Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

723 results about "Clock synchronisation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Source-clock-synchronized memory system and memory unit

InactiveUS6034878ALarge data storage capacity per memoryImprove installation densityMemory adressing/allocation/relocationDigital storageMemory bankComputer module

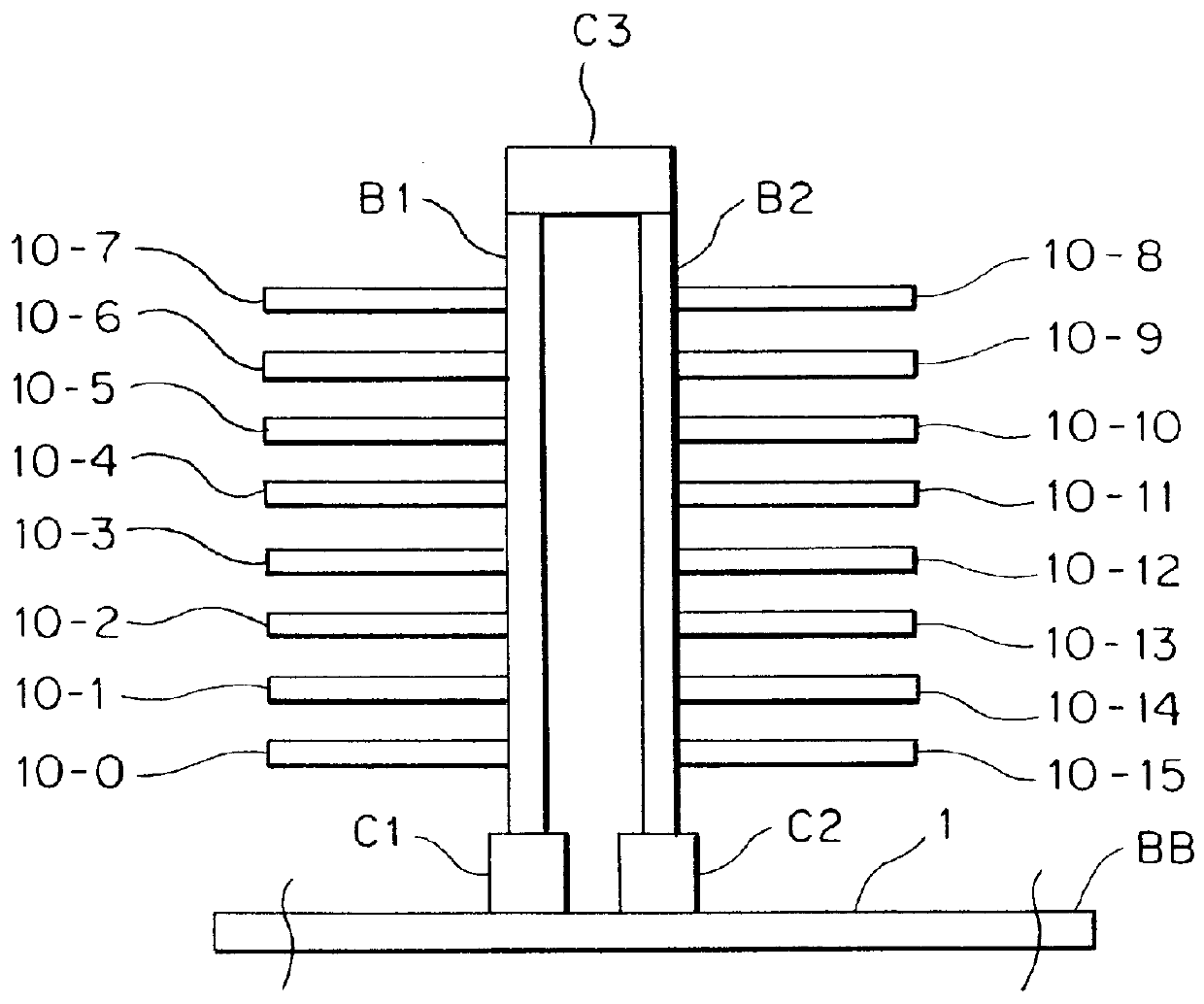

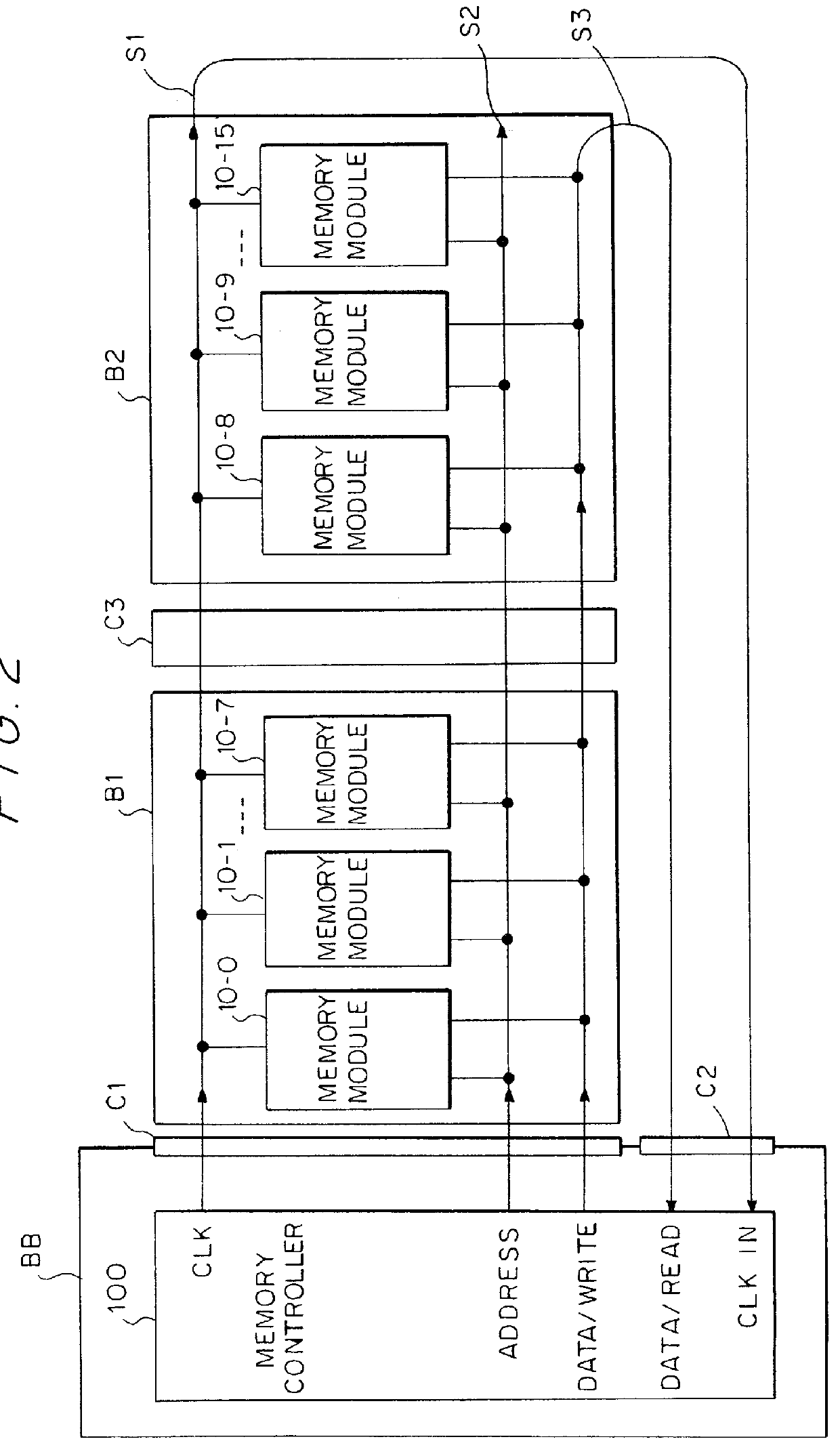

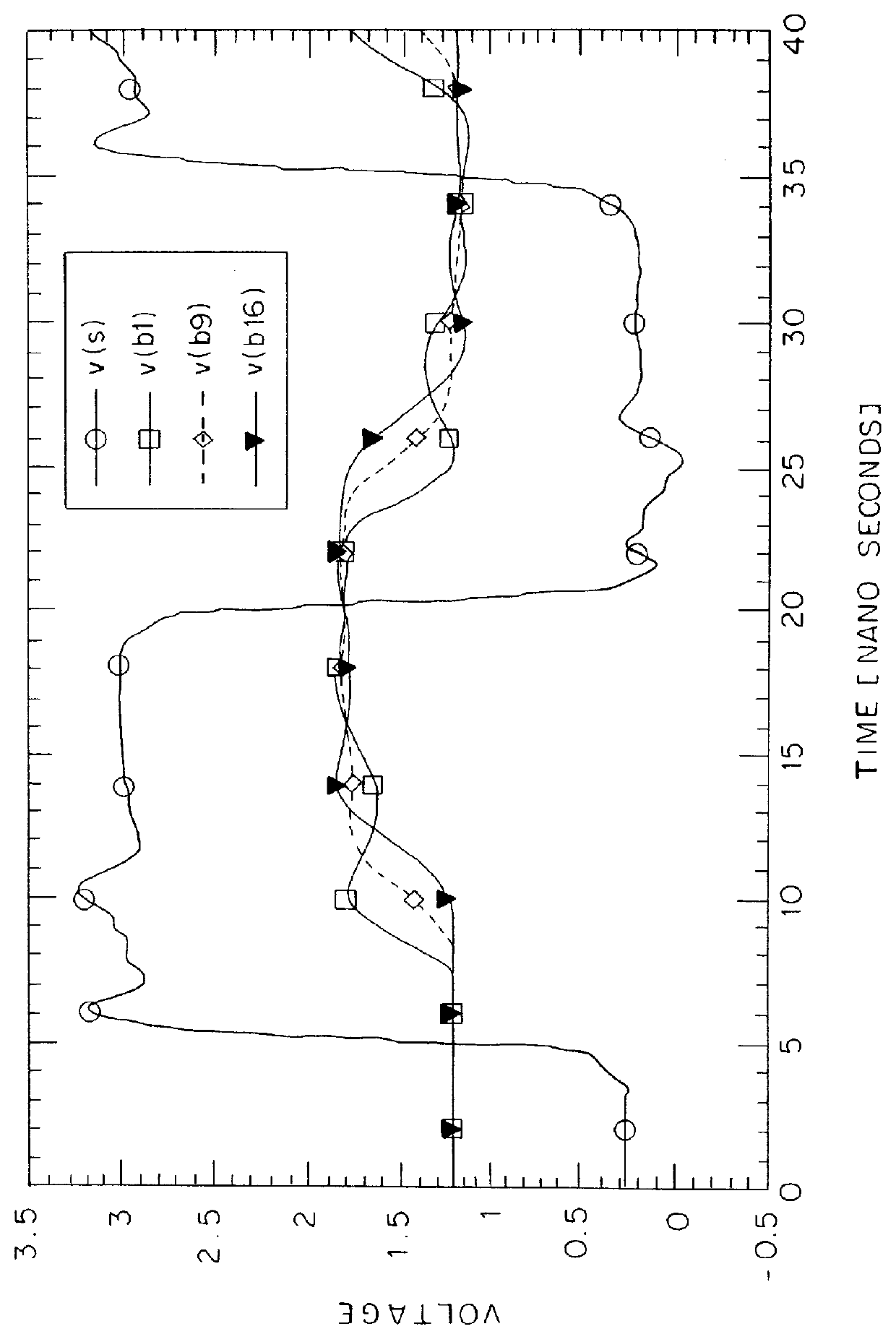

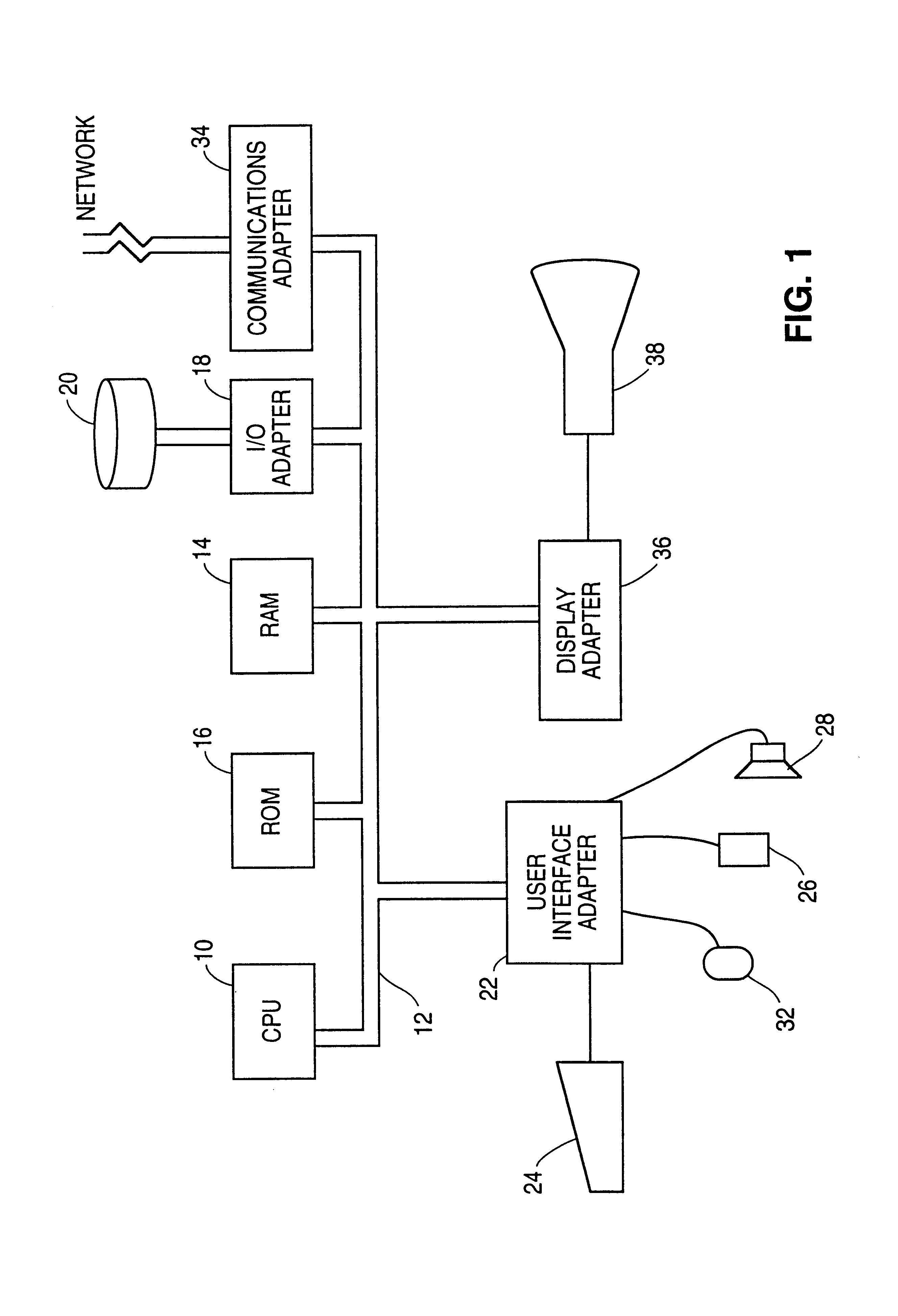

A source-clock-synchronized memory system having a large data storage capacity per memory bank and a high mounting density. The invention includes a memory unit having a first memory riser board B1 mounted on a base board through a first connector C1 and a second memory riser board B2 mounted on the base board BB through a second connector C2. The first memory riser board has a plurality of first memory modules mounted on the front surface thereof and the second memory riser board has a plurality of second memory modules mounted on the front surface thereof. The first and second memory riser boards are arranged in such a way that the back surface of the first memory riser board faces the back surface of the second memory riser board. The invention further includes a board linking connector for connecting signal lines on the first memory riser board to corresponding signal lines on the second memory riser board.

Owner:DELTA KOGYO CO LTD +1

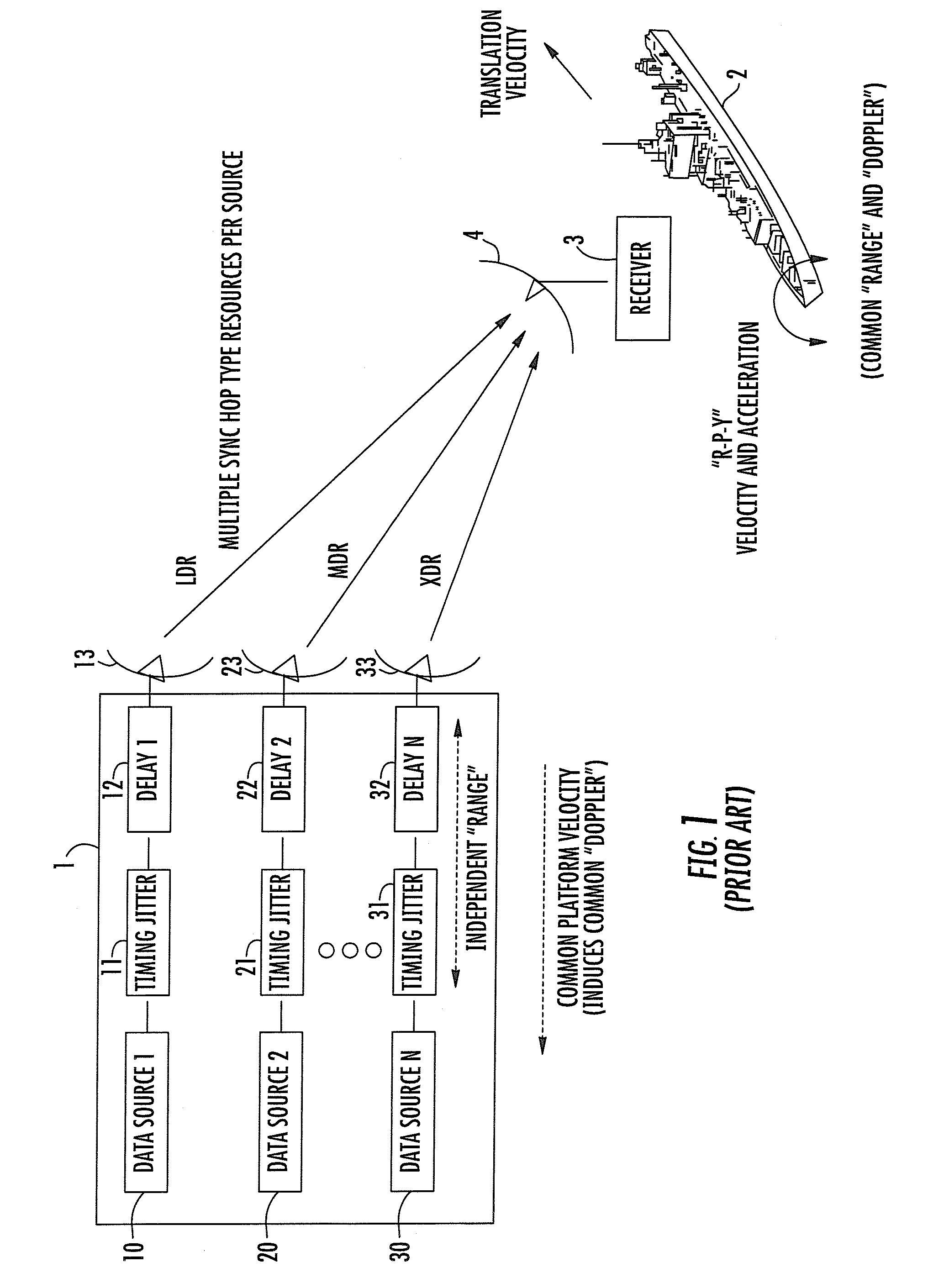

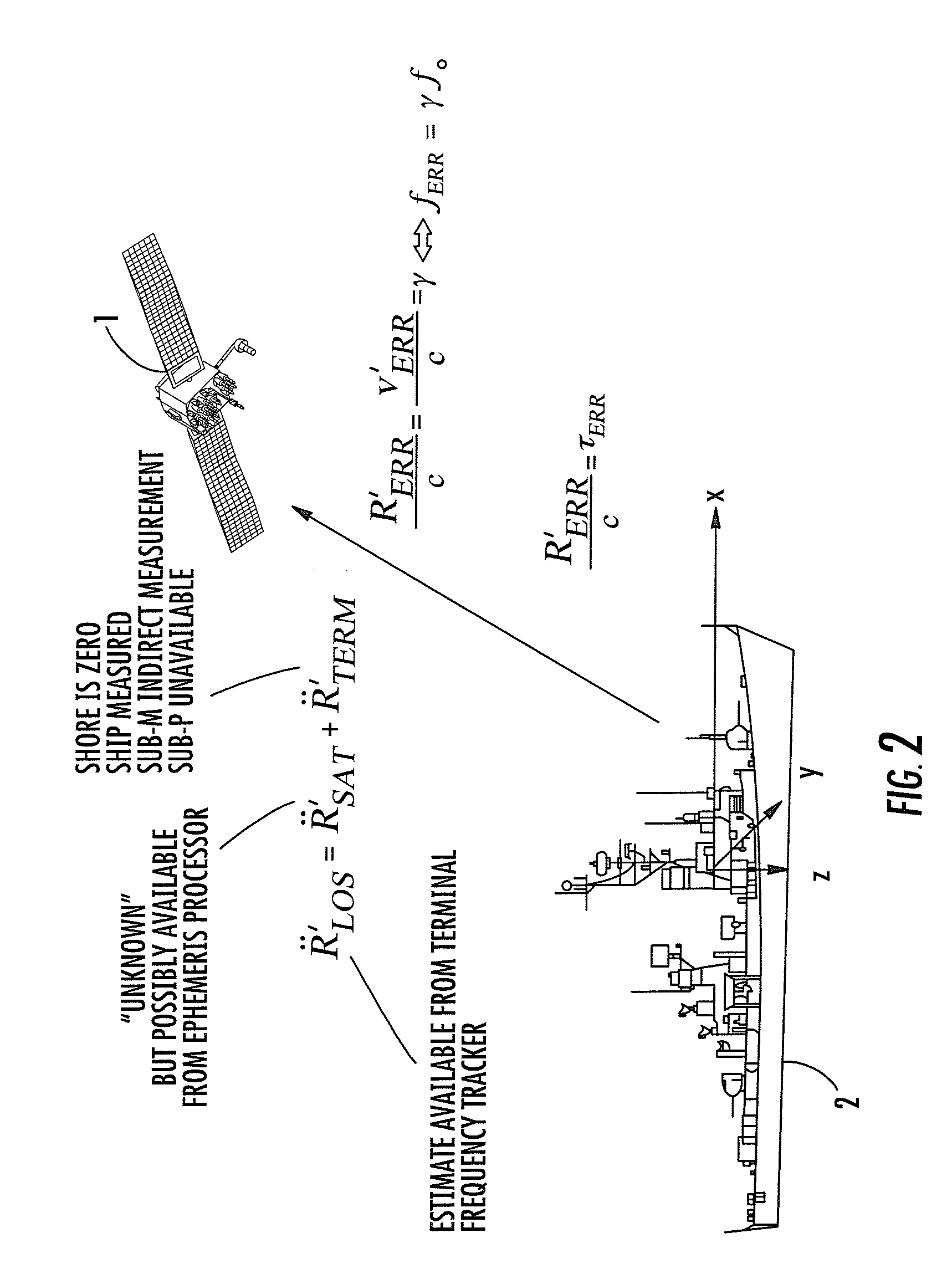

Time/frequency recovery of a communication signal in a multi-beam configuration using a kinematic-based kalman filter and providing a pseudo-ranging feature

InactiveUS20070218931A1Inability to efficientlyEffectively obviatedSynchronisation arrangementRadio transmissionErrors measurementKalman filter

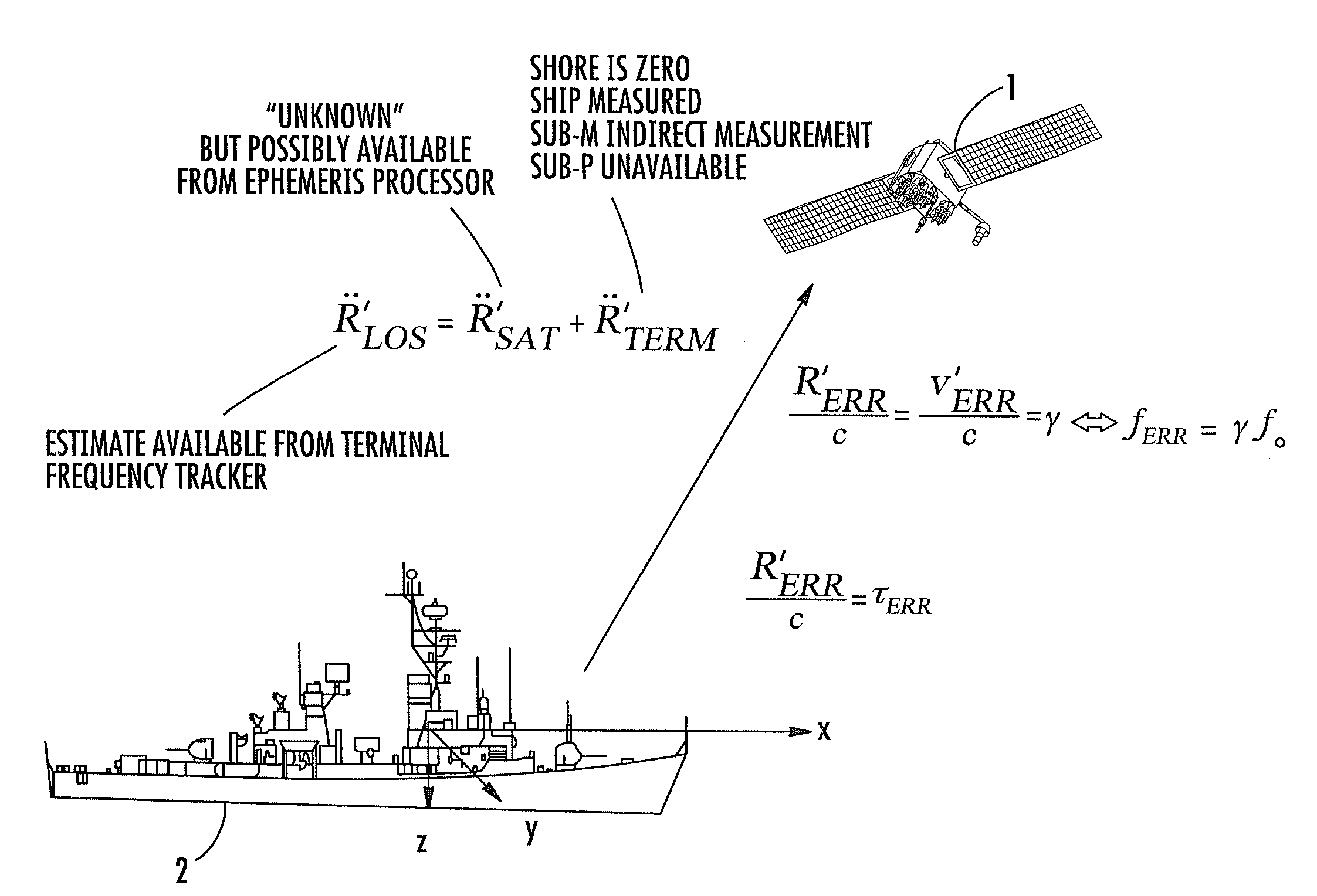

A downlink time / frequency tracker for a receiver terminal, which may be mounted to a static platform on the earth, or to a dynamic platform, such as a ship. The tracker is operative to acquire and track time and frequency variations in time- and frequency-hopped synchronization signals from different data rate sources in a dynamic platform, such as a satellite. Characteristics of the Kalman filter are updated in accordance with data representative of timing error and frequency error measurements carried out on the synchronization signals, as well as data representative of local kinematic domain measurements carried out with respect to the receiver terminal. The Kalman filter outputs minimum mean square error estimates of timing and frequency errors in the receiver terminal's demodulator clock. These error estimates are used to synchronize the demodulator's clock with the clock embedded in the downlink signal, so as to enable demodulation and recovery of data.

Owner:HARRIS CORP

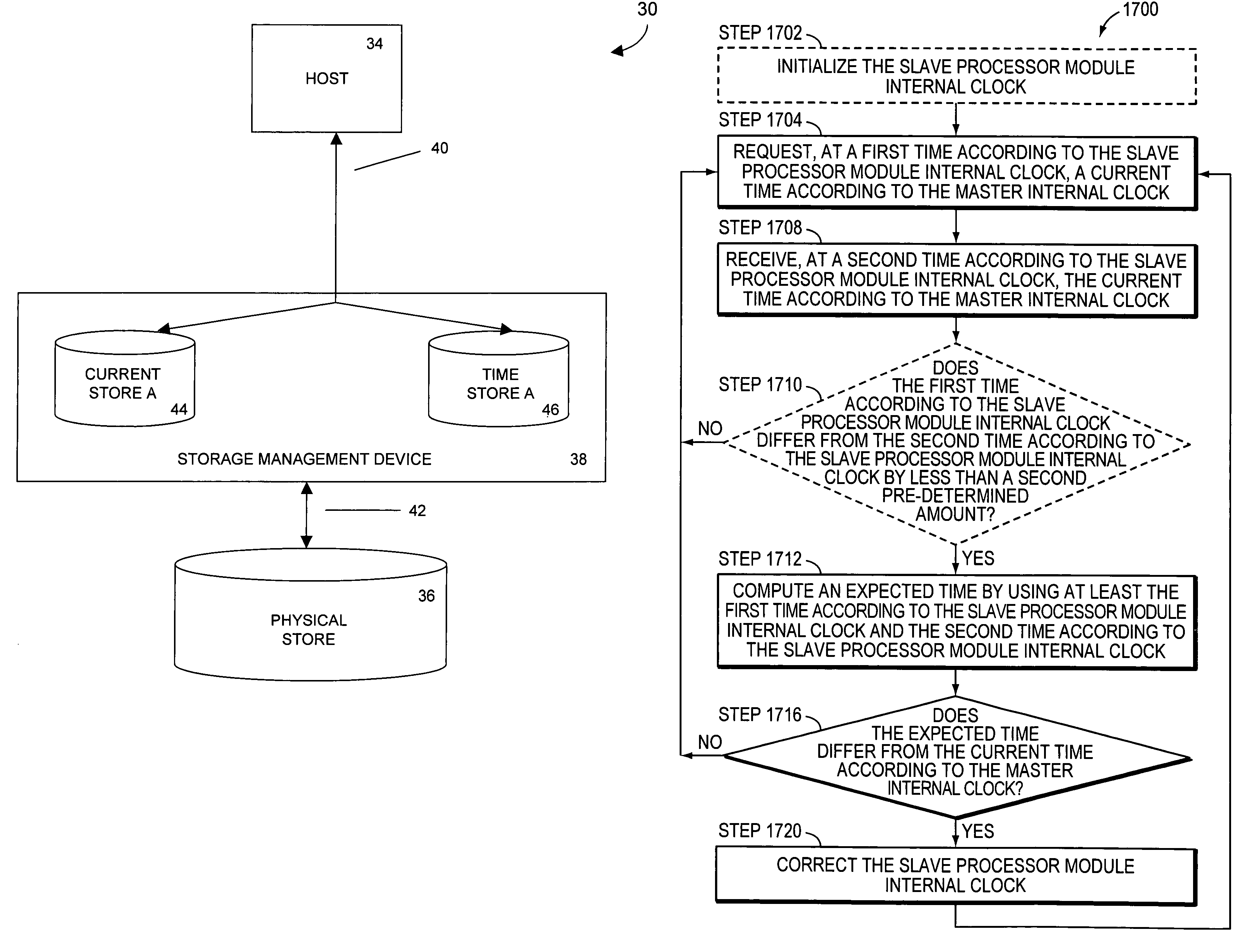

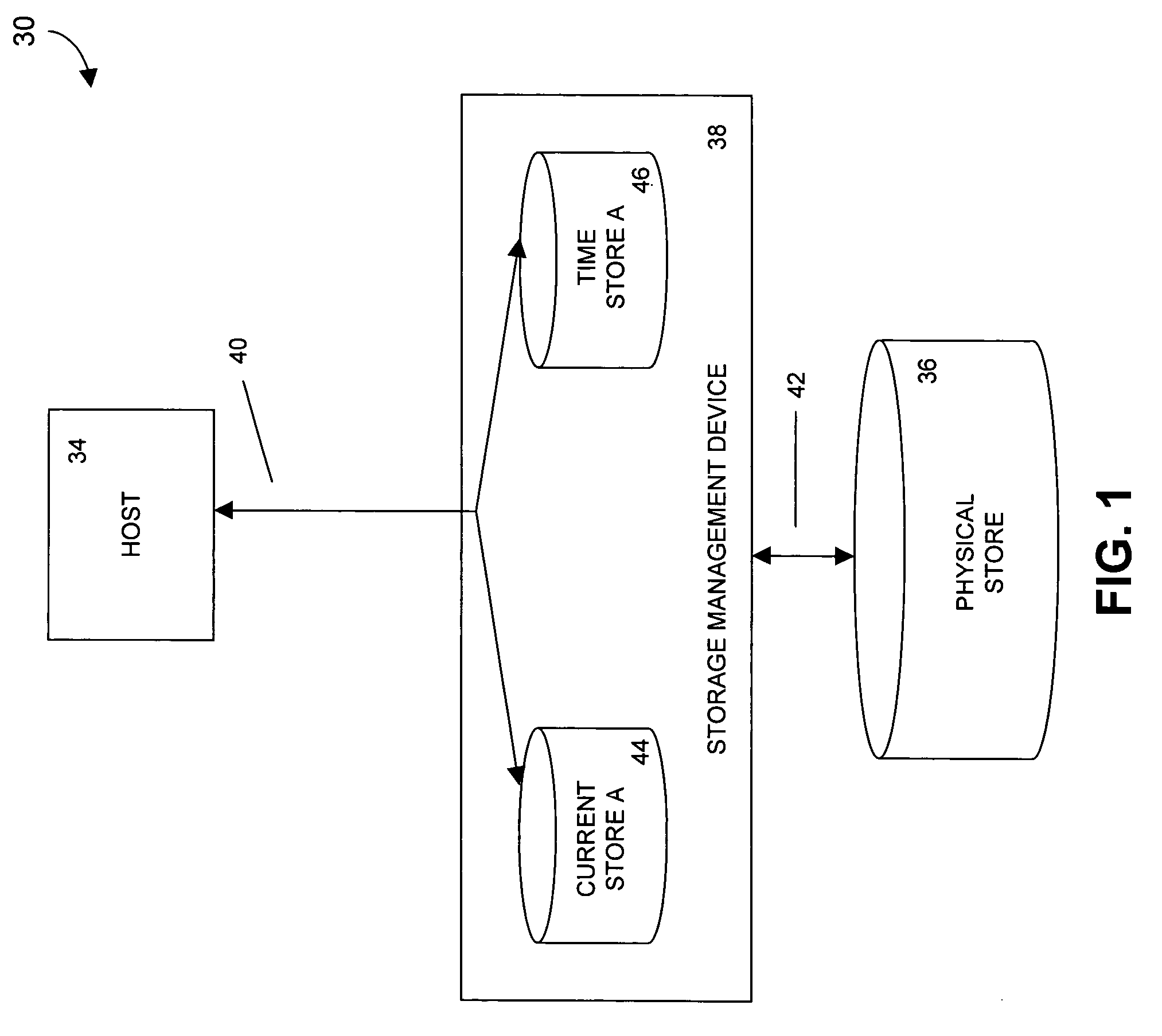

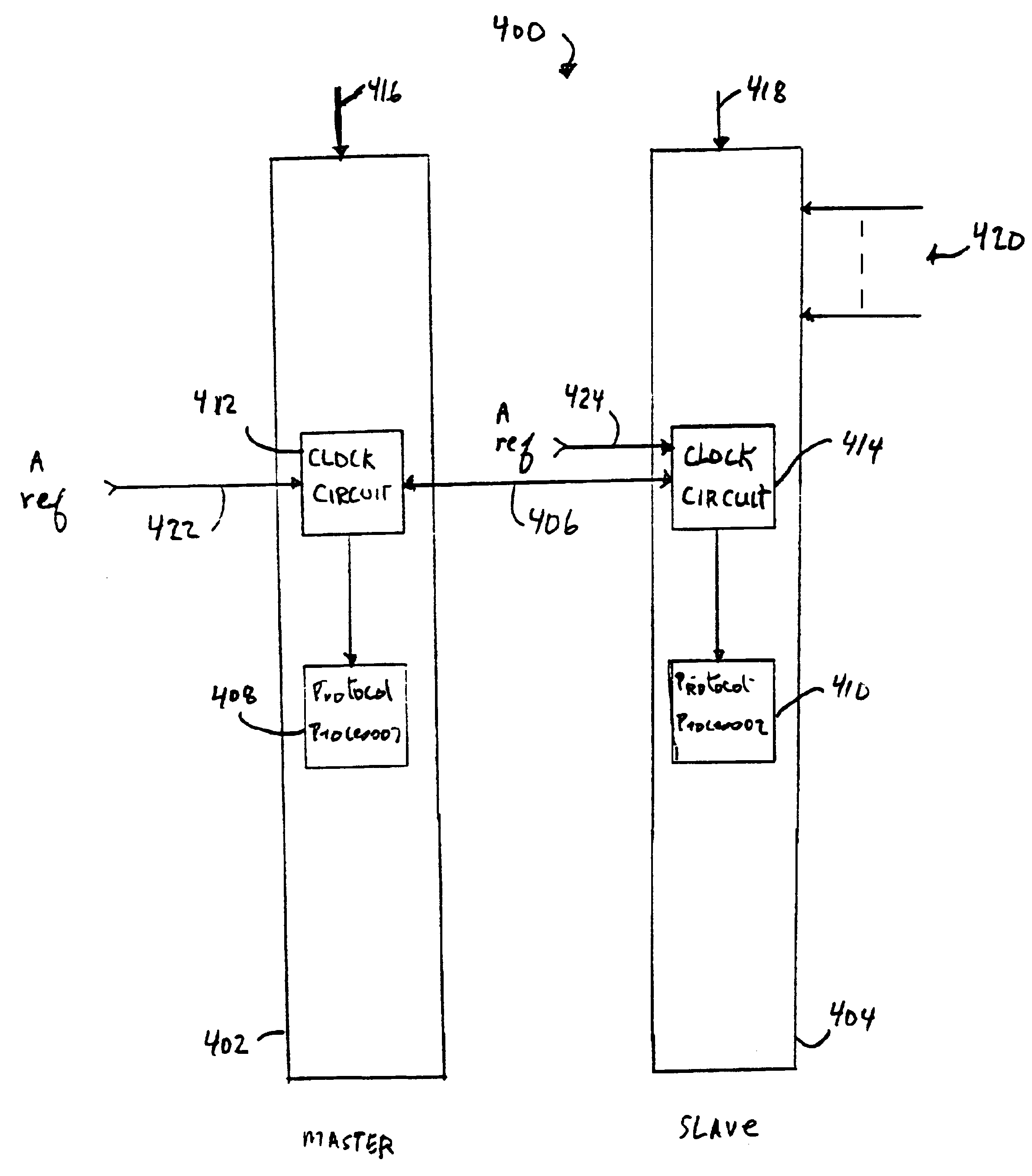

Systems and methods for synchronizing the internal clocks of a plurality of processor modules

ActiveUS7239581B2Data storage is convenientMechanical clocksSynchronous motors for clocksComputer architectureMulti processor

In a multiprocessor system that includes a plurality of processor modules, each one of which includes its own internal clock, one of the plurality of processor modules is designated as a master processor module having a master internal clock. Each other processor module is designated as a slave processor module having a slave processor module internal clock. Each slave processor module synchronizes its internal clock with the master internal clock.

Owner:SYMANTEC OPERATING CORP

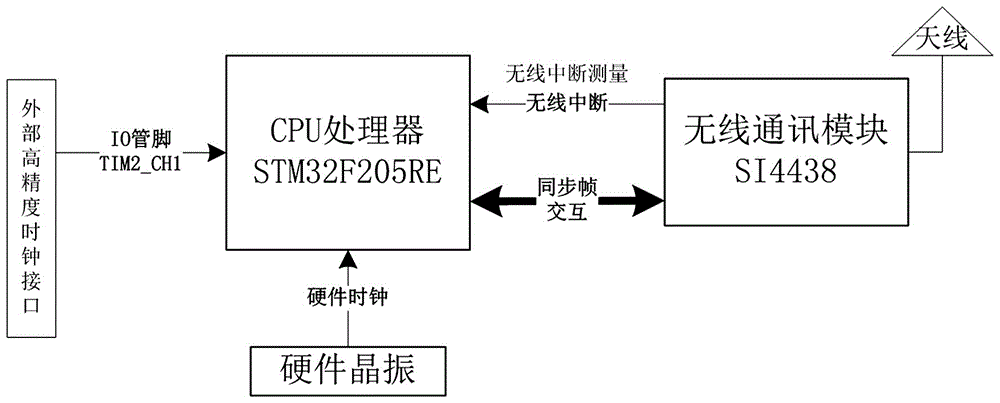

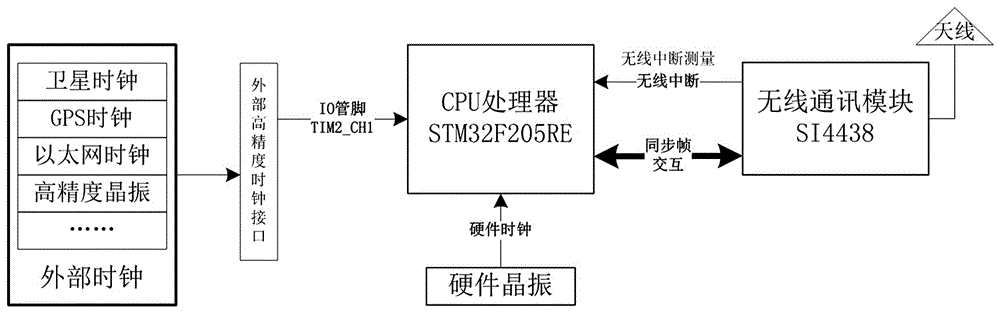

Clock synchronization method among wireless network devices

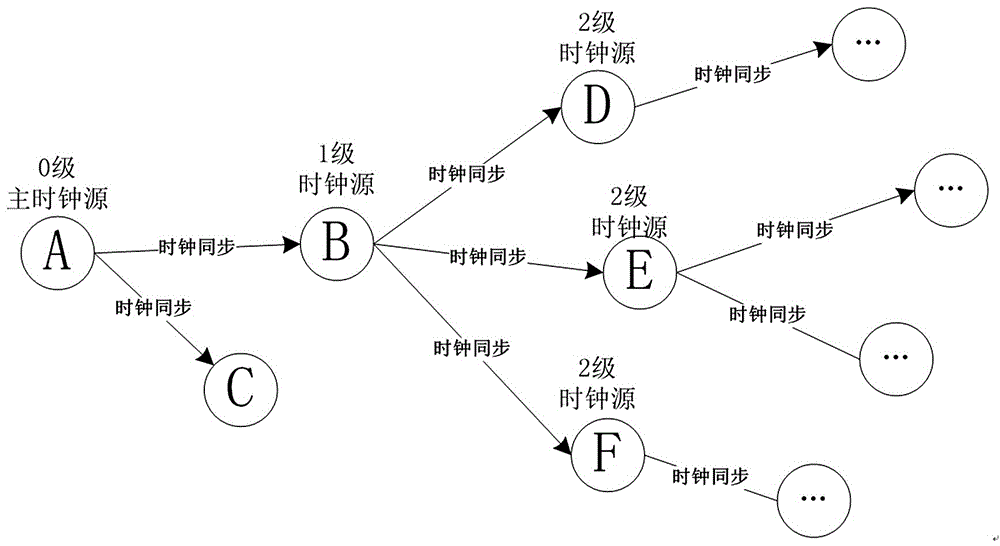

ActiveCN106131947AGuaranteed synchronizationEnsure consistencySynchronisation arrangementTime-division multiplexSynchronous controlInterconnection

The invention provides a clock synchronization method among wireless network devices. The method comprises the steps that 1, a clock source device and at least one clock slave device are in network interconnection; 2, the clock source device obtains a reference clock, and the clock slave devices obtain unsynchronized reference clocks; 3, the clock source device interacts clock information with the clock slave devices through clock synchronization frames; 4, the clock source device transmits information containing the frequency and phase of the reference clock to the clock slave devices; the CPU processors in the clock slave devices calculate the reference clock of the clock source device and calibrate own reference clocks according to the reference clock; and the clock synchronization among the wireless network devices is realized through the steps. The synchronized reference clock can be used for synchronous scheduling of CPU system tasks, synchronous control of performance of instructions, high-precision synchronous measurement of external signals and synchronous measurement of high-speed moving objects, basic wireless take scheduling can be satisfied, and the synchronous awakening tasks of the devices in an ultra low-power-consumption application can be satisfied.

Owner:潘进

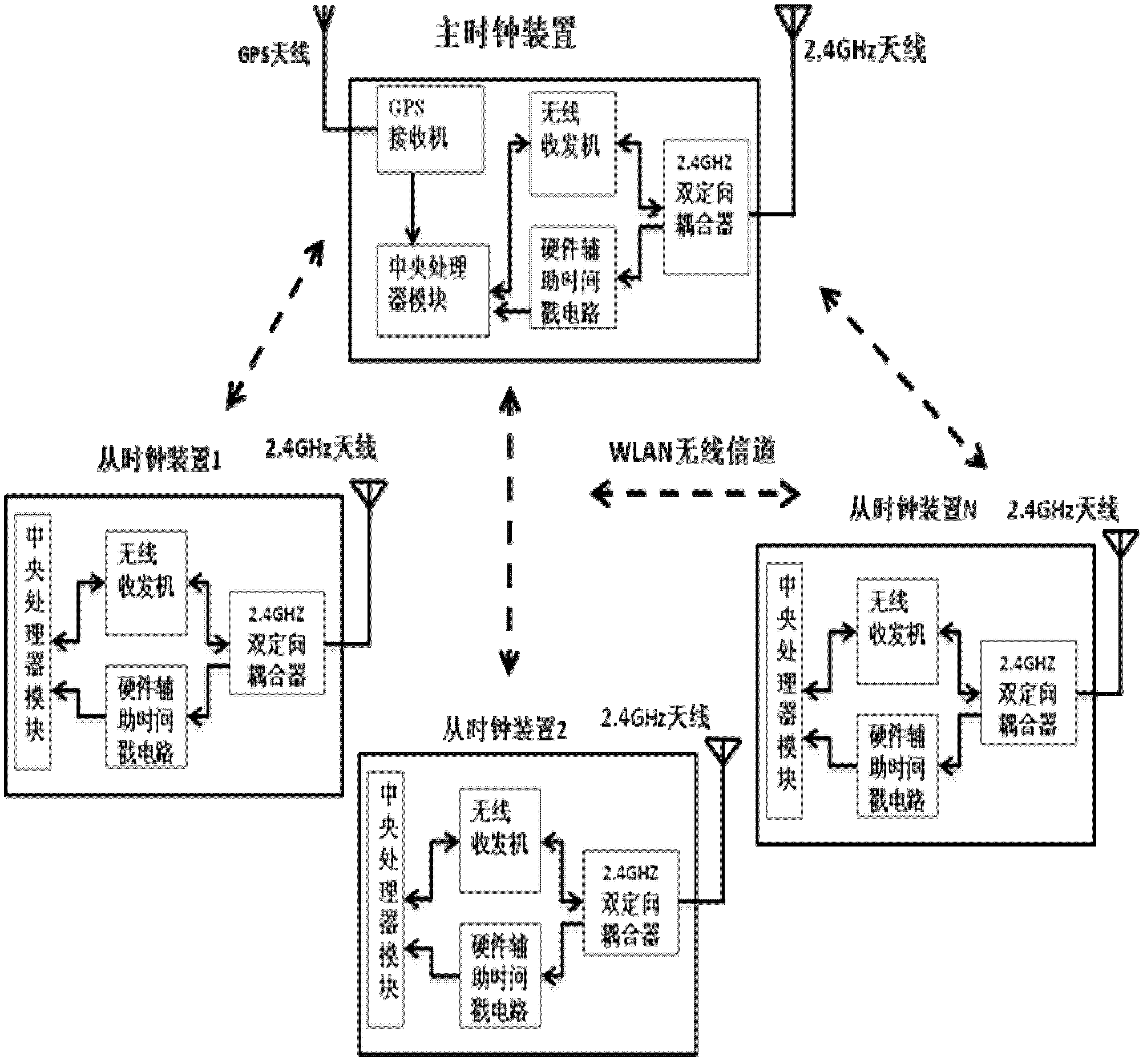

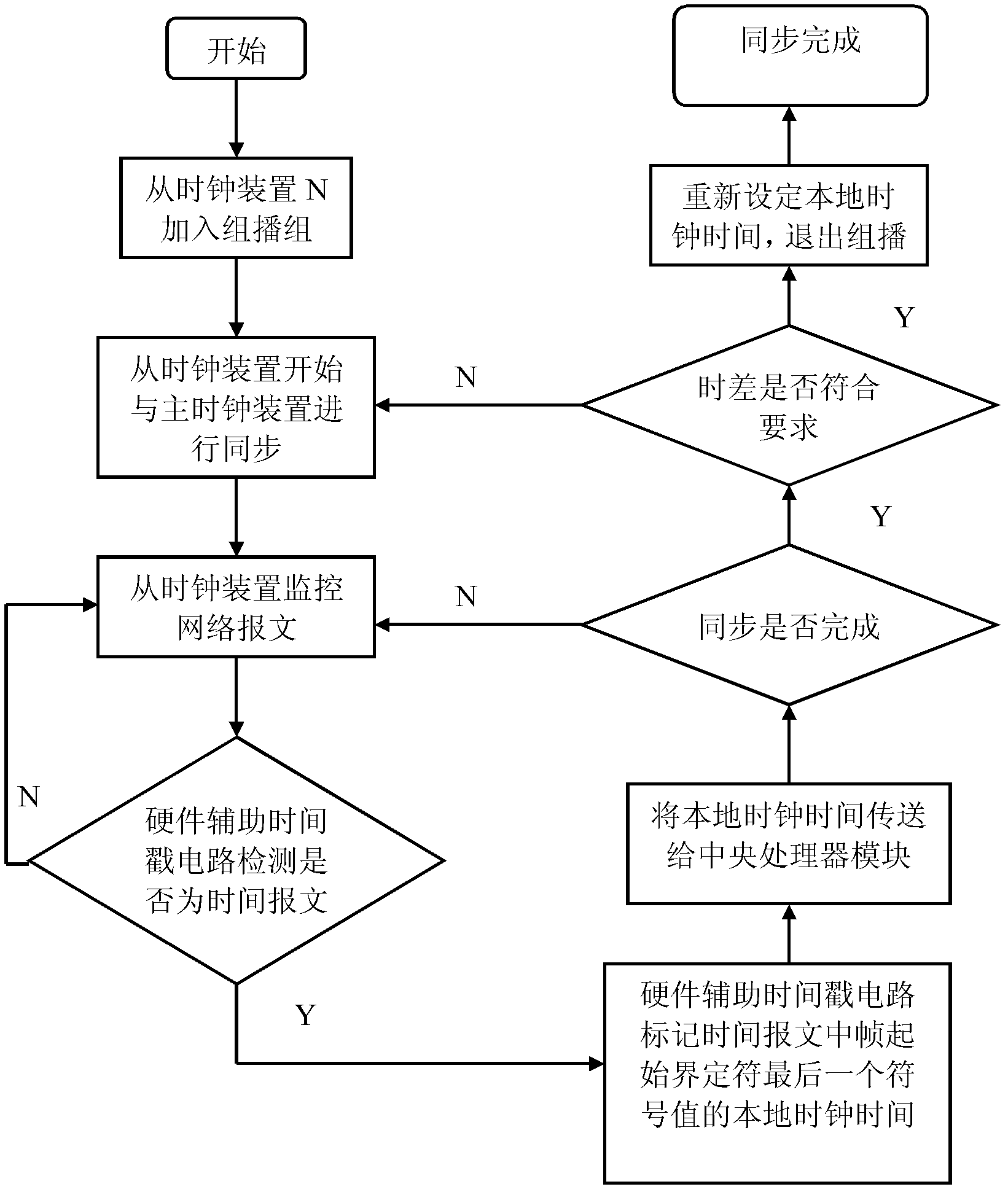

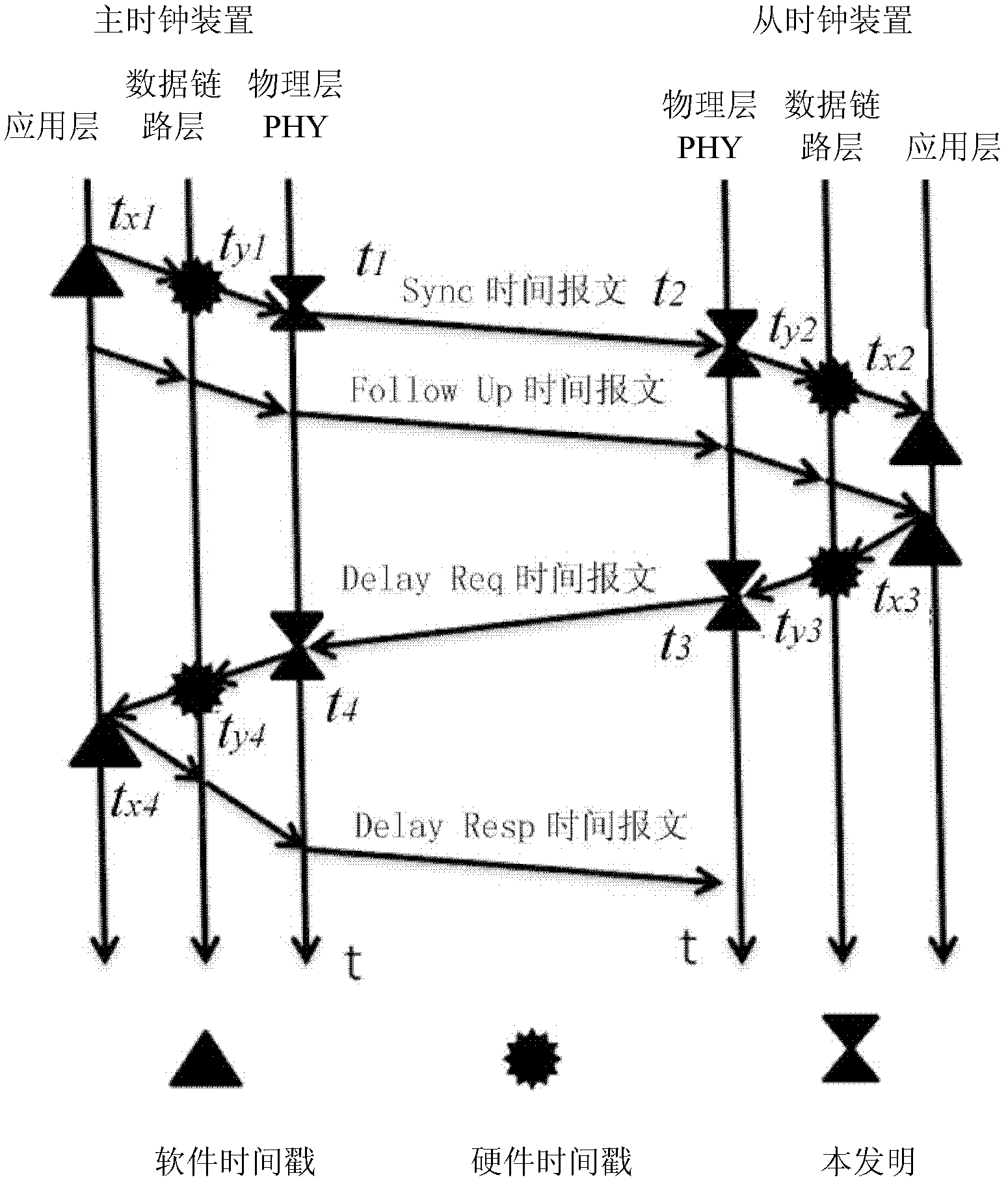

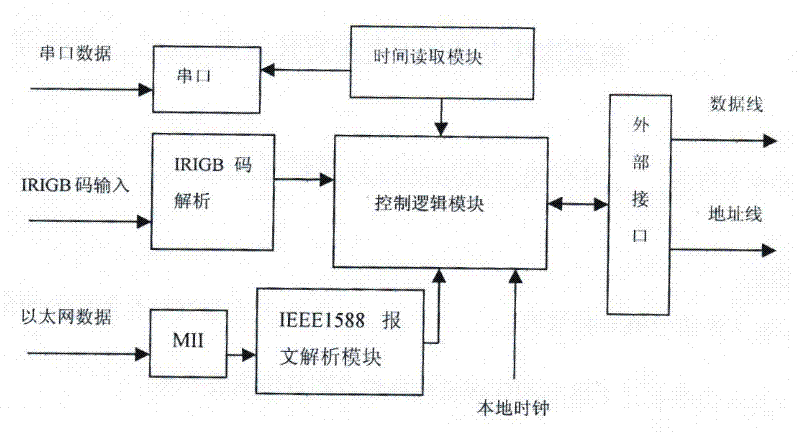

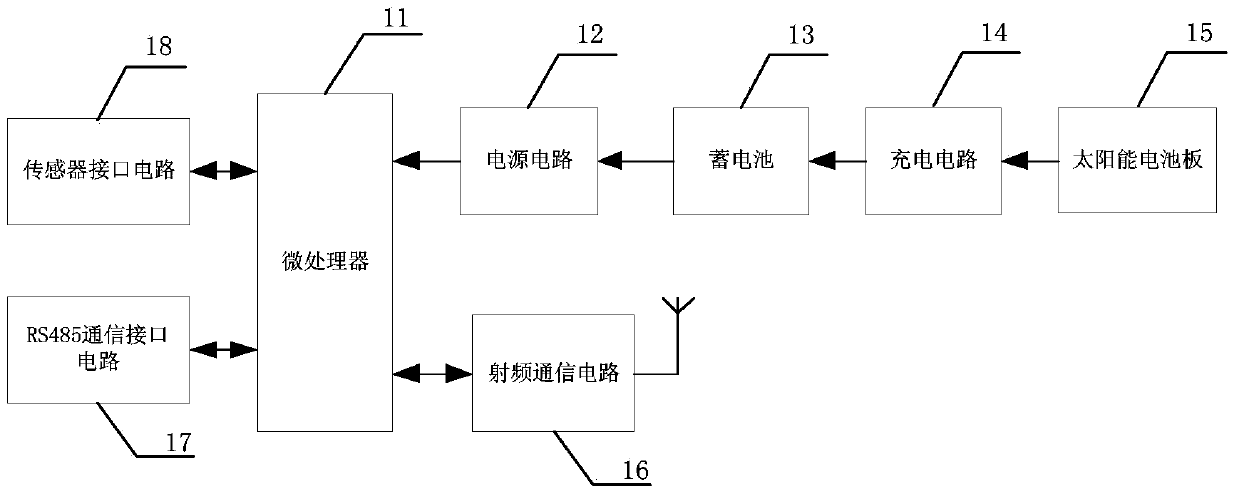

High-accuracy wireless clock synchronization system for power system

InactiveCN102547969AAvoid Uncertain LatencyImprove reliabilitySynchronisation arrangementTransmissionTimestampElectric power system

The invention discloses a high-accuracy wireless clock synchronization system for a power system. A hardware assisting timestamp circuit is added in a physical layer, the identification of the timestamp is transferred from a traditional application layer or a MAC (Medium Access Control) sub-layer of a data link layer to a PHY (physical layer); the timestamp information is transferred to a central processor. Compared with the hardware timestamp method of the prior art, because the driving program of the MAC (Medium Access Control) sub-layer and the uncertain time delay for the interruption response of the driving program are avoided further, the time synchronization accuracy is higher, at the same time, the reliability and the safety are improved further, the requirement that each distribution-type system has high clock synchronization accuracy is met, and the power system oriented high-accuracy wireless clock synchronization system is not suitable for application occasions with laid cables.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA +1

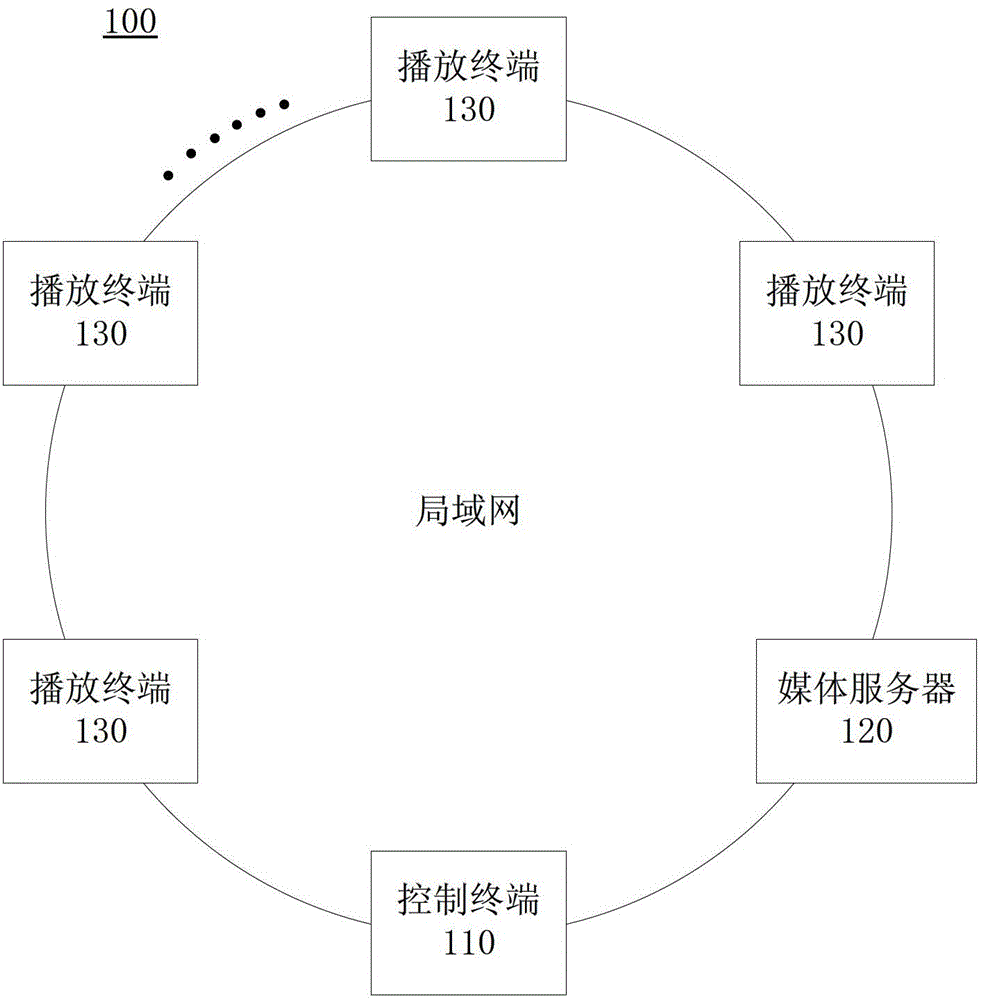

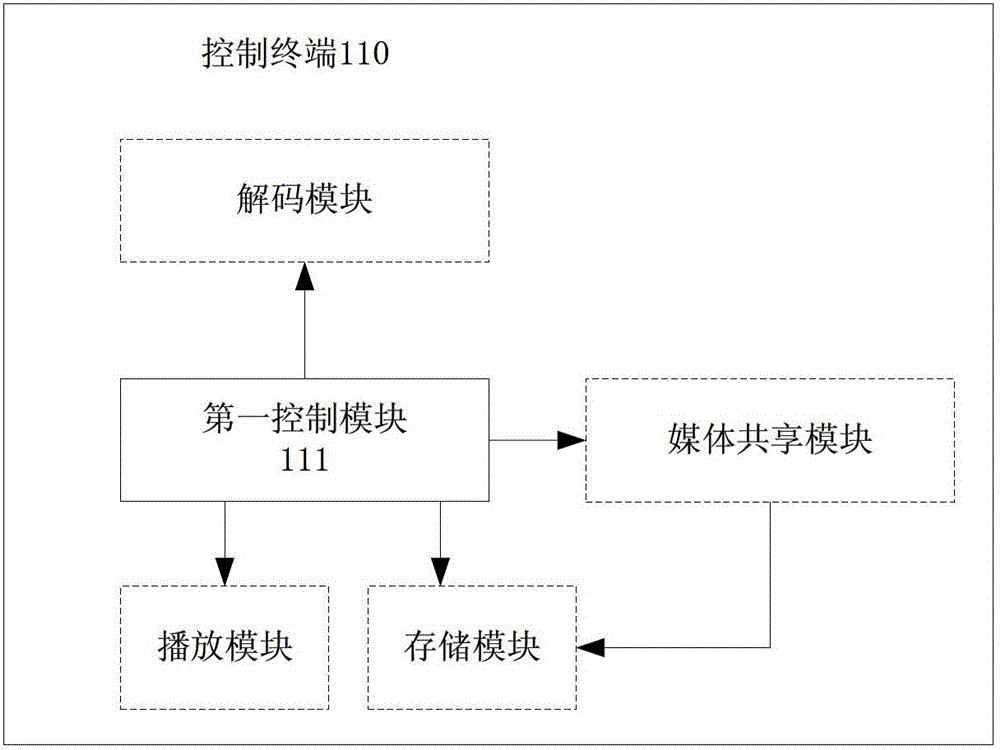

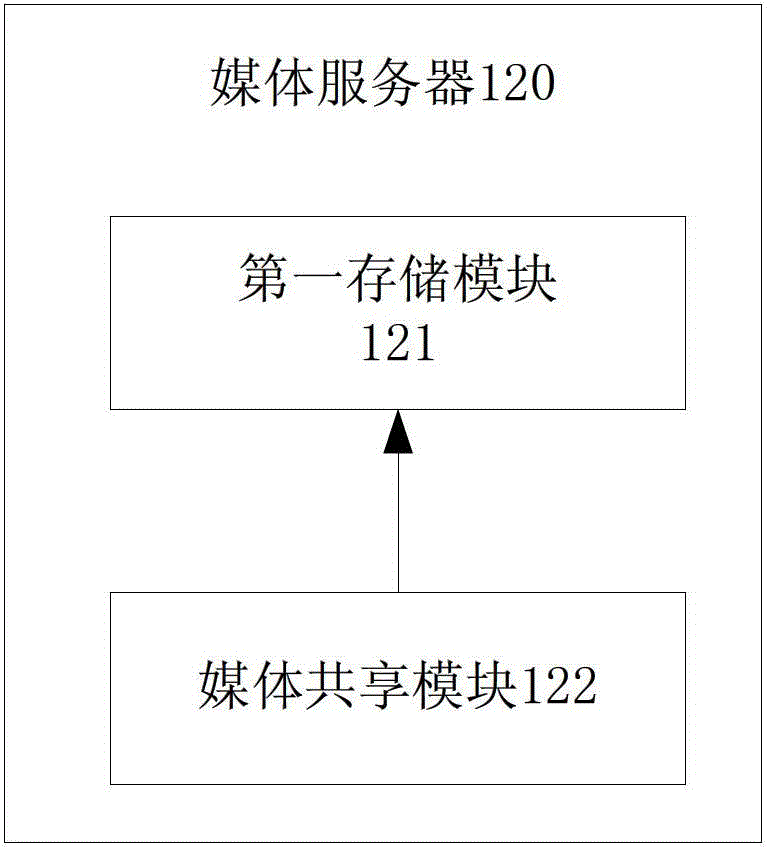

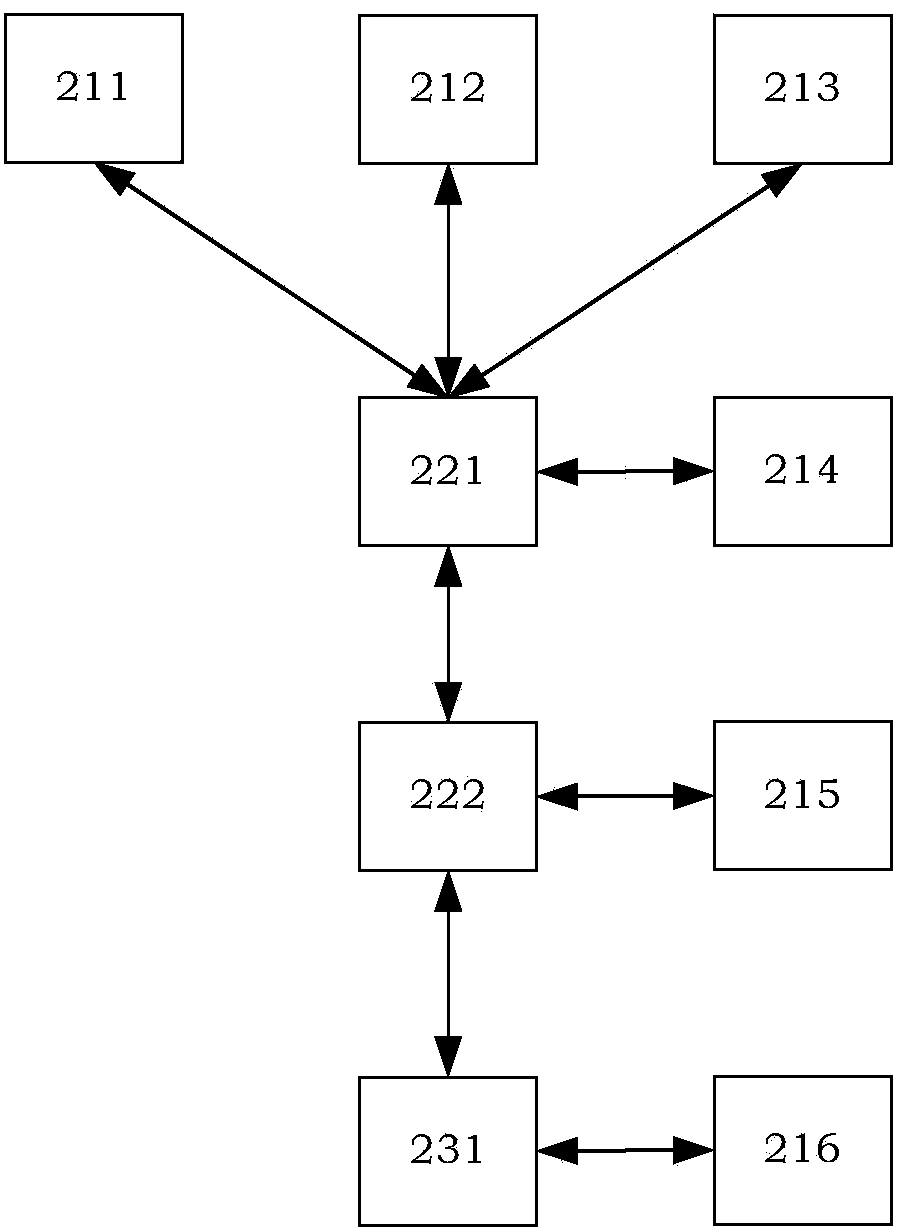

Audio synchronization output method and system

ActiveCN103338204AQuality improvementReduce playback time errorTime-division multiplexSelective content distributionTime errorComputer terminal

The invention discloses an audio synchronization output method and a system. The system comprises a control terminal, a media server and a plurality of play terminals which are accessed to a local area network. The method comprises the steps that S1, the control terminal selects one play terminal from the local area network to serve as a reference terminal, and sends a synchronization instruction to the reference terminal; S2, the reference terminal downloads specified audio information from the media server, decodes the audio information for generating digital audio information, and sends a clock synchronization coordination instruction to the specified play terminals, and the clock synchronization coordination instruction enables the play terminals to send clock synchronization coordination instruction return values to the reference terminal, and synchronizes a clock to the reference time; and S3, the reference terminal sends the digital audio information to the play terminals feeding back the clock synchronization coordination instruction return values within the required time for synchronously playing the digital audio information on the play terminals. Play time errors among the play terminals are reduced, and the quality of an audio is guaranteed.

Owner:SHENZHEN AIRSMART TECH CO LTD

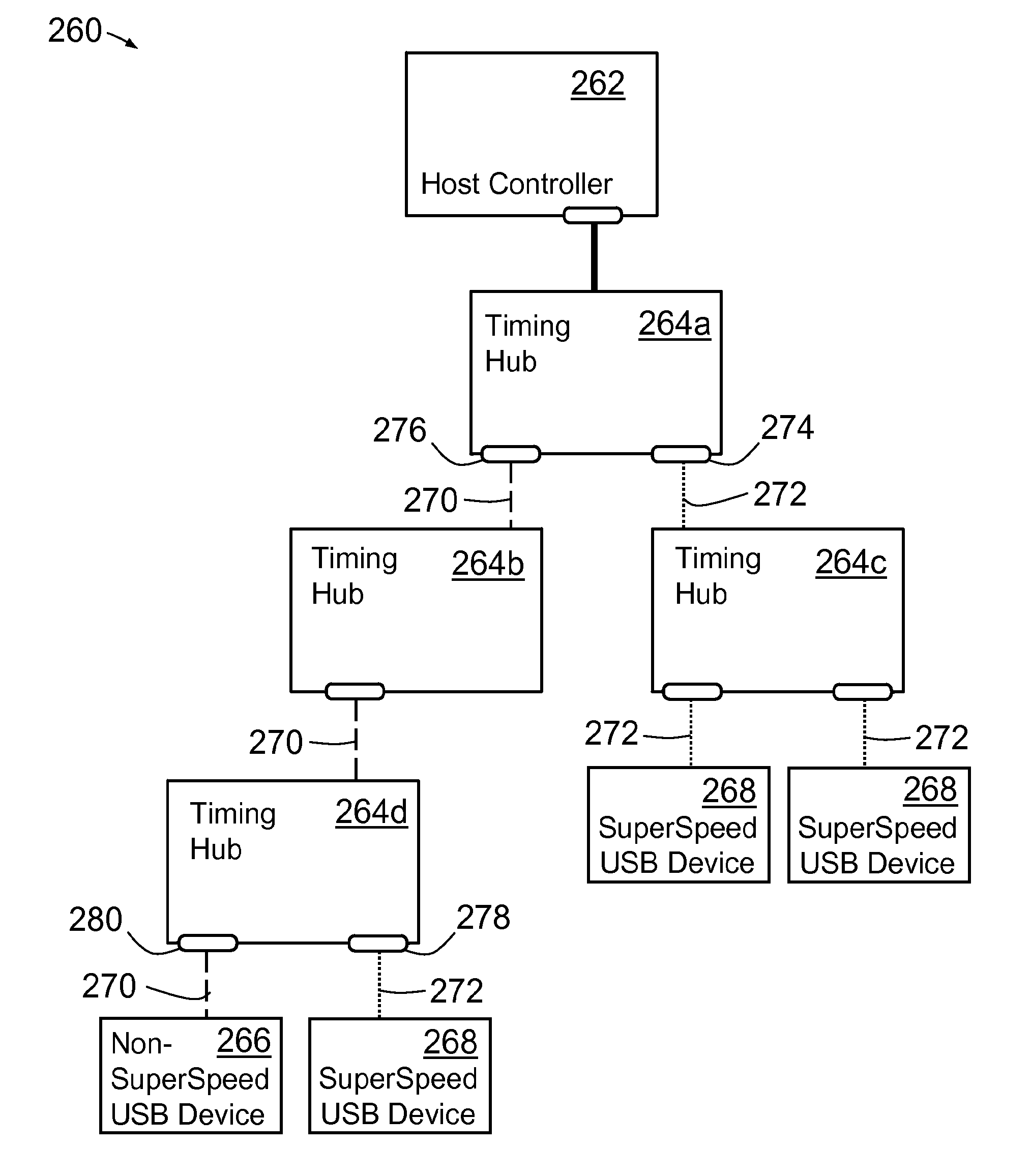

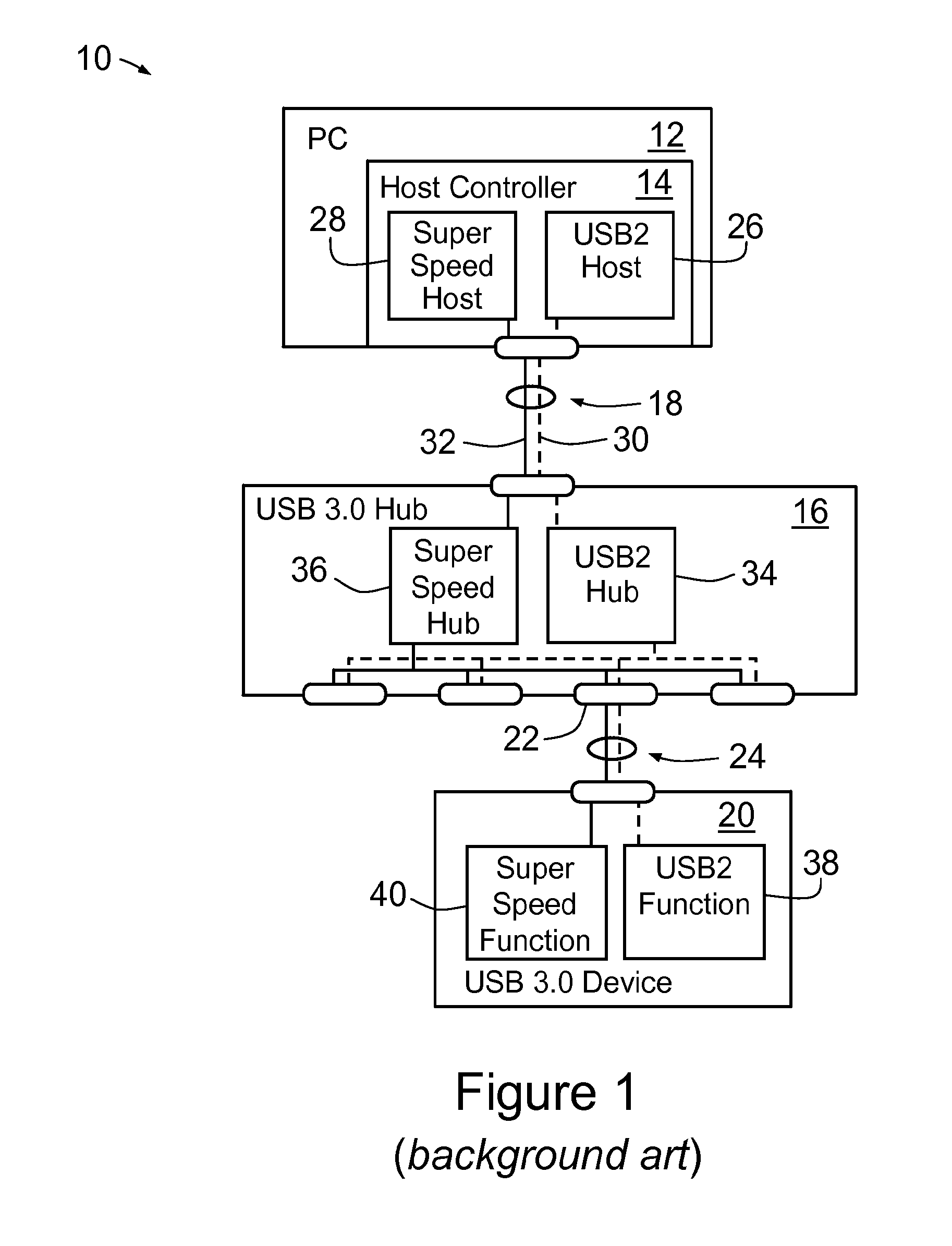

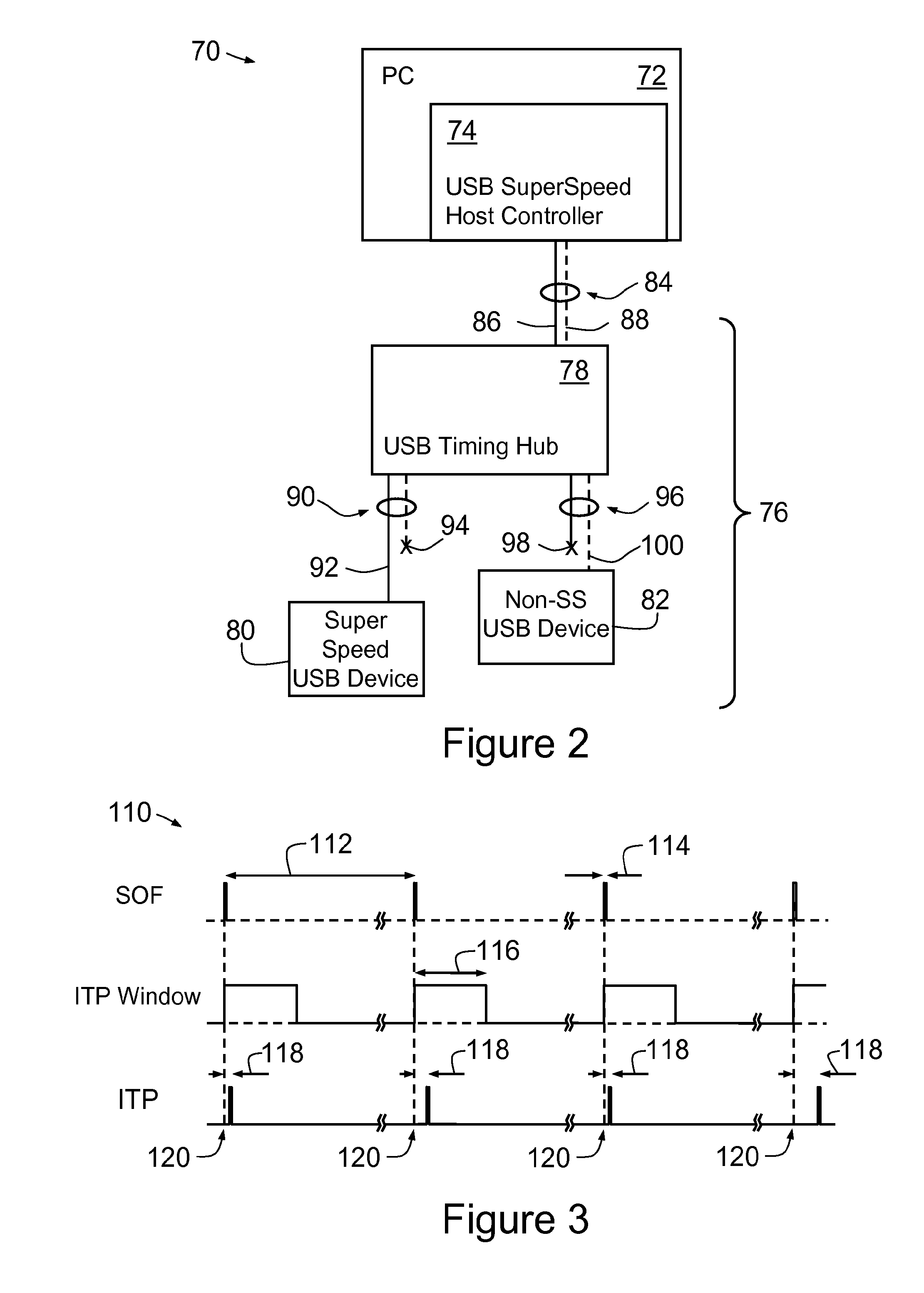

Synchronous network of superspeed and non-superspeed USB devices

InactiveUS20120066418A1Improve accuracyError detection/correctionSynchronisation signal speed/phase controlSynchronous networkUSB

Owner:CHRONOLOGIC PTY LTD

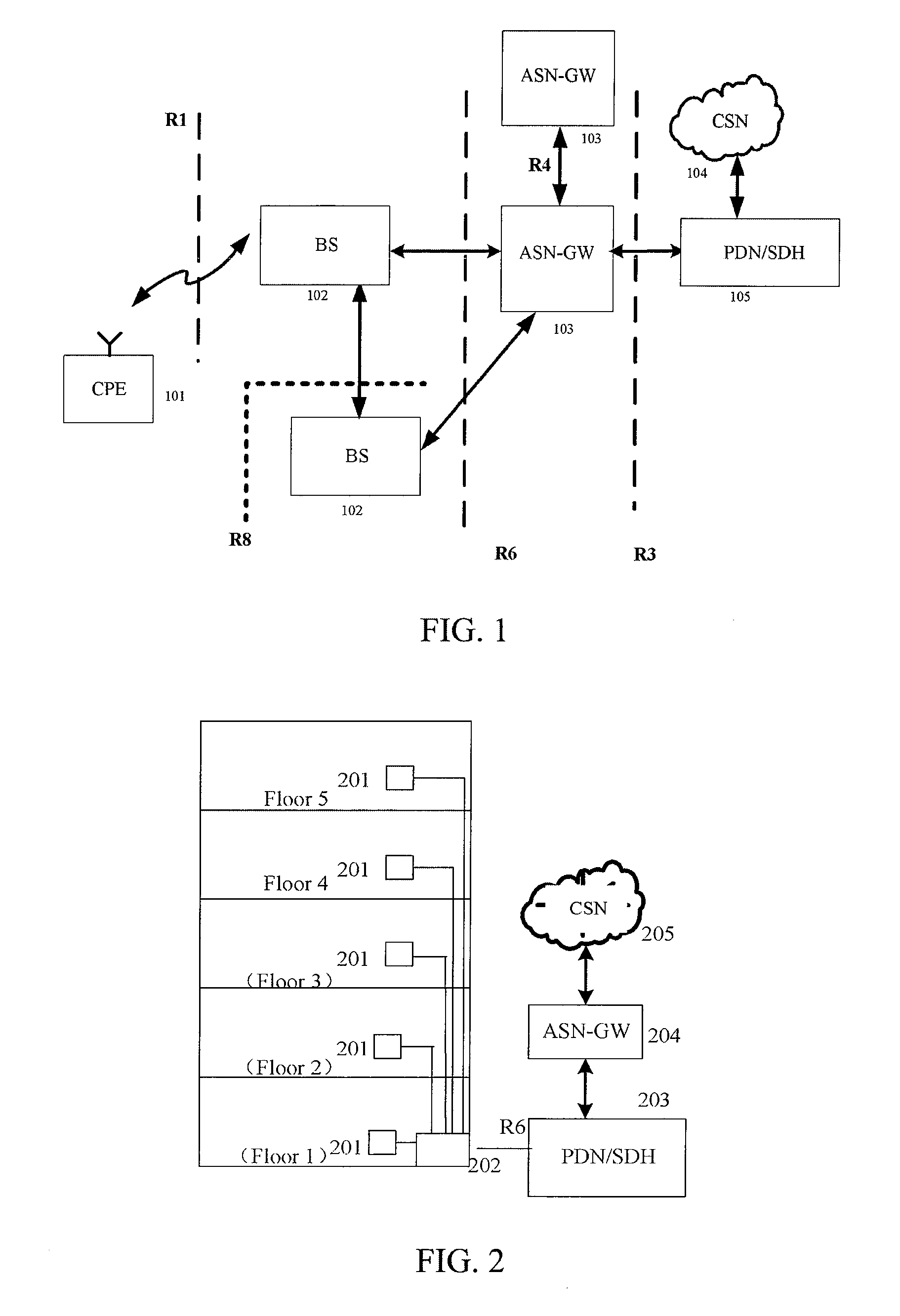

Synchronization, scheduling, network management and frequency assignment method of a layered wireless access system

InactiveUS20110122769A1Improve synchronicitySmooth upgradeError preventionFrequency-division multiplex detailsManagement unitNetwork management

The present invention discloses as synchronization method of a layered wireless access system, which is applied to the layered wireless access system including an access point management unit located in an access layer and its linked access points. The access point management unit has a timing server, each access point having a timing client. The timing server generates timing information and distributes it to the timing client of each linked access point, and the timing client recovers the timing information as a local timing reference signal. The method may implement clock synchronization between the access point management unit and the access points to ensure the normal operation of the system. The present invention also provides network management, scheduling, frequency assignment and flow control methods based on the layered wireless access system.

Owner:ZTE CORP

Simulation system of simulating switched Ethernet clock synchronization

ActiveCN103647682AEasy to implementImprove Clock Synchronization AccuracyTime-division multiplexData switching networksExtensibilityRole management

The invention discloses a simulation system of simulating switched Ethernet clock synchronization. The simulation system comprises an Ethernet protocol instruction database, a timer, nodes, a link attribute configuration module, a synchronization topology generation module, a state management module, a state conversion module, a data processing module, a fault detection and processing module, a clock correction module and a result output module. The Ethernet protocol instruction database and the timer satisfy an IEEE802.3ISO / IEC8802-3 standard specification and instruction and state association information indicated in SAEAS6802. The nodes and the link attribute configuration module are used to carry out simulation role configuration so as to obtain a synchronization topology structure. Then, state role management is performed on each node in the synchronization topology structure and different state roles are used to carry out data processing, clock correction and fault detection. And then a state and clock correction result is output. Compared to the current simulation system, by using the simulation system of the invention, strong scalability is showed on an aspect of network model establishment, which is convenient to carry out an effective analysis on a clock synchronization process.

Owner:BEIHANG UNIV

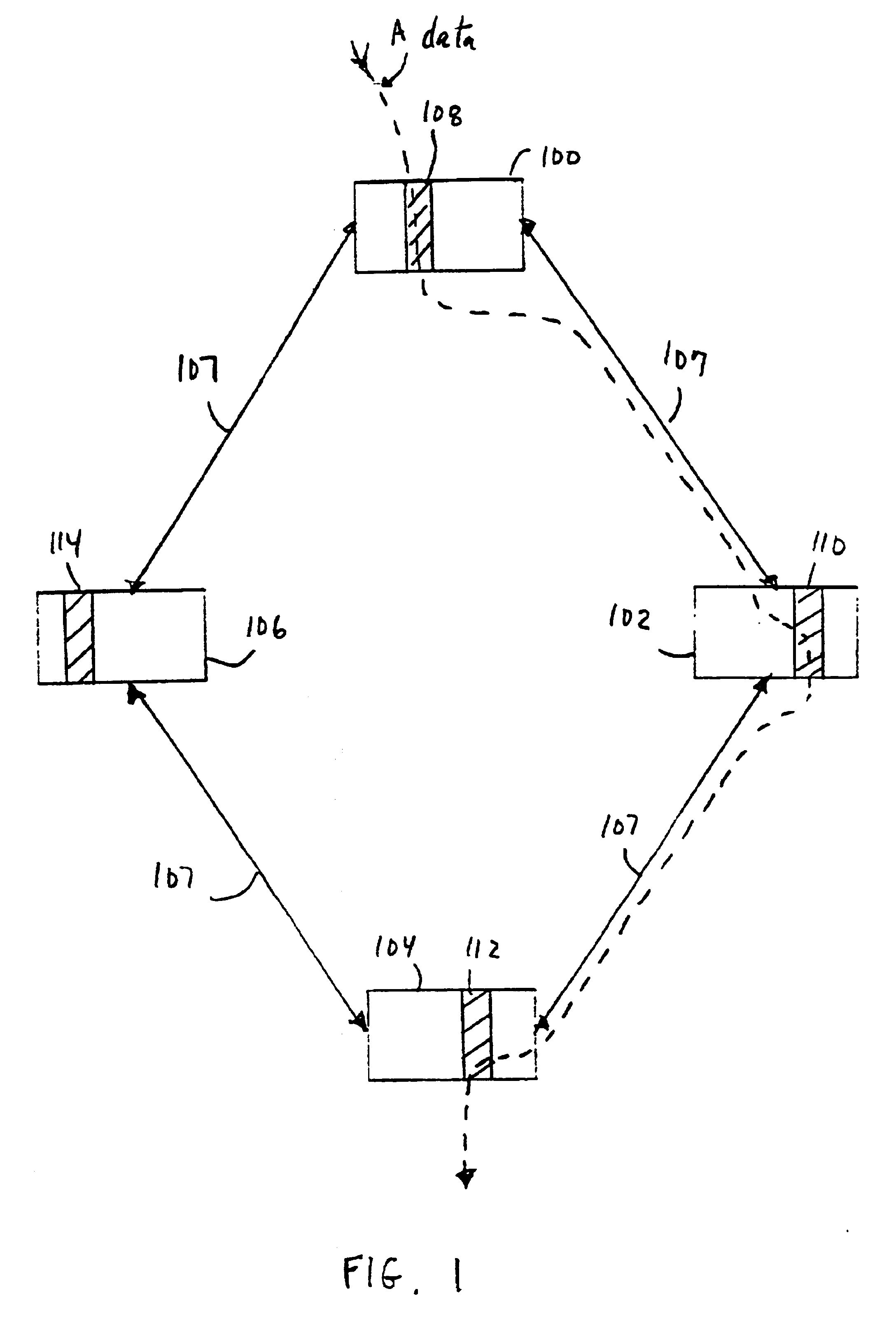

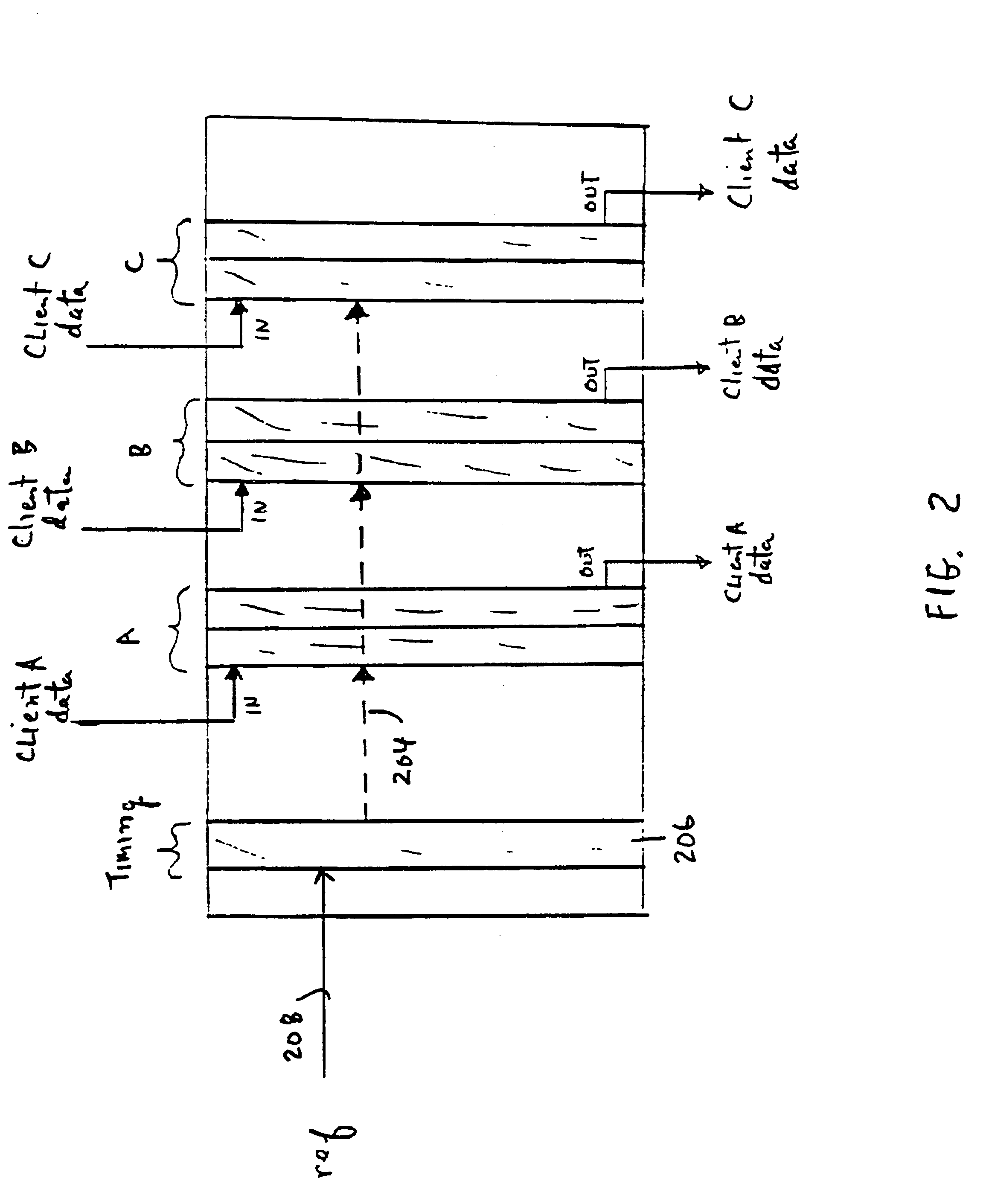

System for clock synchronization

InactiveUS6839858B1Eliminate needTime-division multiplexGenerating/distributing signalsSignal onComputer science

A timing circuit for use with transport logic in a network element is provided. The network element forms part of a data network and the timing circuit includes a timing receiver having a timing input, a timing output, and a selection input, the timing receiver operable to receive one or more timing signals at the timing input and to select a selected timing signal for distribution to the transport logic via the timing output based on a selection signal received at the selection input. The timing circuit also includes a determination circuit that is operable to determine whether the timing circuit is one of a master timing circuit and slave timing circuit, and based on the determination, produce the selection signal. A sync transmitter is also included in the timing circuit. The sync transmitter is coupled to the timing output, the determination circuit, and a communication channel. The sync transmitter is operable to receive the selected timing signal and to transmit the selected timing signal on the communication channel when the determination circuit determines that the timing circuit is the master timing circuit.

Owner:CIENA

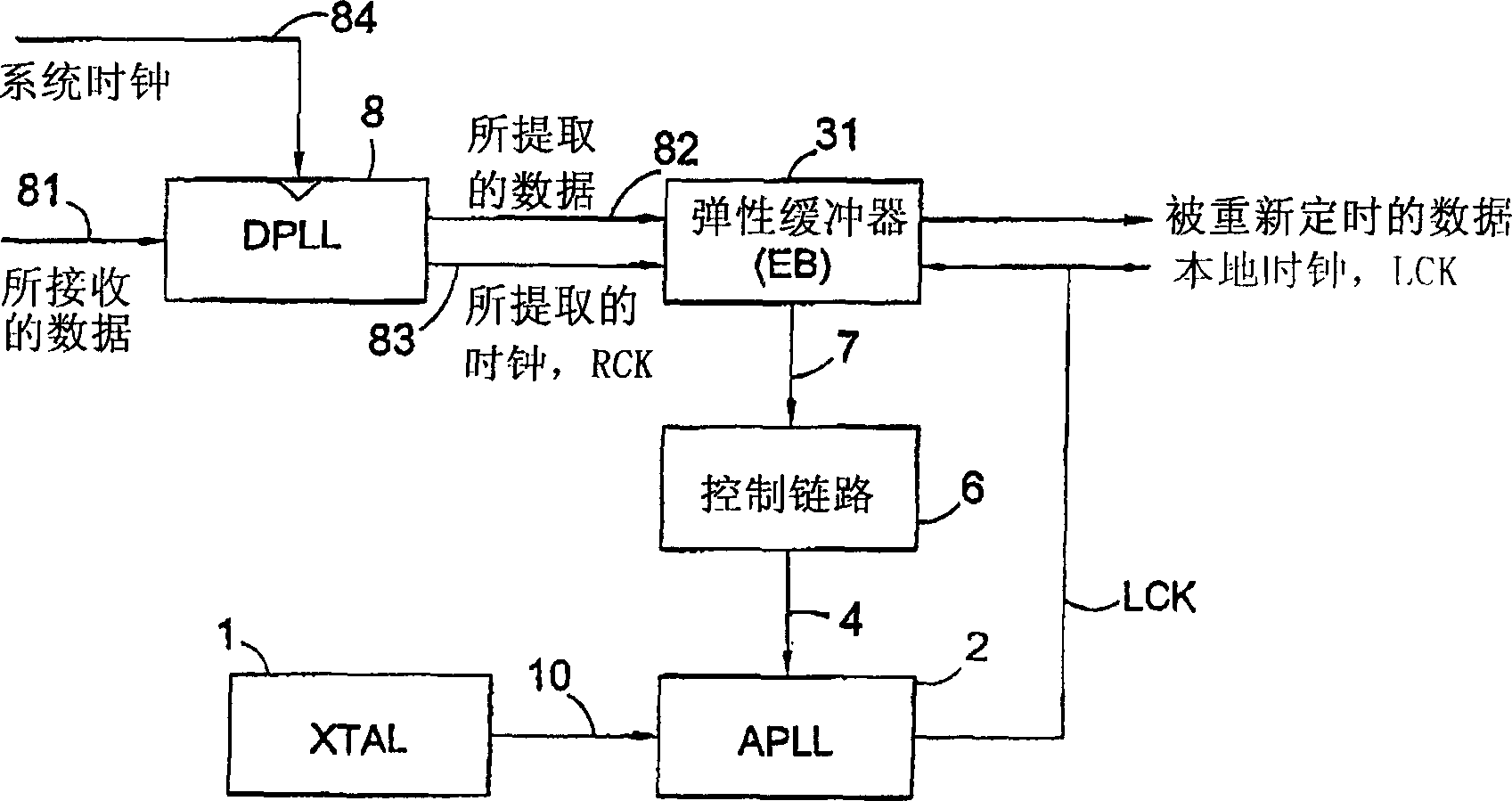

Clock synchronizer and clock and data recovery apparatus and method

A clock synchroniser, and clock and data recovery apparatus incorporating the clock synchroniser, are described, together with corresponding clock synchronisation methods. The clock synchroniser incorporates an elastic buffer. A received clock signal RCK is used to clock data into the buffer, and a locally generated clock LCK is used to clock data out of the buffer. The local clock is synthesised using a PLL, and a fill-level signal from the elastic buffer is used to control to local clock frequency to maintain a desired average quantity of data in the buffer, thereby achieving synchronisation of the received and local clocks. In preferred embodiments the fill-level signal is used to control a variable divider in the feedback path of the PLL, which is supplied with a highly stable reference signal. A synchronised, and low-jitter local clock is thus produced. Preferably, the elastic buffer employs counters of relatively wide word width, and a storage array of much reduced depth, read and write pointers being provided by just a few of the least significant bits of the words.

Owner:CIRRUS LOGIC INT SEMICON

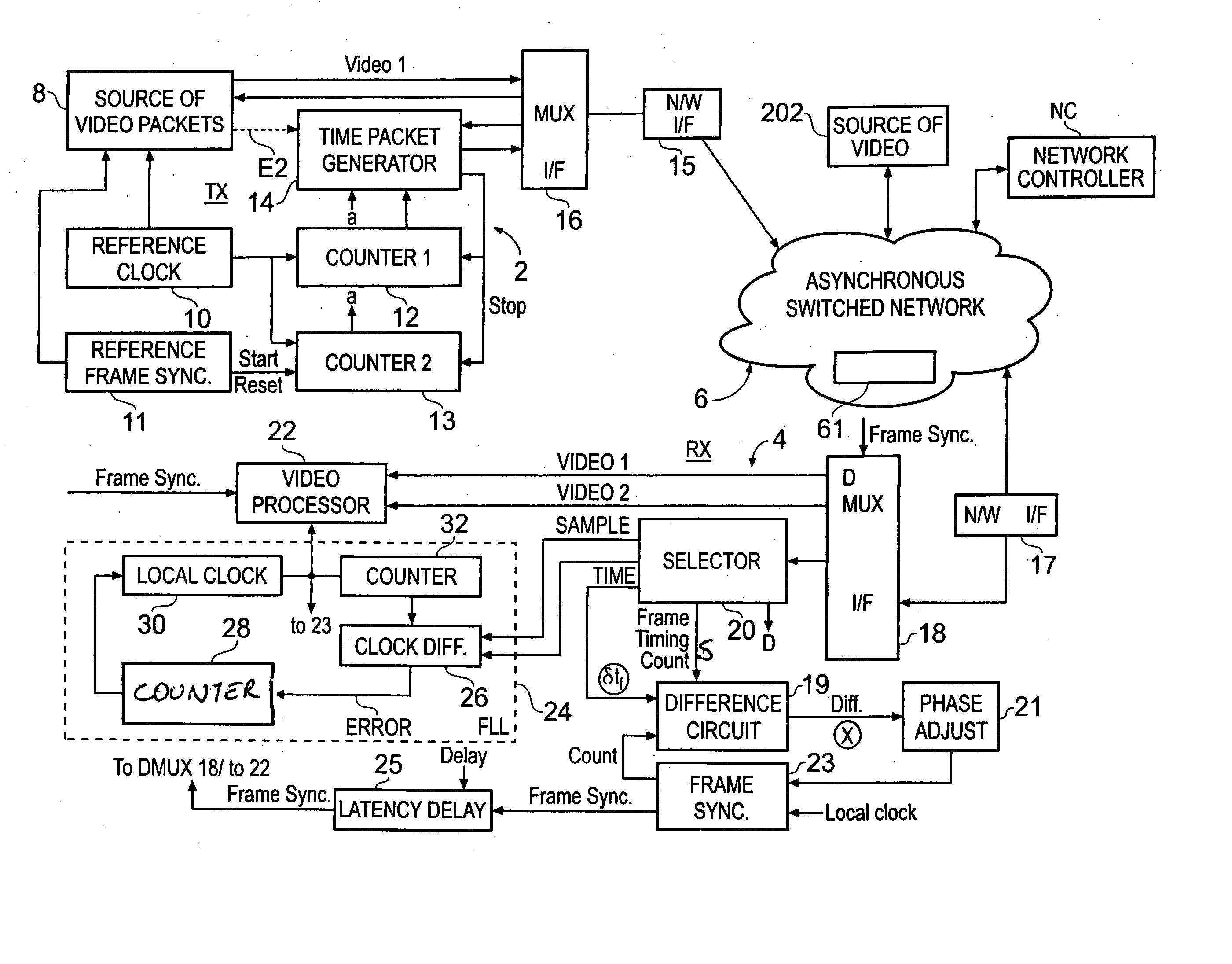

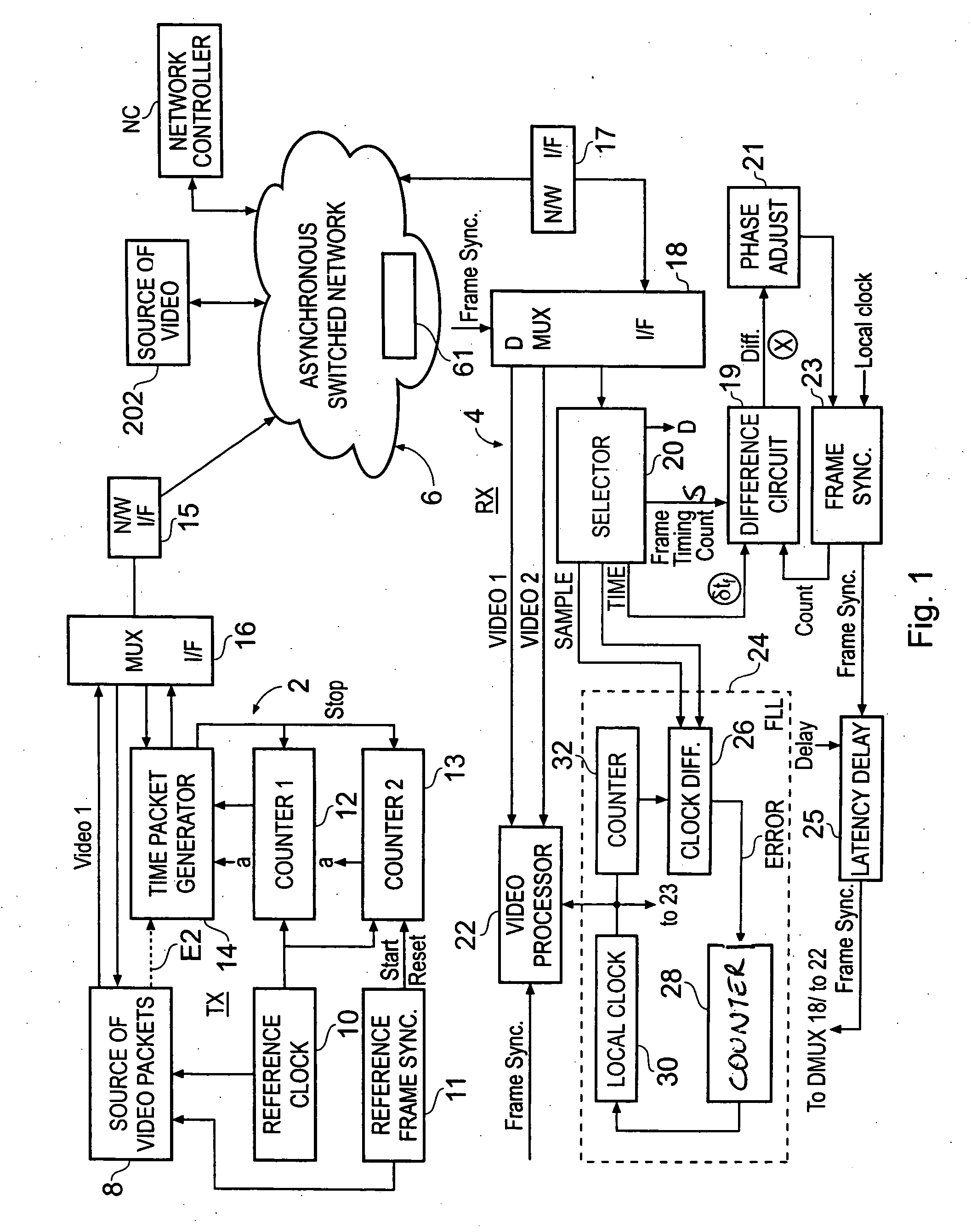

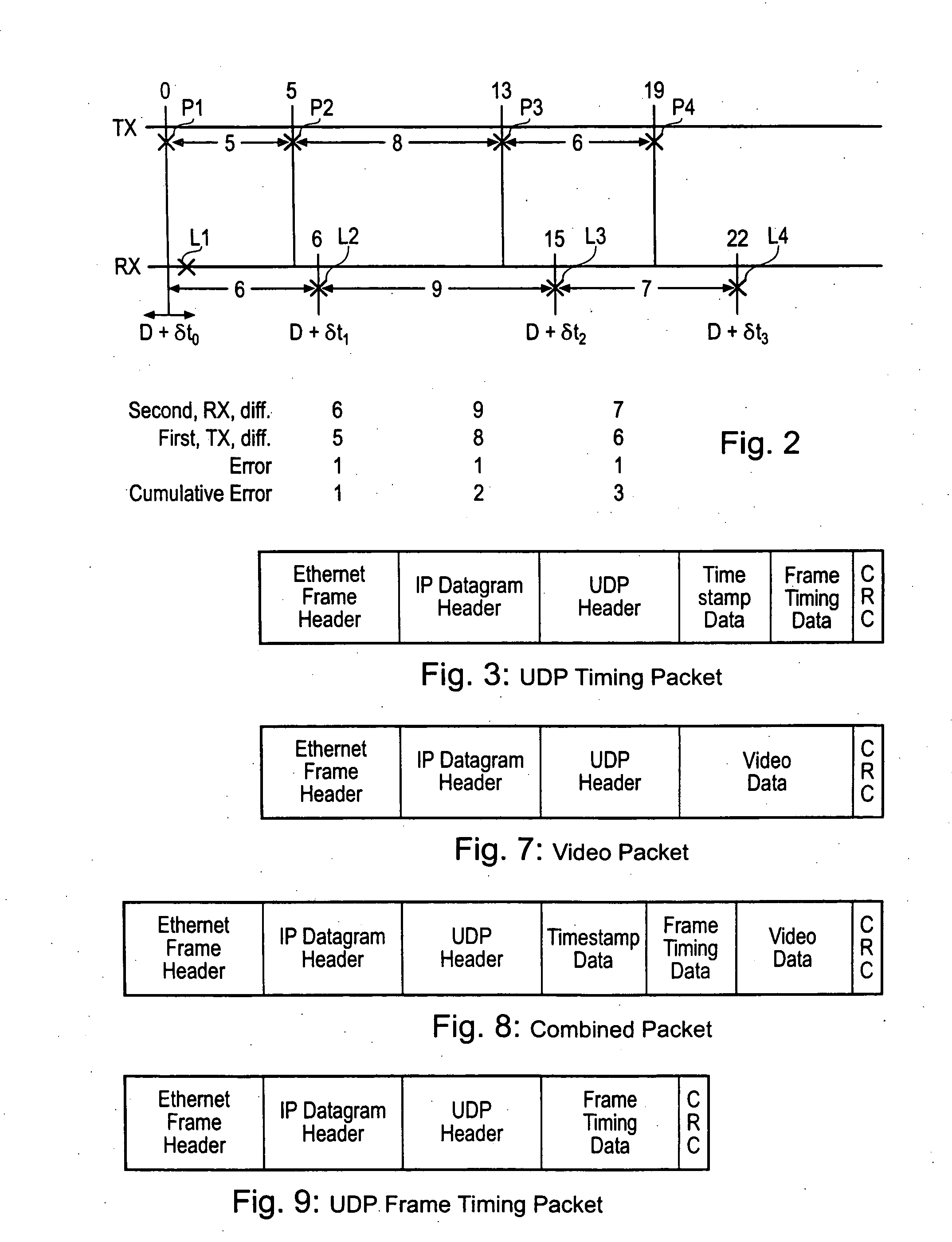

Video snychronisation

ActiveUS20040257469A1Reduce dataEliminate the effects ofTelevision system detailsColor burst signal generation/insertionReference imageData treatment

A method of synchronising the phase of a local image synchronisation signal generator of a local video data processor in communication with an asynchronous switched packet network to the phase of a reference image synchronisation signal generator of a reference video data processor also coupled to the network, the local and reference processors having respective clocks, the reference and local image synchronisation signal generators generating periodic image synchronisation signals in synchronism with the reference and local clocks respectively comprises the steps of: frequency synchronising the local and reference clocks; the reference video data processor sending, via the network, to the local data processor an image timing packet providing reference image synchronisation data indicating the difference in timing, measured with respect to the reference processor's clock, between the time at which the image timing packet is launched onto the network and the time of production of a reference image synchronisation signal; and the local processor controlling the timing of the production of the local image synchronisation signal in dependence on the reference image synchronisation data and the time of arrival of the timing packet.

Owner:SONY EUROPE BV

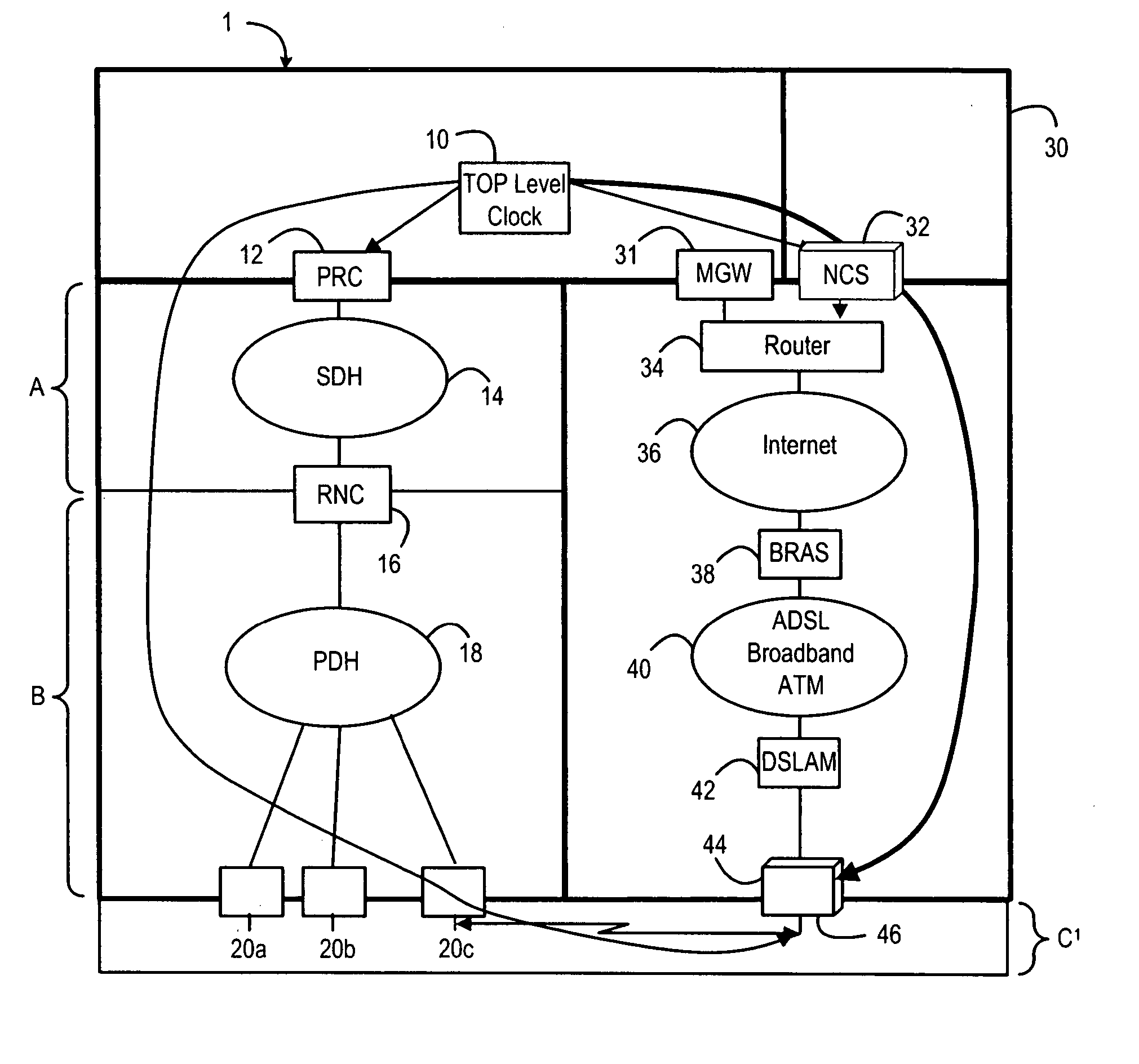

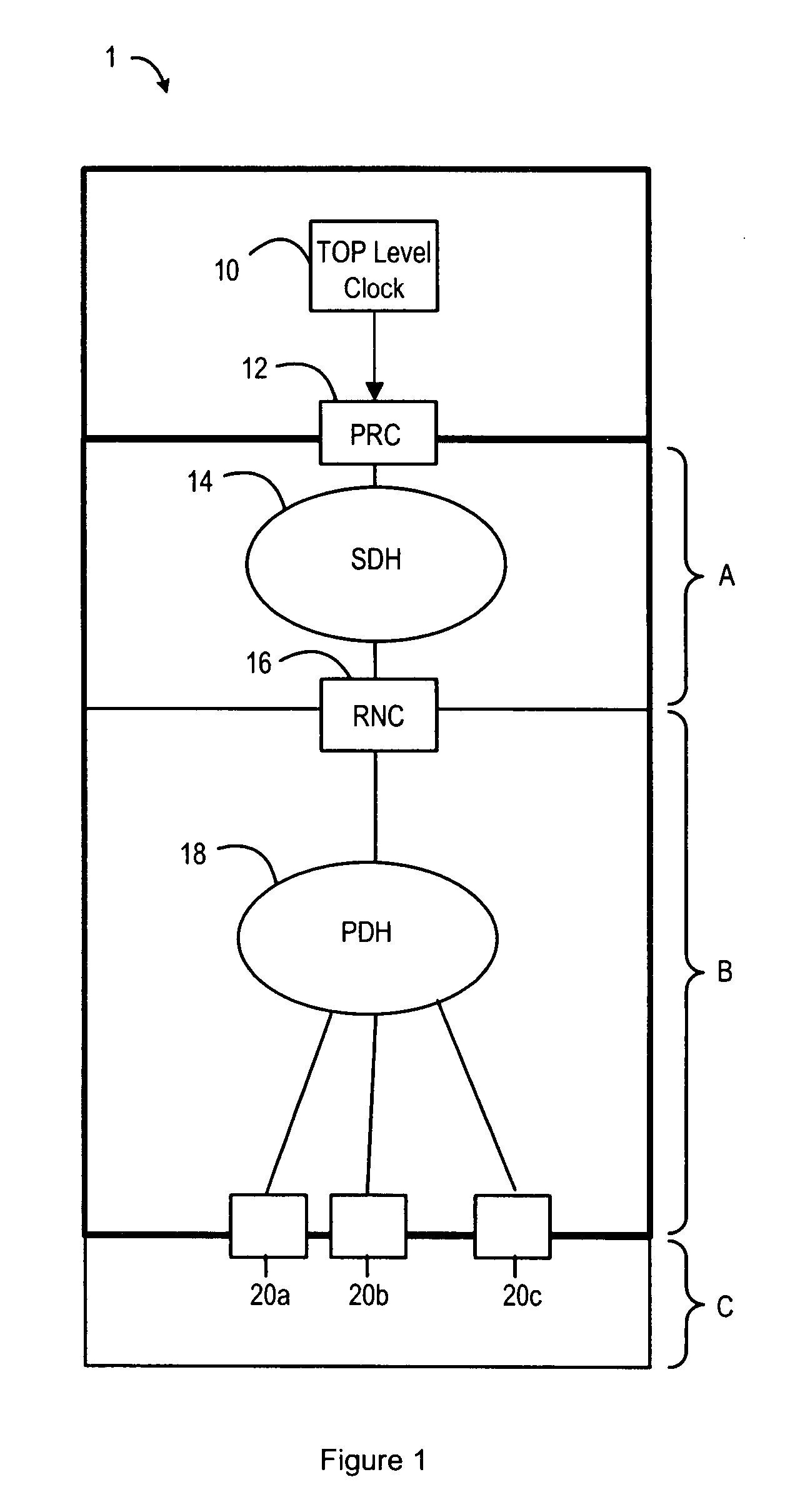

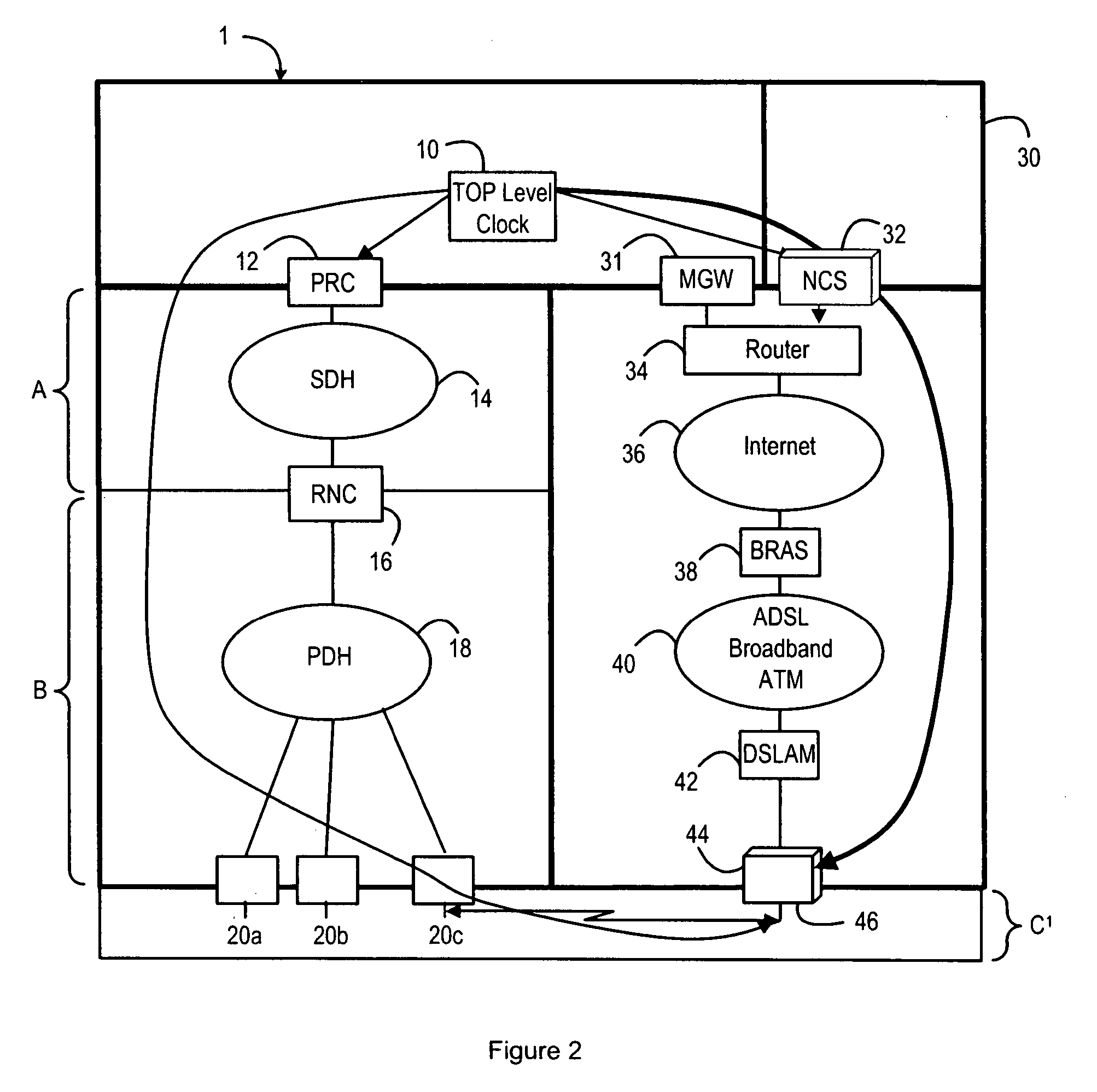

Synchronising base stations

InactiveUS20080075061A1Synchronisation arrangementTime-division multiplexTelecommunications networkPacket switched

A method for synchronising a clock signal in a basestation of a wireless telecommunications system is described. The basestation has a reference clock signal and is operable to communicate with wireless mobile terminals and with a packet switched network. The method comprises detecting a radio frequency clock synchronisation signal from a wireless telecommunications network, and synchronising the reference clock signal of the basestation in dependence upon the detected radio frequency clock synchronisation signal.

Owner:CISCO TECH INC

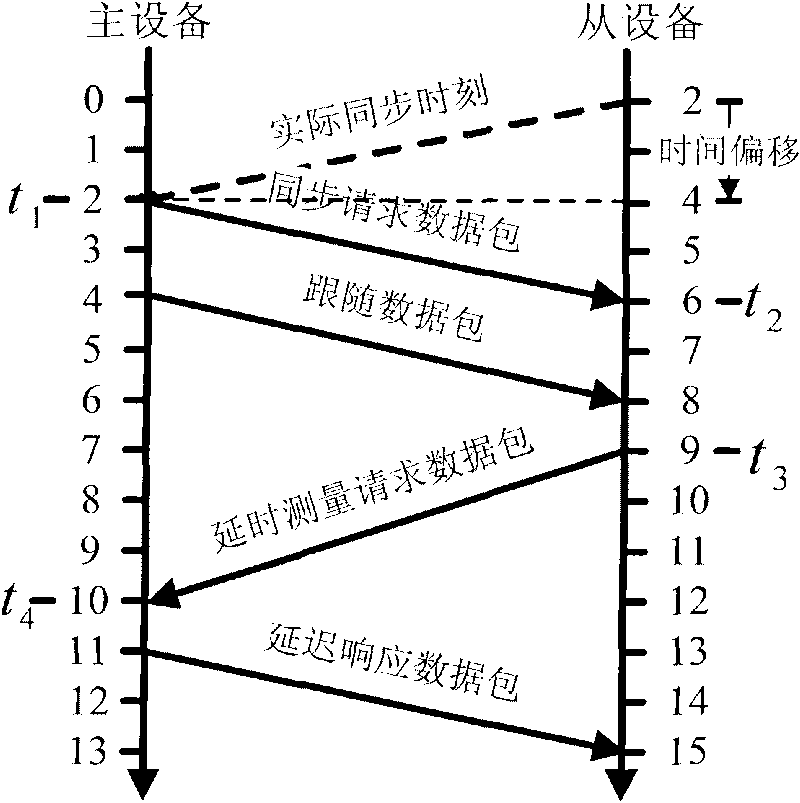

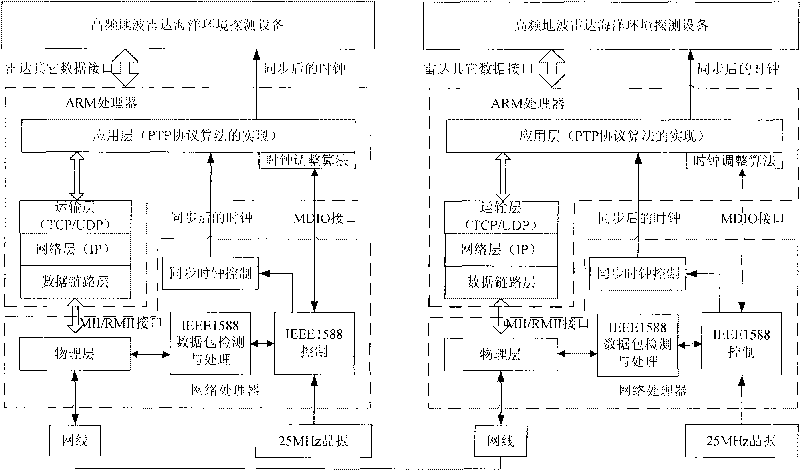

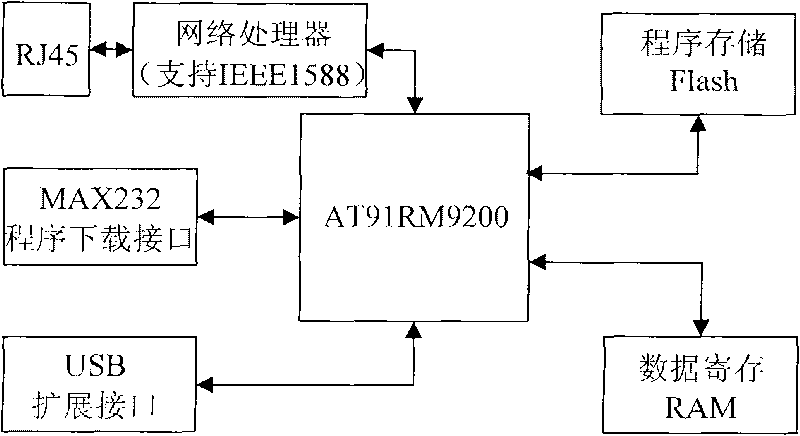

High-frequency ground wave radar networking clock synchronization control method and device thereof

InactiveCN101738600AIncrease independenceHigh synchronization accuracyWave based measurement systemsEmbedded systemSpecific function

The invention discloses a high-frequency ground wave radar networking clock synchronization control method which is characterized in that each piece of radar detection equipment in the network is respectively configured with a synchronization control part for high-frequency ground wave radar networking, and clock synchronization between any two pieces of radar detection equipment is realized by the synchronization control part. The method comprises the following steps: 1. selecting one from two pieces of detecting equipment to serve as the master equipment of clock benchmark, and the other equipment serves as the slave equipment for adjusting clock and master equipment synchronization; 2. carrying out shift measurement from the master equipment to the slave equipment, and carrying out delay measurement between the master equipment and the slave equipment; 3. calculating the clock offset of the master equipment and the slave equipment by the synchronization control part of the slave equipment according to the shift measurement result obtained in step 2 and the delay measurement result obtained in step 3; and correcting the work clock of the slave equipment according to the clock offset. The device of the invention has favorable generality, and the synchronization control part is suitable for circuits with any specific function, has high flexibility and is convenient for research personnel to work in cooperation with a due division of labour.

Owner:WUHAN UNIV

Multi-channel synchronous high-speed data collection device

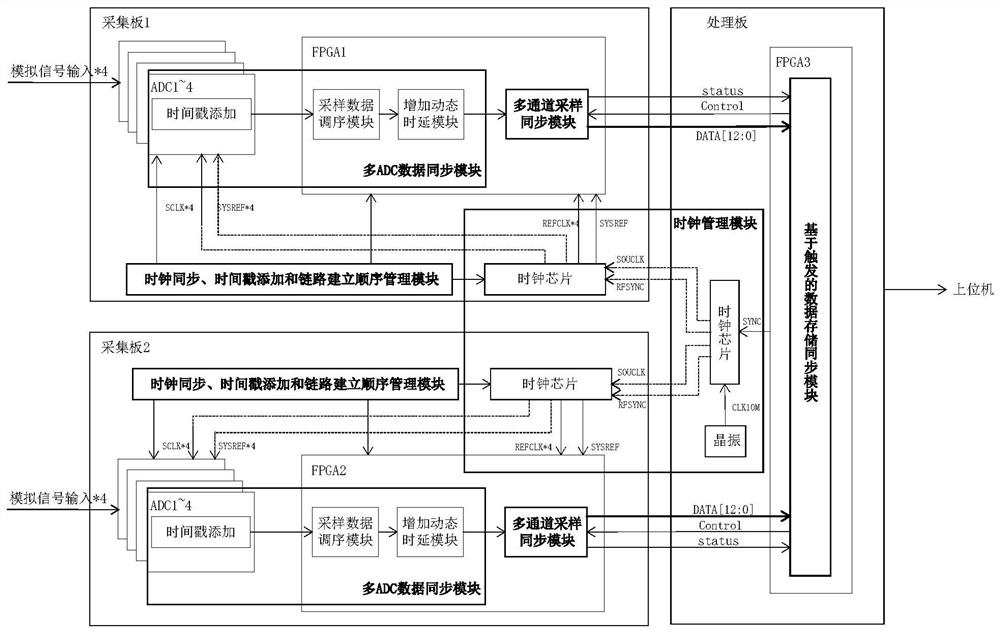

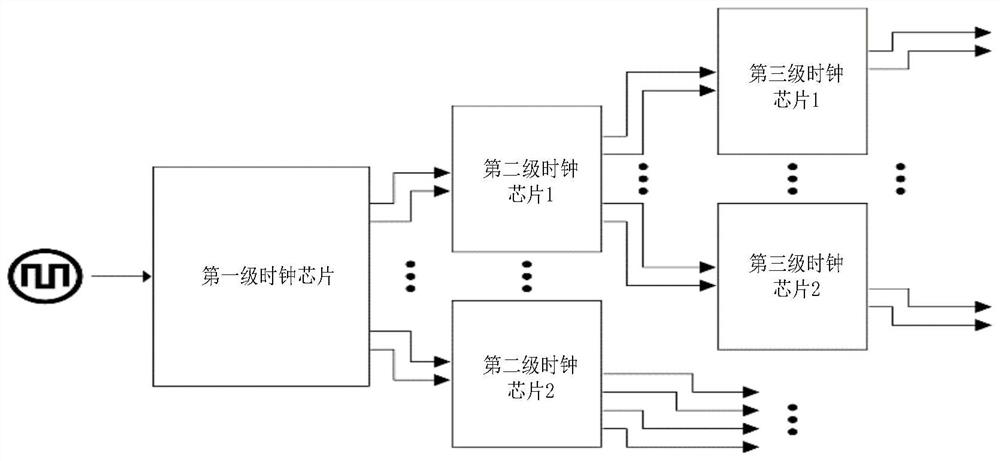

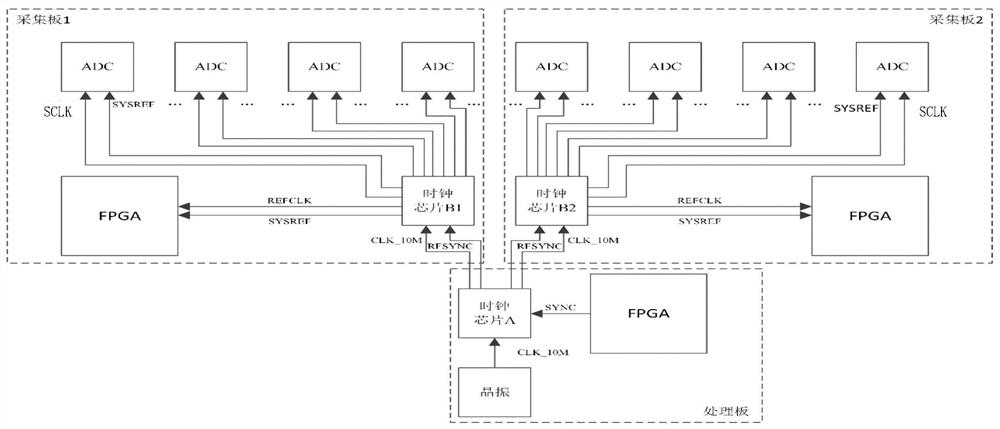

ActiveCN113535620AAvoid random delaysHigh precisionDigital variable displayGenerating/distributing signalsData synchronizationData stream

The invention discloses a multi-channel synchronous high-speed data collection device. A synchronous clock is provided through a clock management module, an ADC (Analog to Digital Converter) is driven by a sampling clock to sample a signal to obtain sampling data and then transmit the sampling data to an collection FPGA (Field Programmable Gate Array), a multi-ADC data synchronization module adds a timestamp mark for the sampling data in the ADC, the sampling data is subjected to sequence adjustment in the collection FPGA, a sampling point with a flag bit is adjusted to be a first path, and multi-ADC data stream synchronization is realized by increasing dynamic time delay; the clock synchronization timestamp adding and link establishment sequence management module manages the working sequence of three independent processes of clock synchronization, a timestamp function and a JESD204B link, and solves the conflict of the three independent processes in multi-ADC data synchronization, and the multi-channel sampling synchronization module adjusts the phase relation between a timestamp signal and a sending end device clock. The random delay caused by taking the time sequence of the two as an example is avoided, the accurate delay adjustment is performed on the signal based on the triggered data storage synchronization module, and the data synchronous storage between different boards is realized.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

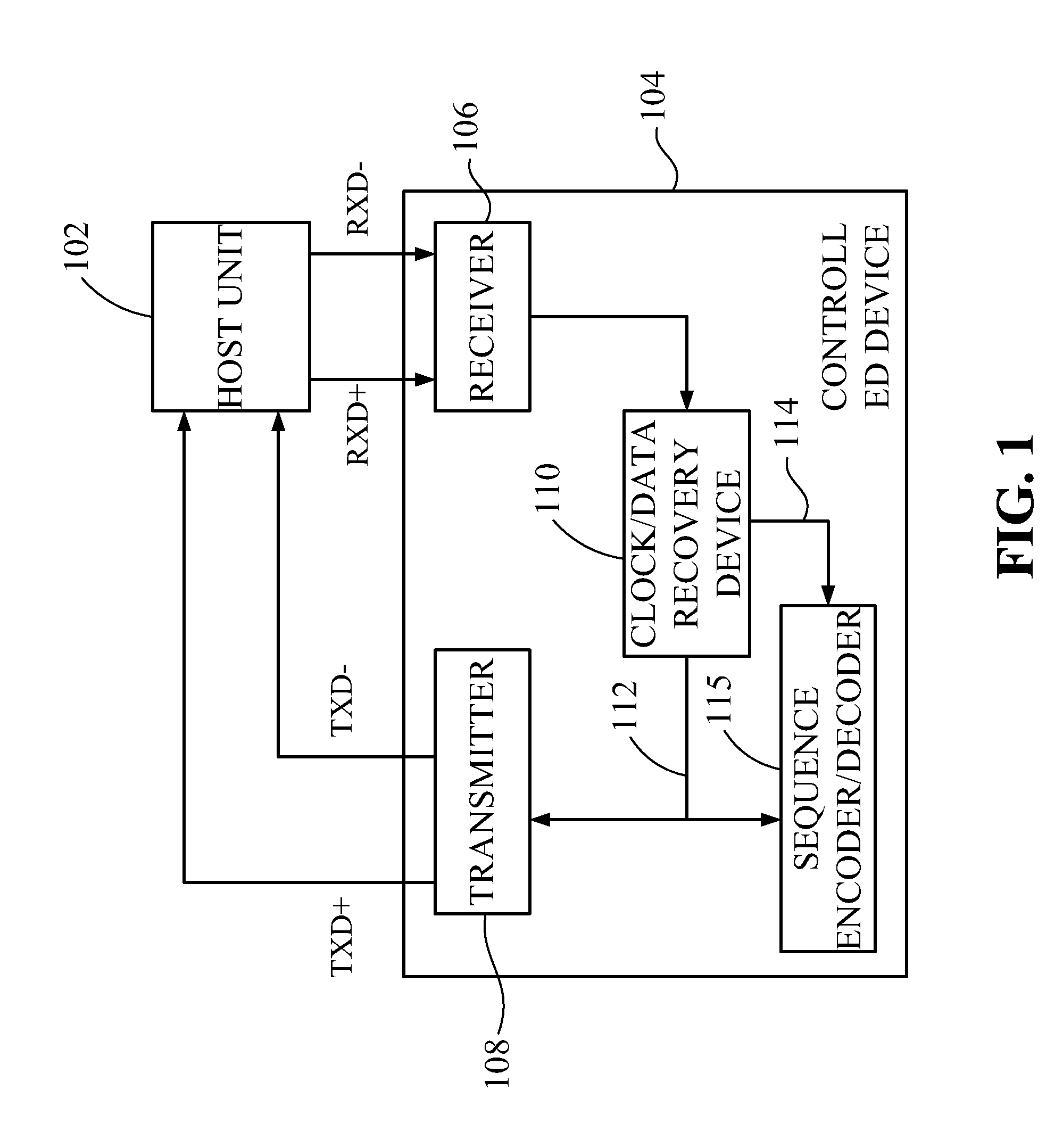

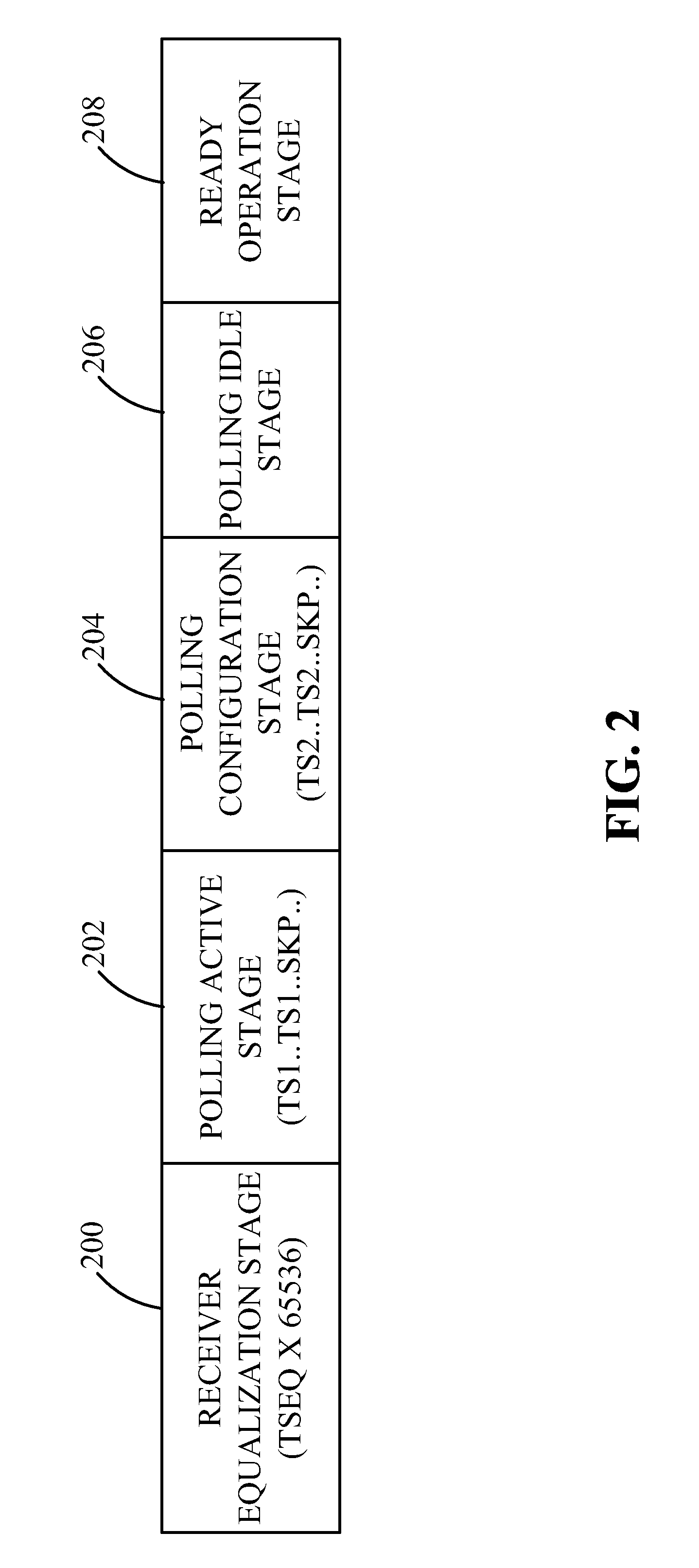

Clock-synchronized method for universal serial bus (USB)

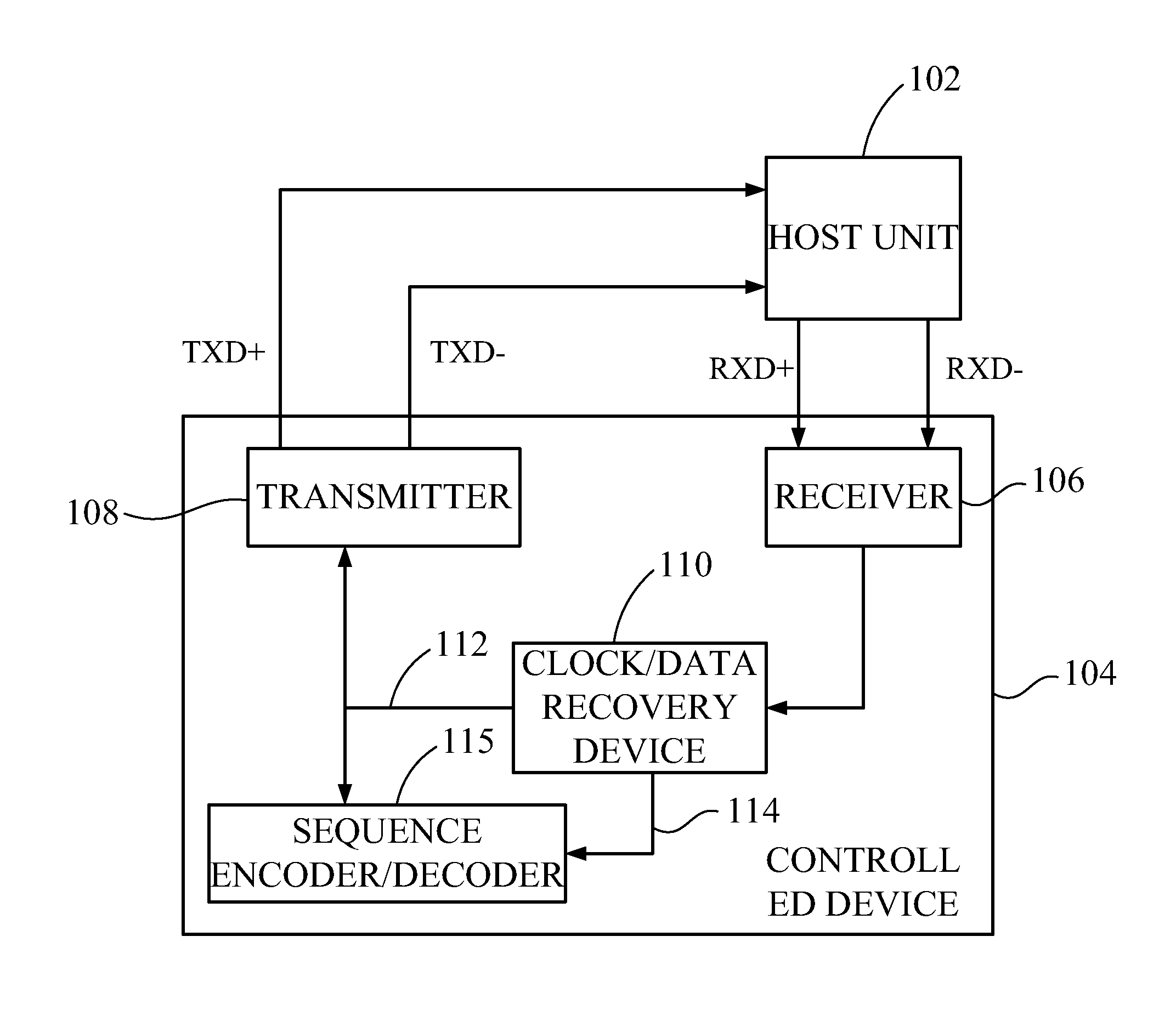

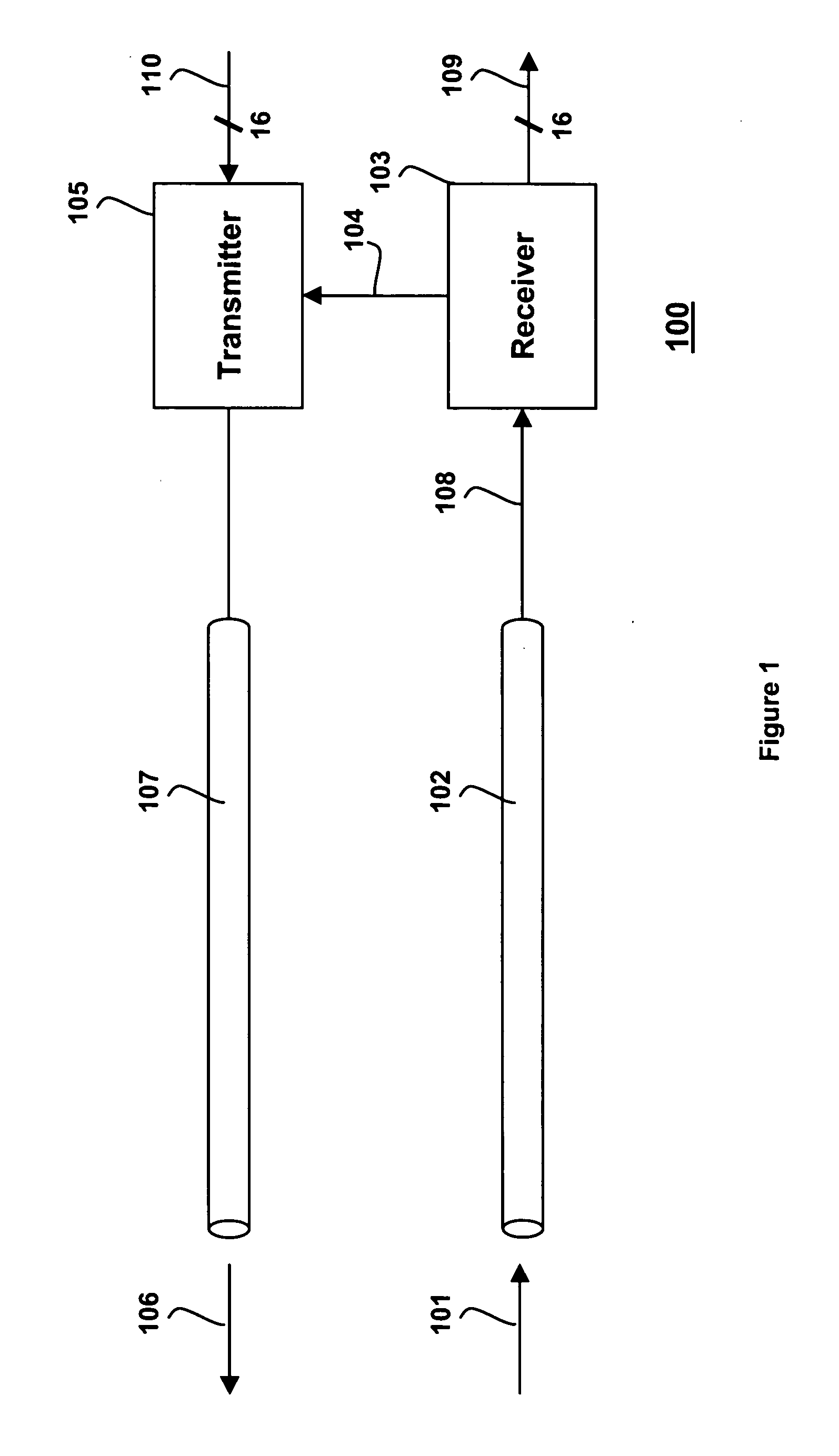

ActiveUS20120020404A1Conserve costLow costMultiple-port networksDelay line applicationsSequence signalData signal

A clock-synchronized method for universal serial bus (USB) is described. The method includes the following steps of: (a) a transmitter sends a periodic signal to a host unit during a first time interval; (b) the host unit transmits a first equalization training sequence signal to a receiver during a second time interval to train the receiver and the transmitter continuously sends the periodic signal to the host unit; (c) a clock and data recovery device extracts the first equalization training sequence signal during the second time interval to generate a extracted clock signal and a data signal; and (d) the transmitter sends a second equalization training sequence signal to the host unit based on the extracted clock signal during the third time interval to train the host unit and the receiver and the transmitter commonly utilize the extracted clock signal as a reference clock.

Owner:GENESYS LOGIC INC

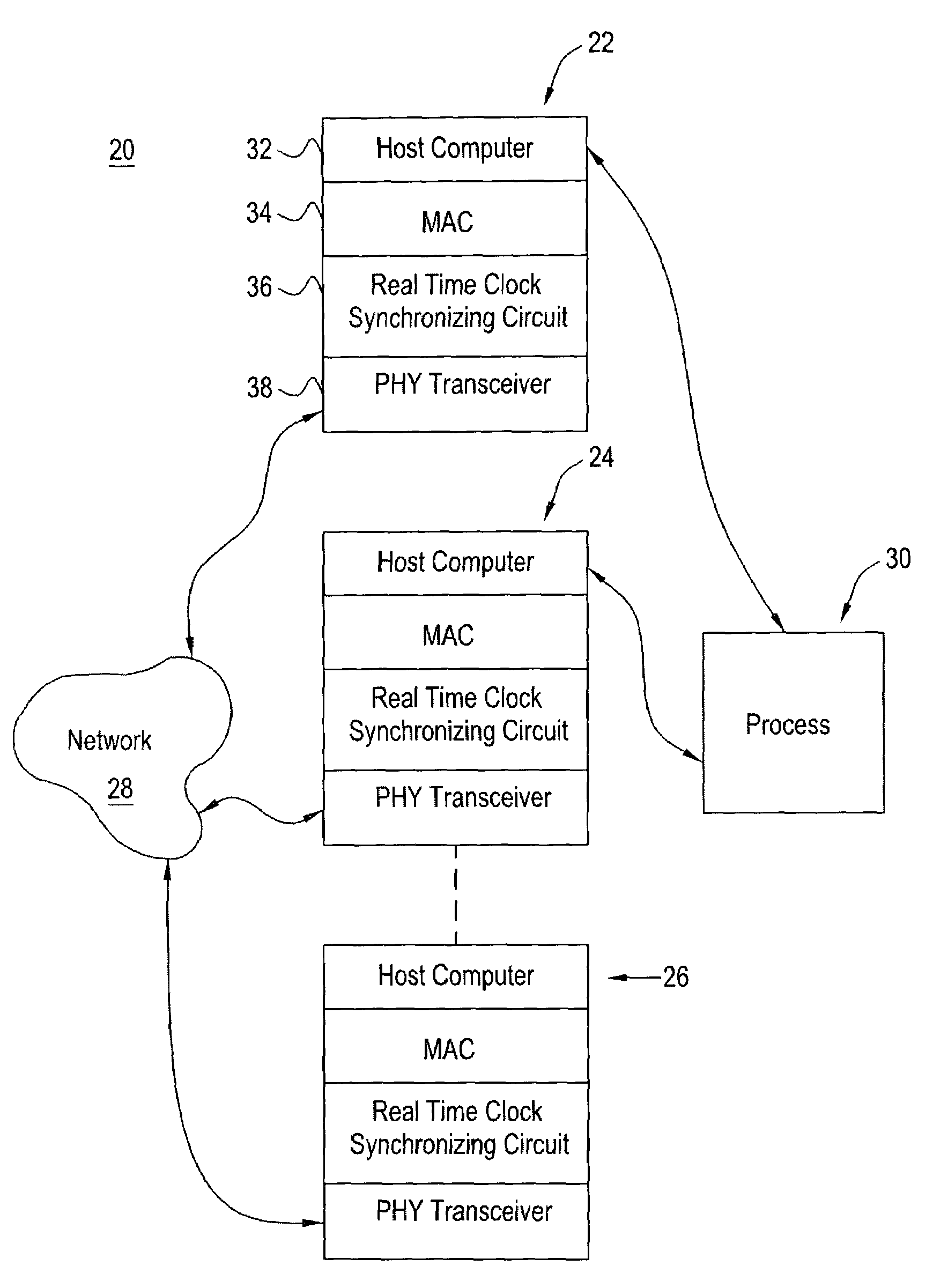

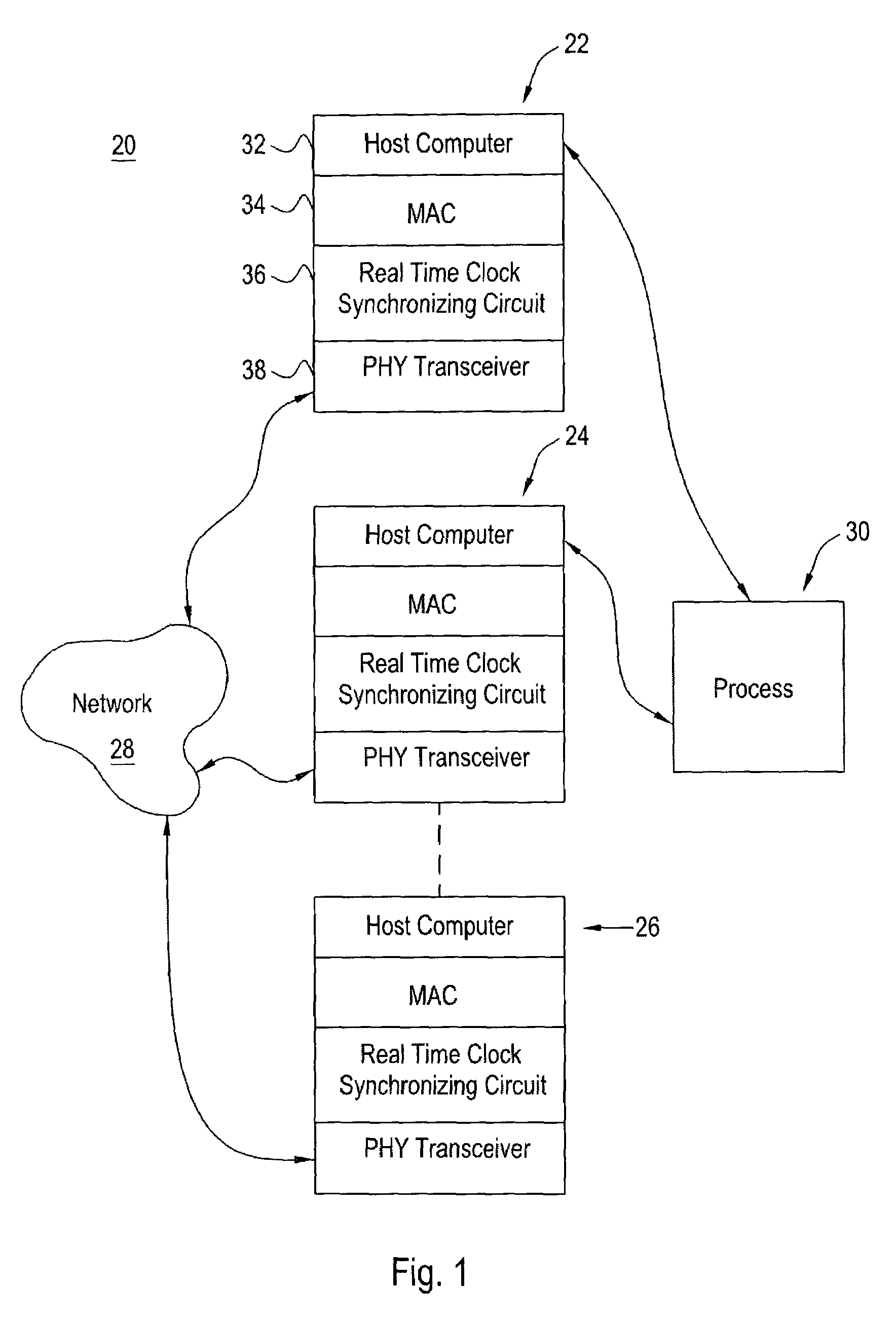

Clock synchronizing method over fault-tolerant Ethernet

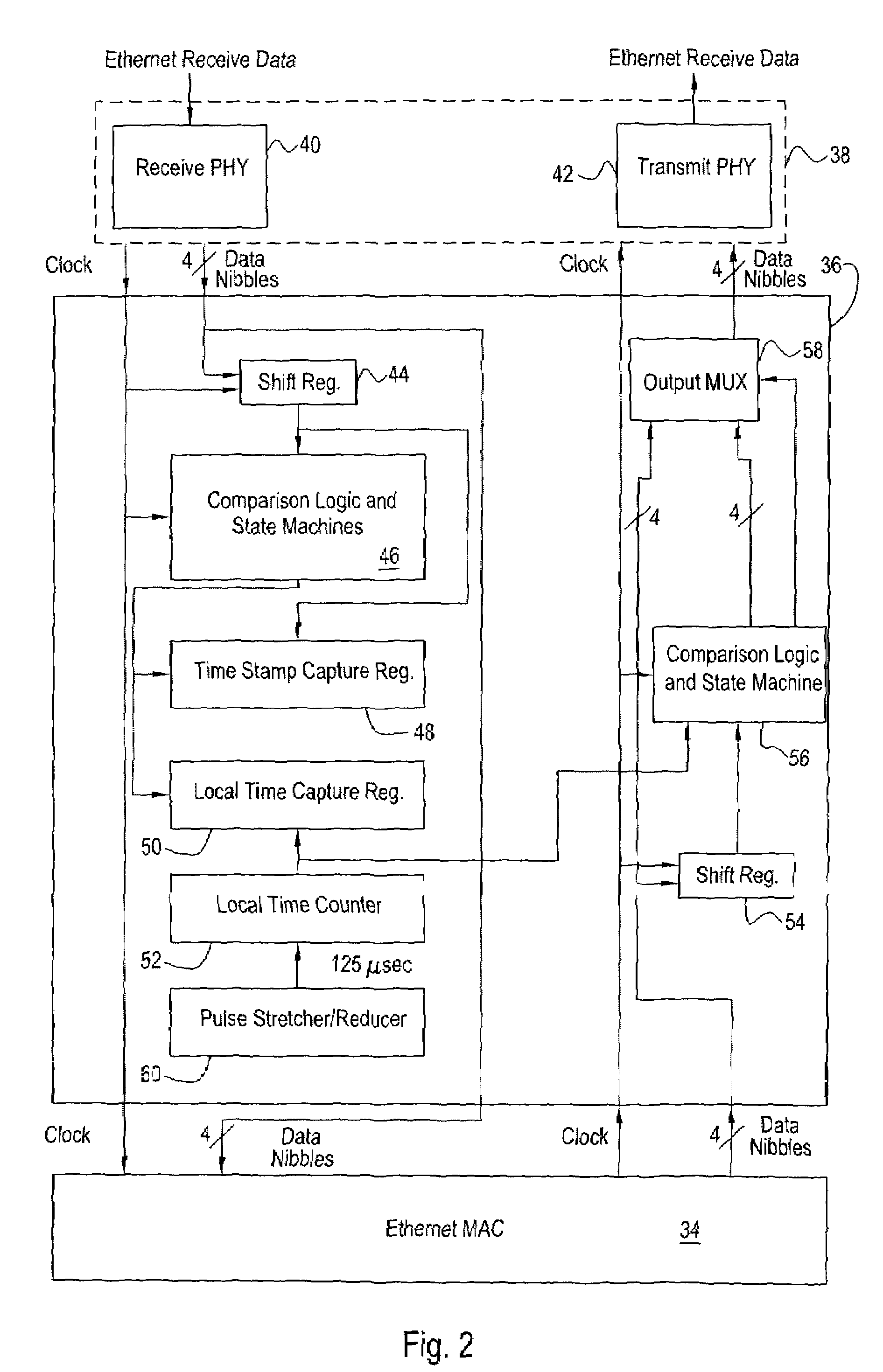

ActiveUS7200158B2Compensation delayTime-division multiplexData switching by path configurationTransceiverMedia access controller

A device that recognizes the time synchronization packet and substitutes a real-time value from the master internal counter into the proper place in a data packet is placed between an Ethernet Media Access Controller (MAC) and a Physical Interface Transceiver (PHY). A second device monitors the packet passing from the MAC to the PHY and determines when it is a time synchronization packet from the time master. Upon recognition of the proper packet, the second device simultaneously captures the master's time value and captures the value of a local real-time clock. The result of these captures are presented to the local host computer which controls the time base clock that increments the local real-time clock to either speed up or slow down this local clock, thereby synchronizing the local clock to the time master clock. The offset and skew of the local clock to the master clock is reduced to only the network latency plus variability due to network congestion.

Owner:HONEYWELL INT INC

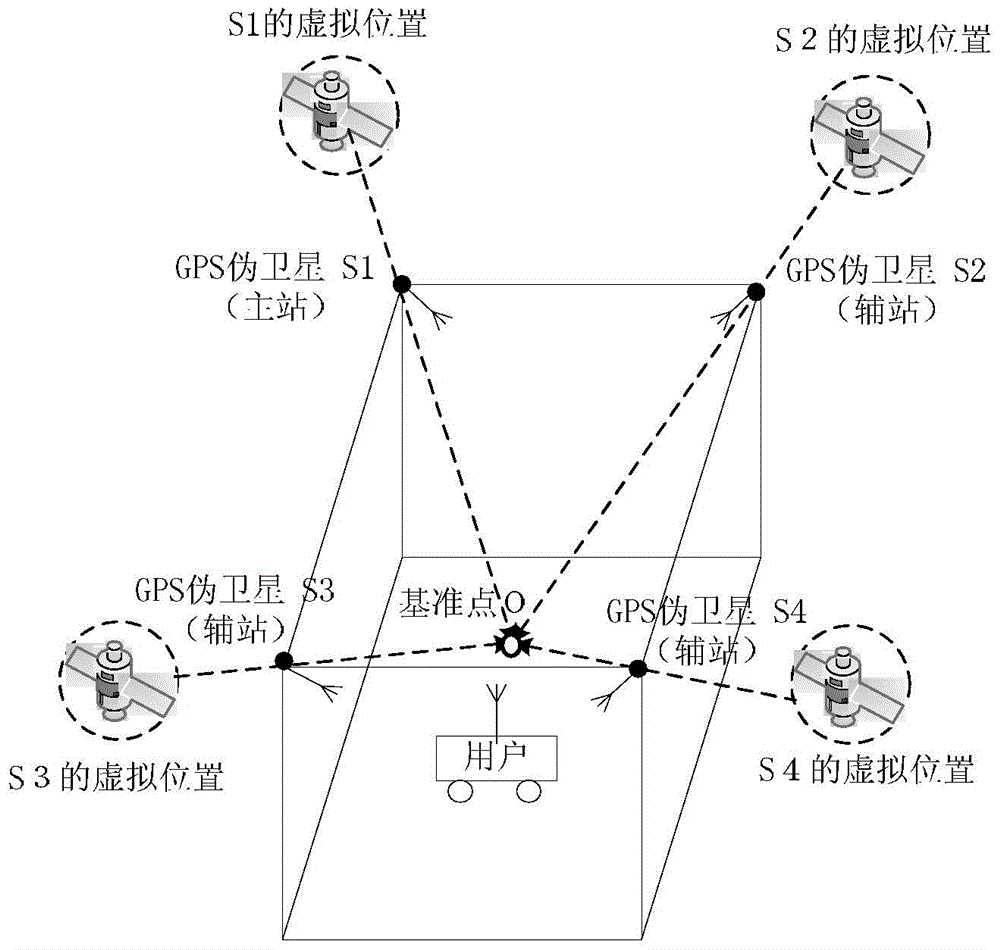

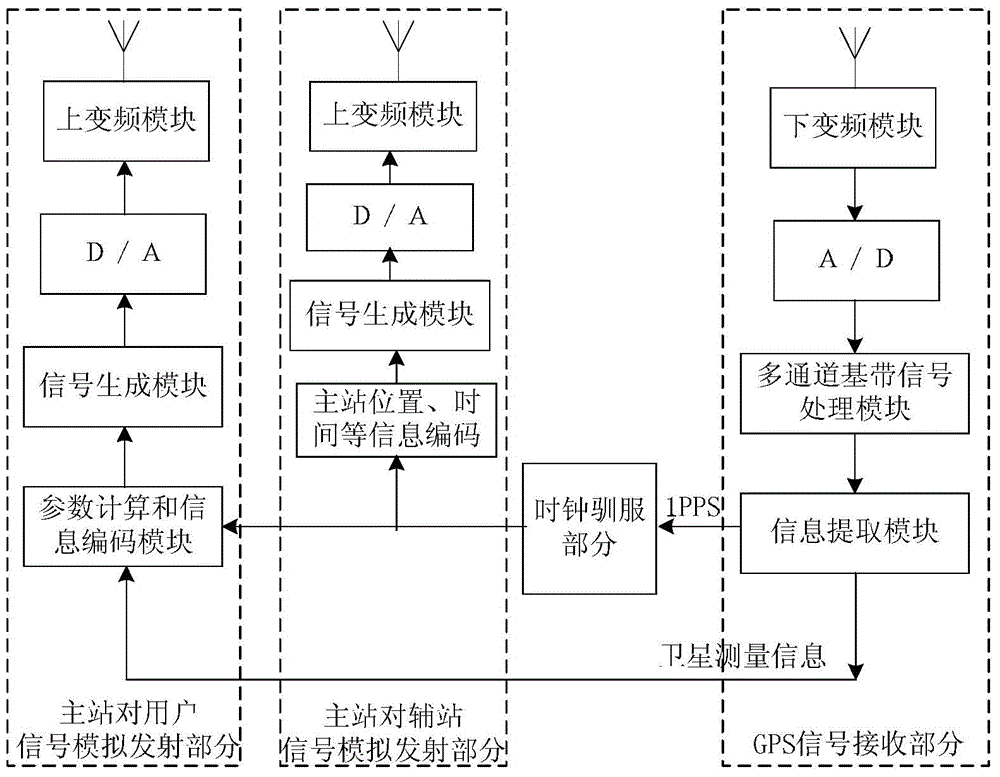

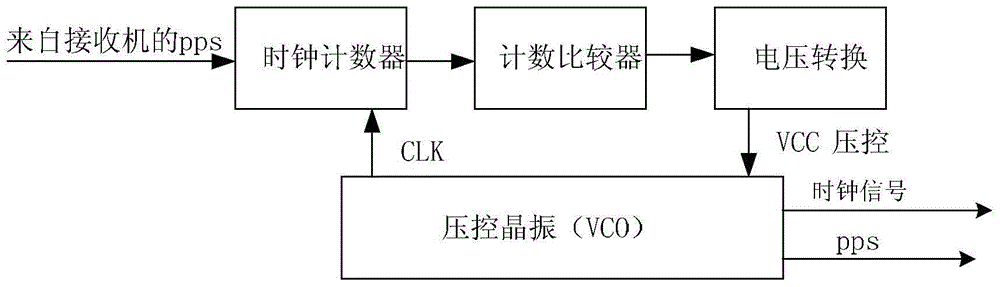

Universal GPS indoor and outdoor positioning system and method

The invention discloses a universal GPS indoor and outdoor positioning system and method. The universal GPS indoor and outdoor positioning system comprises a GPS pseudo satellite main station, three or more GPS pseudo satellite auxiliary stations, and a user receiver. The GPS pseudo satellite main station receives outdoor GPS signals in real time, acquires PPS (pulse per second) signal and a current visible satellite parameter, disciplines the clock of a local pseudo satellite main station by means of the PPS signal, synchronously generates two radiofrequency signals by means of a local disciplined clock, sends one radiofrequency signal to a user, and send the other radiofrequency signal to the GPS pseudo satellite auxiliary stations. The GPS pseudo satellite auxiliary stations receive signal sent from the GPS pseudo satellite main station, achieve synchronization between the local clocks of the GPS pseudo satellite auxiliary stations and the clock of the GPS pseudo satellite main station, and synchronously generate virtual GPS satellite simulating signals. The user synchronously receives the virtual GPS satellite signals sent from the visible pseudo satellite main station and pseudo satellite auxiliary stations and completes indoor and outdoor positioning of the user in real time. The universal GPS indoor and outdoor positioning system is simple and is not required to change the software and the hardware of a conventional GPS receiver.

Owner:GUILIN UNIV OF ELECTRONIC TECH

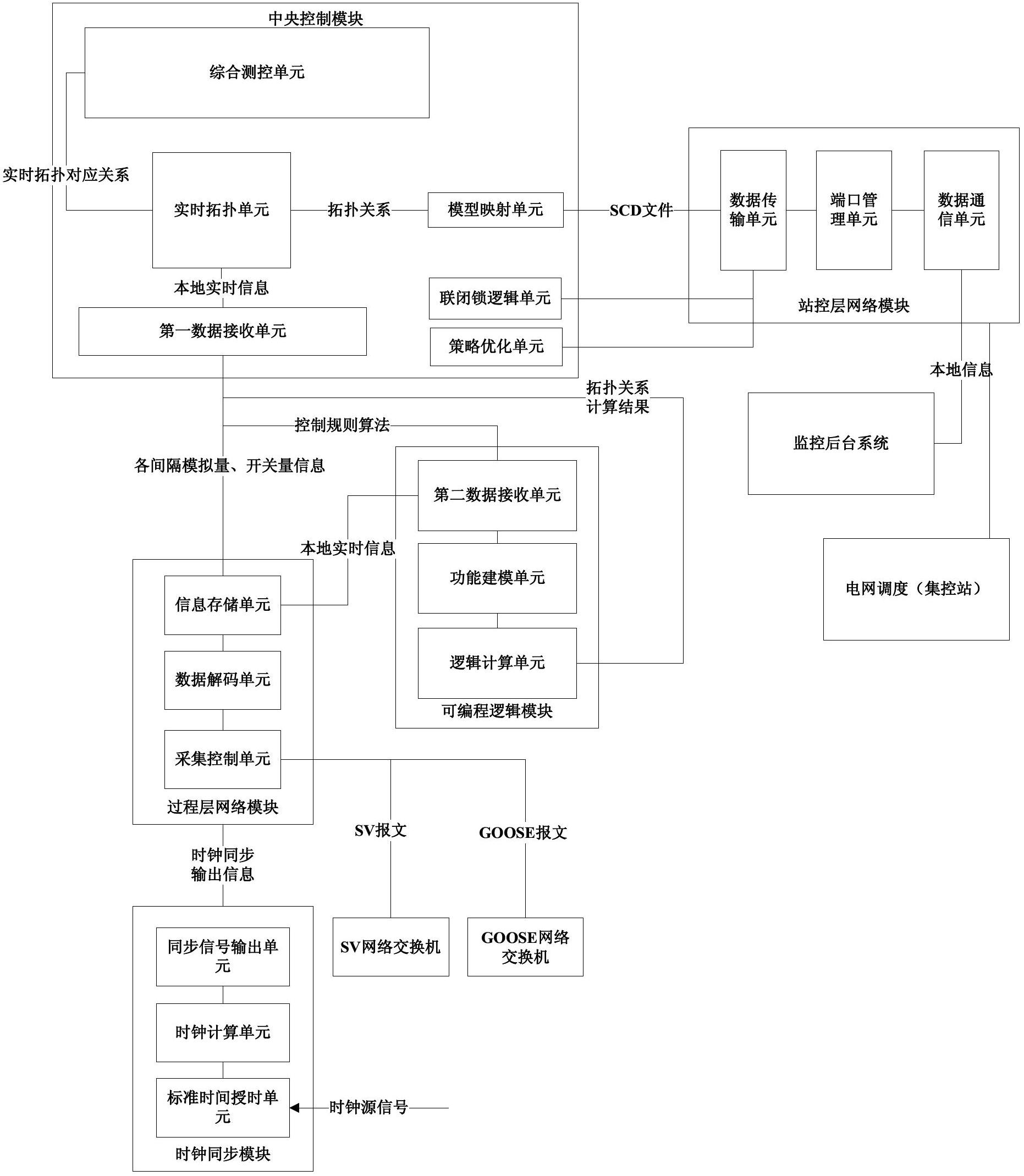

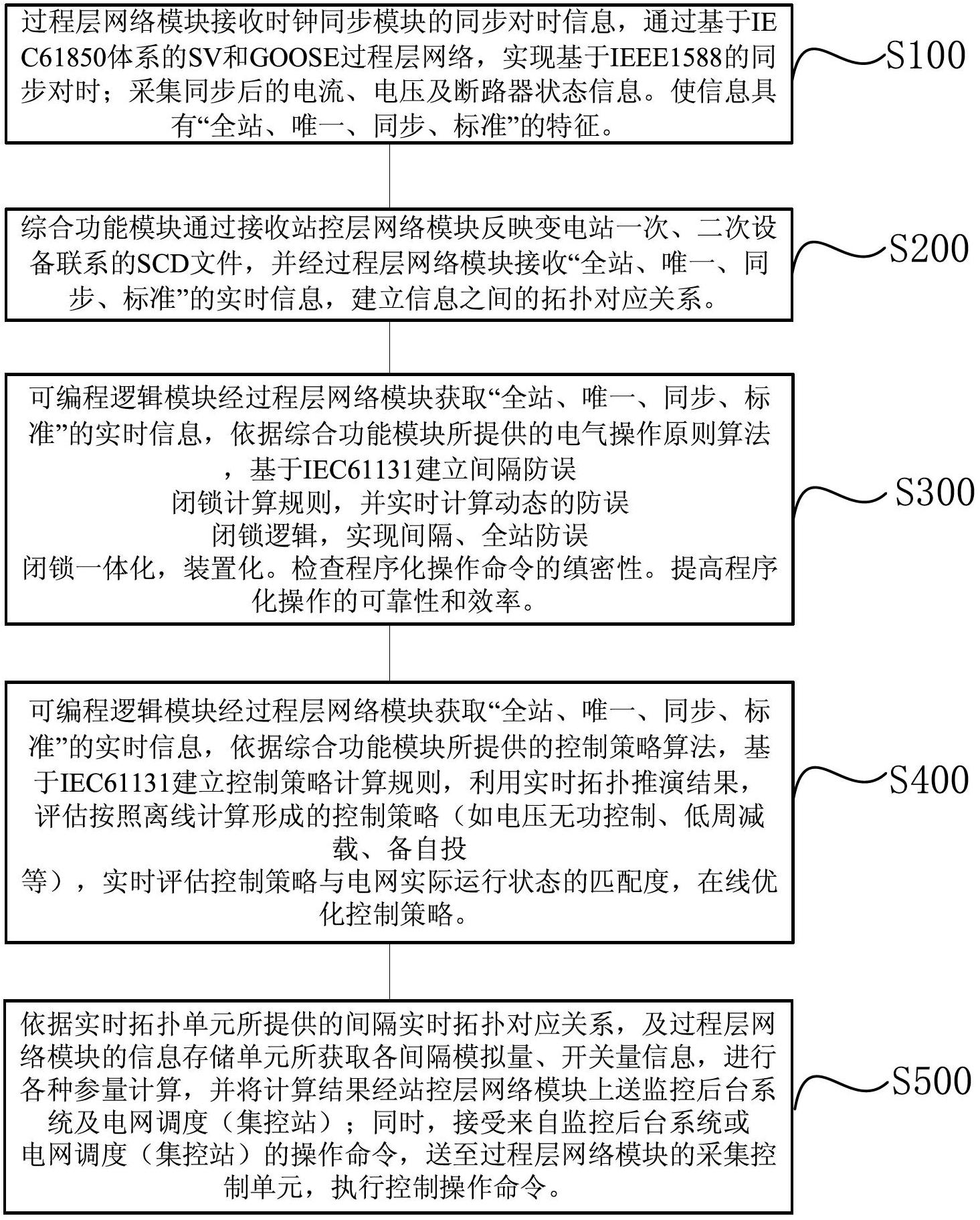

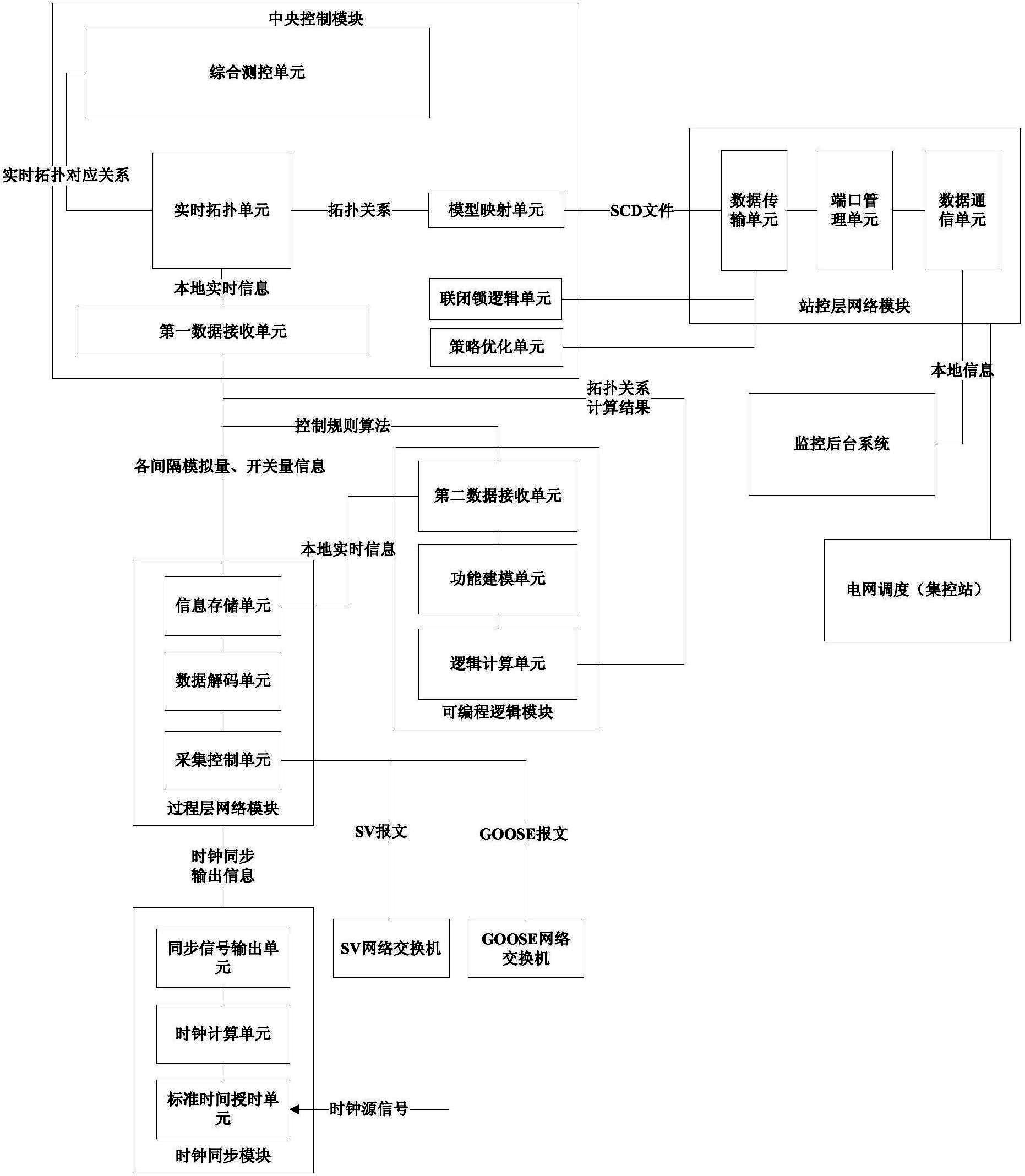

Intelligent transformer networked measurement and control system and method

InactiveCN102694420AHighly integratedSimplified automation system configuration schemeCircuit arrangementsInformation technology support systemTime informationControl layer

The invention discloses an intelligent transformer networked measurement and control system and an intelligent transformer networked measurement and control method in the technical field of intelligent transformer secondary control. The system comprises a clock synchronization module, a process layer network module, a station control layer network module, a programmable logic module and a central control module, wherein the clock synchronization module is connected with the process layer network module and outputs clock synchronization output information; the process layer network module is connected with the programmable logic module and the central control module respectively and outputs each interval analog quantity and switch quantity information and local real-time information; the programmable logic module is connected with the central control module and outputs a control rule algorithm; and the station control layer network module is connected with the central control module, receives an anti-operation lockout rule algorithm and a strategy optimization algorithm and outputs system configuration description (SCD) files from a monitoring background system. According to the system and the method, networked measurement and control can cover a plurality of intervals and even the whole station, so that highly integrated application of an intelligent transformer based on a networked information sharing mechanism is realized; and therefore, the system and the method contribute to optimizing a system configuration scheme, reducing system failure rate and improving system stability.

Owner:SHANGHAI YIHAO AUTOMATION CO LTD

Method and apparatus for synchronizing graphical presentations

InactiveUSRE37418E1Digital data processing detailsElectronic editing digitised analogue information signalsVisual ObjectsCurrent time

A method and system for providing synchronization of the timing of various multimedia events, including a visual event is disclosed. Clock objects are defined in the storage and associated with an internal or external source of current time. The clock objects are able to be displayed on the display, but can be hidden once their linkages are defined. One or more multimedia objects representative of audio, visual or other multimedia events, including an audio object, are defined and linked to a particular clock object or clock objects. Then, a processor synchronizes the multimedia objects, including a visual object, with the associated clock object or objects. Finally, the various multimedia events are performed in synchronization with their associated clocks. The multimedia objects, including the visual object, may include external multimedia sources managed by the computer system.

Owner:APPLE INC

Line loop back for very high speed application

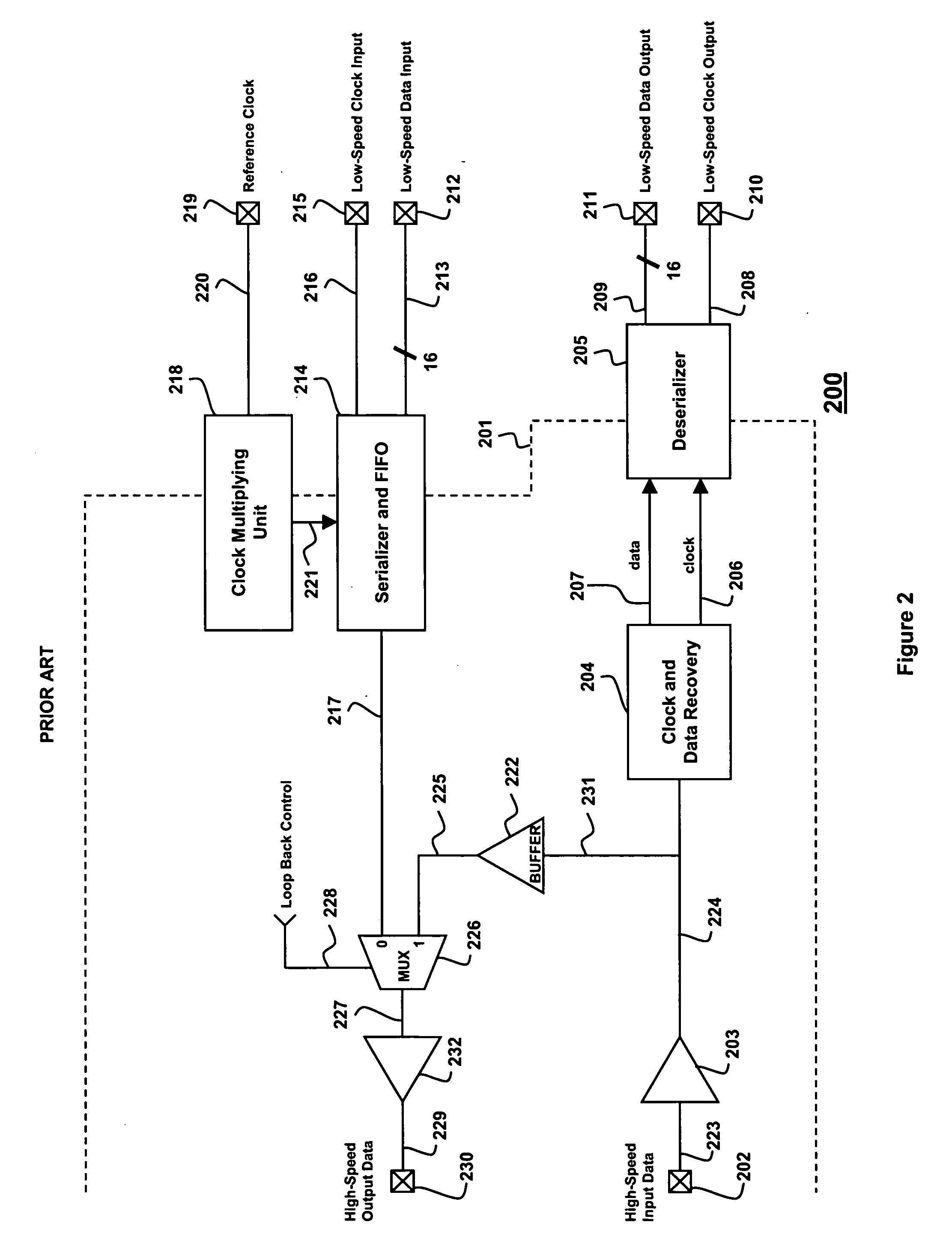

ActiveUS7099278B2Increase heightReduce coupling effectMultiplex system selection arrangementsError prevention/detection by using return channelHemt circuitsEngineering

Method and circuitry for performing a line loop back test includes a receiver, a deserializer, and a low speed parallel loop back data multiplexer selects either the low speed parallel data from the deserializer when in loop back mode or low speed parallel input data when in normal mode. The deserializer produces a low speed clock output signal that is fed to a low speed loop back reference clock multiplexer and also to a low speed loop back clock multiplexer. Both the loop back reference clock multiplexer and the loop back clock multiplexer select the low speed clock output signal from the deserializer when in line loop back mode. A clock multiplying unit converts the output of the low speed loop back reference clock multiplexer into a high speed clock signal. The serializer generates the high speed serial transmitter data in synchronization with the high speed clock signal received from a clock multiplying unit. A clock divider circuit converts the high speed clock signal from the clock multiplying unit into a low speed FIFO output clock. A first-in-first-out buffer receives the low speed parallel output data in synchronization with a clock multiplexer output, and transmits low speed parallel FIFO data to the serializer in synchronization with the low speed FIFO output clock. A low speed parallel loop back data buffer provides coupling between the deserializer and the low speed parallel loop back data multiplexer, and a low speed loop back clock buffer provides coupling between the deserializer and the loop back reference clock multiplexer and the loop back clock multiplexer.

Owner:AVAGO TECH INT SALES PTE LTD

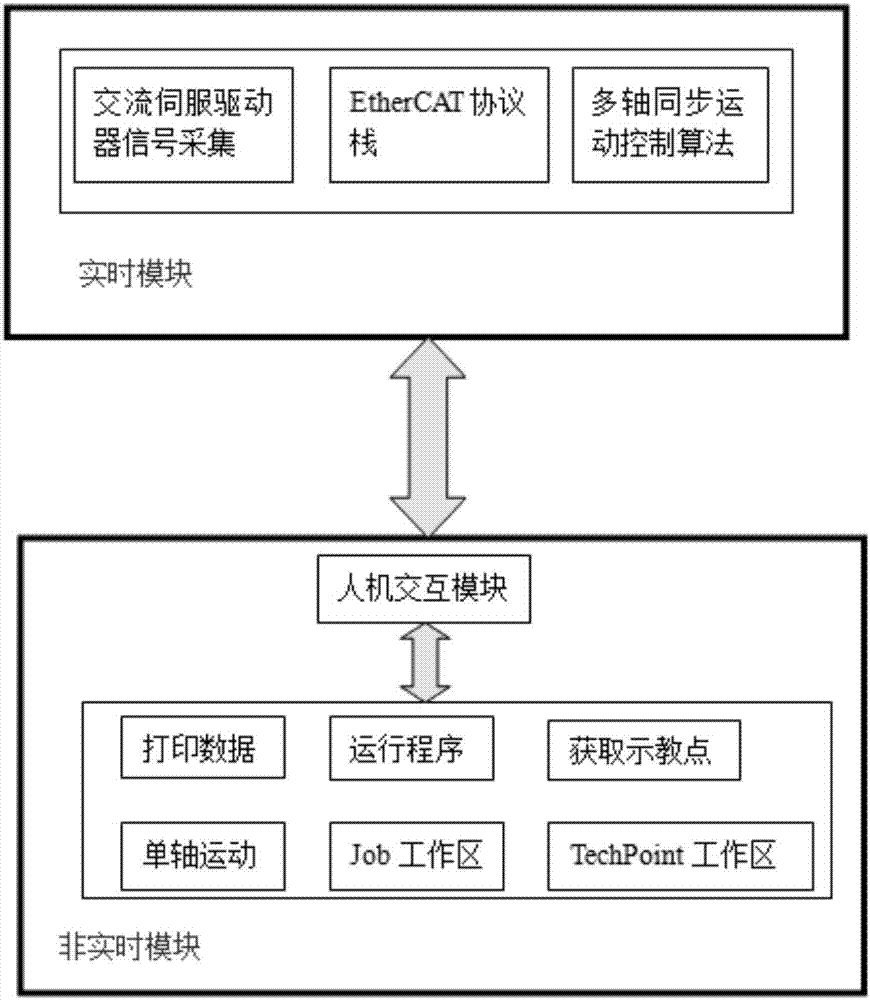

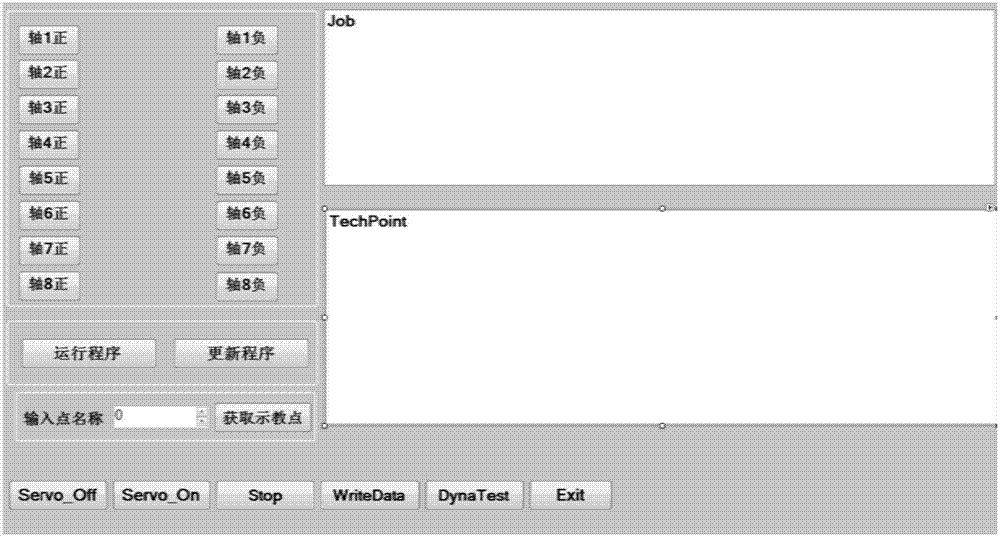

EtherCAT-based multi-axis synchronization control device and method

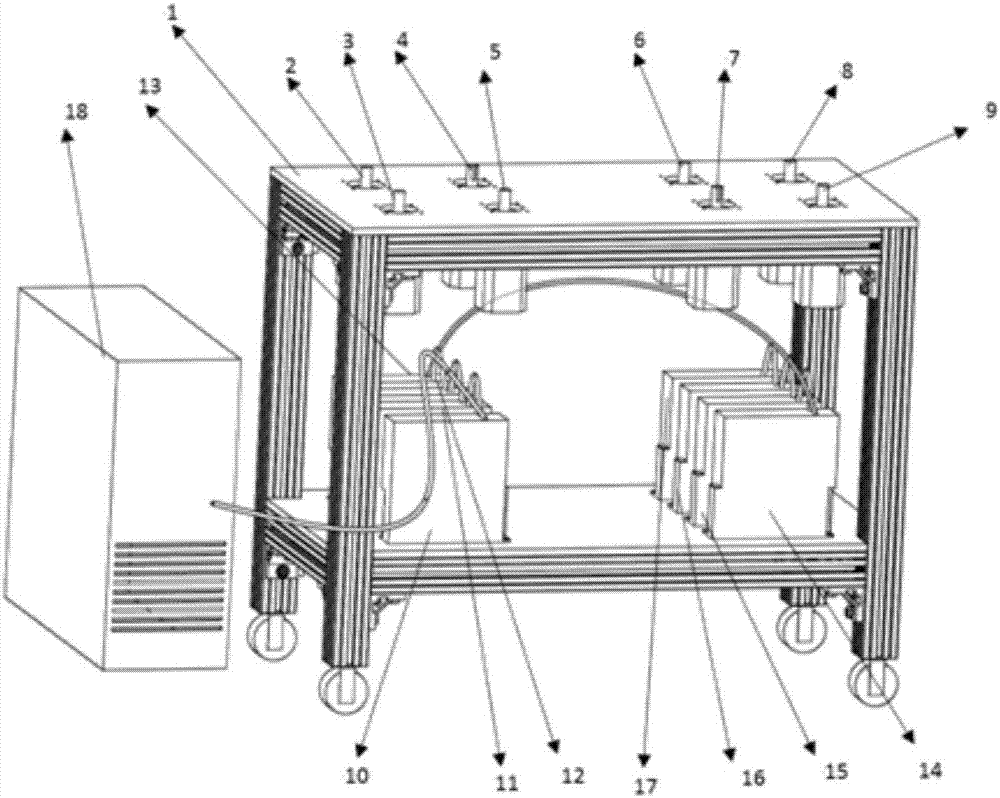

ActiveCN107229240ARealize the integration of drive and controlFast transmissionProgramme controlComputer controlIndustrial EthernetSynchronous control

The invention discloses an EtherCAT-based multi-axis synchronization control device, which comprises a mechanical body part, an AC servo driving part and a control part, wherein the mechanical body part comprises a support platform and a plurality of AC servo motors; the AC servo driving part comprises a plurality of AC servo driver slave stations in one-to-one corresponding connection with the AC servo motors; and the control part comprises a PC master station, which is in circuit connection with the AC servo driver slave stations by means of an EtherCAT network, and used for initializing the EtherCAT network, realizing master and slave clock synchronization of the PC master station and the AC servo driver slave stations as well as clock synchronization among the AC servo driver slave stations, and transmitting position signals to the AC servo driver slave stations. The invention further discloses an EtherCAT-based multi-axis synchronization control method. The EtherCAT-based multi-axis synchronization control device can realize the multi-axis synchronization control and signal acquisition based on an industrial Ethernet EtherCAT protocol.

Owner:SOUTH CHINA UNIV OF TECH

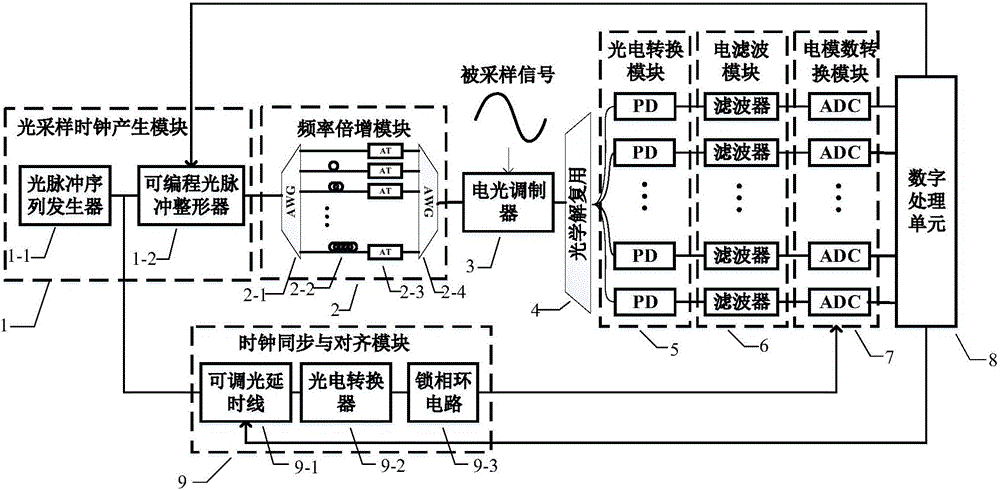

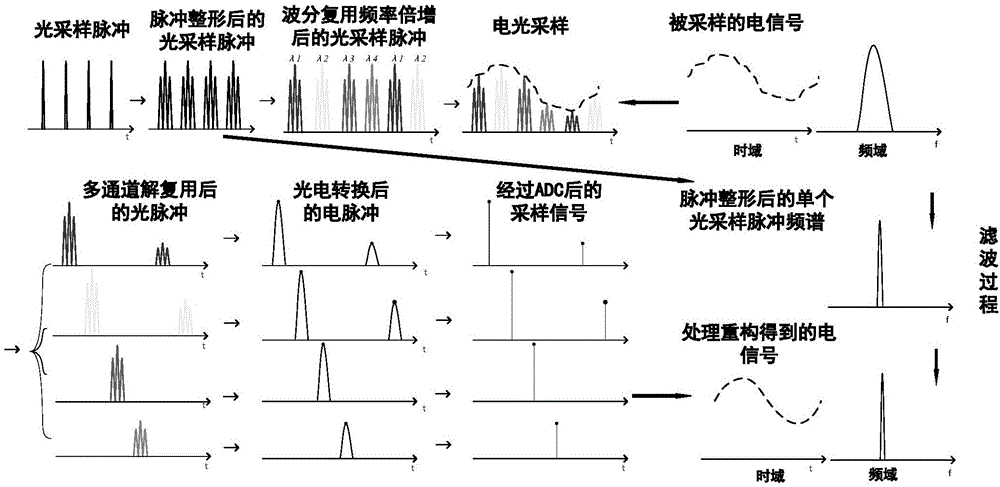

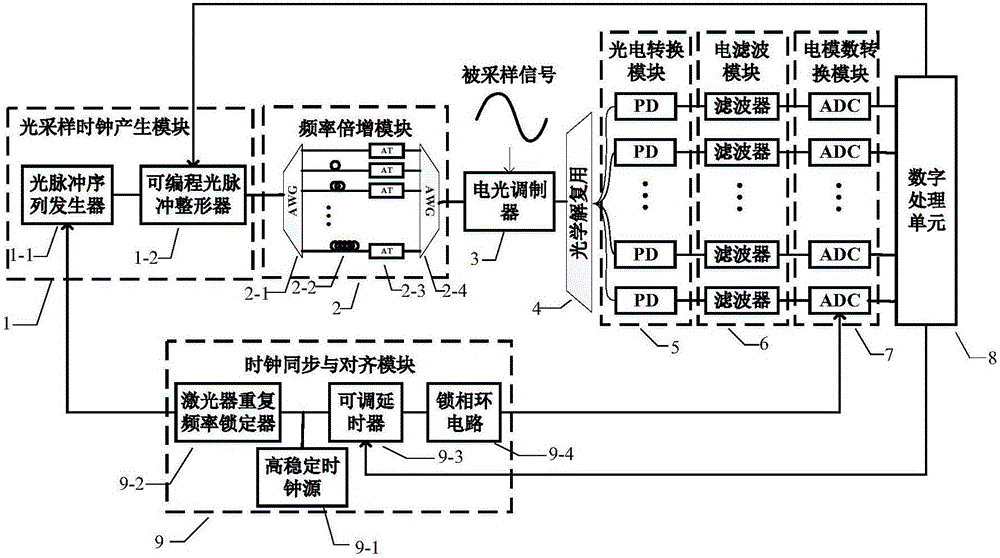

Optical analog-digital converter with configurable frequency response

ActiveCN106444215AReduced analog input performance requirementsReduce complexityOptical analogue/digital convertersDigital down converterFiltration

An optical analog-digital converter with configurable frequency response sequentially comprises a controllable pulse shape optical sampling clock generating module, a repetition frequency doubling module, an electro-optical modulator, a multi-channel module, a photoelectric conversion module, an electric filter module, an electric analog-digital conversion module, a digital processing unit and a clock synchronization and aligning module. The optical analog-digital converter with configurable frequency response provides both analog processing and digitalization for broadband input microwave signals, system complexity is greatly reduced, and the problems, such as high insertion loss and signal distortion, due to respective filtration and sampling are avoided; system equivalent frequency response may be configured flexibly by adjusting time-domain shape of an optical sampling clock.

Owner:SHANGHAI JIAO TONG UNIV

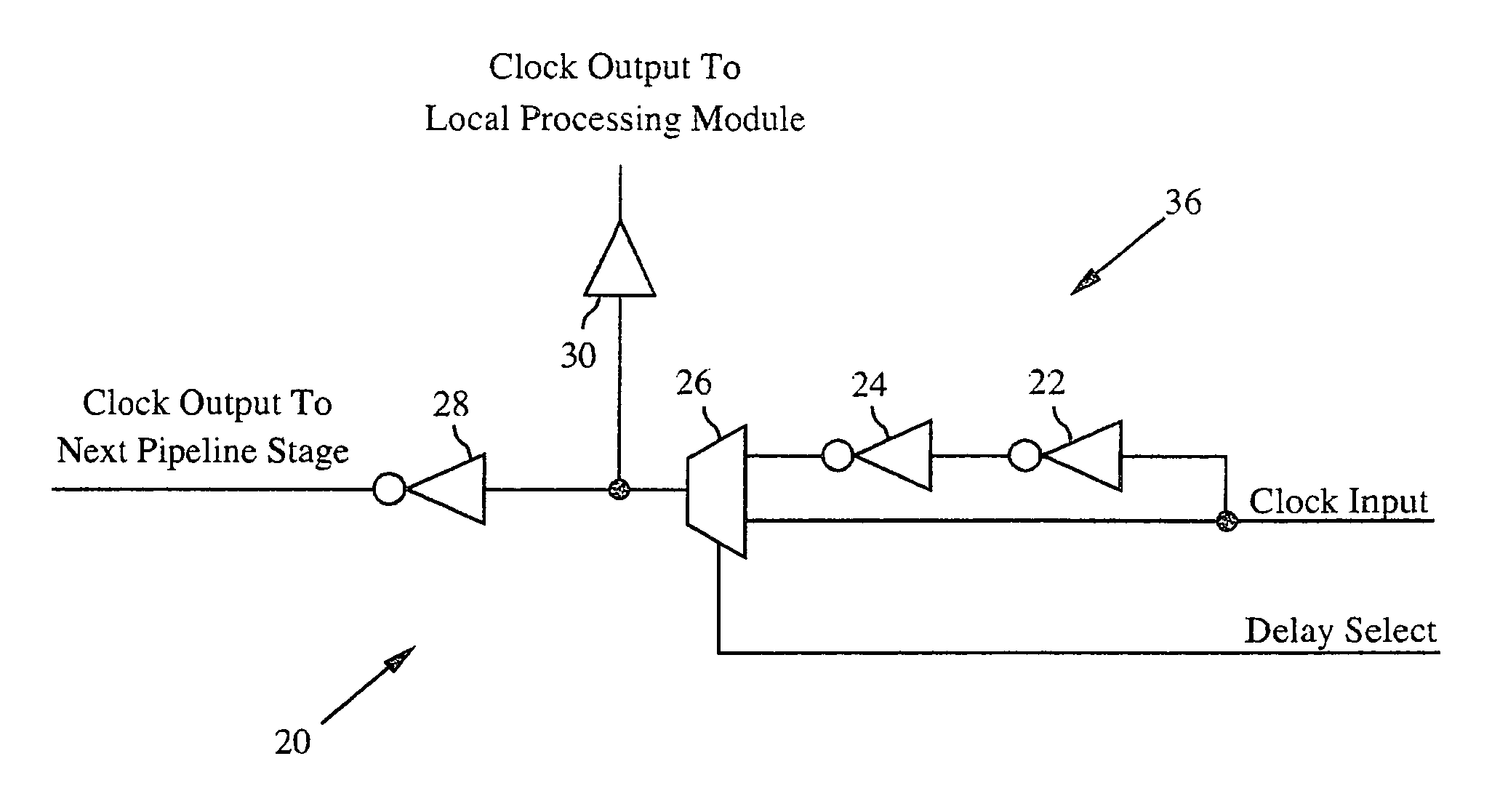

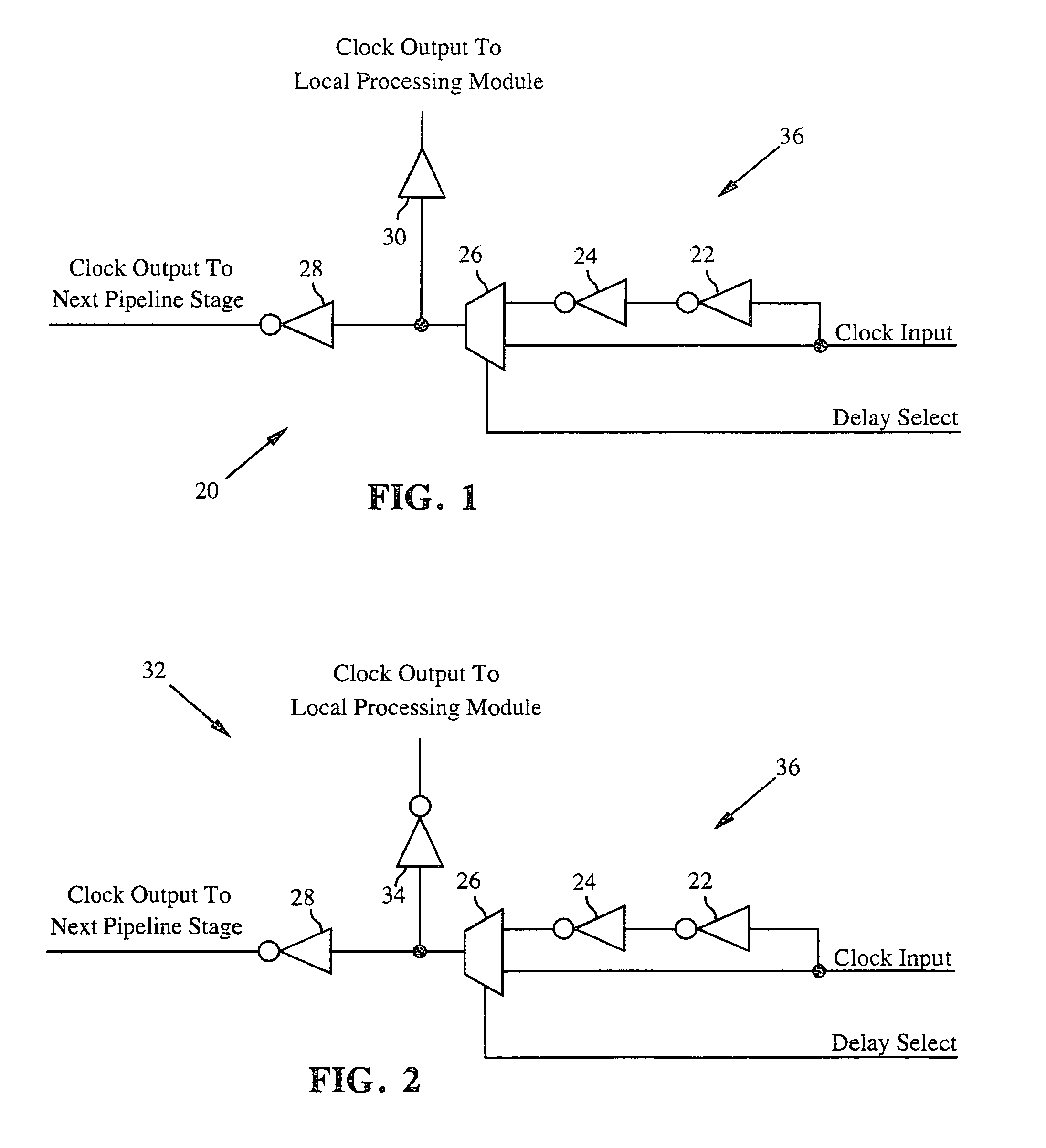

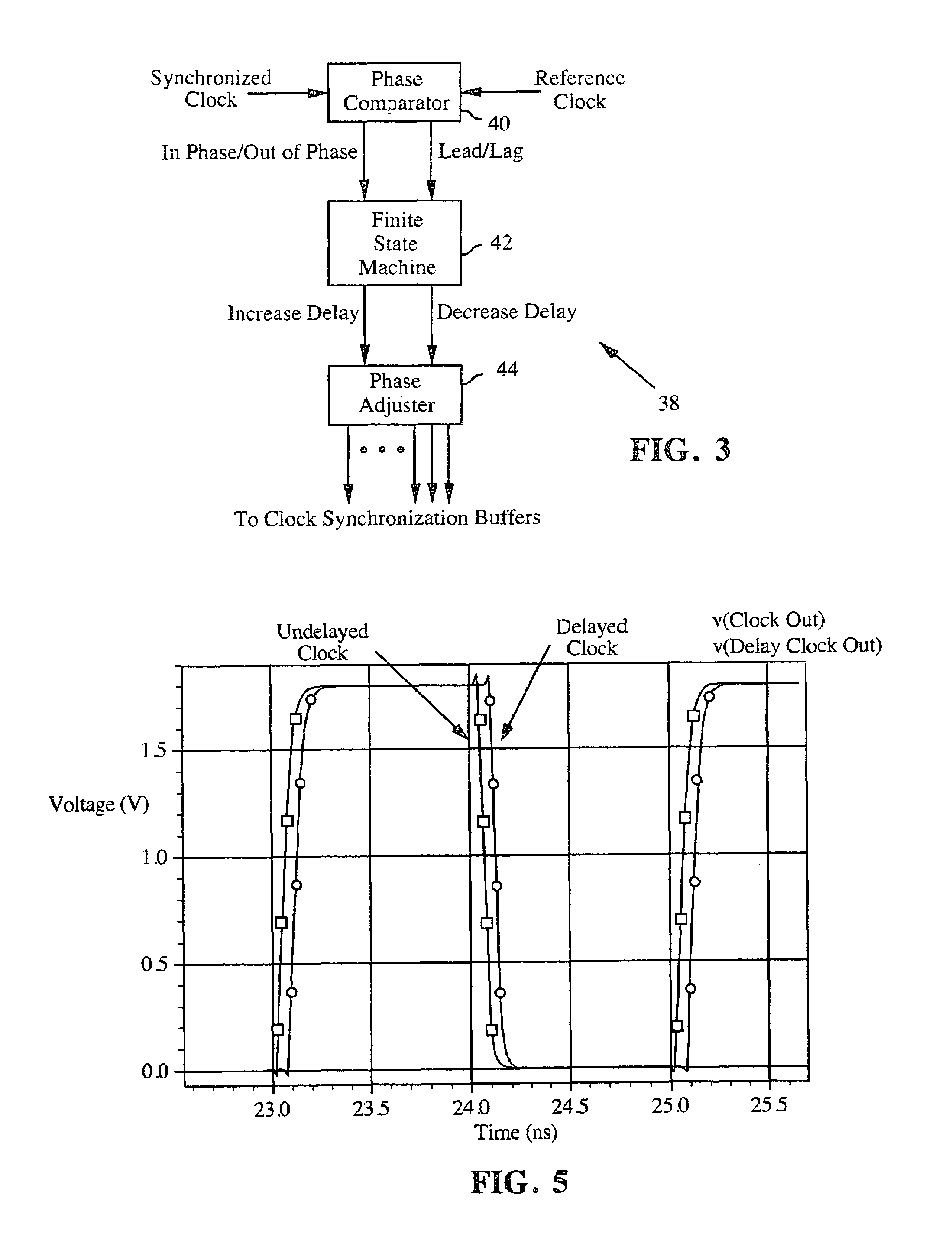

Automatic clock synchronization and distribution circuit for counter clock flow pipelined systems

InactiveUS7627003B1Pulse automatic controlTime-division multiplexAudio power amplifierComputer science

A clock synchronization buffer for a counter clock flow pipelined circuit including a cascade of processing modules that receive data from a previous module and provide output results to a following module. The clock synchronization buffer receives a clock input signal and provides clock signals to a local processing module and to the next pipeline stage. The clock synchronization buffer includes a selectable delay stage that receives a clock input signal and a delay select signal and outputs a clock signal having a selected delay. An amplifier connected to the selectable delay stage provides the delayed clock signal to a local processing module that corresponds to the clock synchronization buffer circuit. An inverting amplifier connected to the selectable delay stage provides the delayed clock signal to the next pipeline stage. A clock synchronization controller synchronizes the phases of reference clock input and synchronized clock input signals.

Owner:NAVY UNITED STATES OF AMERICA THE REPRESENTED BY THE SEC

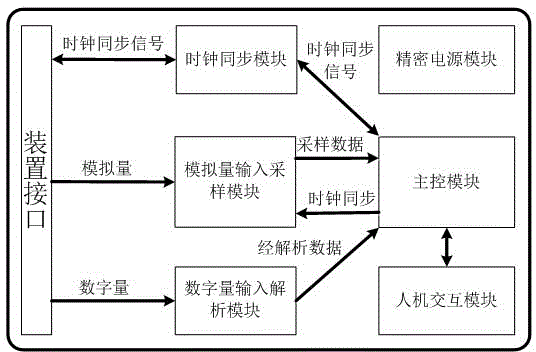

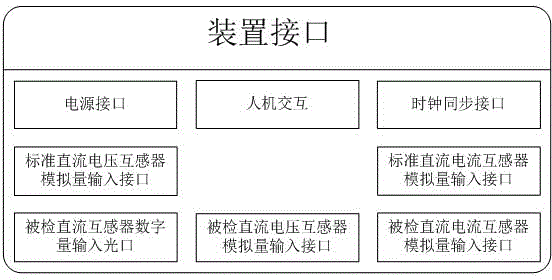

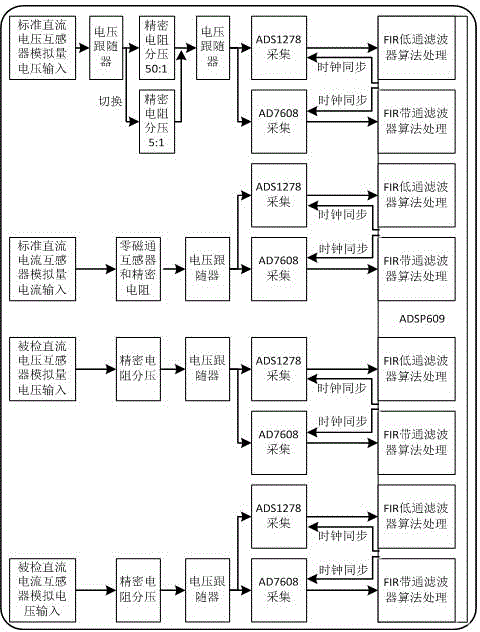

DC mutual inductor check meter combining analog quantity and digital quantity verification function

ActiveCN104833941AHigh measurement accuracySampling implementationElectrical measurementsComputer moduleMan machine

A DC mutual inductor check meter combining analog quantity and digital quantity verification functions comprises a main control module, an analog input sampling module, a digital quantity input parse module, a clock synchronization module, a man-machine exchange module, and a power supply module powering corresponding modules; the check meter also comprises following device interfaces: a clock synchronization interface, at least two analog input interfaces, and at least one digital quantity input optical network port; the analog input interfaces are connected with the analog input sampling module; the digital quantity input optical network port is connected with the digital quantity input parse module; the clock synchronization module is connected with the clock synchronization interface and the main control module; the main control module further processes the data sent by the analog input sampling module and the digital quantity input parse module, and processed data is sent to and displayed by the man-machine exchange module. The check meter can check the DC mutual inductors of either analog output type or digital quantity output type.

Owner:ELECTRIC POWER RES INST OF GUANGDONG POWER GRID

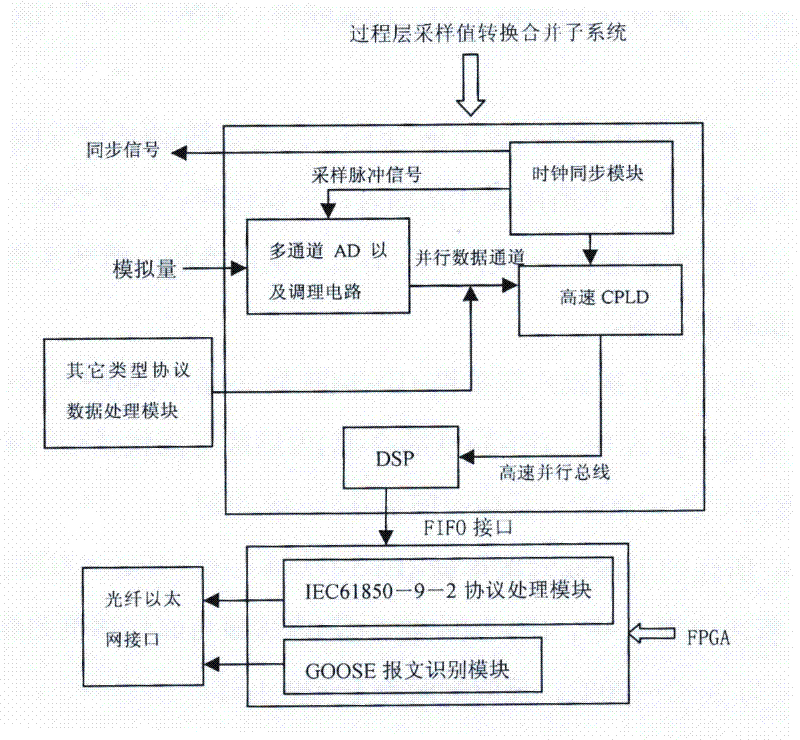

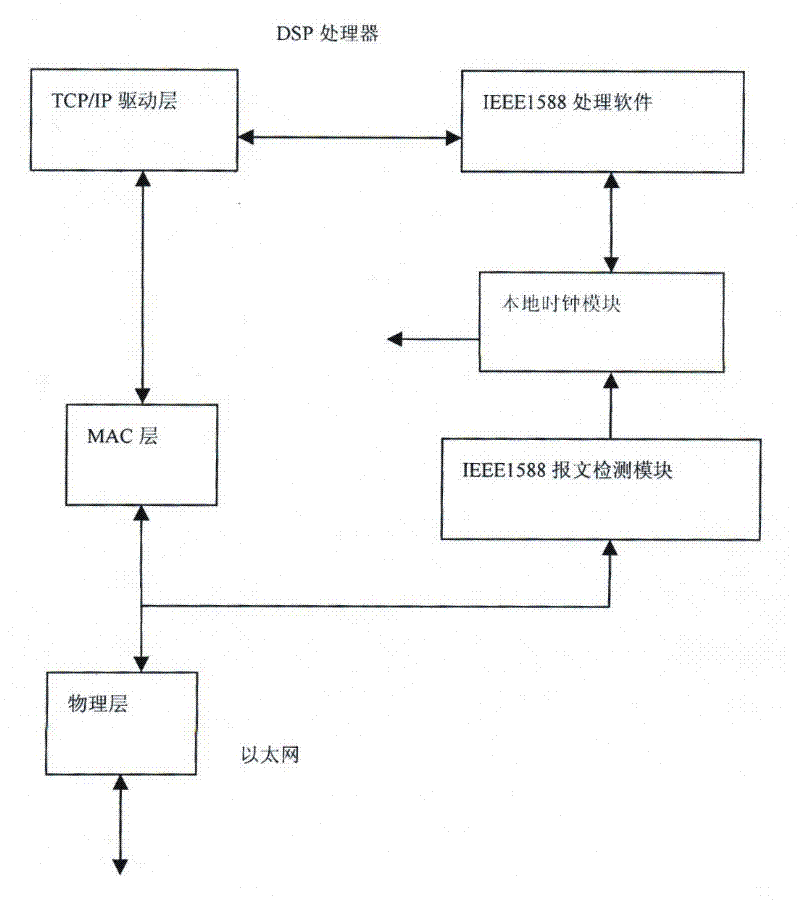

Intelligent transformer station process layer data acquisition, conversion and transmission device and control method thereof

InactiveCN102377781AEasy to transformSimultaneous acquisition for easy controlTransmissionData acquisitionComplex programmable logic device

The invention discloses an intelligent transformer station process layer information acquisition, conversion and transmission device and a control method thereof. The intelligent transformer station process layer data acquisition, conversion and transmission device comprises a process layer sampled value conversion and merging subsystem and an FPGA (Field Programmable Gate Array) subsystem, wherein the process layer sampled value conversion and merging subsystem comprises a multi-channel AD (Analog-to-digital Conversion) and conditioning circuit module, a clock synchronization module, a high-speed CPLD (Complex Programmable Logic Device) module, a DSP (Digital Signal Processor) module and other protocol processing modules; the FPGA subsystem comprises GOOSE (Generic Object Oriented Substation Event) message identification module, and an IEC (International Electrotechnical Commission) 61850-9-2 protocol processing model module; the DSP module is connected with the CPLD module and the clock synchronization module through a parallel bus; the CPLD module is connected with the multi-channel AD and conditioning circuit module through a parallel data channel; pulse signals are collected by the clock synchronization module through a parallel port; and the FPGA subsystem is connected with the process layer sampled value conversion and merging subsystem through an FIFO (First-in, First-out) interface. The intelligent transformer station process layer information acquisition, conversion and transmission device integrates sampling, protocol conversion and data merging, the intermediate process for data transmission is reduced, and real-time transmission of data is facilitated.

Owner:四川电力职业技术学院 +1

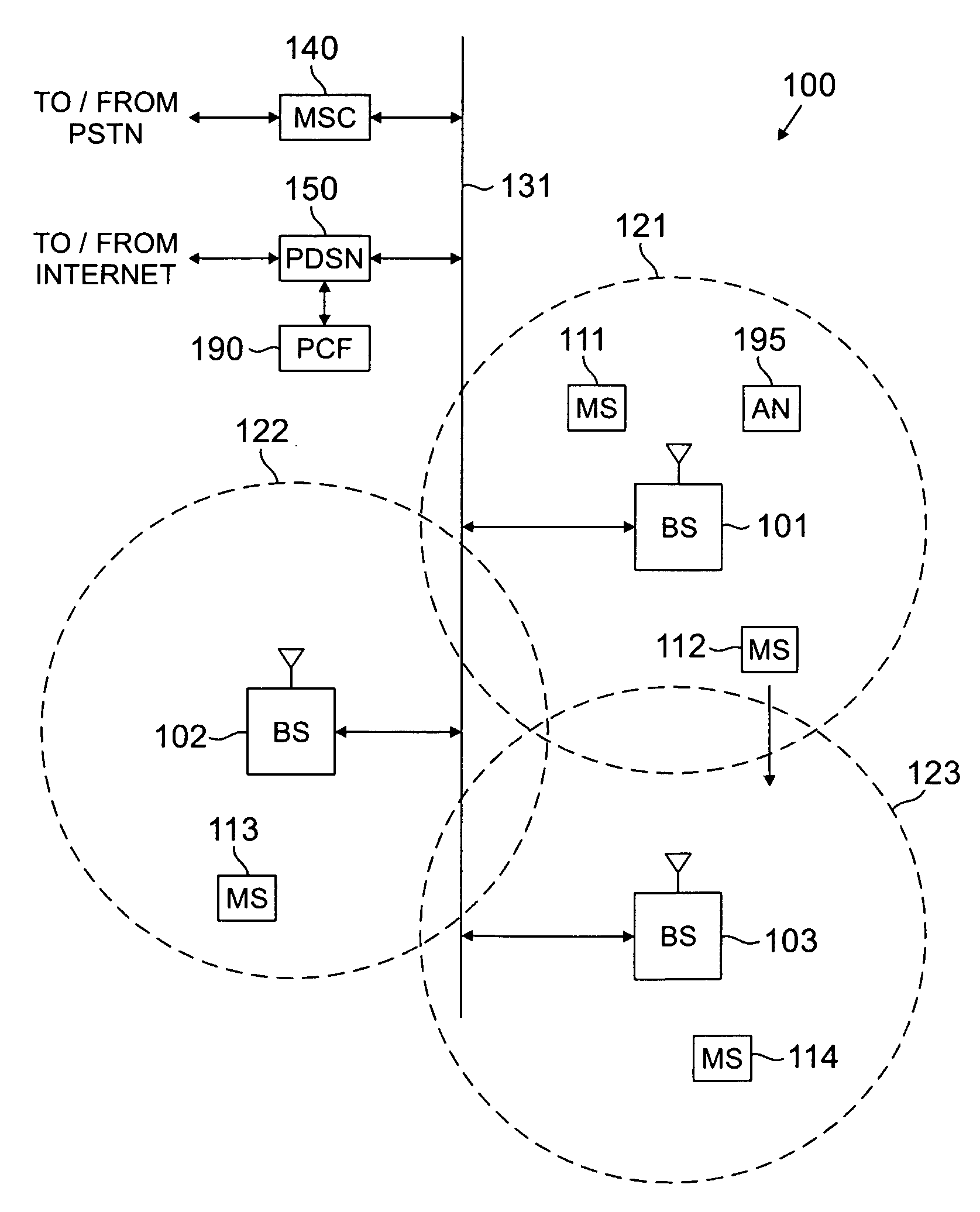

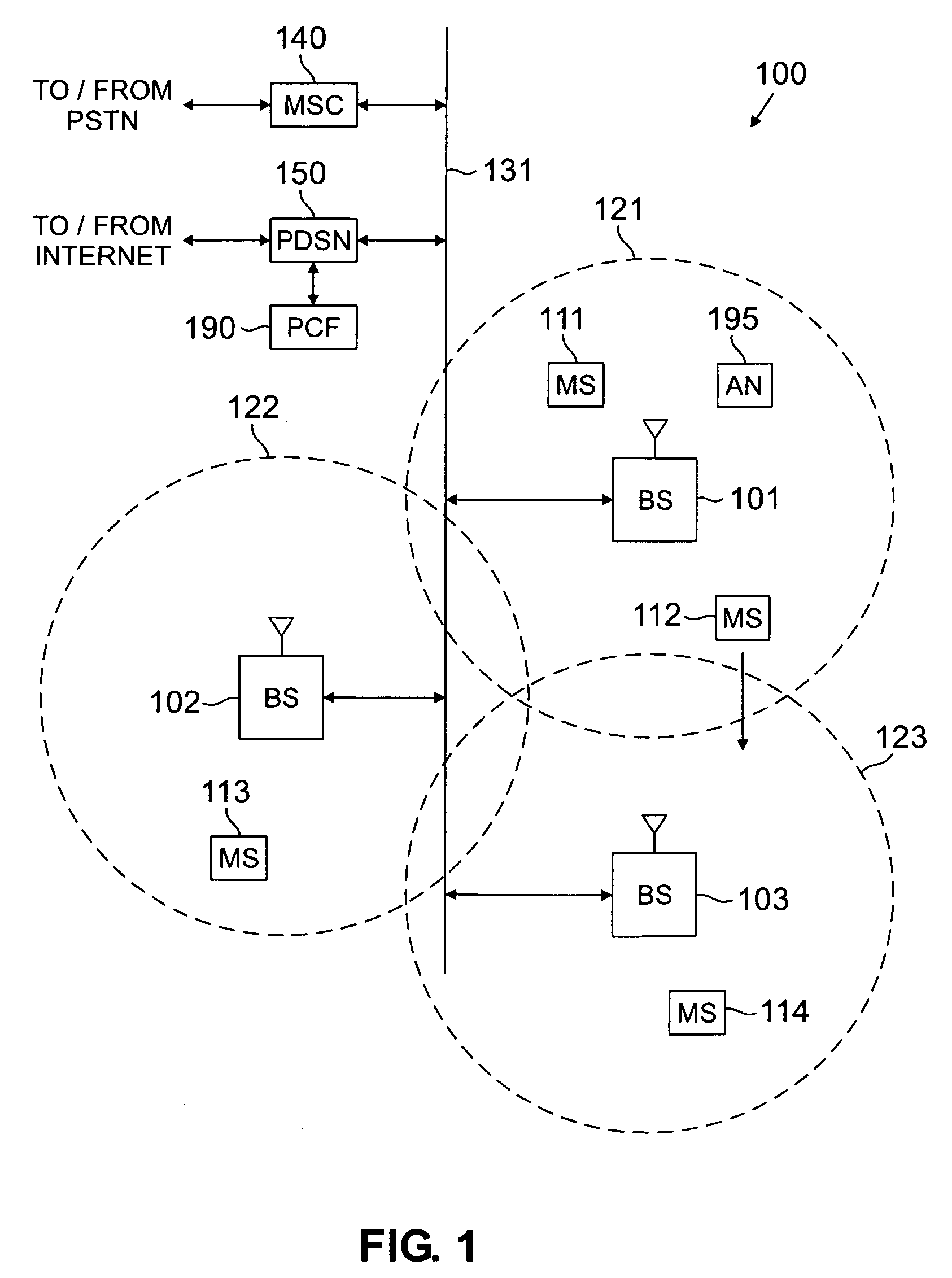

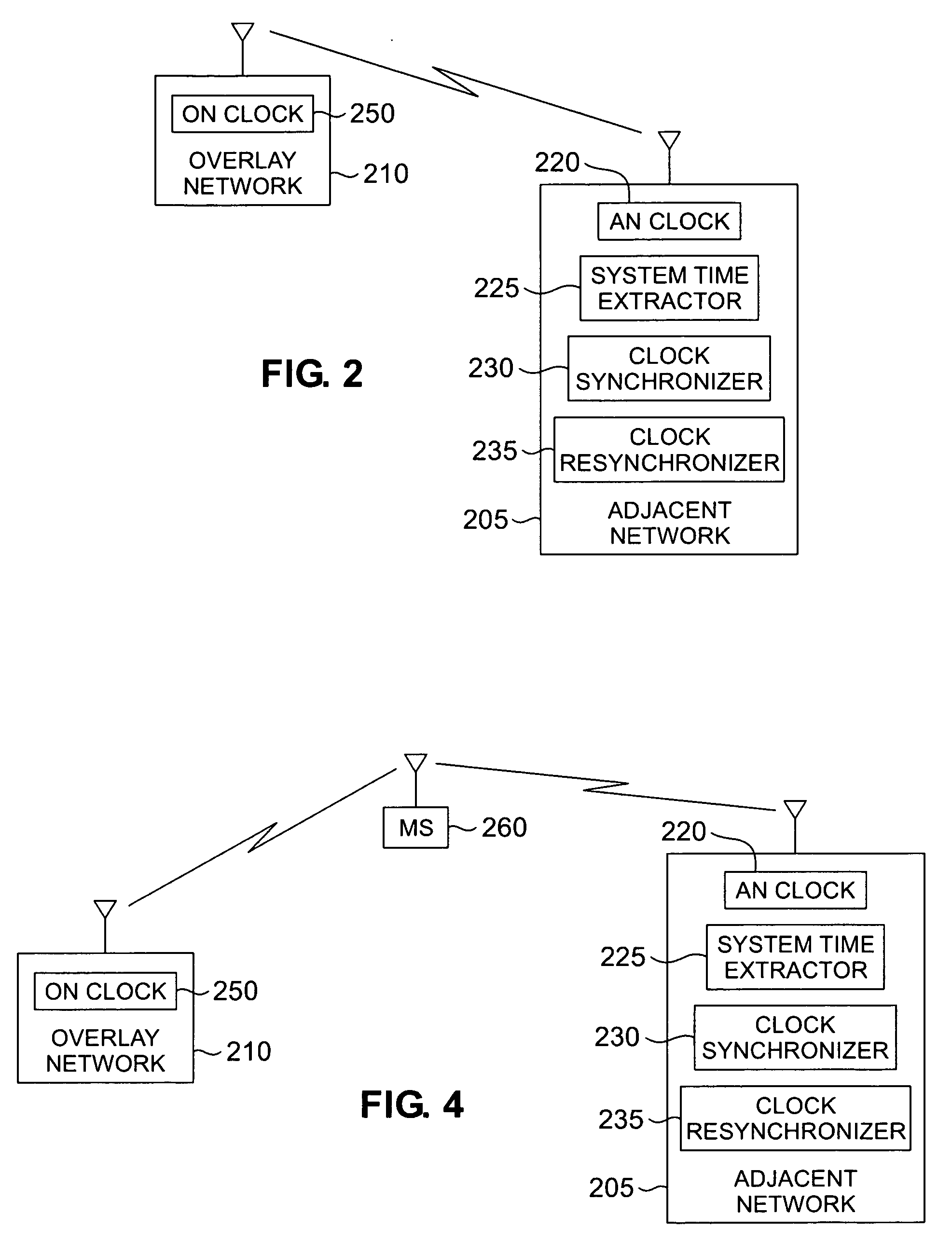

Method and system for synchronizing a clock for an adjacent network to a clock for an overlay network

ActiveUS20060234739A1Synchronisation arrangementTime-division multiplexClock synchronizationOverlay network

A method of synchronizing a clock for an adjacent network (AN) to a clock for an overlay network (ON) is provided. The method includes extracting an ON clock signal from an outgoing signal transmitted from the overlay network. The AN clock is synchronized to the ON clock based on the extracted ON clock signal.

Owner:SAMSUNG ELECTRONICS CO LTD

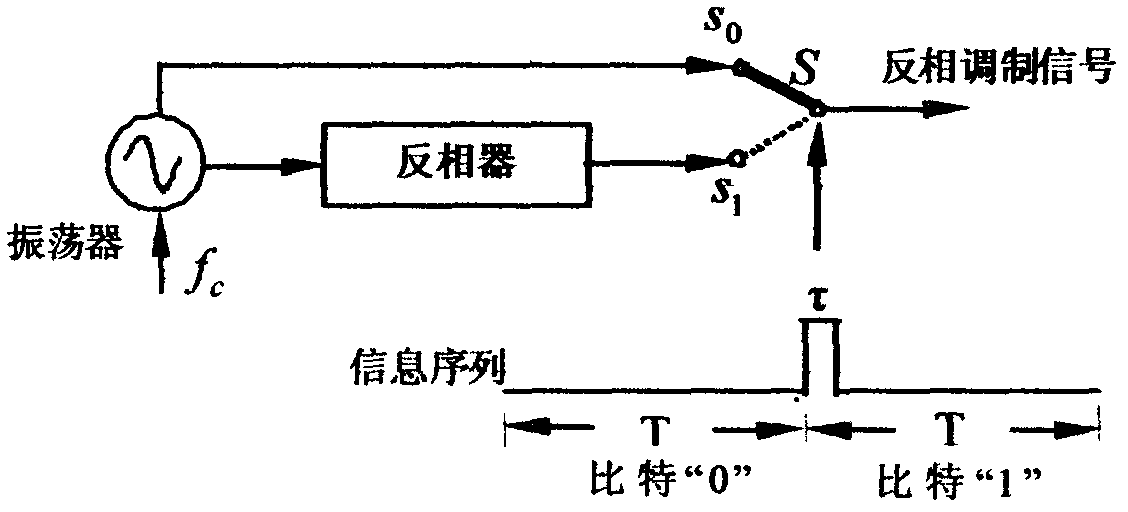

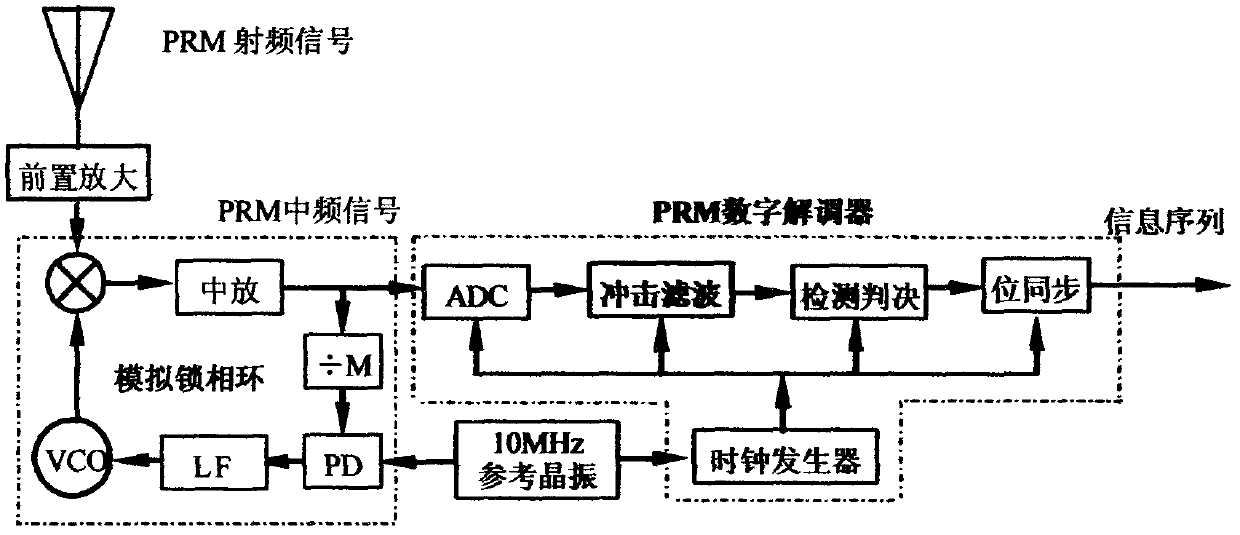

Power supply self-synchronizing phase inversion modulator-demodulator for power line communication

ActiveCN102684744APrecise synchronization of working clocksEasy to filterPower distribution line transmissionModem deviceCarrier signal

The invention discloses a power supply self-synchronizing phase inversion modulator-demodulator for power line communication, which adopts asymmetrical phase inversion modulation as a transmission signal, and utilizes the characteristic that a receiving terminal and a transmitting terminal have the same supply frequency, a typical phase-locked loop frequency synthesizer is firstly adopted to realize a signal generator which is strictly synchronous with the supply frequency, the synchronous signal generator is then utilized to replace a conventional crystal oscillator, accordingly, the receiving-transmitting frequency difference is thoroughly eliminated, the required steps of synchronization of carrier wave, sampling and clock for a power line digital communication receiver are completely omitted, so the self-synchronizing of a phase inversion modulation digital receiver demodulator for power line communication is realized.

Owner:苏州东奇信息科技股份有限公司

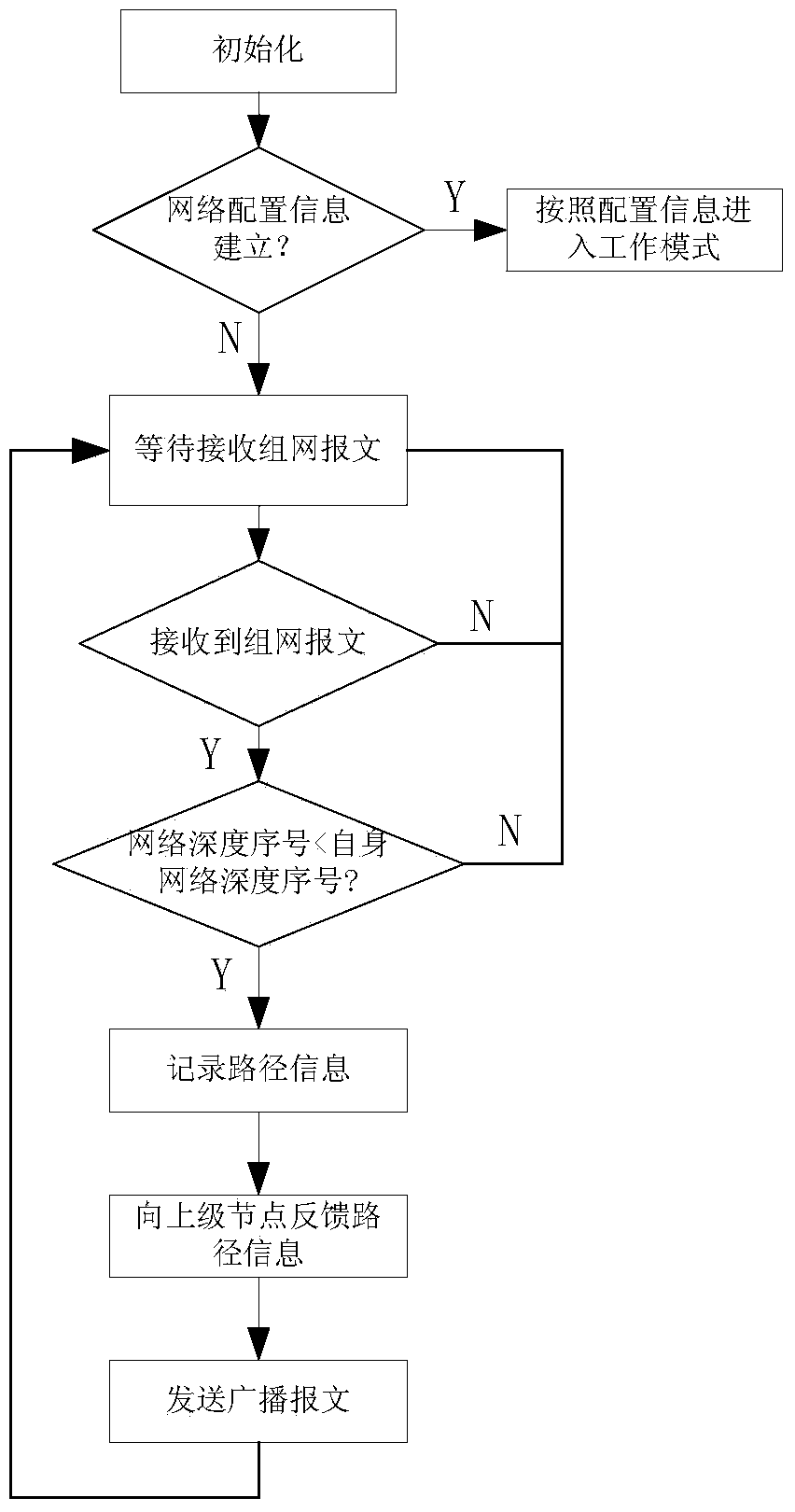

A wireless sensor self-organized networking method

InactiveCN104394581AReduce some overheadReduce power consumption energyPower managementSynchronisation arrangementTelecommunicationsNetworking protocol

The invention discloses a wireless sensor self-organized networking method comprising: self-defining a wireless sensor network networking protocol, transmitting a network command layer upon layer by broadcasting, completing a function of communication path storage during the process of broadcasting, completing a networking function. Based on a clock synchronization technology, the method implements simultaneous dormancy and simultaneous wakeup of the whole wireless sensor network, thus reducing efficiently power consumption in the wireless sensor network.

Owner:NANJING NARI GROUP CORP +1

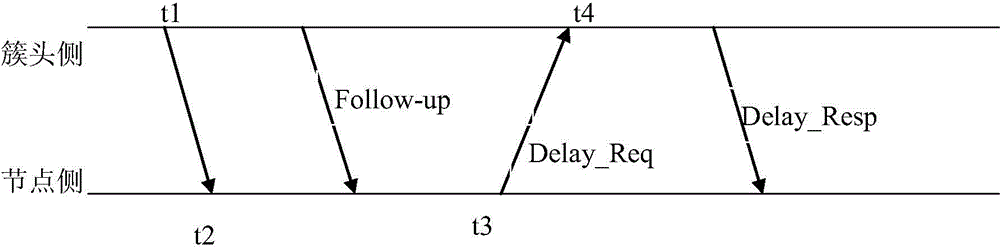

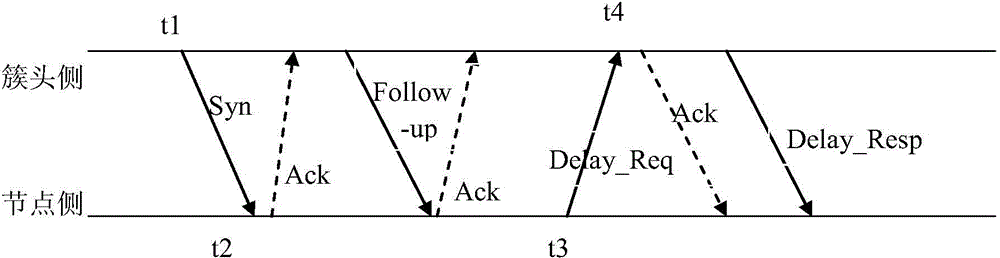

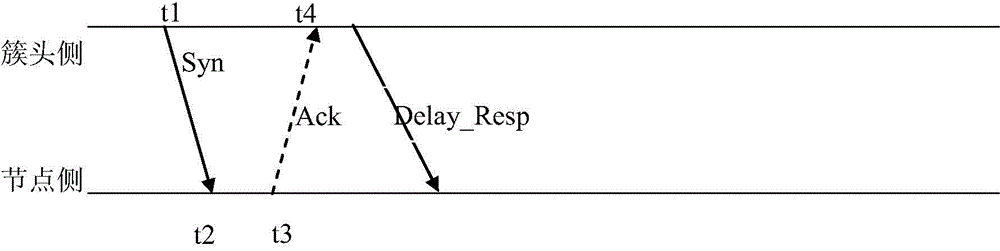

Clock synchronization simplified information exchange method applied to wireless sensor network

InactiveCN104918319AReduce overheadThin Computing CycleSynchronisation arrangementNetwork topologiesRecording durationLine sensor

The invention provides a clock synchronization simplified information exchange method applied to a wireless sensor network. The method comprises steps: a cluster head side sends a message and records a time stamp t1, and a node side receives the message and records a time stamp t2; the node side sends and feeds back the message adn records a time stamp t3; the cluster head side receives the feedback message and records a time stamp t4; the cluster head side combines the time stamps t1 and t4 into a data packet and sends the data packets to the node side; according to the time stamps t2 and t3 and t1 and t4 analyzed from the data packet, the node side calculates clock offset for local clock calibration. The method is simple, synchronization time is greatly reduced, realization is convenient, an IEEE1588 accurate clock synchronization protocol and an IEEE802.15.4 wireless sensor network protocol are combined, at least two message sending and receiving times are saved during each time synchronization process, reliability is high, and the working efficiency is improved.

Owner:NORTH CHINA UNIVERSITY OF TECHNOLOGY

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com