Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

457results about How to "Reduce coupling effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

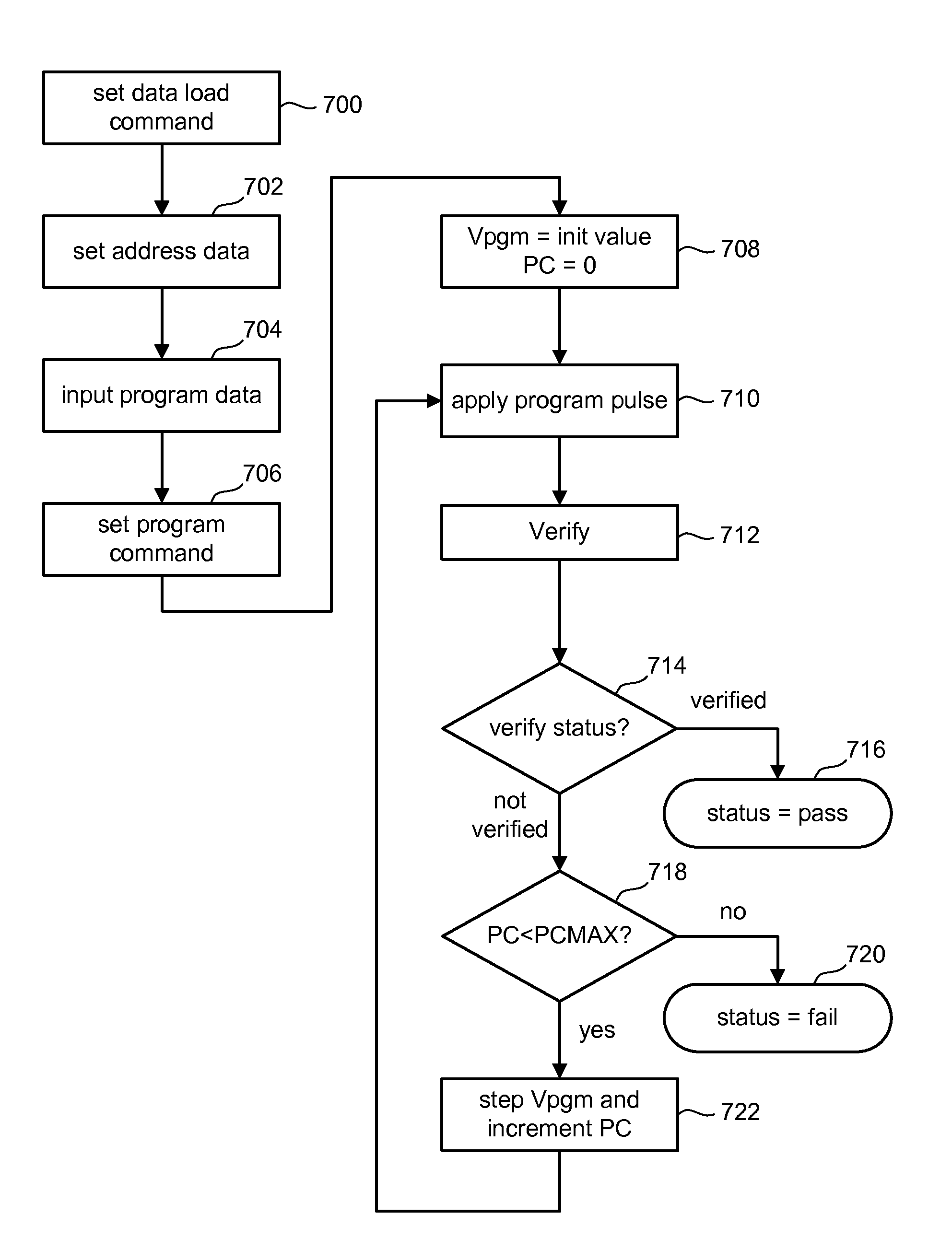

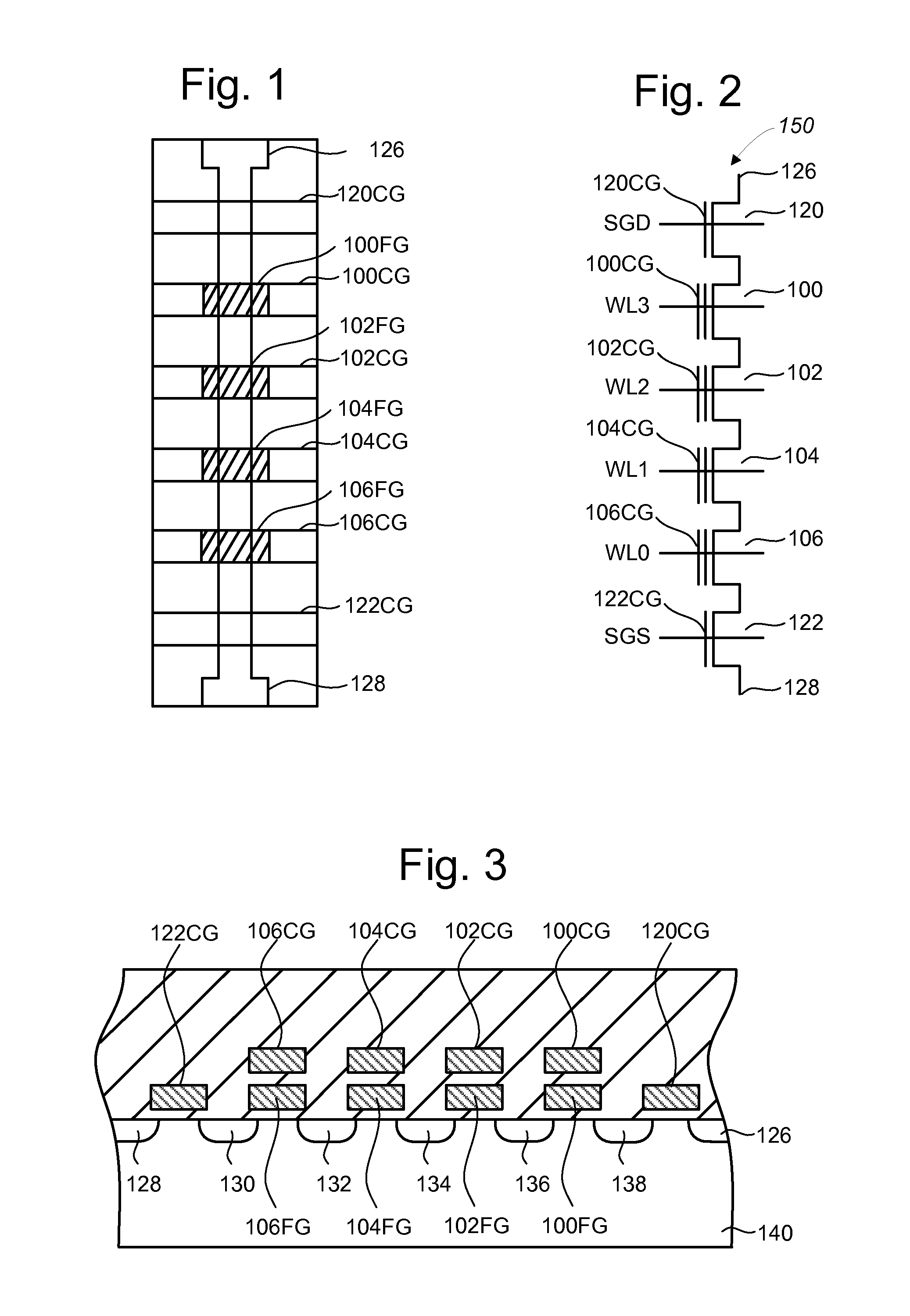

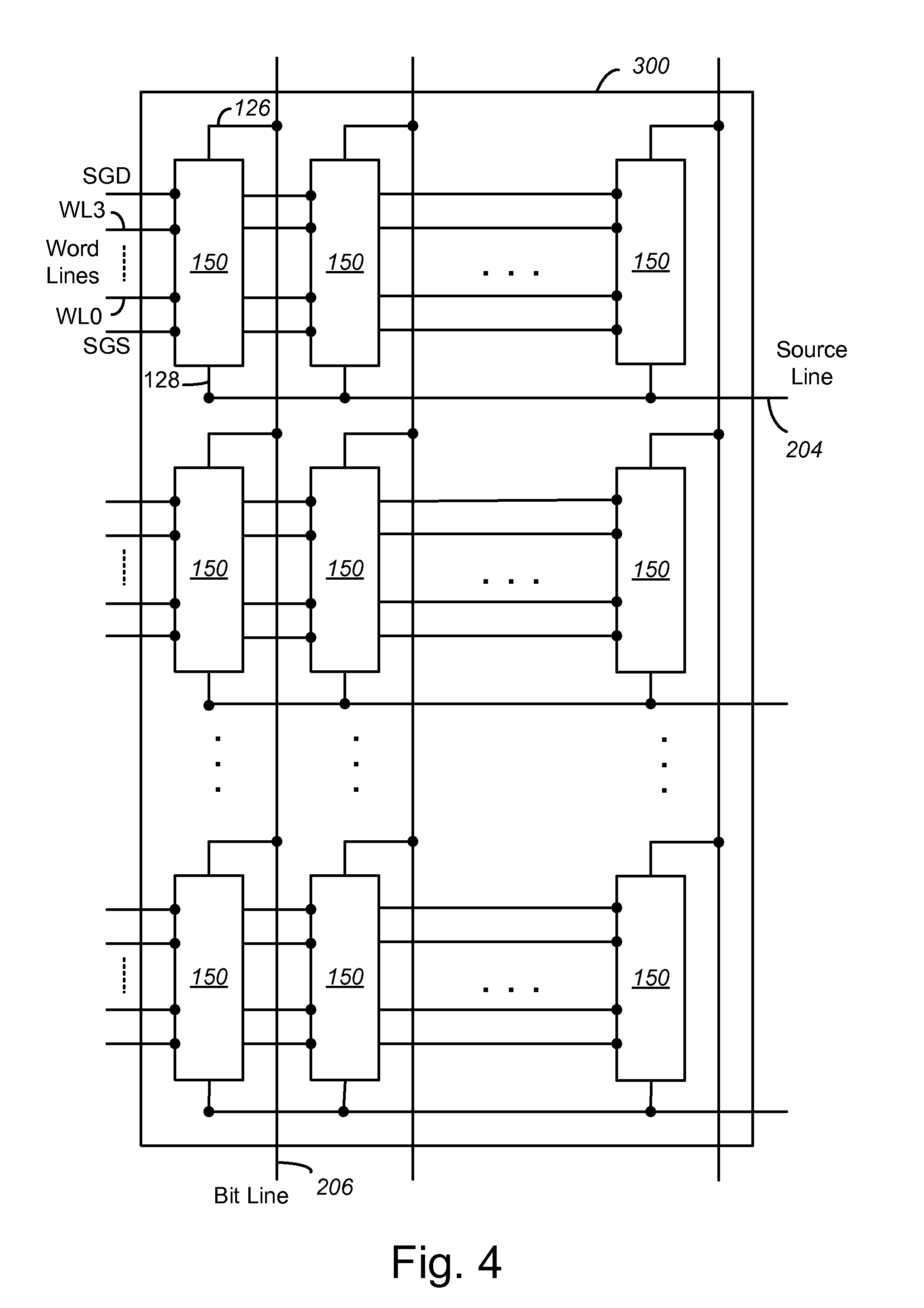

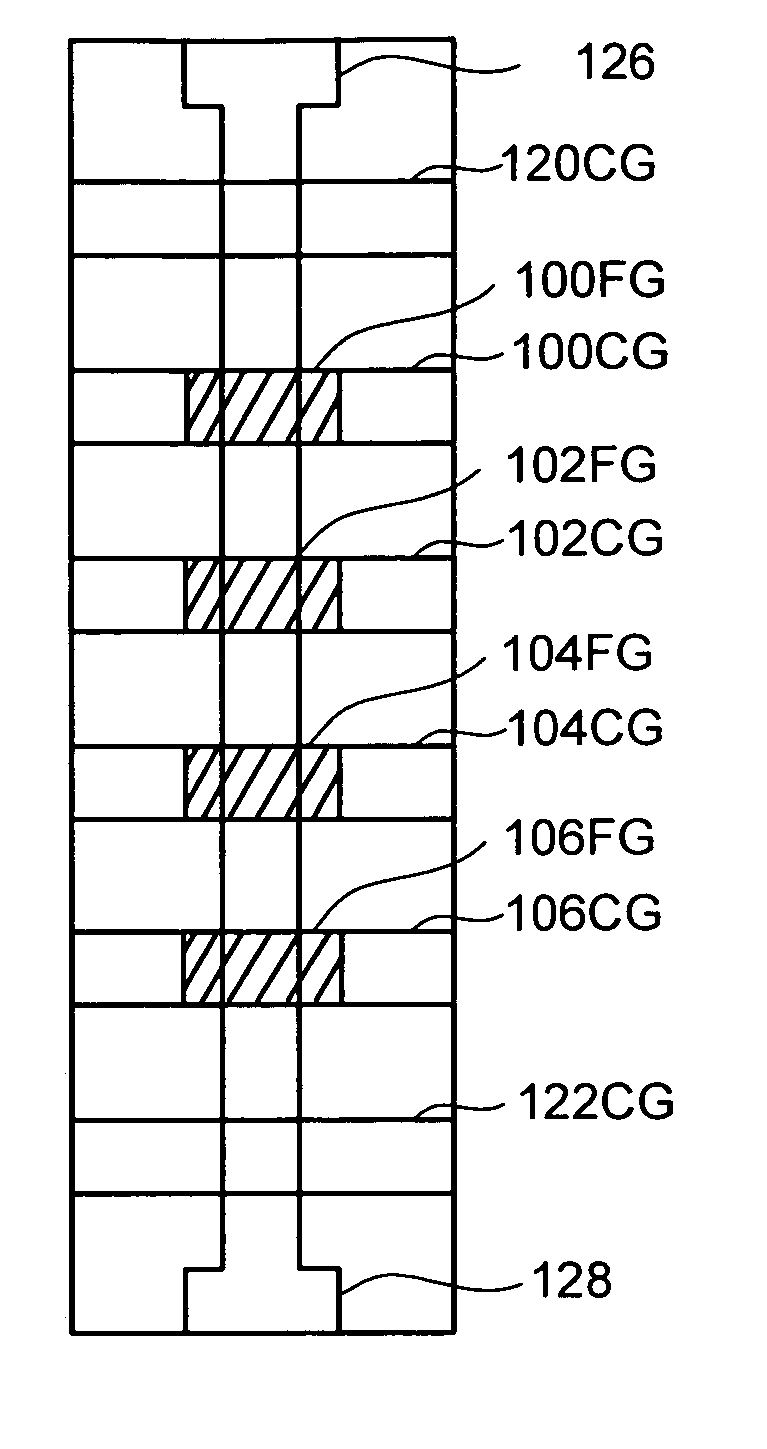

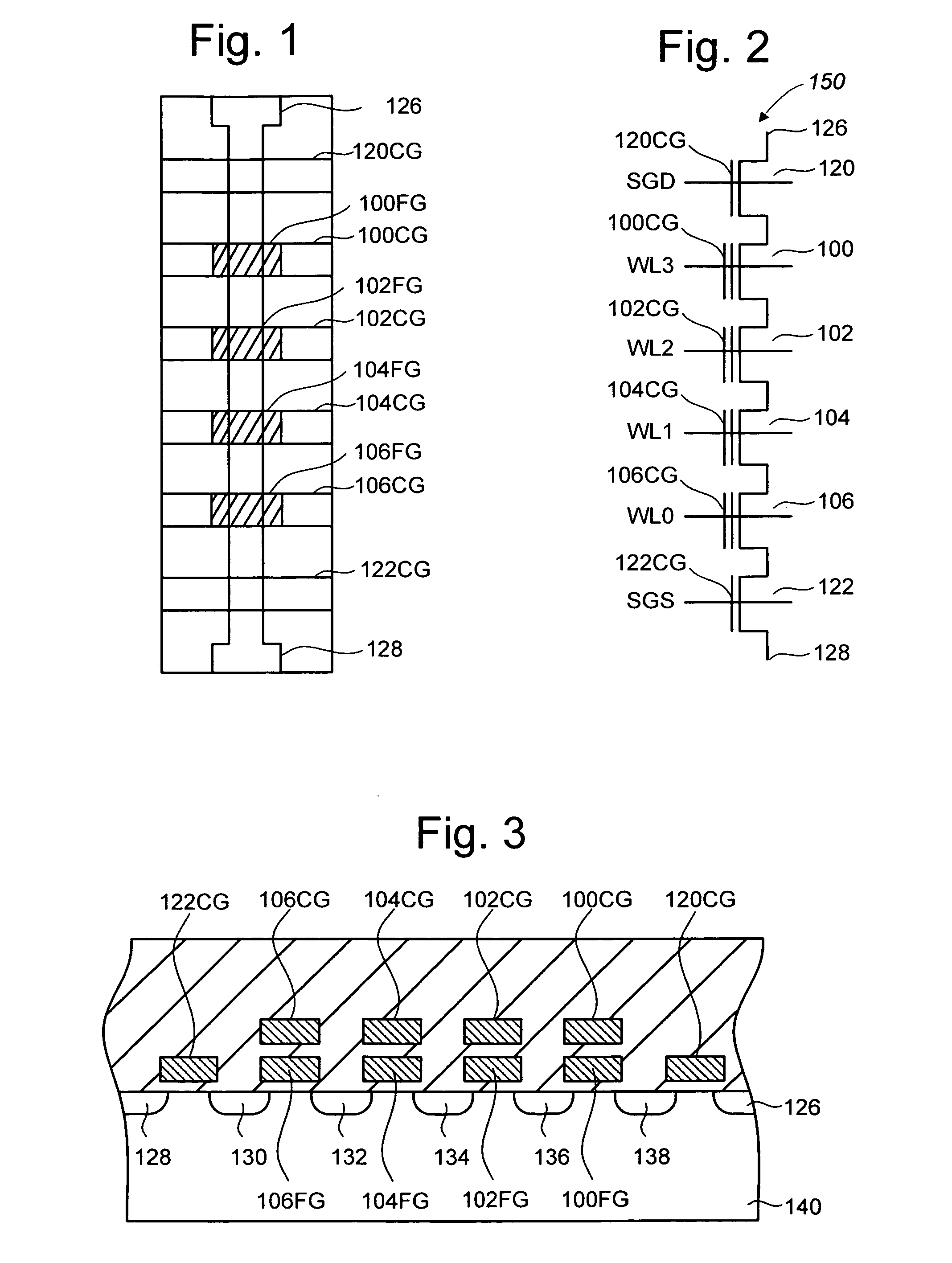

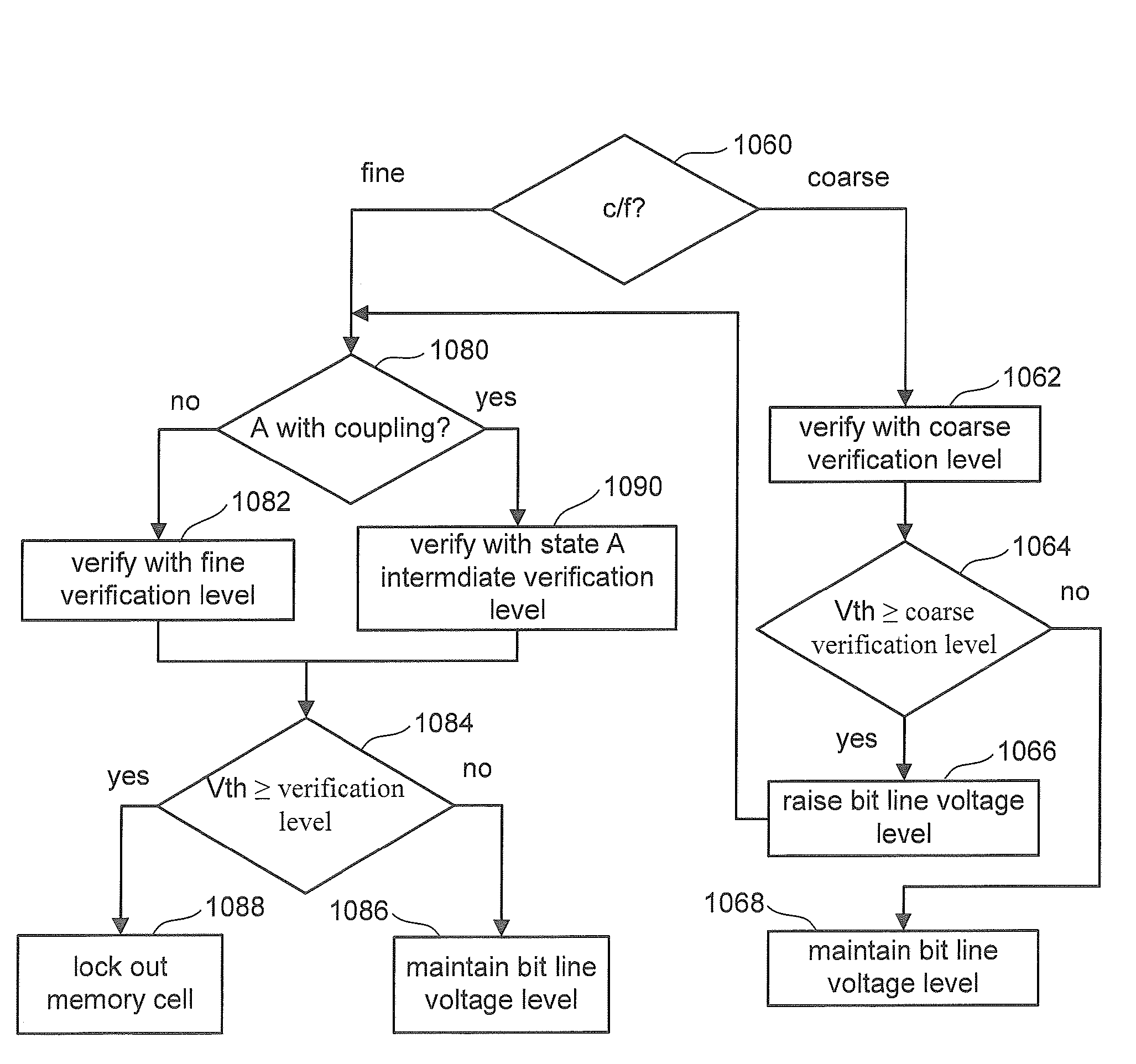

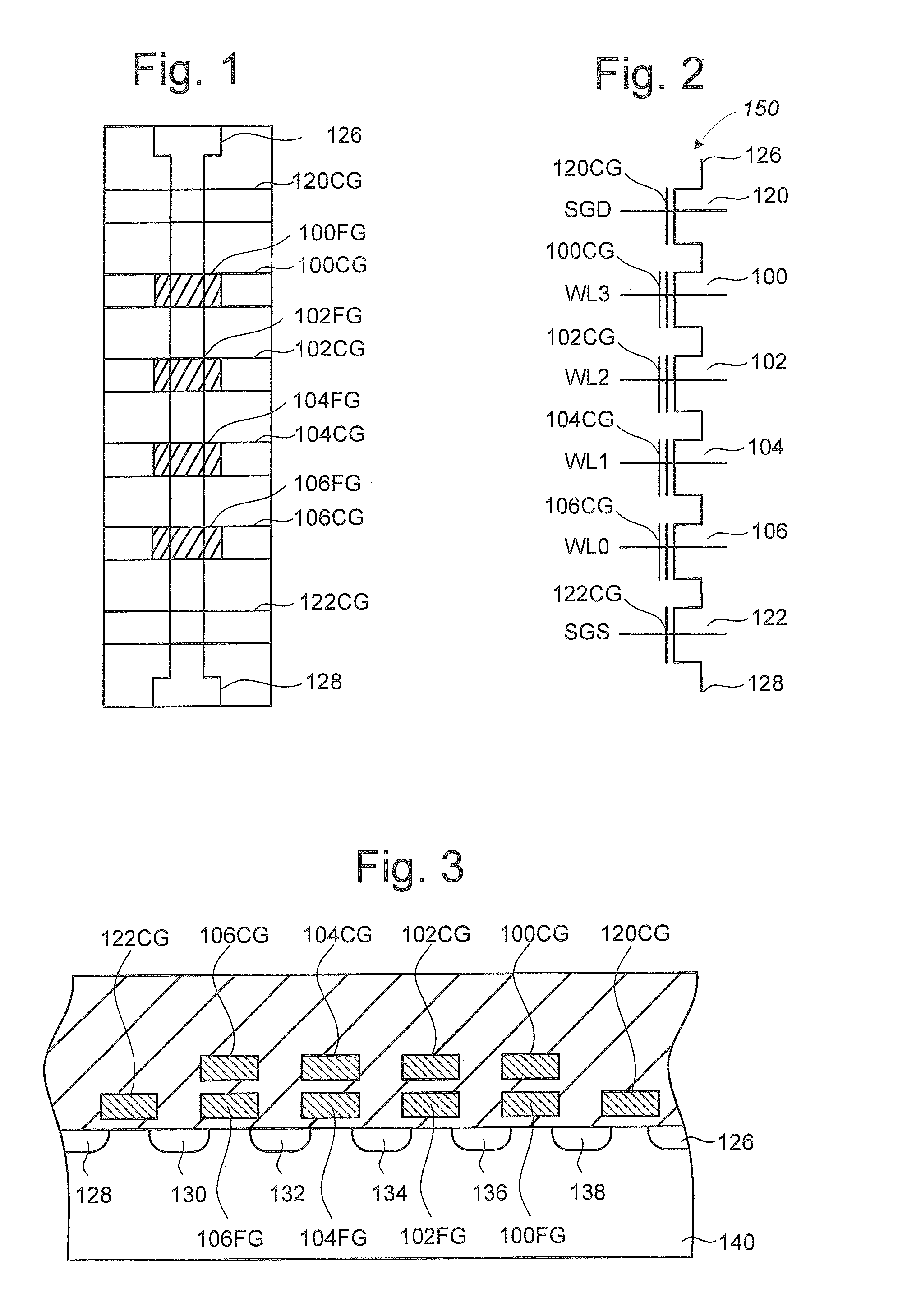

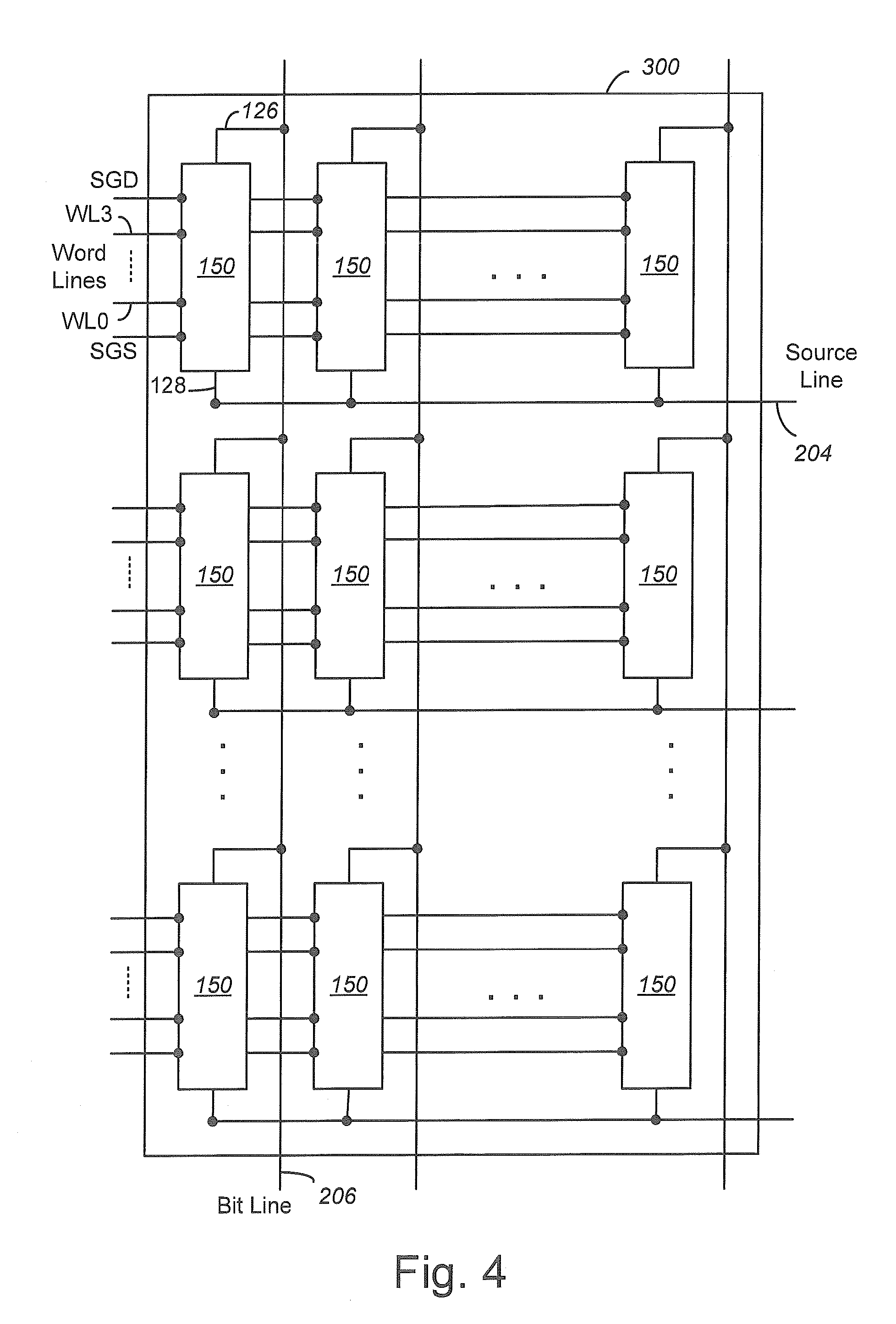

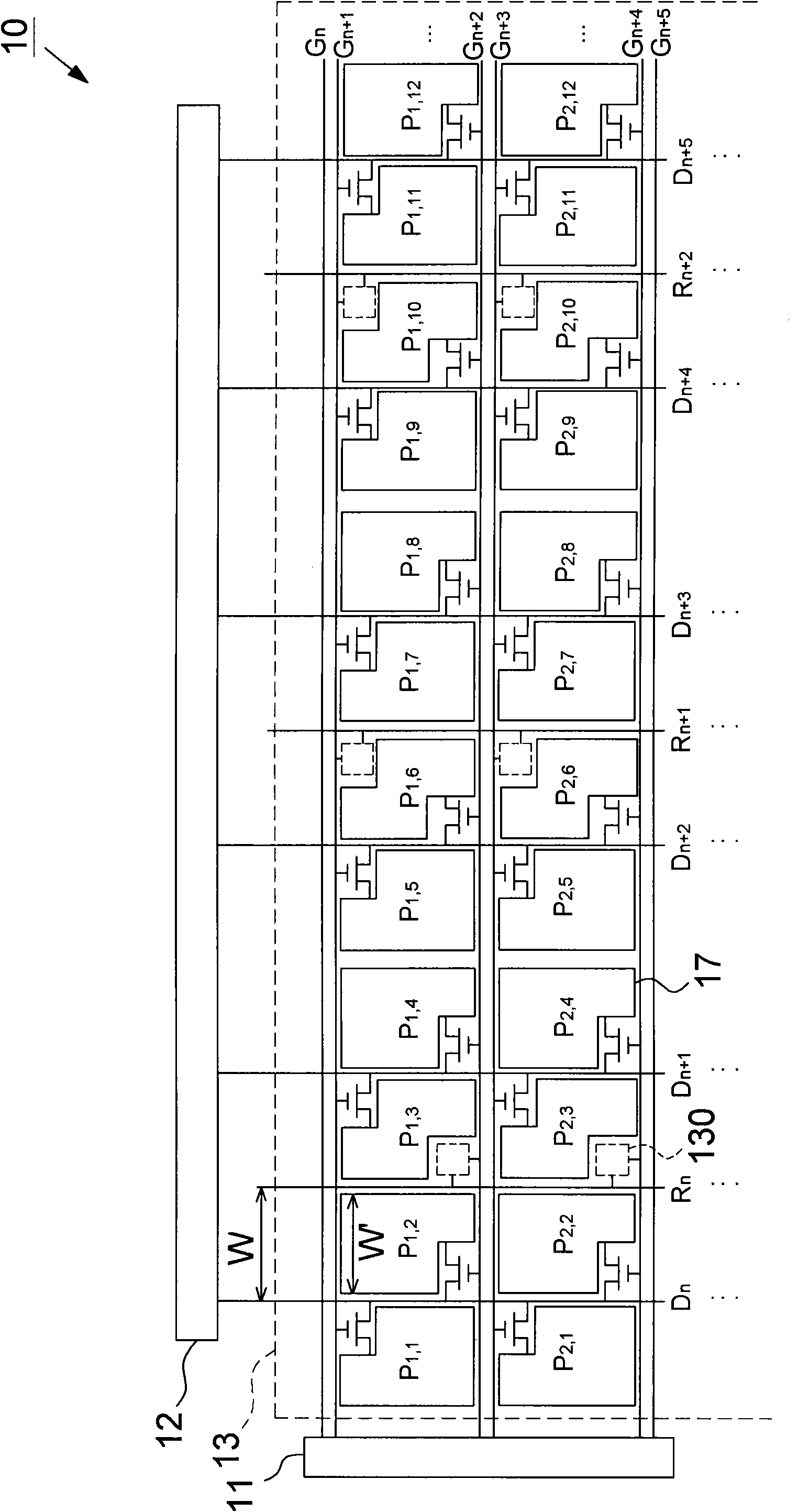

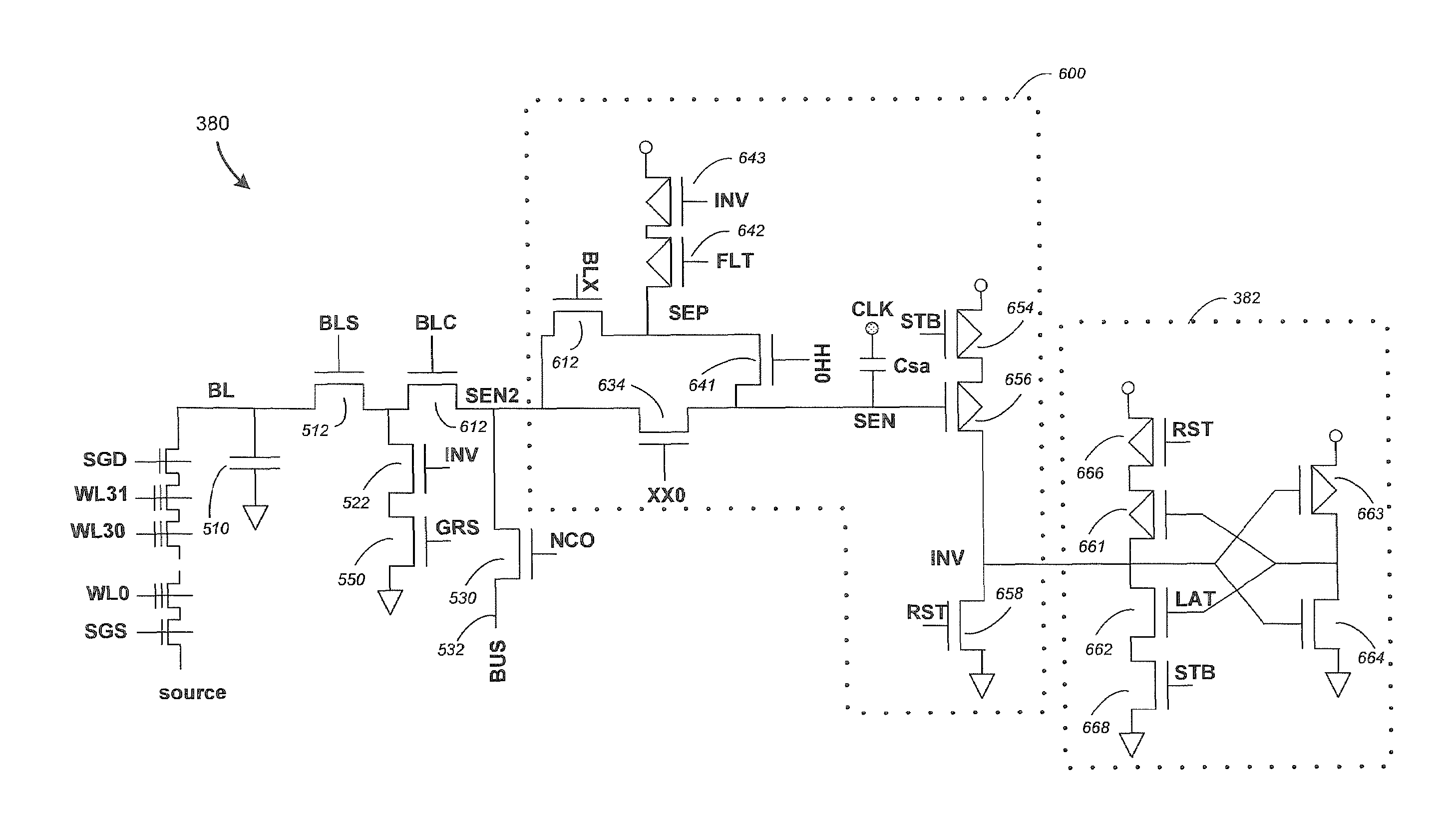

Compensating for coupling during programming

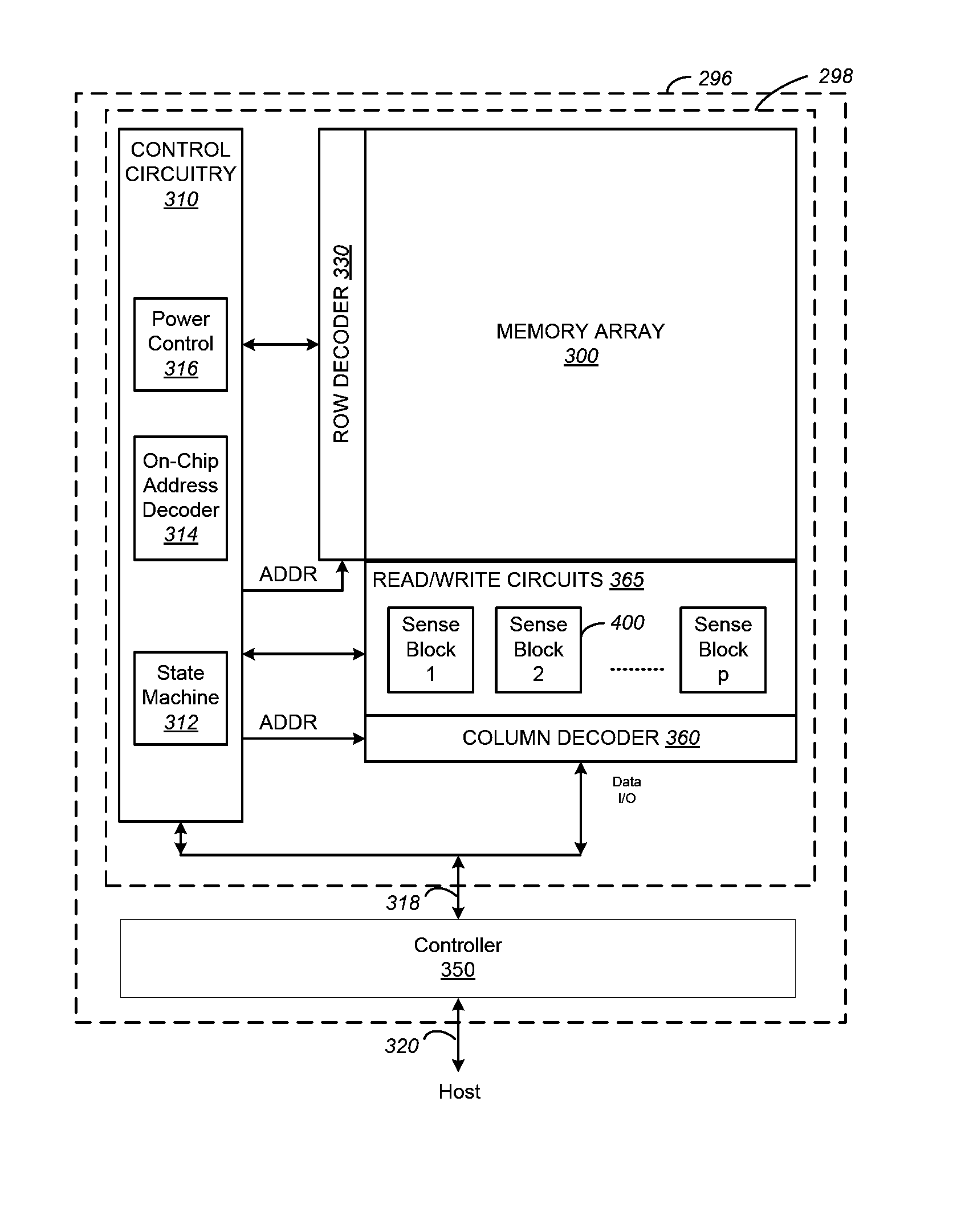

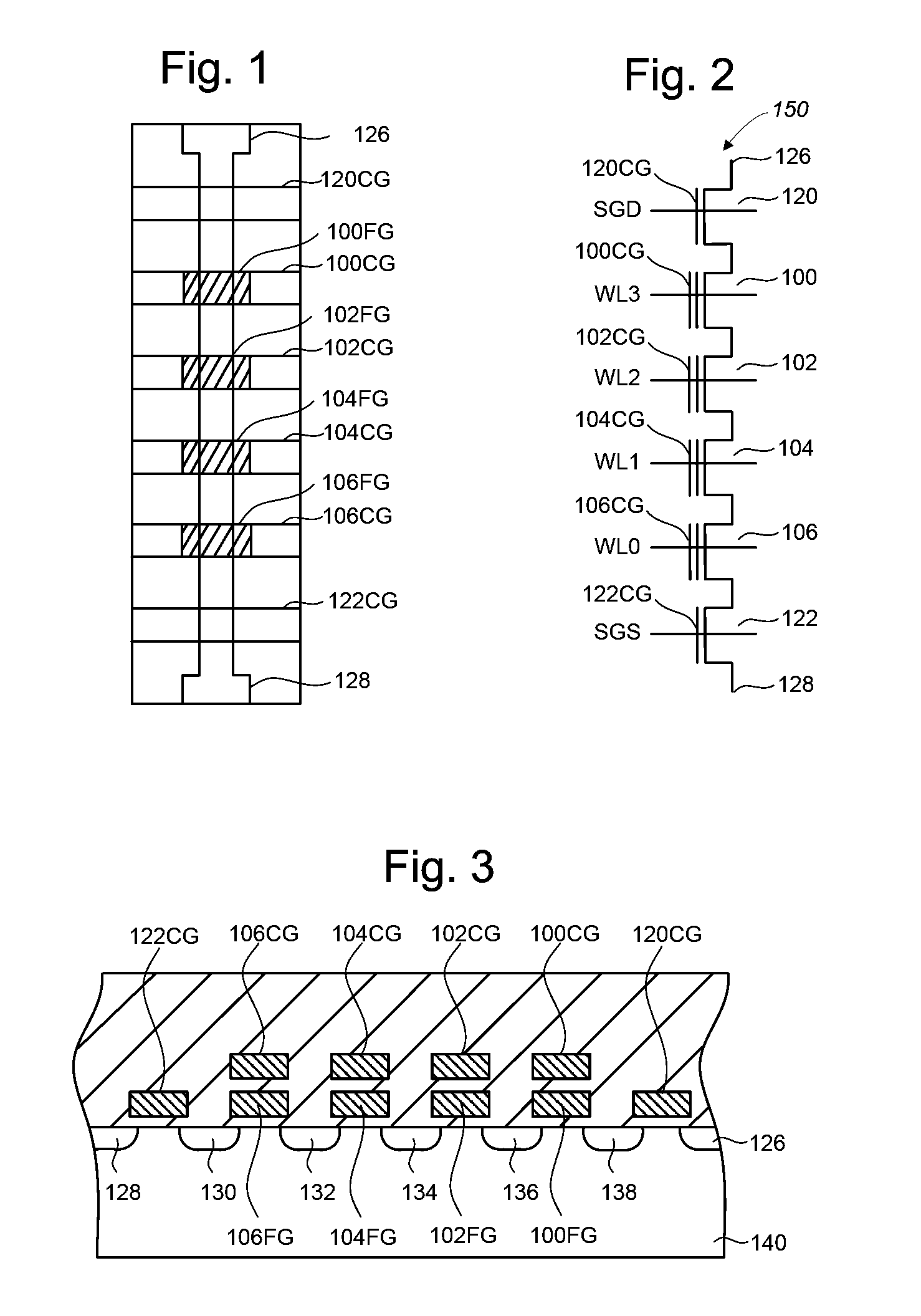

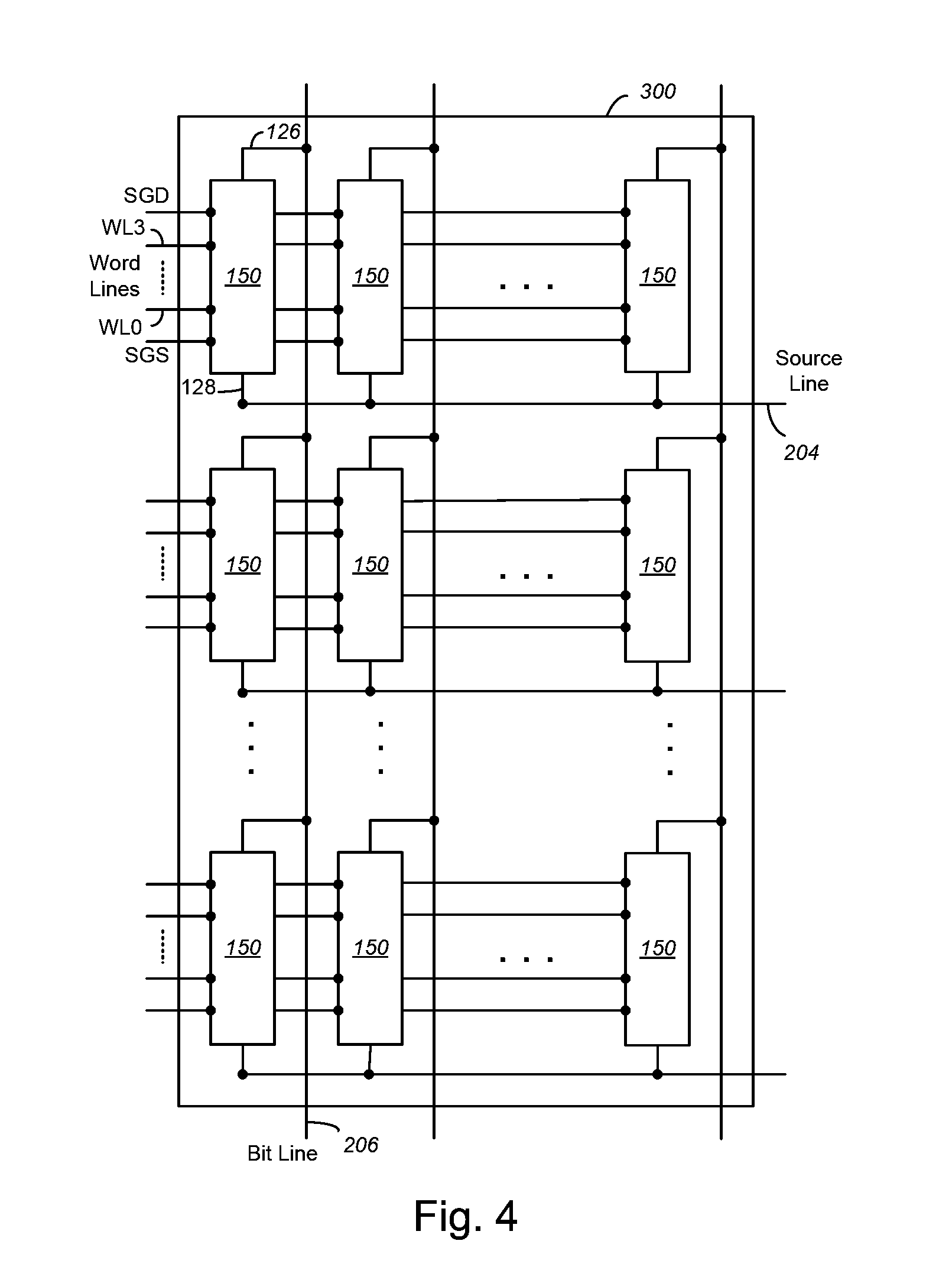

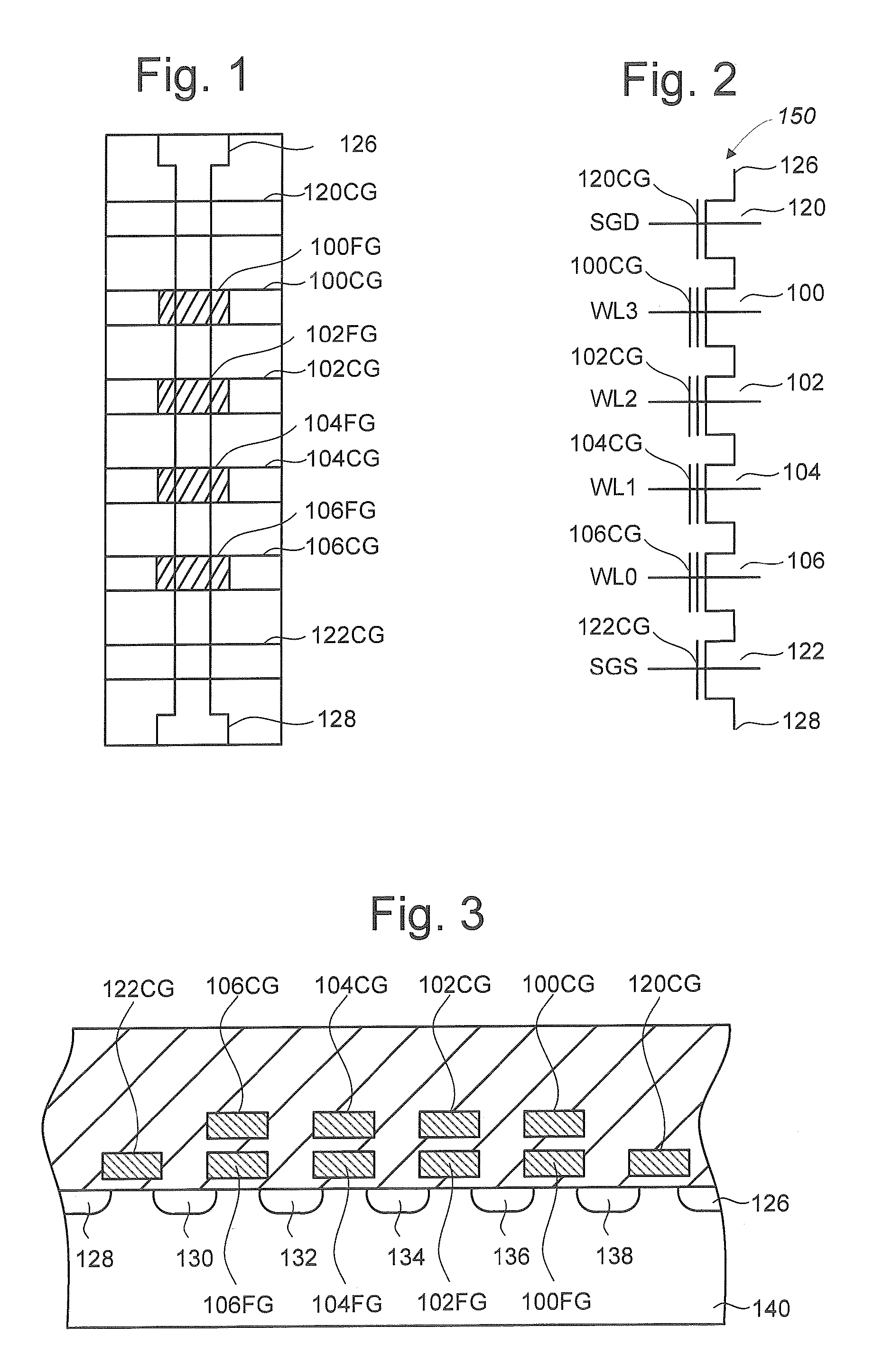

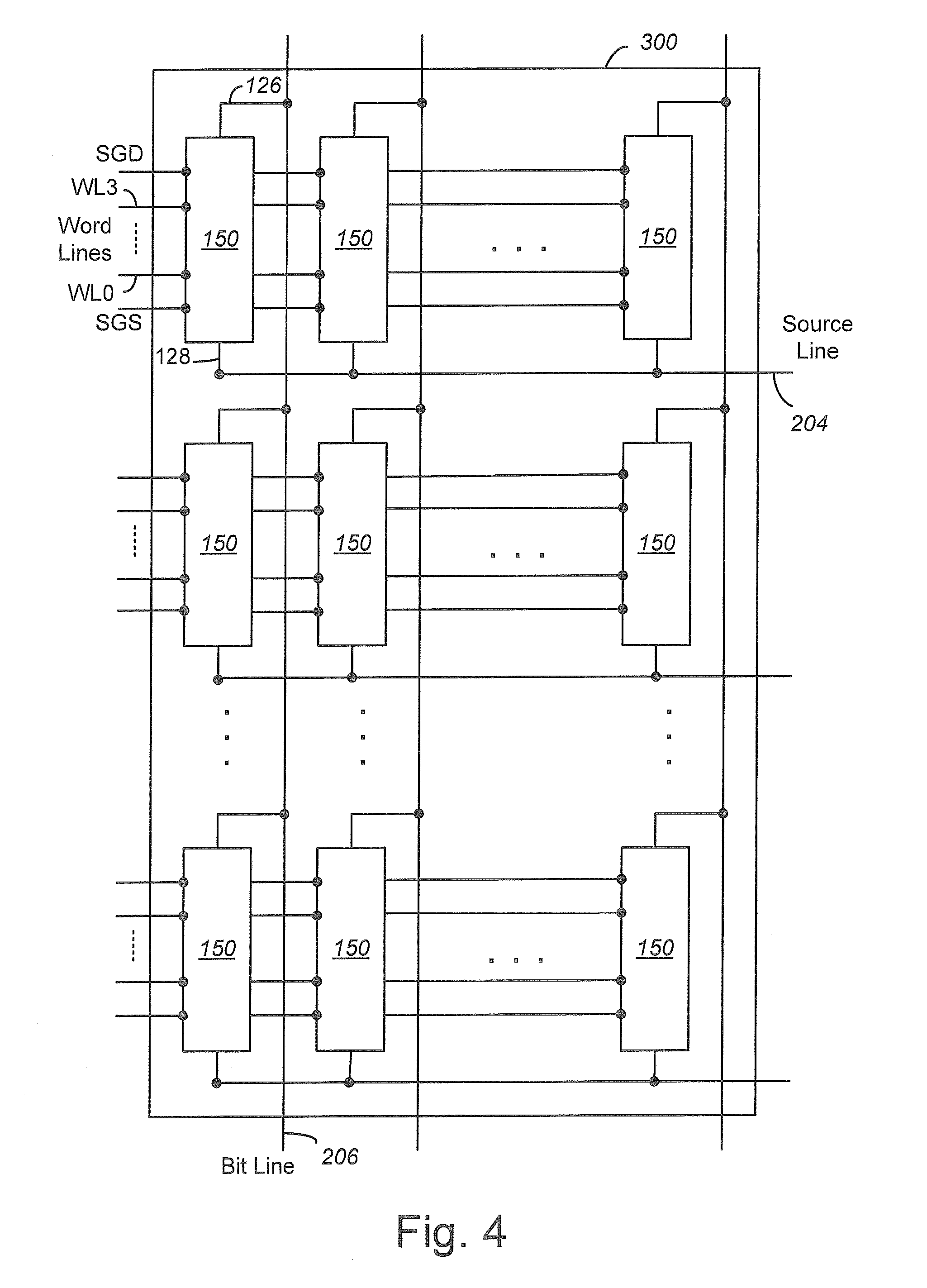

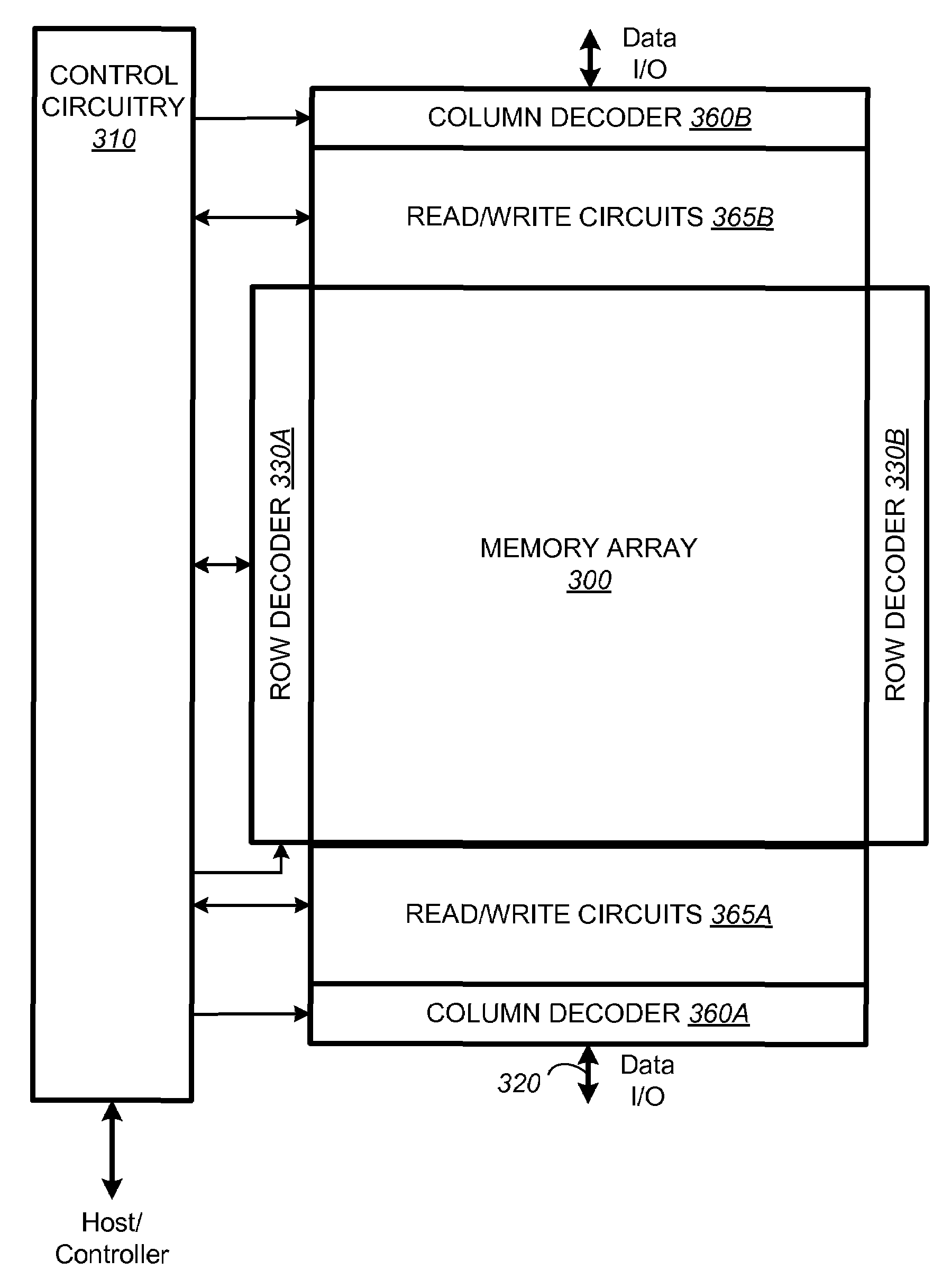

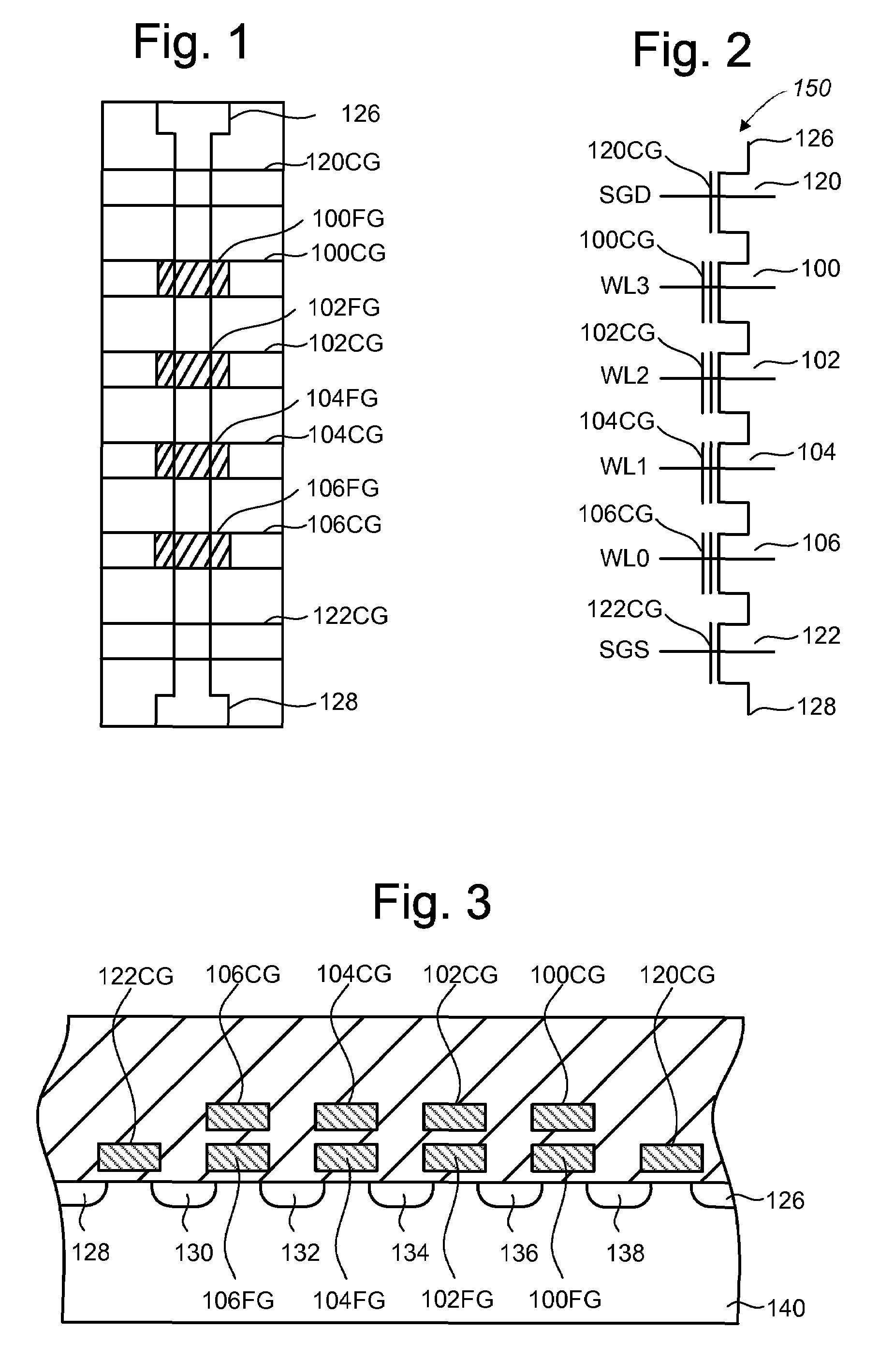

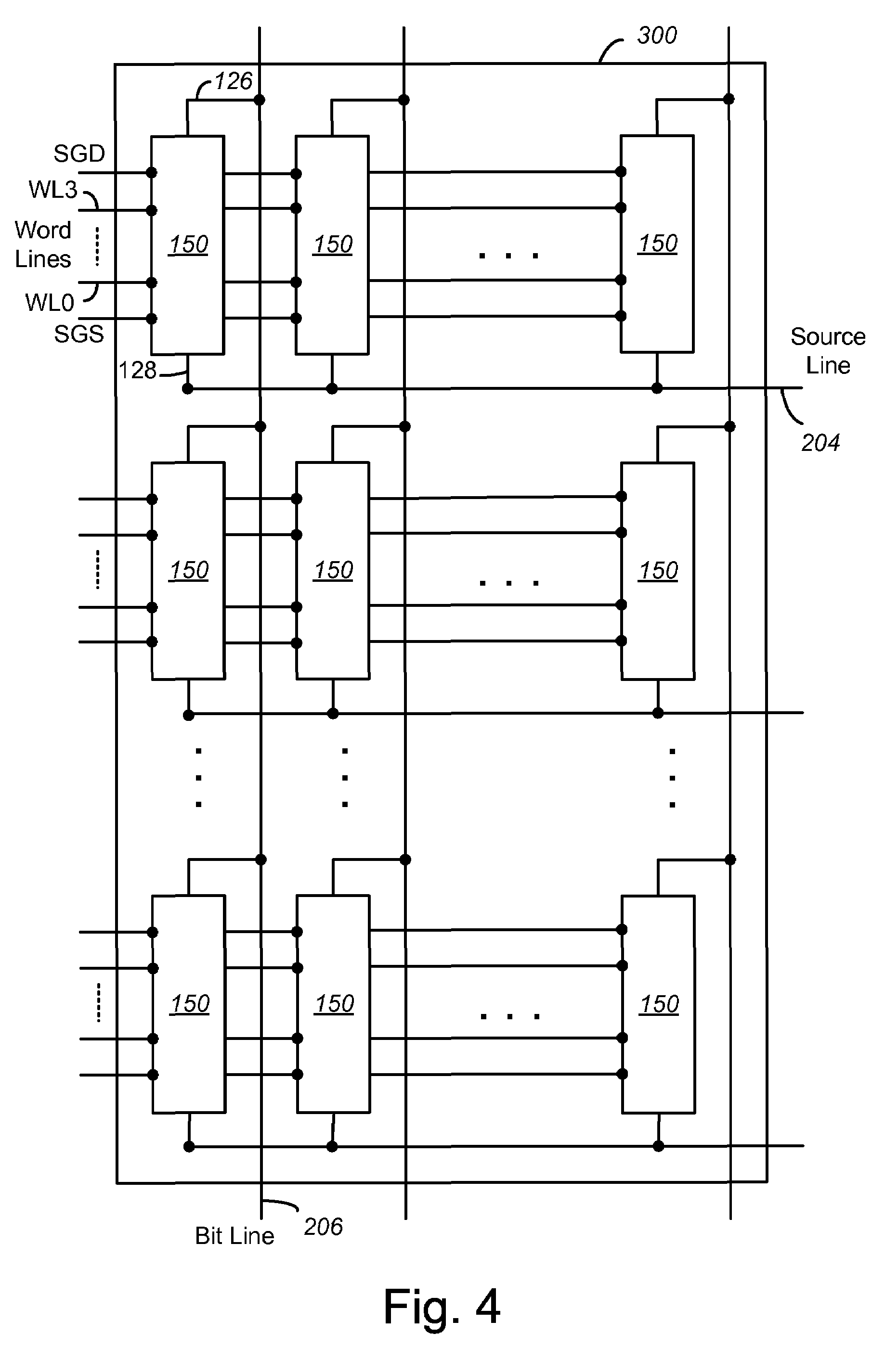

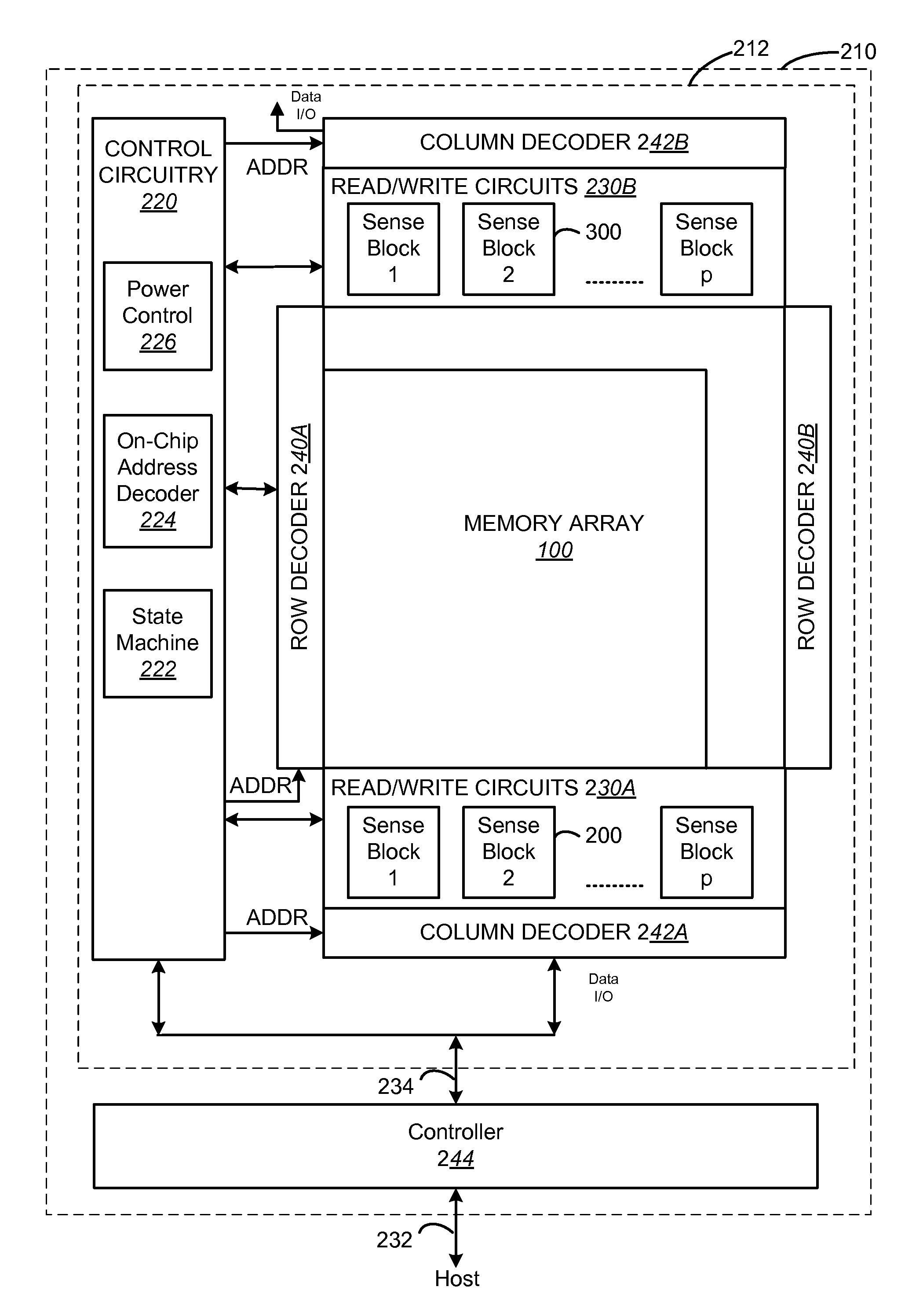

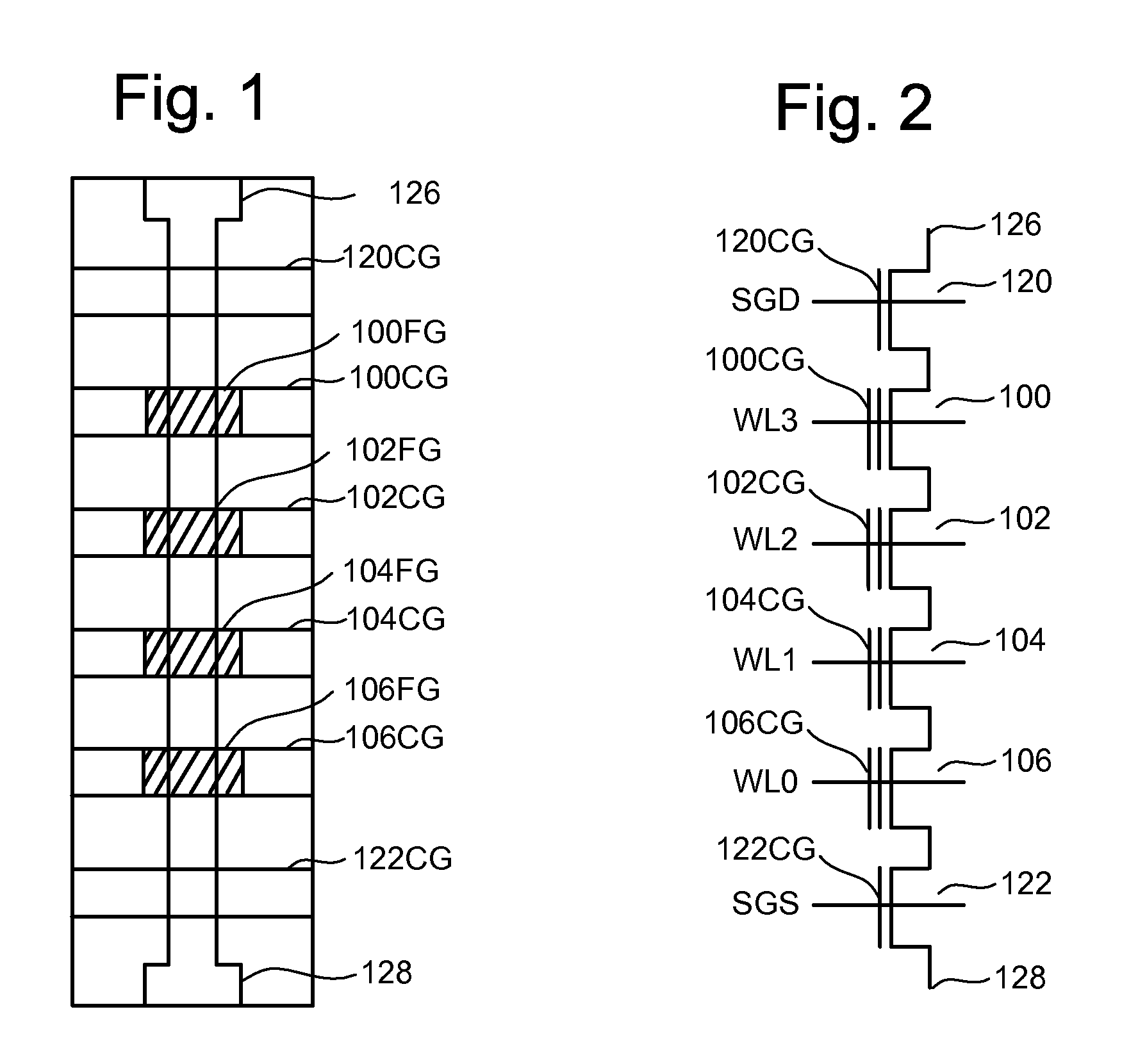

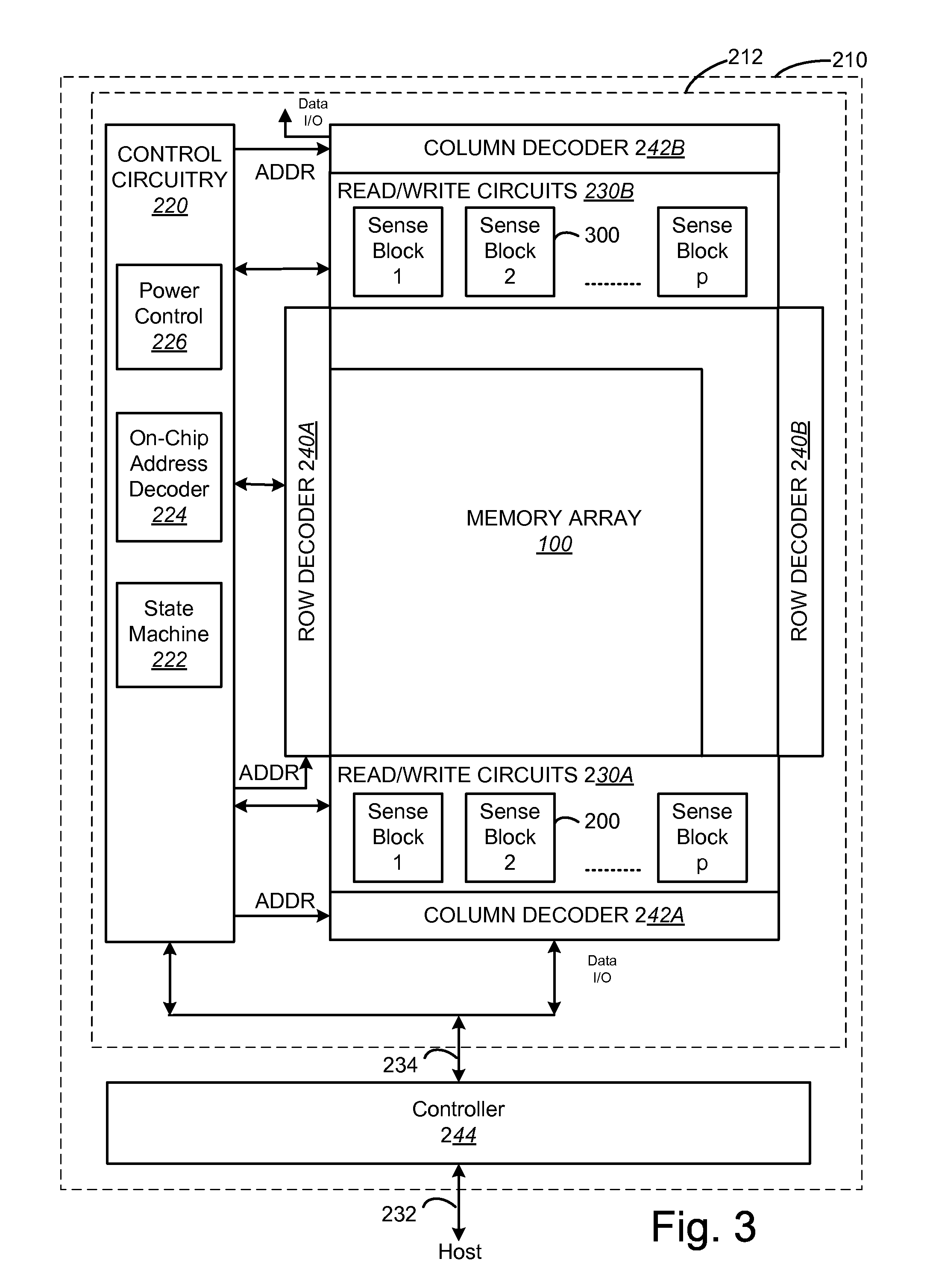

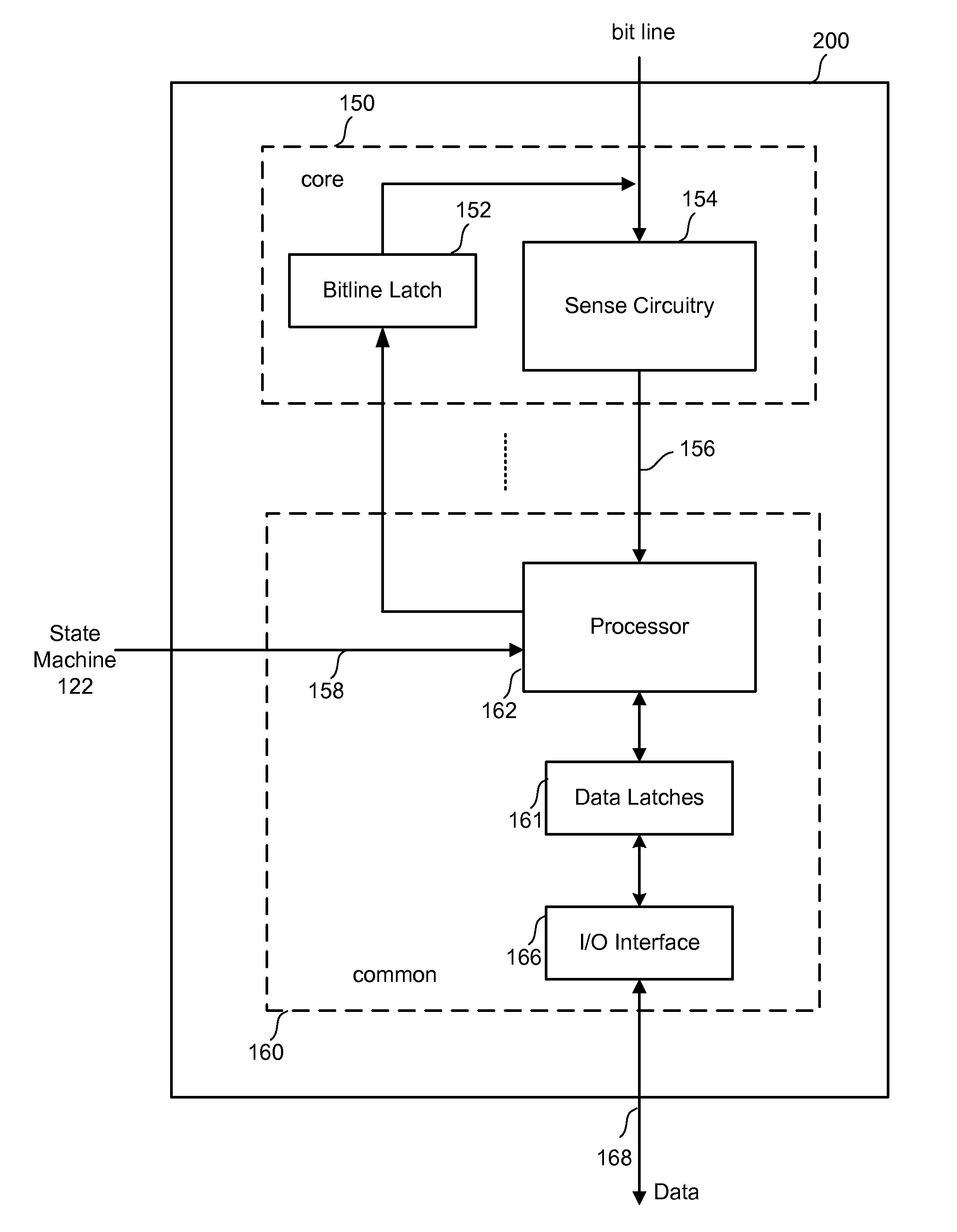

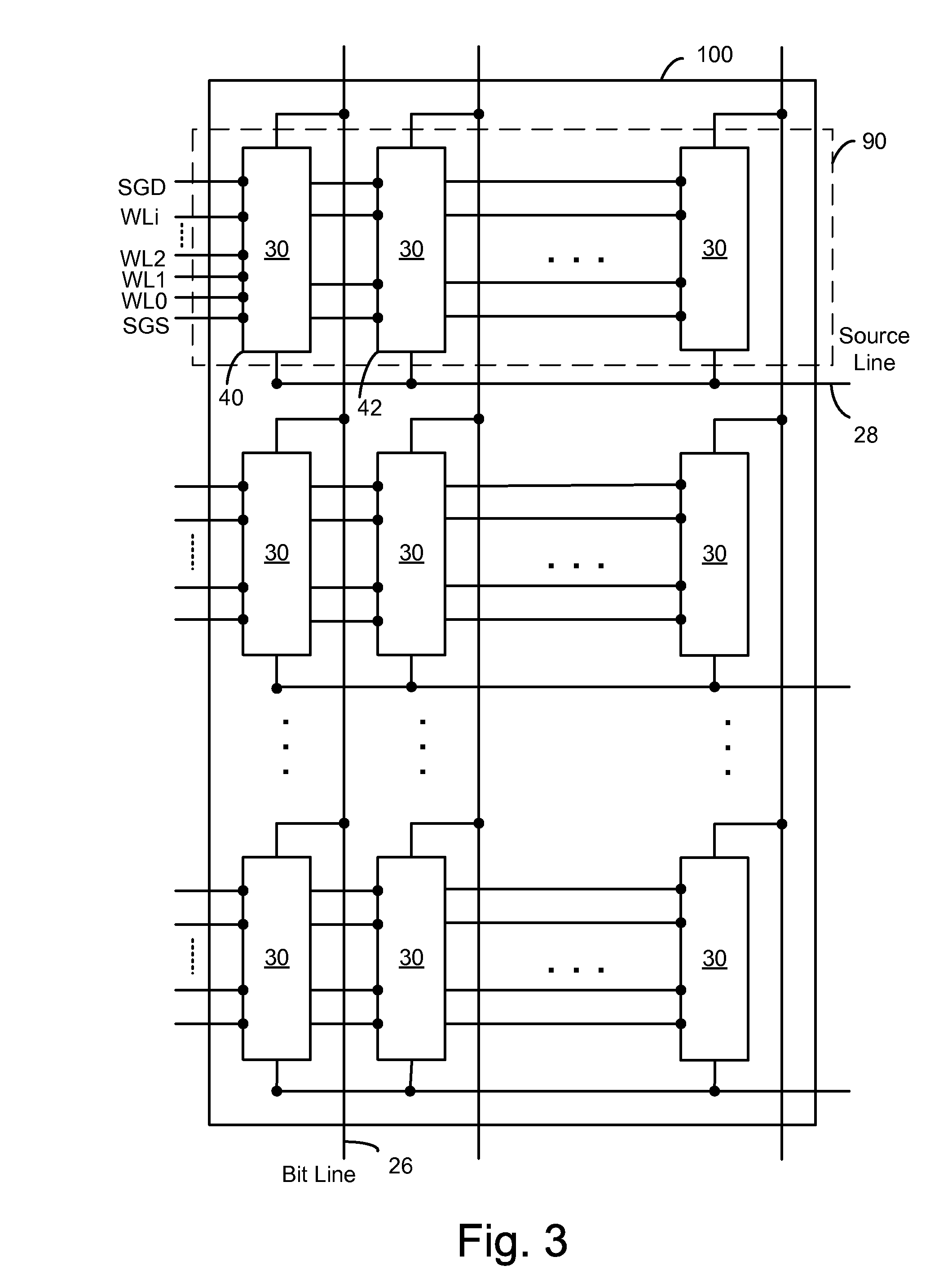

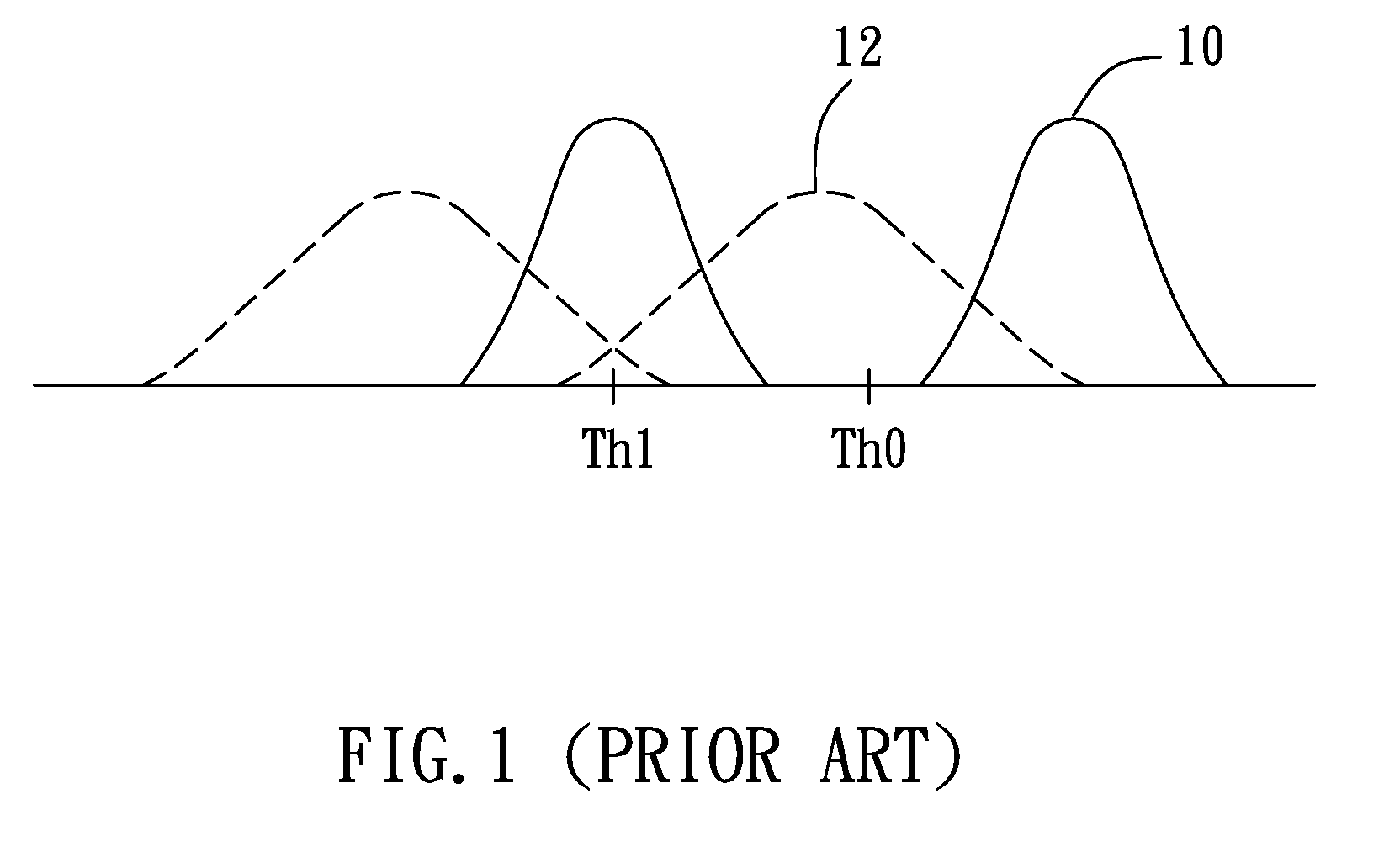

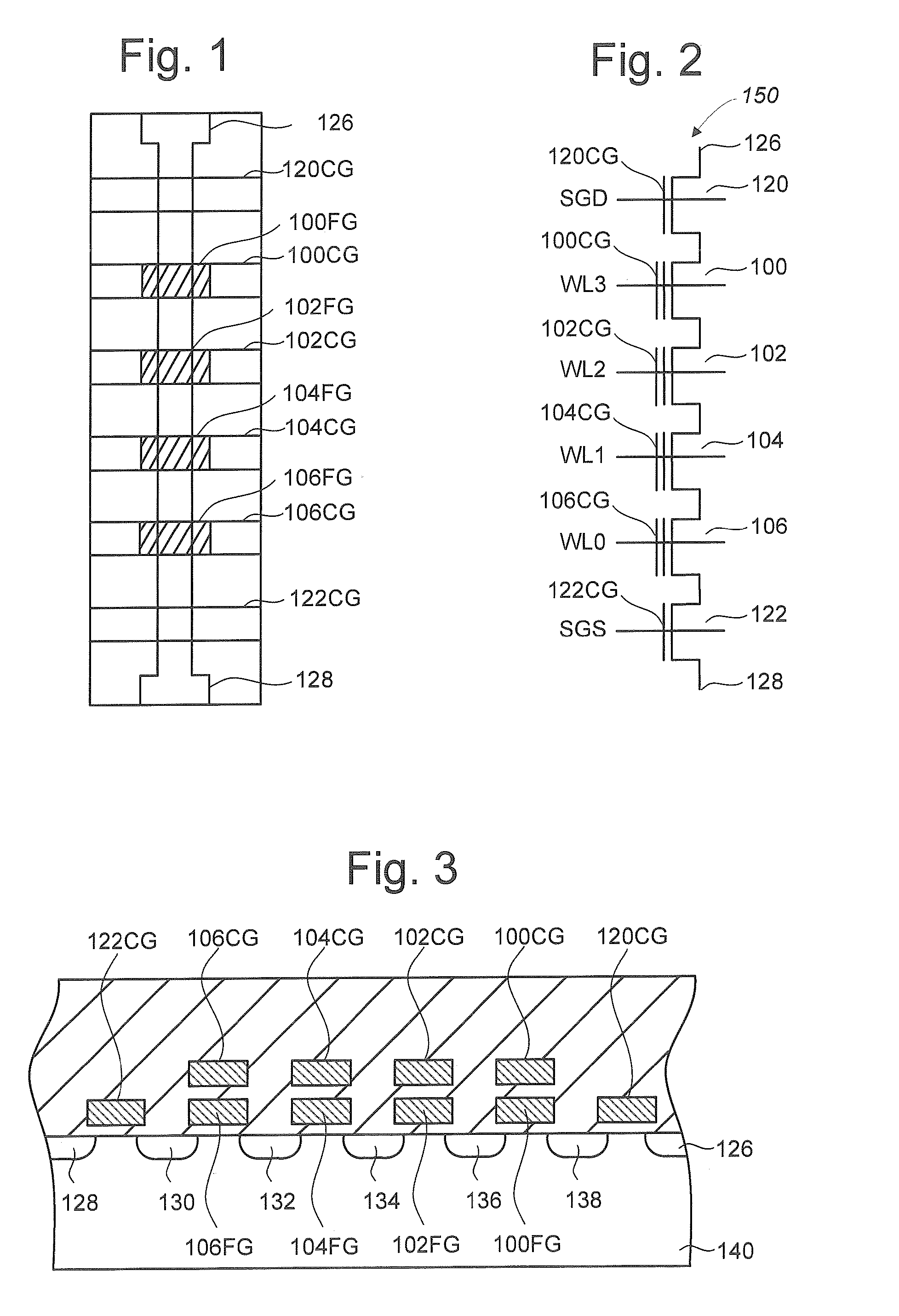

Shifts in the apparent charge stored on a floating gate (or other charge storing element) of a non-volatile memory cell can occur because of the coupling of an electric field based on the charge stored in adjacent floating gates (or other adjacent charge storing elements). To compensate for this coupling, the read or programming process for a given memory cell can take into account the programmed state of an adjacent memory cell. To determine whether compensation is needed, a process can be performed that includes sensing information about the programmed state of an adjacent memory cell (e.g., on an adjacent bit line or other location).

Owner:SANDISK TECH LLC

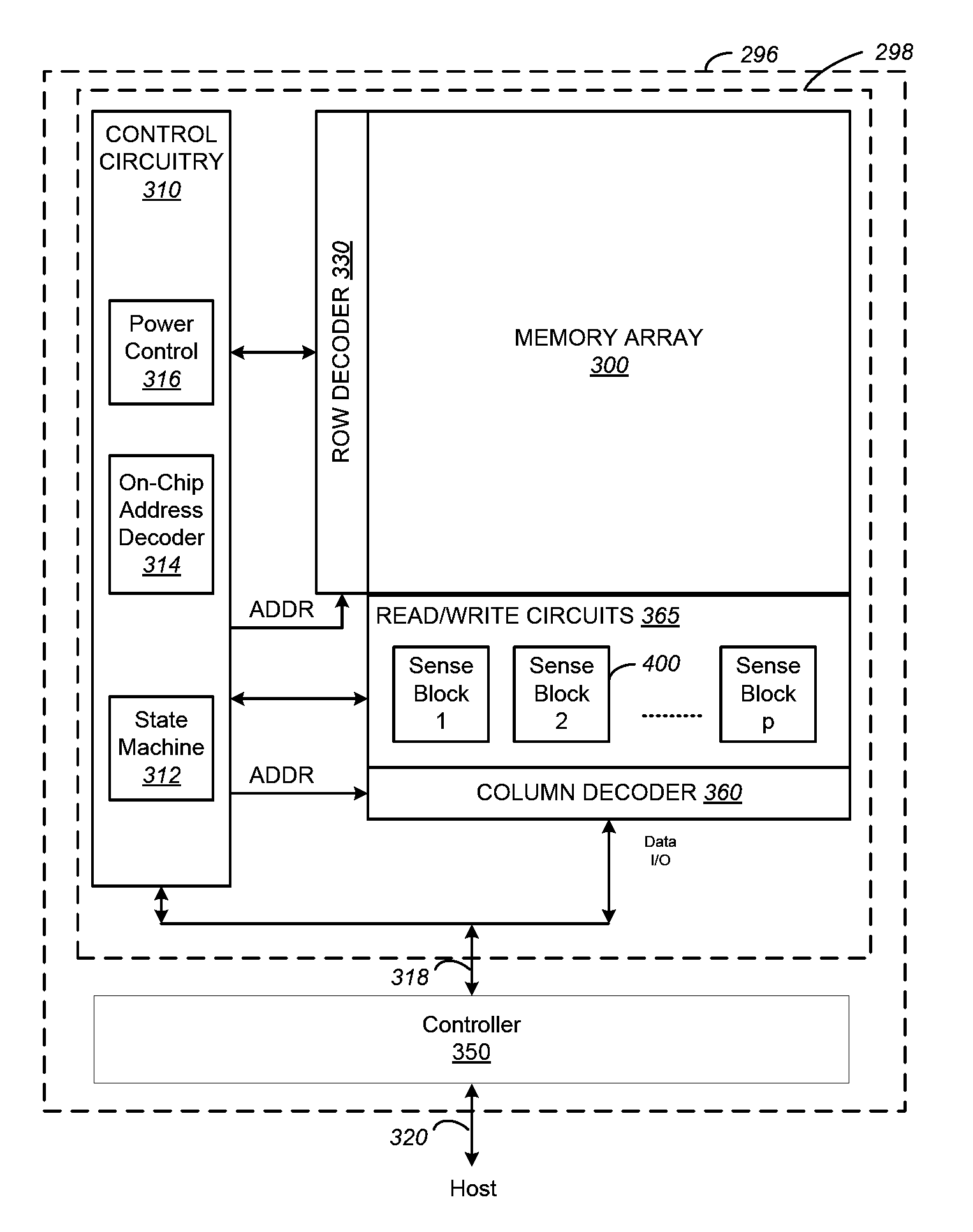

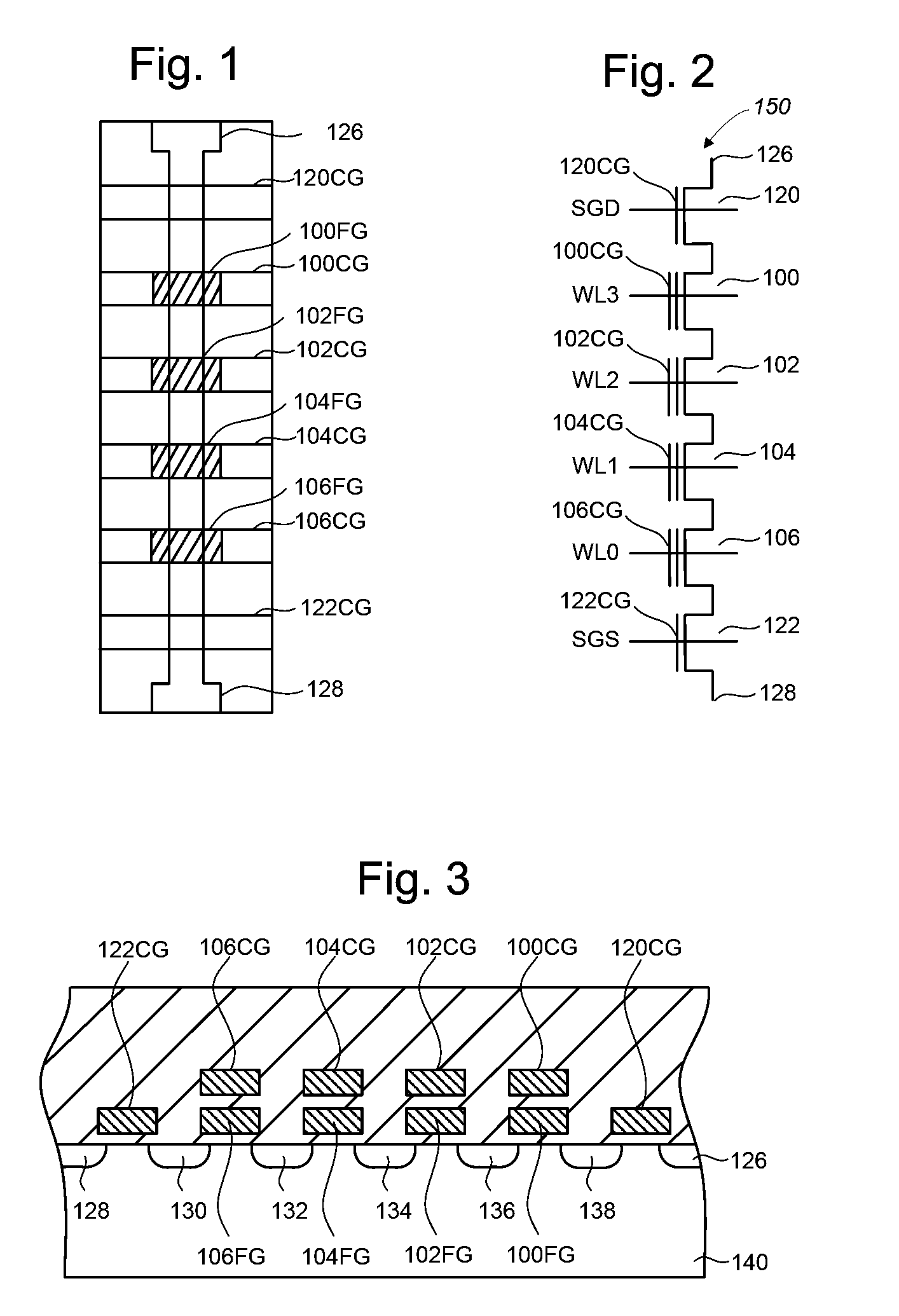

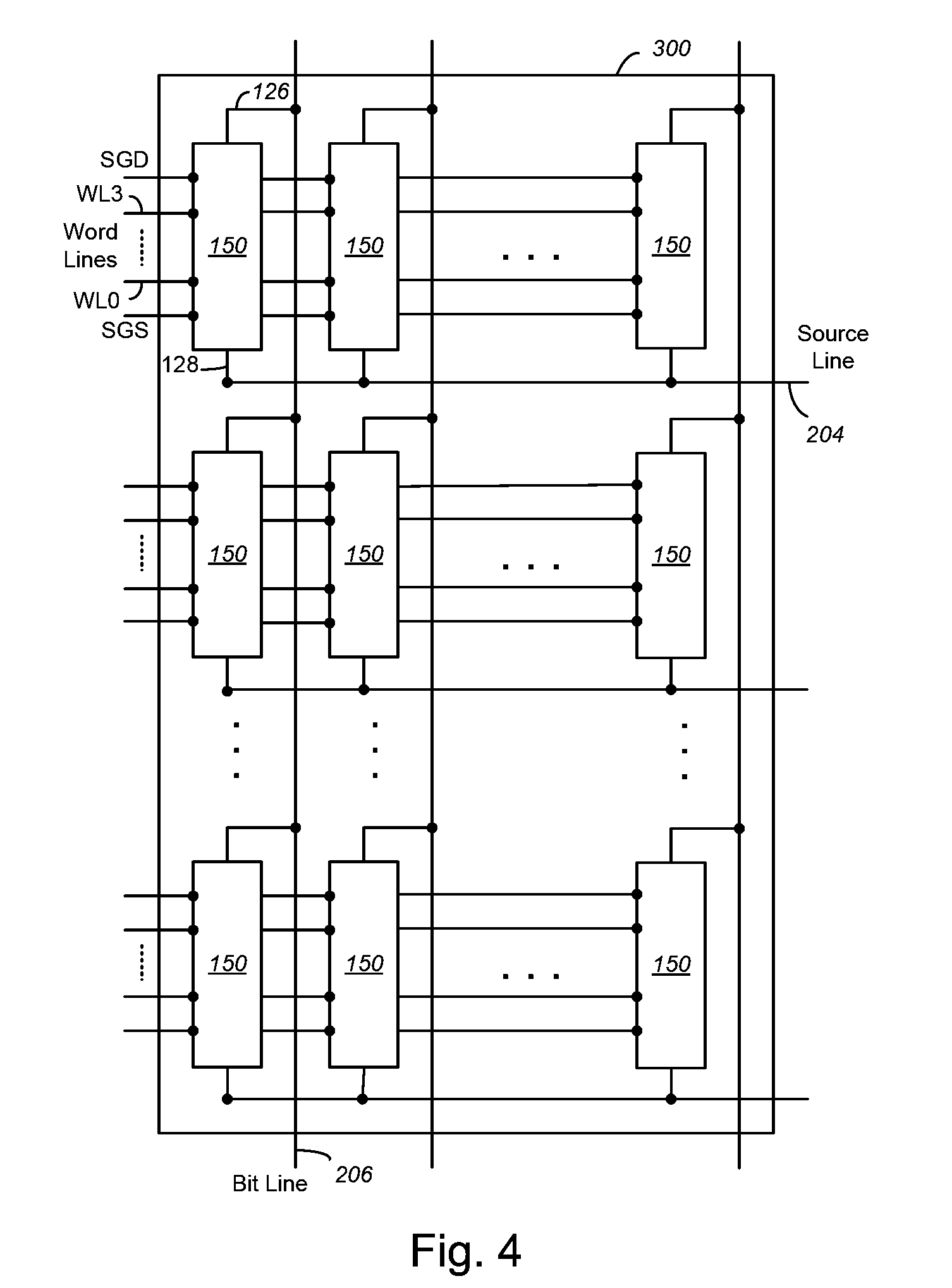

System for performing read operation on non-volatile storage with compensation for coupling

ActiveUS20070206426A1Reduce coupling effectSolid-state devicesRead-only memoriesComputer scienceElectric field

Shifts in the apparent charge stored on a floating gate (or other charge storing element) of a non-volatile memory cell can occur because of the coupling of an electric field based on the charge stored in adjacent floating gates (or other adjacent charge storing elements). The problem occurs most pronouncedly between sets of adjacent memory cells that have been programmed at different times. To account for this coupling, the read process for a particular memory cell will provide compensation to an adjacent memory cell in order to reduce the coupling effect that the adjacent memory cell has on the particular memory cell.

Owner:SANDISK TECH LLC

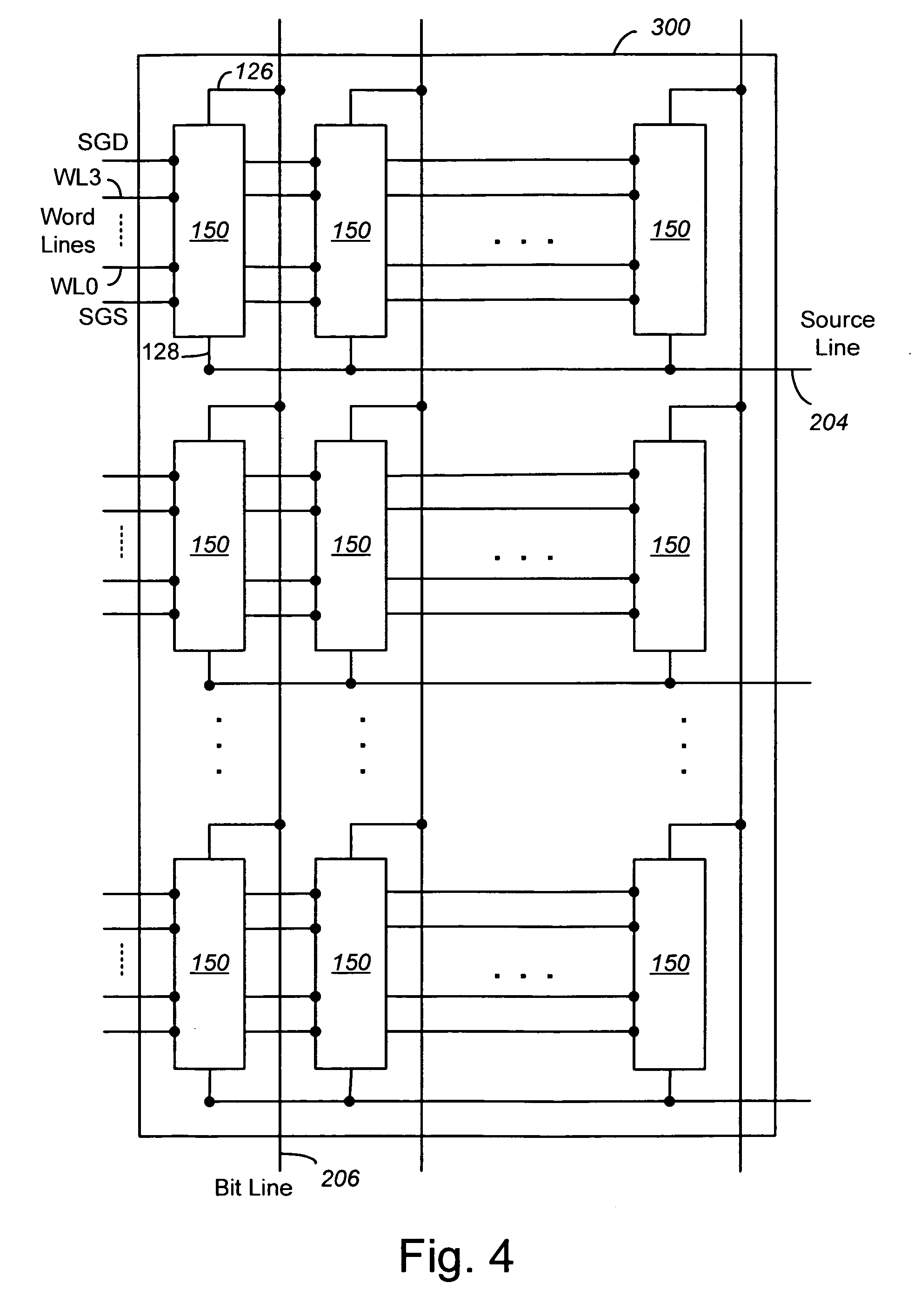

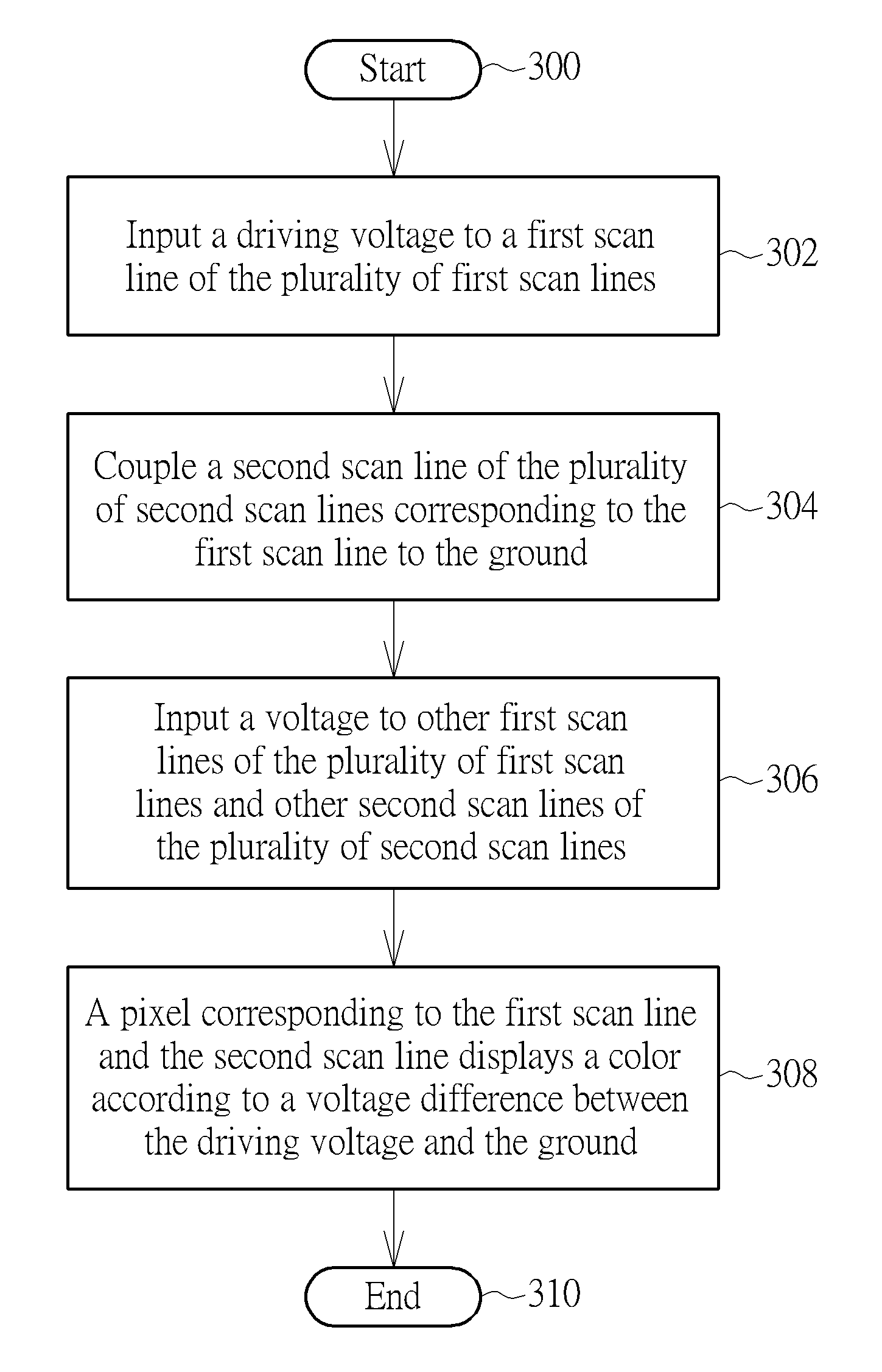

Electrophoretic display capable of reducing passive matrix coupling effect and method thereof

Owner:YUANHAN MATERIALS INC

System for performing data pattern sensitivity compensation using different voltage

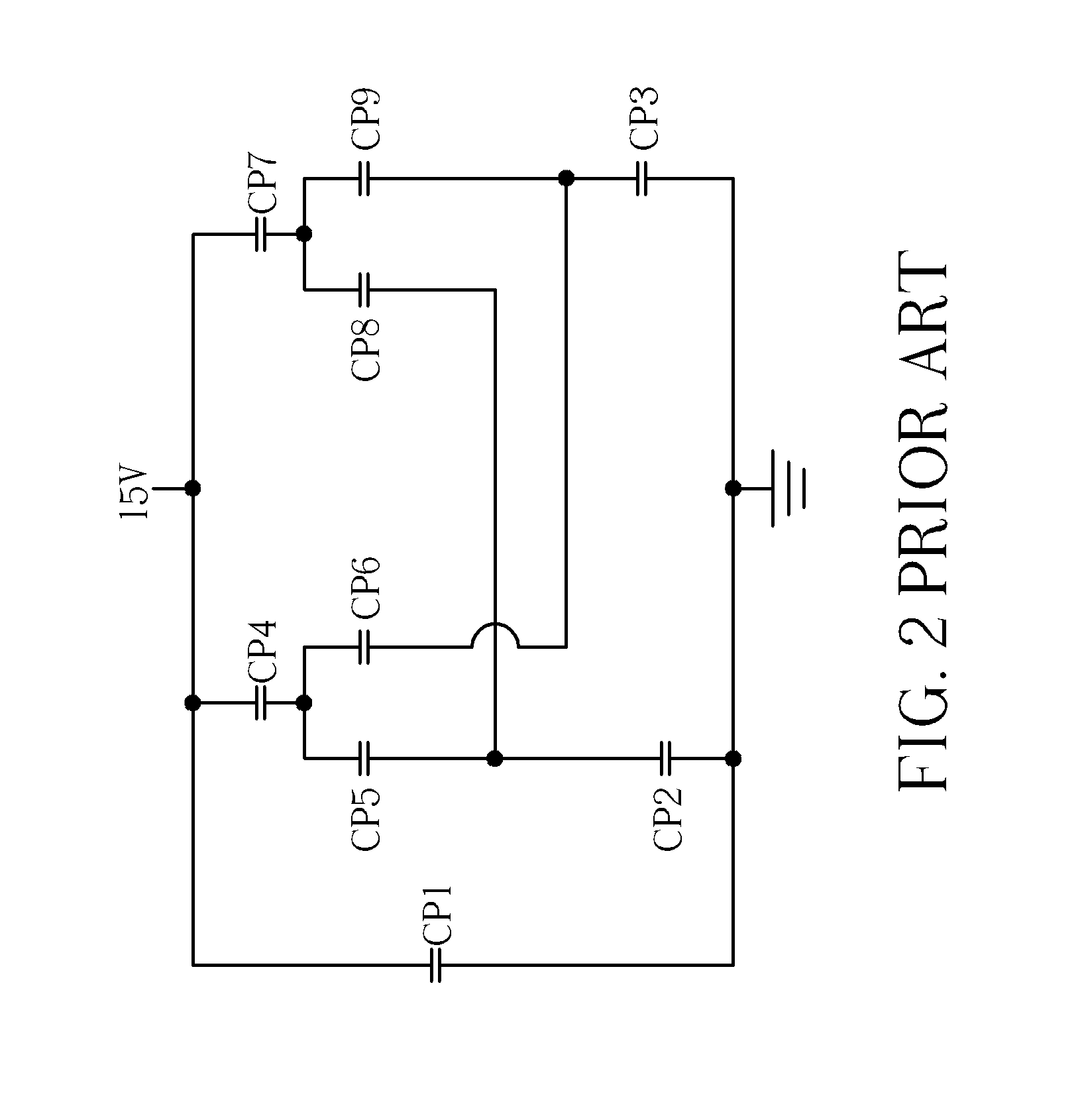

ActiveUS7310272B1Reduce coupling effectExact searchRead-only memoriesDigital storageCapacitanceCapacitive coupling

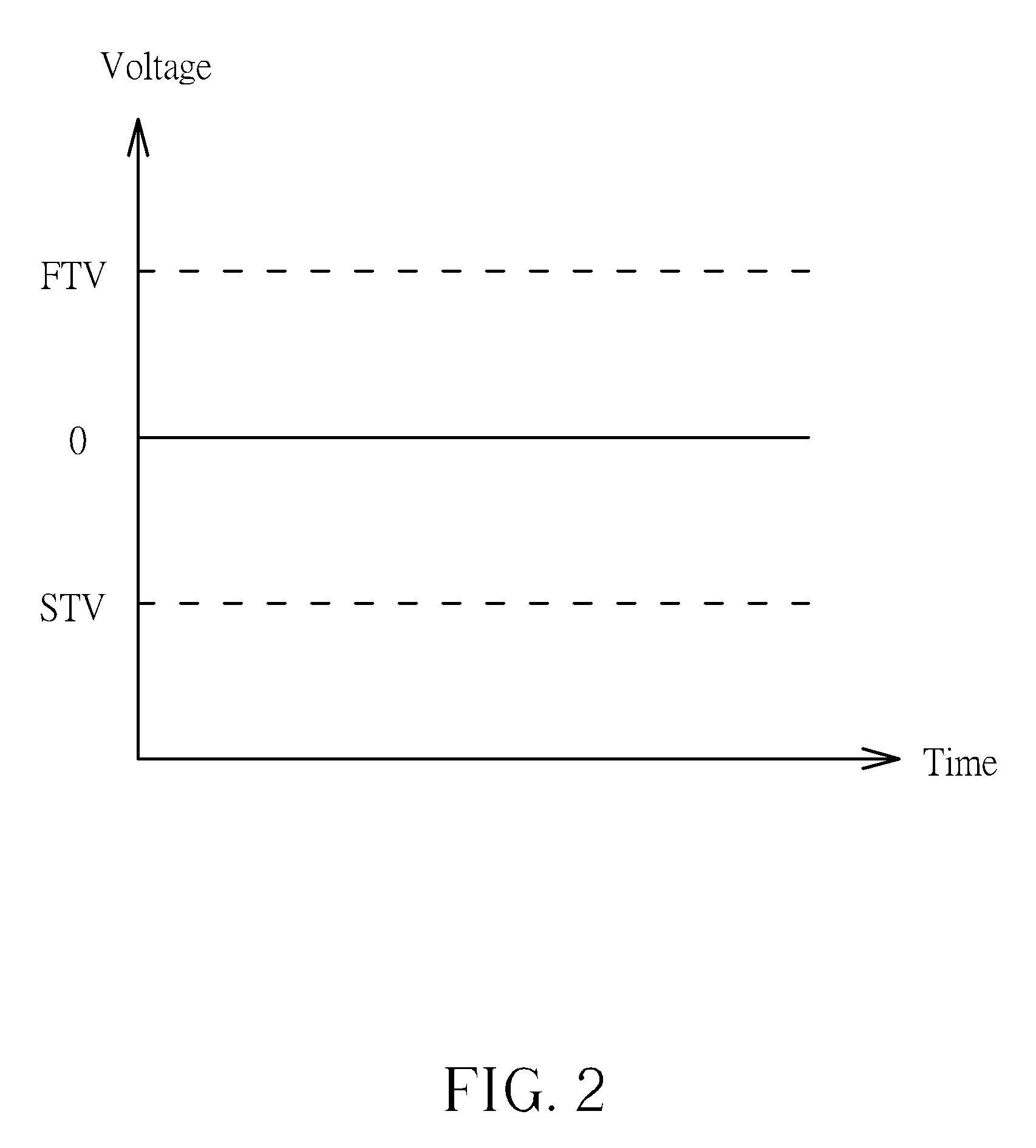

Errors can occur when reading the threshold voltage of a programmed non-volatile storage element due to at least two mechanisms: (1) capacitive coupling between neighboring floating gates and (2) changing conductivity of the channel area after programming (referred to as back pattern effect). To account for coupling between neighboring floating gates, the read process for a particular memory cell will provide compensation to an adjacent memory cell in order to reduce the coupling effect that the adjacent memory cell has on the particular memory cell. To account for the back pattern effect, a first voltage is used during a verify operation for unselected word lines that have been subjected to a programming operation and a second voltage is used for unselected word lines that have not been subjected to a programming operation. The combination of these two techniques provides for more accurate storage and retrieval of data.

Owner:SANDISK TECH LLC

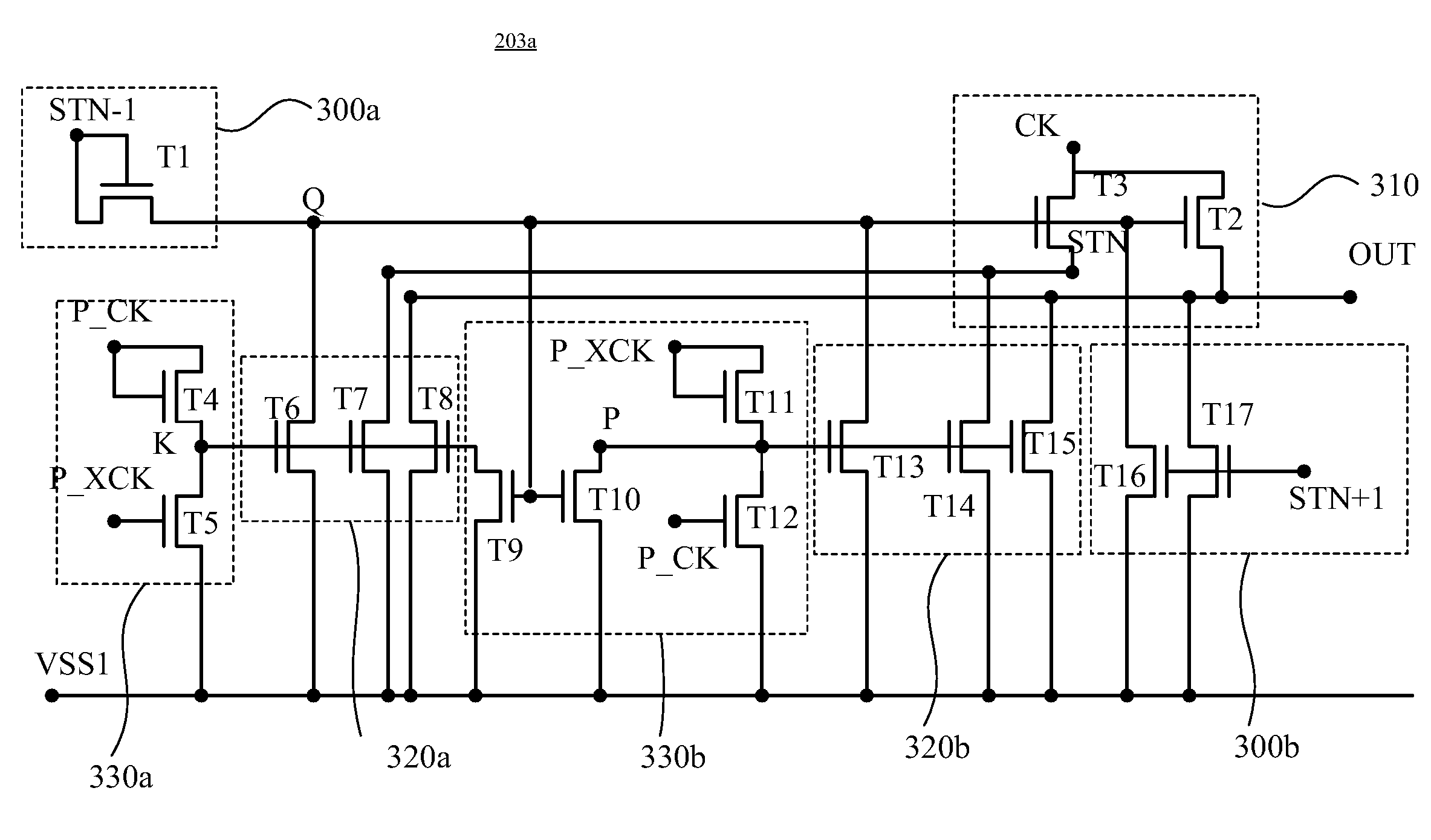

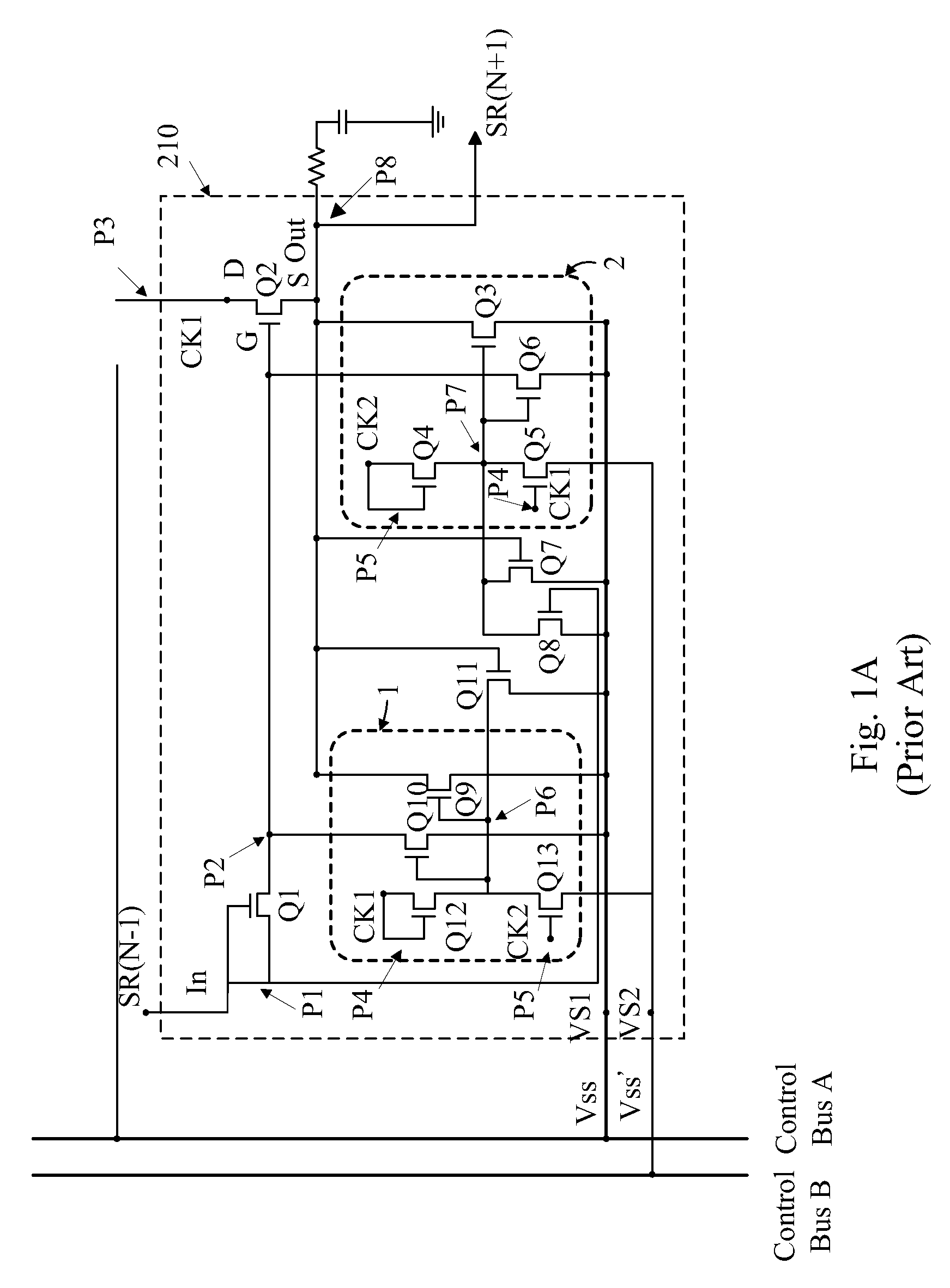

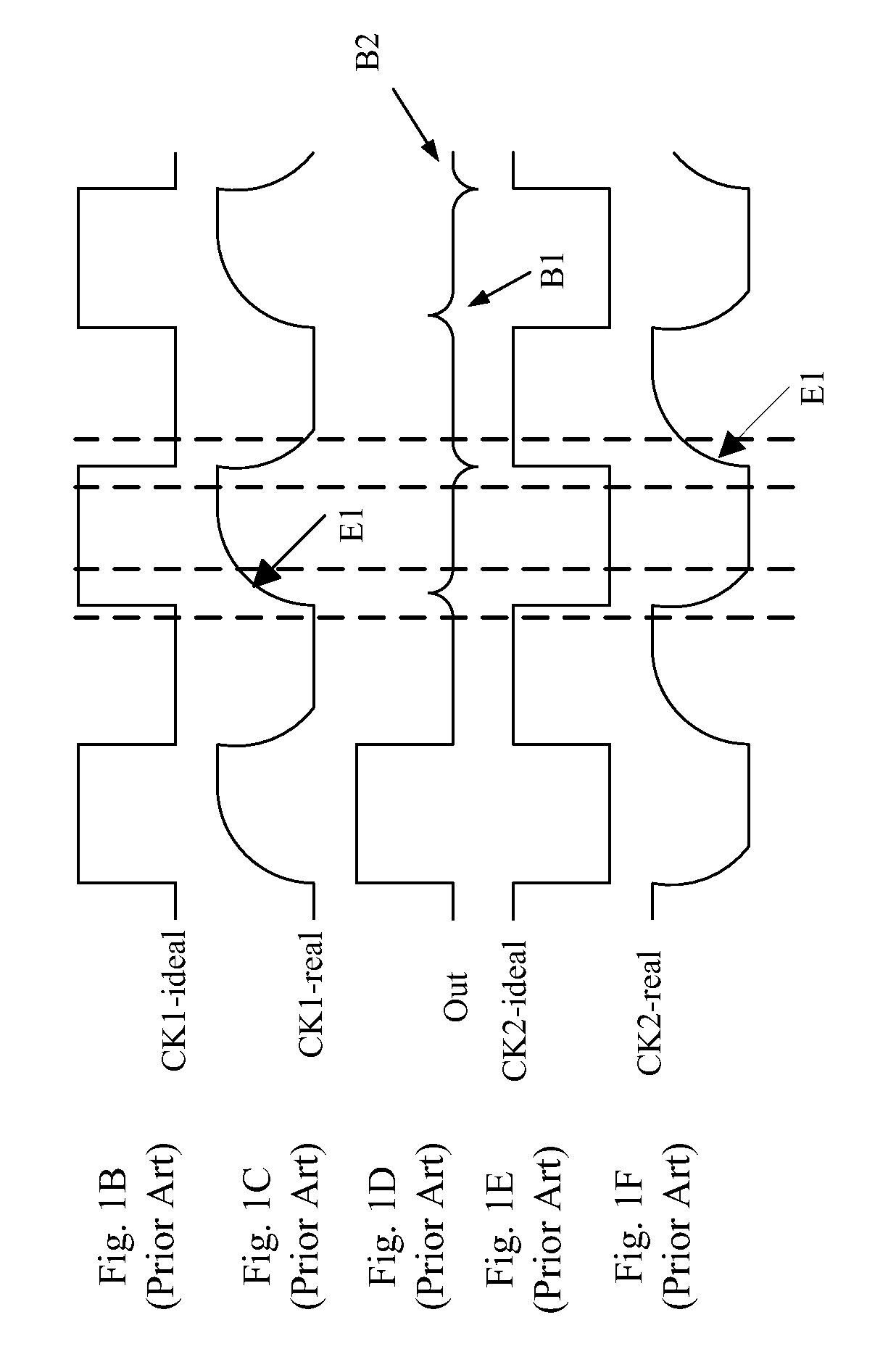

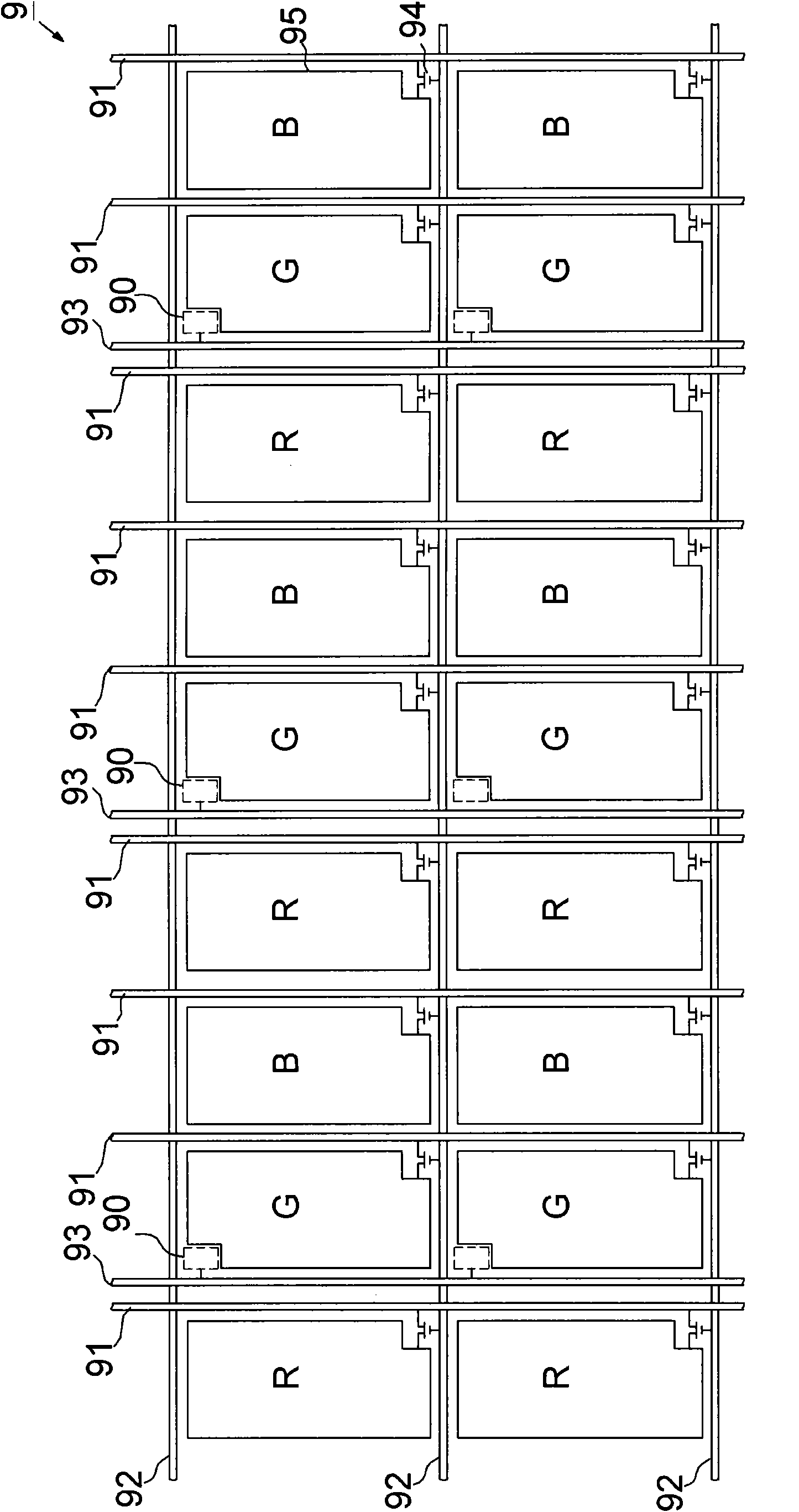

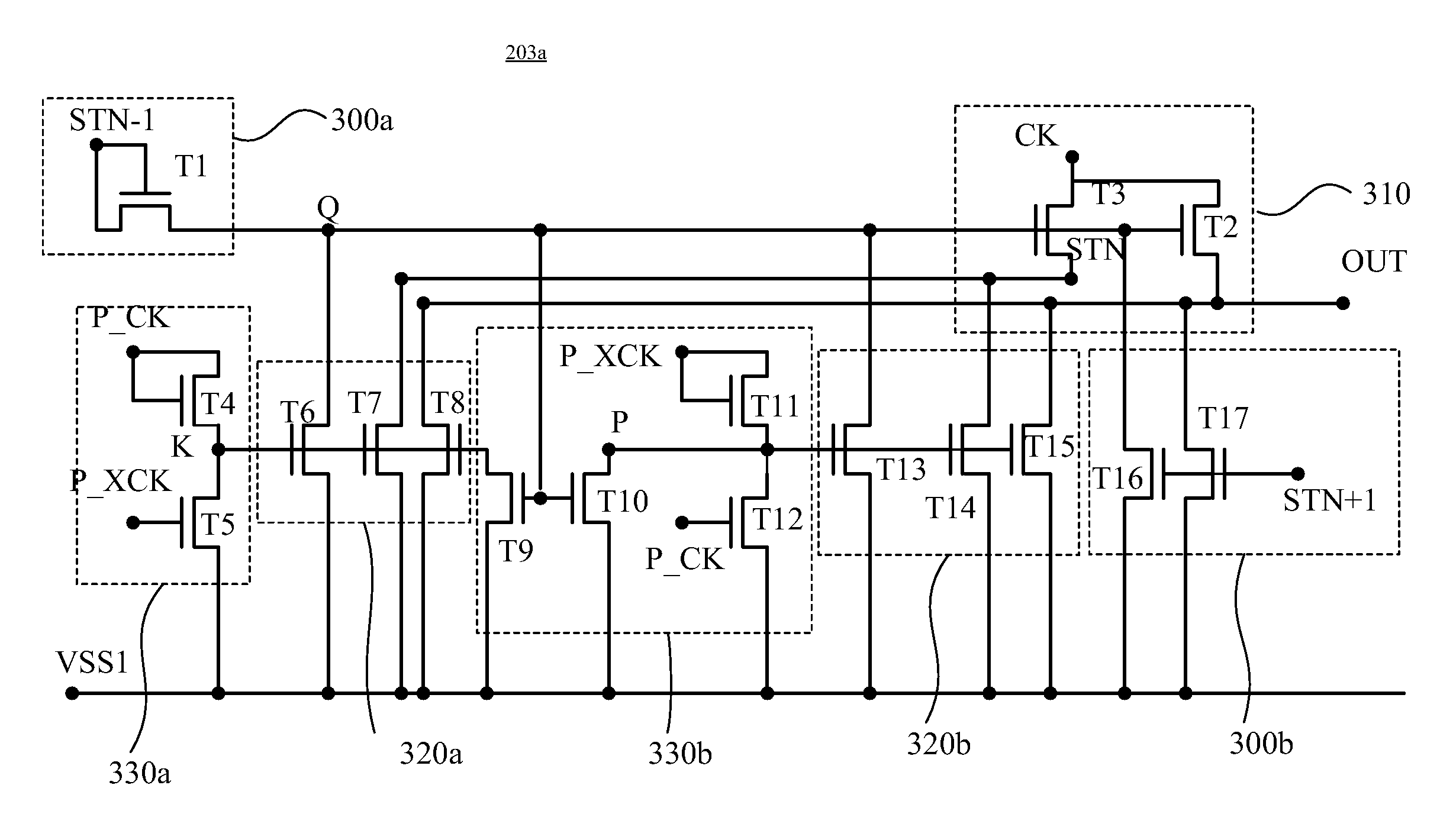

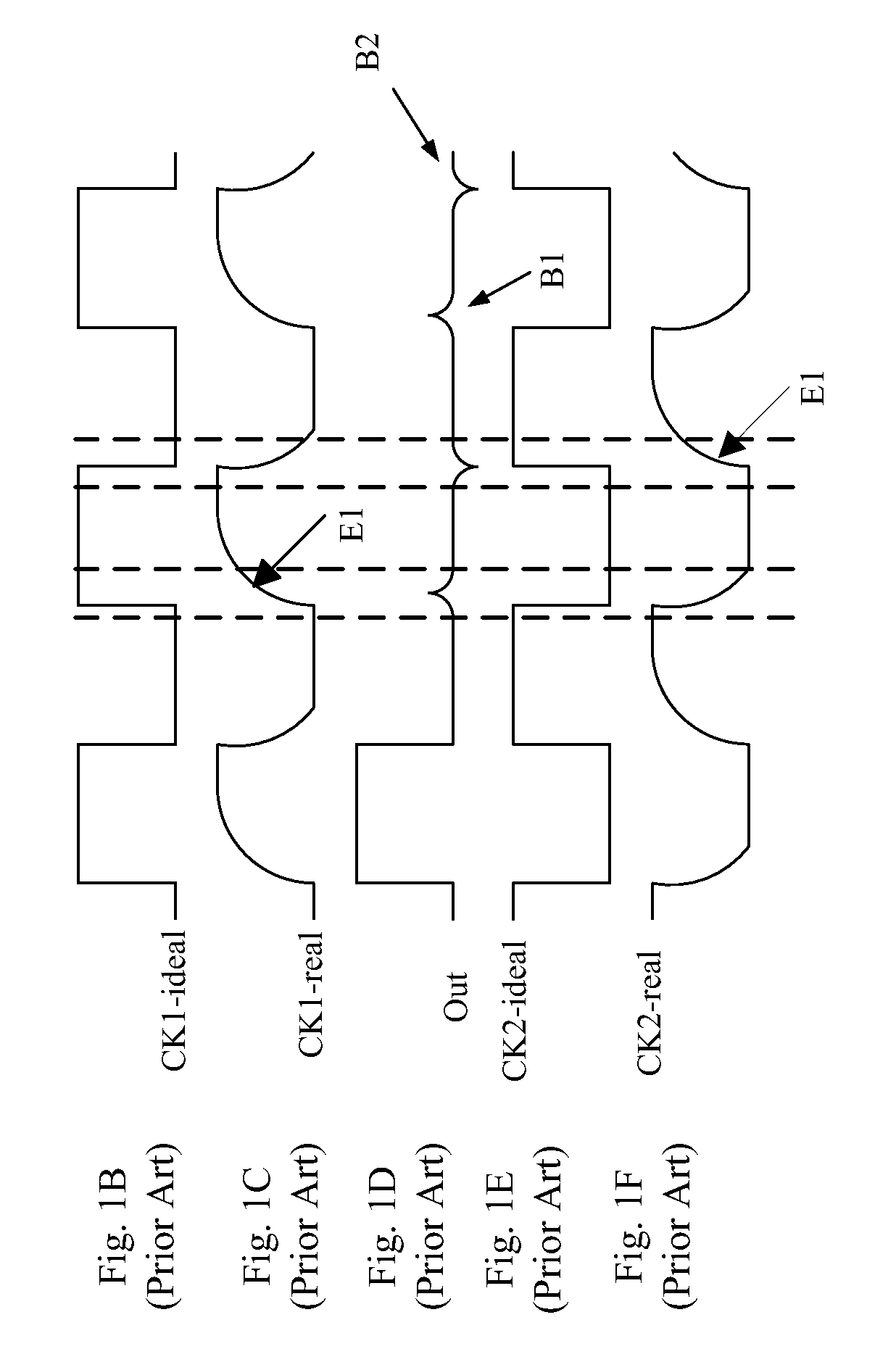

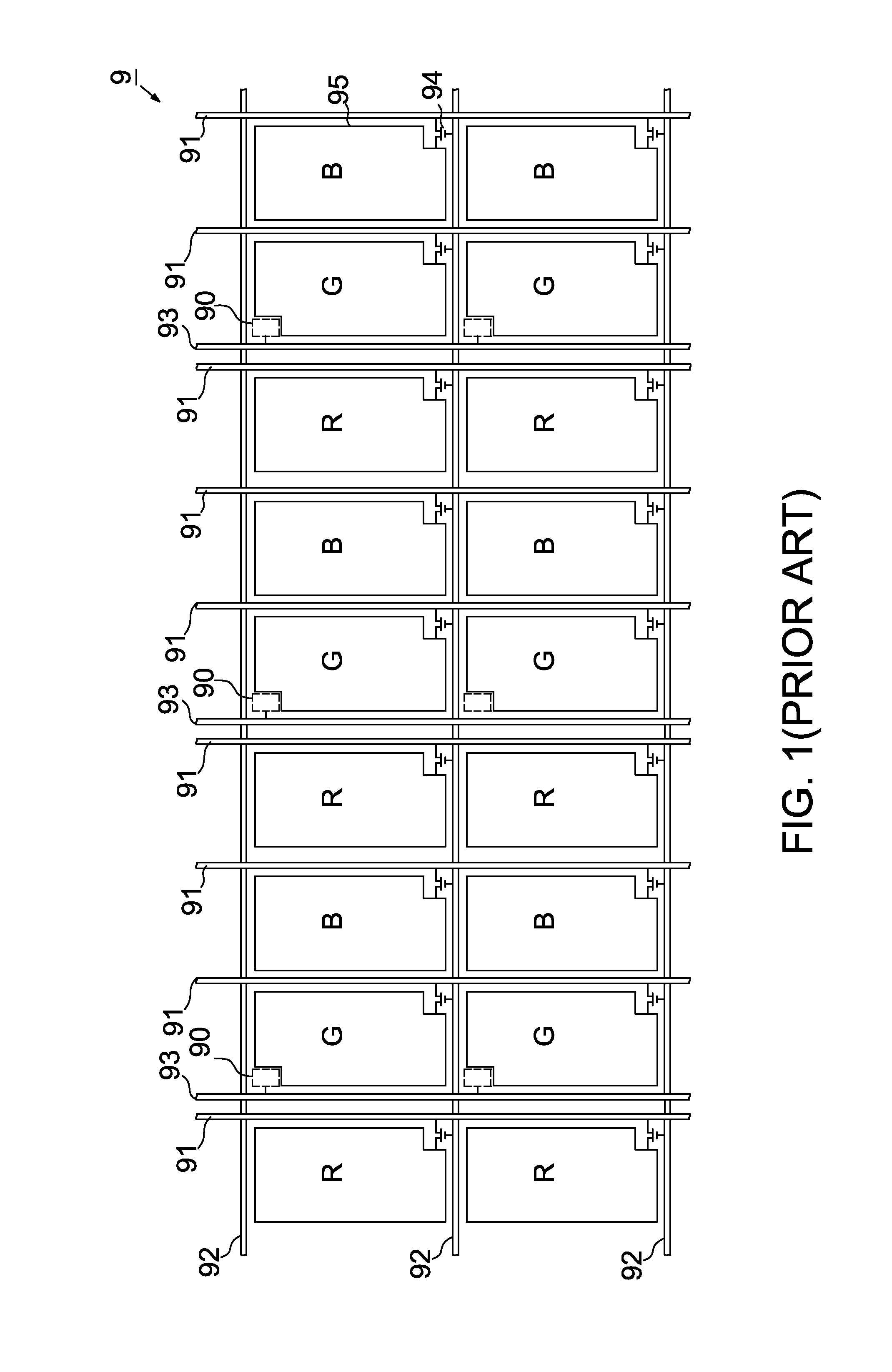

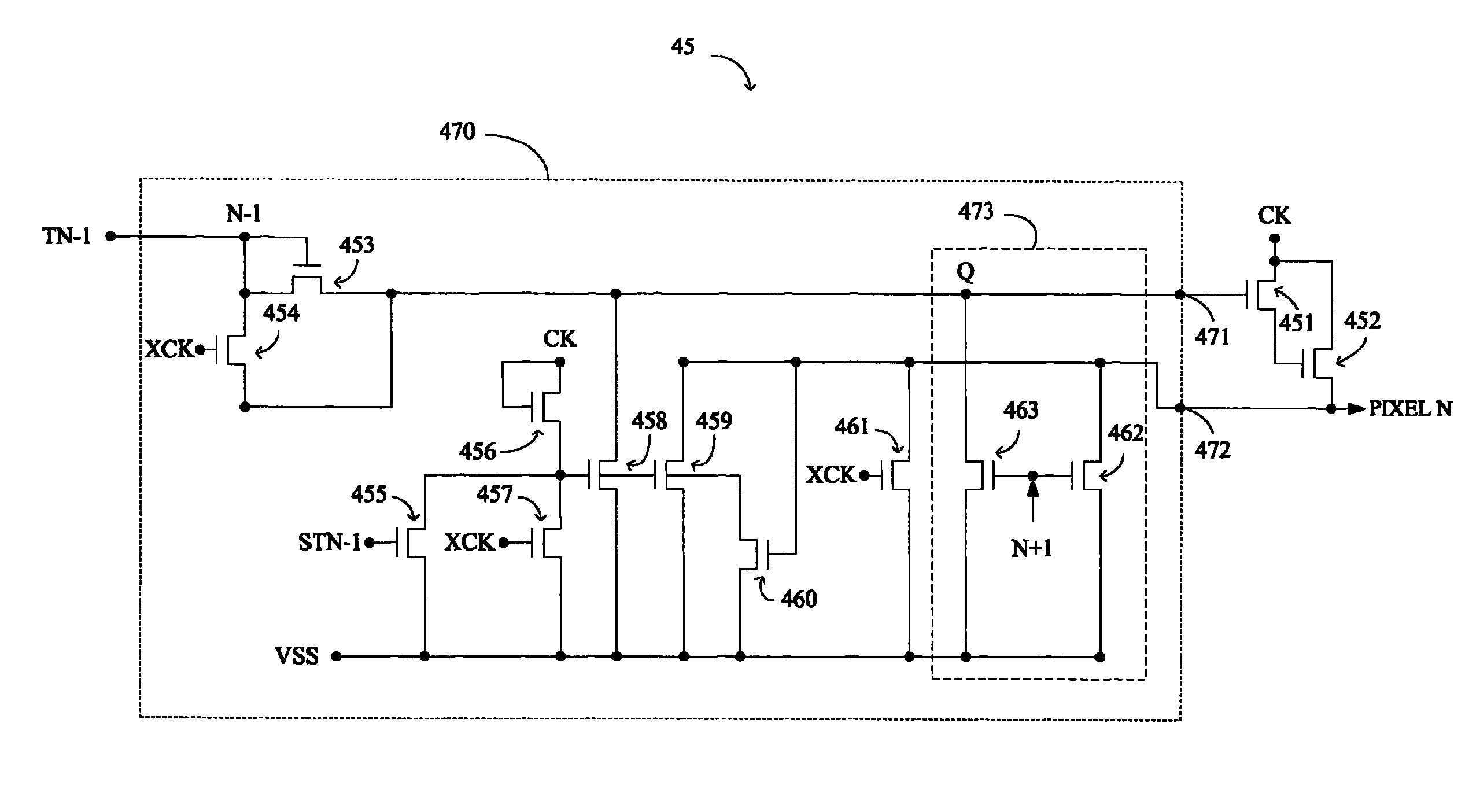

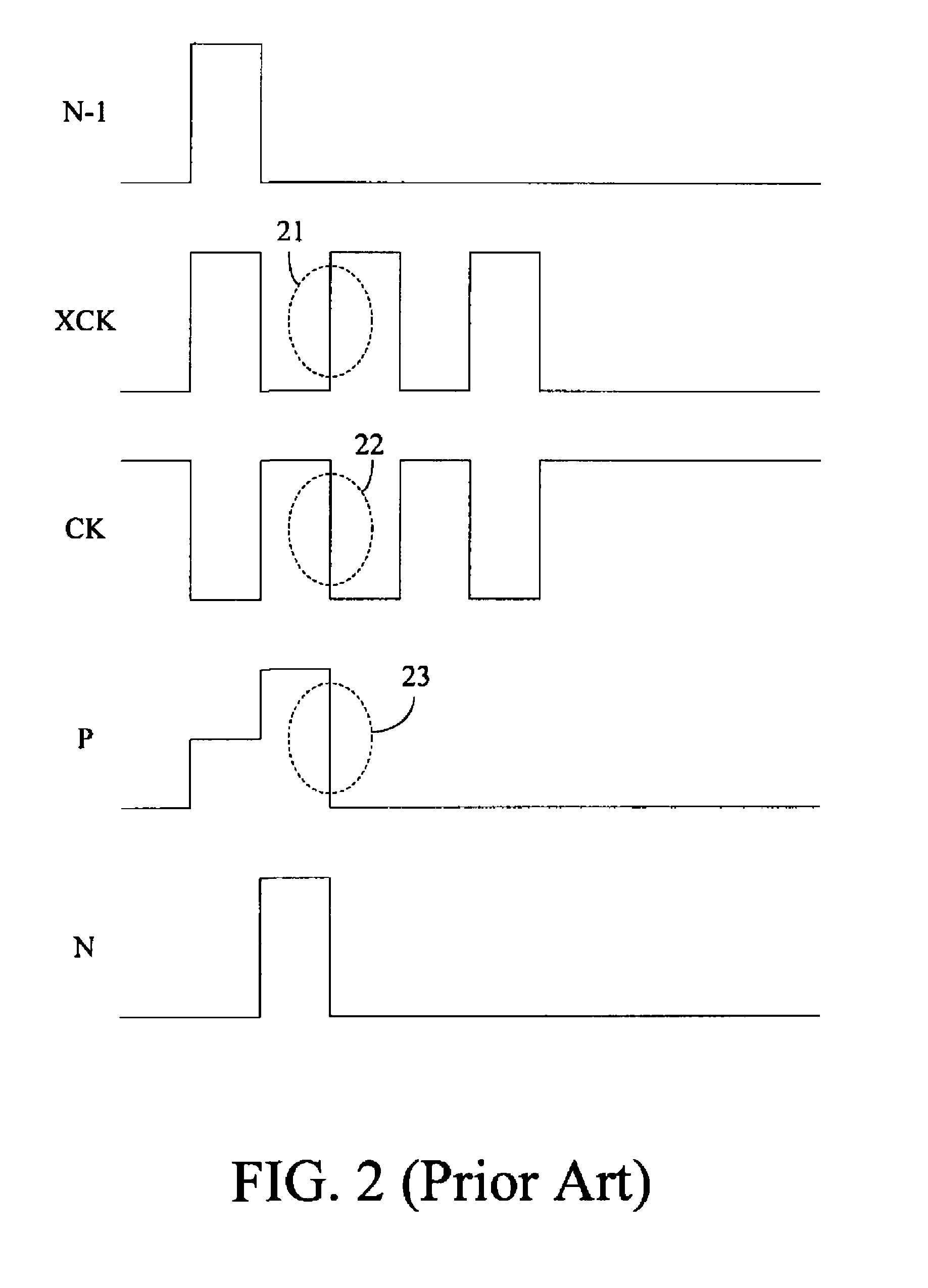

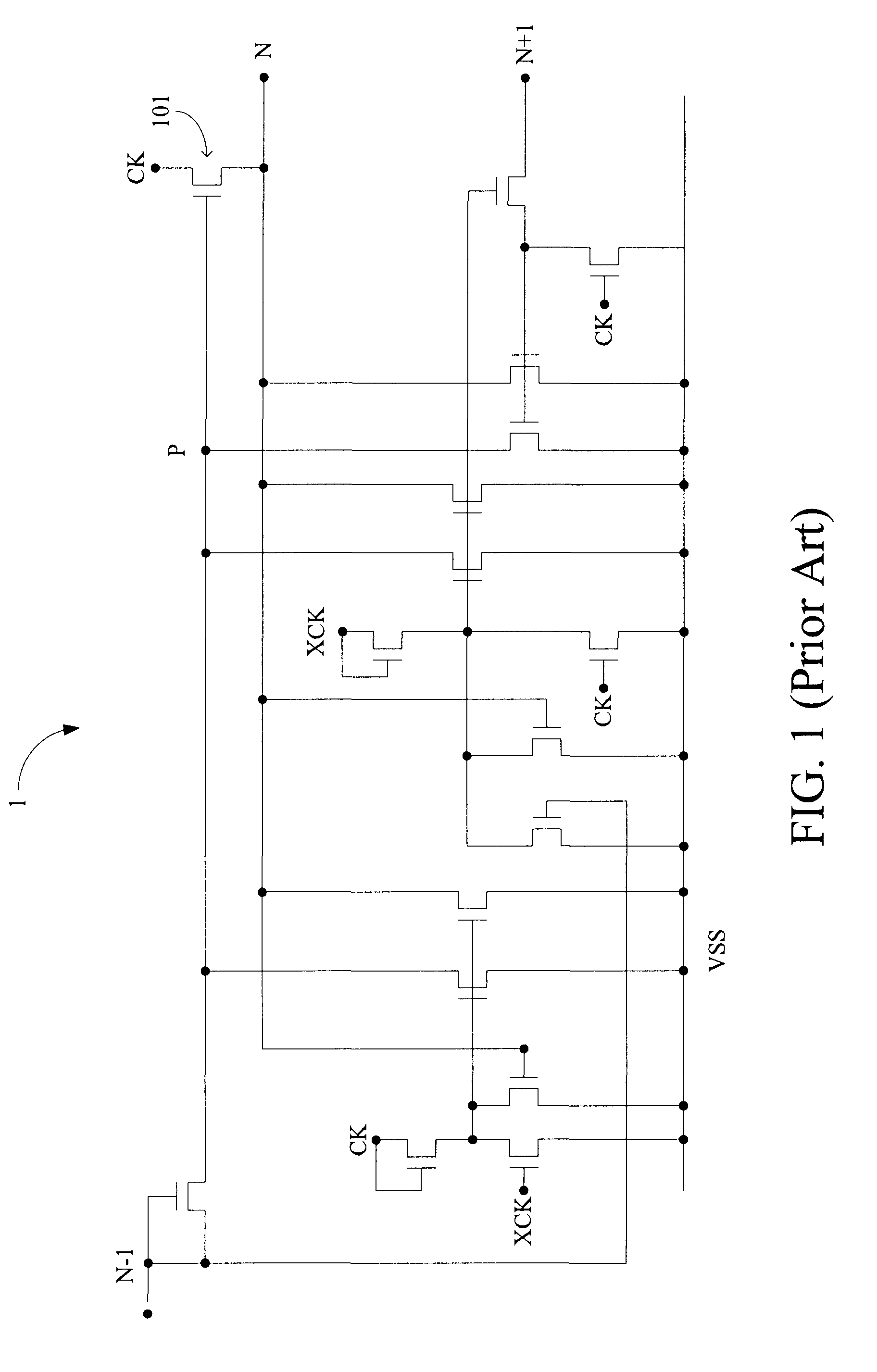

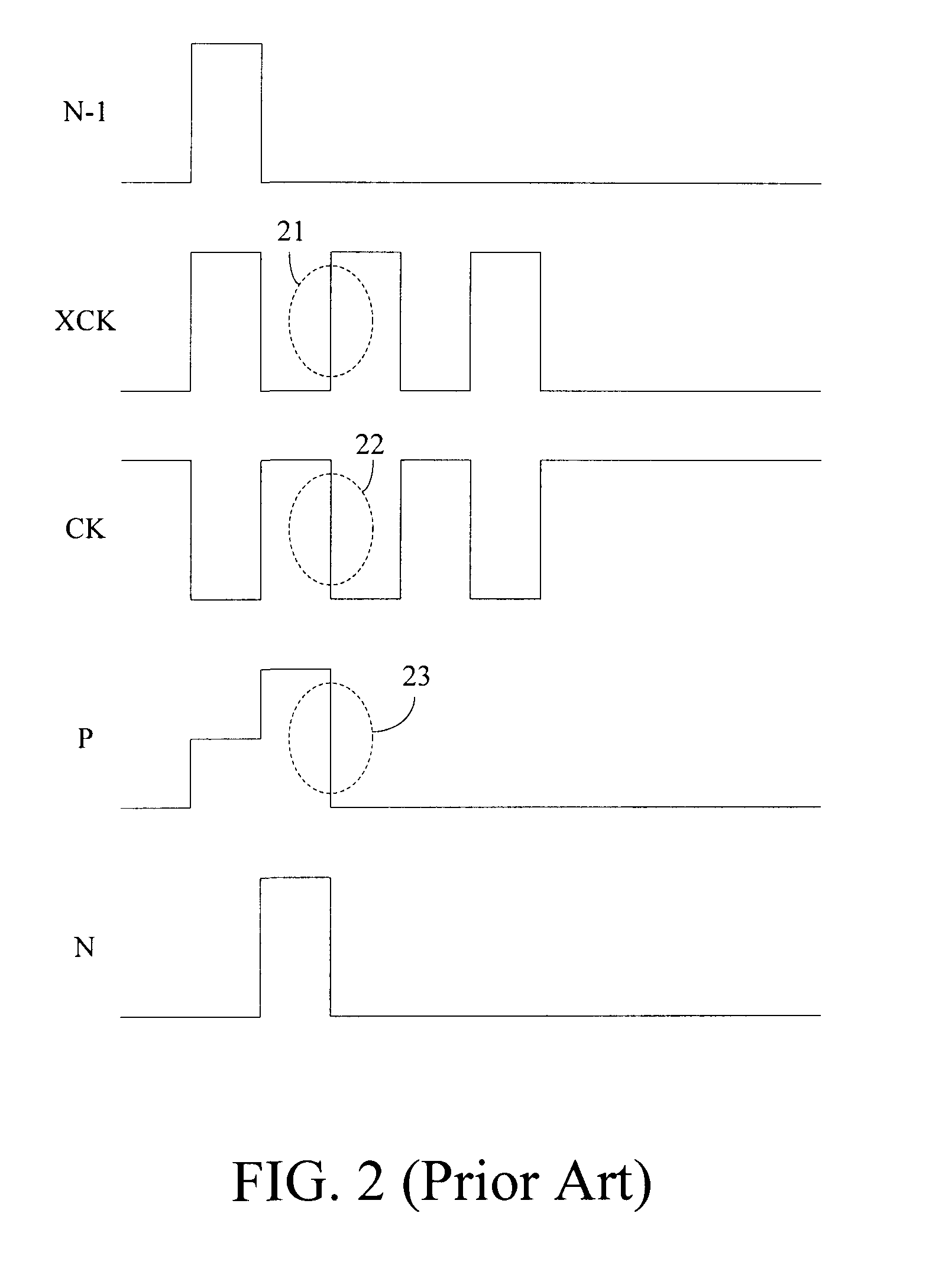

Shift register and shift register unit for diminishing clock coupling effect

ActiveUS20090304138A1Optimize outputOptimize waveform outputStatic indicating devicesDigital storageWave shapeEngineering

A shift register and a shift register unit for diminishing clock coupling effect are introduced herein. Each stage shift register unit includes at least one pull-up driving module, a pull-up module, at least one pull-down module and a pull-down driving module. Before a waveform of either a first clock signal or a second clock signal employed by the pull-up module transits into a rising edge, the pull-down driving module employs a first periodic signal to turn on the pull-down module in advance for a specific period, and / or before the waveform of the first or second clock signal employed by the pull-up module transits into a falling edge, the pull-down driving module employs a second periodic signal to turn off the pull-down module in advance for a specific period. Accordingly, the pull-down module can gain a sufficient capability against the clock coupling effect so as to optimize the waveform outputted from the shift register unit.

Owner:AU OPTRONICS CORP

System that compensates for coupling based on sensing a neighbor using coupling

Shifts in the apparent charge stored on a floating gate (or other charge storing element) of a non-volatile memory cell can occur because of the coupling of an electric field based on the charge stored in adjacent floating gates (or other adjacent charge storing elements). To compensate for this coupling, the read or programming process for a given memory cell can take into account the programmed state of an adjacent memory cell. To determine whether compensation is needed, a process can be performed that includes sensing information about the programmed state of an adjacent memory cell (e.g., on an adjacent bit line or other location).

Owner:SANDISK TECH LLC

Data pattern sensitivity compensation using different voltage

ActiveUS7450421B2Reduce coupling effectExact searchRead-only memoriesDigital storageCapacitanceCapacitive coupling

Owner:SANDISK TECH LLC

Apparatus with alternating read mode

ActiveUS7440324B2Reduce coupling effectRead-only memoriesDigital storageParallel computingElectric field

Shifts in the apparent charge stored on a floating gate (or other charge storage element) of a non-volatile memory cell can occur because of the coupling of an electric field based on the charge stored in adjacent floating gates (or other charge storing elements). To account for this coupling, the read process for a targeted memory cell will provide compensation to an adjacent memory cell (or other memory cell) in order to reduce the coupling effect that the adjacent memory cell has on the targeted memory cell. The compensation applied is based on a condition of the adjacent memory cell. To apply the correct compensation, the read process will at least partially intermix read operations for the adjacent memory cell with read operations for the targeted memory cell.

Owner:SANDISK TECH LLC

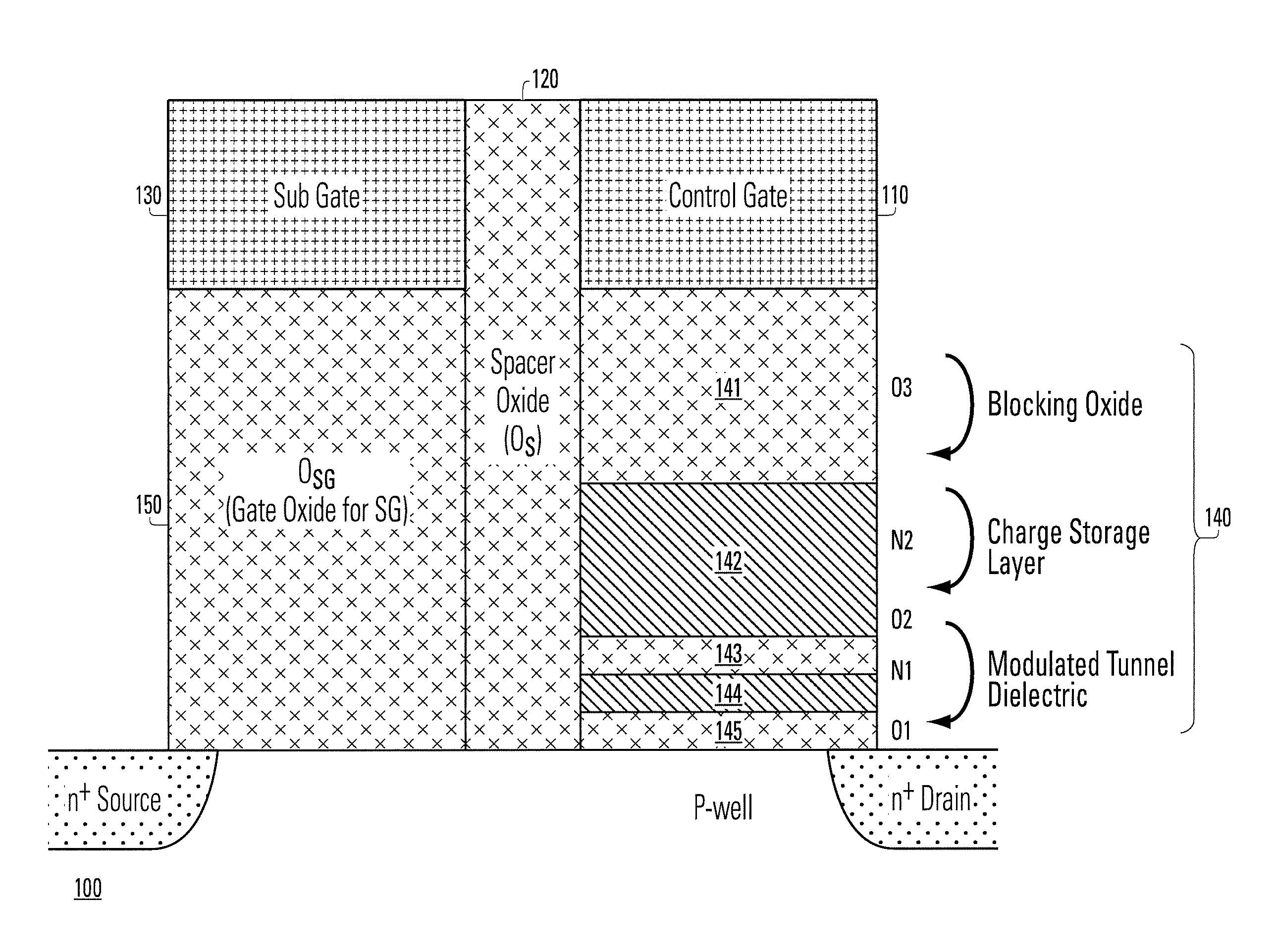

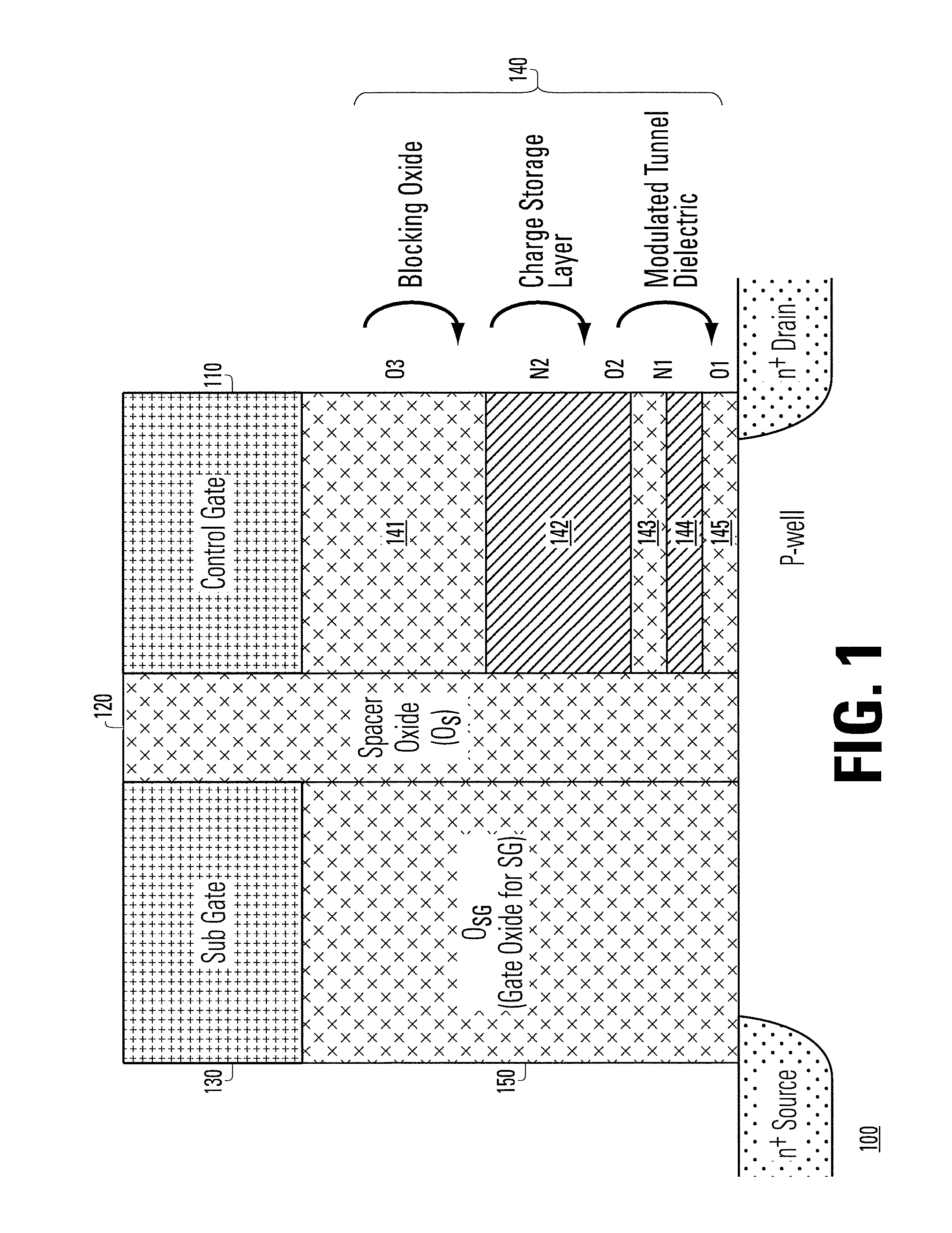

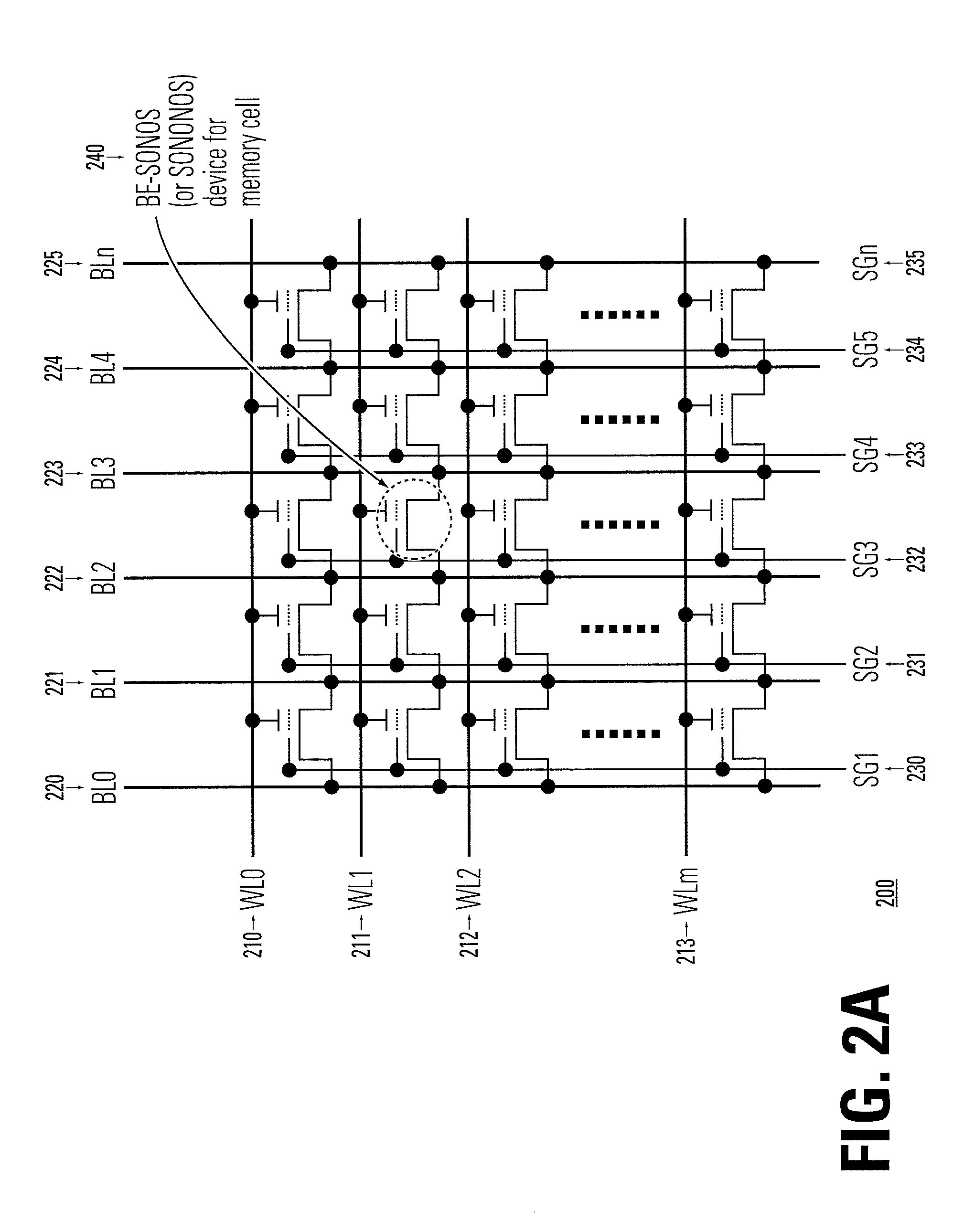

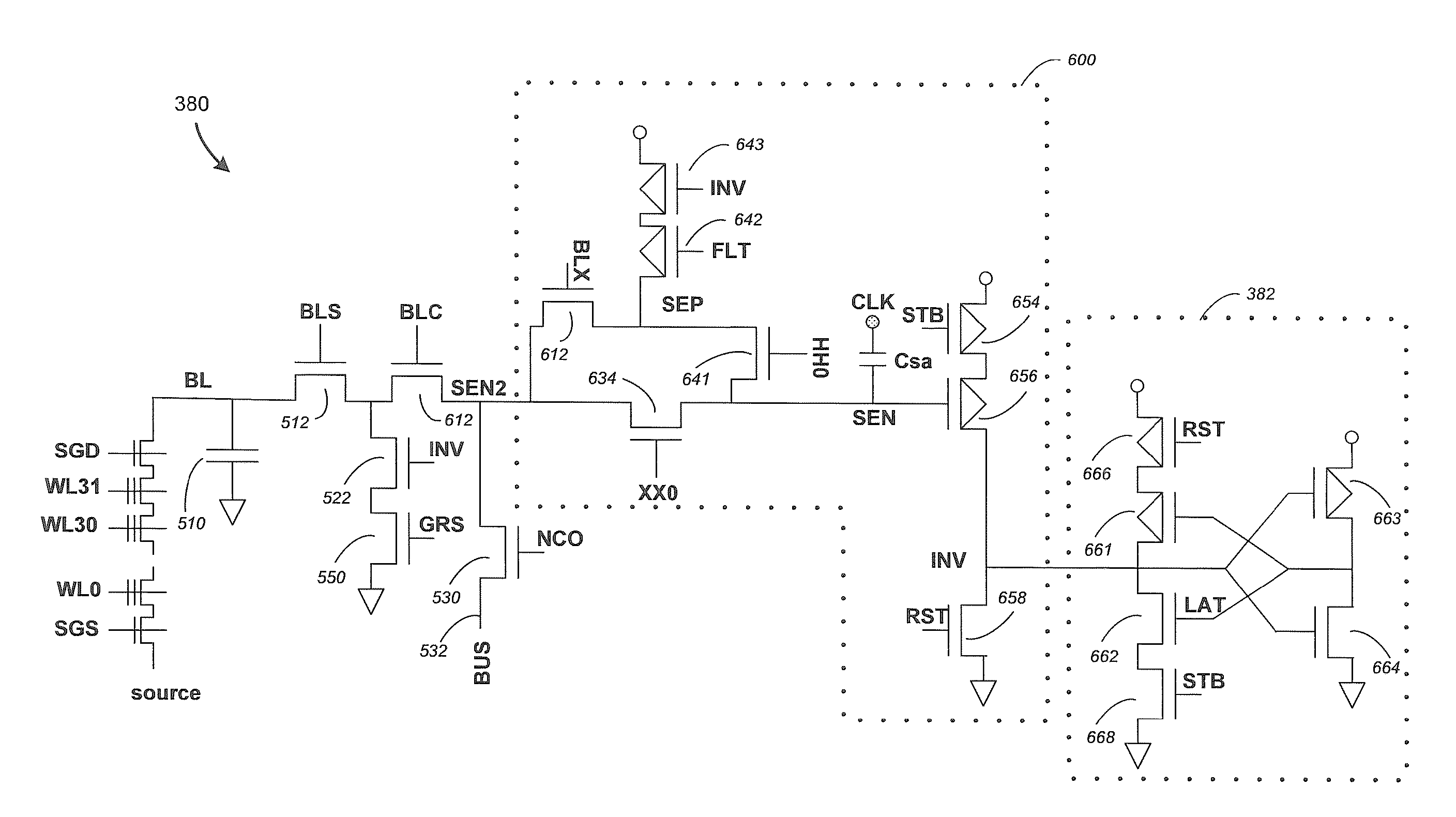

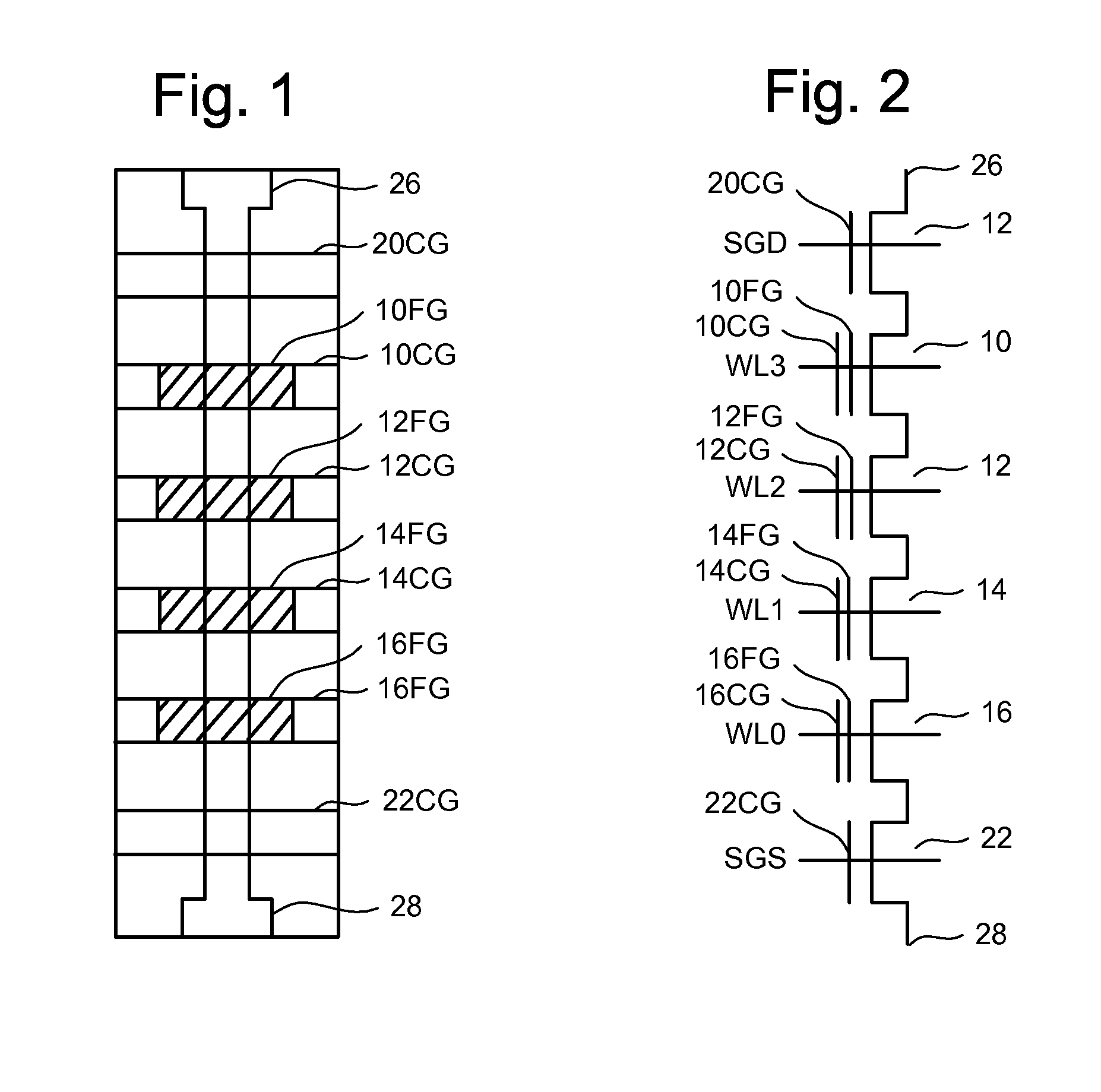

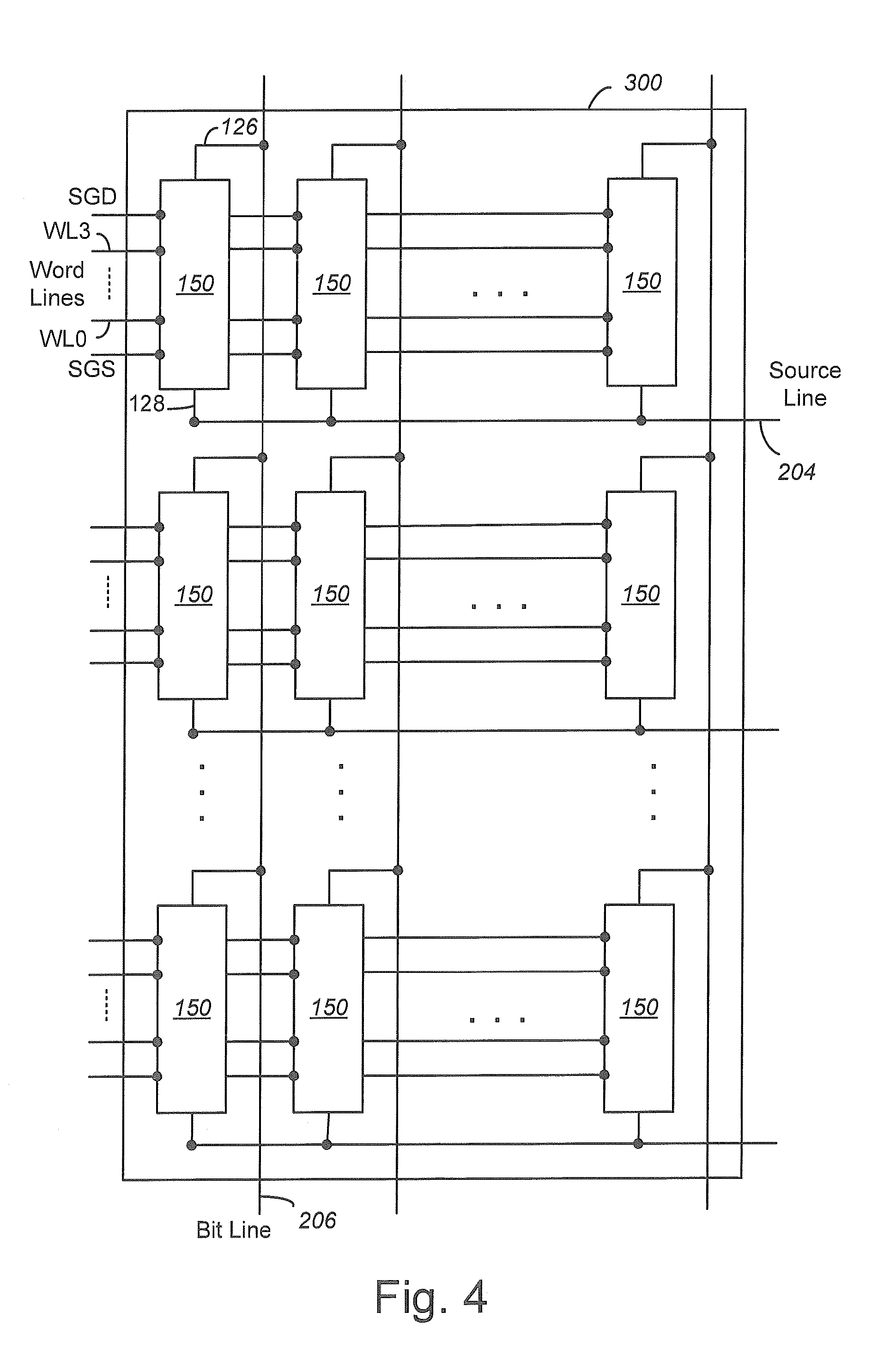

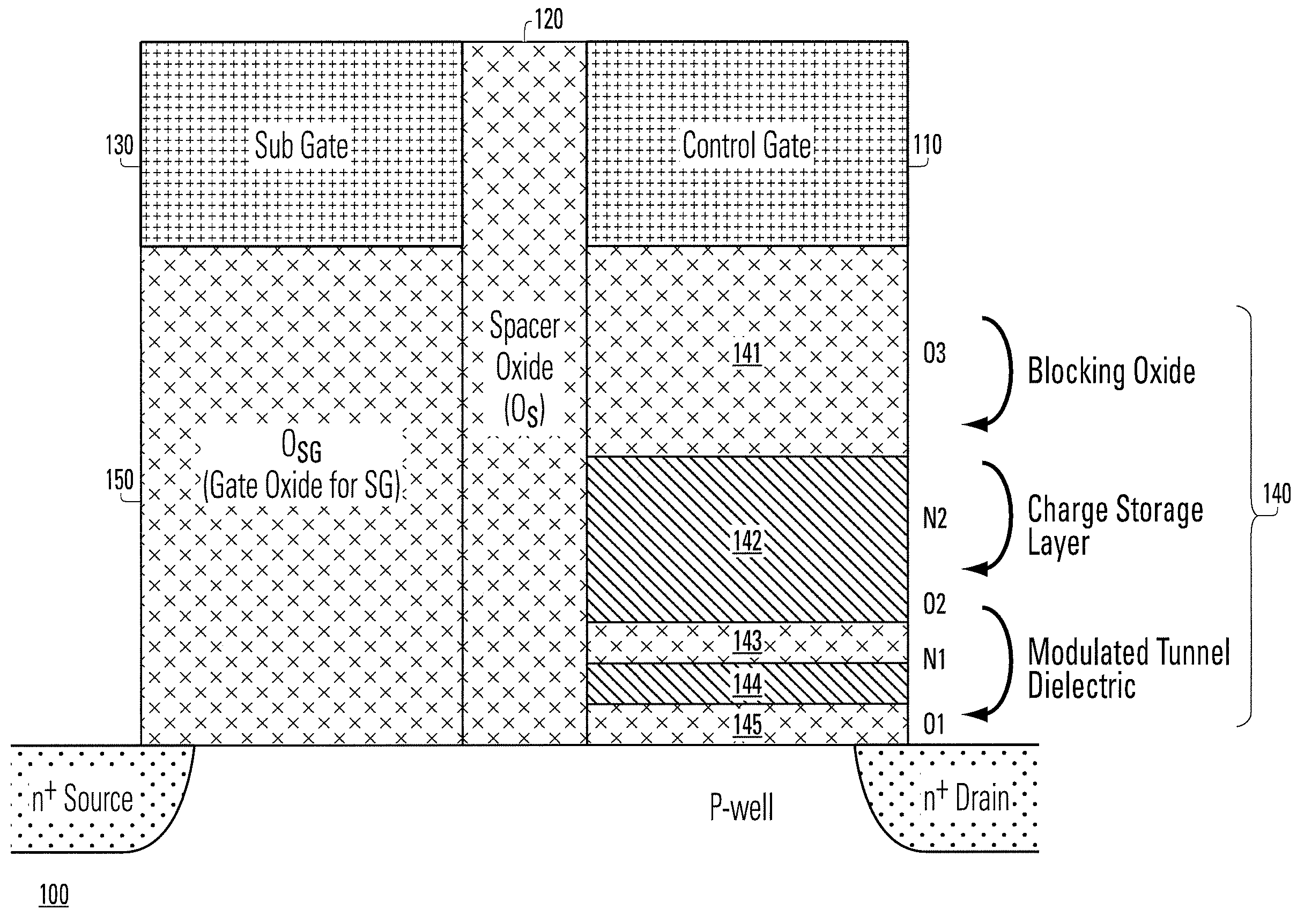

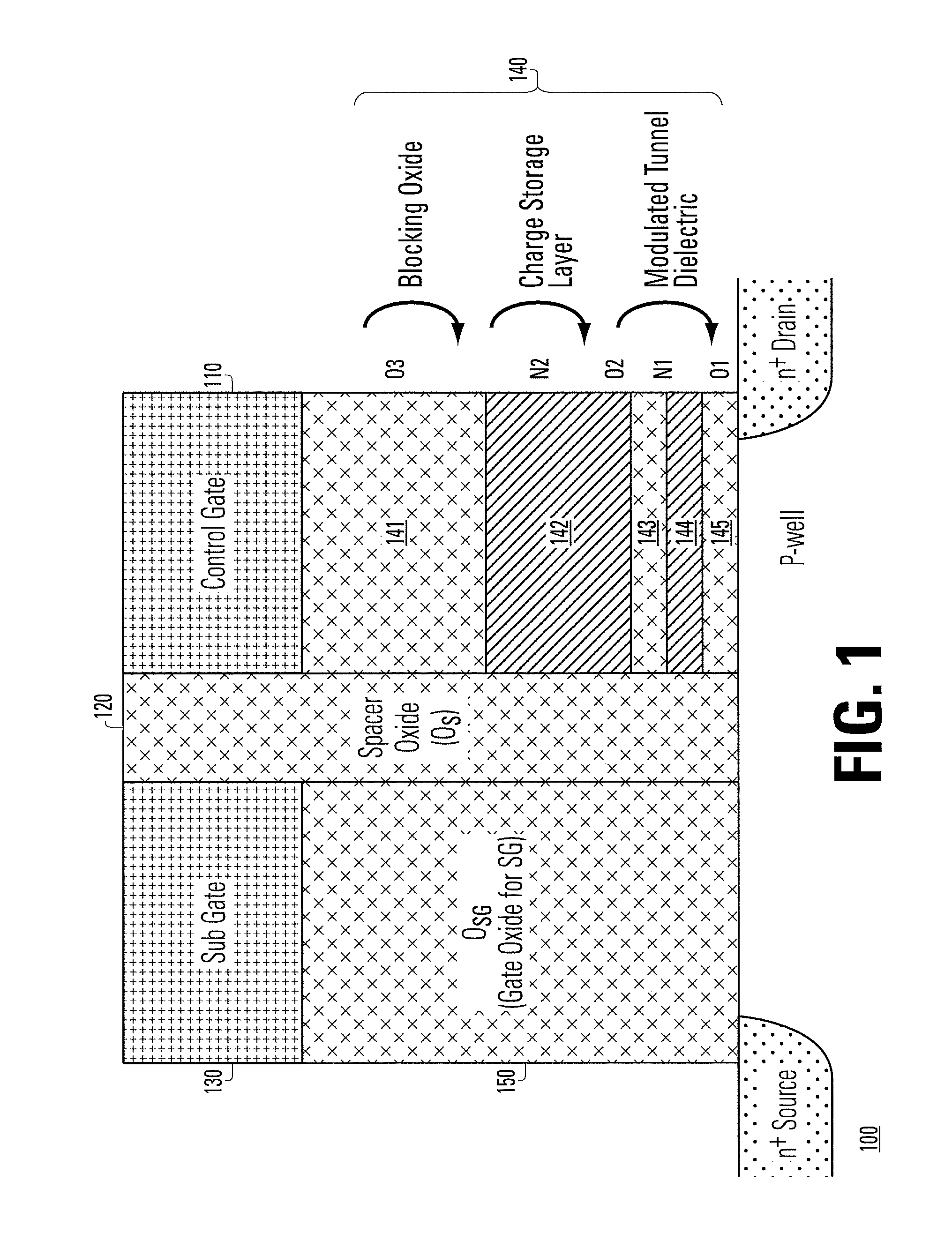

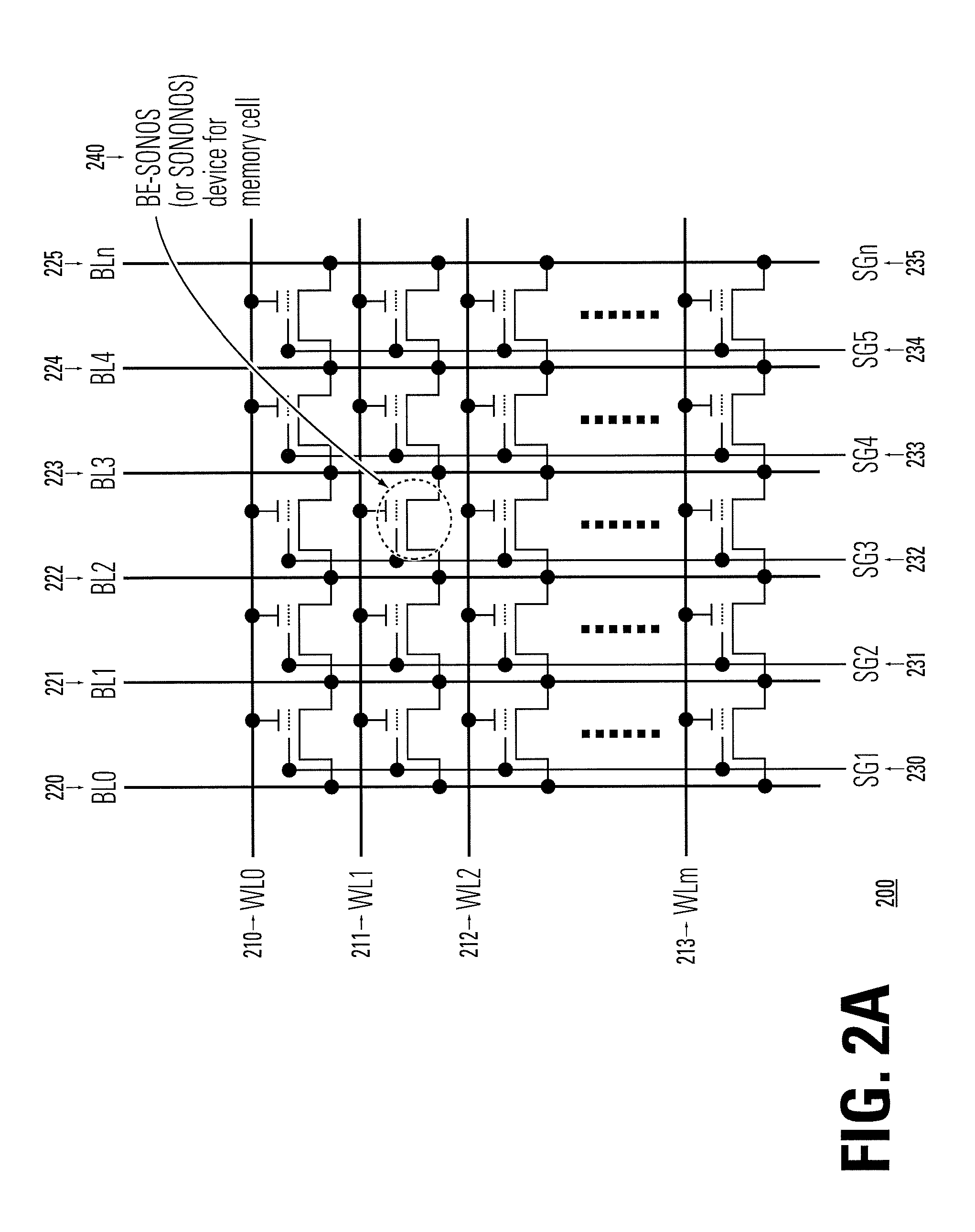

Structure and Method of Sub-Gate NAND Memory with Bandgap Engineered SONOS Devices

ActiveUS20090045452A1Improve good performanceEliminate inter-floating gate coupling effectTransistorSolid-state devicesBit lineEngineering

A bandgap engineered SONOS device structure for design with various AND architectures. The BE-SONOS device structure comprises a spacer oxide disposed between a control gate overlaying an oxide-nitride-oxide-nitride-oxide stack and a sub-gate overlaying a gate oxide. In one example, a BE-SONOS sub-gate-AND array architecture has multiple strings of SONONOS devices with sub-gate lines and diffusion bit lines. In another example, a BE-SONOS sub-gate-AND architecture has multiple strings of SONONOS devices with sub-gate lines, relying on the sub-gate lines that create inversions to substitute for the diffusion bit lines.

Owner:MACRONIX INT CO LTD

Compensating for coupling during programming

ActiveUS20080019185A1Reduce coupling effectReduce the impactRead-only memoriesDigital storageBit lineCoupling

Shifts in the apparent charge stored on a floating gate (or other charge storing element) of a non-volatile memory cell can occur because of the coupling of an electric field based on the charge stored in adjacent floating gates (or other adjacent charge storing elements). To compensate for this coupling, the read or programming process for a given memory cell can take into account the programmed state of an adjacent memory cell. To determine whether compensation is needed, a process can be performed that includes sensing information about the programmed state of an adjacent memory cell (e.g., on an adjacent bit line or other location).

Owner:SANDISK TECH LLC

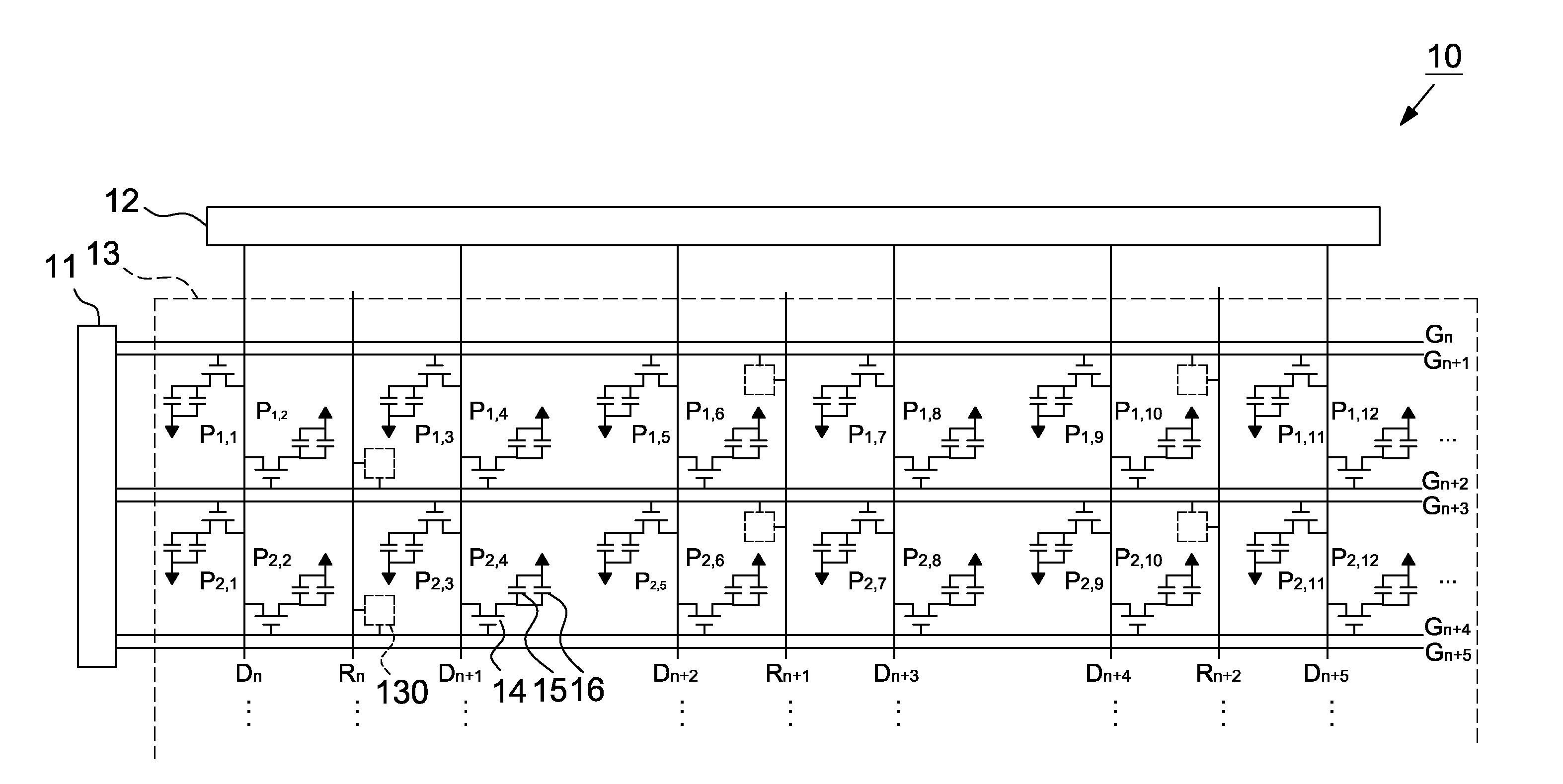

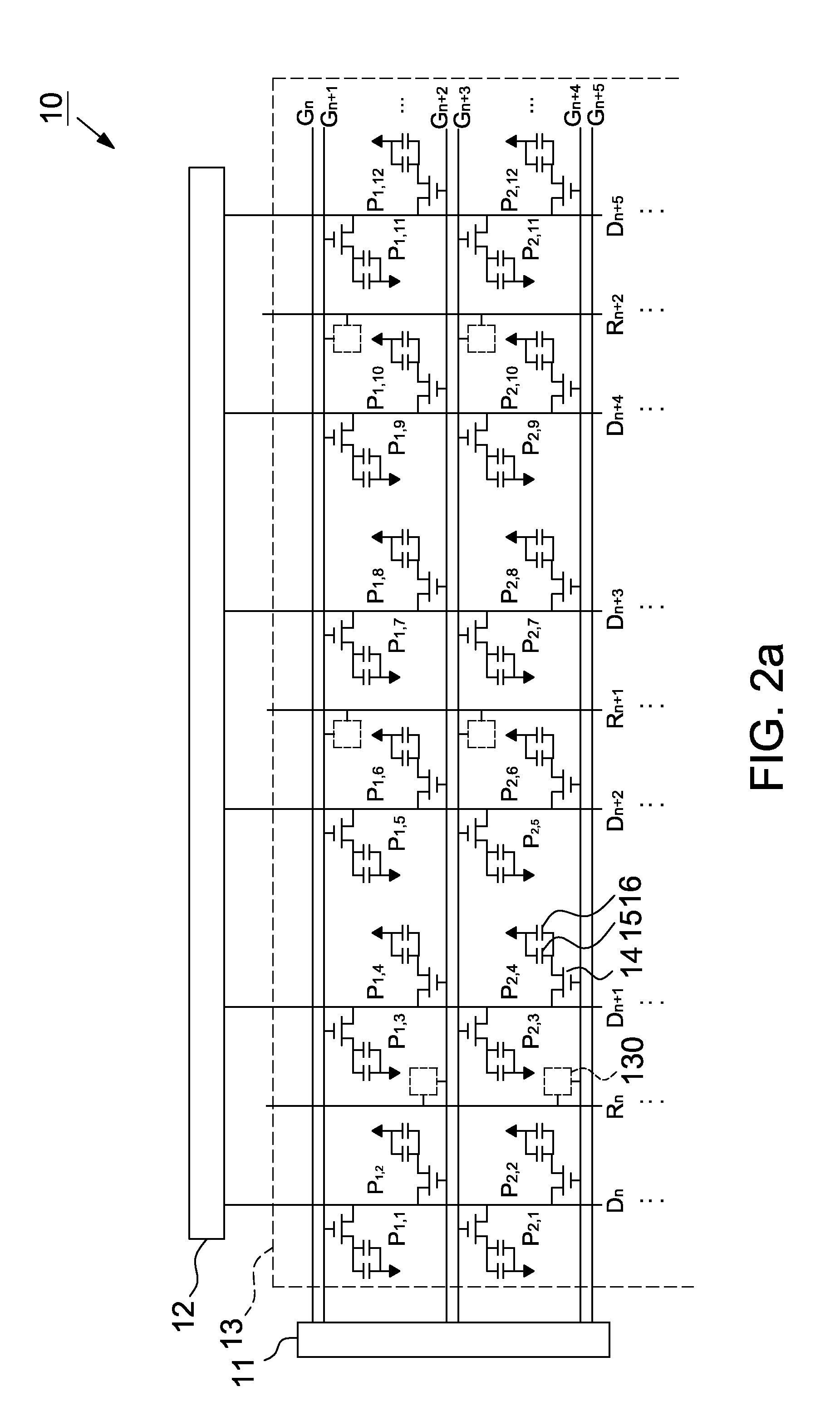

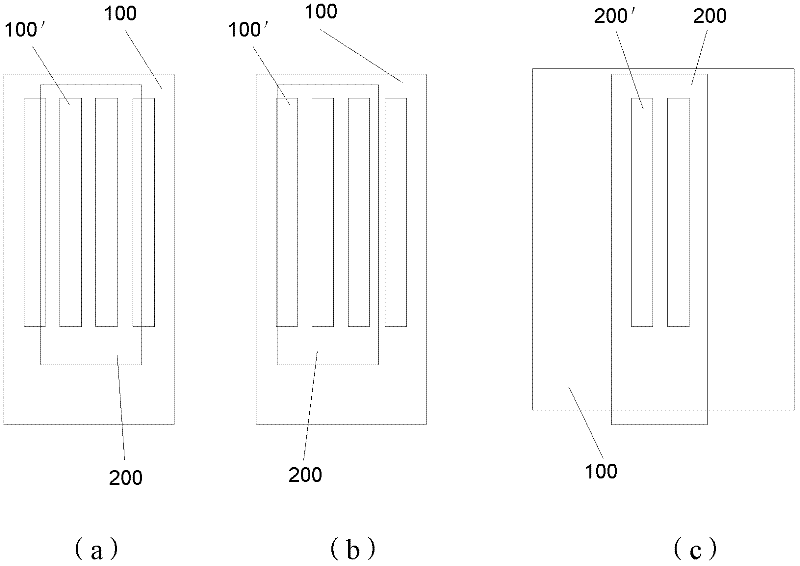

Touch panel and pixel array thereof

InactiveCN102314248AImprove pixel aperture ratioReduce coupling effectStatic indicating devicesInput/output processes for data processingComputer scienceTouch panel

The invention discloses a pixel array, comprising a plurality of pixels, a plurality of data lines, a plurality of reading lines and a plurality of gate lines, wherein the data lines and the reading lines are configured between two adjacent pixels in turn; two adjacent pixels at two sides of each data line are coupled to the same data line and coupled to different gate lines; and at least one part of reading lines is coupled to one of two adjacent pixels at two sides. The invention also provides a touch panel comprising the pixel array.

Owner:HANNSTAR DISPLAY CORPORATION

System for performing data pattern sensitivity compensation using different voltage

ActiveUS20070279995A1Reduce coupling effectExact searchRead-only memoriesDigital storageCapacitanceCapacitive coupling

Errors can occur when reading the threshold voltage of a programmed non-volatile storage element due to at least two mechanisms: (1) capacitive coupling between neighboring floating gates and (2) changing conductivity of the channel area after programming (referred to as back pattern effect). To account for coupling between neighboring floating gates, the read process for a particular memory cell will provide compensation to an adjacent memory cell in order to reduce the coupling effect that the adjacent memory cell has on the particular memory cell. To account for the back pattern effect, a first voltage is used during a verify operation for unselected word lines that have been subjected to a programming operation and a second voltage is used for unselected word lines that have not been subjected to a programming operation. The combination of these two techniques provides for more accurate storage and retrieval of data.

Owner:SANDISK TECH LLC

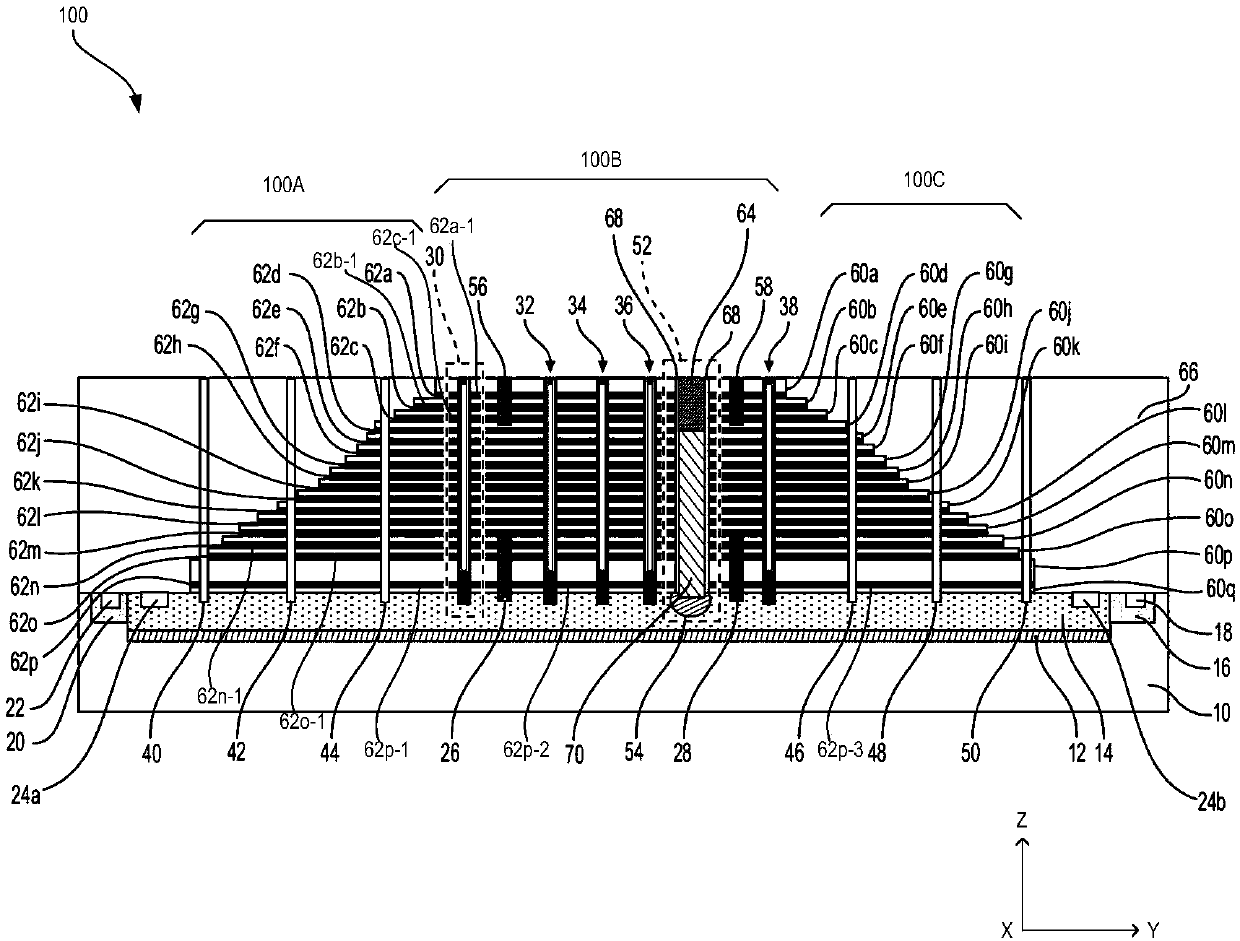

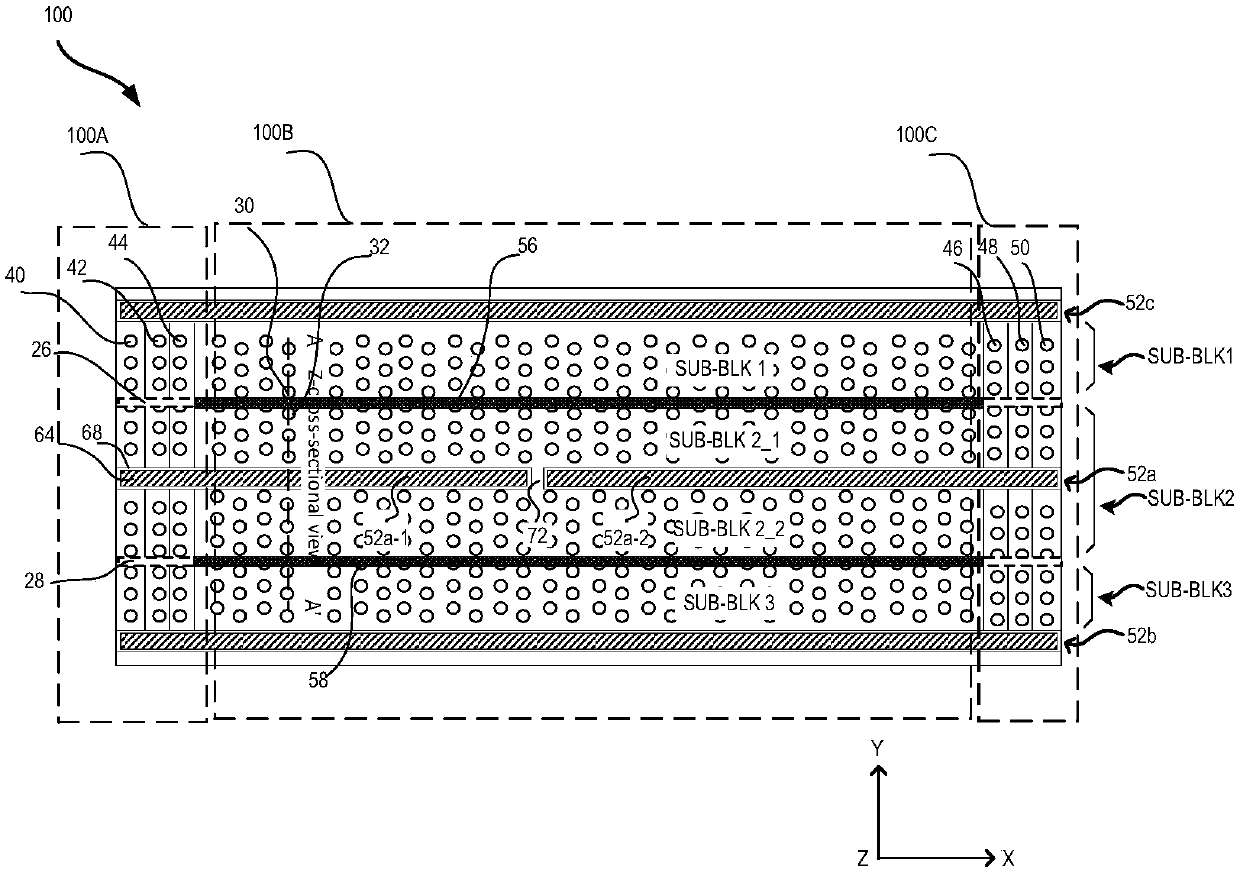

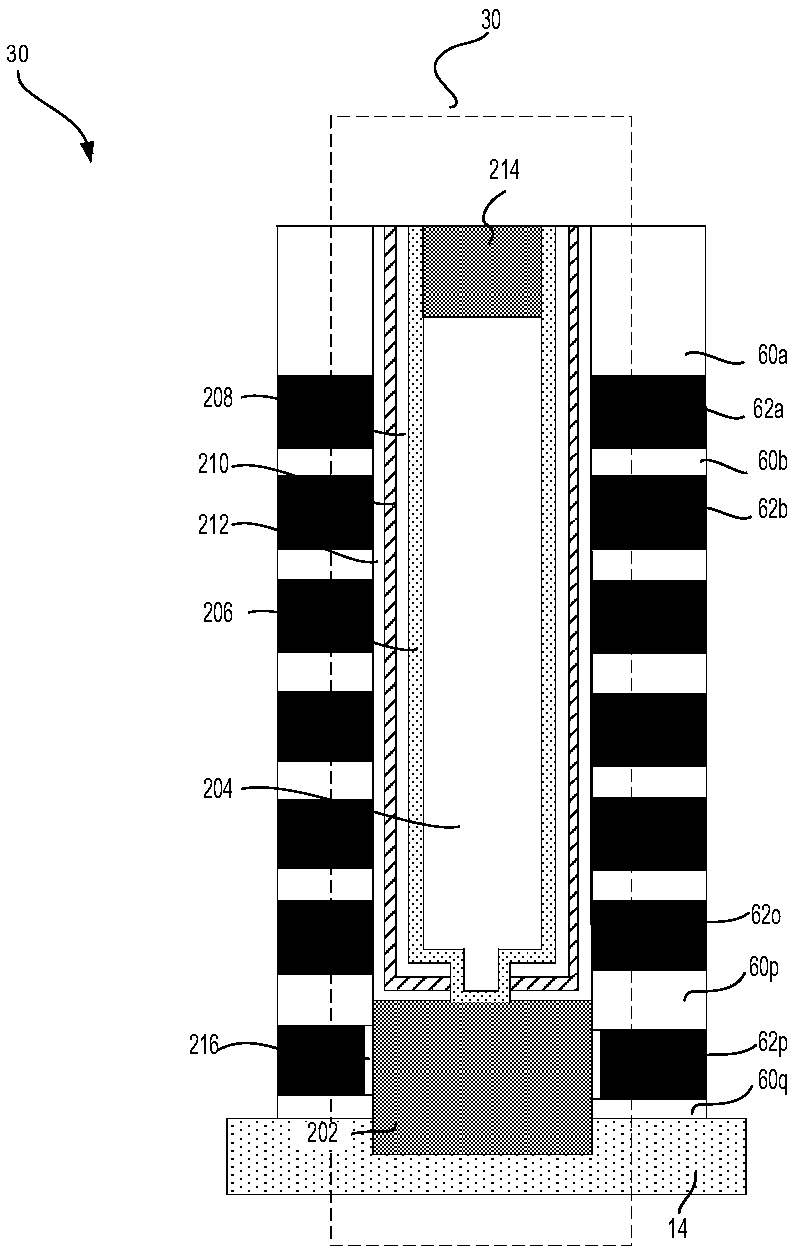

Novel 3D NAND memory device and method of forming same

ActiveCN109690776AReduce coupling effectImprove V

<sub>t</sub>

performanceSemiconductor/solid-state device detailsSolid-state devicesInsulation layerComputer science

A 3D NAND memory device is provided and includes: a substrate, a bottom select gate (BSG) disposed over the substrate, a plurality of word lines disposed above the BSG and having a stepped configuration, and a plurality of insulation layers disposed between the substrate, the BSG, and the plurality of word lines. In the disclosed memory device, one or more first dielectric trenches are formed in the BSG and extend along the length of the substrate to separate the BSG into a plurality of sub-BSGs. Further, one or more common source regions are formed over the substrate and extend in the lengthdirection of the substrate. One or more common source regions also extend through the BSG, the plurality of word lines, and the plurality of insulating layers.

Owner:YANGTZE MEMORY TECH CO LTD

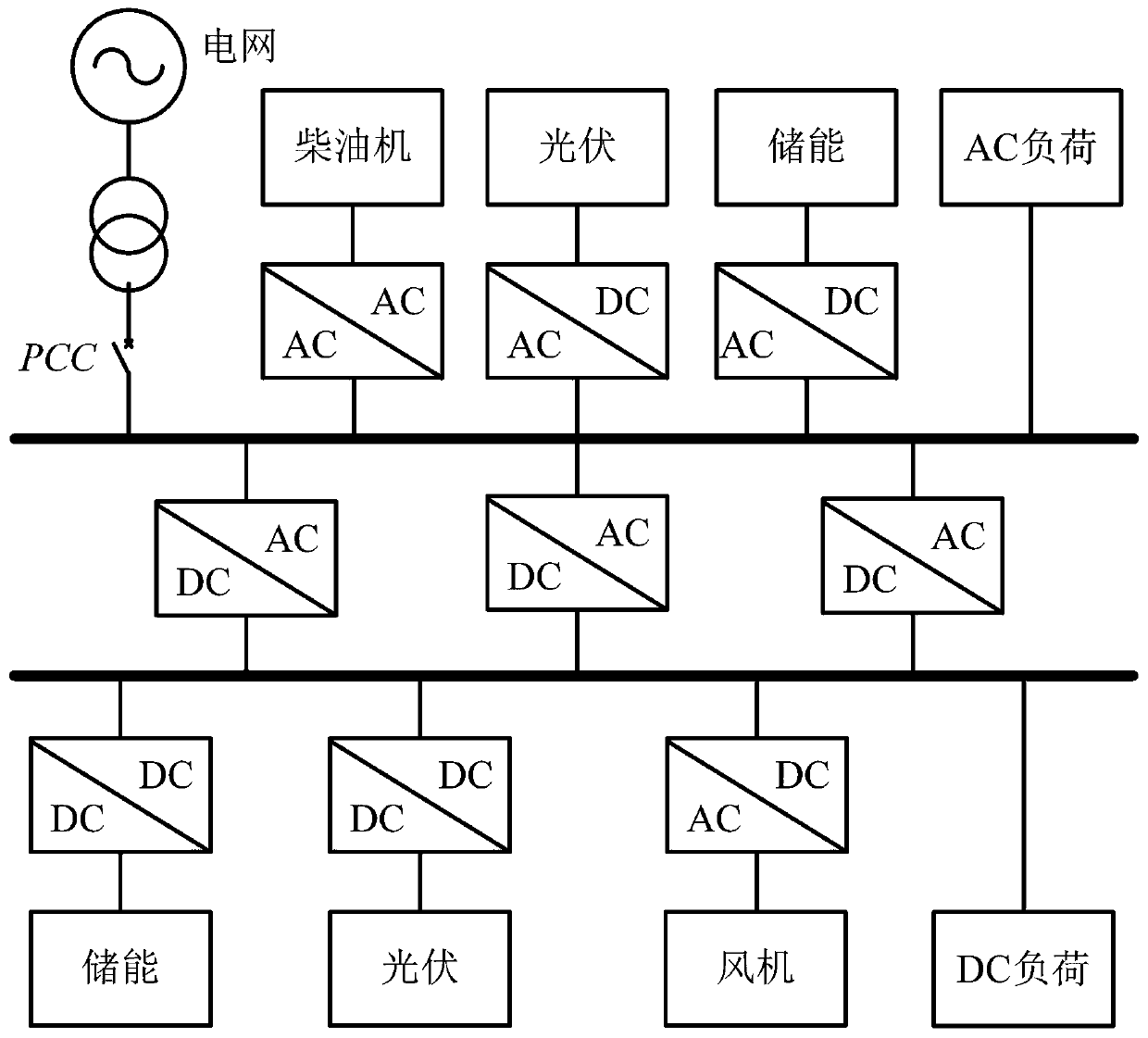

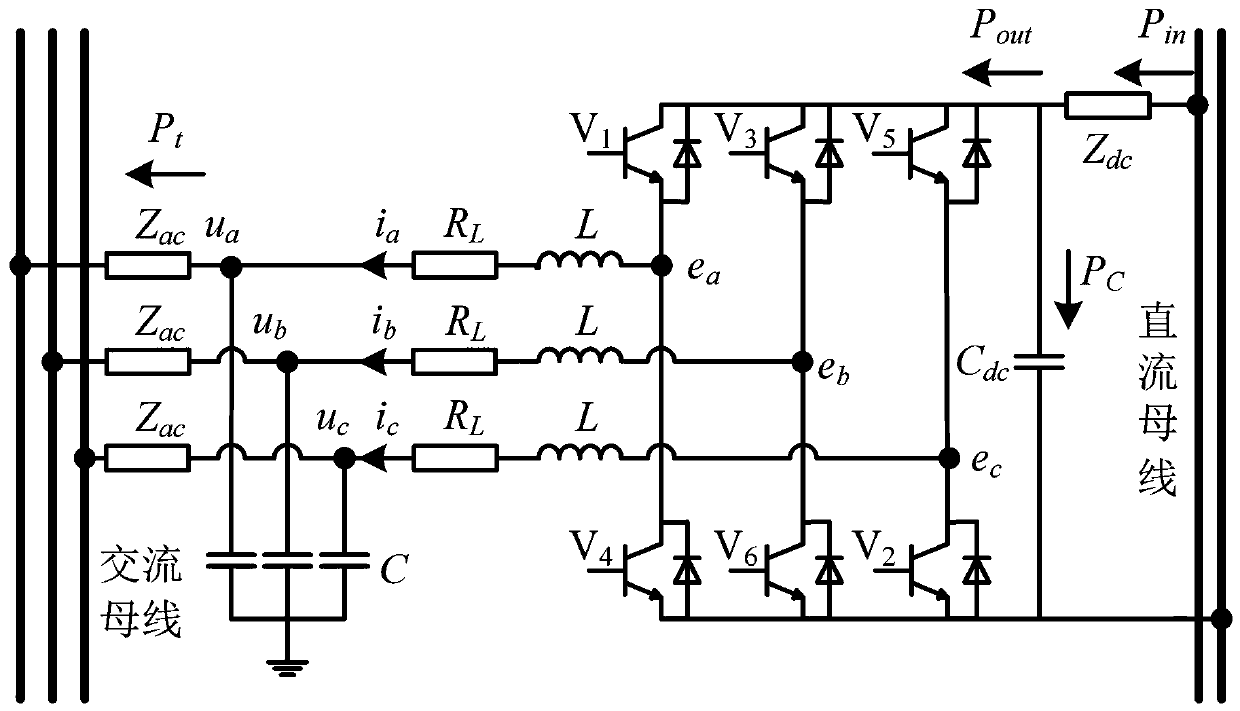

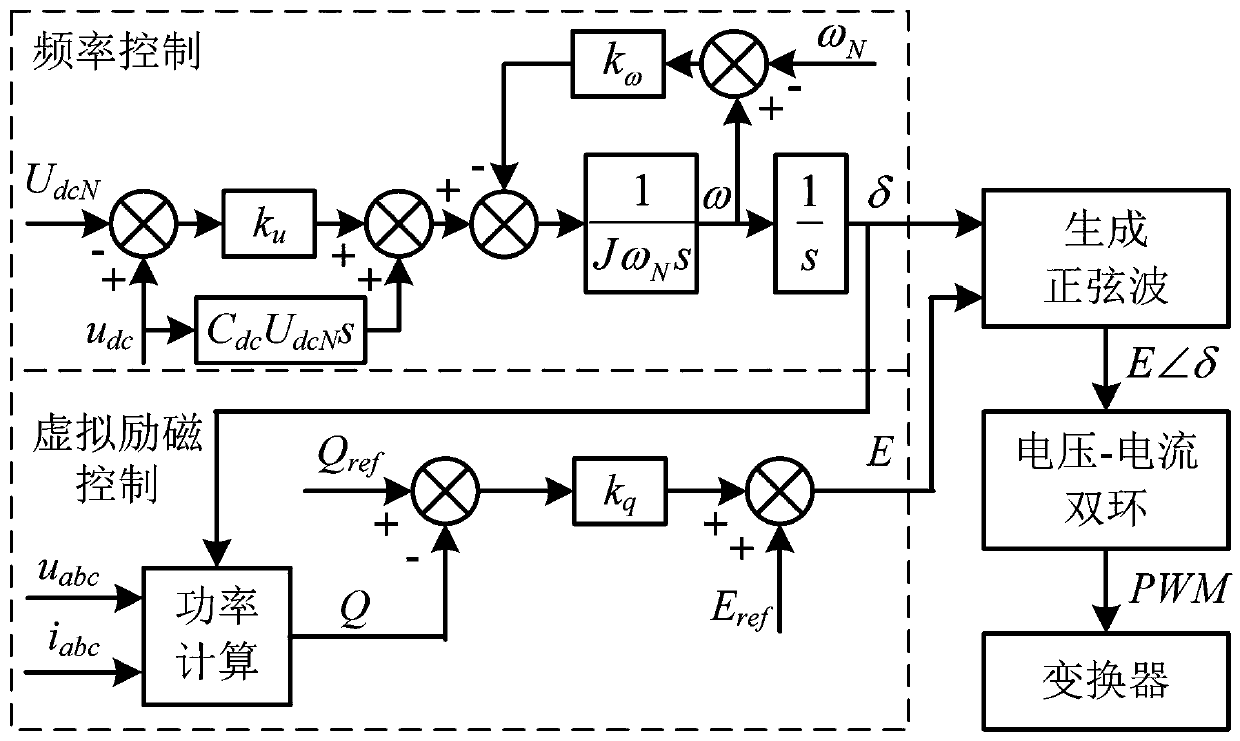

AC-DC hybrid micro grid bidirectional power converter virtual synchronization motor control method

ActiveCN108832657AWith FMFunctionalSingle network parallel feeding arrangementsPower oscillations reduction/preventionDc capacitorClosed loop

The invention discloses an AC-DC hybrid micro grid bidirectional power converter virtual synchronization motor control method, and relates to the AC-DC hybrid micro grid virtual synchronization motorcontrol field; the bidirectional power converter is a three-phase voltage source type PWM converter formed by IGBT switch tubes; the AC side is connected to a AC bus via a LC filter and a line impedance Z ac; the DC side is connected to a DC bus via a DC capacitor Cdc and an line impedance Zdc; the energy bidirectional transmission can be realized respectively via a frequency control unit, a virtual excitation control unit and a bidirectional power transmission control unit; the AC frequency and DC voltage can be directly controlled so as to keep AC-DC subnet load balancing; throughput characteristics of various types of power supplies and loads of the AC-DC subnet can be fully utilized so as to provide inertia for the AC frequency and DC voltage, thus enabling the bidirectional power converter to present sagging characteristics under a stable state, and building a bidirectional power converter closed loop system small signal model so as to provide a key parameter design method.

Owner:TAIYUAN UNIV OF TECH

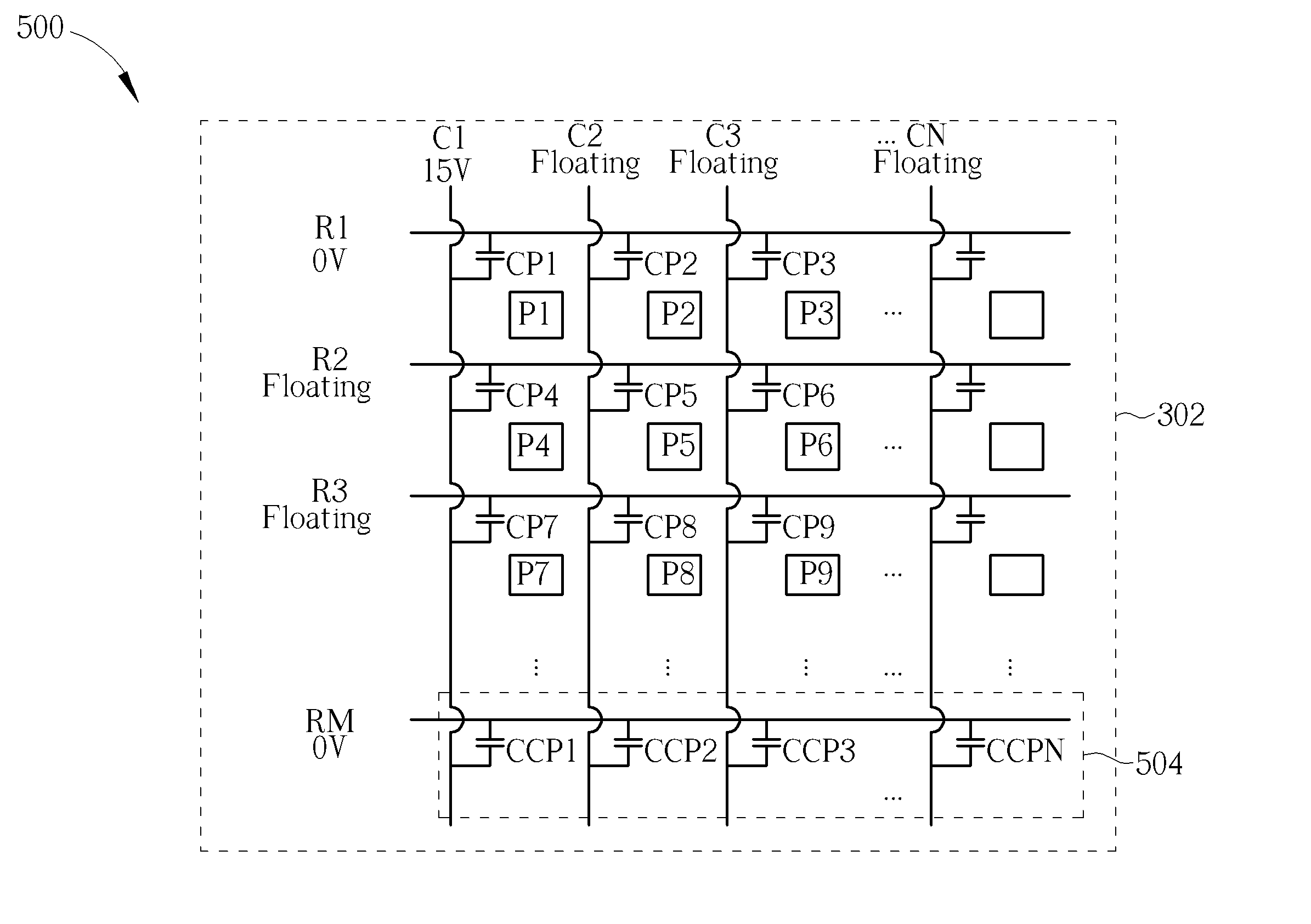

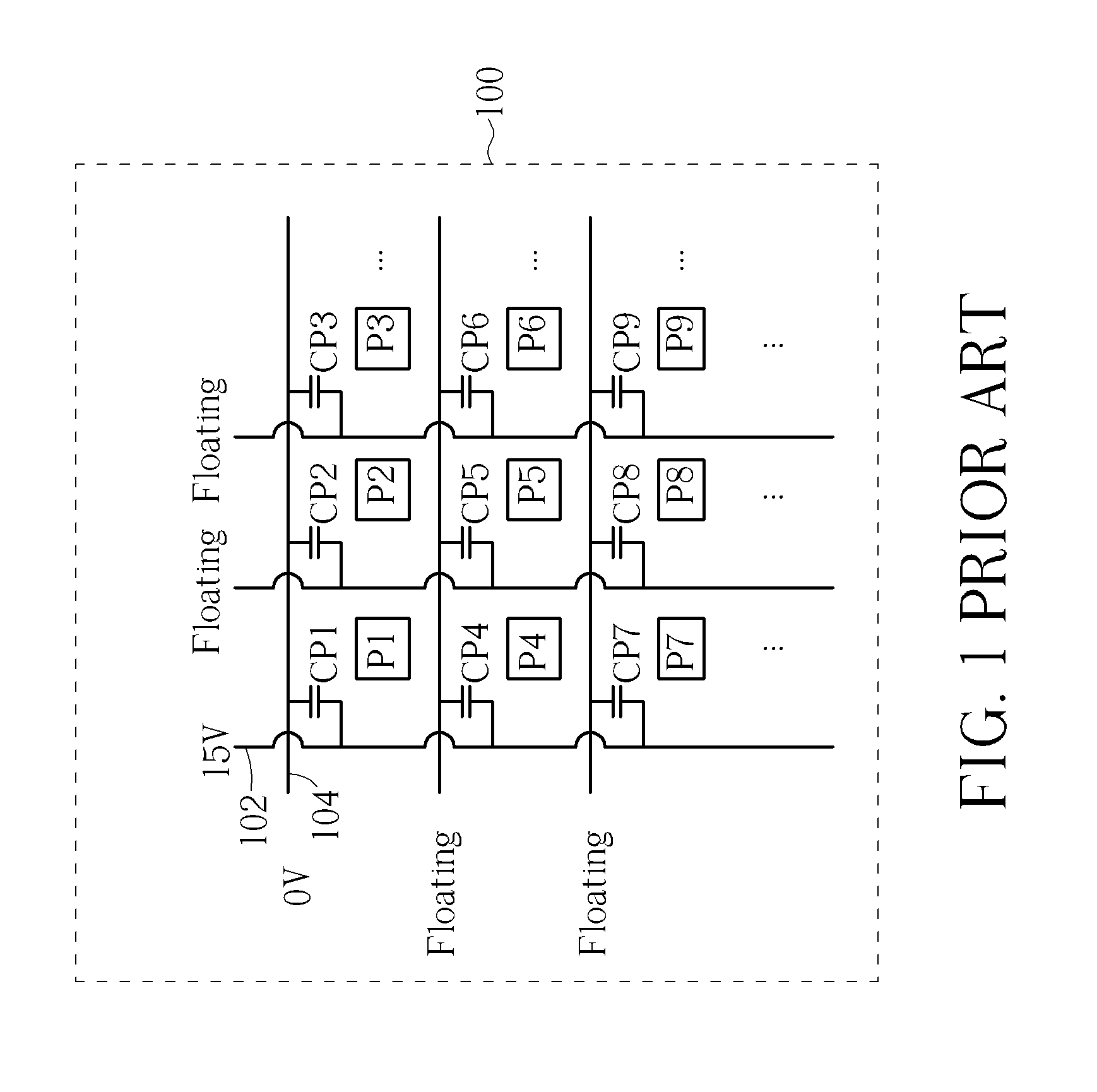

Electrophoretic display capable of reducing passive matrix coupling effect

ActiveUS9147364B2Reduce coupling effectStatic indicating devicesNon-linear opticsScan lineDisplay device

An electrophoretic display capable of reducing passive matrix coupling effect includes an electrophoretic panel, a coupling capacitor group, a plurality of first scan lines, and a plurality of second scan lines. The electrophoretic panel includes a plurality of pixels. The coupling capacitor group includes a plurality of coupling capacitors. Each pixel of the plurality of pixels is coupled to a storage capacitor and corresponds to a coupling capacitor, the storage capacitor is coupled to a first scan line and a second scan line, the coupling capacitor is coupled to another first scan line and the second scan line, and the coupling capacitor is not coupled to any pixel.

Owner:YUANHAN MATERIALS INC

Systems for margined neighbor reading for non-volatile memory read operations including coupling compensation

Shifts in the apparent charge stored on a floating gate (or other charge storing element) of a non-volatile memory cell can occur because of the coupling of an electric field based on the charge stored in adjacent floating gates (or other adjacent charge storing elements). The problem occurs most pronouncedly between sets of adjacent memory cells that have been programmed at different times. To account for this coupling, the read process for a particular memory cell will provide compensation to an adjacent memory cell in order to reduce the coupling effect that the adjacent memory cell has on the particular memory cell. When reading the adjacent cell to determine the appropriate compensation, margined read voltages can be used.

Owner:SANDISK TECH LLC

Shift register and shift register unit for diminishing clock coupling effect

ActiveUS7688934B2Optimize waveform outputReduce coupling effectStatic indicating devicesDigital storageShift registerWave shape

A shift register and a shift register unit for diminishing clock coupling effect are introduced herein. Each stage shift register unit includes at least one pull-up driving module, a pull-up module, at least one pull-down module and a pull-down driving module. Before a waveform of either a first clock signal or a second clock signal employed by the pull-up module transits into a rising edge, the pull-down driving module employs a first periodic signal to turn on the pull-down module in advance for a specific period, and / or before the waveform of the first or second clock signal employed by the pull-up module transits into a falling edge, the pull-down driving module employs a second periodic signal to turn off the pull-down module in advance for a specific period. Accordingly, the pull-down module can gain a sufficient capability against the clock coupling effect so as to optimize the waveform outputted from the shift register unit.

Owner:OPTRONIC SCI LLC

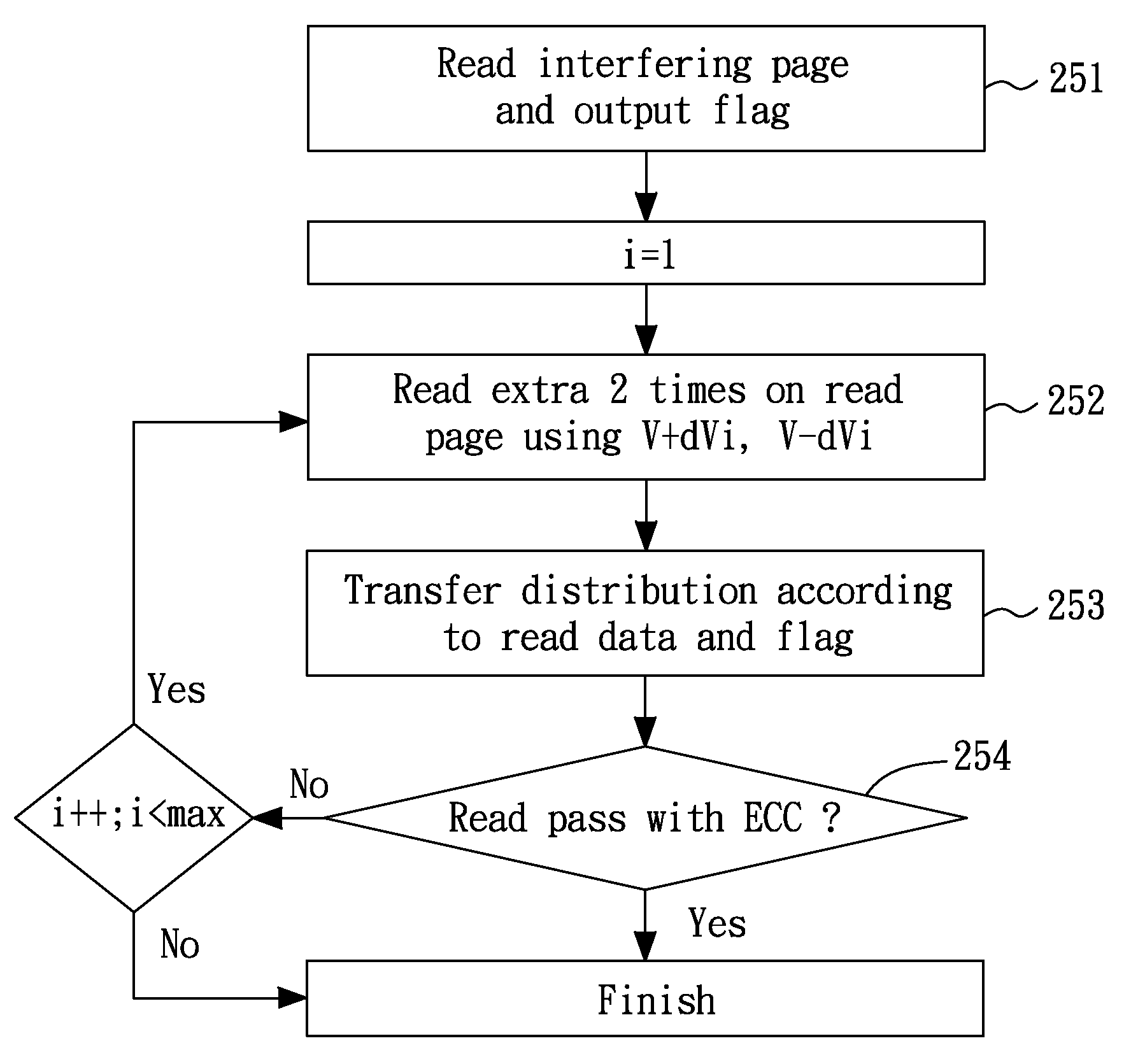

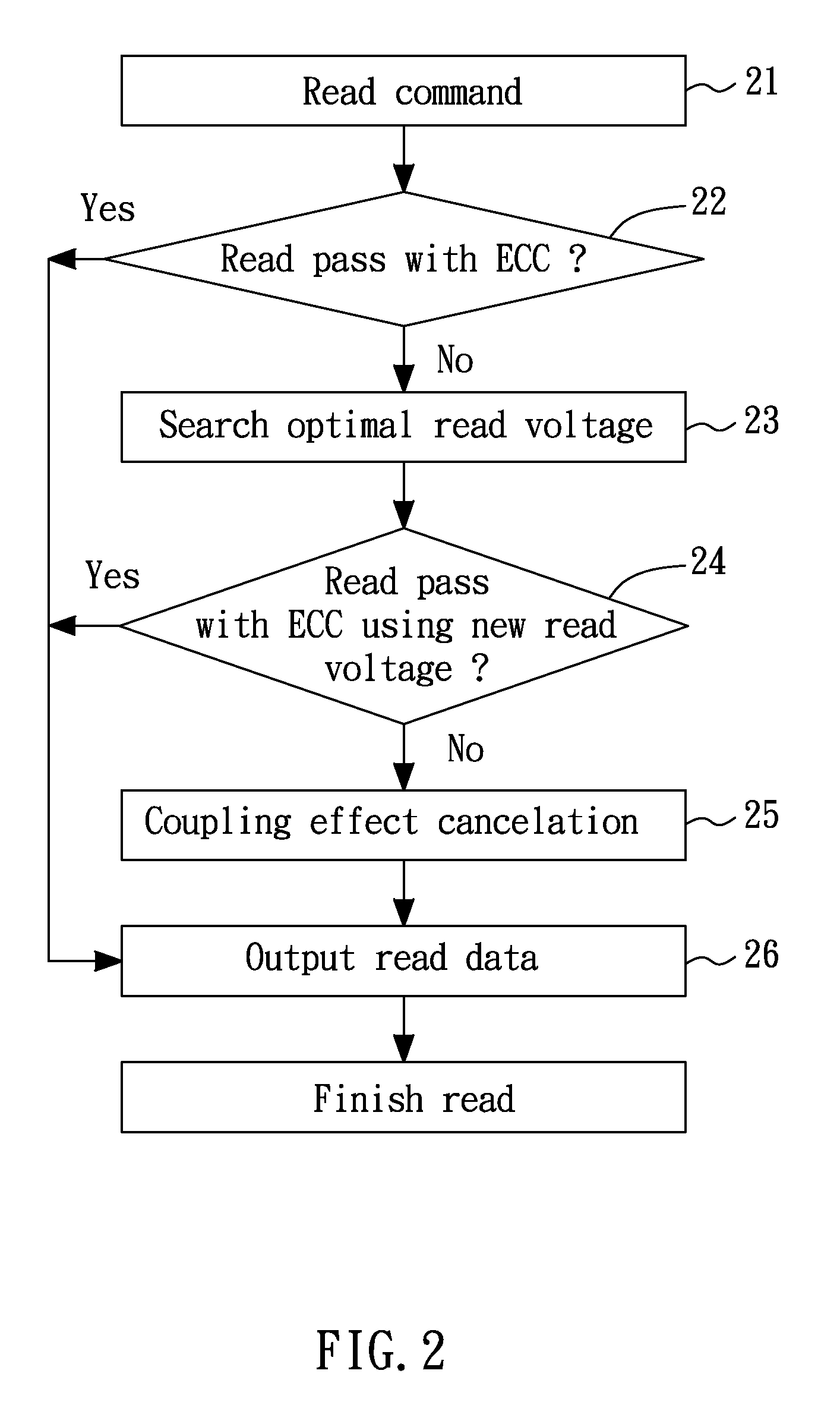

Method Of Reducing Bit Error Rate For A Flash Memory

ActiveUS20110038205A1Reduce coupling effectError detection/correctionRead-only memoriesComputer scienceThreshold voltage

A method of reducing coupling effect in a flash memory is disclosed. A neighboring page is read, and a flag is set active if the neighboring page is an interfering page. Data are read from the neighboring page at least two more times using at least two distinct read voltages respectively. The threshold-voltage distributions associated with an original page and the neighboring page are transferred according to the read data and the flag.

Owner:JIANGSU HUACUN ELECTRONICS TECH CO LTD

Touch panel and pixel aray thereof

InactiveUS20110310036A1Increase the aperture ratioReduce coupling effectInput/output processes for data processingComputer scienceTouch panel

A pixel array includes a plurality of pixels, data lines, readout lines and gate lines, wherein a data line and a readout line are alternatively disposed between every two adjacent pixels; two pixels adjacent to each data line are coupled to the same data line but coupled to different gate lines; and at least a part of the readout lines are coupled to one of the two pixels adjacent thereto. The present invention further provides a touch panel including the above pixel array.

Owner:HANNSTAR DISPLAY CORPORATION

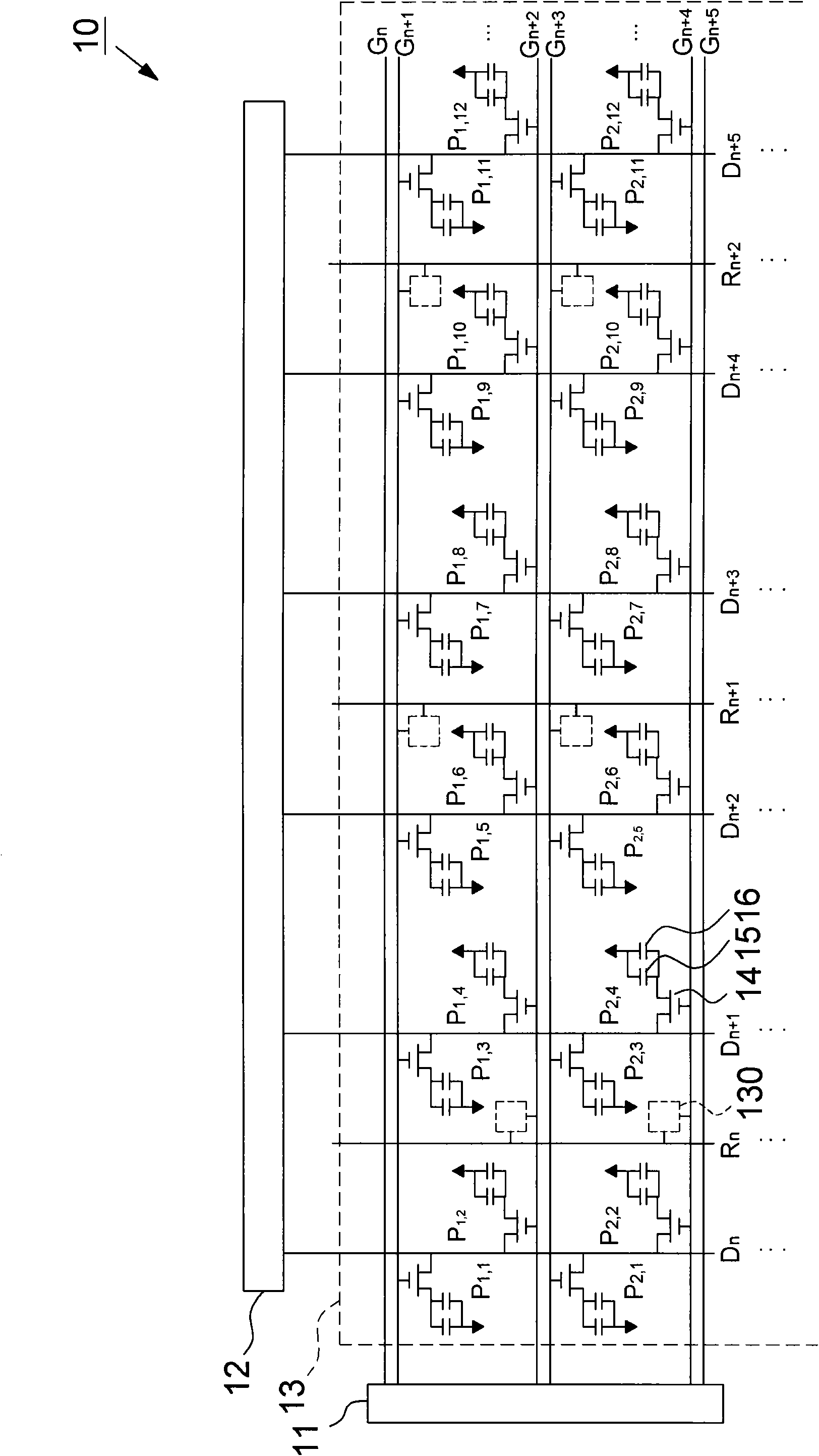

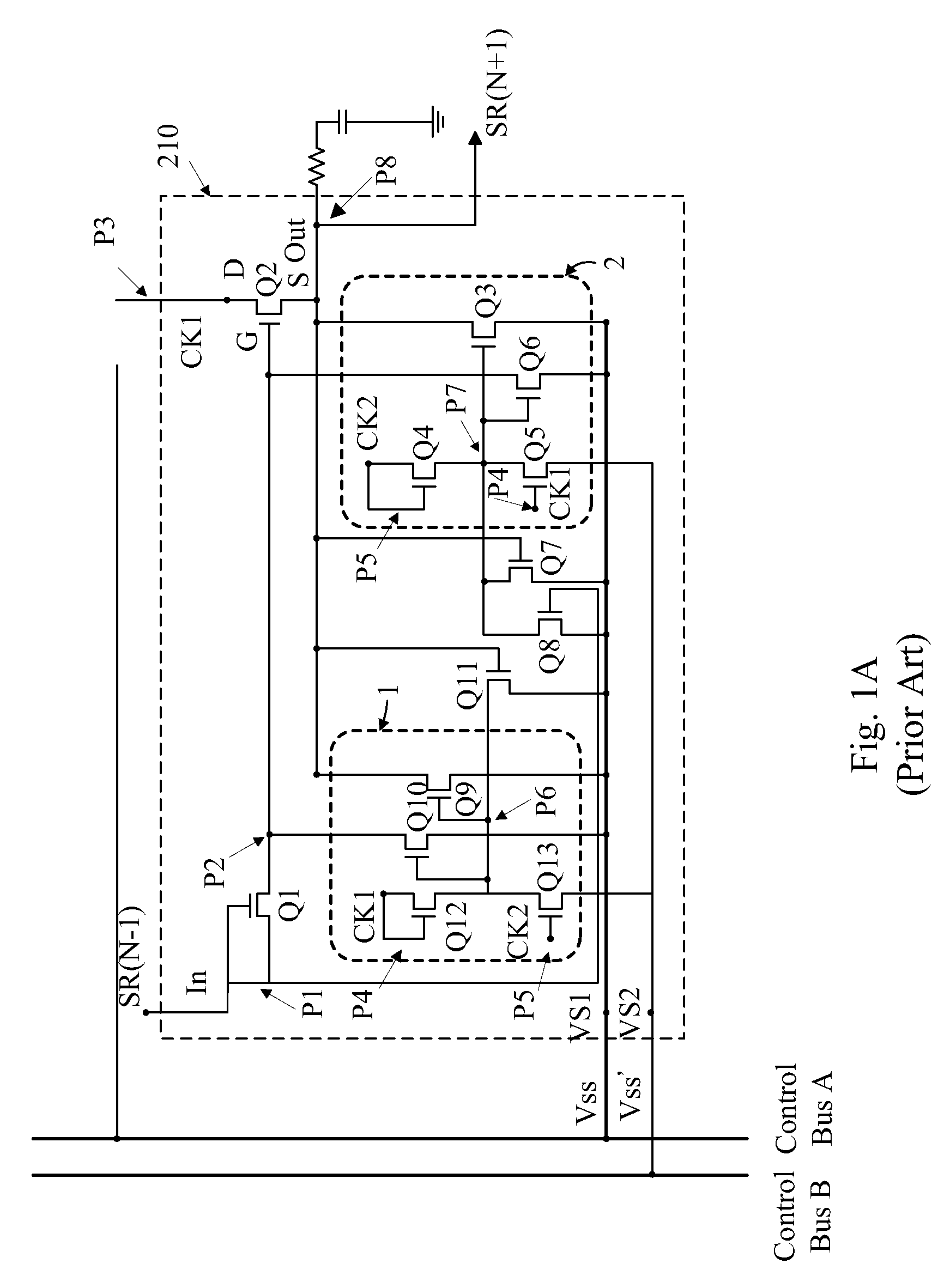

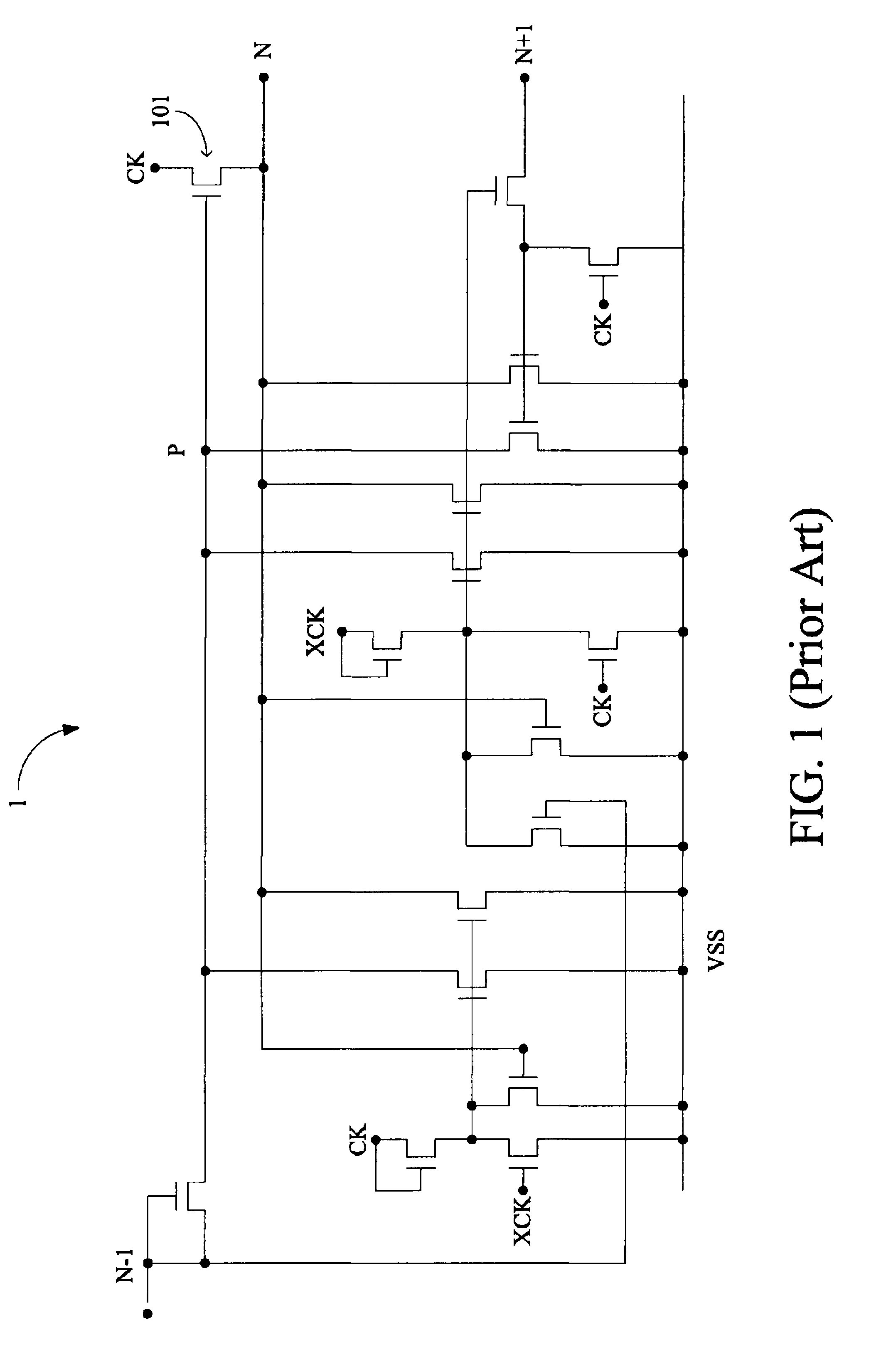

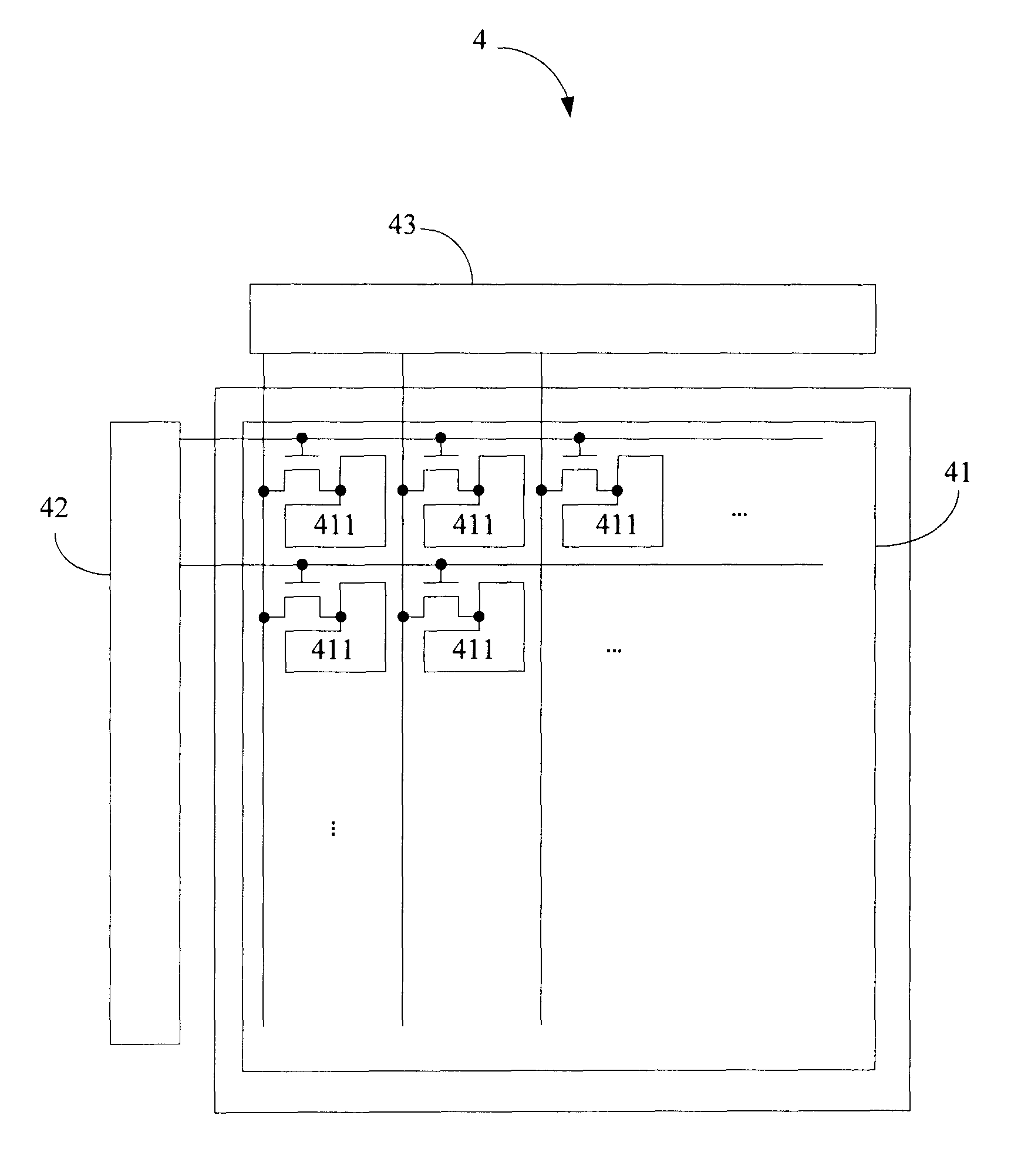

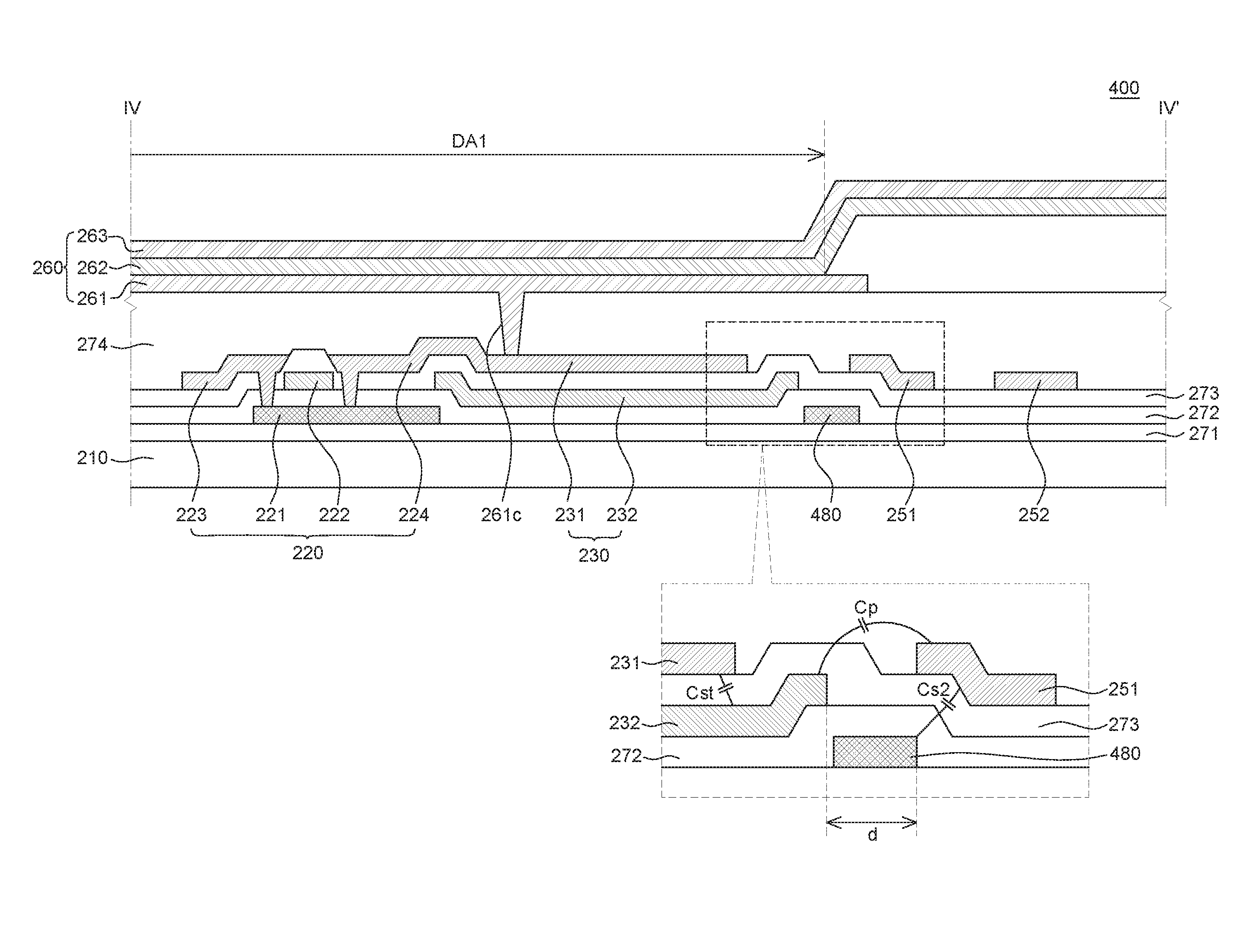

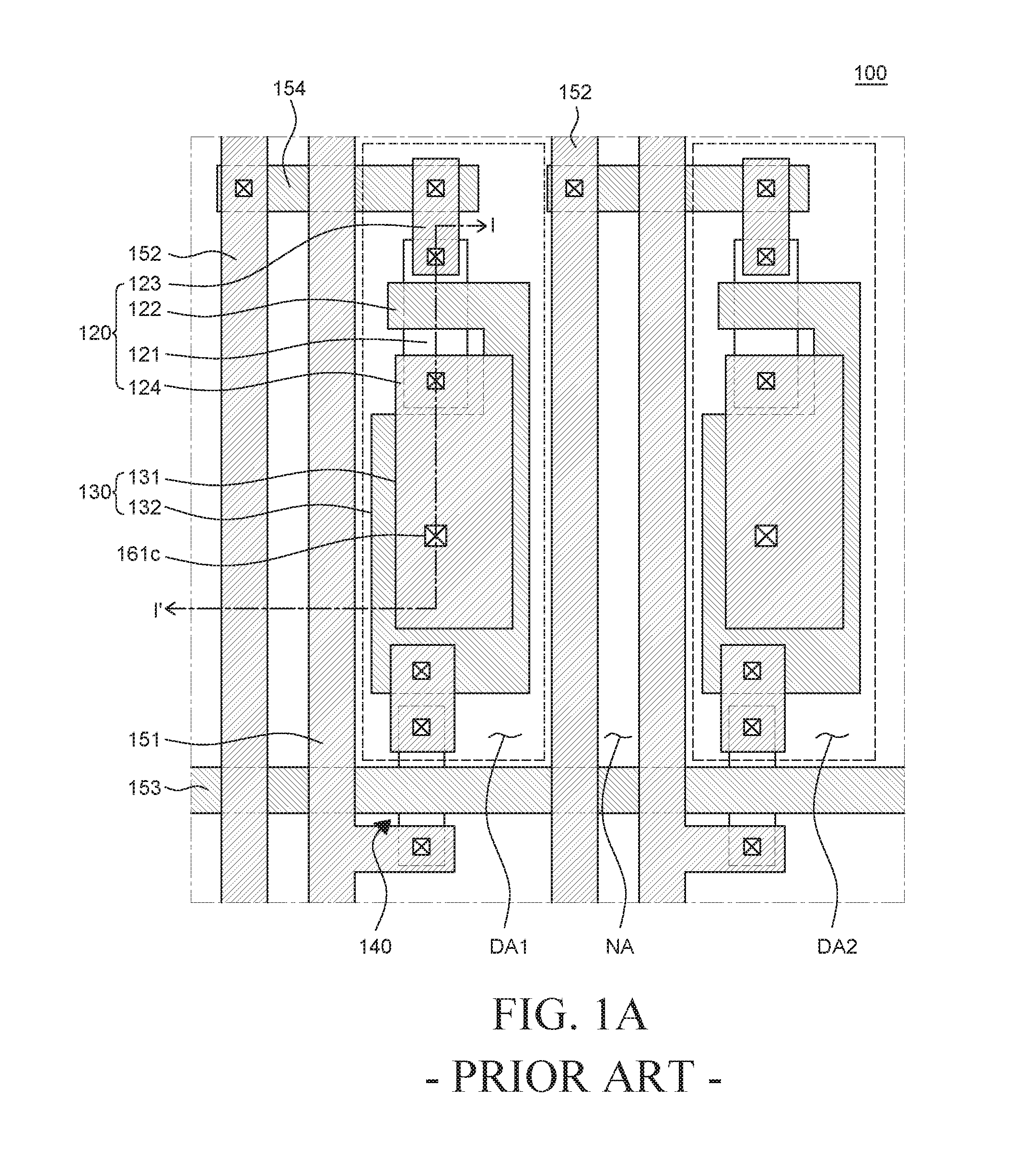

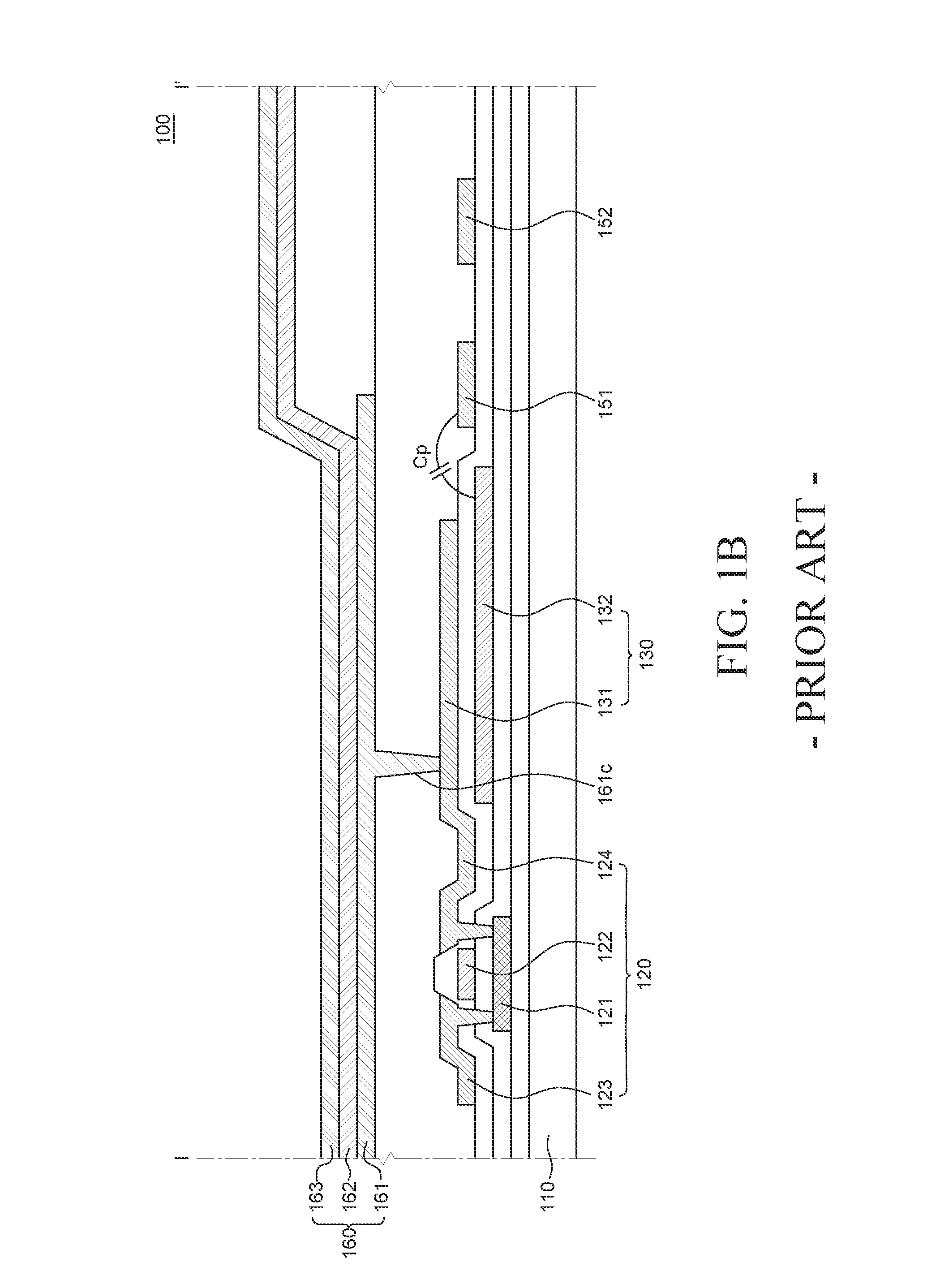

Shift register, shift register array, and flat display apparatus

ActiveUS8031160B2Reduce coupling effectReduce output timeStatic indicating devicesDigital storageShift registerEngineering

A flat display apparatus comprising a shift register array is provided. The shift register array comprises a plurality of shift registers. At least one of these shift registers comprises a shift register unit, a first TFT, and a second TFT. The shift register unit is configured to receive an activation signal and comprises a first output terminal and a second output terminal. The gate of the first TFT is coupled to the first output terminal. The second electrode of the first TFT receives a clock signal. The gate of the second TFT is coupled to the first electrode of the first TFT. The second electrode of the second TFT is coupled to the second electrode of the first TFT. The first electrode of the second TFT is coupled to the second output terminal.

Owner:OPTRONIC SCI LLC

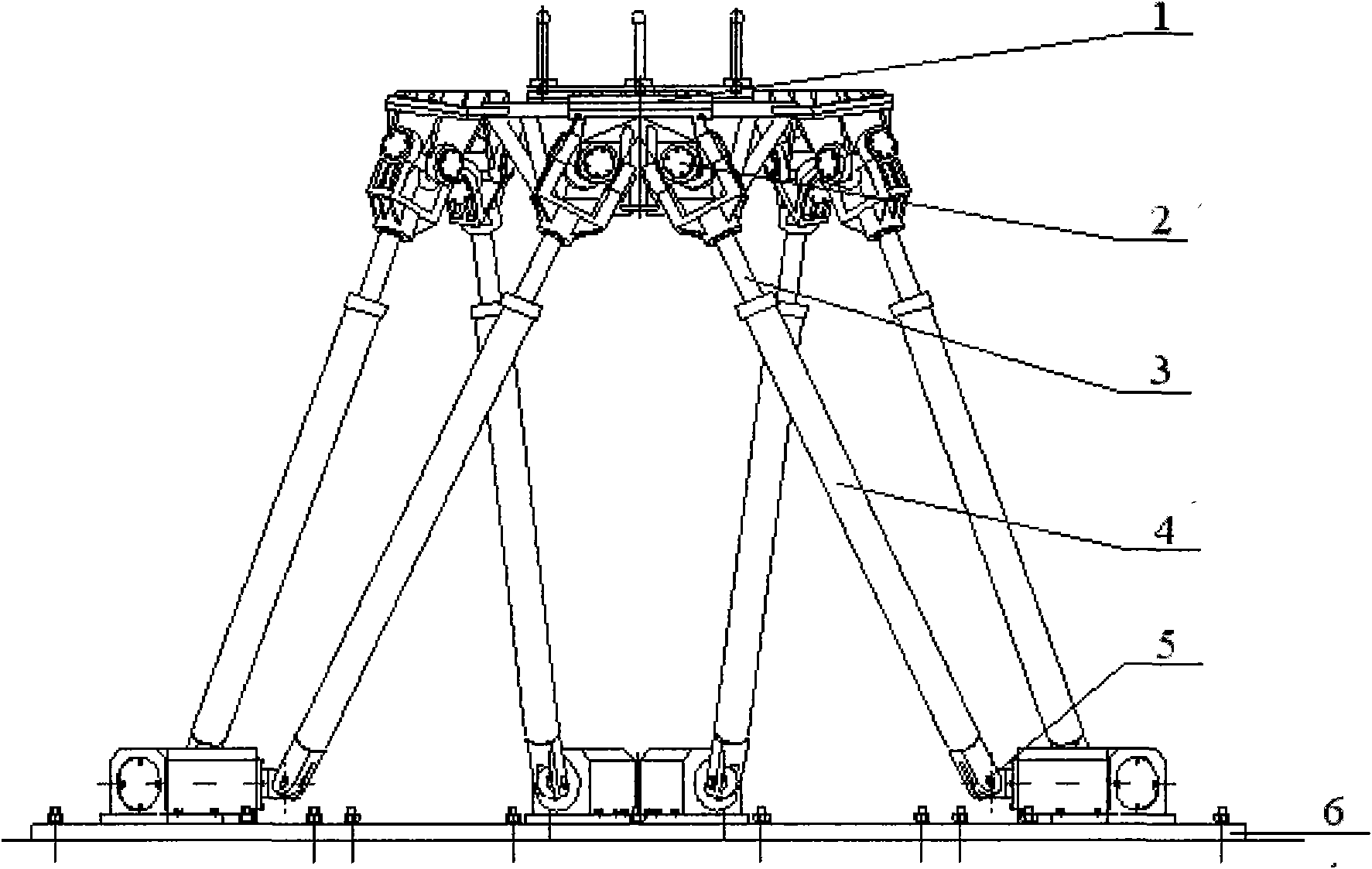

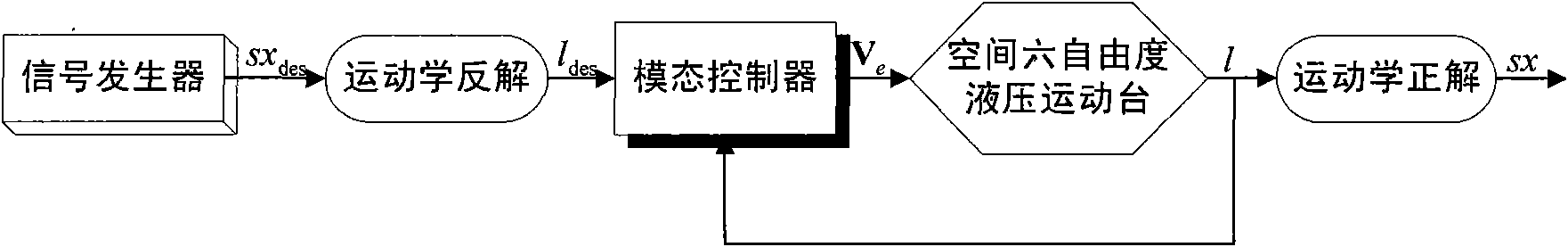

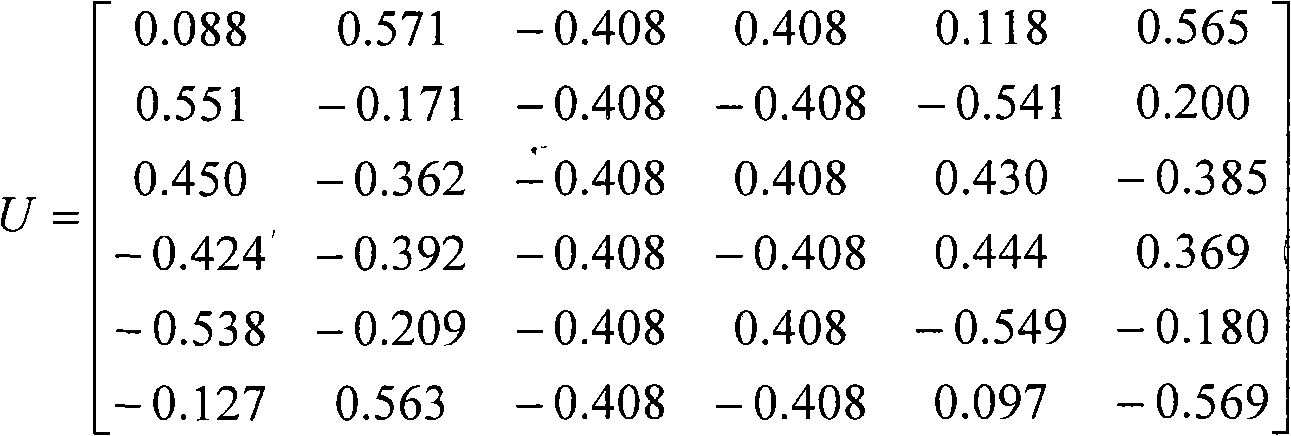

Spatial six-degree-of-freedom motion platform modal control method

InactiveCN102063122AWeaken coupling effectsImprove single-degree-of-freedom motion and multi-degree-of-freedom compound motion reproductionVehicle position/course/altitude controlPosition/direction controlKinetic couplingDynamic coupling

The invention provides a spatial six-degree-of-freedom motion platform modal control method. In the invention, a spatial six-degree-of-freedom motion platform modal matrix is used to convert a strong-coupling physical space system into a decoupled modal space system, a modal control concept is introduced on the basis of the conventional spatial six-degree-of-freedom hydraulic motion platform control, the modal conversion matrix is used to decouple a strong dynamic coupling six-degree-of-freedom hydraulic motion platform, an expected physical input signal and a motion platform actual output signal are converted into modal signals to perform independent modal control regulation, the drive and control of the spatial six-degree-of-freedom hydraulic motion platform are realized, the coupling influences among the actuators and degrees of freedom in a spatial six-degree-of-freedom hydraulic motion are weakened effectively, indexes such as the single degree of freedom motion and multiple degree of freedom motion reproduction of the six-degree-of-freedom hydraulic motion platform are improved, and the bandwidths of degrees of freedoms besides the close degree of freedom of a first order modal are improved.

Owner:HARBIN INST OF TECH

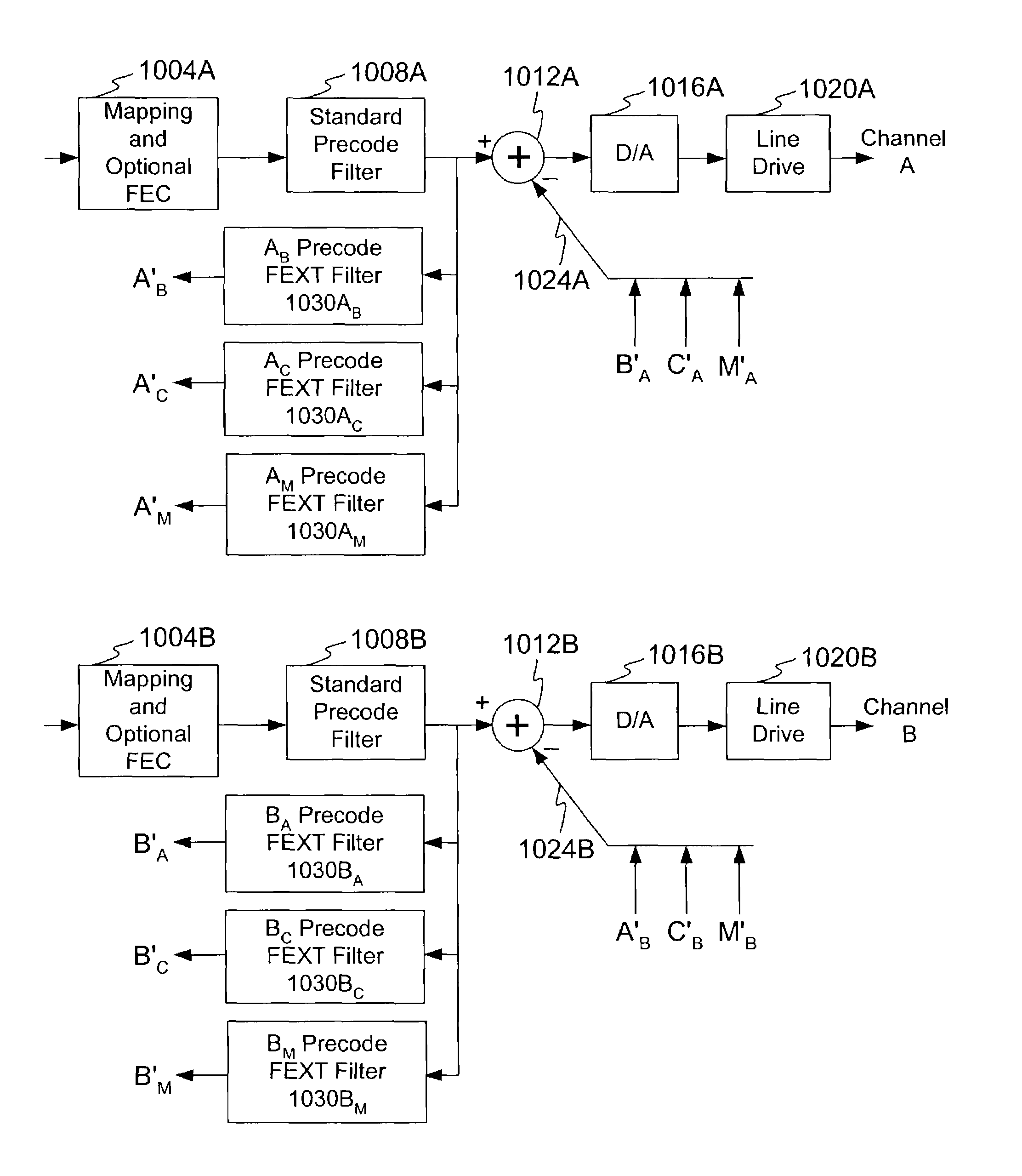

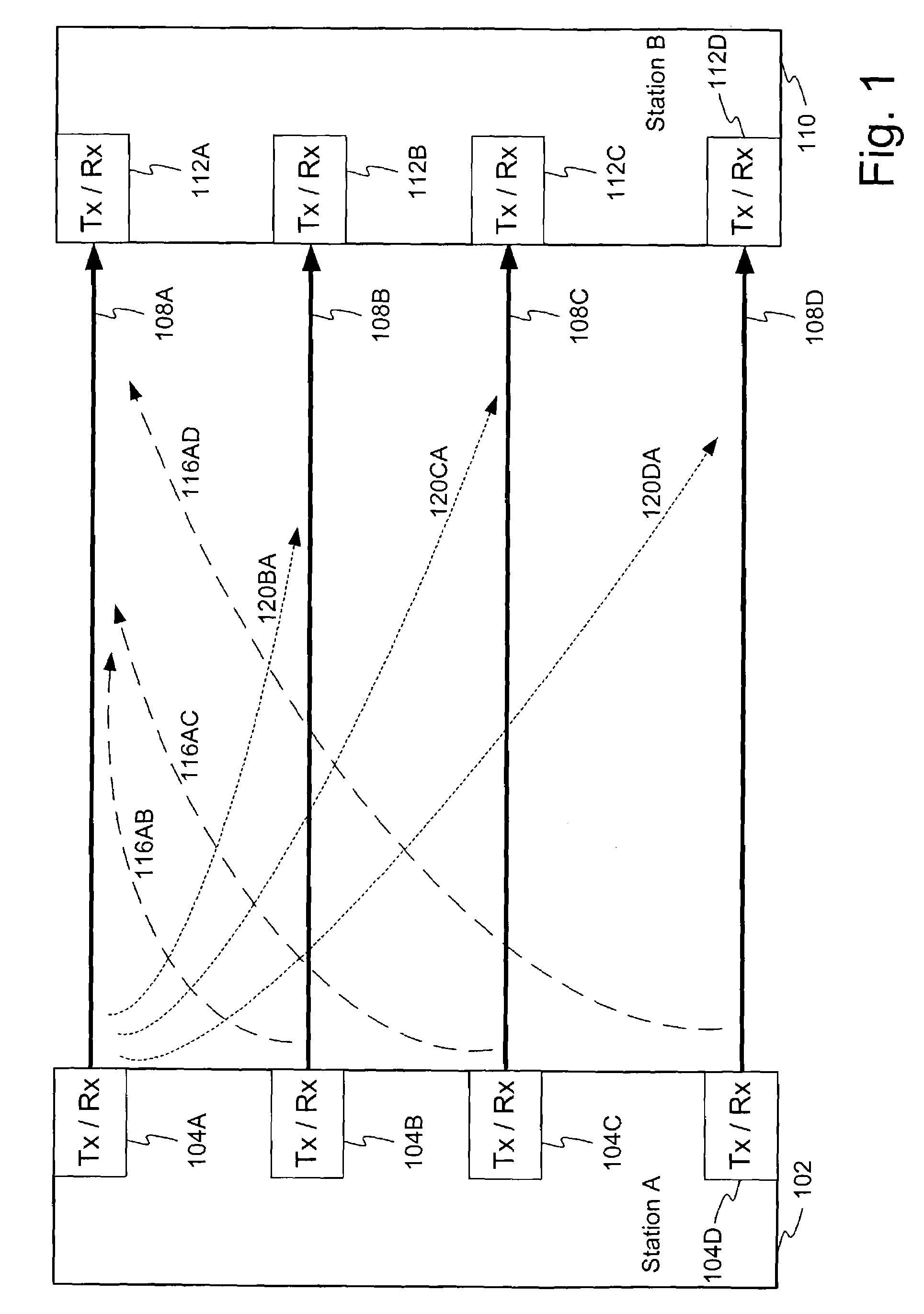

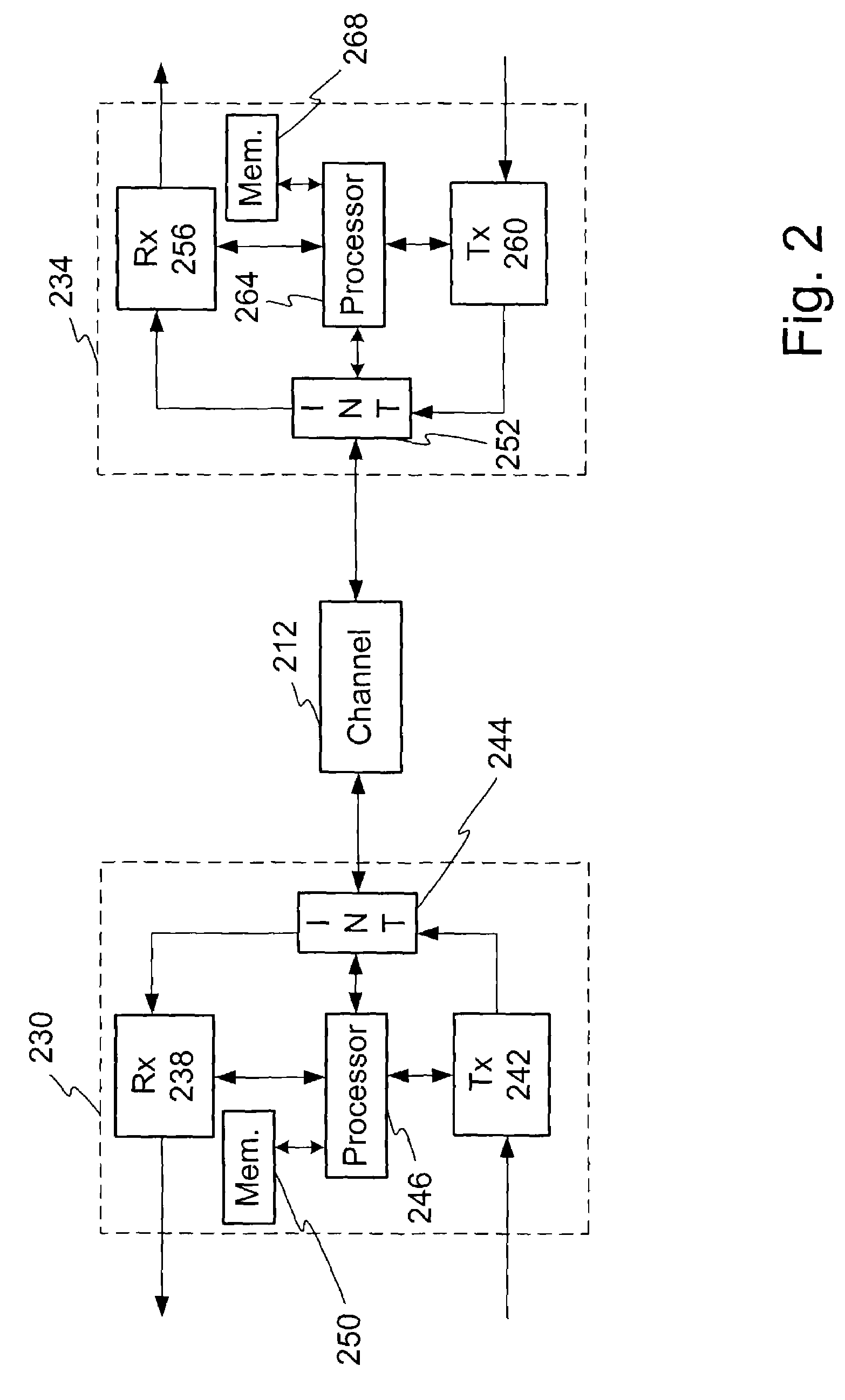

Method and apparatus for precode crosstalk mitigation

ActiveUS7164764B2Reduce coupling effectReduce noiseMultiplex system selection arrangementsSpecial service provision for substationCommunications systemEngineering

A method and apparatus for noise cancellation in a multi-channel communication system is disclosed. In one embodiment this system is configured to cancel FEXT on a victim channel utilizing the signals received on the other channels. The processing benefits gained by a receiver's other filters, such as for example, the FFE and DFE filters, is utilized when generating a FEXT cancellation signal. As a result, the complexity of the apparatus that generates the FEXT cancellation signal may be made less complex since part of the processing burden is performed by other filter apparatus. In one configuration pre-code FEXT cancellation occurs in that a pre-code FEXT filter generates one or more pre-code FEXT cancellation signals corresponding to each of the other channels. The pre-code FEXT cancellation signals are combined, prior to transmission, with the signals associated with each of the other channels, to thereby pre-cancel FEXT prior to transmission.

Owner:MARVELL ASIA PTE LTD

Shift register, shift register array, and flat display apparatus

ActiveUS20080068326A1Reduce coupling effectReduce output timeStatic indicating devicesDigital storageFlat panelClock signal

A flat display apparatus comprising a shift register array is provided. The shift register array comprises a plurality of shift registers. At least one of these shift registers comprises a shift register unit, a first TFT, and a second TFT. The shift register unit is configured to receive an activation signal and comprises a first output terminal and a second output terminal. The gate of the first TFT is coupled to the first output terminal. The second electrode of the first TFT receives a clock signal. The gate of the second TFT is coupled to the first electrode of the first TFT. The second electrode of the second TFT is coupled to the second electrode of the first TFT. The first electrode of the second TFT is coupled to the second output terminal.

Owner:AU OPTRONICS CORP

Organic light emitting display device

ActiveUS20160163780A1Reduce coupling effectReduce parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceActive layer

An organic light emitting display device is discussed. The organic light emitting display device includes a driving thin film transistor including an active layer and a gate electrode; a storage capacitor including a first electrode and a second electrode; a first pattern electrode including the gate electrode and the first electrode; an anode disposed on the driving thin film transistor and the storage capacitor; a second pattern electrode connected with an anode contact part which connects an output electrode connected with the active layer and the anode; and a patterned semiconductor layer including the active layer having a semiconductive characteristic and a shield unit having a conductive characteristic.

Owner:LG DISPLAY CO LTD

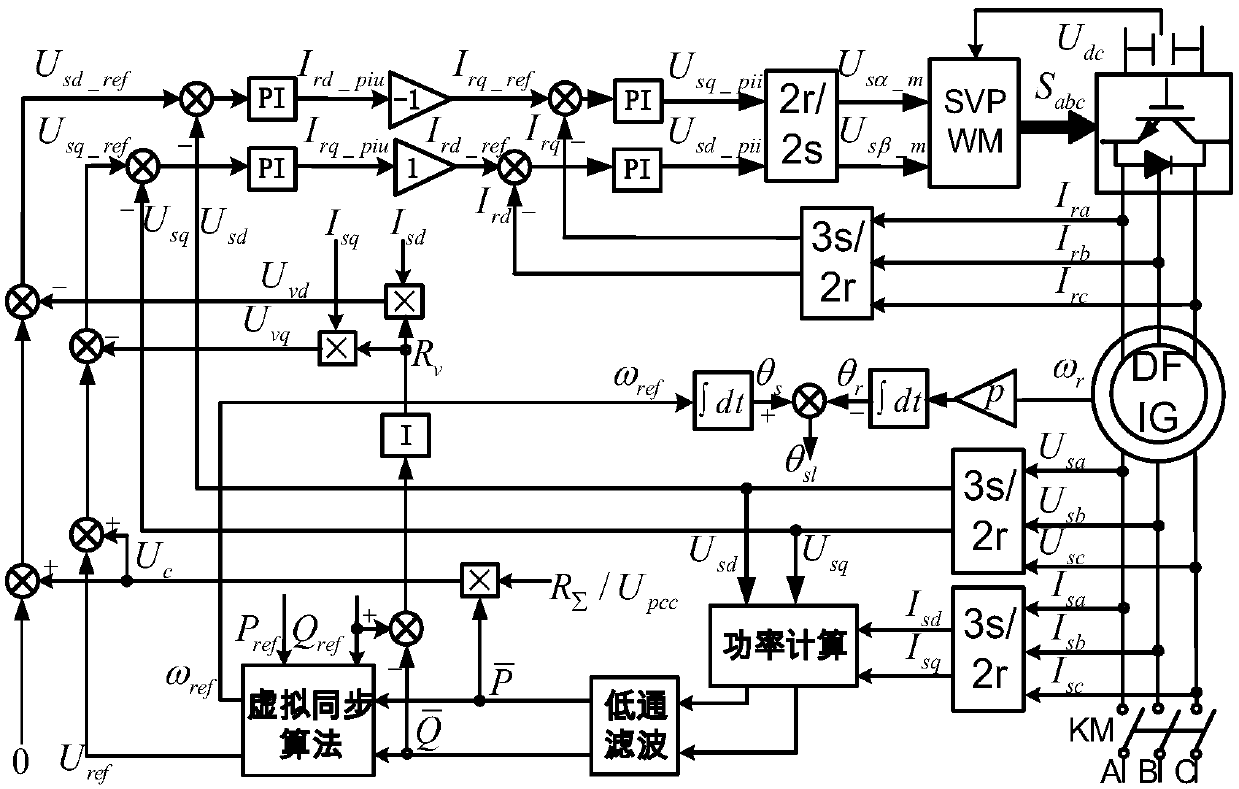

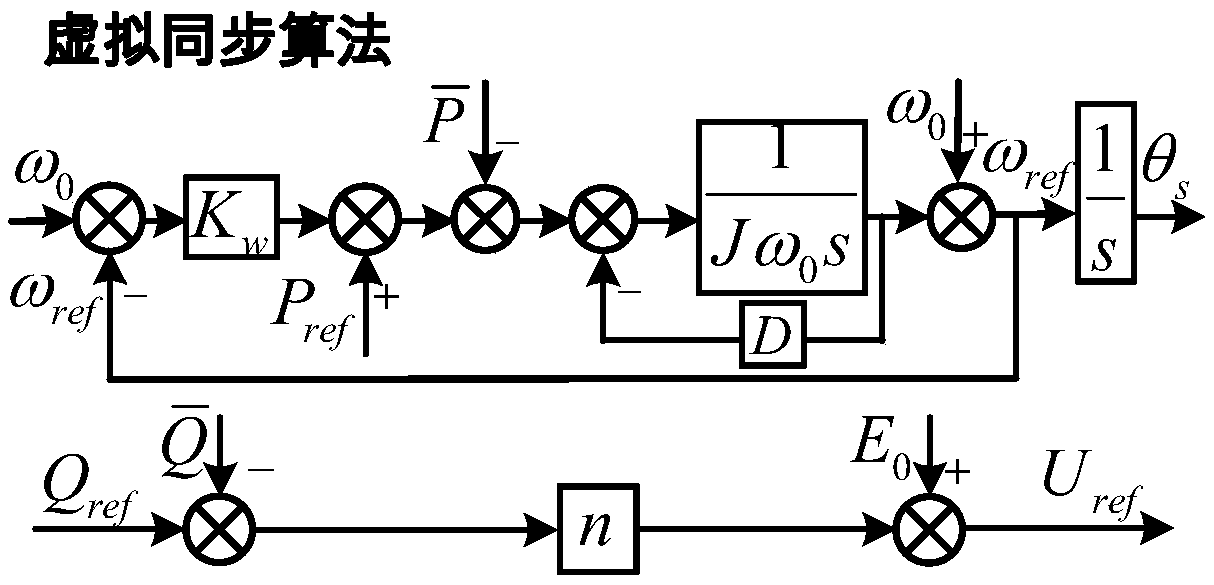

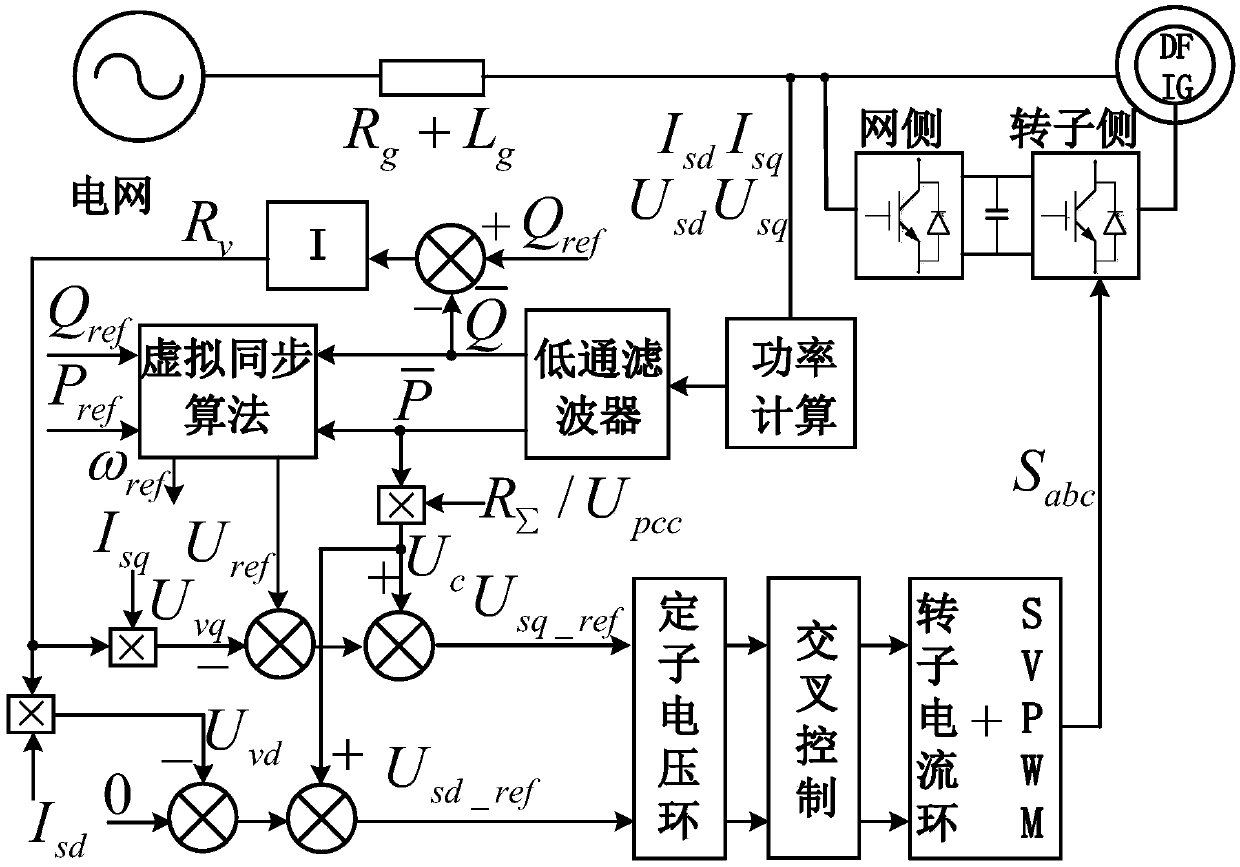

Voltage control type virtual synchronizing method of double-feed wind power generator set

ActiveCN108683198AAccurately offsets estimation errorsSpeed up the dynamic process of power regulationClimate change adaptationSingle network parallel feeding arrangementsControl mannerClosed loop

The invention discloses a voltage control type virtual synchronizing method of a double-feed wind power generator set. Through simulating inertia and a frequency-modulating and voltage-modulating characteristic of a synchronizer, the set can be different from a characteristic of no electric grid frequency change response in a traditional current control type, thereby possessing capability of supporting voltage and frequency of a weak power grid based on the voltage control type through virtual inertia. The method provides and realizes a VCT-DFIC virtual synchronous control structure of which an inner ring is controlled by an improved double-feed generator stator voltage rotor current double-closed-loop structure based on adaptive stator virtual impedance and transmission line sag voltage feedforward compensation in a control manner which includes crossed control between stator voltage and rotor current and furthermore an outer ring is controlled by a virtual synchronous realizing algorithm. The method realizes output power control in VCT-DFIG grid integration operation in a weak grid condition with any actual impedance and effective decoupling, and furthermore a designed control structure realizes higher inertia and frequency supporting capability of the double-feed generator.

Owner:HEFEI UNIV OF TECH

Compensating for coupling based on sensing a neighbor using coupling

Shifts in the apparent charge stored on a floating gate (or other charge storing element) of a non-volatile memory cell can occur because of the coupling of an electric field based on the charge stored in adjacent floating gates (or other adjacent charge storing elements). To compensate for this coupling, the read or programming process for a given memory cell can take into account the programmed state of an adjacent memory cell. To determine whether compensation is needed, a process can be performed that includes sensing information about the programmed state of an adjacent memory cell (e.g., on an adjacent bit line or other location).

Owner:SANDISK TECH LLC

Array substrate and manufacturing method and display device thereof

InactiveCN102651371ALower resistanceReduce coupling effectSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceOptoelectronics

The invention discloses an array substrate, relating to the technical field of display. The array substrate comprises a plurality of grid lines and data lines formed on a substrate and a plurality of film transistor pixel structures formed between the grid lines and the data lines; each film transistor pixel structure comprises a film transistor and a display area; each display area is provided with a common electrode; and the array substrate further comprises at least one common electrode line which is connected with the common electrodes. The invention further discloses a manufacturing method and a display device of the array substrate. The array substrate provided by the invention prevents pictures from generating a crosstalk phenomenon.

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD

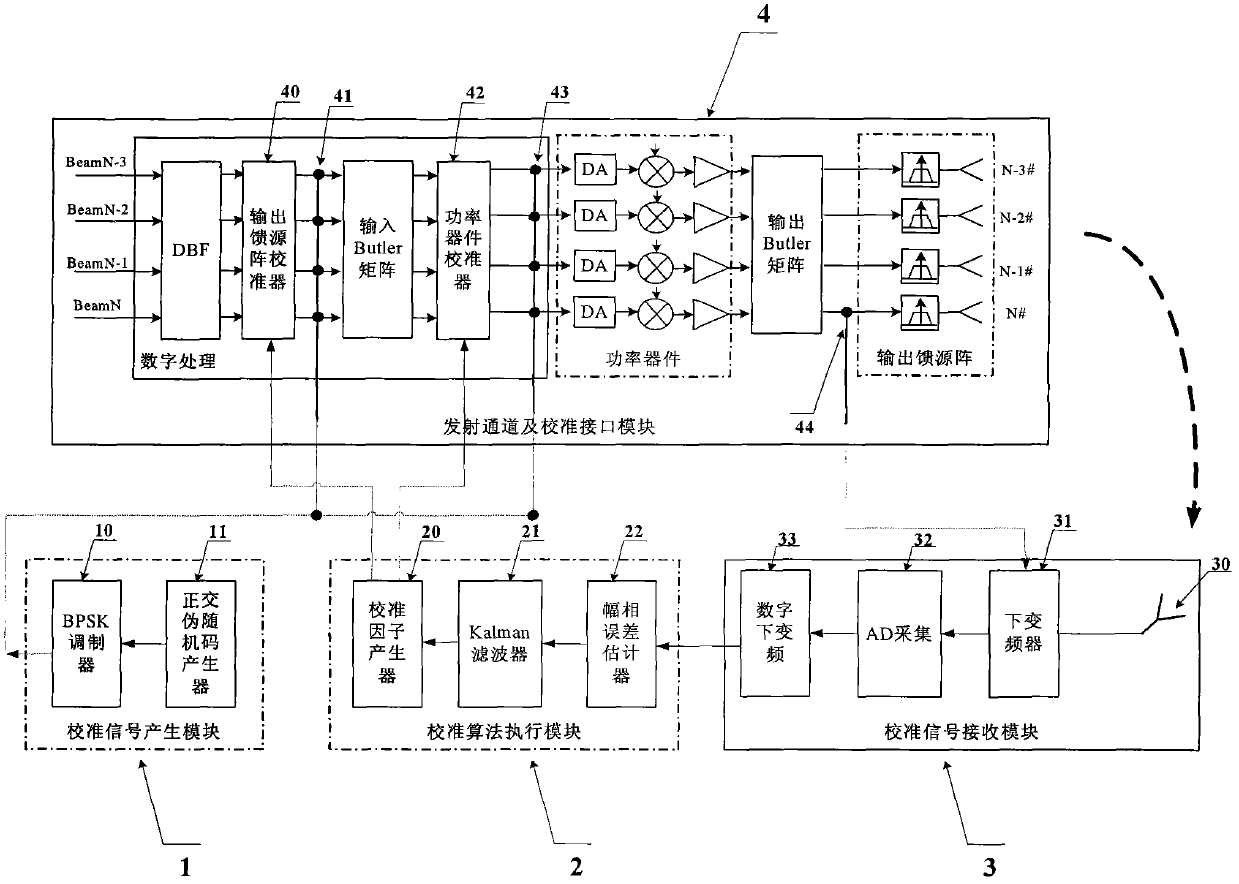

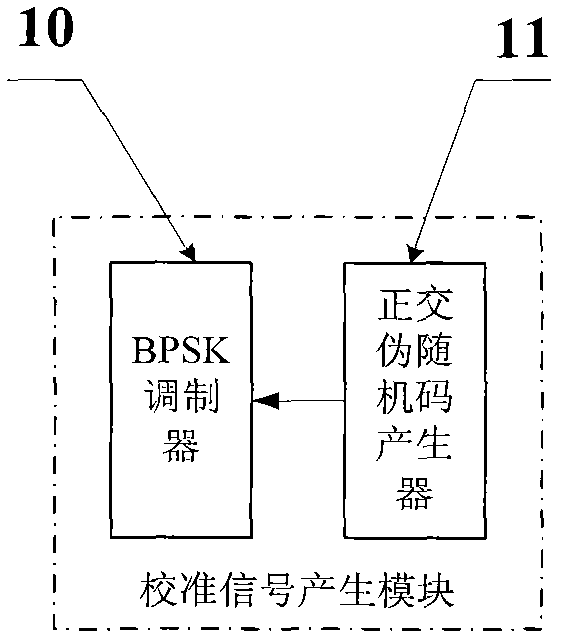

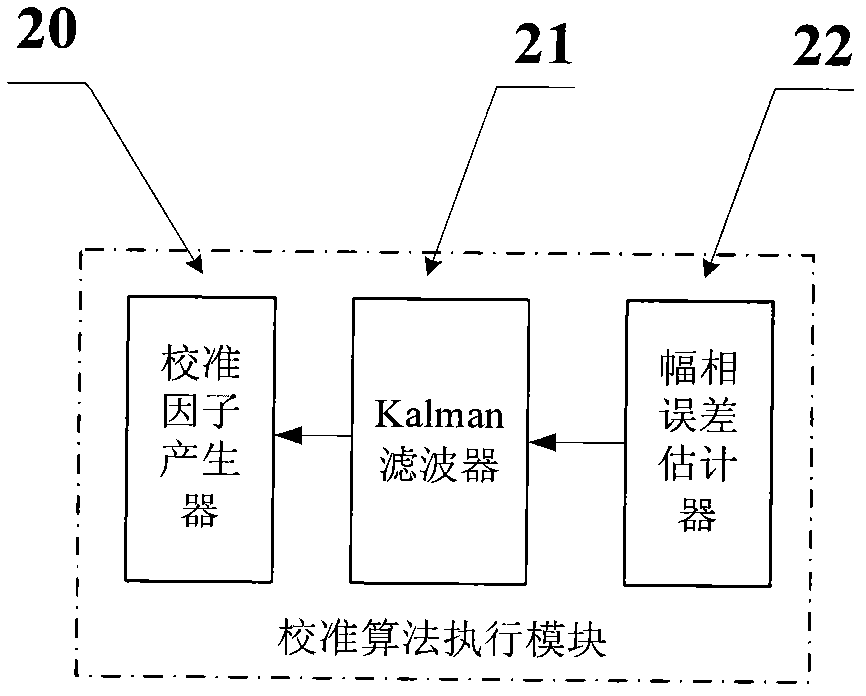

Calibration method and calibration system for amplitude phase error of satellite-borne DBF (Digit Beam Forming) transmitting channel

ActiveCN102413082ADifficult to measureDifficult to calibrateRadio transmissionTransmitter/receiver shaping networksAudio power amplifierFrequency mixer

The invention provides a calibration method and calibration system for the amplitude phase error of a satellite-borne DBF (Digit Beam Forming) transmitting channel. The calibration method and the calibration system respectively comprise two levels of calibration schemes, and the two levels of calibration schemes are composed of output Butler front-end channel part amplitude phase calibration and output Butler rear-end channel part amplitude phase calibration. The method comprises the following steps of: firstly, injecting a calibration signal after inputting the Butler, and coupling the calibration signal at a test port which transmits the Butler, thereby realizing the calibration of a frequency mixer and a power amplifier; and then, keeping the original calibration signal injection mode, and receiving the calibration signal through a far field, thereby realizing the calibration of a filter and a feed source array. Through the method and system provided by the invention, the measurement accuracy of the amplitude phase error is improved greatly, so that the method and the system can be used for effective loads of communication satellites, detection satellites and navigation satellites, and also can be used in the technical fields of ground radars and the like.

Owner:XIAN INSTITUE OF SPACE RADIO TECH

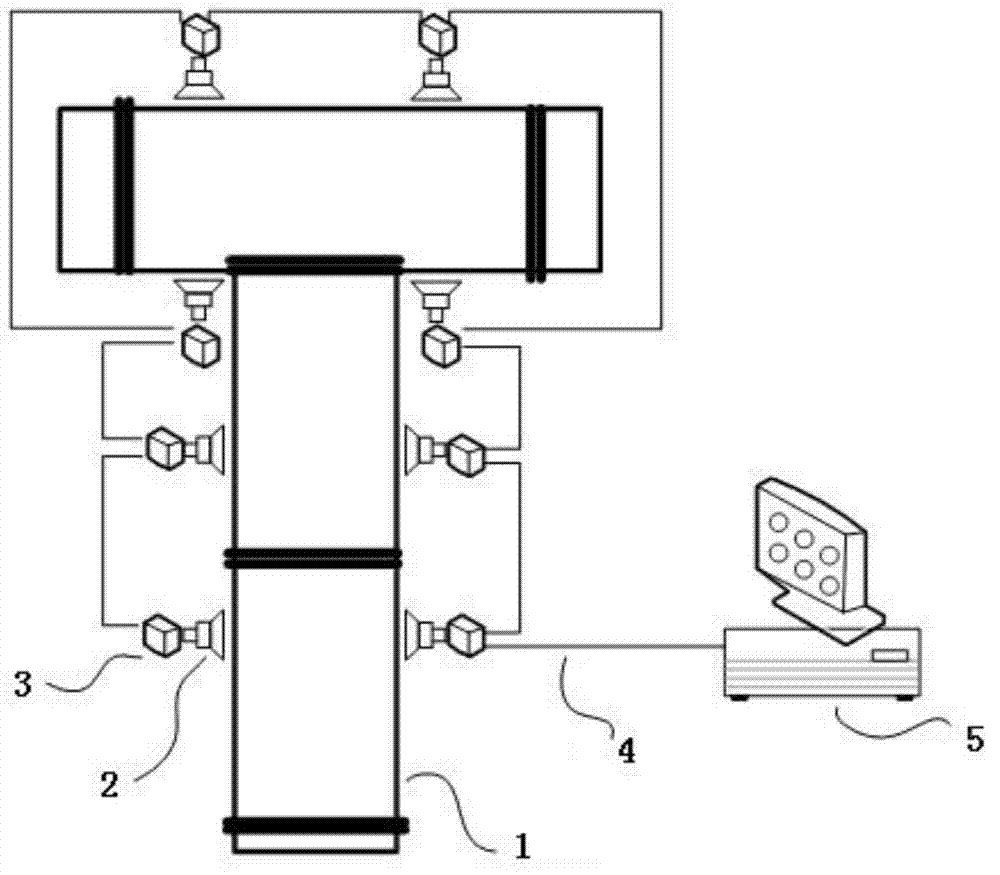

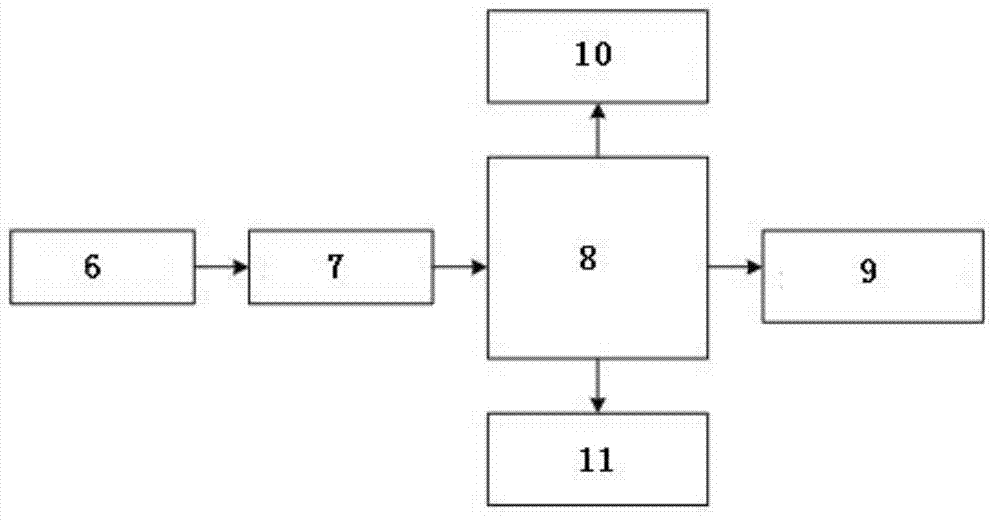

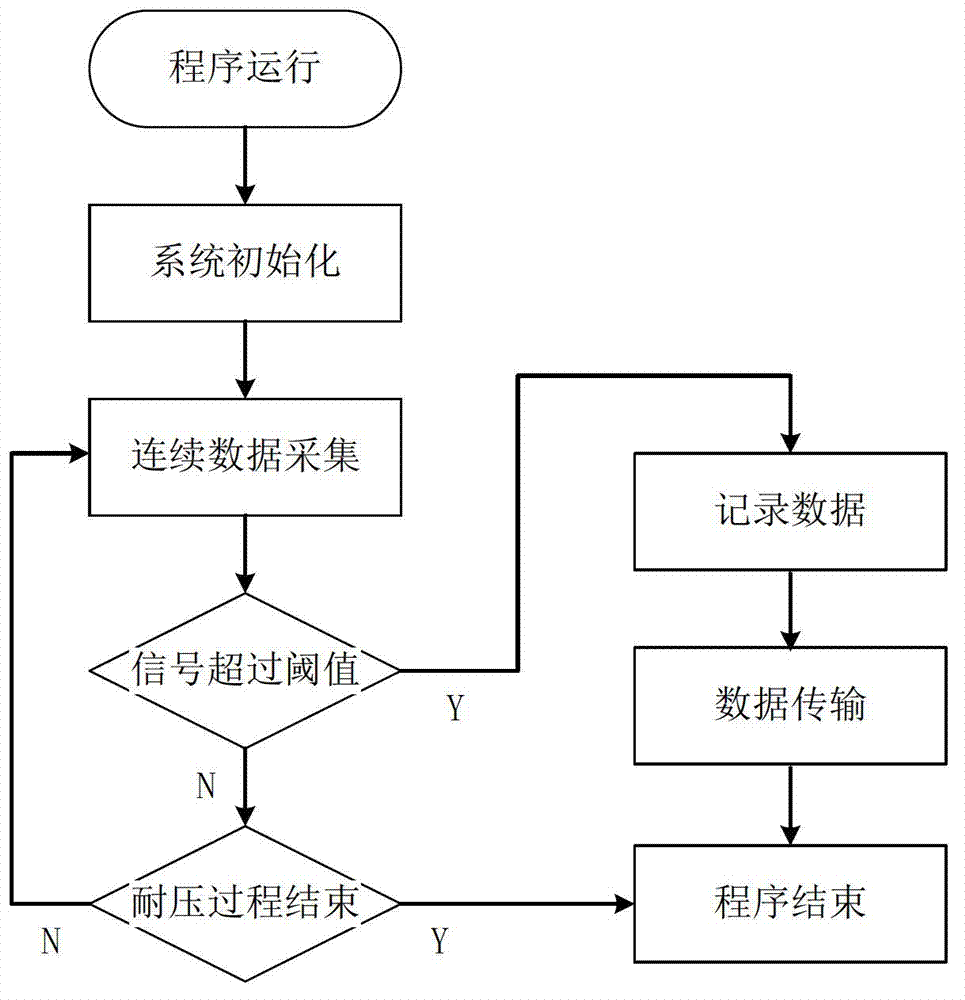

System and method for discharge fault location of geographic information system (GIS) alternating current (AC) voltage withstand test

ActiveCN103197215ACompact structureEasy to carry and detectTesting dielectric strengthFault locationUltrasonic sensorSonification

The invention discloses a system and a method for discharge fault location of a geographic information system (GIS) alternating current (AC) voltage withstand test, can effectively acquire the discharge fault signals of the GIS AC voltage withstand test, and can accurately locate a discharge air chamber. The system comprises a signal processing server, a plurality of ultrasonic sensors and a plurality of signal collectors. The signal processing server is used for analyzing partial discharge signals, abstracting discharge pulse signals, judging the position of a partial discharge source, and evaluating the serious degree of partial discharge. The plurality of ultrasonic sensors are dispersedly fixed on the outer surface of a GIS shell body, and used for acquiring the discharge fault signals inside the GIS through an ultrasonic detecting method. The plurality of signal collectors adopting single data bus cascade connections are respectively connected with the ultrasonic sensors, and the signal collectors at one end are connected with the signal processing server to be used for amplifying and collecting the signals from the ultrasonic sensors, storing fault signals, and transmitting data results to the signal processing server.

Owner:STATE GRID CORP OF CHINA +1

Structure and method of sub-gate NAND memory with bandgap engineered SONOS devices

ActiveUS7948799B2Improve good performanceReduce coupling effectTransistorSolid-state devicesBit lineEngineering

A bandgap engineered SONOS device structure for design with various AND architectures. The BE-SONOS device structure comprises a spacer oxide disposed between a control gate overlaying an oxide-nitride-oxide-nitride-oxide stack and a sub-gate overlaying a gate oxide. In one example, a BE-SONOS sub-gate-AND array architecture has multiple strings of SONONOS devices with sub-gate lines and diffusion bit lines. In another example, a BE-SONOS sub-gate-AND architecture has multiple strings of SONONOS devices with sub-gate lines, relying on the sub-gate lines that create inversions to substitute for the diffusion bit lines.

Owner:MACRONIX INT CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com