Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

230results about How to "Reduce data transfer time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

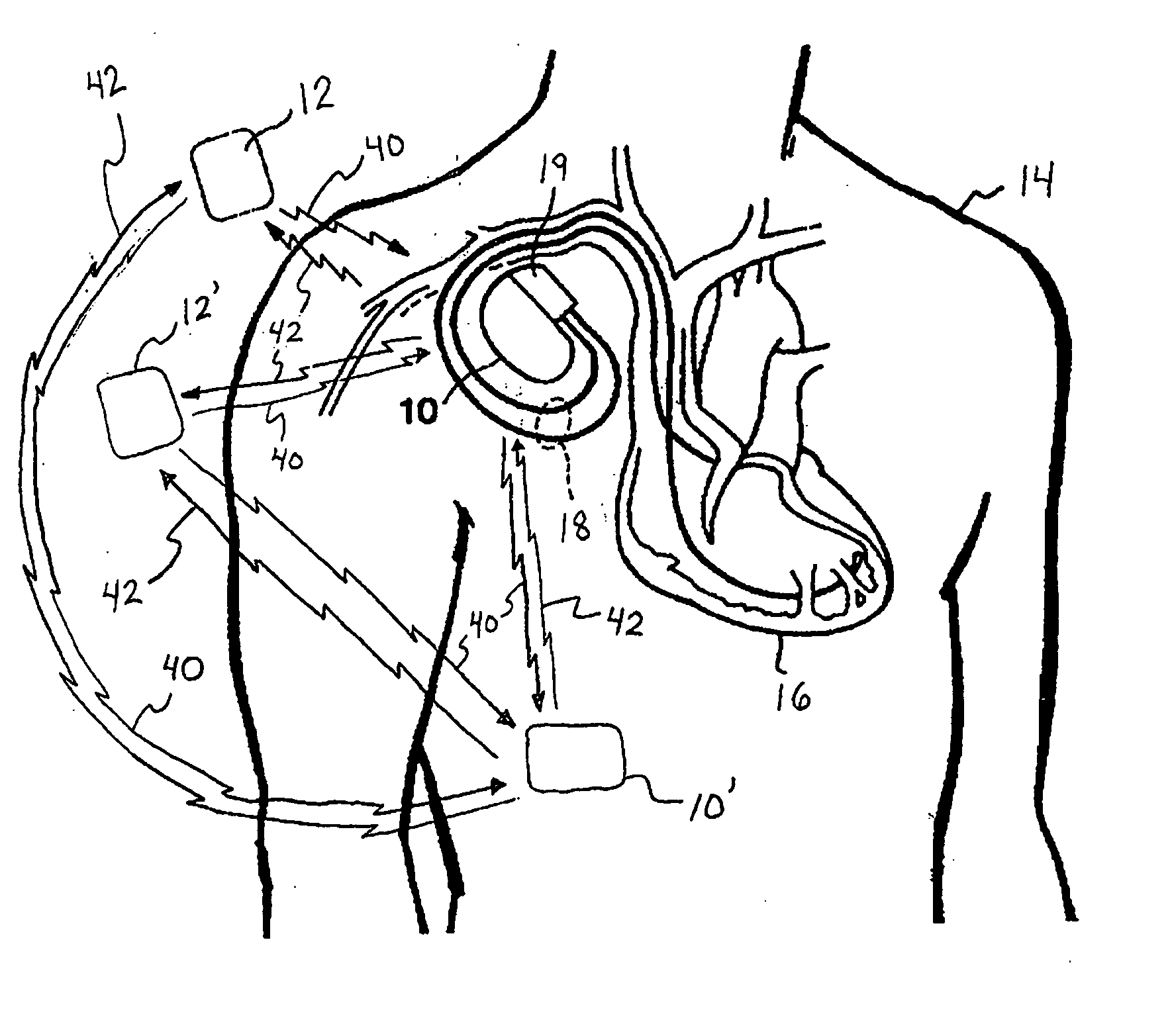

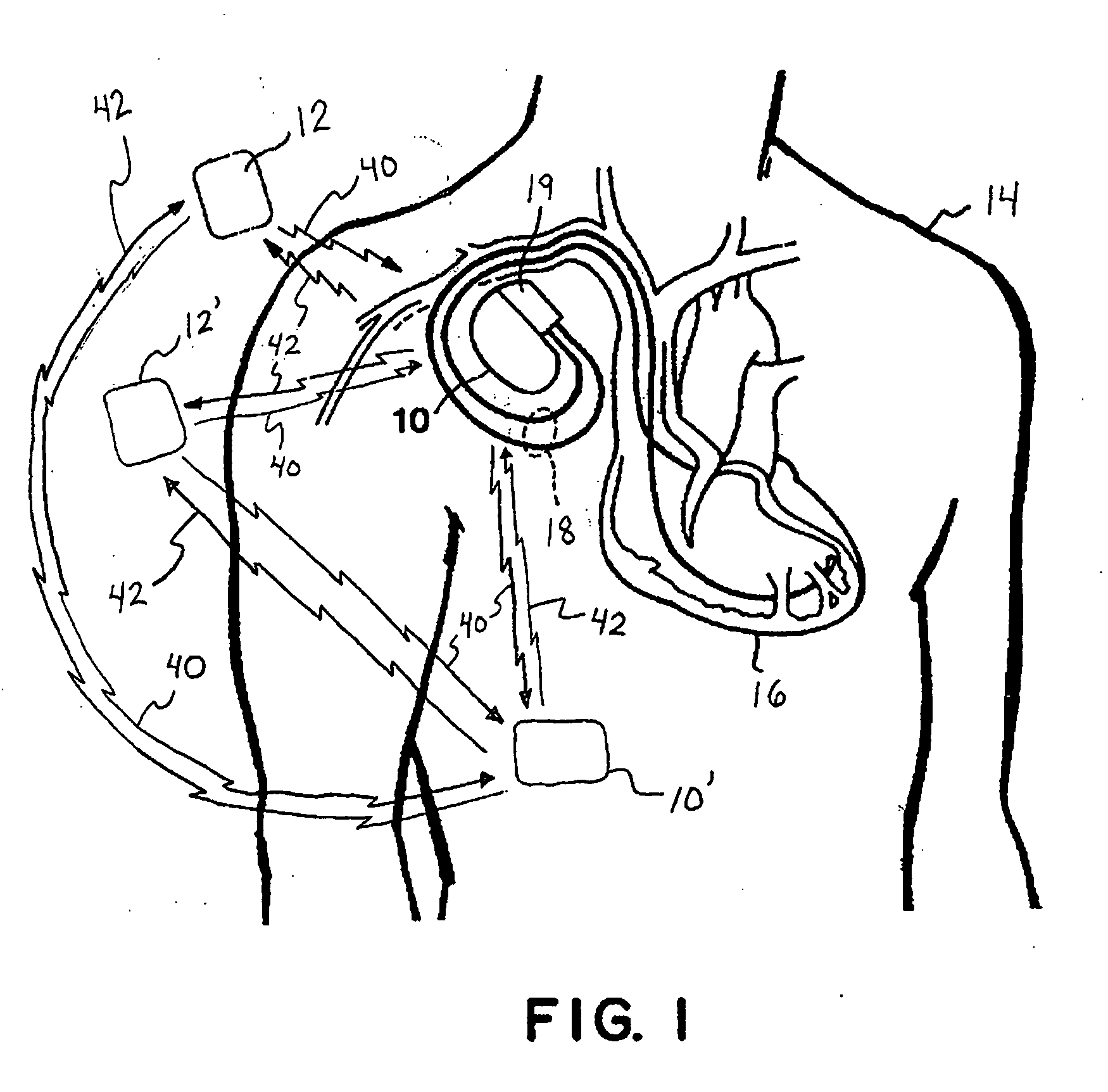

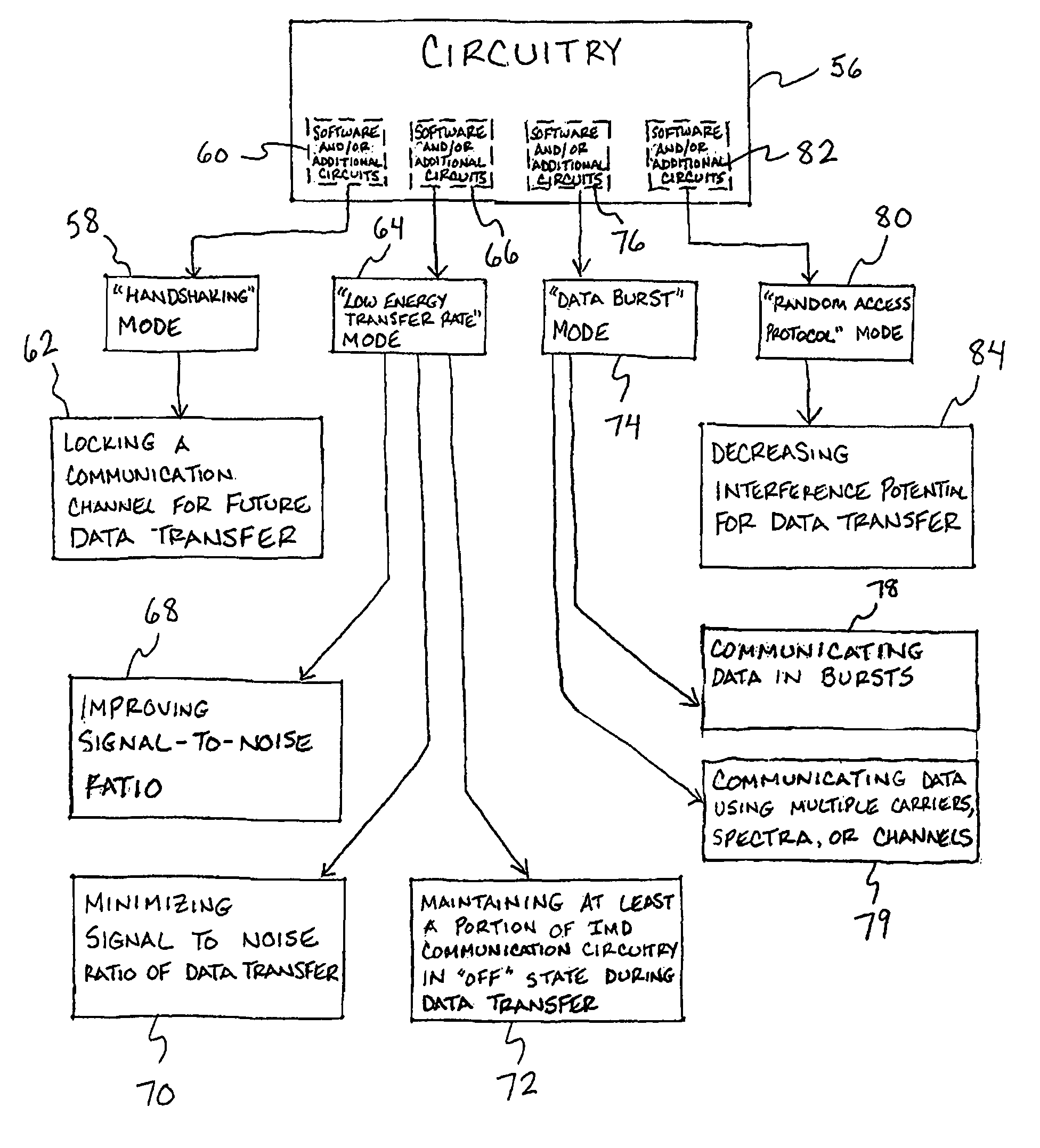

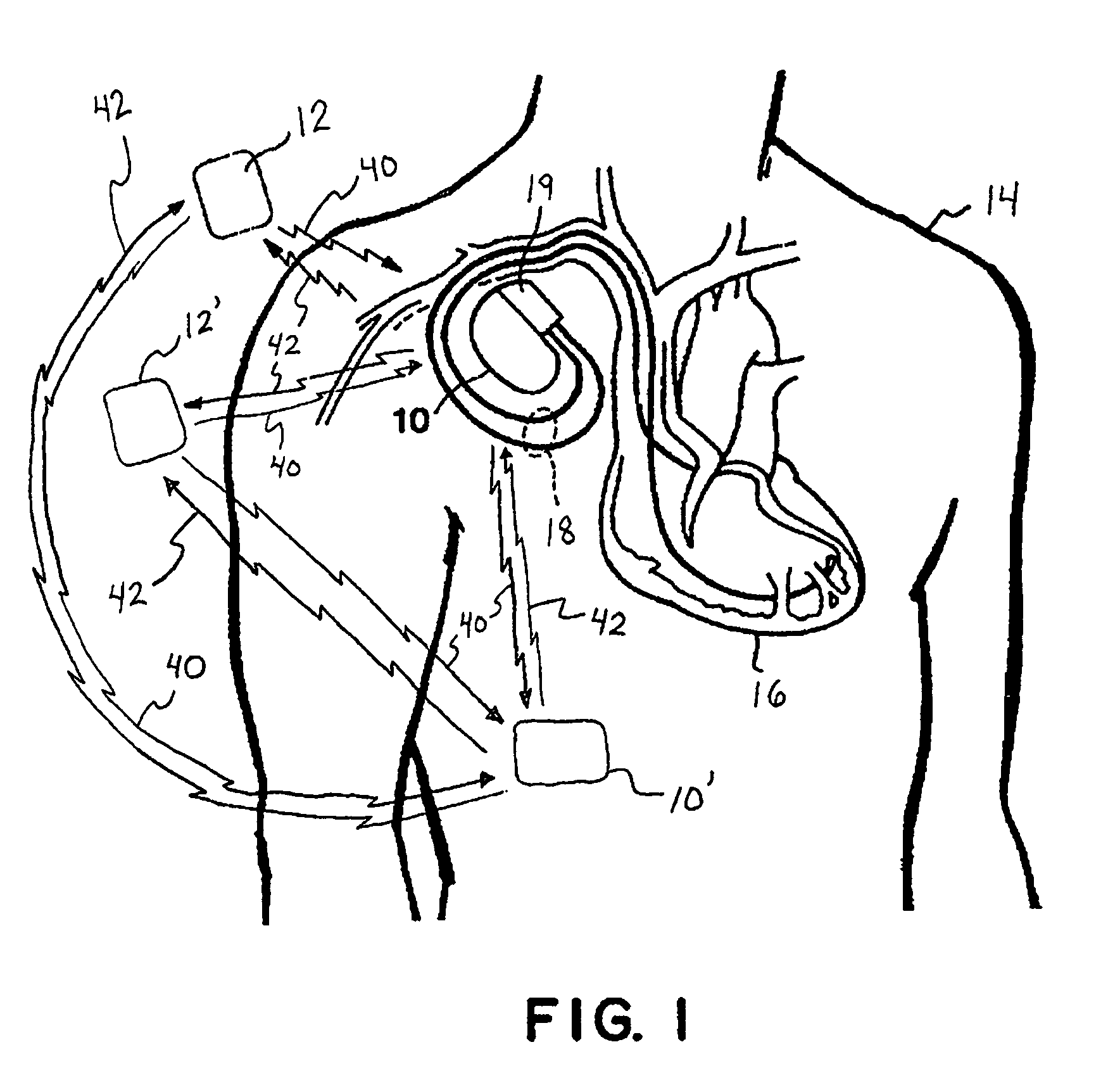

Protocol implementation for telemetry communications involving implantable medical devices

ActiveUS20070123946A1Minimize interferenceOptimizing telemetry communicationElectrotherapySurgeryElectrical devicesEngineering

Embodiments of the invention relate to optimizing telemetry communication involving one or more medical devices and one or more electrical devices. The telemetry communication is optimized by implementing software and / or one or more additional circuits within at least one medical device and at least one electrical device to provide one or more modes or functions of optimizing transfer of data between the medical device and the at least one electrical device, minimizing interference of the data transfer, and reducing data transfer time and / or preserving electrical energy sources of one or more of the medical device and the at least one electrical device.

Owner:MEDTRONIC INC

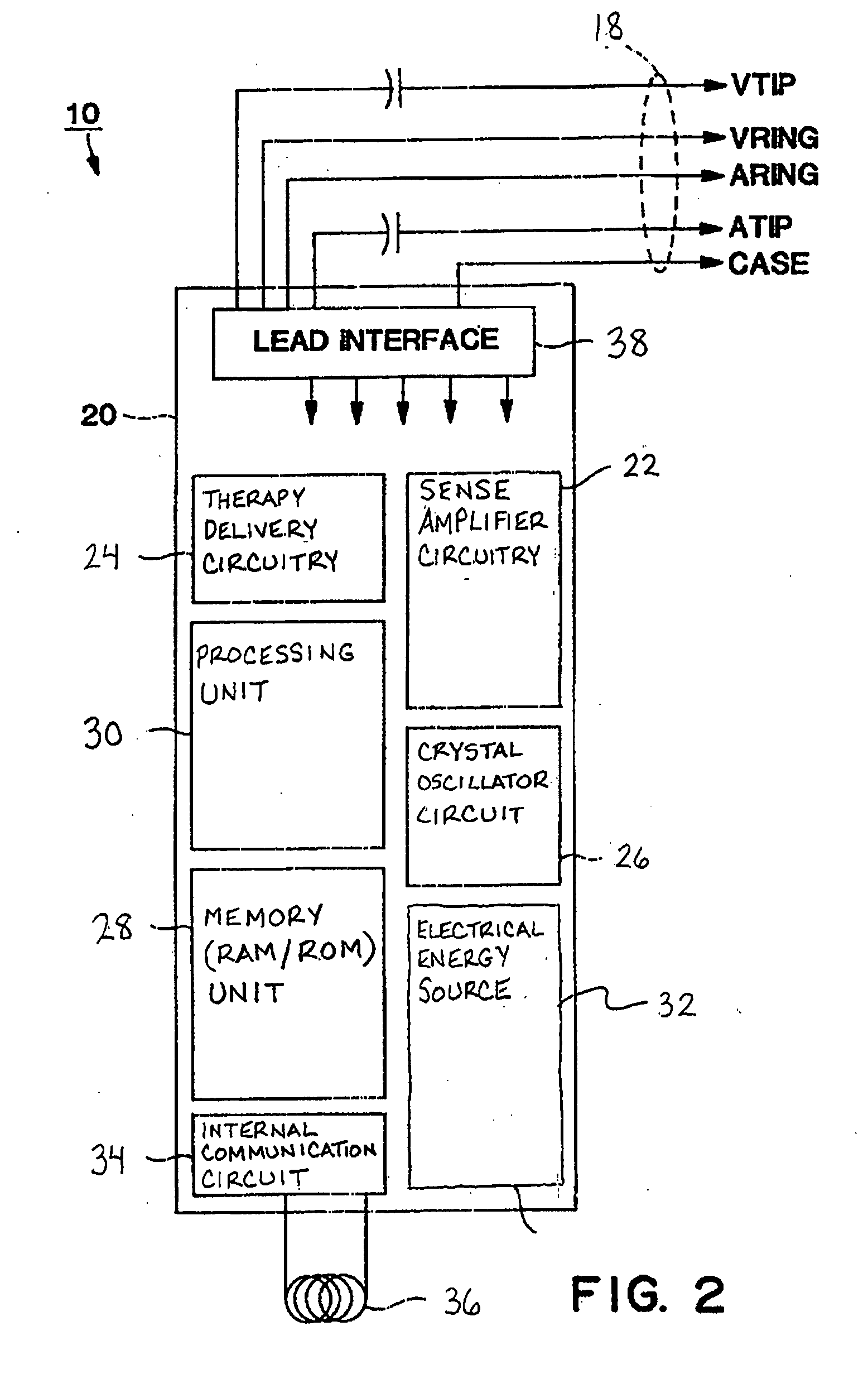

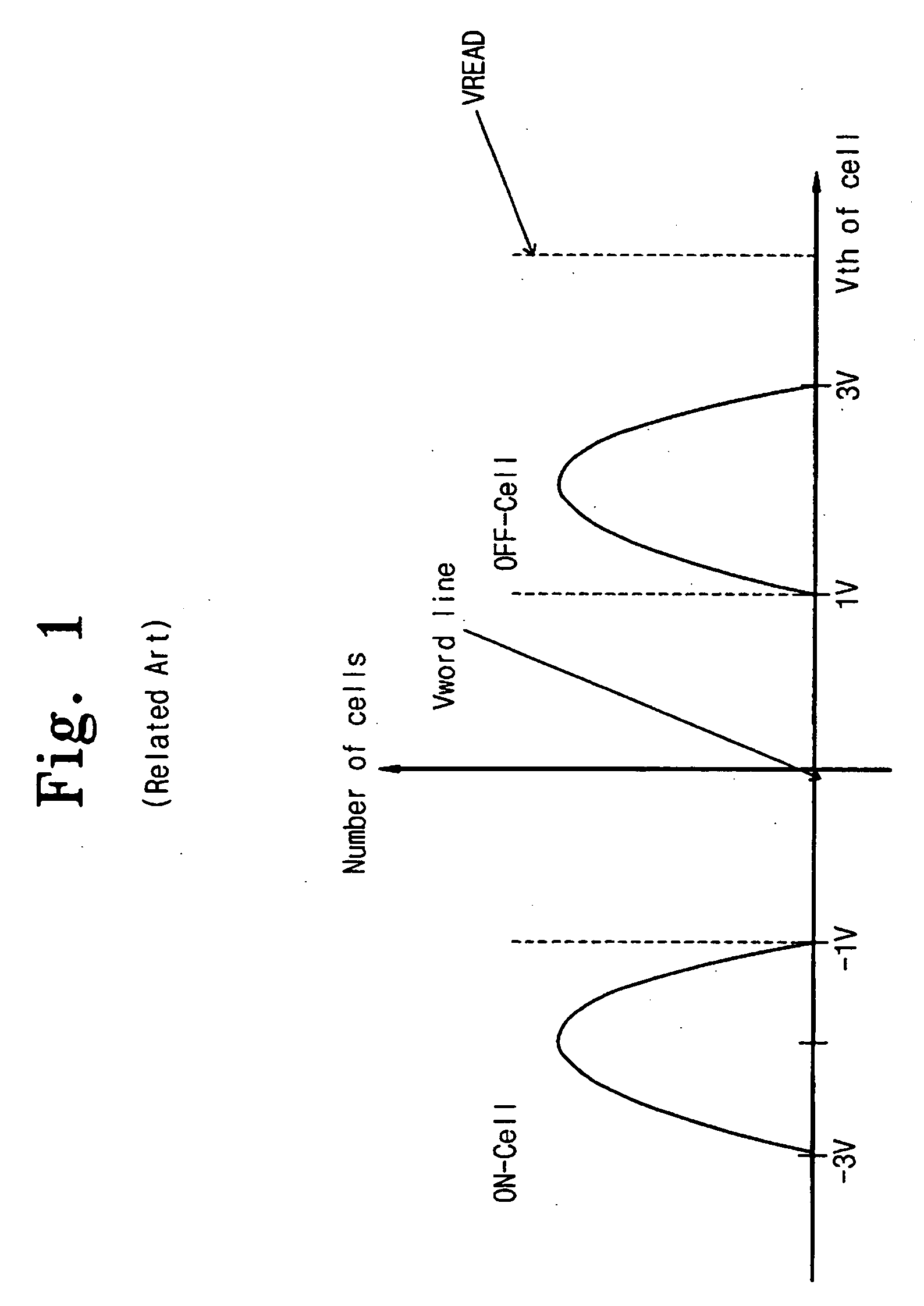

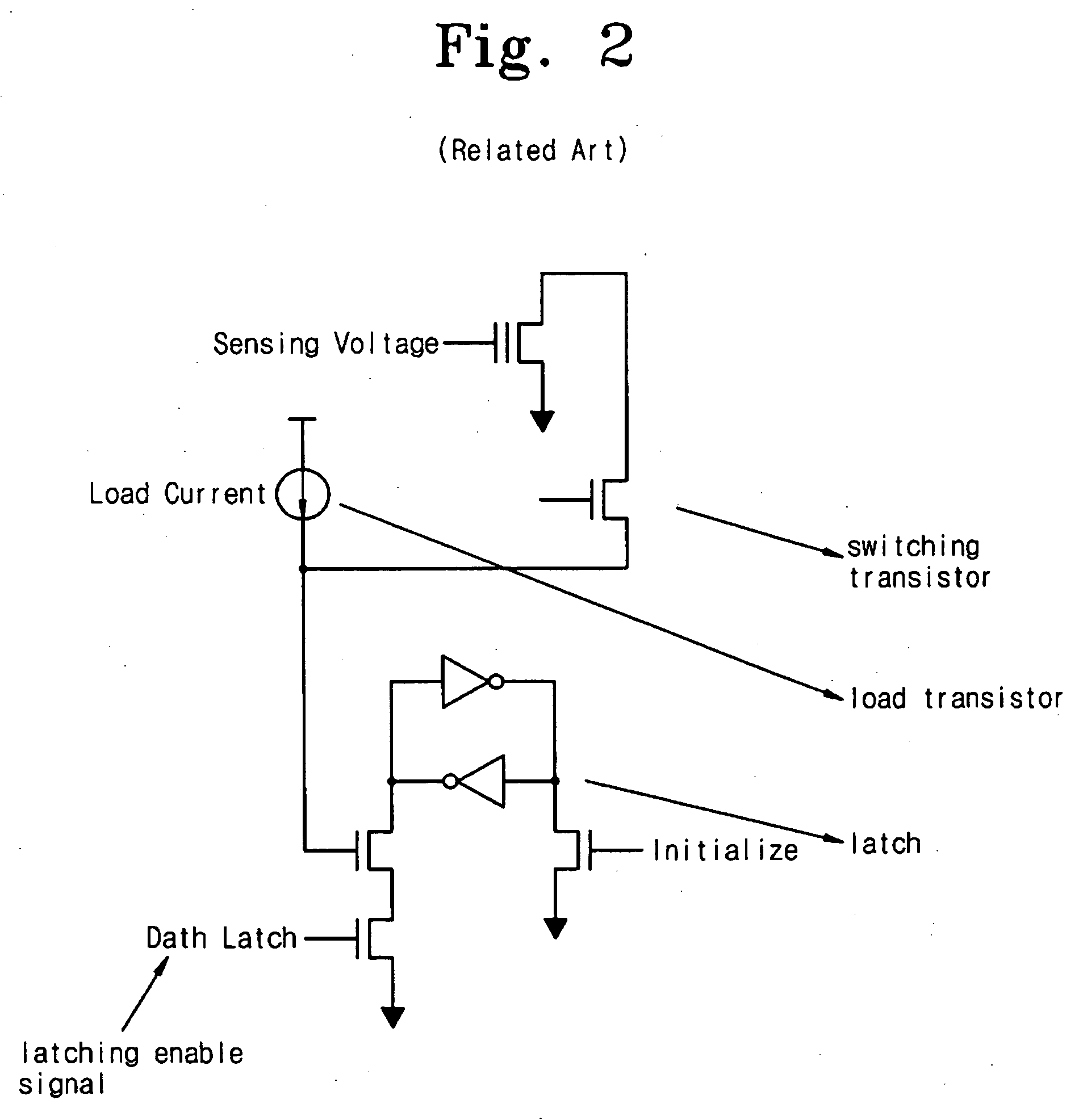

Method and device for performing cache reading

ActiveUS20050226046A1Reduce data transfer timeReduce transfer timeMemory adressing/allocation/relocationRead-only memoriesDevice materialSemiconductor

Method and device for reading data from a semiconductor device, where tR is a read operation time, tT is a buffer transfer time, and tH is a host transfer time, where at least two of tR, tT, and tH may be overlapped to reduce a total transfer time.

Owner:SAMSUNG ELECTRONICS CO LTD

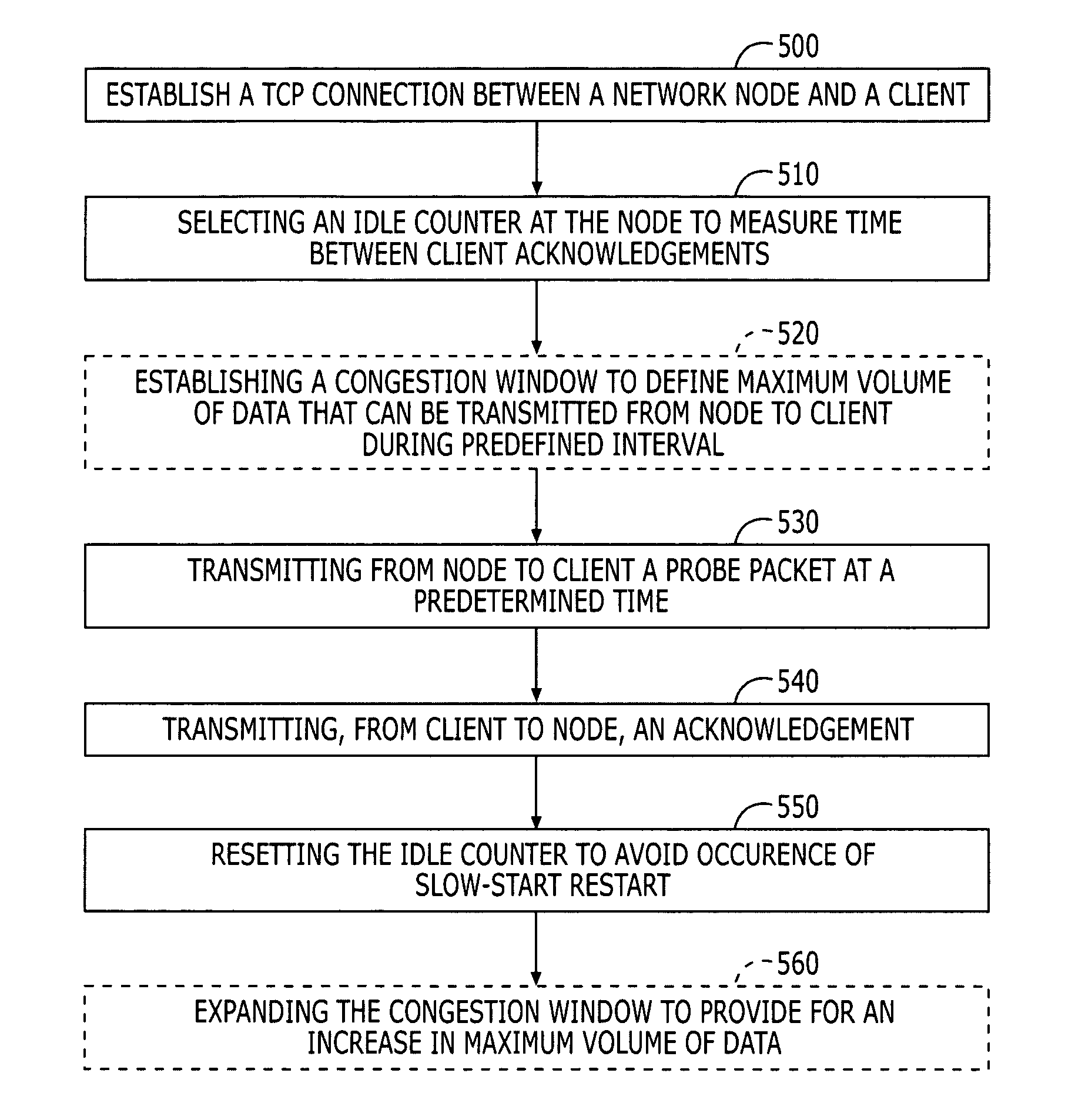

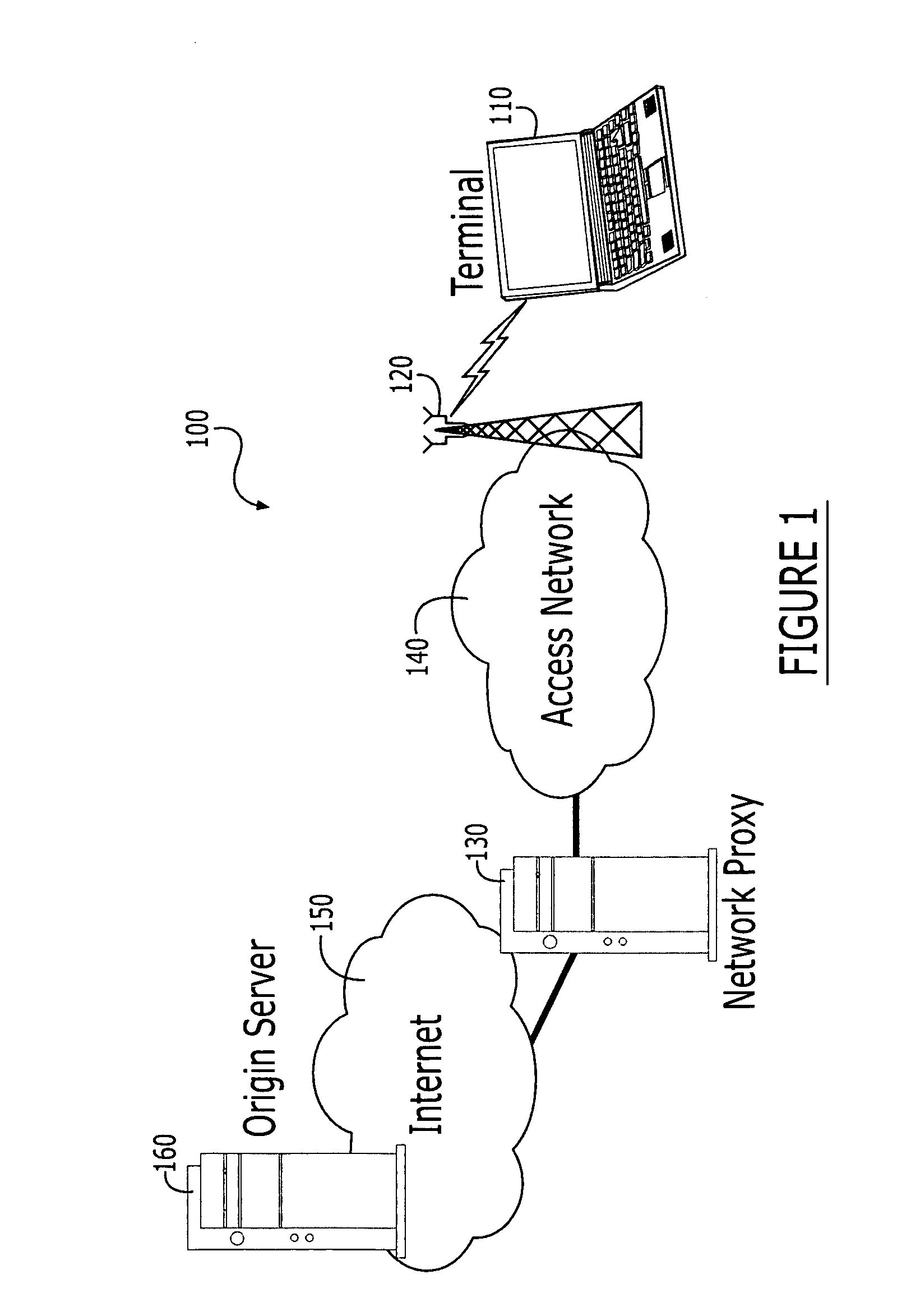

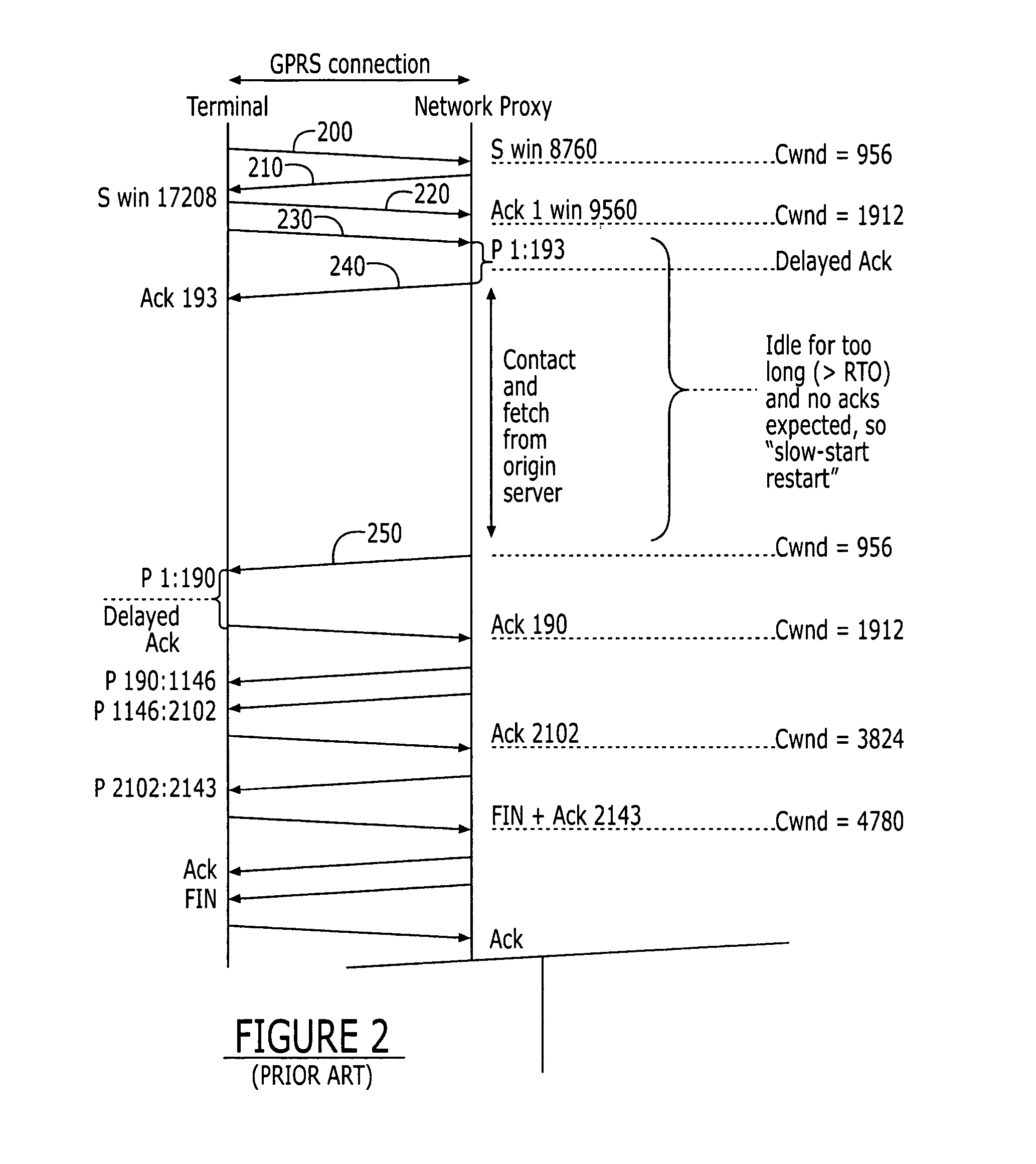

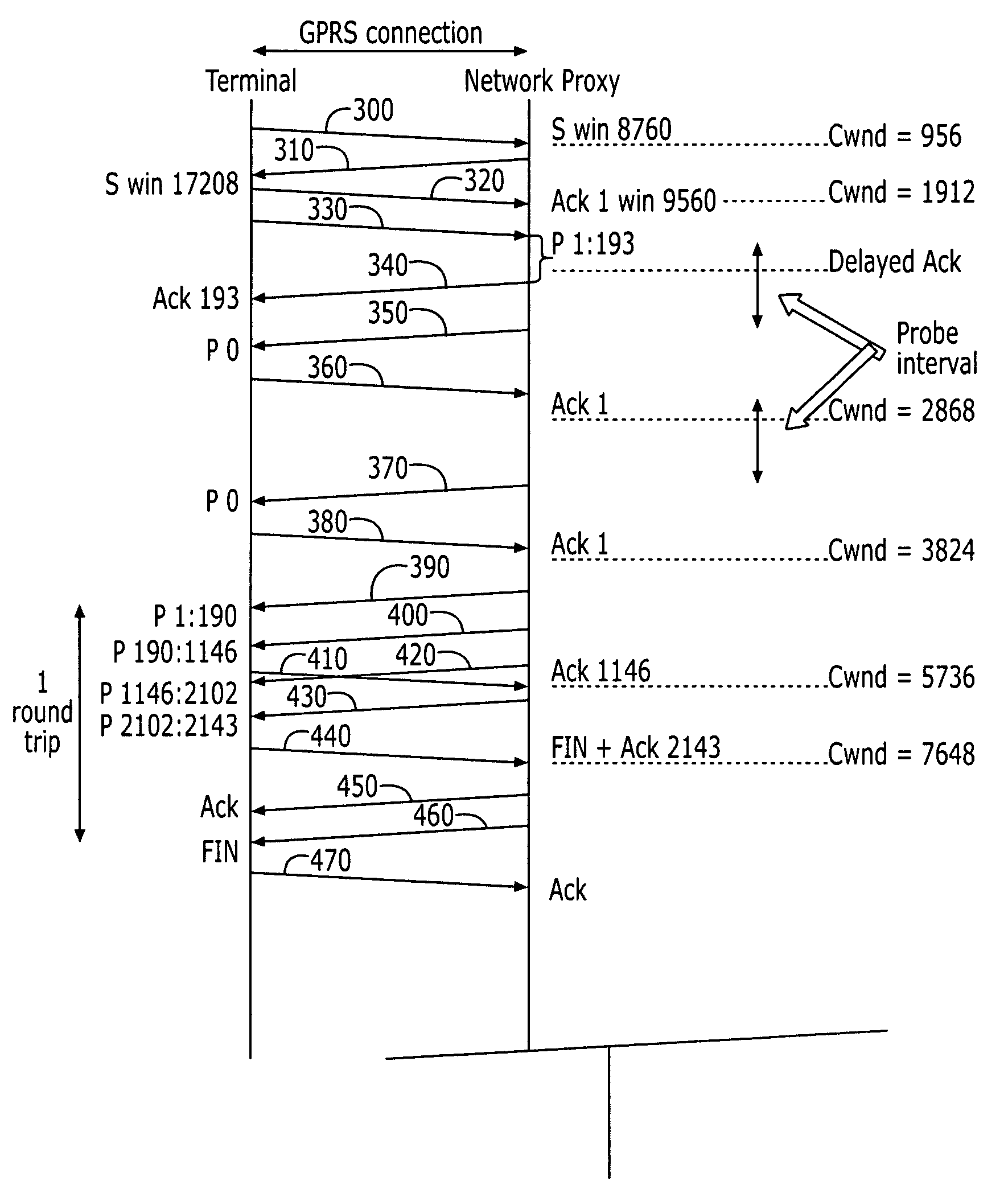

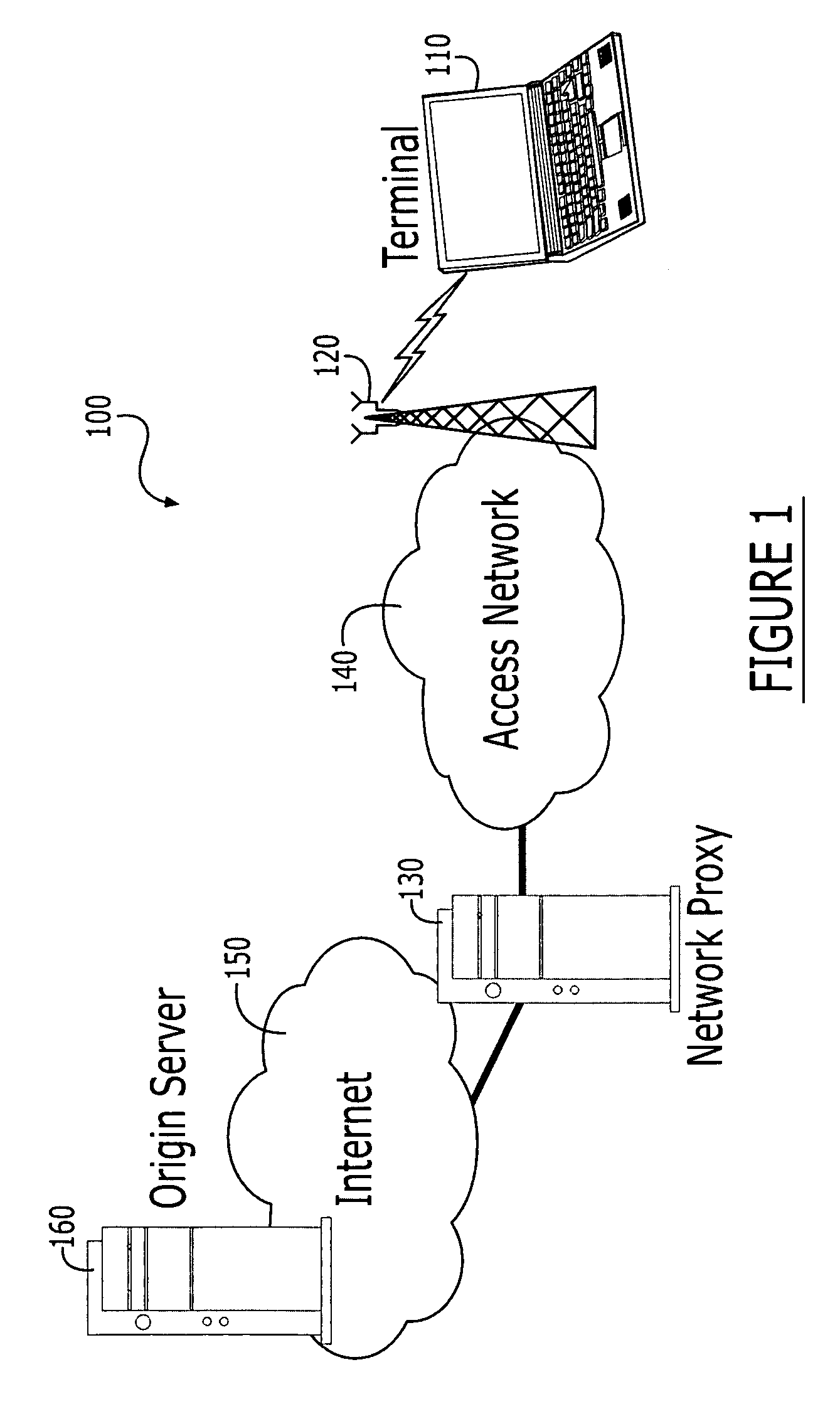

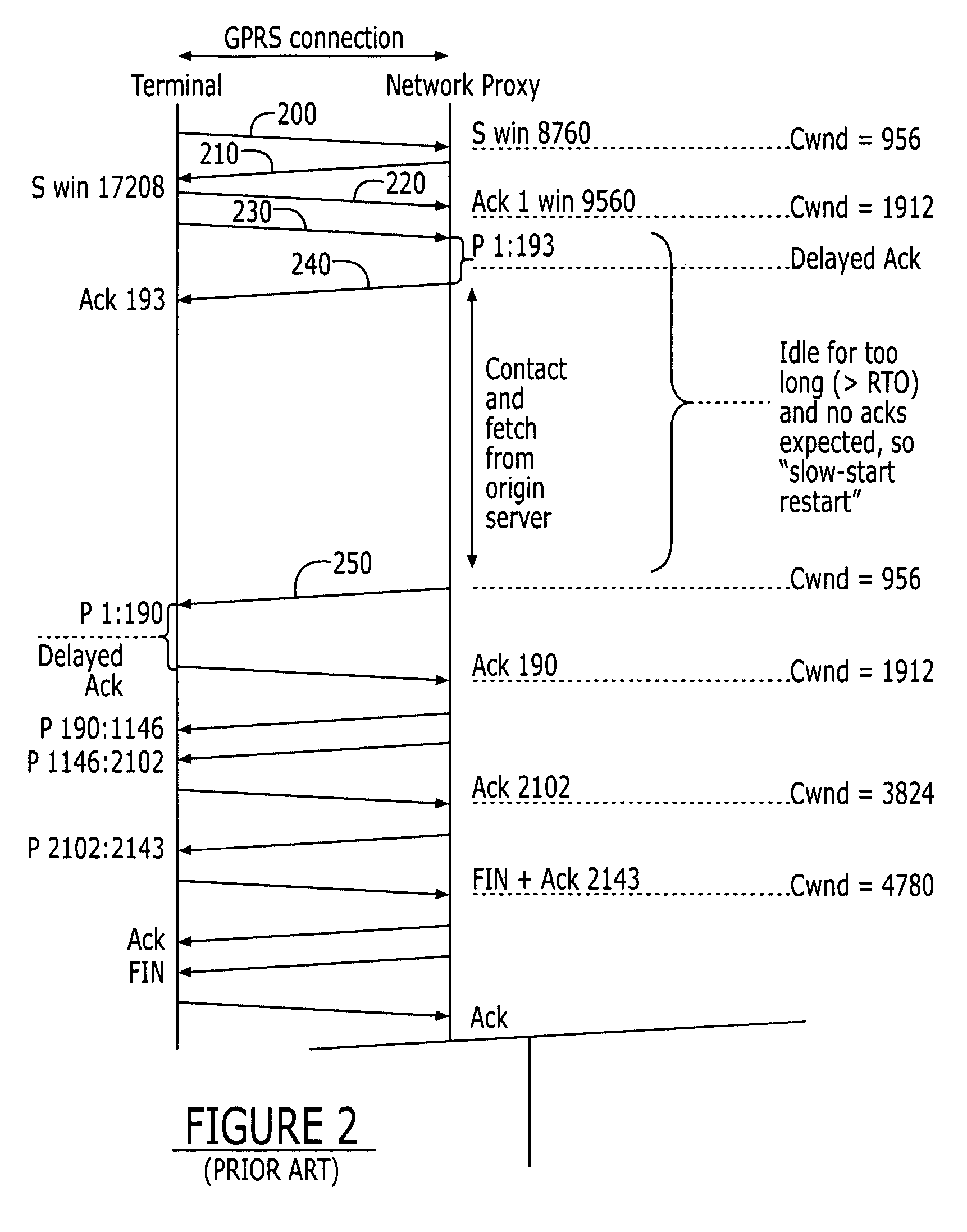

Methods and applications for avoiding slow-start restart in transmission control protocol network communications

InactiveUS20050135248A1Avoid occurrence“slow-start restart” is avoidedError preventionTransmission systemsReal-time computingSlow-start

A novel approach is provided for avoiding the “slow-start restart” in TCP communications when network conditions dictate such. The disclosed approach serves to overcome the latency related to the “slow-start restart” by assessing network conditions and avoiding the “slow-start restart” when network conditions justify the avoidance. The disclosed methods, applications and devices implement the periodic communication of a probe packet that is generated and transmitted from a TCP sender to a TCP receiver during the period that the TCP network connection remains idle. Receipt of the probe packet by the TCP receiver will trigger transmission of an acknowledgment message by the TCP receiver. Upon receipt of the acknowledgement message the TCP sender will restart measurement of the idleness period and, as such the “slow-start restart” is avoided.

Owner:CORE WIRELESS LICENSING R L

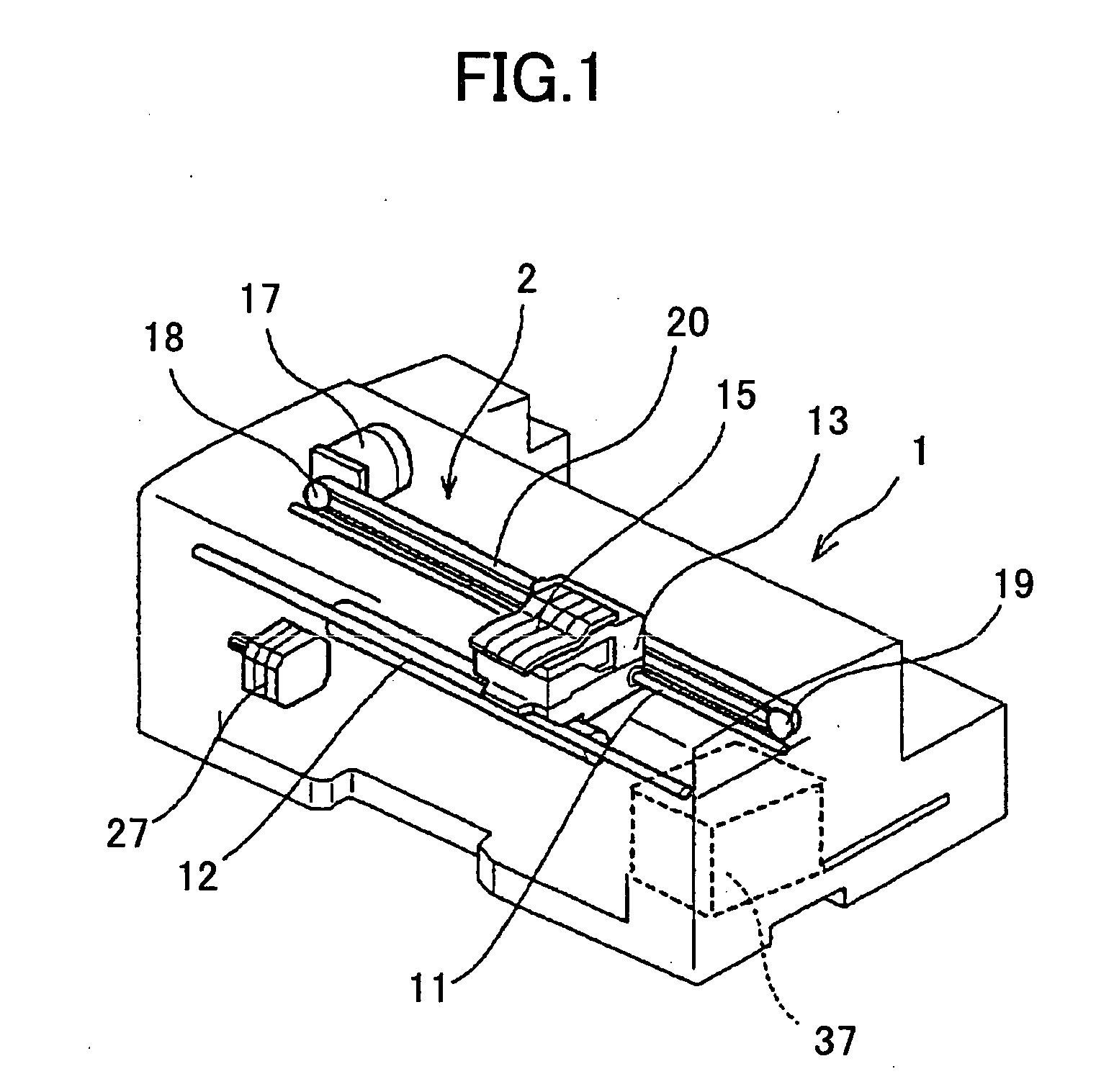

Recording/reproducing apparatus, data reproducing method, and data recording/reproducing method

InactiveUS6993567B1Reduce data transfer timeCharging process can be smoothlyTelevision system detailsMagneto-optical discsData transmission timeData recording

Although music program data has been recorded on a disc, imperfect index data or a signal has been recorded so that music program data is prohibited from being reproduced. To allow music program data to be reproduced, the index data is rewritten to perfect index data or a permission signal that allows music program data to be reproduced is transmitted through a communication line. Thus, music program data can be reproduced from the disc. Since music program data is not directly transmitted, the data transmission time is shortened. The music program data can be downloaded at high speed. In addition, the charging process can be smoothly performed. Moreover, music program data can be prevented from being illegally used.

Owner:SONY CORP

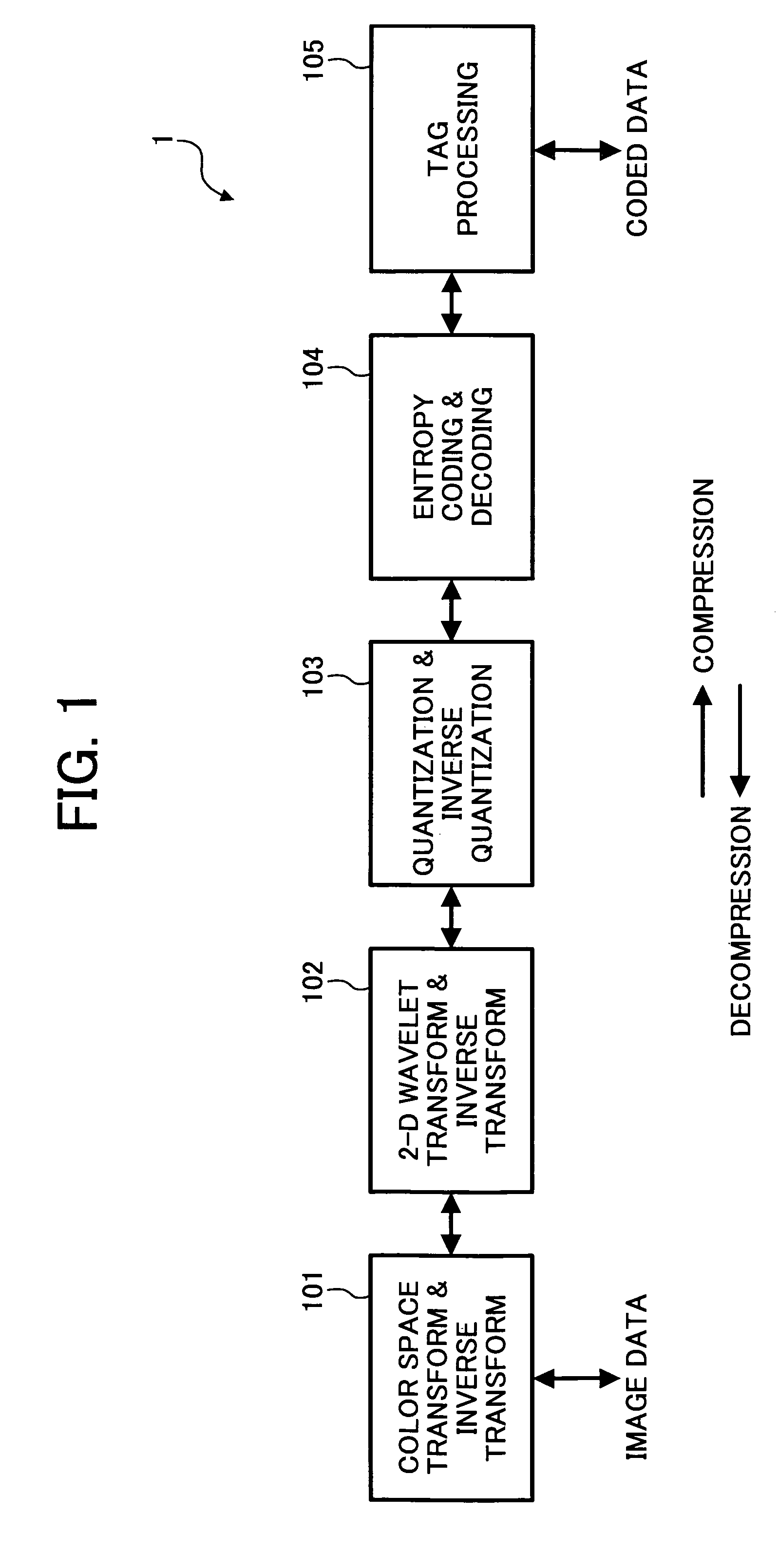

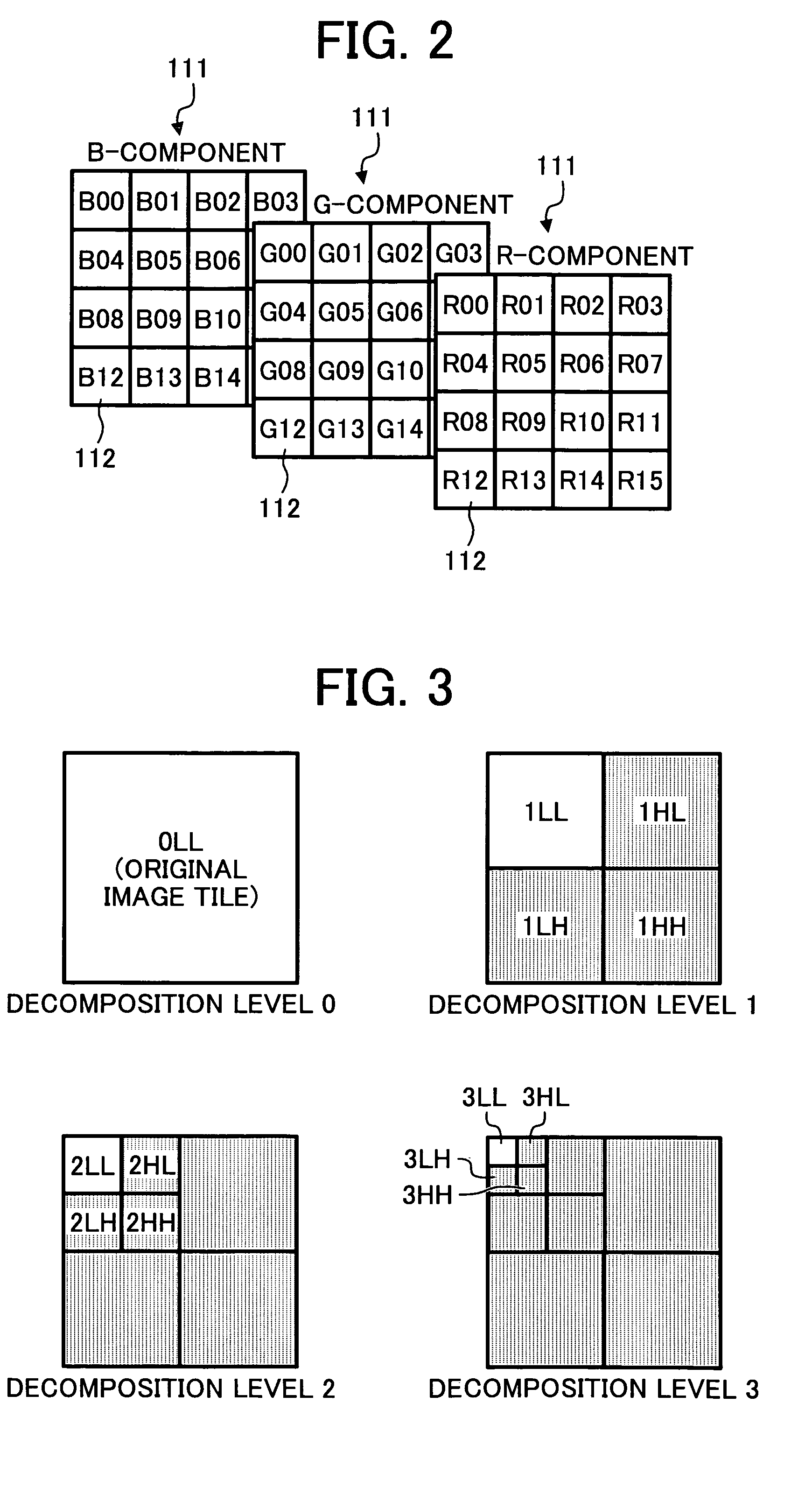

Method, program and apparatus for image processing capable of effectively performing image transmission, and a medium storing the program

ActiveUS20050201624A1Reduce data transfer timeEasy to confirmCharacter and pattern recognitionImage codingImaging processingNetwork connection

An image processing apparatus includes a receiving mechanism configured to receive a request, from at least one different image processing apparatus connected via a network, for transmission of a codestream generated in a way such that image data is divided into at least one region, each region being hierarchically compressed and stored in the image processing apparatus, a decomposing mechanism configured to decompose a codestream and retrieve the codestream in a component unit, an extracting mechanism configured to extract a target region from the codestream, a primary priority assigning mechanism configured to assign priority to the target region extracted by the extracting mechanism, and a primary transmitting mechanism configured for transmission of the codestream, decomposed in a component unit corresponding to the target region, to the different image processing apparatus requesting transmission of the codestream based on the priority assigned by the primary priority assigning mechanism.

Owner:RICOH KK

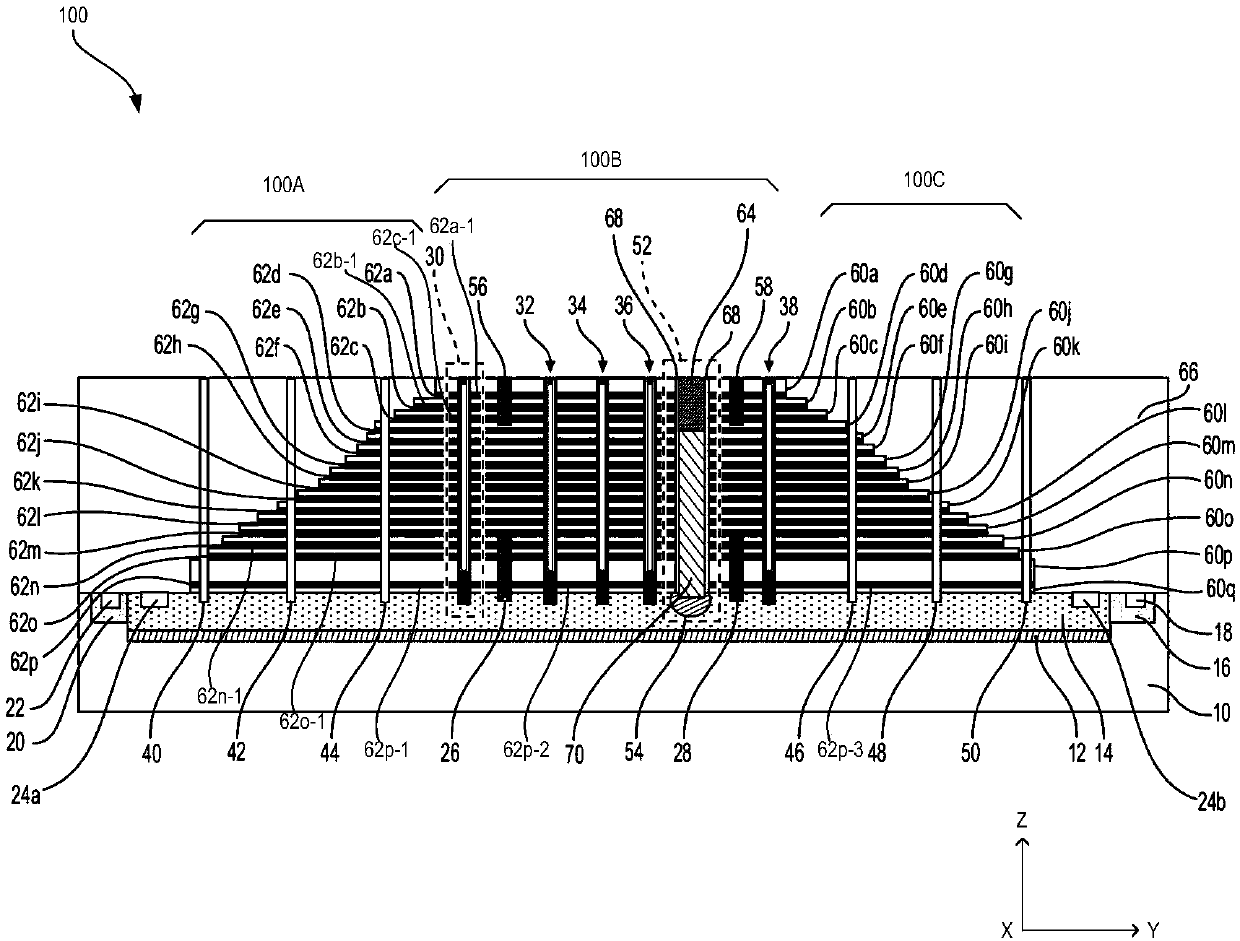

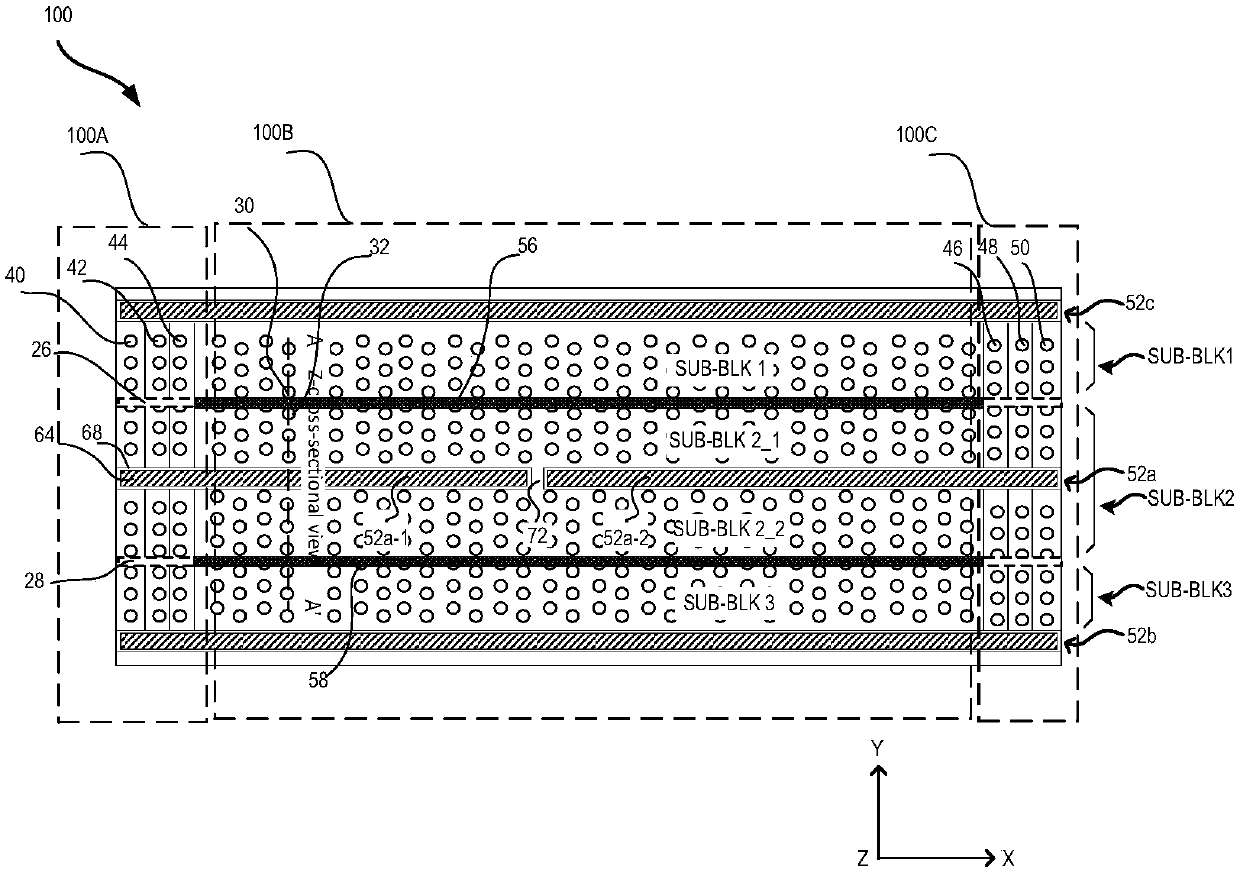

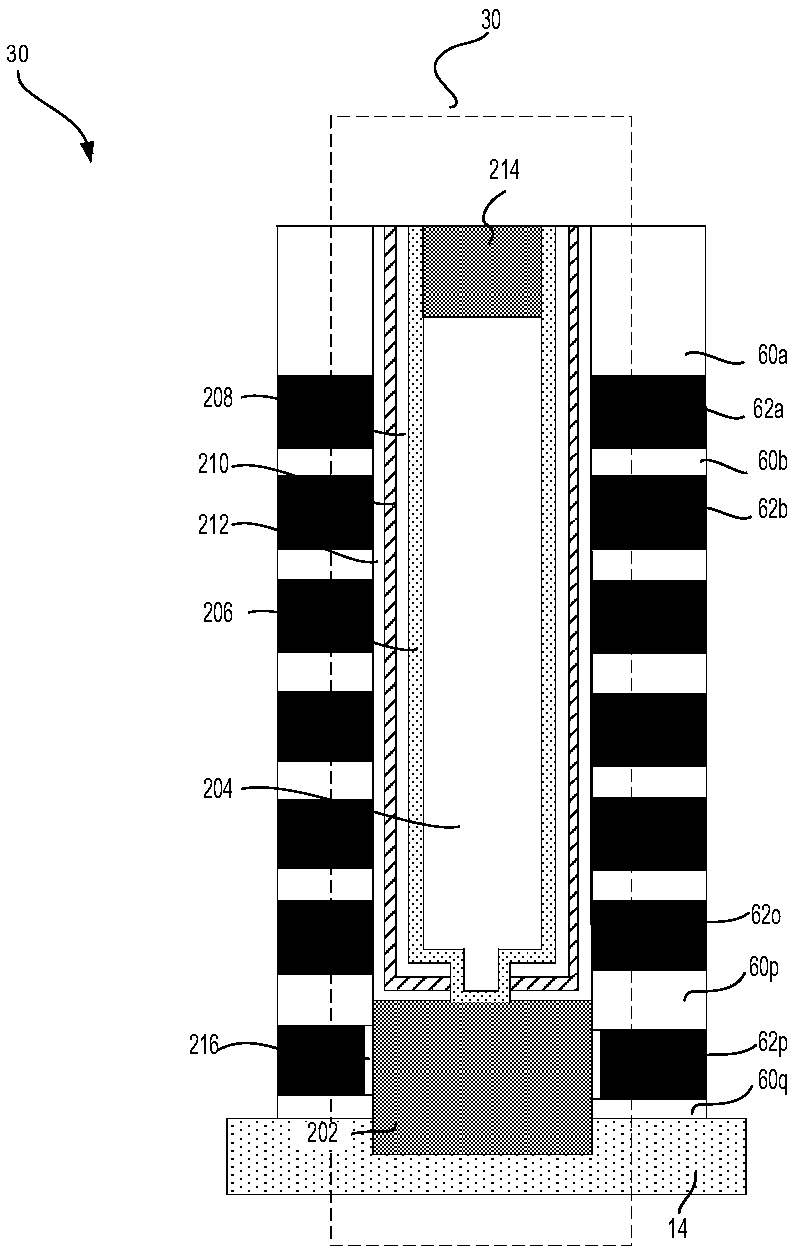

Novel 3D NAND memory device and method of forming same

ActiveCN109690776AReduce coupling effectImprove V

<sub>t</sub>

performanceSemiconductor/solid-state device detailsSolid-state devicesInsulation layerComputer science

A 3D NAND memory device is provided and includes: a substrate, a bottom select gate (BSG) disposed over the substrate, a plurality of word lines disposed above the BSG and having a stepped configuration, and a plurality of insulation layers disposed between the substrate, the BSG, and the plurality of word lines. In the disclosed memory device, one or more first dielectric trenches are formed in the BSG and extend along the length of the substrate to separate the BSG into a plurality of sub-BSGs. Further, one or more common source regions are formed over the substrate and extend in the lengthdirection of the substrate. One or more common source regions also extend through the BSG, the plurality of word lines, and the plurality of insulating layers.

Owner:YANGTZE MEMORY TECH CO LTD

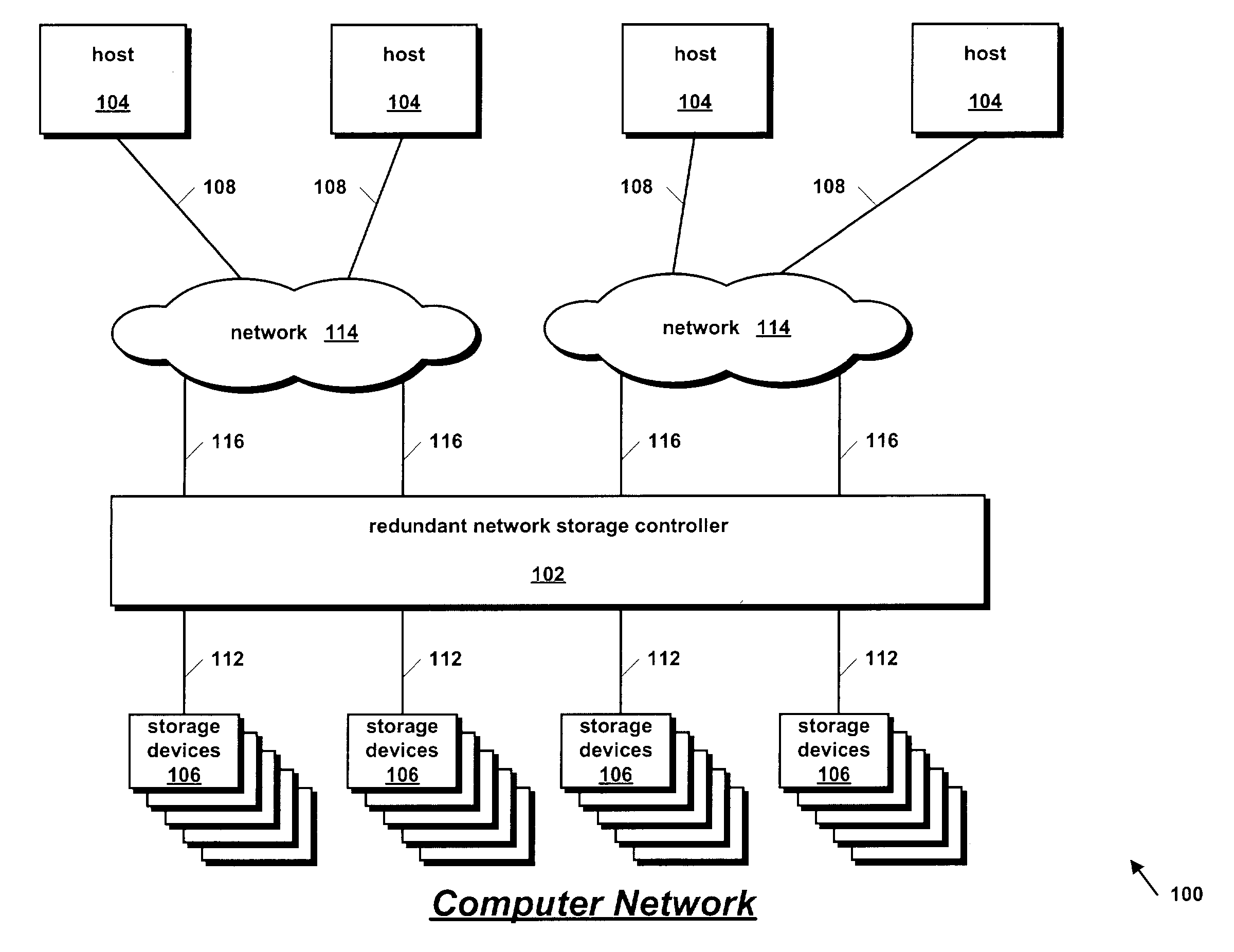

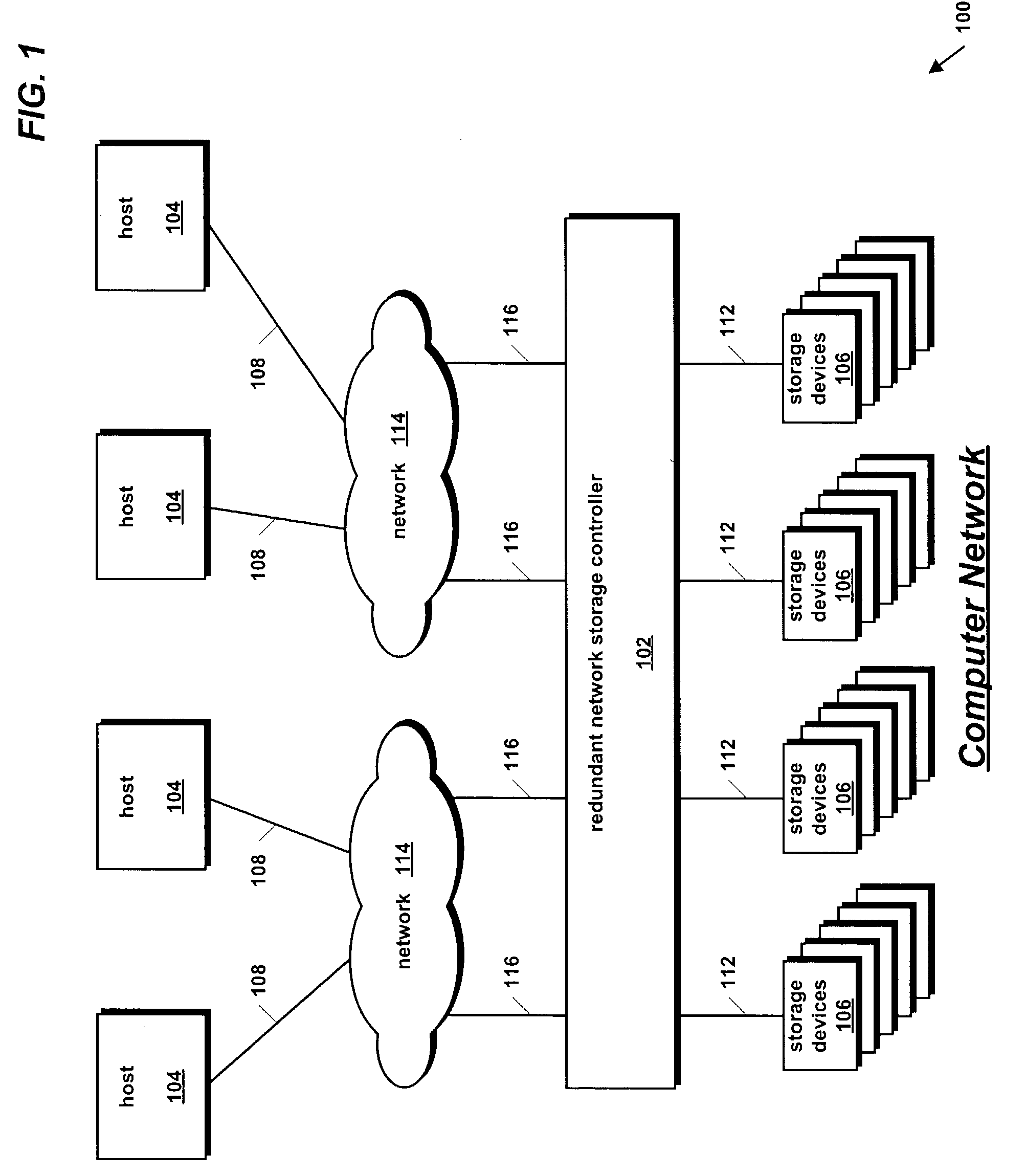

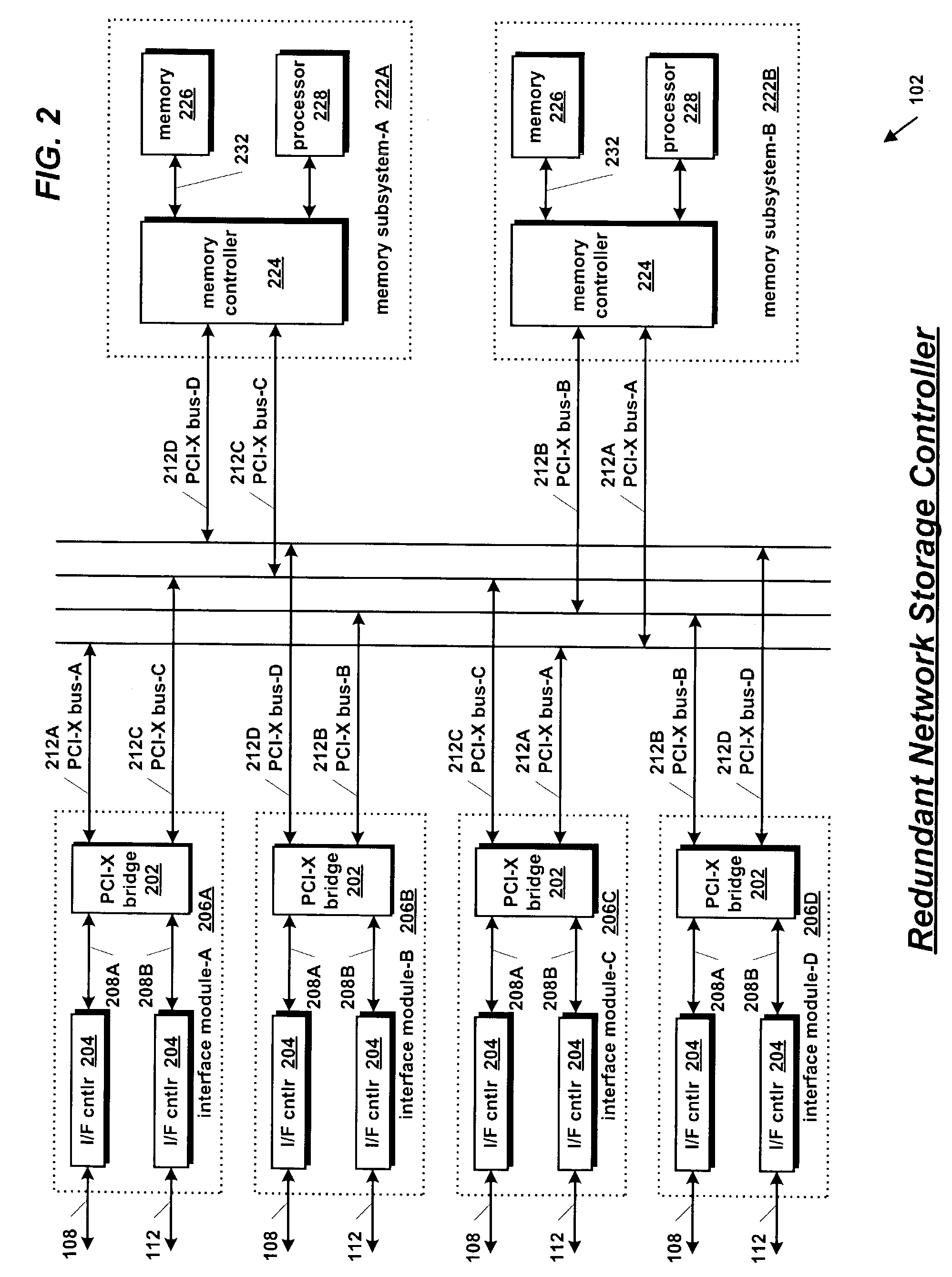

Broadcast bridge apparatus for transferring data to redundant memory subsystems in a storage controller

ActiveUS7143227B2Reduce data transfer timeReduce development timeInput/output to record carriersMultiple digital computer combinationsAuxiliary memoryBroadcast address

A bus bridge apparatus for performing broadcasted writes to redundant memory subsystems in a network storage controller is disclosed. The bus bridge includes a PCI-X target that receives a write command on a first PCI-X bus on one side of the bridge. The target is coupled to two PCI-X masters coupled to primary and secondary memory subsystems by respective PCI-X buses on the other side of the bridge. A first FIFO buffers the write command data between the target and the first master, and a second FIFO buffers a copy of the data between the target and the second master. The first and second masters concurrently retransmit the write command on their respective PCI-X buses to the primary and secondary memory subsystems. However, the second master only retransmits if broadcasting is enabled and the write command address is in a broadcast address range known by the bus bridge.

Owner:DOT HILL SYST

Protocol implementation for telemetry communications involving implantable medical devices

ActiveUS8108048B2Minimize interferenceOptimizing telemetry communicationElectrotherapySurgeryElectrical devicesEngineering

Embodiments of the invention relate to optimizing telemetry communication involving one or more medical devices and one or more electrical devices. The telemetry communication is optimized by implementing software and / or one or more additional circuits within at least one medical device and at least one electrical device to provide one or more modes or functions of optimizing transfer of data between the medical device and the at least one electrical device, minimizing interference of the data transfer, and reducing data transfer time and / or preserving electrical energy sources of one or more of the medical device and the at least one electrical device.

Owner:MEDTRONIC INC

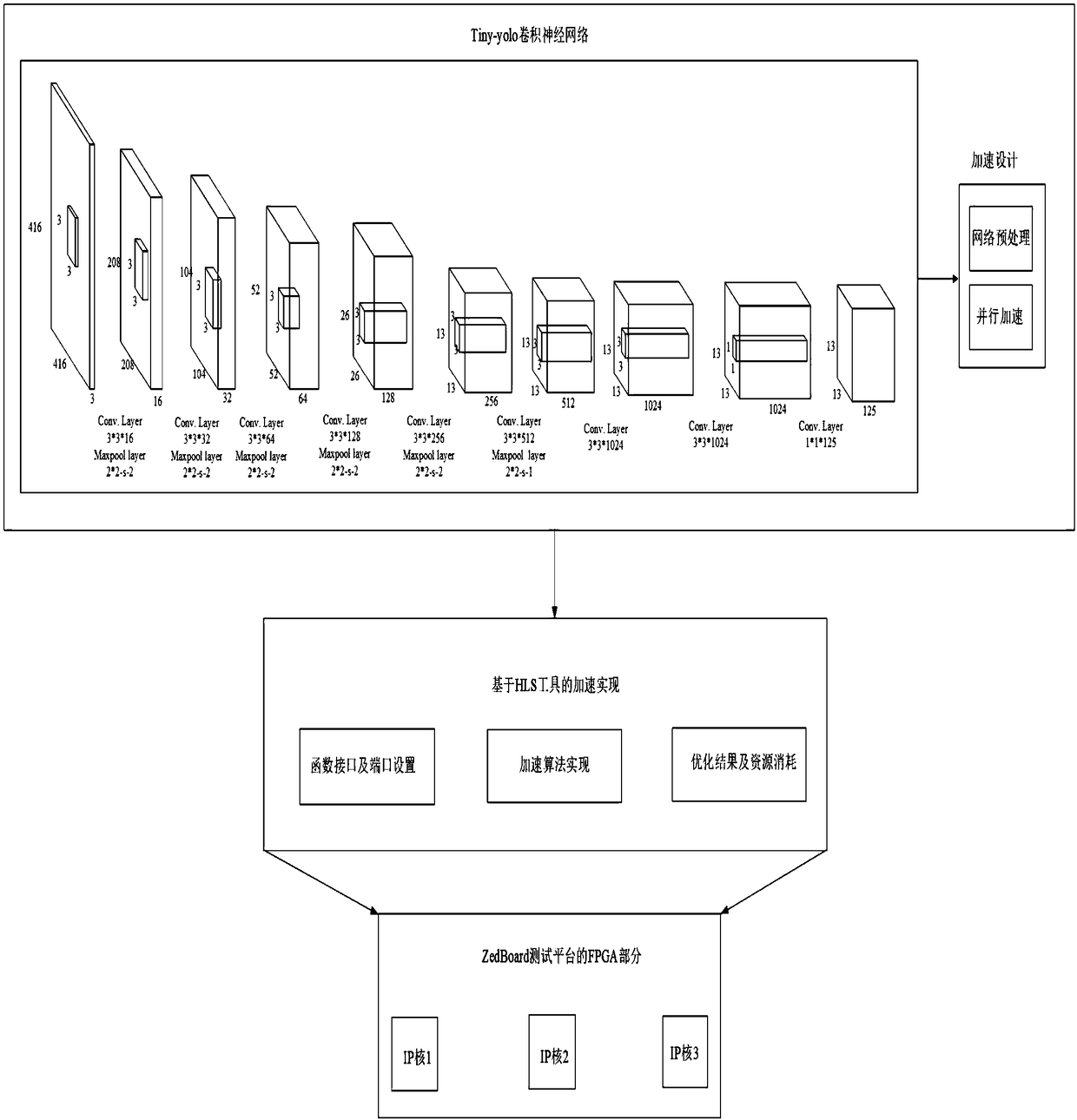

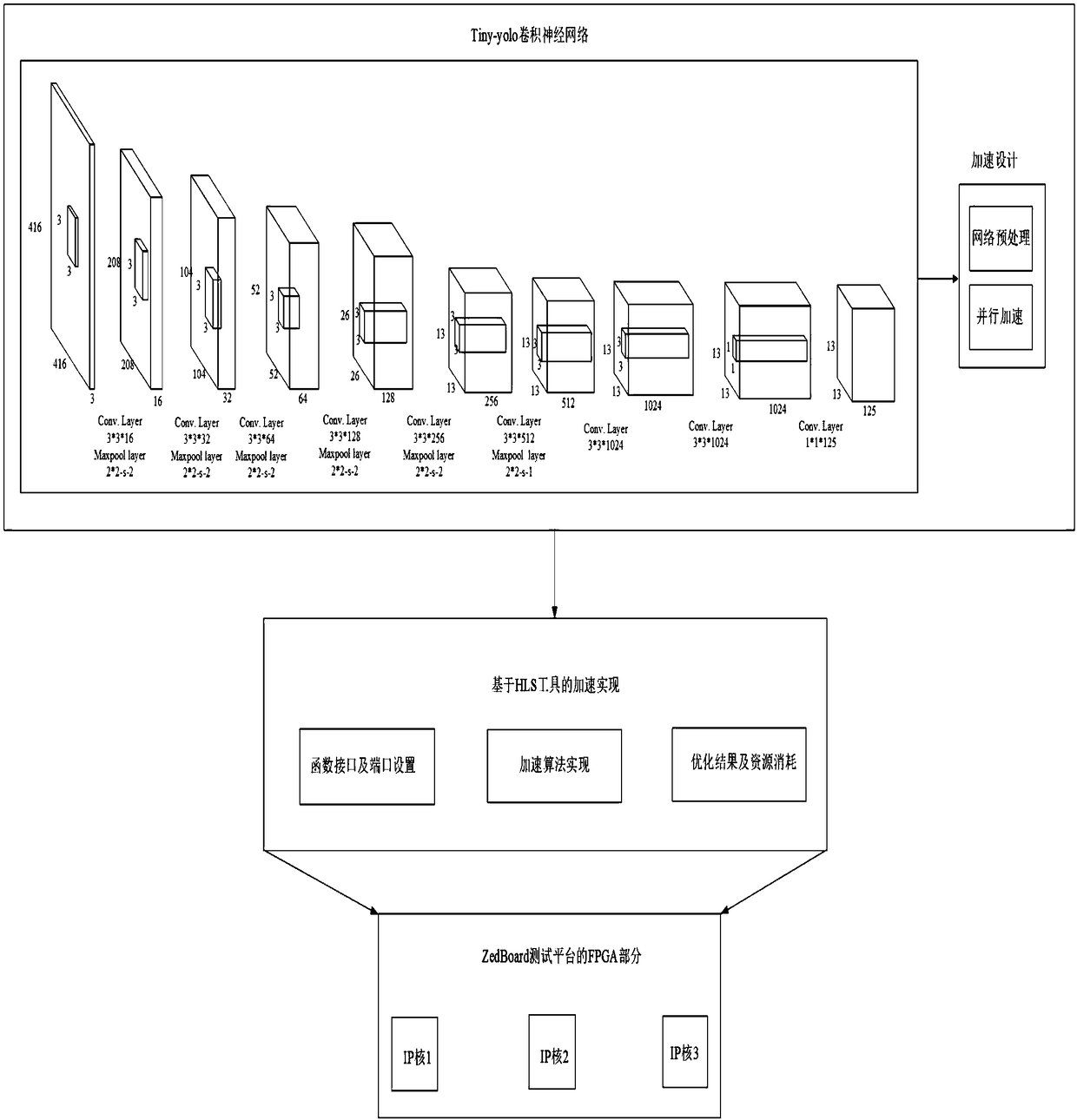

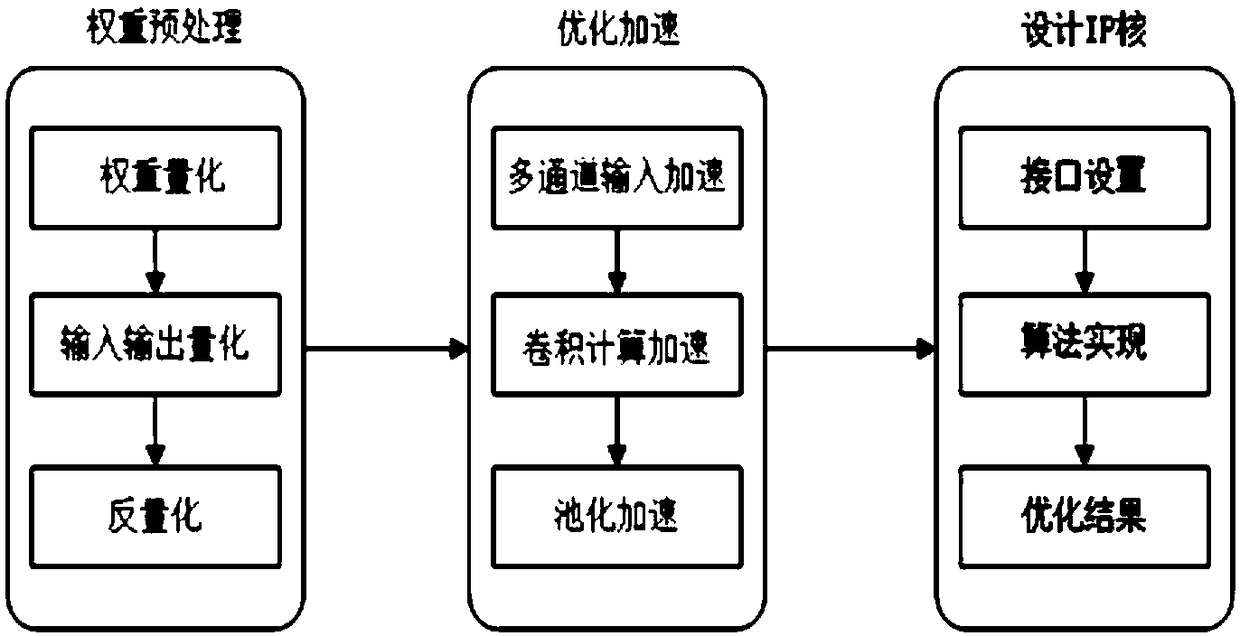

Data processing method for hardware acceleration of convolutional neural network

ActiveCN108805267ASave resourcesFast operationNeural architecturesParallel processingHardware acceleration

The invention discloses a data processing method for hardware acceleration of a convolutional neural network. By analyzing the parallel characteristics of the convolutional neural network, and in combination with the parallel processing capability of hardware, the hardware acceleration is carried out on the convolutional neural network. The acceleration scheme is used for performing acceleration improvement on the Tiny-yolo network from three aspects that (1) the processing speed of the Tiny-yolo network is increased through multi-channel parallel input; (2) the convolution computing speed ofthe Tiny-yolo network is increased through parallel computing; and (3) the pooling process time of the Tiny-yolo network is shortened through pooling embedding. The method greatly increases the detection speed of the convolutional neural network.

Owner:CHONGQING UNIV

Method, program and apparatus for image processing capable of effectively performing image transmission, and a medium storing the program

ActiveUS7508988B2Easy to confirmReduce data transfer timeImage codingCharacter and pattern recognitionImaging processingNetwork connection

An image processing apparatus includes a receiving mechanism configured to receive a request, from at least one different image processing apparatus connected via a network, for transmission of a codestream generated in a way such that image data is divided into at least one region, each region being hierarchically compressed and stored in the image processing apparatus, a decomposing mechanism configured to decompose a codestream and retrieve the codestream in a component unit, an extracting mechanism configured to extract a target region from the codestream, a primary priority assigning mechanism configured to assign priority to the target region extracted by the extracting mechanism, and a primary transmitting mechanism configured for transmission of the codestream, decomposed in a component unit corresponding to the target region, to the different image processing apparatus requesting transmission of the codestream based on the priority assigned by the primary priority assigning mechanism.

Owner:RICOH KK

Methods and applications for avoiding slow-start restart in transmission control protocol network communications

InactiveUS7609640B2“slow-start restart” is avoidedReduce data transfer timeError preventionFrequency-division multiplex detailsSlow-startNetwork connection

A novel approach is provided for avoiding the “slow-start restart” in TCP communications when network conditions dictate such. The disclosed approach serves to overcome the latency related to the “slow-start restart” by assessing network conditions and avoiding the “slow-start restart” when network conditions justify the avoidance. The disclosed methods, applications and devices implement the periodic communication of a probe packet that is generated and transmitted from a TCP sender to a TCP receiver during the period that the TCP network connection remains idle. Receipt of the probe packet by the TCP receiver will trigger transmission of an acknowledgment message by the TCP receiver. Upon receipt of the acknowledgement message the TCP sender will restart measurement of the idleness period and, as such the “slow-start restart” is avoided.

Owner:CORE WIRELESS LICENSING R L

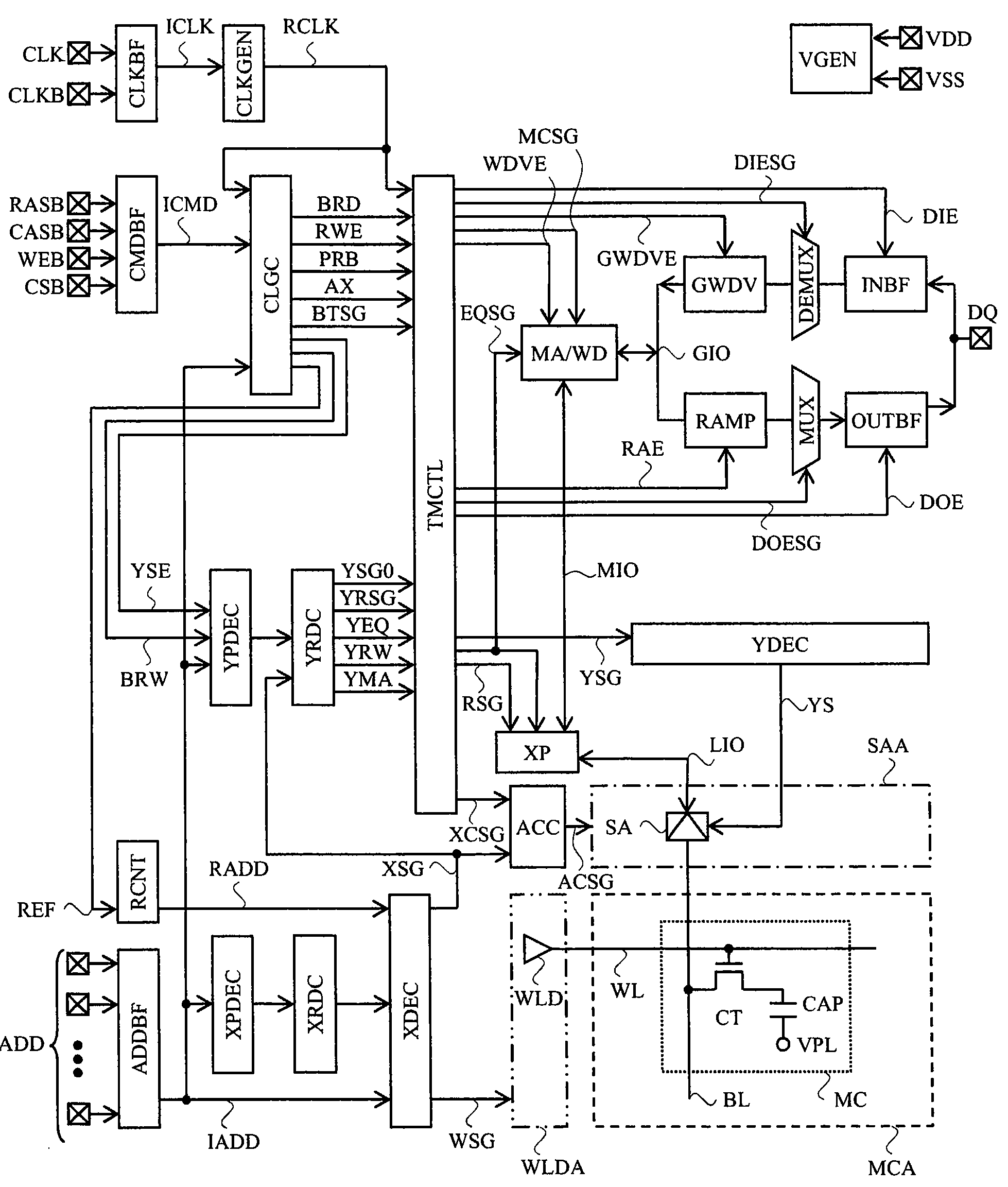

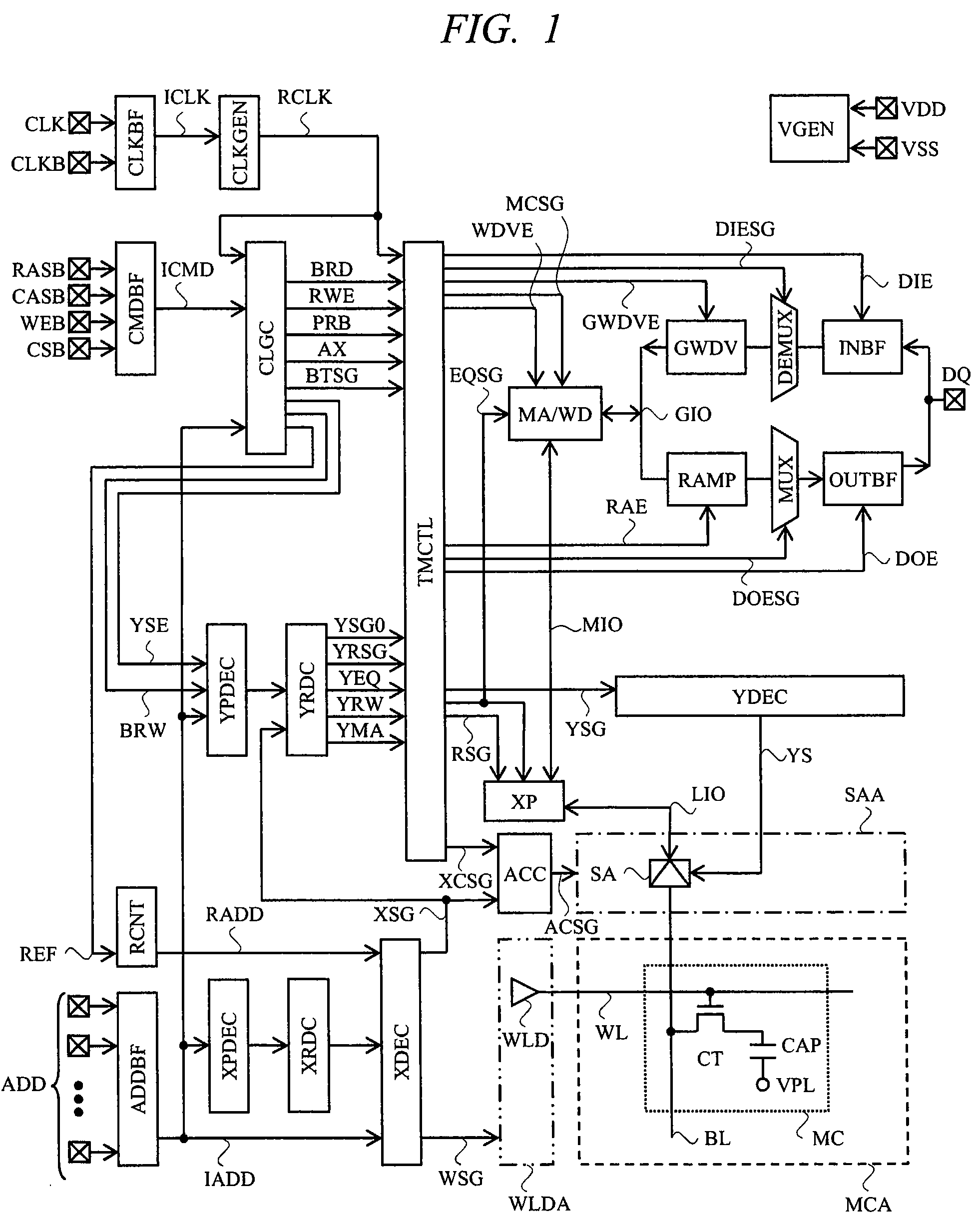

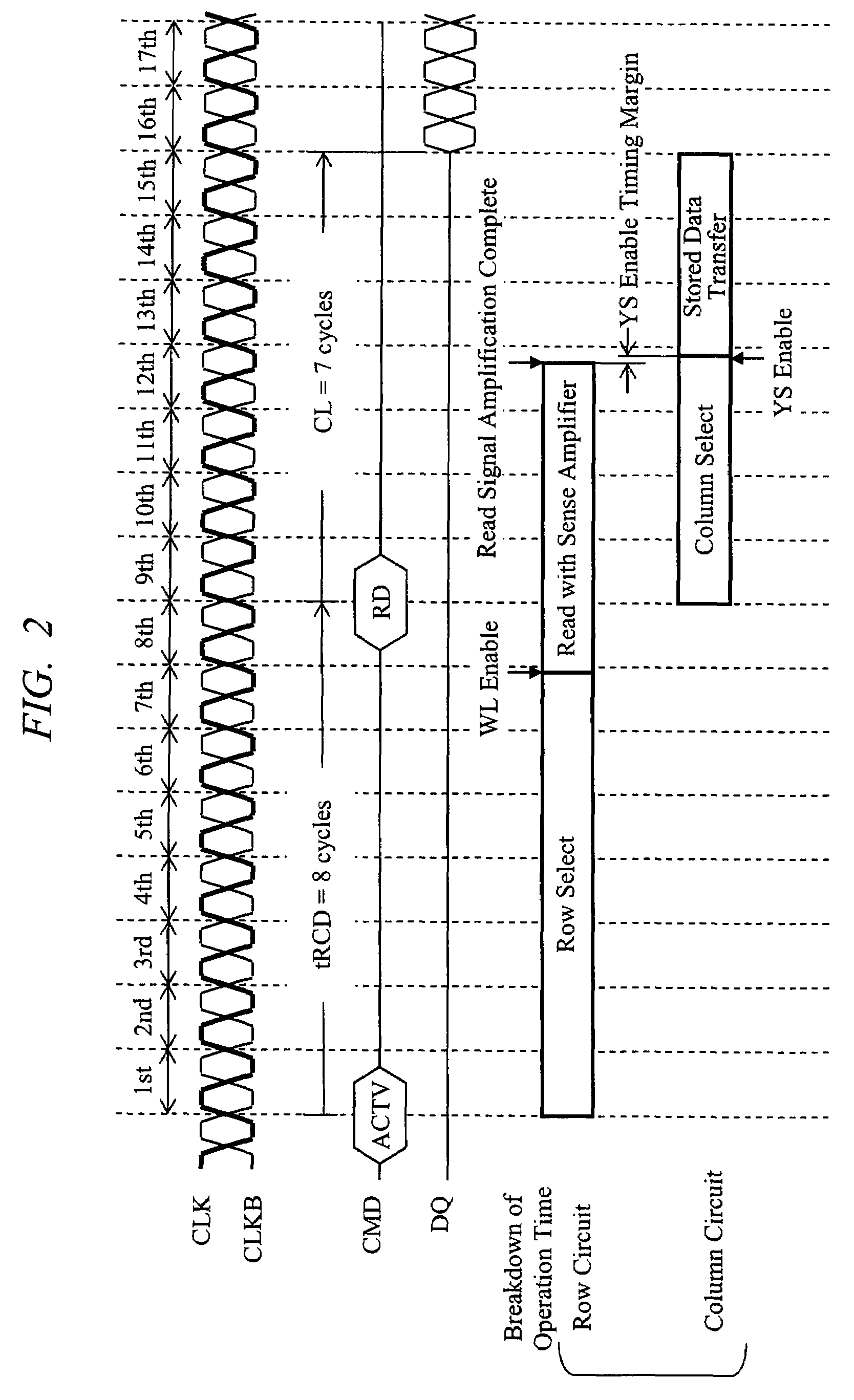

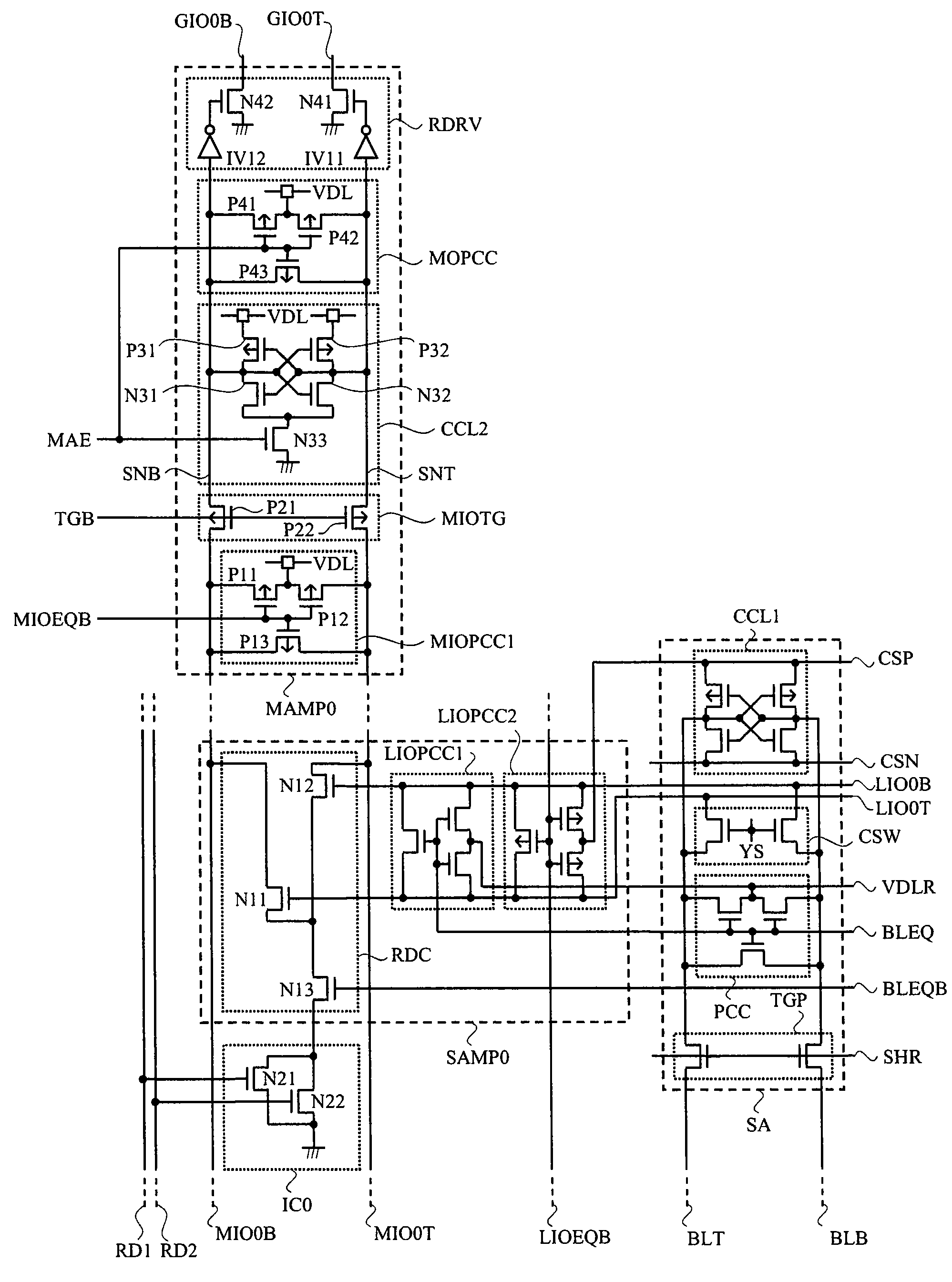

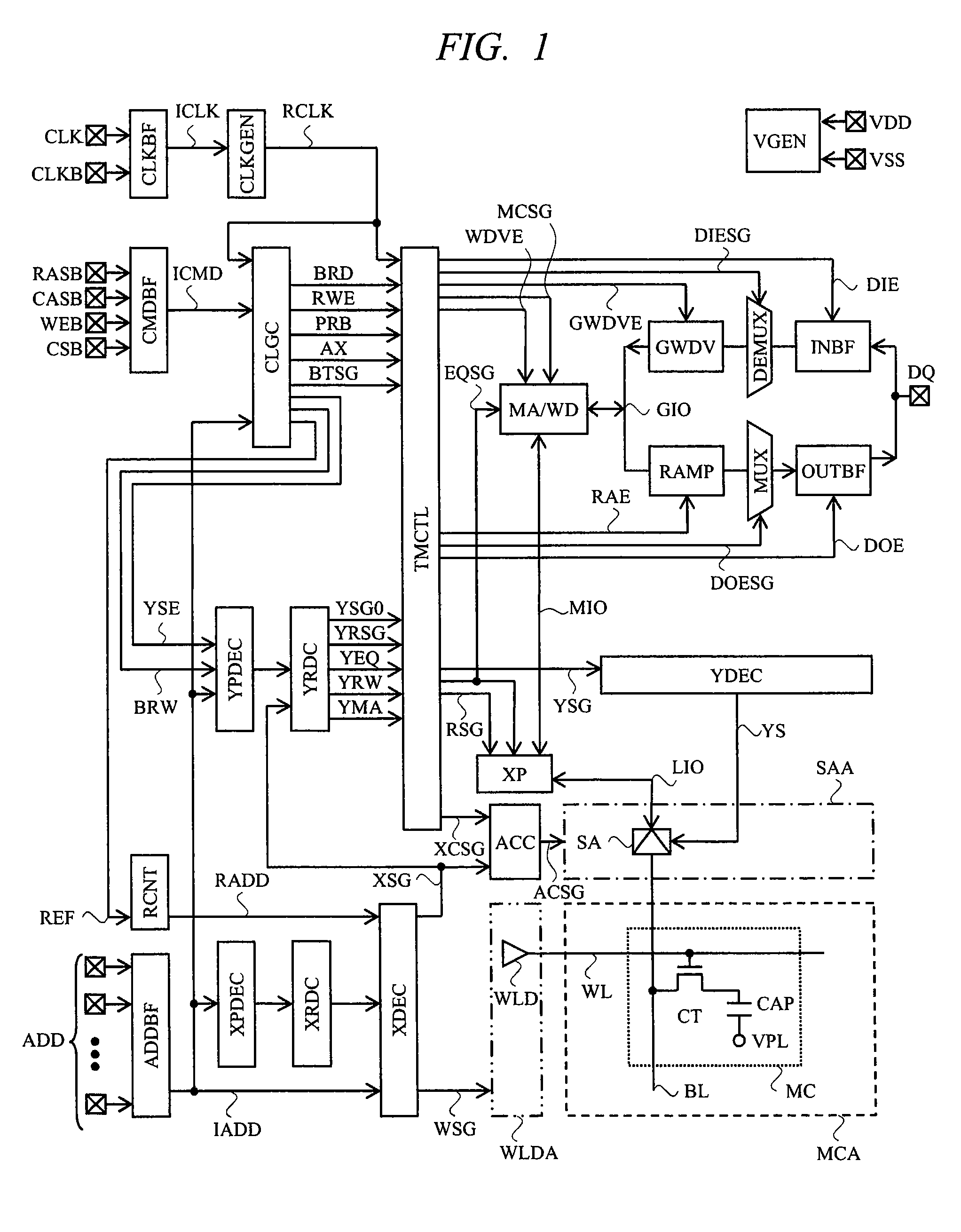

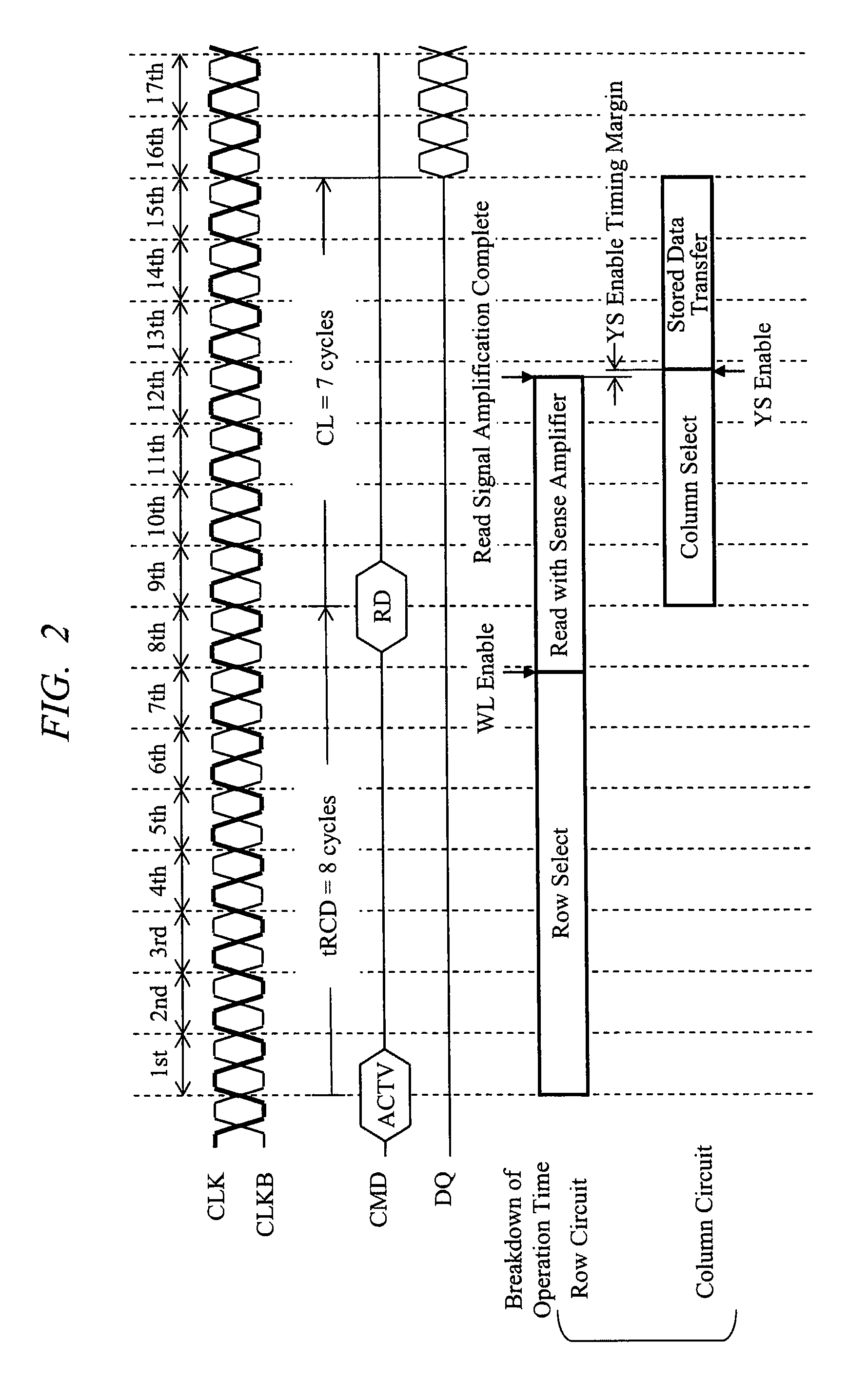

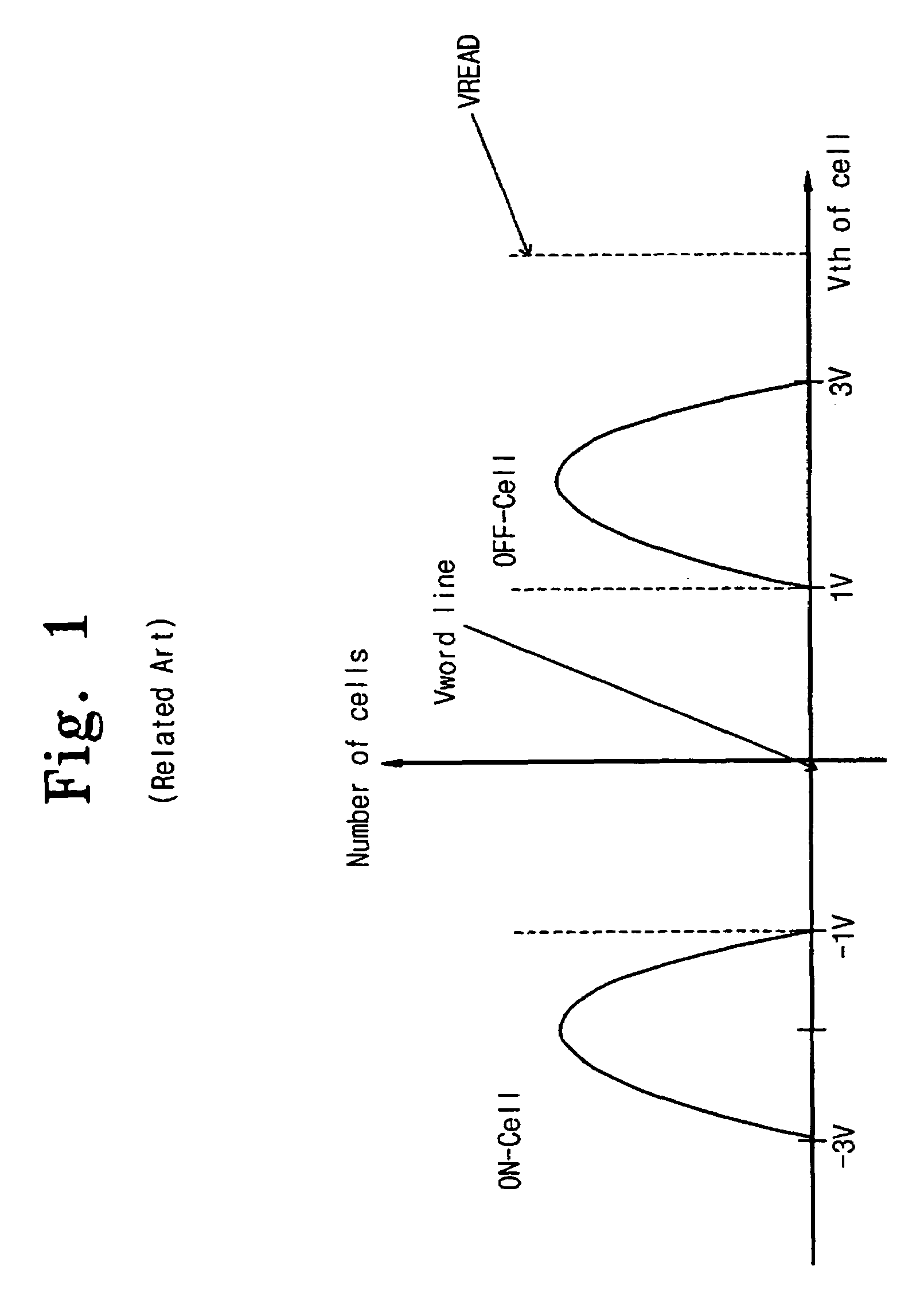

Semiconductor Device

InactiveUS20070147160A1Reduce data transfer timeExpand read operation marginDigital storageSense amplifierInput/output

A column circuit that amplifies signals read from a sense amplifier array SAA to local input / output lines LIO in sub-amplifiers SAMP to transfer the amplified signals to main input / output lines MIO is provided. A current control circuit IC that can set one of two kinds of currents according to read enable signals RD1, RD2 is provided in each sub-amplifier SAMP. The read enable signals RD1, RD2 are generated at timings corresponding to the number of cycles in burst read operation under control of the timing controller. Current in the current control circuit IC is set to be large by the RD1 in burst read operation cycle just after activation of a memory bank, while current in the current control circuit IC is set to be small by the RD2 in the next and subsequent burst read cycles. Accordingly, expansion of an operation margin or reduction of power consumption can be realized in a semiconductor device including a semiconductor memory such as a DRAM.

Owner:LONGITUDE LICENSING LTD

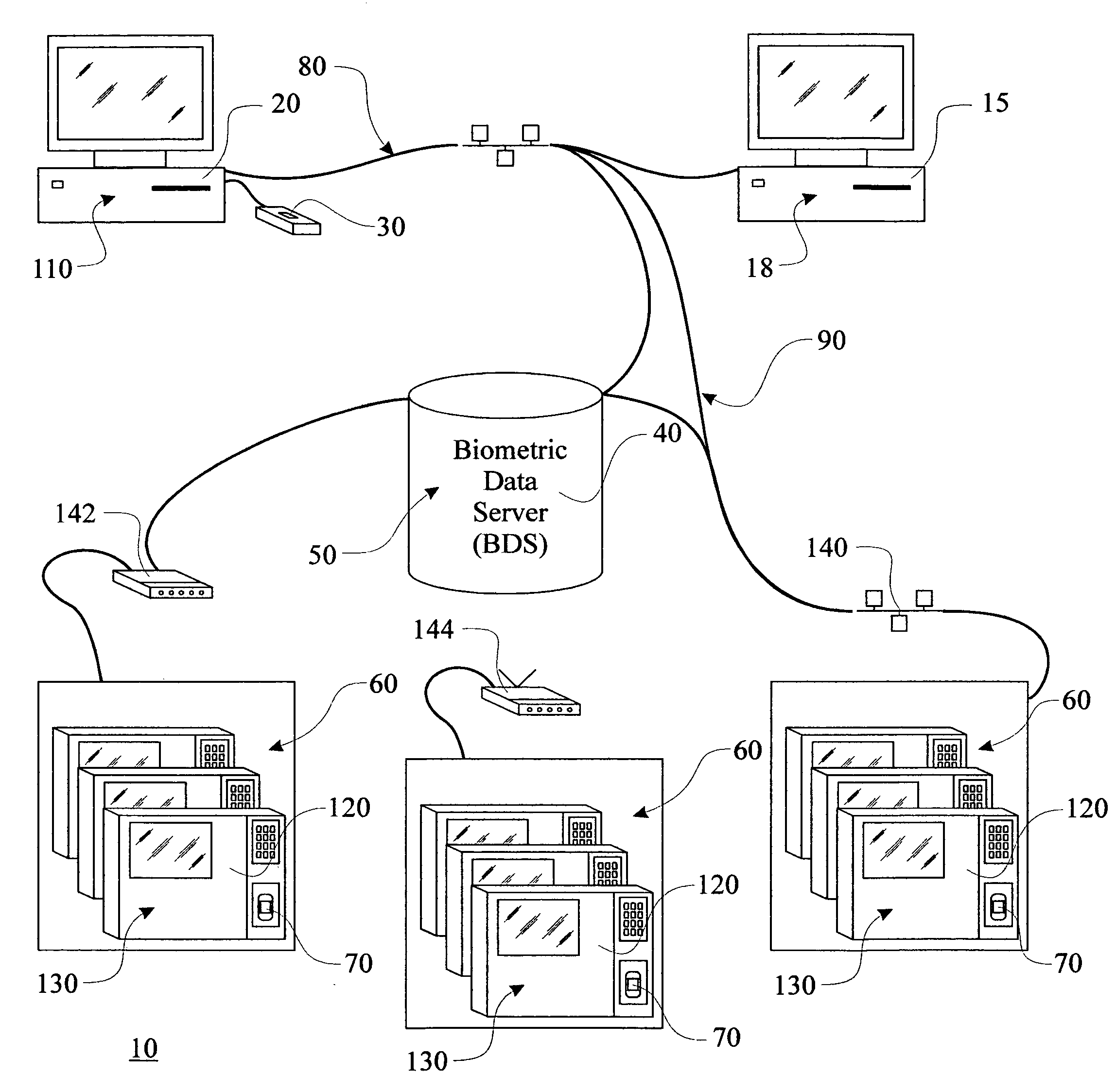

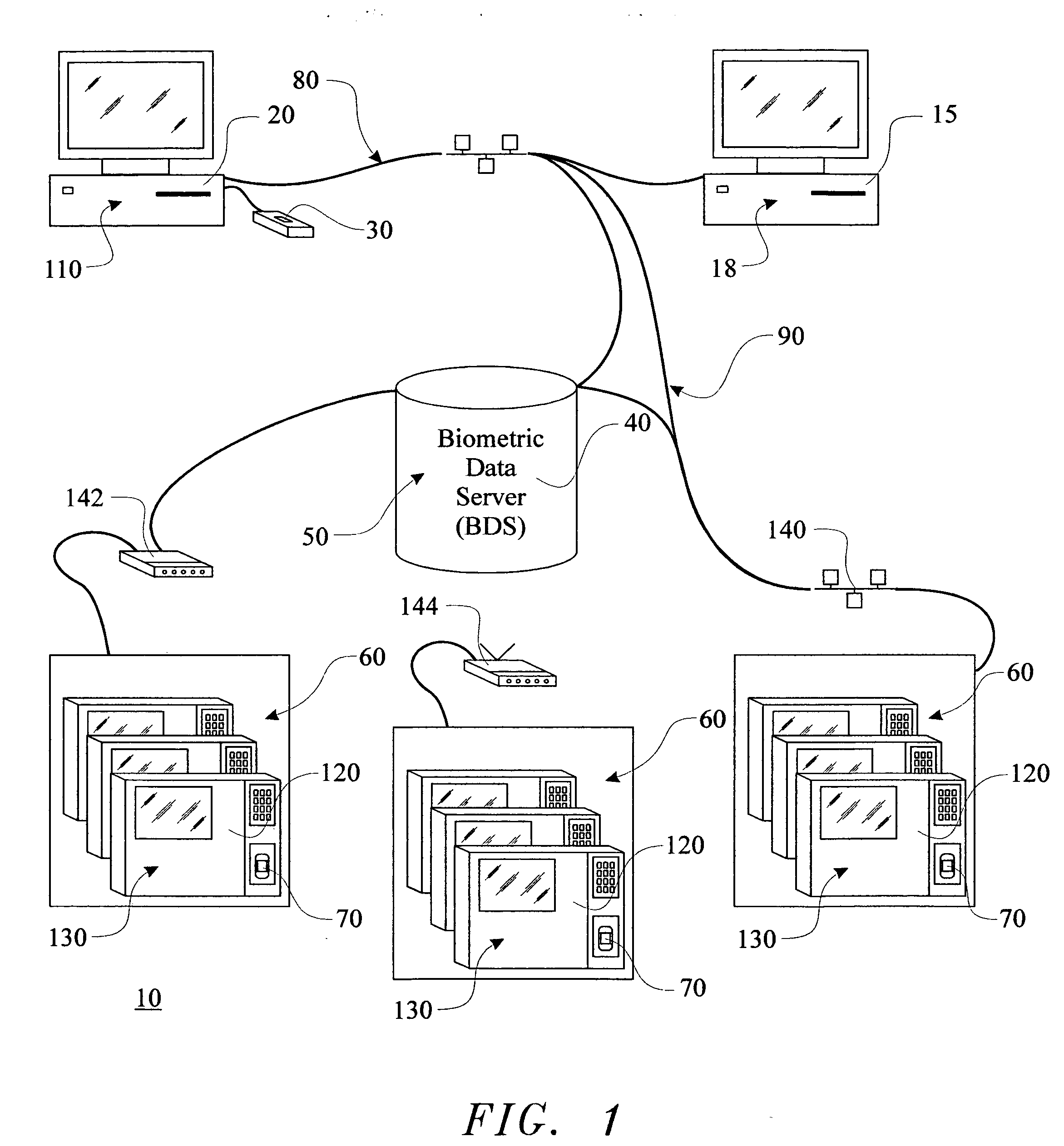

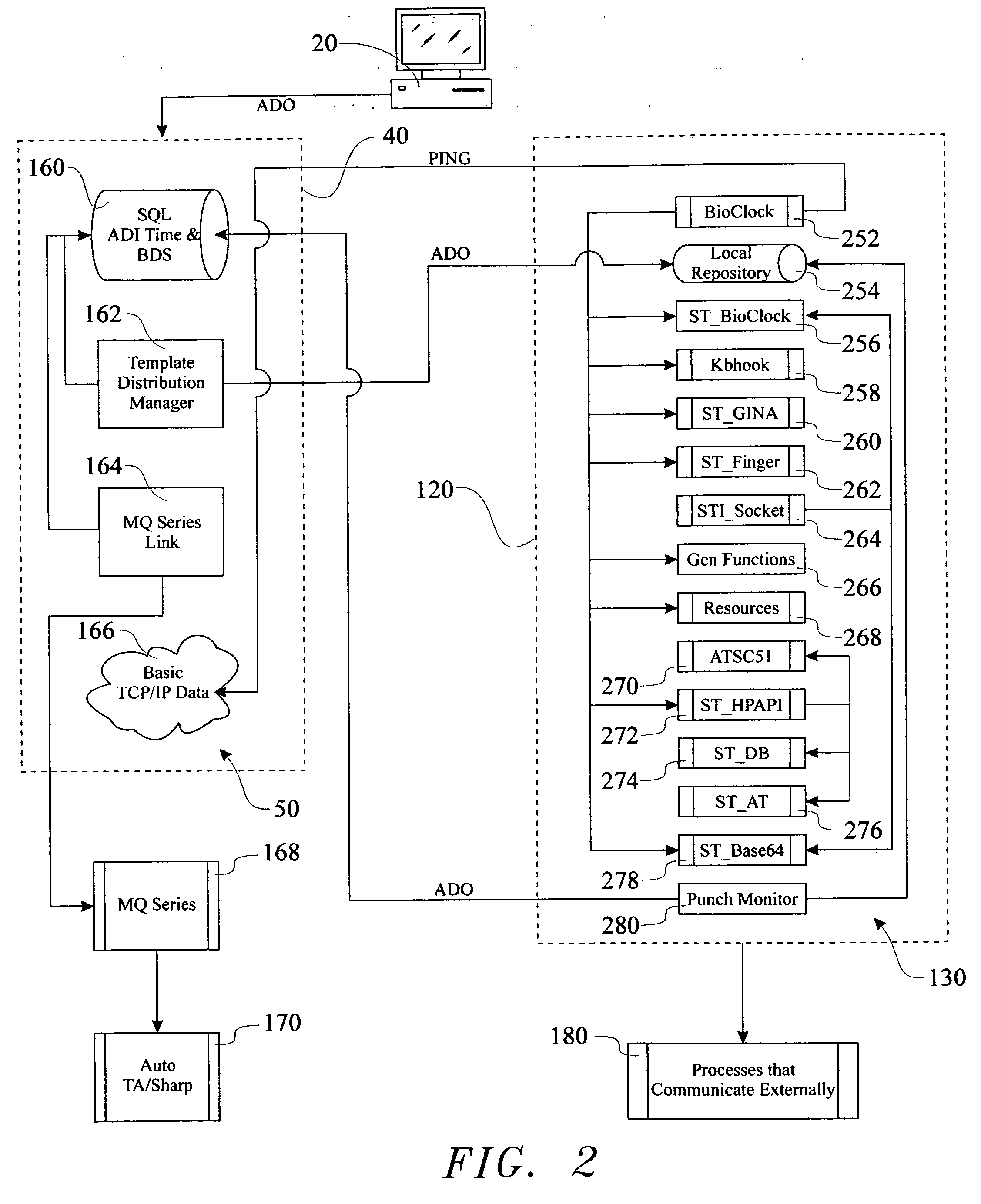

Method and apparatus for biometric template data management

InactiveUS20050154920A1Lower requirementData transfer timeDigital data processing detailsUser identity/authority verificationComputer hardwareBiometric data

The invention is for a method and apparatus of biometric data collection, distribution and management. The method allows for the collection of biometric data and the management and distribution of that data though at least one but preferably a network of biometric reading devices. The biometric reading devices can be used in conjunction with currently known applications or custom developed applications that can utilize data collected and managed throughout a network of remote biometric devices. These remote biometric reading devices can be used to perform time and attendance functions, access control functions, work release prisoner monitoring or any end use where information is managed and gathered to identify a person scheduled to be at a particular remote biometric device at a particular time. The system utilizes a Biometric Data Server (BDS) to manage and maintain Biometric templates, placing a removing the Biometric templates on remote biometric reading devices in conjunction with a predetermined directive. This process increases the efficiency and speed of the remote biometric device.

Owner:SENSE HLDG

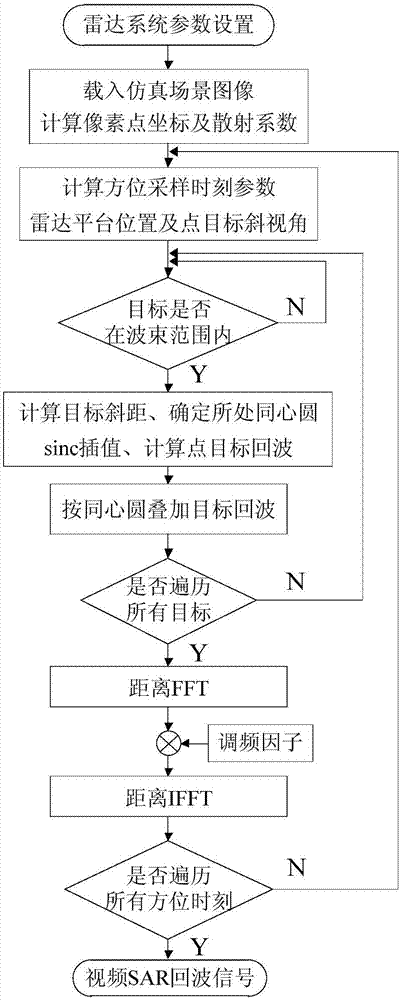

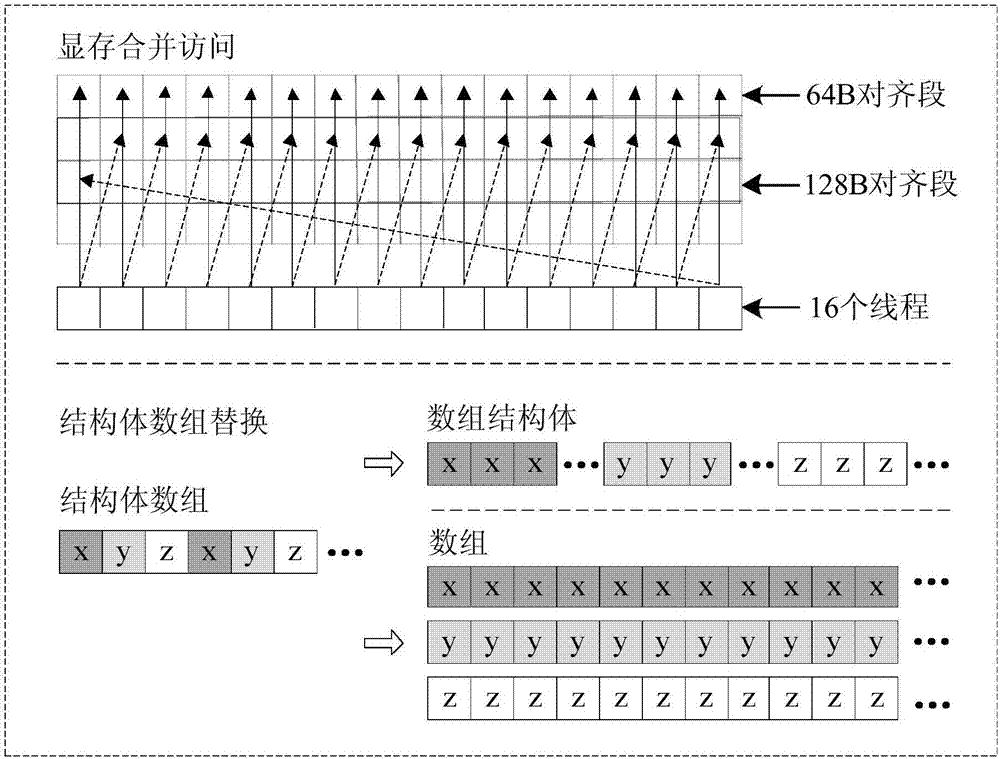

GPU-based video SAR echo simulation parallel implementation method

ActiveCN107229051AAchieve parallelismReduce overheadRadio wave reradiation/reflectionVideo memoryRadar systems

The invention belongs to the field of radar signal processing and discloses a GPU-based video SAR echo simulation parallel implementation method. The method comprises the following steps: copying radar system parameter values from a memory of a CPU to a constant memory of a GPU; transmitting original scene image data in the memory of the CPU to a video memory of the GPU; setting a kernel function and parallelly calculating space coordinates and backscattering coefficients of each point target; setting a kernel function and parallelly calculating space coordinates of a radar platform and instantaneous squint angle between the radar platform and each point target in each azimuth sampling moment; setting a kernel function and carrying out segmentation on all point targets and obtaining echo signals of the point targets in all segmented data; setting a kernel function and obtaining an initial echo signal of the radar at all azimuth moments; and setting a kernel function and obtaining a final echo signal obtained after linear frequency modulation processing as a video SAR echo signal. The method has the advantages of high real-time performance and high efficiency.

Owner:XIDIAN UNIV +1

Image processing apparatus, image forming apparatus, printer driver, image processing method and computer-readable storage medium

ActiveUS20050200905A1Eliminate the problemSatisfactory picture qualityImage enhancementDigitally marking record carriersGraphicsImaging processing

An image forming apparatus forms an image by a plurality of dots, by forming a periphery of a stepped transition portion of a contour portion of at least a character and / or graphics of the image by dots having a smaller size than dots forming portions other than the stepped transition portion, and determining a method of forming the dots having the smaller size depending on an inclination of the contour portion.

Owner:RICOH KK

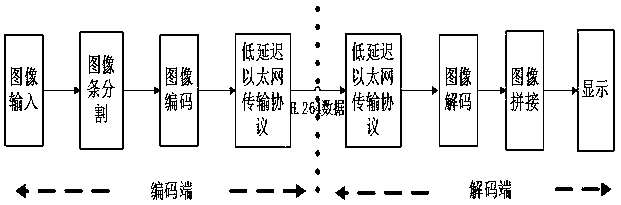

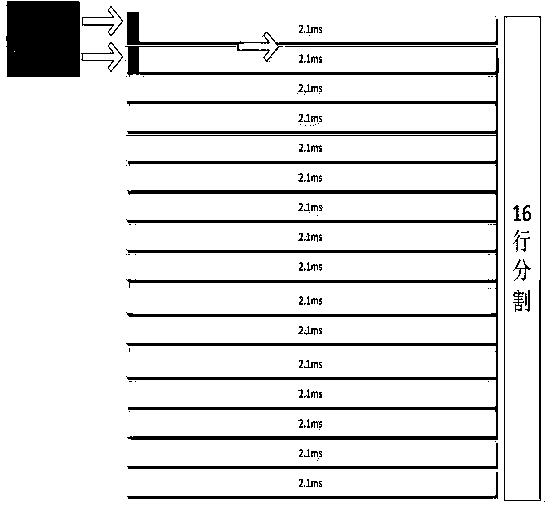

Method and system for realizing ultra-low latency encoding, decoding and transmission of high-definition video

ActiveCN108833932AReduce data transfer timeReduce waiting timeClosed circuit television systemsSelective content distributionLatency (engineering)Image segmentation

The invention provides a method and a system for realizing ultra-low latency encoding, decoding and transmission of a high-definition video. The method comprises the steps that: an encoder receives the high-definition video, segments each frame of images constituting the high-definition video into a plurality of cut frames, and completes caching, compressed encoding and uploading in sequence by regarding each of the cut frames as a unit one by one; an Ethernet transmits compressed encoded data of the cut frames; and a decoder receives the compressed encoded data of the cut frames, completes caching and independent decoding in sequence by regarding each of the cut frames as a unit, and splices the images after independent decoding to complete the restoration of each frame of the images. Themethod and the system solve the problem that high real-time video transmission application cannot be satisfied because the existing encoding and decoding system cannot cut flexibly and is difficult to adjust and optimize, realize the effect that the total time delay from encoding, transmission to decoding is less than 50 ms, and can meet the low latency requirements of the high real-time application.

Owner:HUNAN JUNHAN INFORMATION TECH CO LTD

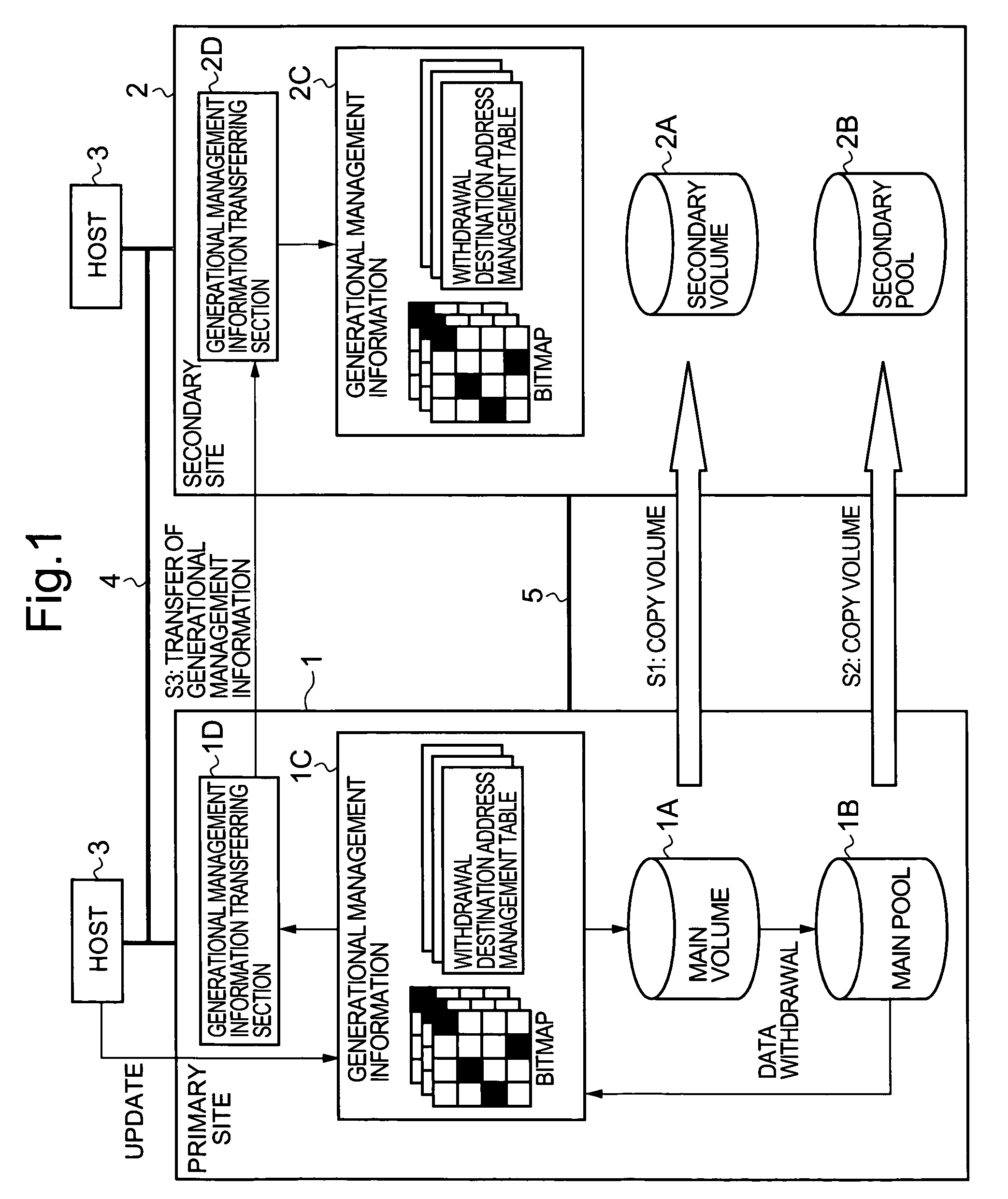

Storage system and back-up method for storage system

ActiveUS7272693B2Reduce storageReduce data transfer timeInput/output to record carriersMemory loss protectionPrimary sitesDisk array

Owner:RAKUTEN GRP INC

Semiconductor memory device with sub-amplifiers having a variable current source

InactiveUS7304910B1Lower performance requirementsShorten operation timeDigital storageHemt circuitsEngineering

A column circuit that amplifies signals read from a sense amplifier array SAA to local input / output lines LIO in sub-amplifiers SAMP to transfer the amplified signals to main input / output lines MIO is provided. A current control circuit IC that can set one of two kinds of currents according to read enable signals RD1, RD2 is provided in each sub-amplifier SAMP. The read enable signals RD1, RD2 are generated at timings corresponding to the number of cycles in burst read operation under control of the timing controller. Current in the current control circuit IC is set to be large by the RD1 in burst read operation cycle just after activation of a memory bank, while current in the current control circuit IC is set to be small by the RD2 in the next and subsequent burst read cycles. Accordingly, expansion of an operation margin or reduction of power consumption can be realized in a semiconductor device including a semiconductor memory such as a DRAM.

Owner:LONGITUDE LICENSING LTD

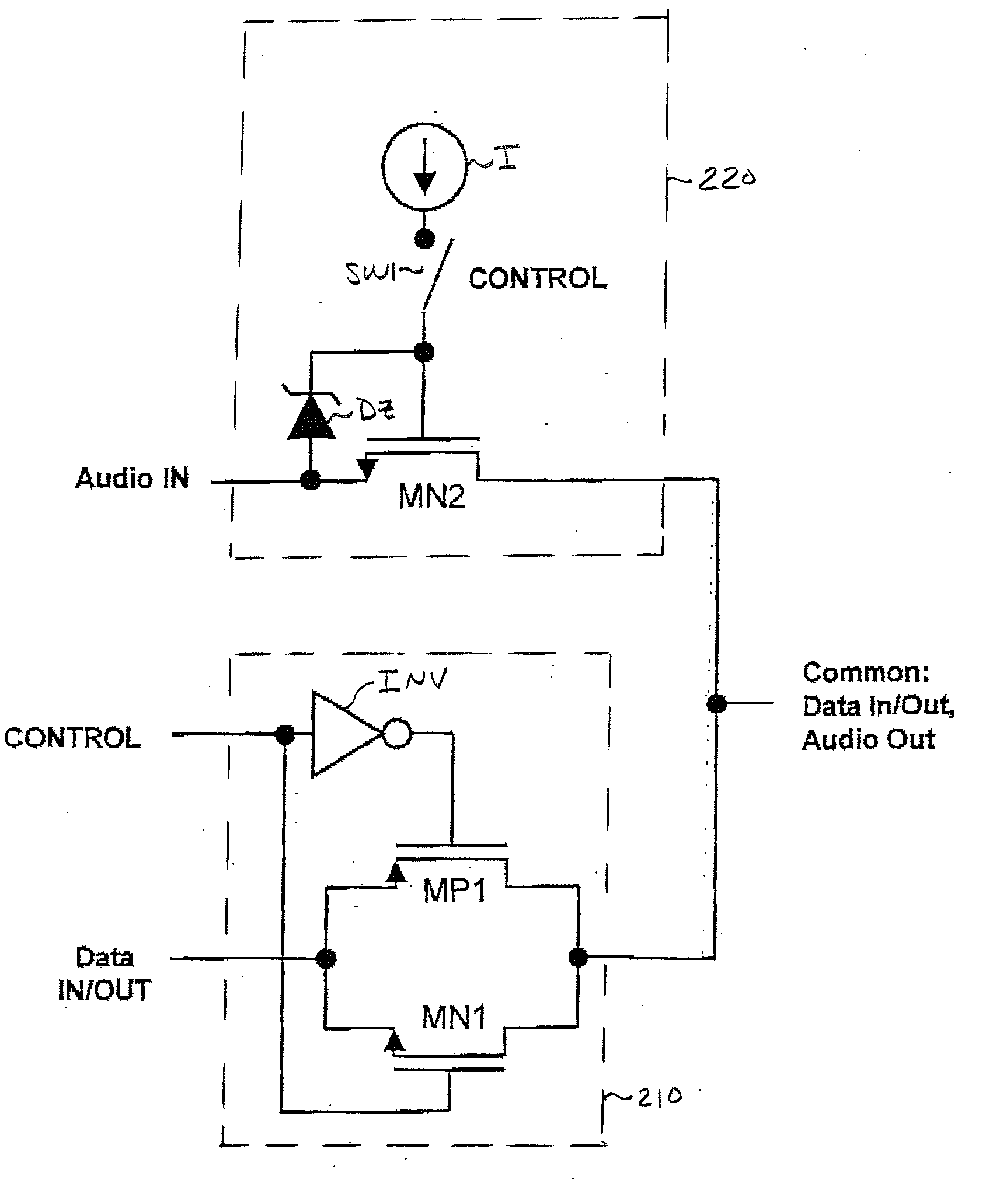

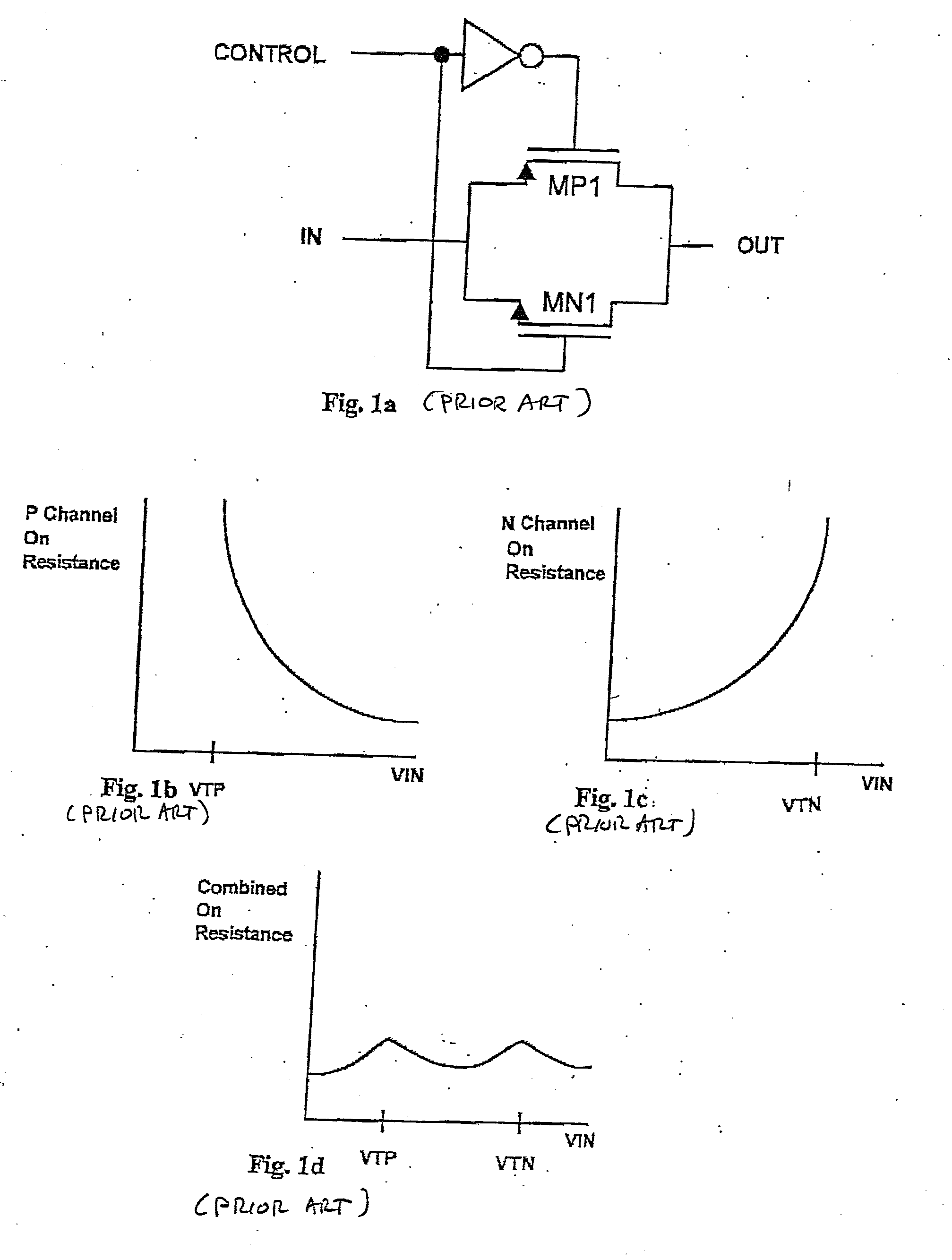

Method And Apparatus For Switching Audio And Data Signals Through A Single Terminal

ActiveUS20070132501A1Minimal distortionIncrease the areaTransistorElectronic switchingDigital dataMOSFET

A MOSFET-based, multi signal-switching circuit controllably passes analog / audio signals and digital signals through a common terminal to a single connector. Analog / audio signals are coupled through a single N-channel MOSFET analog signal switch which, when turned-ON, minimizes distortion of the analog / audio signal and capacitive loading to an adjacent, MOS-based or CMOS-based digital data signal switch. A respective turn-OFF circuit maintains its associated switch MOSFET turned OFF.

Owner:INTERSIL INC

FPGA-based Tiny-yolo convolutional neural network hardware acceleration method and system

ActiveCN108805274ASave resourcesFast operationImage memory managementProcessor architectures/configurationNeural network hardwareParallel processing

The invention discloses an FPGA-based Tiny-yolo convolutional neural network hardware acceleration method and system. By analyzing the parallel characteristics of a Tiny-yolo network, and in combination with the parallel processing capability of hardware, the hardware acceleration is carried out on the Tiny-yolo convolutional neural network. The acceleration scheme is used for performing acceleration improvement on the Tiny-yolo network from three aspects that (1) the processing speed of the Tiny-yolo network is increased through multi-channel parallel input; (2) the convolution computing speed of the Tiny-yolo network is increased through parallel computing; and (3) the pooling process time of the Tiny-yolo network is shortened through pooling embedding. The method greatly increases the detection speed of the Tiny-yolo convolutional neural network.

Owner:CHONGQING UNIV

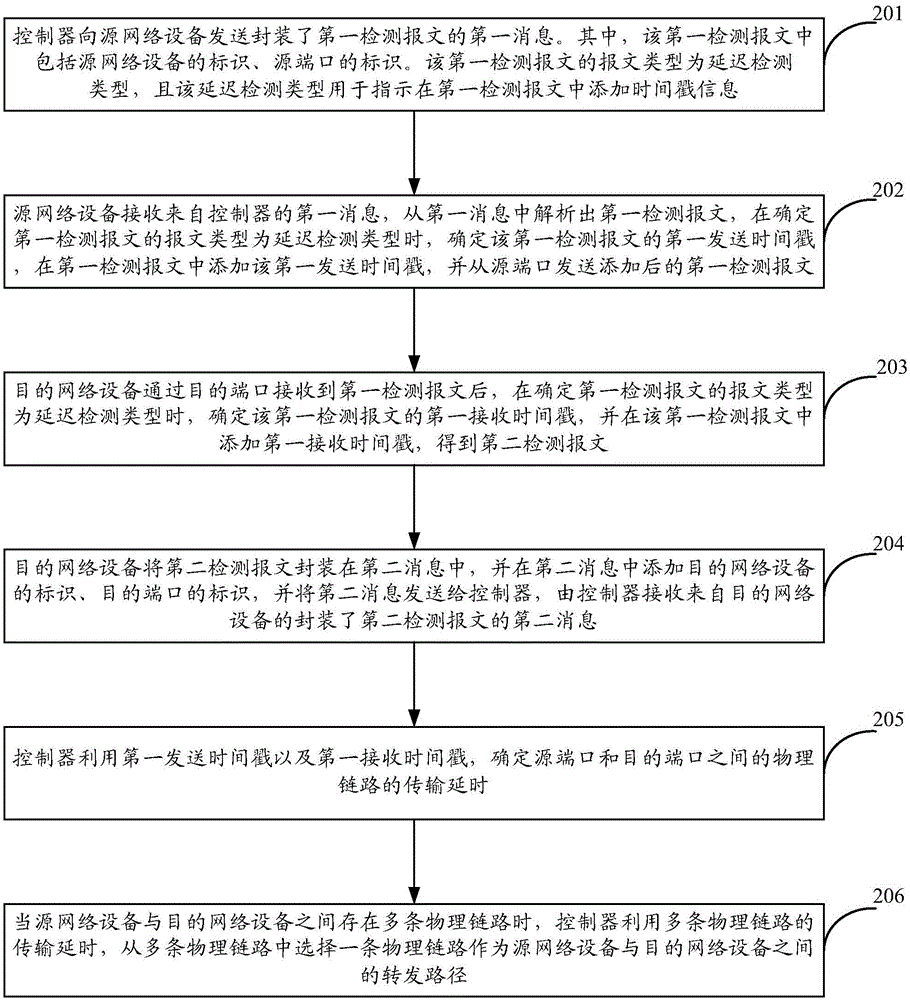

Forwarding path selection method and device

ActiveCN105591912AImprove forwarding efficiencyReduce data transfer timeData switching networksData transmission timeMessage type

The invention provides a forwarding path selection method and a forwarding path selection device. The forwarding path selection method comprises the steps that: a controller sends a first message packaged with a first detection message to source network equipment, wherein a message type of the first detection message is a delay detection type; the controller receives a second message packaged with a second detection message from target network equipment, wherein the second detection message comprise a first sending time stamp of the first detection message determined by the source network equipment, and a first receiving time stamp of the first detection message determined by the target network equipment; and the controller utilizes the first sending time stamp and the first receiving time stamp, determines transmission delay time of a physical link between a source port and a target port, and selects a forwarding path between the source network equipment and the target network equipment by utilizing the transmission delay time. By adopting the forwarding path selection method and the forwarding path selection device, data transmission time can be shortened, and data transmission efficiency can be increased.

Owner:NEW H3C TECH CO LTD

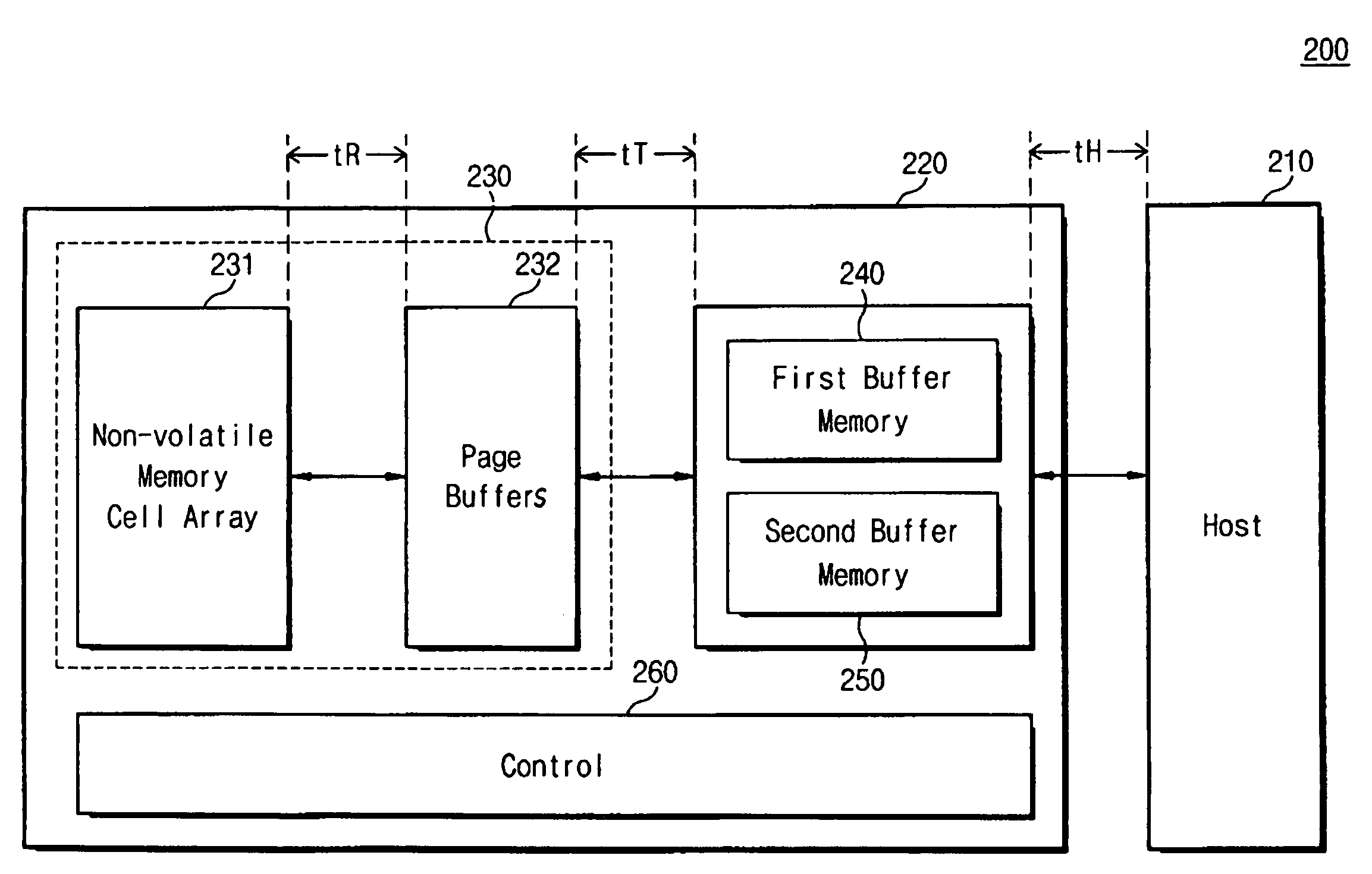

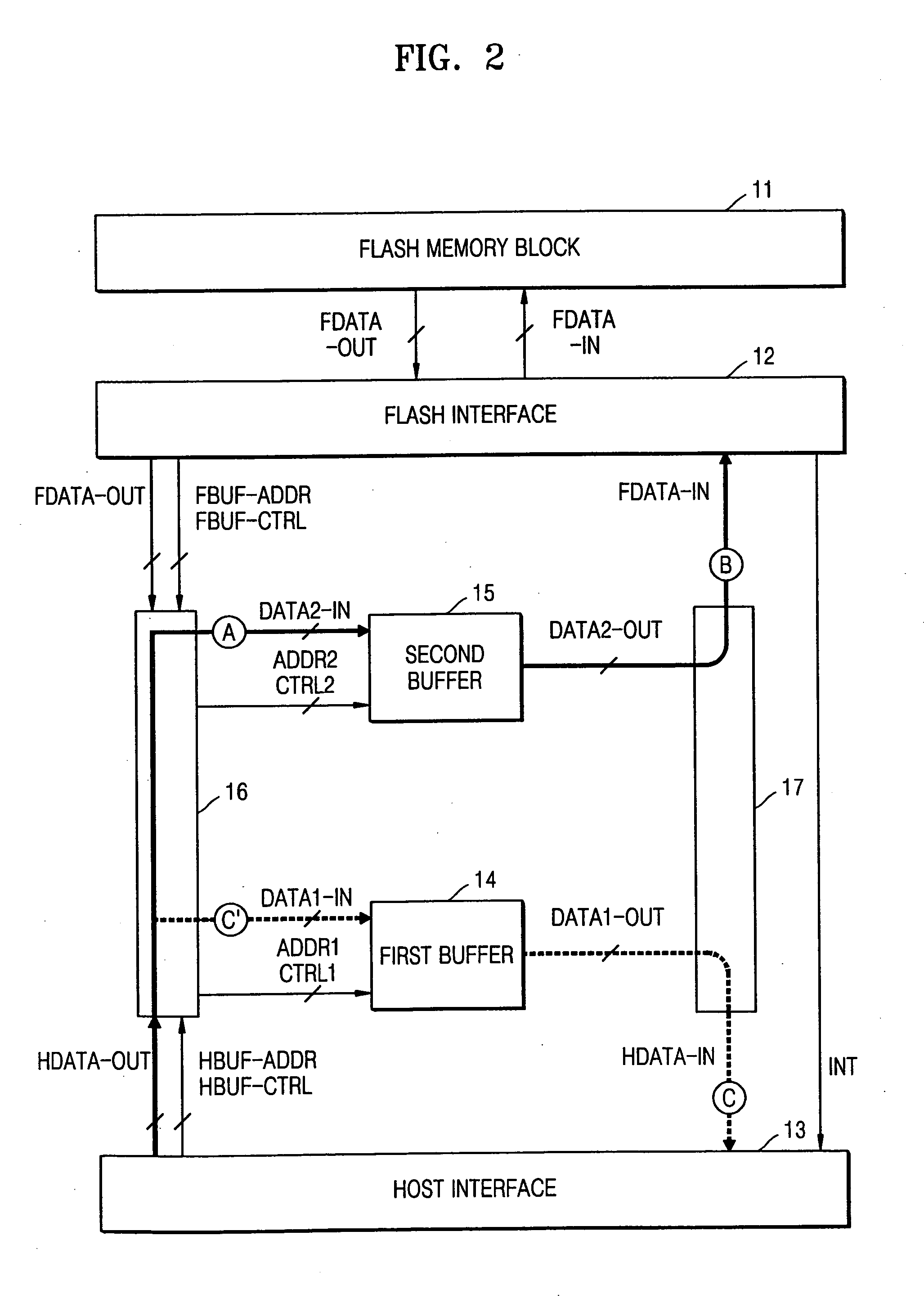

Method and device for performing cache reading

ActiveUS7421557B2Reduce data transfer timeReduce transfer timeMemory adressing/allocation/relocationRead-only memoriesDevice materialSemiconductor

Method and device for reading data from a semiconductor device, where tR is a read operation time, tT is a buffer transfer time, and tH is a host transfer time, where at least two of tR, tT, and tH may be overlapped to reduce a total transfer time.

Owner:SAMSUNG ELECTRONICS CO LTD

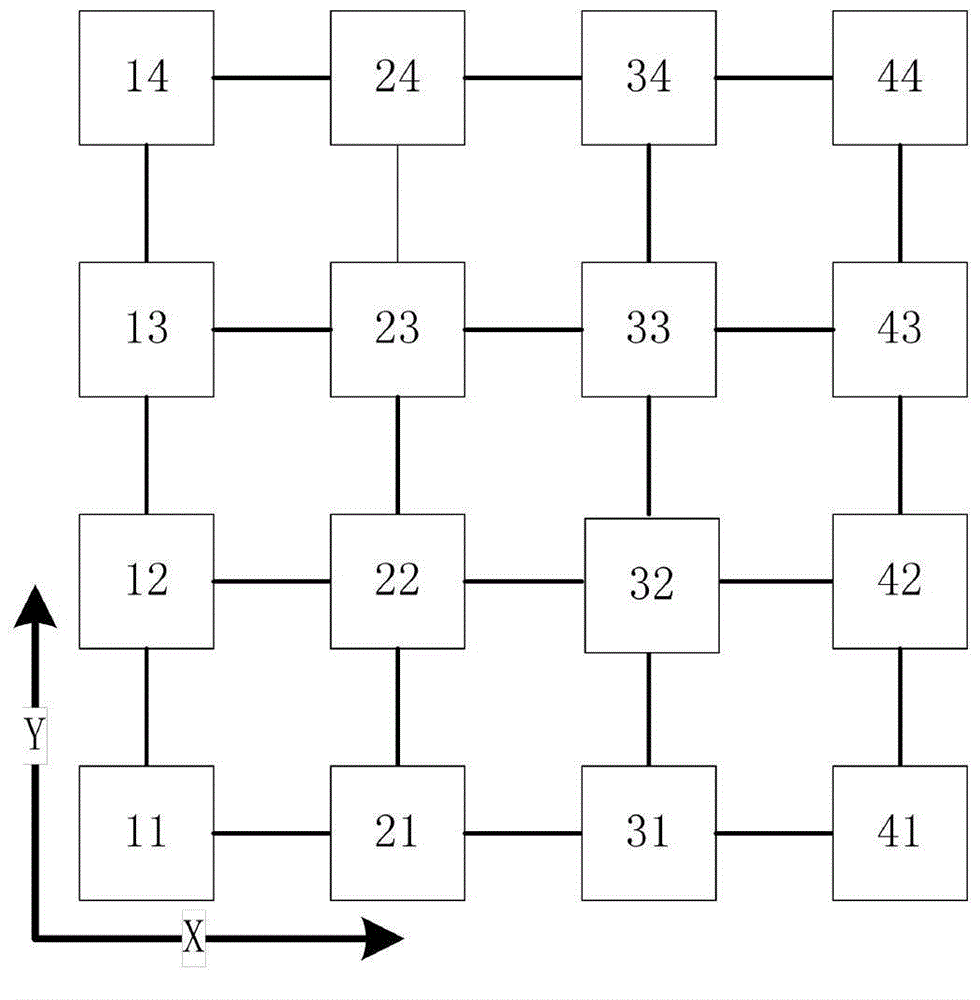

Multicast router based on package and circuit switching technology and working mode thereof

ActiveCN105007226AReduce consumptionReduce data transfer timeData switching networksComputer moduleInterconnection

The invention discloses a multicast router based on package and circuit switching technology and a working mode thereof. The multicast router based on package and circuit switching technology is characterized by being applied to a network on chip which includes a plurality of multicast routers, a plurality of resource nodes and a plurality of interconnection channels; each multicast router comprises an input state machine module, a priority encoder module, a decoder module, an address filtering module, an arbiter module, a crossbar module and an output state machine module; in a multicast data transmission event, a single requester node can simultaneously support sending the same batch of data to at most eight target nodes at the same time; and the success rate of establishing a link can be improved by the priority encoder module, and the target nodes are prevented from repeatedly routing by the address filtering module. The multicast router based on package and circuit switching technology can fully utilize the parallelism characteristic of the network on chip to save time consumed for the event of sending the same batch of data to the plurality of target nodes by the single requester node, and consumption on cache resources of the multicast routers in the network on chip is reduced.

Owner:HEFEI UNIV OF TECH

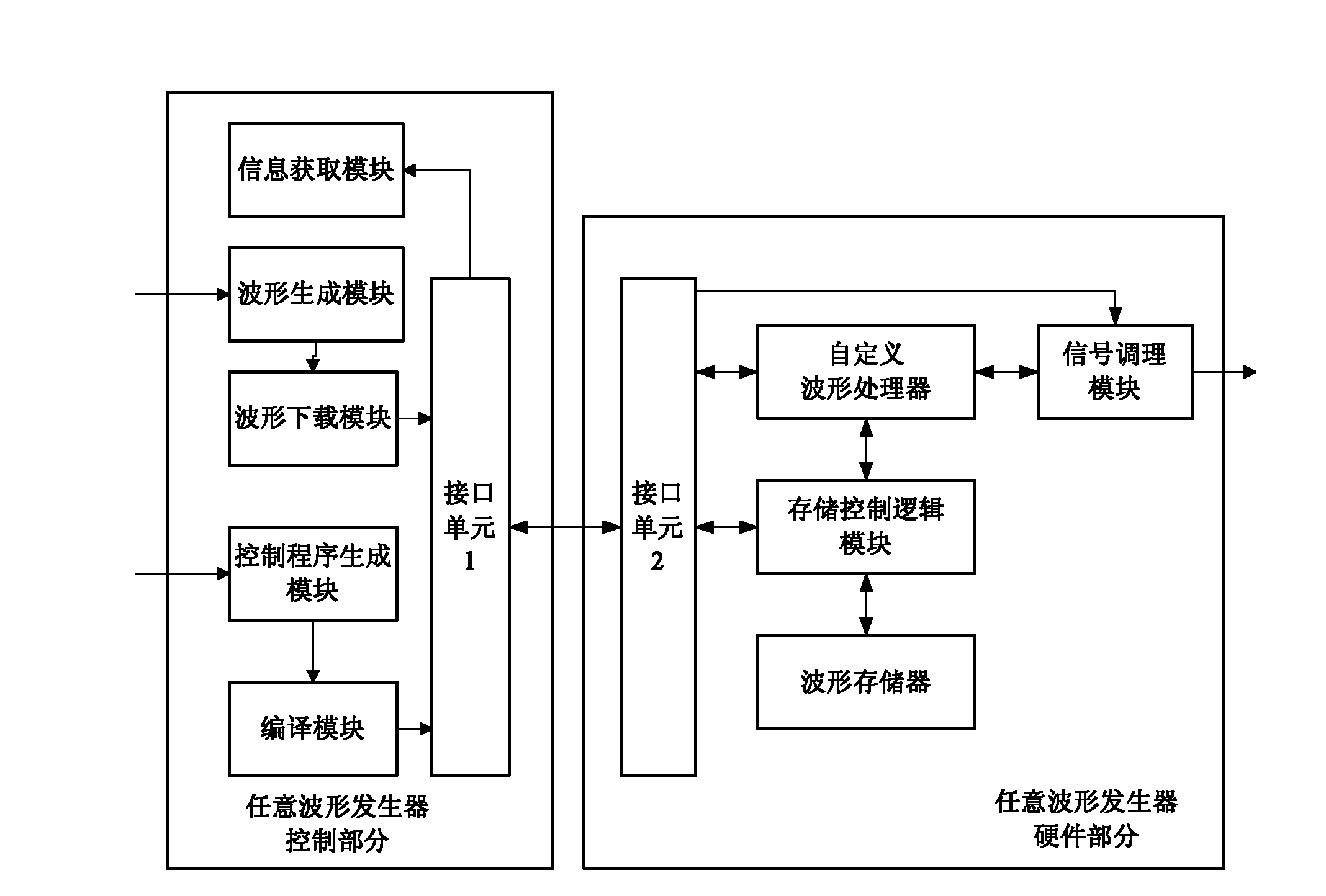

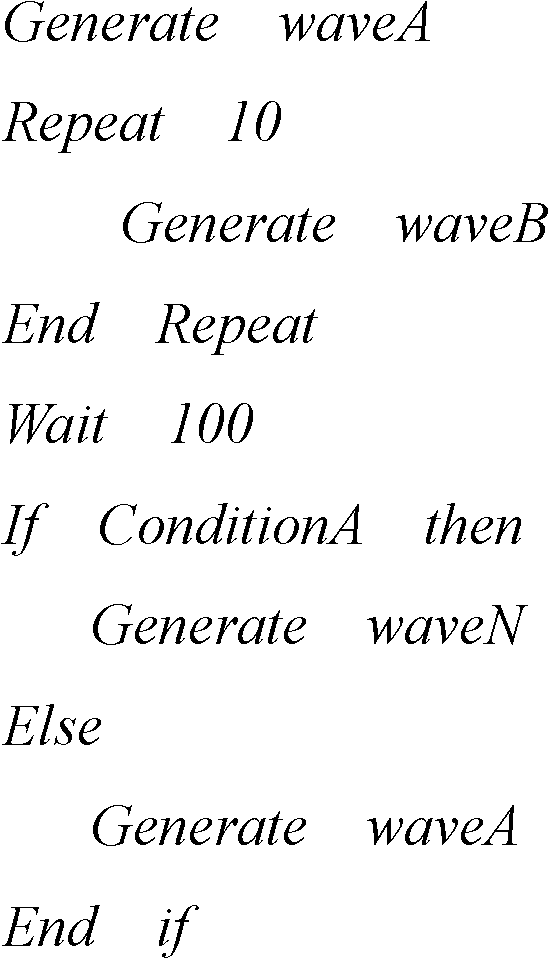

Arbitrary waveform generating system based on user-defined processor

InactiveCN102520761AFunctionality and performance improvementsReduce data transfer timeDigital function generatorsEmbedded systemInstruction set

The invention discloses an arbitrary waveform generating system based on a user-defined processor. In a control portion, a waveform generating module generates various waveform segment data downloaded to a hardware portion through a waveform downloading module, a control program generating module receives an externally inputted instruction set, and the instruction set is downloaded to the hardware portion after compiling of a compiling module. In the hardware portion, a storage control logic module controls reading and writing of a waveform memory, the user-defined waveform processor receives and analyzes the instruction set, generates call instructions for corresponding waveform segments according to names of the waveform segments indicated by the instruction set, transmits the call instructions to the storage control logic module and receives the waveform segment data read by the storage control logic module, and analog signals are outputted after combined waveform segment data are conditioned according to the call sequence and the call frequency of the waveform segment indicated by the instruction set. By the aid of the arbitrary waveform generating system, data transmission time of the control portion and the hardware portion during waveform generation can be shortened.

Owner:BEIJING AEROSPACE MEASUREMENT & CONTROL TECH

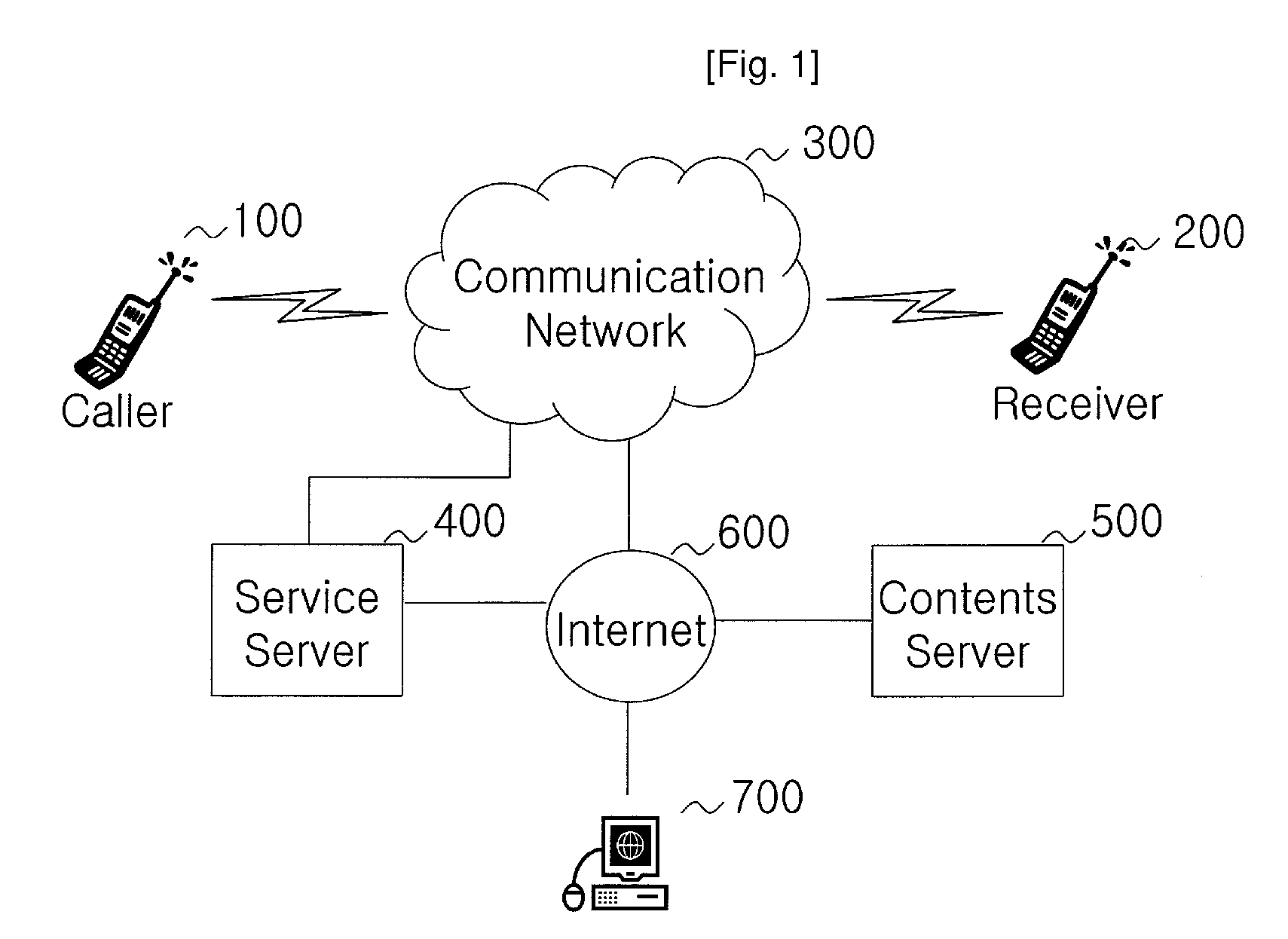

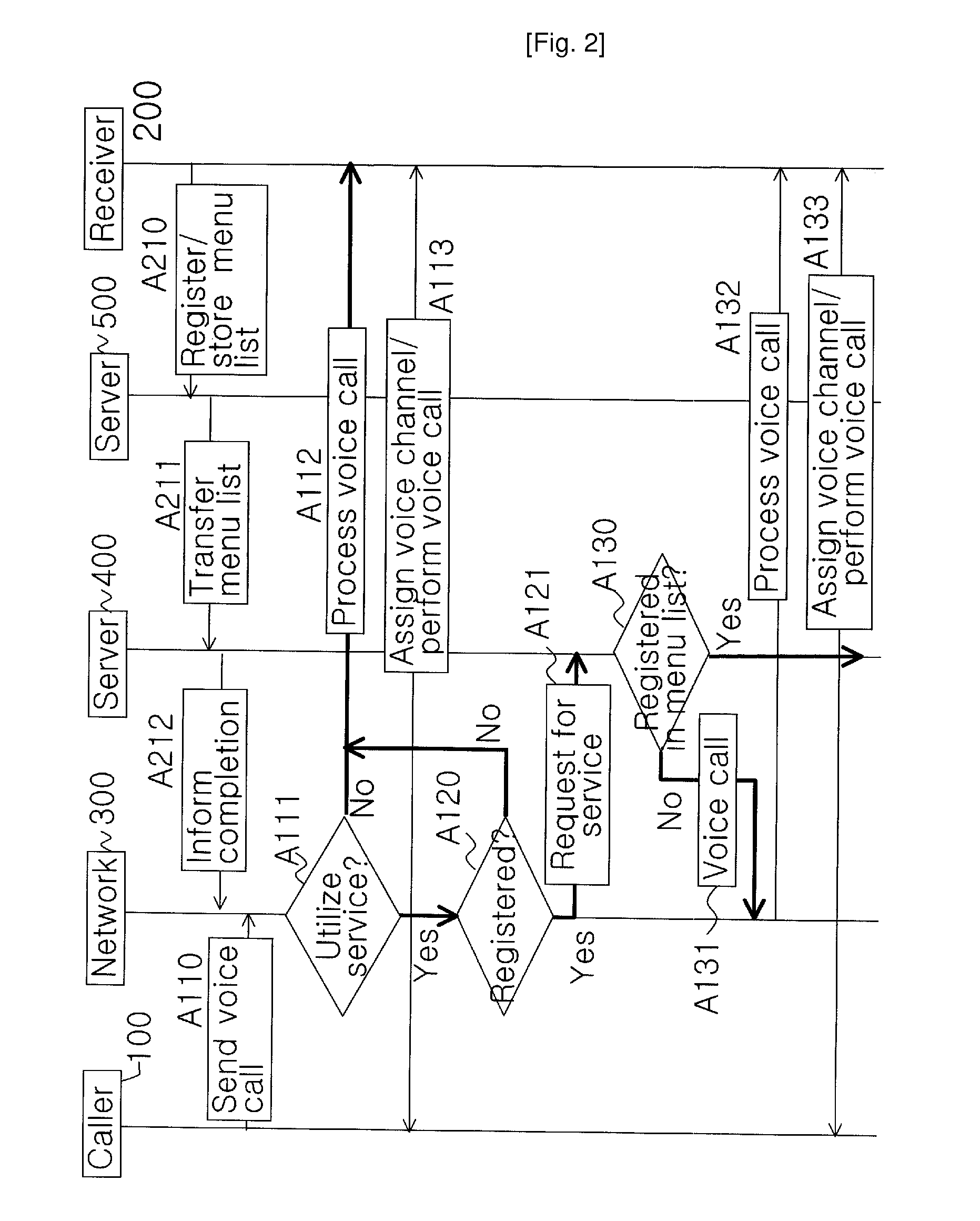

Dynamic URL self-formation in accordance with combining caller & receiver's information

InactiveUS20090305731A1Save resourcesReduces display volumeAutomatic exchangesMessaging/mailboxes/announcementsCommunications systemApplication software

The present invention relates to data communication system and method enabling the utilization of contents by accessing the wireless Internet through self-formation of a dynamic URL by the caller's terminal application. When the caller attempts a voice call or a data call, the contents menu list registered by the receiver (or contents provider) and the caller / receiver information are transferred to the caller's terminal through a paging channel. Then, an application software stored in the caller's terminal processes the service option and displays the menu based on the menu list and caller / receiver information. Subsequently, in response to the caller's menu utilization request, a dynamic URL is formed from the combination of the identification number and contents type of the menu selected by the caller and the caller / receiver information.

Owner:CALL GATE CO LTD

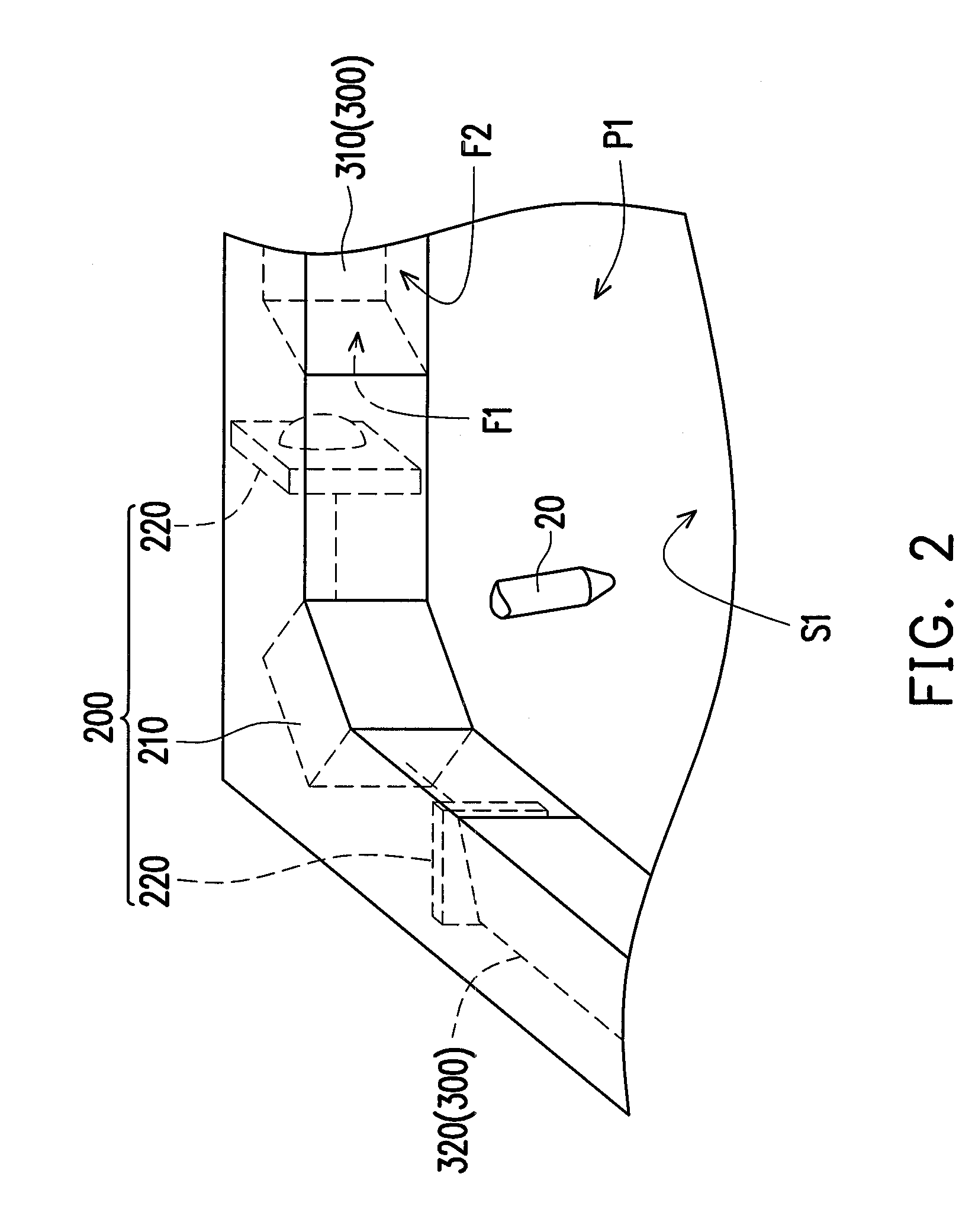

Optical touch-sensing display

InactiveUS20110096034A1Improve touch effectImprove lighting qualityInput/output processes for data processingTouch SensesLight guide

An optical touch-sensing display including a display device, at least three light guides, at least two optical touch-sensing devices and a transmission interface is provided. The display device has a display surface and a sensing space upon the display surface. Each of the light guides disposed at periphery of the display surface has two light incident surfaces and a light-emitting surface there between. Each of the optical touch-sensing devices disposed outside of the display surface includes a sensing module and a light source. When an object enters the sensing space, each sensing module senses a light variation induced by the object to generate a first signal, and then the first signals are transmitted to one sensing module and processed to a second signal, and then the second signal is output from the optical touch-sensing device through the transmission interface.

Owner:SONIX TECH

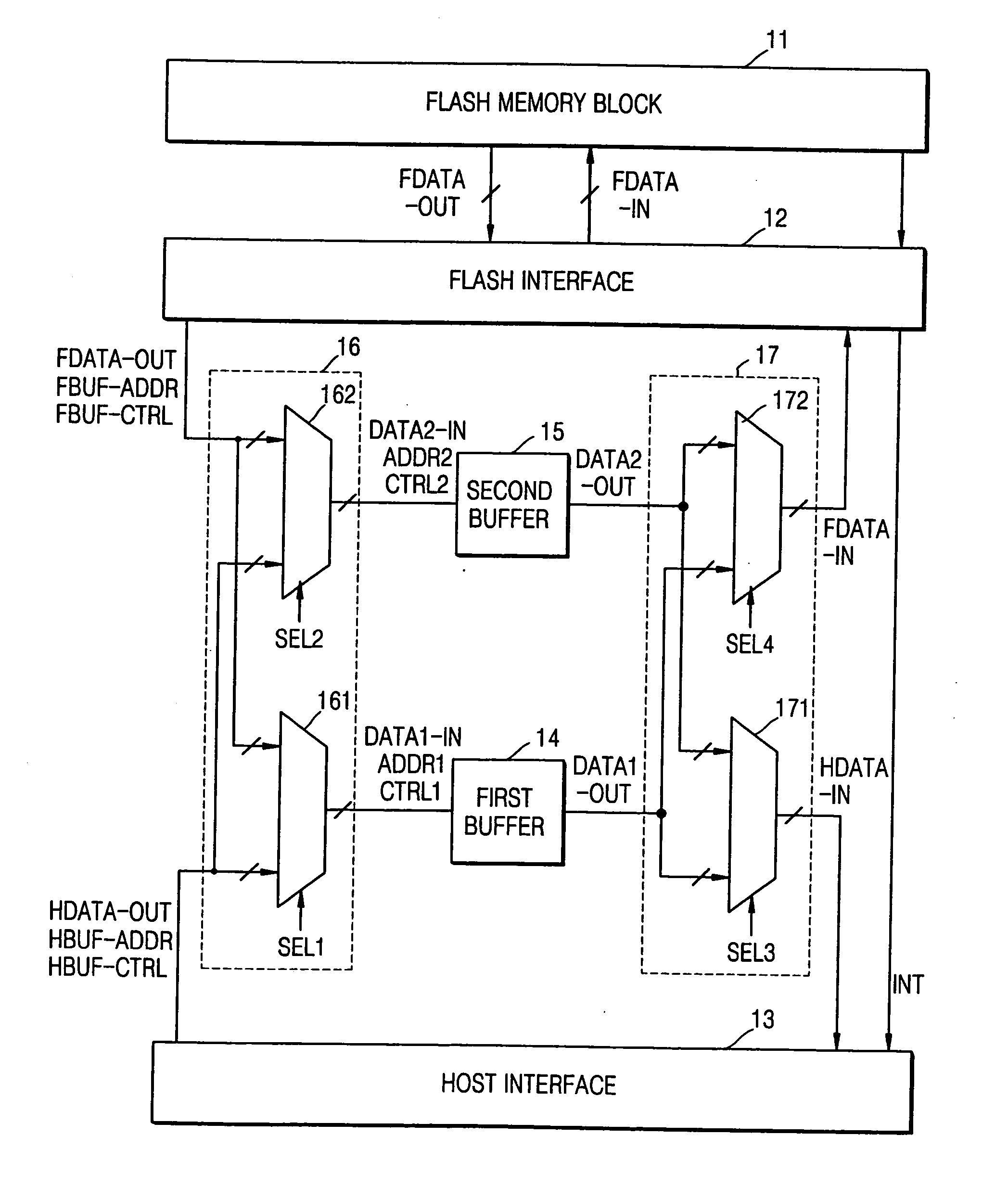

Dual buffer memory system for reducing data transmission time and control method thereof

ActiveUS20050060486A1Improve system performanceReduce data transfer timeMultiple digital computer combinationsDigital storageData transmission timeSystem usage

A dual buffer memory system capable of improving system performance by reducing a data transmission time and a control method thereof are provided. The dual buffer memory system includes a flash memory block and a plurality of buffers. The dual buffer memory system uses a dual buffering scheme in which one buffer among the plurality of buffers interacts with the flash memory block and simultaneously a different buffer among the plurality of buffers interacts with a host. Therefore, it is possible to reduce a data transmission time between the flash memory and the host, thereby improving system performance.

Owner:SAMSUNG ELECTRONICS CO LTD

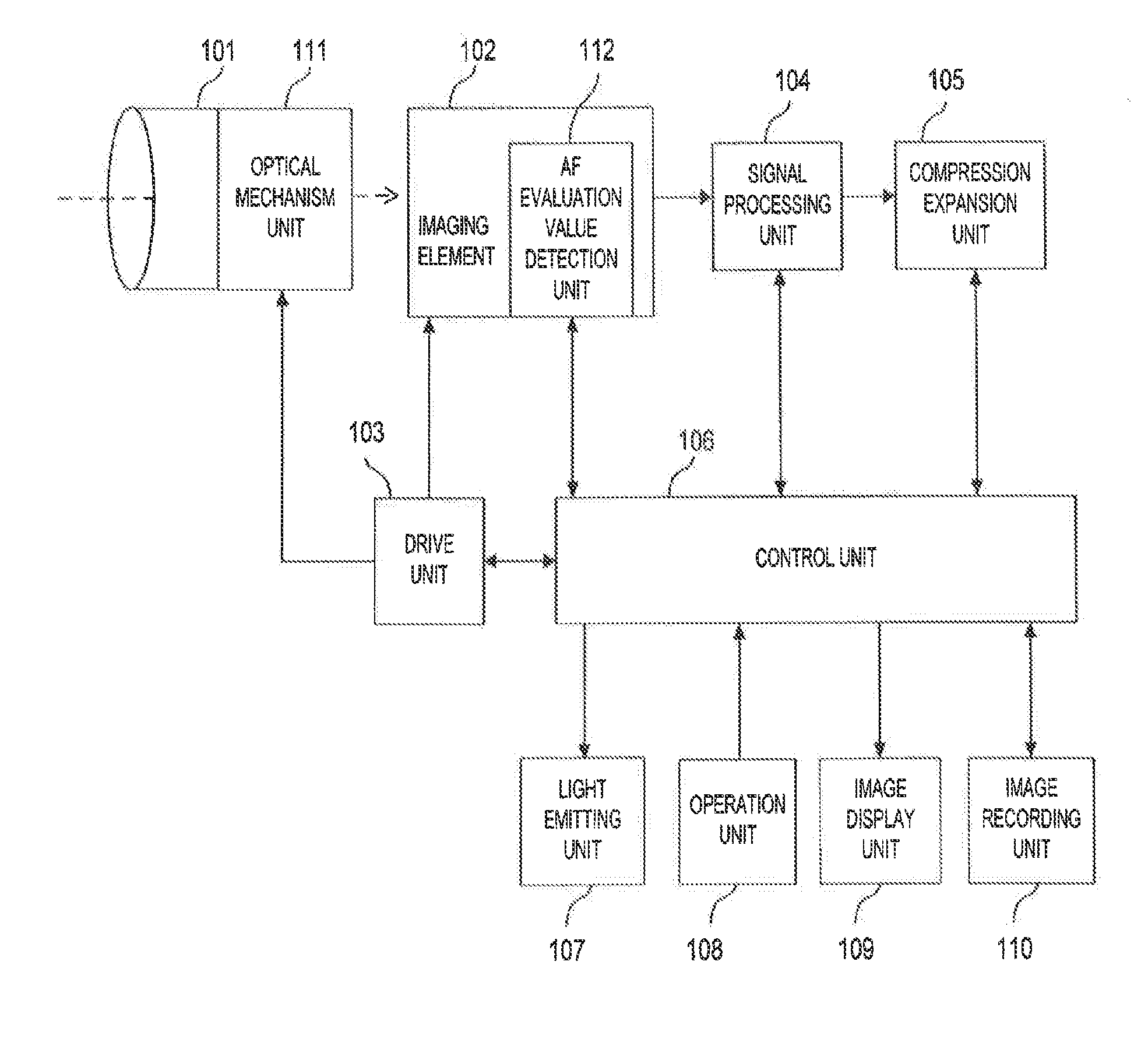

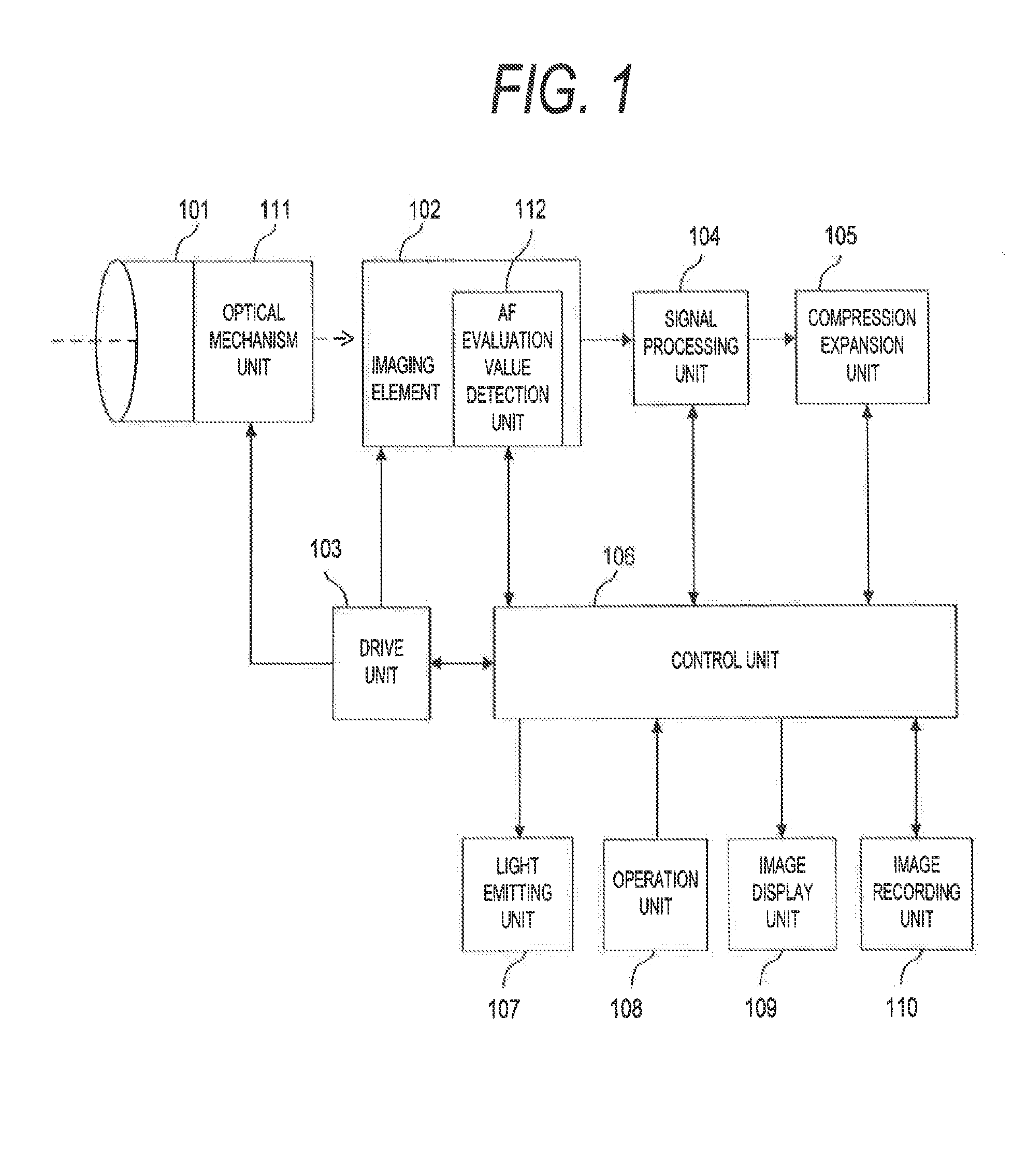

Imaging element, imaging apparatus, its control method, and control program

ActiveUS20150002715A1Data transfer time be shortenReduce data transfer timeTelevision system detailsTelevision system scanning detailsLayered structureOptical image

An imaging element having a layered structure including a first chip having a pixel portion in which pixels for photoelectrically converting an optical image of an object and generating a pixel signal are arranged two-dimensionally and a second chip in which a drive means of the pixel portion is arranged, and having a first output path to output the pixel signals of at least a first pixel group in the pixel portion and a second output path to output the pixel signals of a second pixel group, comprises the a conversion means for converting the pixel signals of the first and second output paths into digital signals and a control information generation means for generating control information of a photographing operation of the object by using the digital signal converted by the conversion means, wherein at least a part of the conversion means is arranged in the first chip.

Owner:CANON KK

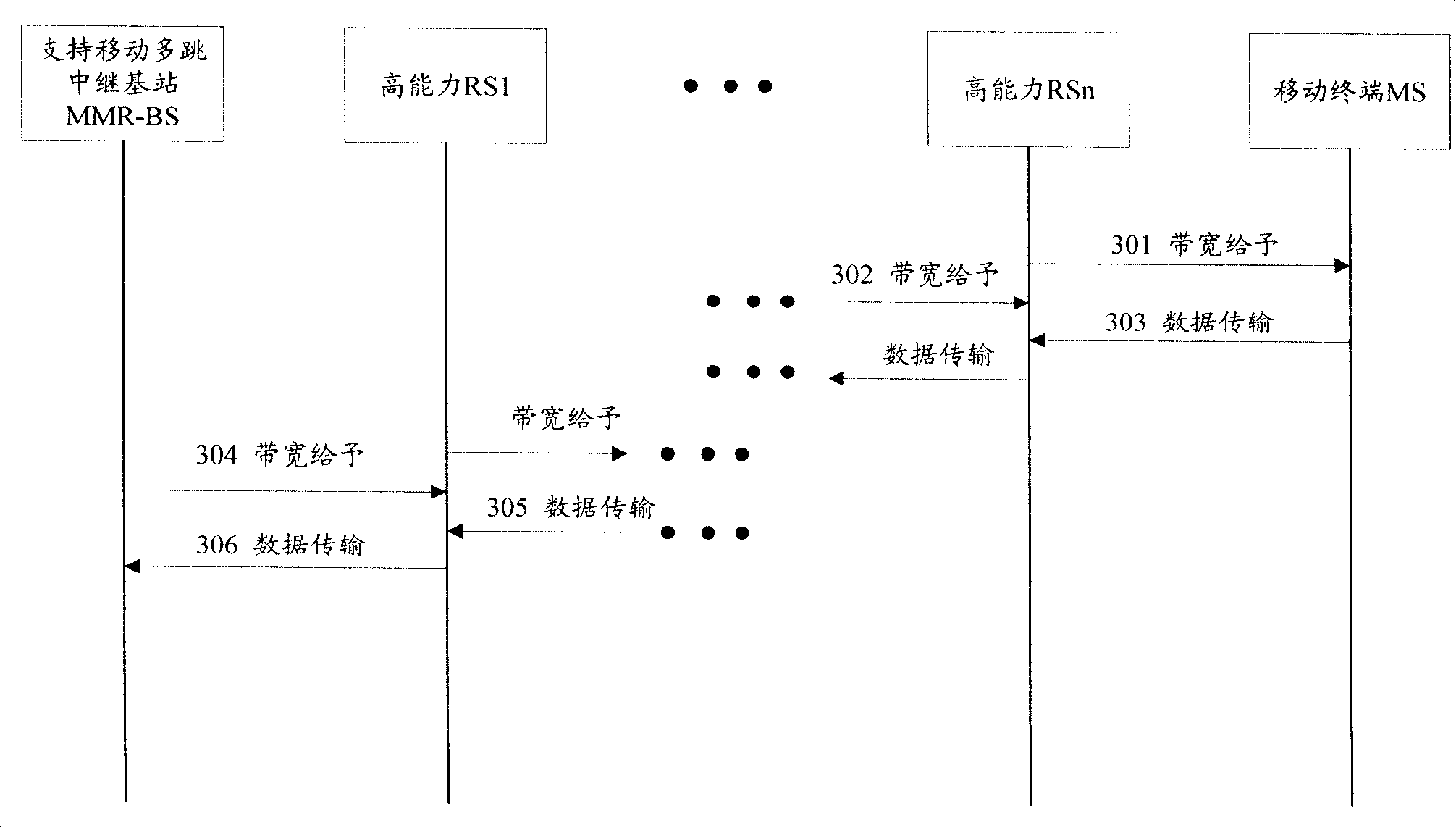

Method and system for scheduling of resource based on wireless system

InactiveCN101203037AAvoid failureReduce intervalNetwork topologiesRadio/inductive link selection arrangementsTime conditionMulti hop relay

The invention provides a resource dispatching method and a system based on a wireless system, applied to a multi-hop network, and the specific realization method is: a bandwidth is given to MS by a mobile terminal MS synchronous station, and data are transmitted to the synchronous station of MS through the acquired bandwidth by MS; data is transmitted to an upper node through the bandwidth given by the upper node from each level of nodes between MS and MMR-BS supporting a mobile multi-hop relay station, after a bandwidth given by the upper node is acquired between a lower node given by the bandwidth and the data received from the lower node and data of the lower node are received. The invention has the advantages that the application of the scheme can assure the acquirement of the bandwidth before receiving the transmitted data from the lower node; the space between the acquired bandwidth and the received transmission data is relatively small; not only can the whole data transmission time be effectively compressed, but also the distributed bandwidth is in line with the real-time condition of a link of the network; a problem of disabled bandwidth distribution can be effectively avoided.

Owner:HUAWEI TECH CO LTD

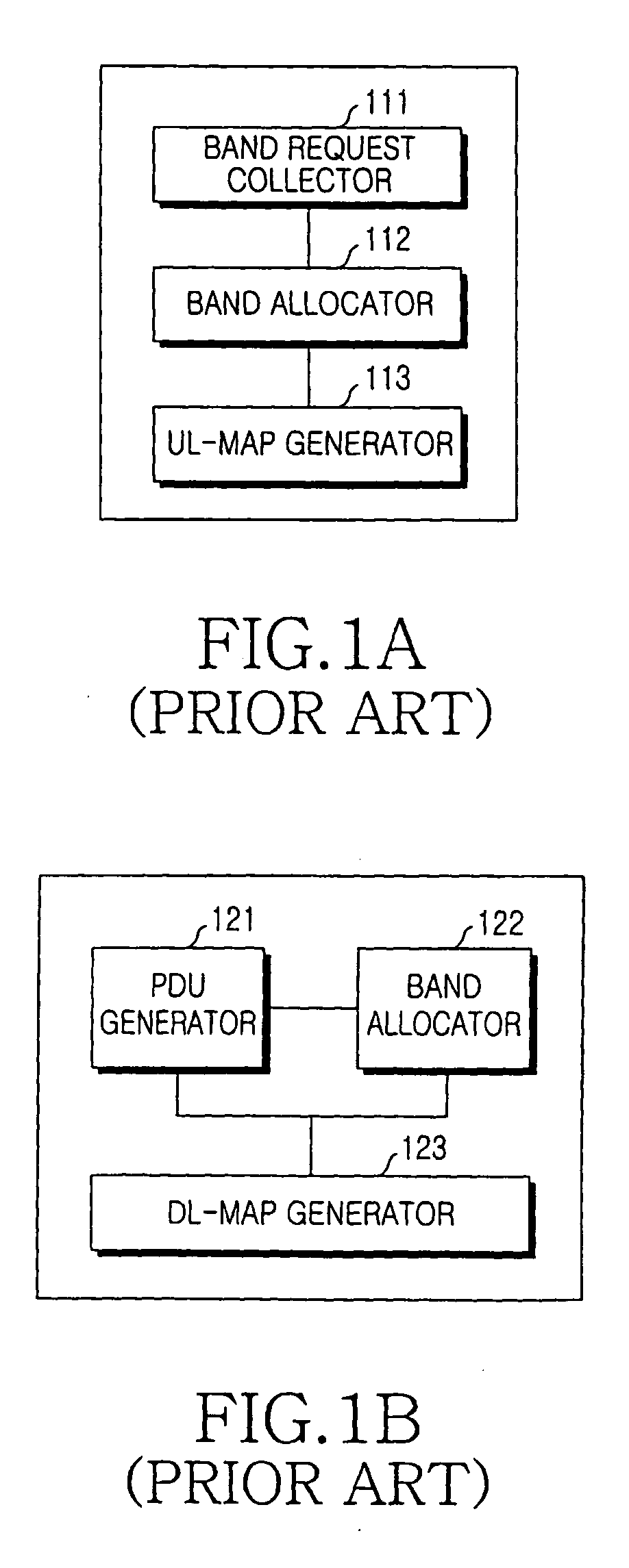

Uplink scheduling method and apparatus in communication system

InactiveUS20080152031A1Reduce data transmission timeShorten timeNetwork traffic/resource managementSecret communicationFrequency bandDelayed time

Provided is an uplink scheduling method and apparatus of a Base Station, in which total packet transmission time can be reduced by reducing the time required for a Subscriber Station to request a frequency band for packet transmission to the BS through a series of contention procedures and to be allocated to the frequency band. Therefore, even an SS that is not allocated a frequency band in an UpLink-MAP can immediately transmit a frequency band allocation request without overhead, thereby reducing initial delay time.

Owner:SAMSUNG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com