Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

4373 results about "Process time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

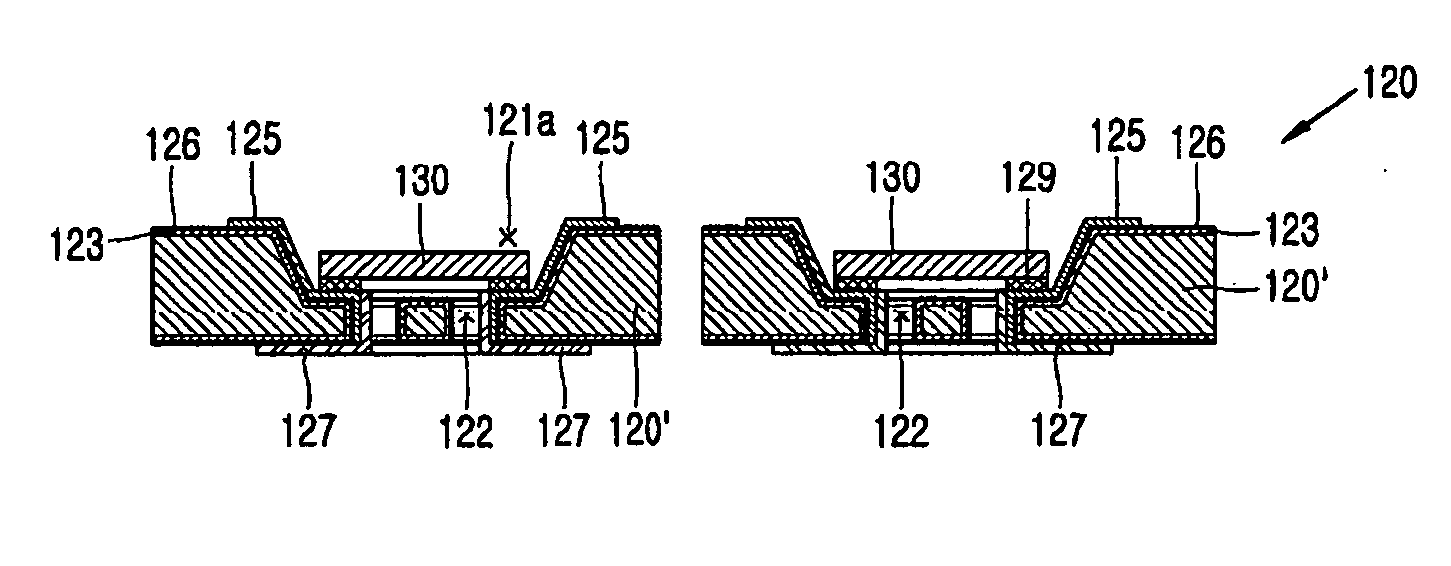

Etch system

InactiveUS20090139657A1Electric discharge tubesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

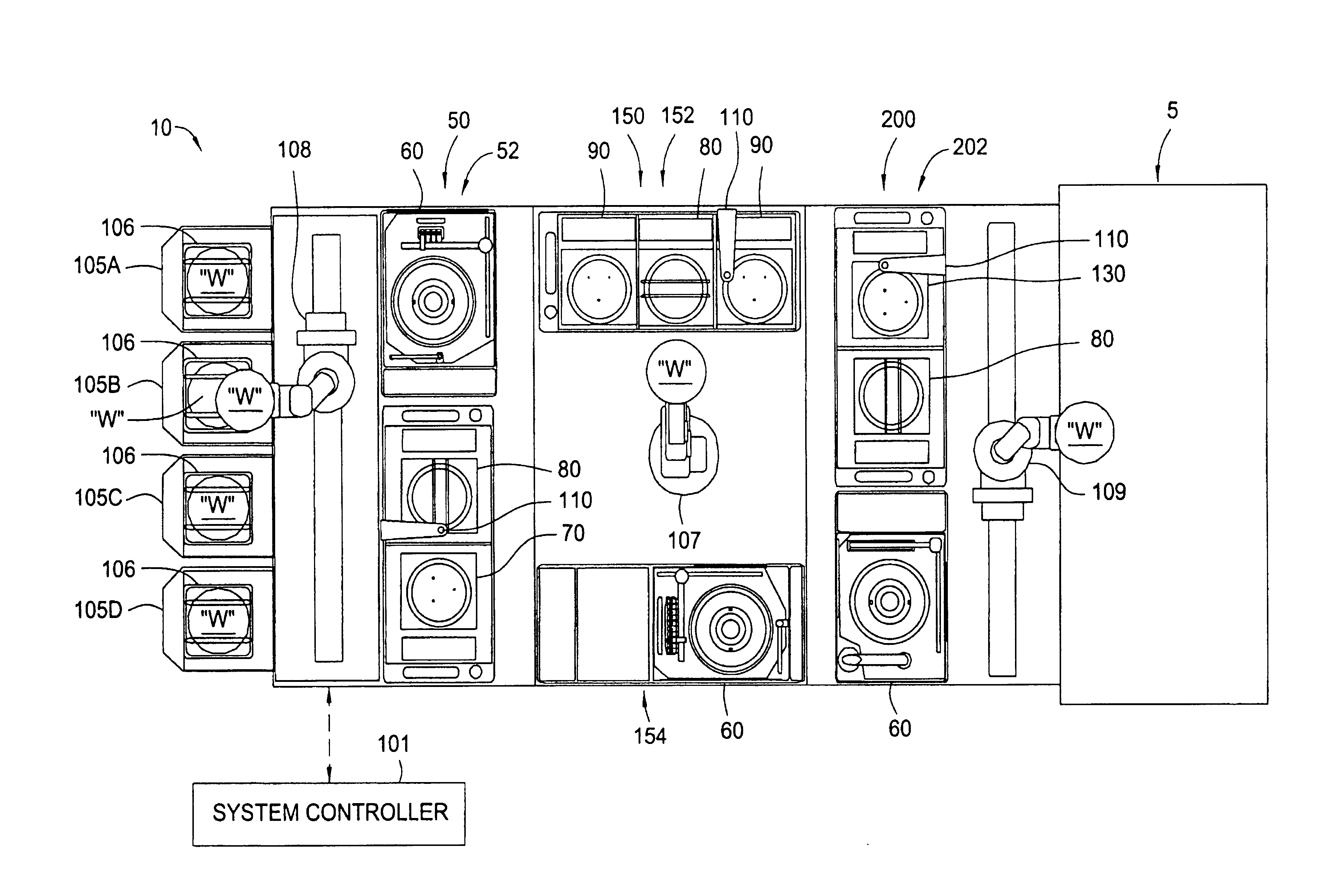

A semiconductor processing system includes a factory interface. A central transfer chamber is coupled to the factory interface. A first number of etch chambers are coupled to the central transfer chamber. The first number of etch chambers are configured to etch a substrate at about a first processing time. A second number of post-etch treatment chambers are coupled to the central transfer chamber. The second number of post-etch treatment chambers are configured to process the substrate at about a second processing time, wherein a ratio of the first number to the second number is substantially proportional to a ratio of the first processing time to the second processing time.

Owner:APPLIED MATERIALS INC

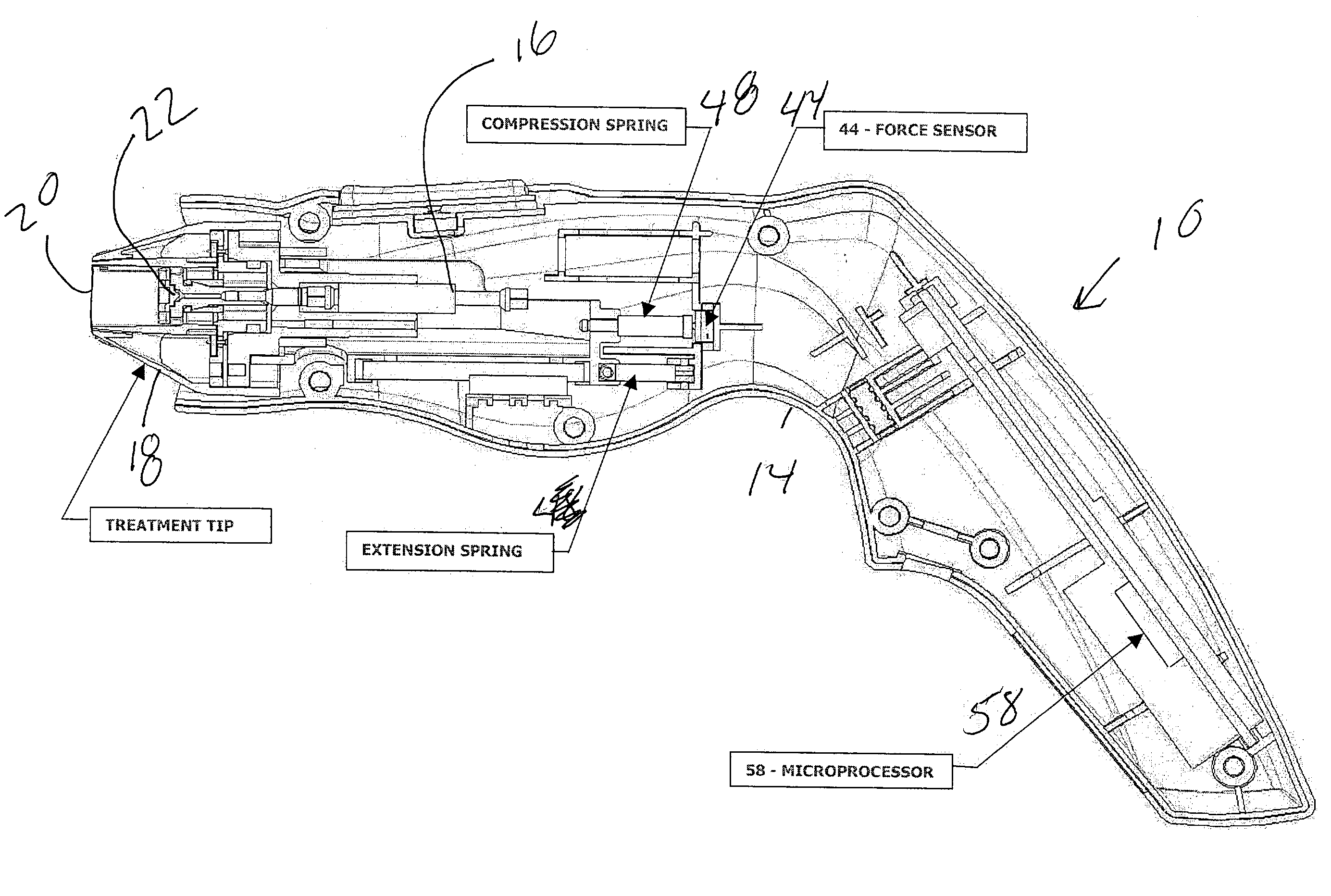

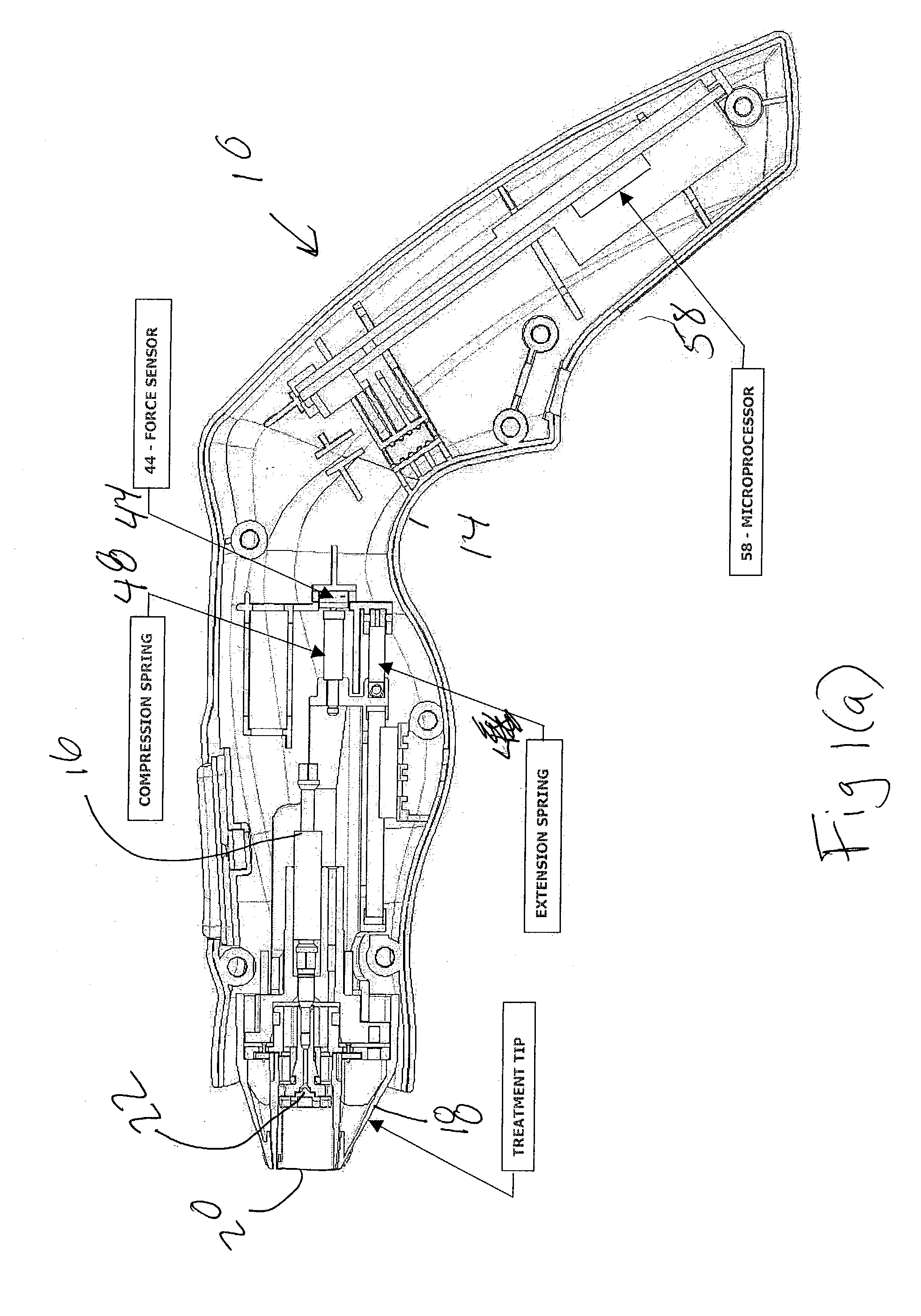

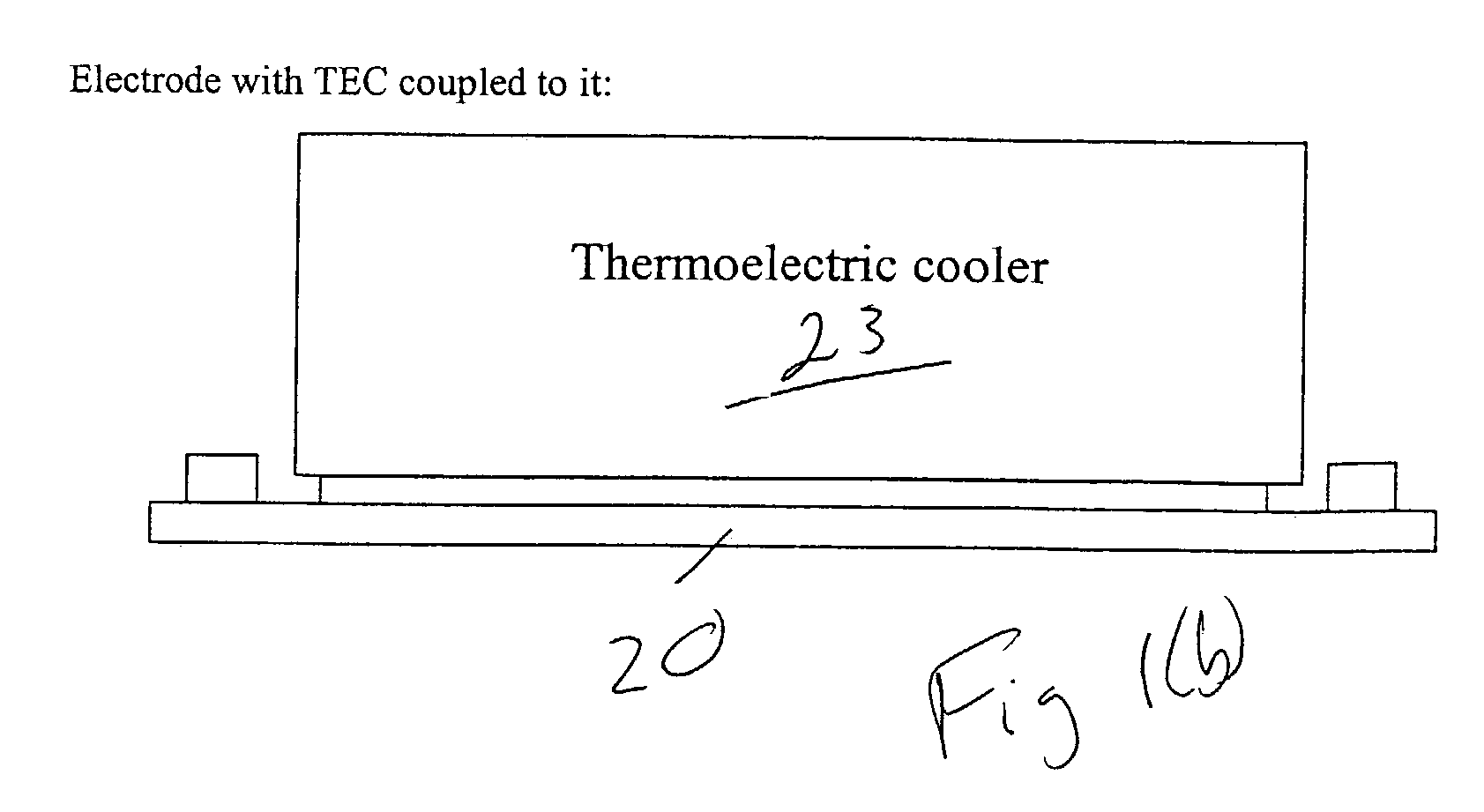

Treatment apparatus with electromagnetic energy delivery device and non-volatile memory

An apparatus for cooling a skin surface includes a support structure coupled to an electromagnetic energy delivery device. The electromagnetic energy delivery device is configured to be coupled to an electromagnetic energy source. A cooling member is coupled to the electromagnetic energy delivery device and is configured to create a reverse thermal gradient through a skin surface. A memory is coupled to the electromagnetic energy delivery device and is positioned at the support structure or the electromagnetic energy delivery device. The memory is configured to store information to facilitate operation of at least one of the cooling member, and the electromagnetic energy source. Resources are coupled to the cooling member to permit different levels of cooling at different times of treatment.

Owner:THERMAGE INC

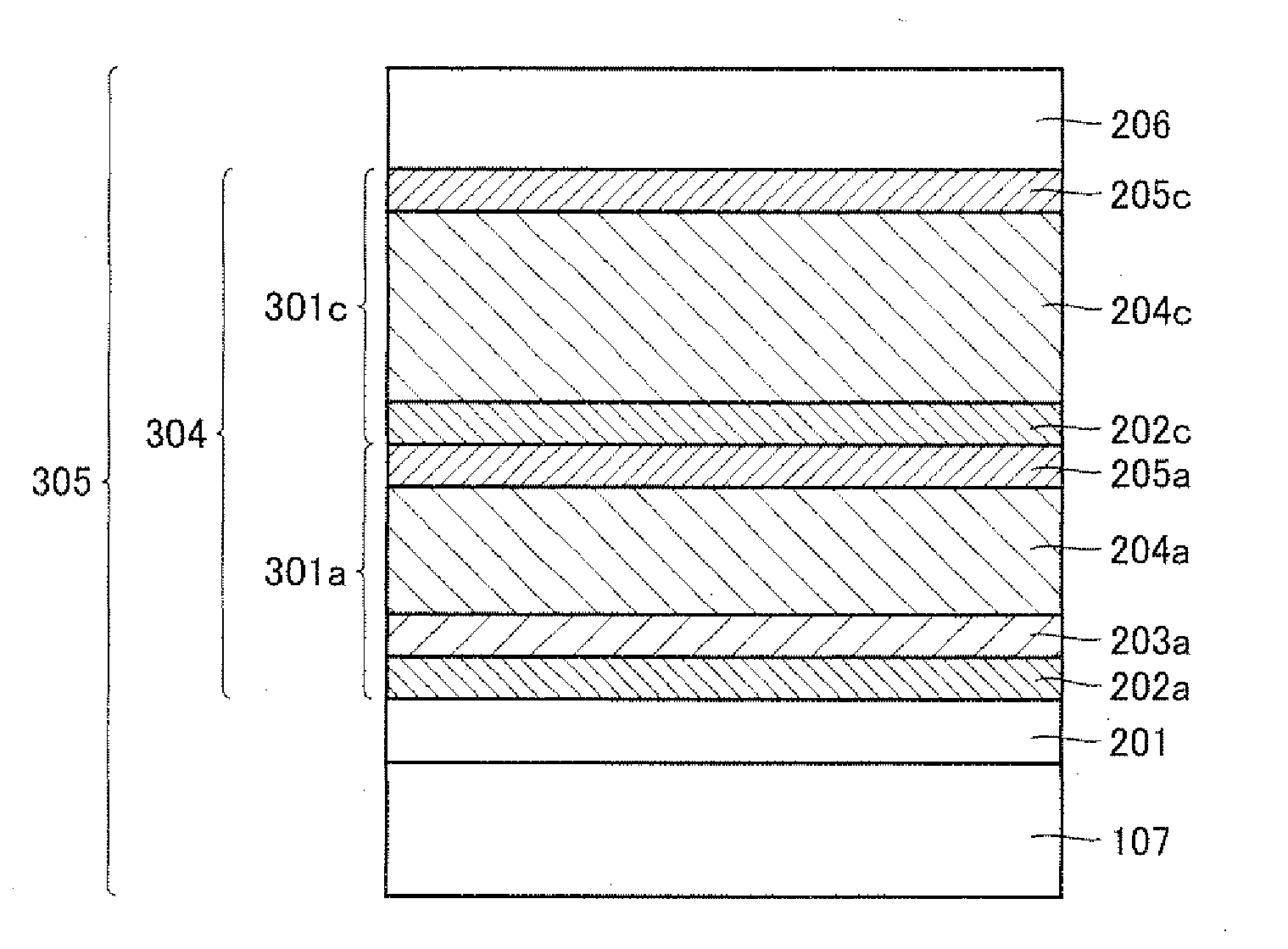

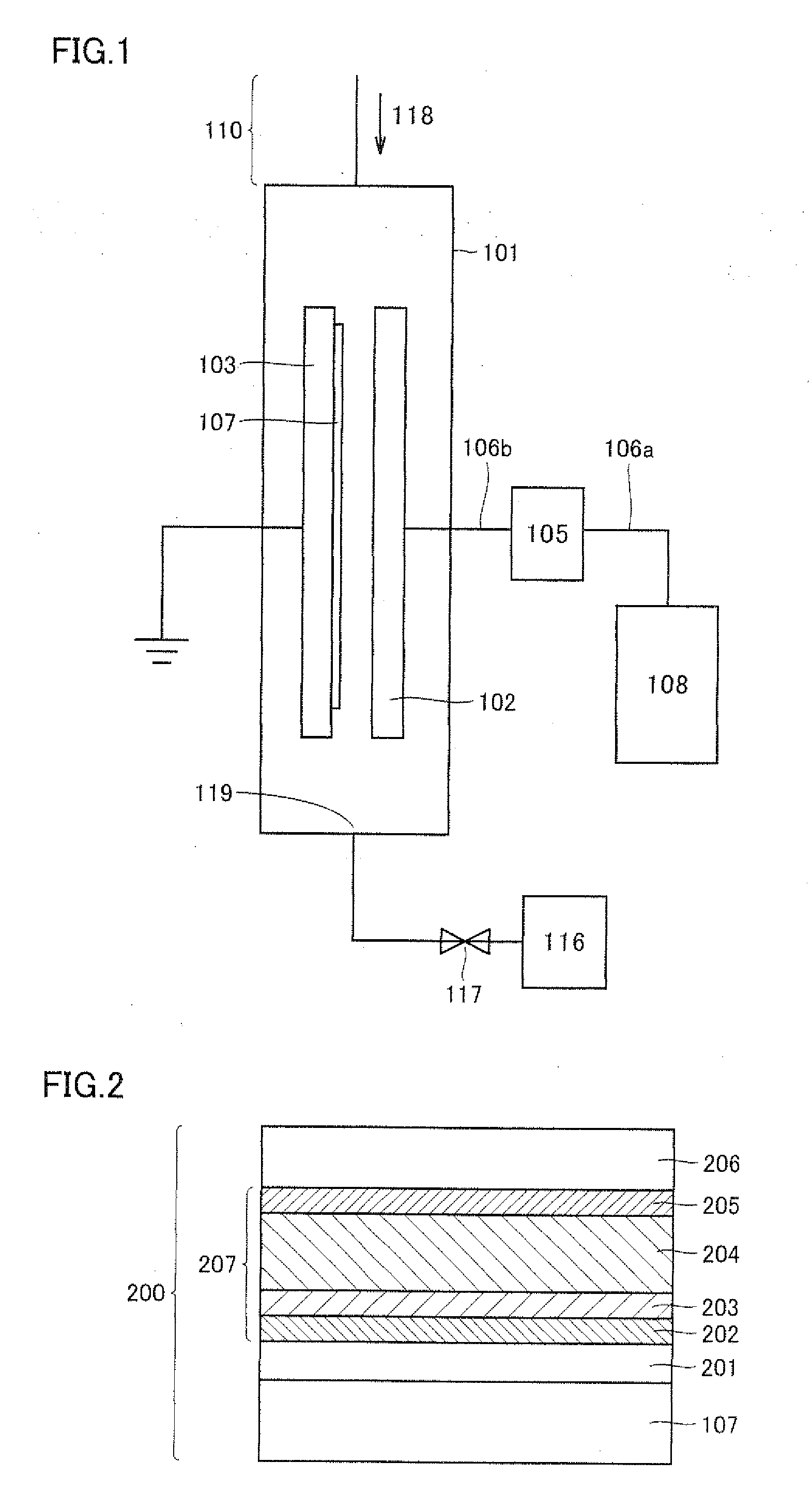

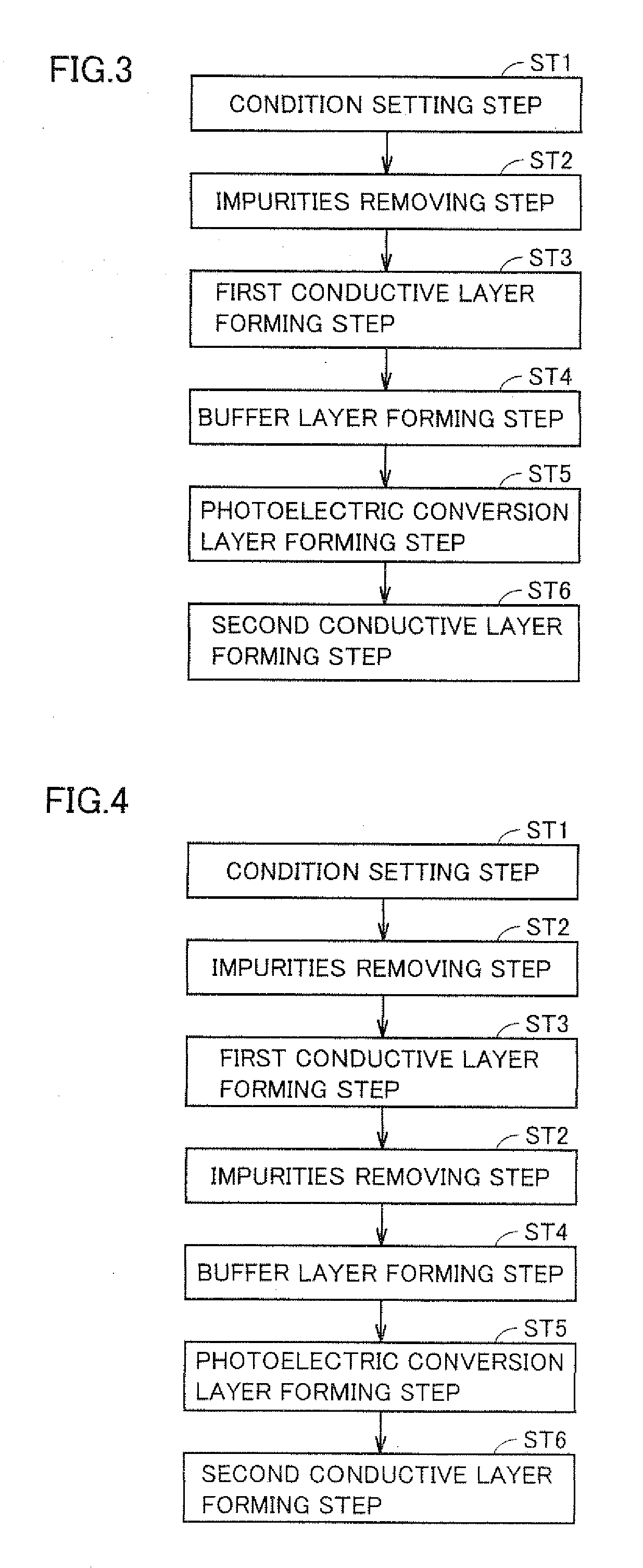

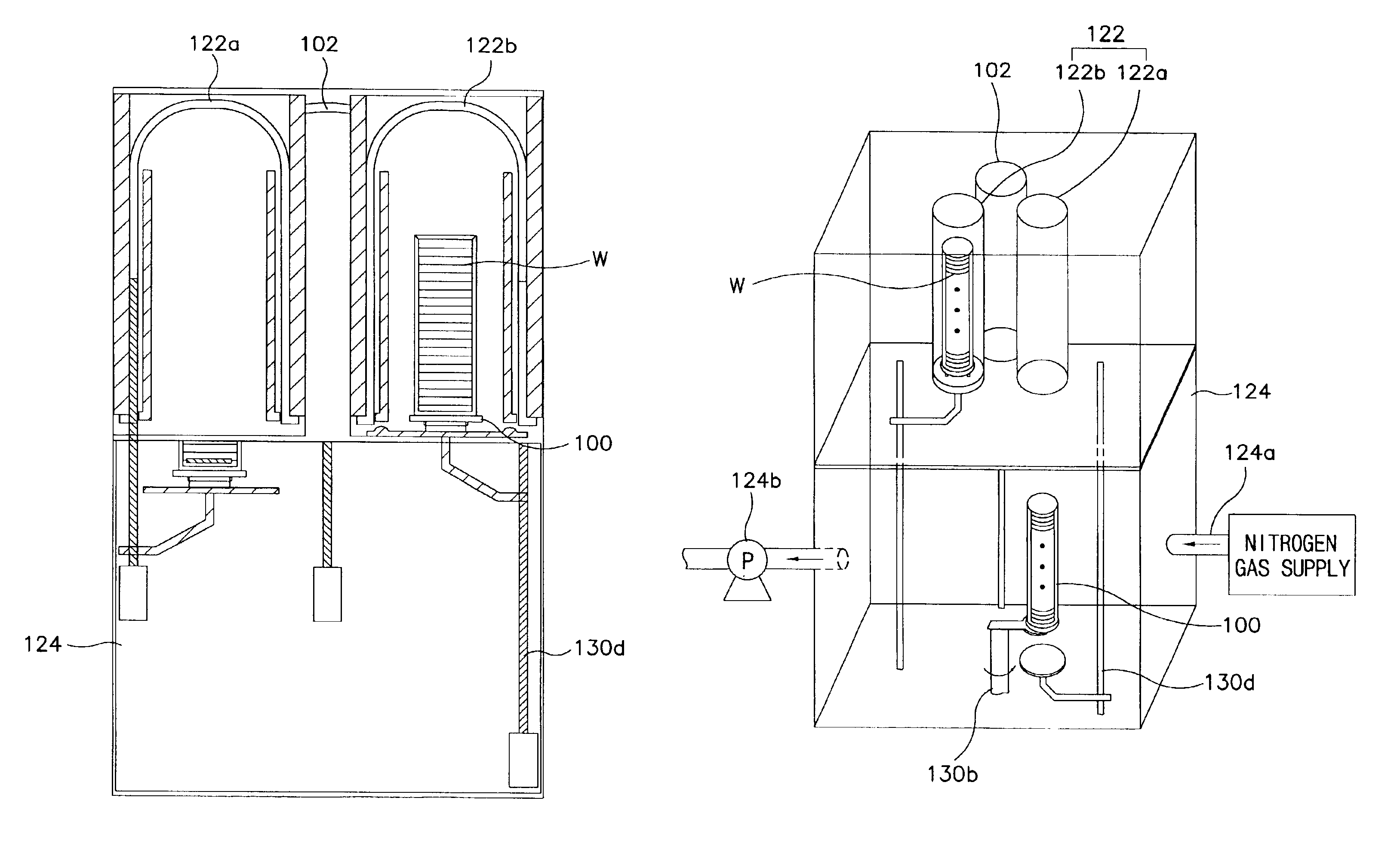

Semiconductor layer manufacturing method, semiconductor layer manufacturing apparatus, and semiconductor device manufactured using such method and apparatus

InactiveUS20100024872A1Quality improvementImprove batch productivityLiquid surface applicatorsFinal product manufactureHermetic sealManufactured apparatus

Provided are a semiconductor layer manufacturing method and a semiconductor manufacturing apparatus capable of forming a high quality semiconductor layer even by a single chamber system, with a shortened process time required for reducing a concentration of impurities that exist in a reaction chamber before forming the semiconductor layer. A semiconductor device manufactured using such a method and apparatus is also provided. The present invention relates to a semiconductor layer manufacturing method of forming a semiconductor layer inside a reaction chamber (101) capable of being hermetically sealed, including an impurities removing step of removing impurities inside the reaction chamber (101) using a replacement gas, and a semiconductor layer forming step of forming the semiconductor layer, the impurities removing step being a step in which a cycle composed of a replacement gas introducing step of introducing the replacement gas into the reaction chamber (101) and an exhausting step of exhausting the replacement gas is repeated a plurality of times, the impurities removing step being performed at least before the semiconductor layer forming step.

Owner:SHARP KK

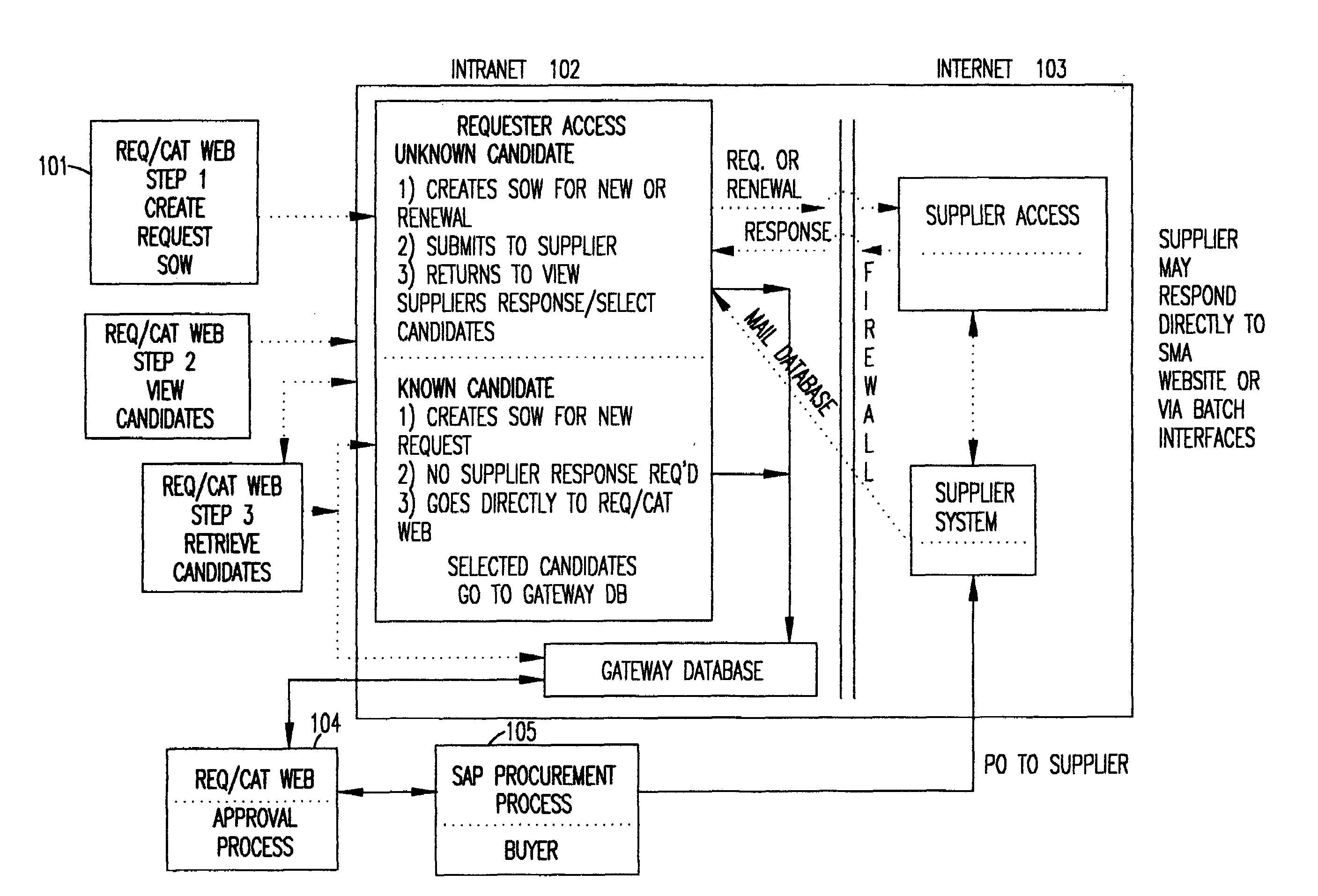

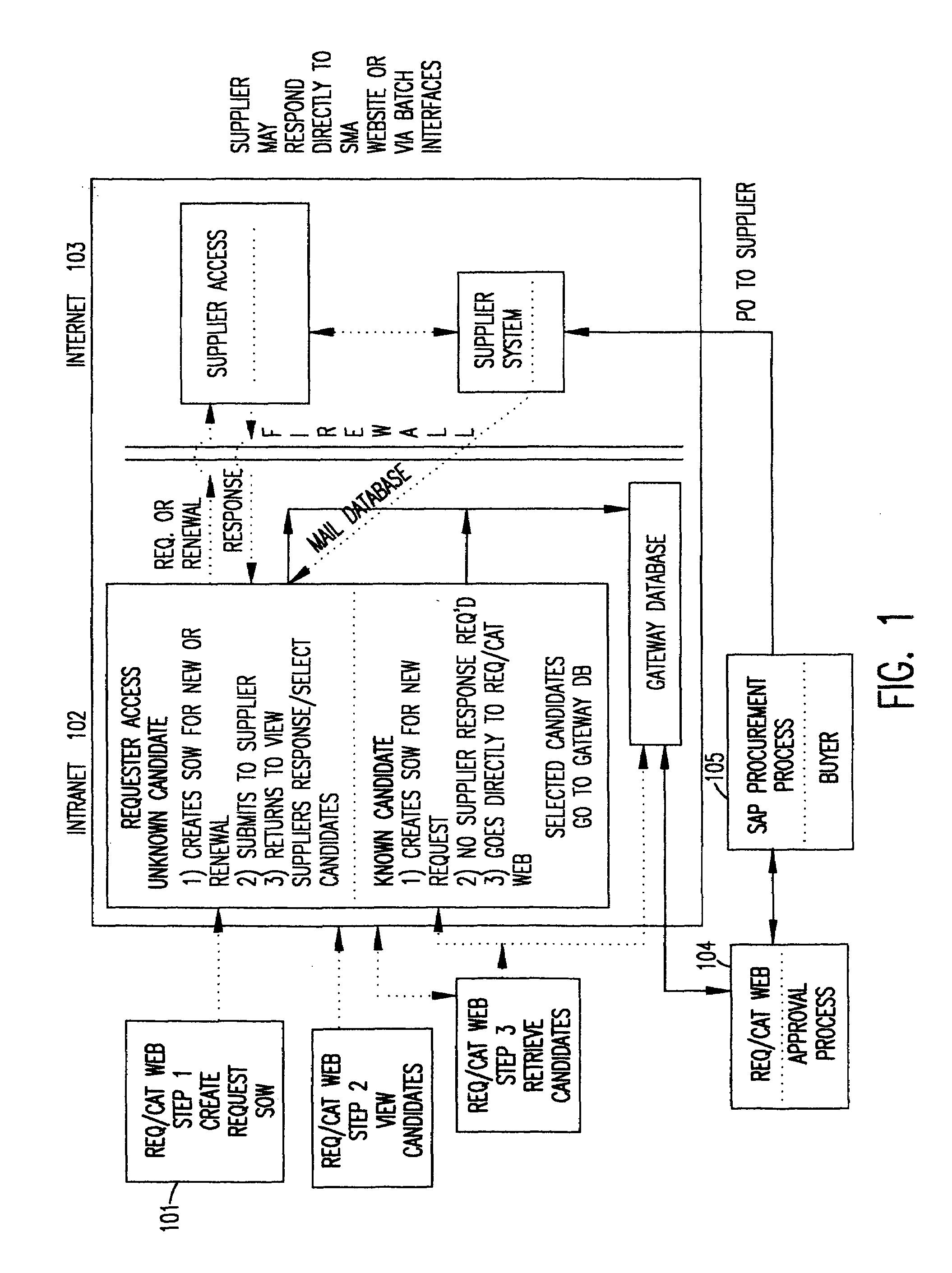

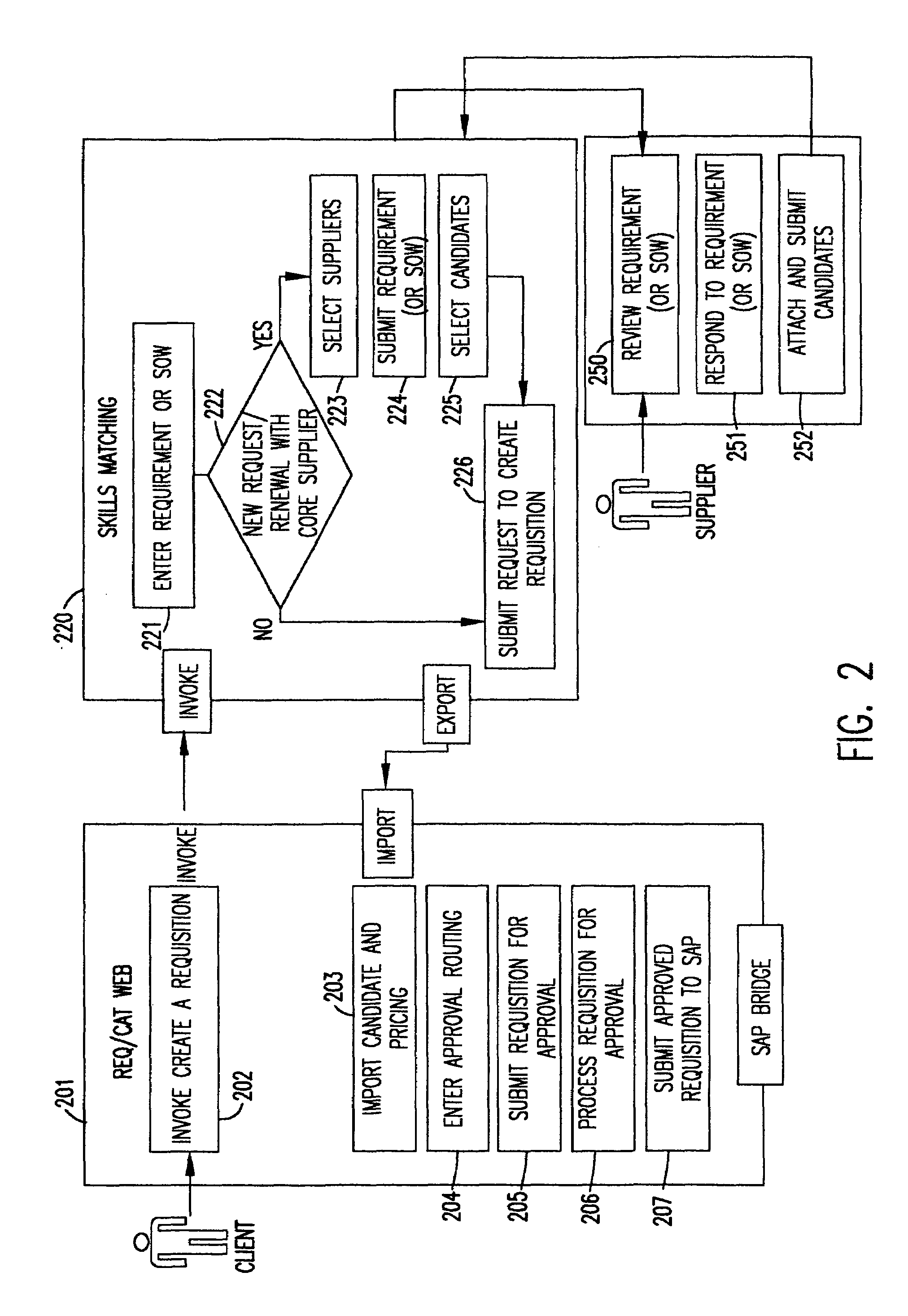

Skills matching application

A tool, called the Skills Matching Application (SMA), allows a user, such as a hiring manager, to communicate requirements to technical service suppliers in a way that significantly reduces the process time and improves the accuracy of requests sent to suppliers. The SMA is accessed from a Web-based Requisition / Catalog (REQ / CAT) Web application. A user who needs to request a technical contractor accesses the REQ / CAT Web application which brings the user to the SMA Web site. The SMA application, after requiring a password and profile (for first time access) to be entered, takes the user through a series of screens which prompts the user to enter a Statement of Work (SOW) and complete a skills detail checklist for each of the technical skills requested. Once the request is completed, it is submitted to contracted suppliers who are sent an e-mail notification notifying the supplier that a new request has been entered into the SMA application for them to review and submit a candidate against. This e-mail has a standard formatted attachment which contains the statement of work and skills detail checklist. The suppliers, when they receive an e-mail request, access the Web site database to view the request details. A supplier provides a candidate or candidates by accessing the SMA Web site and submitting candidates and appending resumes as appropriate. The supplier provides a response to the SOW by responding to the entries with the candidate's skills, experience, etc. The requestor views the supplier responses and associated resumes and can either accept or reject each candidate submitted but cannot accept more than the number of candidates requested.

Owner:IBM CORP

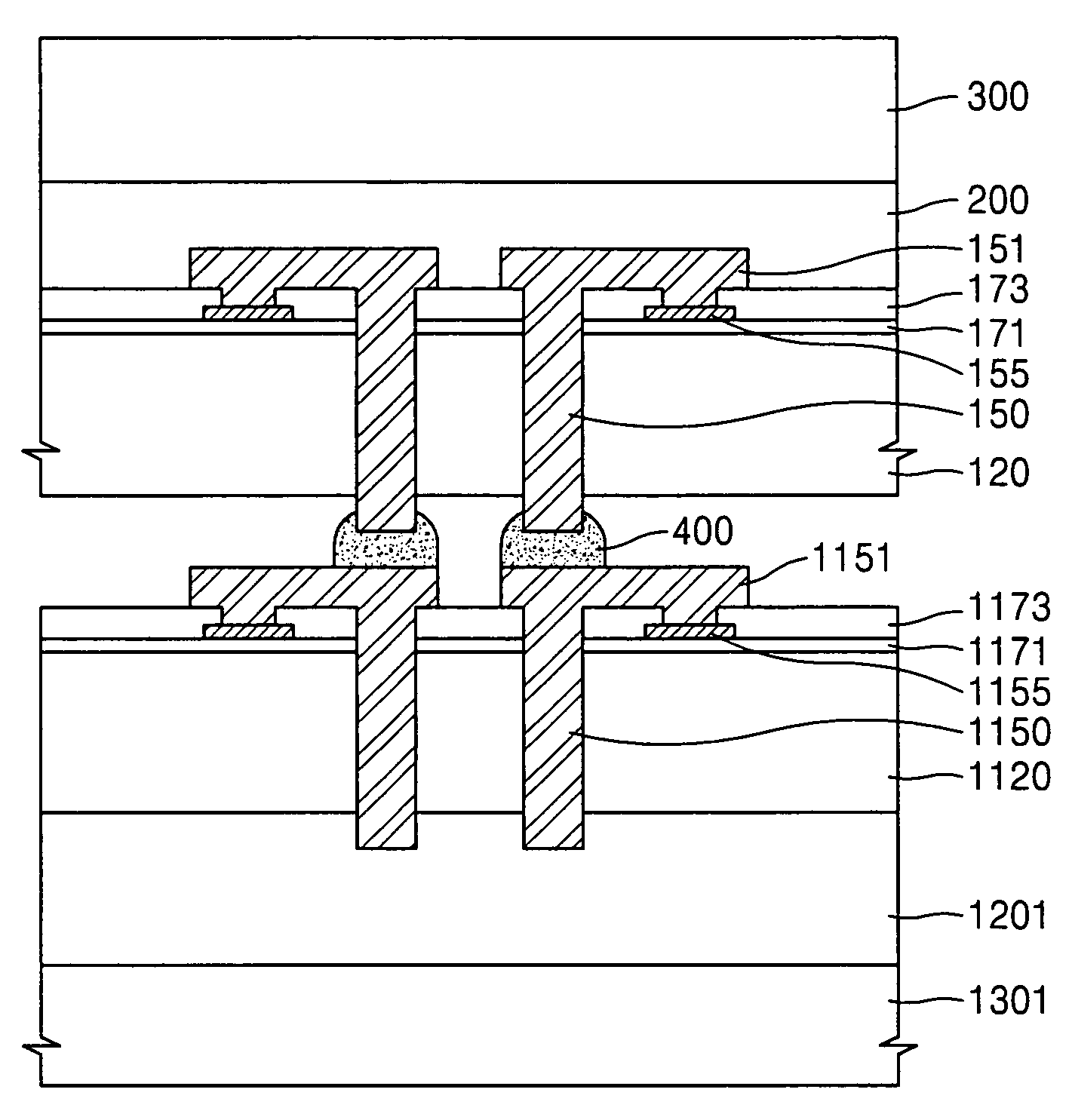

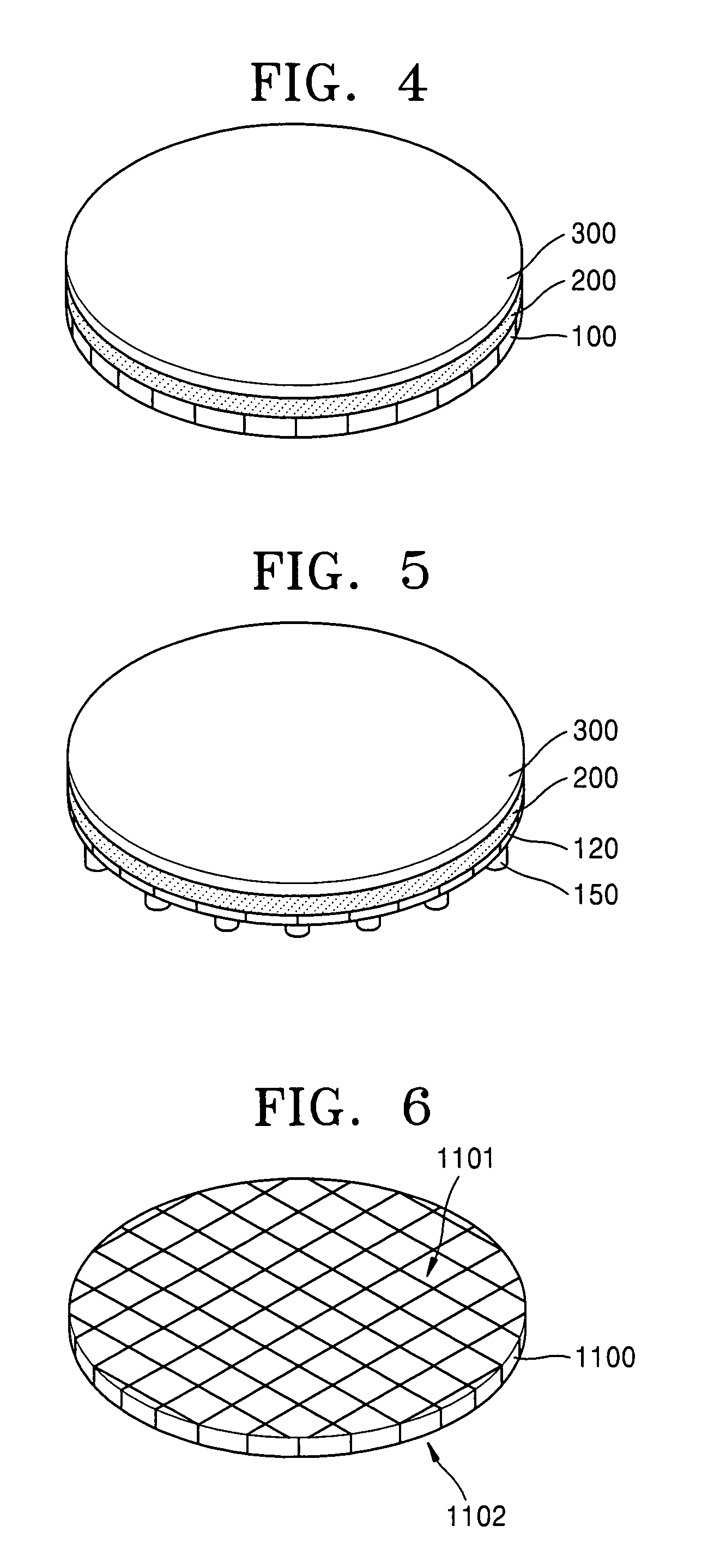

Method of forming a thin wafer stack for a wafer level package

InactiveUS7494845B2Reduce warpageTrend downSemiconductor/solid-state device detailsSolid-state devicesWaferingUltraviolet

A method of forming a stack of thin wafers provides a wafer level stack to greatly reduce process time compared to a method where individually separated chips are stacked after a wafer is sawed. A rigid planar wafer support member stabilizes and planarizes each wafer while it is thin or its thickness is reduced and during subsequent wafer processing. Thinned wafers are stacked and the external support members are removed by applying heat or ultraviolet (UV) light to an expandable adhesive layer between the support members and the thin wafers. The stacked wafers then can be further processed and packaged without thin-wafer warping, cracking or breaking. A wafer level package made in accordance with the invented method also is disclosed.

Owner:SAMSUNG ELECTRONICS CO LTD

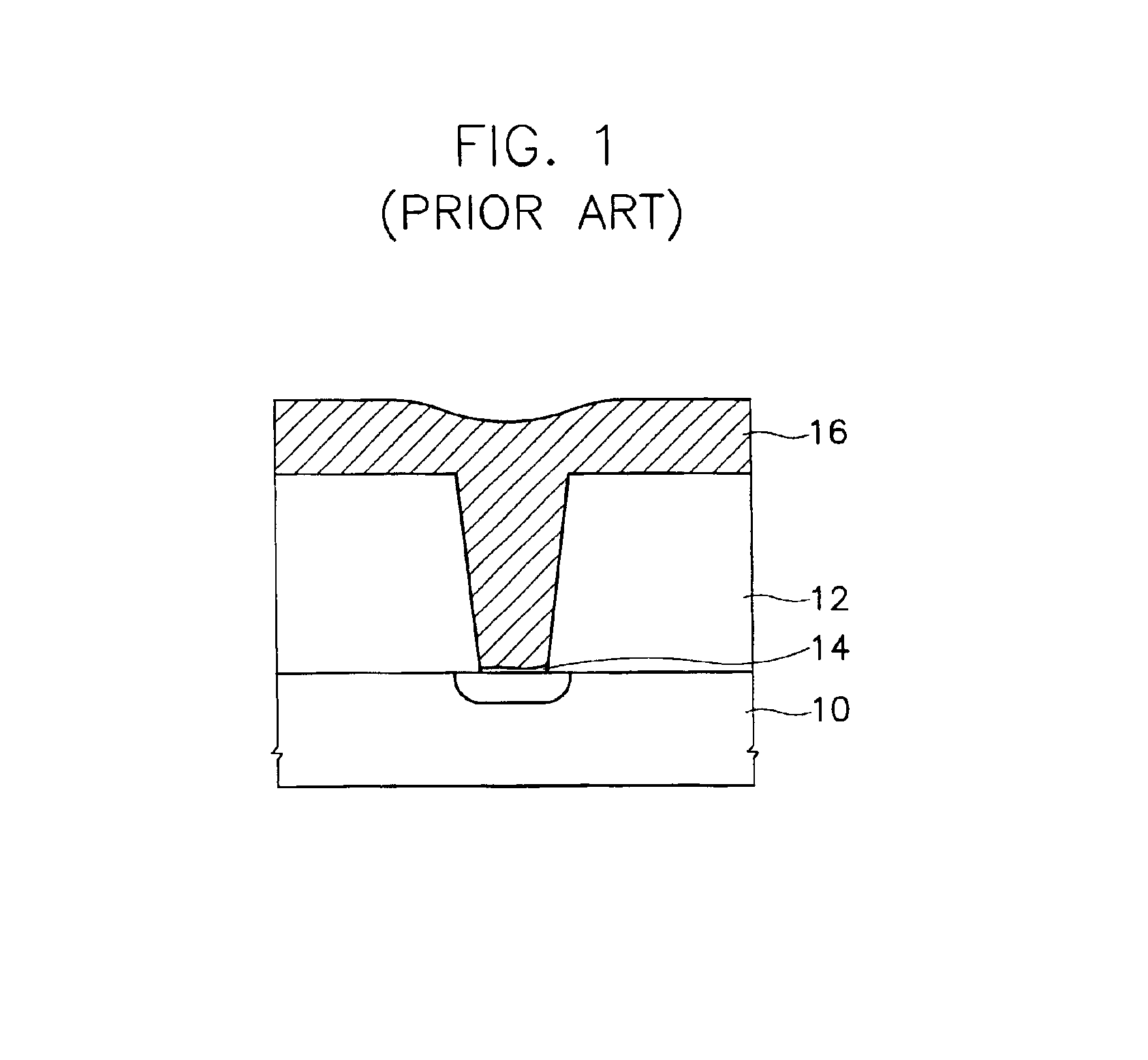

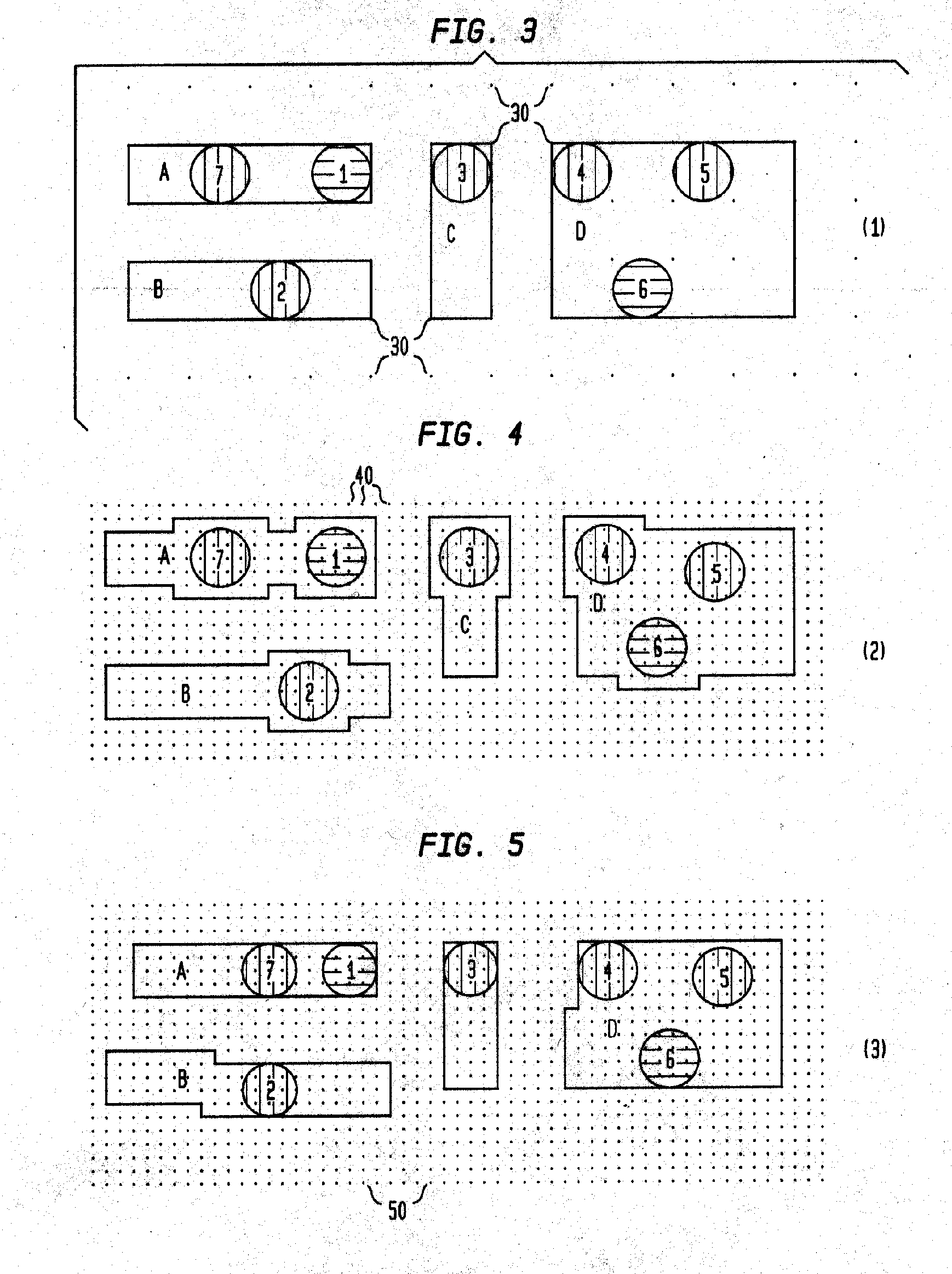

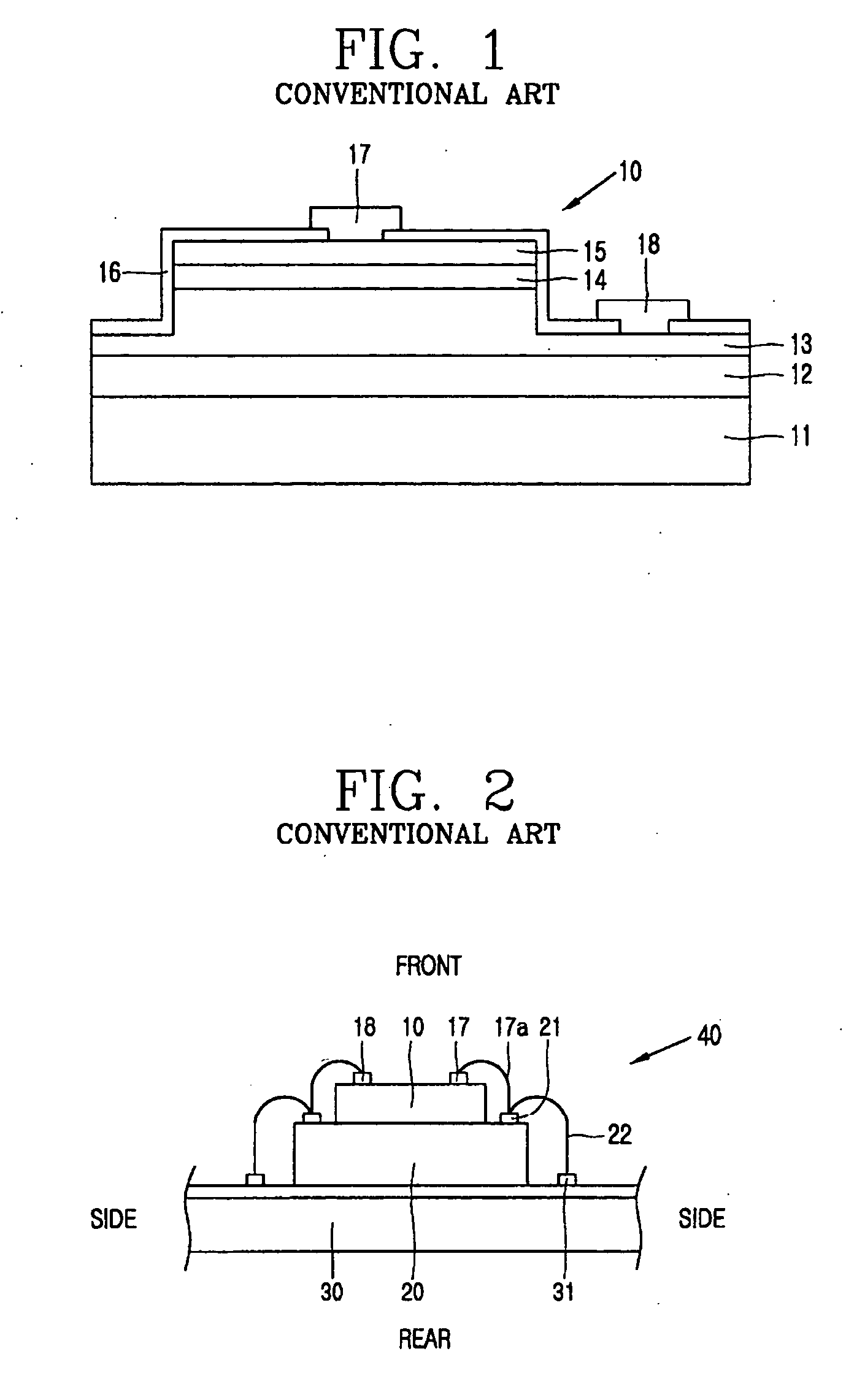

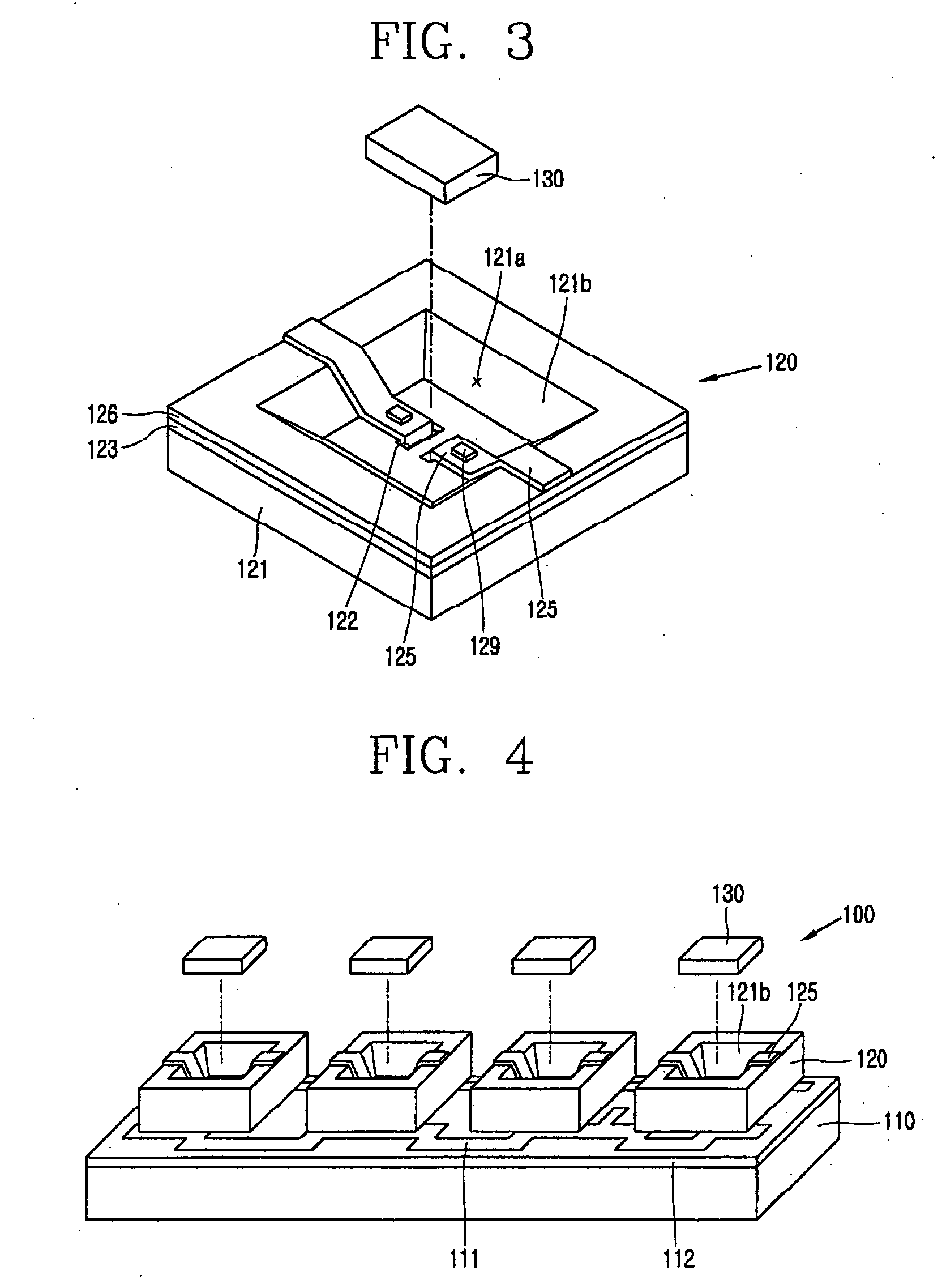

Method of and apparatus for performing sequential processes requiring different amounts of time in the manufacturing of semiconductor devices

InactiveUS6911112B2Without need for significant downtimeHigh productSemiconductor/solid-state device manufacturingCharge manipulationProduction rateDevice material

A method of manufacturing a semiconductor device includes first and second processes, the latter requiring more processing time. An apparatus for performing the semiconductor manufacturing process includes a first reactor, and a plurality of second reactors for each first reactor. A first group of wafers are subjected to the first process within the first reactor, and are then transferred into a second reactor as isolated from the outside air. The first group of wafers is subjected to the second process within the second reactor. At the same time, a second group of wafers are subjected to the first process within the first reactor. After the first process is completed, the second group of wafers is transferred into an unoccupied one of the second reactors as isolated from the outside air. There, the second group of wafers is subjected to the second process. Accordingly, process failures otherwise due to the exposure of the wafers are minimized, and productivity is high despite the difference in the processing times.

Owner:SAMSUNG ELECTRONICS CO LTD

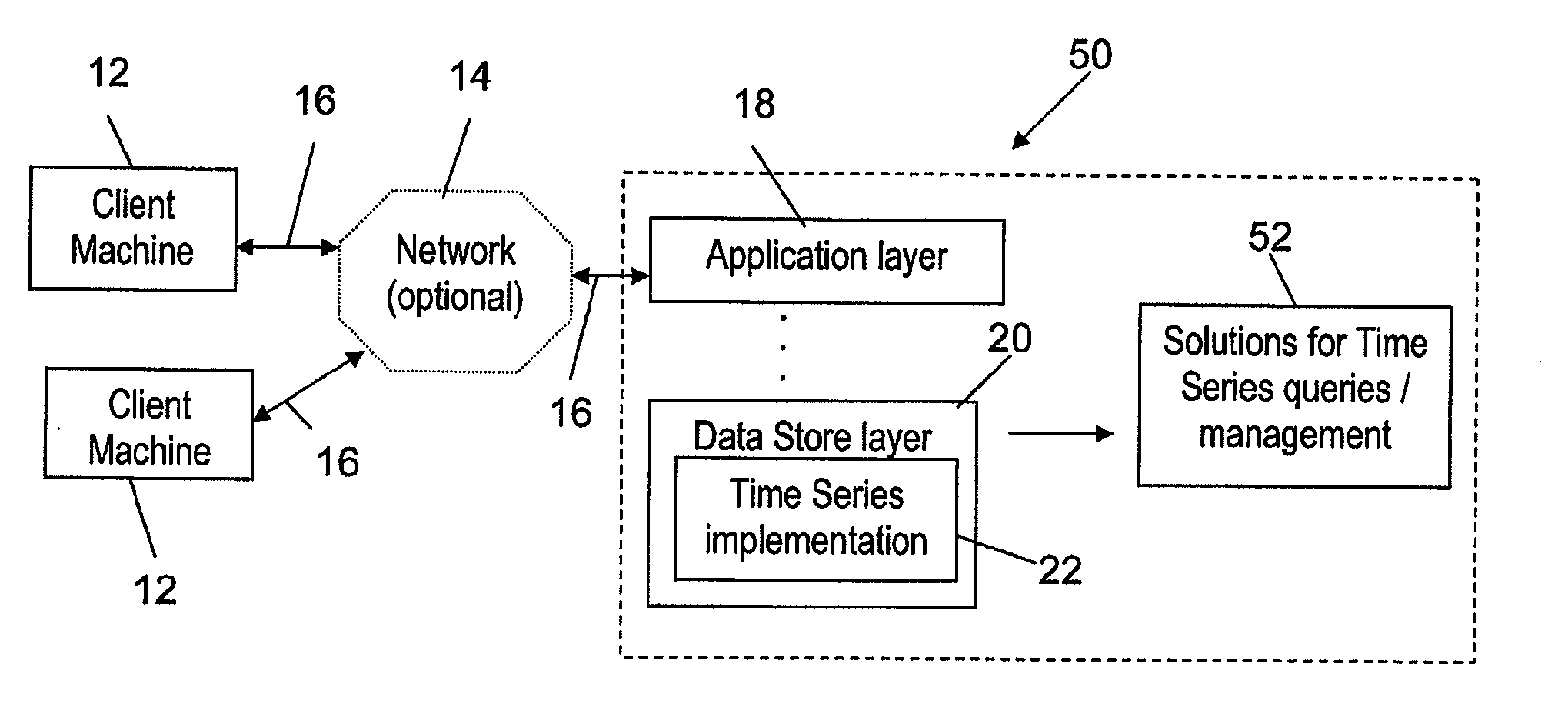

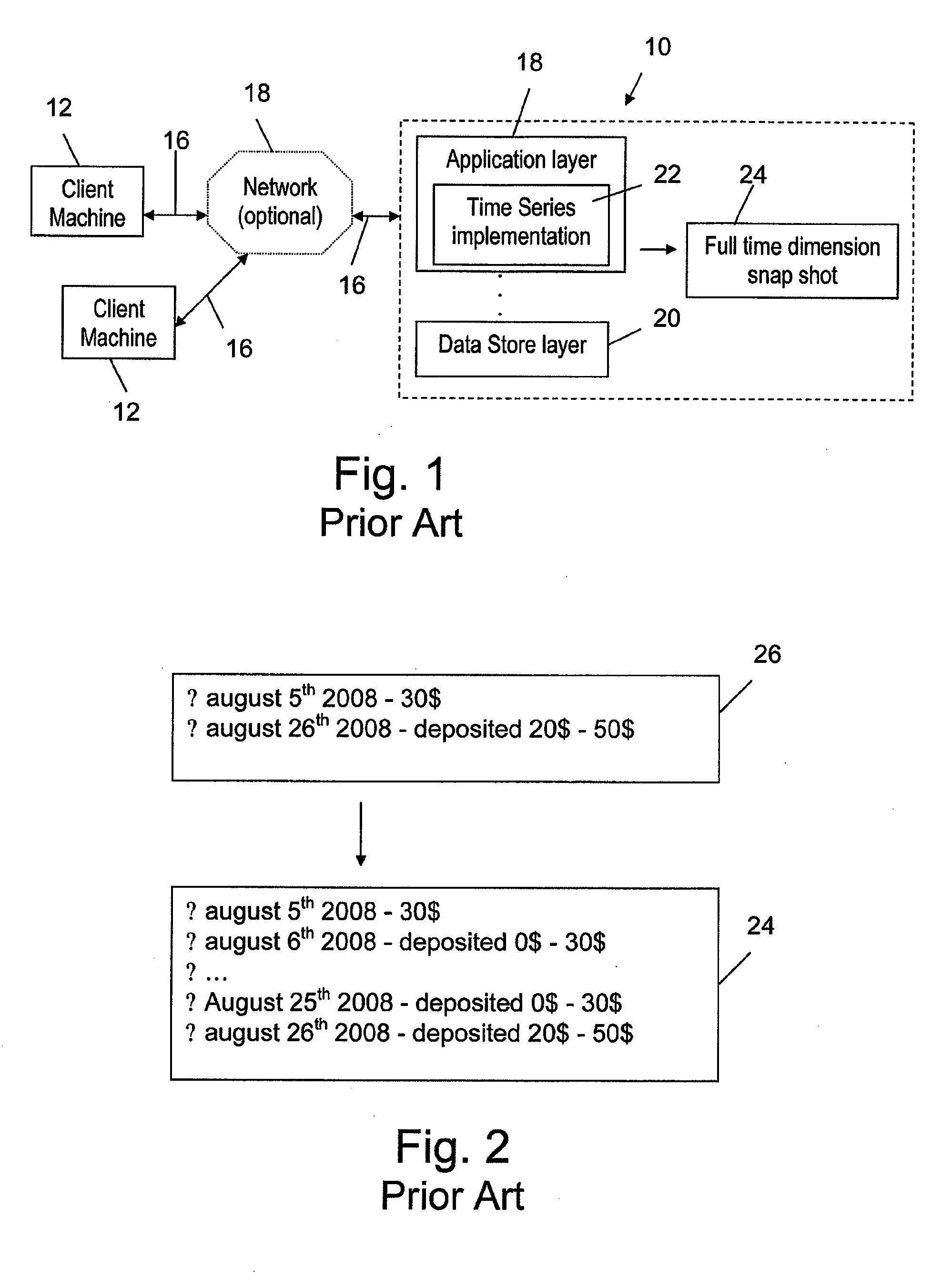

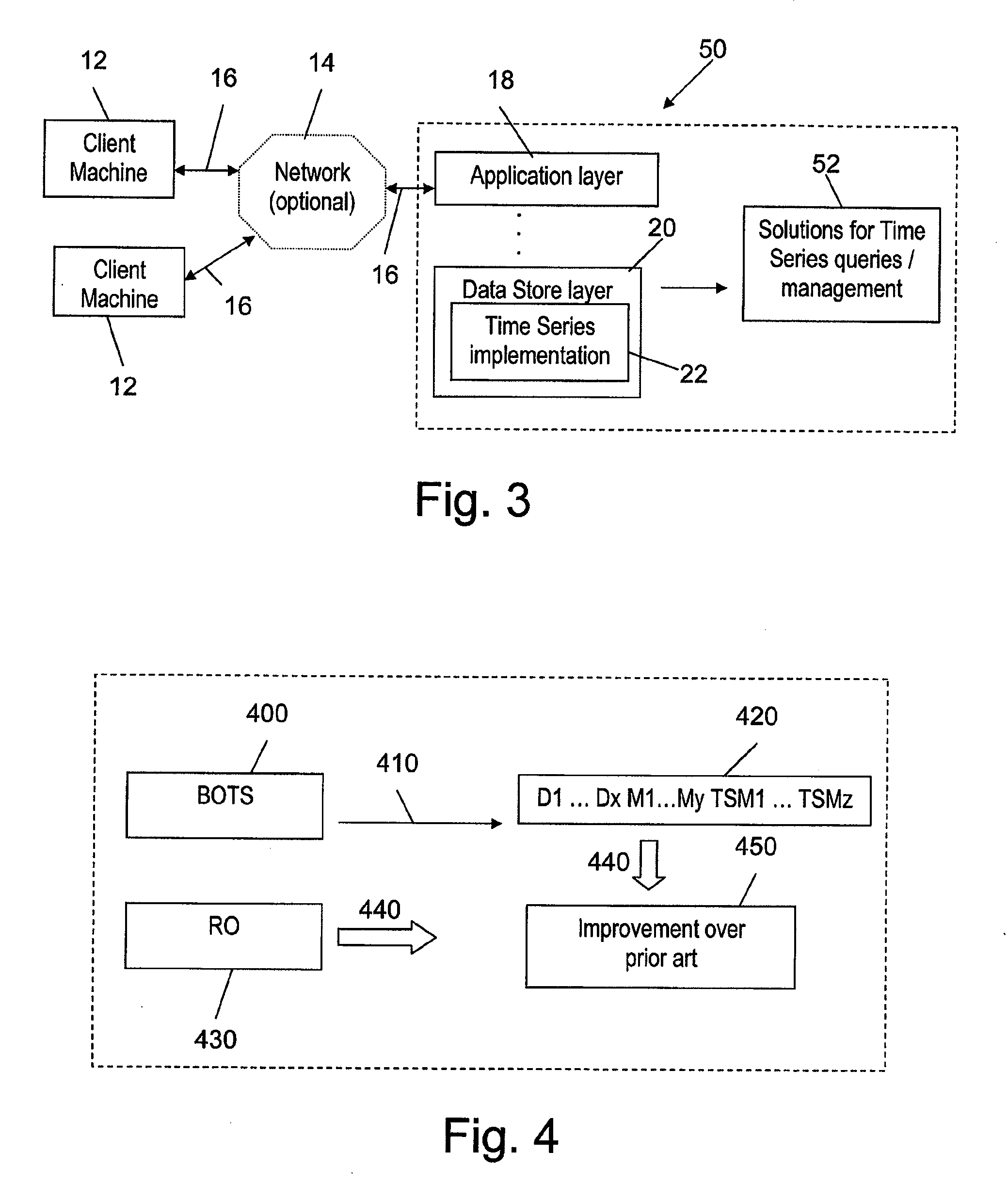

Methods for effective processing of time series

ActiveUS20110060753A1Web data indexingDigital data processing detailsData setTime series representation

A method of effectively representing and processing data sets with time series is disclosed. The method may comprise representing time series as a virtual part of data in a data store layer of a user system, thereby allowing processing of time-series related queries in said data store layer of said user system.

Owner:HYPERROLL ISRAEL

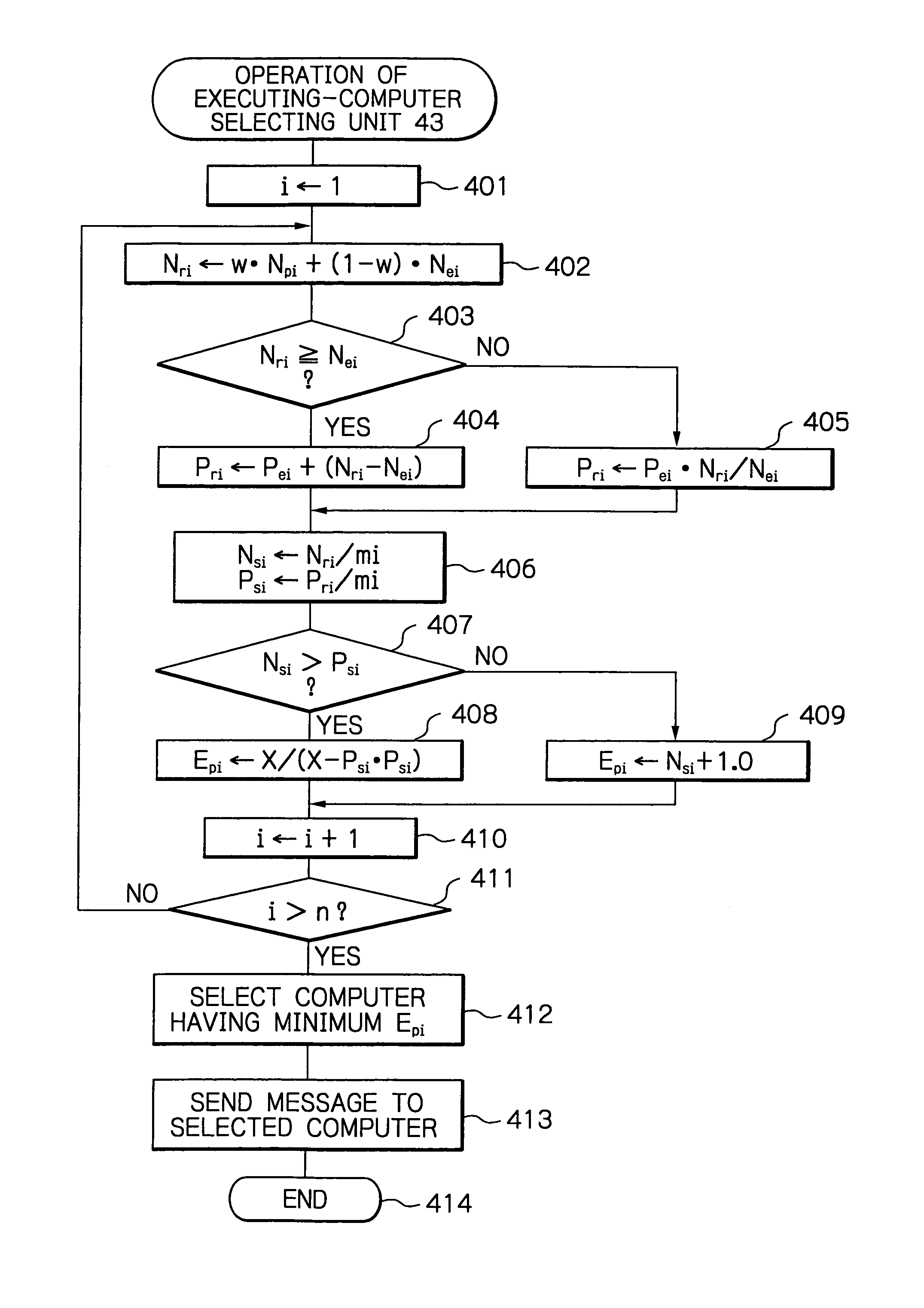

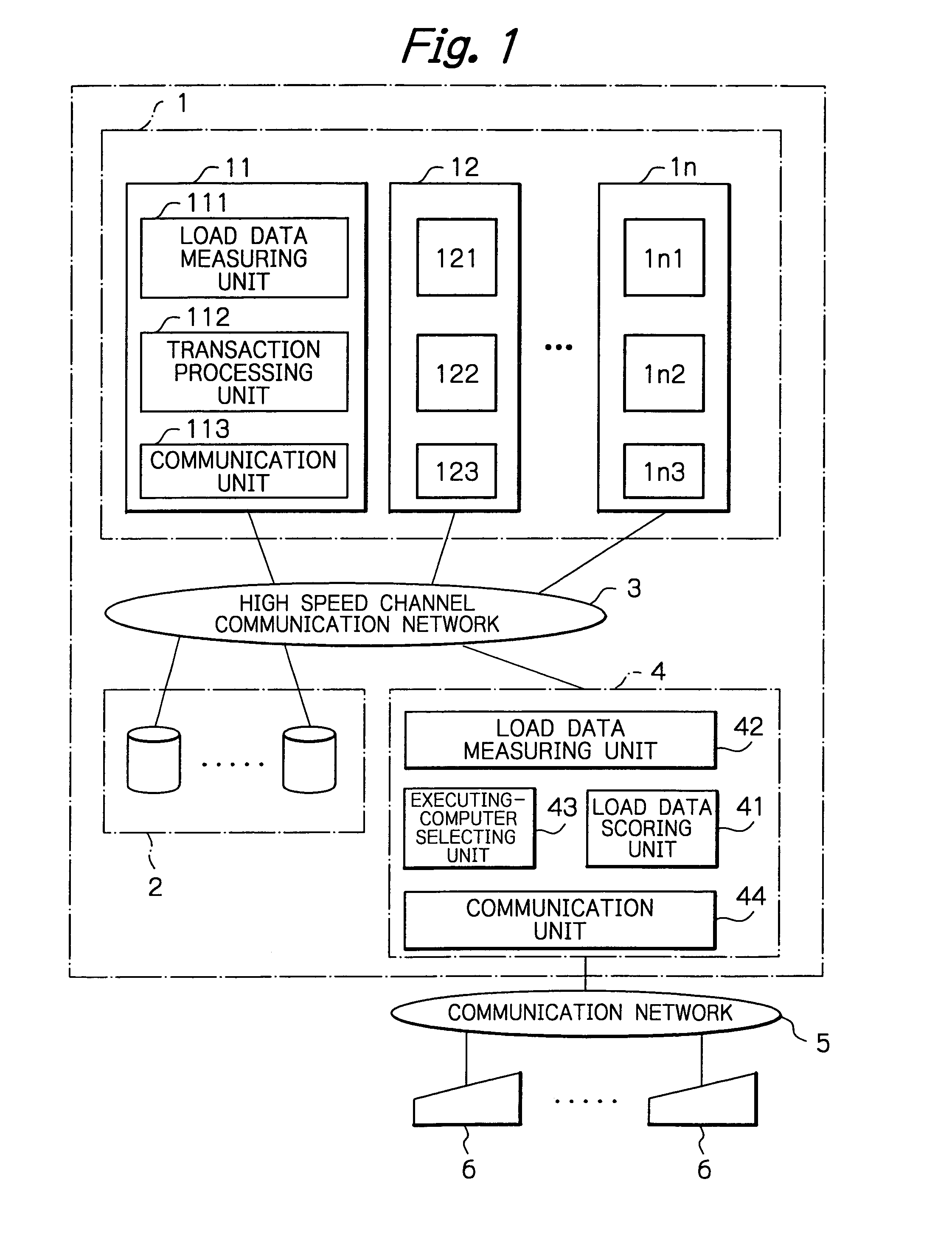

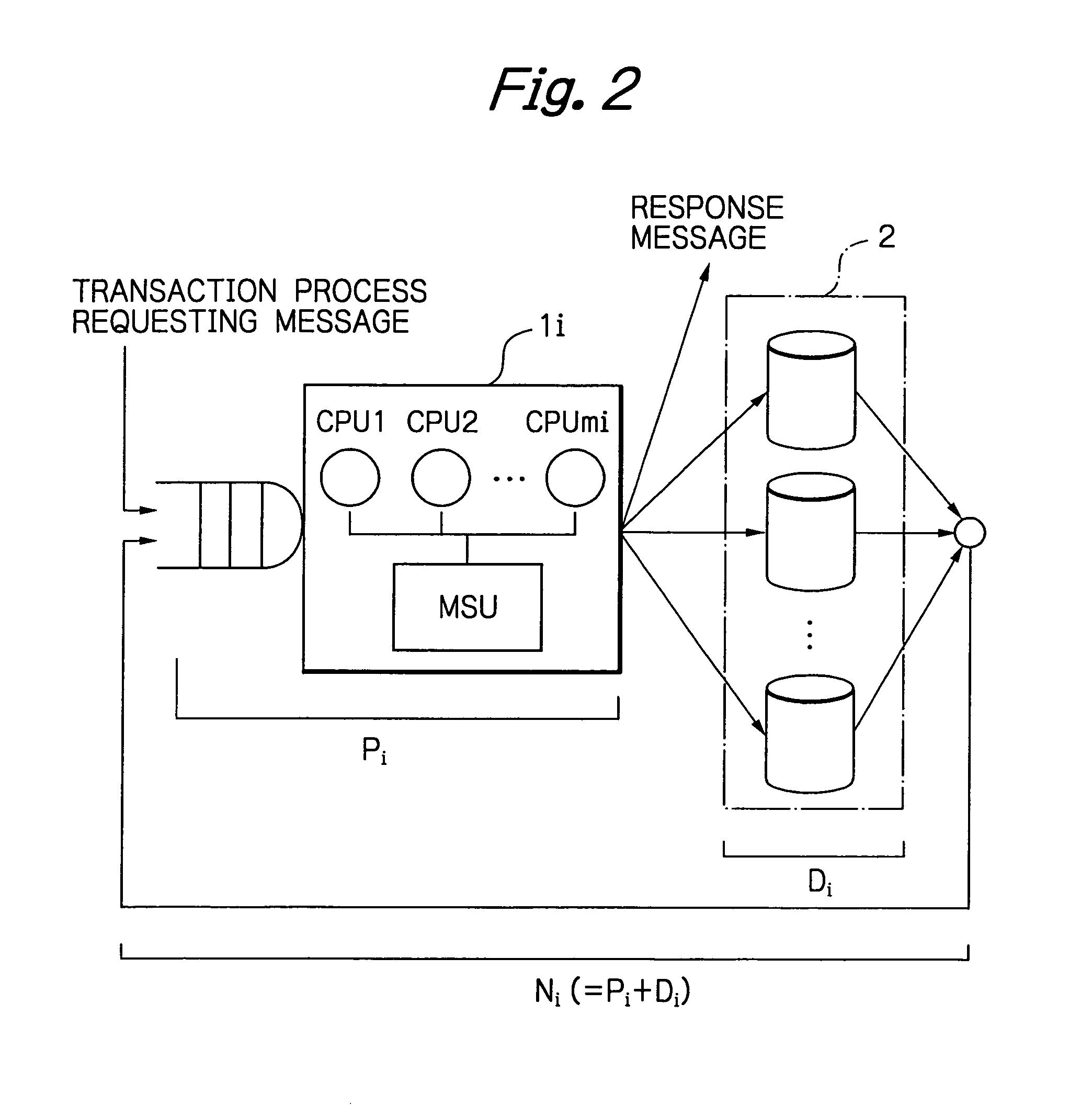

Dynamic load-distributed computer system using estimated expansion ratios and load-distributing method therefor

InactiveUS7062768B2Improve responsivenessResource allocationDigital computer detailsParallel computingSystem usage

In a method for distributing a transaction in a computer system including a plurality of computers each formed by processors, a plurality of estimated loads are calculated for the computers. Then, a plurality of estimated process time expansion ratios are calculated for the computers, in accordance with the estimated loads and the numbers of processors in the computers. Then, a plurality of load indexes one for each of the computers are calculated in accordance with the estimated process time expansion ratios. Finally, the transaction is distributed in accordance with the load indexes.

Owner:NEC CORP

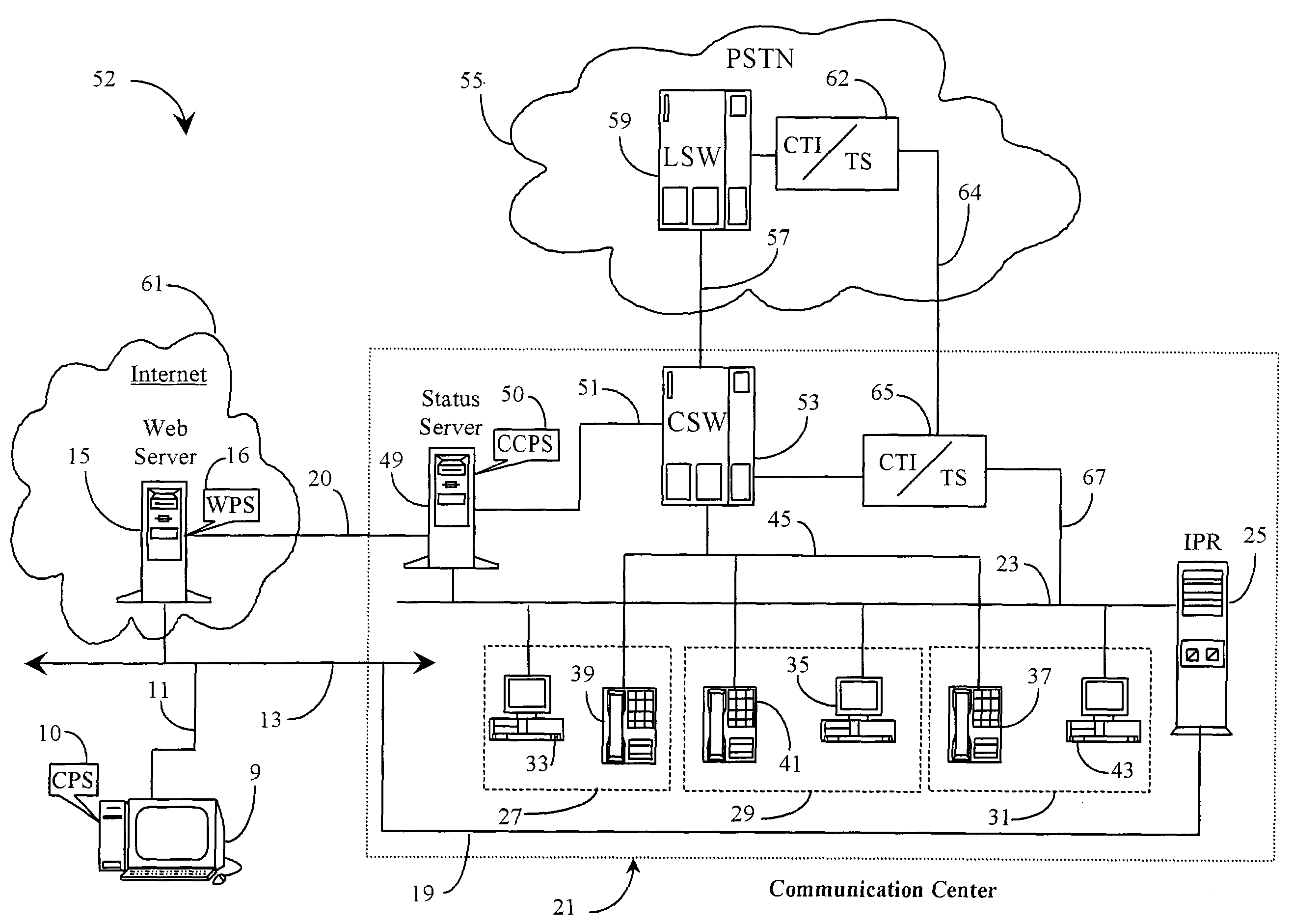

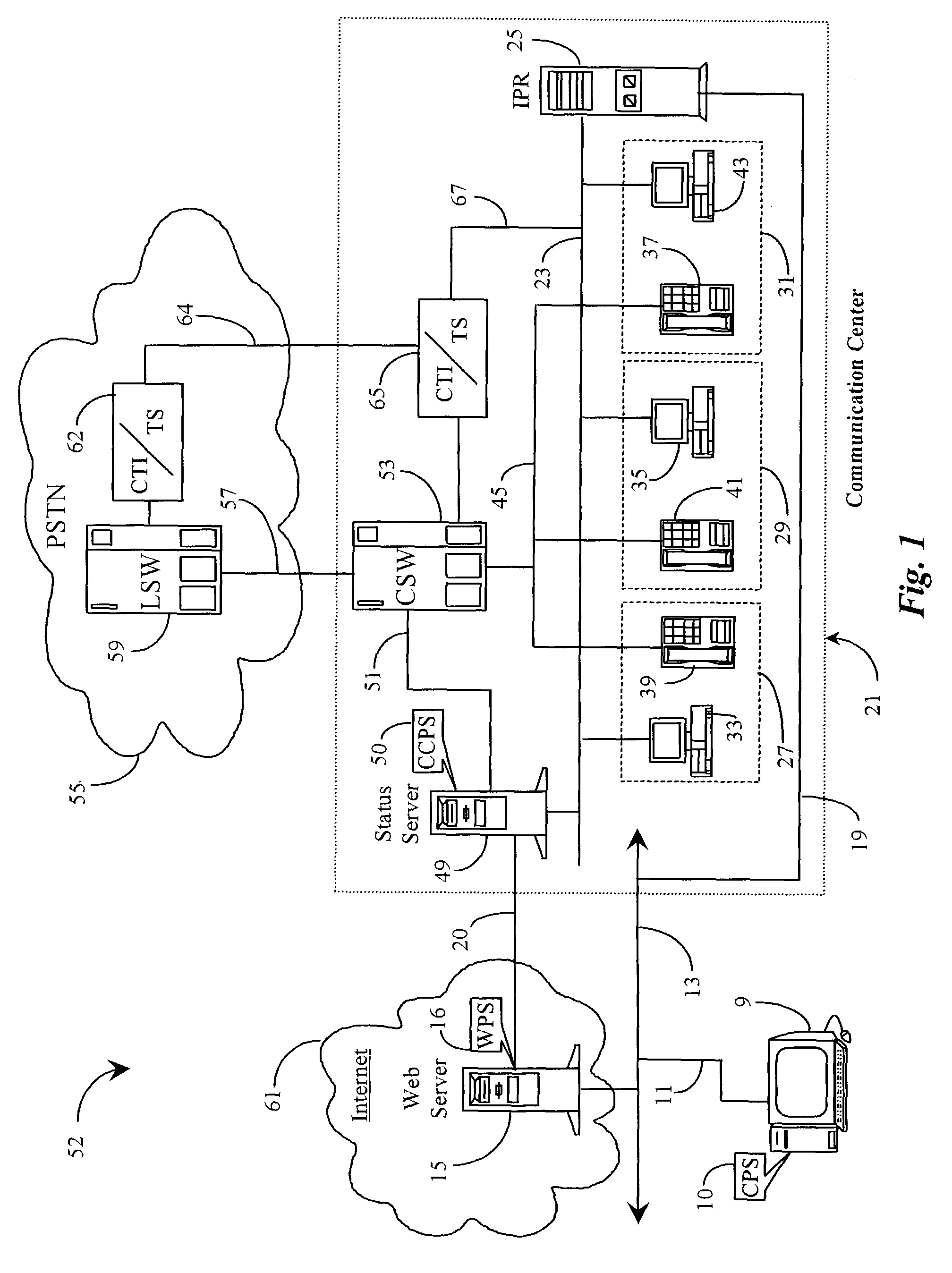

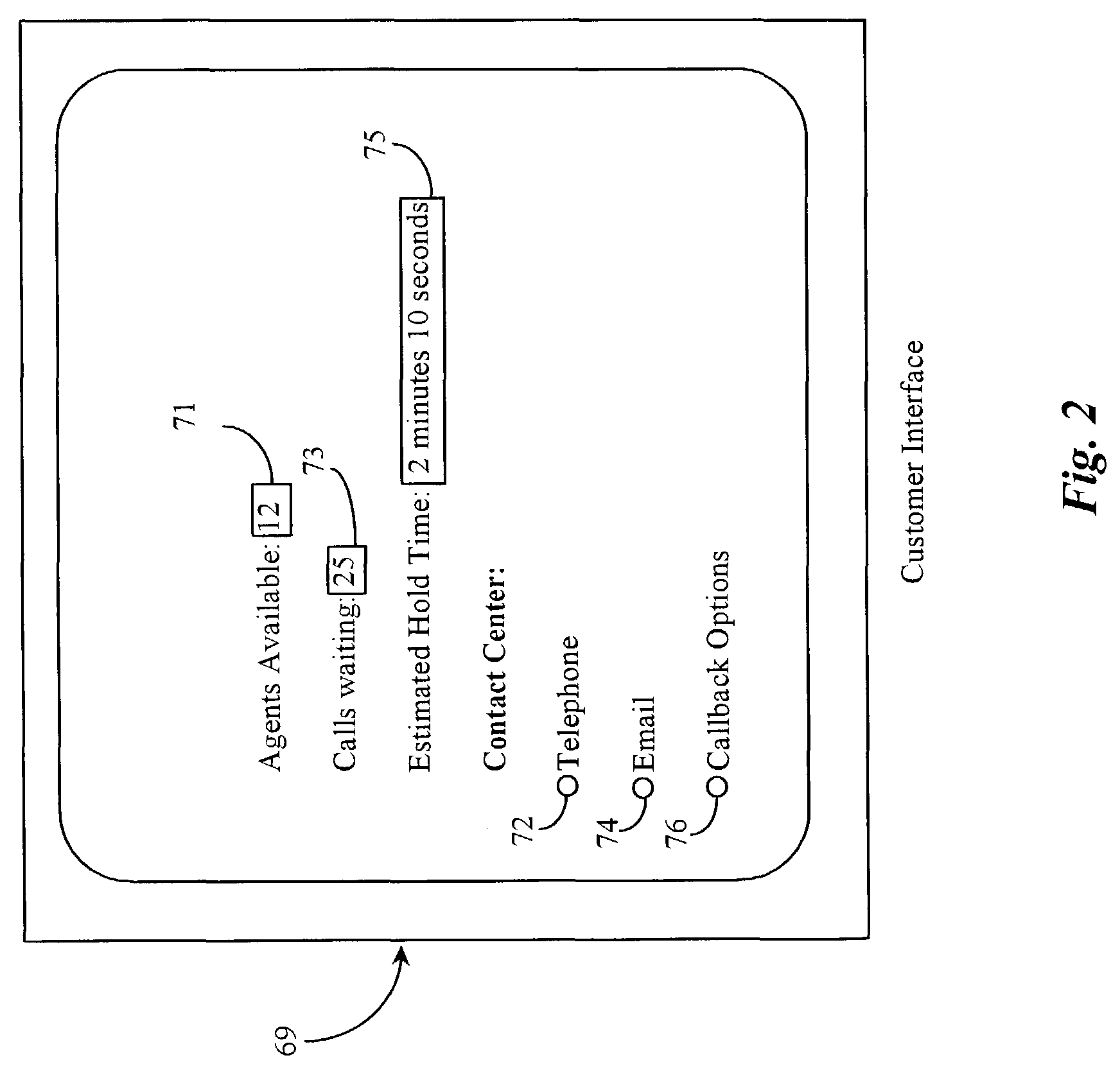

Method and apparatus for optimizing response time to events in queue

ActiveUS7929562B2Short response timeQuick cureError preventionFrequency-division multiplex detailsApplication softwareProcess time

A system for optimizing response time to events or representations thereof waiting in a queue has a first server having access to the queue; a software application running on the first server; and a second server accessible from the first server, the second server containing rules governing the optimization. In a preferred embodiment, the software application at least periodically accesses the queue and parses certain ones of events or tokens in the queue and compares the parsed results against rules accessed from the second server in order to determine a measure of disposal time for each parsed event wherein if the determined measure is sufficiently low for one or more of the parsed events, those one or more events are modified to a reflect a higher priority state than originally assigned enabling faster treatment of those events resulting in relief from those events to the queue system load.

Owner:GENESYS TELECOMMUNICATIONS LABORATORIES INC

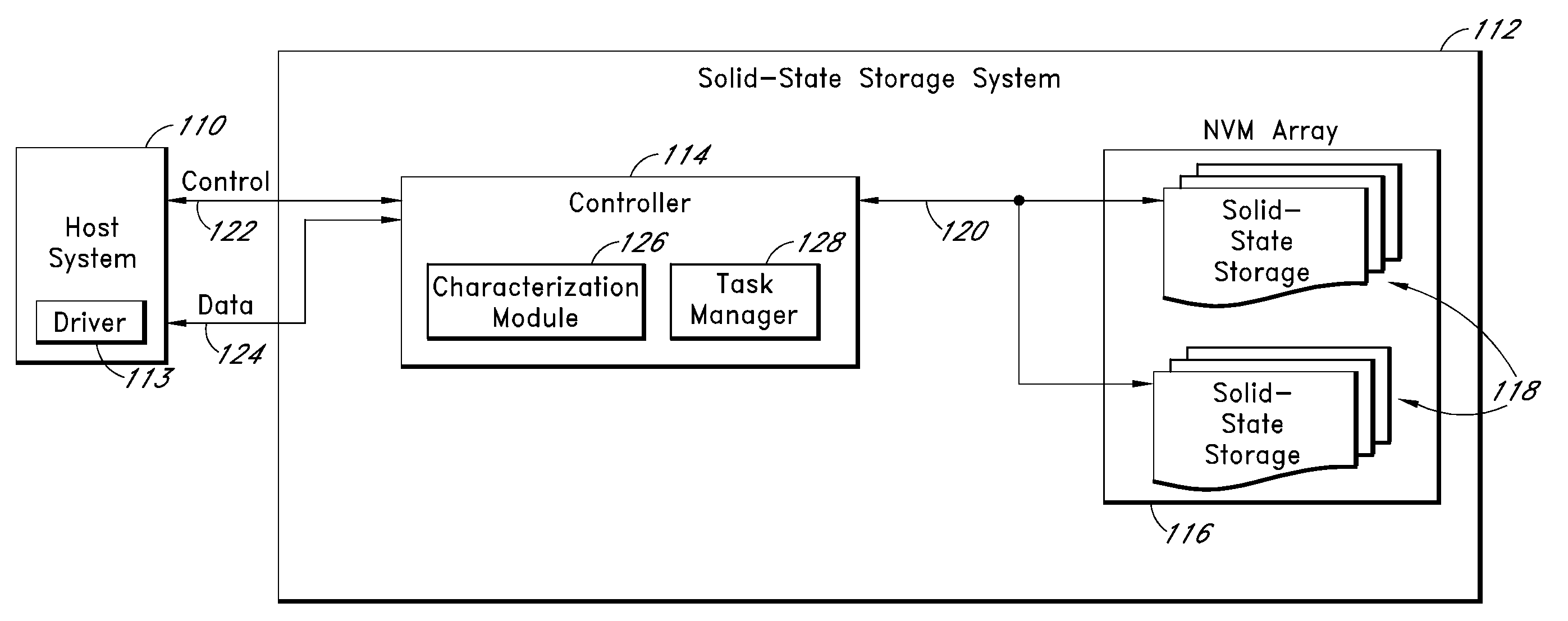

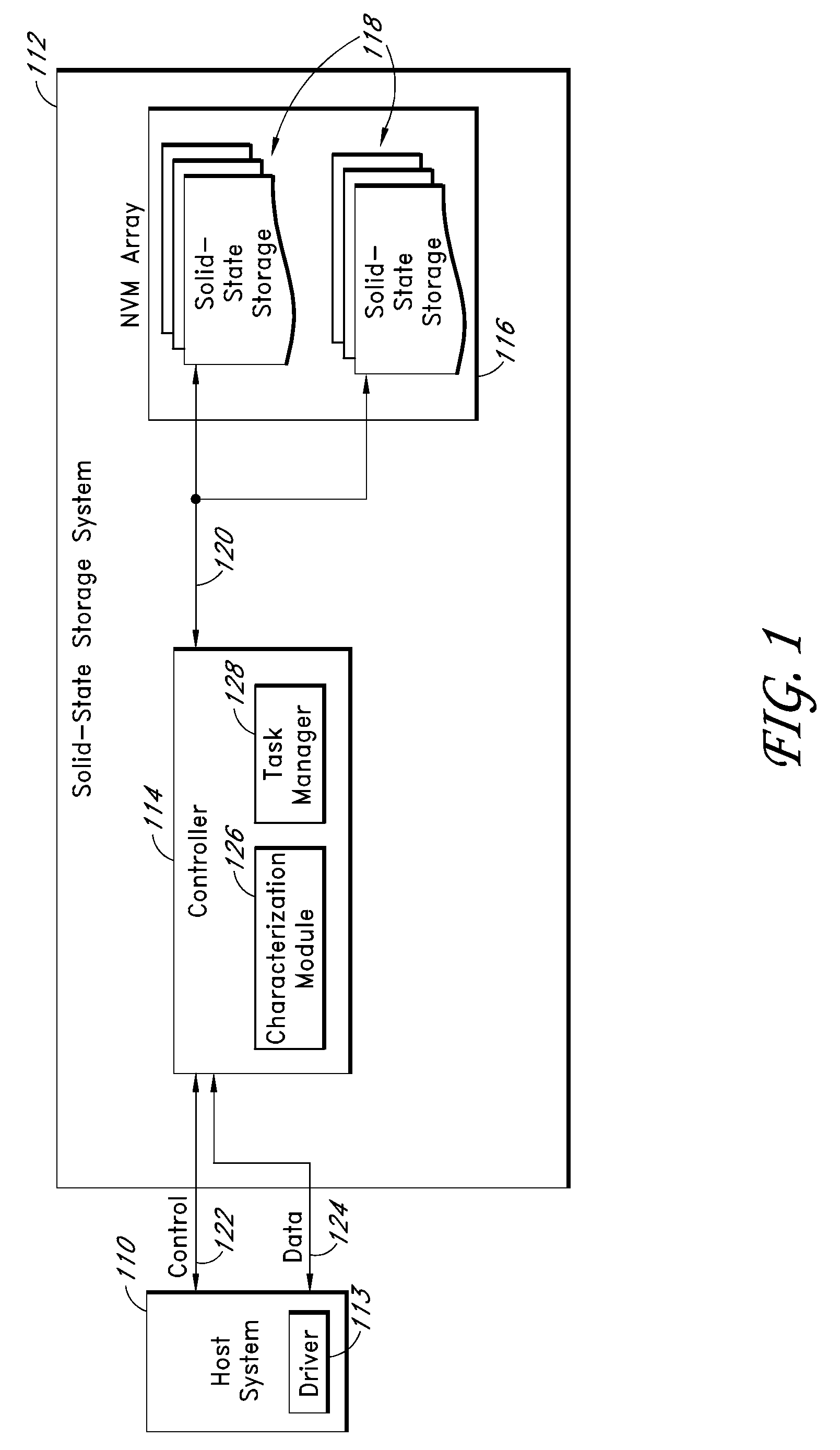

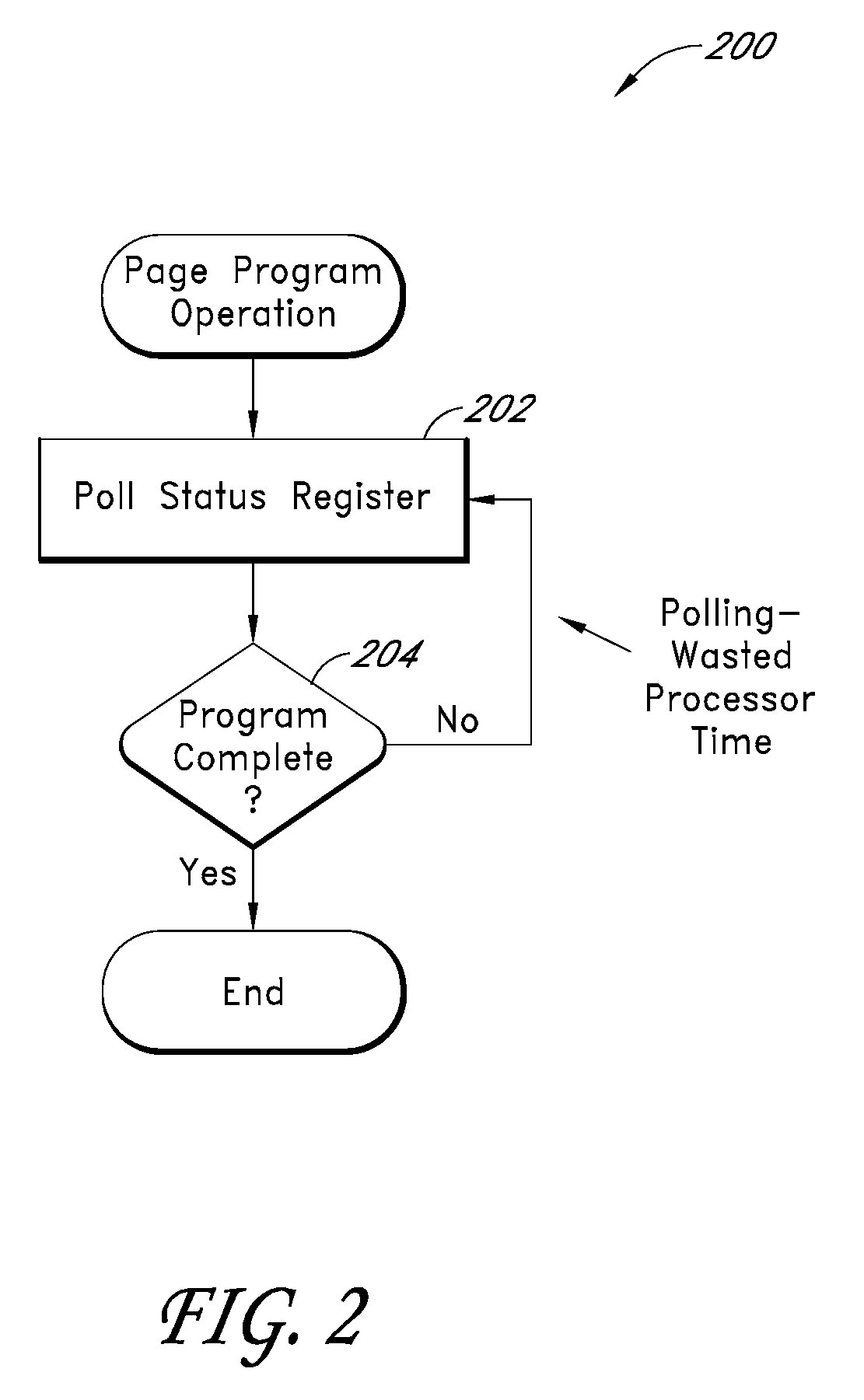

Systems and methods for improving the performance of non-volatile memory operations

ActiveUS20100174849A1Efficient use ofMemory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingStart up

Disclosed herein are systems and methods that recognize and recapture potentially unused processing time in typical page program and block erase operations in non-volatile memory (NVM) devices. In one embodiment, a characterization module within a controller executes a characterization procedure by performing page program and block erase operations on one or more NVM devices in an array and storing execution time data of the operations in a calibration table. The procedure may be executed at start-up and / or periodically so that the time values are reflective of the actual physical condition of the individual NVM devices. A task manager uses the stored time values to estimate the time needed for completing certain memory operations in its task table. Based on the estimated time for completion, the task manager assigns tasks to be executed during page program and / or block erase cycles, so that otherwise unused processing time can be utilized.

Owner:WESTERN DIGITAL TECH INC

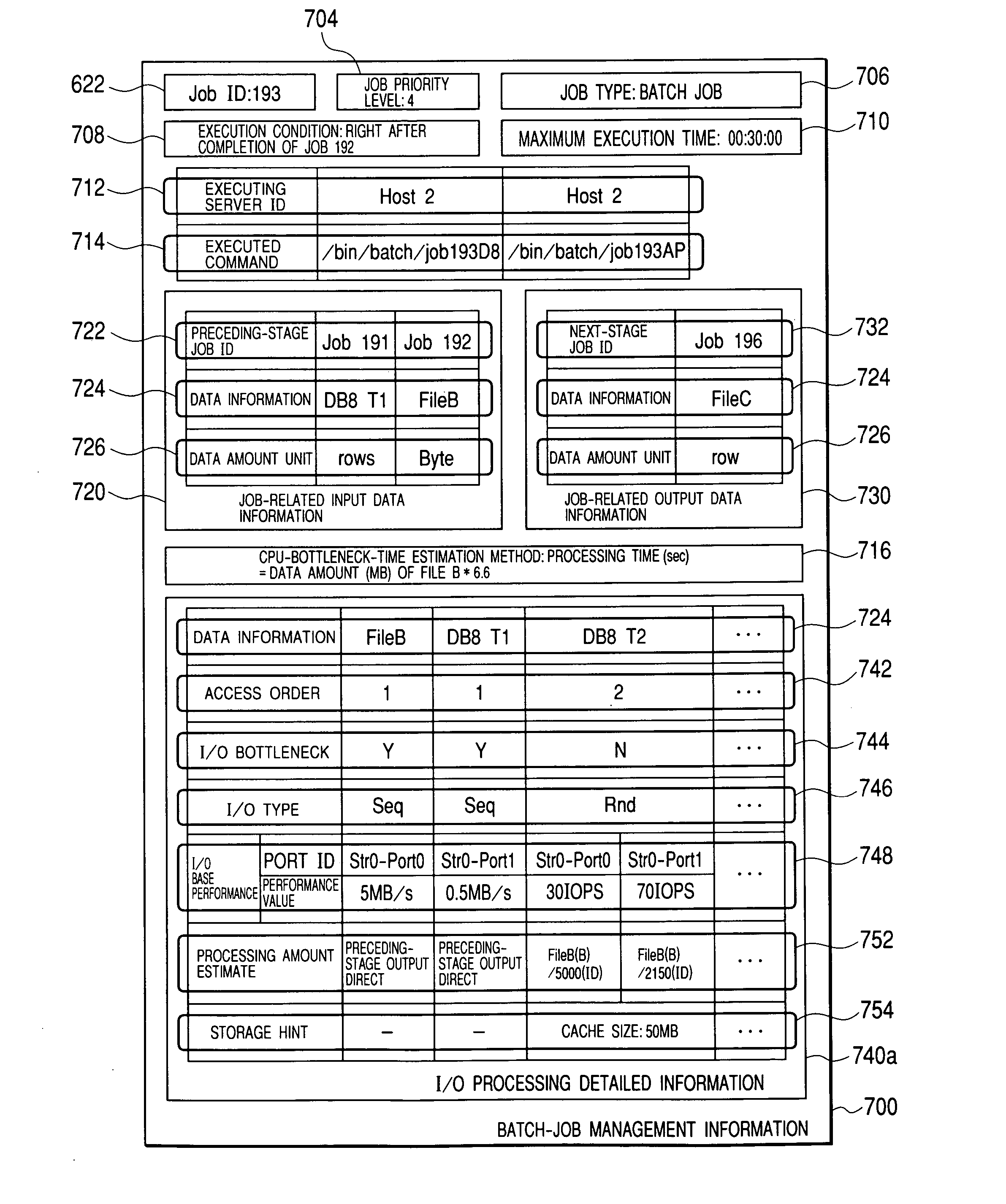

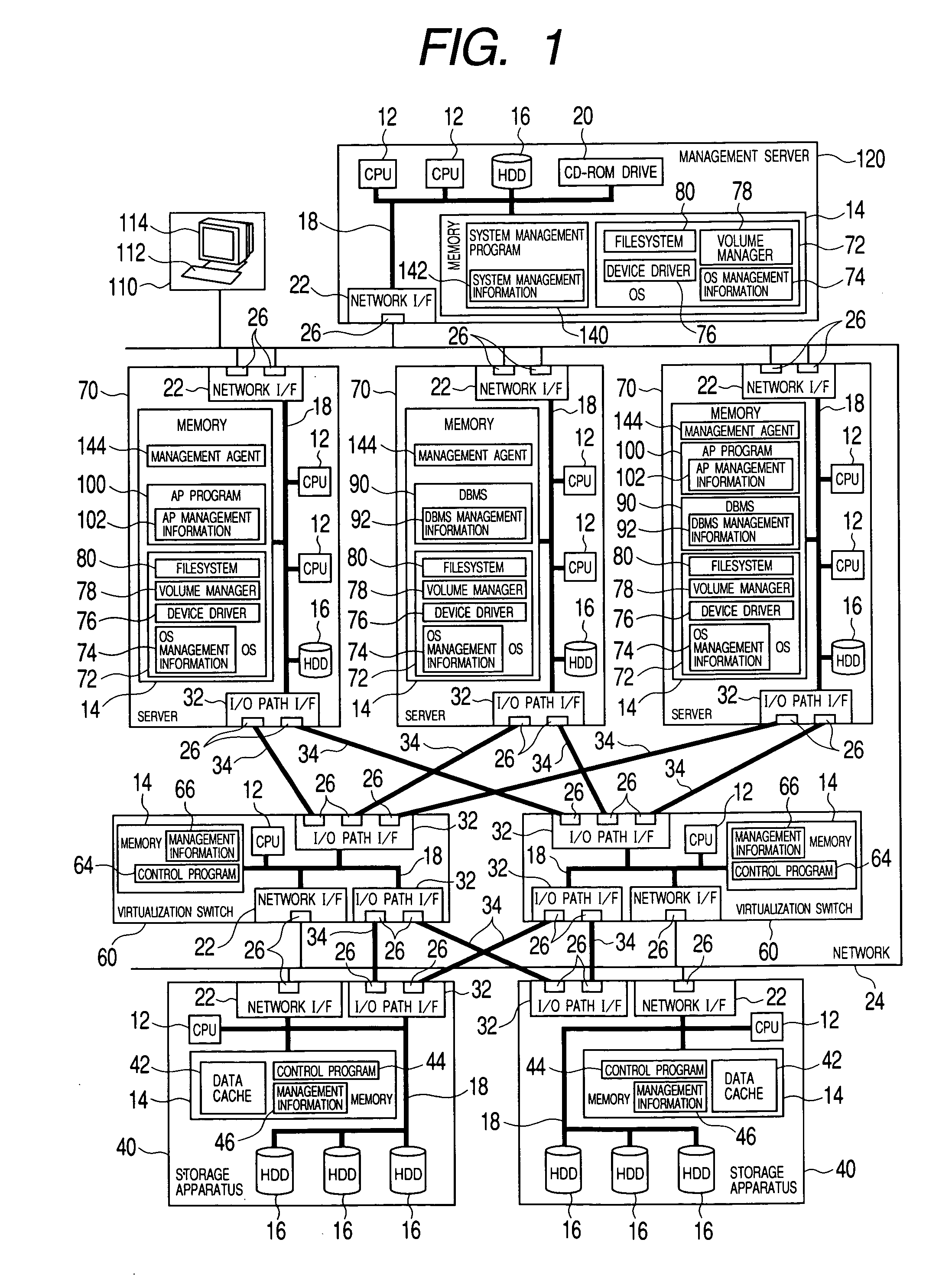

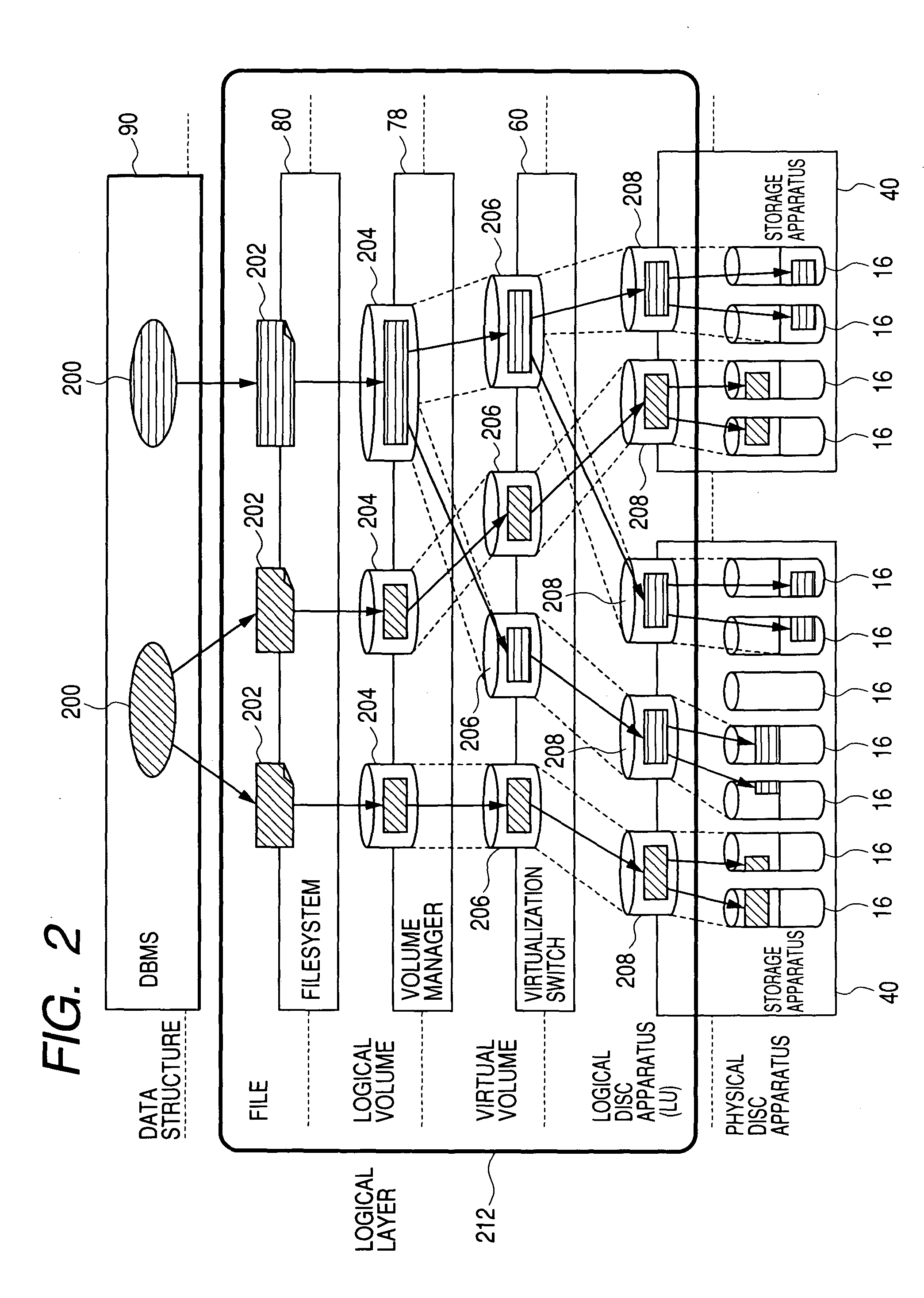

Computer system for managing performances of storage apparatus and performance management method of the computer system

InactiveUS20040193827A1Low costInput/output to record carriersDigital data information retrievalSystem elementSystem monitor

In a computer system with a DBMS running thereon, management of the performance of a storage apparatus is executed by using a performance indicator provided by a user job so as to simplify the management of the performance. For this reason, a management server employed in the computer system monitors an operating state of each system element, a response time onto a job and other information. Pre-given information on a process such as a performance requirement the collected monitored information are used by the management server in issuing a command to change allocation of a processing amount to a port, an allocation of a cache area for data, the logical configuration of disc drives and other parameters in order to carry out the new process or in the case where a result of a judgment based on the monitored information indicates that tuning is necessary. In the case of a process for a batch job, a method for estimating a processing time is given to the management server, which issues a setting modification command based on an estimated processing time. In the case of a process for an on-line job, on the other hand, a command to modify settings of a member bearing a heavy load is issued in the case where a response time on a process and / or a throughput do not meet their performance requirement.

Owner:HITACHI LTD

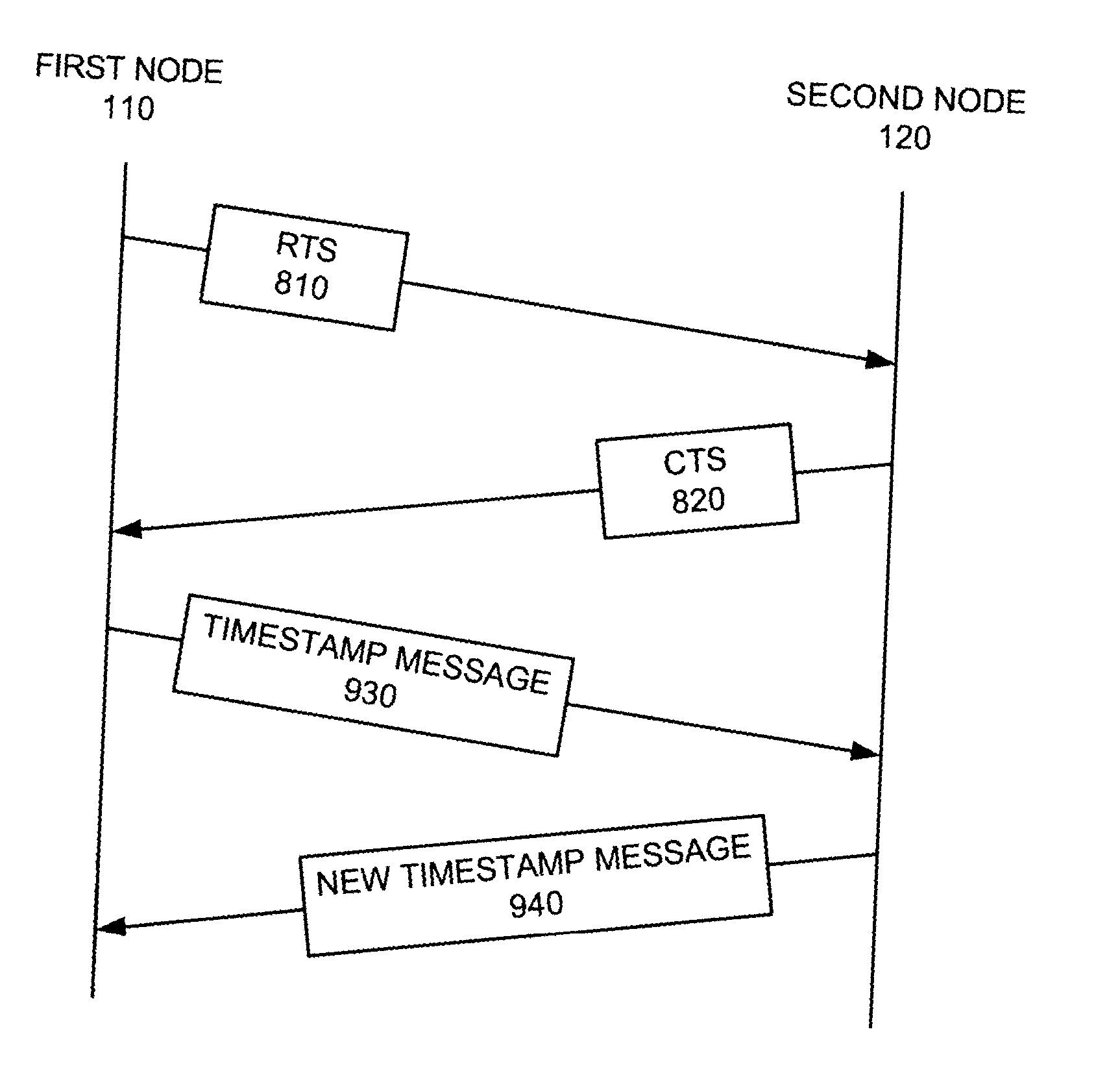

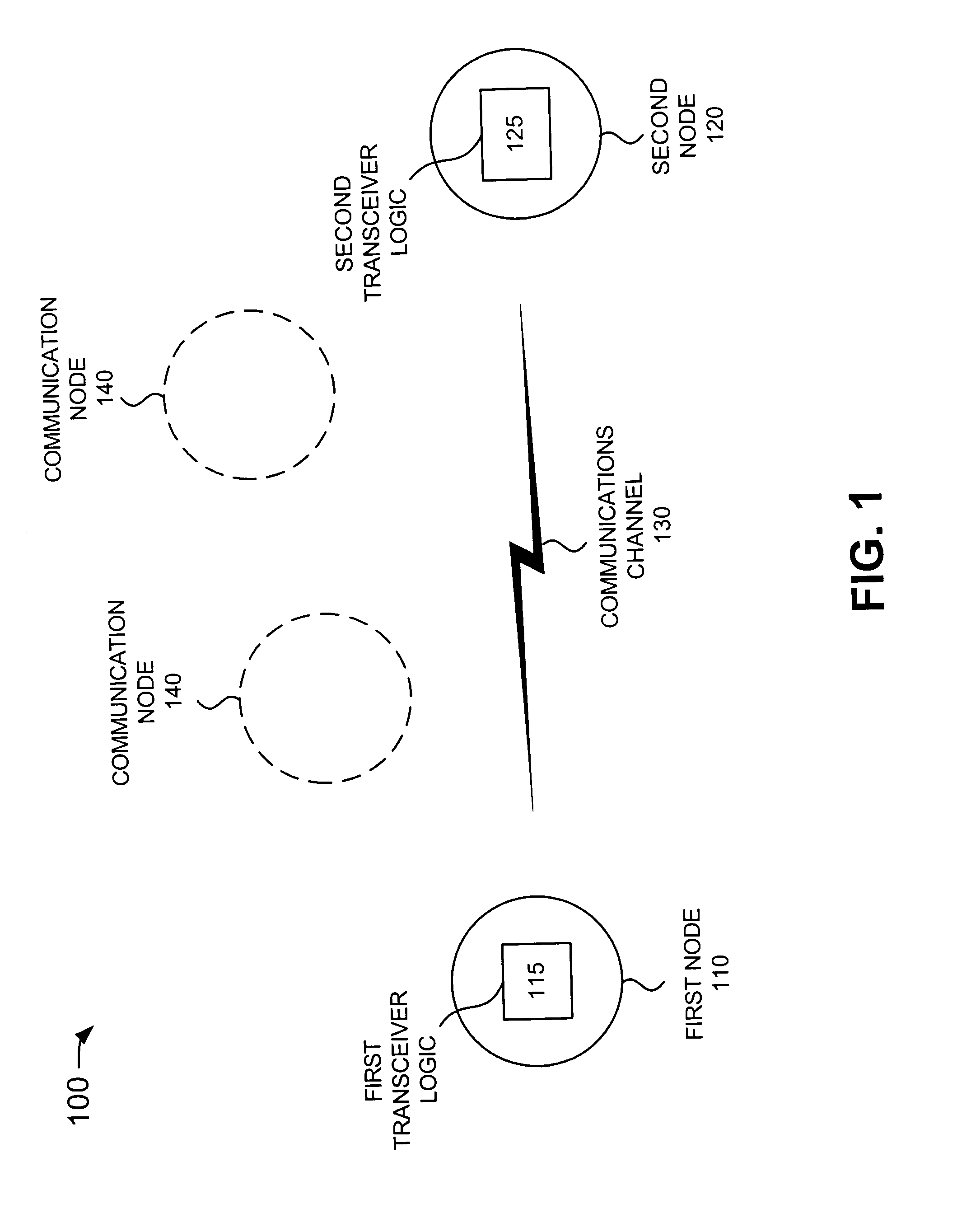

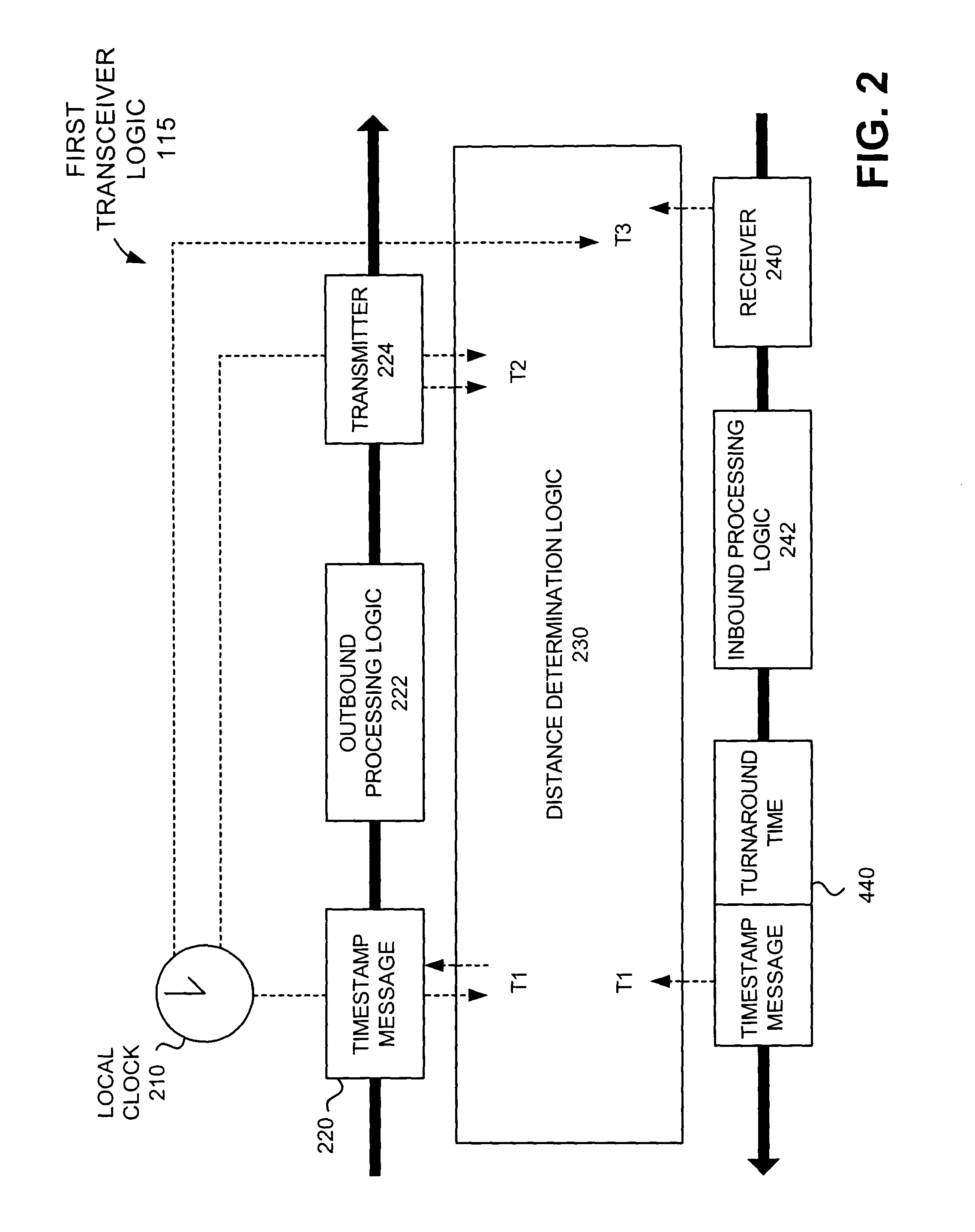

Systems and methods for measuring the distance between devices

InactiveUS20050058081A1Simplified and easily deployable techniqueSynchronisation arrangementError preventionTime informationTimestamp

A network includes a first node (110) and a second node (120). The first node (110) generates a timestamp message (220) that includes a first value, transmits the timestamp message (220) to the second node (120), and records a second time value representing a time at which a portion of the timestamp message (220) is being transmitted. The second node (120) receives the timestamp message (220), generates a new timestamp message (440) in response to receiving the timestamp message (220), stores the first value from the timestamp message (220) in the new timestamp message (440), stores second node processing time information in the new timestamp message (440), and transmits the new timestamp message (440) to the first node (110). Upon receipt of the new timestamp message (440), the first node (110) records a third time value representing a time at which a portion of the new timestamp message (440) is received, and determines the distance between the first node (110) and the second node (120) using the first value, the second time value, the third time value, and the second node processing time information.

Owner:BBN TECHNOLOGIES CORP

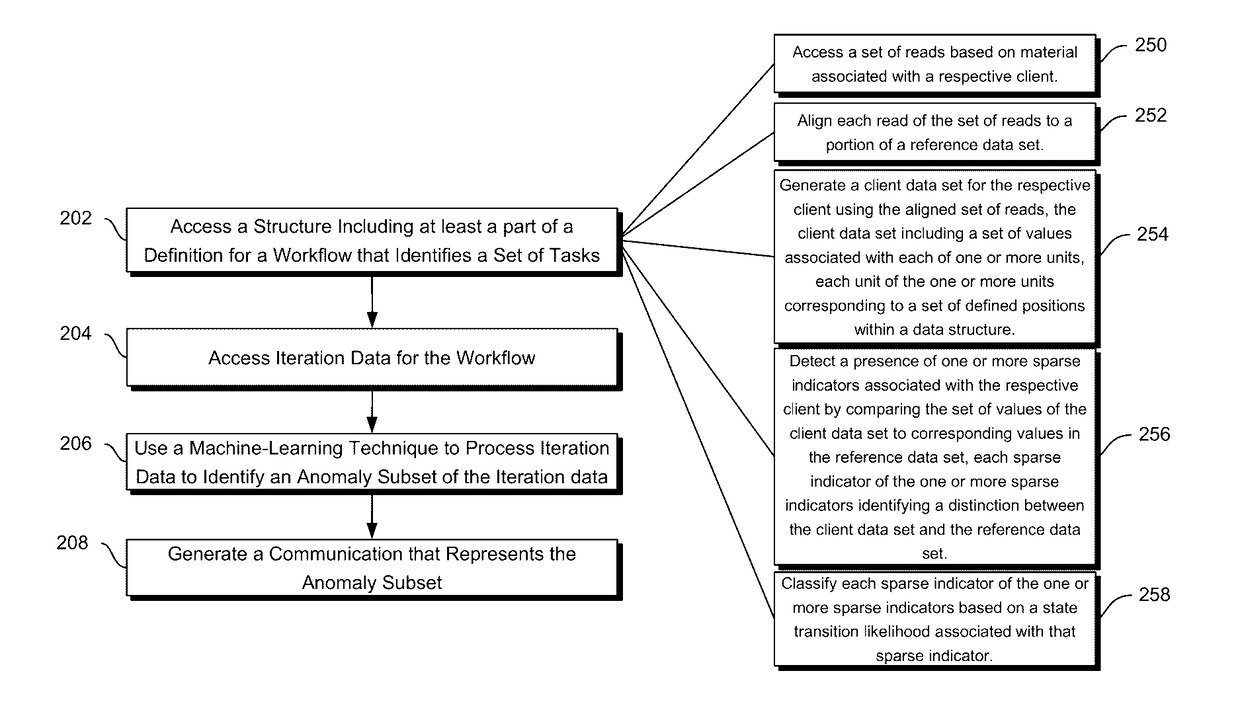

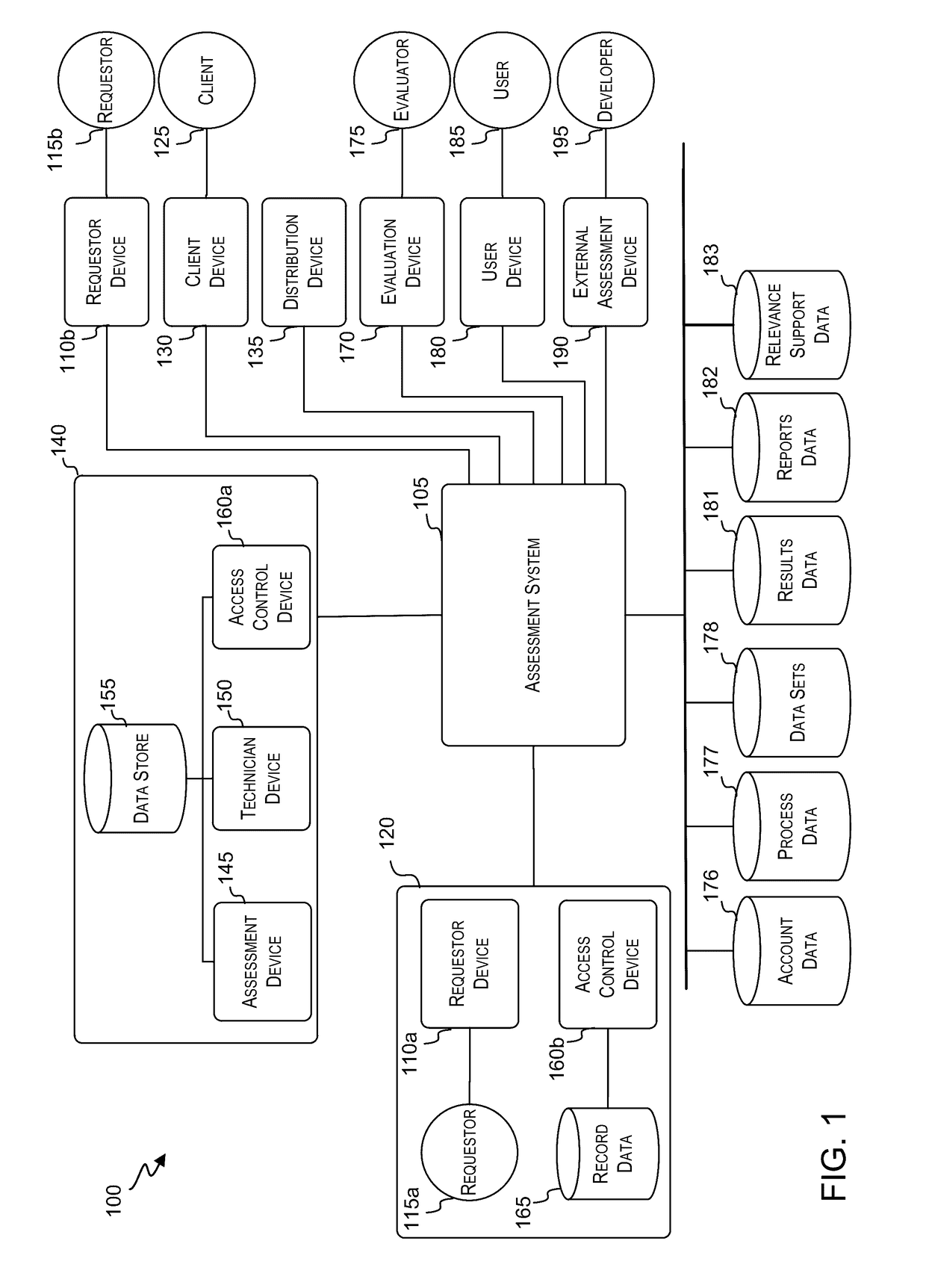

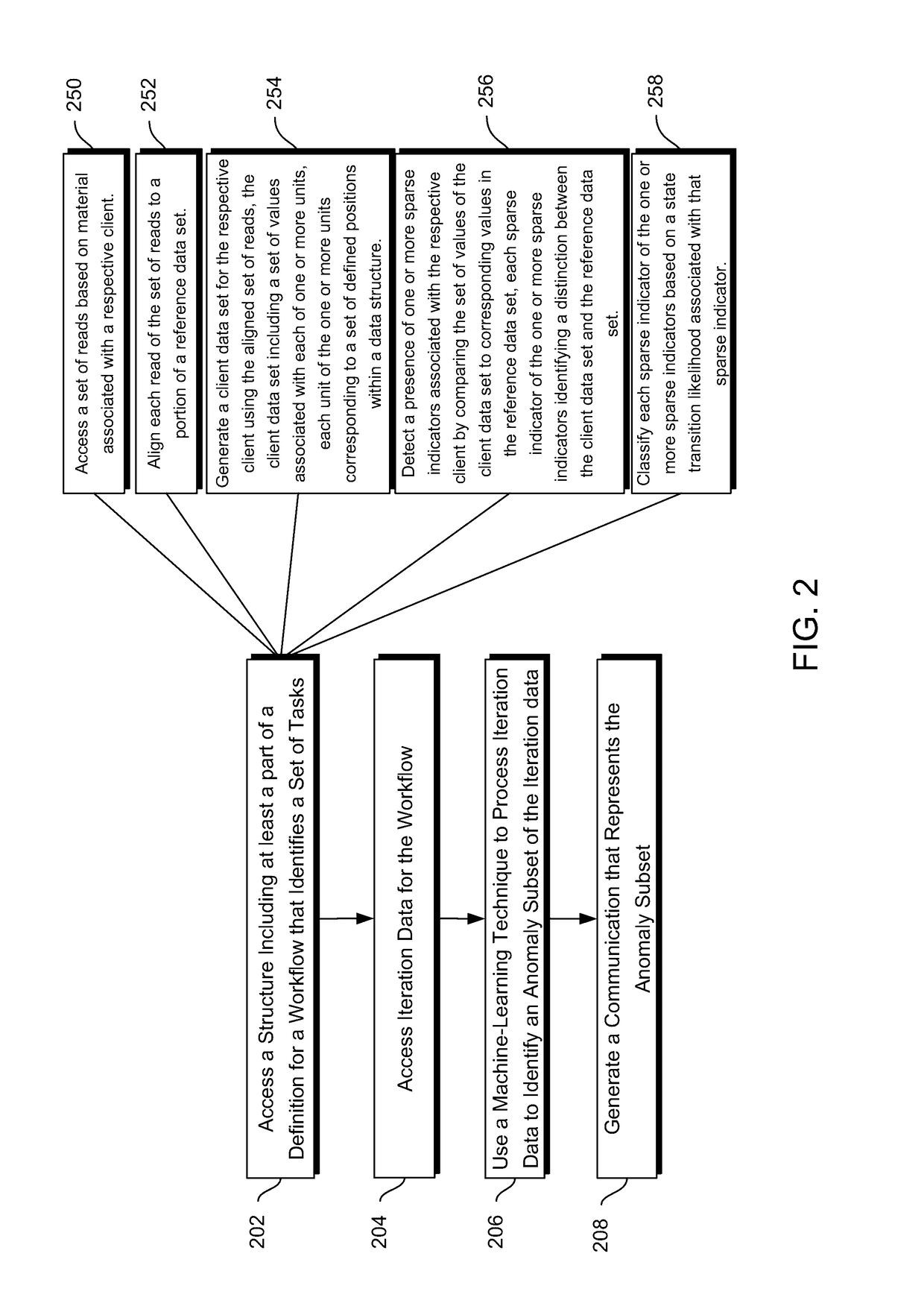

Techniques for processing queries relating to task-completion times or cross-data-structure interactions

Methods and systems disclosed herein relate generally to data processing by applying machine learning techniques to iteration data to identify anomaly subsets of iteration data. More specifically, iteration data for individual iterations of a workflow involving a set of tasks may contain a client data set, client-associated sparse indicators and their classifications, and a set of processing times for the set of tasks performed in that iteration of the workflow. These individual iterations of the workflow may also be associated with particular data sources. Using the iteration data, anomaly subsets within the iteration data can be identified, such as data items resulting from systematic error associated with particular data sources, sets of sparse indicators to be validated or double-checked, or tasks that are associated with long processing times. The anomaly subsets can be provided in a generated communication or report in order to optimize future iterations of the workflow.

Owner:COLOR HEALTH INC

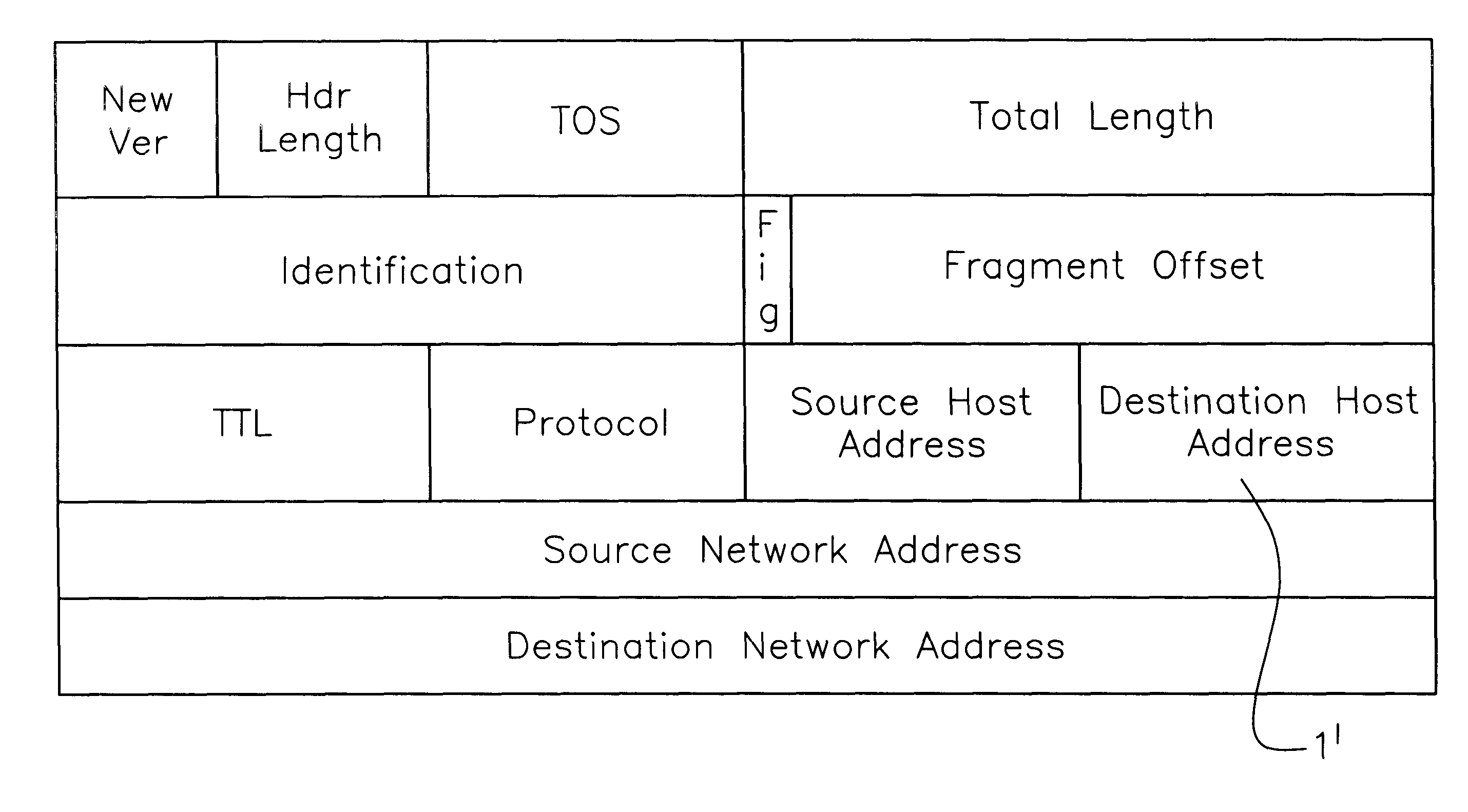

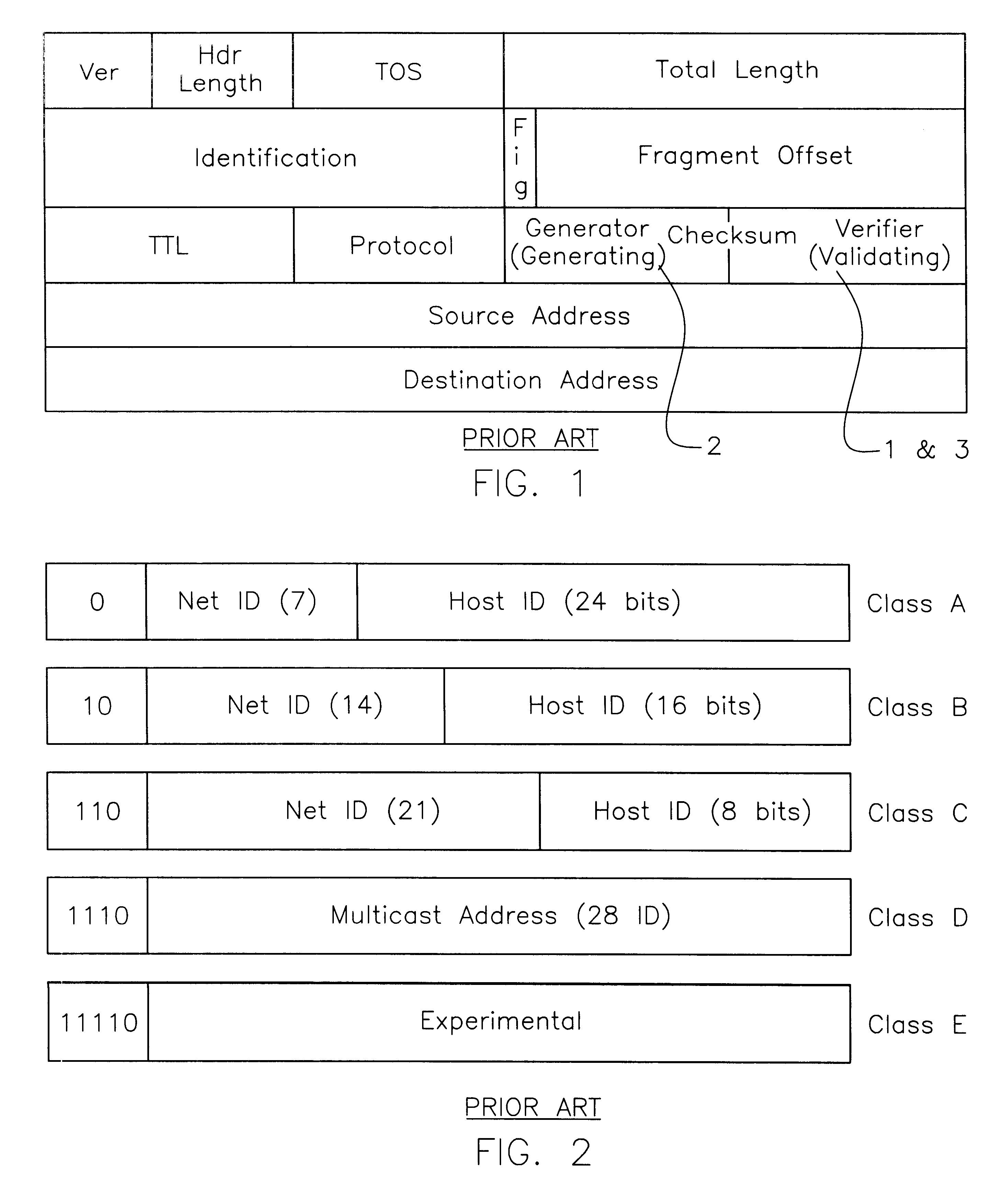

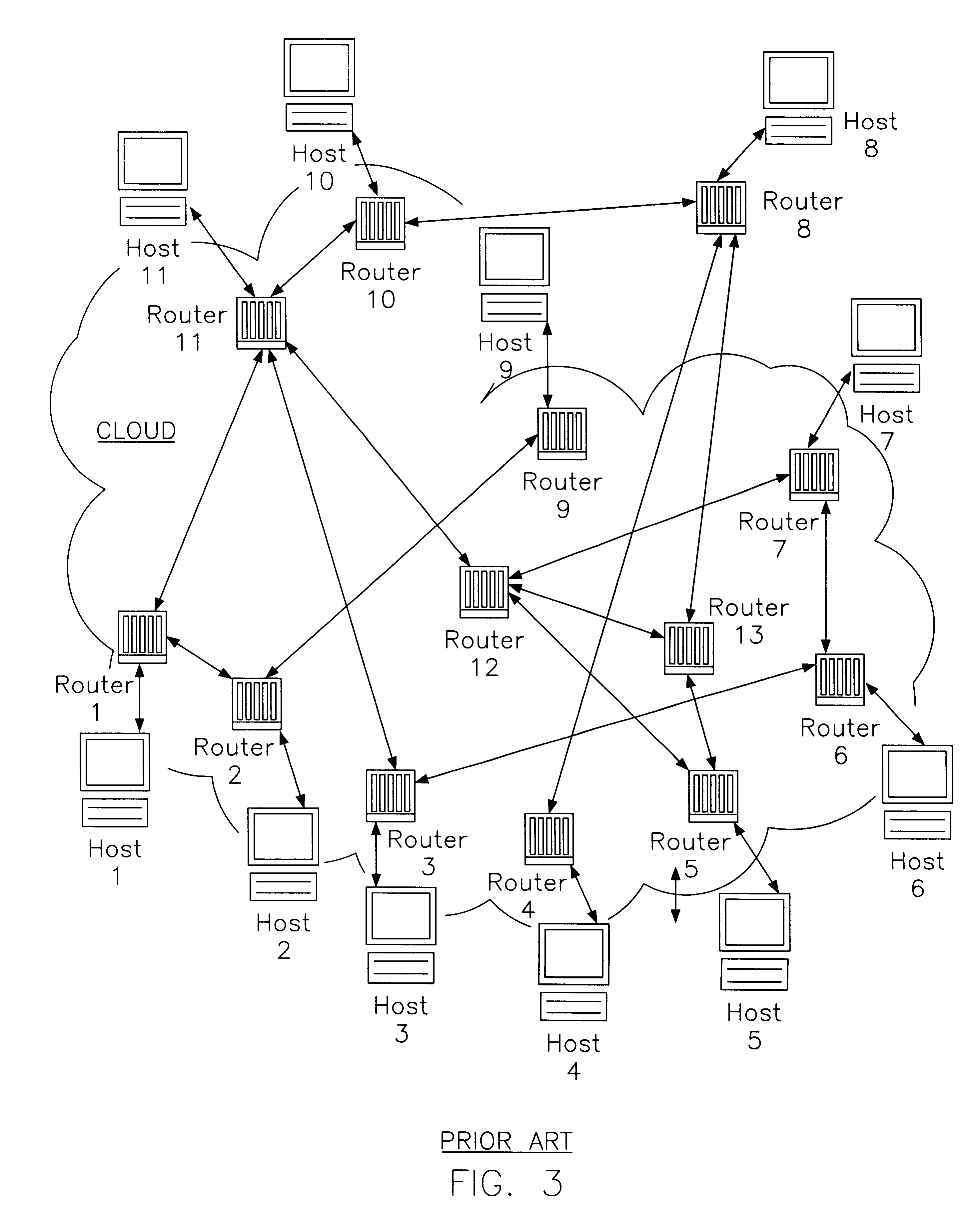

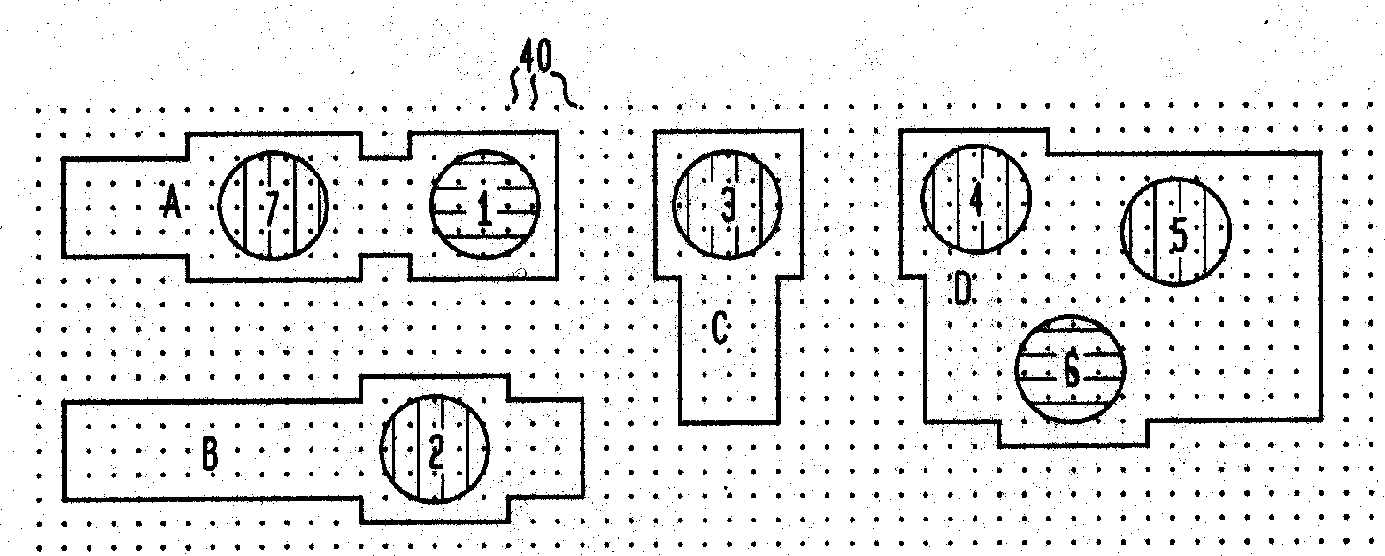

Internet and related networks, a method of and system for substitute use of checksum field space in information processing datagram headers for obviating processing speed and addressing space limitations and providing other features

InactiveUS6330614B1Add featureIncrease internet speedElectric signal transmission systemsTime-division multiplexInformation processingPrivate network

In Internet and related networks, a method of and system for substitute use of the normal checksum field space in information processing (IP) datagram headers for obviating current processing time and addressing space limitations, involving replacing the current checksum usage in the checksum field with its attendant processing time with further source host and destination host addresses of lesser processing time, thereby increasing the address space for the network and decreasing the require header processing time, and / or providing space for autonomous system numbers, a higher layer protocol-based routing information (including of the MPLS type) or for Virtual Private Networks Indentifiers in the header.

Owner:NEXABIT NETWORKS

Circuit layout methodology

InactiveUS20060195809A1Simplifies design/layout ruleReduce data volumeCAD circuit designSpecial data processing applicationsManufacturing technologyData preparation

A circuit layout methology is provided for eliminating the extra processing time and file-space requirements associated with the optical proximity correction (OPC) of a VLSI design. The methodology starts with the design rules for a given manufacturing technology and establishes a new set of layer-specific grid values. A layout obeying these new grid requirements leads to a significant reduction in data preparation time, cost, and file size. A layout-migration tool can be used to modify an existing layout in order to enforce the new grid requirements.

Owner:IBM CORP

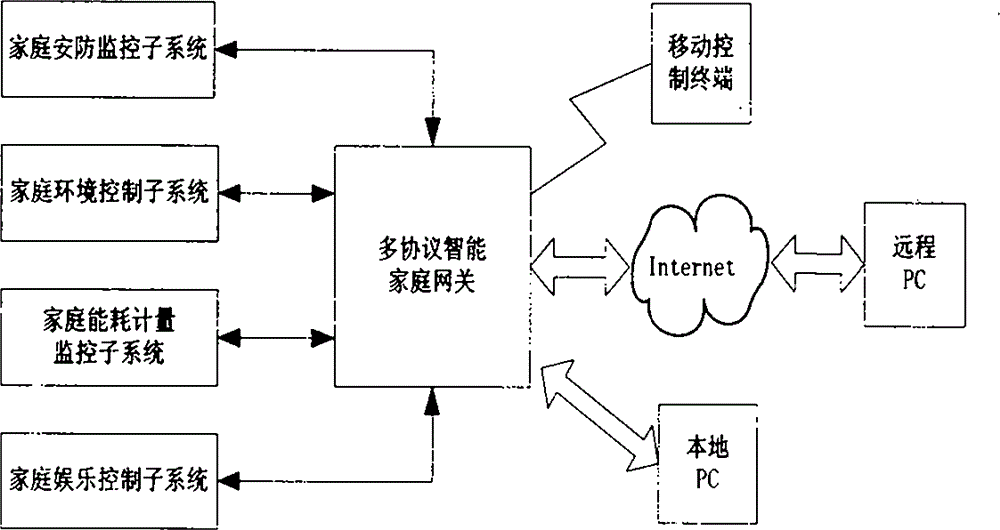

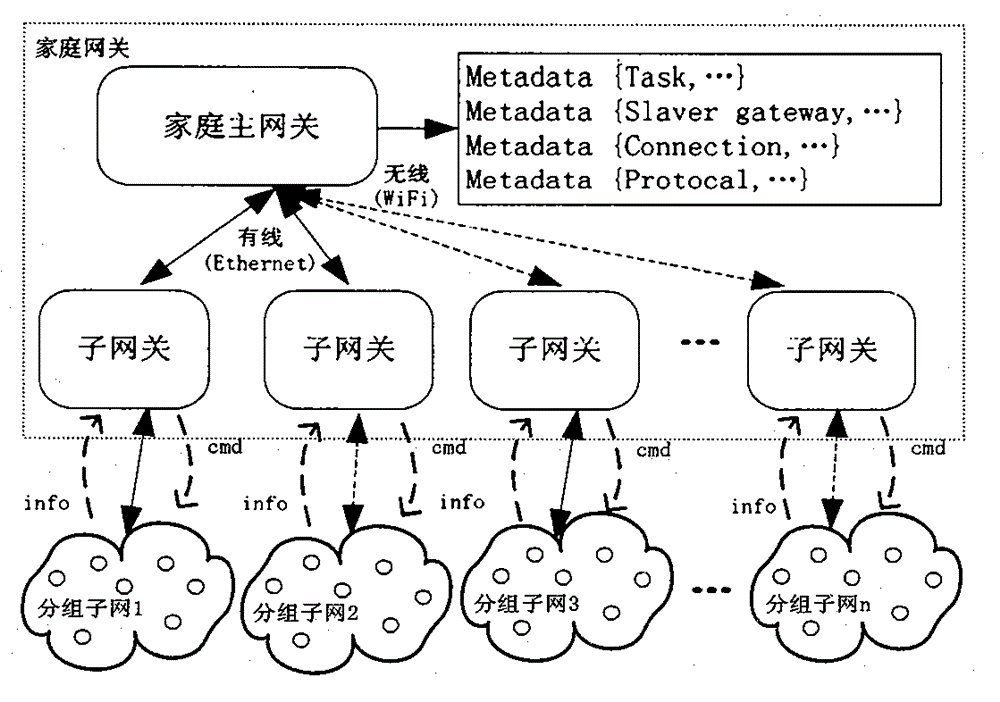

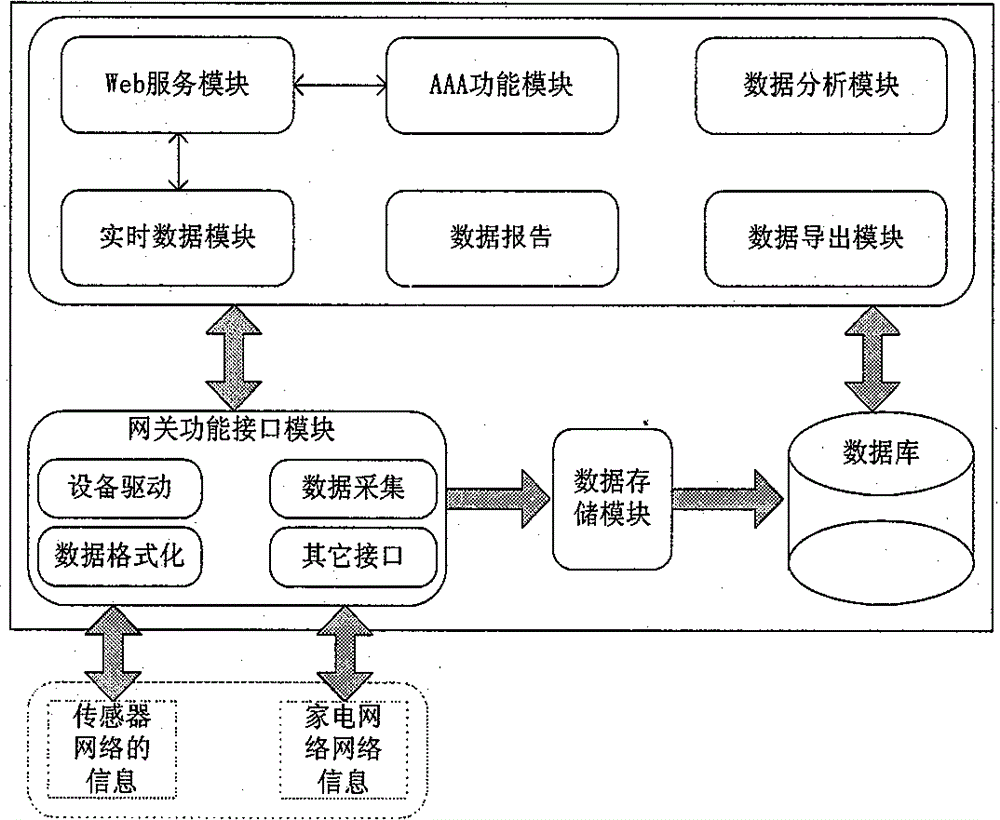

Multiprotocol intelligent household gateway apparatus and system thereof

The invention supports access and integration of multiple heterogeneous networks including a wireless network, an on-site bus, an Ethernet and the like, and provides a household gateway protocol conversion and configuration method and device, and a device description file. A configurable protocol method is mainly employed to solve the problem of conversion among multiple heterogeneous protocols. A gateway is provided with configurable protocol software, the software generates description files of various device protocols, and a protocol conversion driving file is generated through a configuration method according to protocol attributes by use of a software tool. The gateway, after loading the driving file, converts the driving file to a communication protocol which can be identified by a device and automatically maps to generate a unified TCP / IP protocol frame routing table. The description files, based on a ClassAD task description language, are used for providing a flexible and extensible heterogeneous network model to describe any services or data. The gateway, through identification and description of device information, determines the type and meaning of the information, omits information parsing, reduces the time for processing the information by the gateway, and improves the real-time performance of a system.

Owner:JIANGNAN UNIV

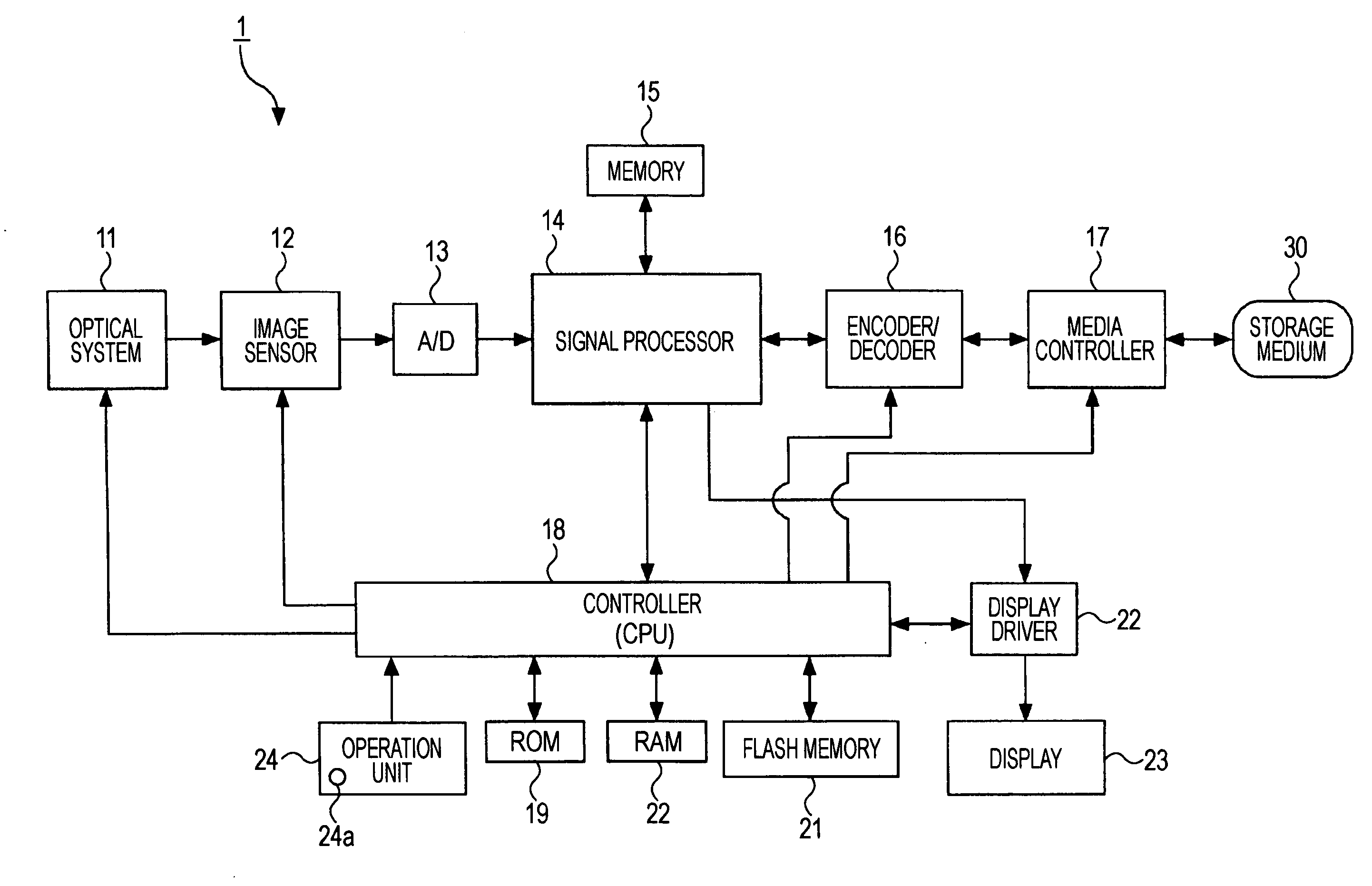

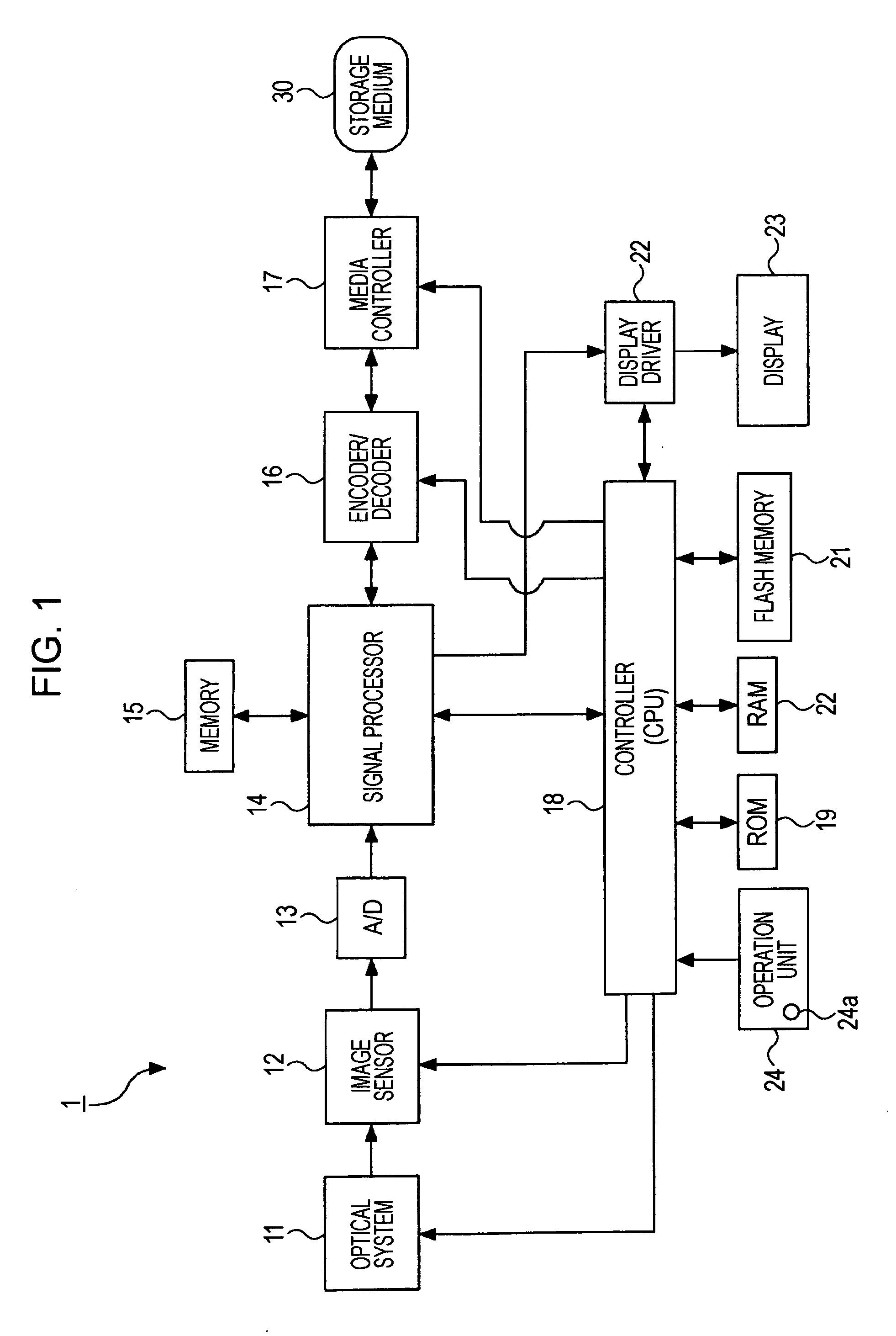

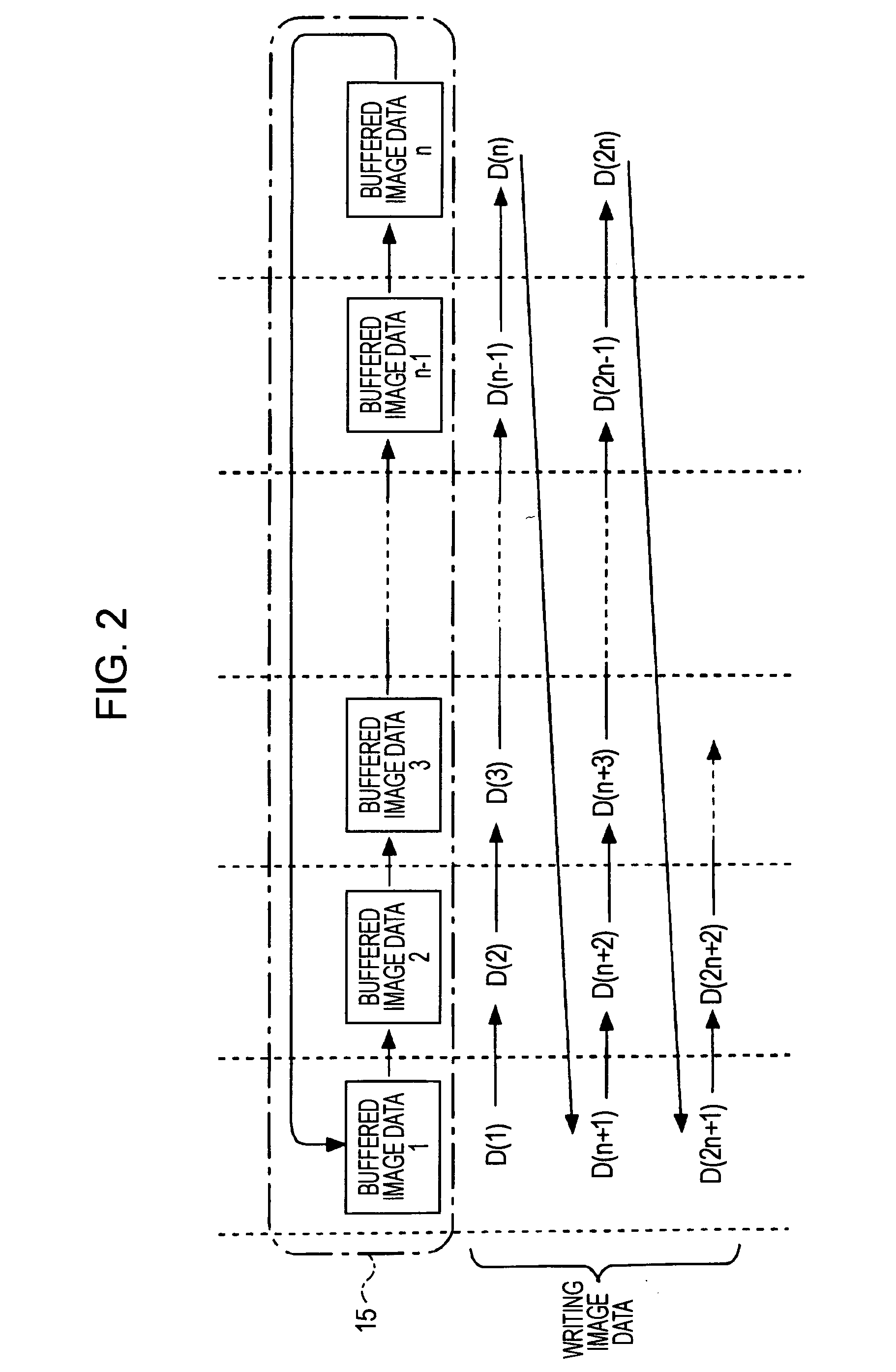

Imaging device, method of processing captured image signal and computer program

InactiveUS20080284866A1Increase the number ofQuality improvementTelevision system detailsColor television detailsComputer hardwareImaging quality

A constant amount of new portion of image data as still images is always stored on a memory in an image taking operation. In response to a shutter release operation, the image data stored on the memory is recorded onto a recording medium. A next new portion of the image data generated subsequent to the shutter release operation is then recorded on the recording medium. A predetermined pixel count, smaller than a standard pixel count set in the image data subsequent to the shutter release operation, is set in the image data prior to the shutter release operation. Process time for multi-shot operation is shortened in order to prevent photo opportunity missing. The pixel count in the image data subsequent to the shutter release operation remains unchanged so that the image data of high image quality is acquired.

Owner:SONY CORP +1

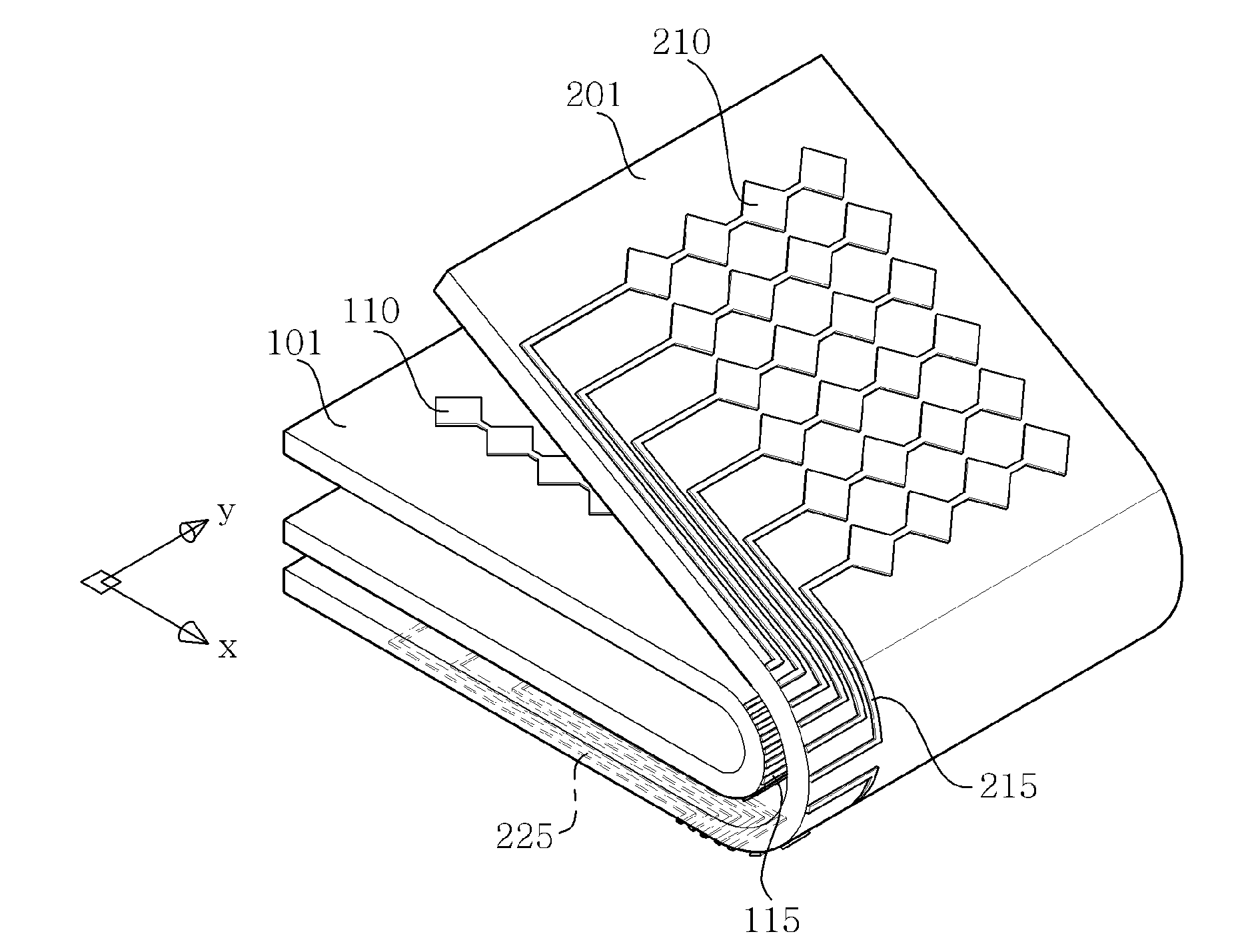

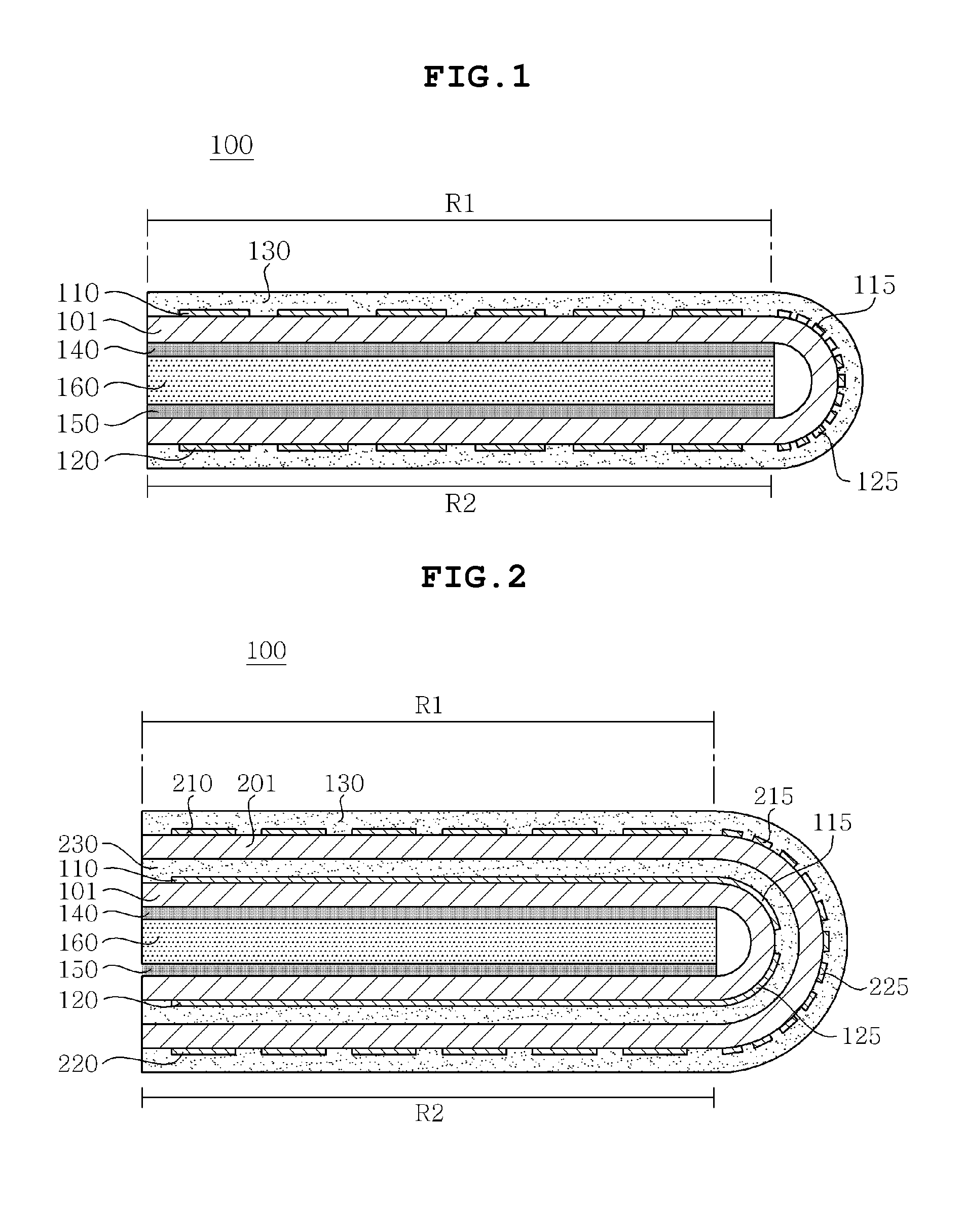

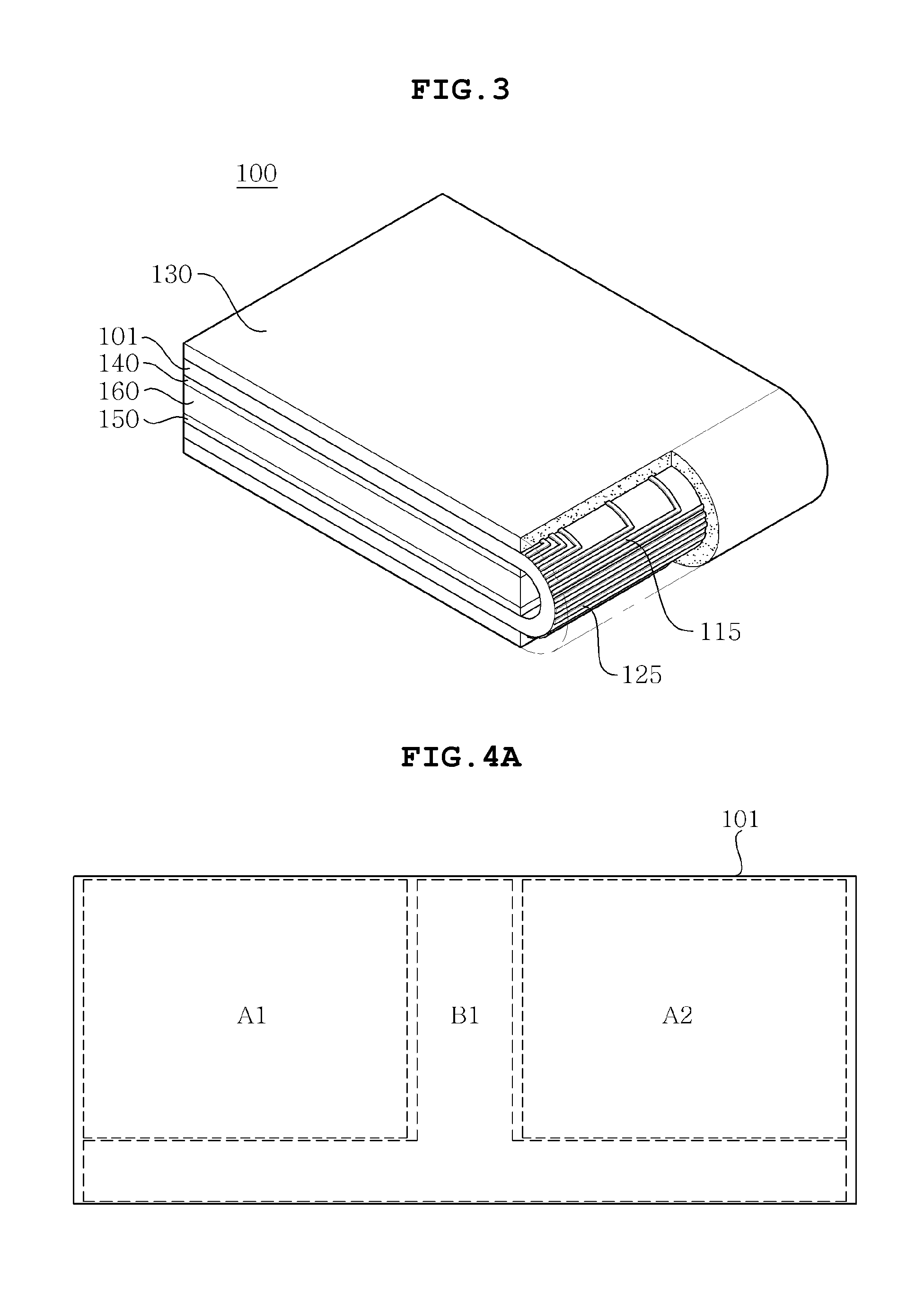

Touch screen

InactiveUS20120162099A1Improve production yieldReduce processing timeInput/output processes for data processingTouchscreenComputer science

Disclosed herein is a touch screen 100 designed to control an image displayed on image display units 140 and 150 on both-sides of the touch screen. The touch screen 100 according to the present invention may overcome an obscured screen problem caused by an input device, increase production yield while reducing a process time of the touch screen 100 by simultaneously forming transparent electrodes and electrode wires on a transparent substrate and, after forming an image display unit and an active region on the transparent substrate, folding the transparent substrate, and minimize an area of a bezel region.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

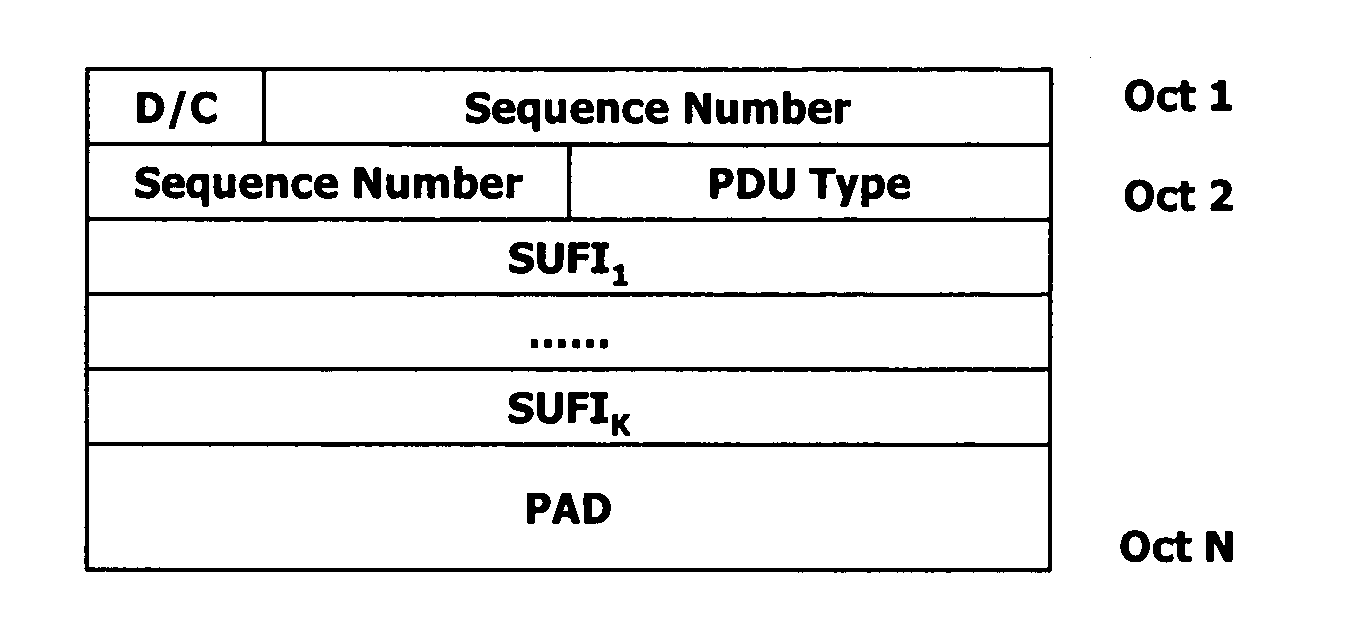

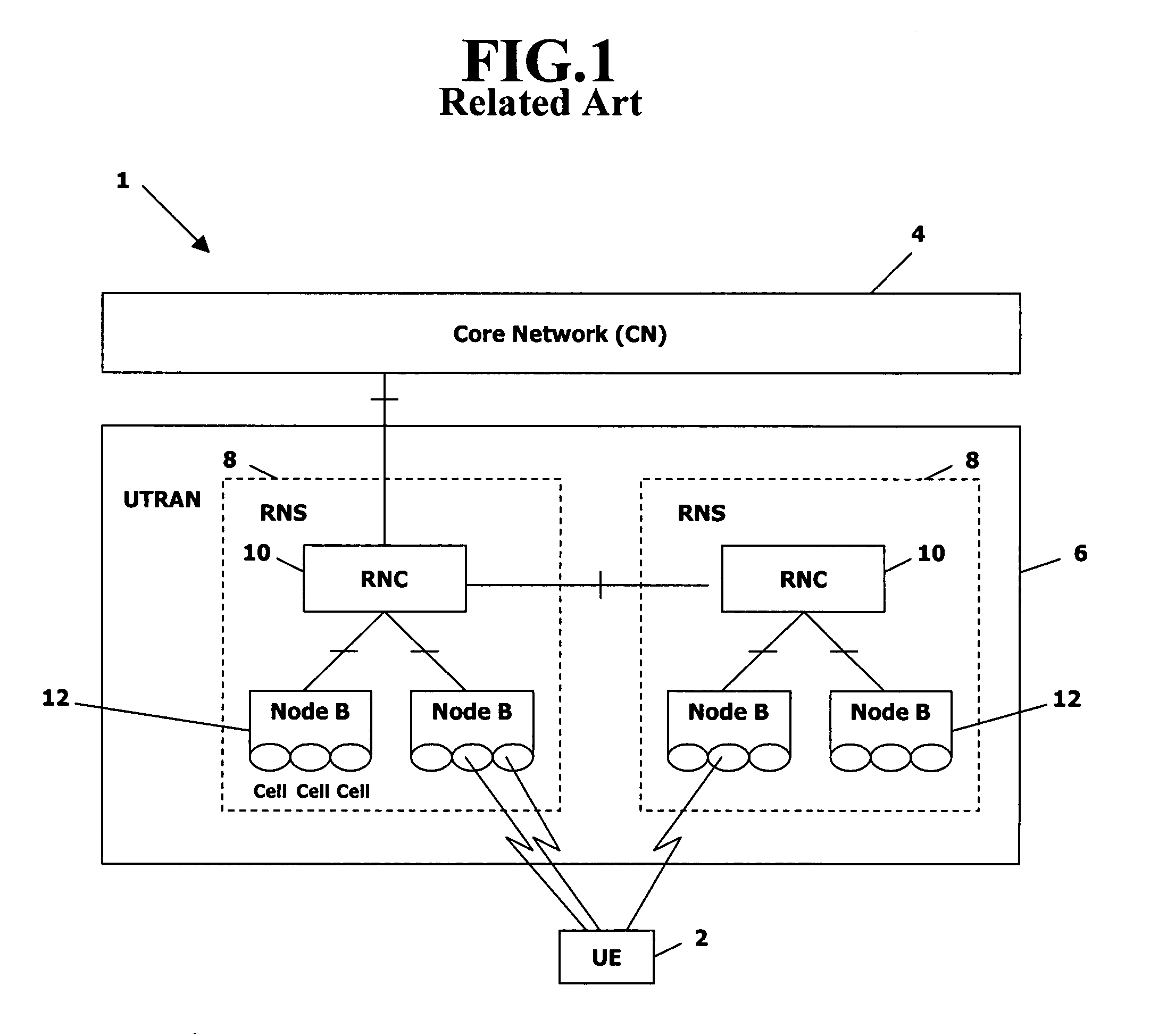

Transmitting and receiving control protocol data unit having processing time information

ActiveUS20050287957A1Error prevention/detection by using return channelNetwork traffic/resource managementTime informationTransmitter

The present invention relates to transmitting and receiving control protocol data. A transmitter transmits a control protocol unit having processing time information, wherein the processing time information indicates to a receiver of when to process the control protocol data unit. Accordingly, the receiver processes the control protocol data unit according to the processing time information.

Owner:LG ELECTRONICS INC

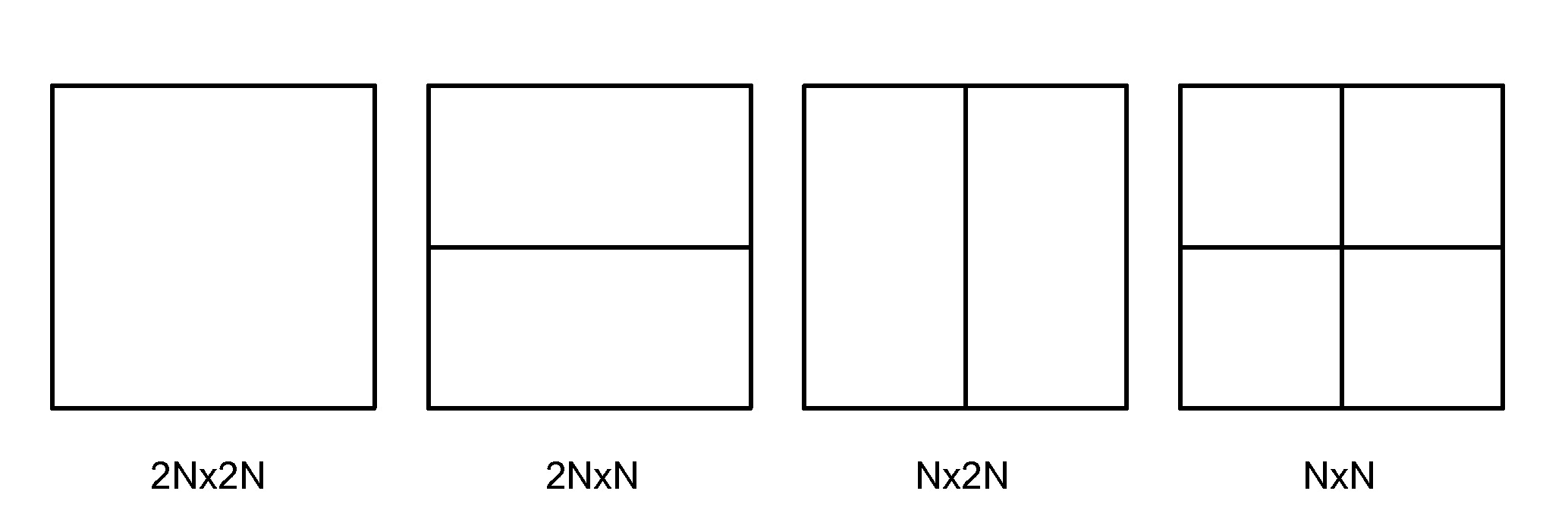

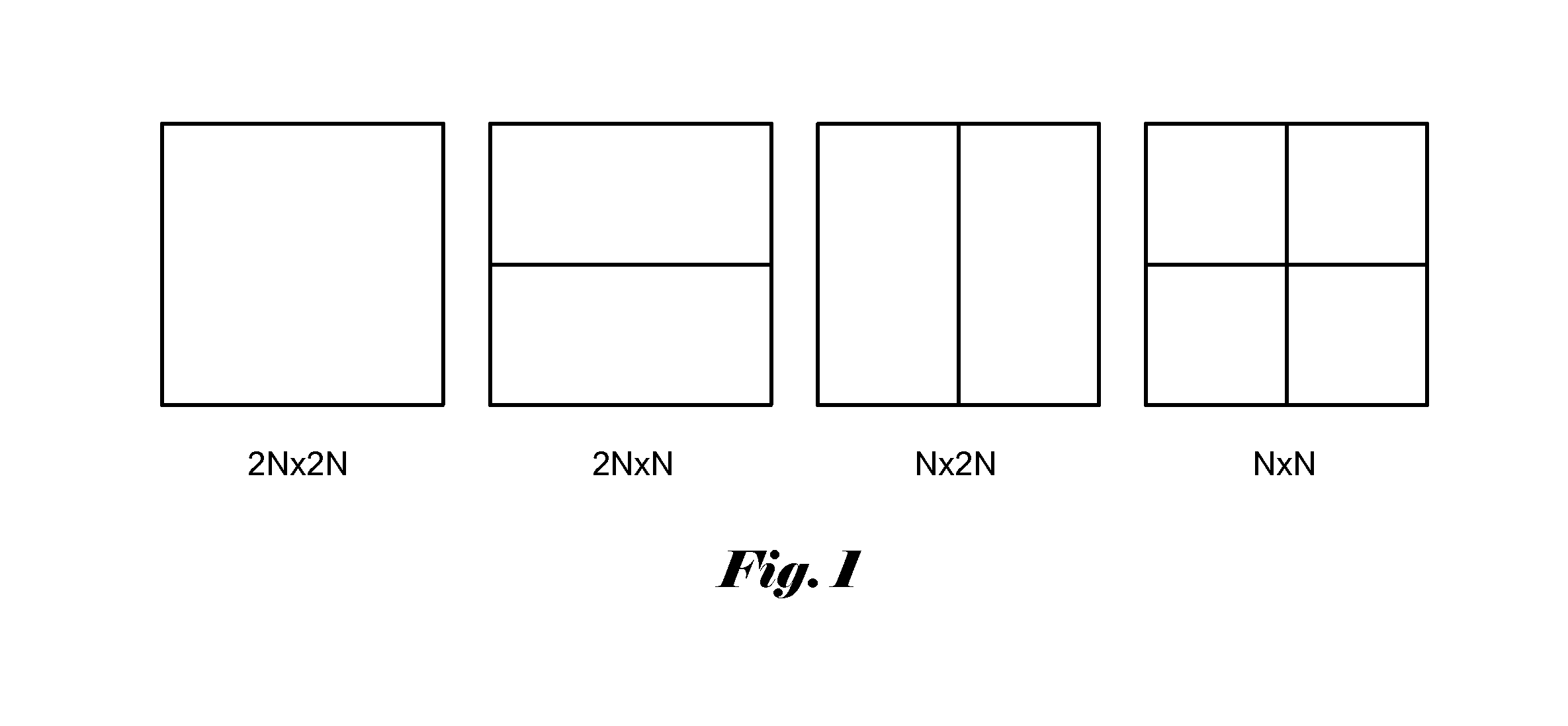

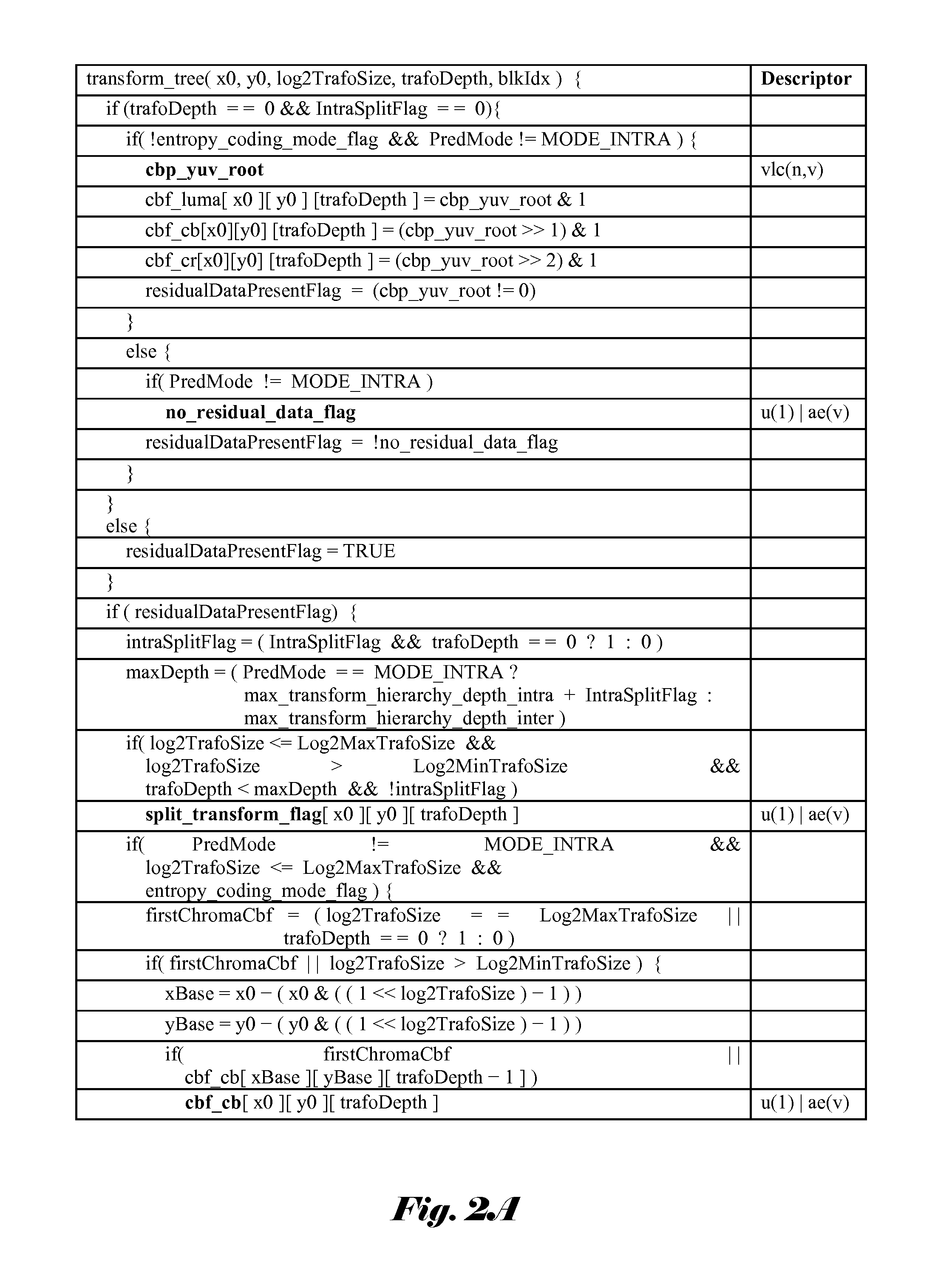

Method and Apparatus of Transform Unit Partition with Reduced Complexity

ActiveUS20120230411A1Reduced encoding computational complexitySmall motion estimation costColor television with pulse code modulationColor television with bandwidth reductionRound complexityMotion vector

Three block concepts are introduced in HEVC: coding unit (CU), prediction unit (PU), and transform unit (TU). The overall coding structure is characterized by the various sizes of CU, PU and TU in a recursive fashion. For transform processing in current HEVC, a hierarchy RQT (Residual Quad Tree) is used and the TU size is related to the CU size, but independent of the PU size. This results in high encoding complexity and also causes increased processing time to process the syntax of residual quad tree. Accordingly a modified transform unit partition with reduced complexity is disclosed. According to an embodiment, the TU size may be restricted to the minimum of PU width and height, except for a 2N×2N coding unit with the 2N×2N partition type. In another embodiment, the maximum TU size equals to maximum of PU width and height, and the minimum TU size equals to minimum of the PU width and height, except for a 2N×2N coding unit with the 2N×2N partition type. In yet another embodiment, the TU size is selected between 2N×2N and N×N for the 2N×2N, 2N×N, N×2N and N×N partition types. The syntax element, split_transform_flag, is used to indicate the selection of 2N×2N or N×N TU size when needed. Furthermore, a method with reduced complexity of selecting the best merge candidate for the 2N×2N CU merge mode is disclosed. The method relies on R-D cost associated with the motion vector of merge candidate to reduce required computation.

Owner:HFI INNOVATION INC

Method and apparatus for controlling semiconductor wafer fabrication equipment based on a remaining process time applicable to the processors

InactiveUS6134482ASemiconductor/solid-state device manufacturingCharge manipulationSemiconductor wafer fabricationSemiconductor

Semiconductor wafer fabrication equipment comprising a selecting device for selecting semiconductor wafers destined to a processor on the basis of a remaining process time applicable to that processor in the equipment, a transporting device for transporting the selected semiconductor wafers to the processor, another selecting device for selecting a processor or a storage device constituting a transport destination to which to transport processed semiconductor wafers, and another transporting device for transporting the semiconductor wafers to the destination processor or storage device in accordance with a transport control changeover code read from the processors and storage devices of the equipment.

Owner:MITSUBISHI ELECTRIC CORP

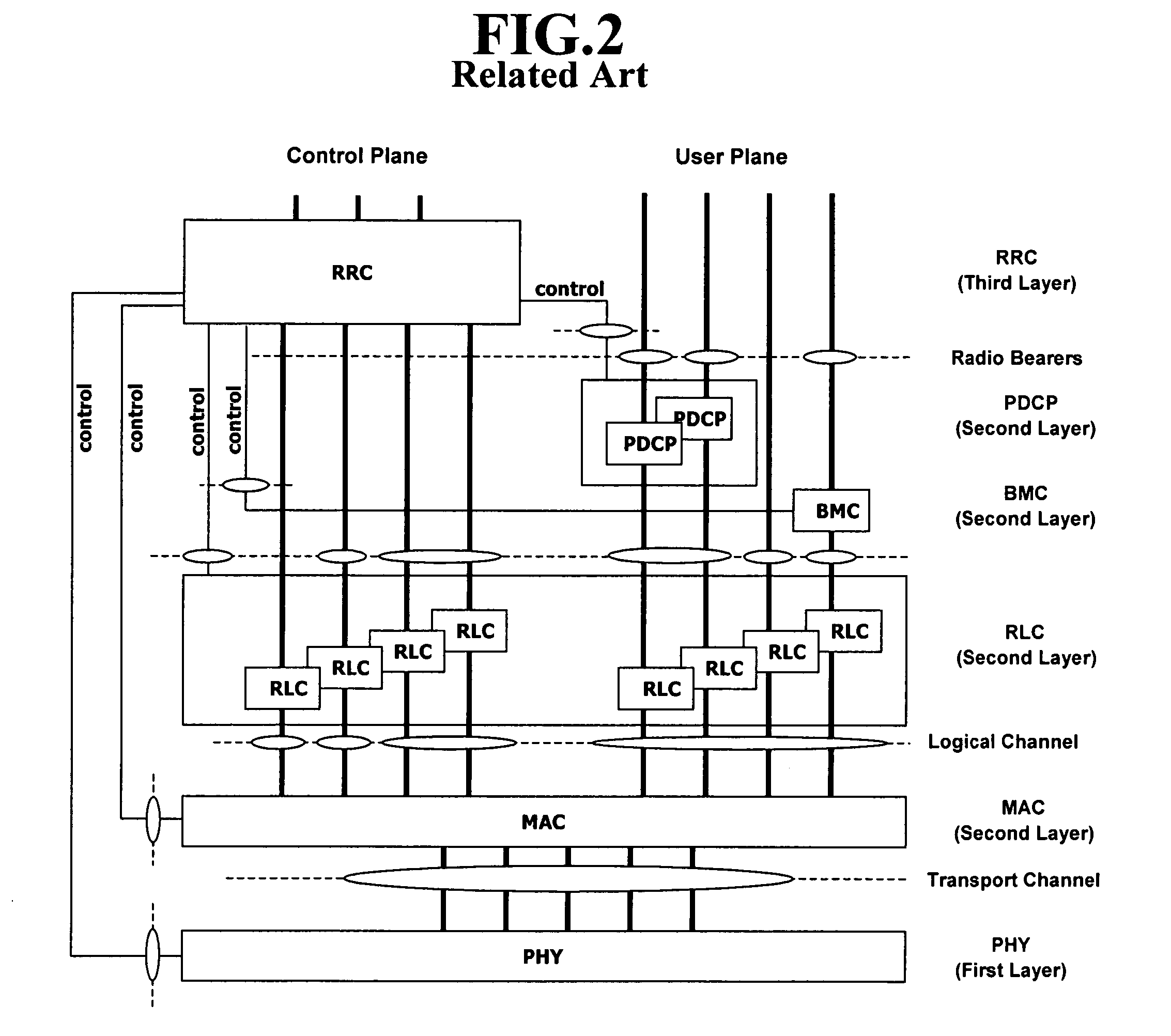

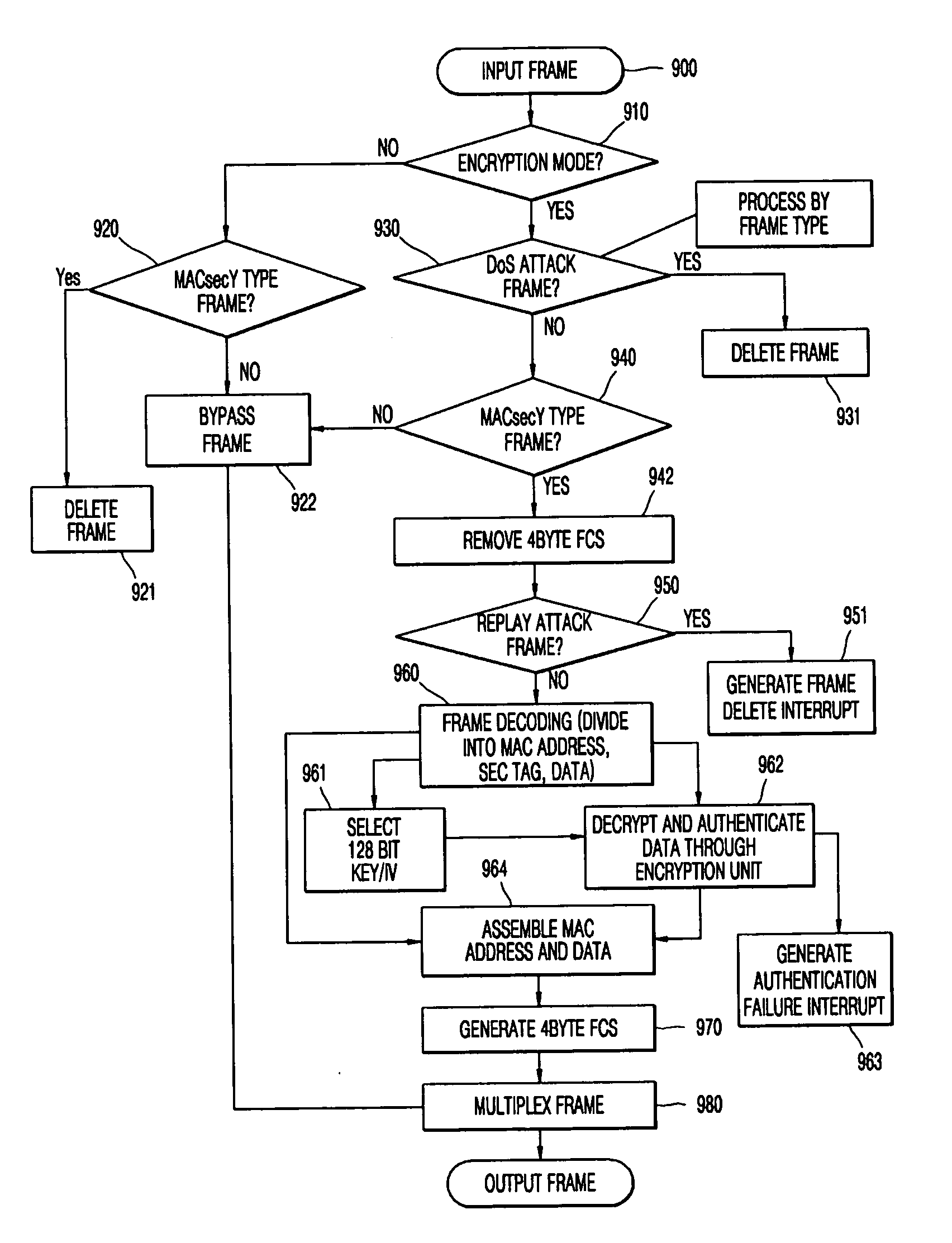

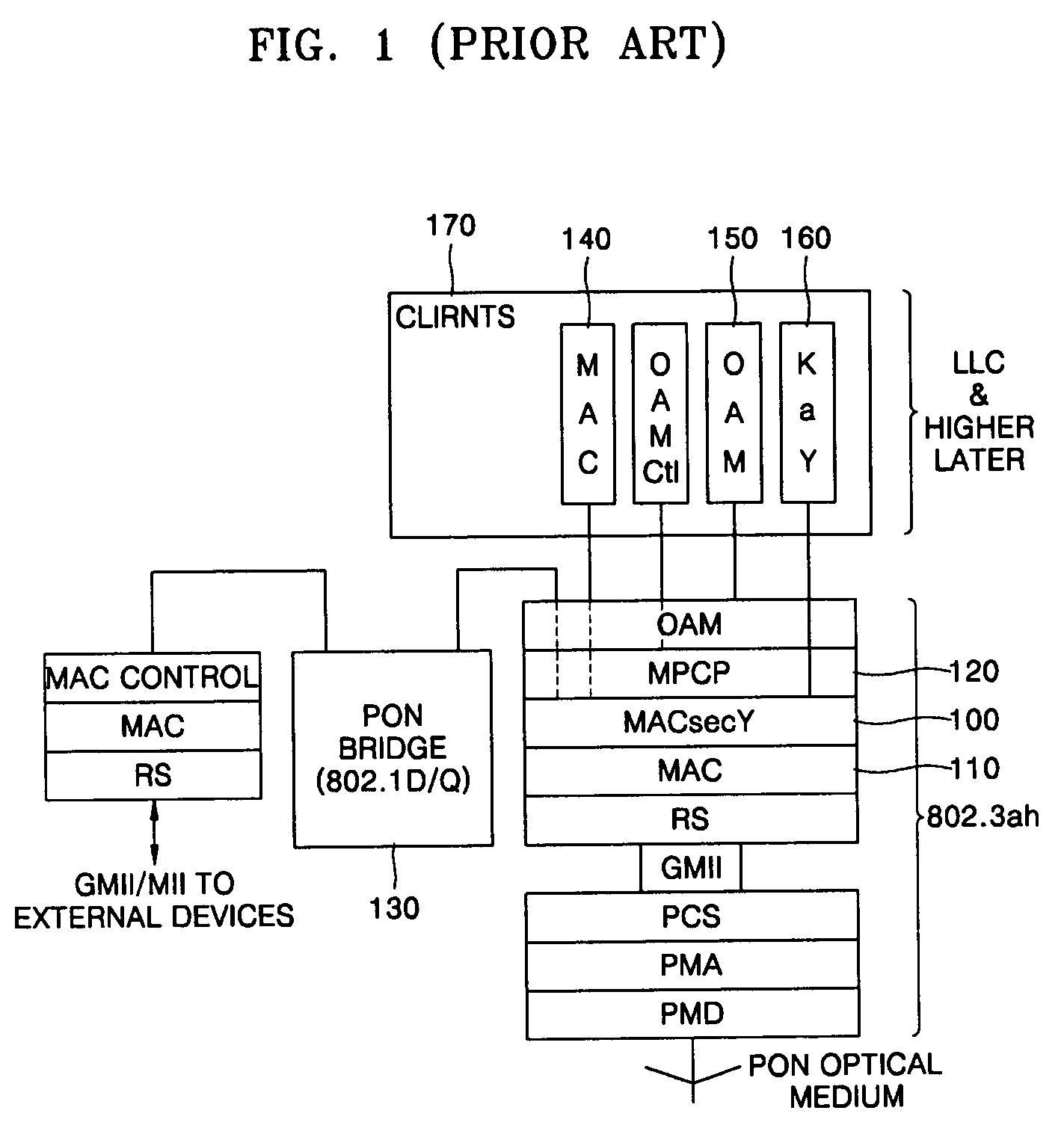

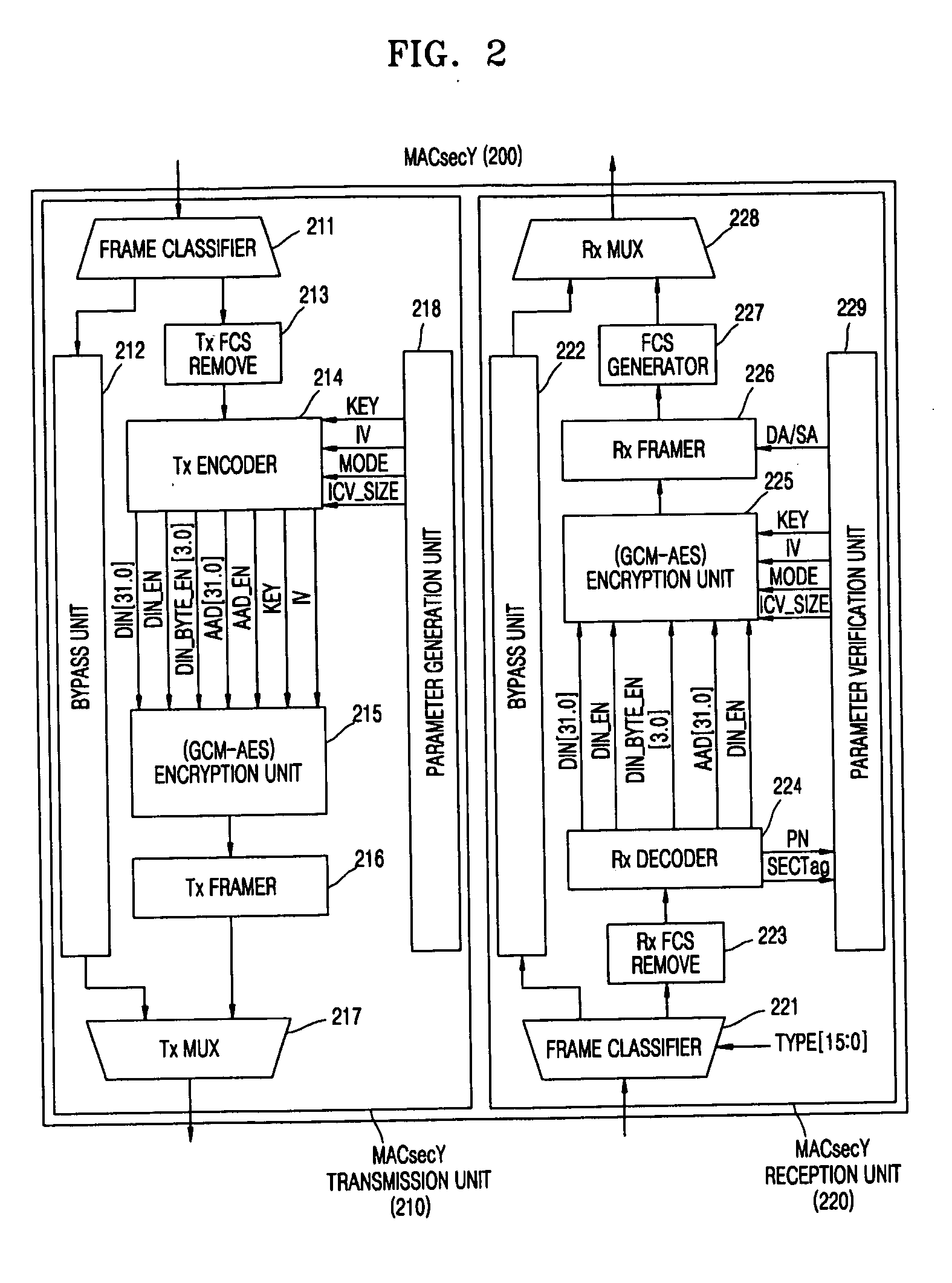

MAC security entity for link security entity and transmitting and receiving method therefor

InactiveUS20060136715A1Memory loss protectionUnauthorized memory use protectionMedia access controlOptical network unit

An apparatus and method for providing a security function of frames transmitted between optical network terminals (OLTs) and optical network units (ONUs) in an Ethernet passive optical network (EPON) providing media access control (MAC) services are provided. The apparatus includes: a frame classifier distinguishing the type of a frame, and based on the logical link identifier (LLID) of the distinguished frame, determining whether or not the frame is a security link to which a security function is to be applied; a bypass unit delaying a no-security-function frame so that a processing time for converting the security-function-applied frame classified in the frame classifier into an encrypted frame is the same as a time for processing the no-security-function frame; and a parameter generation unit transmitting in relation to each of the LLIDs, a parameter set value including a security-function-application setting signal used in the encryption, decryption and authentication of the frame, a frame decryption signal, an encryption mode selection signal, and an authentication intensity adjustment signal.

Owner:ELECTRONICS & TELECOMM RES INST

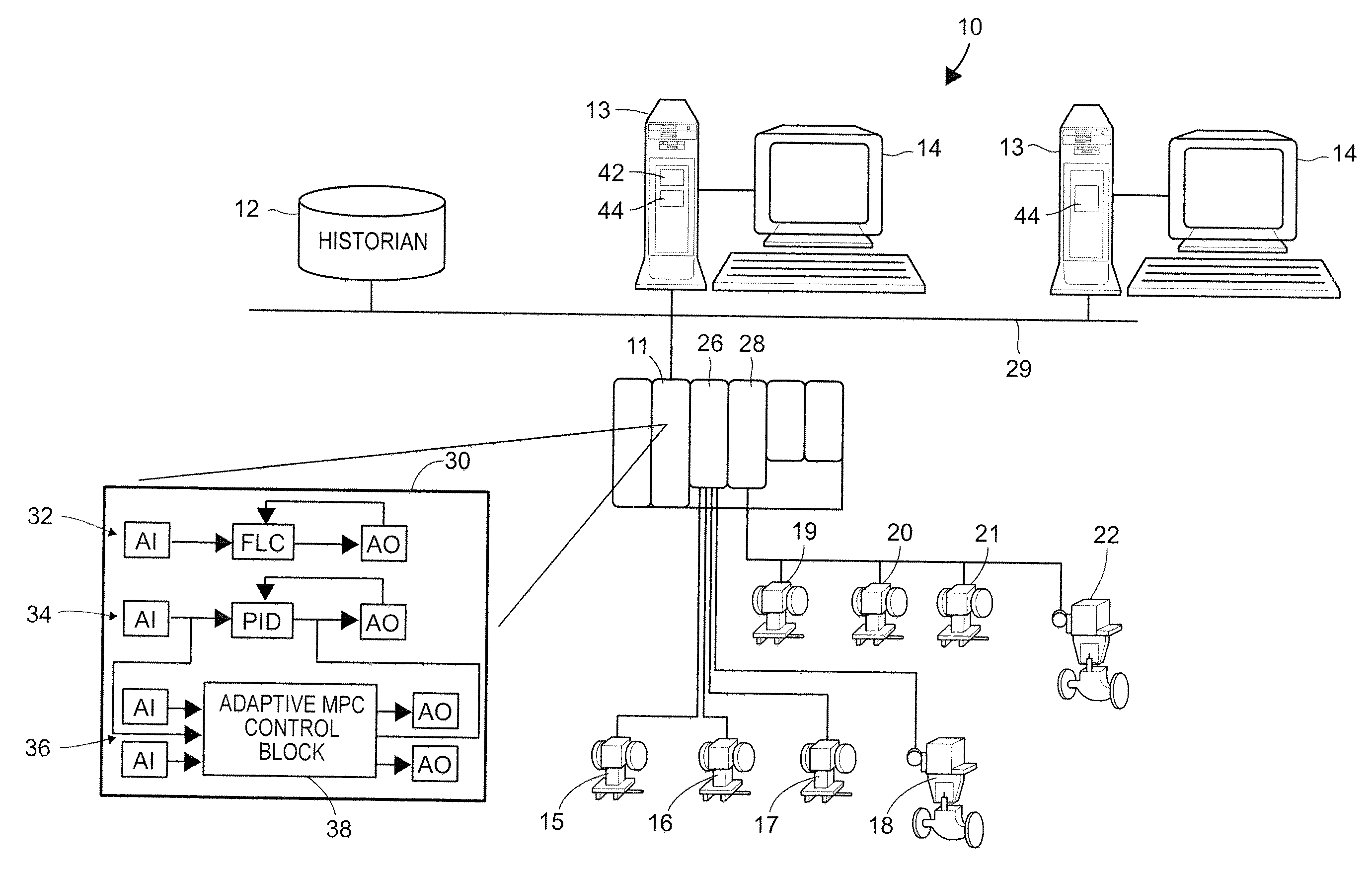

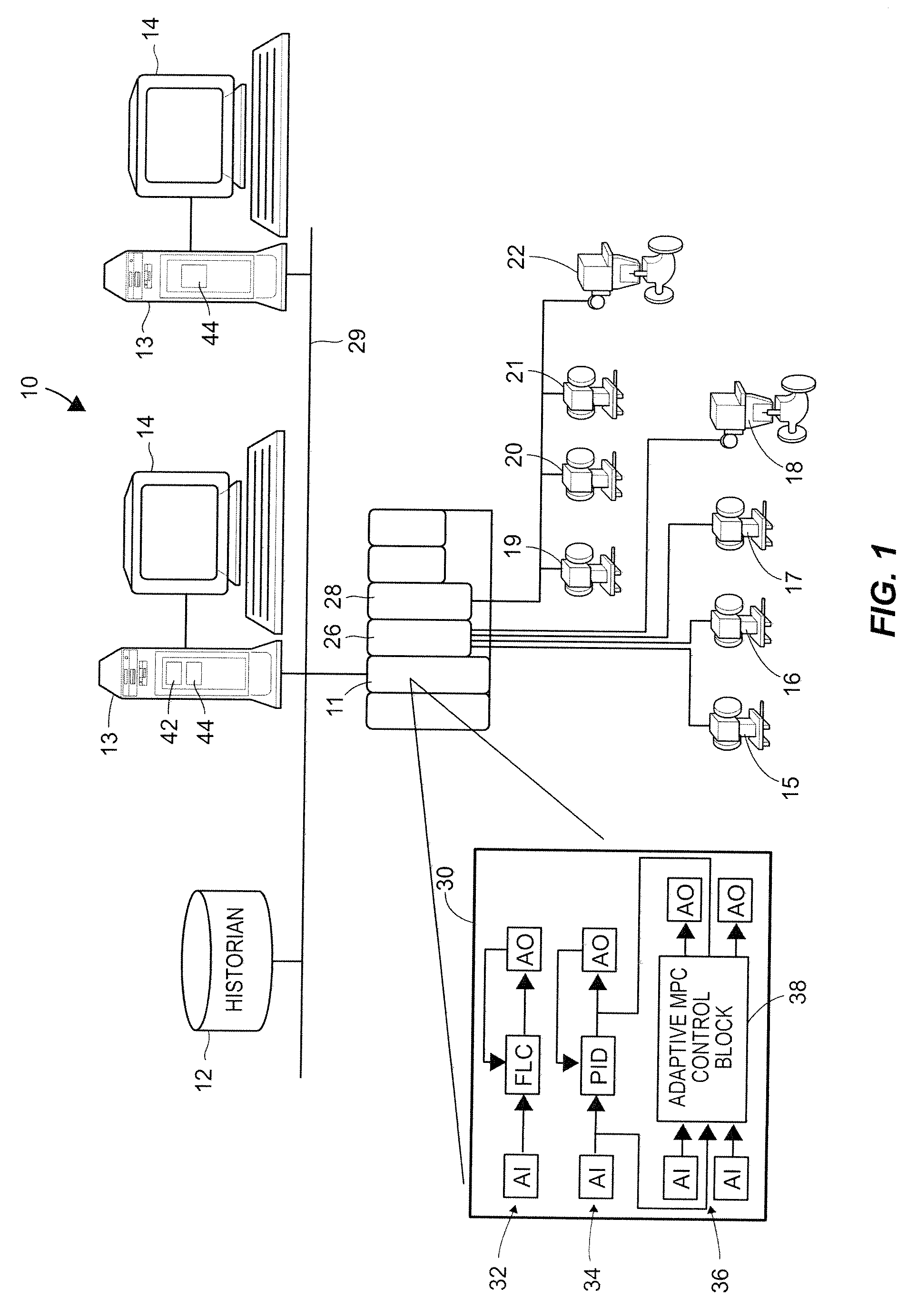

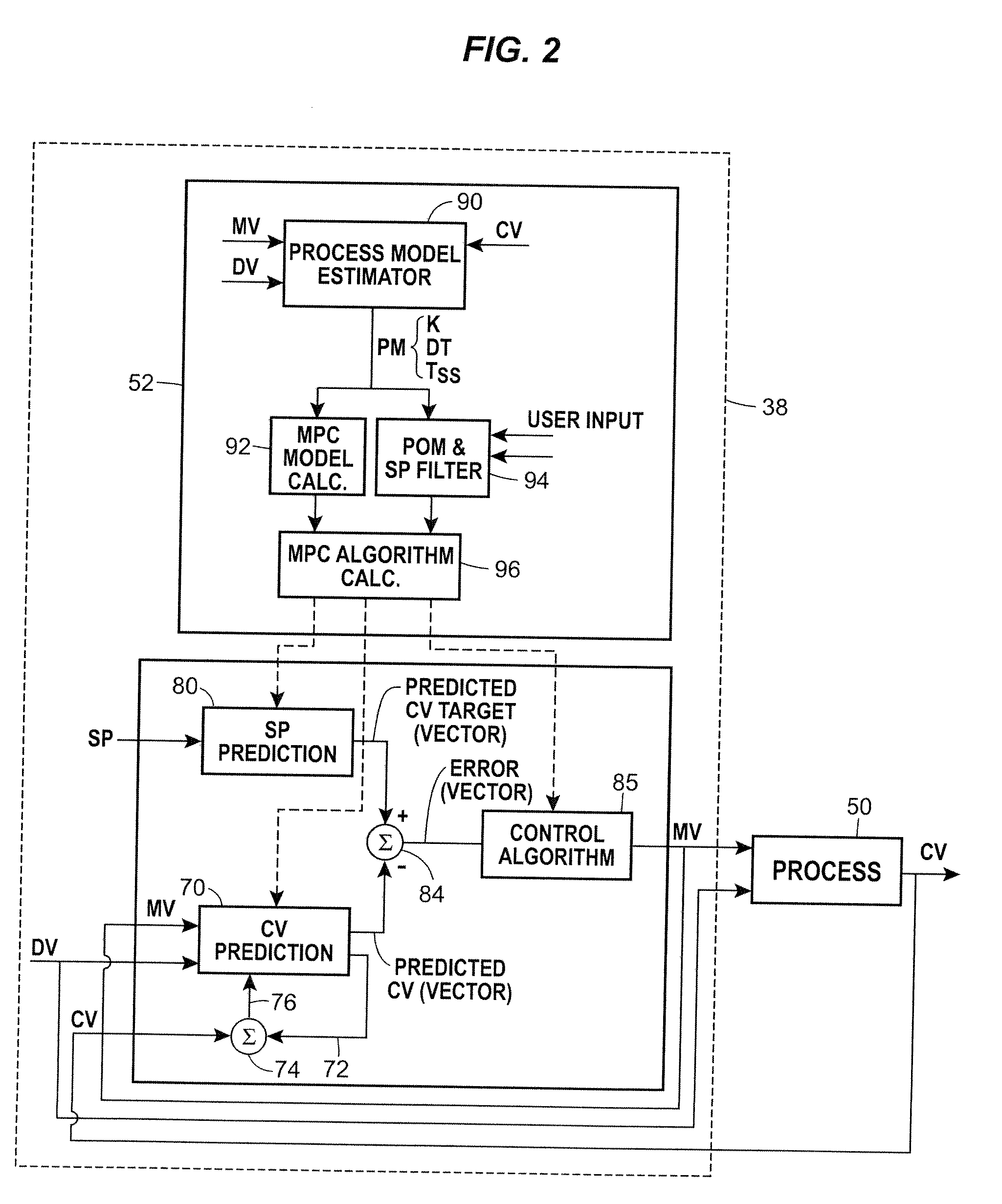

On-line adaptive model predictive control in a process control system

A method of creating and using an adaptive DMC type or other MPC controller includes using a model switching technique to periodically determine a process model, such as a parameterized process model, for a process loop on-line during operation of the process. The method then uses the process model to generate an MPC control model and creates and downloads an MPC controller algorithm to an MPC controller based on the new control model while the MPC controller is operating on-line. This technique, which is generally applicable to single-loop MPC controllers and is particularly useful in MPC controllers with a control horizon of one or two, enables an MPC controller to be adapted during the normal operation of the process, so as to change the process model on which the MPC controller is based to thereby account for process changes. The adaptive MPC controller is not computationally expensive and can therefore be easily implemented within a distributed controller of a process control system, while providing the same or in some cases better control than a PID controller, especially in dead time dominant process loops, and in process loops that are subject to process model mismatch within the process time to steady state.

Owner:FISHER-ROSEMOUNT SYST INC

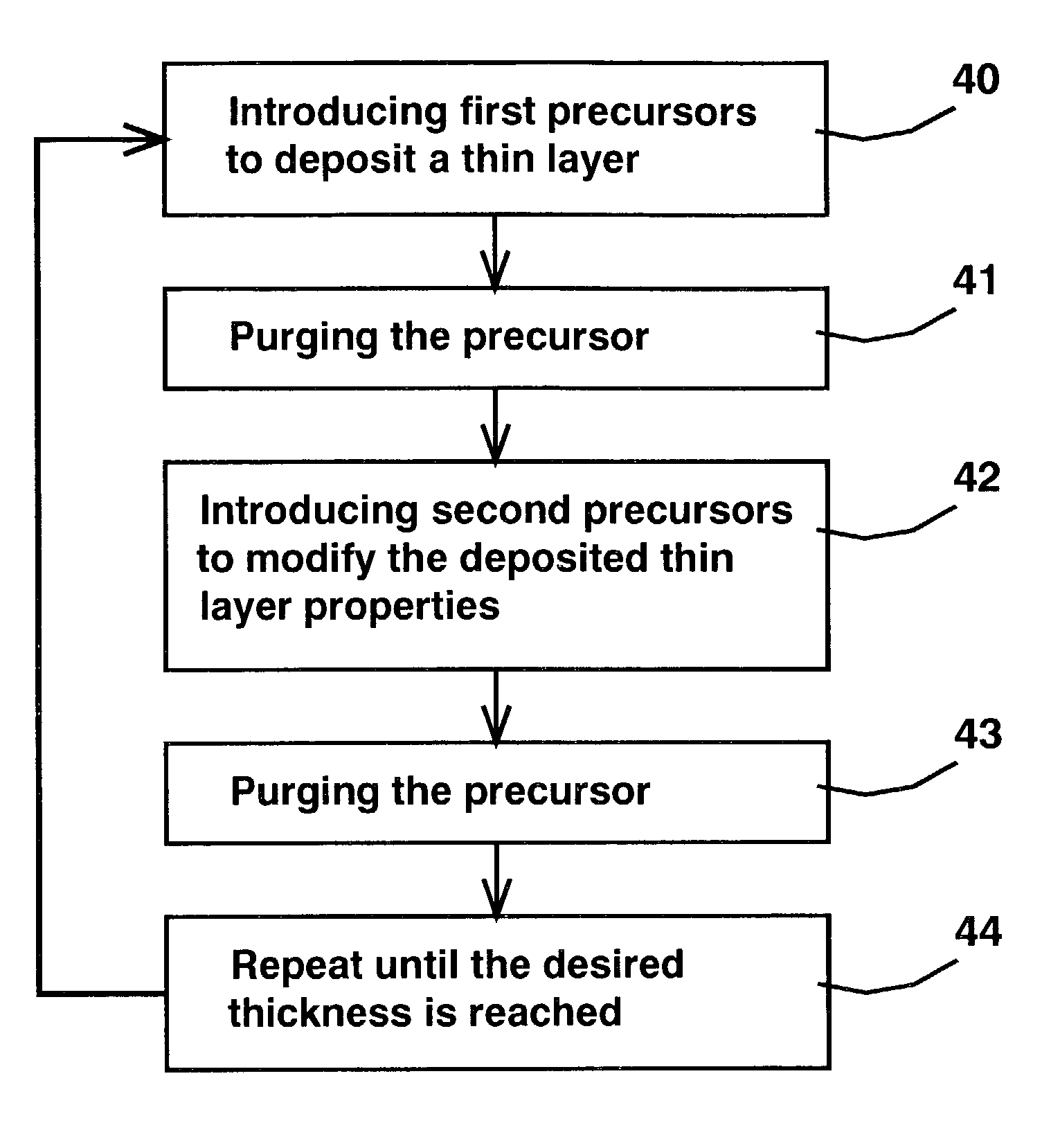

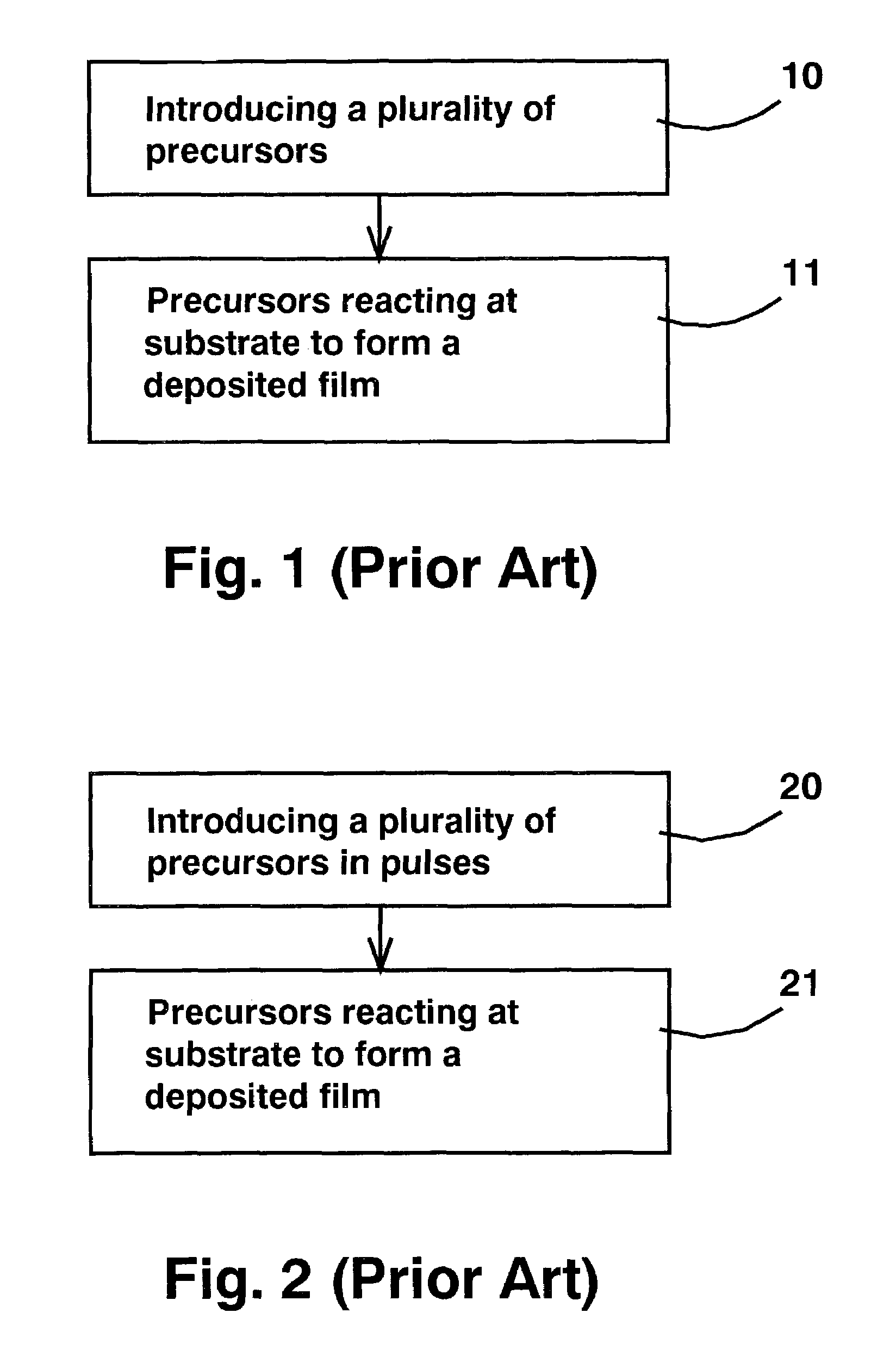

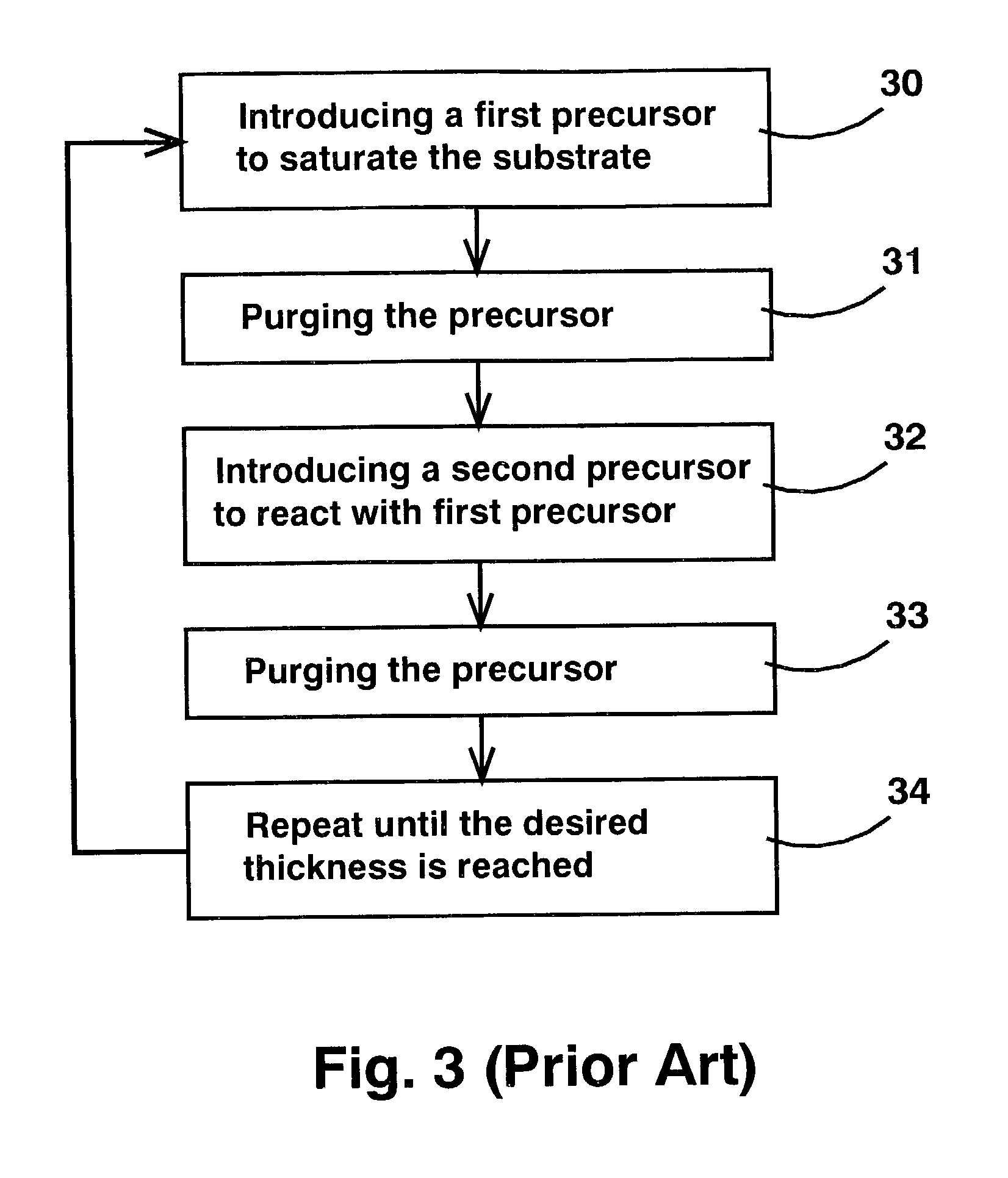

Nanolayer deposition process

InactiveUS7713592B2High energyIncrease powerMaterial nanotechnologyLiquid/solution decomposition chemical coatingSelf limitingDeposition process

A hybrid deposition process of CVD and ALD, called NanoLayer Deposition (NLD) is provided. The nanolayer deposition process is a cyclic sequential deposition process, comprising the first step of introducing a first plurality of precursors to deposit a thin film with the deposition process not self limiting, then a second step of purging the first set of precursors and a third step of introducing a second plurality of precursors to modify the deposited thin film. The deposition step in the NLD process using the first set of precursors is not self limiting and is a function of substrate temperature and process time. The second set of precursors modifies the already deposited film characteristics. The second set of precursors can treat the deposited film such as a modification of film composition, a doping or a removal of impurities from the deposited film. The second set of precursors can also deposit another layer on the deposited film. The additional layer can react with the existing layer to form a compound layer, or can have minimum reaction to form a nanolaminate film.

Owner:ASM INTERNATIONAL

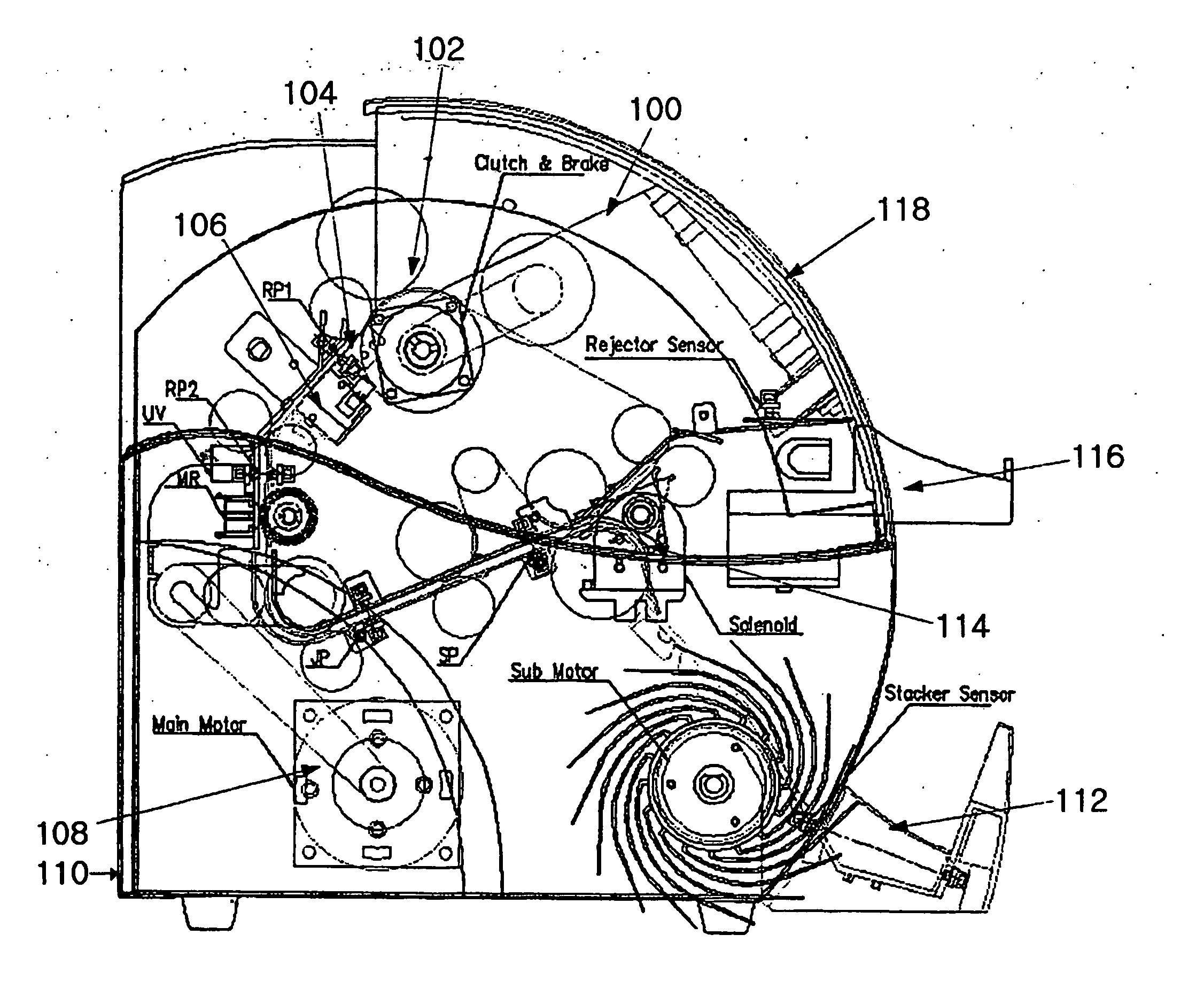

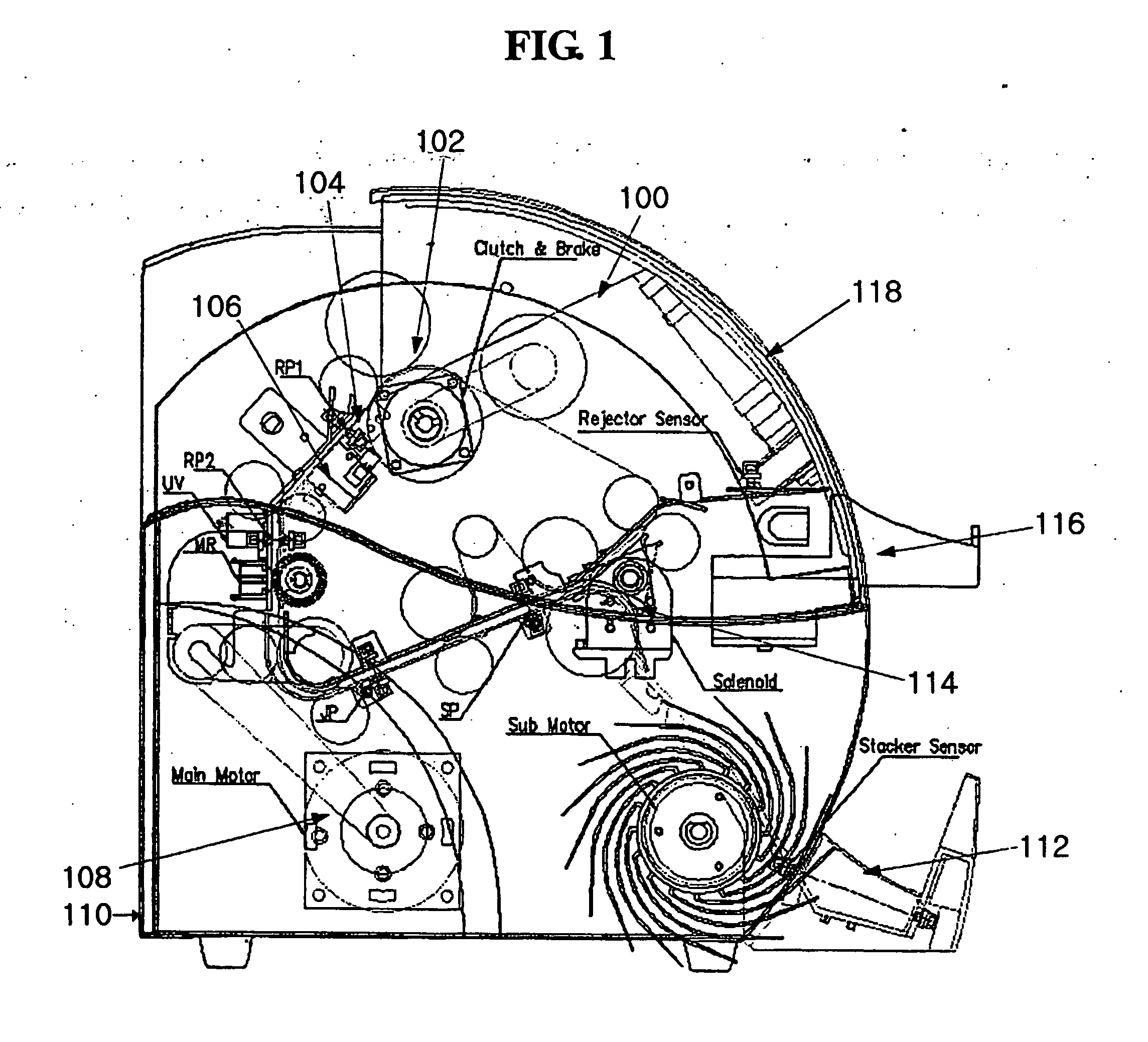

Apparatus for currency calculation which can extract serial number and method for the same

InactiveUS20060054454A1Paper-money testing devicesCounting objects on conveyorsTemporal informationPayment

The present invention relates generally to an apparatus and method for counting currency notes, and more particularly, to an apparatus and method that automatically feed and count a plurality of currency notes, recognize the denominations thereof by reading the images thereof, and extract, store and output the serial numbers thereof. In accordance with the present invention, it is possible to database apparatus-related information, such as the denominations, serial numbers, amounts, serial number region images, and installation locations of continuously fed currency notes, together with processed time information, and to effectively use the currency note counting apparatus in receipt / payment management through the management of the serial numbers of currency notes.

Owner:SHIN WOO INFORMATION & TELECOMM

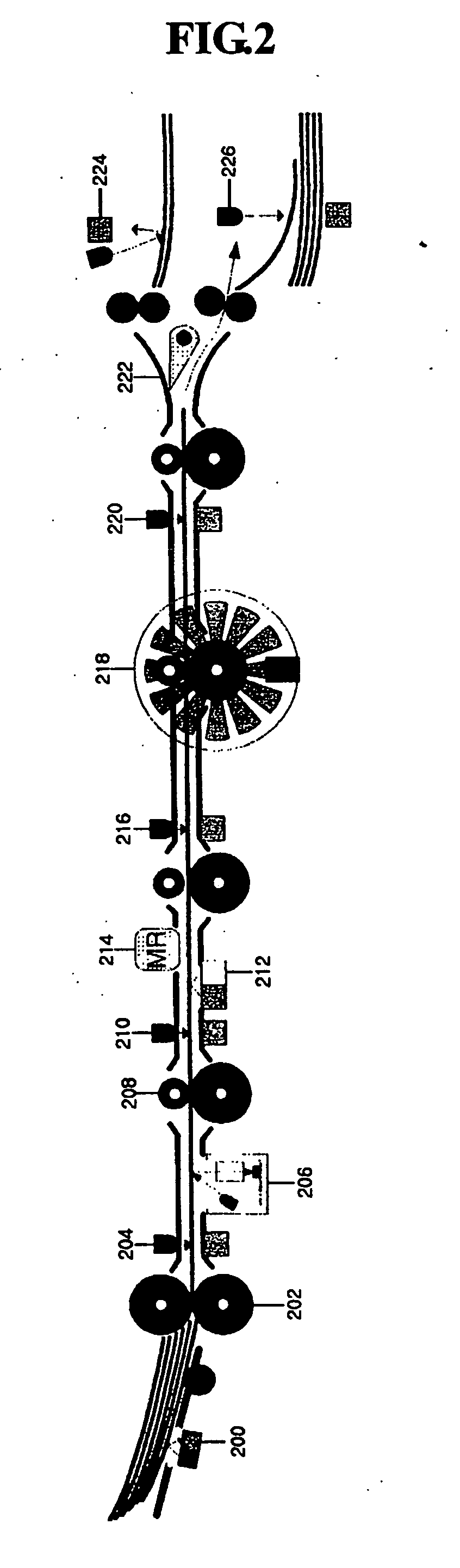

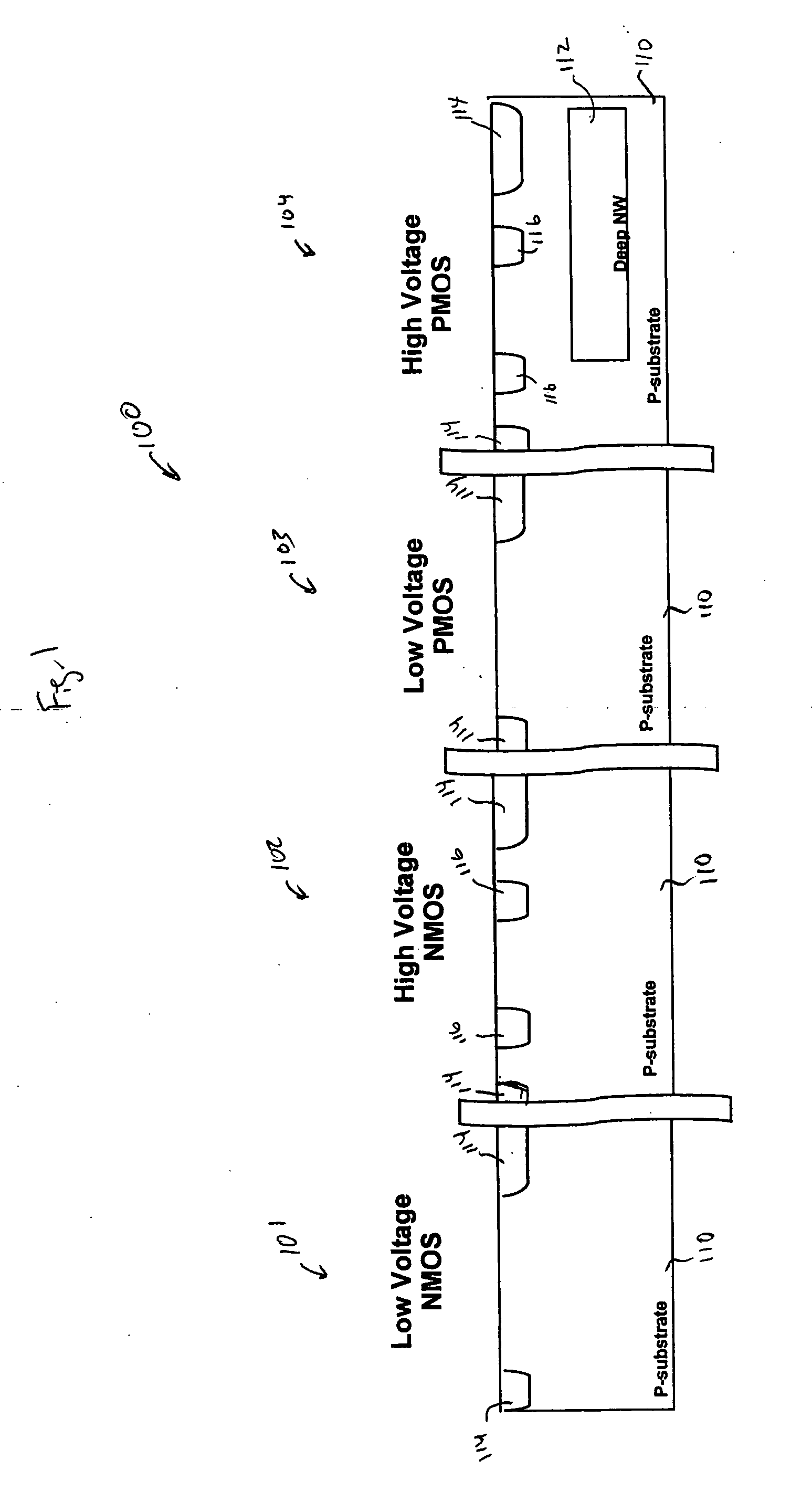

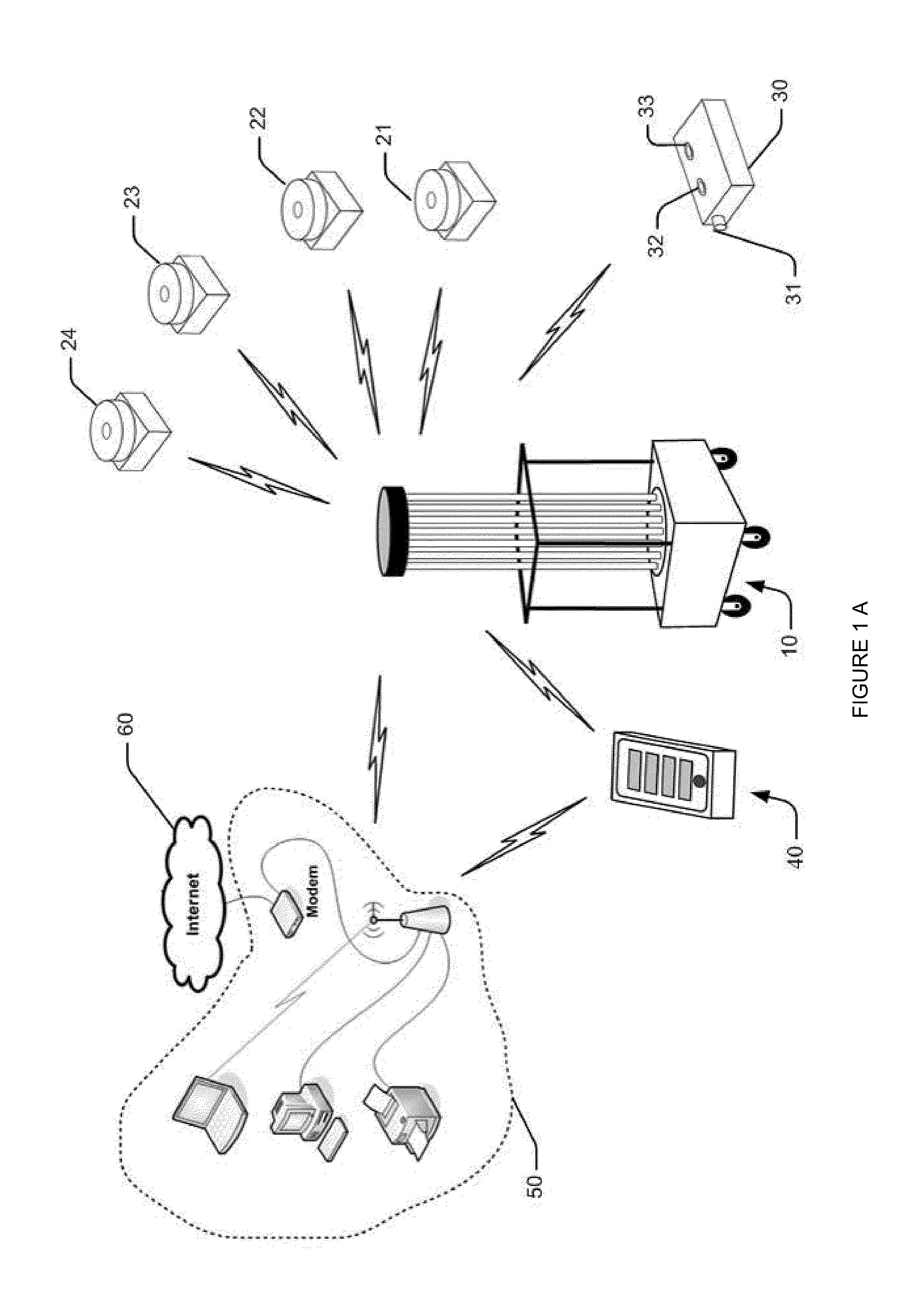

High voltage CMOS devices

A transistor suitable for high-voltage applications is provided. The transistor is formed on a substrate having a deep well of a first conductivity type. A first well of the first conductivity type and a second well of a second conductivity type are formed such that they are not immediately adjacent each other. The well of the first conductivity type and the second conductivity type may be formed simultaneously as respective wells for low-voltage devices. In this manner, the high-voltage devices may be formed on the same wafer as low-voltage devices with fewer process steps, thereby reducing costs and process time. A doped isolation well may be formed adjacent the first well on an opposing side from the second well to provide further device isolation.

Owner:TAIWAN SEMICON MFG CO LTD

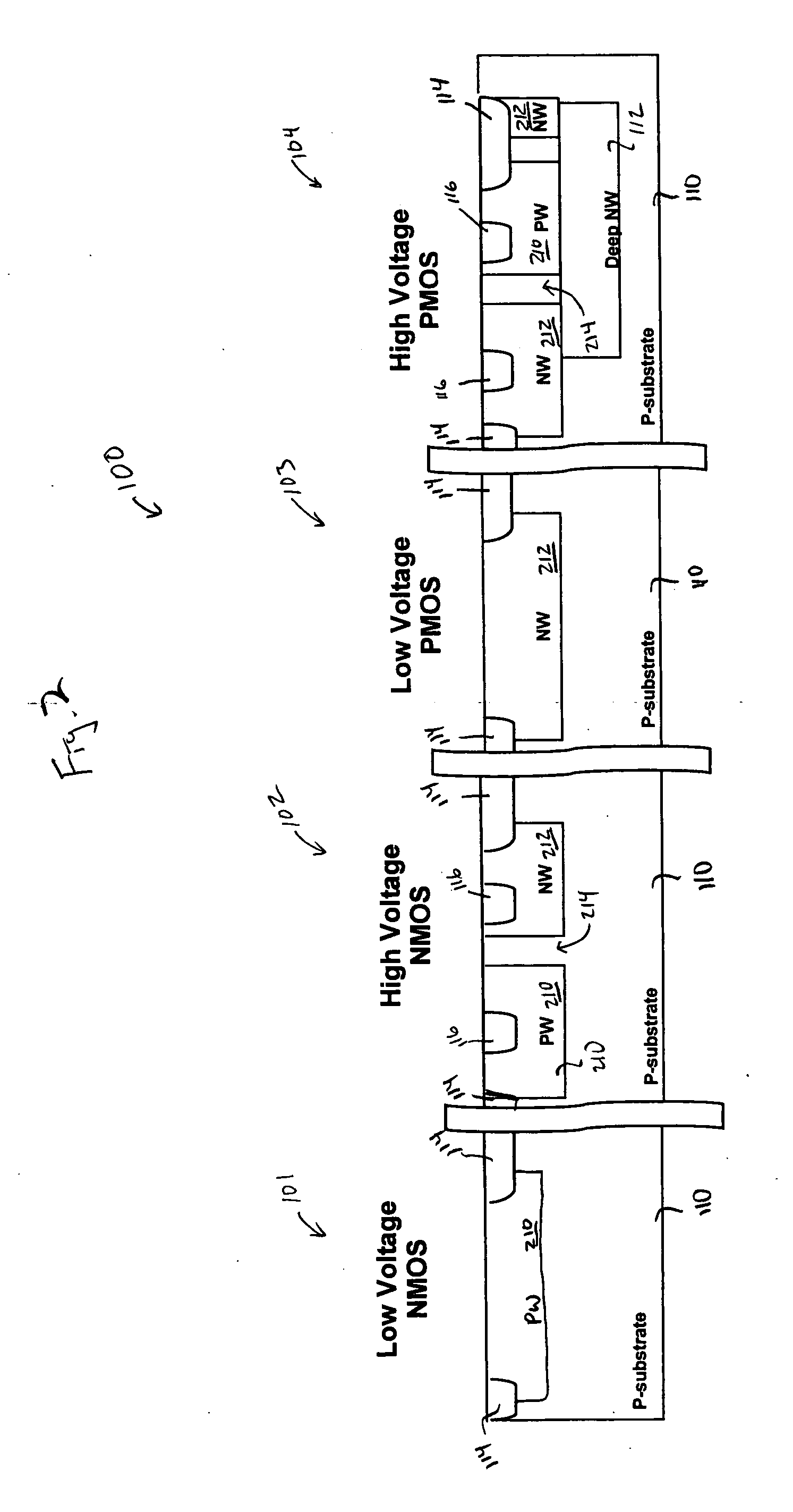

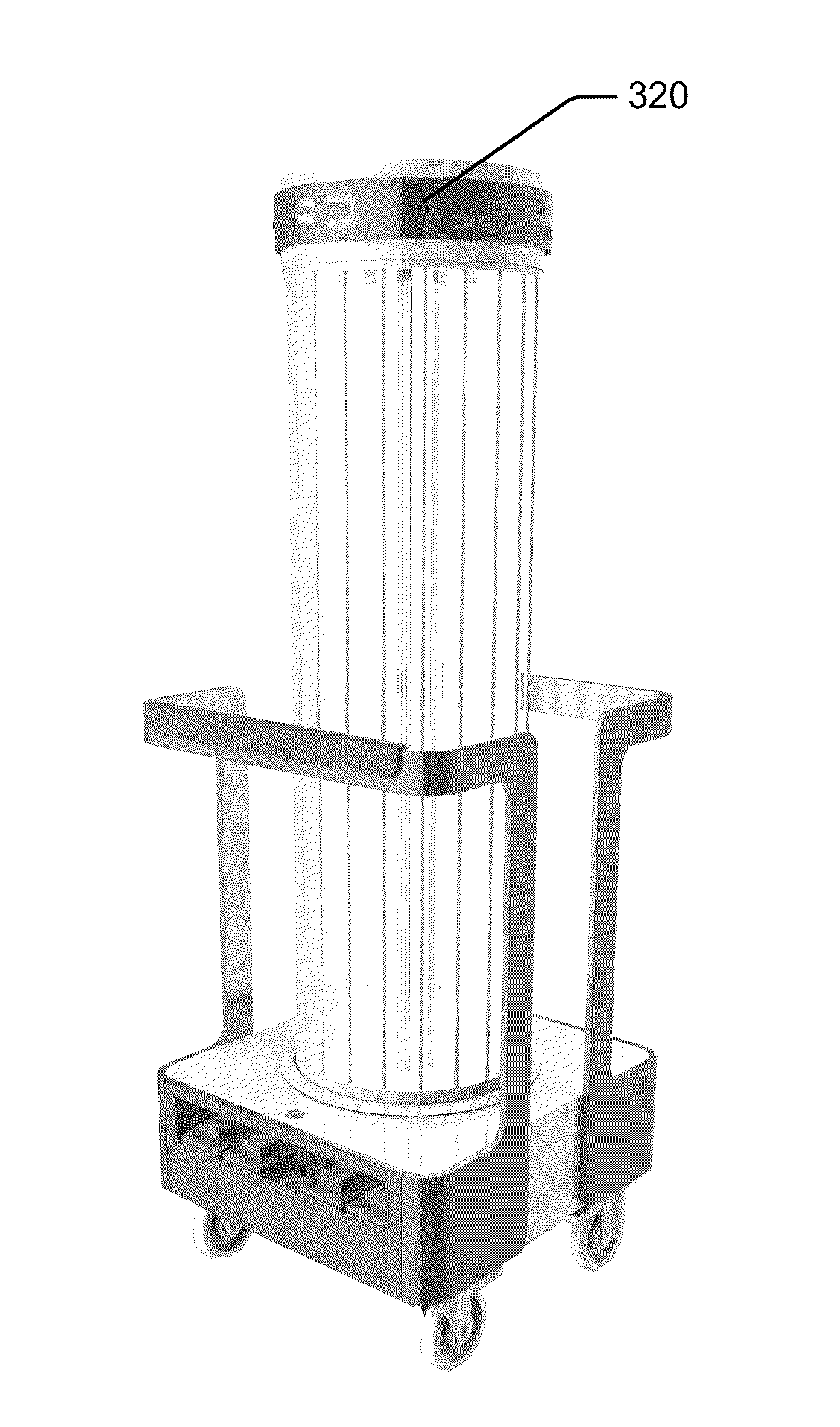

Room sterilization method and system

ActiveUS20150086420A1Environment safetyFaster processing-timeMaterial analysis by optical meansLavatory sanitoryRemote controlPassword

A sterilization system consisting of a mobile emitter, a sensing subsystem and a data logging subsystem is described. The emitter has one or more UV emitting lamps or devices. The sensing system comprises at least one remote UV sensor and at least one door sensor. The door sensor comprises a safety shut off door detector and may contain an emergency stop detector and arming detector to protect people from being exposed to UV energy. The system has a remote control for starting, stopping and setting system parameters which include but are not limited to: treatment time, dosage, room size, room number, unit number, floor, facility name, operator name, operator identification number, password, default dosage values, dosage, and patient identification number. The number of treatments per unit of time can be maximized because of the use of incident light measurement.

Owner:STERILIZ

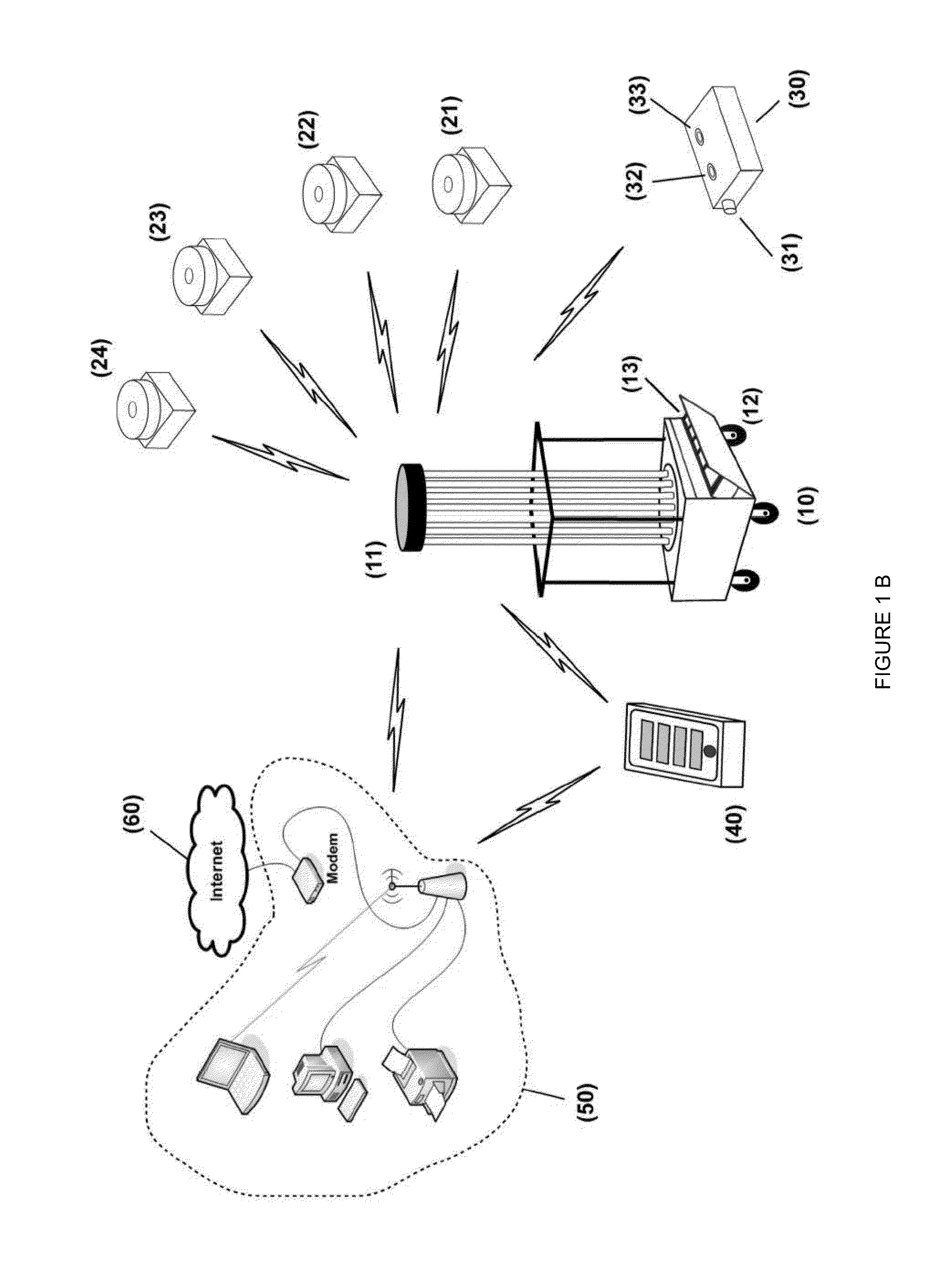

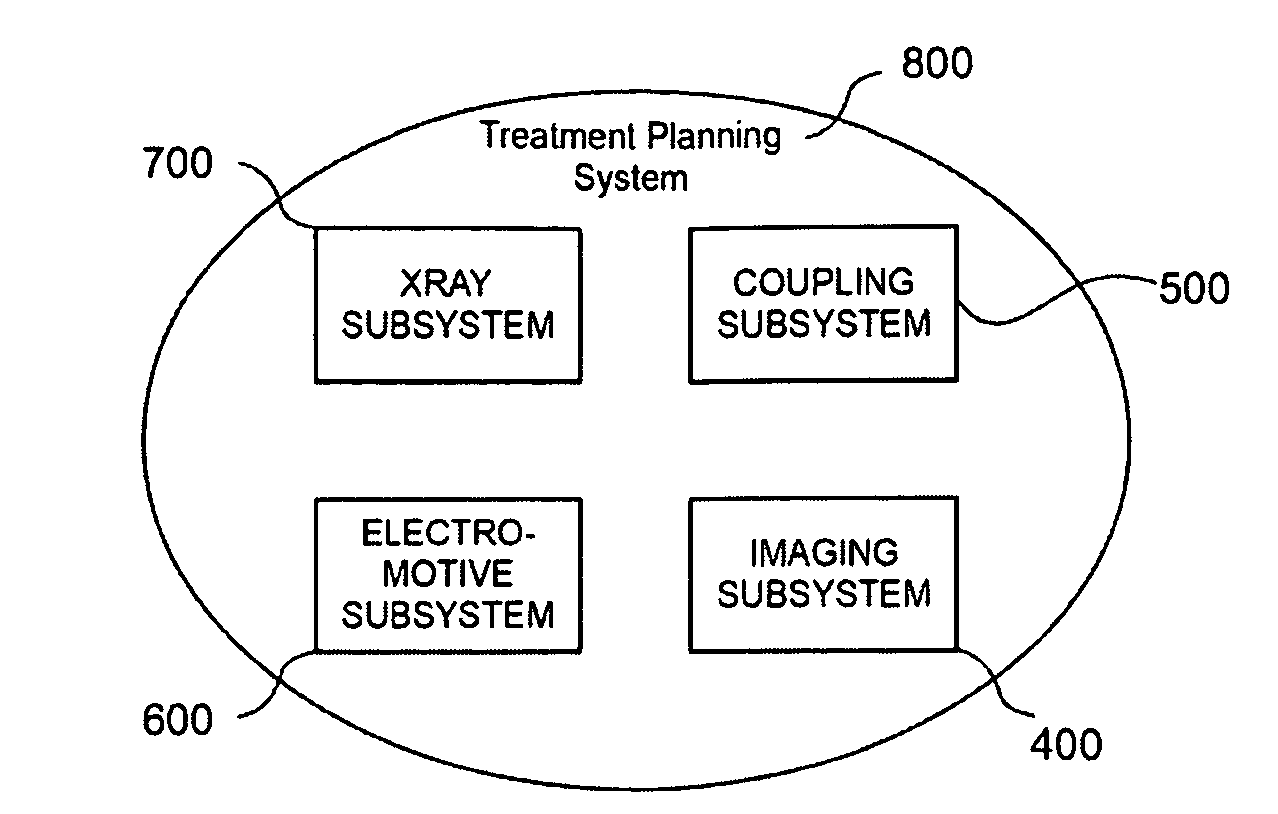

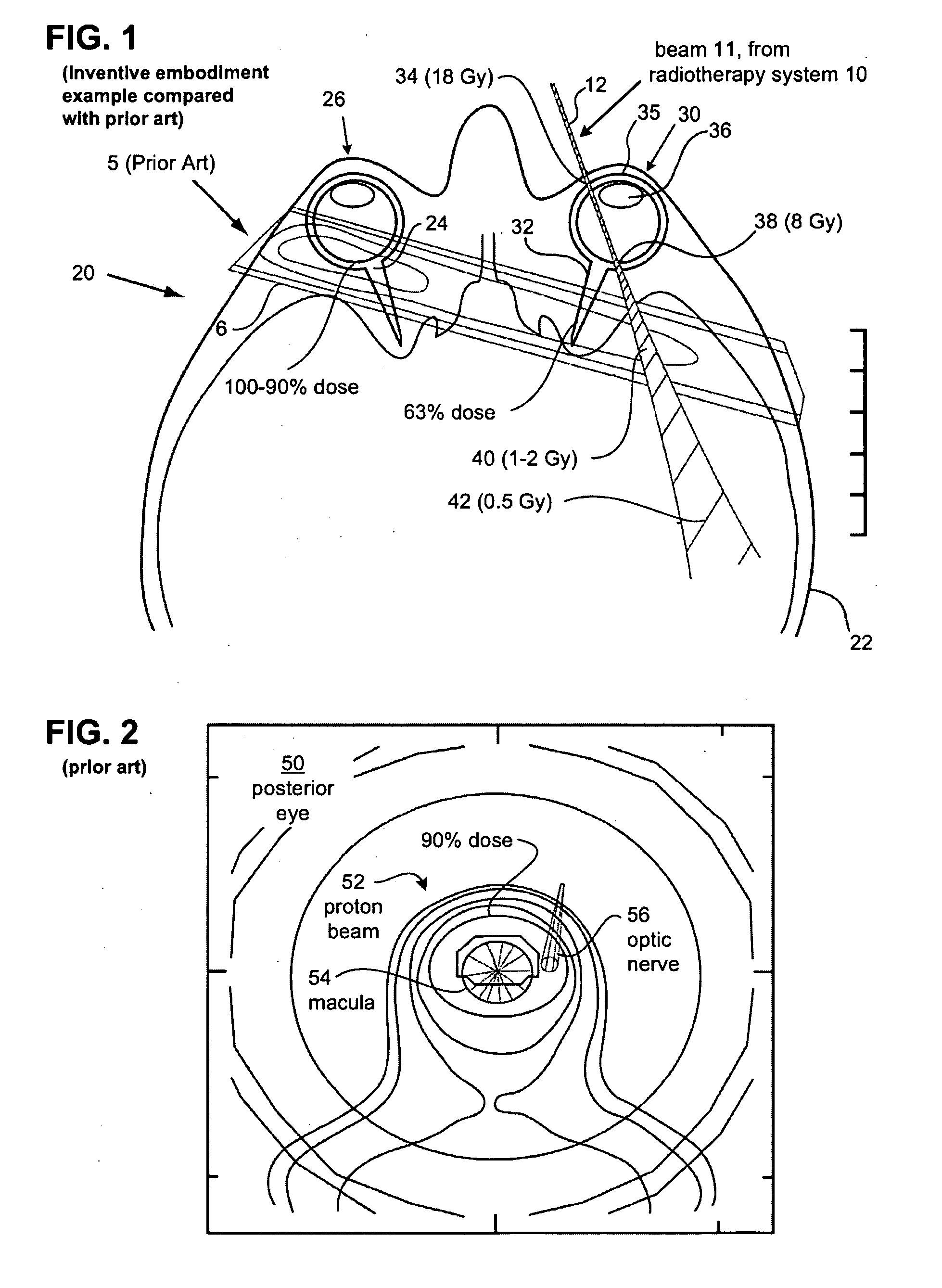

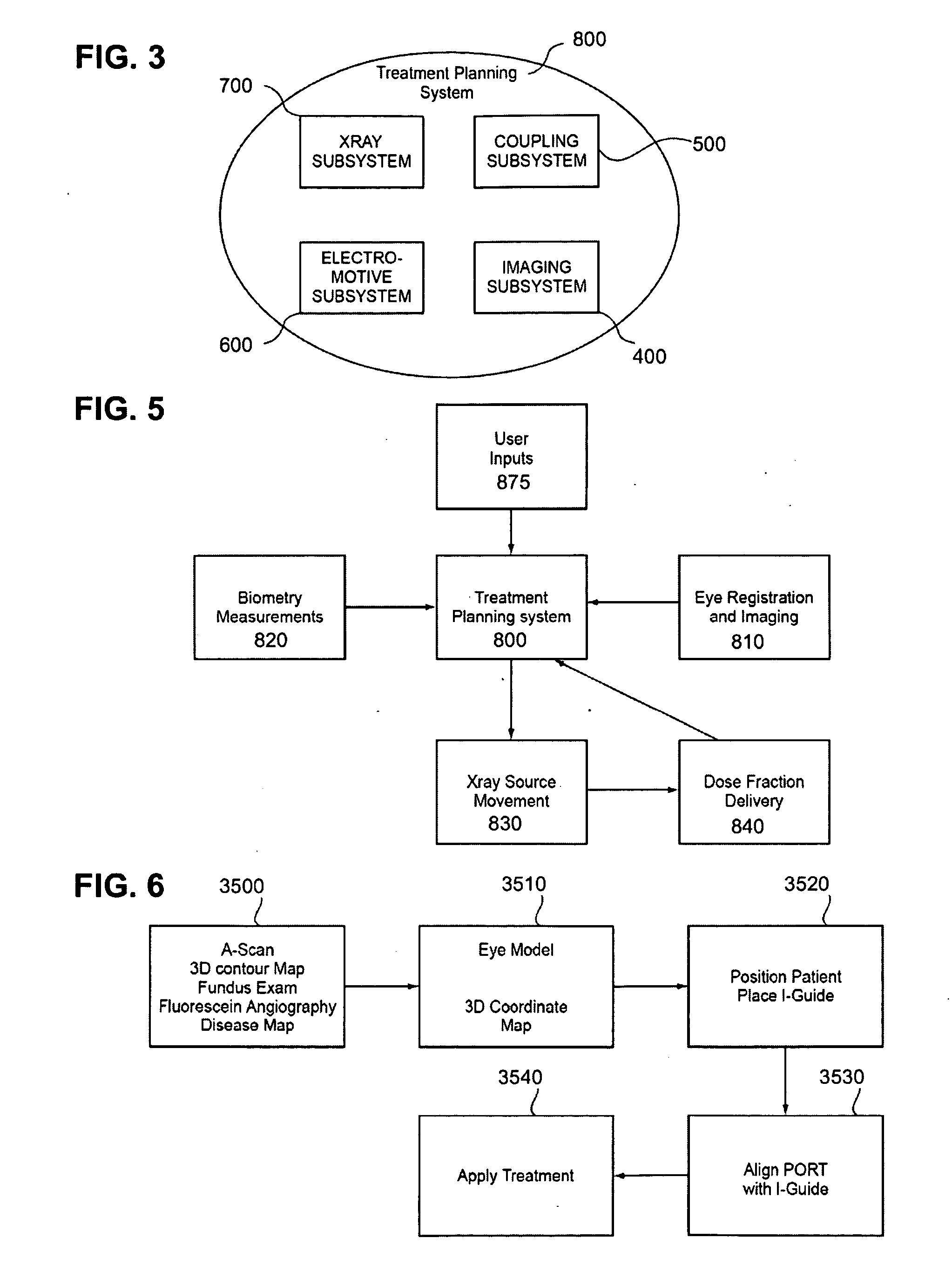

Methods and devices for orthovoltage ocular radiotherapy and treatment planning

ActiveUS20090161826A1Reduce eye motionEfficient relationshipSurgical instrument detailsX-ray/gamma-ray/particle-irradiation therapyX-rayDose level

A method, code and system for planning the treatment a lesion on or adjacent to the retina of an eye of a patient are disclosed. There is first established at least two beam paths along which x-radiation is to be directed at the retinal lesion. Based on the known spectral and intensity characteristics of the beam, a total treatment time for irradiation along each beam paths is determined. From the coordinates of the optic nerve in the aligned eye position, there is determined the extent and duration of eye movement away from the aligned patient-eye position in a direction that moves the patient's optic nerve toward the irradiation beam that will be allowed during treatment, while still maintaining the radiation dose at the patient optic nerve below a predetermined dose level.

Owner:CARL ZEISS MEDITEC INC

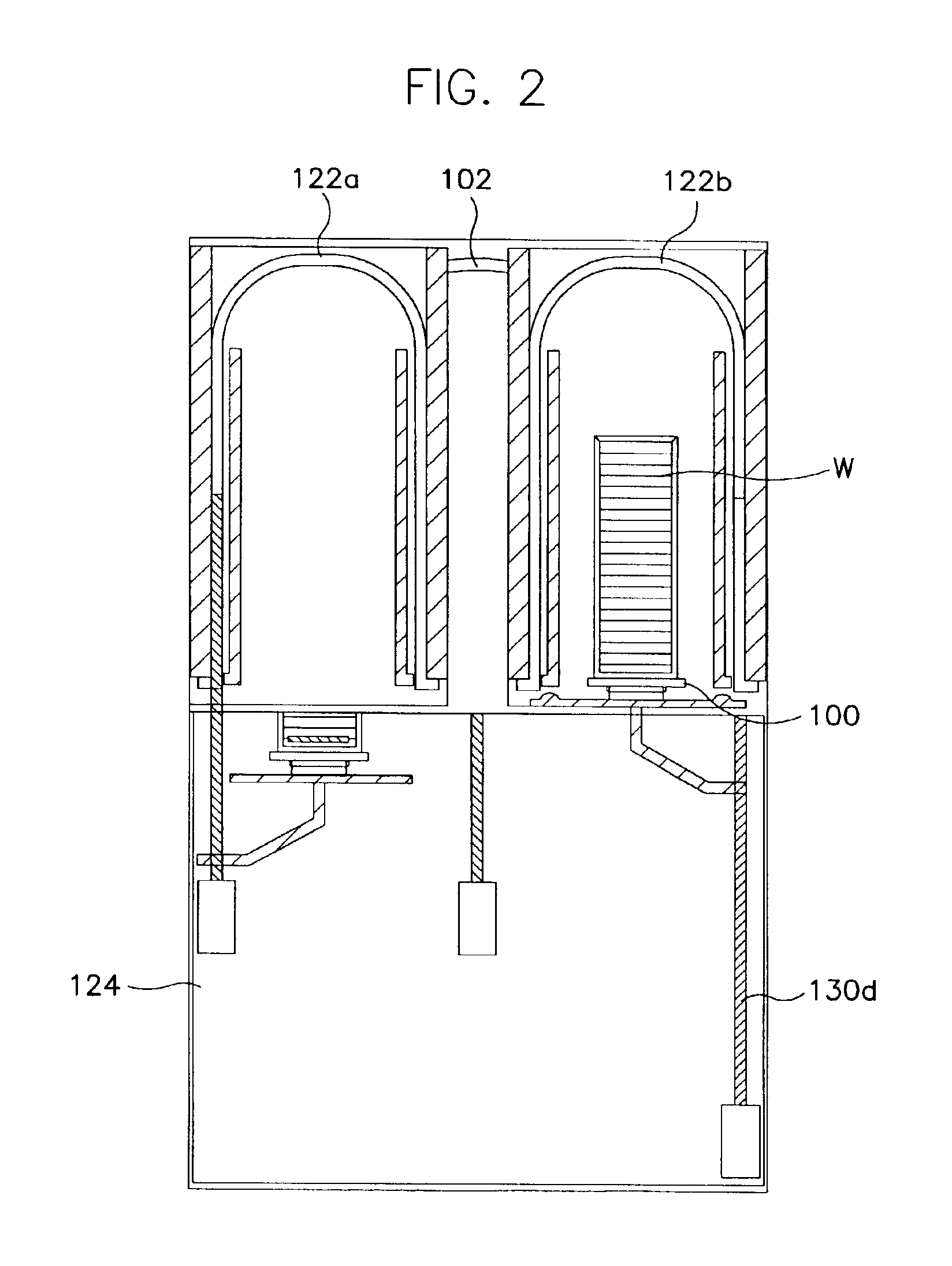

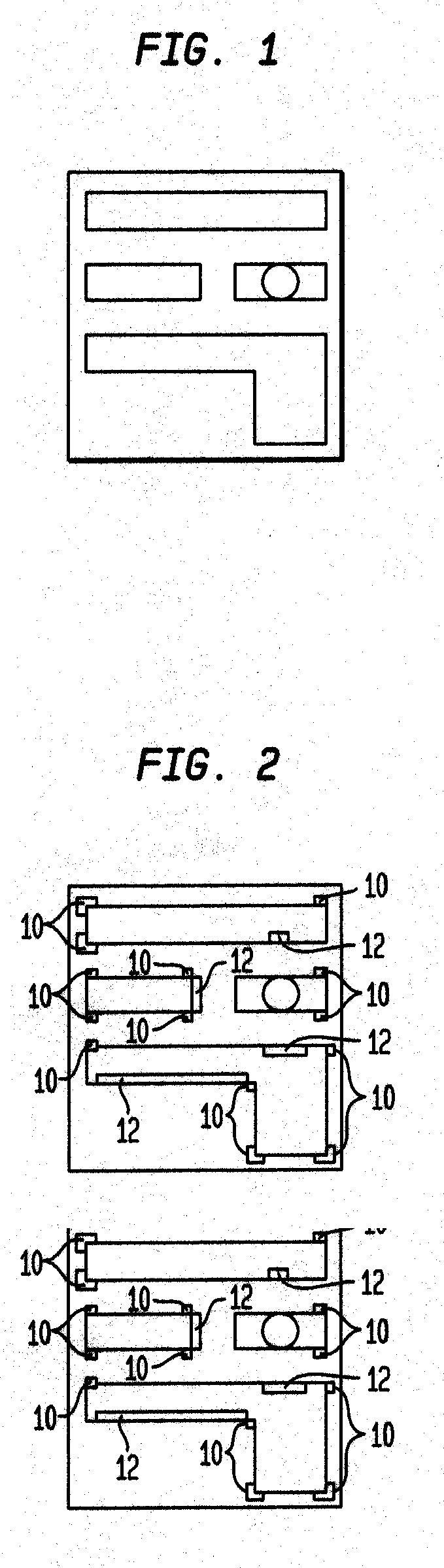

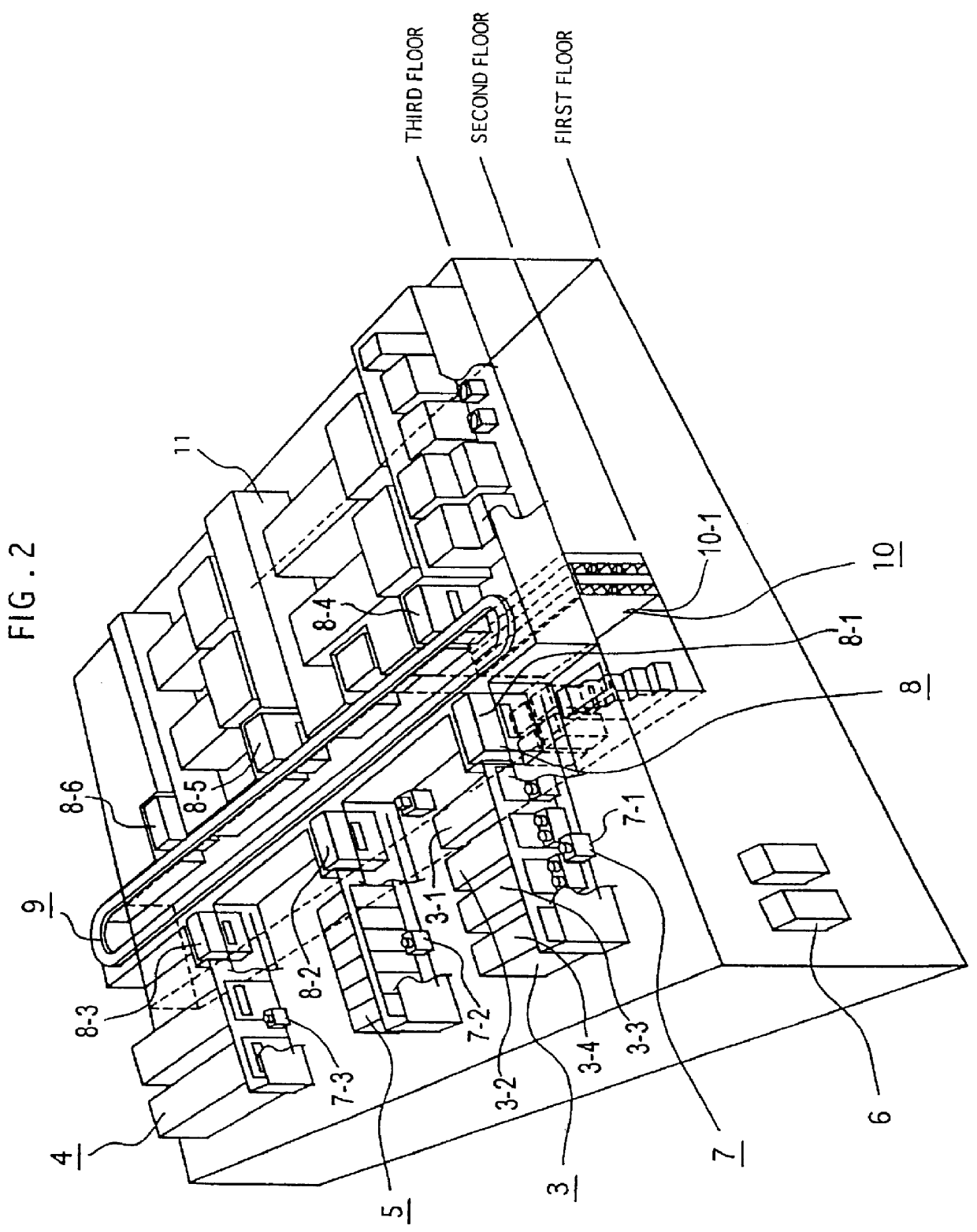

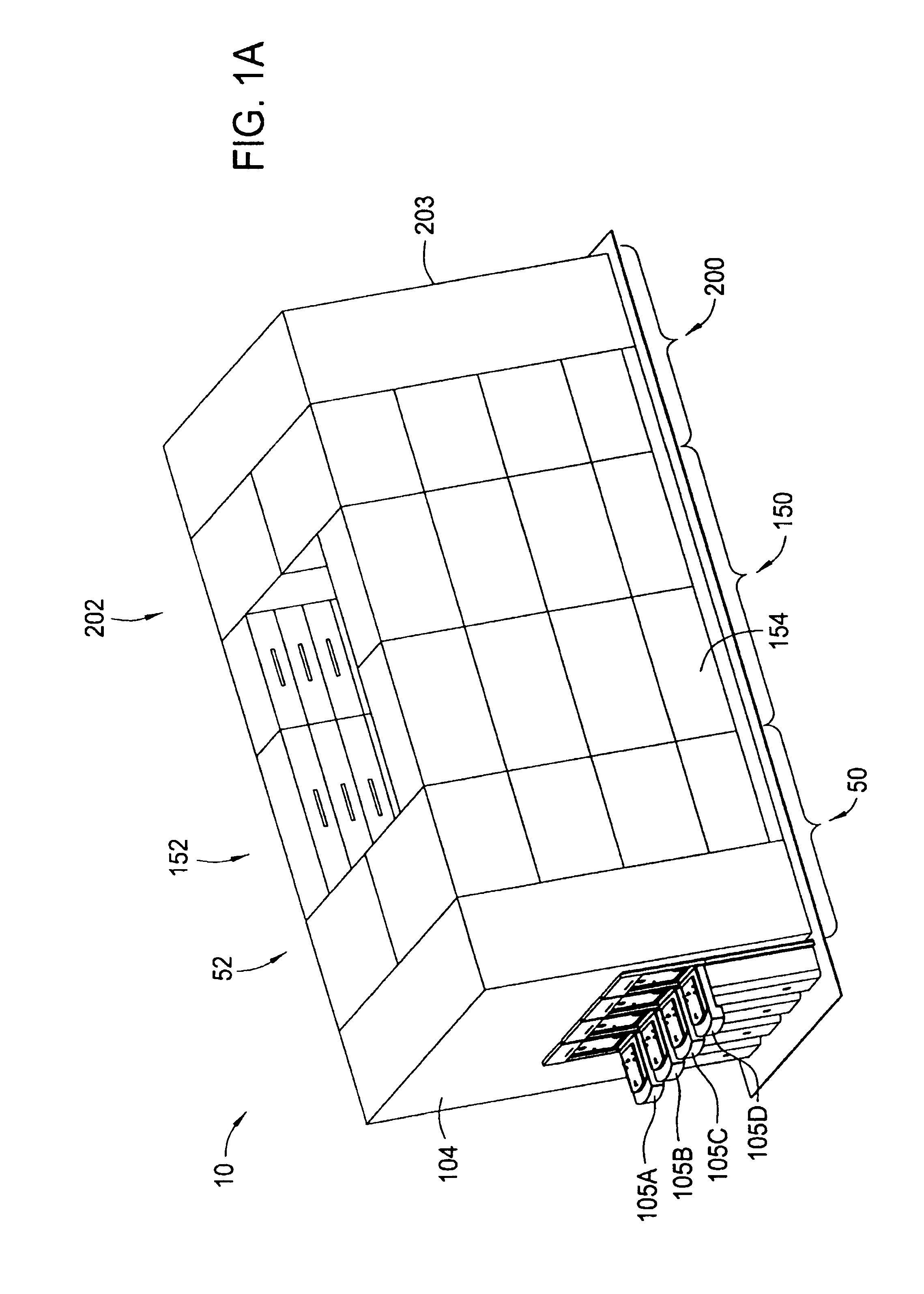

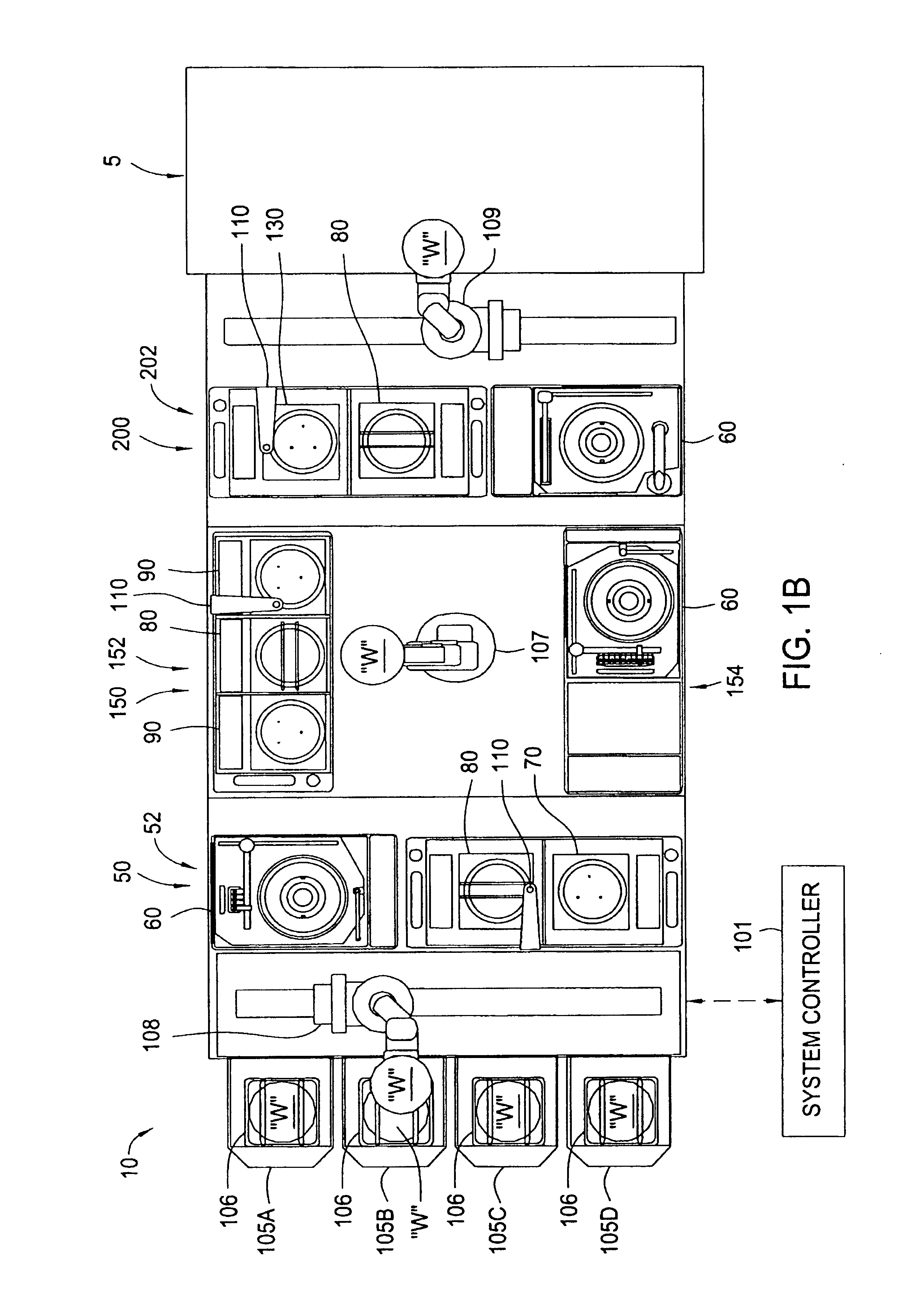

Cluster tool architecture for processing a substrate

ActiveUS20060130750A1Temperature controlMore repeatable wafer processing historyLiquid surface applicatorsSemiconductor/solid-state device testing/measurementLithography processEngineering

Embodiments generally provide an apparatus and method for processing substrates using a multi-chamber processing system (e.g., a cluster tool) that has an increased system throughput, increased system reliability, substrates processed in the cluster tool have a more repeatable wafer history, and also the cluster tool has a smaller system footprint. In one embodiment, the cluster tool is adapted to perform a track lithography process in which a substrate is coated with a photosensitive material, is then transferred to a stepper / scanner, which exposes the photosensitive material to some form of radiation to form a pattern in the photosensitive material, which is then removed in a developing process completed in the cluster tool. In track lithography type cluster tools, since the chamber processing times tend to be rather short, and the number of processing steps required to complete a typical track system process is large, a significant portion of the time it takes to process a substrate is taken up by the processes of transferring the substrates in a cluster tool between the various processing chambers. In one embodiment of the cluster tool, the cost of ownership is reduced by grouping substrates together and transferring and processing the substrates in groups of two or more to improve system throughput, and reduces the number of moves a robot has to make to transfer a batch of substrates between the processing chambers, thus reducing wear on the robot and increasing system reliability. In one aspect of the invention, the substrate processing sequence and cluster tool are designed so that the substrate transferring steps performed during the processing sequence are only made to chambers that will perform the next processing step in the processing sequence. Embodiments also provide for a method and apparatus that are used to improve the coater chamber, the developer chamber, the post exposure bake chamber, the chill chamber, and the bake chamber process results. Embodiments also provide for a method and apparatus that are used to increase the reliability of the substrate transfer process to reduce system down time.

Owner:SCREEN SEMICON SOLUTIONS CO LTD

Light source apparatus and fabrication method thereof

InactiveUS20060208271A1Enhance heat radiation effectSolve low luminous efficiencySemiconductor/solid-state device detailsSolid-state devicesLight emitting deviceTroffer

A light source apparatus and a fabrication method thereof can prevent light interference between light emitting devices adjacent to each other by forming a groove in a sub-mount and bonding a light emitting device to the groove, enhance heat radiating effect as well as luminous efficiency by collecting light emitted from the side of the light emitting device toward the front of the light source apparatus, reduce the process time and costs and increase reliability by directly connecting the sub-mount to the stem by the first electrode and the second electrode which pass through holes of the sub-mount, and extend a life span of the light emitting device because of the enhanced heat radiating effect.

Owner:LG ELECTRONICS INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com