Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

356results about How to "Improve batch productivity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

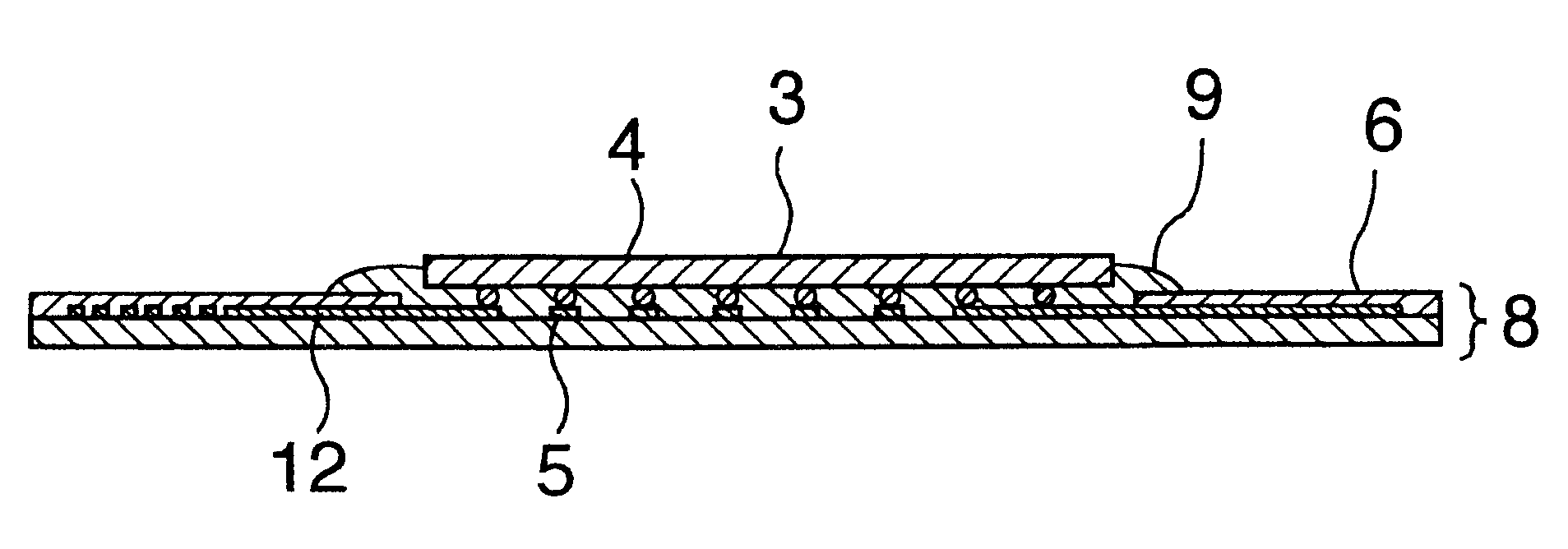

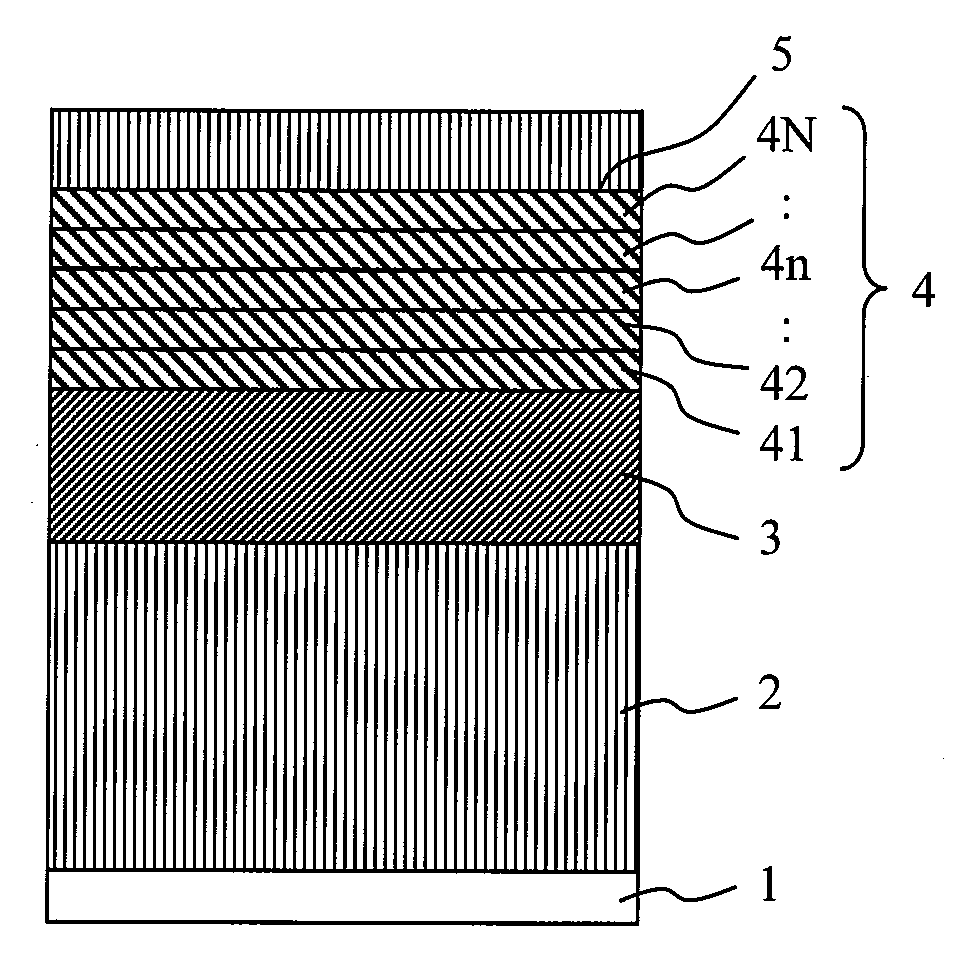

Bottom gate type thin film transistor, method of manufacturing the same, and display apparatus

InactiveUS8148721B2Optimise total massImprove batch productivityTransistorElectroluminescent light sourcesDesorptionBottom gate

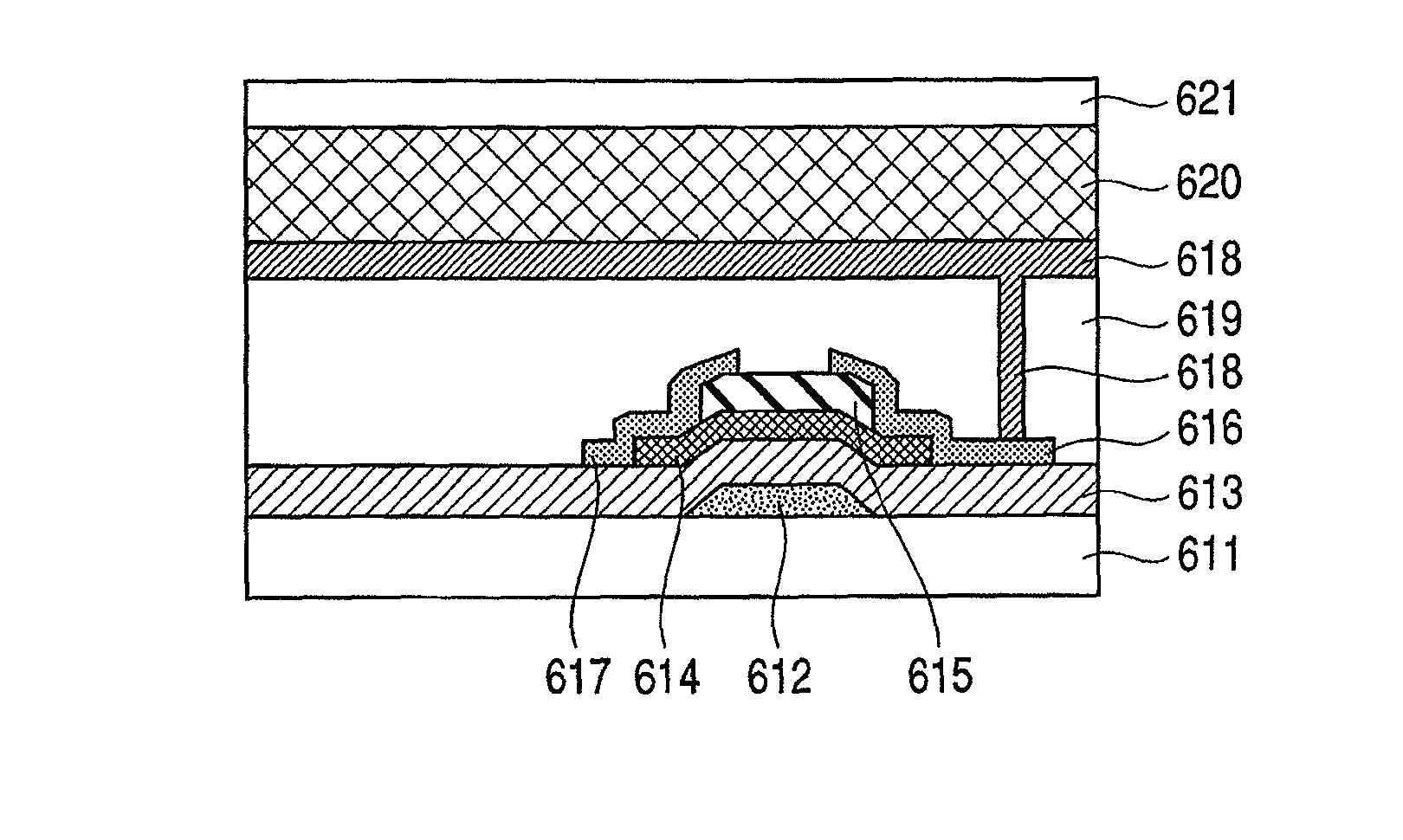

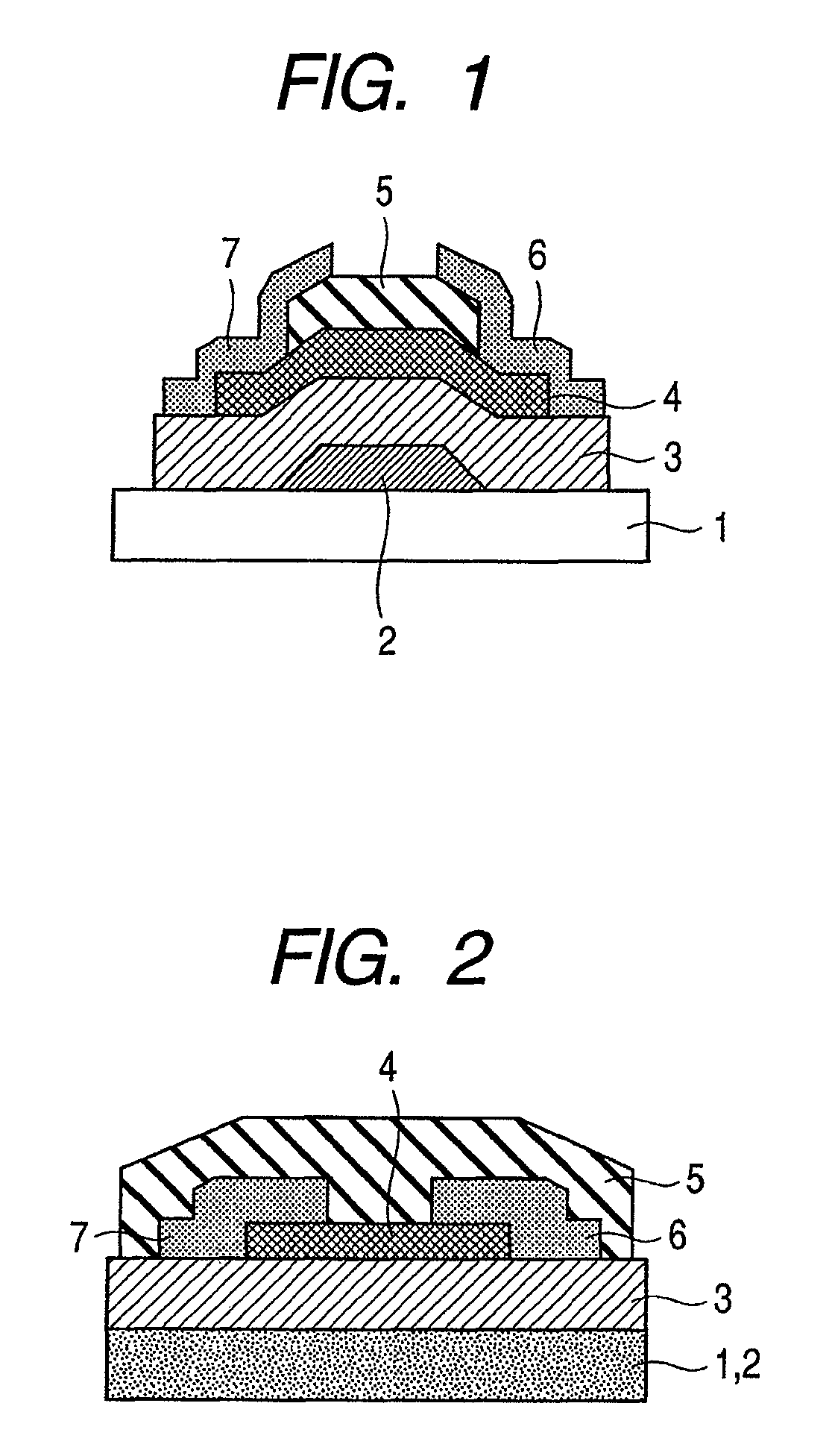

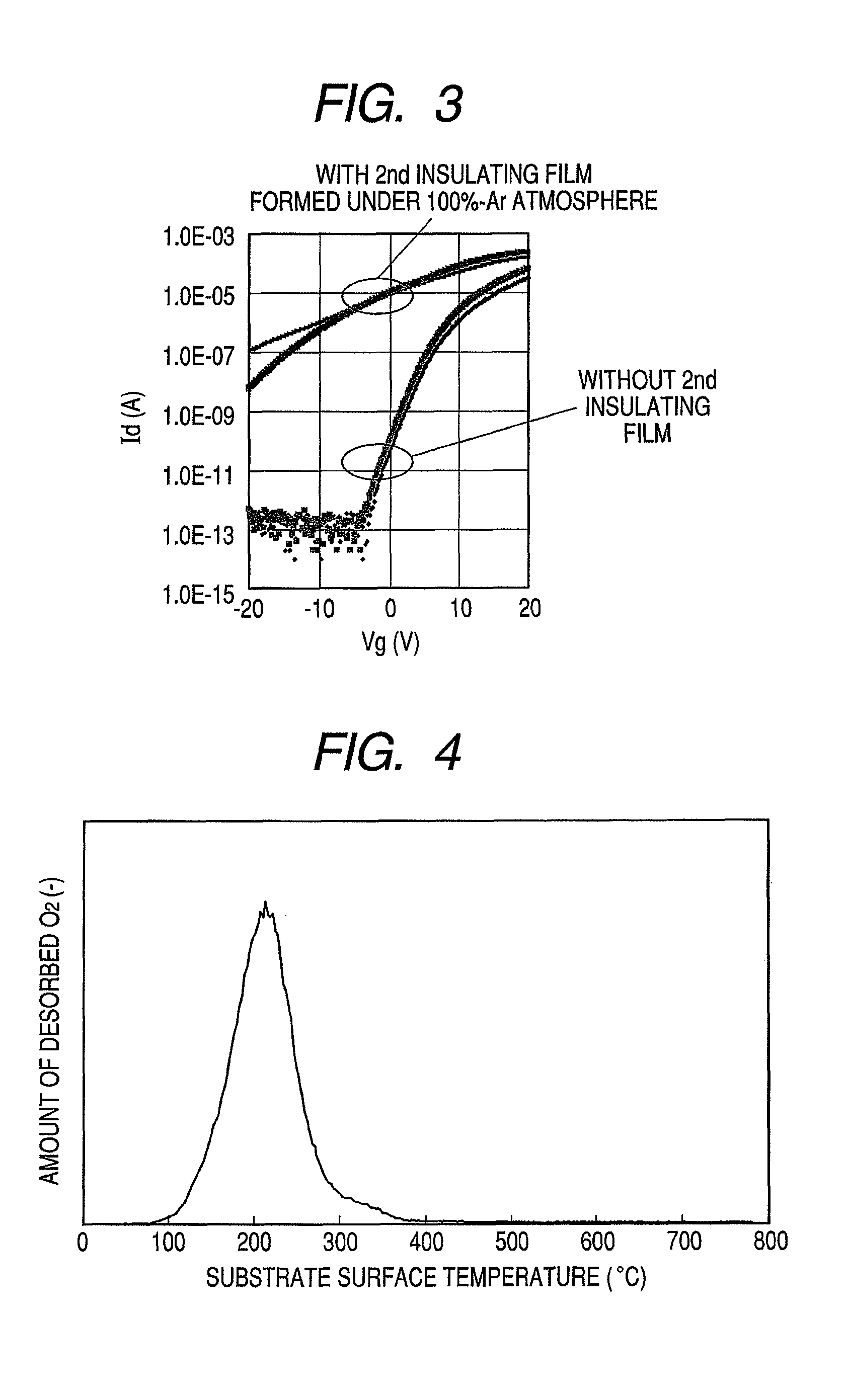

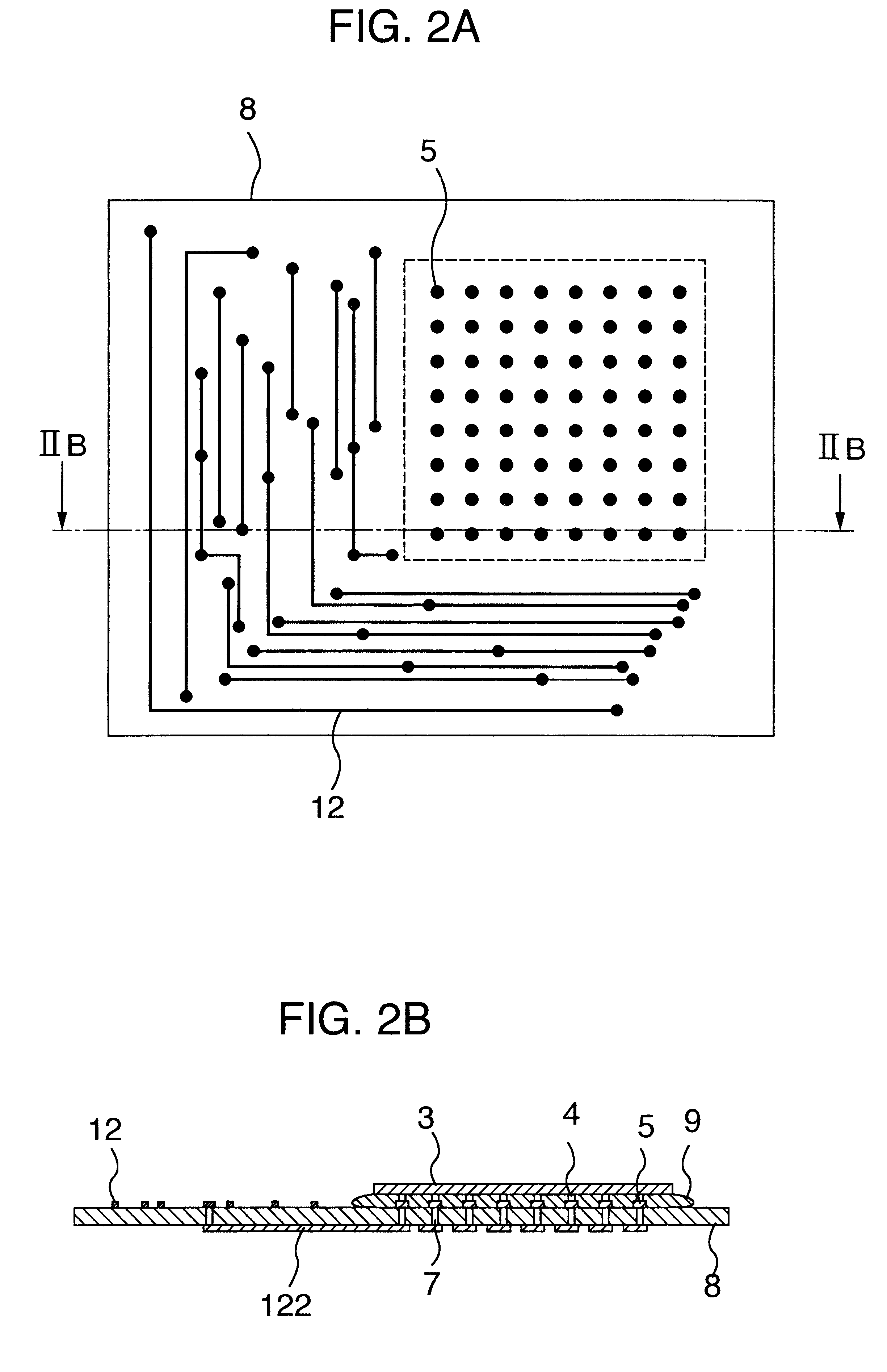

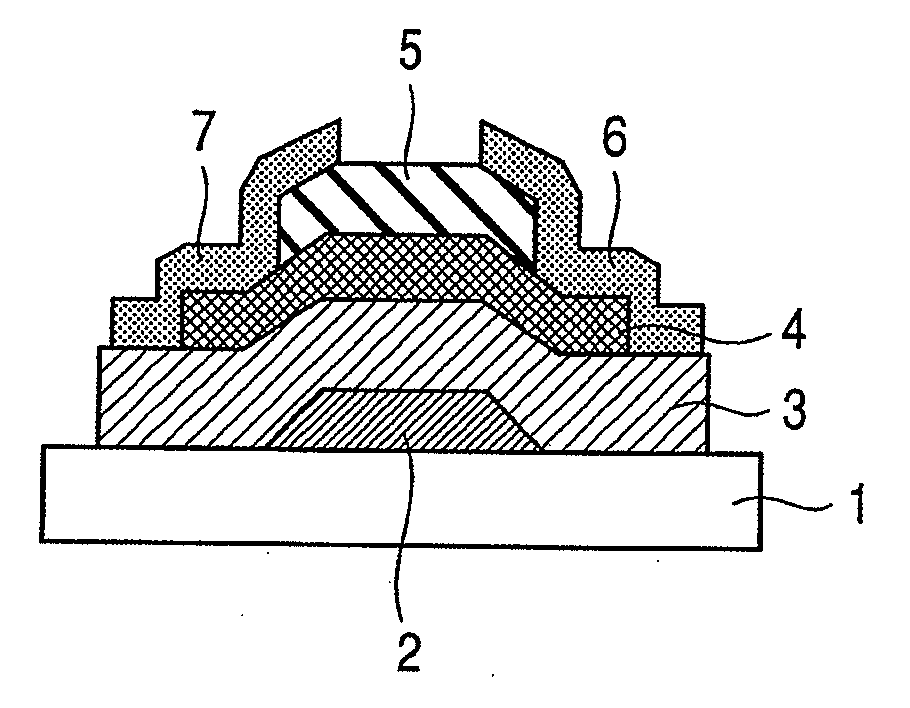

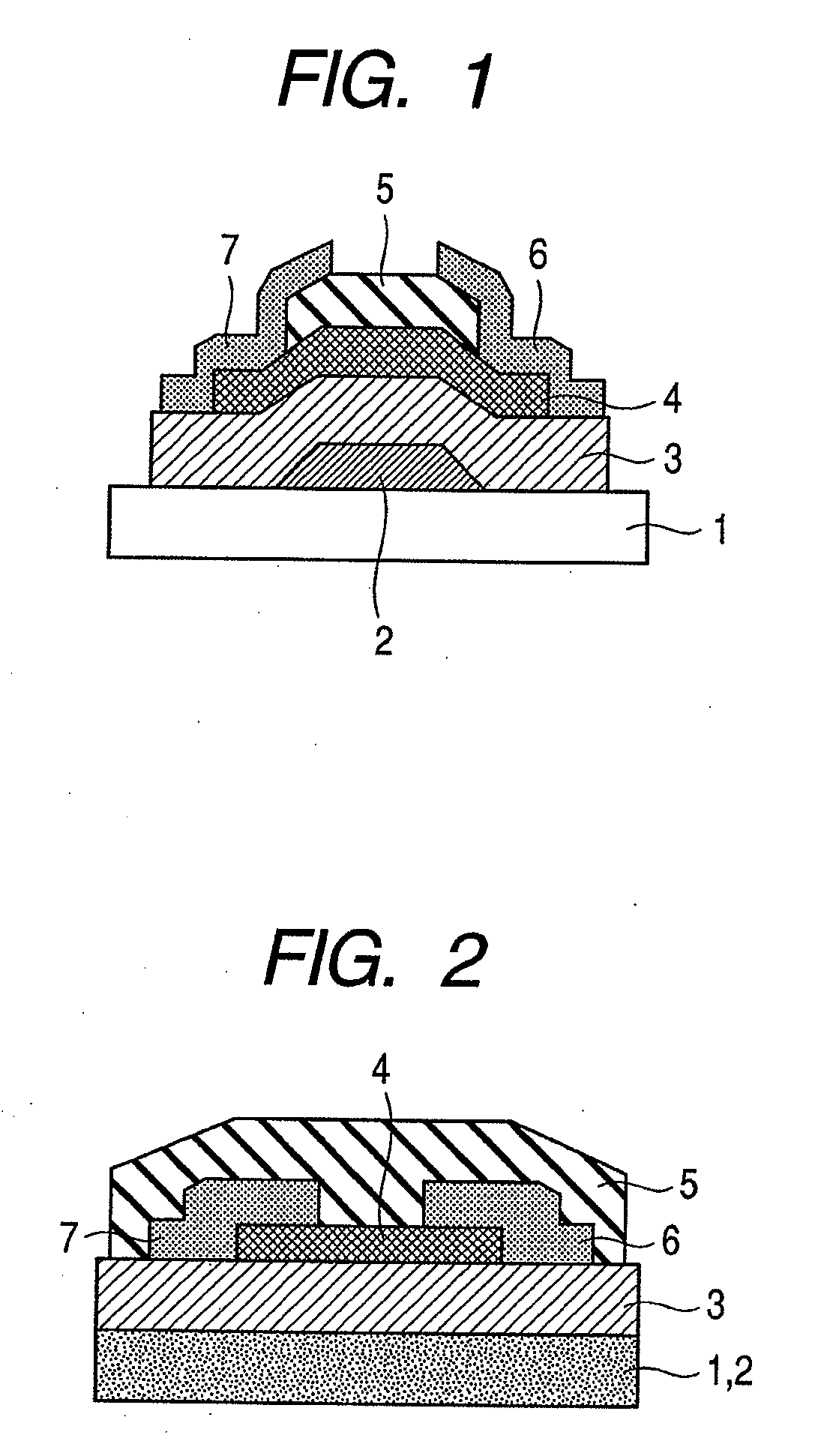

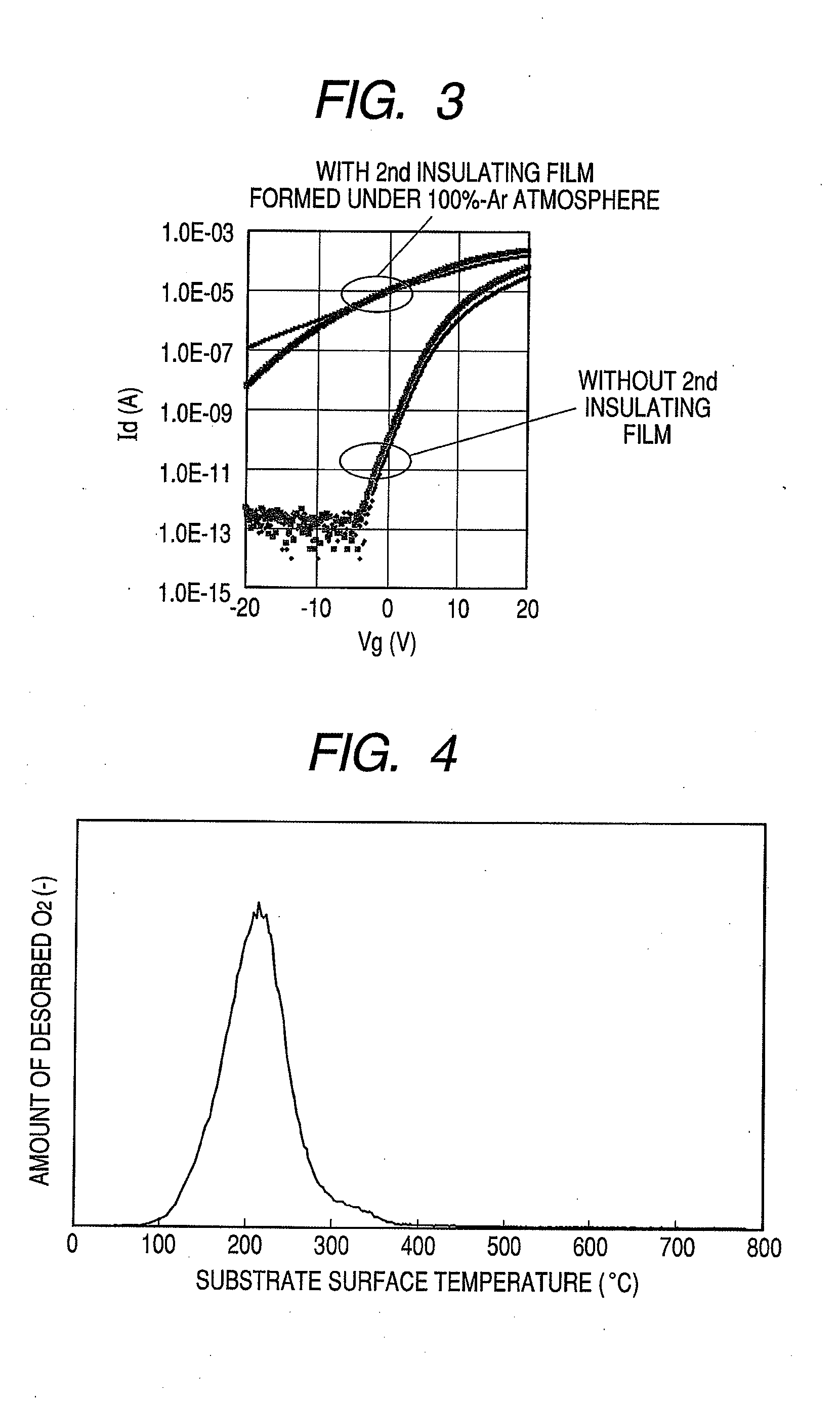

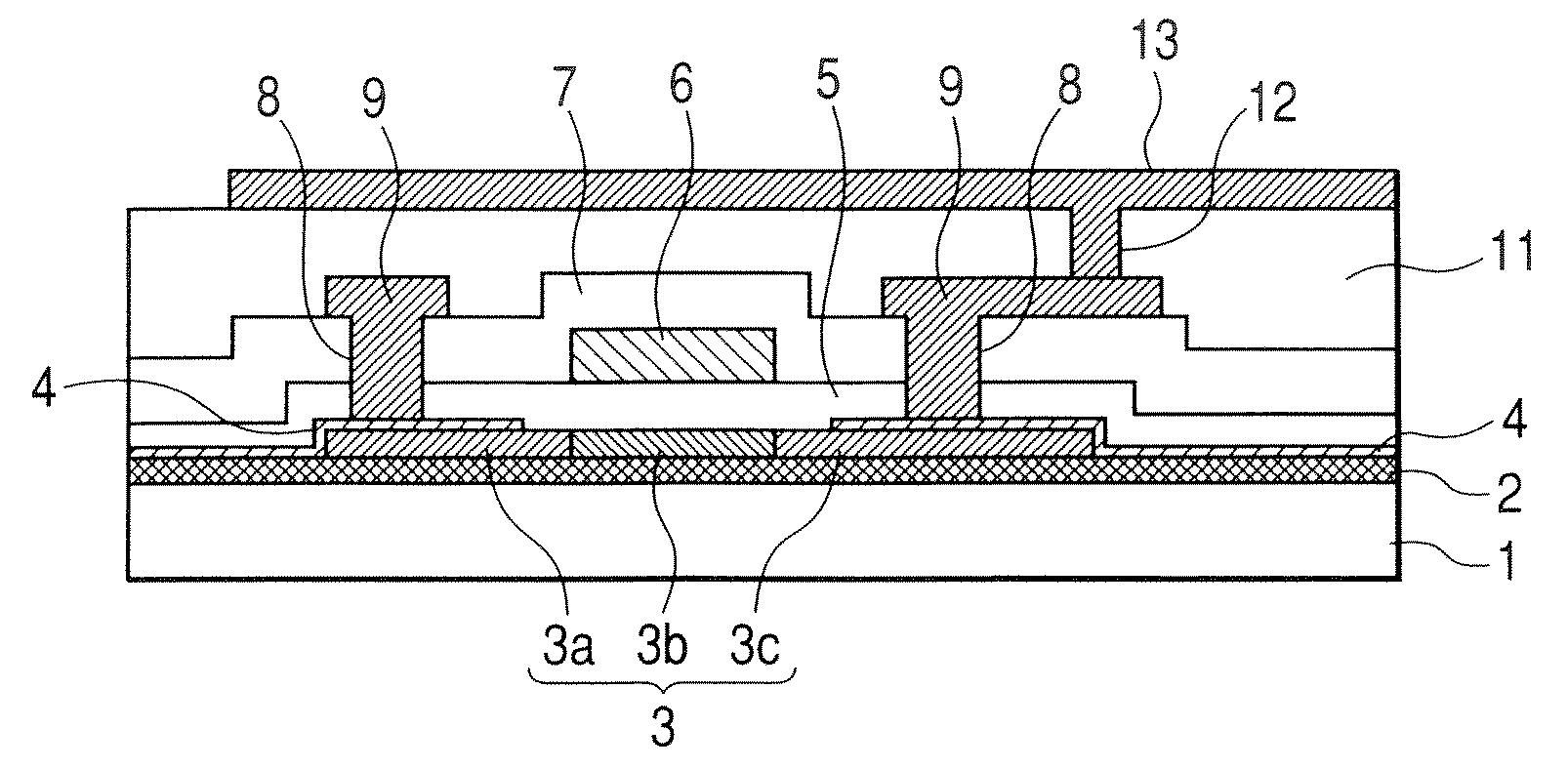

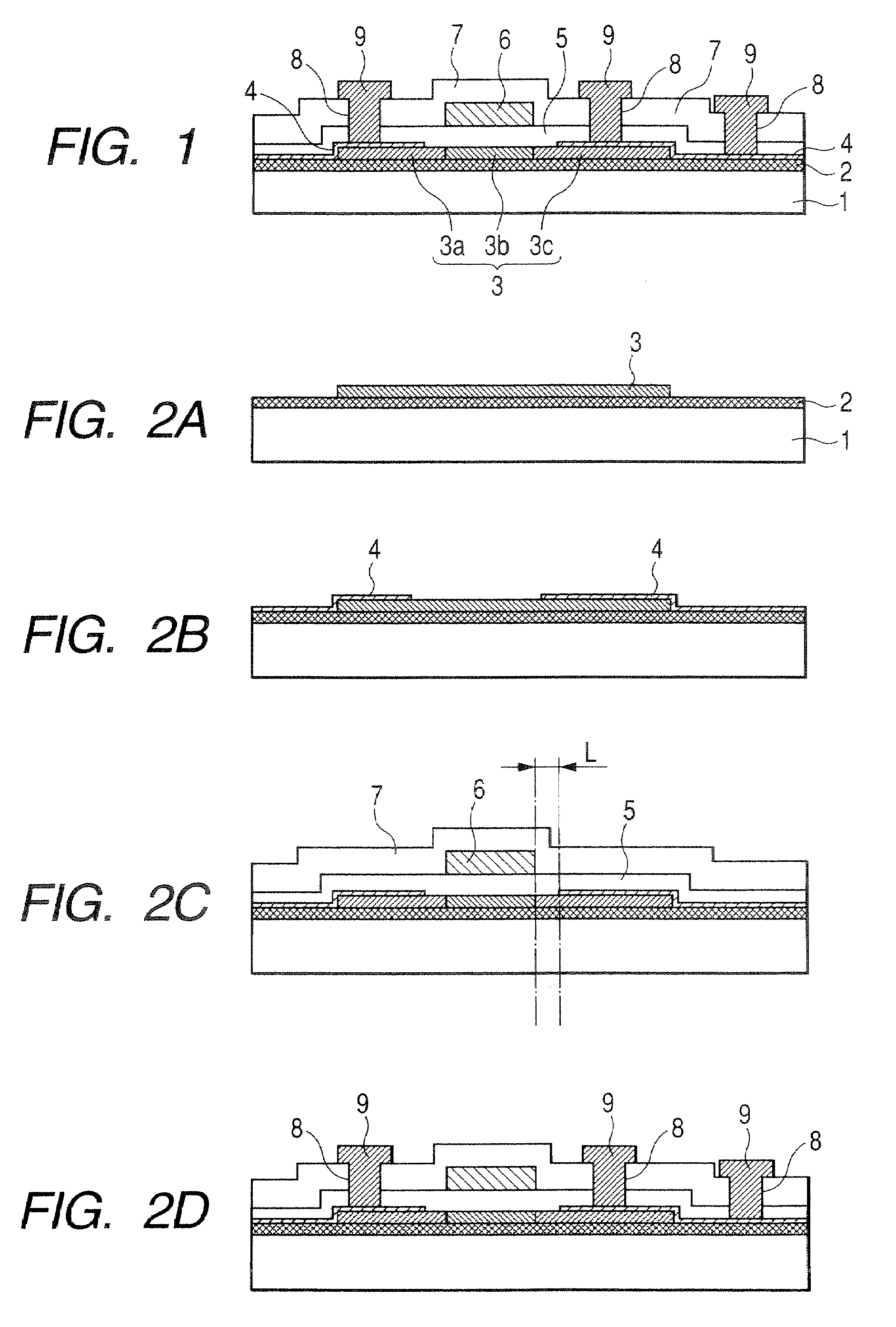

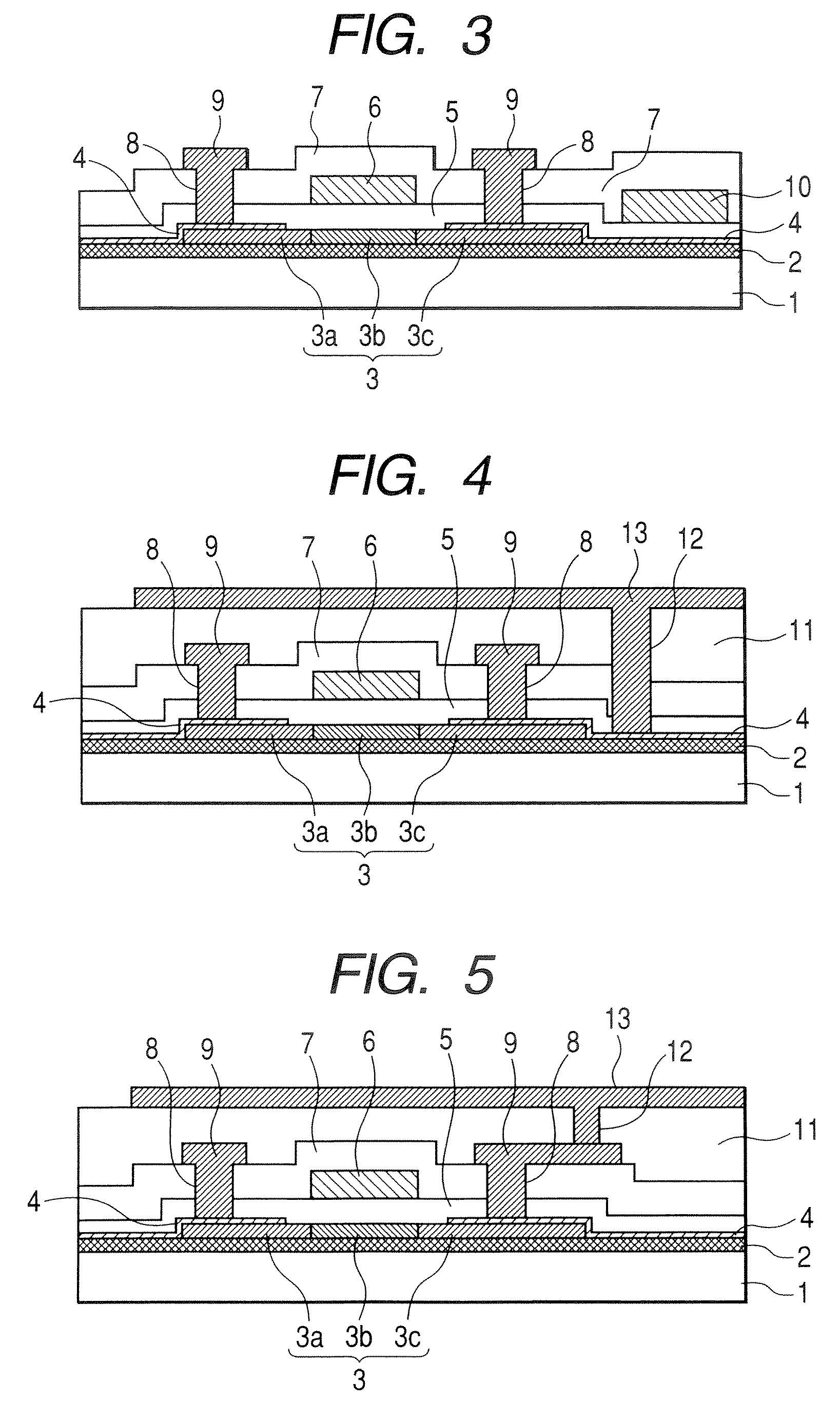

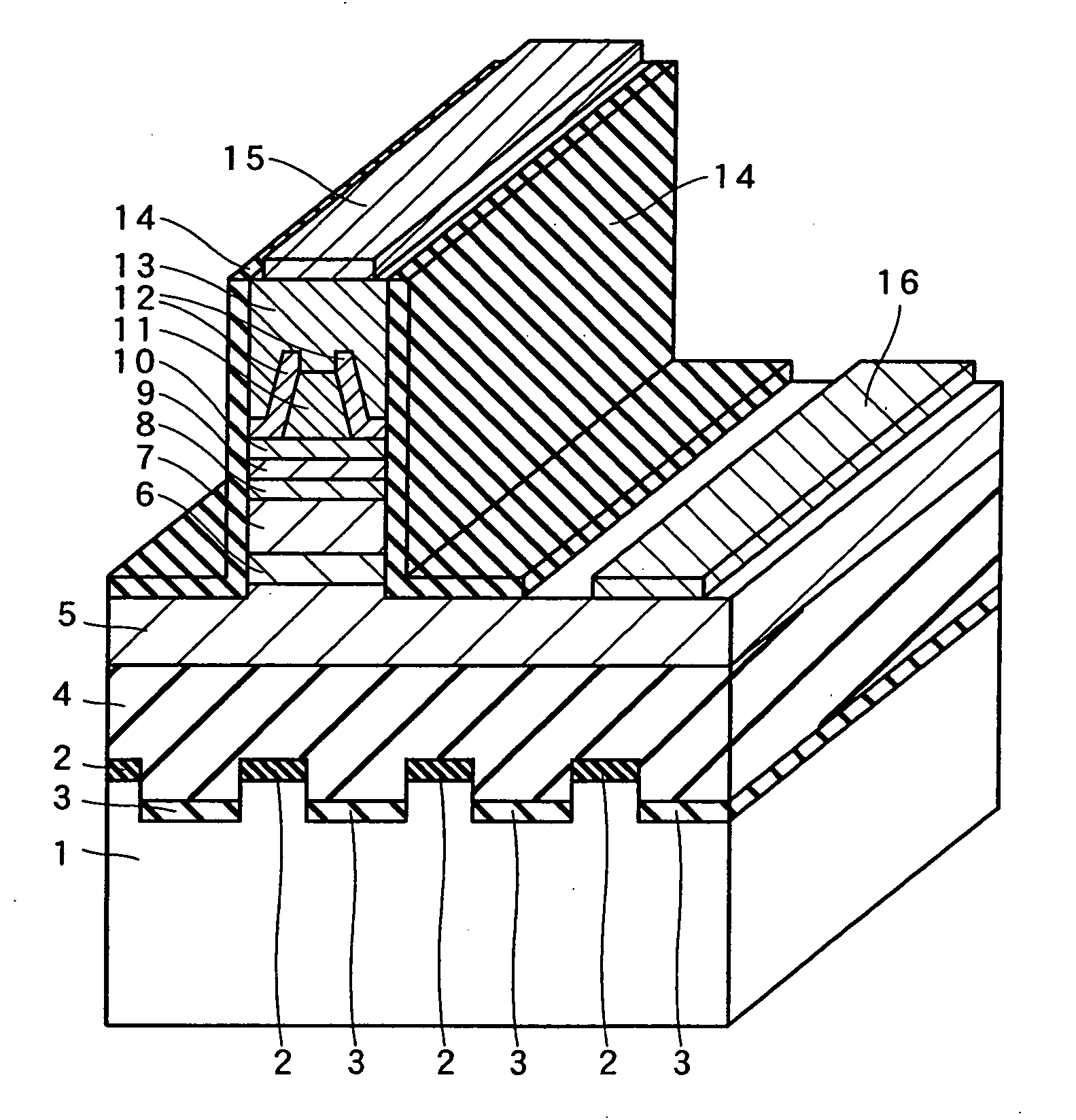

Provided is a bottom gate type thin film transistor including on a substrate (1) a gate electrode (2), a first insulating film (3) as a gate insulating film, an oxide semiconductor layer (4) as a channel layer, a second insulating film (5) as a protective layer, a source electrode (6), and a drain electrode (7), in which the oxide semiconductor layer (4) includes an oxide including at least one selected from the group consisting of In, Zn, and Sn, and the second insulating film (5) includes an amorphous oxide insulator formed so as to be in contact with the oxide semiconductor layer (4) and contains therein 3.8×1019 molecules / cm3 or more of a desorbed gas observed as oxygen by temperature programmed desorption mass spectrometry.

Owner:CANON KK

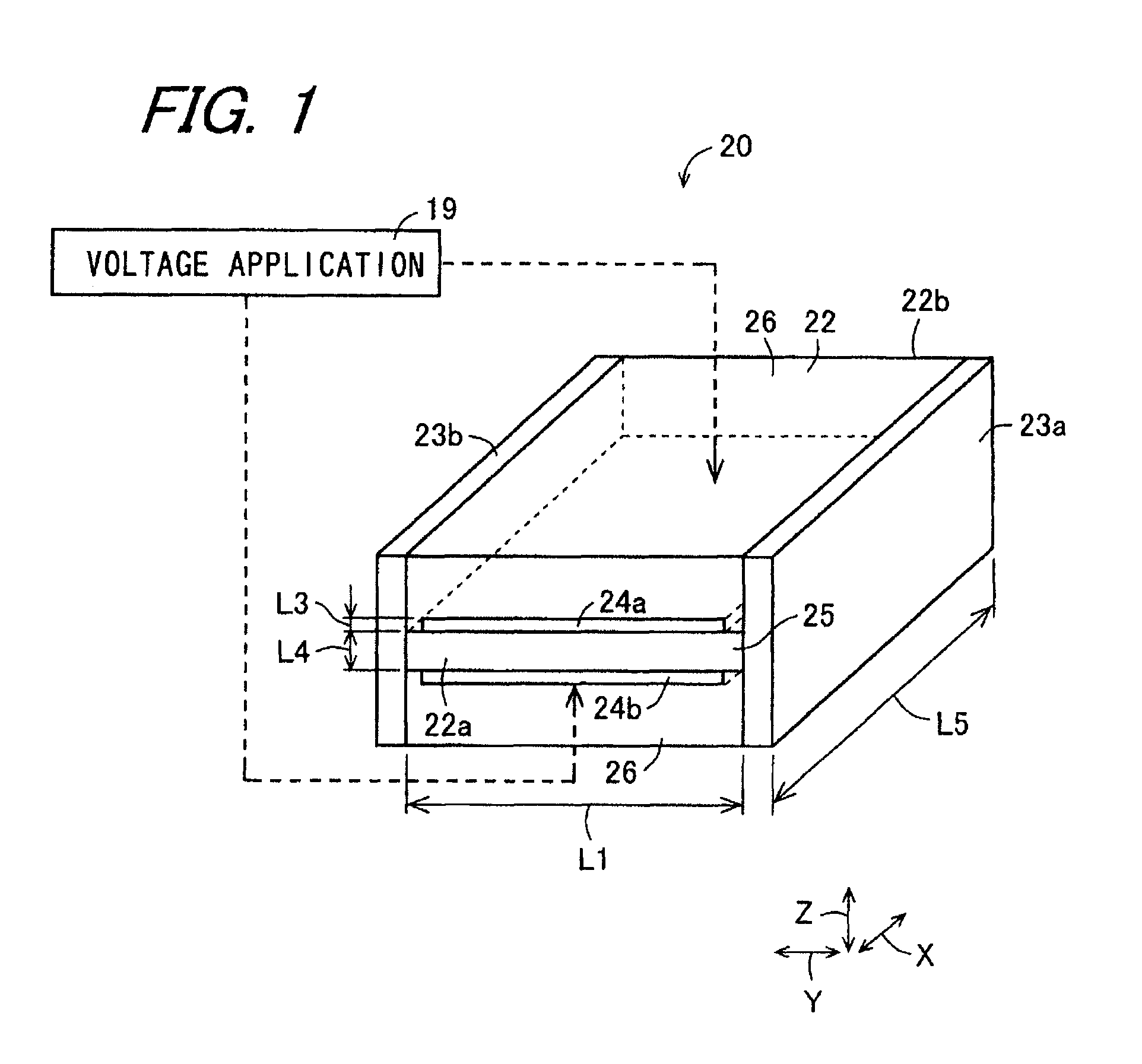

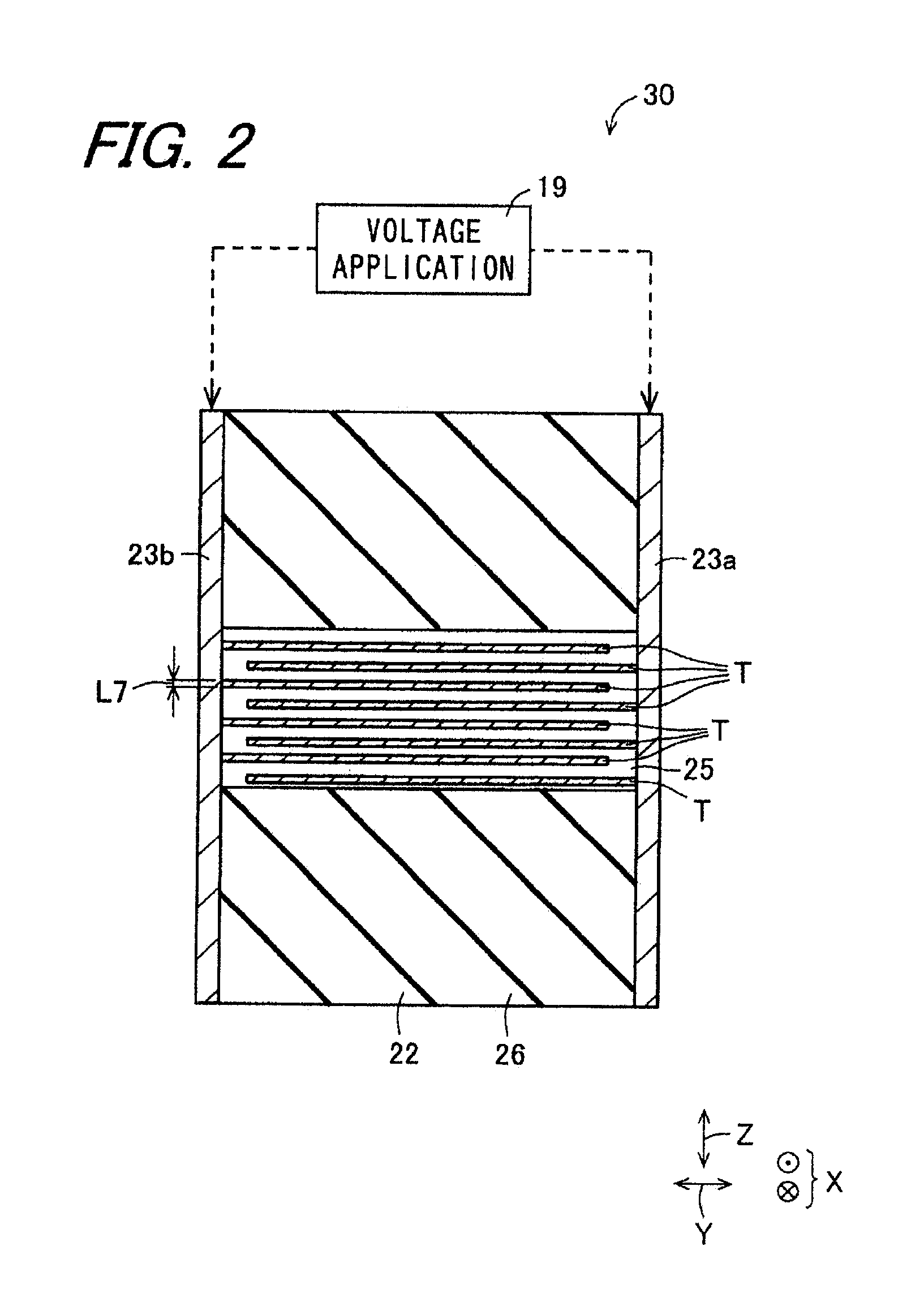

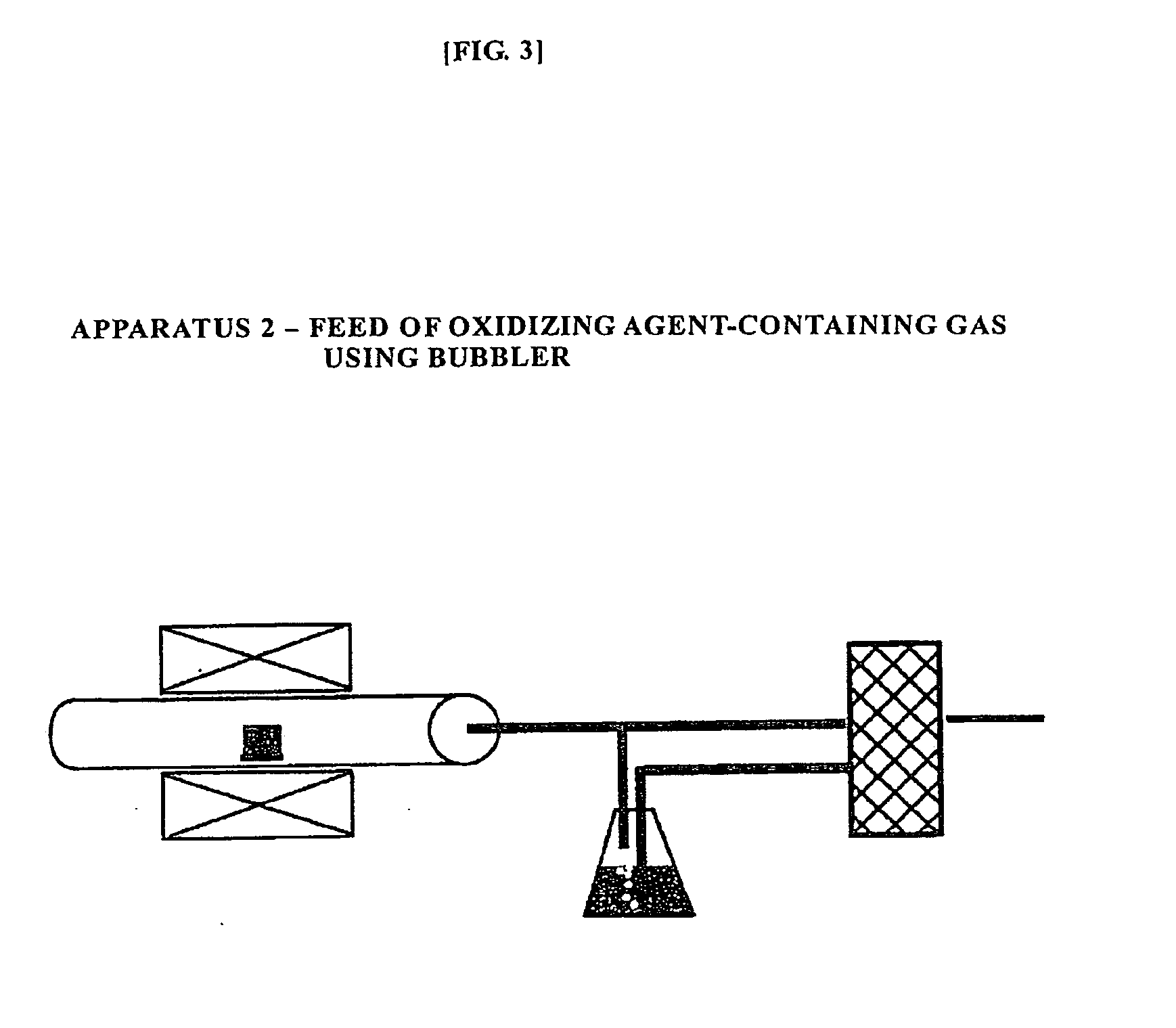

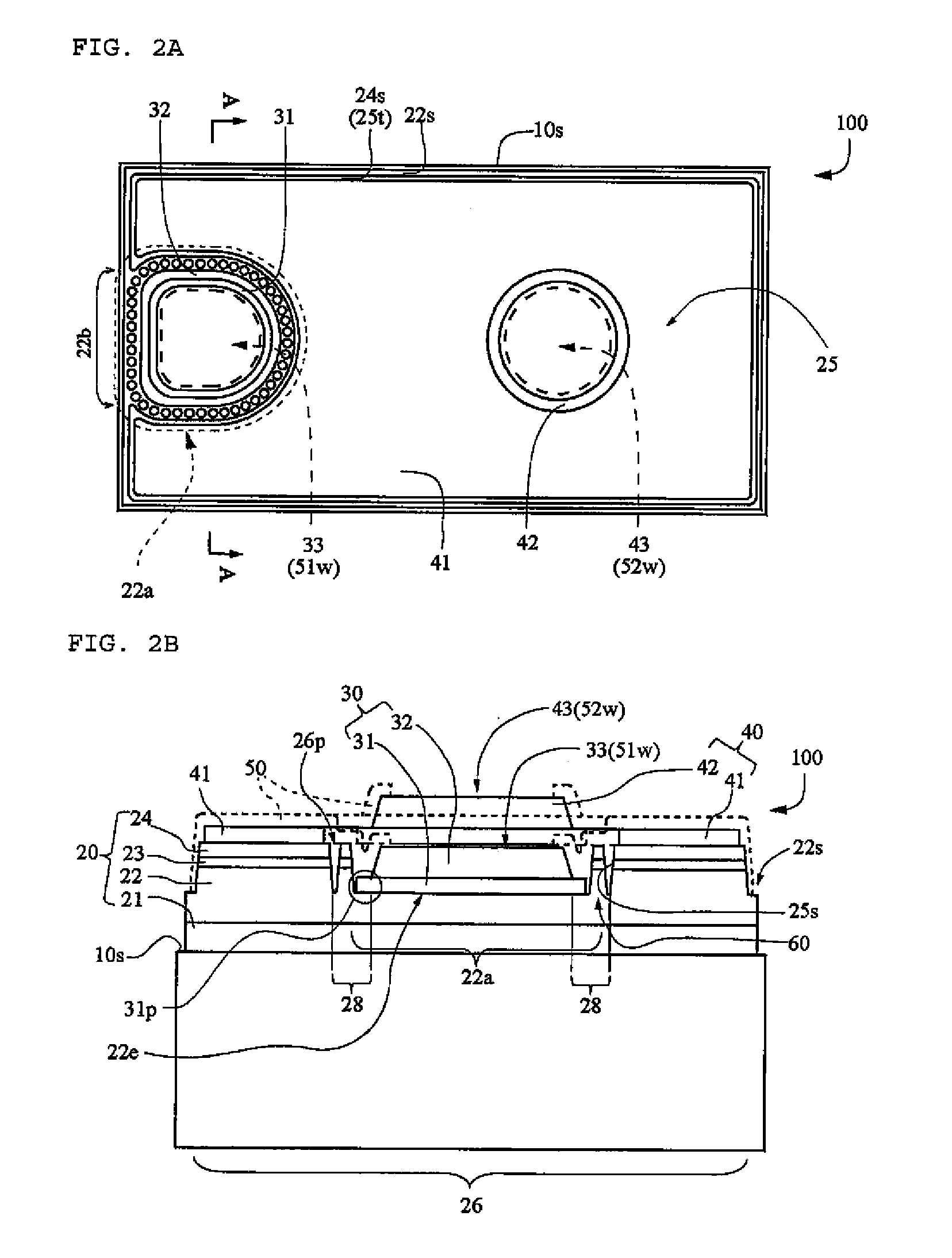

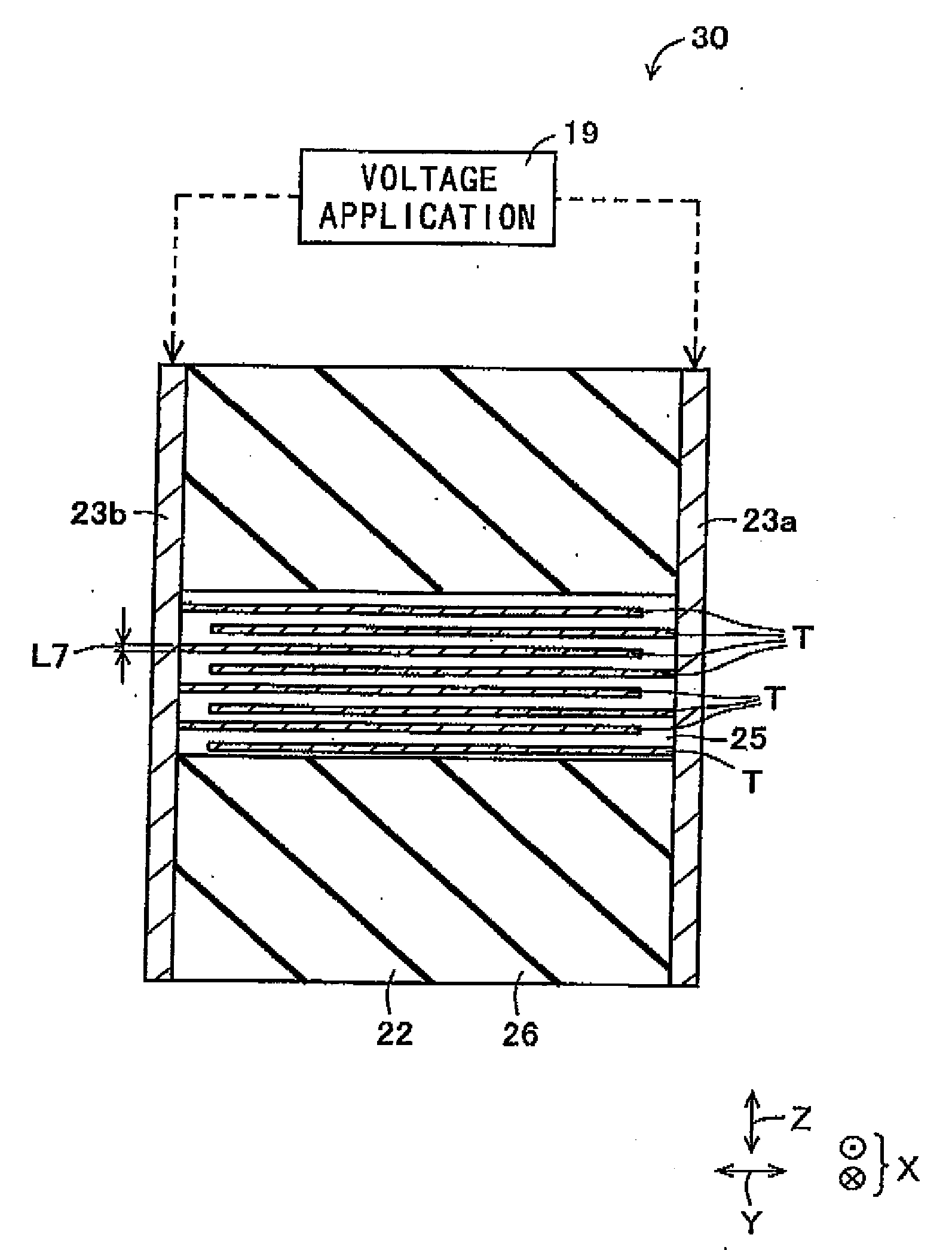

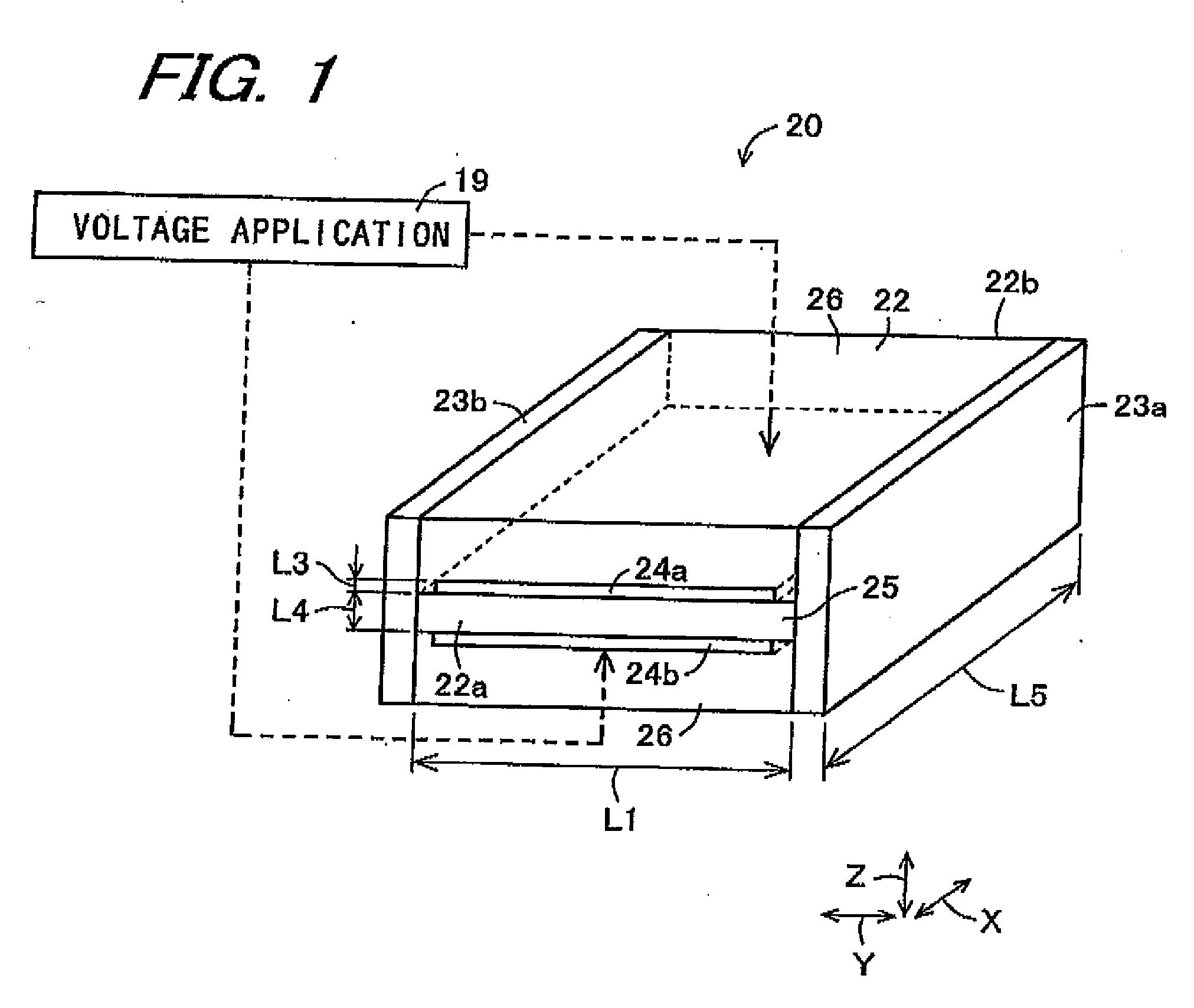

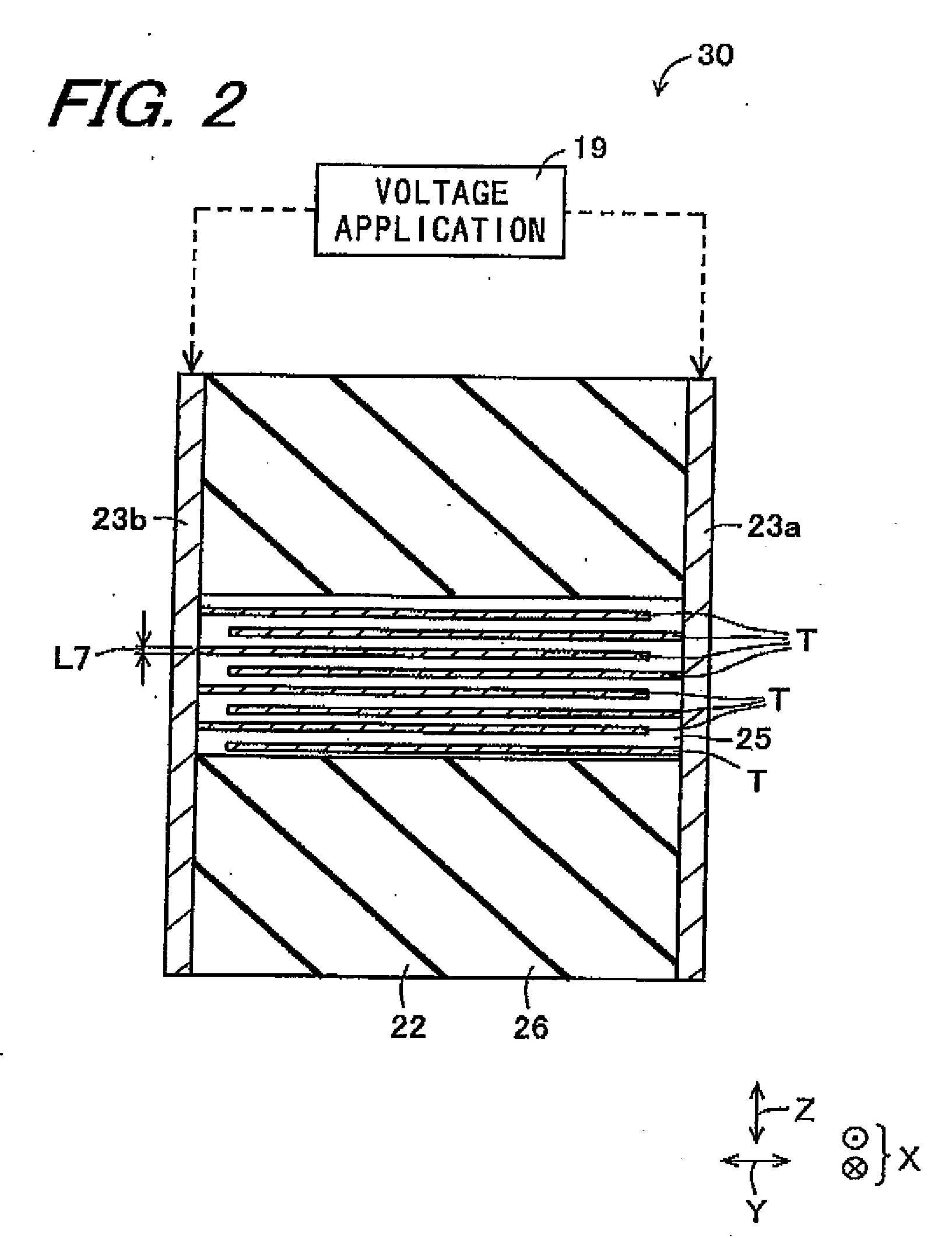

Dielectric waveguide device, phase shifter, high frequency switch, and attenuator provided with dielectric waveguide device, high frequency transmitter, high frequency receiver, high frequency transceiver, radar device, array antenna, and method of manufacturing dielectric waveguide device

InactiveUS8013694B2Small sizeImprove batch productivityWaveguidesRadio wave reradiation/reflectionElectricityTransceiver

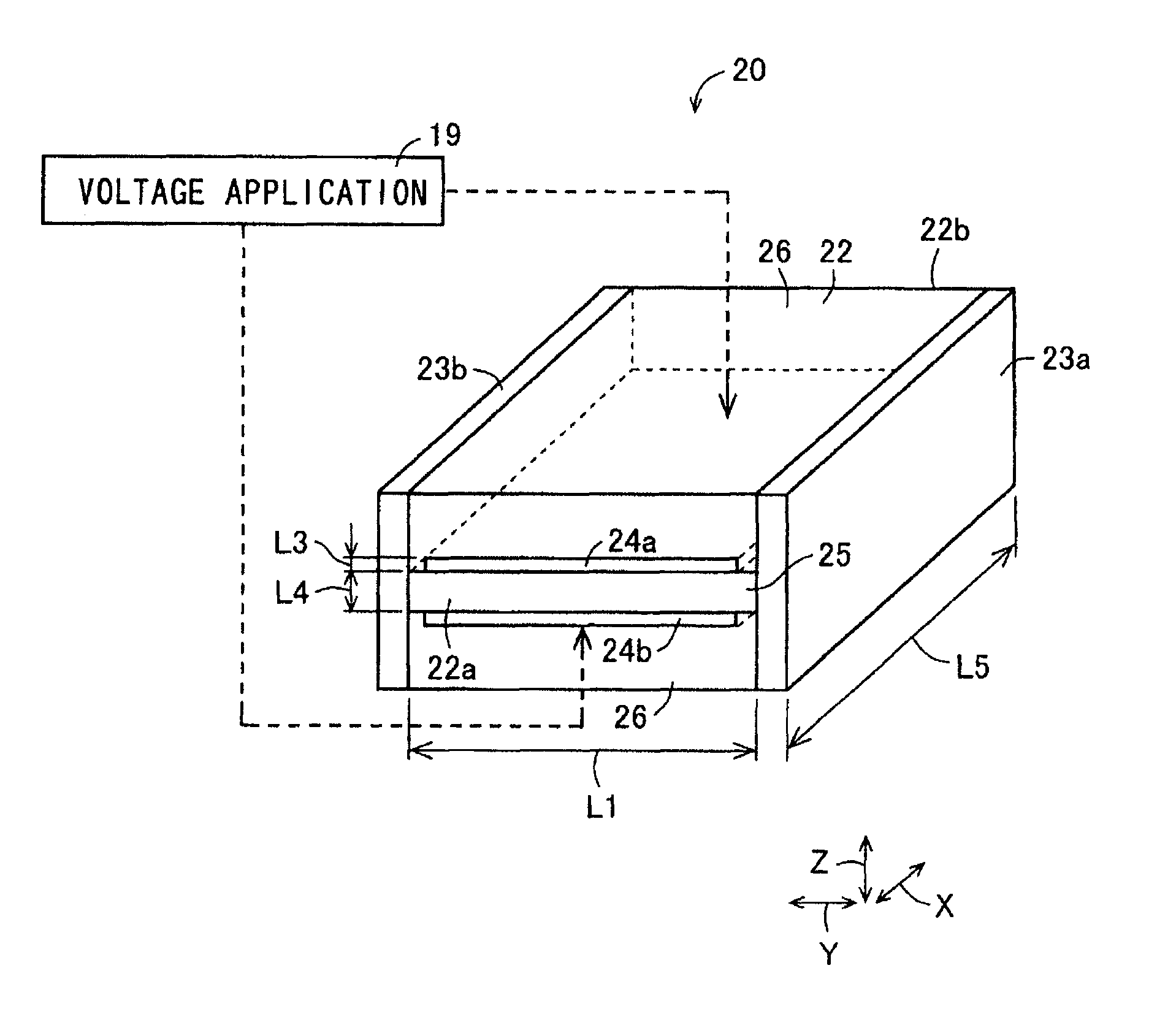

The invention relates to a small and low-voltage operable dielectric waveguide device. First and second electrode are embedded in a dielectric part and are formed to be thinner than a skin depth for a frequency of electromagnetic wave propagating along a first dielectric part included in the dielectric part. Thereby, even if the first and second electrodes are arranged to be in contact with the first dielectric part, the propagating electromagnetic wave can transmit the first and second electrodes, and therefore the electromagnetic wave can propagate without being cut off and there is no influence on waveguide modes of the electromagnetic wave. Further, in a state where a transmission loss due to the embedded of the electrode is suppressed, an electric field with large electric field strength can be applied to the first dielectric part by the first and second electrodes, and a small and low-voltage operable dielectric waveguide device can be achieved.

Owner:KYOCERA CORP

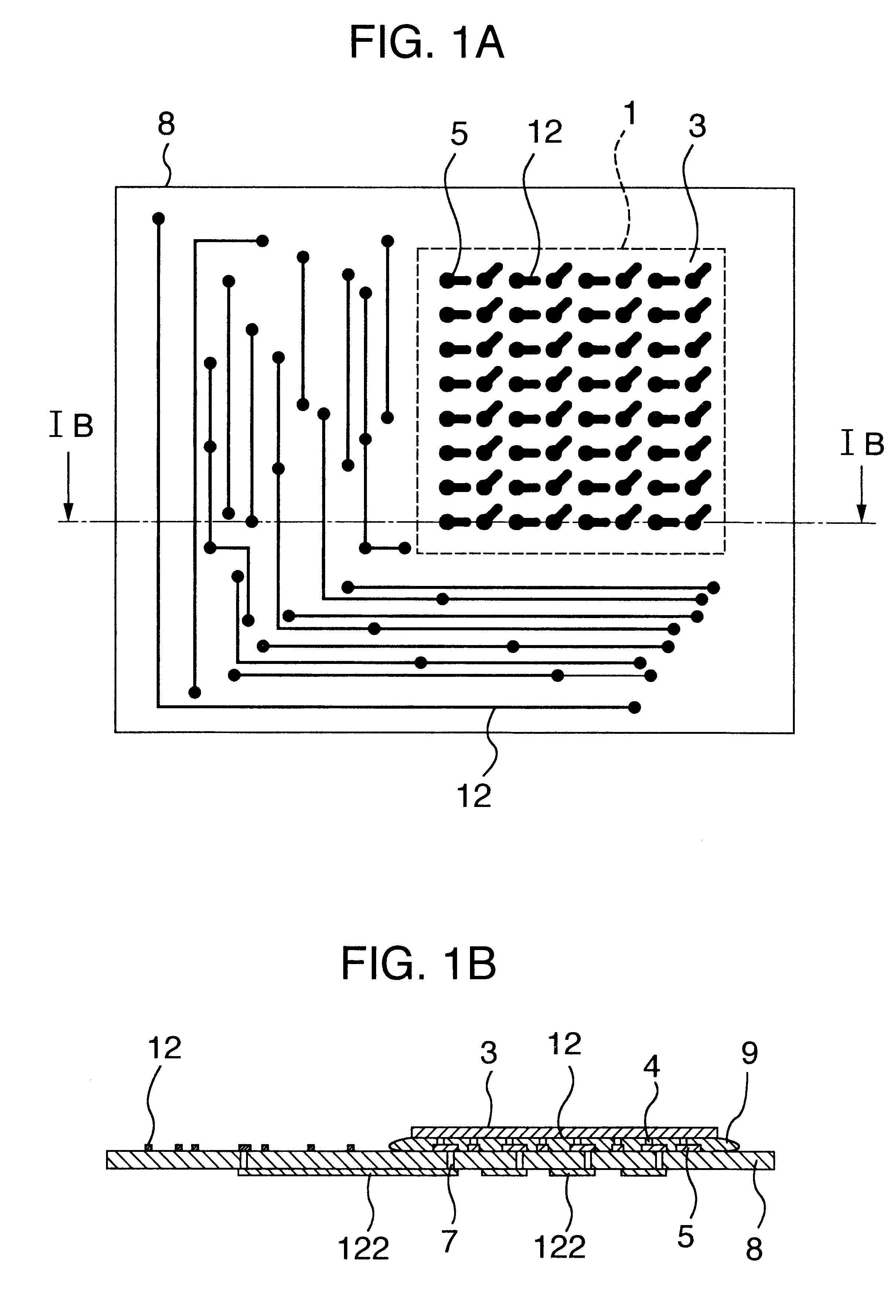

Substrate for mounting semiconductor chips

InactiveUS6281450B1Improve connection reliabilityImprove batch productivitySemiconductor/solid-state device detailsSolid-state devicesProduction rateElectrical conductor

A substrate for mounting a semiconductor chip having bumps using an adhesive thereon, said substrate being, for instance, provided with an insulating coating having an opening in the semiconductor chip mounting area so that the wiring conductors will not be exposed to the substrate surface near the boundary of the semiconductor chip mounting area, is improved in connection reliability and has high mass productivity.

Owner:HITACHI CHEM CO LTD

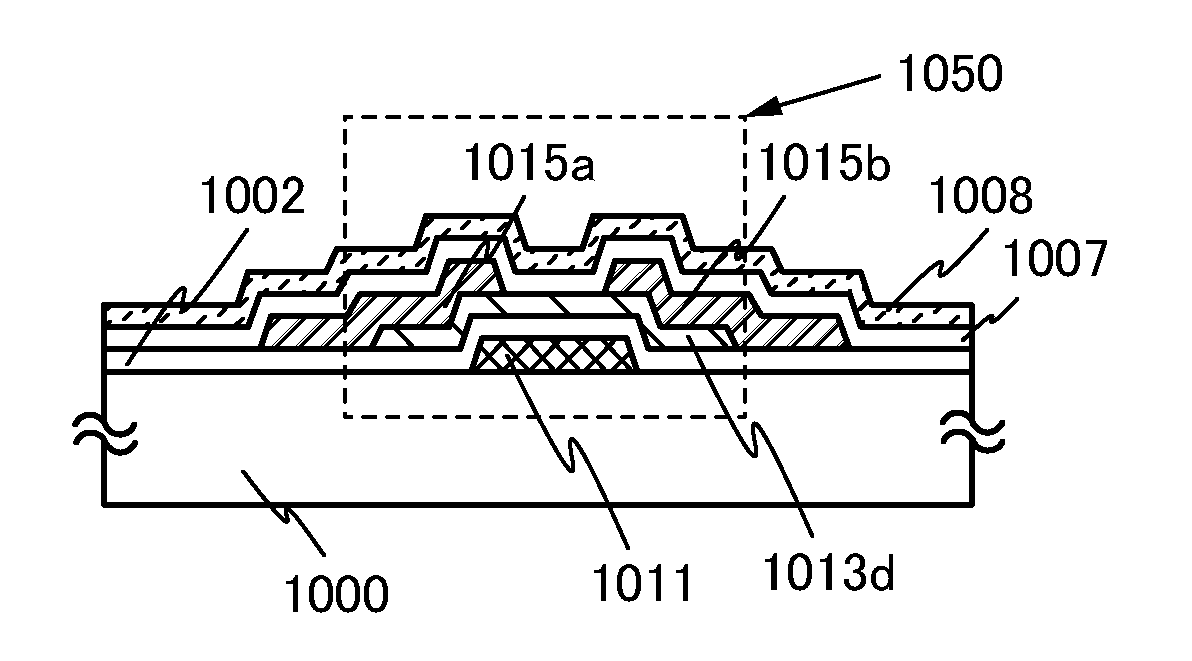

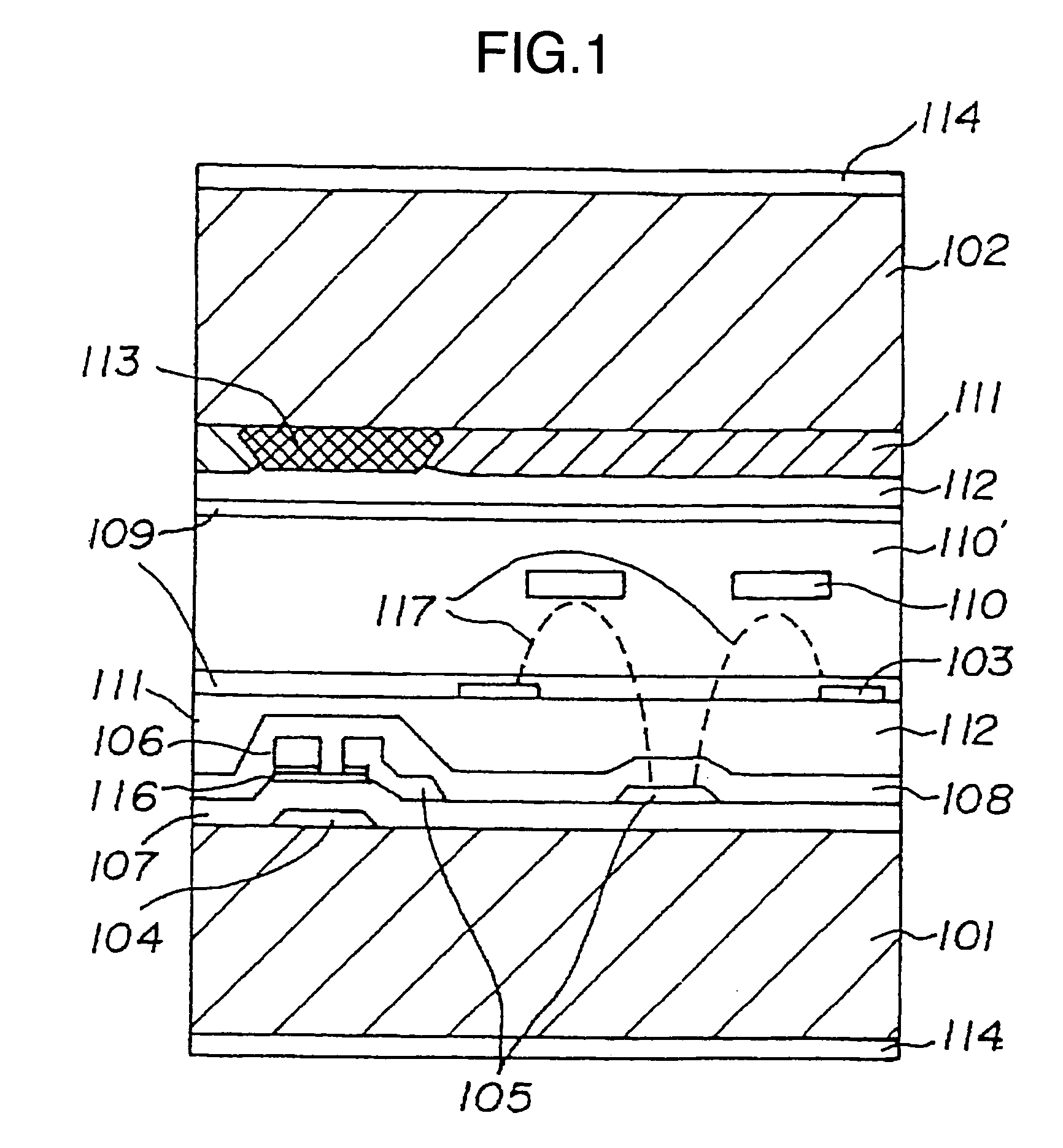

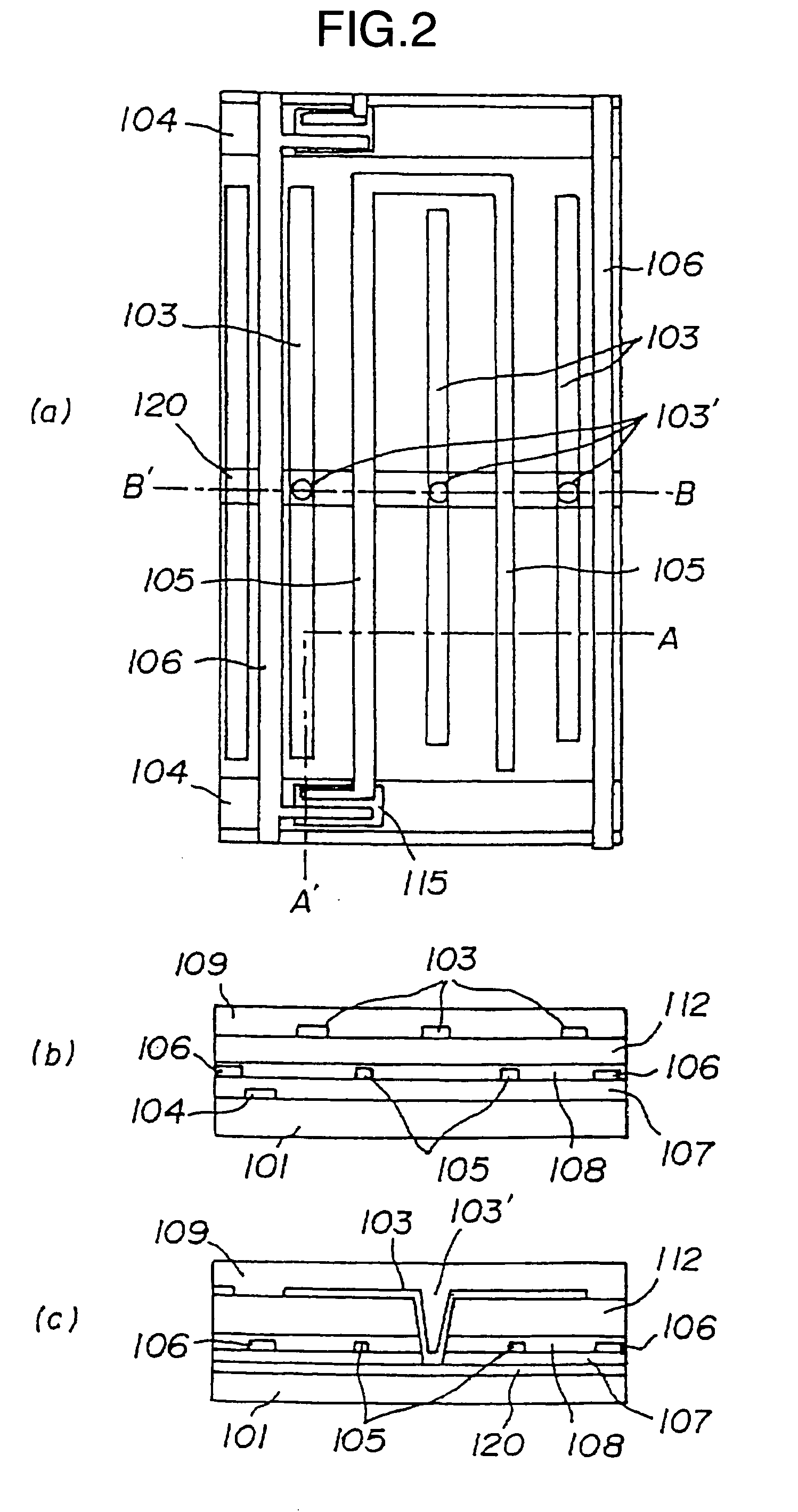

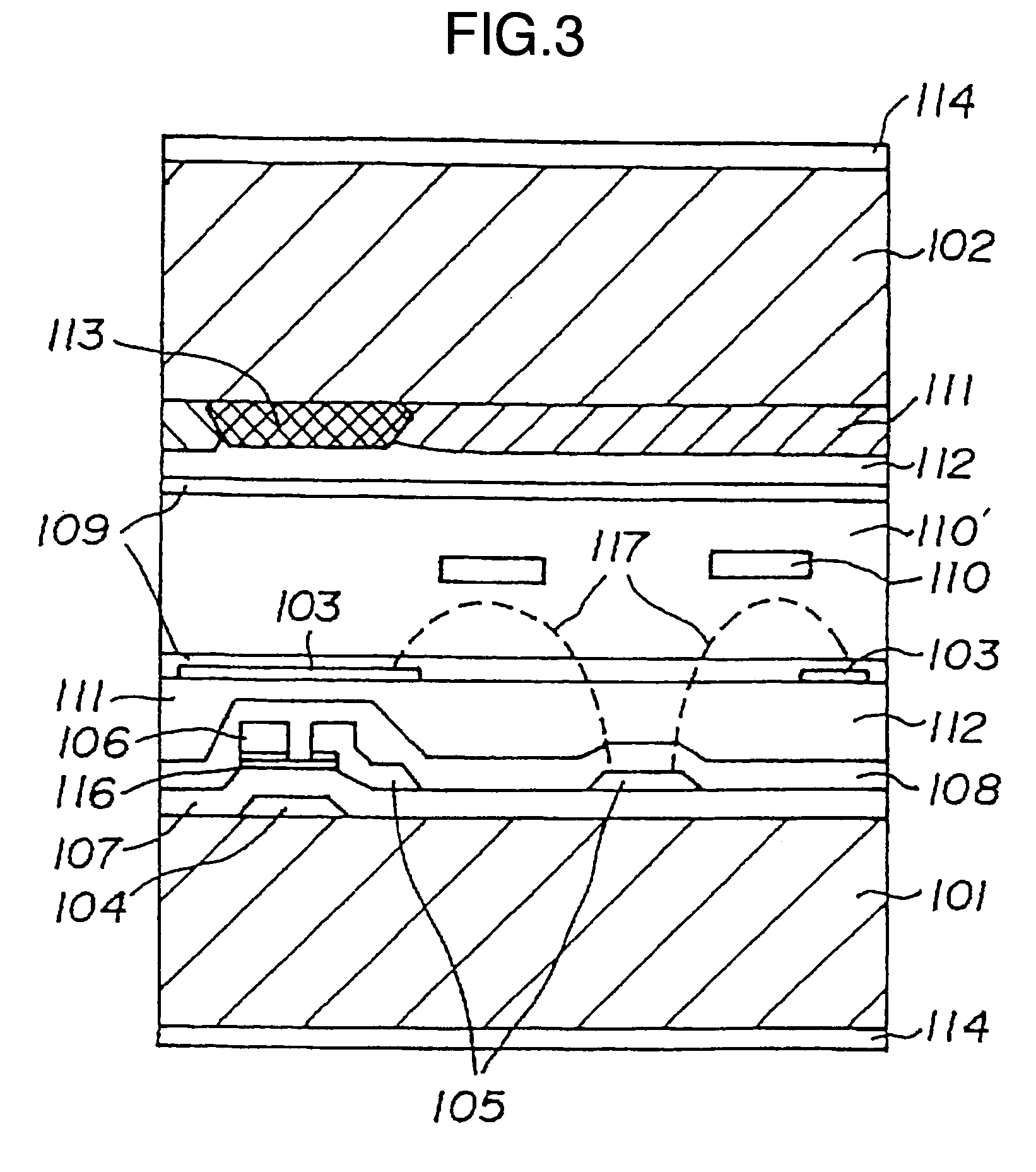

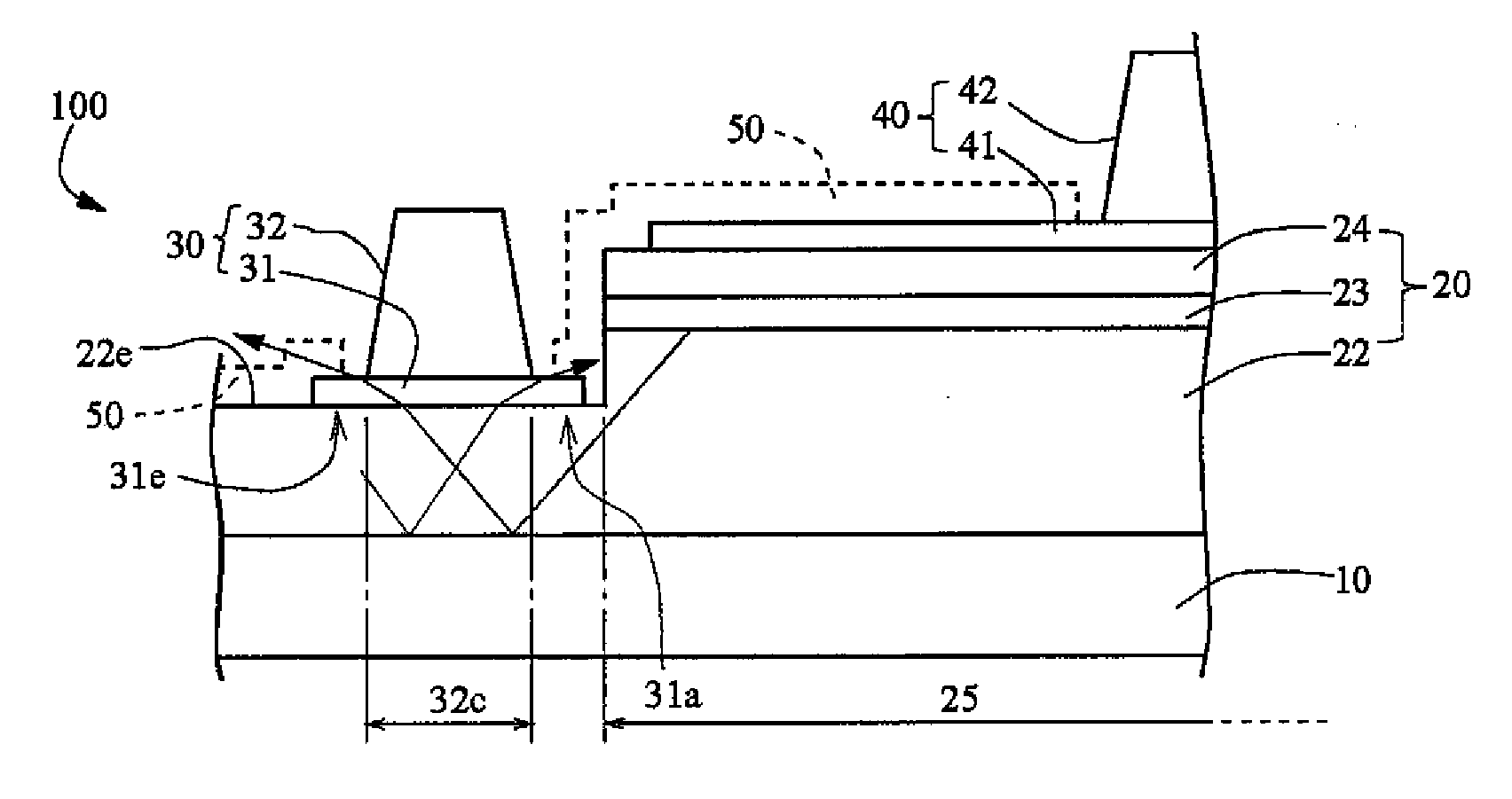

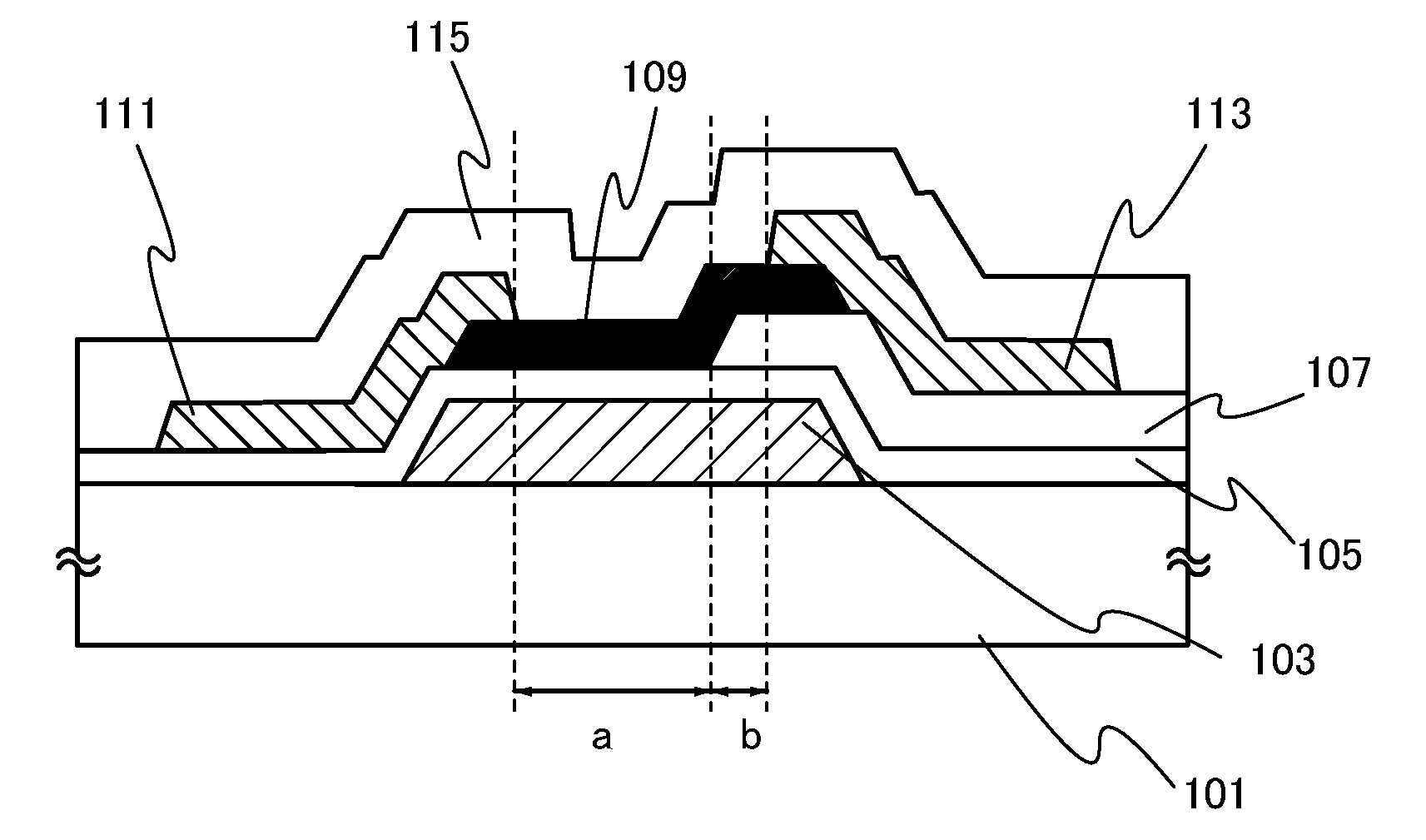

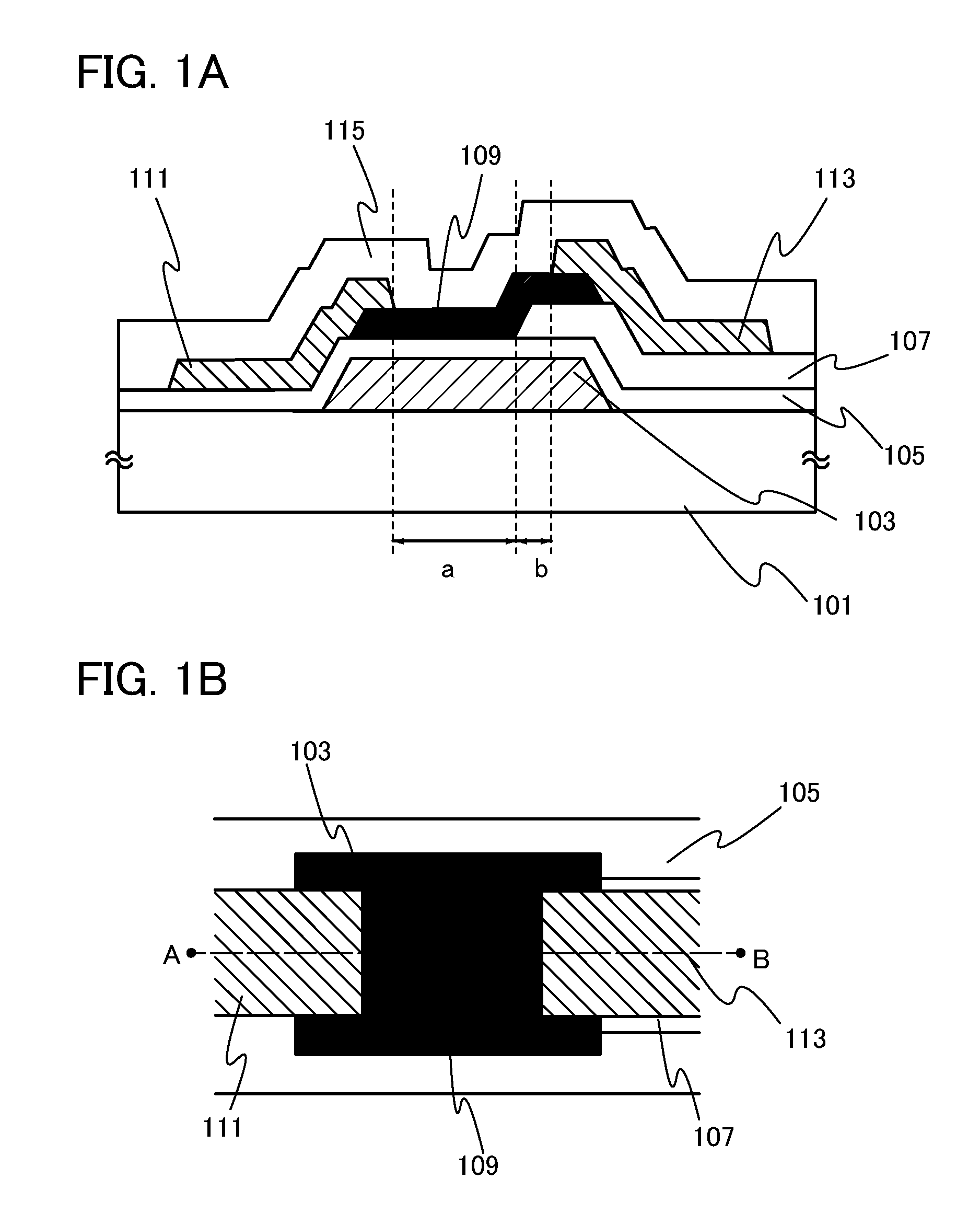

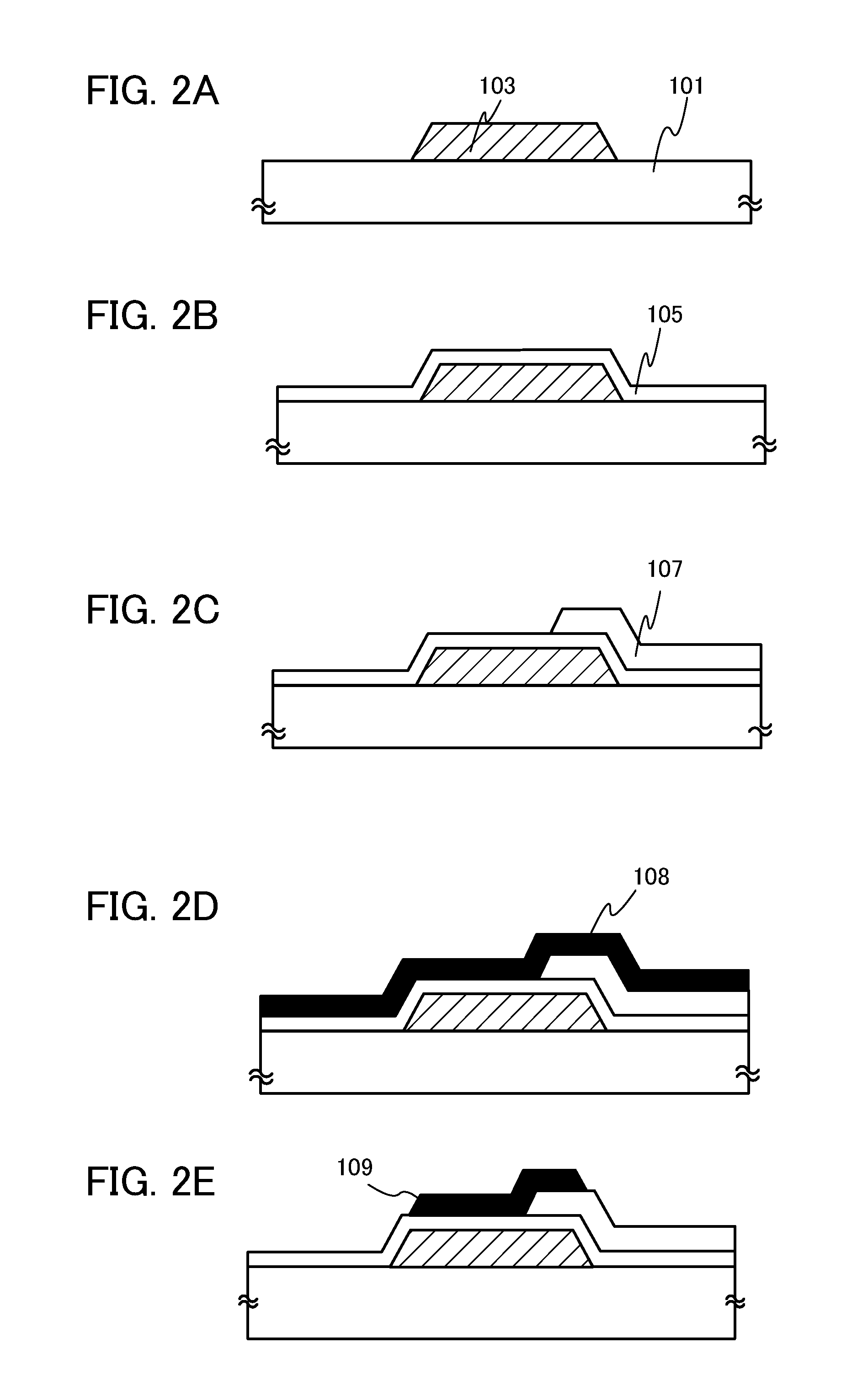

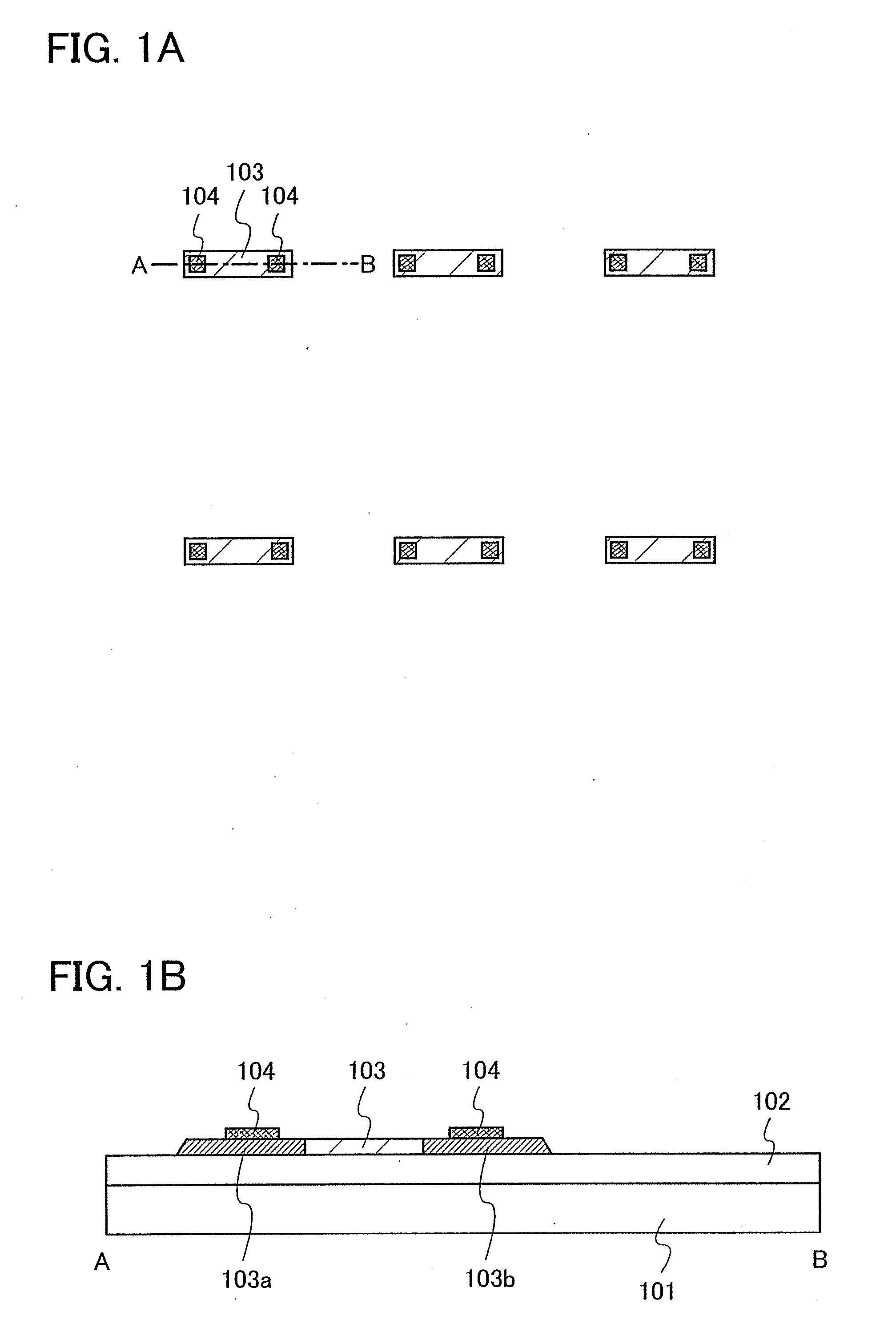

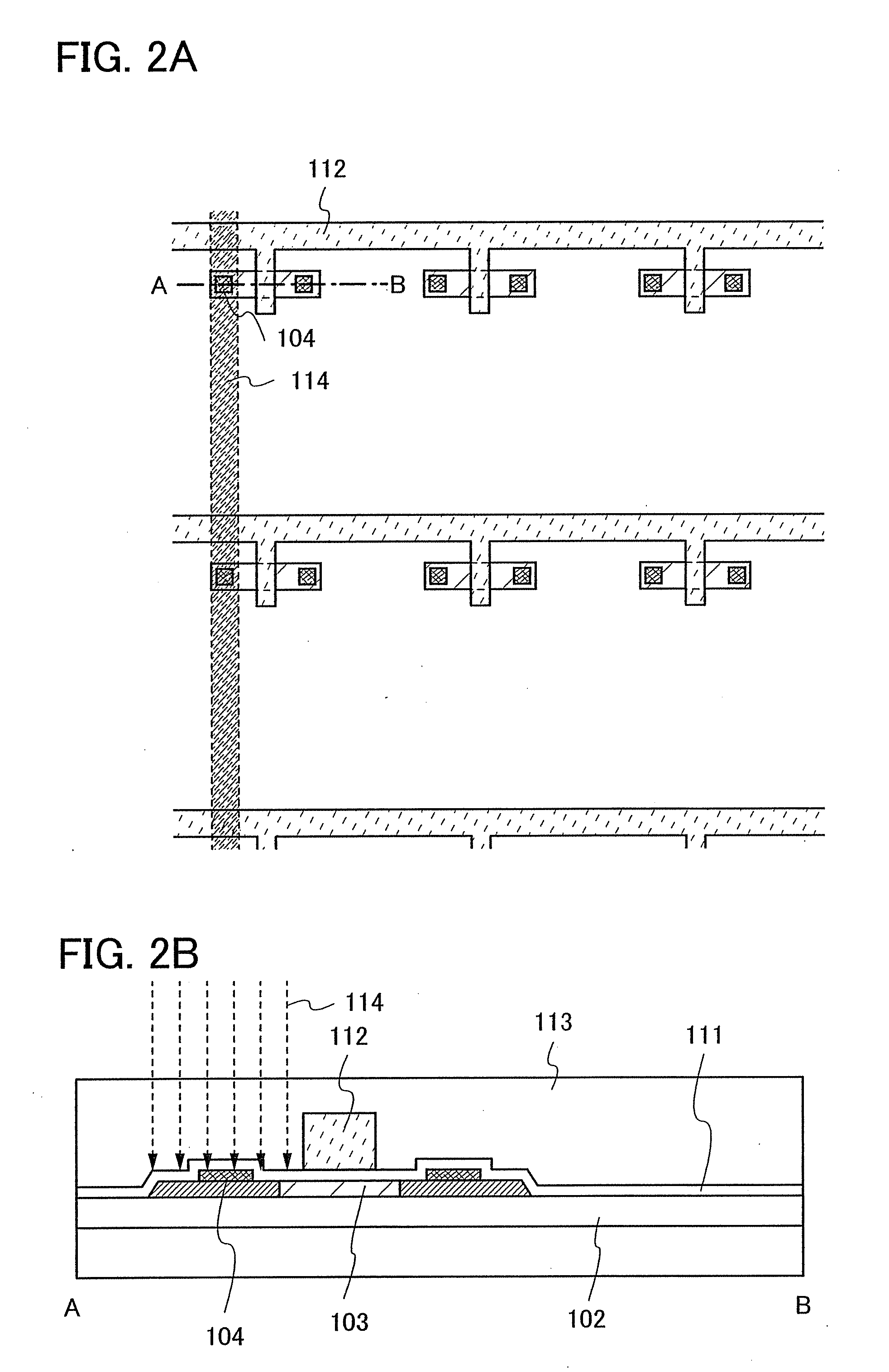

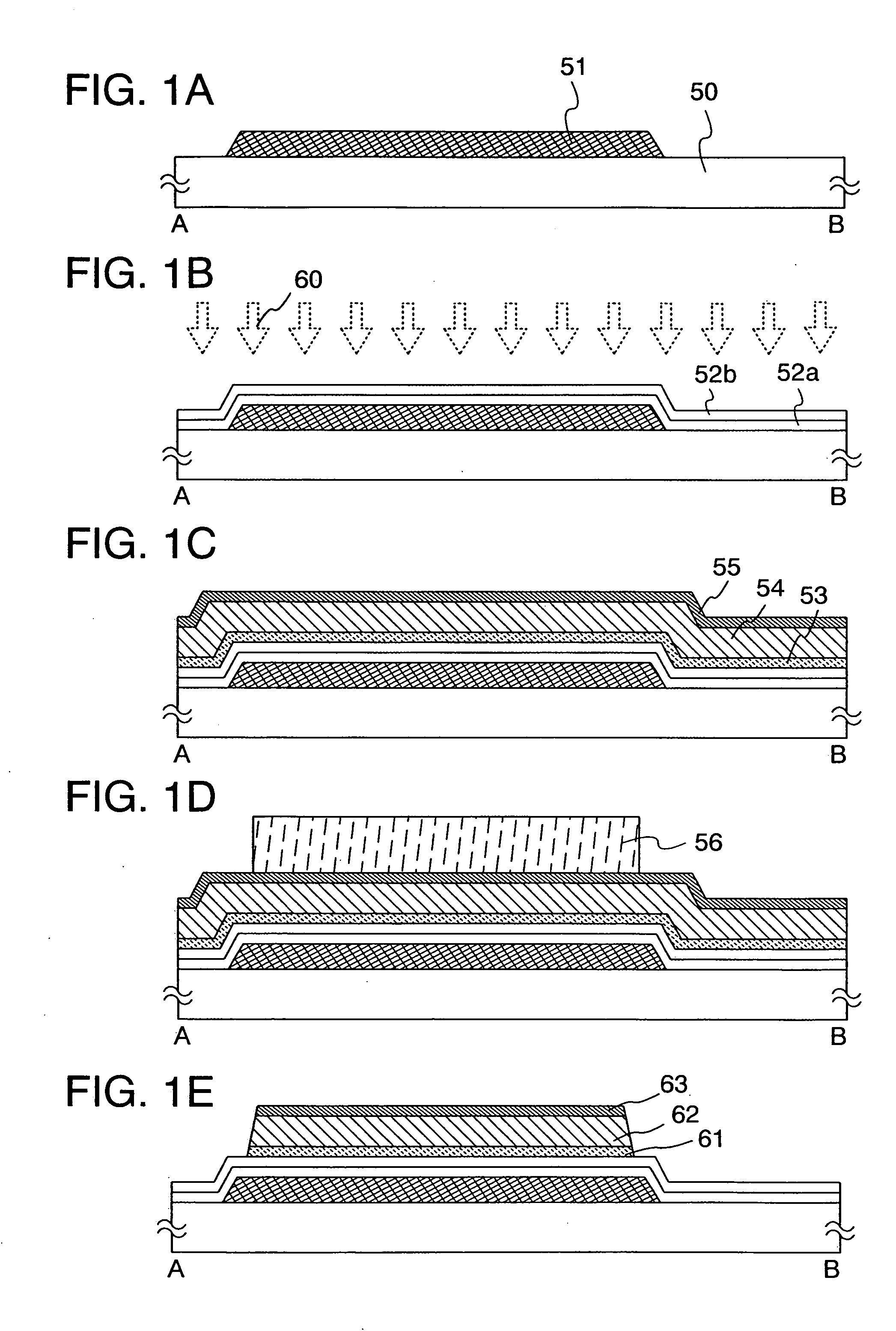

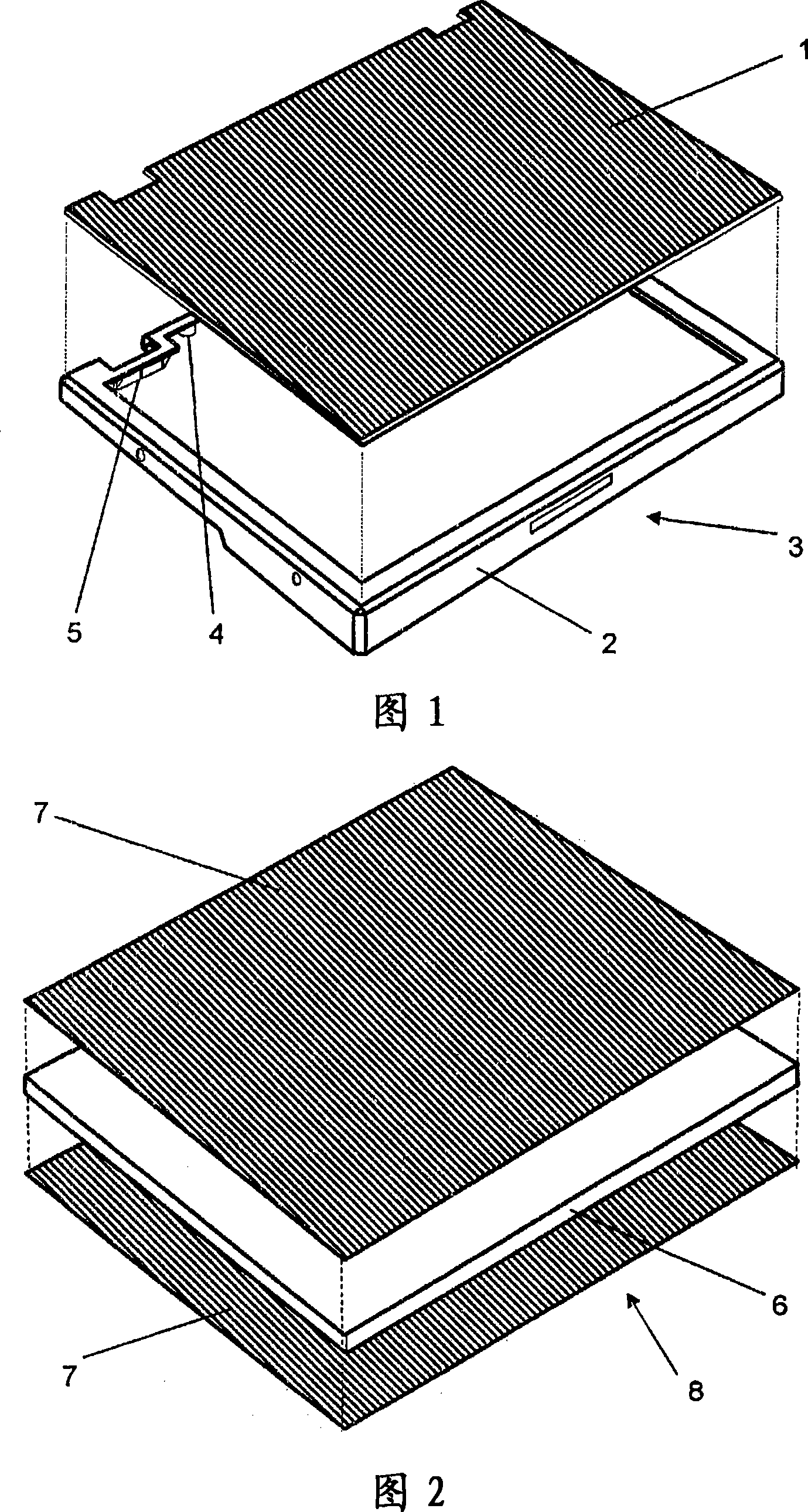

Display Device and Method for Manufacturing Display Device

ActiveUS20140014960A1Reduce thicknessImprove batch productivitySolid-state devicesSemiconductor/solid-state device manufacturingProduction rateDisplay device

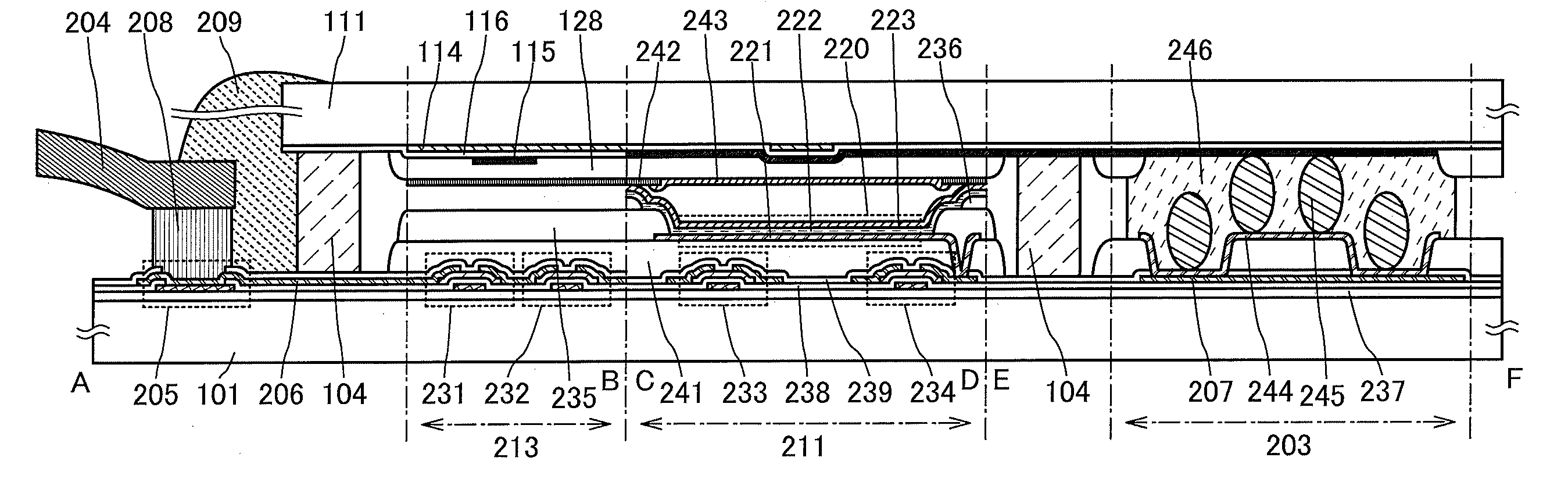

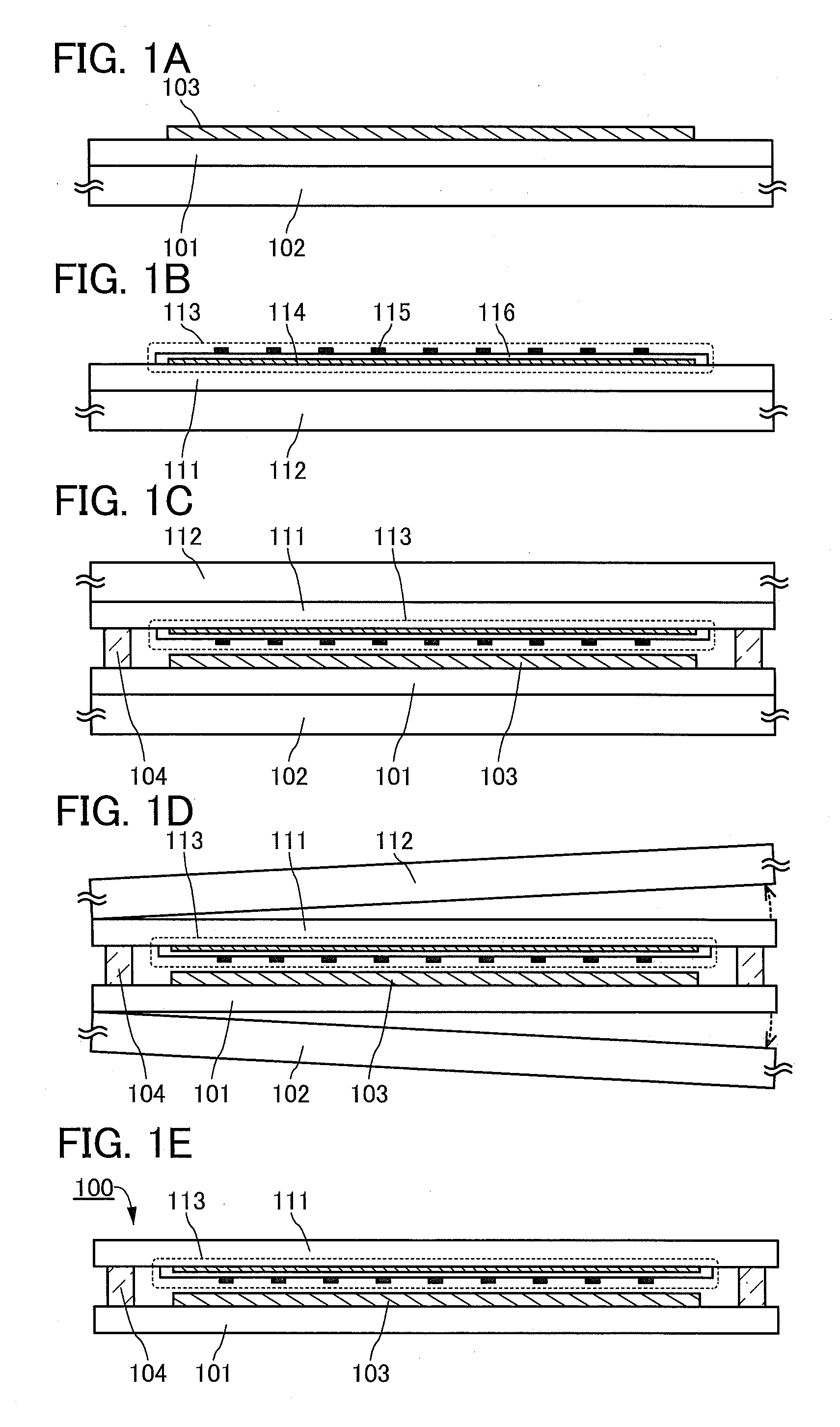

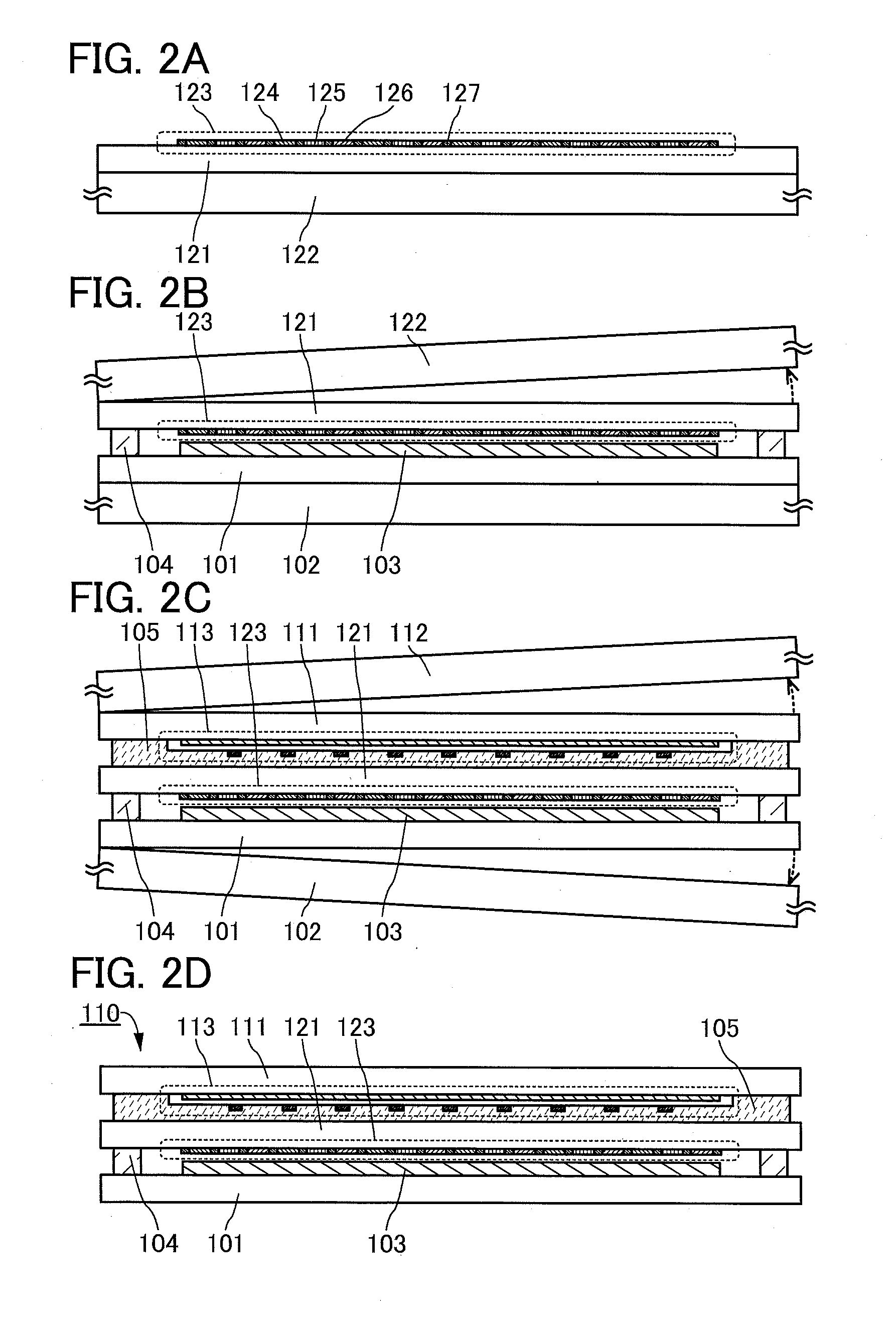

The thickness of a display device including a touch sensor is reduced. Alternatively, the thickness of a display device having high display quality is reduced. Alternatively, a method for manufacturing a display device with high mass productivity is provided. Alternatively, a display device having high reliability is provided. Stacked substrates in each of which a sufficiently thin substrate and a relatively thick support substrate are stacked are used as substrates. One surface of the thin substrate of one of the stacked substrates is provided with a layer including a touch sensor, and one surface of the thin substrate of the other stacked substrate is provided with a layer including a display element. After the two stacked substrates are attacked to each other so that the touch sensor and the display element face each other, the support substrate and the thin substrate of each stacked substrate are separated from each other.

Owner:SEMICON ENERGY LAB CO LTD

Bottom gate type thin film transistor, method of manufacturing the same, and display apparatus

InactiveUS20100051936A1Excels in mass productionOptimise total massTransistorElectroluminescent light sourcesDesorptionBottom gate

Provided is a bottom gate type thin film transistor including on a substrate (1) a gate electrode (2), a first insulating film (3) as a gate insulating film, an oxide semiconductor layer (4) as a channel layer, a second insulating film (5) as a protective layer, a source electrode (6), and a drain electrode (7), in which the oxide semiconductor layer (4) includes an oxide including at least one selected from the group consisting of In, Zn, and Sn, and the second insulating film (5) includes an amorphous oxide insulator formed so as to be in contact with the oxide semiconductor layer (4) and contains therein 3.8×1019 molecules / cm3 or more of a desorbed gas observed as oxygen by temperature programmed desorption mass spectrometry.

Owner:CANON KK

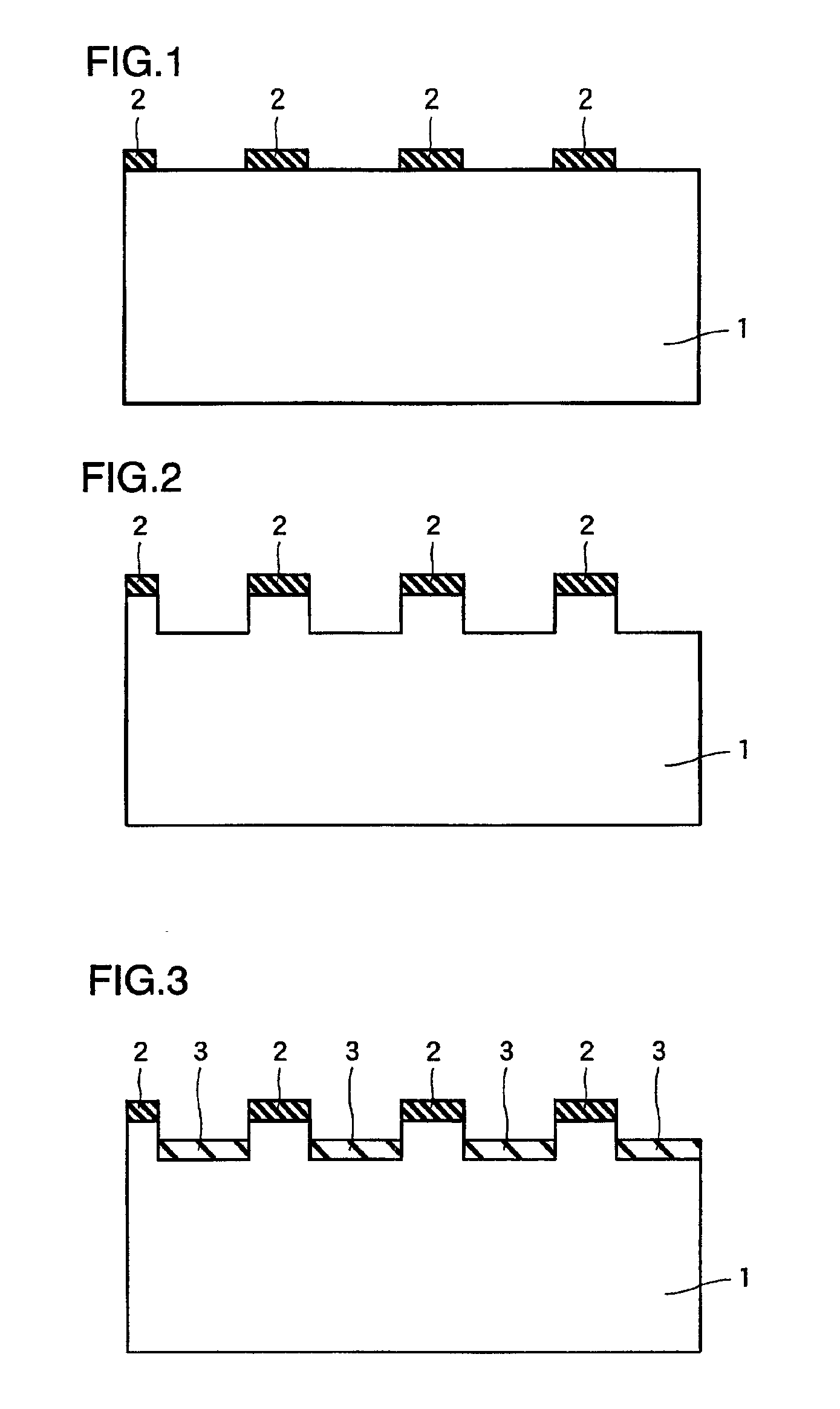

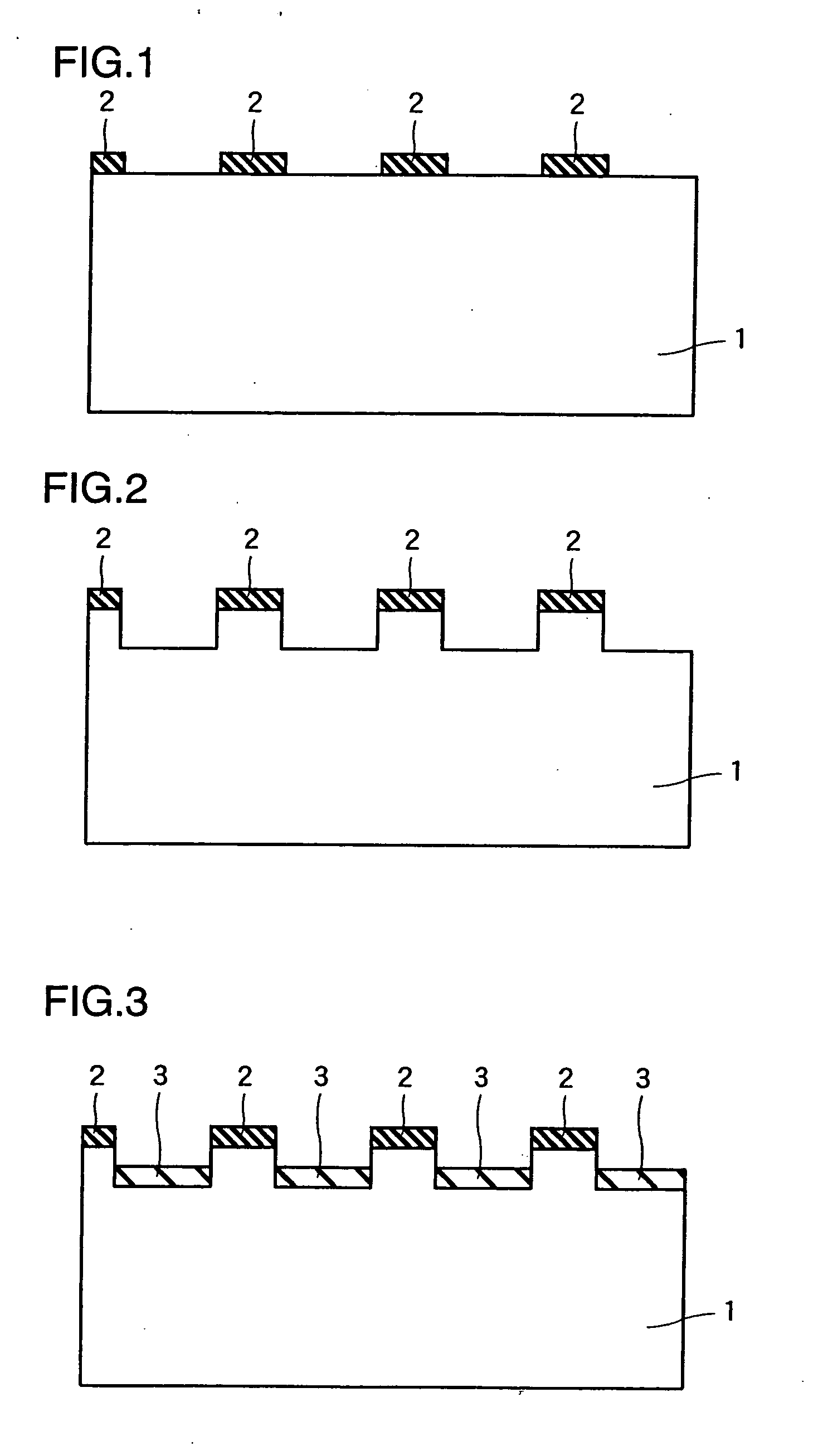

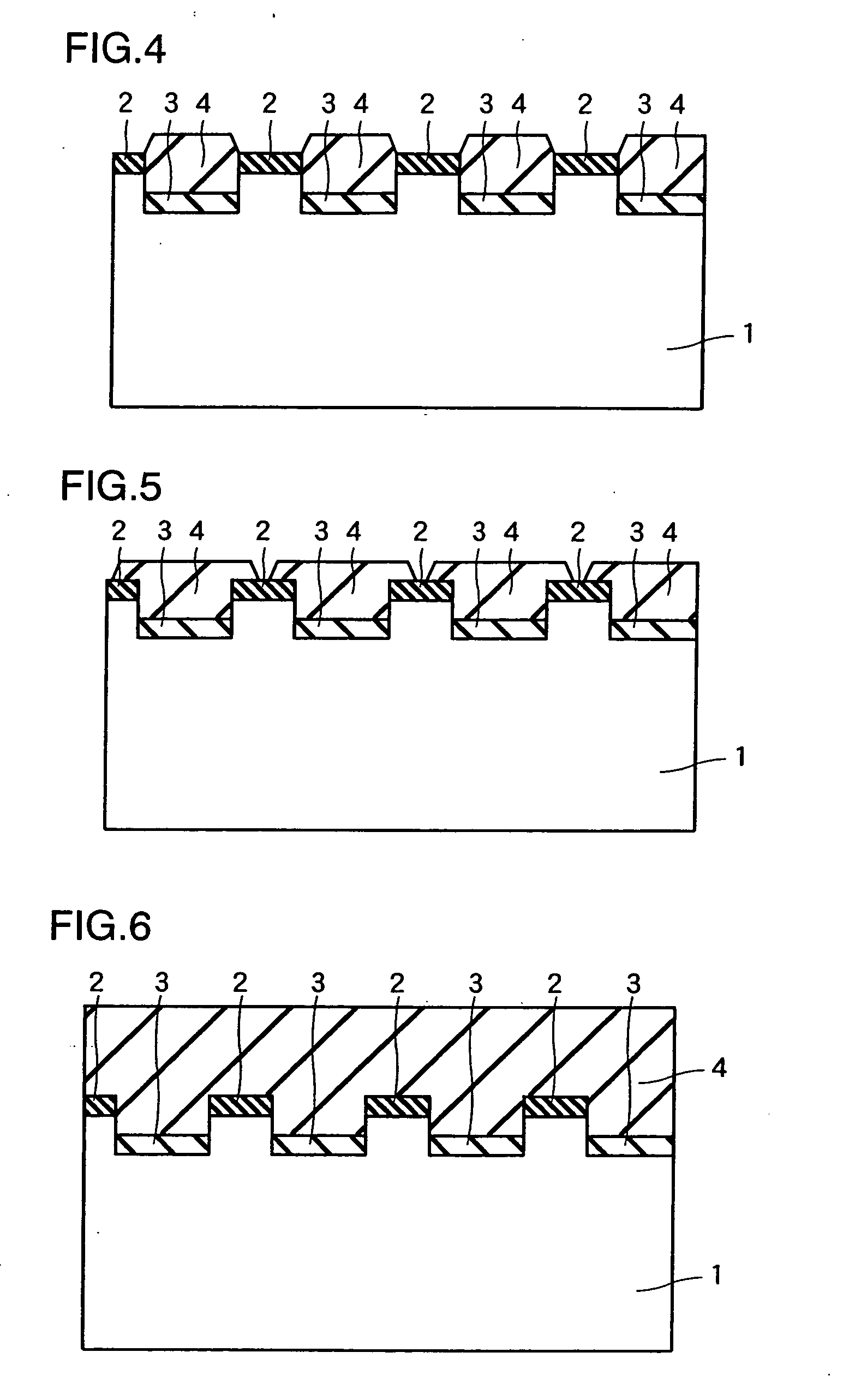

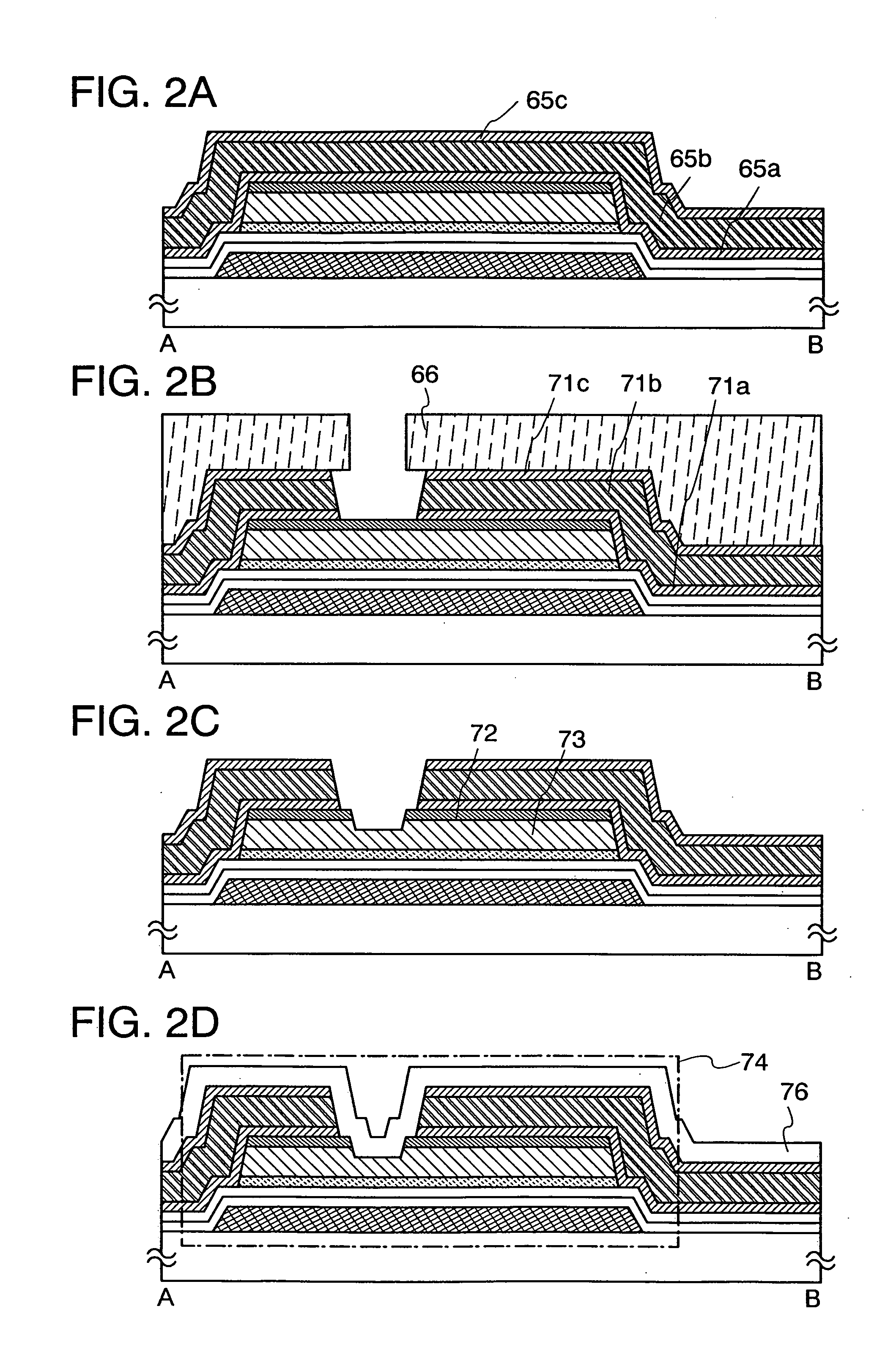

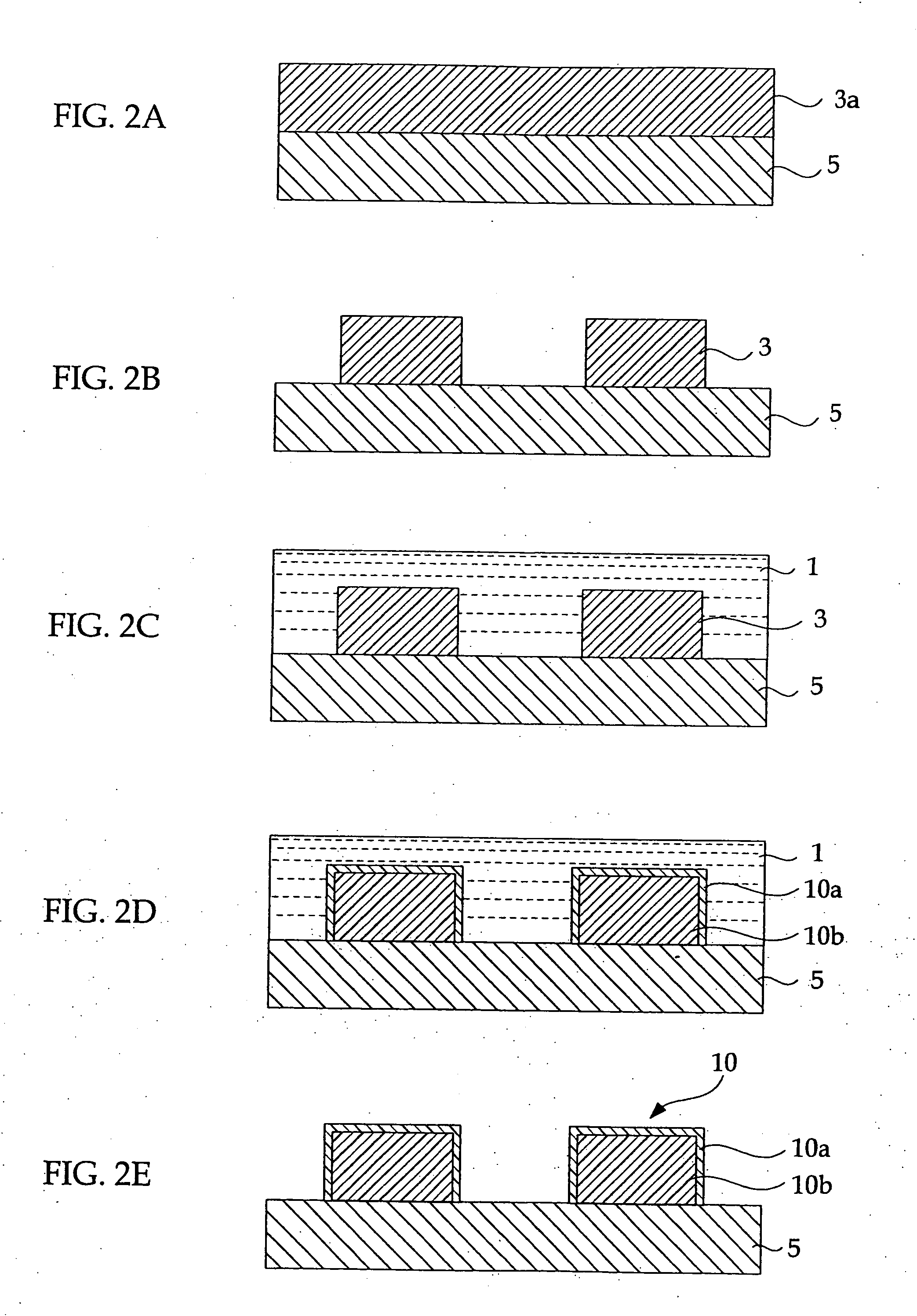

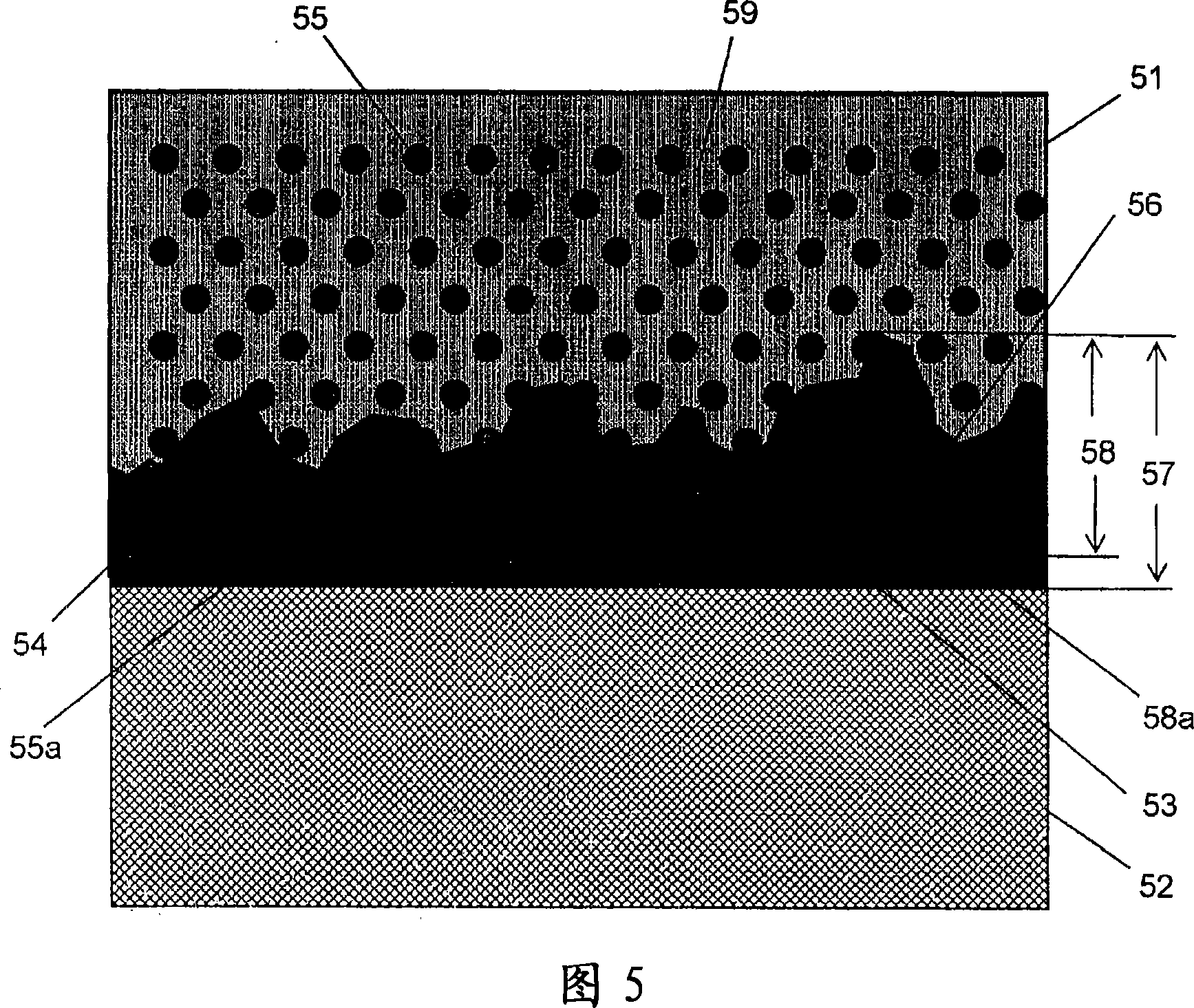

Nitride-based semiconductor element and method of forming nitride-based semiconductor

InactiveUS6994751B2Improve batch productivityExcellent element characteristicOptical wave guidancePolycrystalline material growthProduction rateDislocation

A nitride-based semiconductor element having superior mass productivity and excellent element characteristics is obtained. This nitride-based semiconductor element comprises a substrate comprising a surface having projection portions, a mask layer formed to be in contact with only the projection portions of the surface of the substrate, a first nitride-based semiconductor layer formed on recess portions of the substrate and the mask layer and a nitride-based semiconductor element layer, formed on the first nitride-based semiconductor layer, having an element region. Thus, the first nitride-based semiconductor layer having low dislocation density is readily formed on the projection portions of the substrate and the mask layer through the mask layer serving for selective growth. When the nitride-based semiconductor element layer having the element region is grown on the first nitride-based semiconductor layer having low dislocation density, a nitride-based semiconductor element having excellent element characteristics can be readily obtained. The first nitride-based semiconductor layer is formed through only single growth on the substrate, whereby a nitride-based semiconductor element having excellent mass productivity is obtained.

Owner:LEDVANCE GMBH

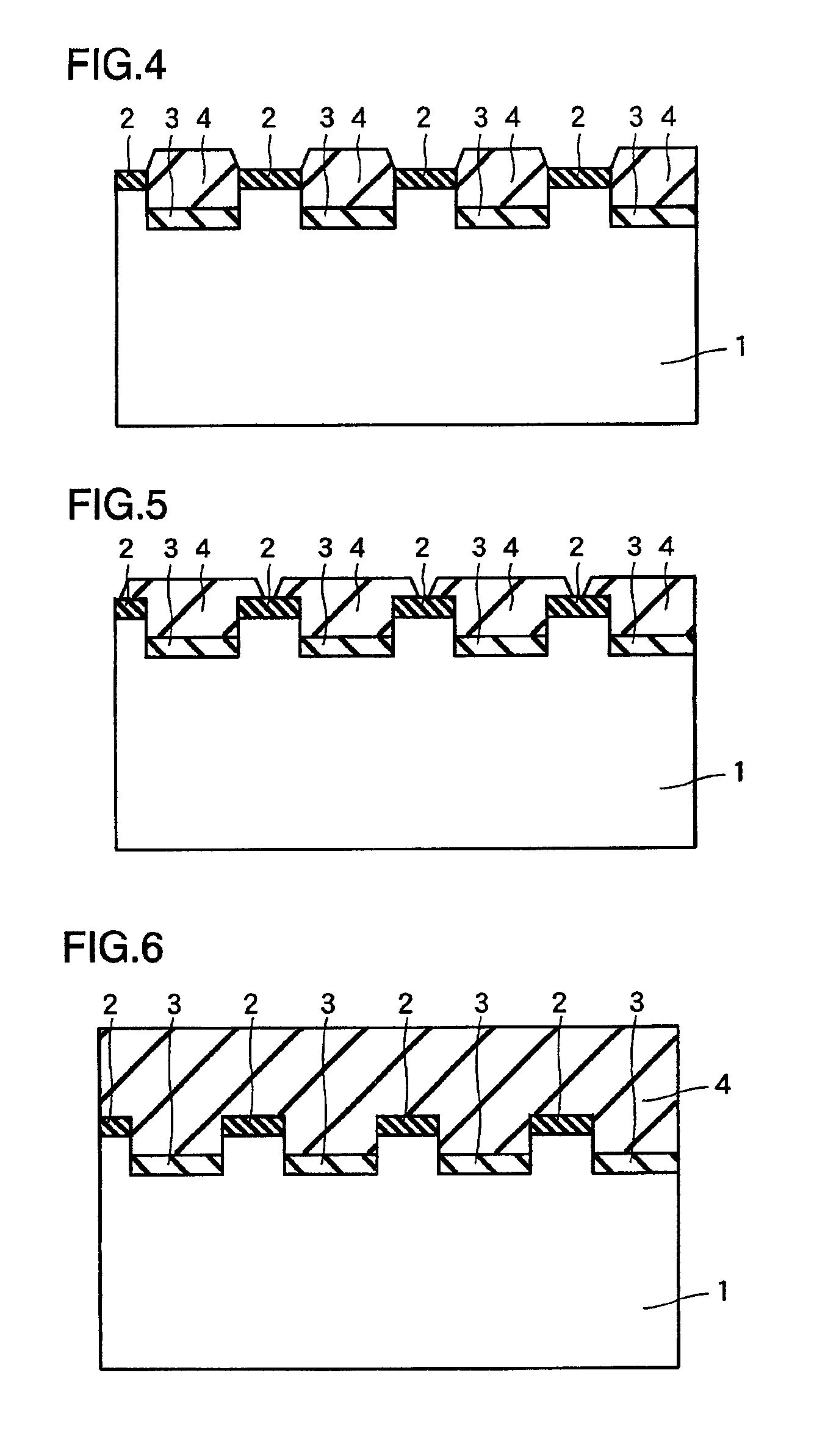

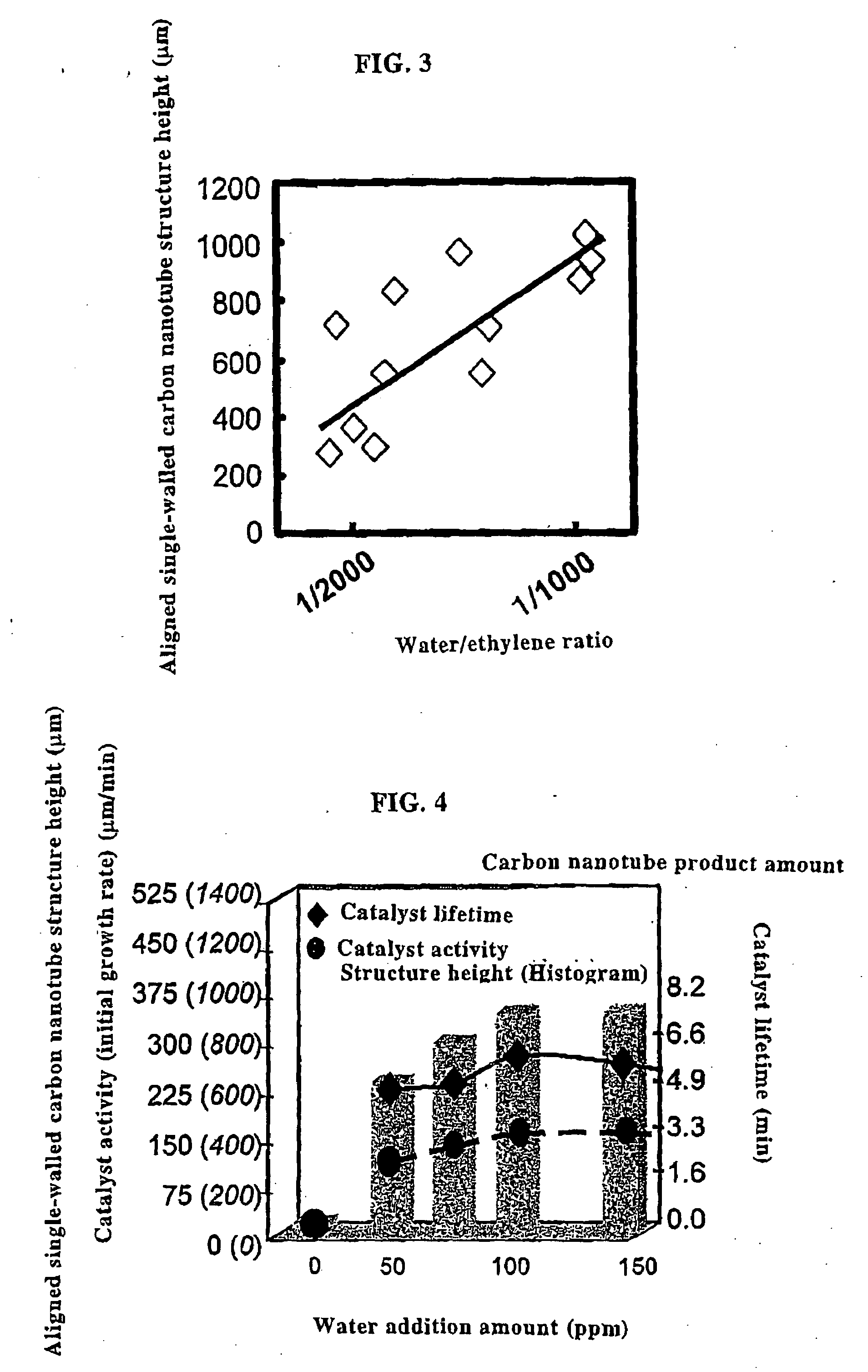

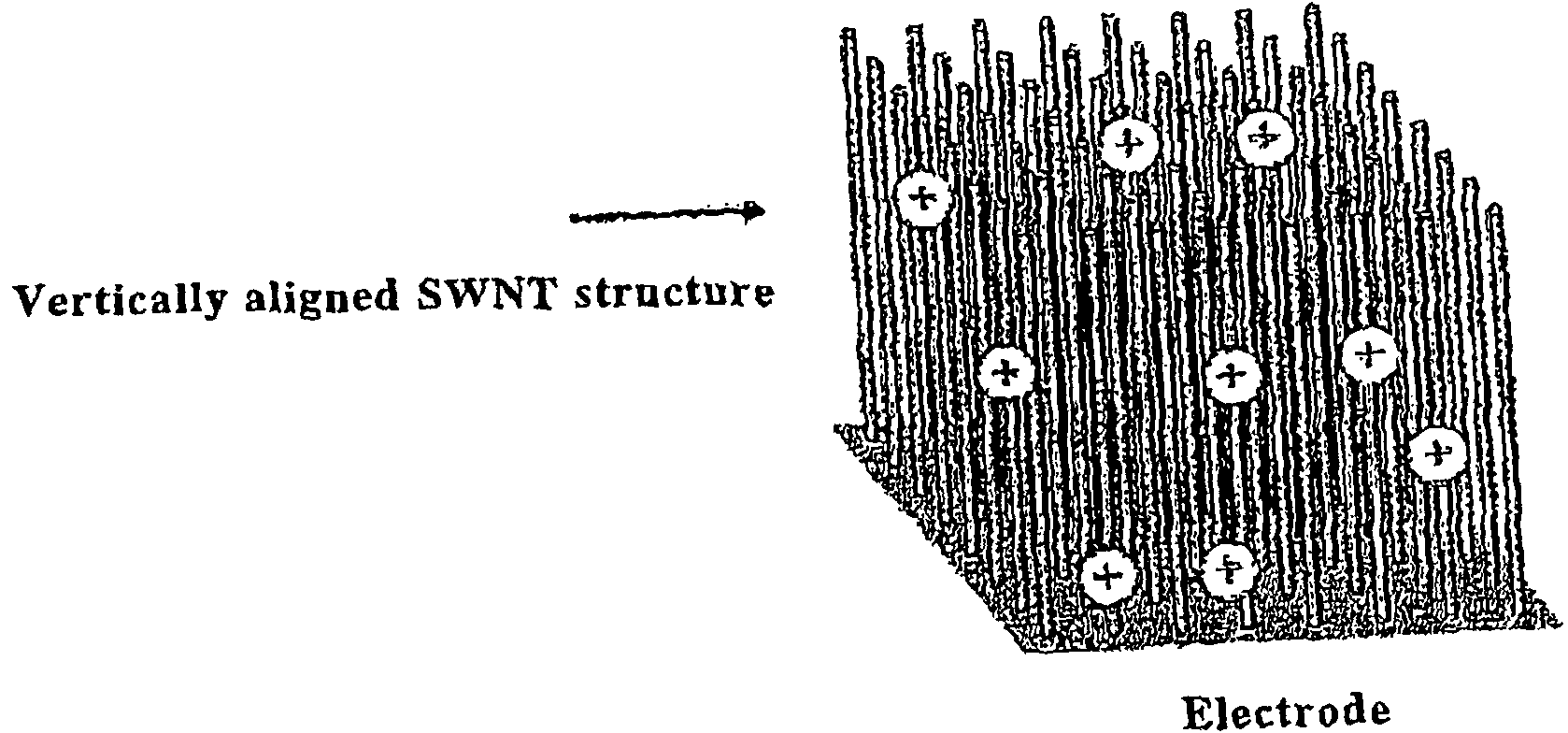

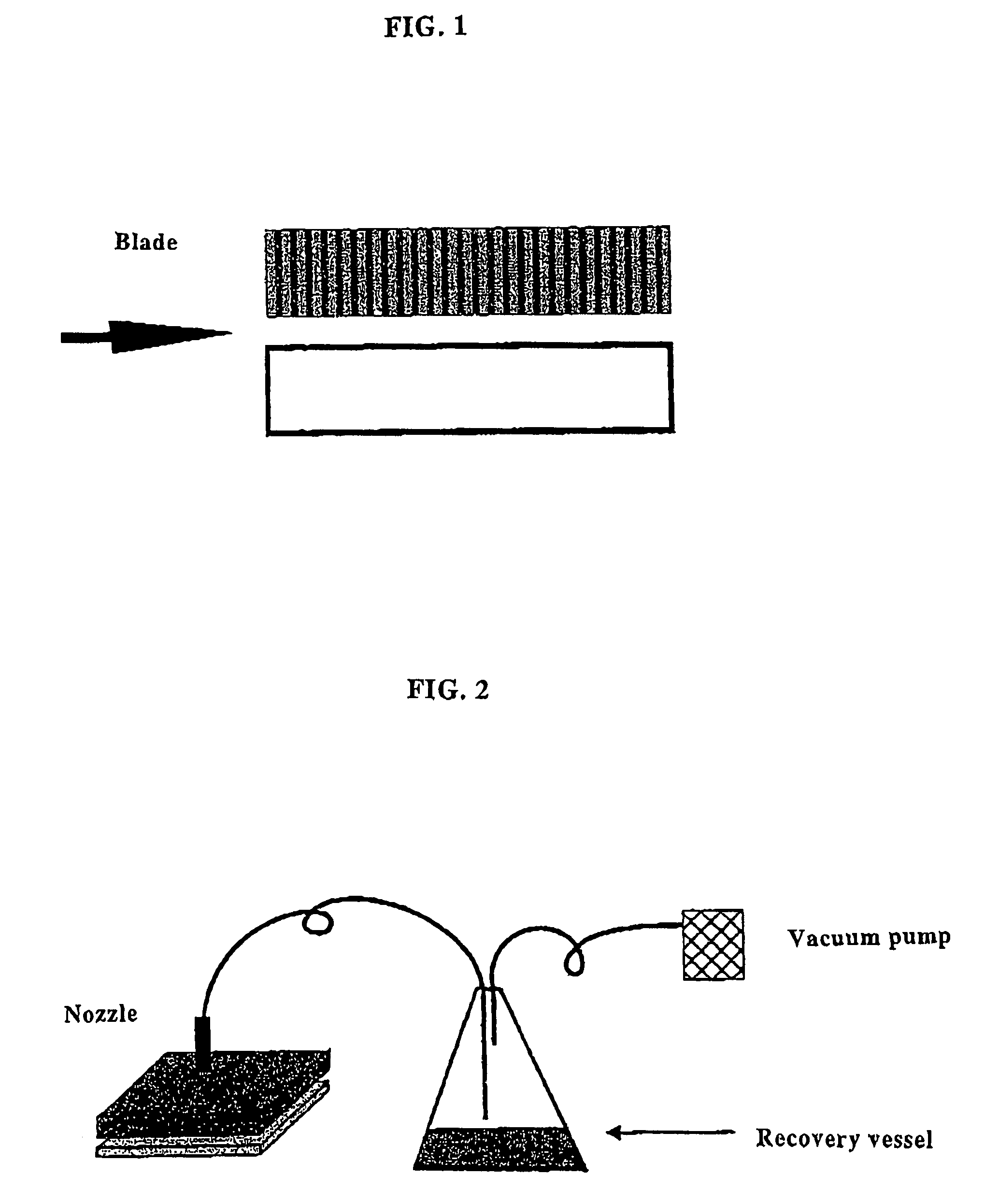

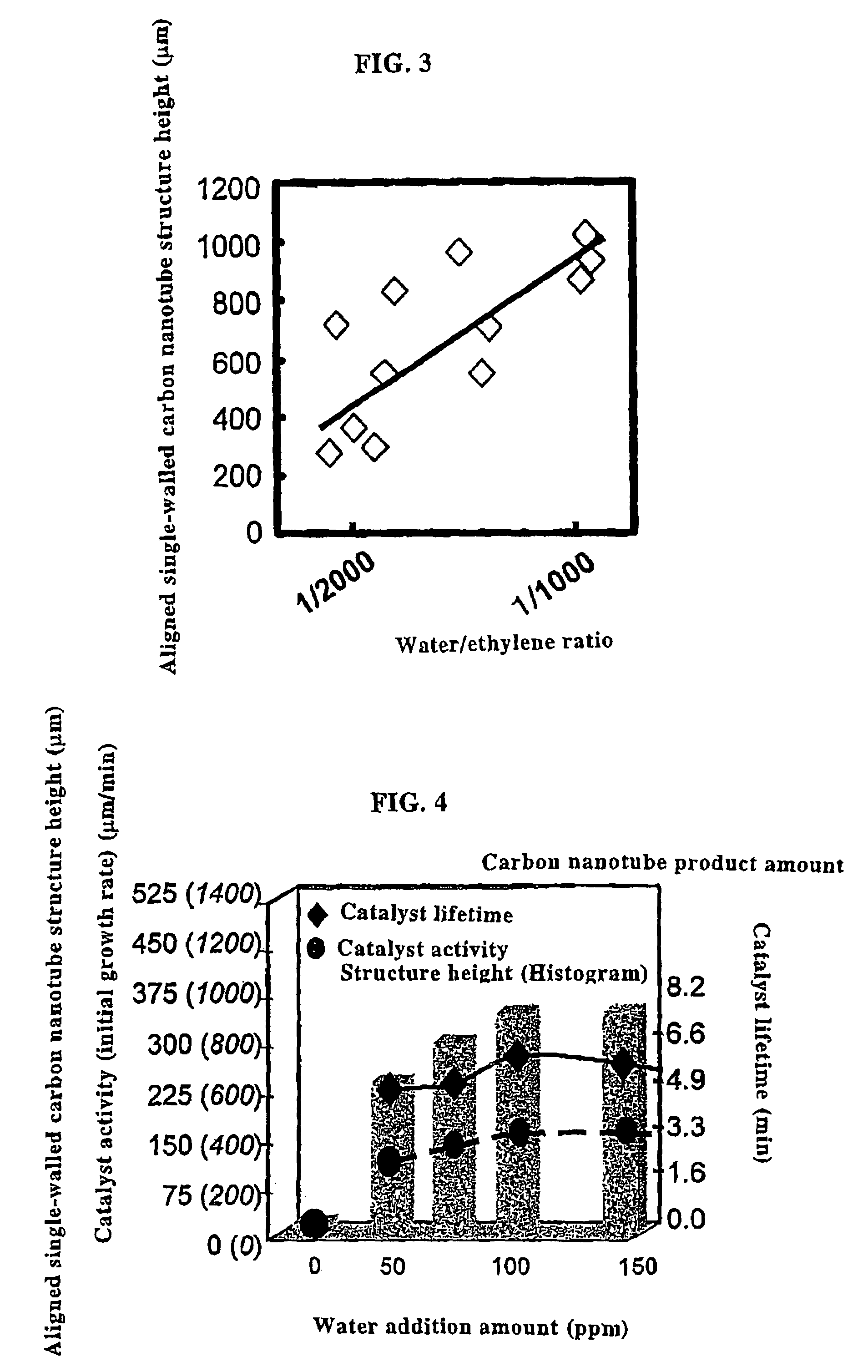

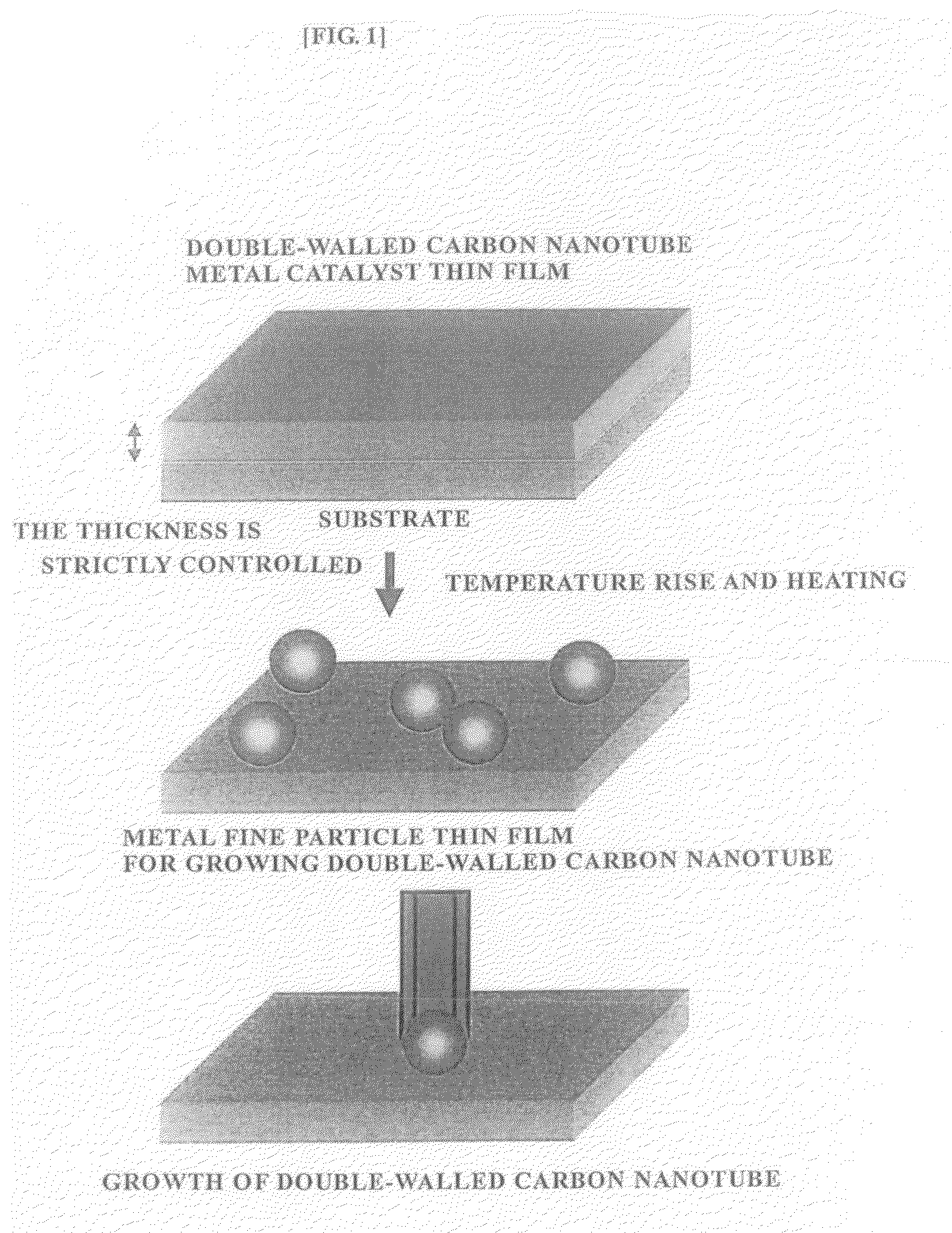

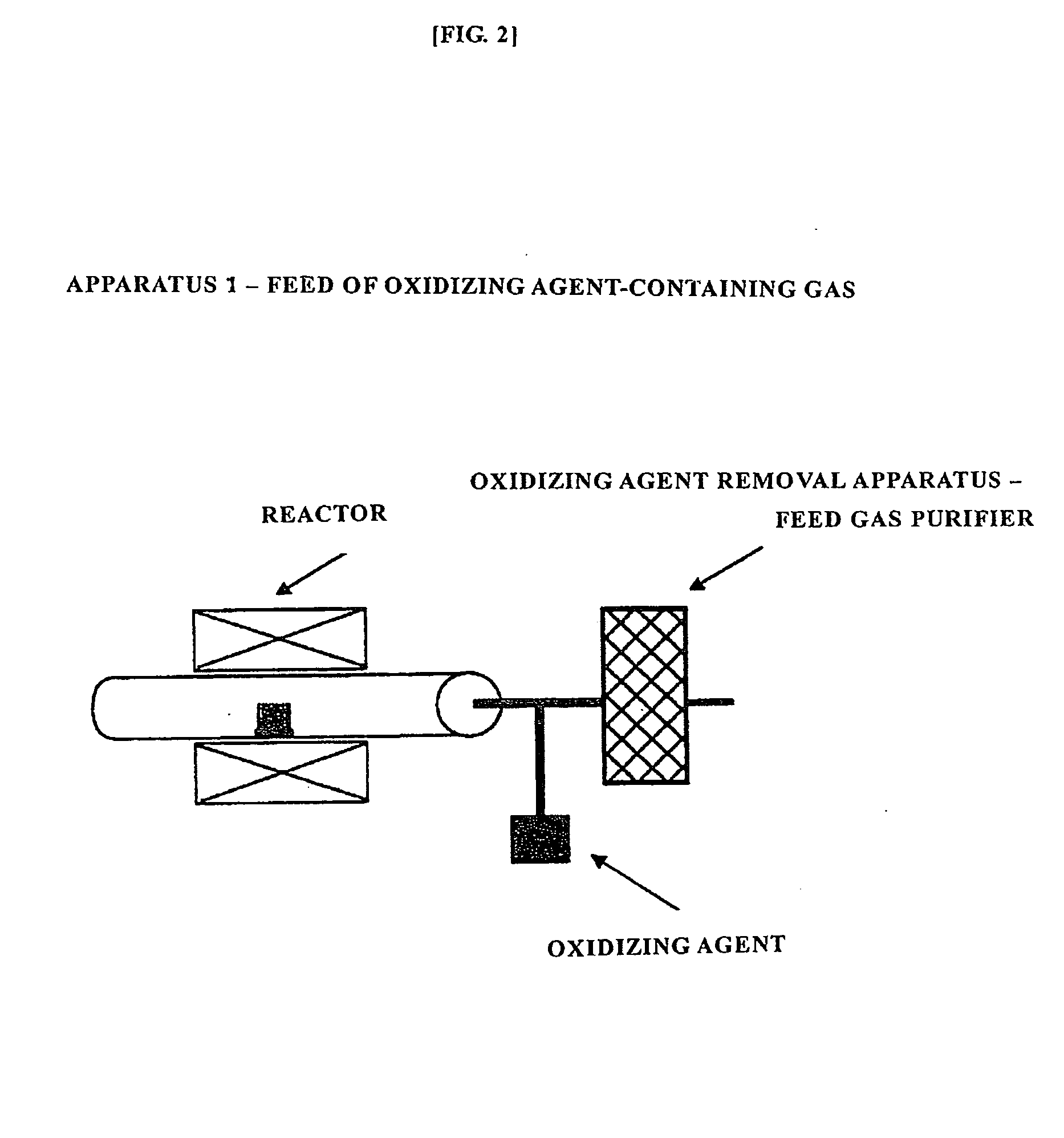

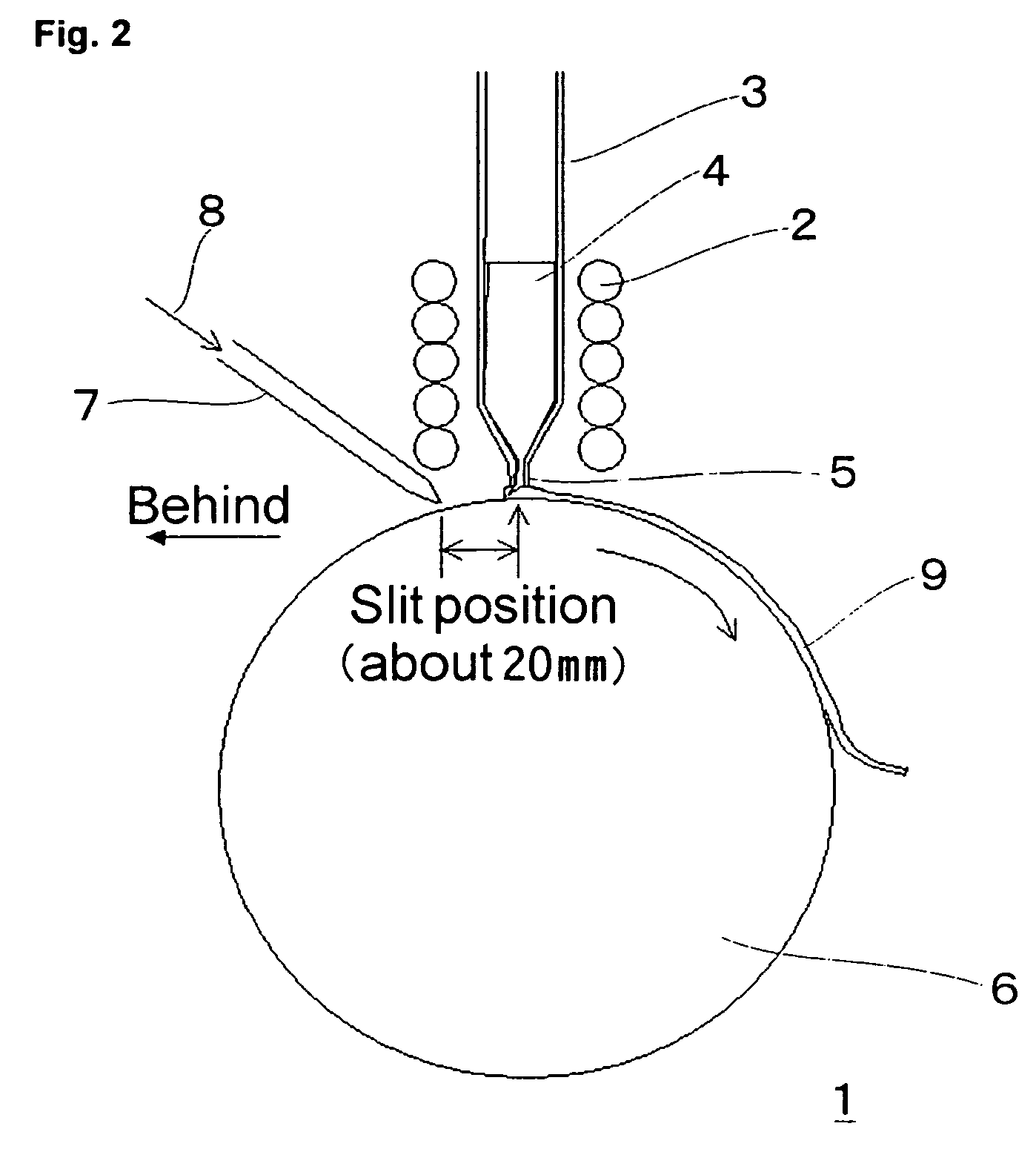

Single-Walled Carbon Nanotube and Aligned Single-Walled Carbon Nanotube Bulk Structure, and Their Production Process, Production Apparatus and Application Use

ActiveUS20080318049A1Efficient productionIncrease freedomMaterial nanotechnologyCell electrodesMetal catalystCarbon nanotube

This invention provides an aligned single-layer carbon nanotube bulk structure, which comprises an assembly of a plurality of aligned single-layer carbon nanotube and has a height of not less than 10 μm, and an aligned single-layer carbon nanotube bulk structure which comprises an assembly of a plurality of aligned single-layer carbon nanotubes and has been patterned in a predetermined form. This structure is produced by chemical vapor deposition (CVD) of carbon nanotubes in the presence of a metal catalyst in a reaction atmosphere with an oxidizing agent, preferably water, added thereto. An aligned single-layer carbon nanotube bulk structure, which has realized high purify and significantly large scaled length or height, its production process and apparatus, and its applied products are provided.

Owner:NAT INST OF ADVANCED IND SCI & TECH

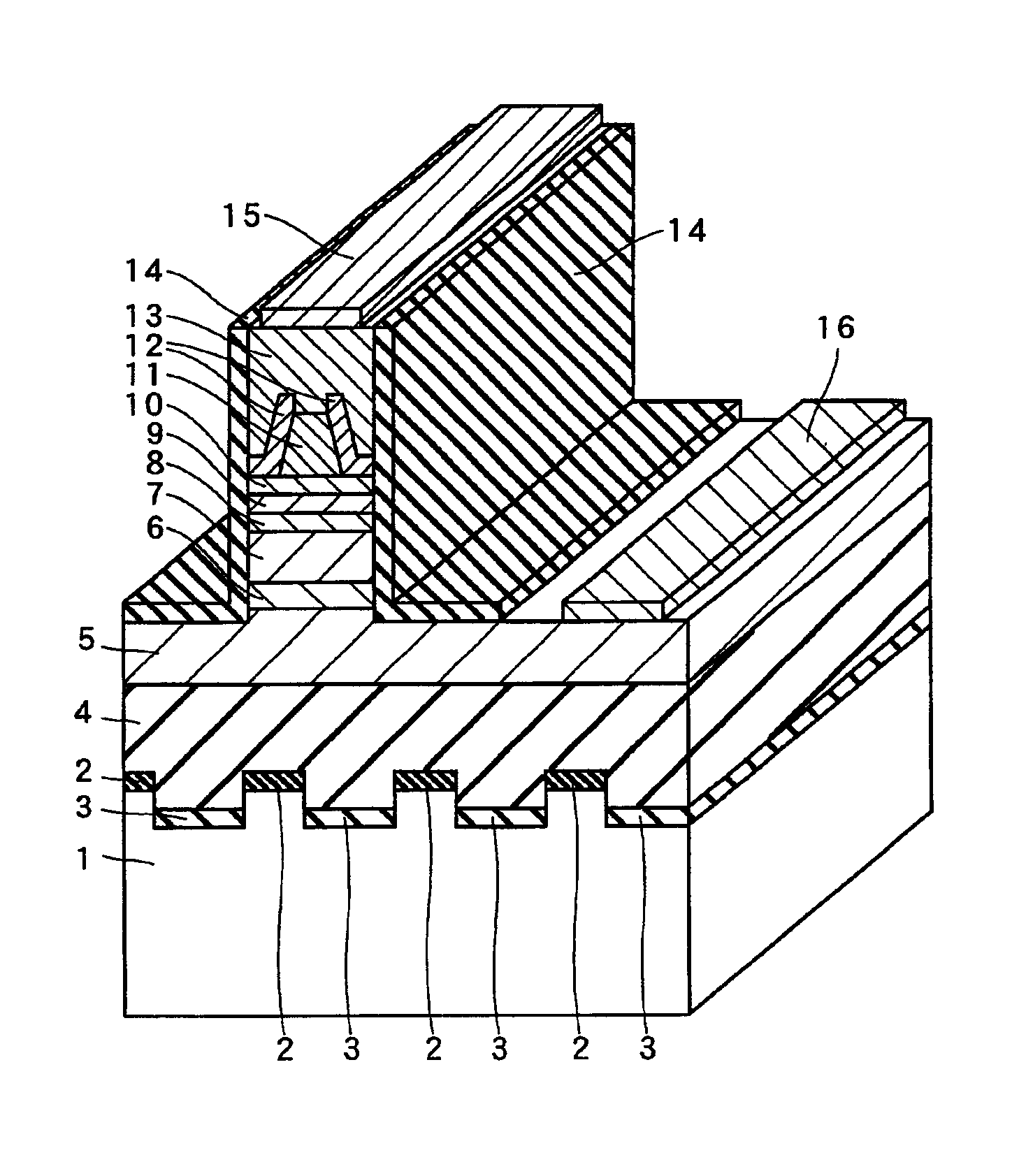

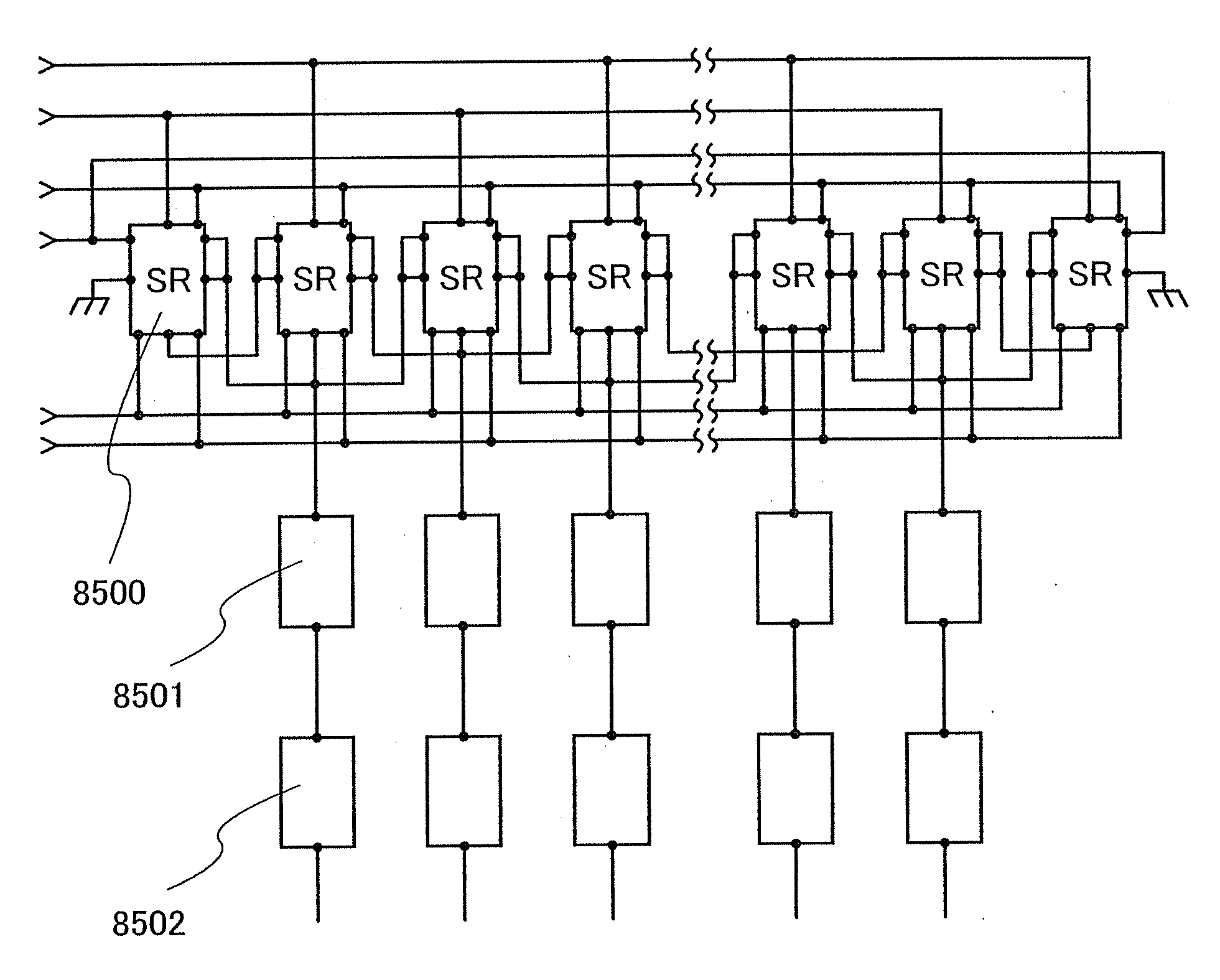

Semiconductor device and manufacturing method thereof

ActiveUS20110215331A1Improve reliabilityReduce power consumptionTransistorStatic indicating devicesDevice materialEngineering

An object of the present invention to provide a highly reliable semiconductor device. Another object is to provide a manufacturing method of a highly reliable semiconductor device. Still another object is to provide a semiconductor device having low power consumption. Yet another object is to provide a manufacturing method of a semiconductor device having low power consumption. Furthermore, another object is to provide a semiconductor device which can be manufactured with high mass productivity. Another object is to provide a manufacturing method of a semiconductor device which can be manufactured with high mass productivity. An impurity remaining in an oxide semiconductor layer is removed so that the oxide semiconductor layer is purified to have an extremely high purity. Specifically, after adding a halogen element into the oxide semiconductor layer, heat treatment is performed to remove an impurity from the oxide semiconductor layer. The halogen element is preferably fluorine.

Owner:SEMICON ENERGY LAB CO LTD

Single-walled carbon nanotube and aligned single-walled carbon nanotube bulk structure, and their production process, production apparatus and application use

ActiveUS7854991B2Prolong lifeIncrease probabilityMaterial nanotechnologyCell electrodesMetal catalystCarbon nanotube

This invention provides an aligned single-layer carbon nanotube bulk structure, which comprises an assembly of a plurality of aligned single-layer carbon nanotube and has a height of not less than 10 μm, and an aligned single-layer carbon nanotube bulk structure which comprises an assembly of a plurality of aligned single-layer carbon nanotubes and has been patterned in a predetermined form. This structure is produced by chemical vapor deposition (CVD) of carbon nanotubes in the presence of a metal catalyst in a reaction atmosphere with an oxidizing agent, preferably water, added thereto. An aligned single-layer carbon nanotube bulk structure, which has realized high purify and significantly large scaled length or height, its production process and apparatus, and its applied products are provided.

Owner:NAT INST OF ADVANCED IND SCI & TECH

Liquid crystal display and method for manufacturing same

ActiveUS20060061719A1Improve light transmittanceImprove light efficiencyLiquid crystal compositionsCoatingsHigh contrastLiquid-crystal display

A liquid crystal display is provided which is capable of reducing the occurrence of defective display due to variations in the initial alignment direction of a liquid crystal alignment control film in a liquid crystal display of an IPS scheme, realizing the stable liquid crystal alignment, providing excellent mass productivity, and having high image quality with a higher contrast ratio. The liquid crystal display has a liquid crystal layer disposed between a pair of substrates, at least one of the substrates being transparent, and an alignment control film formed between the liquid crystal layer and the substrate. At least one of the alignment control films comprises photoreactive polyimide and / or polyamic acid provided with an alignment control ability by irradiation of substantially linearly polarized light.

Owner:NISSAN CHEM IND LTD

Thermoelectric conversion materials

InactiveUS20050268956A1Improve thermoelectric conversion efficiencyImprove batch productivityThermoelectric device with peltier/seeback effectThermoelectric device manufacture/treatmentProduction rateCore component

The main object of the present invention is to provide the thermoelectric conversion materials having a high thermoelectric conversion performance and the excellent mass productivity. The object of the present invention is achieved by providing the thermoelectric conversion materials comprising a core-shell structure having a plurality of core parts and shell parts for covering the above-mentioned core parts, wherein the plurality of the above-mentioned core parts are independent with each other and the above-mentioned shell parts are provided continuously.

Owner:DAI NIPPON PRINTING CO LTD

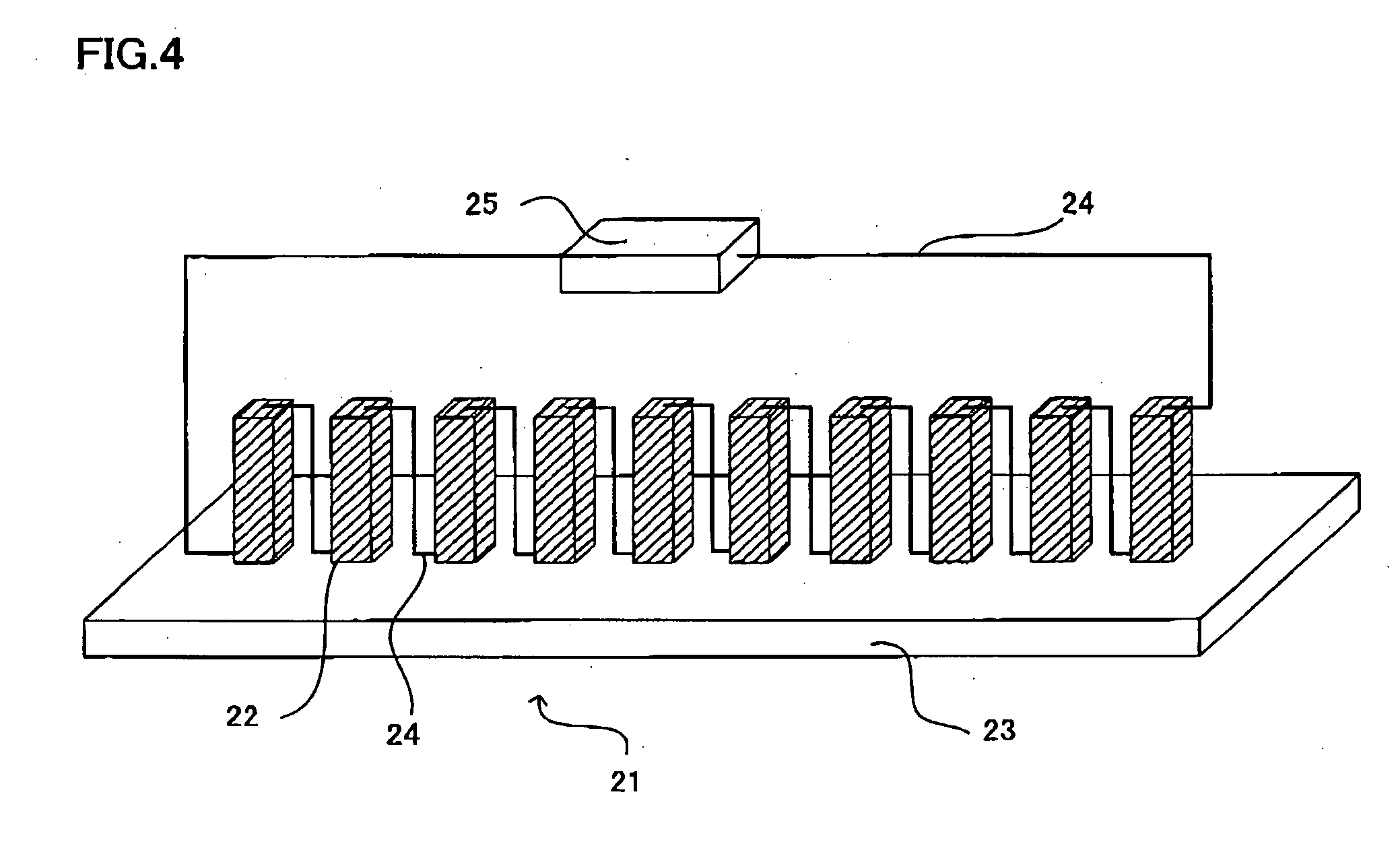

Double-Walled Carbon Nanotube, Aligned Double-Walled Carbon Nanotube Bulk Structure and Process for Producing the Same

InactiveUS20090297846A1High purityEasy to control alignmentMaterial nanotechnologyCarbon compoundsMetal catalystChemical vapor deposition

An aligned double-walled carbon nanotube bulk structure composed of plural aligned double-walled carbon nanotubes and having a height of 0.1 μm or more and a double-walled carbon nanotube are produced by chemically vapor depositing (CVD) a carbon nanotube in the presence of a metal catalyst with controlled particle size and thickness, preferably in the presence of moisture. According to this, it is possible to provide a double-walled nanotube which is free from inclusion of the catalyst, has high purity, is easy to control the alignment and growth, is able to achieve the fabrication through the formation of a bulk structure and has excellent electron emission characteristic (particularly, a double-walled carbon nanotube bulk structure) and also to provide a production technology thereof.

Owner:NAT INST OF ADVANCED IND SCI & TECH

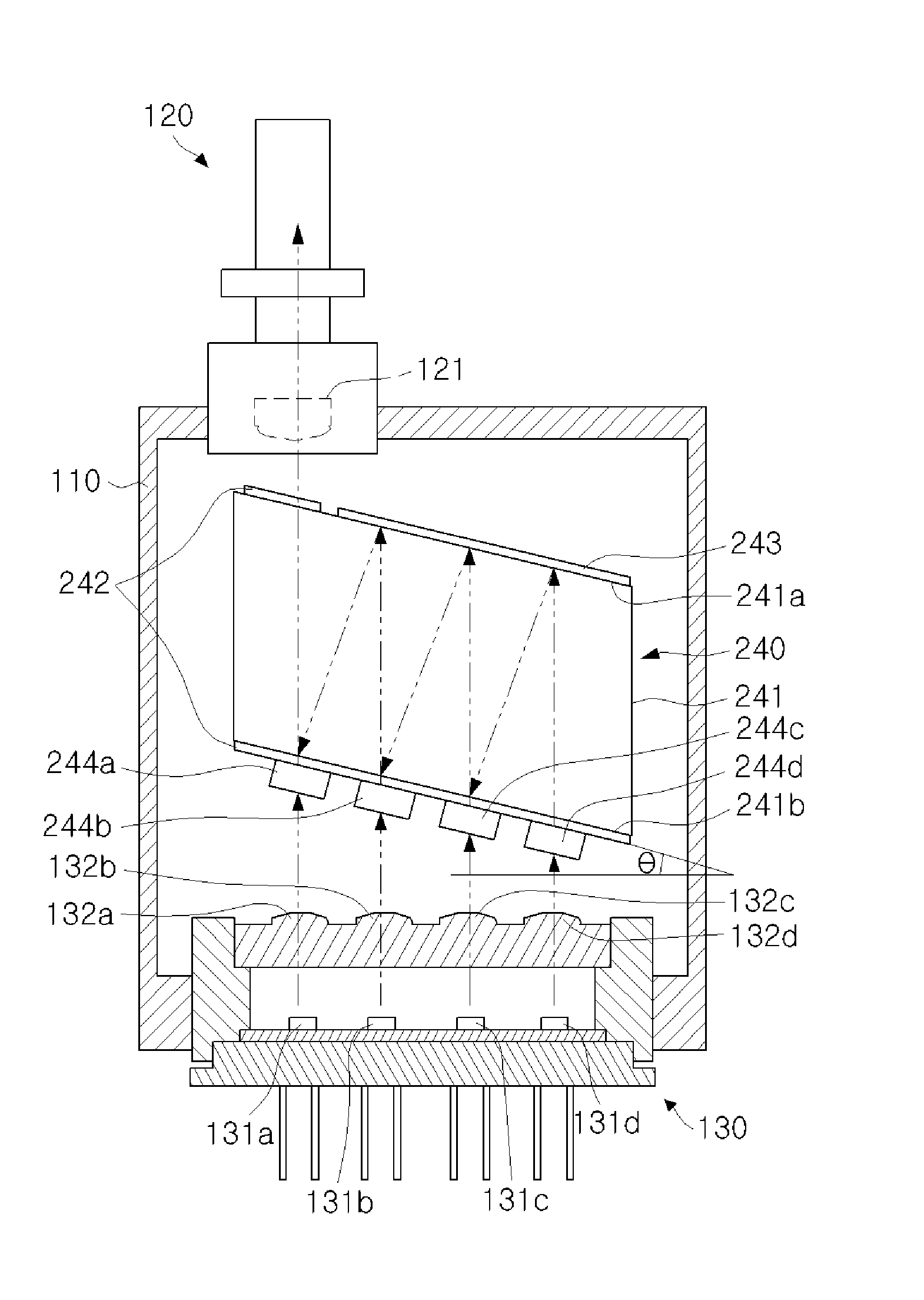

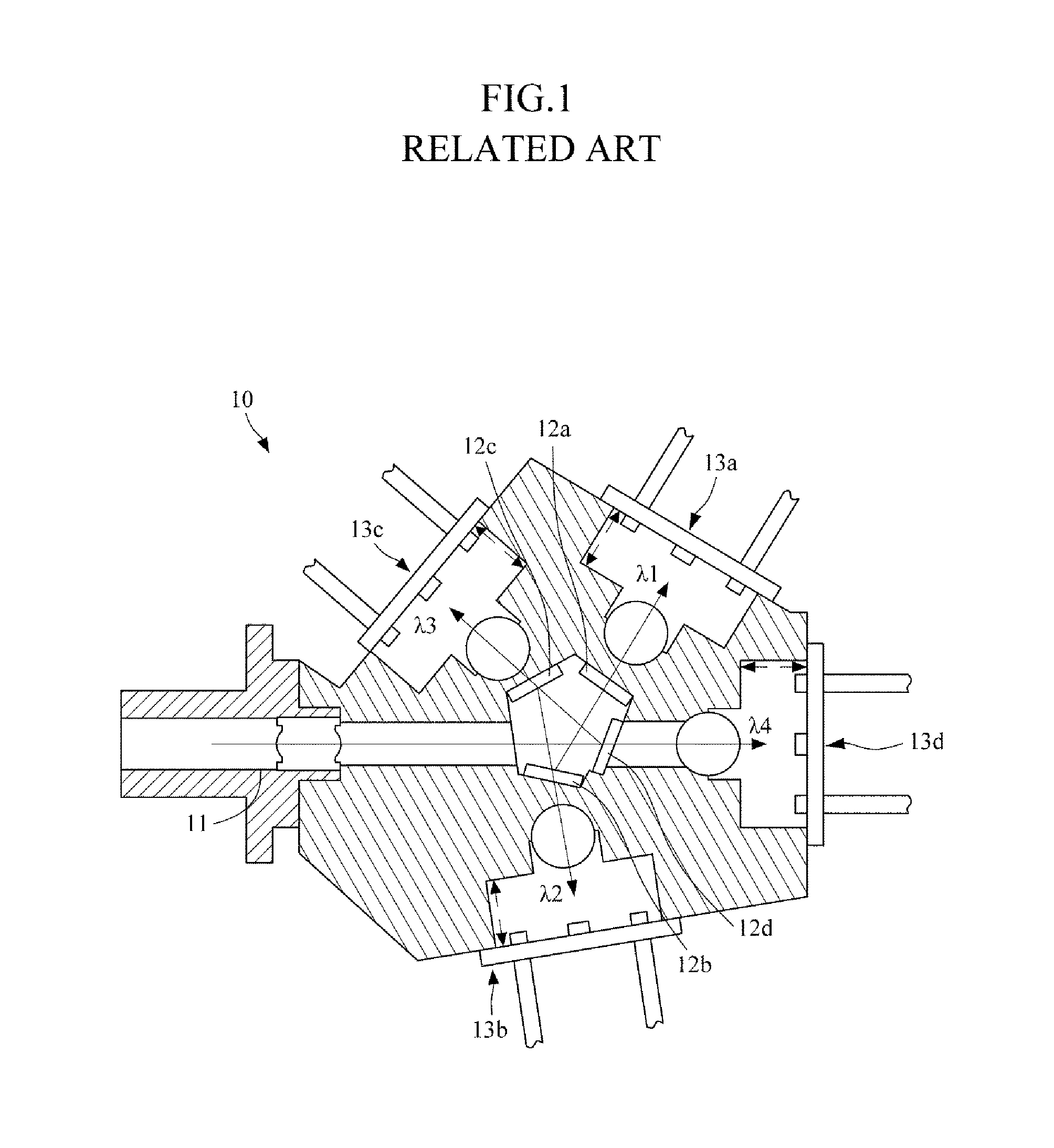

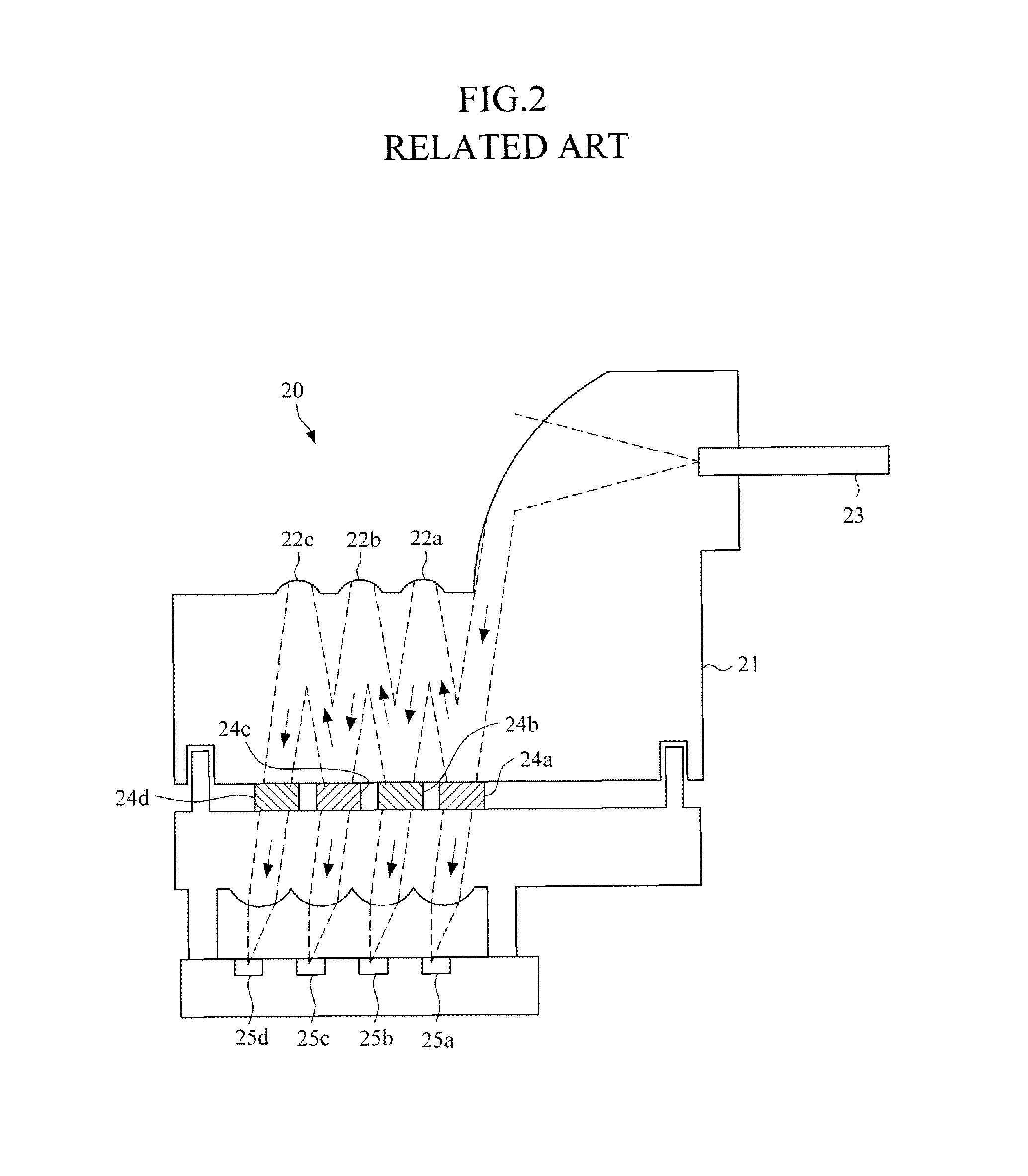

Multi-wavelength optical transmitting and receiving modules

A multi-wavelength optical transmitting module includes a housing, an optical output block, an optical transmitting block, and an optical multiplexer (MUX) block. The optical output block is coupled to a first coupling hole of the housing and to an optical signal connector, and includes a first lens. The optical transmitting block is coupled to a second coupling hole of the housing and to an electrical signal connector. The optical transmitting block includes a plurality of transmitting devices which respectively output light having different wavelengths and are arranged parallel to the optical output block, and a plurality of second lenses which correspond respectively to the transmitting devices. The optical multiplexer (MUX) block multiplexes optical signals of multiple wavelengths, which were output from the transmitting devices and passed through the second lenses, and transmits the multiplexed optical signals to the optical output block.

Owner:ELECTRONICS & TELECOMM RES INST

Semiconductor light emitting device

ActiveUS20080142821A1Decreases mass-productivityExcellent ElectricalSolid-state devicesSemiconductor devicesLight emitting deviceSemiconductor

Owner:NICHIA CORP

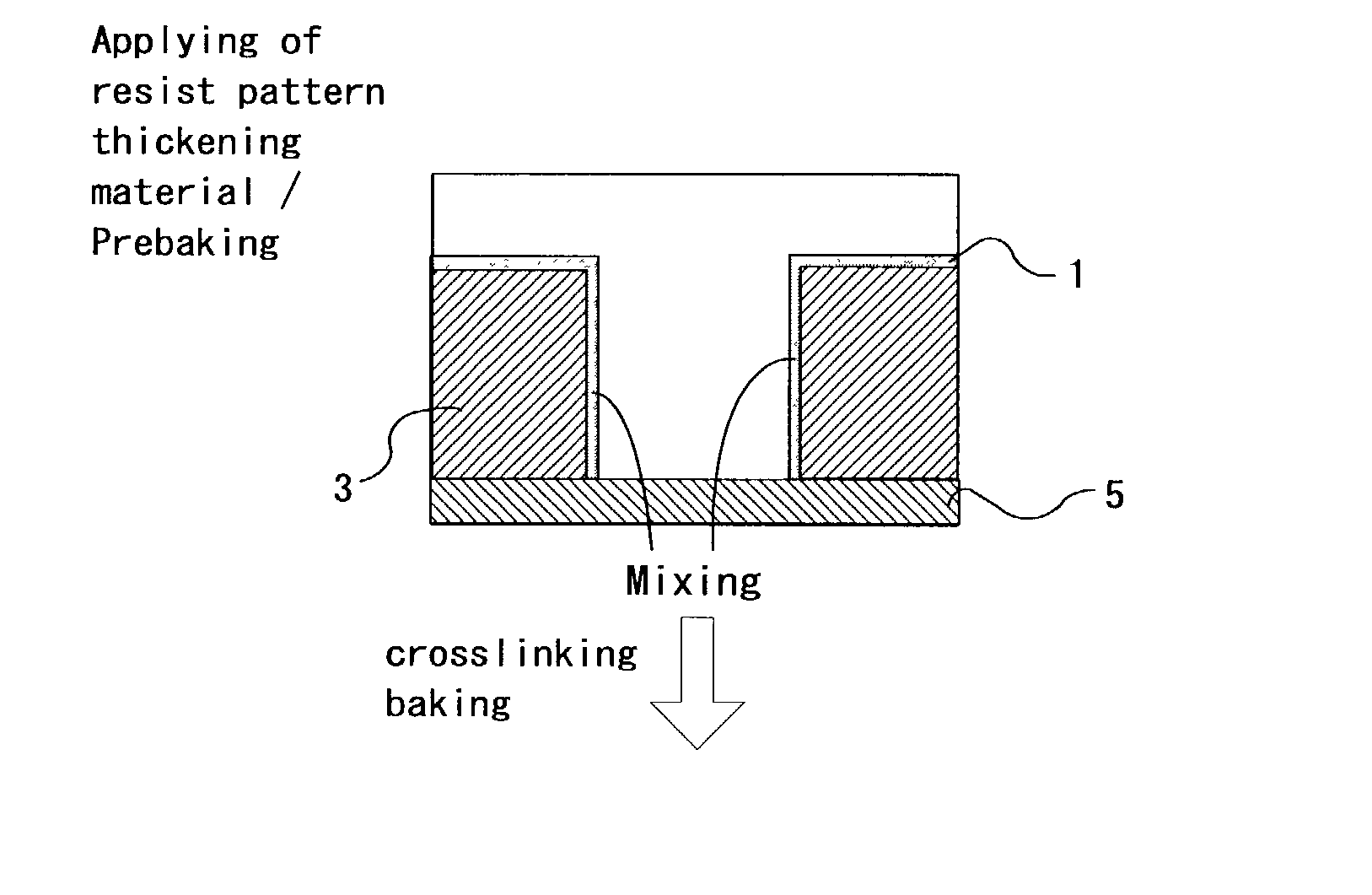

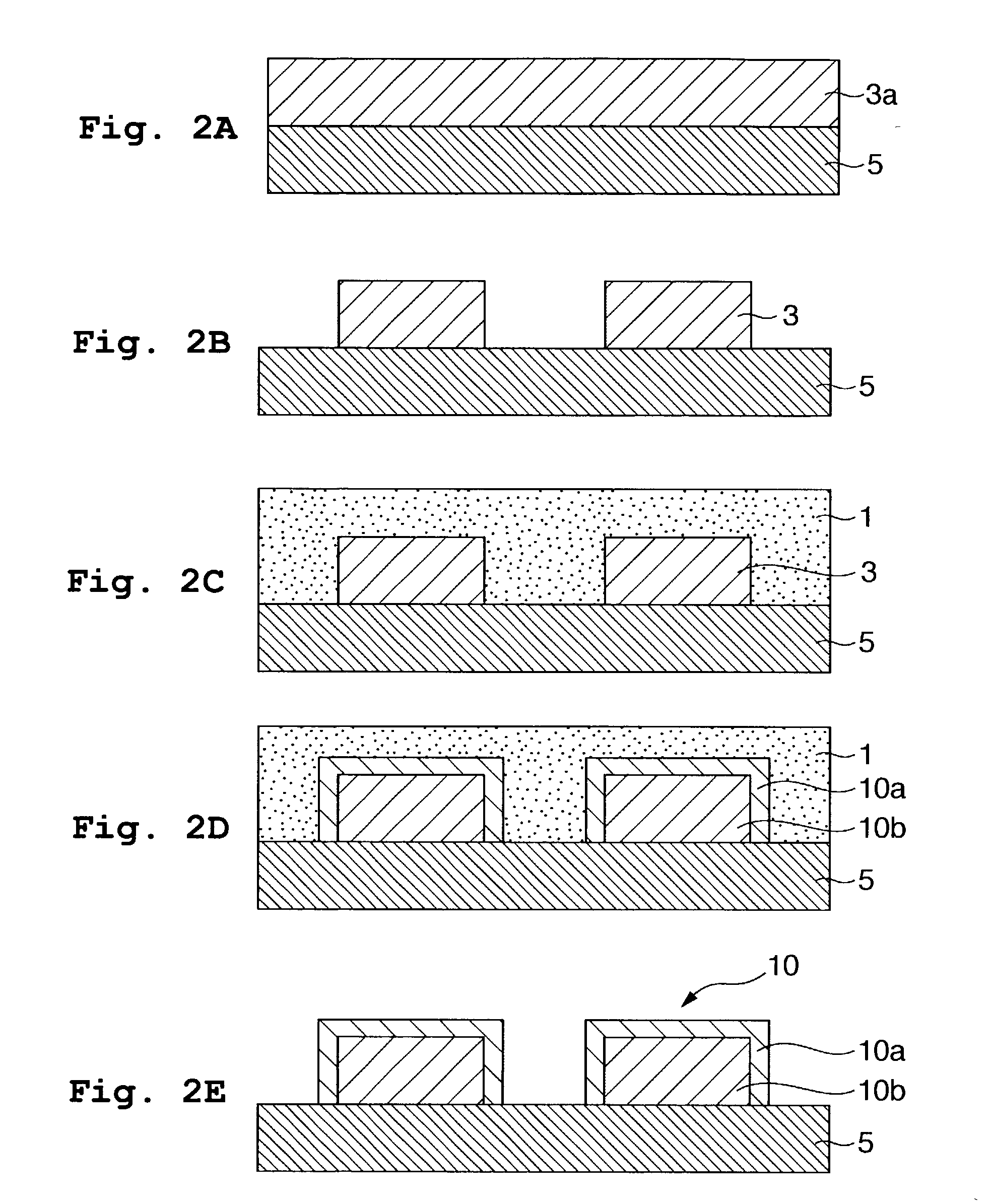

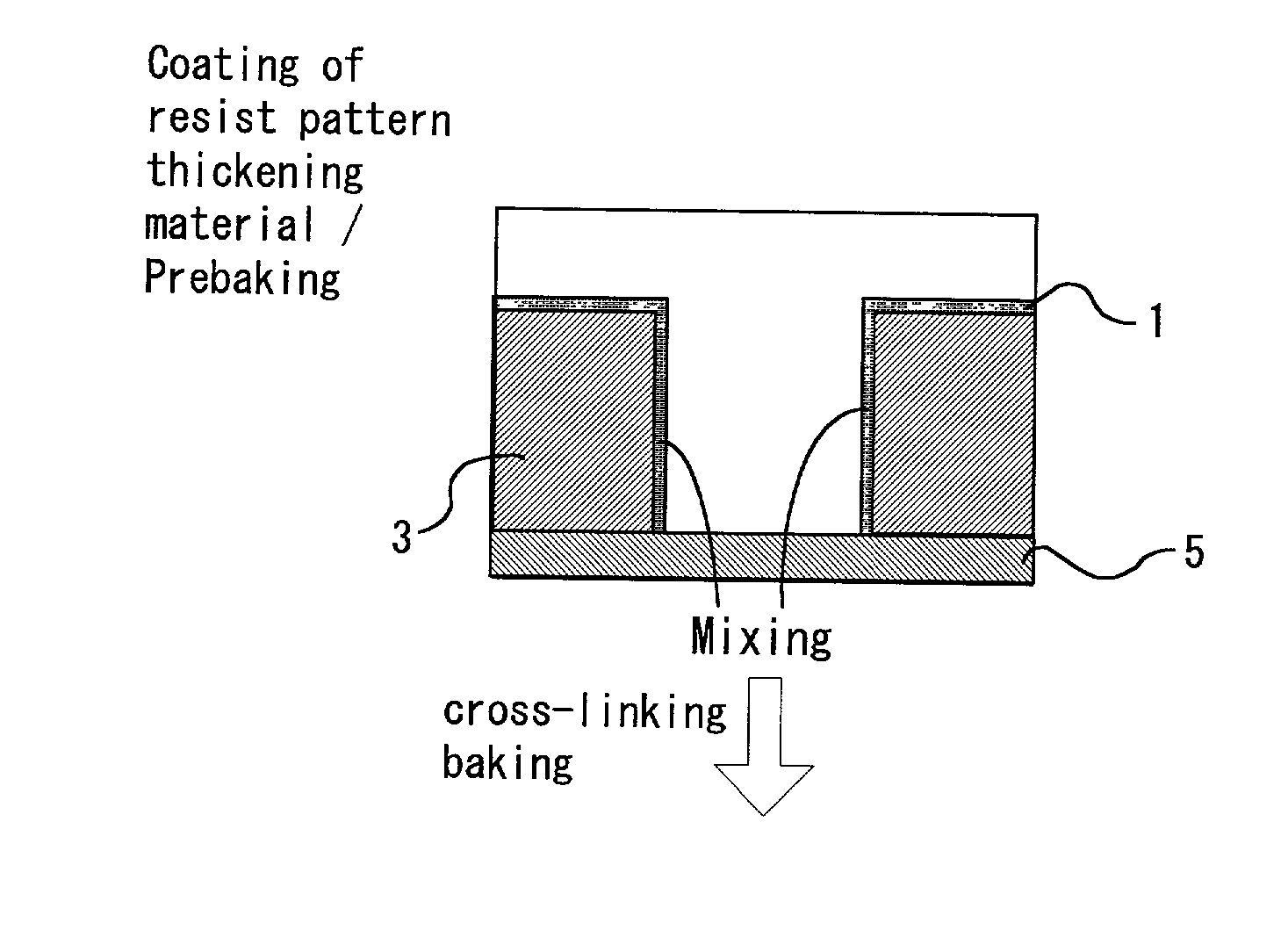

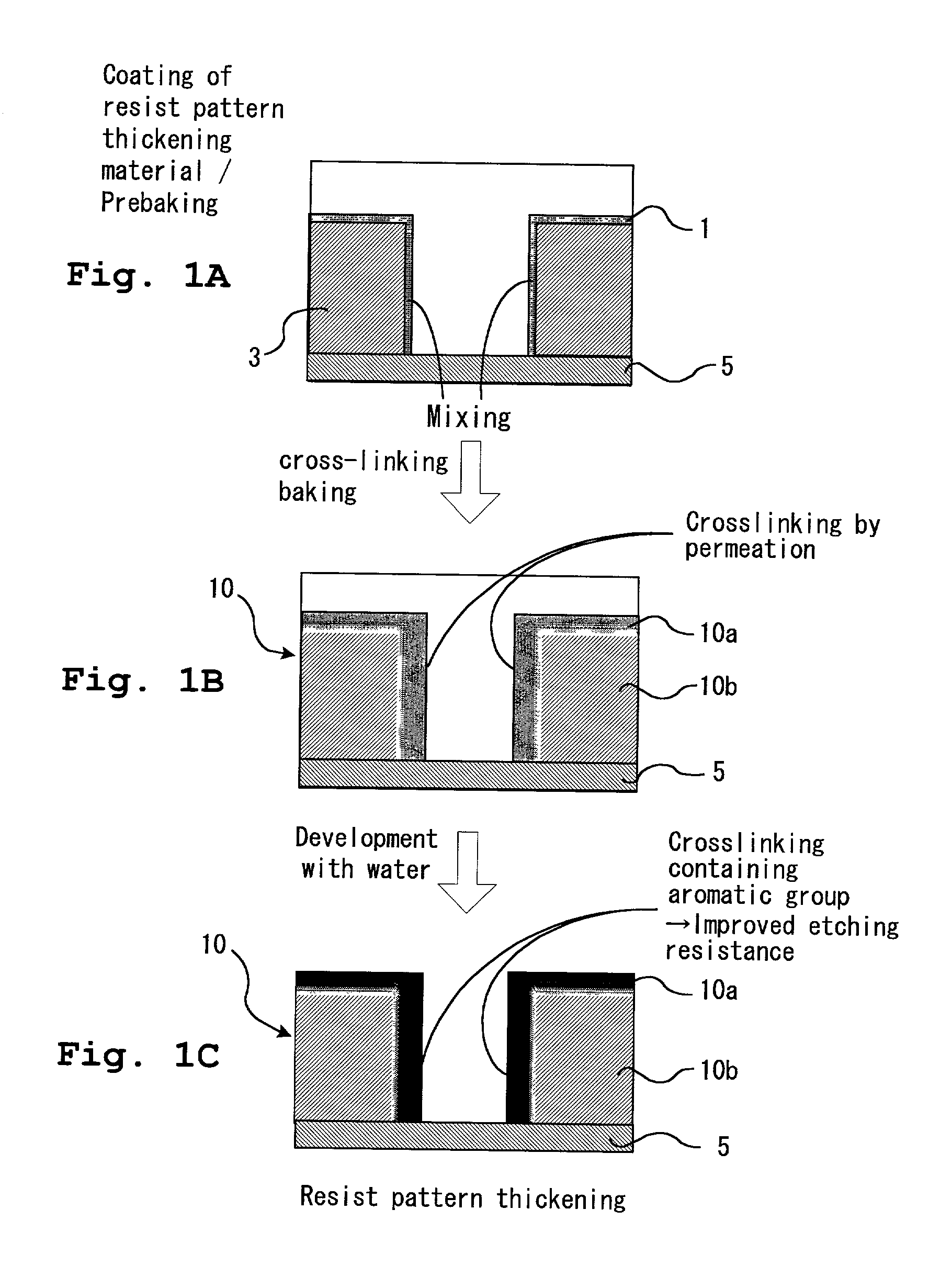

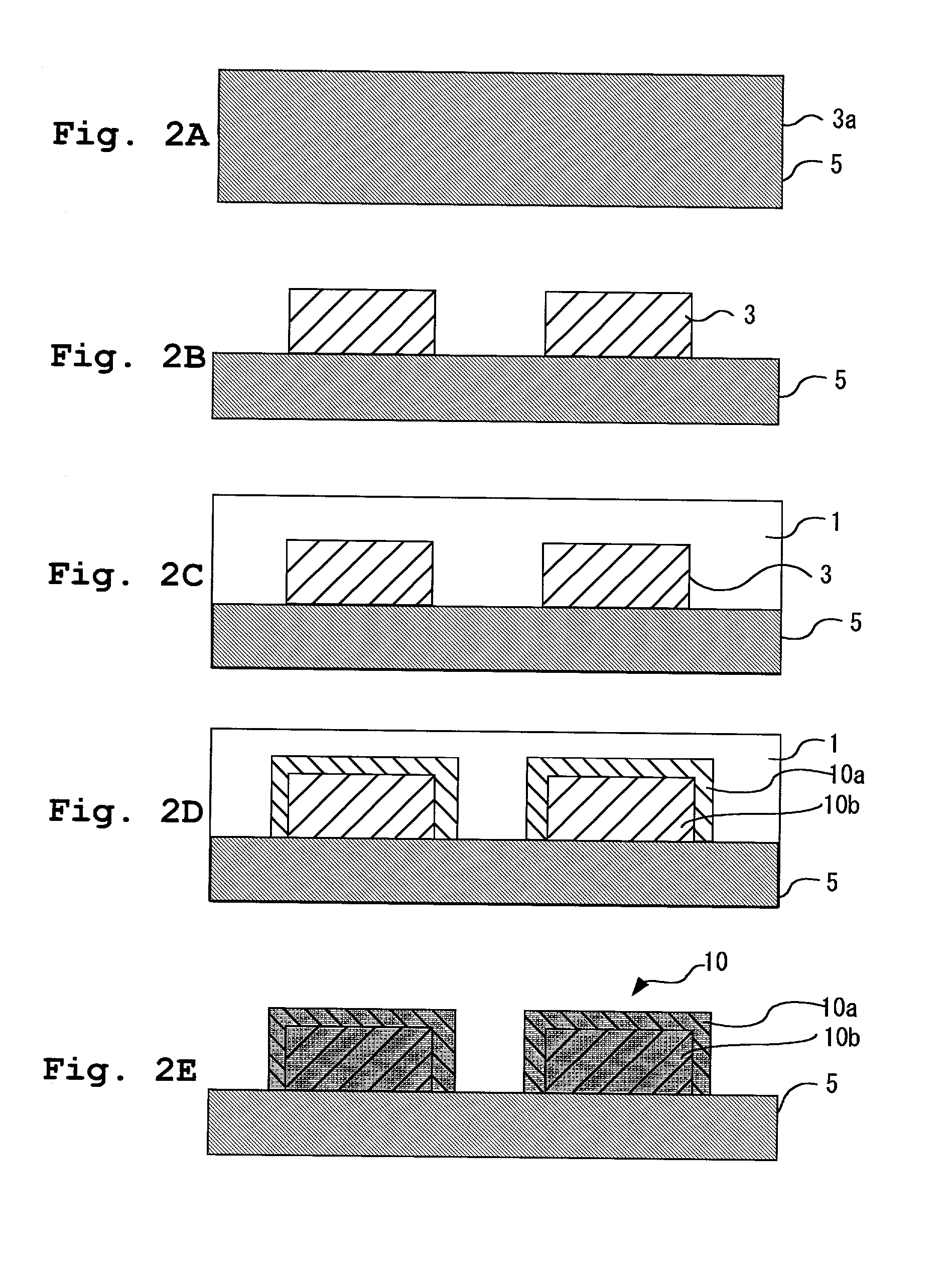

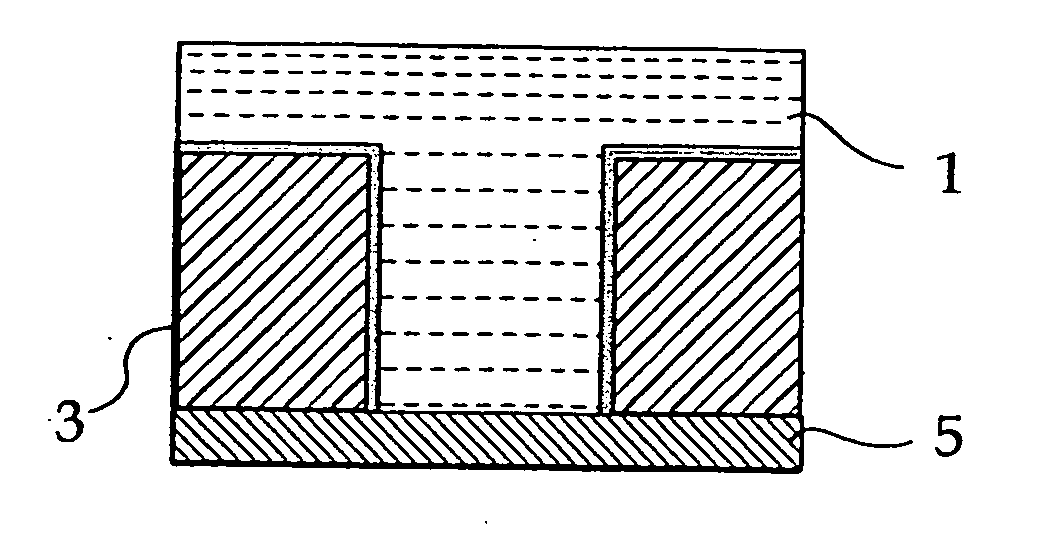

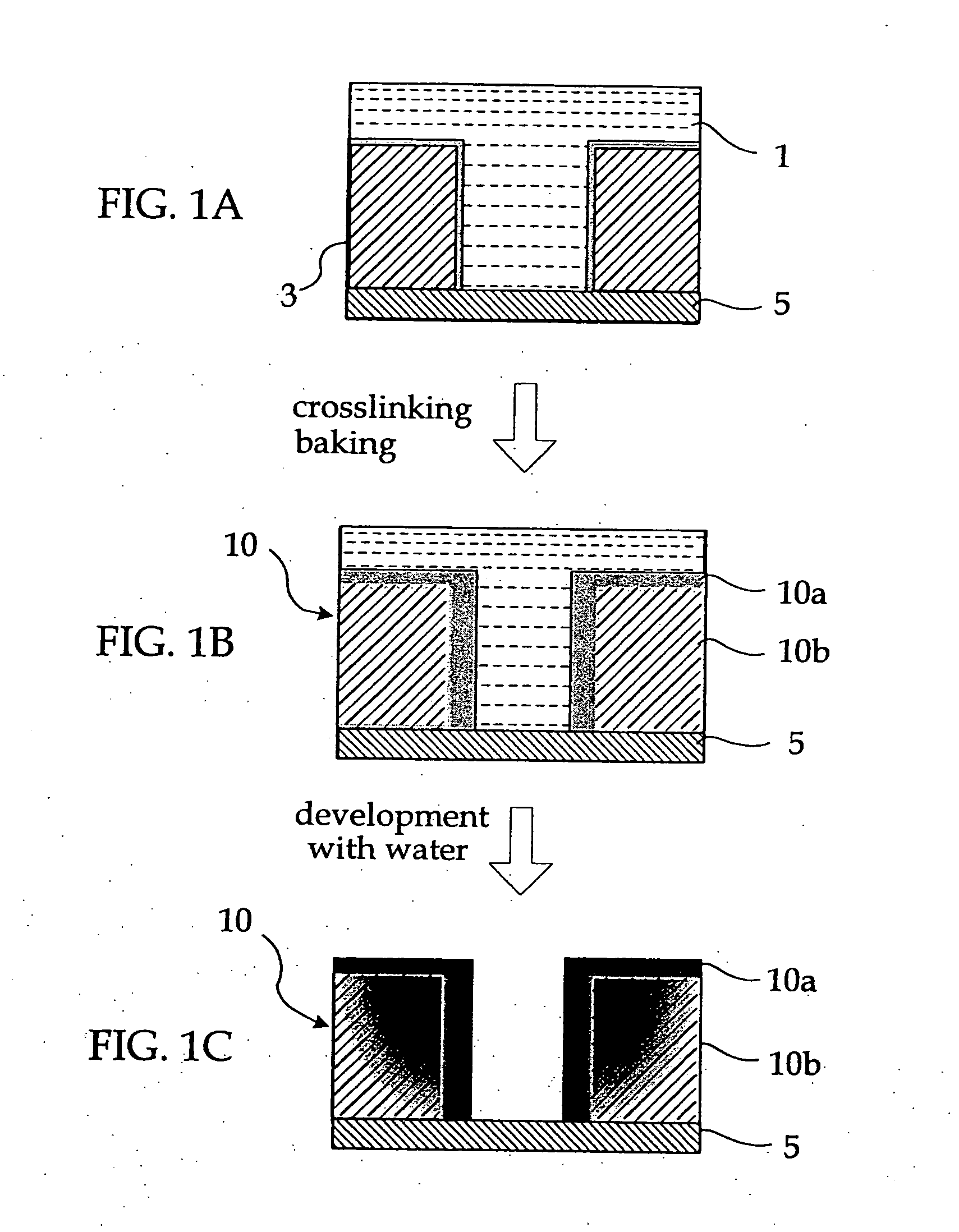

Resist pattern thickening material, resist pattern and forming process thereof, and semiconductor device and manufacturing process thereof

InactiveUS20030157801A1Simple structureImprove the immunityConstruction of head windingsDecorative surface effectsResistSurface layer

A resist pattern thickening material has resin, a crosslinking agent and a compound having a cyclic structure, or resin having a cyclic structure at a part. A resist pattern has a surface layer on a resist pattern to be thickened with etching rate (nm / s) ratio of the resist pattern to be thickened the surface layer of 1.1 or more, under the same condition, or a surface layer to a resist pattern to be thickened. A process for forming a resist pattern includes applying the thickening material after forming a resist pattern to be thickened on its surface. A semiconductor device has a pattern formed by the resist pattern. A process for manufacturing the semiconductor device has applying, after forming a resist pattern to be thickened, the thickening material to the surface of the resist pattern to be thickened, and patterning the underlying layer by etching, the pattern as a mask.

Owner:FUJITSU LTD

Resist pattern thickening material, resist pattern and forming method thereof, and semiconductor device and manufacturing method thereof

InactiveUS20030102285A1Excellent etch resistanceExquisite patternConstruction of head windingsDecorative surface effectsResistWater soluble

A resist pattern thickening material comprises a resin, a crosslinking agent and a water-soluble aromatic compound. A resist pattern comprises an upperlayer on an underlayer resist pattern with an etching rate (Å / s) ratio of the underlayer resist pattern to the upper layer under the same condition of 1.1 or more, or comprises an upperlayer containing an aromatic compound on an underlayer resist pattern. A method for forming a resist pattern comprises applying a resist pattern thickening material after forming an underlayer resist pattern, on the surface of the pattern. A semiconductor device comprises a pattern formed by the resist pattern. A method for manufacturing the semiconductor device comprises applying after forming an underlayer resist pattern on an underlying layer, the thickening material to the surface of the pattern to thicken the pattern, and patterning the underlying layer by etching using the pattern as a mask.

Owner:FUJITSU LTD

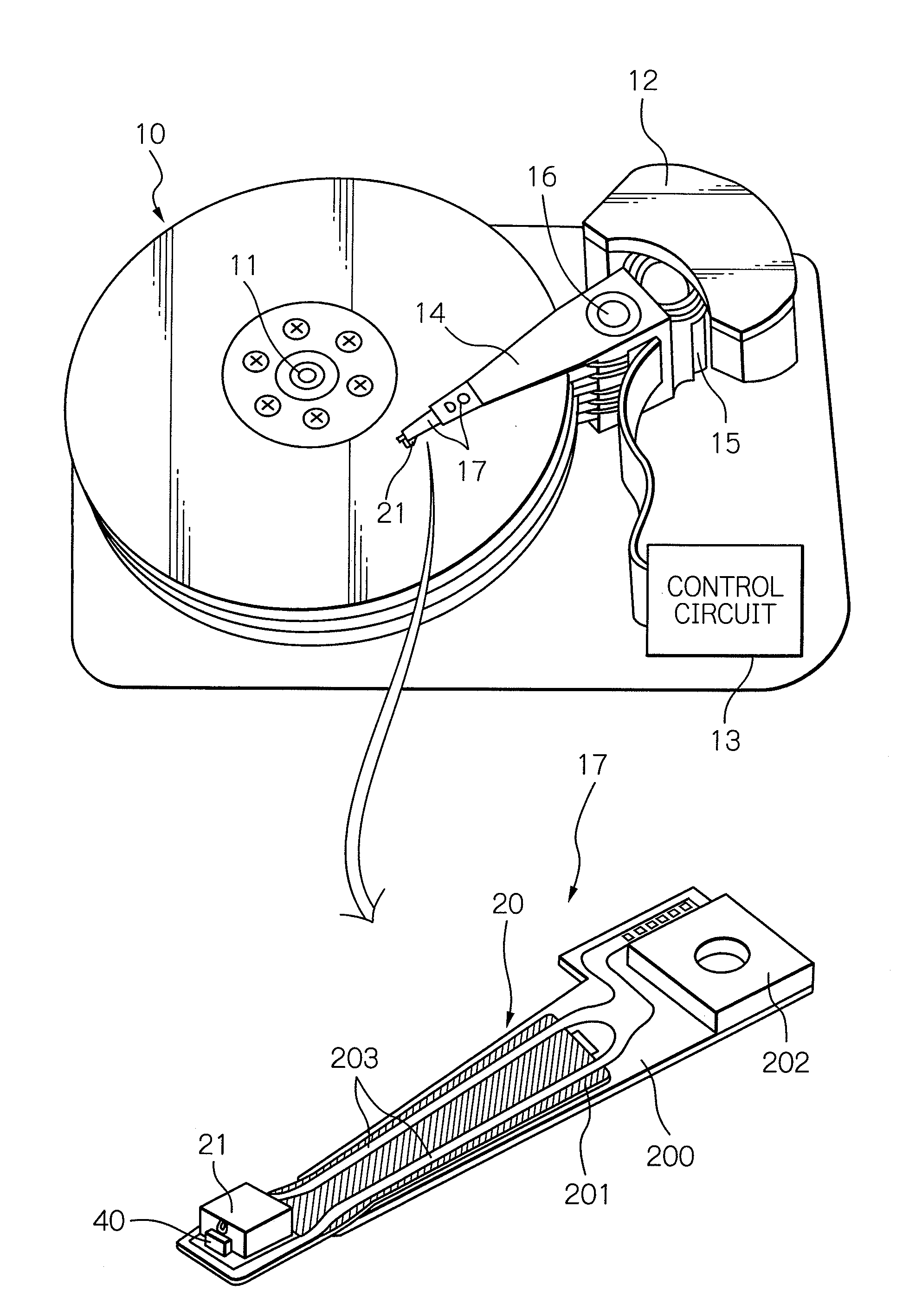

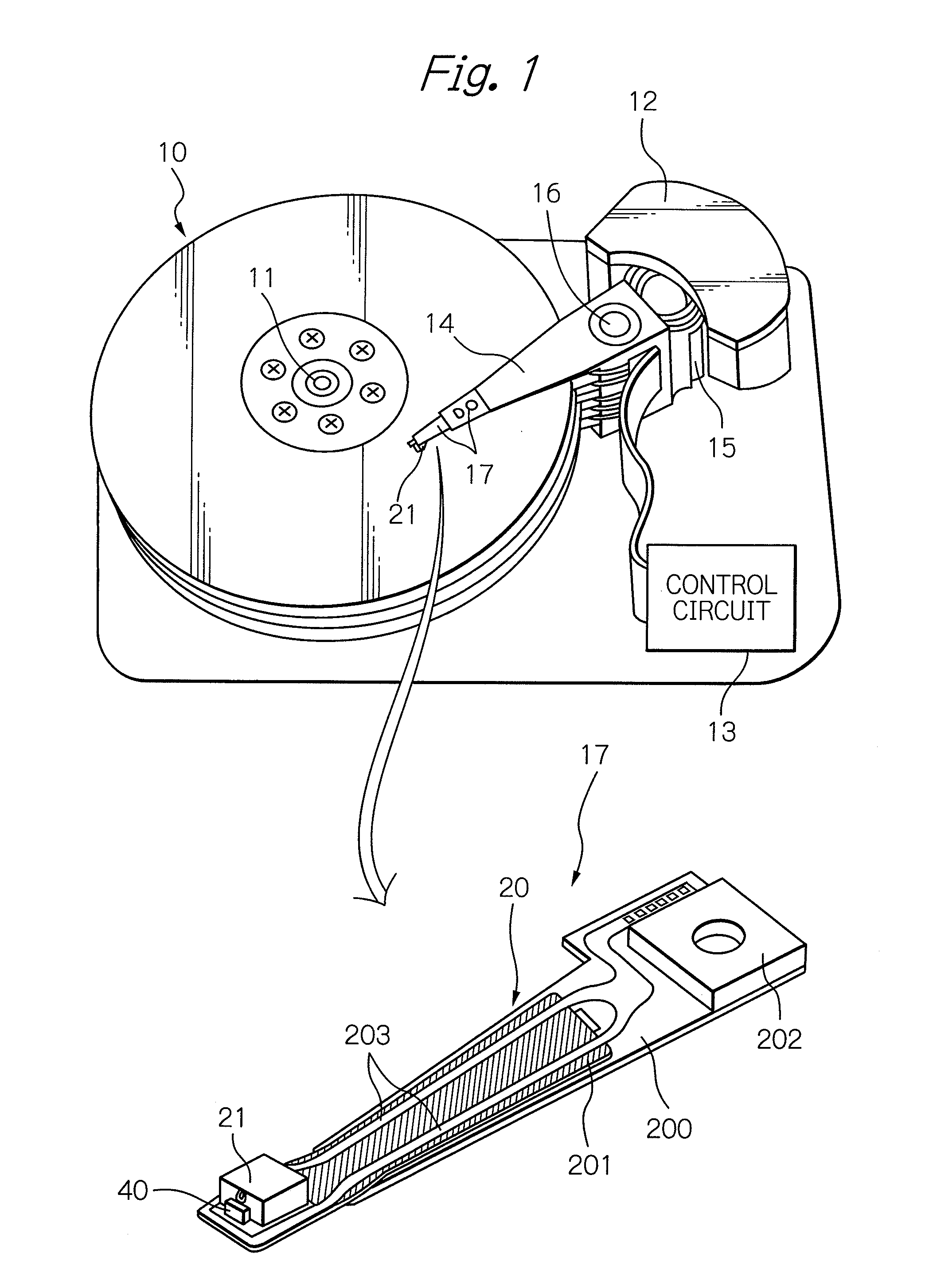

Thermally-Assisted Magnetic Recording Head Comprising Light Source with Photonic-Band Layer

ActiveUS20110026377A1Increase output powerMass productivity can be improvedCombination recordingRecord information storageProduction rateHeat-assisted magnetic recording

A thermally-assisted magnetic recording head is provided, in which a light source having sufficiently high output power for performing thermal-assist is disposed in the element-integration surface of the substrate to achieve improved mass-productivity. The head includes: a light source having a multilayered structure including a photonic-band layer and having a light-emitting surface opposed to the element-integration surface; a diffraction optical element that converges the emitted light; a light-path changer that changes the direction of the converged light; a waveguide that propagates the direction-changed light toward the opposed-to-medium surface; and a magnetic pole that generates write field. The surface-emitting type light source includes a photonic-band layer having a periodic structure in which a light from an active region resonates, and thus emits laser light on a quite different principle from a VCSEL. Therefore, the light source can be disposed in the element-integration surface, even though having sufficiently high output power.

Owner:TDK CORPARATION

Amorphous Alloy Ribbon, Nanocrystalline Soft Magnetic Alloy and Magnetic Core Consisting of Nanocrystalline Soft Magnetic Alloy

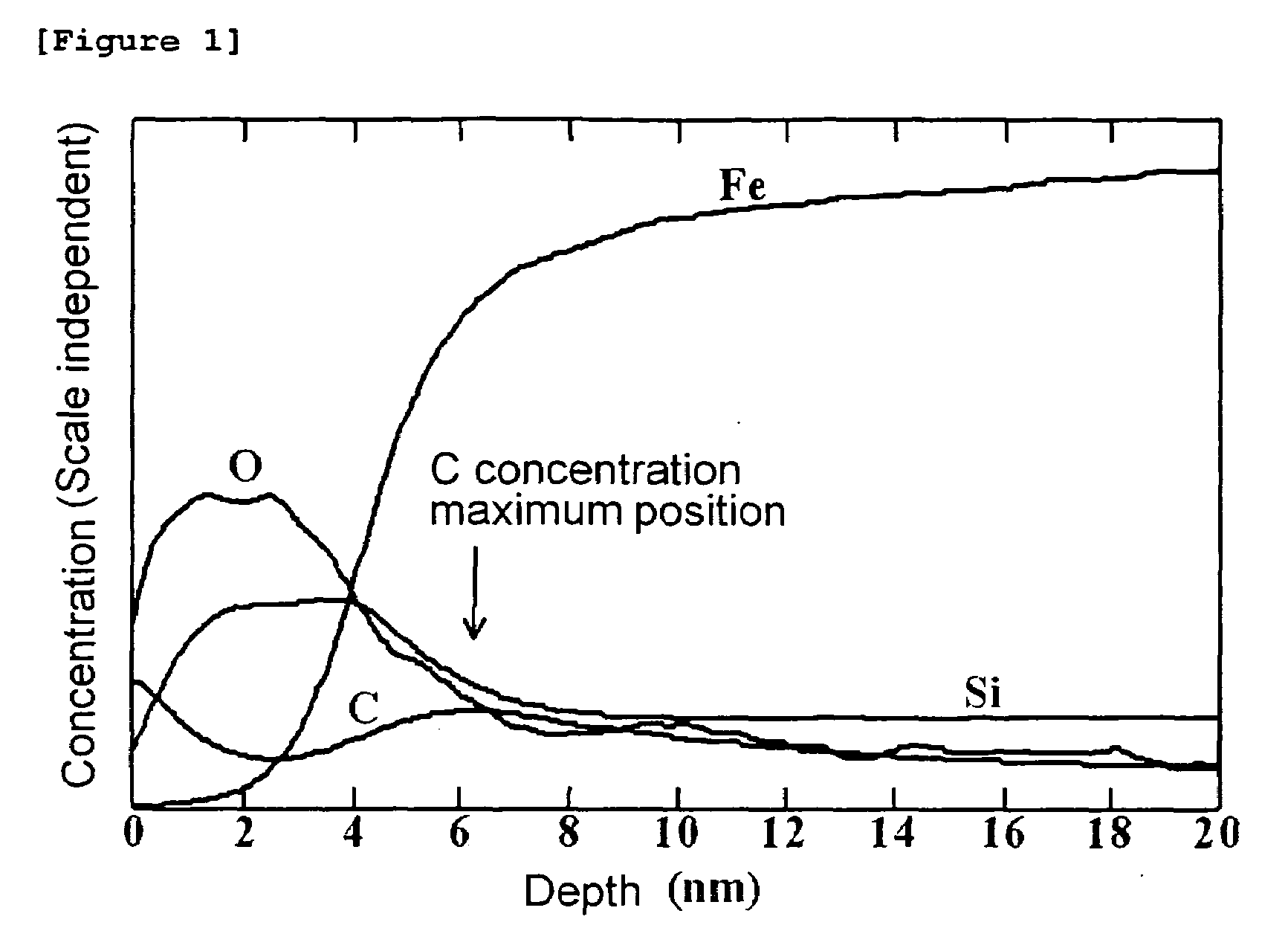

ActiveUS20090065100A1Excellent mass productivityExcellent magnetic propertyInorganic material magnetismInductances/transformers/magnets manufactureMagnetic coreAlloy composition

Even if produced from a broad amorphous alloy ribbon, a nano crystal soft magnetic alloy, a magnetic core made of a nano crystal soft magnetic alloy, and the amorphous alloy ribbon for a nano crystal soft magnetic alloys which has the excellent alternate magnetic property, the small dispersion, the excellent temporal stability in high temperature, the excellent mass productivity can be provided.An amorphous alloy ribbon, wherein the alloy composition is represented by Fe100-a-b-c-dMaSibBcCd (atomic %), 0<a≦10, 0≦b≦20, 2≦c≦20, 0<d≦2, 9≦a+b+c+d≦35, and an amorphous alloy ribbon consists of inevitable impurities, and said M is at least one element selected from Ti, V, Zr, Nb, Mo, Hf, Ta, and W, and C concentration takes maximum value at 2-20 nm depth from the surface of said amorphous alloy with equivalent SiO2.

Owner:HITACHI METALS LTD

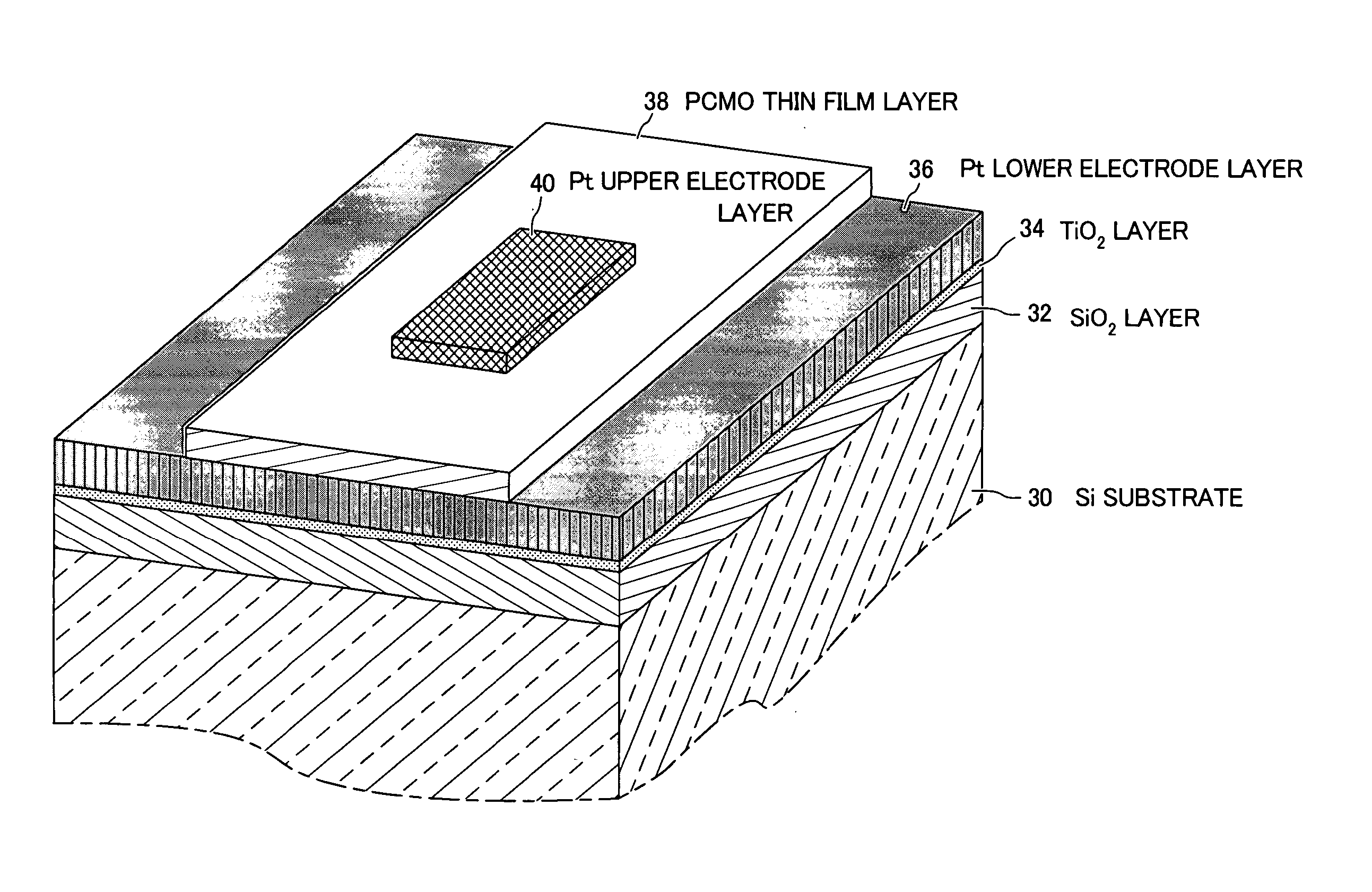

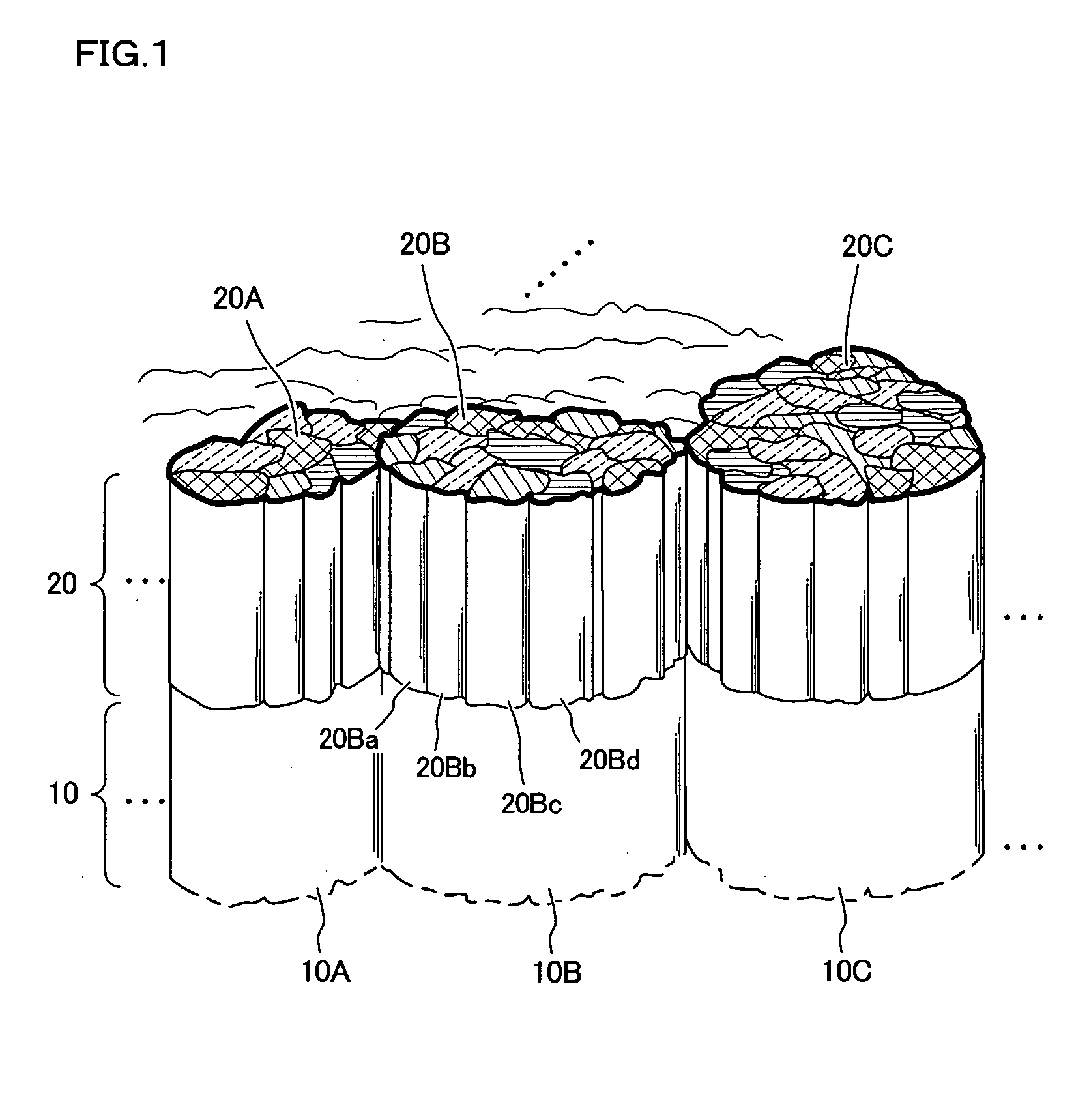

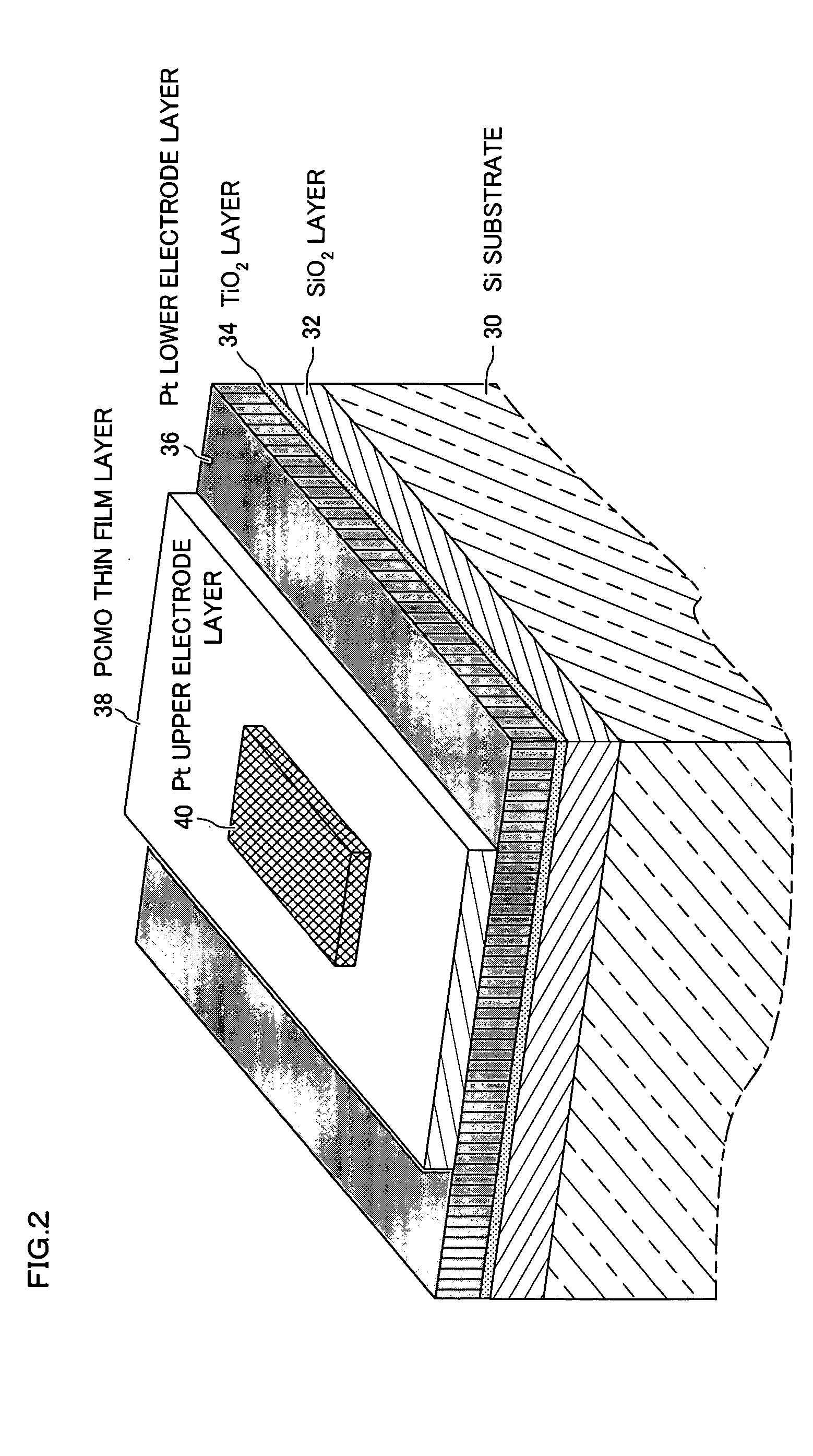

EPIR device and semiconductor devices utilizing the same

InactiveUS20050040482A1Improve batch productivityHigh in practical utilityTransistorNanoinformaticsSemiconductorSubstrate surface

There is provided an EPIR device which is excellent in mass productivity and high in practical utility. The EPIR device includes a lower electrode layer, a CMR thin film layer and an upper electrode layer which are laminated in this order on any of various substrates. A Pt polycrystal thin film 10 forming the lower electrode layer includes columnar Pt crystal grains 10A, 10B, 10C, . . . and over 90% of these crystal grains is oriented to a (1 1 1) face. Columnar PCMO crystal grain groups 20A, 20B, 20C, . . . are respectively locally grown epitaxially on the respective outermost surfaces of the Pt crystal grains 10A, 10B, 10C, Then, the crystal faces of the crystal grains included in the PCMO crystal grain groups 20A, 20B, 20C, . . . and vertical in the substrate surface normal direction are any one of (1 0 0)p, (1 1 0)p and (1 1 1)p planes.

Owner:XENOGENIC DEV LLC

Transistor and semiconductor device

ActiveUS20120193620A1Increase in channel resistanceImprove the immunitySemiconductor devicesCapacitanceSemiconductor

A transistor which withstands a high voltage and controls large electric power can be provided. A transistor is provided which includes a gate electrode, a gate insulating layer over the gate electrode, an oxide semiconductor layer which is over the gate insulating layer and overlaps with the gate electrode, and a source electrode and a drain electrode which are in contact with the oxide semiconductor layer and whose end portions overlap with the gate electrode. The gate insulating layer includes a first region overlapping with the end portion of the drain electrode and a second region adjacent to the first region. The first region has smaller capacitance than the second region.

Owner:SEMICON ENERGY LAB CO LTD

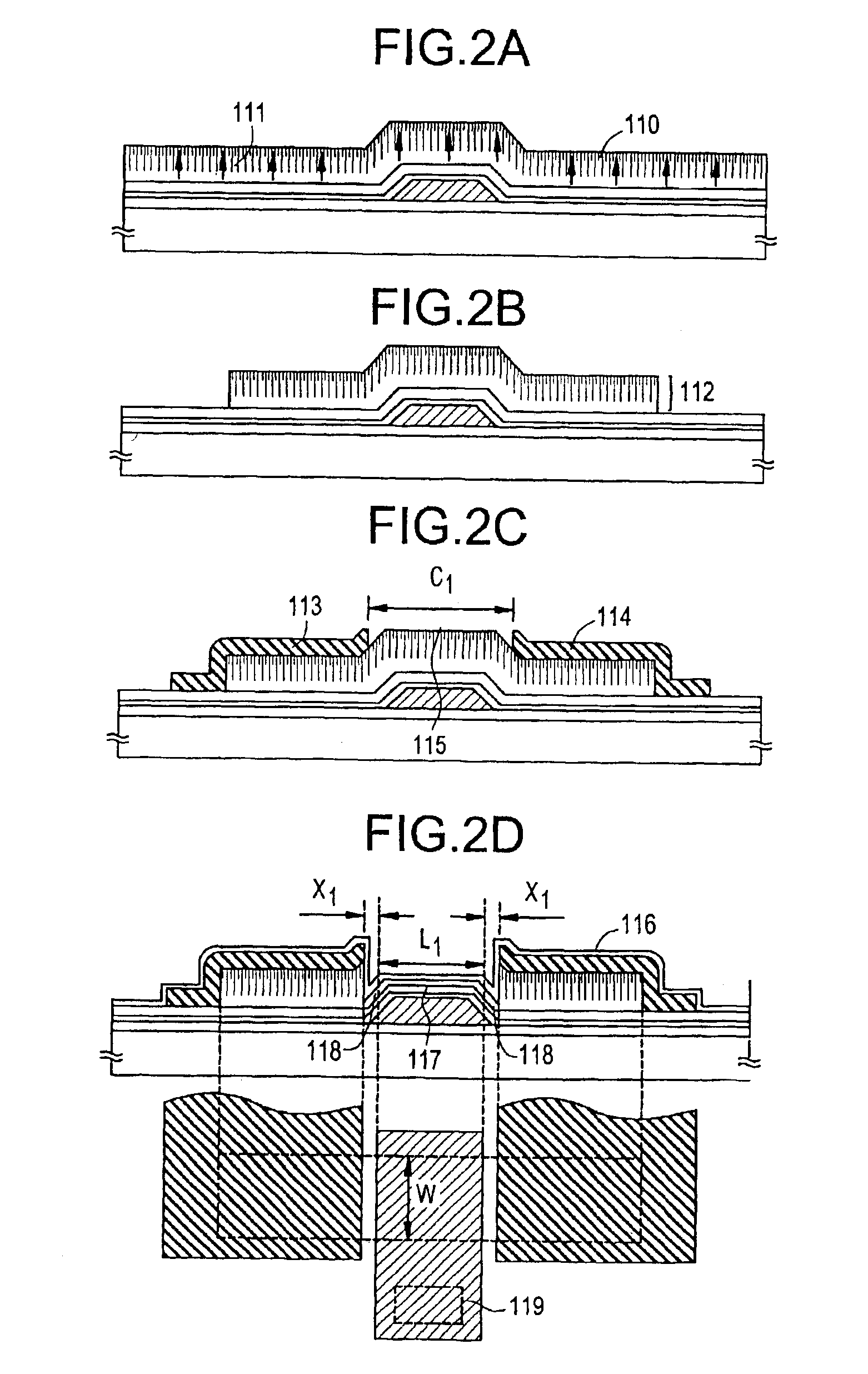

Thin film transistor device, method for manufacturing the same and display apparatus having the same

InactiveUS20070148831A1Easy resistanceImprove batch productivitySolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorMetal

A thin film transistor device includes: an island shaped semiconductor layer; a metal film that covers at least a part of a source region and a drain region of the semiconductor layer; a gate insulating film that covers the semiconductor layer and the metal film; an interlayer insulating film that covers the gate insulating film; and a signal wire that lies on the interlayer insulating film. The gate insulating film and the interlayer insulating film are formed with contact hole that reaches the metal film. The signal wire is connected to the metal film through the contact hole.

Owner:MITSUBISHI ELECTRIC CORP

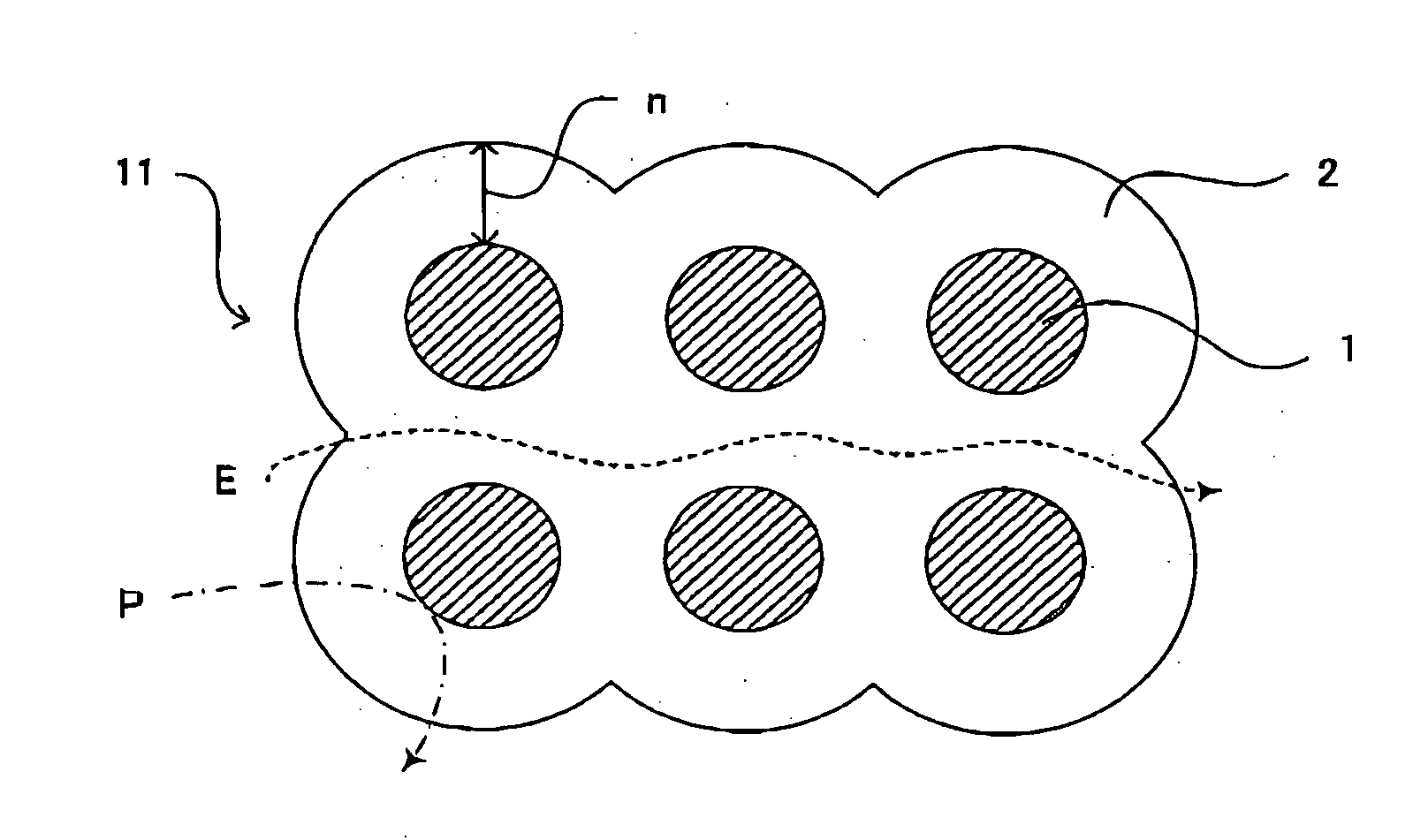

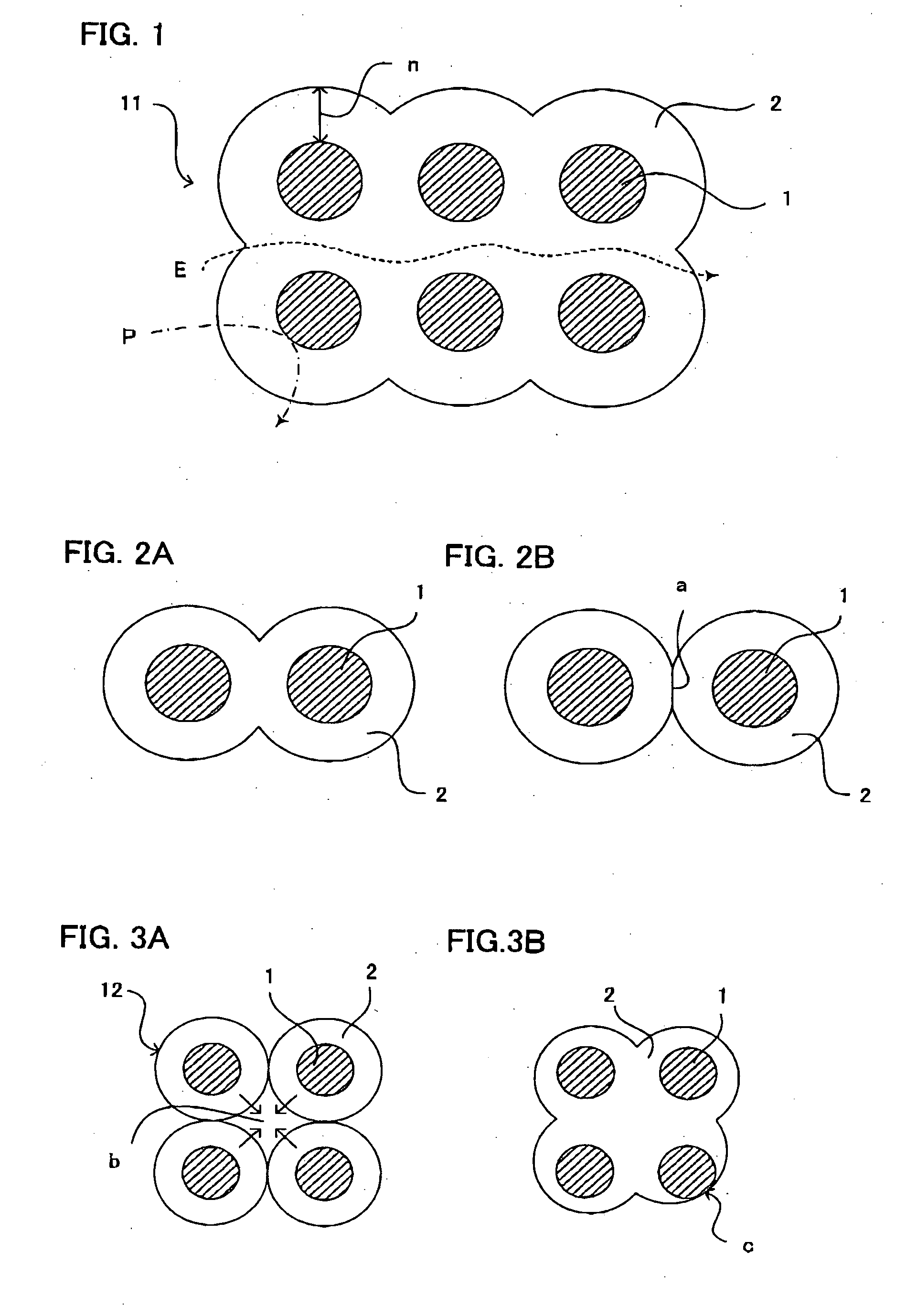

Nitride-based semiconductor element and method of forming nitride-based semiconductor

InactiveUS20050263778A1Improve batch productivityExcellent element characteristicOptical wave guidanceLaser detailsProduction rateNitride

A nitride-based semiconductor element having superior mass productivity and excellent element characteristics is obtained. This nitride-based semiconductor element comprises a substrate comprising a surface having projection portions, a mask layer formed to be in contact with only the projection portions of the surface of the substrate, a first nitride-based semiconductor layer formed on recess portions of the substrate and the mask layer and a nitride-based semiconductor element layer, formed on the first nitride-based semiconductor layer, having an element region. Thus, the first nitride-based semiconductor layer having low dislocation density is readily formed on the projection portions of the substrate and the mask layer through the mask layer serving for selective growth. When the nitride-based semiconductor element layer having the element region is grown on the first nitride-based semiconductor layer having low dislocation density, a nitride-based semiconductor element having excellent element characteristics can be readily obtained. The first nitride-based semiconductor layer is formed through only single growth on the substrate, whereby a nitride-based semiconductor element having excellent mass productivity is obtained.

Owner:EPISTAR CORP

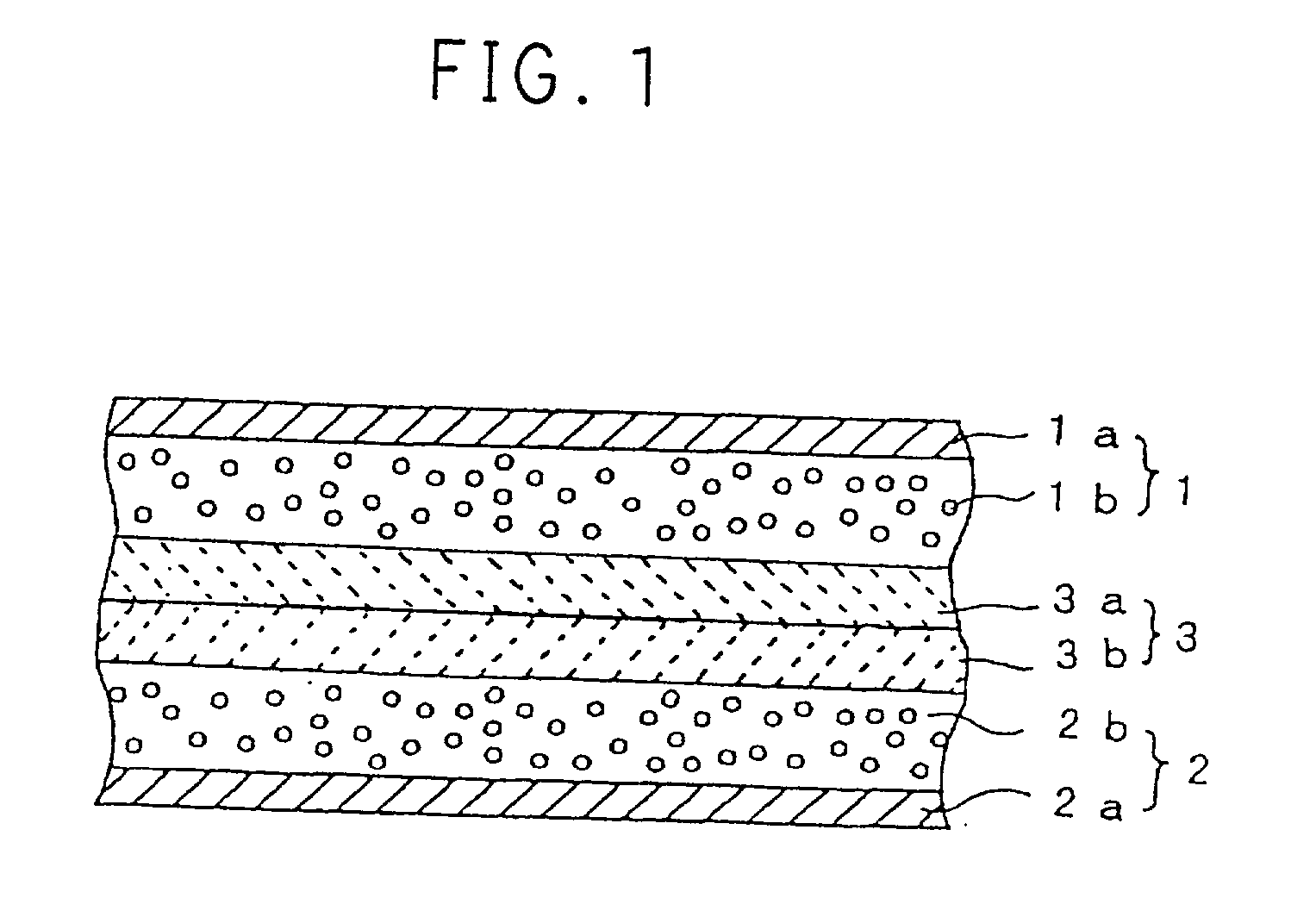

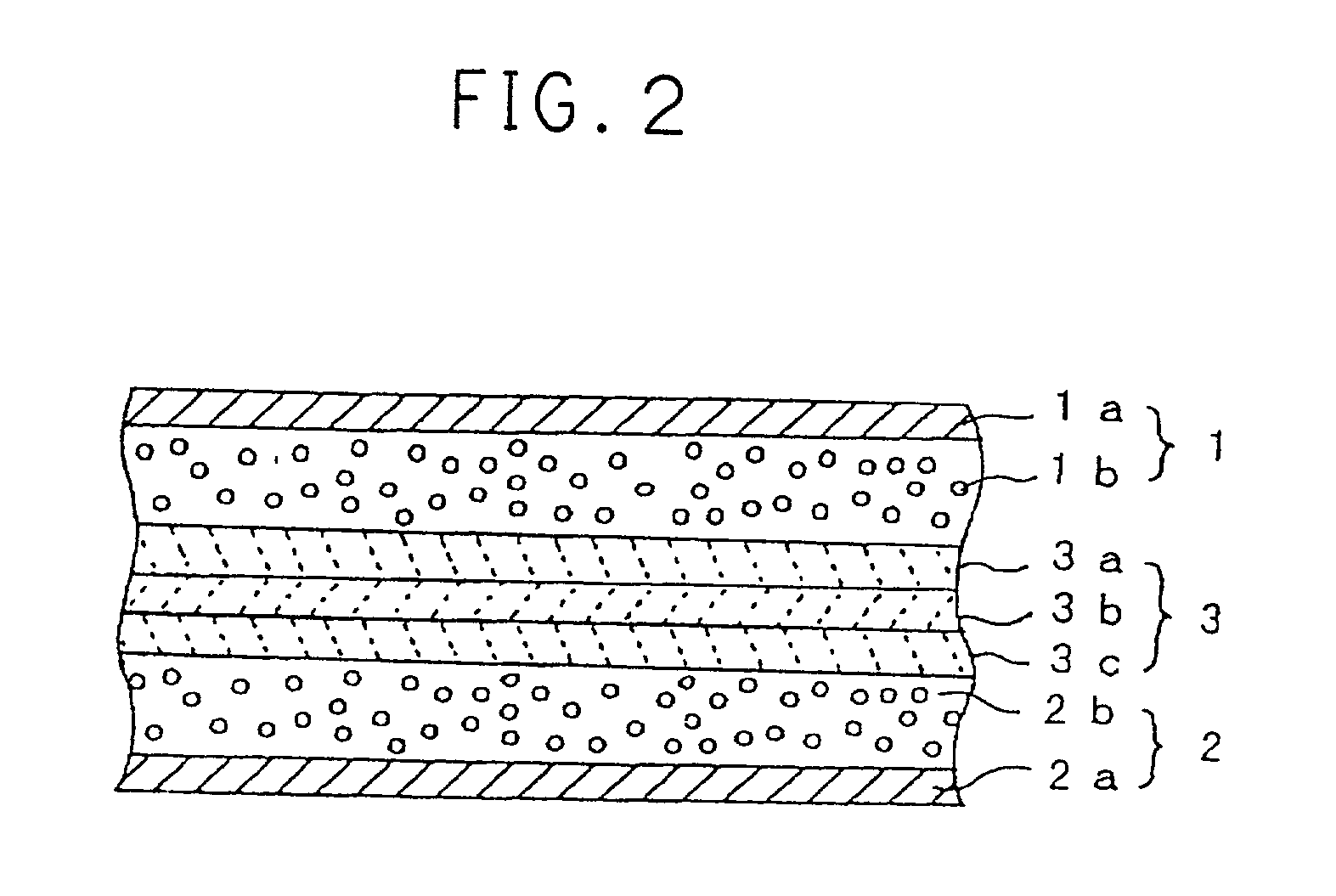

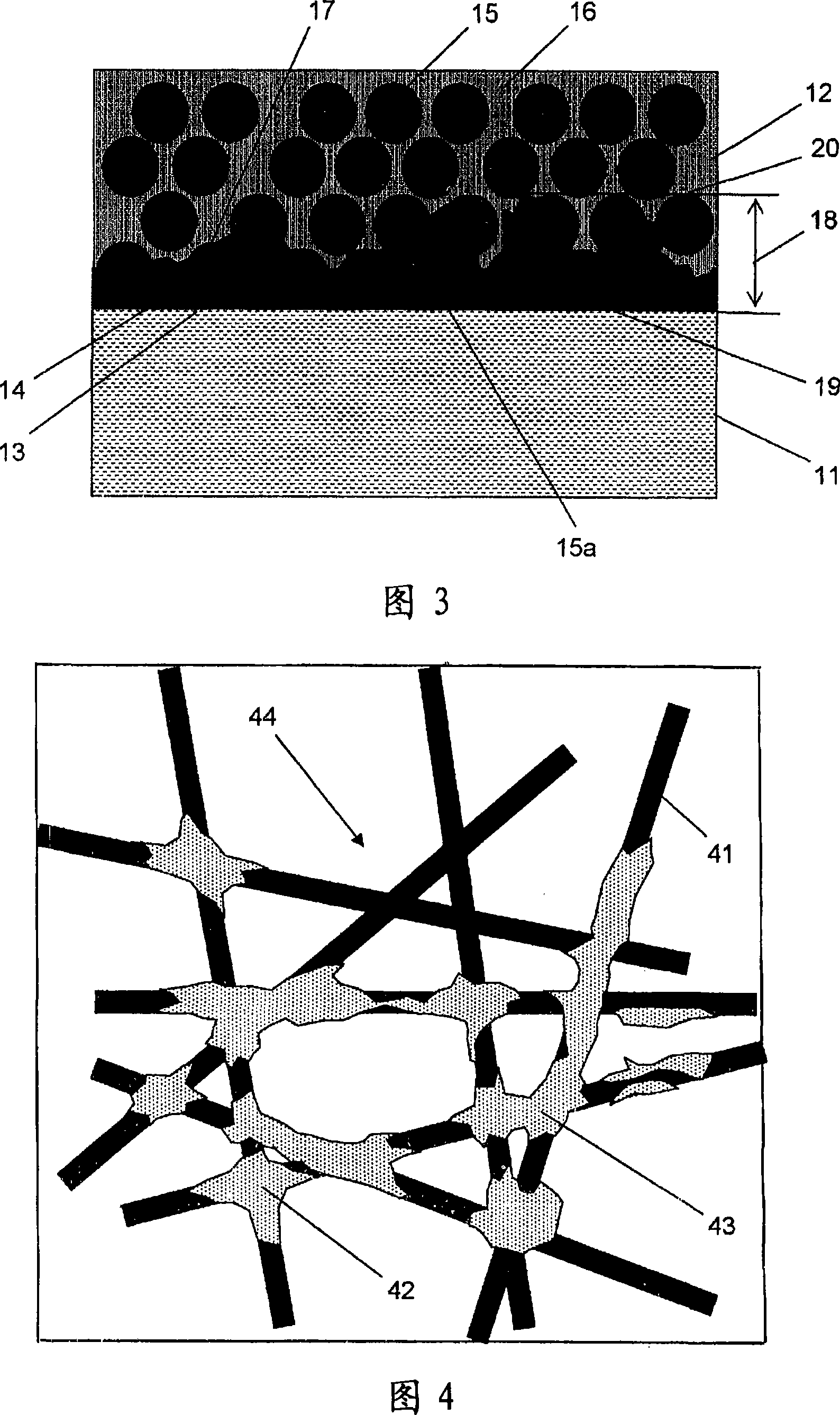

Separator for battery, battery and process for preparing the separator

InactiveUS20010005560A1Improve batch productivityLow costPrimary cell maintainance/servicingCell seperators/membranes/diaphragms/spacersHeat resistancePorous layer

Conventional separators had a function that their melting made minute holes inside the separator smaller, leading to cut off of ion conductivity in temperature increase due to unusual conditions such as short circuit. However, there was a problem that, at a temperature higher than a certain degree, not only the minute holes were closed but also the separator itself was melted to cause deformation of the separator such as shrink and generation of holes due to melting and insulation was broken. The present invention has been carried out in order to solve the above problems. The separator for batteries of the present invention comprises a first porous layer (3a) containing a thermoplastic resin as a main component and a second porous layer (3b) laminated on the first porous layer (3a), which has higher heat resistance than that of the first porous layer (3a).

Owner:MITSUBISHI ELECTRIC CORP

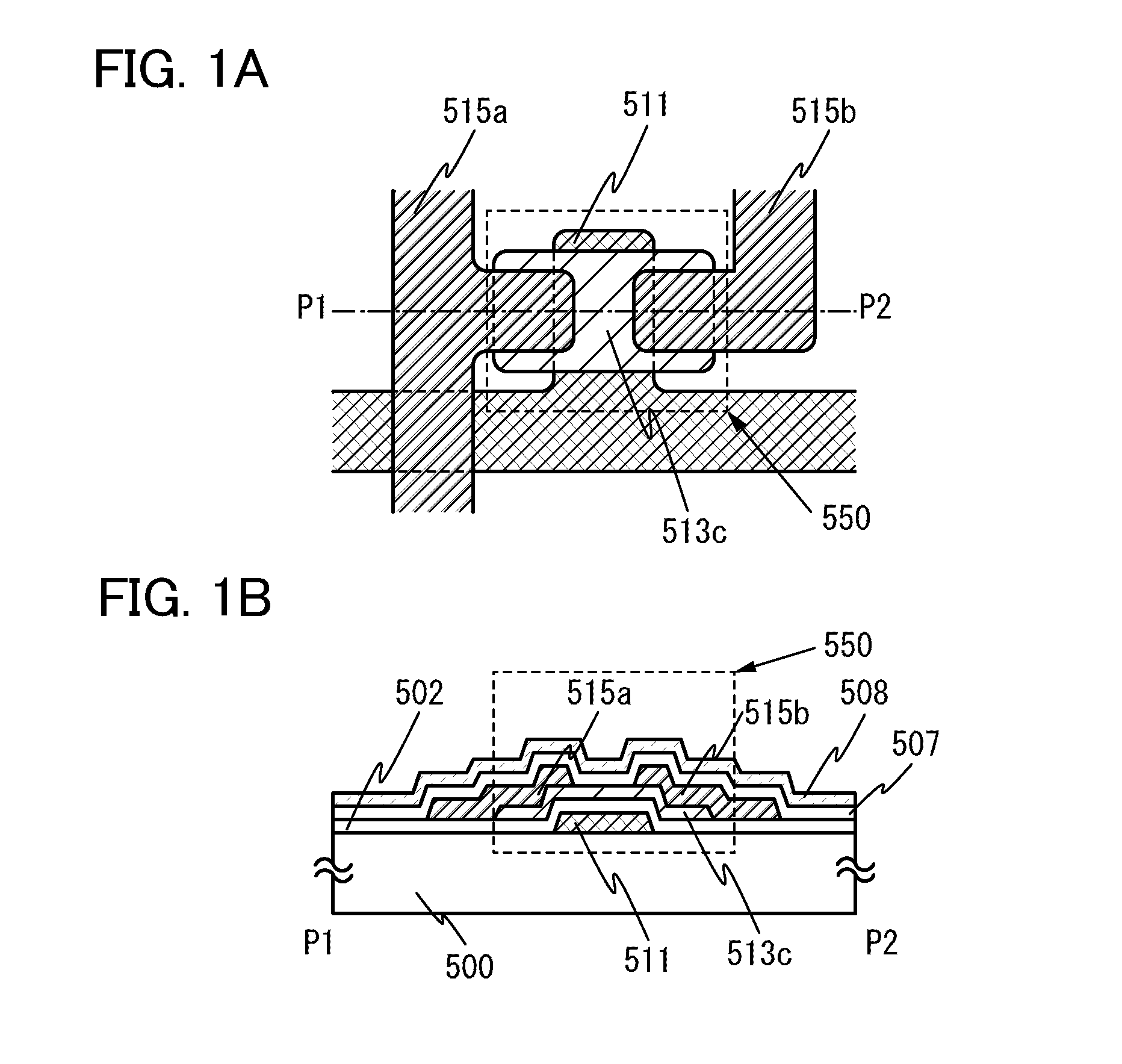

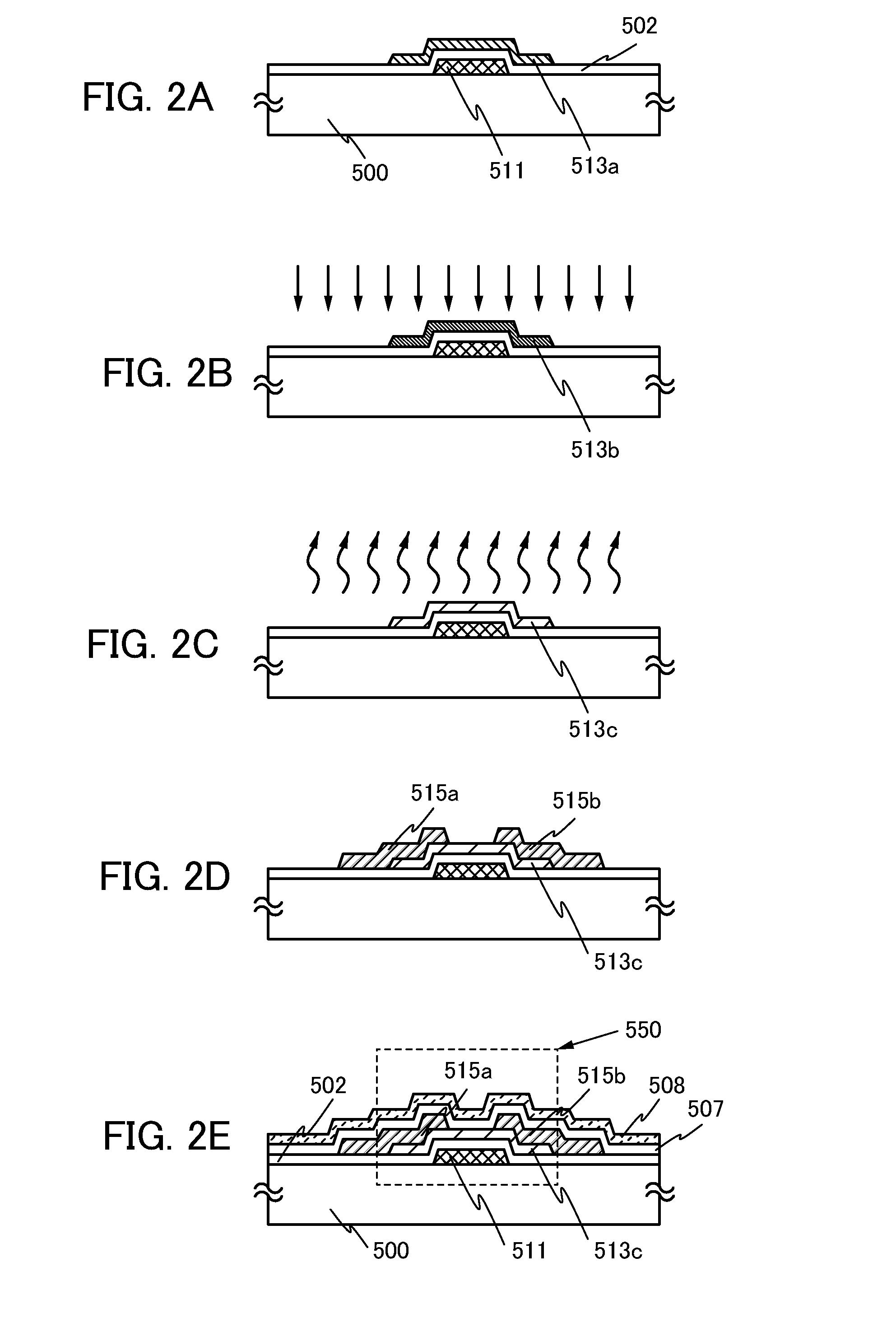

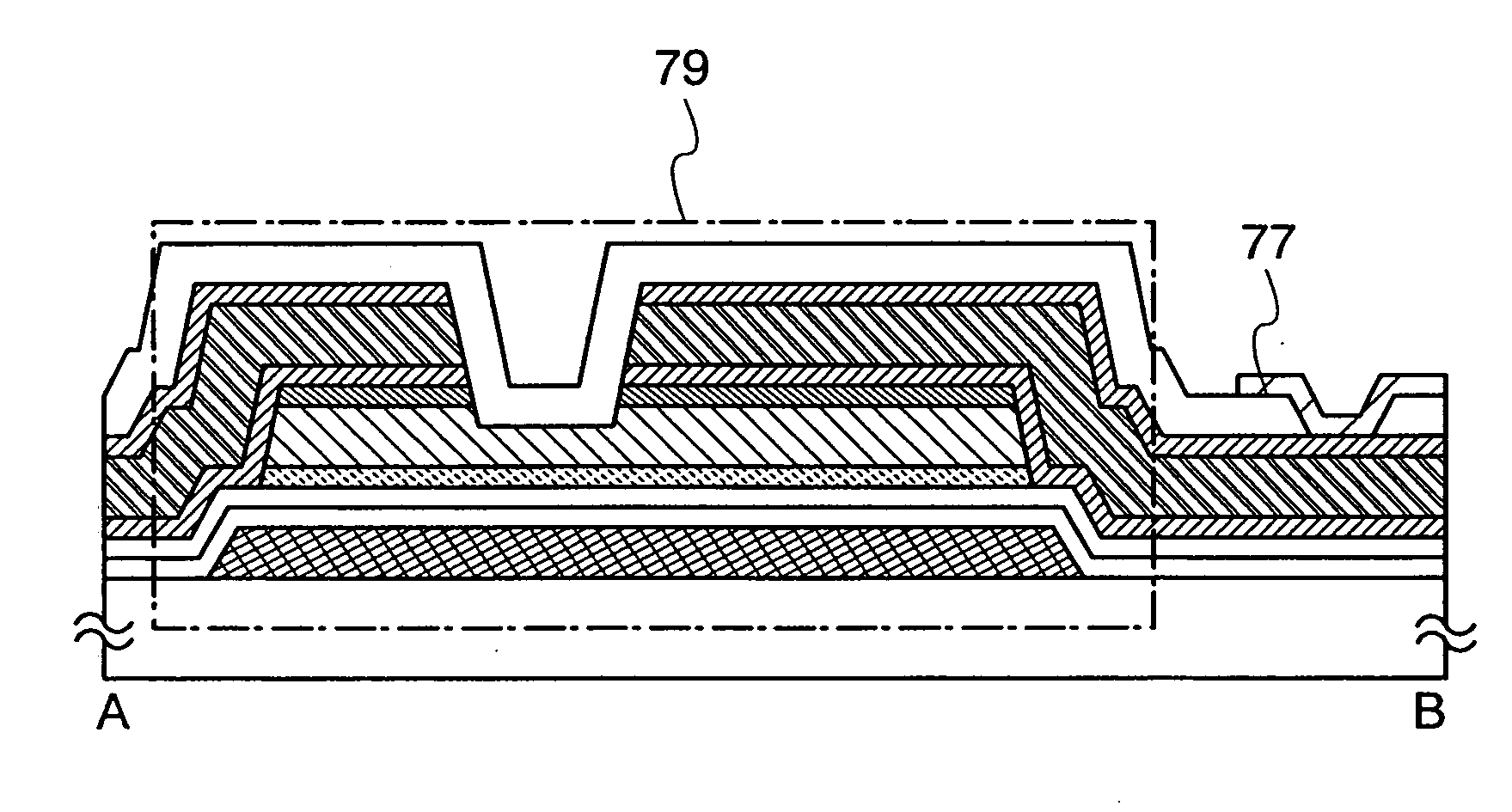

Method for Manufacturing Semiconductor Device

ActiveUS20080057632A1Low cost manufacturingImprove batch productivitySolid-state devicesSemiconductor/solid-state device manufacturingResistLight beam

The present invention offers a method for forming an opening portion by a simple process without using a photomask or a resist. Further, the present invention proposes a method for manufacturing a semiconductor device at low cost. A plurality of light absorbing layers is formed over a substrate, an interlayer insulating layer is formed over the plurality of light absorbing layers, the plurality of light absorbing layers is irradiated with a linear or rectangular laser beam from the interlayer insulating layer side, and at least the interlayer insulating layer which is over the plurality of light absorbing layers is removed and an opening portion is formed; and accordingly, a plurality of opening portions can be formed by removing the plurality of light absorbing layers and an insulating film formed over the plurality of light absorbing layers.

Owner:SEMICON ENERGY LAB CO LTD

Method for manufacturing semiconductor device

InactiveUS20090011551A1Excellent electrical propertiesImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorSemiconductor device

A method for manufacturing a semiconductor device is provided, which comprises at least a steps of forming a gate insulating film over a substrate, a step of forming a microcrystalline semiconductor film over the gate insulating film, and a step of forming an amorphous semiconductor film over the microcrystalline semiconductor film. The microcrystalline semiconductor film is formed by introducing a silicon hydride gas or a silicon halide gas when a surface of the gate insulating film is subjected to hydrogen plasma to generate a crystalline nucleus over the surface of the gate insulating film, and by increasing a flow rate of the silicon hydride gas or the silicon halide gas.

Owner:SEMICON ENERGY LAB CO LTD

Resist pattern thickening material, resist pattern and process for forming the same, and semiconductor device and process for manufacturing the same

InactiveUS20060073420A1Thickening efficiencyImprove batch productivityConstruction of head windingsHeads using thin filmsResistEthylene diamine

The present invention provides a resist pattern thickening material and the like which can thicken a resist pattern and form a fine space pattern. The resist pattern thickening material contains: a resin; a crosslinking agent; and at least one type selected from cationic surfactants, amphoteric surfactants, and non-ionic surfactants selected from alkoxylate surfactants, fatty acid ester surfactants, amide surfactants, alcohol surfactants, and ethylene diamine surfactants. In a process for forming a resist pattern of the present invention, after a resist pattern is formed, the thickening material is applied onto a surface of the pattern. A process for manufacturing a semiconductor device of the present invention includes: after forming a resist pattern on an underlying layer, applying the thickening material on a surface of the pattern so as to thicken the pattern; and a step of patterning the underlying layer by etching by using the pattern.

Owner:FUJITSU LTD

Dielectric Waveguide Device, Phase Shifter, High Frequency Switch, and Attenuator Provided with Dielectric Waveguide Device, High Frequency Transmitter, High Frequency Receiver, High Frequency Transceiver, Radar Device, Array Antenna, and Method of Manufacturing Dielectric Waveguide Device

InactiveUS20090174499A1Small sizeDecreased wavelengthMultiple-port networksConductive pattern formationElectricityTransceiver

The invention relates to a small and low-voltage operable dielectric waveguide device. First and second electrode are embedded in a dielectric part and are formed to be thinner than a skin depth for a frequency of electromagnetic wave propagating along a first dielectric part included in the dielectric part. Thereby, even if the first and second electrodes are arranged to be in contact with the first dielectric part, the propagating electromagnetic wave can transmit the first and second electrodes, and therefore the electromagnetic wave can propagate without being cut off and there is no influence on waveguide modes of the electromagnetic wave. Further, in a state where a transmission loss due to the embedded of the electrode is suppressed, an electric field with large electric field strength can be applied to the first dielectric part by the first and second electrodes, and a small and low-voltage operable dielectric waveguide device can be achieved.

Owner:KYOCERA CORP

Sandwich structure and integrated formed article using the same

ActiveCN101010188AExcellent mechanical propertiesImprove lightnessSynthetic resin layered productsThin material handlingFiberPolymer science

A sandwich structure (III) which has a core material (I) and, arranged on the both surfaces of said core material (I), a fiber-reinforced material (II) composed of a continuous reinforcing fiber (A) and a matrix fiber (B), wherein the above core material (I) comprises a void. The void is formed by bubbles of a foamed material or, the core is composed of a discontinuous reinforcing fiber and a thermoplastic resin and the void is formed by interstices formed at crossings of filaments of said reinforcing fiber.

Owner:TORAY IND INC

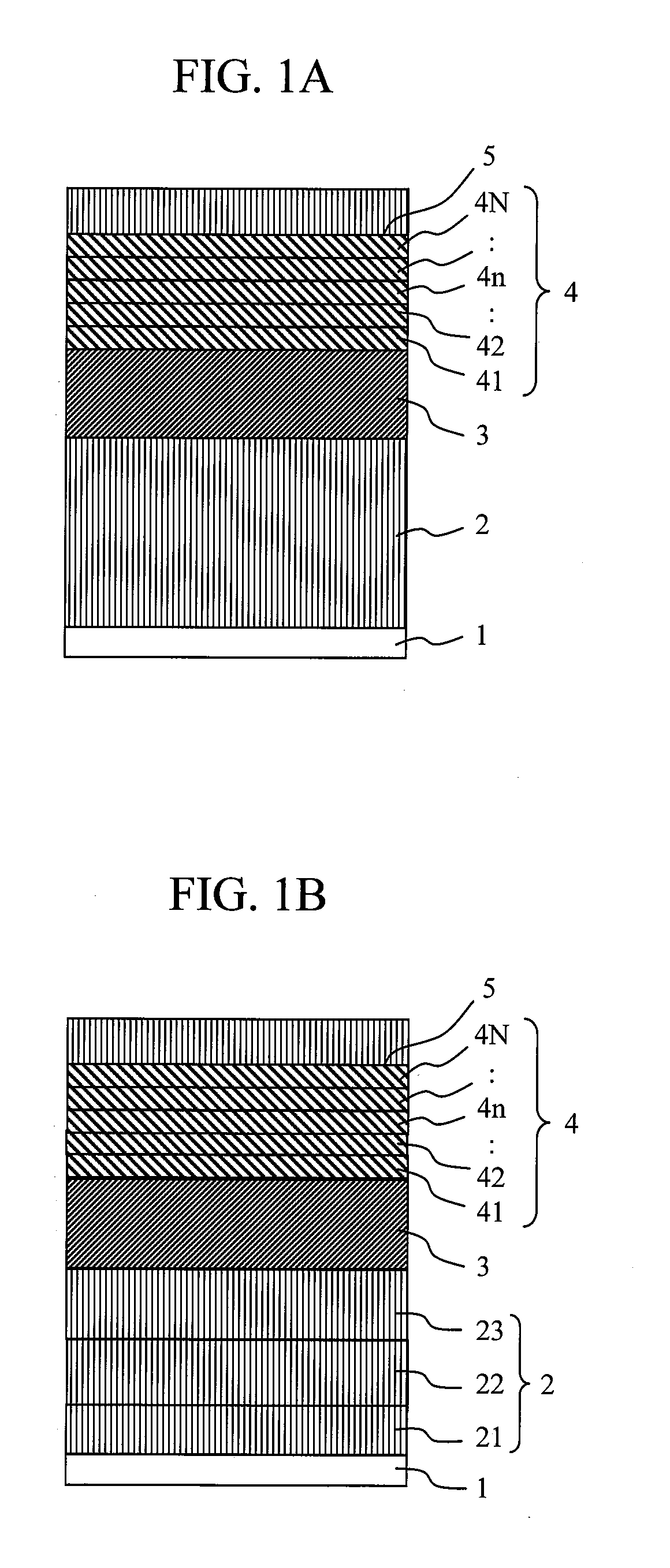

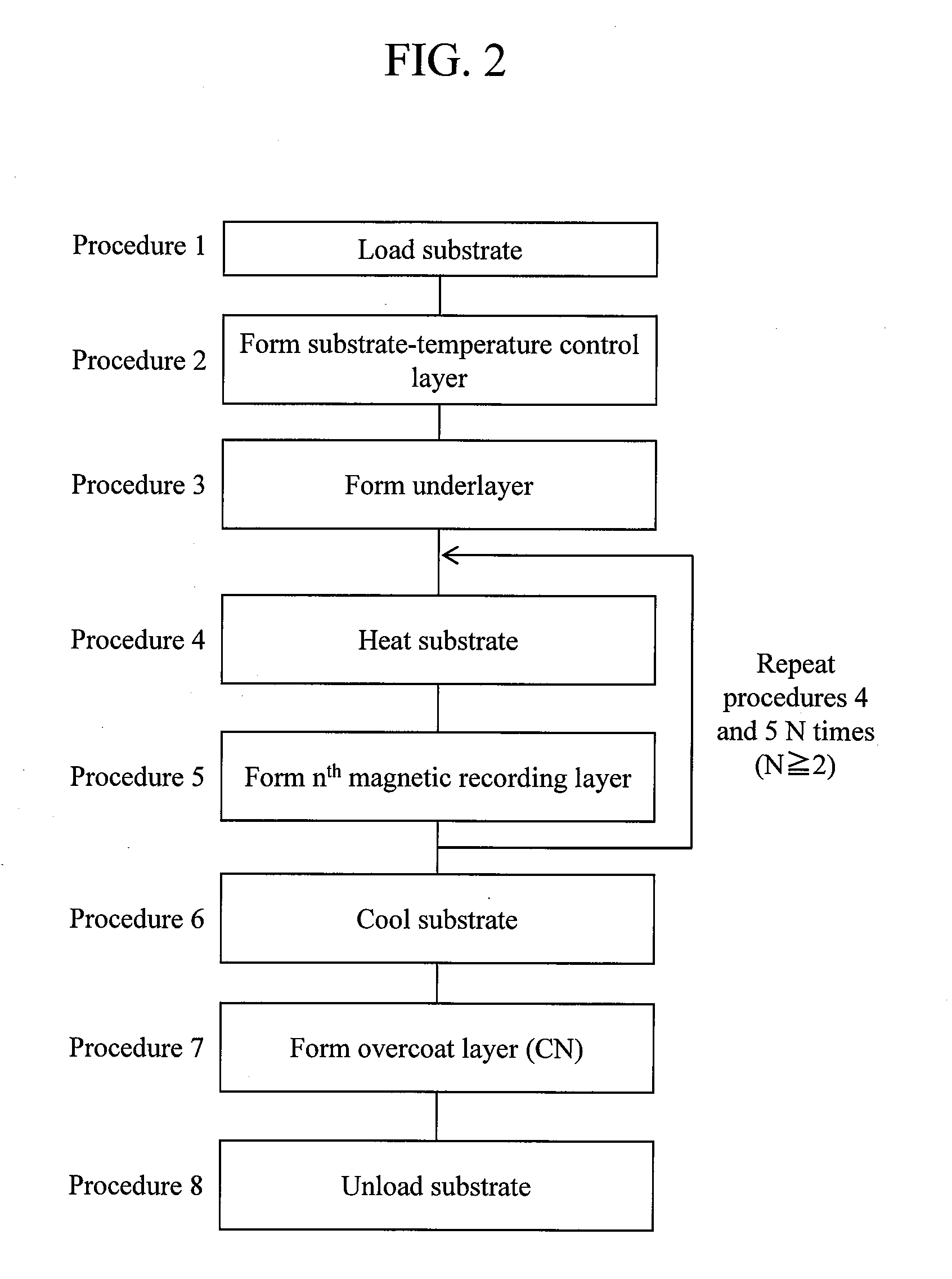

Perpendicular magnetic recording medium and manufacturing method of the same

InactiveUS20120052330A1Large heat capacityTemperature of substrate is reducedRecord information storageCoatingsPhysicsRecording density

A perpendicular magnetic recording medium having sufficient perpendicular uniaxial magnetic anisotropy energy and a crystal grain size for realizing an areal recording density of one terabit or more per one square centimeter, and excellent in mass productivity, and a manufacturing method of the same are provided. On a substrate, a substrate-temperature control layer, an underlayer and a magnetic recording layer are sequentially formed. The magnetic recording layer is formed by repeating a magnetic layer stacking step N times (N≧2), which includes a first step of heating the substrate in a heat process chamber, and a second step of depositing, in a deposition process chamber, the magnetic recording layer constituted of an alloy mainly composed of FePt to which at least one kind of non-magnetic material selected from a group constituted of C and an Si oxide is added.

Owner:HITACHI LTD

Semiconductor device and method of manufacturing the same

InactiveUS6924528B2Improve batch productivityImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingCrystal structureBottom gate

In a bottom gate type semiconductor device made of a semiconductor layer with crystal structure, source / drain regions are constructed by a lamination layer structure including a first conductive layer (n+ layer), a second conductive layer (n− layer) having resistance higher than the first conductive layer, and an intrinsic or substantially intrinsic semiconductor layer (i layer). At this time, the n− layer acts as LDD region, and the i layer acts as an offset region is a film thickness direction.

Owner:SEMICON ENERGY LAB CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com