Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

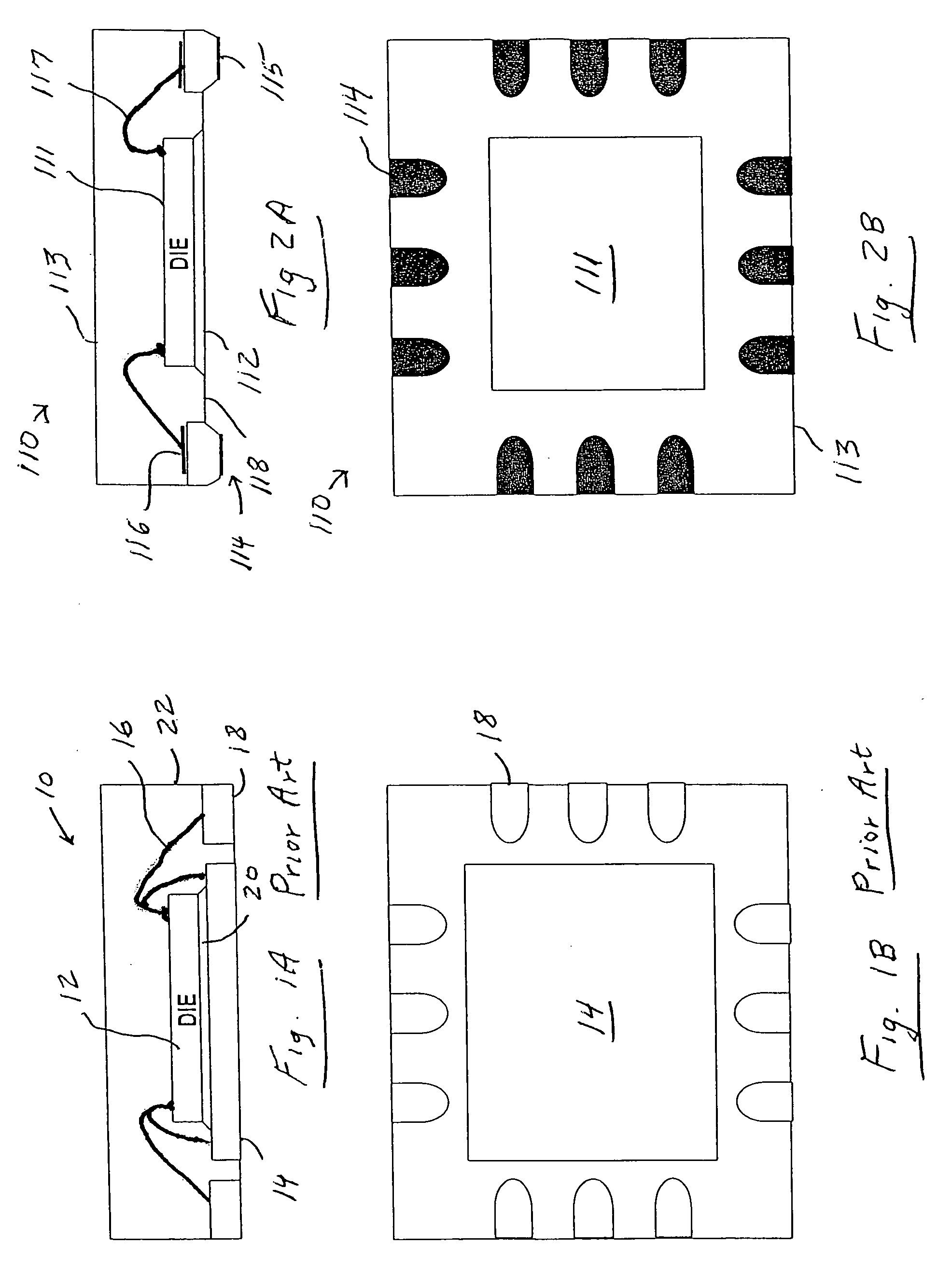

5920 results about "Mask layer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

What are Layer Masks. Layer masks are used in image-editing to control the visibility of the layers present below a layer. Typically, you would delete a part of the image to reveal the underlying layer. But that's what makes layer masks different.

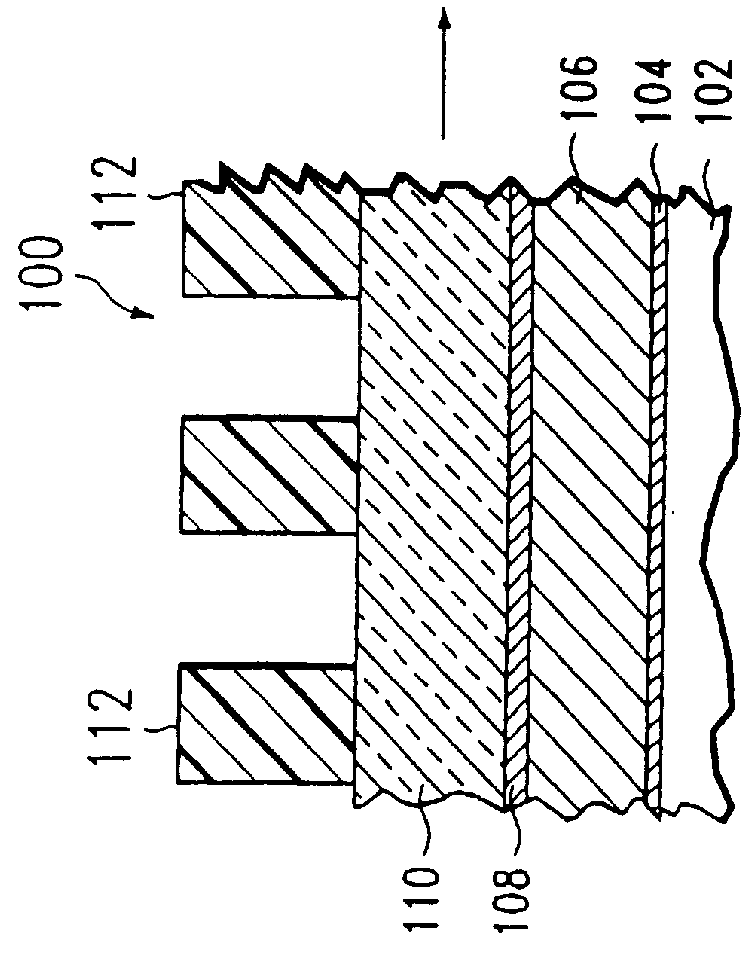

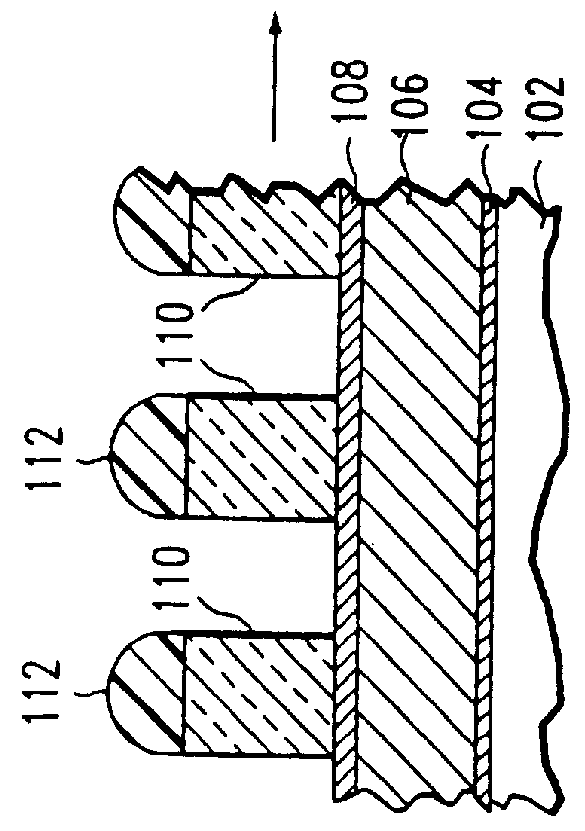

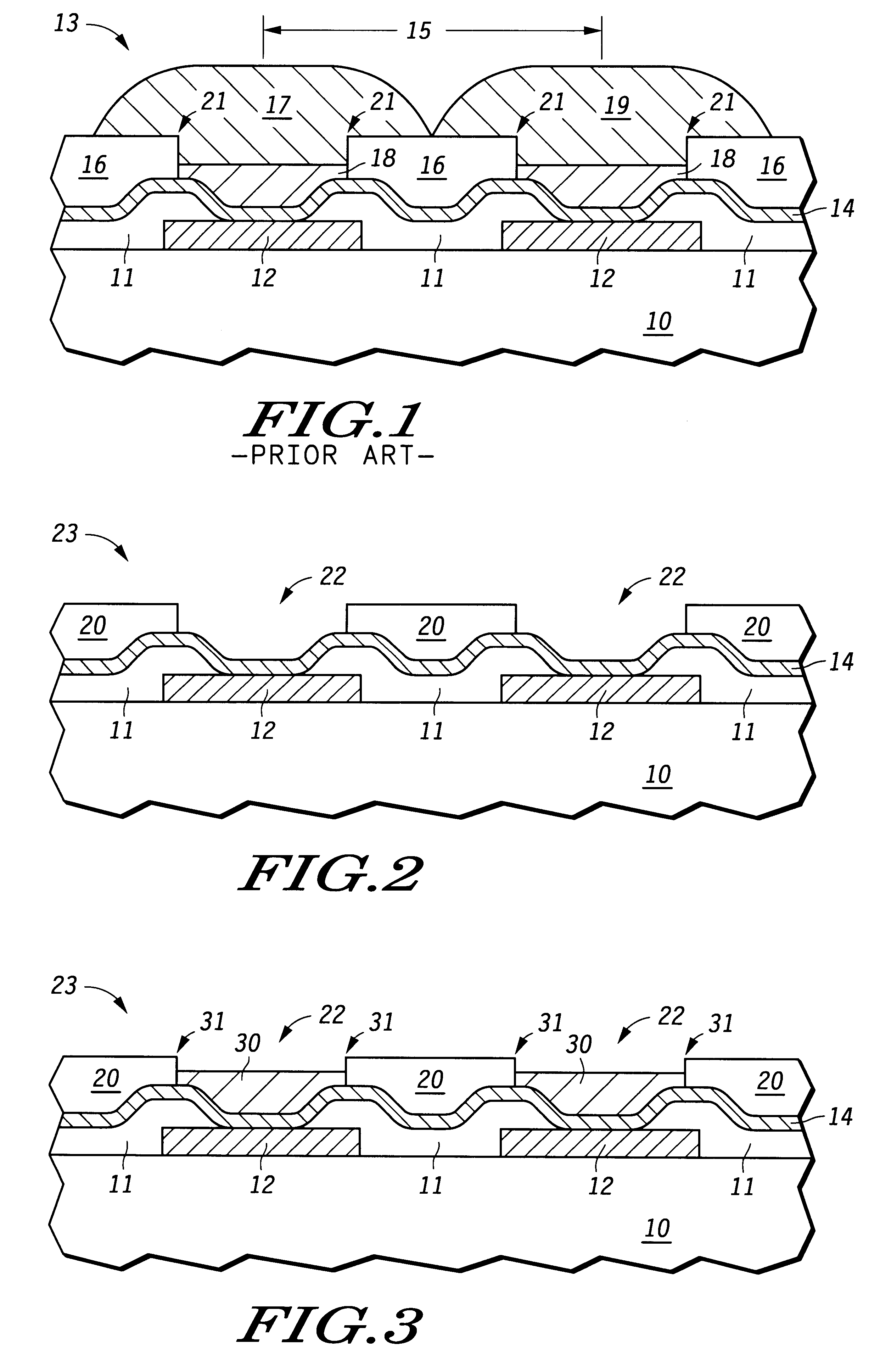

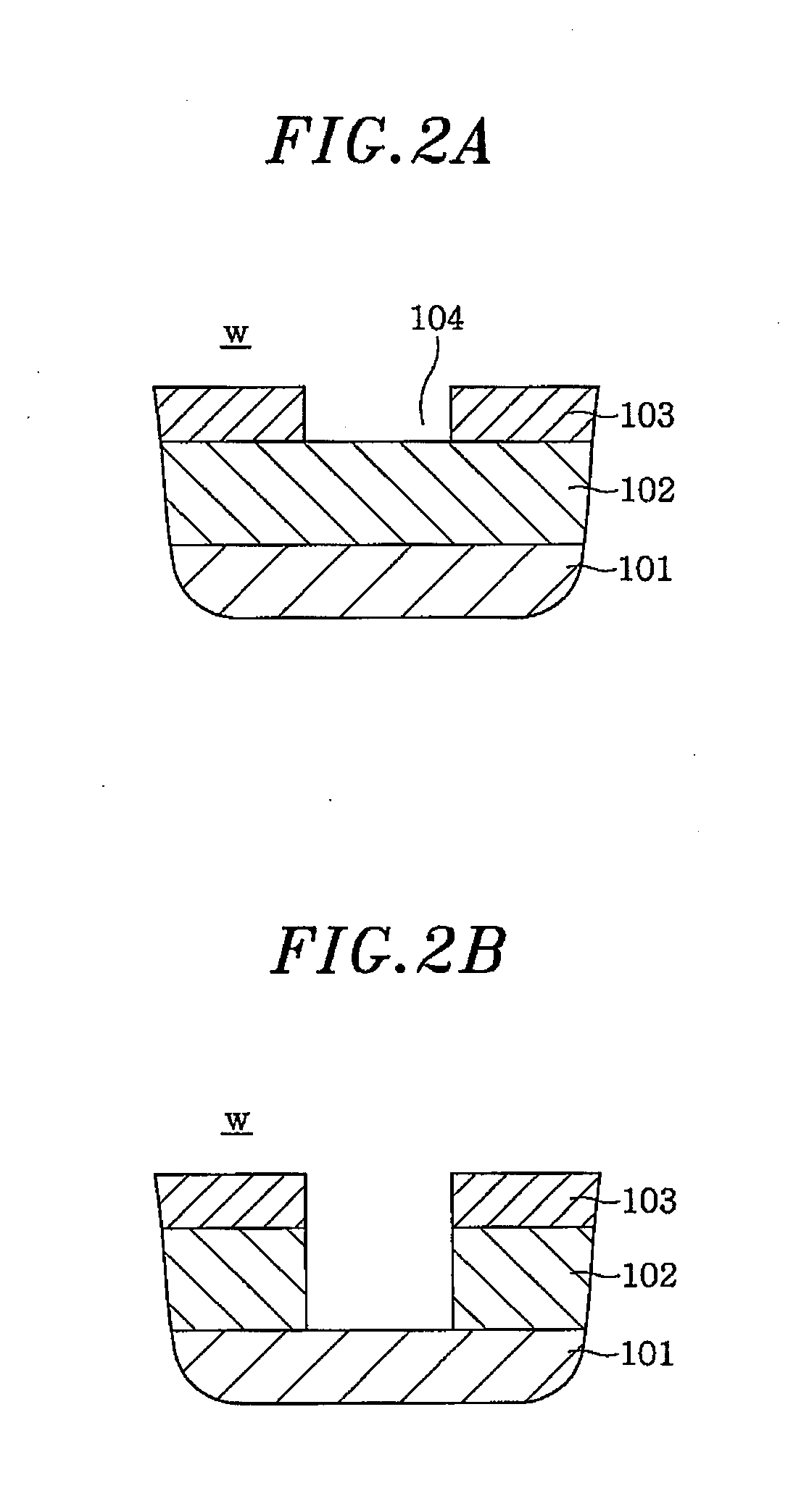

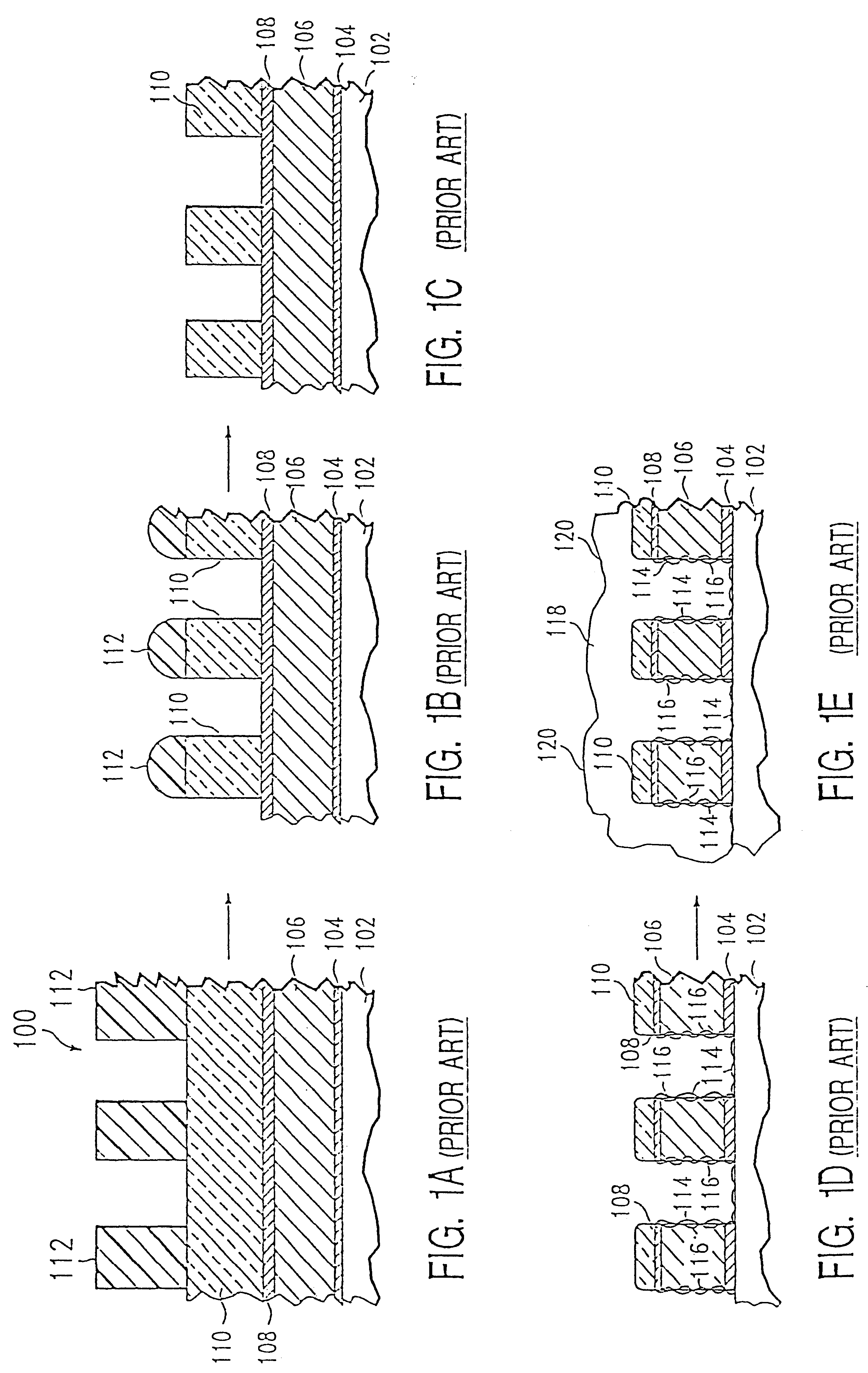

Method of etching patterned layers useful as masking during subsequent etching or for damascene structures

InactiveUS6080529APhotomechanical apparatusSemiconductor/solid-state device manufacturingConductive polymerOrganic base

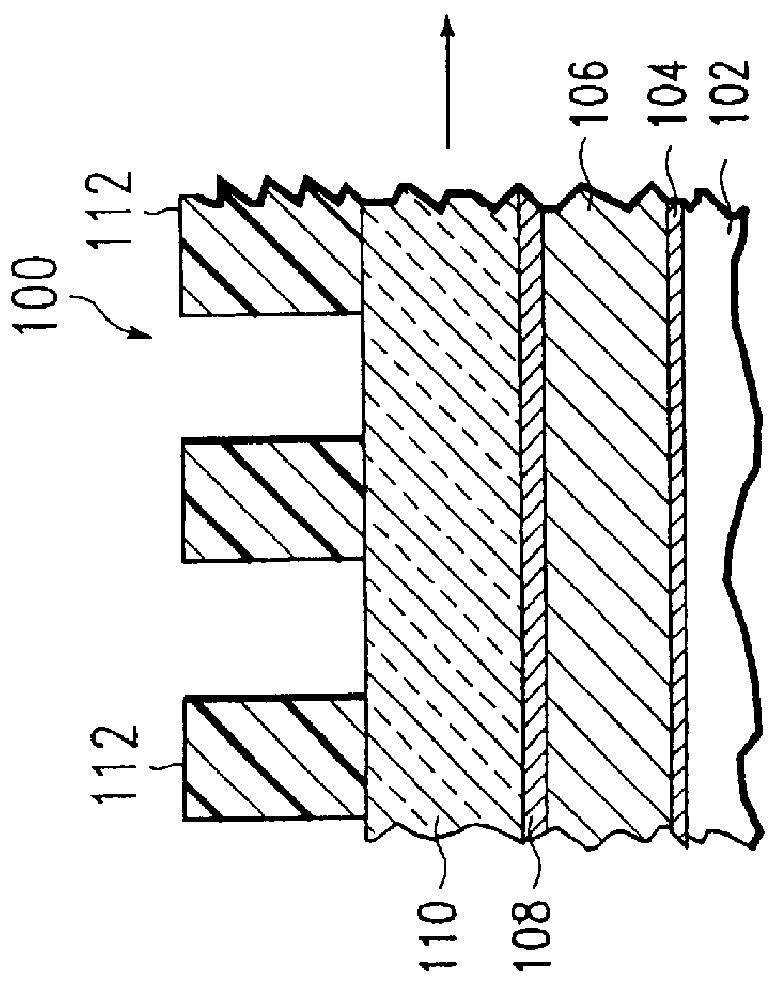

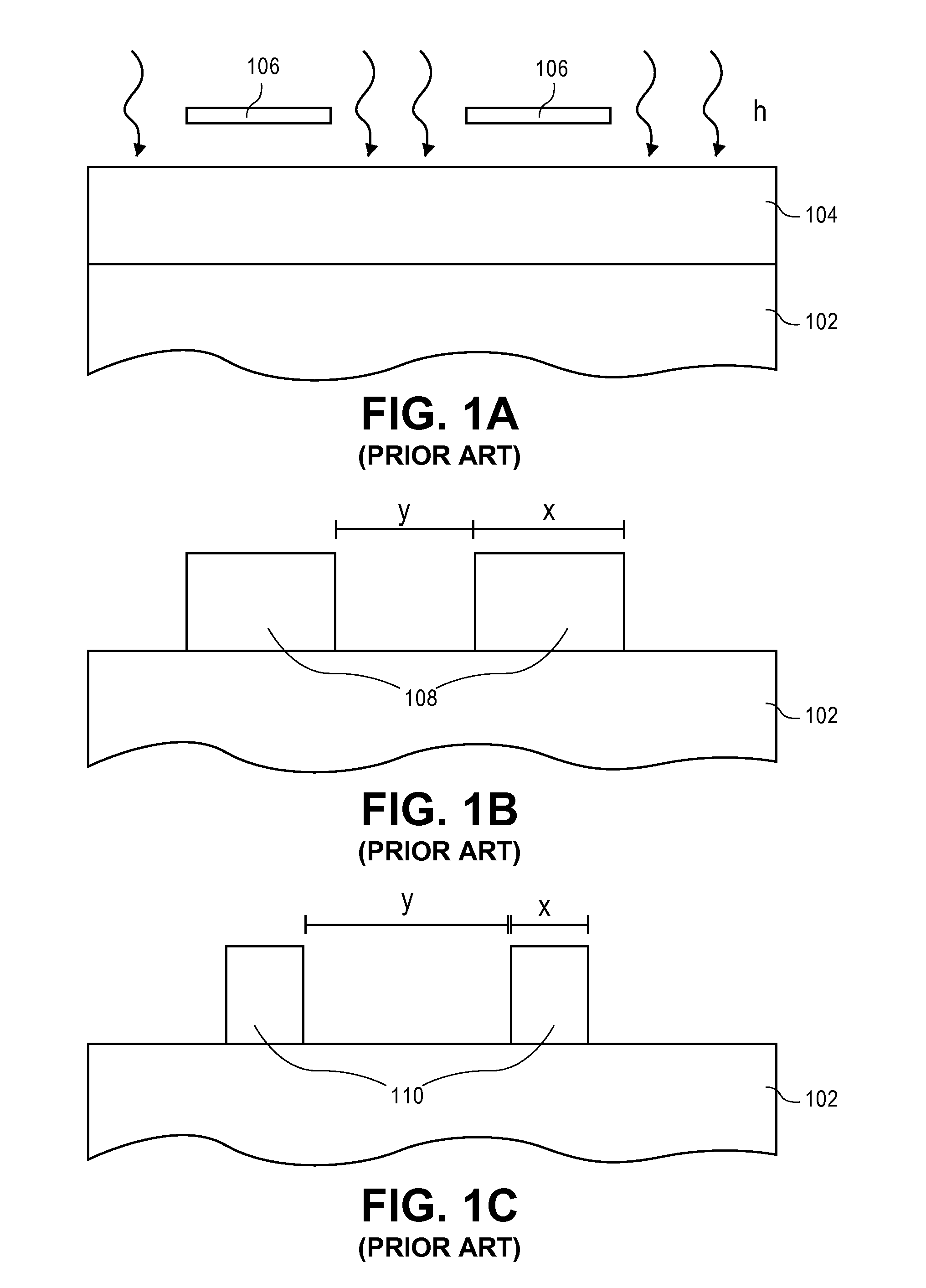

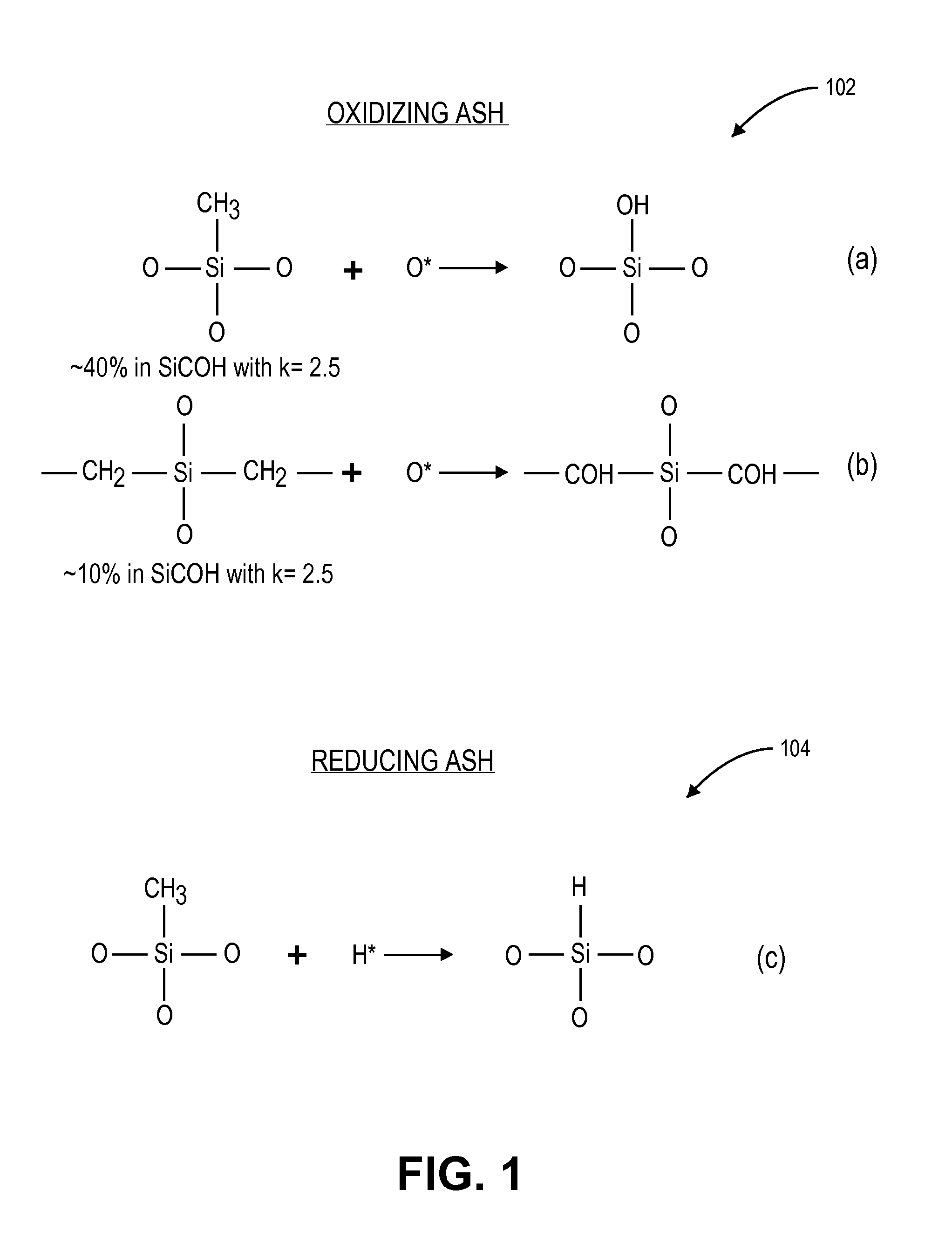

A first embodiment of the present invention pertains to a method of patterning a semiconductor device conductive feature while permitting easy removal of any residual masking layer which remains after completion of the etching process. A multi-layered masking structure is used which includes a layer of high-temperature organic-based masking material overlaid by either a patterned layer of inorganic masking material or by a layer of patterned high-temperature imageable organic masking material. The inorganic masking material is used to transfer a pattern to the high-temperature organic-based masking material and is then removed. The high-temperature organic-based masking material is used to transfer the pattern and then may be removed if desired. This method is also useful in the pattern etching of aluminum, even though aluminum can be etched at lower temperatures. A second embodiment of the present invention pertains to a specialized etch chemistry useful in the patterning of organic polymeric layers such as low k dielectrics, or other organic polymeric interfacial layers. This etch chemistry is useful for mask opening during the etch of a conductive layer or is useful in etching damascene structures where a metal fill layer is applied over the surface of a patterned organic-based dielectric layer. The etch chemistry provides for the use of etchant plasma species which minimize oxygen, fluorine, chlorine, and bromine content.

Owner:APPLIED MATERIALS INC

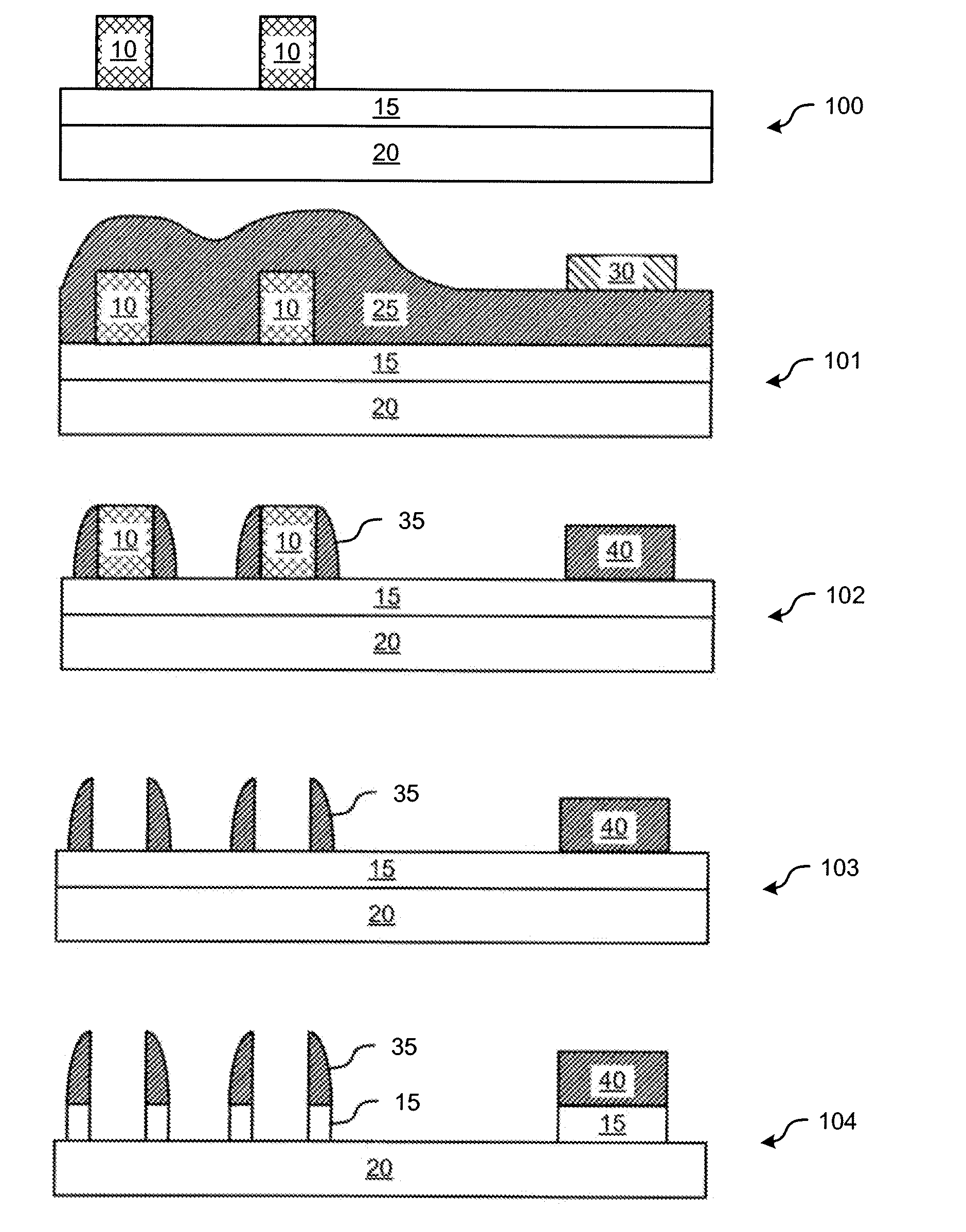

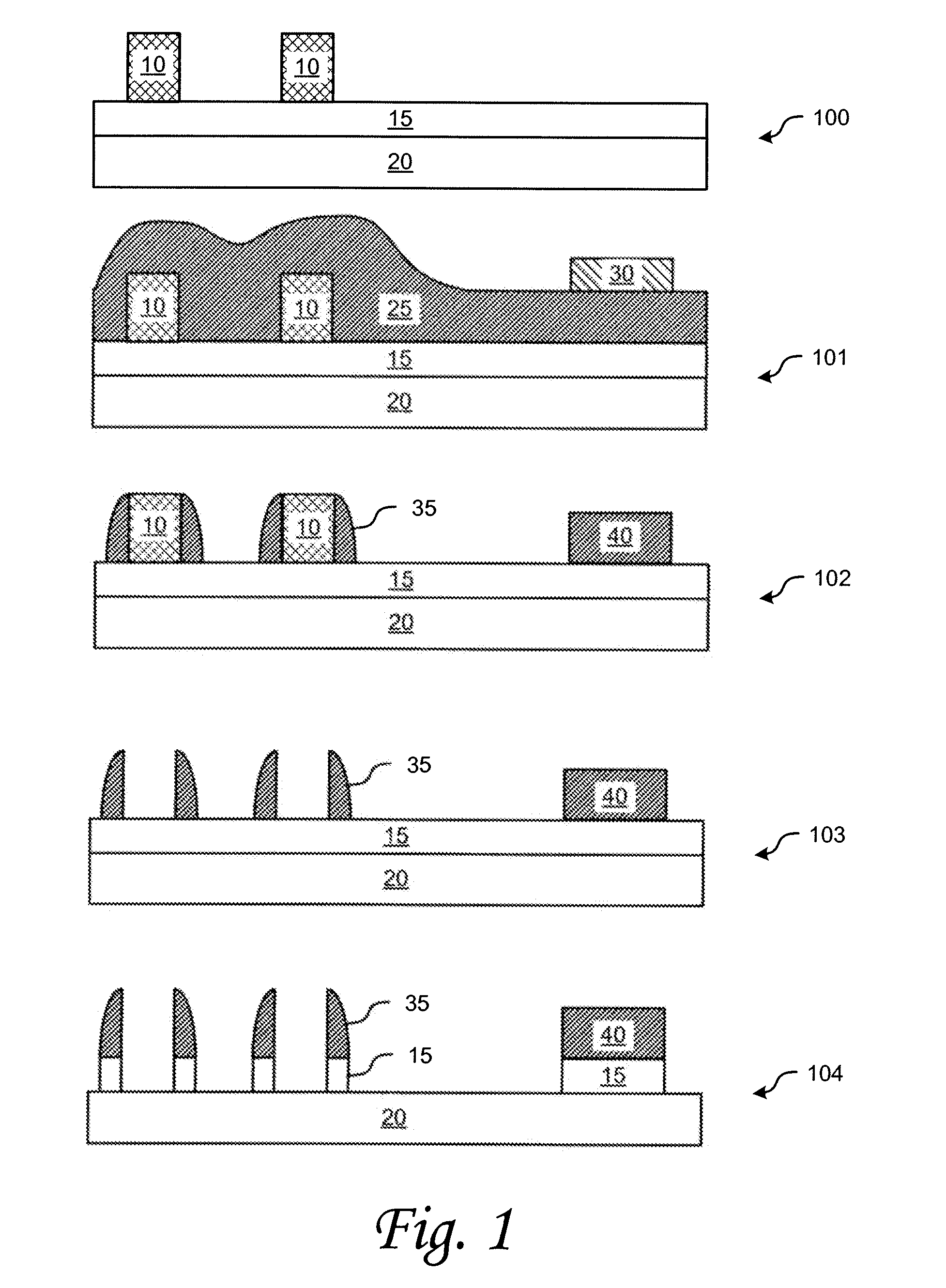

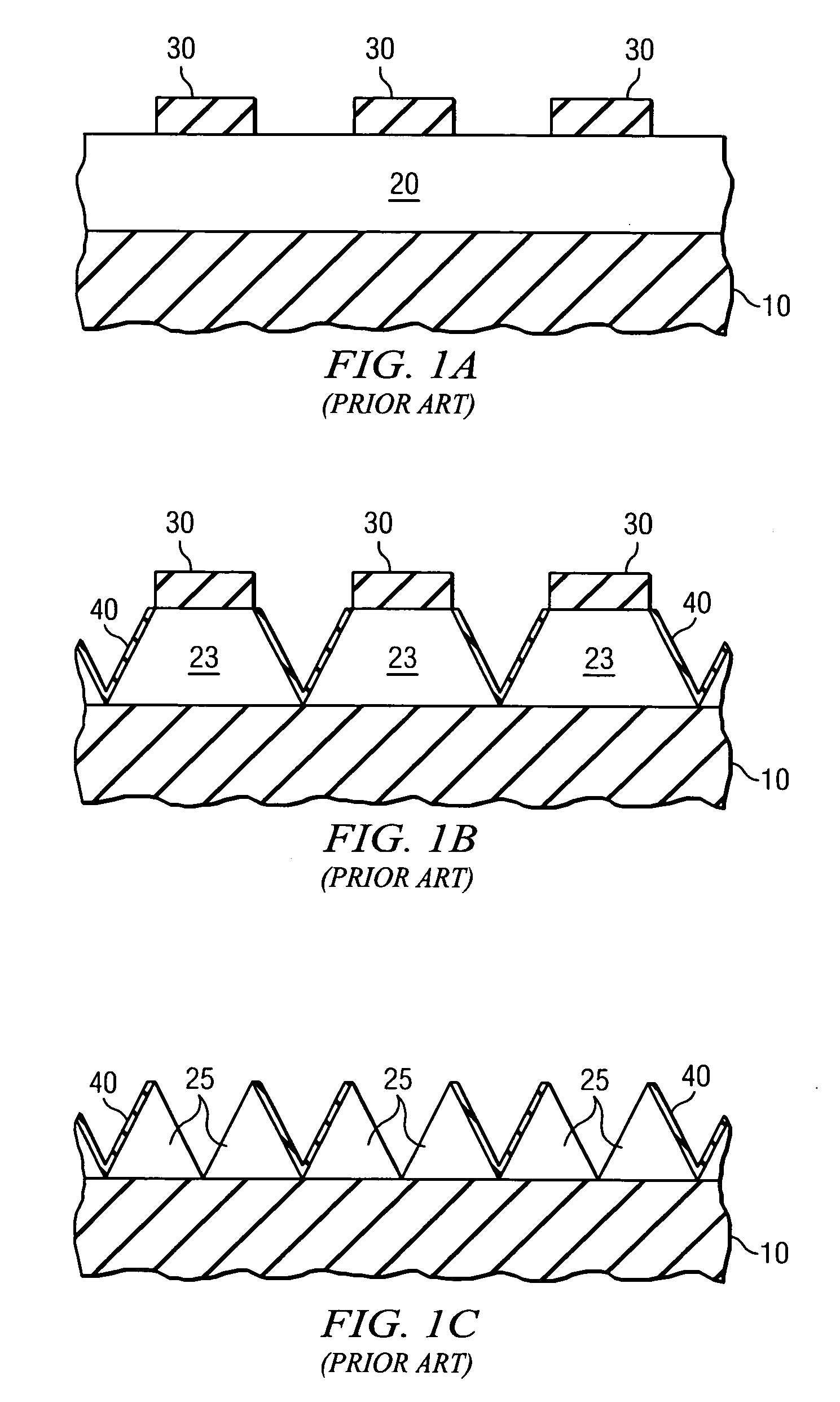

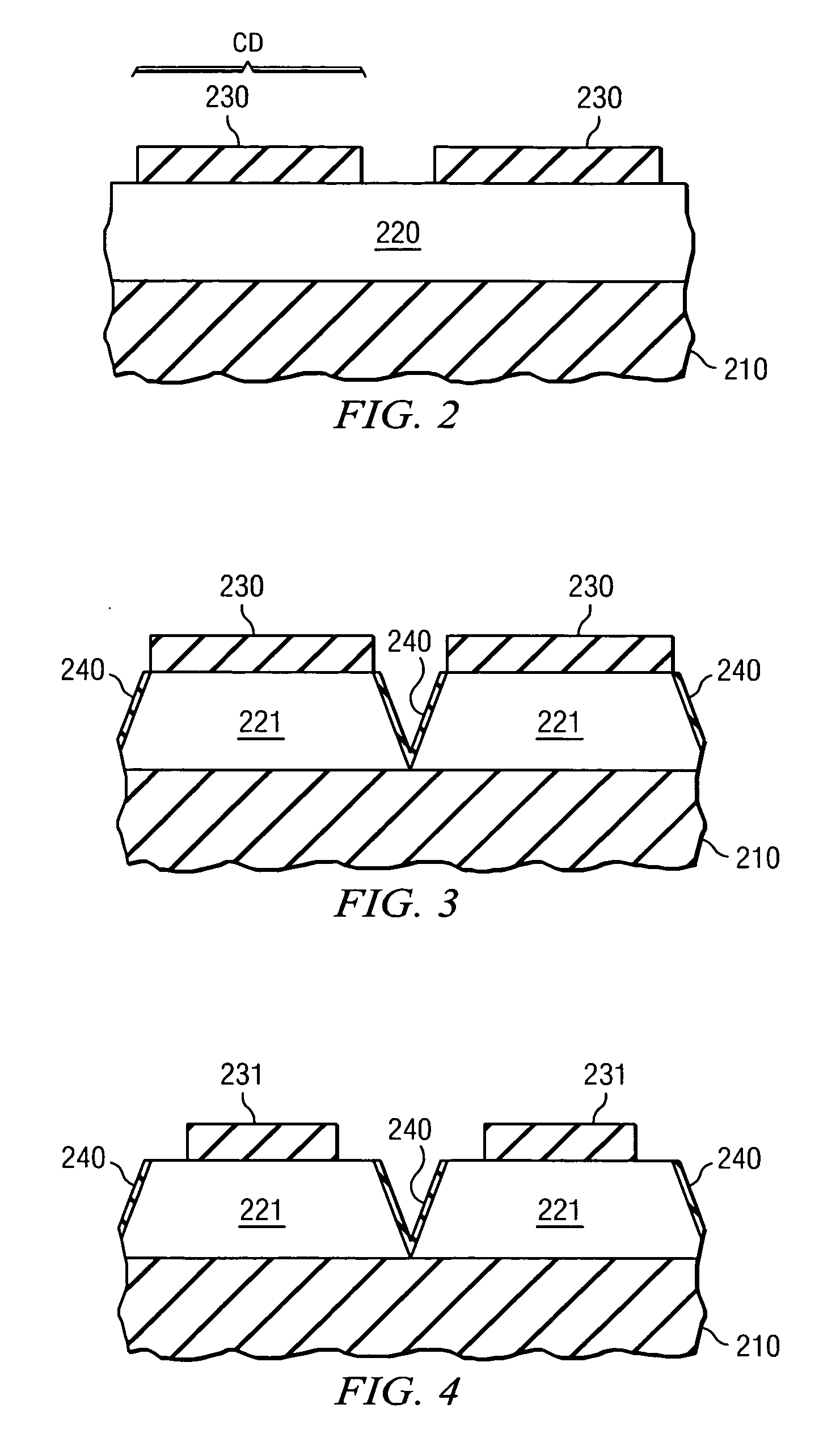

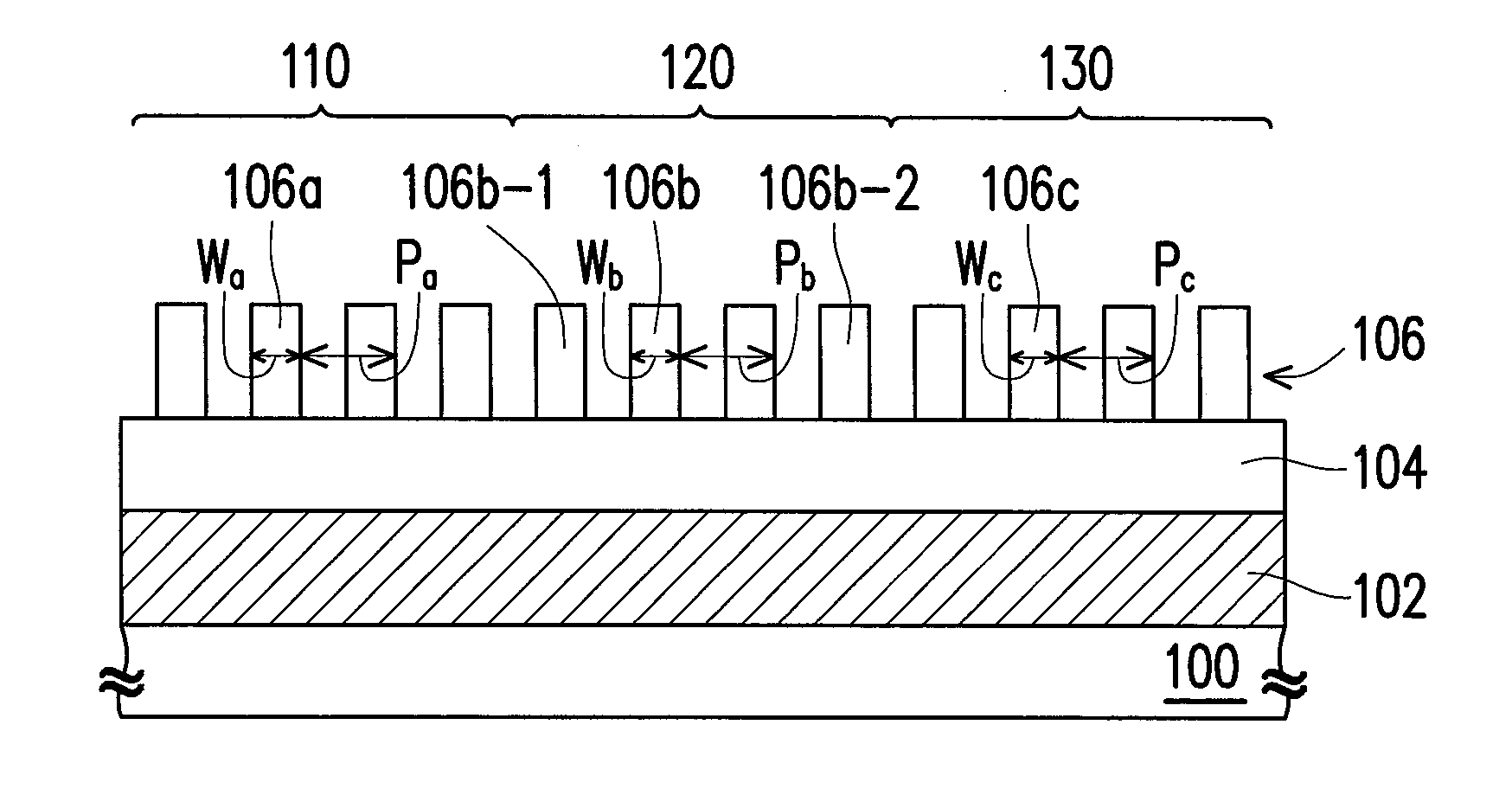

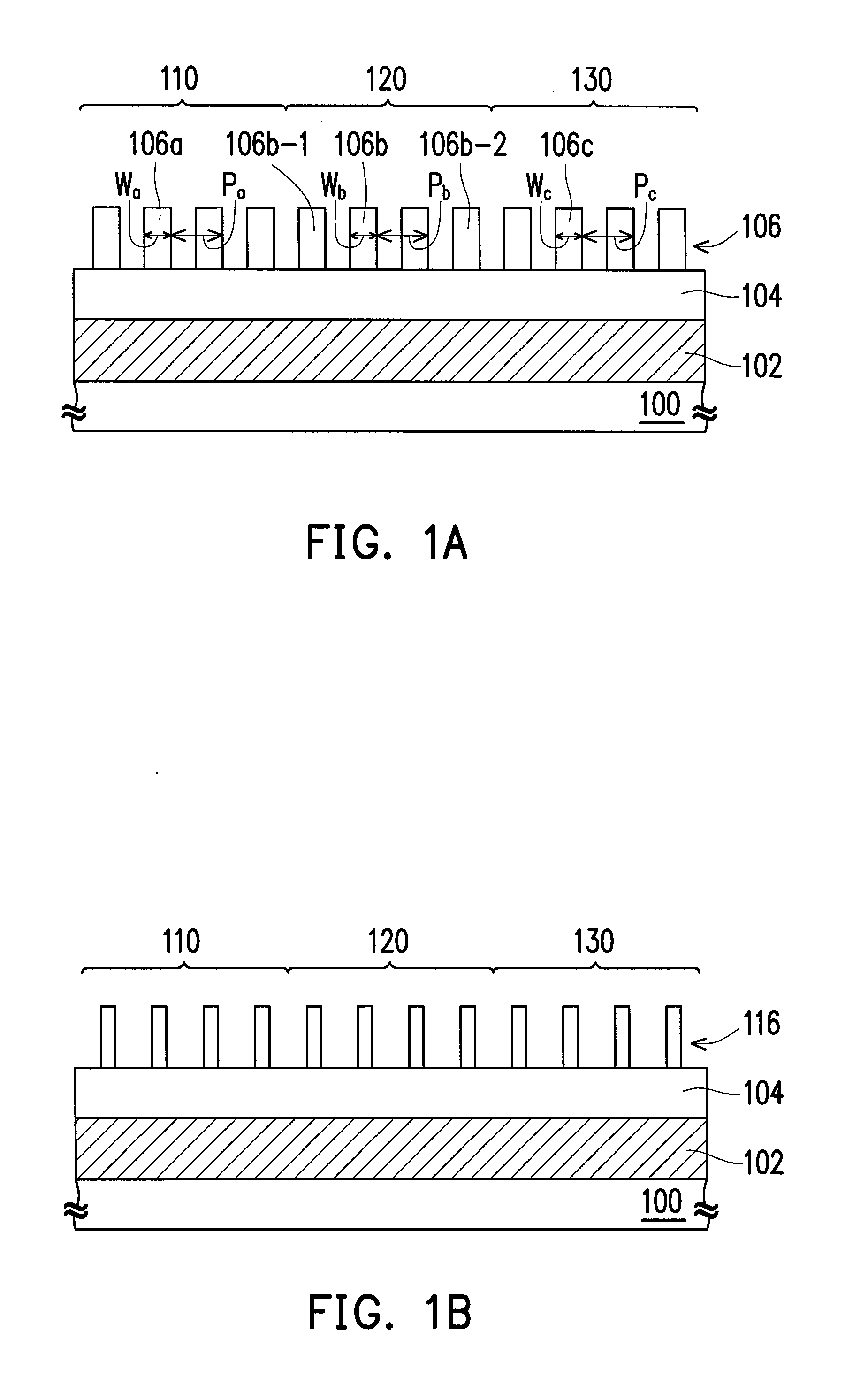

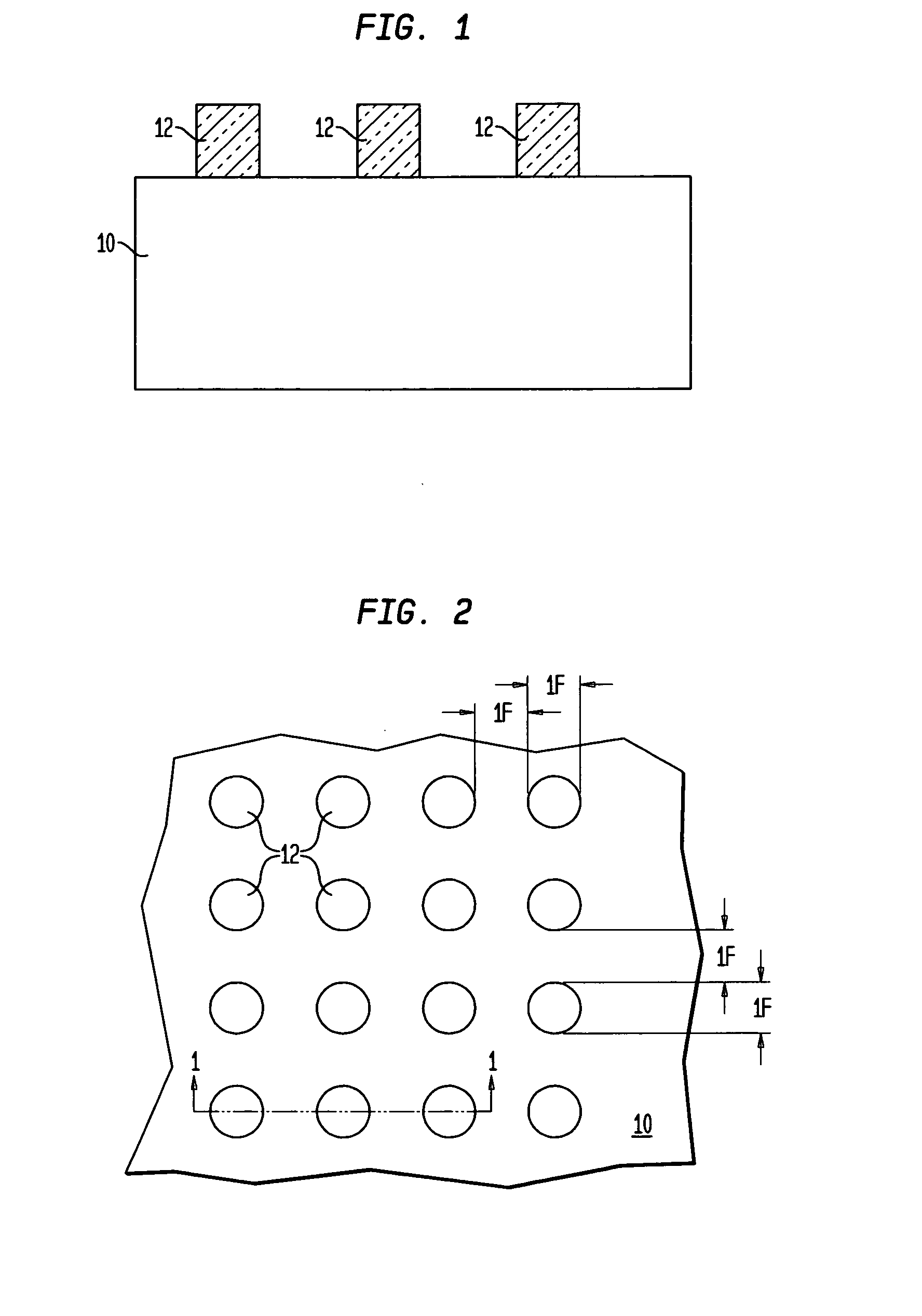

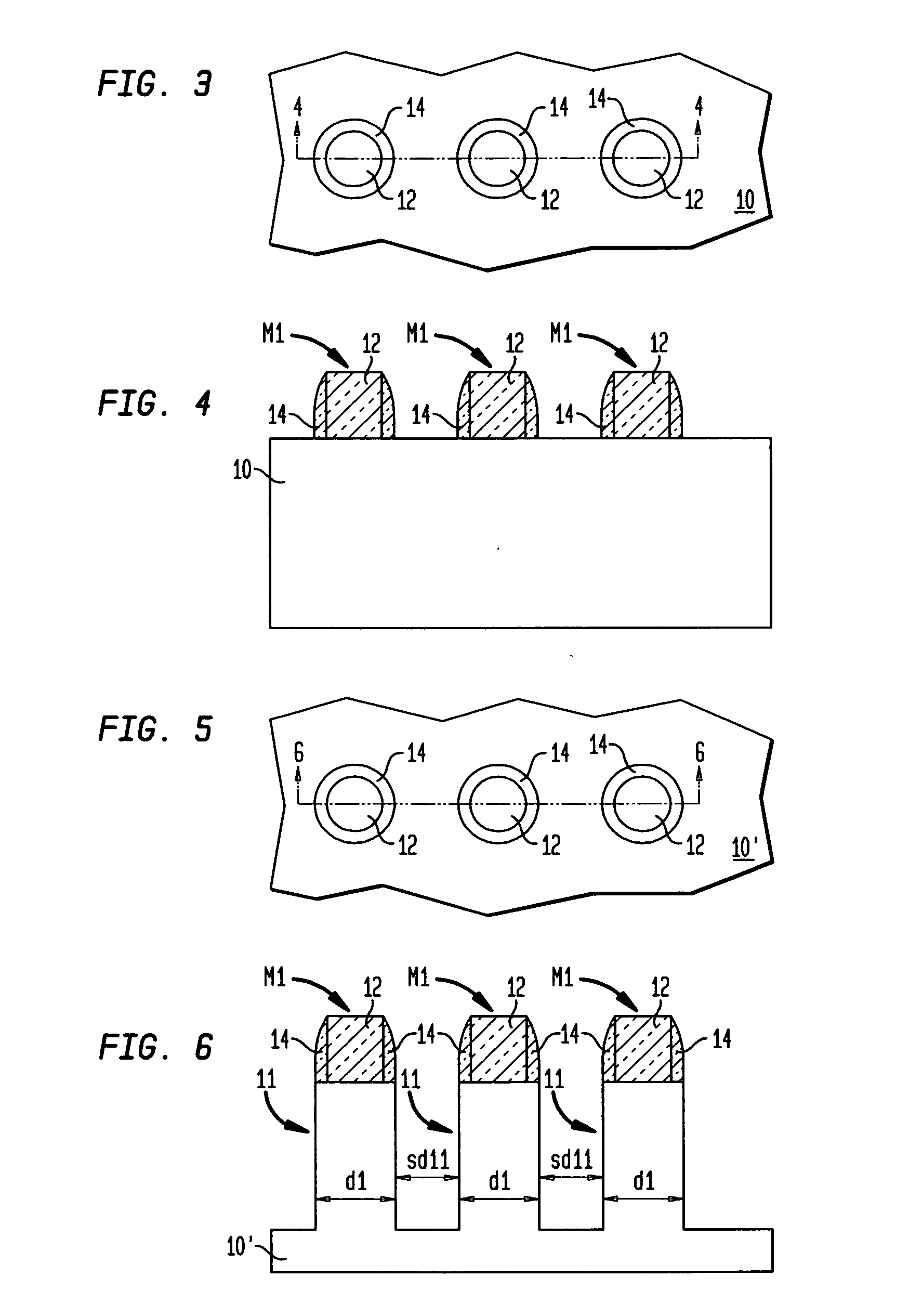

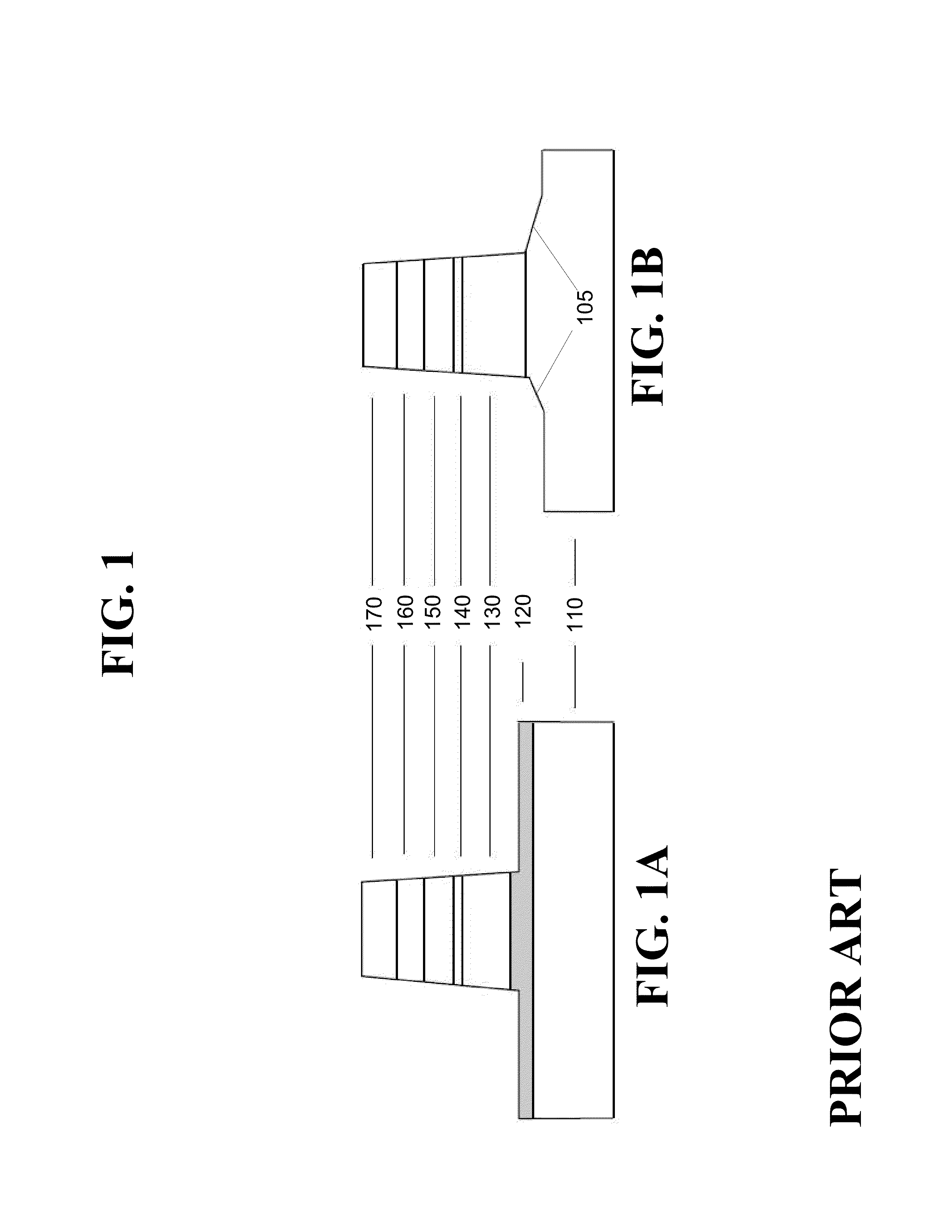

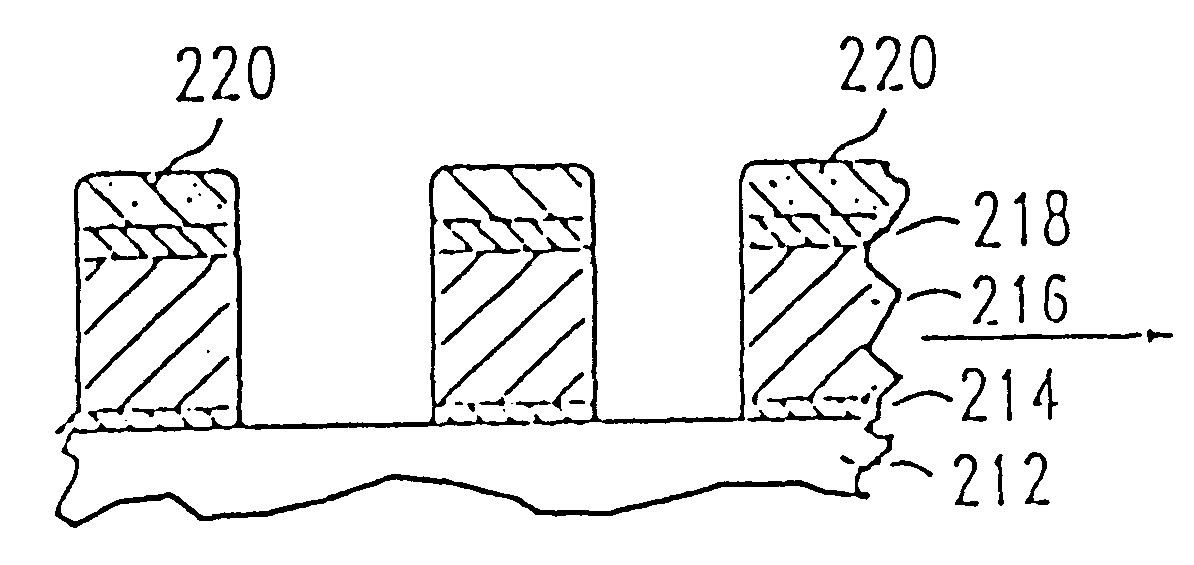

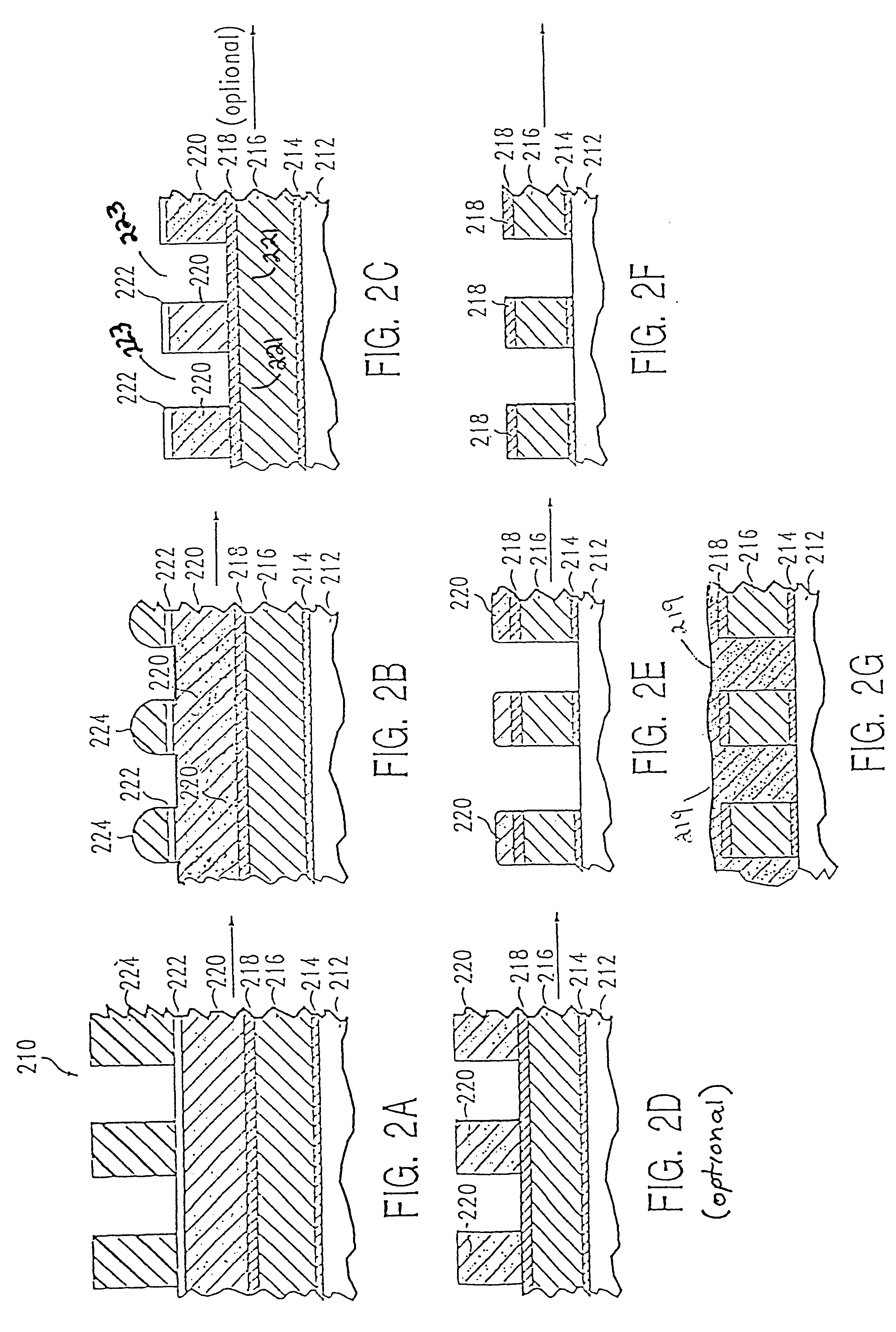

Method for integrated circuit fabrication using pitch multiplication

InactiveUS7115525B2Electric discharge tubesSemiconductor/solid-state device manufacturingResistEngineering

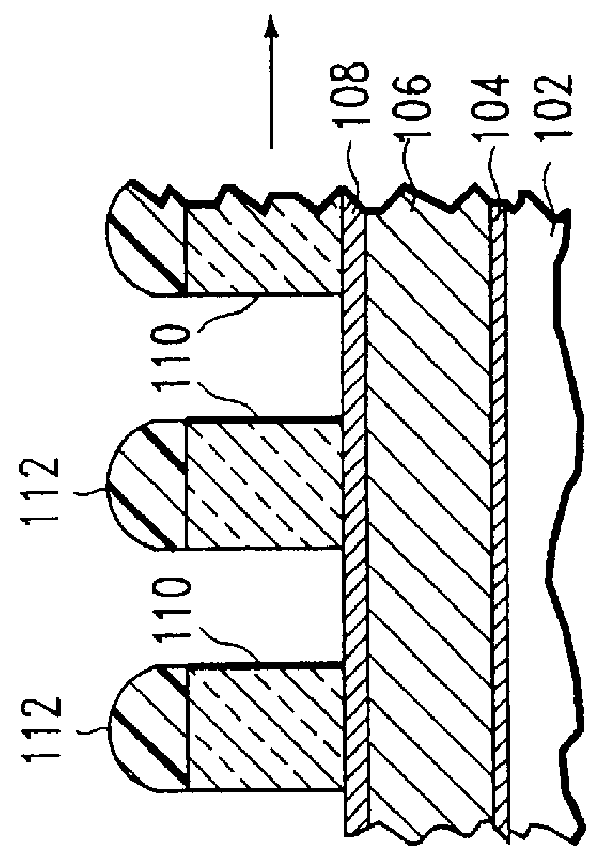

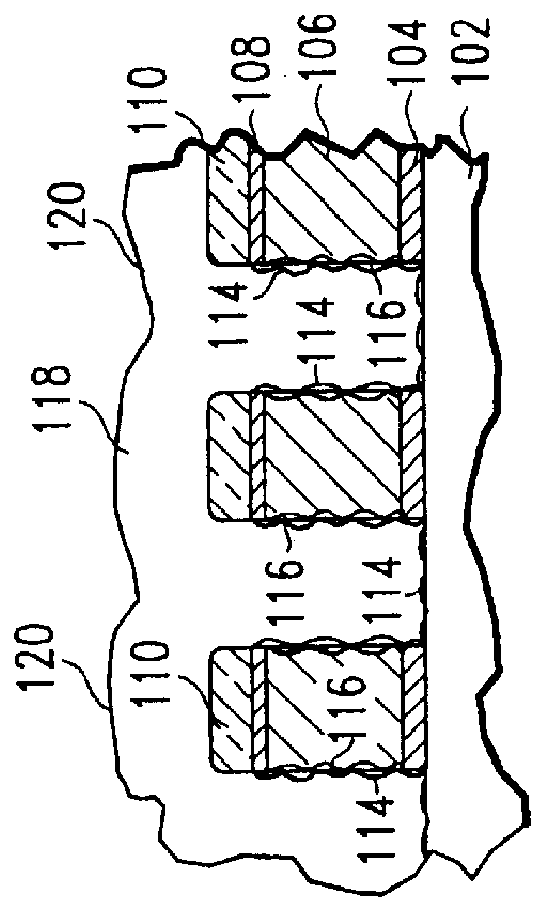

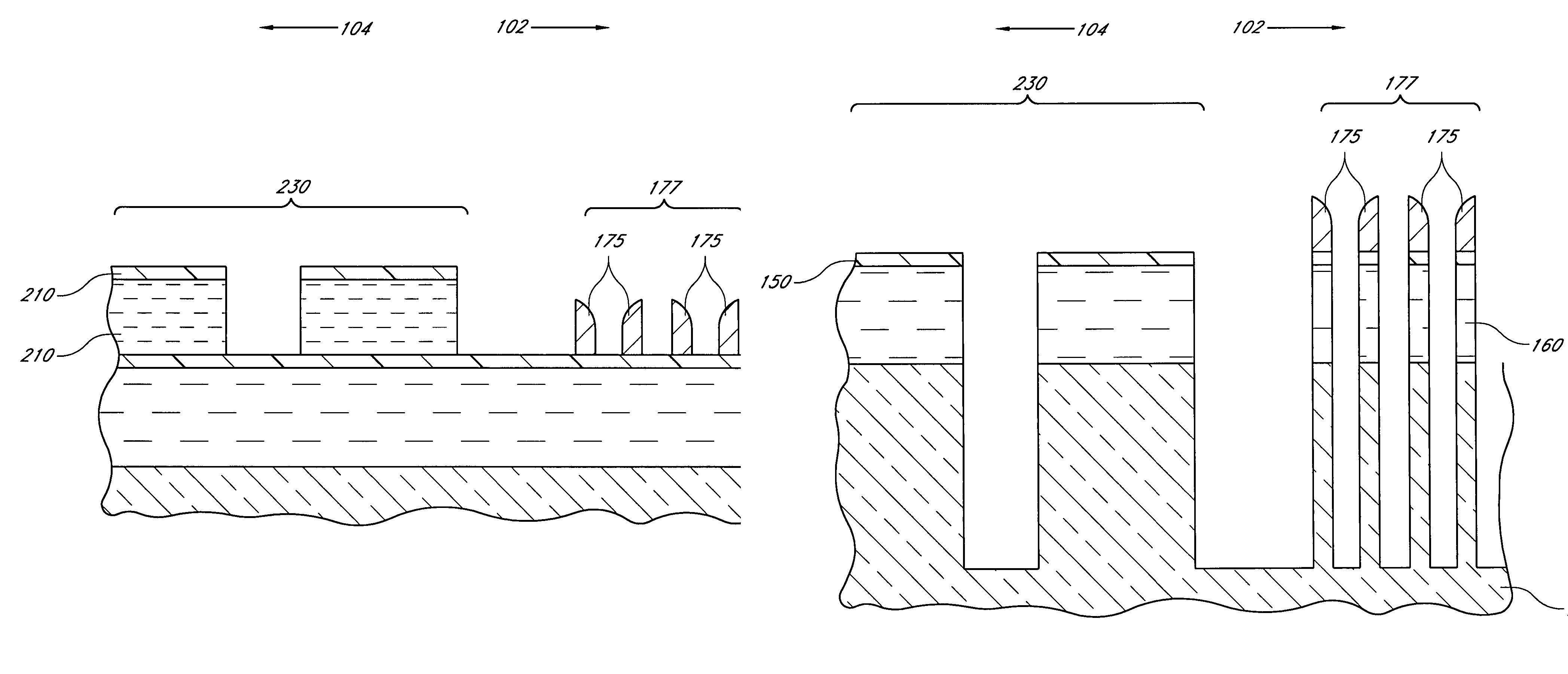

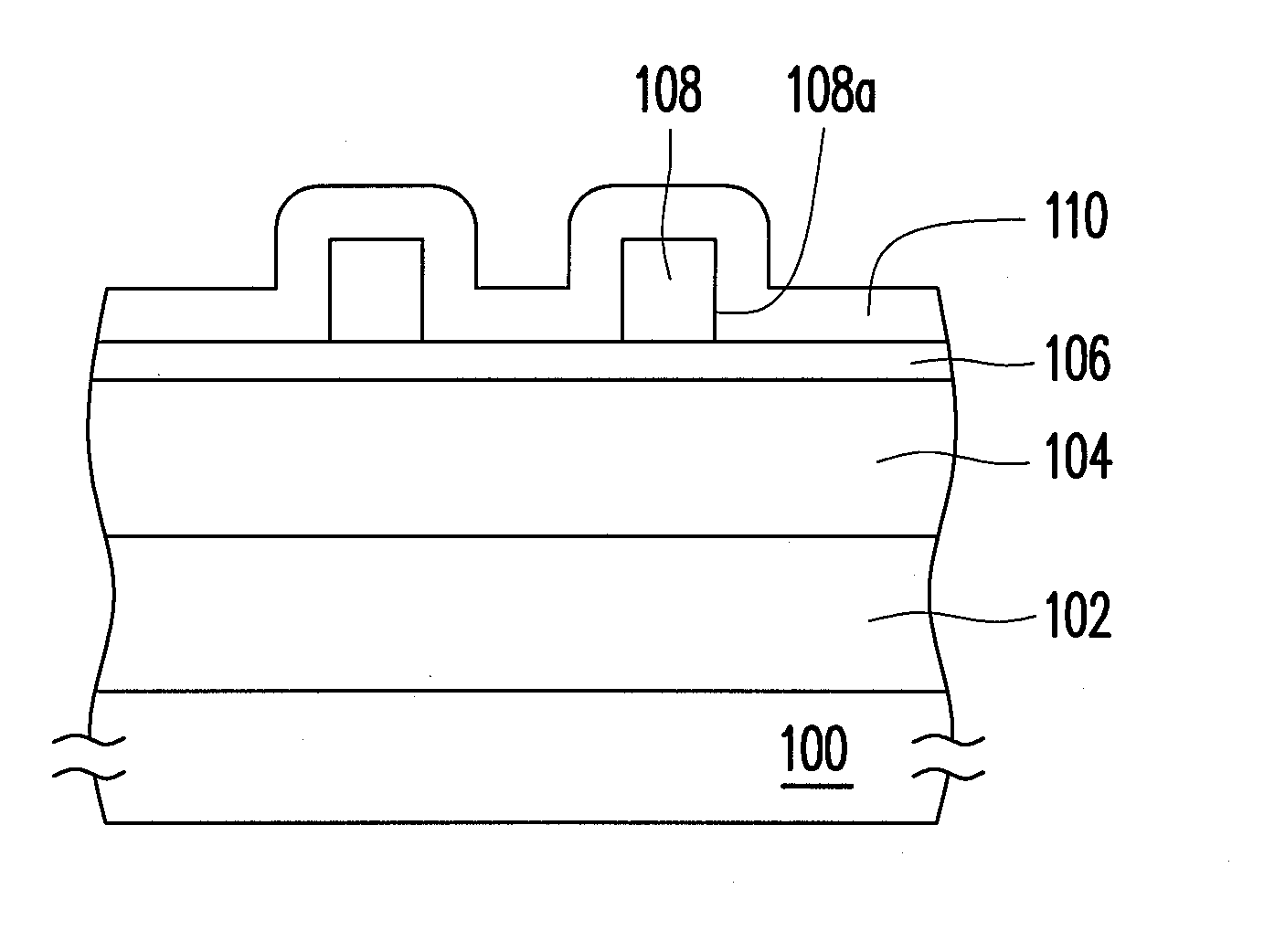

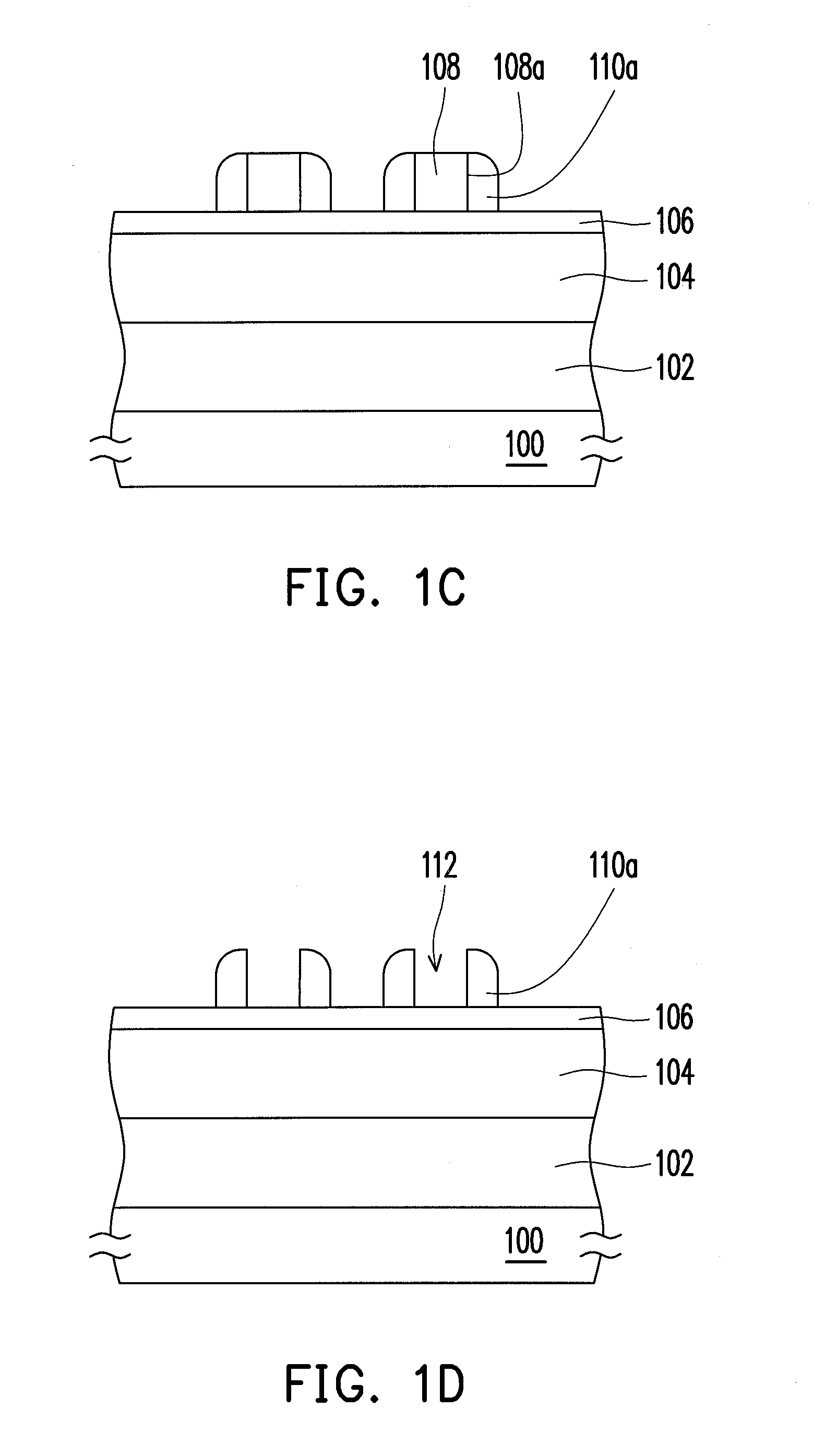

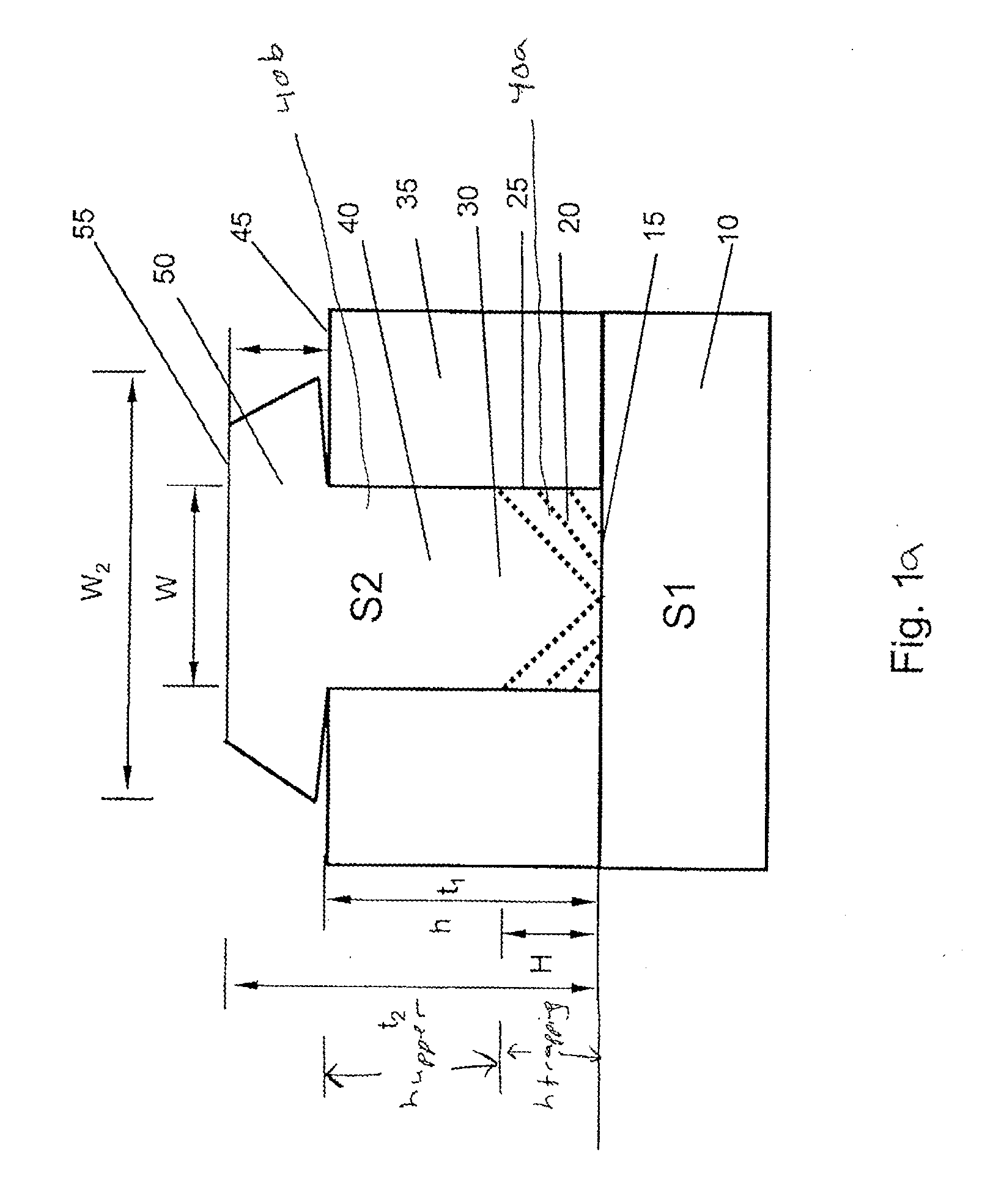

Different sized features in the array and in the periphery of an integrated circuit are patterned on a substrate in a single step. In particular, a mixed pattern, combining two separately formed patterns, is formed on a single mask layer and then transferred to the underlying substrate. The first of the separately formed patterns is formed by pitch multiplication and the second of the separately formed patterns is formed by conventional photolithography. The first of the separately formed patterns includes lines that are below the resolution of the photolithographic process used to form the second of the separately formed patterns. These lines are made by forming a pattern on photoresist and then etching that pattern into an amorphous carbon layer. Sidewall pacers having widths less than the widths of the un-etched parts of the amorphous carbon are formed on the sidewalls of the amorphous carbon. The amorphous carbon is then removed, leaving behind the sidewall spacers as a mask pattern. Thus, the spacers form a mask having feature sizes less than the resolution of the photolithography process used to form the pattern on the photoresist. A protective material is deposited around the spacers. The spacers are further protected using a hard mask and then photoresist is formed and patterned over the hard mask. The photoresist pattern is transferred through the hard mask to the protective material. The pattern made out by the spacers and the temporary material is then transferred to an underlying amorphous carbon hard mask layer. The pattern, having features of difference sizes, is then transferred to the underlying substrate.

Owner:ROUND ROCK RES LLC

Method for integrated circuit fabrication using pitch multiplication

InactiveUS20060046484A1Electric discharge tubesSemiconductor/solid-state device manufacturingImage resolutionDifferences size

Different sized features in the array and in the periphery of an integrated circuit are patterned on a substrate in a single step. In particular, a mixed pattern, combining two separately formed patterns, is formed on a single mask layer and then transferred to the underlying substrate. The first of the separately formed patterns is formed by pitch multiplication and the second of the separately formed patterns is formed by conventional photolithography. The first of the separately formed patterns includes lines that are below the resolution of the photolithographic process used to form the second of the separately formed patterns. These lines are made by forming a pattern on photoresist and then etching that pattern into an amorphous carbon layer. Sidewall pacers having widths less than the widths of the un-etched parts of the amorphous carbon are formed on the sidewalls of the amorphous carbon. The amorphous carbon is then removed, leaving behind the sidewall spacers as a mask pattern. Thus, the spacers form a mask having feature sizes less than the resolution of the photolithography process used to form the pattern on the photoresist. A protective material is deposited around the spacers. The spacers are further protected using a hard mask and then photoresist is formed and patterned over the hard mask. The photoresist pattern is transferred through the hard mask to the protective material. The pattern made out by the spacers and the temporary material is then transferred to an underlying amorphous carbon hard mask layer. The pattern, having features of difference sizes, is then transferred to the underlying substrate.

Owner:ROUND ROCK RES LLC

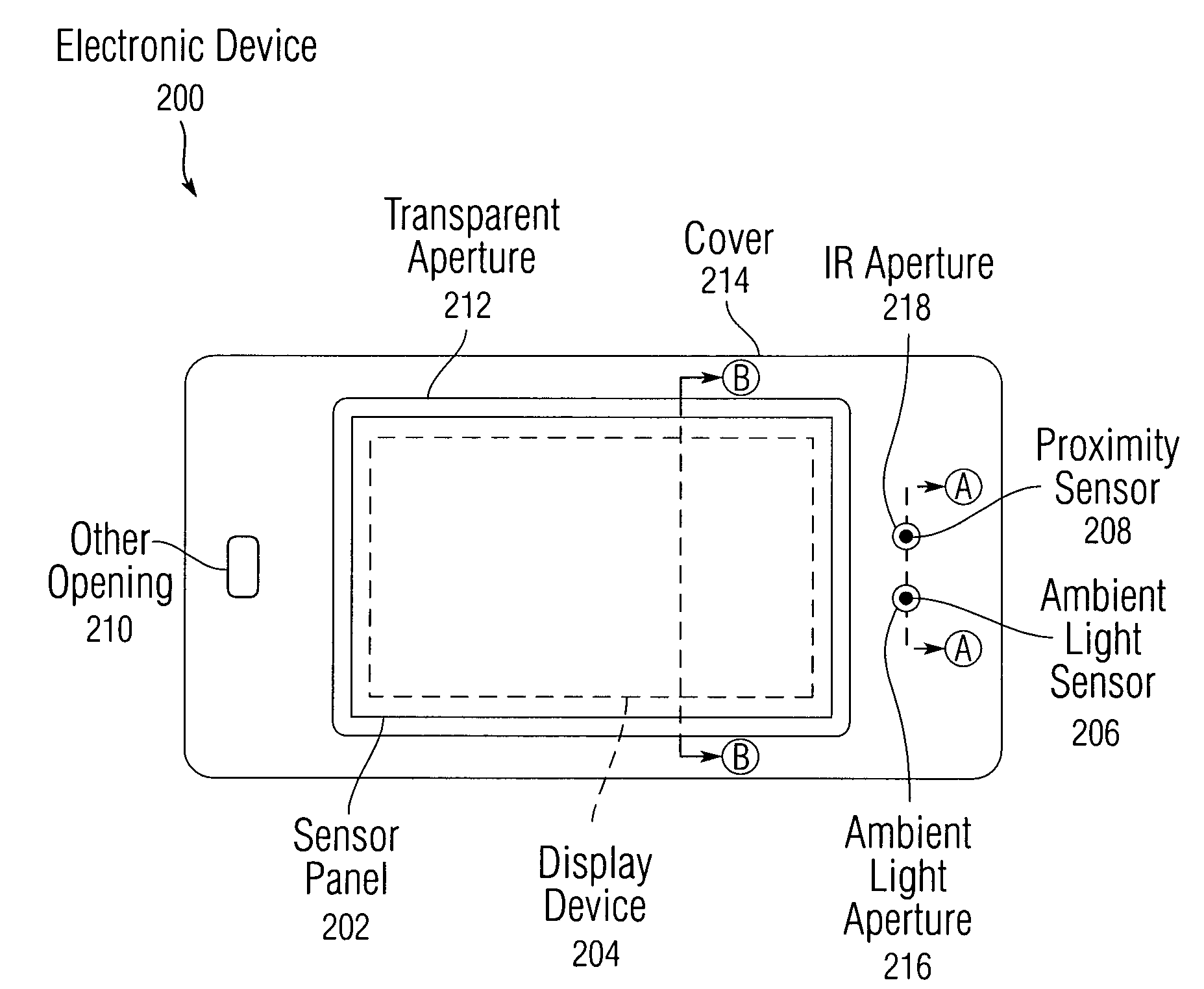

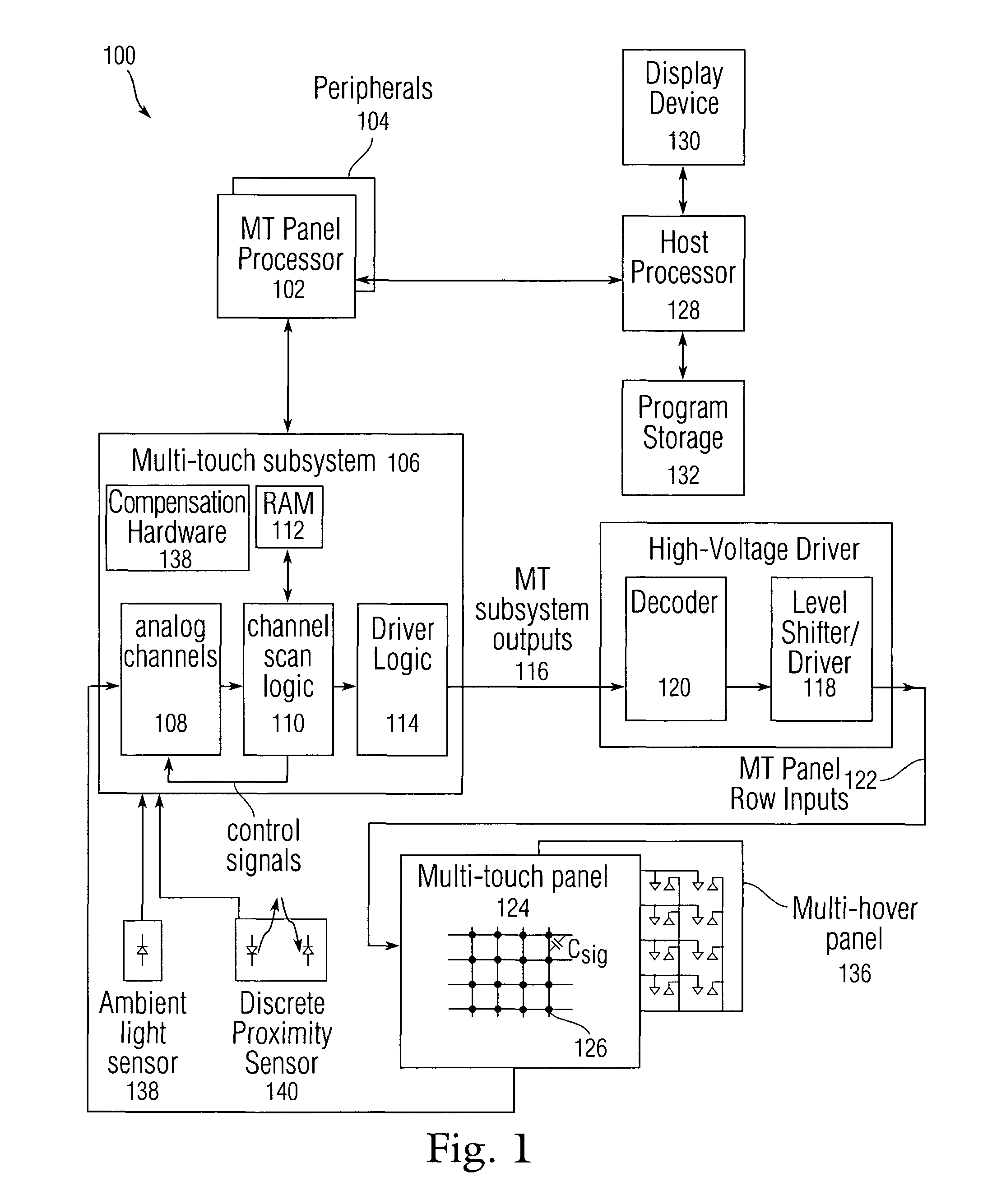

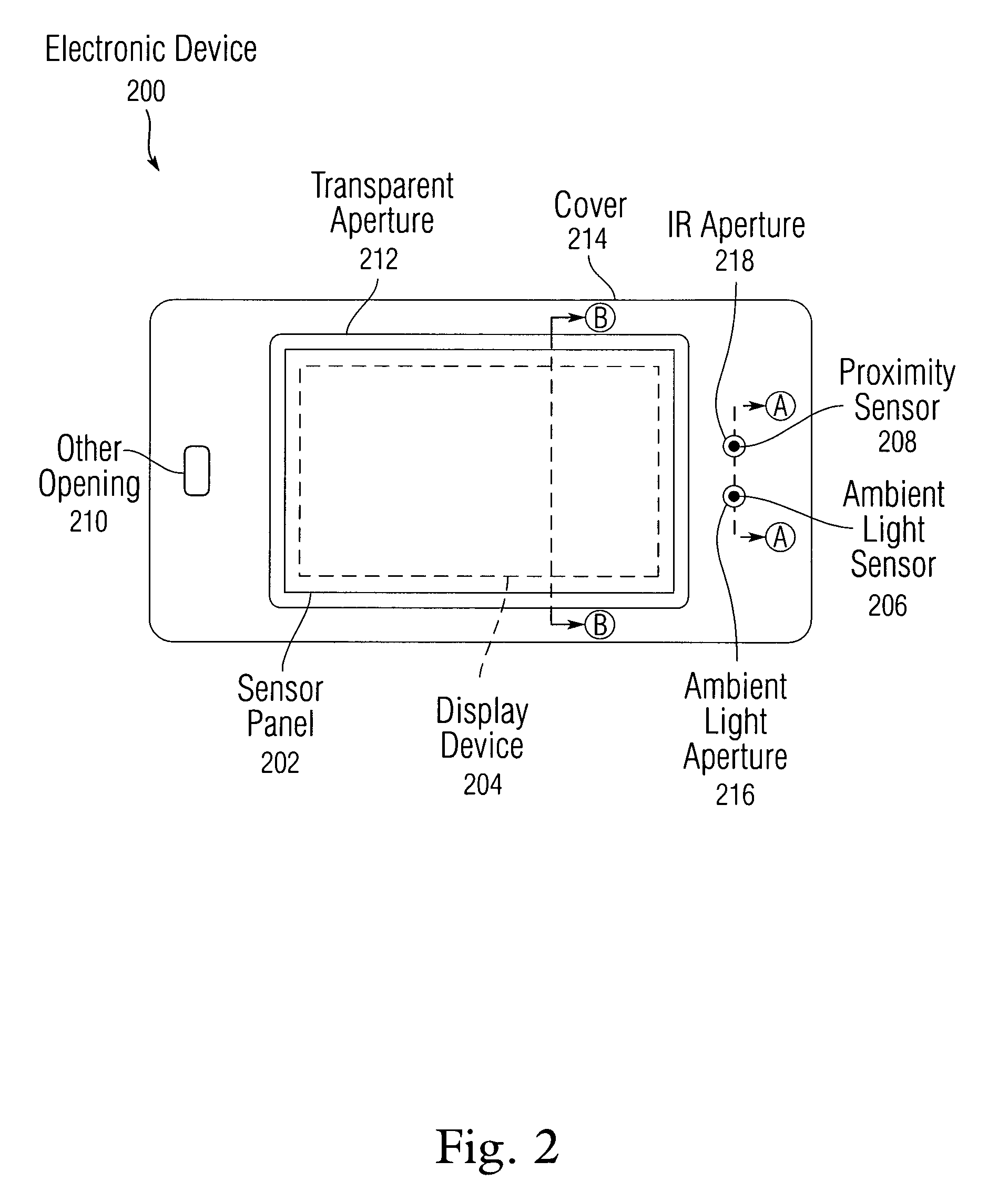

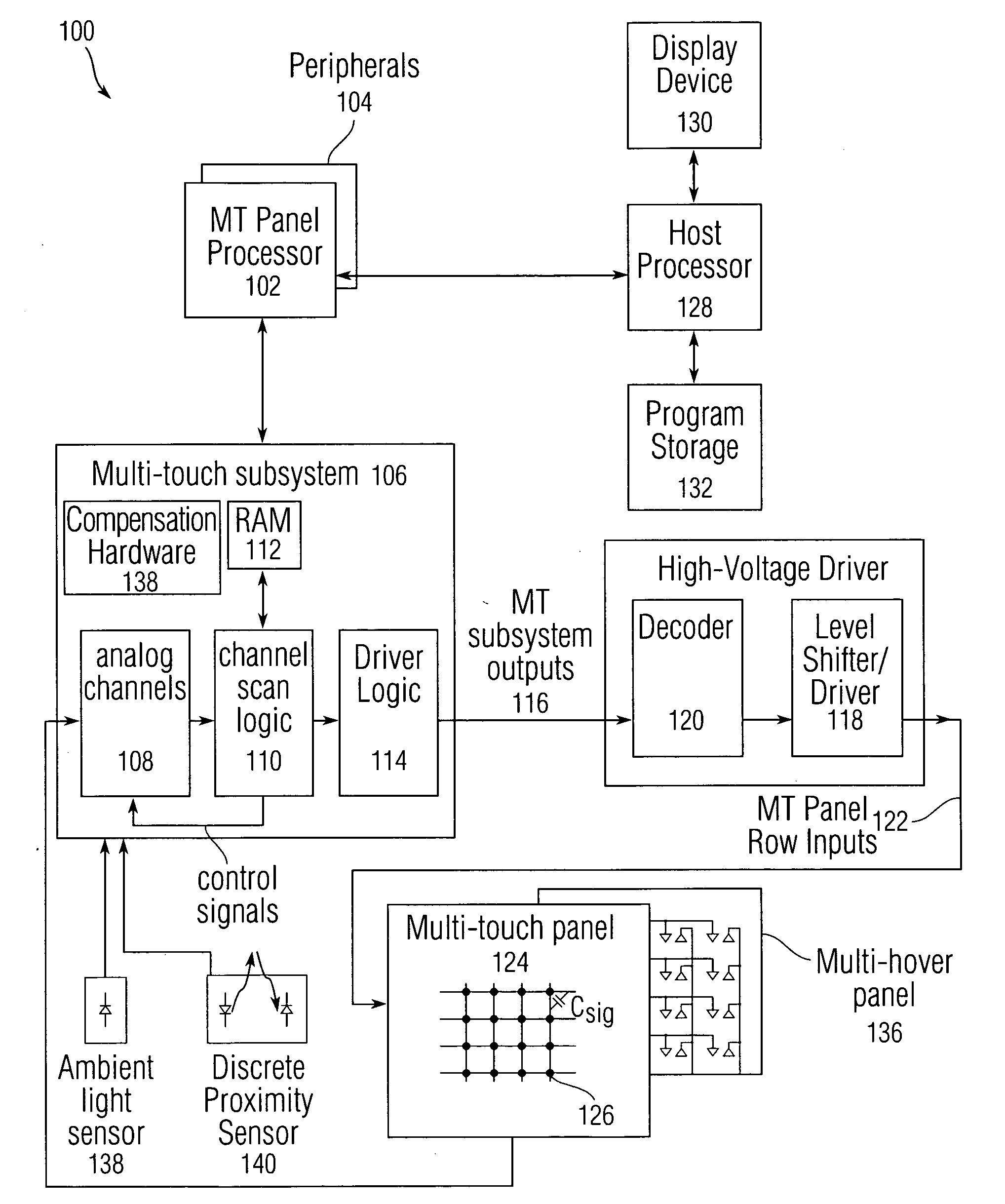

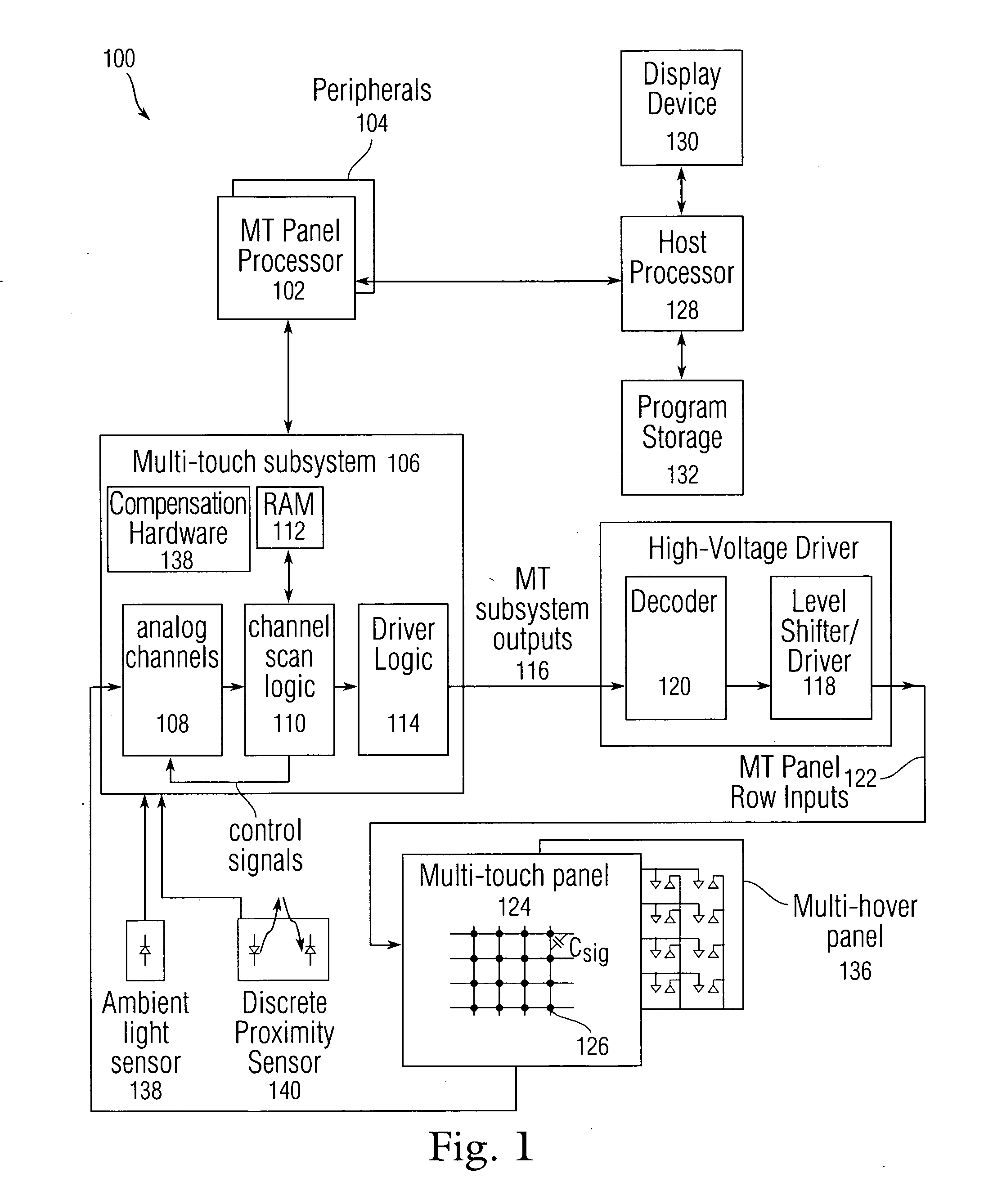

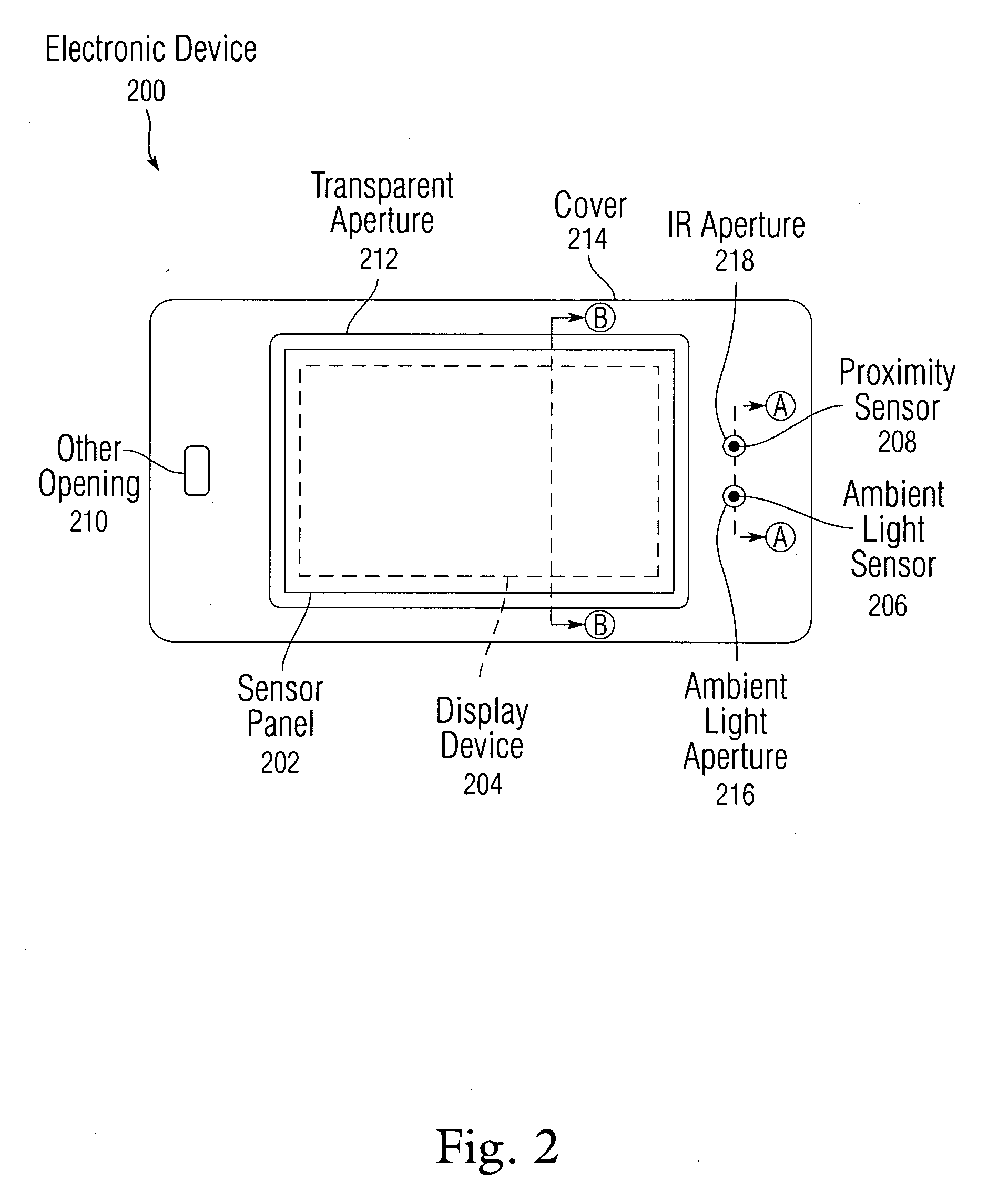

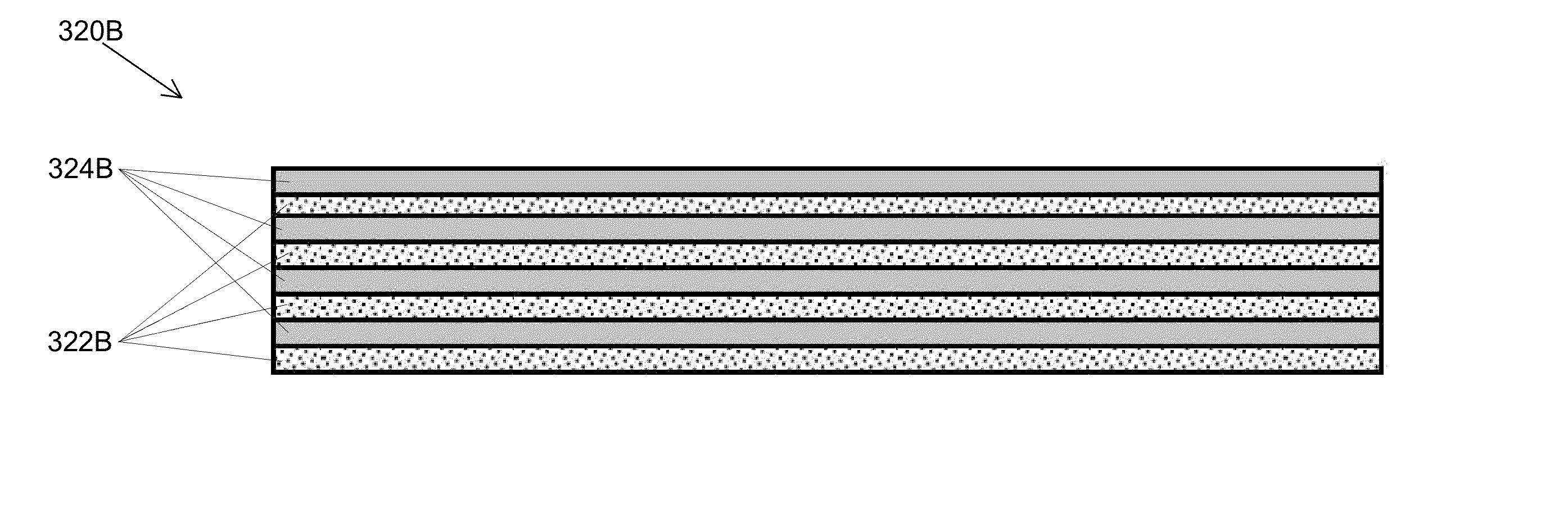

Multi-touch surface stackup arrangement

ActiveUS8031174B2Reduce cover warpageFull surfaceInput/output for user-computer interactionNon-enclosed substationsProximity sensorDisplay device

A multi-layer cover for an electronic device having one or more of a sensor panel, a proximity sensor, an ambient light sensor, and a display device can include an outer hardcoat, a structural layer, an IR transmissive ink layer, a mask layer, and a backside hardcoat. The backside hardcoat can reduce cover warpage, enable full surface lamination of the cover to the sensor panel, prevent bubbles from forming in transparent windows in the cover, enable a wider range of functional inks to be applied in various layering orders to allow certain types of light to pass through while blocking others, and hide the sensors to provide a seamless, uncluttered visual appearance.

Owner:APPLE INC

Method of eliminating a lithography operation

ActiveUS20090146322A1Semiconductor/solid-state device detailsSolid-state devicesLithographic artistEngineering

Methods of semiconductor device fabrication are disclosed. An exemplary method includes processes of depositing a first pattern on a semiconductor substrate, wherein the first pattern defines wide and narrow spaces; depositing spacer material over the first pattern on the substrate; etching the spacer material such that the spacer material is removed from horizontal surfaces of the substrate and the first pattern but remains adjacent to vertical surfaces of a wide space defined by the first pattern and remains within narrow a space defined by the first pattern; and removing the first pattern from the substrate. In one embodiment, the first pattern can comprise sacrificial material, which can include, for example, polysilicon material. The deposition can comprise physical vapor deposition, chemical vapor deposition, electrochemical deposition, molecular beam epitaxy, atomic layer deposition or other deposition techniques. According to another embodiment, features for lines and logic device components having a width greater than that of the lines are formed in the spacer material in the same mask layer.

Owner:CADENCE DESIGN SYST INC

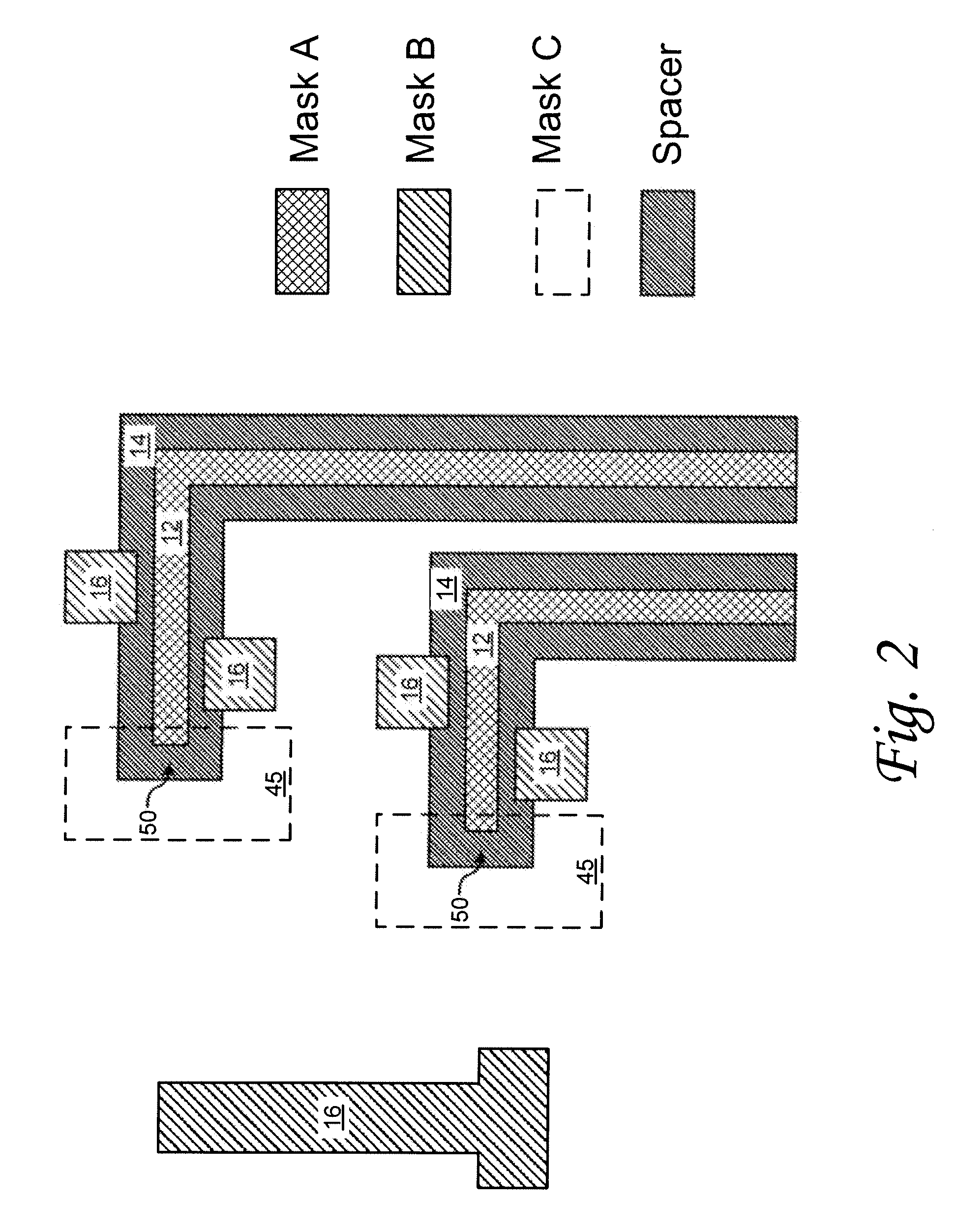

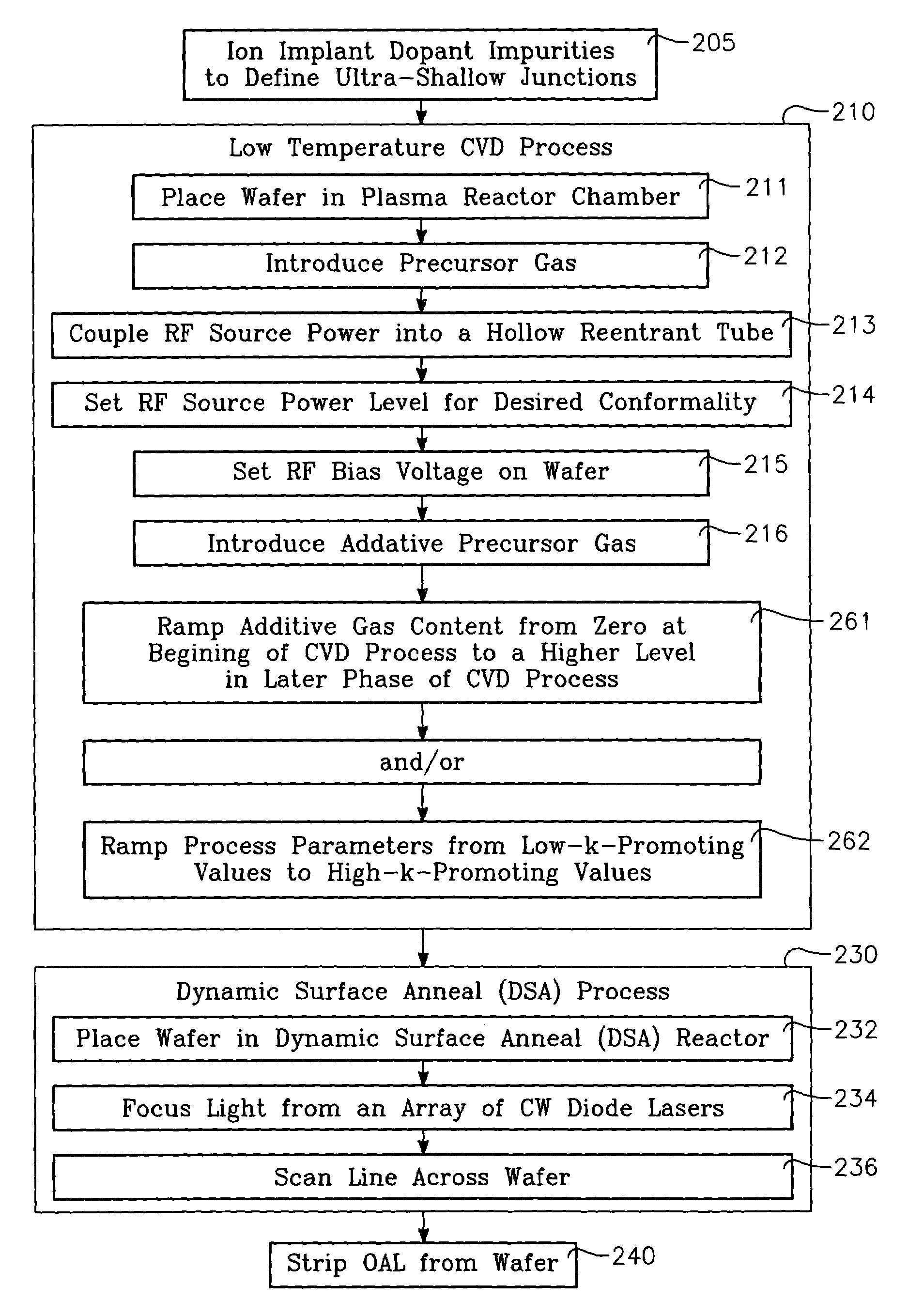

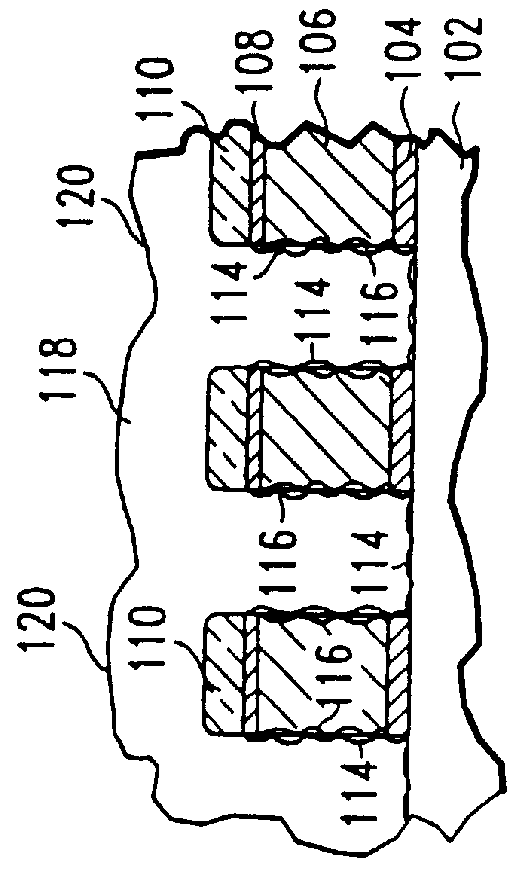

Semiconductor substrate process using an optically writable carbon-containing mask

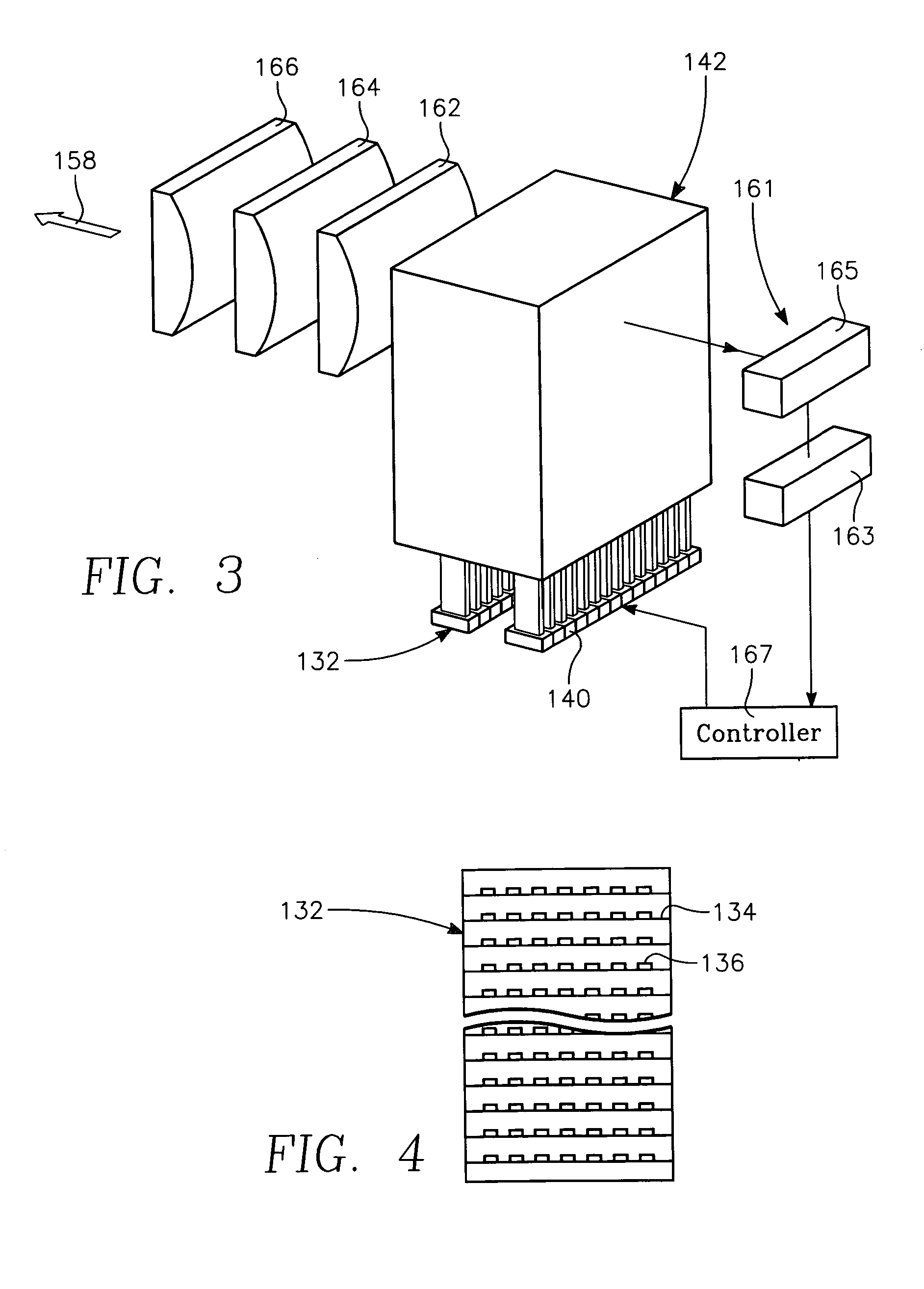

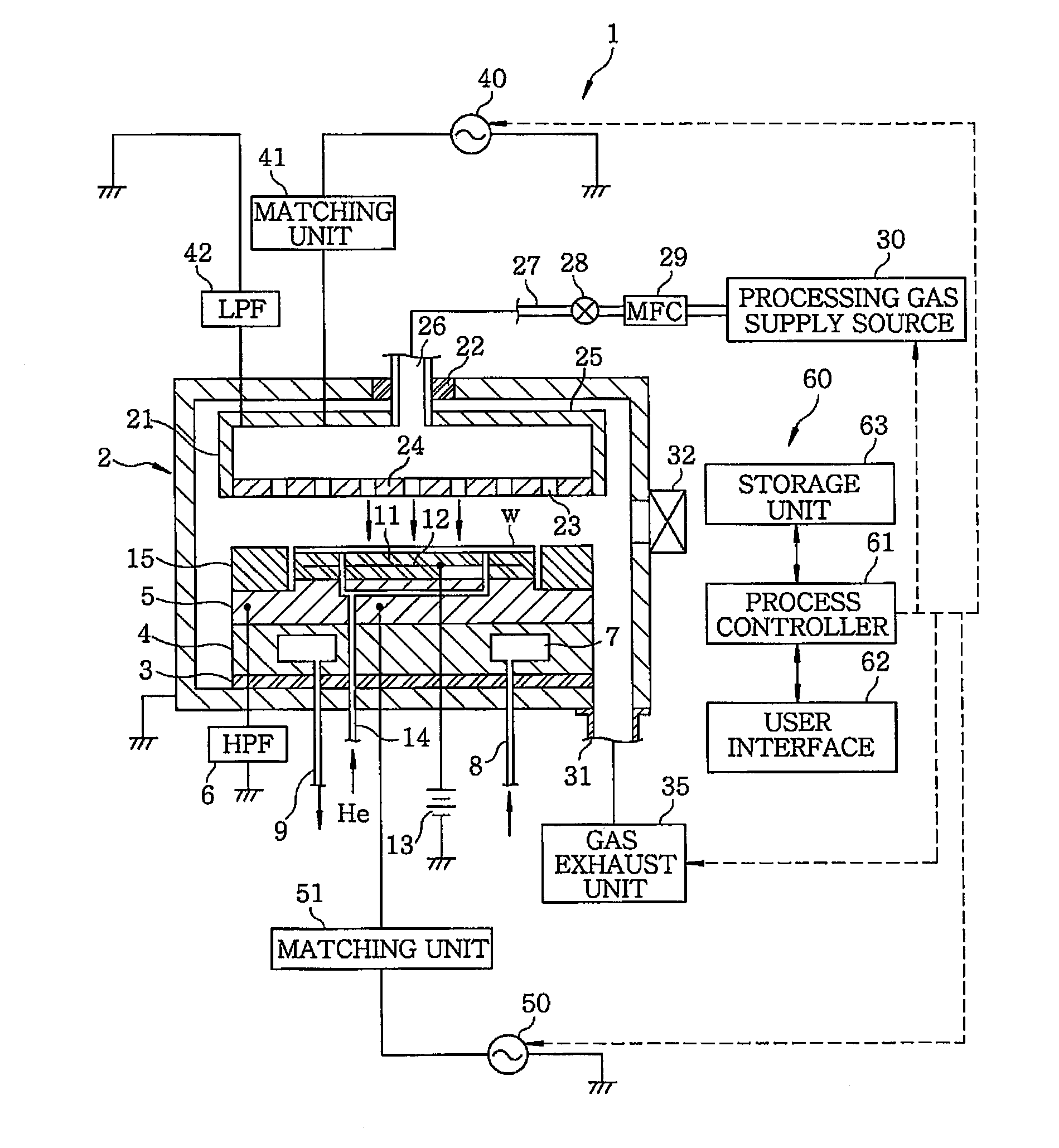

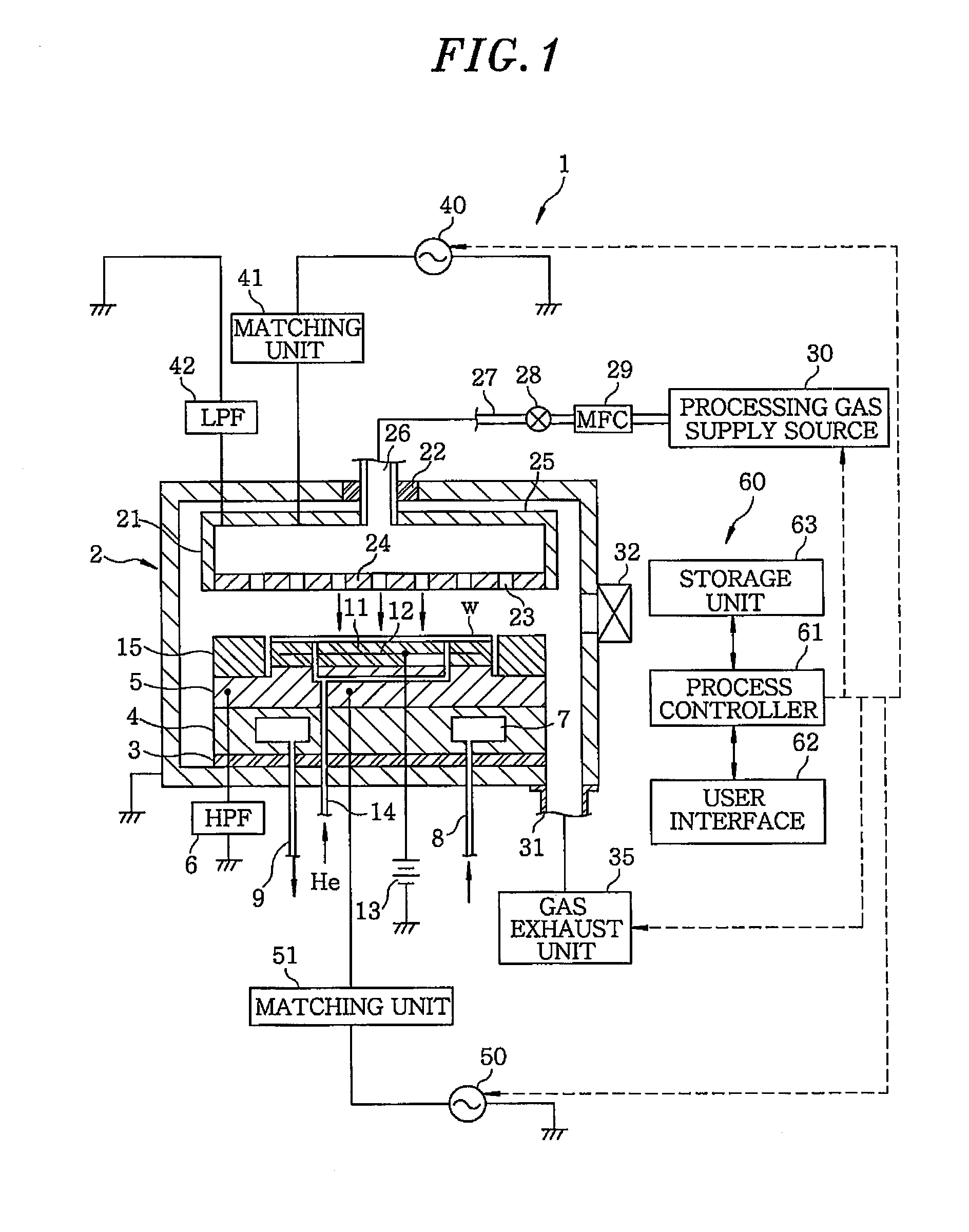

ActiveUS7429532B2Photomechanical apparatusSemiconductor/solid-state device manufacturingPlasma currentCoupling

A method of processing a thin film structure on a semiconductor substrate using an optically writable mask, the method includes placing the substrate in a reactor chamber, the substrate having on its surface a target layer to be exposed to a light source in accordance with a predetermined pattern, depositing an optically writable carbon-containing mask layer on the substrate by (a) introducing a carbon-containing process gas into the chamber, (b) generating a reentrant toroidal RF plasma current in a reentrant path that includes a process zone overlying the workpiece by coupling plasma RF source power to an external portion of the reentrant path, (c) coupling RF plasma bias power or bias voltage to the workpiece. The method further includes optically writing on the carbon-containing mask layer in accordance with the predetermined pattern with writing light of a characteristic suitable for transforming the transparency or opacity of the optically writable mask layer and exposing through the mask layer the target layer with reading light of a characteristic different from that of the writing light.

Owner:APPLIED MATERIALS INC

Semiconductor substrate process using an optically writable carbon-containing mask

ActiveUS20070032082A1Photomechanical apparatusSemiconductor/solid-state device manufacturingPlasma currentCoupling

A method of processing a thin film structure on a semiconductor substrate using an optically writable mask, the method includes placing the substrate in a reactor chamber, the substrate having on its surface a target layer to be exposed to a light source in accordance with a predetermined pattern, depositing an optically writable carbon-containing mask layer on the substrate by (a) introducing a carbon-containing process gas into the chamber, (b) generating a reentrant toroidal RF plasma current in a reentrant path that includes a process zone overlying the workpiece by coupling plasma RF source power to an external portion of the reentrant path, (c) coupling RF plasma bias power or bias voltage to the workpiece. The method further includes optically writing on the carbon-containing mask layer in accordance with the predetermined pattern with writing light of a characteristic suitable for transforming the transparency or opacity of the optically writable mask layer and exposing through the mask layer the target layer with reading light of a characteristic different from that of the writing light.

Owner:APPLIED MATERIALS INC

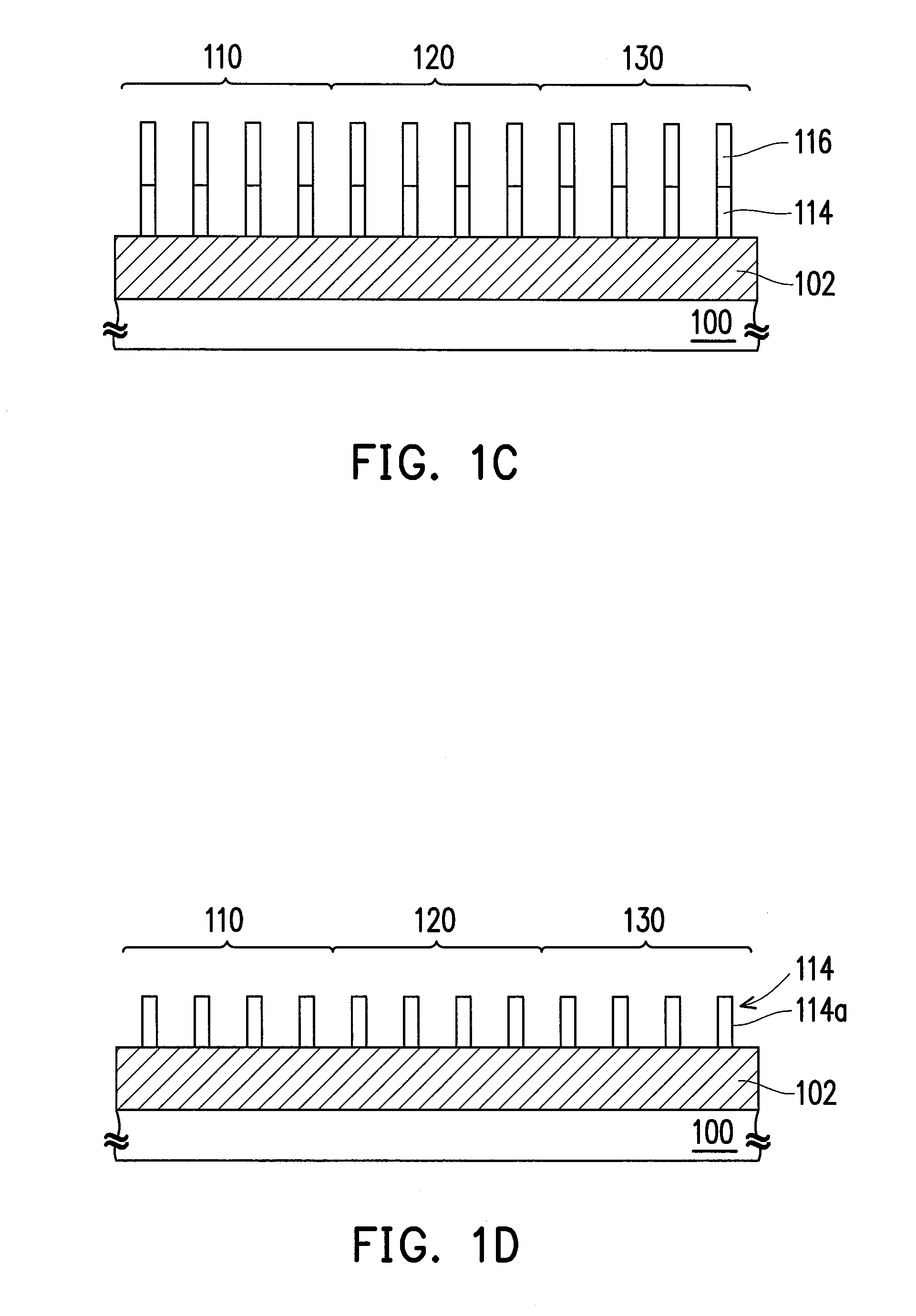

Patterning method

InactiveUS20110294075A1Reduce line widthLow costSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusPhotoresistMask layer

A patterning method of the present invention is described as follows. A mask layer and a patterned photoresist layer are formed on a target layer in sequence, wherein an etching rate of the mask layer is different from an etching rate of the target layer. A plurality of spacers is formed on sidewalls of the patterned photoresist layer respectively, wherein an etching rate of the spacers is different from the etching rate of the mask layer. The patterned photoresist layer is removed to form an opening between any two adjacent spacers. A portion of the mask layer is removed by using the spacers as a mask so as to form a patterned mask layer. A portion of the target layer is removed by using the patterned mask layer as a mask.

Owner:UNITED MICROELECTRONICS CORP

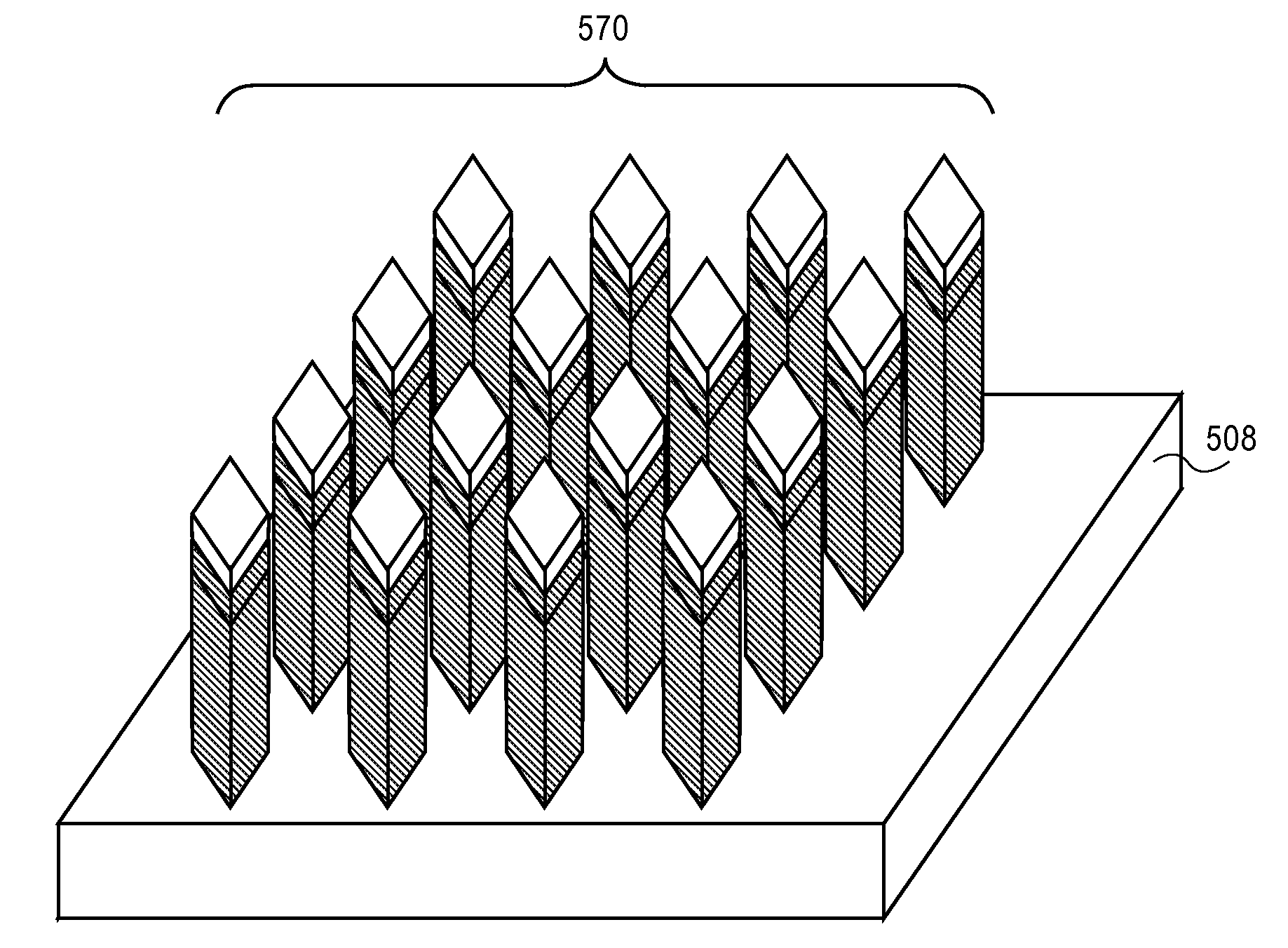

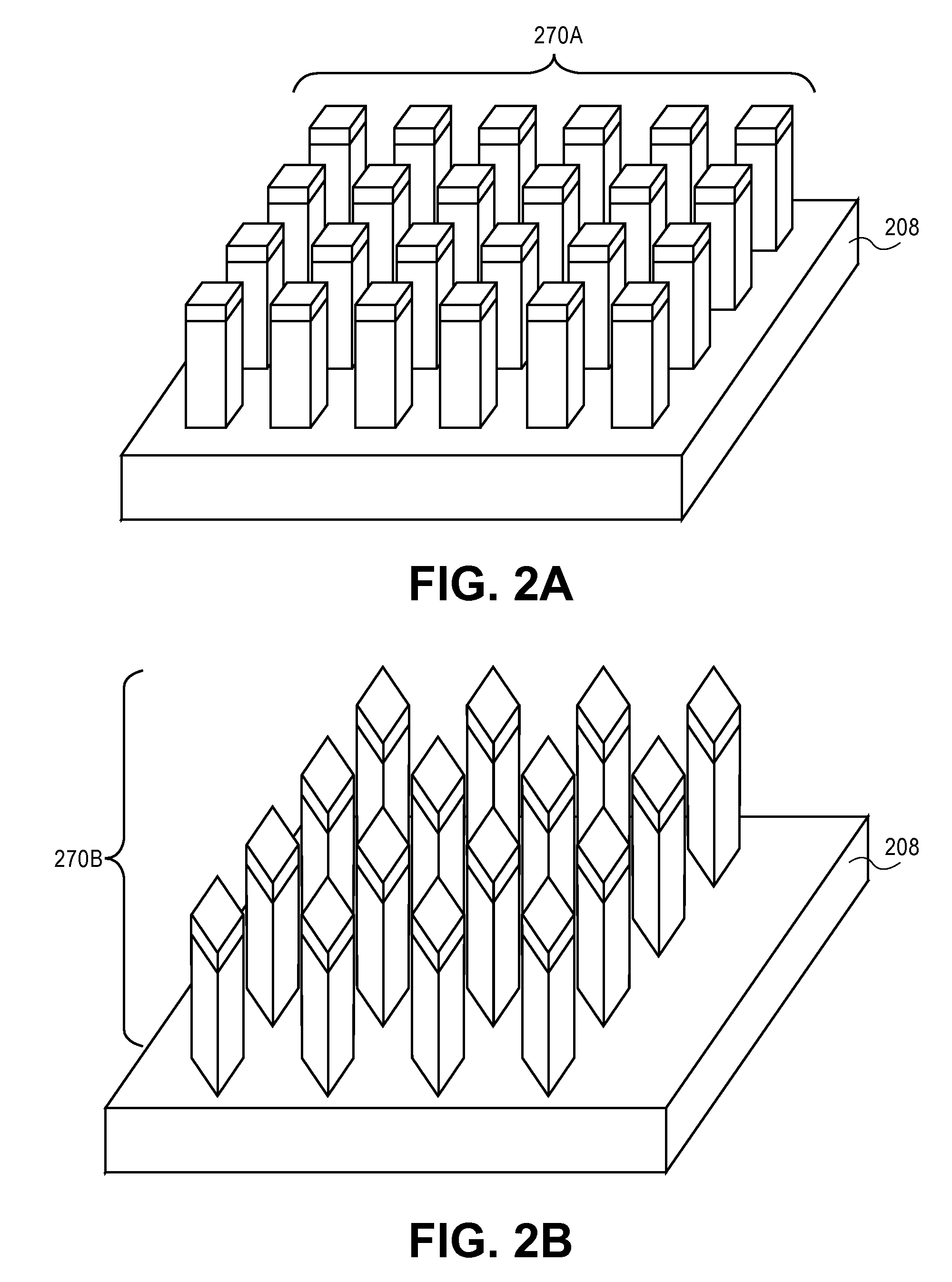

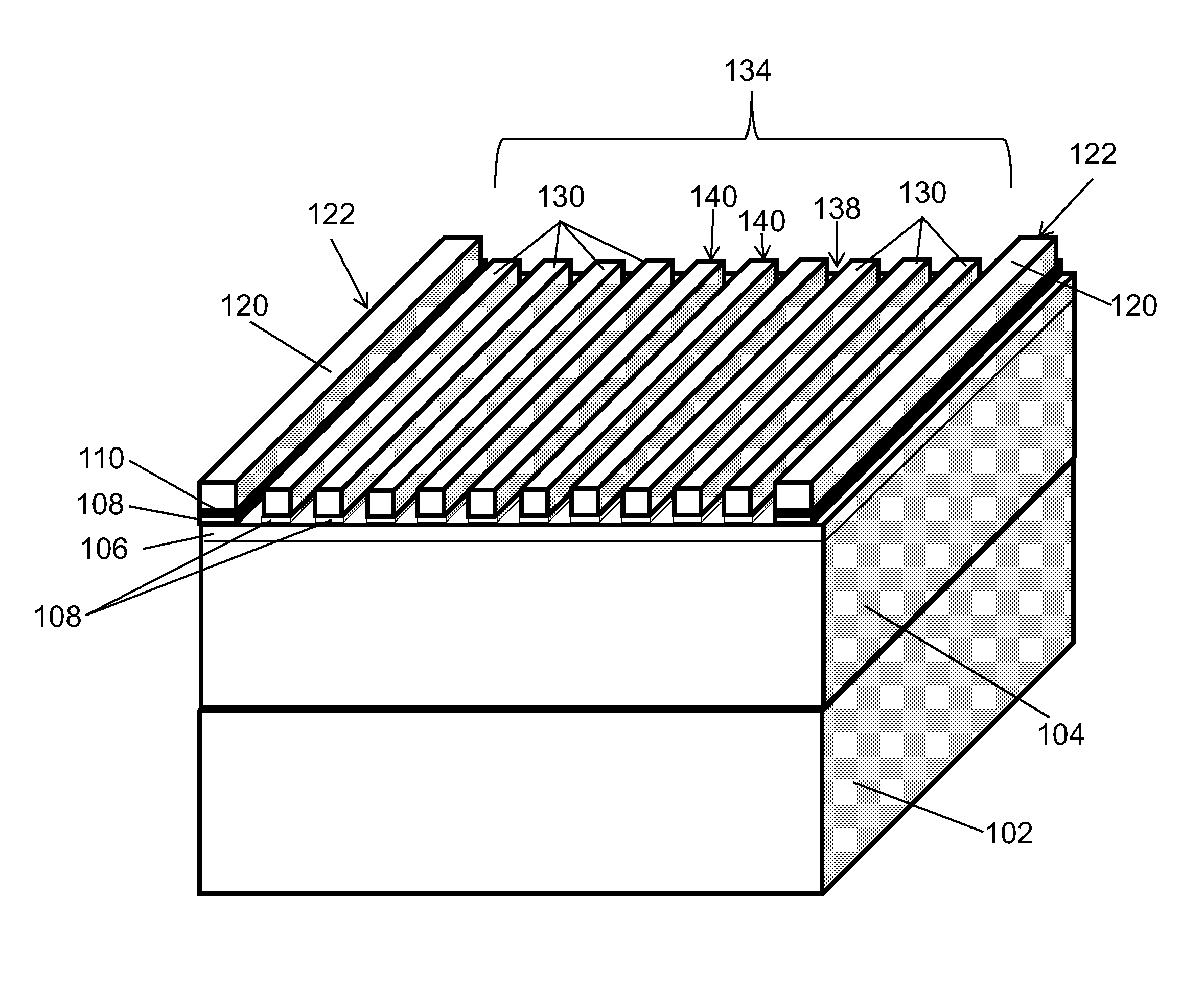

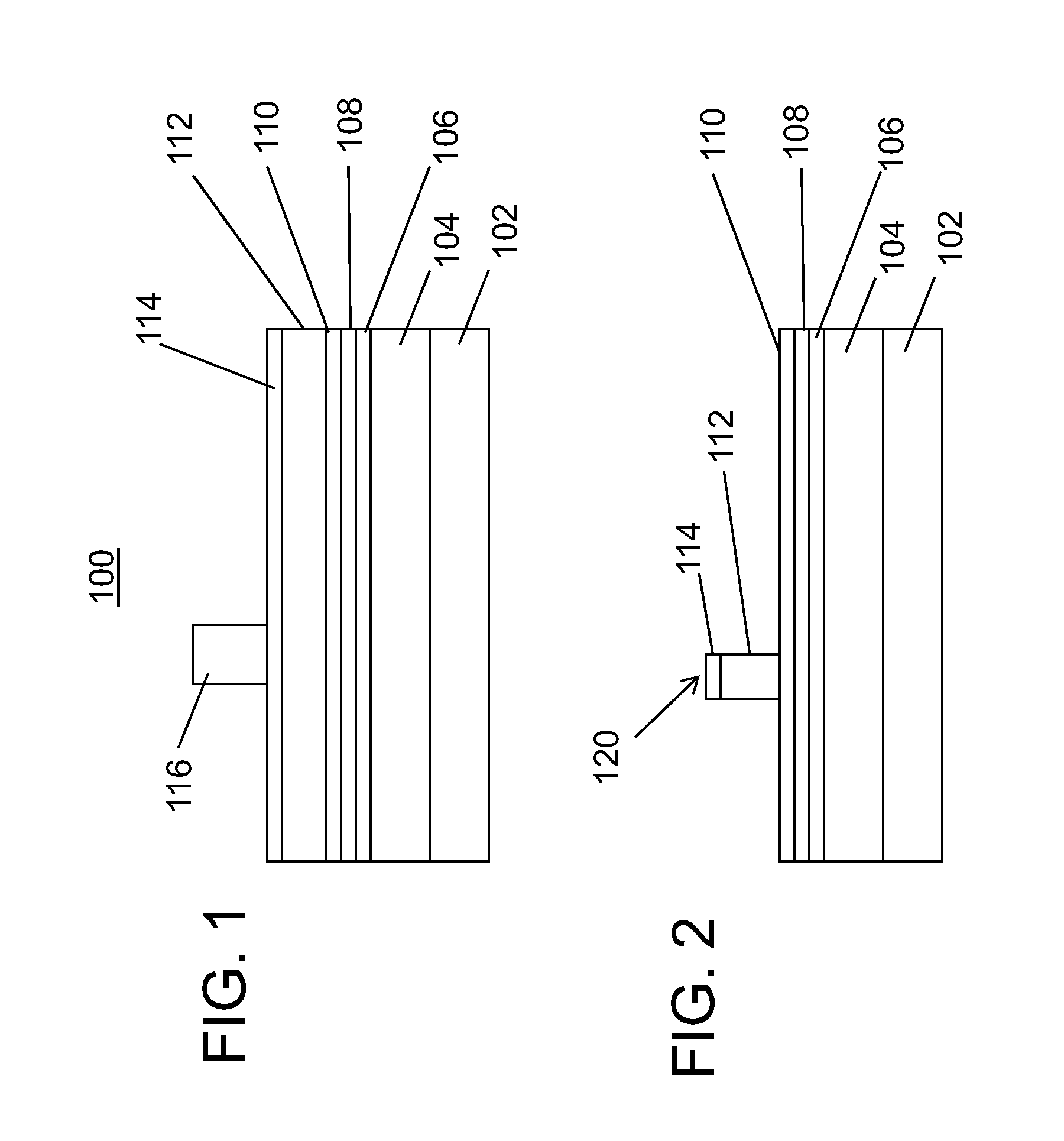

Self-aligned pillar patterning using multiple spacer masks

A method for fabricating a semiconductor mask is described. The image of a series of lines from a first spacer mask is first provided to a mask layer to form a patterned mask layer. The image of a series of lines from a second spacer mask is then provided to the patterned mask layer to form a pillar mask comprised of a series of pillars. The image of the series of lines from the second spacer mask is non-parallel with the series of lines from the first spacer mask.

Owner:APPLIED MATERIALS INC

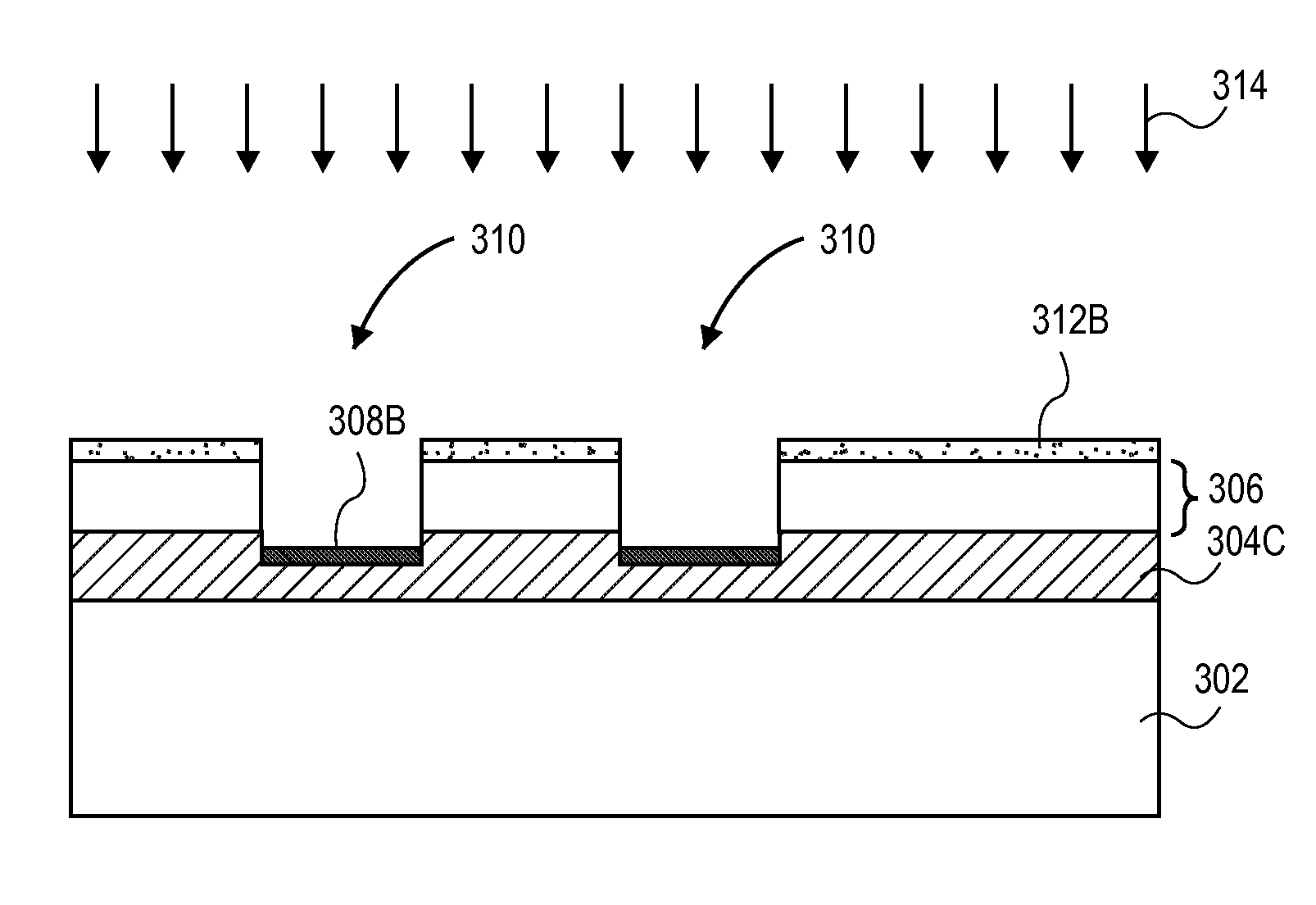

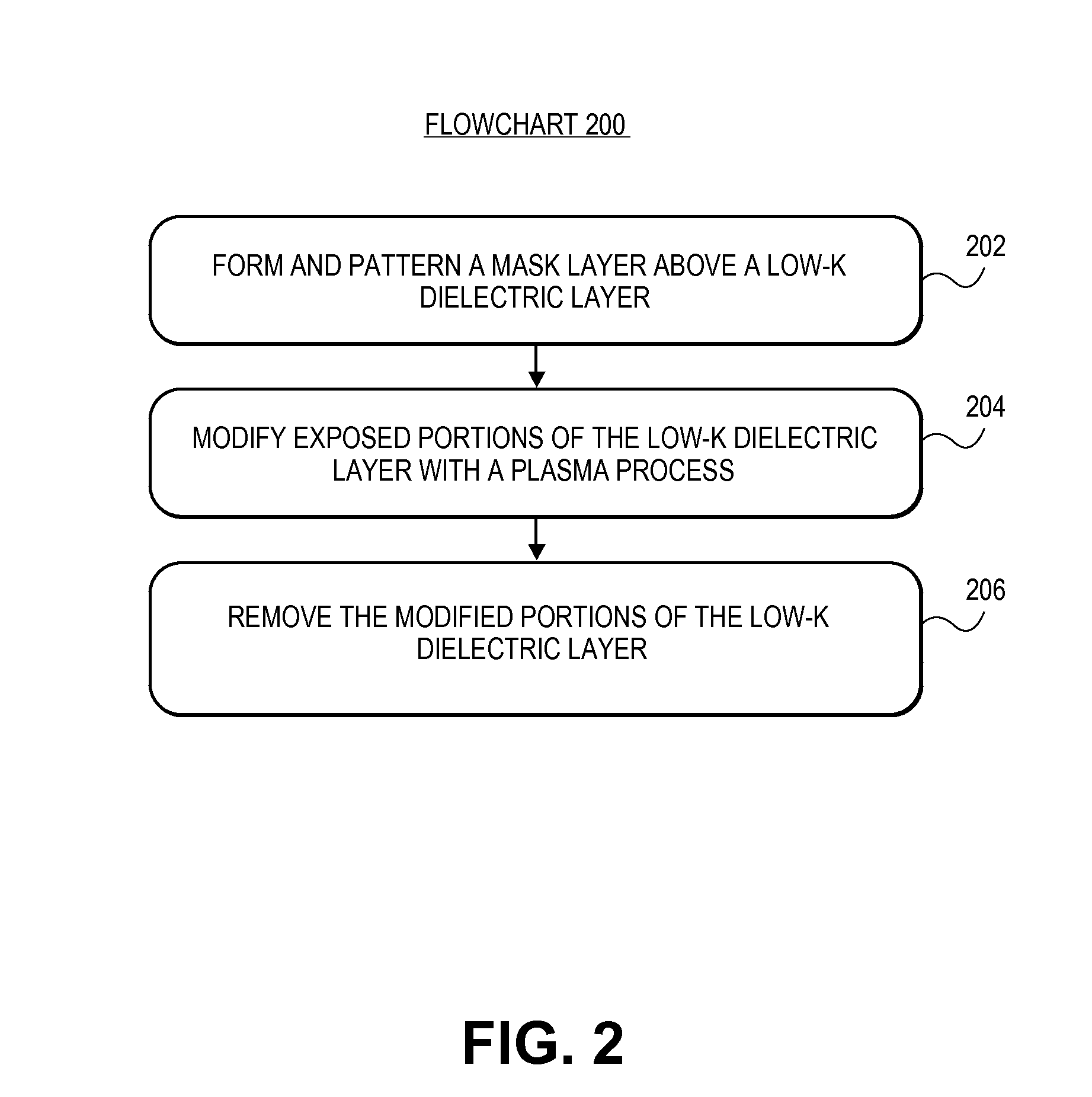

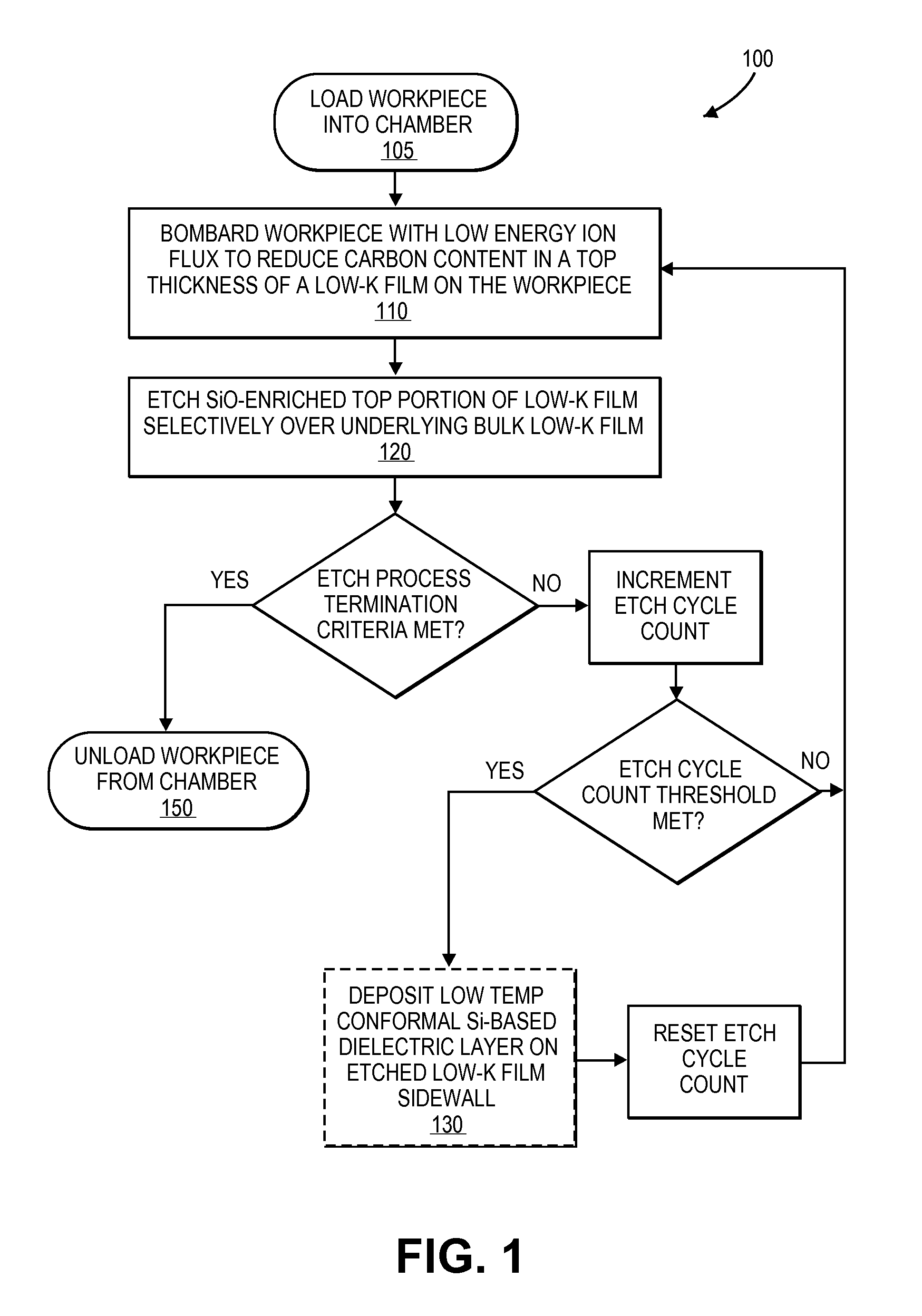

Method of patterning a low-k dielectric film

Methods of patterning low-k dielectric films are described. For example, a method includes forming and patterning a mask layer above a low-k dielectric layer, the low-k dielectric layer disposed above a substrate. Exposed portions of the low-k dielectric layer are modified with a plasma process. The modified portions of the low-k dielectric layer are removed selective to the mask layer and unmodified portions of the low-k dielectric layer.

Owner:APPLIED MATERIALS INC

Hardmask of amorphous carbon-hydrogen (a-C:H) layers with tunable etch resistivity

InactiveUS20040000534A1Decorative surface effectsSemiconductor/solid-state device manufacturingForming gasAmorphous carbon

A process of using a-C:H layer as a hardmask material with tunable etch resistivity in a RIE process that alleviates the addition of a layer forming gas to the etchant when making a semiconductor device, comprising: a) providing a semiconductor substrate; b) forming a hardmask of amorphous carbon-hydrogen (a-C:H) layer by plasma enhancement over the semiconductor substrate; c) forming an opening in the hardmask layer to form an exposed surface portion of the hardmask layer; and d) etching the exposed surface portion of the hardmask layer without the addition of a layer forming gas using RIE to form a trench feature with sufficient masking and side wall protection.

Owner:POLARIS INNOVATIONS

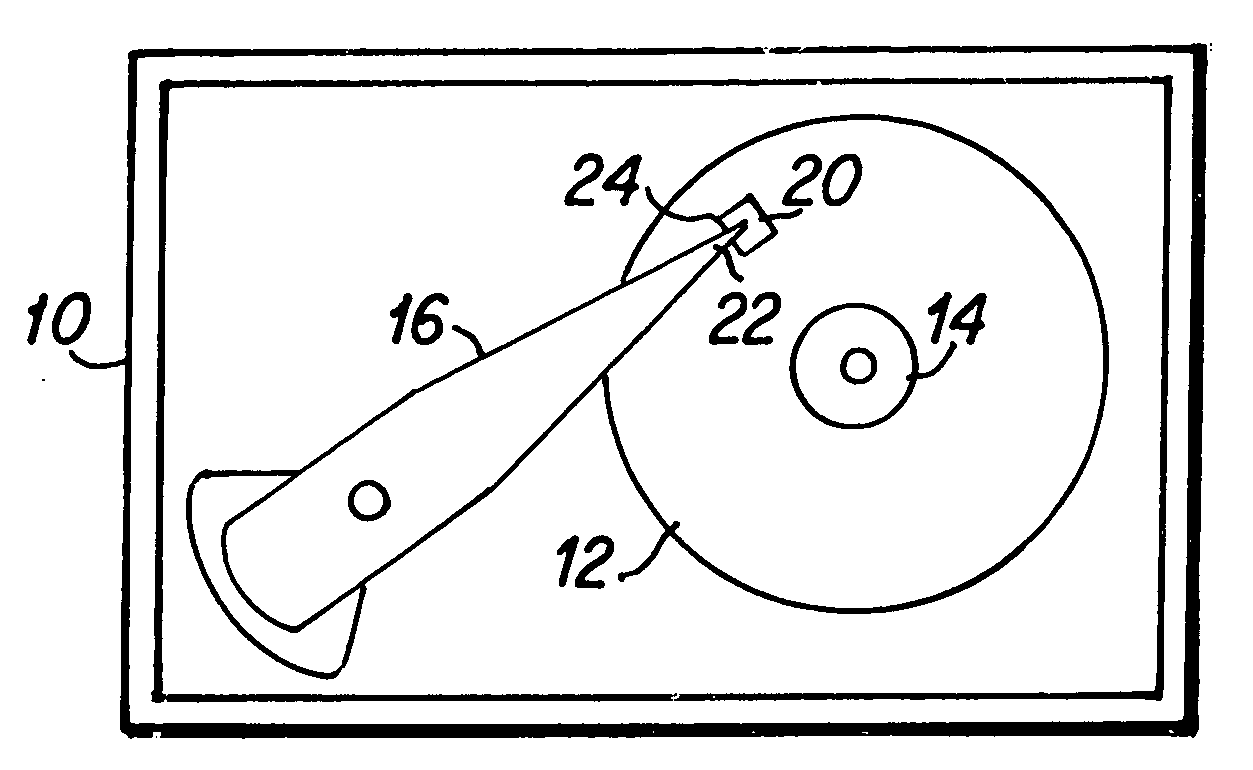

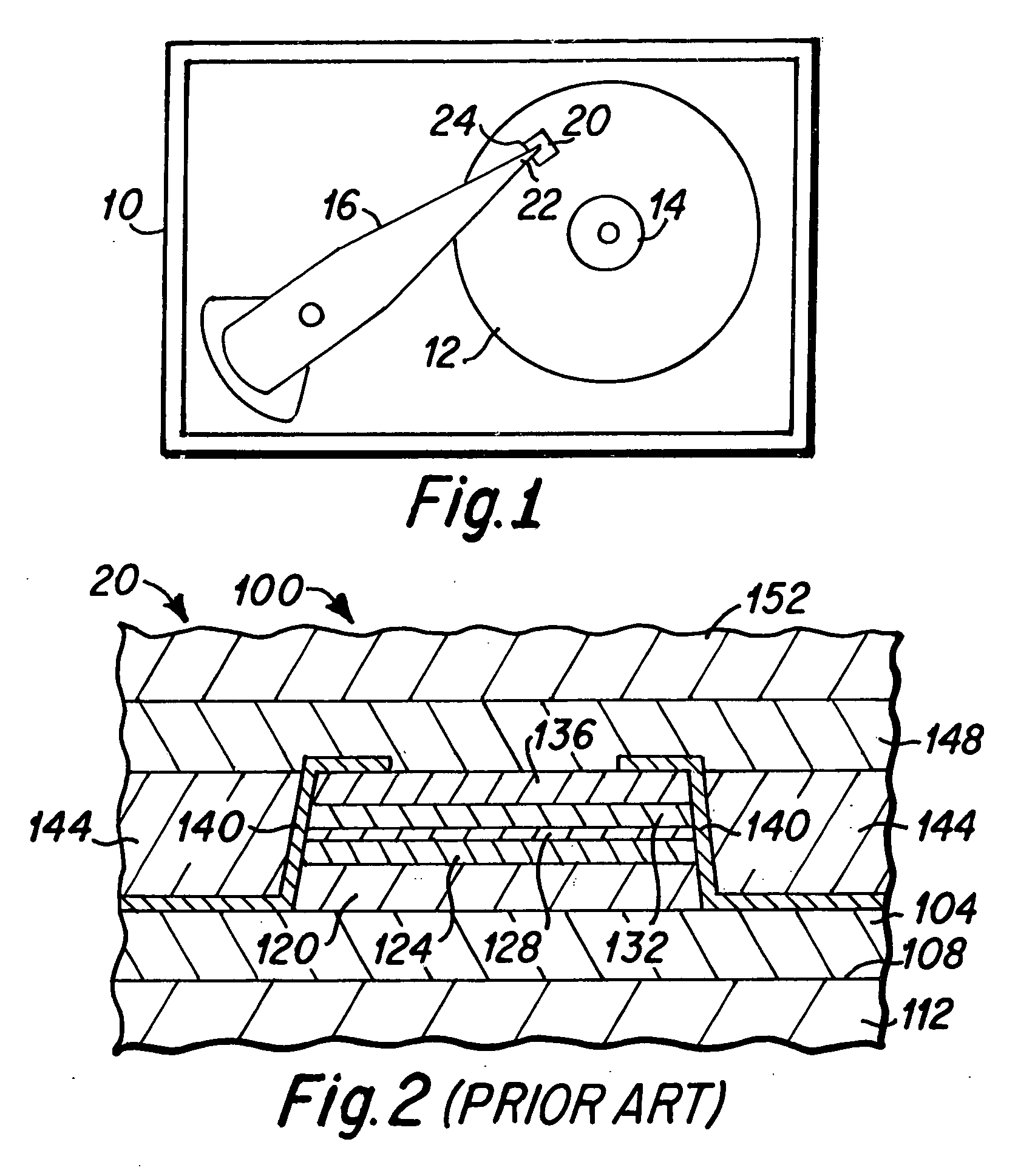

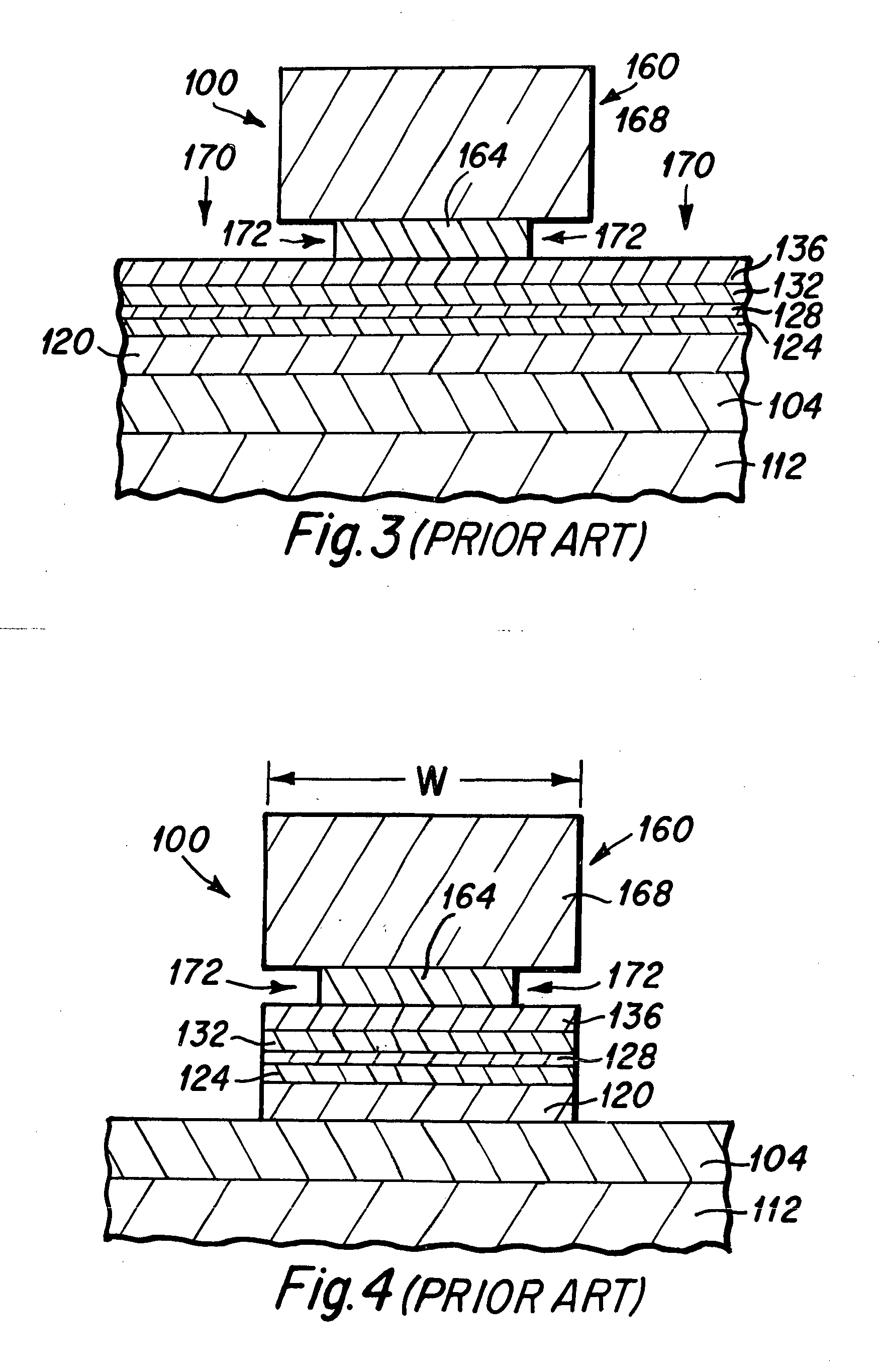

Method to fabricate side shields for a magnetic sensor

InactiveUS20060256482A1Reduce widthElectrical transducersDecorative surface effectsInsulation layerCompound (substance)

A method for fabricating magnetic side shields for an MR sensor of a magnetic head. Following the deposition of MR sensor layers, a first DLC layer is deposited. Milling mask layers are then deposited, and outer portions of the milling mask layers are removed such that a remaining central portion of the milling mask layers is formed having straight sidewalls and no undercuts. Outer portions of the sensor layers are then removed such that a relatively thick remaining central portion of the milling mask resides above the remaining sensor layers. A thin electrical insulation layer is deposited, followed by the deposition of magnetic side shields. A second DLC layer is deposited and the remaining mask layers are then removed utilizing a chemical mechanical polishing (CMP) liftoff step. Thereafter, the first DLC layer and the second DLC layer are removed and a second magnetic shield layer is then fabricated thereabove.

Owner:WESTERN DIGITAL TECH INC

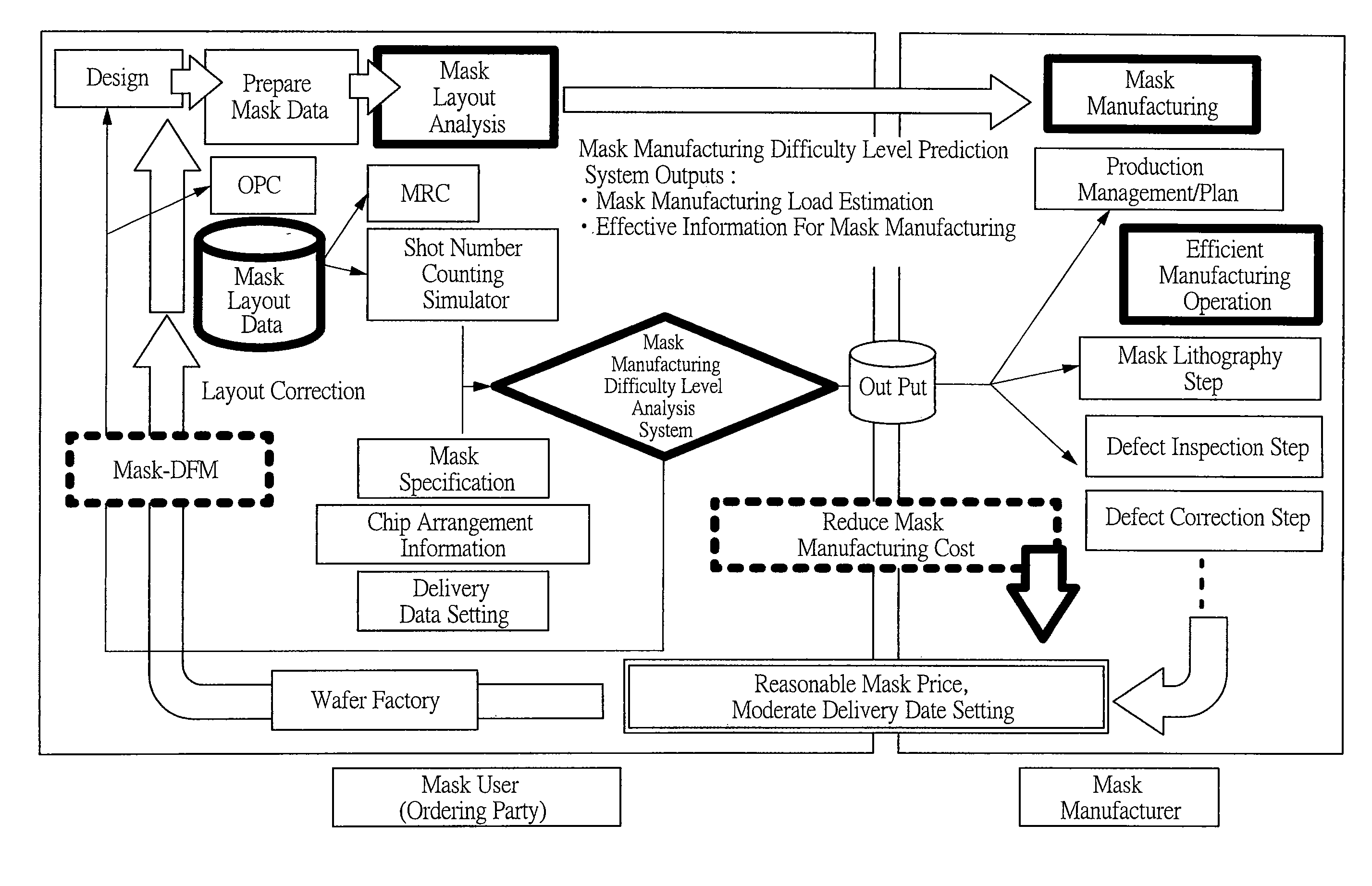

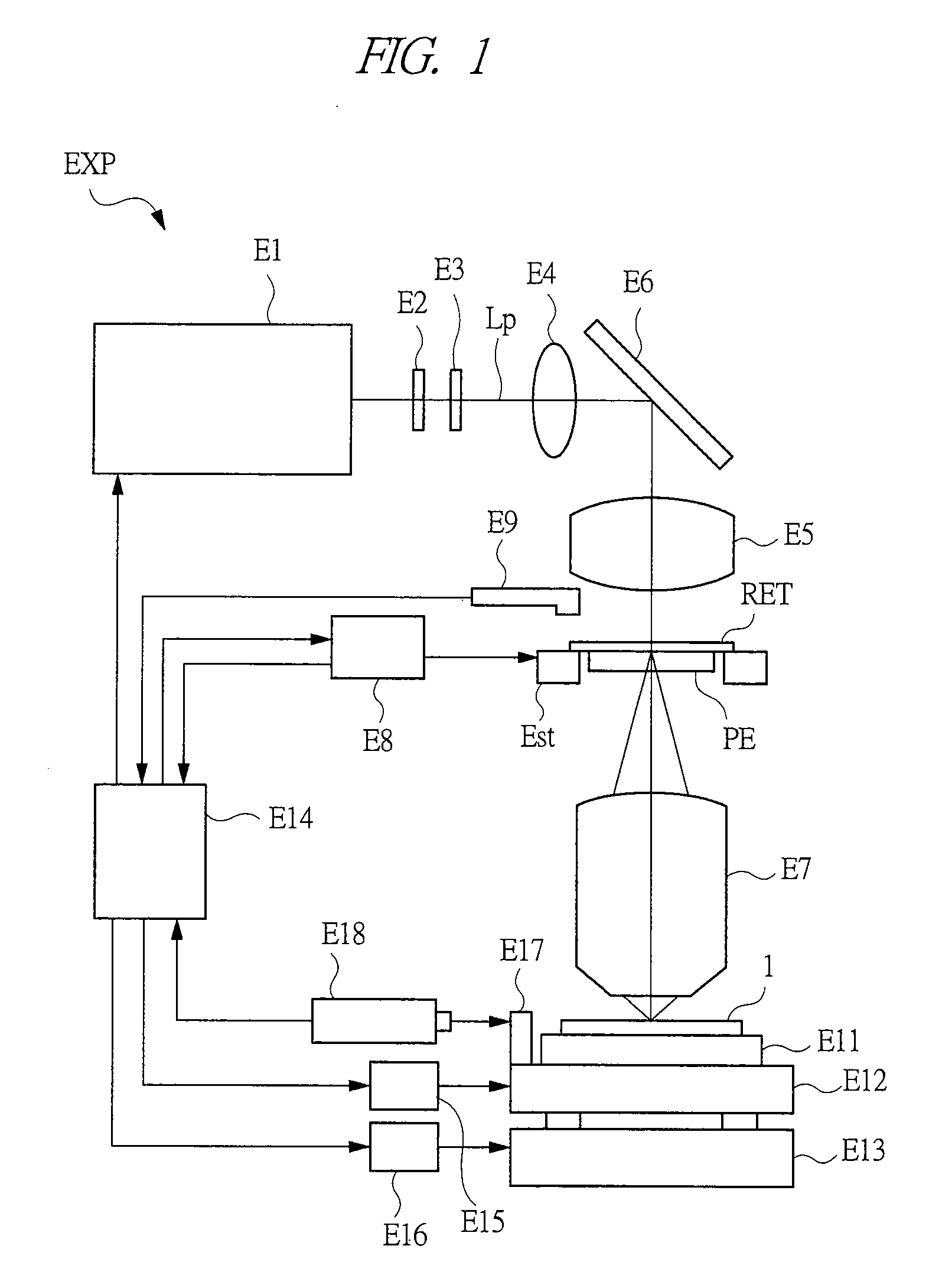

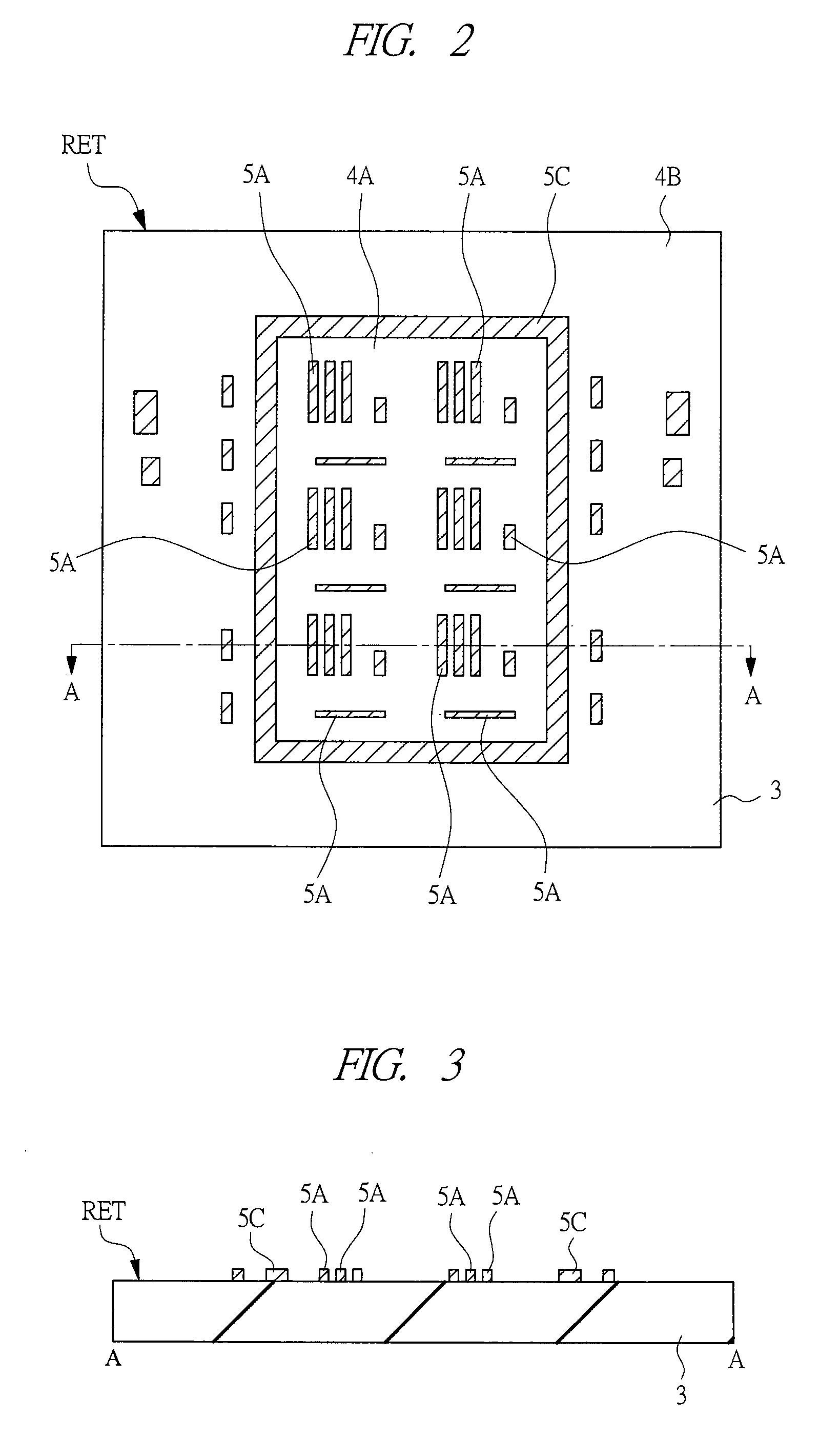

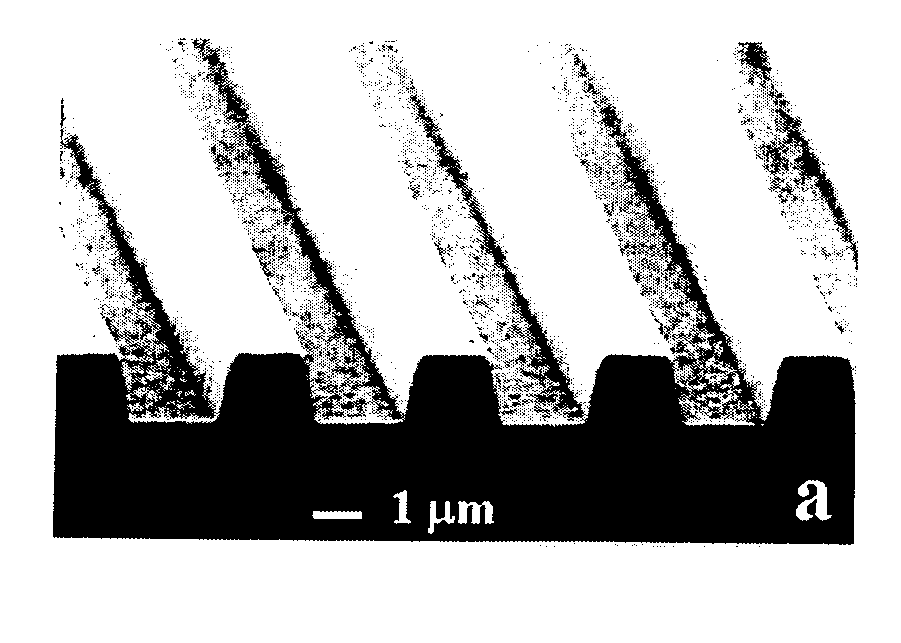

Method of manufacturing photomask

InactiveUS20090077524A1Efficient preparationImprove efficiencyOriginals for photomechanical treatmentSpecial data processing applicationsPrediction systemPhotomask

A technique for quantitatively expressing a manufacturing difficulty level of a photomask and for efficiently manufacturing the photomask is provided. A mask manufacturing difficulty level different for each mask layout, product, and mask layer is relatively recognized with a mask manufacturing load index calculated by a mask manufacturing load prediction system, and when layout correction is possible, the final layout is corrected to a layout with a low difficulty level, and a mask ordering party provides a mask manufacturer with information regarding the mask manufacturing difficulty level in an early stage. The mask manufacturing load index is expressed with a defect guarantee load index and a lithography load index.

Owner:DAI NIPPON PRINTING CO LTD +1

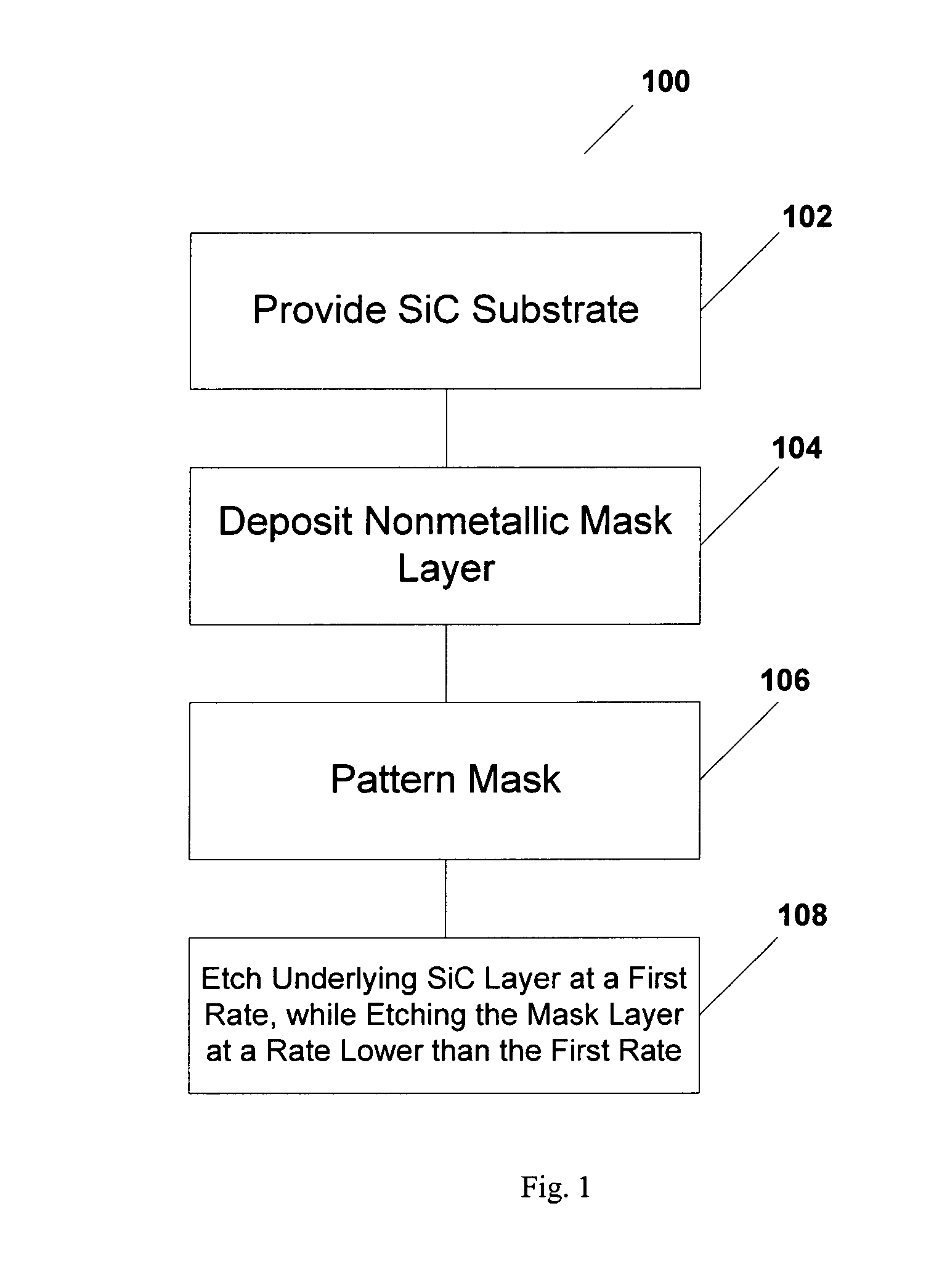

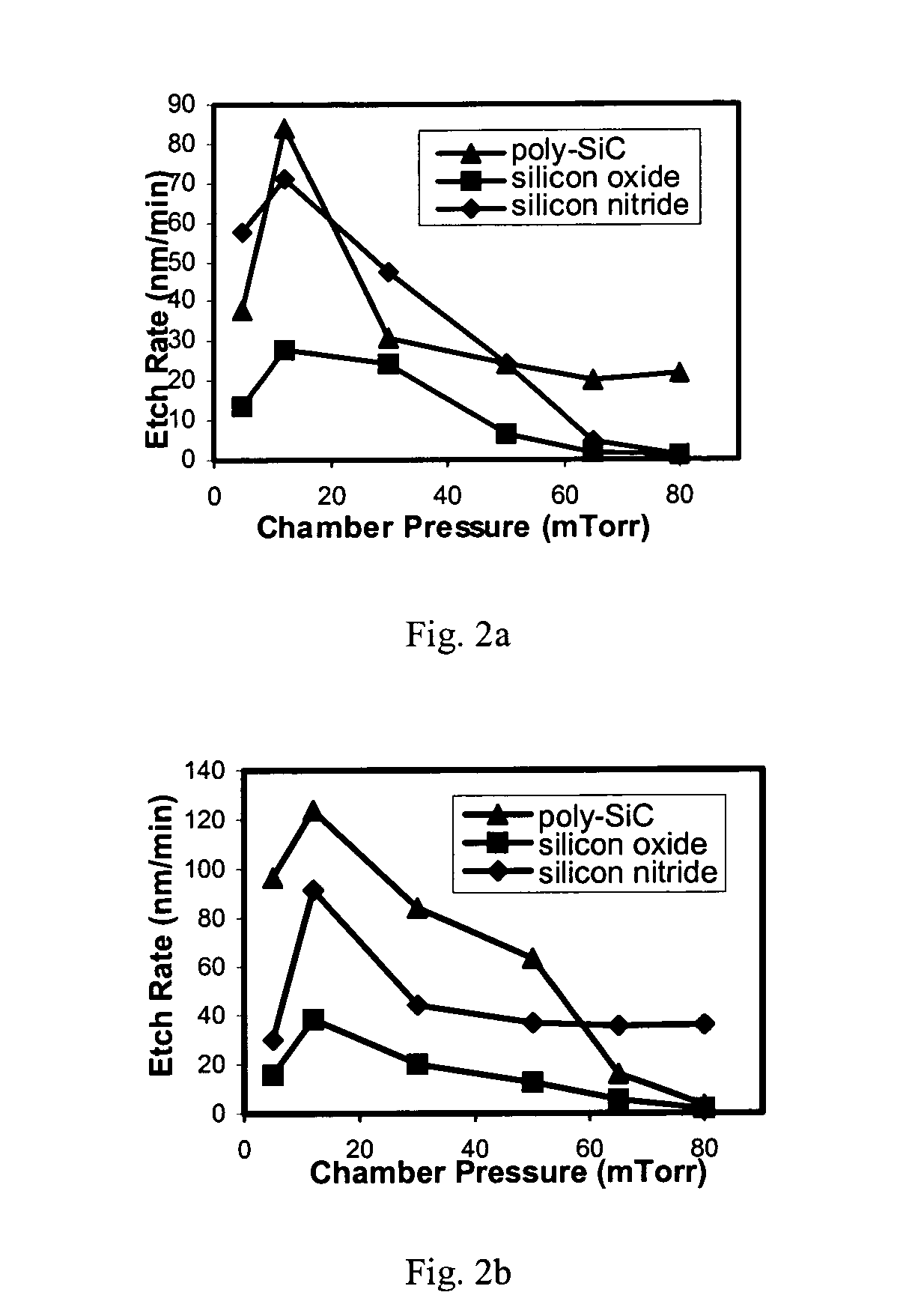

Selective etching of silicon carbide films

ActiveUS20050001276A1Acceleration measurement using interia forcesDecorative surface effectsMask layerSilicon carbide

A method of etching silicon carbide using a nonmetallic mask layer. The method includes providing a silicon carbide substrate; forming a non-metallic mask layer by applying a layer of material on the substrate; patterning the mask layer to expose underlying areas of the substrate; and etching the underlying areas of the substrate with a plasma at a first rate, while etching the mask layer at a rate lower than the first rate.

Owner:RGT UNIV OF CALIFORNIA

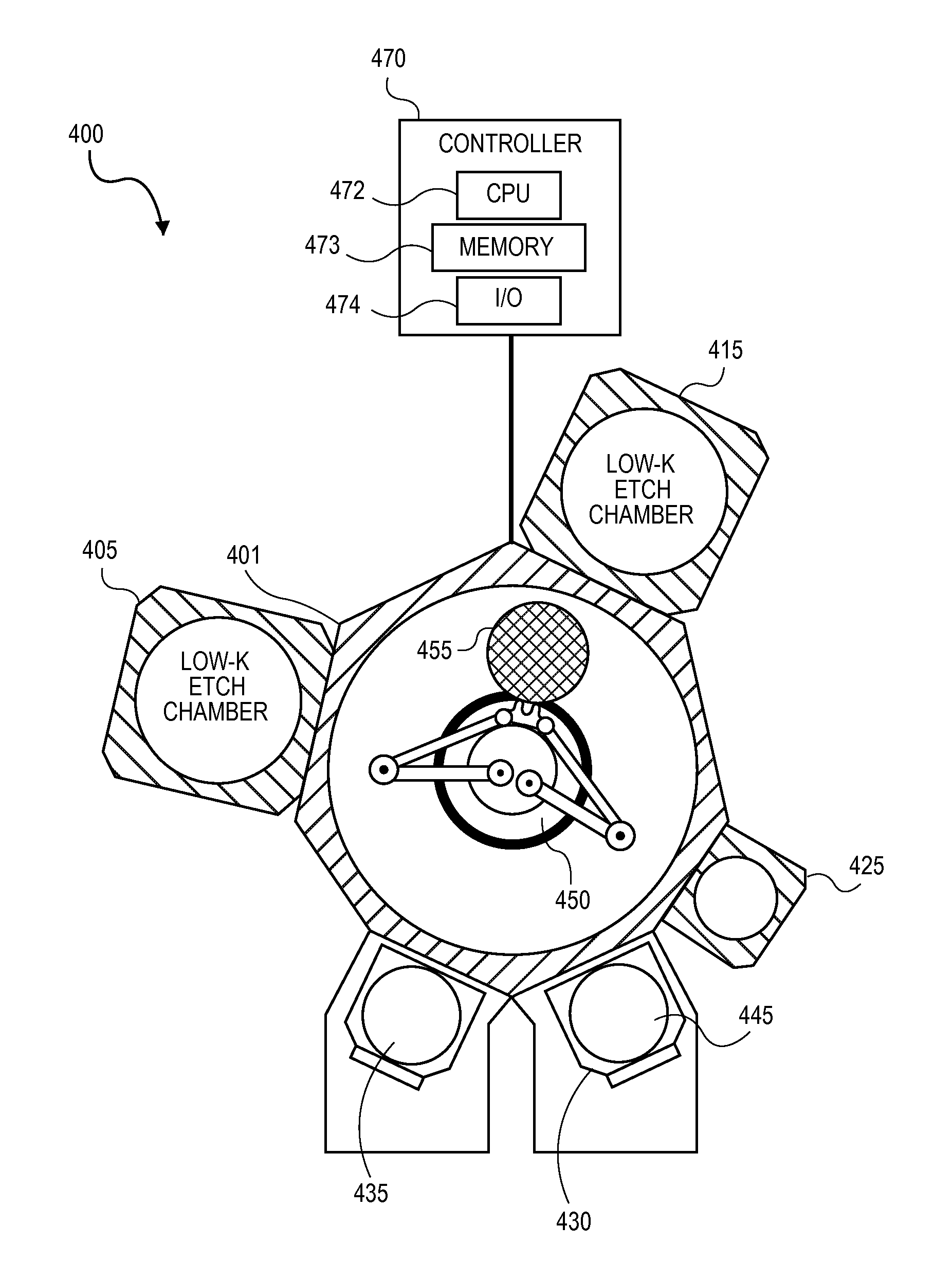

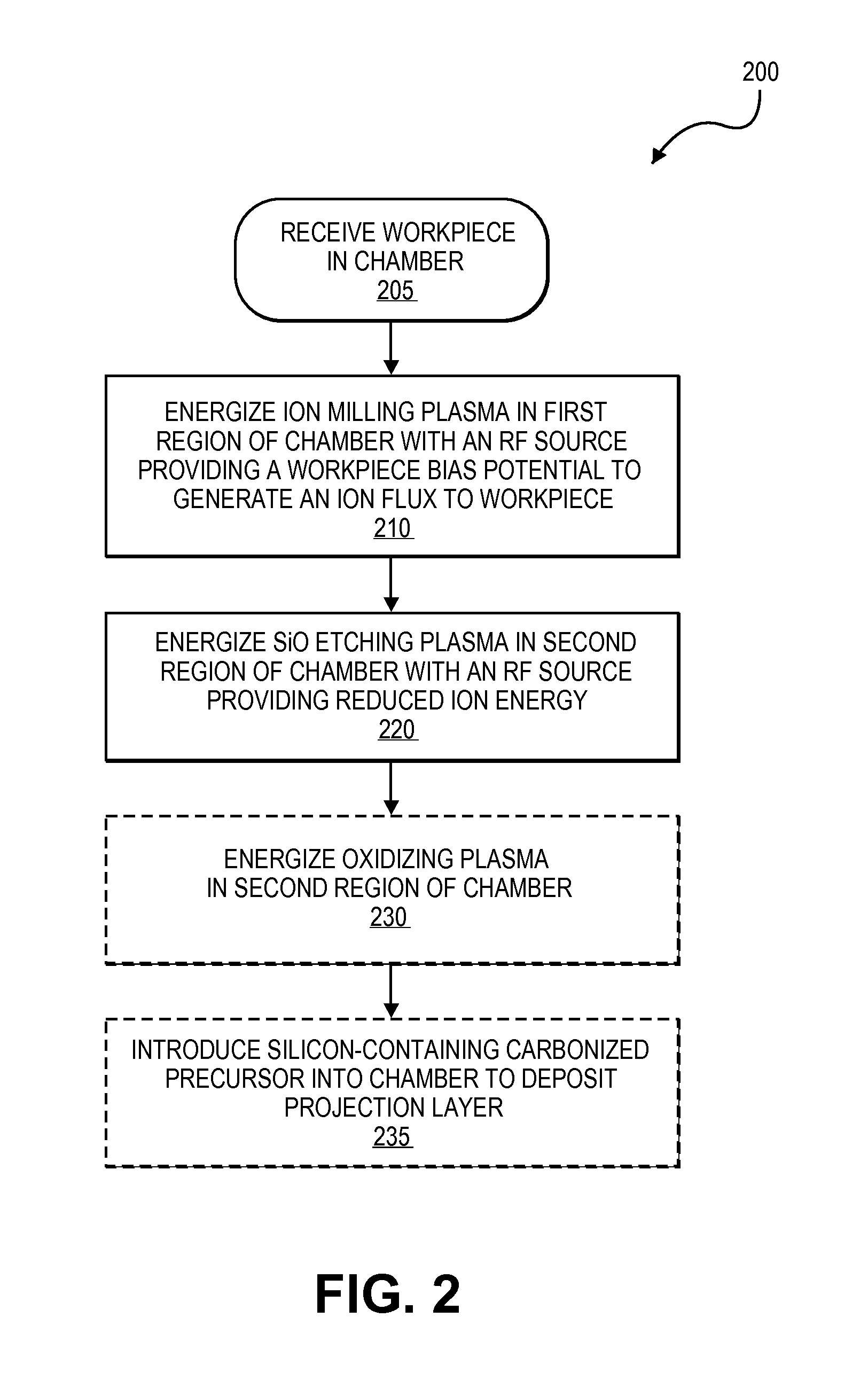

Process chamber for etching low k and other dielectric films

Methods and process chambers for etching of low-k and other dielectric films are described. For example, a method includes modifying portions of the low-k dielectric layer with a plasma process. The modified portions of the low-k dielectric layer are etched selectively over a mask layer and unmodified portions of the low-k dielectric layer. Etch chambers having multiple chamber regions for alternately generating distinct plasmas are described. In embodiments, a first charge coupled plasma source is provided to generate an ion flux to a workpiece in one operational mode, while a secondary plasma source is provided to provide reactive species flux without significant ion flux to the workpiece in another operational mode. A controller operates to cycle the operational modes repeatedly over time to remove a desired cumulative amount of the dielectric material.

Owner:APPLIED MATERIALS INC

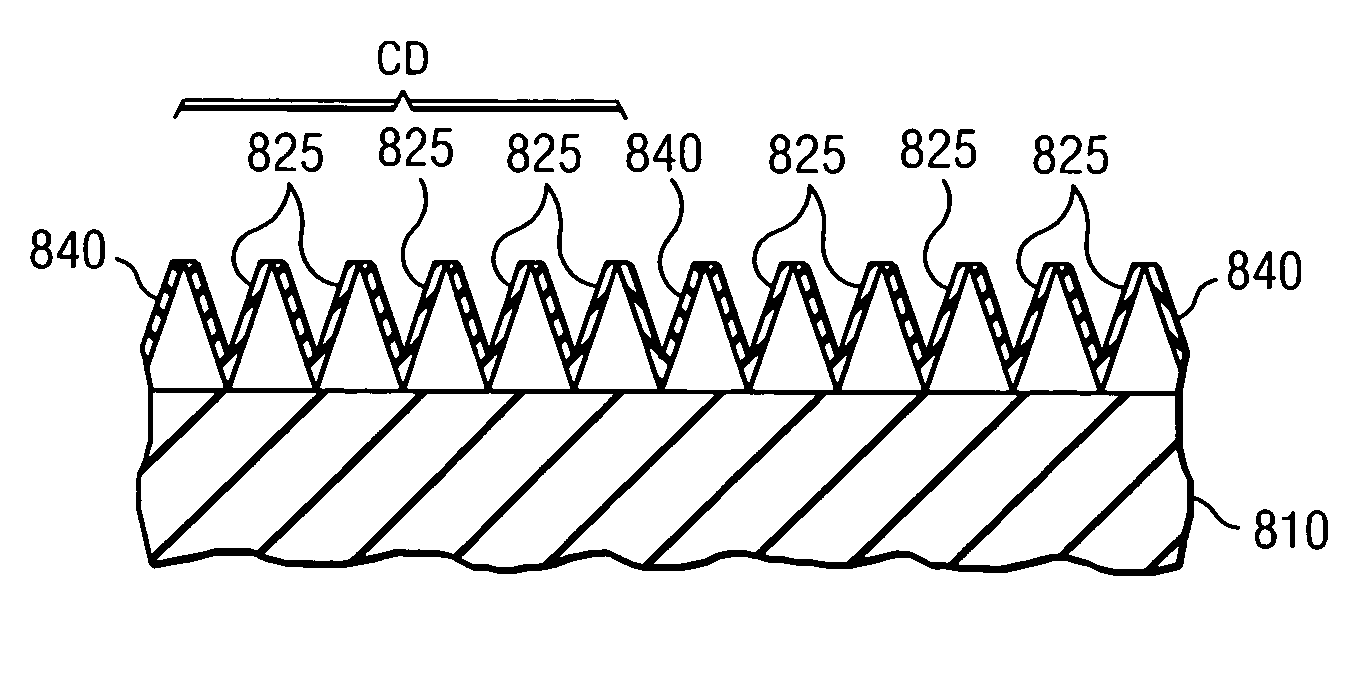

Pitch multiplication process

ActiveUS7208379B2Solid-state devicesSemiconductor/solid-state device manufacturingLine widthOptoelectronics

Owner:TEXAS INSTR INC

Method for high temperature etching of patterned layers using an organic mask stack

InactiveUS6143476APhotomechanical apparatusSemiconductor/solid-state device manufacturingOrganic baseHigh-temperature corrosion

The present disclosure pertains to a method of patterning a semiconductor device feature which provides for the easy removal of any residual masking layer which remains after completion of a pattern etching process. The method provides for a multi-layered masking structure which includes a layer of high-temperature organic-based masking material overlaid by either a layer of a high-temperature inorganic masking material which can be patterned to provide an inorganic hard mask, or by a layer of high-temperature imageable organic masking material which can be patterned to provide an organic hard mask. The hard masking material is used to transfer a pattern to the high-temperature organic-based masking material, and then the hard masking material is removed. The high-temperature organic-based masking material is used to transfer the pattern to an underlying semiconductor device feature.

Owner:APPLIED MATERIALS INC

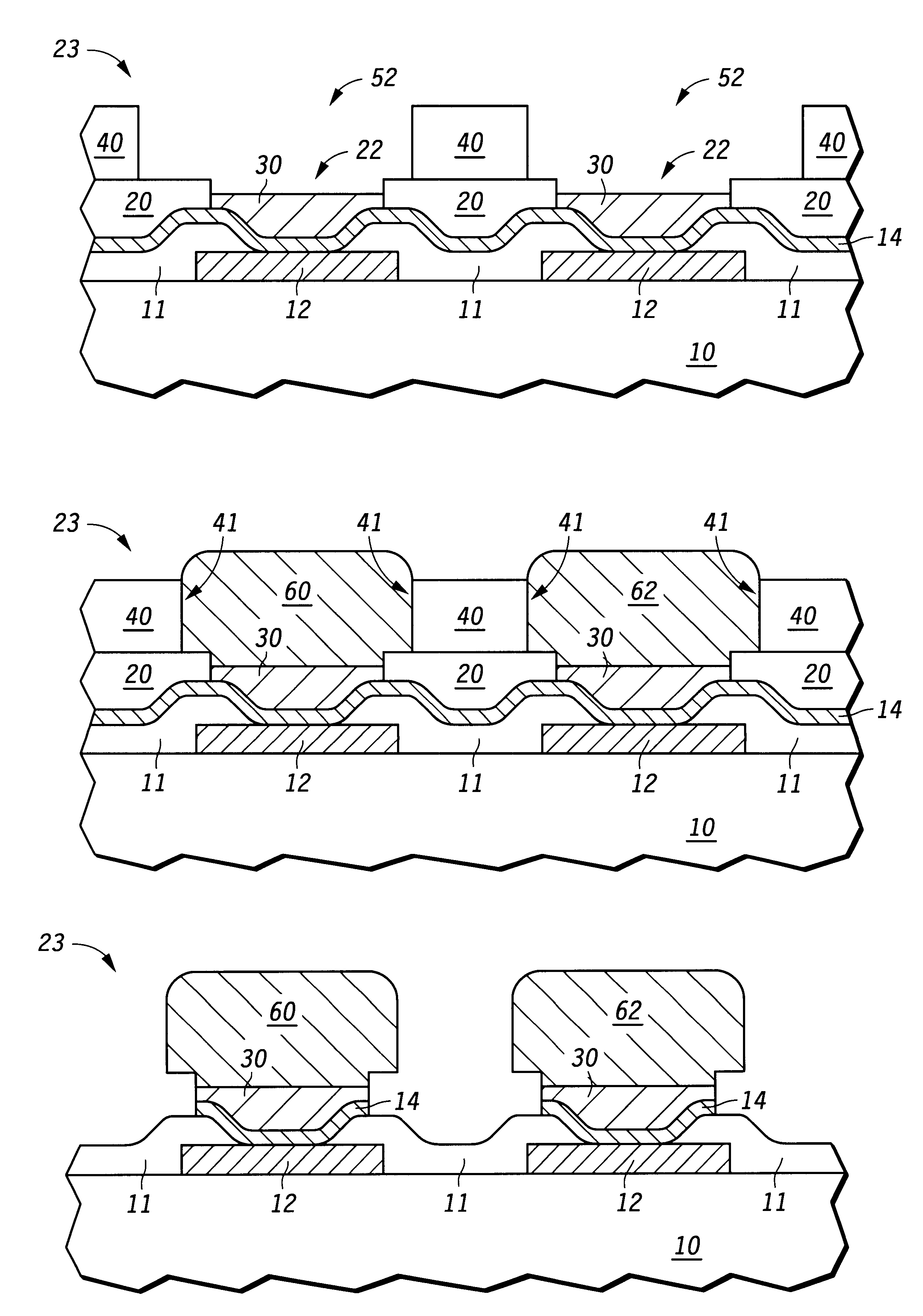

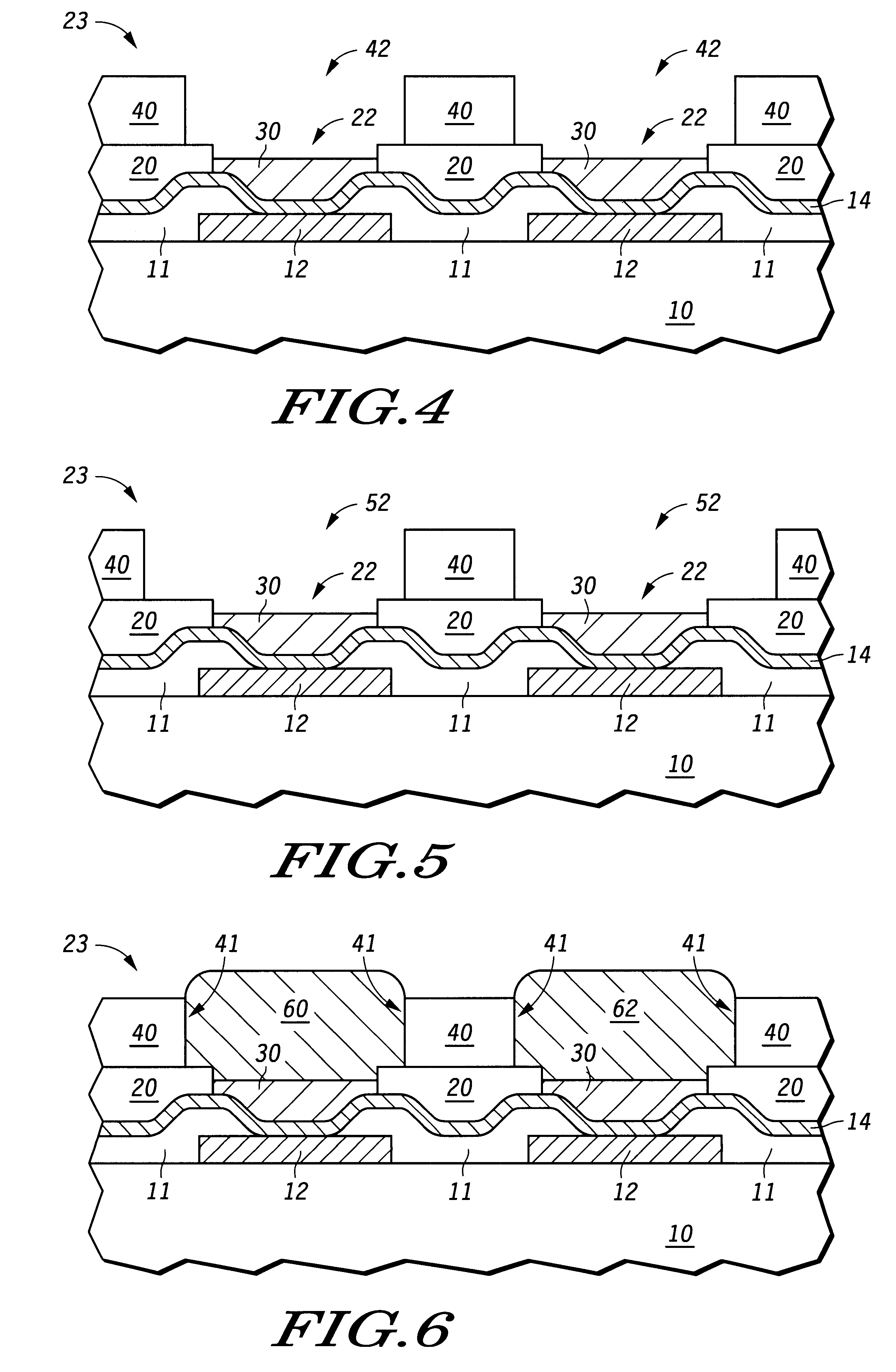

Fine pitch bumping with improved device standoff and bump volume

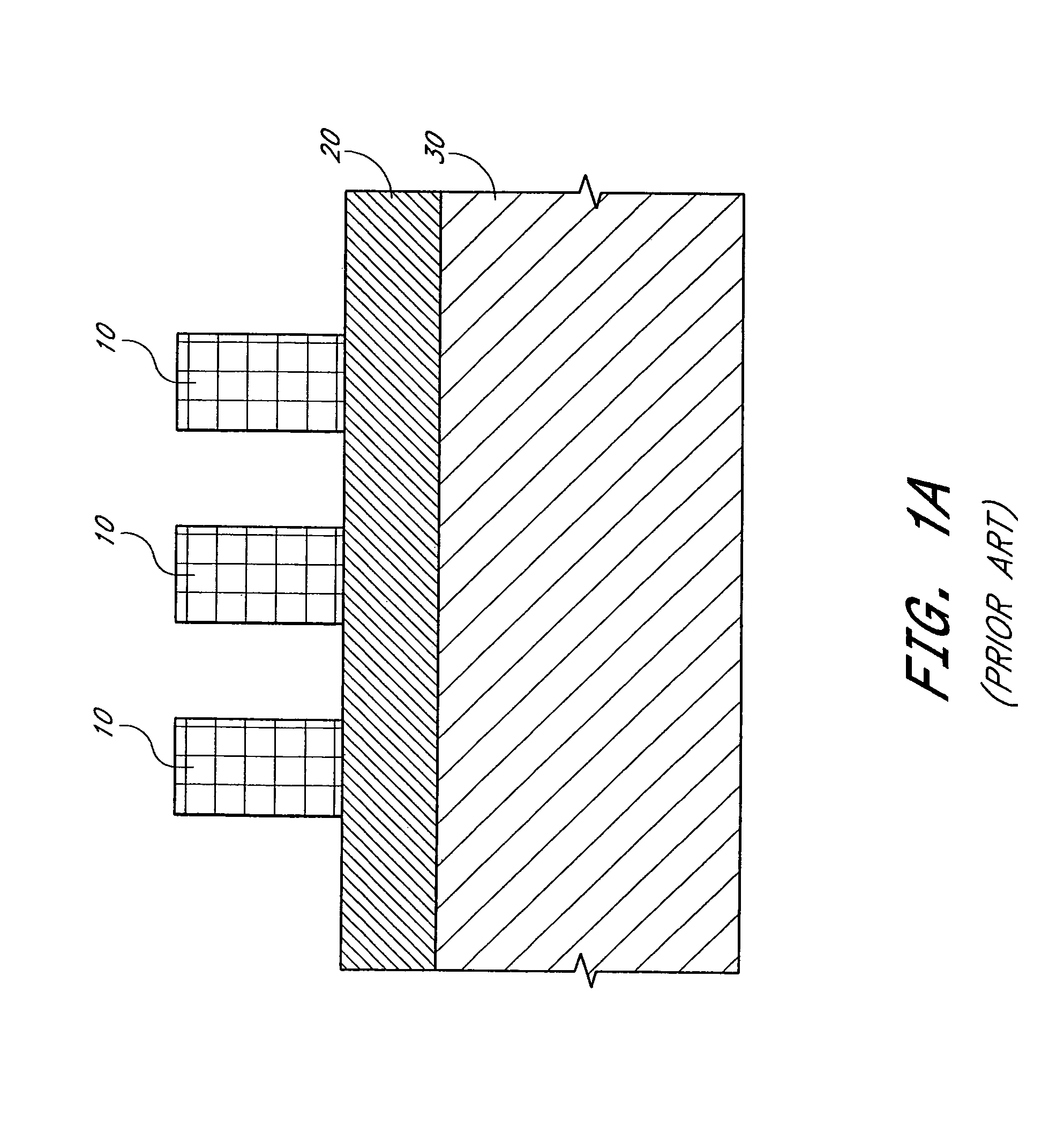

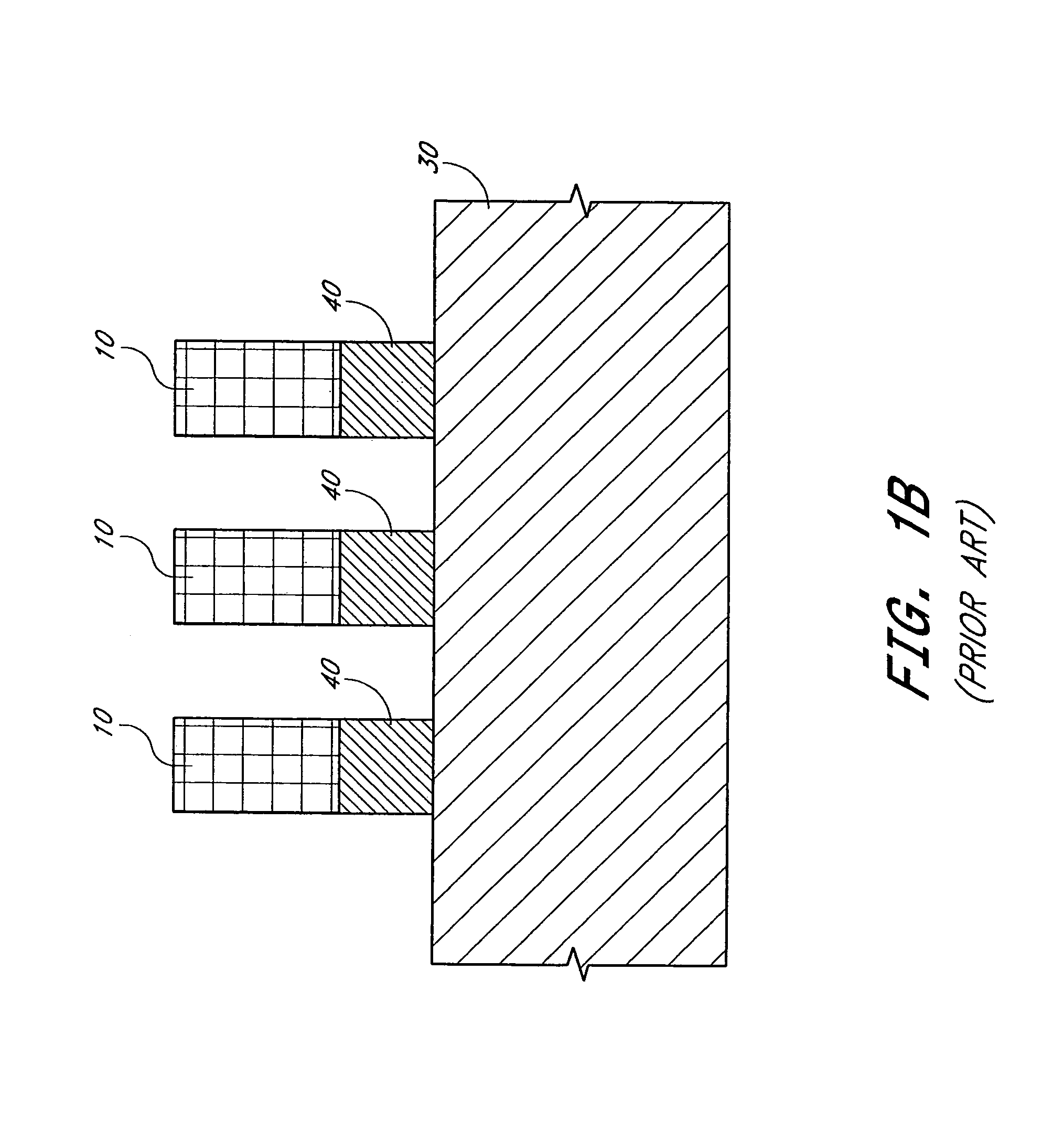

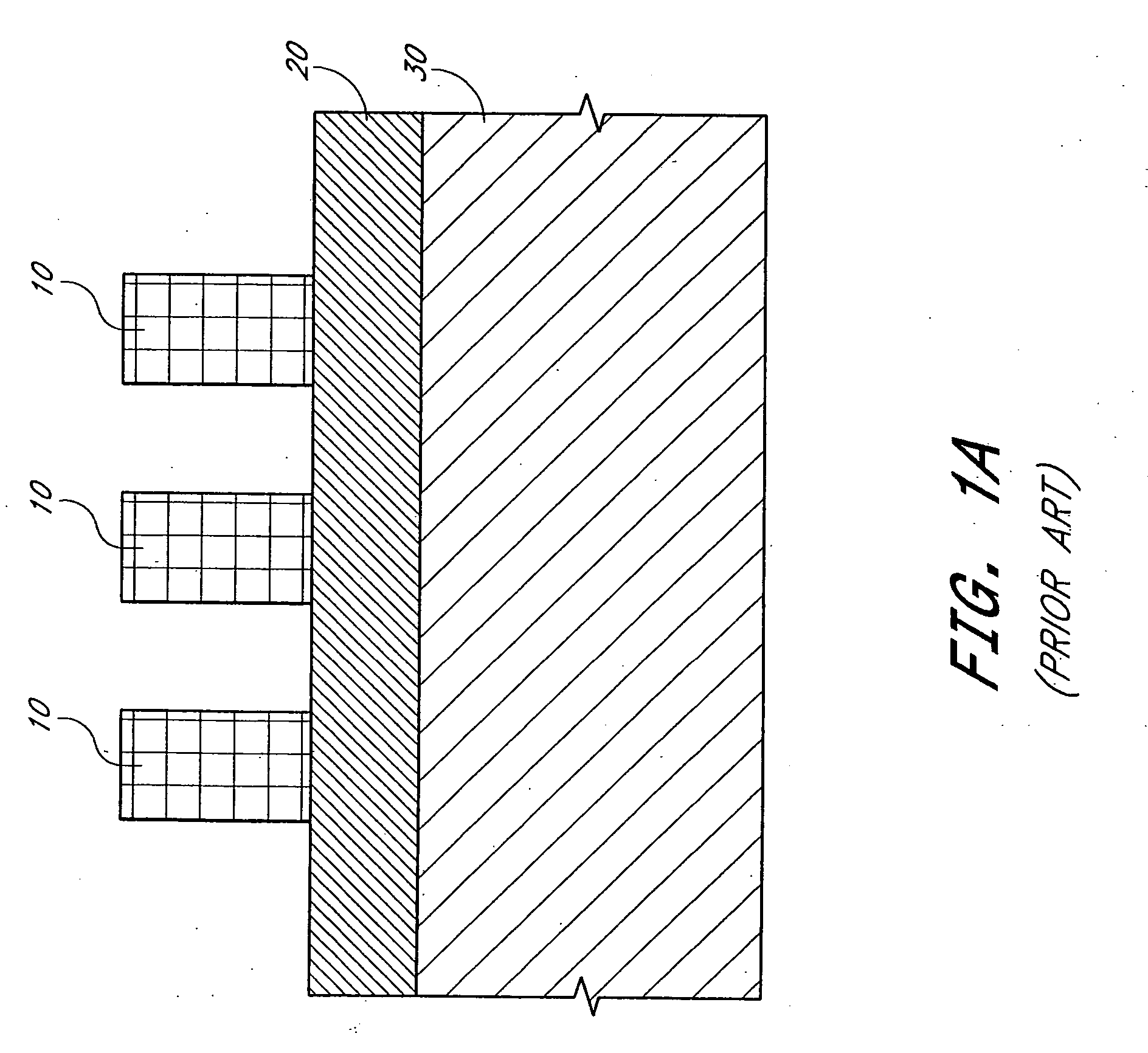

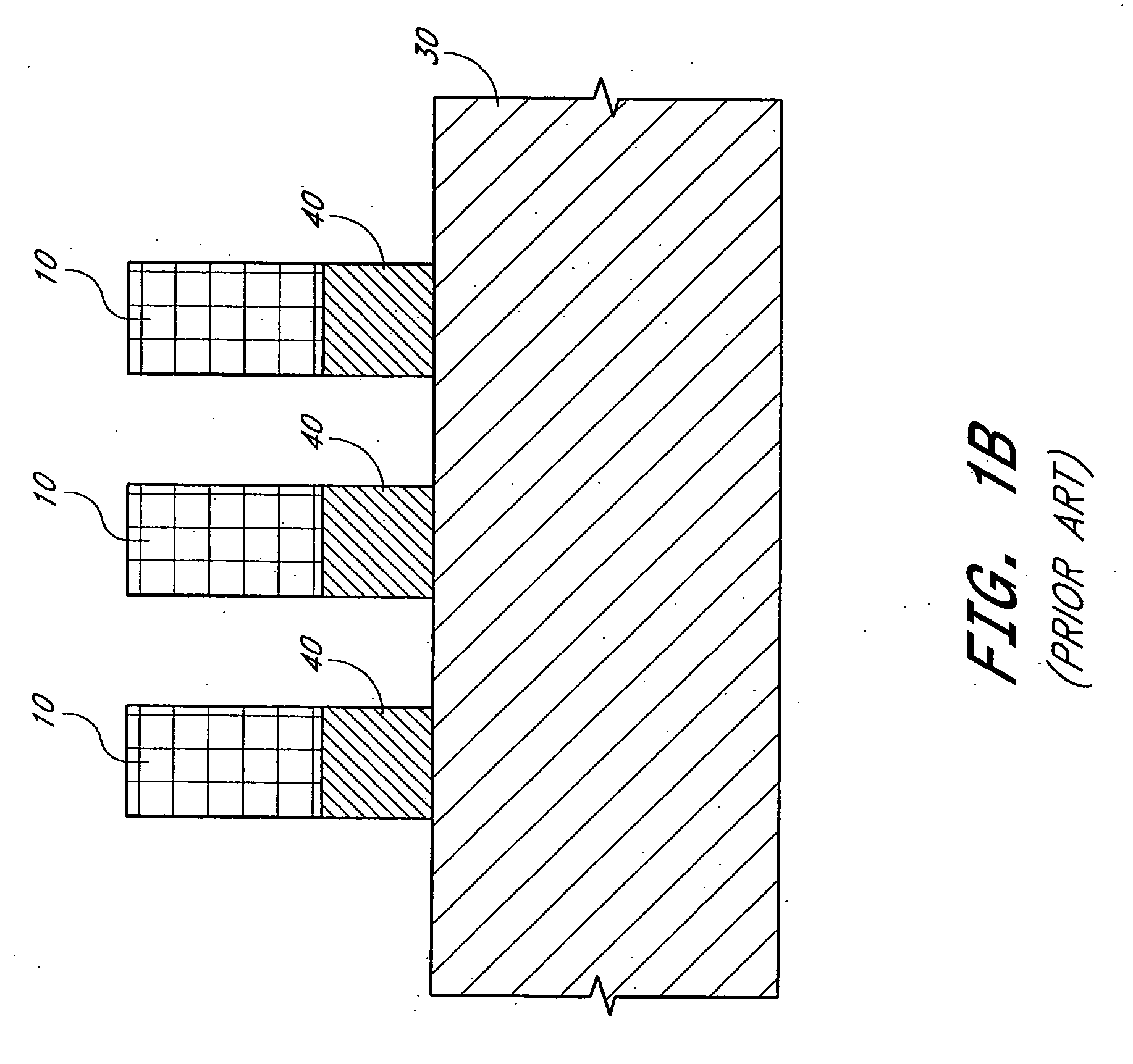

Embodiments of the present invention relate generally to solder bump formation and semiconductor device assemblies. One embodiment related to a method for forming a bump structure includes providing a semiconductor device (10) having a bond pad (12), and forming a first masking layer (20) overlying the bond pad (12). The first masking layer (20) is patterned to form a first opening (22) overlying at least a portion of the bond pad (12). A second masking layer (40) is formed overlying the first masking layer (20), and the second masking layer (40) is patterned to form a second opening (42) overlying at least a portion of the first opening (22). The method further includes forming a stud (30) at least within the first opening (22) and a solder bump (60) at least within the second opening (42).

Owner:NORTH STAR INNOVATIONS

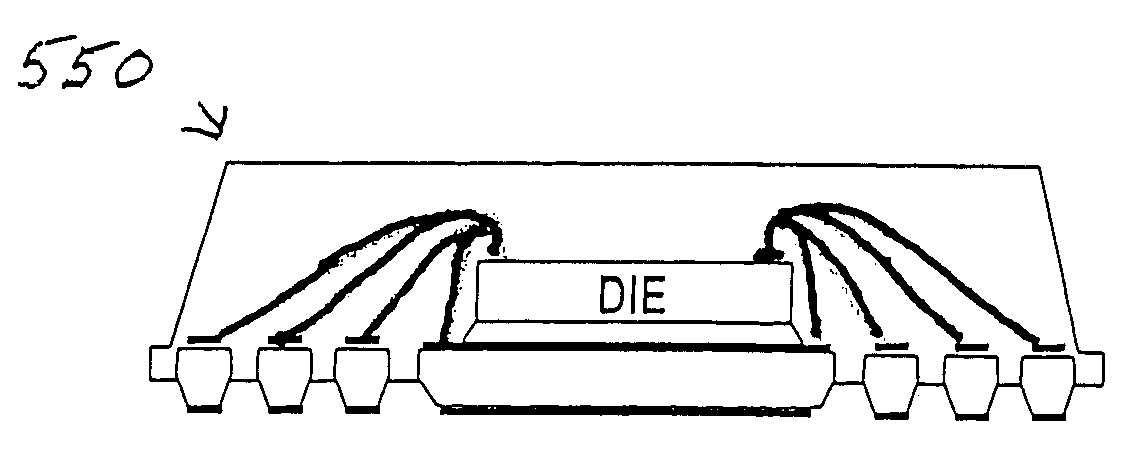

Flat no-lead semiconductor die package including stud terminals

ActiveUS7060535B1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipMetal sheet

A flat no-lead semiconductor die package contains a plurality of studs that protrude from the bottom surface of the capsule and act as electrical contacts, allowing the package to be mounted on a flat surface such as a printed circuit board, while permitting external circuit to be located on the flat surface directly beneath the package. The package may or may not contain a die-attach pad. The die may be mounted flip-chip style on the stud contacts and die-attach pad. A method of fabricating the package includes etching an upper portion of a metal sheet through a mask layer, attaching dice at locations on the surface of the metal sheet, forming a layer of molding compound over the dice, etching the lower portion of the metal sheet through a second mask layer, and separating the packages with a dicing saw or punch tool.

Owner:UTAC HEADQUARTERS PTE LTD

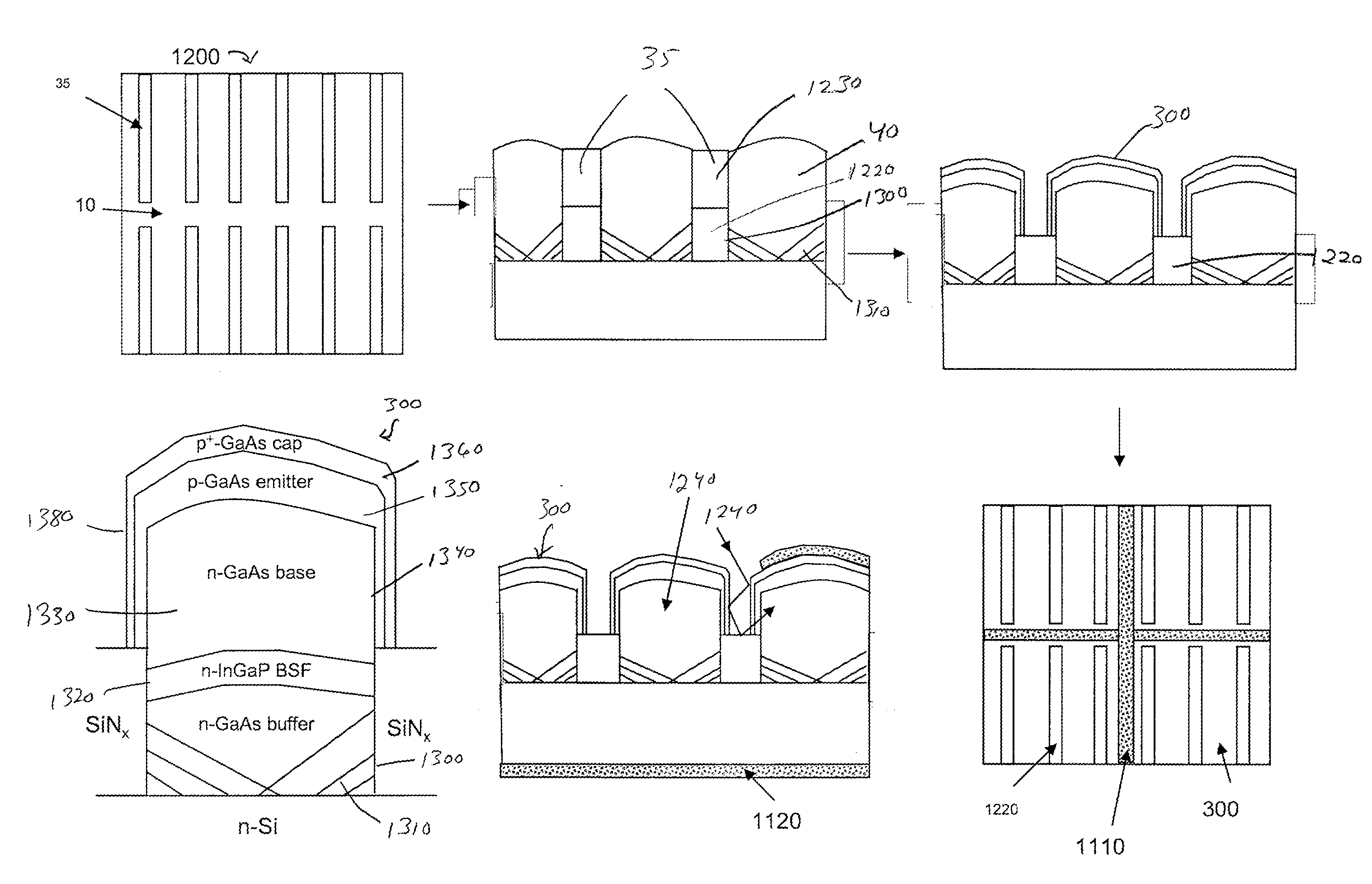

Photovoltaics on silicon

ActiveUS20080257409A1Quality improvementImprove efficiencyFinal product manufactureSemiconductor/solid-state device manufacturingCrystalline materialsSilicon

Owner:TAIWAN SEMICON MFG CO LTD

Multi-touch surface stackup arrangement

ActiveUS20080158173A1Reduce cover warpageFull surfaceNon-enclosed substationsInput/output for user-computer interactionProximity sensorDisplay device

A multi-layer cover for an electronic device having one or more of a sensor panel, a proximity sensor, an ambient light sensor, and a display device can include an outer hardcoat, a structural layer, an IR transmissive ink layer, a mask layer, and a backside hardcoat. The backside hardcoat can reduce cover warpage, enable full surface lamination of the cover to the sensor panel, prevent bubbles from forming in transparent windows in the cover, enable a wider range of functional inks to be applied in various layering orders to allow certain types of light to pass through while blocking others, and hide the sensors to provide a seamless, uncluttered visual appearance.

Owner:APPLE INC

Patterning method and method of forming memory device

ActiveUS20140248773A1Excellent CDUSerious problemSemiconductor/solid-state device manufacturingComputer scienceMask layer

A method of forming memory device is provided. A substrate having at least two cell areas and at least one peripheral area between the cell areas is provided. A target layer, a sacrificed layer and a first mask layer having first mask patterns in the cell areas and second mask patterns in the peripheral area are sequentially formed on the substrate. Sacrificed layer is partially removed to form sacrificed patterns by using the first mask layer as a mask. Spacers are formed on sidewalls of the sacrificed patterns. The sacrificed patterns and at least the spacers in the peripheral area are removed. A second mask layer is formed in the cell areas. Target layer is partially removed, using the second mask layer and remaining spacers as a mask, to form word lines in the cell areas and select gates in a portion of cell areas adjacent to the peripheral area.

Owner:WINBOND ELECTRONICS CORP

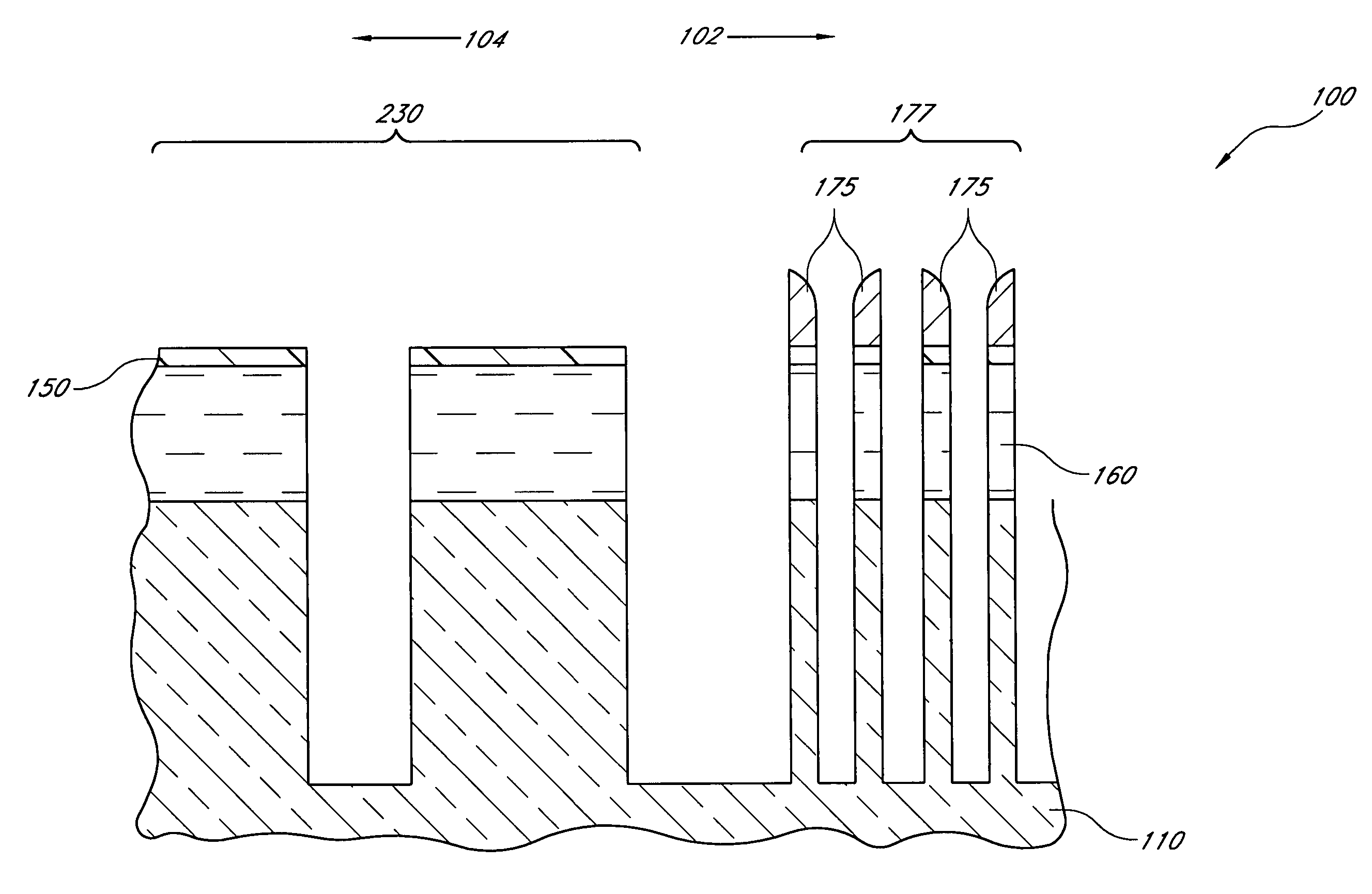

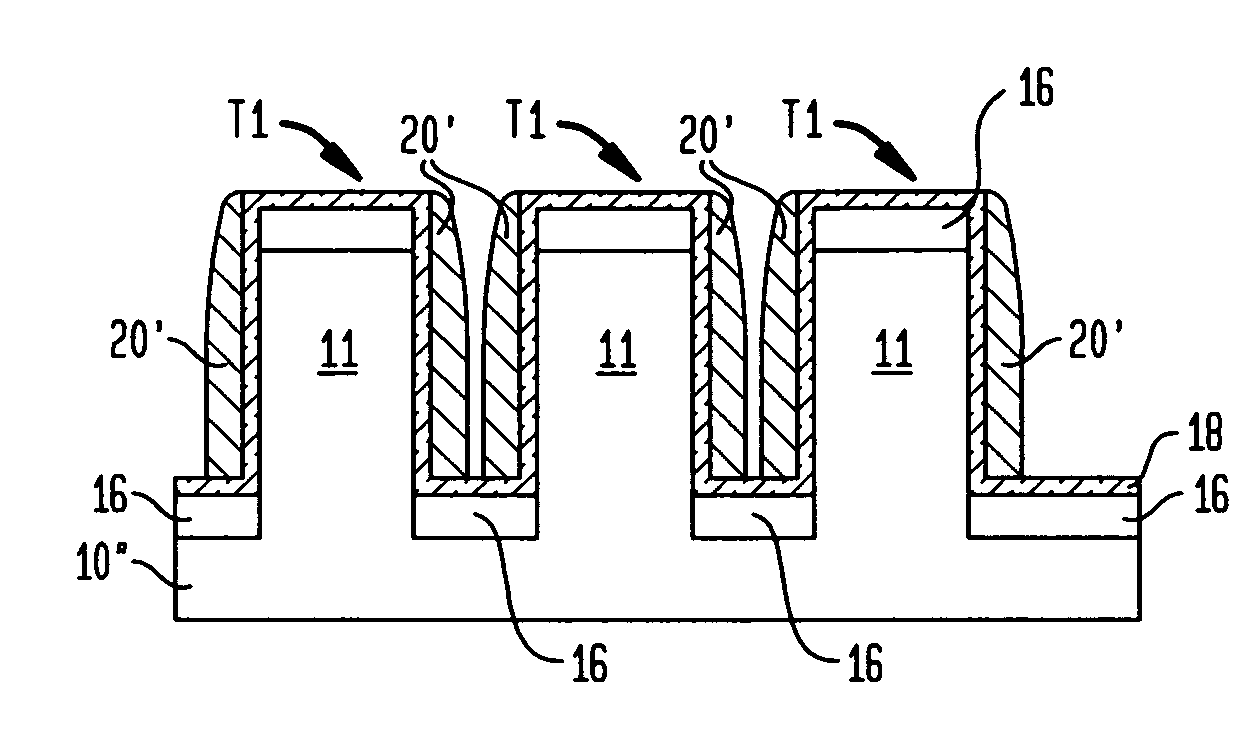

Vertical field effect transistor arrays and methods for fabrication thereof

Vertical field effect transistor semiconductor structures and methods for fabrication of the vertical field effect transistor semiconductor structures provide an array of semiconductor pillars. Each vertical portion of each semiconductor pillar in the array of semiconductor pillars has a linewidth greater than a separation distance to an adjacent semiconductor pillar. Alternatively, the array may comprise semiconductor pillars with different linewidths, optionally within the context of the foregoing linewidth and separation distance limitations. A method for fabricating the array of semiconductor pillars uses a minimally photolithographically dimensioned pillar mask layer that is annularly augmented with at least one spacer layer prior to being used as an etch mask.

Owner:TAIWAN SEMICON MFG CO LTD

Dsa grapho-epitaxy process with etch stop material

InactiveUS20140256145A1Reduce widthForming accuratelySemiconductor/solid-state device manufacturingResistReactive-ion etching

A method for defining a template for directed self-assembly (DSA) materials includes forming an etch stop layer on a neutral material, forming a mask layer on the etch stop layer and forming an anti-reflection coating (ARC) on the mask layer. A resist layer is patterned on the ARC using optical lithography to form a template pattern. The ARC and the mask layer are reactive ion etched down to the etch stop layer in accordance with the template pattern to form a template structure. The ARC is removed from the mask layer and the template structure is trimmed to reduce a width of the template structure. A wet etch is performed to remove the etch stop layer to permit the neutral material to form an undamaged DSA template for DSA materials.

Owner:IBM CORP

Dry etching method for metal film

ActiveUS20130098868A1Decorative surface effectsSemiconductor/solid-state device manufacturingHalogenNoble gas

A method for performing dry etching on a metal film containing Pt via a mask layer includes performing dry etching on the metal film by generating a plasma of an etching gas including a gaseous mixture of H2 gas, CO2 gas, methane gas and rare gas. With the dry etching method, it is possible to make a vertical sidewall of a hole or trench more vertical without using a halogen gas.

Owner:TOKYO ELECTRON LTD

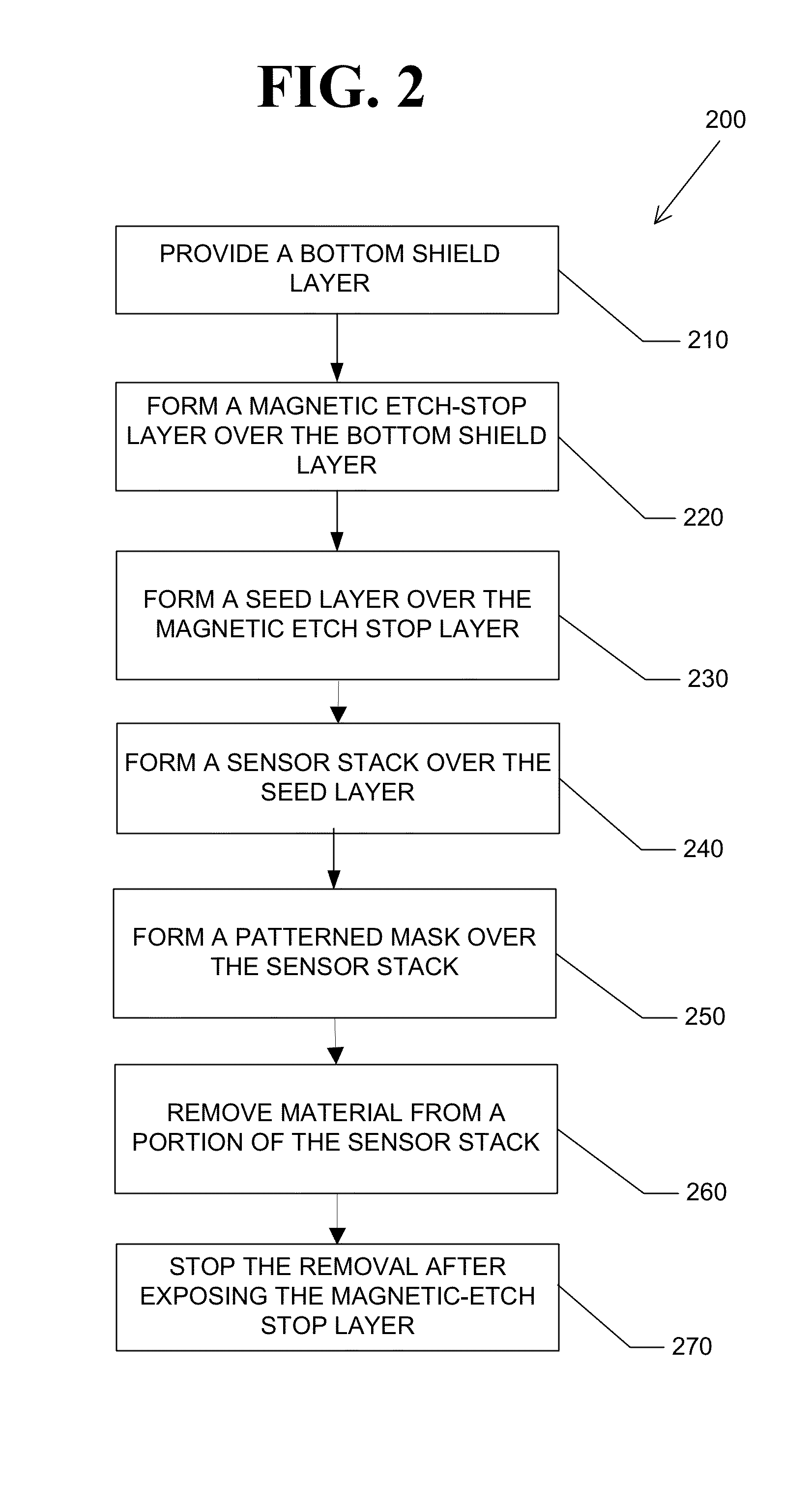

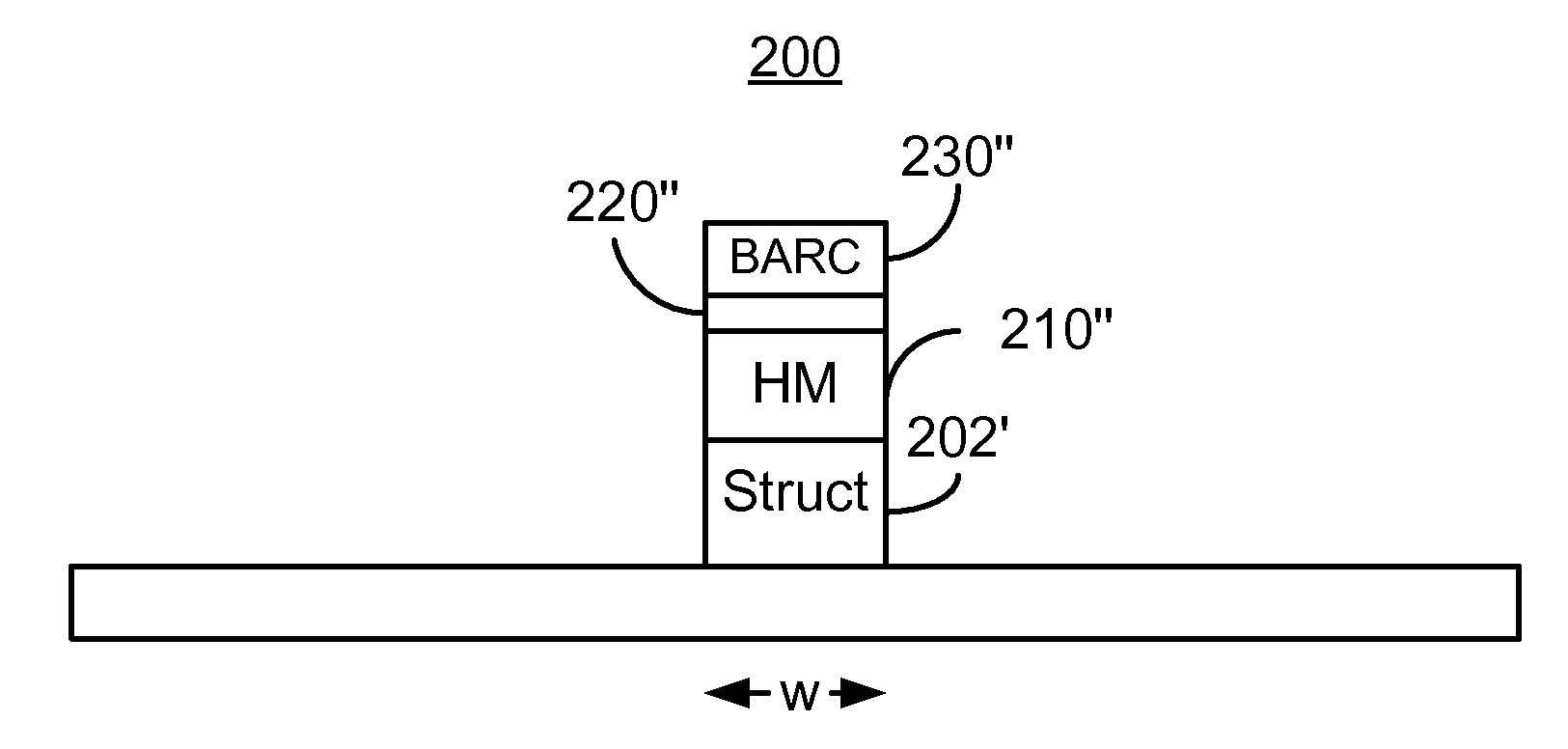

Magnetic etch-stop layer for magnetoresistive read heads

ActiveUS8611055B1Soft magnetic propertyReduce spacingRecord information storageManufacture of flux-sensitive headsEngineeringMask layer

A method of producing a magnetoresistive read head and a tunneling magnetoresistive read head produced thereby are disclosed. A shield layer is provided. A magnetic etch-stop layer is formed over the shield layer, where the magnetic etch-stop layer comprises a nonmagnetic metal and a soft magnetic material with overall property still being magnetically soft. A sensor stack is formed over the magnetic etch-stop layer. A patterned mask layer is formed over the sensor stack. Material from a portion of the sensor stack not covered by the patterned mask is removed.

Owner:WESTERN DIGITAL TECH INC

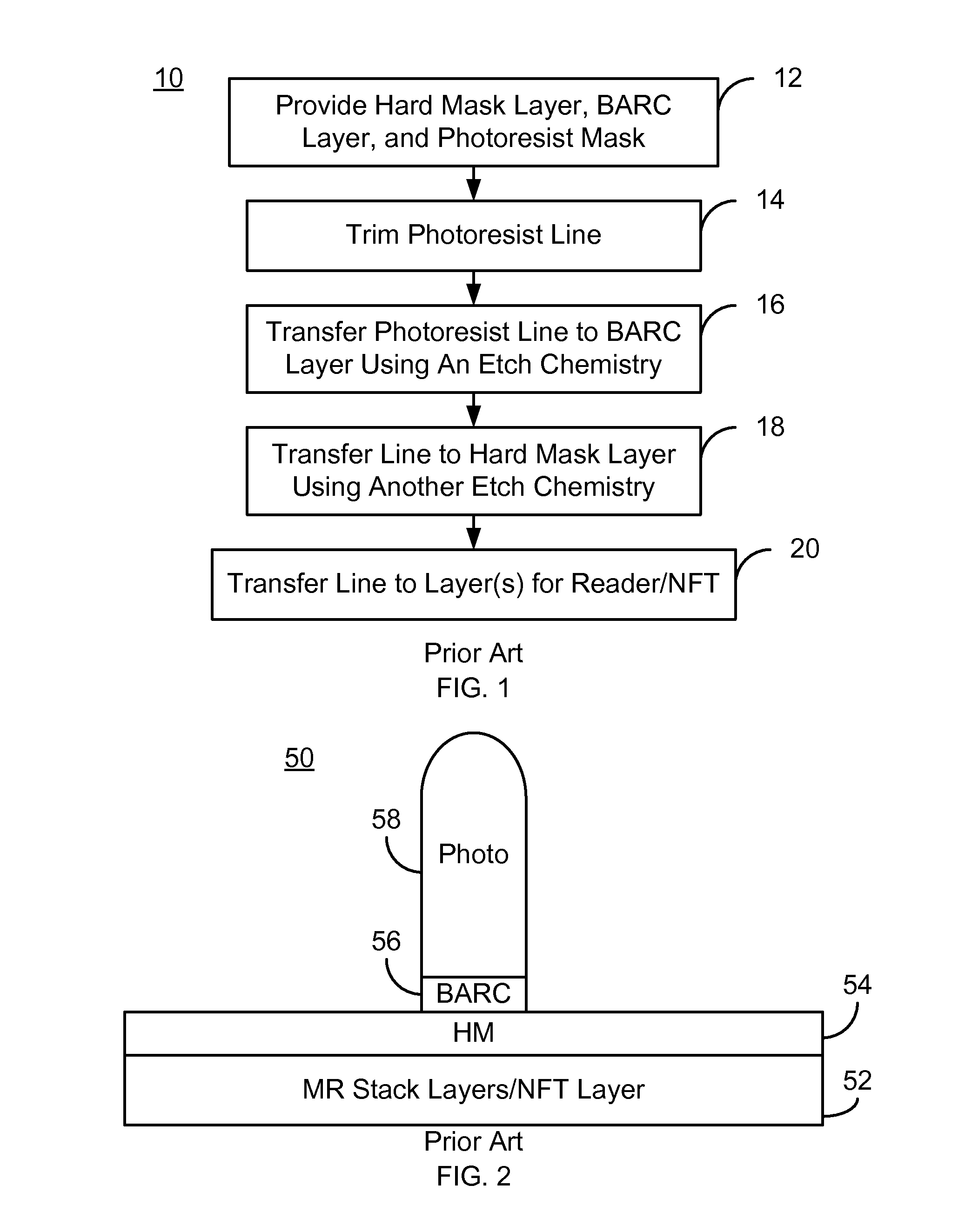

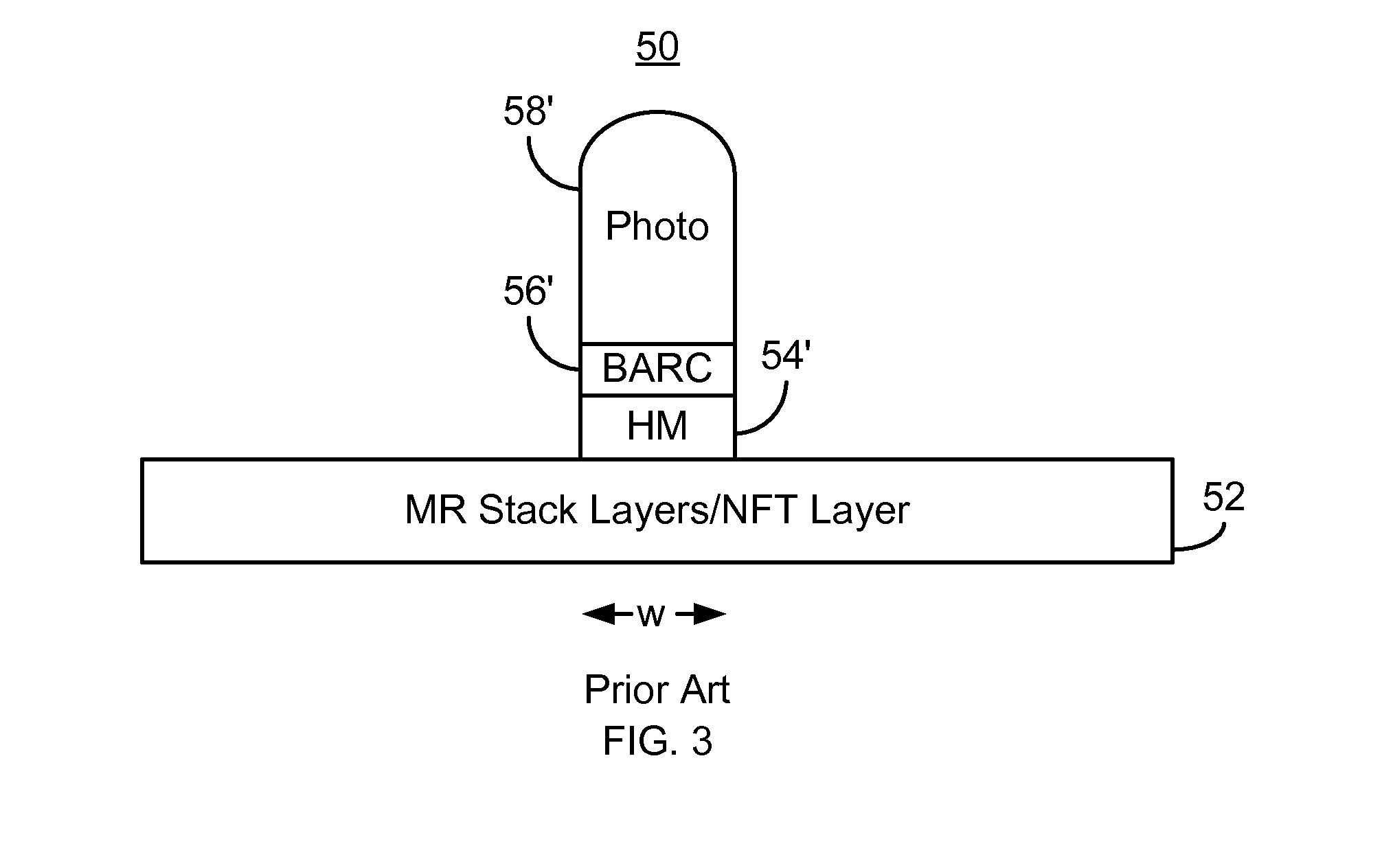

Method and system for fabricating a narrow line structure in a magnetic recording head

A method for fabricating a structure in magnetic recording head is described. First and second hard mask layers are provided on the layer(s) for the structure. A BARC layer and photoresist mask having a pattern are provided on the second hard mask layer. The pattern includes a line corresponding to the structure. The pattern is transferred to the BARC layer and the second hard mask layer in a single etch using an etch chemistry. At least the second hard mask layer is trimmed using substantially the same first etch chemistry. A mask including a hard mask line corresponding to the line and less than thirty nanometers wide is thus formed. The pattern of the second hard mask is transferred to the first hard mask layer. The pattern of the first hard mask layer is transferred to the layer(s) such that the structure has substantially the width.

Owner:WESTERN DIGITAL TECH INC

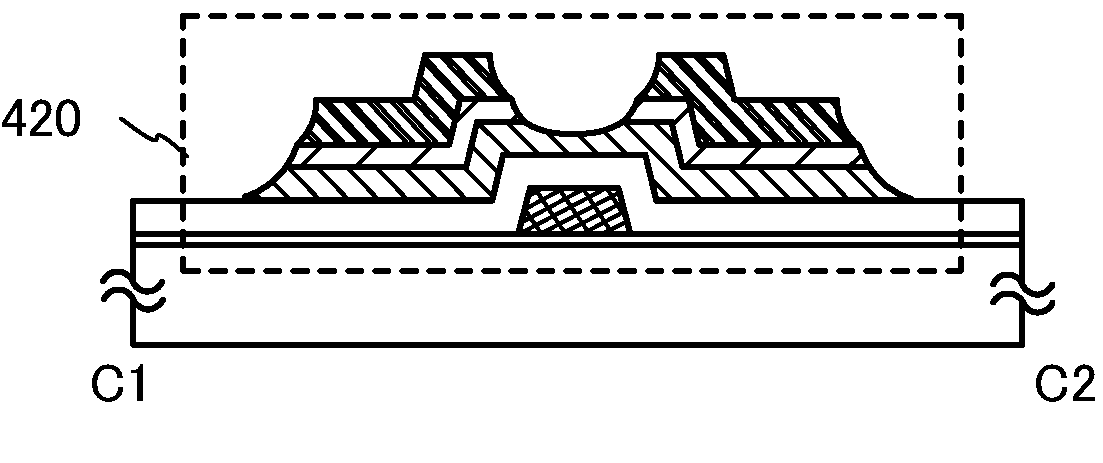

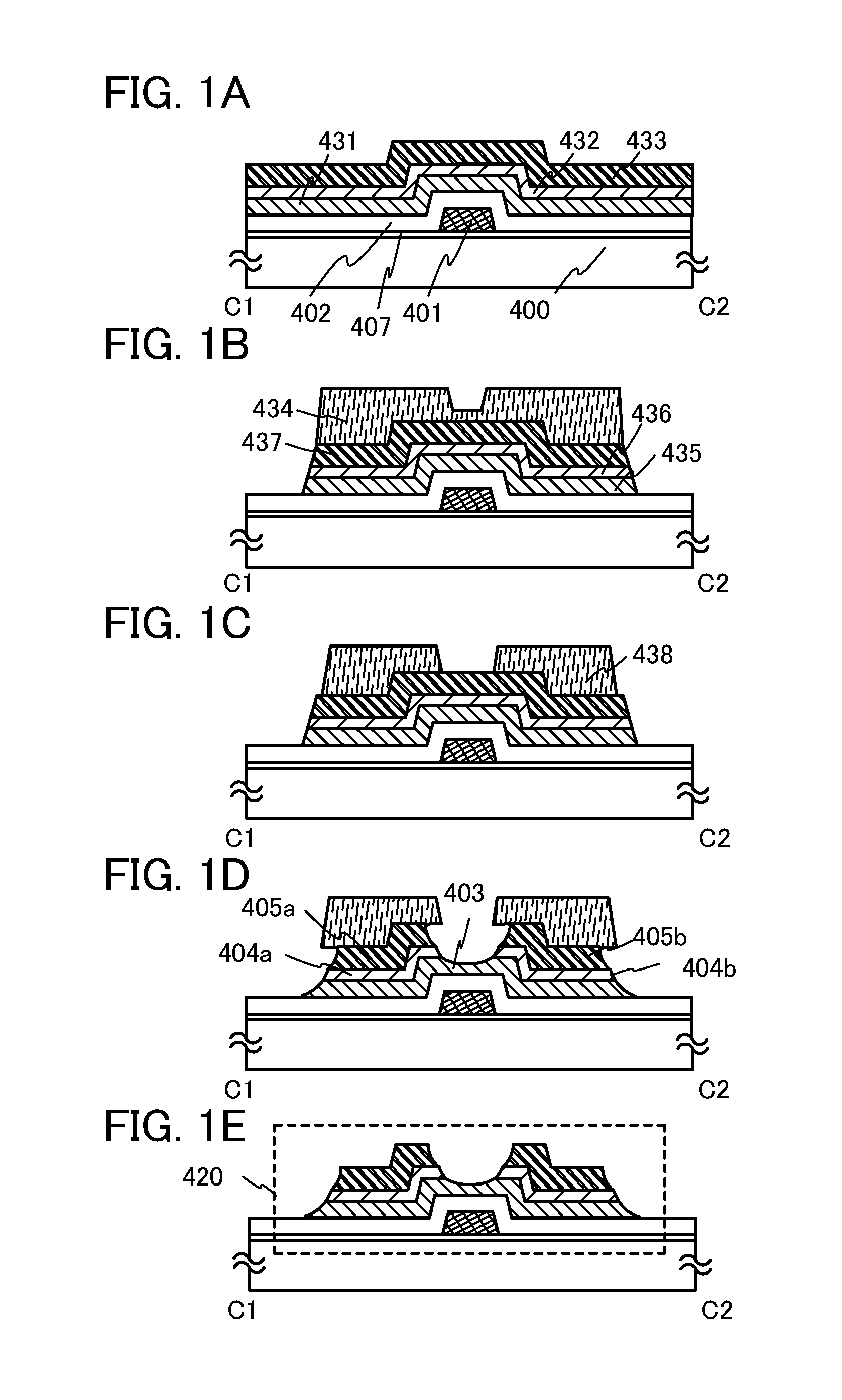

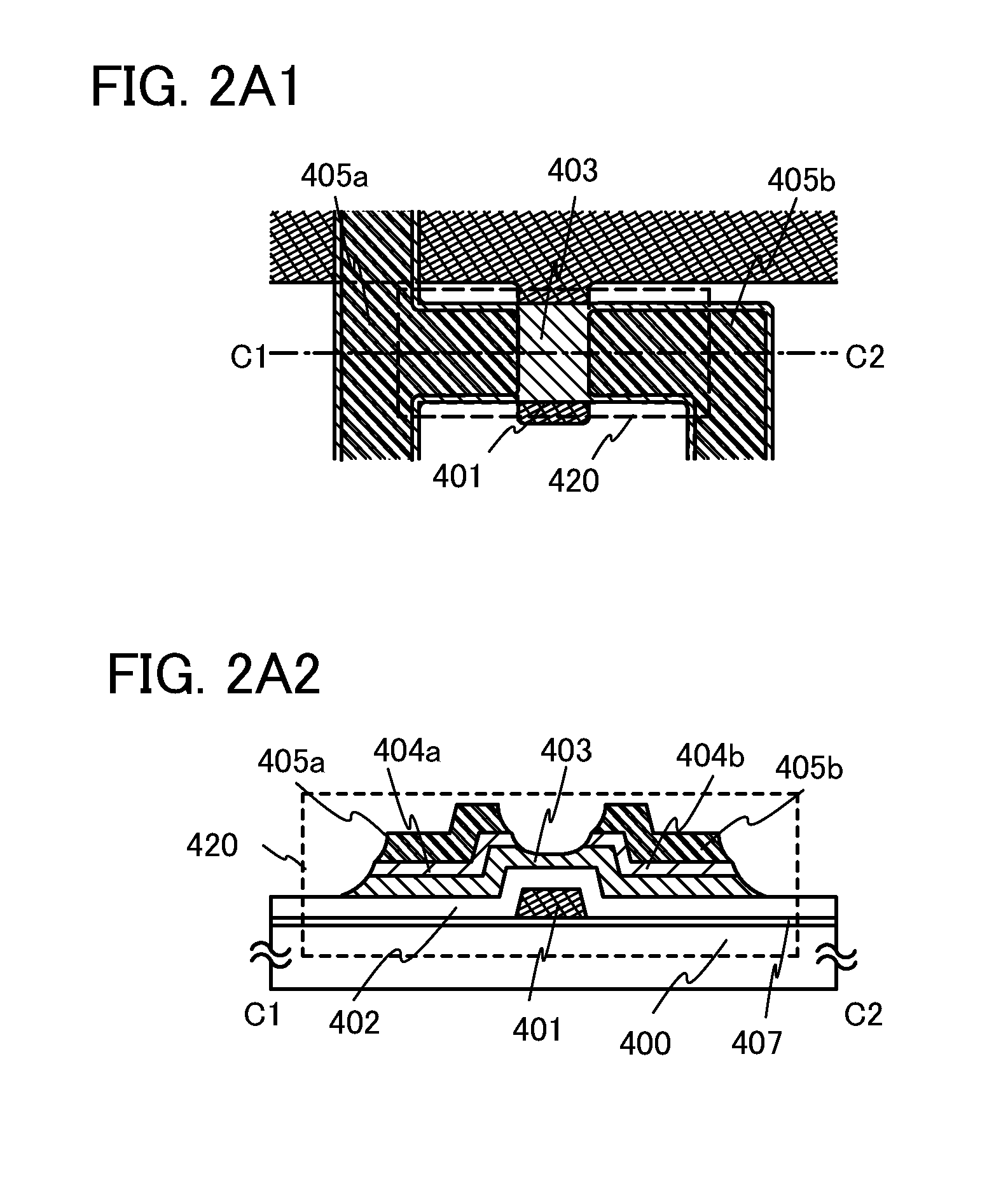

Method for manufacturing semiconductor device

ActiveUS20100105163A1Reduce manufacturing costImprove productivityTransistorElectroluminescent light sourcesProduction rateLight exposure

An object is to manufacture a semiconductor device including an oxide semiconductor at low cost with high productivity in such a manner that a photolithography process is simplified by reducing the number of light-exposure masks. In a method for manufacturing a semiconductor device including a channel-etched inverted-staggered thin film transistor, an oxide semiconductor film and a conductive film are etched using a mask layer formed with the use of a multi-tone mask which is a light-exposure mask through which light is transmitted so as to have a plurality of intensities. In etching steps, a first etching step is performed by dry etching in which an etching gas is used, and a second etching step is performed by wet etching in which an etchant is used.

Owner:SEMICON ENERGY LAB CO LTD

Method of pattern etching a low K dielectric layer

InactiveUS6331380B1Photomechanical apparatusSemiconductor/solid-state device manufacturingOrganic baseOxygen

A first embodiment of the present invention pertains to a method of patterning a semiconductor device conductive feature while permitting easy removal of any residual masking layer which remains after completion of the etching process. A multi-layered masking structure is used which includes a layer of high-temperature organic-based masking material overlaid by either a patterned layer of inorganic masking material or by a layer of patterned high-temperature imageable organic masking material. The inorganic masking material is used to transfer a pattern to the high-temperature organic-based masking material and is then removed. The high-temperature organic-based masking material is used to transfer the pattern and then may be removed if desired. This method is also useful in the pattern etching of aluminum, even though aluminum can be etched at lower temperatures. A second embodiment of the present invention pertains to a specialized etch chemistry useful in the patterning of organic polymeric layers such as low k dielectrics, or other organic polymeric interfacial layers. This etch chemistry is useful for mask opening during the etch of a conductive layer or is useful in etching damascene structures where a metal fill layer is applied over the surface of a patterned organic-based dielectric layer. The etch chemistry provides for the use of etchant plasma species which minimize oxygen, fluorine, chlorine, and bromine content.

Owner:APPLIED MATERIALS INC

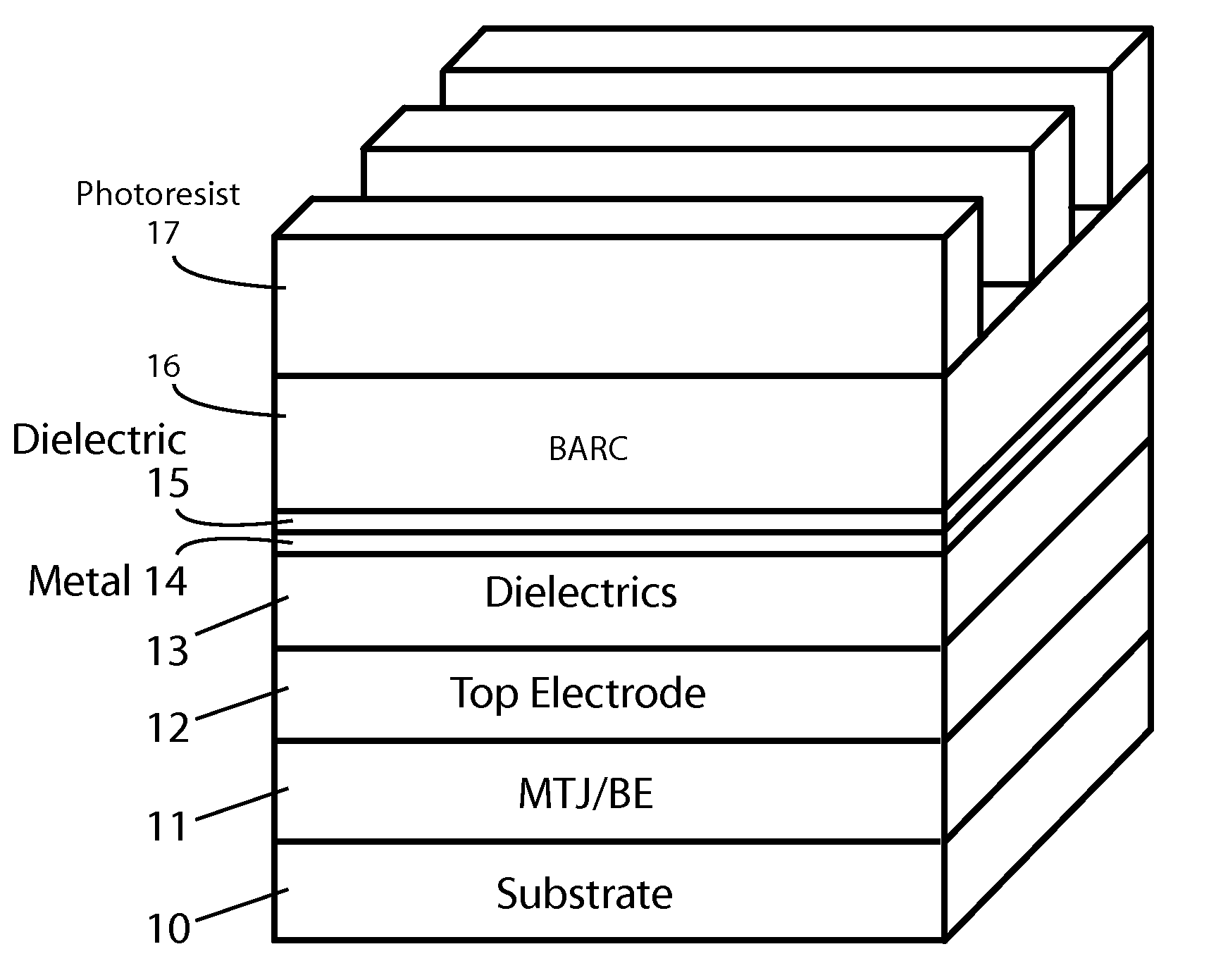

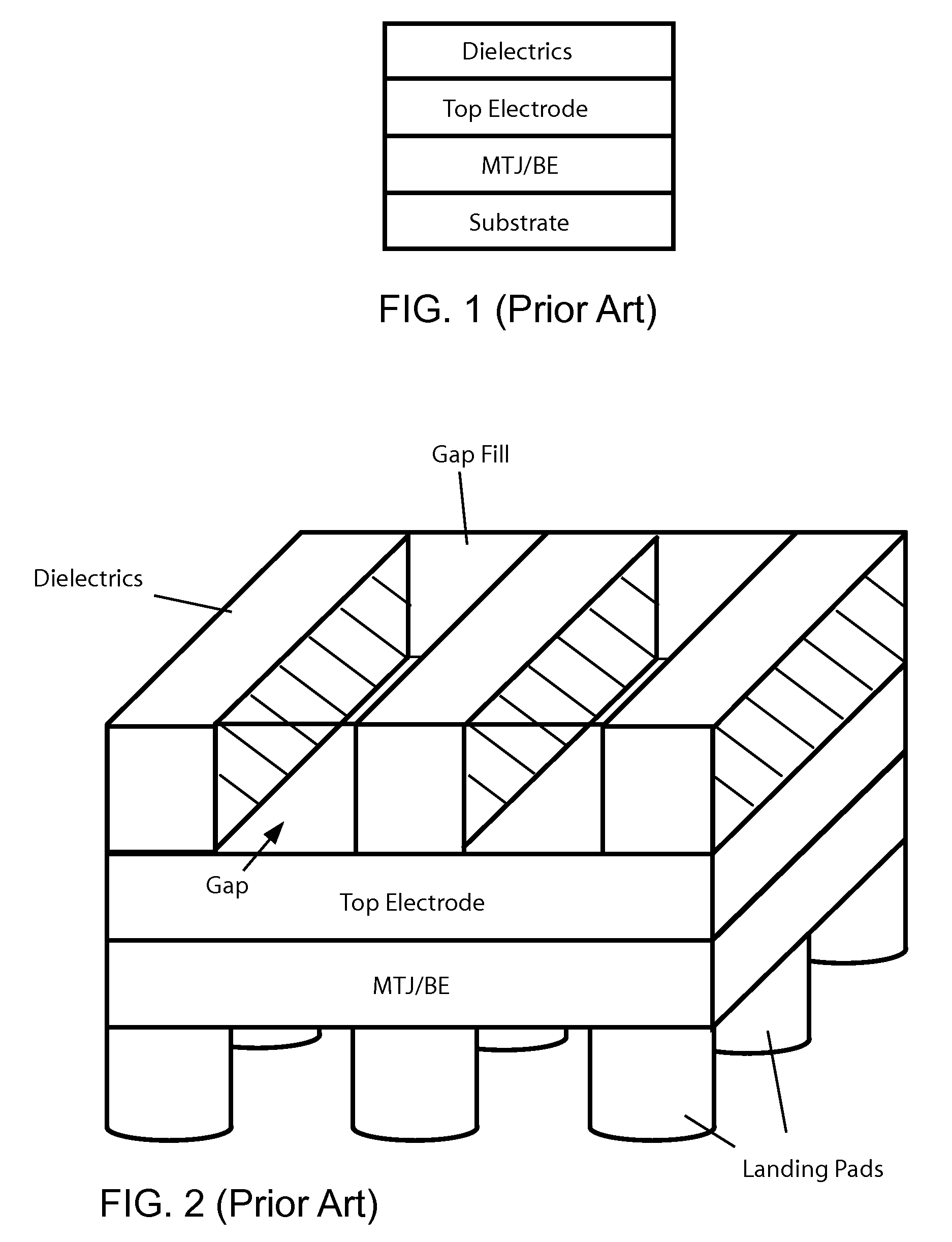

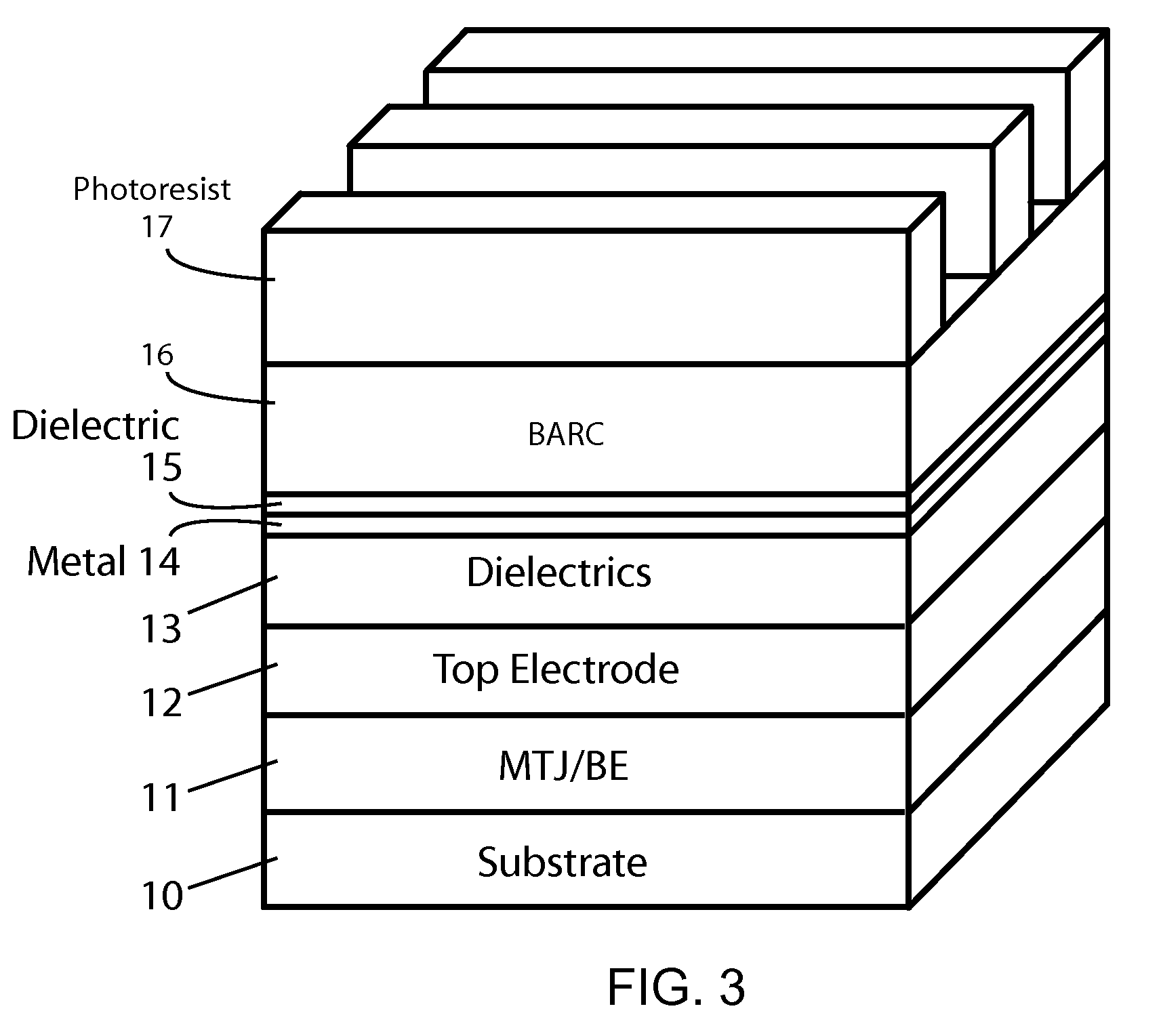

Method for manufacturing high density non-volatile magnetic memory

ActiveUS20130244344A1Reduce programming currentReduced dimensionNanomagnetismNanoinformaticsFeature DimensionLithographic artist

Methods of fabricating MTJ arrays using two orthogonal line patterning steps are described. Embodiments are described that use a self-aligned double patterning method for one or both orthogonal line patterning steps to achieve dense arrays of MTJs with feature dimensions one half of the minimum photo lithography feature size (F). In one set of embodiments, the materials and thicknesses of the stack of layers that provide the masking function are selected so that after the initial set of mask pads have been patterned, a sequence of etching steps progressively transfers the mask pad shape through the multiple mask layer and down through all of the MTJ cell layers to the form the complete MTJ pillars. In another set of embodiments, the MTJ / BE stack is patterned into parallel lines before the top electrode layer is deposited.

Owner:AVALANCHE TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com