Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

3419 results about "Etching rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In a simple sense, etch rate is rate of the peeling off (removing) a compound or changing it into its elemental form from a surface either by some physical or chemical method.

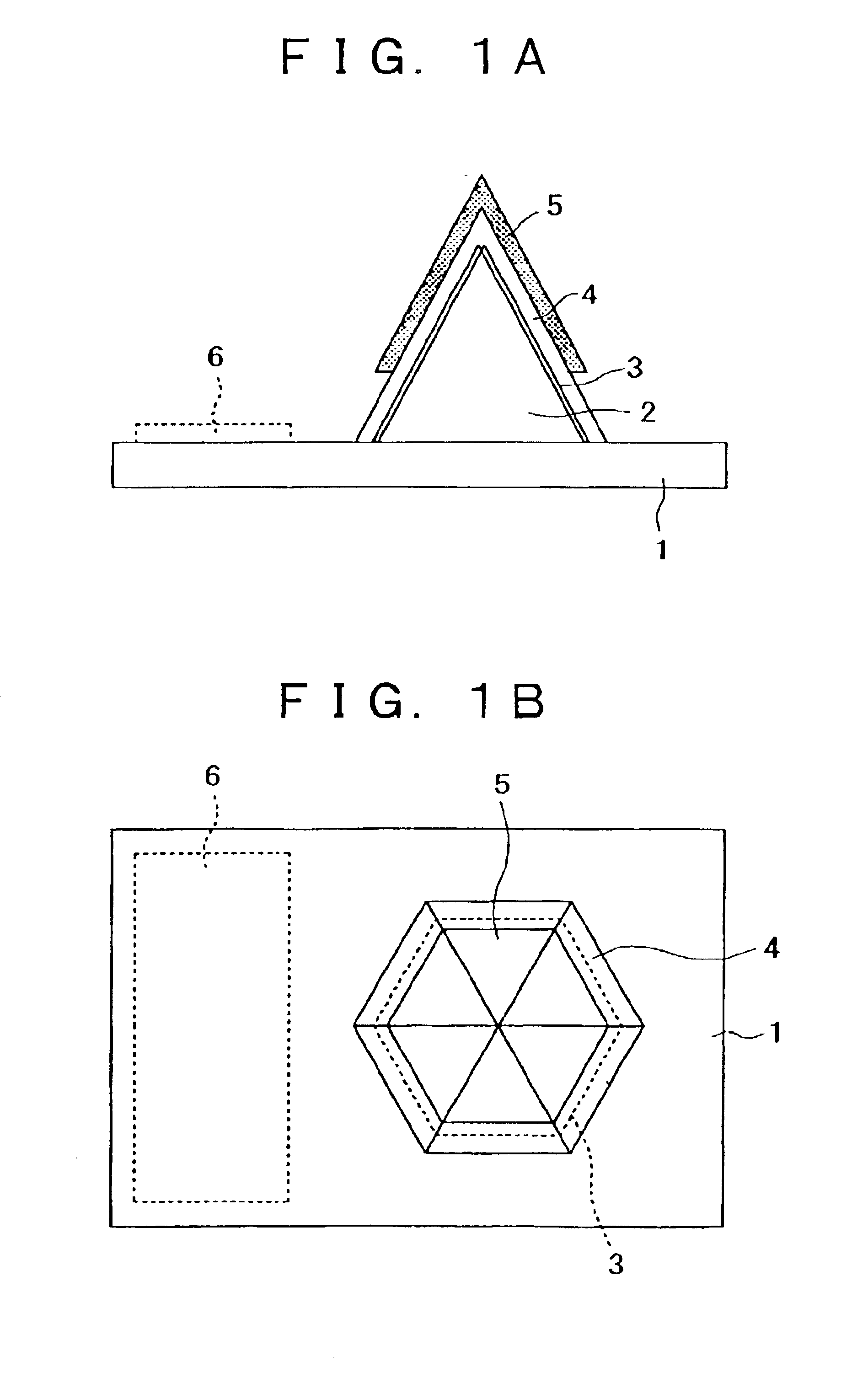

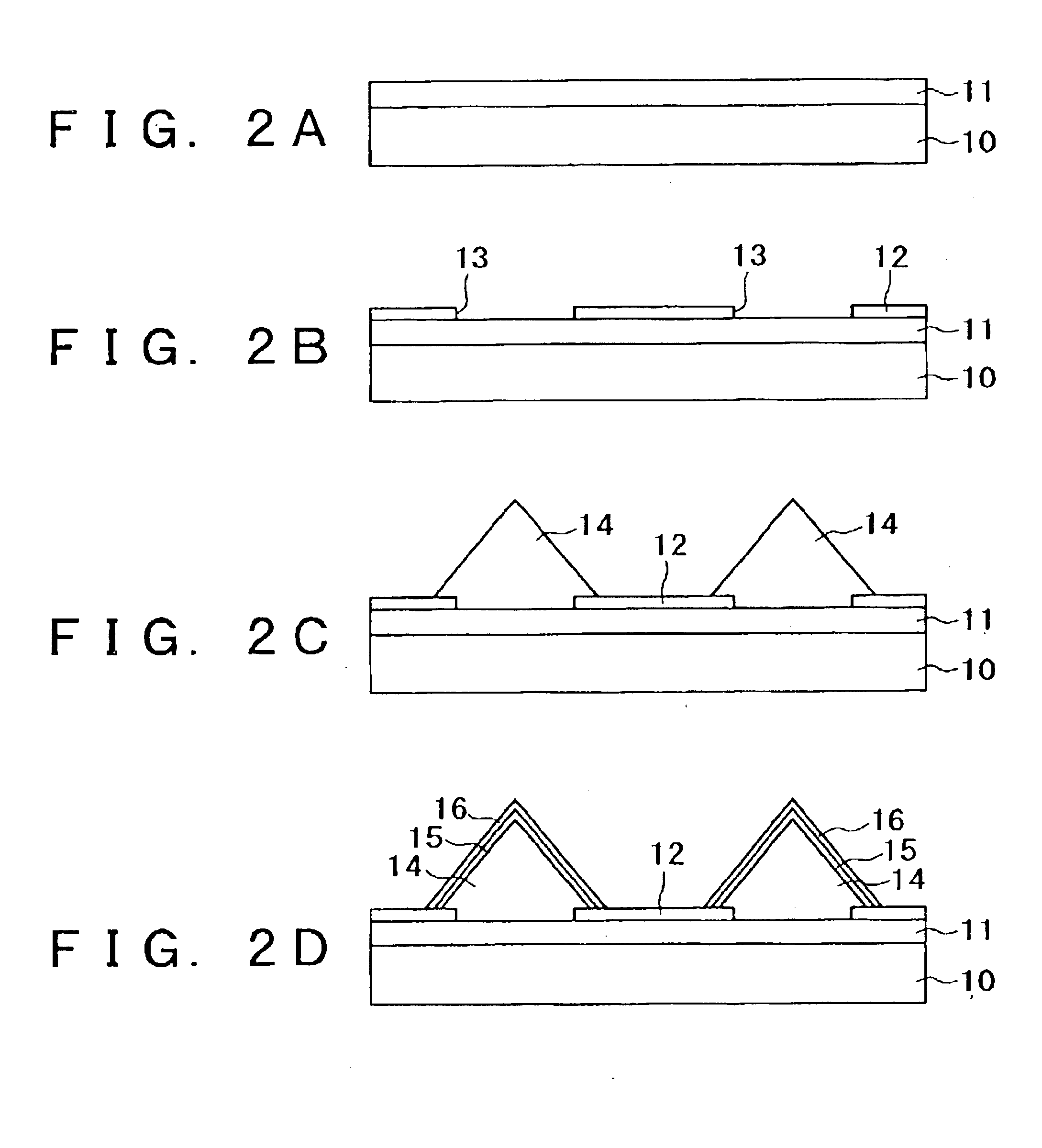

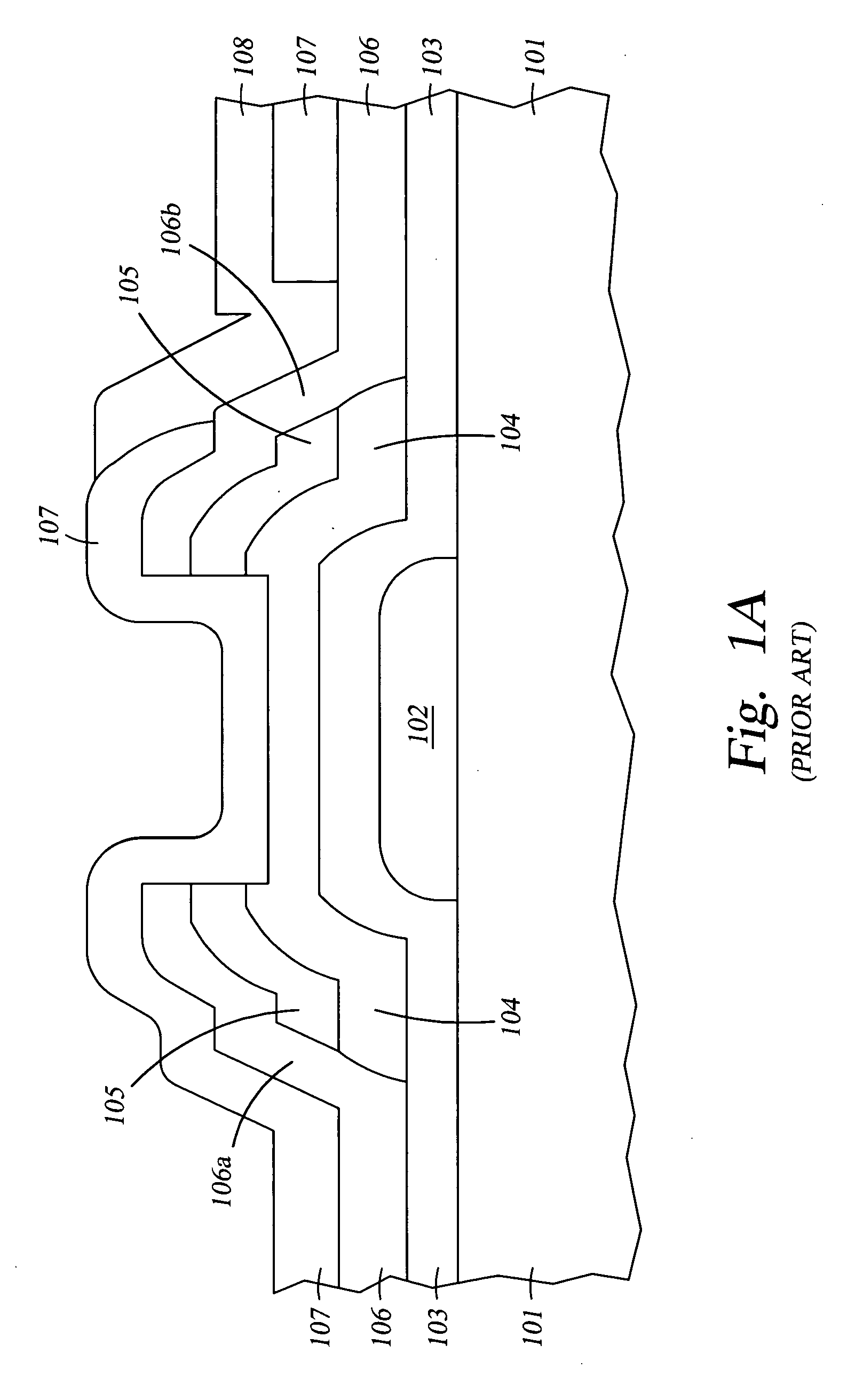

Selective growth method, and semiconductor light emitting device and fabrication method thereof

InactiveUS6858081B2Improve featuresReduce widthPolycrystalline material growthSemiconductor/solid-state device manufacturingThree dimensional shapeActive layer

In a selective growth method, growth interruption is performed at the time of selective growth of a crystal layer on a substrate. Even if the thickness distribution of the crystal layer becomes non-uniform at the time of growth of the crystal layer, the non-uniformity of the thickness distribution of the crystal layer can be corrected by inserting the growth interruption. As a result of growth interruption, an etching rate at a thick portion becomes higher than that at a thin portion, to eliminate the difference in thickness between the thick portion and the thin portion, thereby solving the problem associated with degradation of characteristics due to a variation in thickness of the crystal layer, for example, an active layer. The selective growth method is applied to fabrication of a semiconductor light emitting device including an active layer as a crystal layer formed on a crystal layer having a three-dimensional shape by selective growth.

Owner:SAMSUNG ELECTRONICS CO LTD

Integrated low K dielectrics and etch stops

InactiveUS6340435B1Decorative surface effectsSemiconductor/solid-state device detailsHydrogenFluorocarbon

A method of depositing and etching dielectric layers having low dielectric constants and etch rates that vary by at least 3:1 for formation of horizontal interconnects. The amount of carbon or hydrogen in the dielectric layer is varied by changes in deposition conditions to provide low k dielectric layers that can replace etch stop layers or conventional dielectric layers in damascene applications. A dual damascene structure having two or more dielectric layers with dielectric constants lower than about 4 can be deposited in a single reactor and then etched to form vertical and horizontal interconnects by varying the concentration of a carbon:oxygen gas such as carbon monoxide. The etch gases for forming vertical interconnects preferably comprises CO and a fluorocarbon, and CO is preferably excluded from etch gases for forming horizontal interconnects.

Owner:APPLIED MATERIALS INC

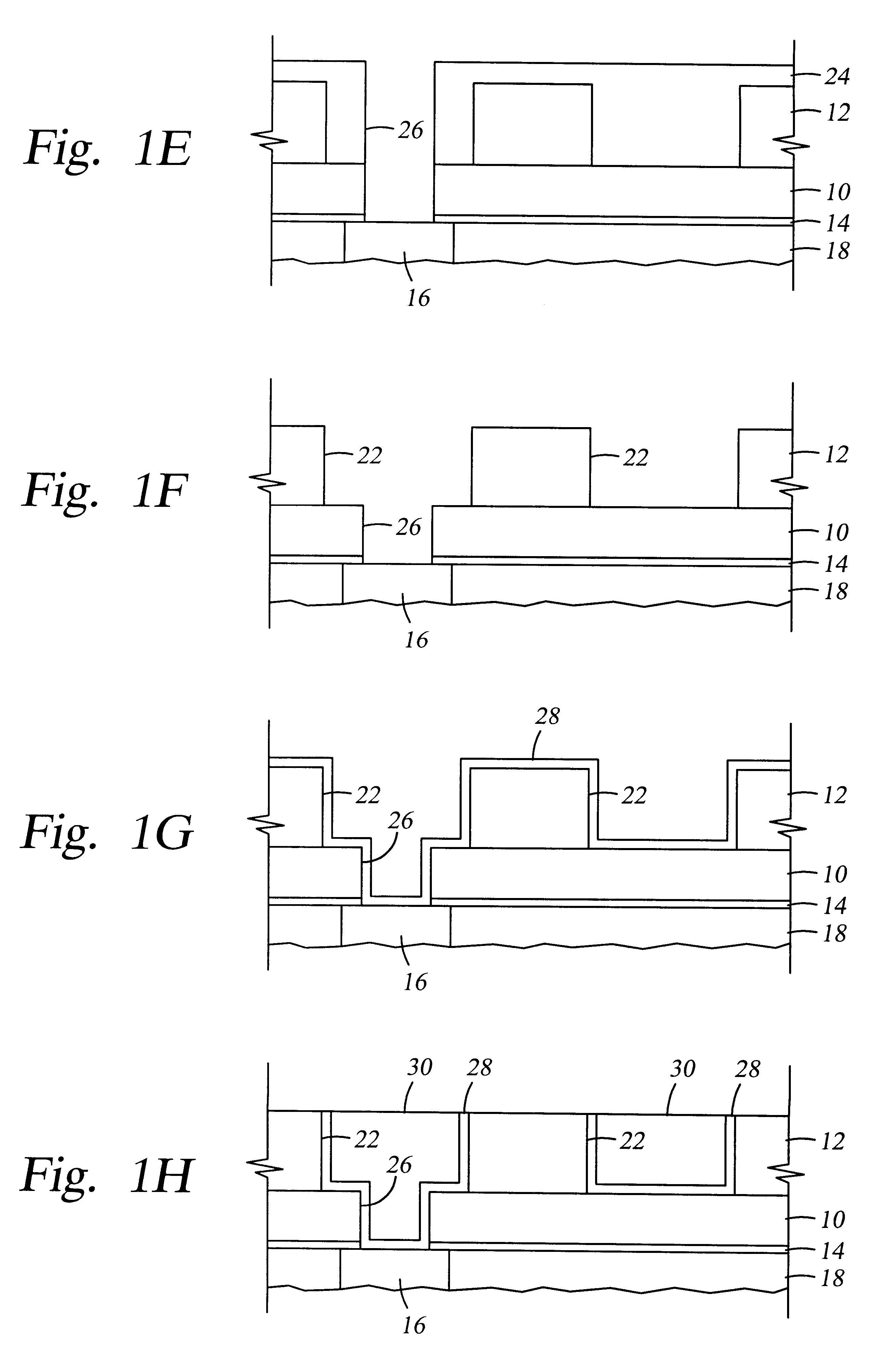

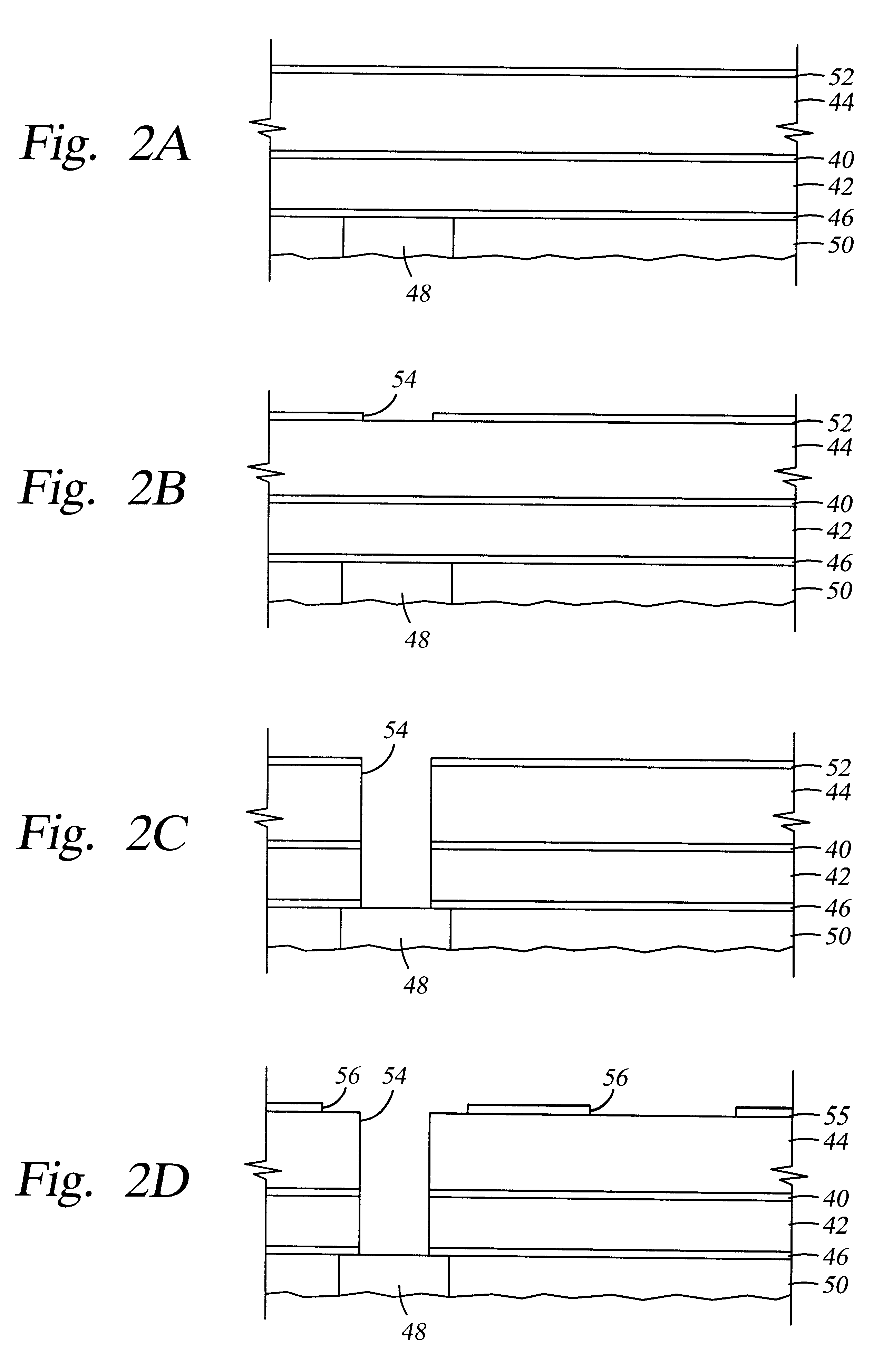

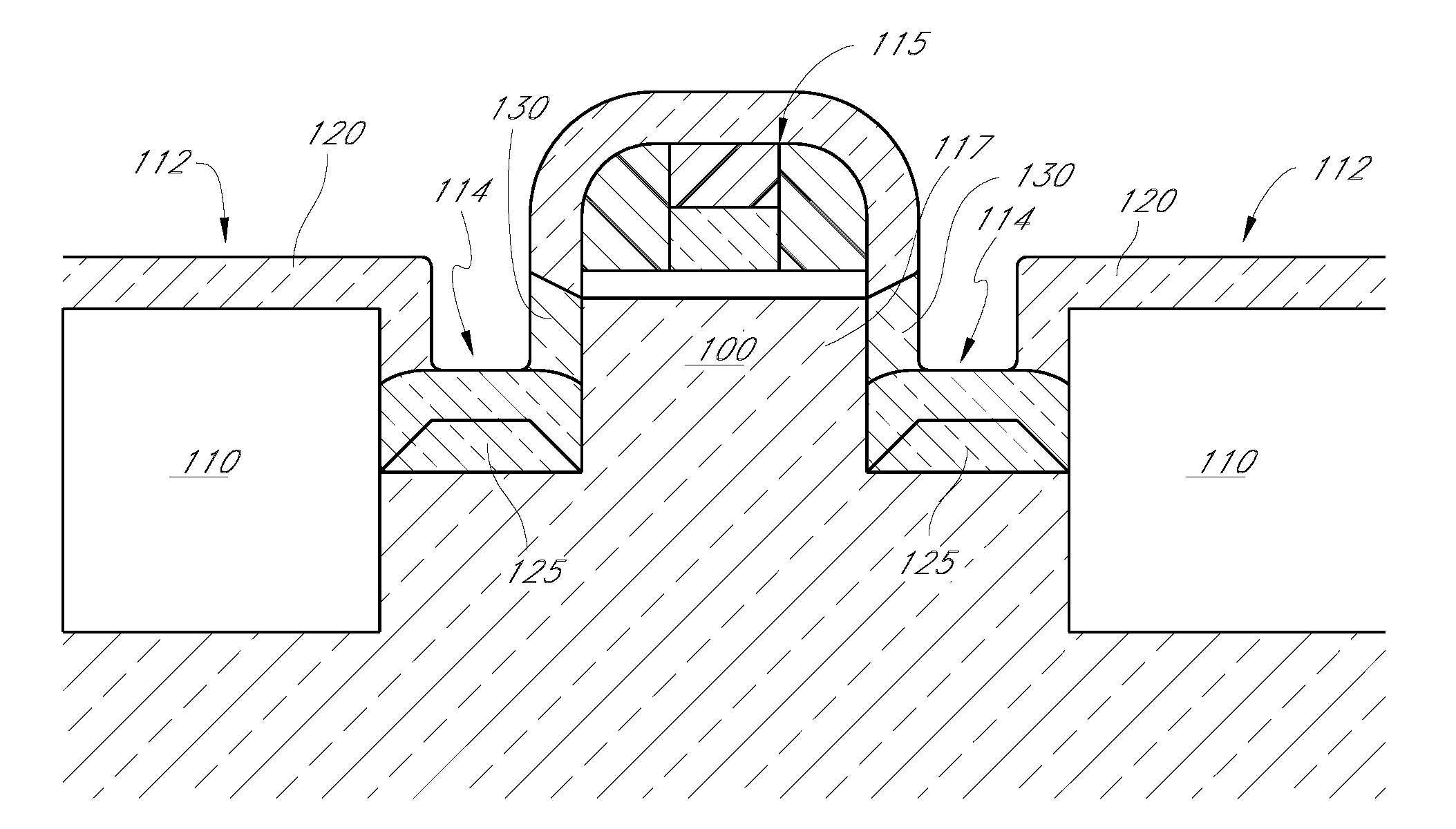

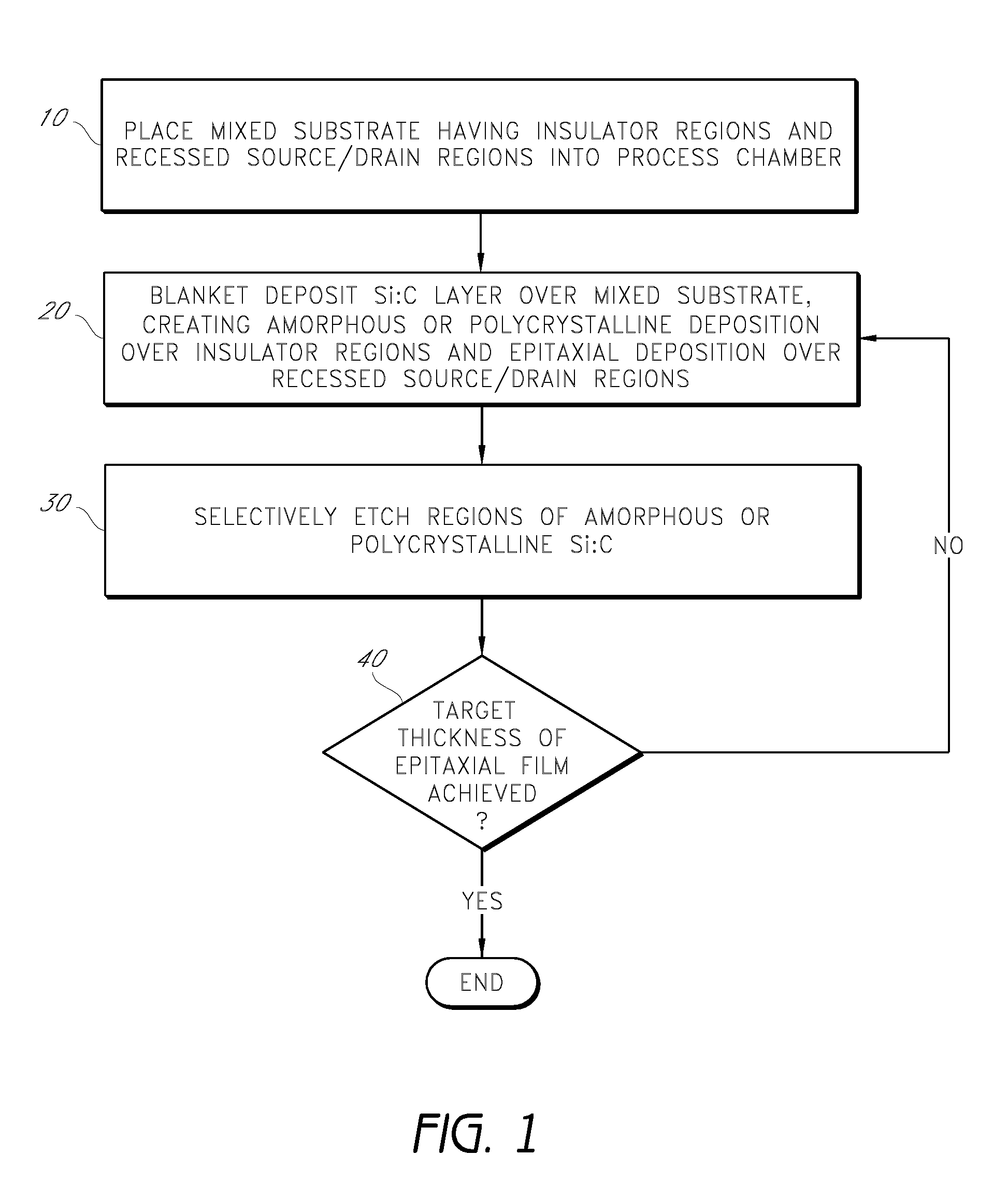

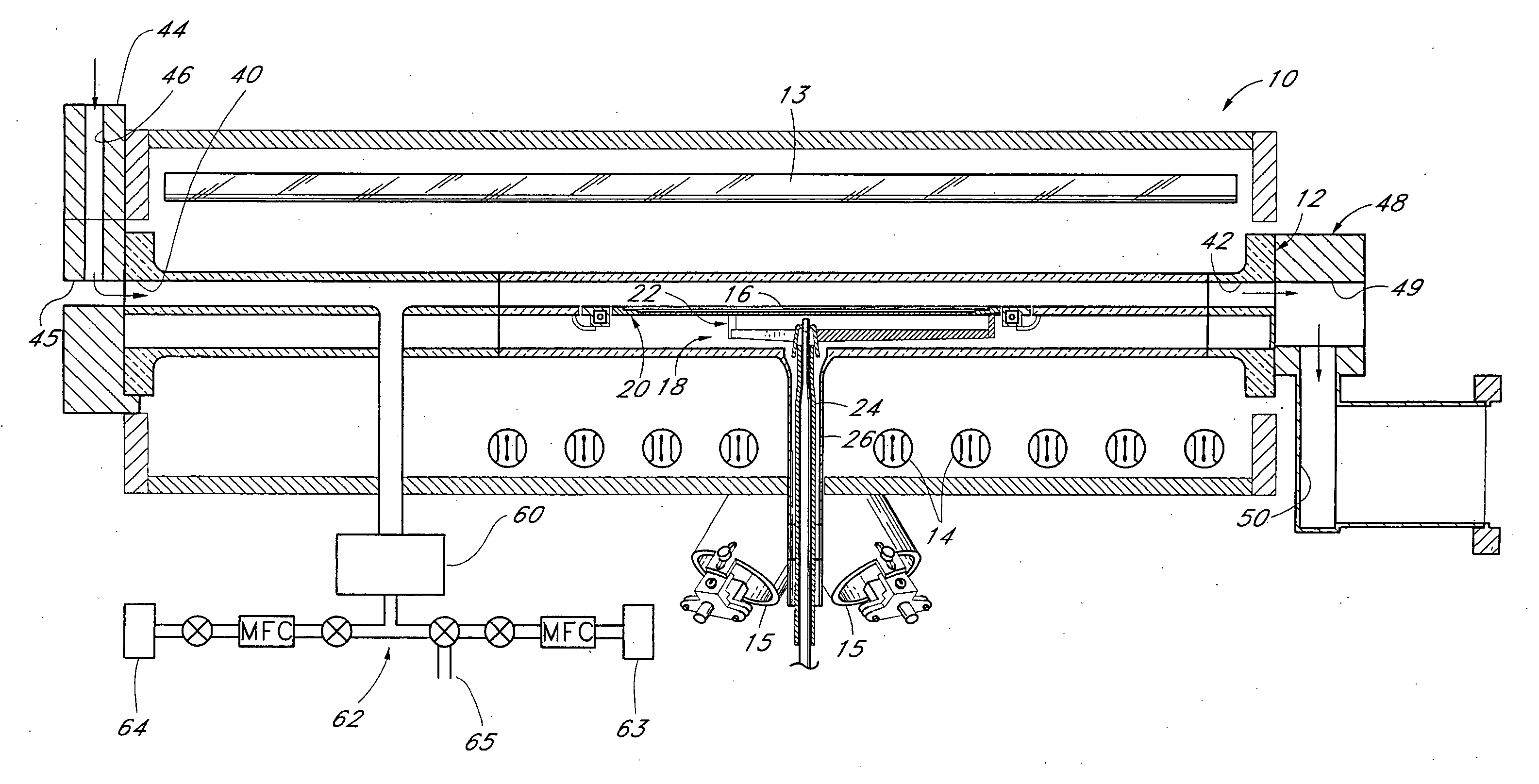

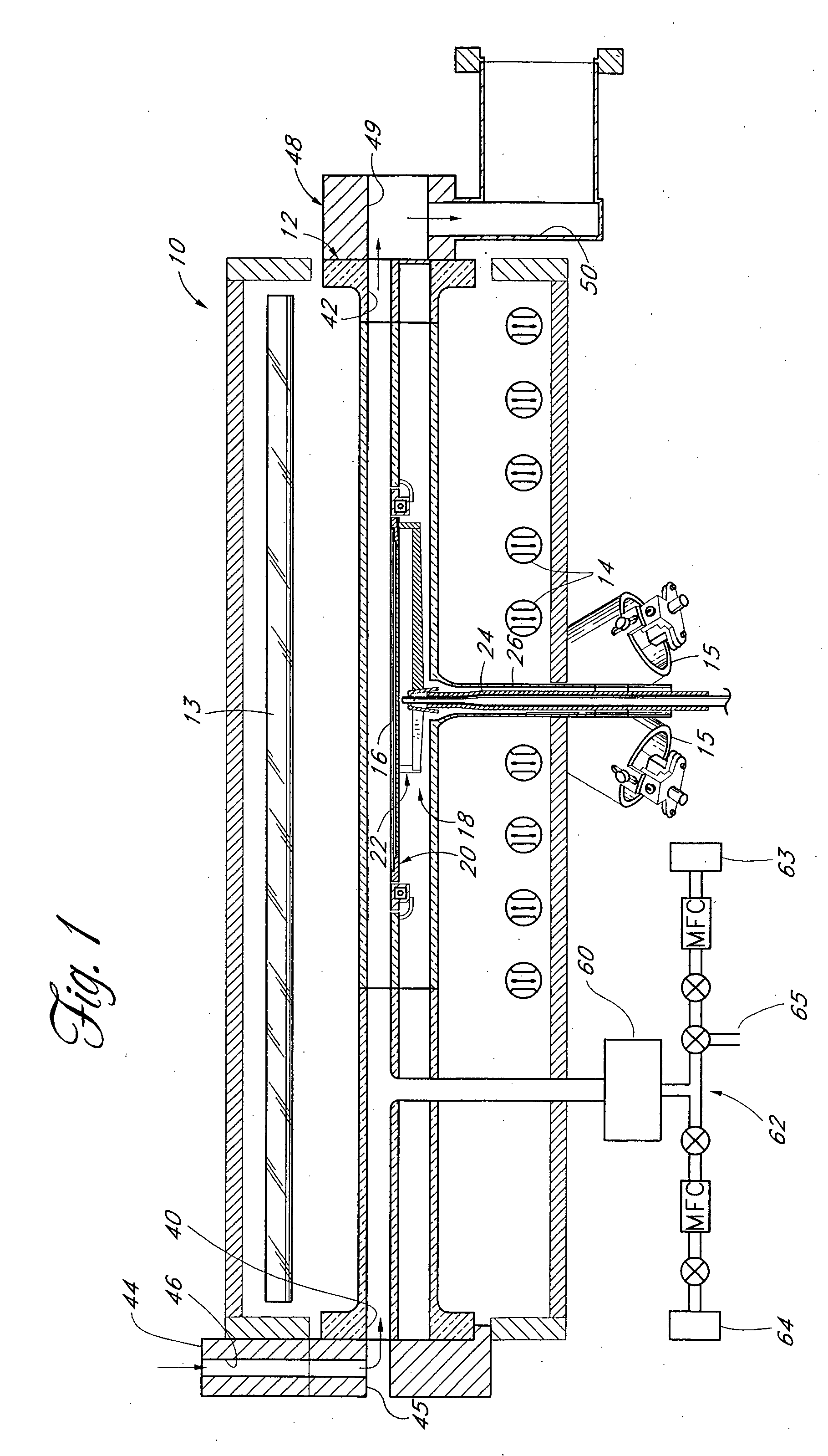

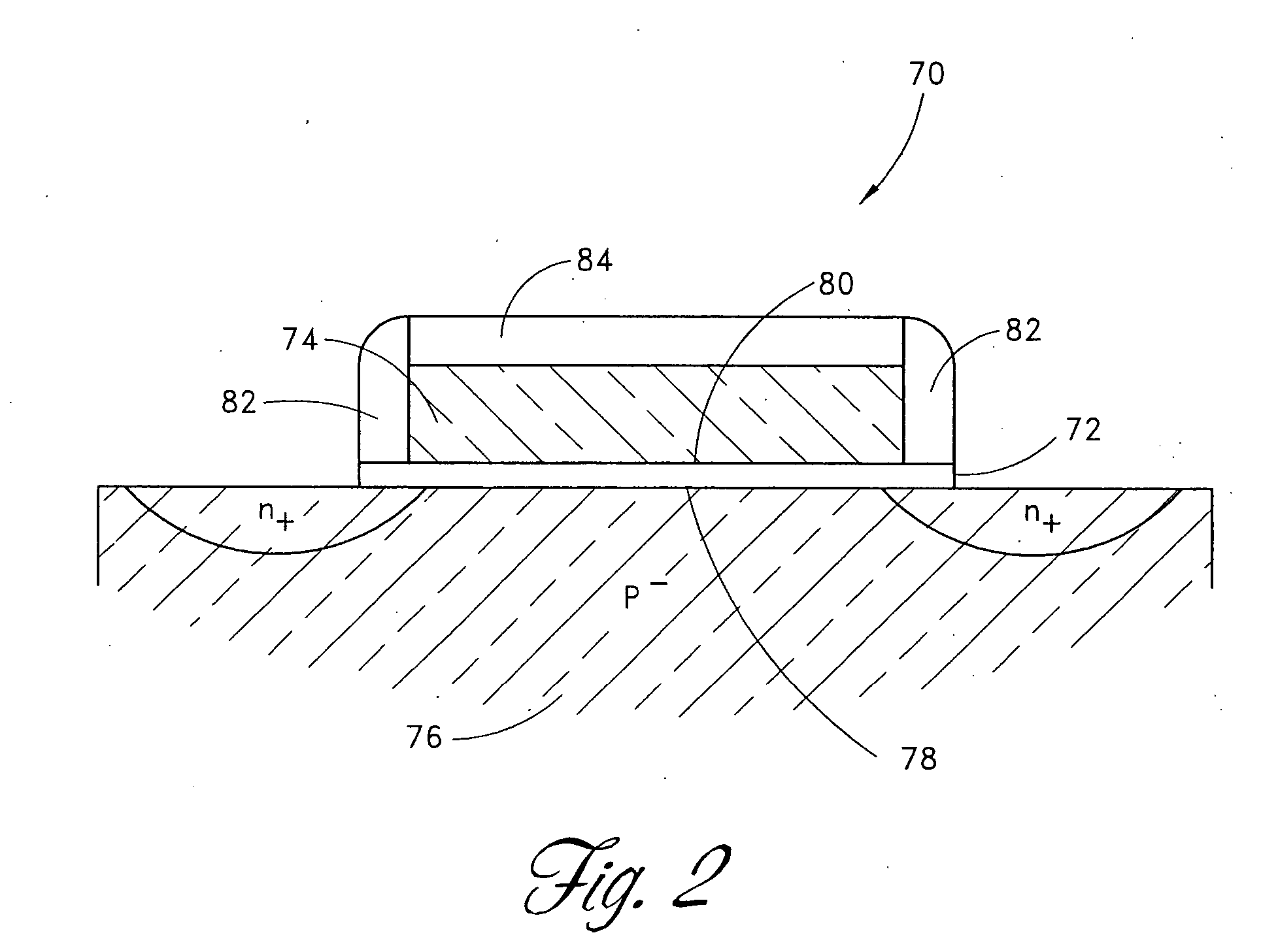

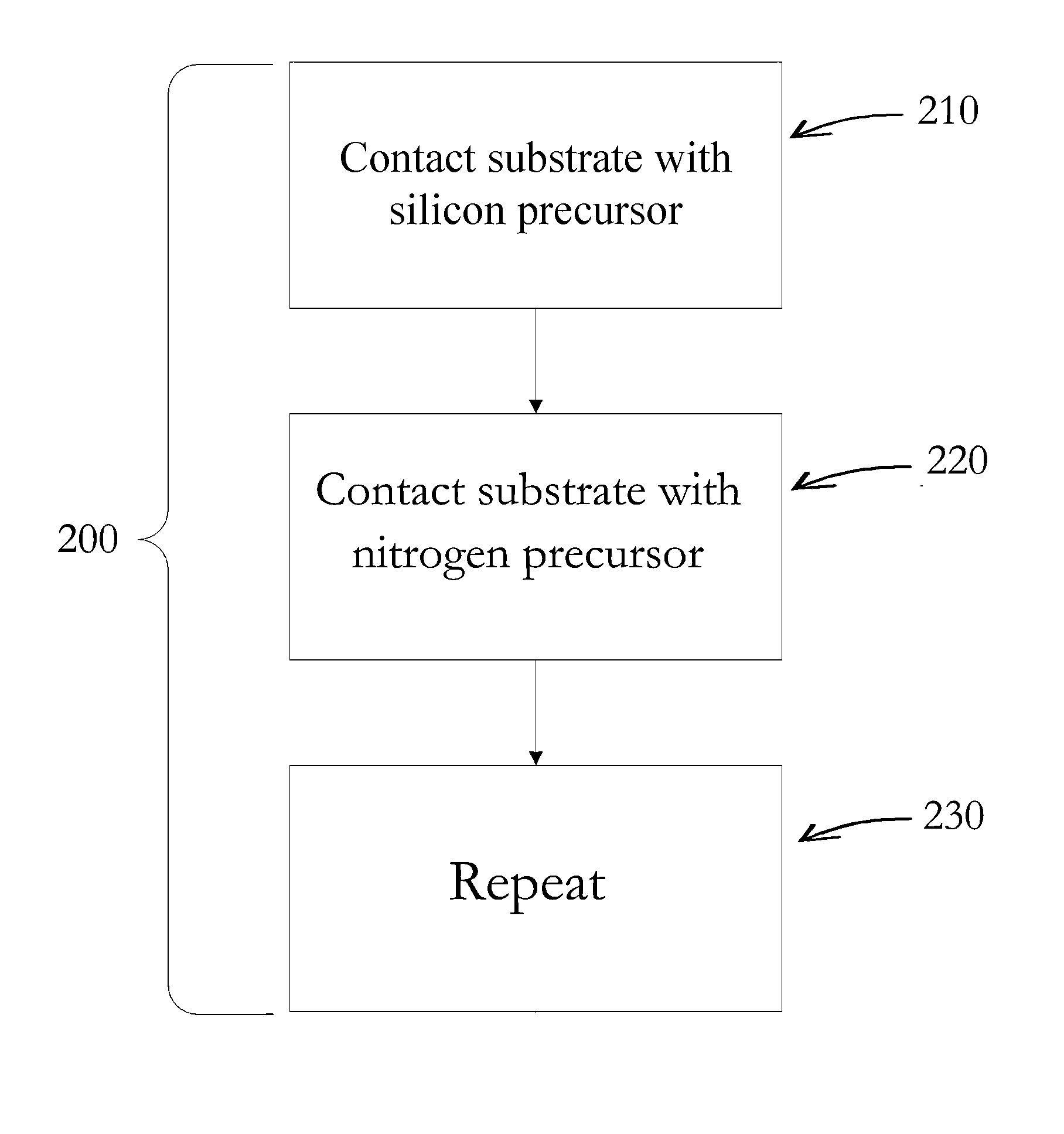

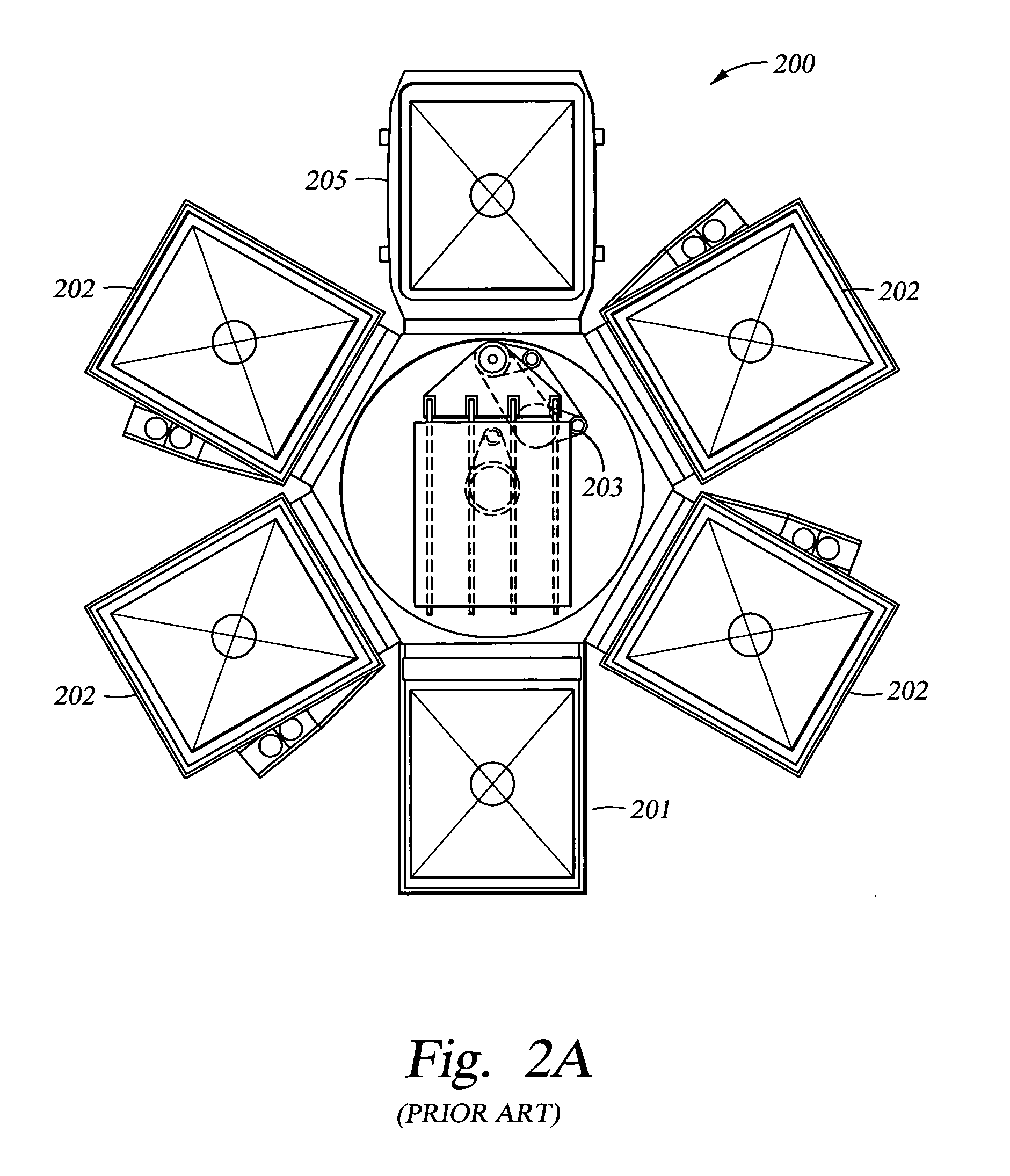

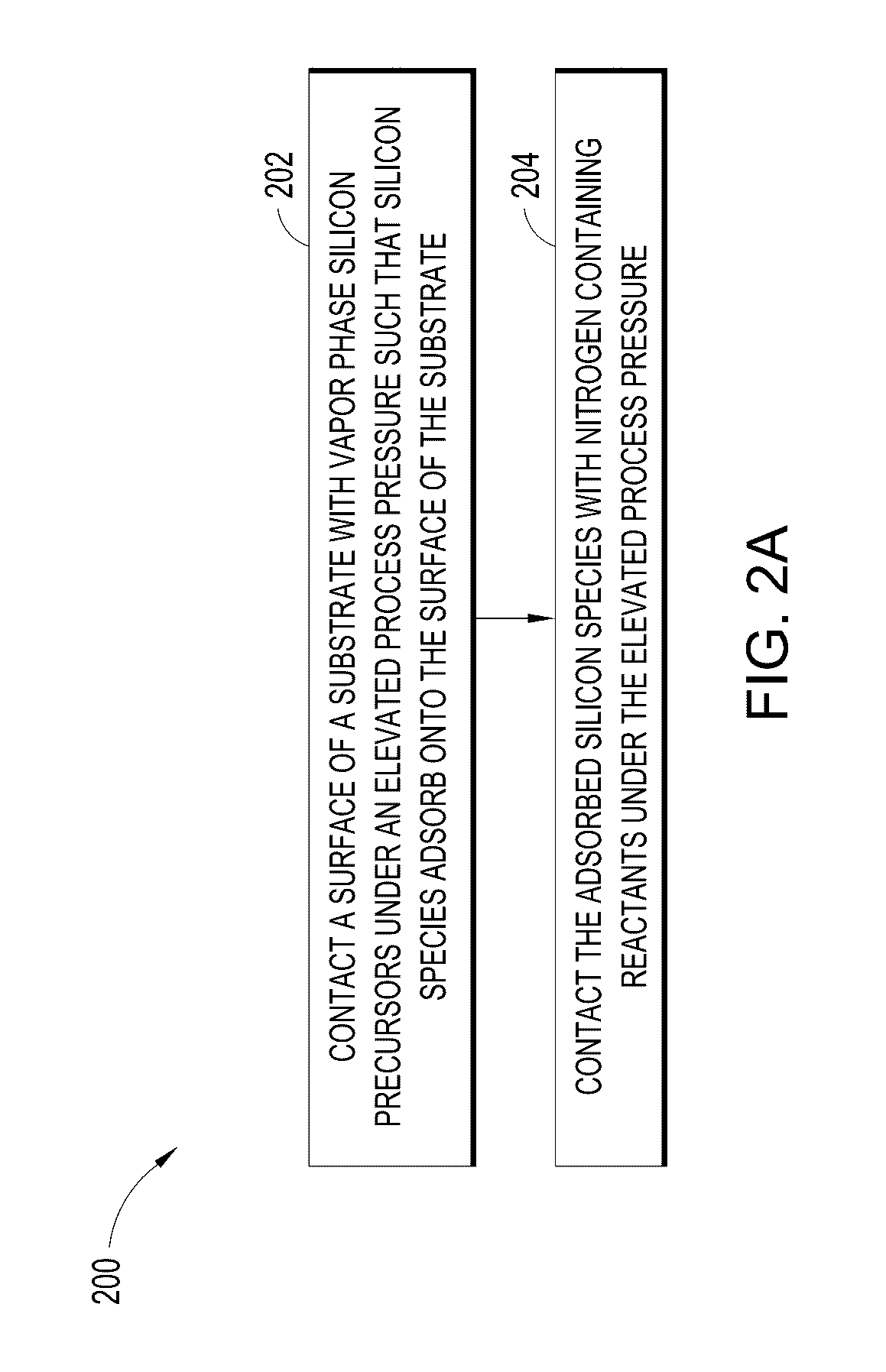

Selective epitaxial formation of semiconductor films

ActiveUS8278176B2Semiconductor/solid-state device manufacturingSemiconductor devicesCyclic processMetallurgy

Epitaxial layers are selectively formed in semiconductor windows by a cyclical process of repeated blanket deposition and selective etching. The blanket deposition phases leave non-epitaxial material over insulating regions, such as field oxide, and the selective etch phases preferentially remove non-epitaxial material while deposited epitaxial material builds up cycle-by-cycle. Quality of the epitaxial material improves relative to selective processes where no deposition occurs on insulators. Use of a germanium catalyst during the etch phases of the process aid etch rates and facilitate economical maintenance of isothermal and / or isobaric conditions throughout the cycles. Throughput and quality are improved by use of trisilane, formation of amorphous material over the insulating regions and minimizing the thickness ratio of amorphous:epitaxial material in each deposition phase.

Owner:ASM IP HLDG BV

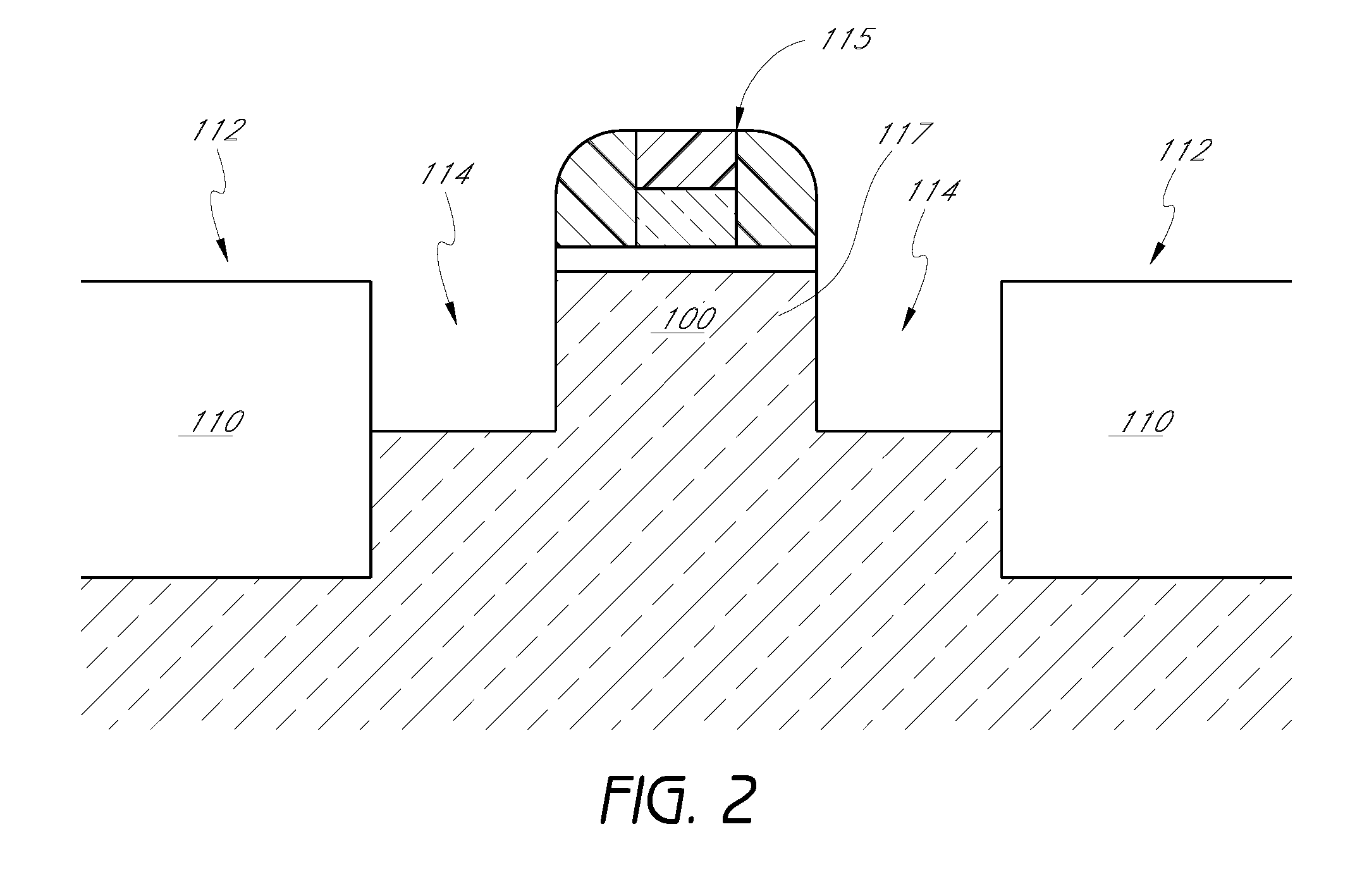

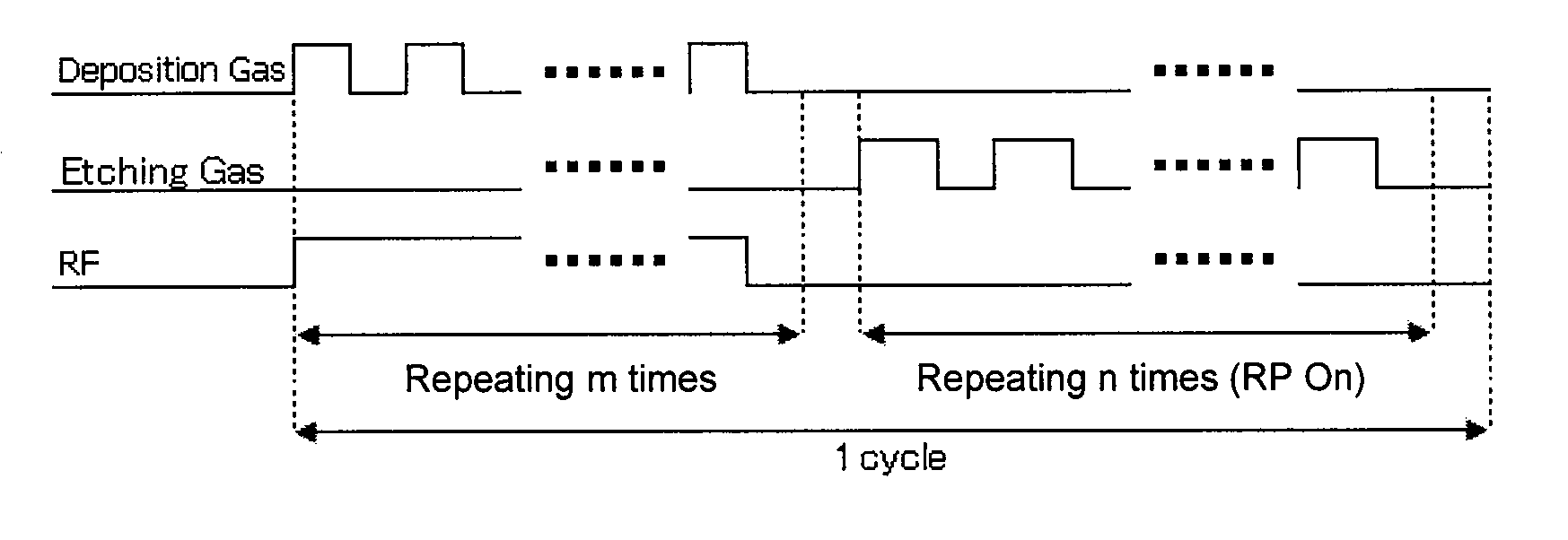

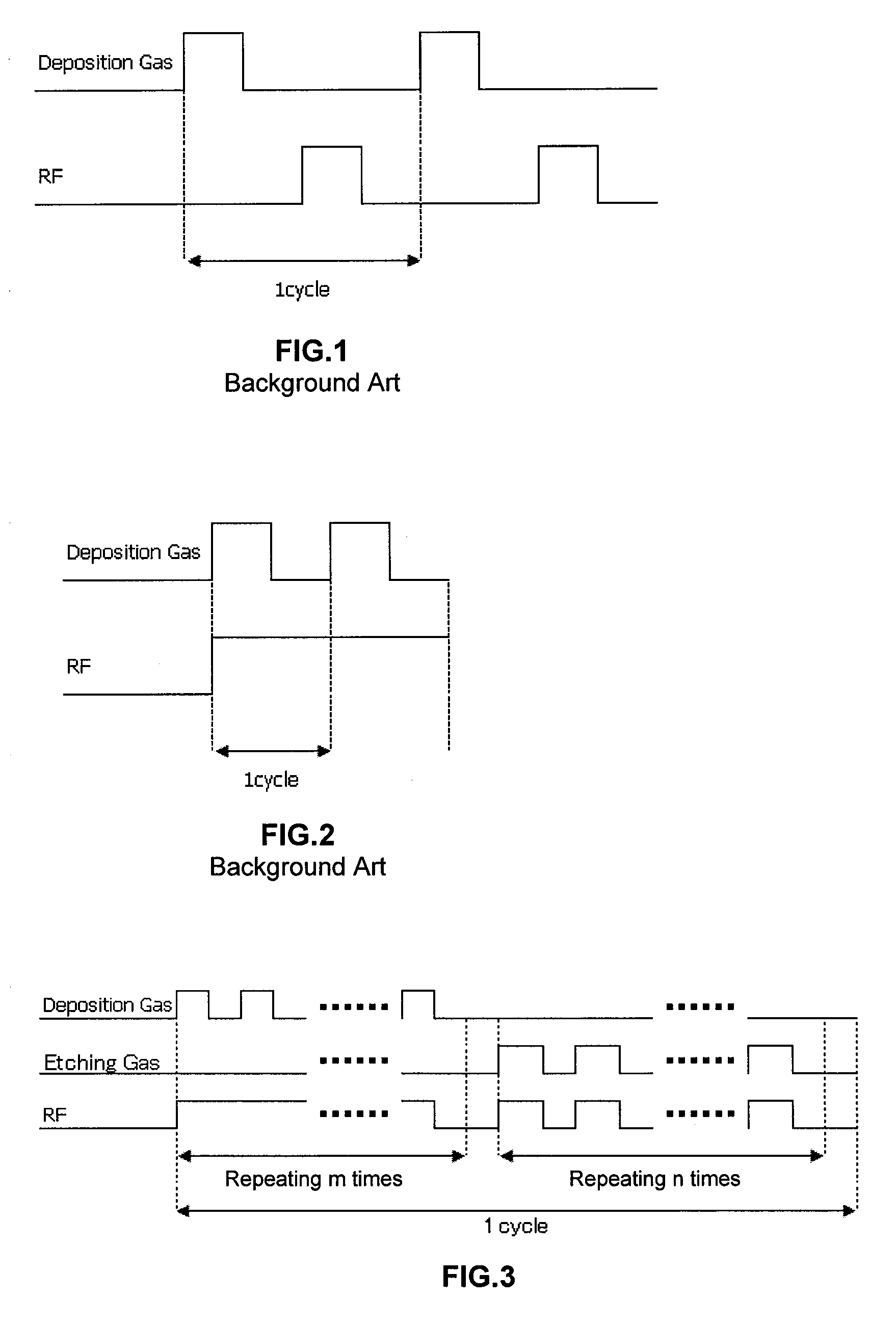

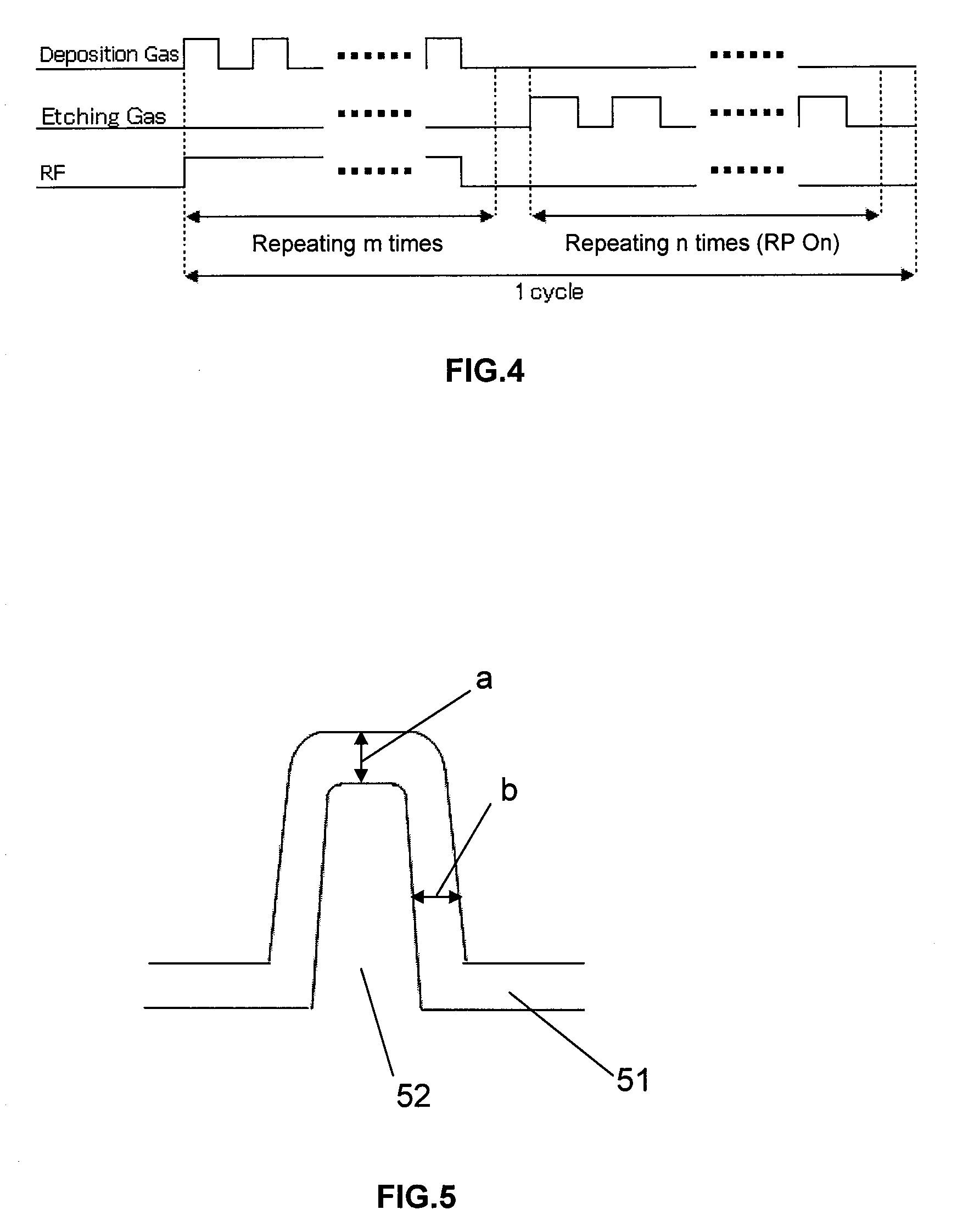

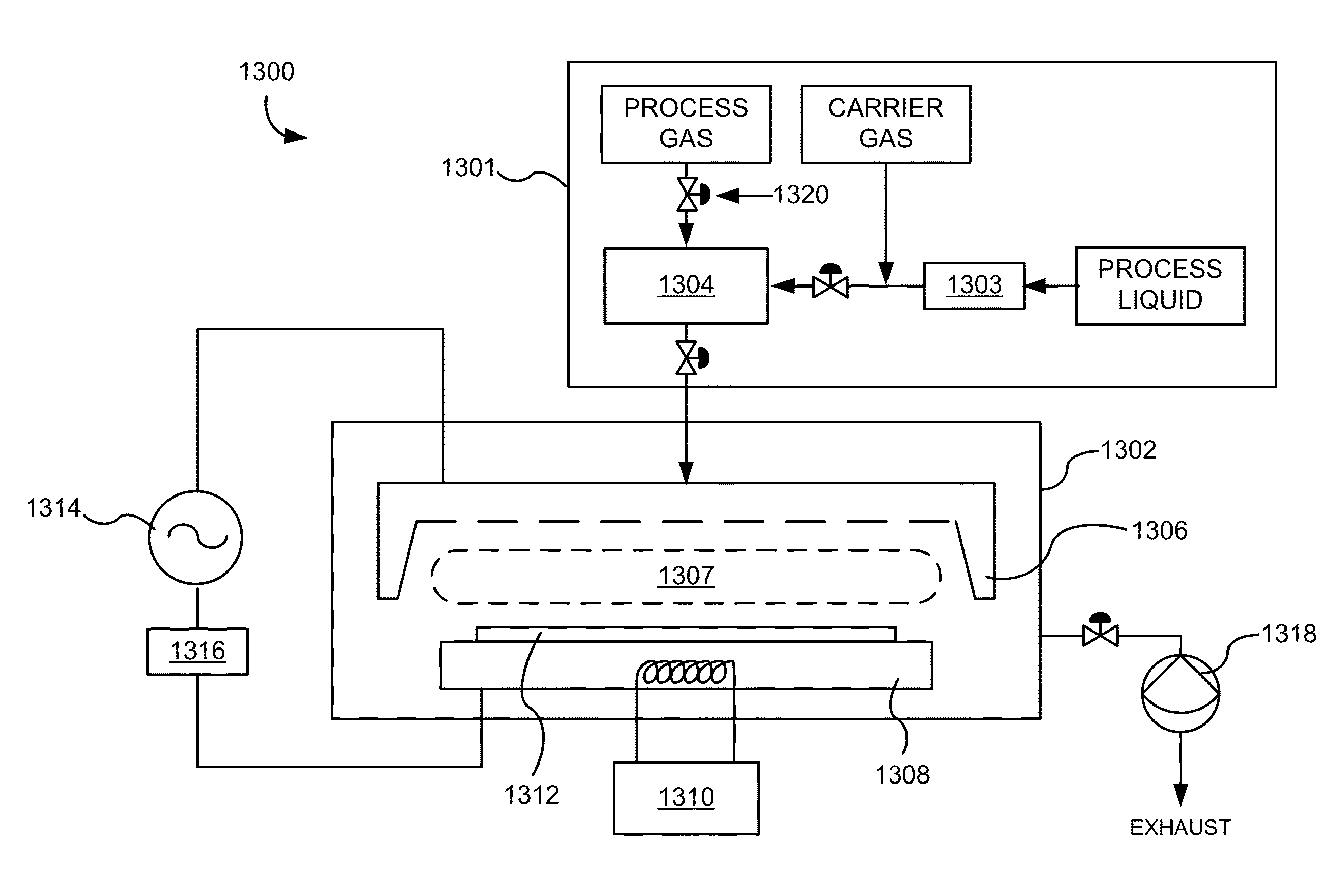

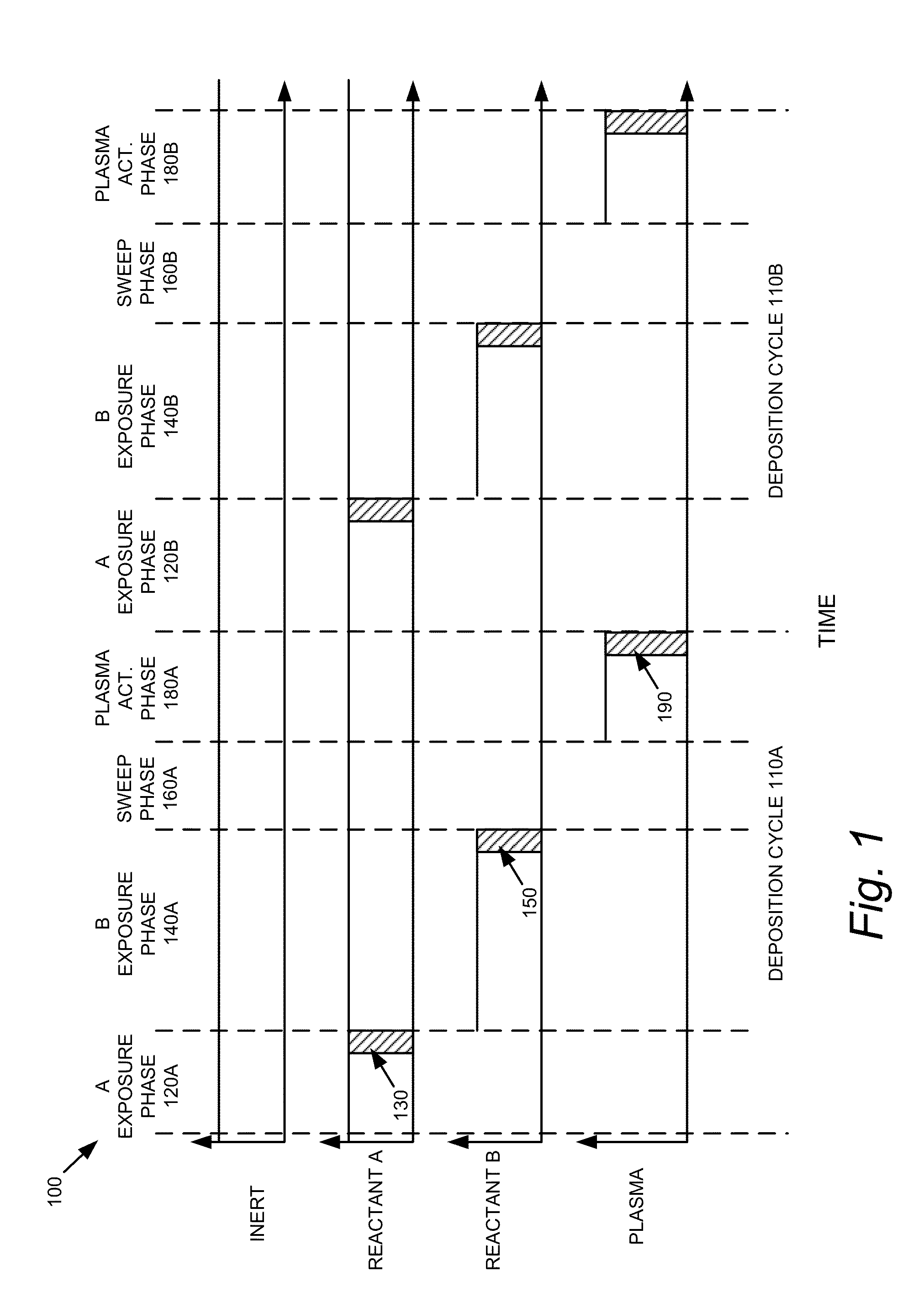

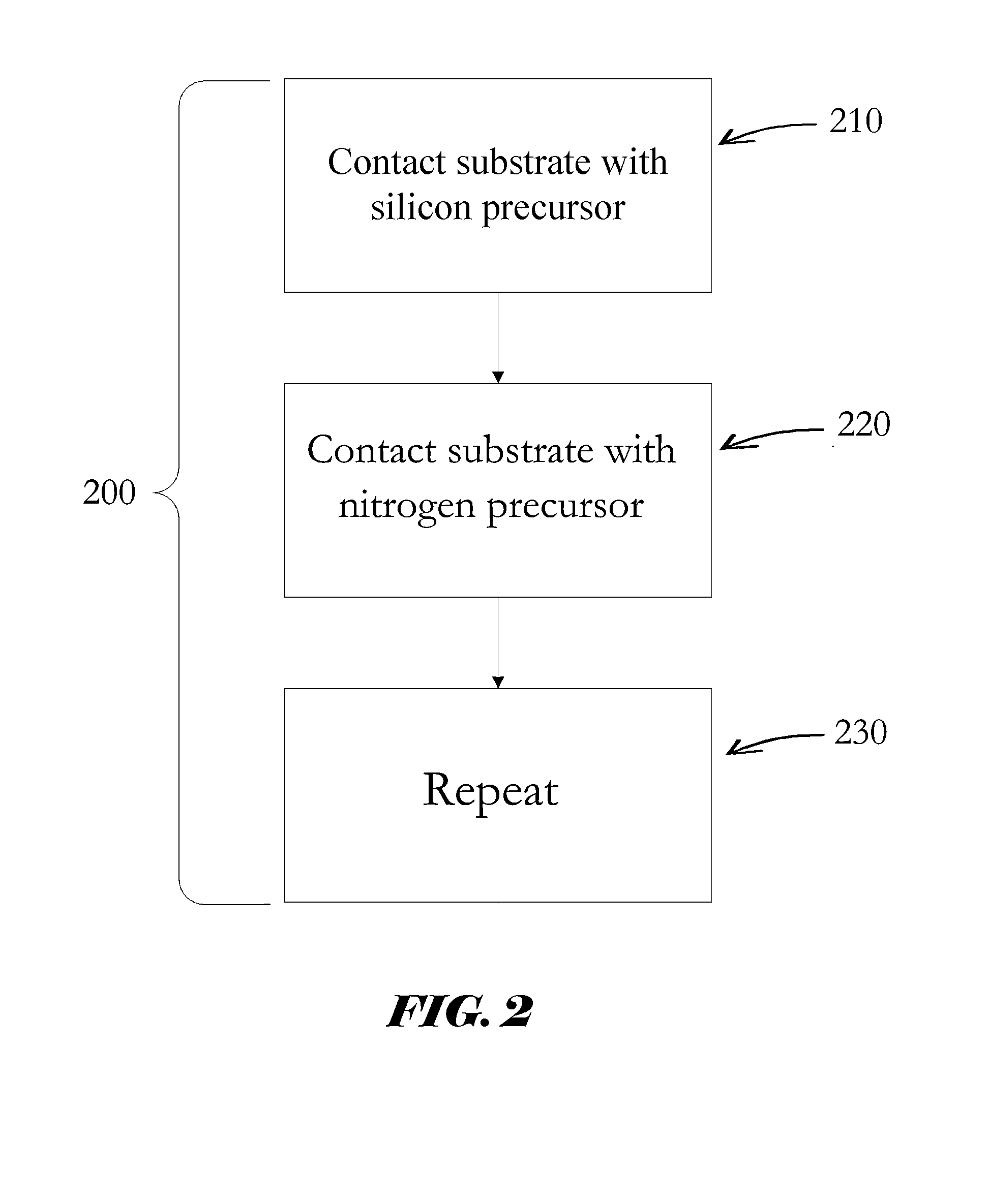

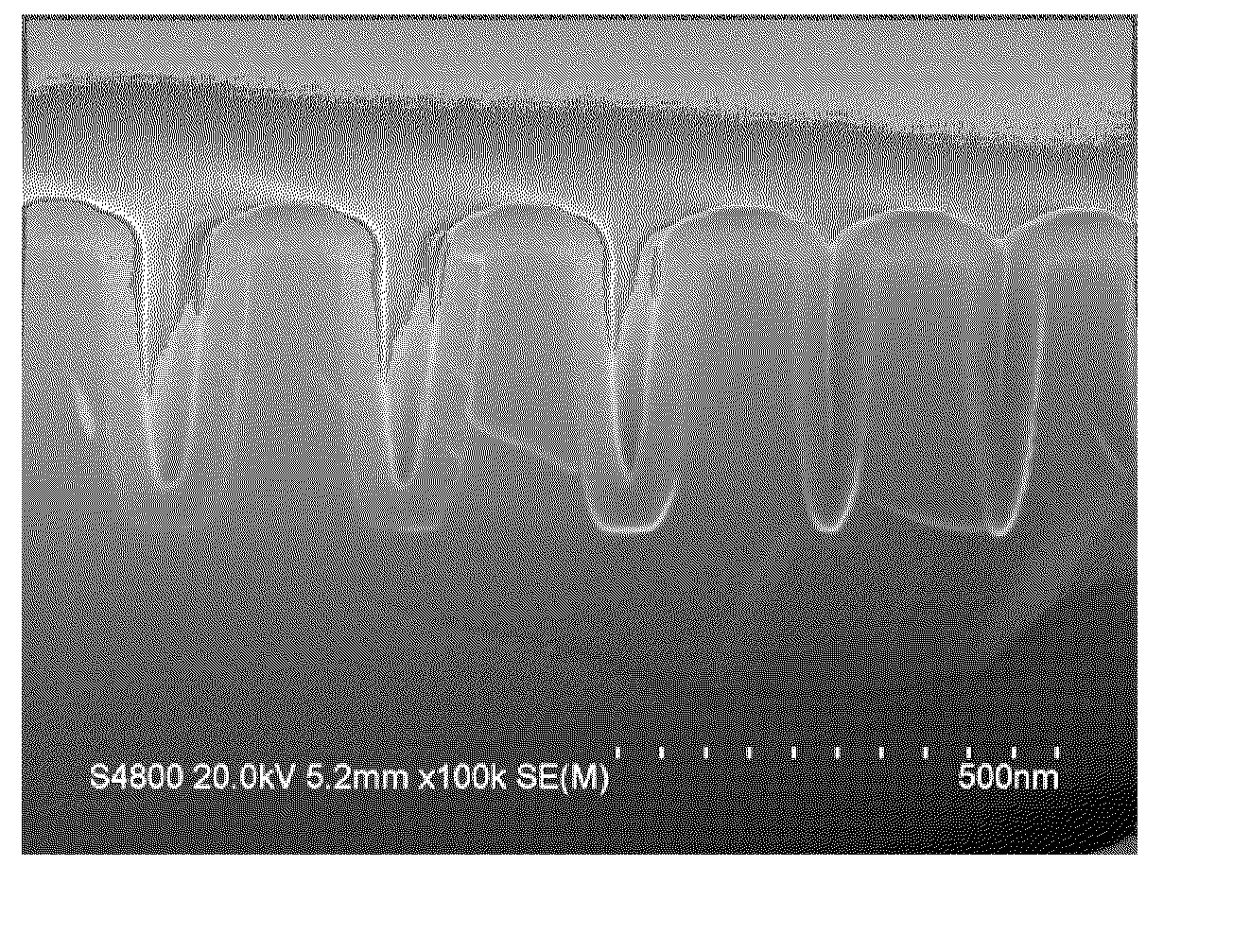

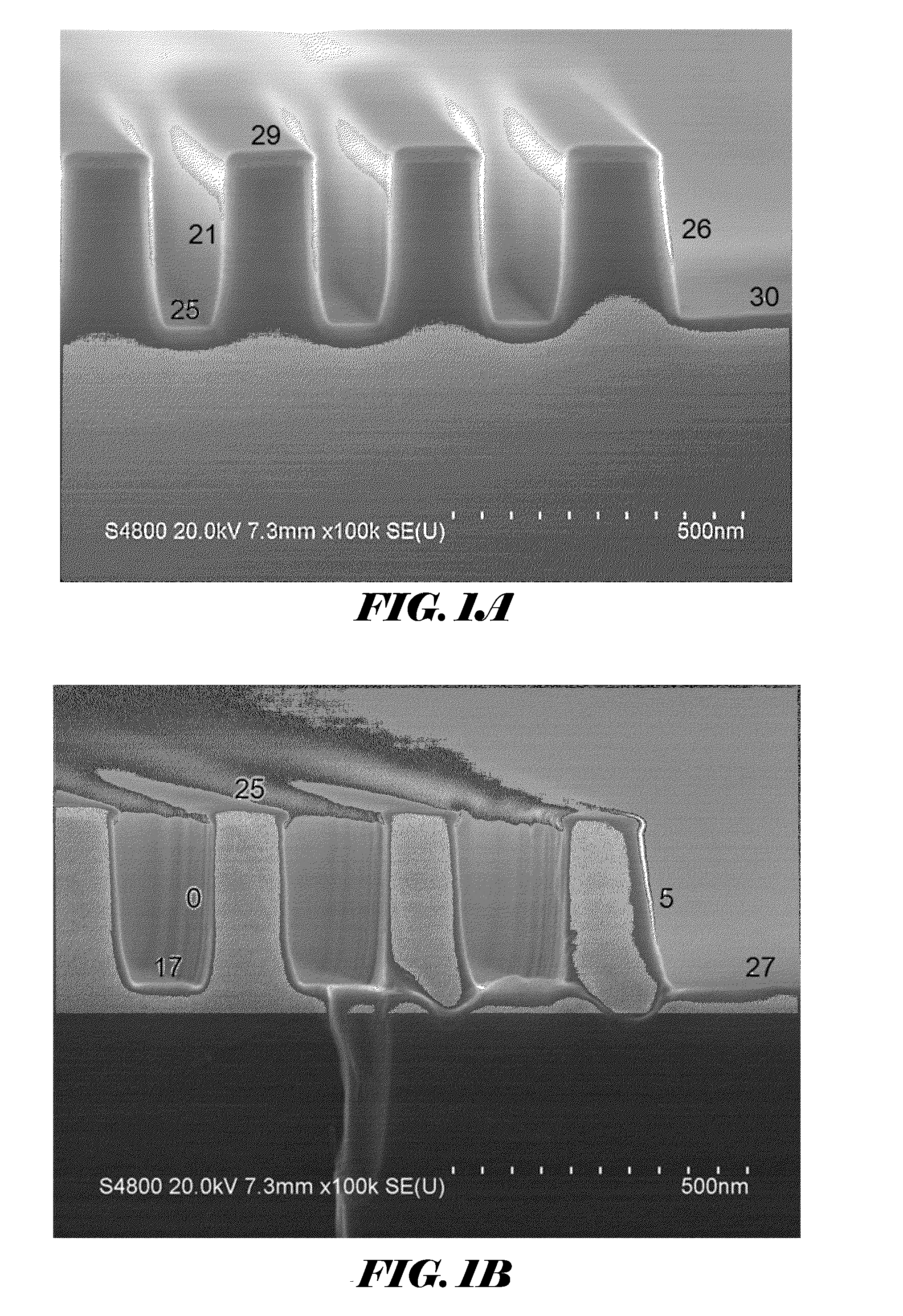

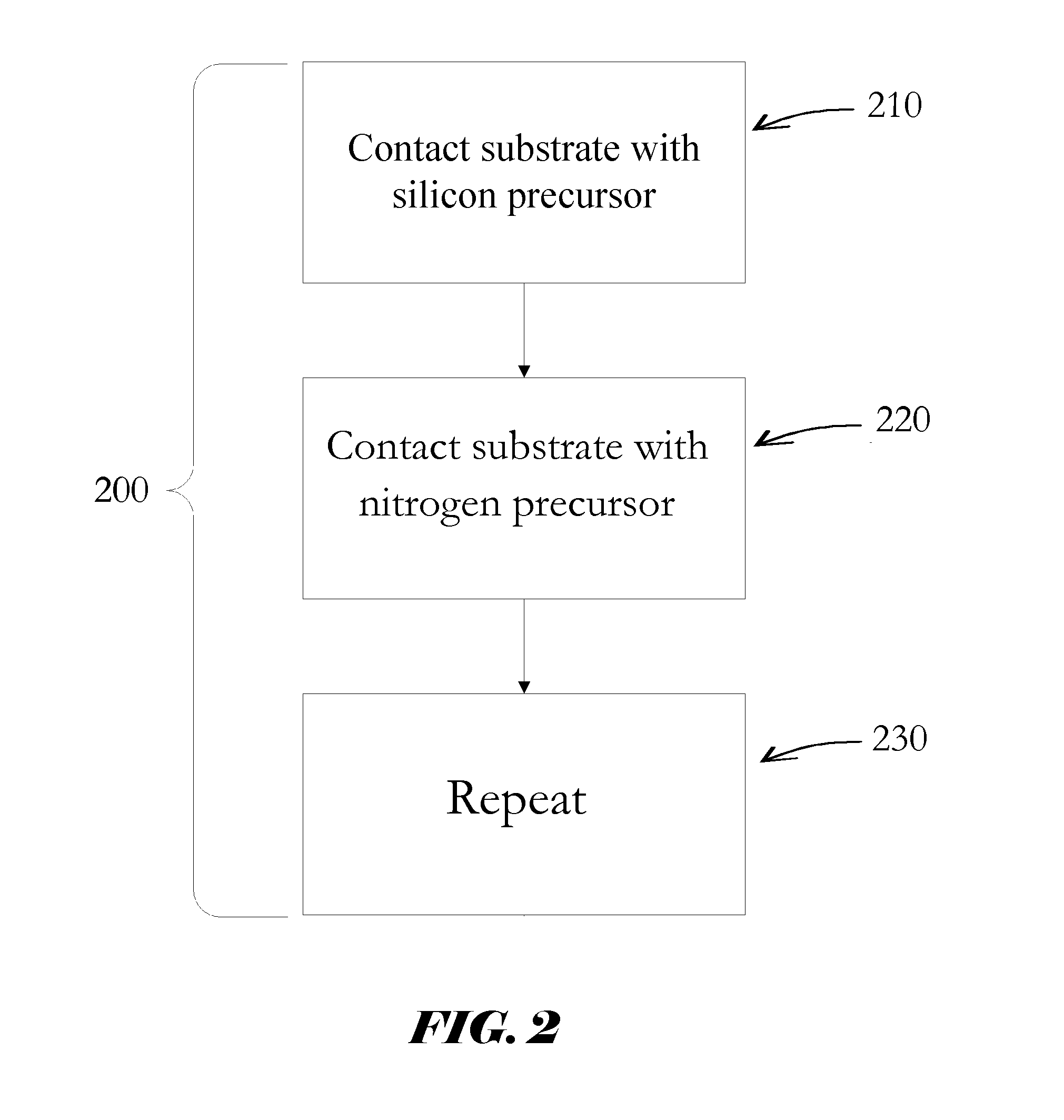

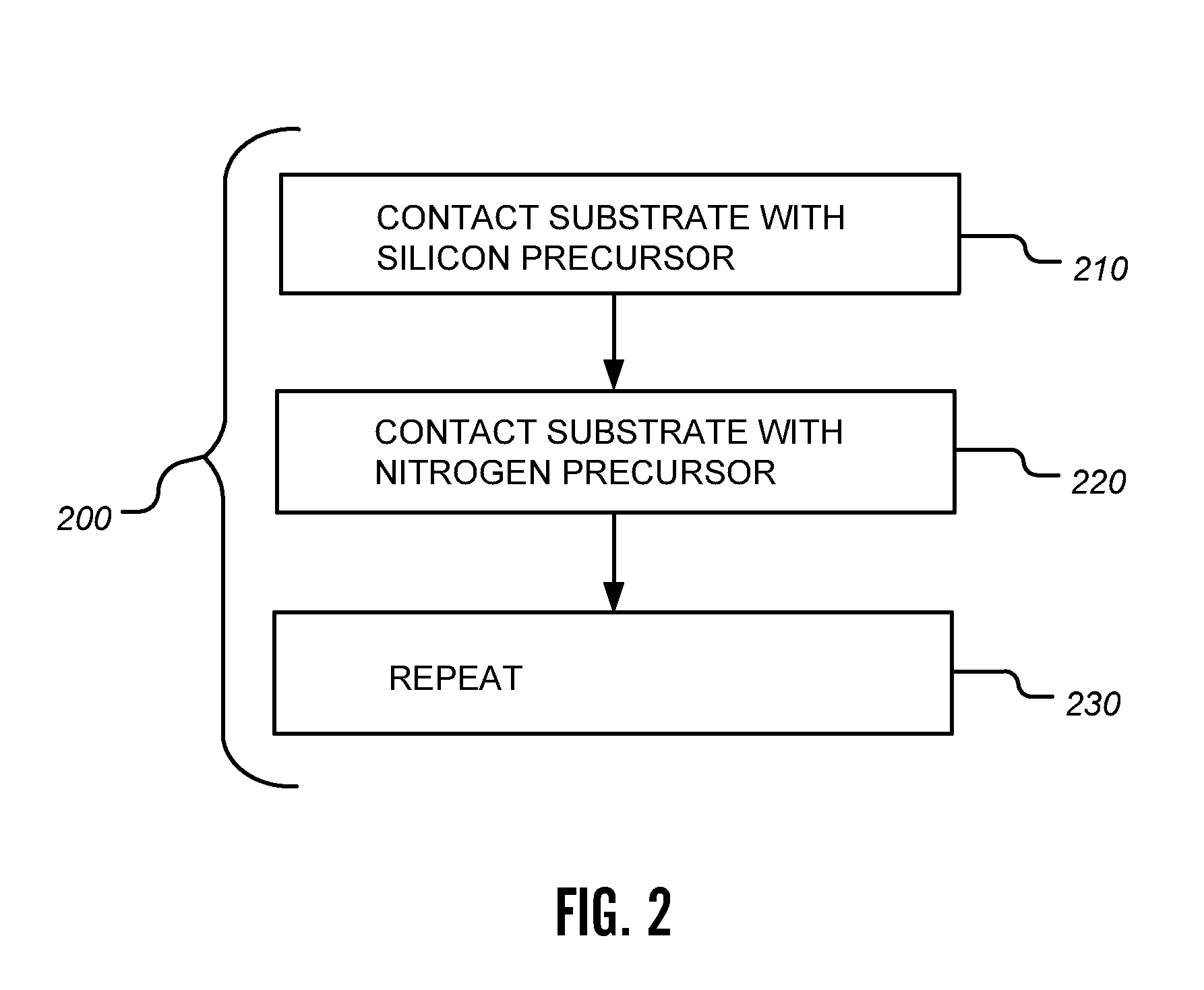

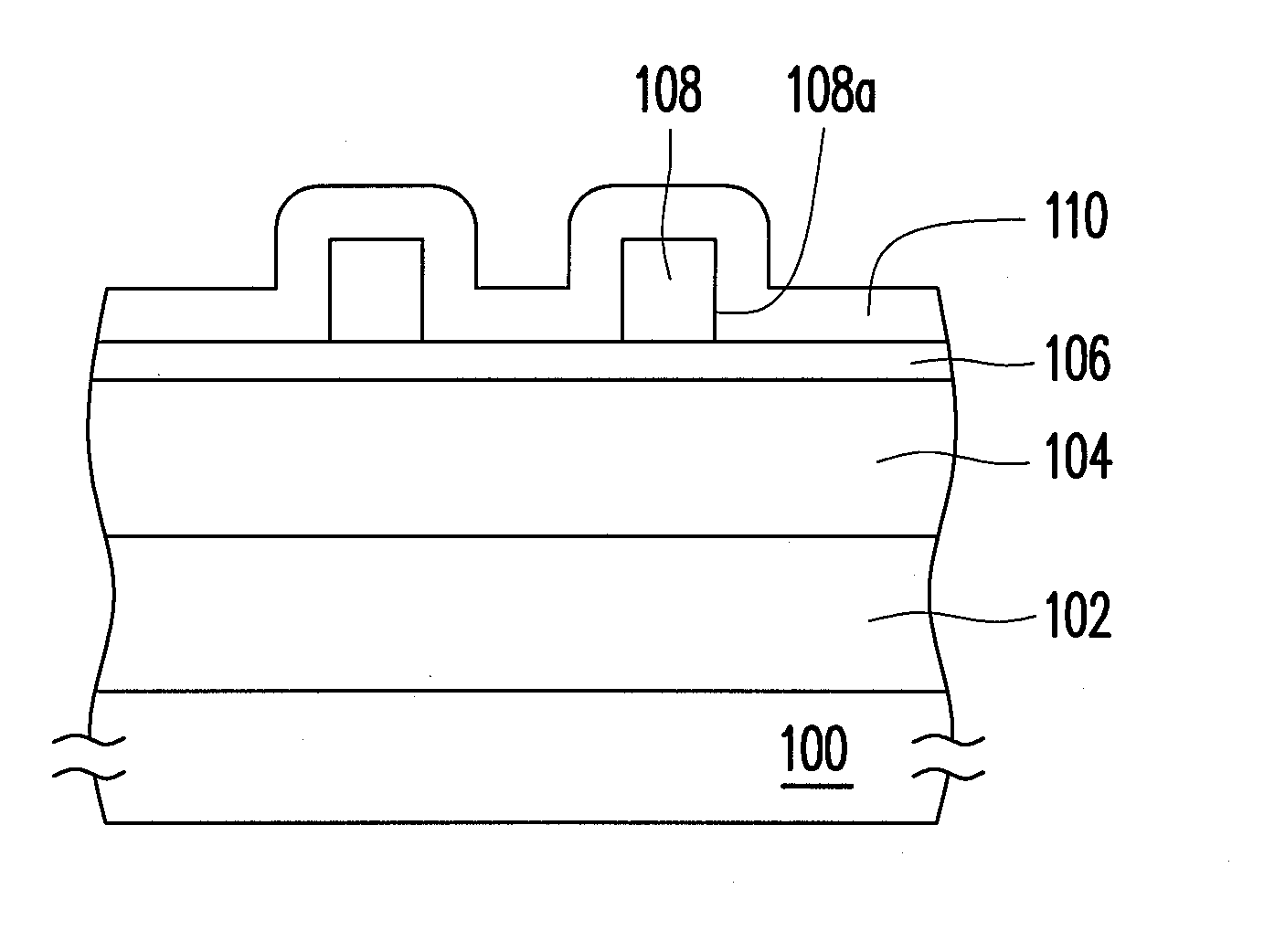

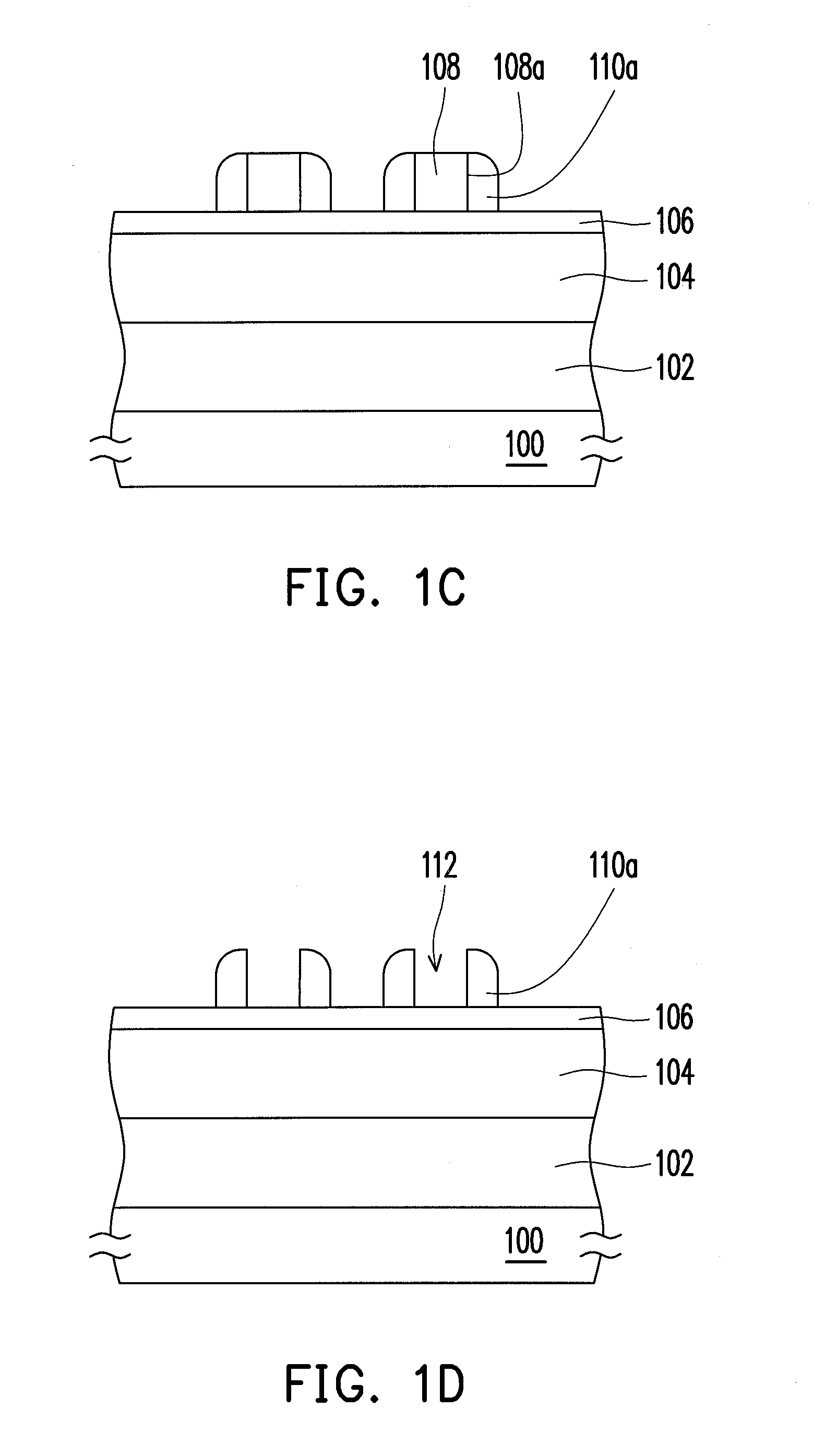

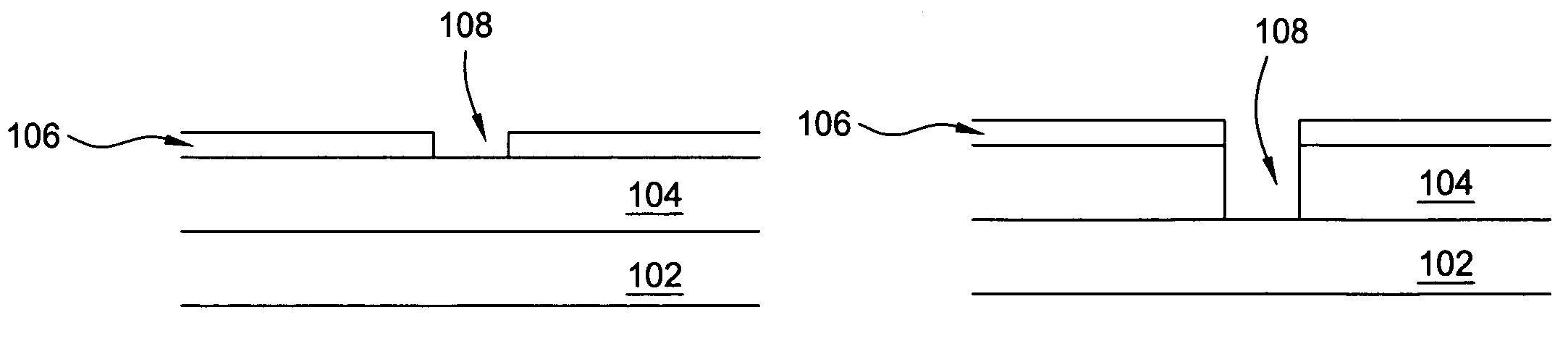

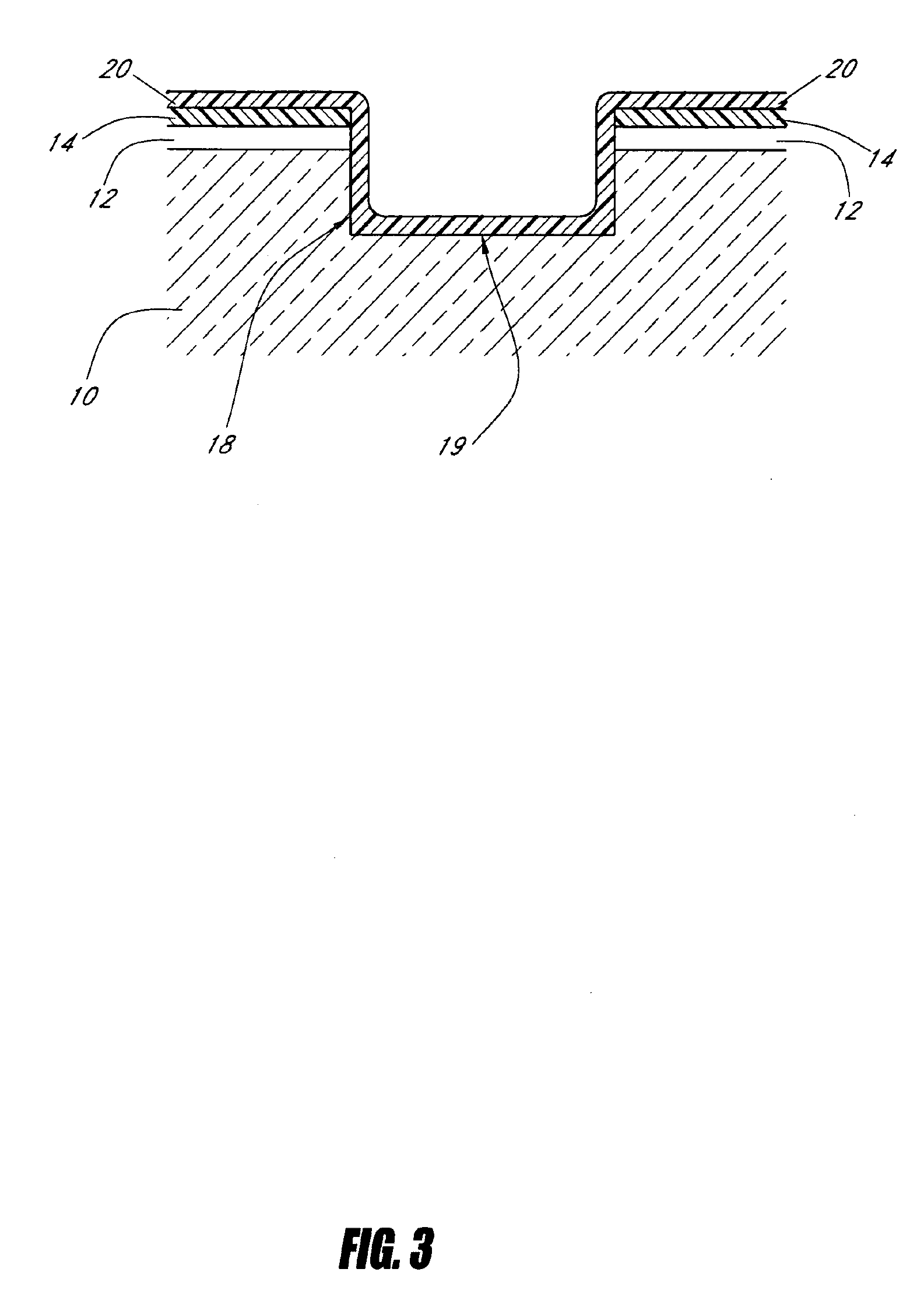

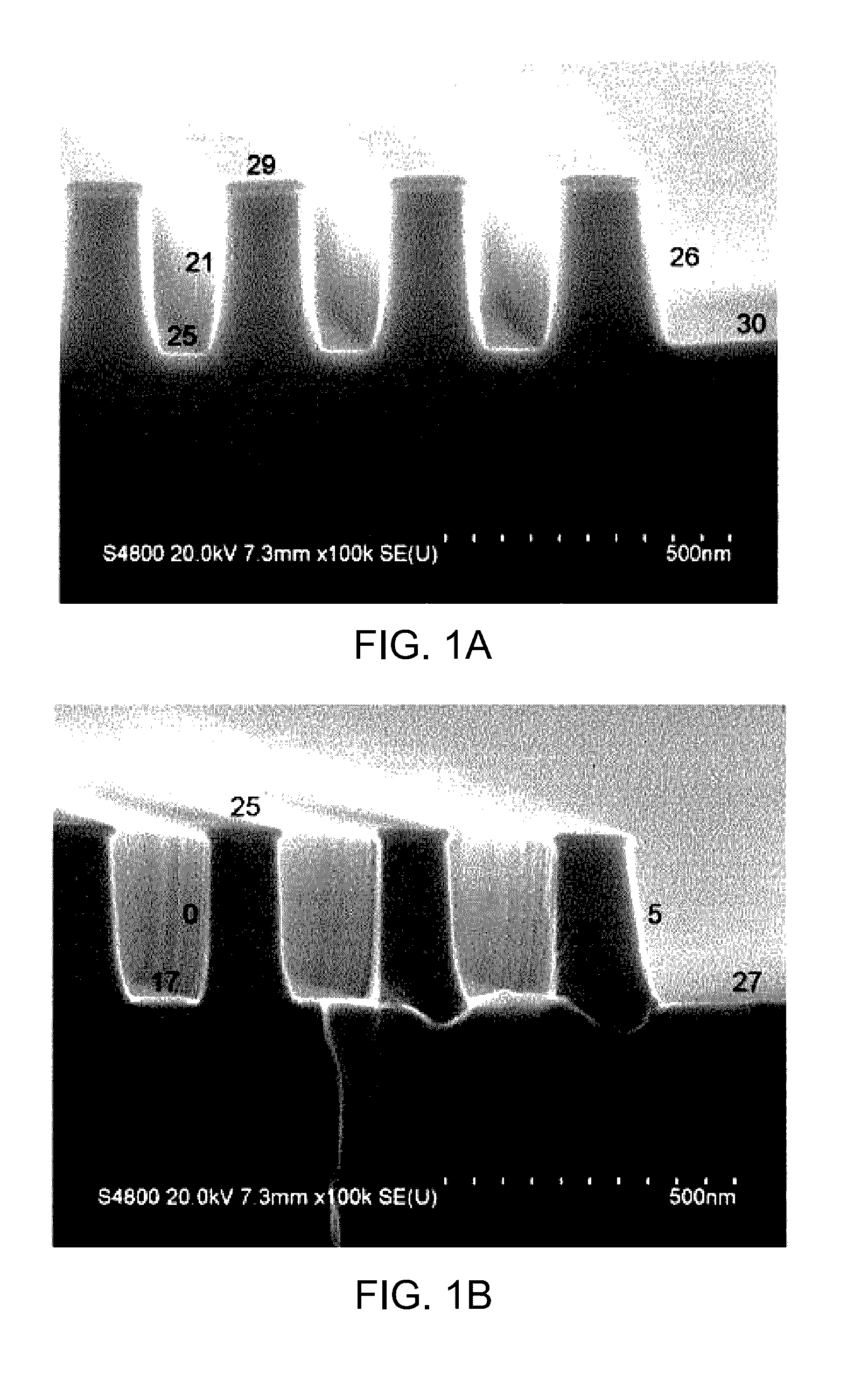

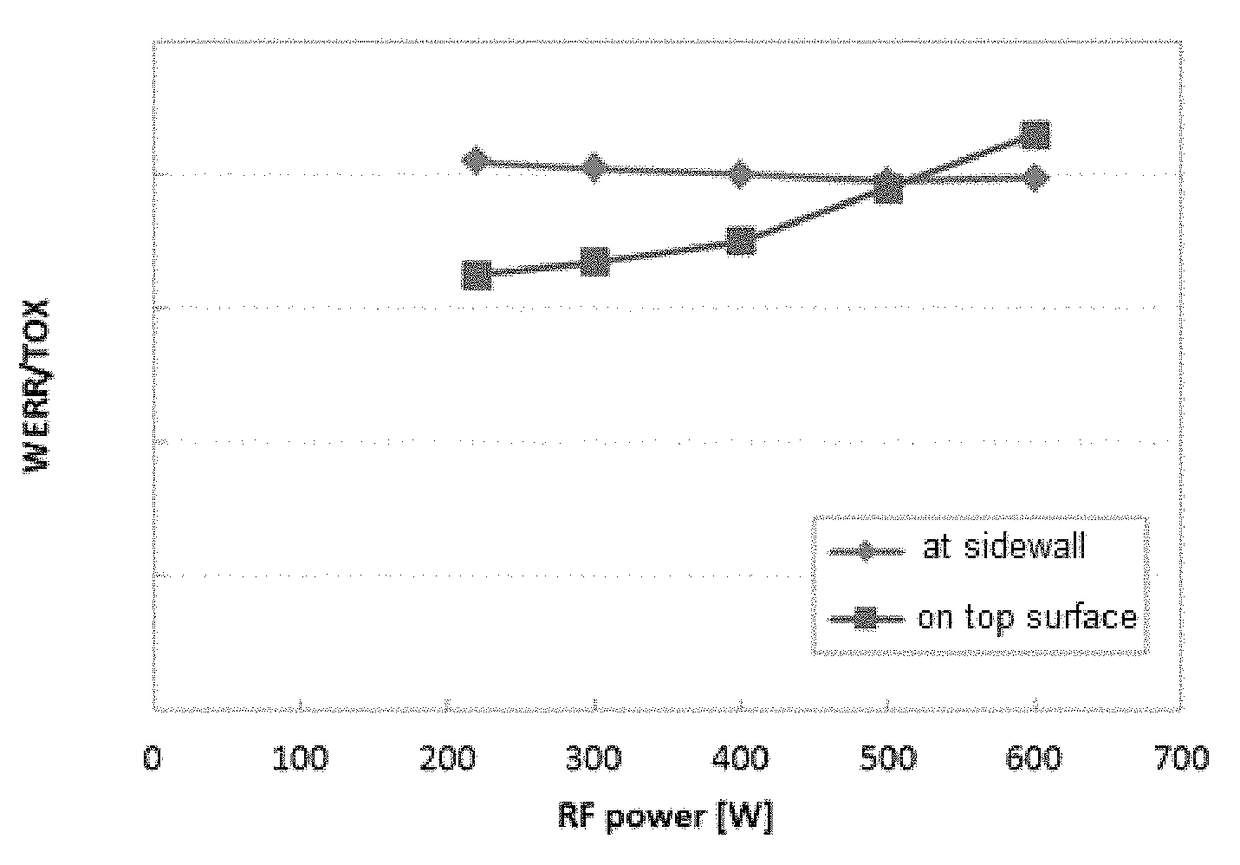

Method of tailoring conformality of Si-containing film

ActiveUS8669185B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingThin membraneEngineering

A method of tailoring conformality of a film deposited on a patterned surface includes: (I) depositing a film by PEALD or pulsed PECVD on the patterned surface; (II) etching the film, wherein the etching is conducted in a pulse or pulses, wherein a ratio of an etching rate of the film on a top surface and that of the film on side walls of the patterns is controlled as a function of the etching pulse duration and the number of etching pulses to increase a conformality of the film; and (III) repeating (I) and (II) to satisfy a target film thickness.

Owner:ASM JAPAN

Thin films

InactiveUS20050181555A1Quality improvementHigh dielectric constantSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSilicon oxide

Thin films are formed by formed by atomic layer deposition, whereby the composition of the film can be varied from monolayer to monolayer during cycles including alternating pulses of self-limiting chemistries. In the illustrated embodiments, varying amounts of impurity sources are introduced during the cyclical process. A graded gate dielectric is thereby provided, even for extremely thin layers. The gate dielectric as thin as 2 nm can be varied from pure silicon oxide to oxynitride to silicon nitride. Similarly, the gate dielectric can be varied from aluminum oxide to mixtures of aluminum oxide and a higher dielectric material (e.g., ZrO2) to pure high k material and back to aluminum oxide. In another embodiment, metal nitride (e.g., WN) is first formed as a barrier for lining dual damascene trenches and vias. During the alternating deposition process, copper can be introduced, e.g., in separate pulses, and the copper source pulses can gradually increase in frequency, forming a transition region, until pure copper is formed at the upper surface. Advantageously, graded compositions in these and a variety of other contexts help to avoid such problems as etch rate control, electromigration and non-ohmic electrical contact that can occur at sharp material interfaces. In some embodiments additional seed layers or additional transition layers are provided.

Owner:ASM INTERNATIONAL

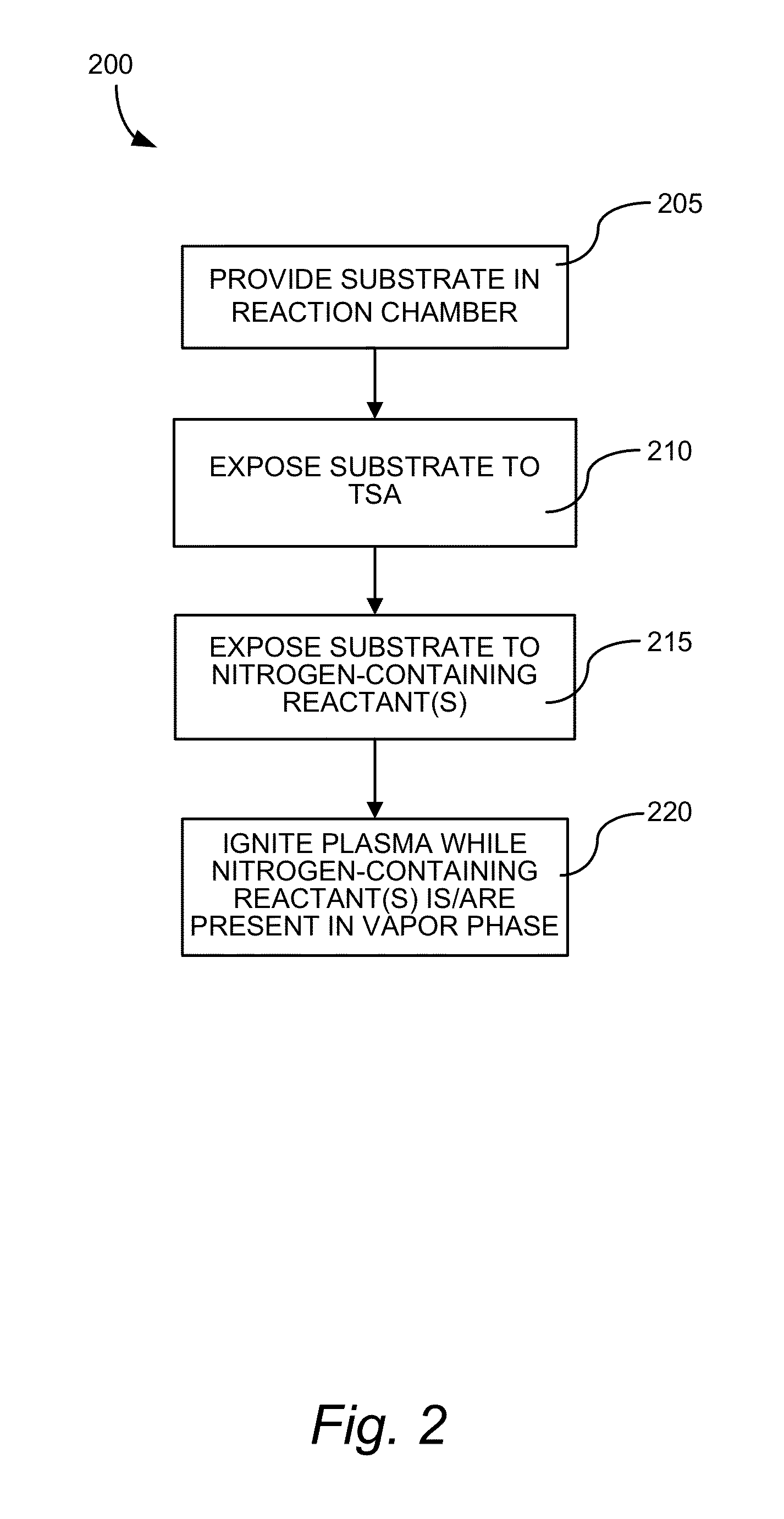

Method for depositing a chlorine-free conformal sin film

ActiveUS20130189854A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingChemistryEtching rate

Described are methods of making silicon nitride (SiN) materials on substrates. Improved SiN films made by the methods are also included. One aspect relates to depositing chlorine (Cl)-free conformal SiN films. In some embodiments, the SiN films are Cl-free and carbon (C)-free. Another aspect relates to methods of tuning the stress and / or wet etch rate of conformal SiN films. Another aspect relates to low-temperature methods of depositing high quality conformal SiN films. In some embodiments, the methods involve using trisilylamine (TSA) as a silicon-containing precursor.

Owner:NOVELLUS SYSTEMS

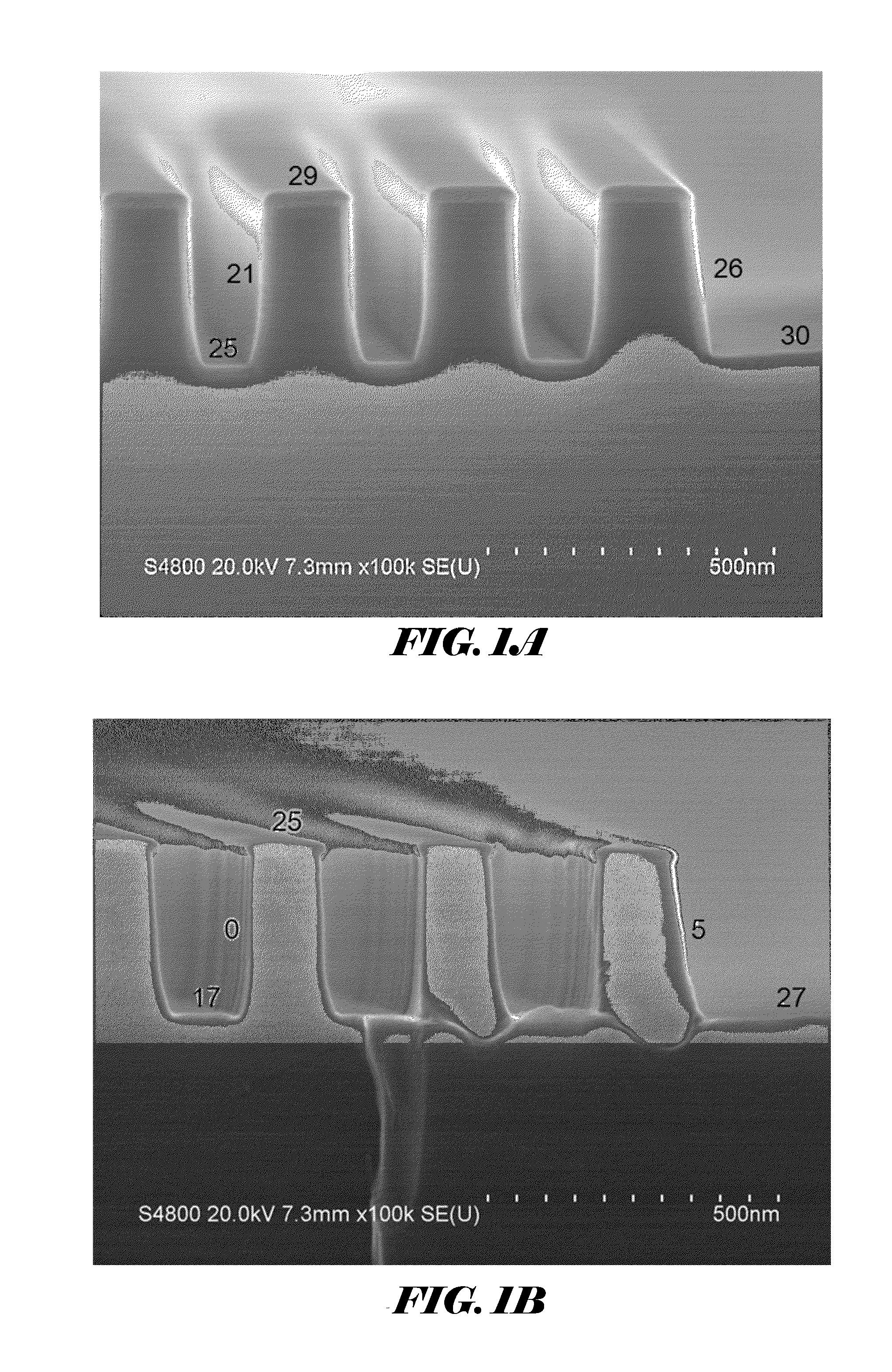

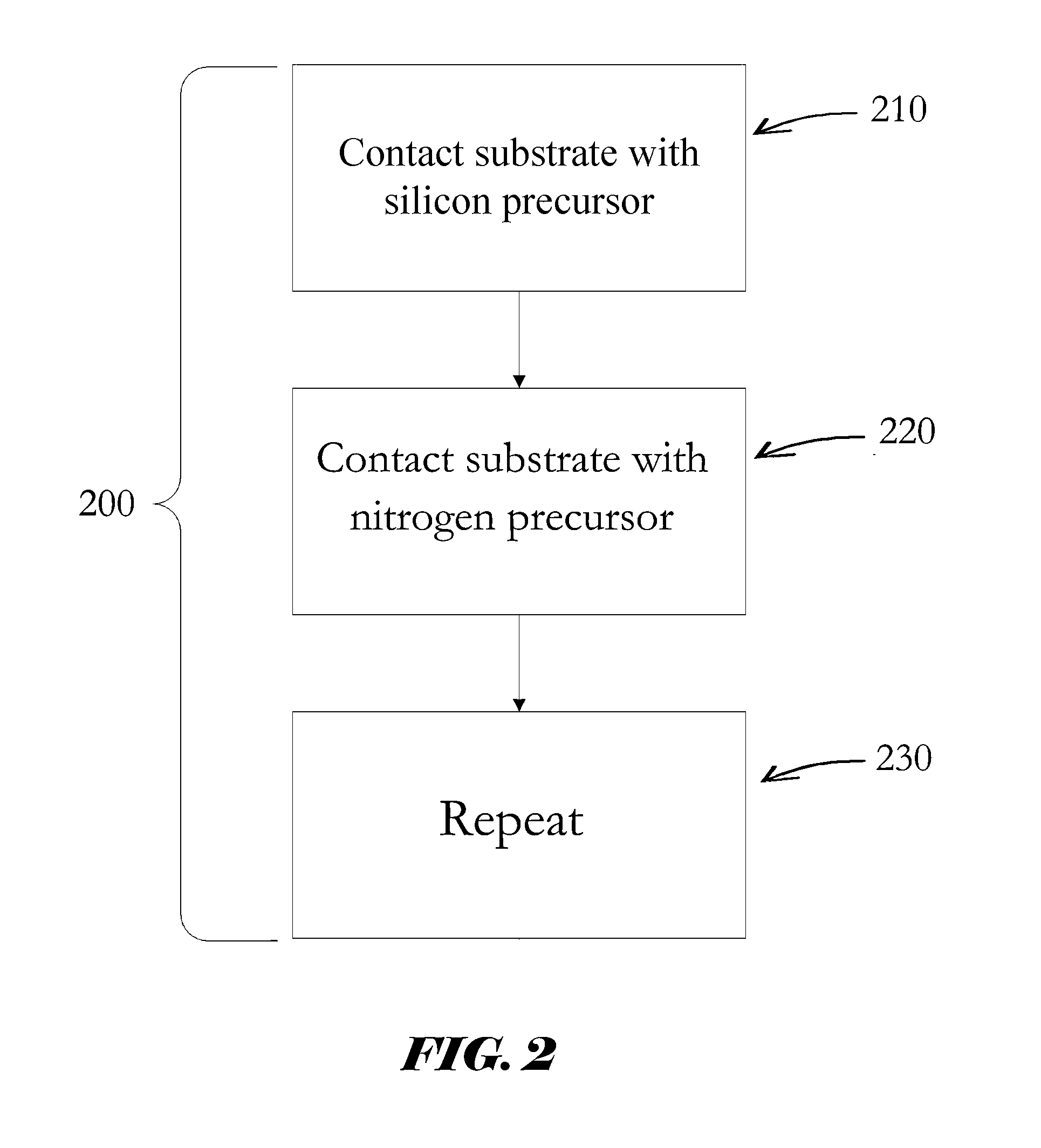

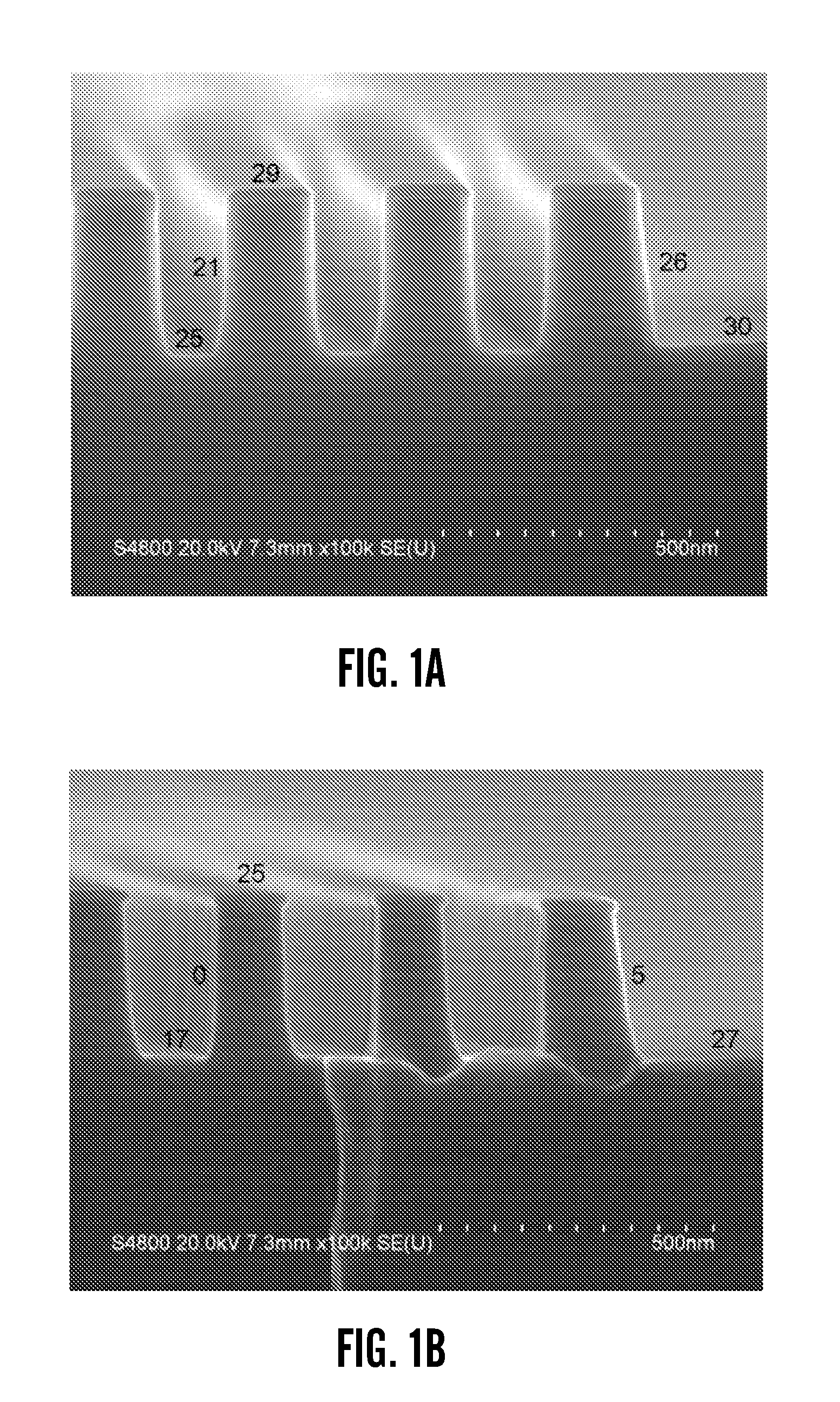

Si PRECURSORS FOR DEPOSITION OF SiN AT LOW TEMPERATURES

ActiveUS20140273528A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingMetallurgyAtomic layer deposition

Methods and precursors for depositing silicon nitride films by atomic layer deposition (ALD) are provided. In some embodiments the silicon precursors comprise an iodine ligand. The silicon nitride films may have a relatively uniform etch rate for both vertical and the horizontal portions when deposited onto three-dimensional structures such as FinFETS or other types of multiple gate FETs. In some embodiments, various silicon nitride films of the present disclosure have an etch rate of less than half the thermal oxide removal rate with diluted HF (0.5%).

Owner:ASM IP HLDG BV

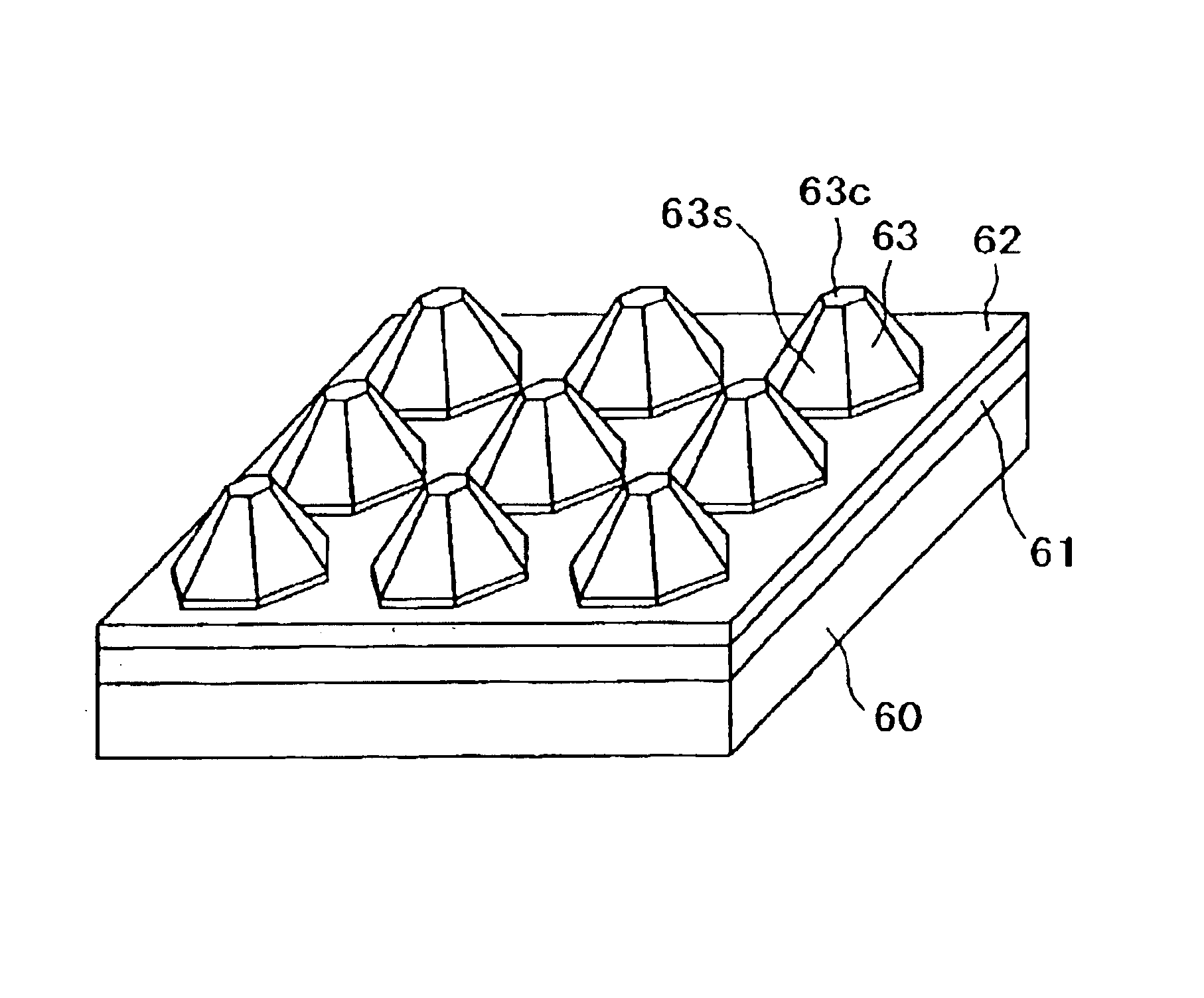

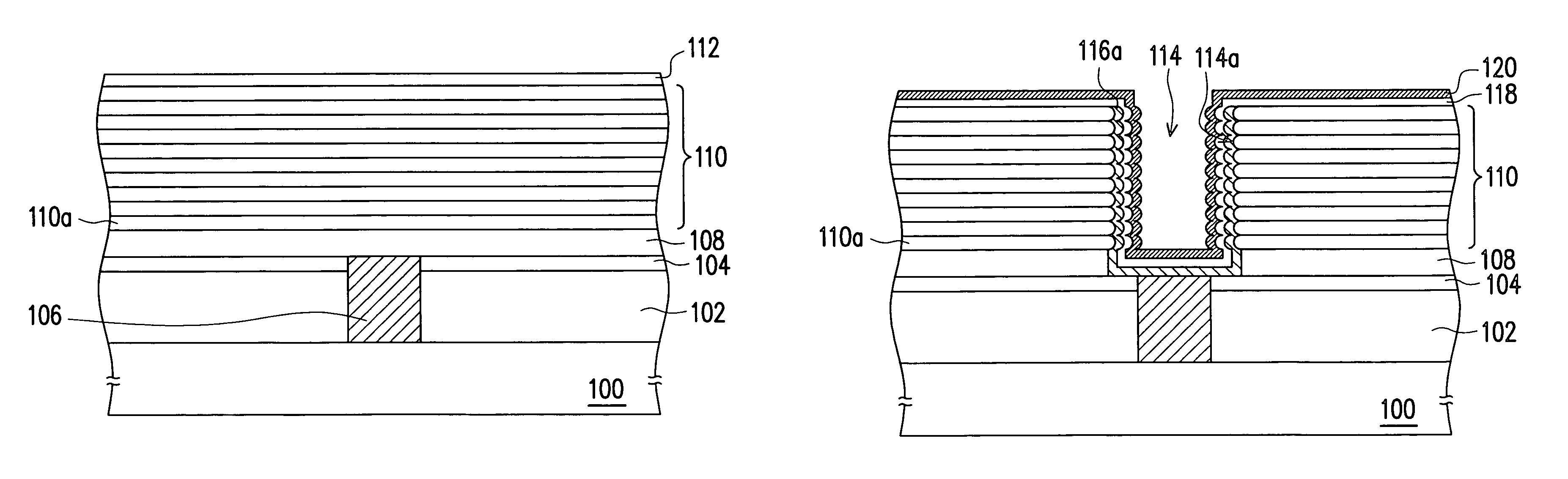

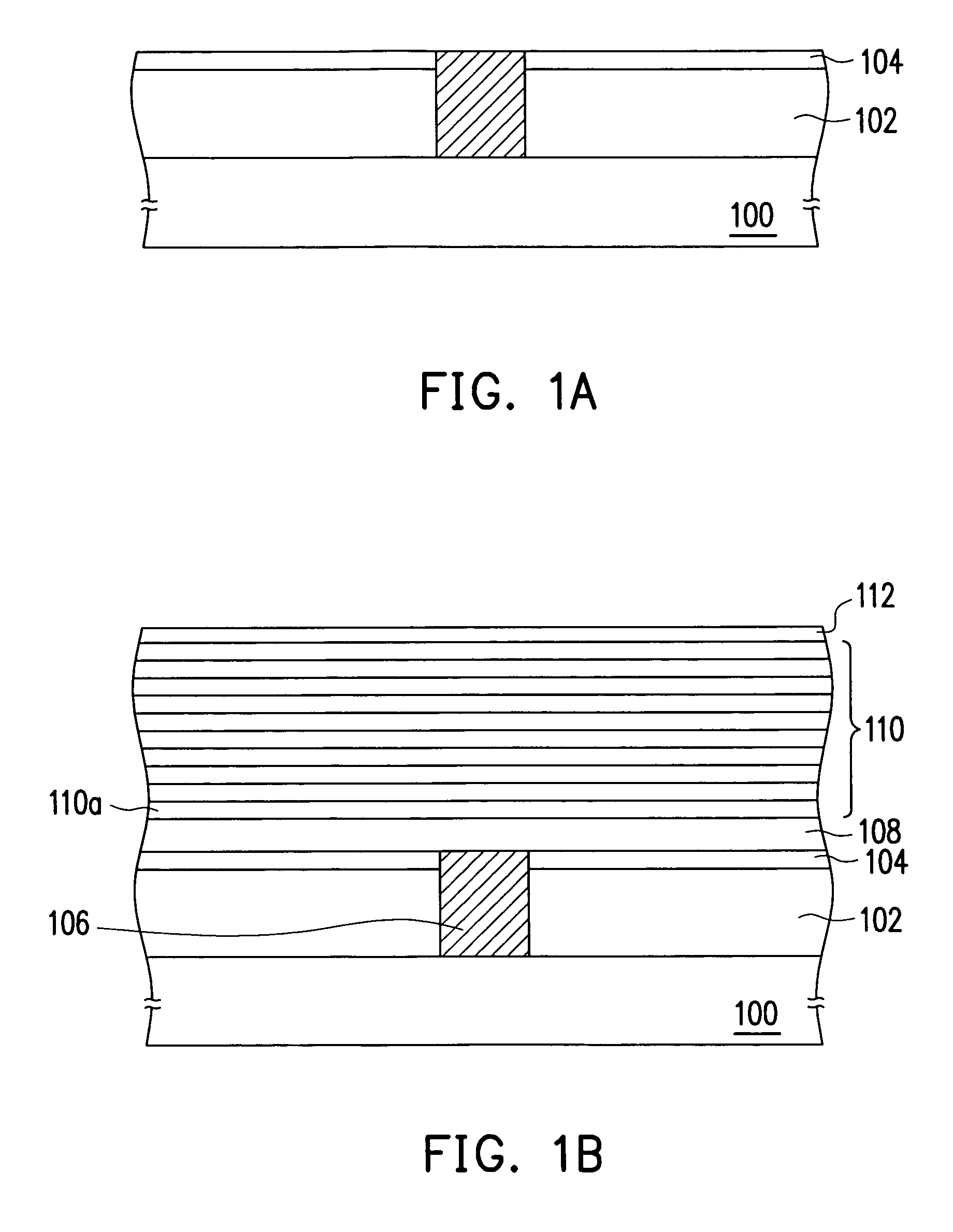

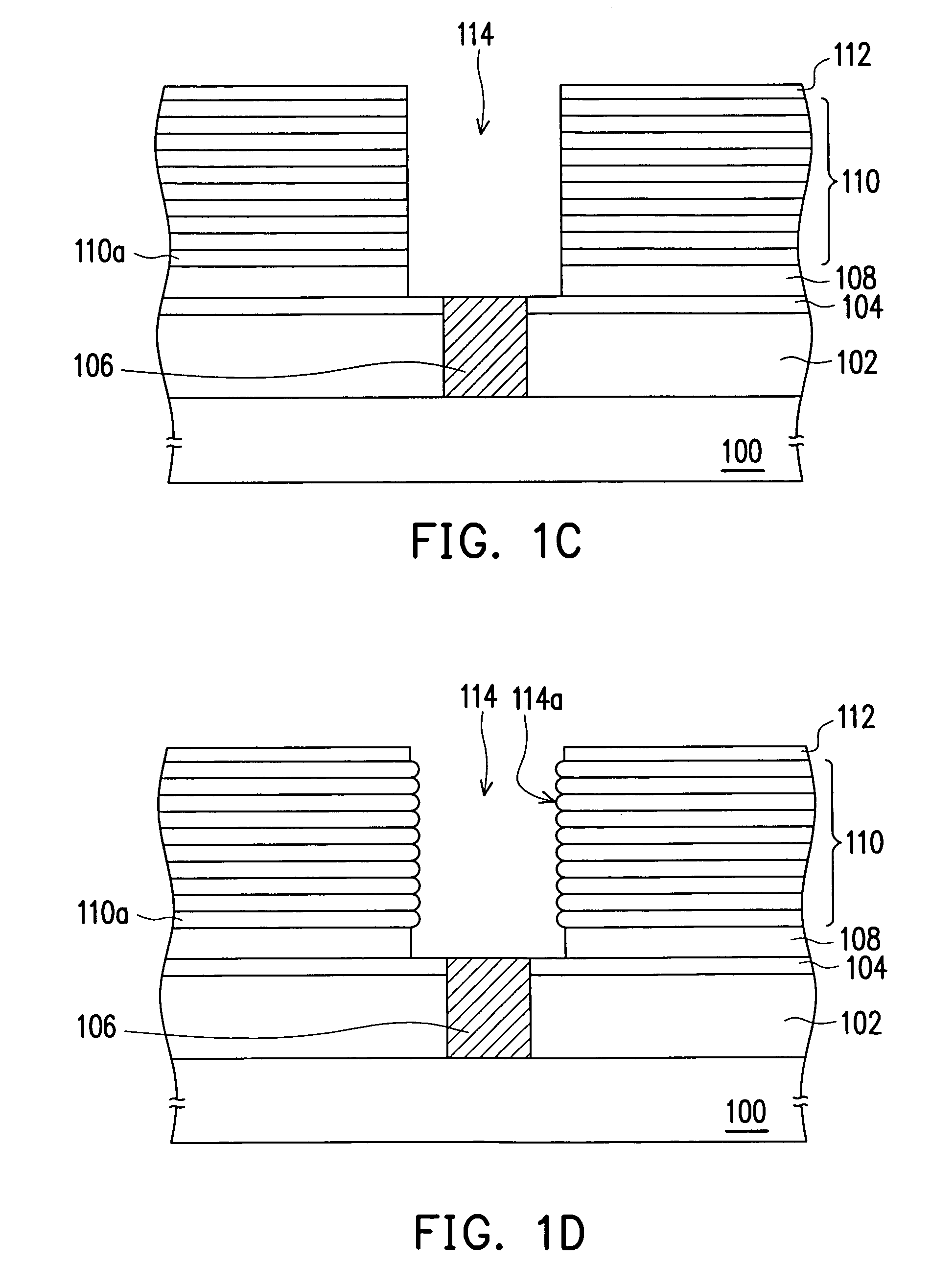

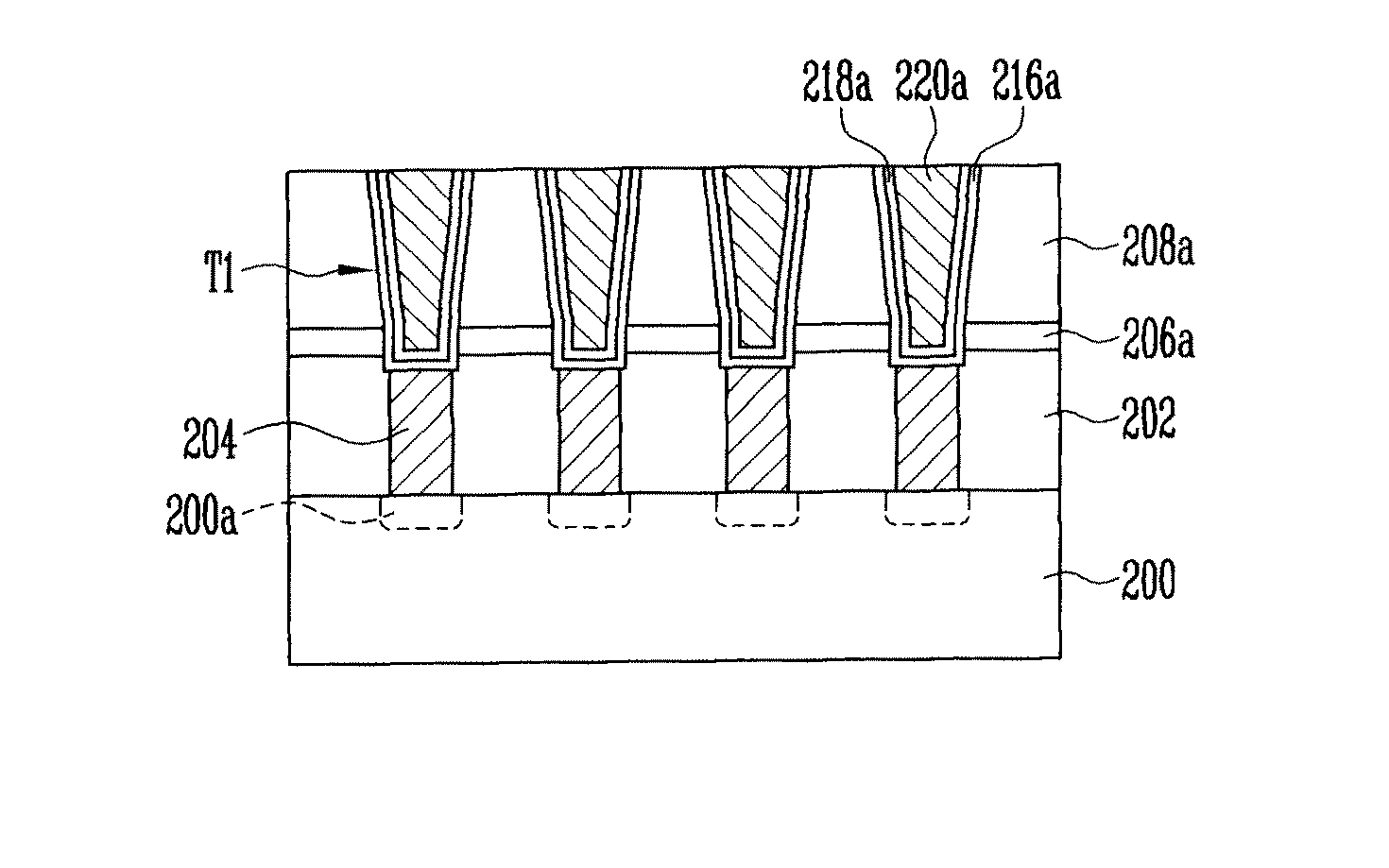

Method of manufacturing charge storage device

InactiveUS7405166B2Increase electrode areaEasy to produceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceHydrogen fluoride

Owner:IND TECH RES INST

Si PRECURSORS FOR DEPOSITION OF SiN AT LOW TEMPERATURES

ActiveUS20140273477A1Semiconductor/solid-state device manufacturingAtomic layer depositionThermal oxide

Methods and precursors for depositing silicon nitride films by atomic layer deposition (ALD) are provided. In some embodiments the silicon precursors comprise an iodine ligand. The silicon nitride films may have a relatively uniform etch rate for both vertical and the horizontal portions when deposited onto three-dimensional structures such as FinFETS or other types of multiple gate FETs. In some embodiments, various silicon nitride films of the present disclosure have an etch rate of less than half the thermal oxide removal rate with diluted HF (0.5%).

Owner:ASM IP HLDG BV

Method for forming layer constituted by repeated stacked layers

ActiveUS9018093B2High wet etching selectivityUniform film qualitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingThin membraneSecondary layer

A method for forming a layer constituted by repeated stacked layers includes: forming a first layer and a second layer on a substrate under different deposition conditions to form a stacked layer, wherein the film stresses of the first and second layers are tensile or compressive and opposite to each other, and the wet etch rates of the first and second layers are at least 50 times different from each other; and repeating the above step to form a layer constituted by repeated stacked layers, wherein the deposition conditions for forming at least one stacked layer are different from those for forming another stacked layer.

Owner:ASM IP HLDG BV

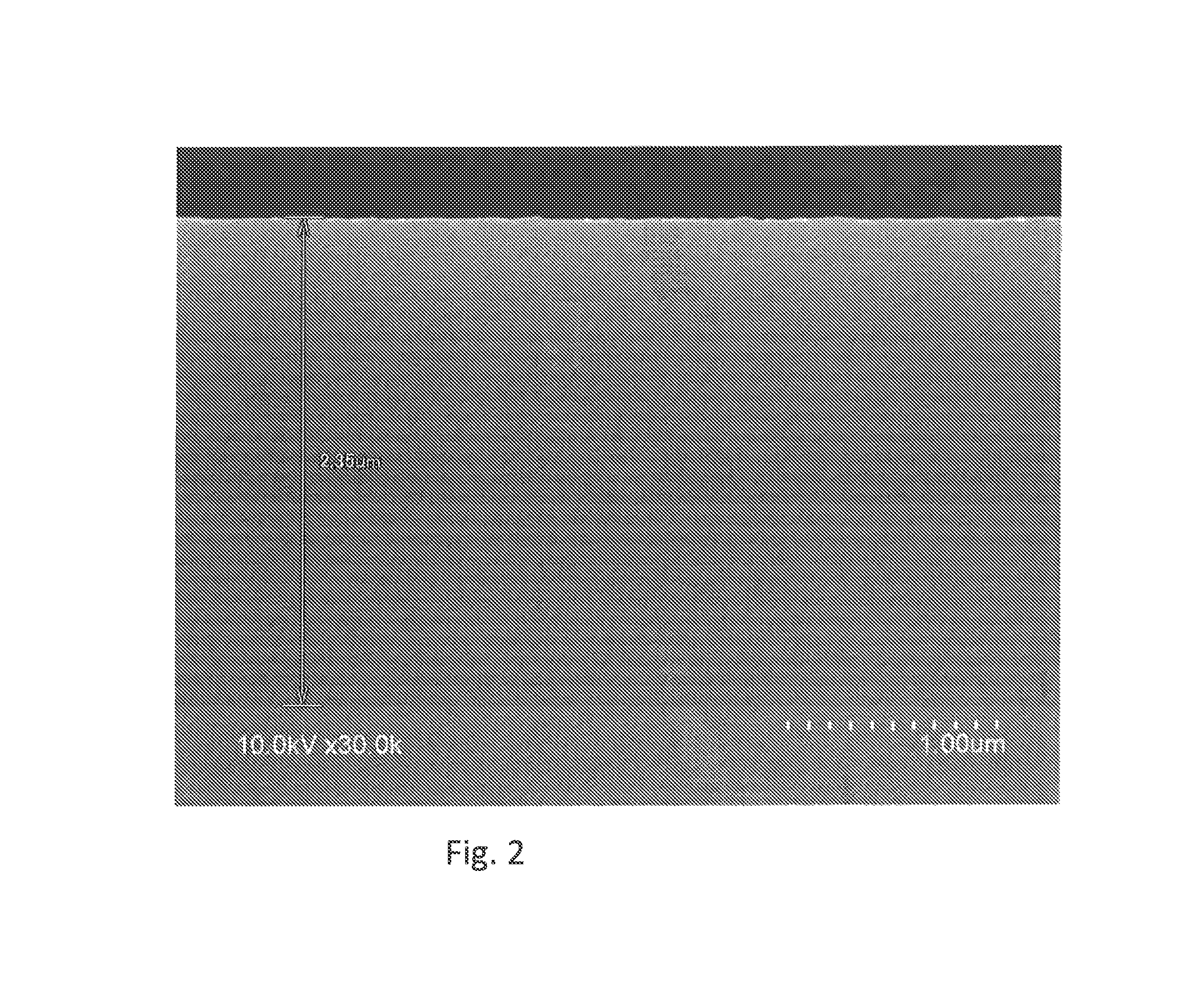

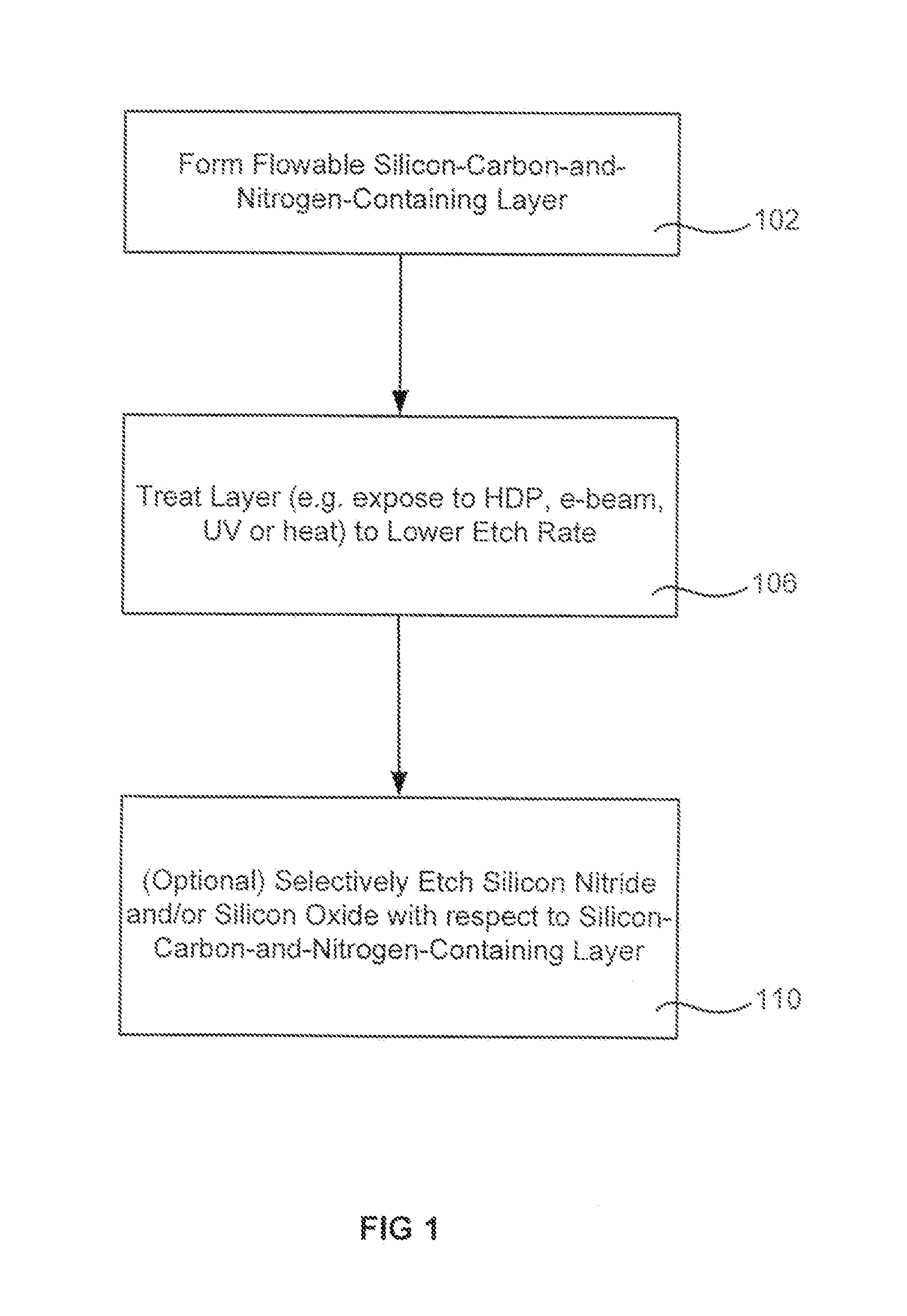

Treatments for decreasing etch rates after flowable deposition of silicon-carbon-and-nitrogen-containing layers

InactiveUS20130217241A1Excellent etch resistanceFilm property decreaseSemiconductor/solid-state device manufacturingNitrogenSemiconductor

Methods are described for forming and curing a flowable silicon-carbon-and-nitrogen-containing layer on a semiconductor substrate. The silicon and carbon constituents may come from a silicon and carbon containing precursor while the nitrogen may come from a nitrogen-containing precursor that has been activated to speed the reaction of the nitrogen with the silicon-and-carbon-containing precursor at lower deposition chamber temperatures. The initially-flowable silicon-carbon-and-nitrogen-containing layer is treated to remove components which enabled the flowability, but are no longer needed after deposition. Removal of the components increases etch resistance in order to allow the gapfill silicon-carbon-and-nitrogen-containing layer to remain intact during subsequent processing. The treatments have been found to decrease the evolution of properties of the film upon exposure to atmosphere.

Owner:APPLIED MATERIALS INC

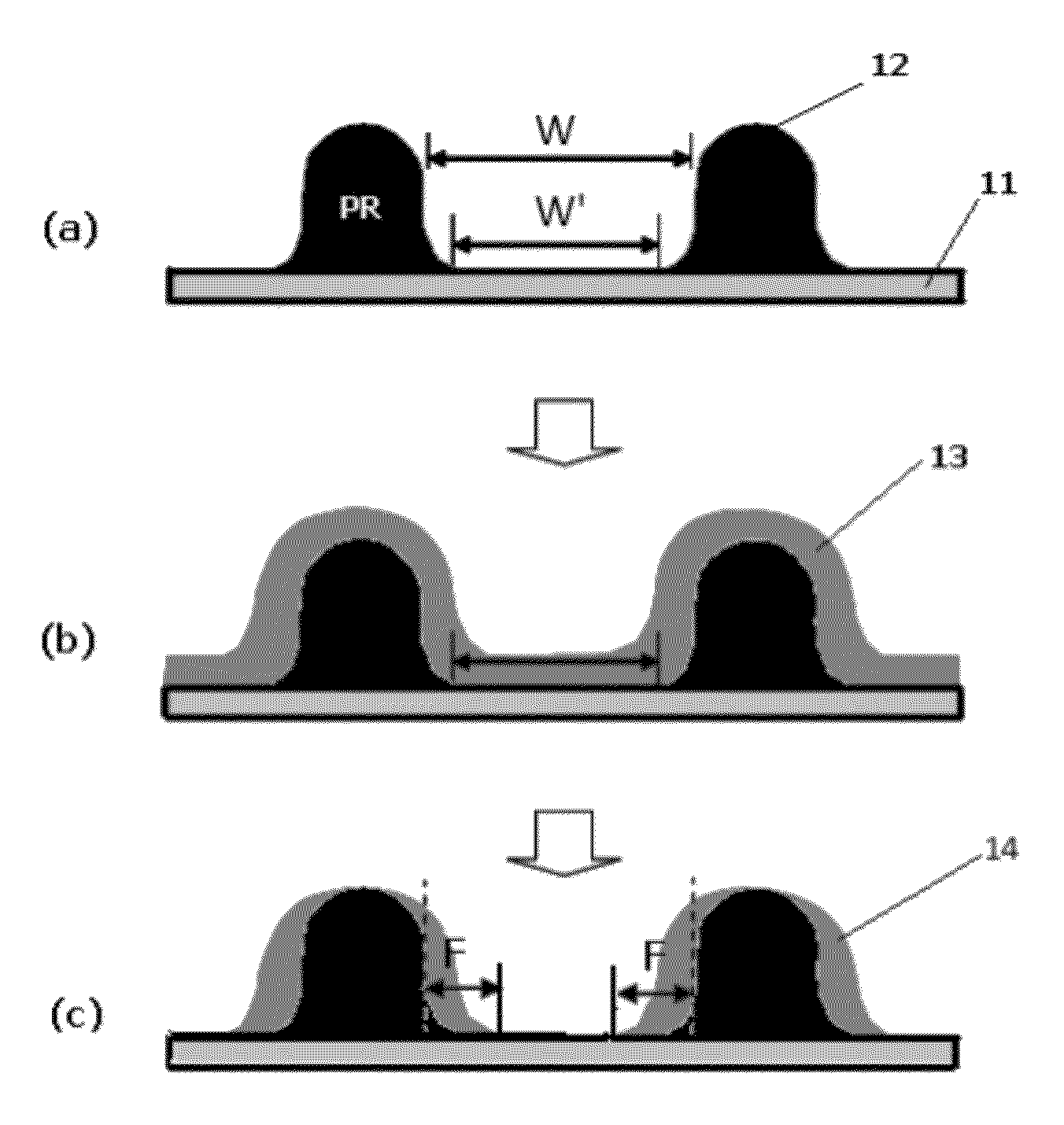

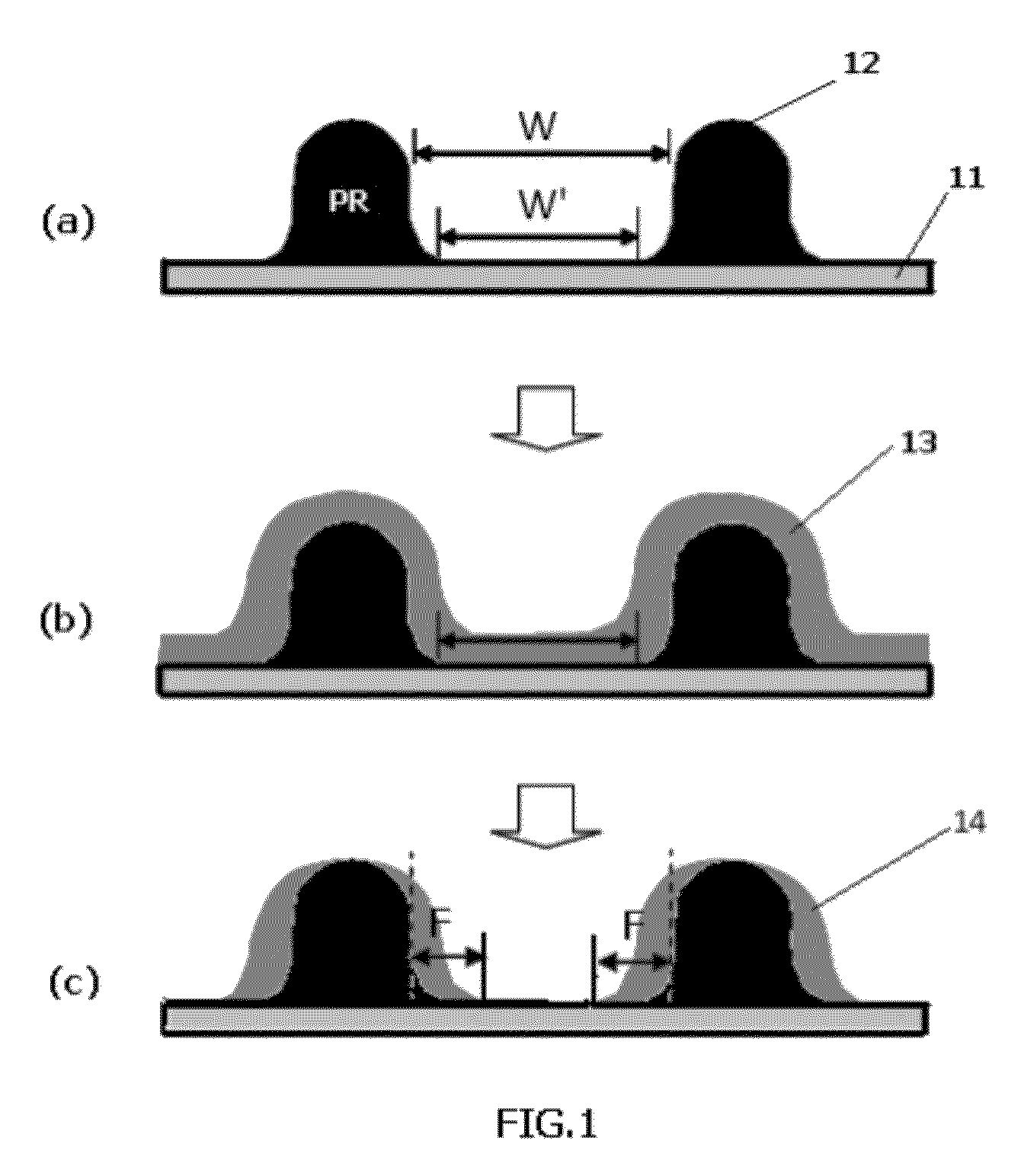

Footing reduction using etch-selective layer

ActiveUS8298951B1Reduce etch rateReducing a widened footing of the photoresistDecorative surface effectsSemiconductor/solid-state device manufacturingEngineeringOxygen

A method of forming side spacers upwardly extending from a substrate, includes: providing a template constituted by a photoresist formed on and in contact with an etch-selective layer laminated on a substrate; anisotropically etching the template in a thickness direction with an oxygen-containing plasma to remove a footing of the photoresist and an exposed portion of the underlying layer; depositing a spacer film on the template by atomic layer deposition (ALD); and forming side spacers using the spacer film by etching. The etch-selective layer has a substantially lower etch rate than that of the photoresist.

Owner:ASM JAPAN

Low wet etch rate silicon nitride film

Owner:APPLIED MATERIALS INC

Polymer sacrificial light absorbing structure and method

InactiveUS6876017B2From solid stateSemiconductor/solid-state device detailsSolubilityLithographic artist

Method and structure for optimizing dual damascene patterning with polymeric dielectric materials are disclosed. Certain embodiments of the invention comprise polymeric sacrificial light absorbing materials (“polymer SLAM”) functionalized to have a controllable solubility switch wherein such polymeric materials have substantially the same etch rate as conventionally utilized polymeric dielectric materials, and subsequent to chemical modification of solubility-modifying protecting groups comprising the SLAM materials by thermal treatment or in-situ generation of an acid, such SLAM materials become soluble in weak bases, such as those conventionally utilized to remove materials in lithography treatments.

Owner:INTEL CORP

Si PRECURSORS FOR DEPOSITION OF SiN AT LOW TEMPERATURES

InactiveUS20140273531A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingAtomic layer depositionThermal oxide

Methods and precursors for depositing silicon nitride films by atomic layer deposition (ALD) are provided. In some embodiments the silicon precursors comprise an iodine ligand. The silicon nitride films may have a relatively uniform etch rate for both vertical and the horizontal portions when deposited onto three-dimensional structures such as FinFETS or other types of multiple gate FETs. In some embodiments, various silicon nitride films of the present disclosure have an etch rate of less than half the thermal oxide removal rate with diluted HF (0.5%).

Owner:ASM IP HLDG BV

Deposition of SiN

ActiveUS20160079054A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingNitrogen plasmaAtomic layer deposition

Methods and precursors for forming silicon nitride films are provided. In some embodiments, silicon nitride can be deposited by atomic layer deposition (ALD), such as plasma enhanced ALD. In some embodiments, deposited silicon nitride can be treated with a plasma treatment. The plasma treatment can be a nitrogen plasma treatment. In some embodiments the silicon precursors for depositing the silicon nitride comprise an iodine ligand. The silicon nitride films may have a relatively uniform etch rate for both vertical and the horizontal portions when deposited onto three-dimensional structures such as FinFETS or other types of multiple gate FETs. In some embodiments, various silicon nitride films of the present disclosure have an etch rate of less than half the thermal oxide removal rate with diluted HF (0.5%). In some embodiments, a method for depositing silicon nitride films comprises a multi-step plasma treatment.

Owner:ASM IP HLDG BV

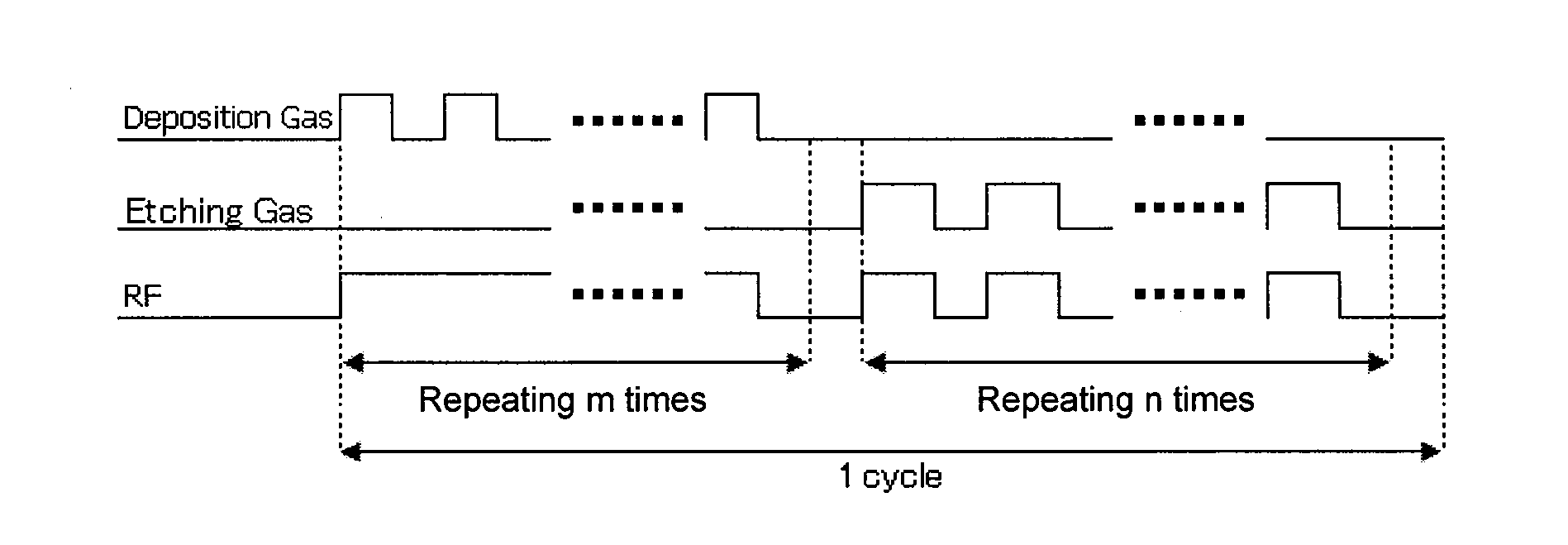

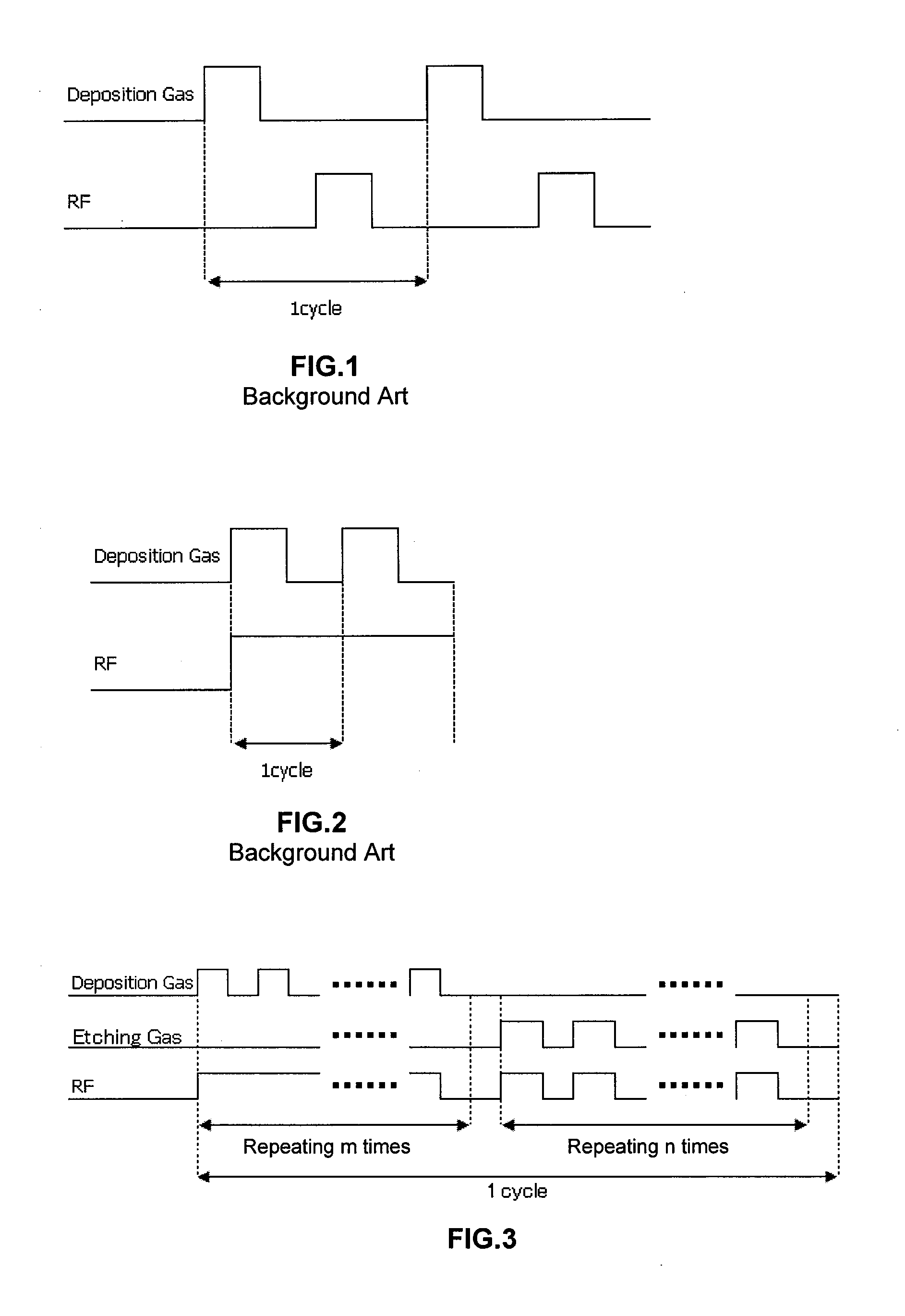

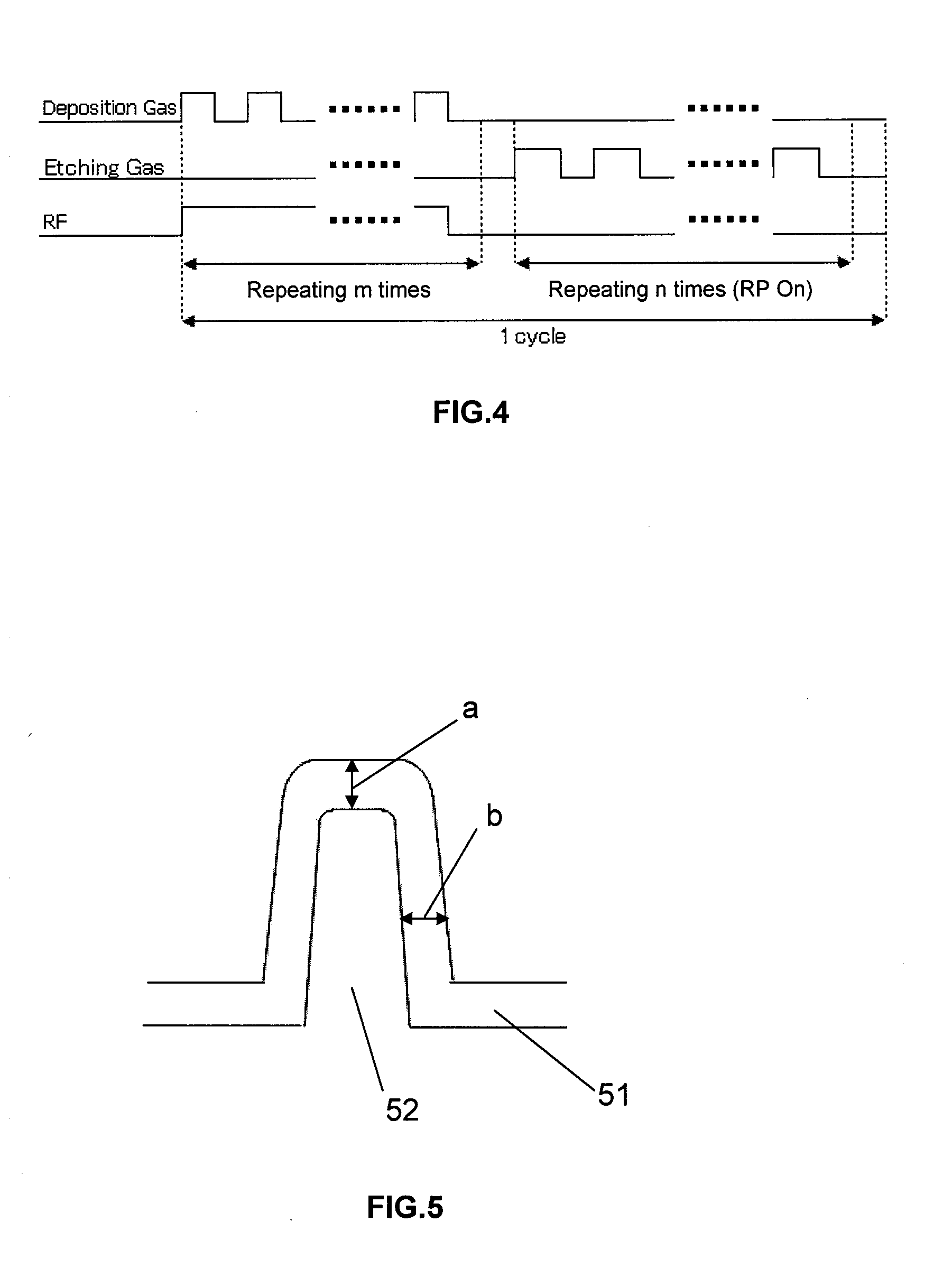

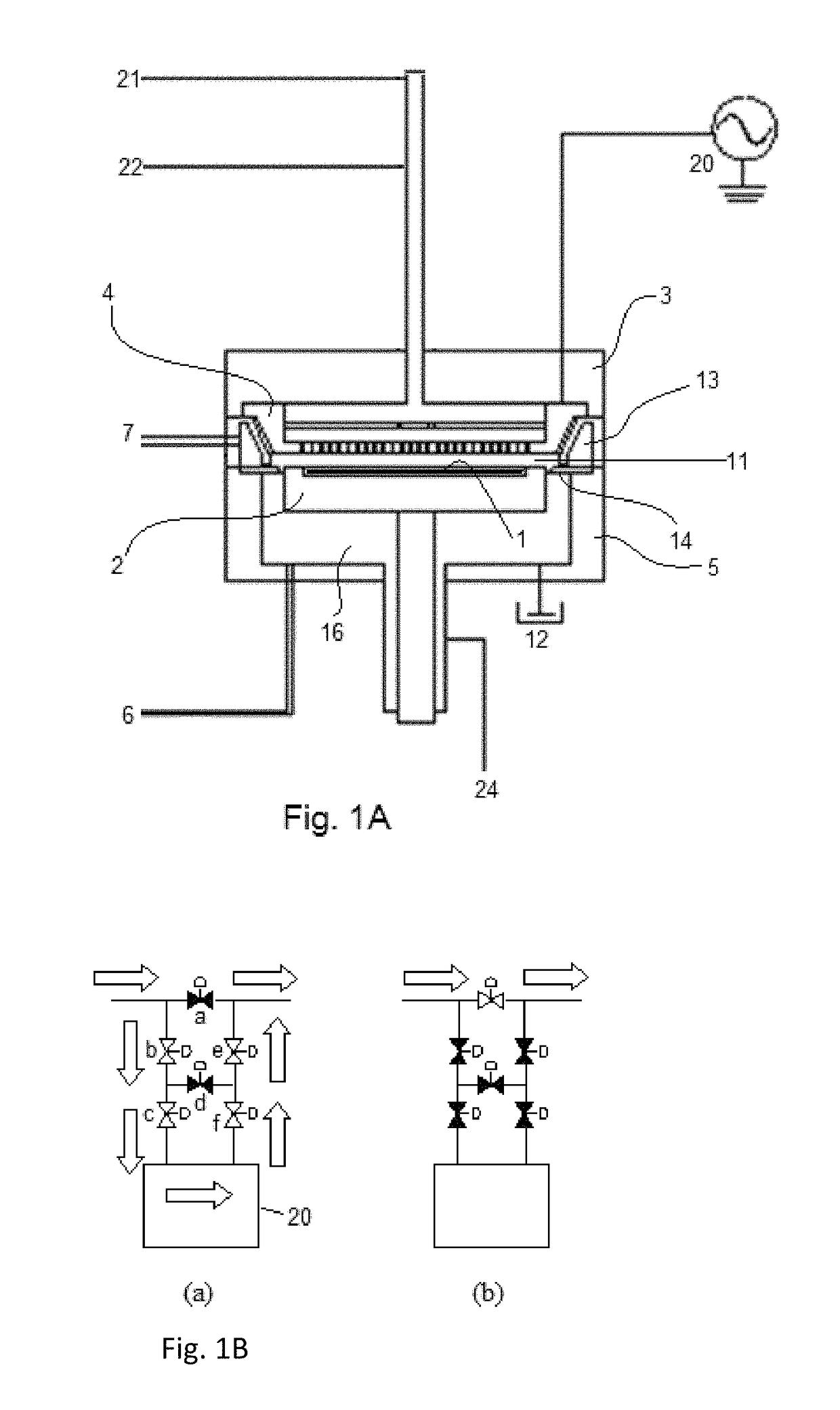

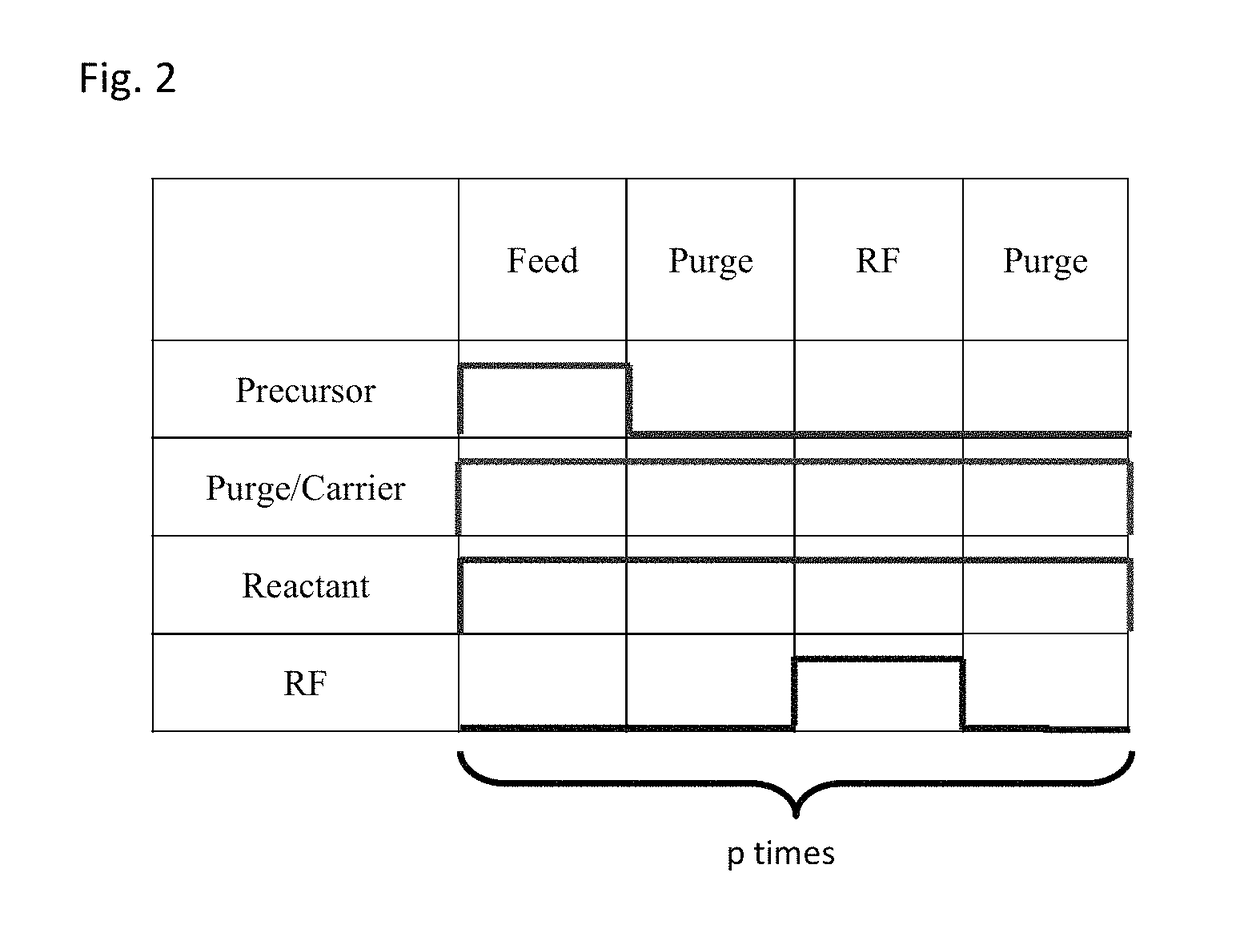

METHOD OF TAILORING CONFORMALITY OF Si-CONTAINING FILM

ActiveUS20120028469A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingThin membraneSilicon thin film

A method of tailoring conformality of a film deposited on a patterned surface includes: (I) depositing a film by PEALD or pulsed PECVD on the patterned surface; (II) etching the film, wherein the etching is conducted in a pulse or pulses, wherein a ratio of an etching rate of the film on a top surface and that of the film on side walls of the patterns is controlled as a function of the etching pulse duration and the number of etching pulses to increase a conformality of the film; and (III) repeating (I) and (II) to satisfy a target film thickness.

Owner:ASM JAPAN

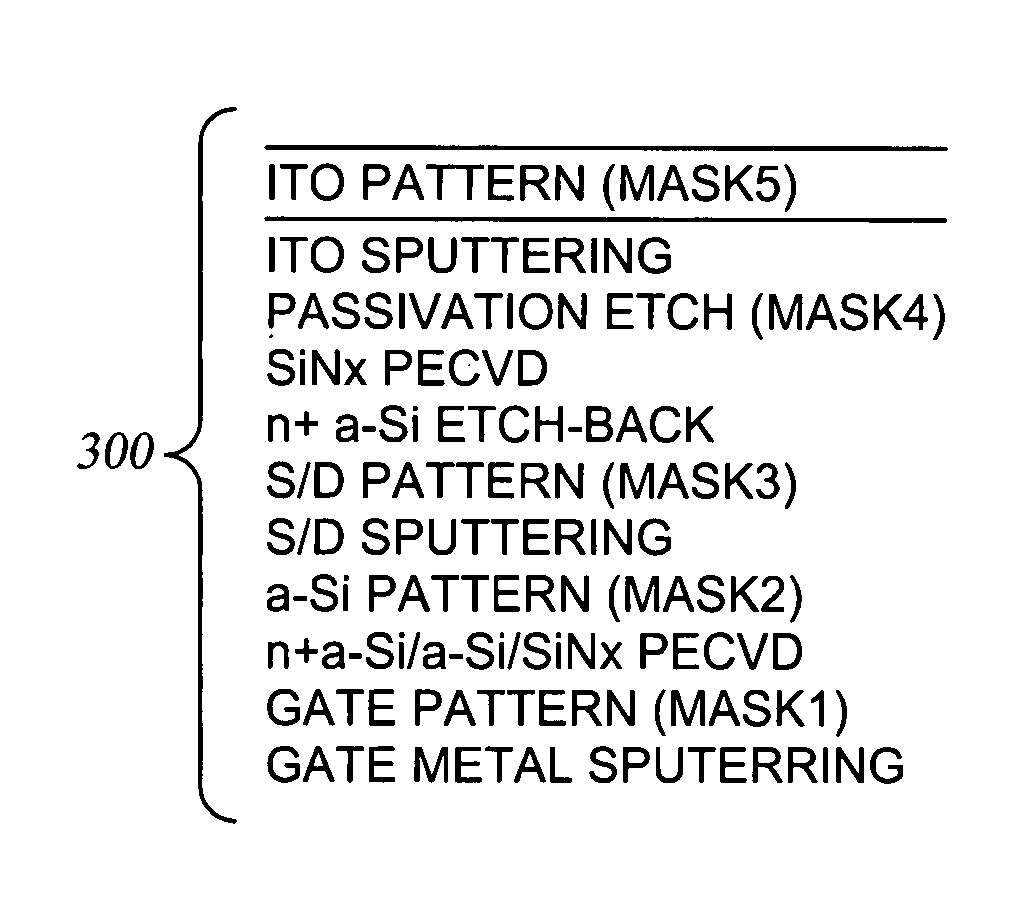

Method of controlling the film properties of a CVD-deposited silicon nitride film

InactiveUS20060019502A1Increase wet etch rateEasy to controlSemiconductor/solid-state device manufacturingChemical vapor deposition coatingGate dielectricGas composition

We have discovered that adding H2 to a precursor gas composition including SiH4, NH3, and N2 is effective at improving the wet etch rate and the wet etch rate uniformity across the substrate surface of a-SiNx:H films which are deposited on a substrate by PECVD. Wet etch rate is an indication of film density. Typically, the lower the wet etch rate, the denser the film. The addition of H2 to the SiH4 / NH3 / N2 precursor gas composition did not significantly increase the variation in deposited film thickness across the surface of the substrate. The a-SiNx:H films described herein are particularly useful as TFT gate dielectrics in the production of flat panel displays. The uniformity of the film across the substrate enables the production of flat panel displays having surface areas of 25,000 cm2 and larger.

Owner:APPLIED MATERIALS INC

Patterning method

InactiveUS20110294075A1Reduce line widthLow costSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusPhotoresistMask layer

A patterning method of the present invention is described as follows. A mask layer and a patterned photoresist layer are formed on a target layer in sequence, wherein an etching rate of the mask layer is different from an etching rate of the target layer. A plurality of spacers is formed on sidewalls of the patterned photoresist layer respectively, wherein an etching rate of the spacers is different from the etching rate of the mask layer. The patterned photoresist layer is removed to form an opening between any two adjacent spacers. A portion of the mask layer is removed by using the spacers as a mask so as to form a patterned mask layer. A portion of the target layer is removed by using the patterned mask layer as a mask.

Owner:UNITED MICROELECTRONICS CORP

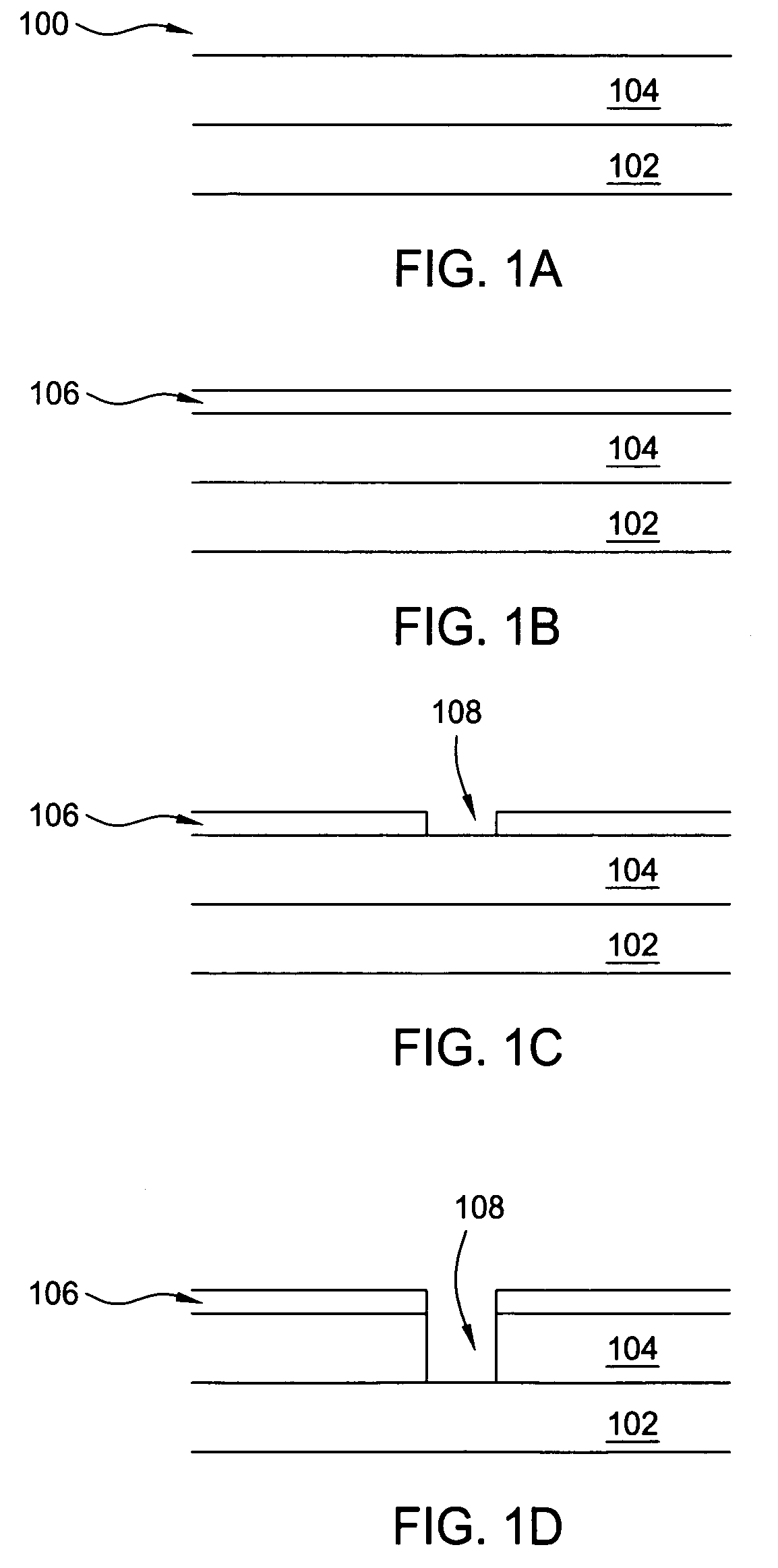

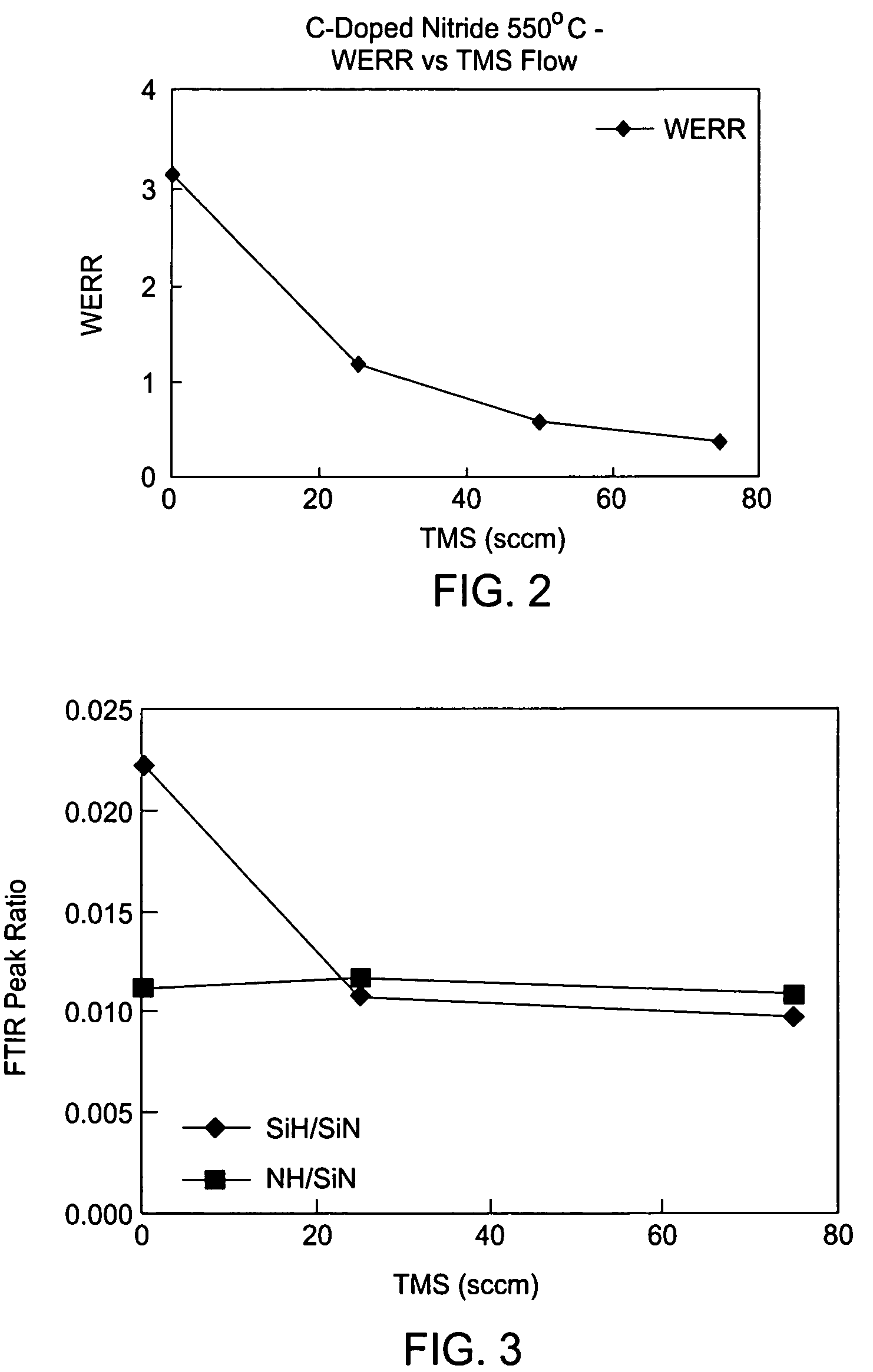

Decreasing the etch rate of silicon nitride by carbon addition

Methods for forming silicon nitride hard masks are provided. The silicon nitride hard masks include carbon-doped silicon nitride layers and undoped silicon nitride layers. Carbon-doped silicon nitride layers that are deposited from a mixture comprising a carbon source compound, a silicon source compound, and a nitrogen source in the presence of RF power are provided. Also provided are methods of UV post-treating silicon nitride layers to provide silicon nitride hard masks. The carbon-doped silicon nitride layers and UV post-treated silicon nitride layers have desirable wet etch rates and dry etch rates for hard mask layers.

Owner:APPLIED MATERIALS INC

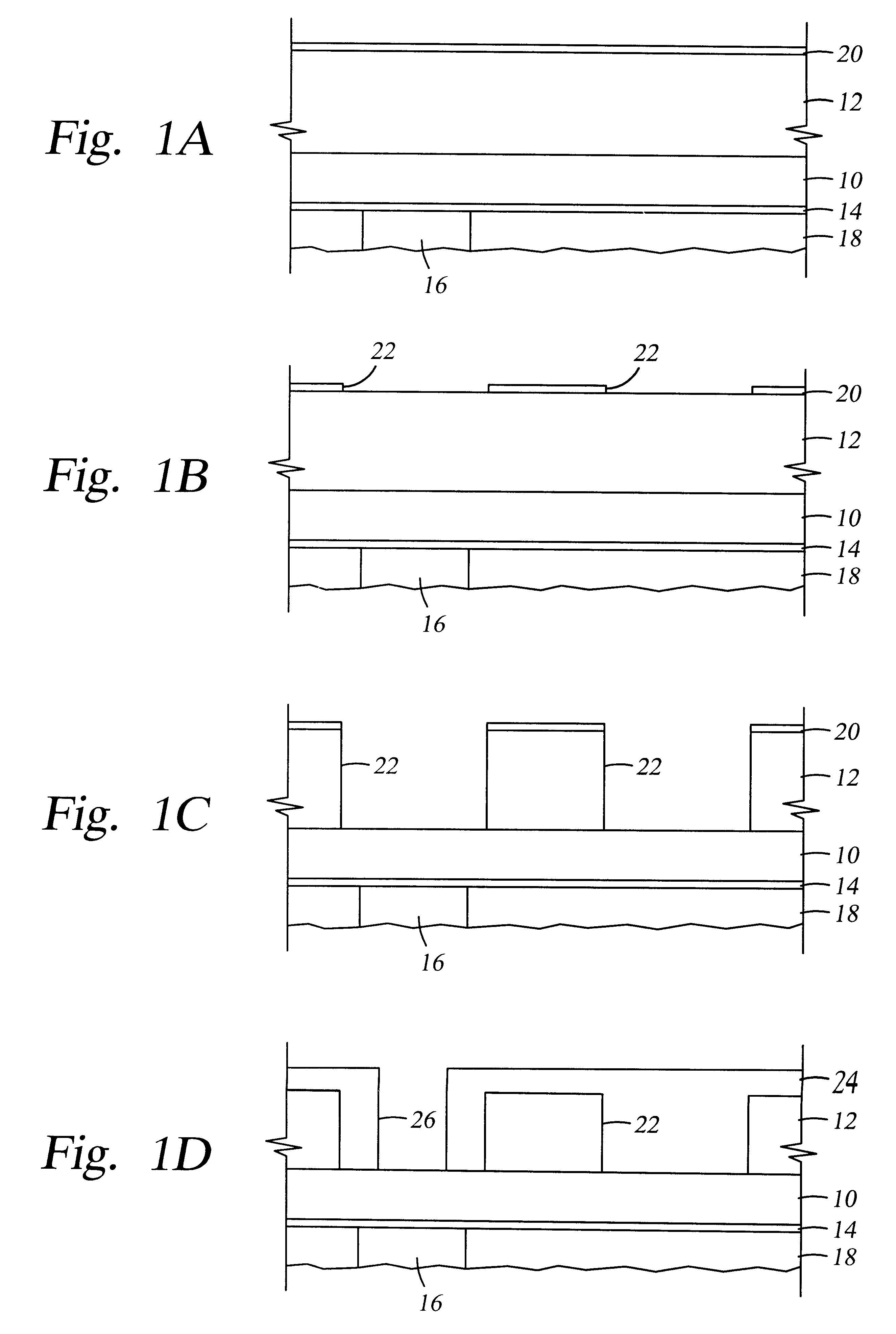

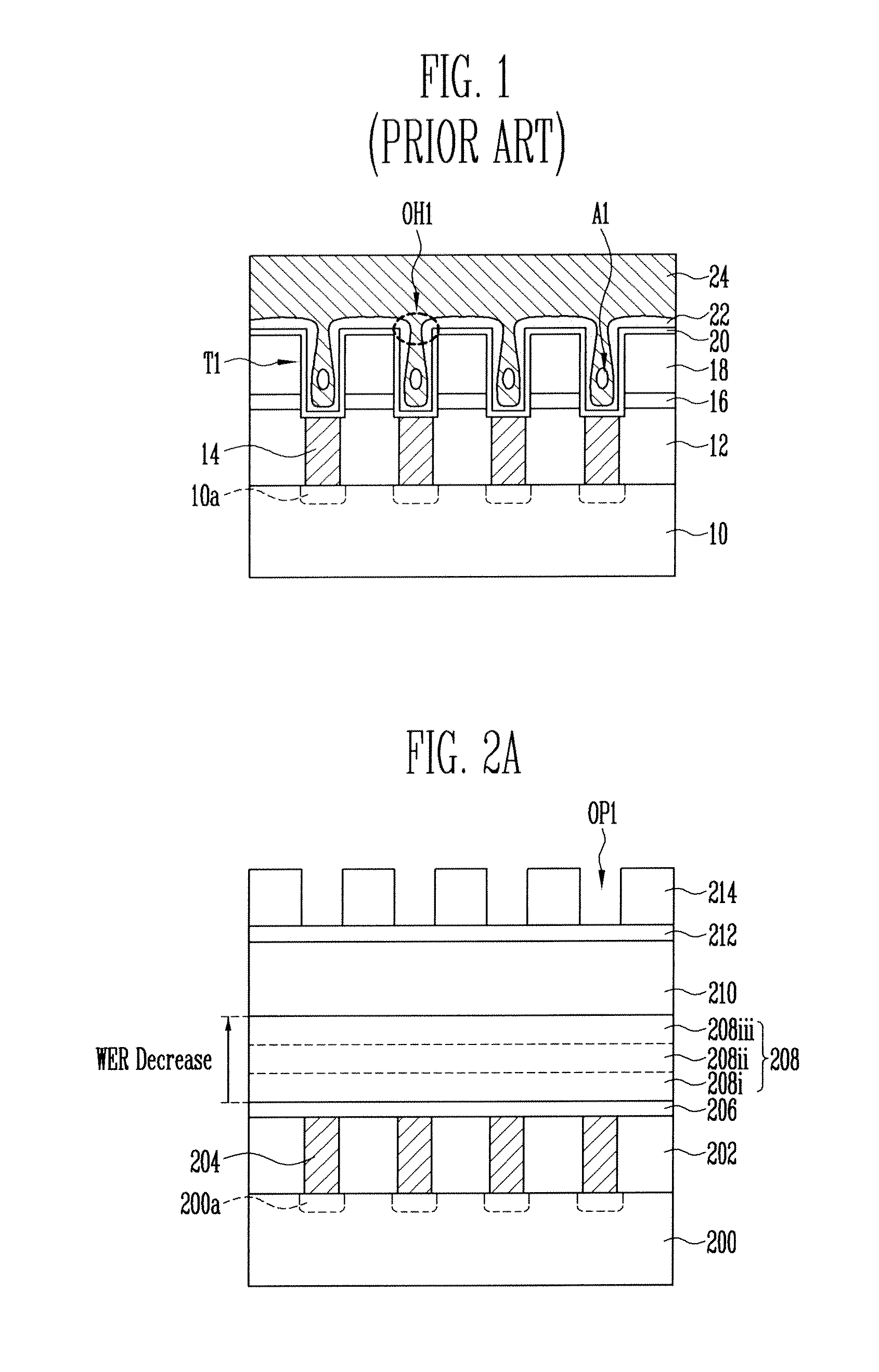

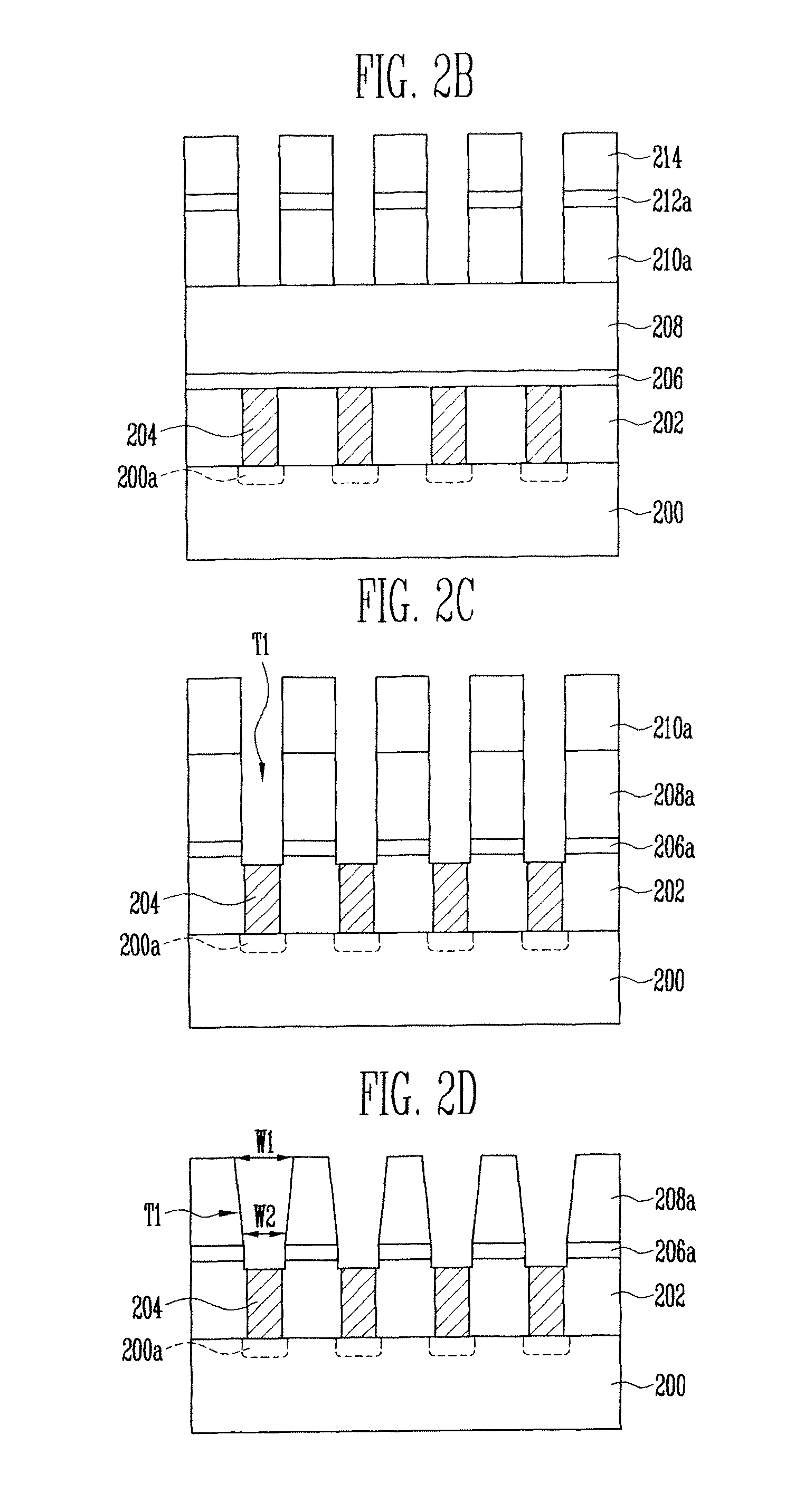

Method of manufacturing semiconductor devices

InactiveUS8293642B2Avoid it happening againIncrease intervalSemiconductor/solid-state device manufacturingEngineeringDielectric layer

A method of manufacturing semiconductor devices includes forming a dielectric interlayer over a semiconductor substrate, wherein a wet etch rate (WER) is faster in an upper part of the dielectric interlayer than in a lower part of the dielectric interlayer, forming trenches in the dielectric interlayer, performing a cleaning process to make a width of an opening portion in an upper part of each of the trenches wider than a width of an opening portion in lower part of the trench, and filling the trenches with a metal layer.

Owner:SK HYNIX INC

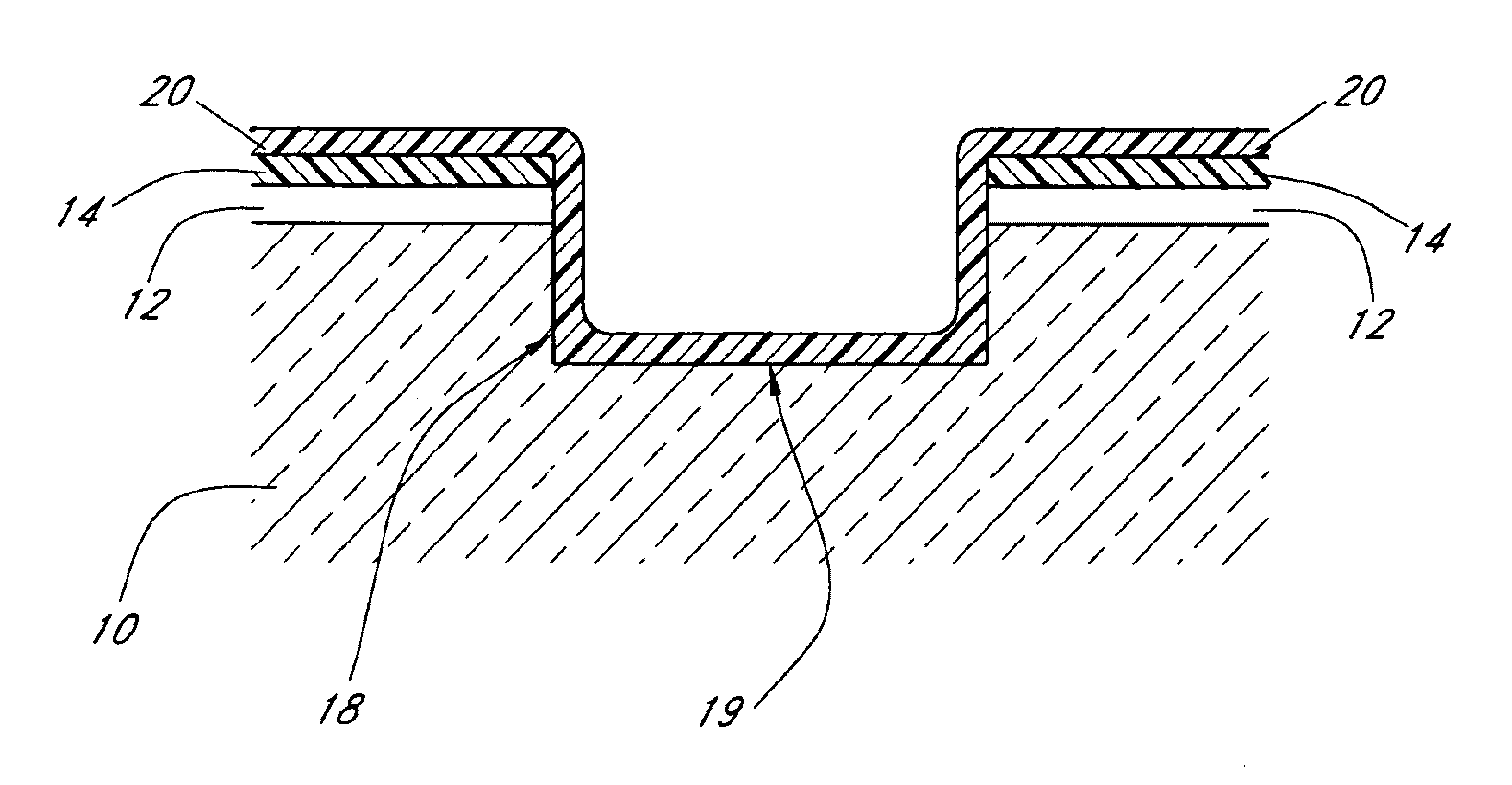

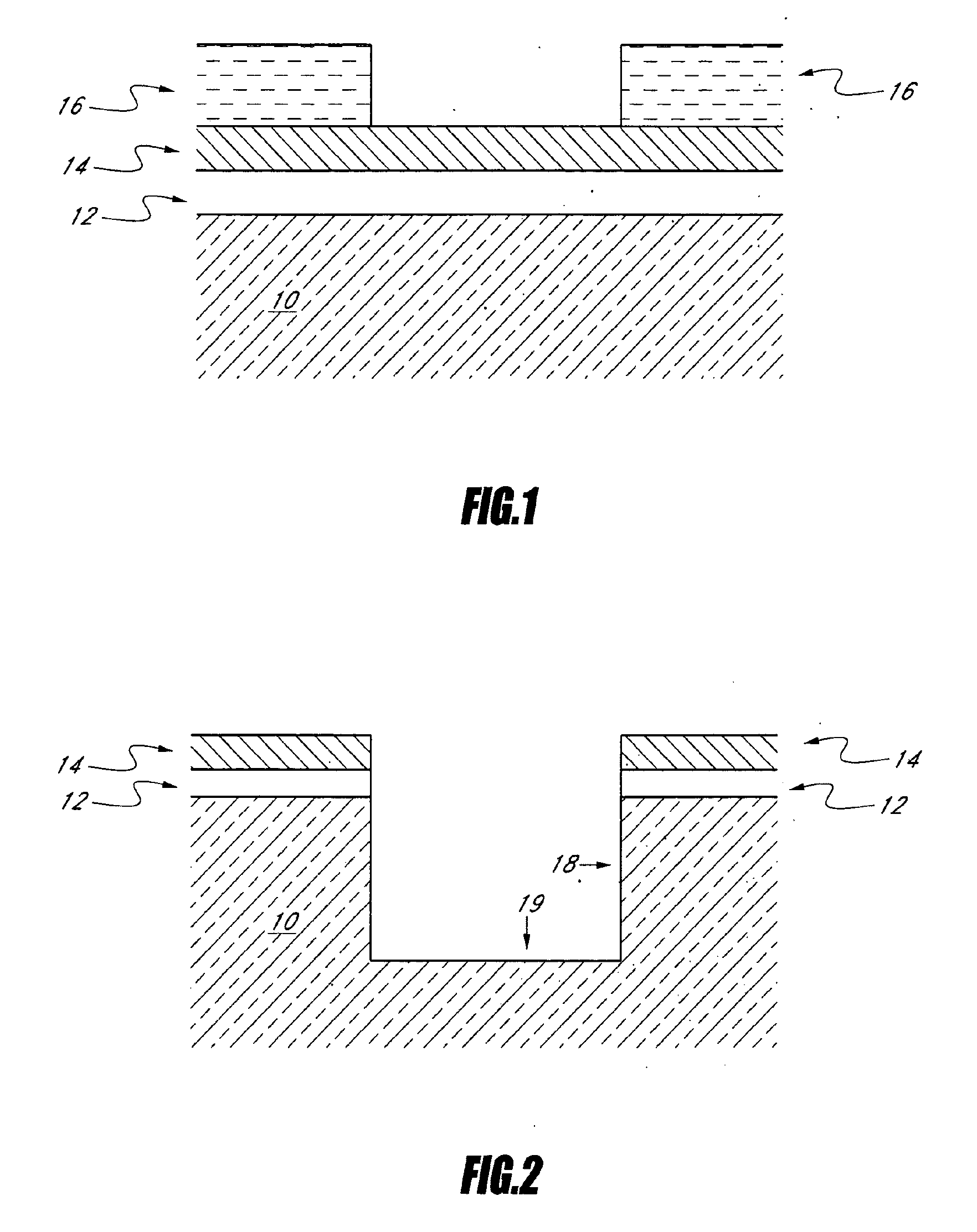

Trench insulation structures and methods

Owner:MICRON TECH INC

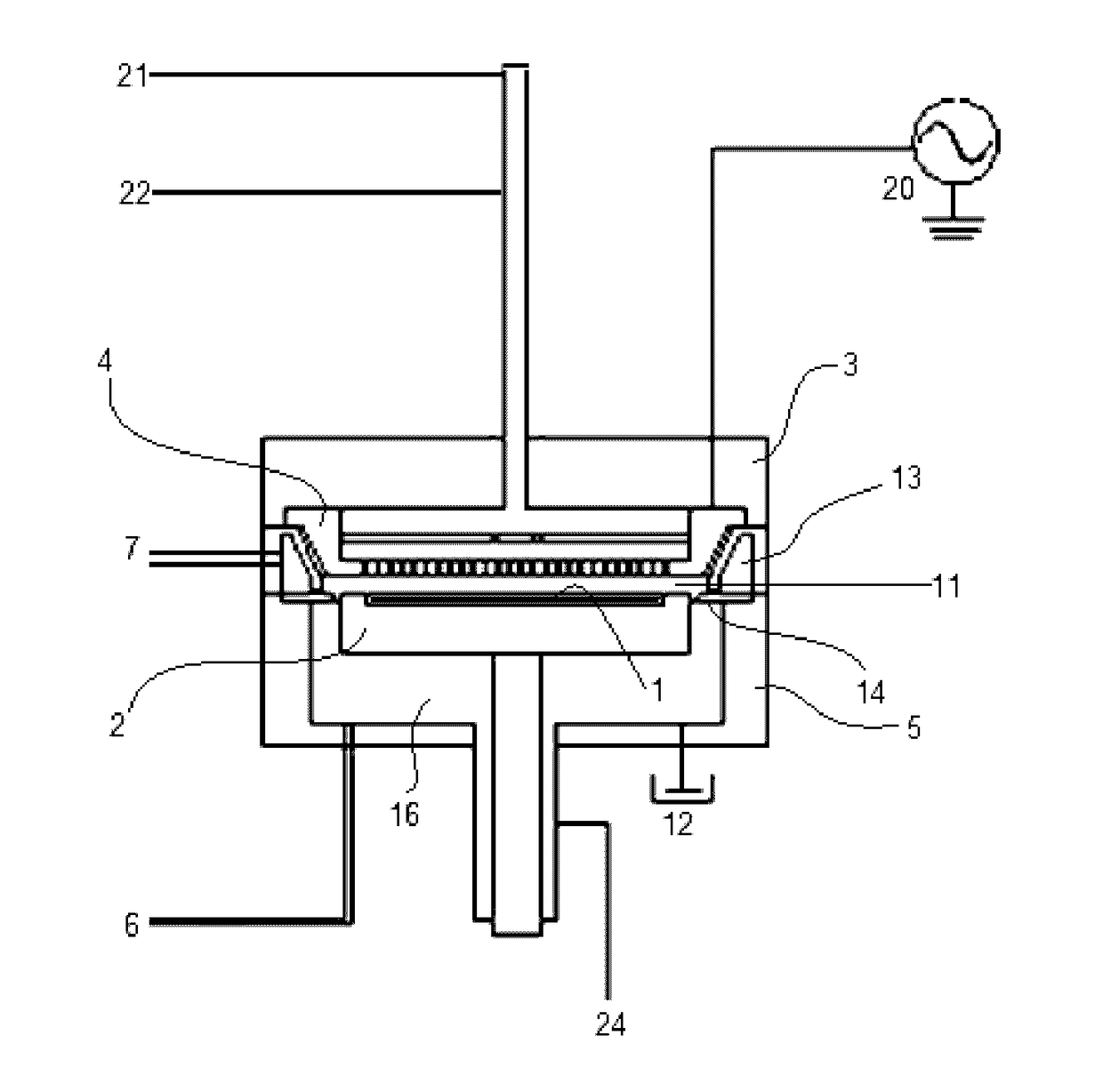

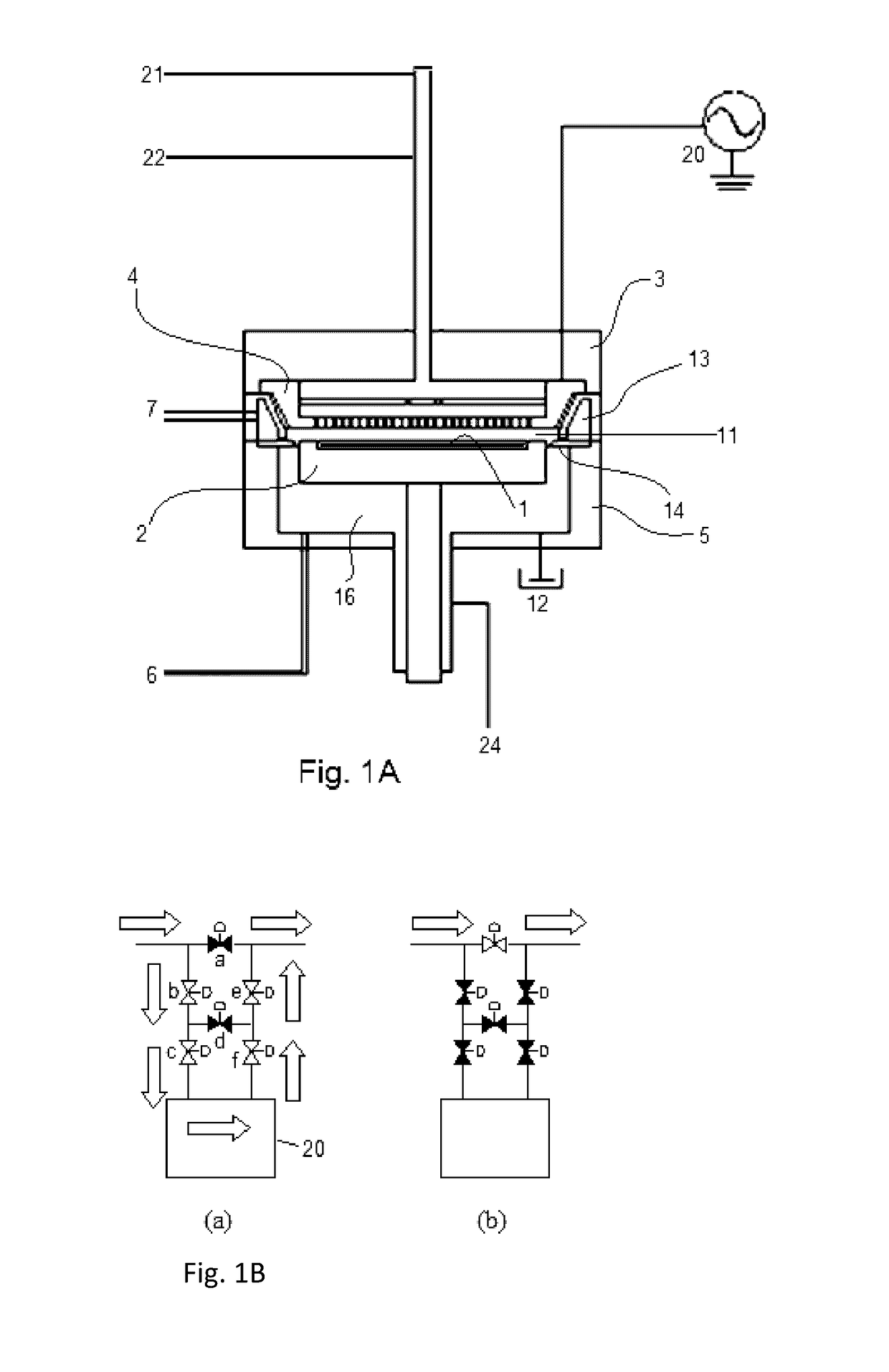

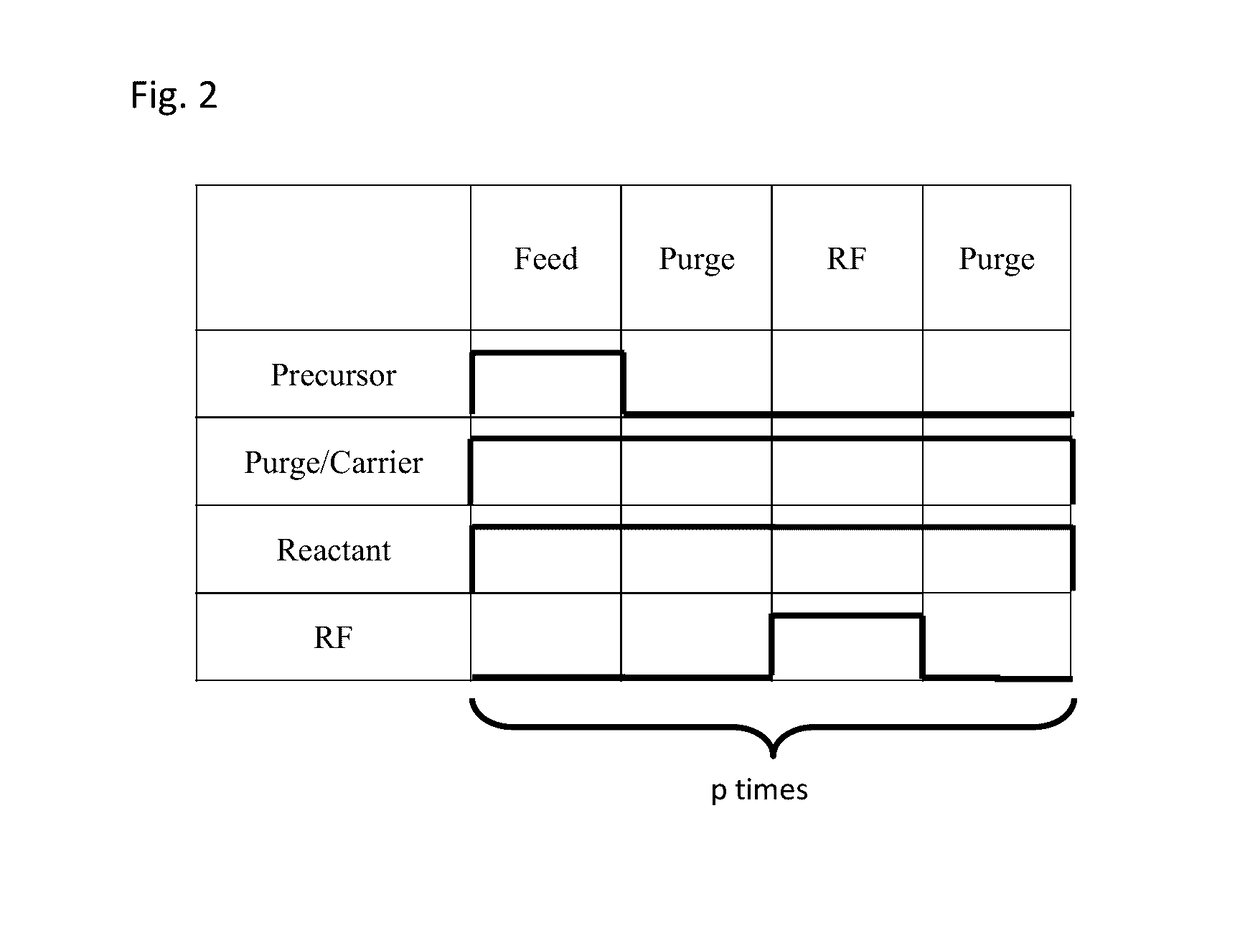

Method for depositing dielectric film in trenches by peald

ActiveUS20170107621A1Quality improvementReduce the differenceElectric discharge tubesSemiconductor/solid-state device manufacturingEngineeringAtomic layer deposition

A method for depositing a dielectric film in a trench by plasma-enhanced atomic layer deposition (PEALD) includes depositing a dielectric film in a trench of a substrate by PEALD under conditions wherein the wet etch rate of the depositing film on a top surface of the substrate is substantially equivalent to or higher than the wet etch rate of the depositing film at a sidewall of the trench, wherein a precursor fed into the reaction space has —N(CH3)2 as a functional group.

Owner:ASM IP HLDG BV

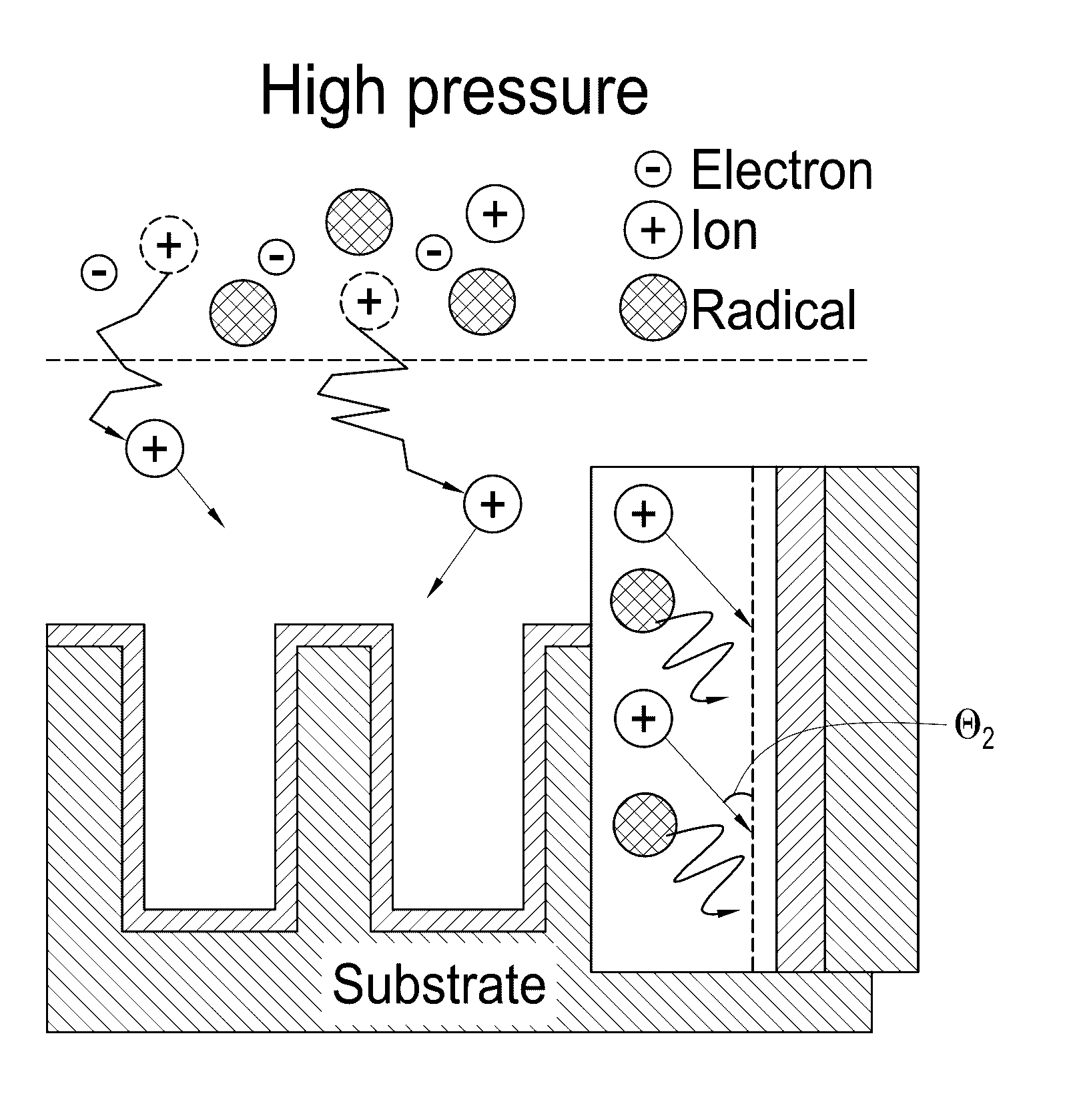

FORMATION OF SiN THIN FILMS

ActiveUS20170062204A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingNitrogen plasmaHigh pressure

Methods of forming silicon nitride thin films on a substrate in a reaction space under high pressure are provided. The methods can include a plurality of plasma enhanced atomic layer deposition (PEALD) cycles, where at least one PEALD deposition cycle comprises contacting the substrate with a nitrogen plasma at a process pressure of 20 Torr to 500 Torr within the reaction space. In some embodiments the silicon precursor is a silyly halide, such as H2SiI2. In some embodiments the processes allow for the deposition of silicon nitride films having improved properties on three dimensional structures. For example, such silicon nitride films can have a ratio of wet etch rates on the top surfaces to the sidewall of about 1:1 in dilute HF.

Owner:ASM IP HLDG BV

Method for depositing dielectric film in trenches by PEALD

ActiveUS9909214B2Quality improvementReduce the differenceElectric discharge tubesDecorative surface effectsDielectric membraneThin membrane

A method for depositing a dielectric film in a trench by plasma-enhanced atomic layer deposition (PEALD) includes depositing a dielectric film in a trench of a substrate by PEALD under conditions wherein the wet etch rate of the depositing film on a top surface of the substrate is substantially equivalent to or higher than the wet etch rate of the depositing film at a sidewall of the trench, wherein a precursor fed into the reaction space has —N(CH3)2 as a functional group.

Owner:ASM IP HLDG BV

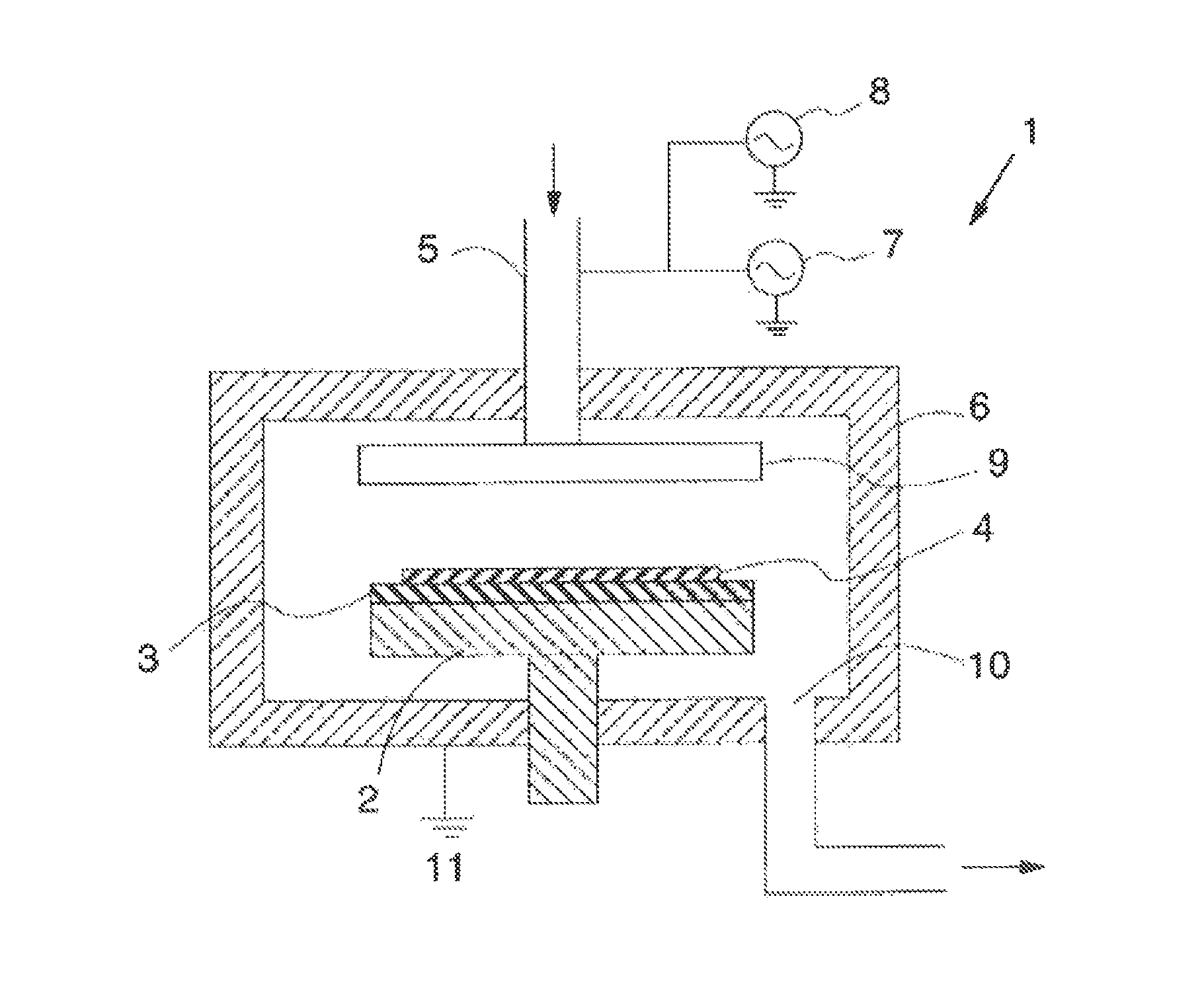

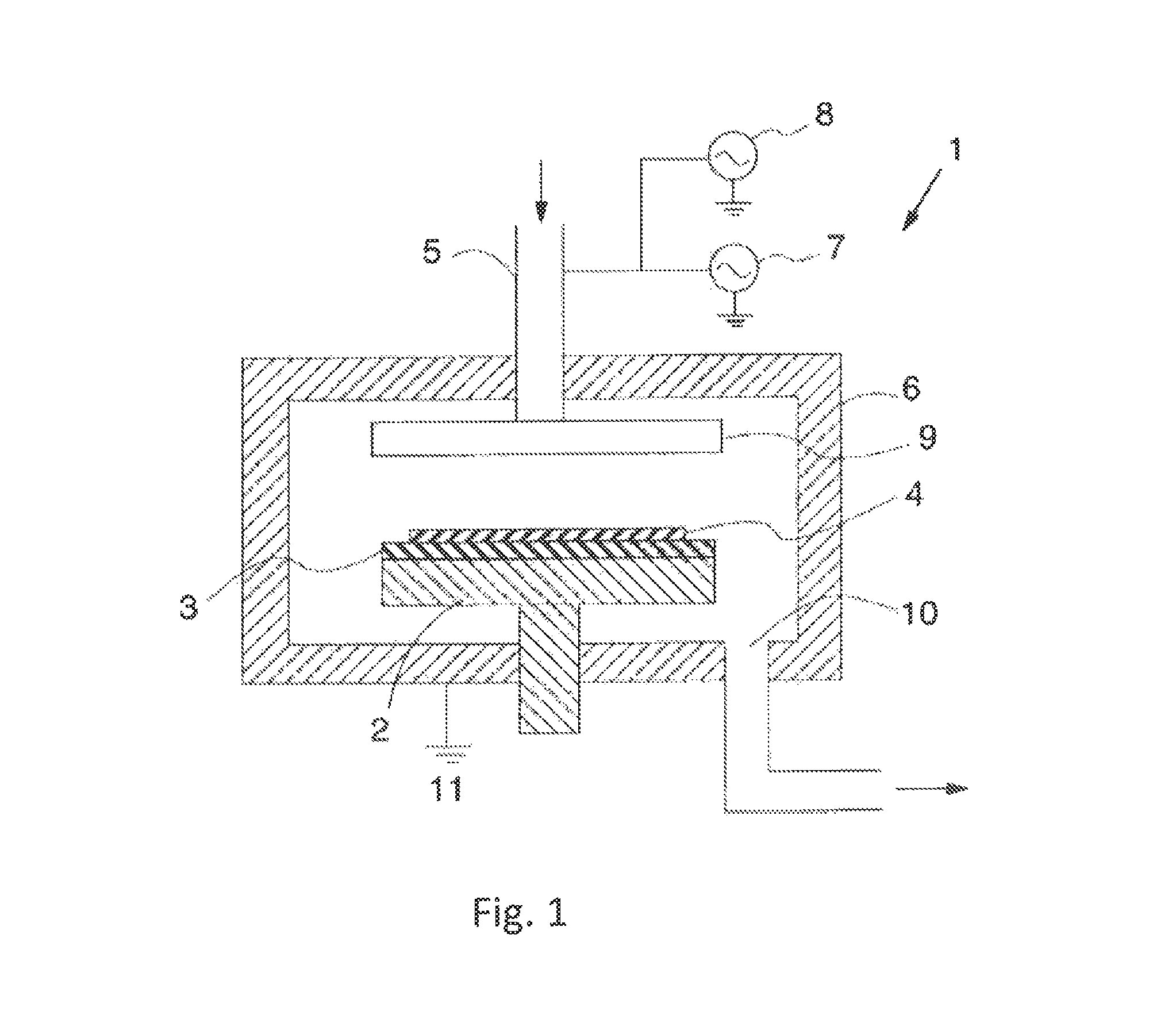

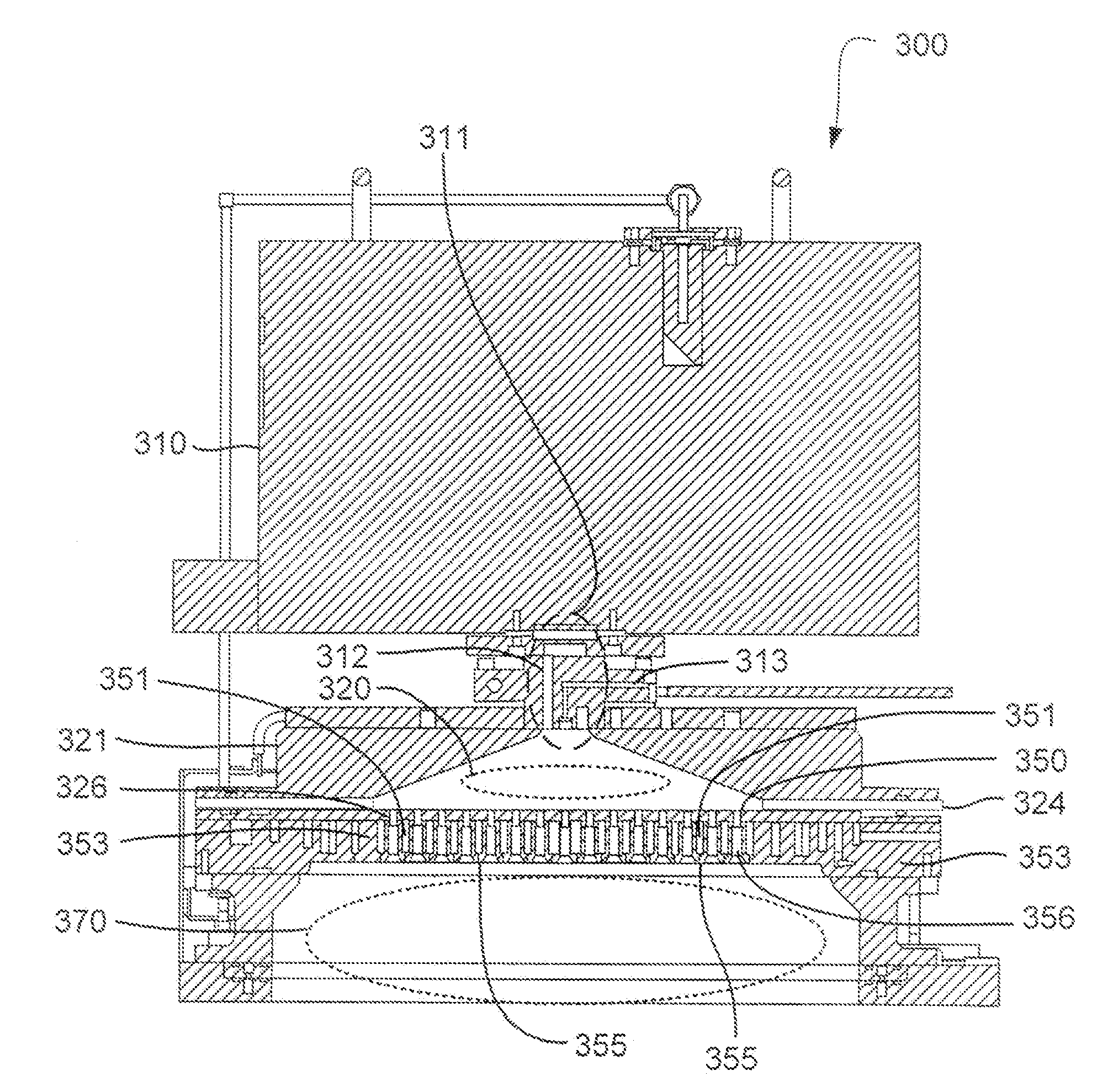

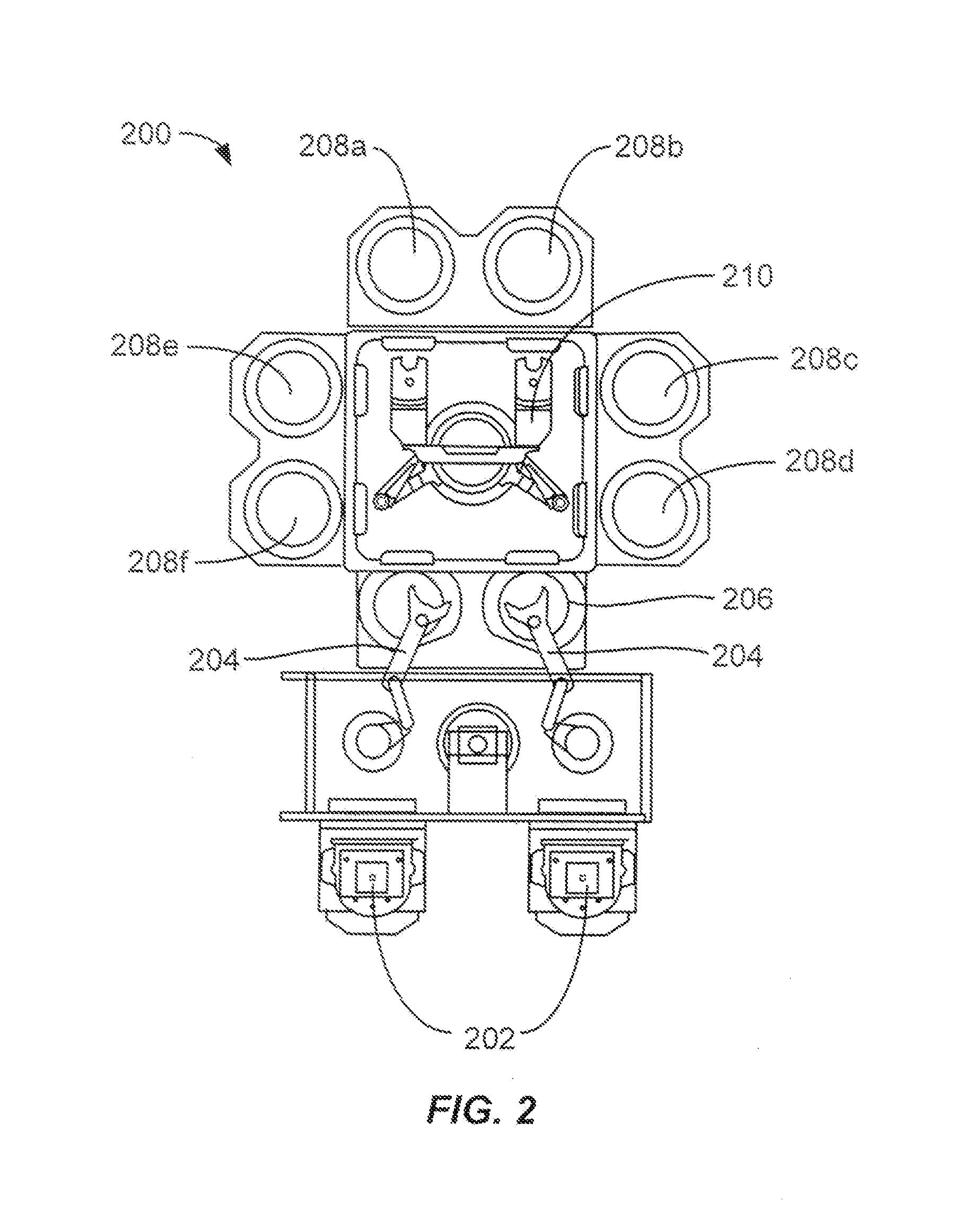

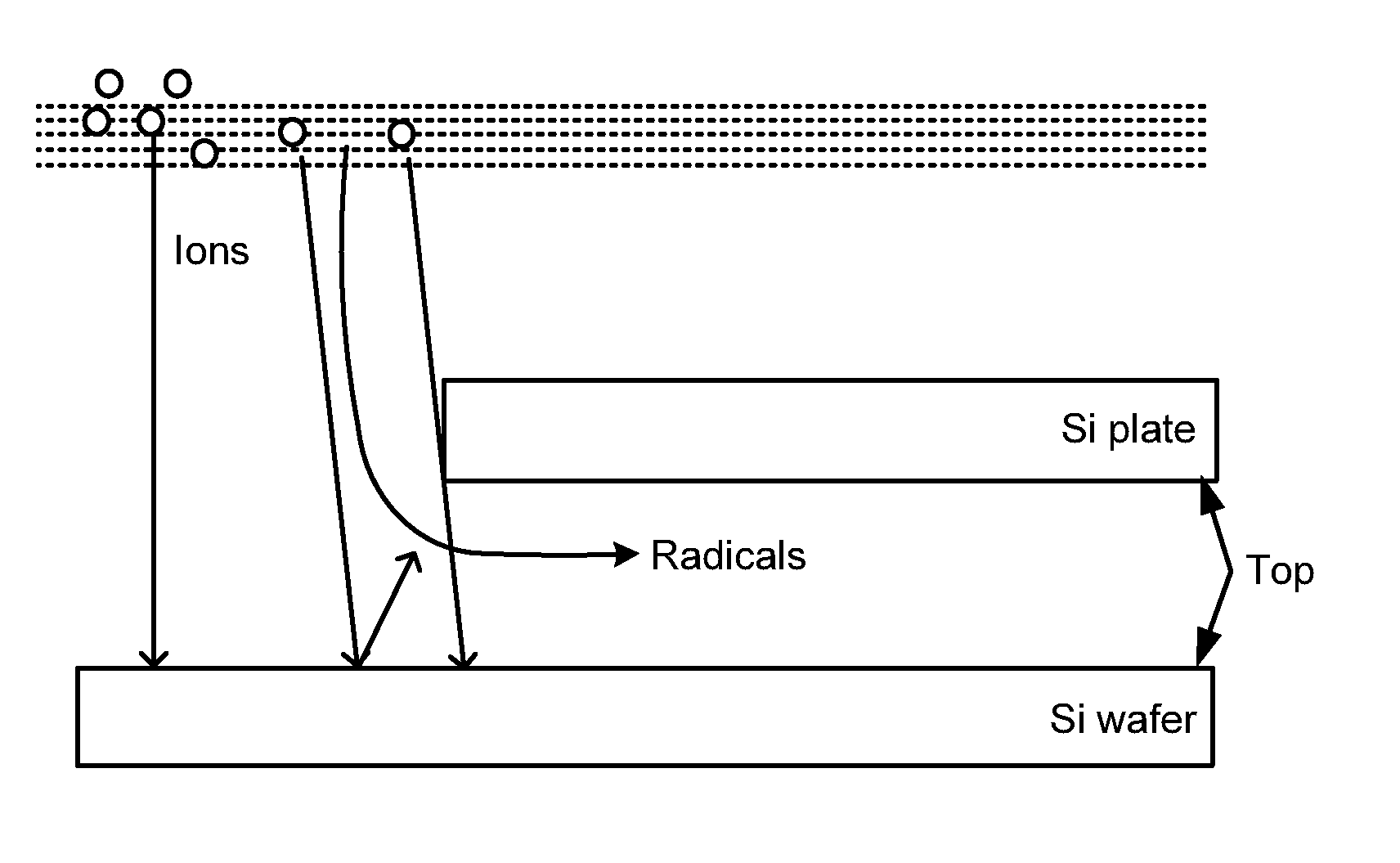

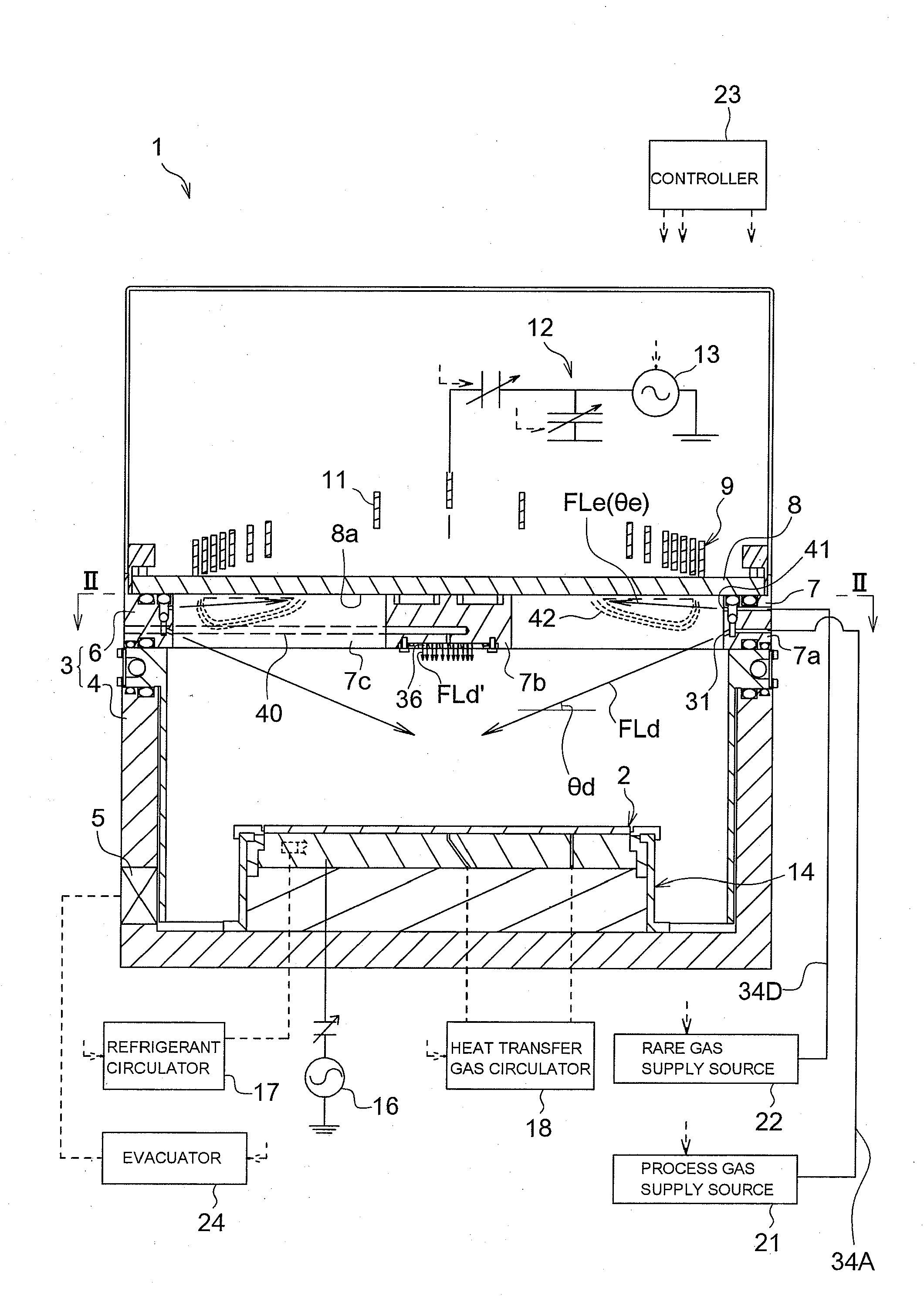

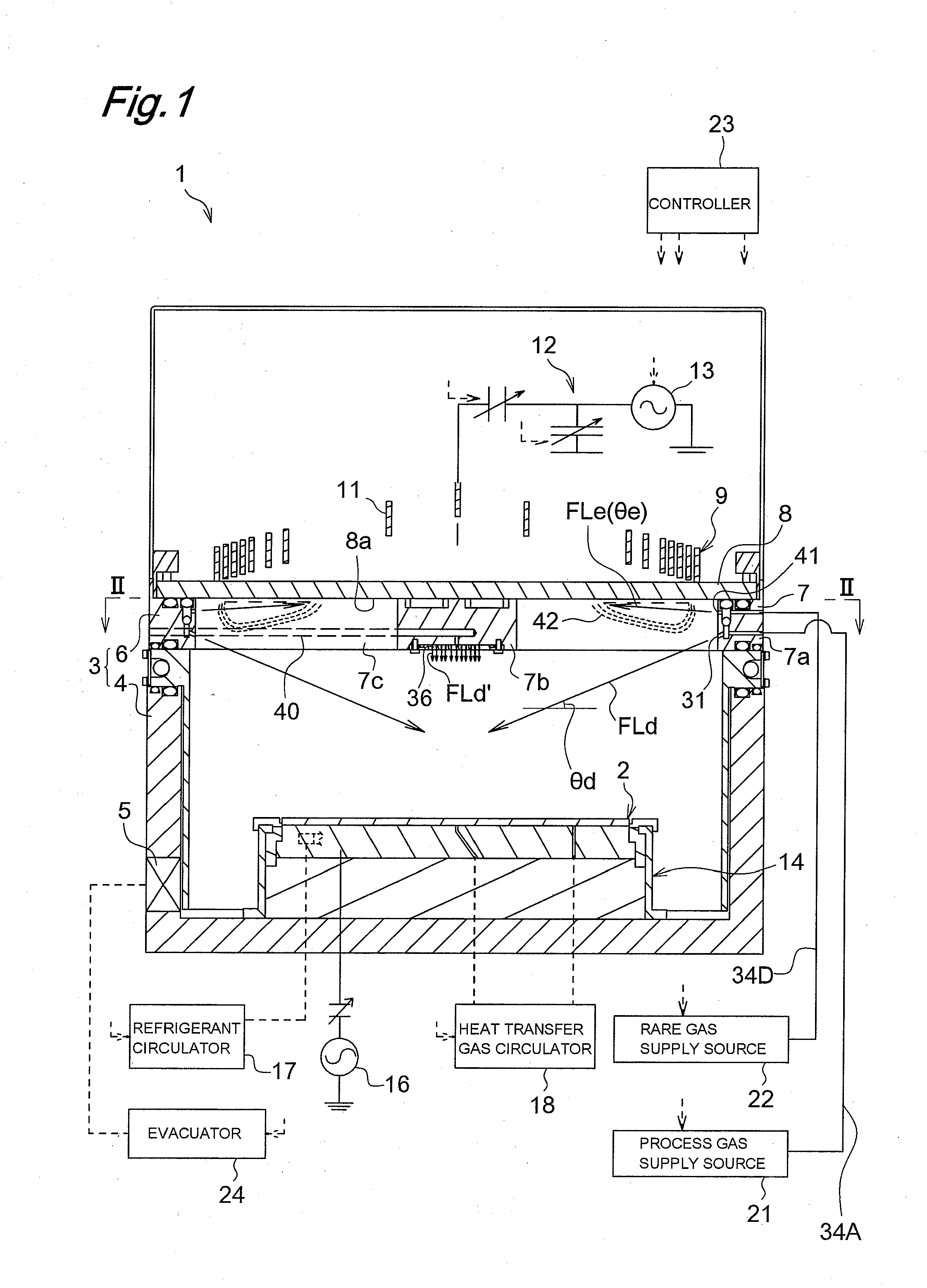

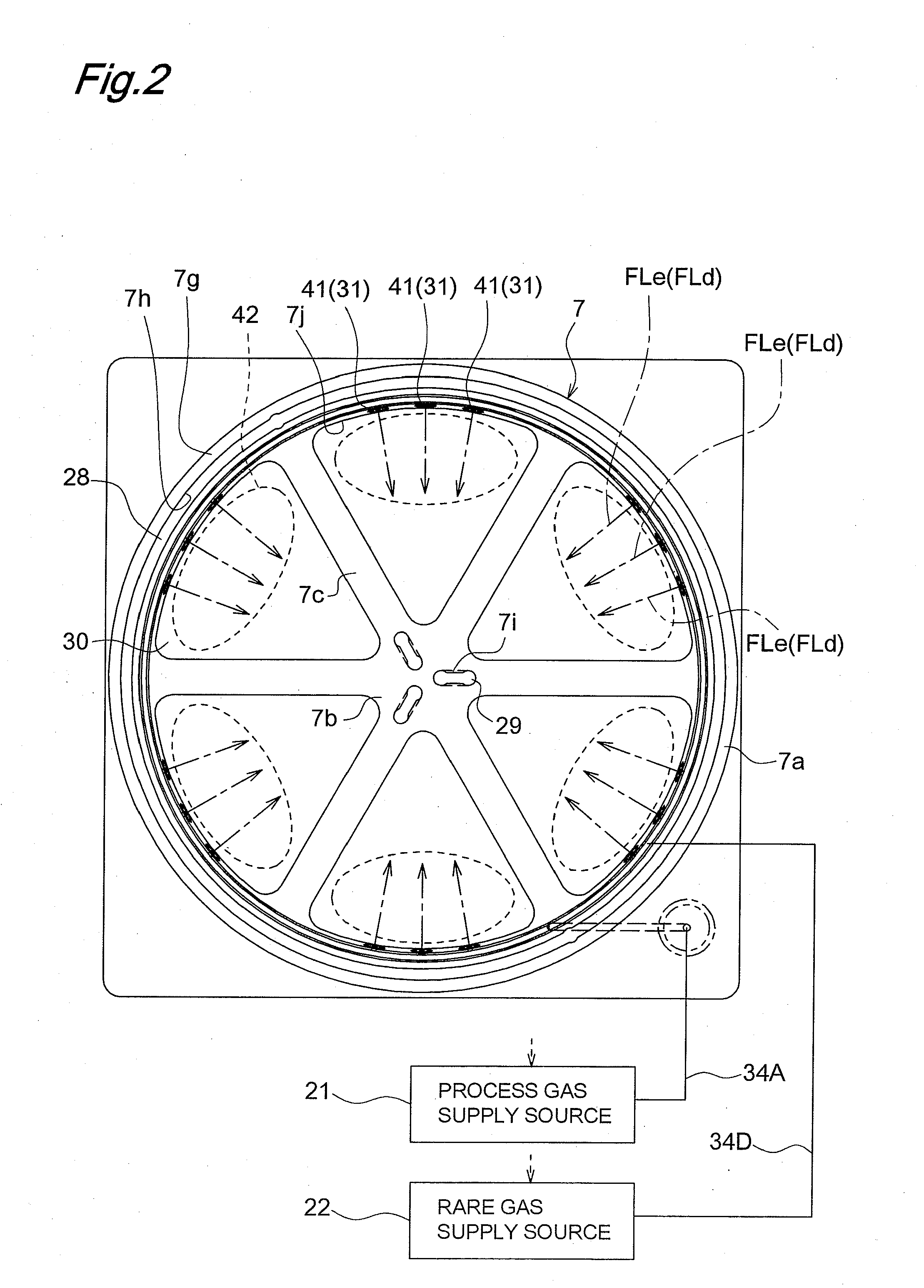

Plasma processing apparatus and plasma processing method

ActiveUS20100089870A1Improve processing speedEffective suppression of wearElectric discharge tubesDecorative surface effectsElevation angleNoble gas

A plasma processing apparatus includes a beam-shaped spacer 7 which is placed at an upper opening of a chamber 3 opposed to a substrate 2 to support a dielectric plate 8. The dielectric plate 8 is supported by the beam-shaped spacer 7. In the beam-shaped spacer 7 are provided a plurality of process gas introducing ports 31, 36 which have a depression angle θd and which are provided downward and directed toward the substrate 2, as well as a plurality of rare gas introducing ports 41 having a elevation angle θe directed toward the dielectric plate 8. Improvement of processing rates such as etching rate as well as effective suppression of wear of the dielectric plate 8 can be achieved.

Owner:PANASONIC CORP

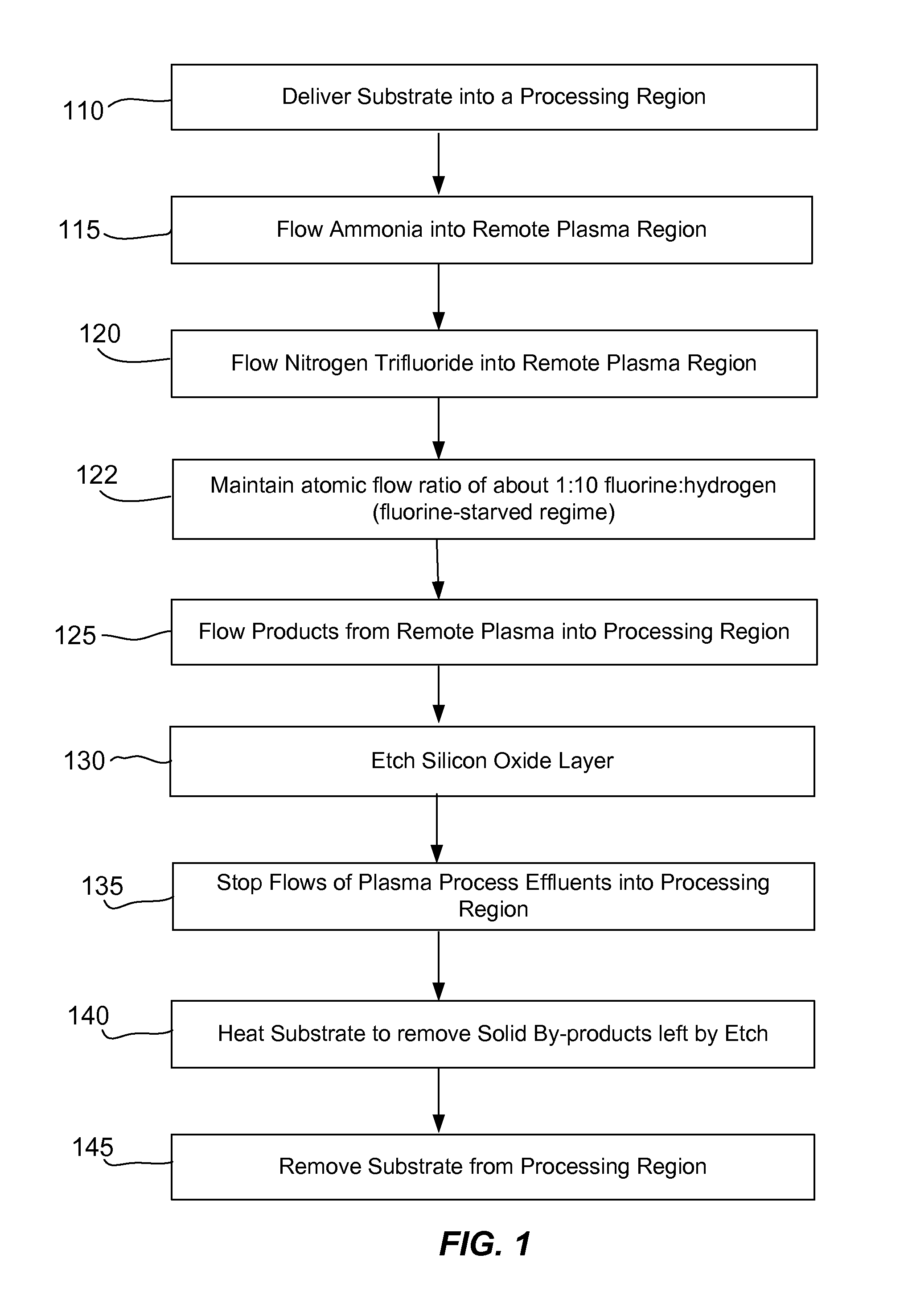

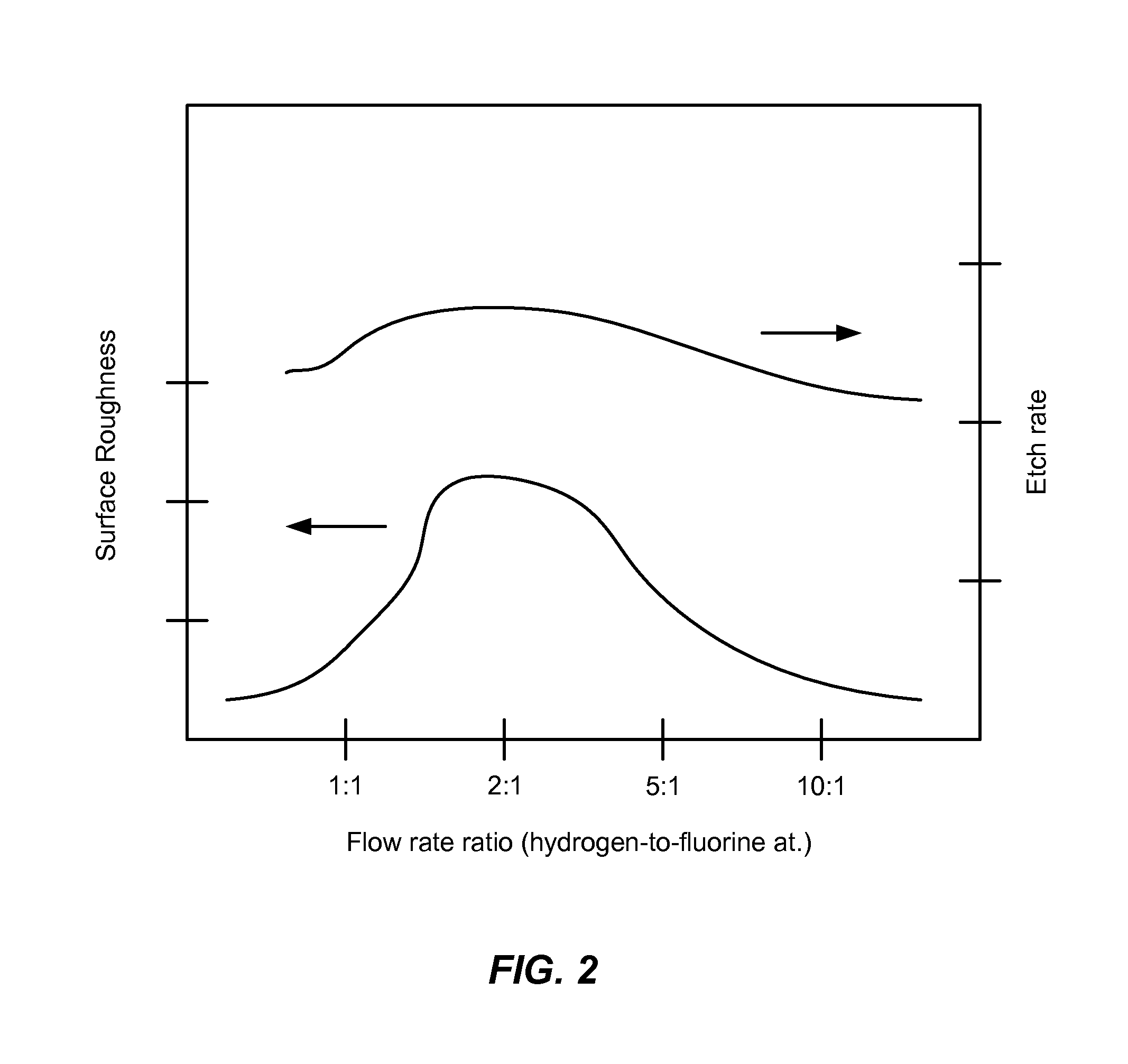

Smooth siconi etch for silicon-containing films

ActiveUS20110151674A1Great and less flow ratioReduce roughnessElectric discharge tubesDecorative surface effectsHydrogenSurface roughness

A method of etching silicon-containing material is described and includes a SiConi™ etch having a greater or lesser flow ratio of hydrogen compared to fluorine than that found in the prior art. Modifying the flow rate ratios in this way has been found to reduce roughness of the post-etch surface and to reduce the difference in etch-rate between densely and sparsely patterned areas. Alternative means of reducing post-etch surface roughness include pulsing the flows of the precursors and / or the plasma power, maintaining a relatively high substrate temperature and performing the SiConi™ in multiple steps. Each of these approaches, either alone or in combination, serve to reduce the roughness of the etched surface by limiting solid residue grain size.

Owner:APPLIED MATERIALS INC

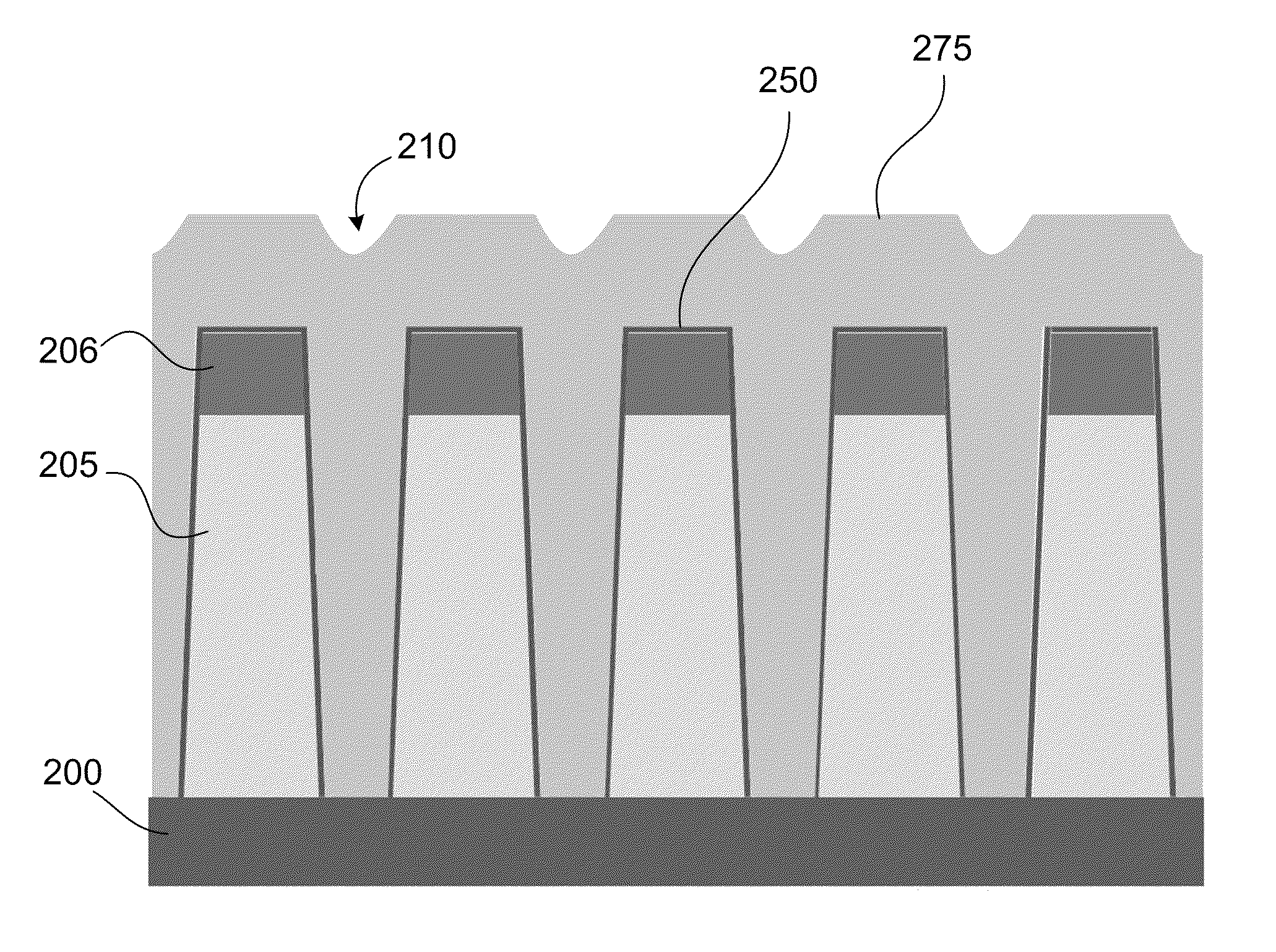

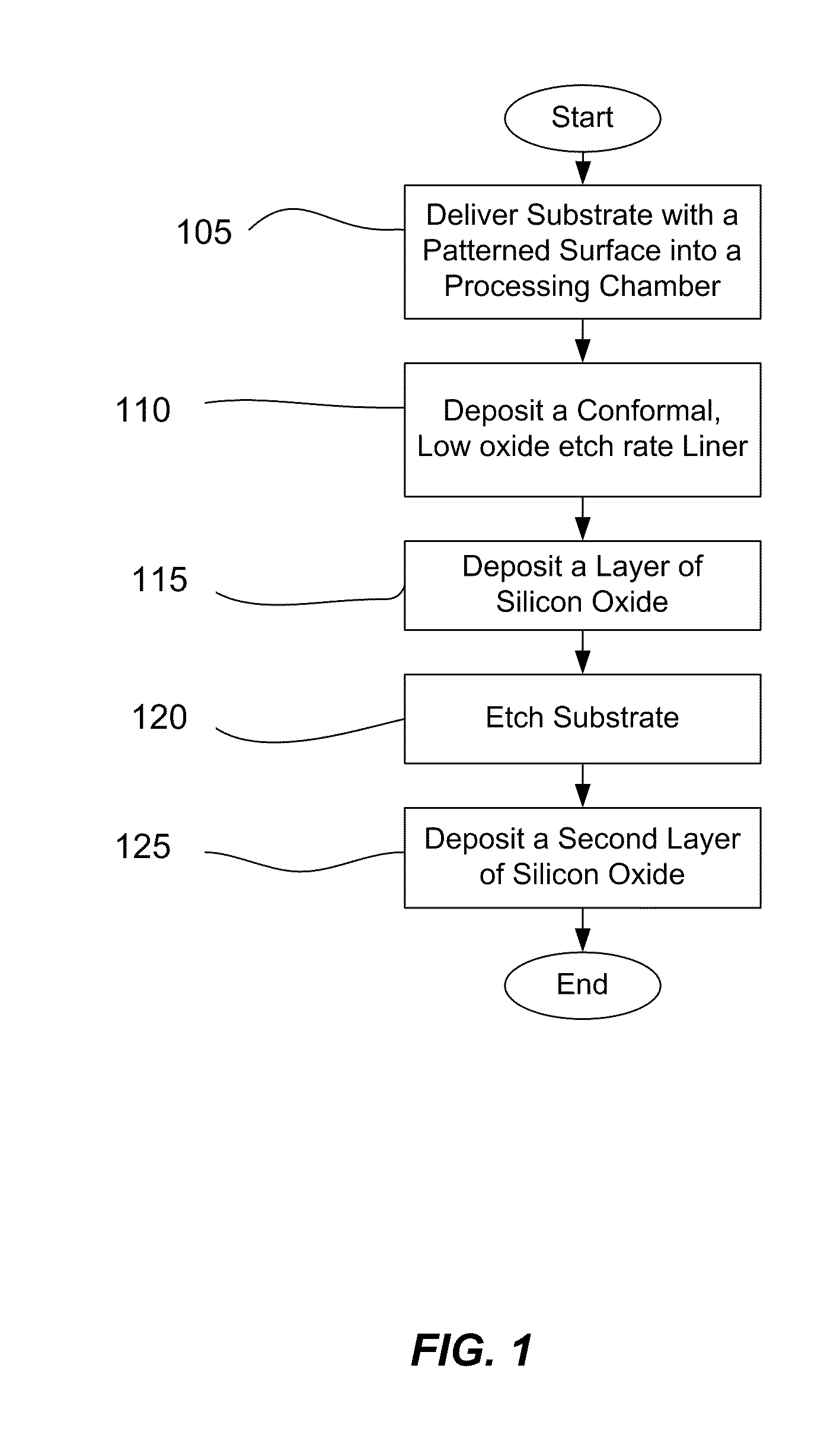

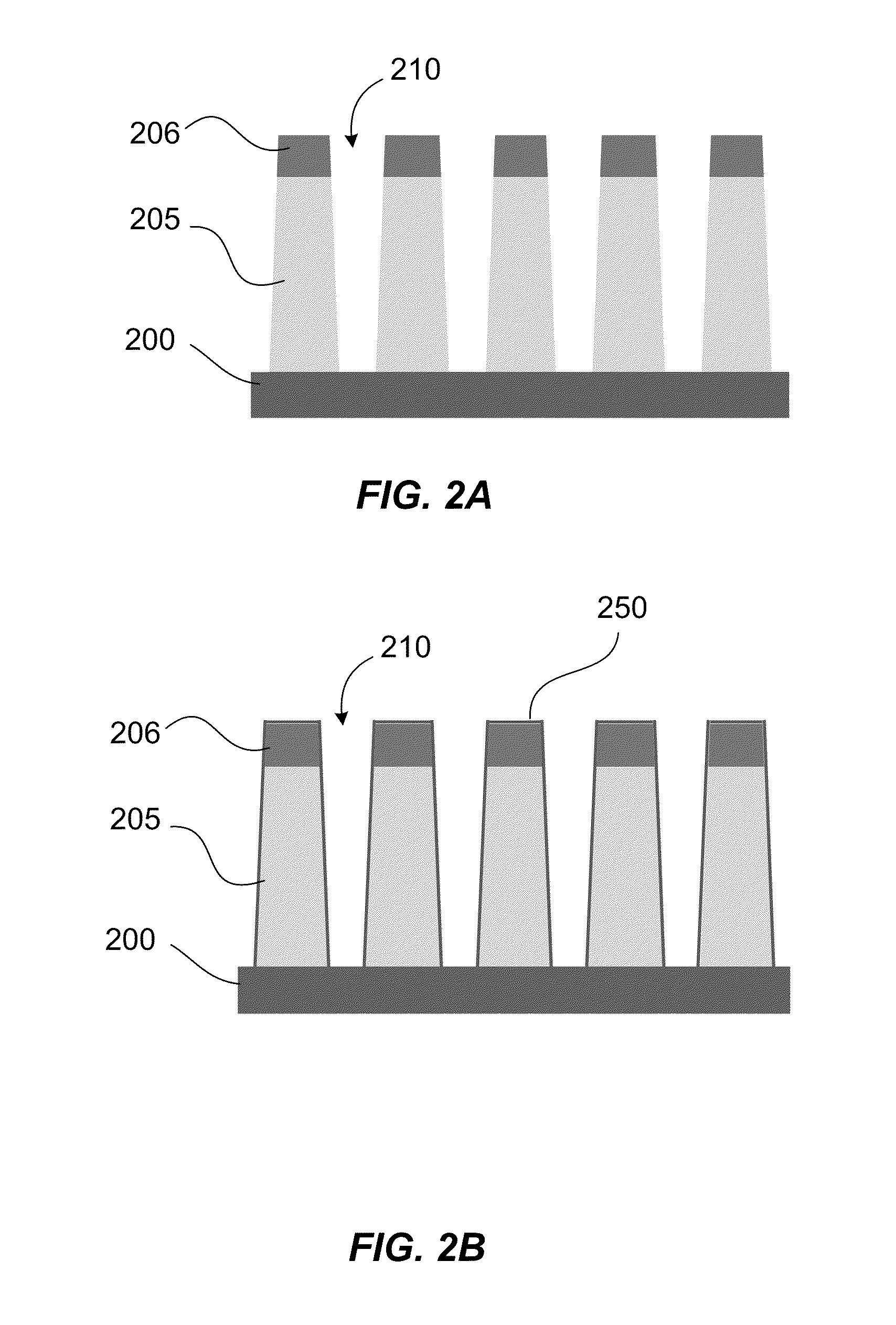

Gapfill improvement with low etch rate dielectric liners

A method of filling a trench is described and includes depositing a dielectric liner with a high ratio of silicon oxide to dielectric liner etch rate in fluorine-containing etch chemistries. Silicon oxide is deposited within the trench and etched to reopen or widen a gap near the top of the trench. The dielectric liner protects the underlying substrate during the etch process so the gap can be made wider. Silicon oxide is deposited within the trench again to substantially fill the trench.

Owner:APPLIED MATERIALS INC

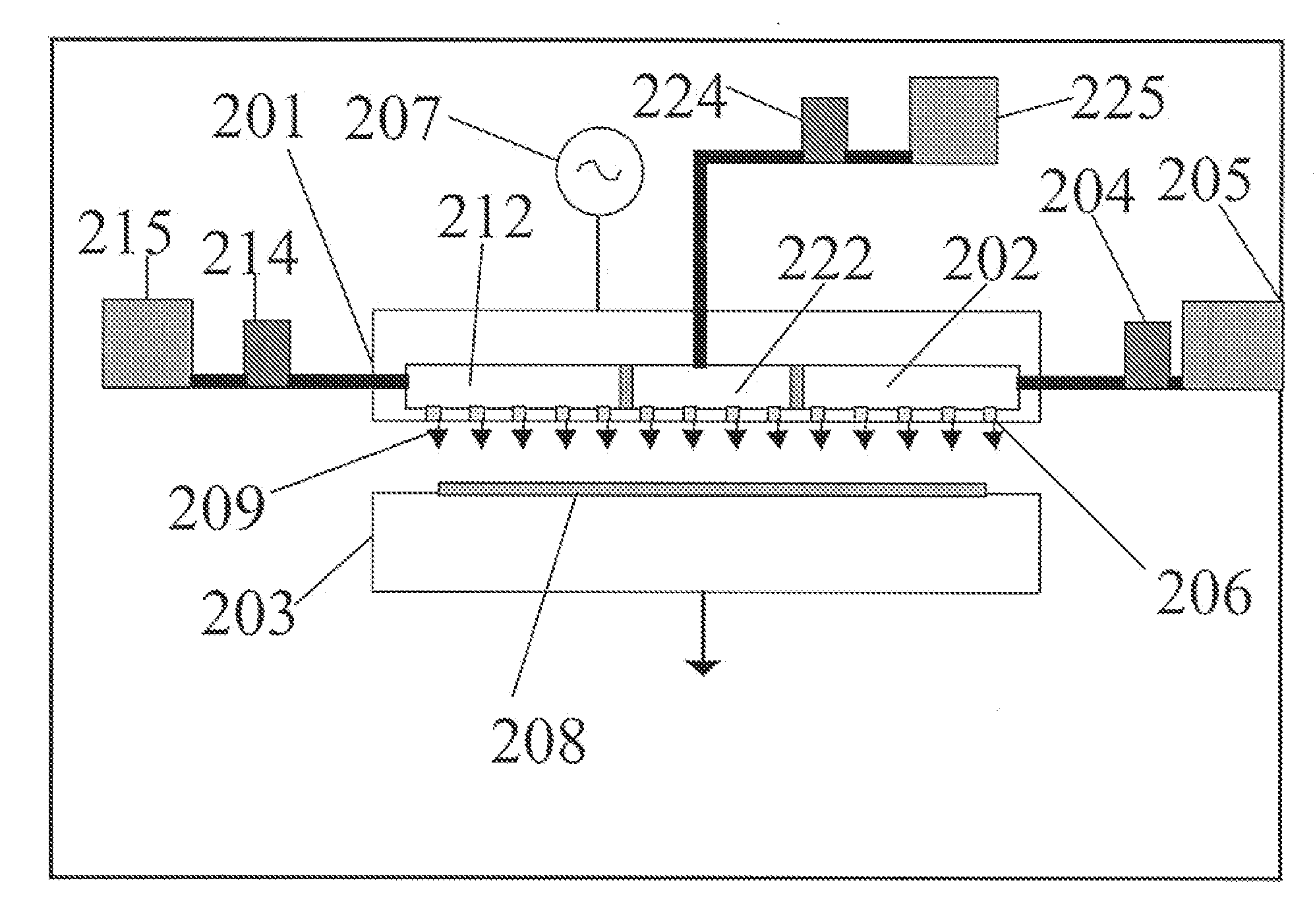

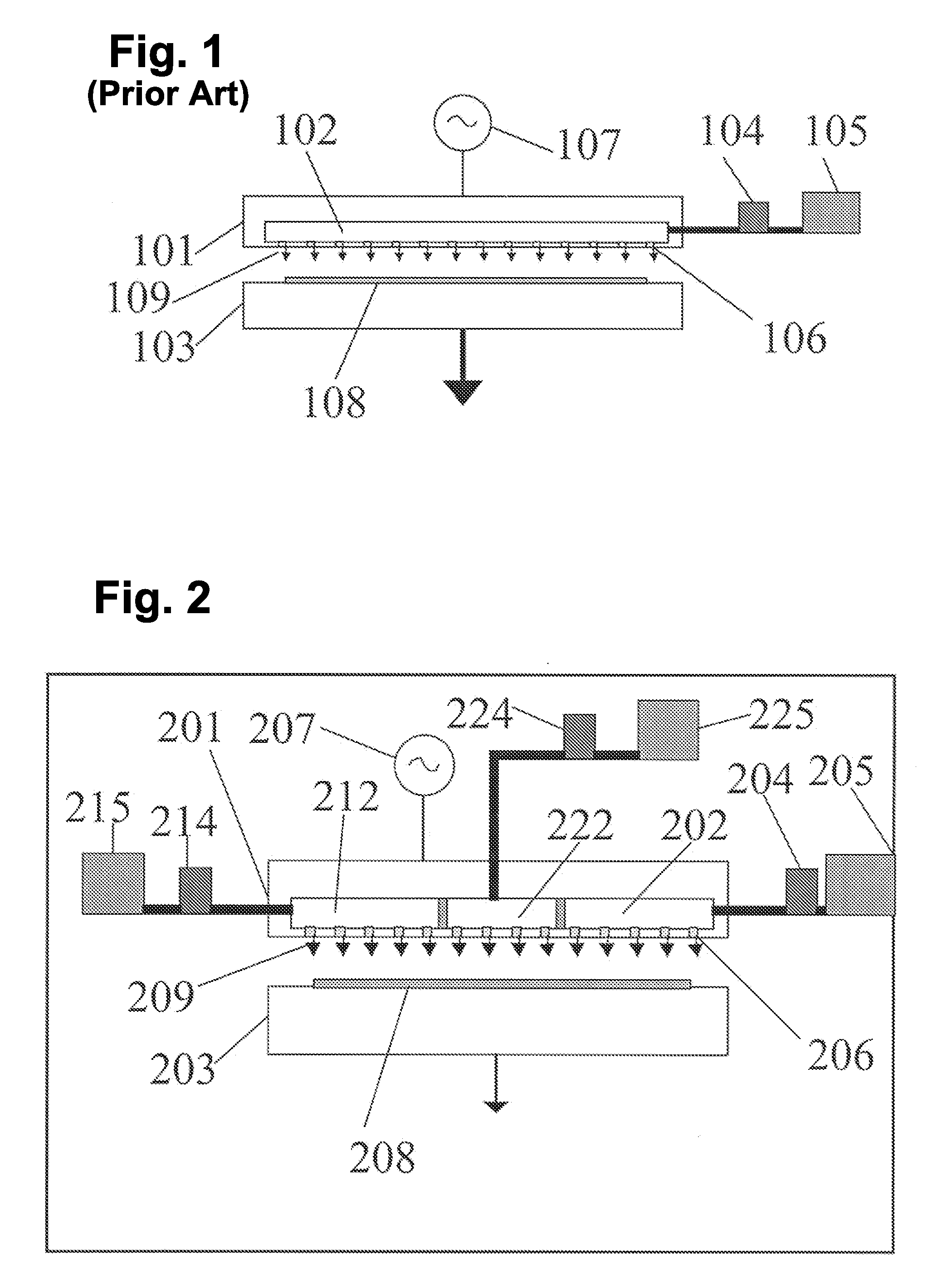

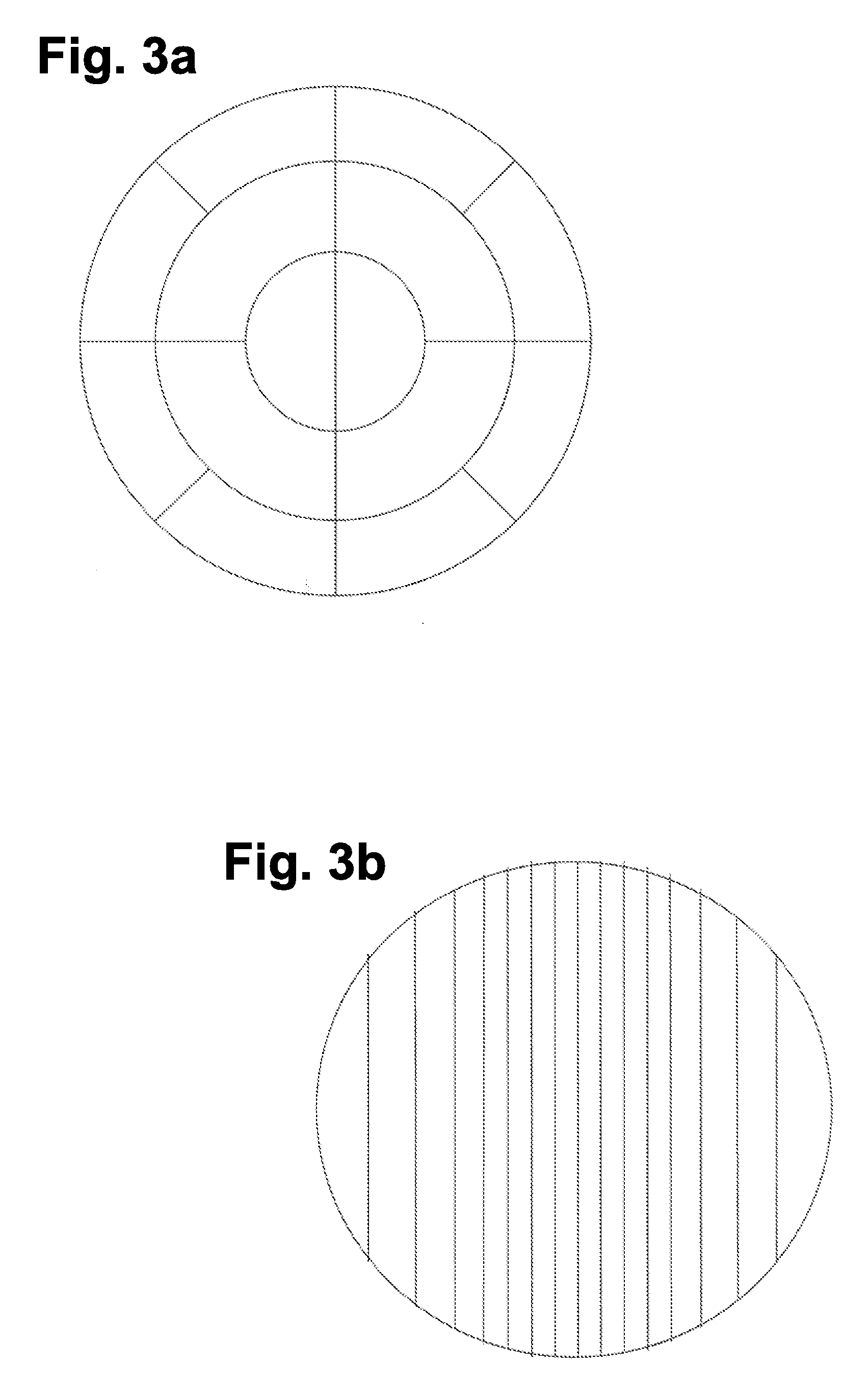

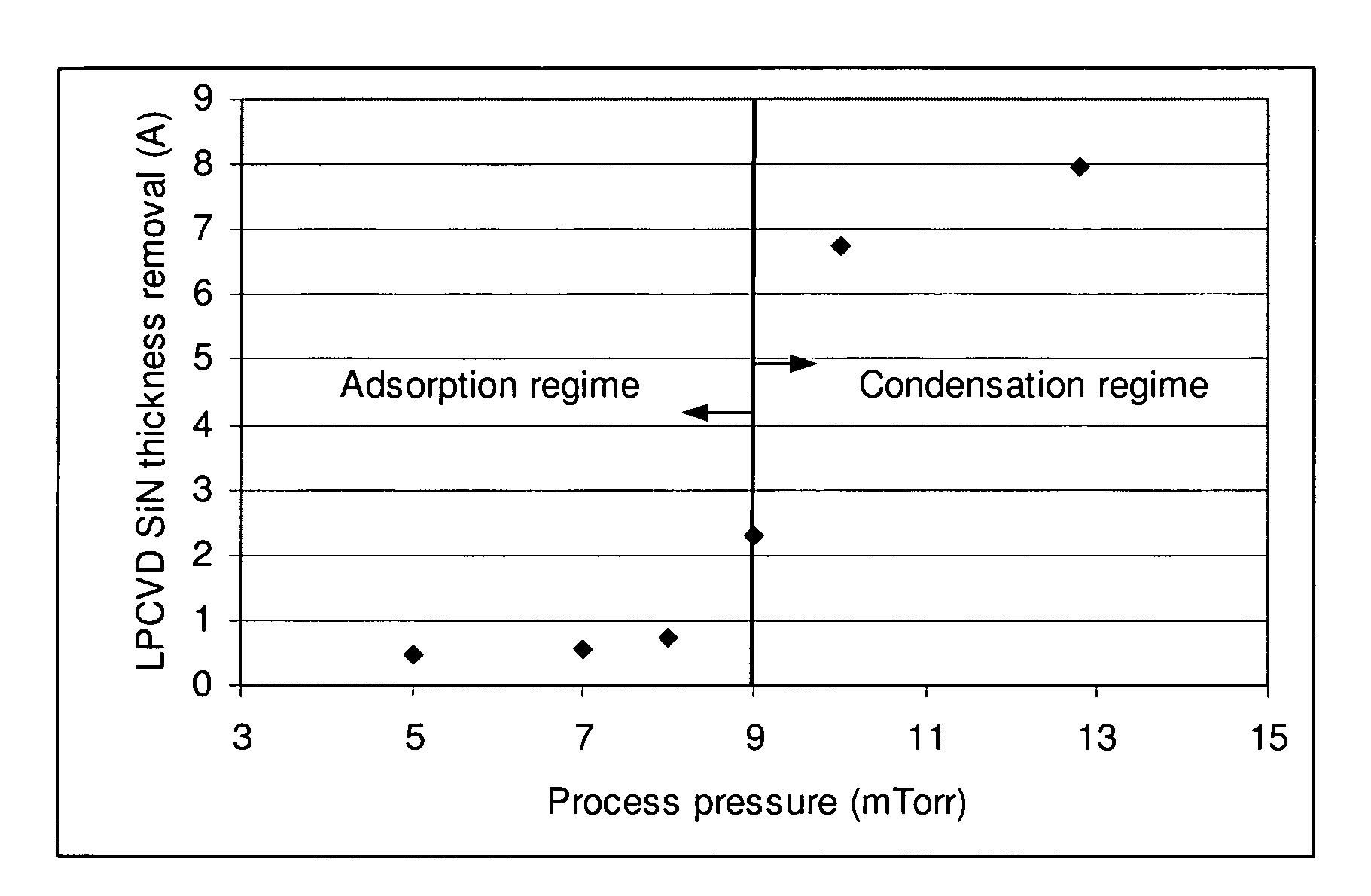

Etching Apparatus and Process with Thickness and Uniformity Control

InactiveUS20060191637A1Improve uniformityReduce unevennessElectric discharge tubesDecorative surface effectsEngineeringFilm material

Apparatus and process for etching semiconductor wafers and the like in which a substrate is supported by a pedestal within a chamber, and at least one gas capable of etching the substrate or a film material on the substrate is introduced into the chamber through a segmented gas injection element which is separated from the substrate by a distance approximately less than its size from which the distribution of the flow or mixture of gas can be altered spatially proximate to the substrate in a controlled and variable way, for each wafer or substrate if desired, by having a varying amount or mixture of gas flow to some or all of the segments such as to cause the etching rate distribution to vary across the substrate.

Owner:ZAJAC JOHN +1

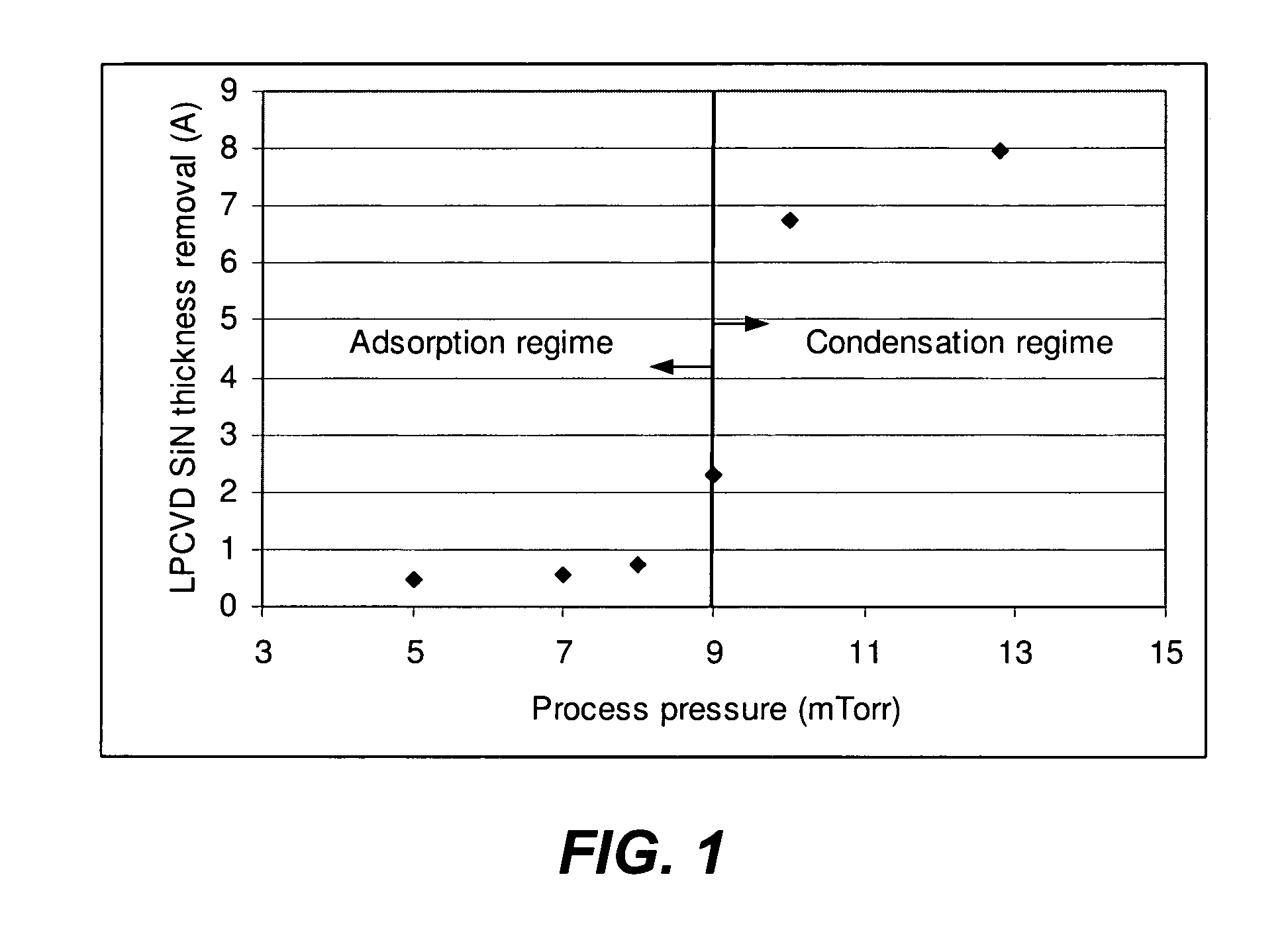

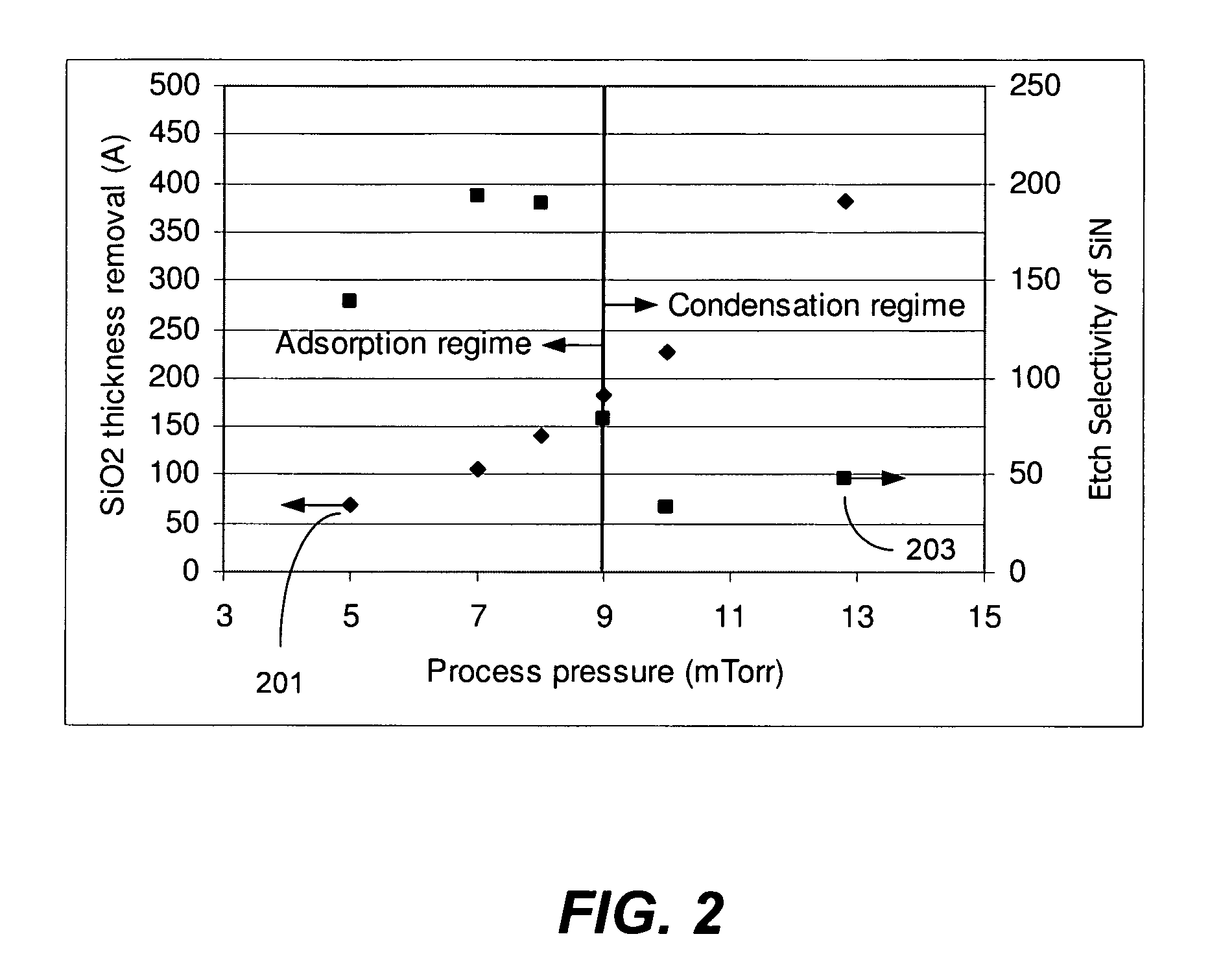

Modulating etch selectivity and etch rate of silicon nitride thin films

ActiveUS8187486B1Decorative surface effectsSemiconductor/solid-state device manufacturingNitrideMolecular physics

Etching of nitride and oxide layers with reactant gases is modulated by etching in different process regimes. High etch selectivity to silicon nitride is achieved in an adsorption regime where the partial pressure of the etchant is lower than its vapor pressure. Low etch selectivity to silicon nitride is achieved in a condensation regime where the partial pressure of the etchant is higher than its vapor pressure. By controlling partial pressure of the etchant, very high etch selectivity to silicon nitride may be achieved.

Owner:NOVELLUS SYSTEMS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com