Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

479results about How to "Reduce line width" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

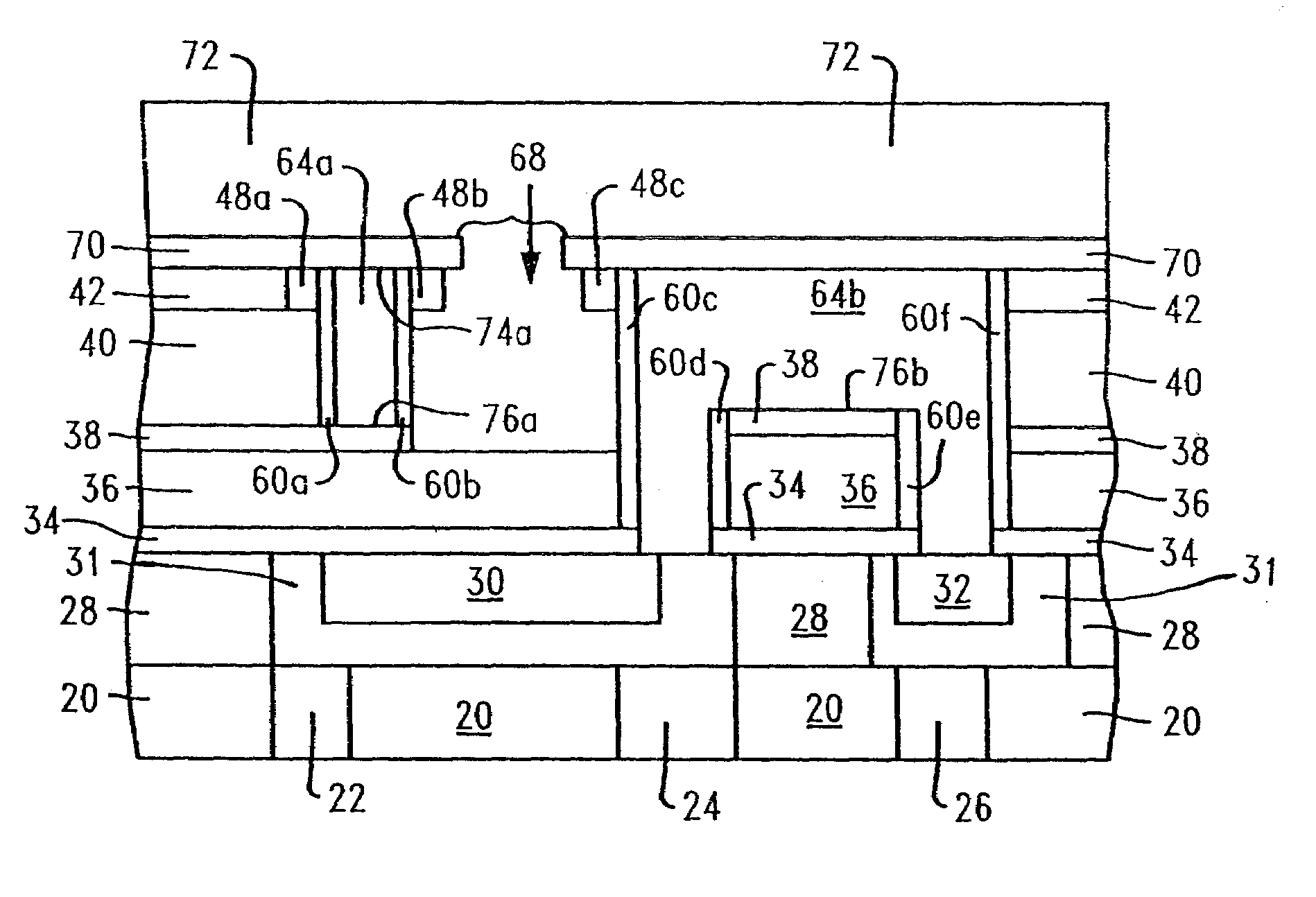

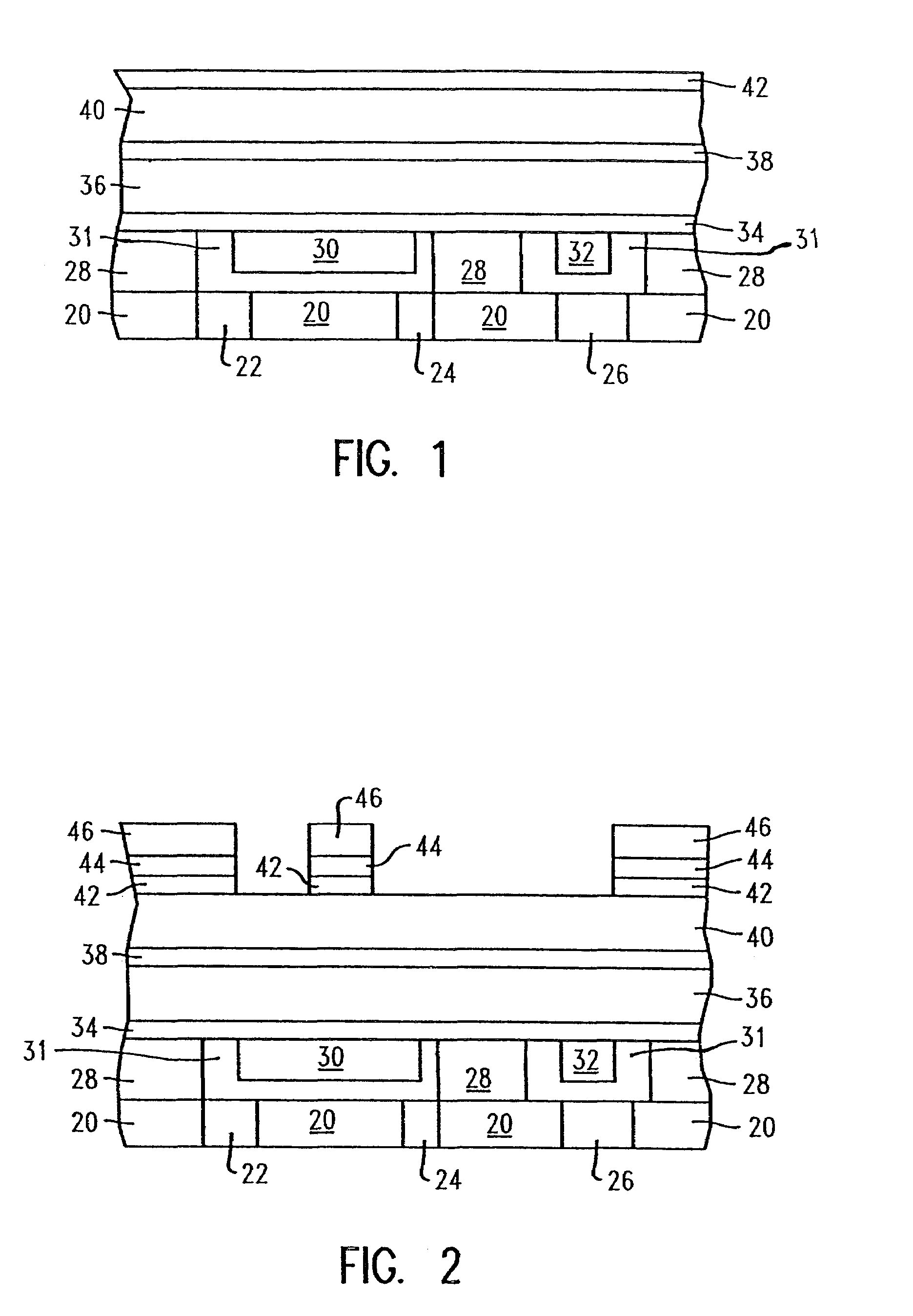

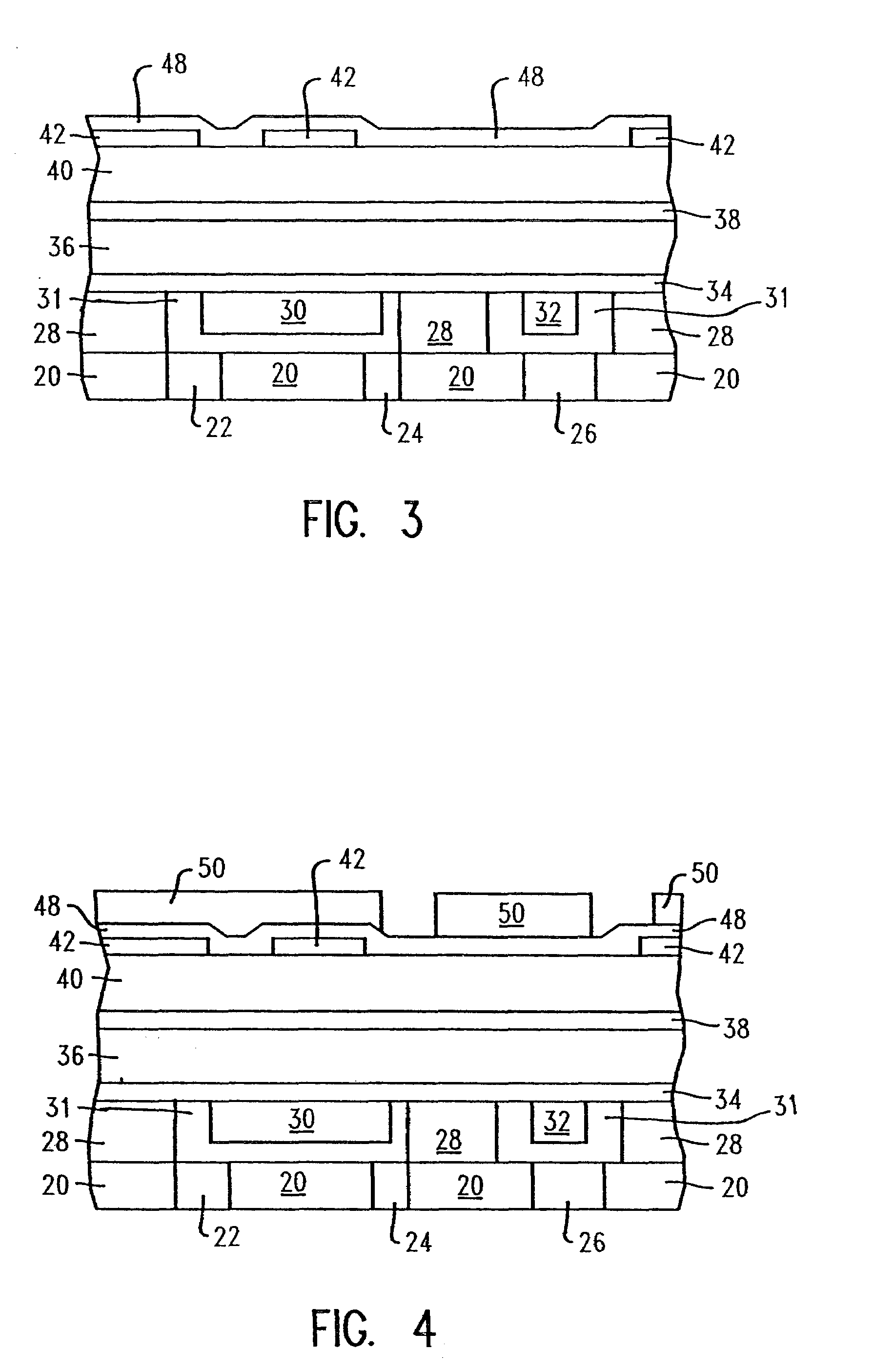

Adjustable self-aligned air gap dielectric for low capacitance wiring

ActiveUS7071532B2Reduce capacitanceReduce line widthSemiconductor/solid-state device detailsSolid-state devicesDielectricCapacitance

Owner:GLOBALFOUNDRIES U S INC

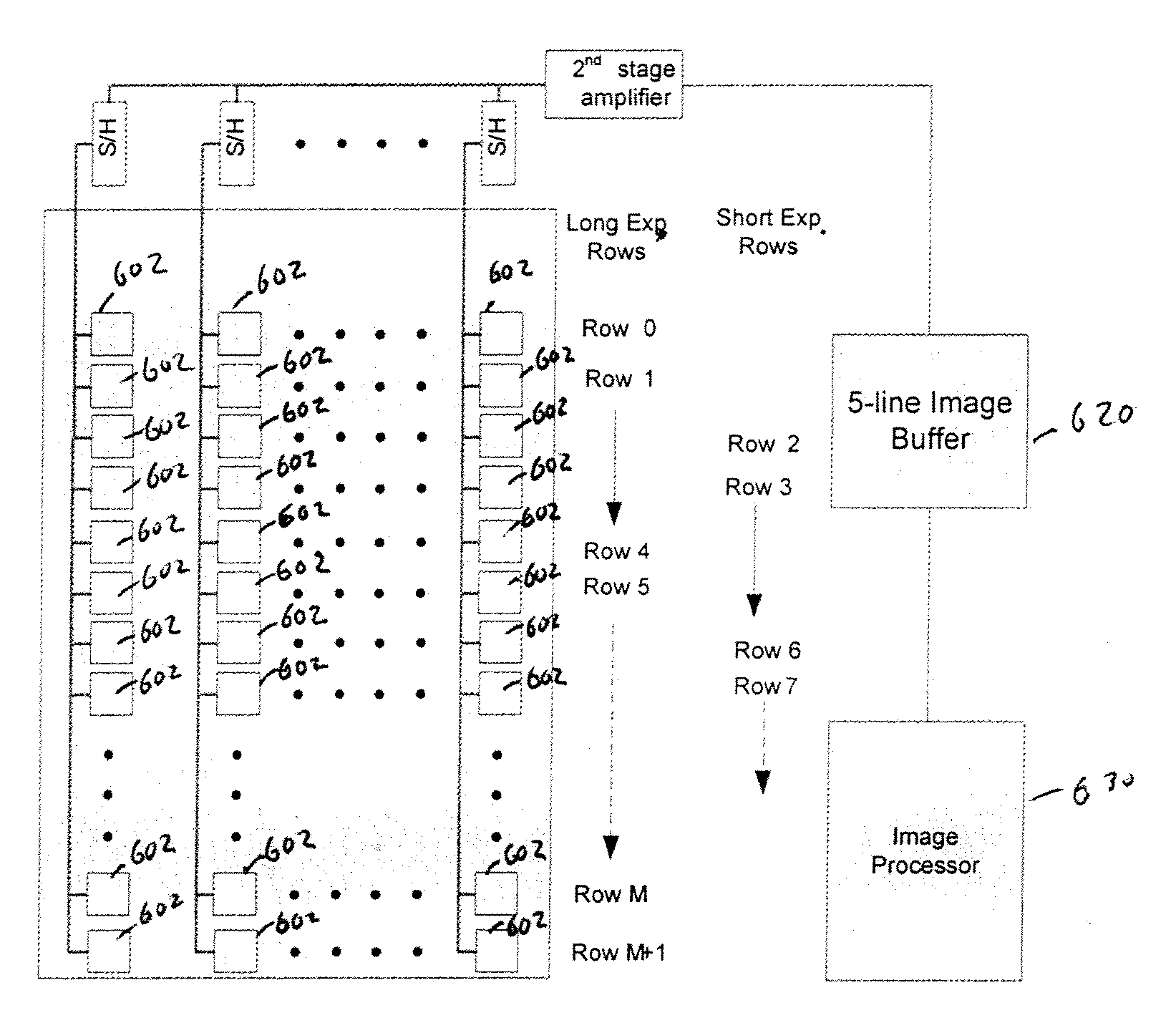

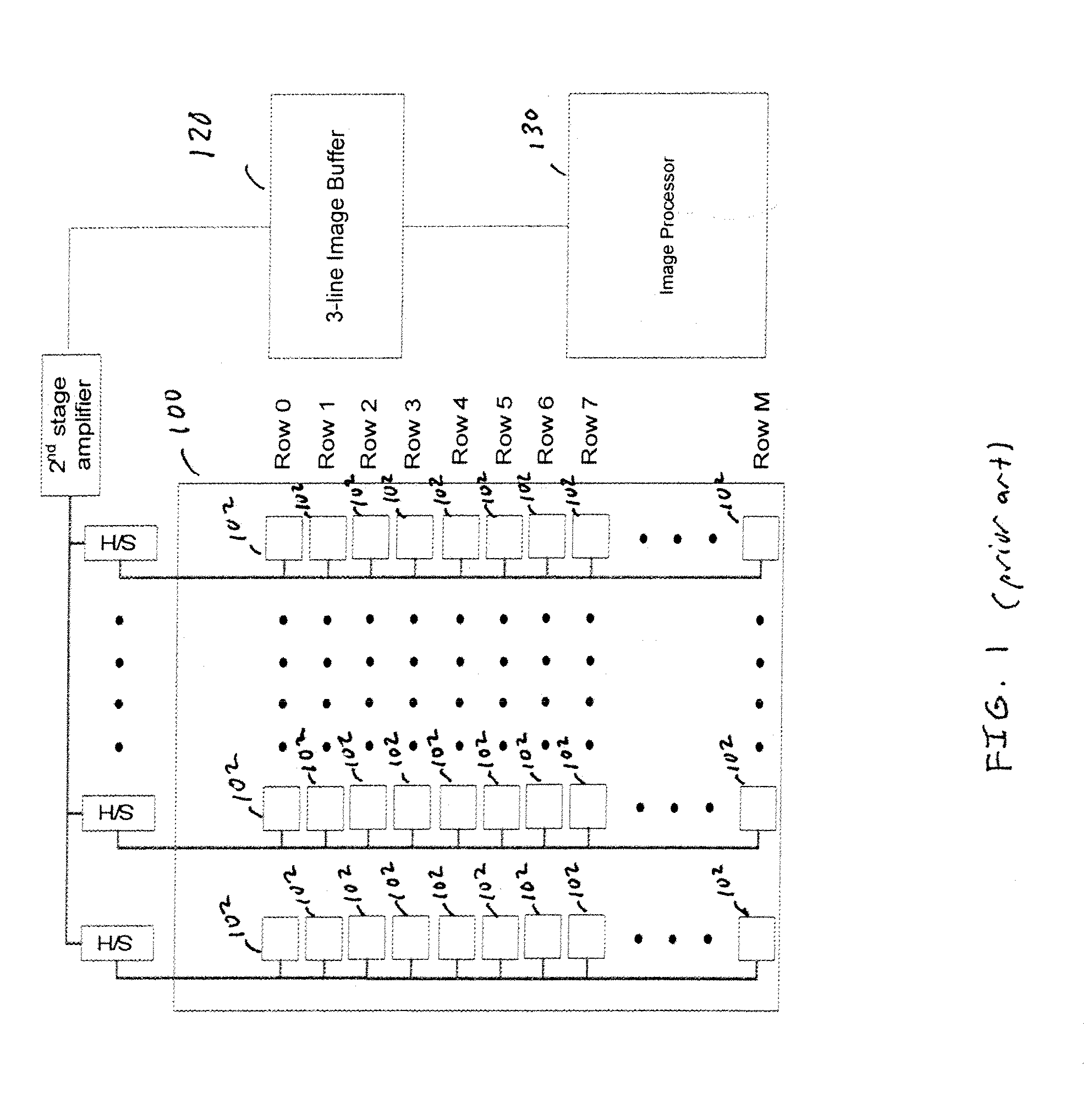

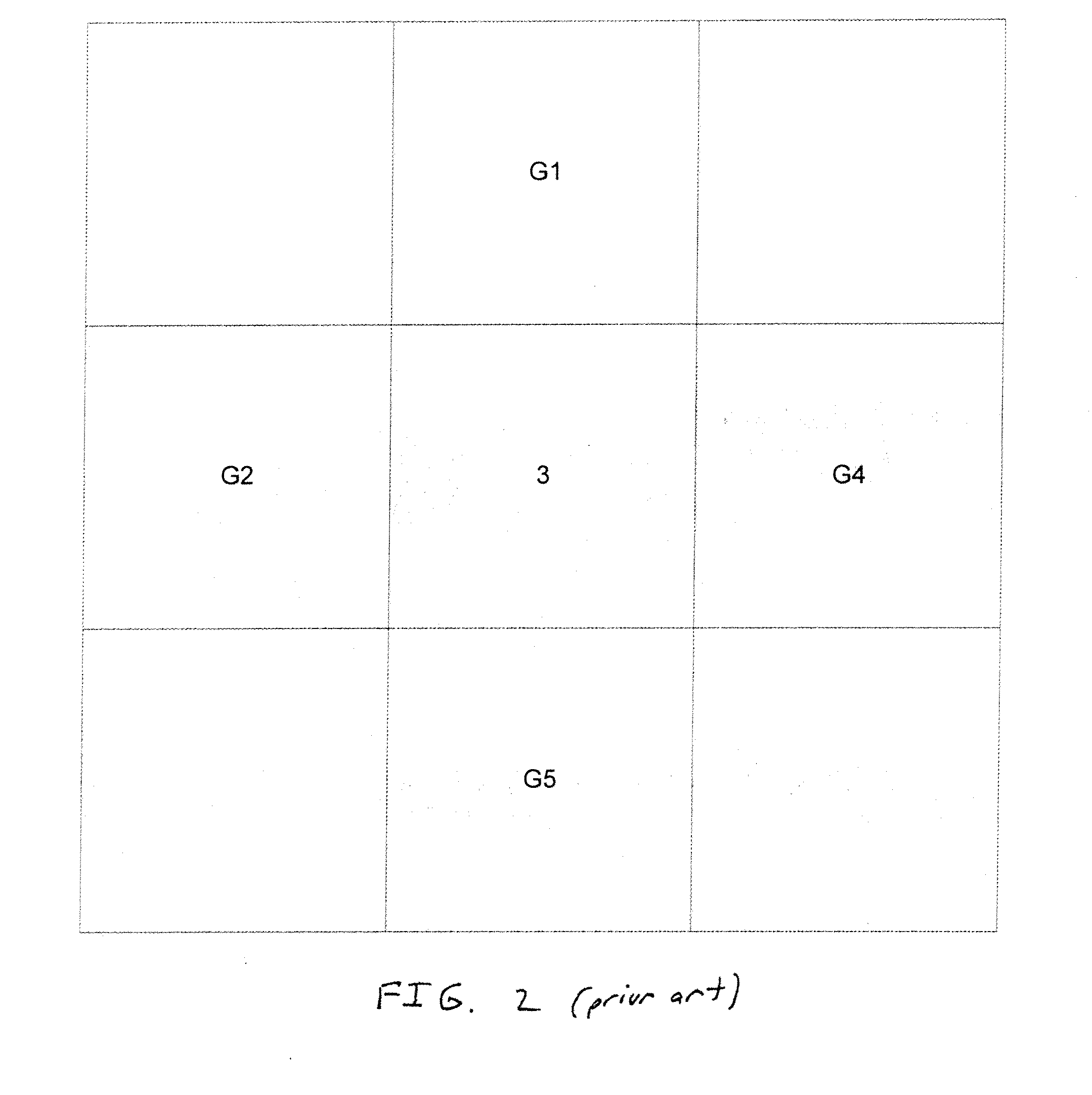

High dynamic range sensor with reduced line memory for color interpolation

ActiveUS20090109306A1Reduction in line widthExtend dynamic rangeTelevision system detailsColor signal processing circuitsImage sensorHigh dynamic range

An image sensor has an array of pixels organized into a row and column format. Pixels are read out in a line-by-line sequence and buffered in a line image buffer. An extended dynamic range is supported by varying a column exposure time according to a periodic sequence. As a result, the pixel exposure times vary within each row. A high dynamic range is generated by combining pixel data of adjacent pixels within the same row that are of the same filter type but having different exposure times. Color interpolation is performed on the combined line data.

Owner:OMNIVISION TECH INC

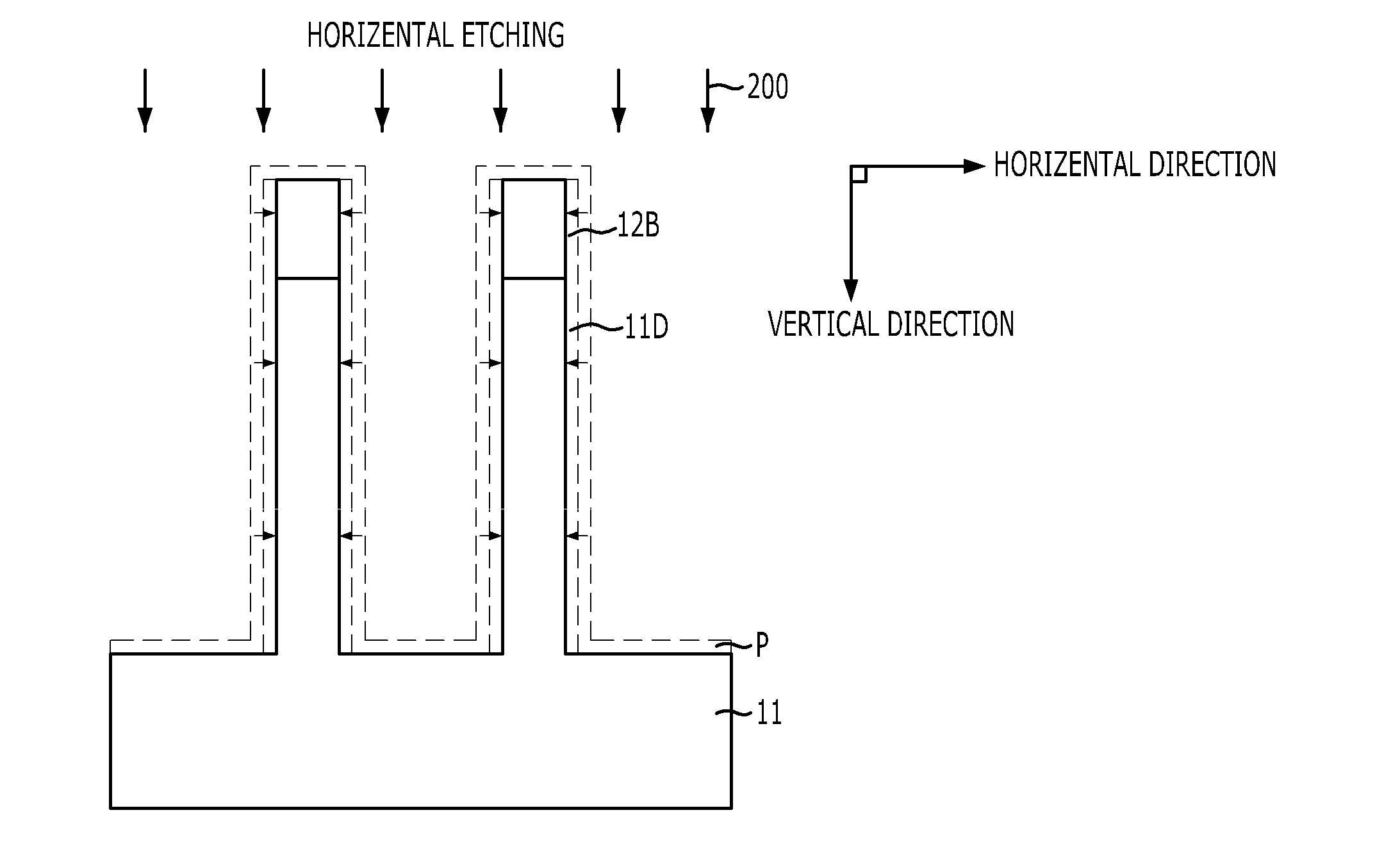

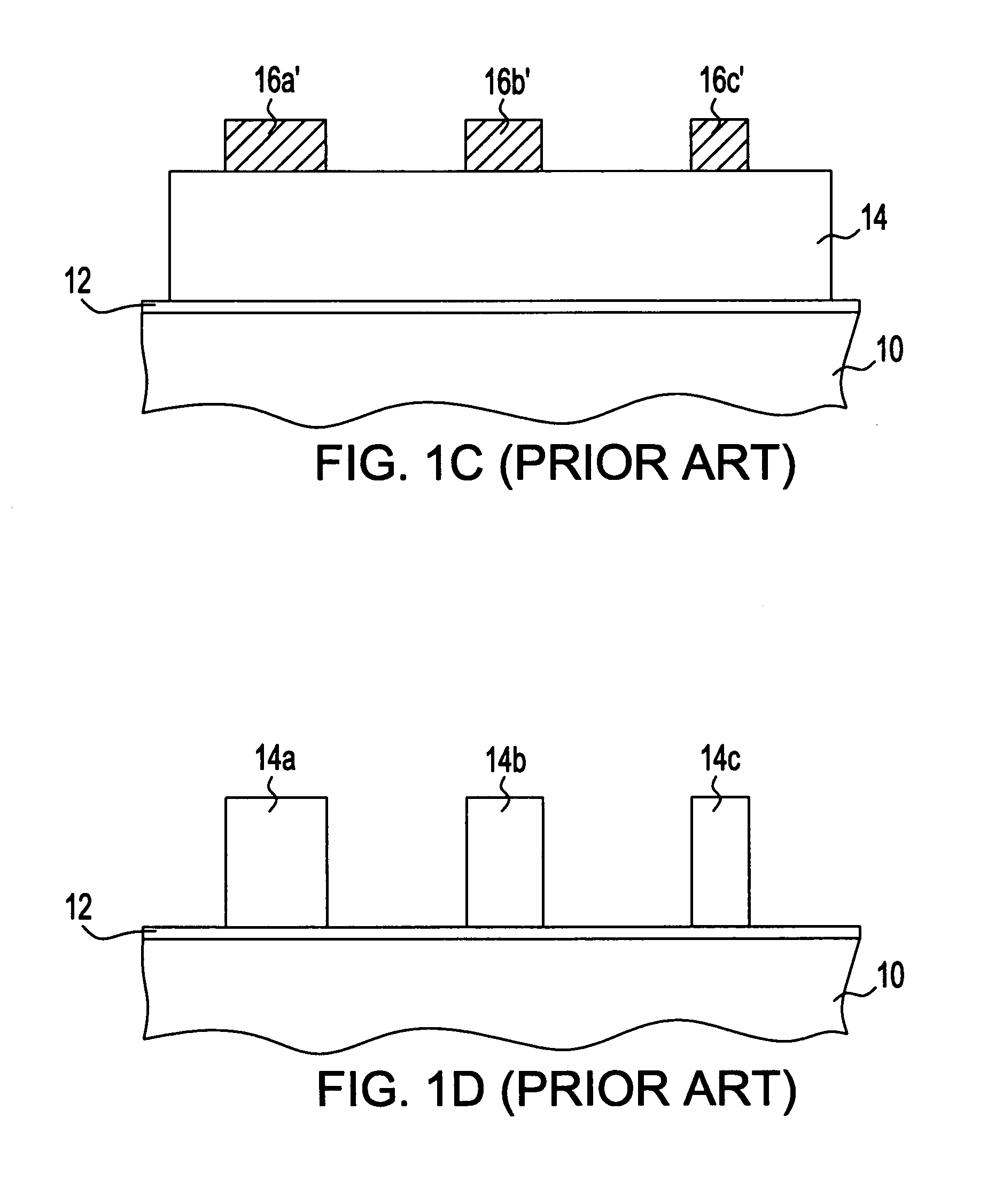

Method for forming active pillar of vertical channel transistor

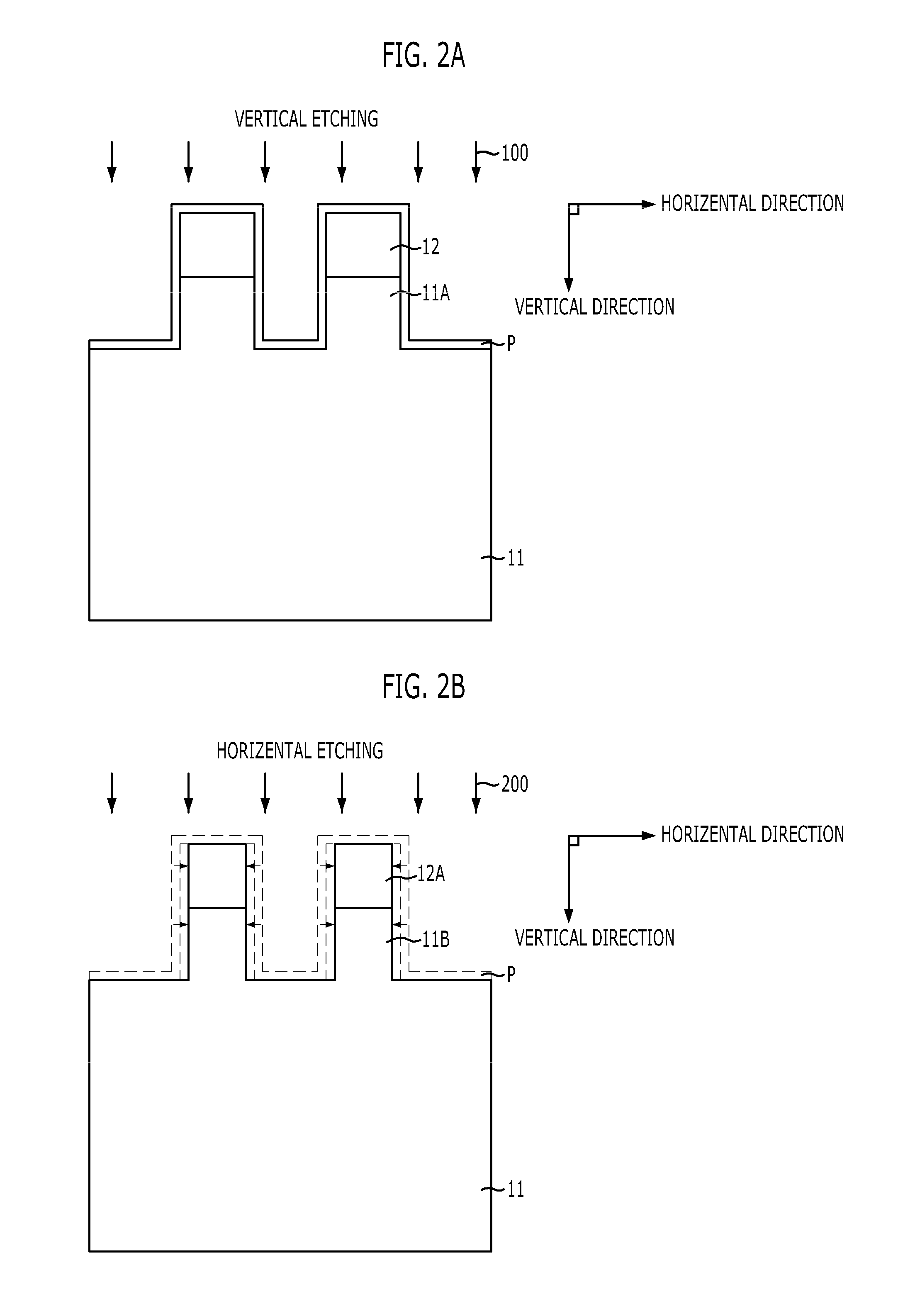

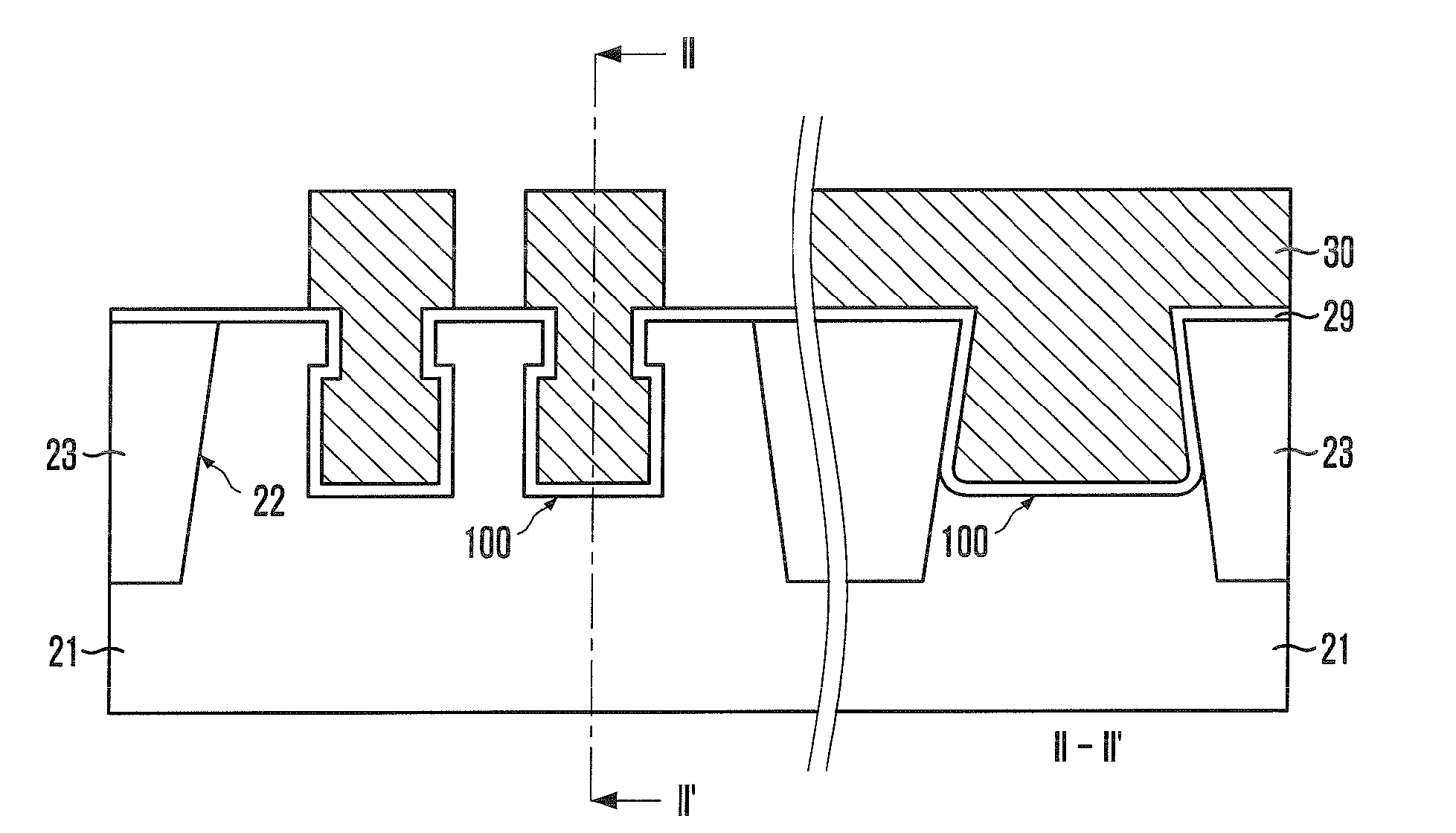

ActiveUS20100055917A1Reduce horizontal widthOvercome limitationsSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingLine width

A method for forming an active pillar of a vertical channel transistor includes forming a hard mask pattern on a substrate, etching vertically the substrate using the hard mask pattern as an etch barrier to form an active pillar, and etching horizontally to remove by-product remaining on the exposed substrate, the hard mask pattern and the active pillar and at the same time to reduce line width of the hard mask pattern and the active pillar, wherein a unit cycle in which the vertical etching and the horizontal etching are each performed subsequently once, respectively, is performed repeatedly at least two times or more. According to the present invention, an active pillar having vertical profiles on its sidewalls and having height and line width (or diameter) required in a highly integrated vertical channel transistor can be provided.

Owner:SK HYNIX INC

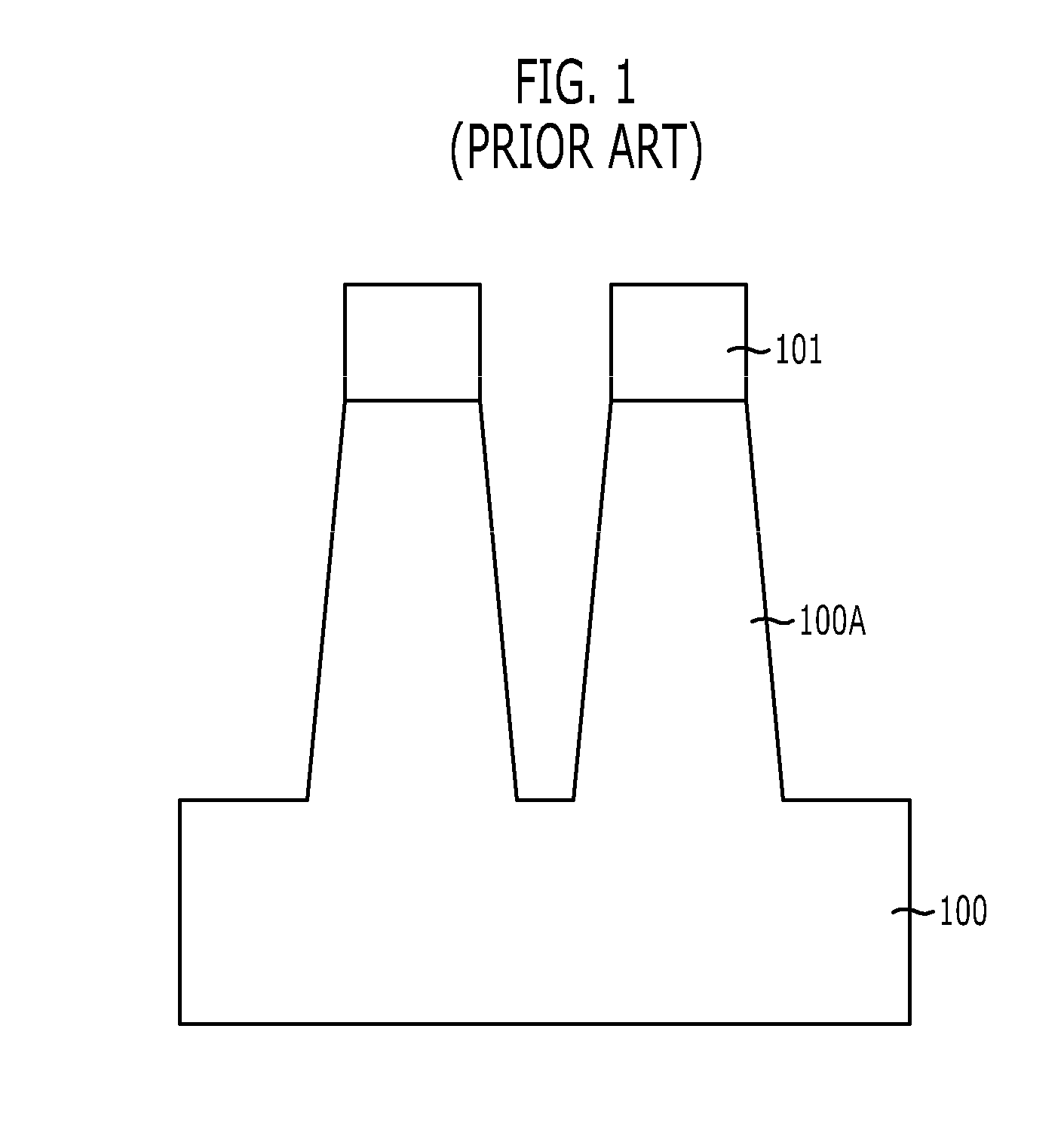

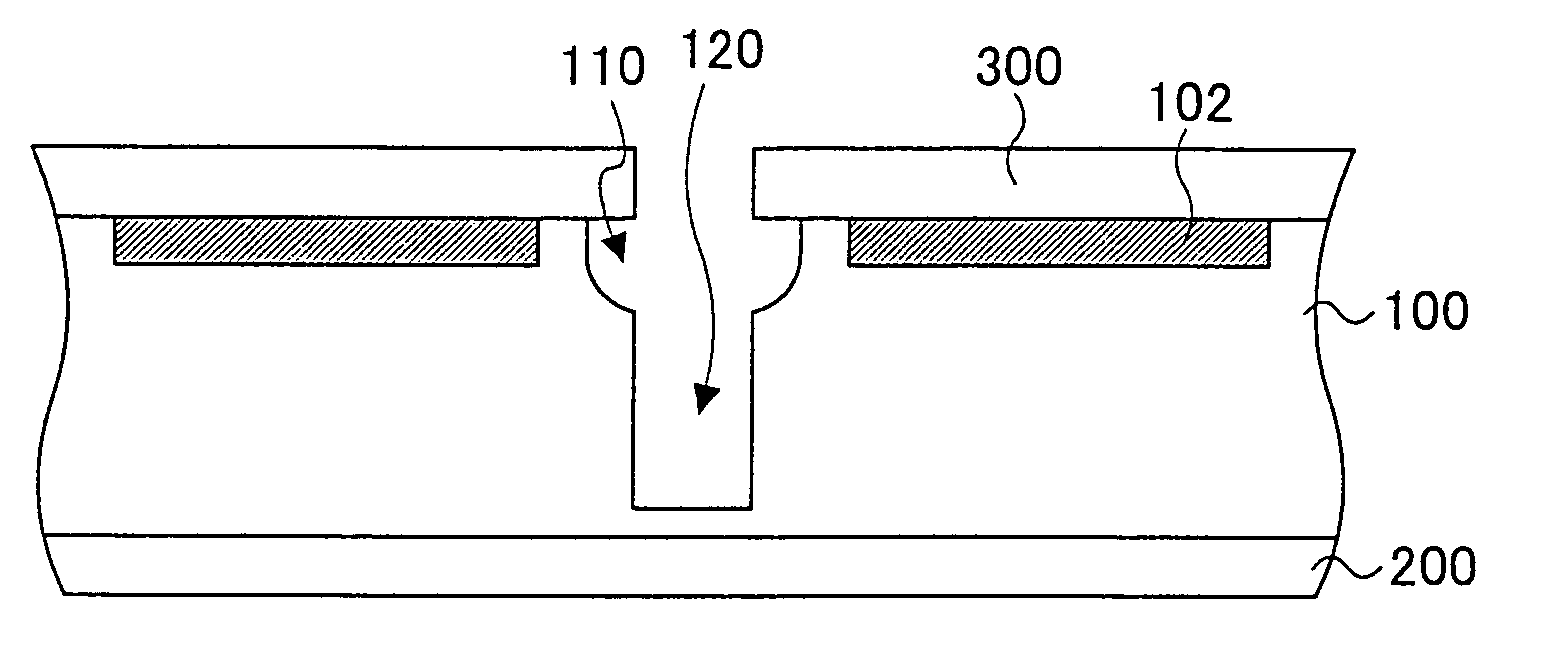

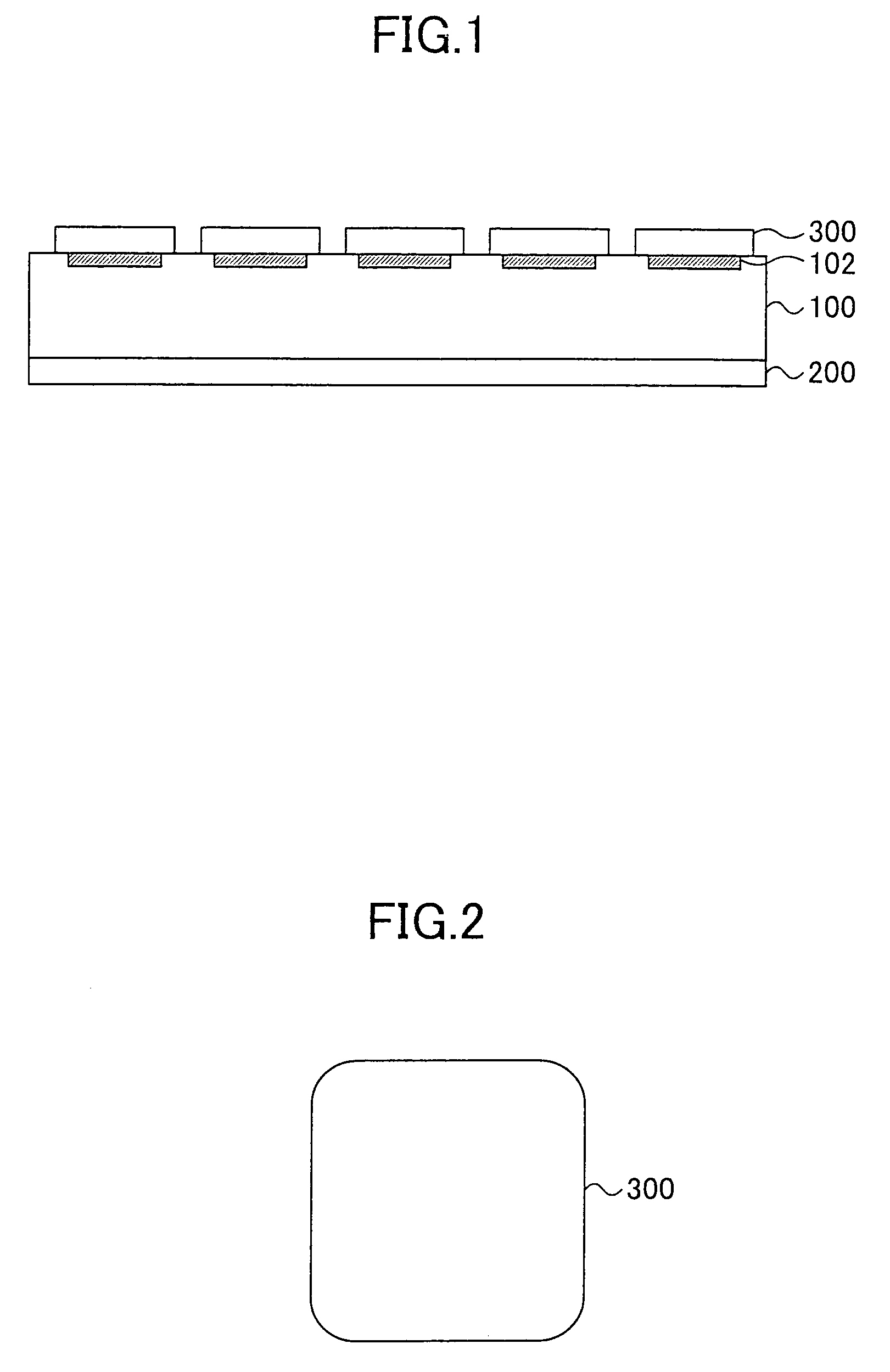

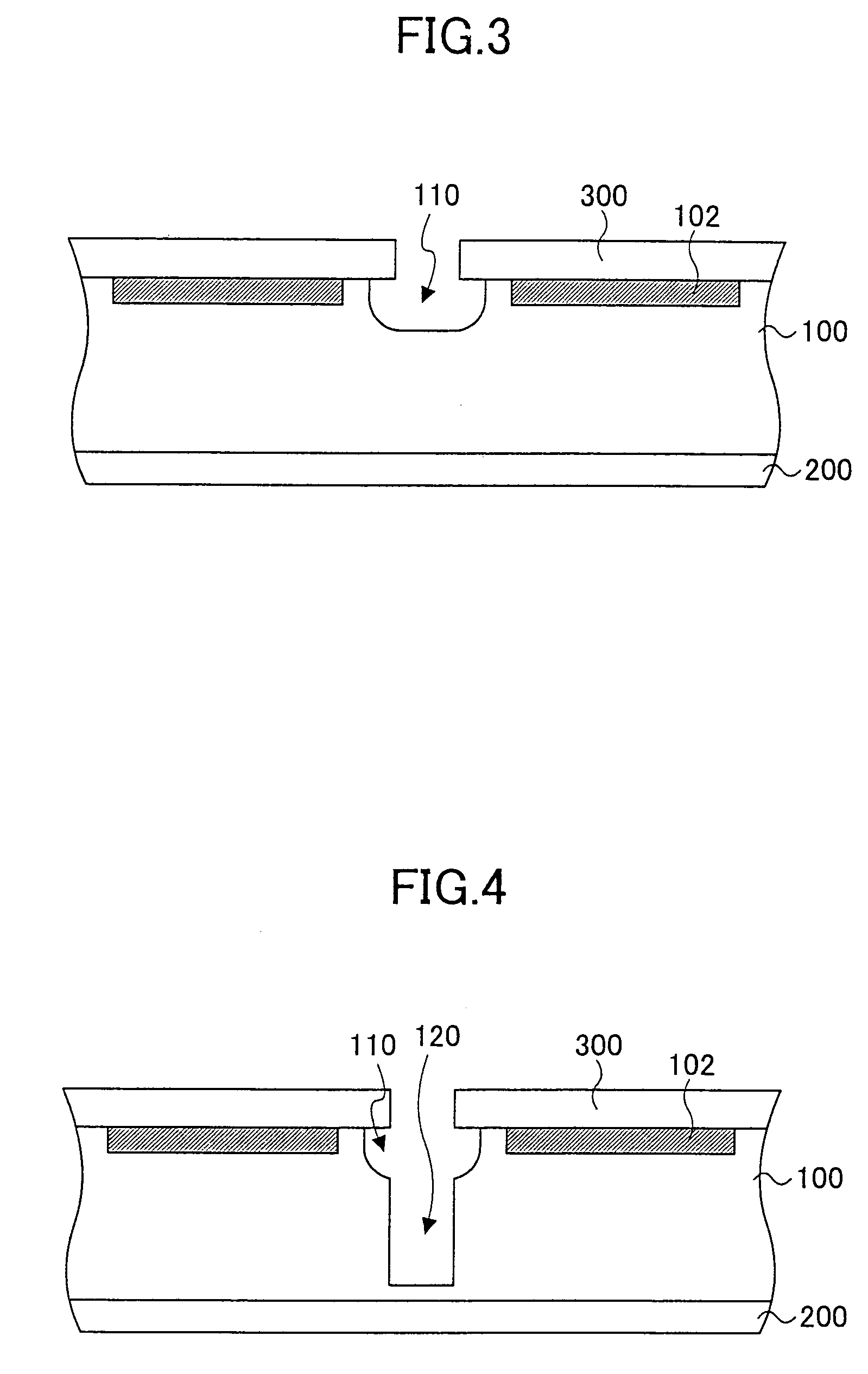

Method for fabricating recess gate in semiconductor device

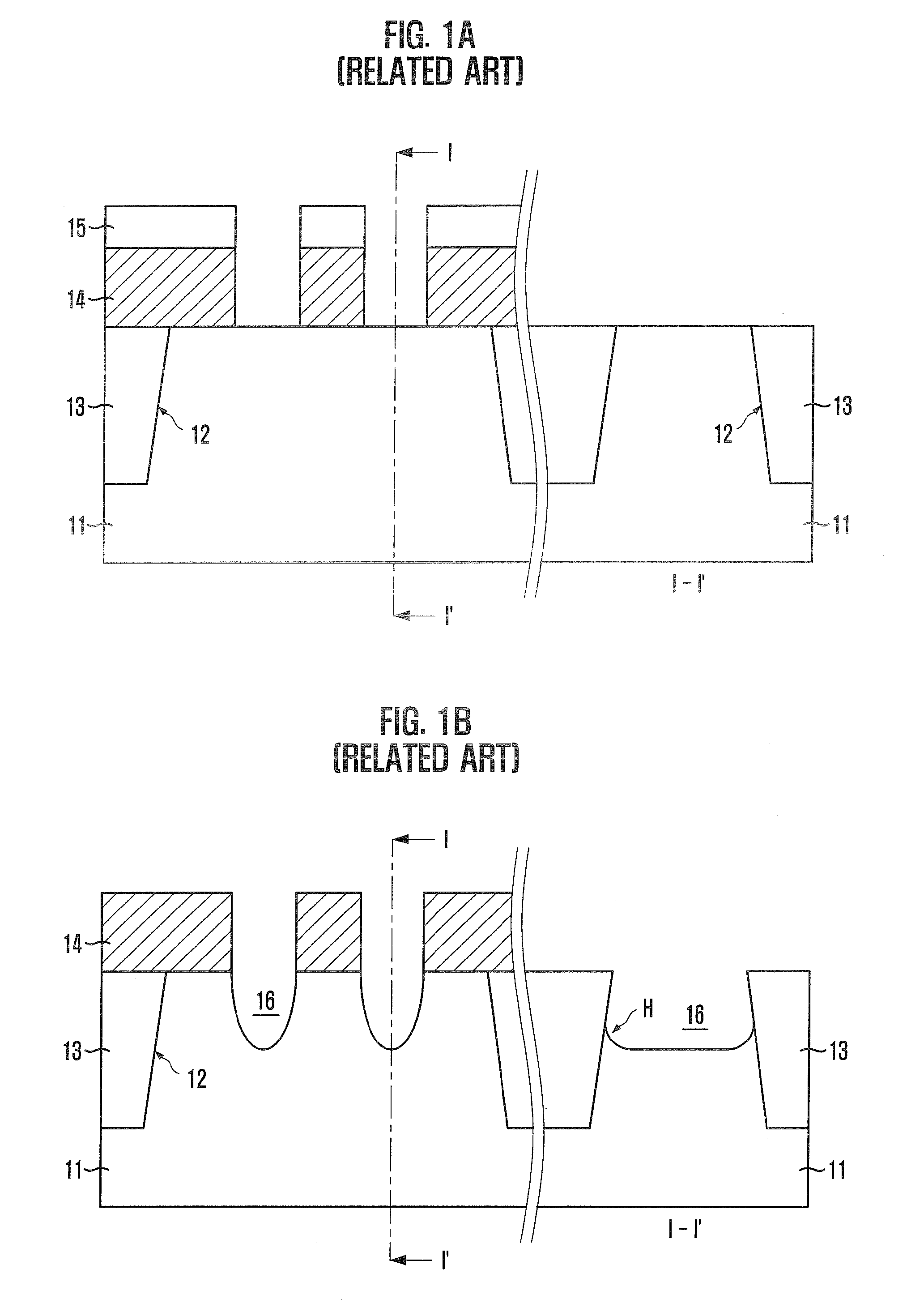

InactiveUS20090087960A1Suppress generationReduce line widthTransistorSolid-state devicesEtchingOxide

A method for fabricating a recess gate in a semiconductor device includes etching a silicon substrate to form a trench that defines an active region, forming a device isolation layer that gap-fills the trench, forming a hard mask layer over the silicon substrate, the hard mask layer comprising a stack of an oxide layer and an amorphous carbon layer, wherein the hard mask layer exposes a channel target region of the active region, and forming a recess region with a dual profile by first etching and second etching the channel target region using the hard mask layer as an etch barrier, wherein the second etching is performed after removing the amorphous carbon layer.

Owner:SK HYNIX INC

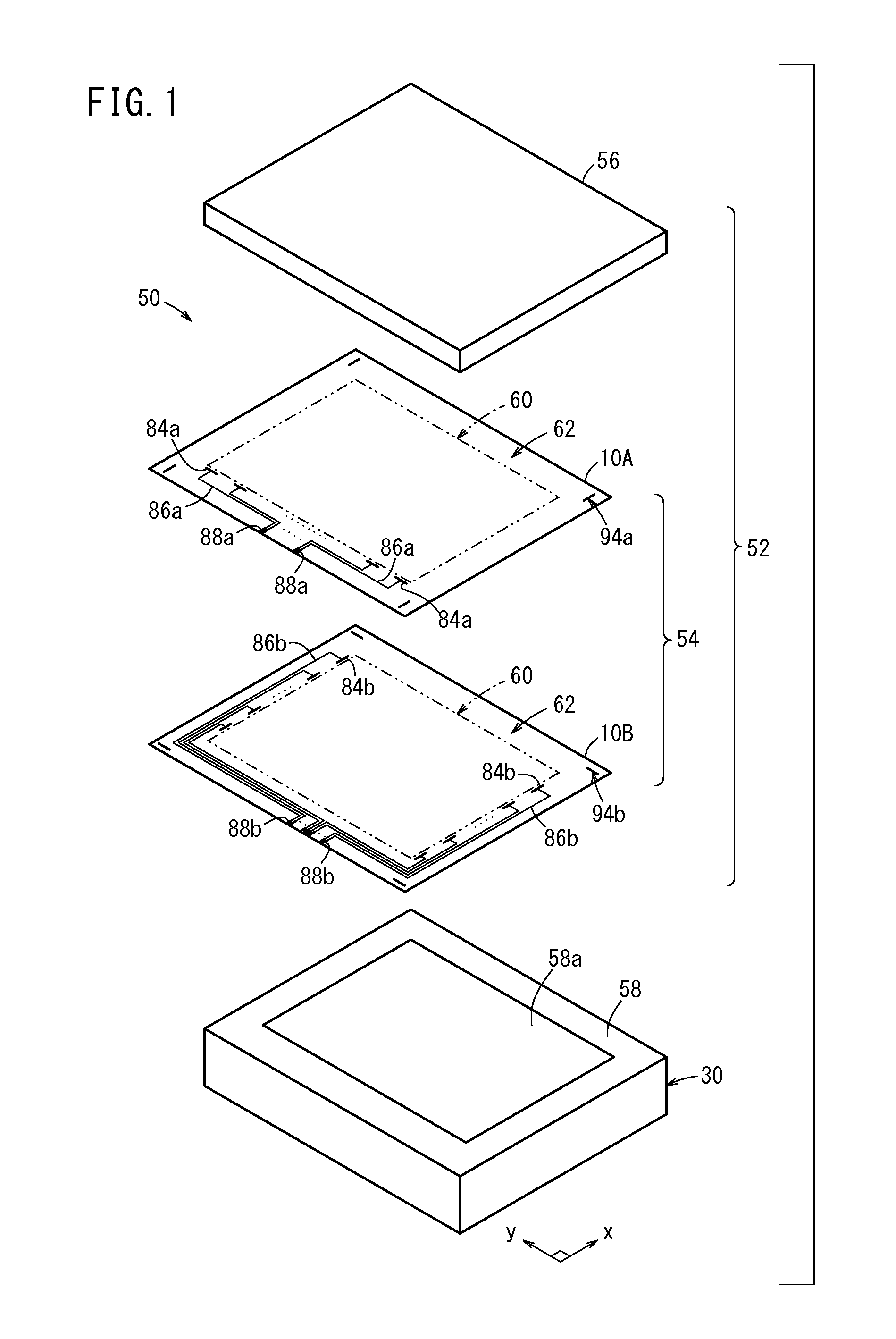

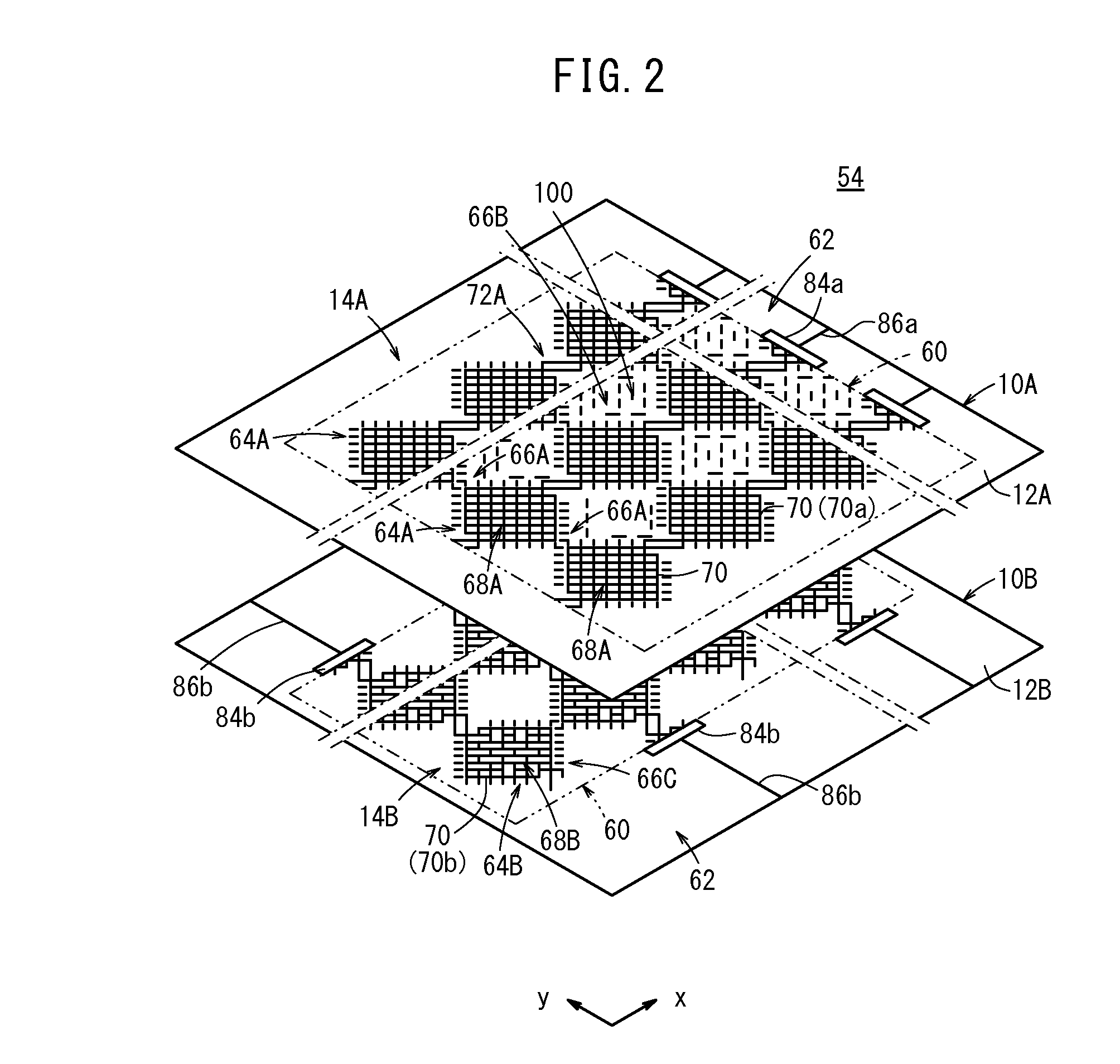

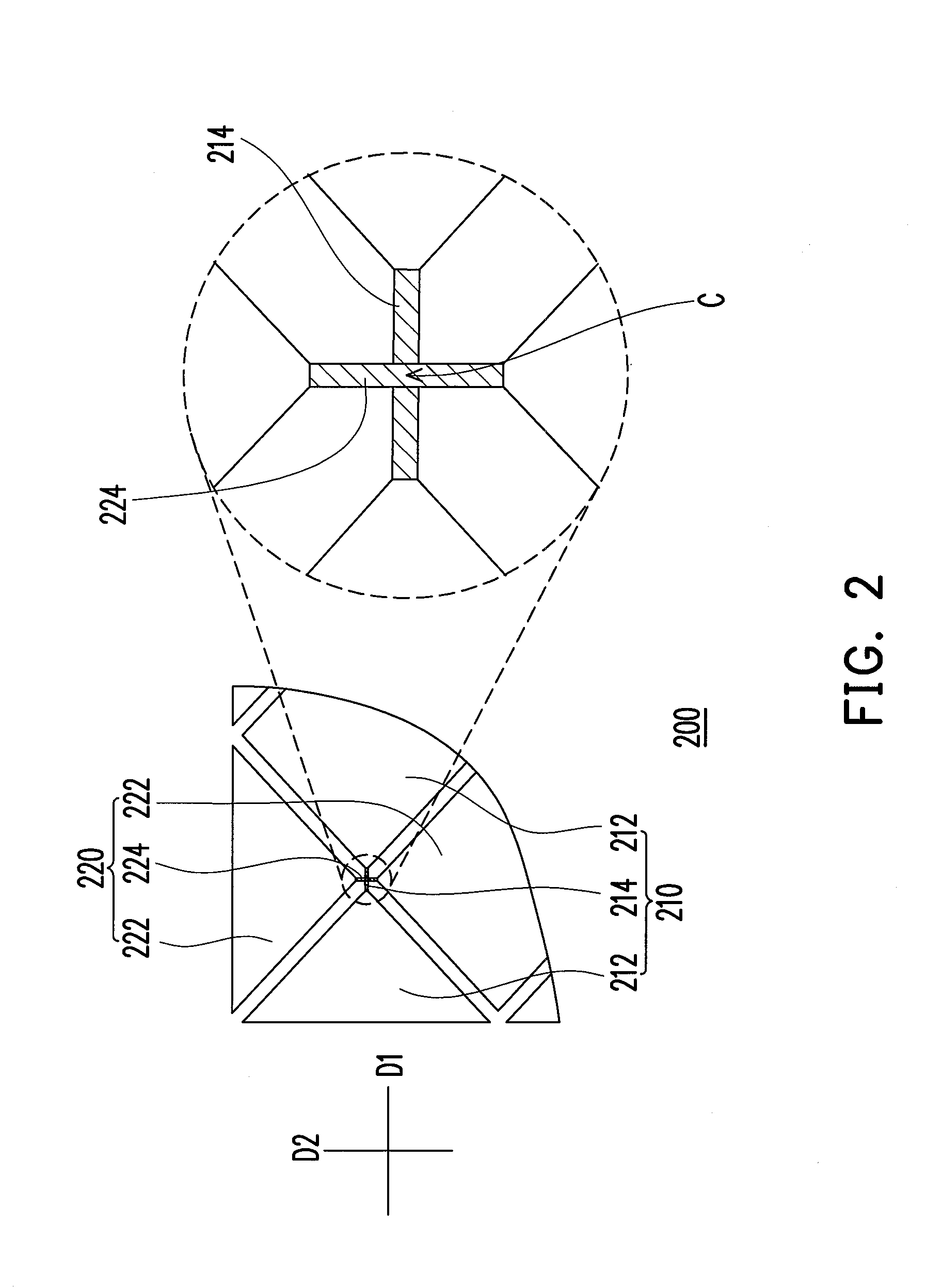

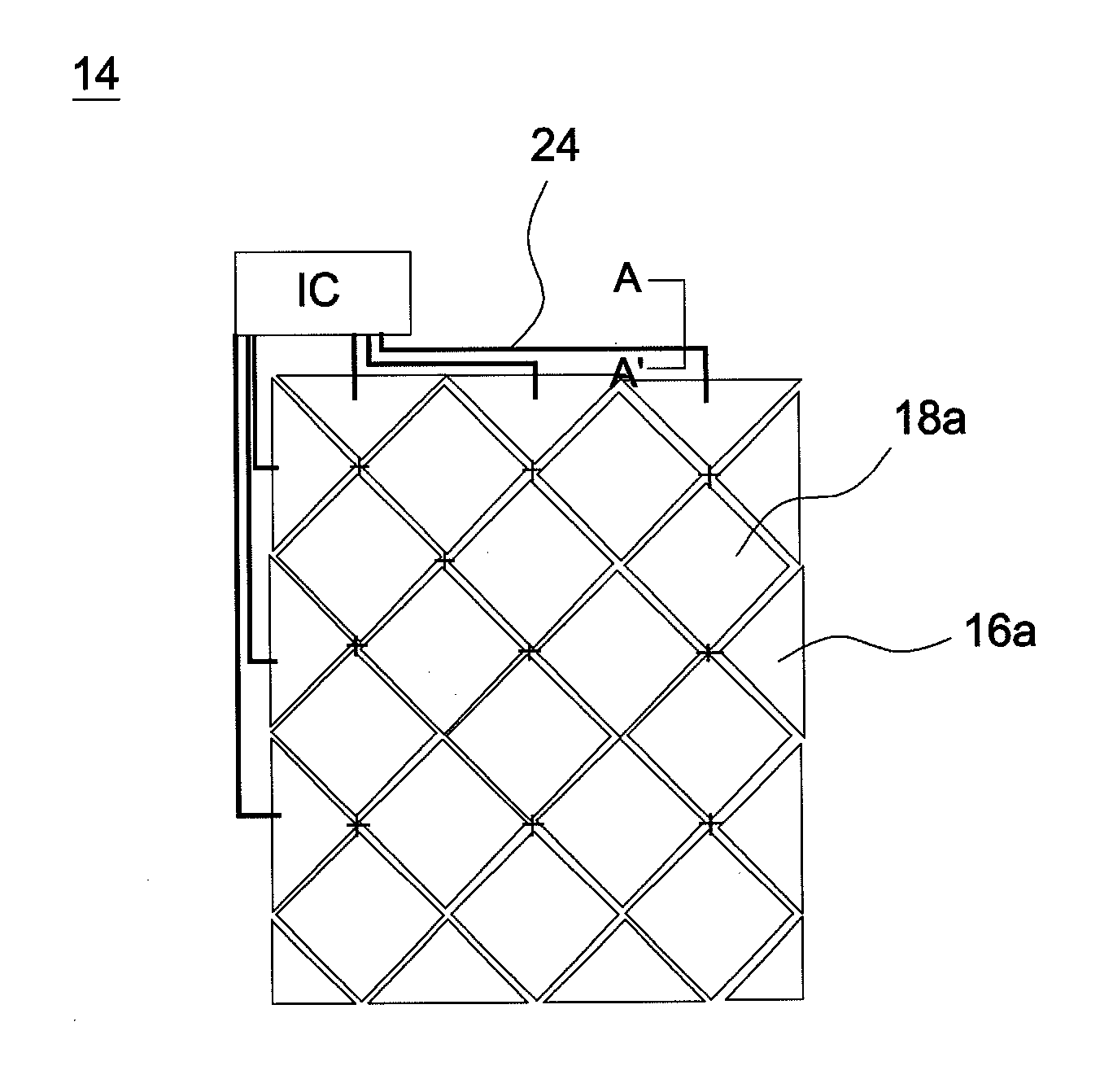

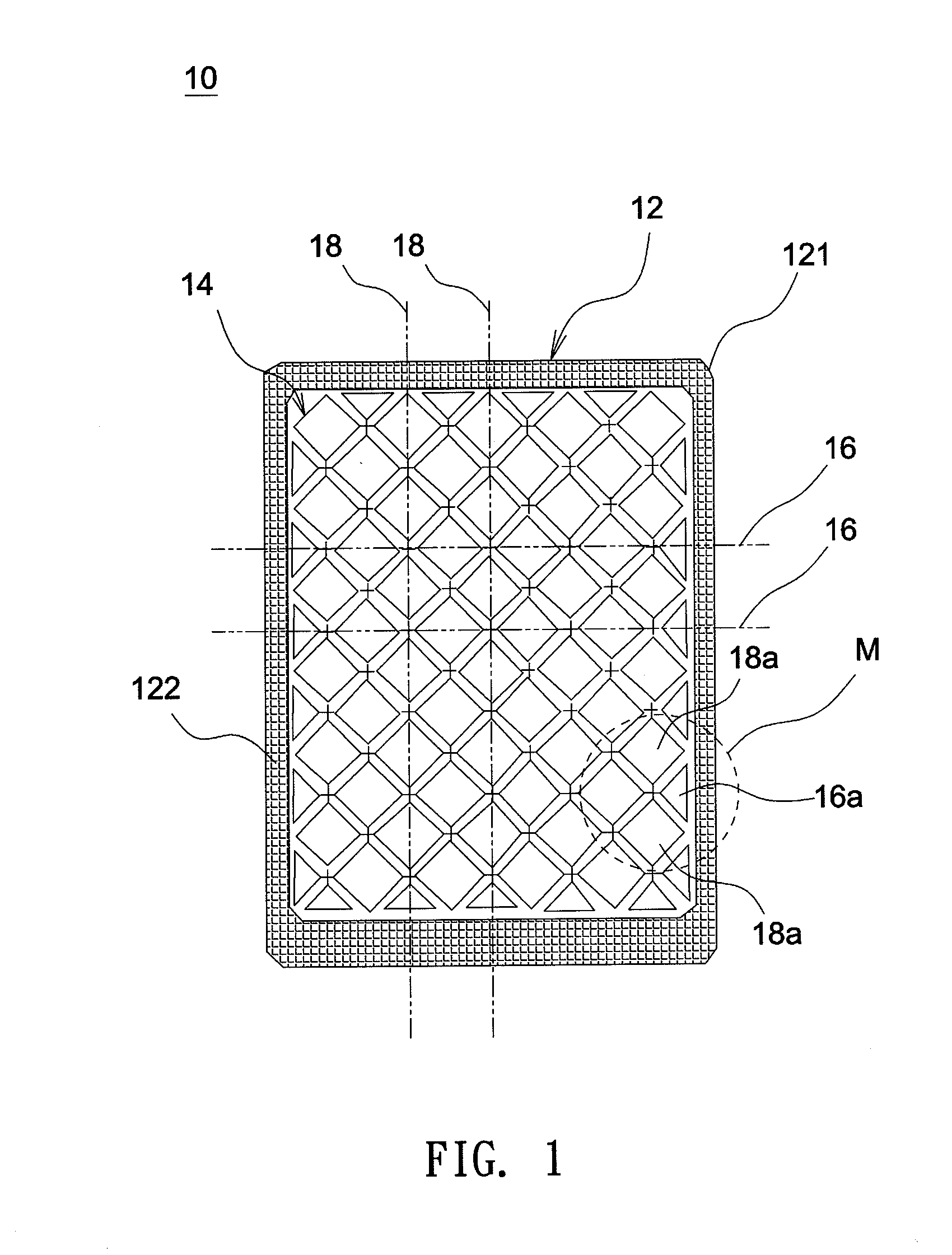

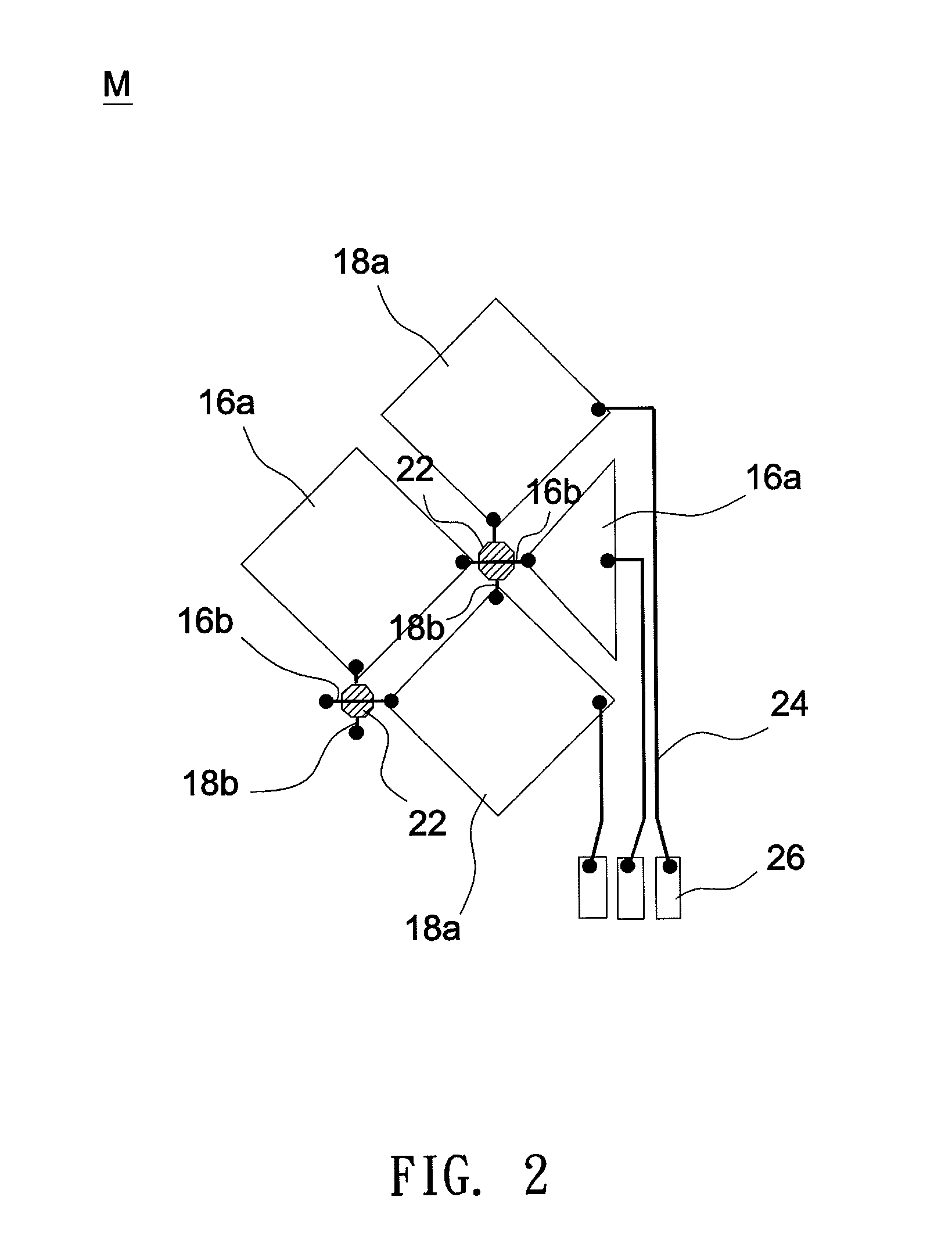

Electroconductive sheet and touch panel

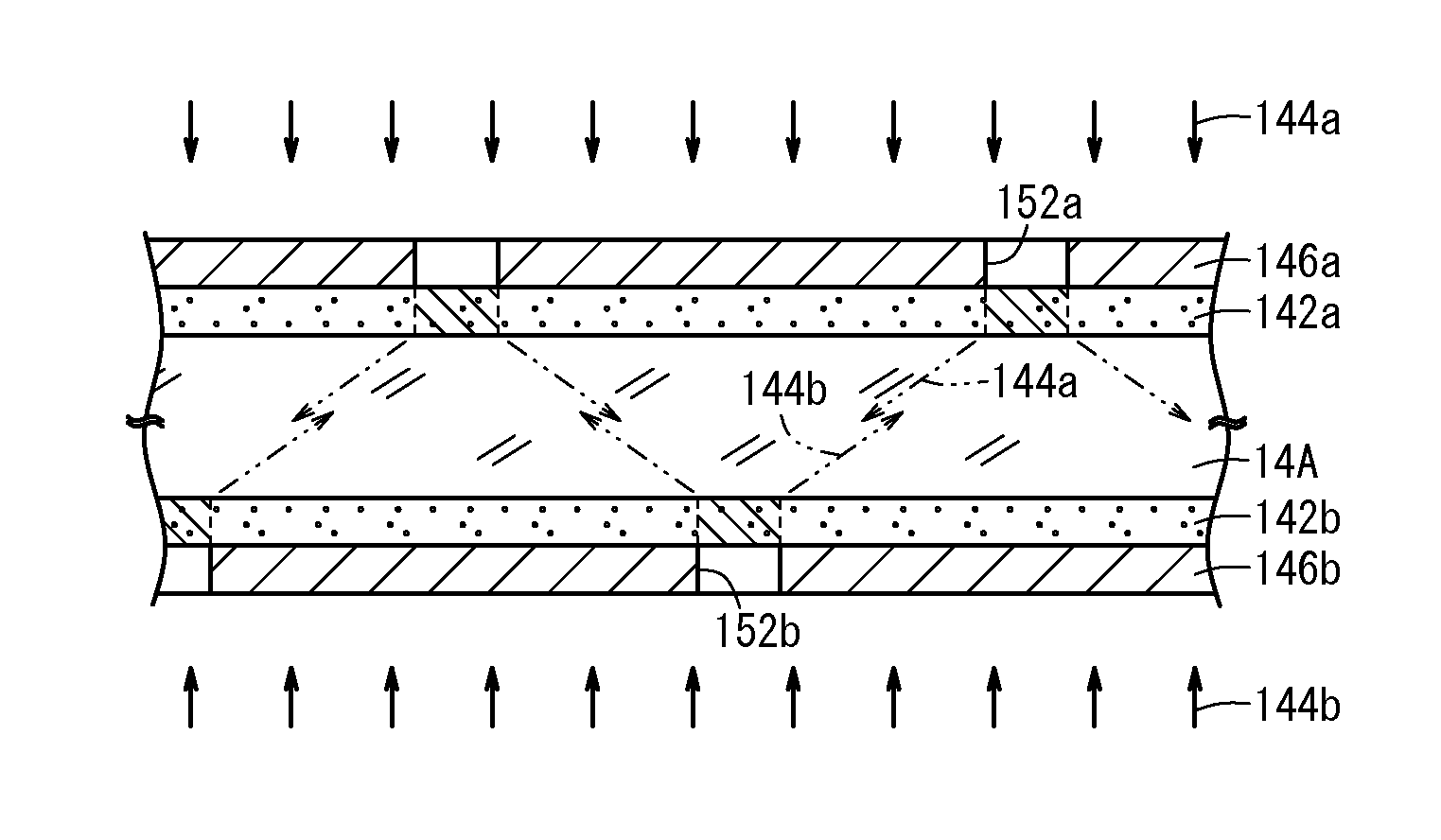

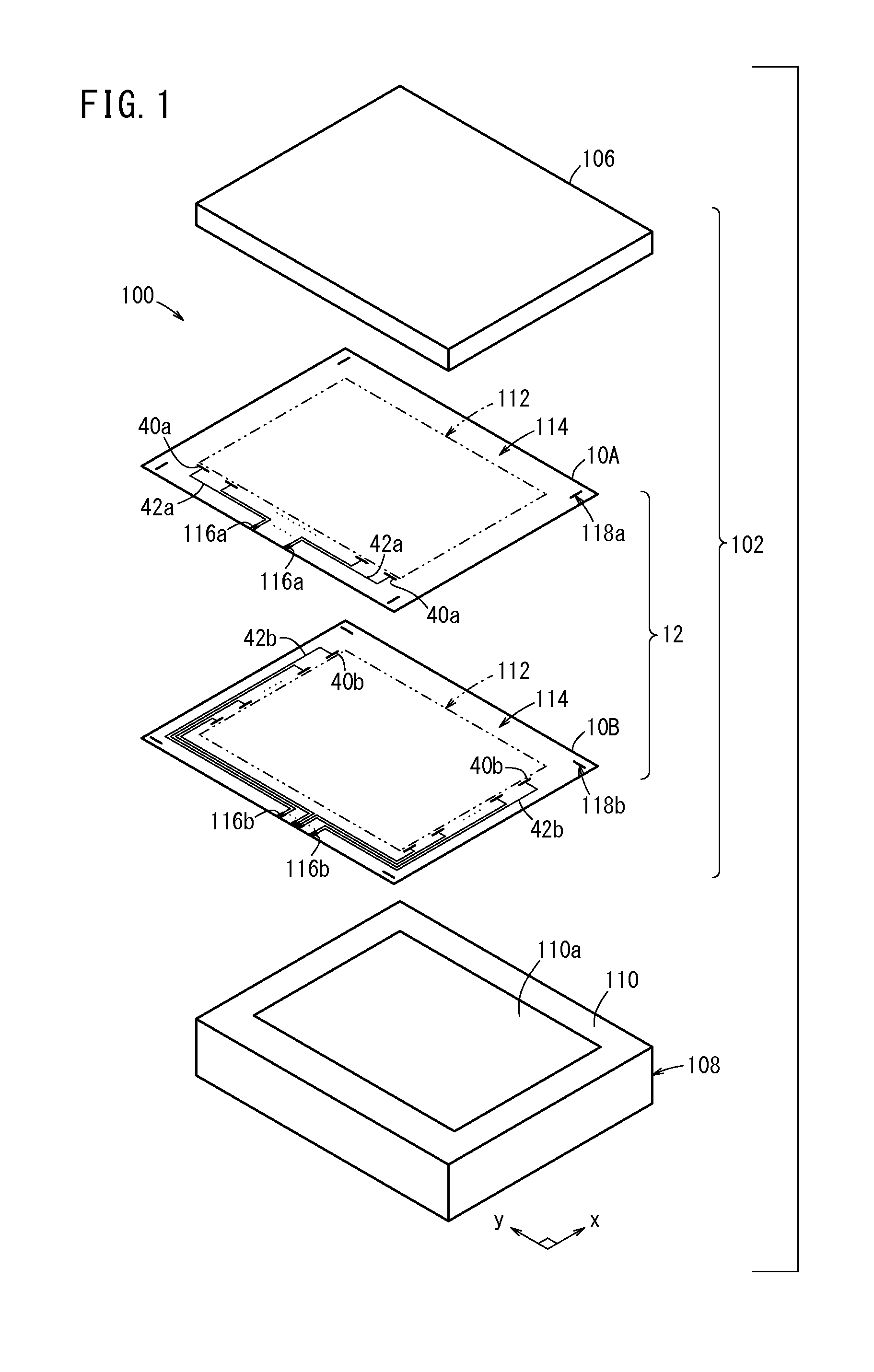

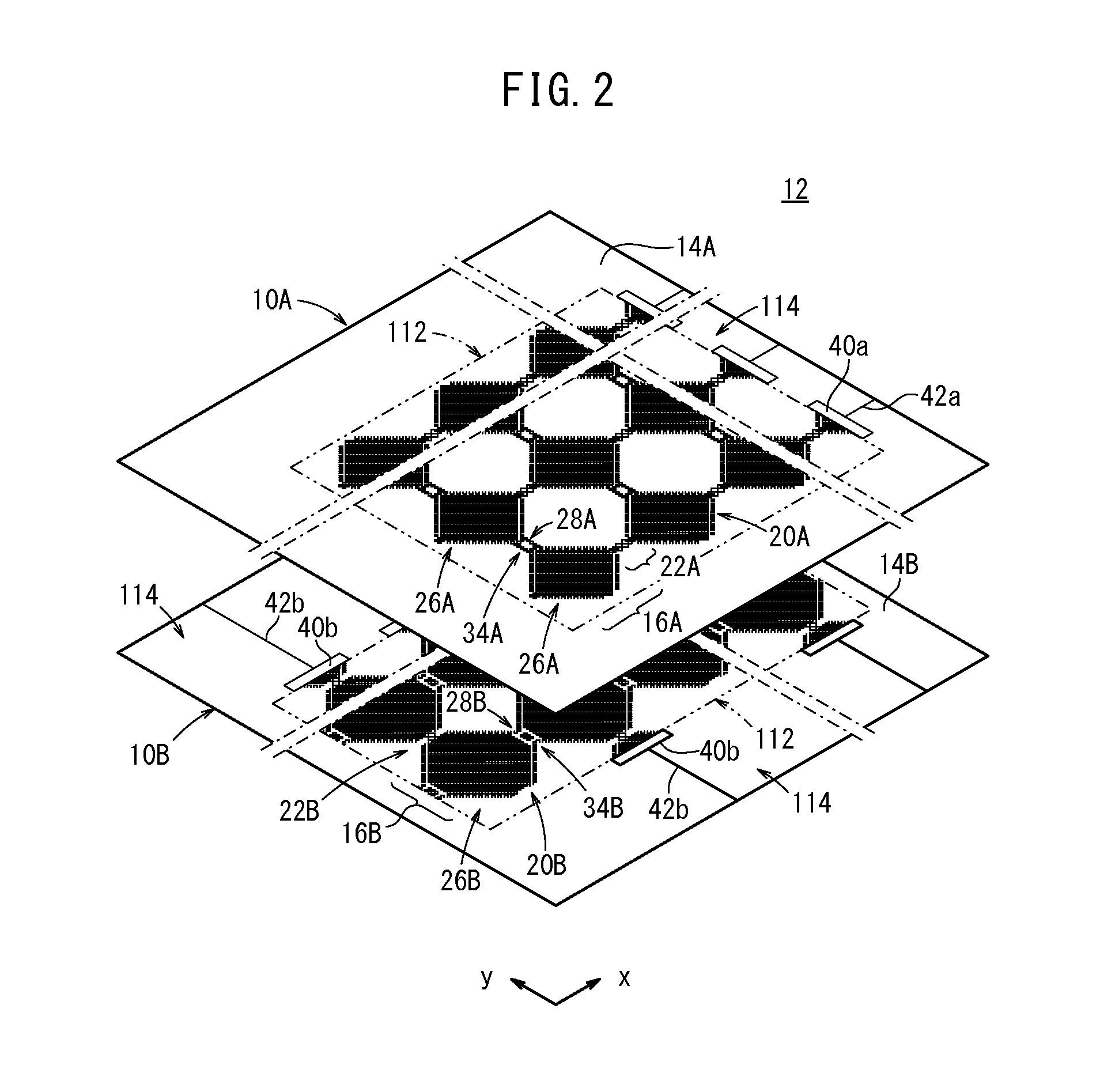

ActiveUS20130327560A1High transparencyHigh detection sensitivityNon-insulated conductorsSuperimposed coating processThin metalEngineering

An electroconductive sheet and a touch panel having a first electroconductive section and a second electroconductive section, the second electroconductive section being disposed on the display-panel side. The first electroconductive section has a plurality of first electroconductive patterns arranged in the x-direction, a plurality of first large grids being respectively connected to the first electroconductive patterns. The second electroconductive section has a plurality of second electroconductive patterns arranged in the y-direction, a plurality of second large grids being respectively connected to the second electroconductive patterns. The area occupied by thin metal wires in the second electroconductive patterns is larger than the area occupied by thin metal wires in the first electroconductive patterns. The area occupied by thin metal wires in the second large grids is larger than the area occupied by thin metal wires in the first large grids.

Owner:FUJIFILM CORP

Electroconductive sheet and touch panel

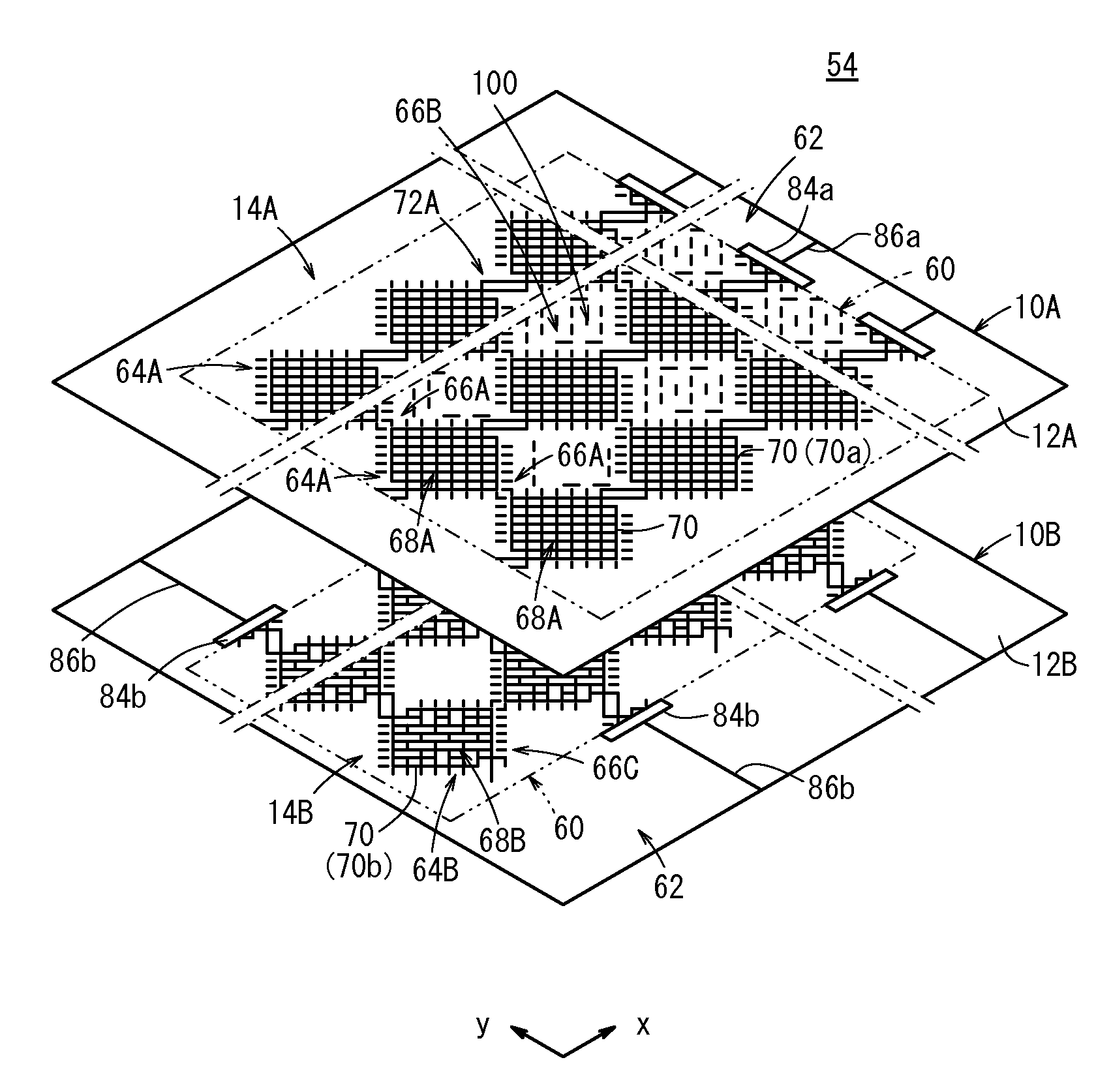

InactiveUS20140054070A1Increase awarenessThin line widthCircuit optical detailsPrinted circuit aspectsTouch panelElectrical and Electronics engineering

An electroconductive sheet and a touch panel, wherein the electroconductive sheet has a first electroconductive section and a second electroconductive section; the first electroconductive section has a plurality of first electroconductive patterns arrayed in one direction and to which a plurality of first electrodes, respectively, are connected; the second electroconductive section has a plurality of second electroconductive patterns arrayed in a direction orthogonal to the arrayed direction of the first electroconductive patterns and to which a plurality of second electrodes, respectively, are connected; and the electroconductive sheet has dummy electrodes disposed between the first electrodes and the second electrodes, and other dummy electrodes disposed in portions corresponding to the second electrodes.

Owner:FUJIFILM CORP

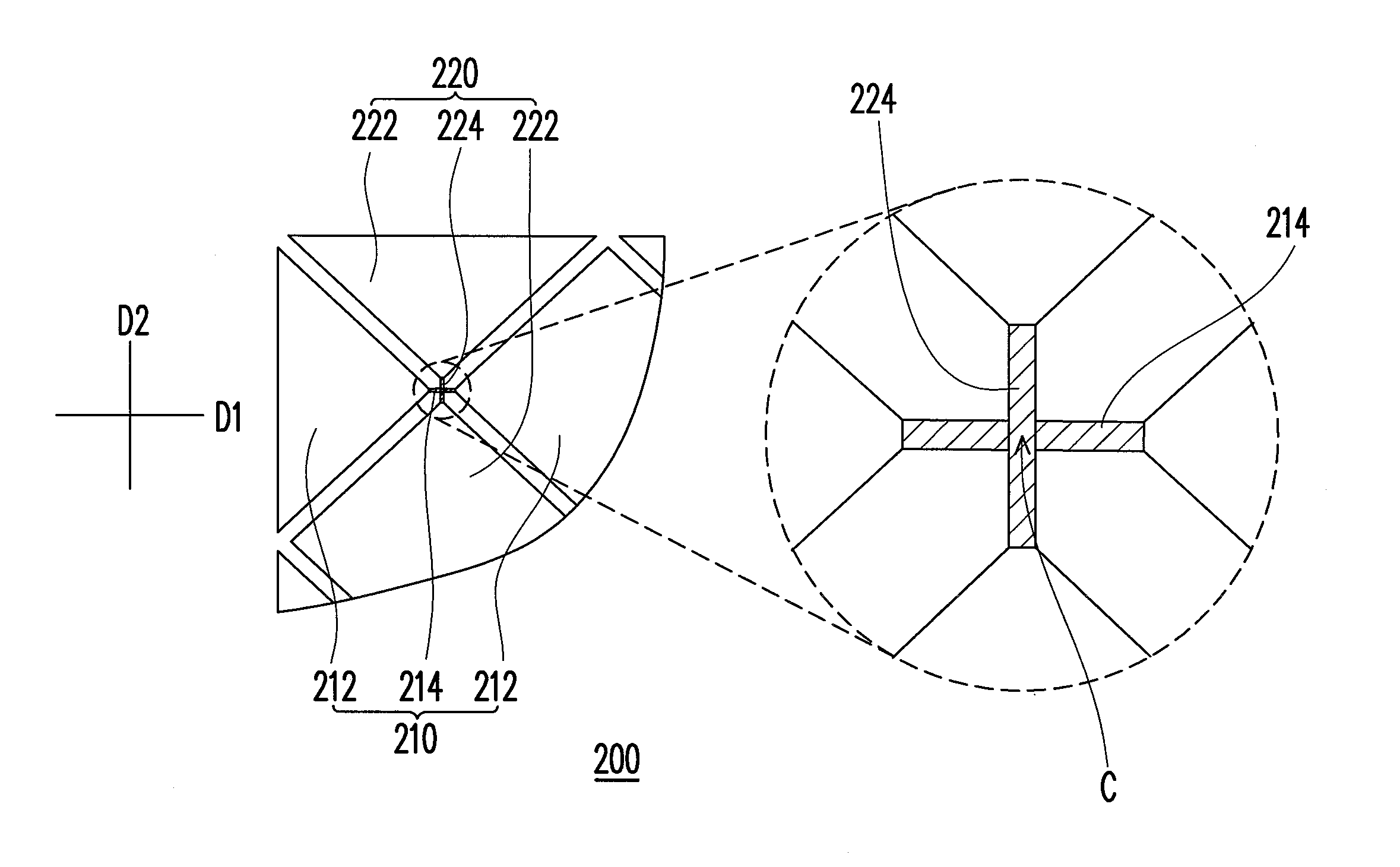

Touch panel

InactiveUS20100123674A1Satisfactory touch sensitivityLow resistivityInput/output processes for data processingTouch panelElectrical and Electronics engineering

A touch panel including at least a first sensing string and at least a second sensing string is provided. The first sensing string arranged in a first direction includes first sensing pads electrically connecting with each other and at least a first connecting pattern. The first connecting patterns are located between two adjacent first sensing pads. The second sensing string does not contact the first sensing string and is arranged in a second direction which crosses with the first direction. The second sensing string includes second sensing pads and at least a second connecting pattern. The second sensing pads electrically connected with one another are located among the first sensing pads. The second connecting pattern is located between two adjacent second sensing pads. Resistivities of the first connecting pattern and the second connecting pattern are lower than those of the first sensing pad and the second sensing pad respectively.

Owner:WINTEK CORP

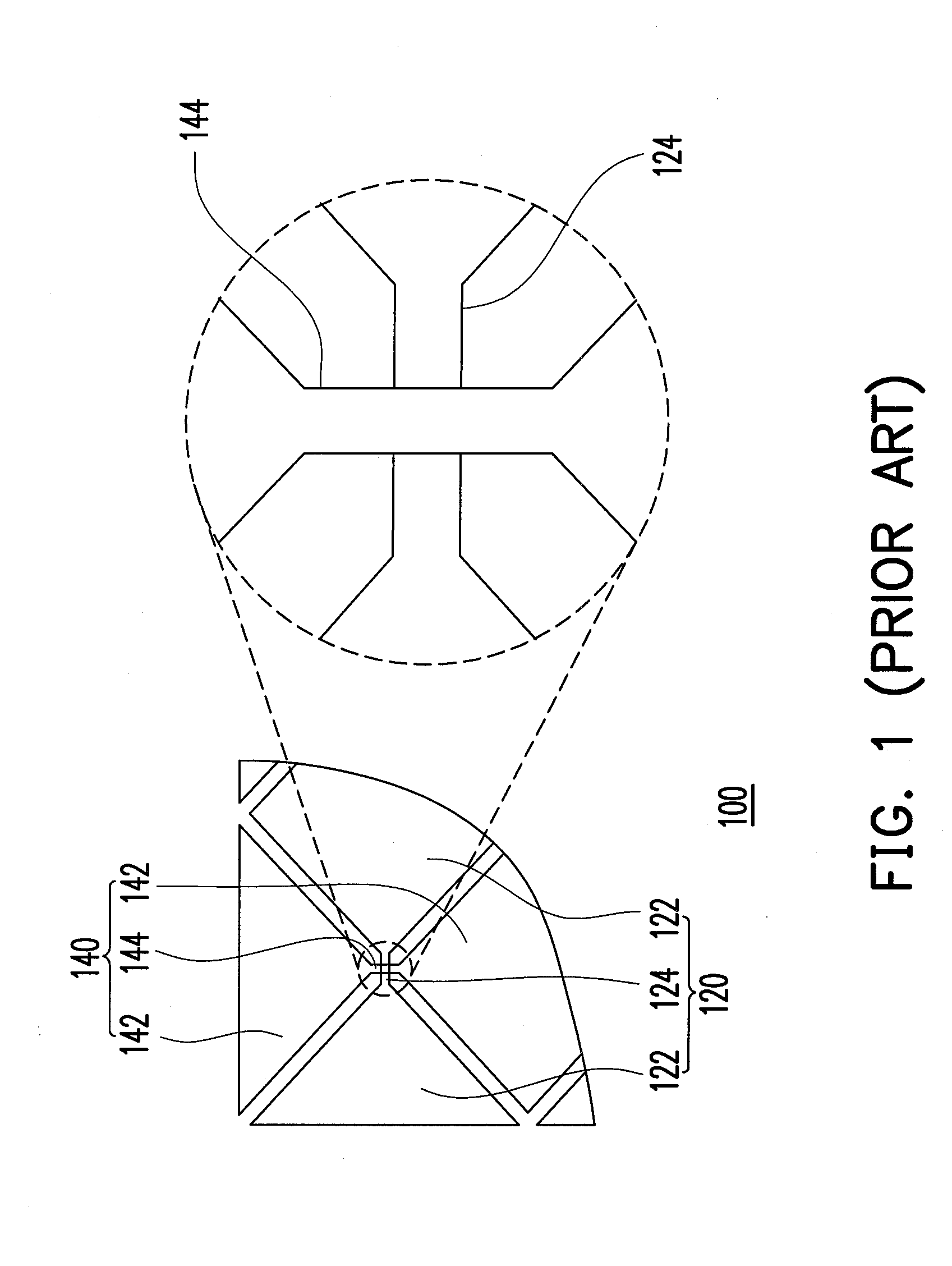

Capacitive touch sensor and fabrication method thereof and capacitive touch panel

InactiveUS20110187673A1Reduce capacitanceLower impedanceConductive pattern formationConverting sensor output electrically/magneticallyInsulation layerTouch Senses

A capacitive touch sensor includes multiple first-axis traces, multiple second-axis traces, an insulation layer and multiple metal traces. Each first-axis trace includes multiple first touch-sensing pads and first connecting lines connected therebetween. Each second-axis trace includes multiple second touch-sensing pads and second connecting lines connected therebetween. At least one of the first connecting line and the second connecting line is a metal printing line.

Owner:WINTEK CHINA TECH LTD +1

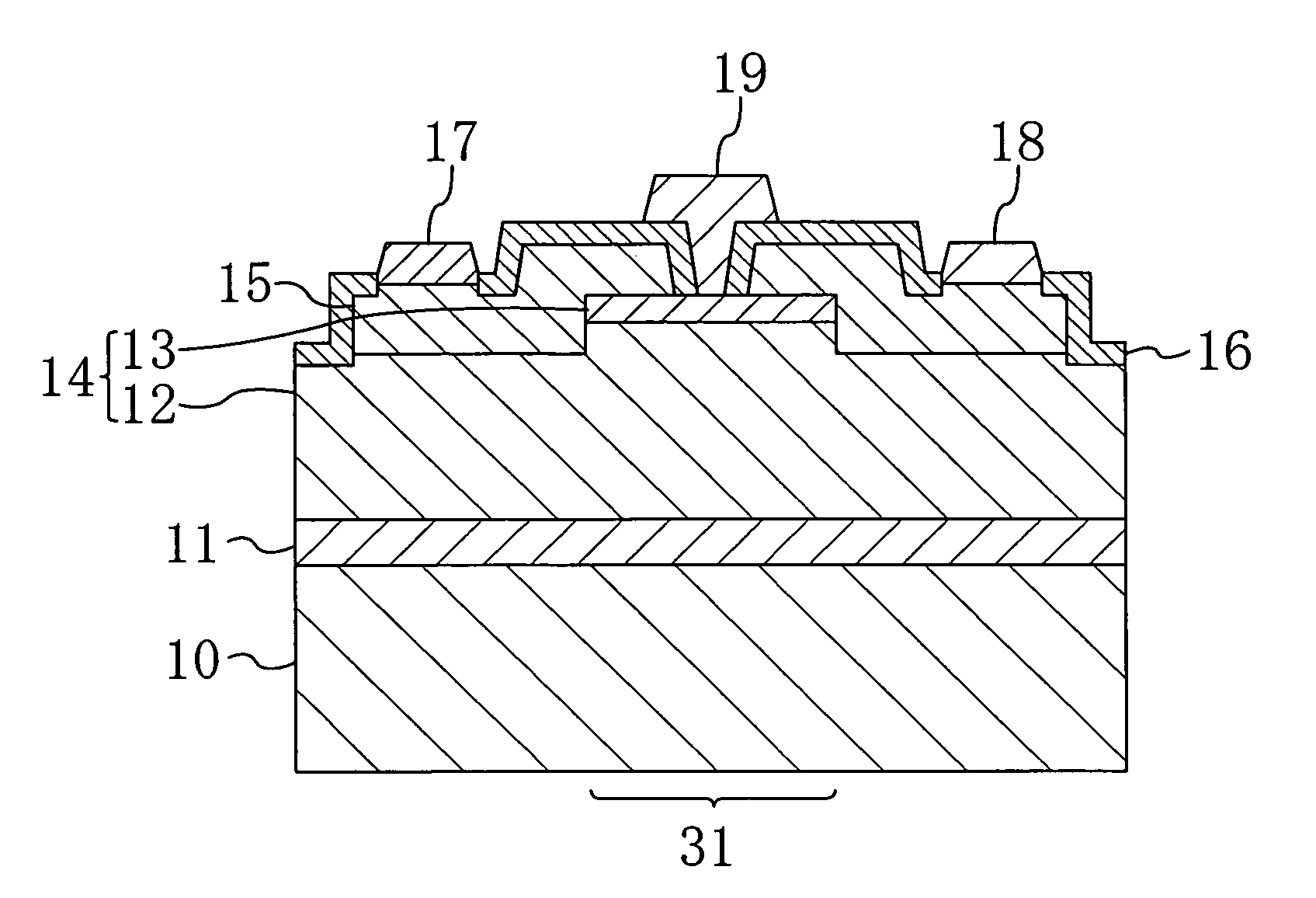

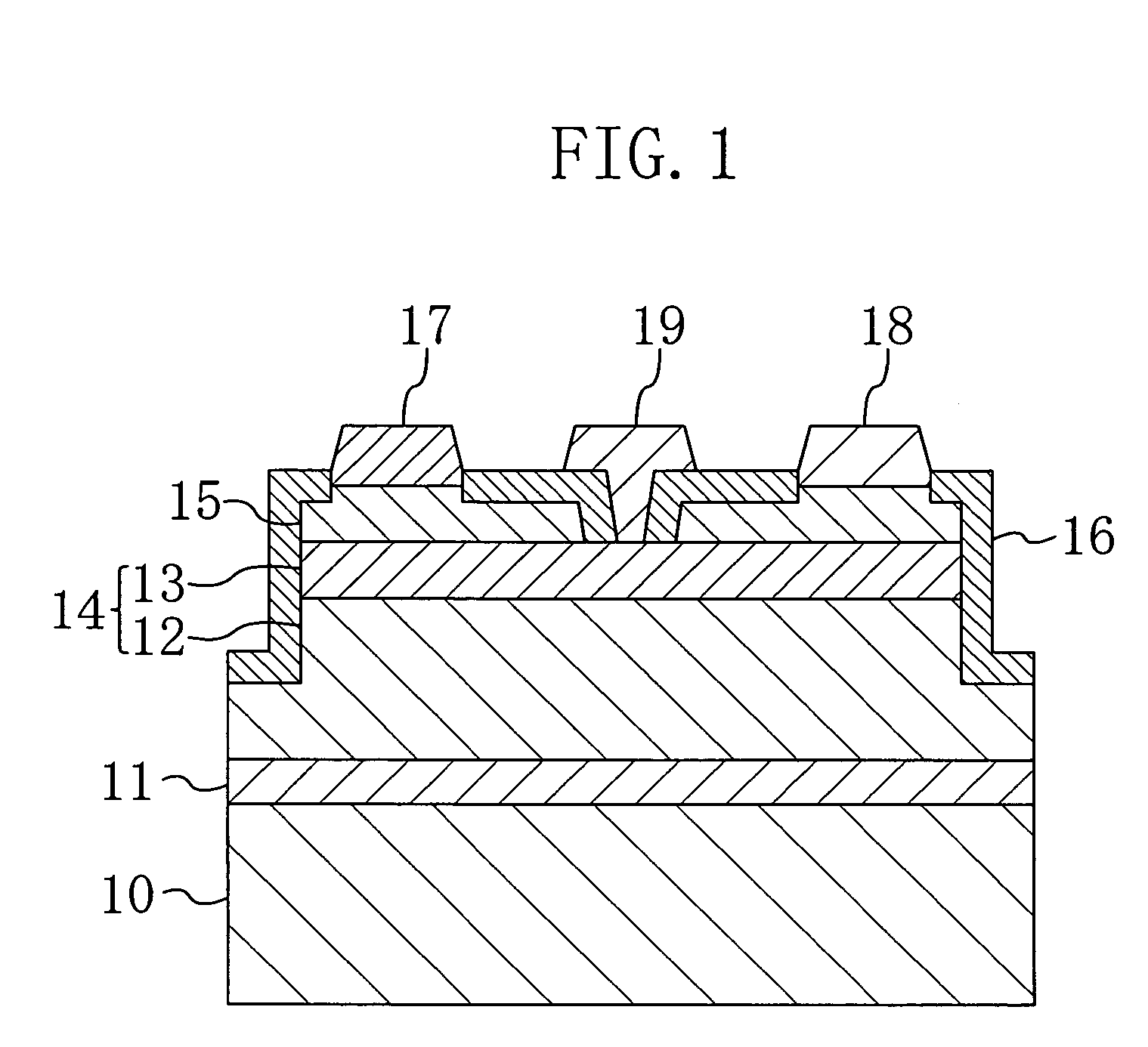

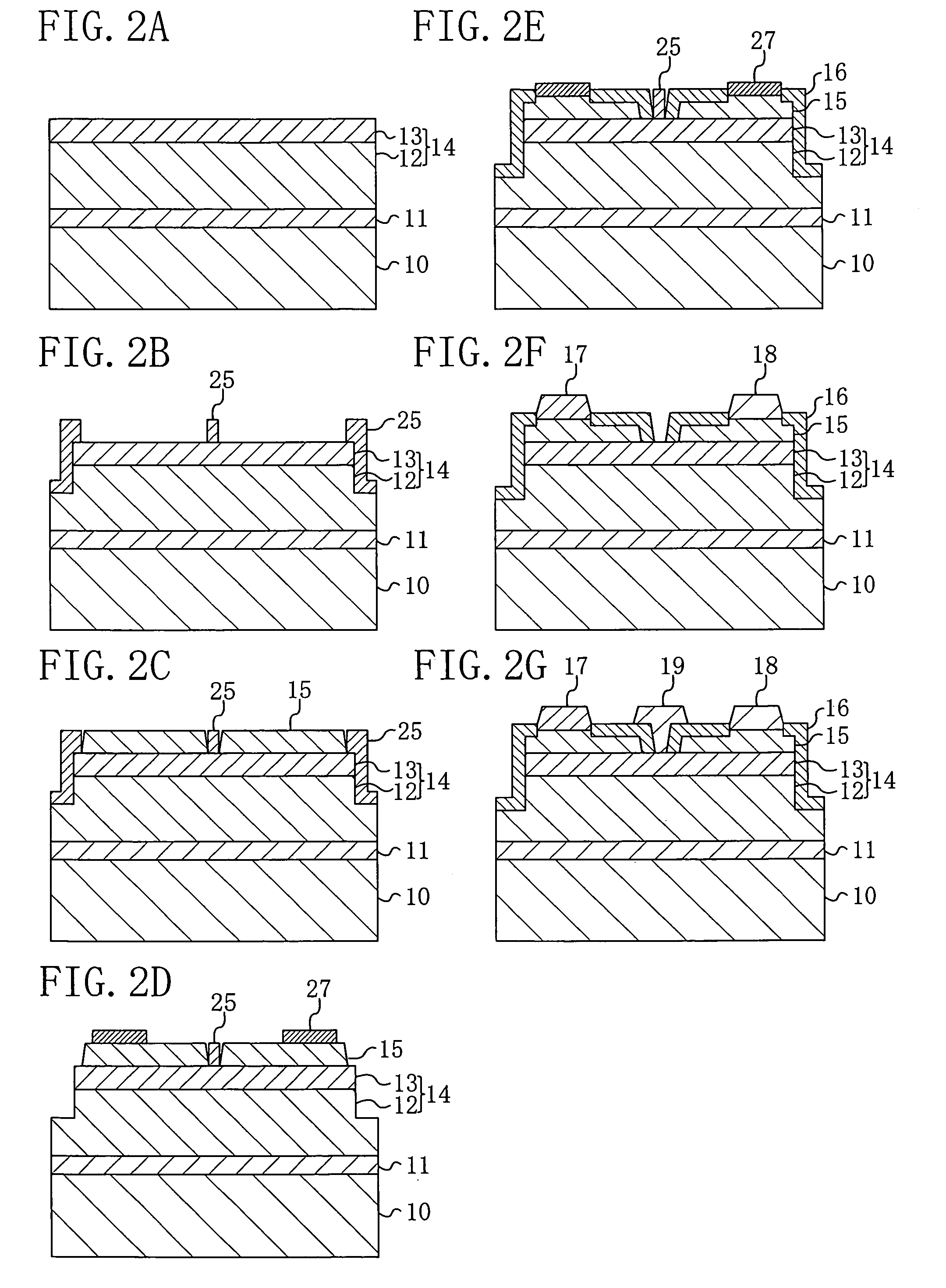

Semiconductor chip and fabrication method thereof

ActiveUS7052975B2Improve integration and yieldShorten production timeSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

Owner:SHINKO ELECTRIC IND CO LTD

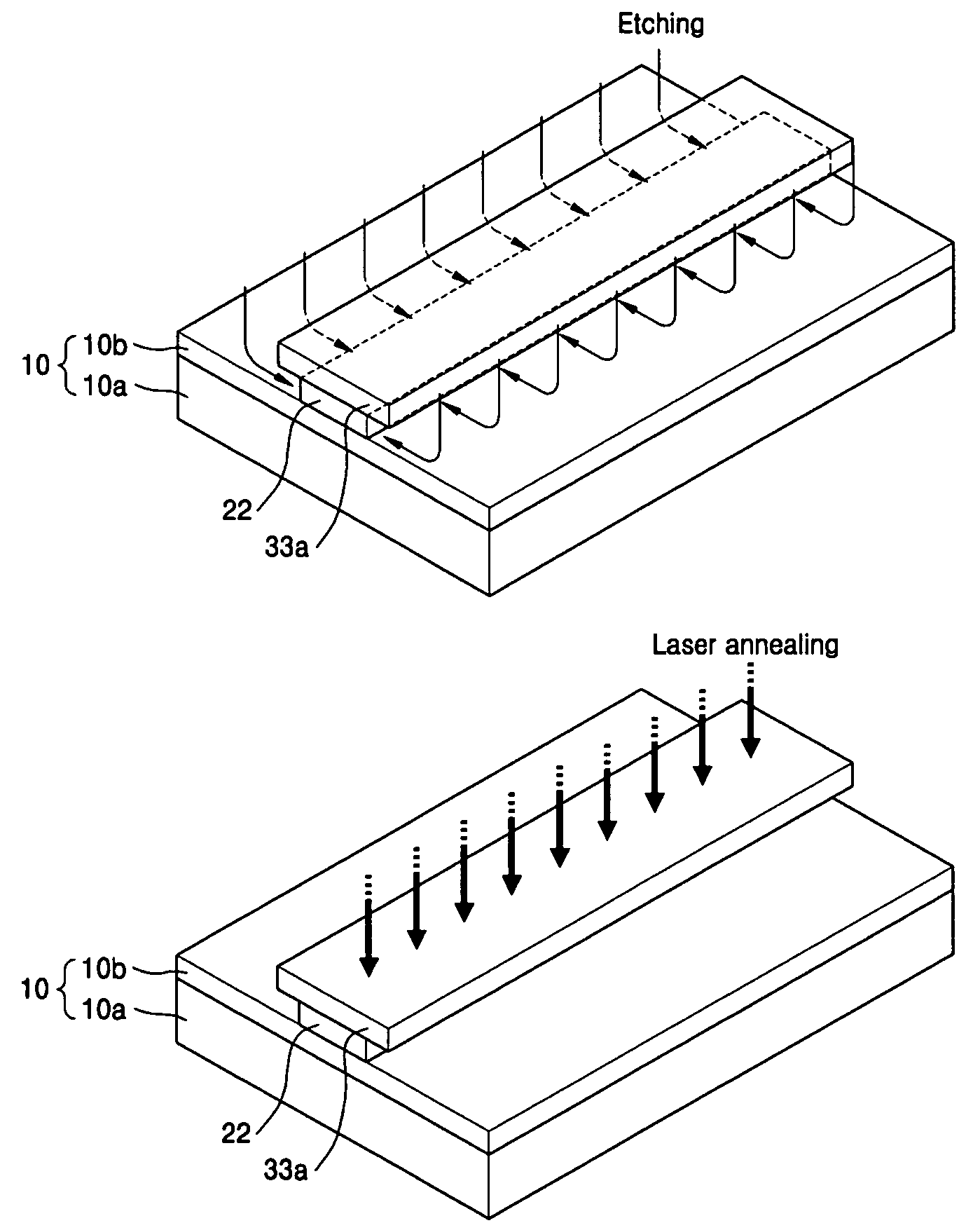

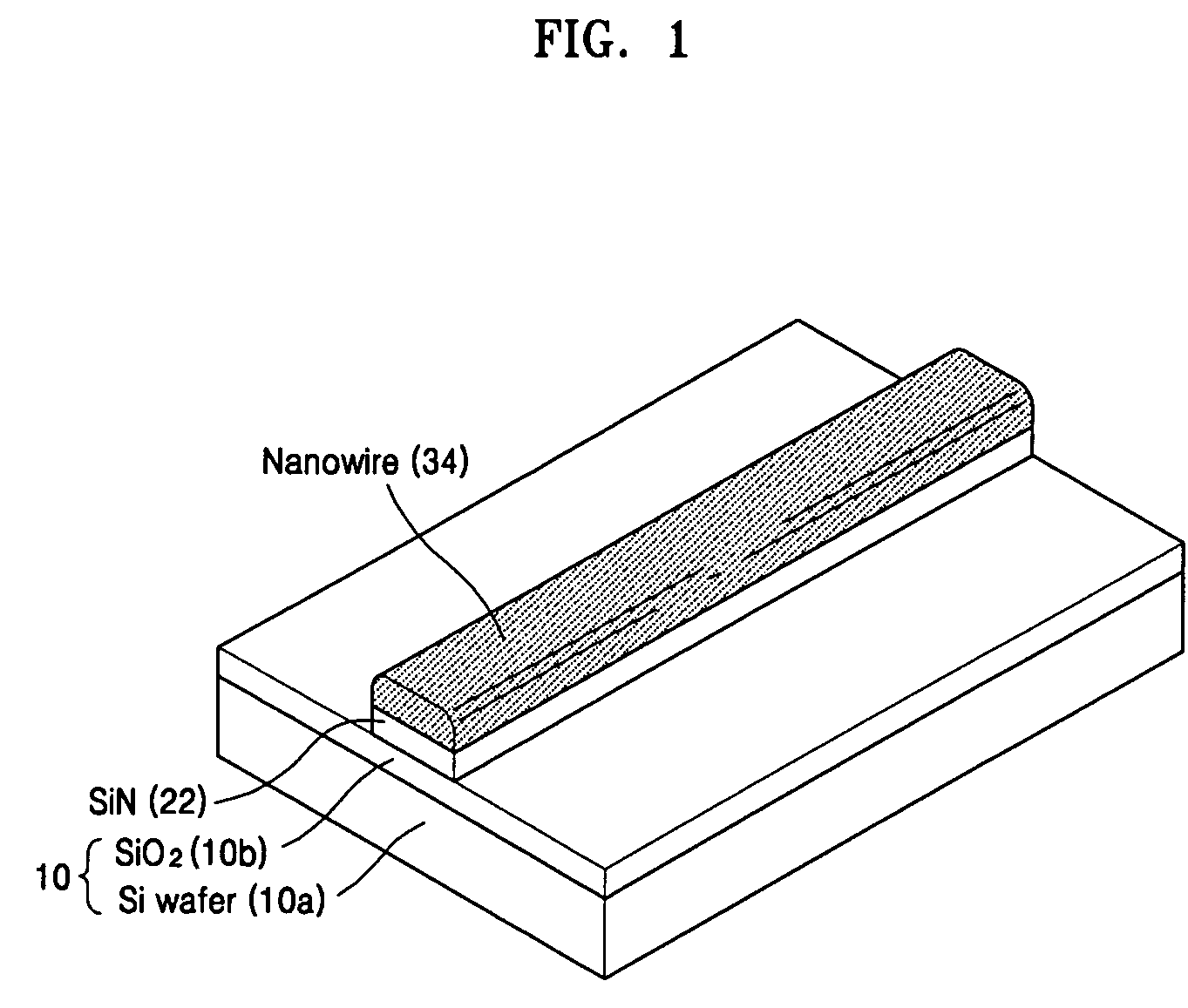

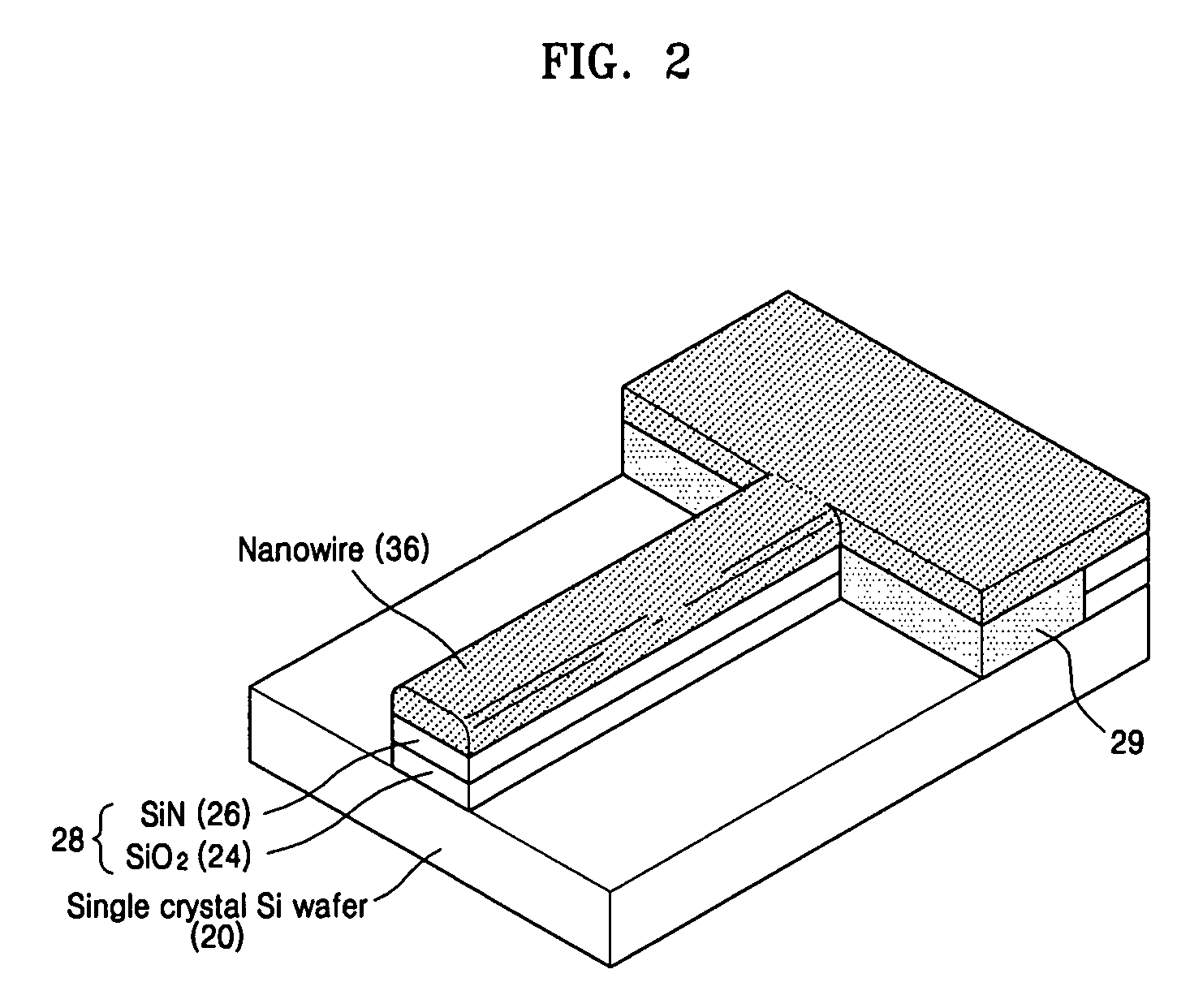

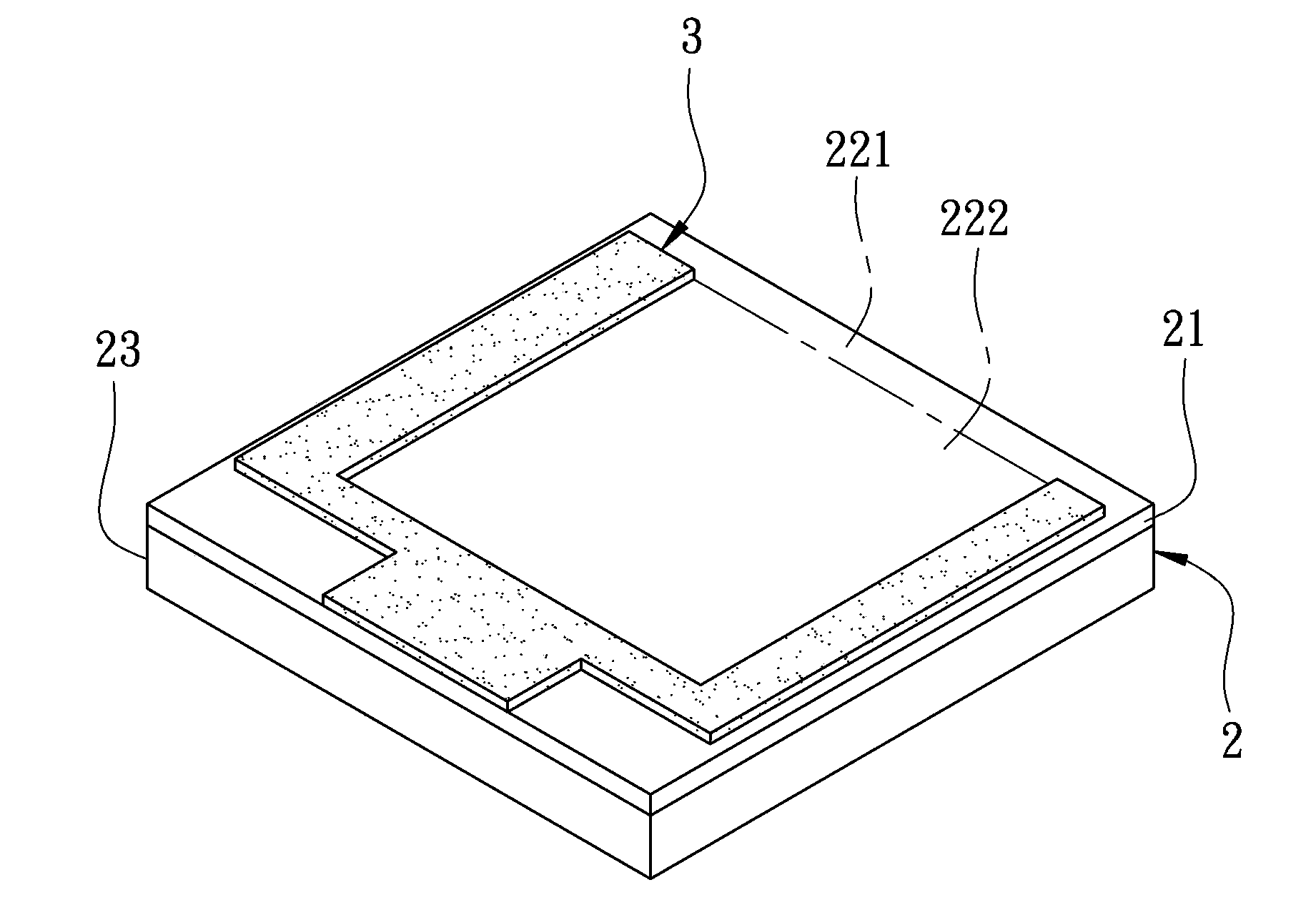

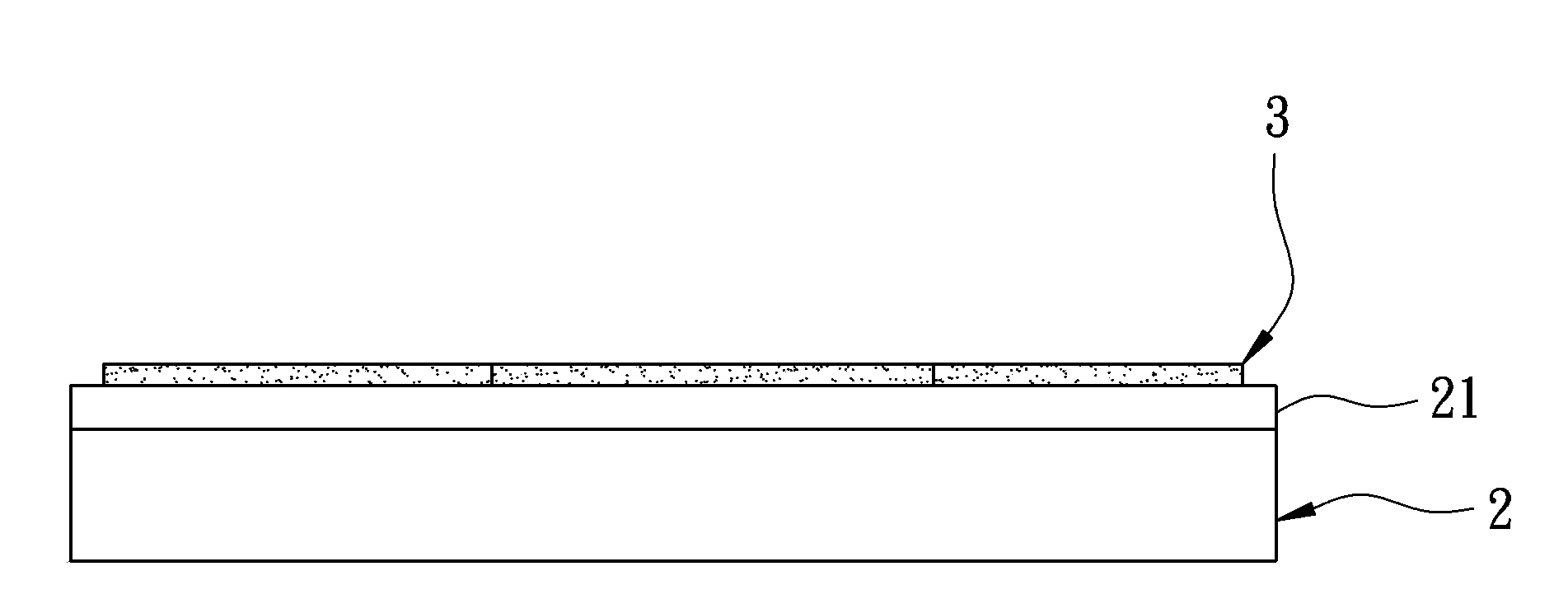

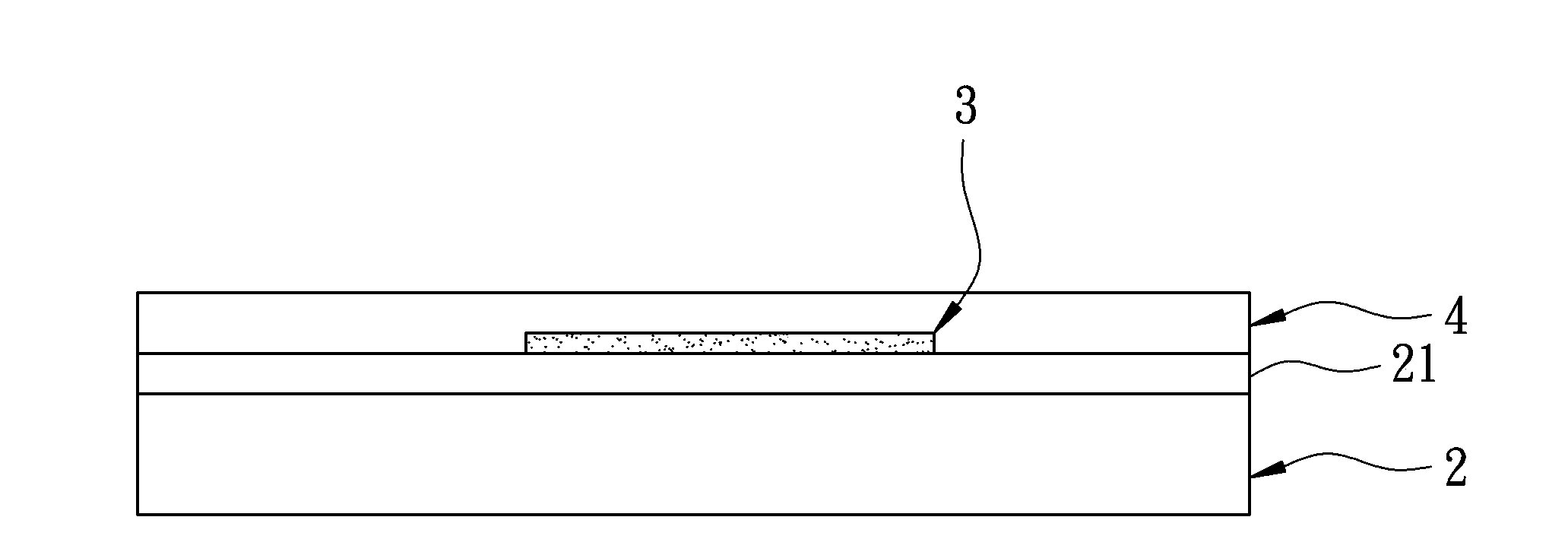

Si nanowire substrate, method of manufacturing the same, and method of manufacturing thin film transistor using the same

A silicon nanowire substrate having a structure in which a silicon nanowire film having a fine line-width is formed on a substrate, a method of manufacturing the same, and a method of manufacturing a thin film transistor using the same. The method of manufacturing the silicon nanowire substrate includes preparing a substrate, forming an insulating film on the substrate, forming a silicon film on the insulating film, patterning the insulating film and the silicon film into a strip shape, reducing the line-width of the insulating film by undercut etching at least one lateral side of the insulating film, and forming a self-aligned silicon nanowire film on an upper surface of the insulating film by melting and crystallizing the silicon film.

Owner:SAMSUNG ELECTRONICS CO LTD

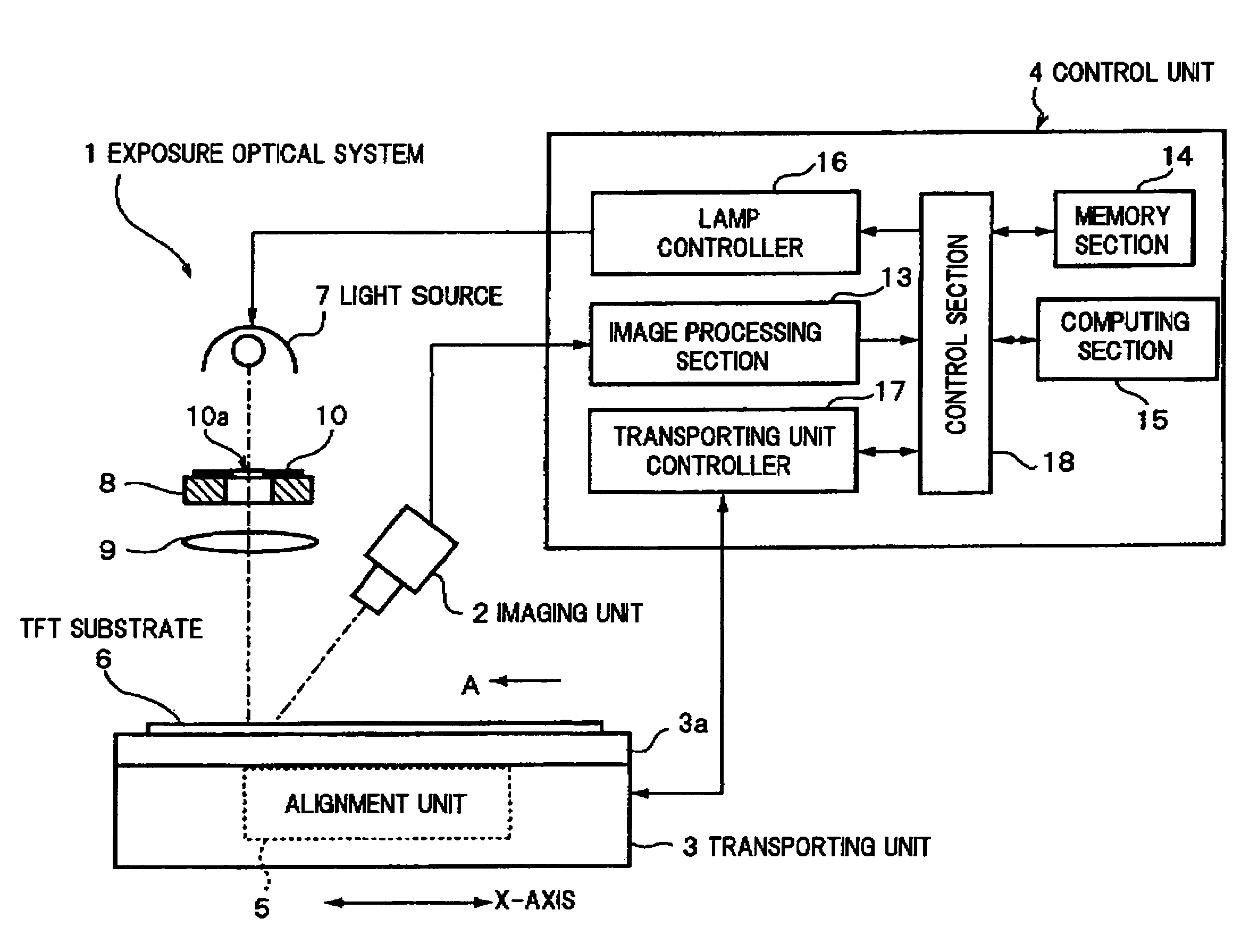

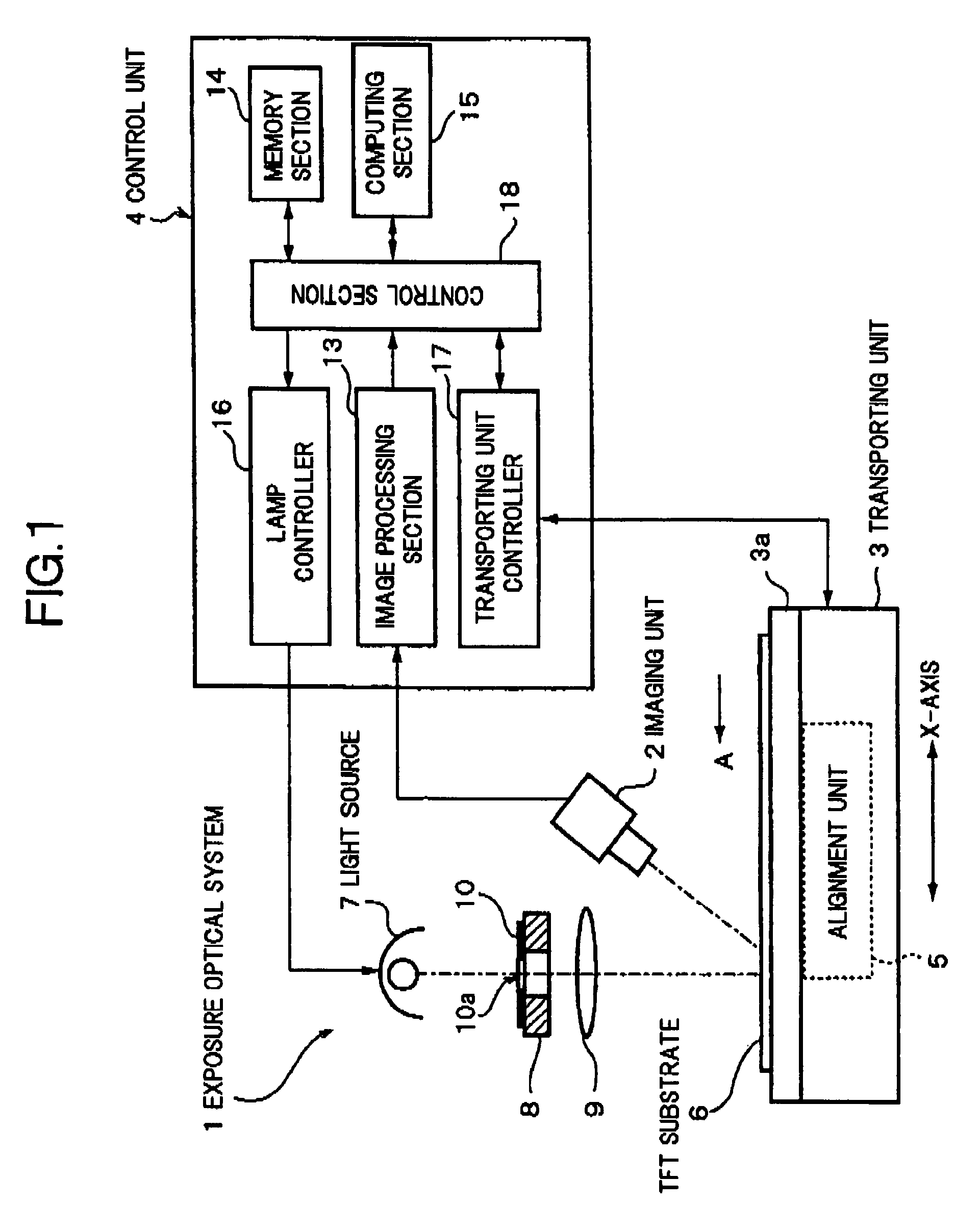

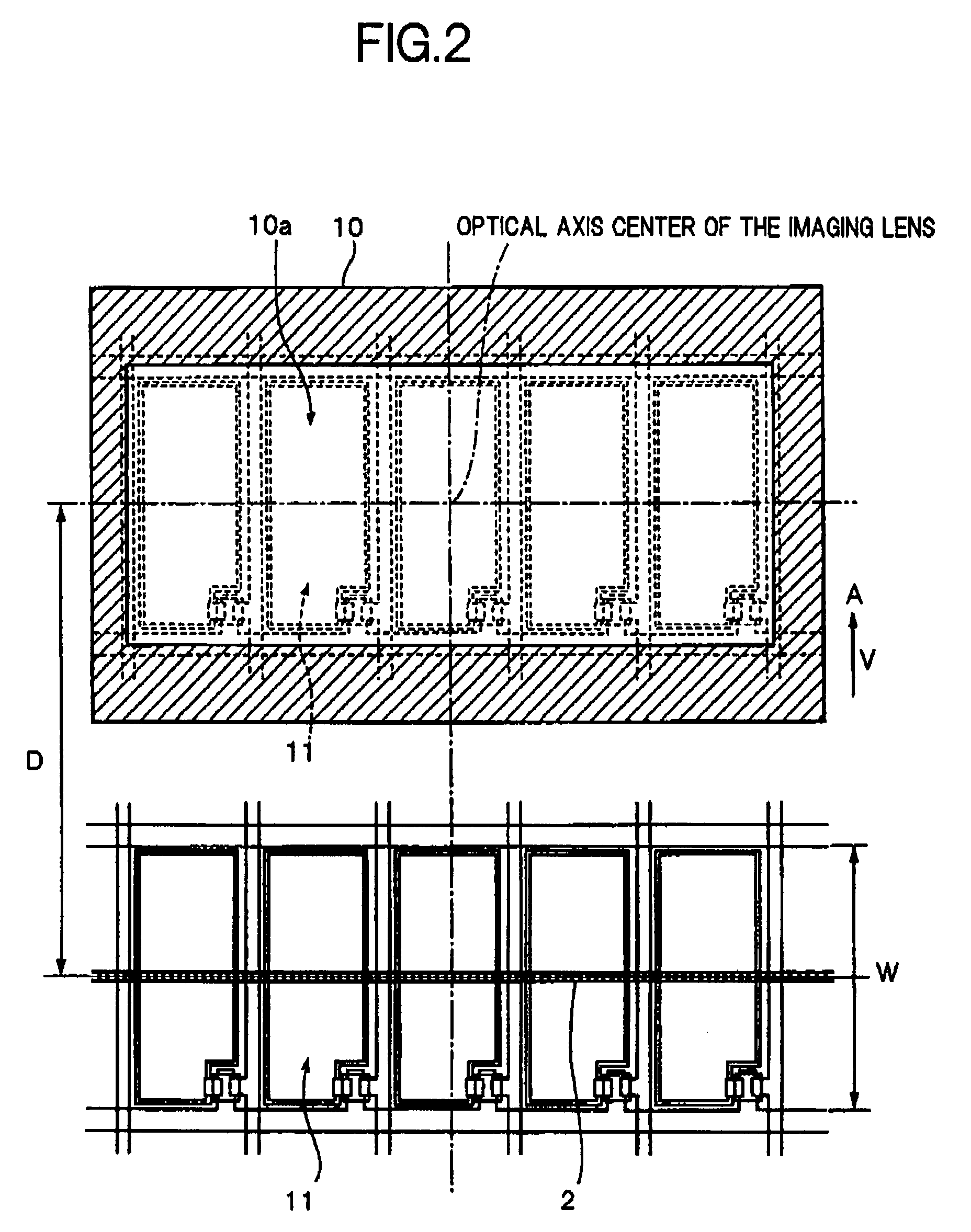

Production method of substrate for liquid crystal display using image-capturing and reference position detection at corner of pixel preset in TFT substrate

InactiveUS7812920B2High precisionReduce line widthTelevision system detailsPhotomechanical apparatusLiquid-crystal displayImaging processing

A production method of a substrate for a liquid crystal display in which an exposure pattern of a color filter or a black matrix is formed in a predetermined position of a TFT substrate at a high level of precision. Therefore the production method includes following steps: applying a photosensitive material for a color filter or a black matrix onto a TFT substrate; image-capturing a pixel region by an imaging unit while transporting the TFT substrate coated with the photosensitive material at a predetermined velocity by a transporting unit; detecting a reference position preset in the pixel region image-captured by the imaging unit at an image processing section of a control unit; and controlling irradiation timing of a light source in an exposure optical system by a lamp controller with reference to the detected reference position, and forming an exposure pattern of a color filter or a black matrix at a predetermined position of the TFT substrate.

Owner:V TECH CO LTD

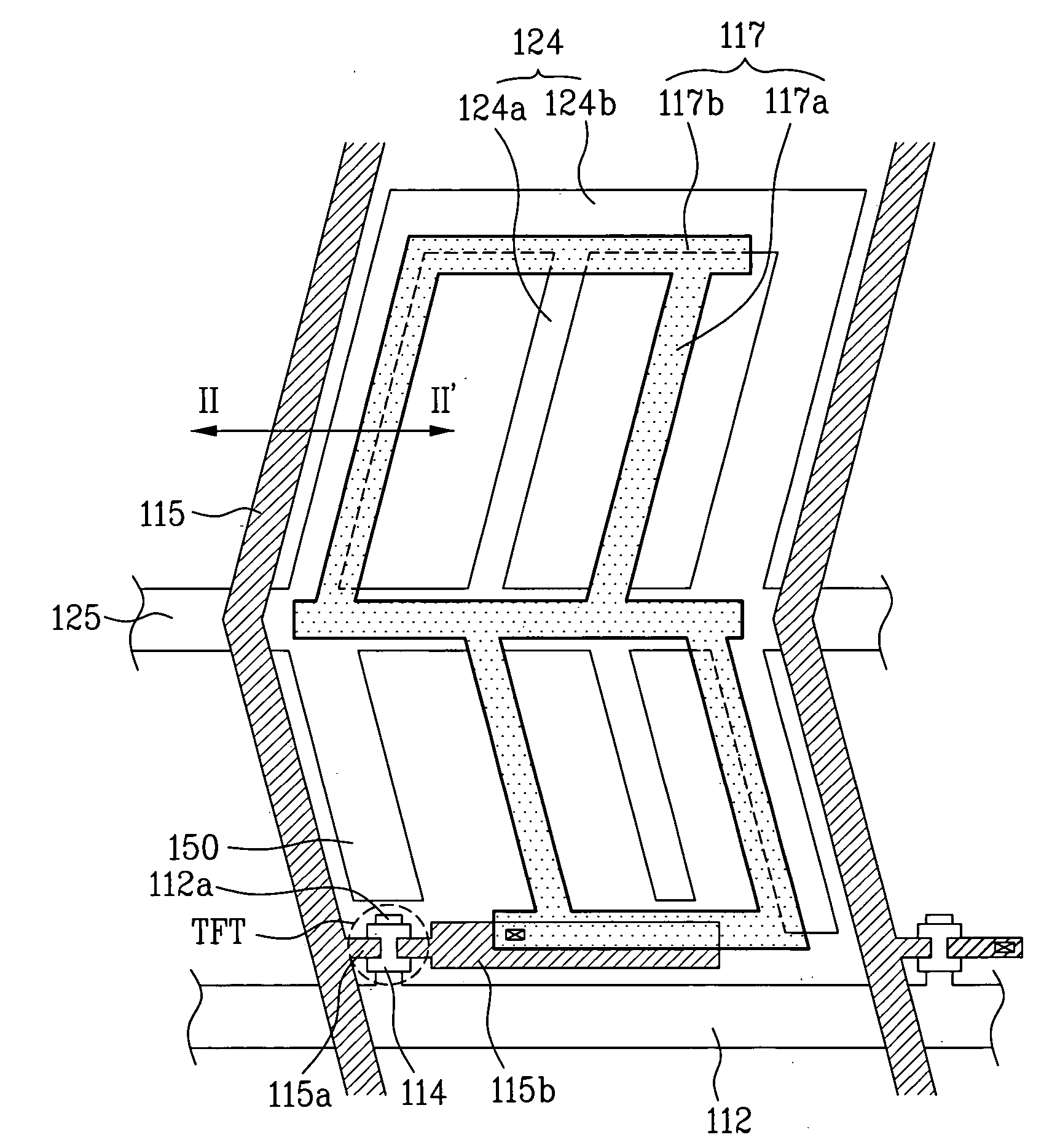

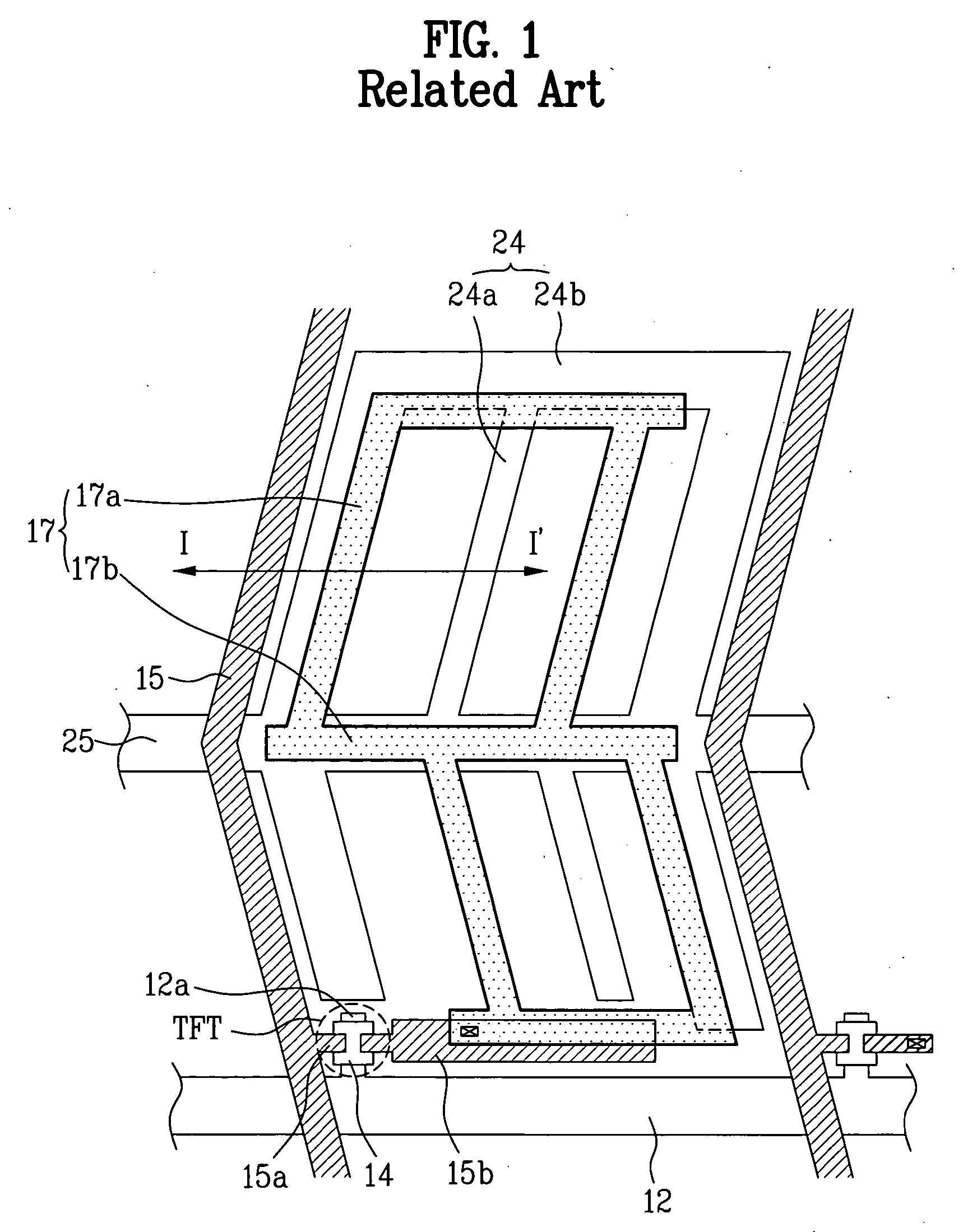

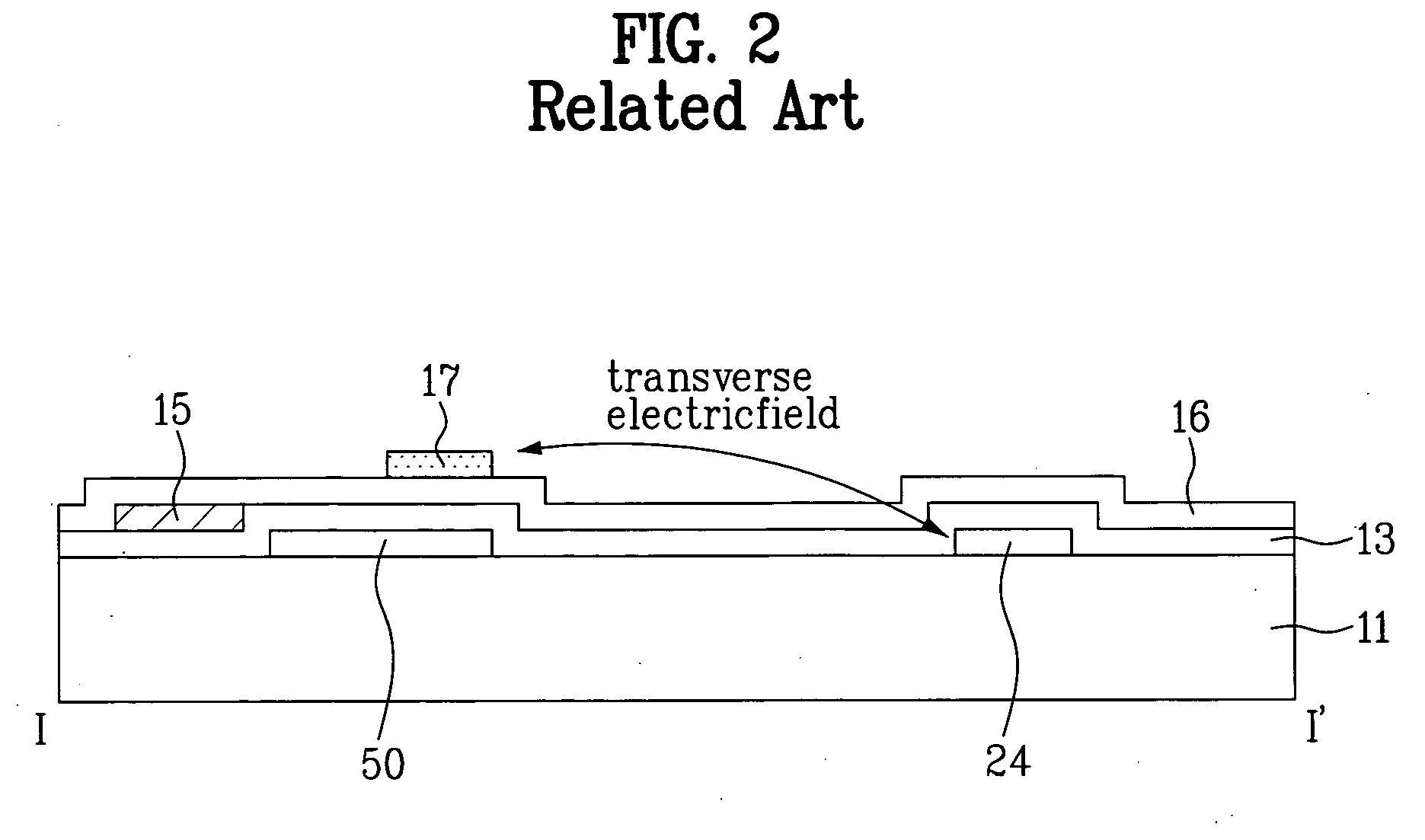

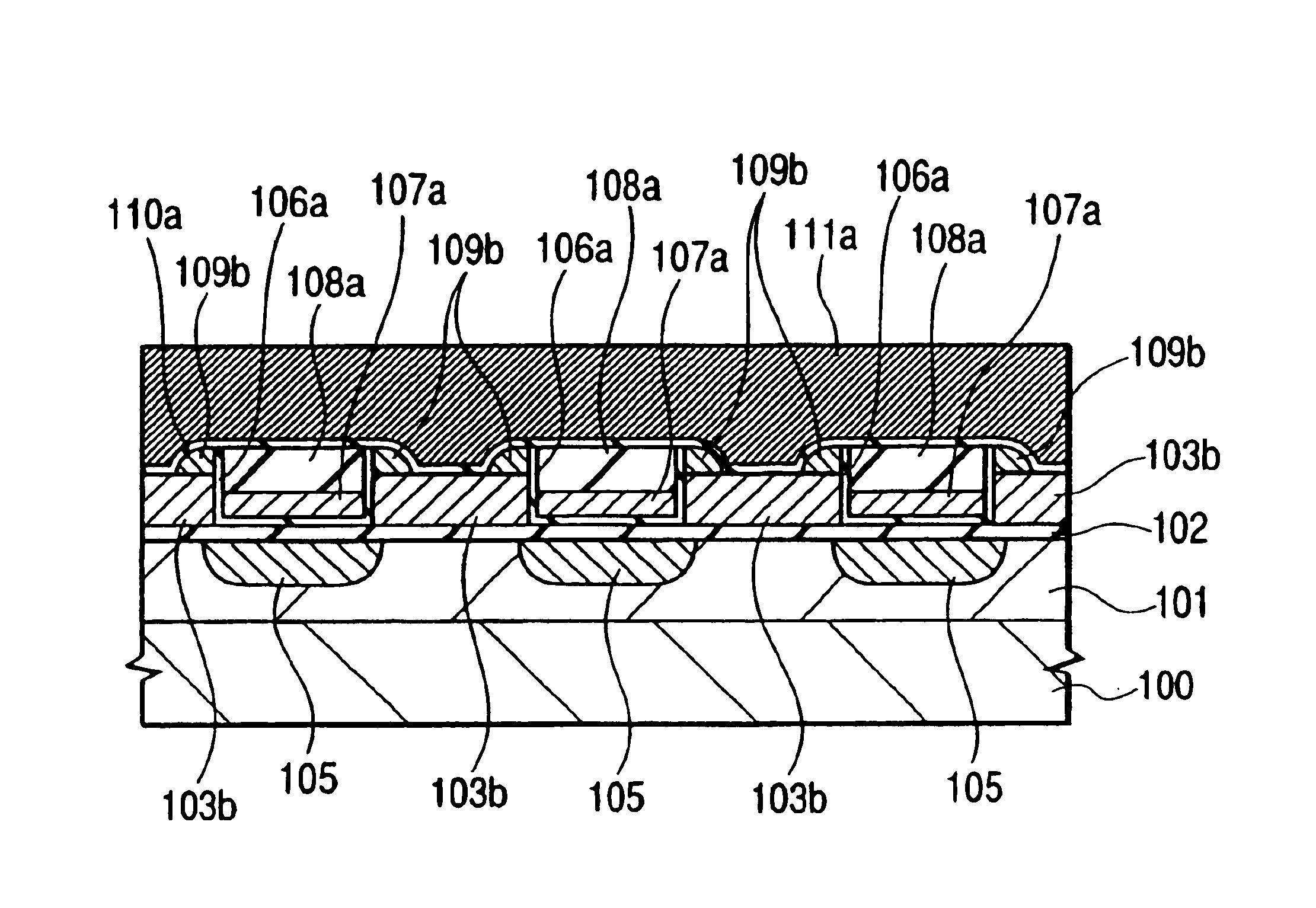

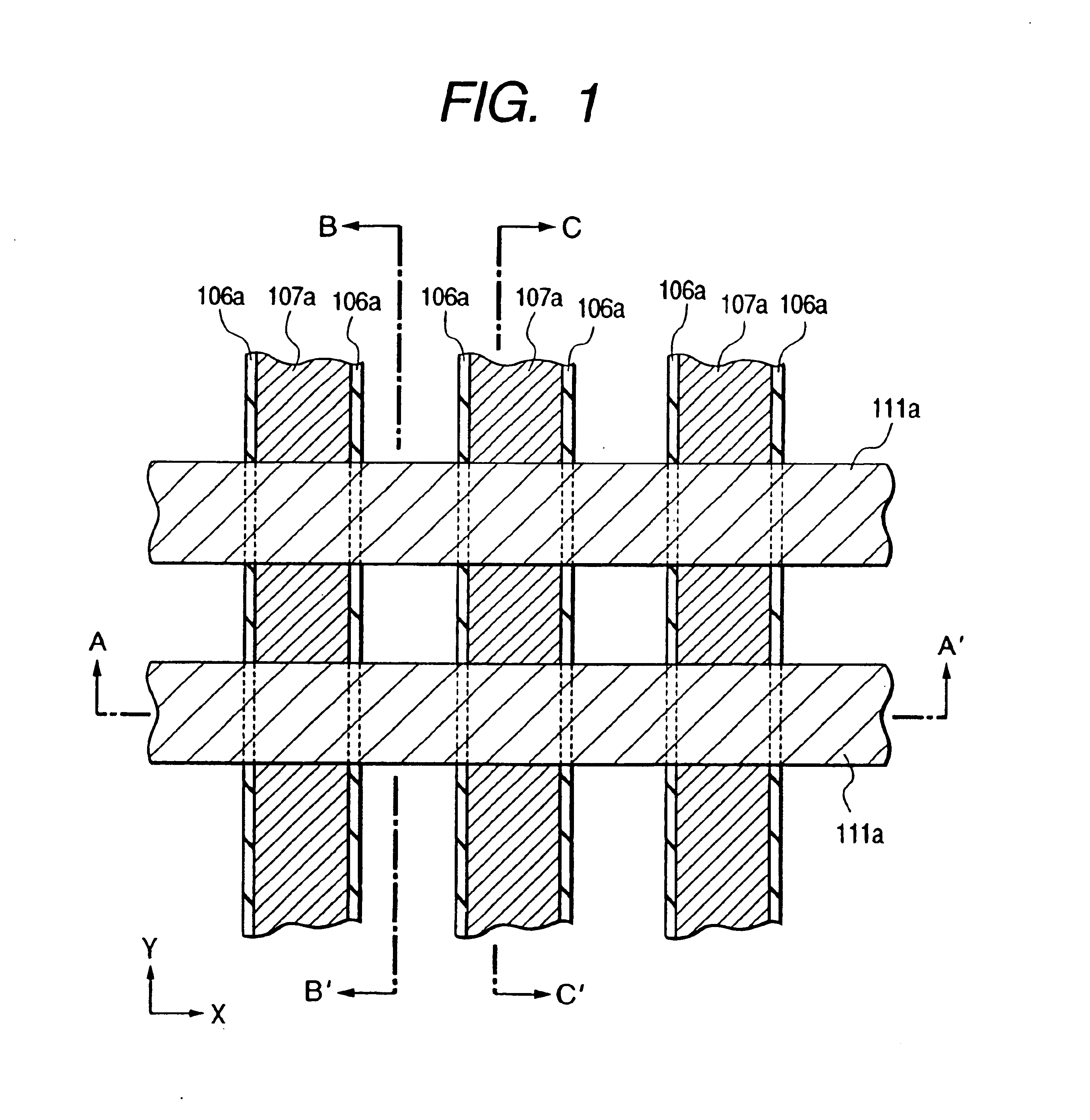

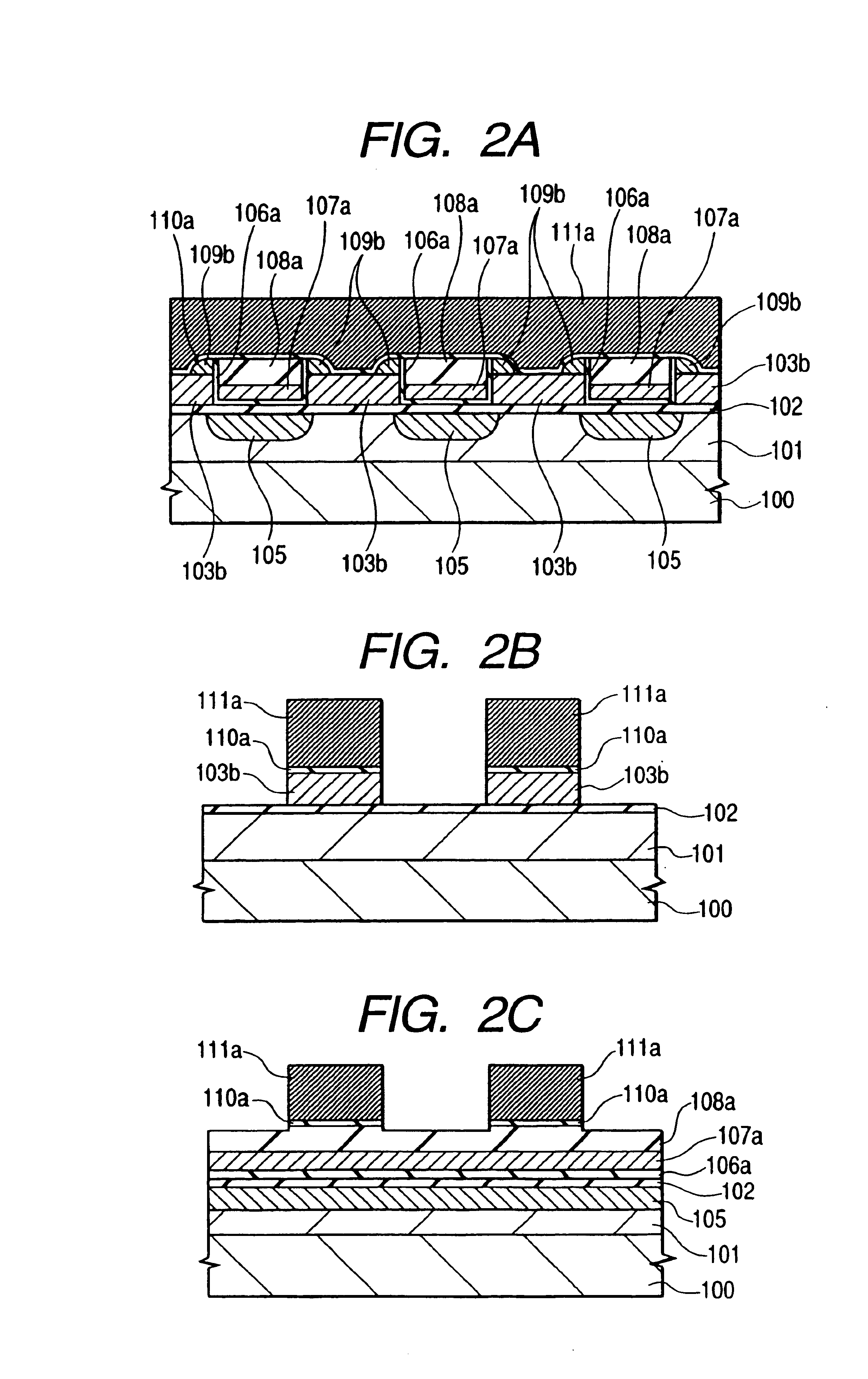

In-plane switching mode liquid crystal display device

ActiveUS20050280763A1Avoid distortionReduce line widthNon-linear opticsIn planeLiquid-crystal display

An In-Plane Switching (IPS) mode LCD device is disclosed, to prevent the distortion of transverse electric field in a method of decreasing a line width of a common electrode overlapped with a pixel electrode, which includes intersecting gate and data lines that define a pixel region; thin film transistors at an intersection point of the gate and data lines; pixel electrodes formed in the pixel region and connected with a thin film transistor; and common electrodes arranged between the pixel electrodes of the pixel region; wherein, the outermost common electrode, formed adjacent to the data line, is partially overlapped with the pixel electrode, and the line width of the predetermined portion of the outermost common electrode overlapped with the pixel electrode is smaller than the remaining portions of the outermost common electrode.

Owner:LG DISPLAY CO LTD

Field effect transistor and method for fabricating the same

ActiveUS7834380B2Well formedShorten the lengthSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorField-effect transistor

A field effect transistor includes a first semiconductor layer made of a multilayer of a plurality of semiconductor films and a second semiconductor layer formed on the first semiconductor layer. A source electrode and a drain electrode are formed on the second semiconductor layer to be spaced from each other. An opening having an insulating film on its inner wall is formed in a portion of the second semiconductor layer sandwiched between the source electrode and the drain electrode so as to expose the first semiconductor layer therein. A gate electrode is formed in the opening to be in contact with the insulating film and the first semiconductor layer on the bottom of the opening.

Owner:PANASONIC CORP

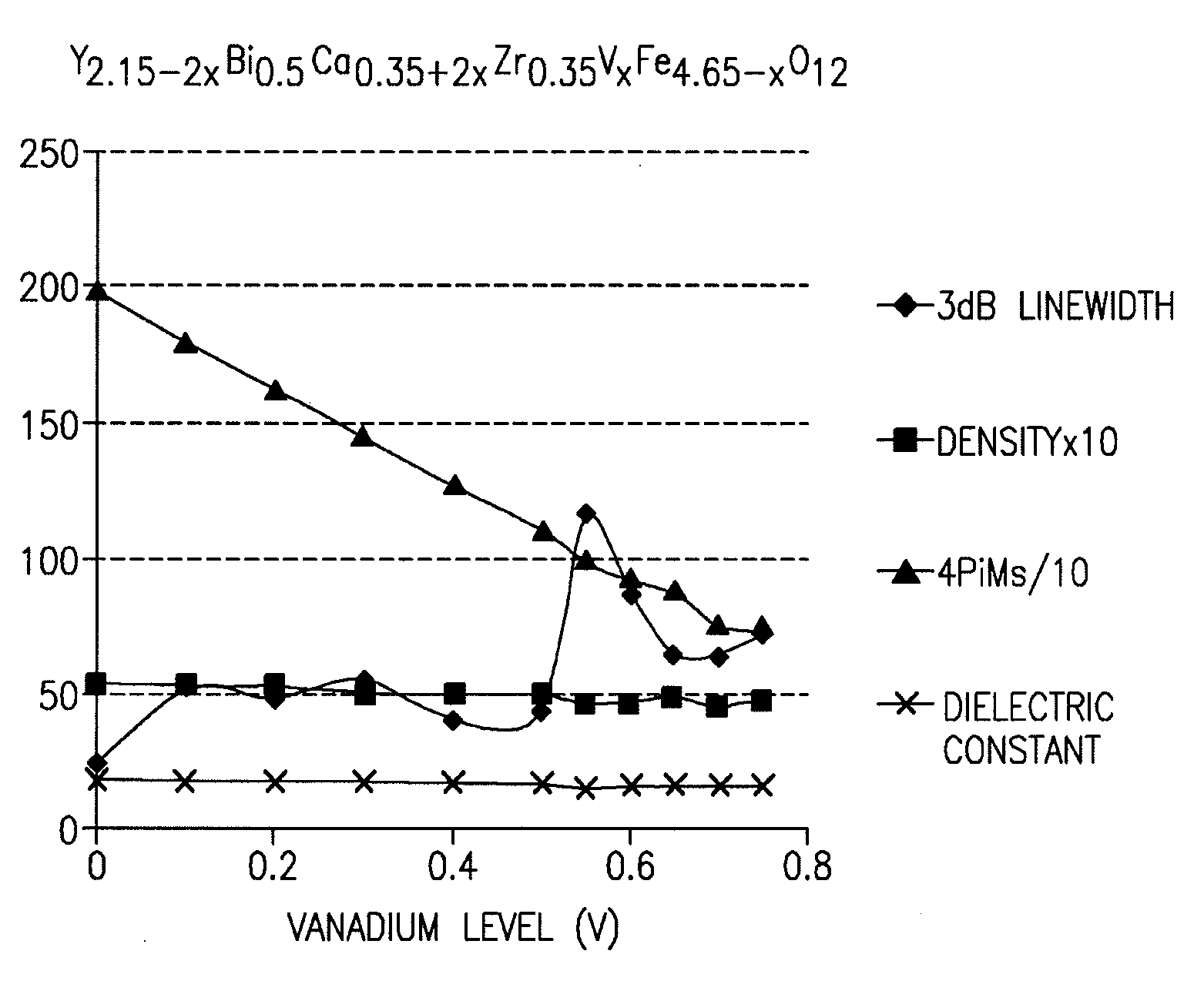

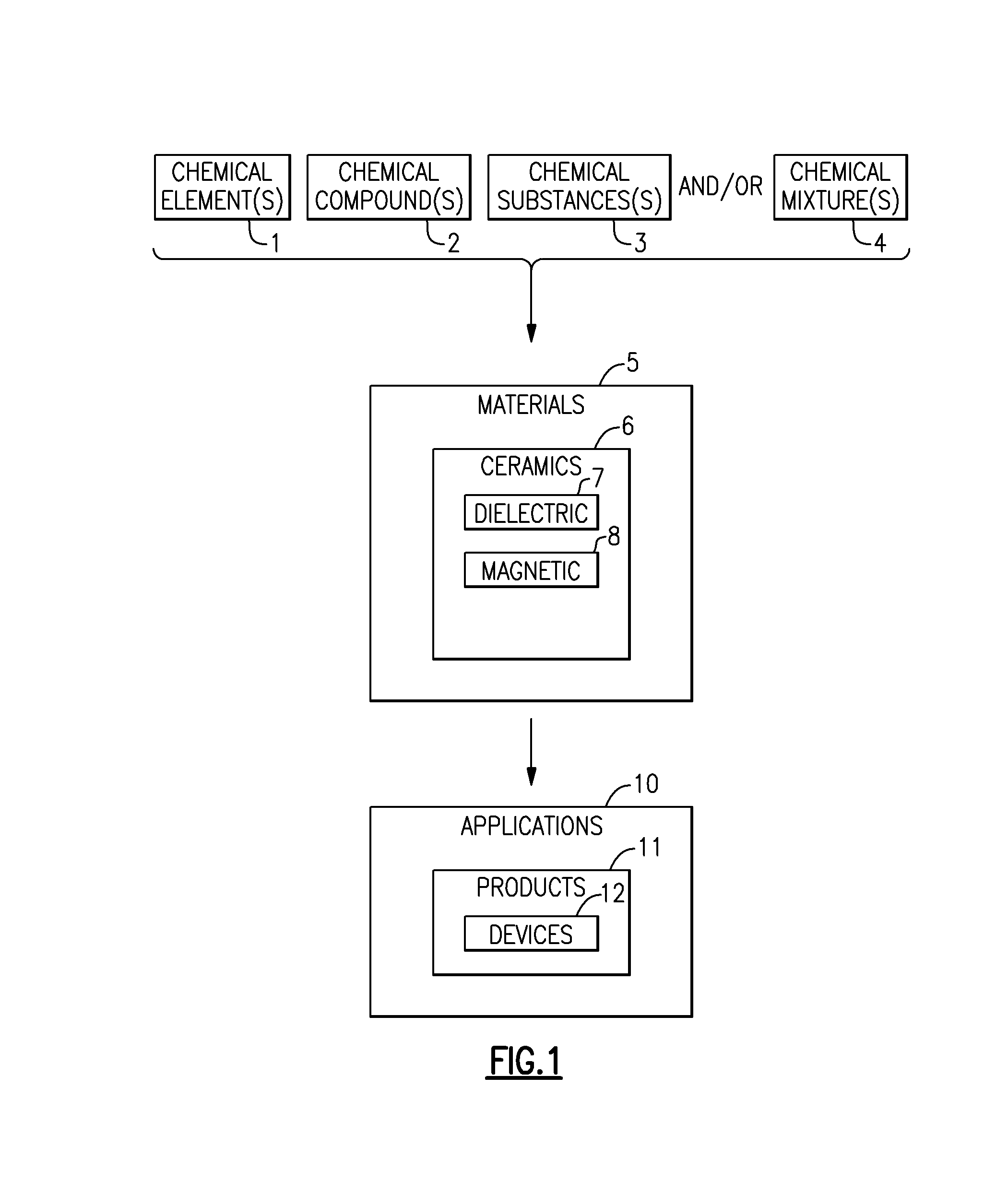

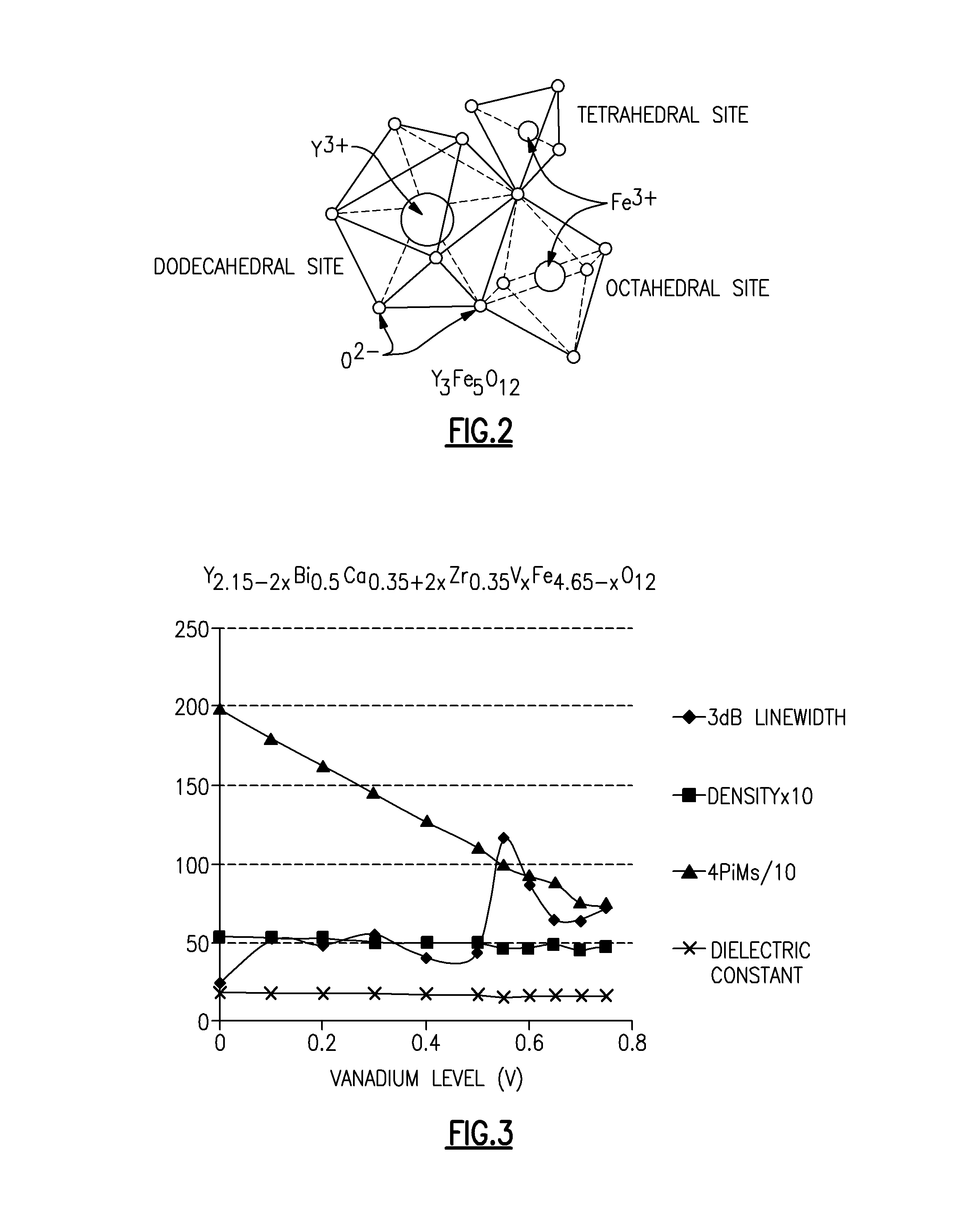

Effective substitutions for rare earth metals in compositions and materials for electronic applications

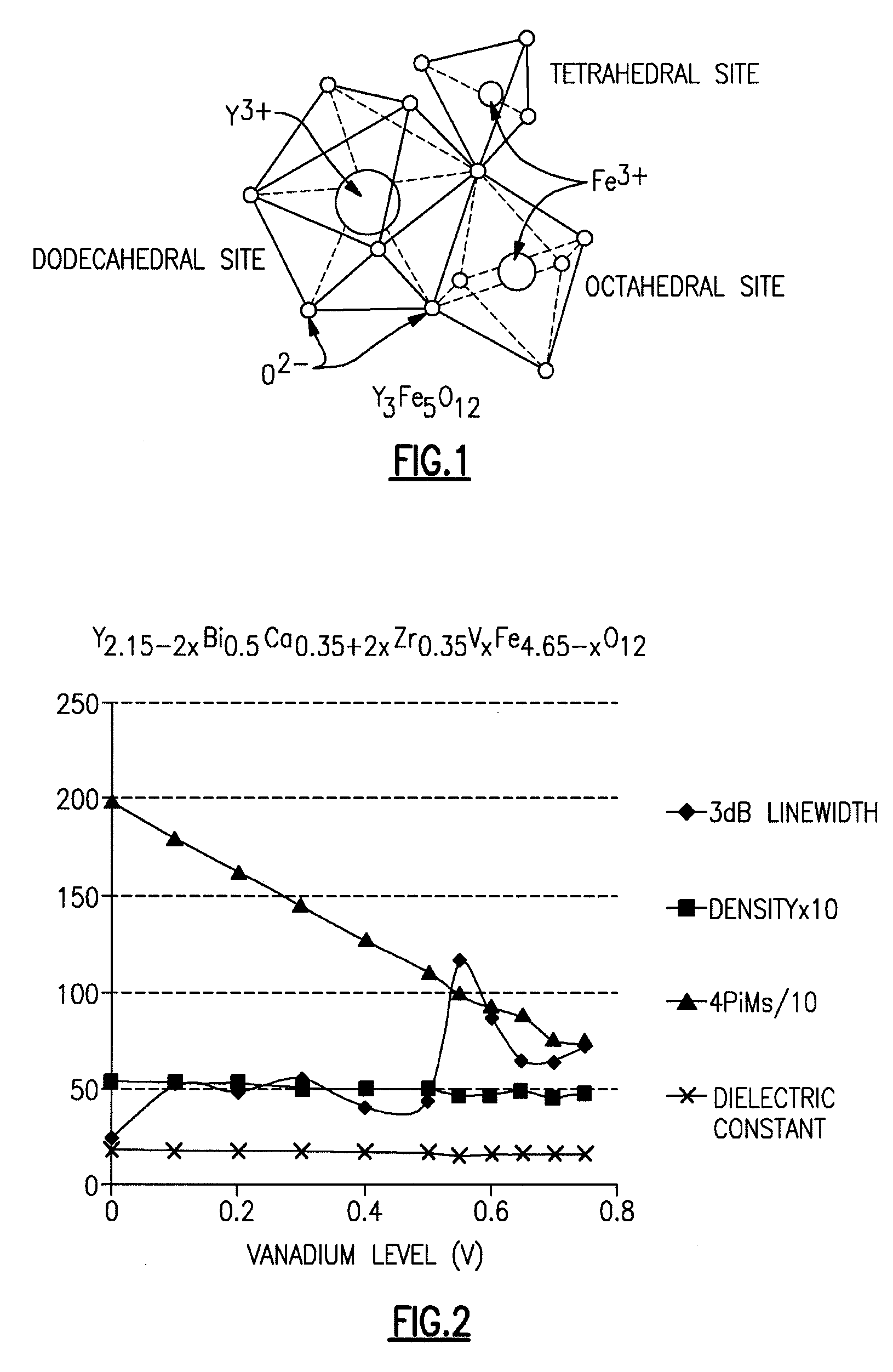

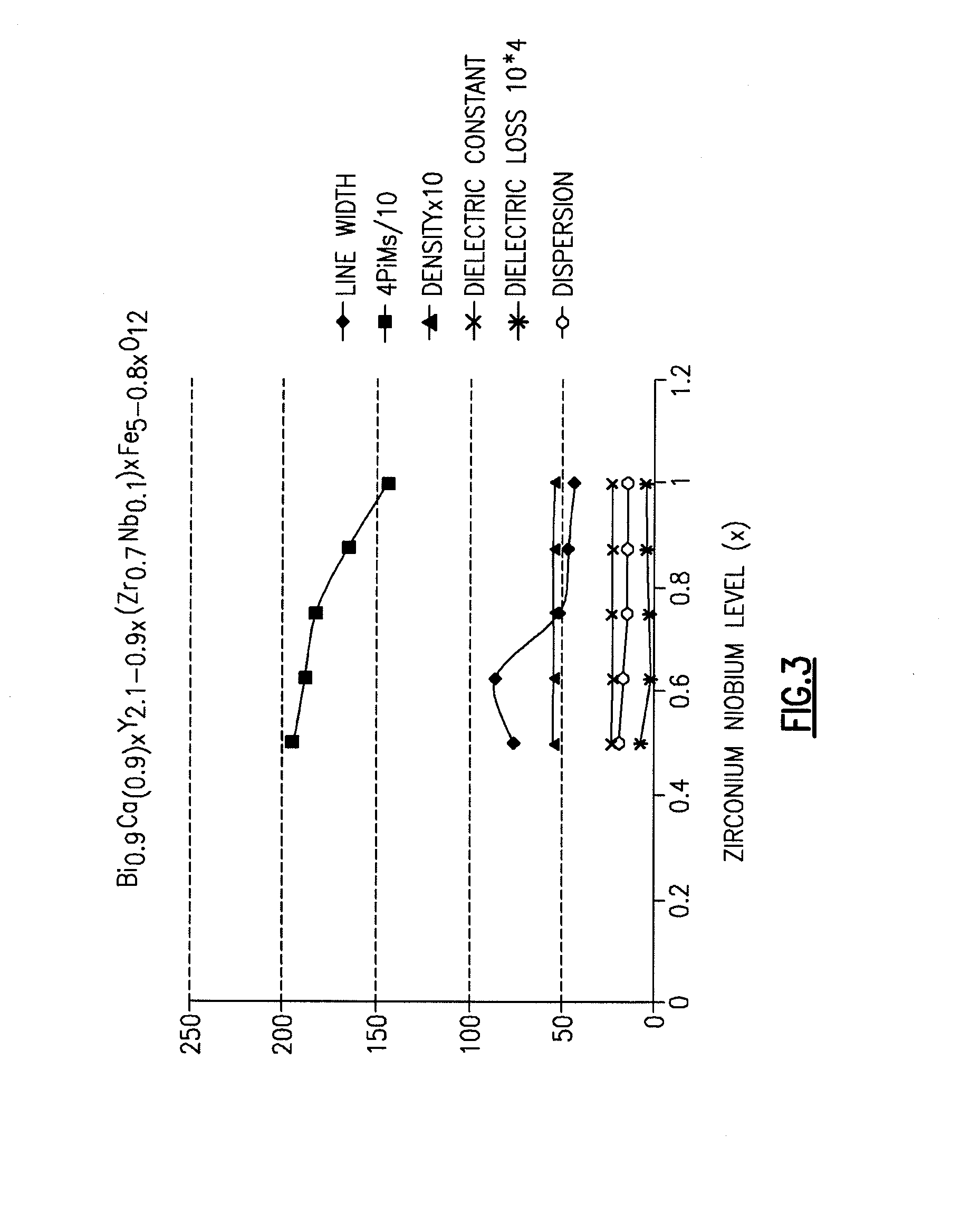

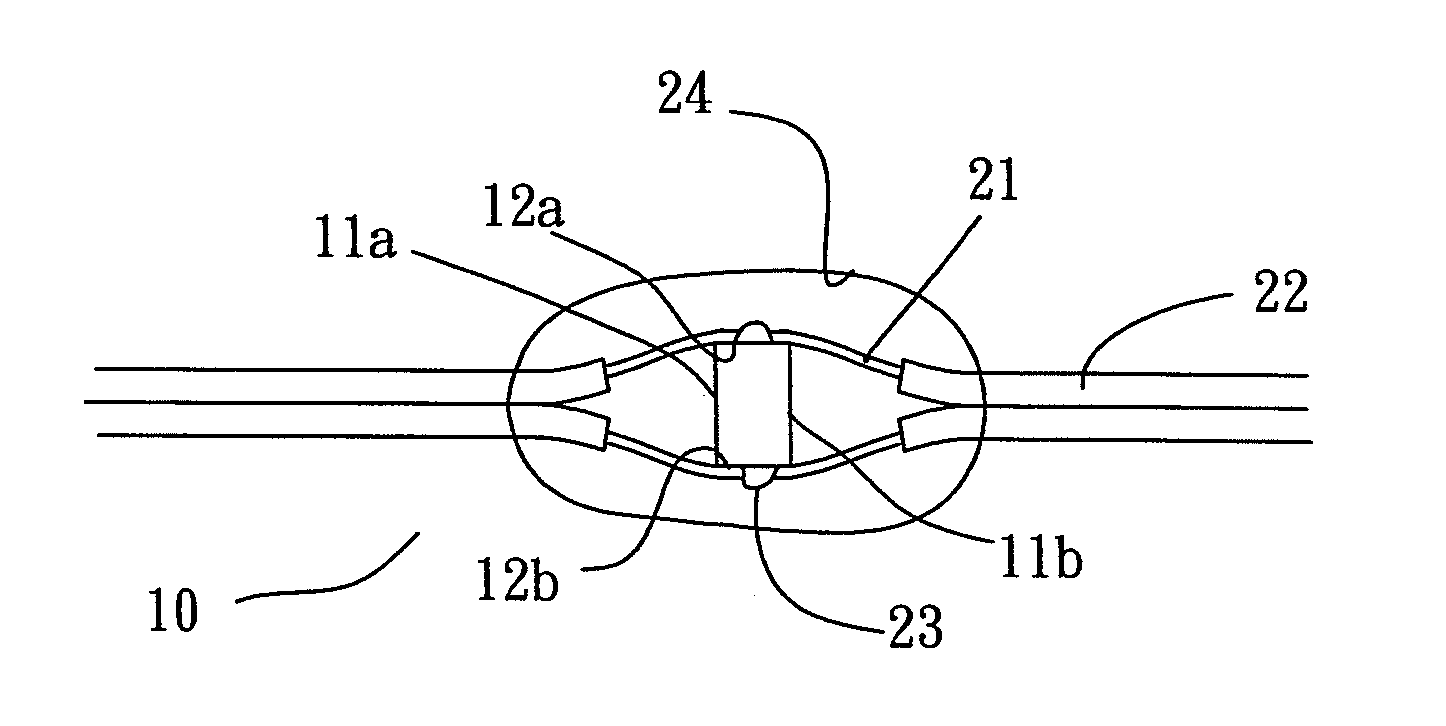

ActiveUS8696925B2Increase contentHigh valencyPolycrystalline material growthRuthenium/rhodium/palladium/osmium/iridium/platinum compoundsOctahedronMicrowave

Embodiments disclosed herein include methods of modifying synthetic garnets used in RF applications to reduce or eliminate Yttrium or other rare earth metals in the garnets without adversely affecting the magnetic properties of the material. Some embodiments include substituting Bismuth for some of the Yttrium on the dodecahedral sites and introducing one or more high valency ions to the octahedral and tetrahedral sites. Calcium may also be added to the dodecahedral sites for valency compensation induced by the high valency ions, which could effectively displace all or most of the Yttrium (Y) in microwave device garnets. The modified synthetic garnets with substituted Yttrium (Y) can be used in various microwave magnetic devices such as circulators, isolators and resonators.

Owner:SKYWORKS SOLUTIONS INC

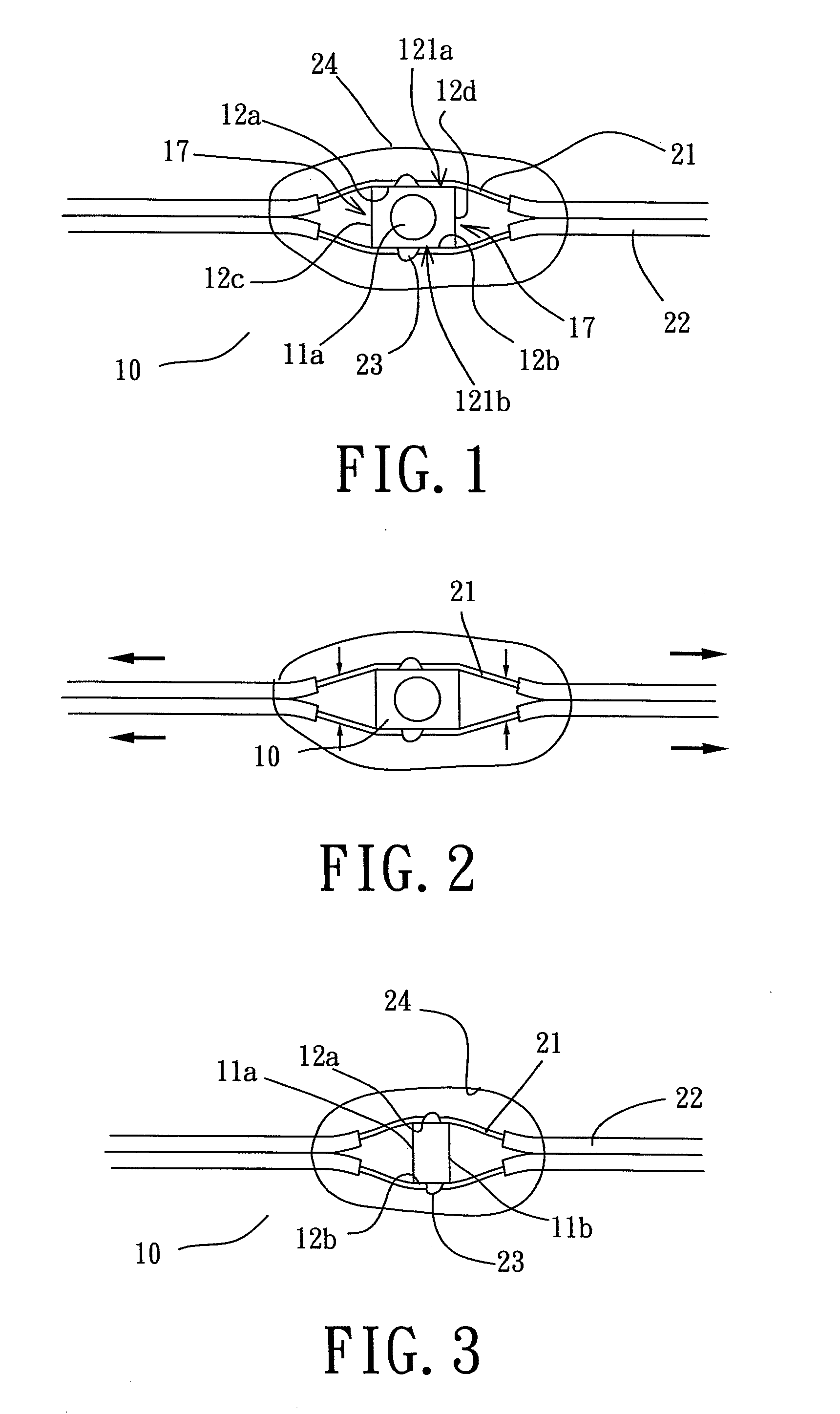

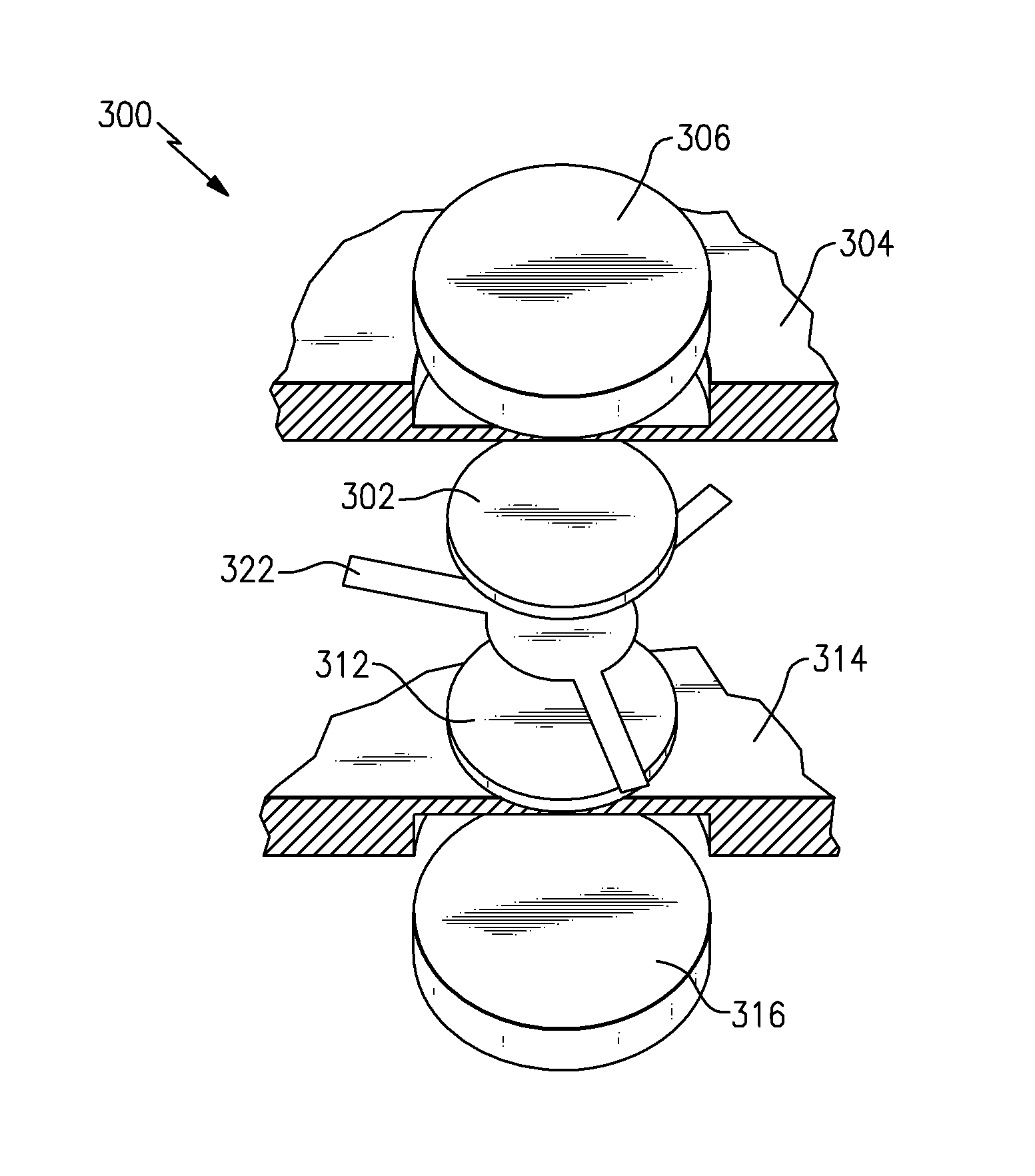

Method and structures of a miniaturized line lamp

InactiveUS20110228535A1Small sizeReduce line widthPoint-like light sourceLighting support devicesMiniaturizationEngineering

The present invention discloses a method and structures of a miniaturized line lamp. Metal wires are crossed over at two sides of an LED and are in a state of clipping, allowing the LED to be located at a same plane of the metal wires of an electric wire. Electrode positions at shorter edges of two sides of the LED are perpendicular to the metal wires and each across corner is formed respectively with a notch area which is free of electrode. A no-notch position of electrode at the other end of each side provides exactly for contact of two metal wires to form a loop. Therefore, a size of the line lamp device can better comply with a requirement of miniaturization.

Owner:SHAO YI SHIANG

Semiconductor integrated circuit device including first, second and third gates

InactiveUS6901006B1Increase computing speedReduce defect densityTransistorSolid-state devicesMiniaturizationConnection control

In a semiconductor integrated circuit device including a third gate, the present invention improves miniaturization and operation speed and reduces a defect density of an insulator film. In a semiconductor integrated circuit device including a well of a first conductivity type formed in a semiconductor substrate, a source / drain diffusion layer of a second conductivity type inside the well, a floating gate formed over the semiconductor substrate through an insulator film, a control gate formed and isolated from the floating gate through an insulator film, word lines formed by connecting the control gates and a third gate formed and isolated from the semiconductor substrate, the floating gate and the control gate through an insulator film and different from the floating gate and the control gate, the third gate is buried into a space of the floating gates existing in a direction vertical to the word line and a channel.

Owner:RENESAS ELECTRONICS CORP

Metal silicide nano-wire and its making method

InactiveCN1979828APosition is easy to controlControllable line widthSemiconductor/solid-state device detailsSolid-state devicesSalicideSputtering

The method for preparing metal silicides Nano wire with width being as 7 nm includes following steps: developing a layer of insulation film on substrate of monocrystalline silicon; etching grooves in use for producing metal silicides Nano wires through process technology in Nano scale; using method of metal sputtering and coating by vaporization to deposit layer of metal film on silicon substrate with Nano grooves being prepared; carrying out high temperature annealing to make reaction between metal and monocrystalline silicon exposed on bases of grooves so as to produce metal silicides; using chemical corrosion to eat off unreacted metal on surface; producing discrete metal silicides Nano wires in Nano grooves. The method can control position, shape, and width of wire of metal silicides Nano wire to be made. Thus, the invention is applicable to IC to prepare interconnection wires, source pole, drain pole and grid pole based on need.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

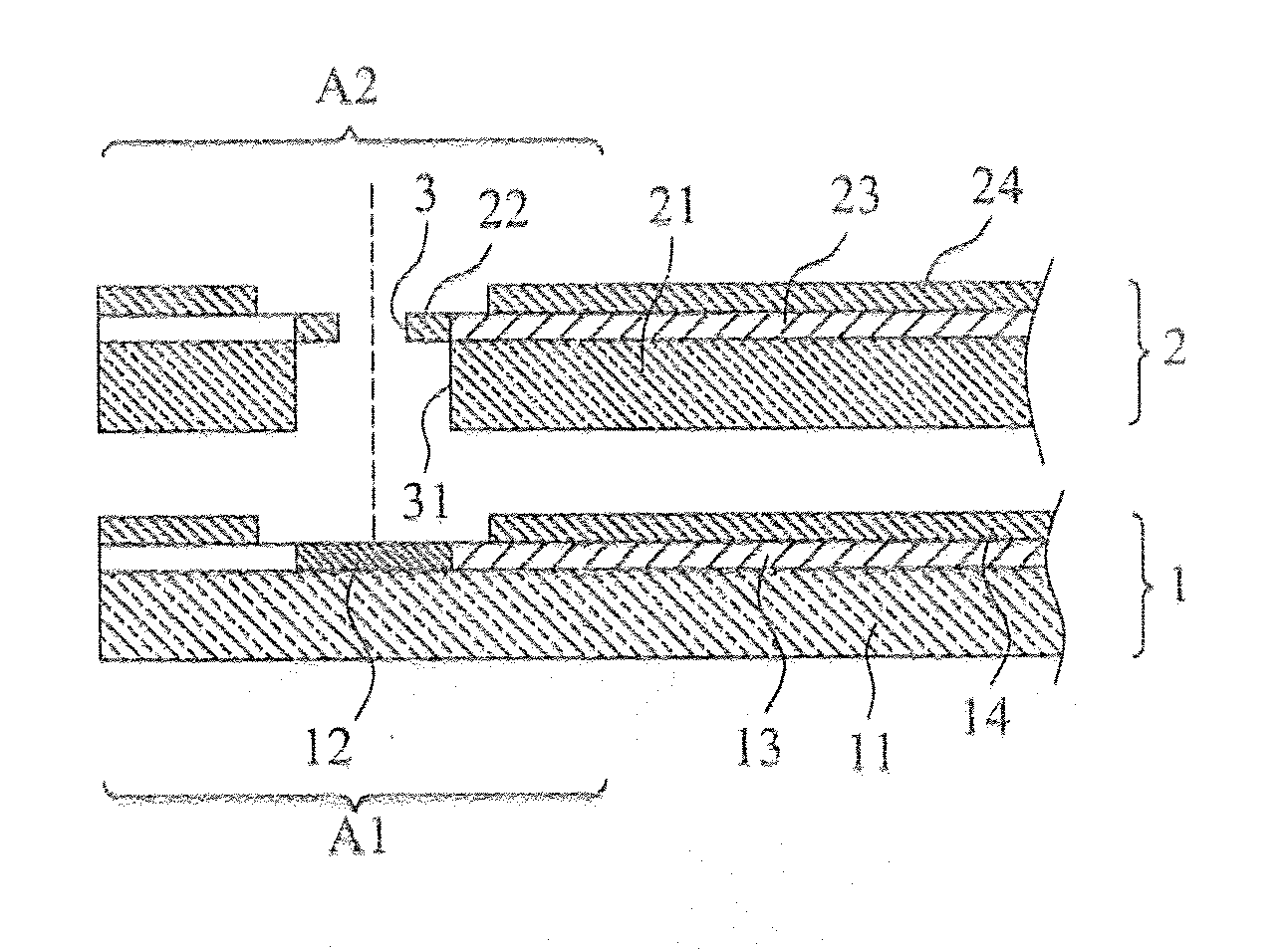

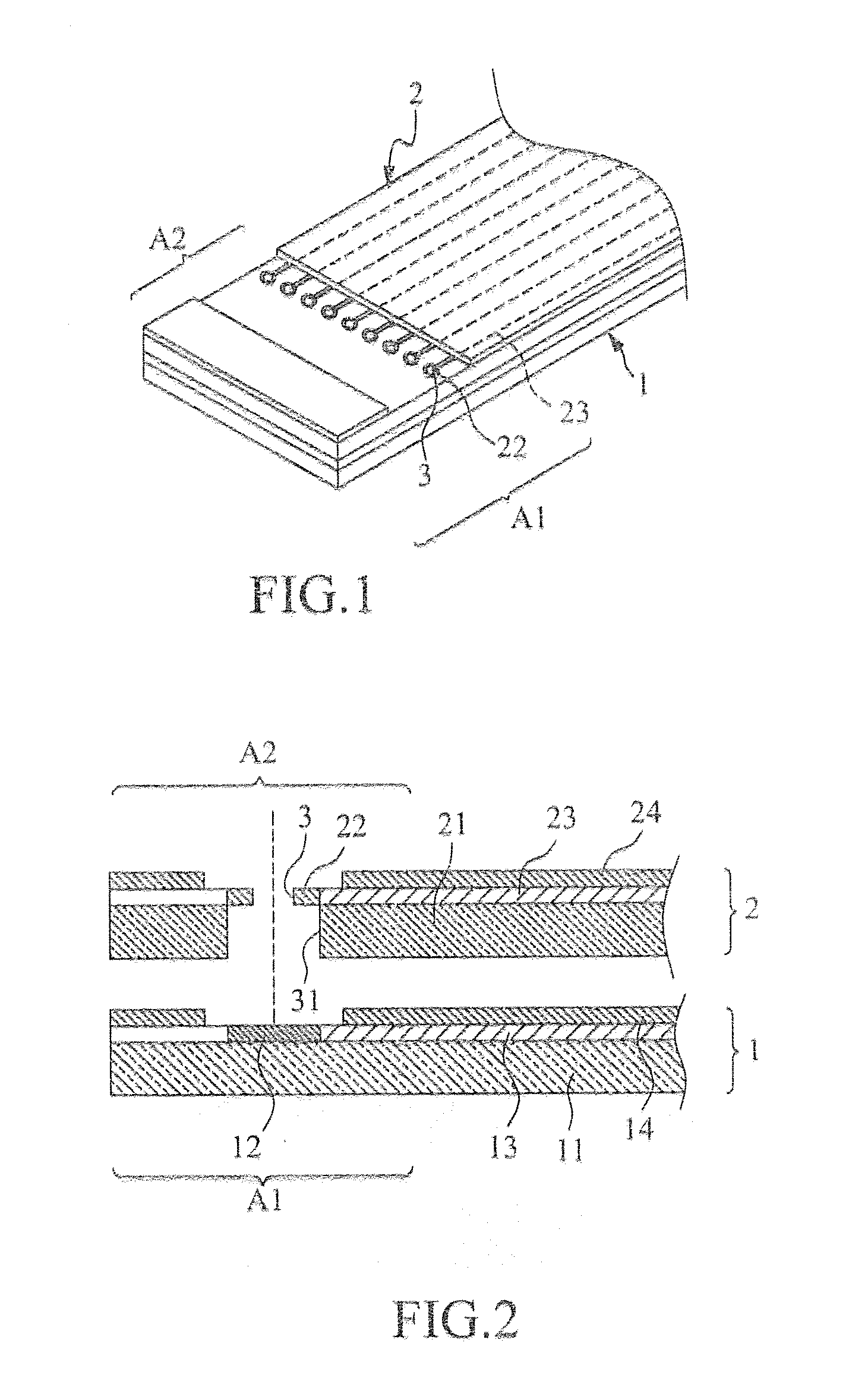

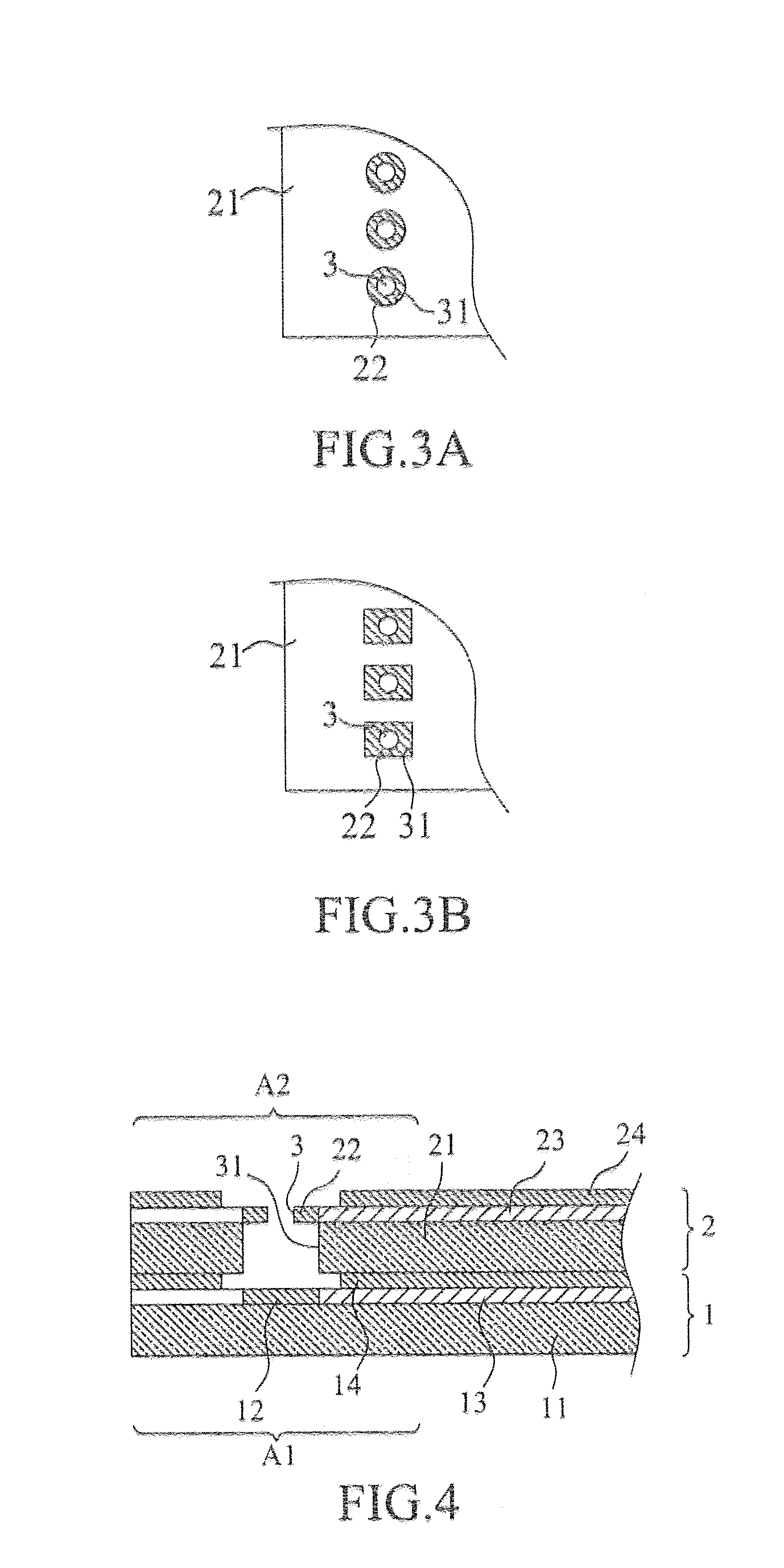

Interconnecting conduction structure for electrically connecting conductive traces of flexible circuit boards

ActiveUS20150327368A1Line width decreaseExpand sizePrinted circuit groundingCross-talk/noise/interference reductionSolder pasteFlexible circuits

Owner:ADVANCED FLEXIBLE CIRCUITS

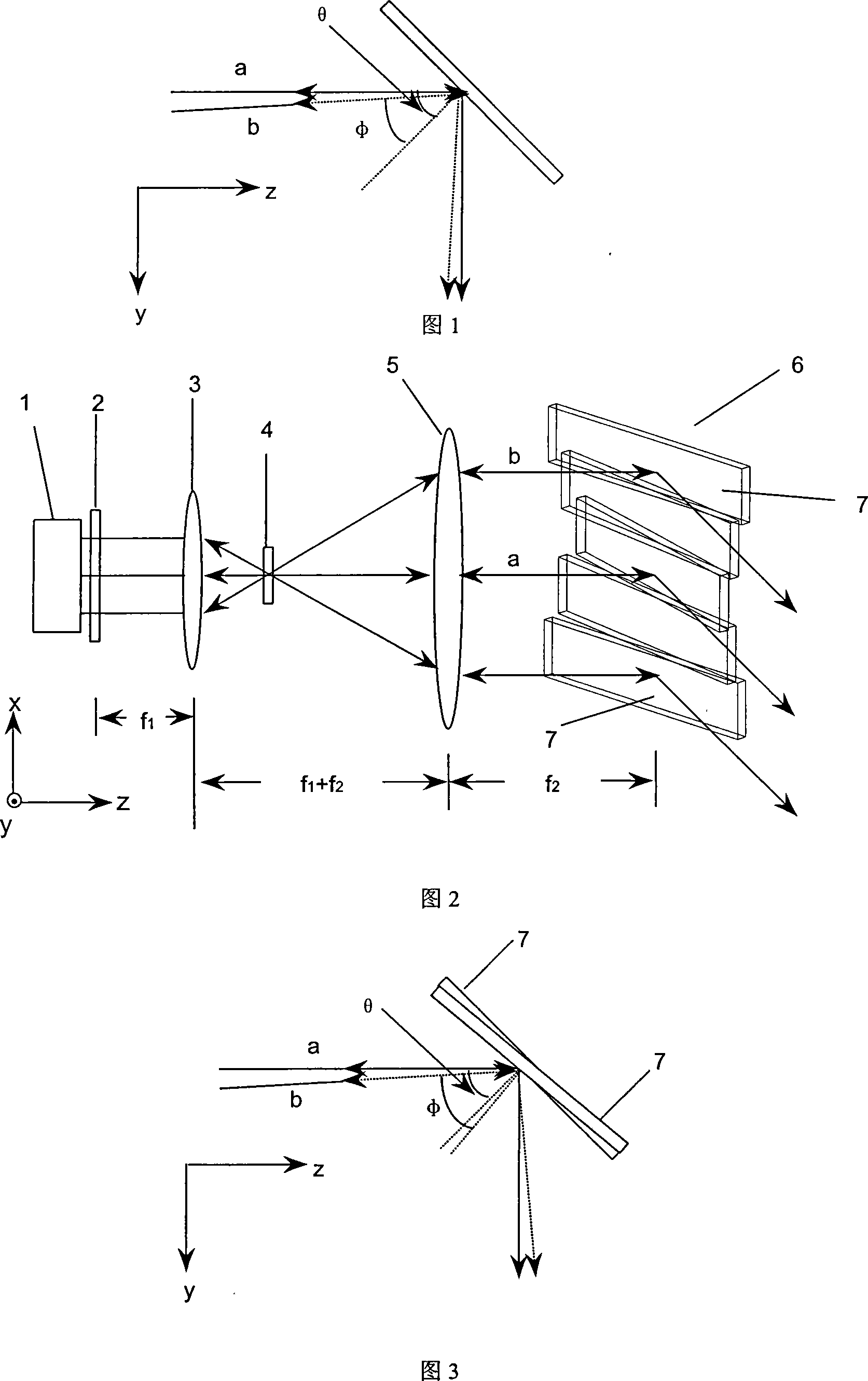

Diffraction grid array external cavity semiconductor laser linear array and method of producing the same

InactiveCN101141051AHigh-resolutionIncrease the degree of narrowingSemiconductor laser arrangementsLaser arrangementsLine widthLength wave

A semiconductor laser linear array of the iffraction grating array exocoele and its preparation method is provided, which belongs to the field of semiconductor laser and comprises a semiconductor laser linear array, a fastaxis collimation lens, a slow lens, a half wave plate, a high-aperture lens and an iffraction grating array. The said semiconductor laser linear array is characterized in making exocoele feedback through the iffraction grating array to make one or more luminescent units of the semiconductor laser linear array incident onto the corresponding iffraction grating unit. By adjusting each of the iffraction grating units, the central wavelength of the luminescent unit in different degrees of crook through the iffraction grating unit and the feedback light retraced back are equal or closely similar with each other, thus the whole spectral line width is reduced. The invention has the advantages of using a plurality of small-area gratings, low cost, easy processing, simple light path adjustment and high output power.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

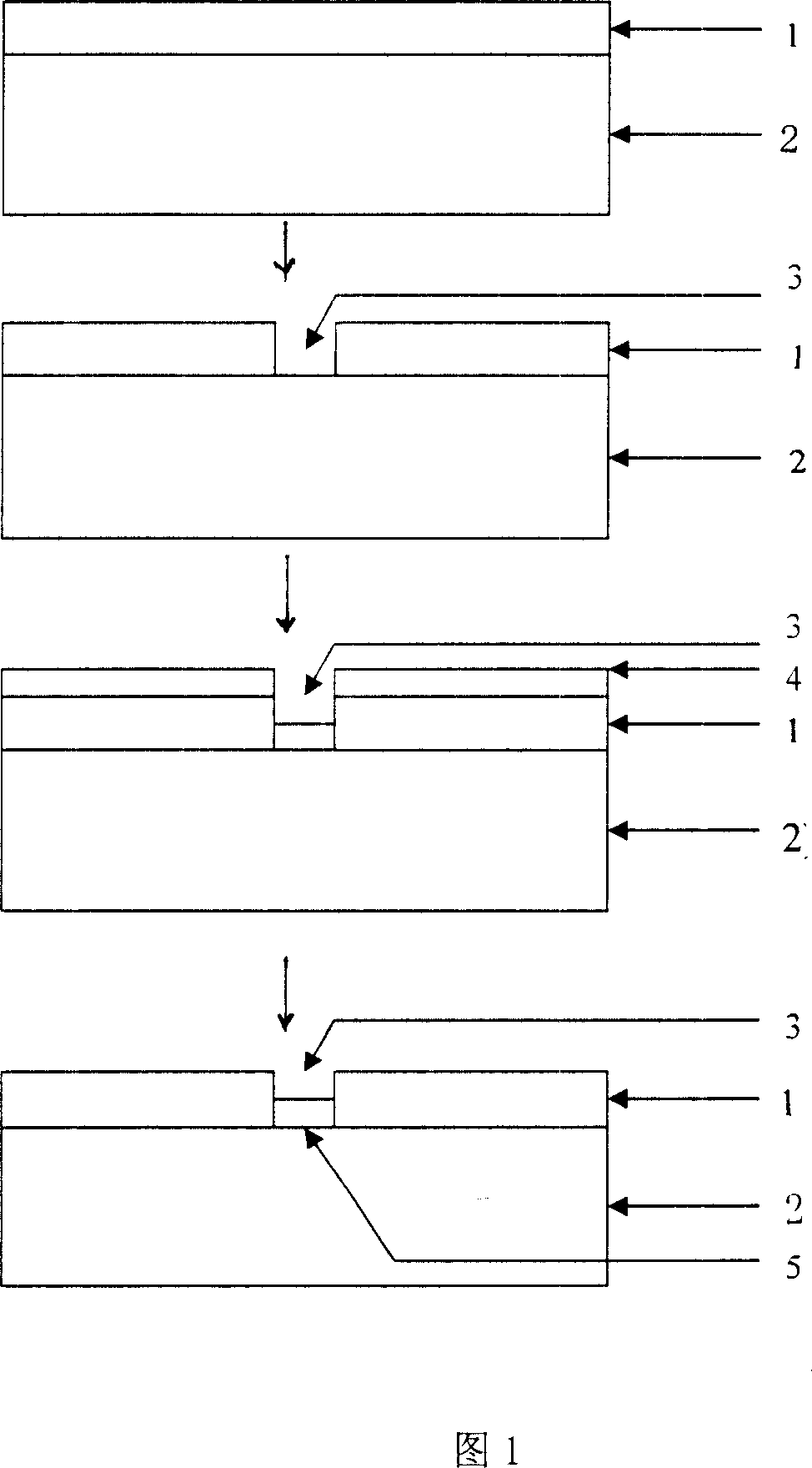

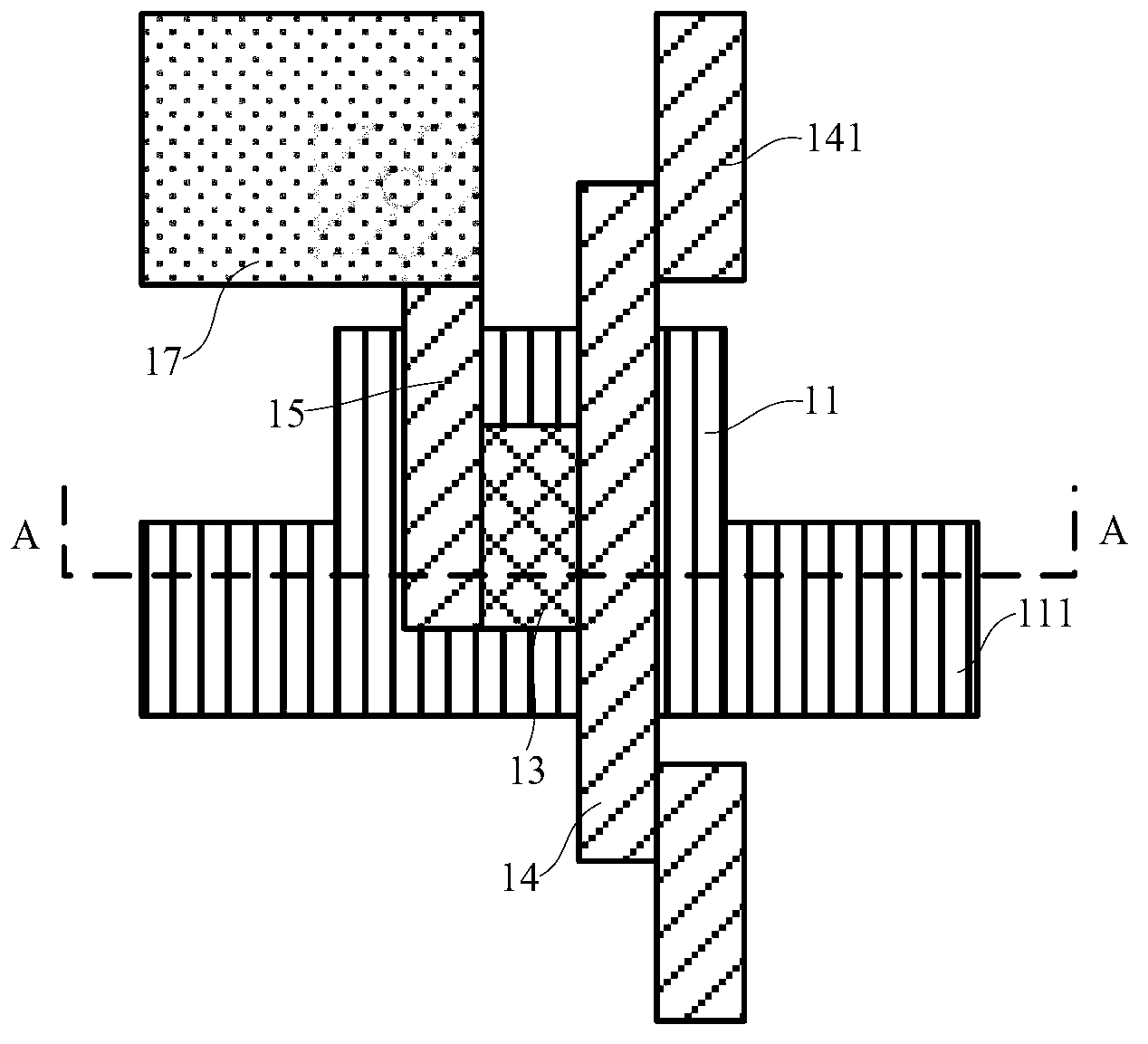

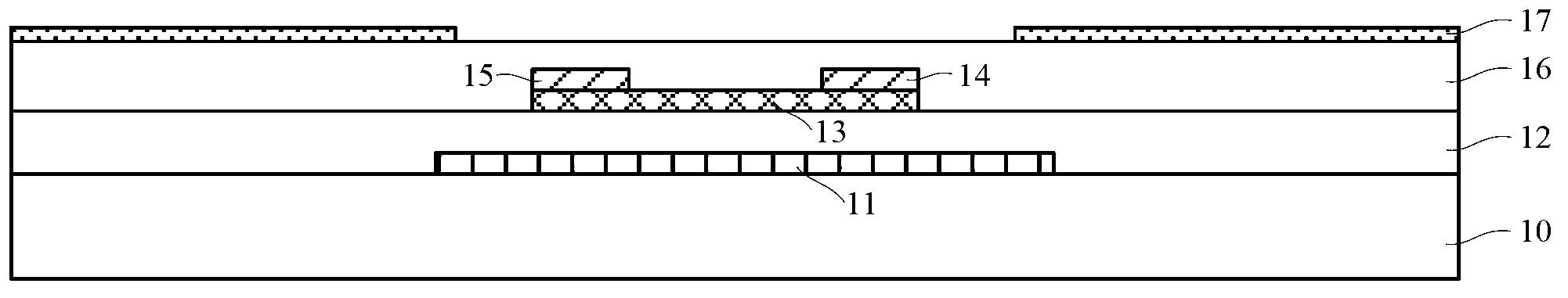

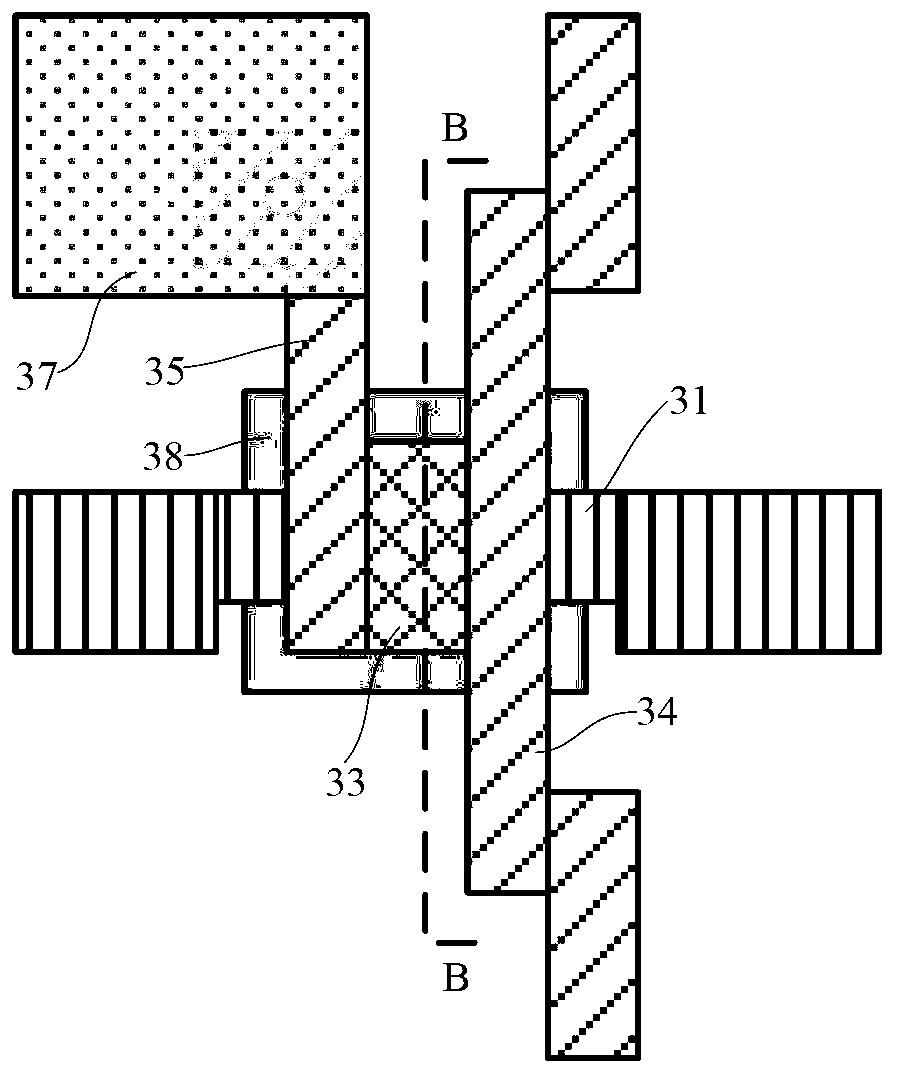

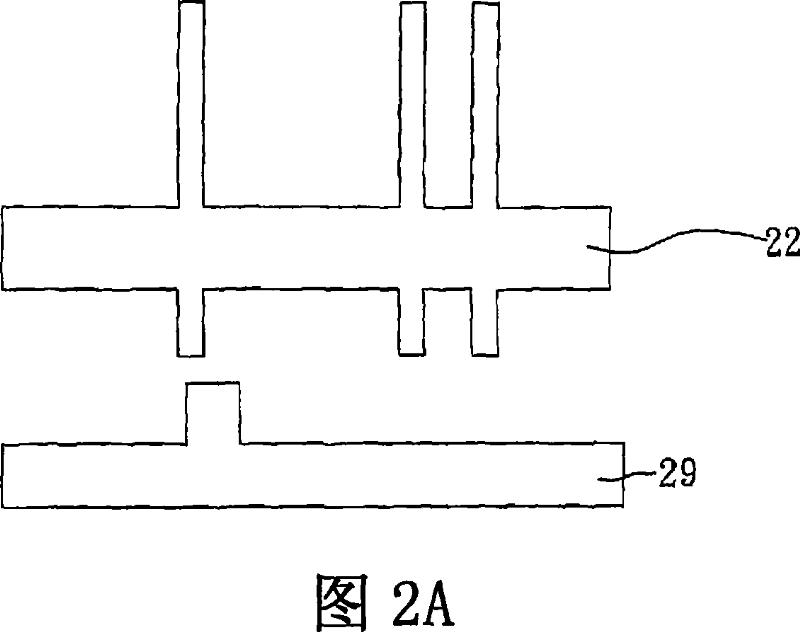

Array base plate, manufacturing method thereof and liquid crystal display device

InactiveCN103018989AReduce line widthReduce overlap areaSemiconductor/solid-state device manufacturingNon-linear opticsCapacitanceLiquid-crystal display

The invention relates to the field of liquid crystal display and particularly relates to an array base plate, a manufacturing method thereof and a liquid crystal display device which are used for solving the problems of large grid electrode size and increased feed-in voltage value in the prior art. The array base plate provided by the embodiment of the invention comprises a thin film transistor arranged on a substrate base plate, a grid line connected with the thin film transistor and a shielding layer positioned between the substrate base layer and an active layer of the thin film transistor; the shielding layer is used for shielding light rays injected into the active layer; and the line width of a grid electrode is less than that of the grid line in which the grid electrode is positioned. According to the embodiment of the invention, the shielding layer shields the light rays injected into the active layer, and the line width of the grid electrode is less than that of the grid line in which the grid electrode is positioned, so that the value of the interelectrode capacitance of a TFT (Thin Film Transistor) is reduced, and further feed-in voltages influencing the frame level of a TFT-LCD (Liquid Crystal Display) can be reduced.

Owner:BOE TECH GRP CO LTD

Rare earth reduced garnet systems and related microwave applications

ActiveUS9263175B2Increase contentHigh valencyPolycrystalline material growthInorganic material magnetismMicrowave applicationsRare-earth element

Disclosed are synthetic garnets and related devices that can be used in radio-frequency (RF) applications. In some embodiments, such RF devices can include garnets having reduced or substantially nil Yttrium or other rare earth metals. Such garnets can be configured to yield high dielectric constants, and ferrite devices, such as TM-mode circulators / isolators, formed from such garnets can benefit from reduced dimensions. Further, reduced or nil rare earth content of such garnets can allow cost-effective fabrication of ferrite-based RF devices. In some embodiments, such ferrite devices can include other desirable properties such as low magnetic resonance linewidths. Examples of fabrication methods and RF-related properties are also disclosed.

Owner:SKYWORKS SOLUTIONS INC

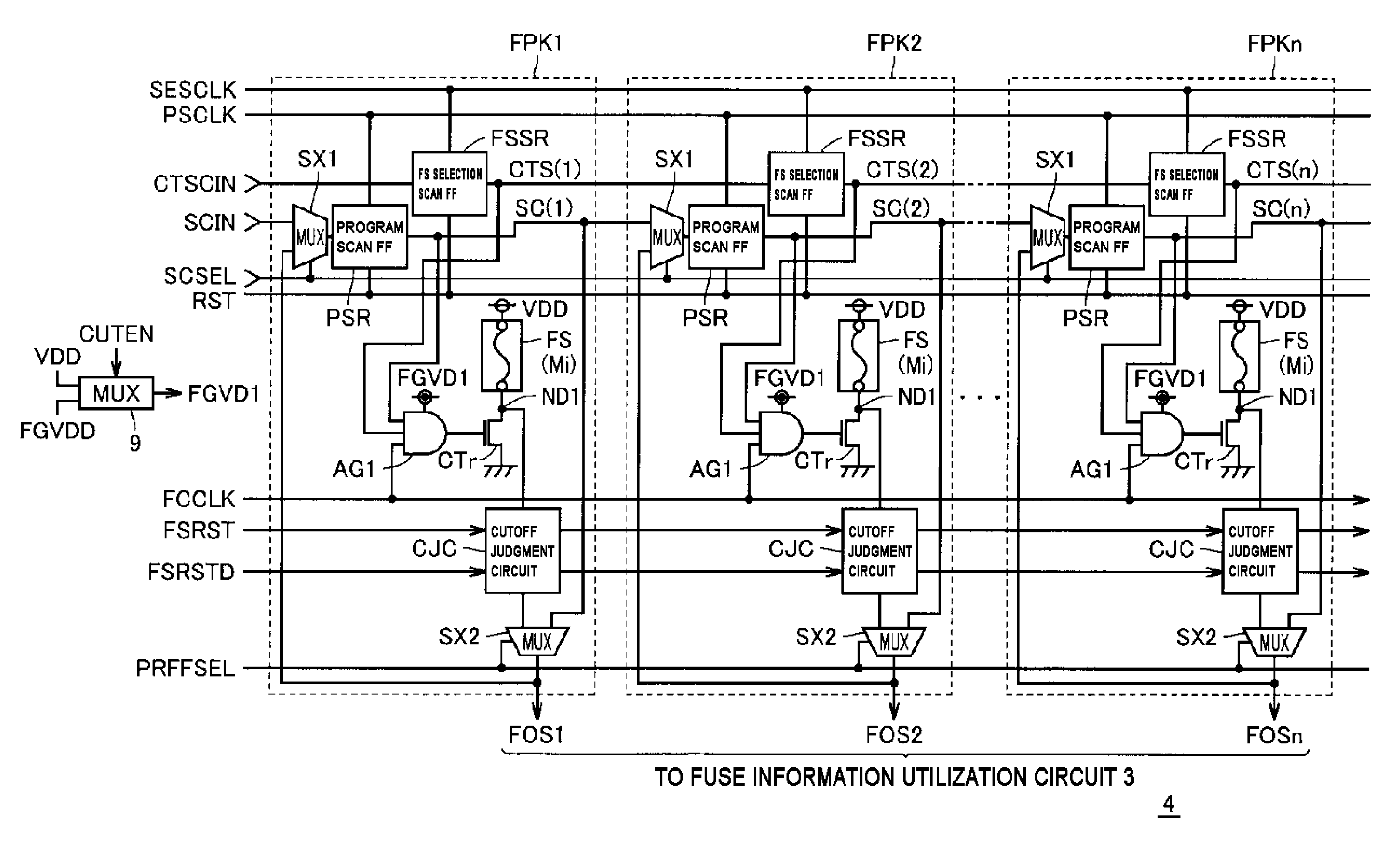

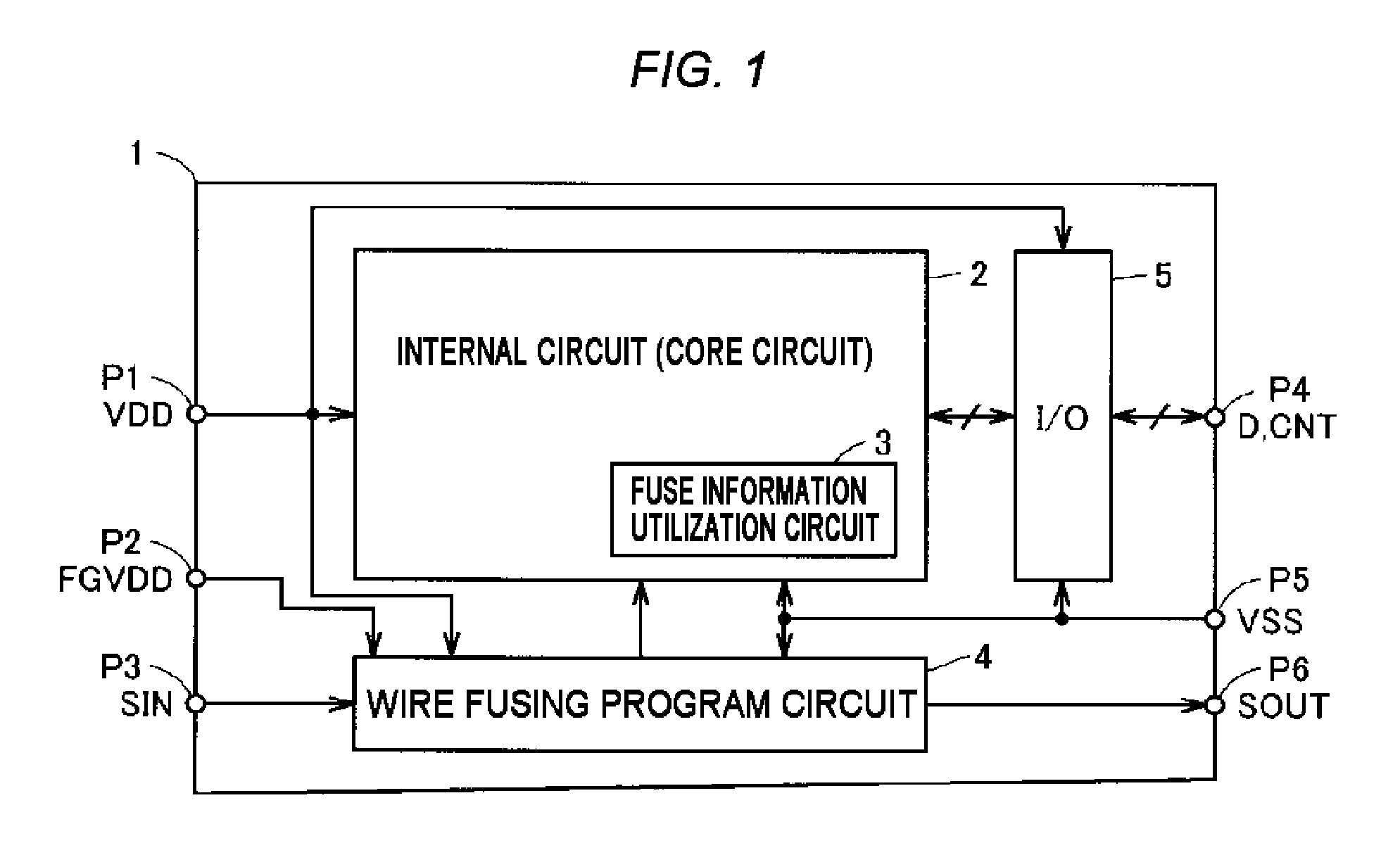

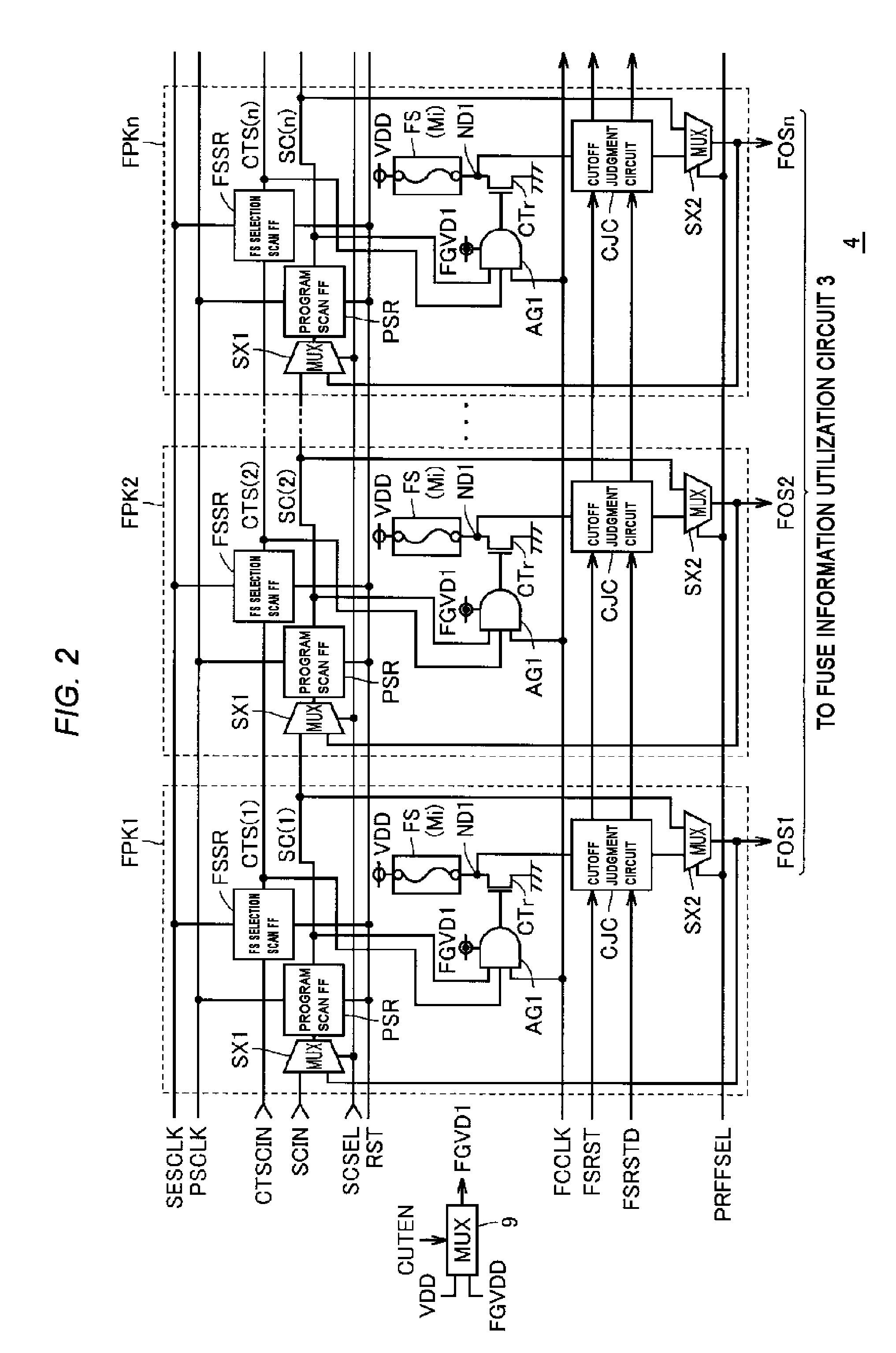

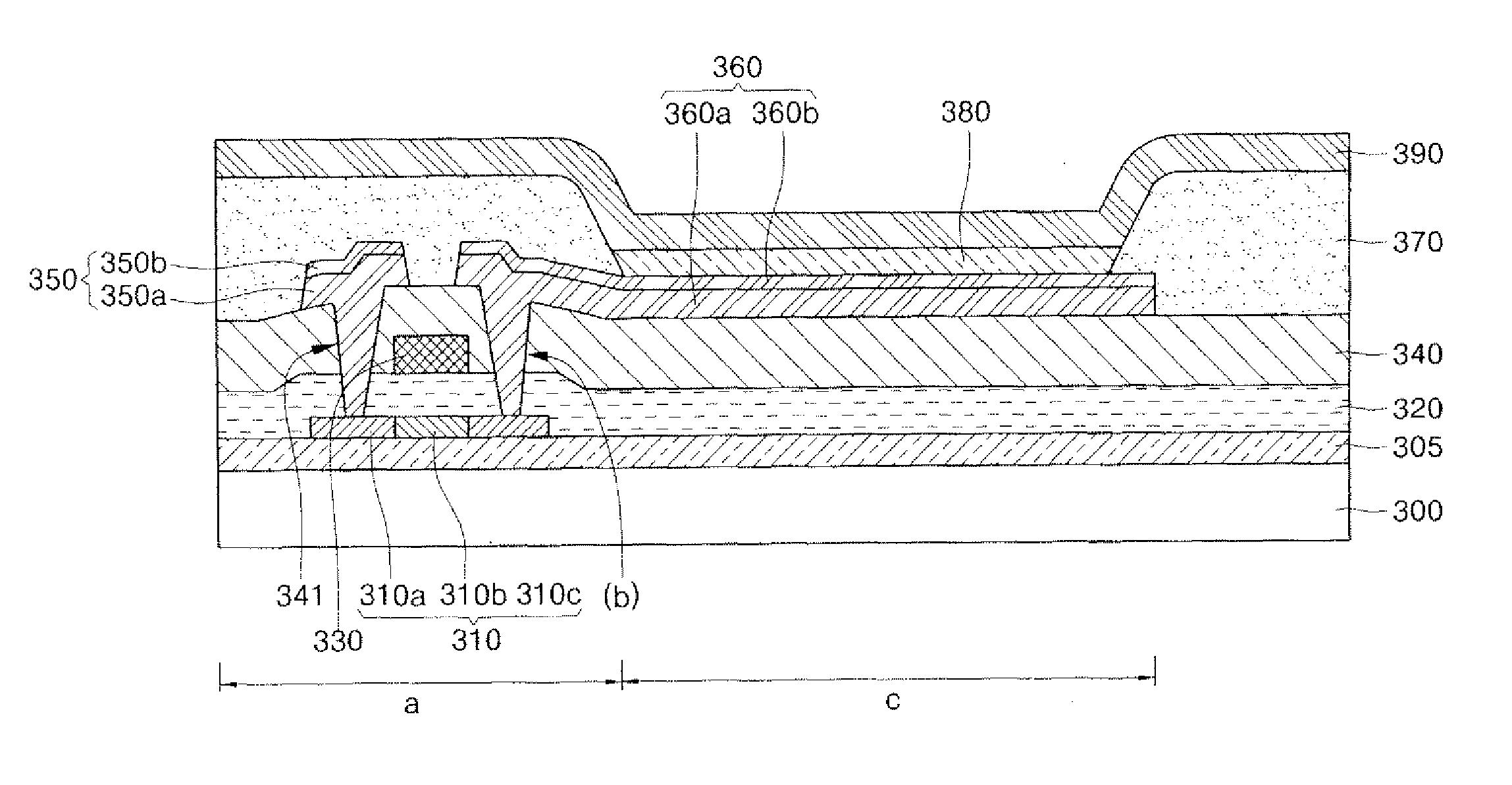

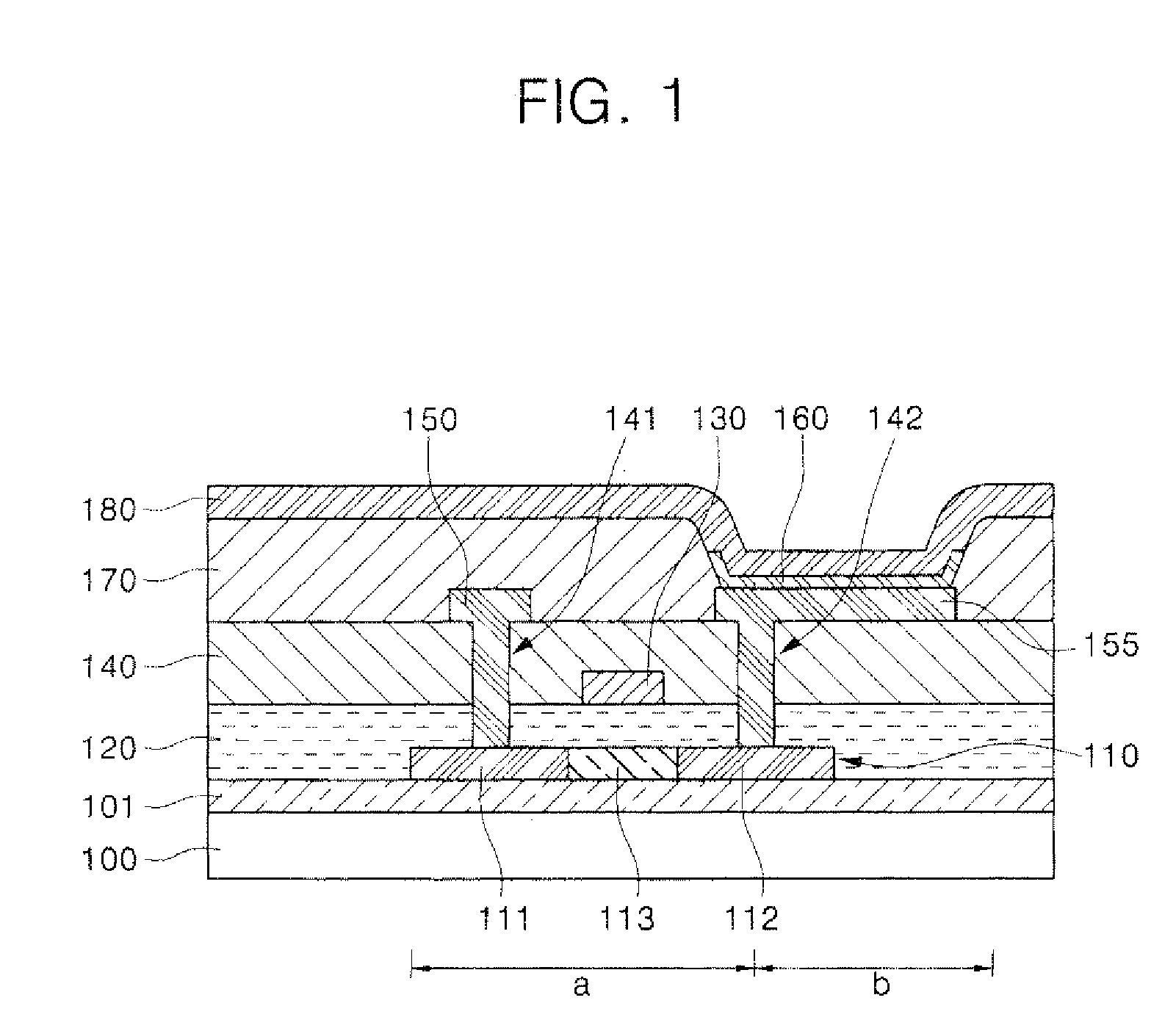

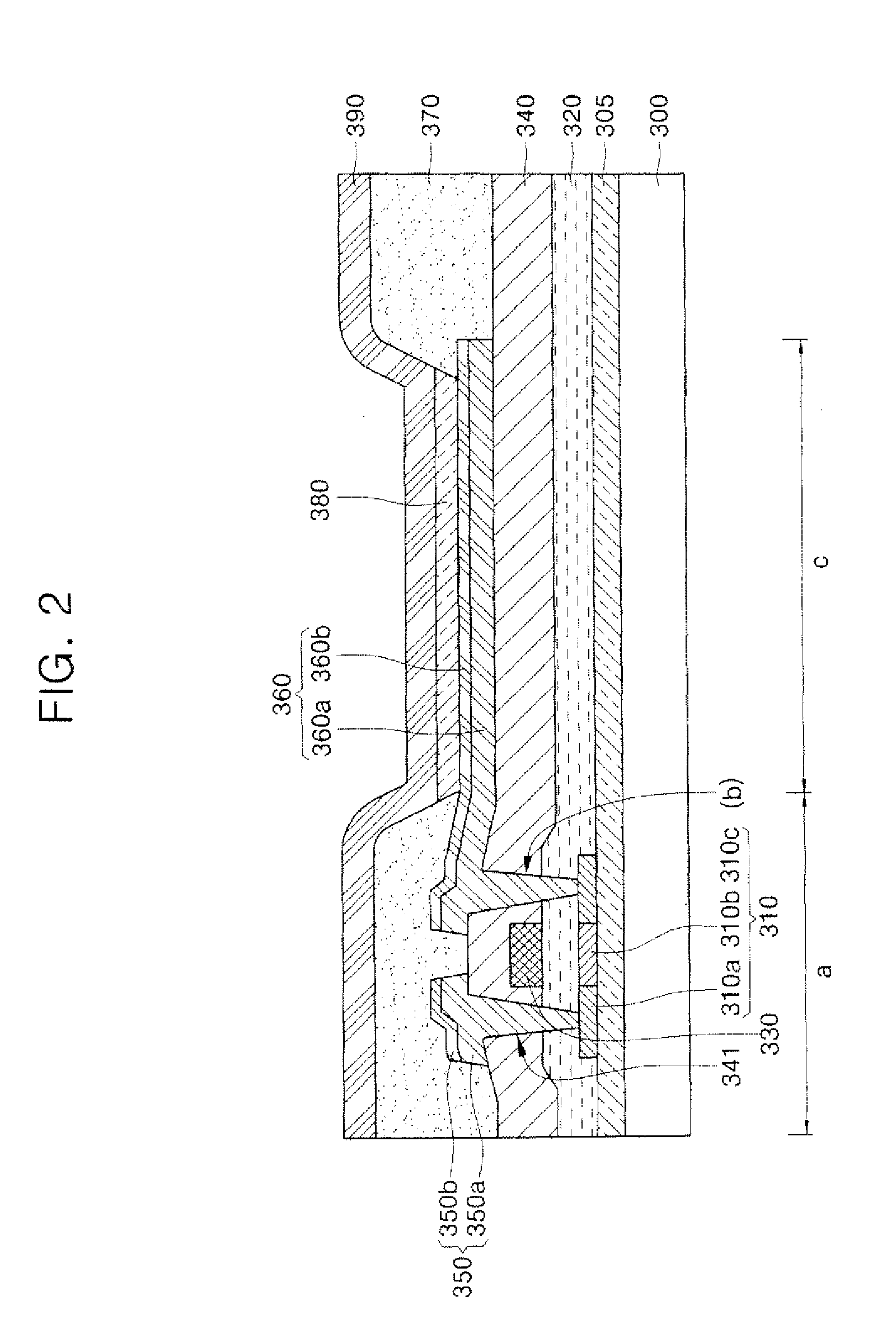

Semiconductor device

ActiveUS20110116299A1Reduce line widthReduce layout areaSemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceSemiconductor

To provide a semiconductor device capable of reducing the line width of a fuse.In the semiconductor device, a dummy fuse is provided adjacent to a fuse, each wiring width of the fuse and the dummy fuse is set to the minimum line width, and the interval between the fuse and the dummy fuse is set to the minimum interval. Consequently, the exposure condition of the fuse and the dummy fuse is optimized by OPC, and therefore, it is possible to form the fuse with the minimum line width.

Owner:RENESAS ELECTRONICS CORP

Organic light emitting display device and method of fabricating the same

ActiveUS20060243976A1Increasing reflectivity and efficiencyReducing the organic light emitting display device panel sizeElectroluminescent light sourcesSolid-state devicesLine widthDisplay device

An organic light emitting display device and a method of fabricating the same are provided, which employ an Ag alloy containing Sm, Tb, Au, and Cu to simultaneously form a source electrode, a drain electrode, and a first electrode of the organic light emitting display device for increasing the reflectivity and efficiency of the organic light emitting display device and reducing the organic light emitting display device panel size by reducing a line width of the source and drain electrodes due to the low resistance of the source and drain electrodes.

Owner:SAMSUNG DISPLAY CO LTD

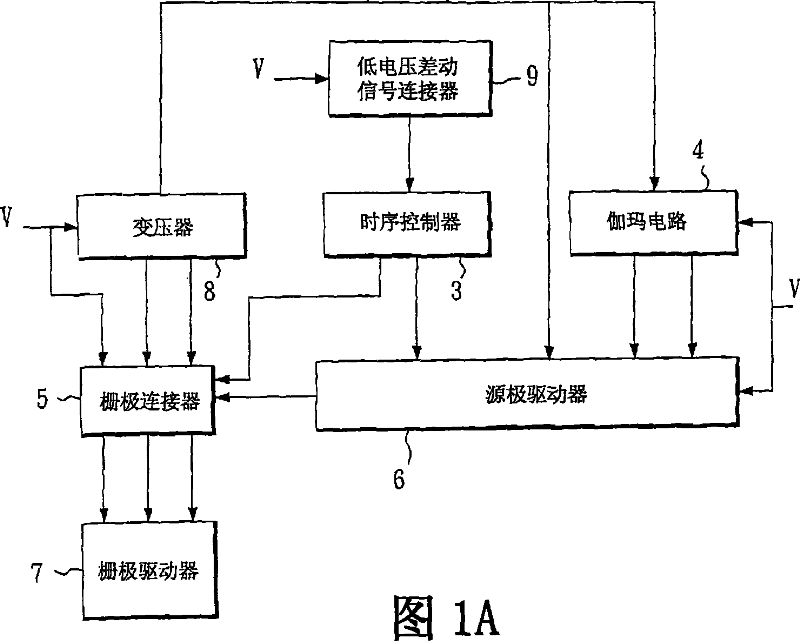

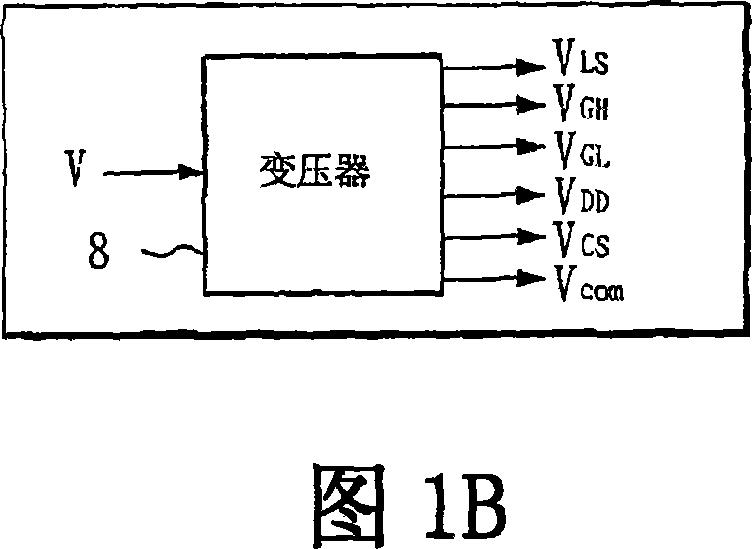

Liquid crystal display device and its driving method

InactiveCN101038716AImprove side light leakageReduce line widthStatic indicating devicesCapacitanceLiquid-crystal display

The invention provides a liquid crystal display driving system and a driving method thereof, the method comprises: supplying a special voltage to an auxiliary shade storage capacitor electrode plate on a liquid crystal display panel having an upper substrate, a lower substrate, and a liquid crystal layer; applying a common electrode voltage on a common electrode, and applying a special voltage to a storage capacitor so that a predetermined voltage difference is formed between the voltages of the auxiliary shade storage capacitor electrode plate and the common electrode, thereby improving side light-leakage of the liquid crystal display, increasing manufacturing ability when the upper substrate and the lower substrate are assembled, and reducing a line width of an upper substrate black matrix shade sheet to increase an opening degree.

Owner:AU OPTRONICS CORP

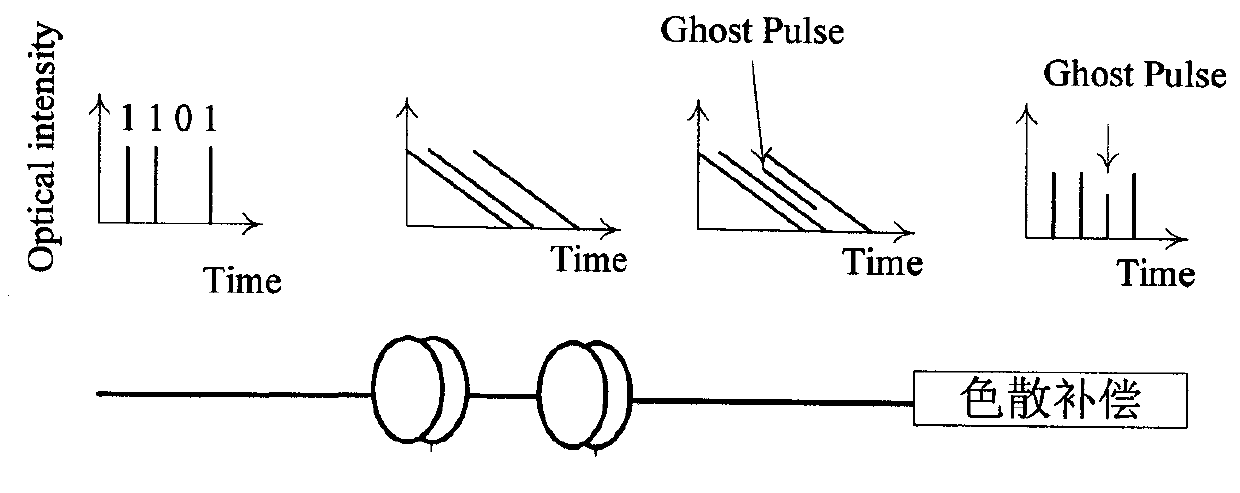

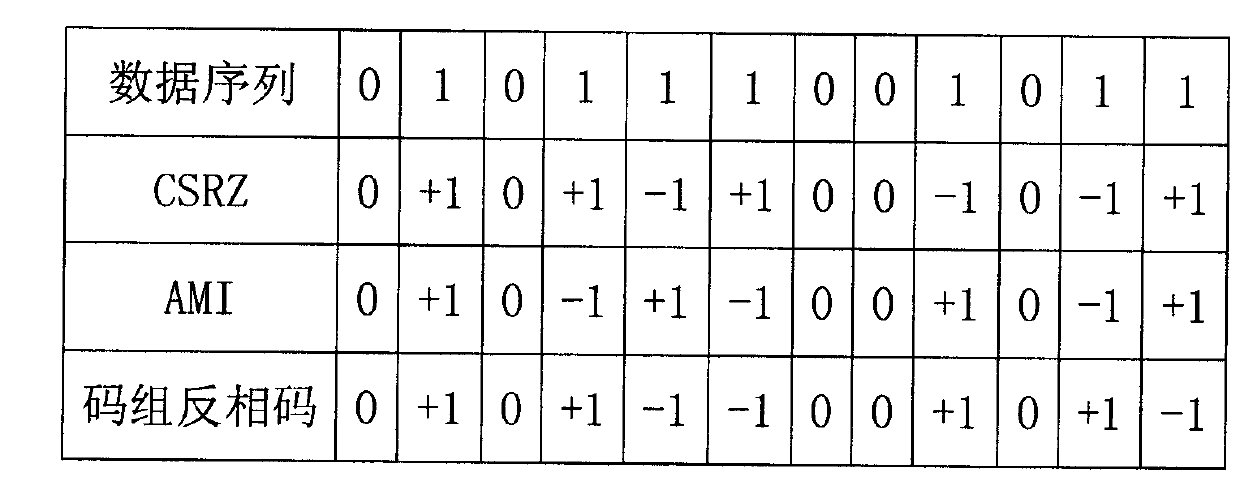

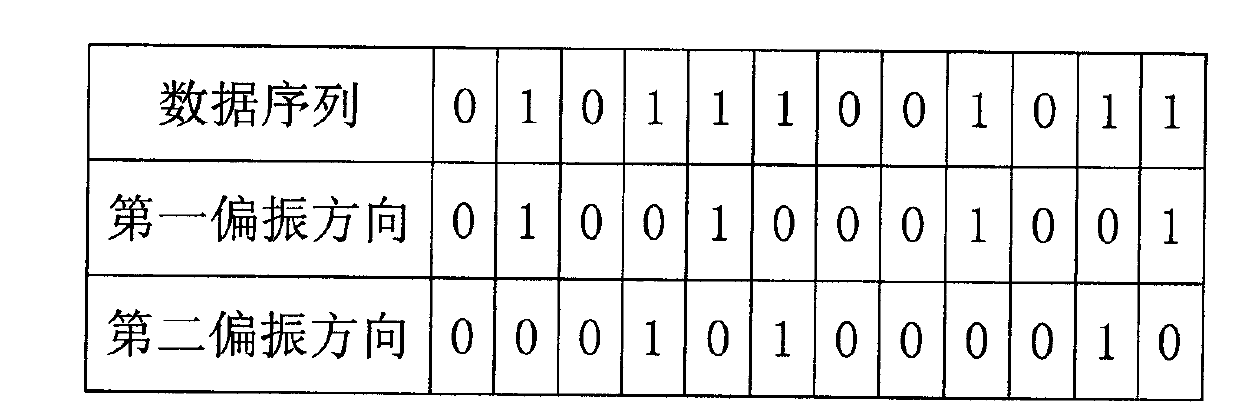

High-speed WDM (Wavelength Division Multiplexing) light communication system and method for resisting non-linearity effect in same

ActiveCN101795159AReduce line widthLower requirementWavelength-division multiplex systemsElectromagnetic transmissionLine widthEngineering

The invention discloses a high-speed WDM (Wavelength Division Multiplexing) light communication system and a method for resisting non-linearity effect in the same. The method comprises the following steps of: (A10) respectively dividing linearly polarized light into polarized light in a first polarization direction and polarized light in a second polarization direction, wherein the two paths of polarized light have orthogonal polarization states; (A20) coding and modulating digital signals by adopting polarization interleaved codes, i.e. respectively modulating code 1 of the same group of the digital signals to the polarized light in the first polarization direction and the polarized light in the second polarization direction; (A30) merging the polarized light in the first polarization direction and the polarized light in the second polarization direction into a transmission light wave, multiplexing by a wavelength division multiplexer at a transmitting terminal and outputting to an optical fiber link; and (A40) dividing the transmission light wave by a wavelength division demultiplexer at a receiving terminal and respectively outputting to a light-strength detecting light receiver. The invention damages the forming conditions of iFWM (intra-channel Four-Wave Mixing) by utilizing the polarization characteristics of the light wave. Compared with the traditional method, the invention lowers the requirements for the linear width of a laser and the performance of a modulator so that the actual iFWM-resisting effect is better.

Owner:WUHAN POST & TELECOMM RES INST CO LTD

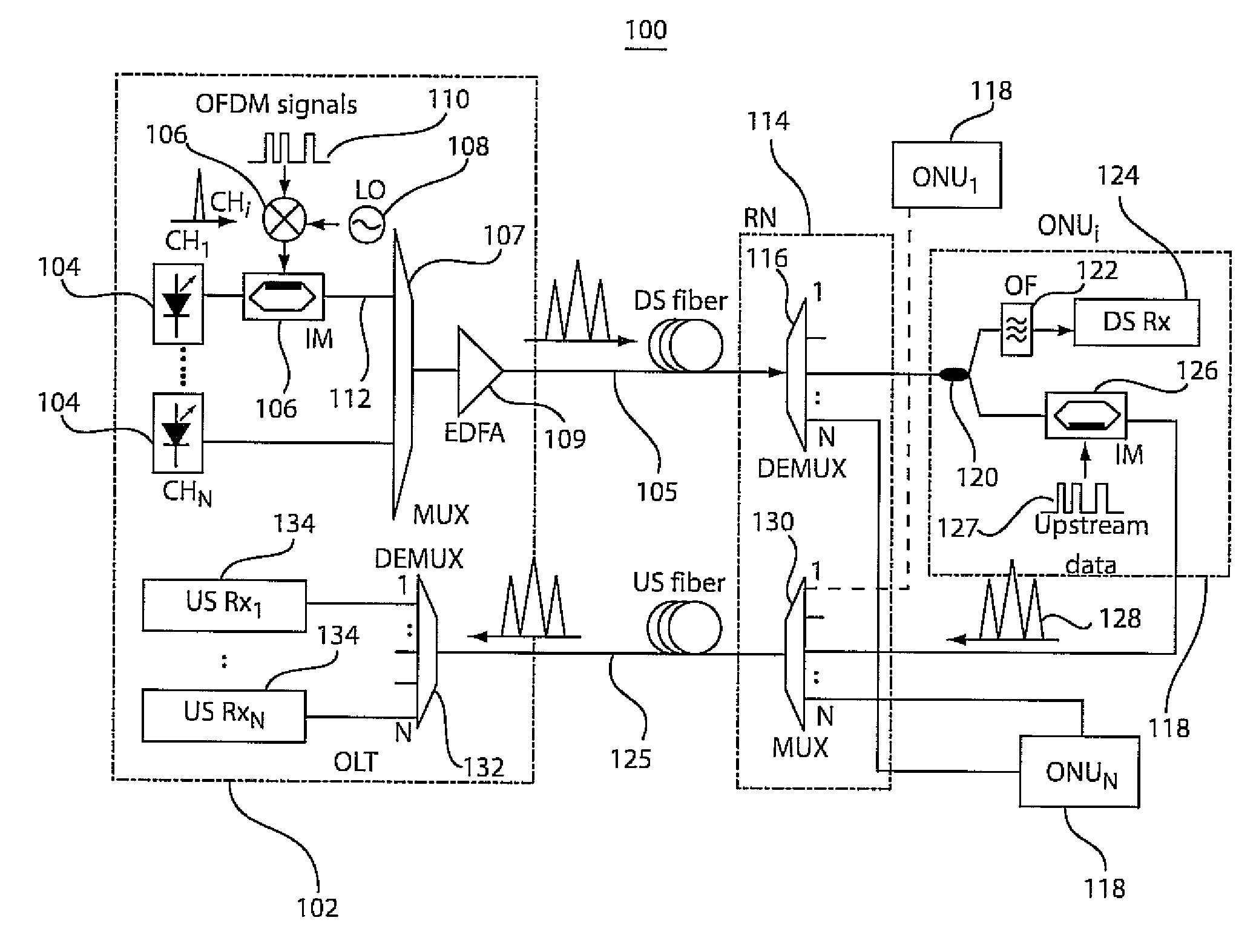

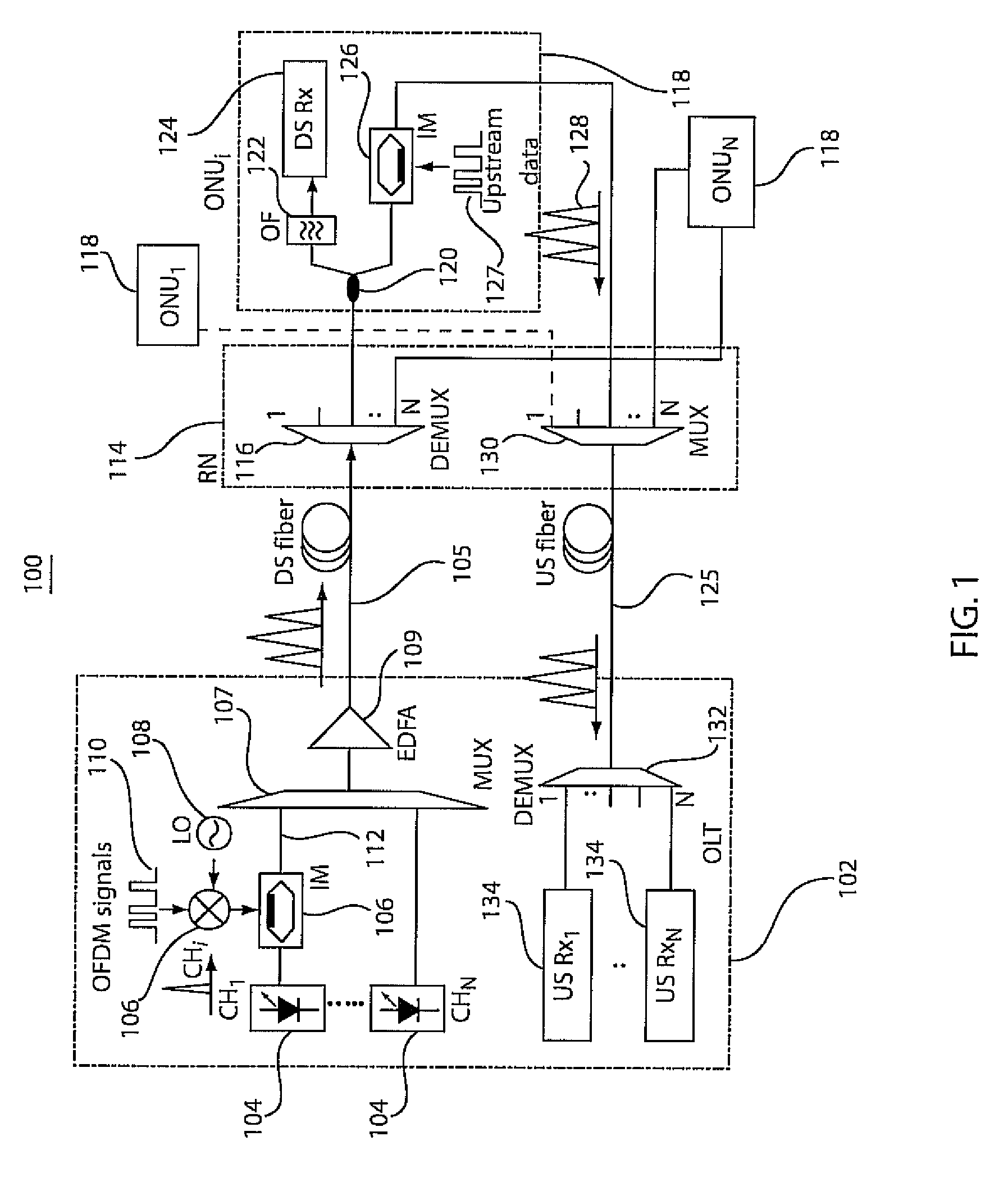

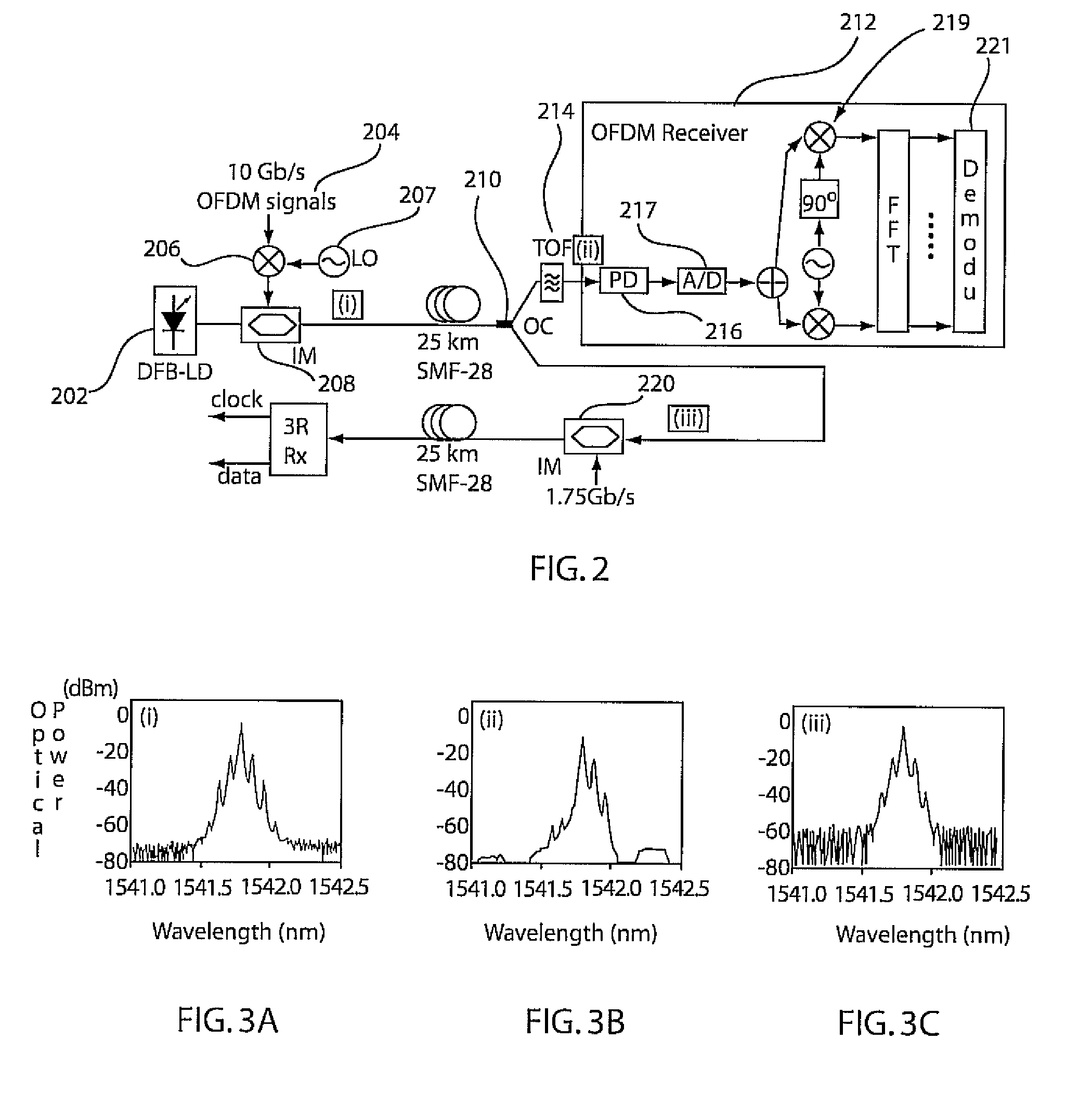

Centralized lightwave WDM-PON employing intensity modulated downstream and upstream

ActiveUS8131156B2Reduce phase noiseReduce line widthModulated-carrier systemsOptical multiplexCarrier signalData signal

An optical system and method includes a source-free optical network unit coupled to an optical fiber for receiving a centralized lightwave carrier signal with downstream data over the optical fiber. The optical network unit includes a coupler configured to split the original carrier signal into a first path and a second path. The first path includes an optical filter configured to reduce fading effects of the carrier signal. The second path includes a modulator configured to remodulate the centralized lightwave carrier signal with upstream data to produce an upstream data signal for upstream transmission.

Owner:NEC CORP

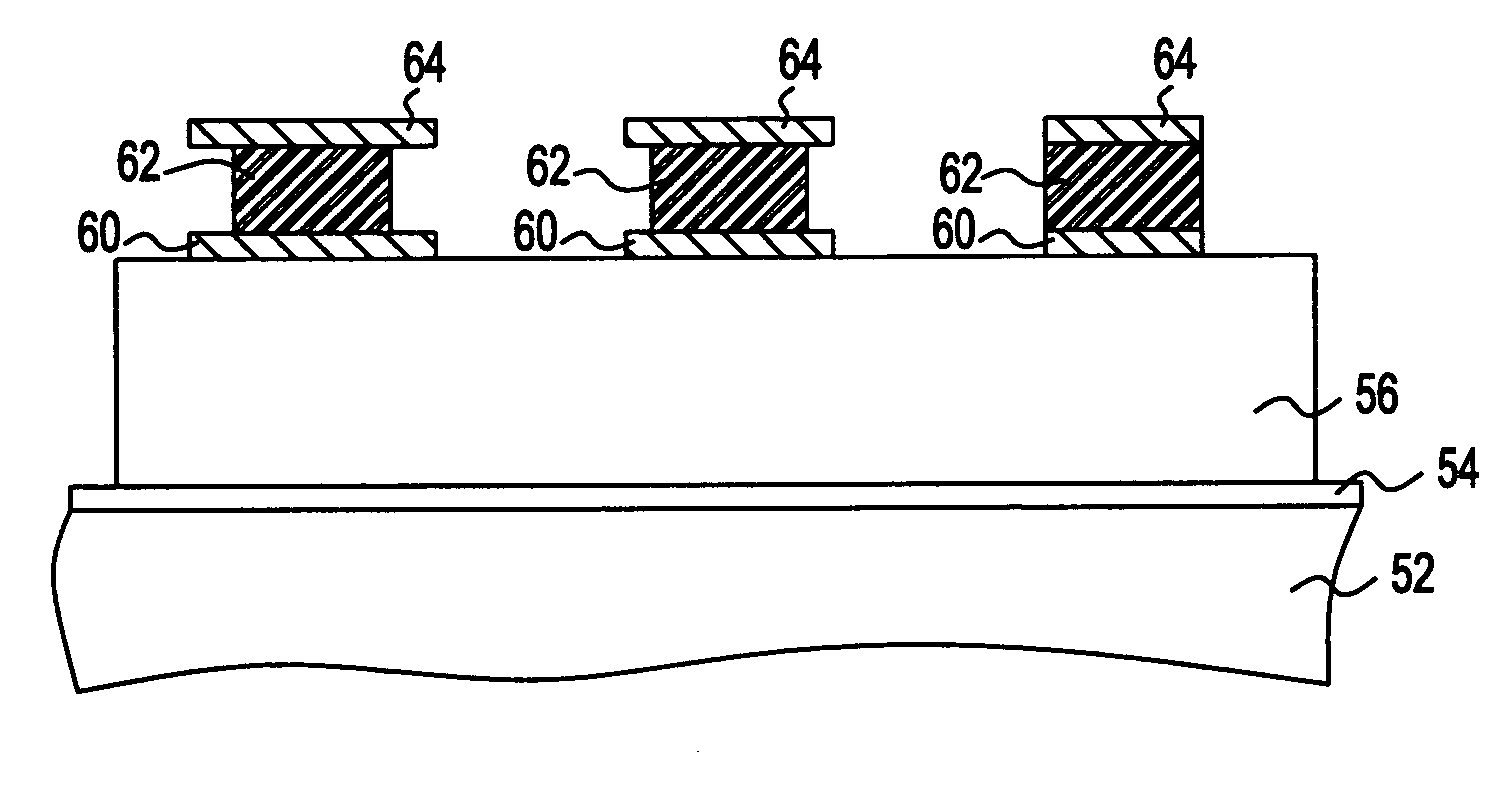

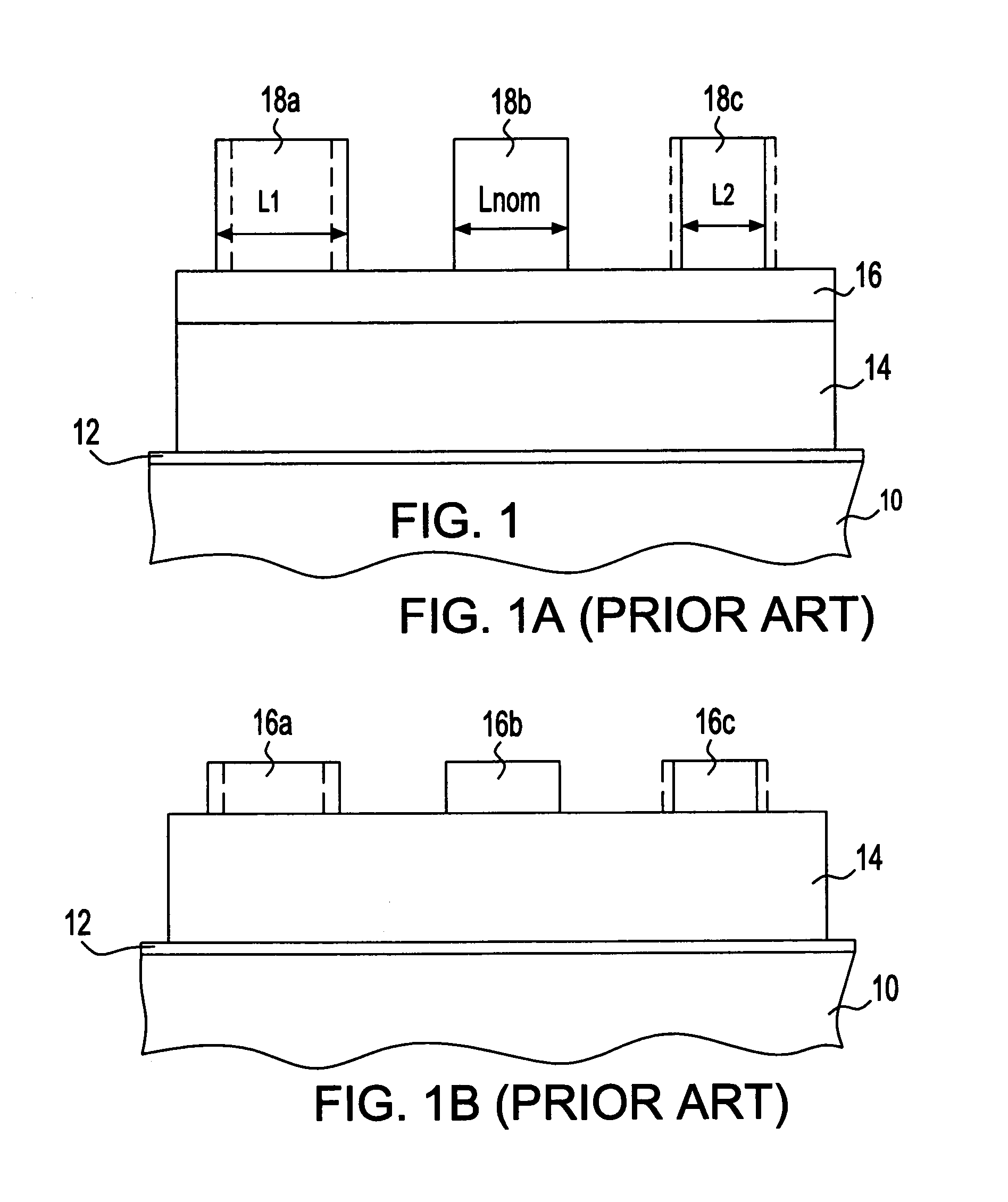

Nanocircuit and self-correcting etching method for fabricating same

InactiveUS7026247B2Reduced feature requirementsProduce some attenuationSemiconductor/solid-state device manufacturingSemiconductor devicesNanostructureCritical dimension

A self-correcting etching (SCORE) process for fabricating microstructure is provided. The SCORE process of the present invention is particularly useful for reducing preselected features of a hard mask without degrading the variation of the critical dimension (CD) within each wafer. Alternatively, the CD variation of the hard mask features' produced during printing can be substantially reduced by applying SCORE. Hence, ultra-sub-lithographic features (e.g., nanostructures) can be reliably fabricated. Consequently, the method of the present invention can be used to increase the circuit performance, while improving the manufacturing yield.

Owner:INT BUSINESS MASCH CORP

Manufacturing method for touch panel edge wire routing, touch panel and touch display device

InactiveCN103384451AAvoid bad situationsBad or error signal goodConductive material chemical/electrolytical removalInput/output processes for data processingTouch panelSurface smoothness

The invention provides a manufacturing method for touch panel edge wire routing, a control panel with the edge wire routing and a touch display device. The manufacturing method comprises the following steps of (a) forming a photosensitive conductive paste layer on an edge area of a substrate with a transparent conductive layer, enabling the photosensitive conductive paste layer to be at least in partial overlapping with the transparent conductive layer, (b) exposing the photosensitive conductive paste layer by using a mask, and (c) carrying out developing on the exposed photosensitive conductive paste layer to form a patterning edge wire routing unit on the edge area of the substrate. The manufacturing method is beneficial to improving the precision of a wire route under the situation that the wire width of the edge wire routing is narrowed, and can enable the wire route to have good surface smoothness.

Owner:INNOCOM TECH SHENZHEN +1

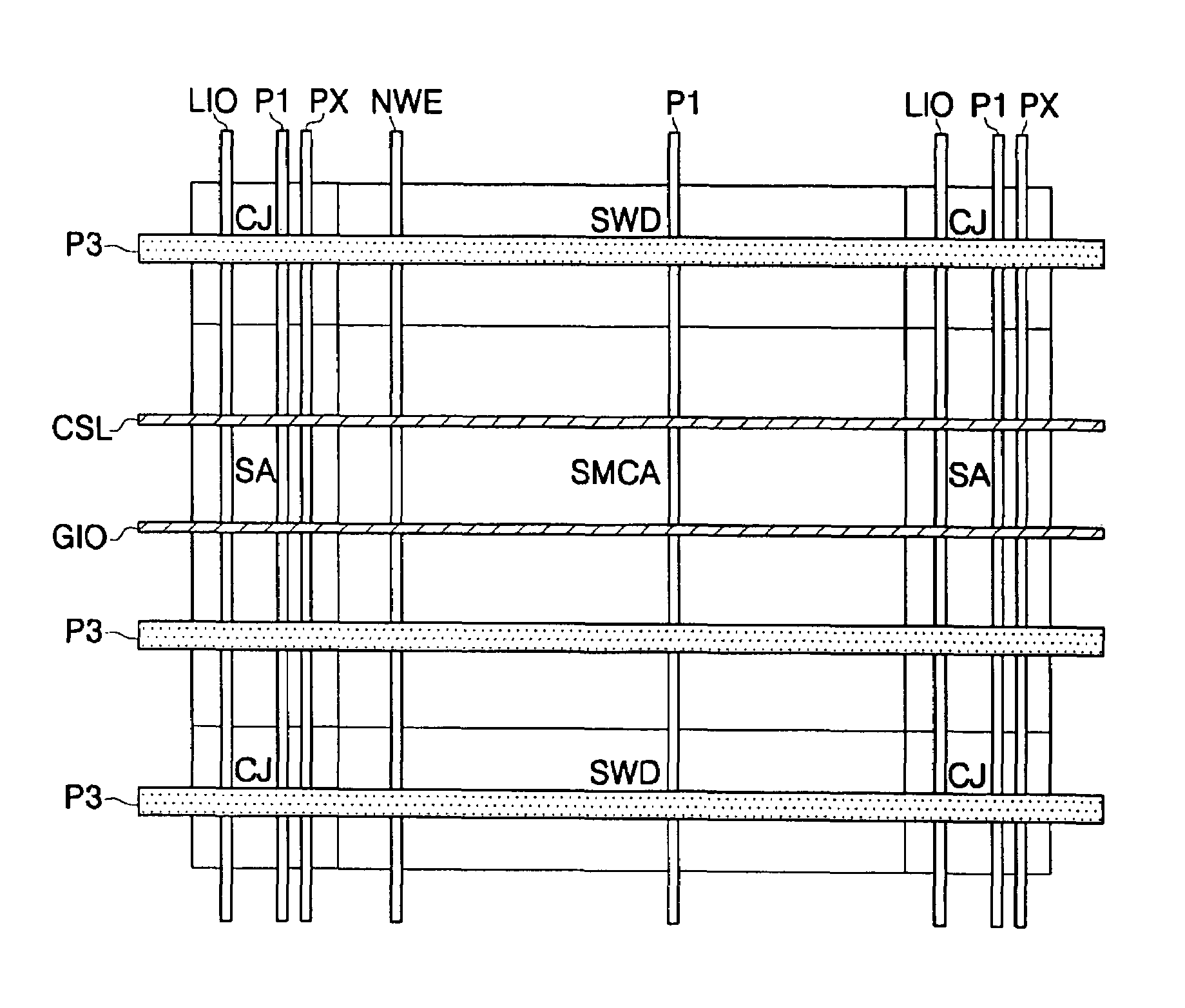

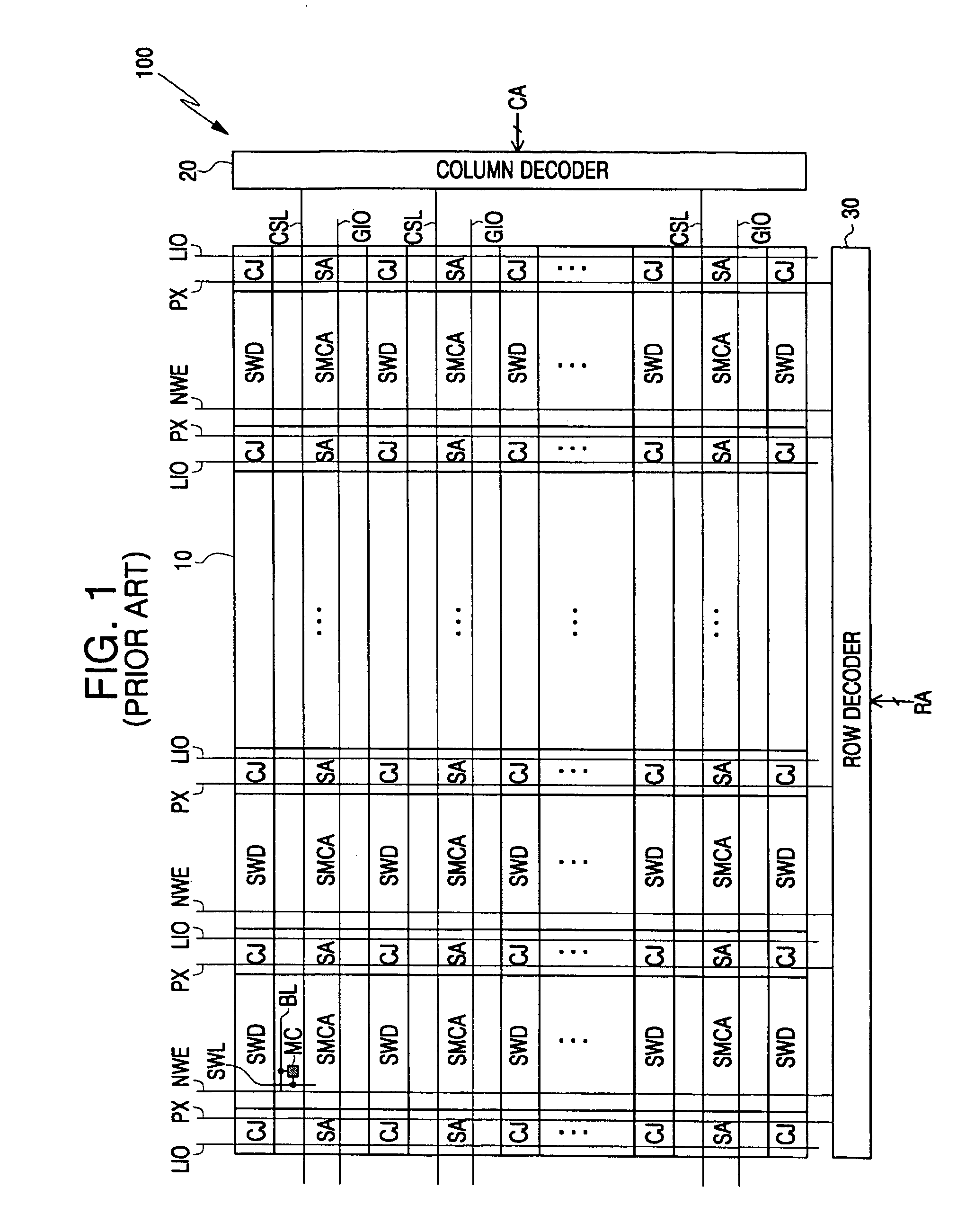

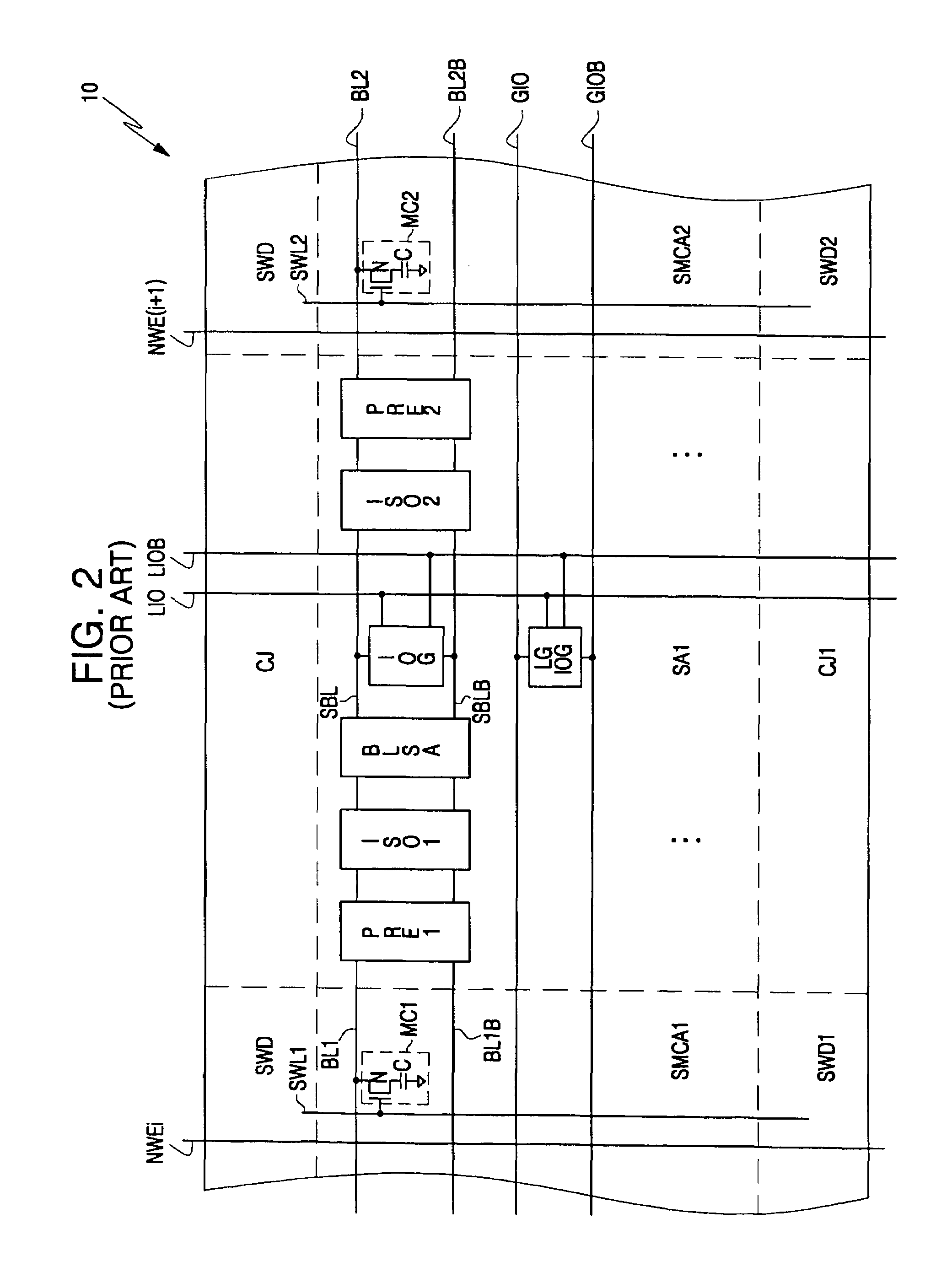

Semiconductor memory device and method of arranging signal and power lines thereof

ActiveUS7161823B2Increase the number of cellsReduce widthDigital storageElectrical conductorRandom access memory

Method and apparatus for use, e.g., with Synchronous Dynamic Random Access Memory (SDRAM) circuits are disclosed. In one described embodiment, three metal layers are deposited and patterned in turn overlying a memory array portion of an SDRAM. Relatively wide power conductors are routed on a third metal layer, allowing power conductors to be reduced in size, or in some cases eliminated, on first and second metal layers. The relatively wide power conductors thus can provide a more stable power supply to the memory array, and also free some space on first and / or second metal for routing of additional and / or more widely spaced signal conductors. Other embodiments are described and claimed.

Owner:SAMSUNG ELECTRONICS CO LTD

Accurately-tunable optical fiber laser microwave source with low phase noise and narrow line width

ActiveCN101794952AReduce phase noiseReduce line widthSolid masersFibre transmissionGratingPhase noise

The invention discloses an accurately-tunable optical fiber laser microwave source with low phase noise and narrow line width, comprising a pumping source, a wavelength division multiplexer, a superstructure active Bragg phase shifted fiber grating, an absorbing liquid, a photoelectric detector and electric control telescopic piezoelectric ceramic. A first end of the wavelength division multiplexer is connected with the pumping source; one end of the superstructure active Bragg phase shifted fiber grating is connected with a second end of the wavelength division multiplexer; one end of the superstructure active Bragg phase shifted fiber grating is immersed into the absorbing liquid; the photoelectric detector is connected with a third end of the wavelength division multiplexer; and the superstructure active Bragg phase shifted fiber grating is fixed on the lateral surface of the electric control telescopic piezoelectric ceramic.

Owner:山东中科际联光电集成技术研究院有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com