Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

90results about How to "Small parasitic capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

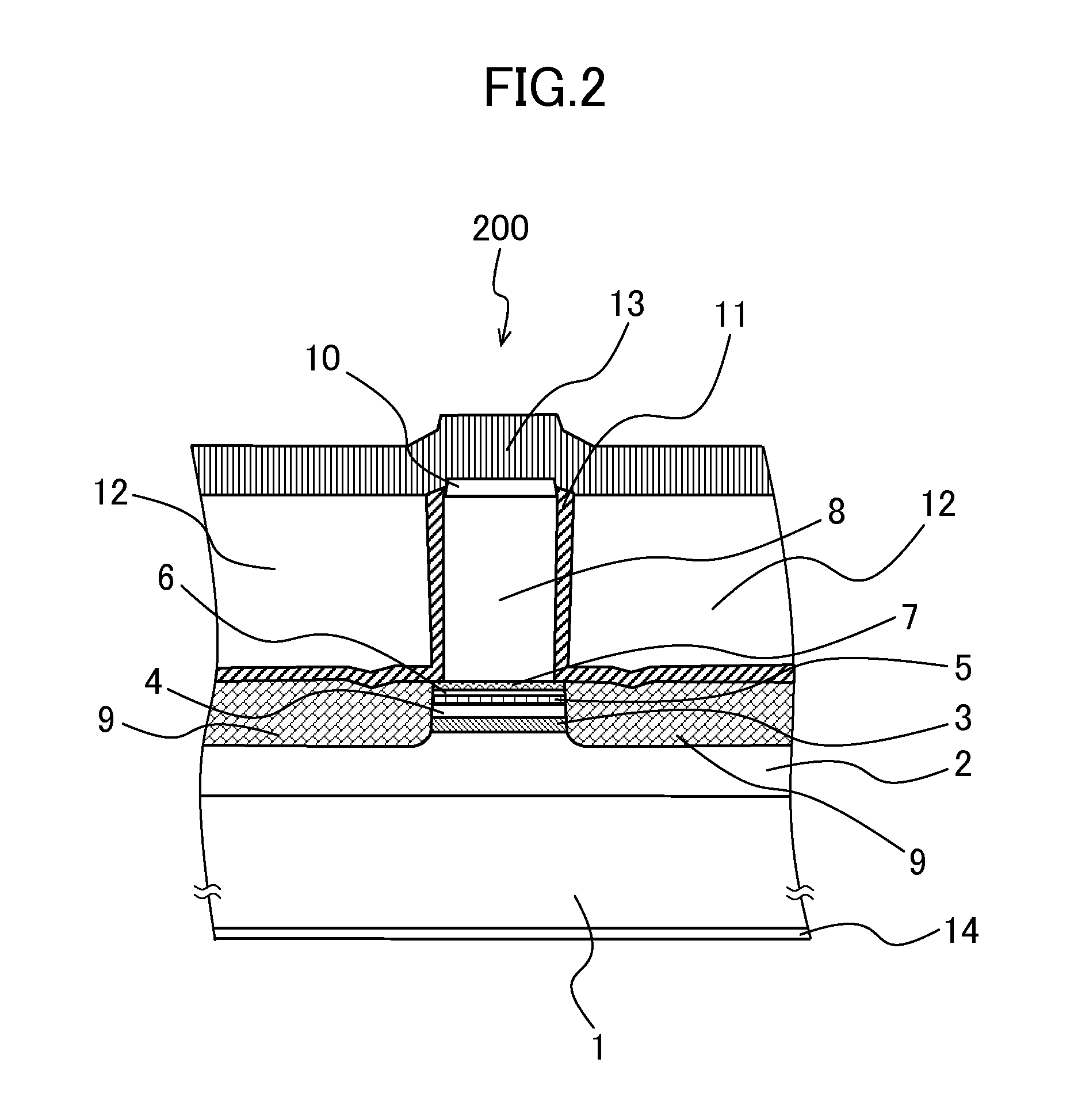

Semiconductor device and method for manufacturing the same

ActiveUS20100025679A1Small currentHigh on-off ratioStatic indicating devicesSolid-state devicesOhmic contactCharge carrier

An embodiment is to include an inverted staggered (bottom gate structure) thin film transistor in which an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer and a buffer layer is provided between the semiconductor layer and a source and drain electrode layers. The buffer layer having higher carrier concentration than the semiconductor layer is provided intentionally between the source and drain electrode layers and the semiconductor layer, whereby an ohmic contact is formed.

Owner:SEMICON ENERGY LAB CO LTD

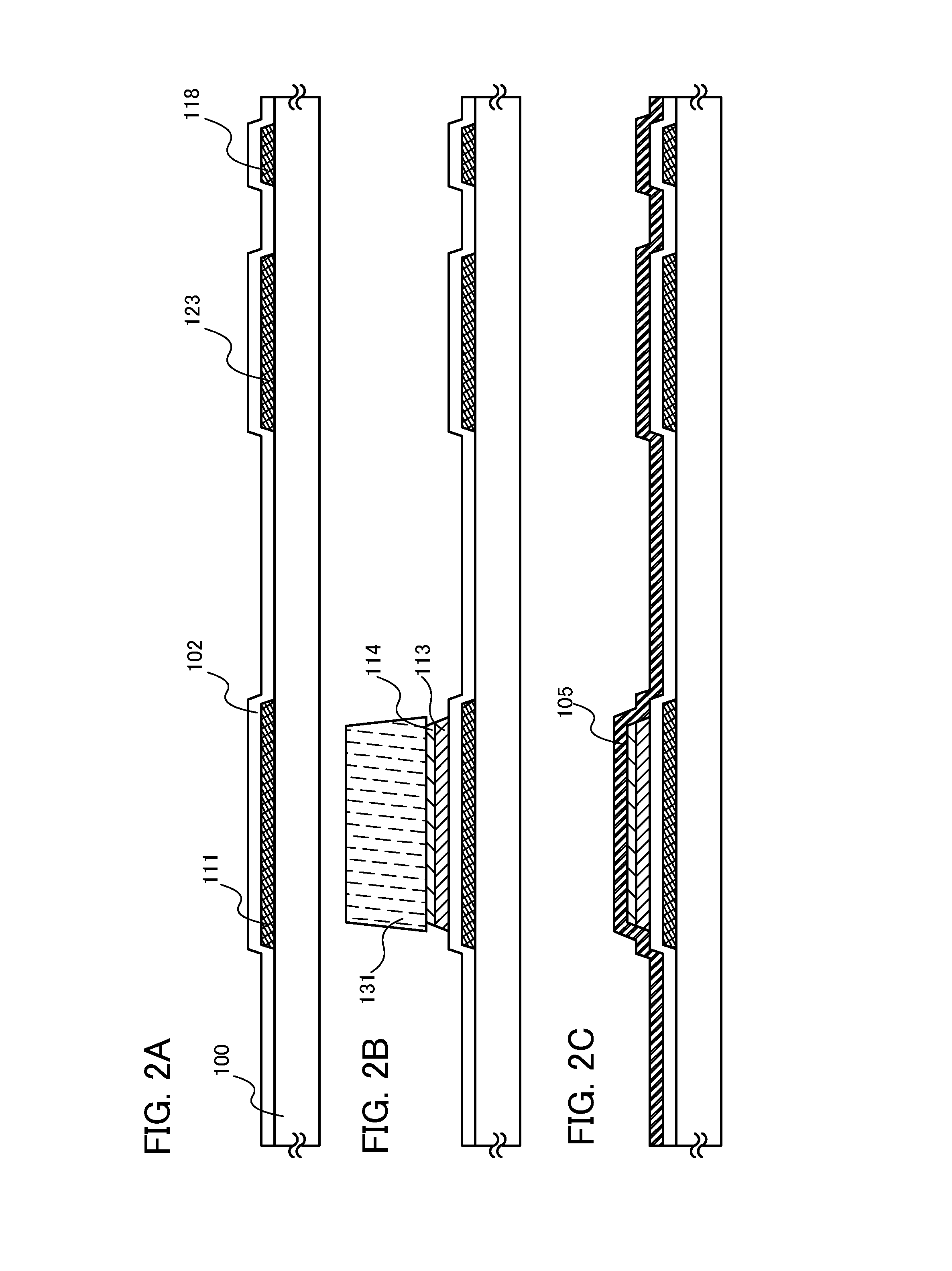

Semiconductor device and method for manufacturing the same

ActiveUS20100065838A1Small currentHigh on-off ratioTransistorSolid-state devicesProduction rateSemiconductor package

An object is to provide a semiconductor device including a thin film transistor with excellent electrical characteristics and high reliability and a method for manufacturing the semiconductor device with high mass productivity. A main point is to form a low-resistance oxide semiconductor layer as a source or drain region after forming a drain or source electrode layer over a gate insulating layer and to form an oxide semiconductor film thereover as a semiconductor layer. It is preferable that an oxygen-excess oxide semiconductor layer be used as a semiconductor layer and an oxygen-deficient oxide semiconductor layer be used as a source region and a drain region.

Owner:SEMICON ENERGY LAB CO LTD

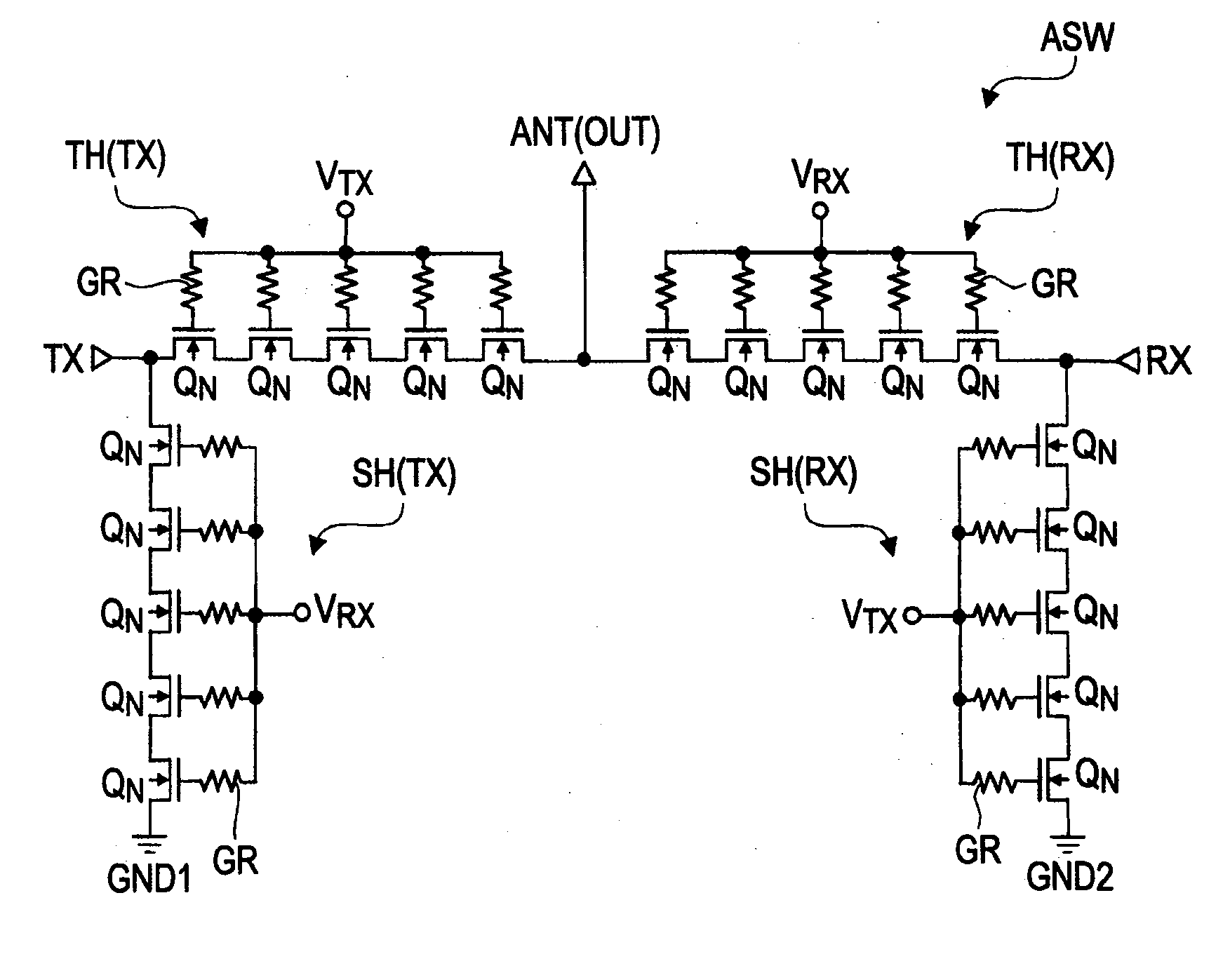

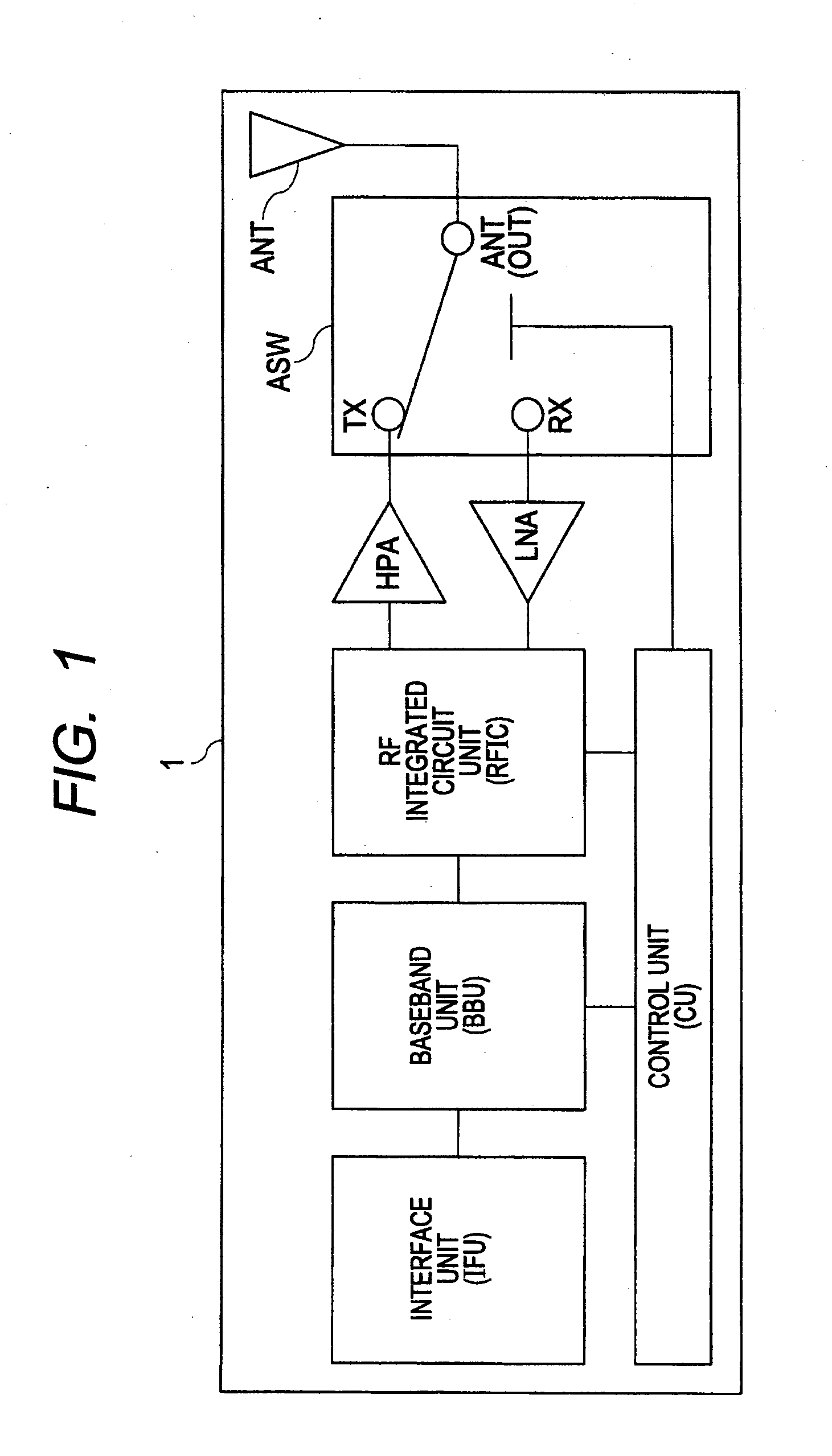

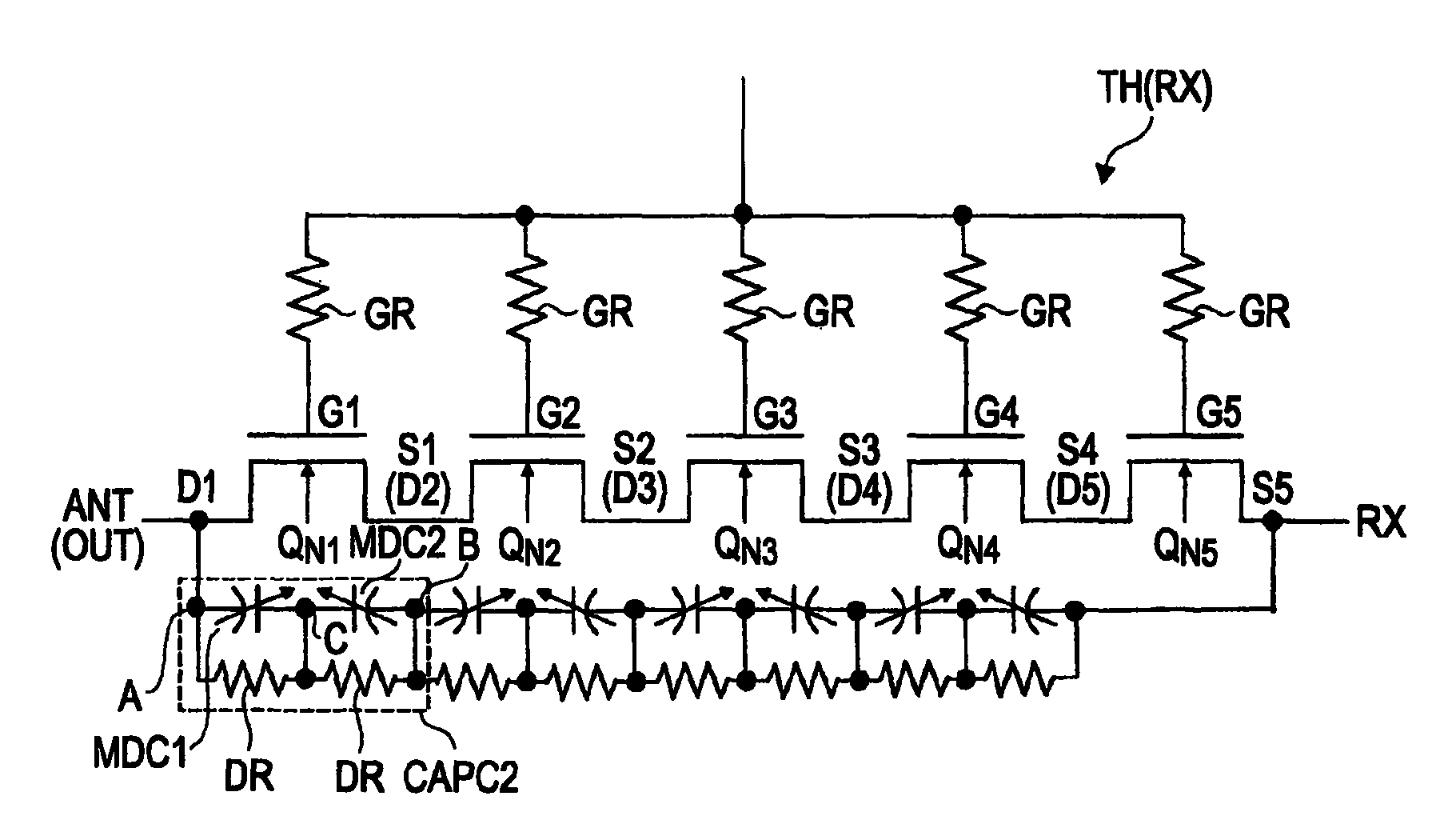

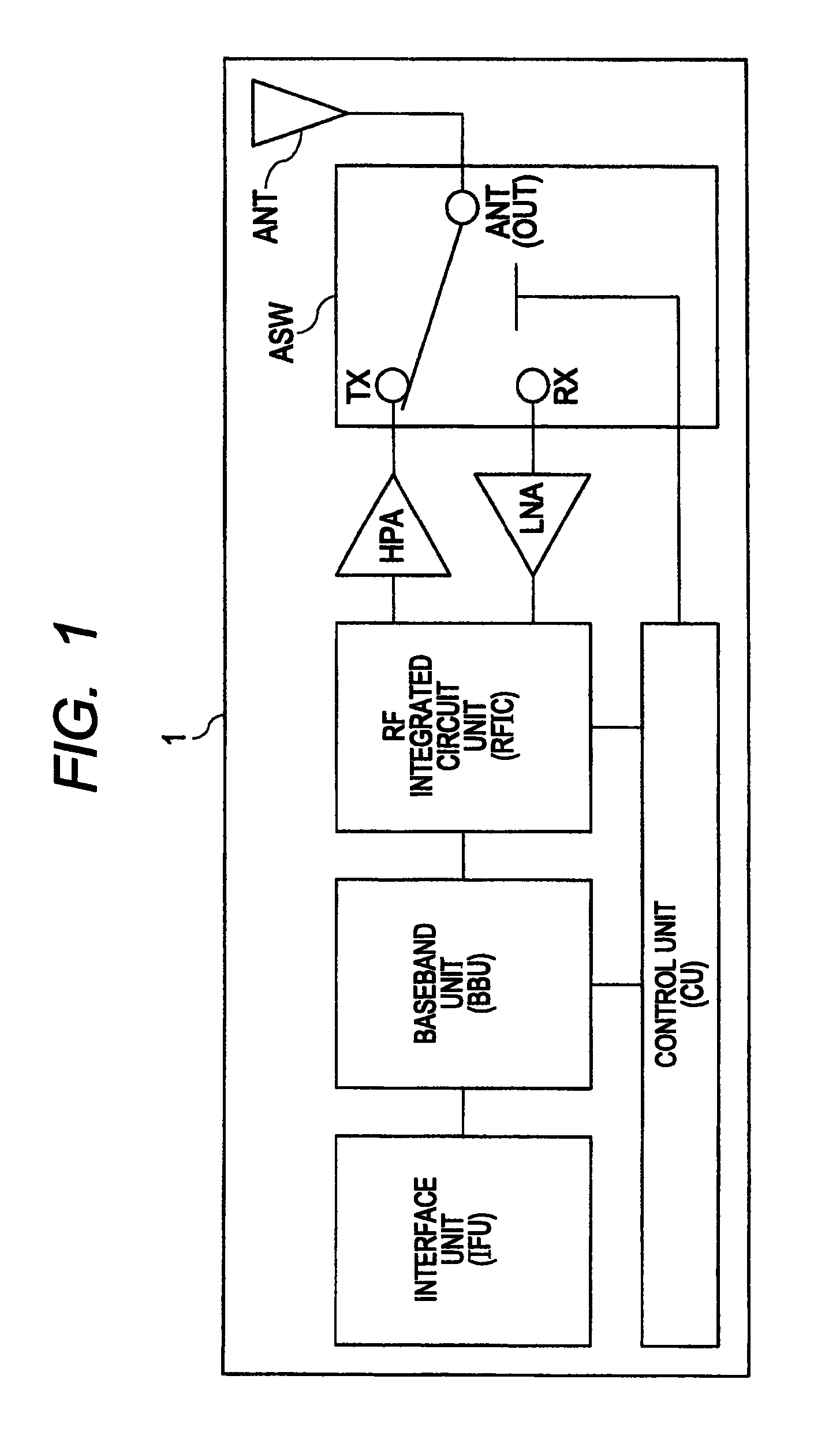

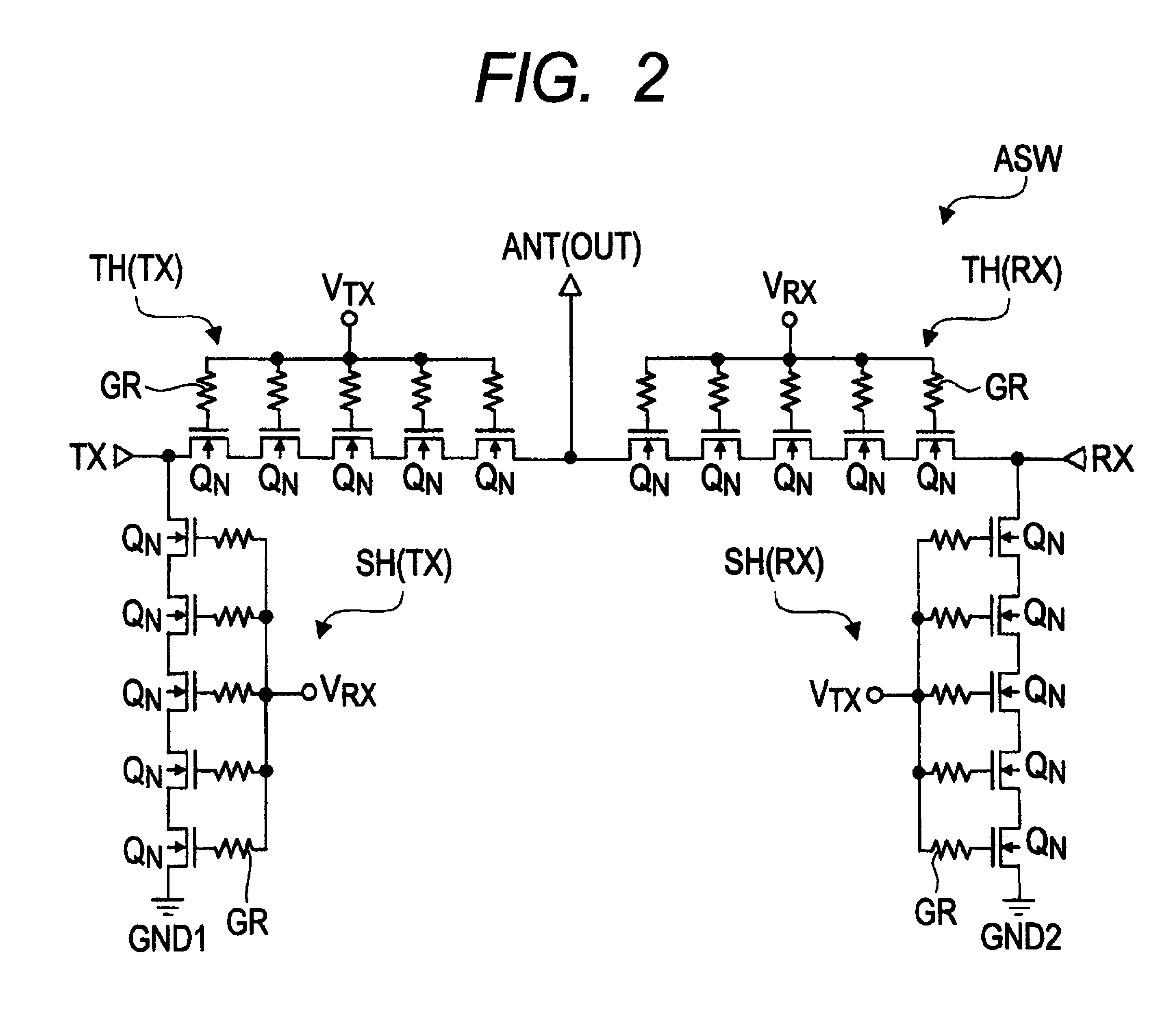

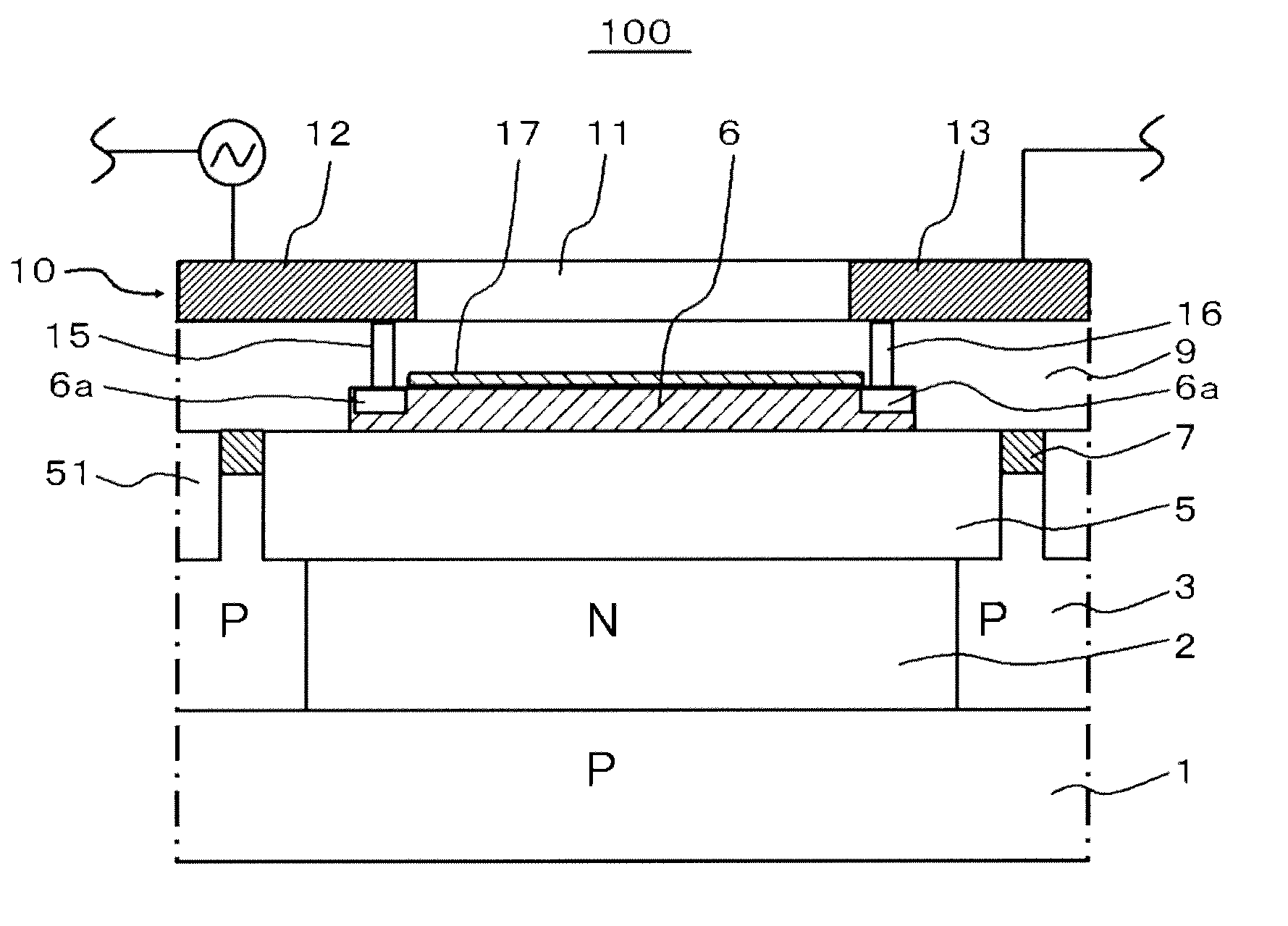

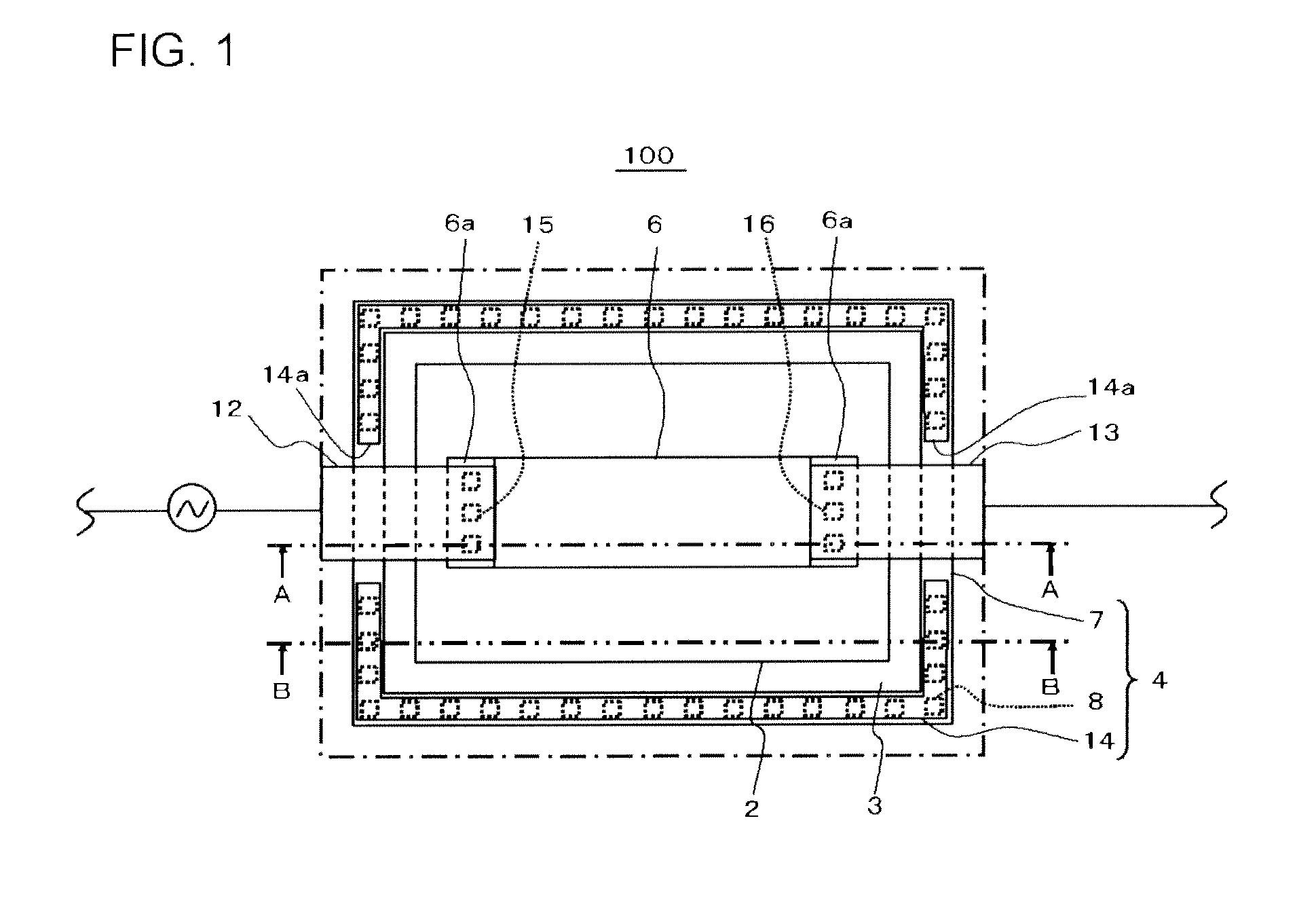

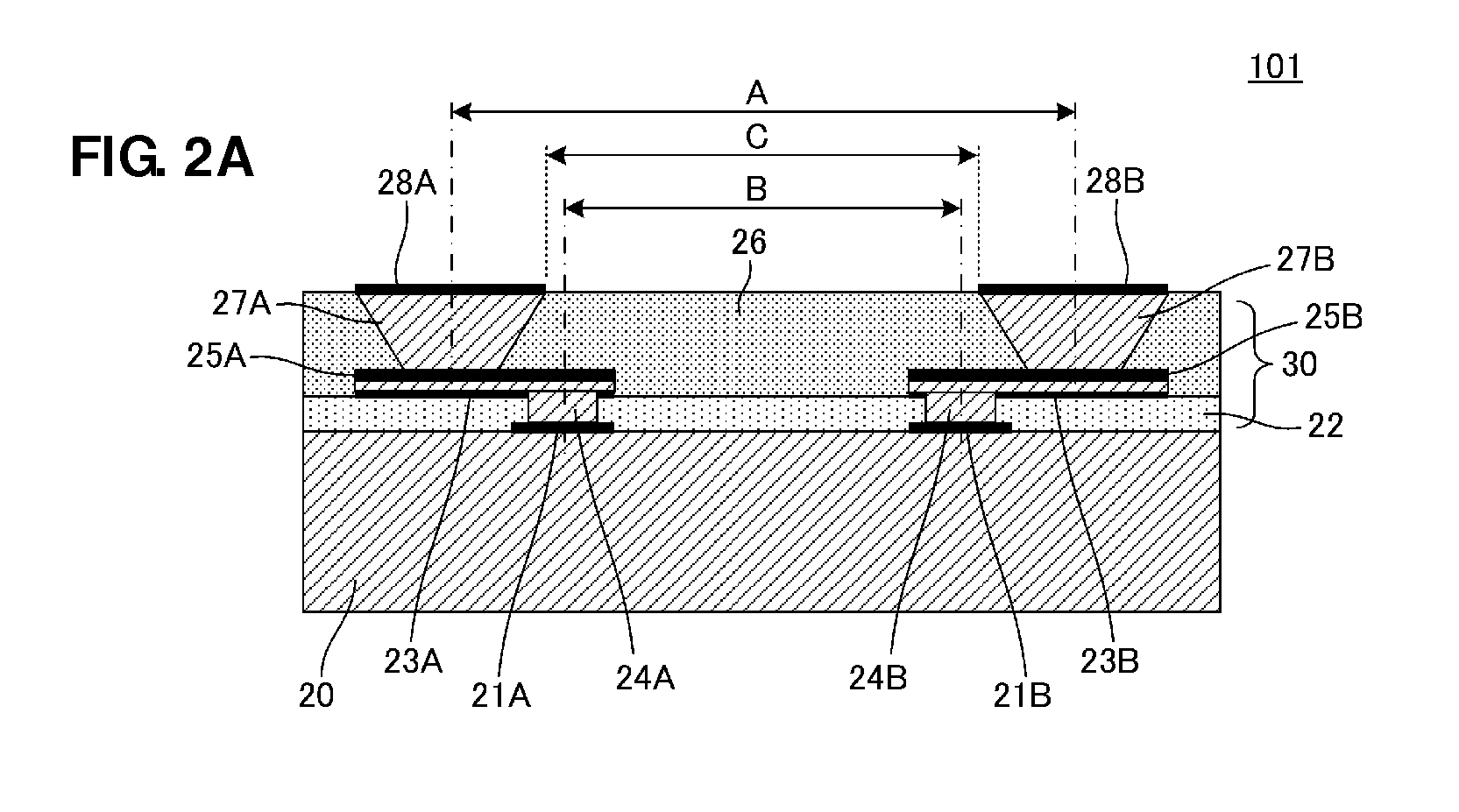

Semiconductor device

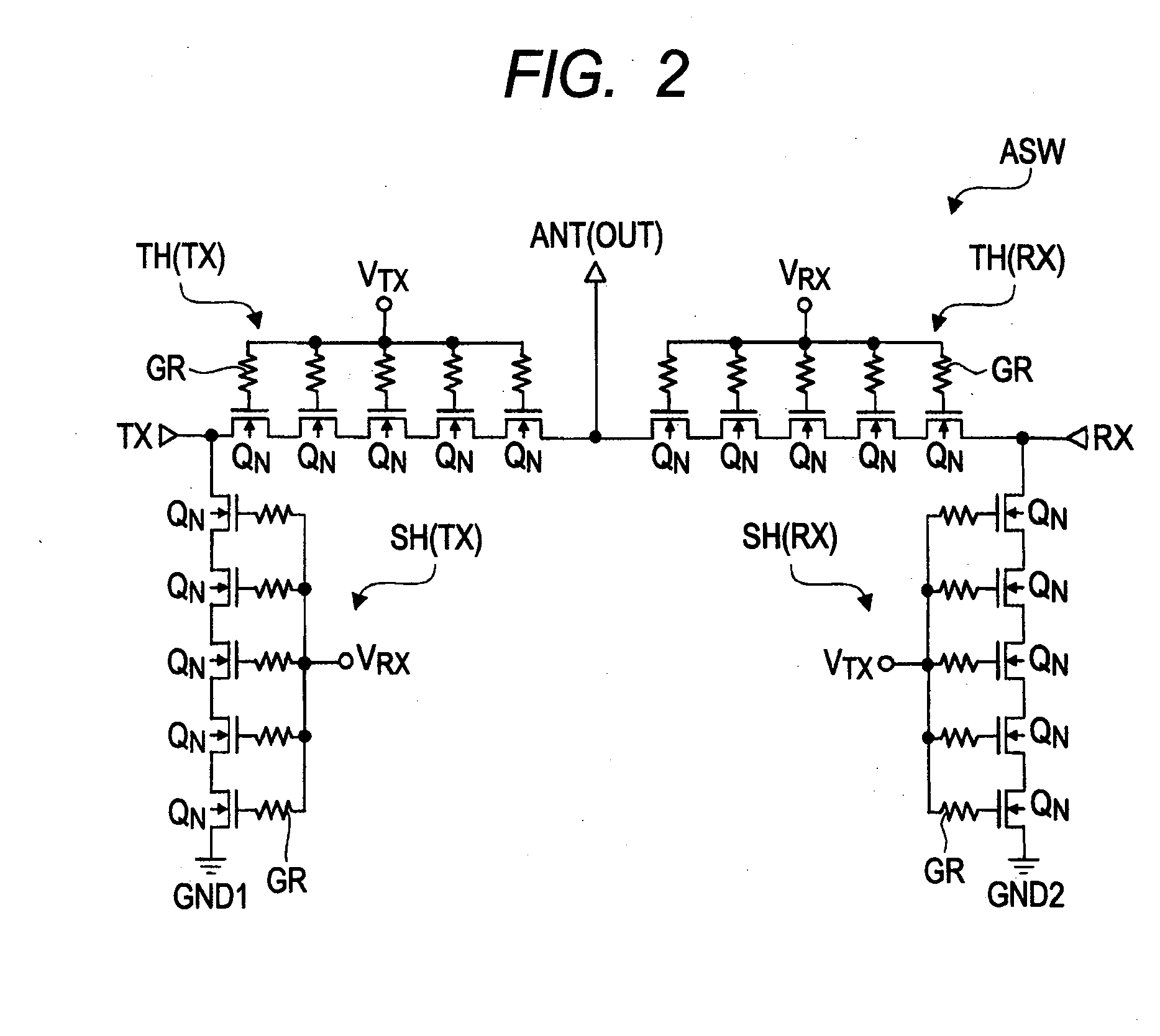

ActiveUS20110316062A1Lower Antenna CostsMinimizing harmonic distortionTransistorSolid-state devicesCapacitanceTotal harmonic distortion

In terms of achieving a reduction in the cost of an antenna switch, there is provided a technology capable of minimizing harmonic distortion generated in the antenna switch even when the antenna switch is particularly formed of field effect transistors formed over a silicon substrate. Between the source region and the drain region of each of a plurality of MISFETs coupled in series, a distortion compensating capacitance circuit is coupled which has a voltage dependency such that, in either of the cases where a positive voltage is applied to the drain region based on the potential of the source region and where a negative voltage is applied to the drain region based on the potential of the source region, the capacitance decreases to a value smaller than that in a state where the potential of the source region and the potential of the drain region are at the same level.

Owner:RENESAS ELECTRONICS CORP

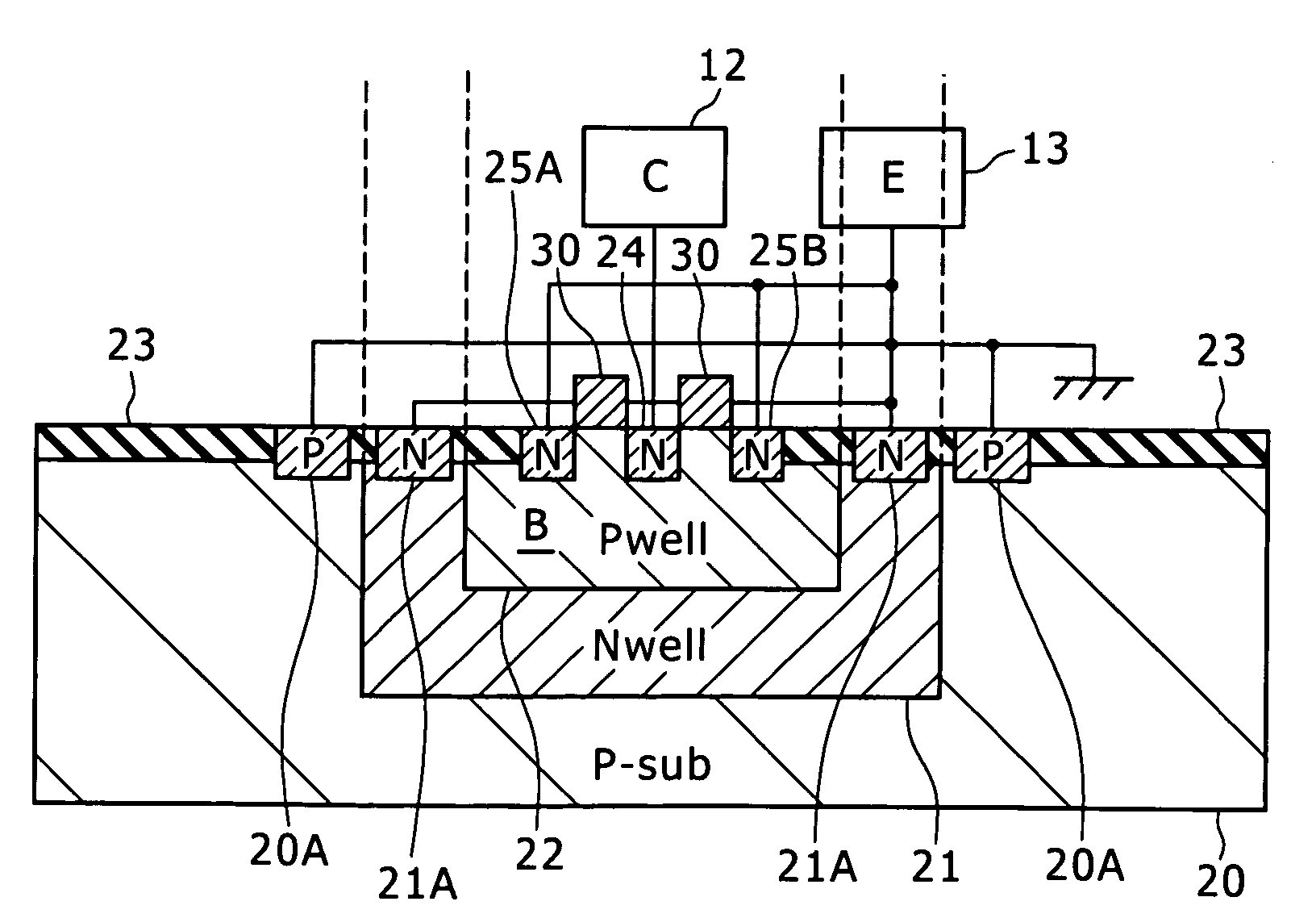

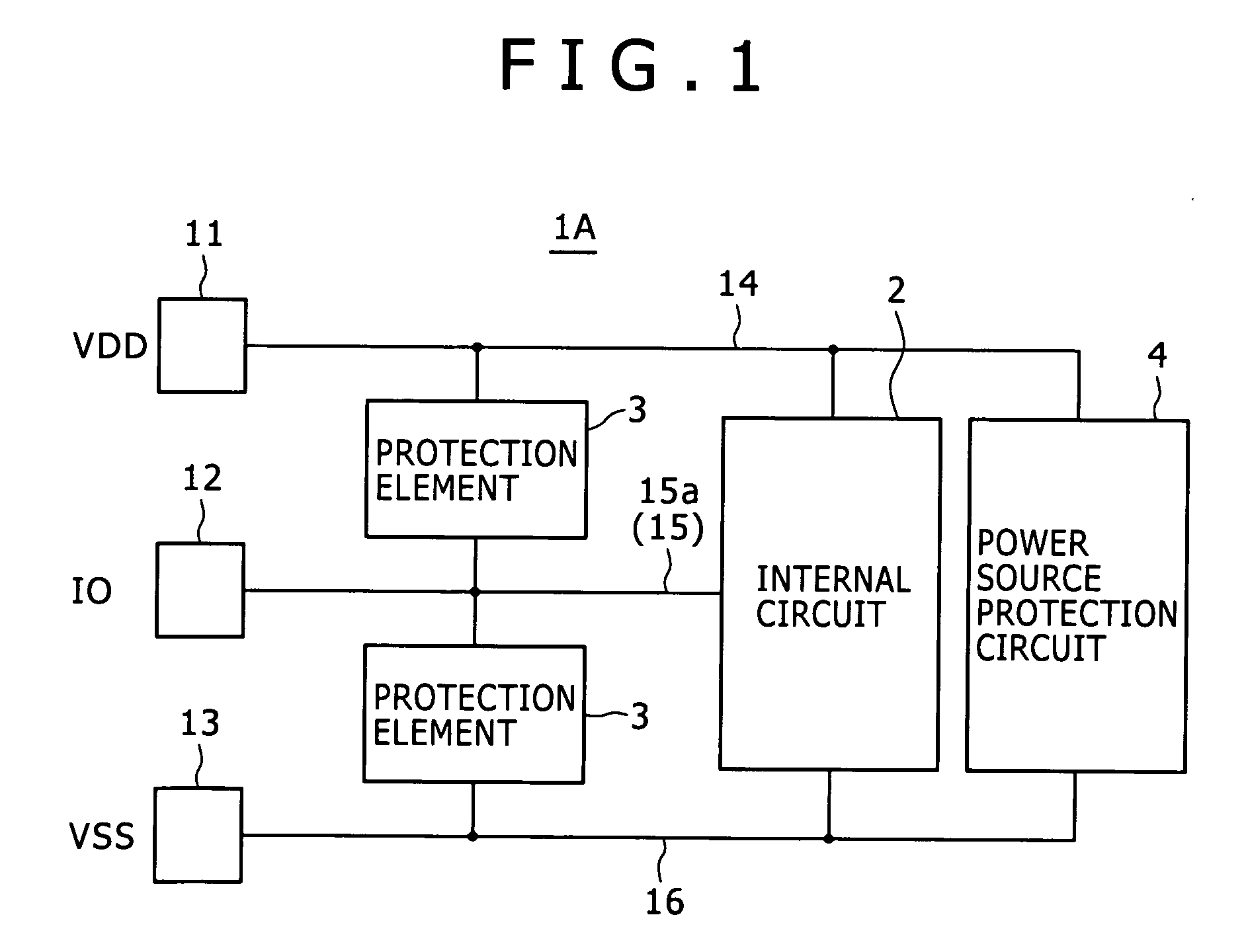

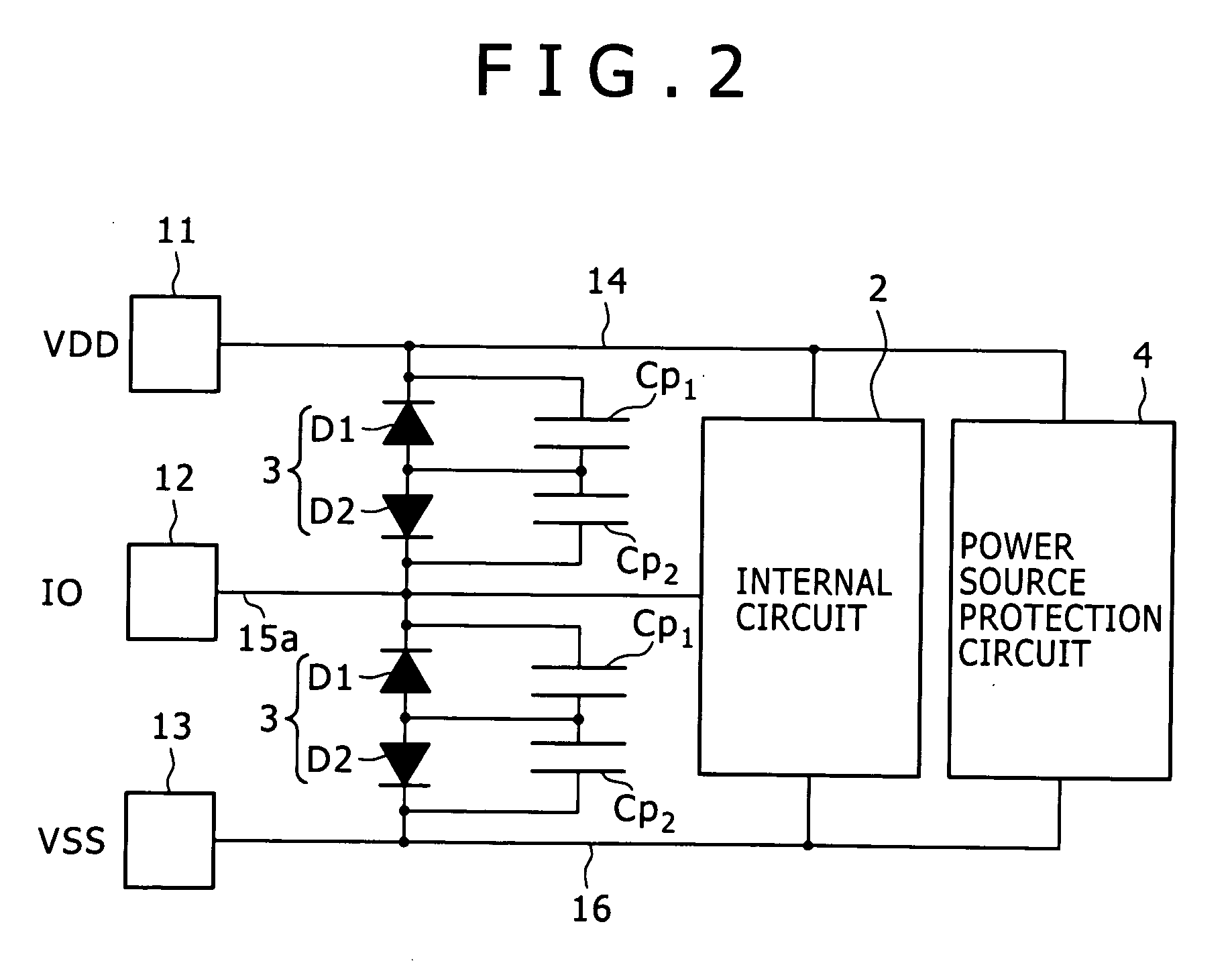

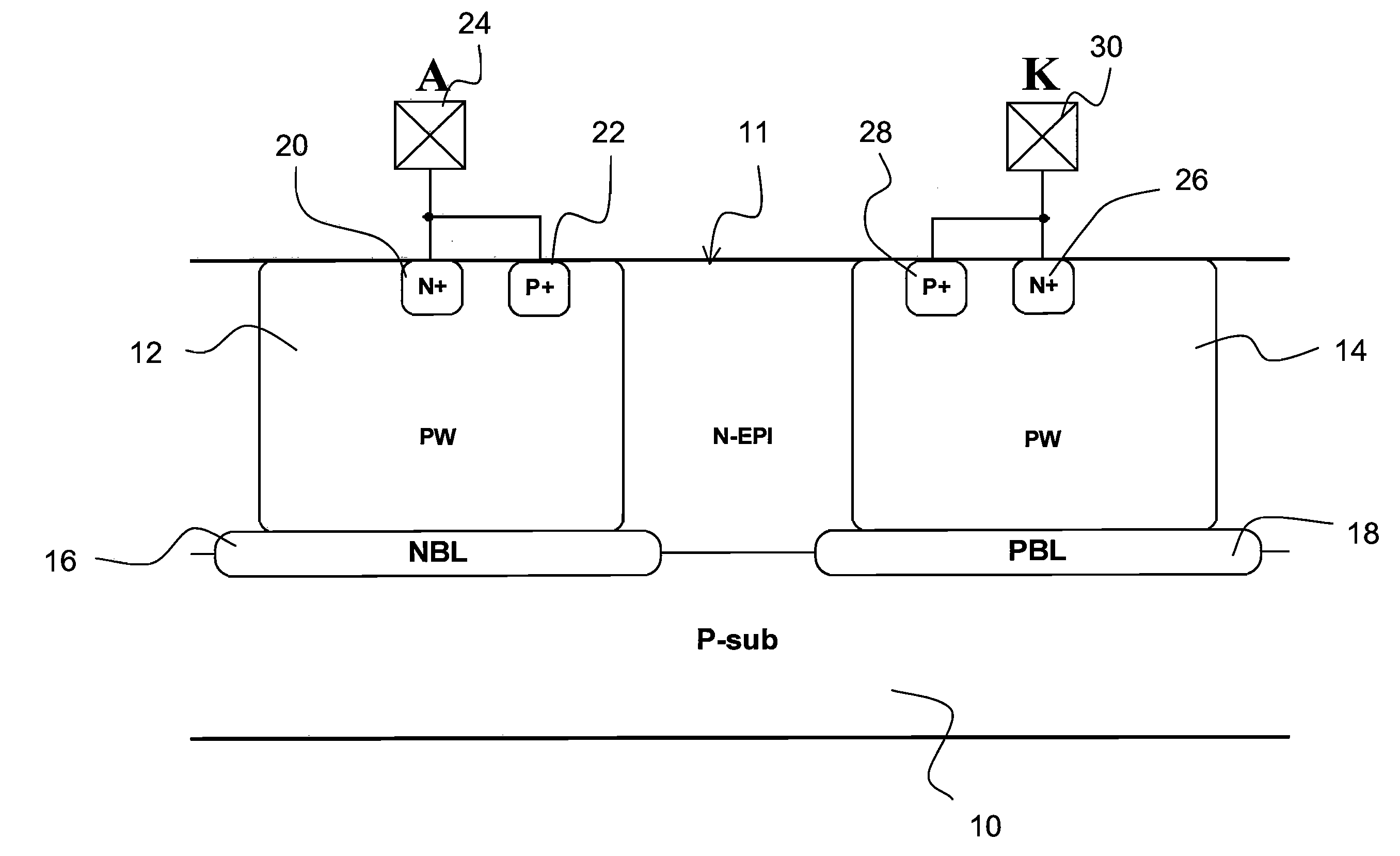

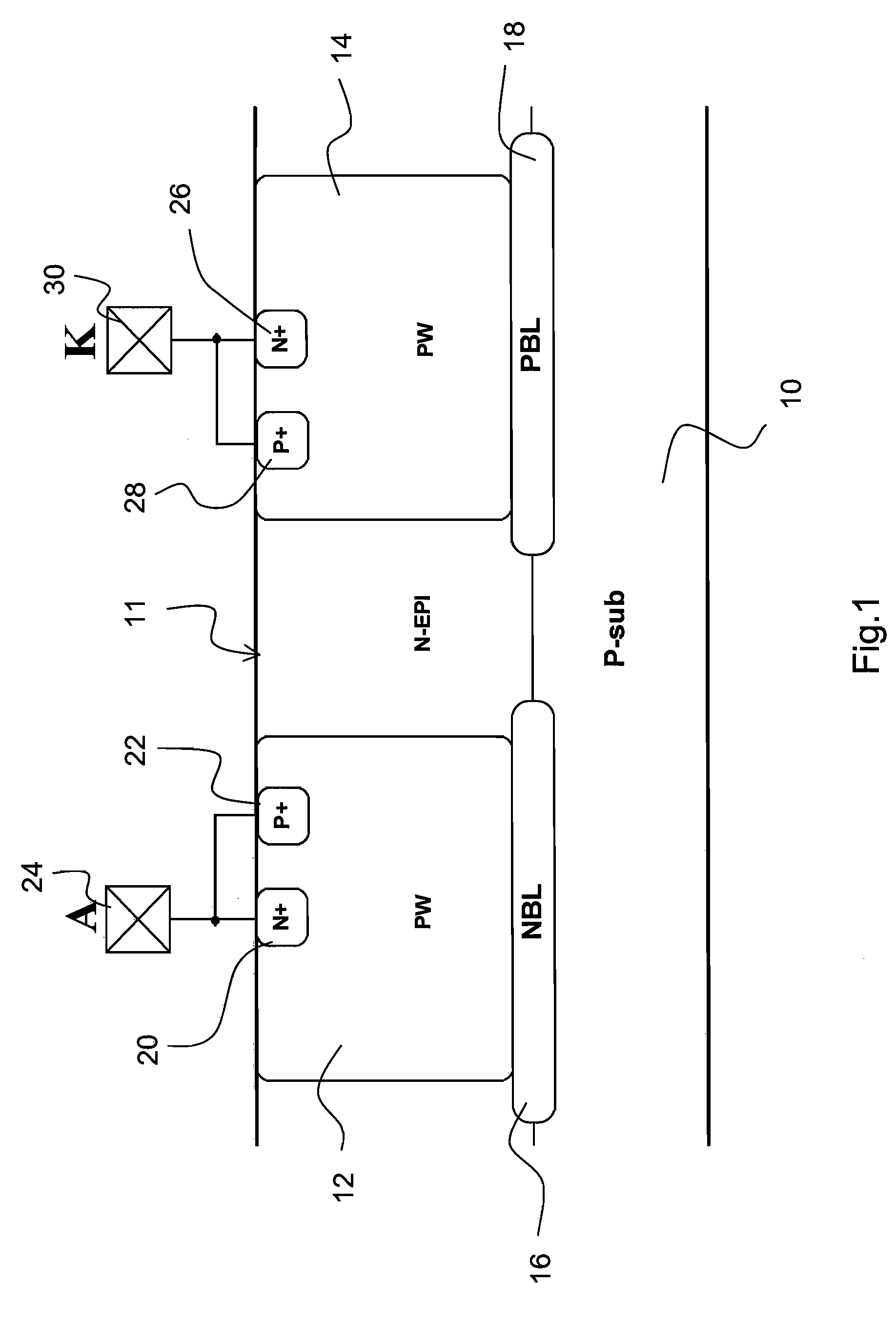

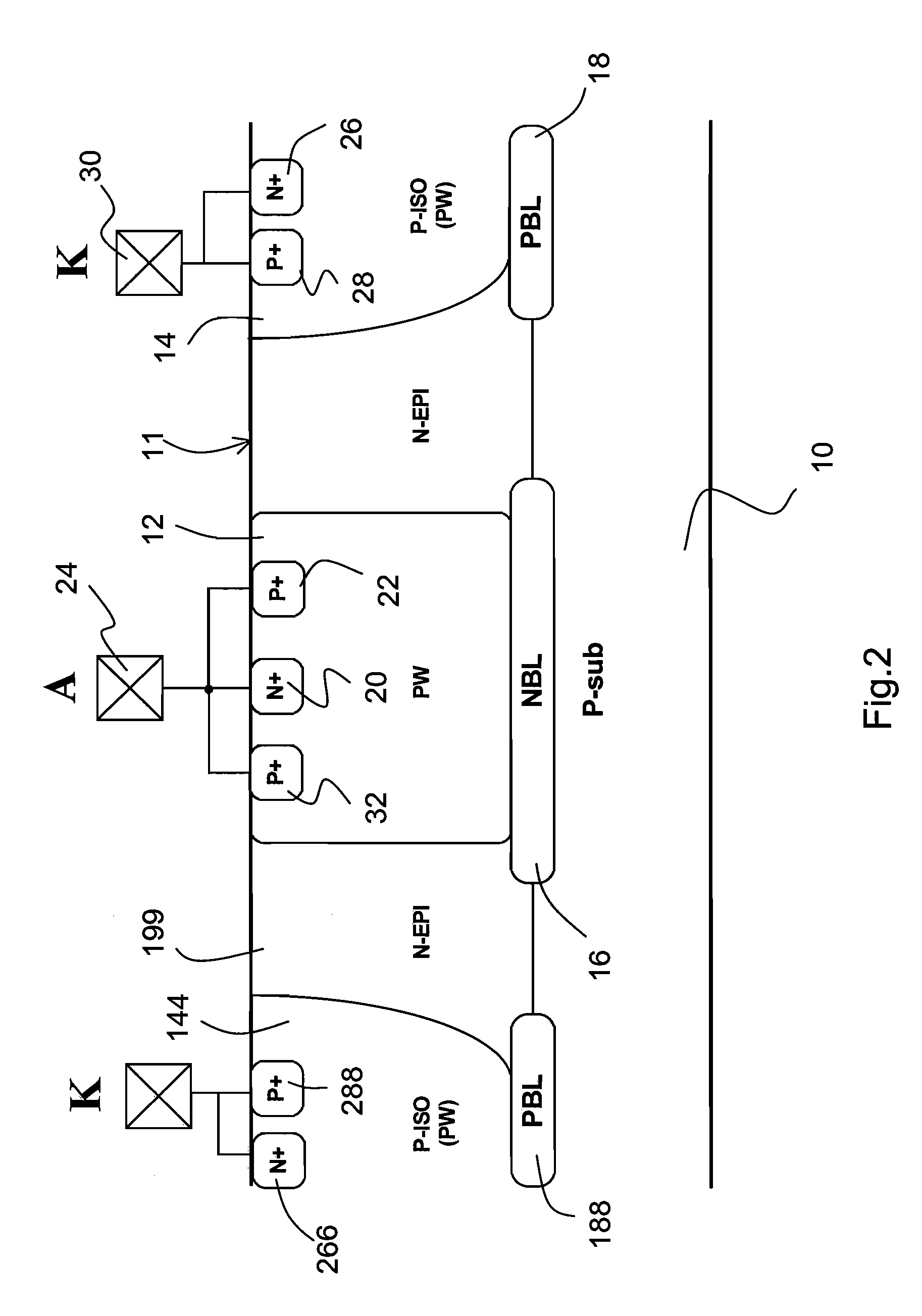

Semiconductor integrated circuit

ActiveUS20100133583A1Rapidly eliminating surgeLower impedanceTransistorThyristorSemiconductorIntegrated circuit

Disclosed herein is a semiconductor integrated circuit including a protected circuit; and a protection element formed on the same semiconductor substrate as the protected circuit and adapted to protect the protected circuit, wherein the protection element includes two diodes having their anodes connected together to form a floating node and two cathodes connected to the protected circuit, the two diodes are formed in a well-in-well structure on the semiconductor substrate, and the well-in-well structure includes a P-type well forming the floating gate, an N-type well which surrounds the surfaces of the P-type well other than that on the front side of the substrate with the deep portion side of the substrate so as to form the cathode of one of the diodes, and a first N-type region formed in the P-type well so as to form the cathode of the other diode.

Owner:SONY CORP

Semiconductor device and method for manufacturing the same

ActiveUS8049225B2Guaranteed high speed operationEasy to makeElectroluminescent light sourcesSolid-state devicesCharge carrierOhmic contact

Owner:SEMICON ENERGY LAB CO LTD

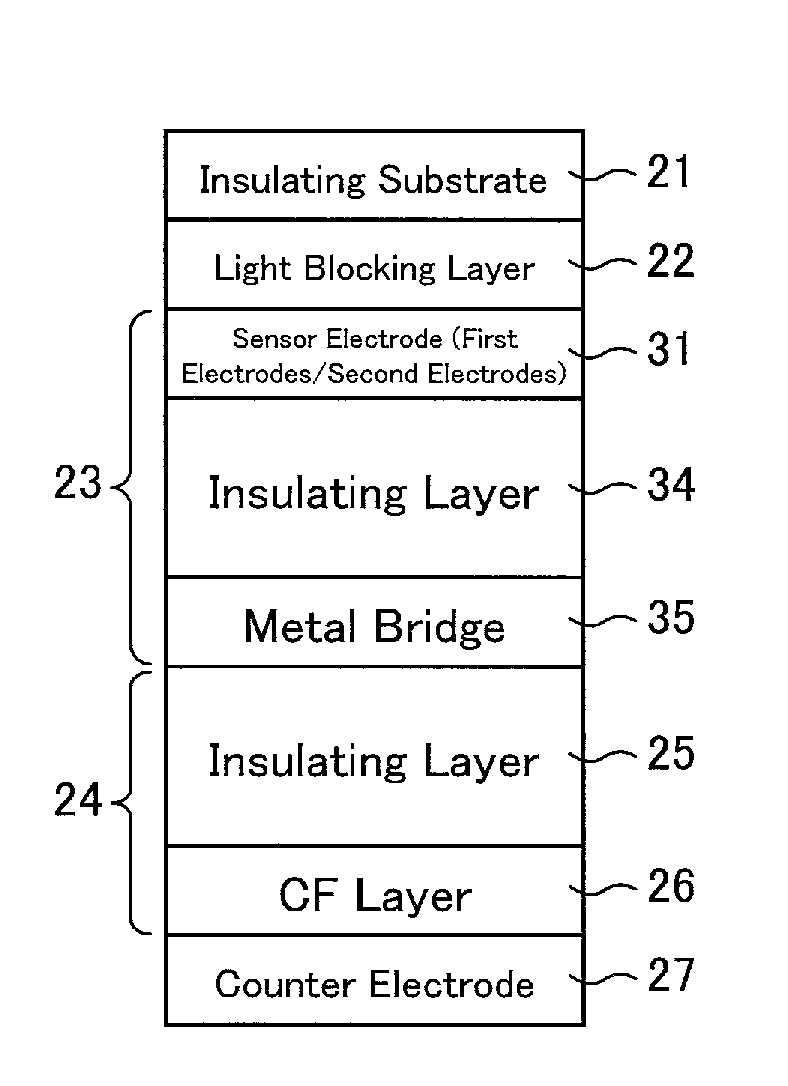

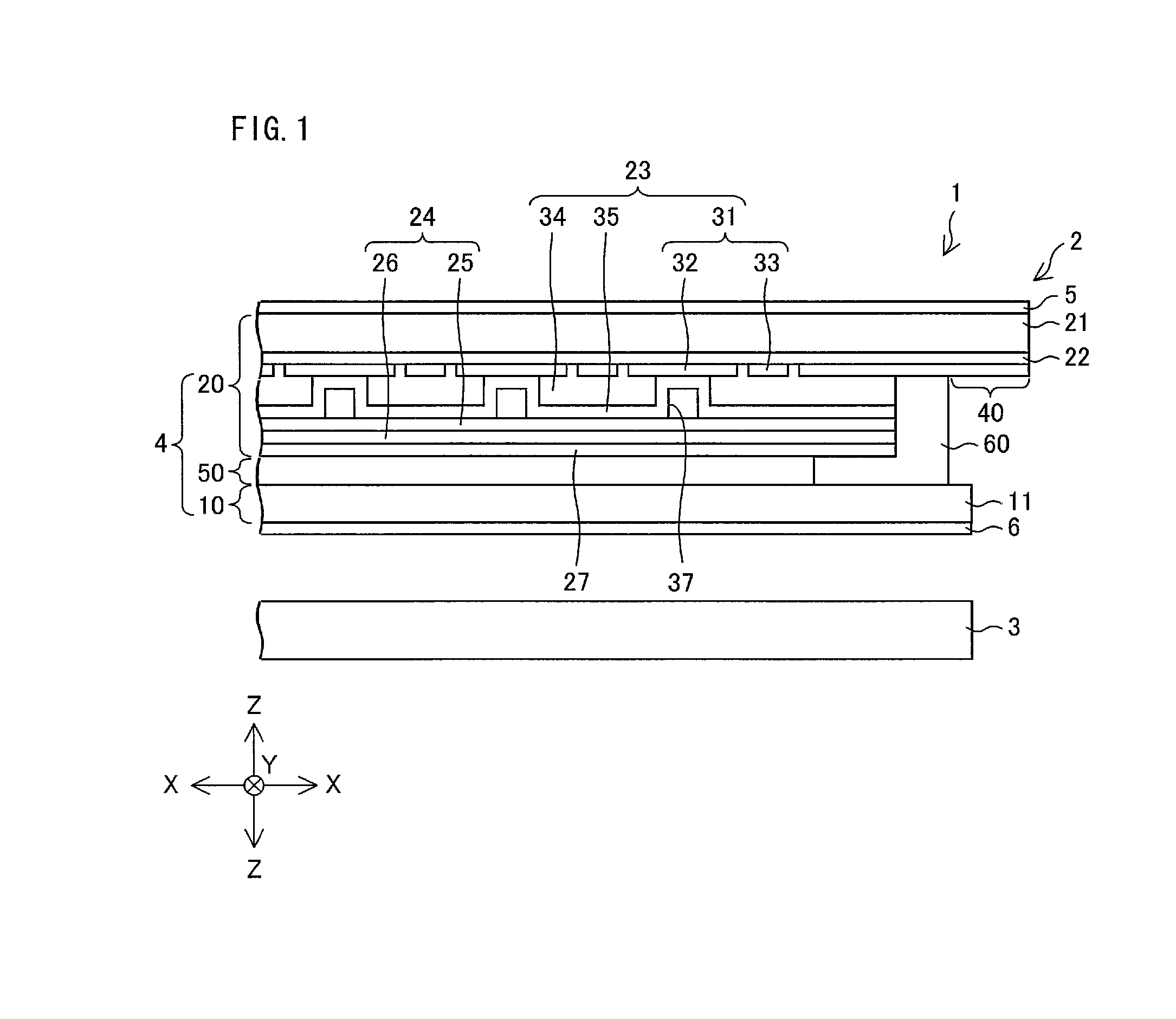

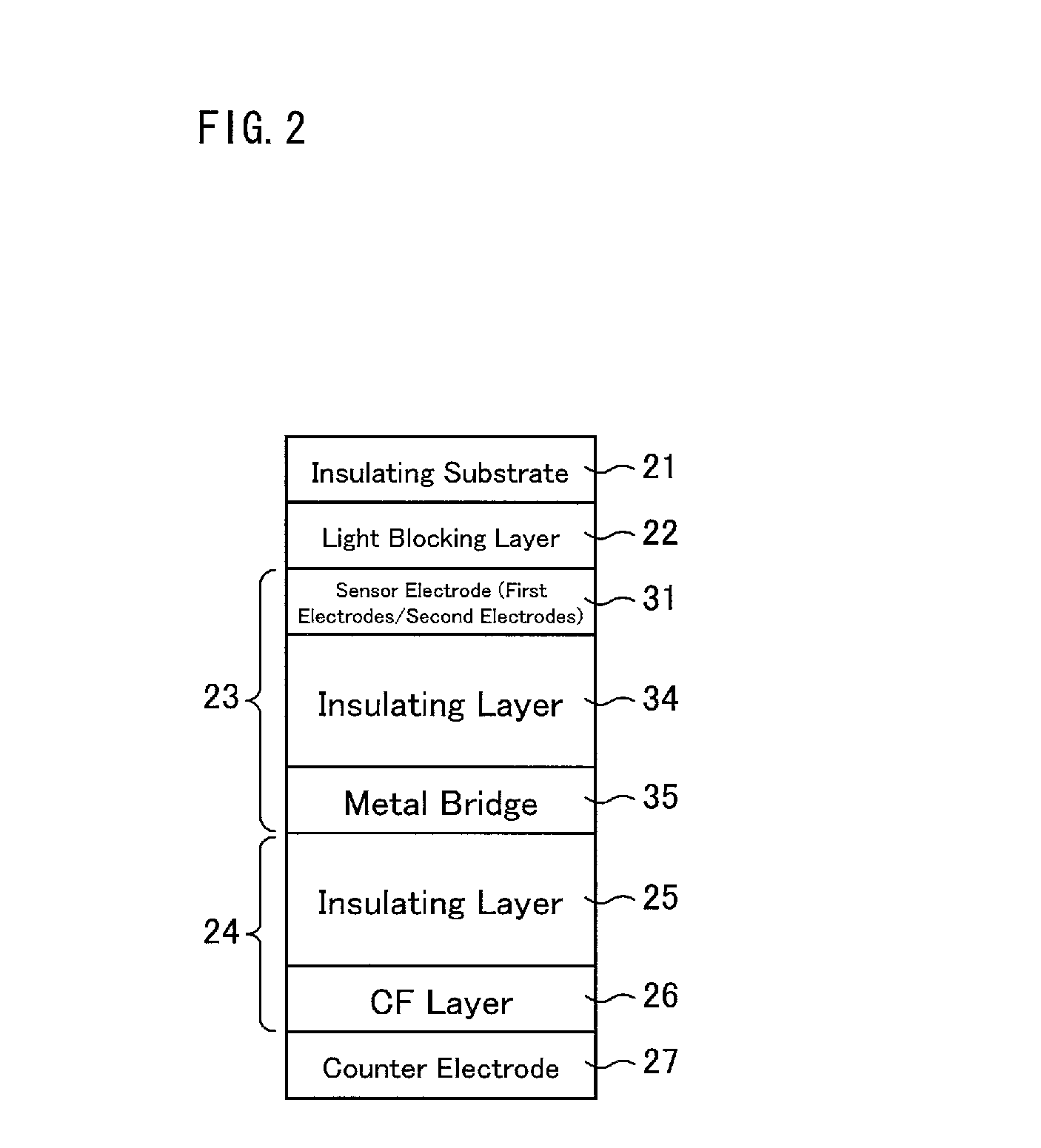

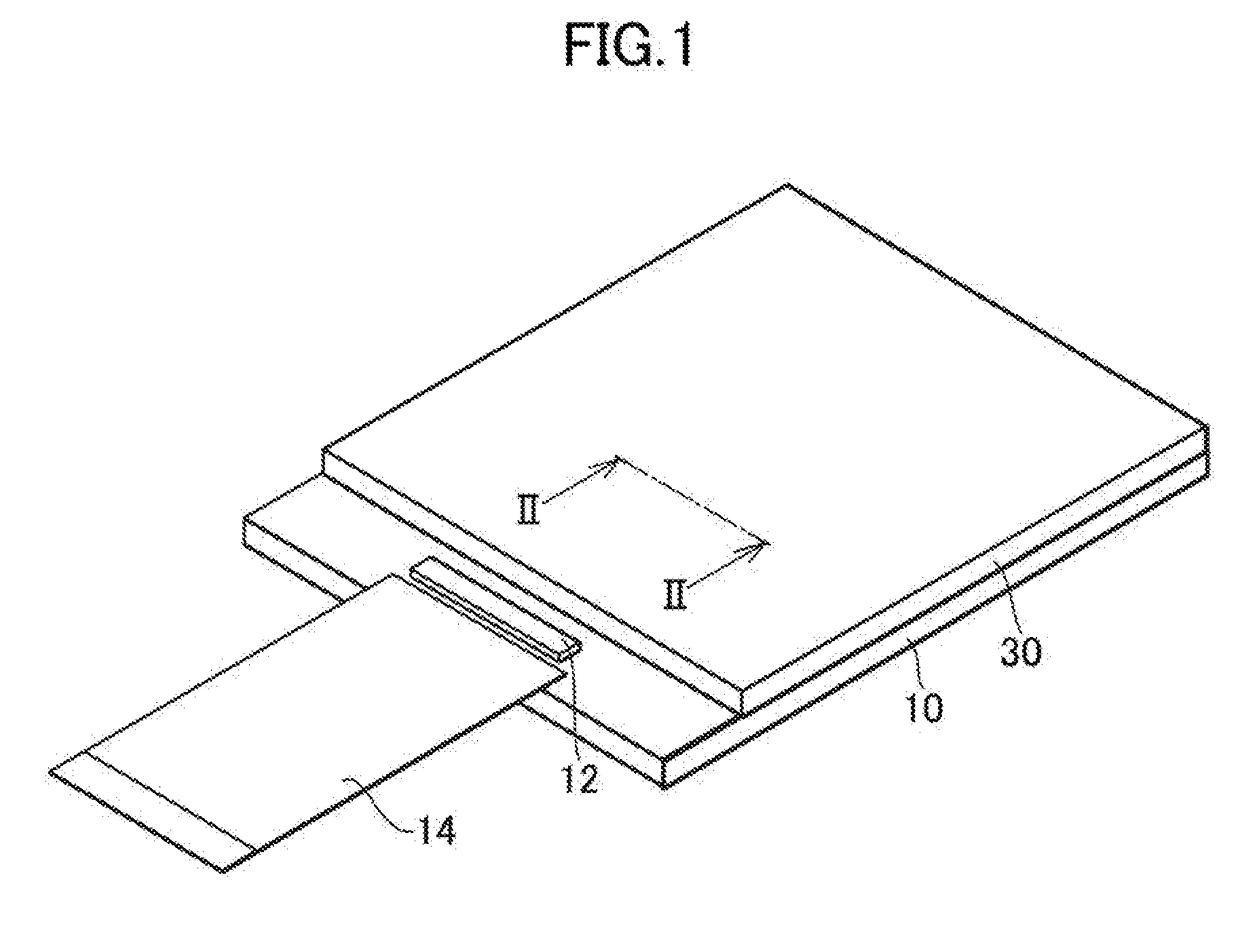

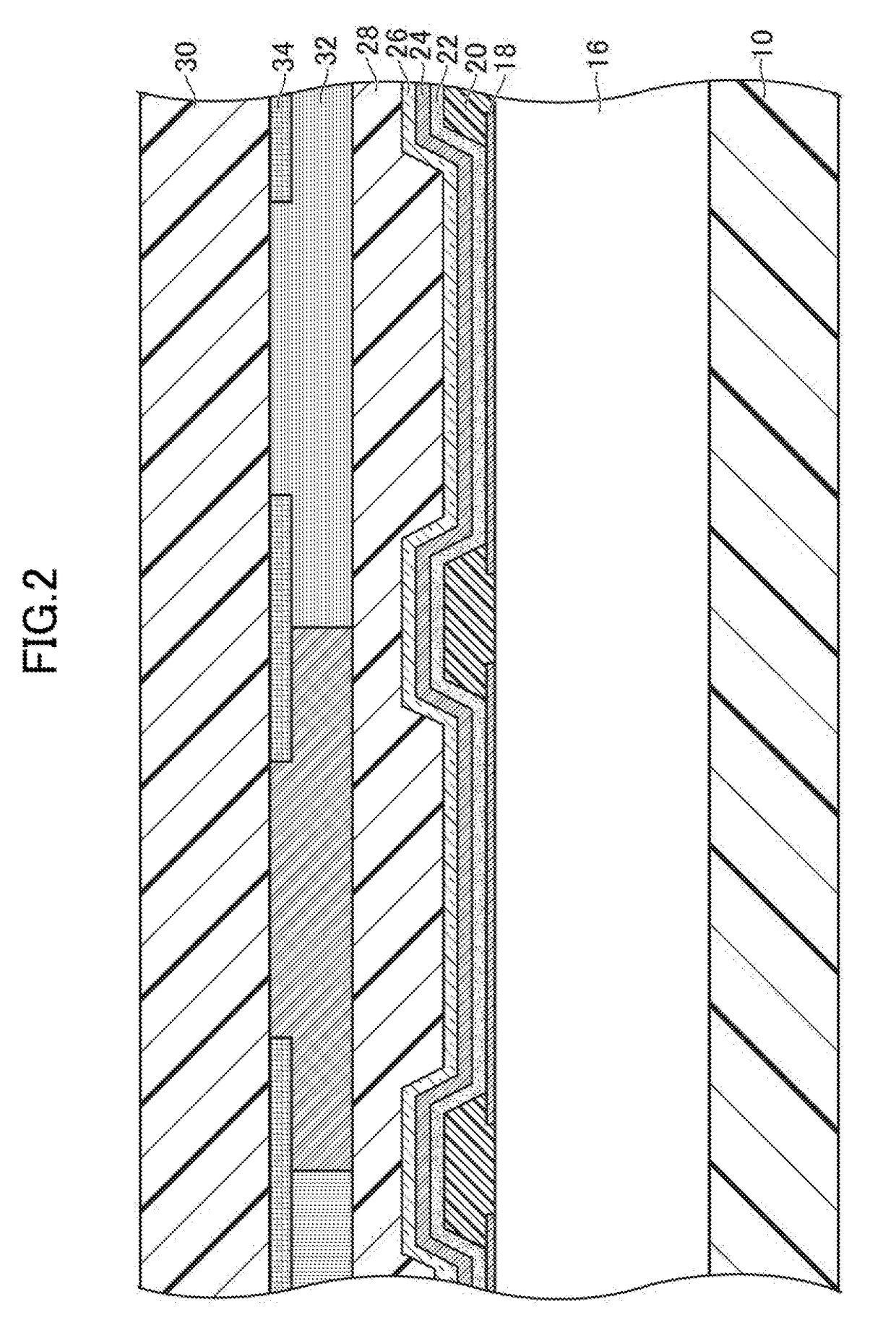

Touch panel substrate and electro-optic device

ActiveUS20140152921A1Small parasitic capacitanceHigh in position detection performanceDigital data processing detailsNon-linear opticsTouch panelEngineering

A sensor electrode (31) provided between an insulating substrate (21) and a counter electrode (27) includes a plurality of electrodes (32) arranged along a first direction and a plurality of electrodes (33) arranged along a second direction perpendicular to the first direction and insulated from the electrodes (32), and these electrodes (32, 33) are formed in the same plane.

Owner:SHARP KK

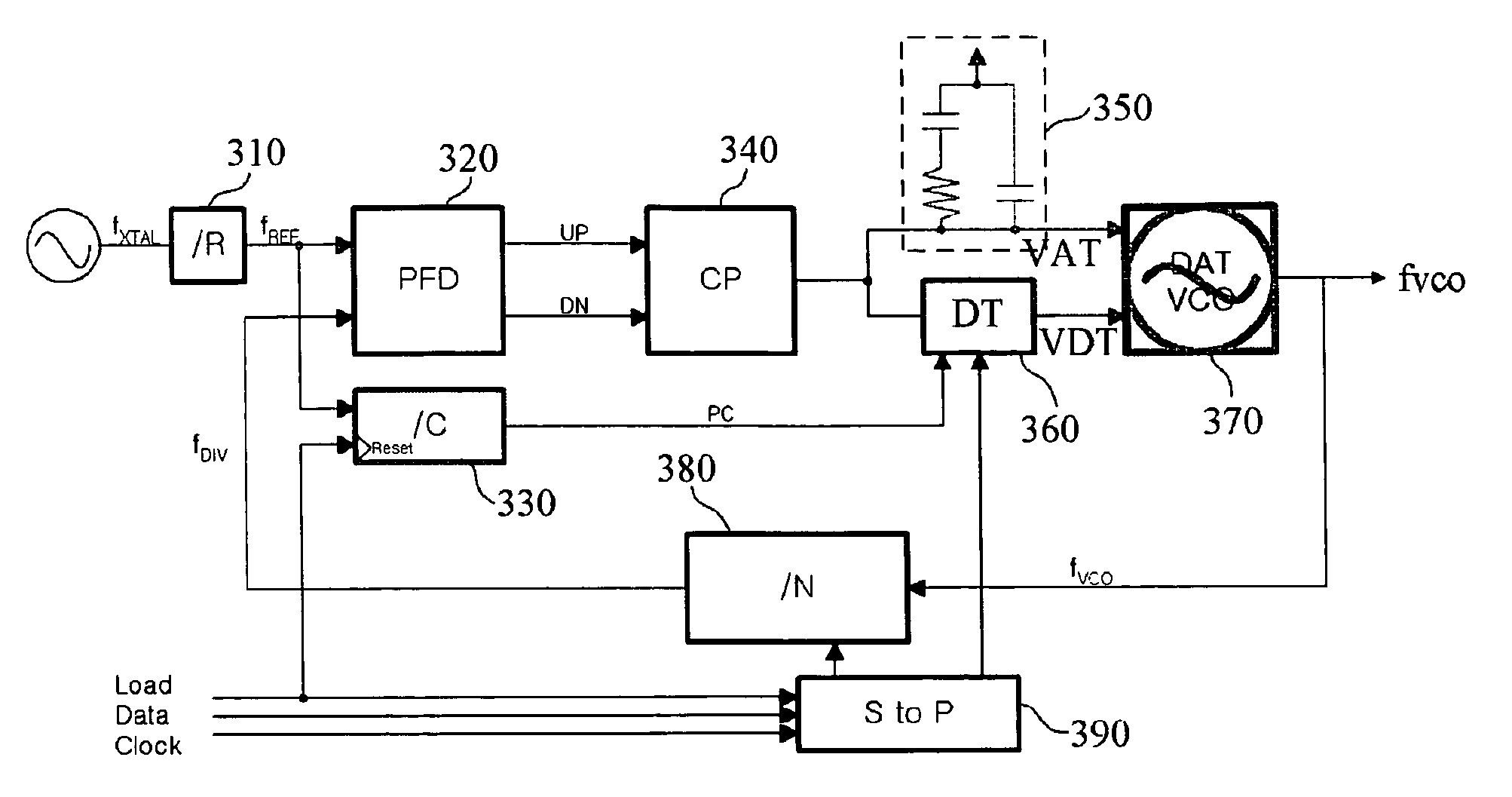

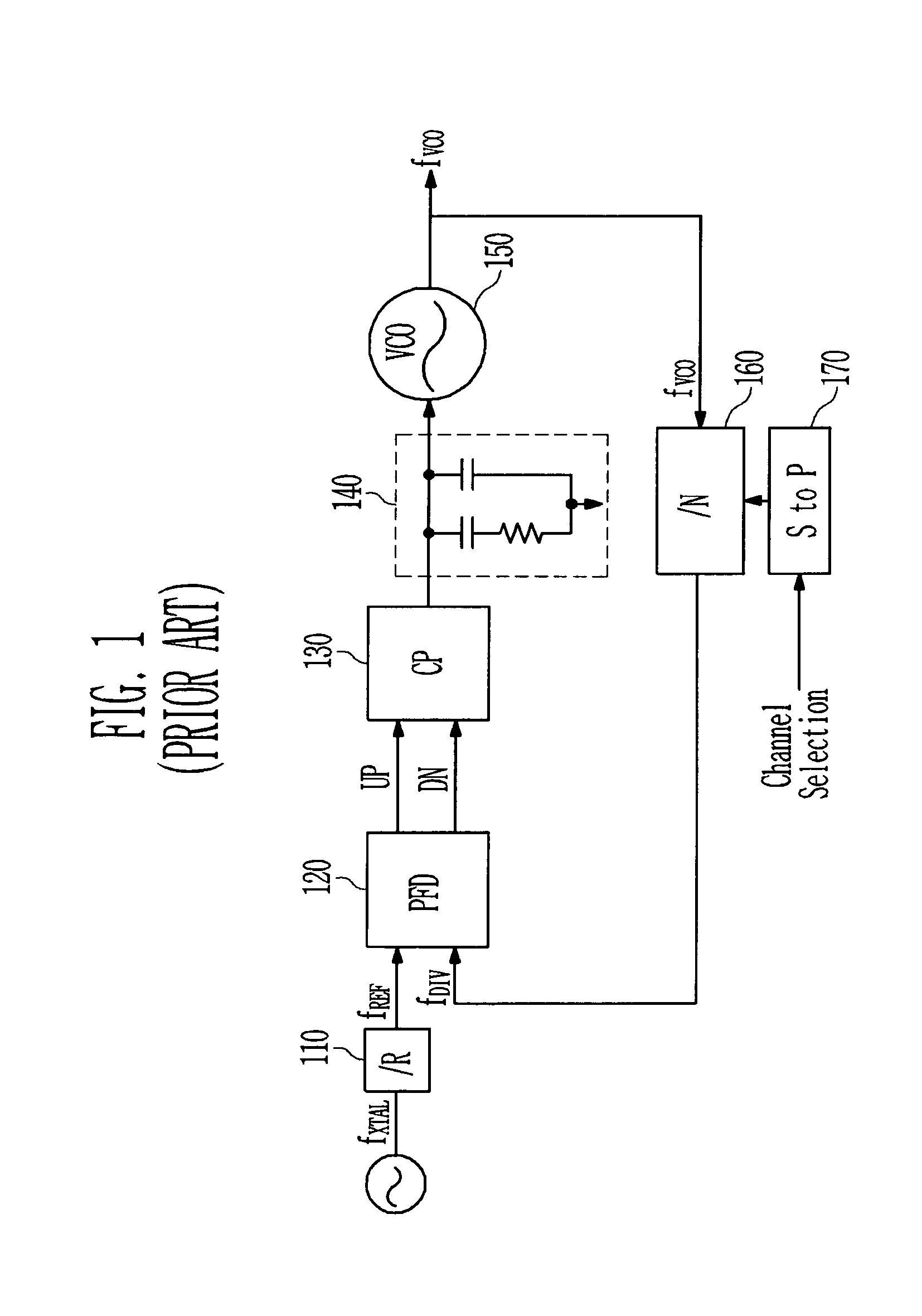

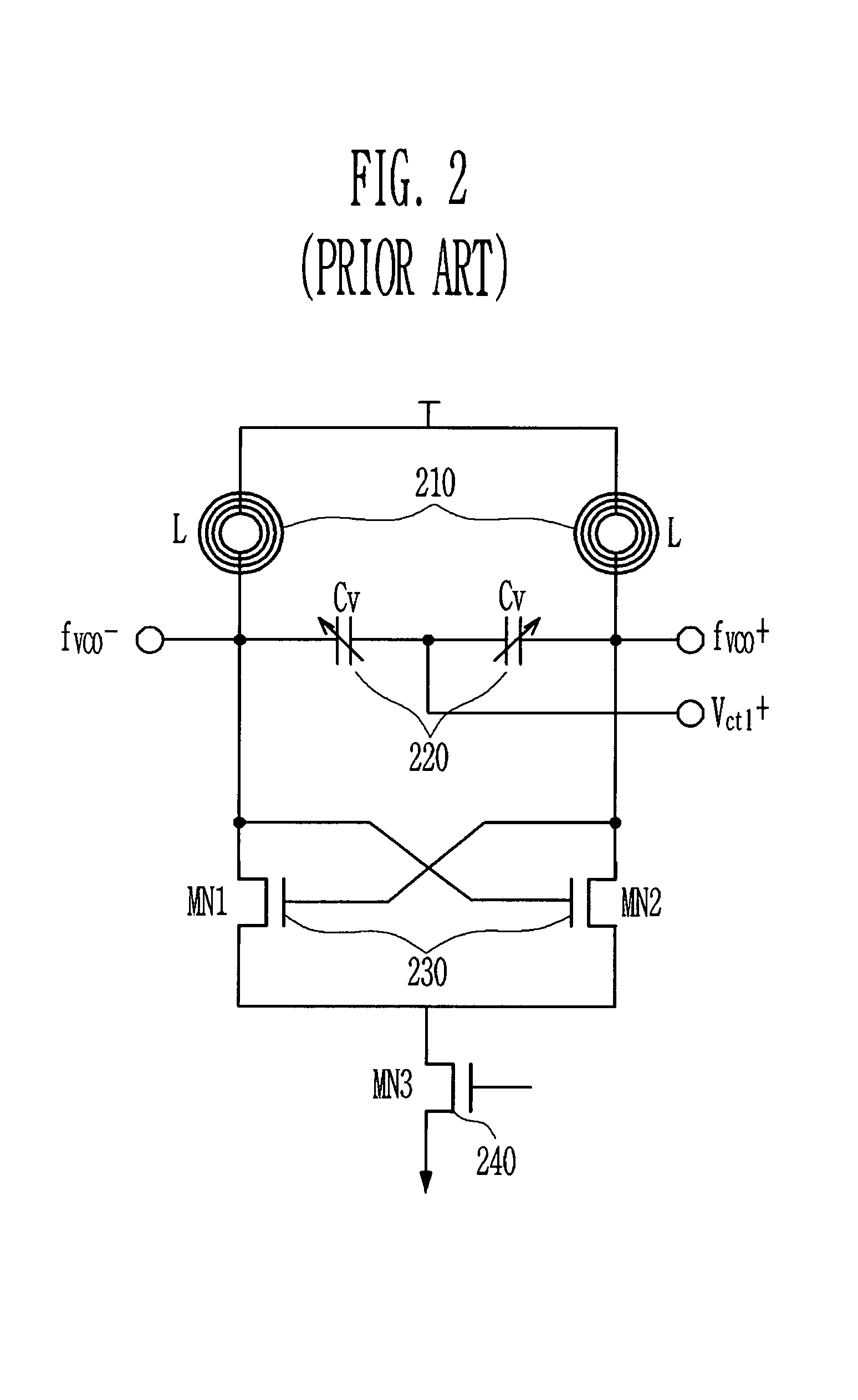

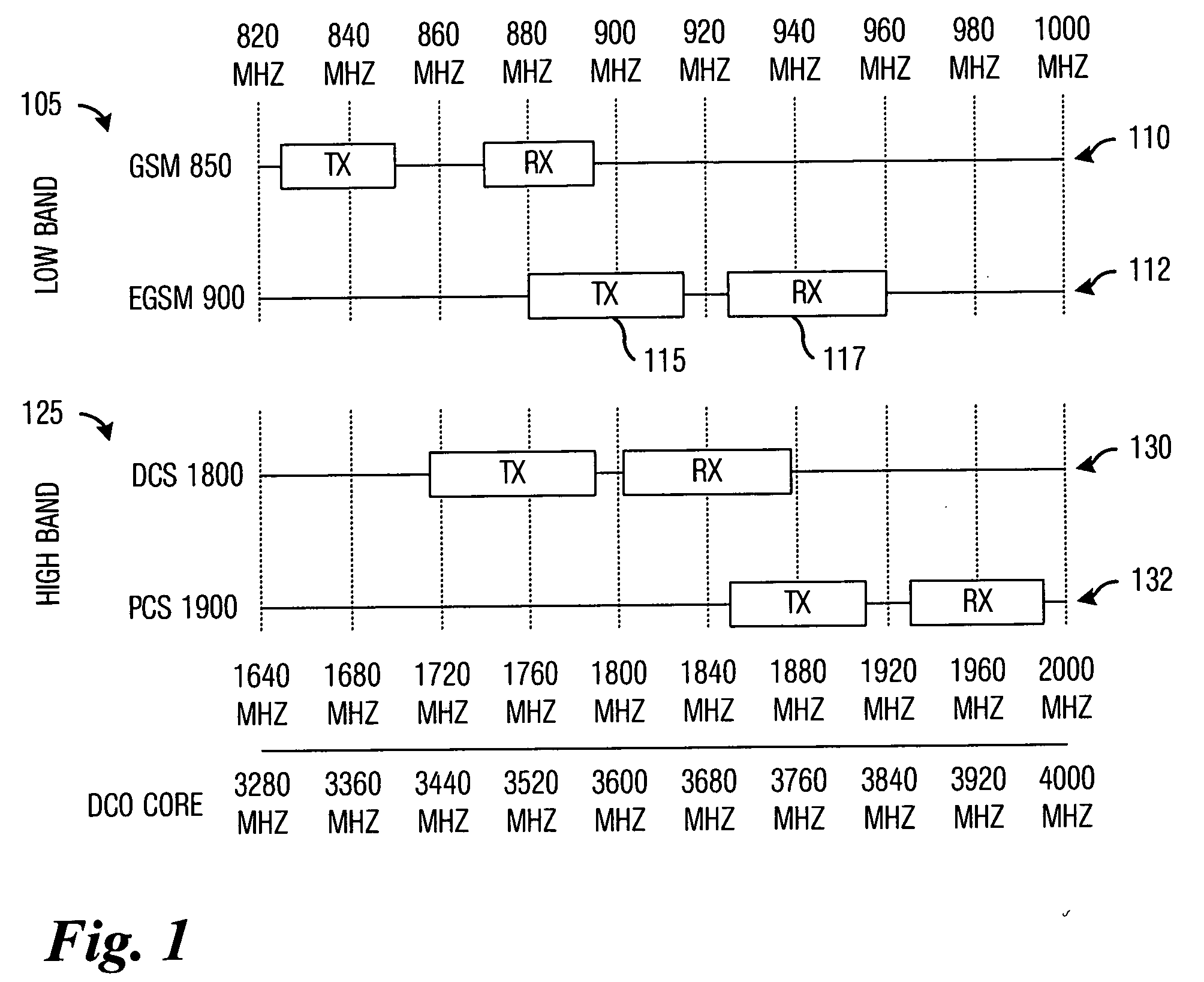

Voltage controlled digital analog oscillator and frequency synthesizer using the same

InactiveUS7432768B2Broad frequency variance rangeSmall VCO gainAngle modulation by variable impedencePulse automatic controlDigital tuningFrequency synthesizer

Provided are a voltage controlled digital analog oscillator and a frequency synthesizer using the same, the oscillator comprising an oscillator having a frequency of an output signal being determined by a voltage inputted to an analog input end and a digital value inputted to a digital input end; and a digital tuner for comparing the voltage inputted to the analog input end to first and second threshold voltages and changing the digital value inputted to the digital input end according to the result, whereby it is possible to obtain a broadband frequency output with less noise.

Owner:ELECTRONICS & TELECOMM RES INST

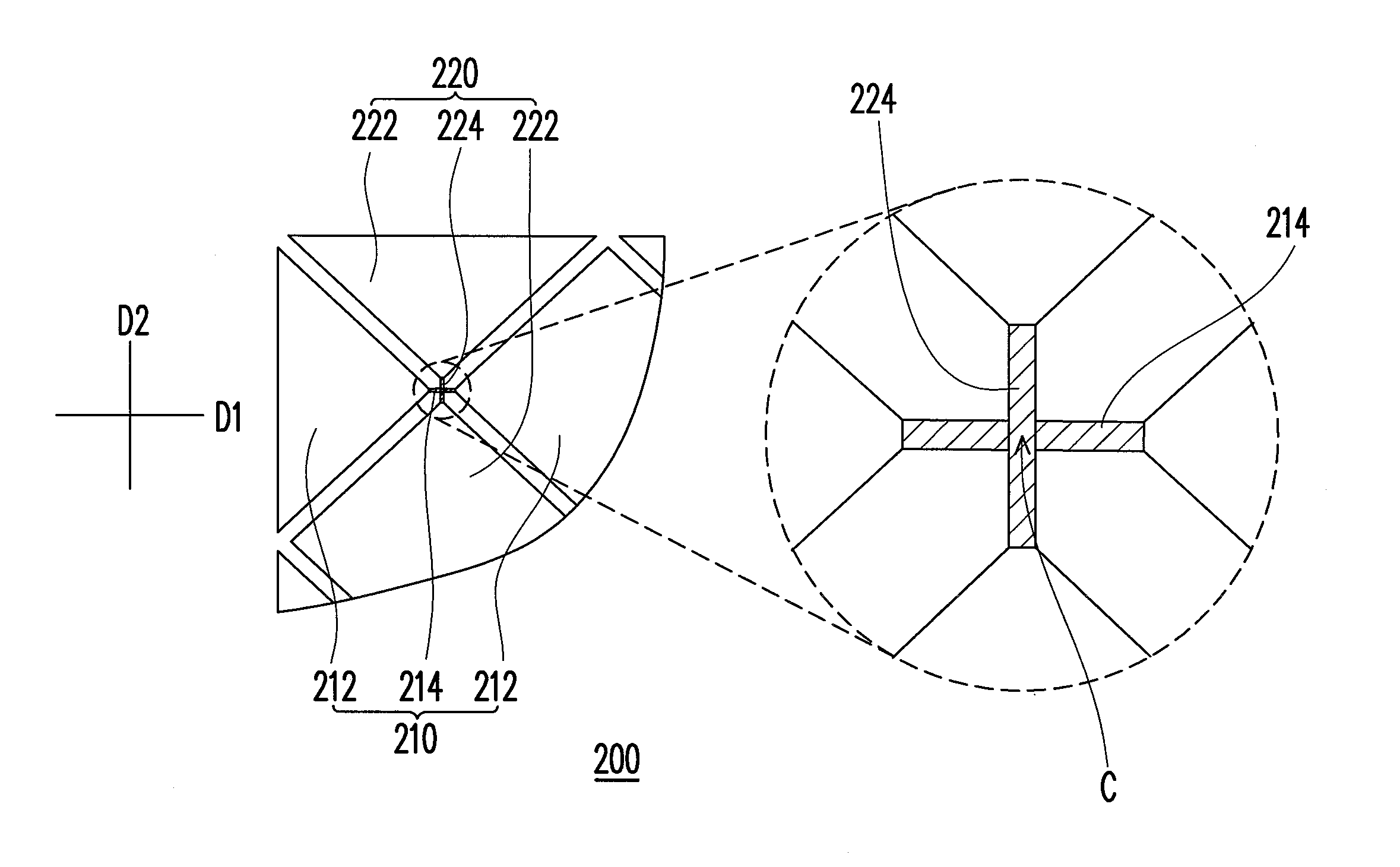

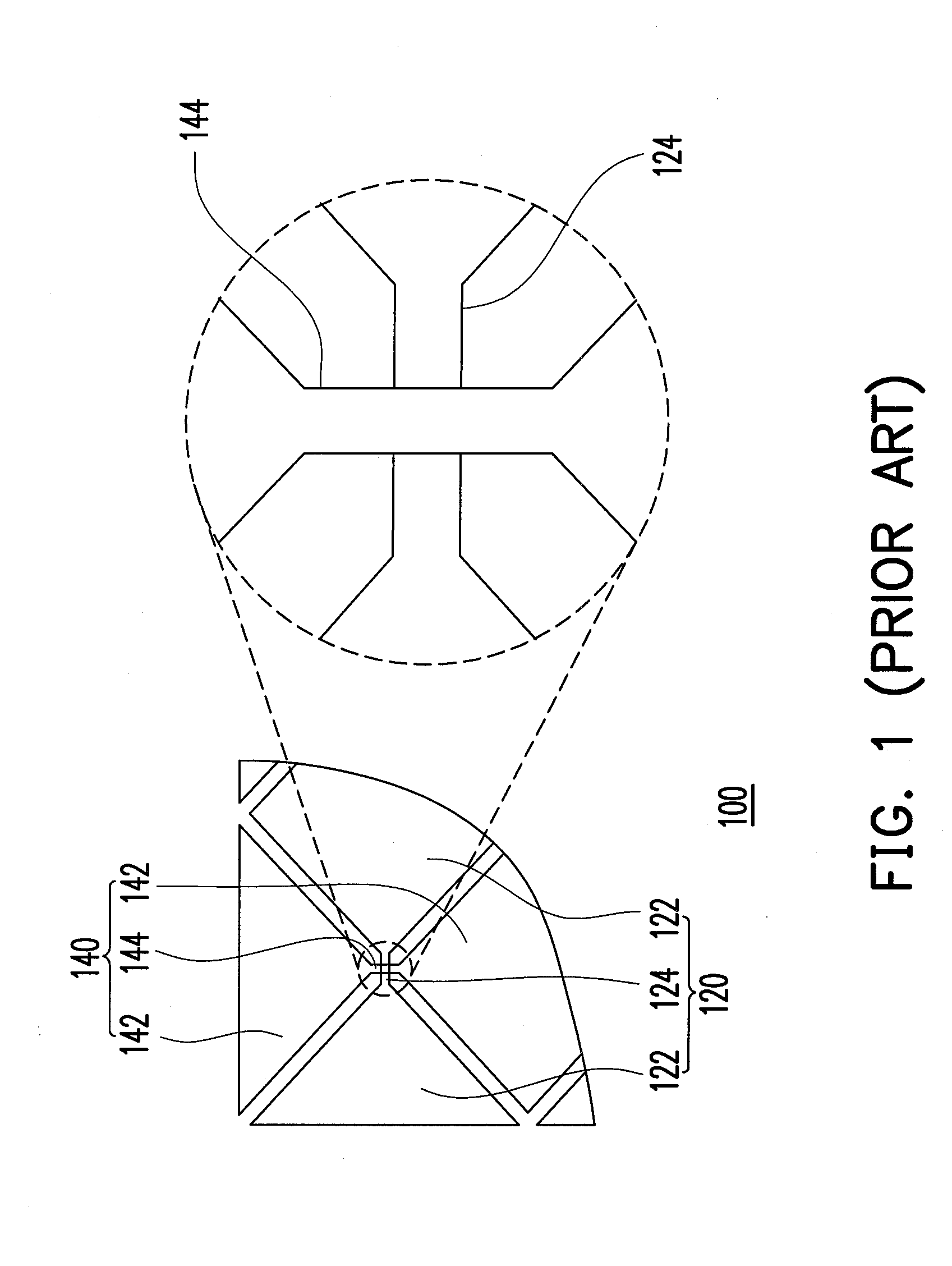

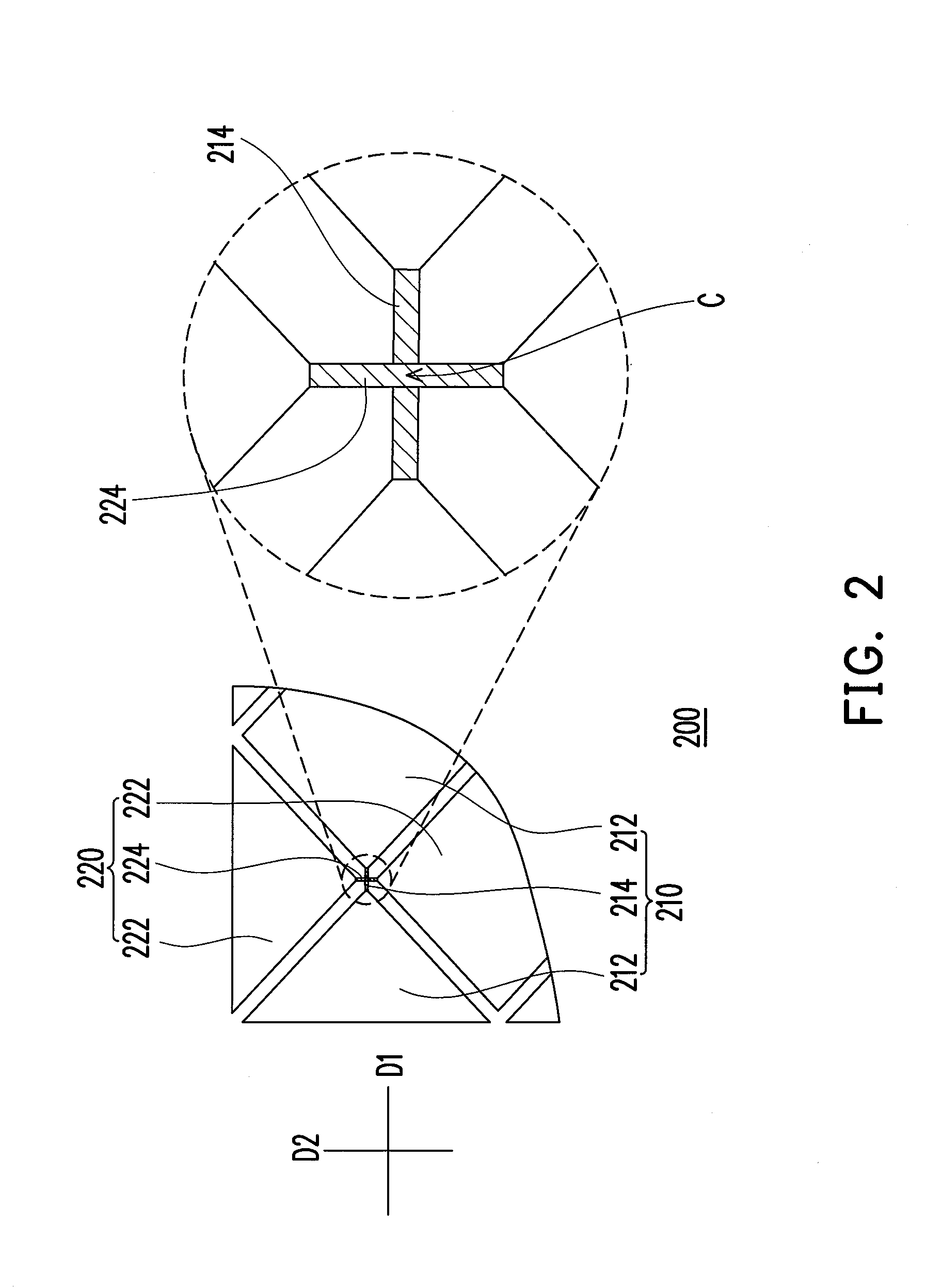

Touch panel

InactiveUS20100123674A1Satisfactory touch sensitivityLow resistivityInput/output processes for data processingTouch panelElectrical and Electronics engineering

A touch panel including at least a first sensing string and at least a second sensing string is provided. The first sensing string arranged in a first direction includes first sensing pads electrically connecting with each other and at least a first connecting pattern. The first connecting patterns are located between two adjacent first sensing pads. The second sensing string does not contact the first sensing string and is arranged in a second direction which crosses with the first direction. The second sensing string includes second sensing pads and at least a second connecting pattern. The second sensing pads electrically connected with one another are located among the first sensing pads. The second connecting pattern is located between two adjacent second sensing pads. Resistivities of the first connecting pattern and the second connecting pattern are lower than those of the first sensing pad and the second sensing pad respectively.

Owner:WINTEK CORP

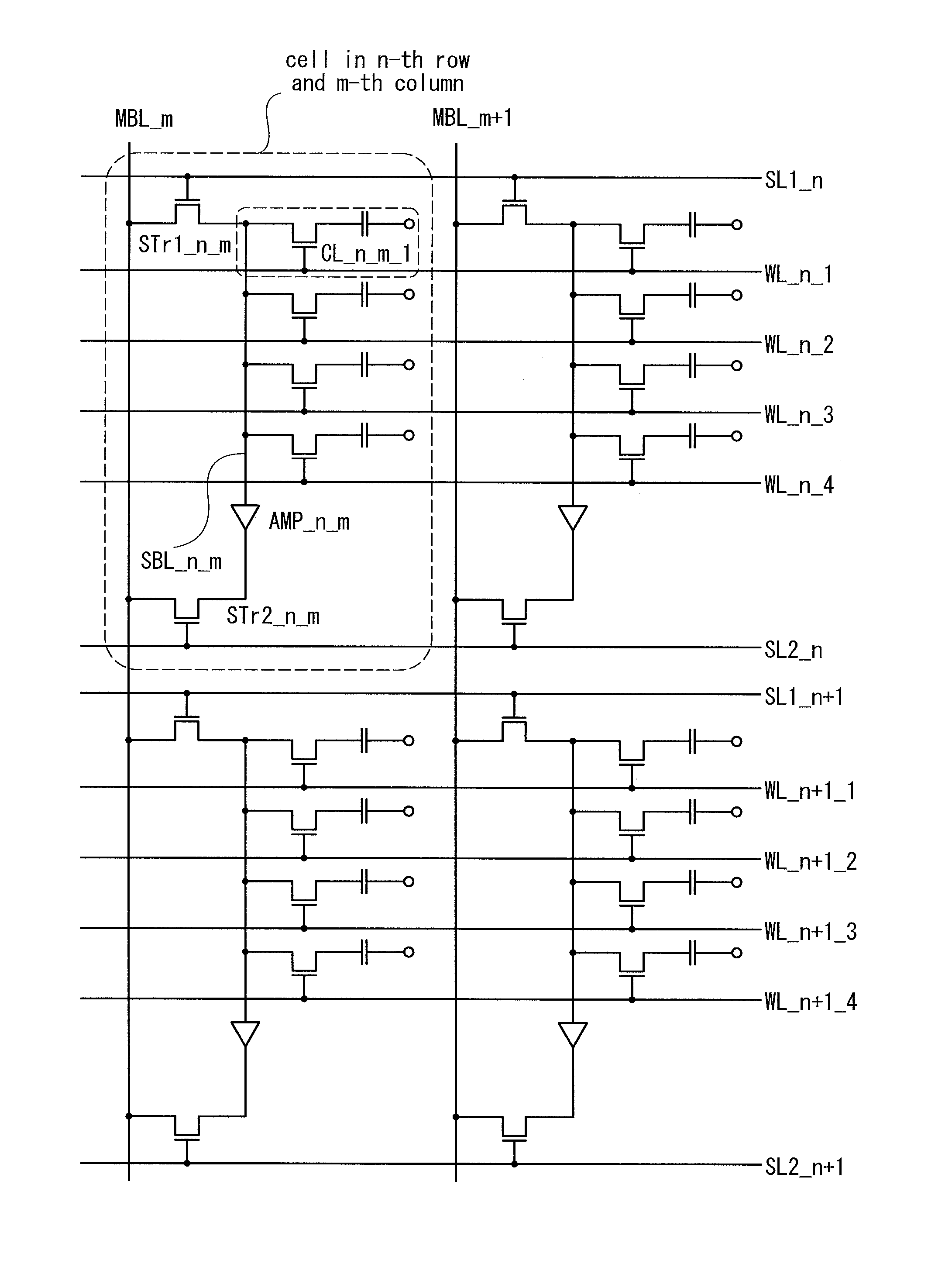

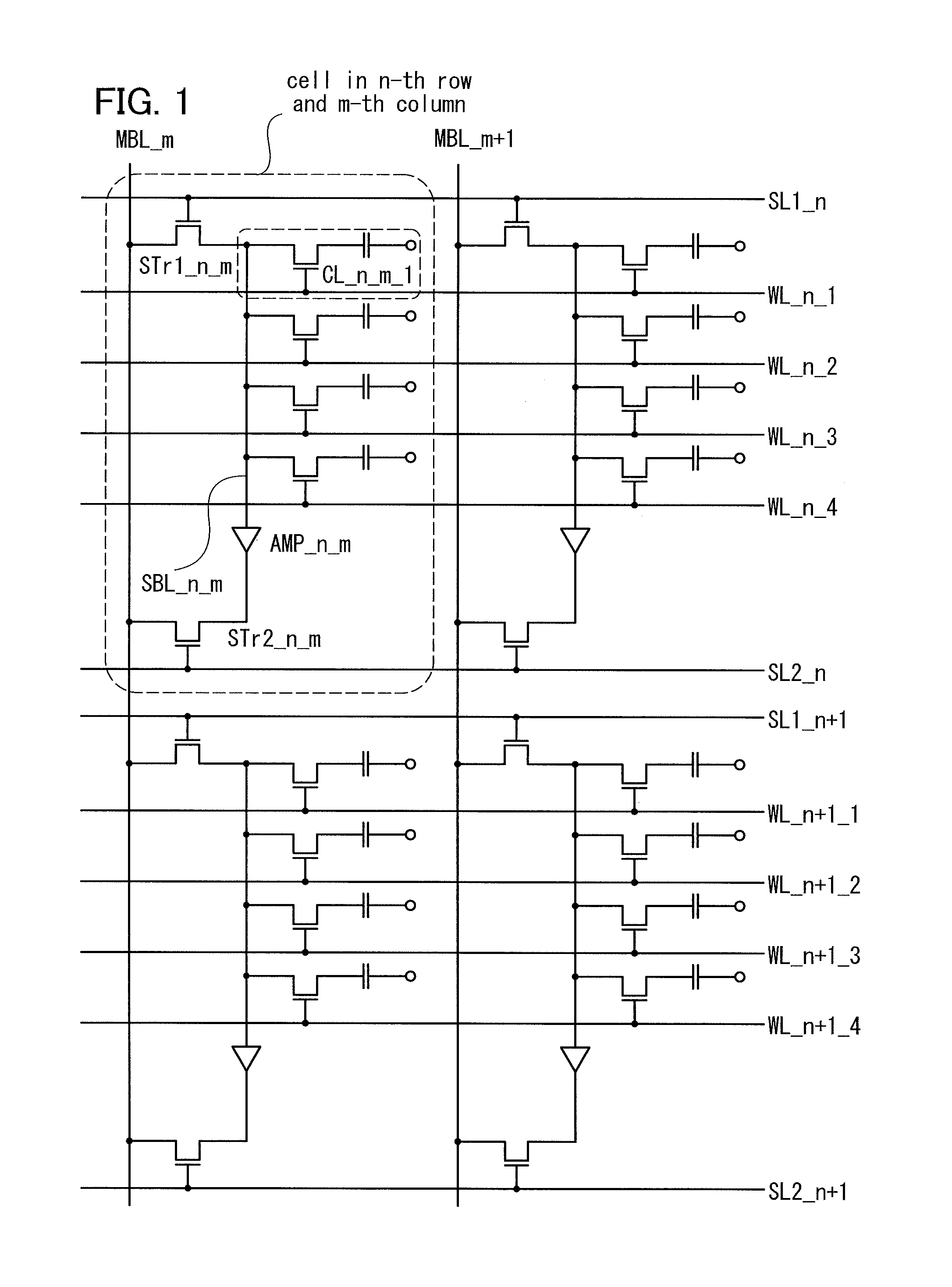

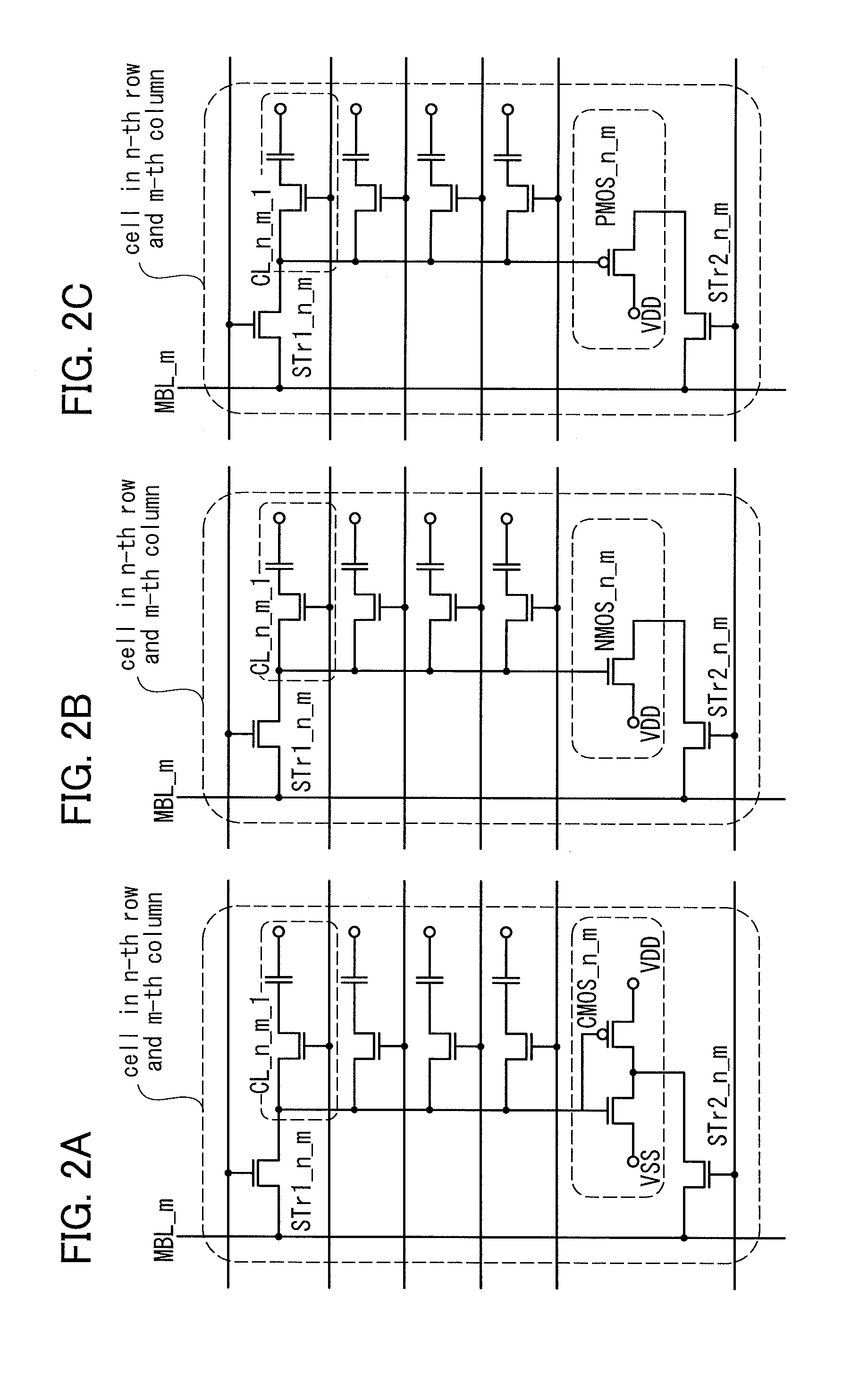

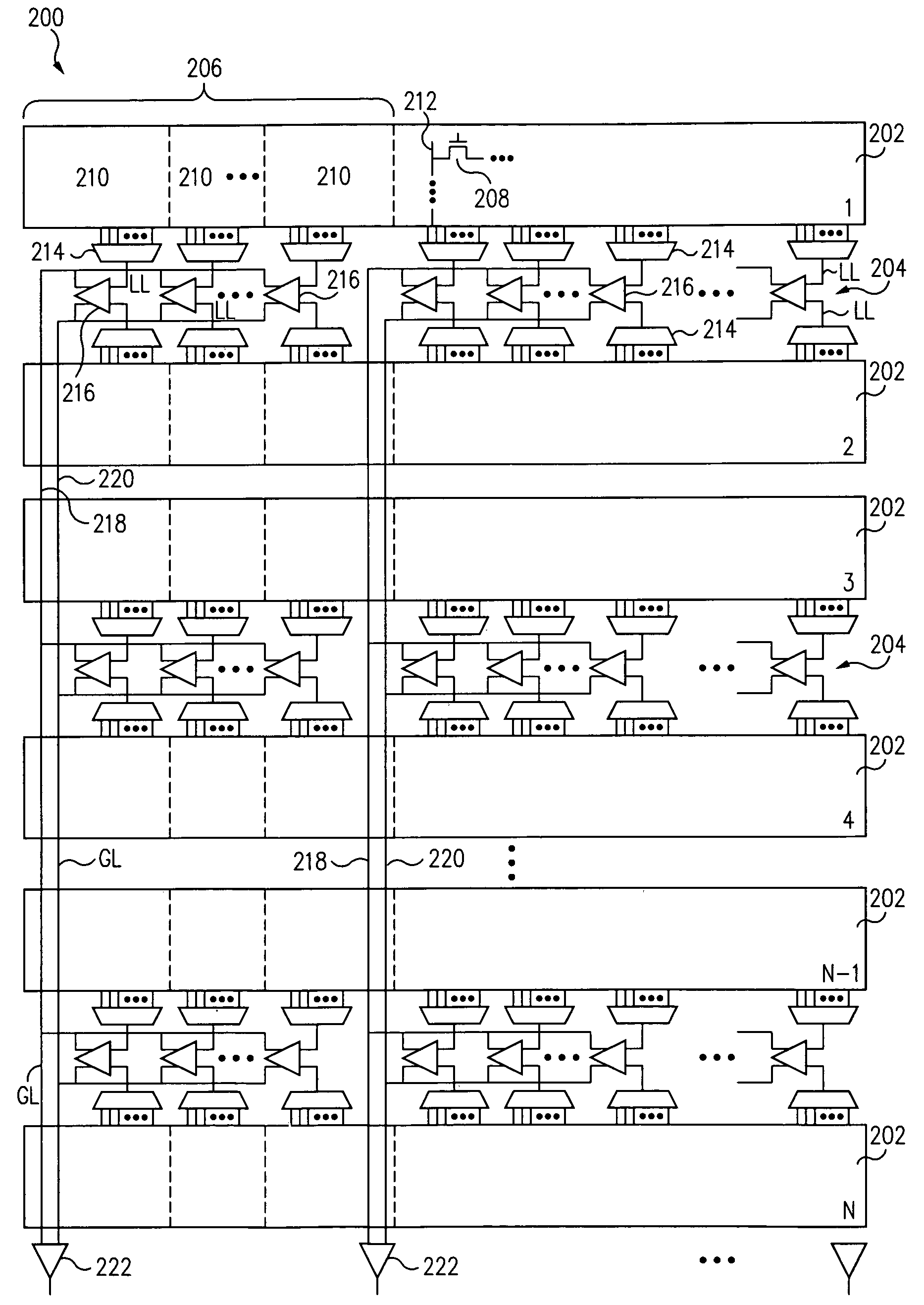

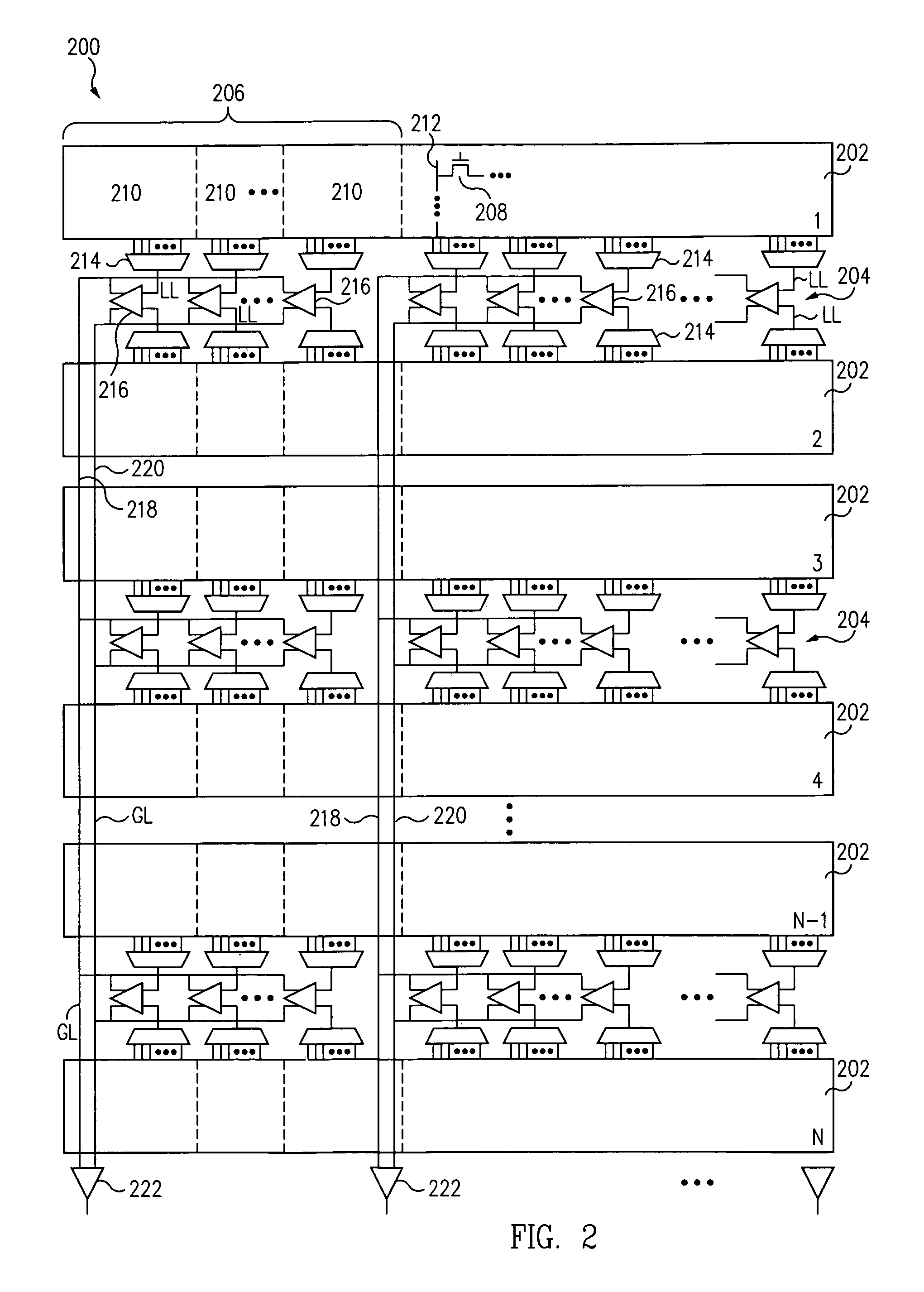

Semiconductor memory device and method for driving the same

InactiveUS20120075917A1Small parasitic capacitanceLarge capacitanceTransistorSolid-state devicesBit linePotential change

In a conventional DRAM, when the capacitance of a capacitor is reduced, an error of reading data easily occurs. A plurality of cells are connected to one bit line MBL_m. Each cell includes a sub bit line SBL_n_m and 4 to 64 memory cells (a memory cell CL_n_m—1 or the like). Further, each cell includes selection transistors STr1_n_m and STr2_n_m and an amplifier circuit AMP_n_m that is a complementary inverter or the like is connected to the selection transistor STr2_n_m. Since parasitic capacitance of the sub bit line SBL_n_m is sufficiently small, potential change due to electric charge in a capacitor of each memory cell can be amplified by the amplifier circuit AMP_n_m without an error, and can be output to the bit line.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and method for manufacturing the same

ActiveUS8338827B2Guaranteed high speed operationEasy to makeElectroluminescent light sourcesSolid-state devicesIndiumNitrogen

In a thin film transistor which uses an oxide semiconductor, buffer layers containing indium, gallium, zinc, oxygen, and nitrogen are provided between the oxide semiconductor layer and the source and drain electrode layers.

Owner:SEMICON ENERGY LAB CO LTD

Asymmetric bidirectional silicon-controlled rectifier

The present invention discloses an asymmetric bidirectional silicon-controlled rectifier, which comprises: a second conduction type substrate; a first conduction type undoped epitaxial layer formed on the substrate; a first well and a second well both formed inside the undoped epitaxial layer and separated by a portion of the undoped epitaxial layer; a first buried layer formed in a junction between the first well and the substrate; a second buried layer formed in a junction between the second well and the substrate; a first and a second semiconductor area with opposite conduction type both formed inside the first well; a third and a fourth semiconductor area with opposite conduction type both formed inside the second well, wherein the first and second semiconductor areas are connected to the anode of the silicon-controlled rectifier, and the third and fourth semiconductor areas are connected to the cathode of the silicon-controlled rectifier.

Owner:AMAZING MICROELECTRONICS

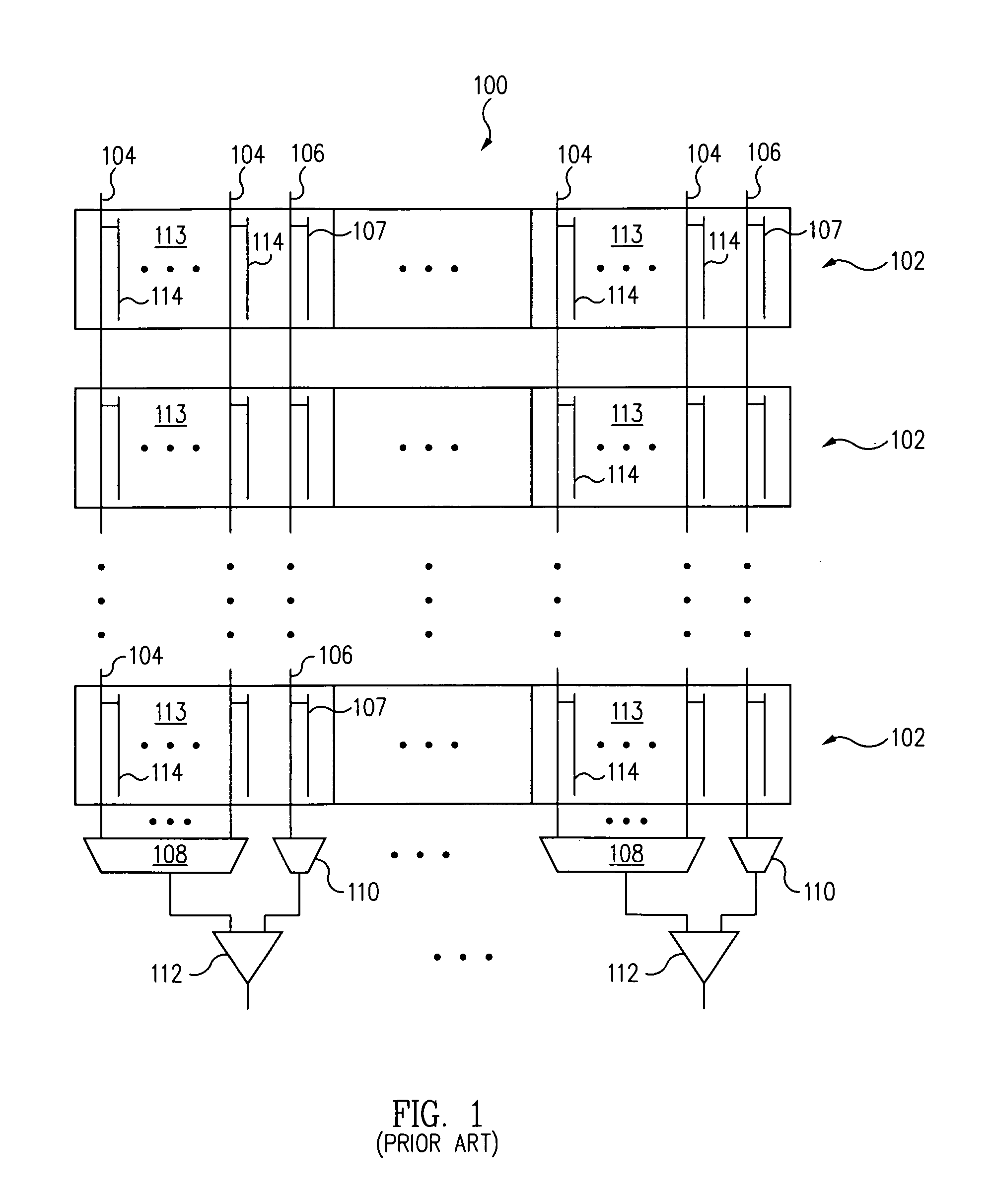

Non-volatile memory architecture to improve read performance

ActiveUS7009880B1Improve read performanceIncrease in sizeRead-only memoriesDigital storageBit lineAudio power amplifier

A memory cell array is physically divided into an even number of sectors, with each pair of sectors sharing read circuitry. The outputs of the shared read circuitry are commonly connected to form data lines spanning the height of the array, which are input to global sense amplifiers. A two-stage sensing scheme is employed, with first stage and global sense amplifiers. The driving capability of the first stage sense amplifier can be used to decrease the time to charge or discharge the data lines, which reduces the total signal development time and consequently improves read performance. Granularity of the array can be adjusted by dividing groups and sub-groups of memory cells within a sector accordingly. In a read operation, the bit line in the opposite sector at the same column location is used as reference bit line, which greatly improves matching of bit line loading for the sensing.

Owner:INTEGRATED SILICON SOLUTION

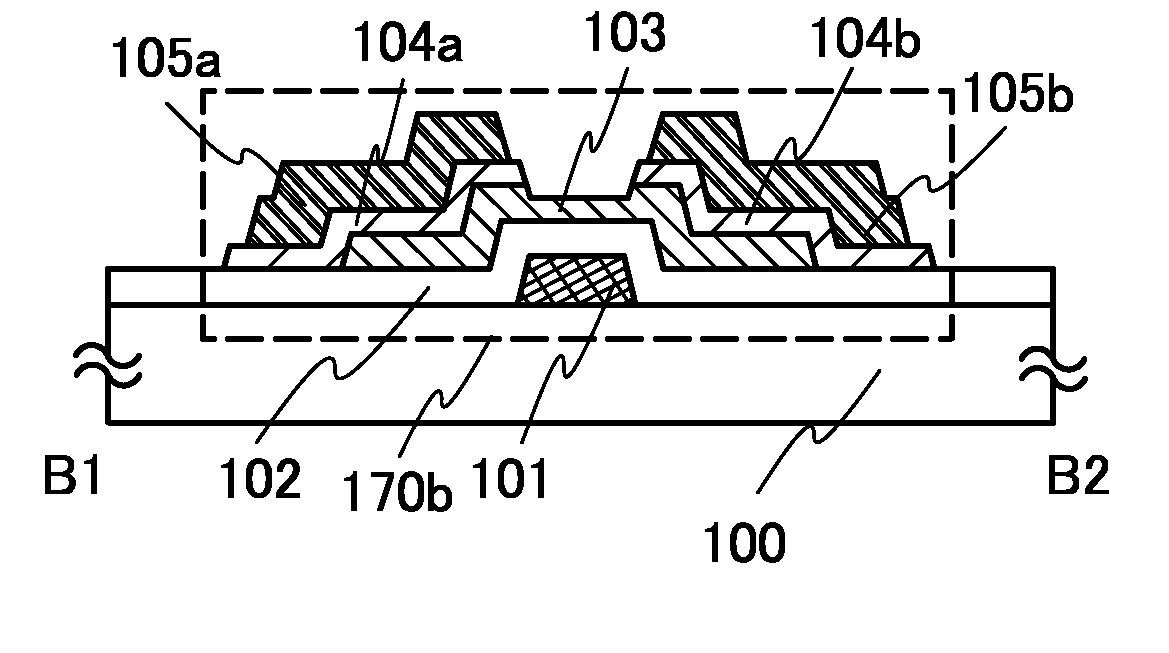

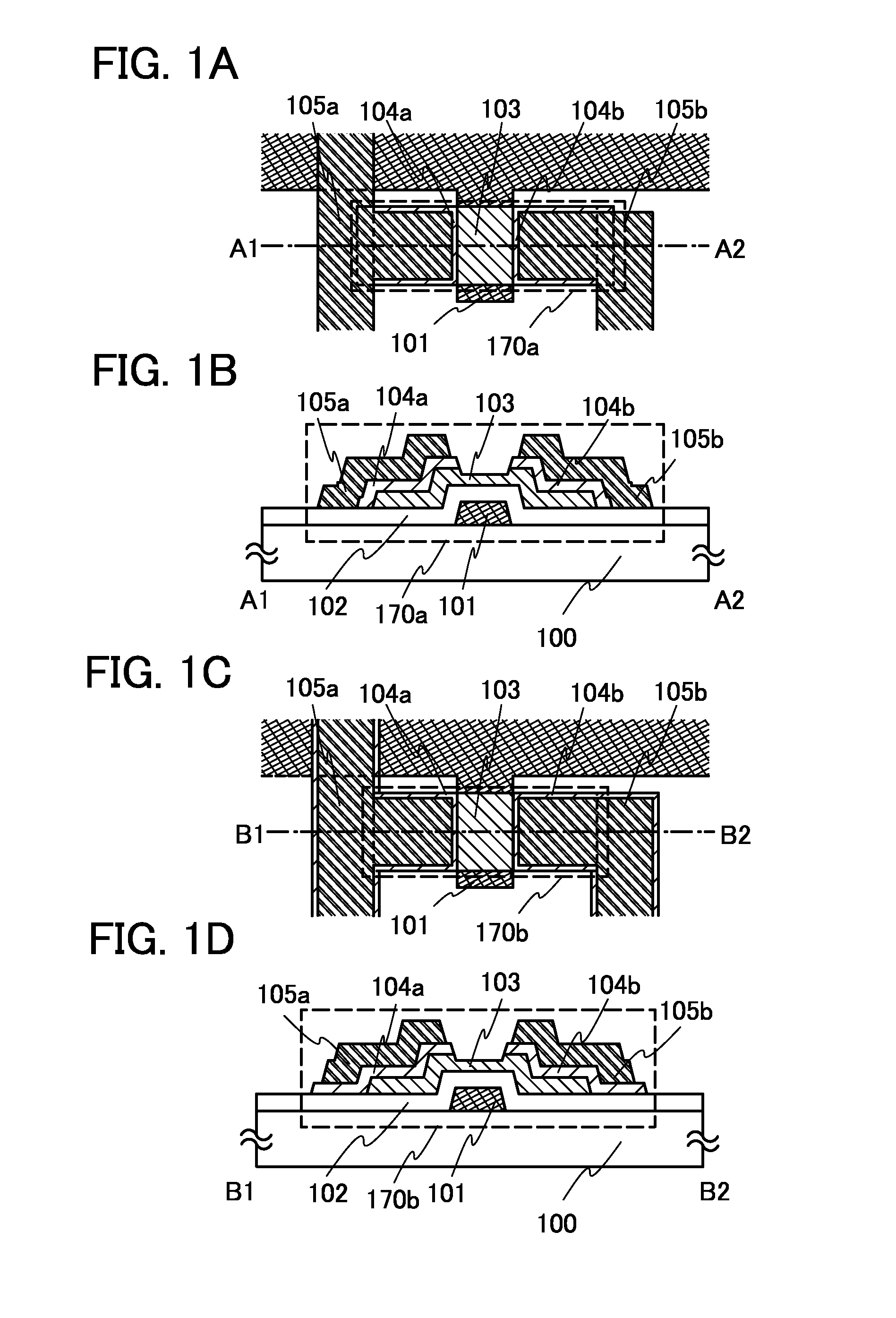

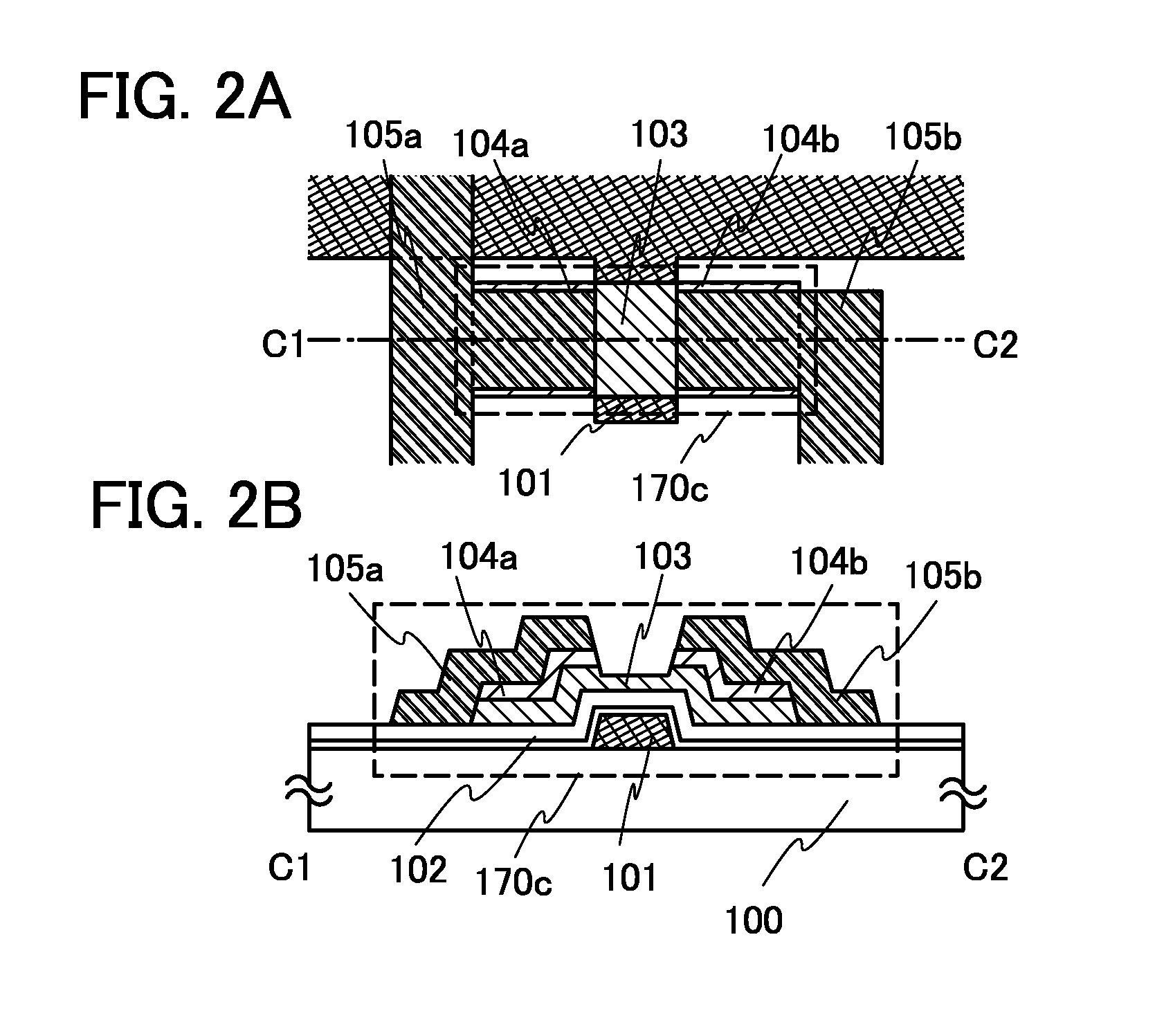

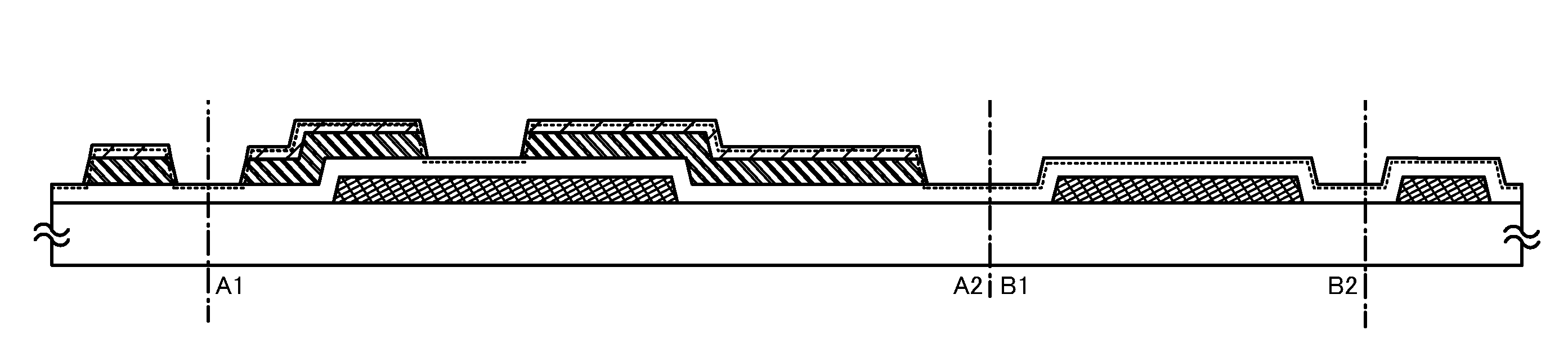

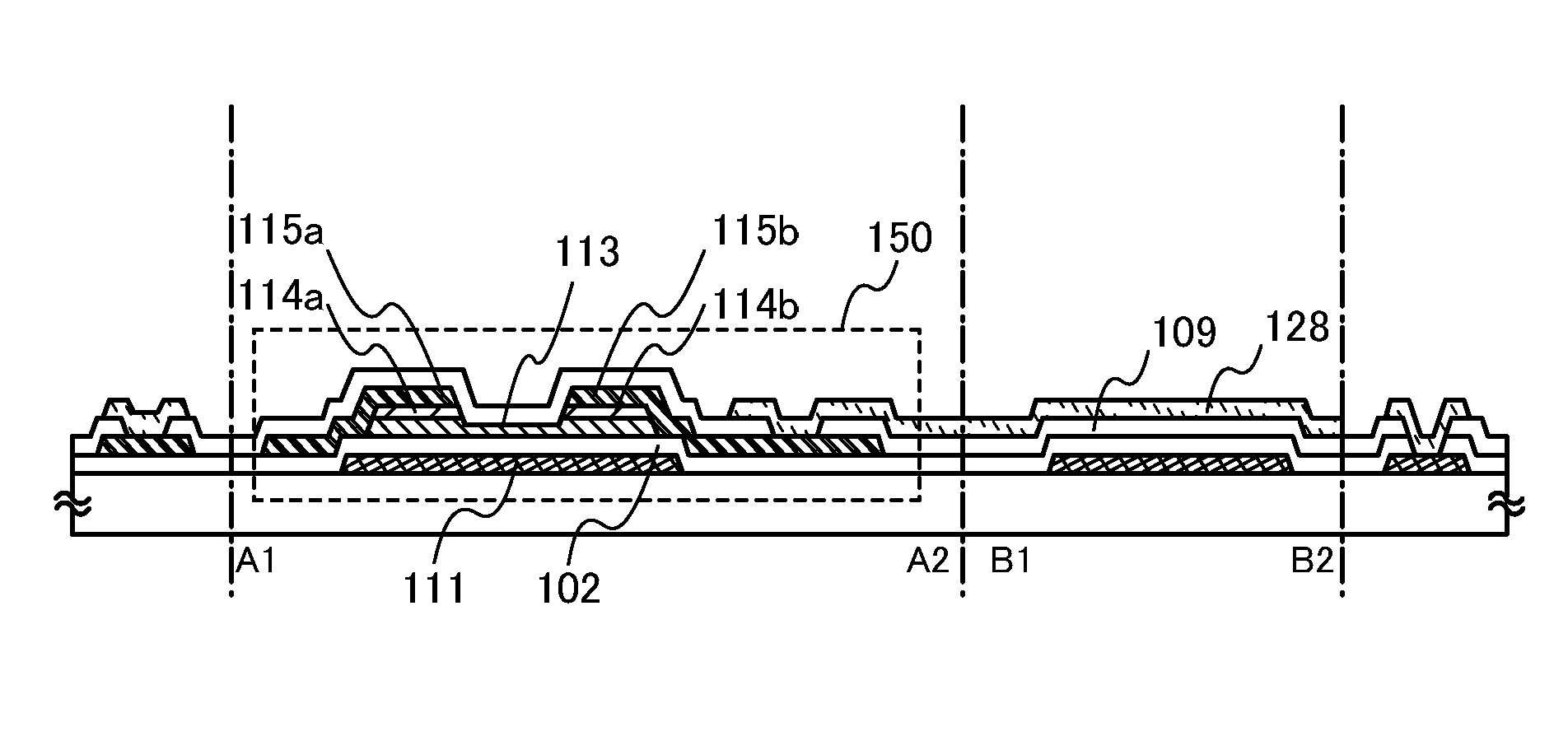

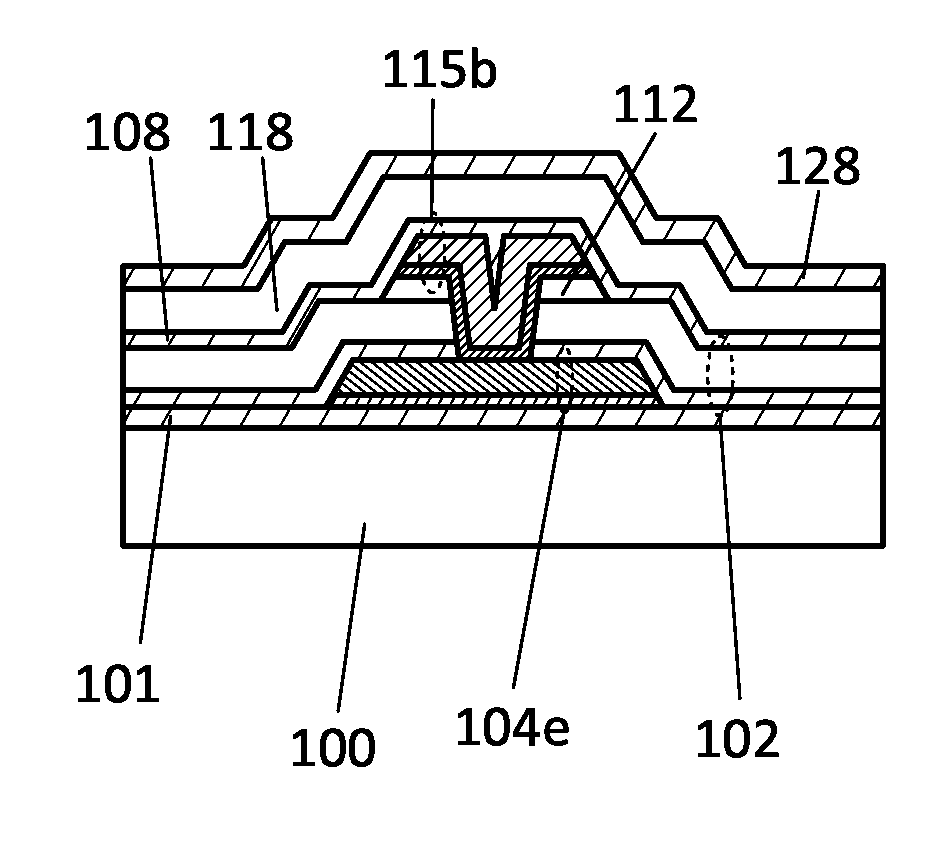

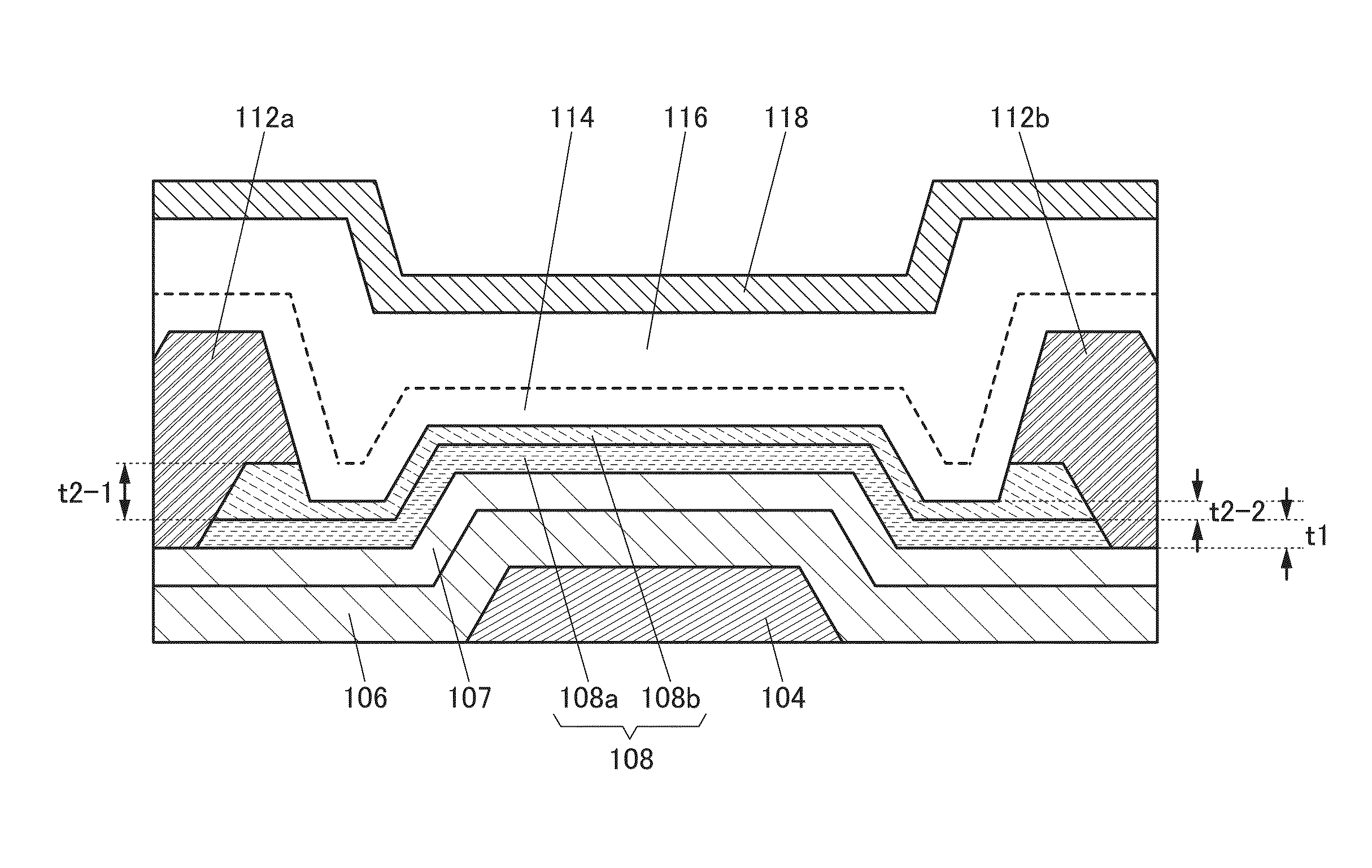

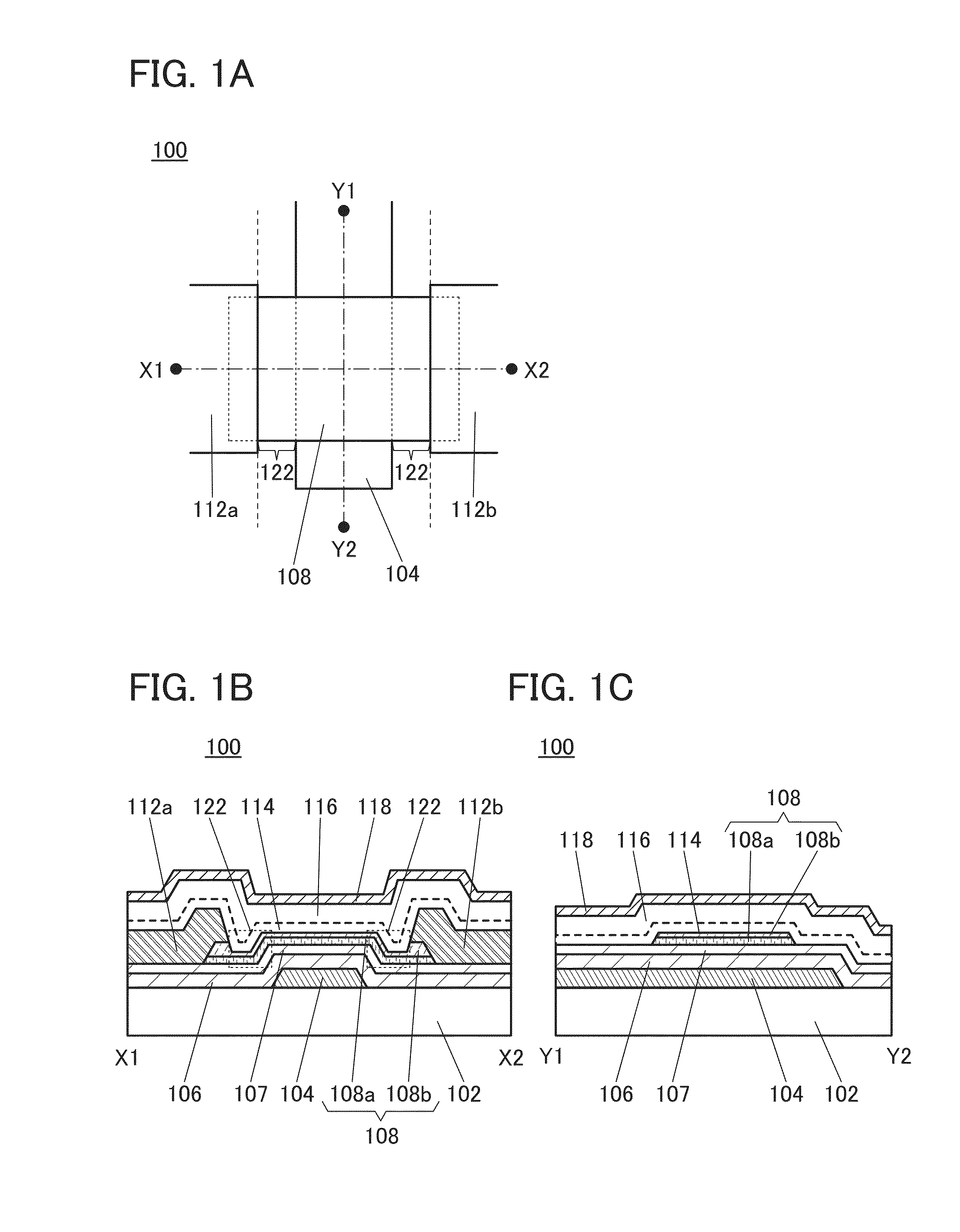

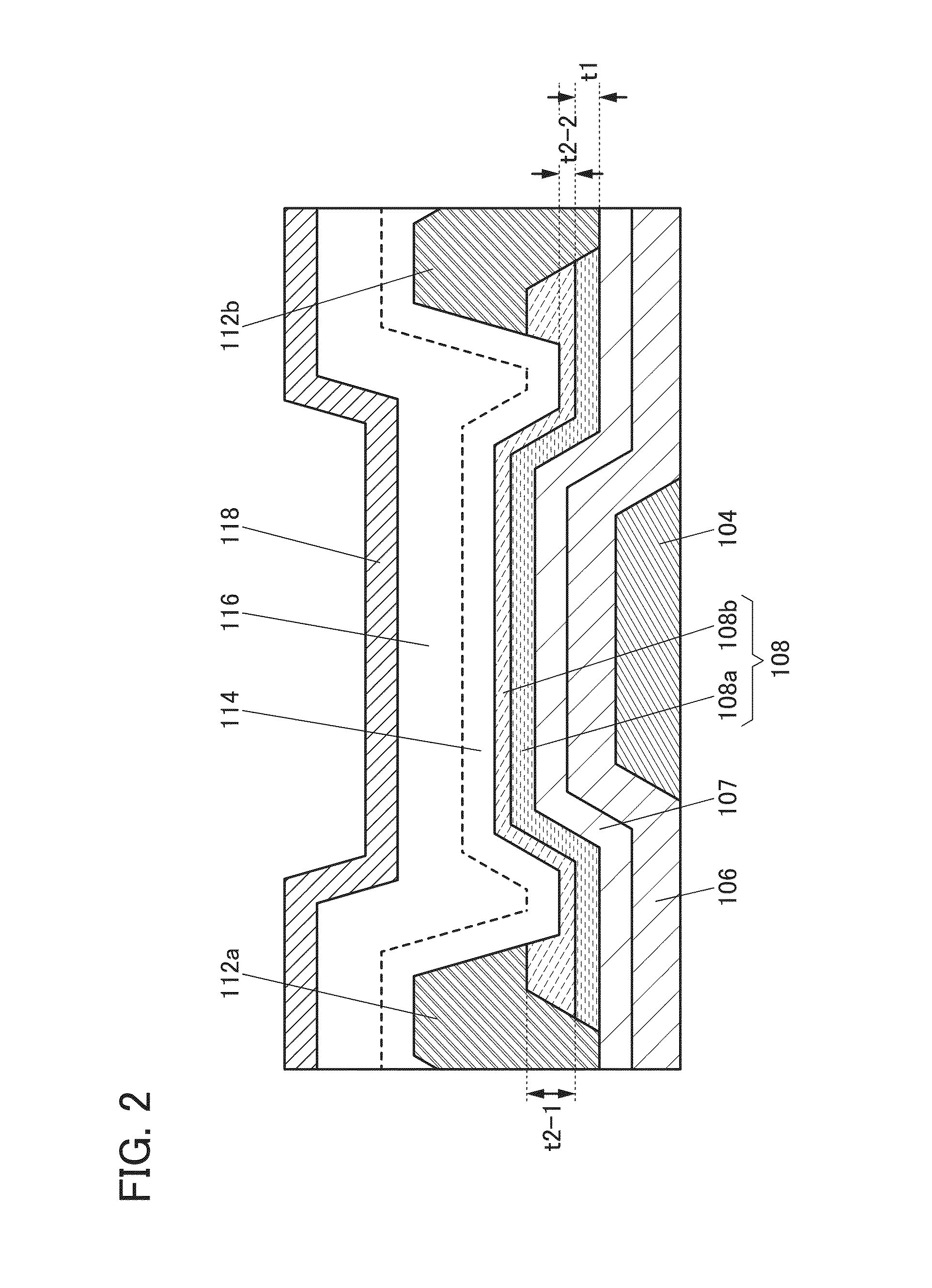

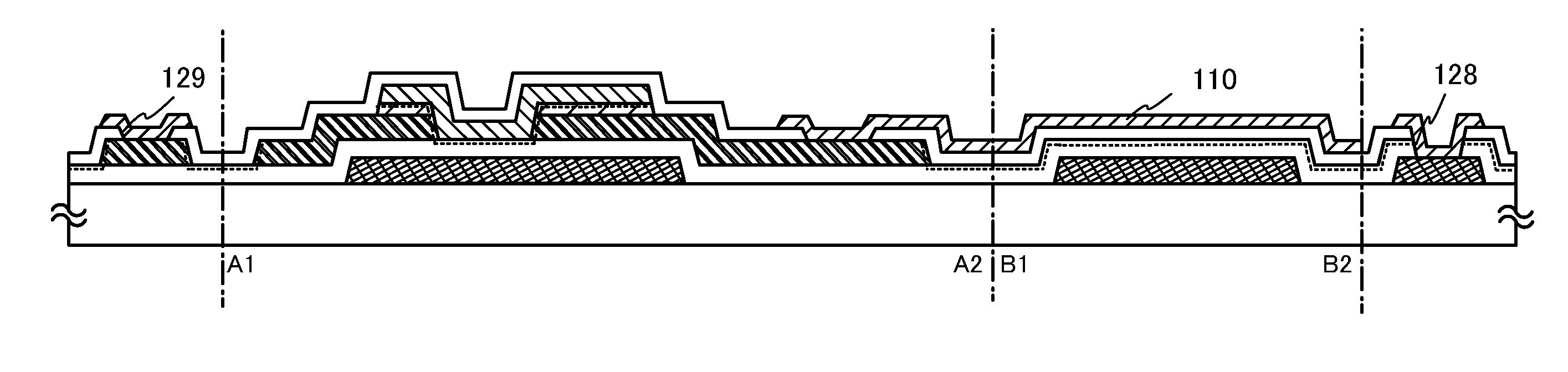

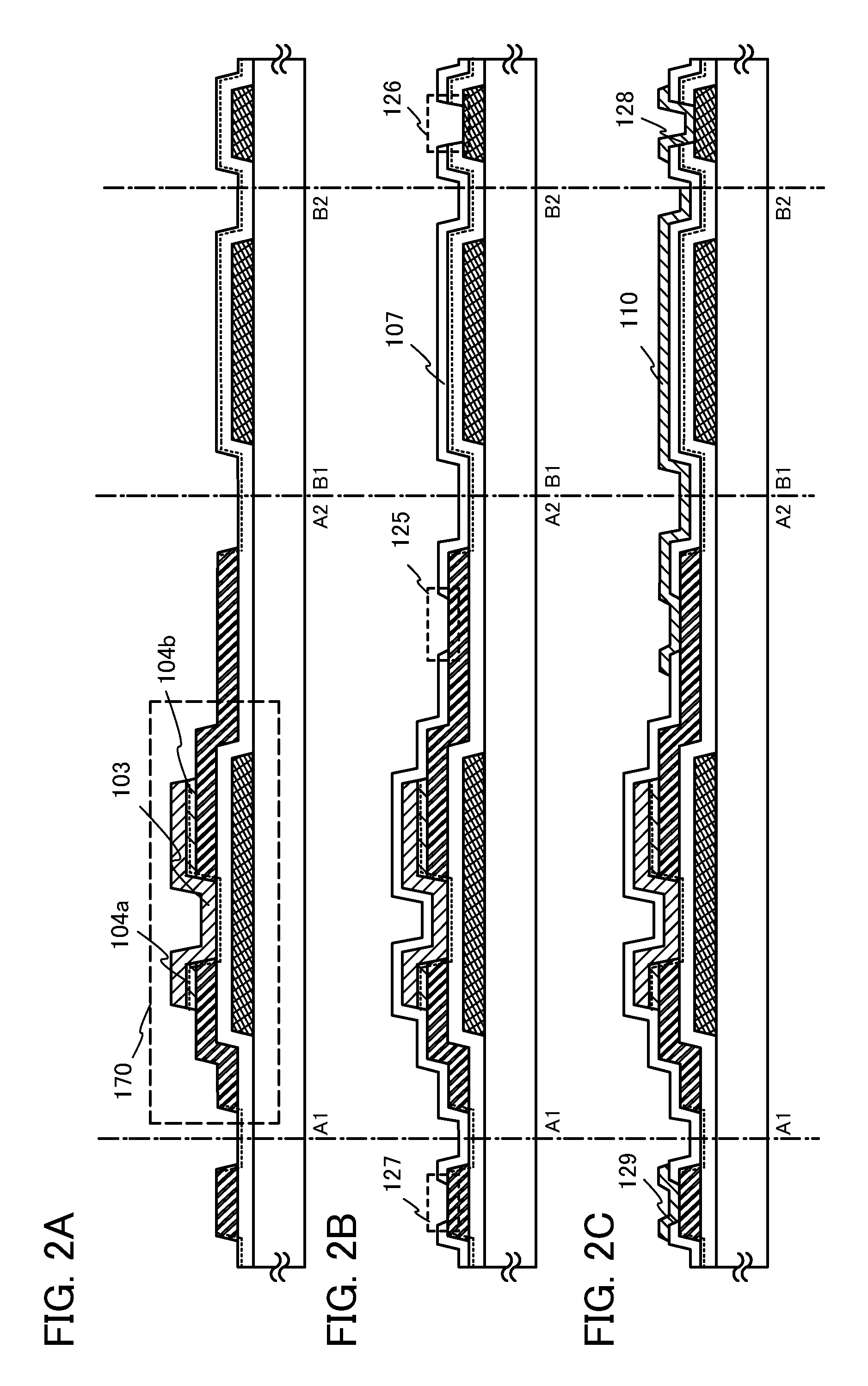

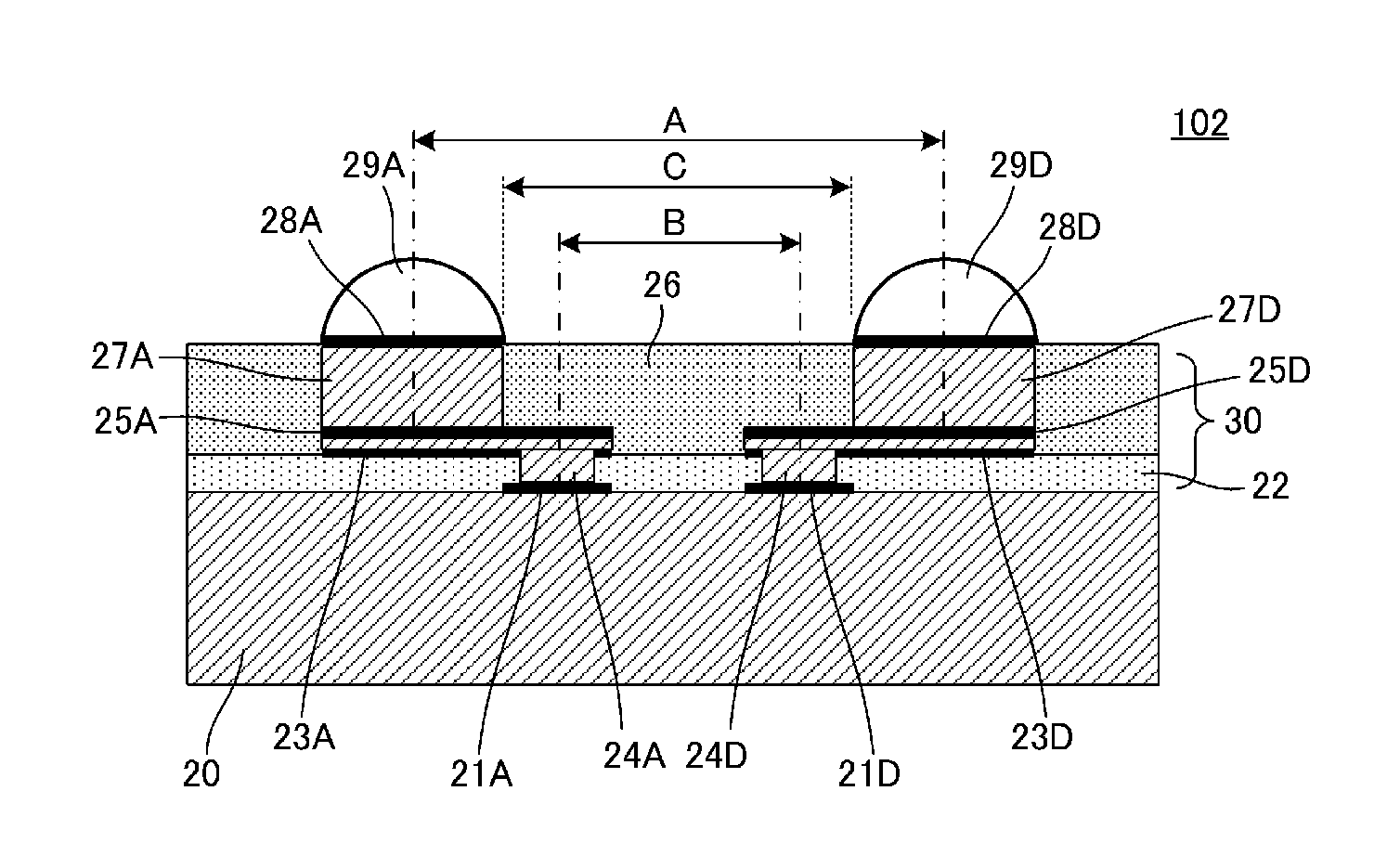

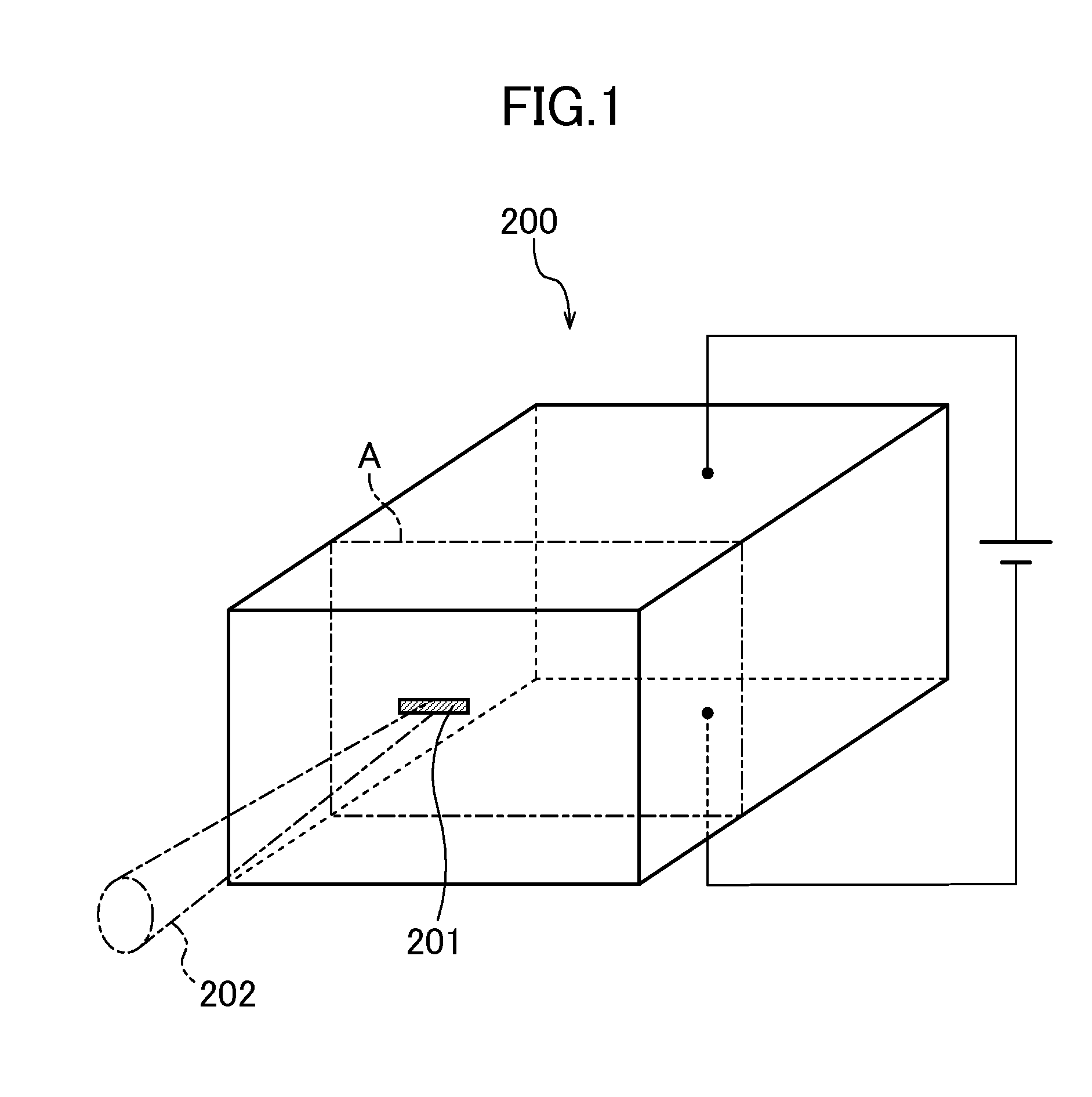

Semiconductor device, module, and electronic device

ActiveUS20150221775A1Small parasitic capacitanceReduce power consumptionTransistorSolid-state devicesElectrical conductorParasitic capacitance

To provide a semiconductor device with small parasitic capacitance. Alternatively, to provide a semiconductor device with low power consumption. The semiconductor device includes a transistor and a capacitor. The transistor includes a first conductor, a first insulator over the first conductor, a semiconductor including a region overlapping with the first conductor with the first insulator interposed therebetween, a second insulator over the semiconductor, a second conductor including a region overlapping with the semiconductor with the second insulator interposed therebetween, and a third conductor and a fourth conductor including a region in contact with a top surface of the semiconductor. The capacitor includes a layer formed from the same layer as the first conductor and a layer formed from the same layer as the third conductor and the fourth conductor.

Owner:SEMICON ENERGY LAB CO LTD

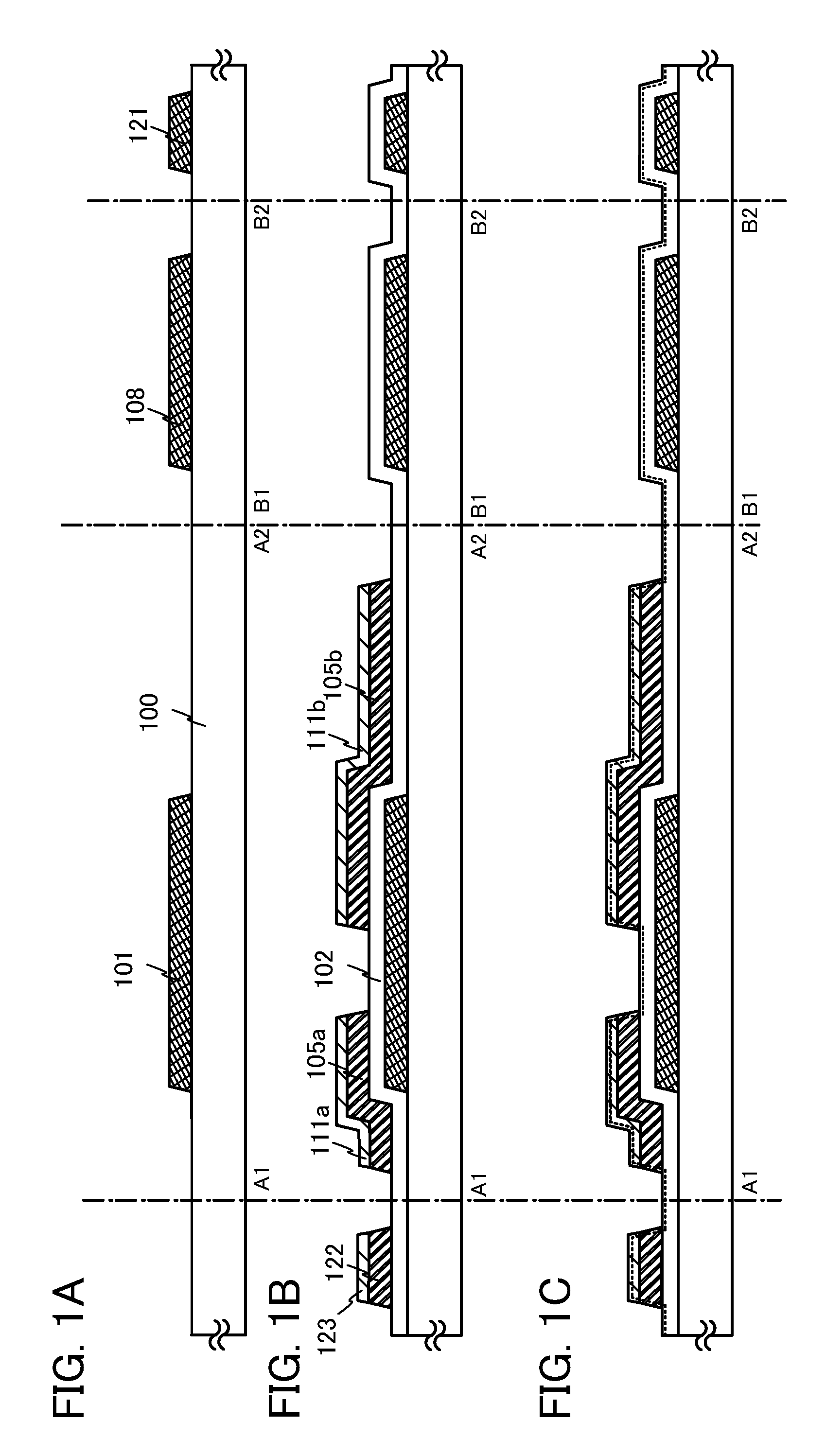

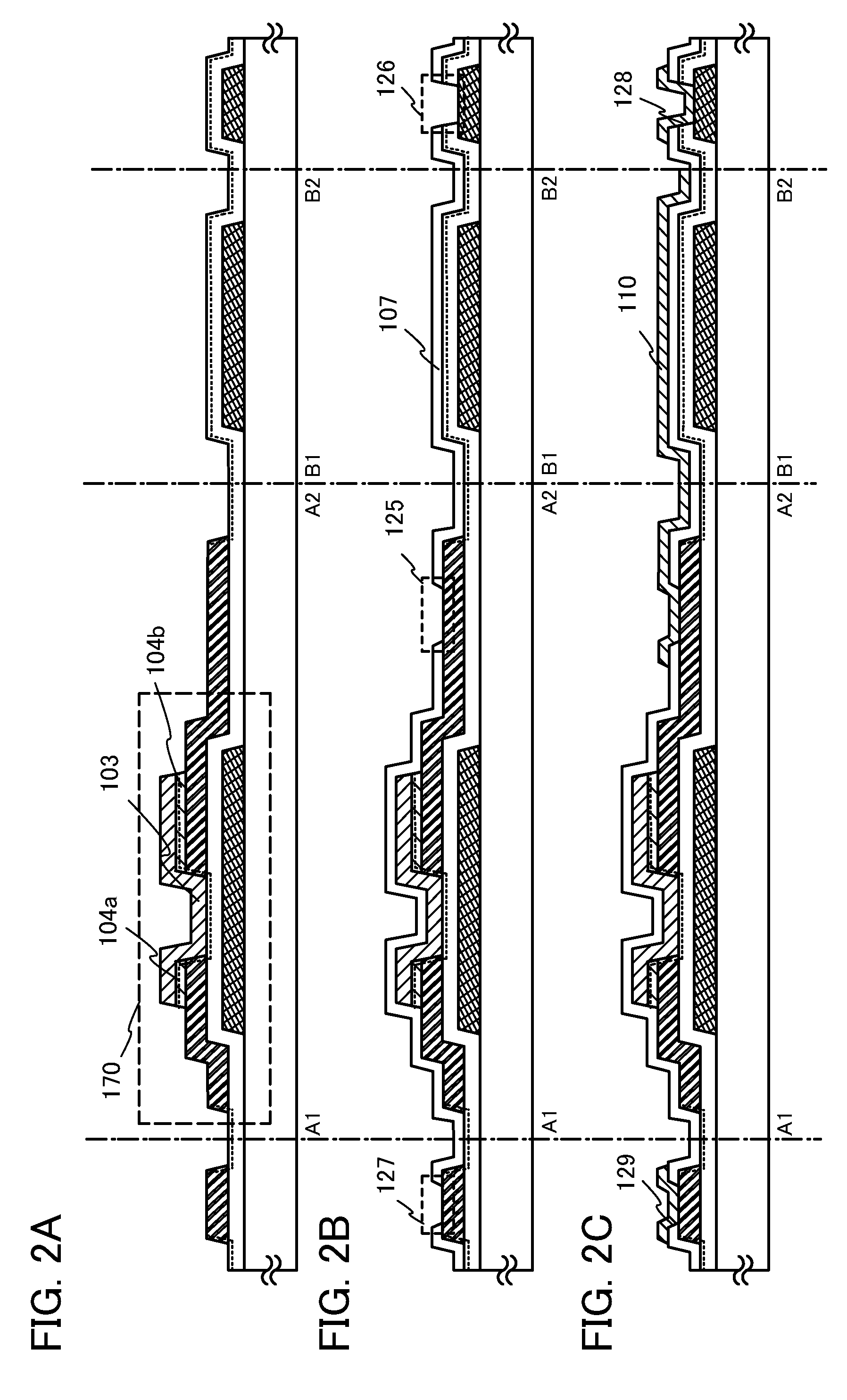

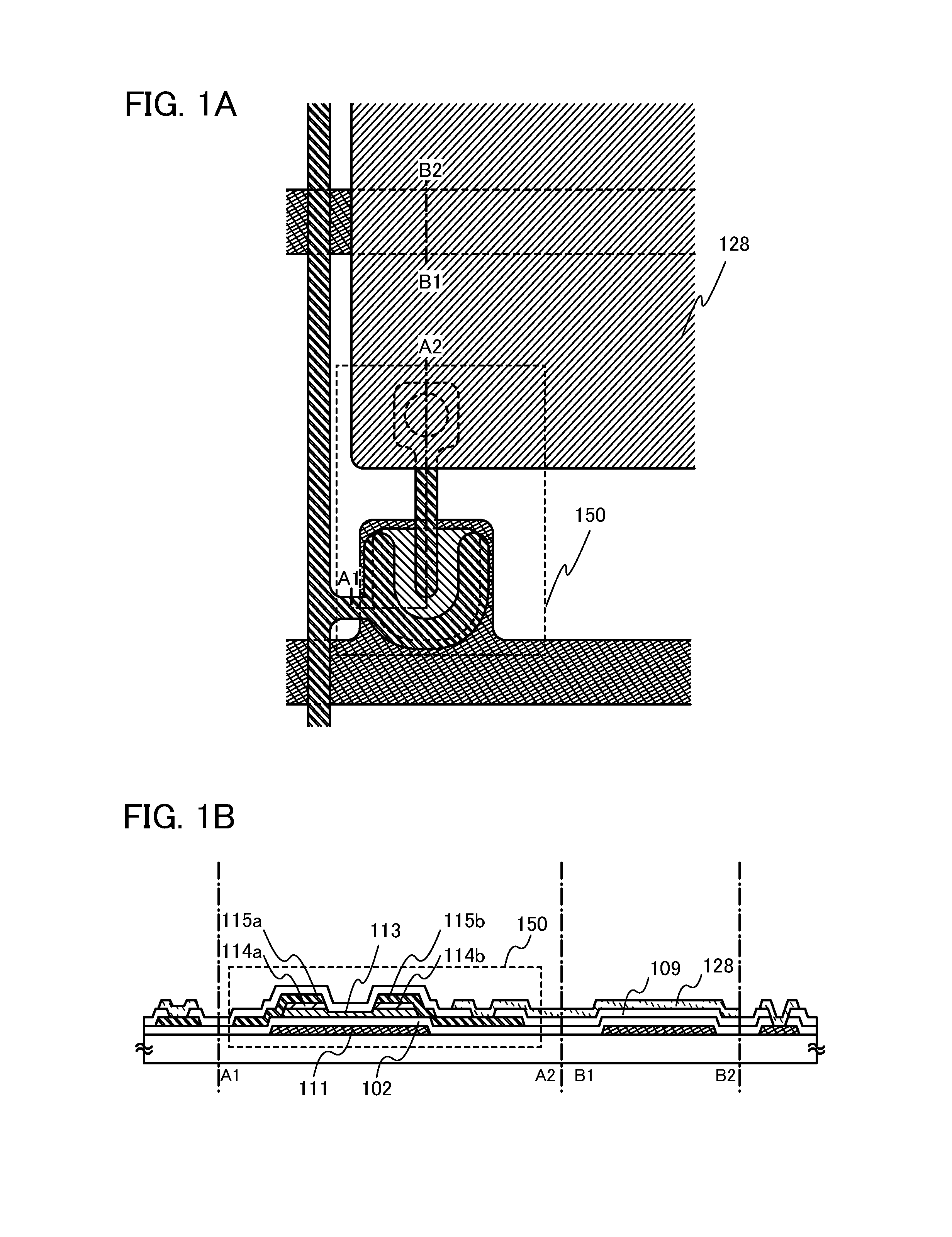

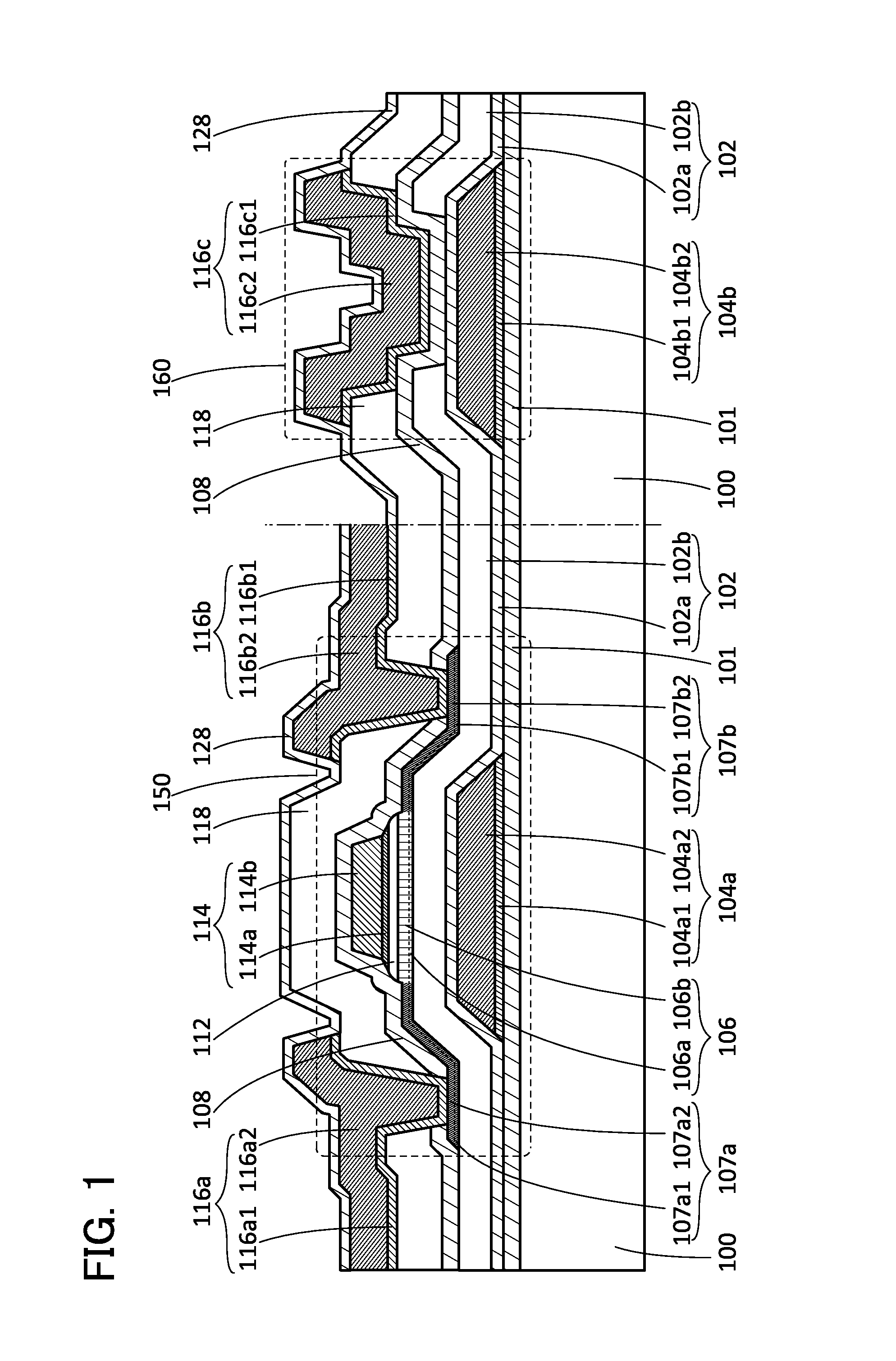

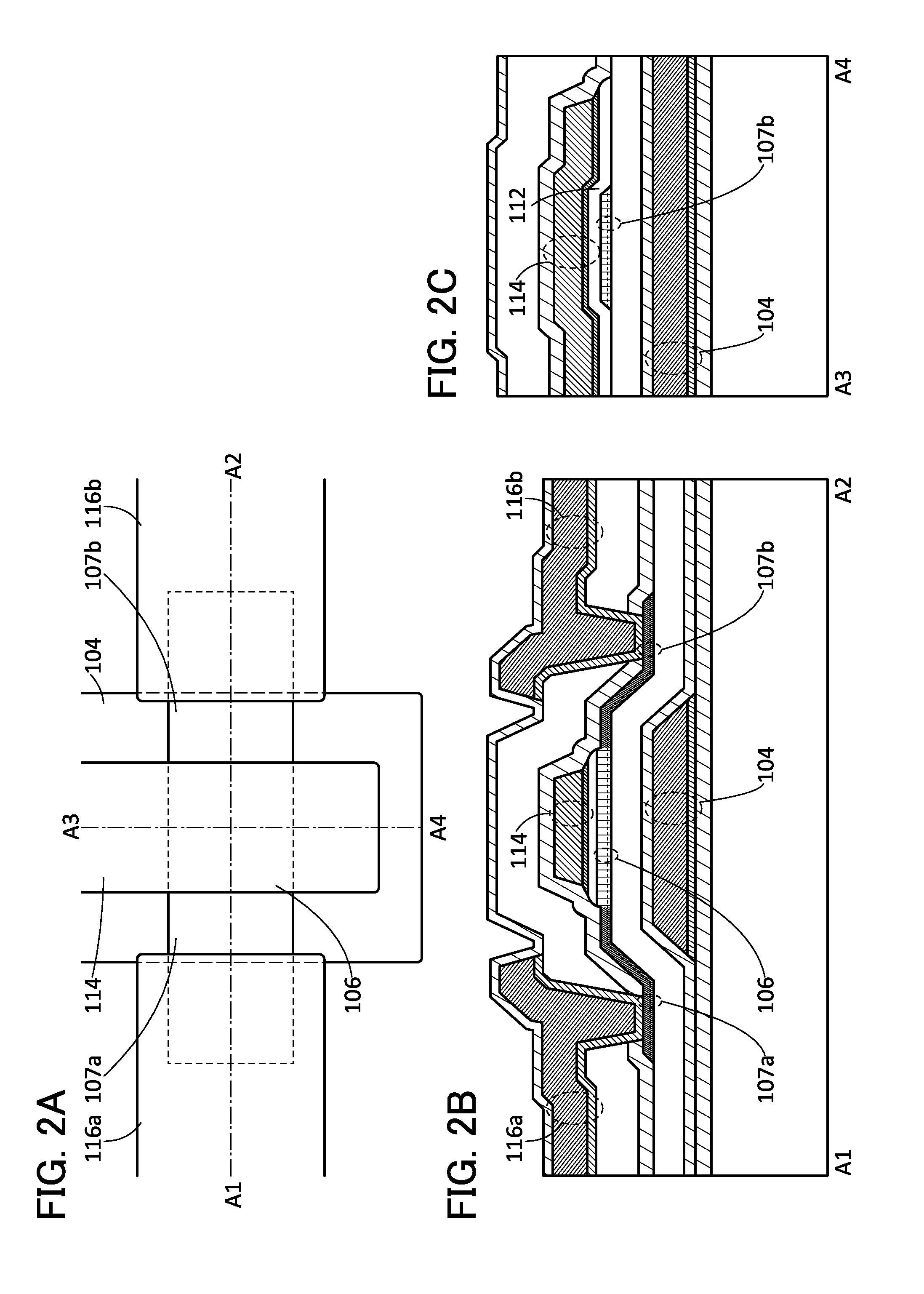

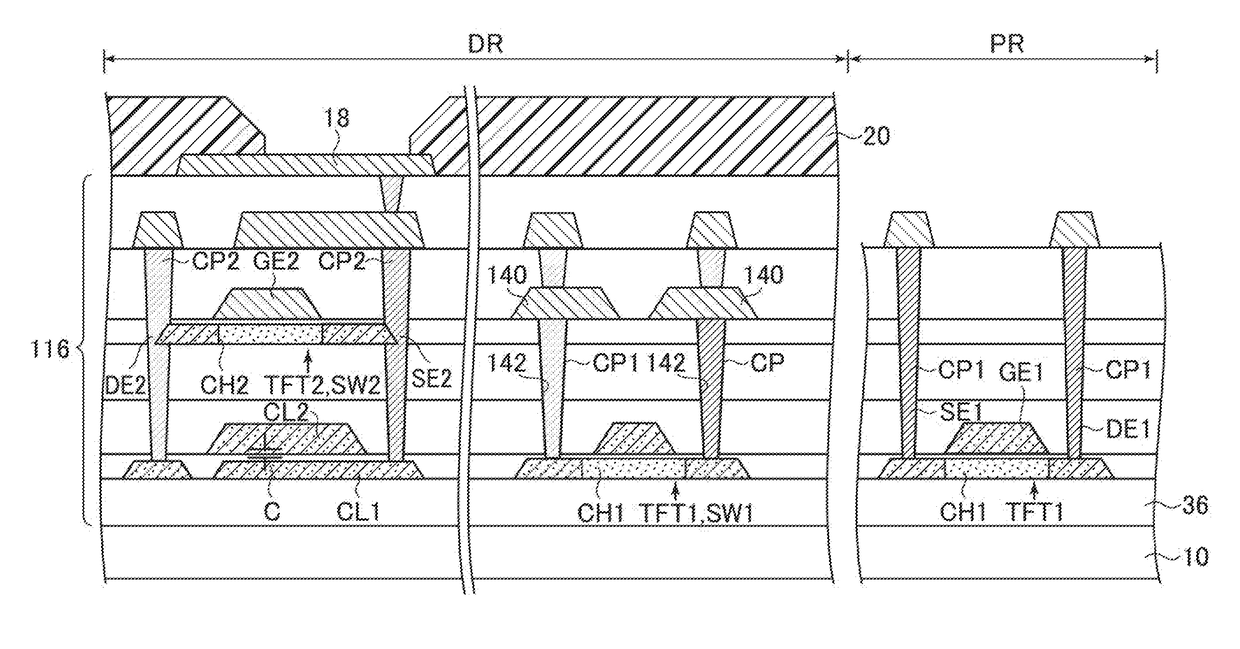

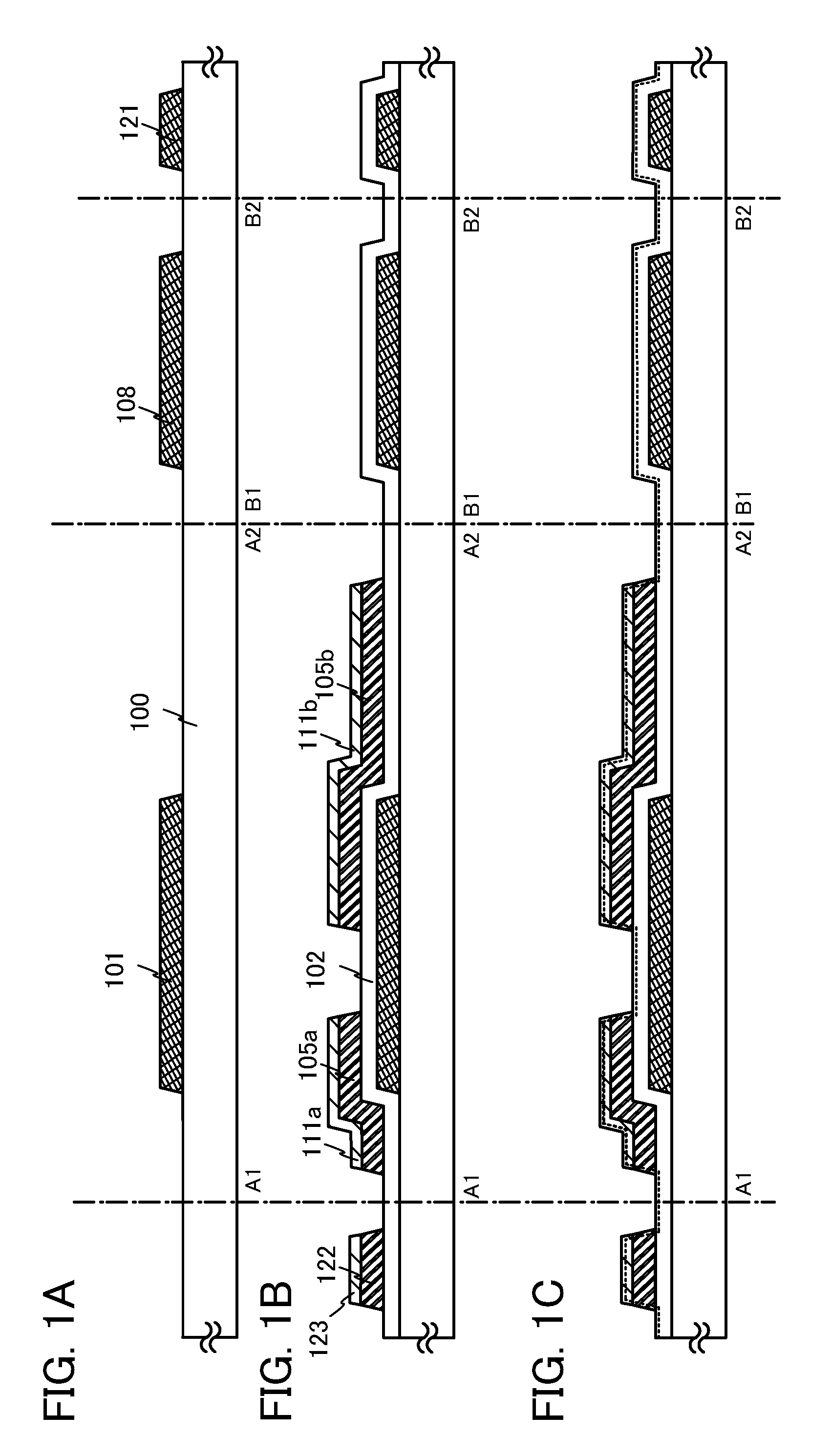

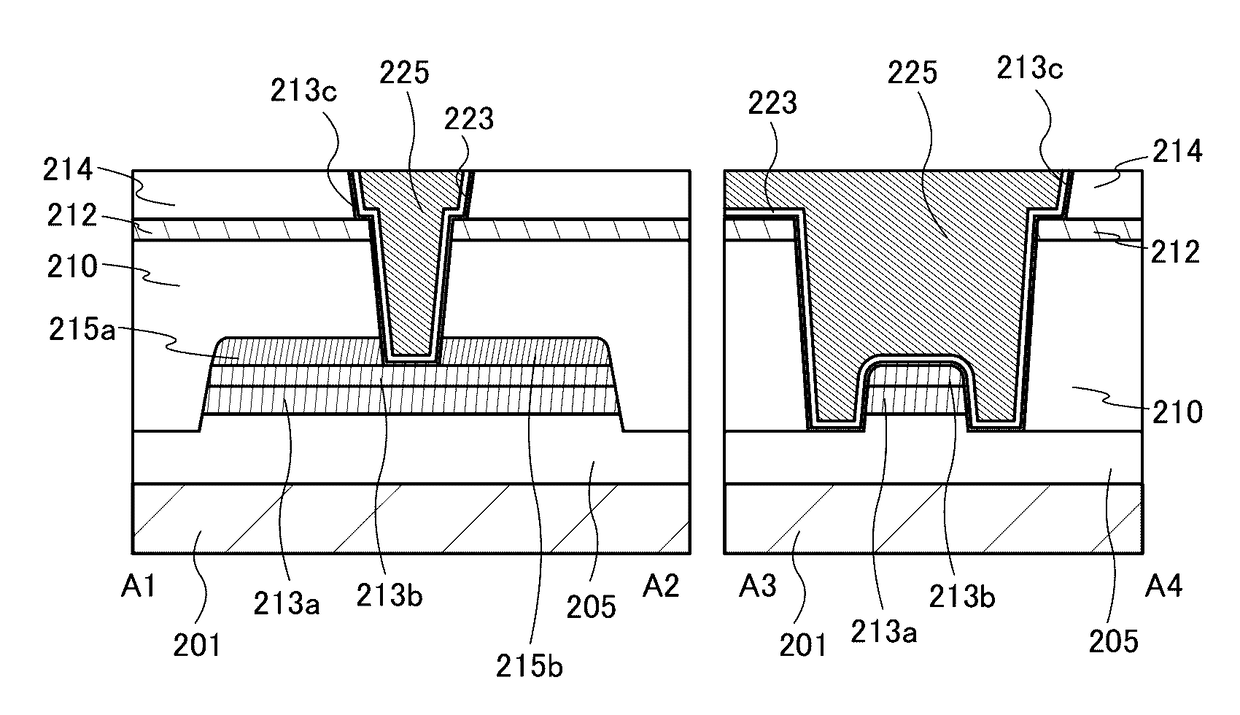

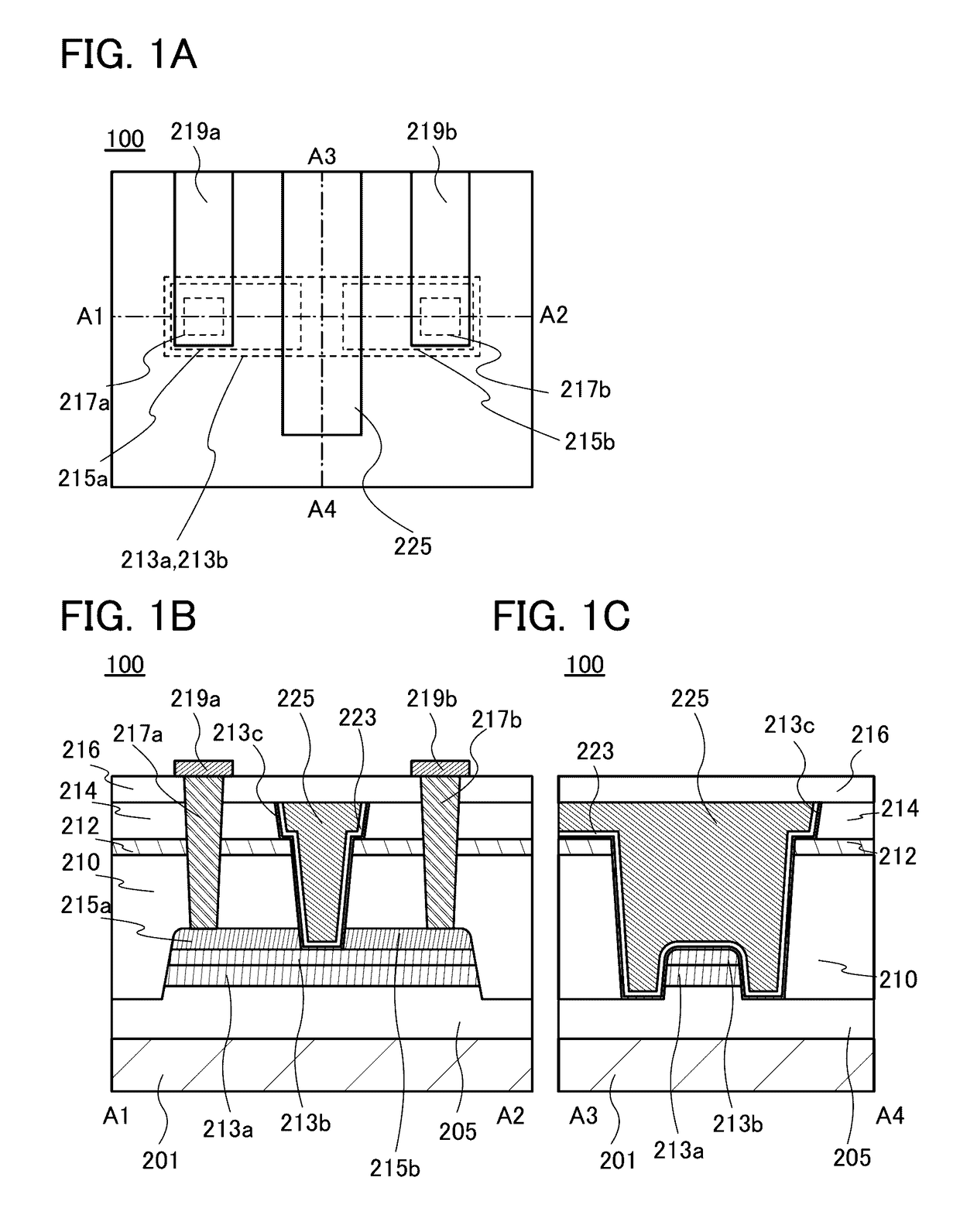

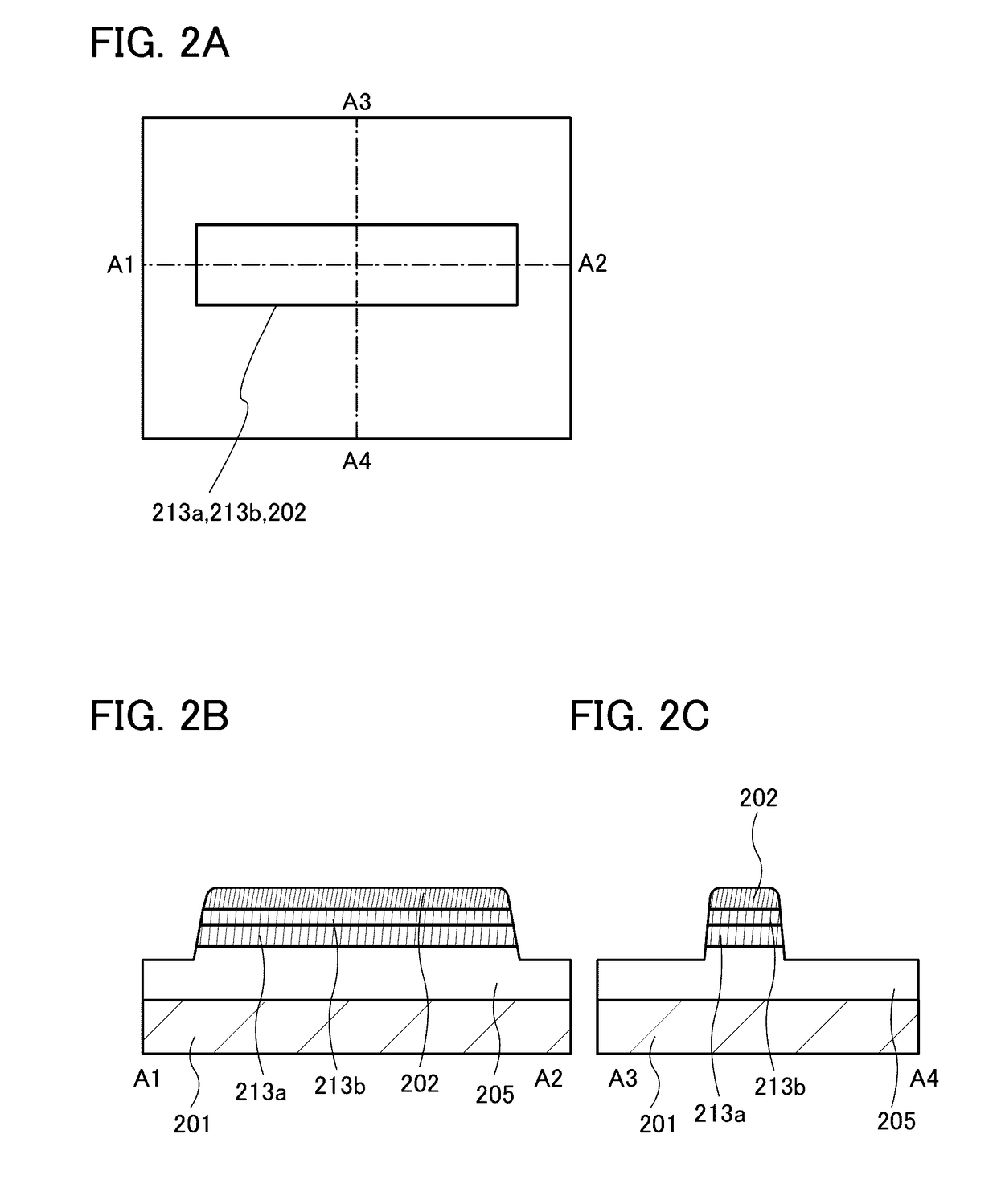

Display device and method for manufacturing the same

ActiveUS20170278916A1Decrease current variationSmall parasitic capacitanceSolid-state devicesSemiconductor devicesDisplay deviceEngineering

A plurality of thin film transistors provided in a peripheral region are first staggered thin film transistors where a first channel layer configured of low-temperature polysilicon is included, and the first channel layer is not interposed between a first source electrode and a first gate electrode, and between a first drain electrode and the first gate electrode. A plurality of thin film transistors provided in a display region are second staggered thin film transistors where a second channel layer configured of an oxide semiconductor is included, and the second channel layer is not interposed between a second source electrode and a second gate electrode, and between a second drain electrode and the second gate electrode. The first thin film transistor is located below the second thin film transistor.

Owner:JAPAN DISPLAY INC

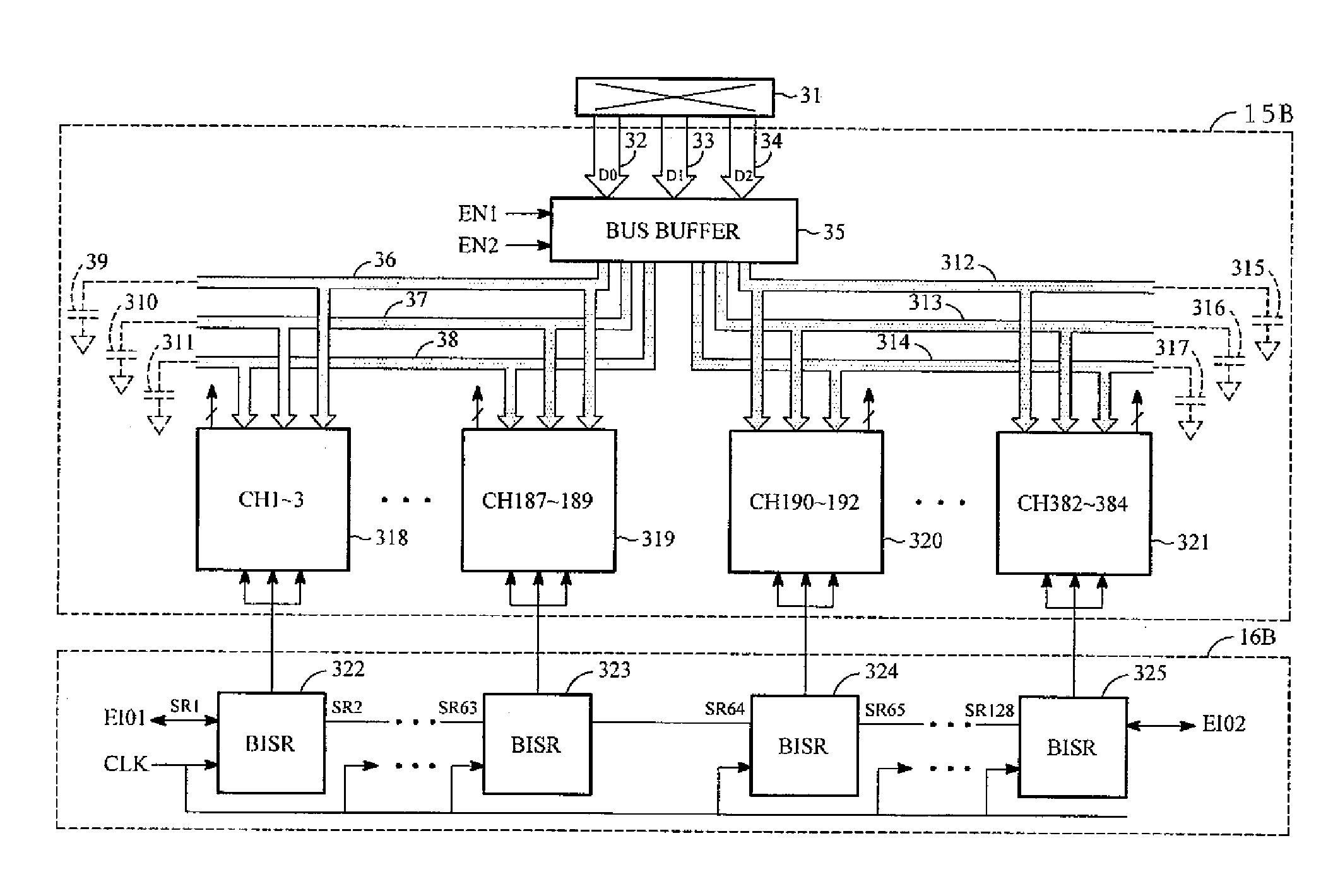

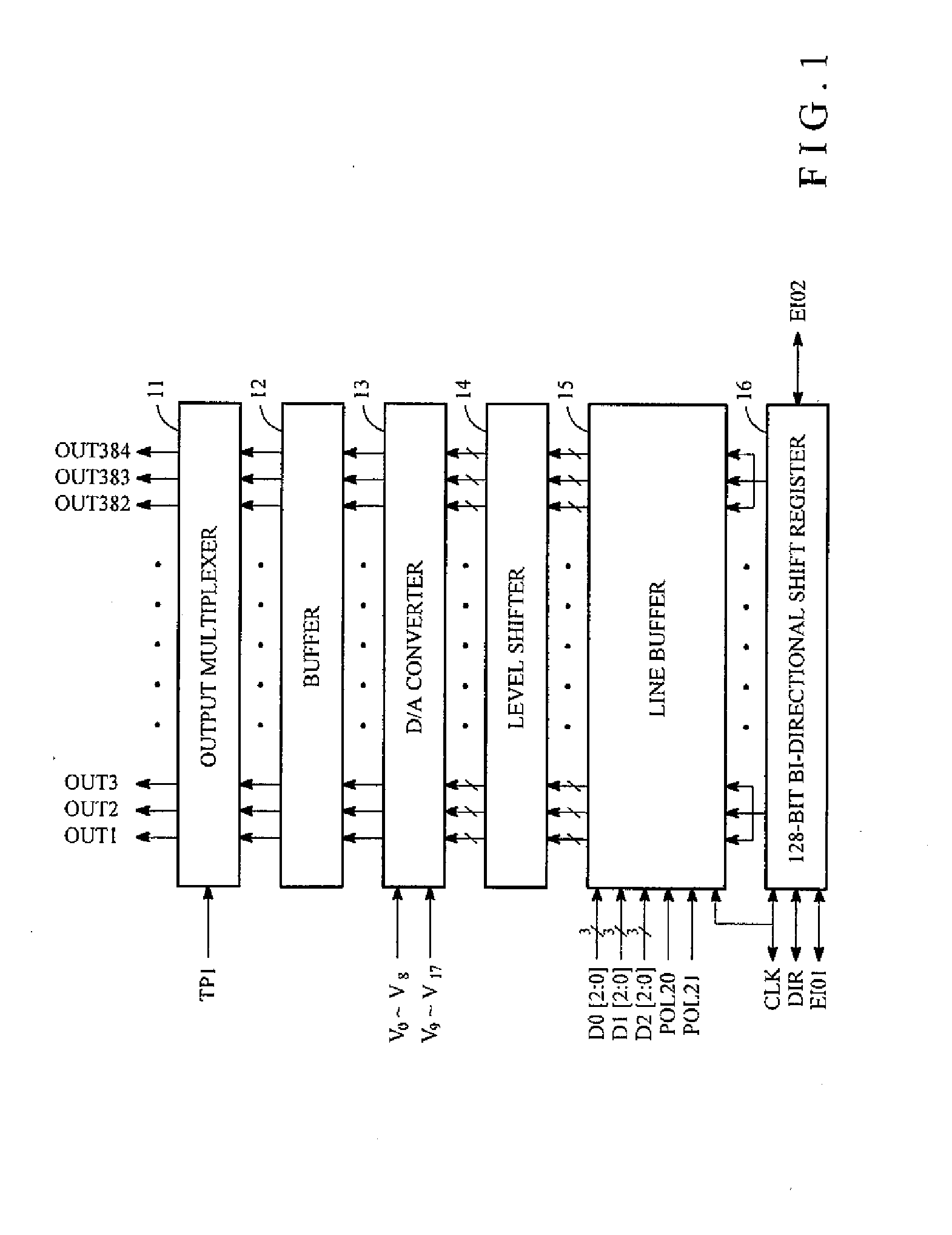

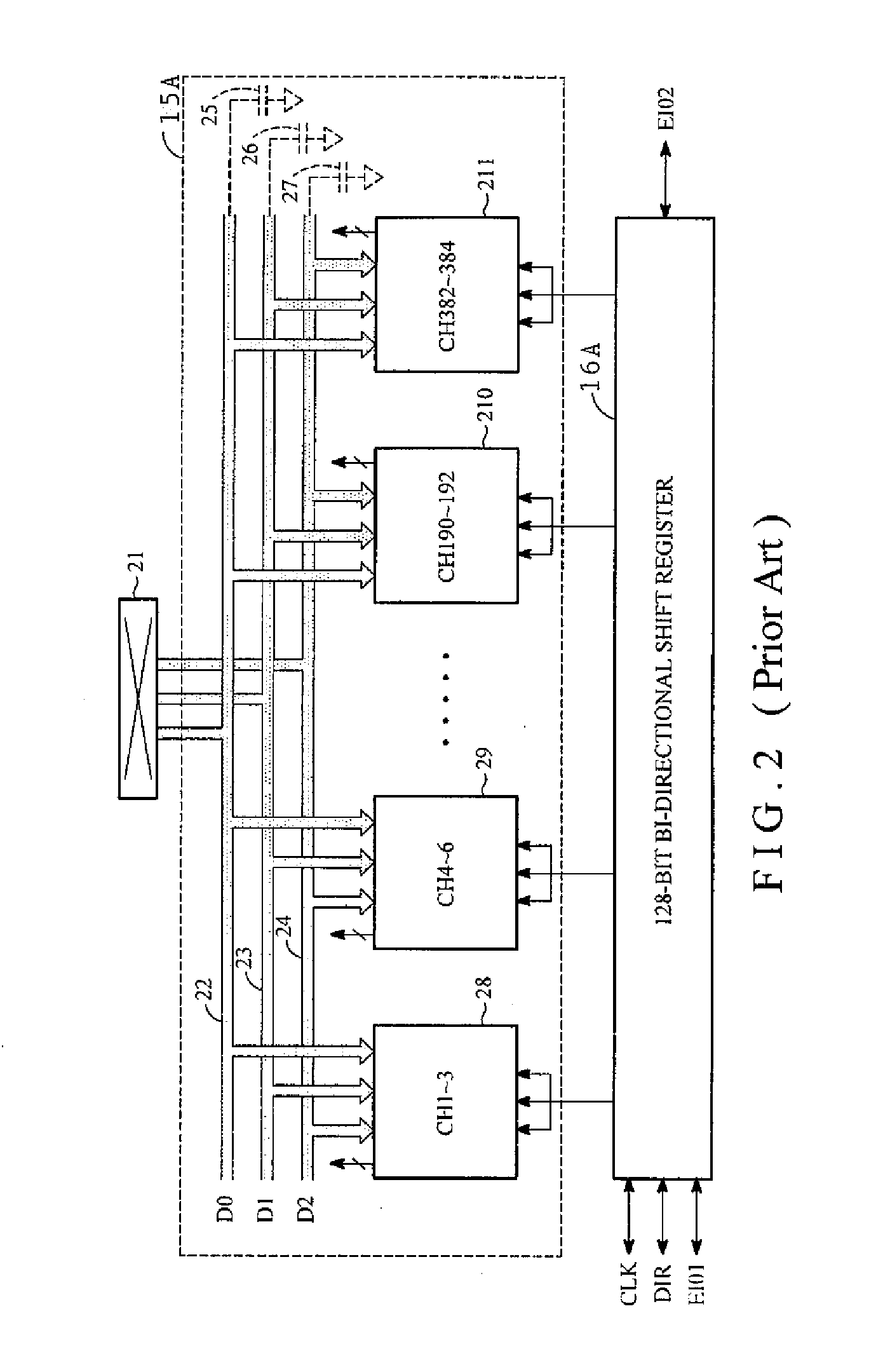

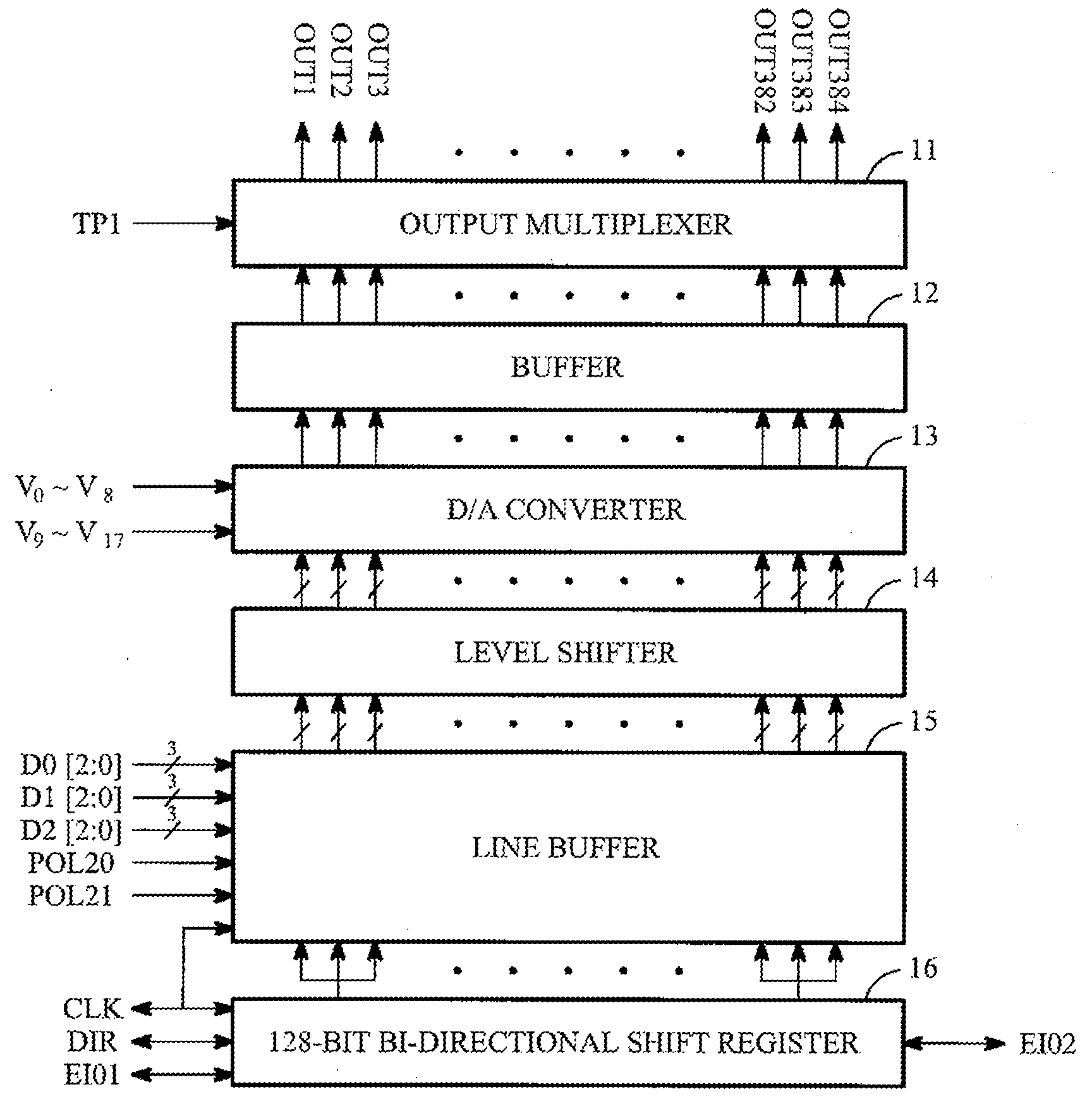

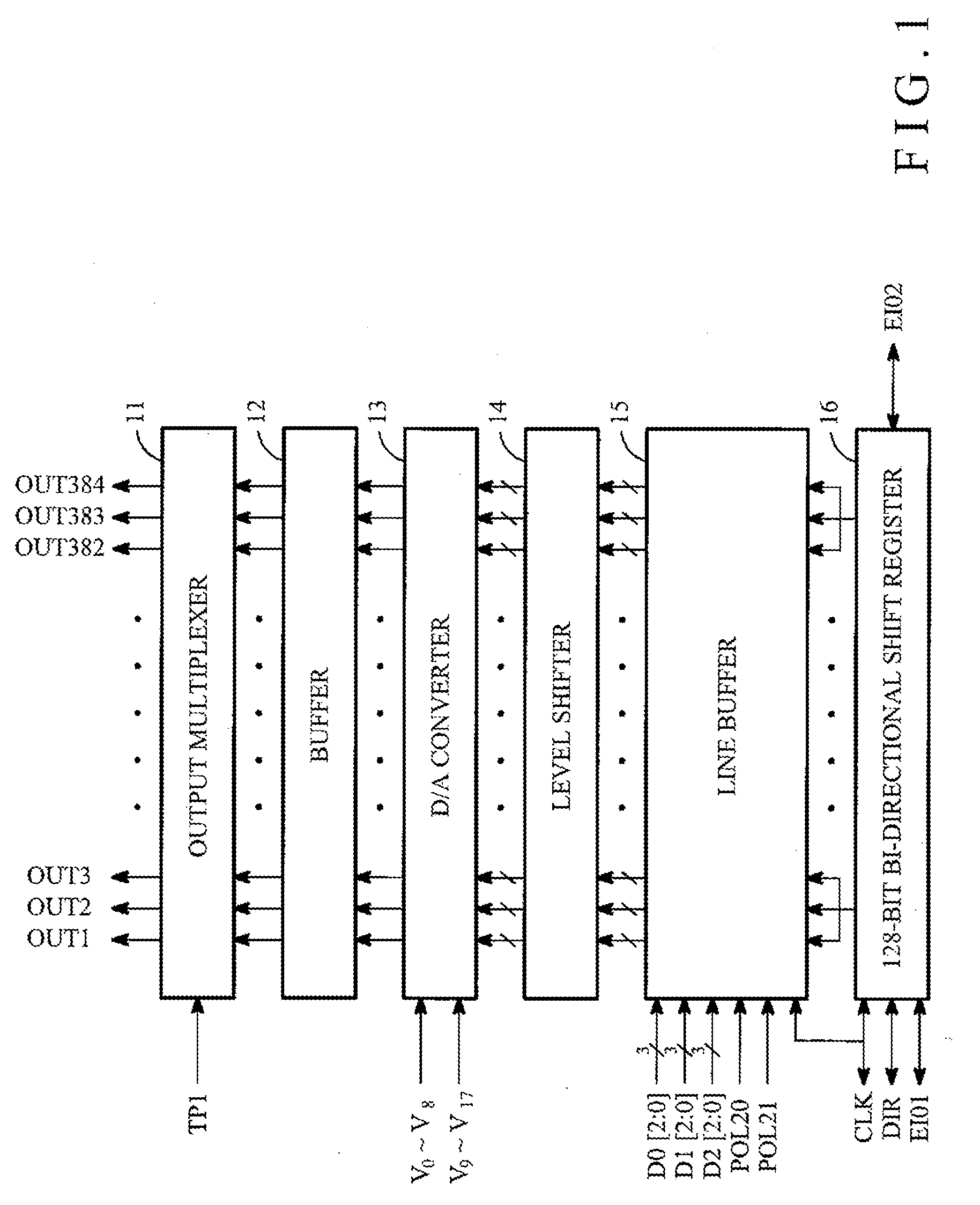

Data bus power down for low power LCD source driver

InactiveUS20080001898A1Reduce data bus power consumptionSmall parasitic capacitanceStatic indicating devicesParasitic capacitanceEmbedded system

The invention provides solutions to solve the power consumption of the image data buses of an LCD source driver. With a bus buffer provided in one embodiment of the invention, a first image data buses are divided into several groups. Each group of image data buses is dispatched by the bus buffer. It is possible in one embodiment of the invention that some groups are active when the others are passive. Therefore, unnecessary power consumption is cut off. Despite the power saved by the management of the bus buffer, the parasitic capacitance of each group of image data buses is much smaller than that of the image data buses in the prior art. Moreover, the management of the bus buffer can depend upon the layout patterns or the layout locations of circuit components so that the driving strength of the bus buffer may be modified according to the layout pattern or the layout locations.

Owner:HIMAX TECH LTD

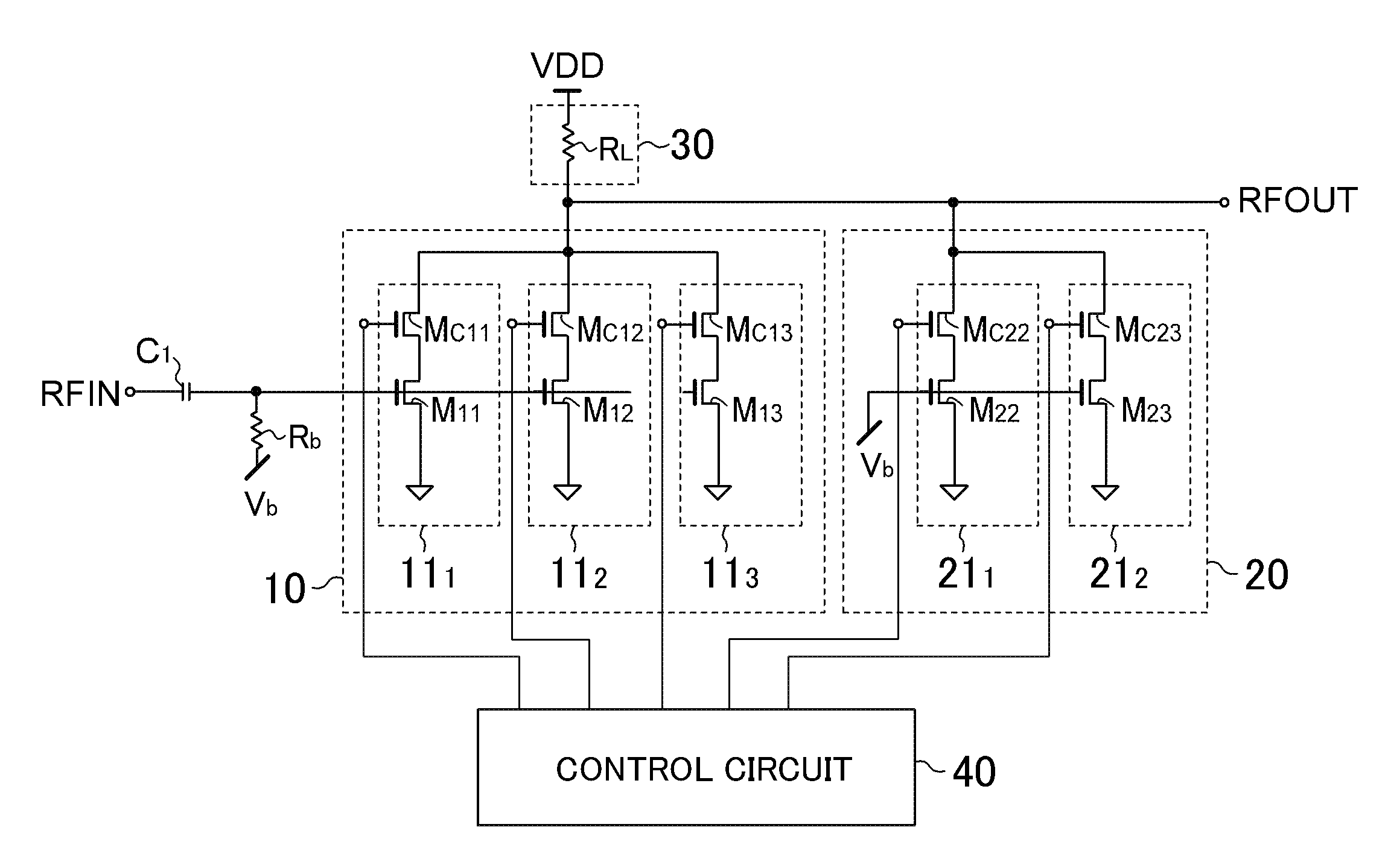

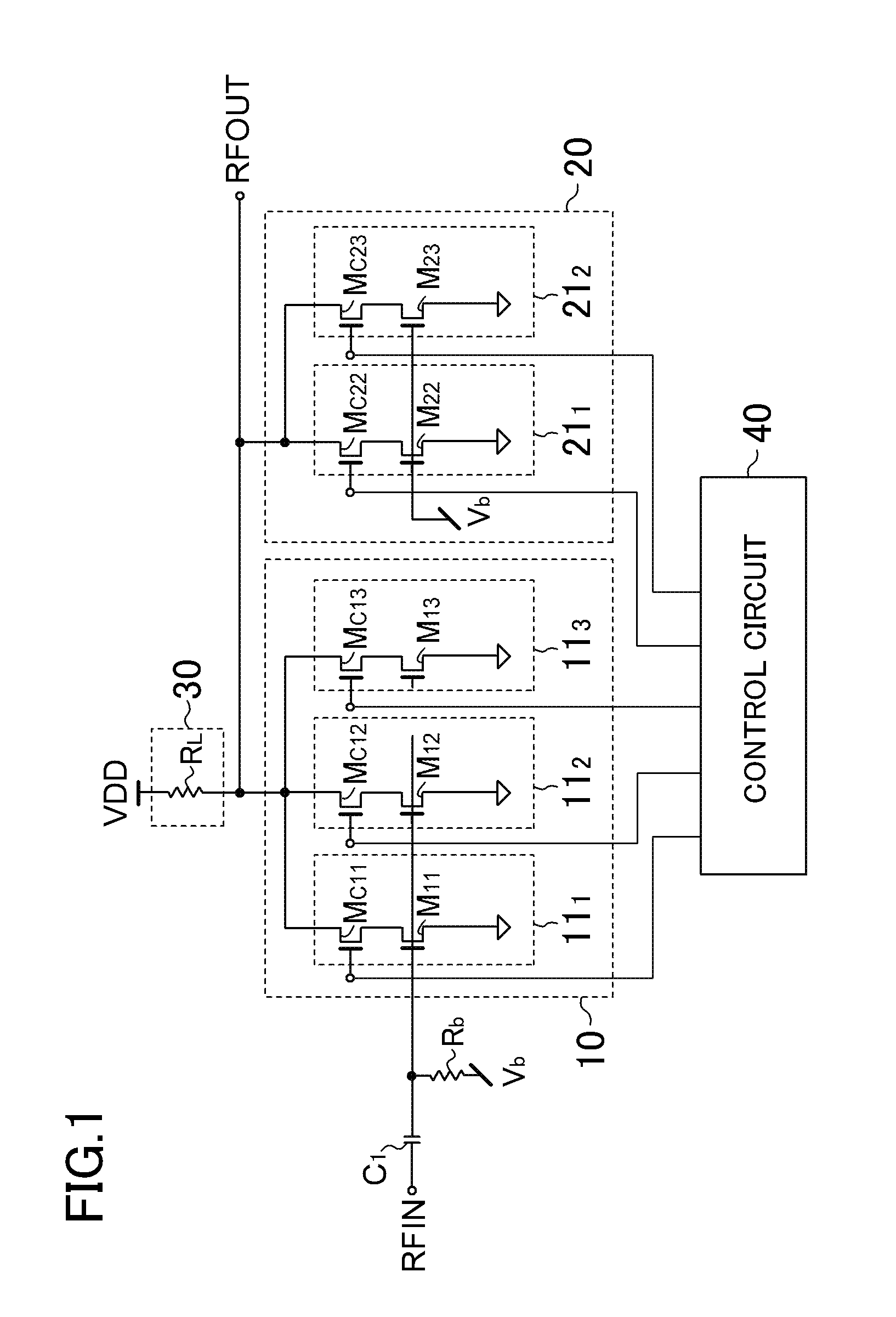

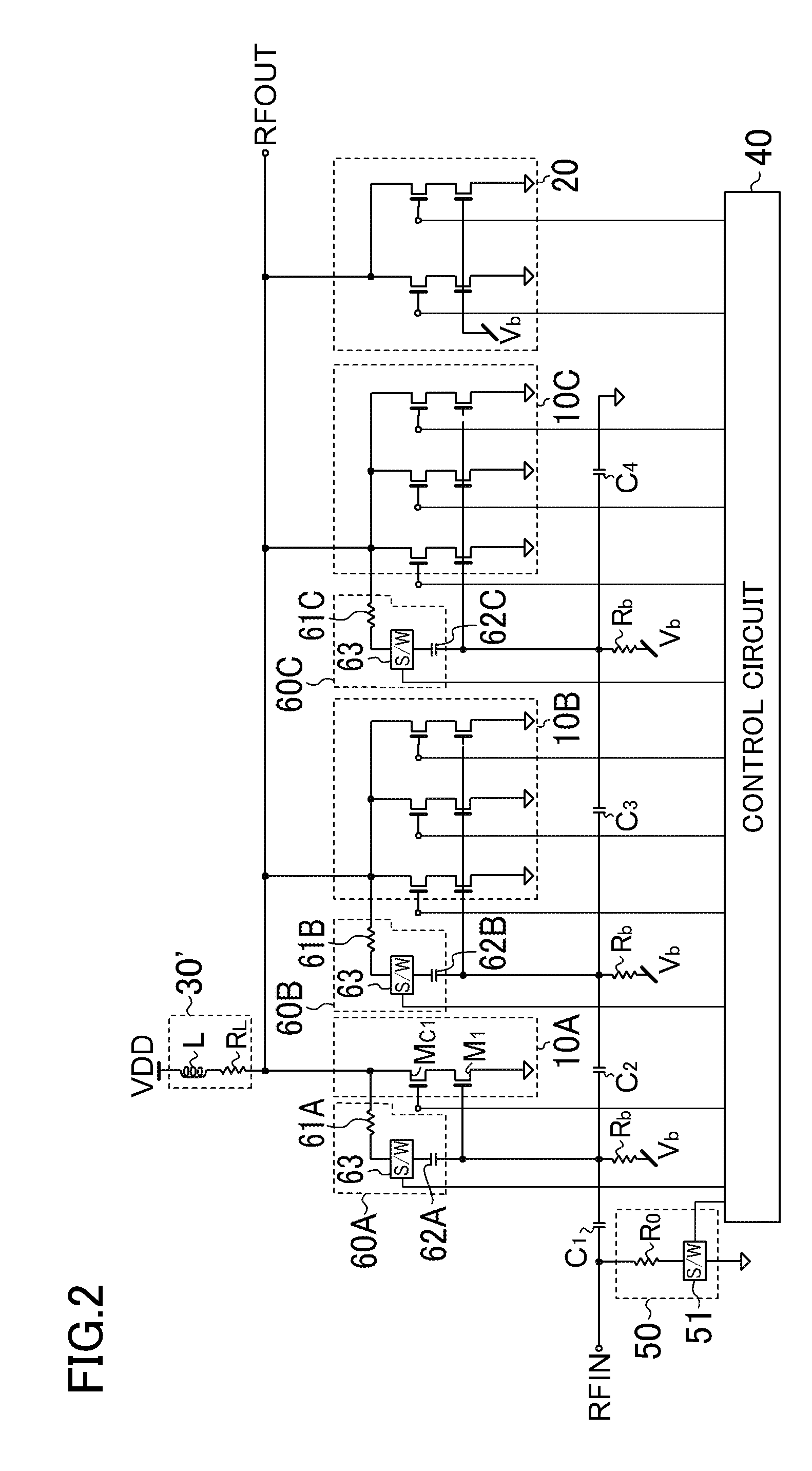

Variable gain amplifier and high-frequency signal receiving apparatus comprising the same

ActiveUS20110221531A1Easy to implementReduce degradationGain controlGated amplifiersLoad circuitAudio power amplifier

A cascode amplification unit includes a plurality of cascode amplifiers connected in parallel. Each of the cascode amplifiers has two transistors. A cascode current source unit includes a plurality of cascode current sources connected in parallel. Each of the cascode current sources has two transistors. Both the output end of the cascode amplification unit and the output end of the cascode current source unit are connected to a load circuit. The control circuit turns on and off each cascode transistor of the cascode amplifier and each cascode transistor of the cascode current source so that an amount of current passing through the load circuit is constant.

Owner:PANASONIC CORP

Low power LCD source driver

InactiveUS20080001944A1Reduce data bus power consumptionSmall parasitic capacitanceCathode-ray tube indicatorsInput/output processes for data processingParasitic capacitanceImaging data

The invention provides solutions to solve the power consumption of the image data buses of an LCD source driver. With a bus buffer provided in one embodiment of the invention, a first image data buses are divided into several groups. Each group of image data buses is dispatched by the bus buffer. It is possible in one embodiment of the invention that some groups are active when the others are passive. Therefore, unnecessary power consumption is cut off. Despite the power saved by the management of the bus buffer, the parasitic capacitance of each group of image data buses is much smaller than that of the image data buses in the prior art. Moreover, the management of the bus buffer can depend upon the layout patterns or the layout locations of circuit components so that the driving strength of the bus buffer may be modified according to the layout pattern or the layout locations.

Owner:HIMAX TECH LTD

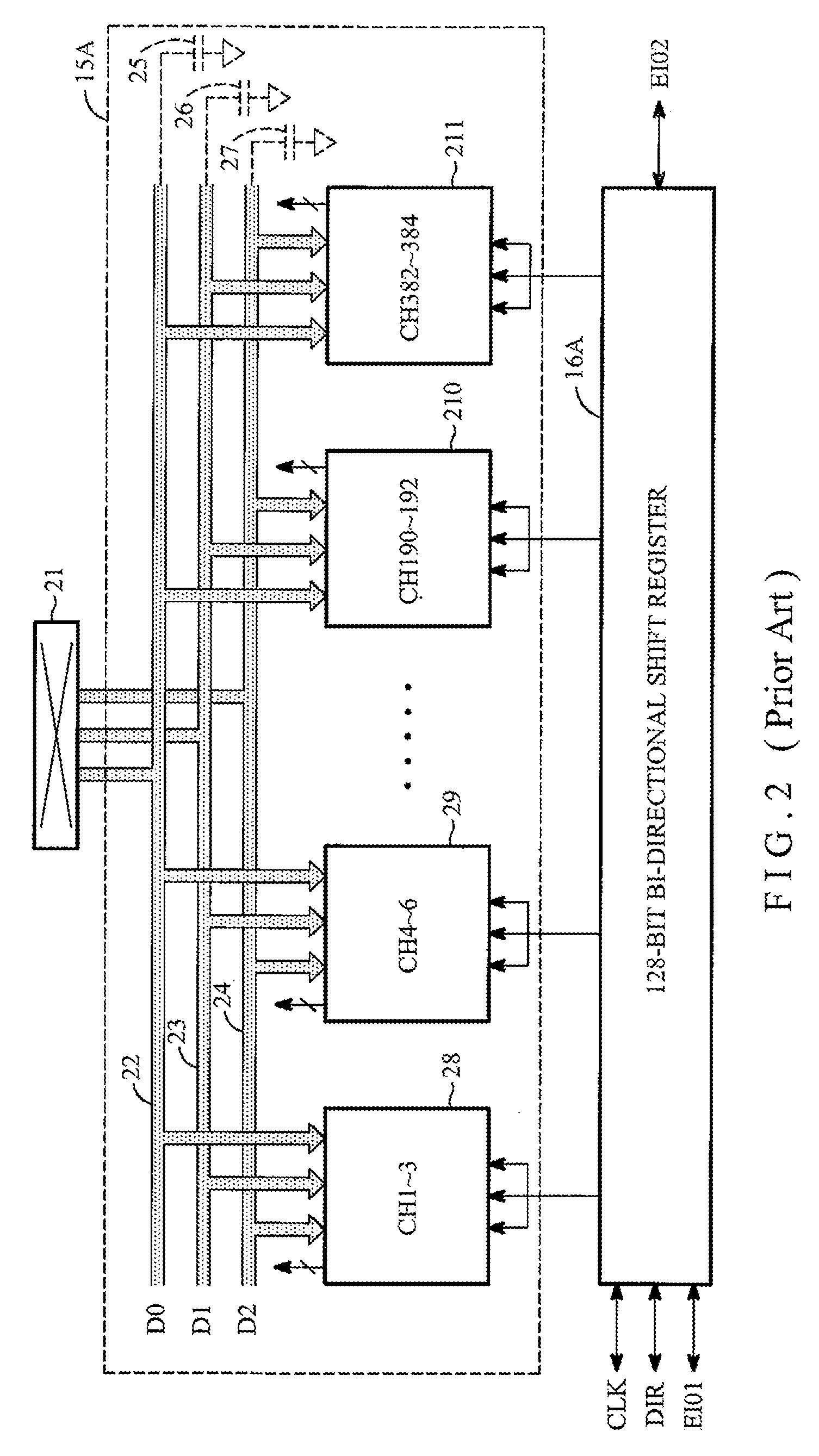

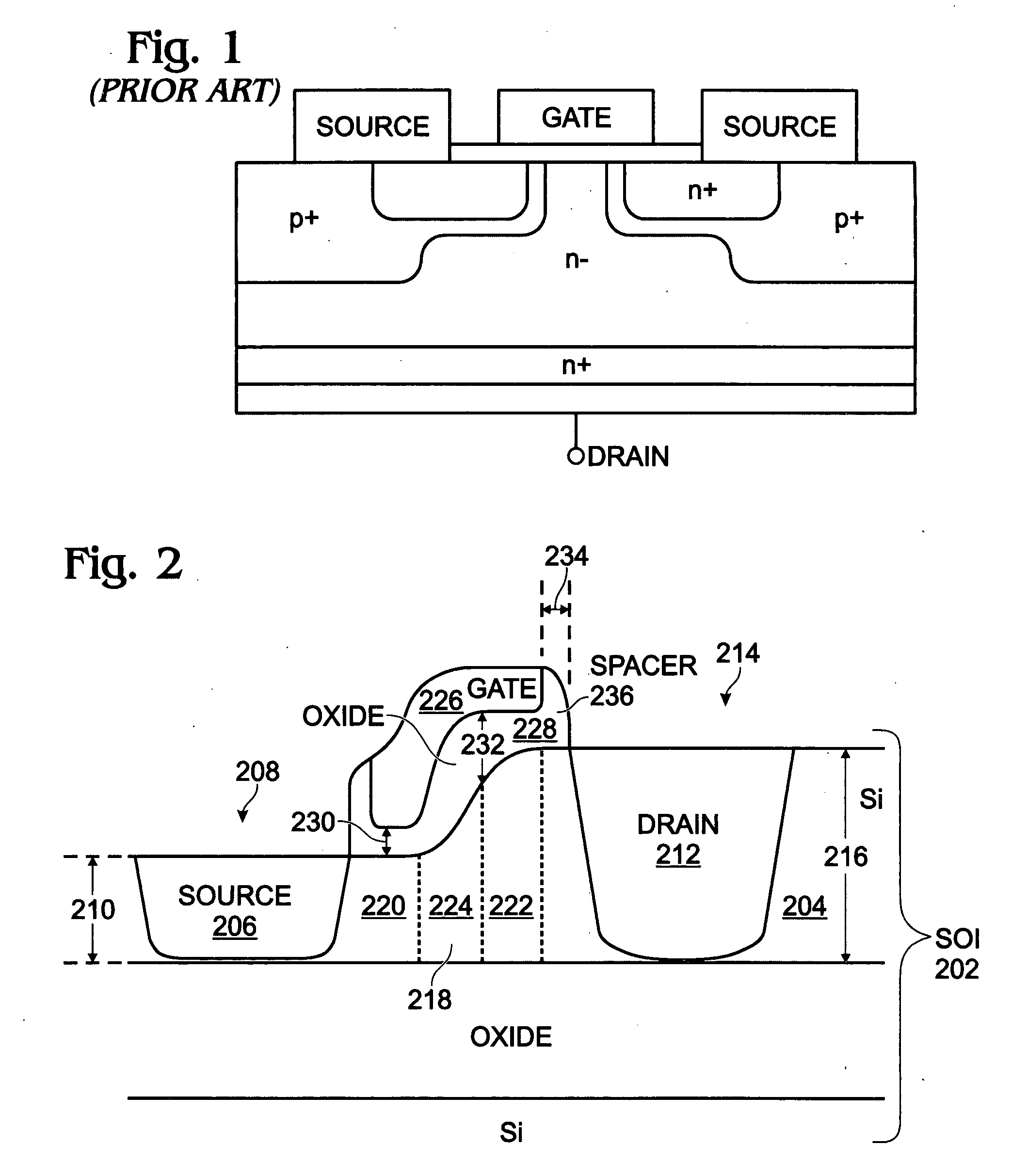

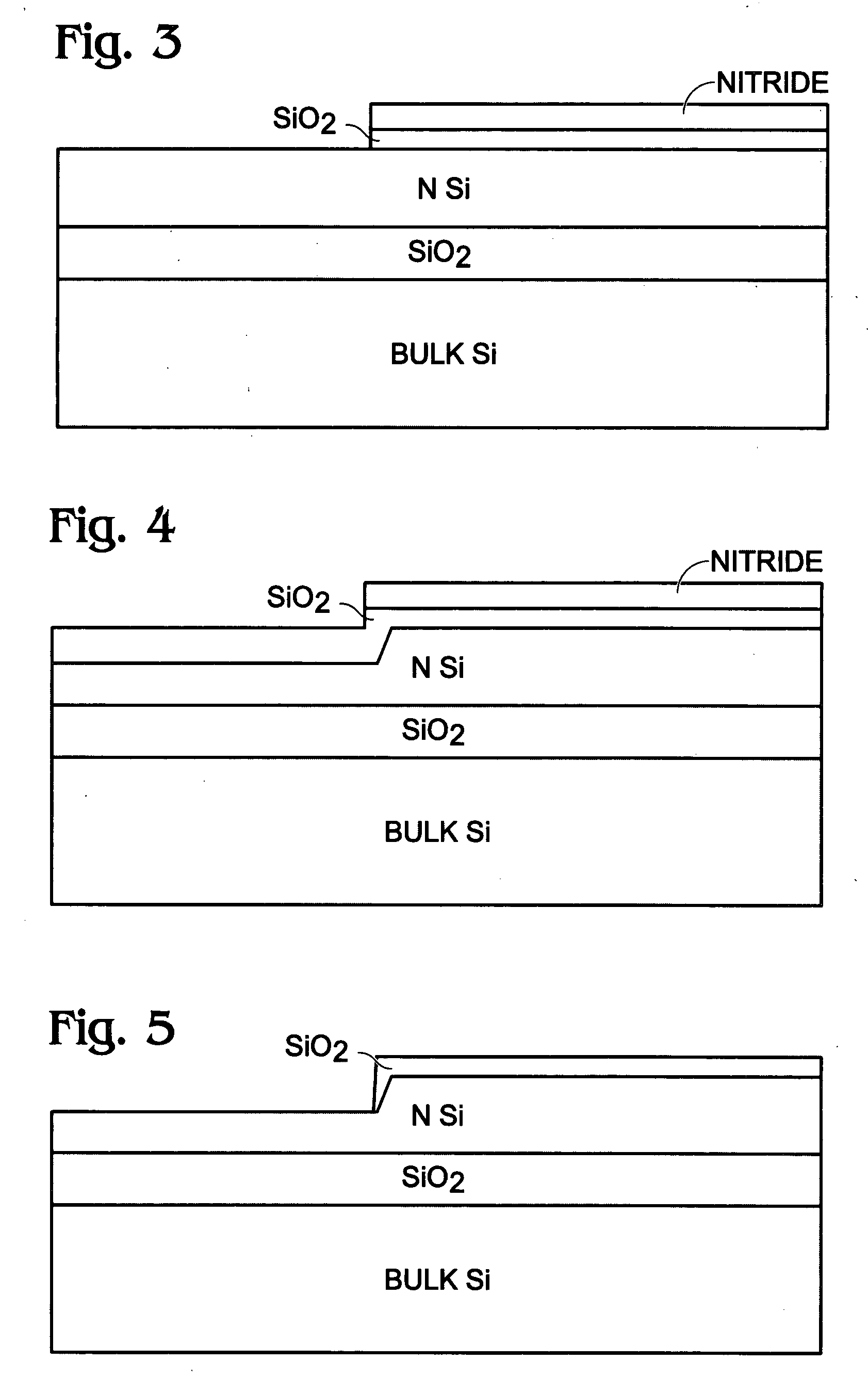

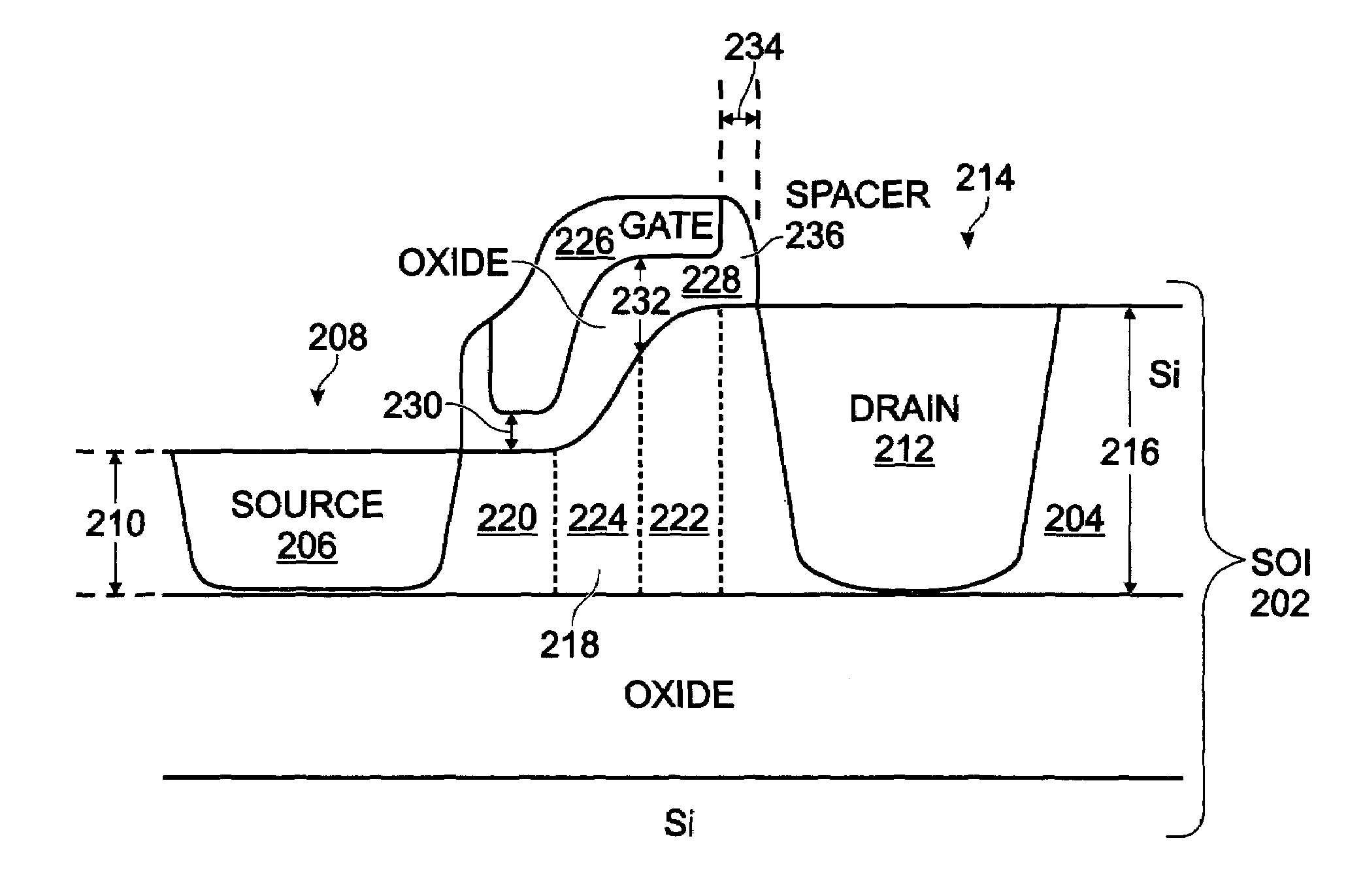

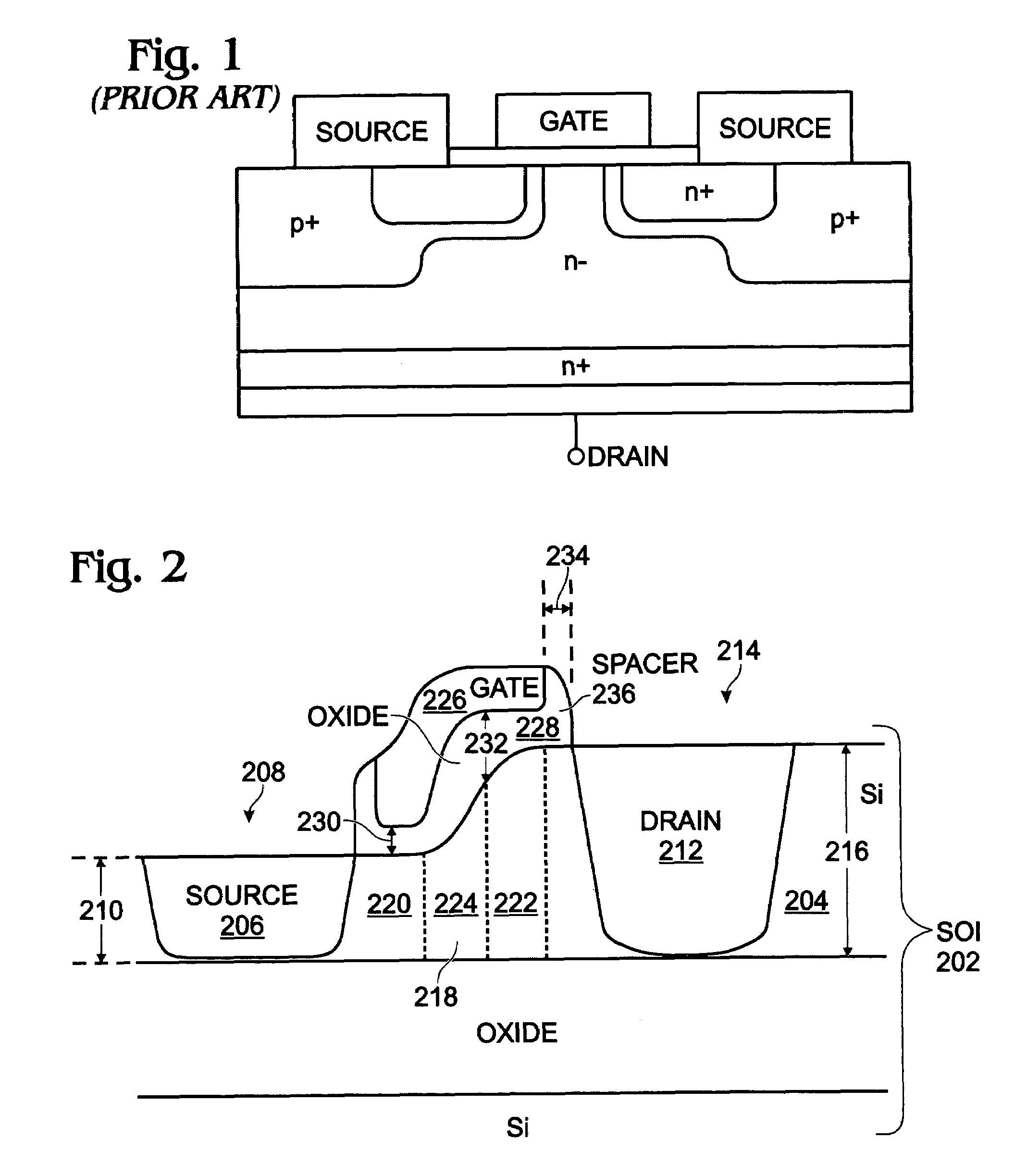

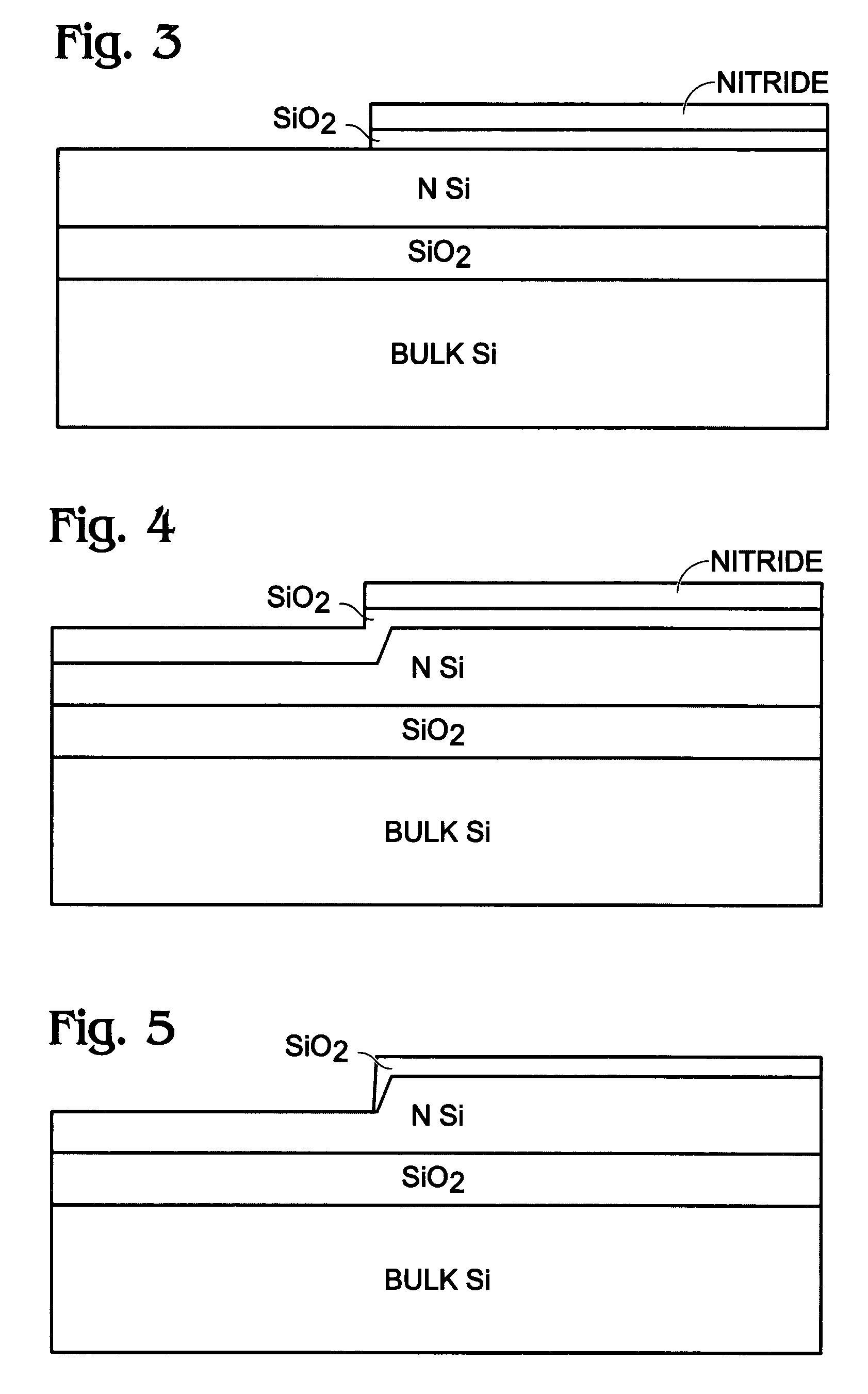

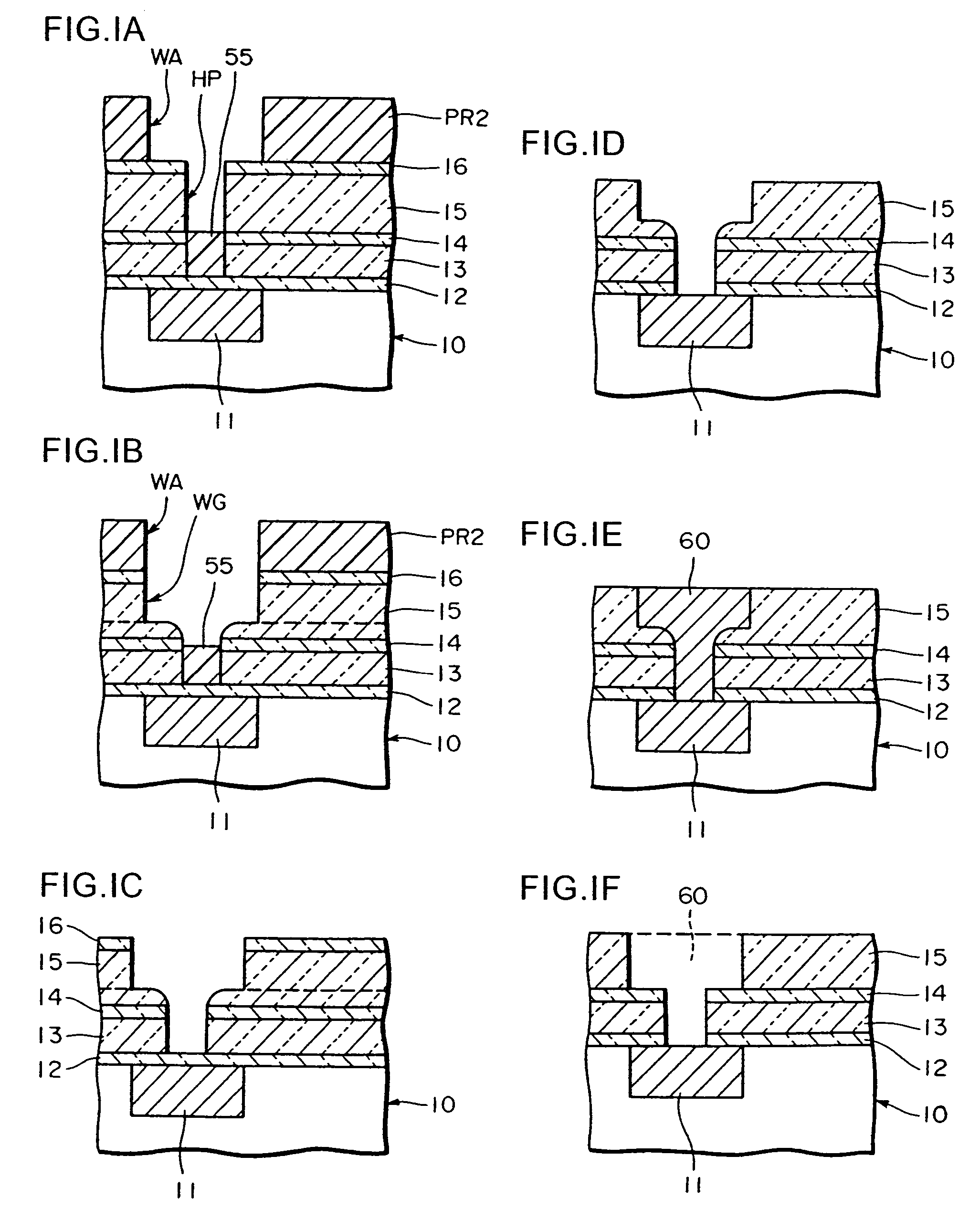

Thin silicon-on-insulator double-diffused metal oxide semiconductor transistor

InactiveUS20080290408A1Small parasitic capacitanceIncrease drive currentTransistorSemiconductor/solid-state device manufacturingDopantSoi substrate

A method is provided for fabricating a silicon (Si)-on-insulator (SOI) double-diffused metal oxide semiconductor transistor (DMOST) with a stepped channel thickness. The method provides a SOI substrate with a Si top layer having a surface. A thinned area of the Si top layer is formed, and a source region is formed in the thinned Si top layer area. The drain region is formed in an un-thinned area of the Si top layer. The channel has a first thickness adjacent the source region with first-type dopant, and a second thickness, greater than the first thickness, adjacent the drain region. The channel also has a sloped thickness between the first and second thicknesses. The second and sloped thicknesses have a second-type dopant, opposite of the first-type dopant. A stepped gate overlies the channel.

Owner:SHARP KK

Thin silicon-on-insulator double-diffused metal oxide semiconductor transistor

InactiveUS7598128B2Increase drive currentLower resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDopantSoi substrate

A method is provided for fabricating a silicon (Si)-on-insulator (SOI) double-diffused metal oxide semiconductor transistor (DMOST) with a stepped channel thickness. The method provides a SOI substrate with a Si top layer having a surface. A thinned area of the Si top layer is formed, and a source region is formed in the thinned Si top layer area. The drain region is formed in an un-thinned area of the Si top layer. The channel has a first thickness adjacent the source region with first-type dopant, and a second thickness, greater than the first thickness, adjacent the drain region. The channel also has a sloped thickness between the first and second thicknesses. The second and sloped thicknesses have a second-type dopant, opposite of the first-type dopant. A stepped gate overlies the channel.

Owner:SHARP KK

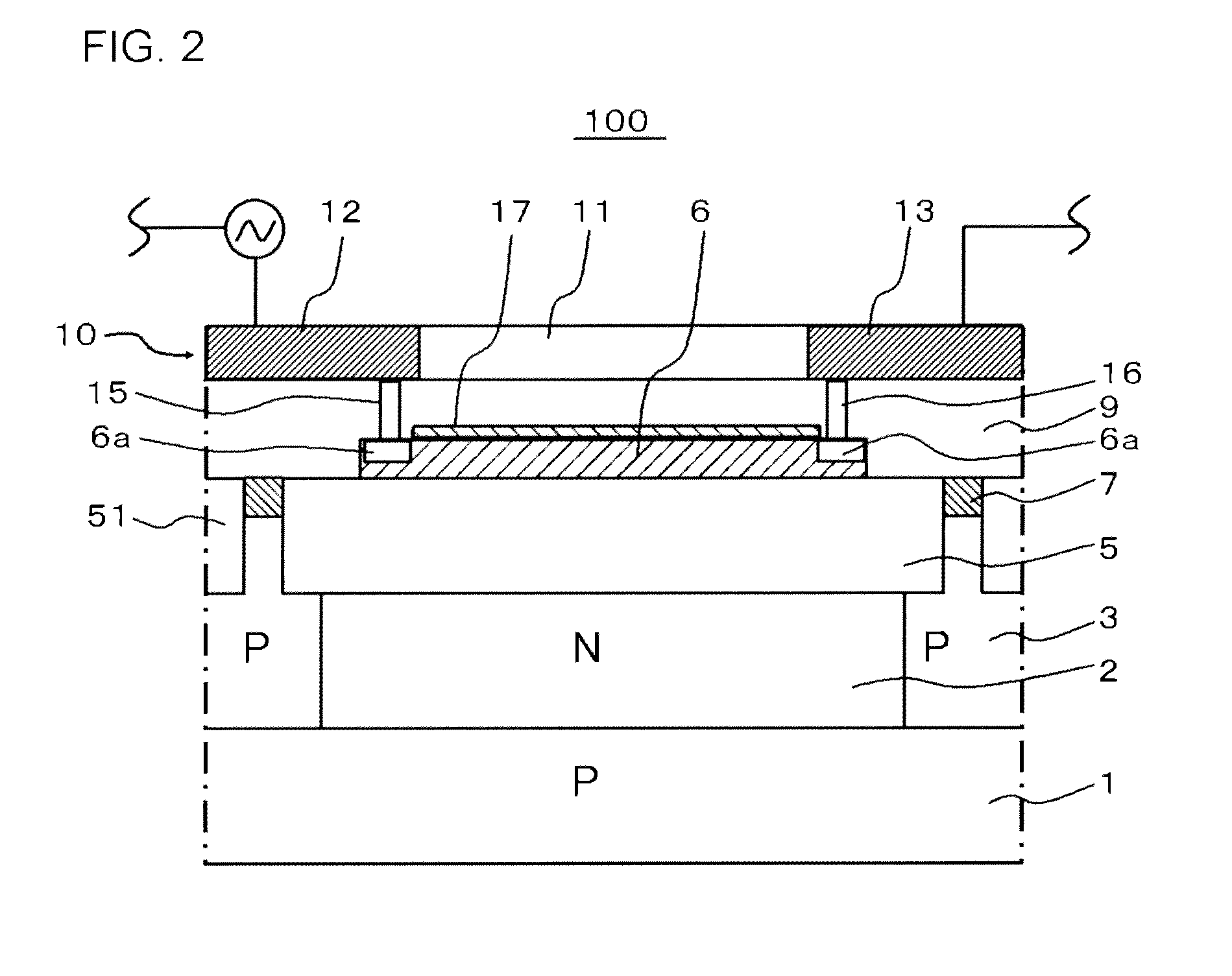

Semiconductor device

ActiveUS8786002B2Improved breakdown voltage performanceQuality improvementTransistorSolid-state devicesCapacitanceTotal harmonic distortion

In terms of achieving a reduction in the cost of an antenna switch, there is provided a technology capable of minimizing harmonic distortion generated in the antenna switch even when the antenna switch is particularly formed of field effect transistors formed over a silicon substrate. Between the source region and the drain region of each of a plurality of MISFETs coupled in series, a distortion compensating capacitance circuit is coupled which has a voltage dependency such that, in either of the cases where a positive voltage is applied to the drain region based on the potential of the source region and where a negative voltage is applied to the drain region based on the potential of the source region, the capacitance decreases to a value smaller than that in a state where the potential of the source region and the potential of the drain region are at the same level.

Owner:RENESAS ELECTRONICS CORP

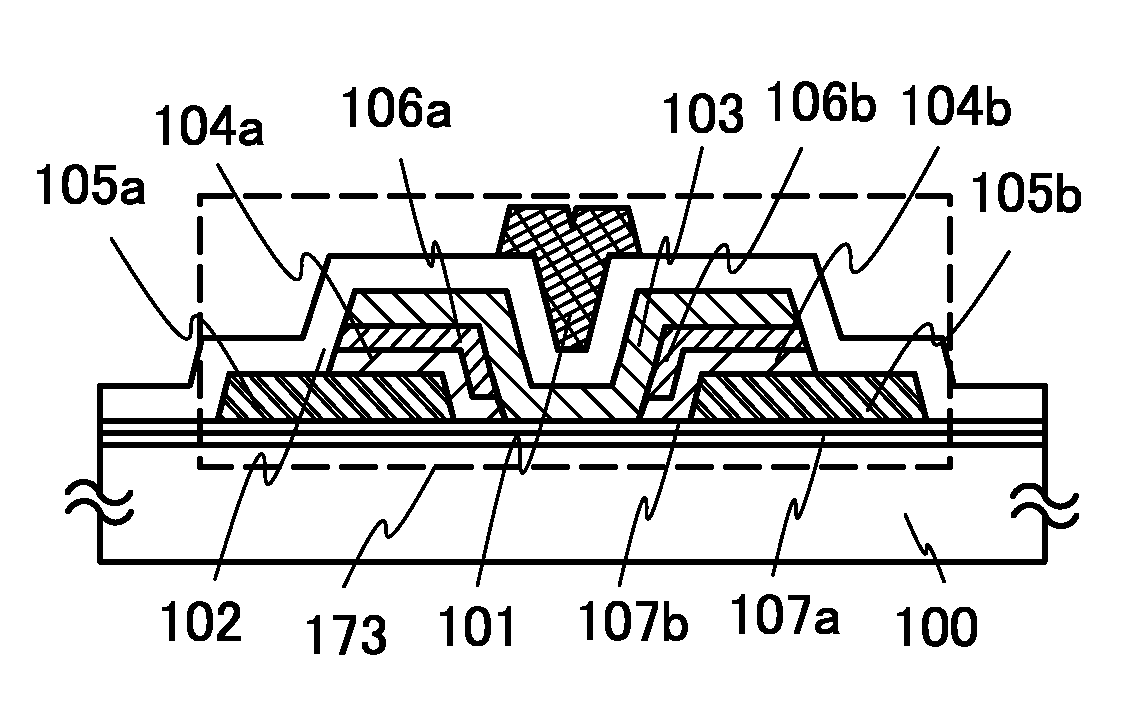

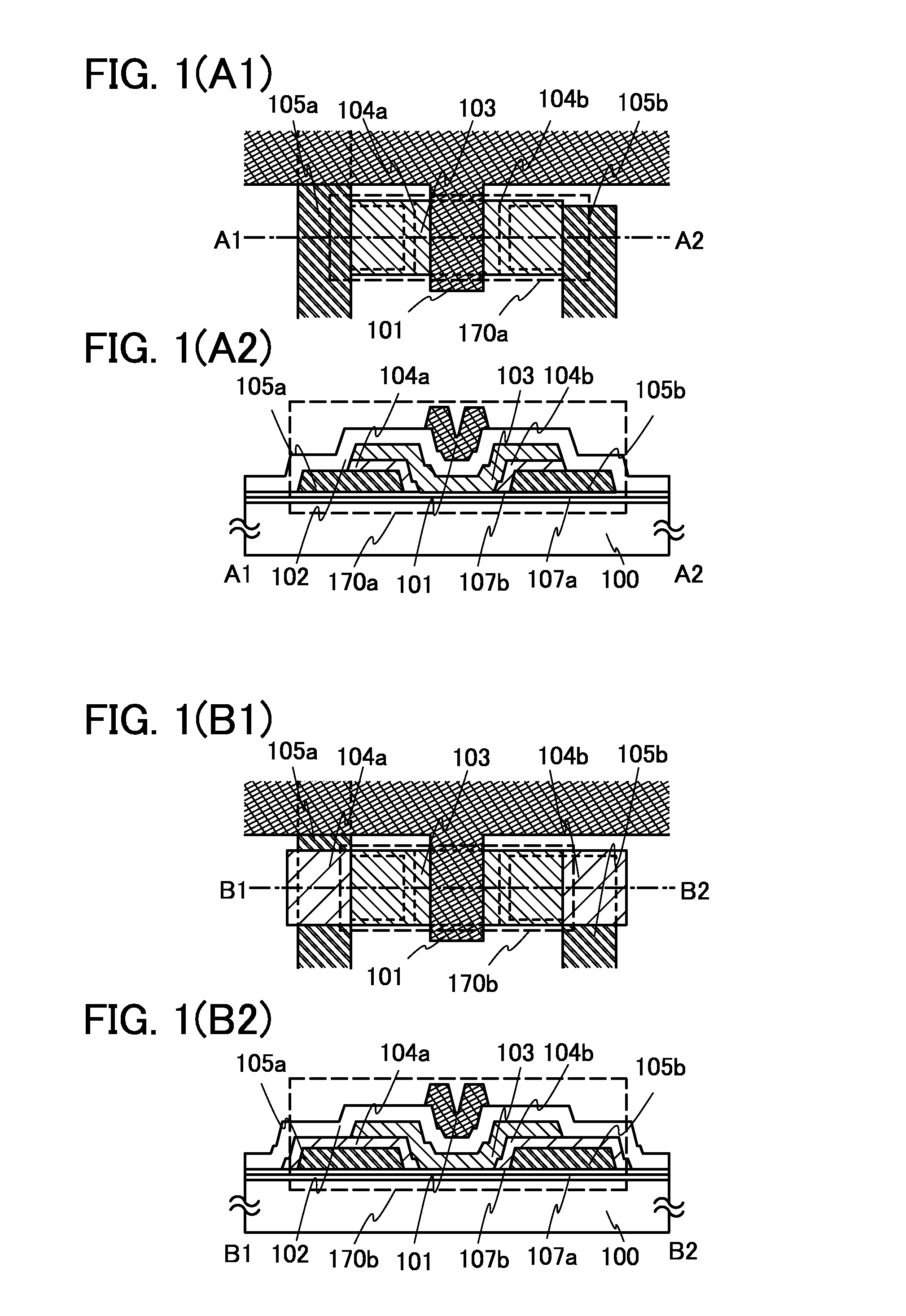

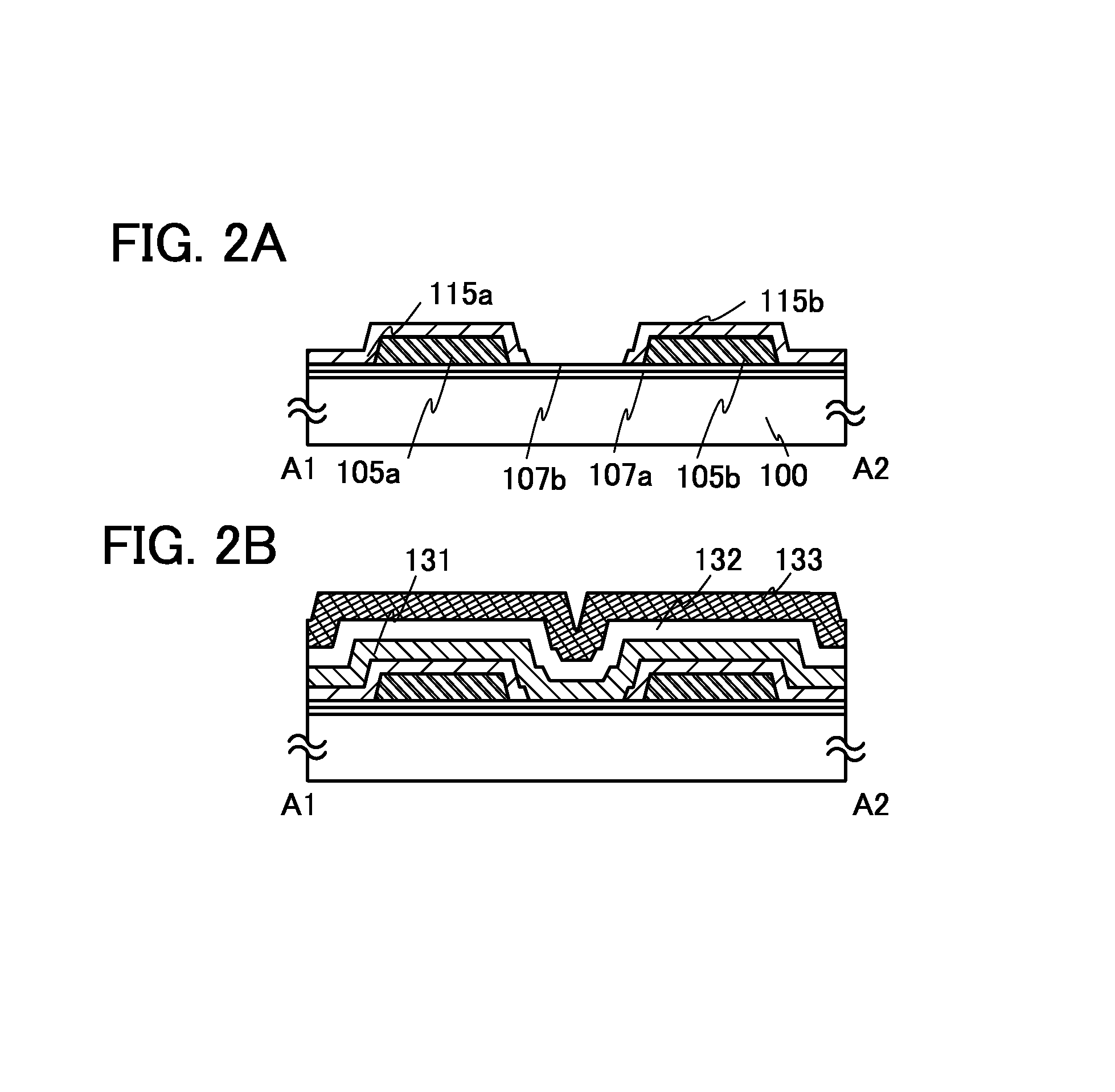

Semiconductor device and display device including the semiconductor device

ActiveUS20160240683A1Reduce electric resistanceDecrease in field-effect mobilityTransistorSolid-state devicesOxide semiconductorPower semiconductor device

To reduce parasitic capacitance in a semiconductor device having a transistor including an oxide semiconductor. The transistor includes a first gate electrode, a first gate insulating film over the first gate electrode, an oxide semiconductor film over the first gate insulating film, and source and drain electrodes electrically connected to the oxide semiconductor film. The oxide semiconductor film includes a first oxide semiconductor film on the first gate electrode side and a second oxide semiconductor film over the first oxide semiconductor film. The atomic proportion of In is larger than the atomic proportion of M (M is Ti, Ga, Sn, Y, Zr, La, Ce, Nd, or Hf) in the first oxide semiconductor film, and the atomic proportion of In in the second oxide semiconductor film is smaller than that in the first oxide semiconductor film.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and method for manufacturing the same

ActiveUS20130092932A1Simple interfaceIncrease oxygen concentrationSolid-state devicesSemiconductor devicesProduction rateDevice material

An object is to provide a semiconductor device including a thin film transistor with excellent electrical characteristics and high reliability and a method for manufacturing the semiconductor device with high mass productivity. A main point is to form a low-resistance oxide semiconductor layer as a source or drain region after forming a drain or source electrode layer over a gate insulating layer and to form an oxide semiconductor film thereover as a semiconductor layer. It is preferable that an oxygen-excess oxide semiconductor layer be used as a semiconductor layer and an oxygen-deficient oxide semiconductor layer be used as a source region and a drain region.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and method for manufacturing the same

InactiveUS20110309466A1Improve stabilitySmall parasitic capacitanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

The semiconductor device includes a first-conductivity-type region (an N-type well region, for example) and a first second-conductivity-type region (a P-type semiconductor substrate, for example) positioned to cover a lower surface of the first-conductivity-type region, a second second-conductivity-type region (a P-type well region, for example) that is positioned to surround the side faces of the first-conductivity-type region and is in contact with the first second-conductivity-type region, a guard ring that is electrically connected to the second second-conductivity-type region and is also electrically connected to a fixed potential terminal, an insulating film positioned to cover an upper surface of the first-conductivity-type region, and an analog element (a resistor element, for example) placed on the insulating film.

Owner:RENESAS ELECTRONICS CORP

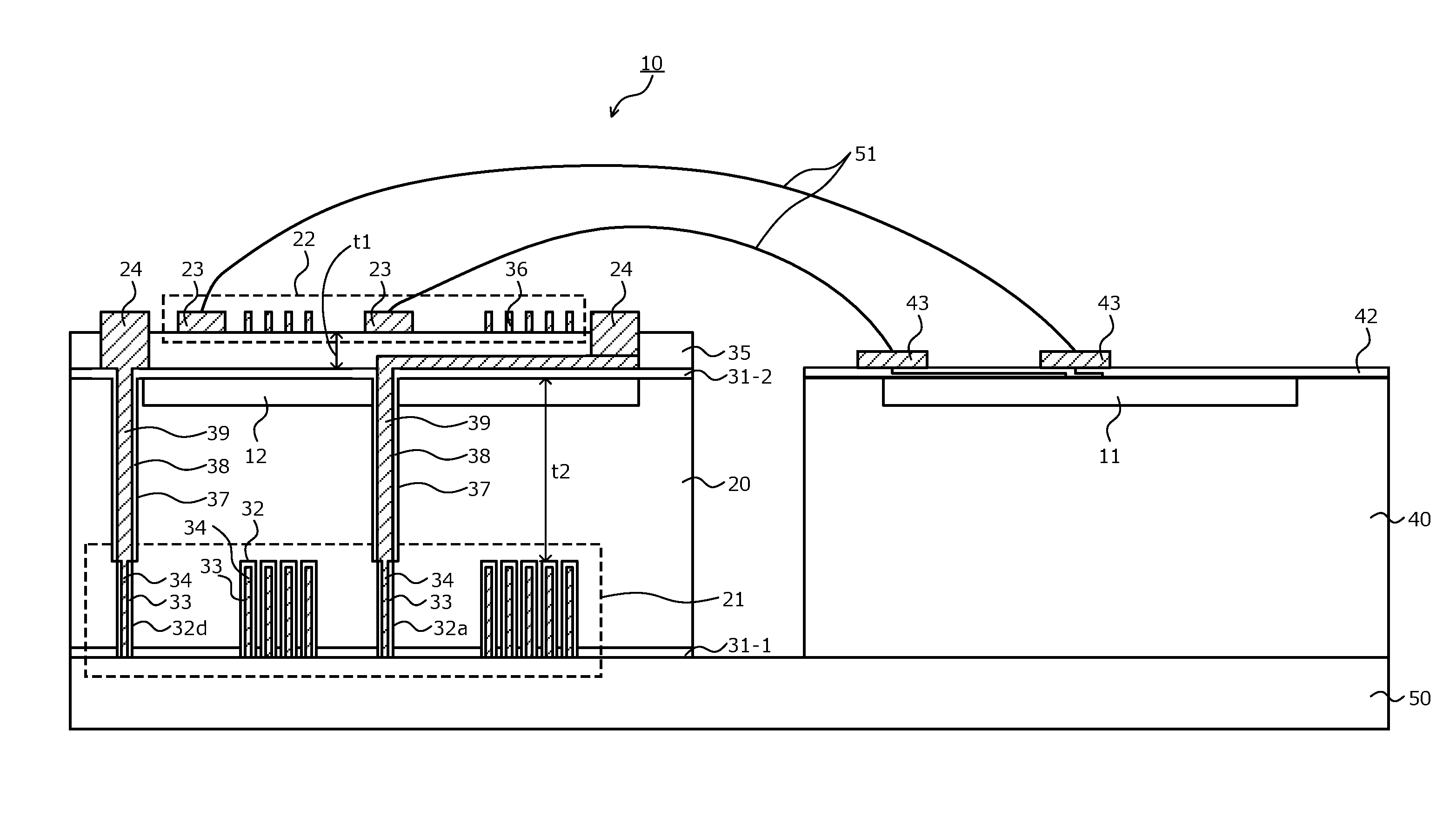

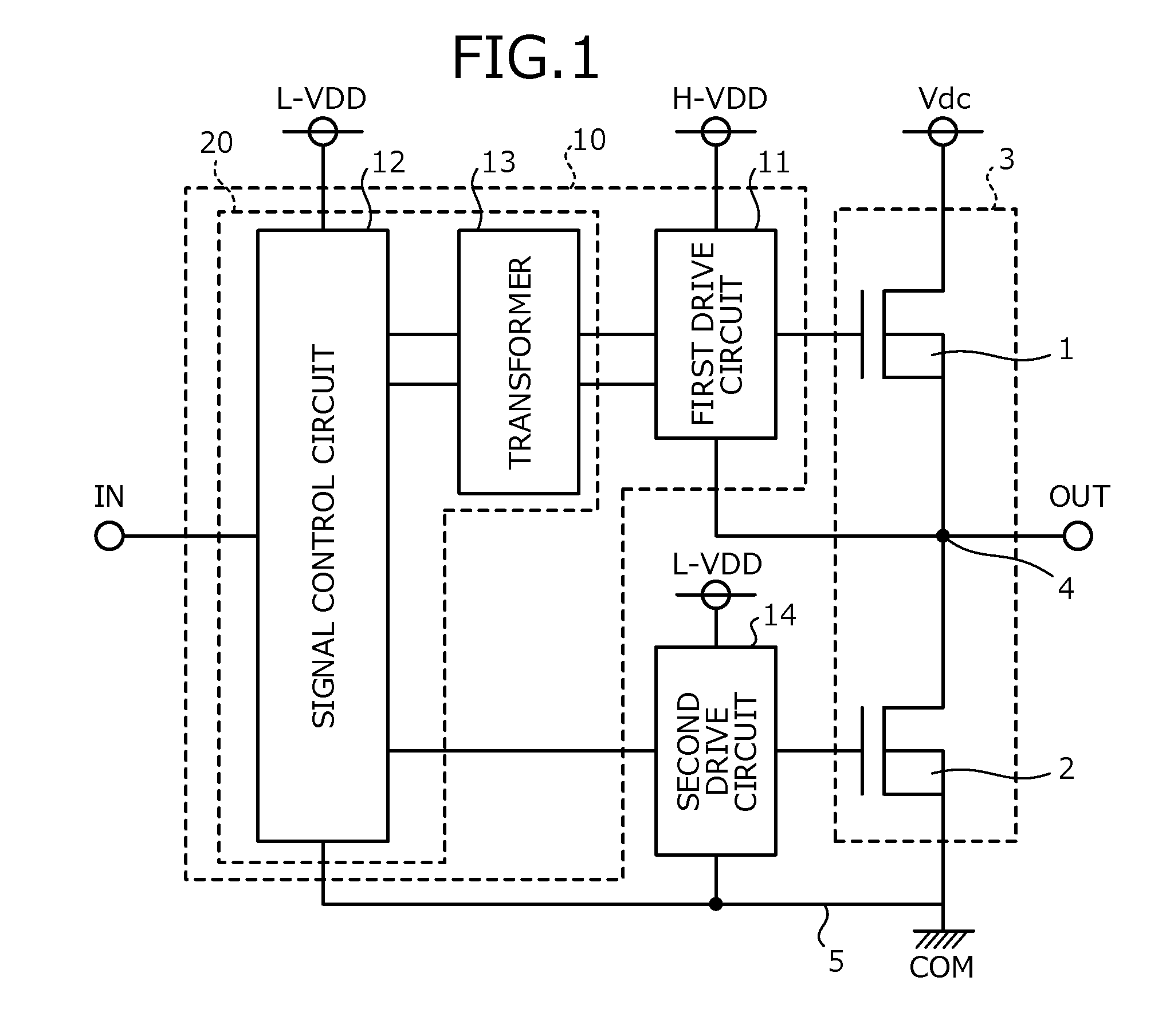

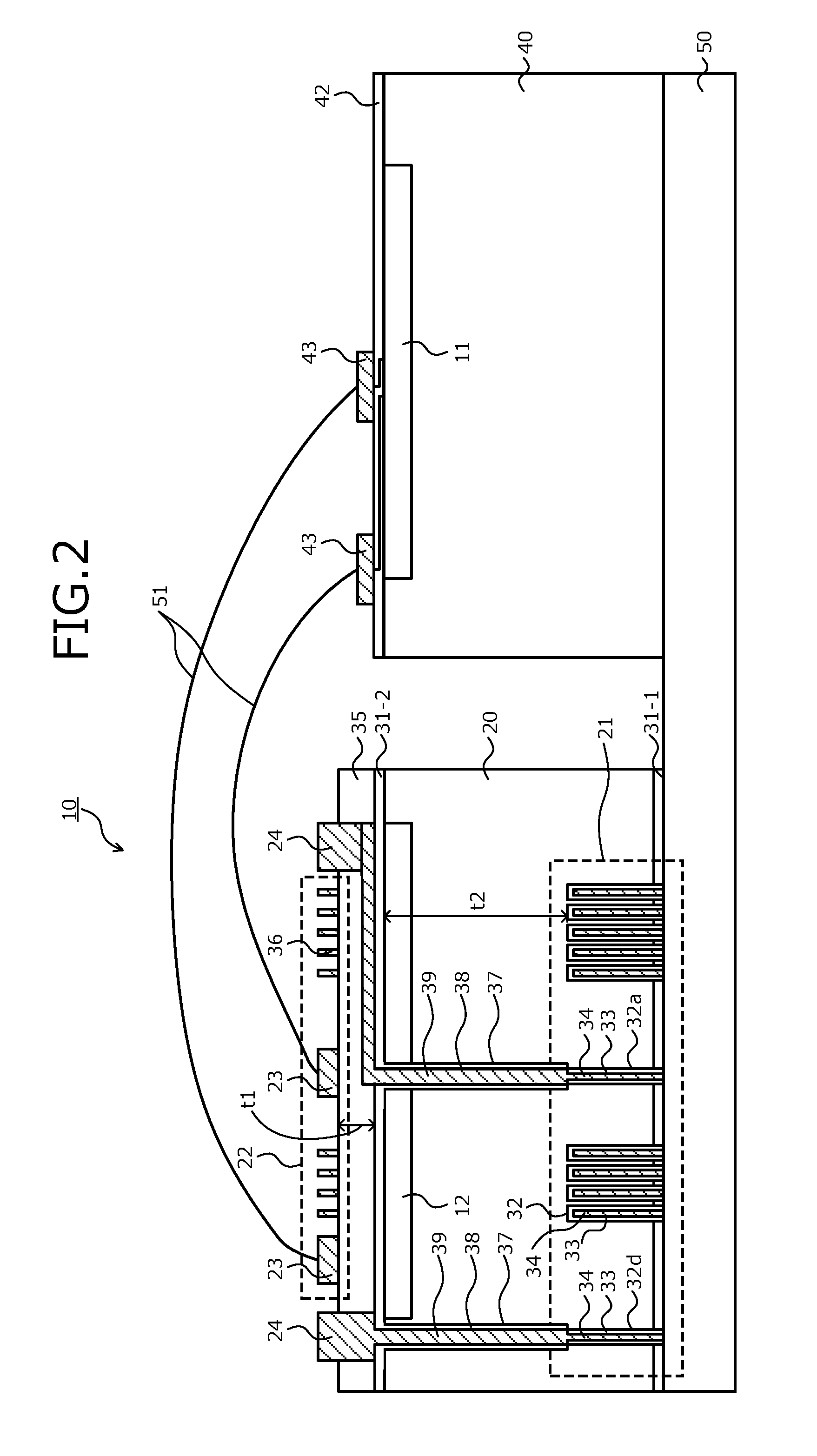

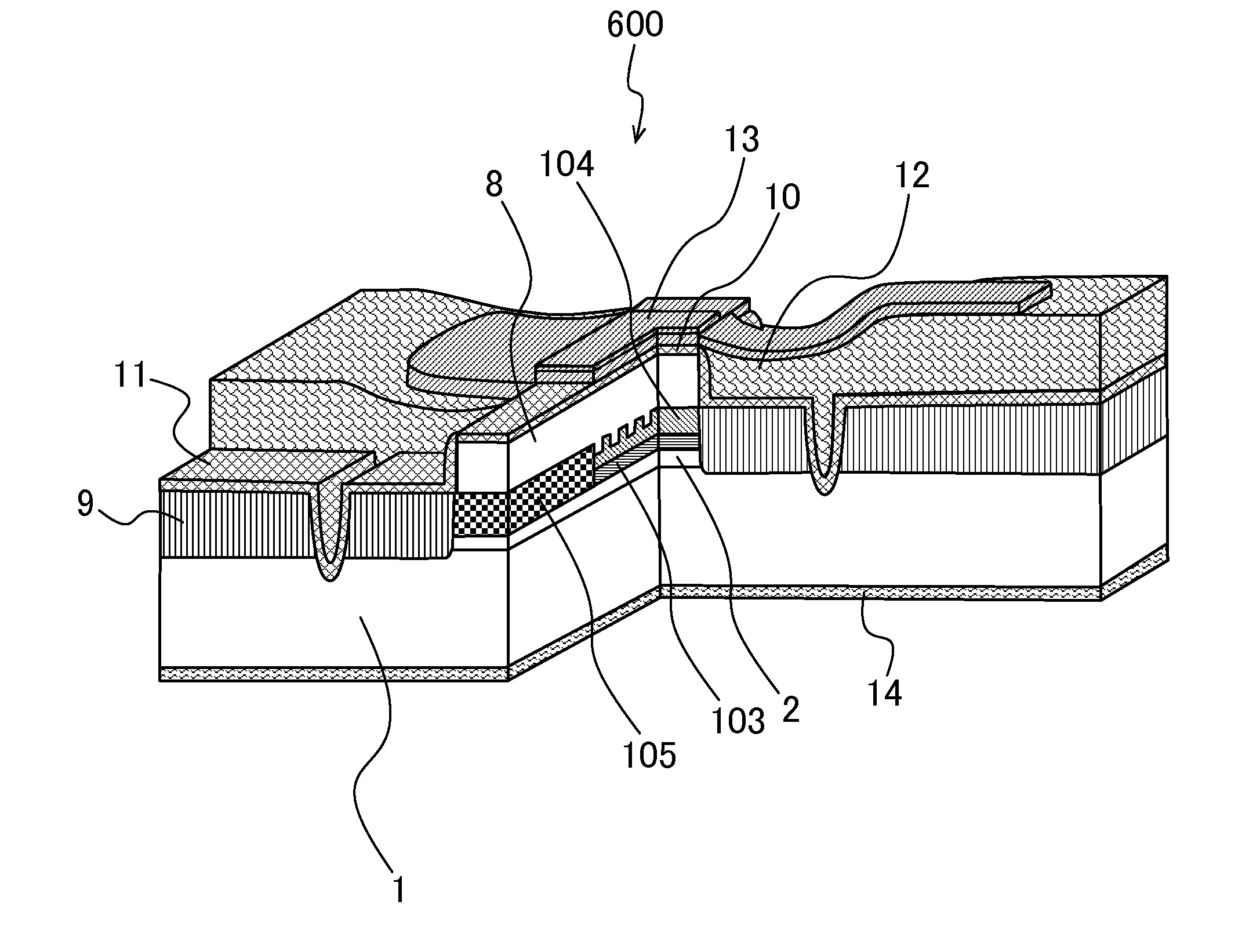

Isolator and method of manufacturing isolator

ActiveUS20170005046A1Small sizeIncrease resistanceSemiconductor/solid-state device detailsSolid-state devicesTransformerEngineering

An isolator is configured by a transmission circuit, a transformer, and a reception circuit. A first coil of the transformer is disposed on a back surface of a first semiconductor substrate; a transmission circuit and a second coil of the transformer are disposed on a front surface. The first coil is embedded within a coil trench, is led out through an embedded via-metal-film to a substrate front surface, and is electrically connected to the transmission circuit. The second coil is disposed on an insulating layer of the substrate front surface. The reception circuit is disposed on a front surface of a second semiconductor substrate. The second coil and the reception circuit are electrically connected to each other by connecting first and third electrode pads disposed respectively on the front surfaces of the first and second semiconductor substrates through wires.

Owner:FUJI ELECTRIC CO LTD

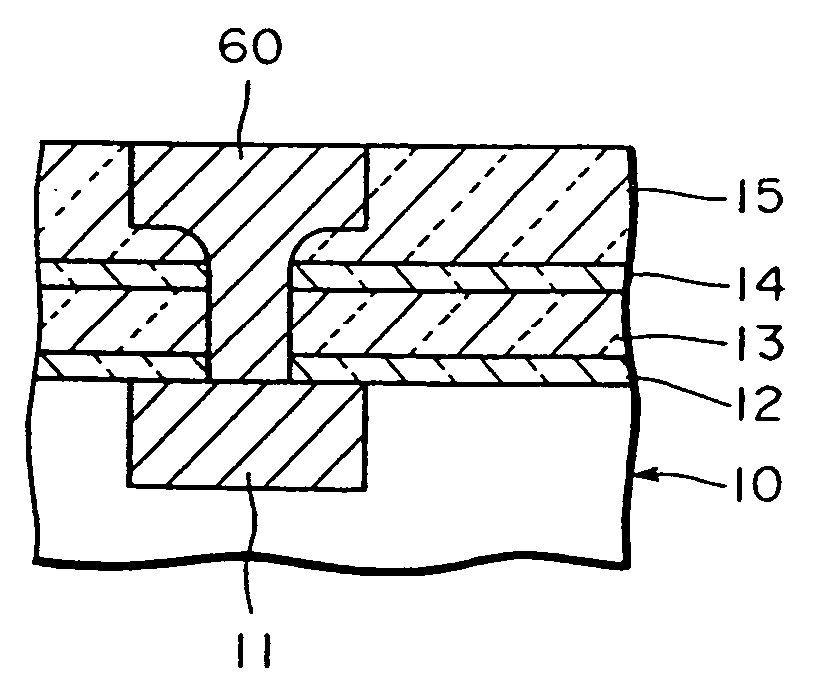

Semiconductor device with dual damascene wiring

InactiveUS7119009B2Small parasitic capacitanceAbnormal etching is preventedSemiconductor/solid-state device detailsSolid-state devicesCapacitanceSurface layer

Owner:TRINITY SEMICON RES

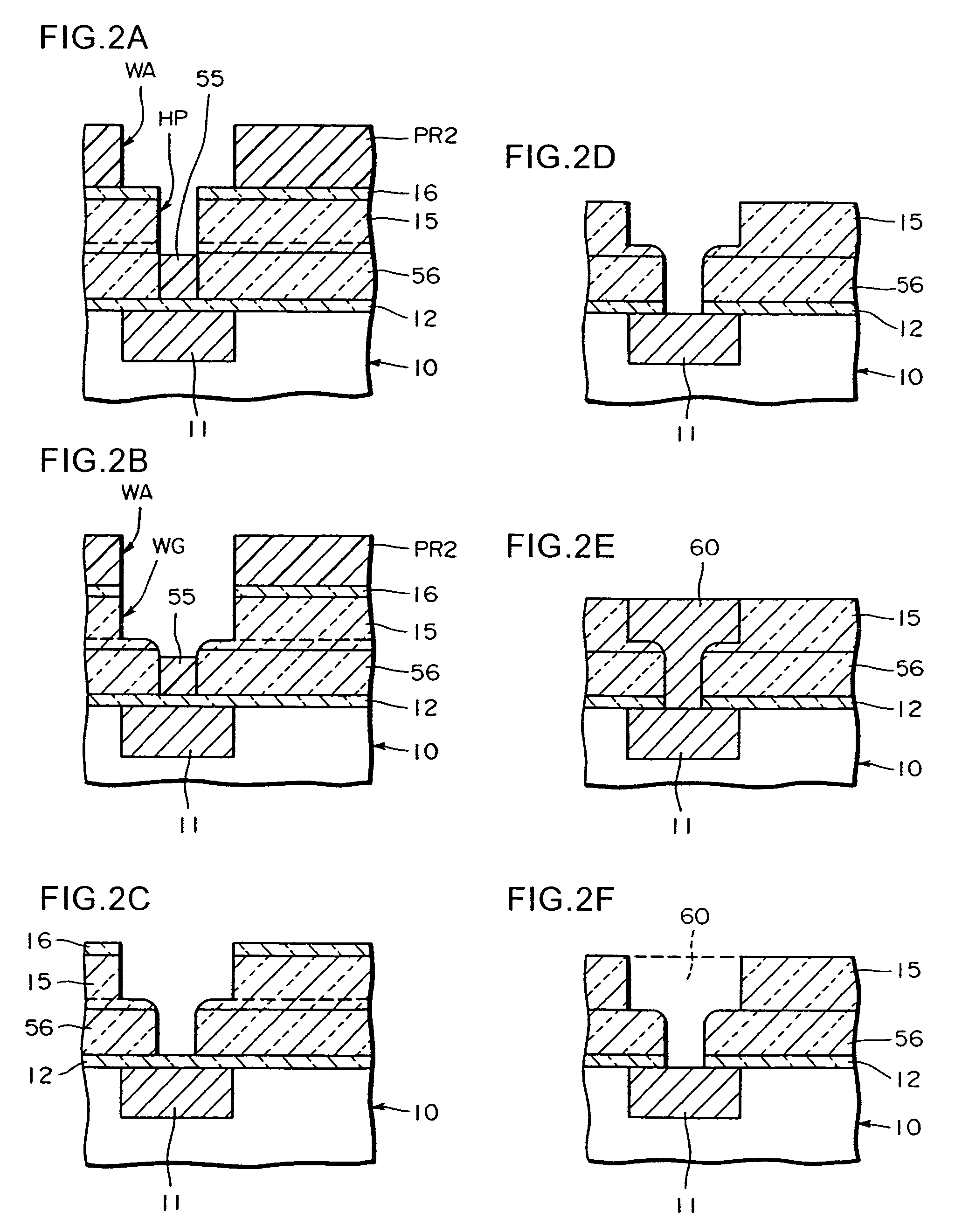

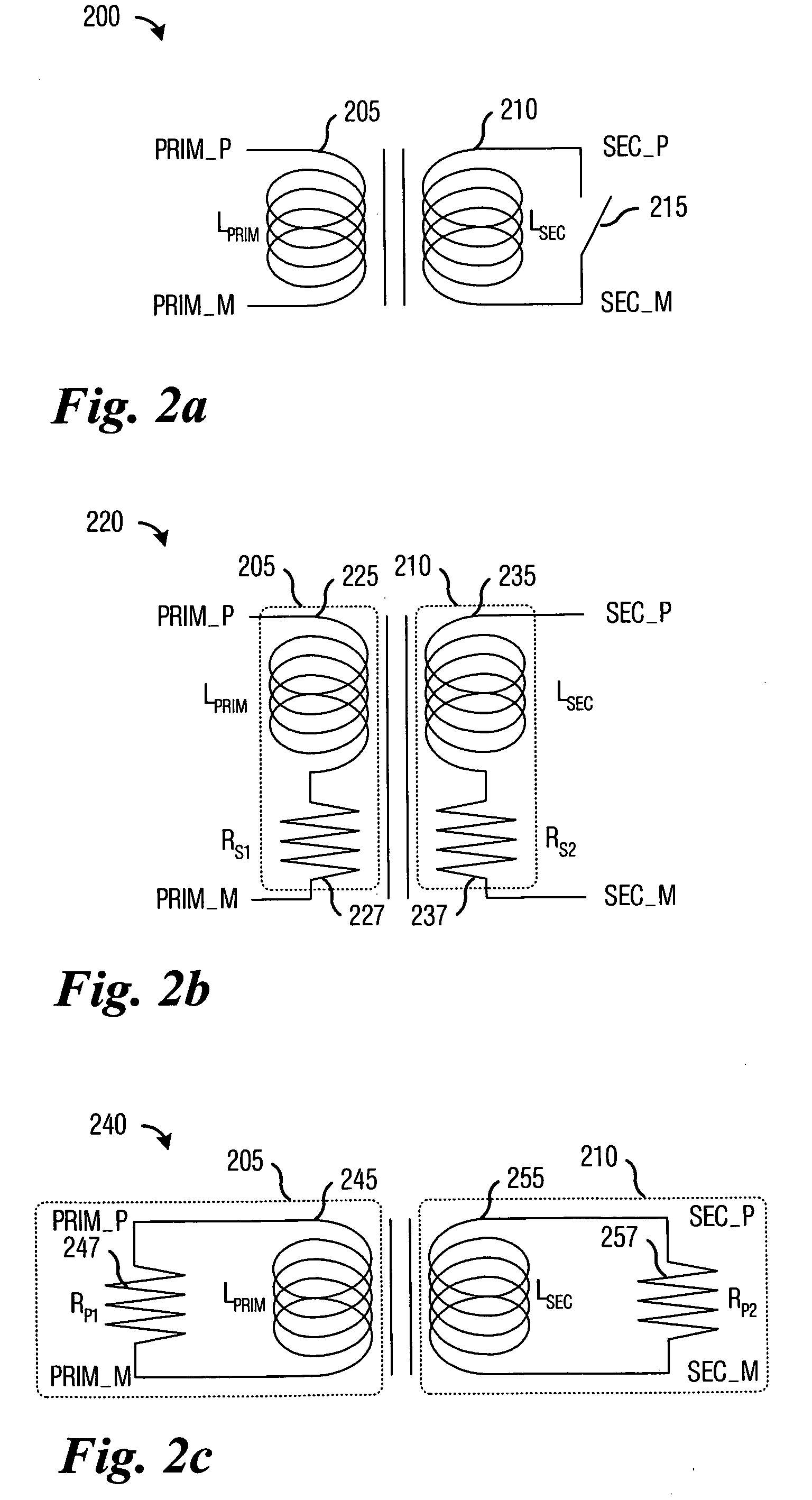

System and method for increasing radio frequency (RF)/microwave inductor-capacitor (LC) oscillator frequency tuning range

ActiveUS20050184820A1Reduced footprintIncrease frequencyPulse automatic controlOscillations generatorsInductorRadio frequency

System and method for increasing the frequency tuning range of a RF / microwave LC oscillator. A preferred embodiment comprises a voltage controlled oscillator (VCO) configured to generate an output signal at a frequency that is dependent upon a magnitude of an input voltage level and an effective inductance of an inductive load and a variable inductor coupled to the VCO. The variable inductor comprises a primary inductor coupled to the VCO to produce a magnetic field based upon a current flowing through the primary inductor and a secondary inductor magnetically coupled to the primary inductor, the secondary inductor to affect the magnitude of the effective inductance of the primary inductor.

Owner:TEXAS INSTR INC

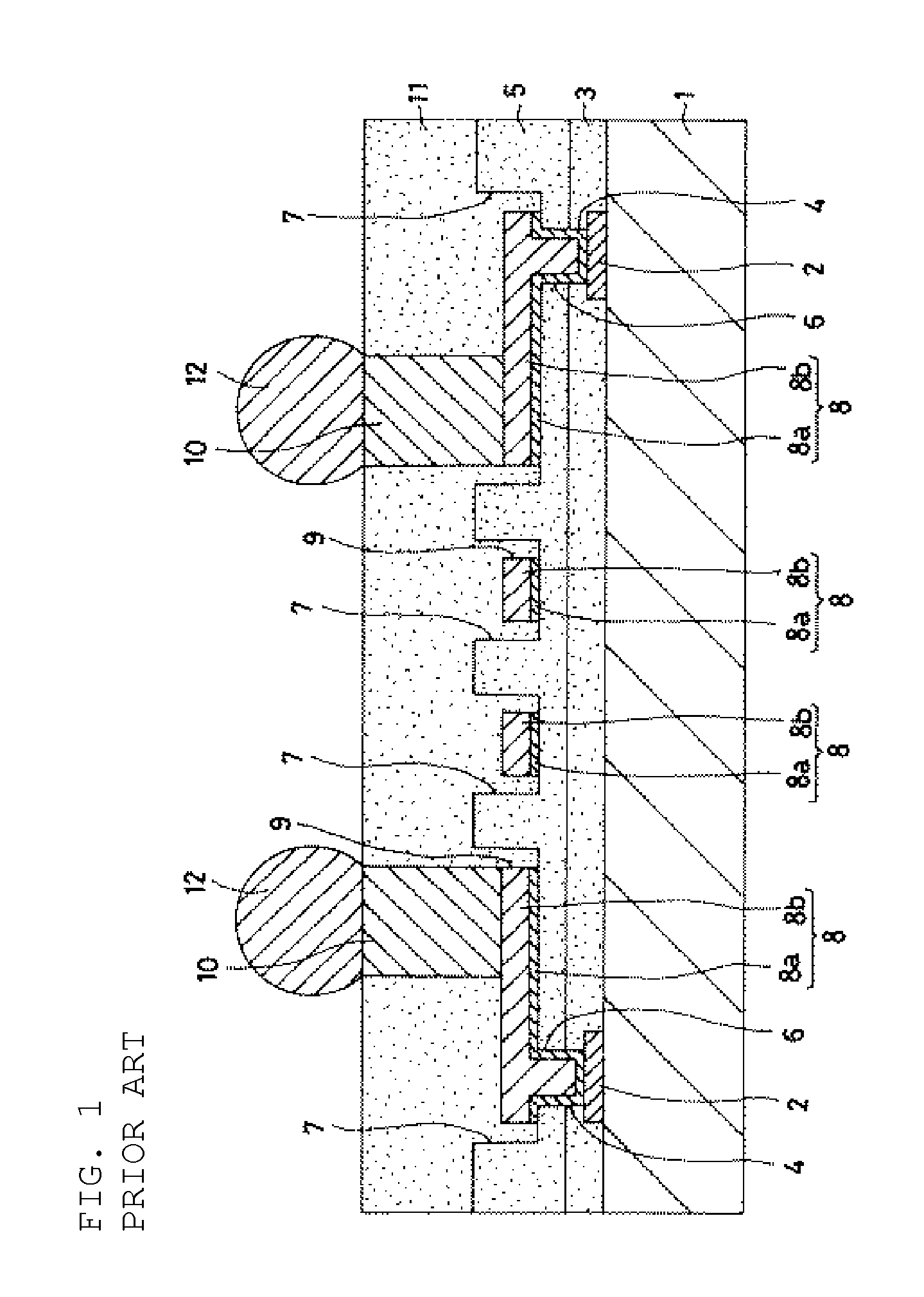

ESD protection device

ActiveUS20130168837A1Small parasitic capacitanceExcellent high frequency characteristicSemiconductor/solid-state device detailsSolid-state devicesPhysicsHemt circuits

An ESD protection device includes a semiconductor substrate including input / output electrodes and a rewiring layer located on the top surface of the semiconductor substrate. An ESD protection circuit is provided in the top layer of the semiconductor substrate, and the input / output electrodes are connected to the ESD protection circuit. The rewiring layer includes interlayer wiring lines, in-plane wiring lines, and post-shaped electrodes. First ends of the interlayer wiring lines provided in the thickness direction are connected to the input / output electrodes provided on the top surface of the semiconductor substrate and the second ends are connected to first ends of the in-plane wiring lines extending in the plane direction. The distance between the centers of the first and second post-shaped electrodes is larger than the distance between the centers of the first and second input / output electrodes.

Owner:MURATA MFG CO LTD

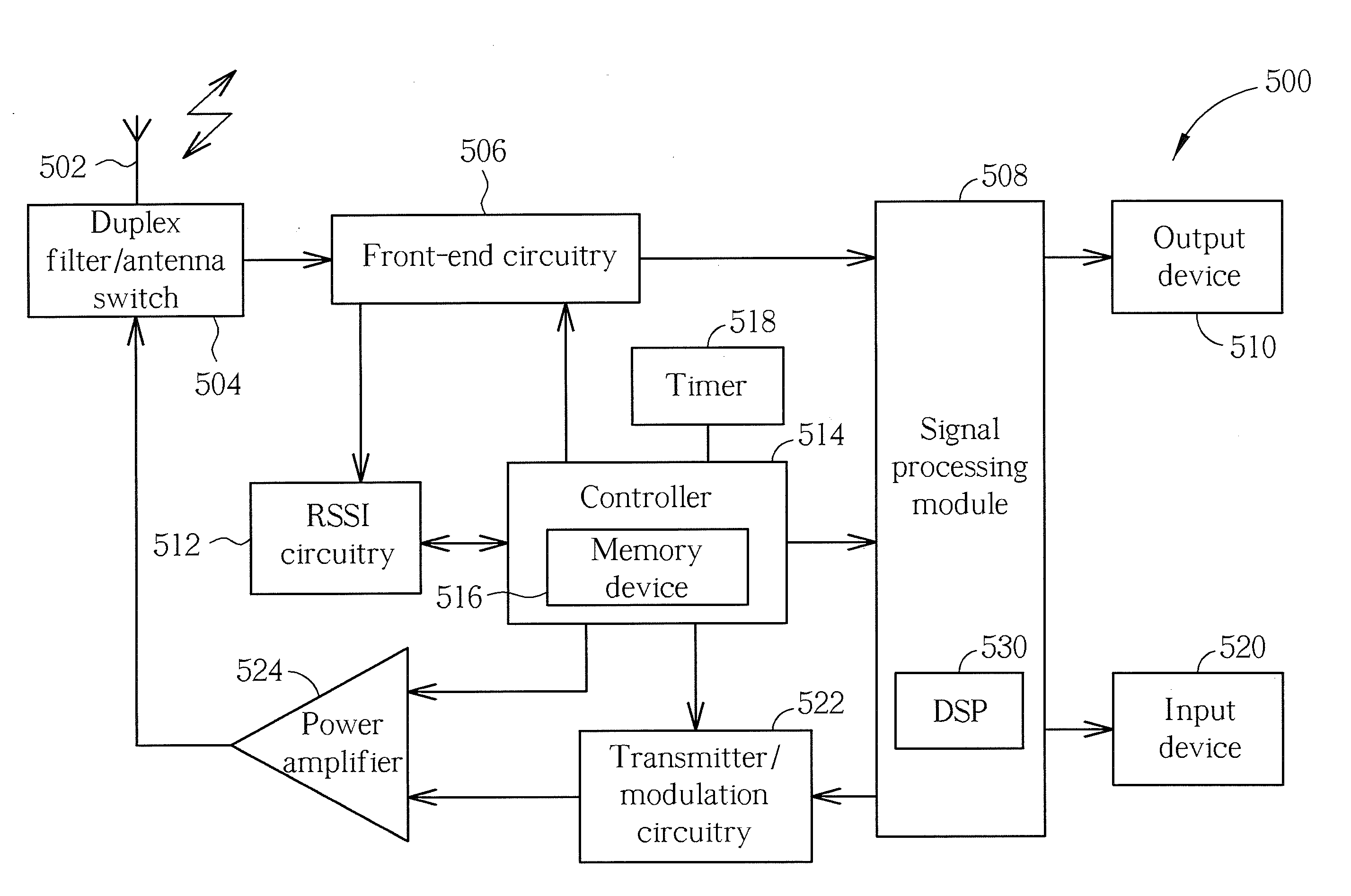

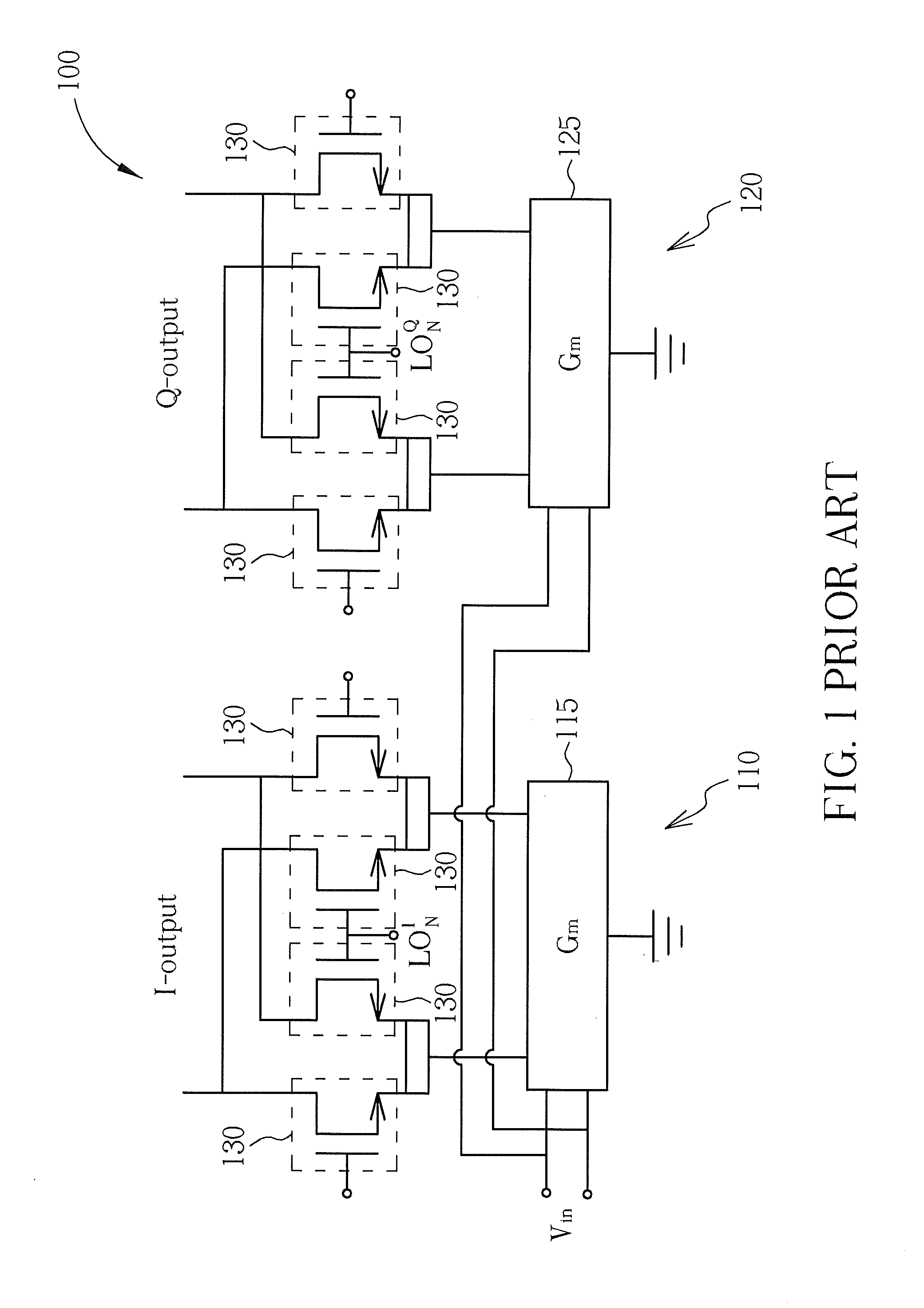

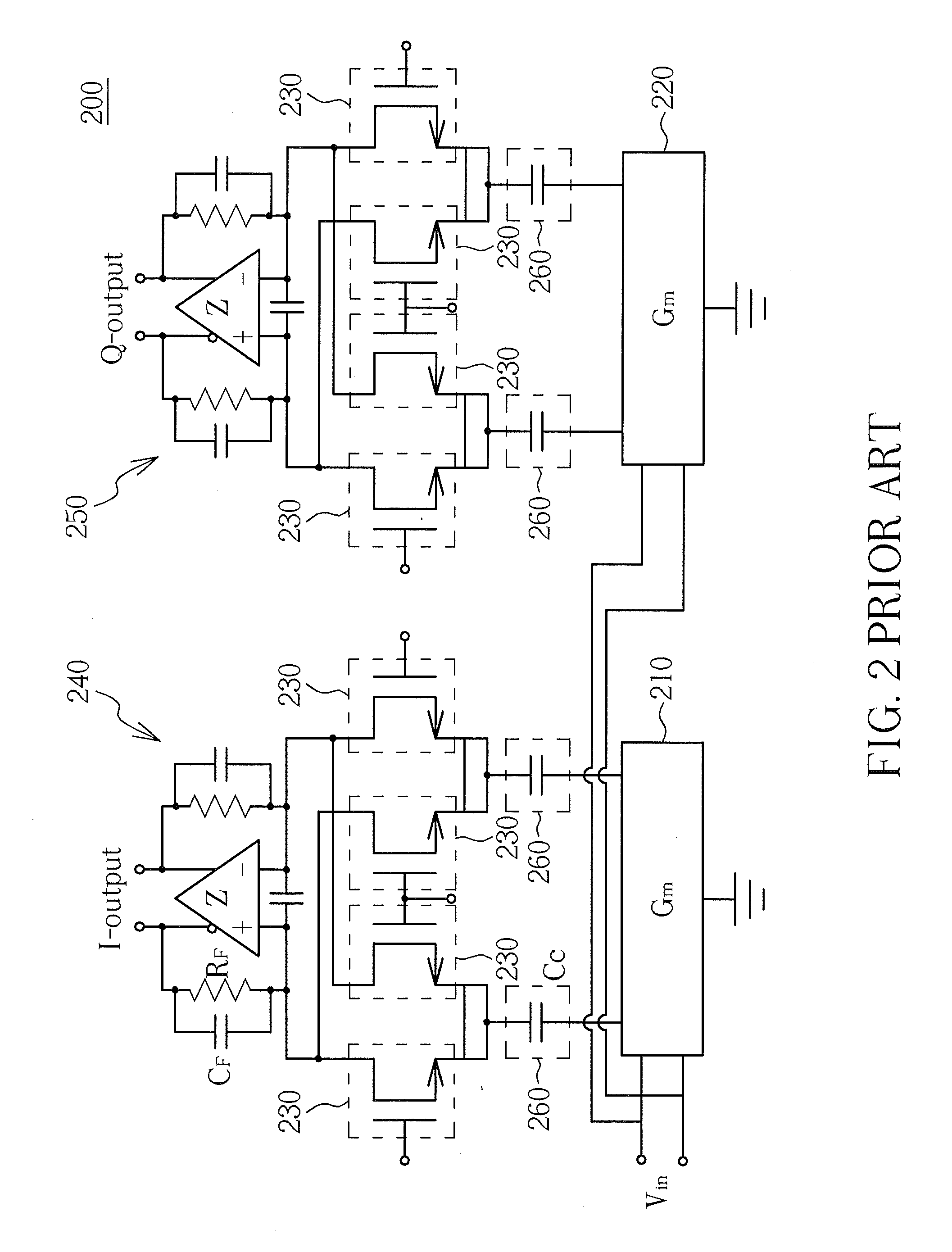

Mixer circuit, integrated circuit device and radio frequency communication unit

ActiveUS20110065412A1Small parasitic capacitanceReduce riskTransmissionFrequency-changer modificationsPower flowFrequency conversion

A mixer circuit comprises an input stage arranged to convert an input voltage signal received at an input of the mixer circuit into at least one current signal, and a frequency conversion stage comprising at least one switching element arranged to convert a signal component of the at least one current signal from an input frequency to a output frequency. The input stage comprises at least one resistance connected between the input of the mixer circuit and the at least one switching element. The at least one switching element and the at least one resistance are arranged such that the at least one switching element comprises a ‘turn-on’ resistance that exhibits a resistivity that is a factor less than the at least one resistance connected thereto.

Owner:MEDIATEK SINGAPORE PTE LTD SINGAPORE

Semiconductor device and method for manufacturing the same

ActiveUS9660100B2ResponsivenessReduced responsivenessTransistorSemiconductor/solid-state device detailsElectrical conductorCompound (substance)

A semiconductor device is formed in such a manner that a first insulator, a first oxide semiconductor, and a first conductor are formed; the first conductor is processed to form a second conductor; the first oxide semiconductor is processed to form a second oxide semiconductor; a second insulator is formed over the second conductor; a third insulator is formed over the second insulator; a fourth insulator is formed over the third insulator; the fourth insulator, the third insulator, the second insulator, and the second conductor are selectively processed to partly expose the second oxide semiconductor; a fifth insulator is formed over the second oxide semiconductor and the fourth insulator; and a third conductor is formed over the fifth insulator and then chemical mechanical polishing treatment is performed to expose a top surface of the fourth insulator.

Owner:SEMICON ENERGY LAB CO LTD

Optical semiconductor device

ActiveUS20130208751A1Guaranteed uptimeSmall parasitic capacitanceLaser detailsLaser optical resonator constructionDevice materialLow leakage

In a BH laser which uses InGaAlAs-MQW in an active layer, Al-based semiconductor multi-layer films including an InP buffer layer and an InGaAlAs-MQW layer, and an InGaAsP etching stop layer are formed in a mesa shape, and a p type InP burial layer is buried in side walls of the mesa shape. An air ridge mesa-stripe of a lateral center that is substantially the same as that of the mesa shape is formed on the mesa shape. According to the present structure, a leakage current can be considerably reduced, the light confinement coefficient can be made to be larger than in a BH laser in the related art, and thereby it is possible to implement a semiconductor laser with a low leakage current and a high relaxation oscillation frequency.

Owner:LUMENTUM JAPAN INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com