Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

4516 results about "Second source" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In the electronics industry, a second source is a company that is licensed to manufacture and sell components originally designed by another company (the first source). It is common for engineers and purchasers to avoid components that are only available from a single source, to avoid the risk that a problem with the supplier would prevent a popular and profitable product from being manufactured. For simple components such as resistors and transistors, this is not usually an issue, but for complex integrated circuits, vendors often react by licensing one or more other companies to manufacture and sell the same parts as second sources. While the details of such licenses are usually confidential, they often involve cross-licensing, so that each company also obtains the right to manufacture and sell parts designed by the other.

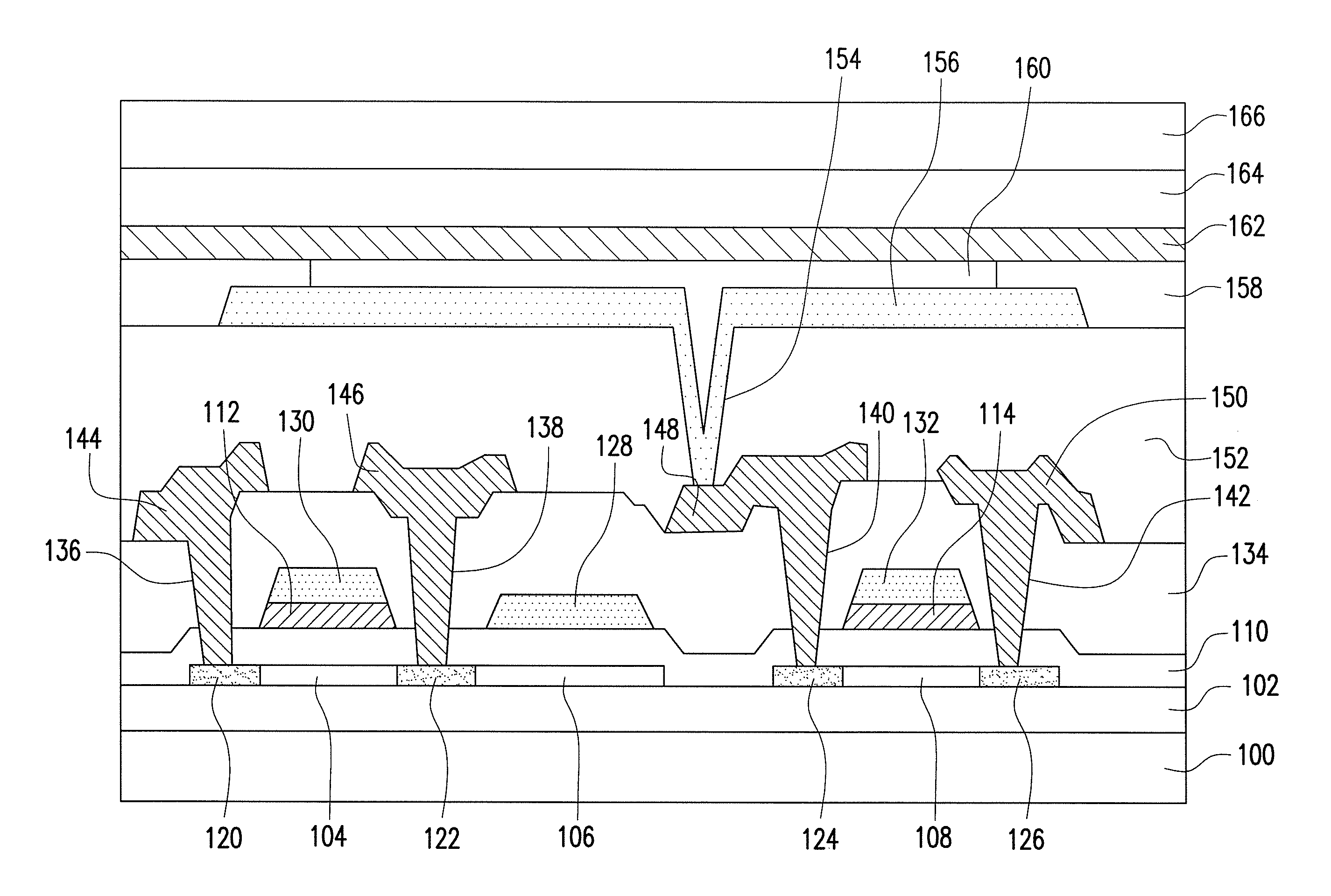

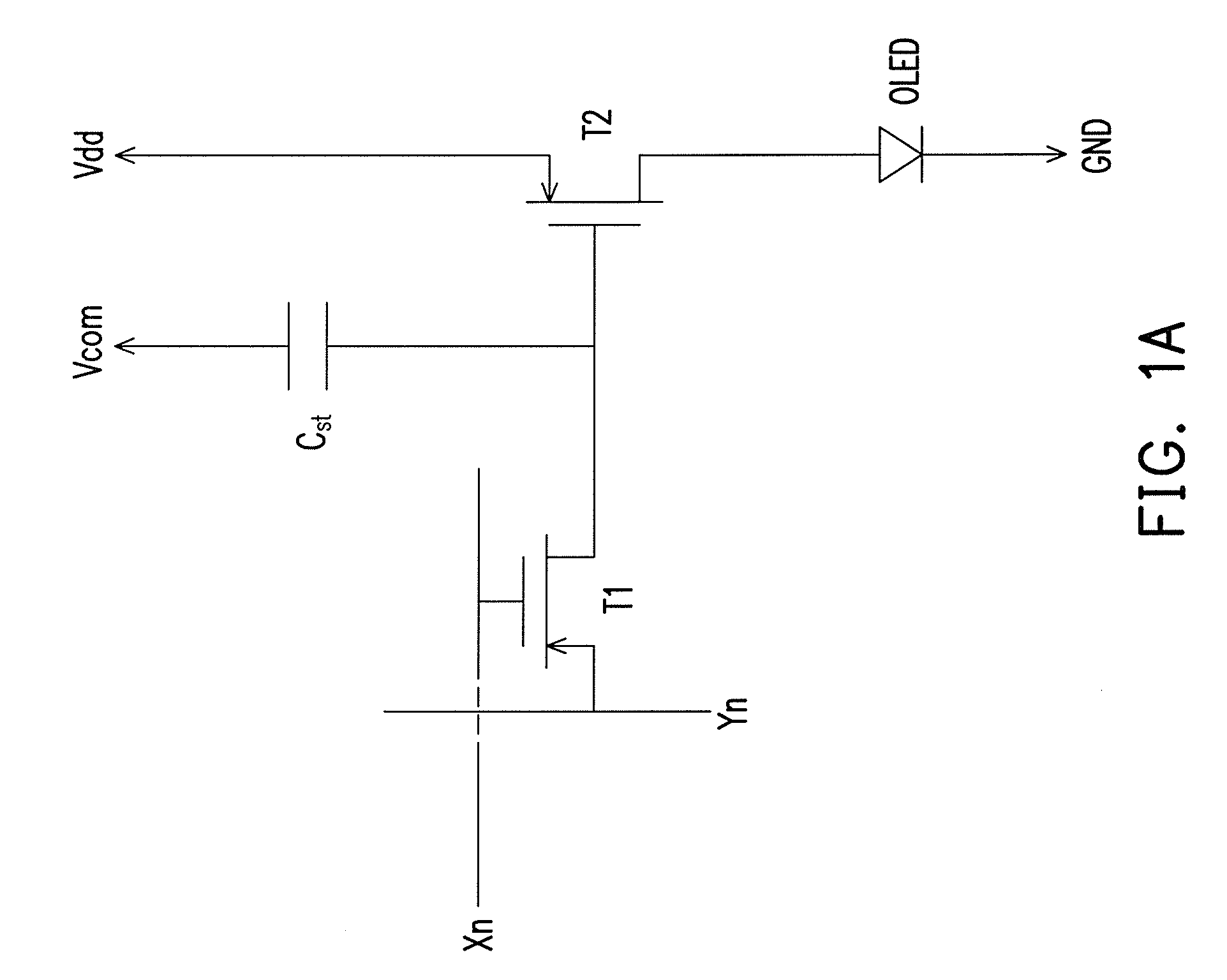

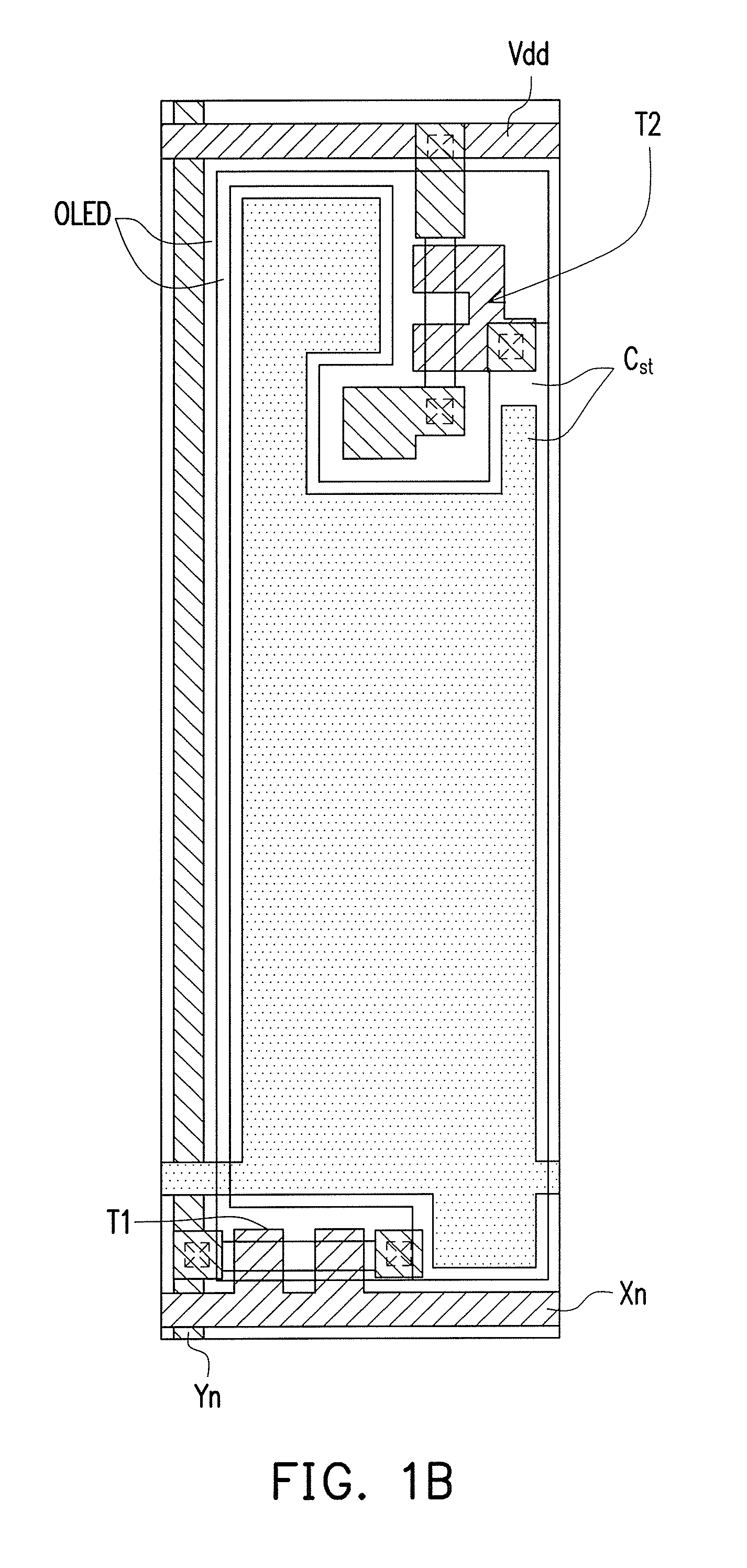

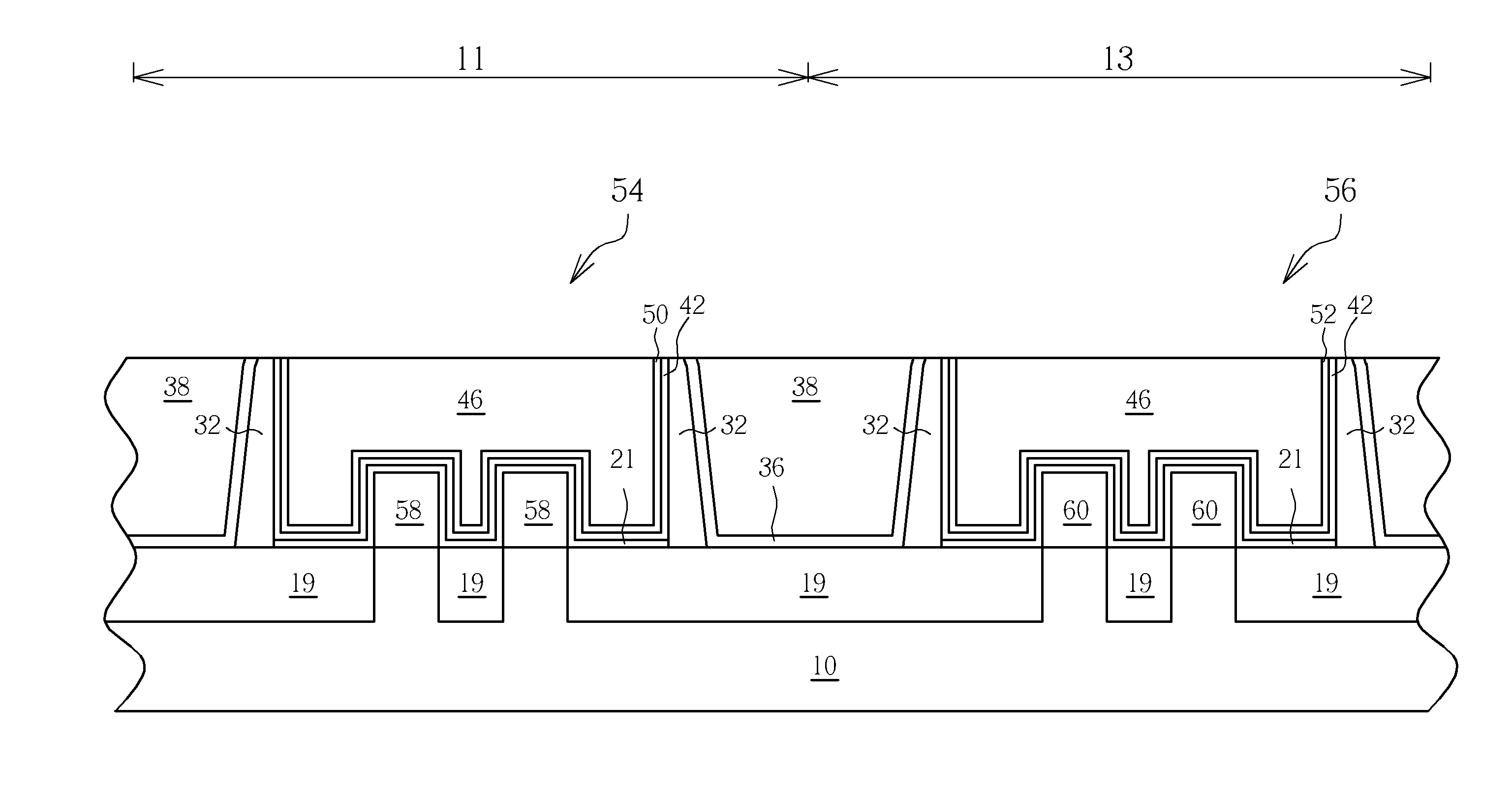

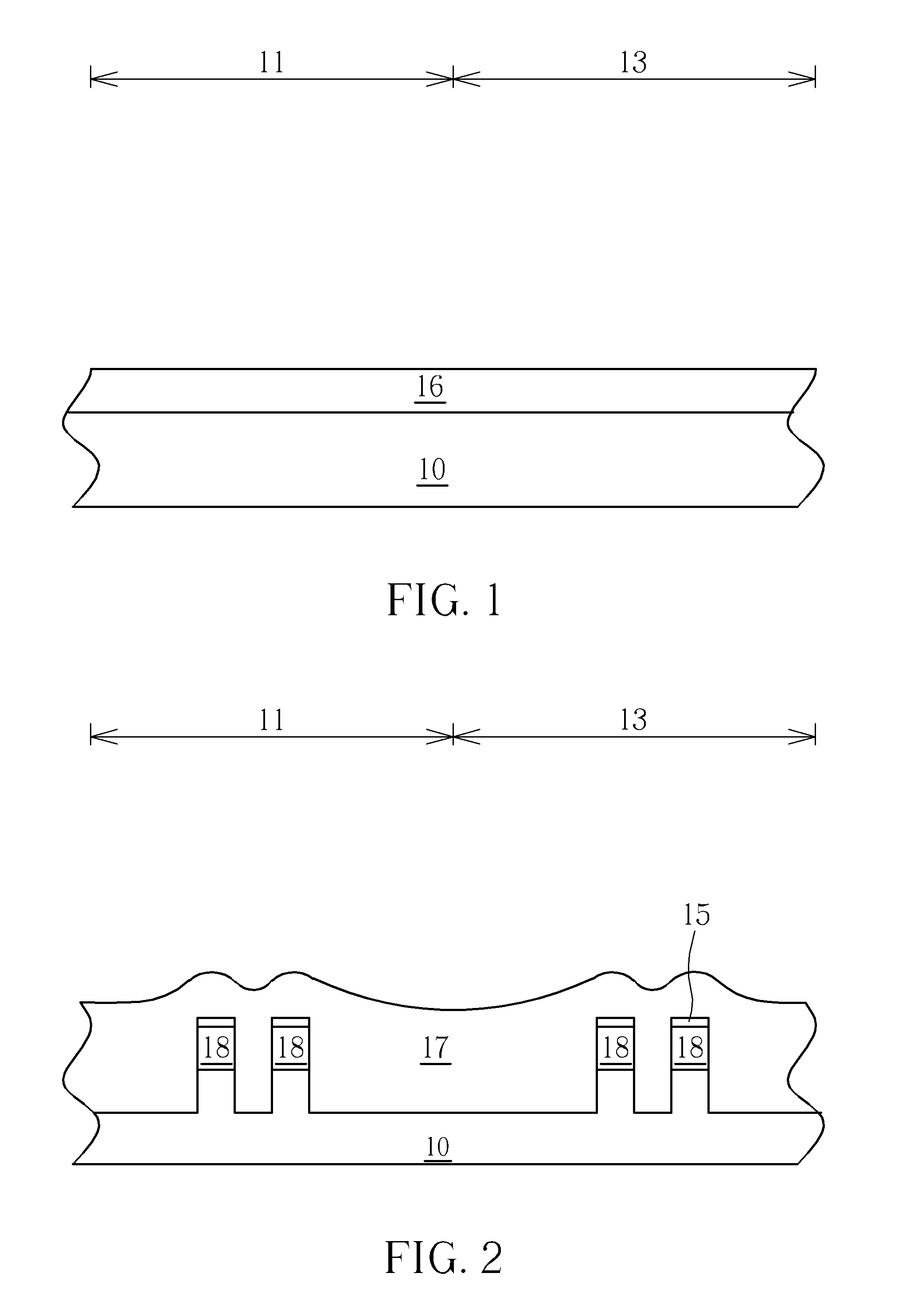

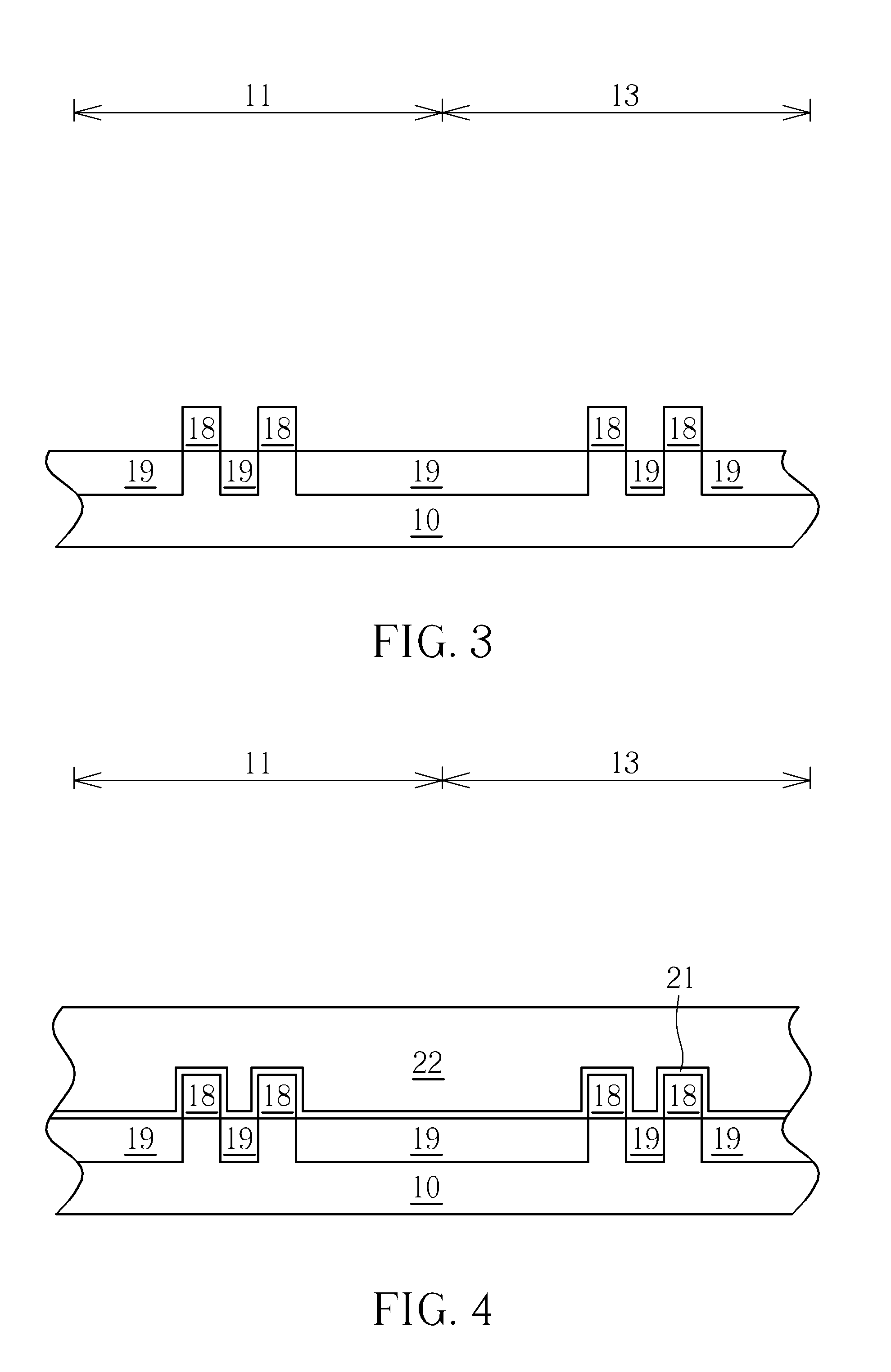

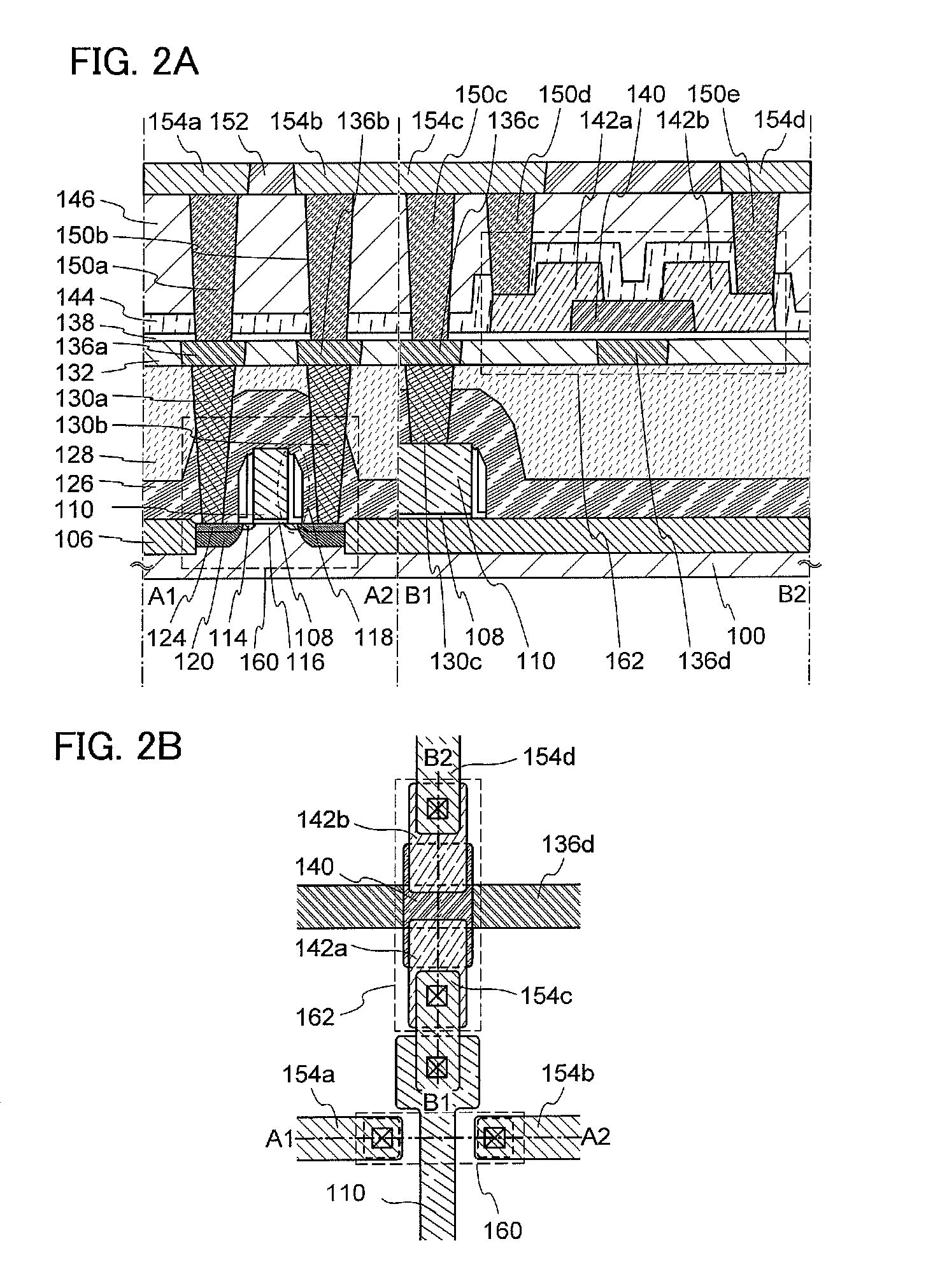

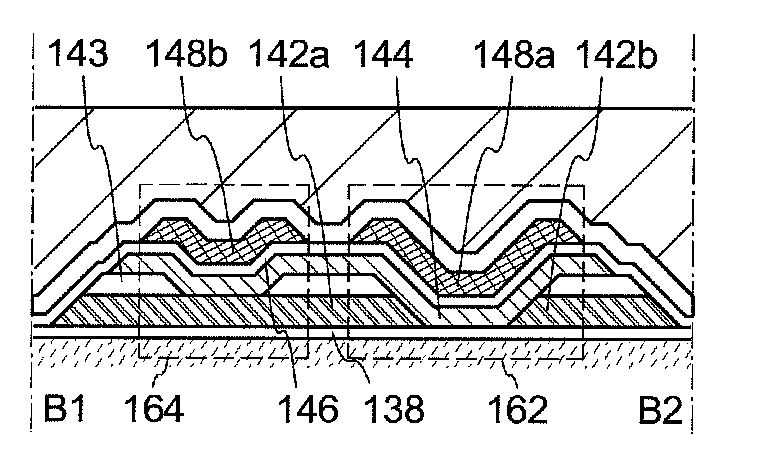

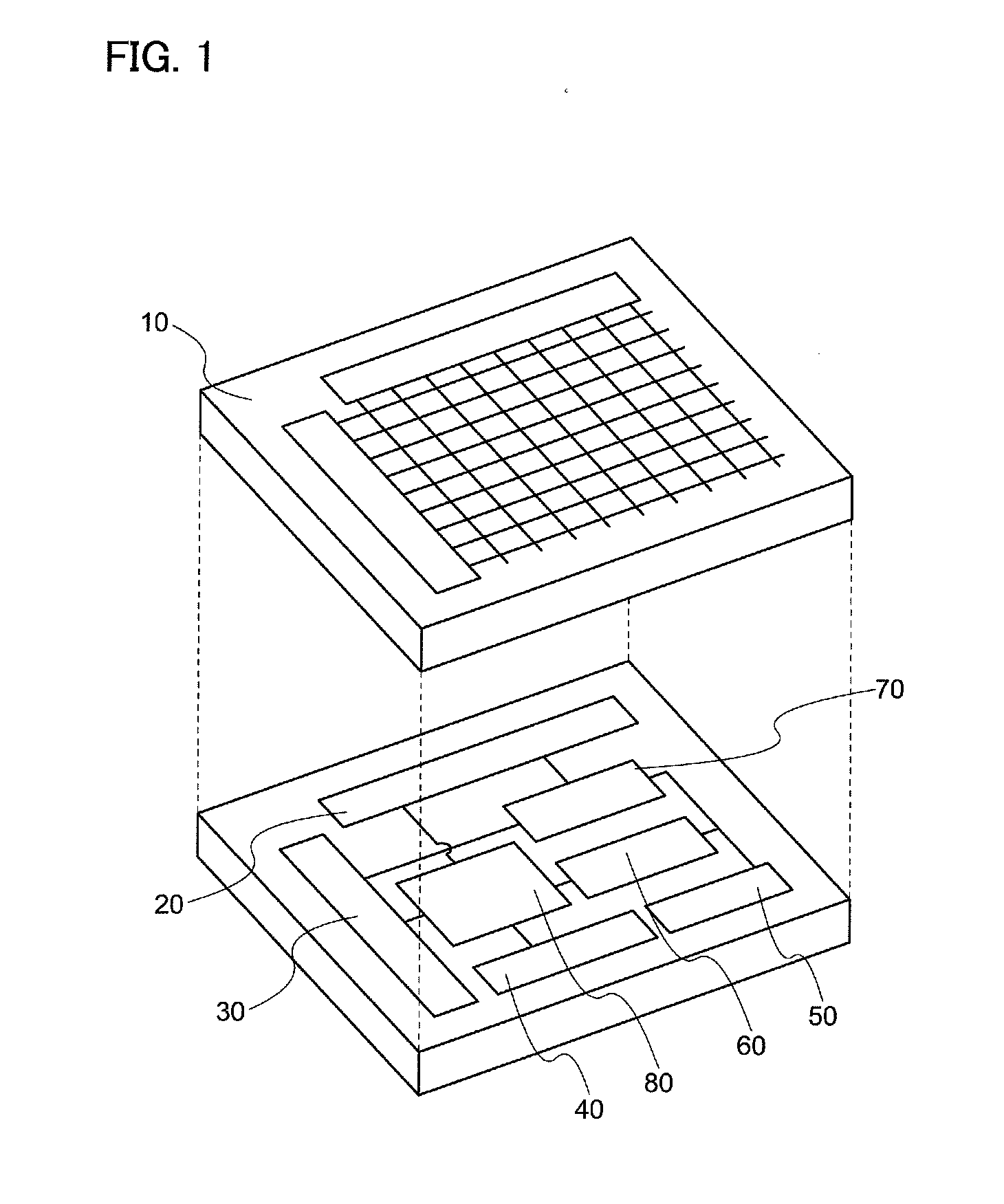

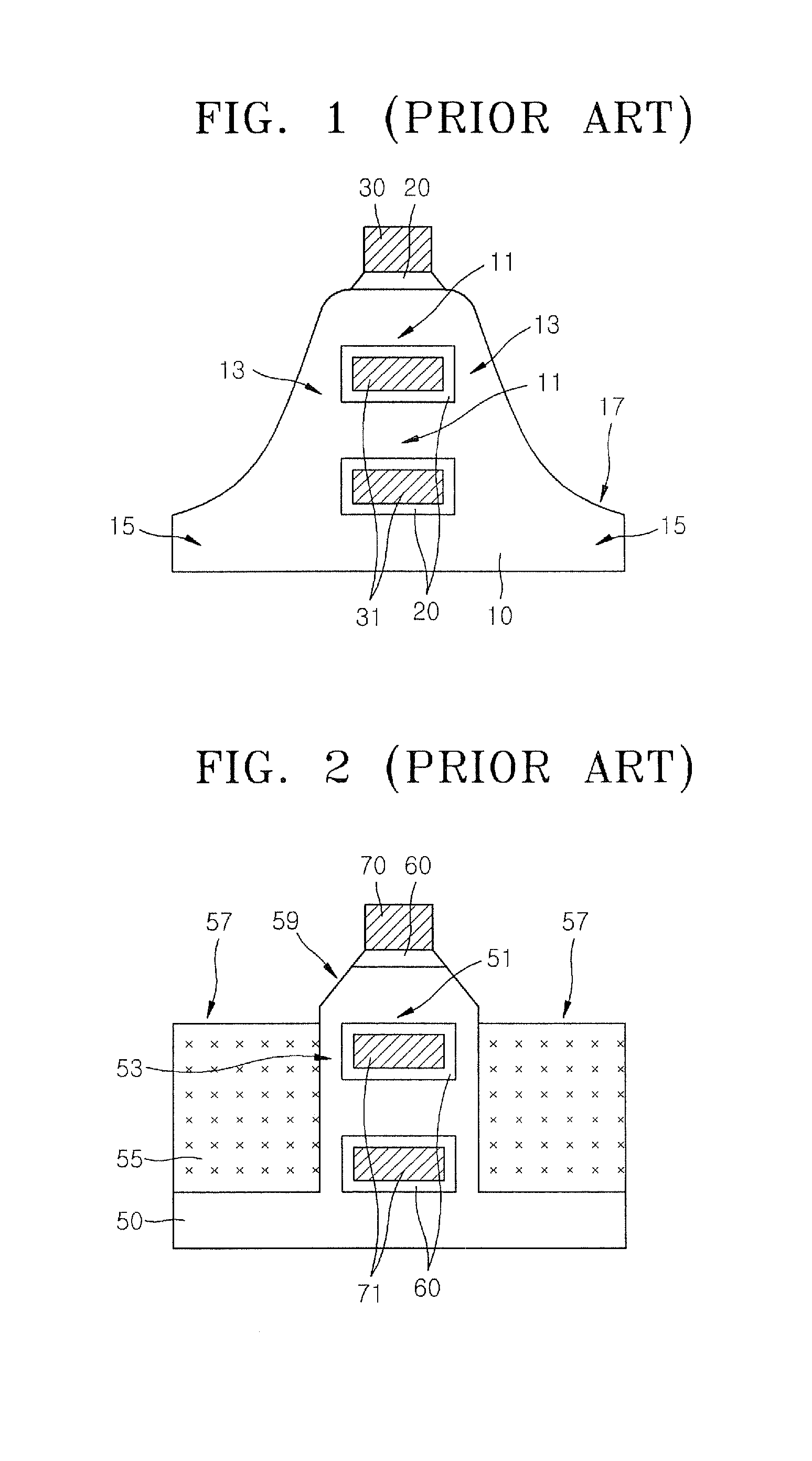

Method for fabricating pixel structure of active matrix organic light-emitting diode

ActiveUS20090068773A1Improve pixel aperture ratioIncrease the aperture ratioSolid-state devicesSemiconductor/solid-state device manufacturingActive matrixScan line

Owner:IND TECH RES INST

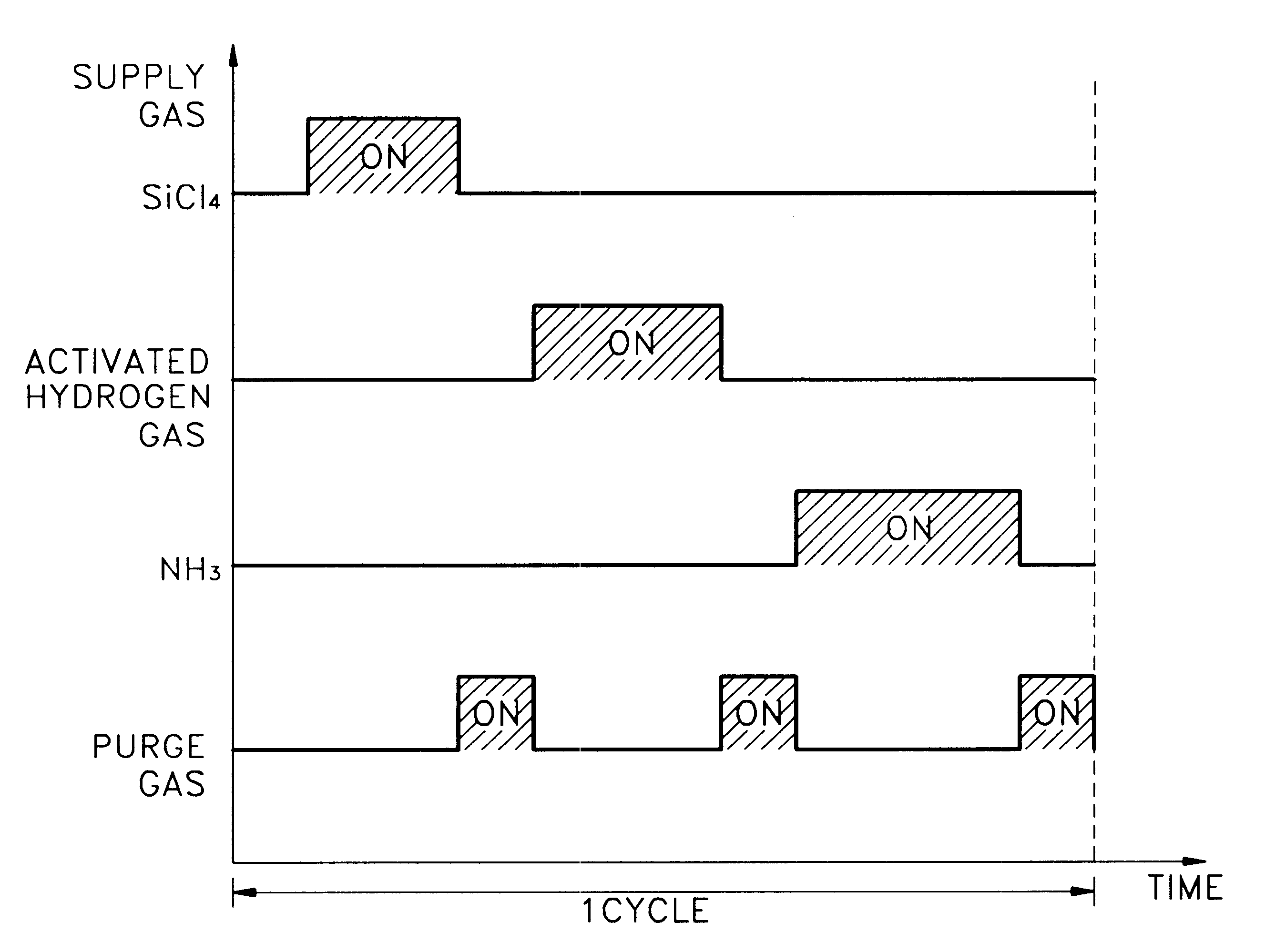

Methods of forming thin films by atomic layer deposition

InactiveUS6468924B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingHydrogenProduct gas

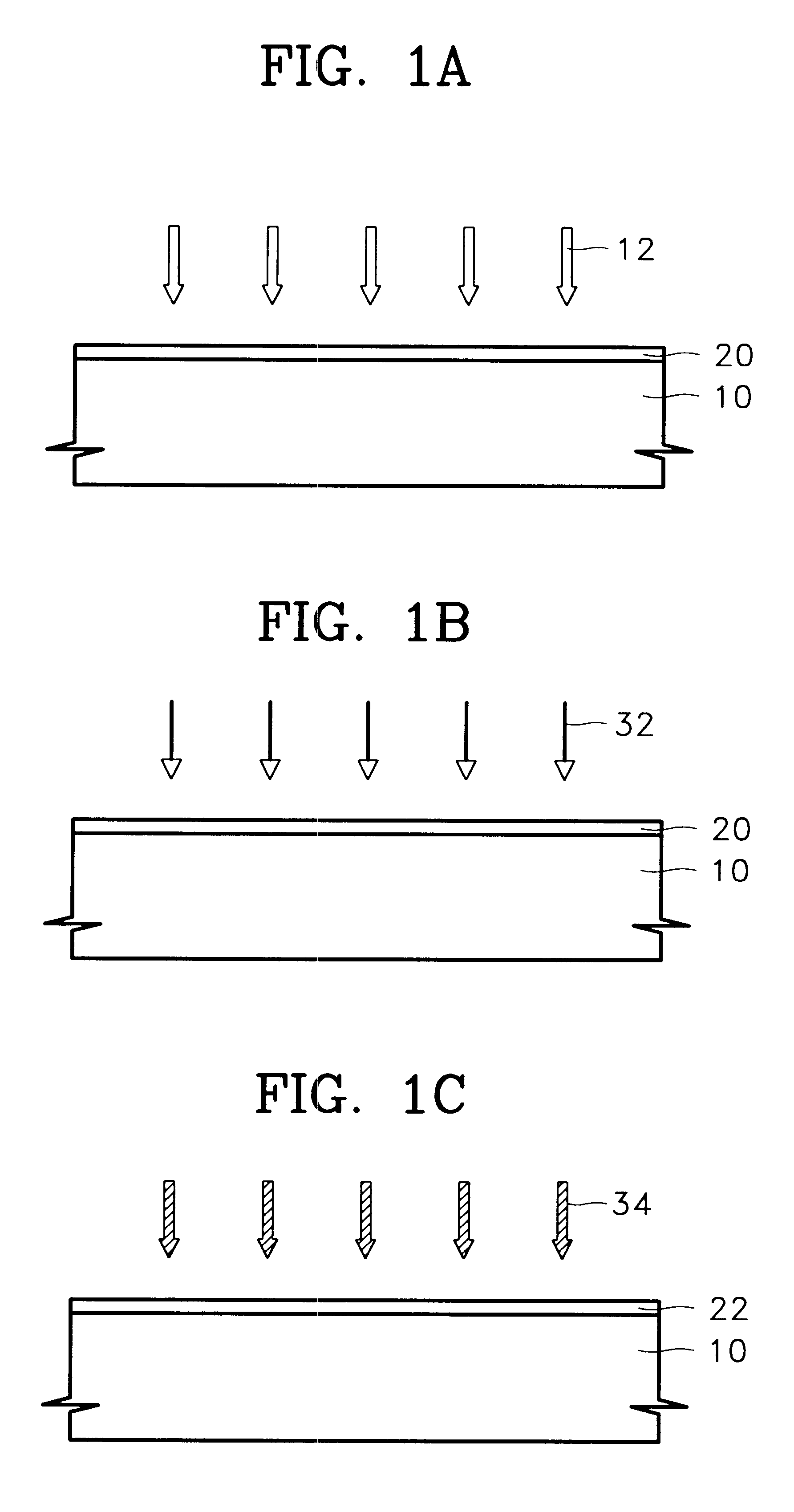

Methods of forming thin films include forming a first layer comprising a first element that is chemisorbed to a surface of a substrate, by exposing the surface to a first source gas having molecules therein that comprise the first element and a halogen. A step is then performed to expose the first layer to an activated hydrogen gas so that halogens associated with the first layer become bound to hydrogen provided by the activated hydrogen gas. The first layer may then be converted to a thin film comprising the first element and a second element, by exposing a surface of the first layer to a second source gas having molecules therein that comprise the second element.

Owner:SAMSUNG ELECTRONICS CO LTD

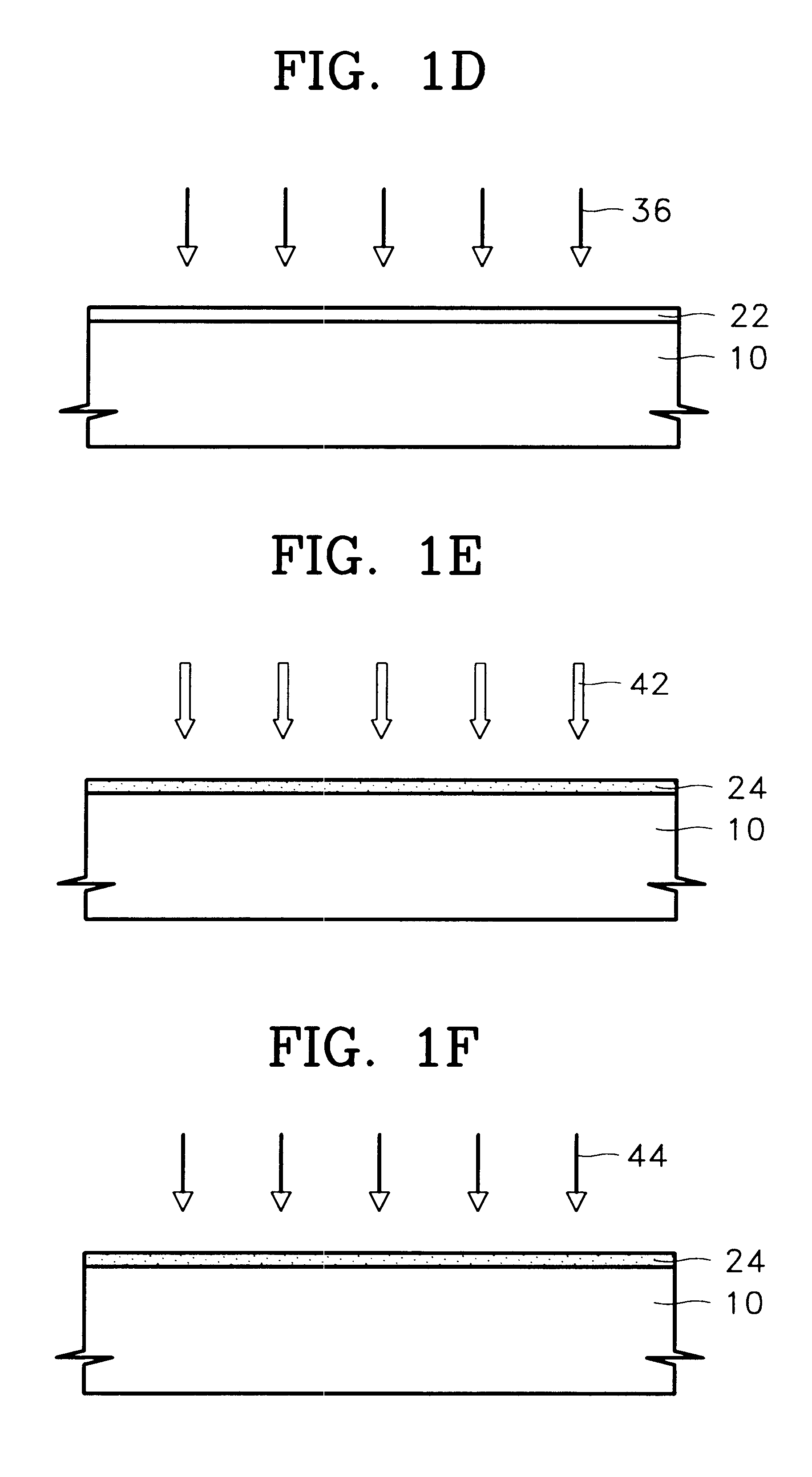

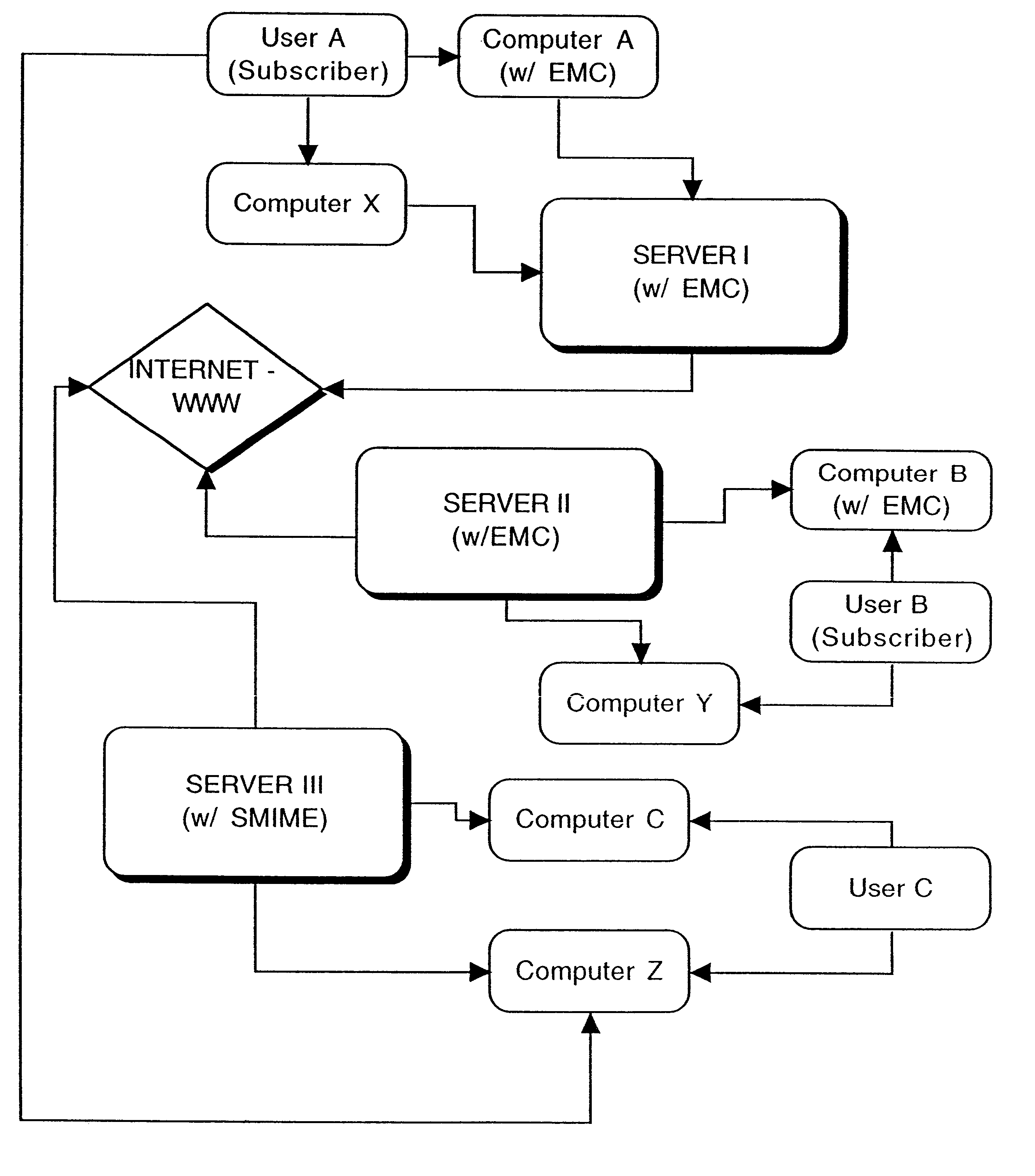

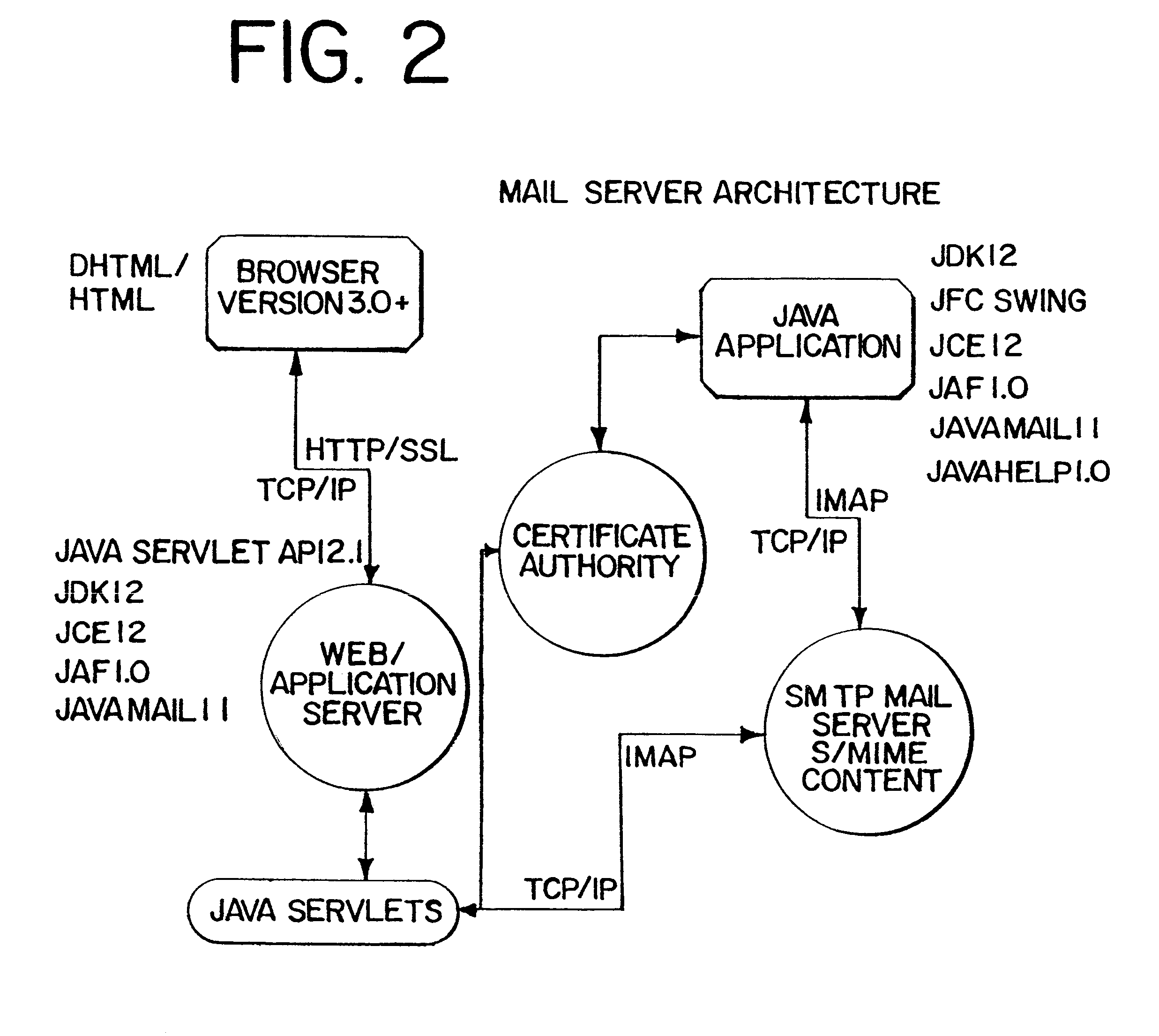

Interoperable full-featured web-based and client-side e-mail system

InactiveUS6356937B1More secure log-inMultiple digital computer combinationsOffice automationApplication softwareProprietary software

A full-featured e-mail system is used in both Internet-based and client-side (personal computer) forms. In each form, either basic e-mail service is provided to system subscribers or a secure, premium service with authentication, concealment, integrity, and non-repudiation functions for electronic messaging services is provided. In either form and at either level of service, subscribers can work off-line on their own computers with proprietary software loaded or, alternatively, on-line on any computer with an Internet connection. The system is interoperable, to preserve security, with all S / MIME compliant software applications, even for those users not subscribing to a service implementing the disclosed system. Digital certificates can be provided as a security service of the disclosed system, rather than requiring a second source with separate verification procedures. As additional optional features, the subscriber can control compression of outgoing attachment files, rather than having that function absent or operate in some automatic way. Decompression of such file attachments when received occurs automatically for subscribers, without having to invoke a different program or system. Interactive help features, book hierarchy uniformity for messages, accounts, certificates, virus warnings, and dual naming capability are also provided and available to subscribers in both the Web-based and the client-side application forms disclosed herein, and in both basic and premium service levels.

Owner:MEC MANAGEMENT LLC

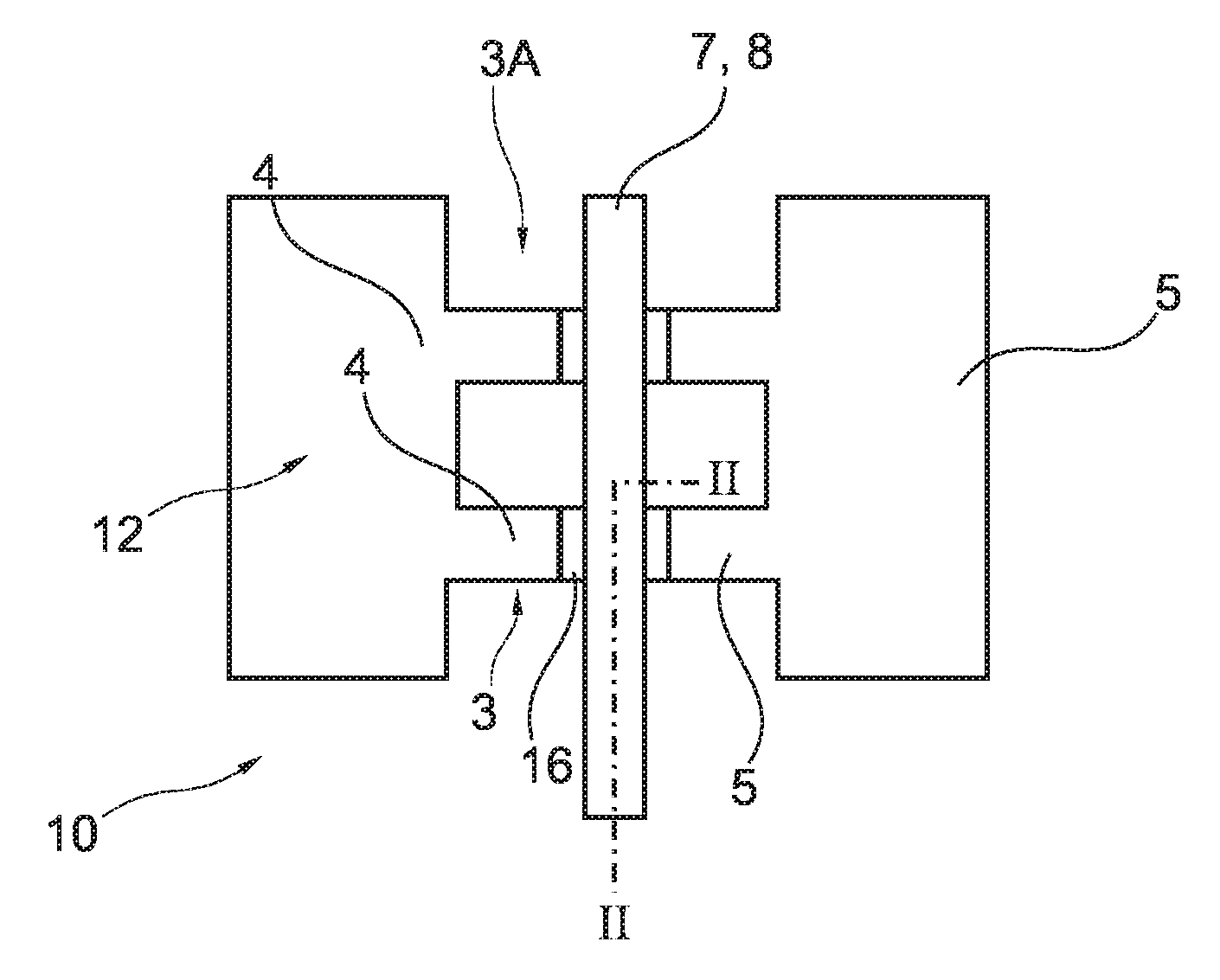

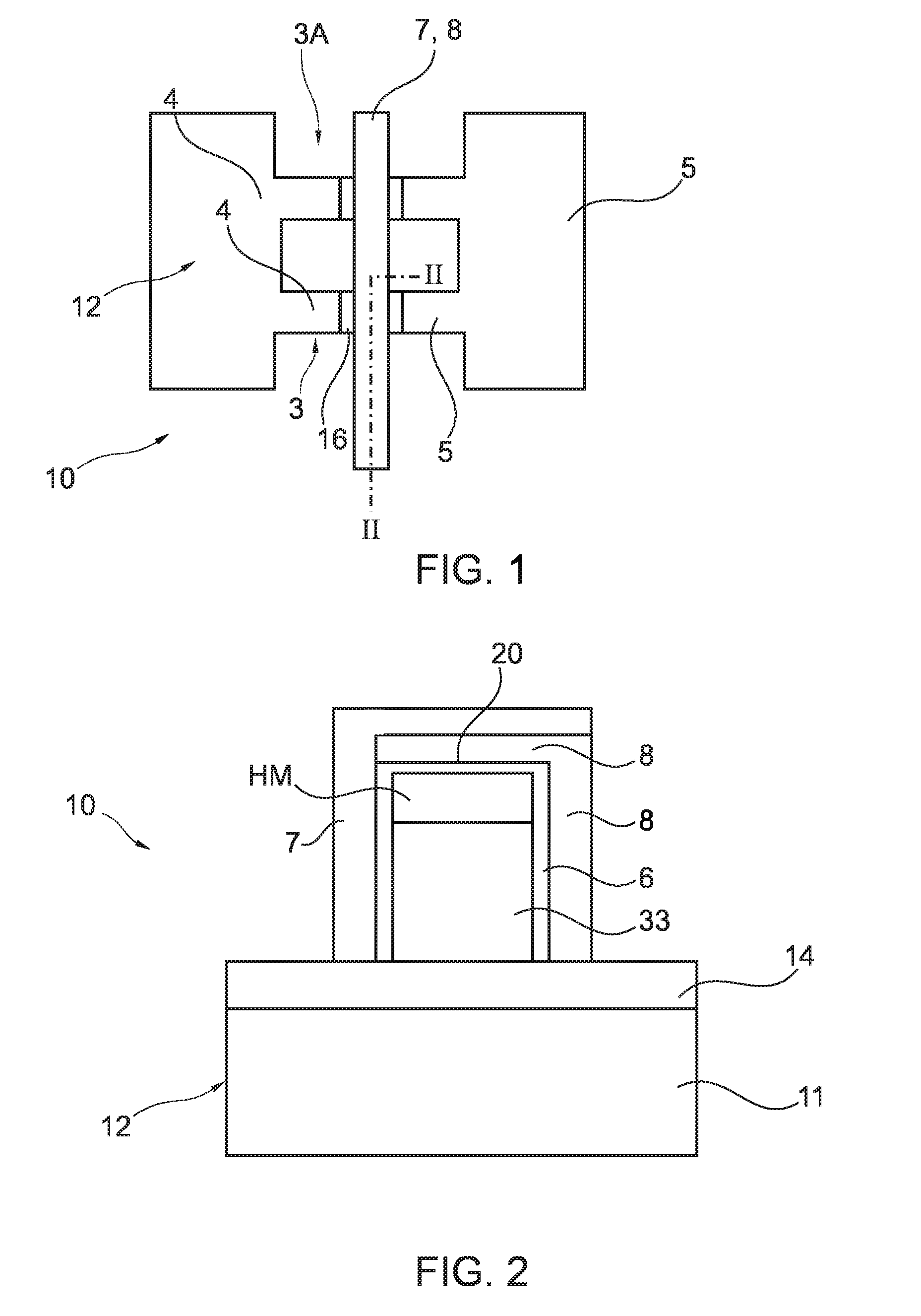

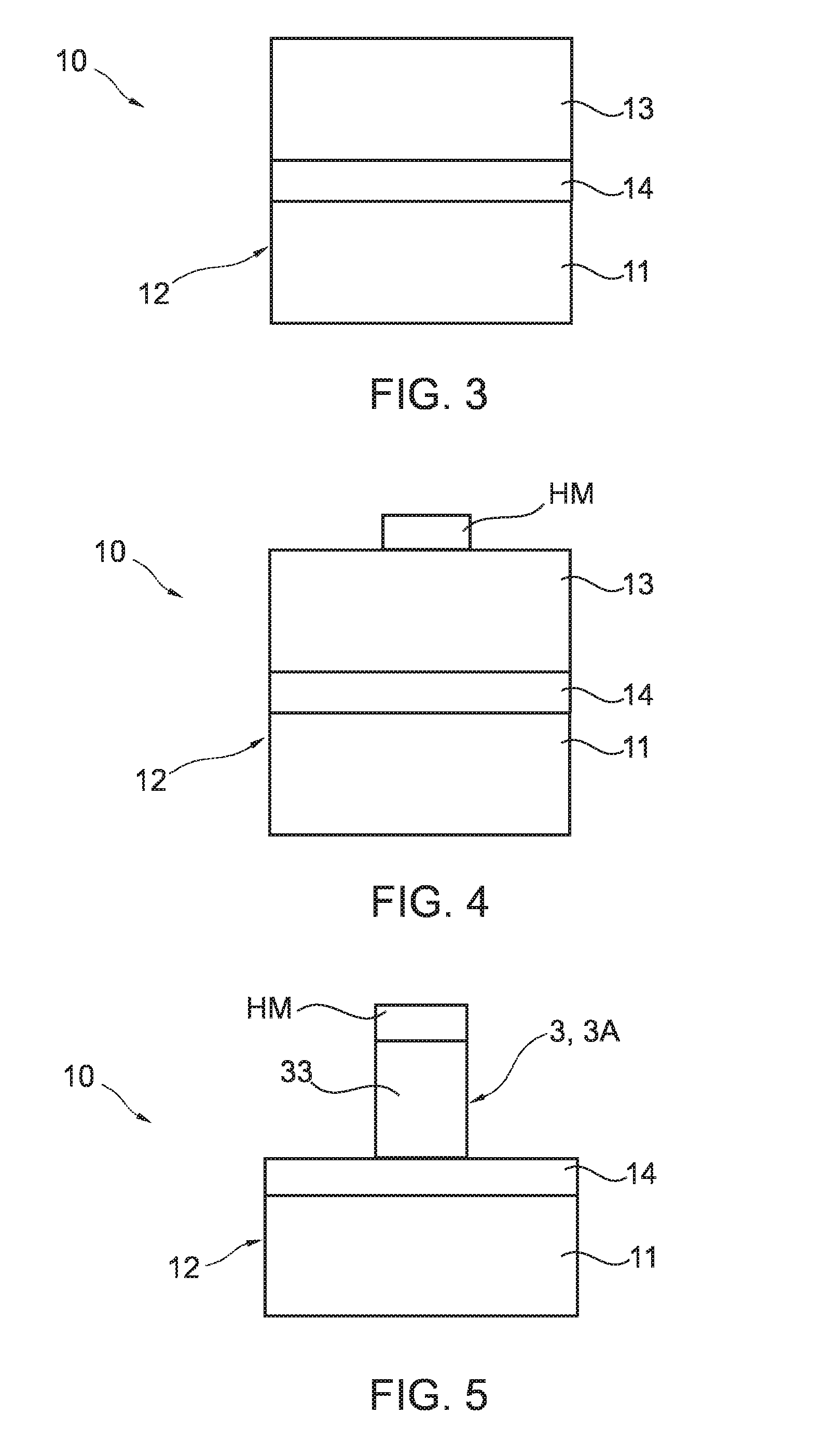

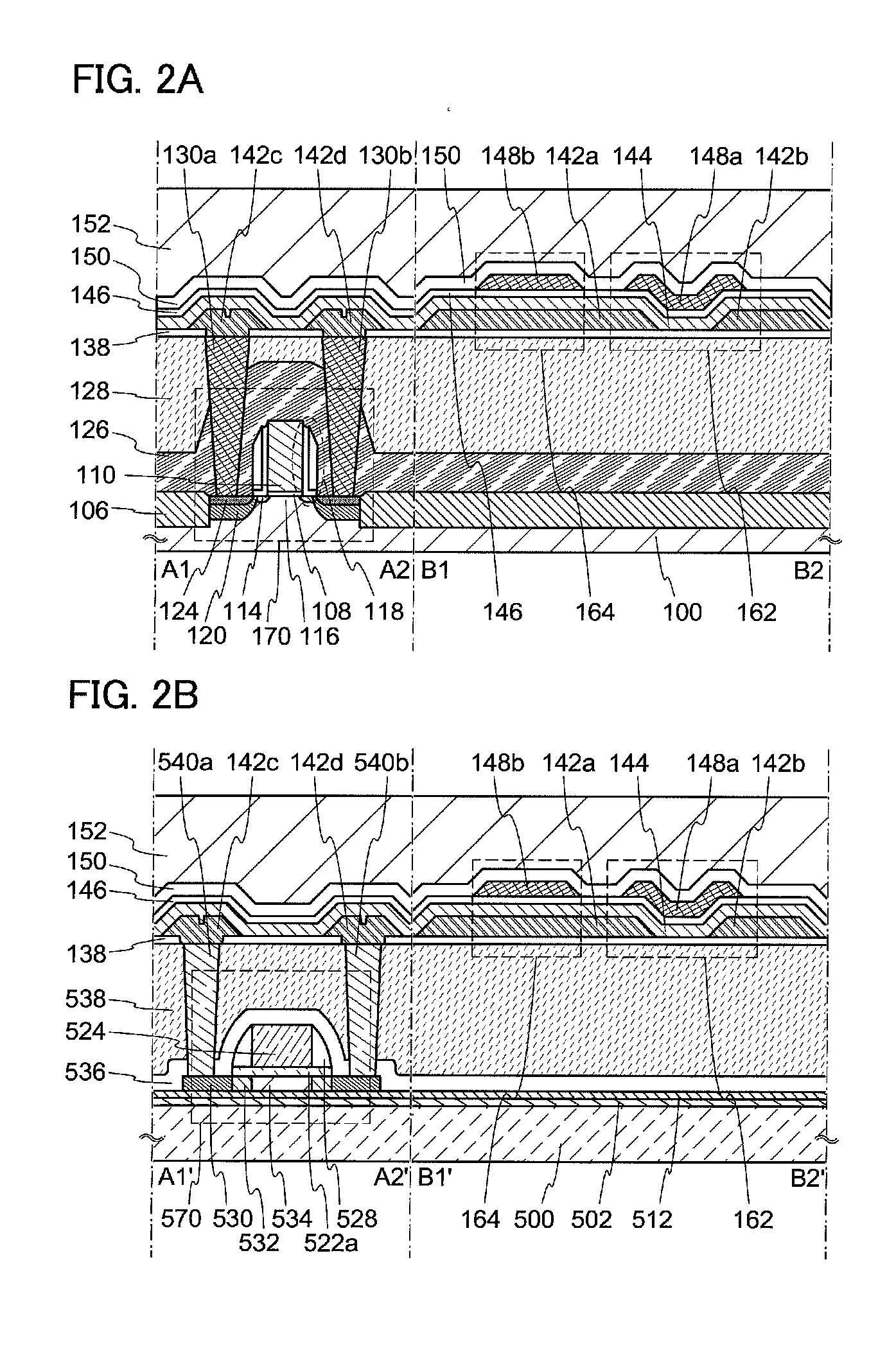

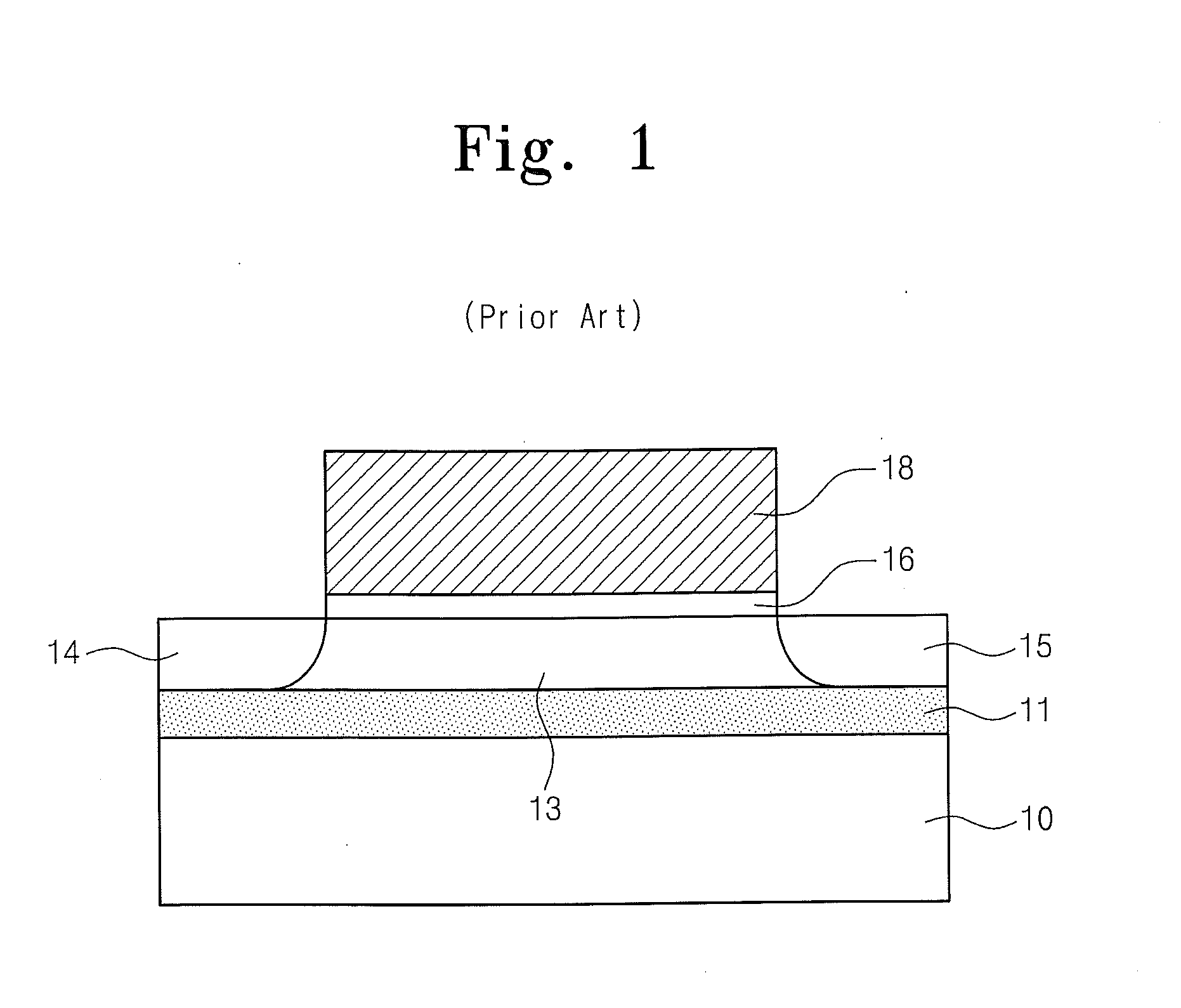

Transistor device and method of manufacturing such a transistor device

ActiveUS20100025766A1Suitable for high-scale integrationImprove device performanceSolid-state devicesSemiconductor/solid-state device manufacturingGate insulatorEngineering

A transistor device (10), the transistor device (10) comprising a substrate (11, 14), a fin (3, 3A) aligned along a horizontal direction on the substrate (11, 14), a first source / drain region (4) of a first type of conductivity in the fin (3, 3A), a second source / drain region (5) of a second type of conductivity in the fin (3, 3A), wherein the first type of conductivity differs from the second type of conductivity, a channel region (33) in the fin (3, 3A) between the first source / drain region (4) and the second source / drain region (5), a gate insulator (6) on the channel region (33), and a gate structure (7, 8) on the gate insulator (6), wherein the sequence of the first source / drain region (4), the channel region (33) and the second source / drain region (5) is aligned along the horizontal direction.

Owner:UNITED MICROELECTRONICS CORP

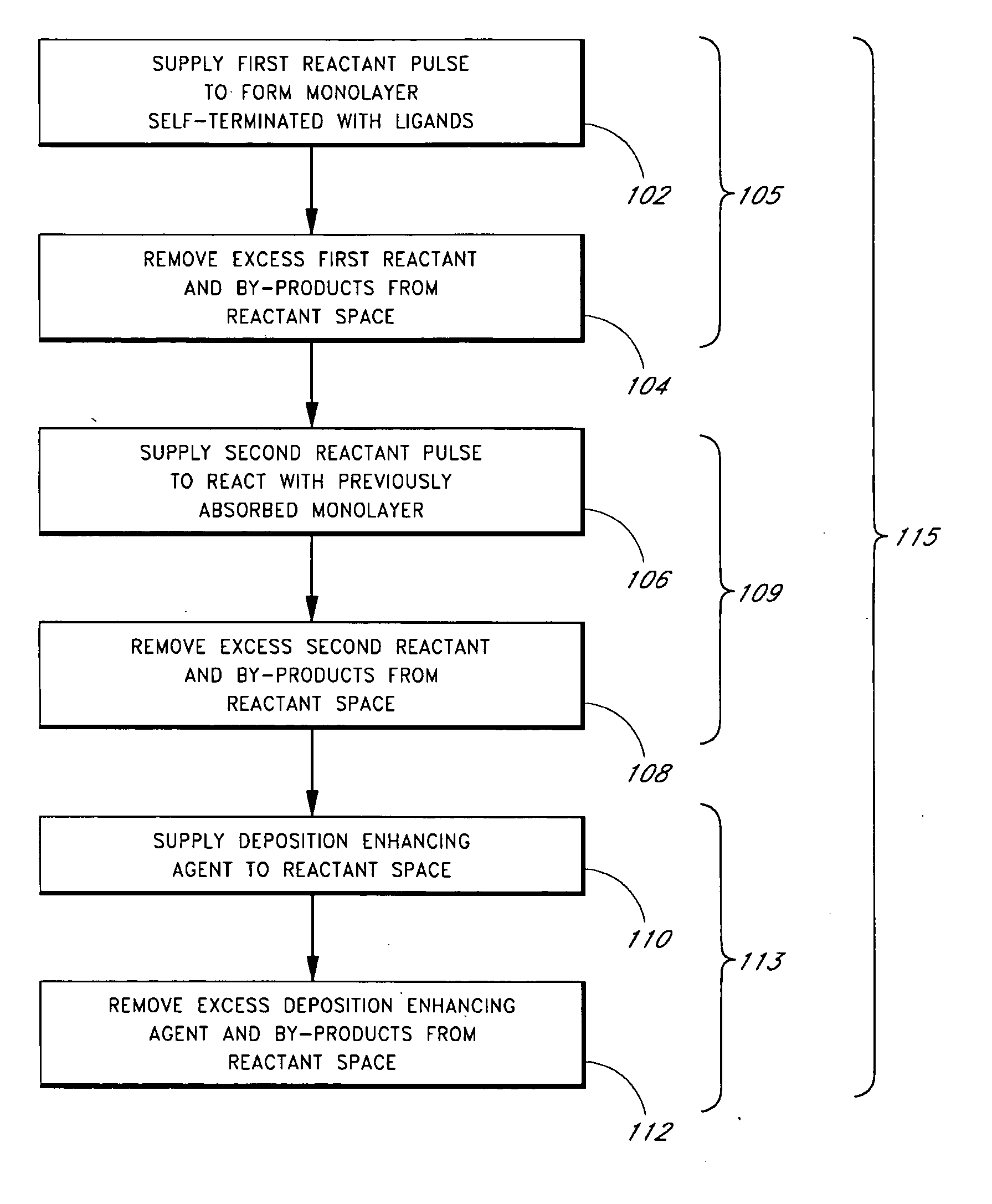

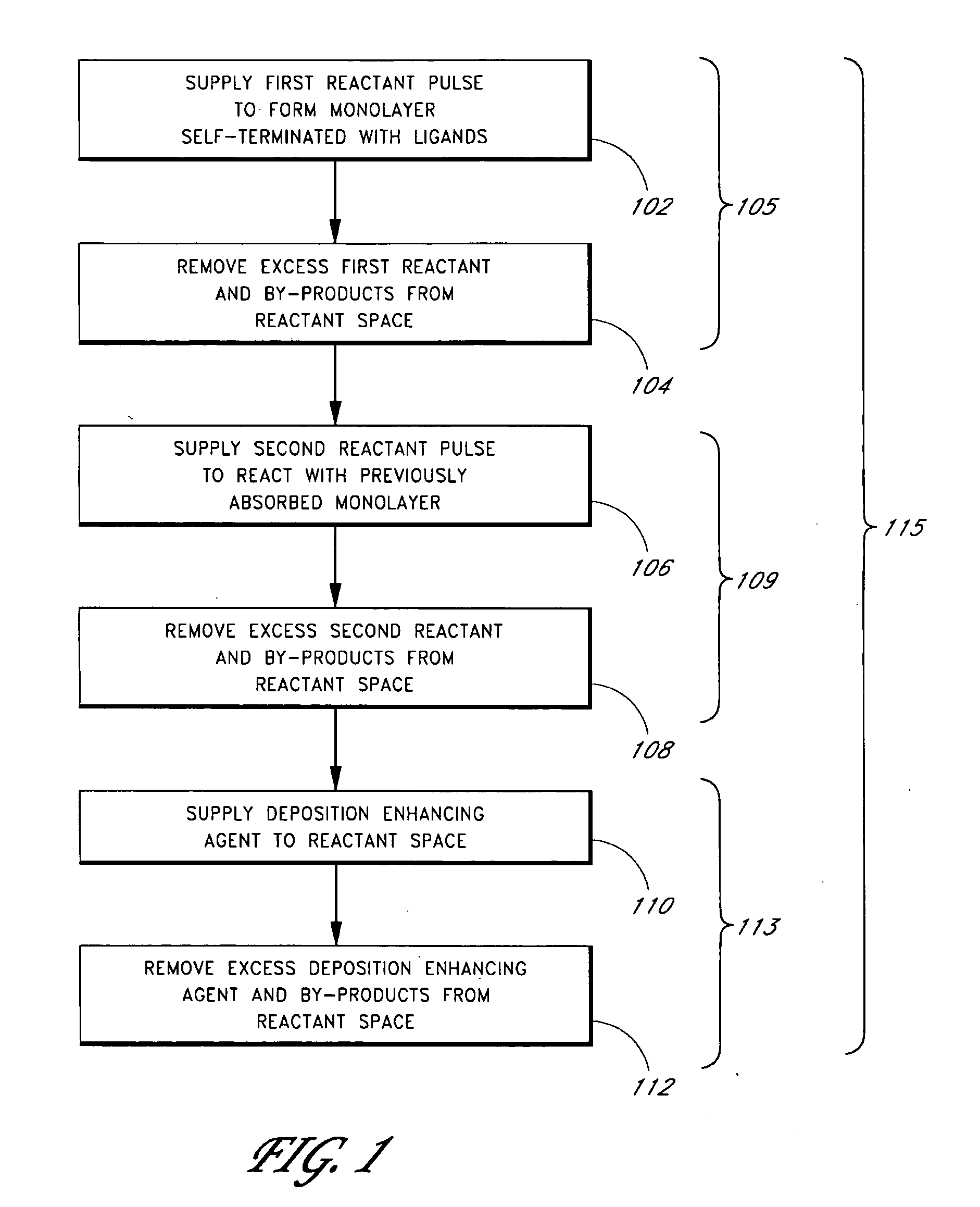

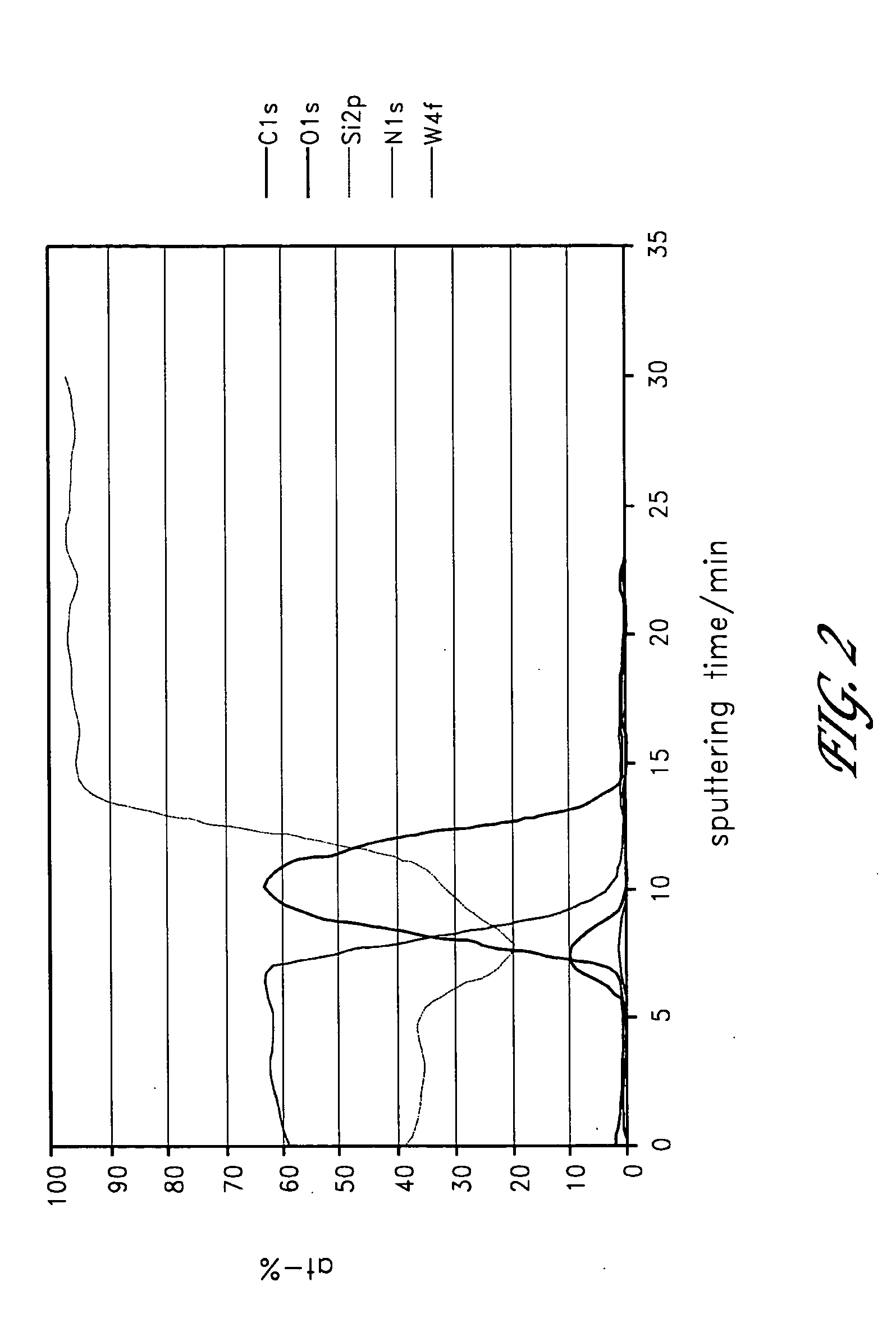

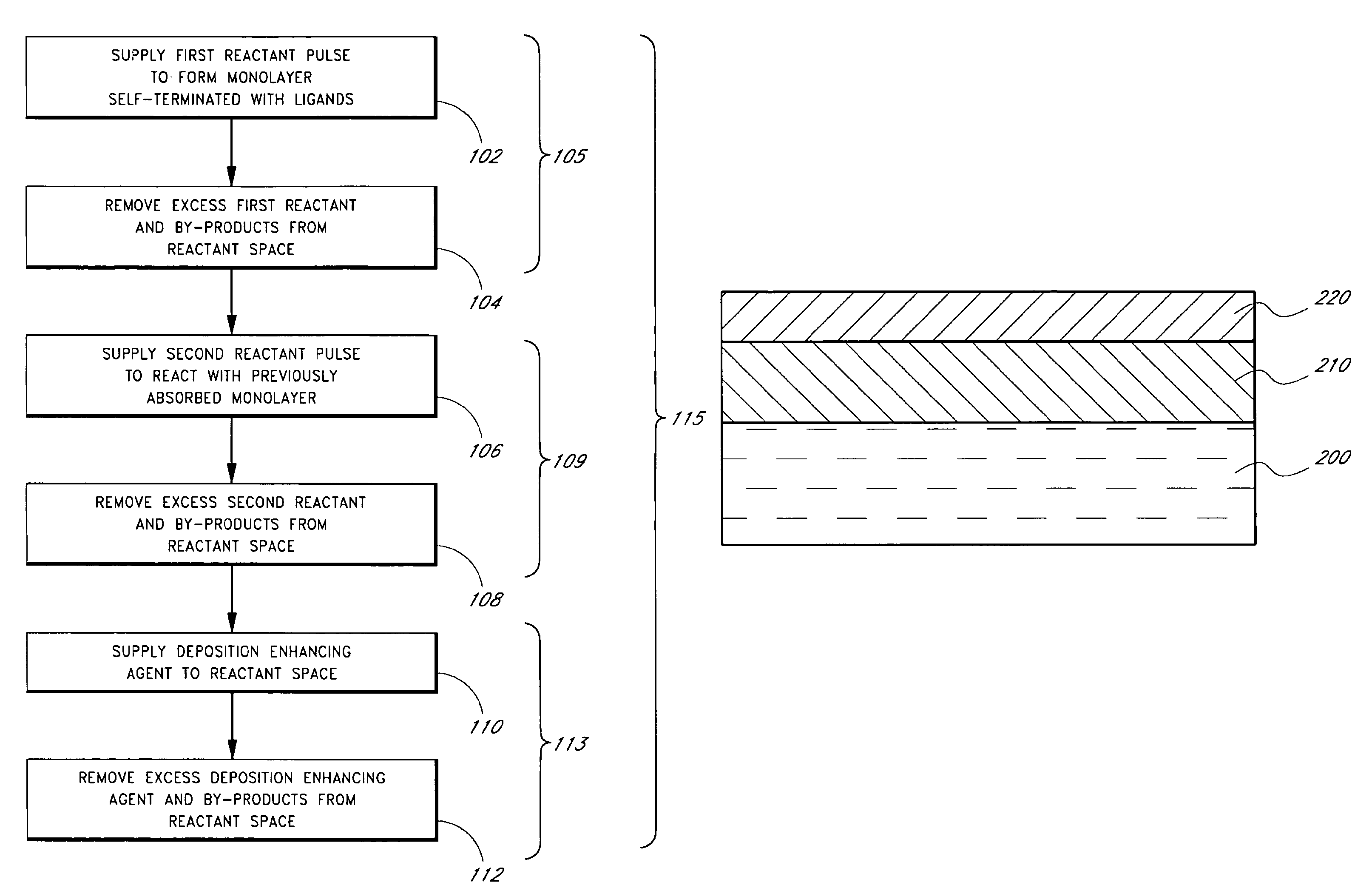

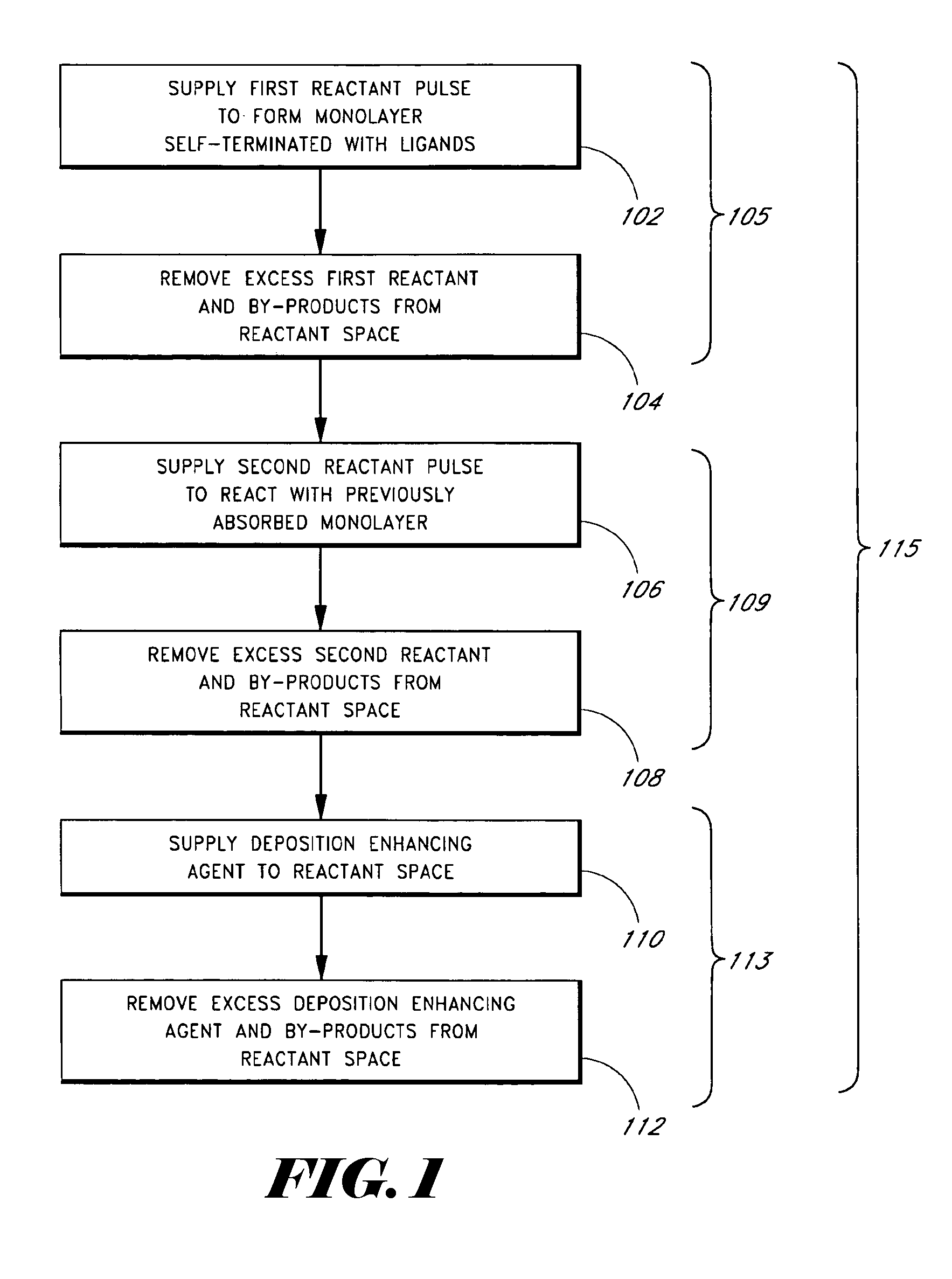

Enhanced thin film deposition

ActiveUS20070148350A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingSilanesNitrogen

Methods of producing metal-containing thin films with low impurity contents on a substrate by atomic layer deposition (ALD) are provided. The methods preferably comprise contacting a substrate with alternating and sequential pulses of a metal source chemical, a second source chemical and a deposition enhancing agent. The deposition enhancing agent is preferably selected from the group consisting of hydrocarbons, hydrogen, hydrogen plasma, hydrogen radicals, silanes, germanium compounds, nitrogen compounds, and boron compounds. In some embodiments, the deposition-enhancing agent reacts with halide contaminants in the growing thin film, improving film properties.

Owner:ASM INTERNATIONAL

Semiconductor device and method of making the same

ActiveUS20130037886A1Improve efficiencyImprove performanceTransistorSolid-state devicesPower semiconductor deviceEngineering

A semiconductor device includes a semiconductor substrate, at least a first fin structure, at least a second fin structure, a first gate, a second gate, a first source / drain region and a second source / drain region. The semiconductor substrate has at least a first active region to dispose the first fin structure and at least a second active region to dispose the second fin structure. The first / second fin structure partially overlapped by the first / second gate has a first / second stress, and the first stress and the second stress are different from each other. The first / second source / drain region is disposed in the first / second fin structure at two sides of the first / second gate.

Owner:UNITED MICROELECTRONICS CORP

Silane and borane treatments for titanium carbide films

ActiveUS8841182B1Reduce oxidized portionPrevent oxidationSemiconductor/solid-state device manufacturingSilanesCompound (substance)

Methods of treating metal-containing thin films, such as films comprising titanium carbide, with a silane / borane agent are provided. In some embodiments a film including titanium carbide is deposited on a substrate by an atomic layer deposition (ALD) process. The process may include a plurality of deposition cycles involving alternating and sequential pulses of a first source chemical that includes titanium and at least one halide ligand, a second source chemical that includes metal and carbon, where the metal and the carbon from the second source chemical are incorporated into the thin film, and a third source chemical, where the third source chemical is a silane or borane that at least partially reduces oxidized portions of the titanium carbide layer formed by the first and second source chemicals. The treatment can form a capping layer on the metal carbide film.

Owner:ASM IP HLDG BV

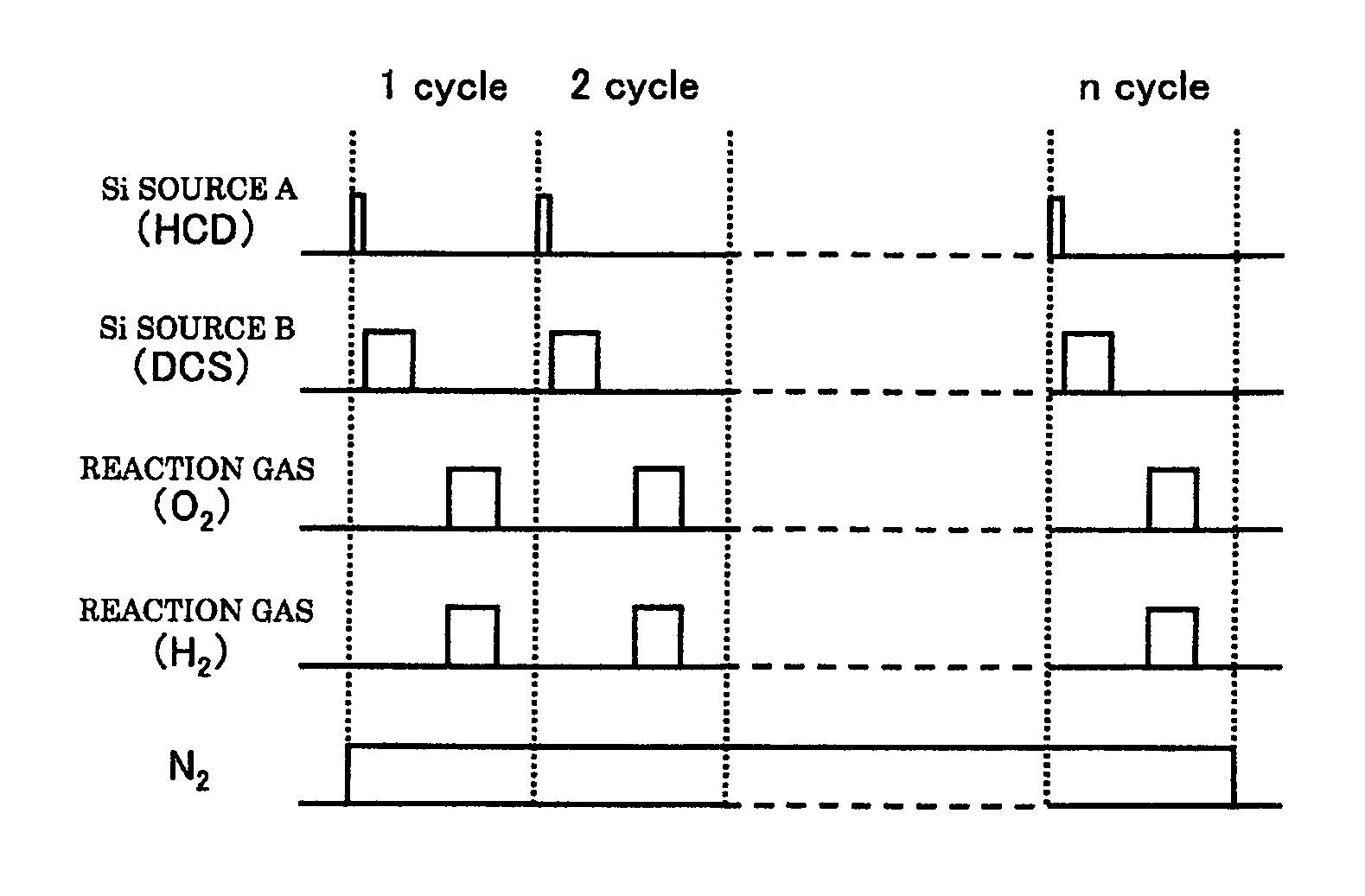

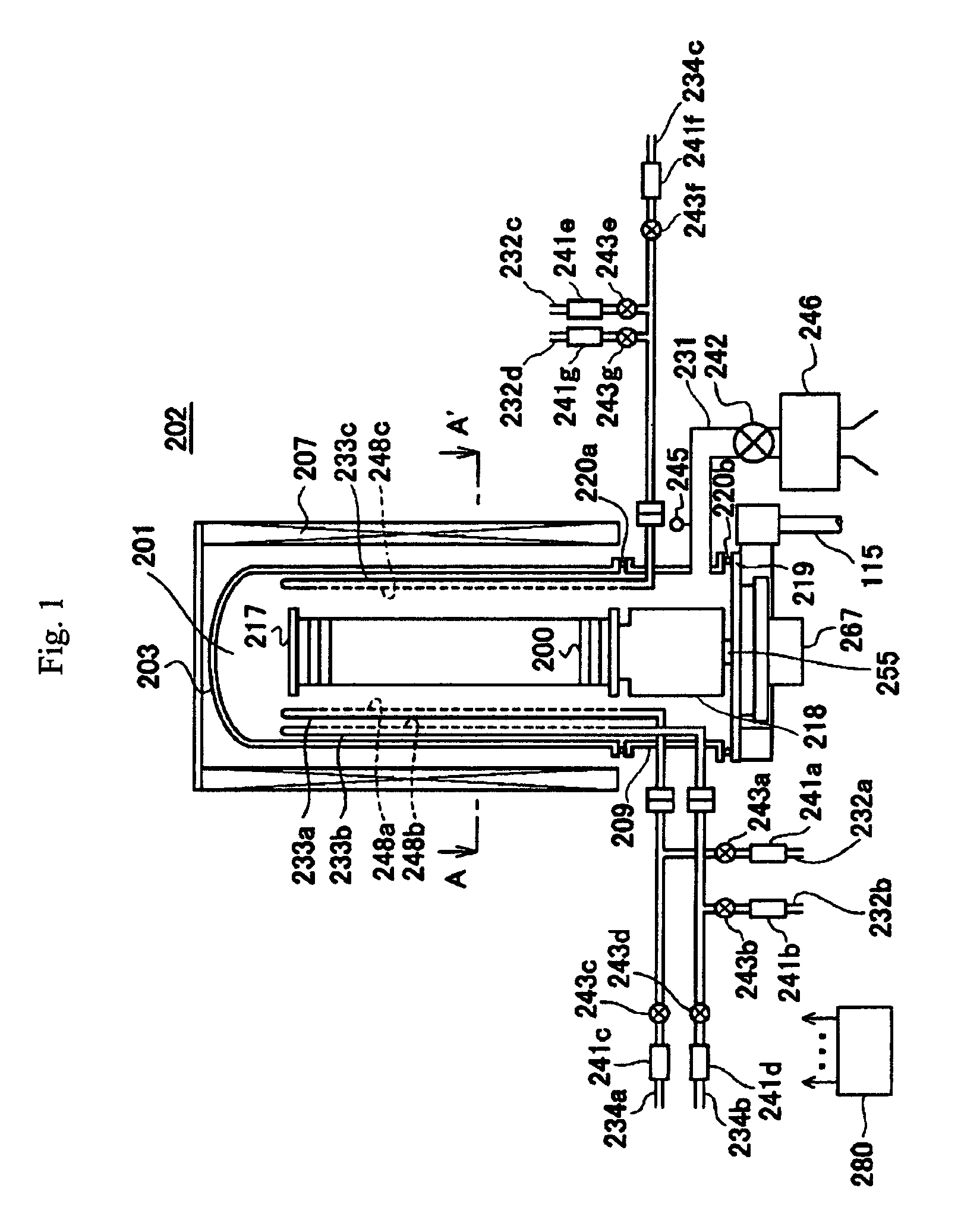

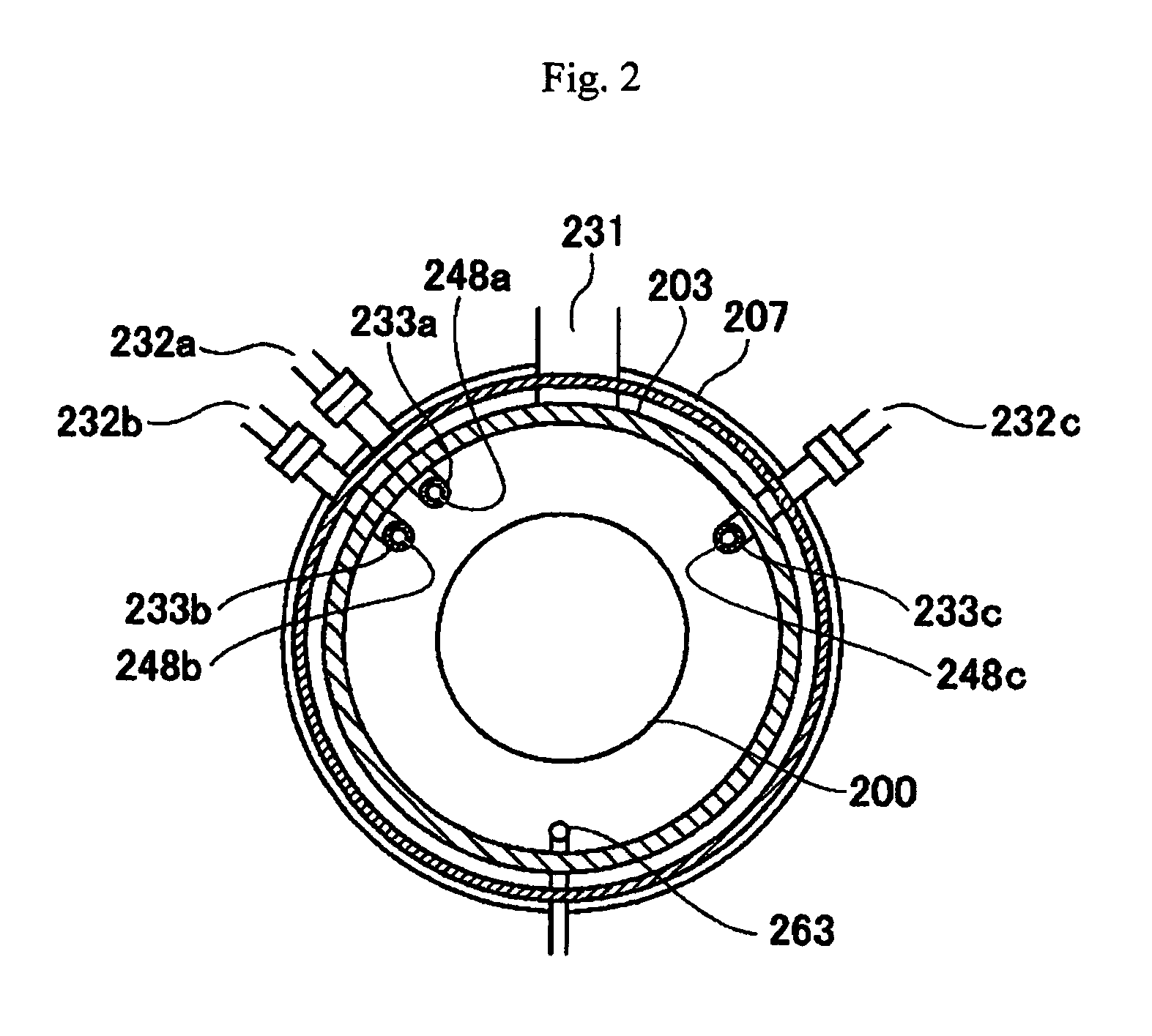

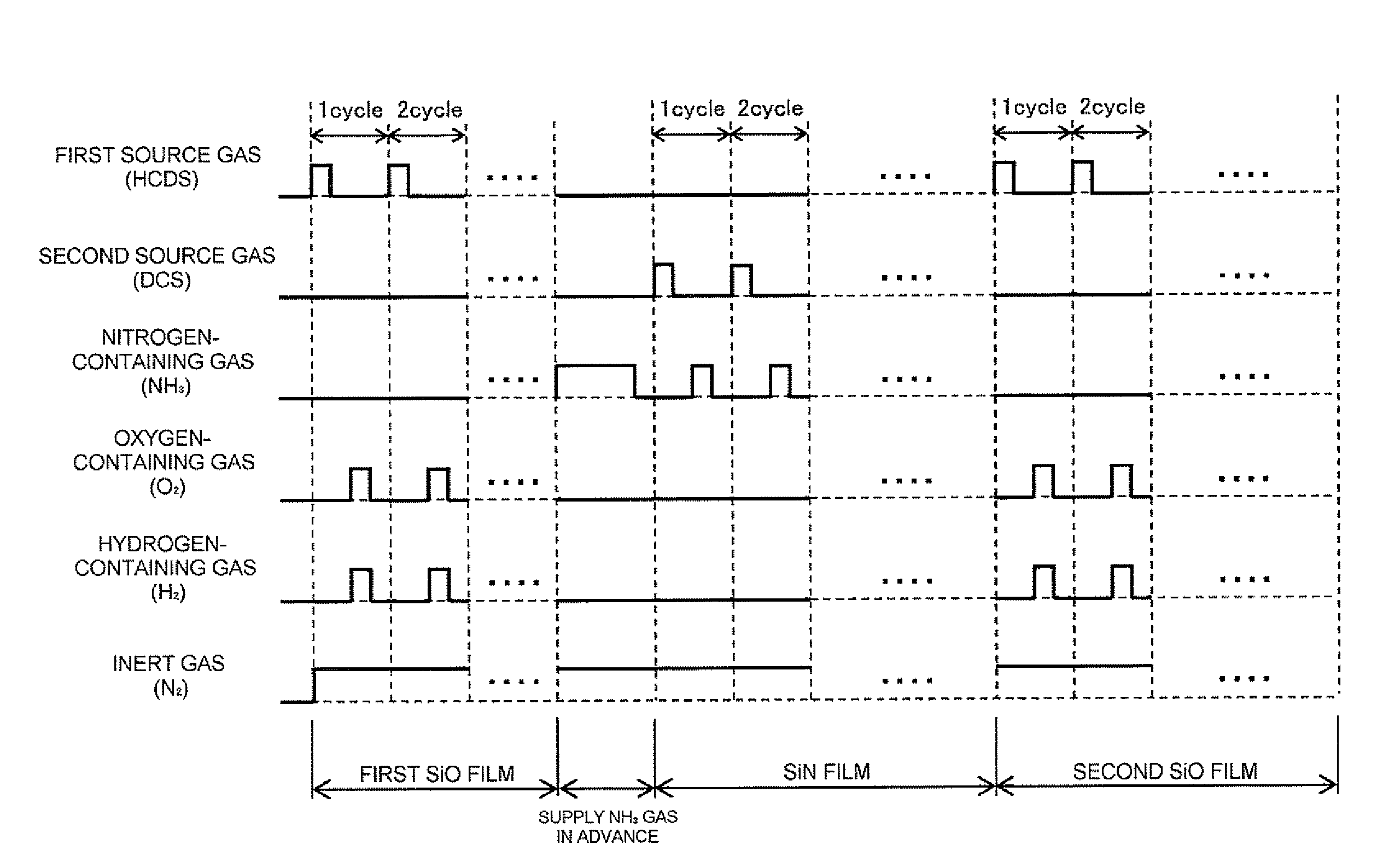

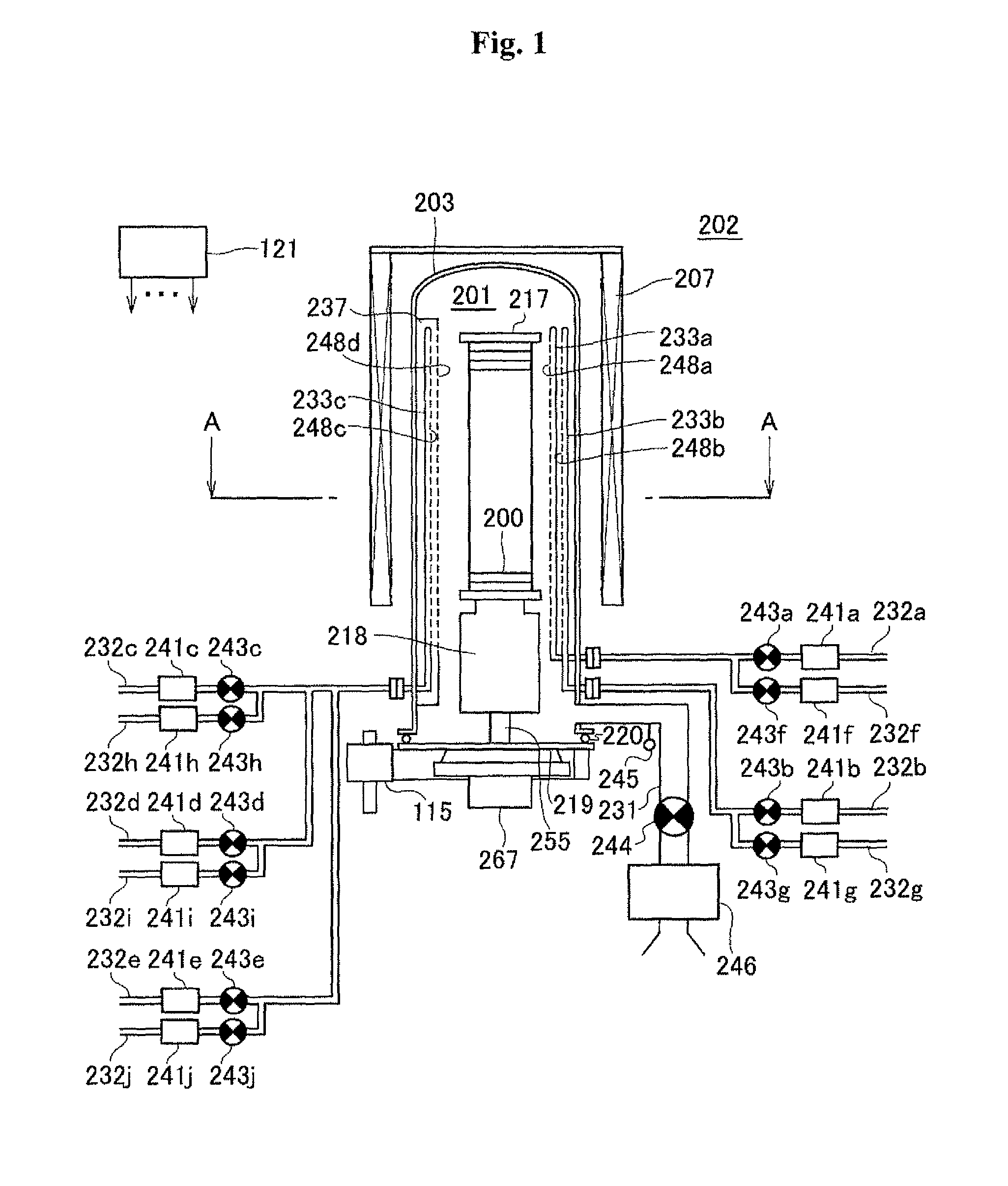

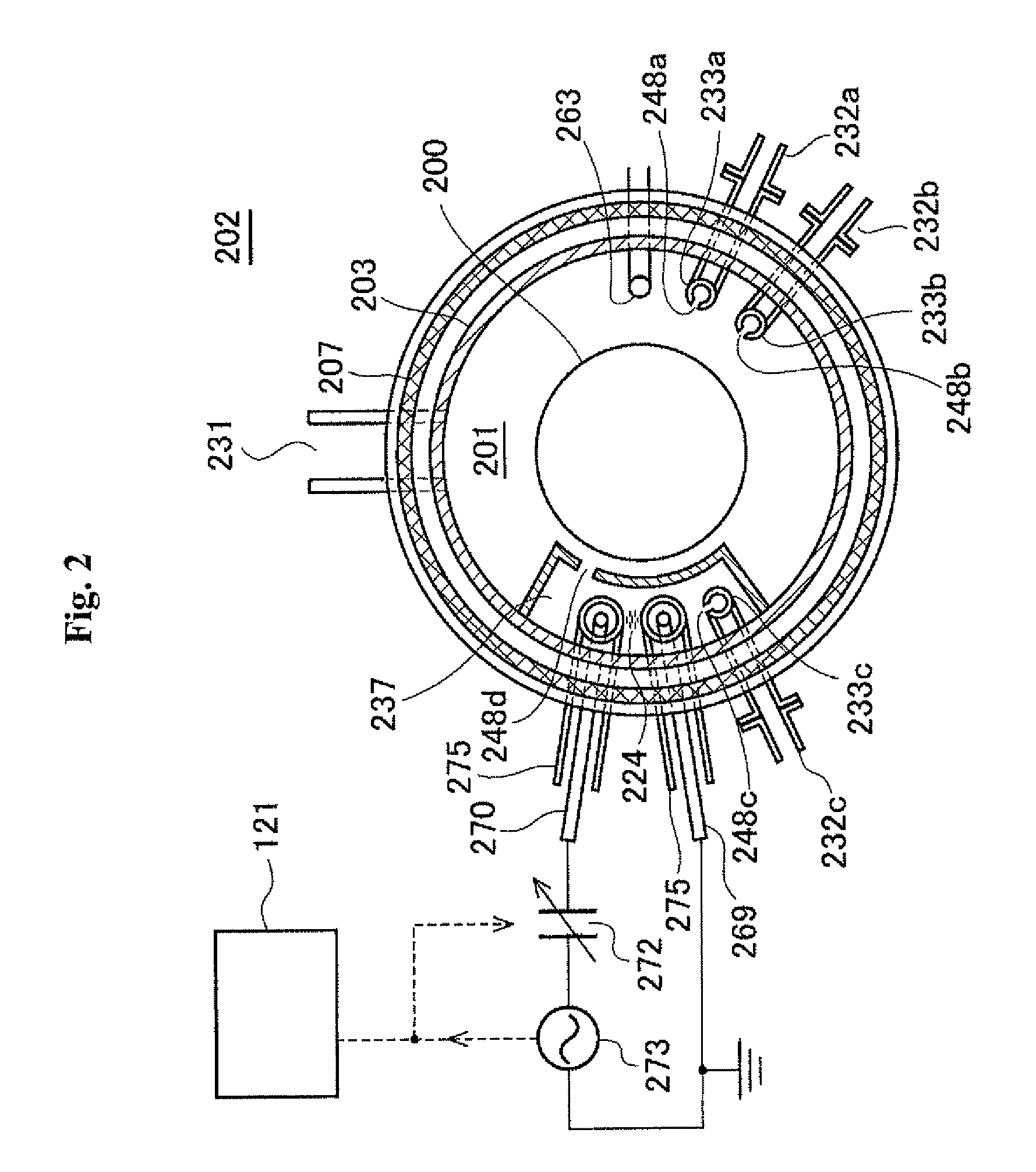

Method of manufacturing semiconductor device, method of processing substrate and substrate processing apparatus

ActiveUS8076251B2Increase probabilityLow costSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDevice materialPhysical chemistry

Provided is a method of manufacturing a semiconductor device. The method includes: loading a substrate into a process vessel; performing a process to form an oxide, nitride, or oxynitride film on the substrate by alternately repeating: (a) forming a layer containing an element on the substrate by supplying and exhausting first and second source gases containing the element into and from the process vessel; and (b) changing the layer containing the element into an oxide, nitride, or oxynitride layer by supplying and exhausting reaction gas different from the first and second source gases into and from the process vessel; and unloading the substrate from the process vessel. The first source gas is more reactive than the second source gas, and an amount of the first source gas supplied into the process vessel is set to be less than that of the second source gas supplied into the process vessel.

Owner:KOKUSA ELECTRIC CO LTD

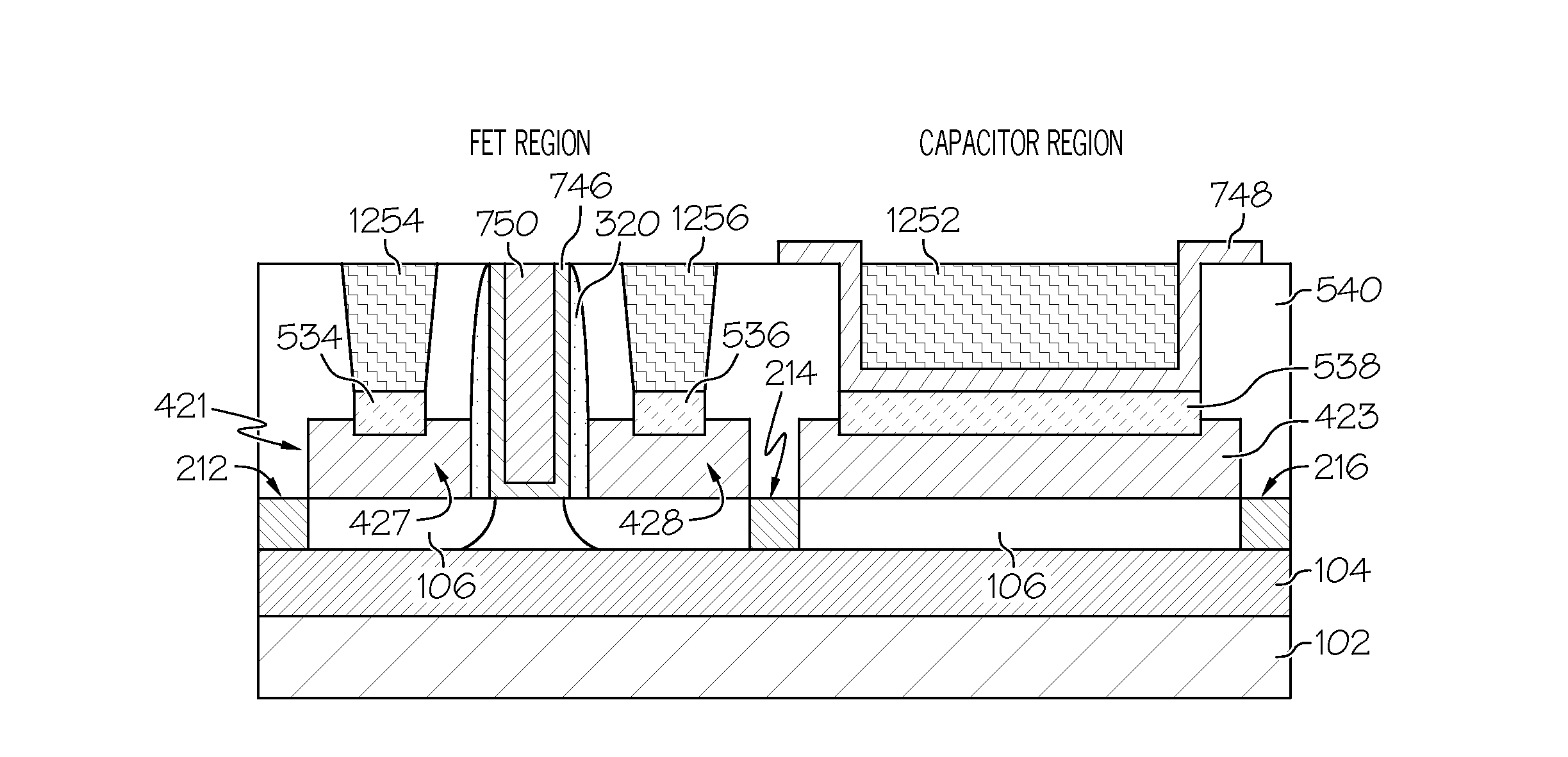

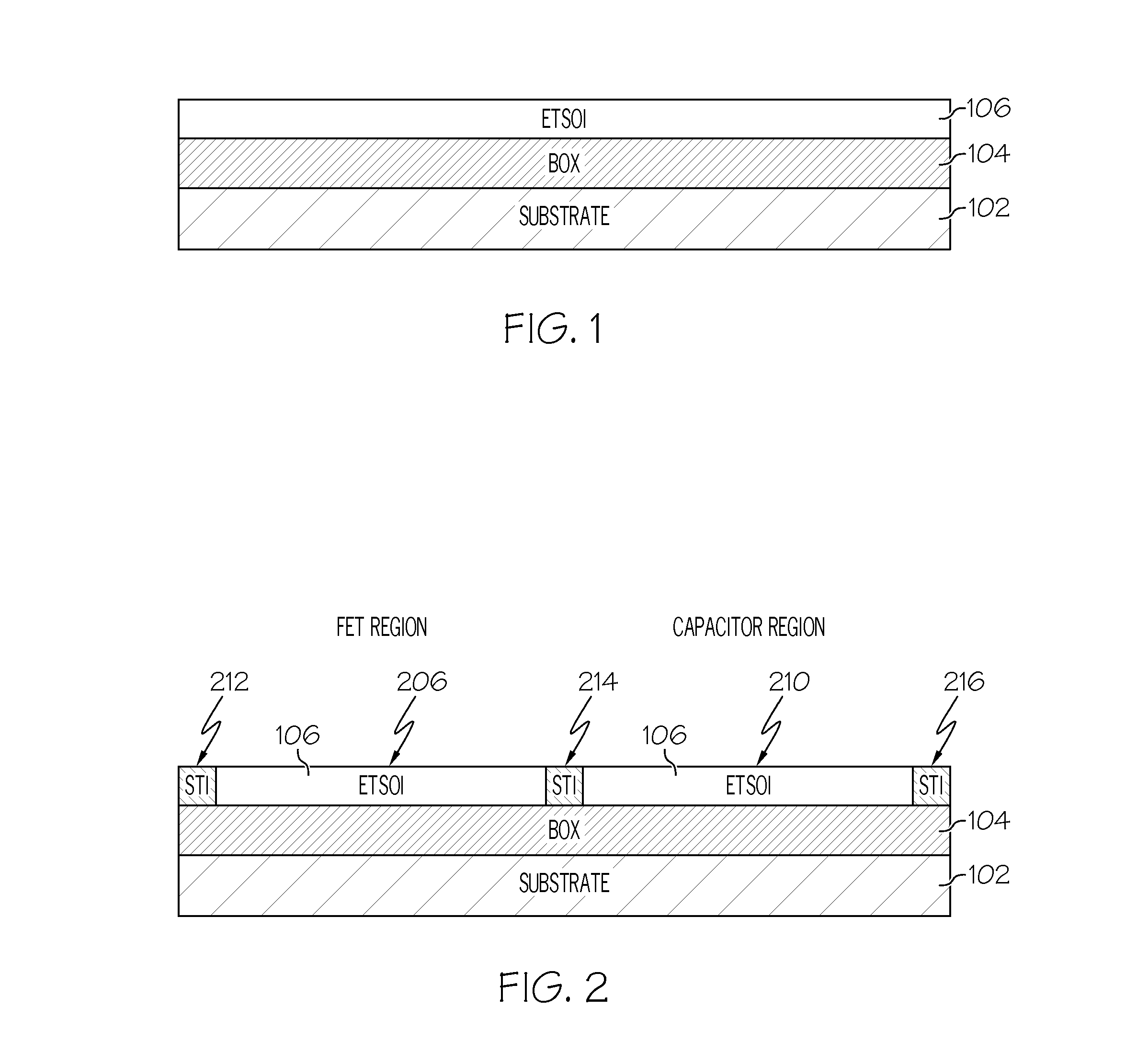

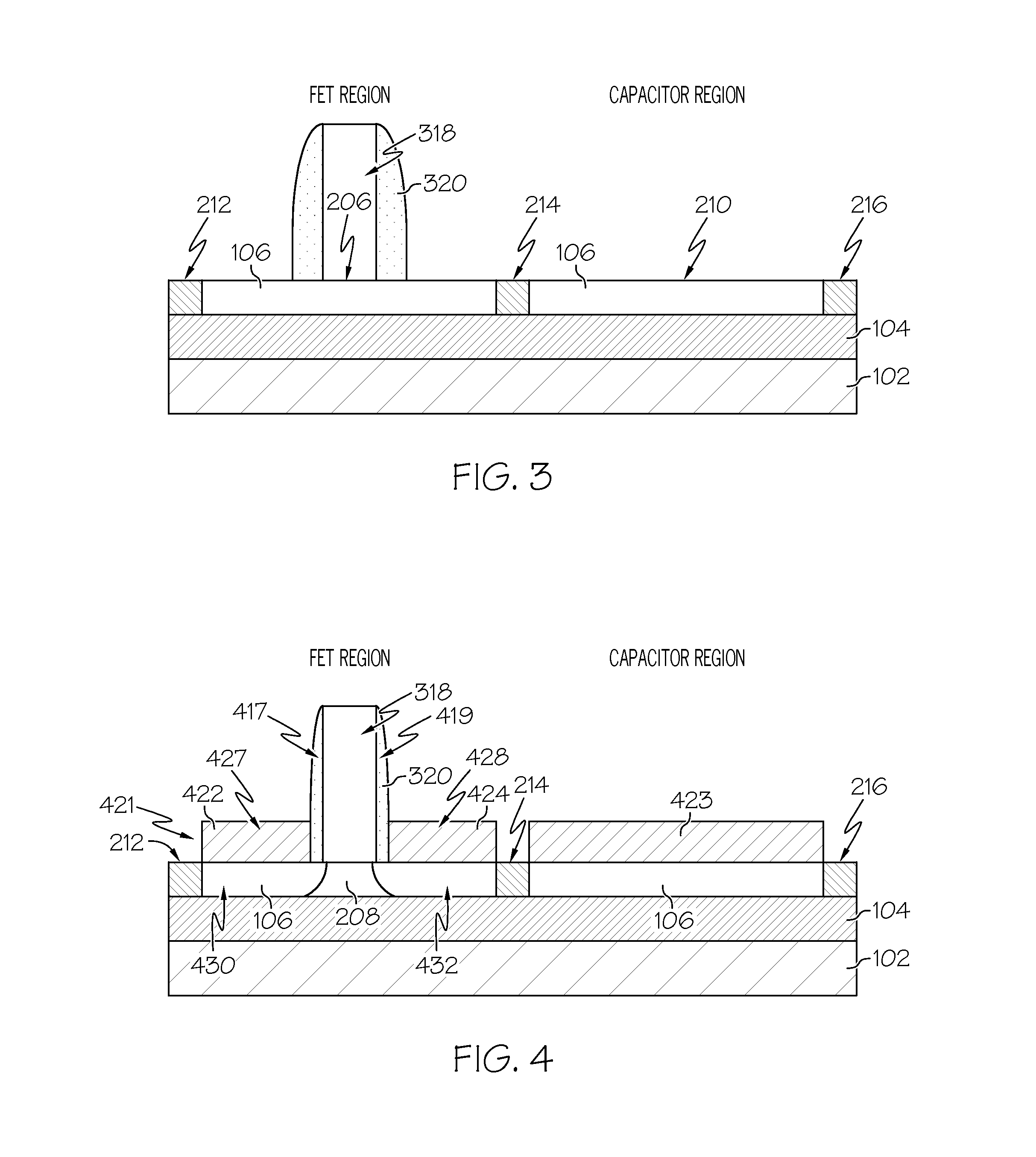

Integrated circuit with a thin body field effect transistor and capacitor

An integrated circuit includes a transistor and a capacitor. The transistor includes a first semiconductor layer and a gate stack located on the first semiconductor layer. The gate stack includes a metal layer and a first high-k dielectric layer. A gate spacer is located on sidewalls of the gate stack. The first high-k dielectric layer is located between the first semiconductor layer and the metal layer and between the gate spacer and sidewalls of the metal layer. A first silicide region is located on a first source / drain region. A second silicide region is located on a second source / drain region. The capacitor includes a first terminal that comprises a third silicide region located on a portion of the second semiconductor. A second high-k dielectric layer is located on the silicide region. A second terminal comprises a metal layer that is located on the second high-k dielectric layer.

Owner:GLOBALFOUNDRIES US INC

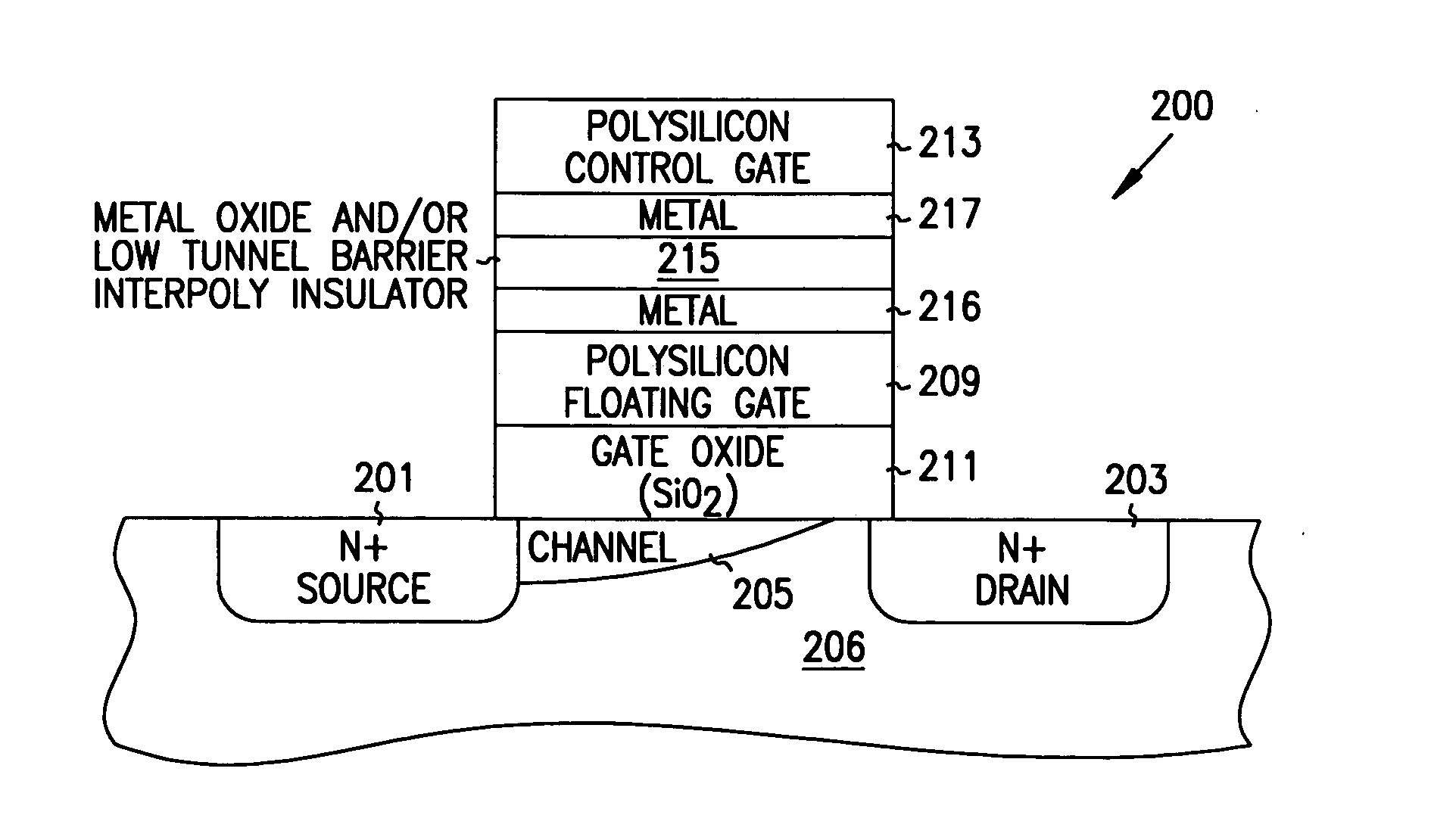

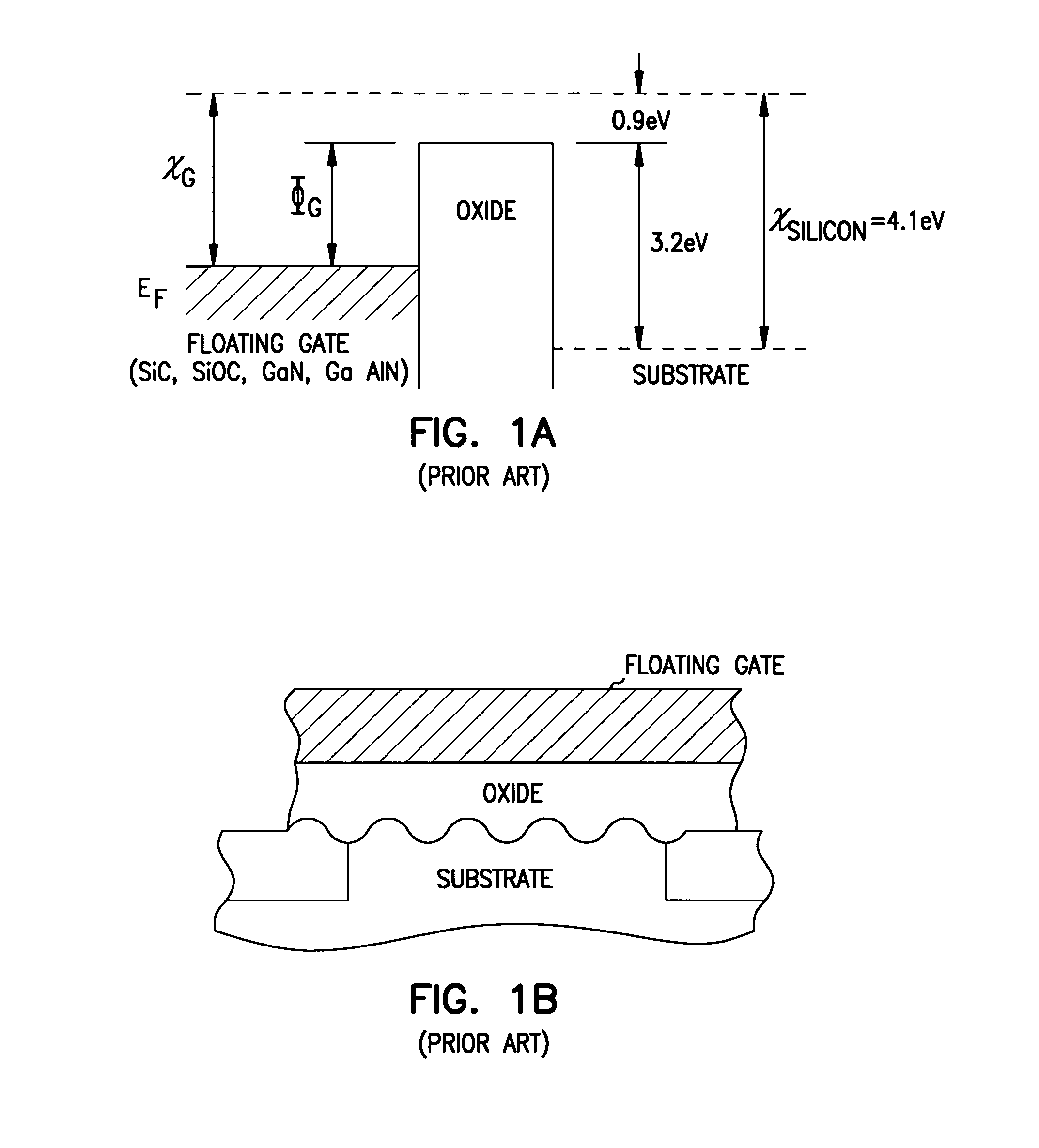

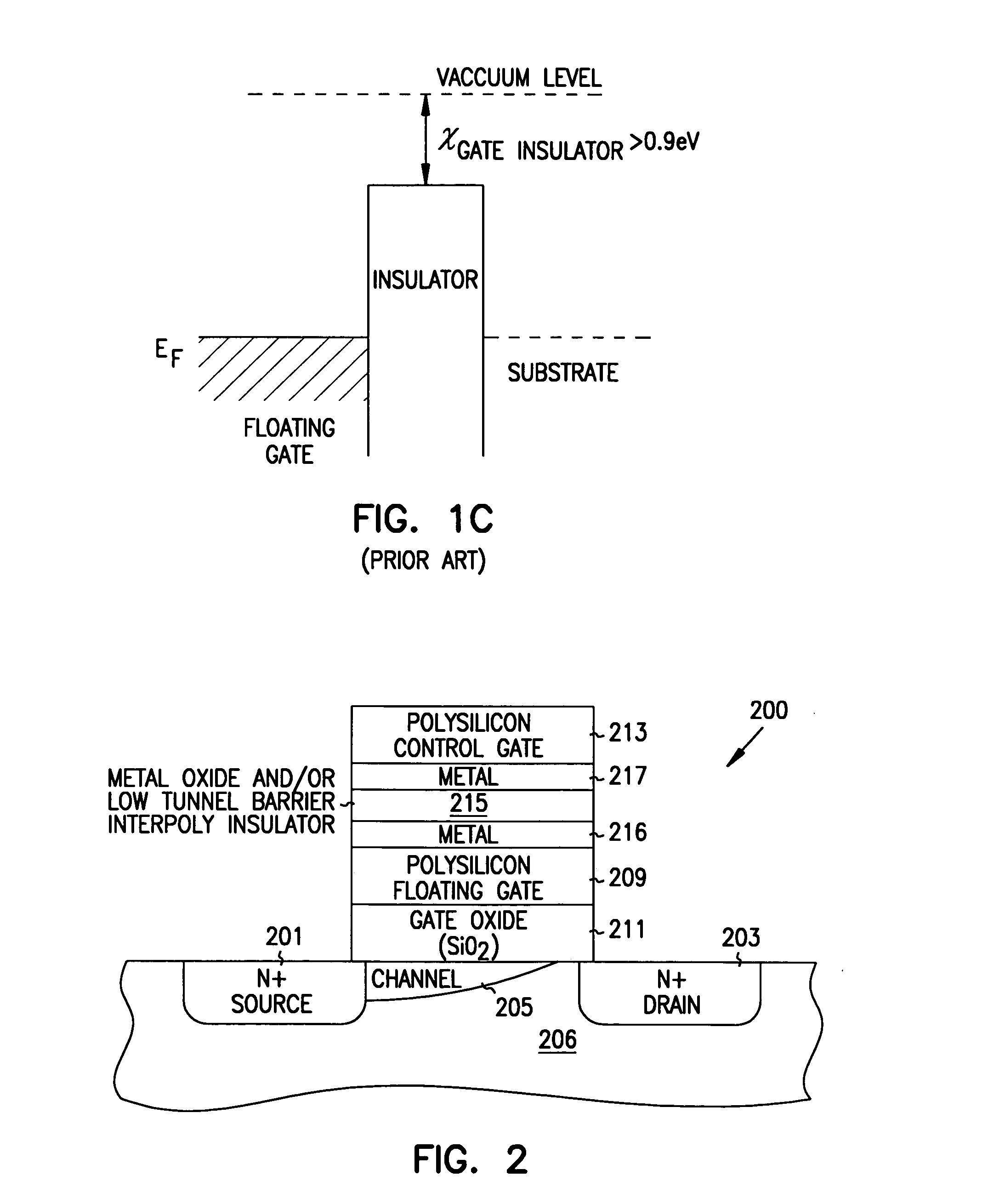

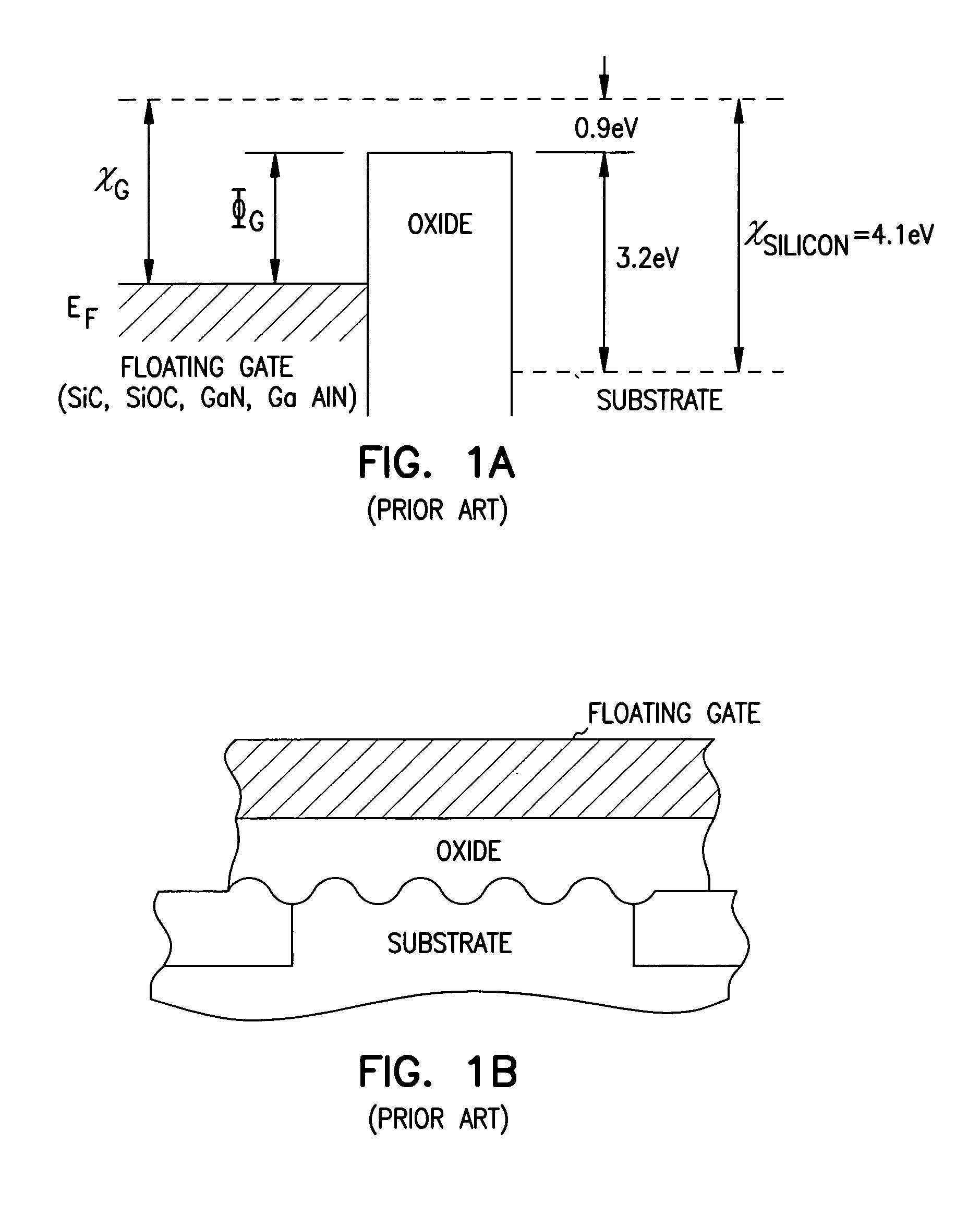

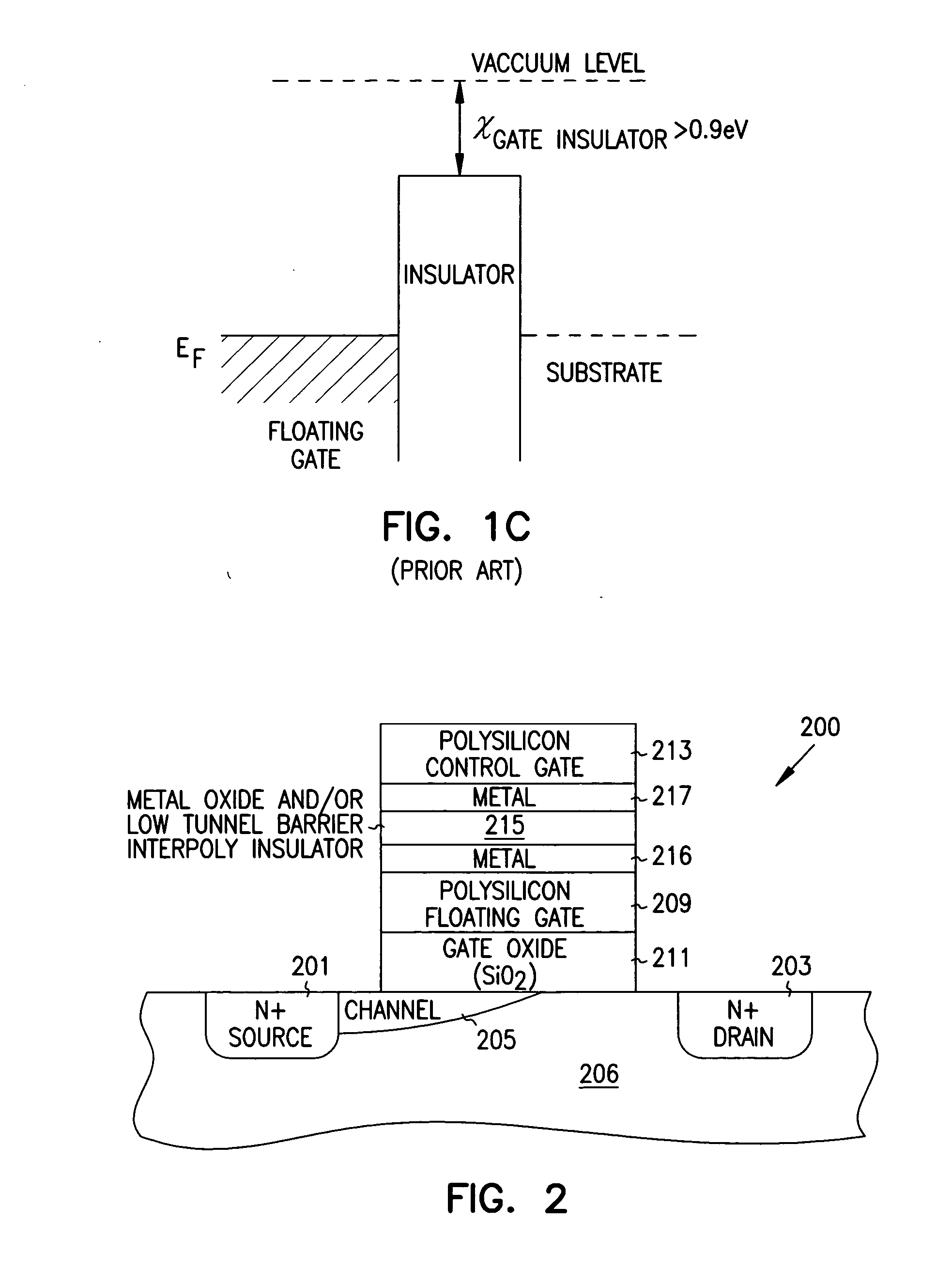

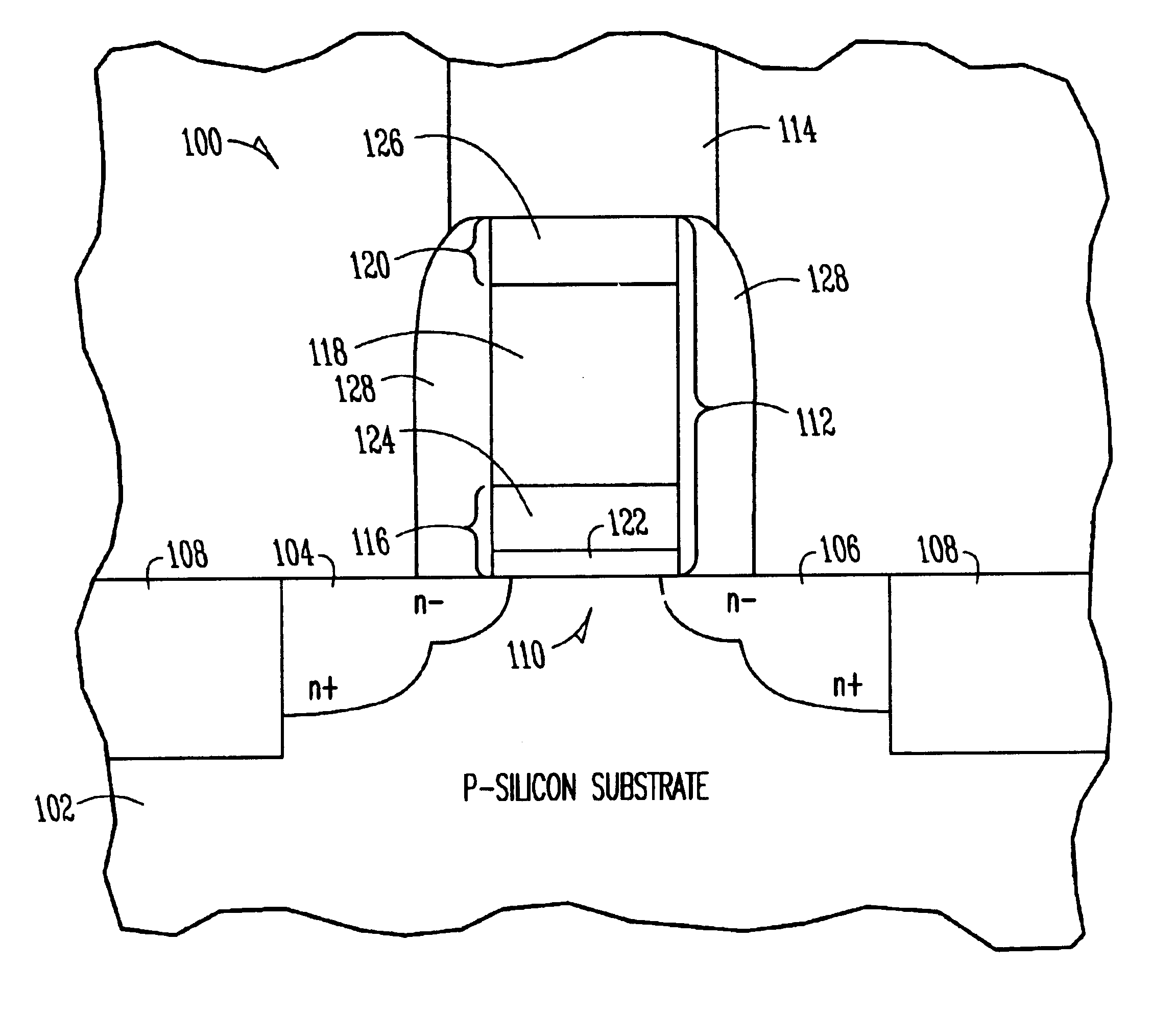

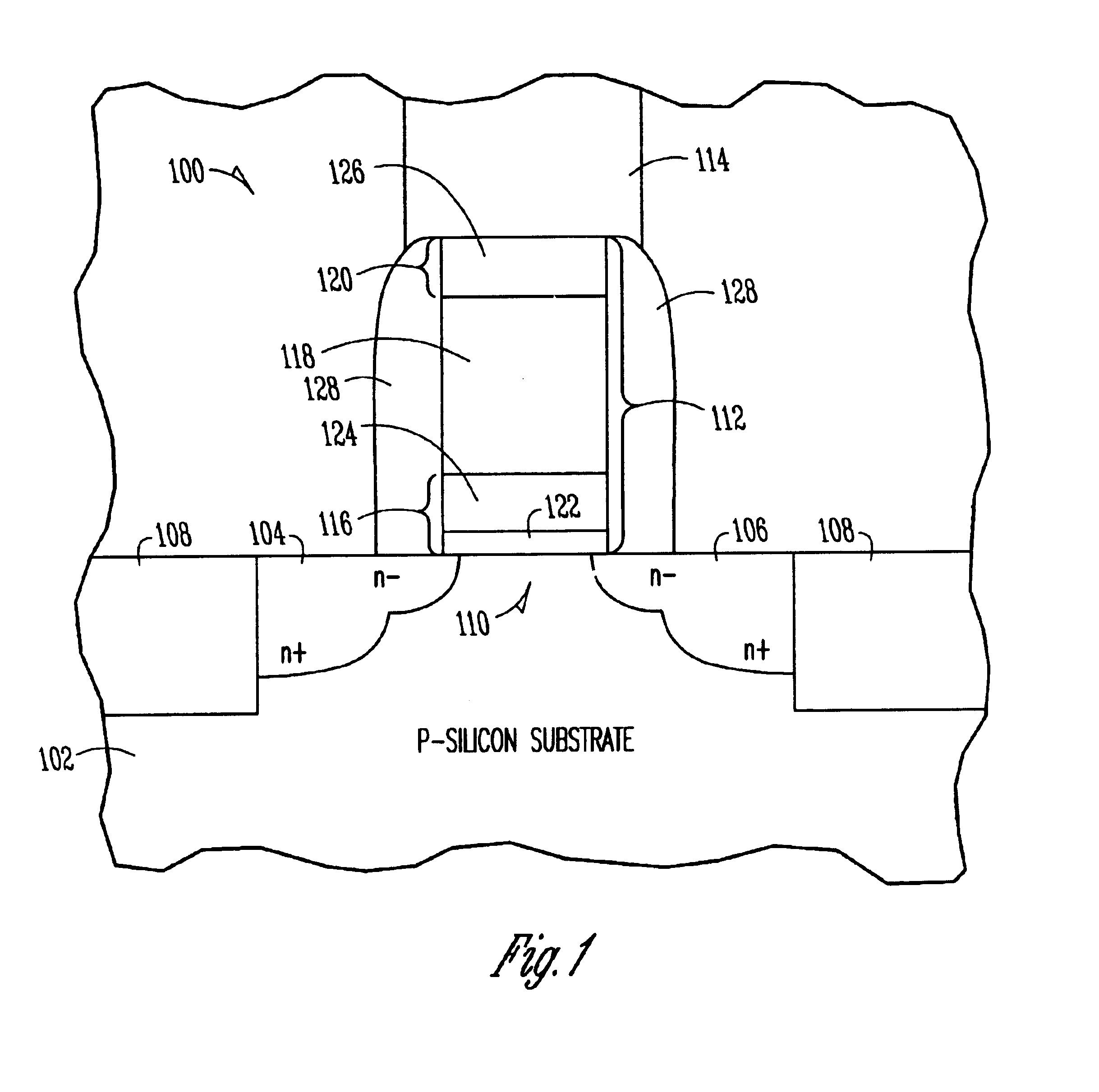

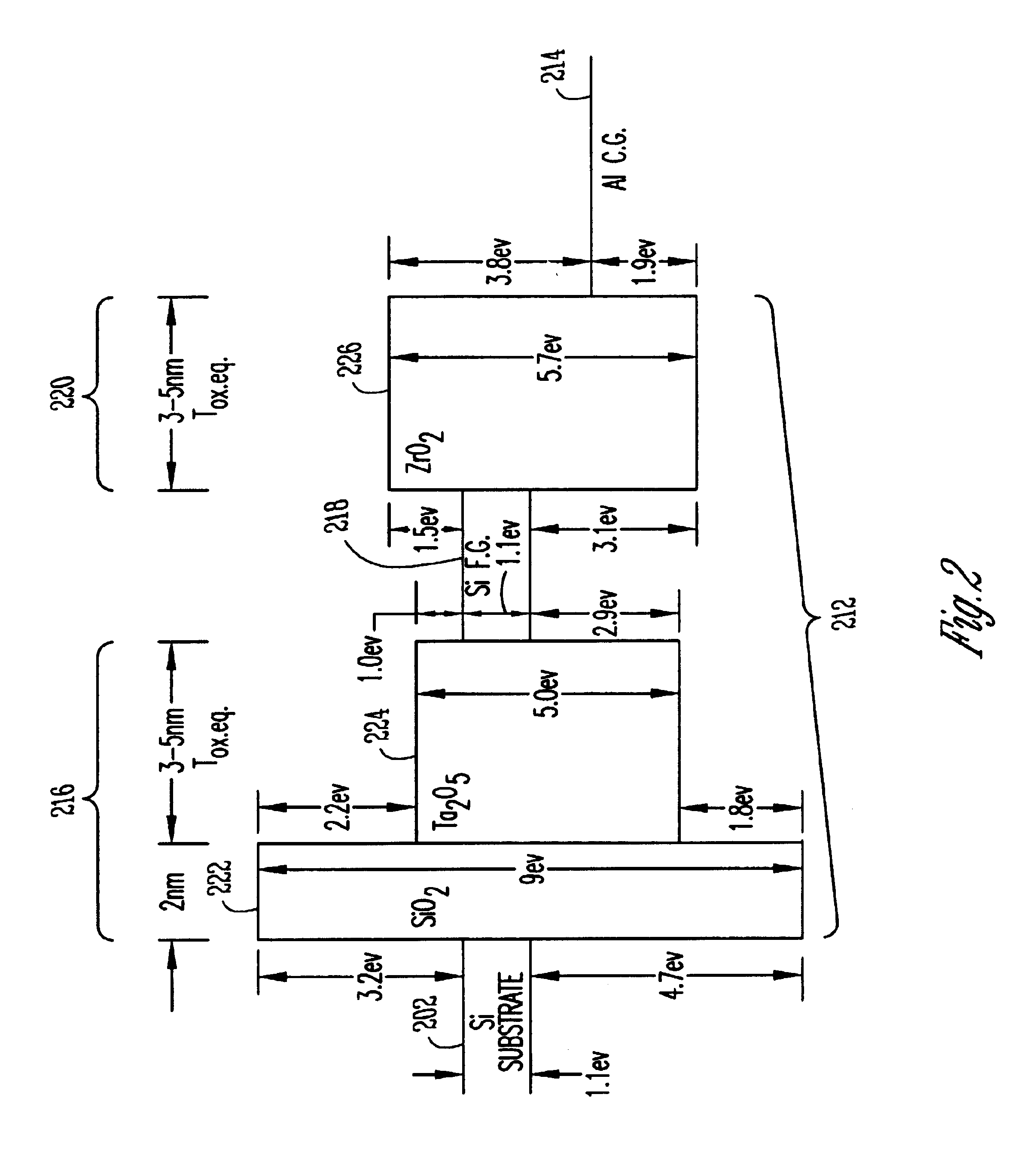

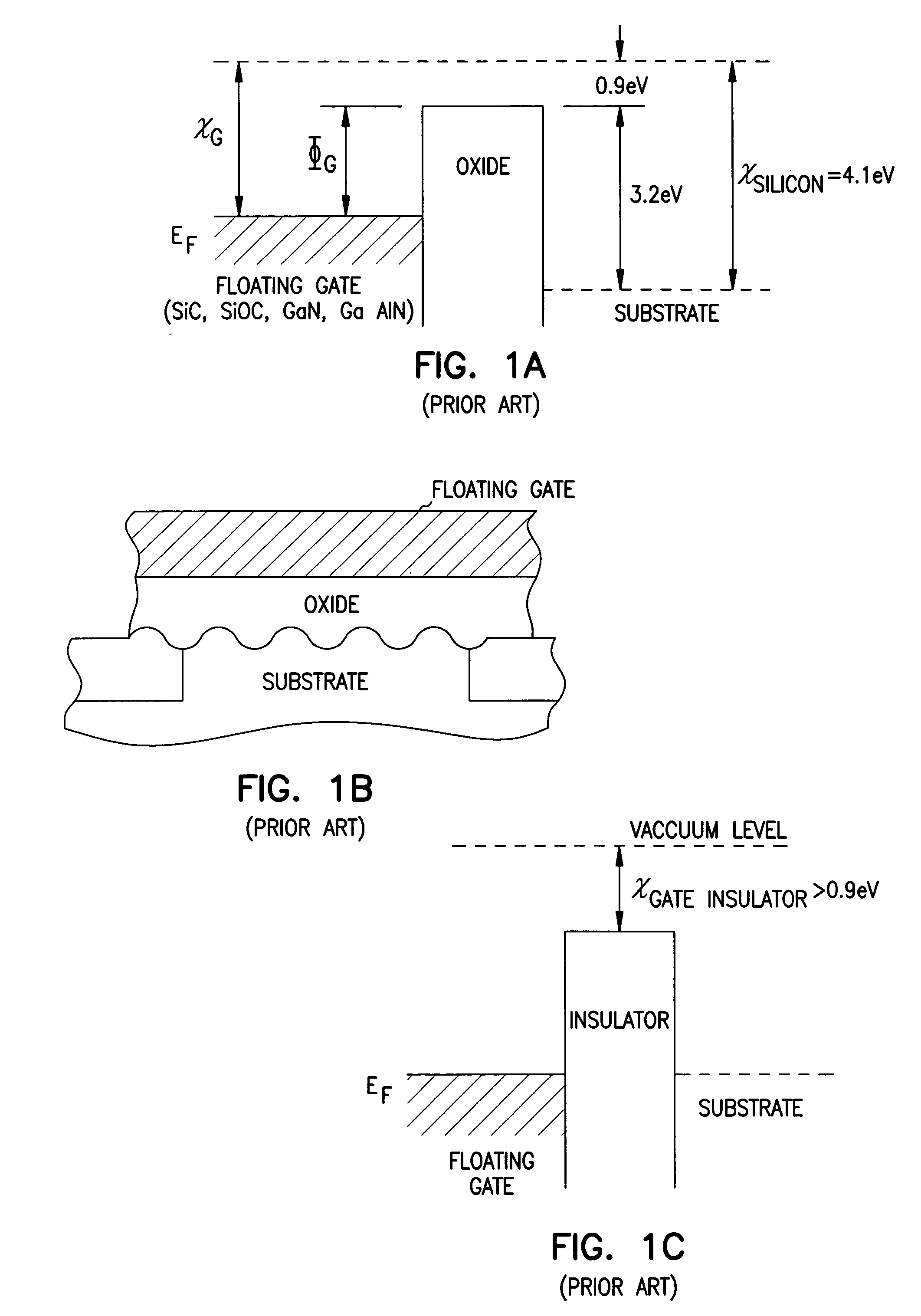

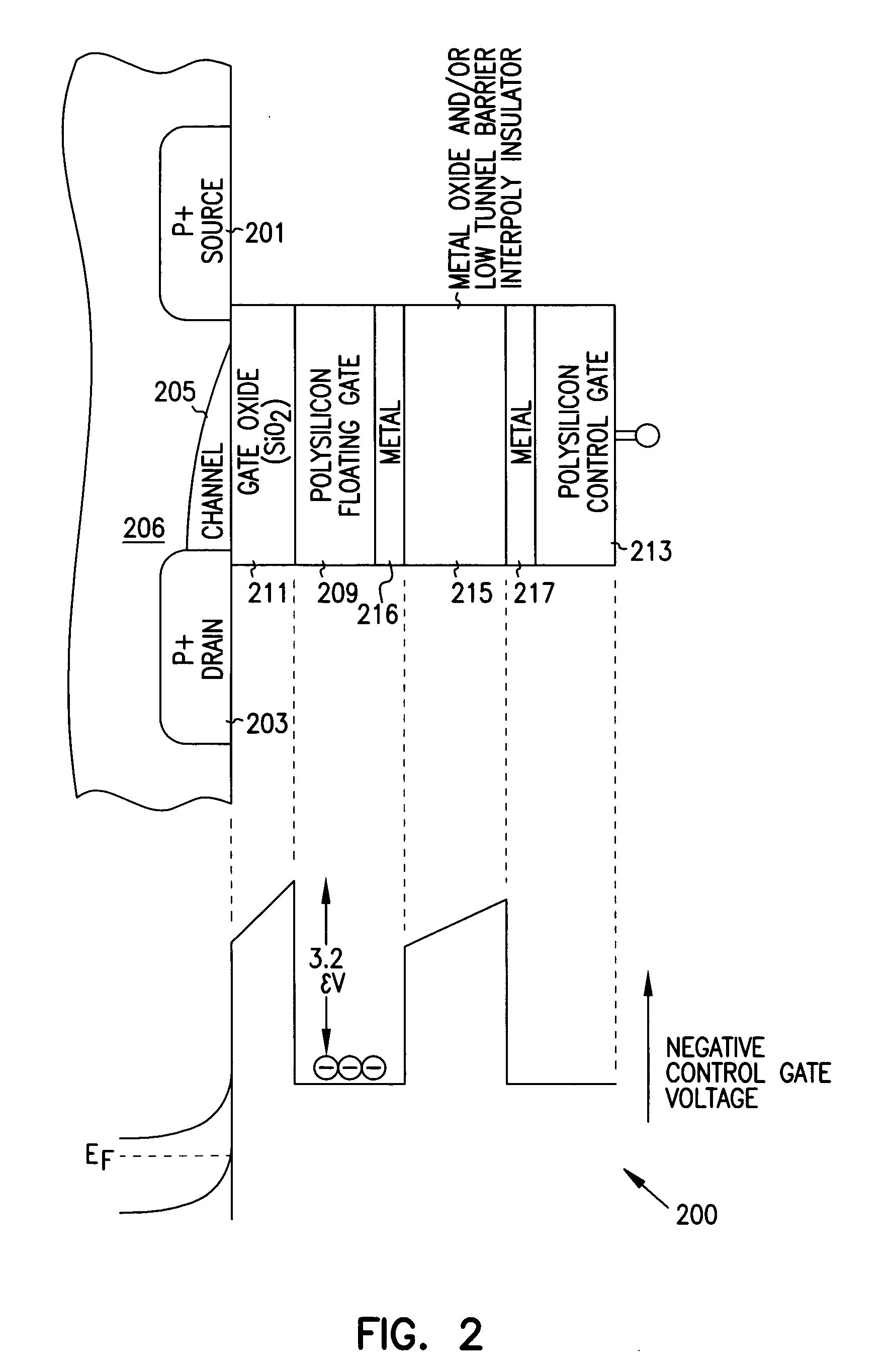

Atomic layer deposition of metal oxide and/or low asymmetrical tunnel barrier interpoly insulators

Structures and methods for programmable array type logic and / or memory devices with asymmetrical low tunnel barrier intergate insulators are provided. The programmable array type logic and / or memory devices include non-volatile memory which has a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposing the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by an asymmetrical low tunnel barrier intergate insulator formed by atomic layer deposition. The asymmetrical low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5, SrBi2Ta2O3, SrTiO3, PbTiO3, and PbZrO3.

Owner:MICRON TECH INC

Method of manufacturing semiconductor device, method of processing substrate and non-transitory computer readable recording medium

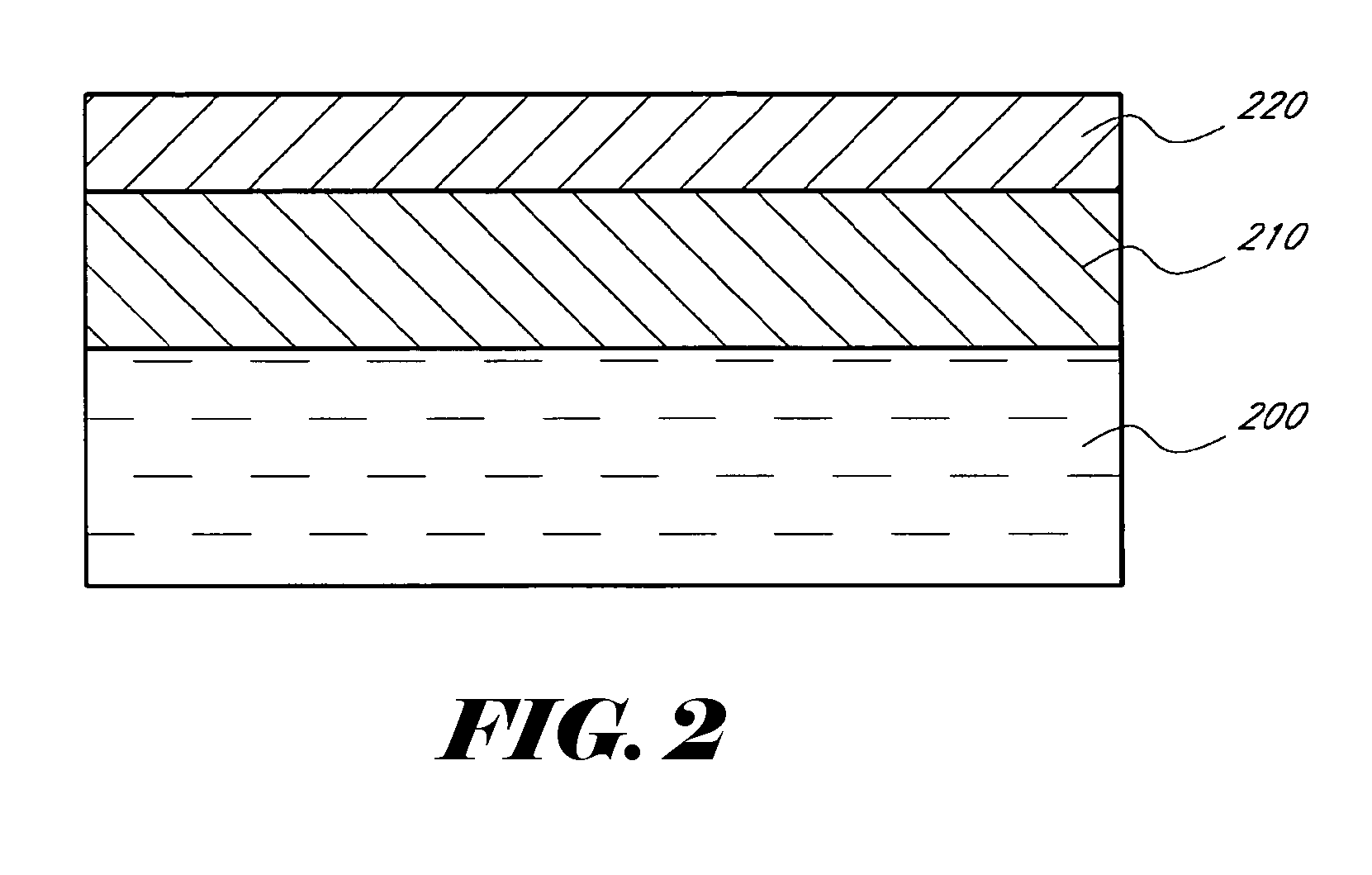

ActiveUS9190264B2Increase productionEasy to operateLiquid surface applicatorsSemiconductor/solid-state device manufacturingPower semiconductor deviceEngineering

A semiconductor manufacturing method includes forming an oxide film on a substrate by performing a first cycle a predetermined number of times, including supplying a first source gas, an oxidizing gas and a reducing gas to the substrate heated to a first temperature in a process container under a sub-atmospheric pressure; forming a seed layer on a surface of the oxide film by supplying a nitriding gas to the substrate in the process container, the substrate being heated to a temperature equal to or higher than the first temperature and equal to or lower than a second temperature; and forming a nitride film on the seed layer formed on the surface of the oxide film by performing a second cycle a predetermined number of times, including supplying a second source gas and the nitriding gas to the substrate heated to the second temperature in the process container.

Owner:KOKUSA ELECTRIC CO LTD

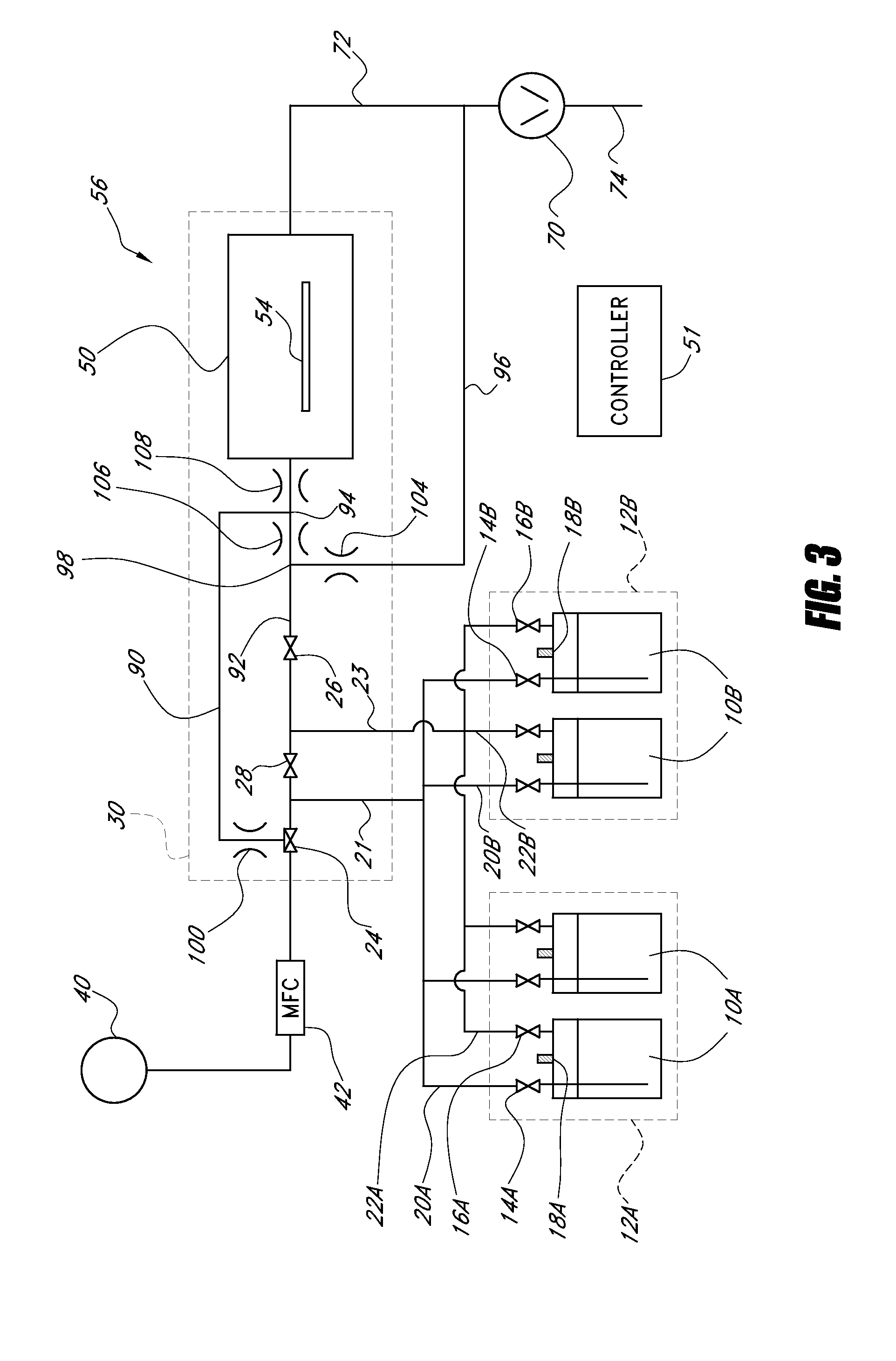

Multiple vapor sources for vapor deposition

Owner:ASM IP HLDG BV

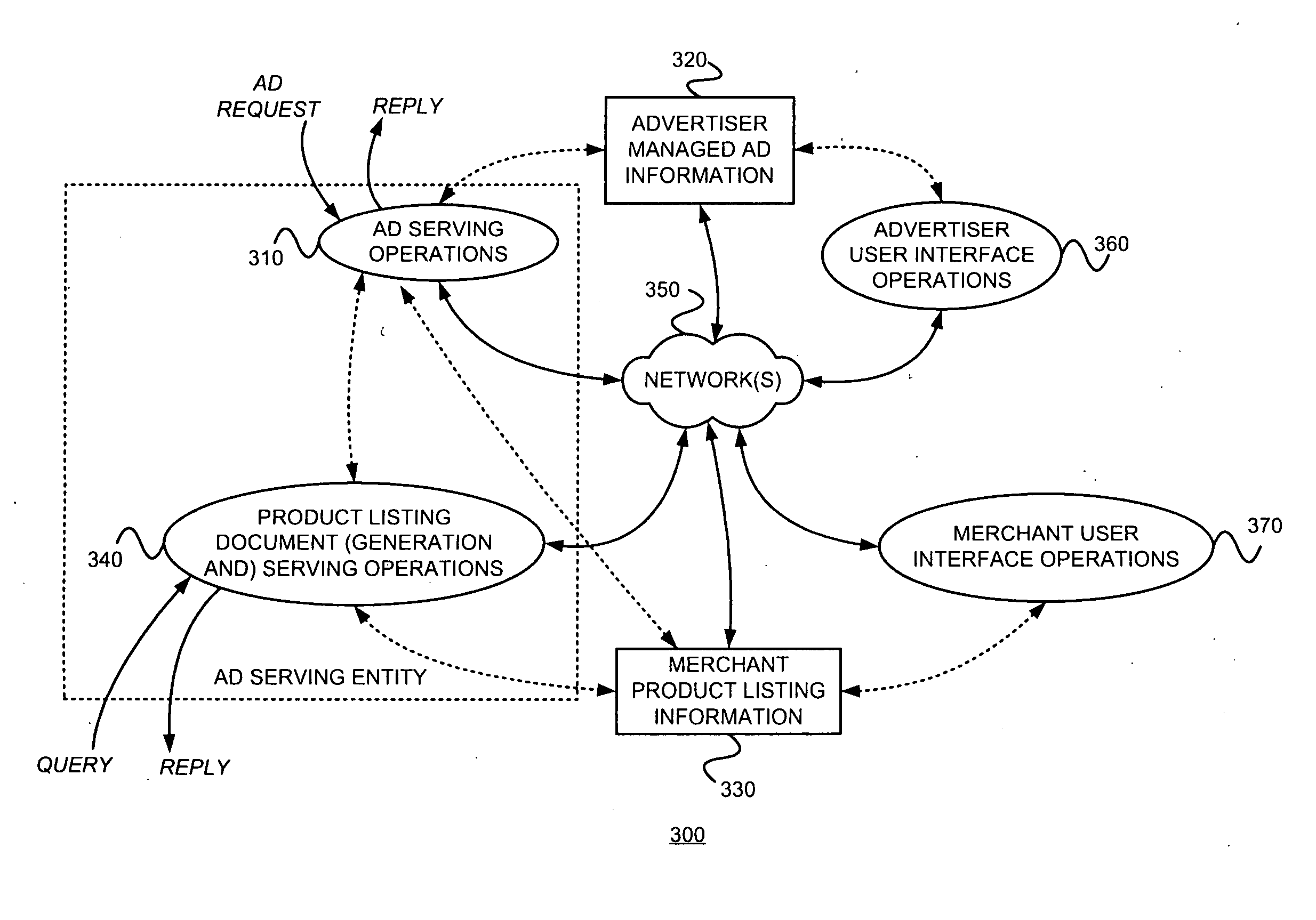

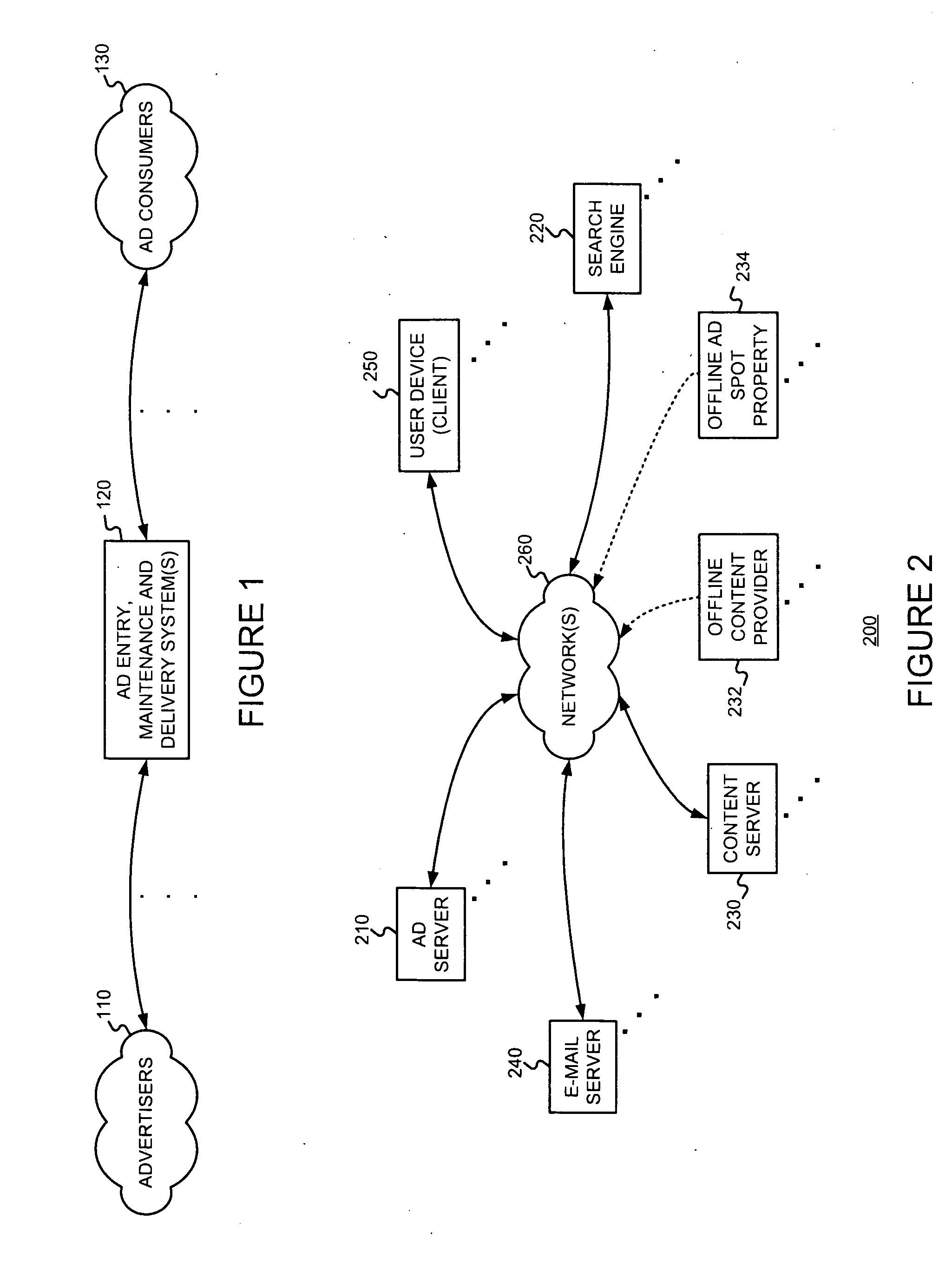

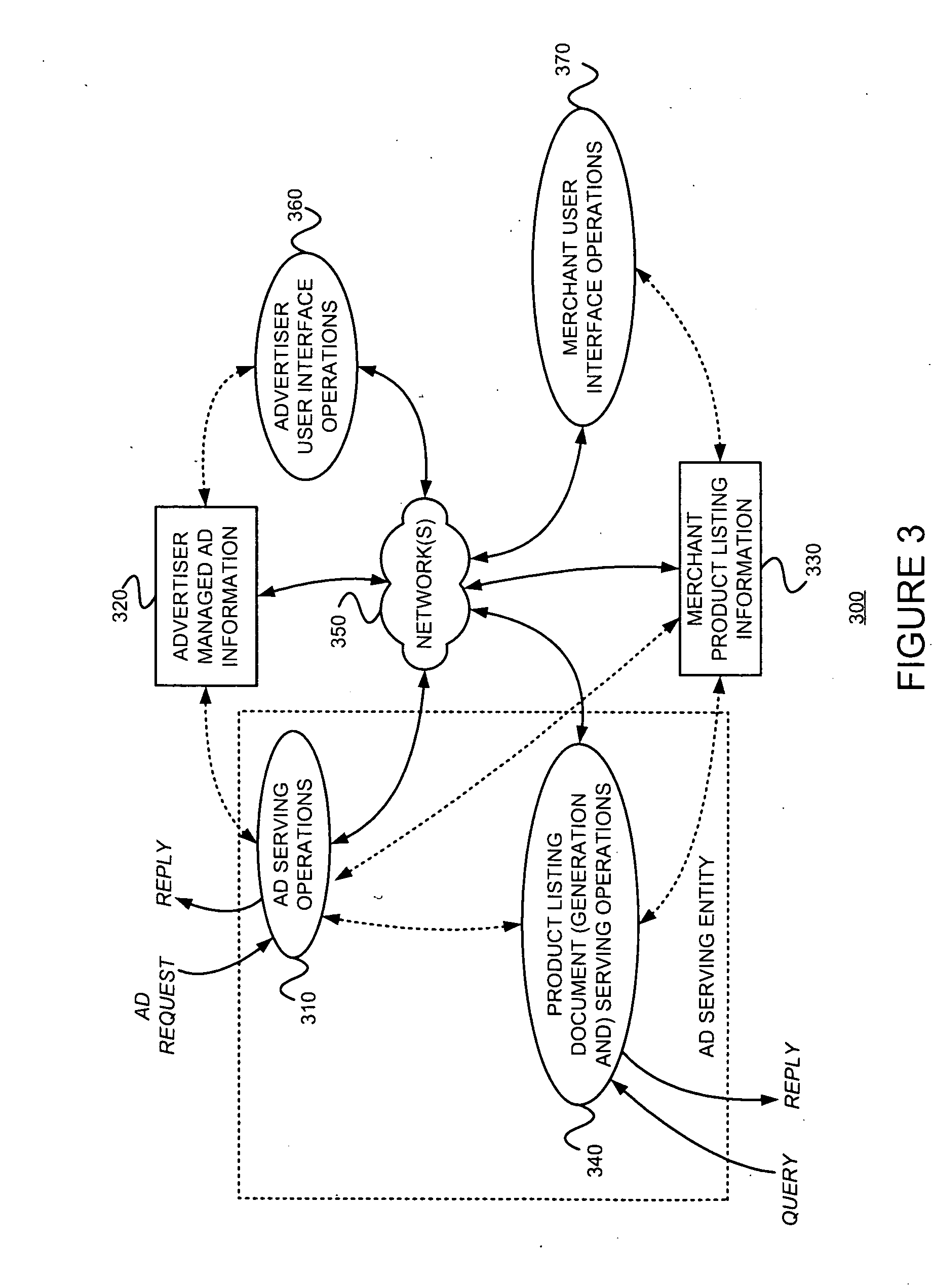

Controlling the serving, with a primary document, of ads from a first source, subject to a first compensation scheme, and ads from a second source, subject to a second compensation scheme

An advertising entity manages determinations, bidding, and / or billing for serving “generic advertisements” on a primary document. Generic ads are not for specific merchants or products; rather they lead users to a secondary document containing more specific information, product listings, and / or merchant listings. Such information and / or listings are determined to be relevant to a generic concept corresponding to the generic ad. For example, when a user selects a generic ad, they may be presented with a secondary document including product listings. If the user selects a merchant's product listing, then that merchant compensates an ad serving entity and / or a publisher of the primary document. Such management might include choosing or generating an appropriate generic advertisement creative for a potential advertising situation. A determination of whether or not to render a generic ad instead of one or more typical advertiser-managed ads may use an expected value of rendering the generic ad versus showing the advertiser-managed ad(s). The result of this determination may be reflected in a bid associated with the generic ad. Generic ads will often be useful for primary documents (e.g., Web pages) that are non-specific.

Owner:GOOGLE LLC

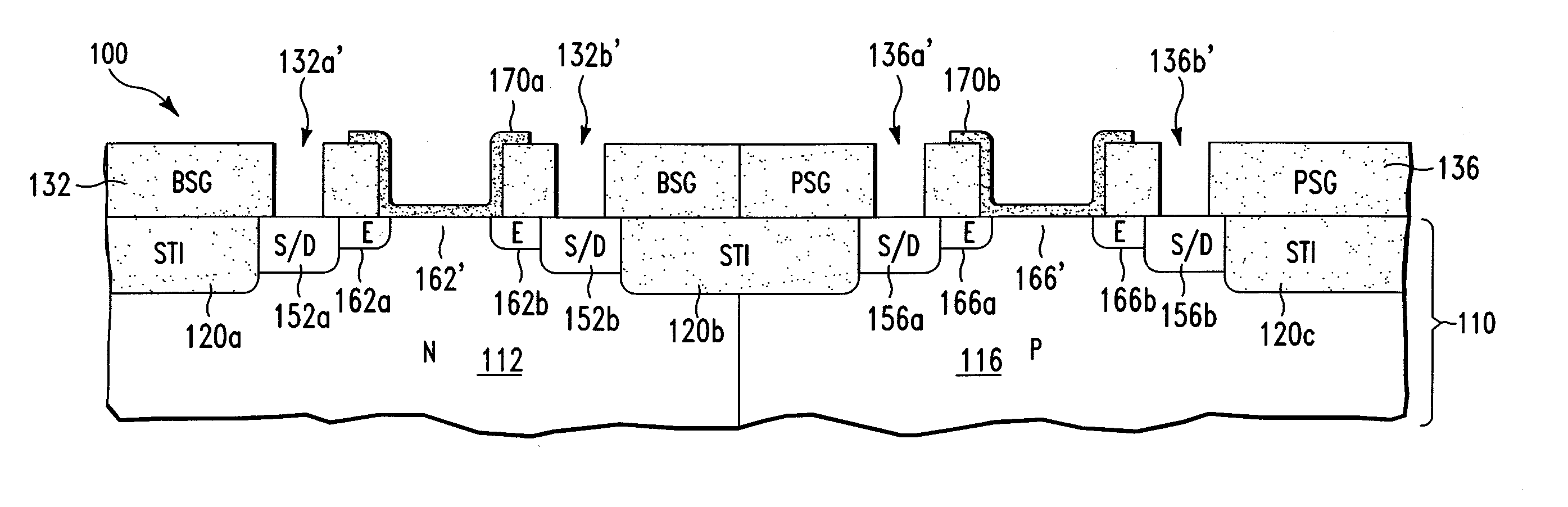

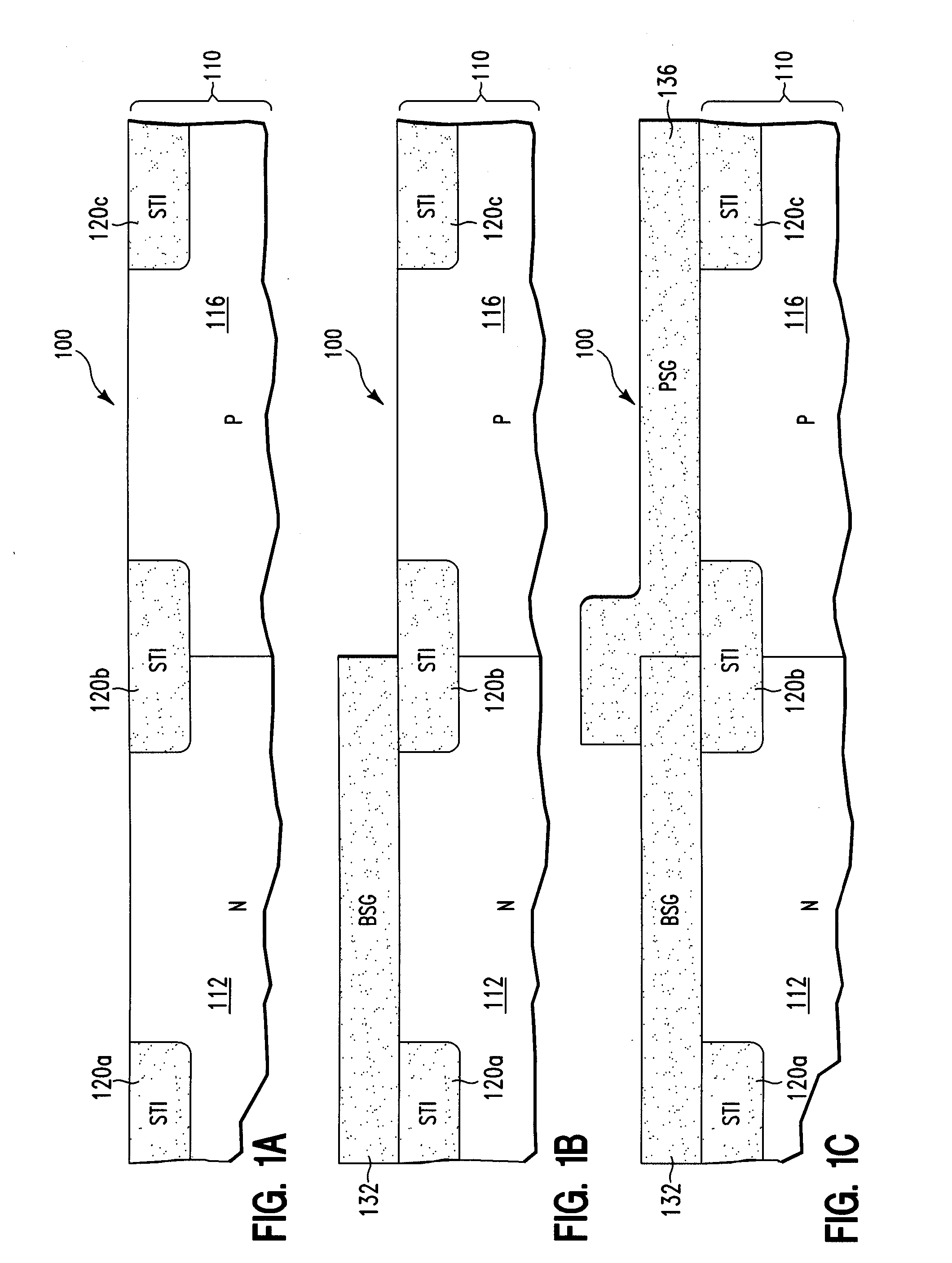

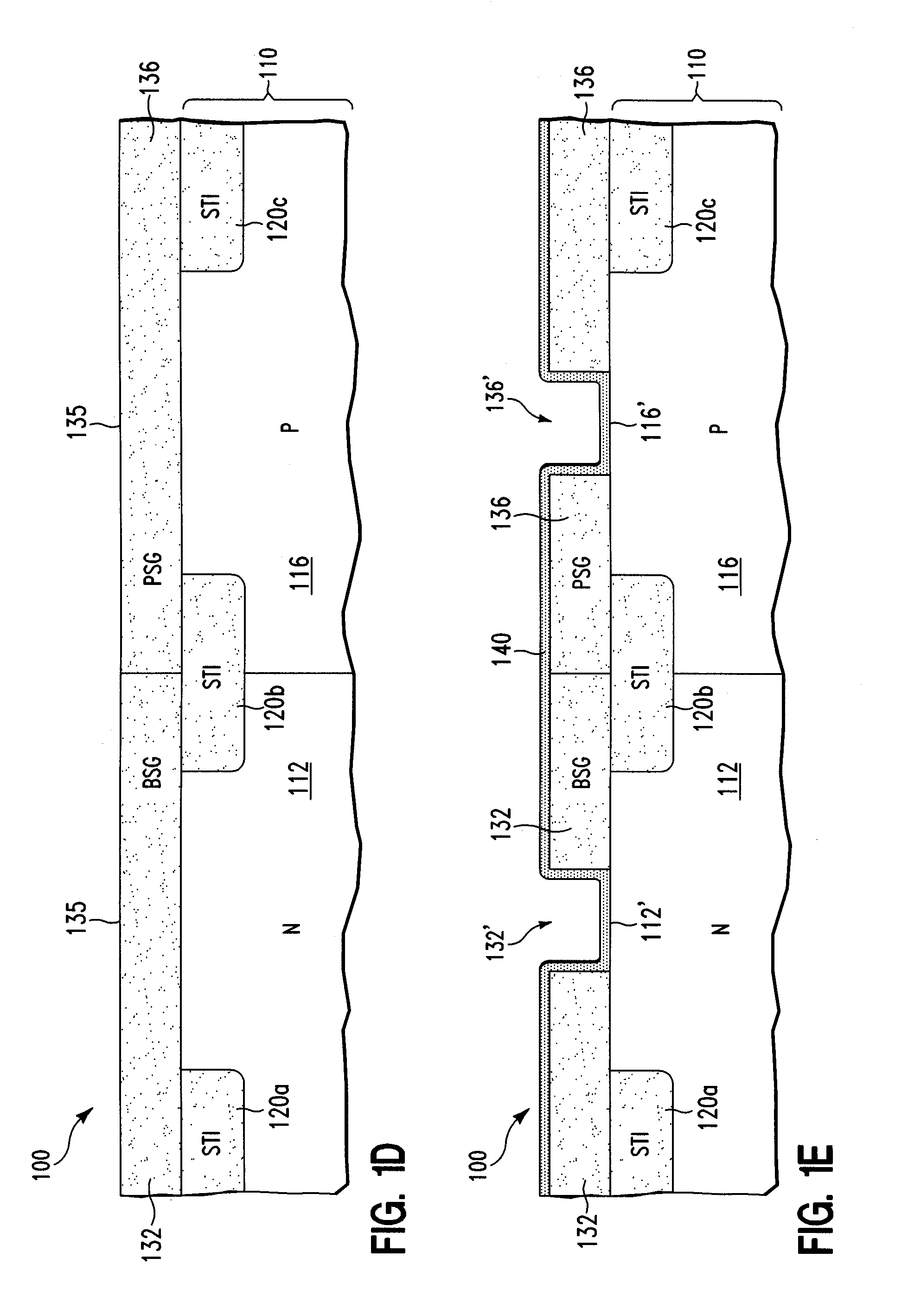

IMPROVED CMOS (Complementary Metal Oxide Semiconductor) TECHNOLOGY

InactiveUS20070020830A1Leakage problemSemiconductor/solid-state device manufacturingSemiconductor devicesDopantCMOS

A method for forming semiconductor transistor. The method comprises providing a structure including (a) a semiconductor region, and (b) first and second dopant source regions on and in direct physical contact with the semiconductor region, wherein each region of the first and second dopant source regions comprises a dielectric material which contains dopants; causing the dopants to diffuse from the first and second dopant source regions into the semiconductor region so as to form first and second source / drain extension regions, respectively, wherein the first and second source / drain extension regions define a channel region disposed between; forming a gate dielectric region on a channel region; and forming a gate region on the gate dielectric region, wherein the gate dielectric region electrically insulates the gate region from the channel region.

Owner:IBM CORP

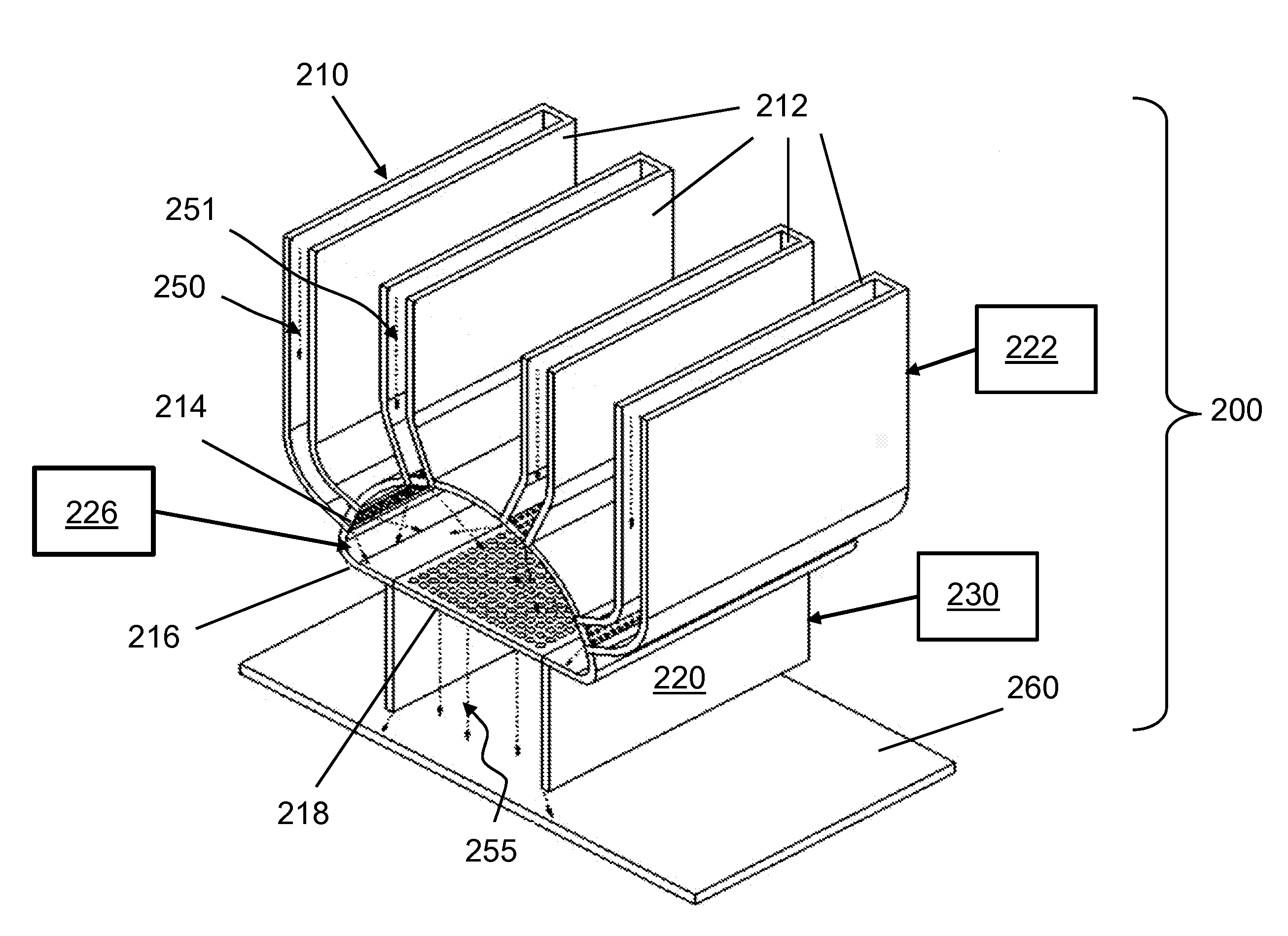

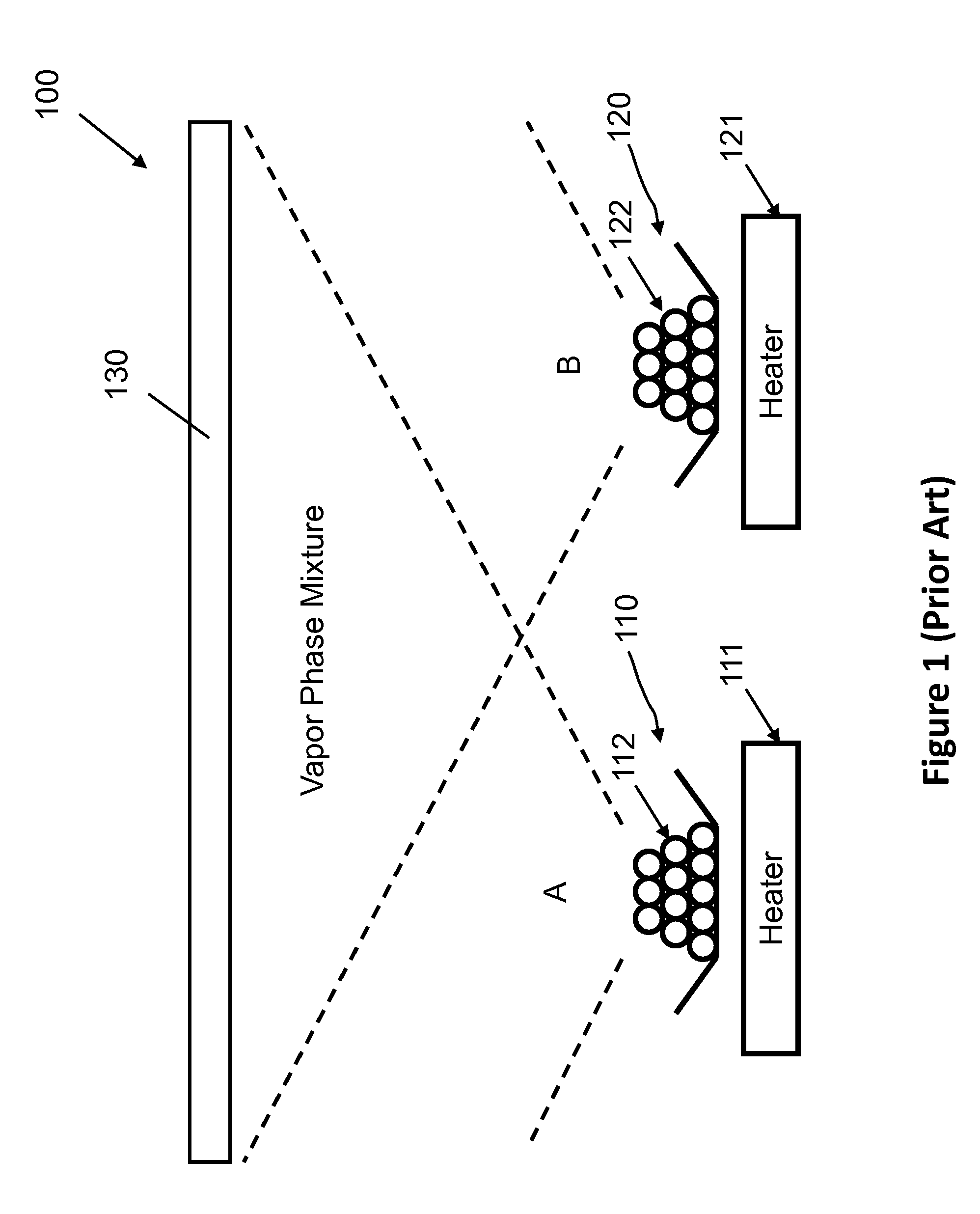

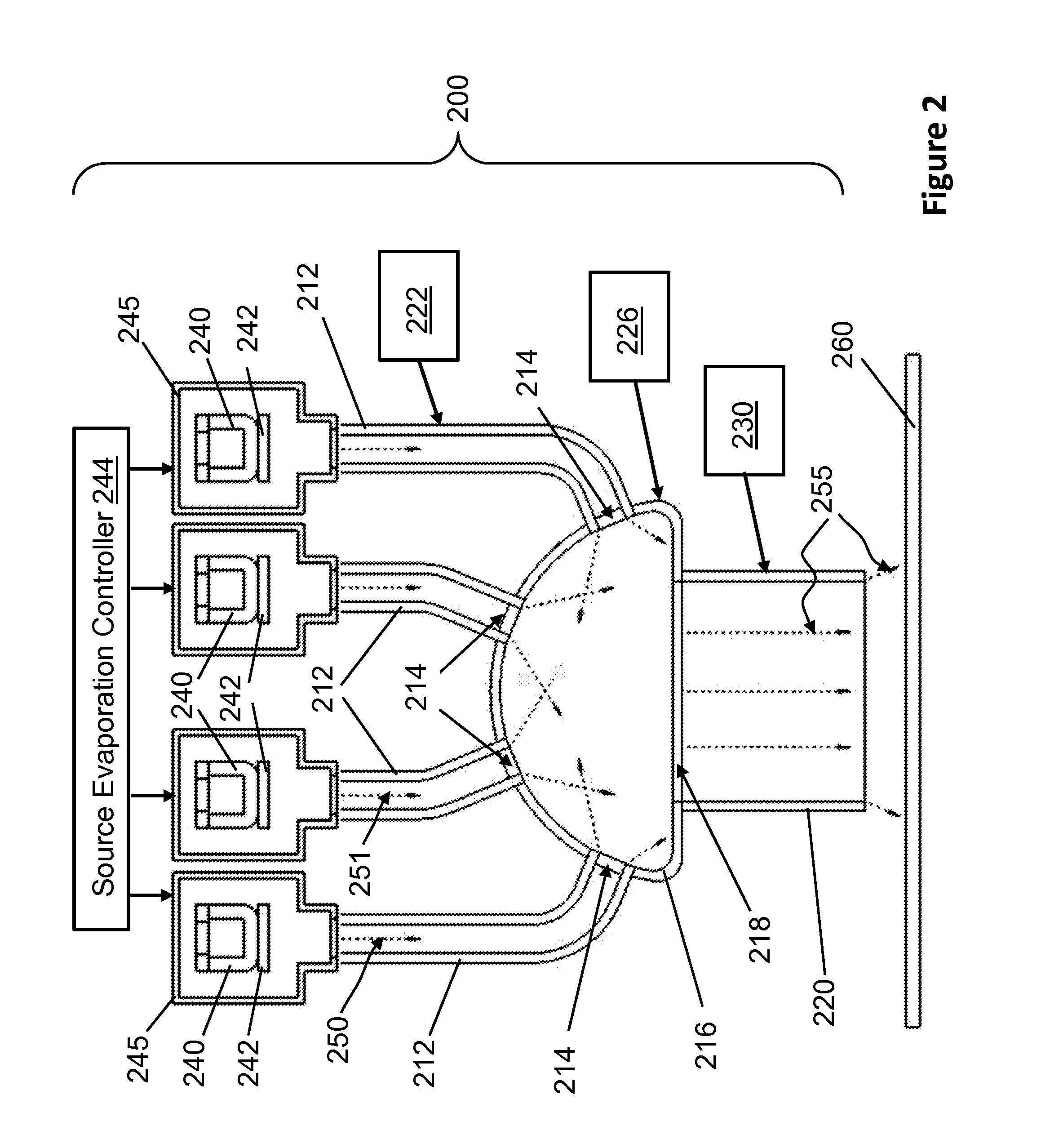

Co-evaporation system comprising vapor pre-mixer

InactiveUS20130302520A1Uniform depositionUniform composition ratioVacuum evaporation coatingSputtering coatingSource materialEvaporation

A processing system for depositing a plurality of source materials on a substrate, includes a first thermal evaporation source that can evaporate a first source material to produce a first vapor, a second thermal evaporation source that can evaporate a second source material to produce a second vapor, a vapor mixing chamber that allows the first vapor and the second vapor to be mixed to produce a mixed vapor, and conduits that can separately transport the first vapor and the second vapor to the vapor mixing chamber. The mixed vapor can be directed toward a substrate to deposit a mixture of the first source material and the second source material on the substrate. The processing system can also include vapor filters configured to regulate flows of the first vapor and the second vapor, and a mixed vapor filter to regulate flow of the mixed vapor.

Owner:WANG KAI AN +4

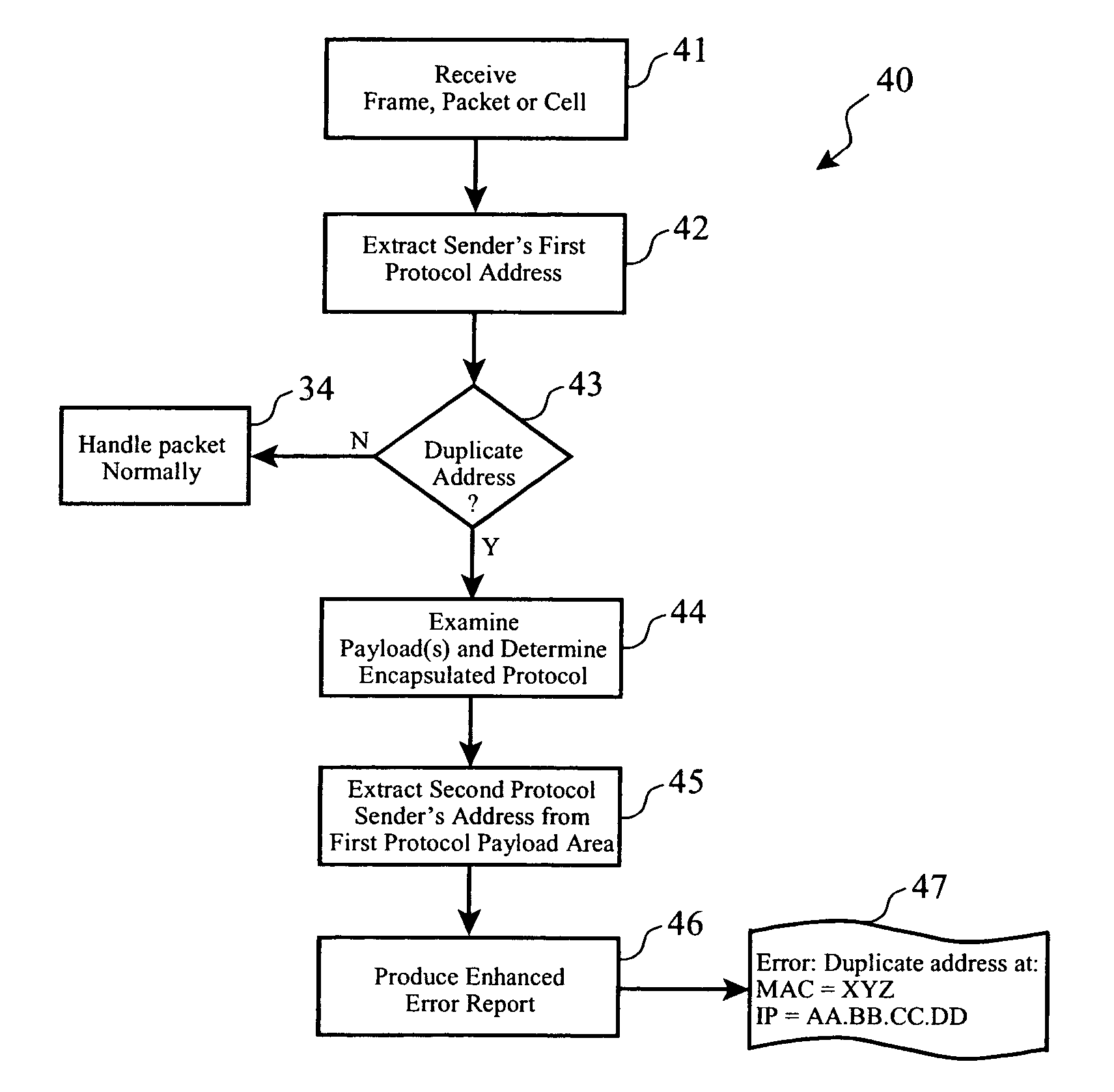

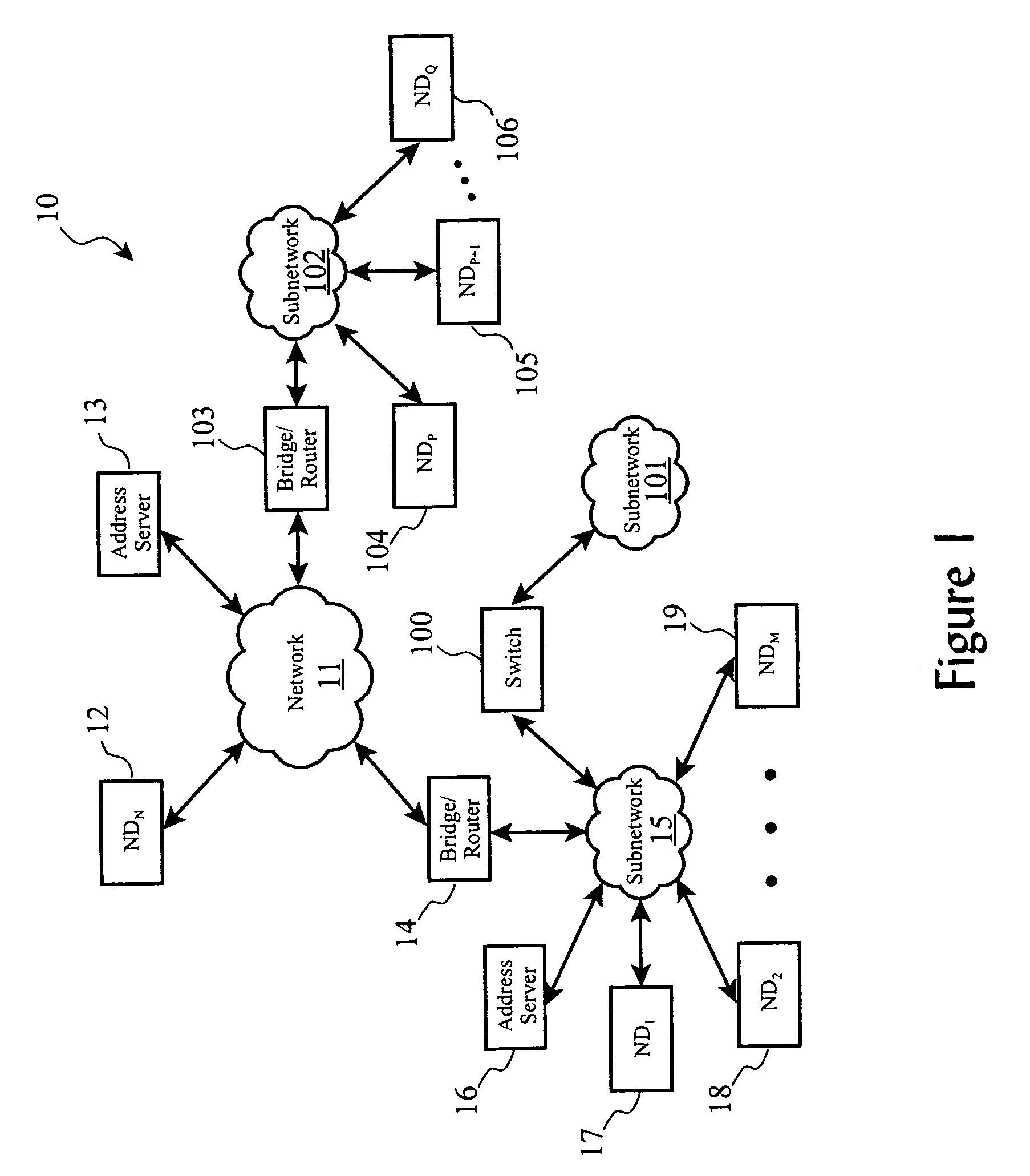

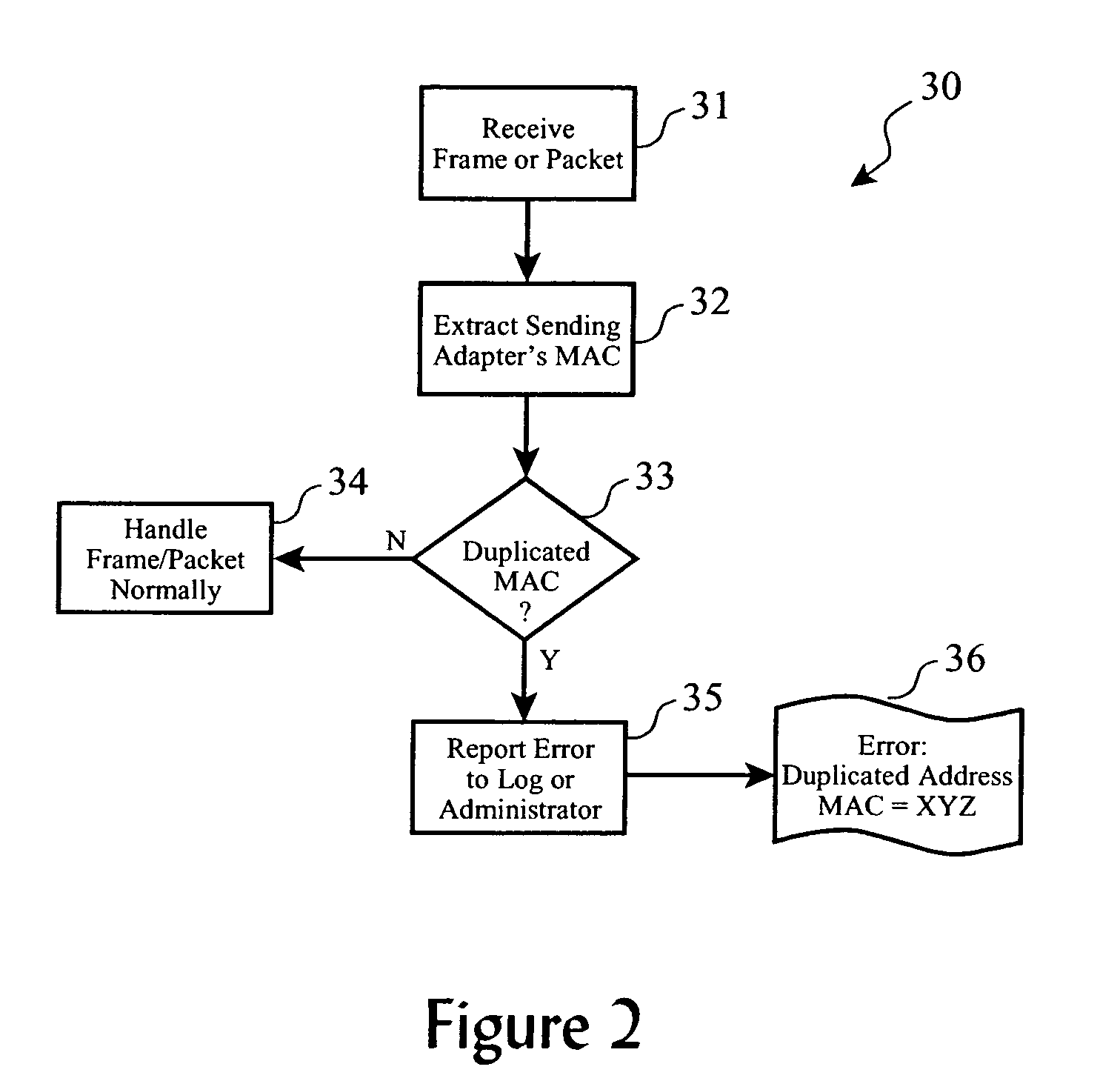

Duplicate network address detection

ActiveUS7246272B2Easy to detectError detection/correctionData switching by path configurationEncapsulated dataNetwork addressing

A plurality of data packets encoded according to a first protocol are received which encapsulate data encoded according to a second protocol. A first source address is extracted from the packets according to the first protocol, it is determined whether or not the first source address is a substantial duplicate of a known assigned address. If it is a duplicate, a second source address is extracted from the encapsulated data according to the second protocol, and the first source address and said second source address are provided in an enhanced error log so that a system administrator may correct the duplicate assigned address. Enhanced embodiments of the invention included analysis of data encapsulated by a third, fourth and subsequent protocols, and automatic determination of each protocol encoding format.

Owner:GOOGLE LLC

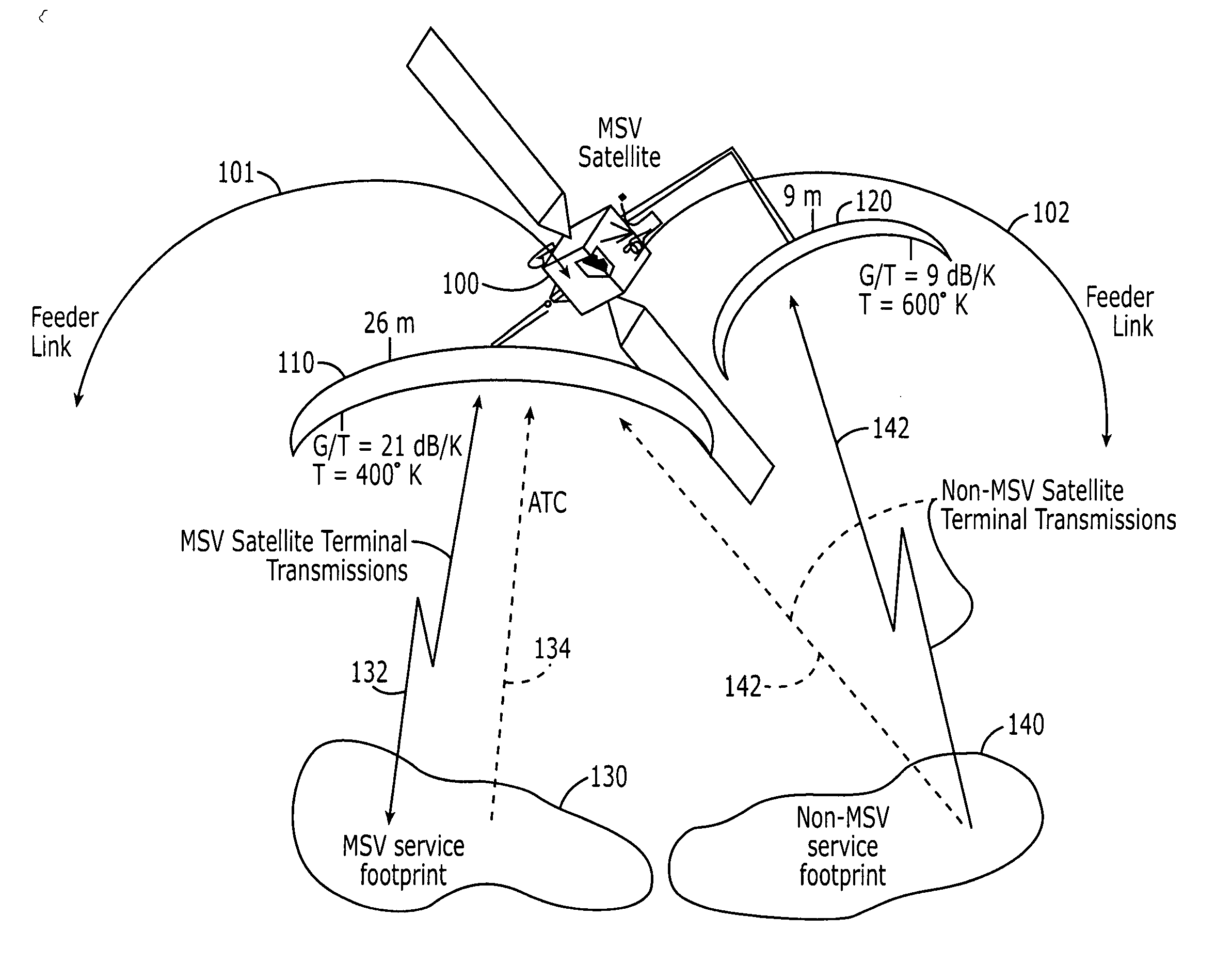

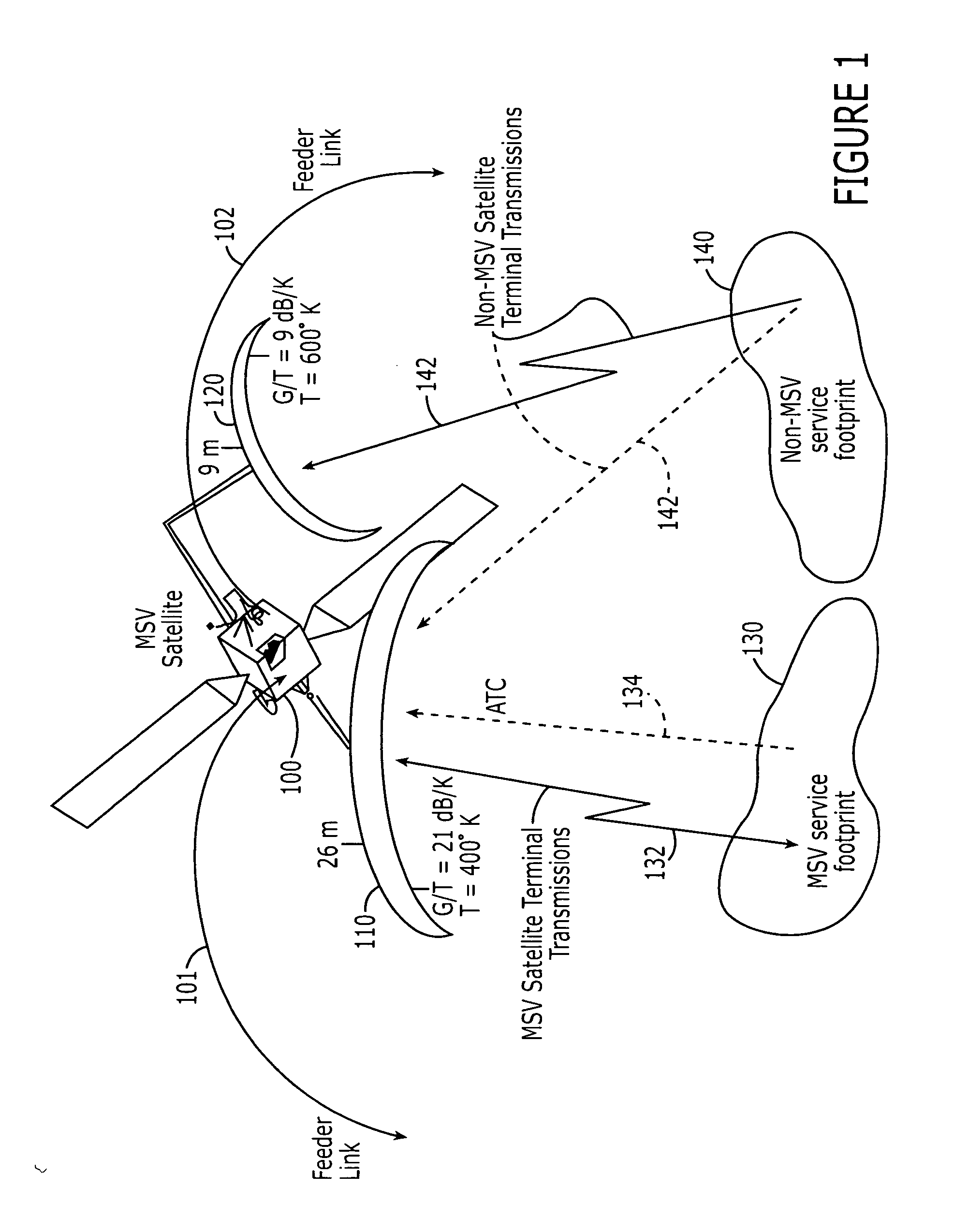

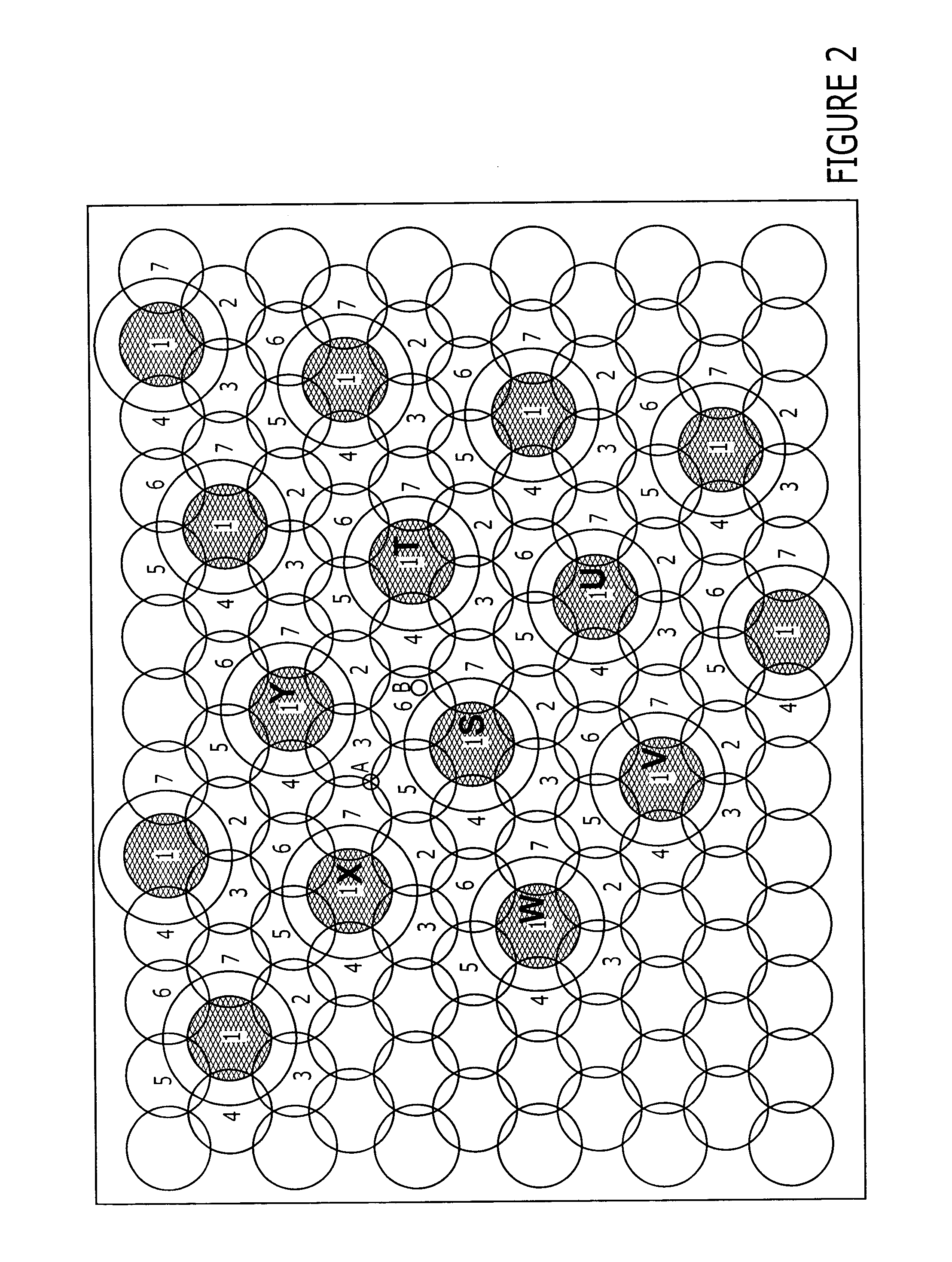

Additional intra-and/or inter-system interference reducing systems and methods for satellite communications systems

ActiveUS20050136836A1Radio/inductive link selection arrangementsRadio transmissionEngineeringSatellite Telecommunications

First radio signals are received by a first satellite, the received first radio signals including a desired satellite uplink signal transmitted from a first source using a frequency assigned to the first source and an interfering signal transmitted from a second source using the frequency assigned to the first source. The first radio signals are combined based on a first performance criterion to generate a first output signal. Second radio signals are received by a second satellite, the received second radio signals including a measure of the desired signal. The second radio signals are combined based on a second performance criterion to produce a second output signal. The first and second output signals are combined to generate an estimate of the desired satellite uplink signal.

Owner:ATC TECH LLC

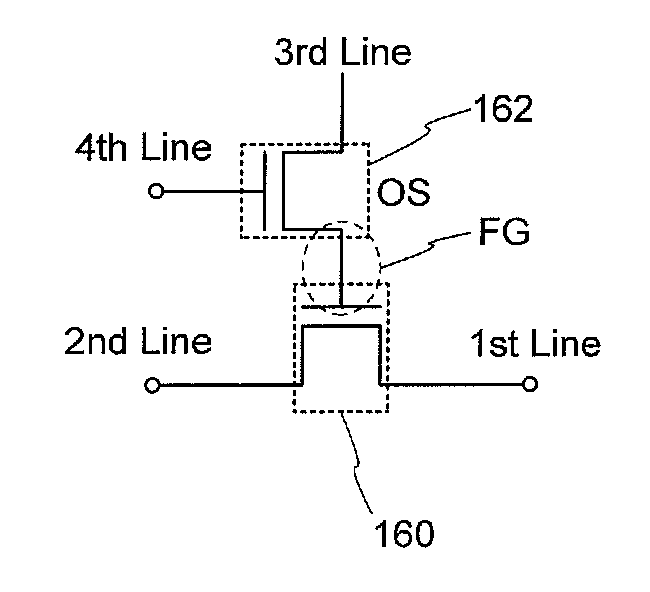

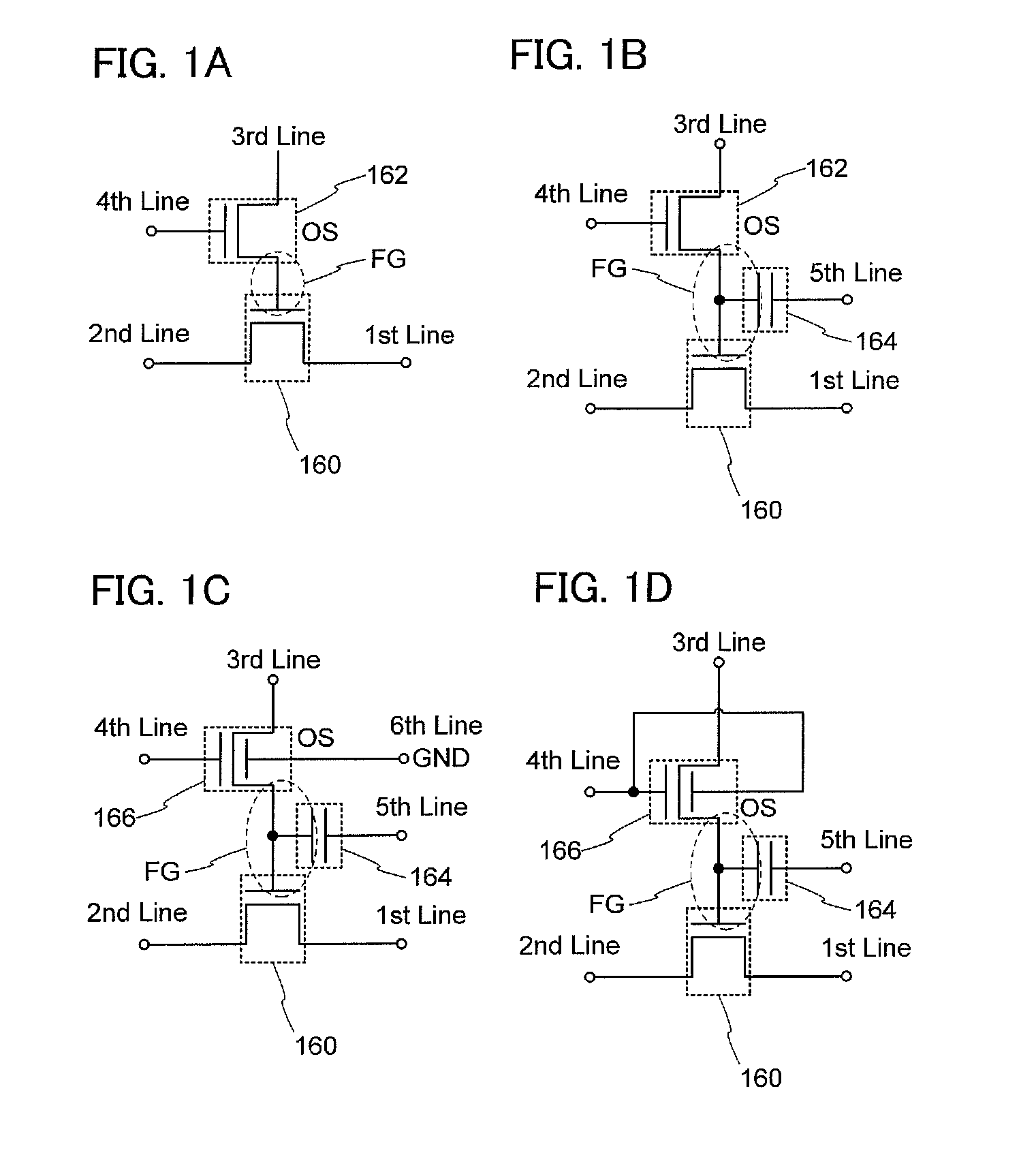

Semiconductor device

InactiveUS20110128777A1Long storageReduce power consumptionSolid-state devicesRead-only memoriesPower semiconductor deviceSemiconductor materials

The semiconductor device includes a first wiring; a second wiring; a third wiring; a fourth wiring; a first transistor having a first gate electrode, a first source electrode, and a first drain electrode; and a second transistor having a second gate electrode, a second source electrode, and a second drain electrode. The first transistor is formed on or in a substrate including a semiconductor material. The second transistor includes an oxide semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

ActiveUS20110156027A1Long storageReduce power consumptionTransistorSolid-state devicesSemiconductor materialsEngineering

An object of one embodiment of the present invention is to provide a semiconductor device with a novel structure in which stored data can be stored even when power is not supplied in a data storing time and there is no limitation on the number of times of writing. The semiconductor device includes a first transistor which includes a first channel formation region using a semiconductor material other than an oxide semiconductor, a second transistor which includes a second channel formation region using an oxide semiconductor material, and a capacitor. One of a second source electrode and a second drain electrode of the second transistor is electrically connected to one electrode of the capacitor.

Owner:SEMICON ENERGY LAB CO LTD

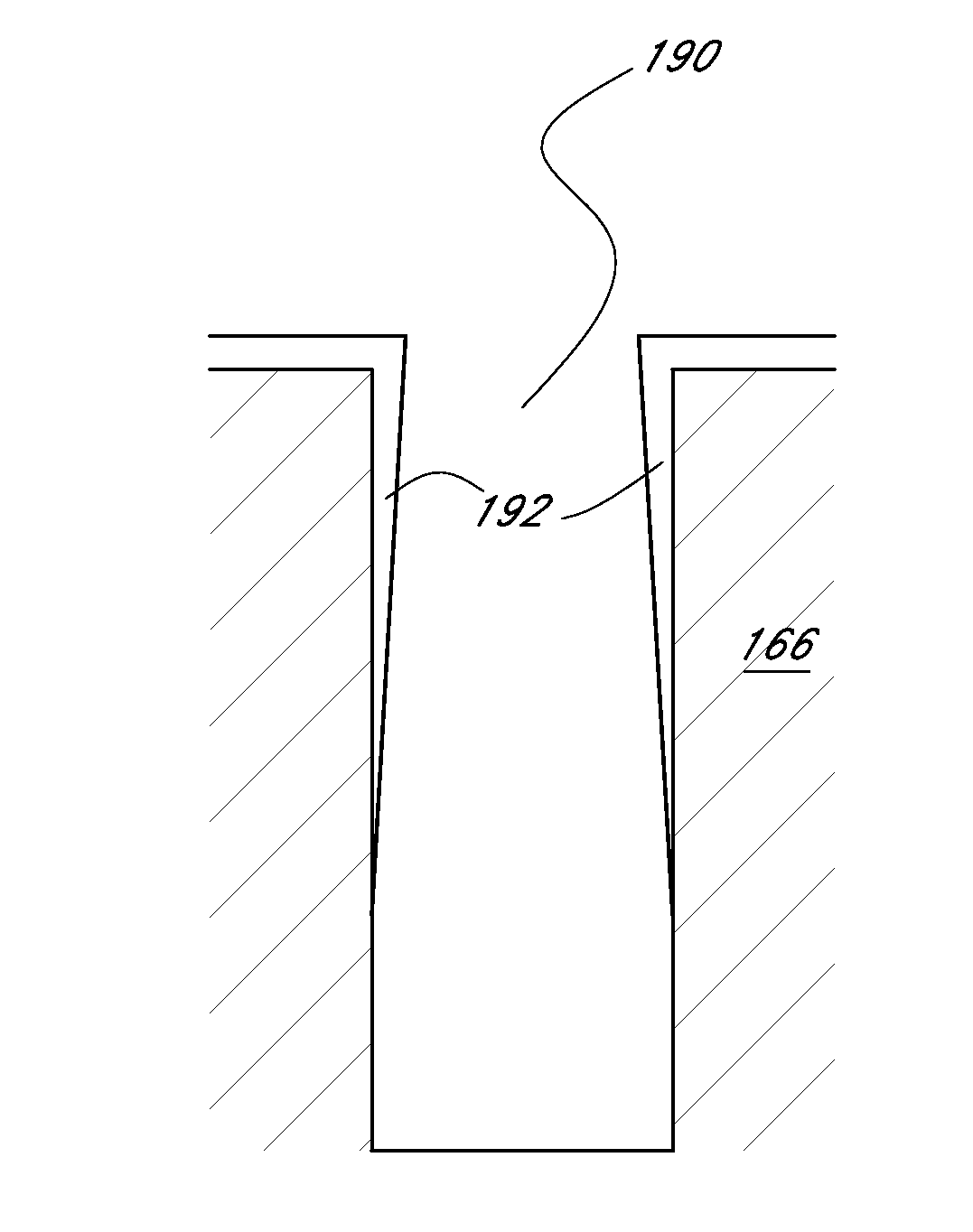

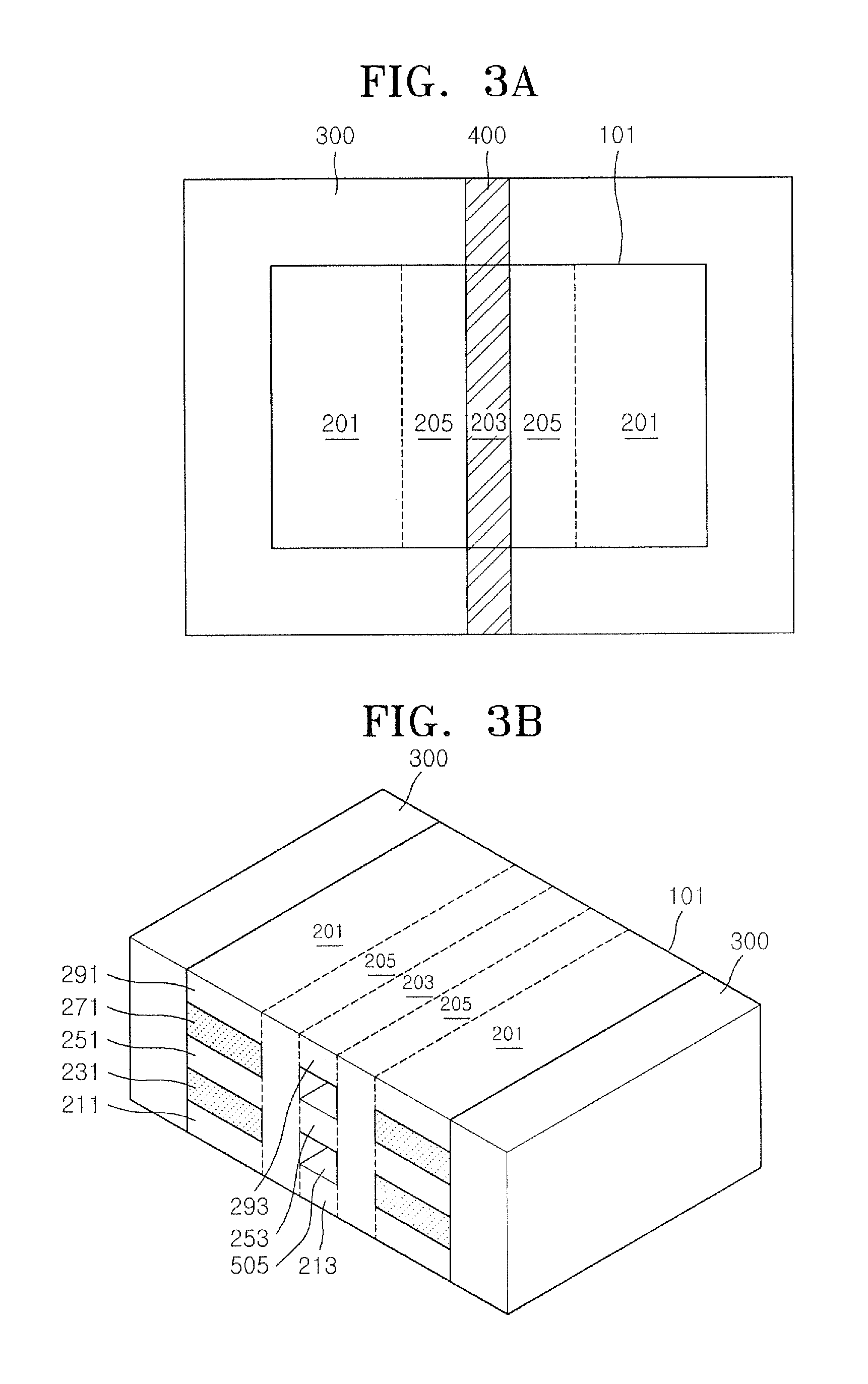

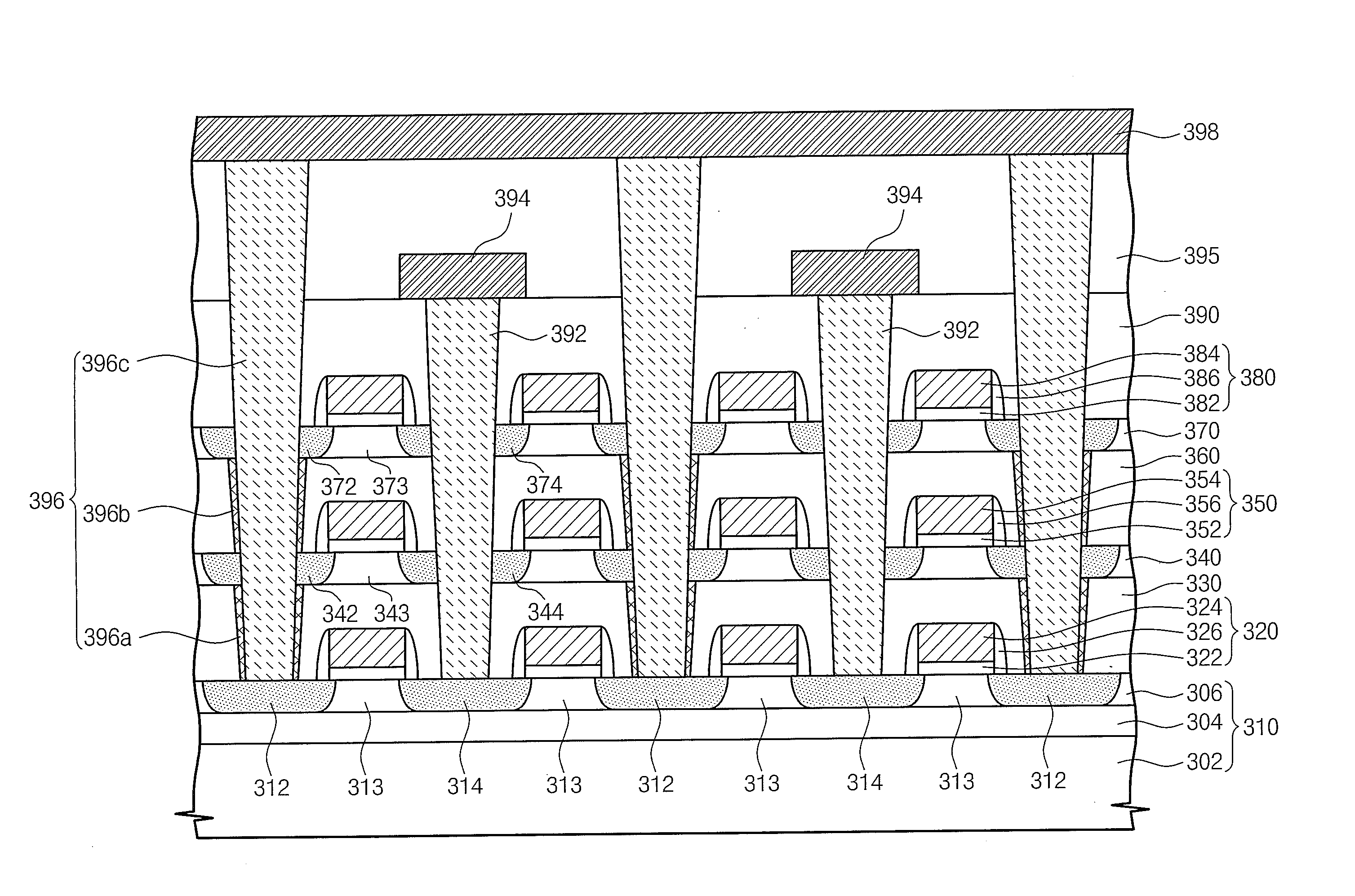

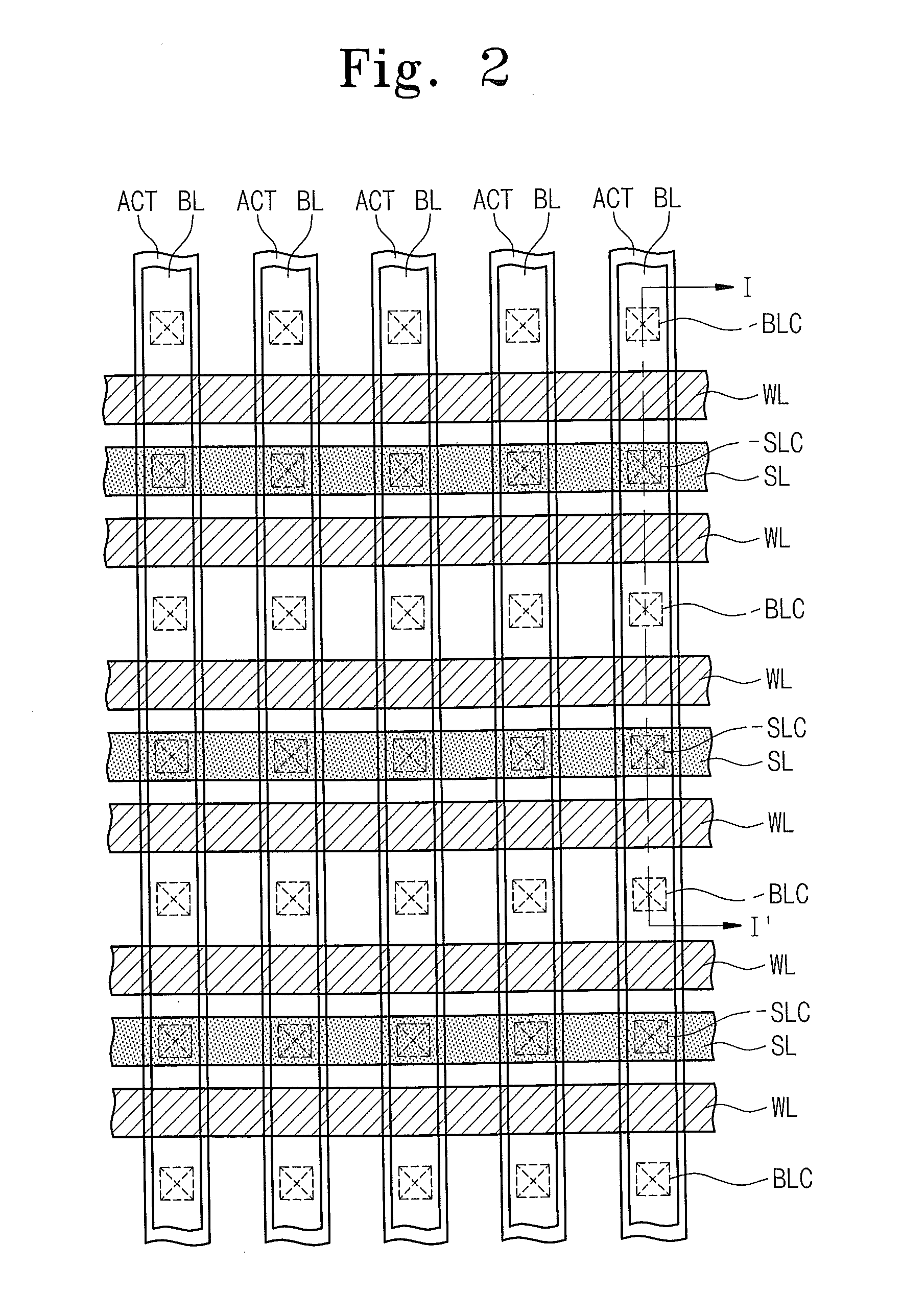

Methods of forming a multi-bridge-channel MOSFET

ActiveUS7402483B2Semiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate dielectric

A multi-bridge-channel MOSFET (MBCFET) may be formed by forming a stacked structure on a substrate that includes channel layers and interchannel layers interposed between the channel layers. Trenches are formed by selectively etching the stacked structure. The trenches run across the stacked structure parallel to each other and separate a first stacked portion including channel patterns and interchannel patterns from second stacked portions including channel and interchannel layers remaining on both sides of the first stacked portion. First source and drain regions are grown using selective epitaxial growth. The first source and drain regions fill the trenches and connect to second source and drain regions defined by the second stacked portions. Marginal sections of the interchannel patterns of the first stacked portion are selectively exposed. Through tunnels are formed by selectively removing the interchannel patterns of the first stacked portion beginning with the exposed marginal sections. The through tunnels are surrounded by the first source and drain regions and the channel patterns. A gate is formed along with a gate dielectric layer, the gate filling the through tunnels and extending onto the first stacked portion.

Owner:SAMSUNG ELECTRONICS CO LTD

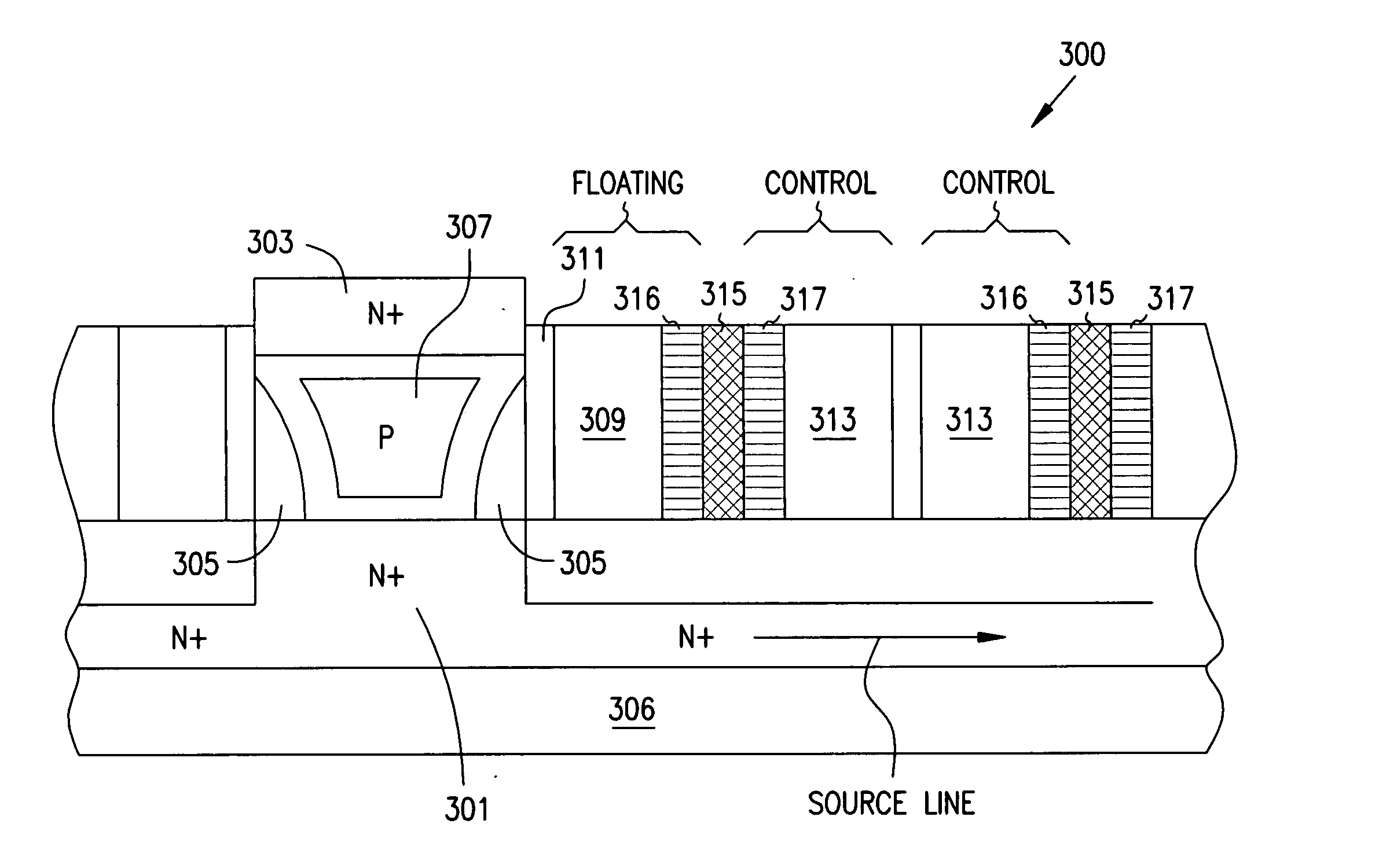

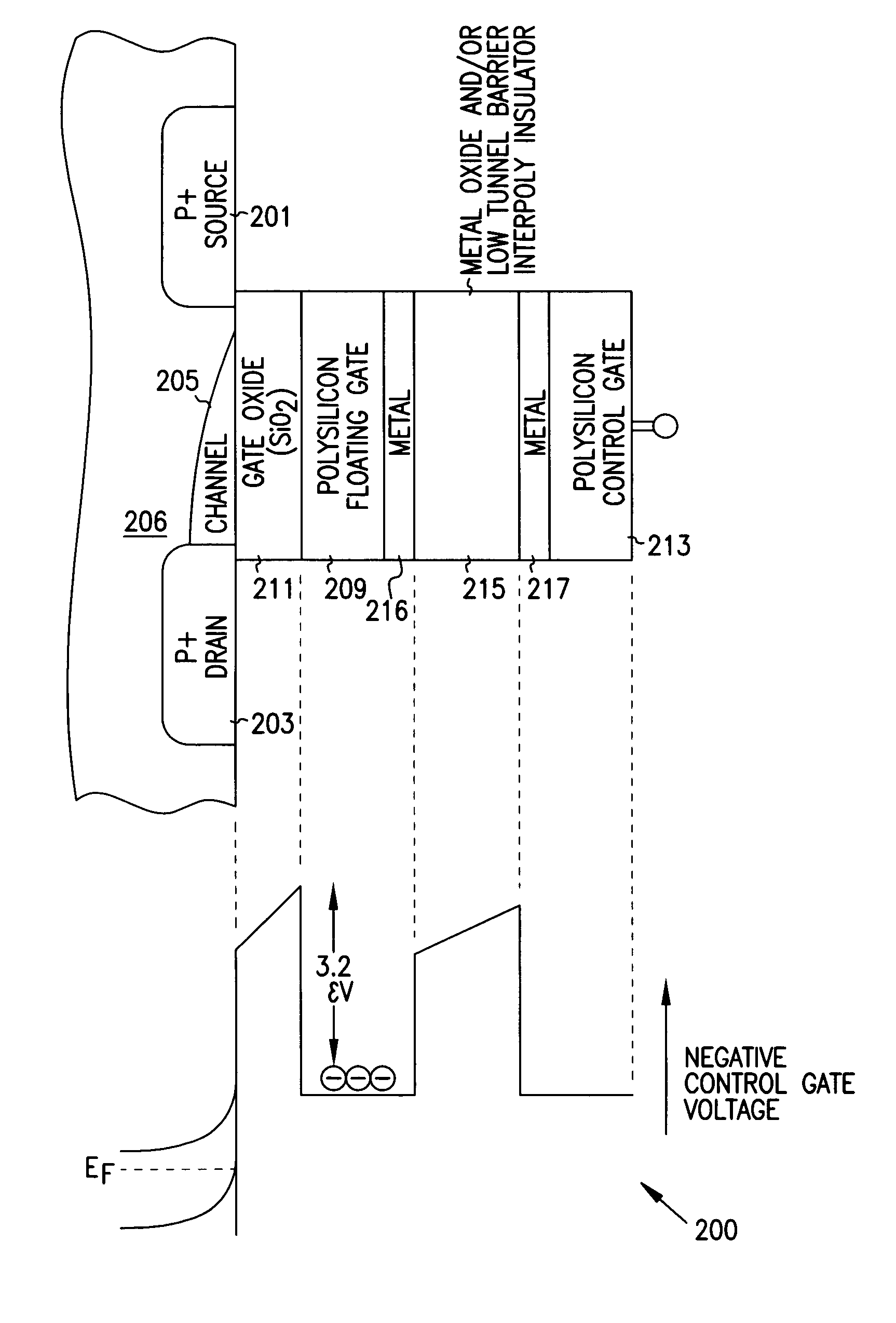

Flash memory with low tunnel barrier interpoly insulators

Structures and methods for Flash memory with low tunnel barrier intergate insulators are provided. The non-volatile memory includes a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposing the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by a low tunnel barrier intergate insulator. The low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of PbO, Al2O3, Ta2O5, TiO2, ZrO2, and Nb2O5. The floating gate includes a polysilicon floating gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator. And, the control gate includes a polysilicon control gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator.

Owner:MICRON TECH INC

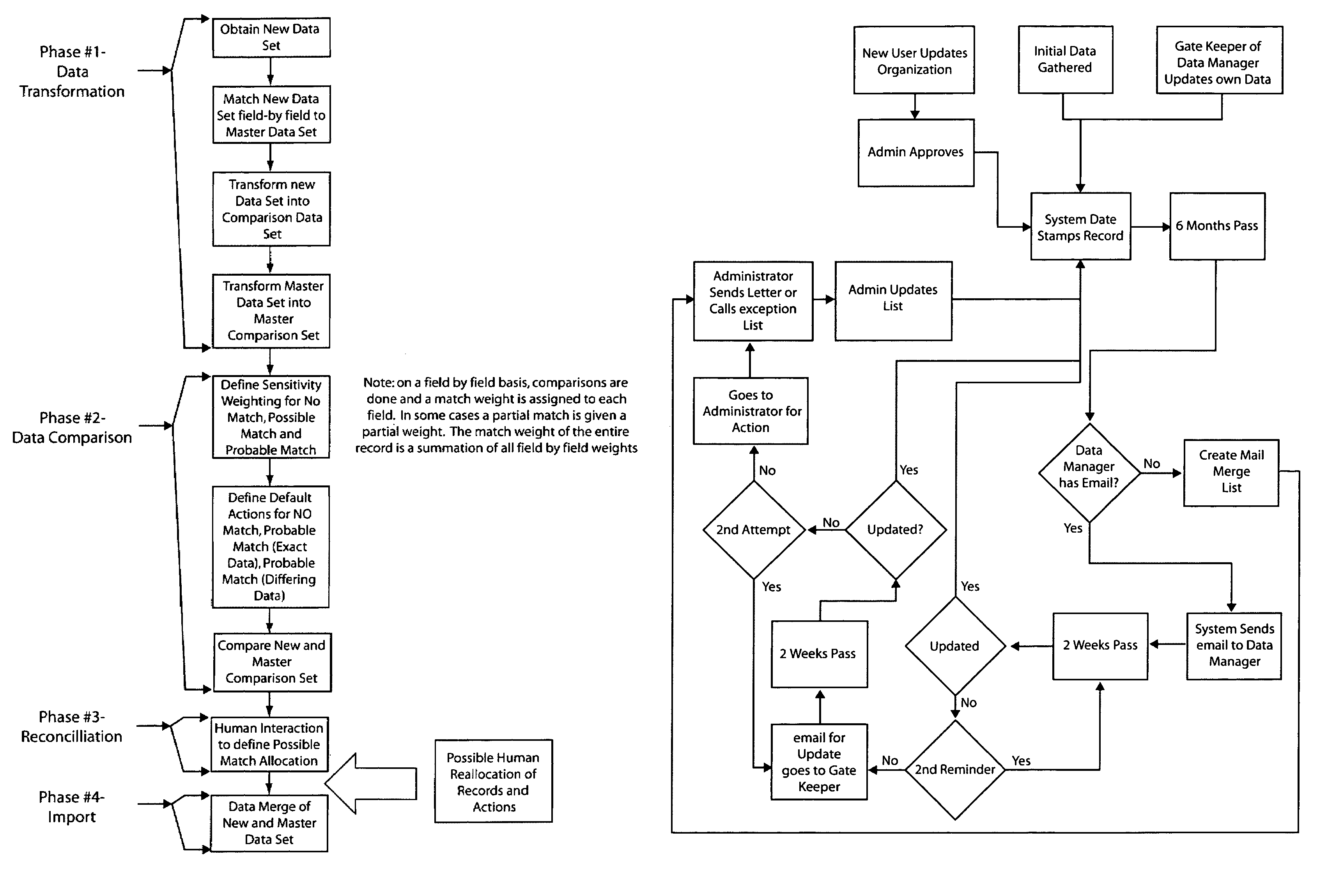

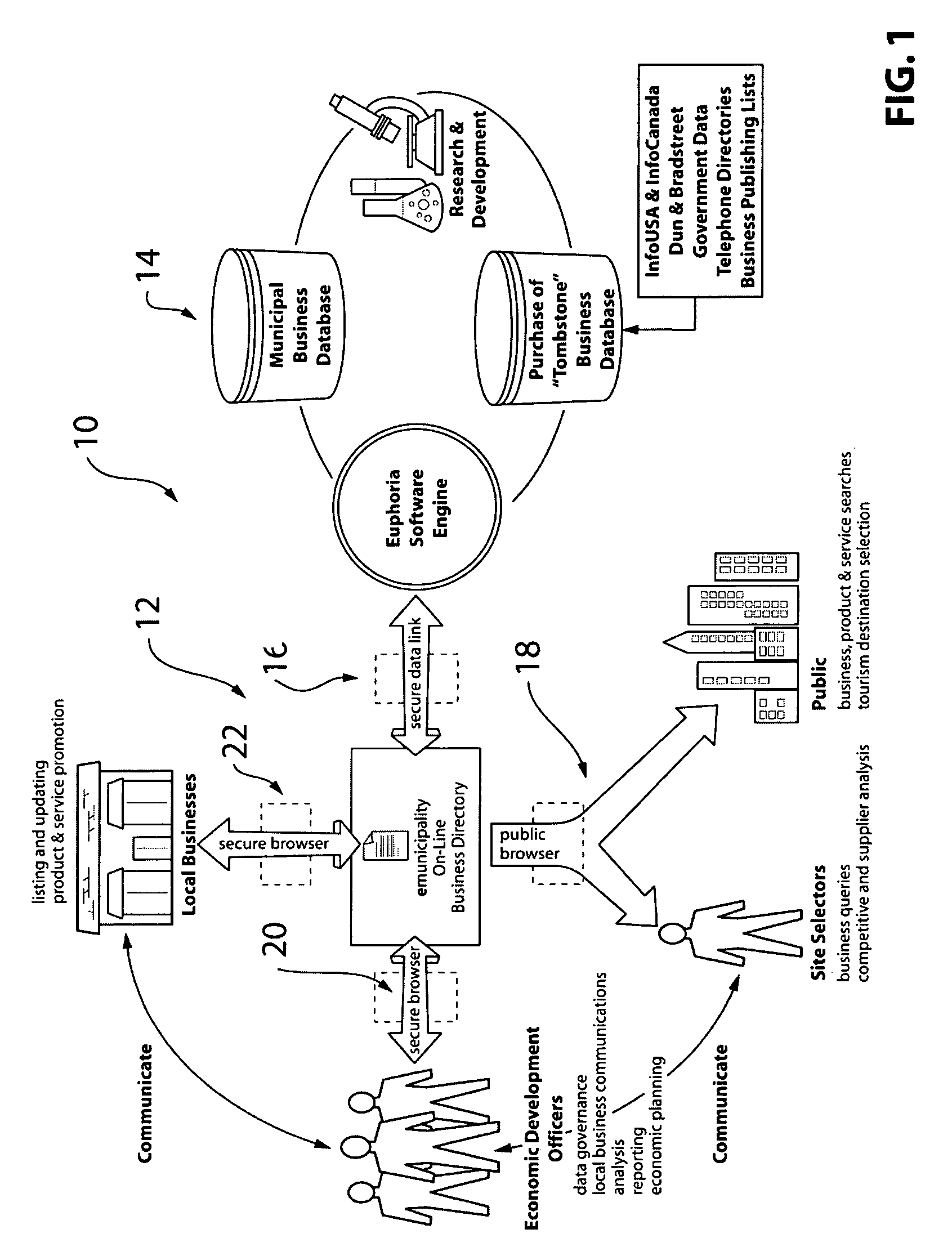

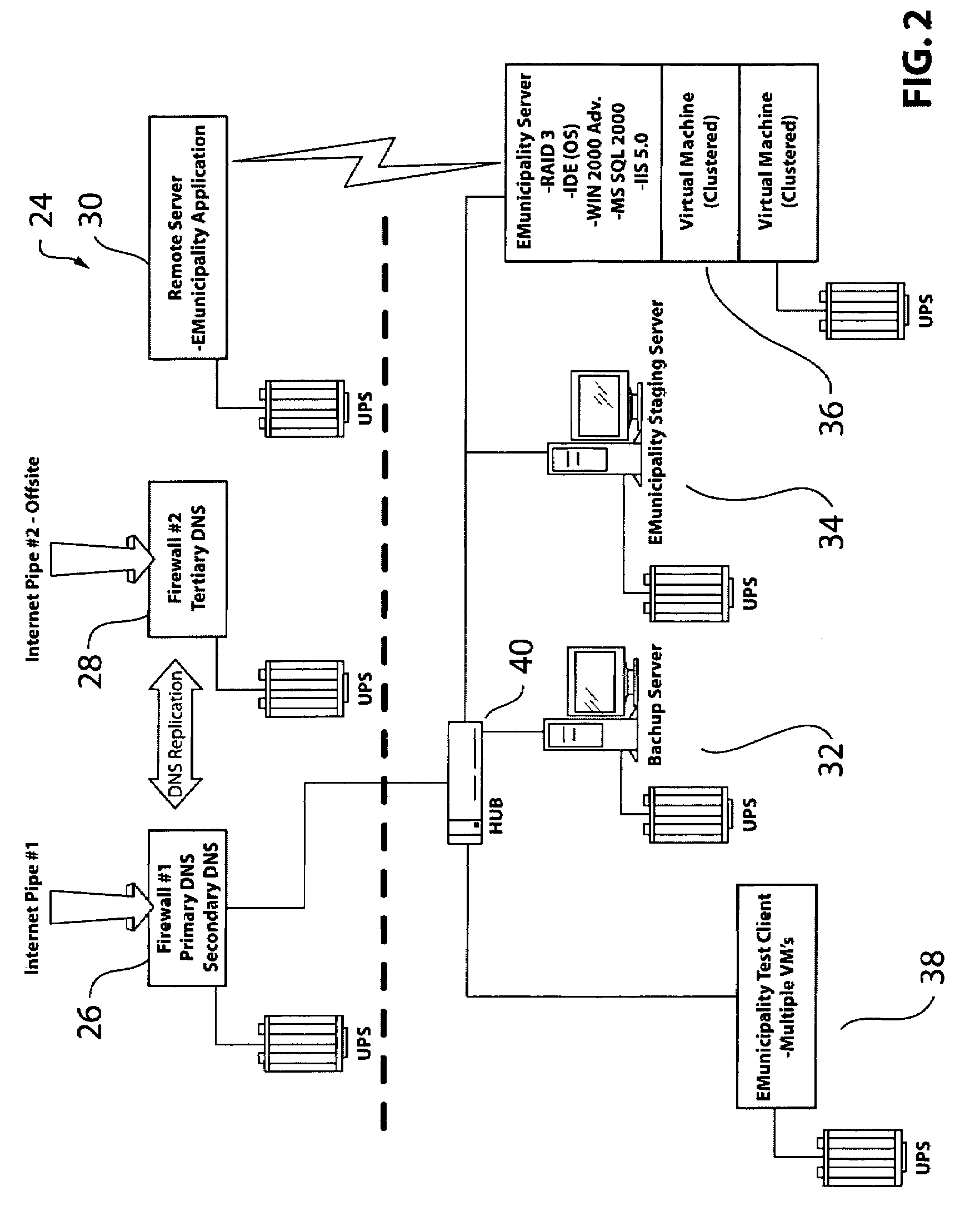

Database management system

A method of creating a database and of providing results from a database, for use by a municipality, and operating a community database, comprises the steps of: providing first and second source databases addressable under first and second data protocols respectively, which protocols are incompatible one with the other; transforming, comparing and reconciling the data in the first and second source databases in order to optimize each field of data in each record; and storing the optimized data for each record as a record in a resulting master database. Records from searches are presented in order of recency. The present invention also provides a method of generating revenue from activities associated with a community.

Owner:BREKEN TECH GROUP

Asymmetric band-gap engineered nonvolatile memory device

Owner:MICRON TECH INC

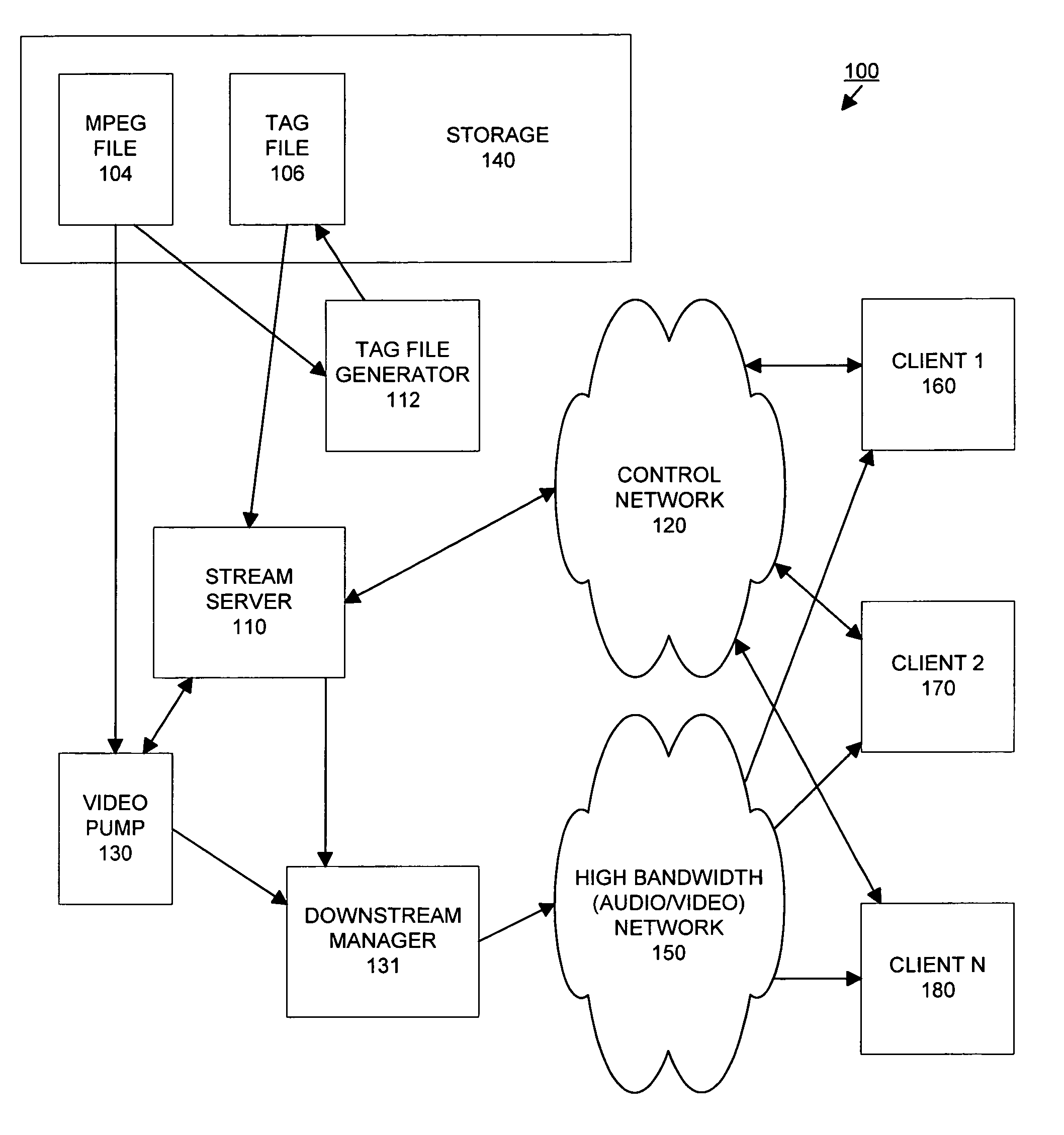

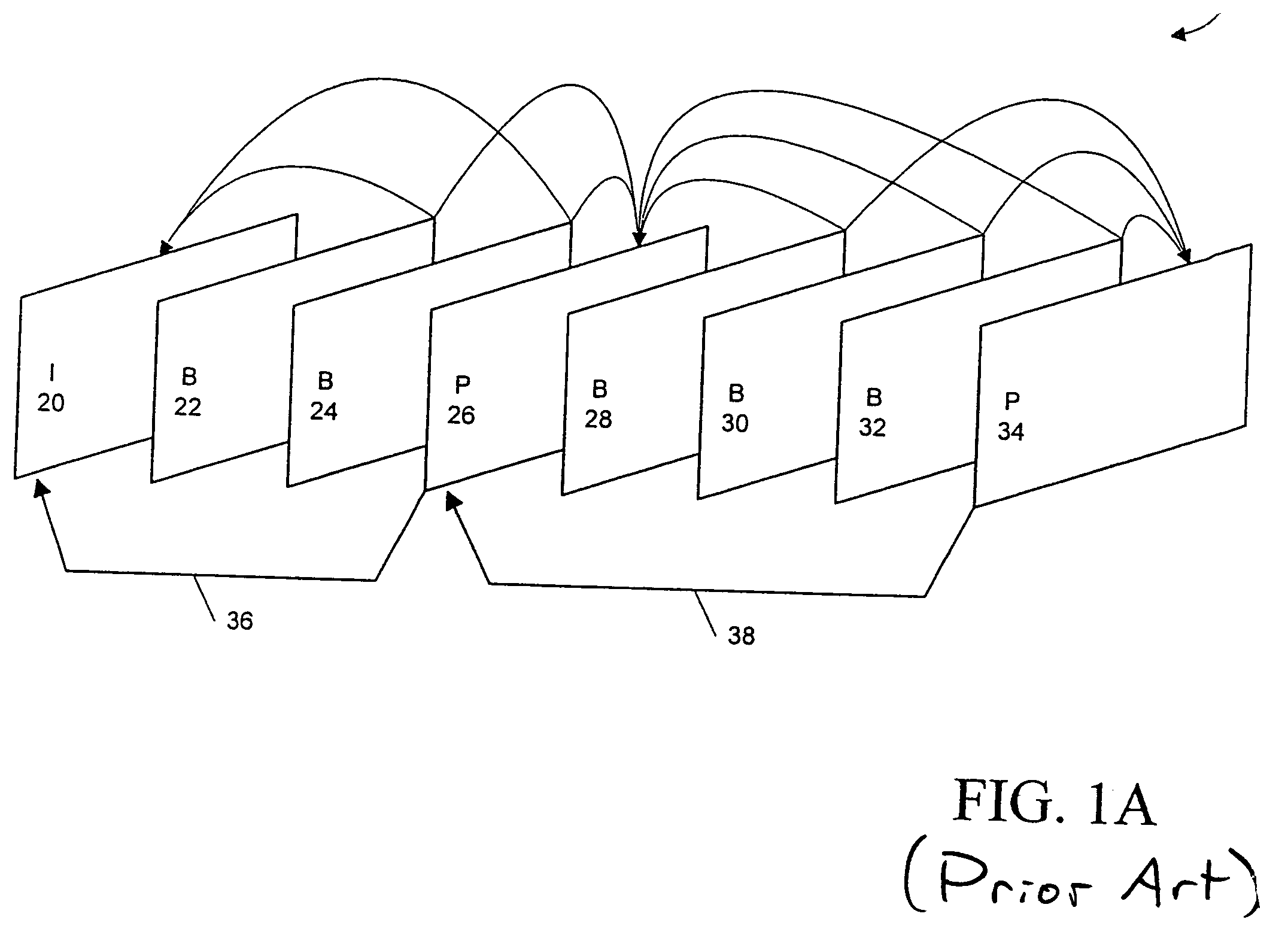

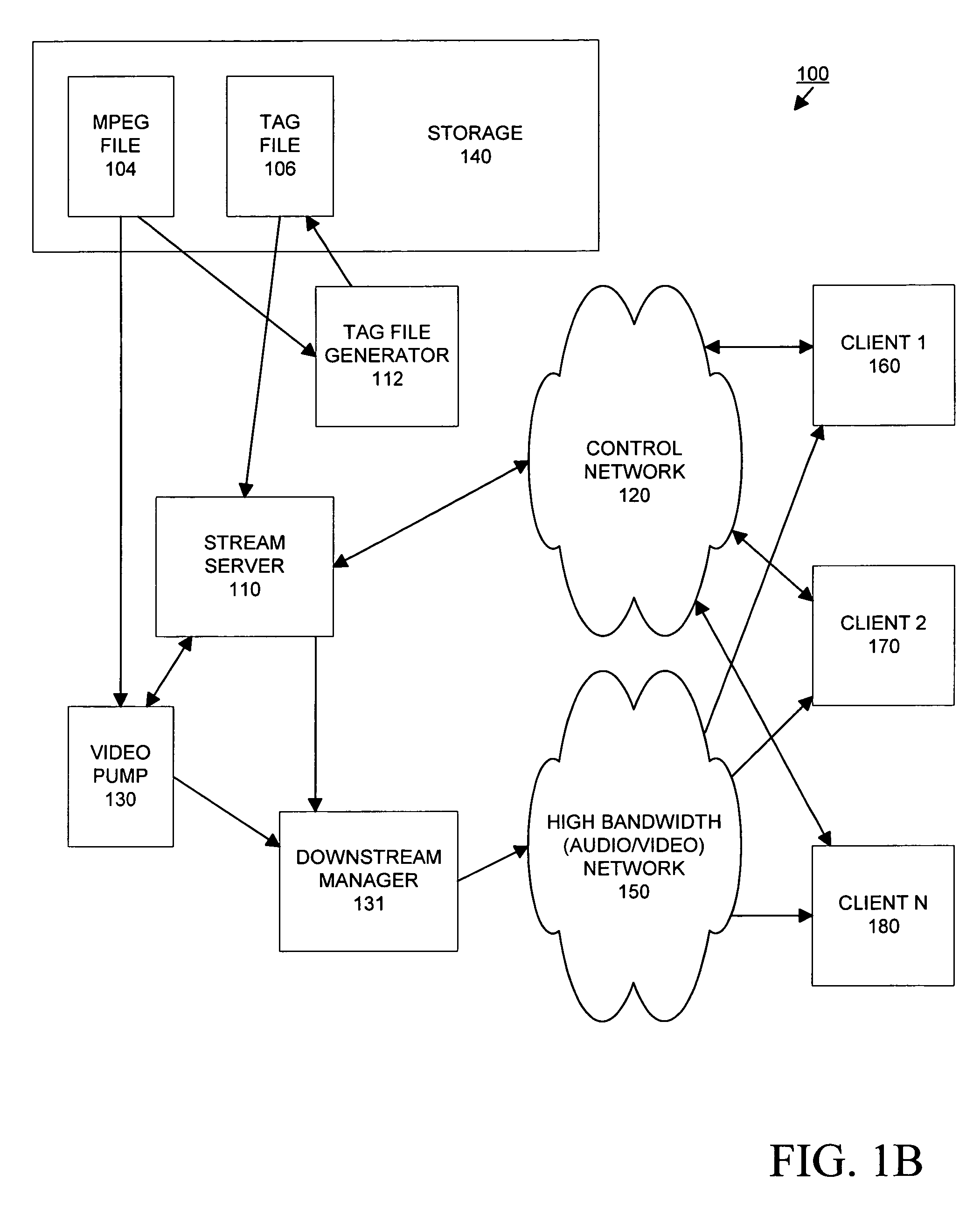

Dynamic quality adjustment based on changing streaming constraints

InactiveUS7058721B1Quality improvementReduce constraintsDisc-shaped record carriersRedundant array of inexpensive disk systemsQuality adjustmentSlow motion

A method and apparatus for dynamic quality adjustment based on changing streaming constraints is provided. According to one aspect of the present invention, a video stream is sent to a client according to a set of streaming constraints. At least a subset of the video information in the video stream is sent from a first source. Next, a signal is received indicating a relaxation of streaming constraints corresponding to the video stream. In one embodiment, the signal is a freeze frame signal. In another embodiment, the signal is a slow motion signal. In response to the signal, a set of improved quality video information from a second source is accessed and sent to the client. According to one embodiment, the set of improved quality video information comprises a still image. According to another embodiment, the set of improved quality video information comprises a set of preprocessed video information ready to be streamed. As a result of the techniques described herein, an improved quality visual image is available for presentation on the client and, consequently, when a viewer requests a presentation rate that reduces the streaming constraints on a video streaming service, the improved quality video information may be sent using the freed-up portion of the bandwidth previously allocated to the client.

Owner:ARRIS SOLUTIONS +1

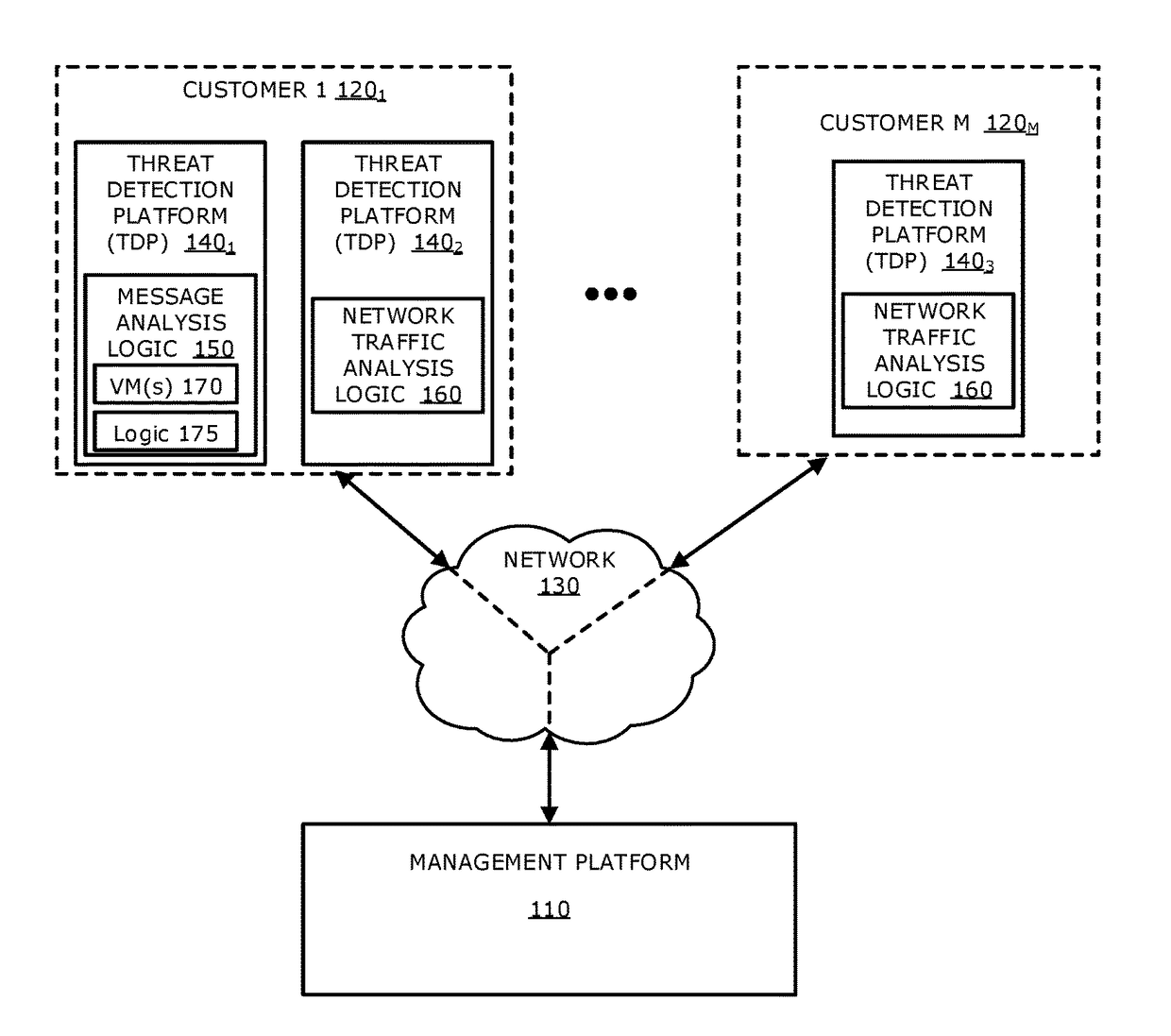

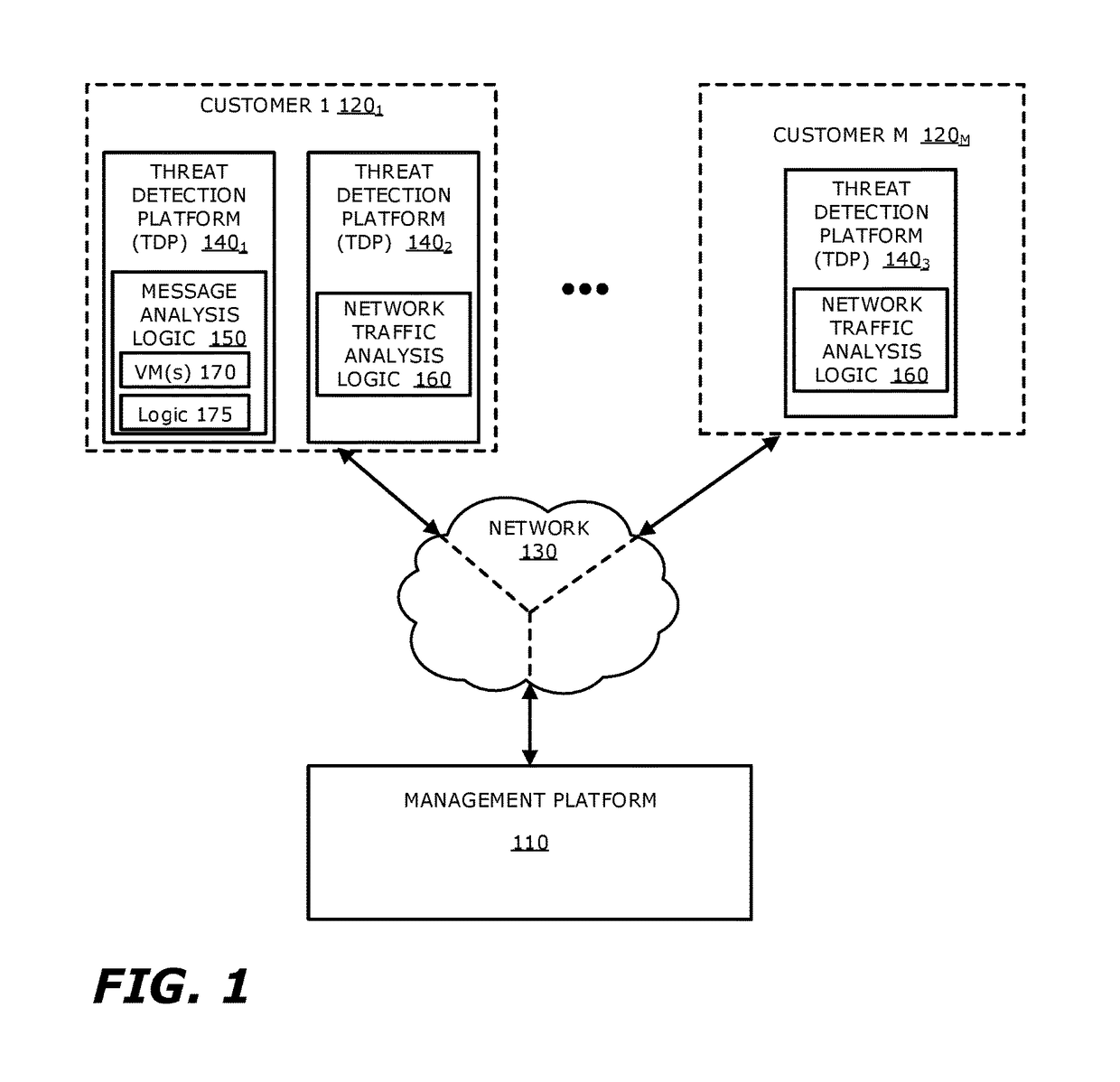

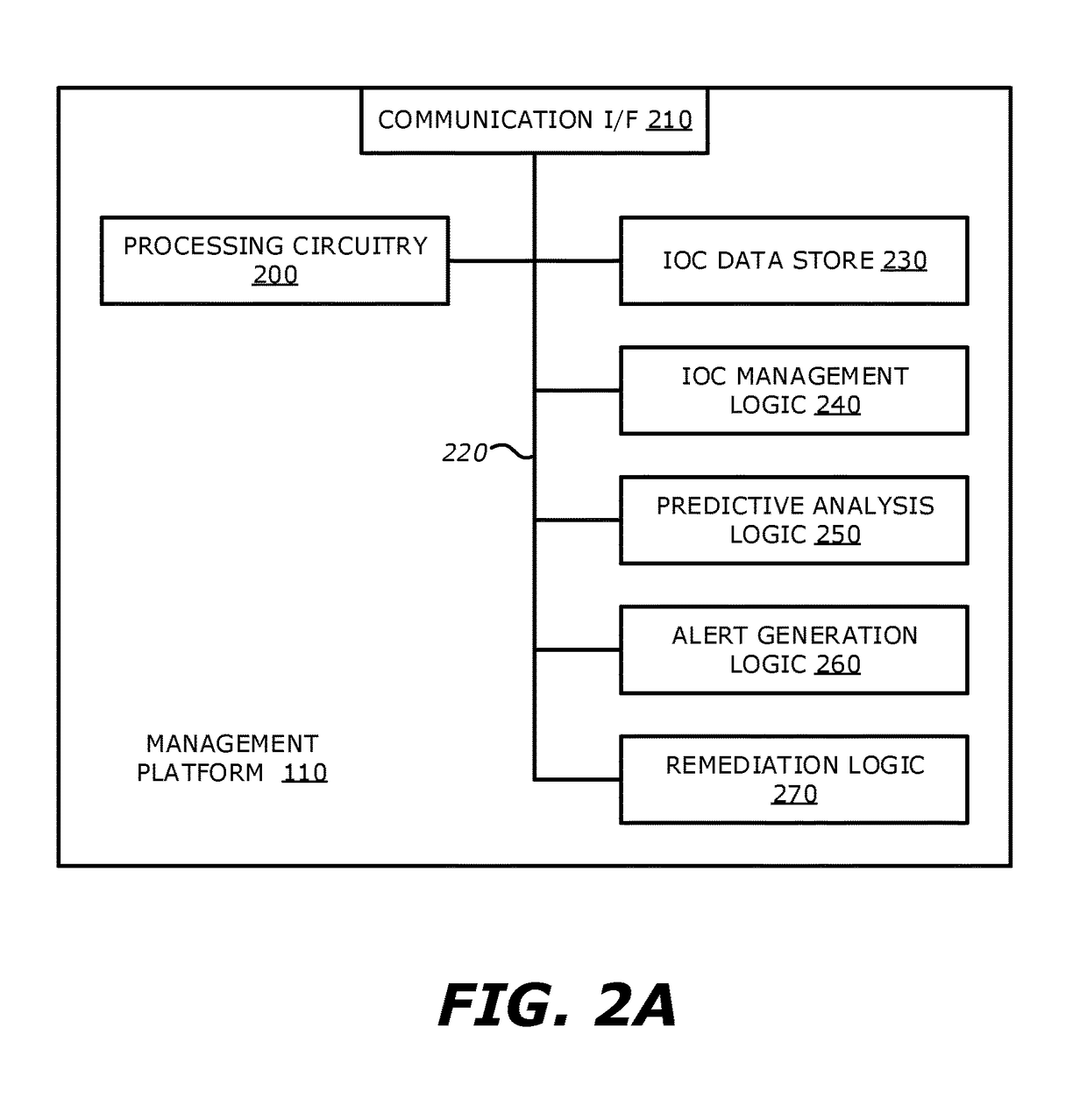

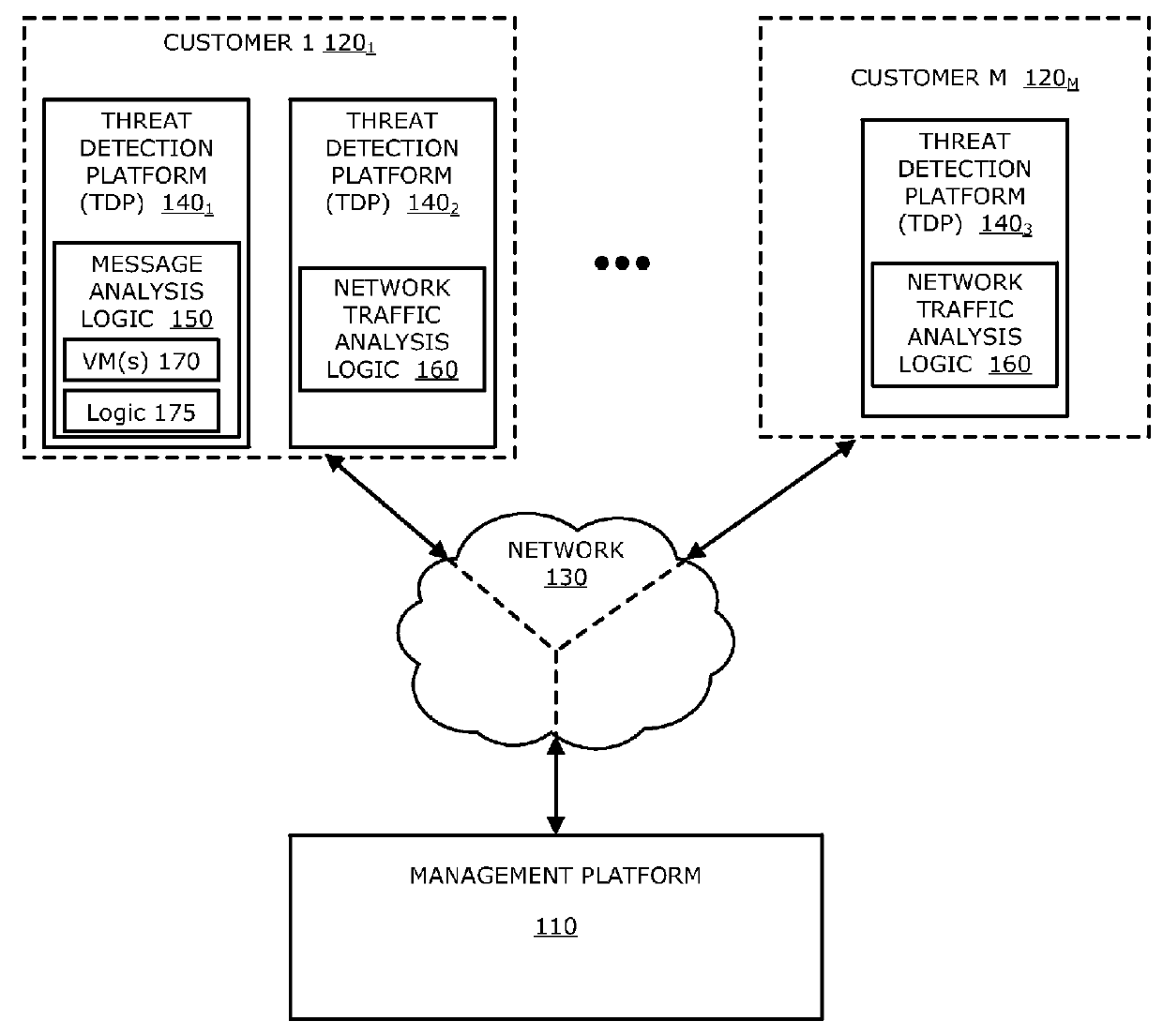

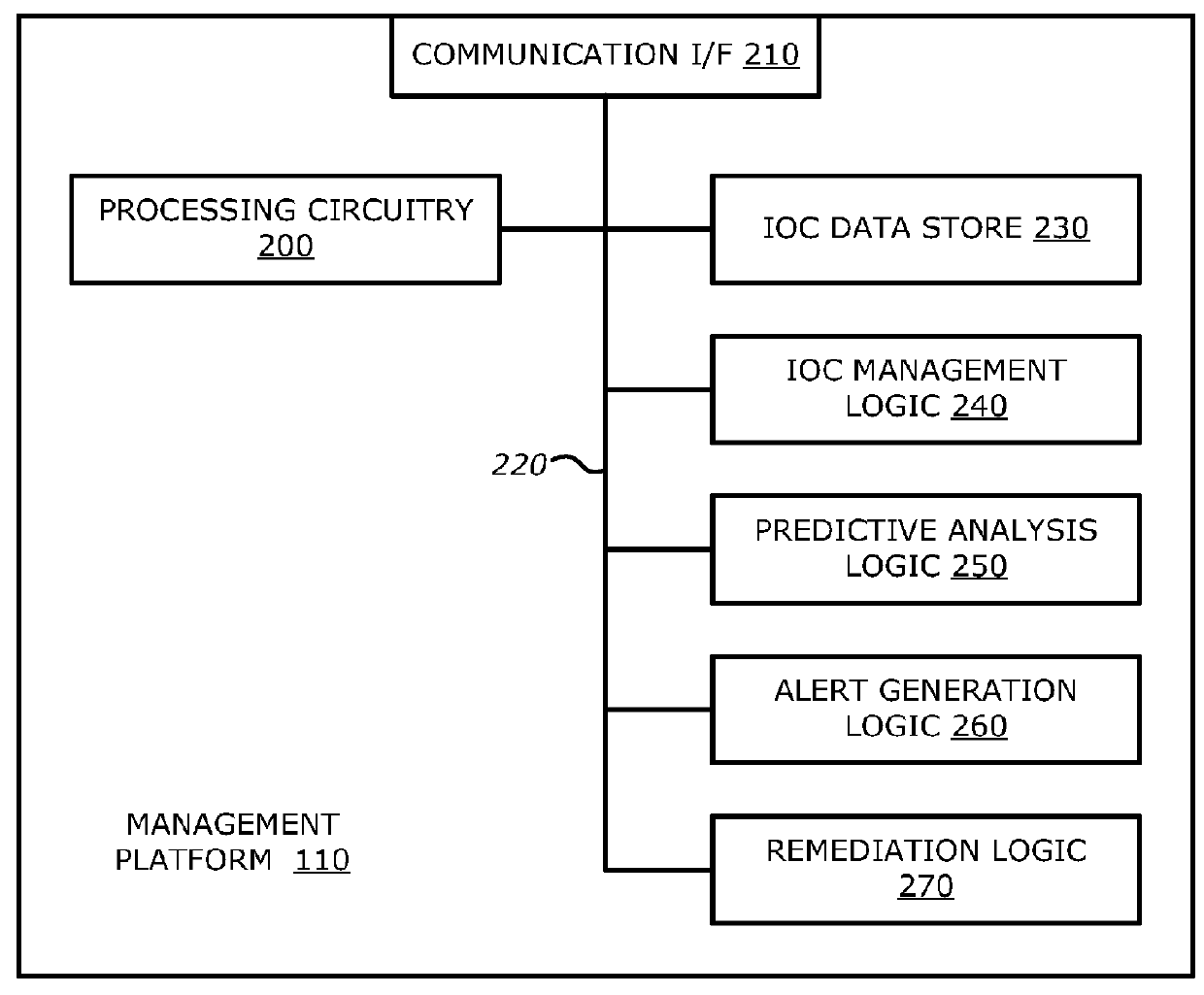

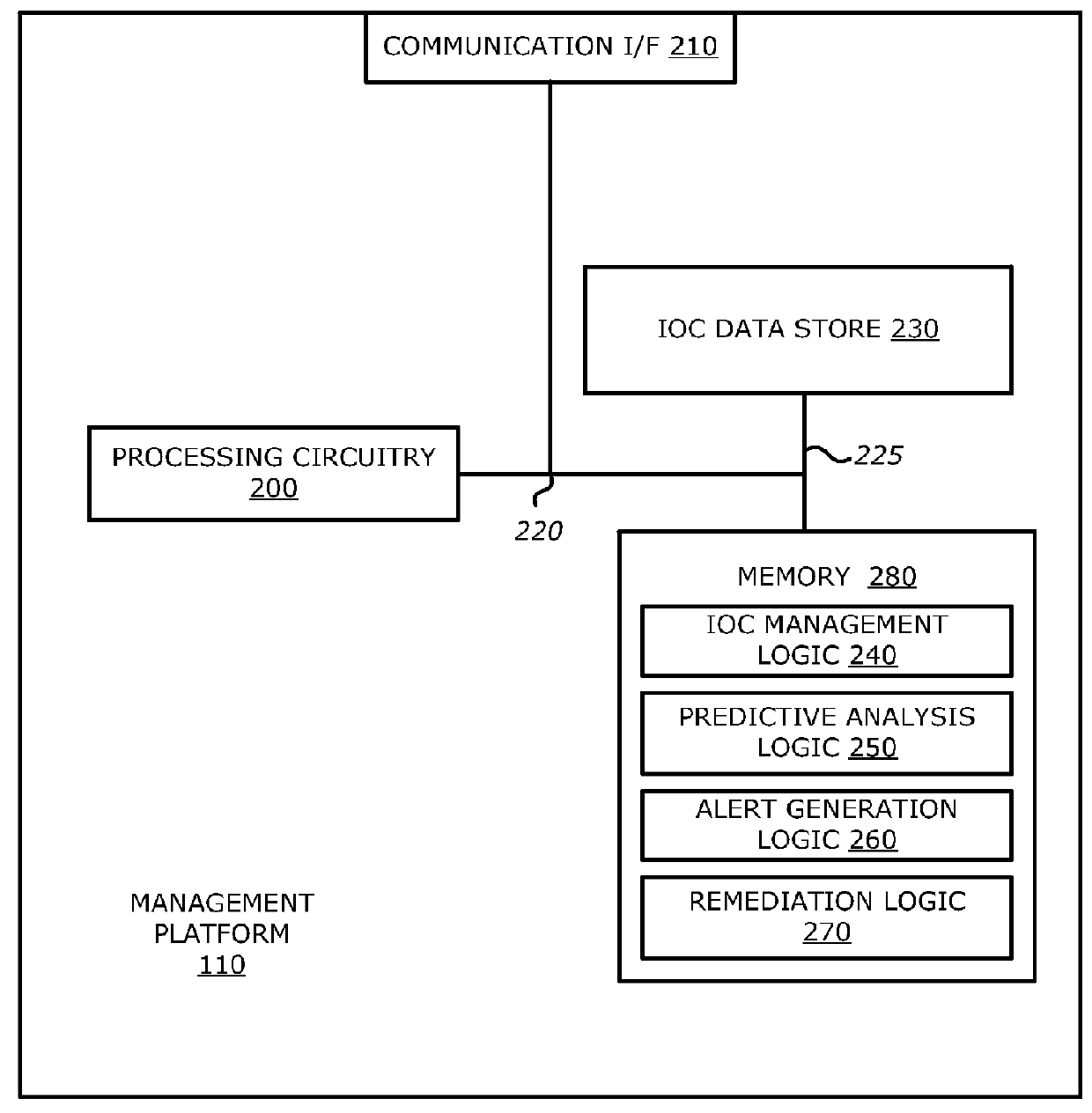

System and method of detecting delivery of malware based on indicators of compromise from different sources

According to one embodiment, a computerized method comprises receiving a set of indicators of compromise (IOCs) associated with a known malware of a first message type from a first source and receiving one or more IOCs (IOC(s)) from a second source that is different from the first source. Thereafter, a determination is made as to whether the received IOC(s) from the second source correspond to the set of IOCs received from the first source. If so, information associated with at least the set of IOCs is used to locate a malware of the first message type that is undetected at the second source.

Owner:FIREEYE SECURITY HLDG US LLC

System and method of detecting delivery of malware using cross-customer data

According to one embodiment, a computerized method comprises receiving a set of indicators of compromise (IOCs) associated with a known malware of a first message type from a first source and receiving one or more IOCs (IOC(s)) from a second source that is different from the first source. Thereafter, a determination is made as to whether the received IOC(s) from the second source correspond to the set of IOCs received from the first source. If so, information associated with at least the set of IOCs is used to locate a malware of the first message type that is undetected at the second source.

Owner:FIREEYE SECURITY HLDG US LLC

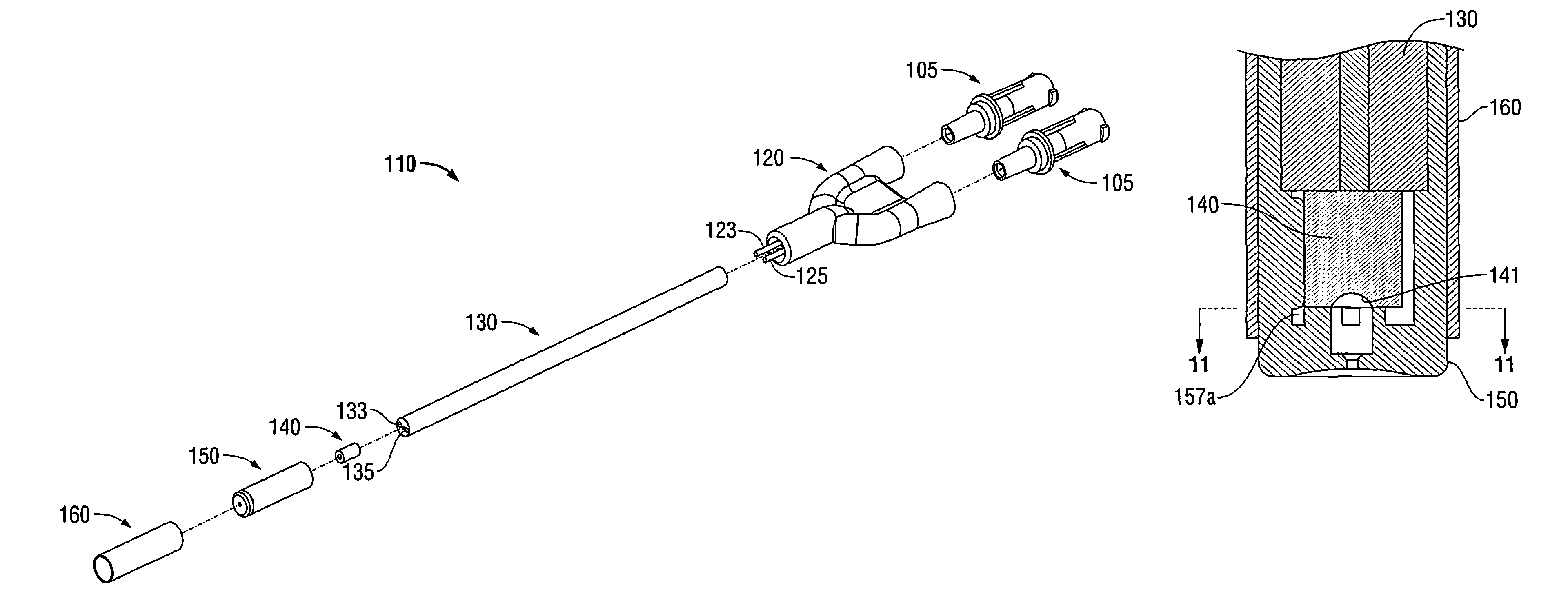

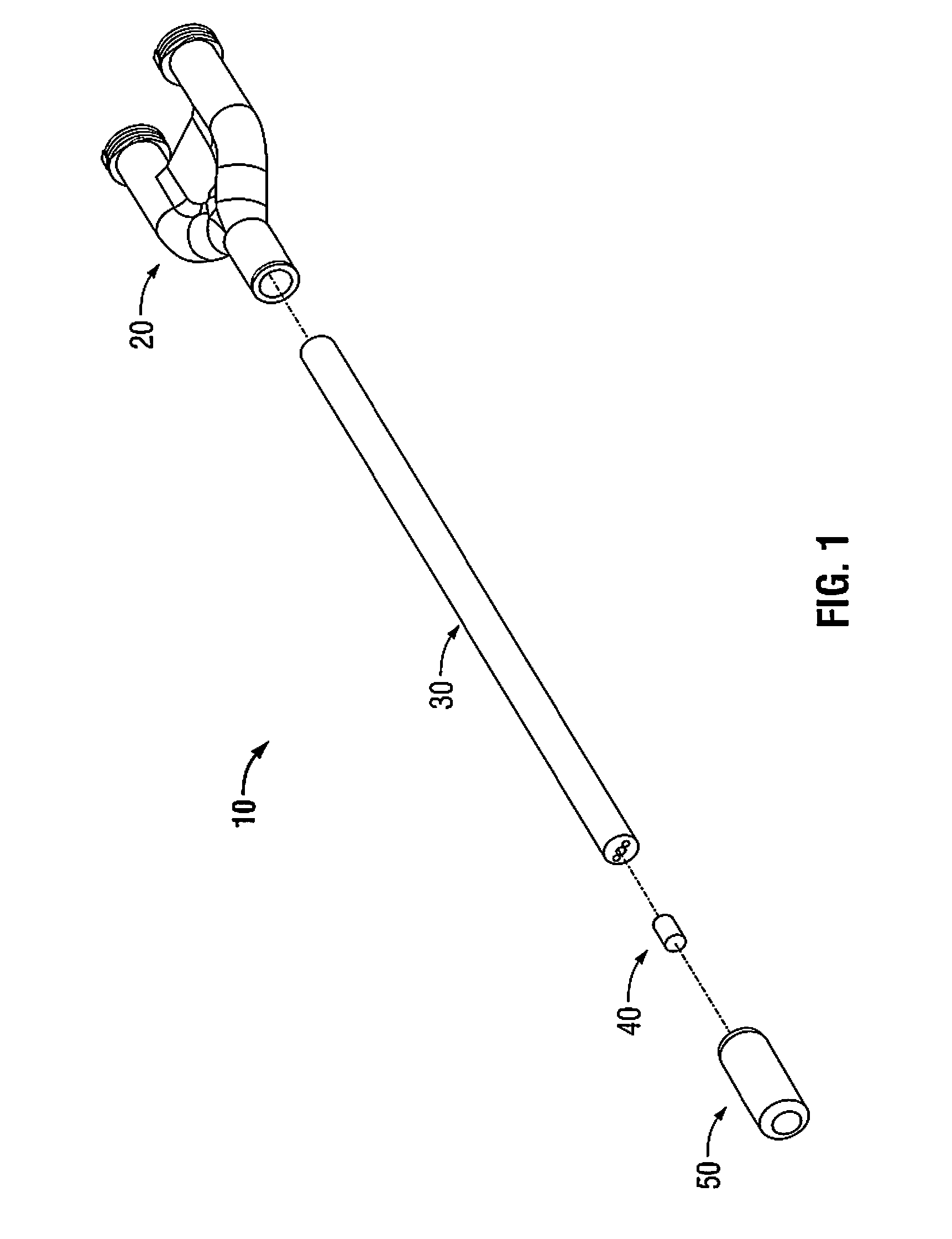

Silicone spray tip

Owner:CONFLUENT SURGICAL

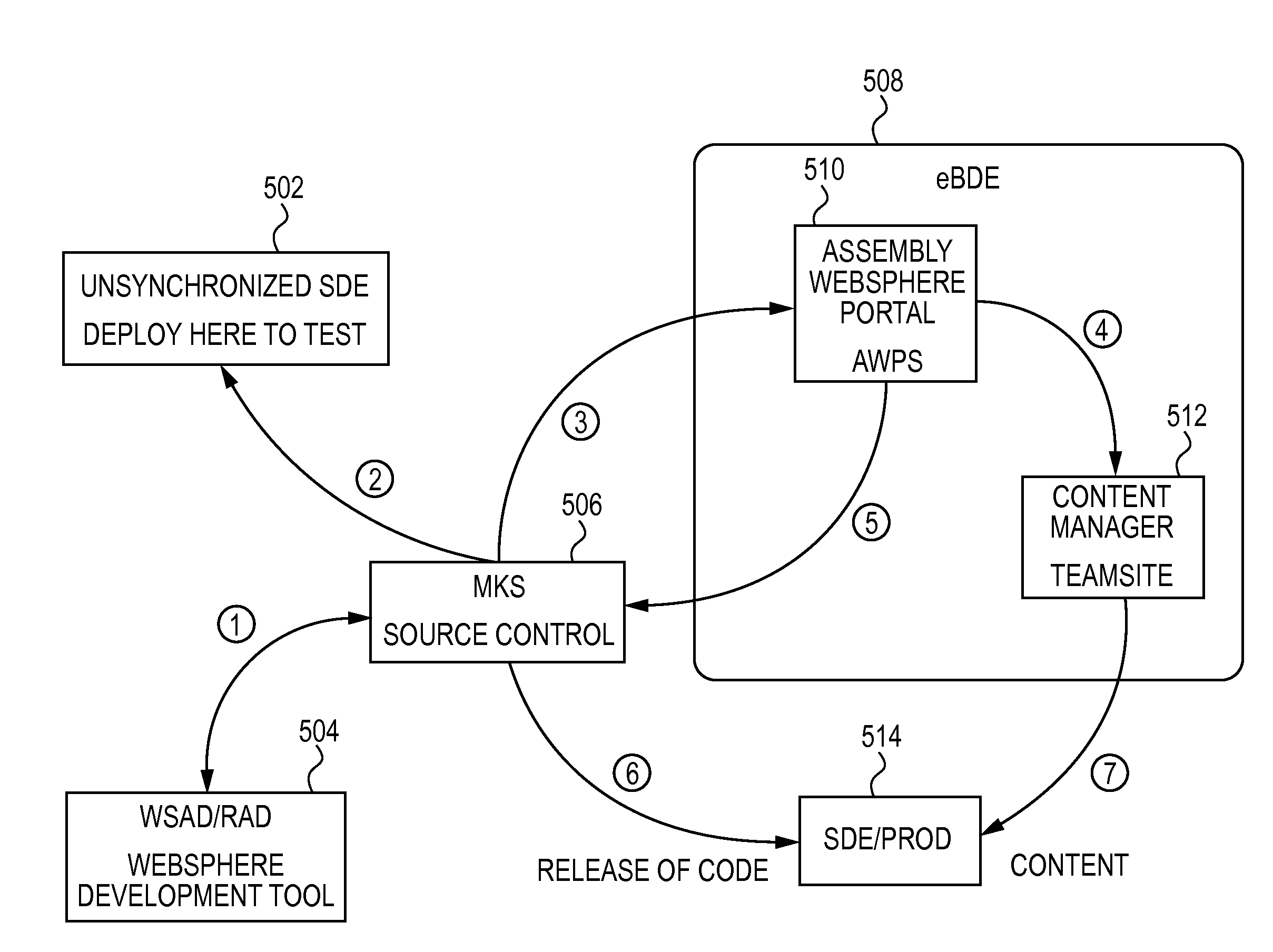

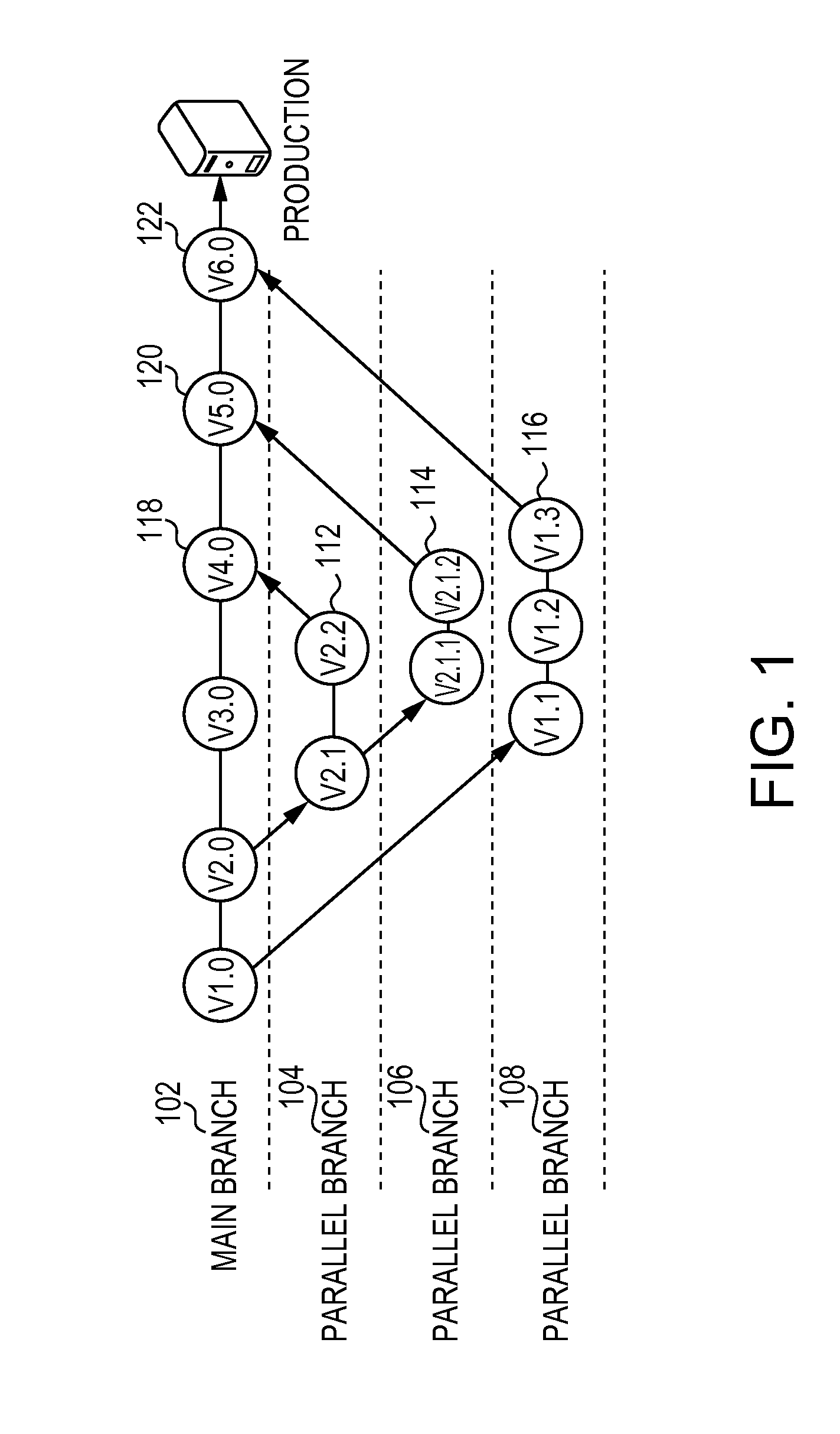

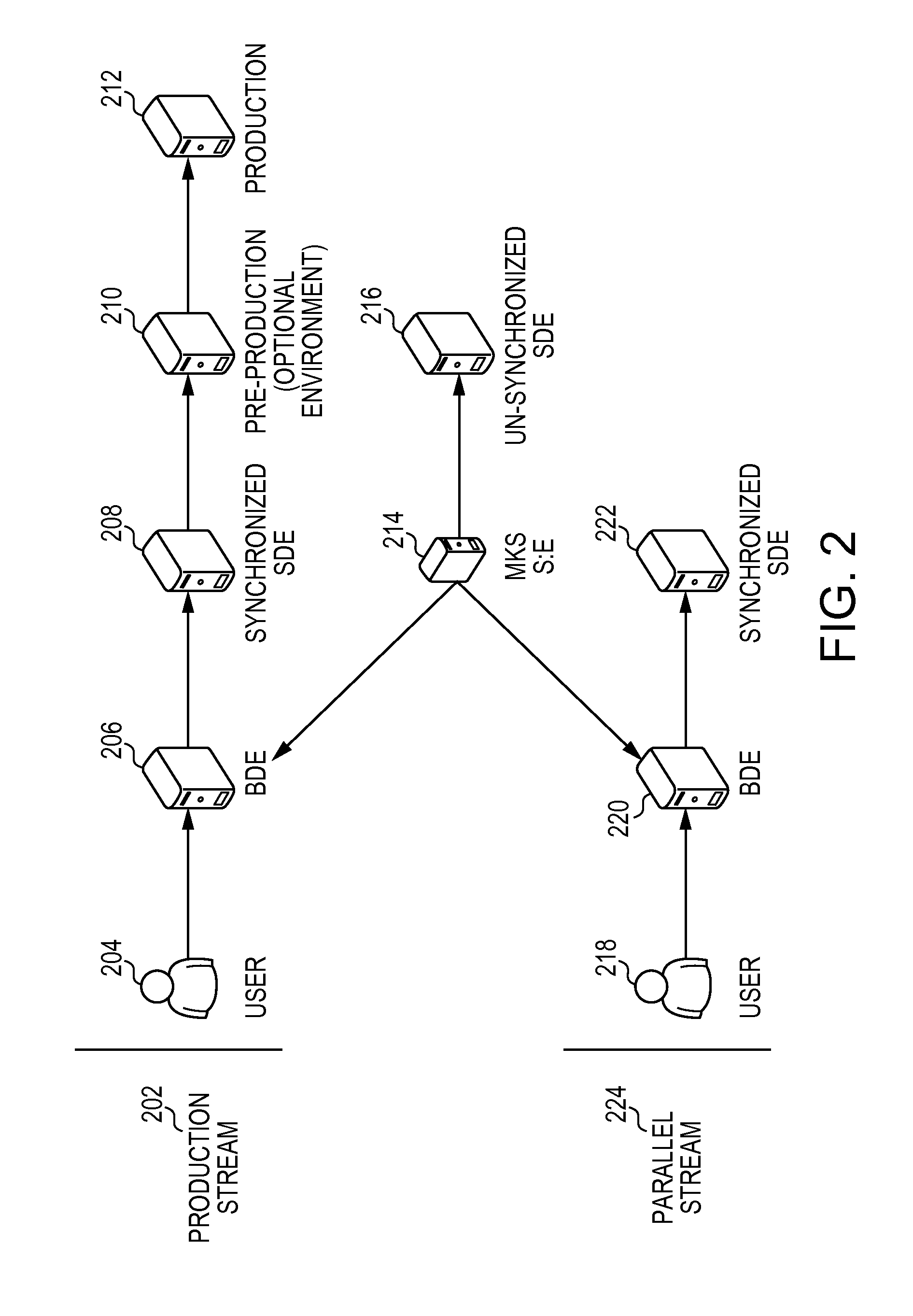

Automated methods and systems for developing and deploying projects in parallel

Embodiments of the invention are directed to system and method for managing parallel development of projects. One embodiment of the invention is a method of automatically managing processes in the parallel development of an application through a graphical user interface. The graphical user interface manages the automated processes, which are able to complete their tasks without further user interaction. The automated processes managed by the graphical user interface include, provisioning a first development environment and second development environment. The processes also includes deploying a second release of an application to the second development environment, and merging modifications to the second source code and the second content of the second release into a first source code and a first content of the first release. After the releases have been merged together, the process automatically deploys the third release of the application to a production environment for use by users.

Owner:HSBC TECH & SERVICES (USA) INC

Methods of Forming One Transistor DRAM Devices

A one transistor DRAM device includes: a substrate with an insulating layer, a first semiconductor layer provided on the insulating layer and including a first source region and a first region which are in contact with the insulating layer and a first floating body between the first source region and the first drain region, a first gate pattern to cover the first floating body, a first interlayer dielectric to cover the first gate pattern, a second semiconductor layer provided on the first interlayer dielectric and including a second source region and a second drain region which are in contact with the first interlayer dielectric and a second floating body between the second source region and the second drain region, and a second gate pattern to cover the second floating body.

Owner:SAMSUNG ELECTRONICS CO LTD

Programmable array logic or memory with p-channel devices and asymmetrical tunnel barriers

Structures and methods for programmable array type logic and / or memory with p-channel devices and asymmetrical low tunnel barrier intergate insulators are provided. The programmable array type logic and / or memory devices include p-channel non-volatile memory which has a first source / drain region and a second source / drain region separated by a p-type channel region in an n-type substrate. A floating gate opposing the p-type channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by an asymmetrical low tunnel barrier intergate insulator. The asymmetrical low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5, SrBi2Ta2O3, SrTiO3, PbTiO3, and PbZrO3. The floating gate includes a polysilicon floating gate having a metal layer formed thereon in contact with the low tunnel barrier intergate insulator. And, the control gate includes a polysilicon control gate having a metal layer, having a different work function from the metal layer formed on the floating gate, formed thereon in contact with the low tunnel barrier intergate insulator.

Owner:MICRON TECH INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com