Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

12630results about How to "Improve electrical performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

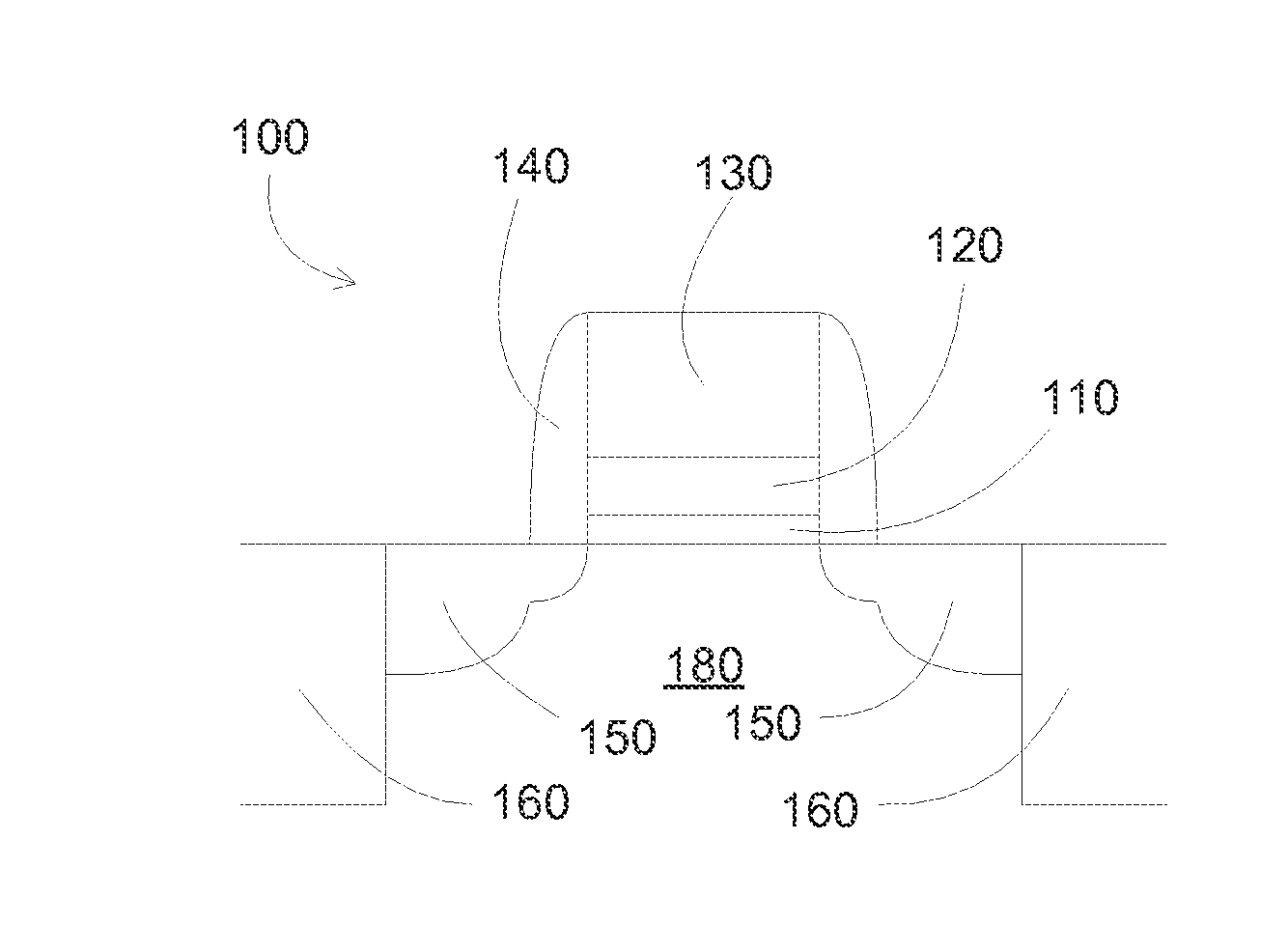

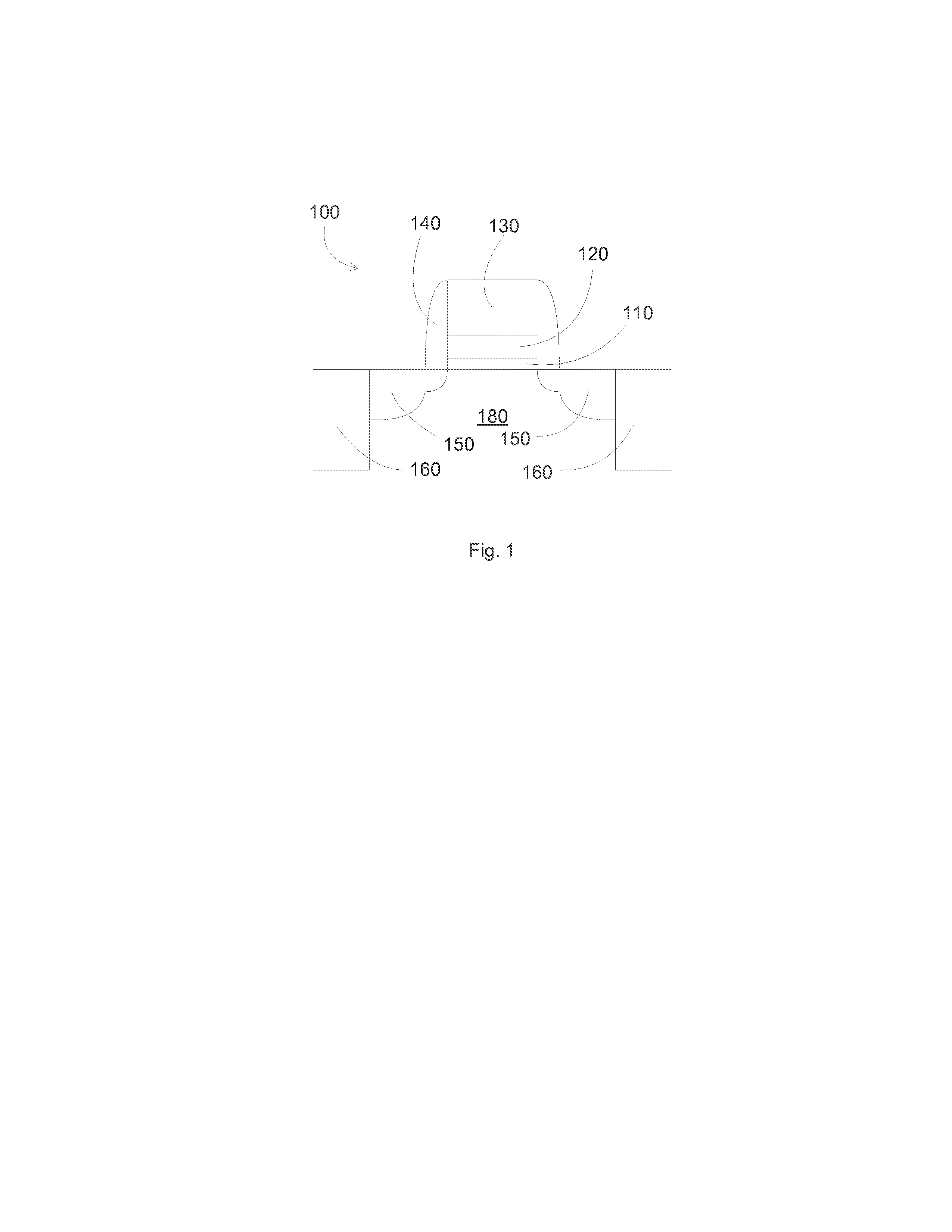

Method of Fabricating a Gate Dielectric for High-K Metal Gate Devices

ActiveUS20100075507A1Facilitate formation of the high-k dielectric layerImprove electrical performanceSemiconductor/solid-state device manufacturingChemical vapor deposition coatingGate dielectricSulfur

The present disclosure provides a method of fabricating a semiconductor device. The method includes providing a substrate, forming an interfacial layer on the substrate by treating the substrate with radicals, and forming a high-k dielectric layer on the interfacial layer. The radicals are selected from the group consisting of hydrous radicals, nitrogen / hydrogen radicals, and sulfur / hydrogen radicals.

Owner:TAIWAN SEMICON MFG CO LTD

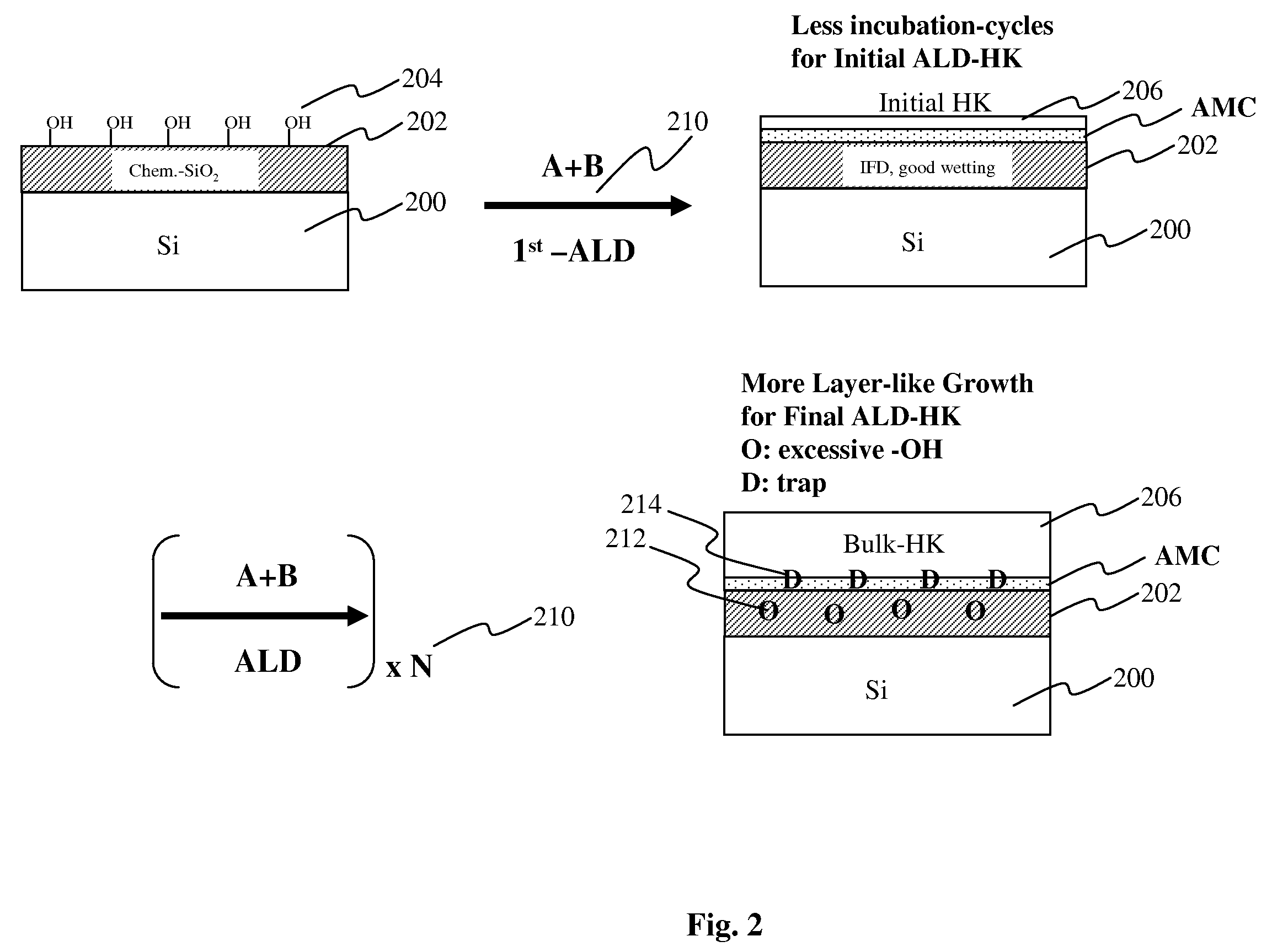

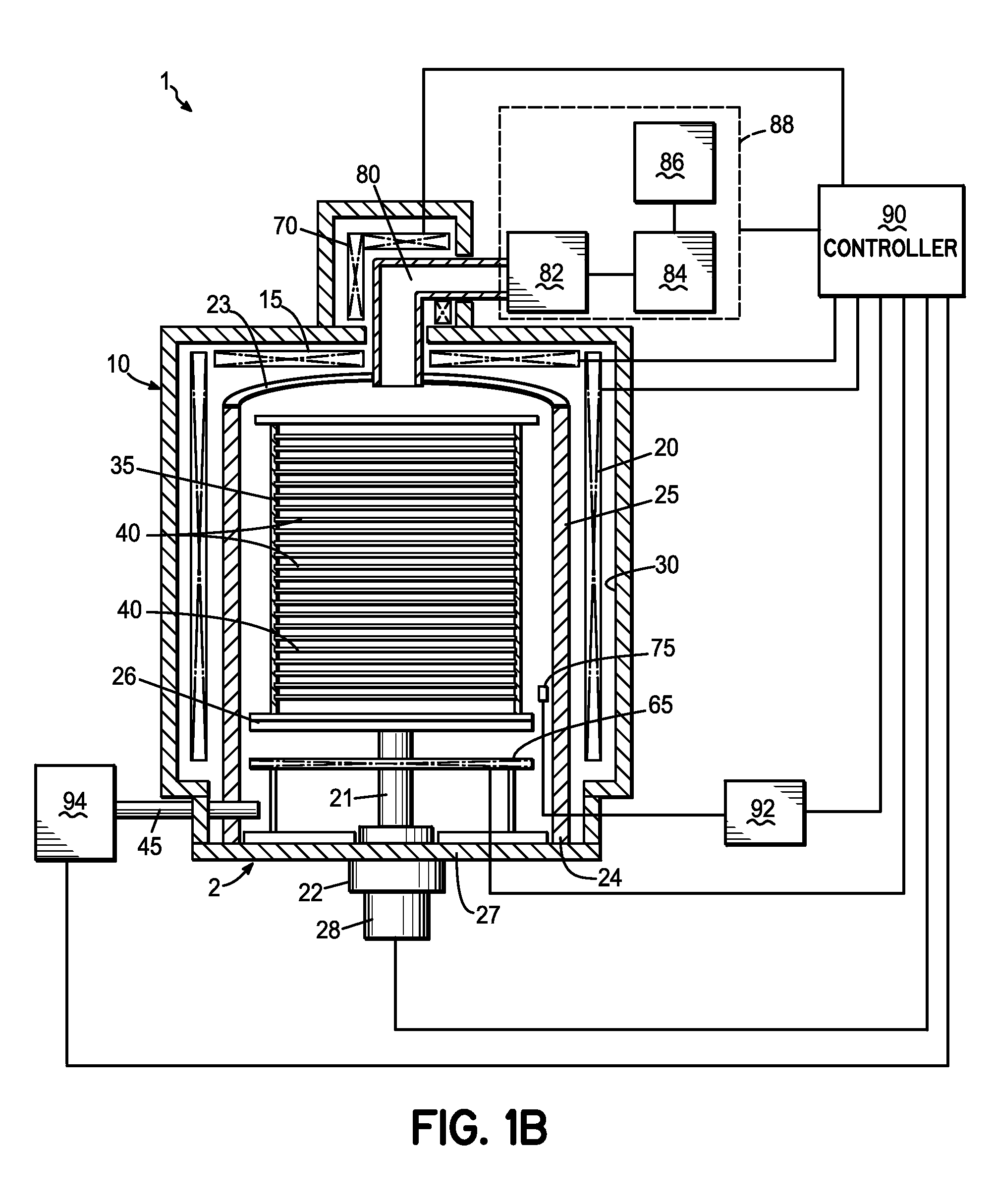

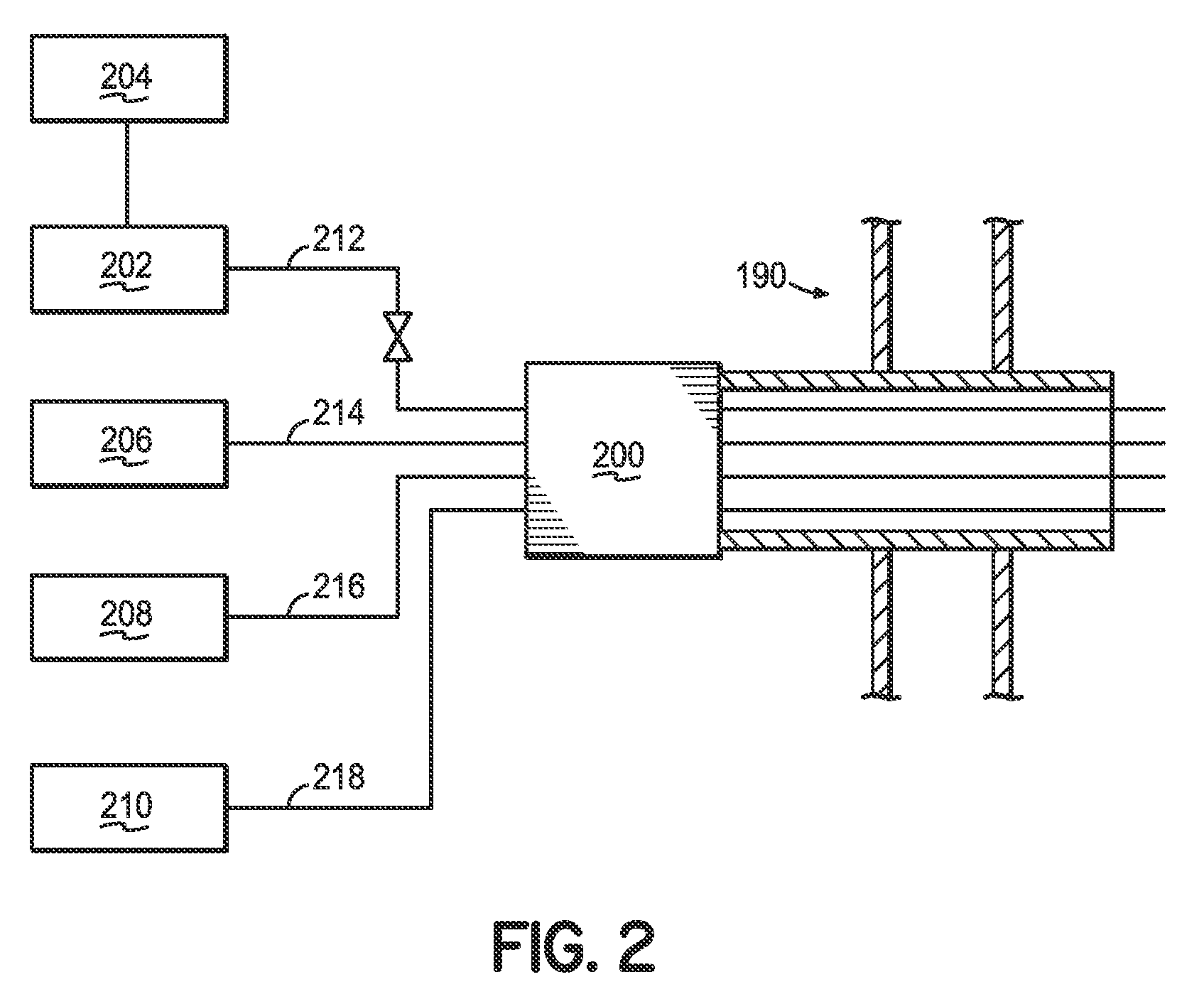

In-situ atomic layer deposition

InactiveUS20070037412A1Improve uniformityImprove electrical performanceSemiconductor/solid-state device manufacturingChemical vapor deposition coatingWaferingHafnium

An in situ method for forming a HfO2 high-k dielectric layer in a batch wafer processing system. The method comprises first loading a plurality of wafers into a process chamber, and then pre-treating the plurality of wafers in the process chamber with a first oxidizer. After pre-treating the wafers, and without removing the wafers from the process chamber, the method then comprises depositing HfO2 on the plurality of wafers by atomic layer deposition, which comprises a plurality of deposition cycles, each cycle comprising alternating exposure of the plurality of wafers in the process chamber to a second oxidizer and a hafnium precursor. The hafnium precursor is selected from hafnium tert-butoxide (HTB) or hafnium tetra-diethylamide (TDEAH).

Owner:TOKYO ELECTRON LTD

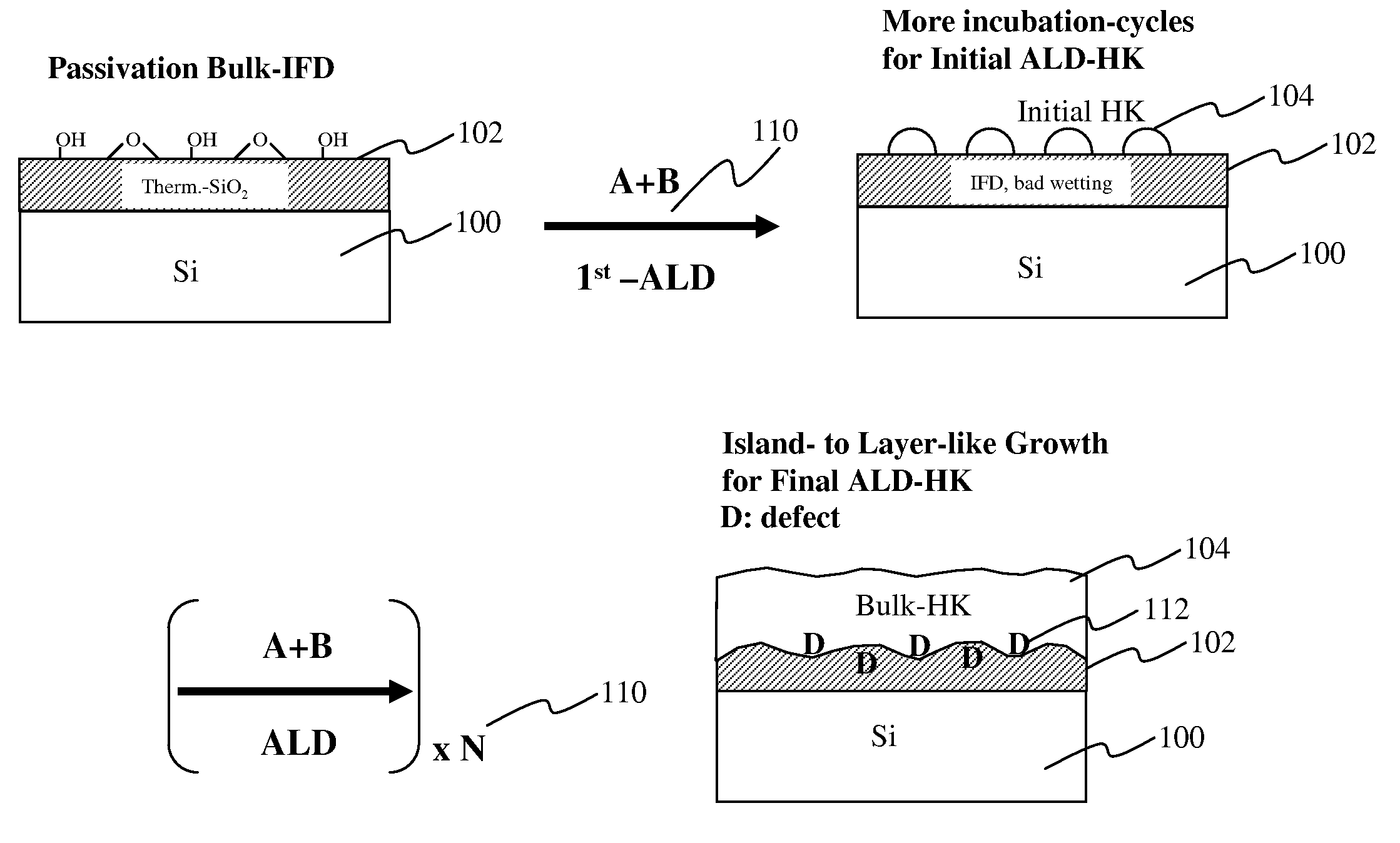

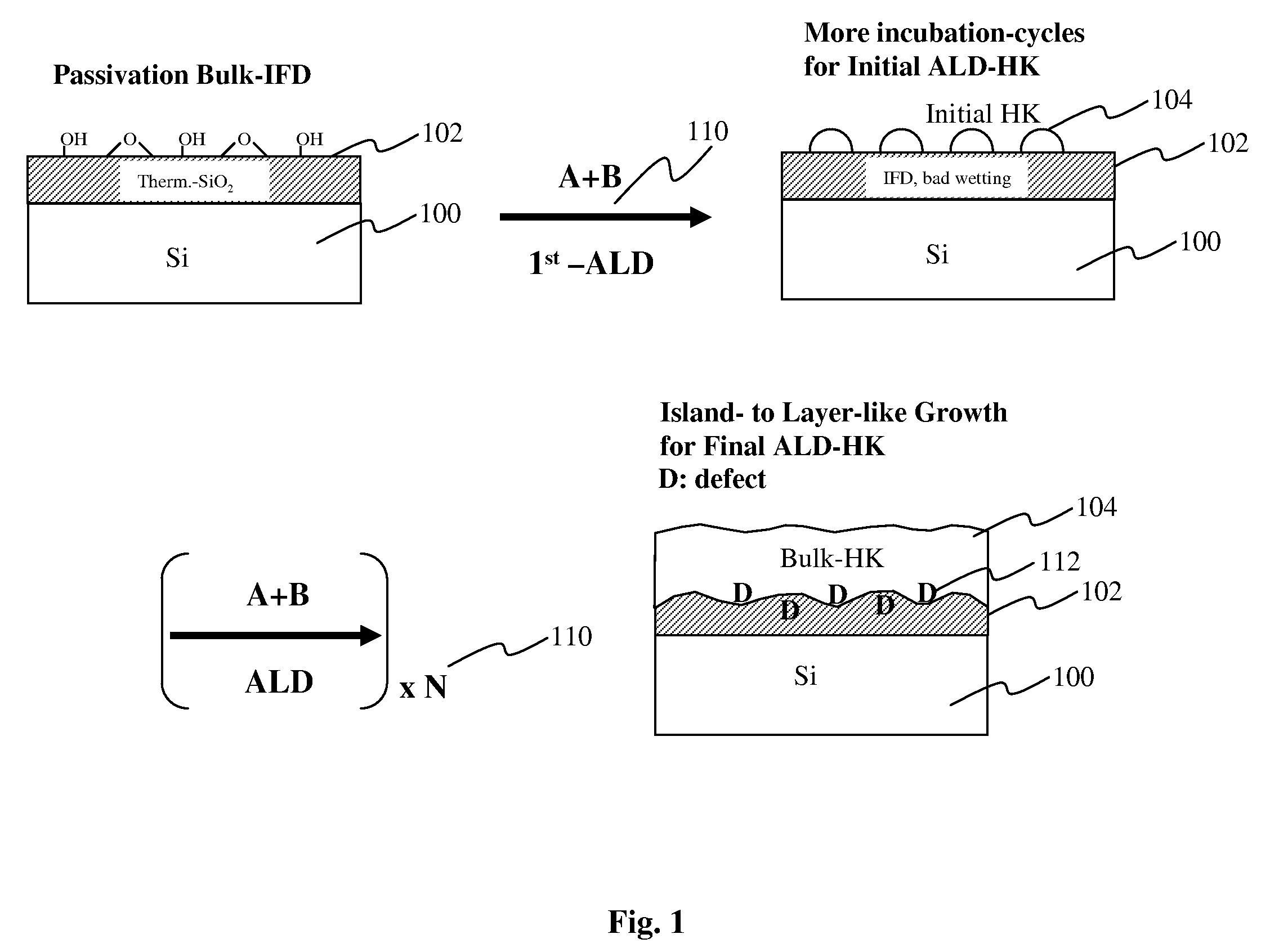

Methods of atomic layer deposition of hafnium oxide / erbium oxide bi-layer as advanced gate dielectrics

InactiveUS20130313656A1Improve electrical performanceFew defectSemiconductor/solid-state device manufacturingChemical vapor deposition coatingGate dielectricHafnium

Provided is a two-step ALD deposition process for forming a gate dielectric involving an erbium oxide layer deposition followed by a hafnium oxide layer deposition. Hafnium oxide can provide a high dielectric constant, high density, large bandgap and good thermal stability. Erbium oxide can act as a barrier against oxygen diffusion, which can lead to increasing an effective oxide thickness of the gate dielectric and preventing hafnium-silicon reactions that may lead to higher leakage current.

Owner:INTERMOLECULAR

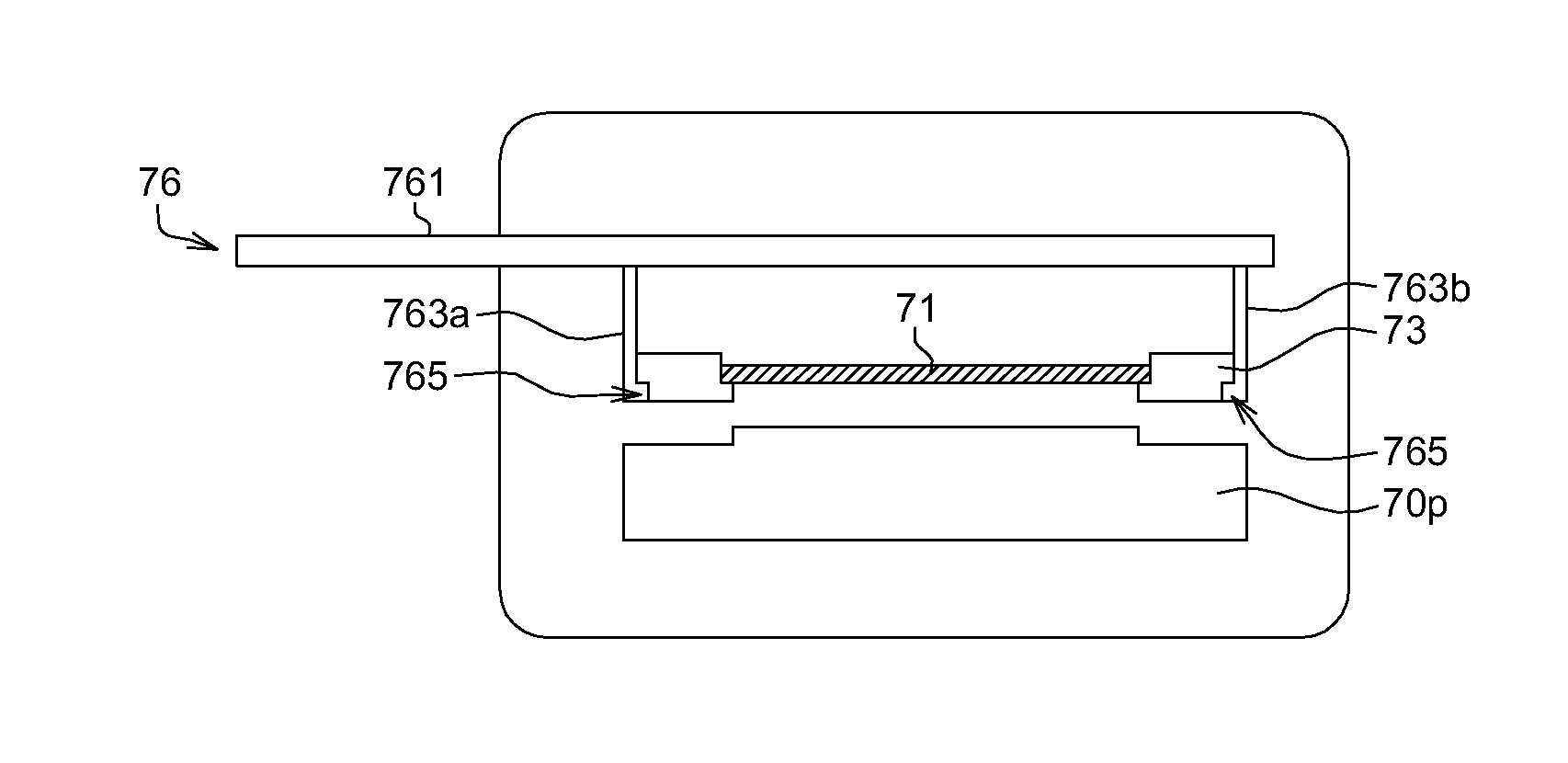

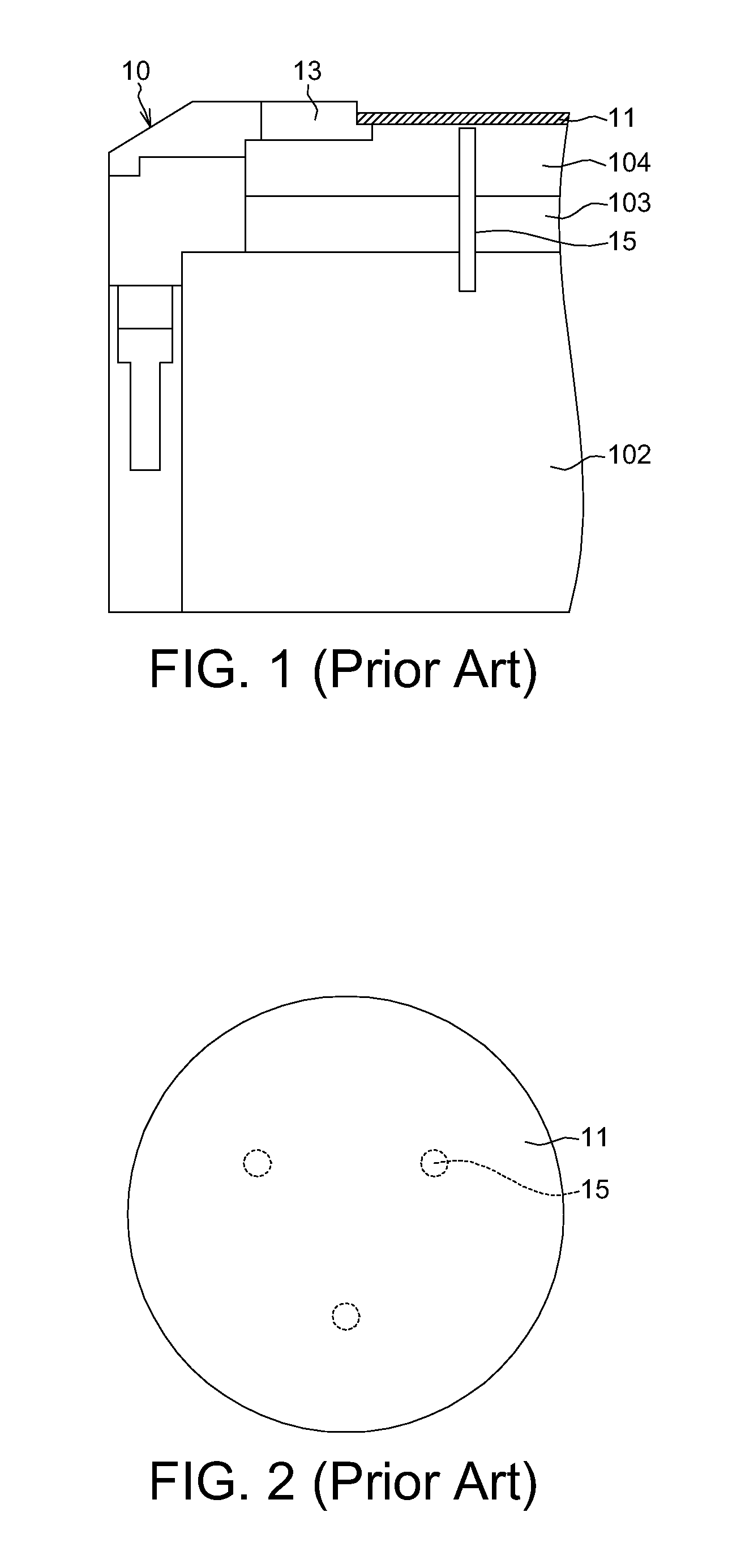

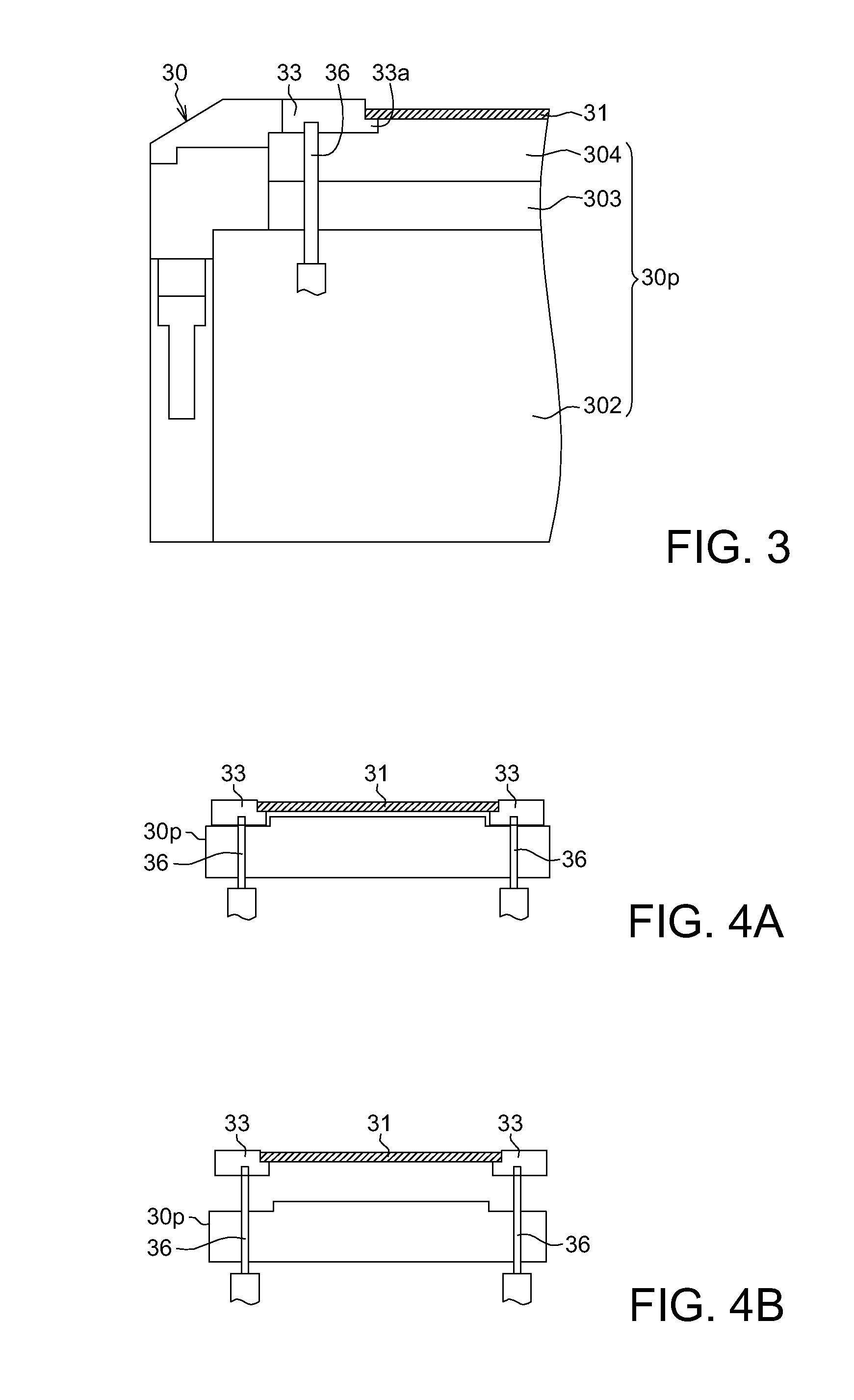

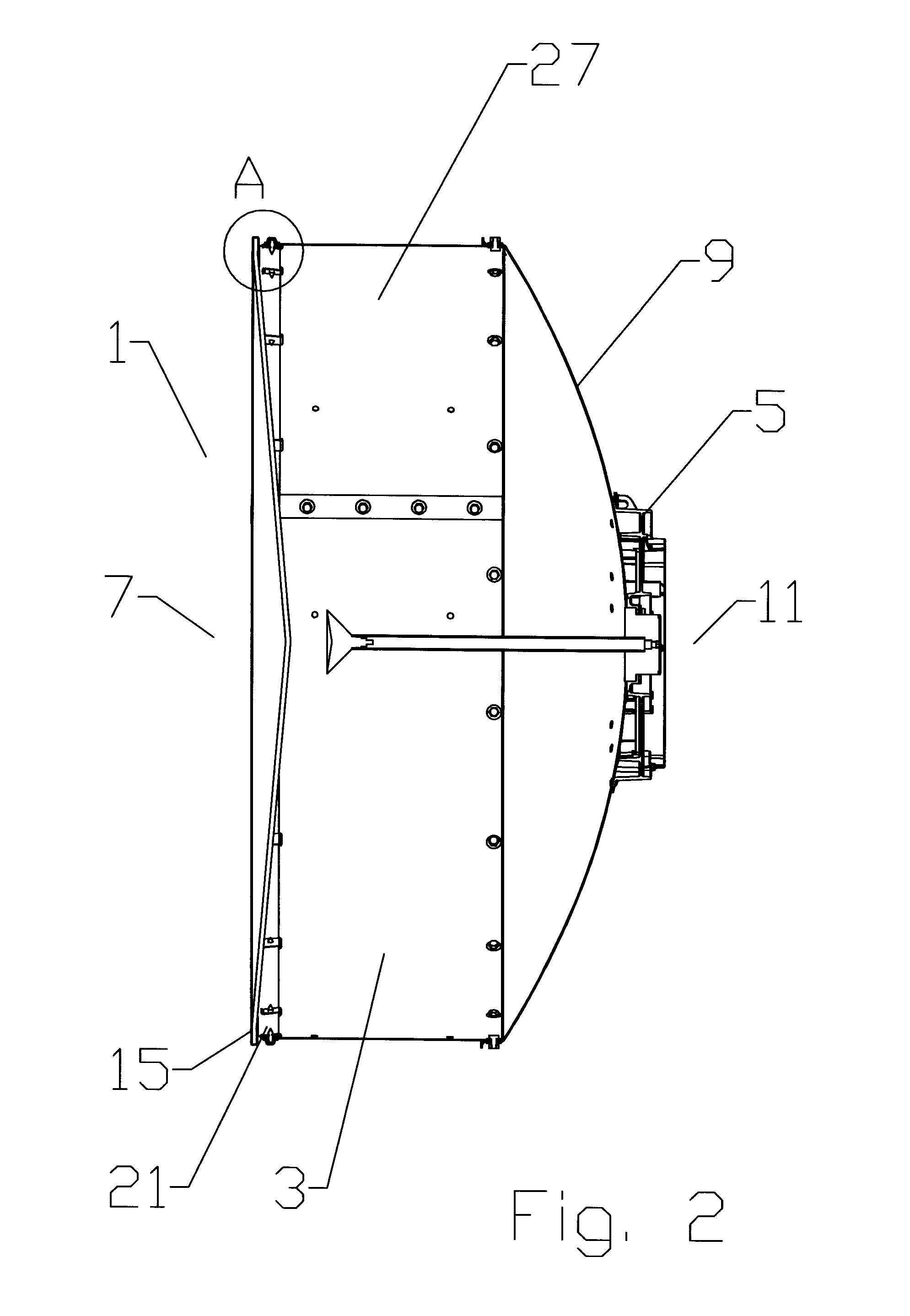

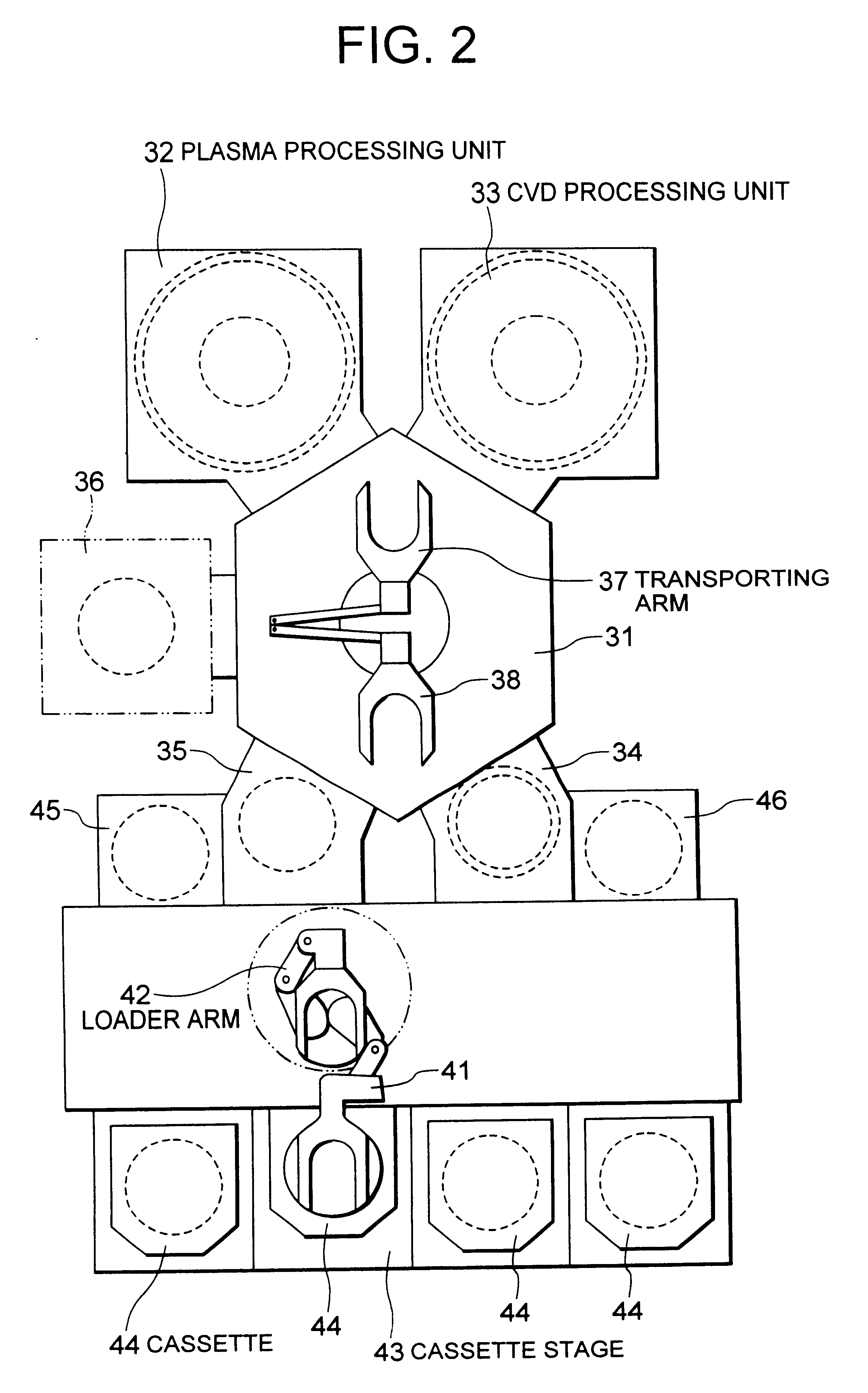

Wafer processing chamber and method for transferring wafer in the same

InactiveUS20150010381A1Improve propertiesArcing issue could be effectively preventedElectric discharge tubesSemiconductor/solid-state device manufacturingEngineeringMechanical engineering

A wafer processing chamber and a method for transferring wafer in the same are provided to prevent the arcing issue. In the embodiments, a wafer is positioned on the focus ring, and a lifting apparatus is provided outside the wafer such as corresponding to the focus ring. The lifting apparatus of the embodiment could be positioned below or above the focus ring. The wafer and the focus ring are lifted together by the lifting apparatus, and transferred together by a transferring unit.

Owner:UNITED MICROELECTRONICS CORP

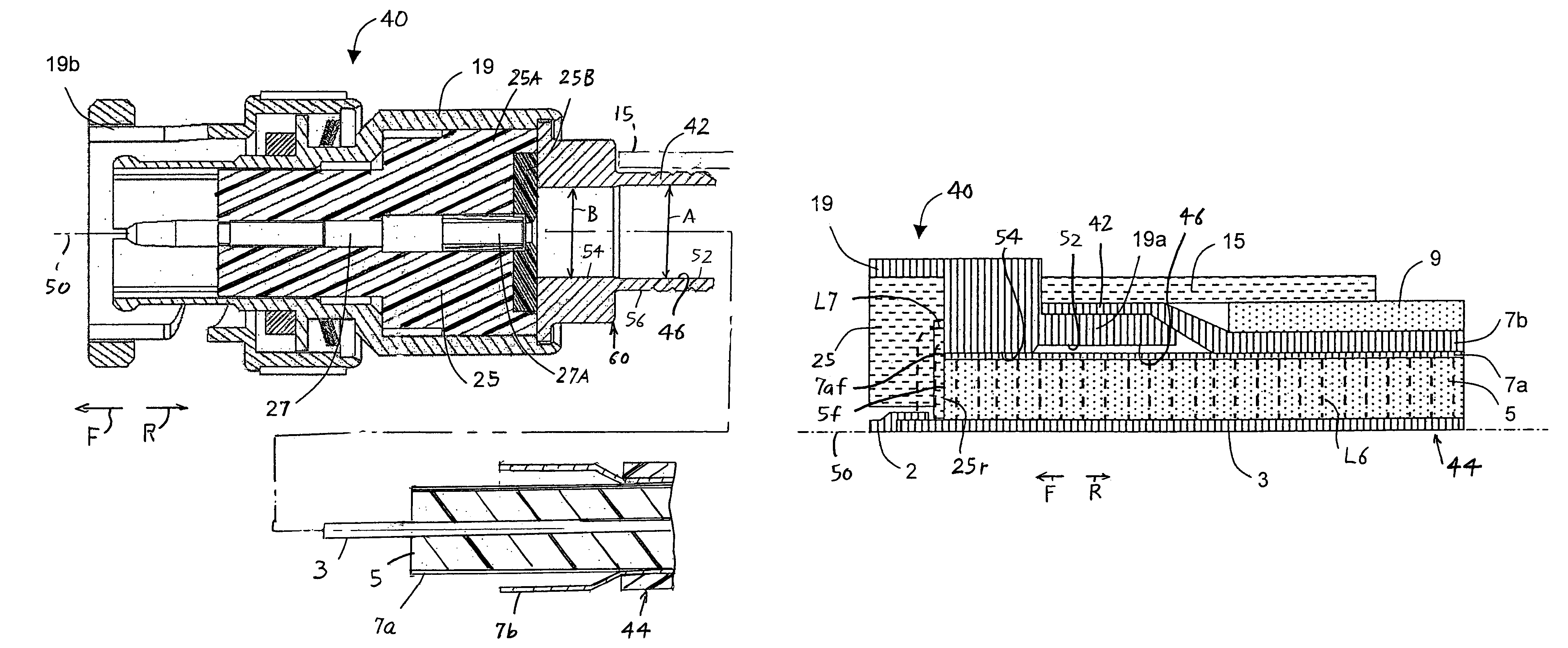

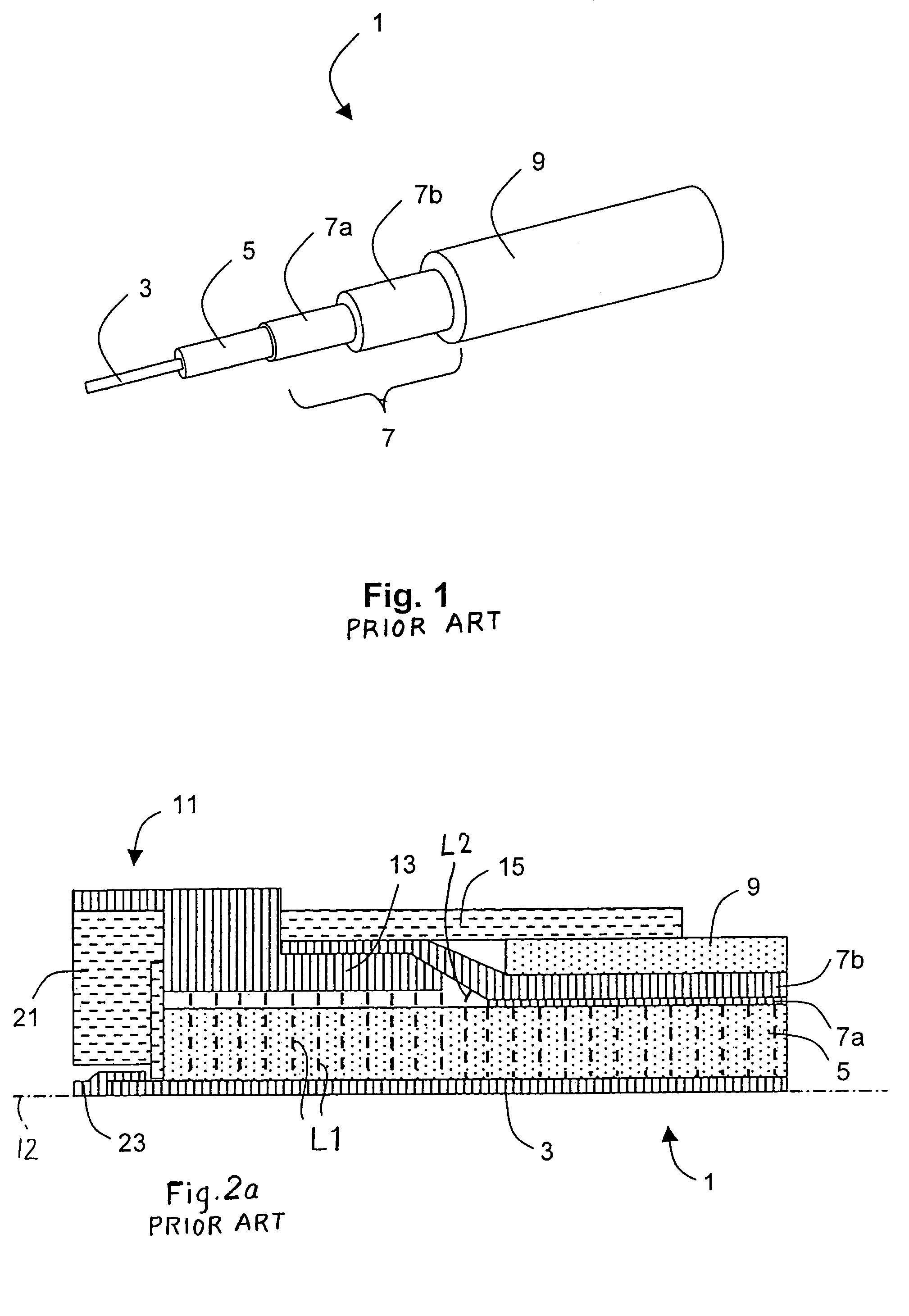

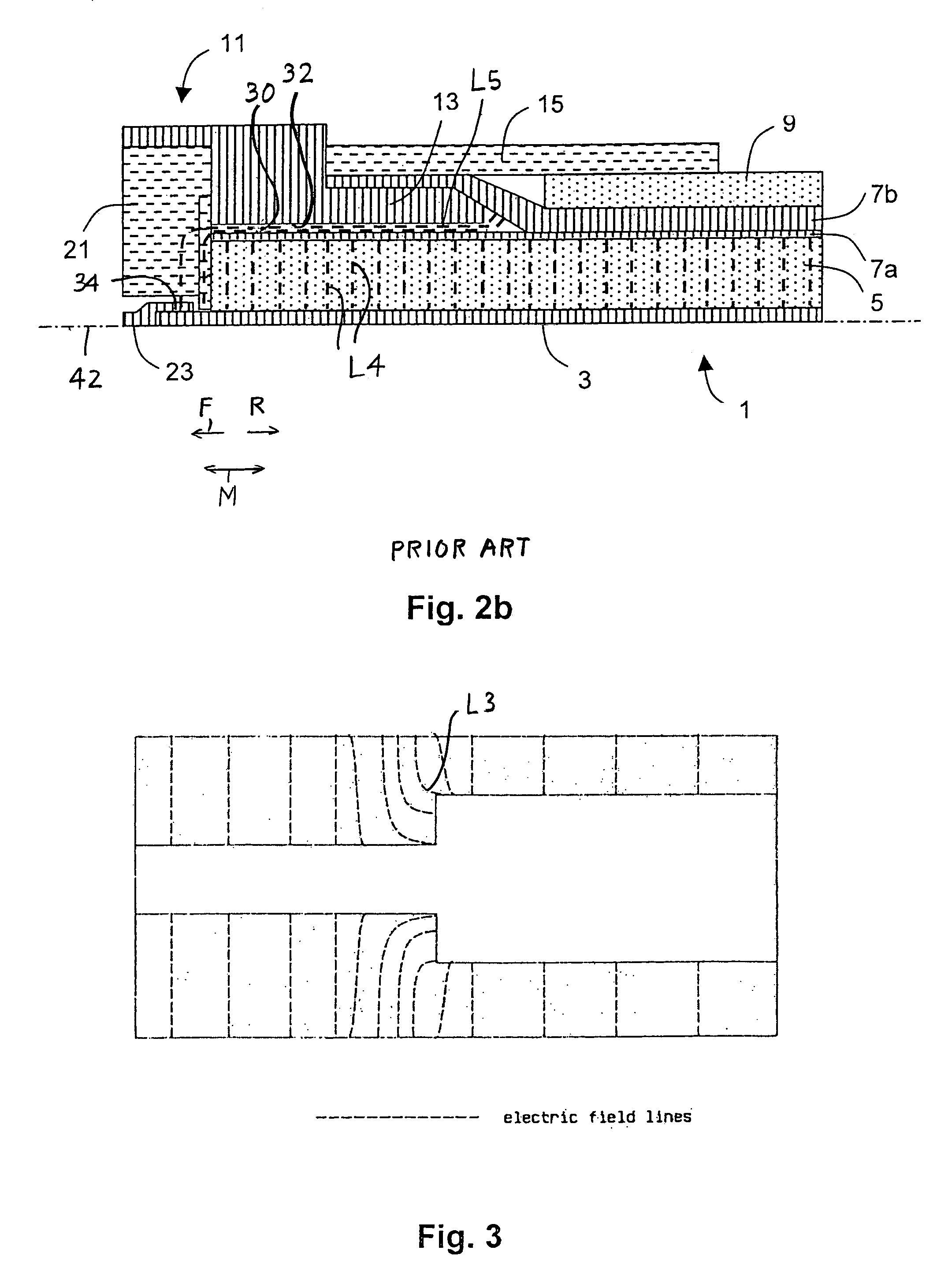

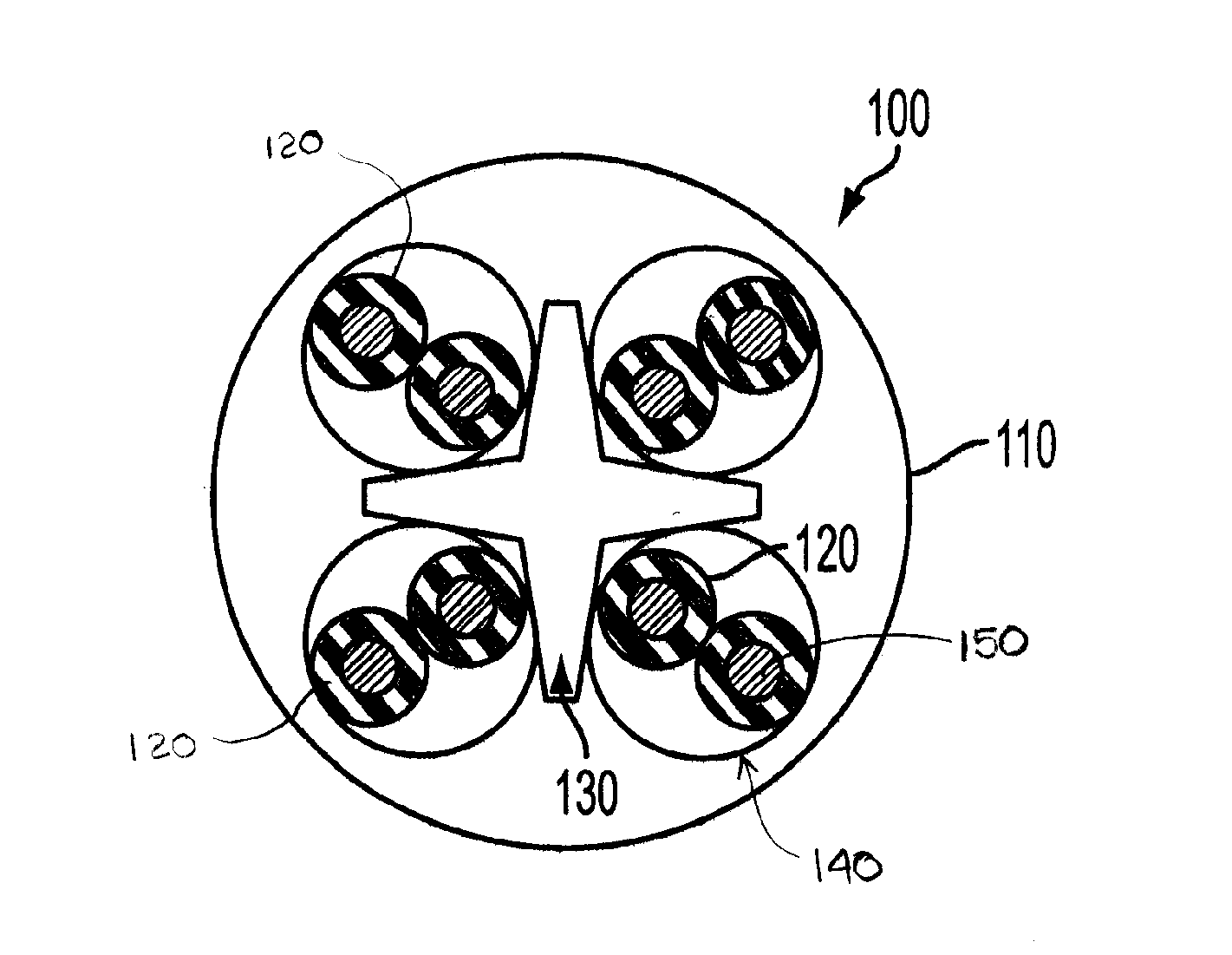

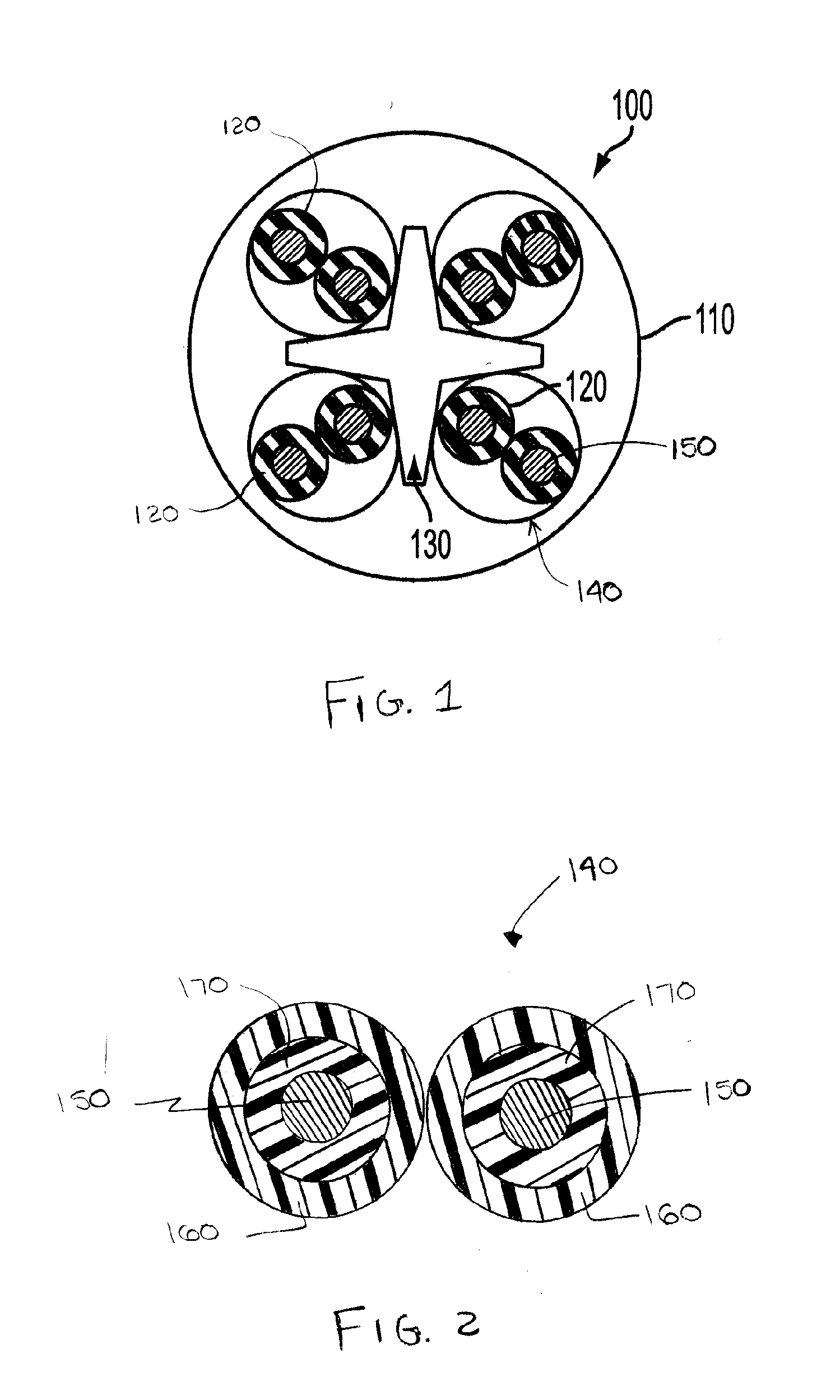

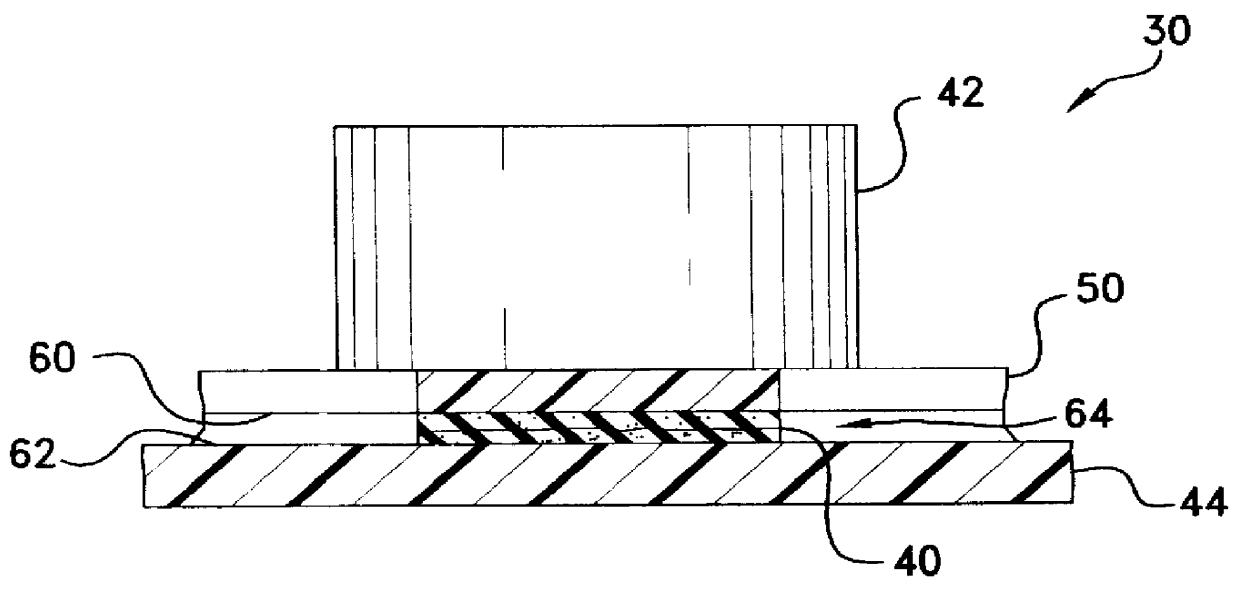

Coaxial cable-connector termination

InactiveUS7381089B2Eliminate spaceEliminates a longitudinal electric fieldElectrically conductive connectionsCoupling device detailsInterference fitElectrical conductor

A high frequency coaxial cable having a foil (7a) between the cable insulator (5) and cable braid (7b), is terminated to a coaxial connector (40) in a manner that allows fast and easy cable preparation and results in a termination with minimal axial electric field lines that cause a high insertion loss and a high VSWR (voltage standing wave ratio). A bore (46) at the rear portion of the connector outer conductor, receives the cable insulator with foil around the cable insulator. The bore has a front part (54) that forms an interference fit around the foil, to avoid an axially-extending gap which might contain axially-extending field lines. The front of cable insulator and foil are flush and both abut the insulation (25) of the connector.

Owner:ITT MFG ENTERPRISES LLC

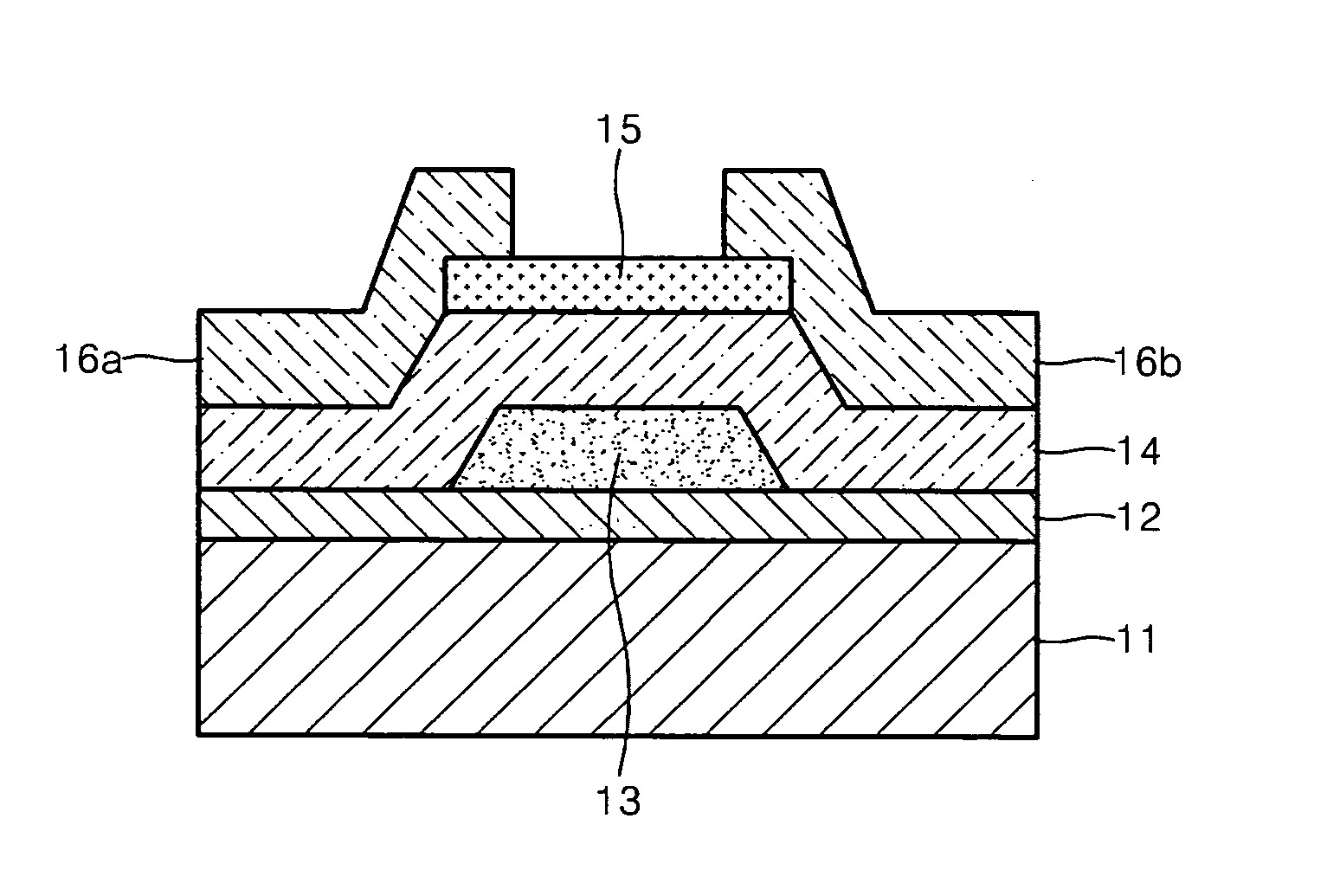

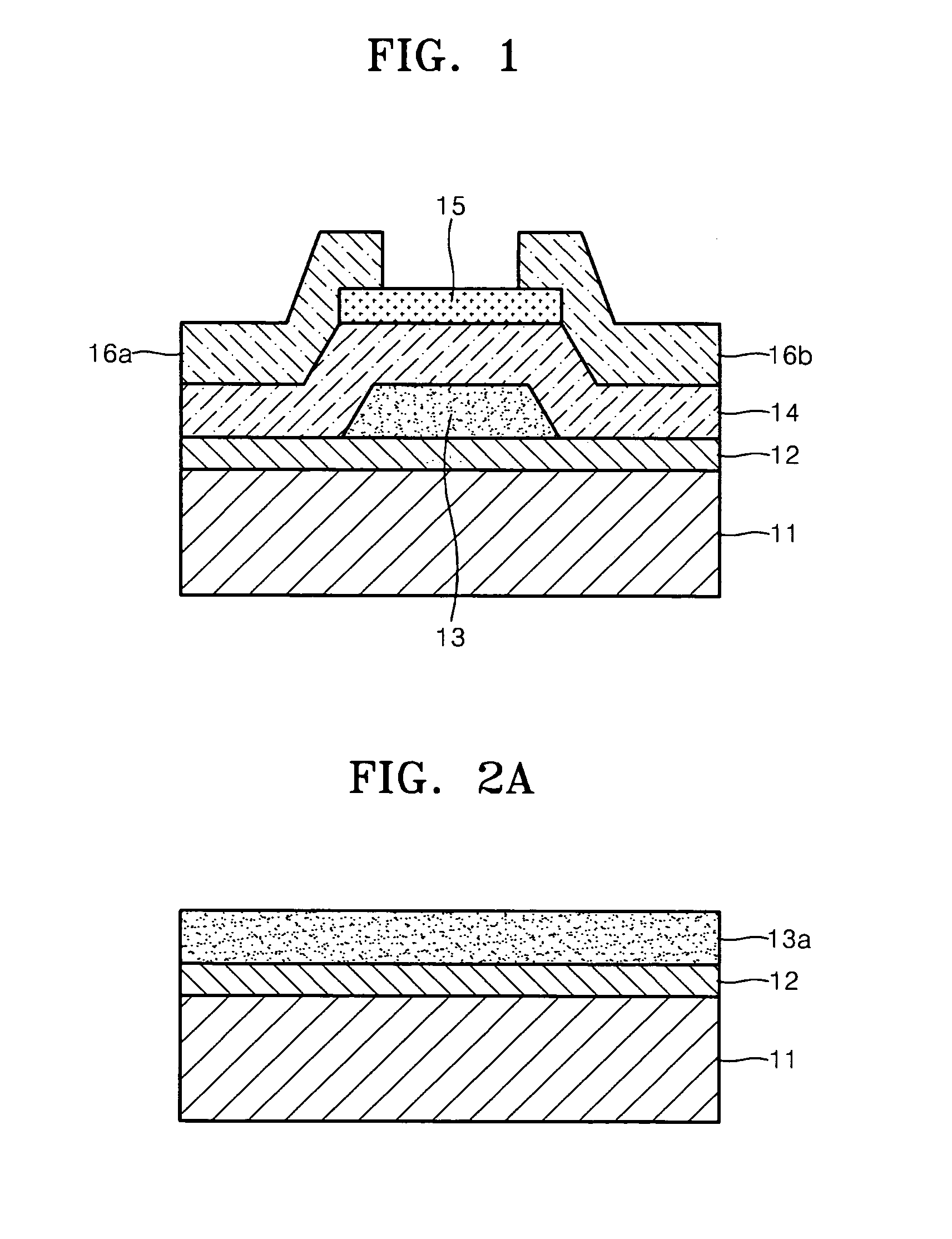

Oxide semiconductor, thin film transistor including the same and method of manufacturing a thin film transistor

InactiveUS20090008638A1Improve electrical performanceSemiconductor/solid-state device manufacturingSemiconductor devicesRare-earth elementGroup element

Example embodiments relate to an oxide semiconductor including zinc oxide (ZnO), a thin film transistor including a channel formed of the oxide semiconductor and a method of manufacturing the thin film transistor. The oxide semiconductor may include a GaxInyZnz oxide and at least one material selected from the group consisting of a 4A group element, a 4A group oxide, a rare earth element and combinations thereof.

Owner:SAMSUNG ELECTRONICS CO LTD

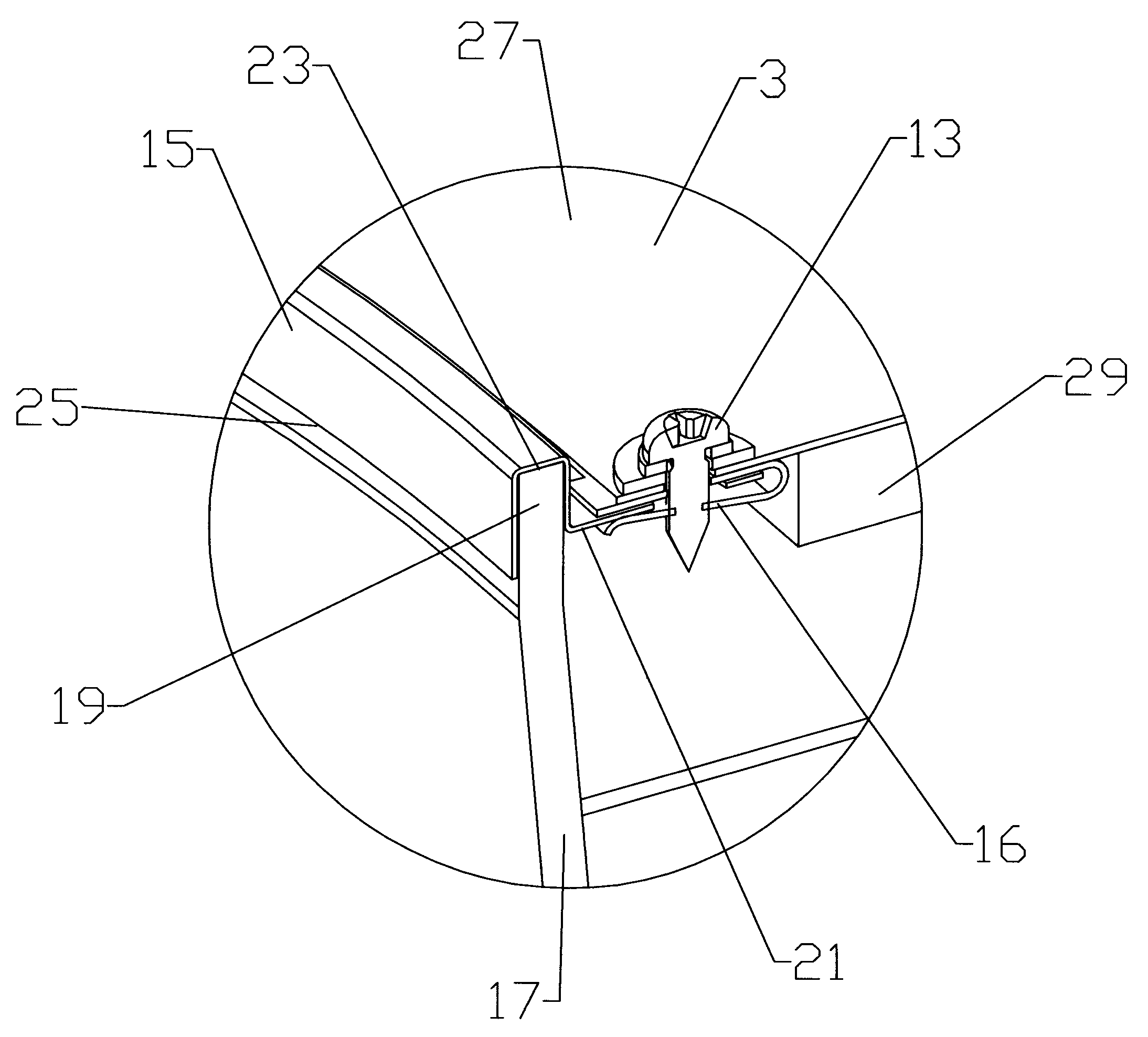

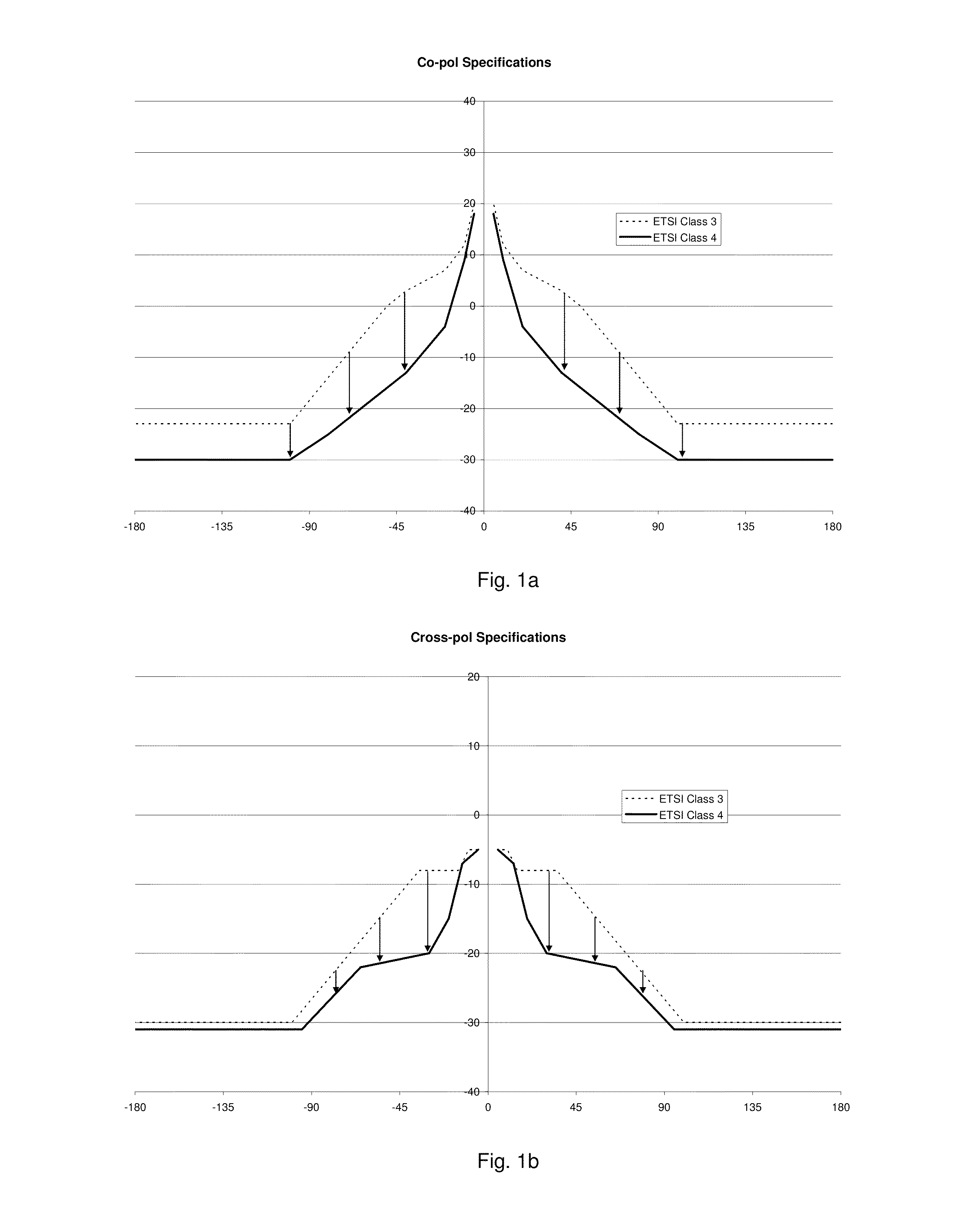

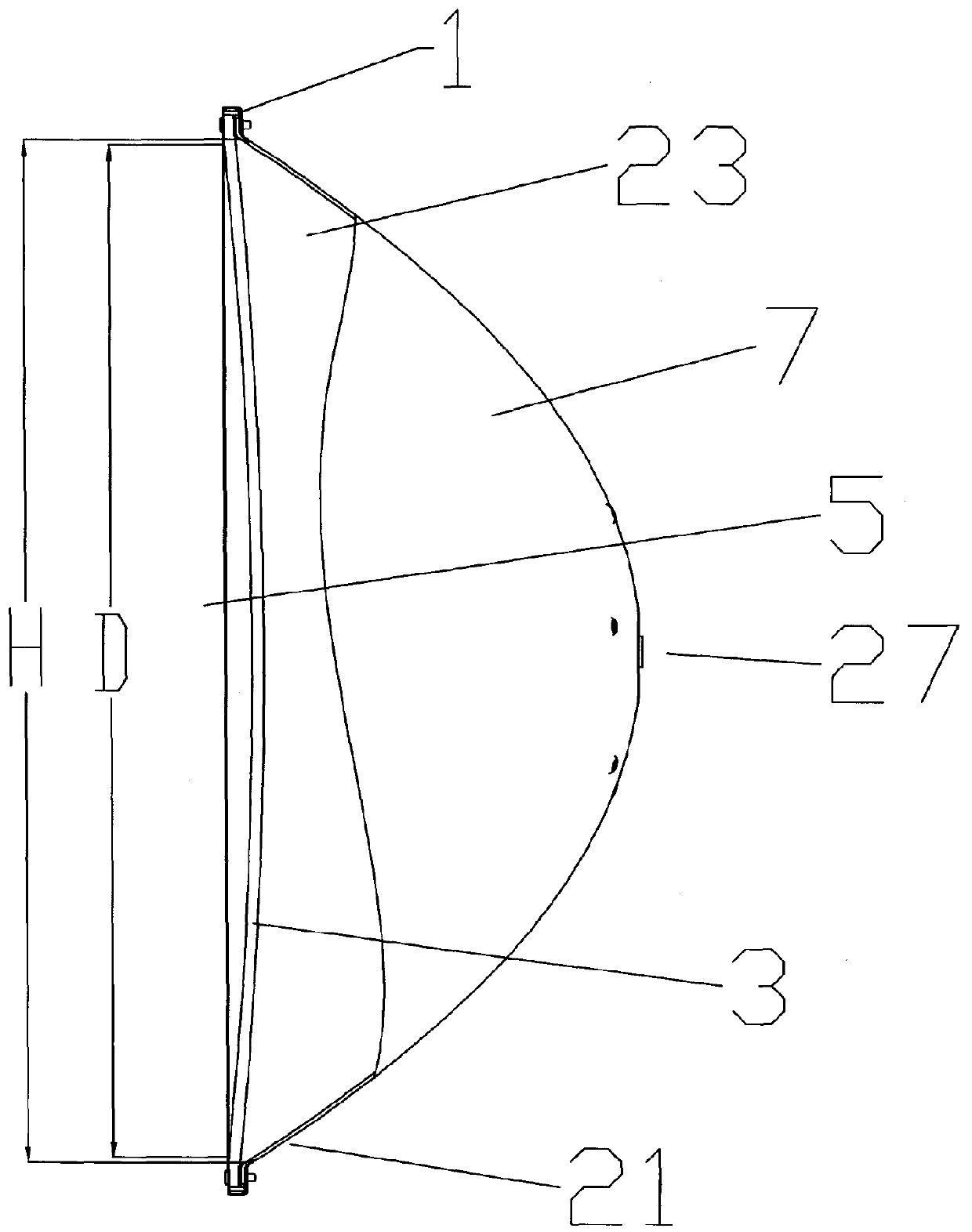

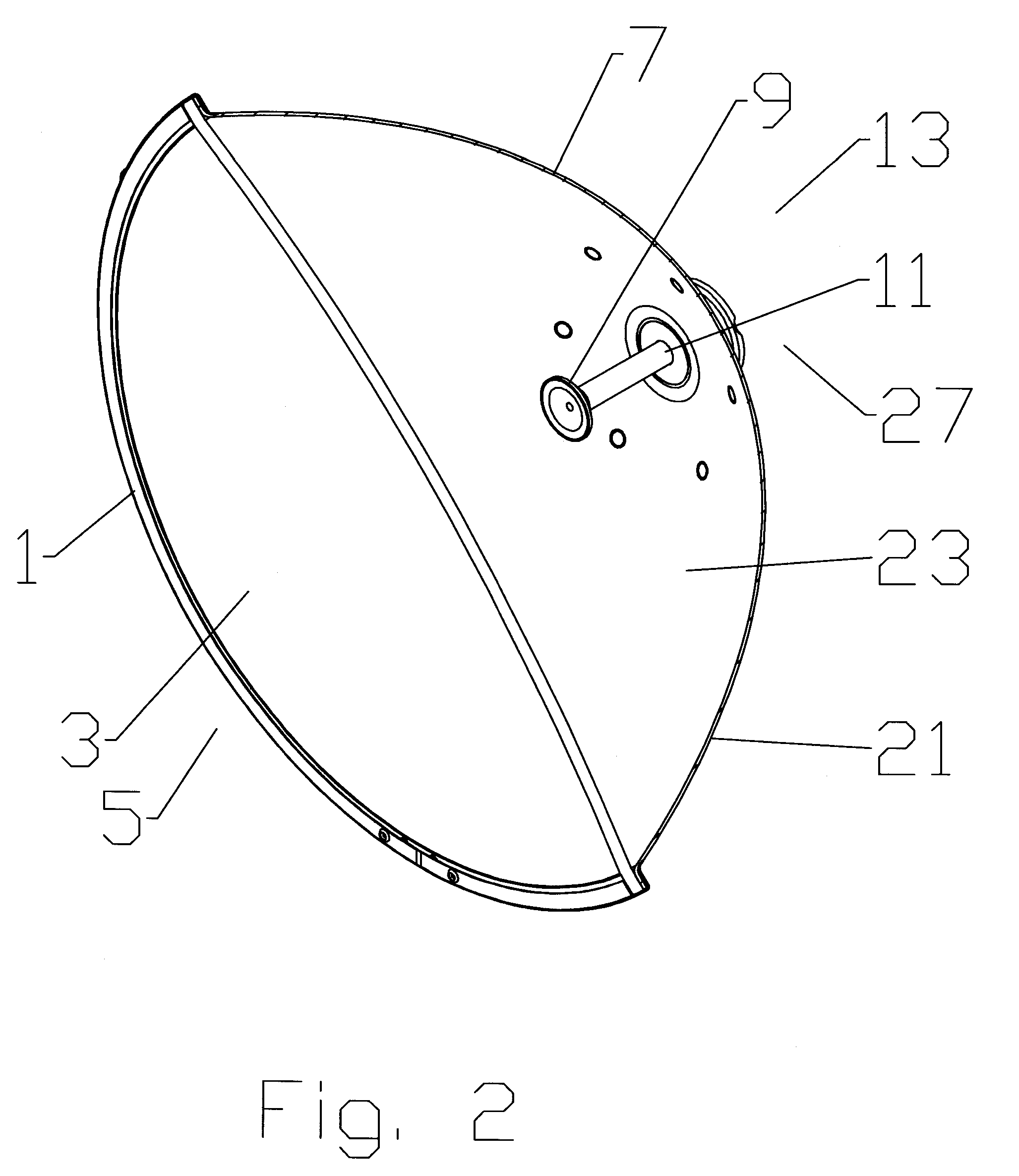

Radome and shroud enclosure for reflector antenna

ActiveUS8077113B2Improved choke effect upon signal energyShorten the lengthRadiating element housingsAntenna couplingsEngineeringRadome

An enclosure for the open end of a reflector antenna includes a cylindrical shroud coupled to a distal end of the reflector antenna, the shroud generally coaxial with a longitudinal axis of the reflector antenna. A retaining band is coupled to an inner diameter of the shroud, proximate a distal end of the shroud. The retaining band is provided with a retaining groove open radially inward towards the longitudinal axis. The retaining groove provided with a bottom extending radially outward beyond an outer diameter of the shroud. A radome is seated within the retaining groove.

Owner:COMMSCOPE TECH LLC

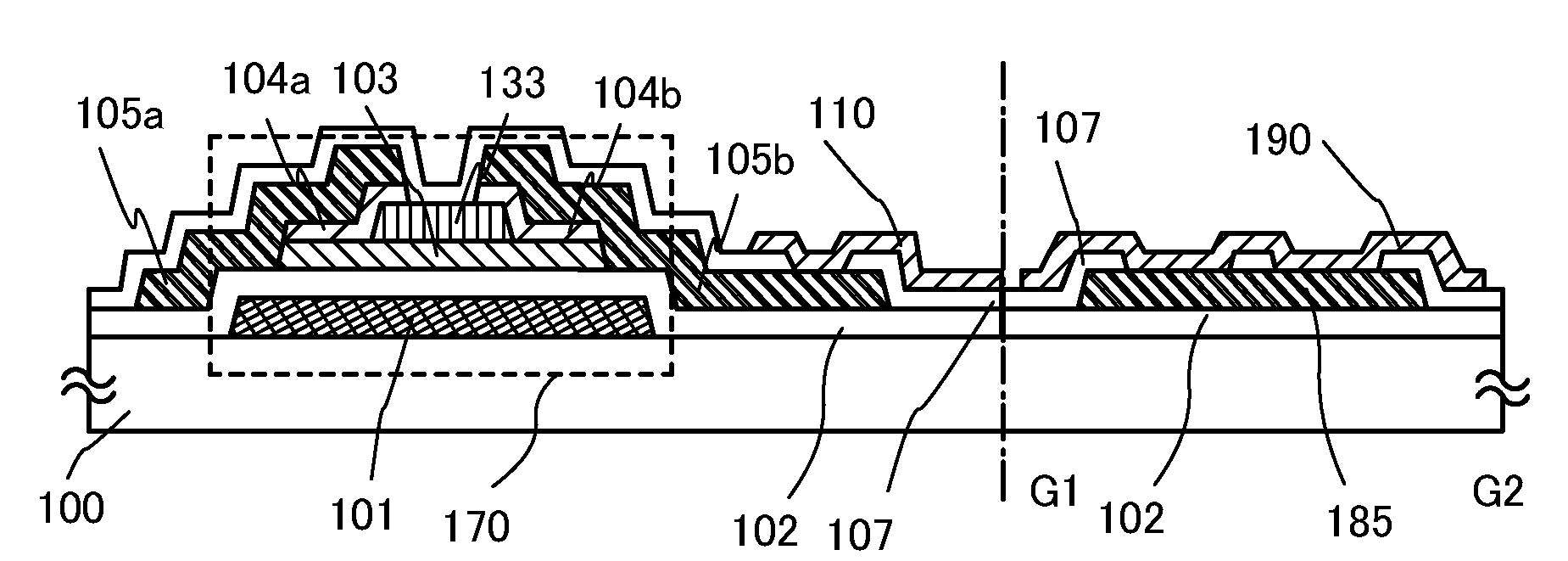

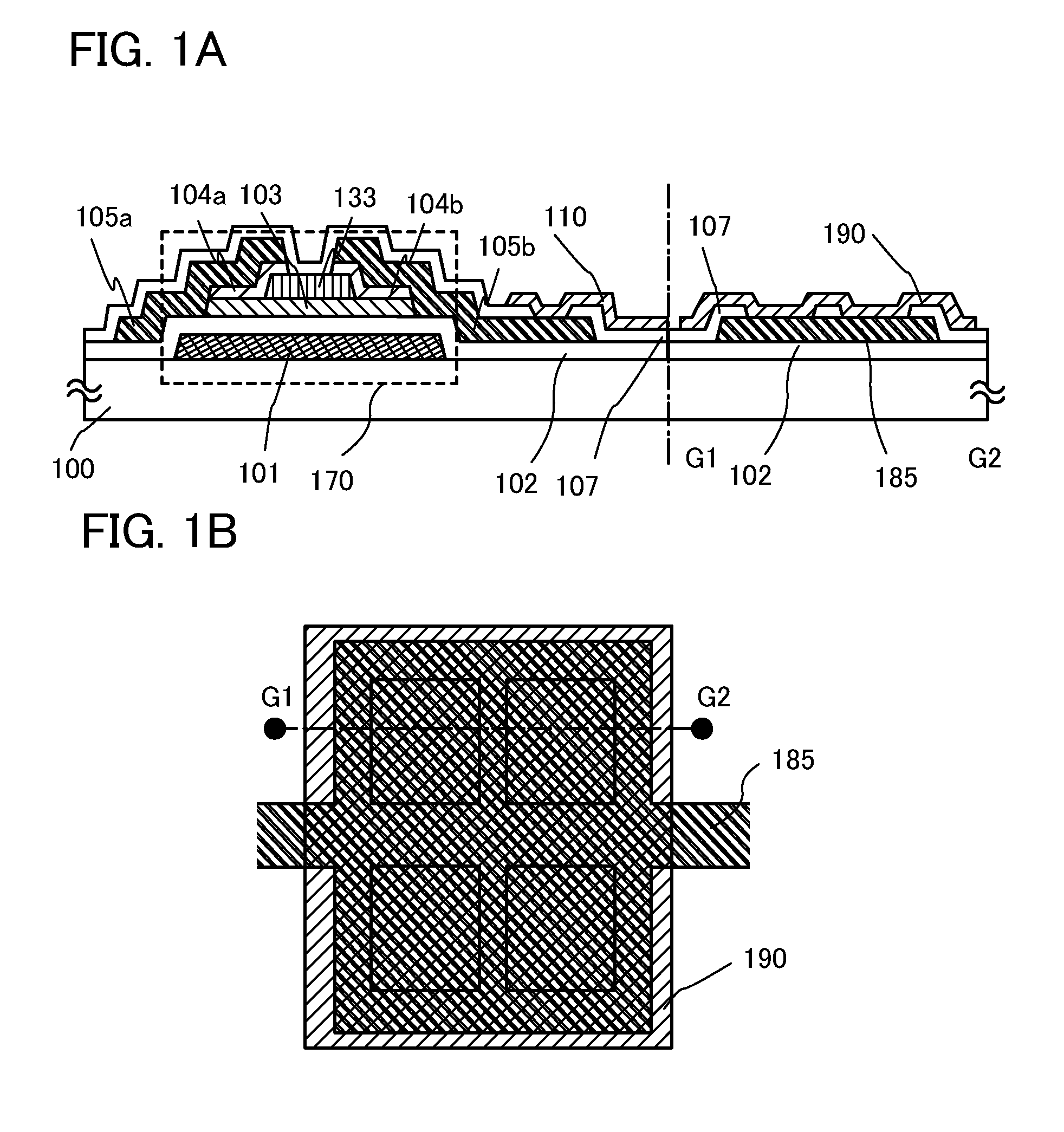

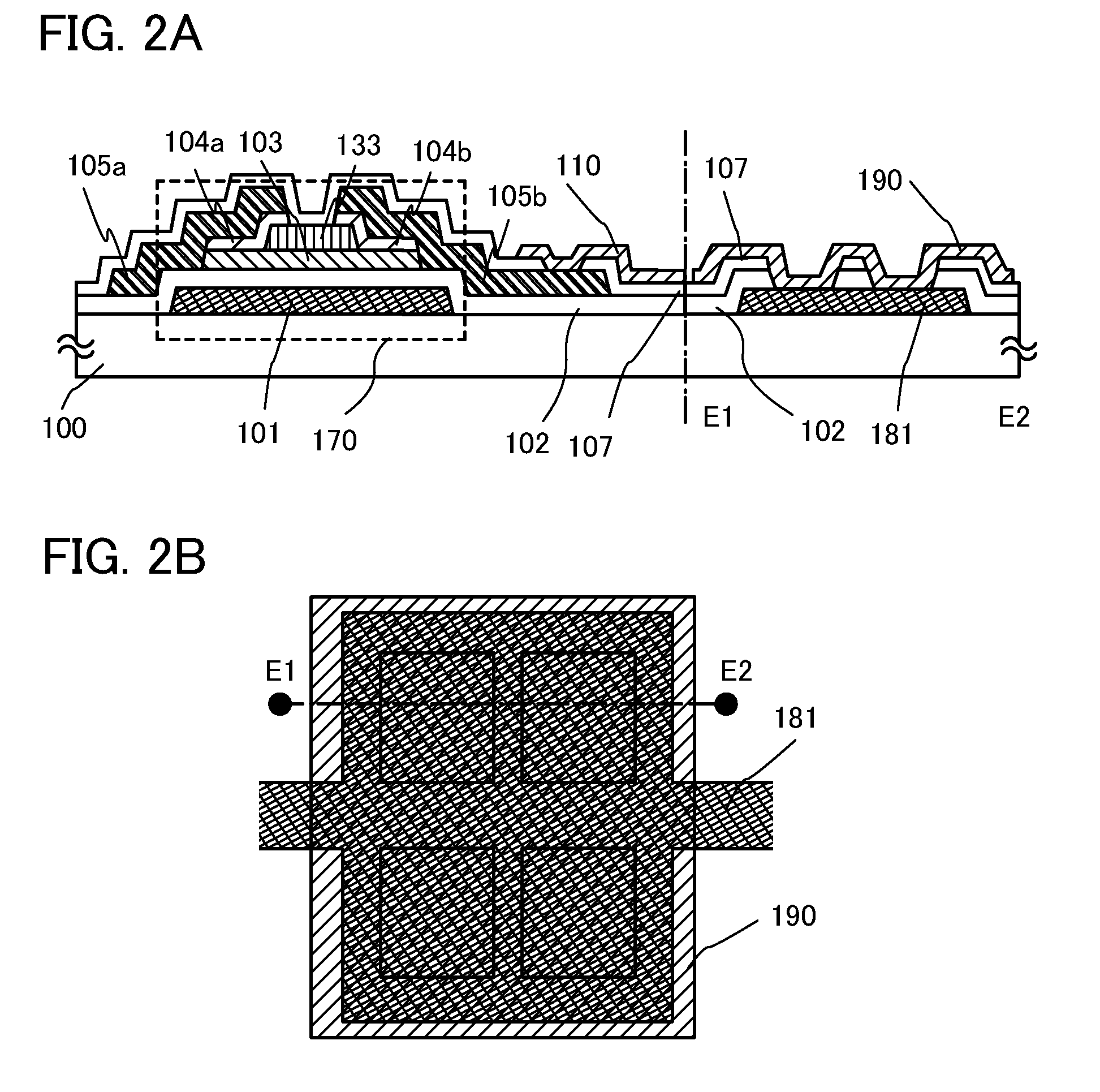

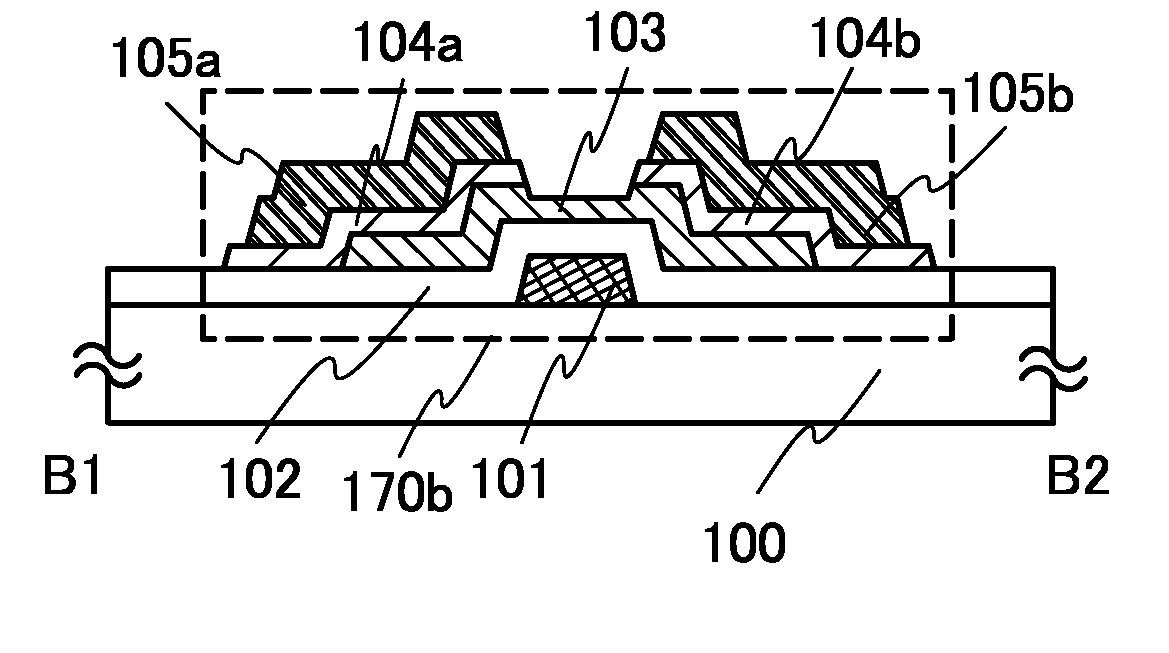

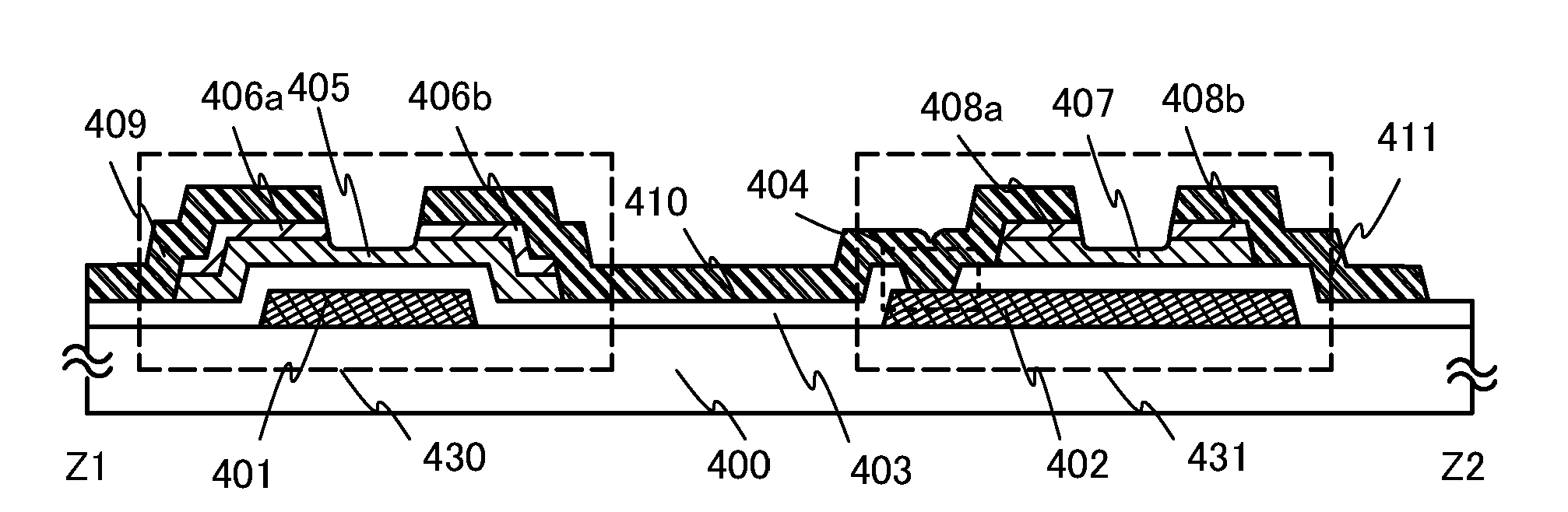

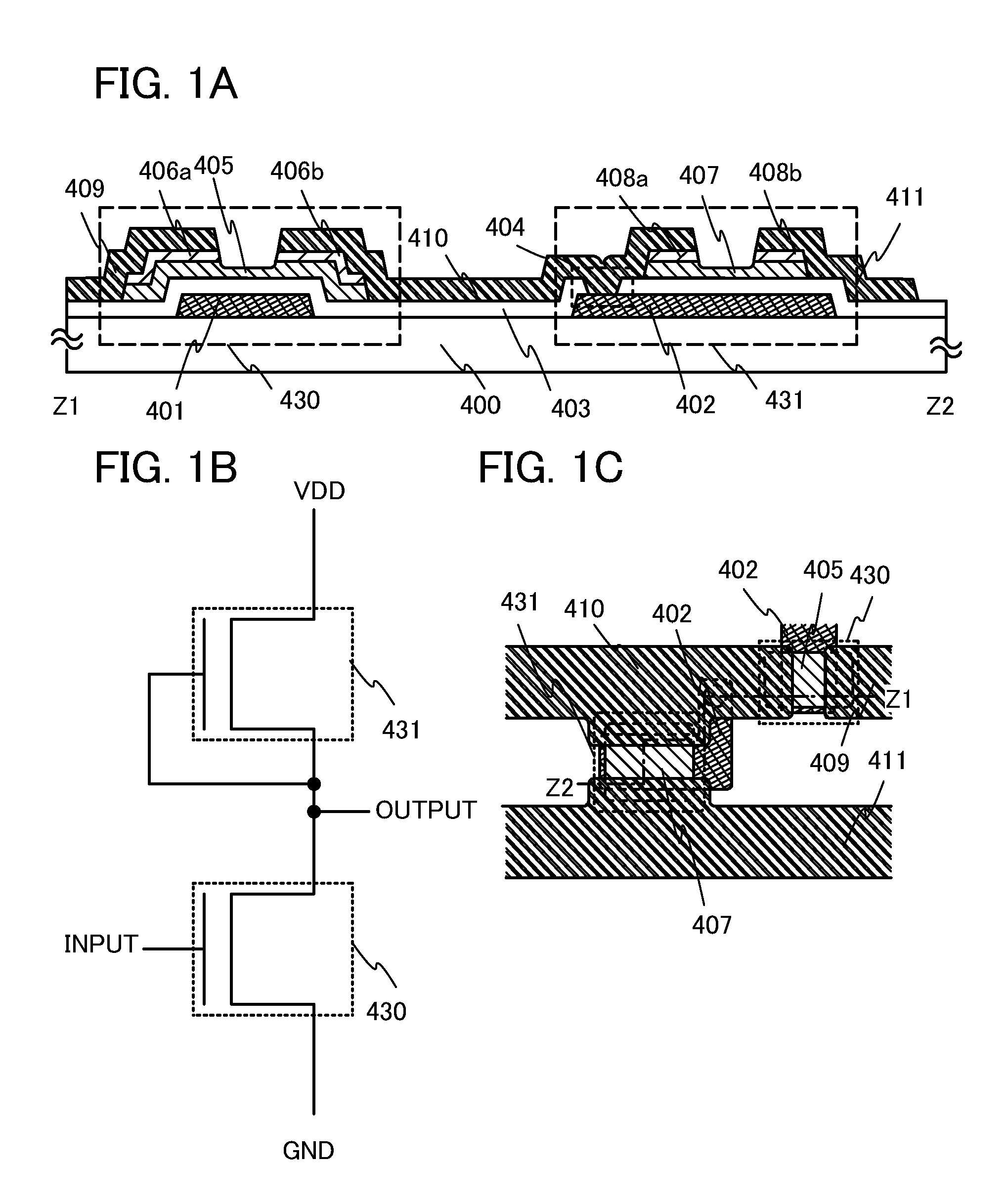

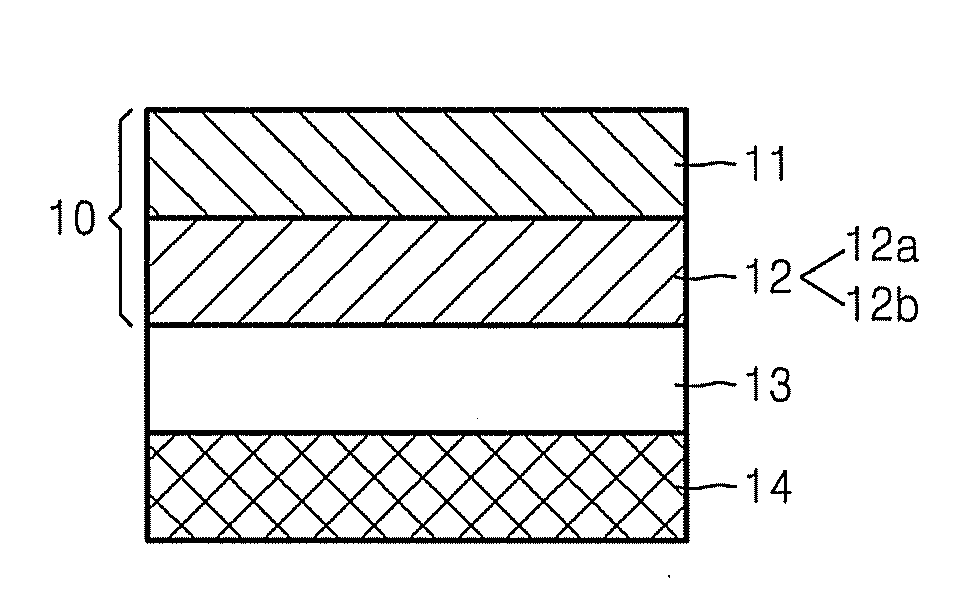

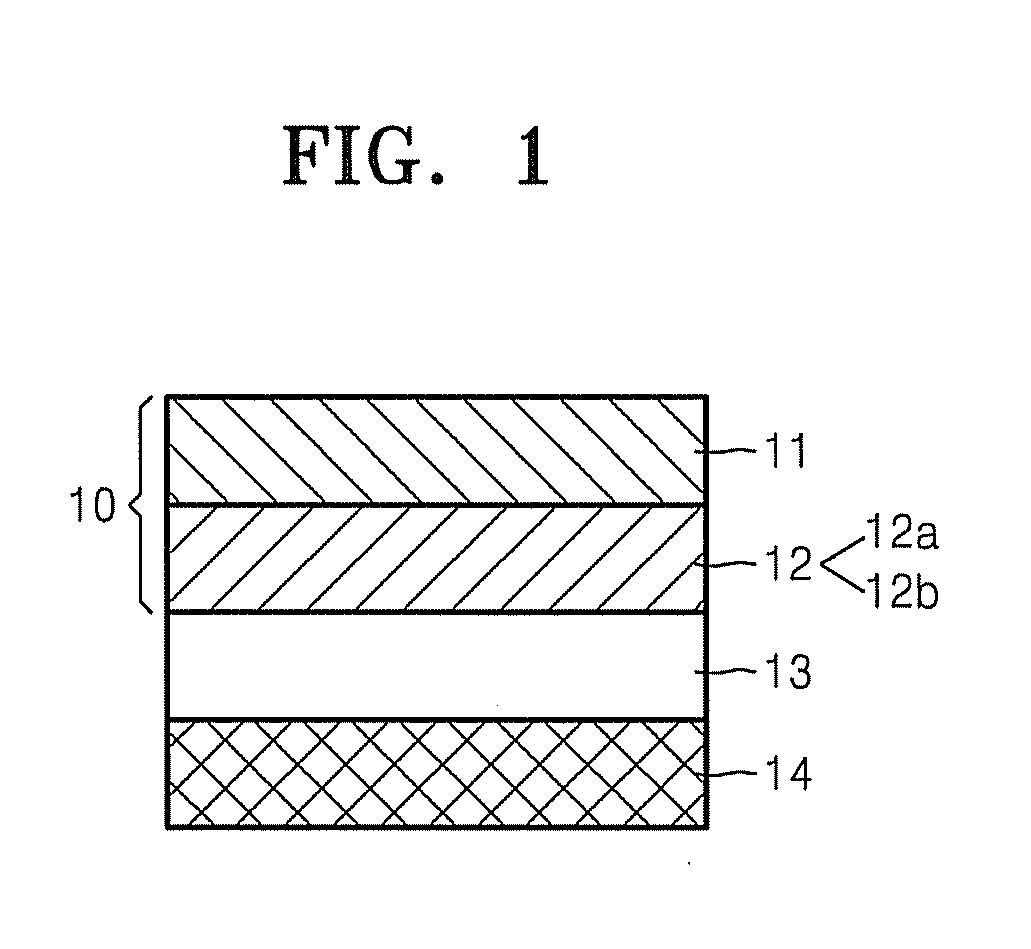

Semiconductor device

ActiveUS20100072467A1Increasing the thicknessAvoid separationTransistorElectroluminescent light sourcesDisplay deviceSemiconductor package

A display device includes a pixel portion in which a pixel is arranged in a matrix, the pixel including an inverted staggered thin film transistor having a combination of at least two kinds of oxide semiconductor layers with different amounts of oxygen and having a channel protective layer over a semiconductor layer to be a channel formation region overlapping a gate electrode layer and a pixel electrode layer electrically connected to the inverted staggered thin film transistor. In the periphery of the pixel portion in this display device, a pad portion including a conductive layer made of the same material as the pixel electrode layer is provided. In addition, the conductive layer is electrically connected to a common electrode layer formed on a counter substrate.

Owner:SEMICON ENERGY LAB CO LTD

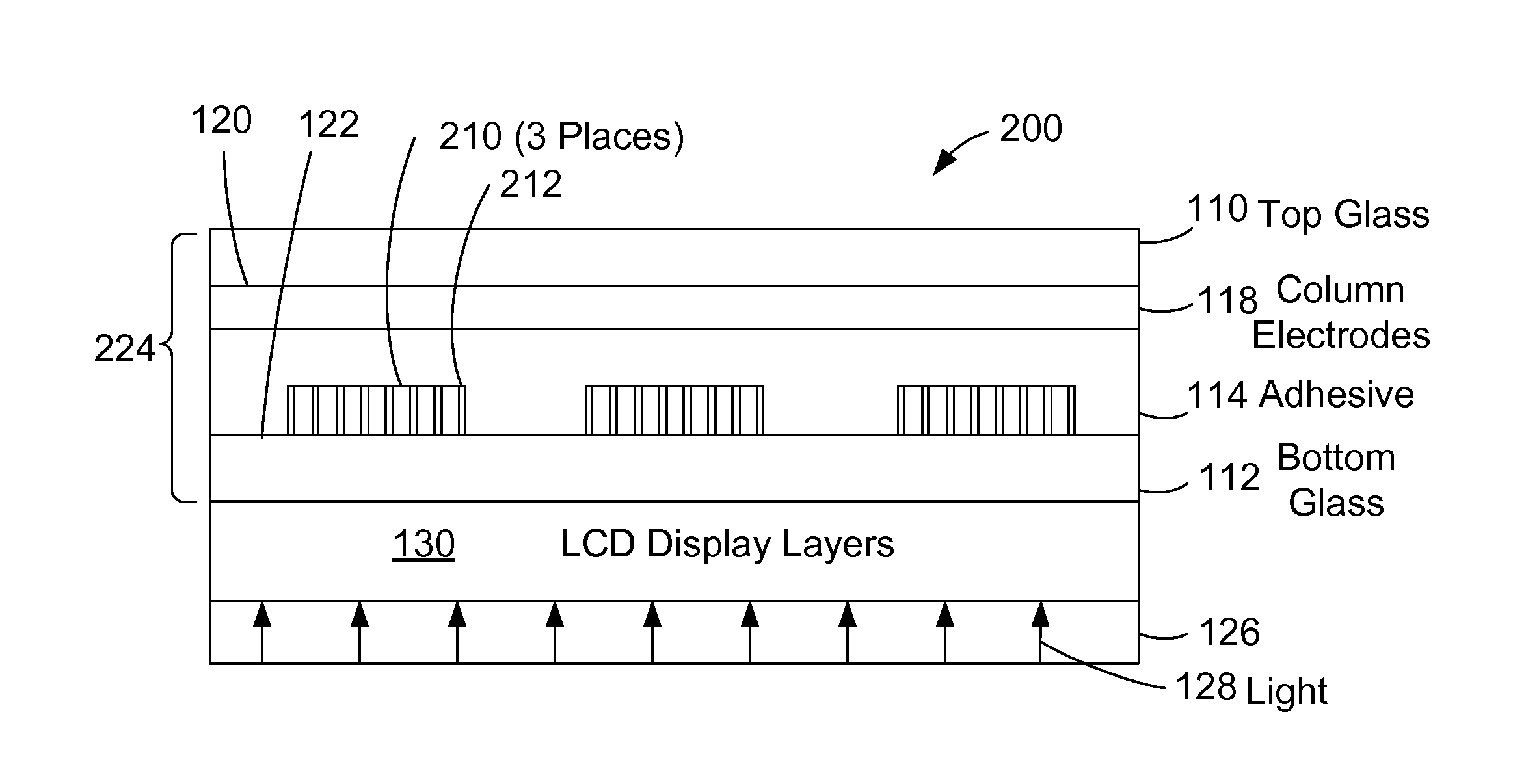

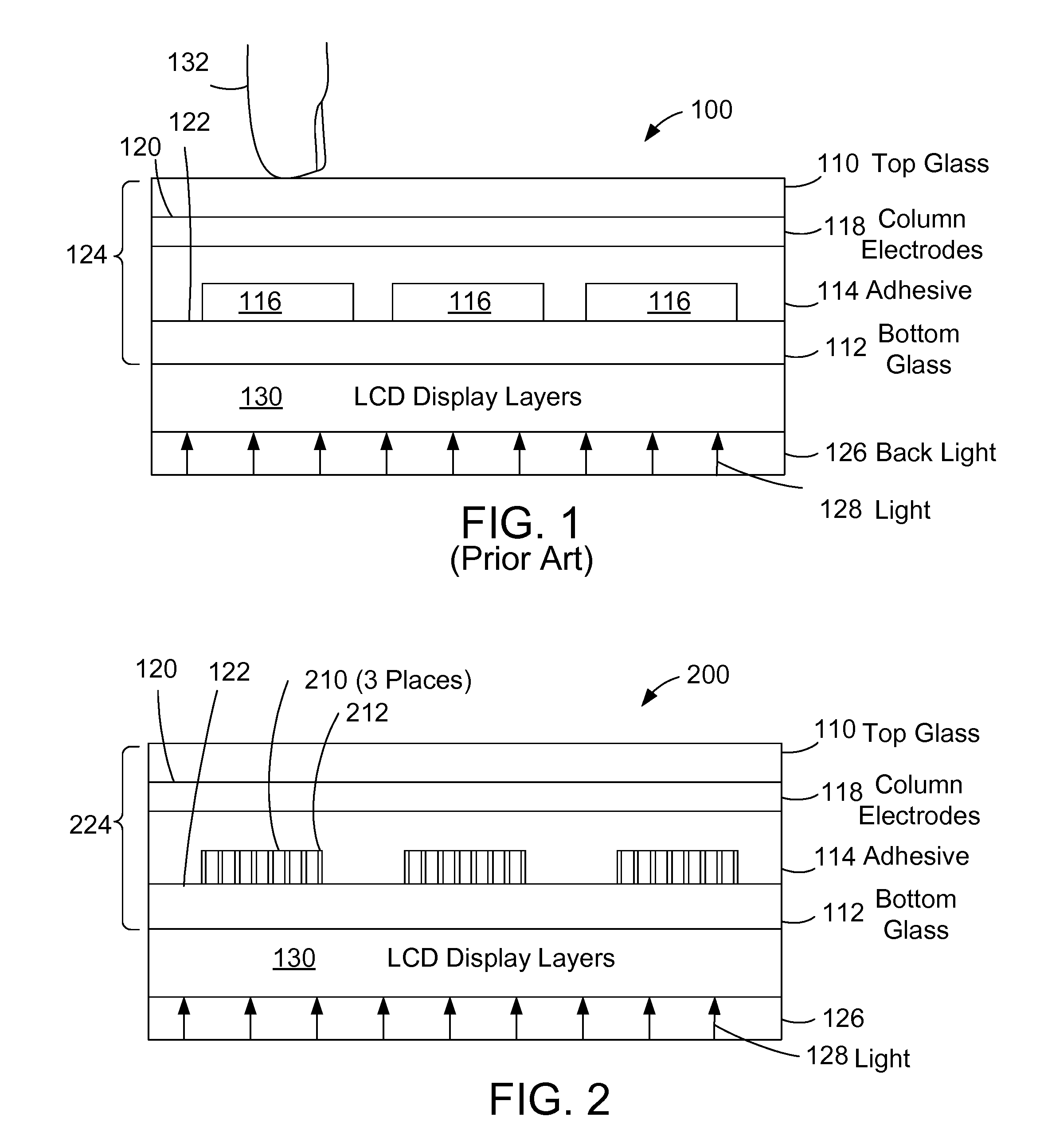

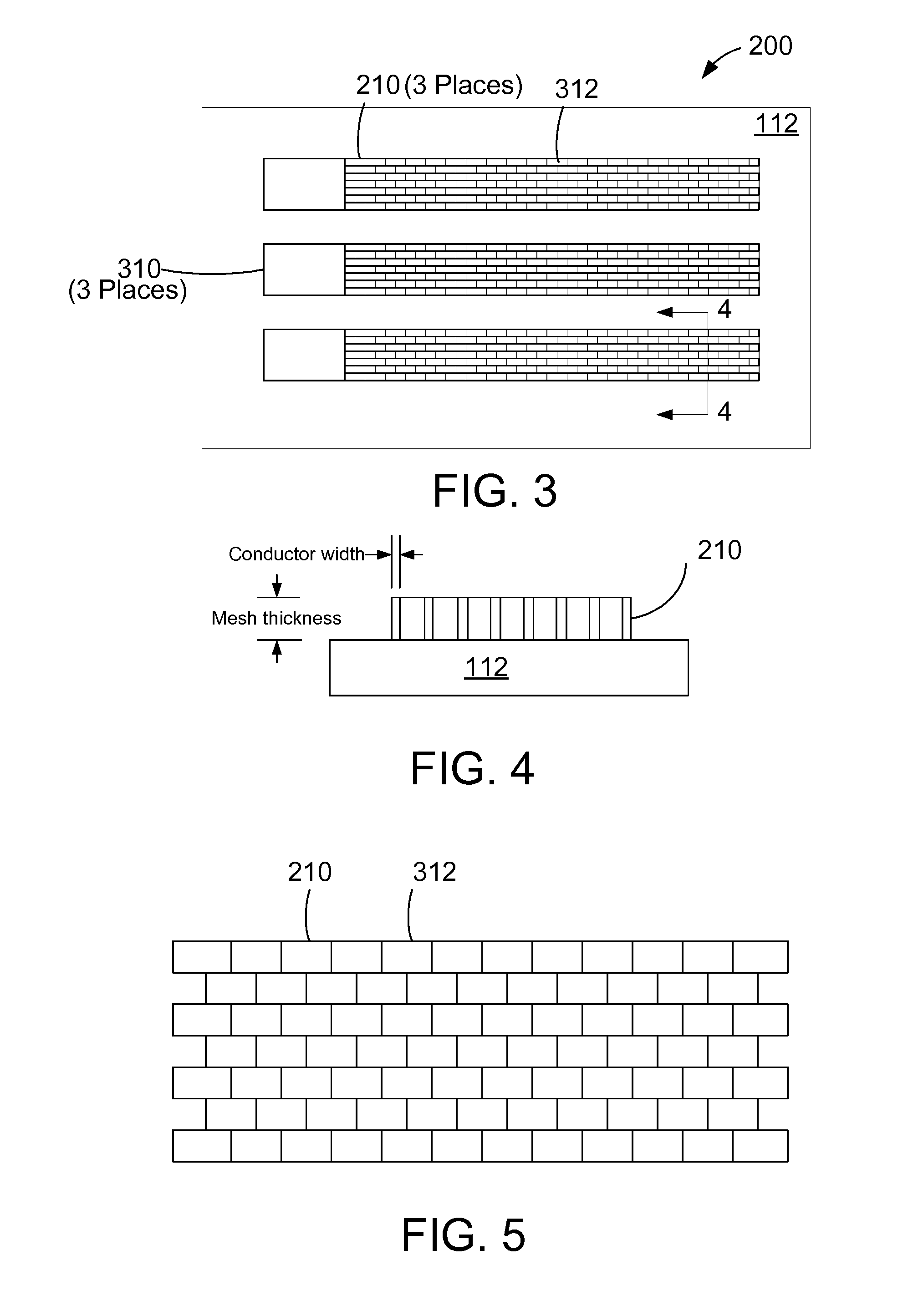

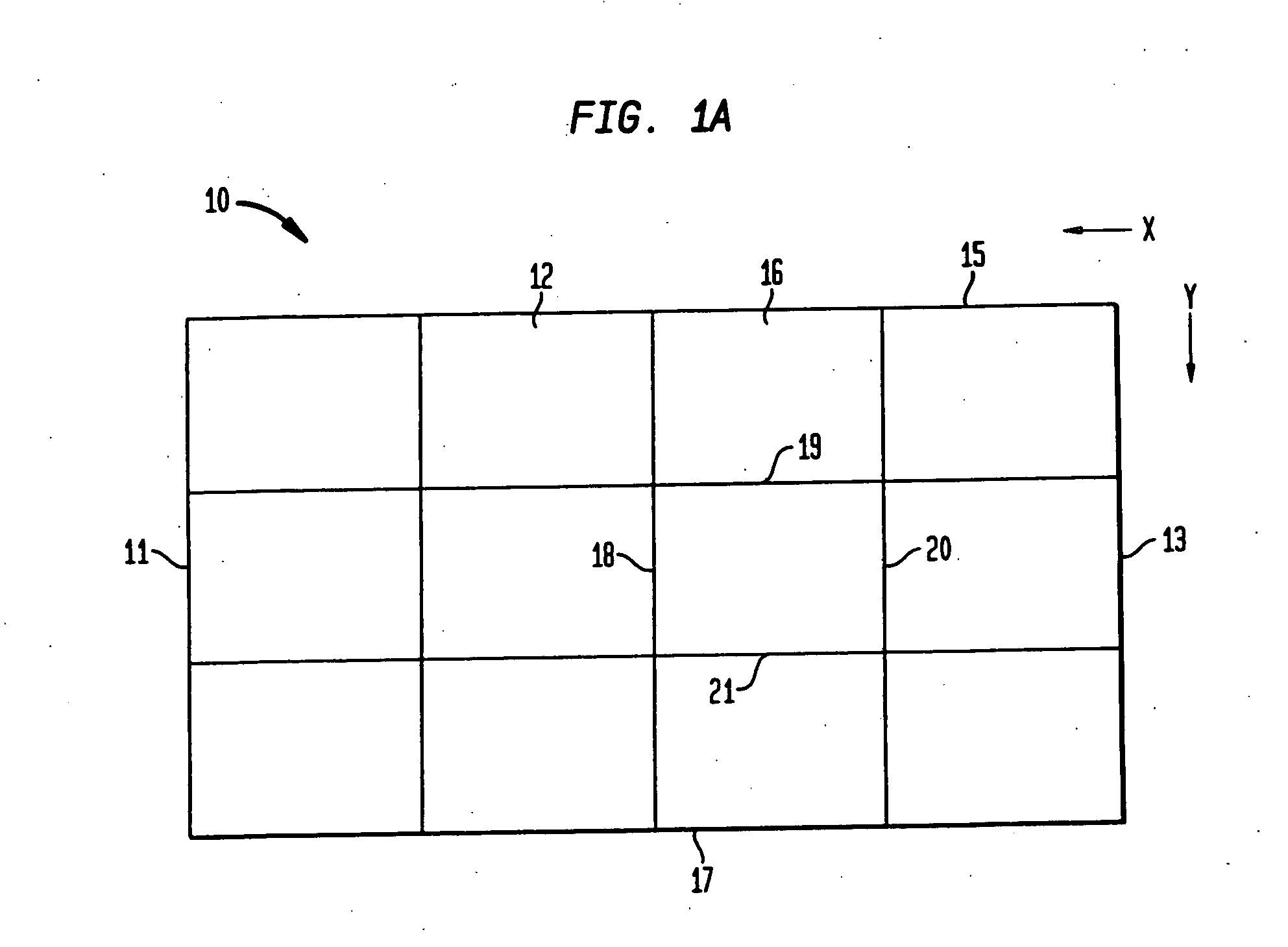

Capacitive touch screen with a mesh electrode

InactiveUS20110007011A1Improve electrical performanceImprove optical qualityInput/output processes for data processingElectrical resistance and conductanceConductive materials

An improved touch screen provides enhanced electrical performance and optical quality. The electrodes on the touch screen are made of a mesh of conductors to reduce the overall electrode resistance thereby increasing the electrical performance without sacrificing optical quality. The mesh electrodes comprise a mesh pattern of conductive material with each conductor comprising the mesh having a very small width such that the conductors are essentially invisible to the user of the touch screen.

Owner:OCULAR LCD

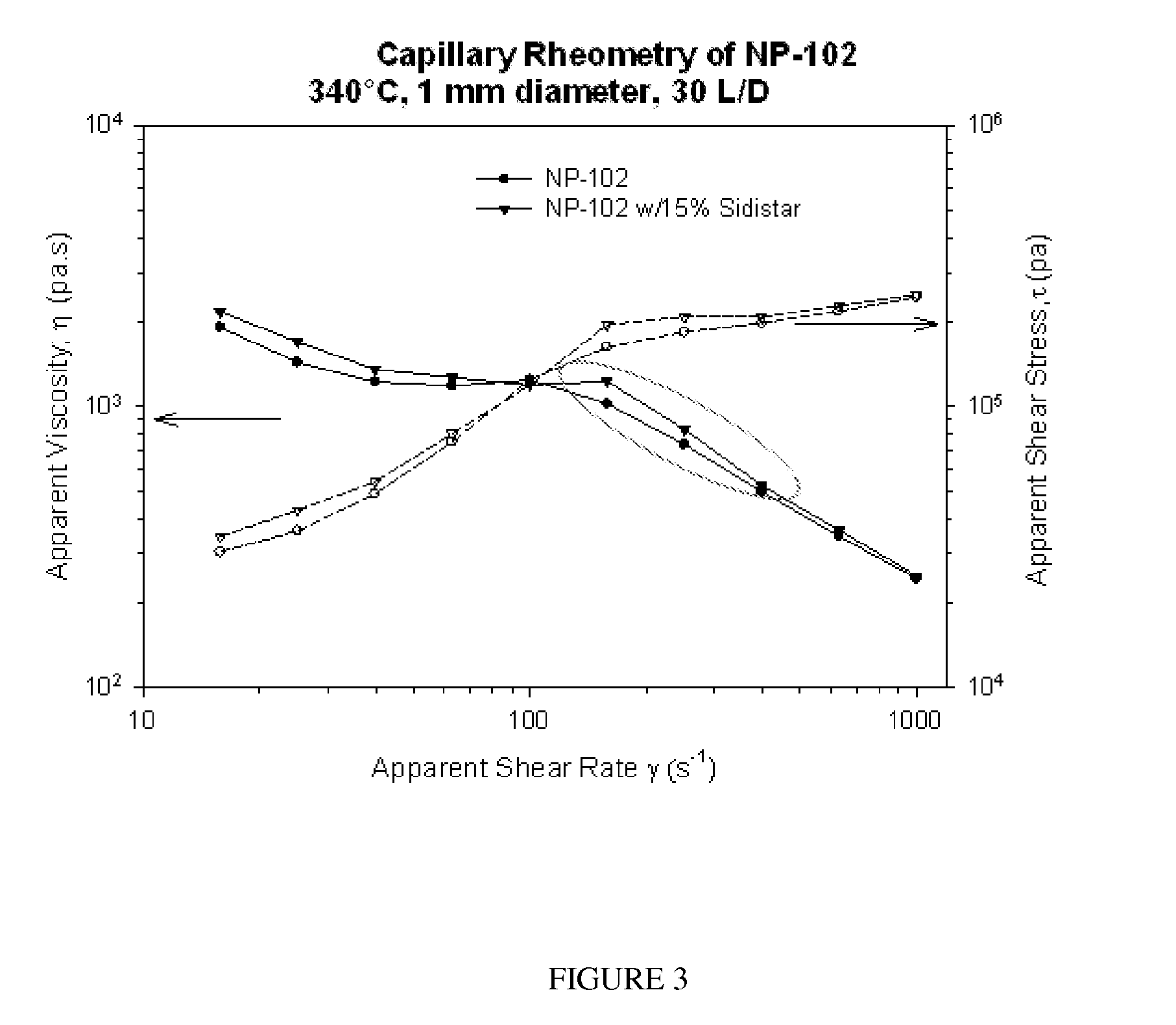

Insulation with micro oxide particles

InactiveUS20110220394A1Improve flame retardant performanceImprove electrical performanceInsulated cablesInsulatorsElectricityOxide

A composite insulation that comprises an insulating material and amorphous micro oxide particles added to the insulating material by at least 1% weight of the composition insulation wherein the micro oxide particles provide at least one of an increase in the flame retardancy of the insulating material, a reduction in smoke generated, and an improvement in the electrical properties of the insulating material.

Owner:GENERAL CABLE TECH CORP

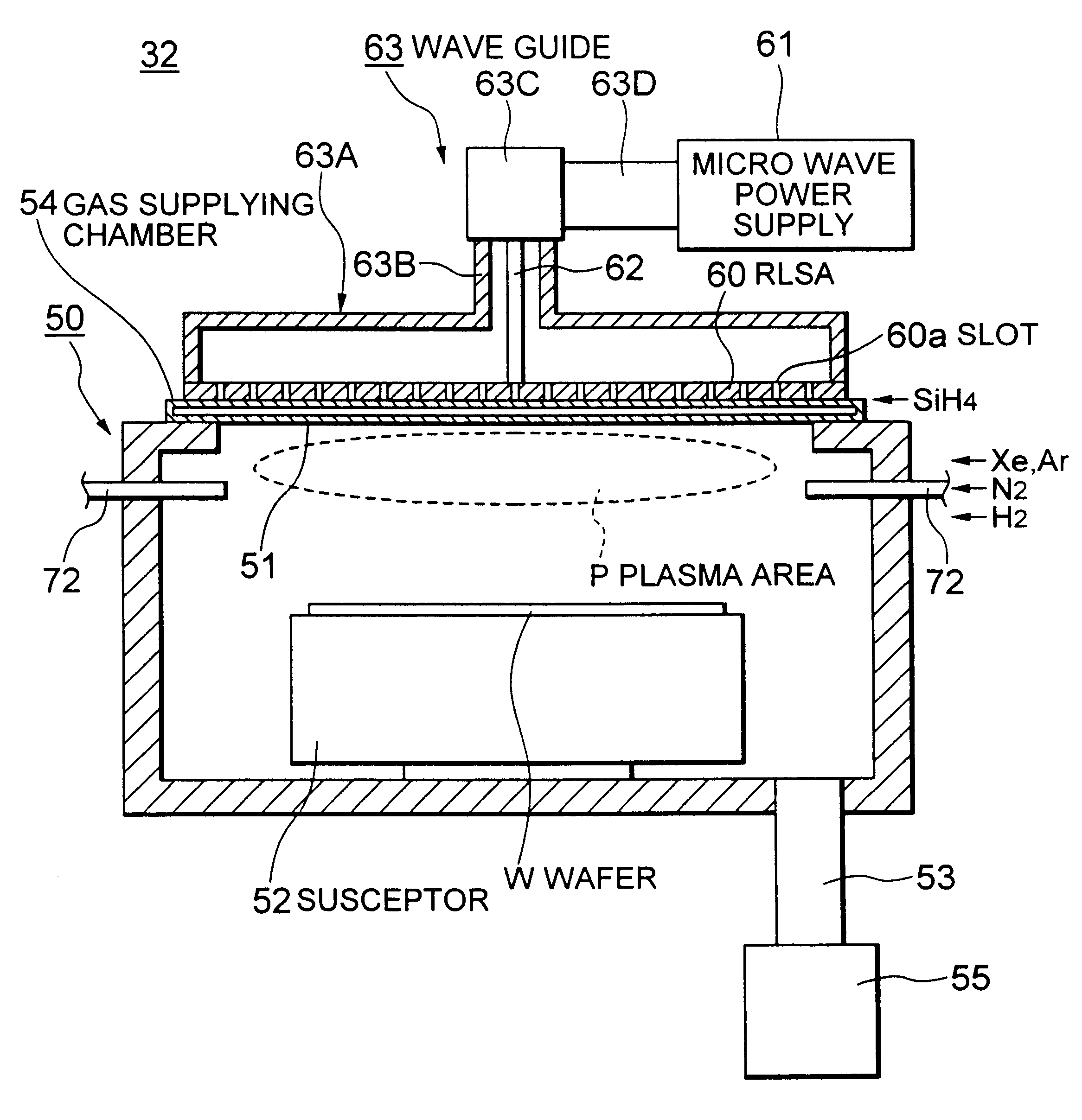

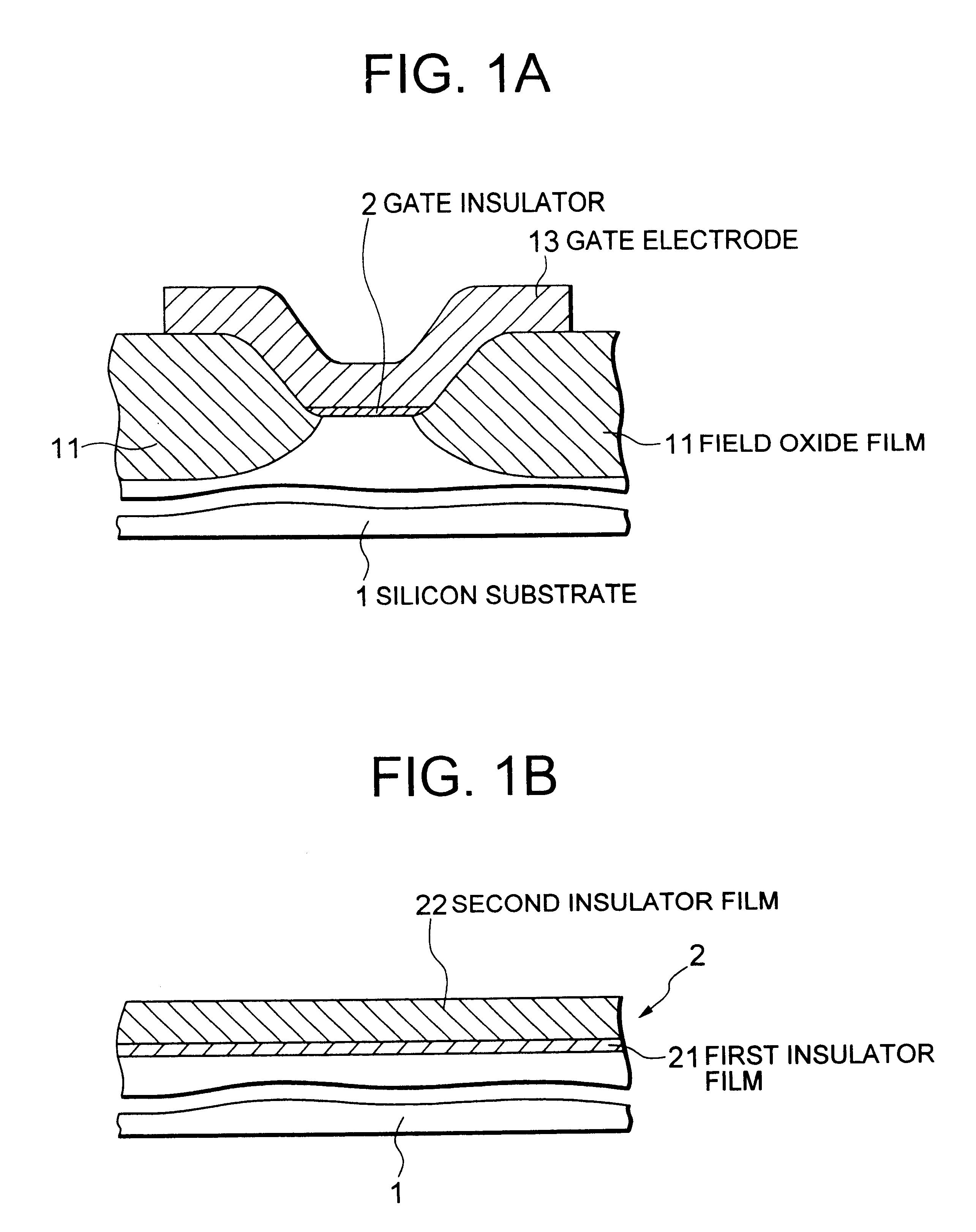

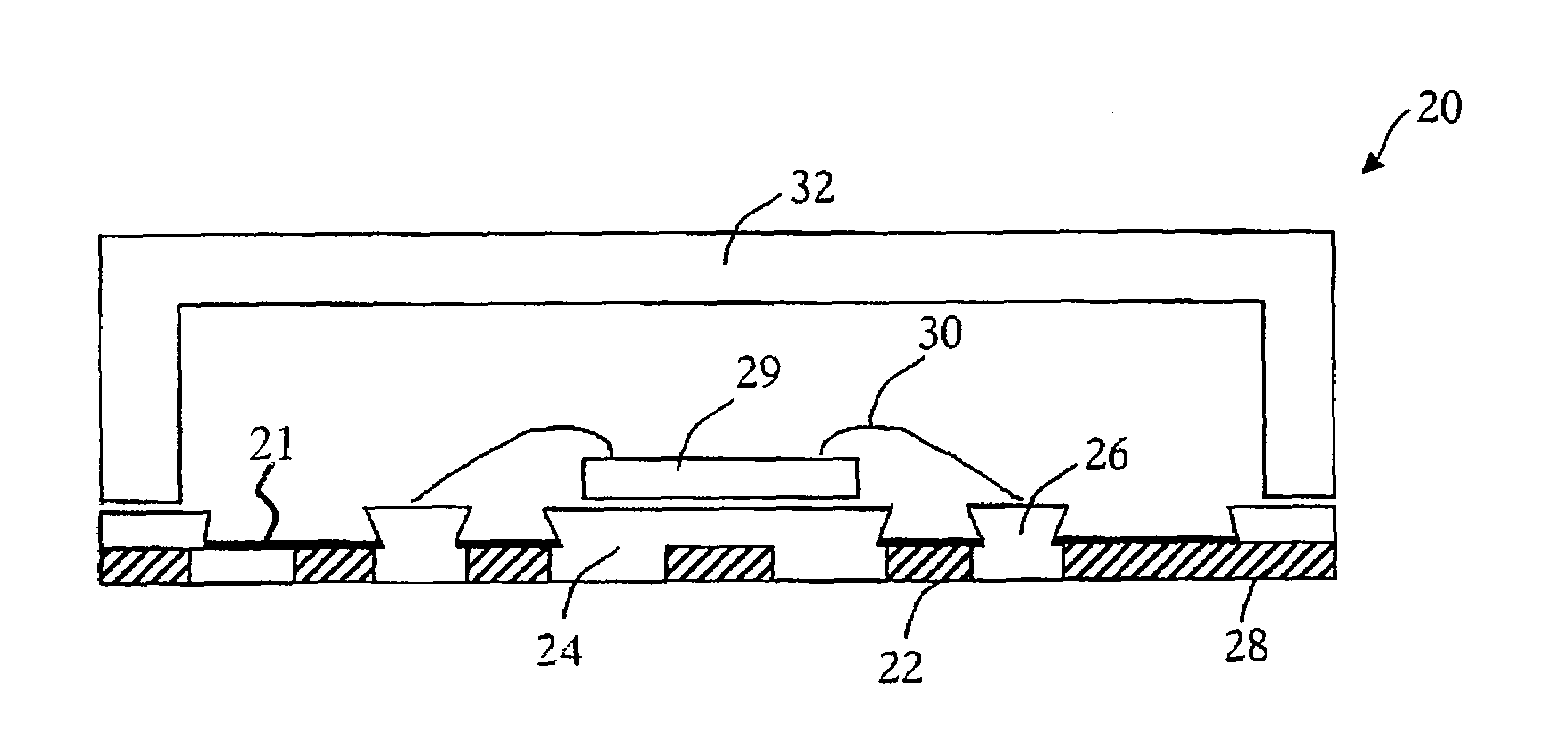

Semiconductor manufacturing method and semiconductor manufacturing apparatus

InactiveUS6399520B1Quality improvementShort timeElectric discharge tubesSemiconductor/solid-state device manufacturingMicrowaveWafering

In an atmosphere of processing gas, on a wafer W consisting mainly of silicon, through a planar-array antenna RLSA 60 having a plurality of slits, microwaves are irradiated to generate plasma containing oxygen, or nitrogen, or oxygen and nitrogen and to implement therewith on the surface of the wafer W direct oxidizing, nitriding, or oxy-nitriding to deposit an insulator film 2 of a thickness of 1 nm or less in terms of oxide film. A manufacturing method and apparatus of semiconductors that can successfully regulate film quality of the interface between a silicon substrate and a SiN film and can form SiN film of high quality in a short time can be obtained.

Owner:TOKYO ELECTRON LTD

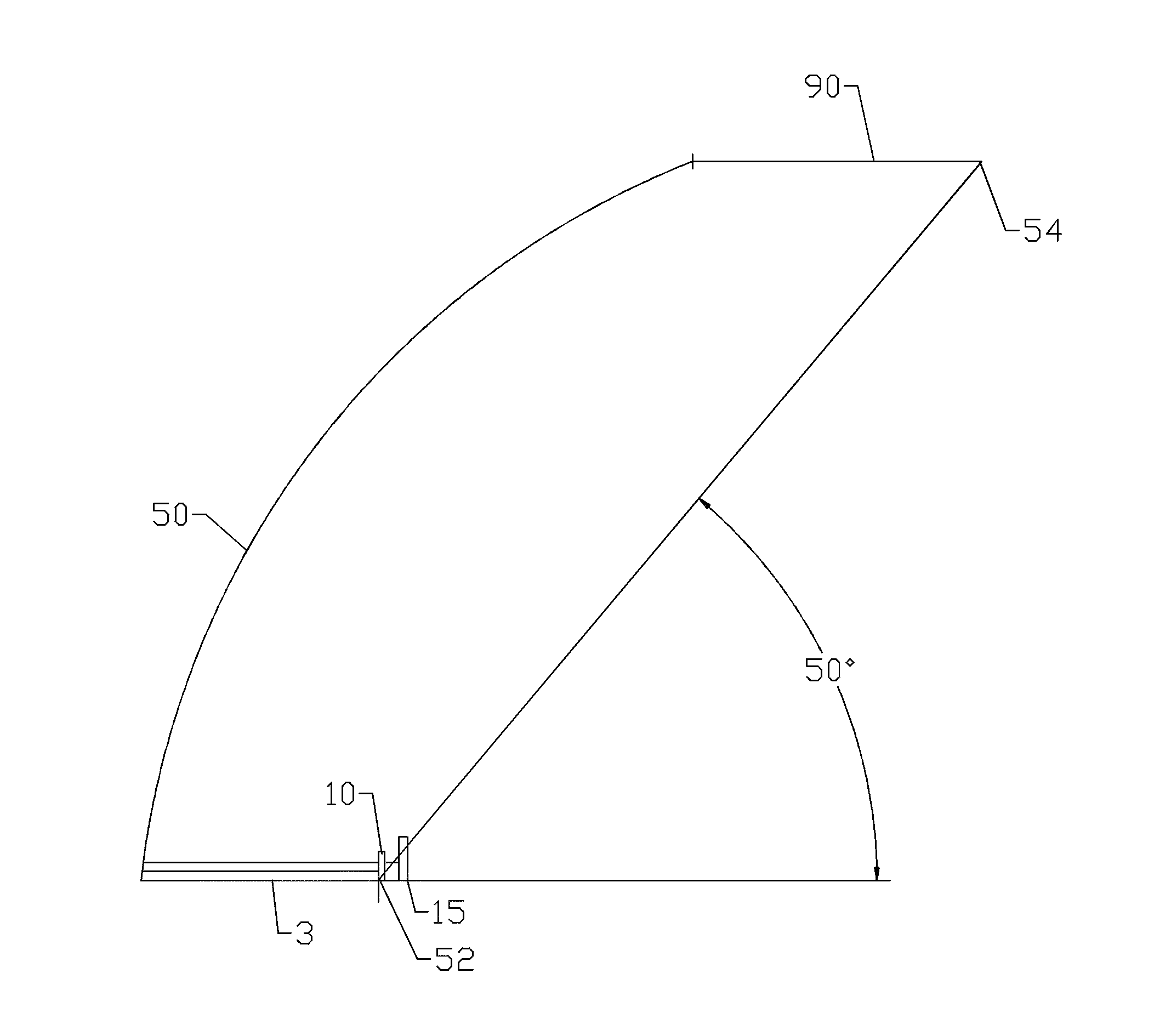

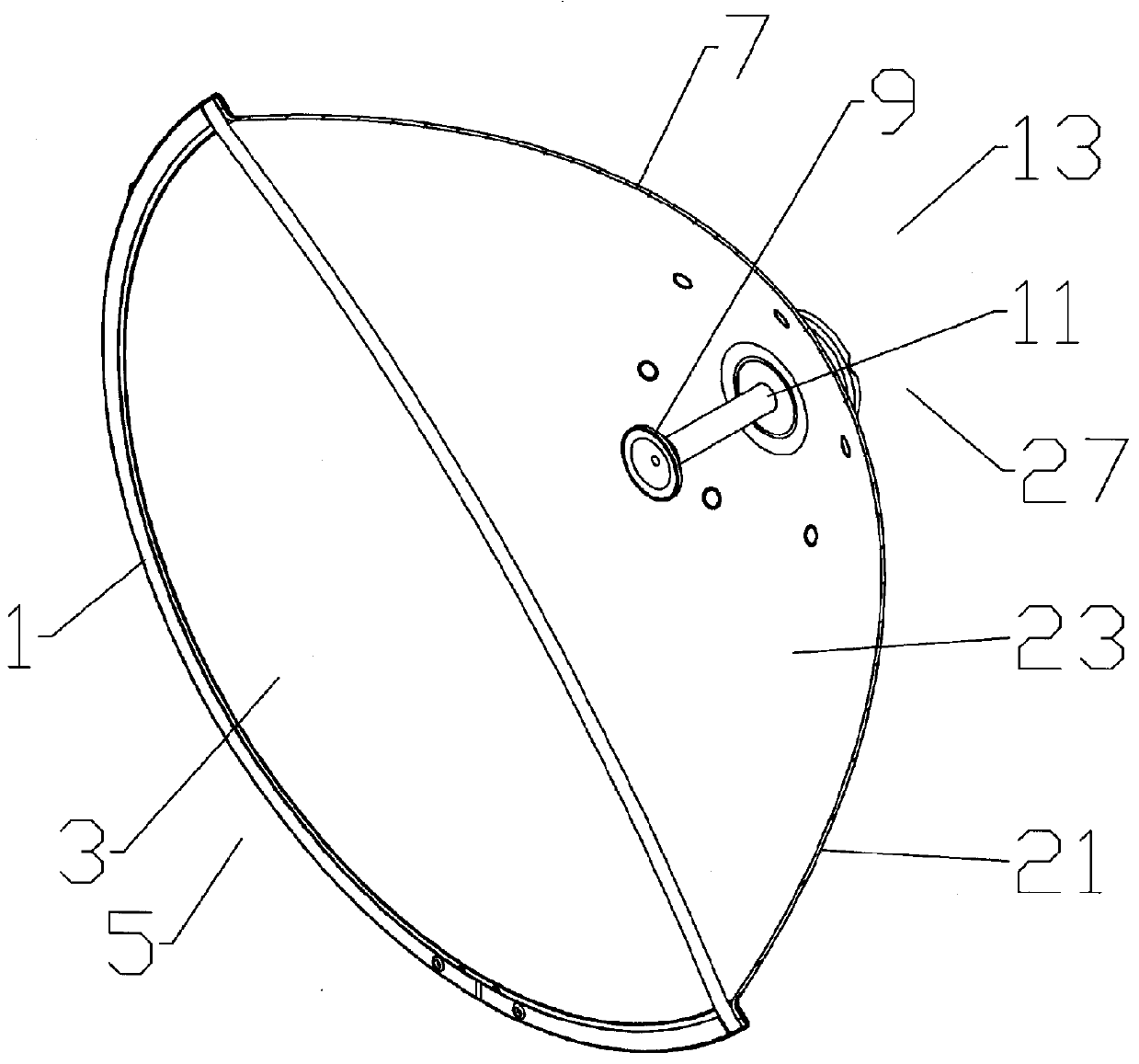

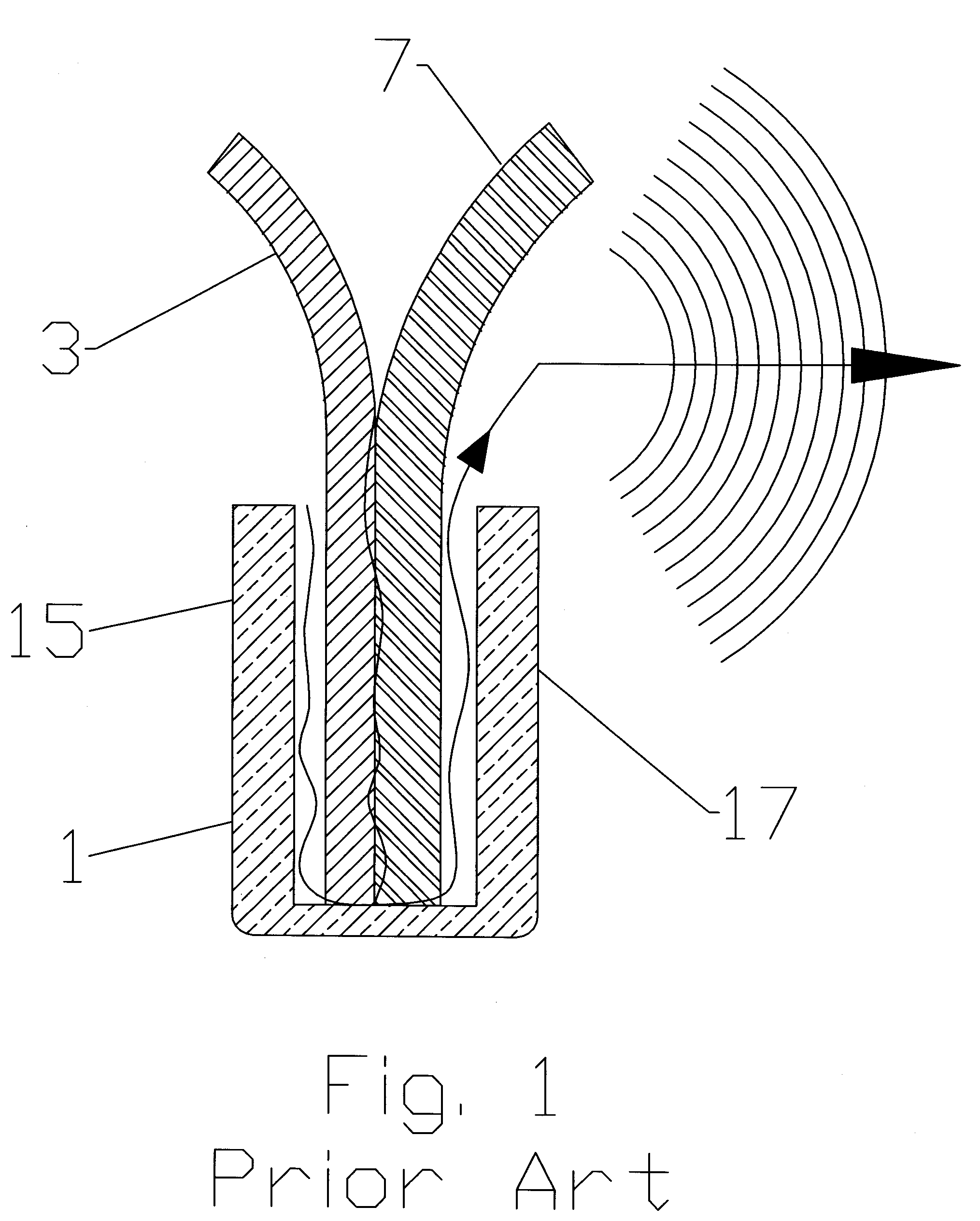

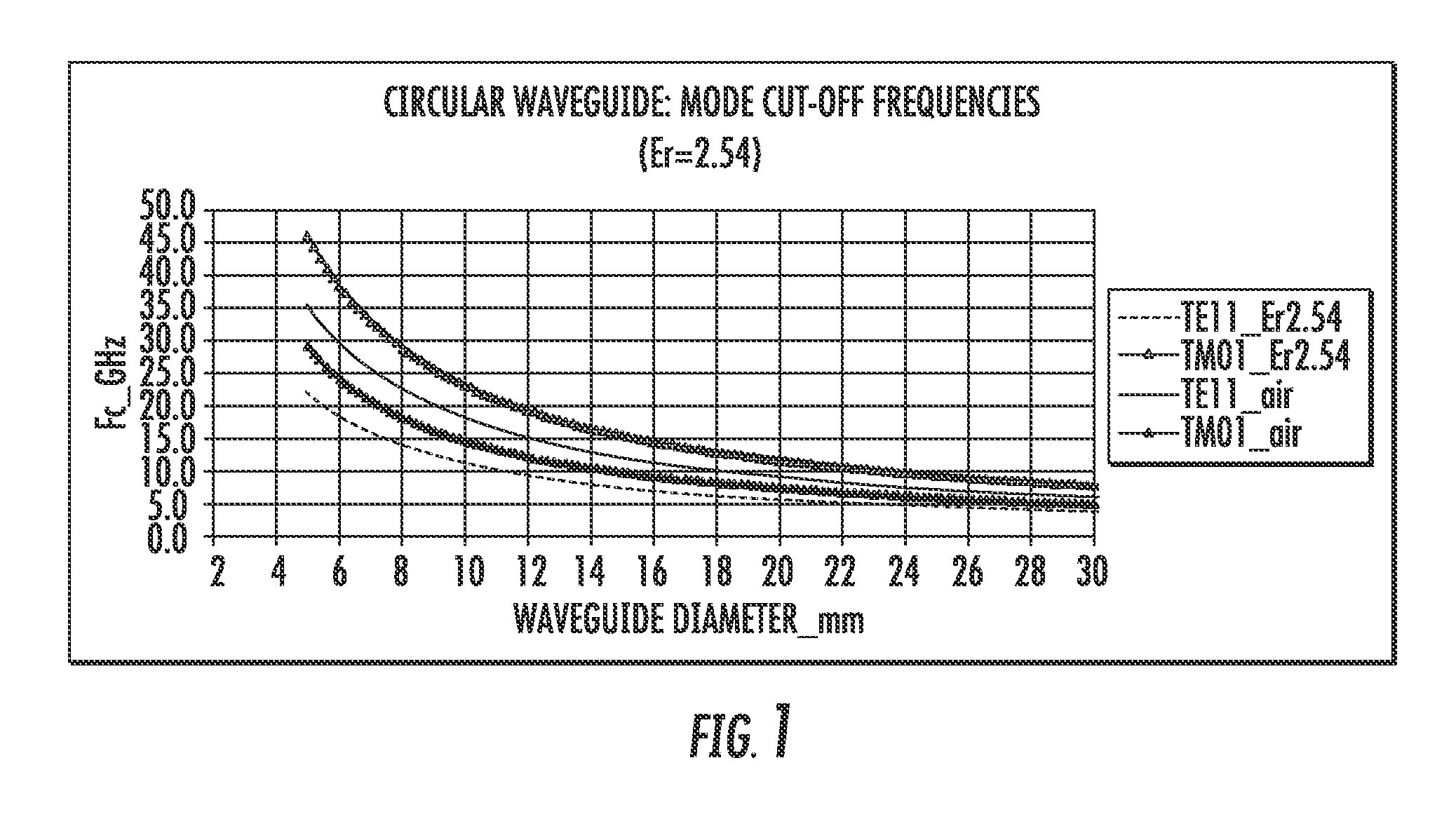

Low sidelobe reflector antenna with shield

ActiveUS9019164B2Area minimizationIncrease in sizeWaveguide hornsRadiating element housingsWaveguidePhysics

A front feed reflector antenna with a dish reflector has a wave guide is coupled to a proximal end of the dish reflector, projecting into the dish reflector along a longitudinal axis. A dielectric block may be coupled to a distal end of the waveguide and a sub-reflector coupled to a distal end of the dielectric block. A shield is coupled to the periphery of the dish reflector. A subtended angle between the longitudinal axis and a line between the focal point and a distal periphery of the shield is 50 degrees or less.

Owner:COMMSCOPE TECH LLC

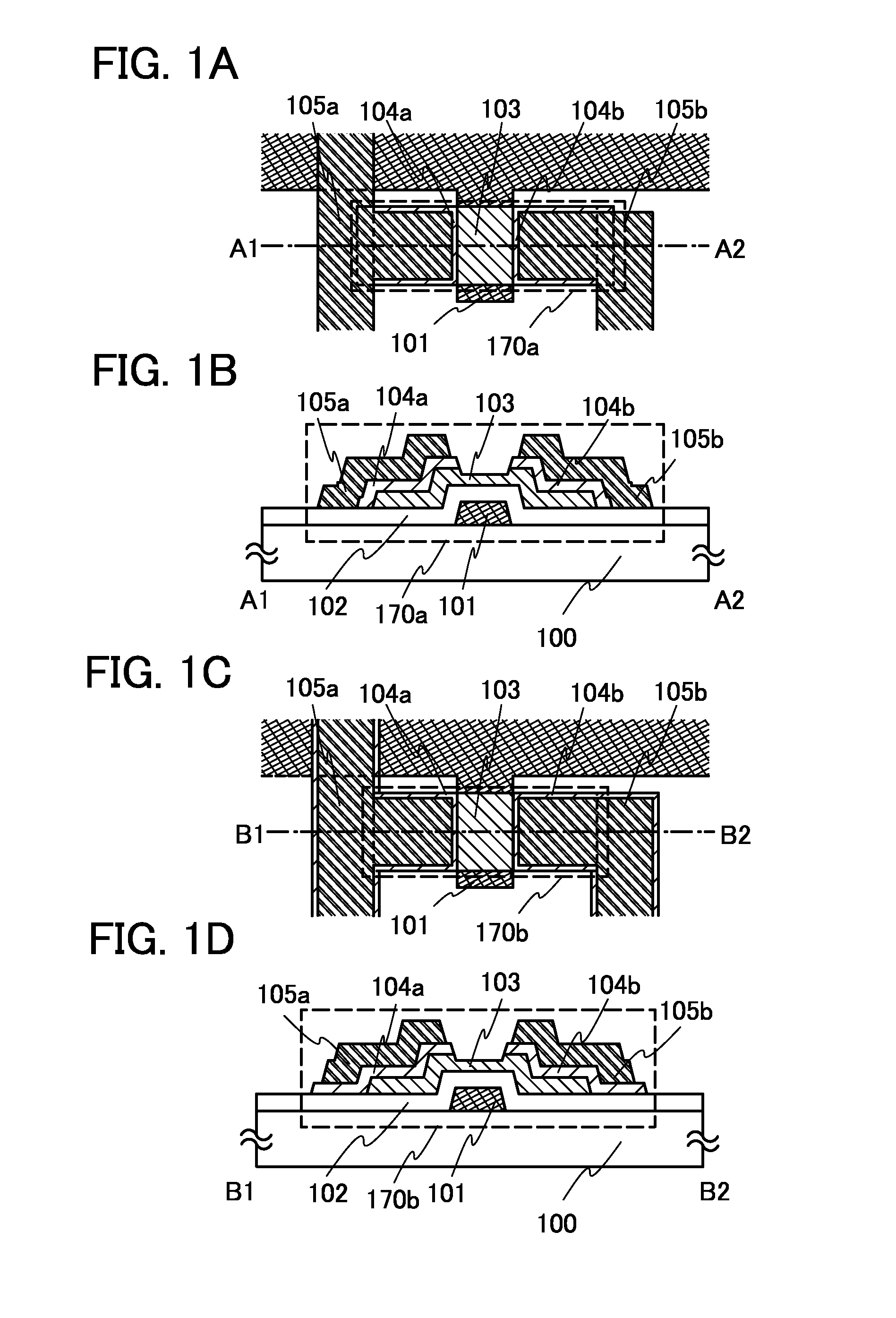

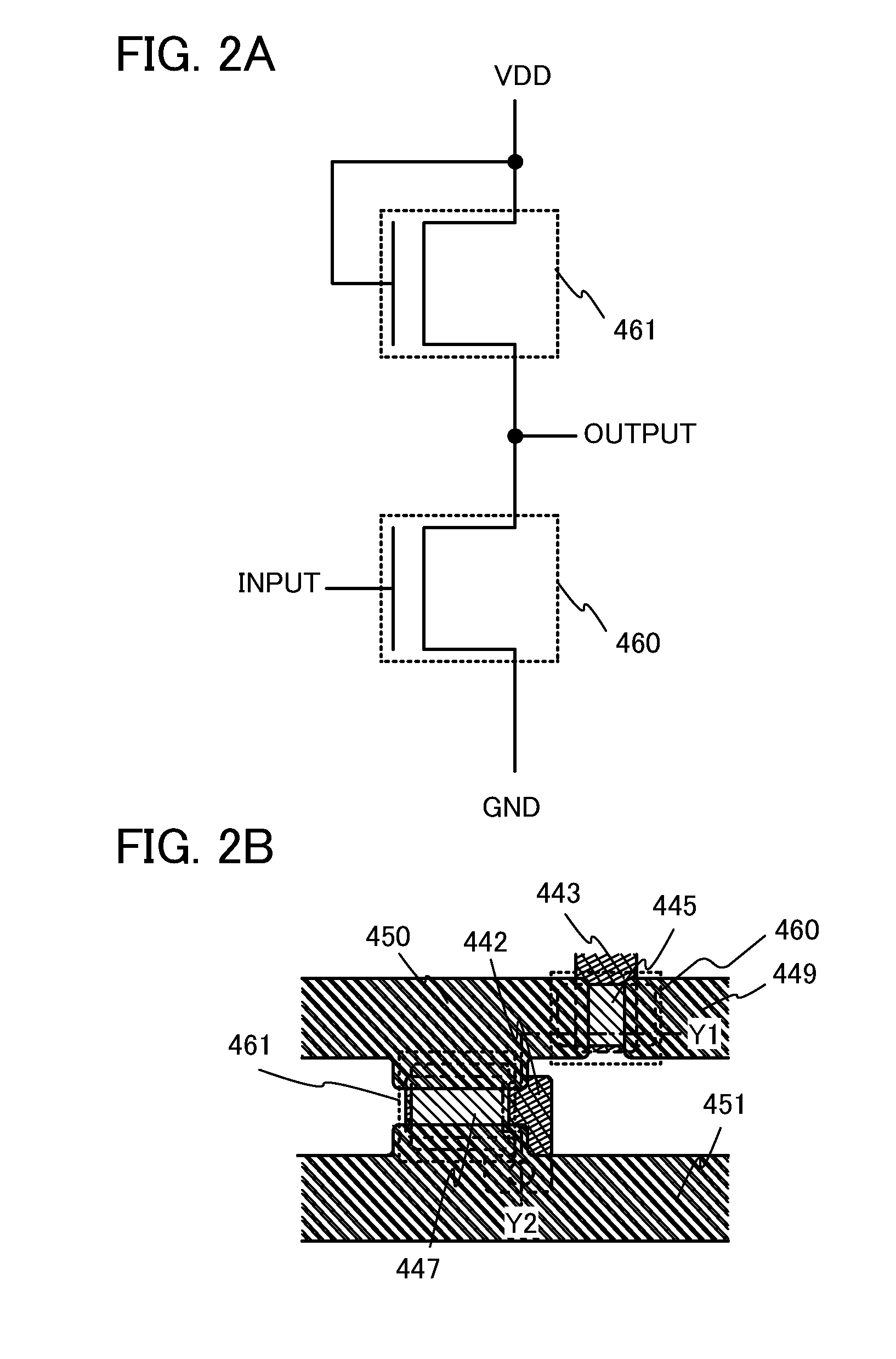

Semiconductor device and method for manufacturing the same

ActiveUS20100025679A1Small currentHigh on-off ratioStatic indicating devicesSolid-state devicesOhmic contactCharge carrier

An embodiment is to include an inverted staggered (bottom gate structure) thin film transistor in which an oxide semiconductor film containing In, Ga, and Zn is used as a semiconductor layer and a buffer layer is provided between the semiconductor layer and a source and drain electrode layers. The buffer layer having higher carrier concentration than the semiconductor layer is provided intentionally between the source and drain electrode layers and the semiconductor layer, whereby an ohmic contact is formed.

Owner:SEMICON ENERGY LAB CO LTD

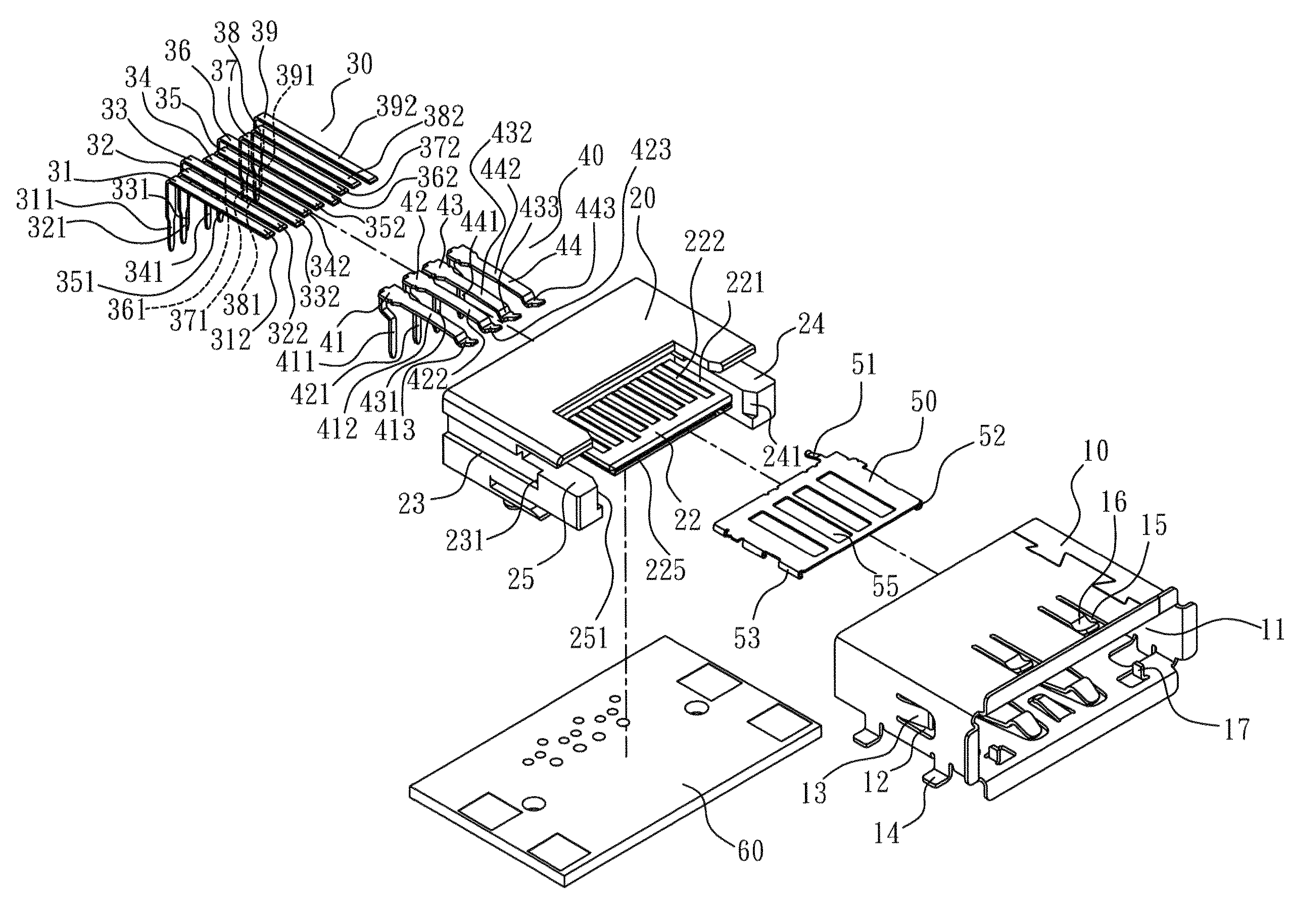

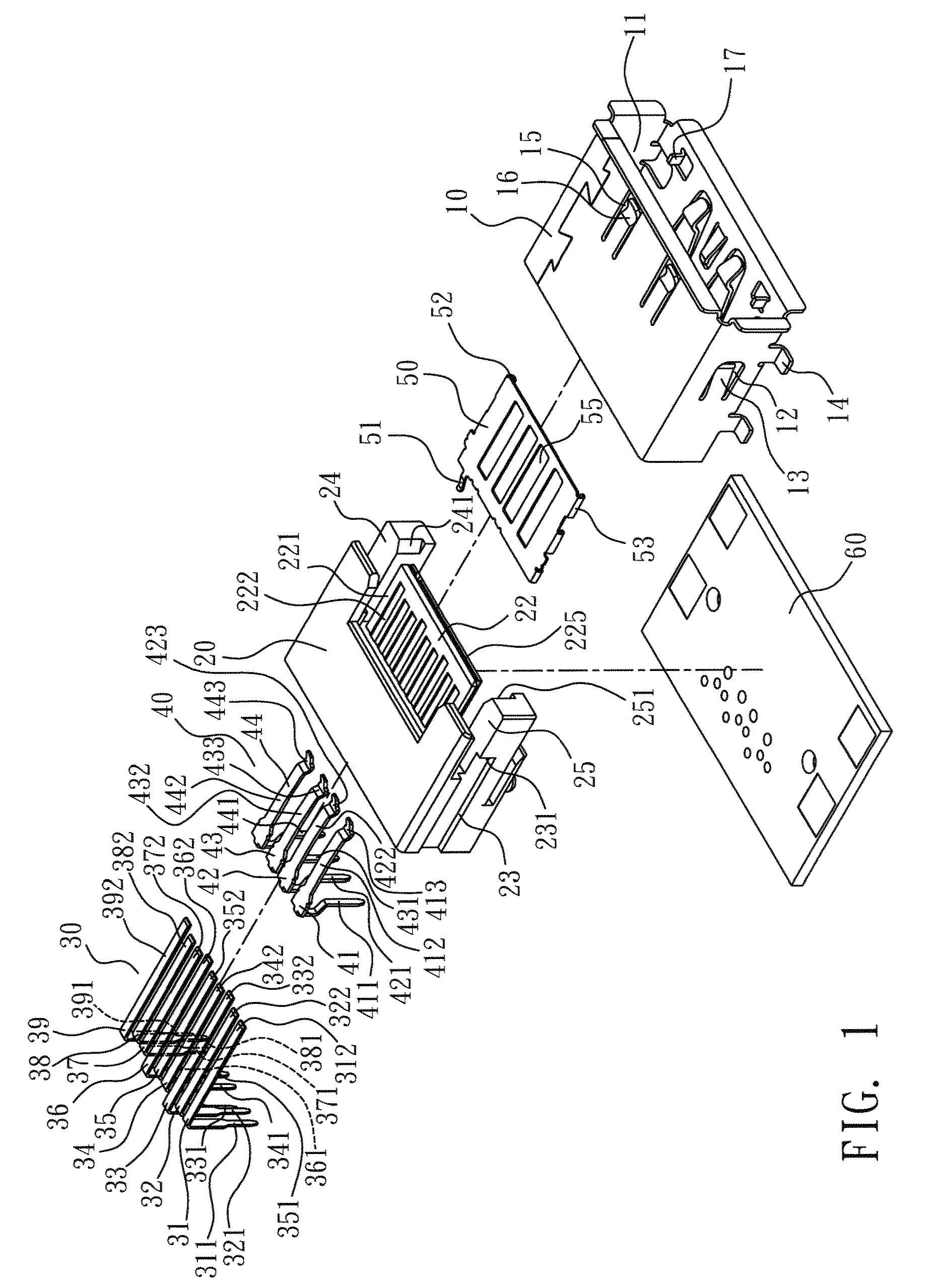

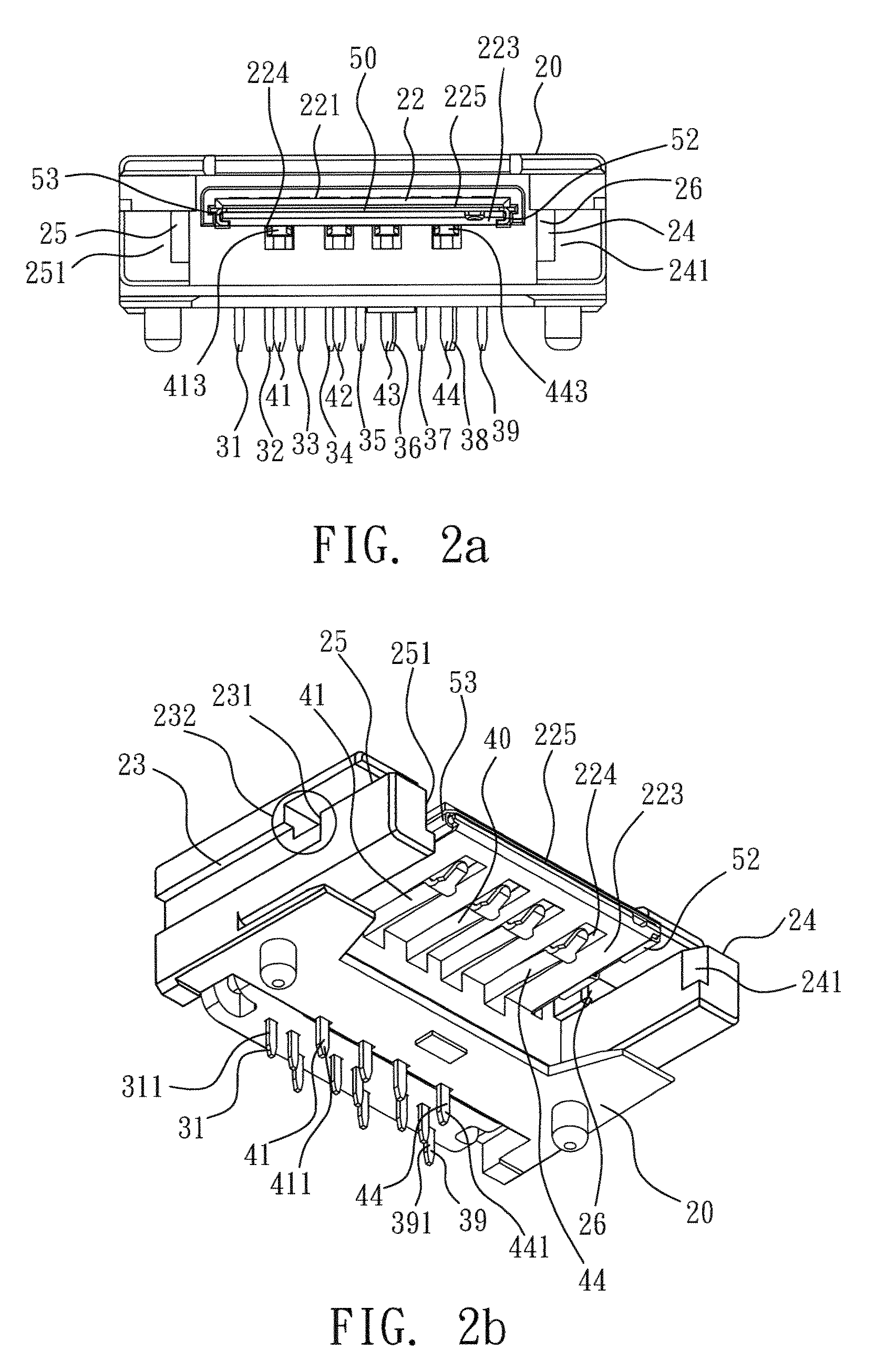

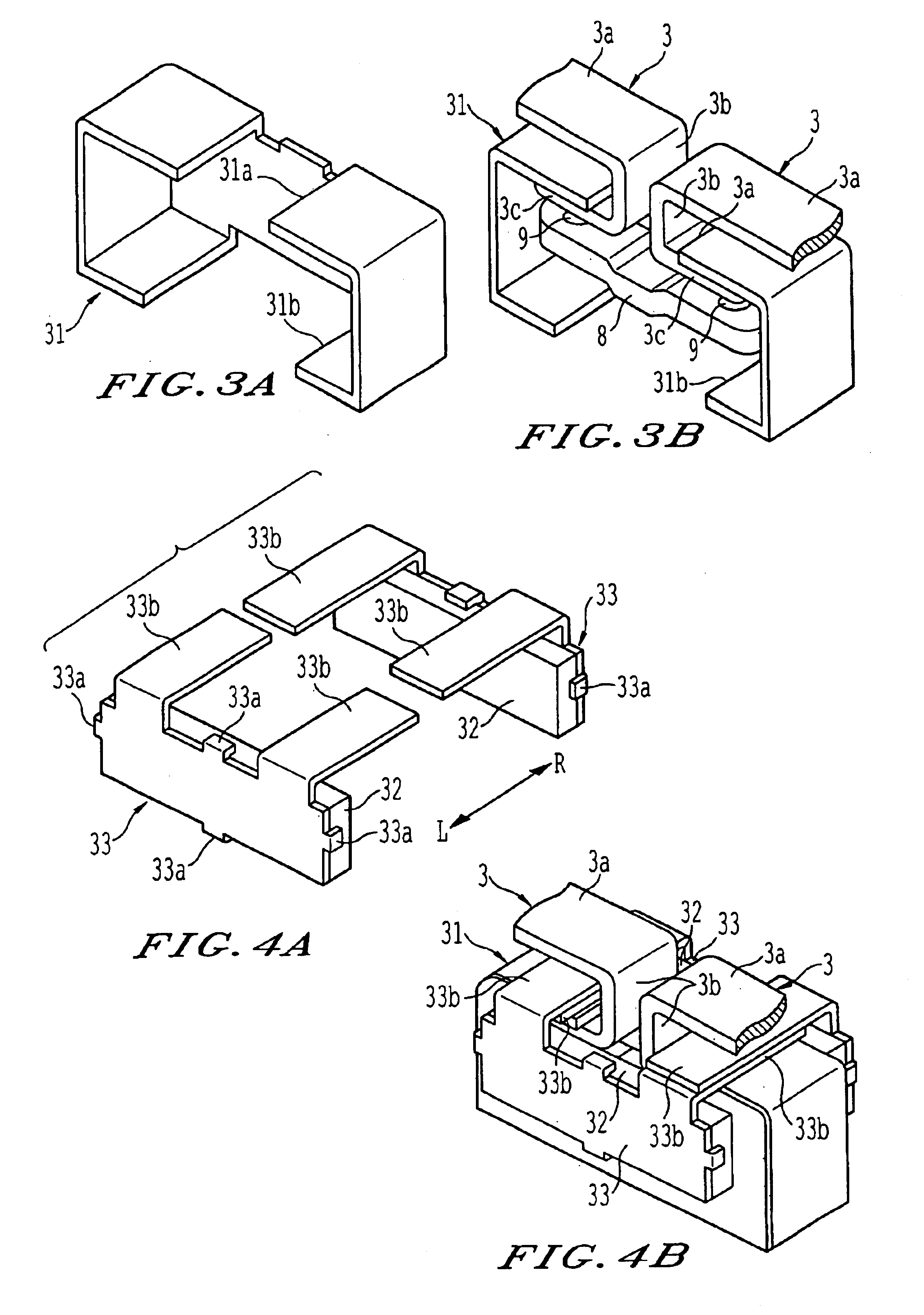

Electrical connector with first and second terminal assemblies

InactiveUS7758379B2Big spaceLow costElectric discharge tubesTwo-part coupling devicesEngineeringElectrical connector

The present invention discloses an electrical connector comprising: a housing; a base body having a tongue, whose one surface is disposed with a plurality of first terminal slots and whose other surface is disposed with a plurality of second terminal slots; a first terminal assembly whose each first terminal is disposed with a leg and a contact portion perpendicular to the leg, respectively, with the legs being alternately arranged; and a second terminal assembly whose each second terminal is disposed with a leg and a contact portion perpendicular to the leg and then bending downward, respectively. For the first terminal assembly the legs of every third terminal are offset from the remaining ones. The terminals of one assembly may be e-SATA type and those of the other assembly may be USB type.

Owner:WONTEN TECH

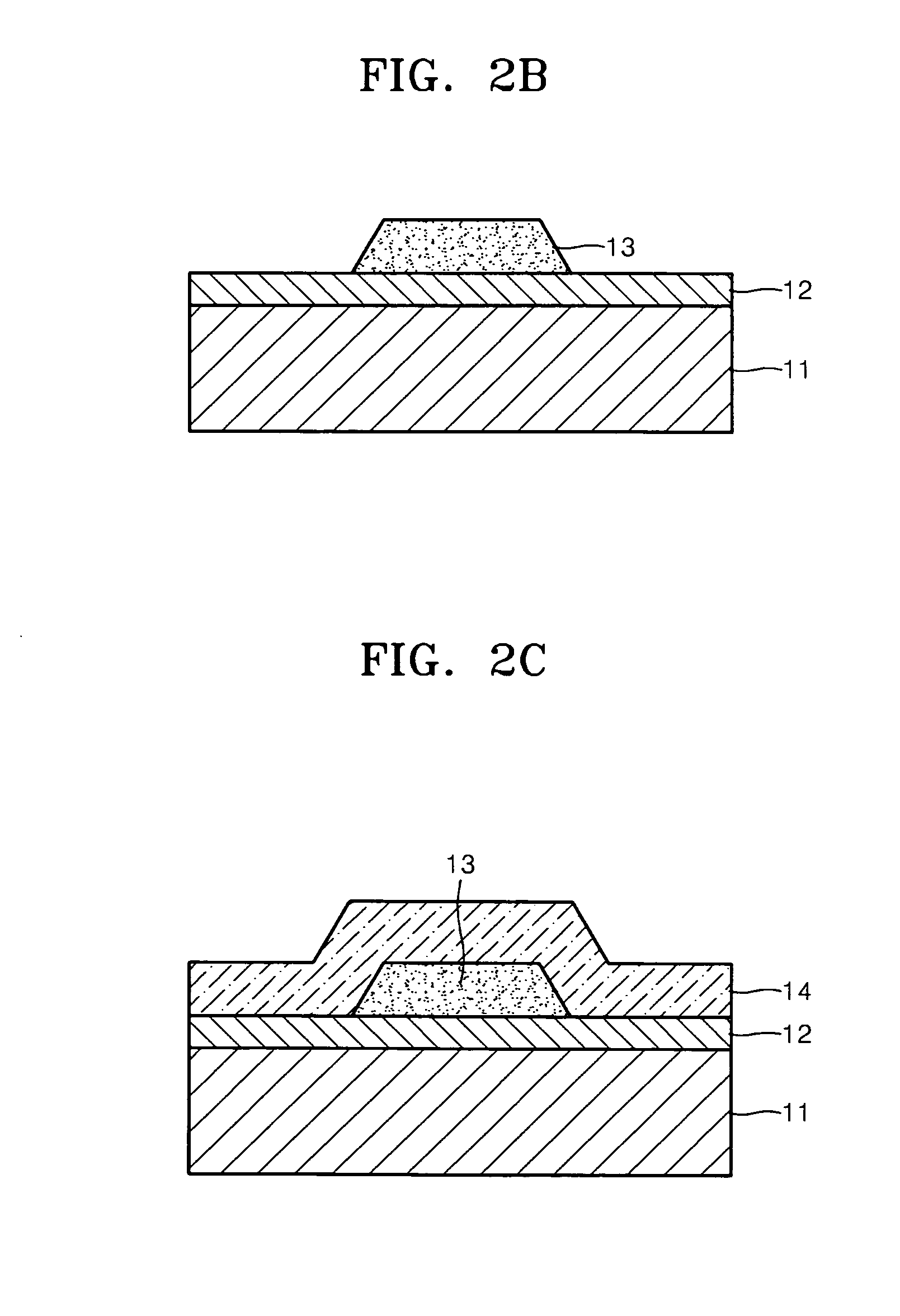

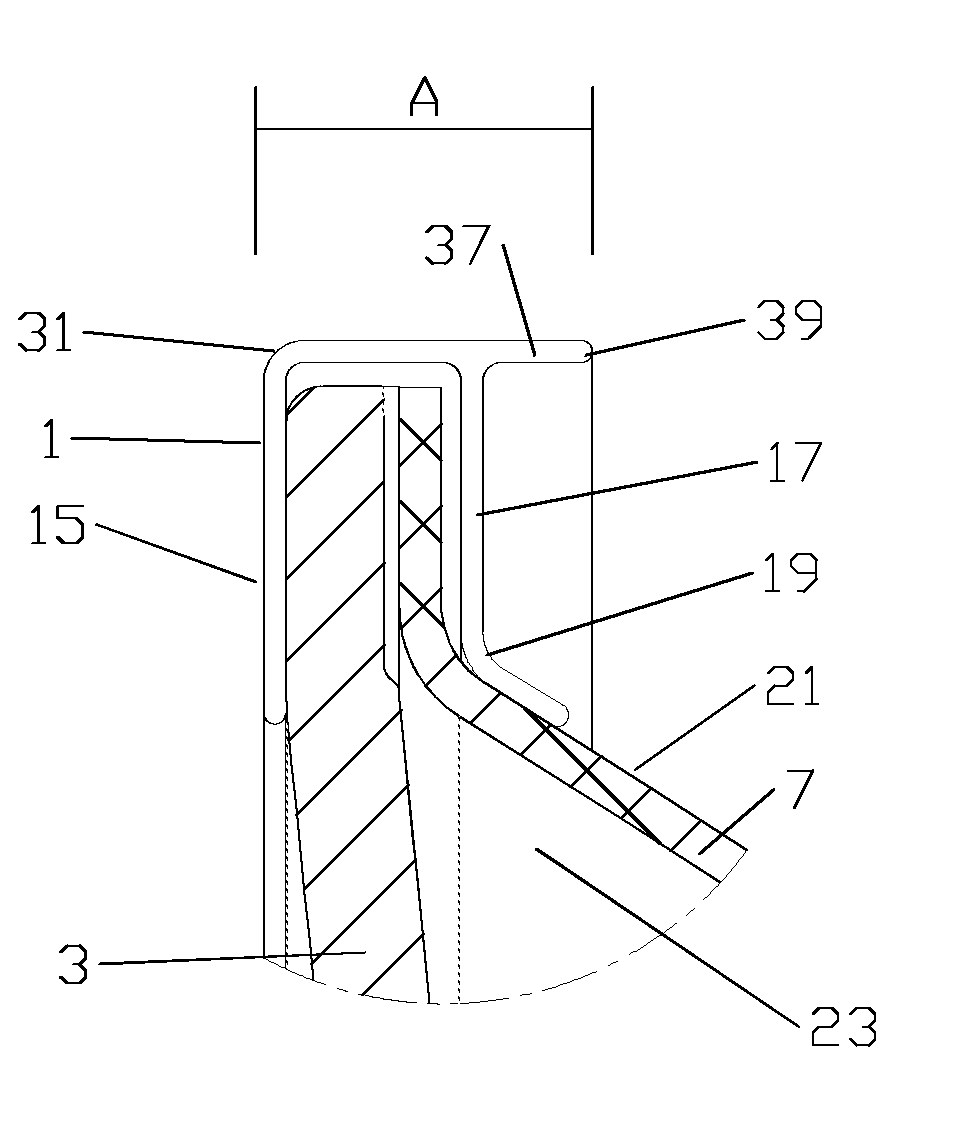

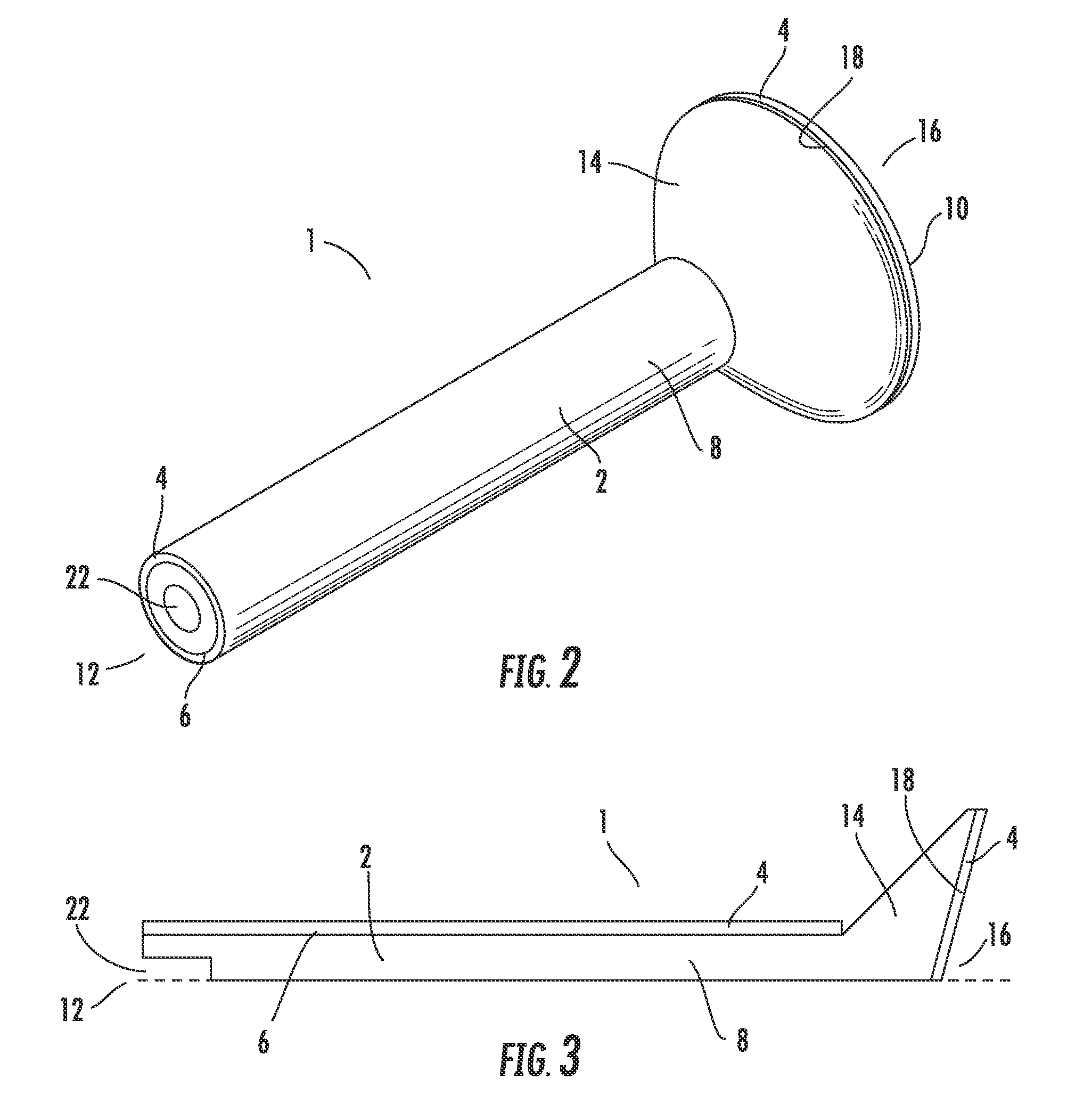

Reflector antenna radome attachment band clamp

A band clamp for coupling a radome to a distal end of a reflector dish for improving the front to back ratio of a reflector antenna, the band clamp provided with an inward projecting proximal lip and an inward projecting distal lip. The distal lip dimensioned with an inner diameter equal to or less than a reflector aperture of the reflector dish. The proximal lip provided with a turnback region dimensioned to engage an outer surface of a signal area of the reflector dish in an interference fit. A width of the band clamp may be dimensioned, for example, between 0.8 and 1.5 wavelengths of an operating frequency.

Owner:COMMSCOPE TECH LLC

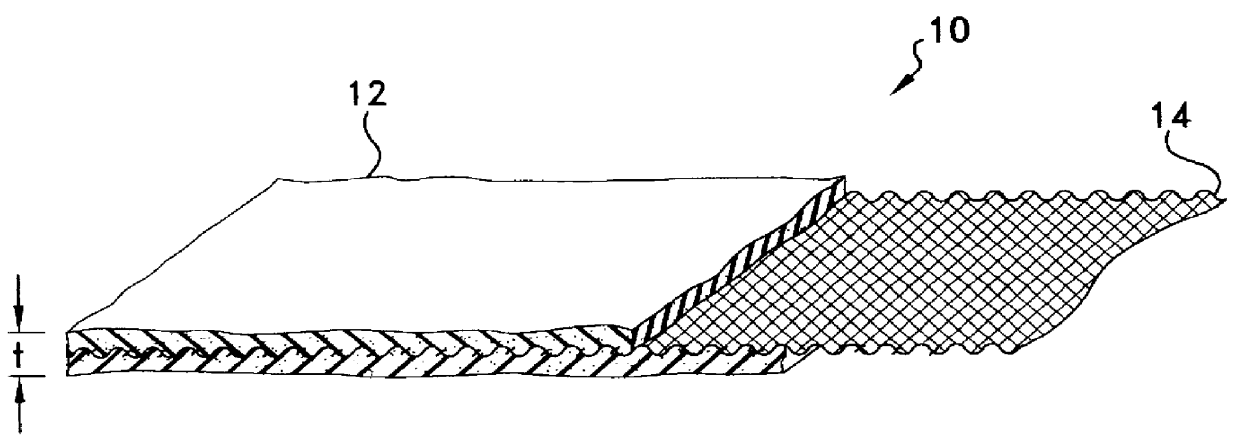

High dielectric strength thermal interface material

InactiveUS6096414AImprove performanceMaintain good propertiesOther chemical processesSynthetic resin layered productsThermal conductivityThermal transmittance

A thermally-conductive, electrically insulative interface for conductively cooling a heat-generating source, such as an electronic component, having an associated thermal dissipation member such as a heat sink. The interface is provided as a cured sheet of a curable material formulated as a blend of a curable silicone binder, and a particulate alumina, i.e., aluminum oxide (Al2O3), filler. The interface is observed to exhibit a thermal conductivity of at least about 0.8 W / m-K and a wet dielectric breakdown strength of at least about 475 Vac / mil.

Owner:PARKER INTANGIBLES LLC

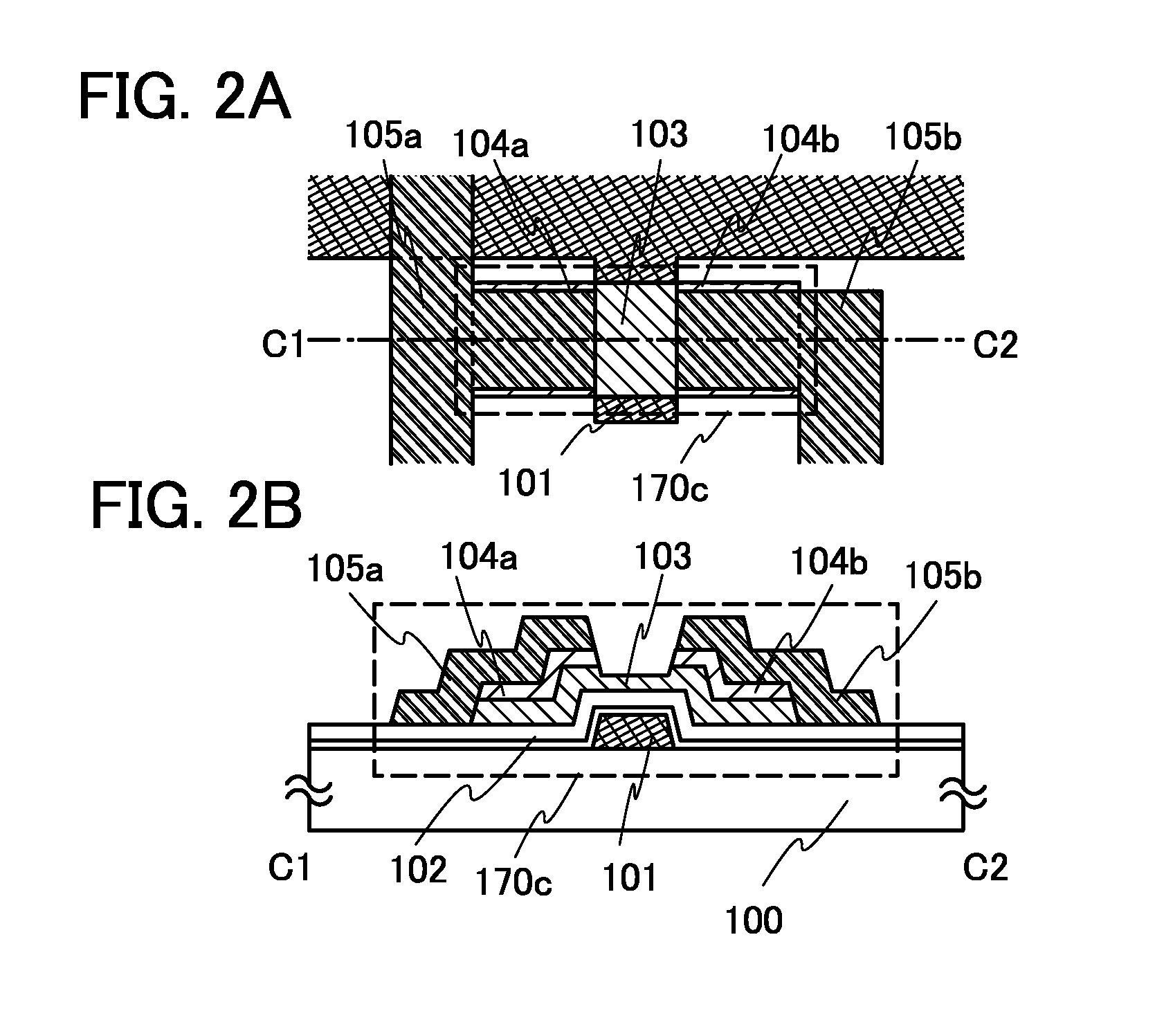

Display device

ActiveUS20100084651A1Reduce manufacturing costReduce areaSolid-state devicesNon-linear opticsDriver circuitDisplay device

With an increase in the definition of a display device, the number of pixels is increased, and thus the numbers of gate lines and signal lines are increased. Due to the increase in the numbers of gate lines and signal lines, it is difficult to mount an IC chip having a driver circuit for driving the gate and signal lines by bonding or the like, which causes an increase in manufacturing costs. A pixel portion and a driver circuit for driving the pixel portion are formed over one substrate. At least a part of the driver circuit is formed using an inverted staggered thin film transistor in which an oxide semiconductor is used. The driver circuit as well as the pixel portion is provided over the same substrate, whereby manufacturing costs are reduced.

Owner:SEMICON ENERGY LAB CO LTD

Radome attachment band clamp

ActiveUS9083083B2RF leakageClamp firmlyPretreated surfacesRadiating element housingsInterference fitElectrical performance

Owner:COMMSCOPE TECH LLC

Fluted anode with minimal density gradients and capacitor comprising same

InactiveUS7116548B2Improve consistencyImprove electrical performanceSolid electrolytic capacitorsLiquid electrolytic capacitorsCapacitorPhysics

Owner:KEMET ELECTRONICS CORP

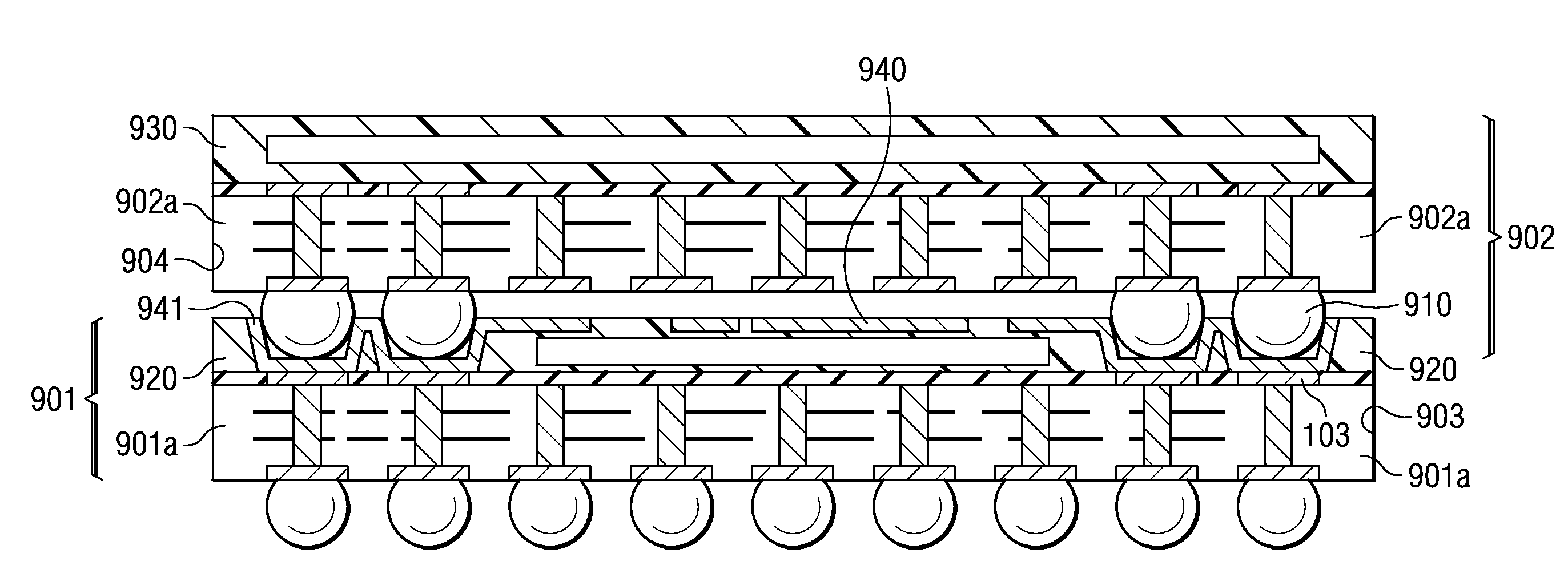

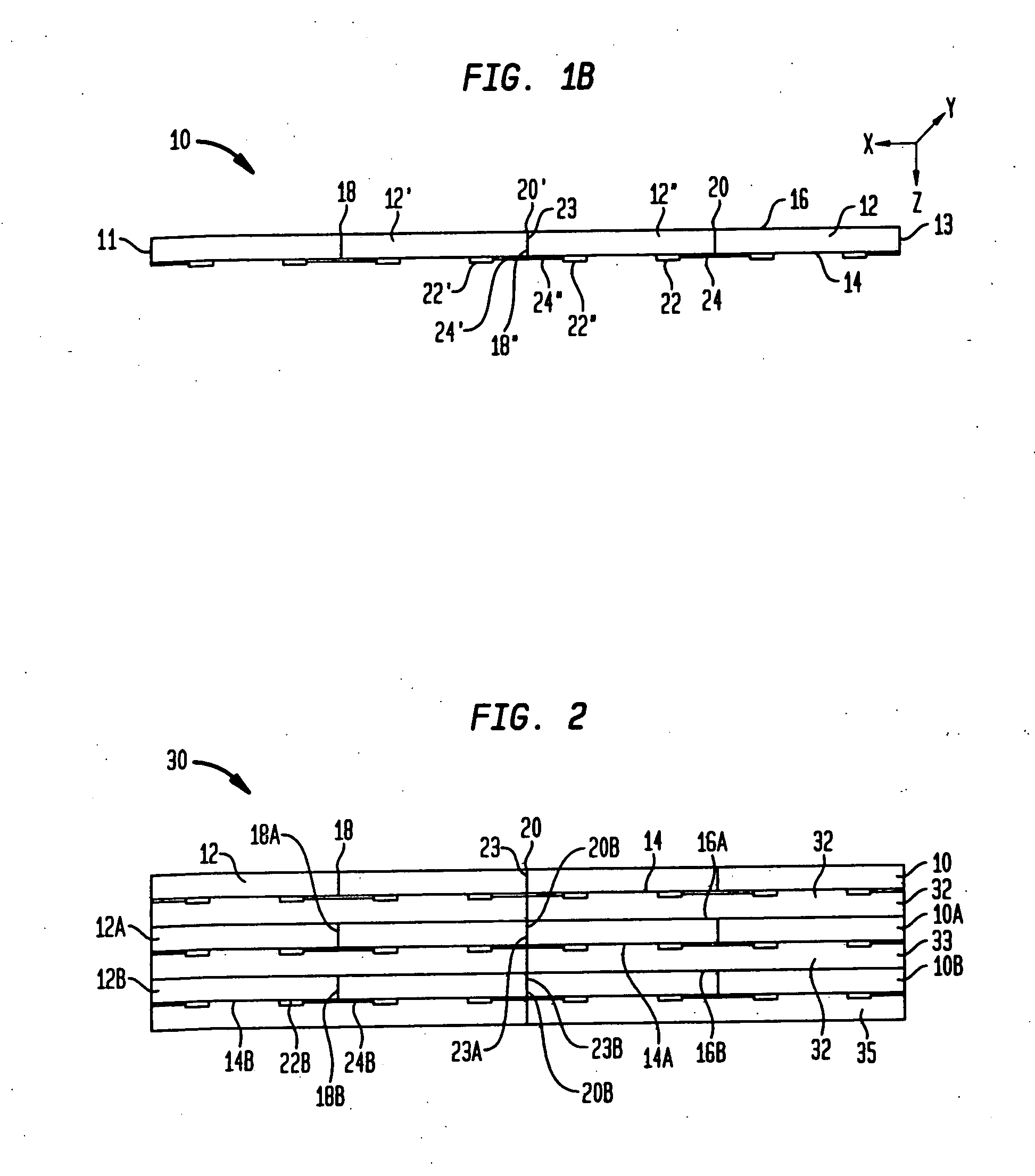

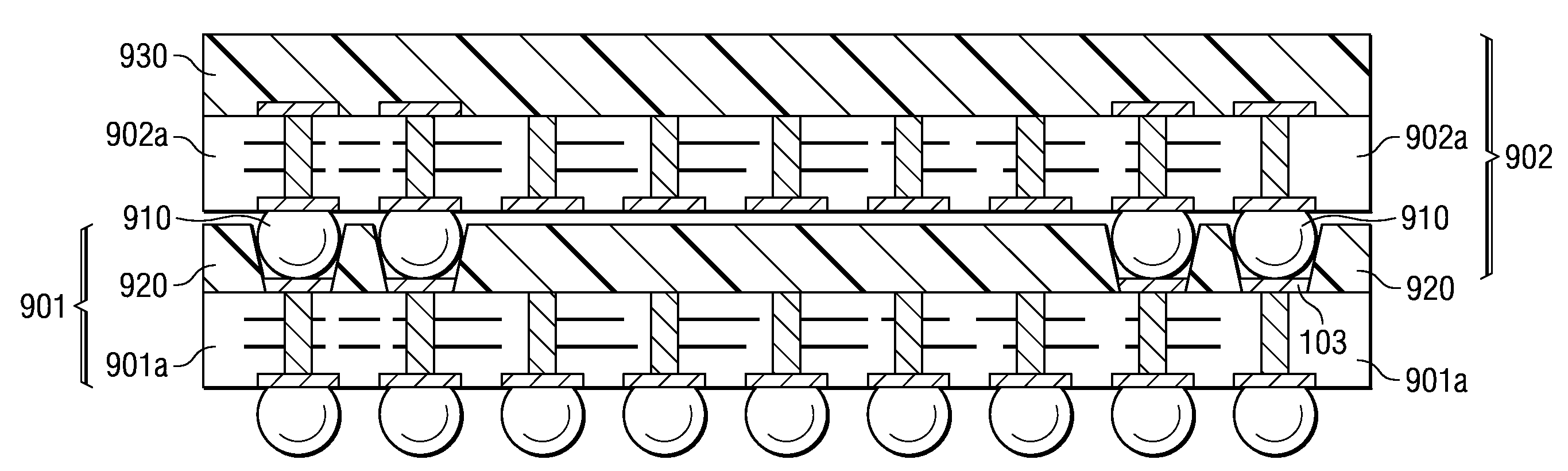

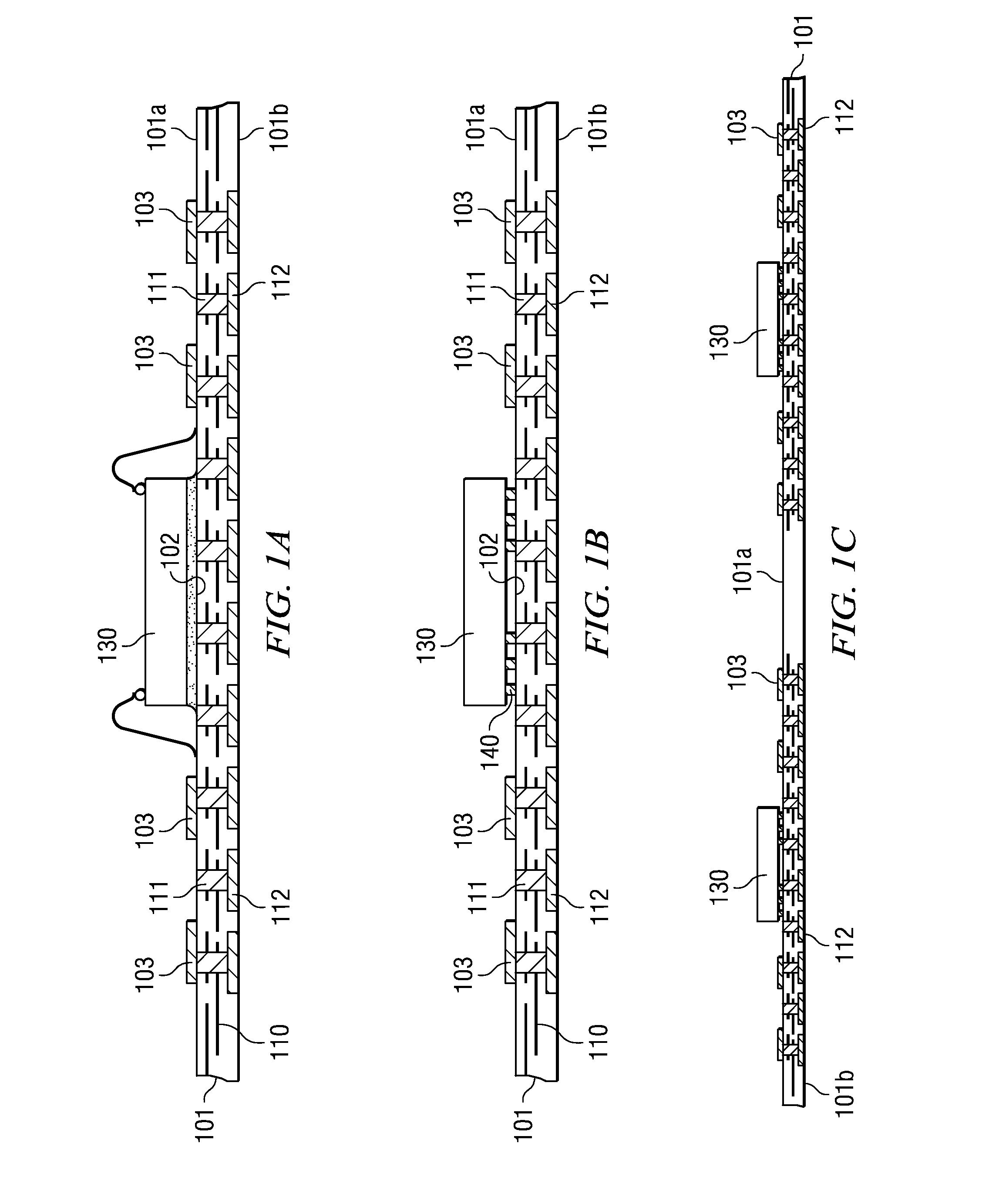

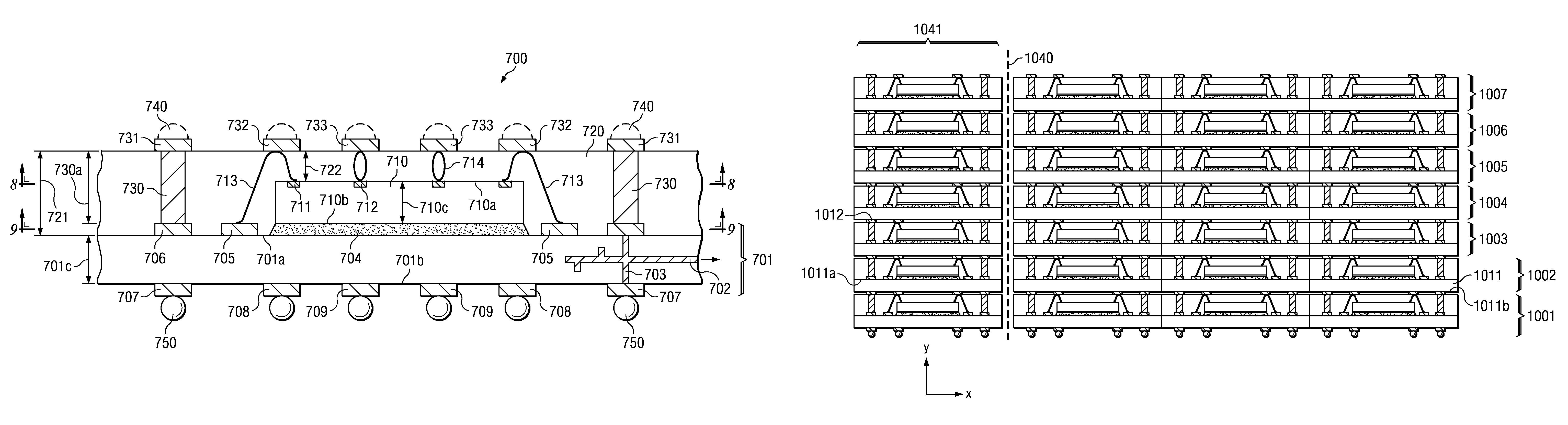

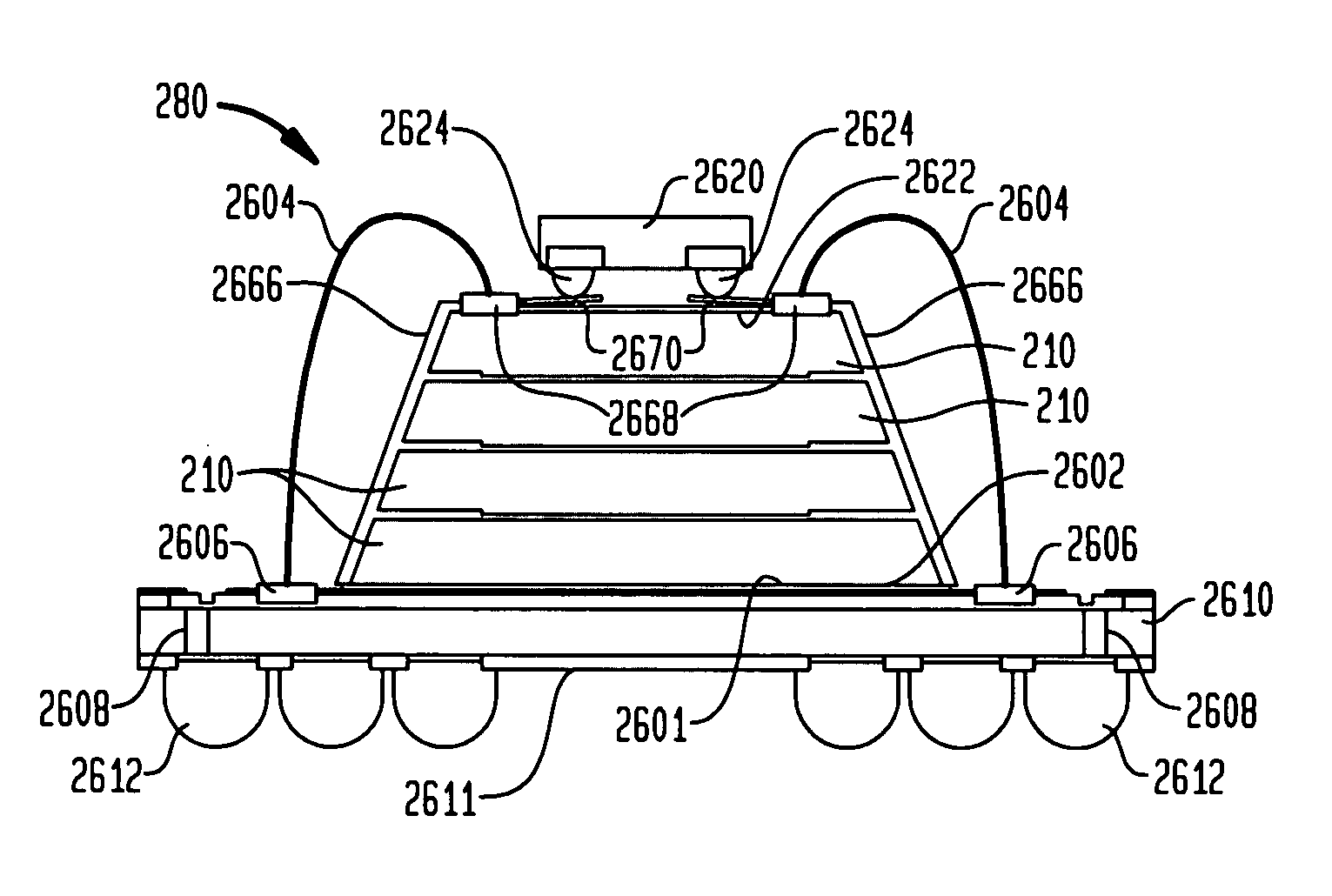

Array molded package-on-package having redistribution lines

ActiveUS20080315385A1Shorten the time to marketSimple methodSemiconductor/solid-state device detailsSolid-state devicesContact padCoupling

A semiconductor device with a sheet-like insulating substrate (101) integral with two or more patterned layers of conductive lines and vias, a chip attached to an assembly site, and contact pads (103) in pad locations has an encapsulated region on the top surface of the substrate, extending to the edge of the substrate, enclosing the chip, and having contact apertures (703) at the pad locations for external communication with the pad metal surfaces. The apertures may have not-smooth sidewall surfaces and may be filled with solder material (704) to contact the pads. Metal-filled surface grooves (710) in the encapsulated region, with smooth groove bottom and sidewalls, are selected to serve as customized routing interconnections, or redistribution lines, between selected apertures and thus to facilitate the coupling with another semiconductor device to form a package-on-package assembly.

Owner:TEXAS INSTR INC

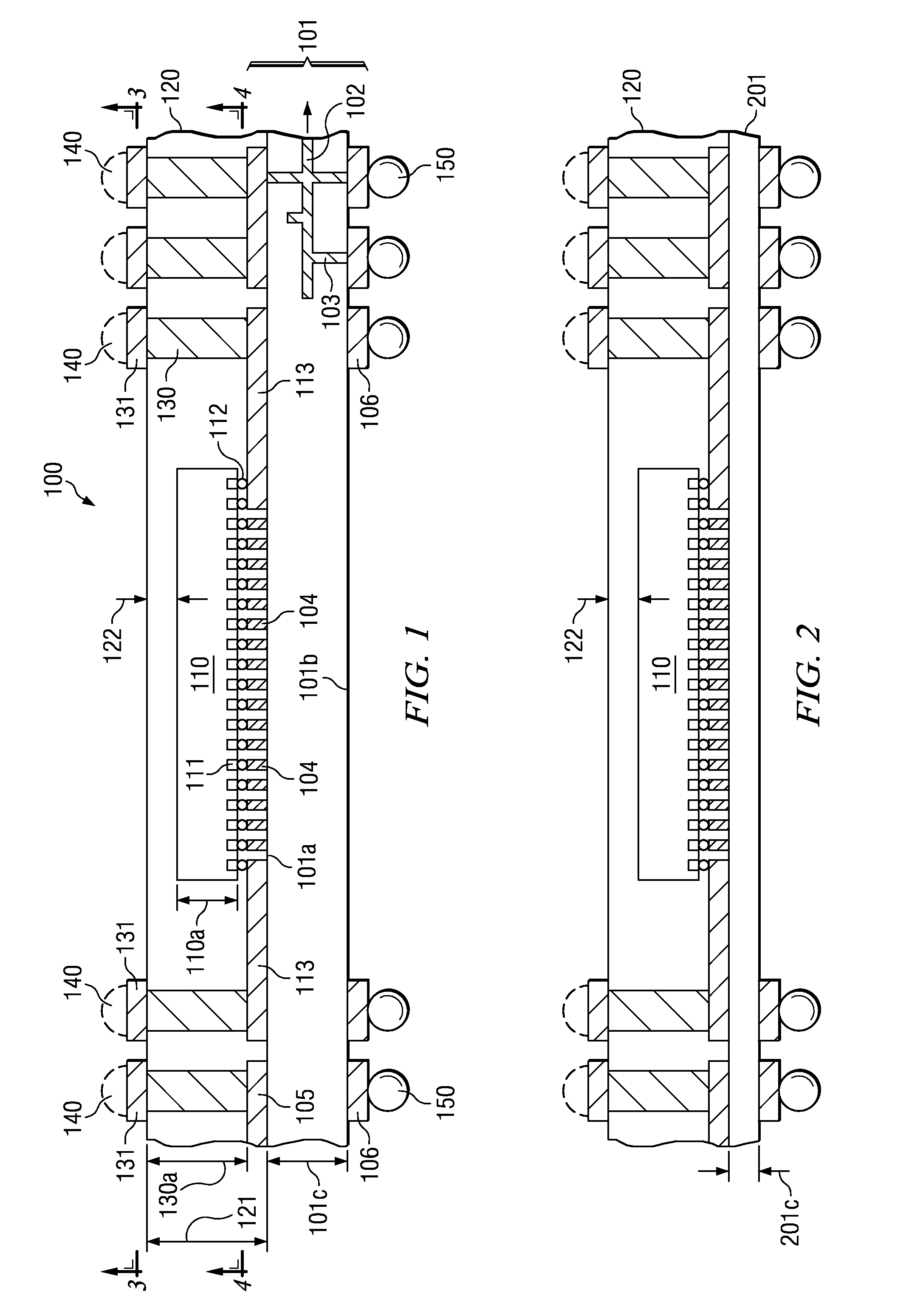

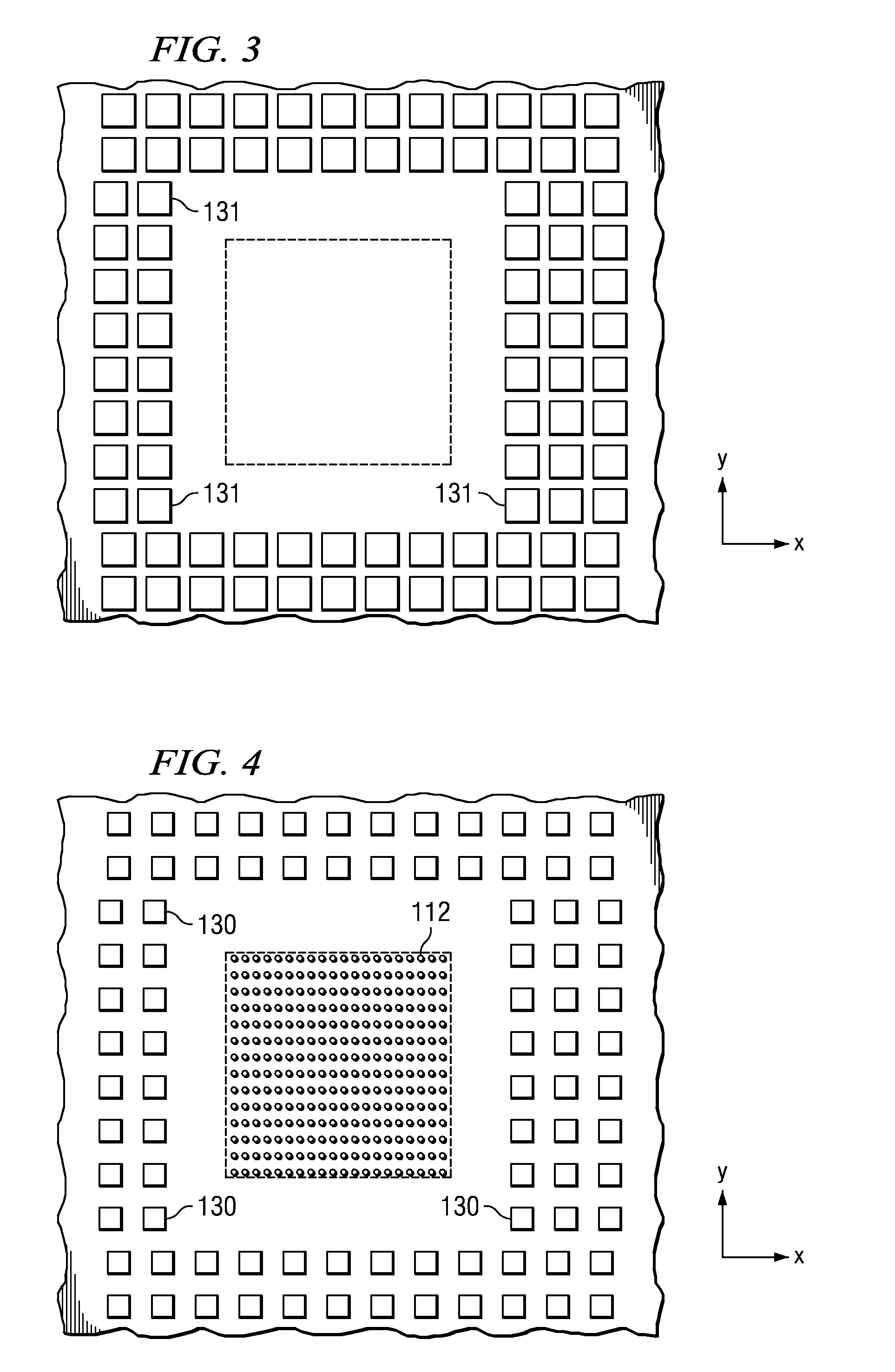

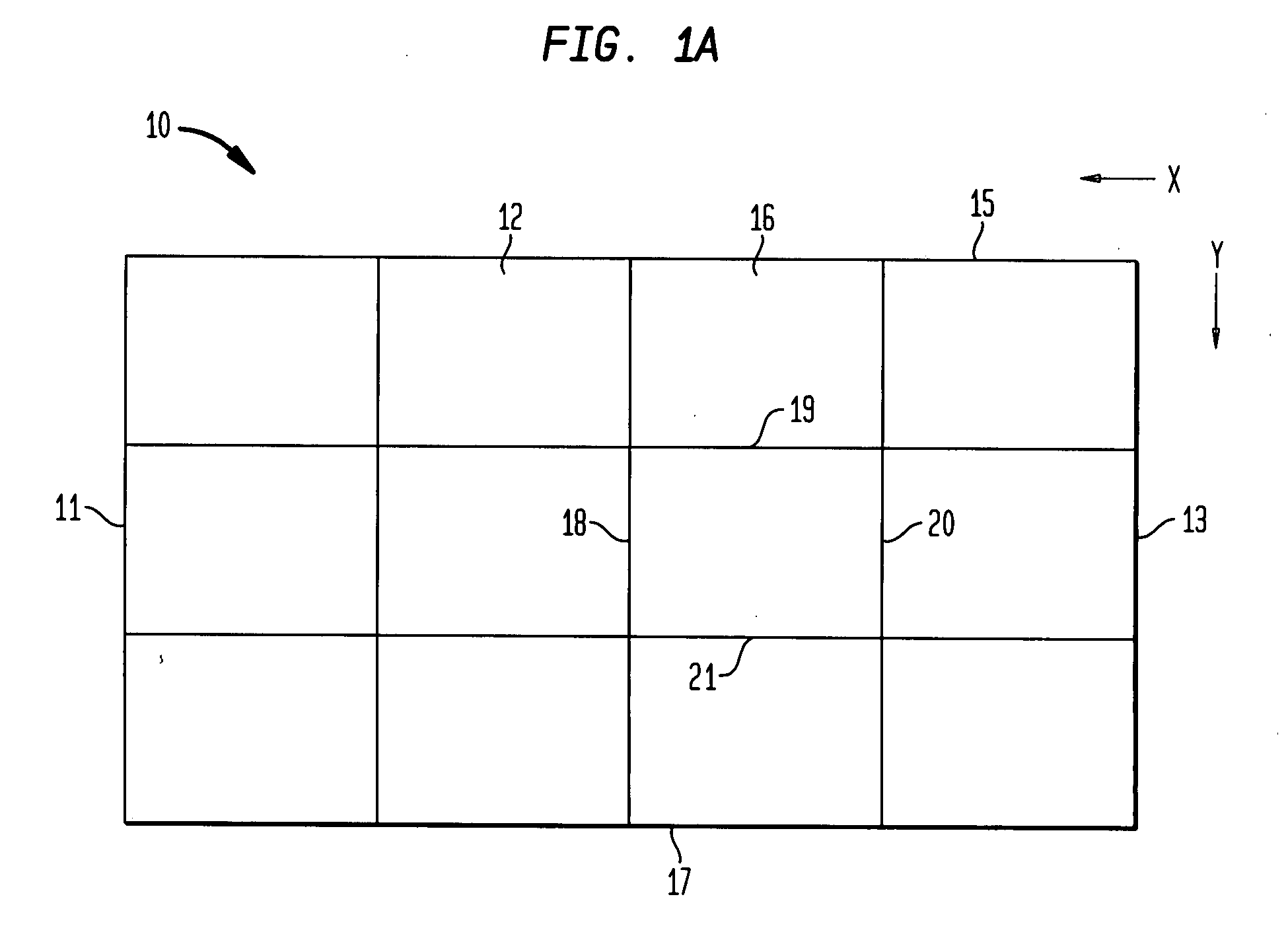

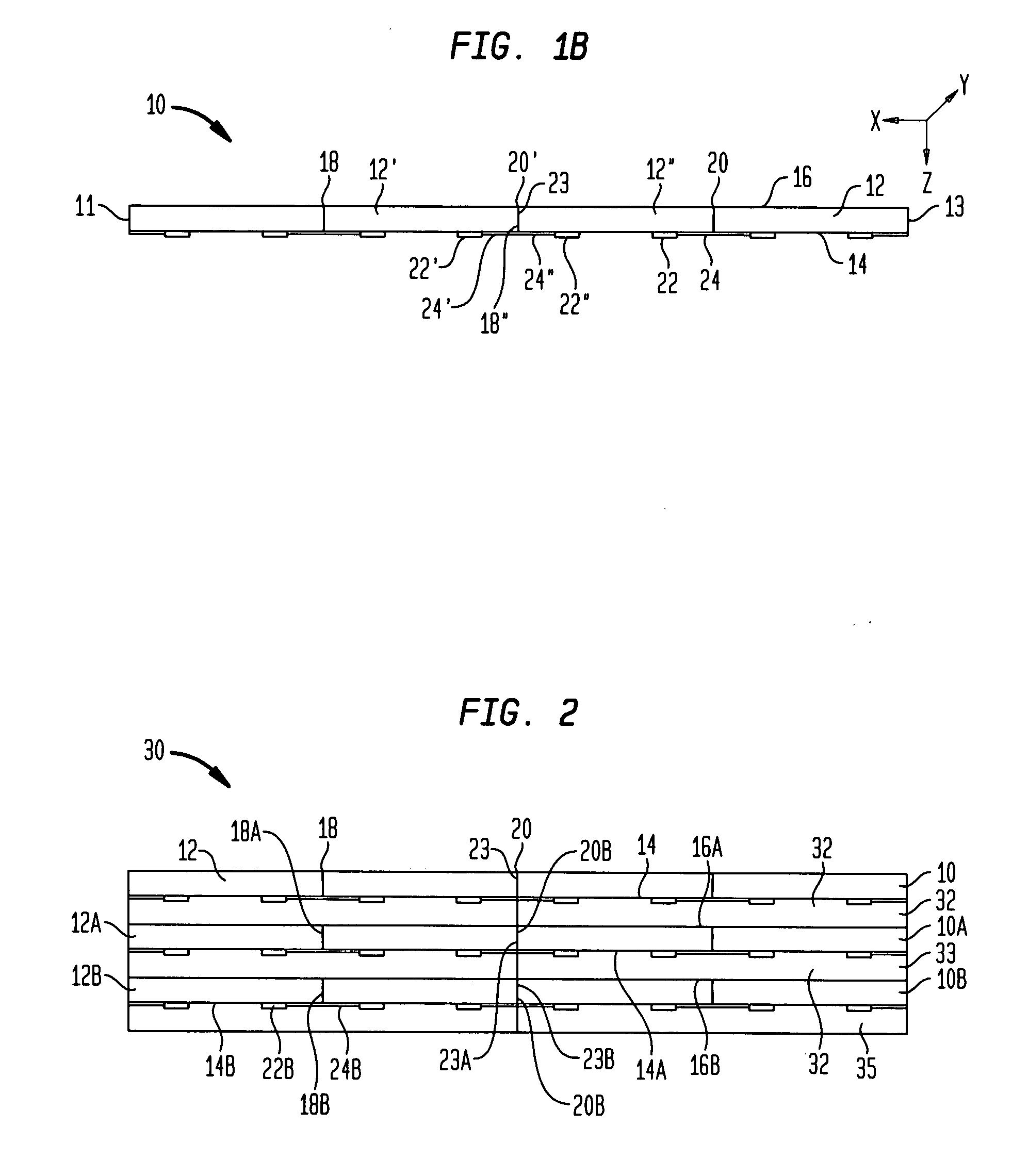

Edge connect wafer level stacking

ActiveUS20080083976A1Low costSmall sizeSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectronic component

A method of making a stacked microelectronic package by forming a microelectronic assembly by stacking a first subassembly including a plurality of microelectronic elements onto a second subassembly including a plurality of microelectronic elements, at least some of the plurality of microelectronic elements of said first subassembly and said second subassembly having traces that extend to respective edges of the microelectronic elements, then forming notches in the microelectronic assembly so as to expose the traces of at least some of the plurality of microelectronic elements, then forming leads at the side walls of the notches, the leads being in electrical communication with at least some of the traces and dicing the assembly into packages. Additional embodiments include methods for creating stacked packages using substrates and having additional traces that extend to both the top and bottom of the package.

Owner:TESSERA INC

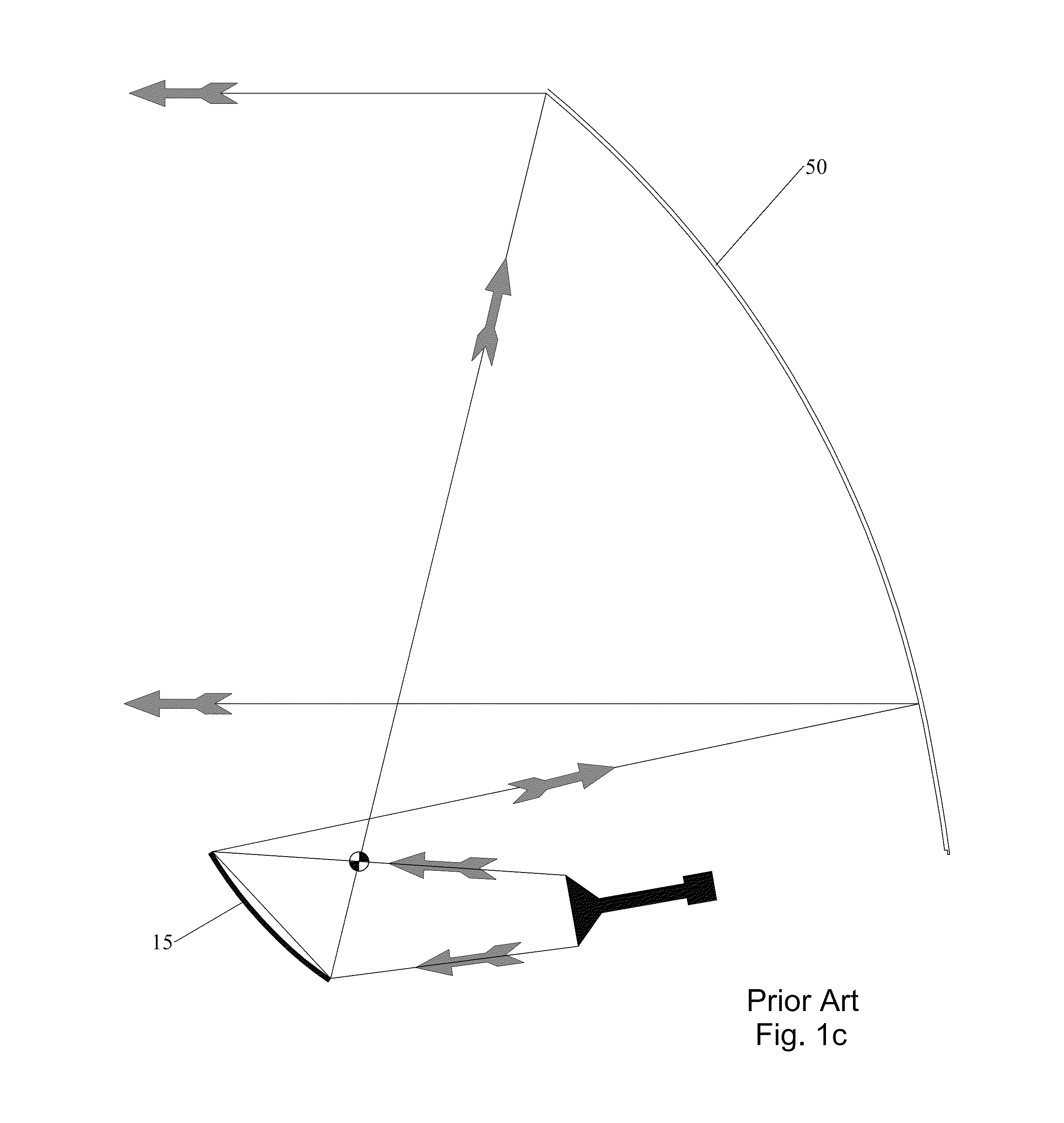

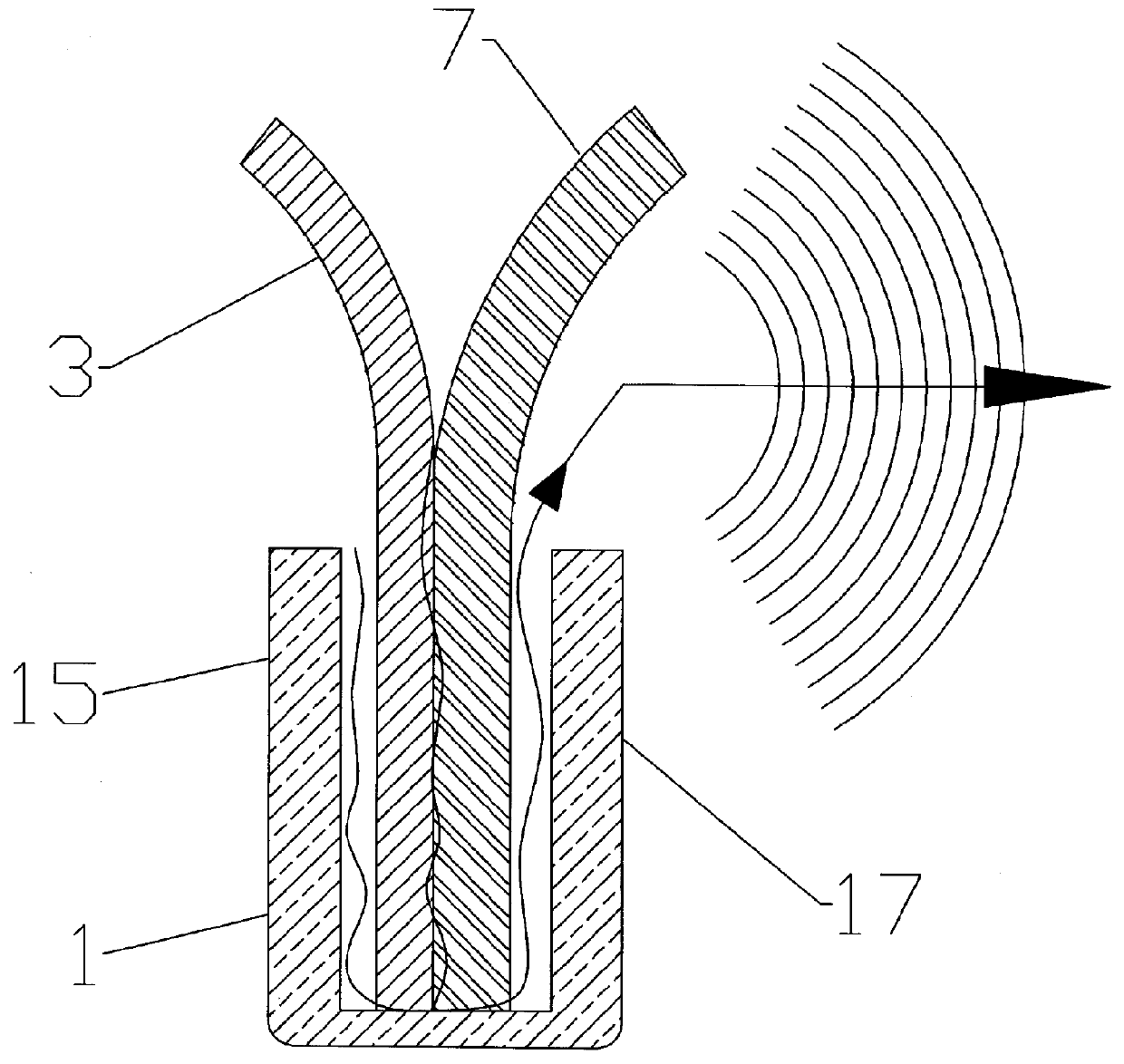

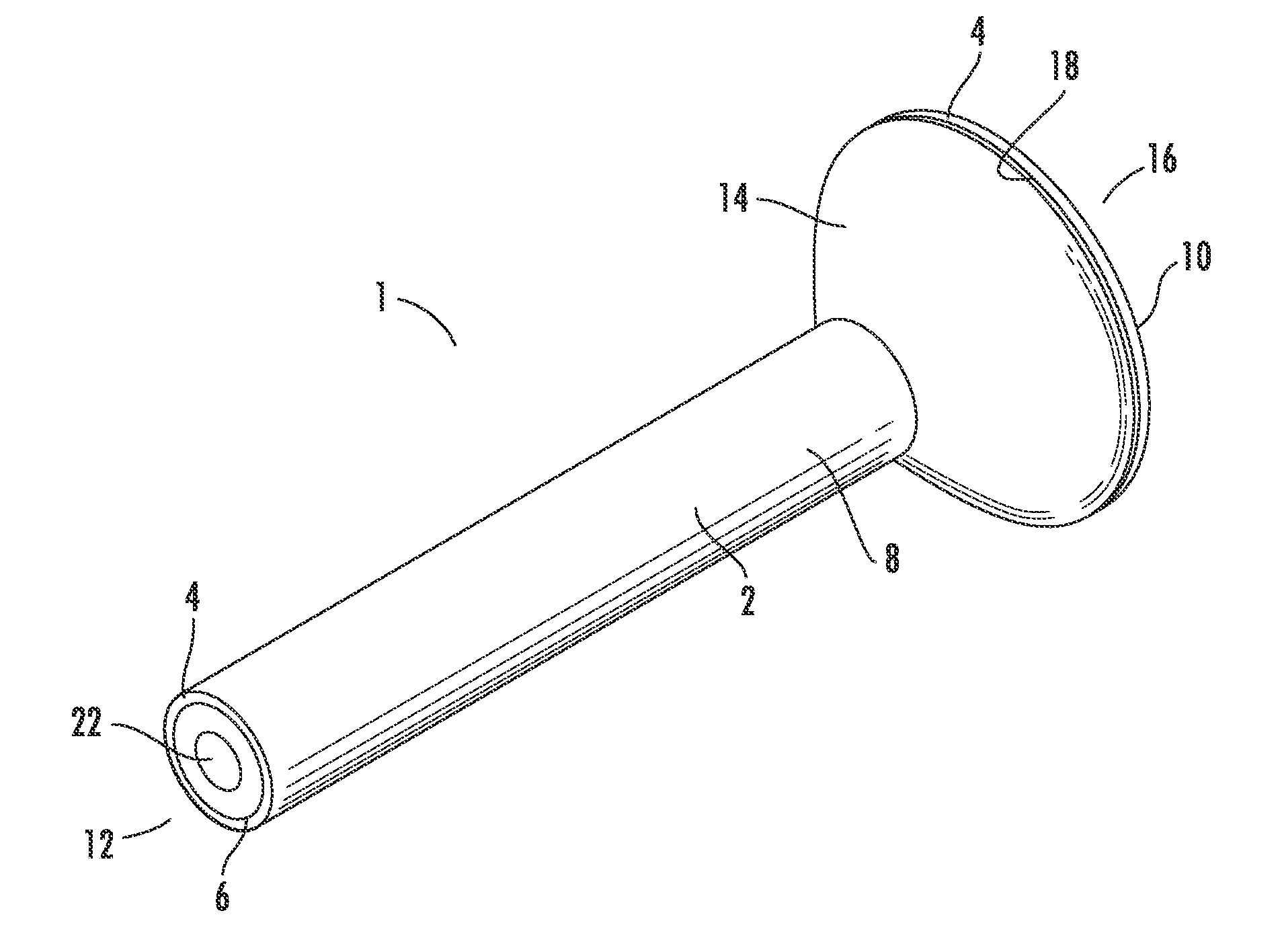

Self-supporting unitary feed assembly

InactiveUS7907097B2Minimize impedance mismatchRepeatedly cost efficiently manufacturedAntenna supports/mountingsEngineeringMachining

A feed assembly for a reflector antenna having a unitary portion of dielectric material, a proximal end of the unitary portion configured for connection with the reflector antenna. The unitary portion having a waveguide portion extending between the proximal end and a sub reflector support having a sub reflector surface at a distal end. The waveguide portion and the sub reflector surface covered with an RF reflective material. The unitary portion may be cost effectively formed via, for example injection molding and or machining. Alternatively, the feed assembly may be formed as a horn feed, without a sub reflector.

Owner:COMMSCOPE TECH LLC

Reduced graphene oxide doped with dopant, thin layer and transparent electrode

InactiveUS20090146111A1Improve electrical performanceMaterial nanotechnologyNon-metal conductorsDopantDisplay device

Disclosed herein is a reduced graphene oxide doped with a dopant, and a thin layer, a transparent electrode, a display device and a solar cell including the reduced graphene oxide. The reduced graphene oxide doped with a dopant includes an organic dopant and / or an inorganic dopant.

Owner:SAMSUNG ELECTRONICS CO LTD

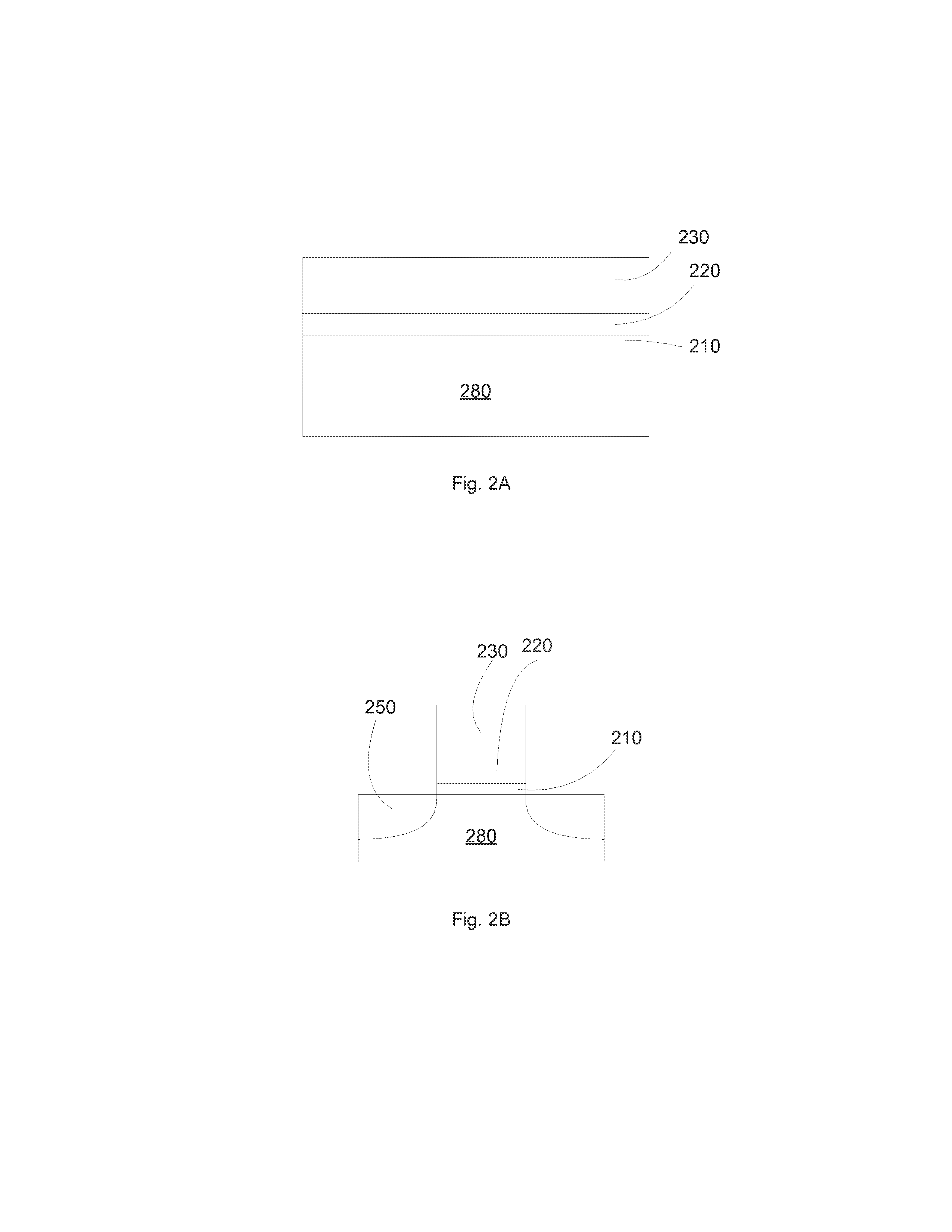

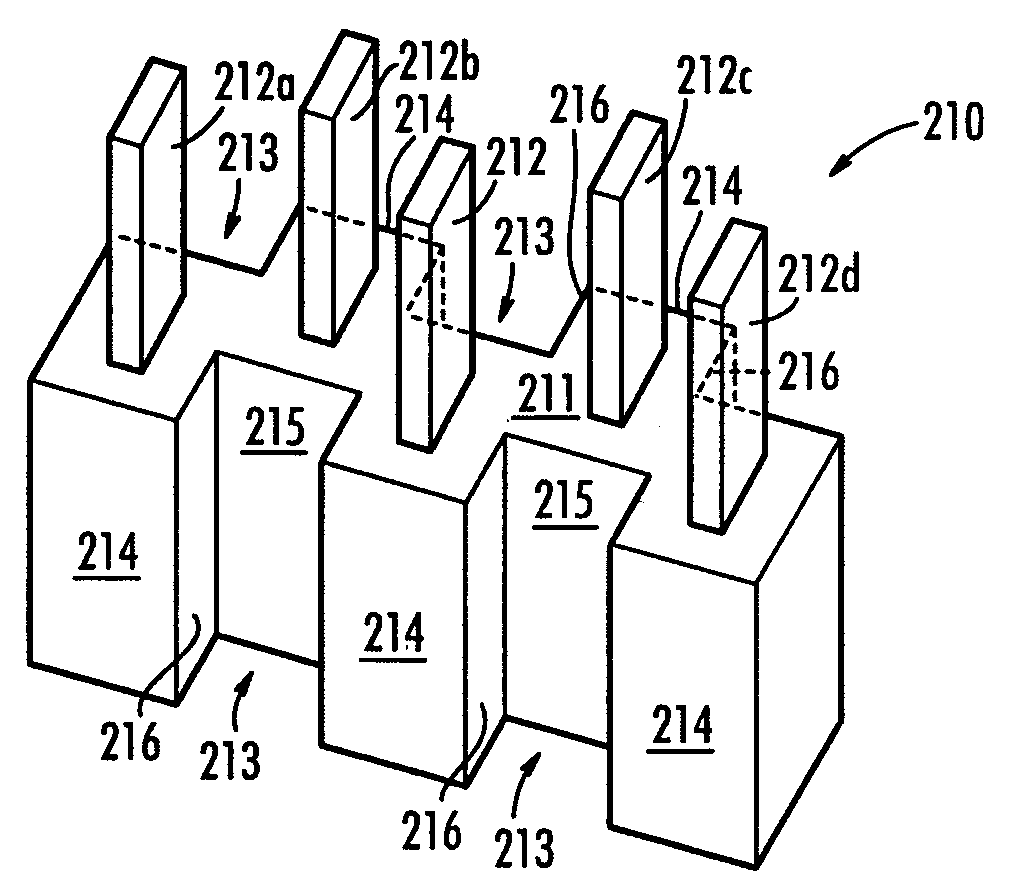

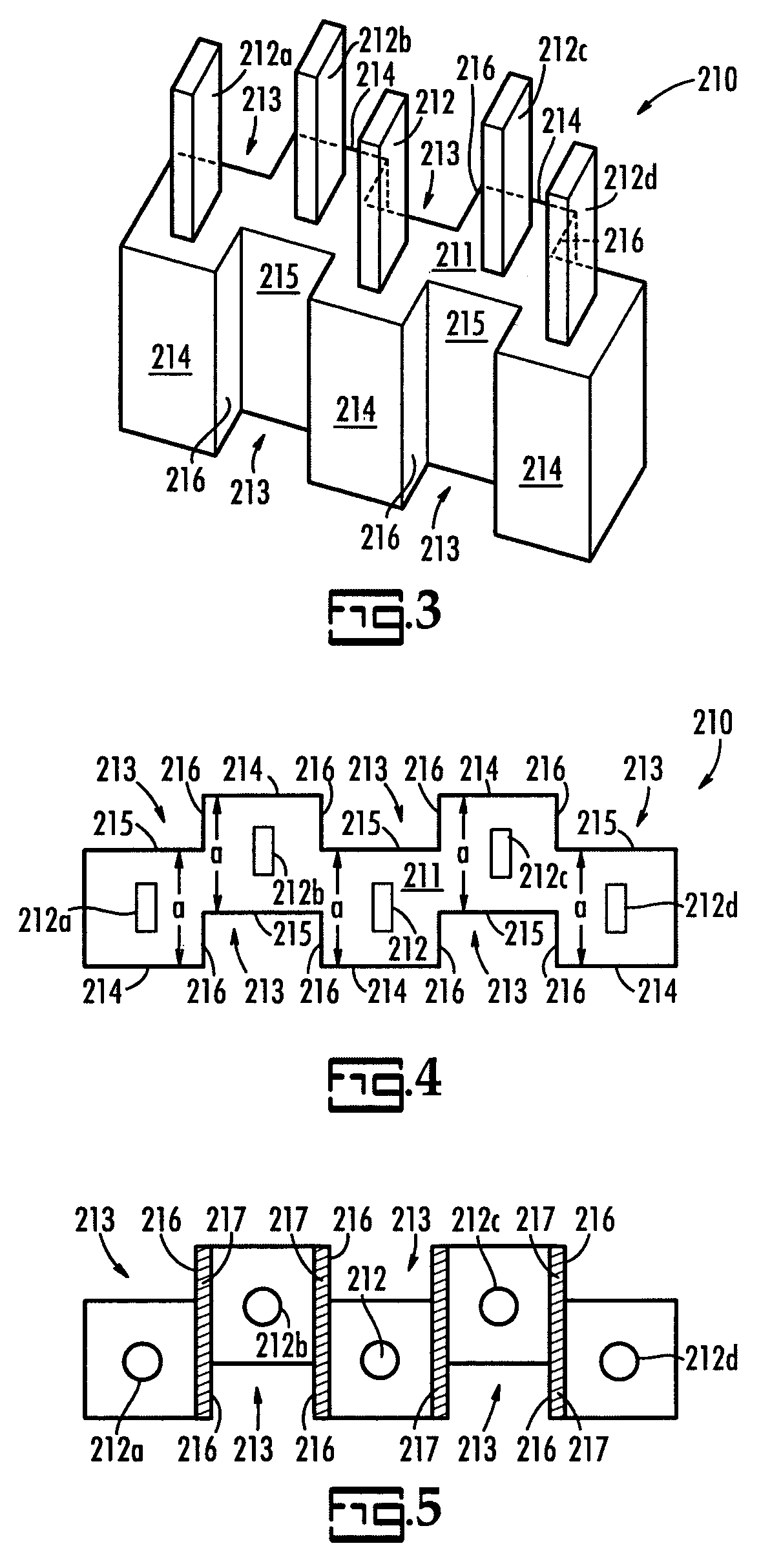

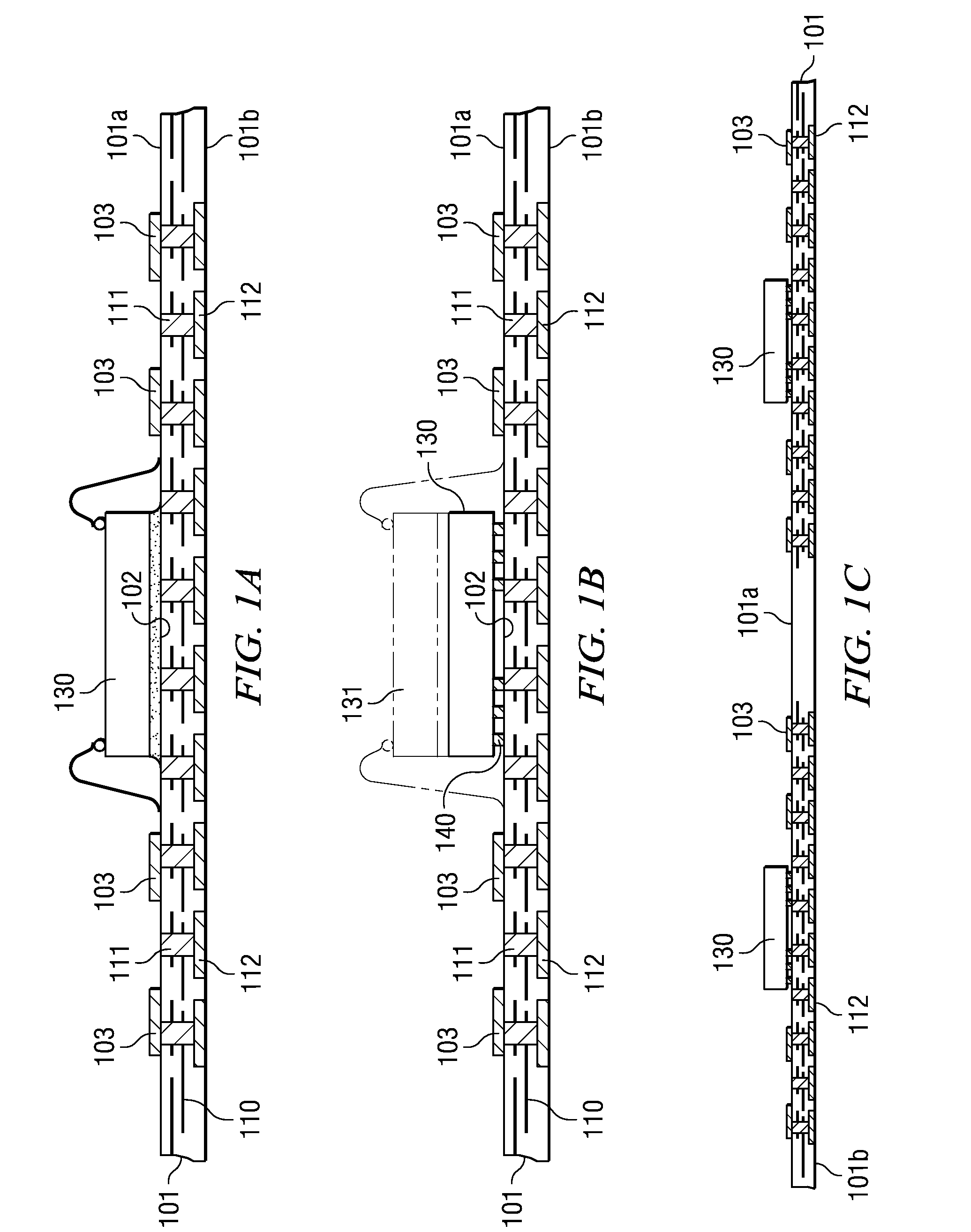

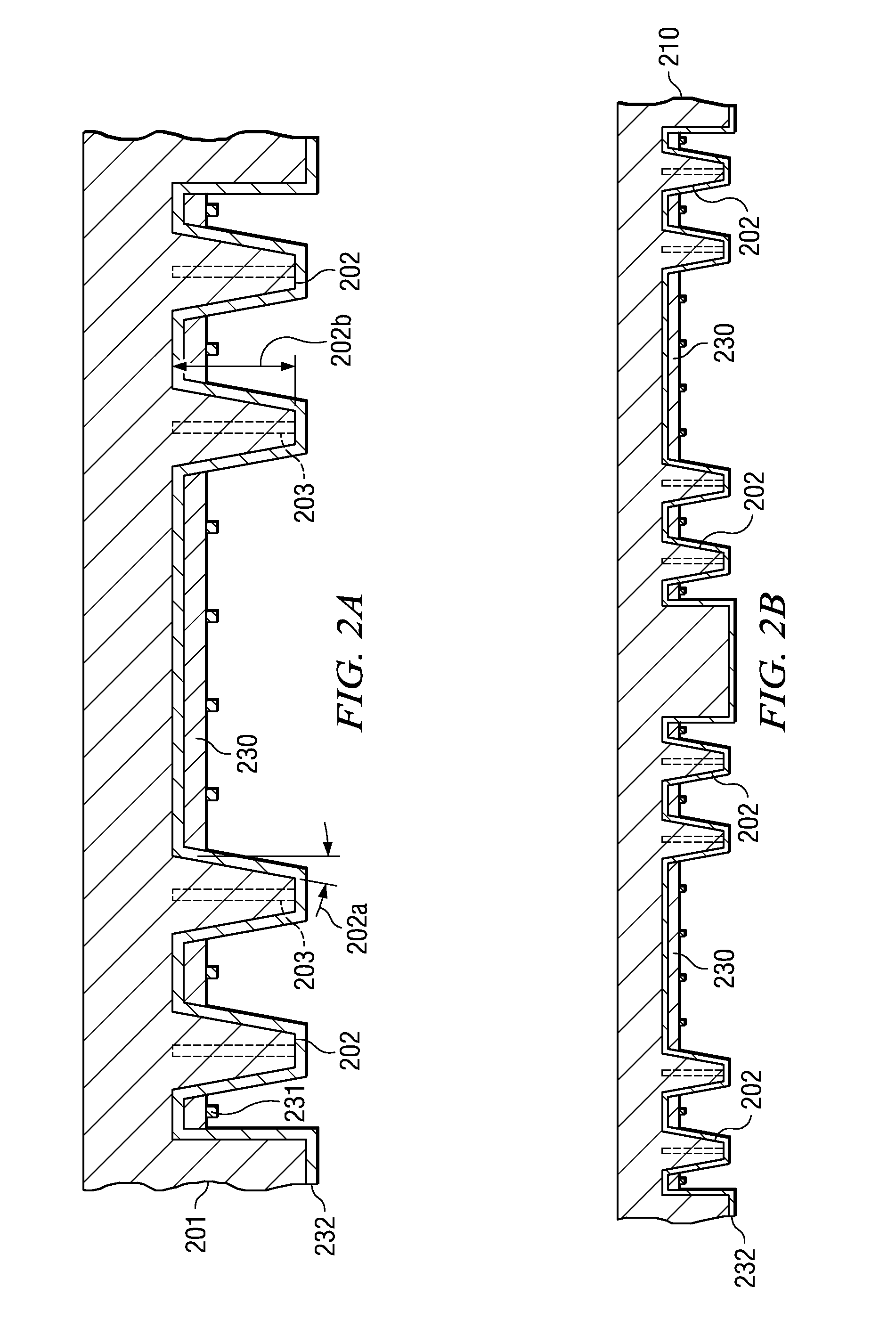

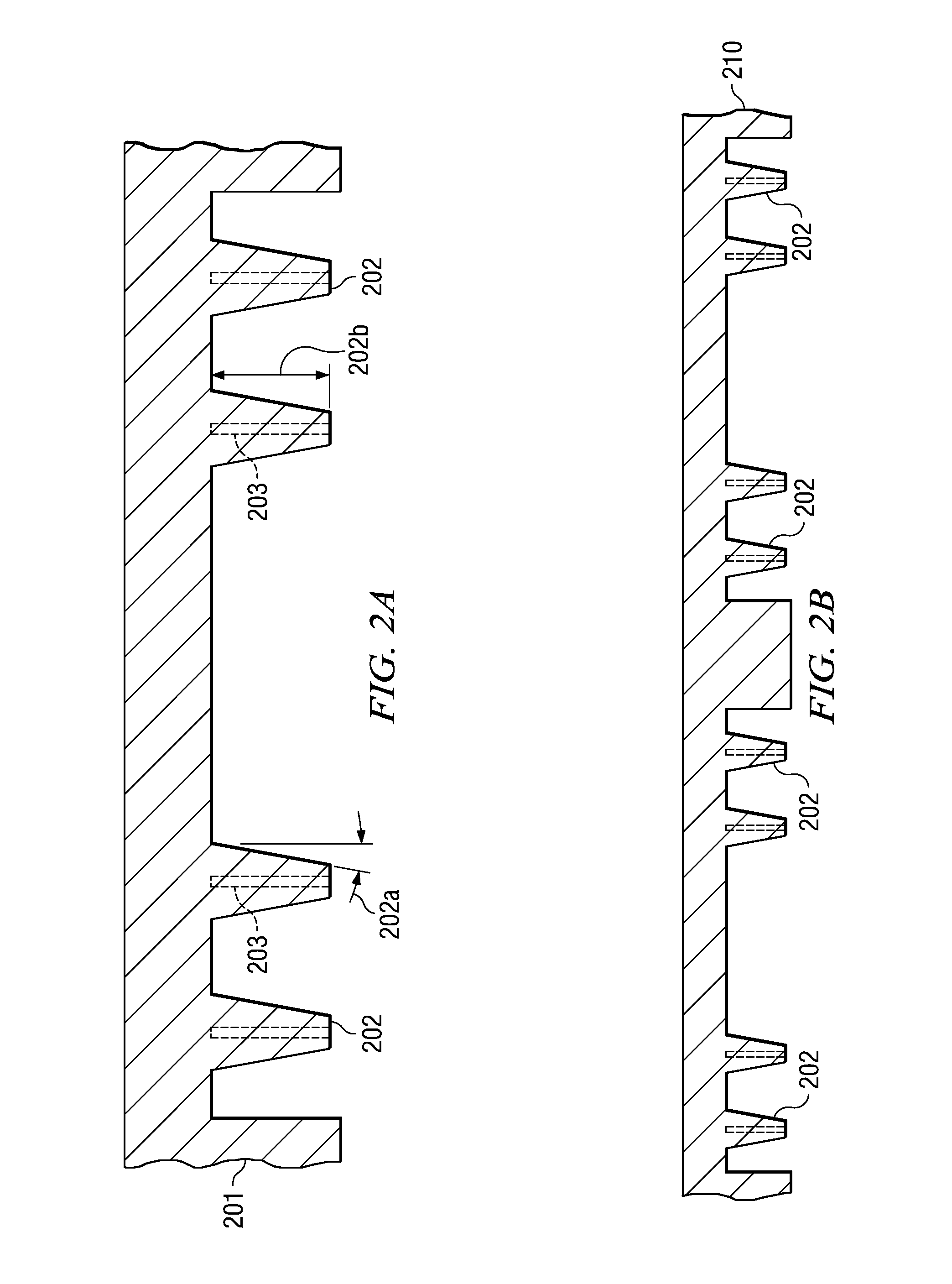

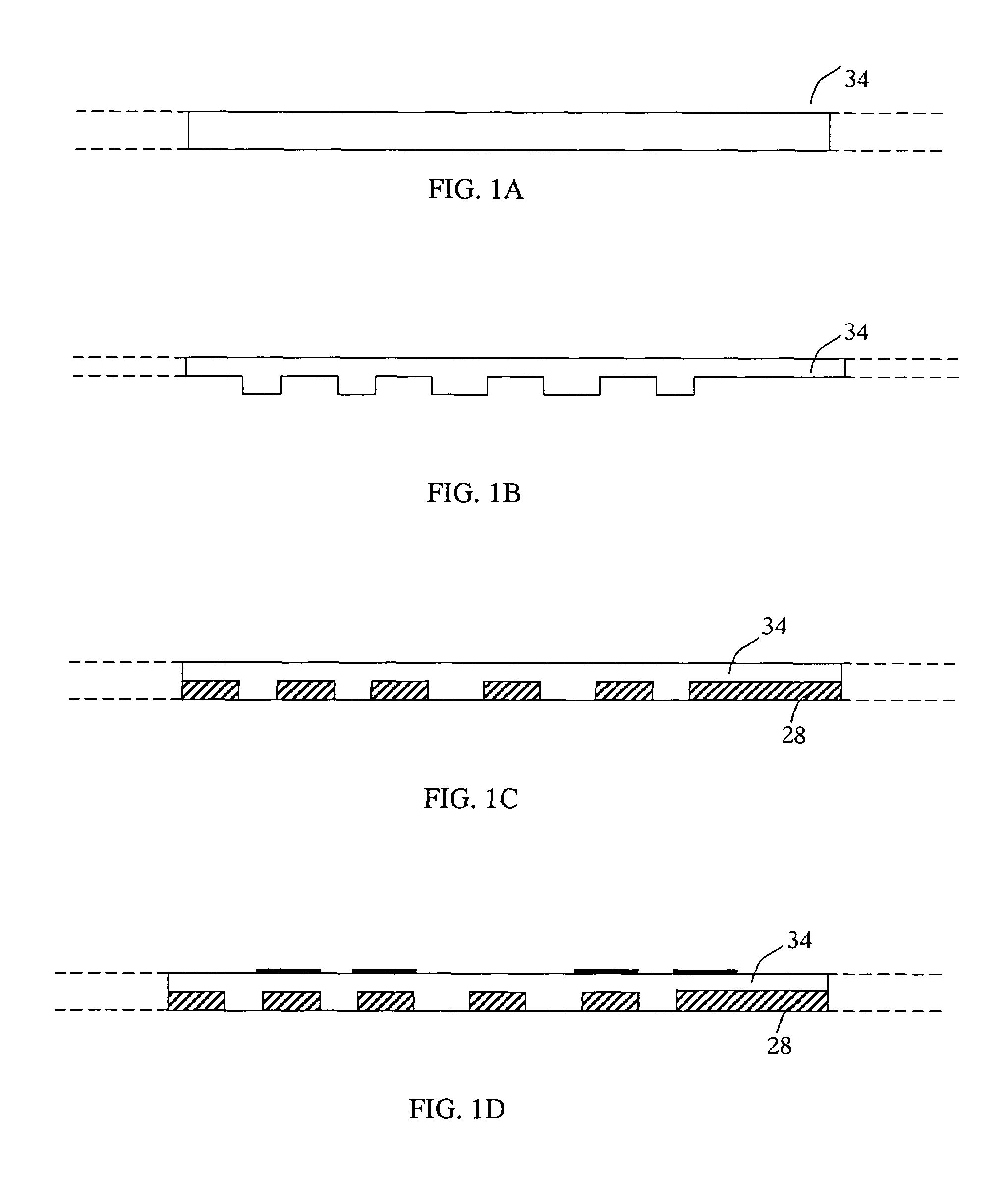

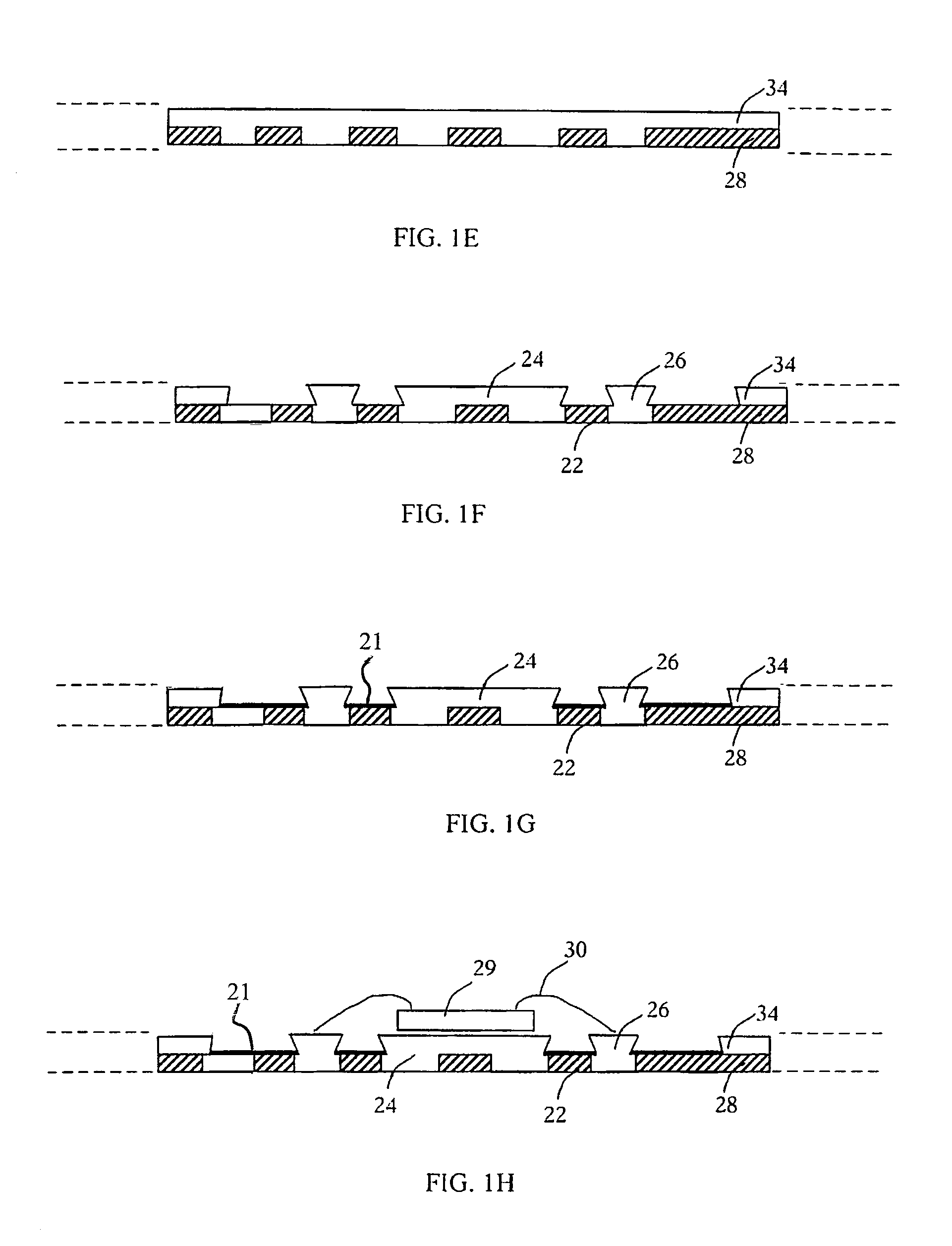

Method for Fabricating Array-Molded Package-On-Package

InactiveUS20080284045A1Low-cost and simplifyImprove testability and thus yieldLiquid surface applicatorsSemiconductor/solid-state device detailsContact padEngineering

A method and apparatus for fabricating a semiconductor device are disclosed. The method attaches semiconductor chips (130) on a sheet-like insulating substrate (101) integral with two or more patterned layers of conductive lines and vias and with contact pads (103) in pad locations. A mold is provided, which has a top portion (210) with metal protrusions (202) at locations matching the pad locations. The protrusions are shaped as truncated cones of a height suitable to approach the pad metal surface in the closed mold cavity. The substrate and the chip are loaded onto the bottom mold portion (310); the mold is closed by clamping the top portion onto the bottom portion so that the protrusions are aligned with the contact pads, approaching the pad surface. After pressuring encapsulation compound into the cavity, the mold is opened; the encapsulated device has apertures to the pad locations. Any residual compound formed on the pads is removed by laser, plasma, or chemical to expose the metal surface.

Owner:TEXAS INSTR INC

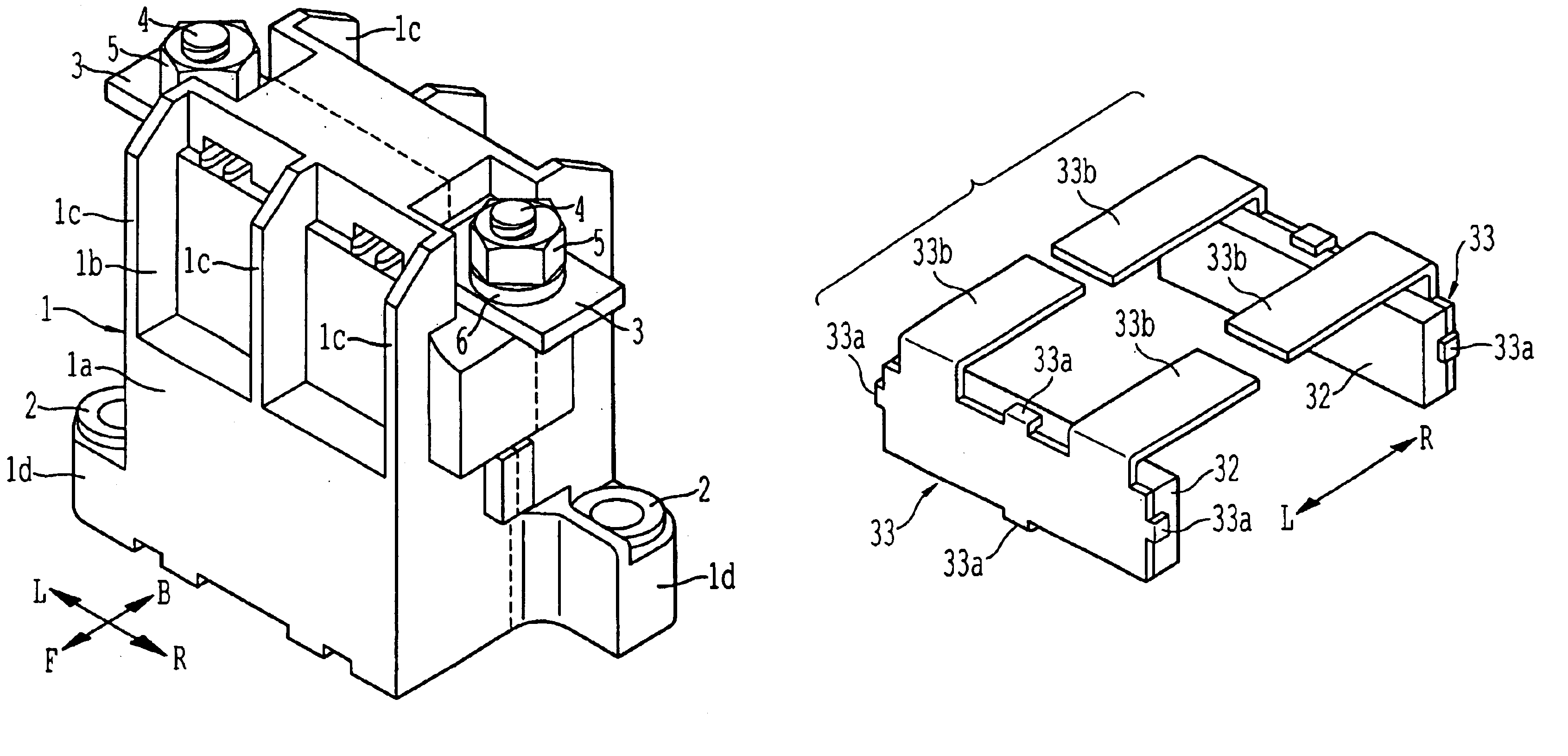

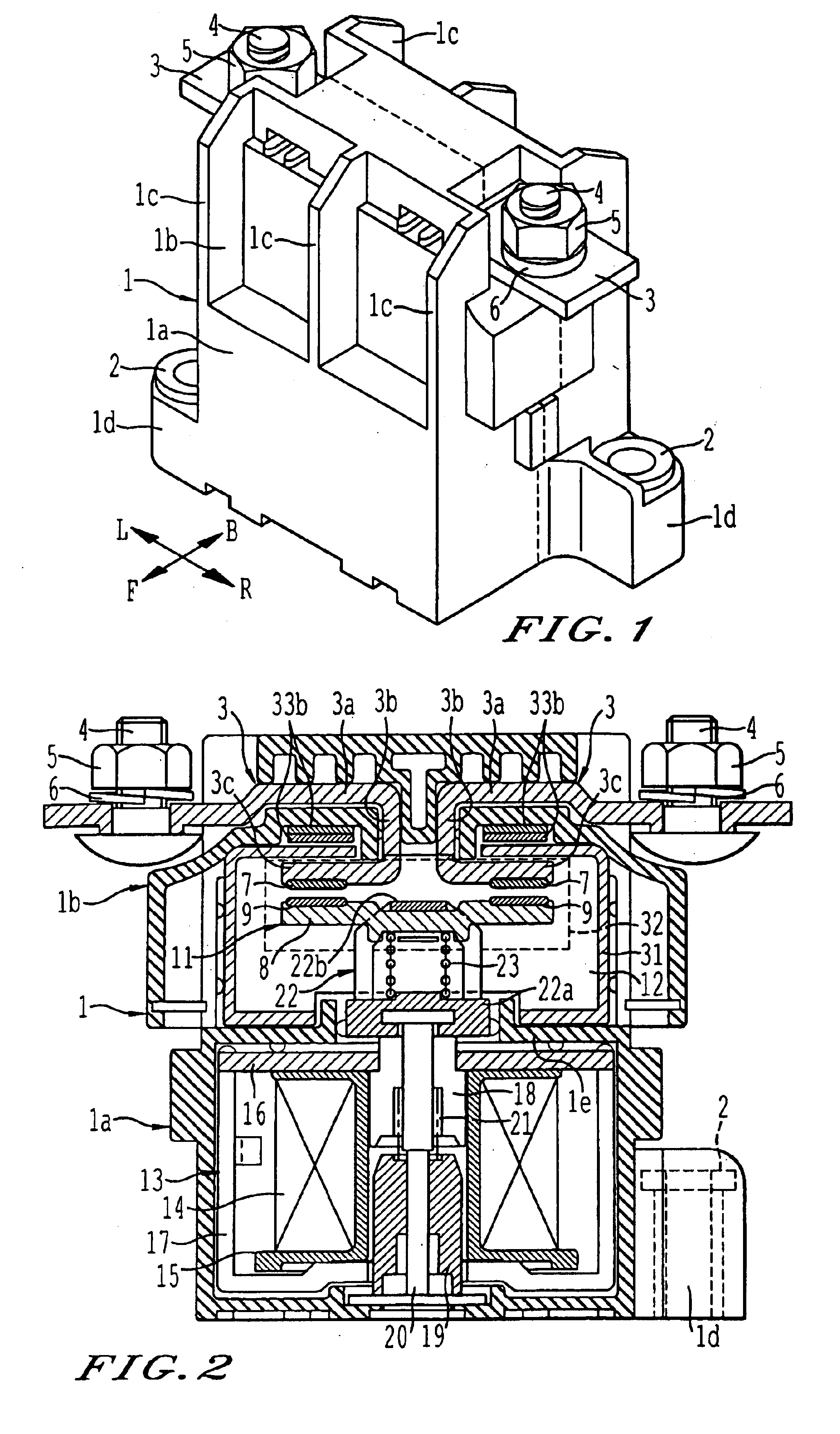

Contactor

InactiveUS6700466B1Increase arc lengthIncrease arc voltageHigh-tension/heavy-dress switchesAir-break switchesEngineeringMagnet

A contact apparatus is provided having a permanent magnet disposed in a region where a fixing contact point is mounted to a fixing contact and a movable contact to which a movable contact point is mounted. An arc generated between both the contact points is moved in a lateral direction by the magnetic force of the permanent magnet and stretched. An arc-extinguishing member which is heated by the arc for generating arc-extinguishing gas is provided such as to surround the fixing contact point and the movable contact point.

Owner:MATSUSHITA ELECTRIC WORKS LTD

Integrated circuit package and method for fabricating same

ActiveUS7348663B1Reduce electrical impedanceImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesDielectricContact pad

A process for fabricating an integrated circuit package includes: selectively etching a first side of a substrate thereby providing etched regions of the substrate to partially define at least a plurality of contact pads; adding a dielectric material to the etched regions of the substrate; selectively etching a second side of the substrate to further define at least the plurality of contact pads and thereby provide a package base of at least the contact pads and the dielectric; mounting a semiconductor die to the package base and connecting the semiconductor die to the contact pads; fixing a lid to the package base to cover the semiconductor die in a cavity between the lid and the package base; and singulating to provide the integrated circuit package.

Owner:UTAC HEADQUARTERS PTE LTD

Array-processed stacked semiconductor packages

ActiveUS7892889B2Raise countLow contour devicesSemiconductor/solid-state device detailsSolid-state devicesLead bondingElectrical connection

One embodiment of the invention is a semiconductor system (1400) of arrays (1401, 1402, etc.) of packaged devices. Each array includes a sheet-like substrate (1411, 1412, etc.) made of insulating material integral with conductive horizontal lines and vertical vias, and terminals on the surfaces. Semiconductor components, which may include more than one active or passive chips, or chips of different sizes, are attached to the substrate; the electrical connections may include flip-chip, wire bond, or combination techniques. Encapsulation compound (1412, 1422, etc.), which adheres to the substrate, embeds the connected components. Metal posts (1431, 1432, etc.) traverse the encapsulation compound vertically, connecting the substrate vias with pads on the encapsulation surface. The pads are covered with solder bodies used to connect to the next-level device array so that a 3-dimensional system of packaged devices is formed.

Owner:TEXAS INSTR INC

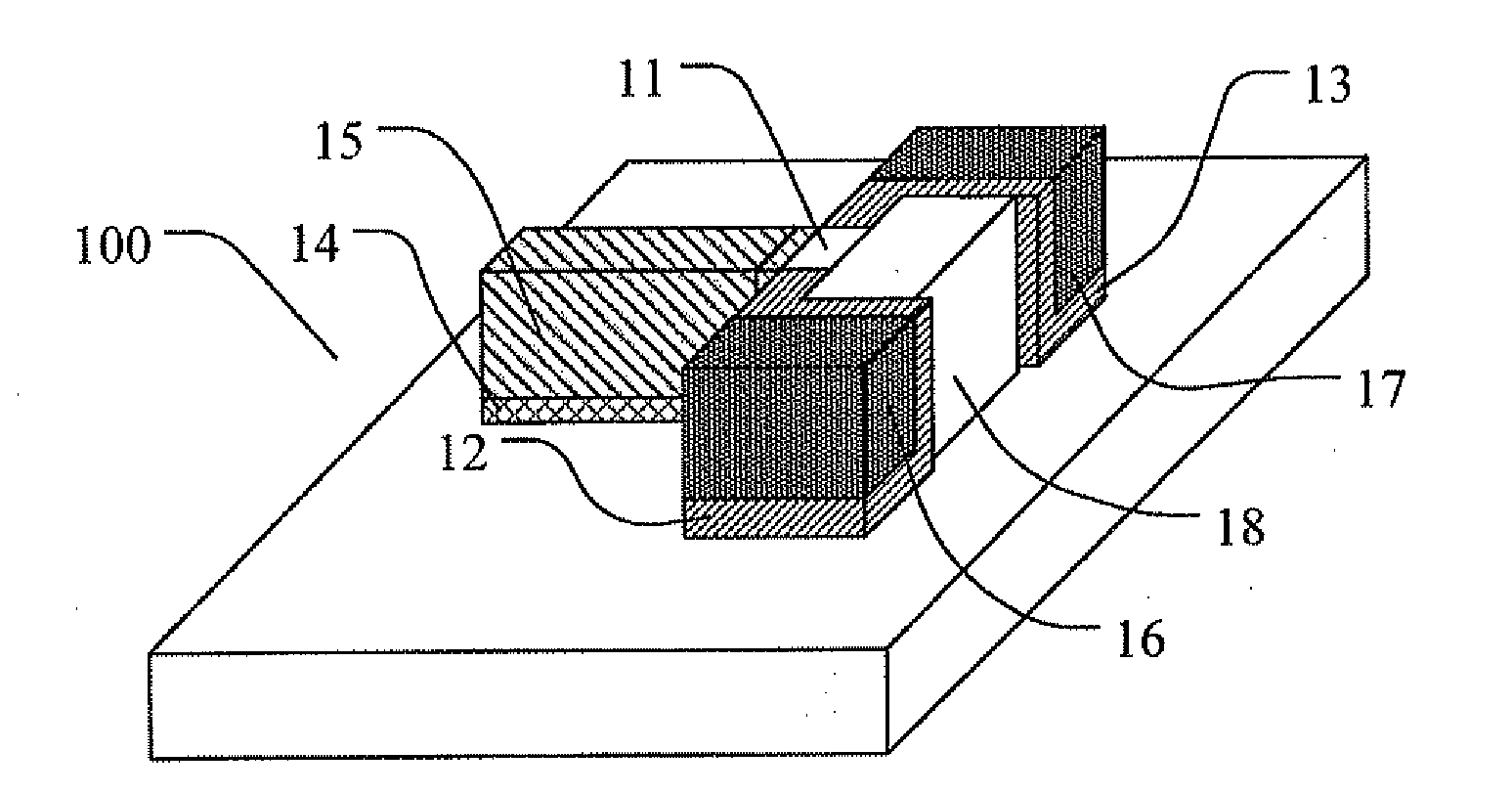

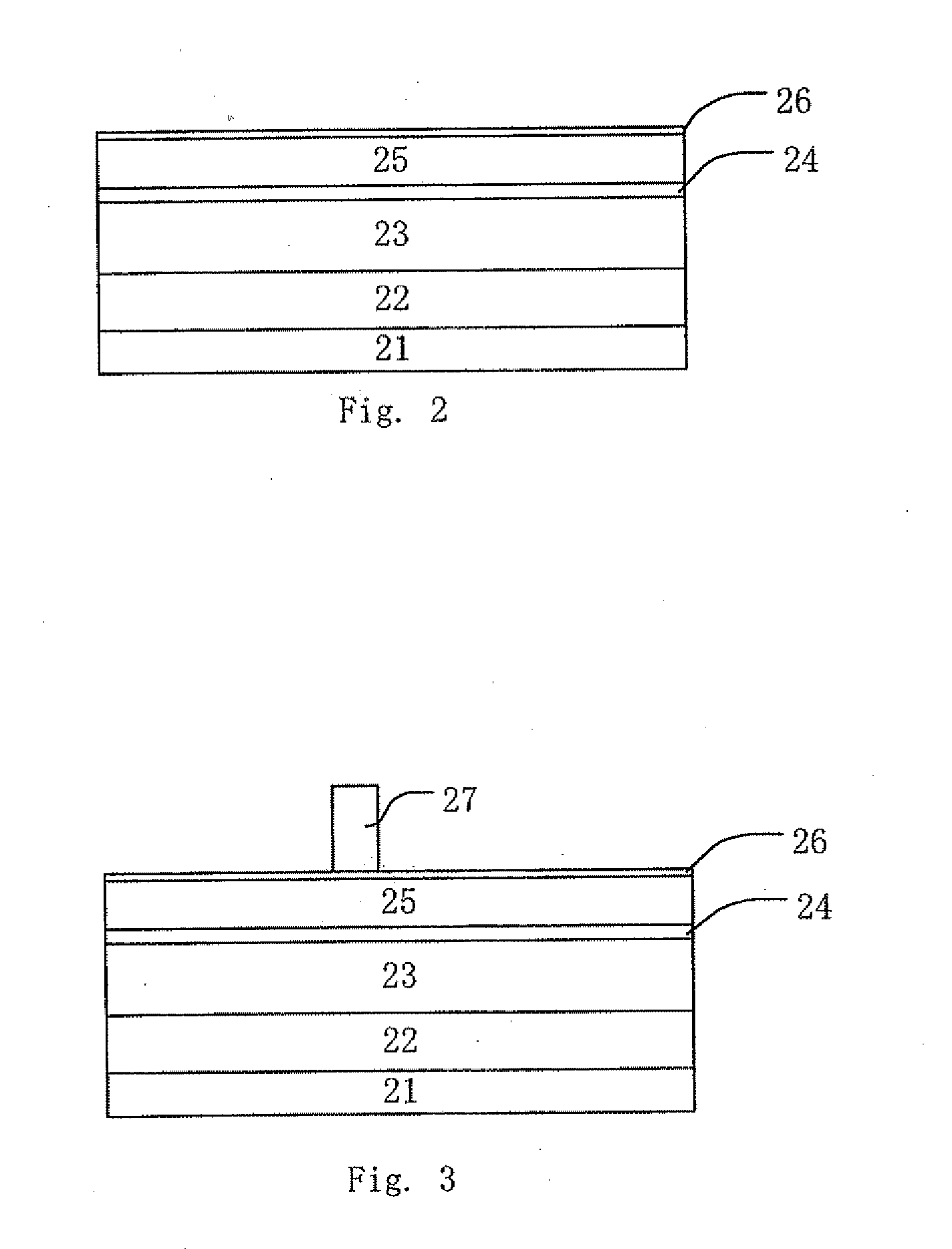

Semiconductor device and method for manufacturing the same

ActiveUS20110193164A1Reduce parasitic capacitanceLarge thicknessSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceGate dielectric

The present application discloses a semiconductor device formed on a SOI substrate which comprises a buried insulating layer and a semiconductor layer on the buried insulating layer and a method for manufacturing the same, wherein a fin of semiconductive material having two opposing sides perpendicular to a main surface of the SOI substrate is provided in the semiconductor layer, said semiconductor device comprising: a source region and a drain region provided at two ends of the fin respectively; a channel region provided at a central portion of the fin; and a stack of gate dielectric and gate conductor provided at one side of the fin, where the gate conductor is isolated from the channel region by the gate dielectric, wherein the gate conductor extends away from the one side of the fin in a direction parallel to the main surface of the SOI substrate. The semiconductor device has an improved short channel effect and a reduced parasitic capacitance and resistance, which contributes to an improved electrical property and facilitates scaling down of the transistor.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Edge connect wafer level stacking

ActiveUS20080083977A1Low costSmall sizeSemiconductor/solid-state device detailsSolid-state devicesMechanical engineering

In accordance with an aspect of the invention, a stacked microelectronic package is provided which may include a plurality of subassemblies, e.g., a first subassembly and a second subassembly underlying the first subassembly. A front face of the second subassembly may confront the rear face of the first subassembly. Each of the first and second subassemblies may include a plurality of front contacts exposed at the front face, at least one edge and a plurality of front traces extending about the respective at least one edge. The second subassembly may have a plurality of rear contacts exposed at the rear face. The second subassembly may also have a plurality of rear traces extending from the rear contacts about the at least one edge. The rear traces may extend to at least some of the plurality of front contacts of at least one of the first or second subassemblies.

Owner:TESSERA INC

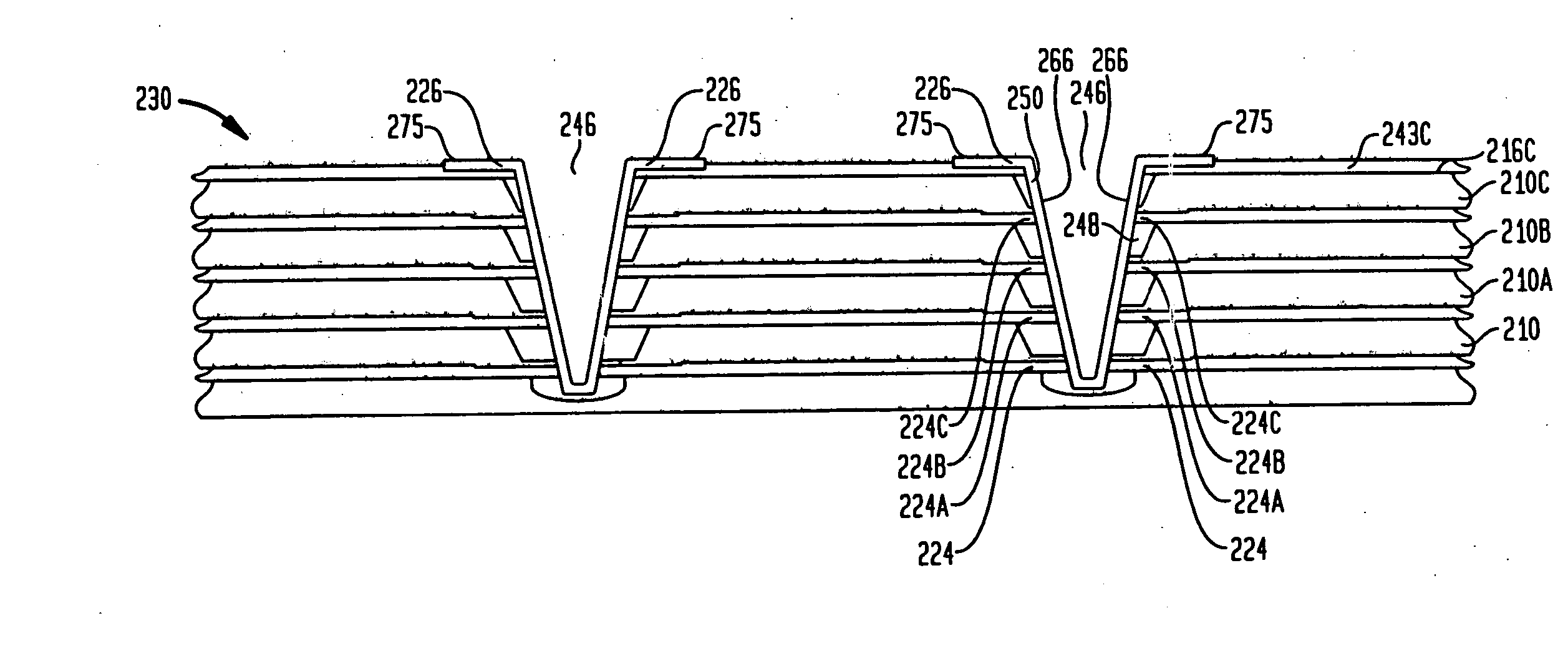

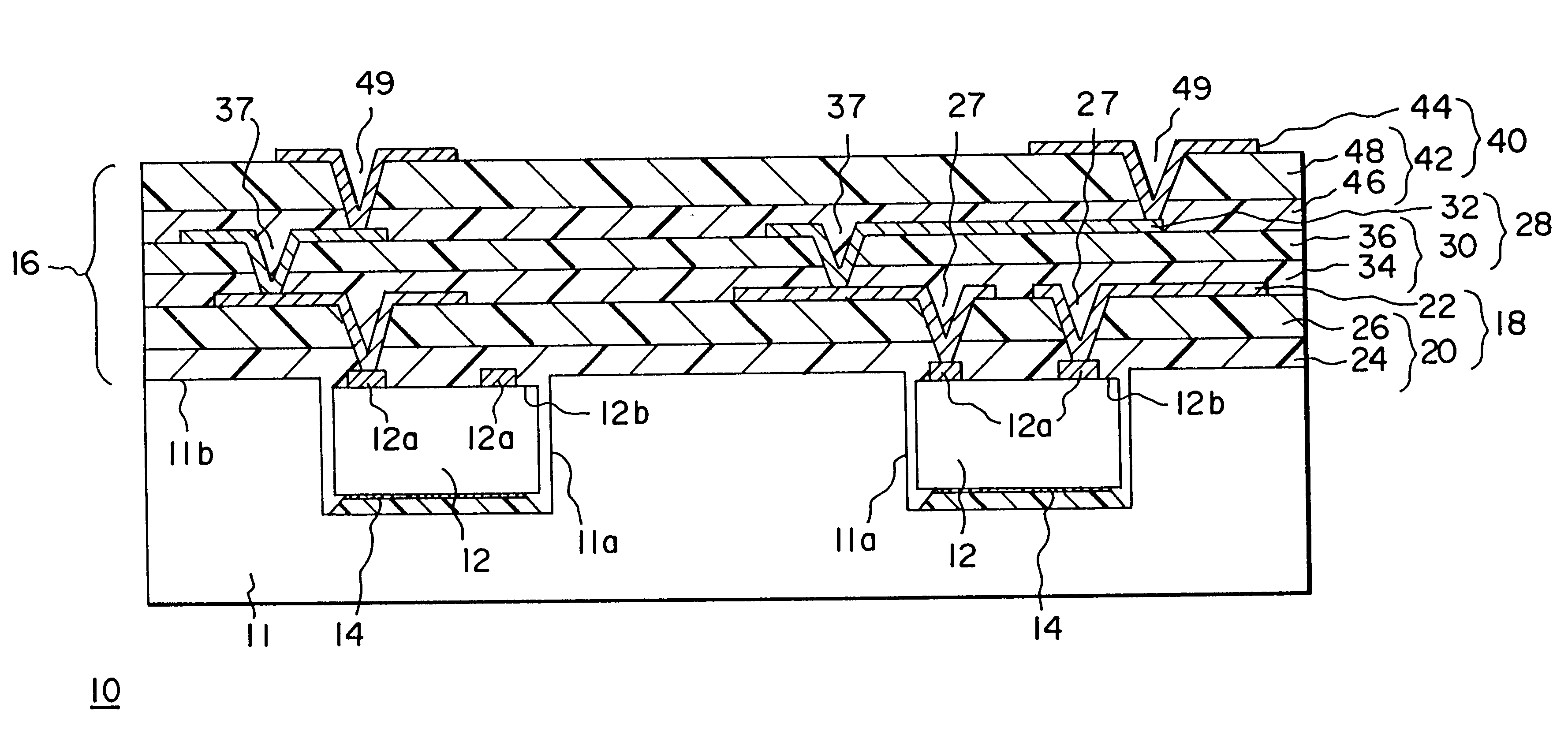

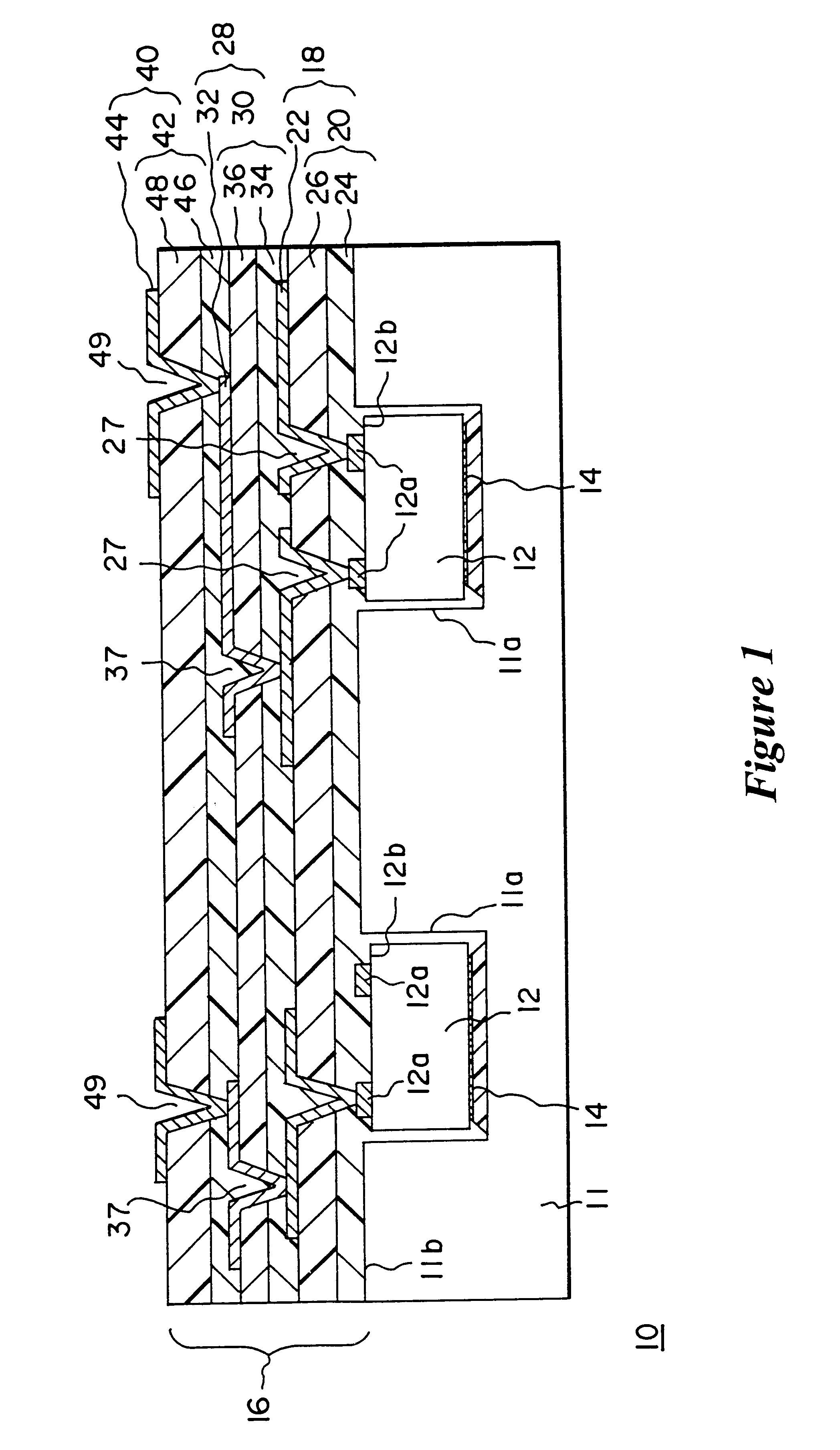

Electronics module having high density interconnect structures incorporating an improved dielectric lamination adhesive

InactiveUS6294741B1Electrical performance be improveHigh densityInsulating substrate metal adhesion improvementSemiconductor/solid-state device detailsPolyimide membraneElectrical structure

A multi-chip electronics module is provided which utilizes benzocyclobutene as a laminate adhesive for bonding the upper dielectric films in a high density interconnect structure. The benzocyclobutene thermosetting polymer is spin coated on a polyimide film, and baked at low temperature to remove any solvent to leave a B-staged coating on the polyimide film. The composite film can be laminated to an underlying electrical structure using a vacuum laminator and heat. As the heat is applied, the BCB layer softens, flows and then cures to bond the polyimide film to the underlying electrical structure.

Owner:LOCKHEED MARTIN CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com