Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1687 results about "Solder material" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Solder is the name of the actual material used in soldering. Historically, many solders contained lead or cadmium, but that has been recently phased out for health reasons. Solder is typically composed of two or more metals combined into an alloy. Silver, antimony, copper, tin, and zinc are all common ingredients.

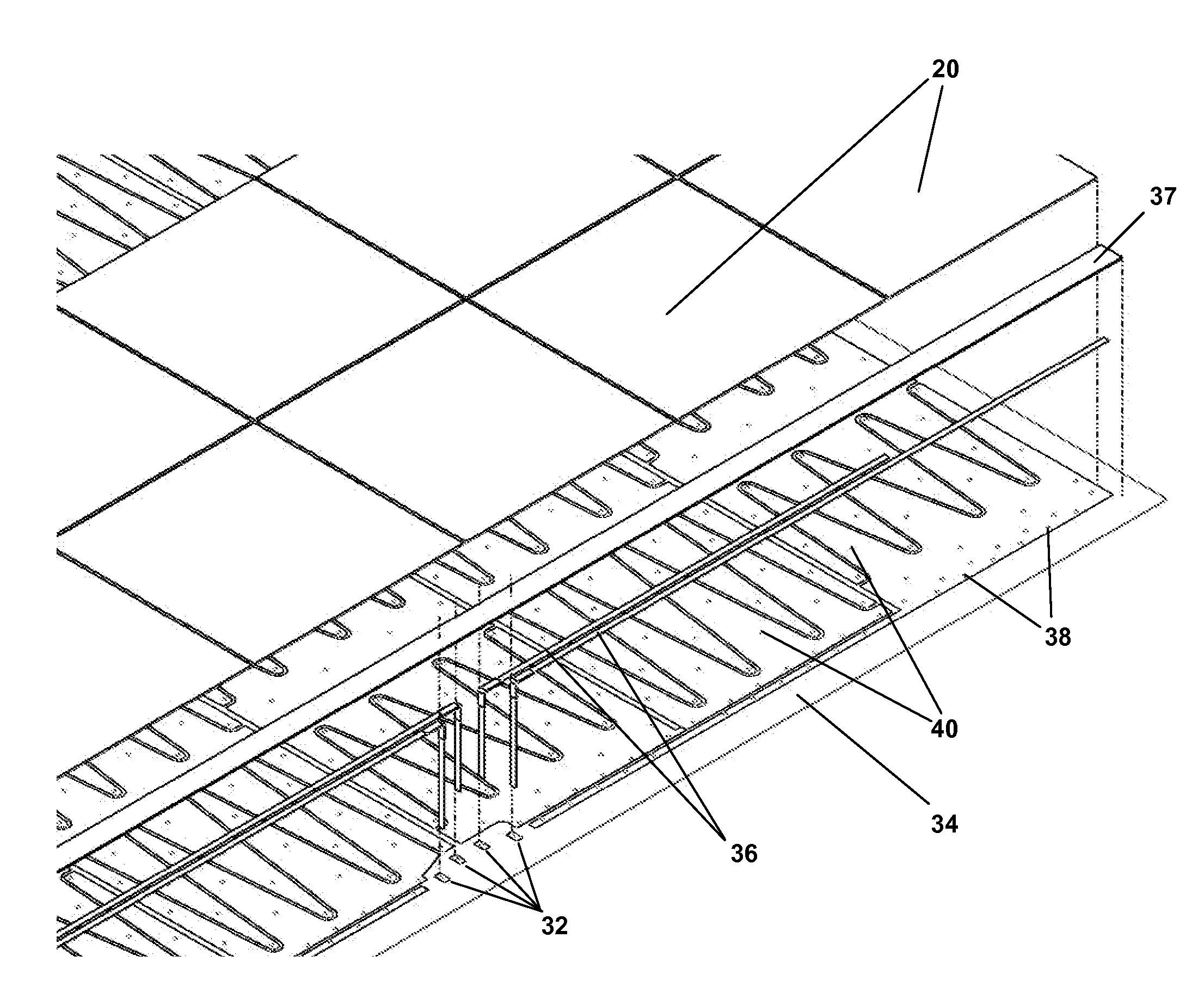

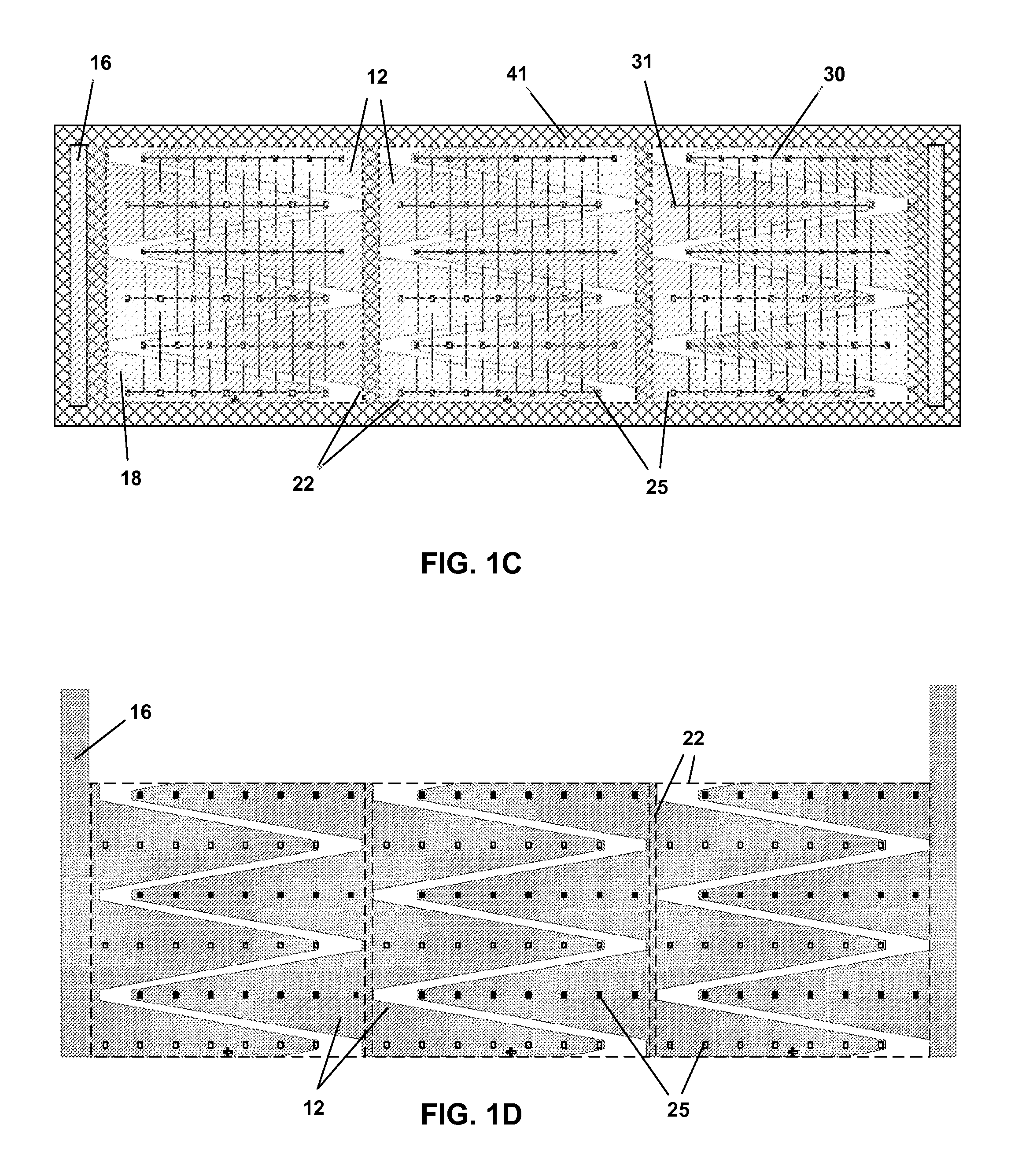

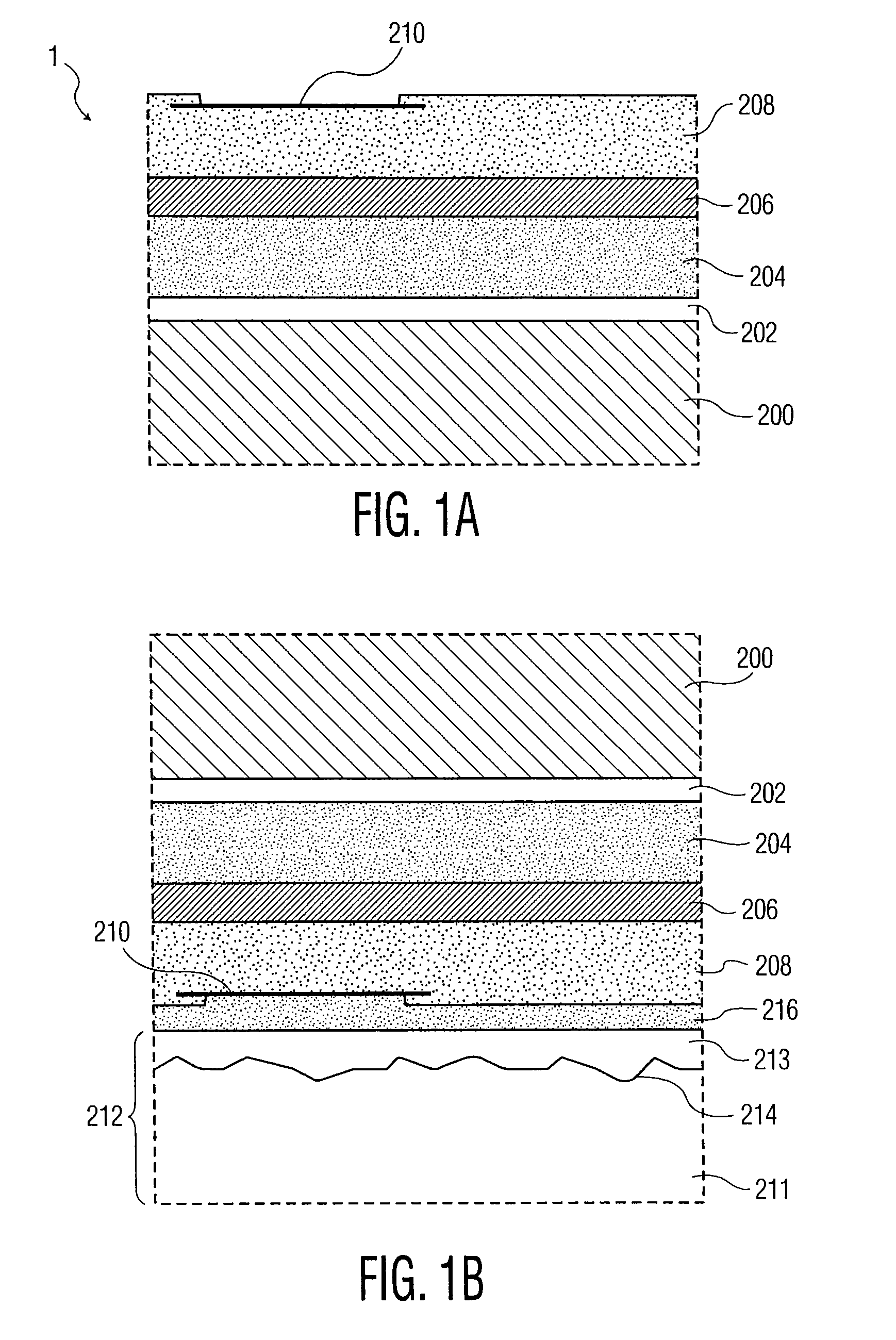

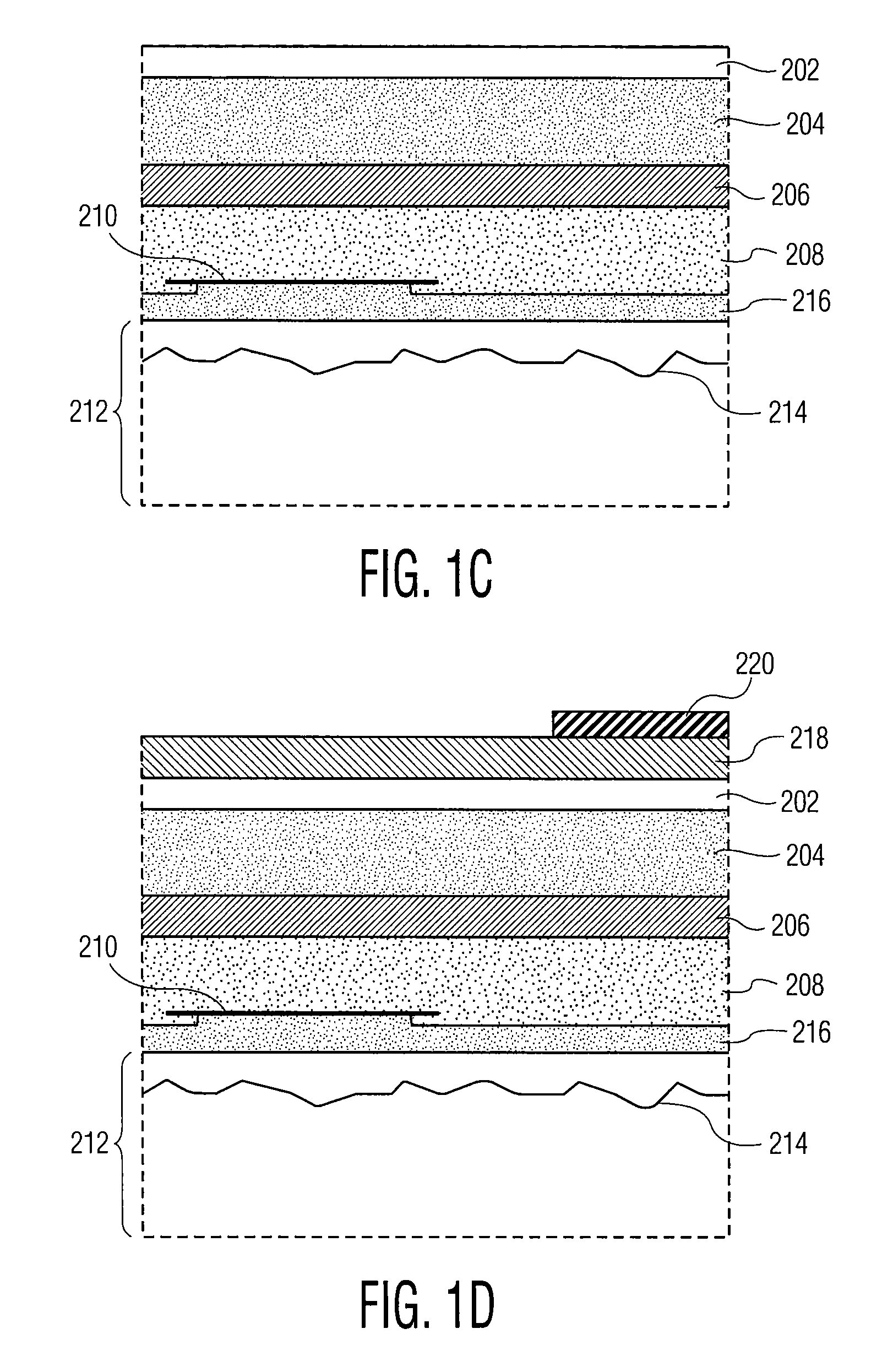

Photovoltaic Modules Manufactured Using Monolithic Module Assembly Techniques

InactiveUS20100012172A1Substantial electrical conductivityLower resistancePV power plantsPhotovoltaic energy generationRoll-to-roll processingFlexible circuits

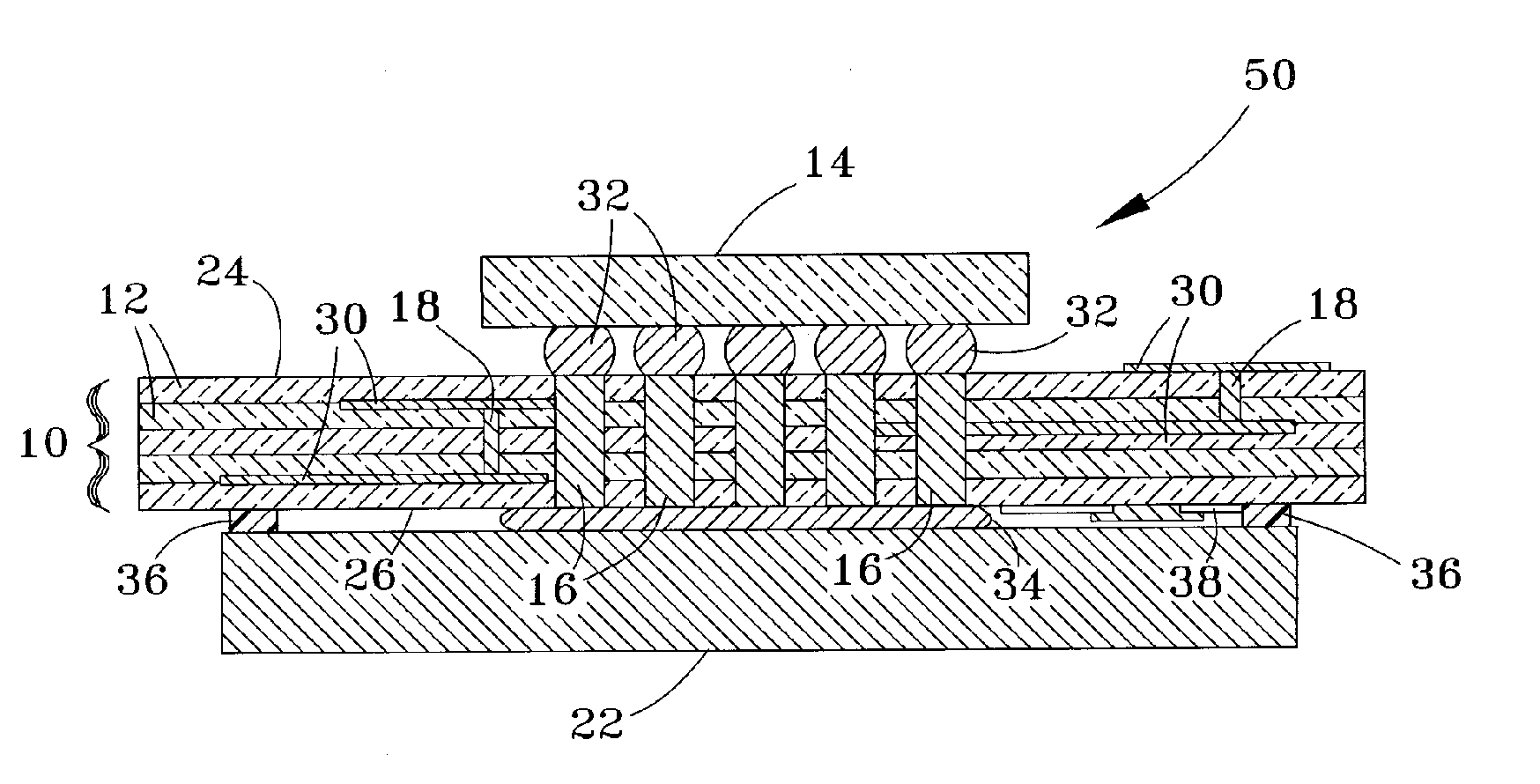

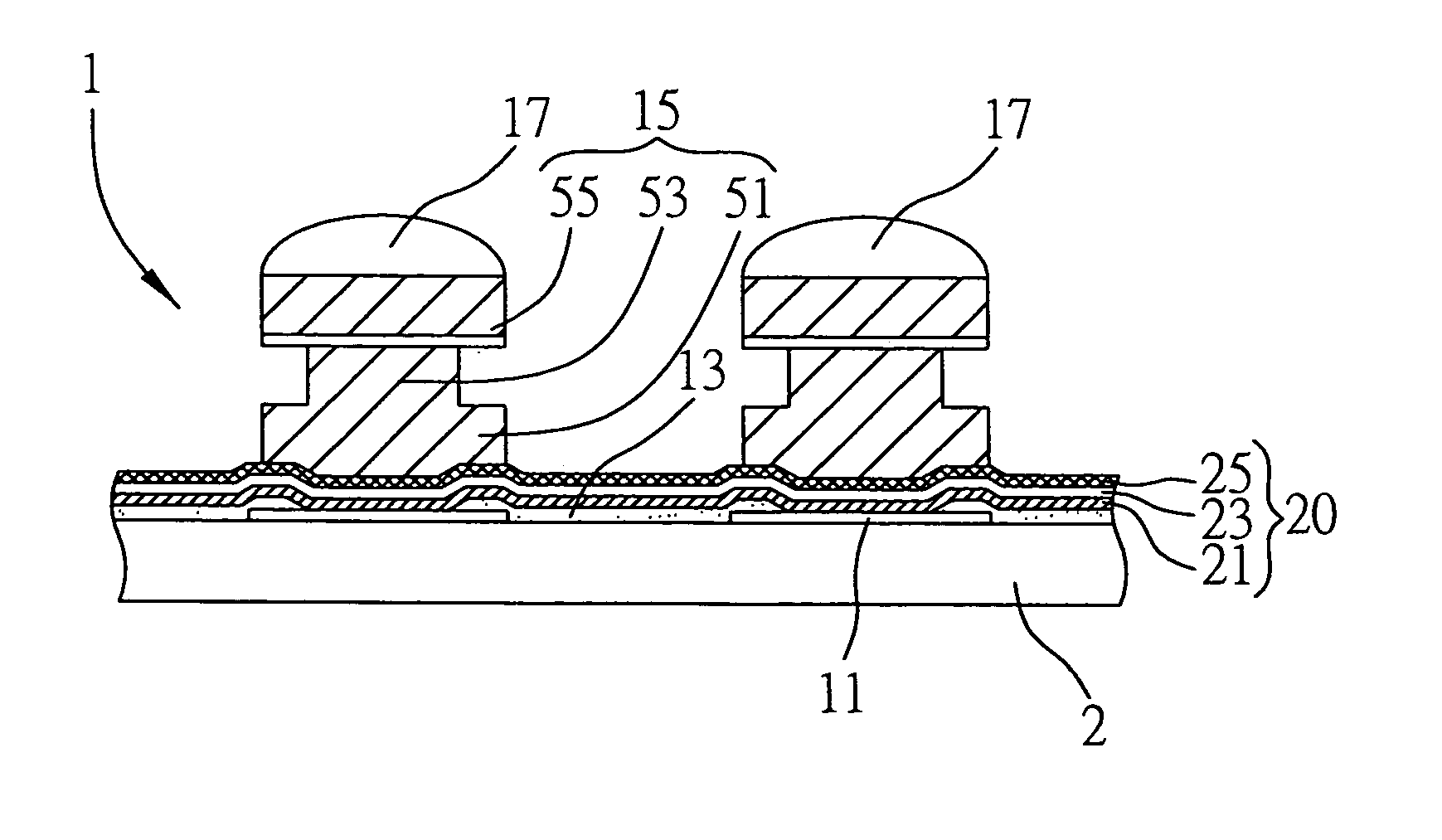

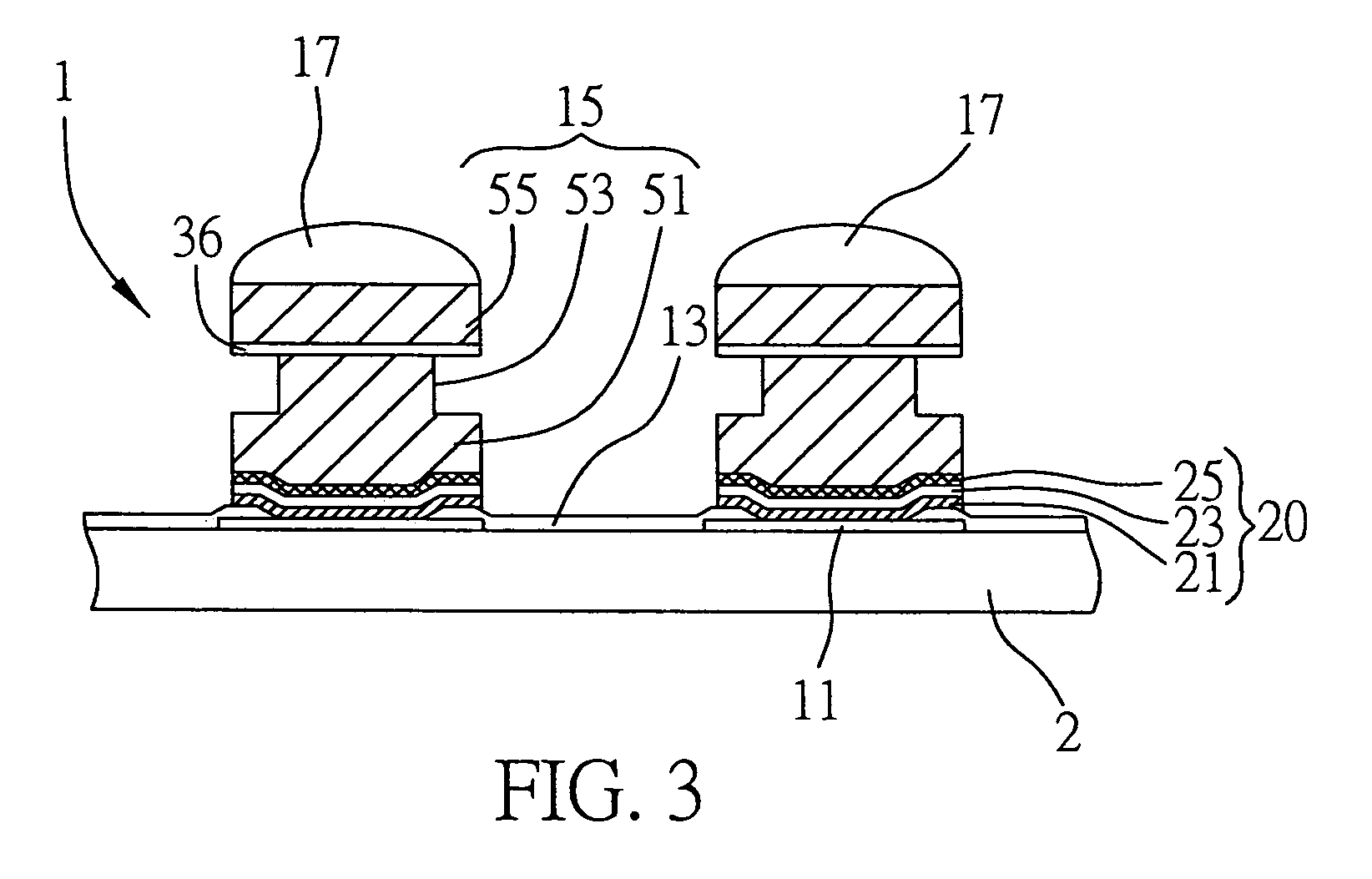

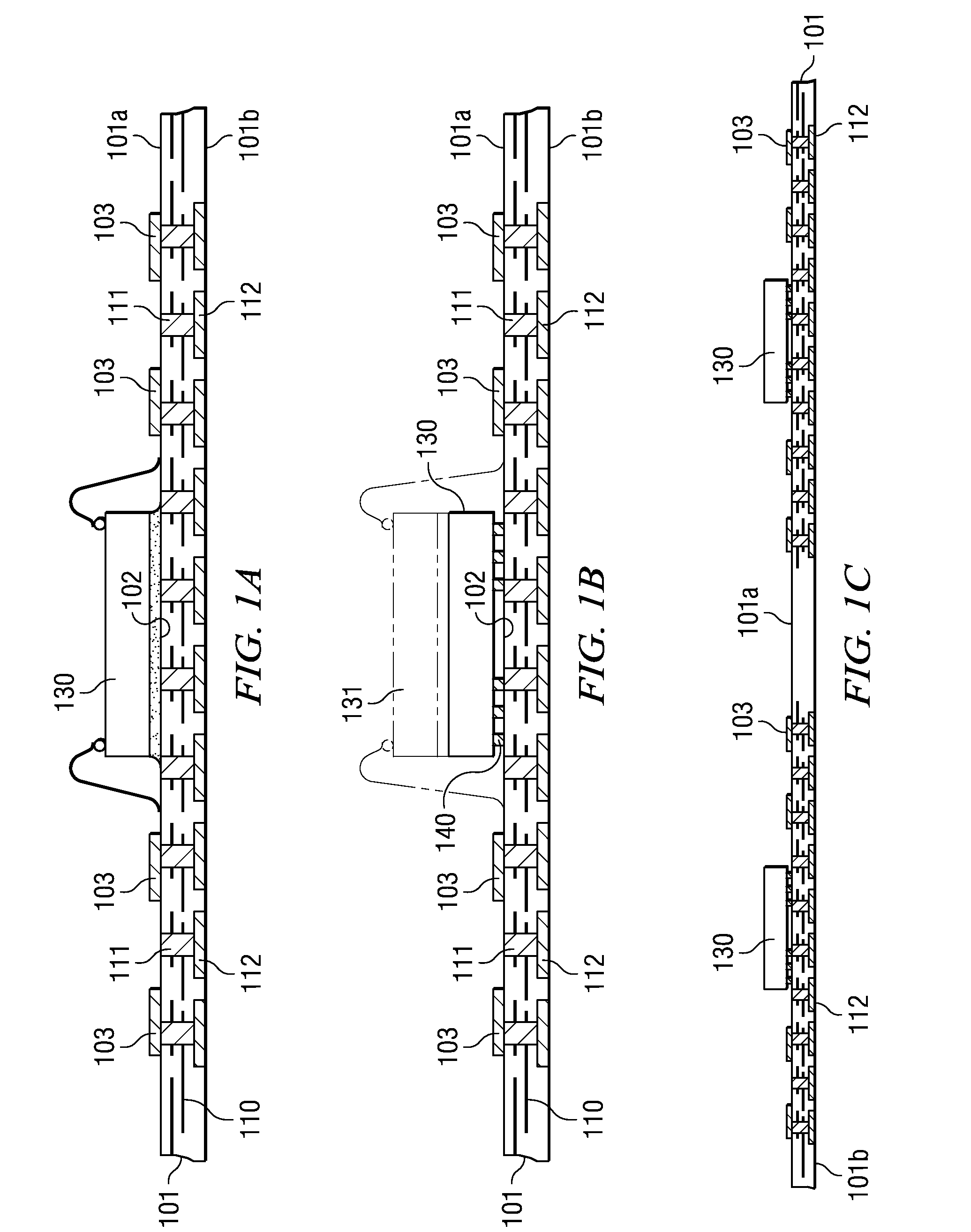

Photovoltaic modules comprising back-contact solar cells manufactured using monolithic module assembly techniques comprising a flexible circuit comprising a back sheet and a patterned metallization. The module may comprise busses in electrical contact with the patterned metallization to extract the current. The module may alternatively comprise multilevel metallizations. Interlayer dielectric comprising islands or dots relieves stresses due to thermal mismatch. The use of multiple cord plates enables flexible circuit layouts, thus optimizing the module. The modules preferably comprise a thermoplastic encapsulant and / or hybrid adhesive / solder materials. An ultrathin moisture barrier enables roll-to-roll processing.

Owner:APPLIED MATERIALS INC

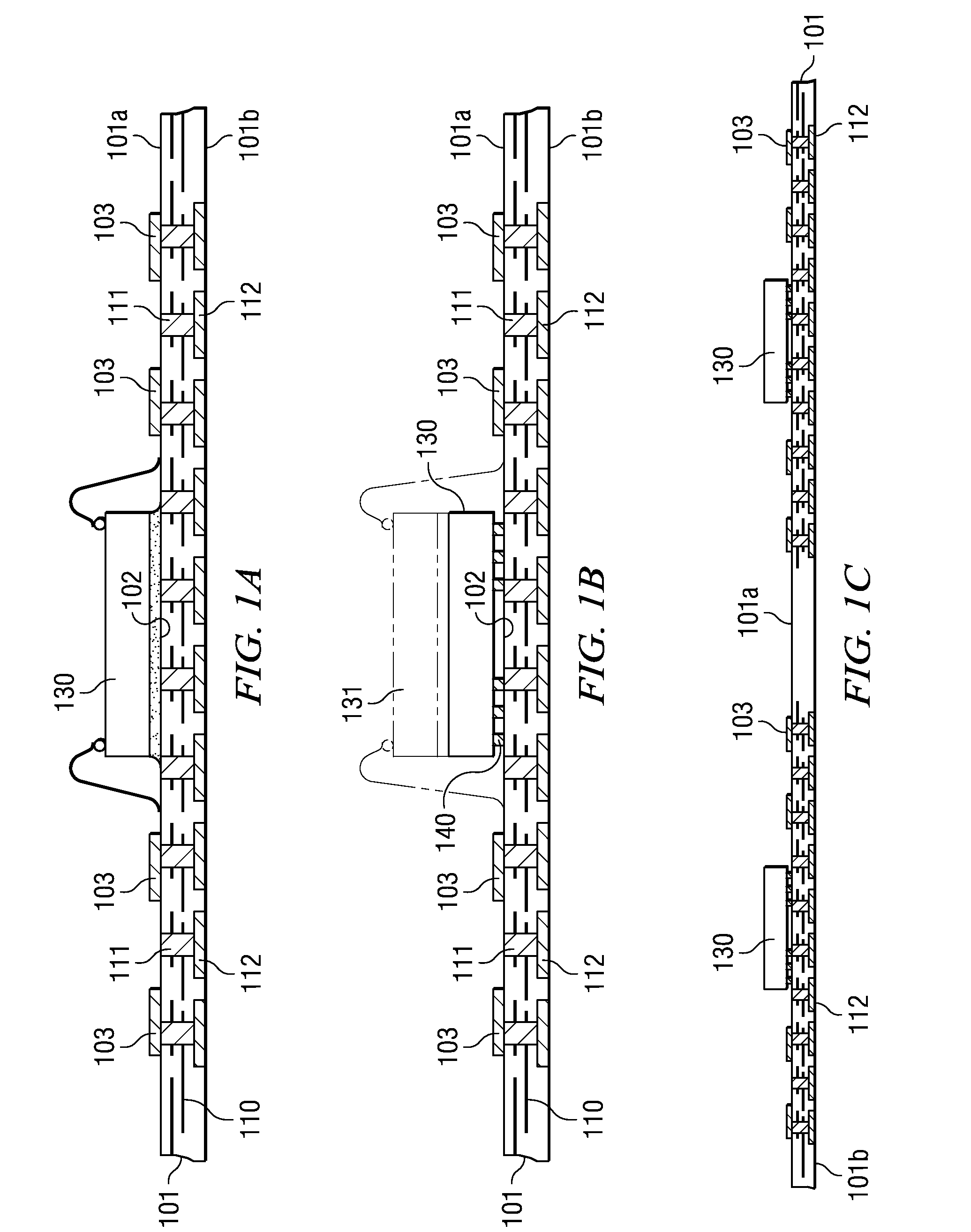

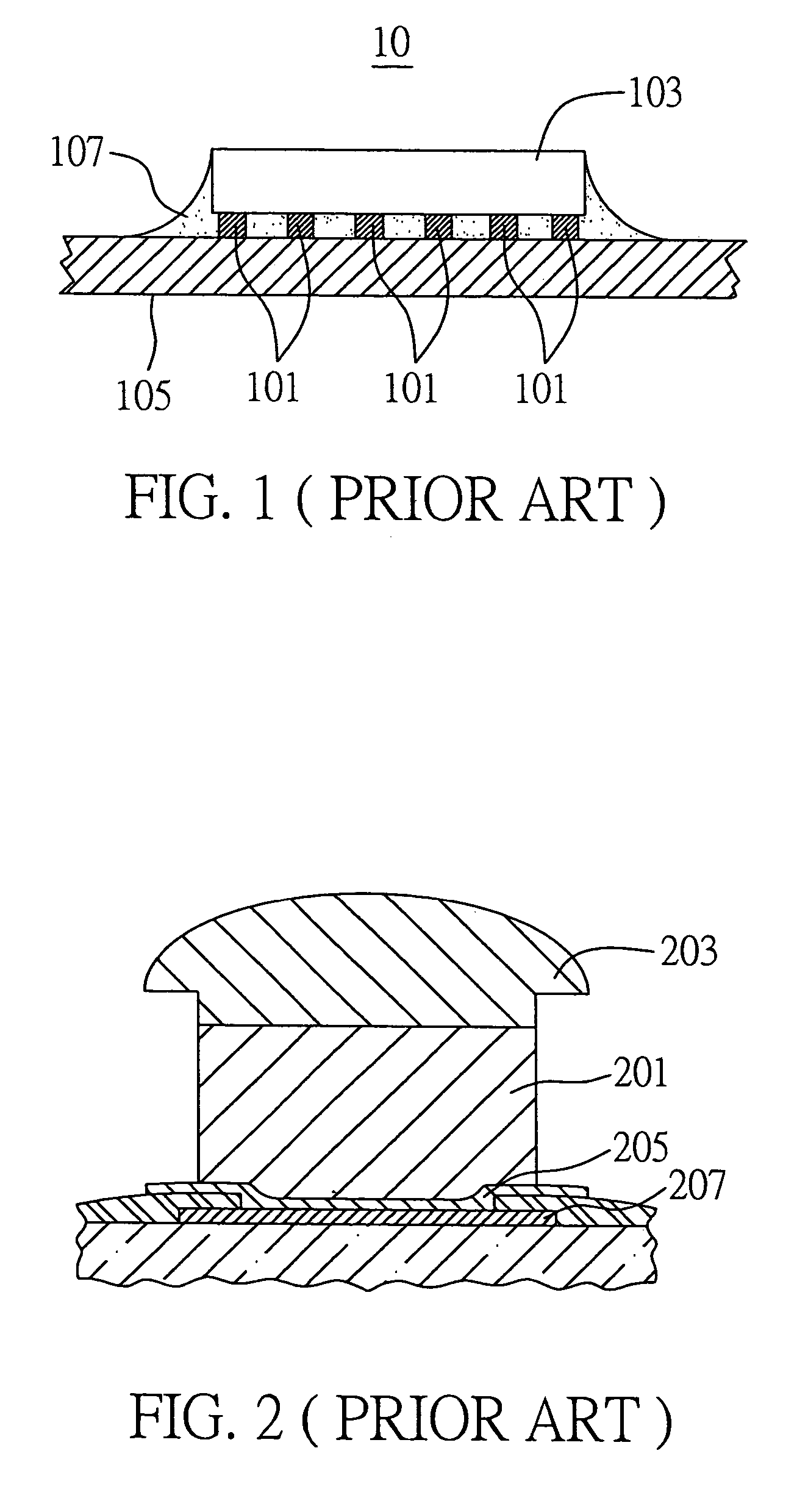

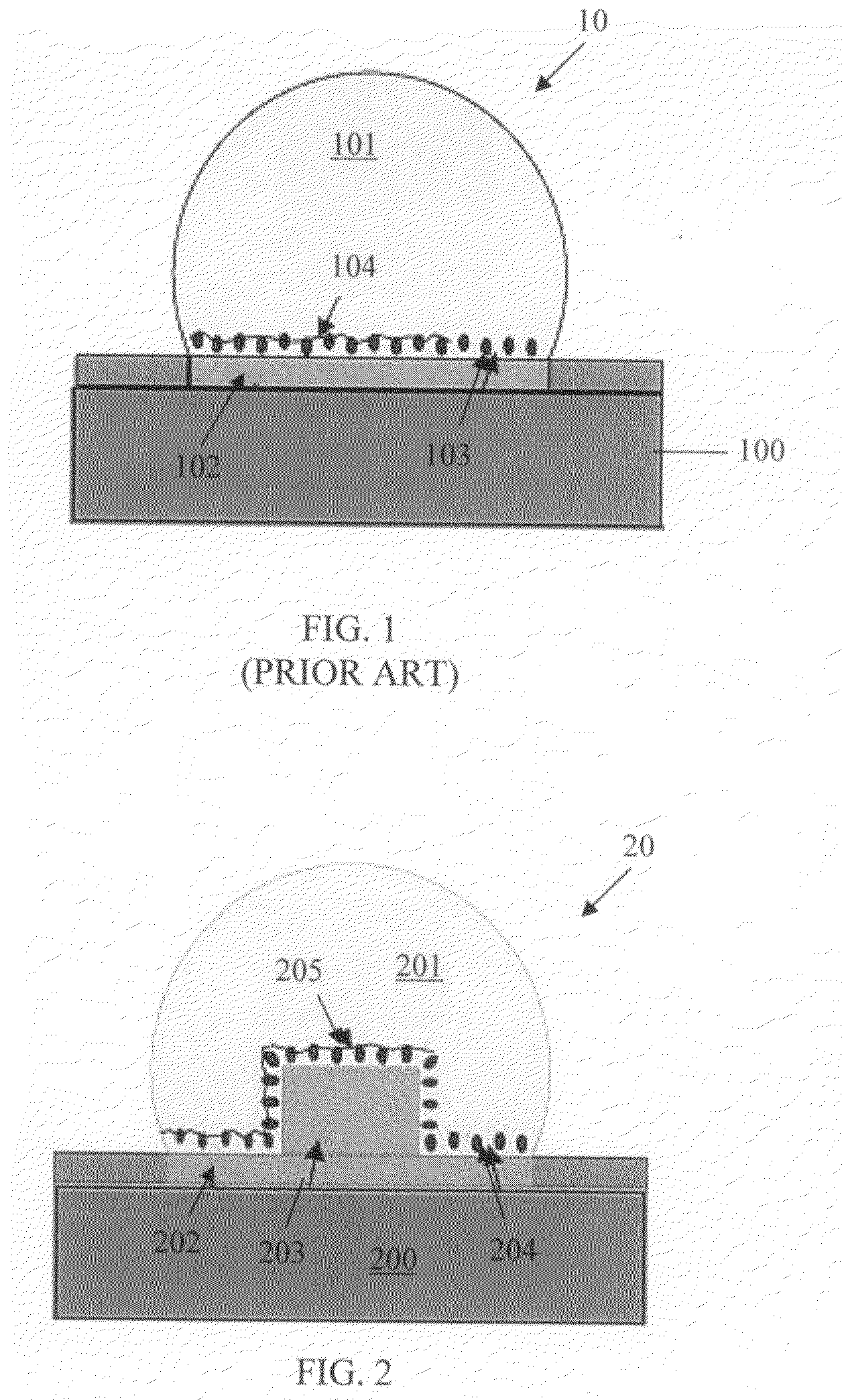

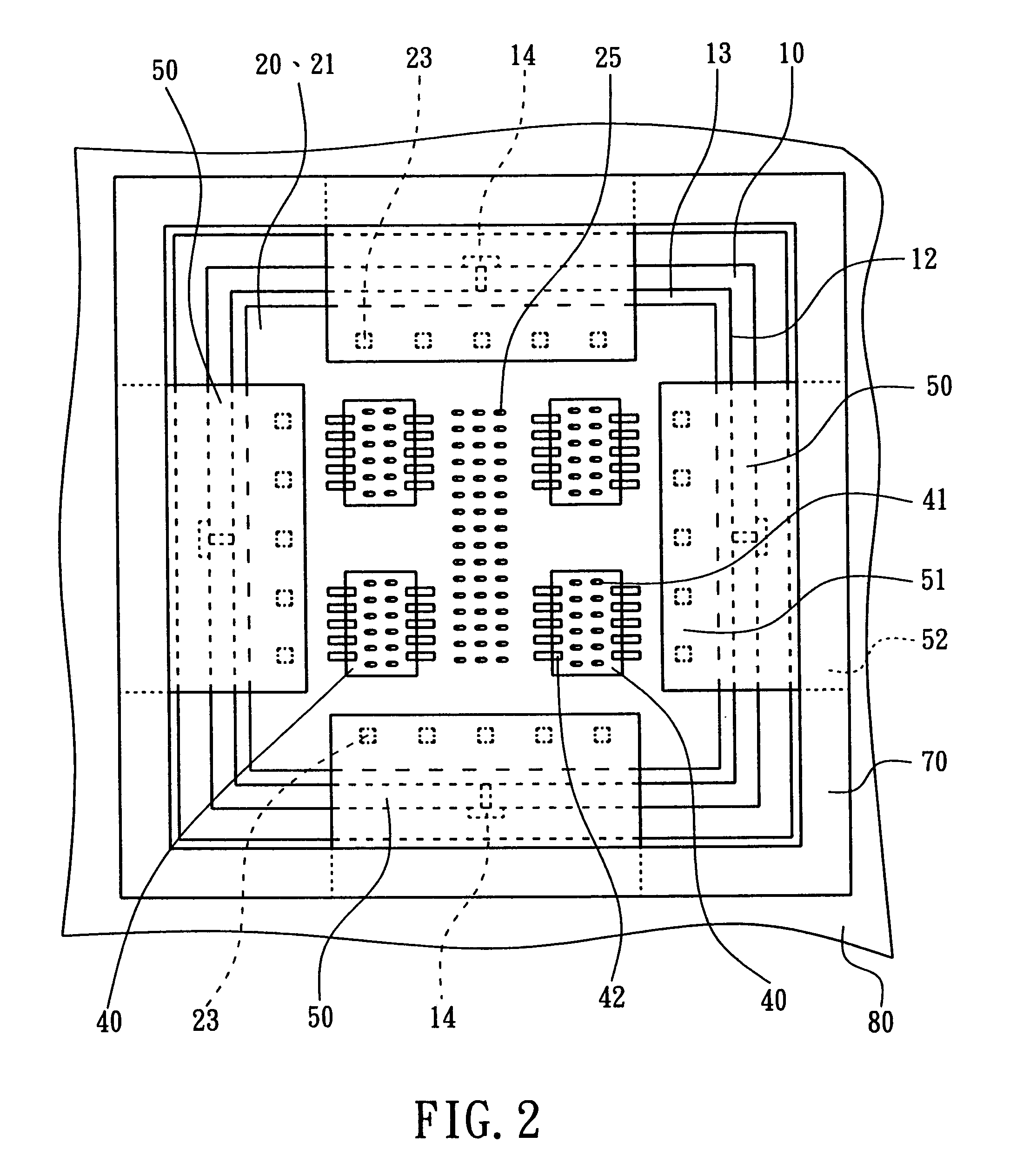

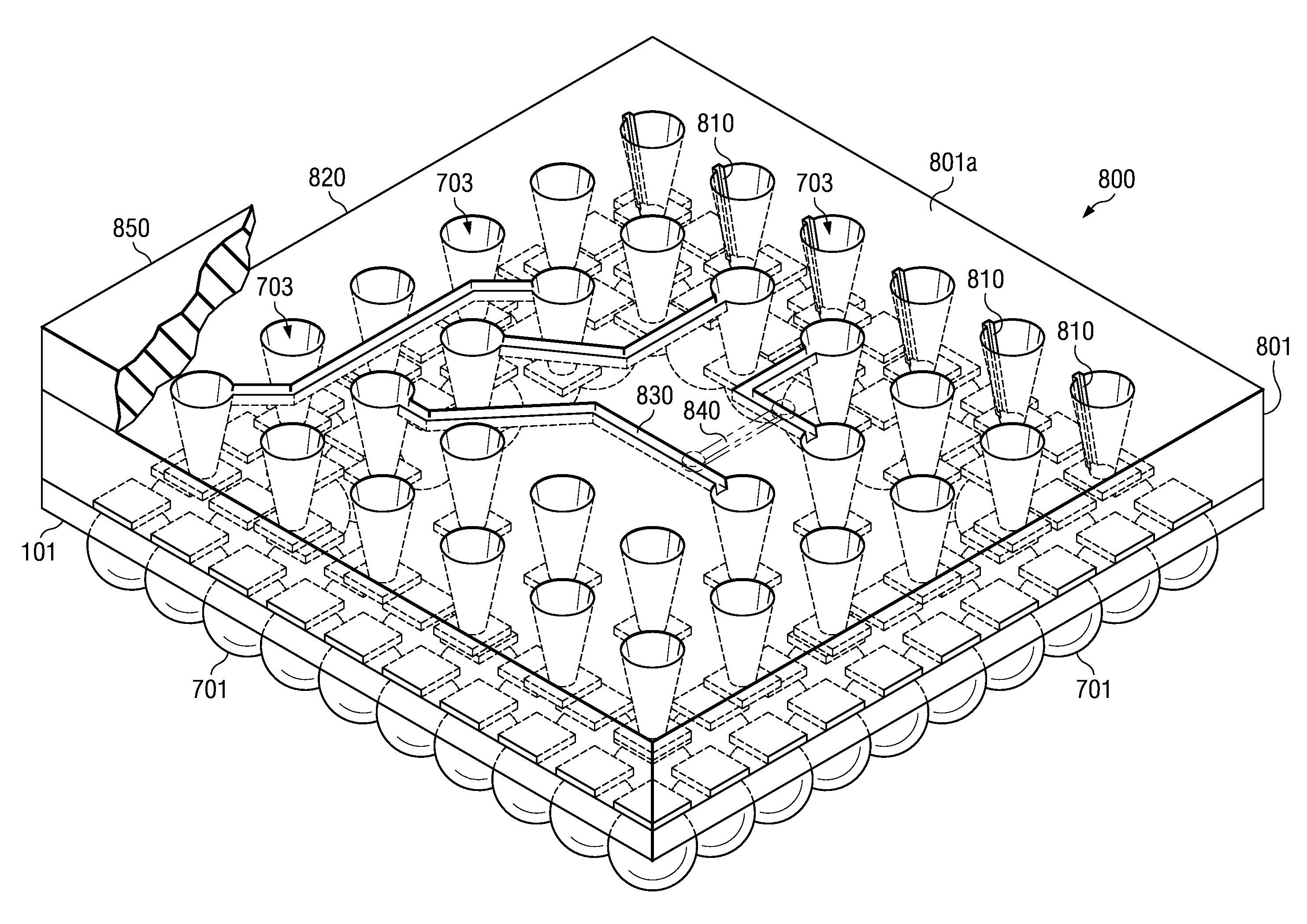

Array molded package-on-package having redistribution lines

ActiveUS20080315385A1Shorten the time to marketSimple methodSemiconductor/solid-state device detailsSolid-state devicesContact padCoupling

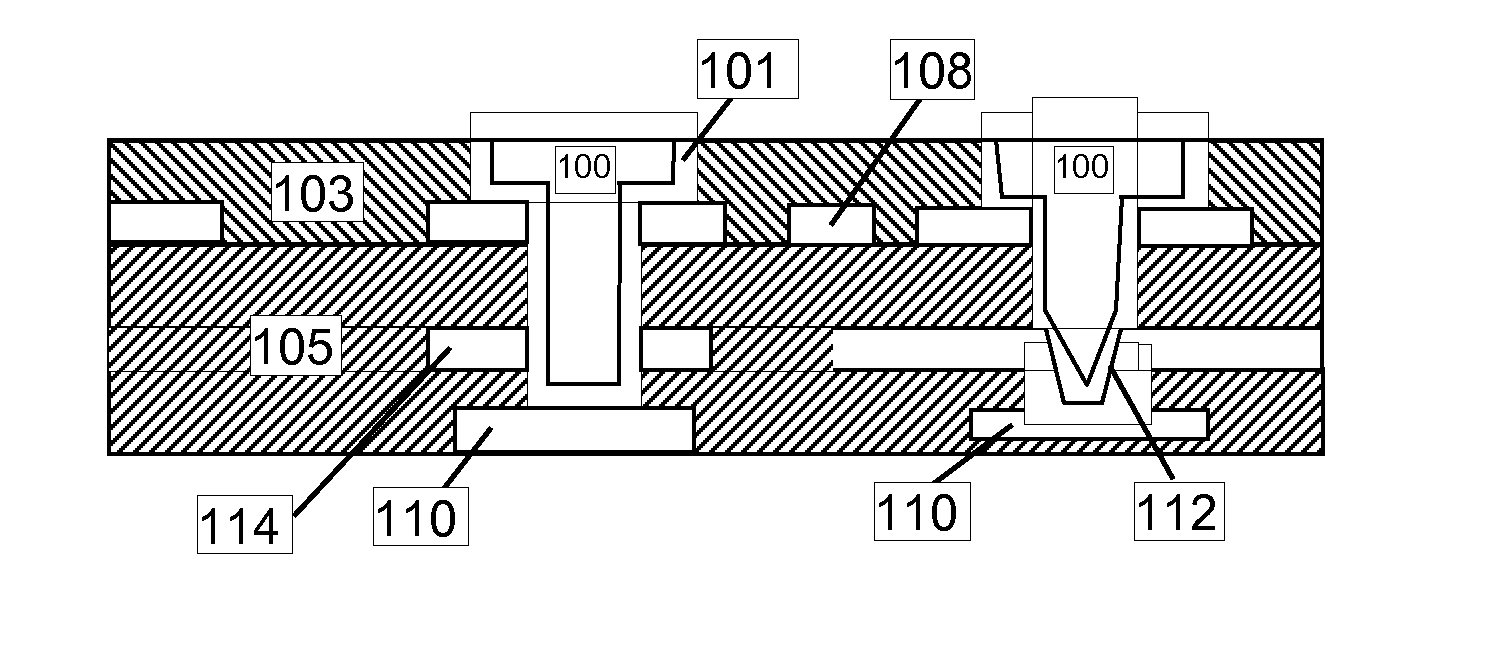

A semiconductor device with a sheet-like insulating substrate (101) integral with two or more patterned layers of conductive lines and vias, a chip attached to an assembly site, and contact pads (103) in pad locations has an encapsulated region on the top surface of the substrate, extending to the edge of the substrate, enclosing the chip, and having contact apertures (703) at the pad locations for external communication with the pad metal surfaces. The apertures may have not-smooth sidewall surfaces and may be filled with solder material (704) to contact the pads. Metal-filled surface grooves (710) in the encapsulated region, with smooth groove bottom and sidewalls, are selected to serve as customized routing interconnections, or redistribution lines, between selected apertures and thus to facilitate the coupling with another semiconductor device to form a package-on-package assembly.

Owner:TEXAS INSTR INC

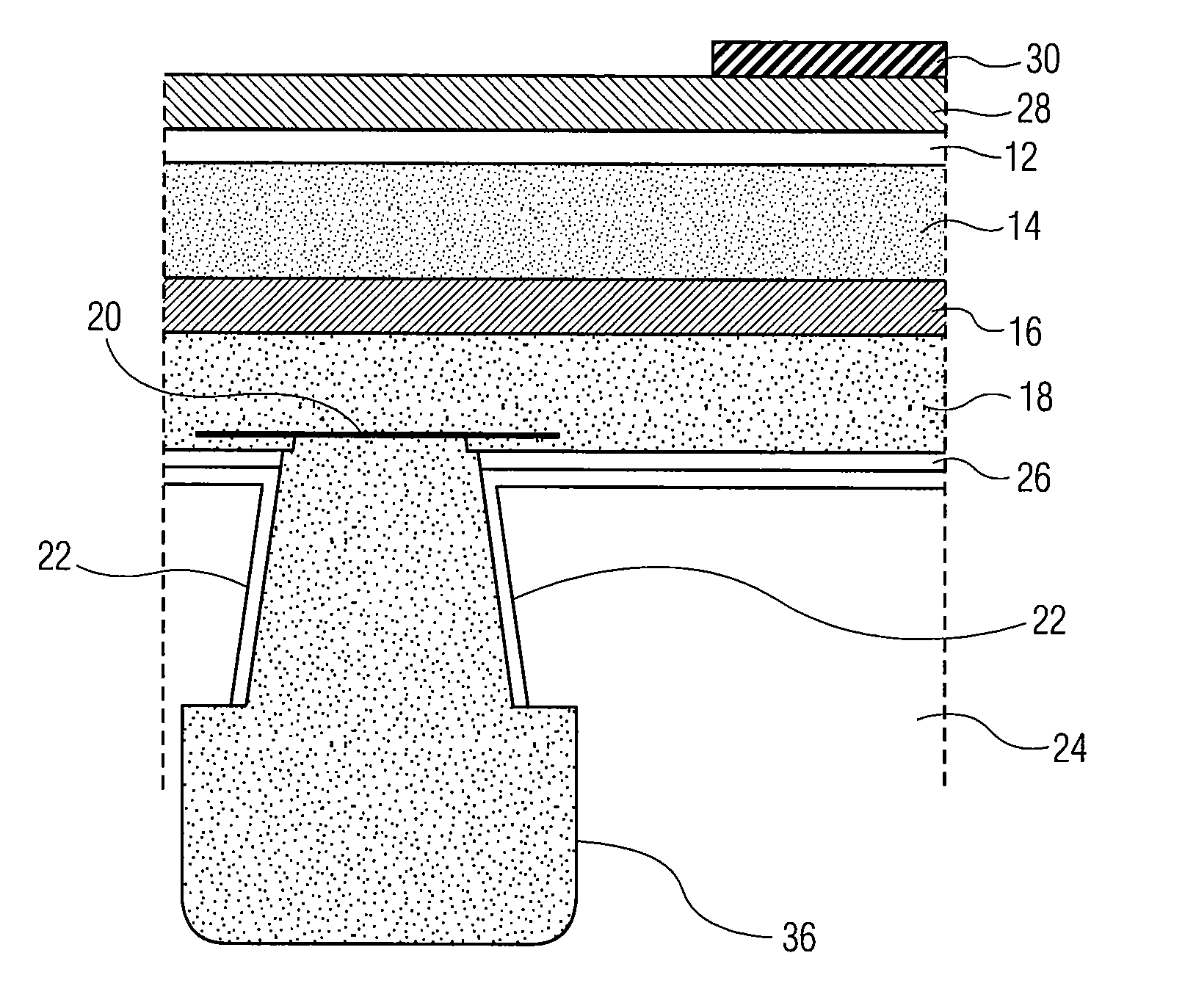

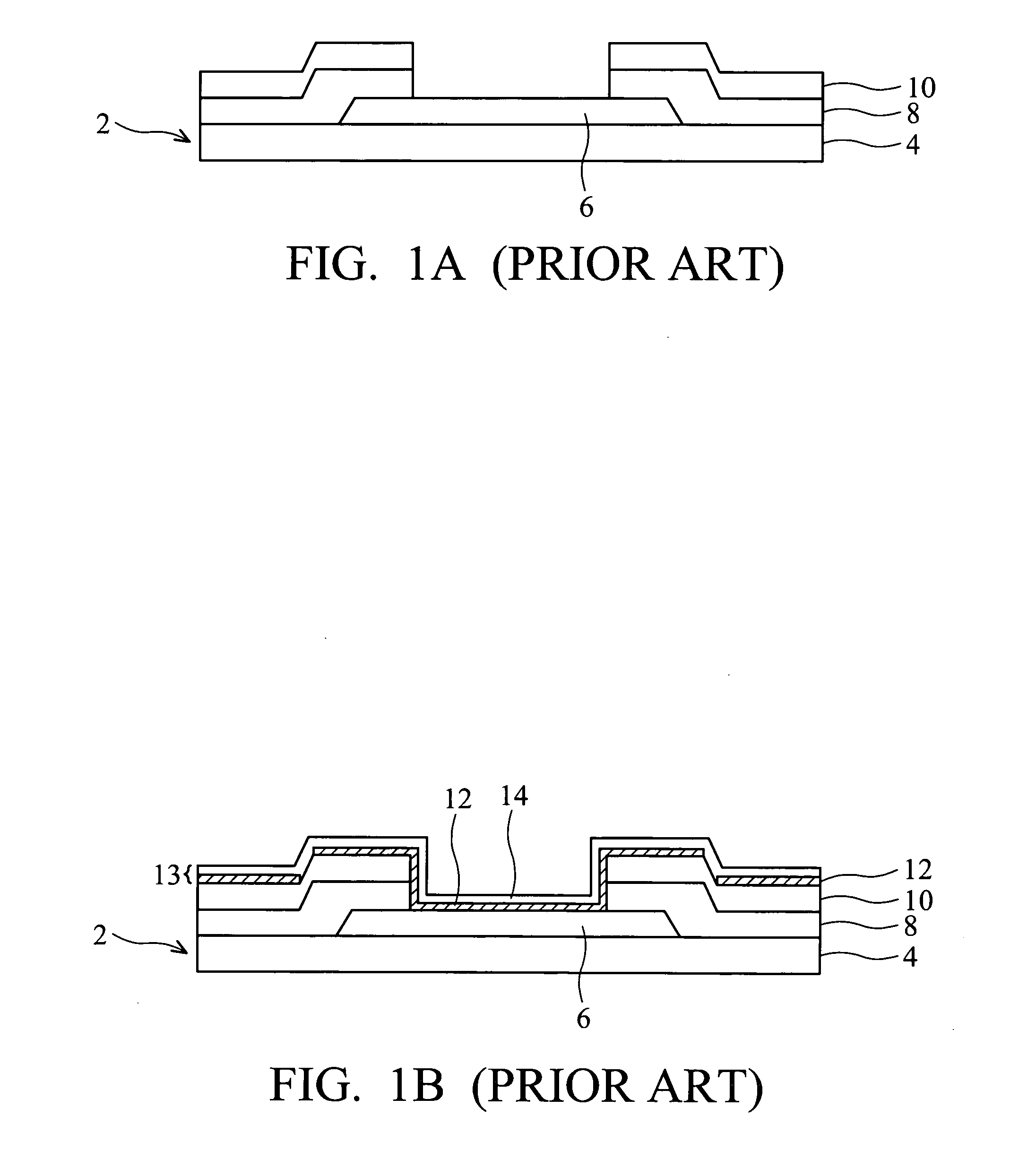

Construction methods for backside illuminated image sensors

InactiveUS20090174018A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringConductive materials

A method of constructing a backside illuminated image sensor is described. The method includes the steps of forming a semiconductor wafer, forming at least electrical contacts in the semiconductor wafer, forming, in a handle wafer separate from the semiconductor wafer, a plurality of via holes, attaching the semiconductor wafer to the handle wafer such that the via holes in the handle wafer are aligned with the respective electrical contacts on the semiconductor wafer, removing the substrate layer from the semiconductor wafer, removing at least a portion of the handle wafer to expose the plurality of via holes, filling each of the exposed via holes with a conductive material and applying a solder material to each of the exposed via holes such that the conductive material in each of the via holes is electrically connected to the solder material.

Owner:APTINA IMAGING CORP

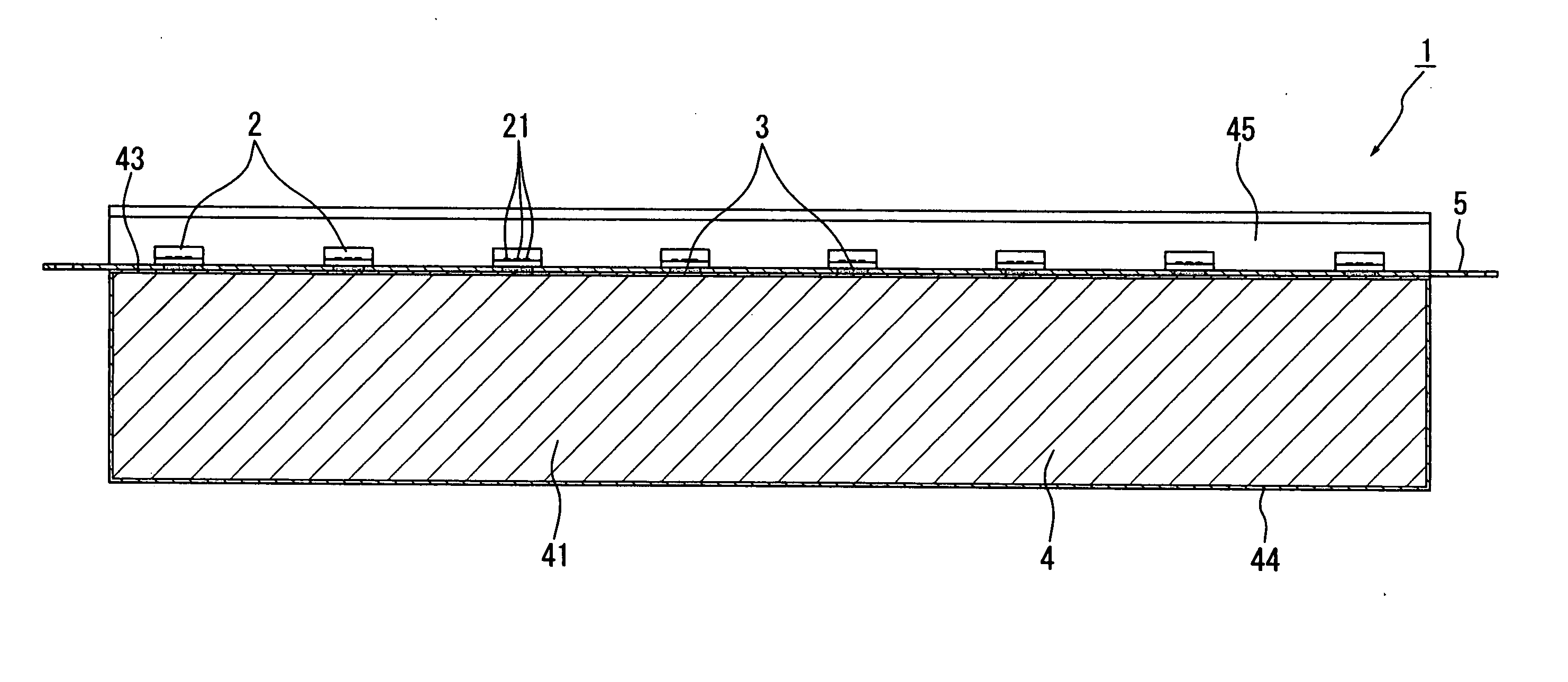

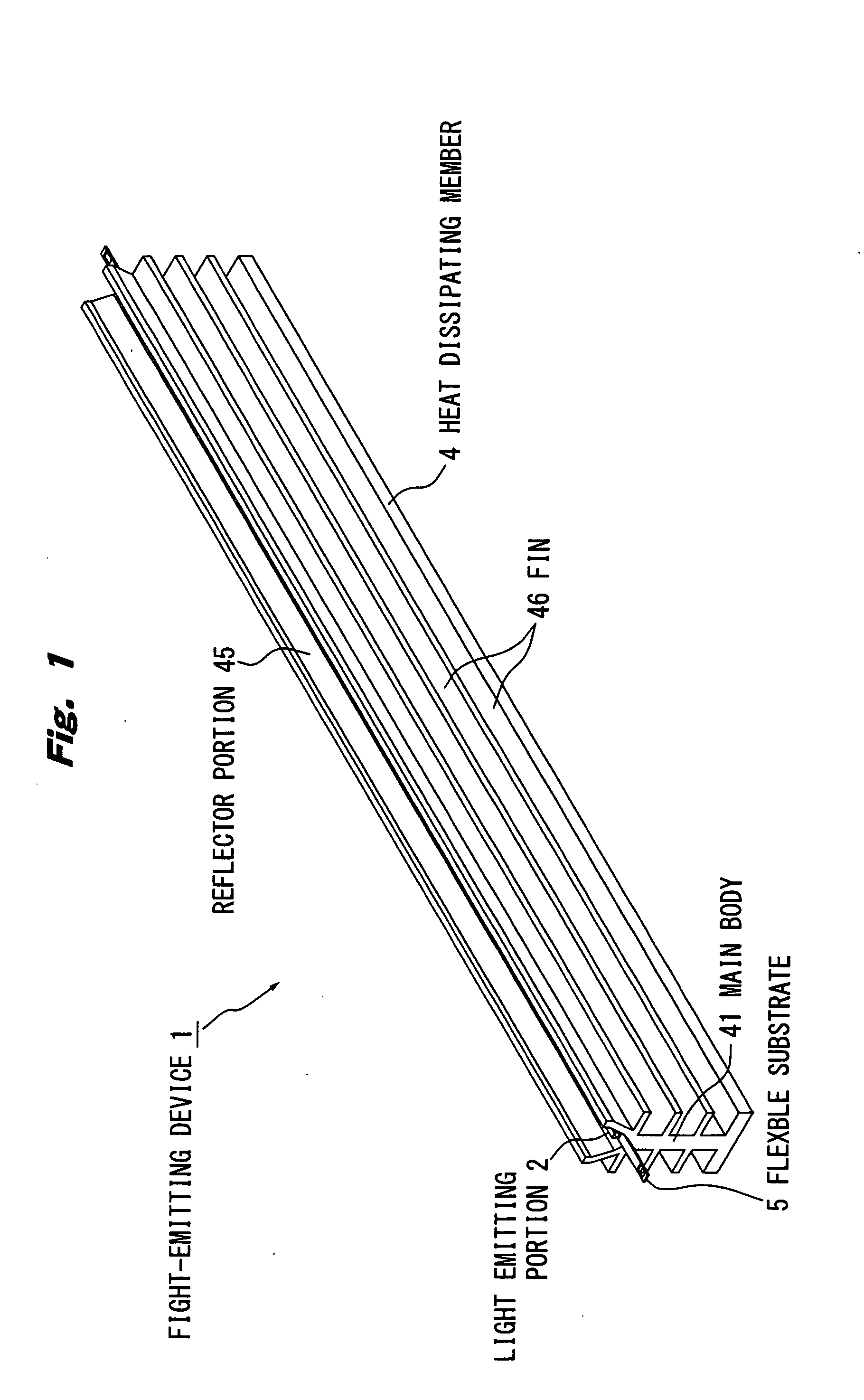

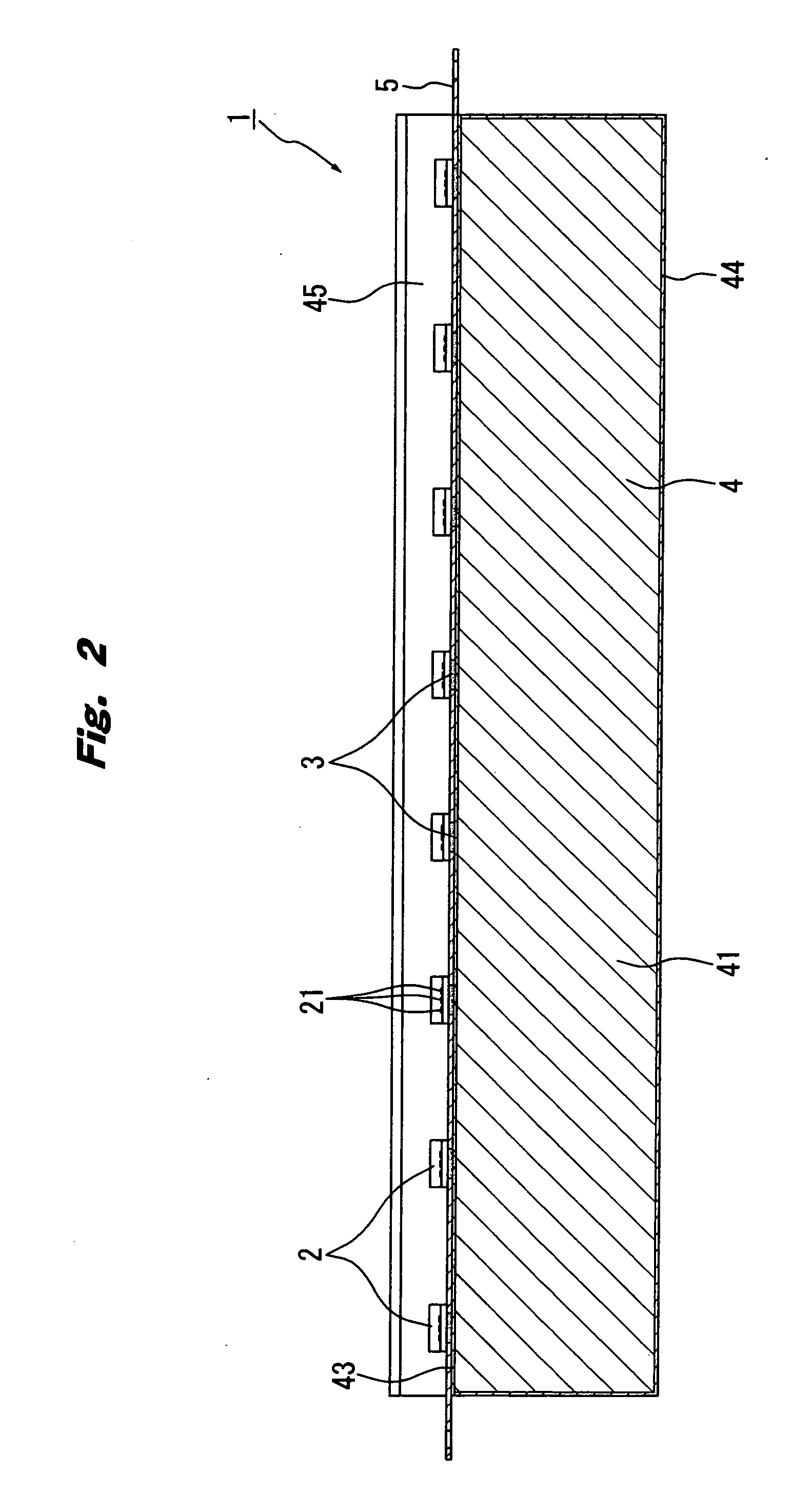

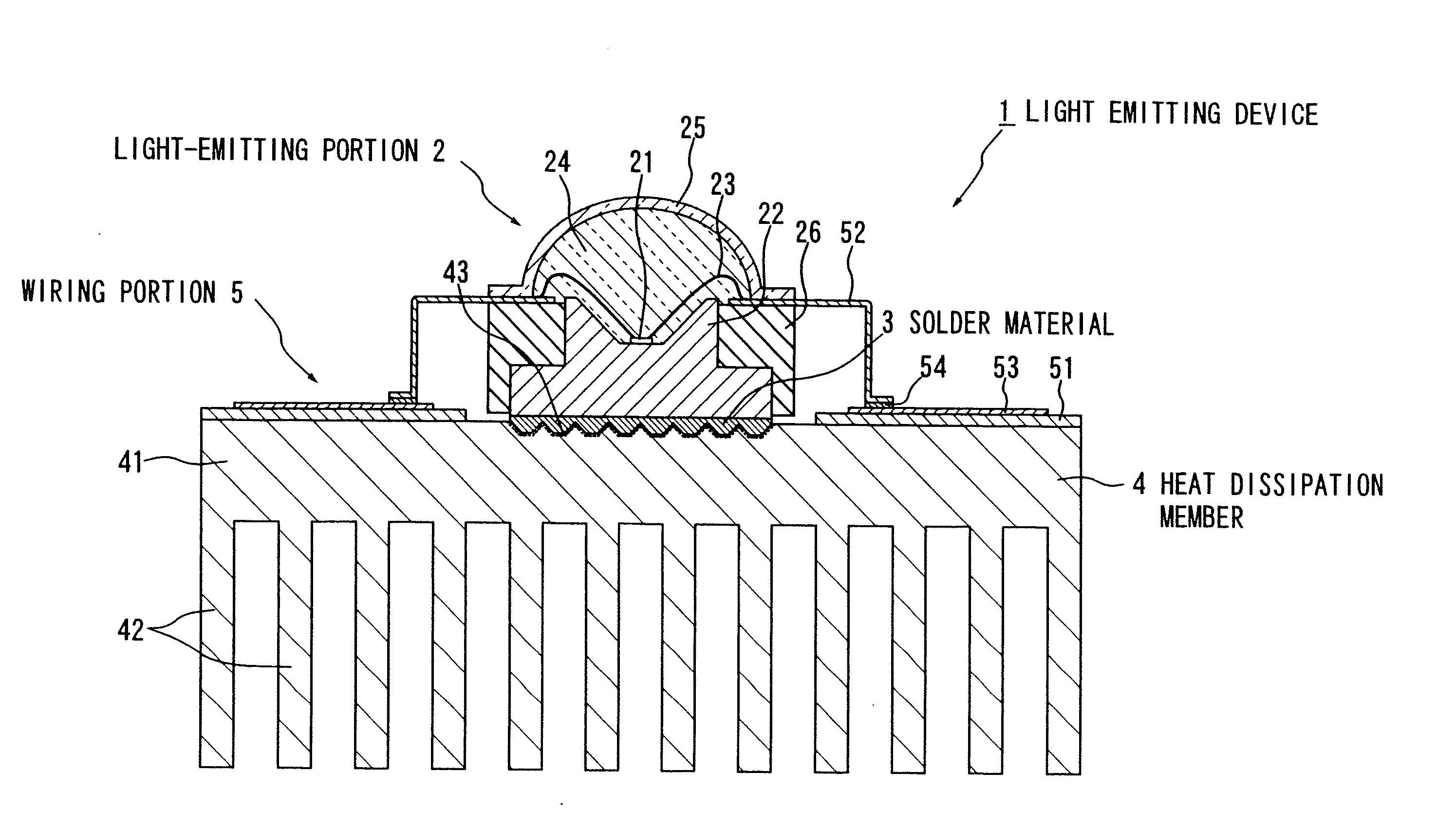

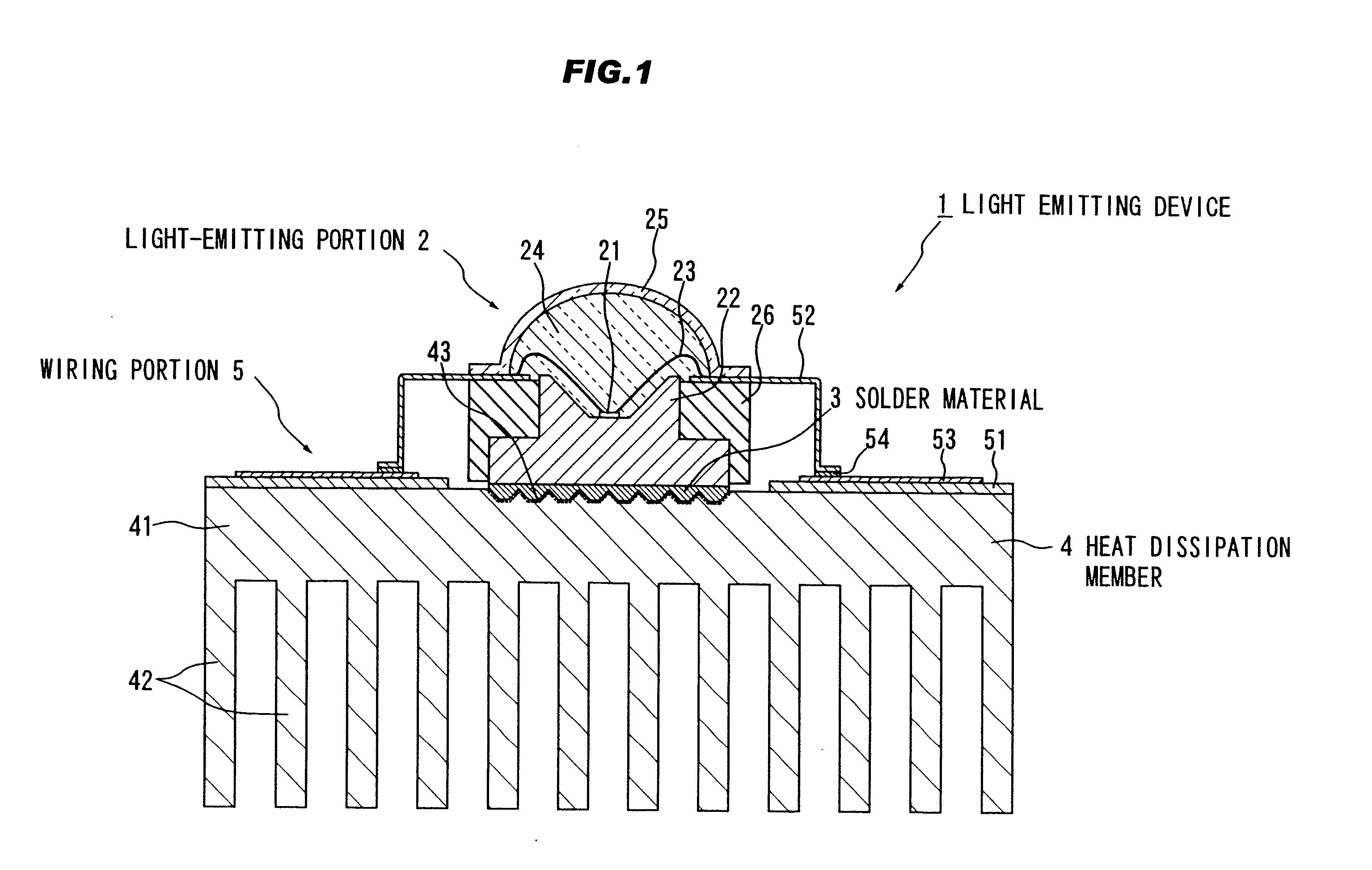

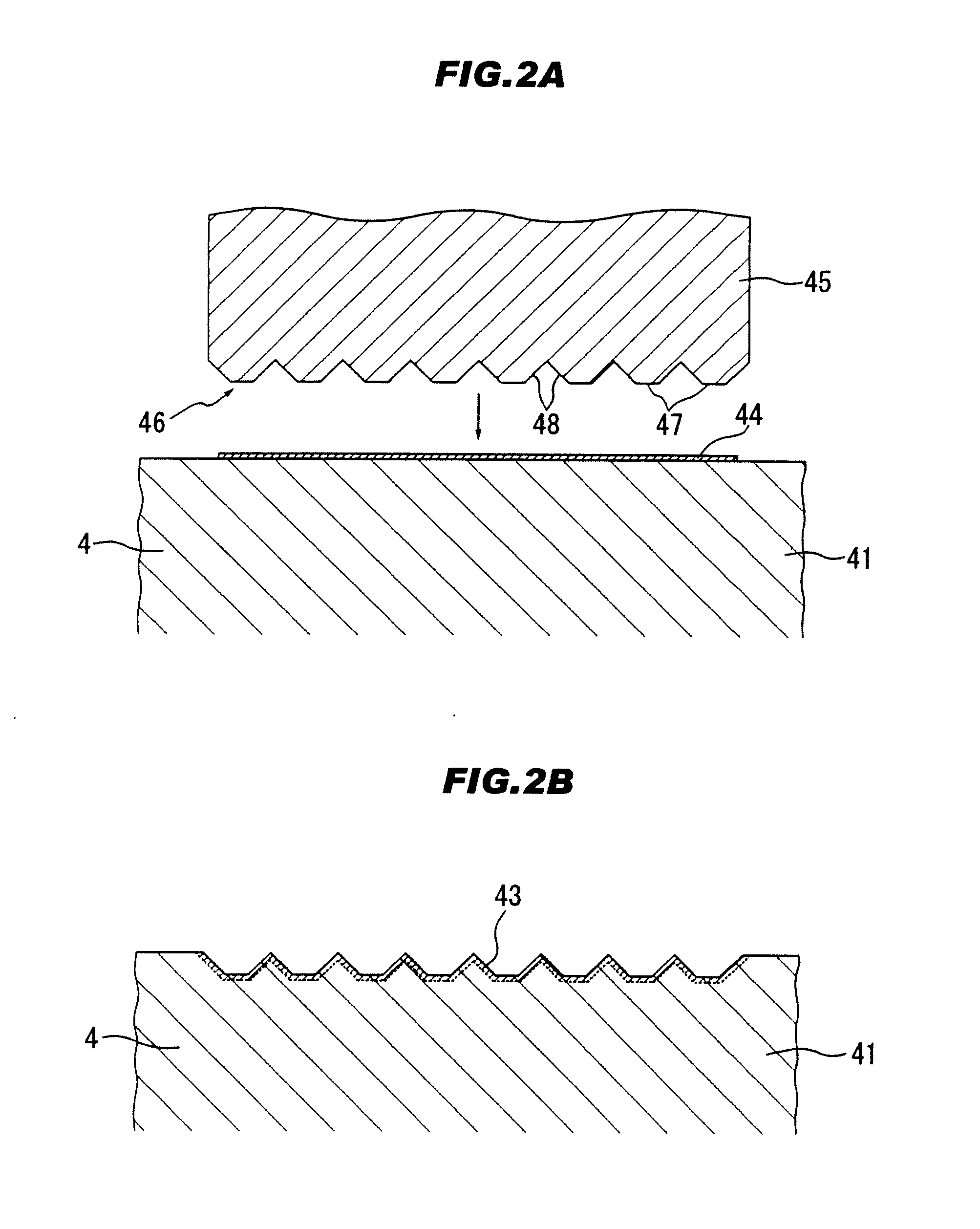

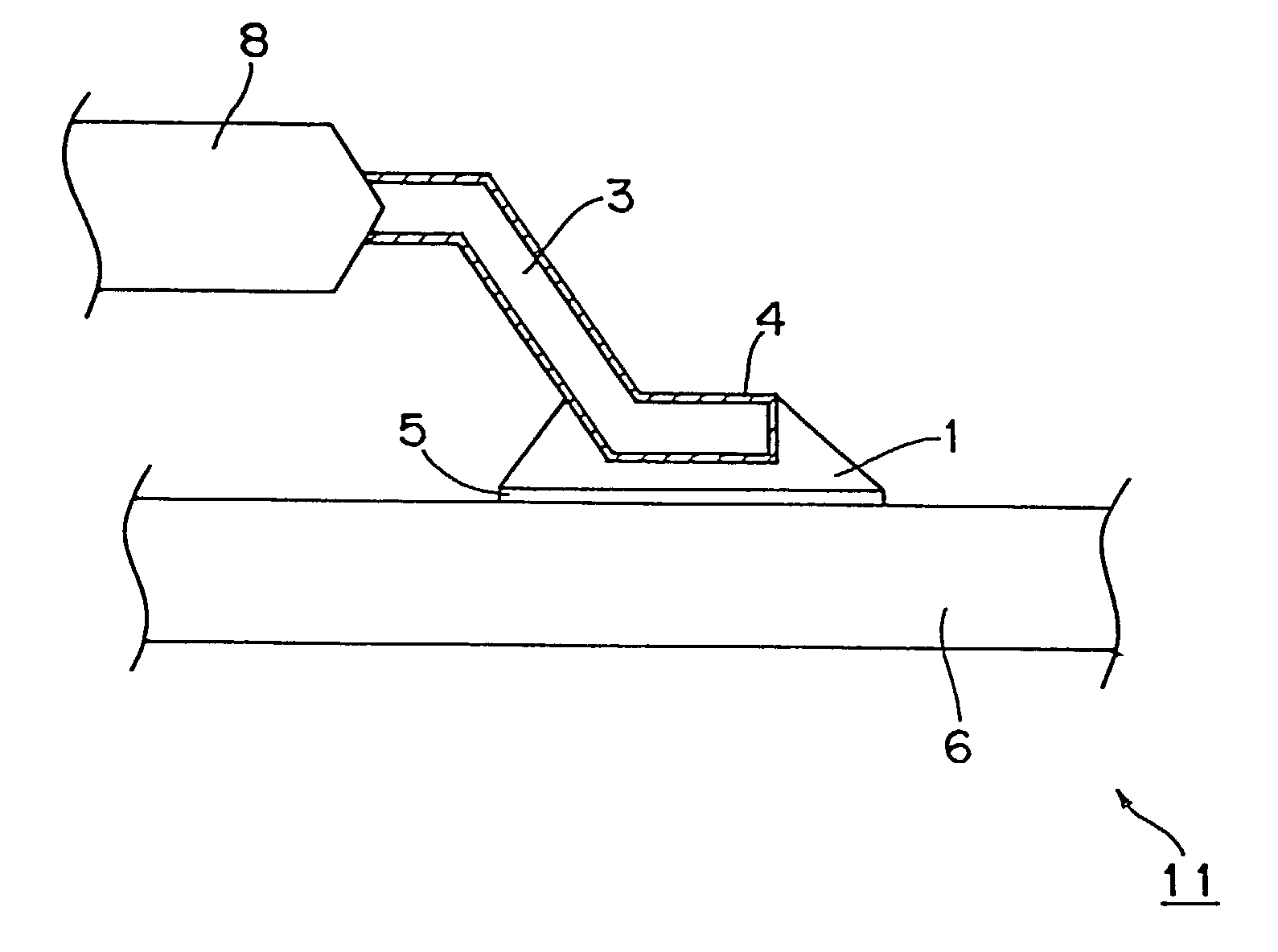

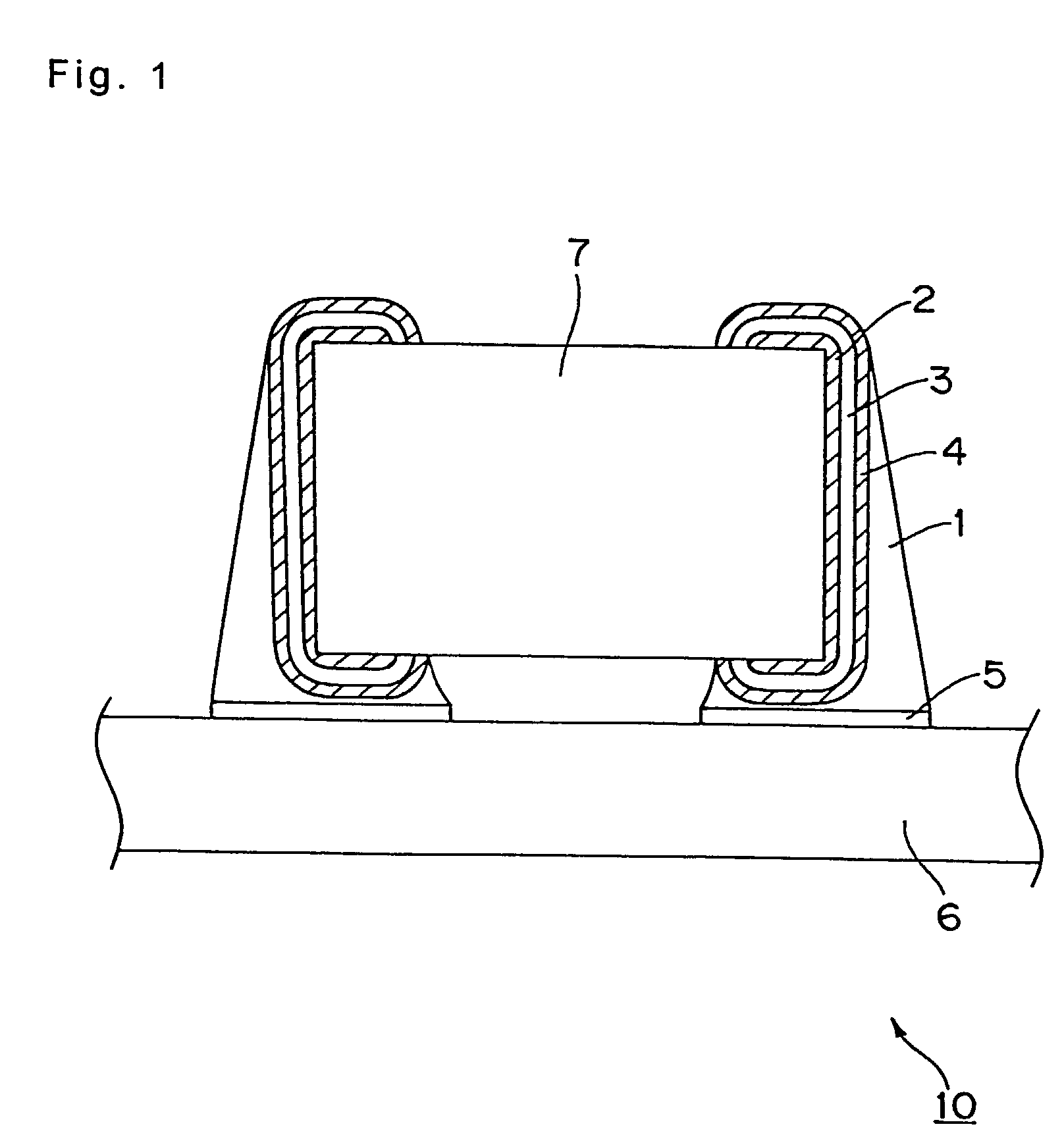

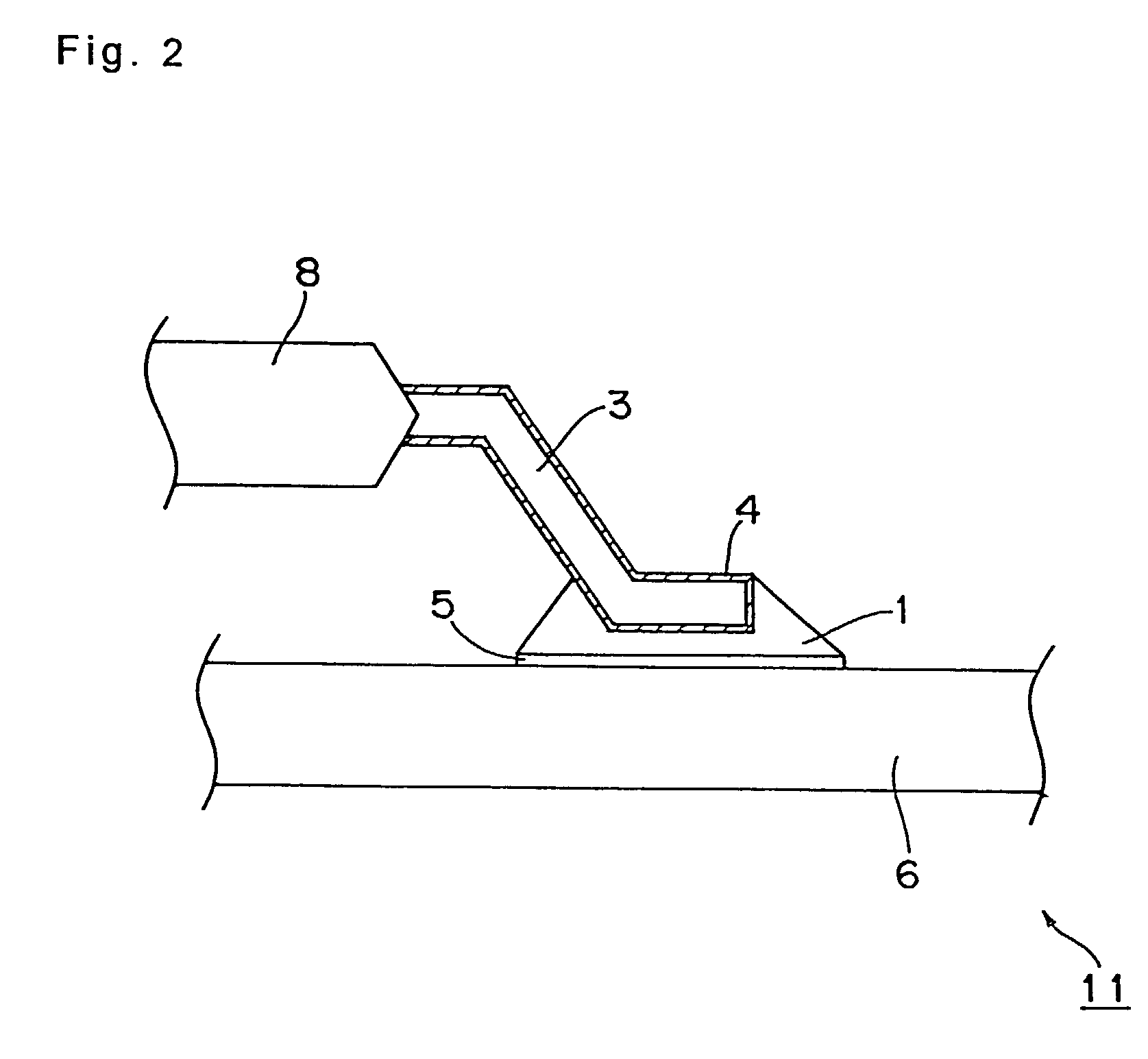

Light-emitting device and method of manufacturing the same

InactiveUS20100214777A1Increase the number ofImprove cooling efficiencyLighting support devicesPoint-like light sourceLight emitting deviceSemiconductor

A light-emitting device includes a light emitting portion comprising a substrate having a mounting surface for mounting a LED element and a metal portion formed on a surface of the substrate opposite to the mounting surface, the substrate comprising ceramic or a semiconductor and the metal portion being bondable to a solder material and a heat dissipating member comprising aluminum, aluminum alloy, magnesium or magnesium alloy, and having, on a surface thereof, a junction treated so as to be bondable to the solder material and a heat dissipating film formed in a periphery of the junction, wherein the metal portion of the light emitting portion is bonded to the junction of the heat dissipating member by the solder material.

Owner:TOYODA GOSEI CO LTD

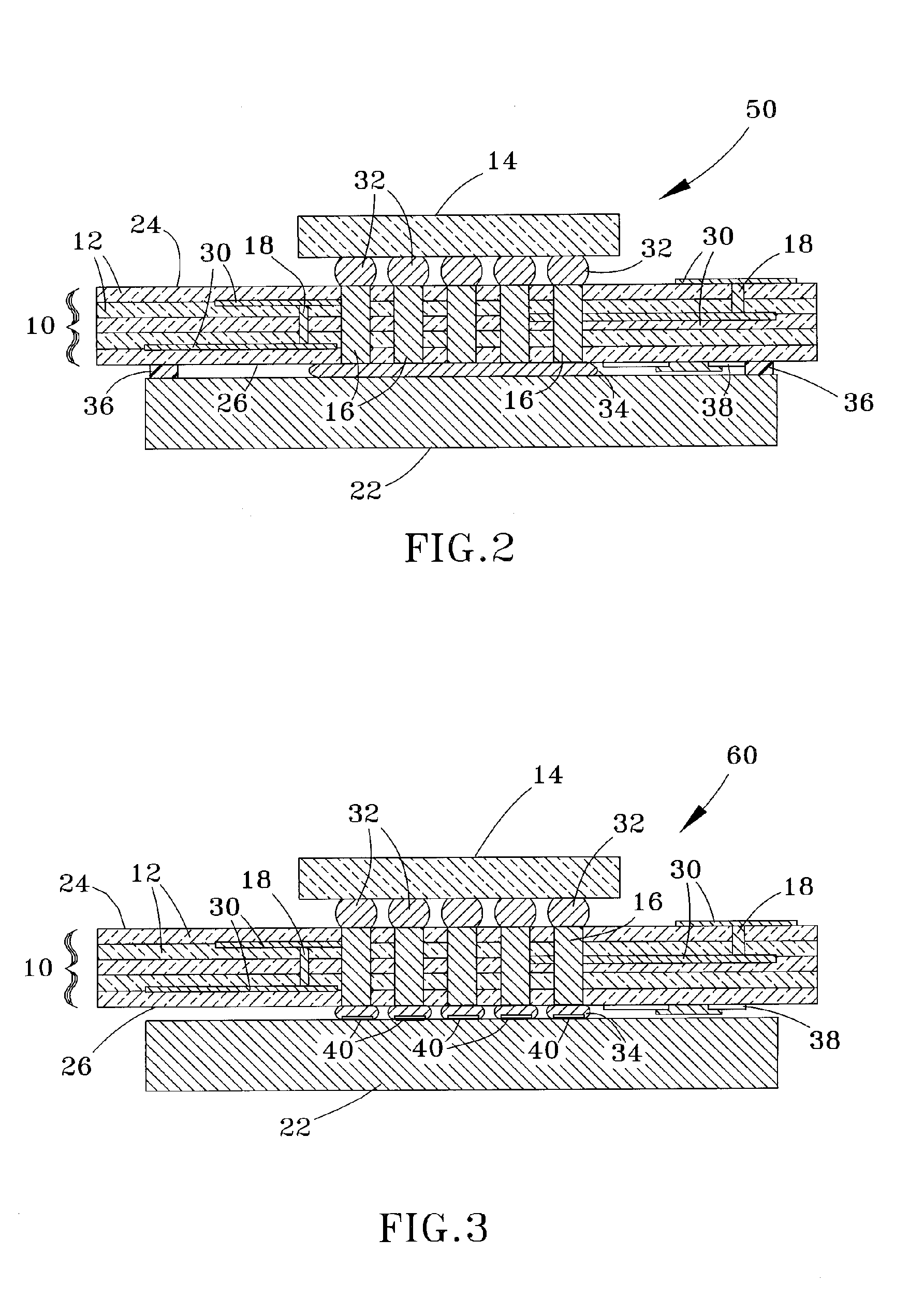

Thermal management of surface-mount circuit devices on laminate ceramic substrate

InactiveUS20060109632A1Improved thermal managementSemiconductor/solid-state device detailsPrinted circuit aspectsSurface mountingPower circuits

Owner:DELPHI TECH INC

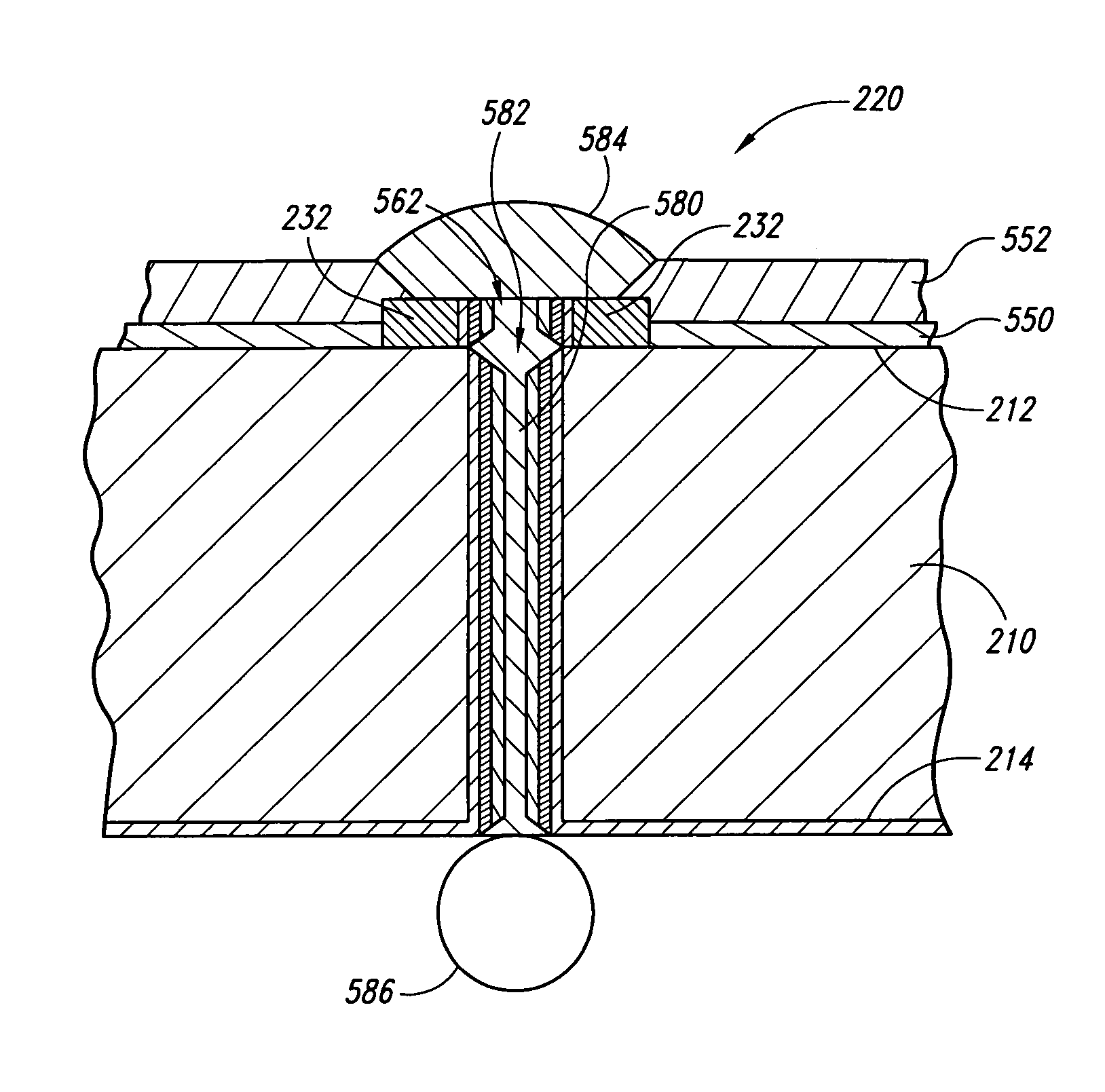

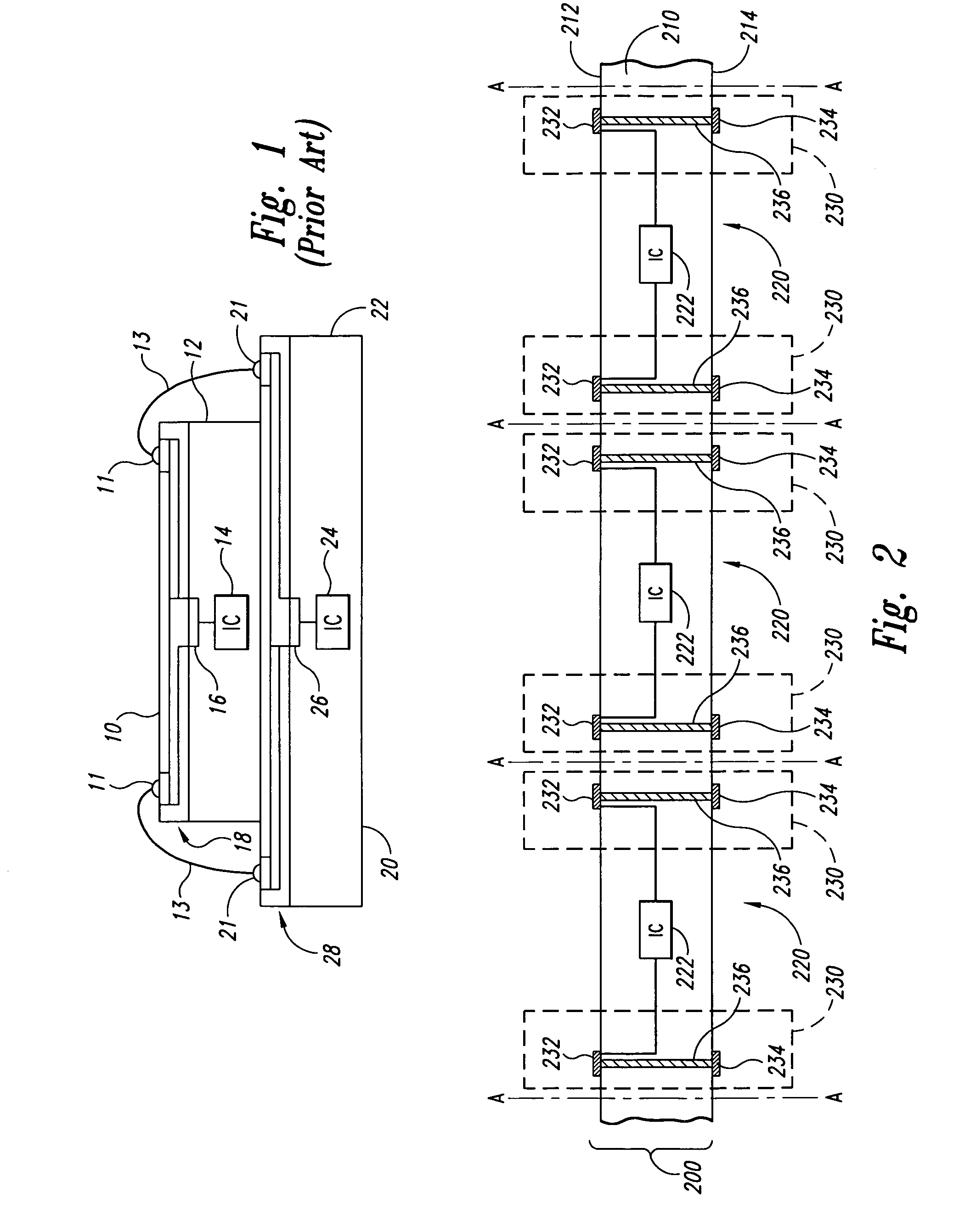

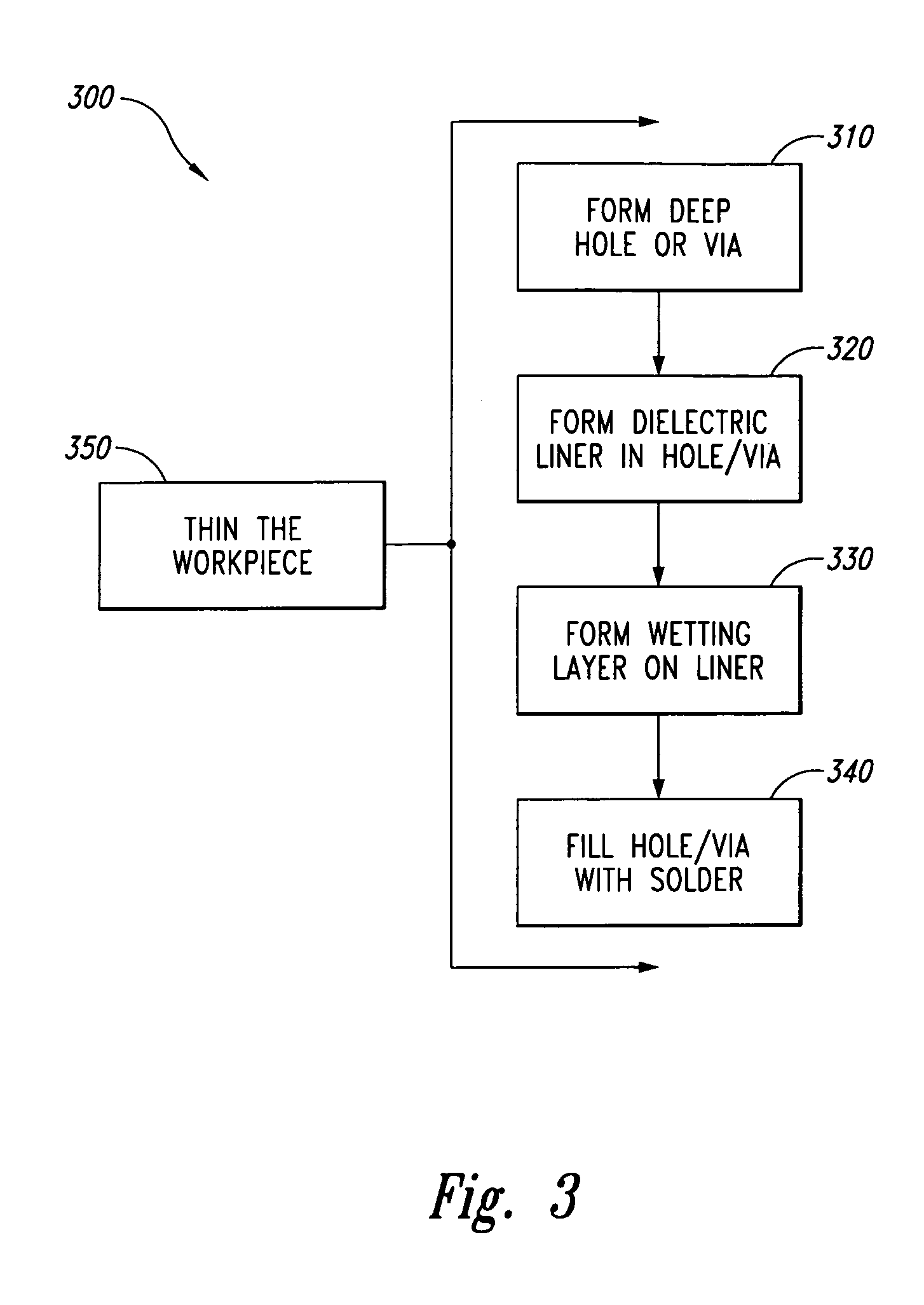

Methods for forming interconnects in microelectronic workpieces and microelectronic workpieces formed using such methods

ActiveUS7271482B2Semiconductor/solid-state device detailsSolid-state devicesEngineeringIntegrated circuit

Methods for forming interconnects in microelectronic workpieces and microelectronic workpieces having such interconnects are disclosed herein. One aspect of the invention is directed toward a method for manufacturing a microelectronic workpiece having a plurality of microelectronic dies. The individual dies include an integrated circuit and a terminal electrically coupled to the integrated circuit. In one embodiment, the method includes forming an opening in the workpiece in alignment with the terminal. The opening can be a through-hole extending through the workpiece or a blind hole that extends only partially through the substrate. The method continues by constructing an electrically conductive interconnect in the workpiece by depositing a solder material into at least a portion of the opening and in electrical contact with the terminal. In embodiments that include forming a blind hole, the workpiece can be thinned either before or after forming the hole.

Owner:MICRON TECH INC

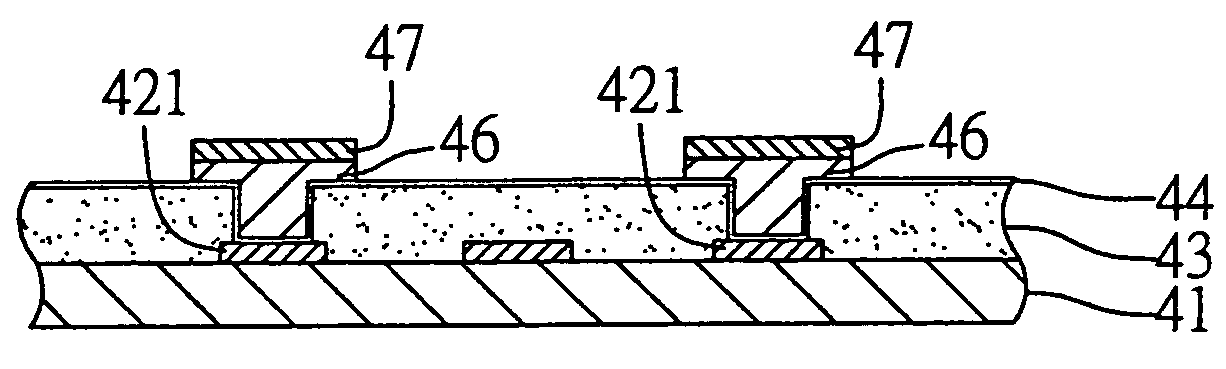

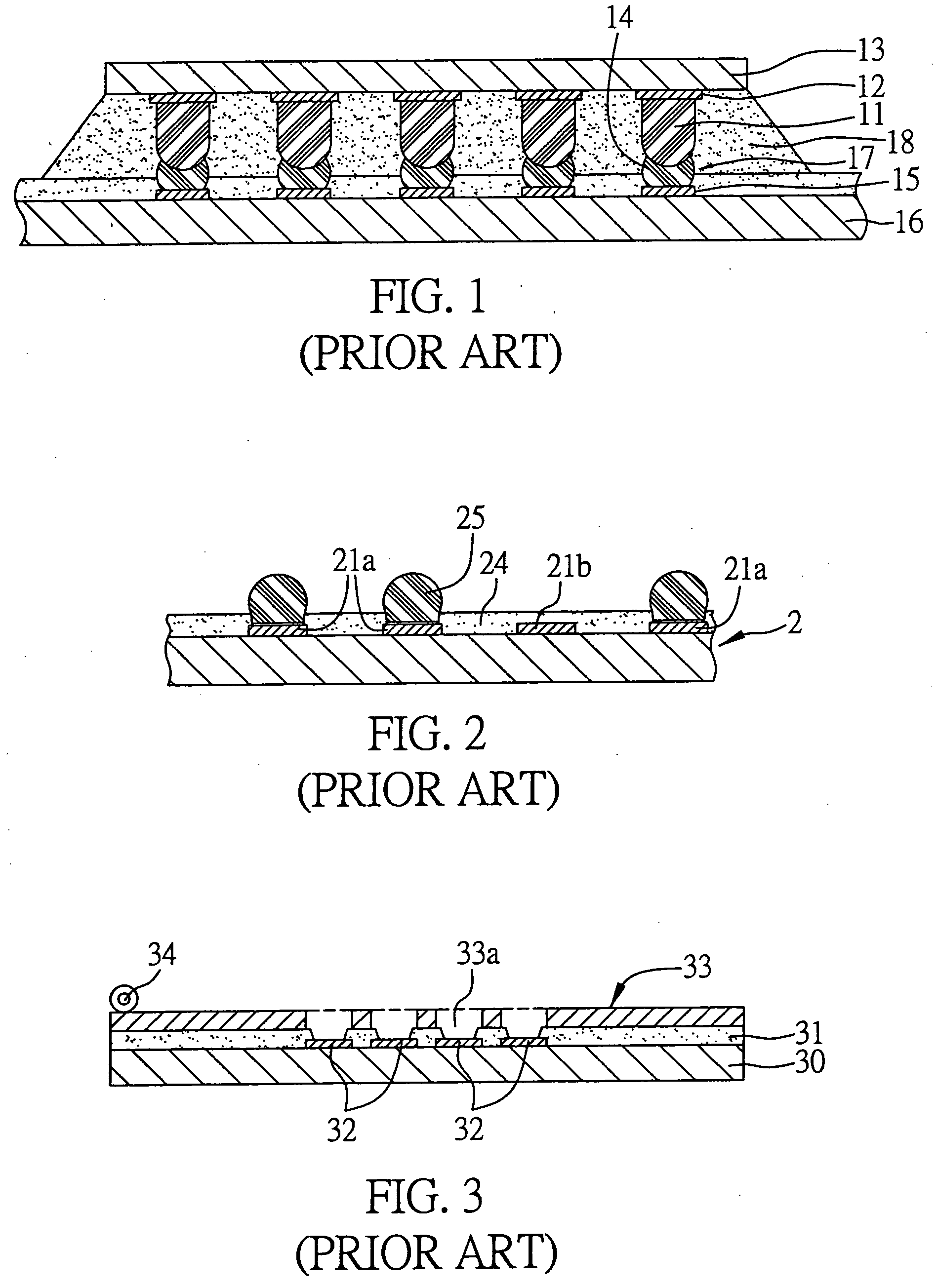

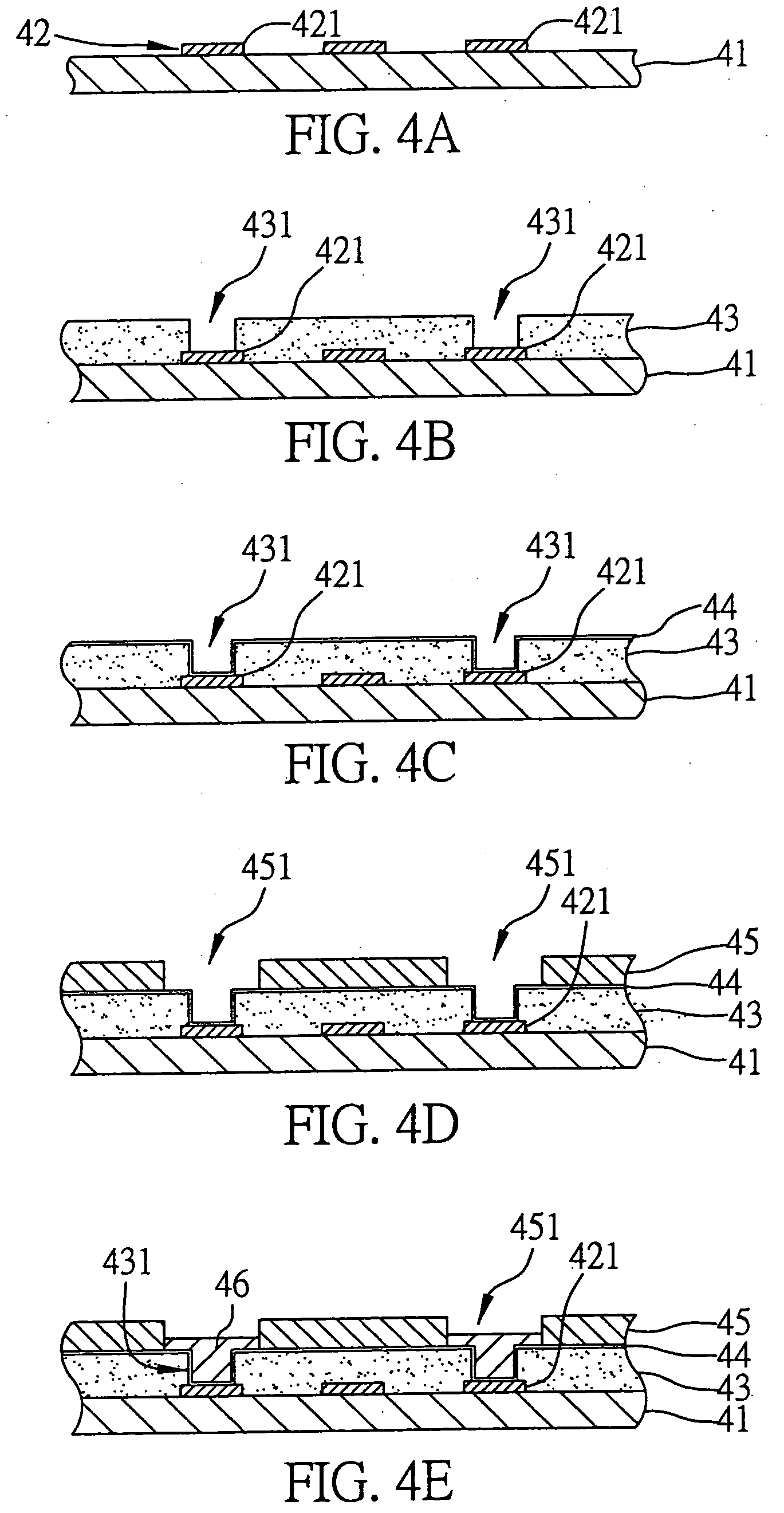

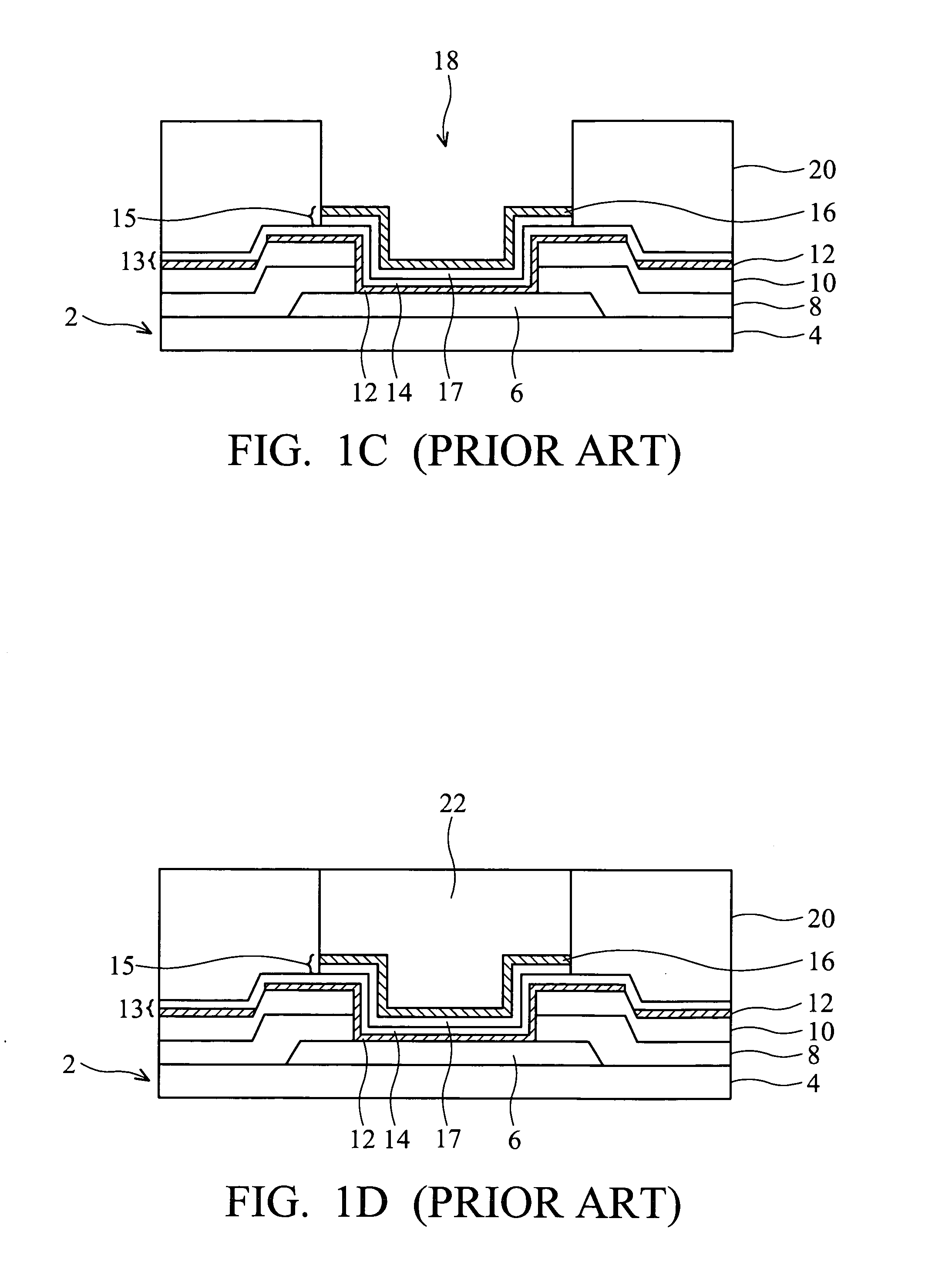

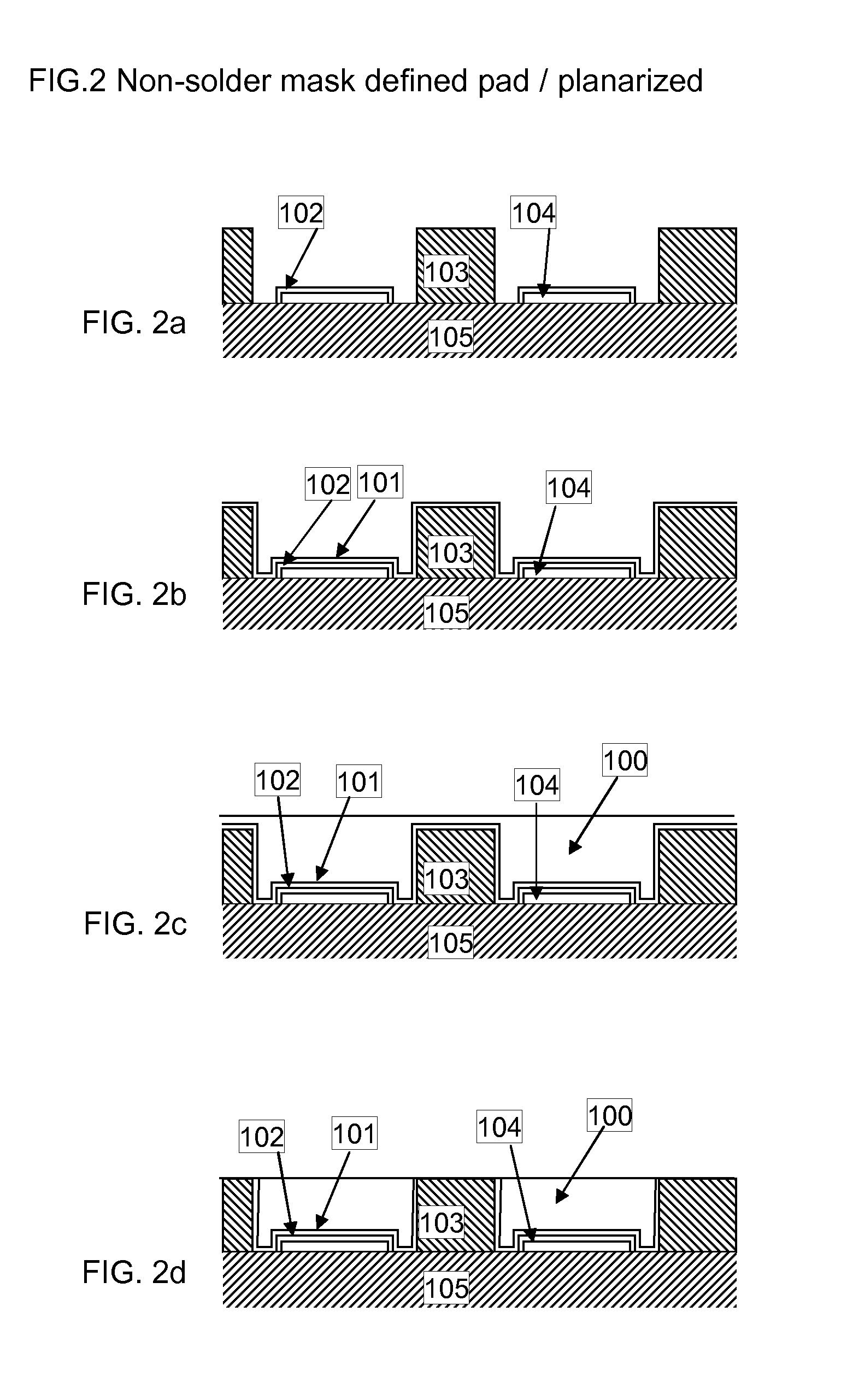

Pre-solder structure on semiconductor package substrate and method for fabricating the same

InactiveUS20050167830A1Pad pitchFabrication cost is increasedPrinted circuit assemblingSemiconductor/solid-state device detailsResistSemiconductor package

A pre-solder structure on a semiconductor package substrate and a method for fabricating the same are proposed. A plurality of conductive pads are formed on the substrate, and a protective layer having a plurality of openings for exposing the conductive pads is formed over the substrate. A conductive seed layer is deposited over the protective layer and openings. A patterned resist layer is formed on the seed layer and has openings corresponding in position to the conductive pads. A plurality of conductive pillars and a solder material are deposited in sequence in each of the openings. The resist layer and the seed layer not covered by the conductive pillars and the solder material are removed. The solder material is subject to a reflow-soldering process to form pre-solder bumps covering the conductive pillars.

Owner:PHOENIX PRECISION TECH CORP

Light emiting device and method of making same

ActiveUS20100123164A1Low production costReduce the number of partsPoint-like light sourceElongate light sourcesThermal expansionLight emitting device

A light emitting device includes a light-emitting portion including a metal part including a metal able to be bonded to a solder material, and a heat dissipation member that includes aluminum, aluminum alloy, magnesium or magnesium alloy and a bonding portion processed to be bonded to the solder material. The metal part of the light-emitting portion is bonded via the solder material to the bonding portion of the heat dissipation member. The solder material includes a material unable to be directly bonded to the heat dissipation member, the metal part of the light-emitting portion is formed by metalizing an insulation of ceramic or semiconductor, and the bonding portion includes a thermal expansion coefficient between that of the heat dissipation member and that of the insulation.

Owner:TOYODA GOSEI CO LTD

Method of solder bumping a circuit component and circuit component formed thereby

InactiveUS20070045840A1Reduce degradationReducing and eliminating dissolutionSemiconductor/solid-state device detailsSolid-state devicesSurface layerLead bonding

A circuit component and method by which degradation of a solder connection by electromigration can be prevented or reduced. The component generally includes an interconnect pad on a surface of the component, a metallic multilayer structure overlying the interconnect pad and having a solderable surface layer, and a solder material on the multilayer structure. According to a preferred aspect of the component and method, a stud is wire-bonded to the solderable surface layer of the multilayer structure and encased by the solder material to provide a low electrical resistance path through the solder material.

Owner:DELPHI TECH INC

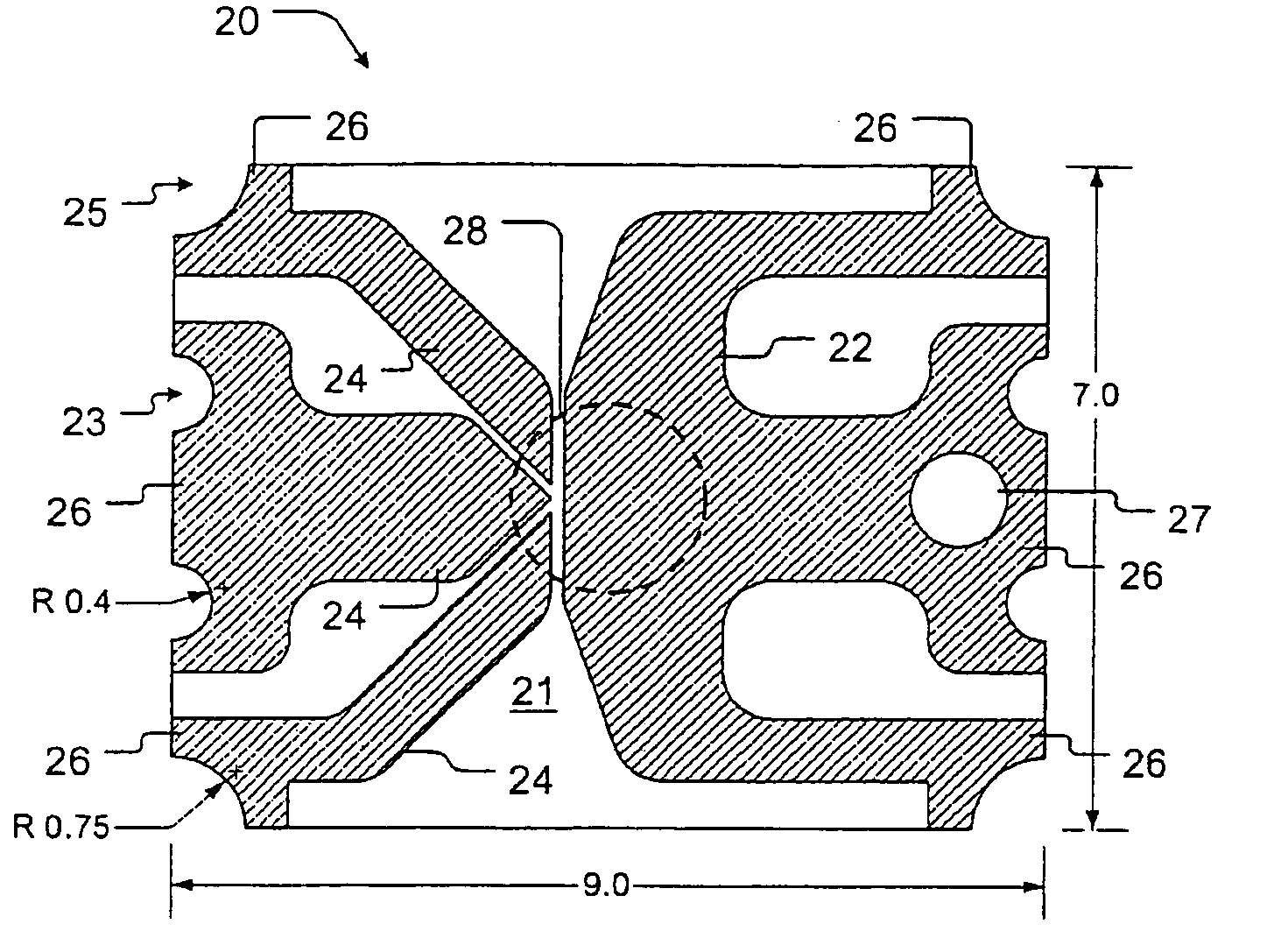

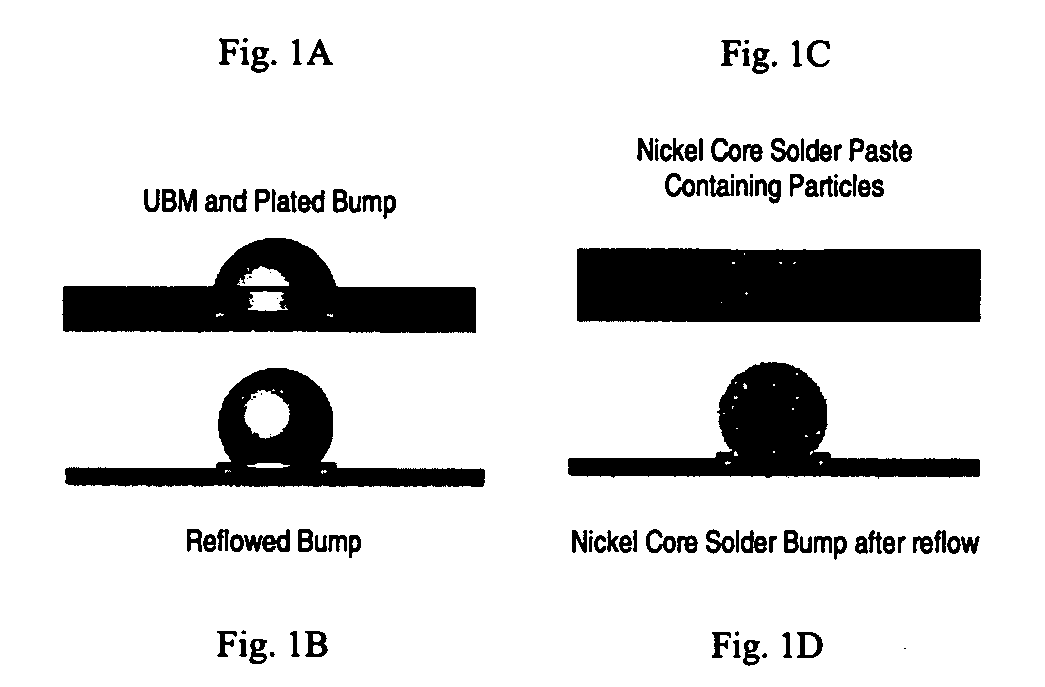

Bump structure of semiconductor package and method for fabricating the same

InactiveUS20060051954A1Increase spacingReduces the formation of voidsSemiconductor/solid-state device detailsPrinted circuit aspectsElectrical connectionSemiconductor package

A bump structure of a semiconductor package and a method for fabricating the same are provided. The bump structure is used to connect a semiconductor element to a carrier of the semiconductor package. The fabrication method primarily employs an electroplating process to form the bump structure including an under bump metallurgy (UBM) layer, at least one I-shaped conductive pillar, and a solder material. This allows fine-pitch electrical connection pads to be arranged in the semiconductor package, and also provides an enhanced support structure and a sufficient height between the semiconductor element and the carrier.

Owner:SILICONWARE PRECISION IND CO LTD

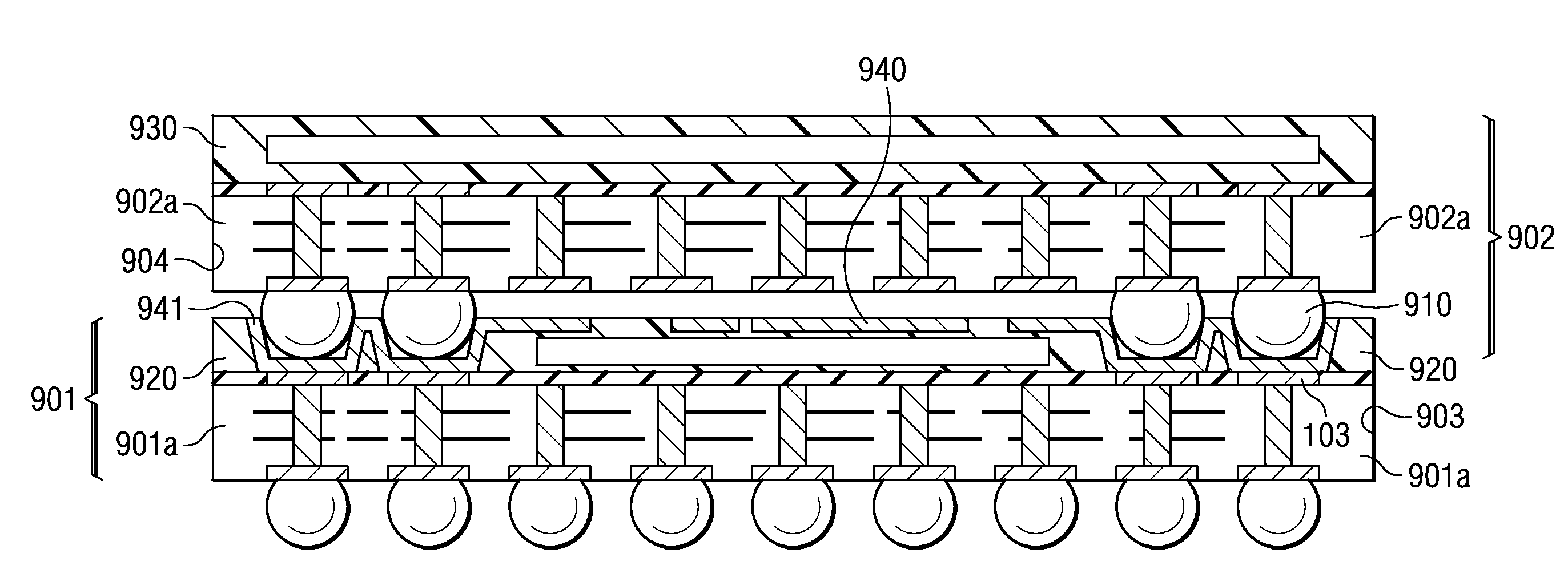

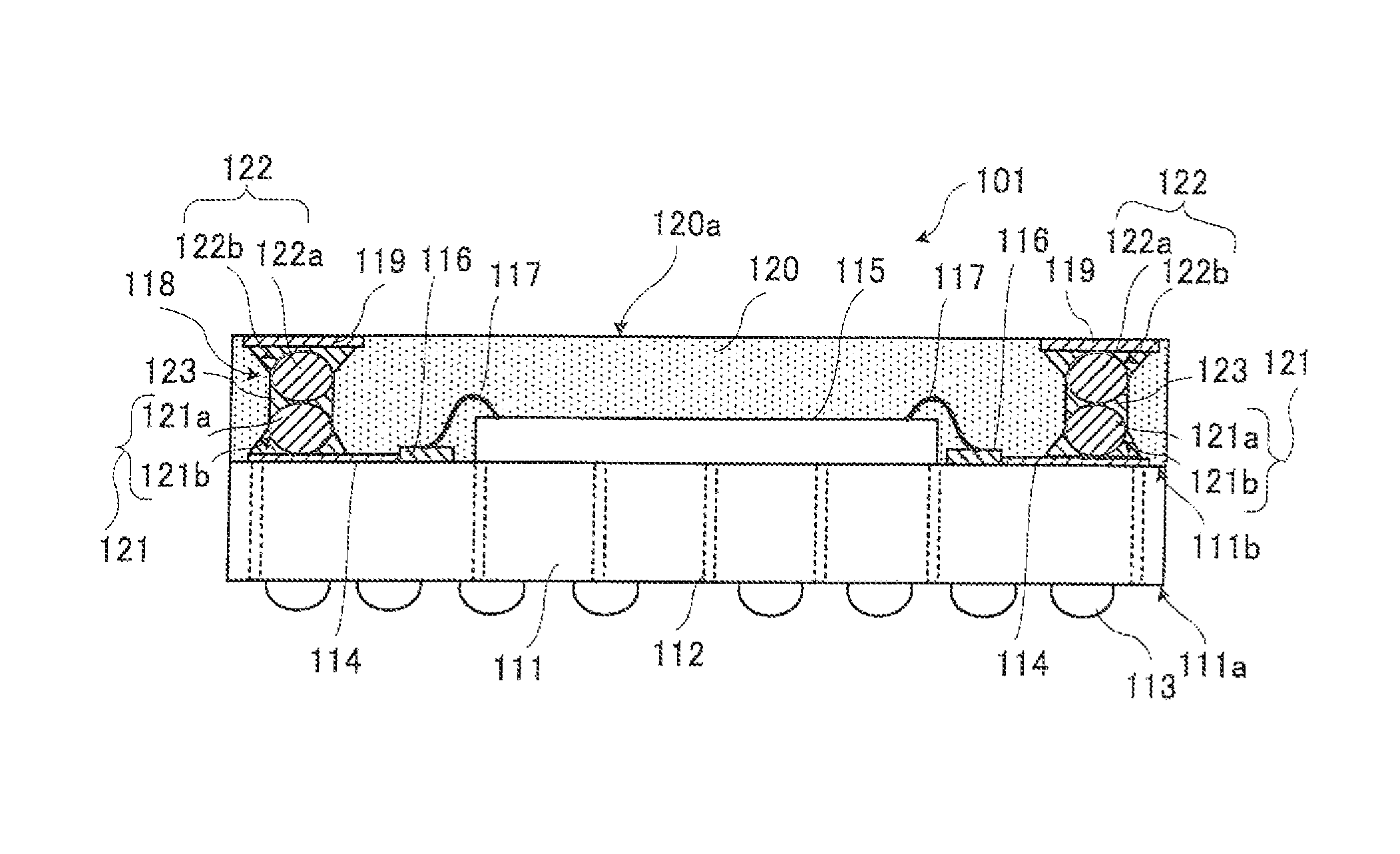

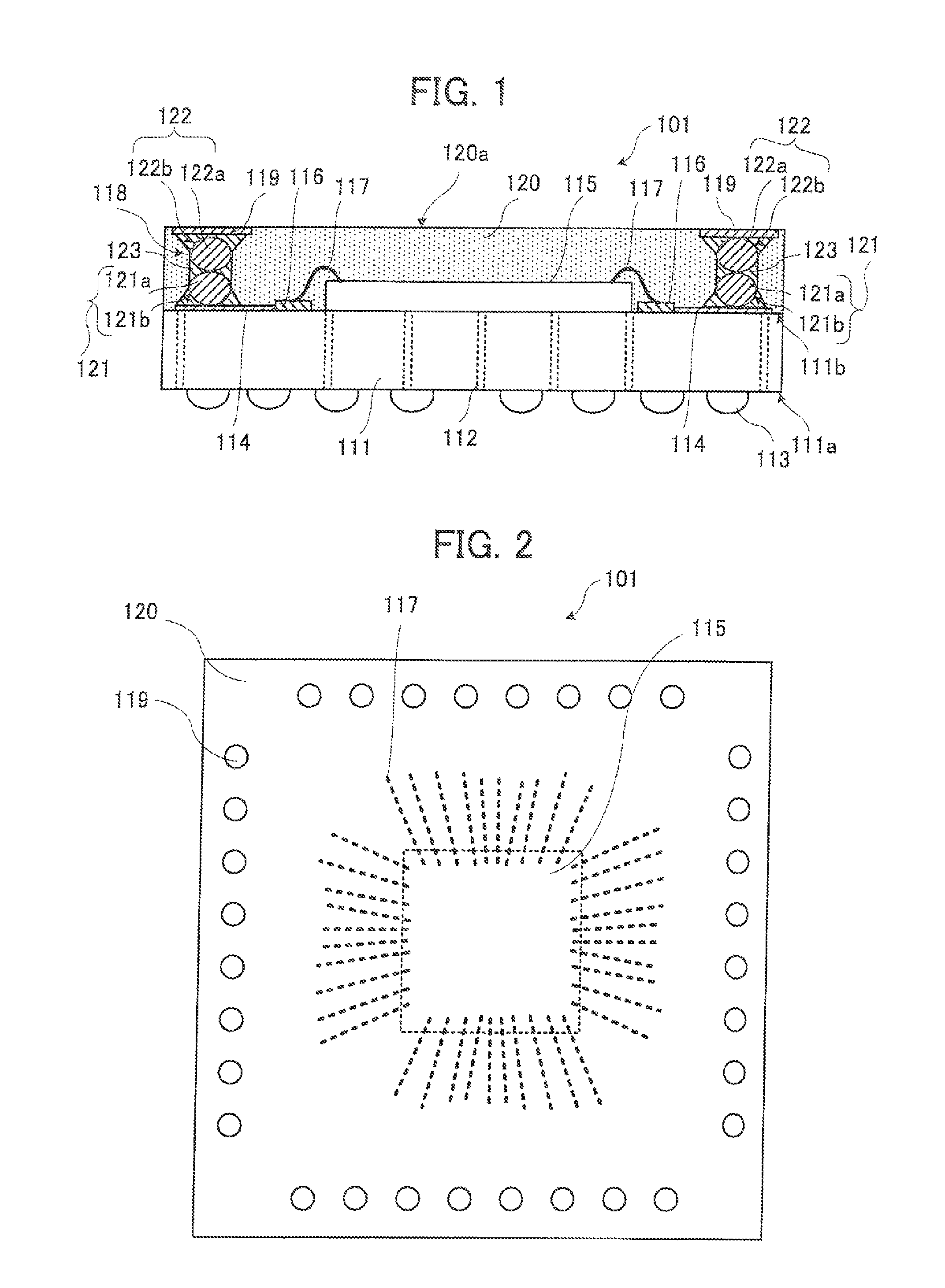

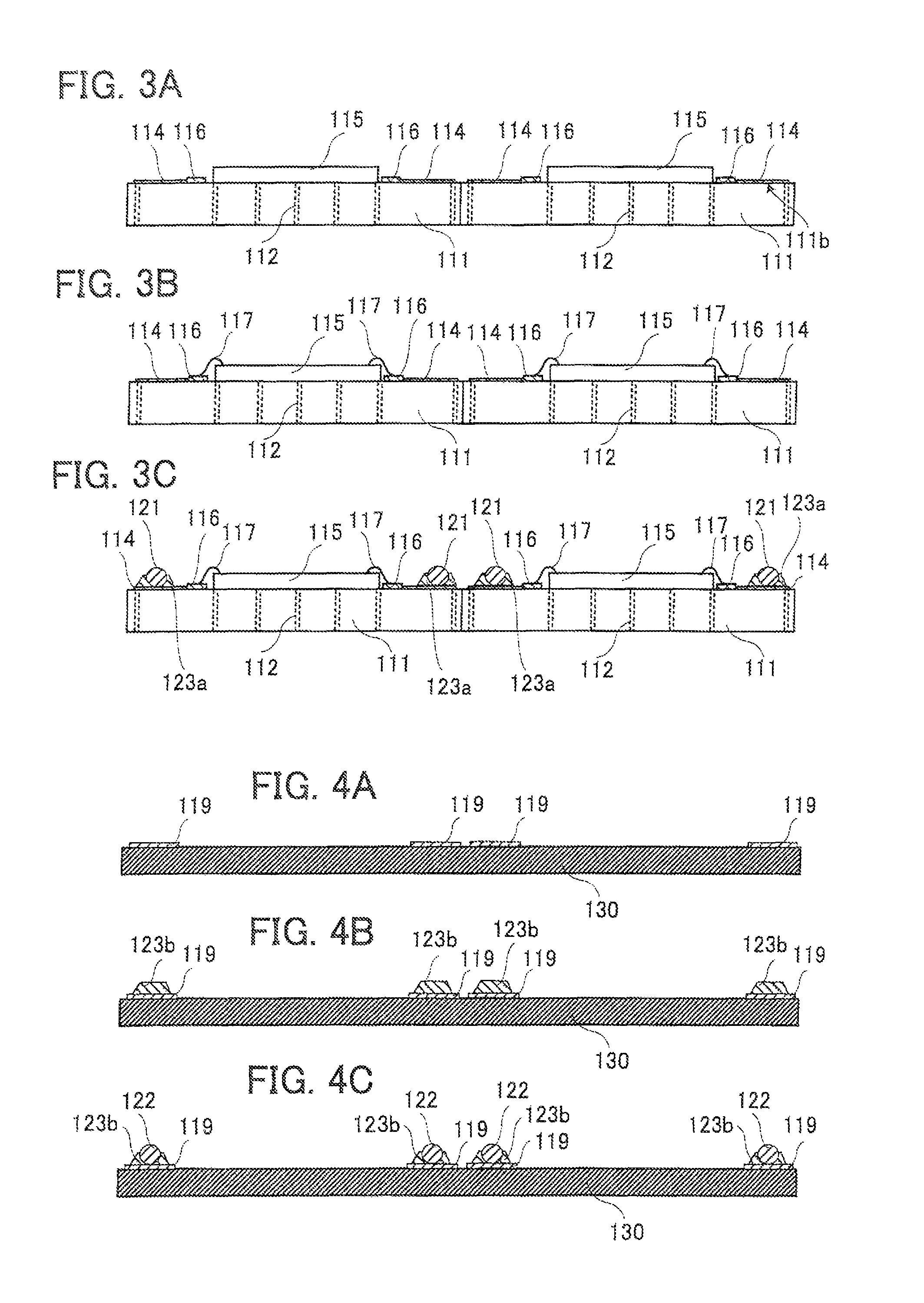

Semiconductor package and package-on-package semiconductor device

ActiveUS8314492B2Low priceLow costSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A semiconductor package includes a wiring board; a first electrode for external connection; a ball pad; a semiconductor chip; a mold resin; an electrode unit connected with the ball pad and penetrating the mold resin; and a second electrode for external connection connected with a portion of the electrode unit on a side of an outer surface of the mold resin. The electrode unit includes a first ball disposed on the ball pad; a second ball disposed between the first ball and the second electrode; and a solder material connecting between the ball pad and the first ball, between the first ball and the second ball, and between the second ball and the second electrode for external connection; each of the first ball and the second ball including a core part having a glass transition temperature which is higher than a melting point of the solder material.

Owner:LAPIS SEMICON CO LTD

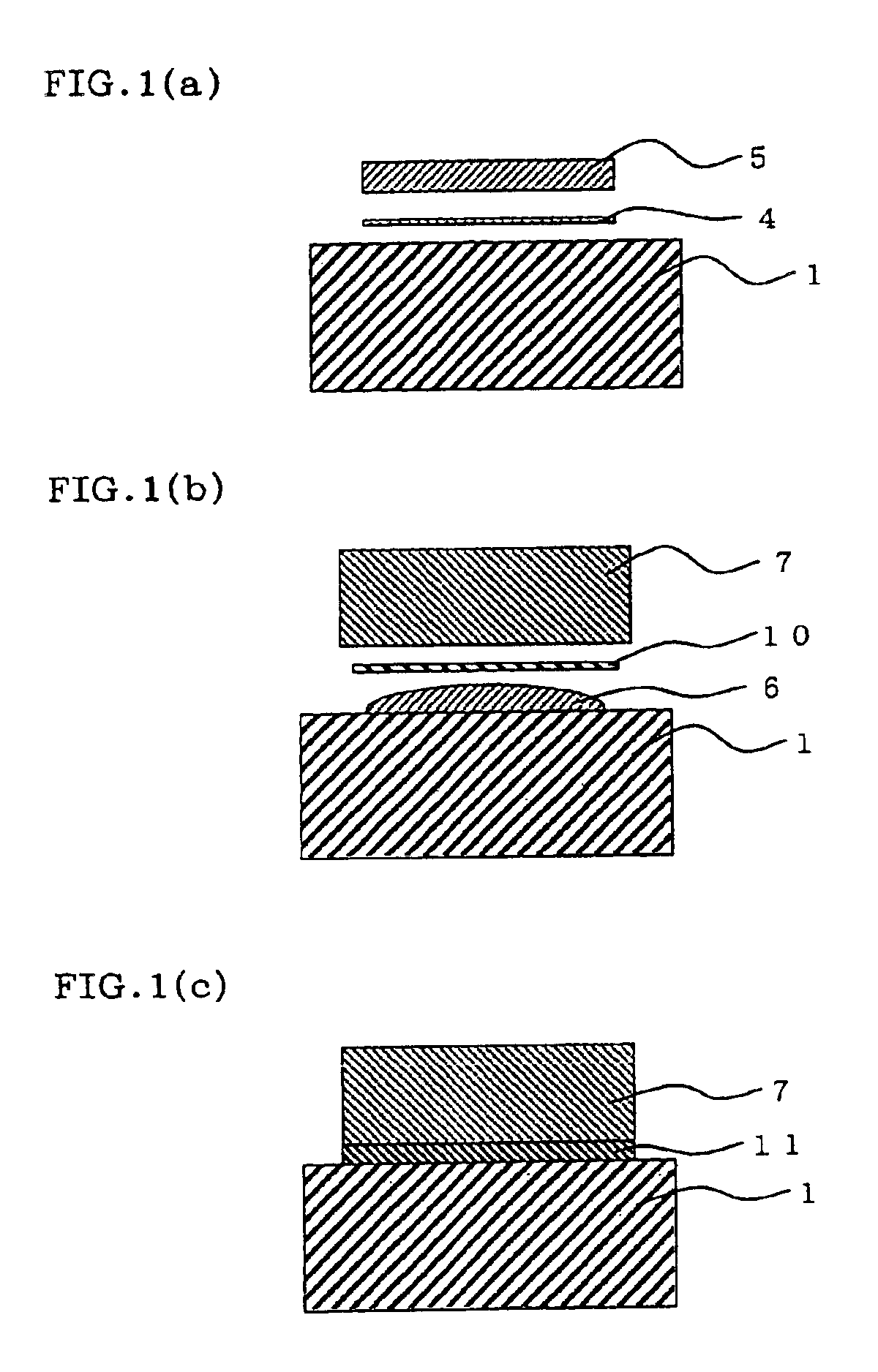

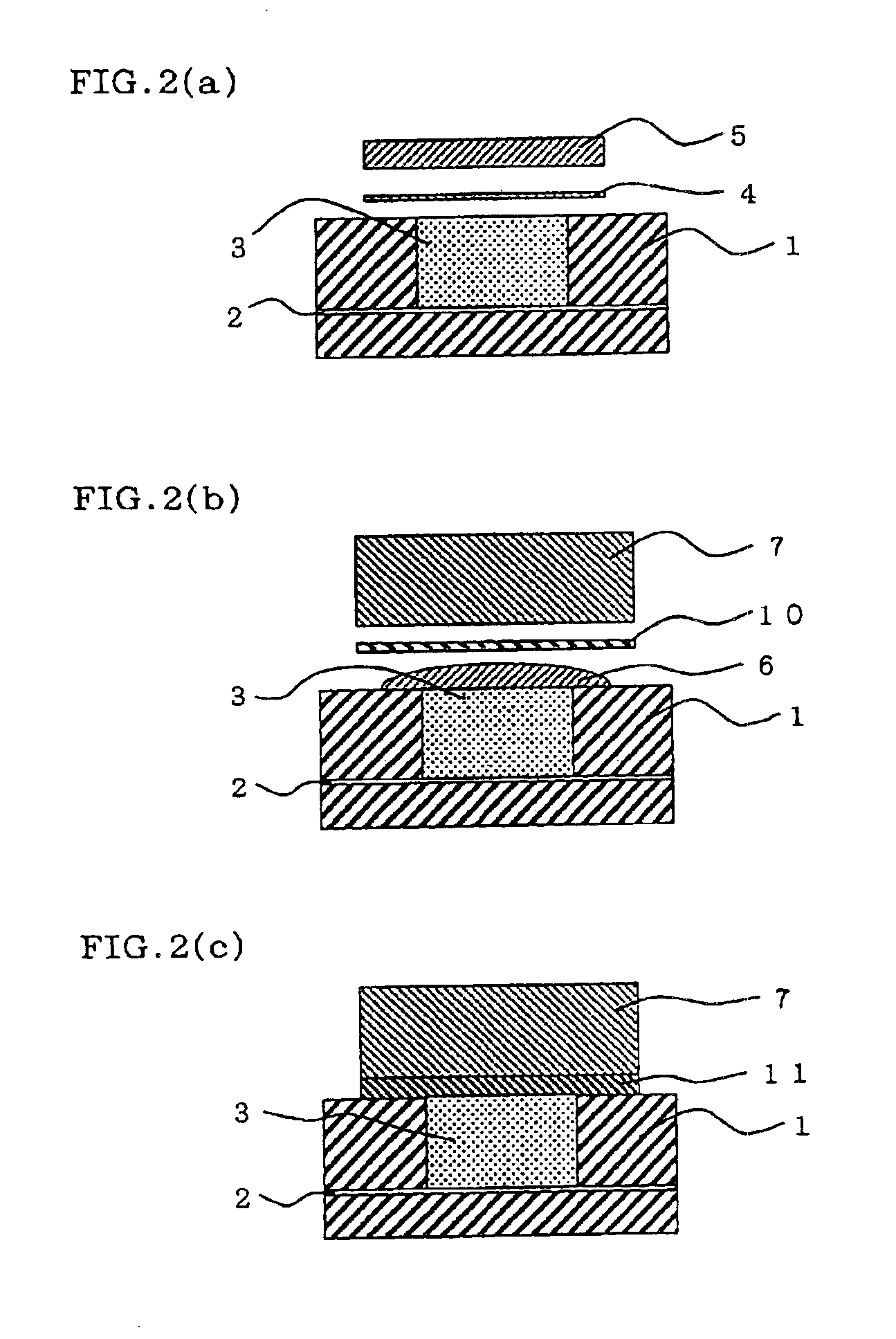

Bonded member comprising different materials, and production method thereof

InactiveUS6918530B2Easy to operateHigh bonding strengthLayered product treatmentSoldered/welded conductive connectionsAlloyLow melting point

A bonded member including a ceramic base material 1 and a metallic member 7 which are bonded together, wherein a solder material 5 comprising Au is disposed on the surface of the ceramic base material 1 via an active metal layer, the active metal layer and the solder material 5 are molten by heating so as to form a precoat layer 6, the metallic member 7 is disposed on the surface of the precoat layer 6 via an insertion metal layer comprising pure metal which may form an alloy having a lower melting point than Au with Au or an alloy of the pure metal and Au, and the insertion metal layer and at least a portion in the vicinity of the interface between the insertion metal layer and the precoat layer 6 are molten by heating to bond the metallic member 7 and the precoat layer 6.

Owner:NGK INSULATORS LTD

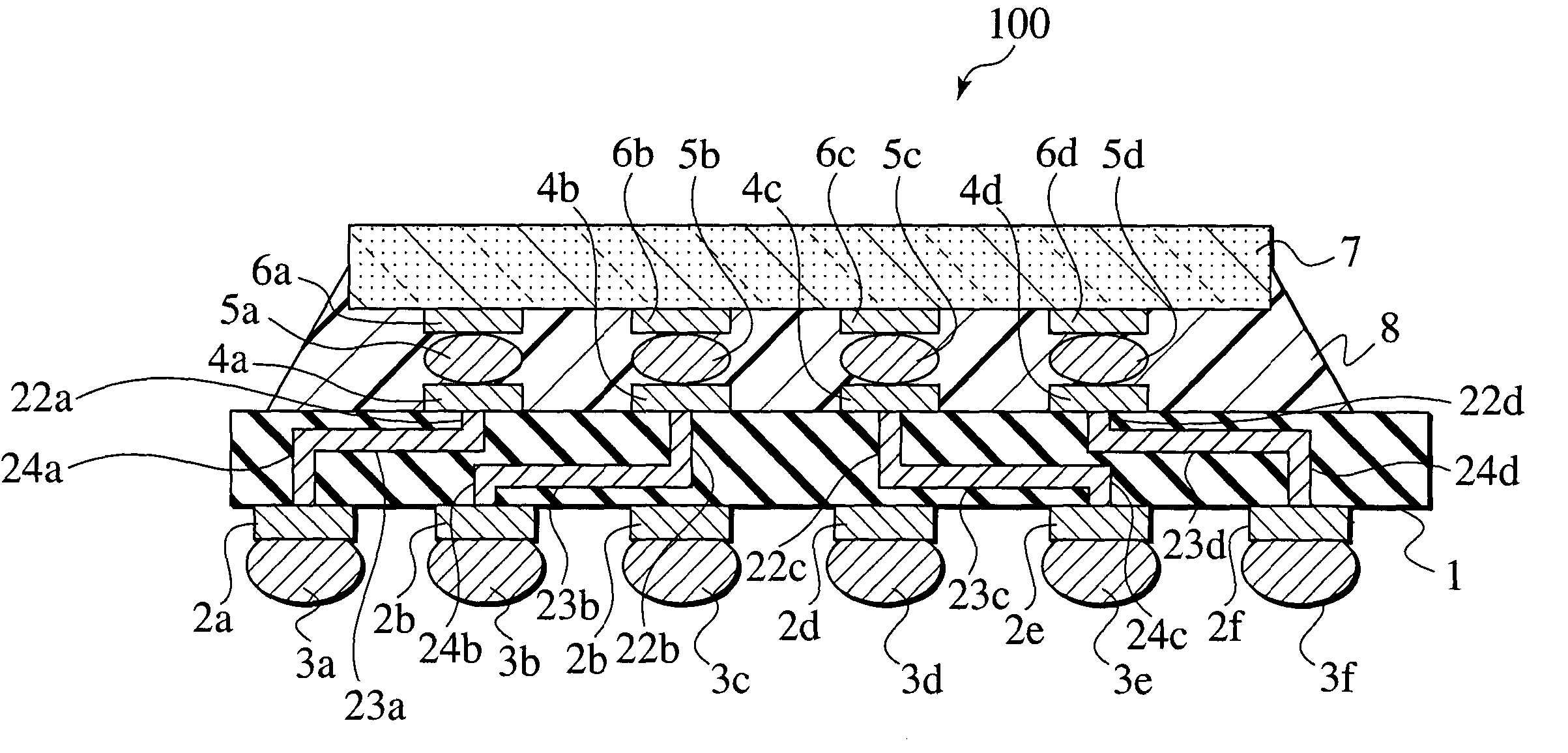

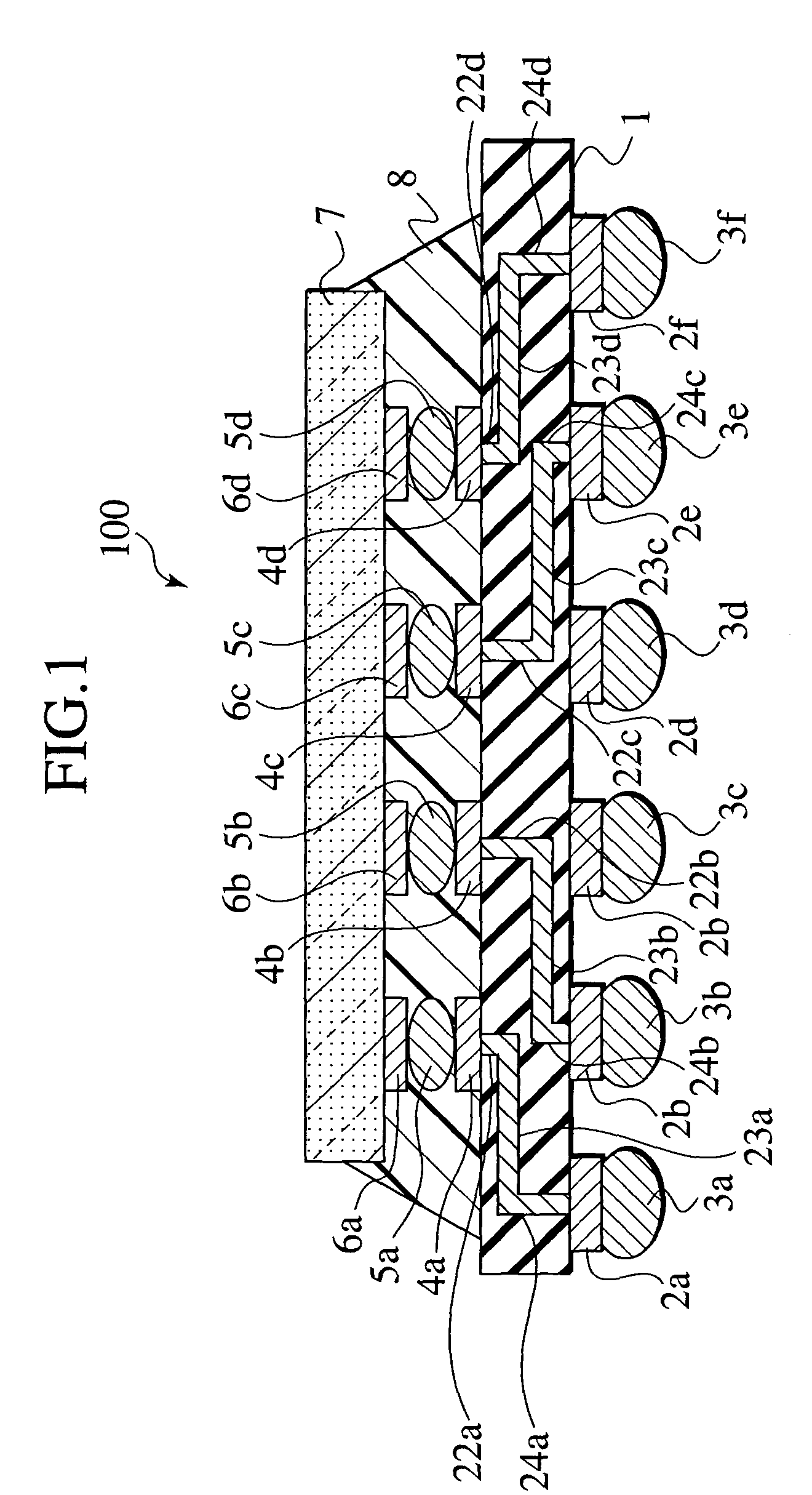

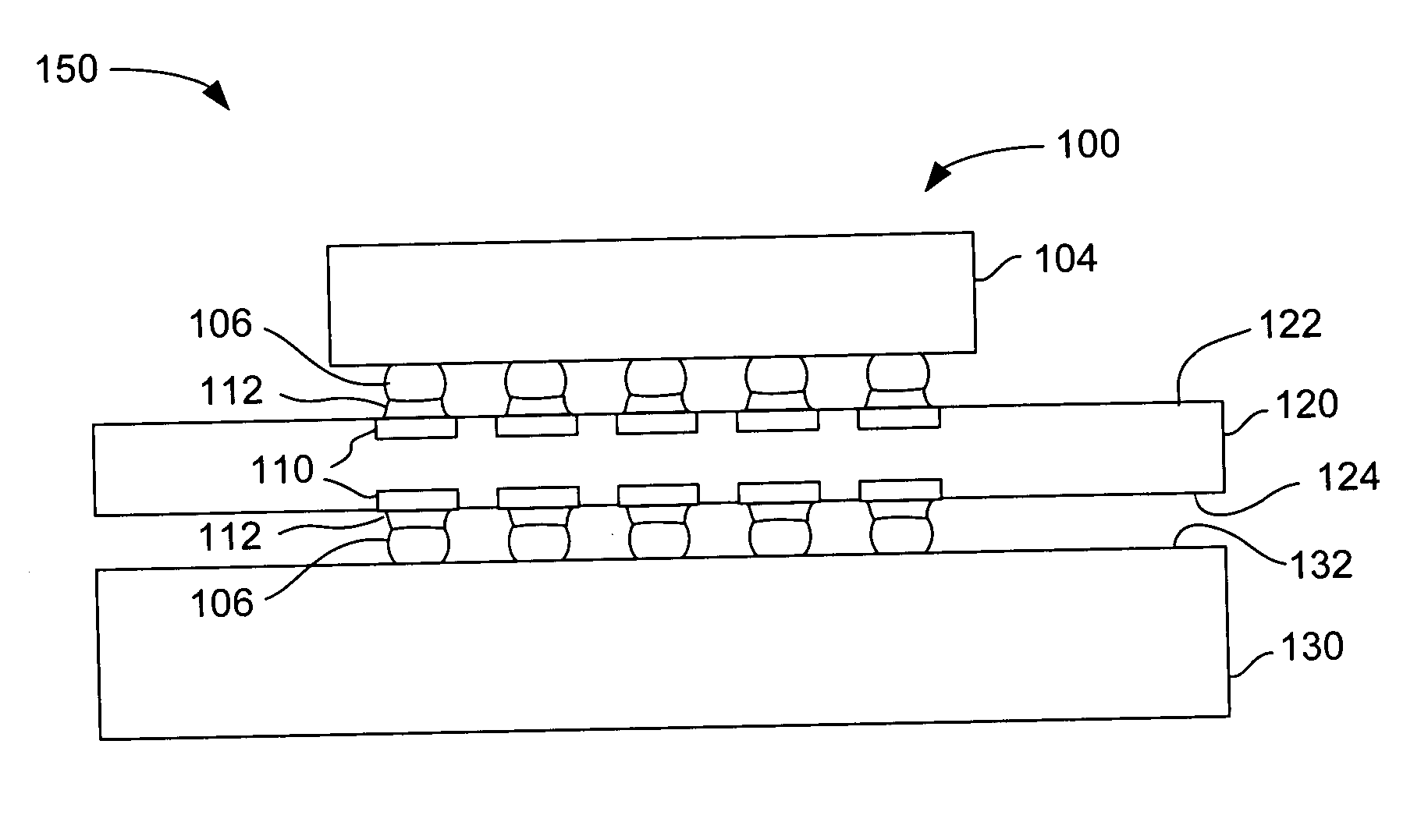

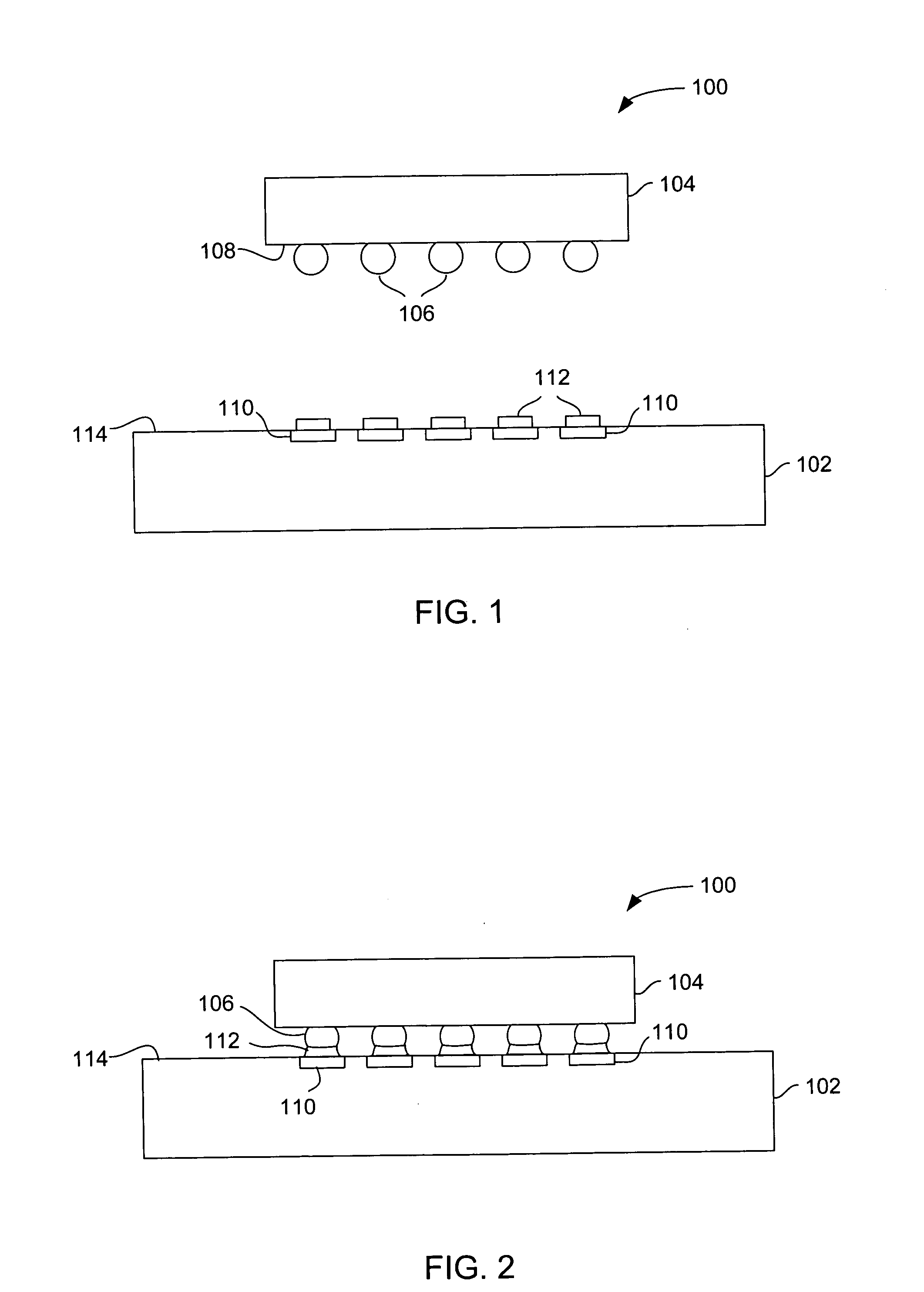

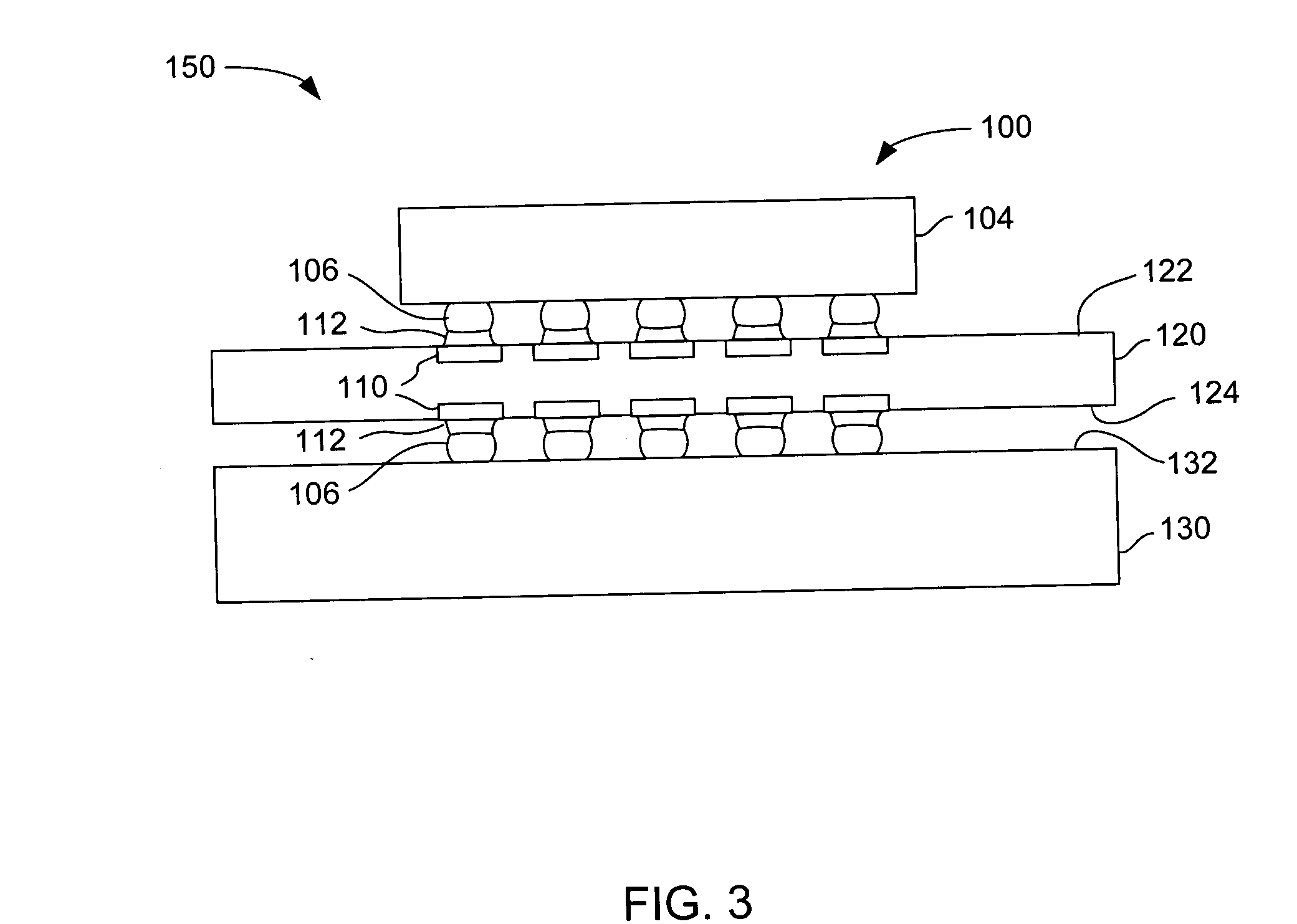

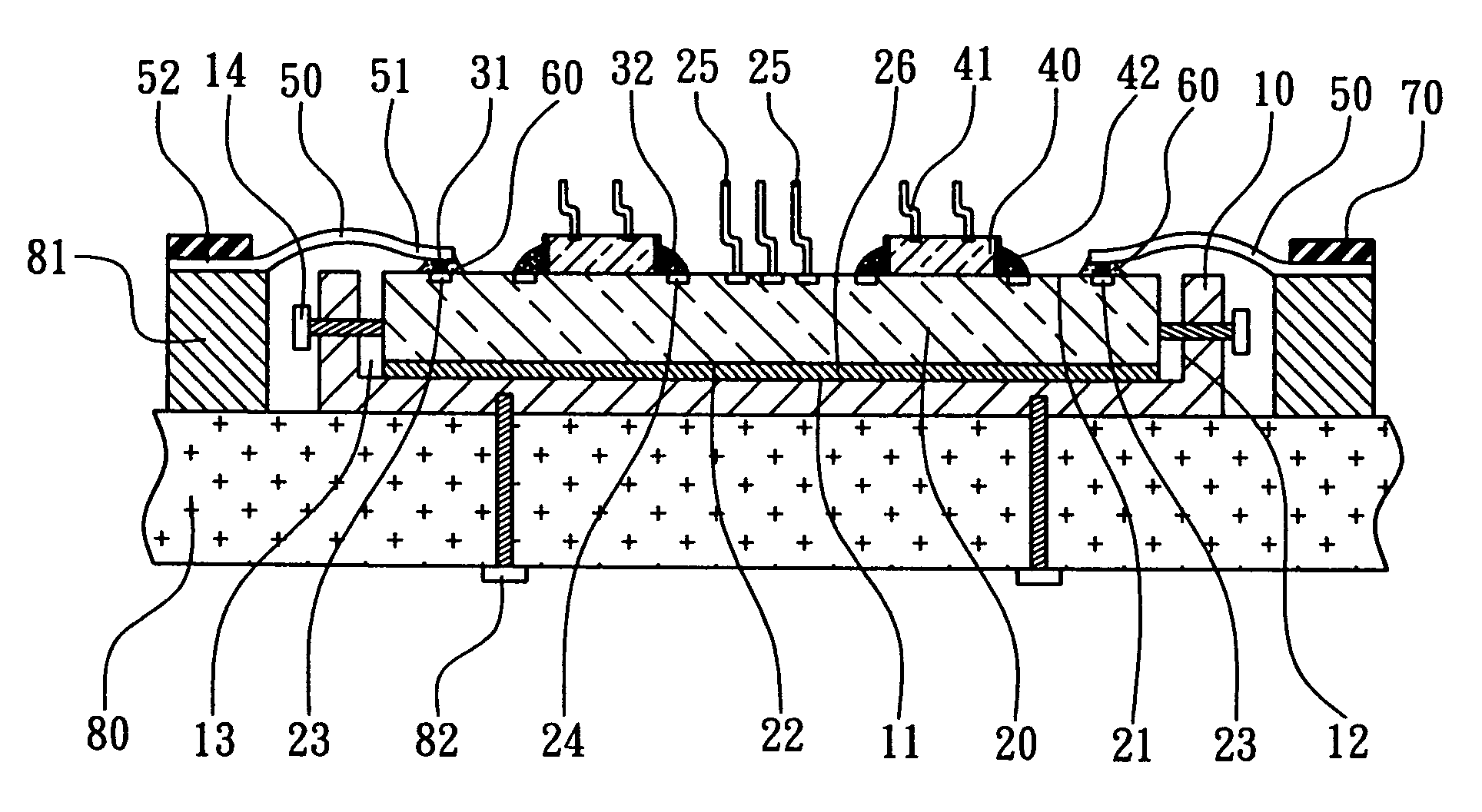

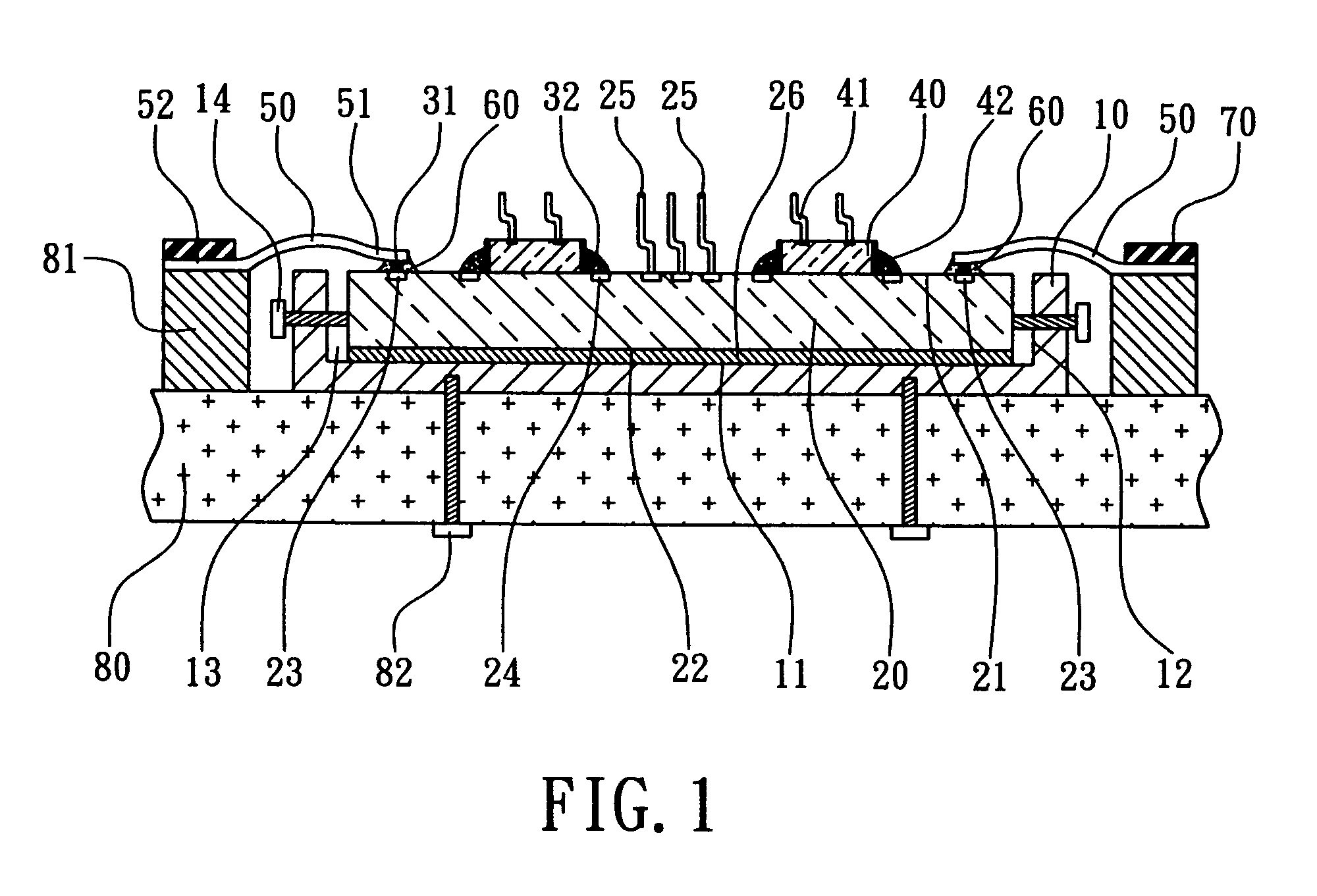

First and second level packaging assemblies and method of assembling package

InactiveUS20040155358A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSolder ball

A first level packaging assembly includes a chip-mounting base defined by a first surface and a second surface opposite to the first surface; a plurality of external connection lands disposed on the first surface; a plurality of solder balls connected to the external connection lands; a plurality of internal connection lands disposed on the second surface; a plurality of solder joints connected to the internal connection lands including solder materials having lower melting temperature than the solder balls; a semiconductor chip defined by a third surface and a fourth surface opposite to the third surface, connected to the solder joints on the third surface; and an underfill resin sandwiched between the second and third surfaces so as to mold the solder joints.

Owner:KK TOSHIBA

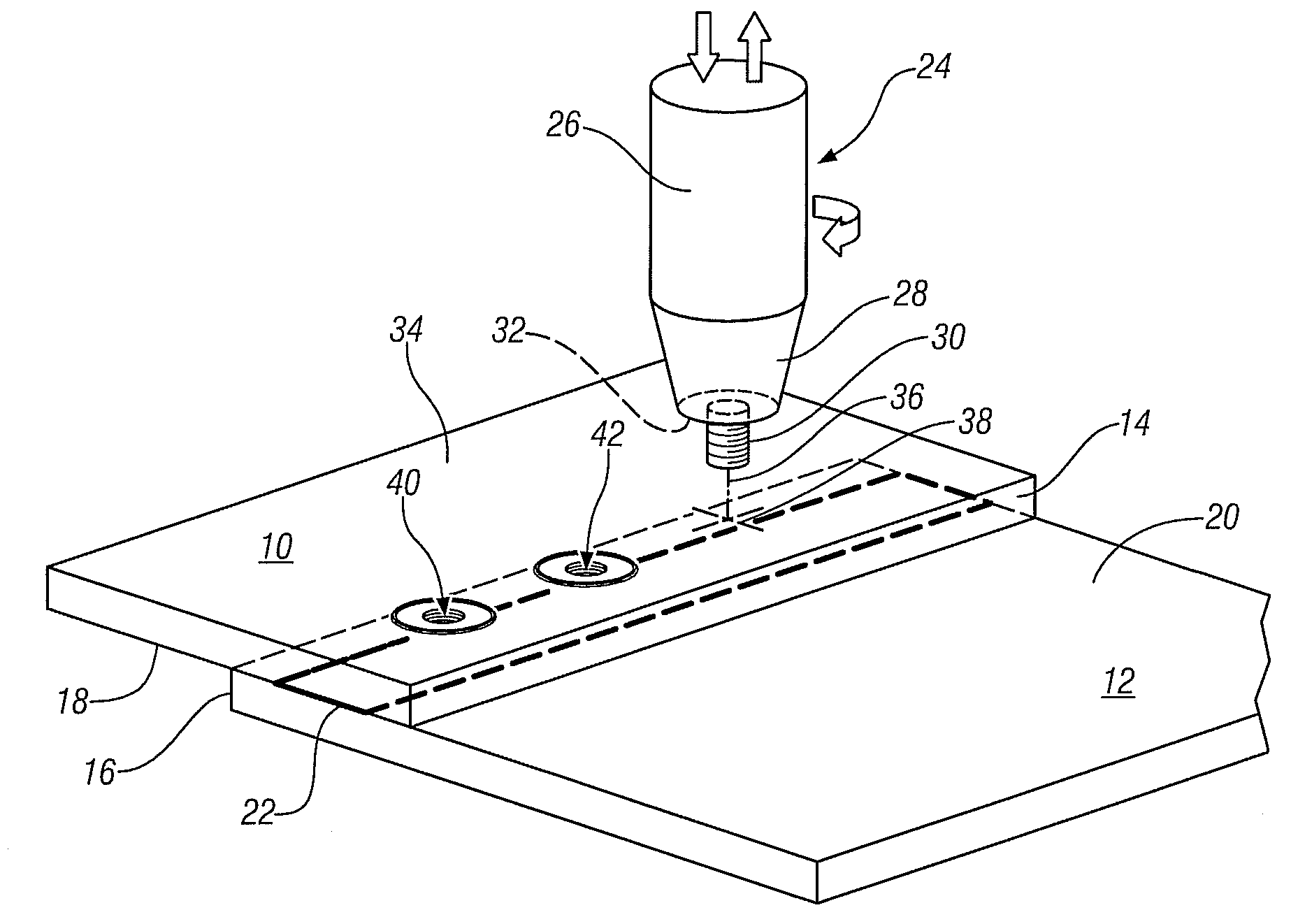

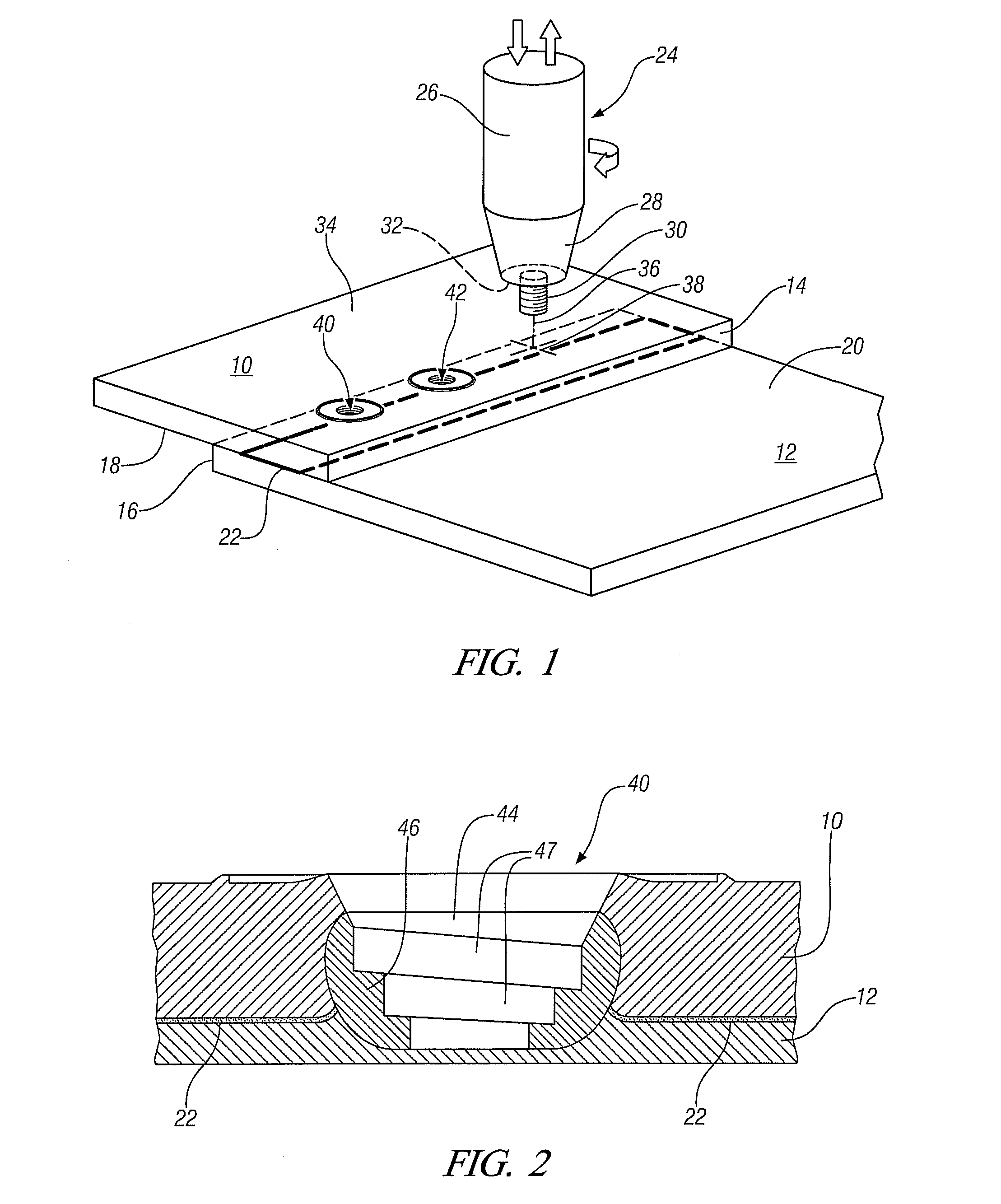

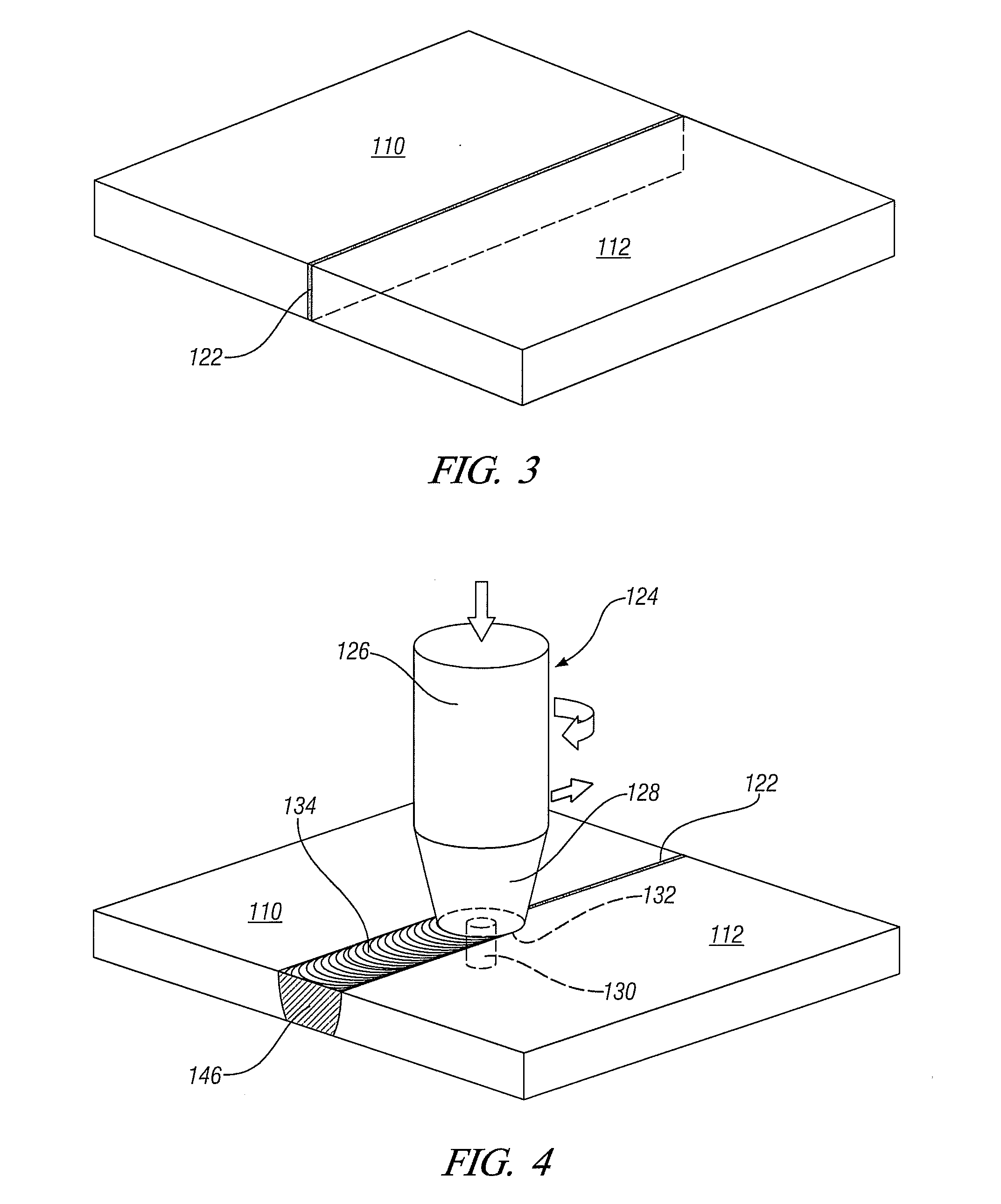

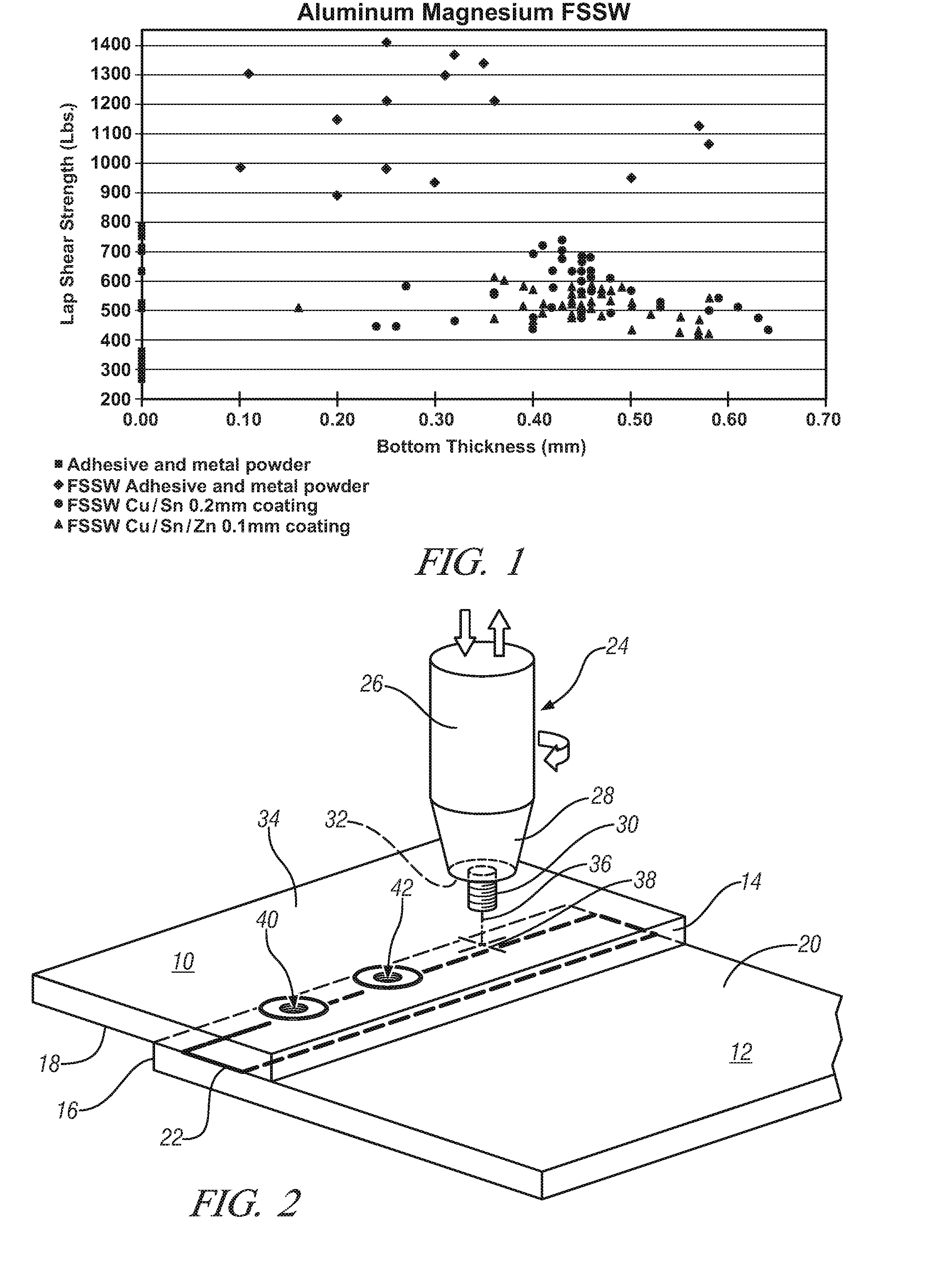

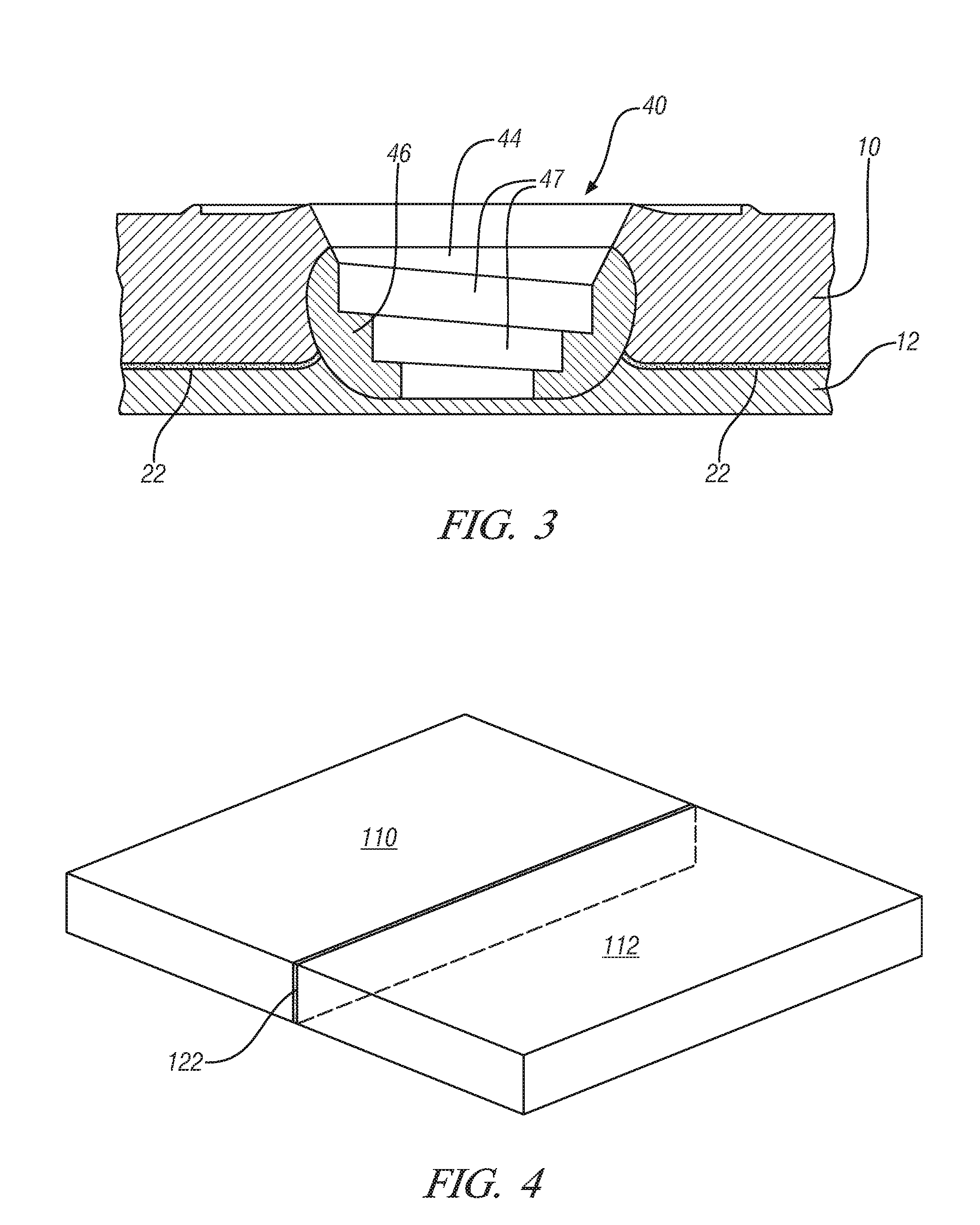

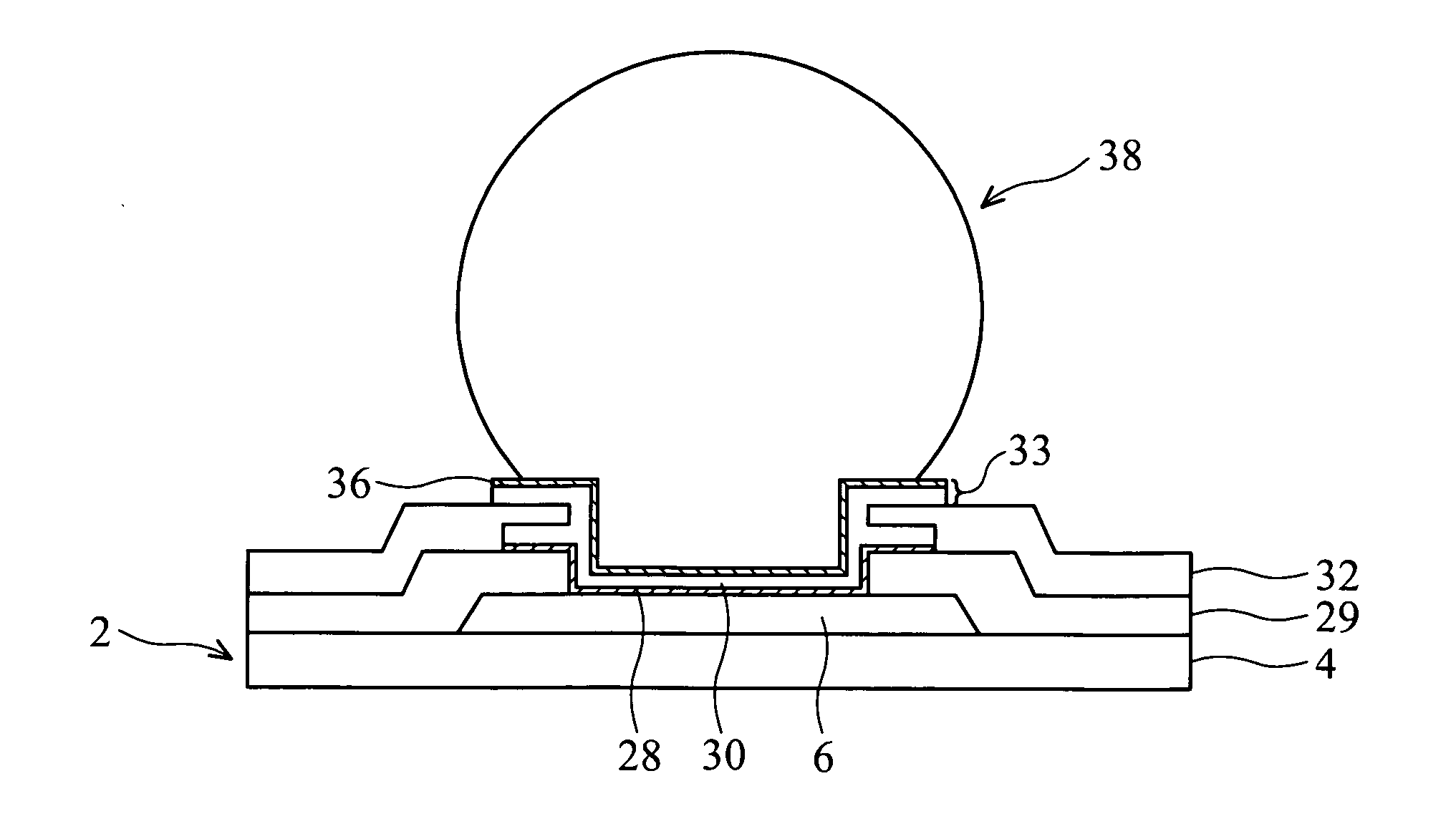

Friction stir welding of dissimilar metals

InactiveUS20100089977A1Improve mechanical propertiesHigh viscosityWelding/soldering/cutting articlesNon-electric welding apparatusFriction stir weldingTin

When a friction stir weld tool penetrates the interface of two workpieces of dissimilar metal alloy materials, the resultant weld of the different alloy materials may produce a weak weld joint. Such weak joints are often experienced, for example, when attempting to form spot welds or other friction stir welds between a magnesium alloy sheet or strip and an aluminum alloy sheet or strip. It is discovered that suitable coating compositions placed at the interface of assembled workpieces can alter the composition of the friction stir weld material and strengthen the resulting bond. In the example of friction stir welds between magnesium alloy and aluminum alloy workpieces, it is found that combinations of copper, tin, and zinc, and other powders can strengthen the magnesium-containing and aluminum-containing friction stir weld material.

Owner:GM GLOBAL TECH OPERATIONS LLC

Bump structure of semiconductor package and method for fabricating the same

InactiveUS7271483B2Increase spacingReduce formationSemiconductor/solid-state device detailsPrinted circuit aspectsSemiconductor packageElectrical connection

A bump structure of a semiconductor package and a method for fabricating the same are provided. The bump structure is used to connect a semiconductor element to a carrier of the semiconductor package. The fabrication method primarily employs an electroplating process to form the bump structure including an under bump metallurgy (UBM) layer, at least one I-shaped conductive pillar, and a solder material. This allows fine-pitch electrical connection pads to be arranged in the semiconductor package, and also provides an enhanced support structure and a sufficient height between the semiconductor element and the carrier.

Owner:SILICONWARE PRECISION IND CO LTD

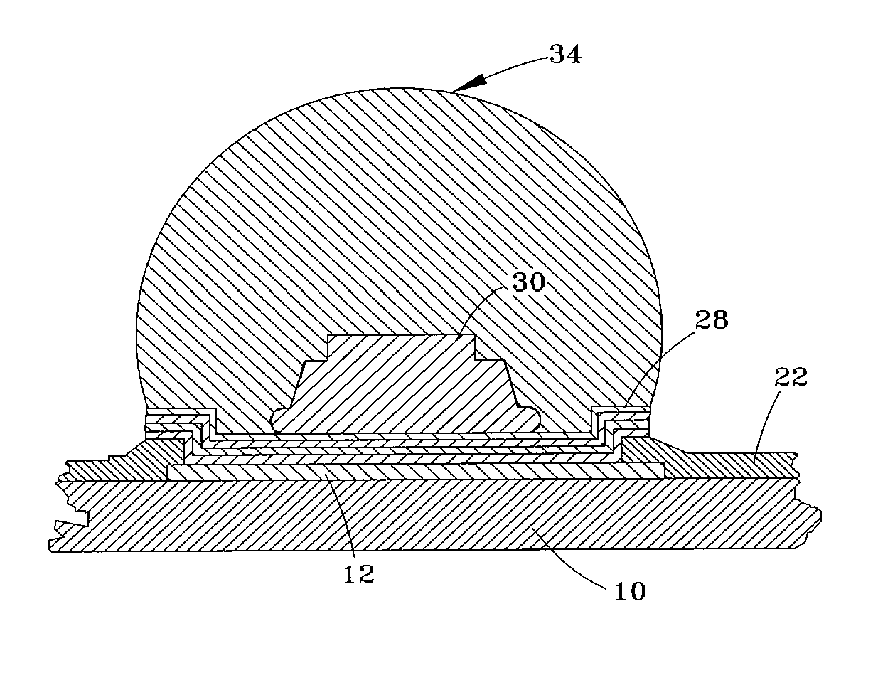

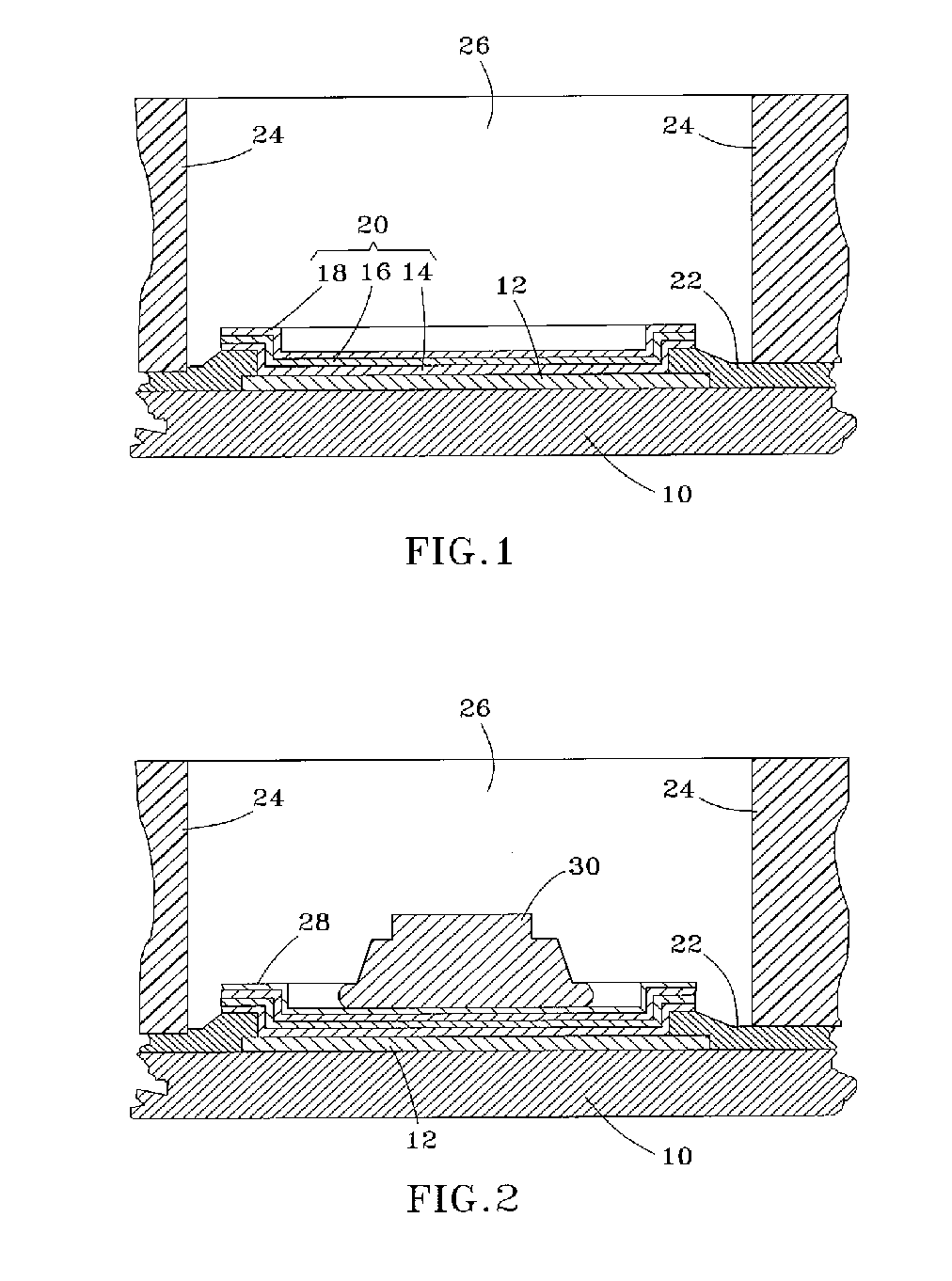

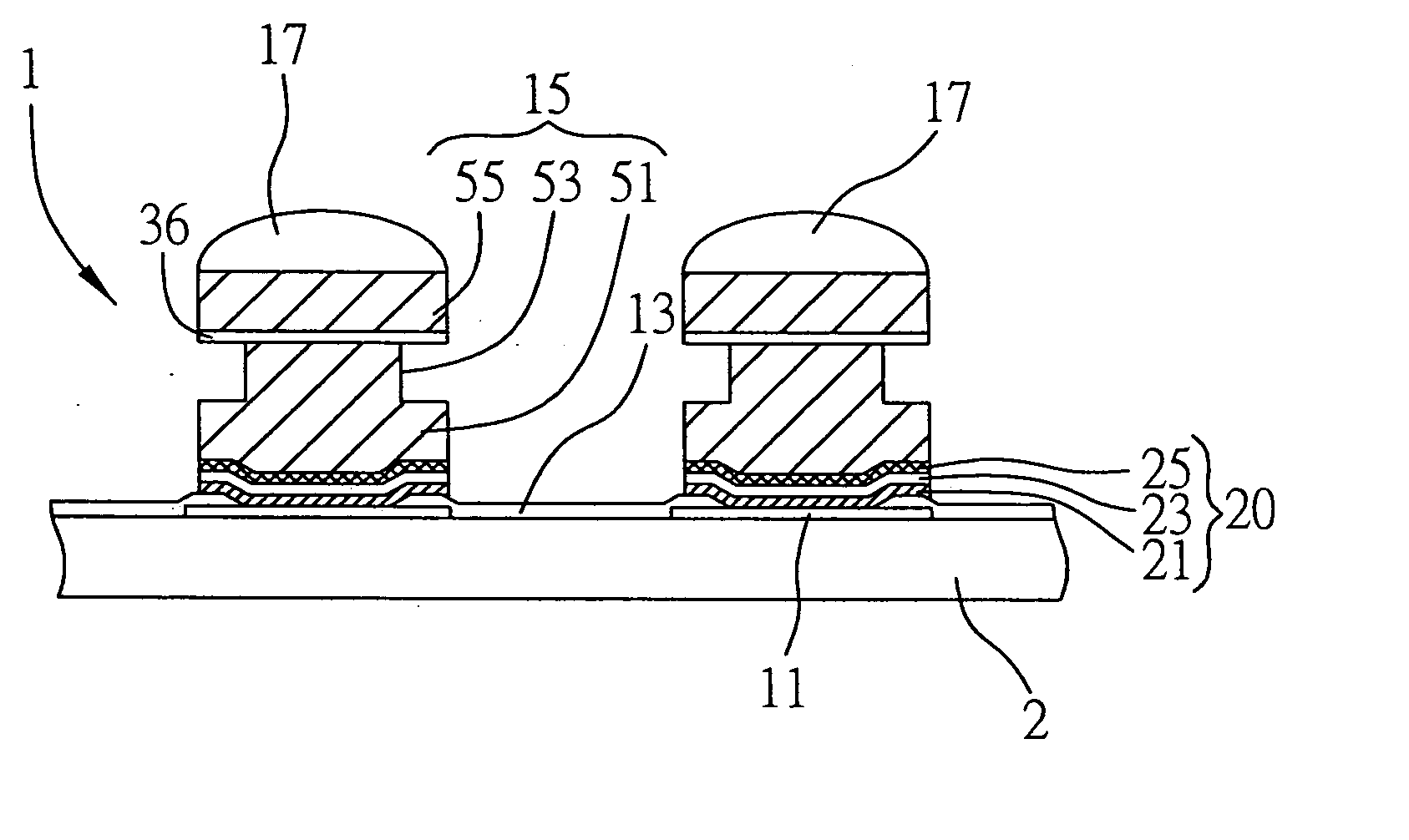

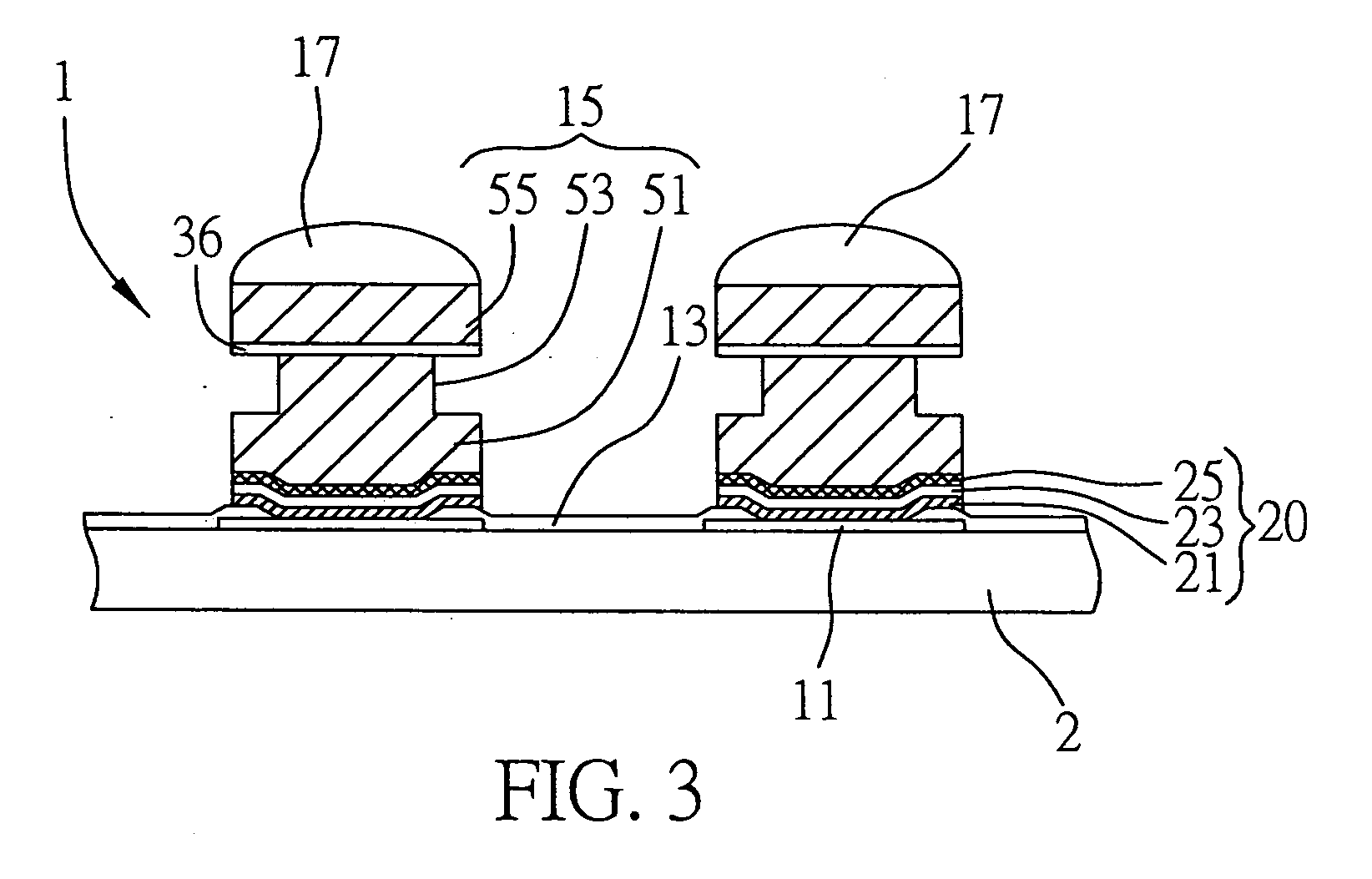

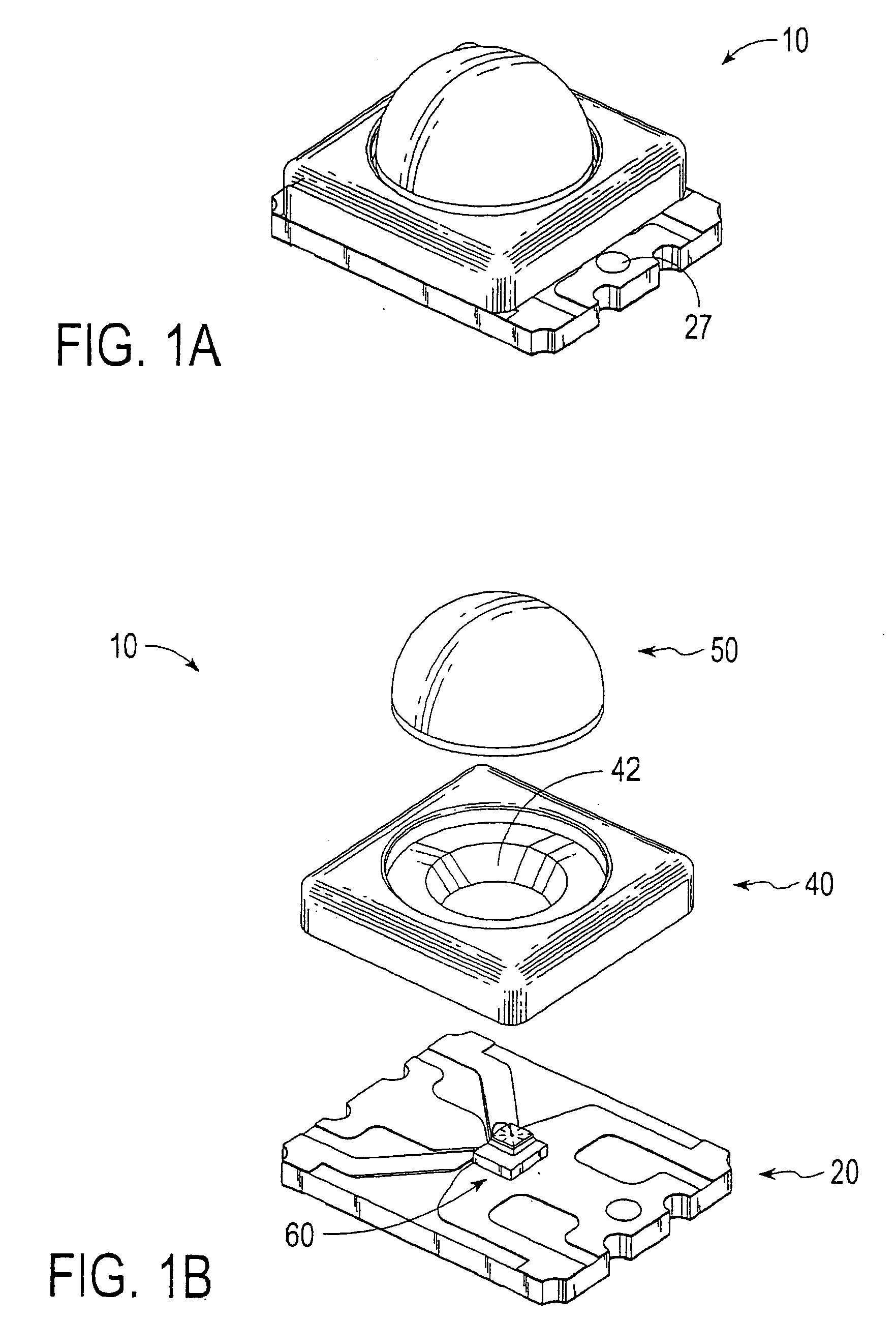

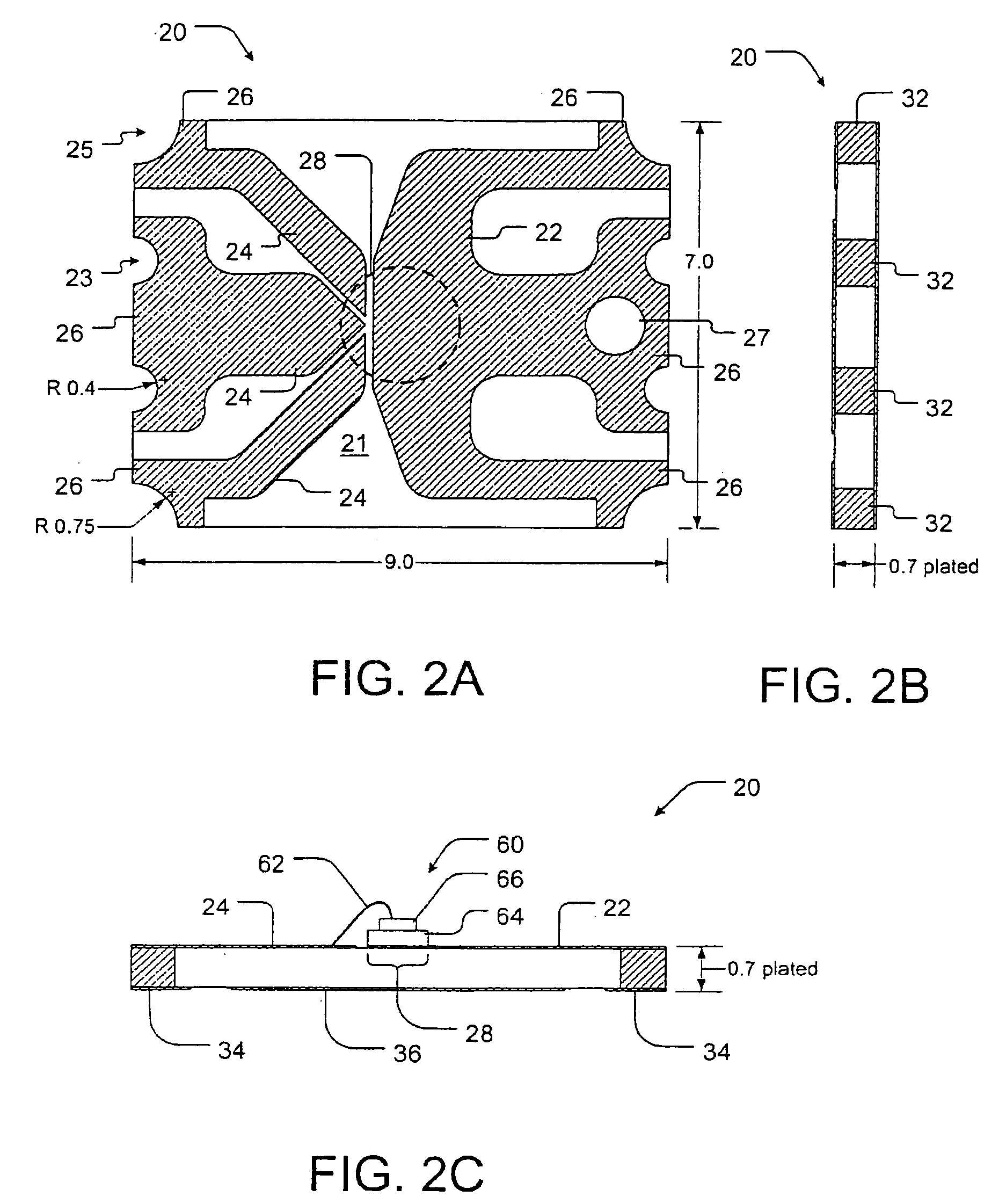

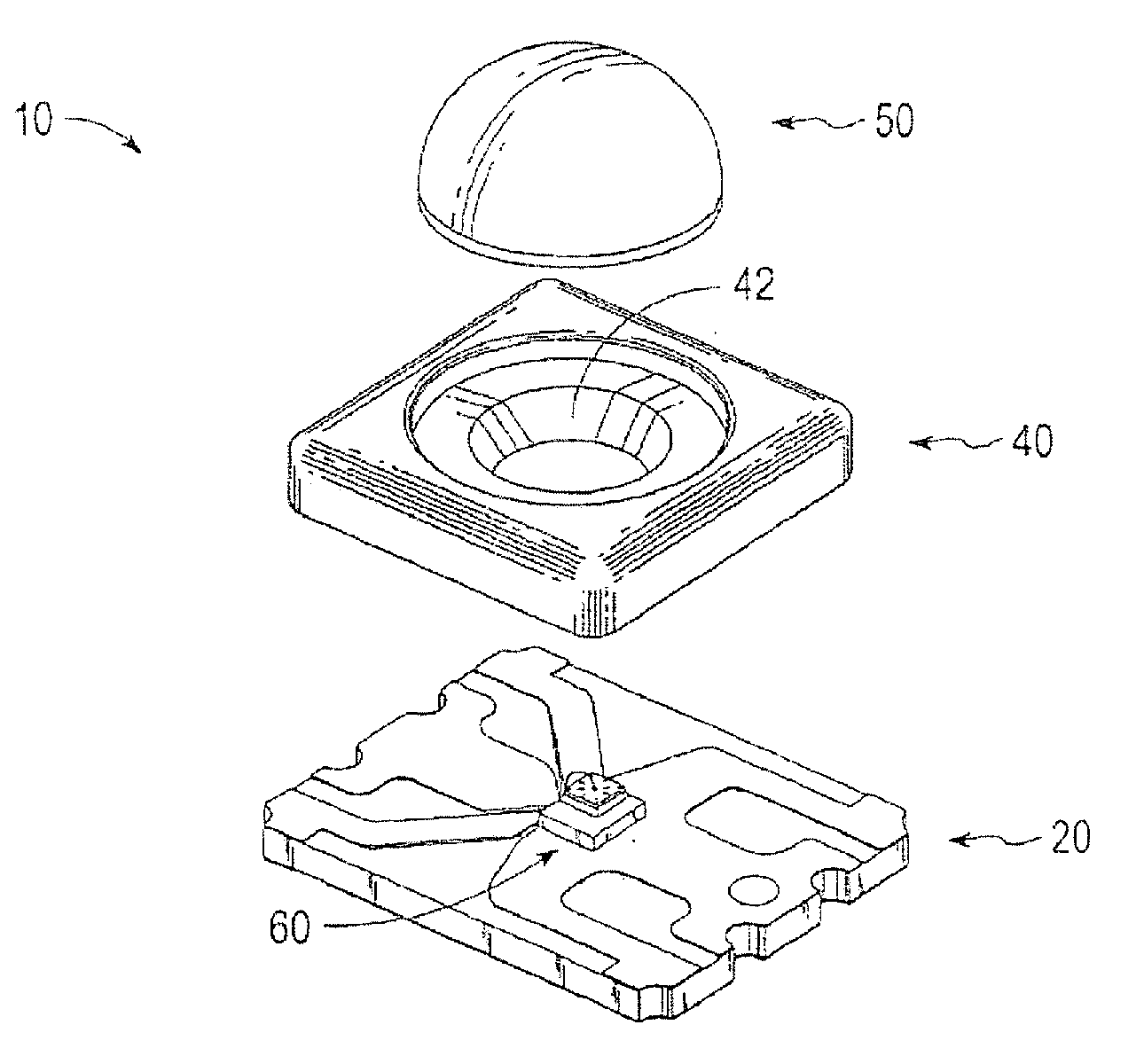

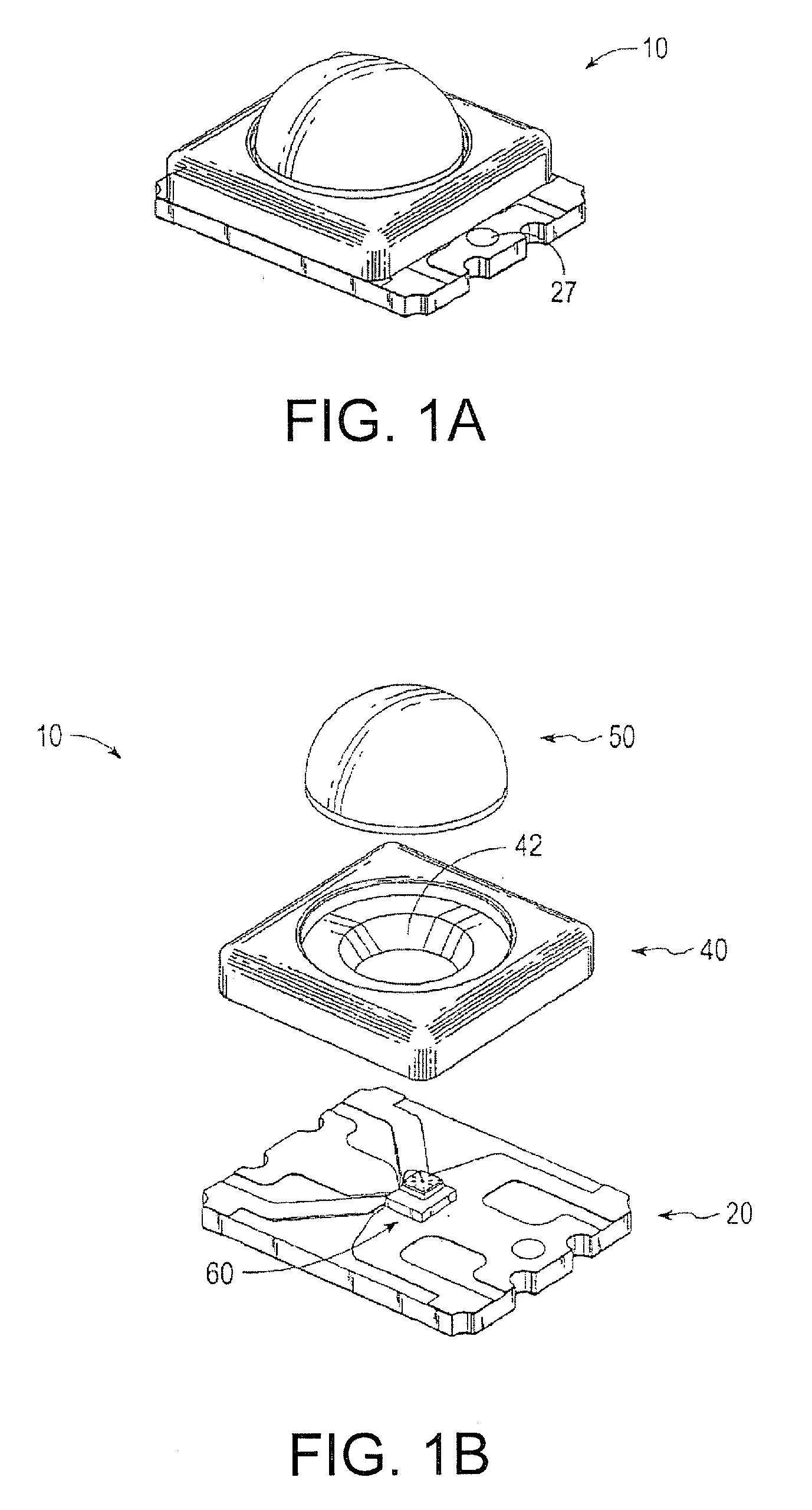

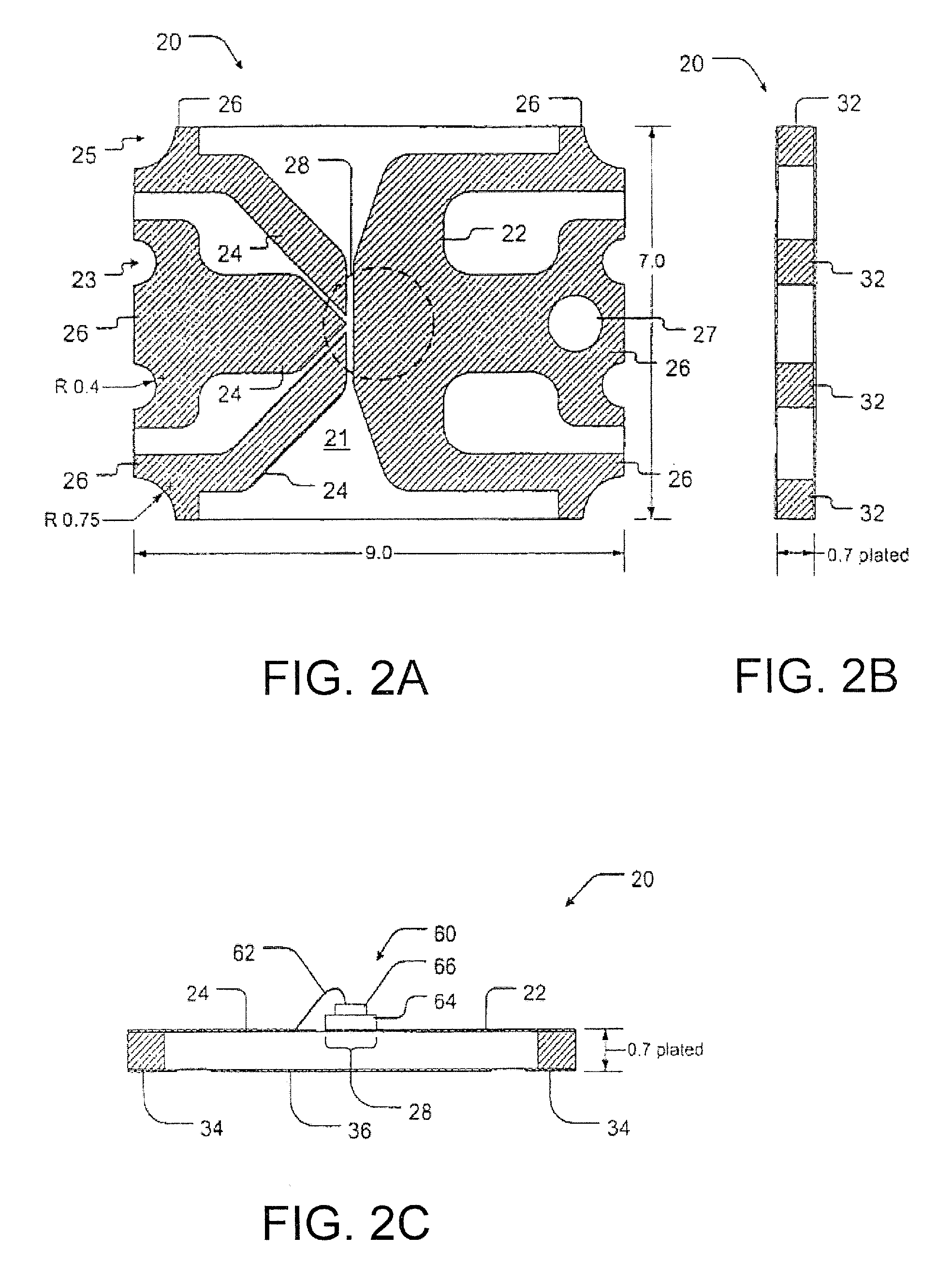

Methods of assembly for a semiconductor light emitting device package

ActiveUS20060063287A1Solid-state devicesSemiconductor/solid-state device manufacturingLight emitting deviceSemiconductor

Methods of assembly for a semiconductor light emitting device package may include positioning a submount on a mounting substrate with a solder material and a flux therebetween. The semiconductor light emitting device is positioned on a top side of the submount with a solder material and a flux therebetween to provide an assembled stack that has not been reflowed. The assembled stack is reflowed to attach the submount to the mounting substrate and the light emitting device to the submount.

Owner:CREELED INC

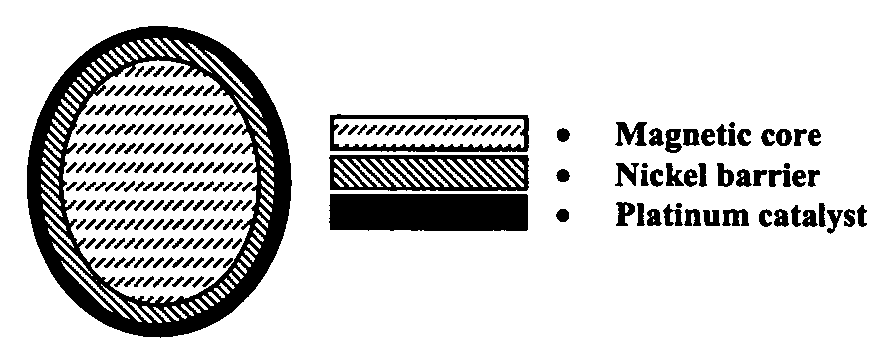

Coated and magnetic particles and applications thereof

InactiveUS20040115340A1Easy to controlImprove catalytic performanceNon-insulated conductorsVolume/mass flow measurementAlloyMaterials science

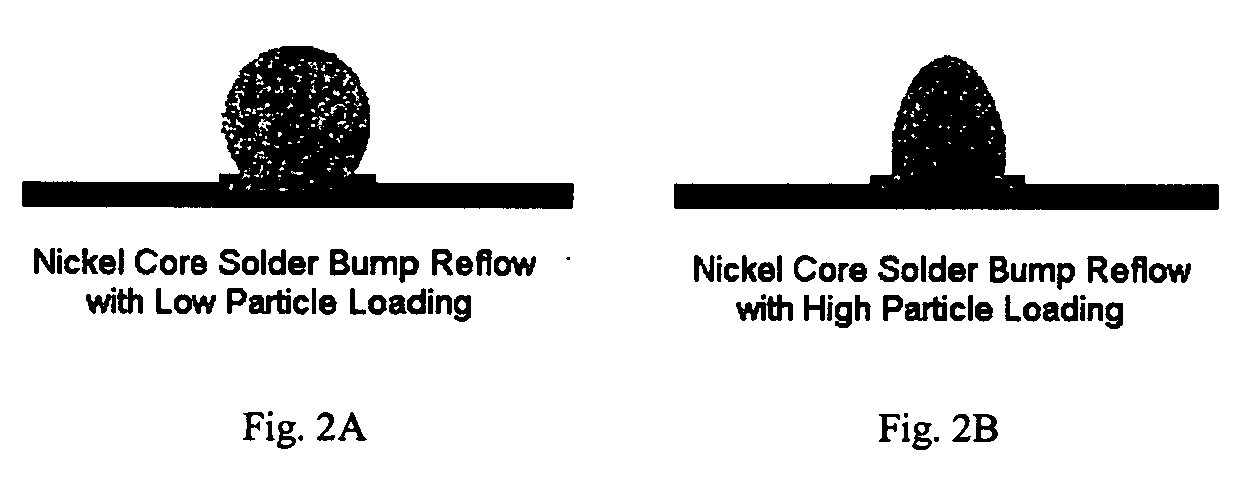

A method of using coated and / or magnetic particles to deposit structures including solder joints, bumps, vias, bond rings, and the like. The particles may be coated with a solderable material. For solder joints, after reflow the solder material may comprise unmelted particles in a matrix, thereby increasing the strength of the joint and decreasing the pitch of an array of joints. The particle and coating may form a higher melting point alloy, permitting multiple subsequent reflow steps. The particles and / or the coating may be magnetic. External magnetic fields may be applied during deposition to precisely control the particle loading and deposition location. Elements with incompatible electropotentials may thereby be electrodeposited in a single step. Using such fields permits the fill of high aspect ratio structures such as vias without requiring complete seed metallization of the structure. Also, a catalyst consisting of a magnetic particle coated with a catalytic material, optionally including an intermediate layer.

Owner:SURFECT TECH

Methods of assembly for a semiconductor light emitting device package

ActiveUS20090315061A1Solid-state devicesSemiconductor/solid-state device manufacturingLight emitting deviceSemiconductor

Methods of assembly for a semiconductor light emitting device package may include positioning a submount on a mounting substrate with a flux material therebetween and at least substantially free of solder material therebetween. The submount has a metal bonding layer facing the mounting substrate. A semiconductor light emitting device is positioned on a top side of the submount with a flux material therebetween to provide an assembled stack. The assembled stack is reflowed to attach the metal bonding layer of the submount to the mounting substrate and to attach the light emitting device to the submount.

Owner:CREELED INC

Low temperature PB-free processing for semiconductor devices

InactiveUS20060043603A1Reduce heat damageFinal product manufactureSemiconductor/solid-state device detailsElectronic systemsMetallurgy

Techniques for utilizing a bonding agent that allows a solder reflow process to occur at a lower reflow temperature. One area of use includes semiconductor device manufacturing processes. The bonding agent is placed between a solder ball and a contact surface. The bonding agent has a melting temperature that is lower than that of the solder ball. Reflow is then performed at a relative low temperature that is high enough for reflowing the bonding agent, yet at the same time, lower than what would be necessary to reflow the solder material. Since, the electrical system is not subjected to the high temperatures necessary for reflowing the solder material, the electronic system experiences less high-temperature related damage.

Owner:LSI CORPORATION

Enhanced copper posts for wafer level chip scale packaging

ActiveUS20080296764A1Increased shear strengthImprove conductivitySemiconductor/solid-state device detailsSolid-state devicesElectrical connectionCopper electrode

An enhanced wafer level chip scale packaging (WLCSP) copper electrode post is described having one or more pins that protrude from the top of the electrode post. When the solder ball is soldered onto the post, the pins are encapsulated within the solder material. The pins not only add shear strength to the soldered joint between the solder ball and the electrode post but also create a more reliable electrical connection due to the increased surface area between the electrode post / pin combination and the solder ball. Moreover, creating an irregularly shaped solder joint retards the propagation of cracks that may form in the intermetal compounds (IMC) layer formed at the solder joint.

Owner:ADVANCED MFG INNOVATIONS INC

Modularized probe head

ActiveUS6946860B2Improve member universalityEasy to reworkElectronic circuit testingIndividual semiconductor device testingContact padProbe card

A modularized probe head for modularly assembling on a probe card is configured for probing a semiconductor wafer under test. The probe head includes a silicon substrate having an active surface and an opposing back surface. The back surface of the silicon substrate is attached on a holder. The silicon substrate has a plurality of peripheral bond pads and contact pads on its active surface. At least a probing chip is mounted on the active surface of the silicon substrate. The probing chip has probing tips and side electrodes. The side electrodes are connected with the contact pads by means of solder material. The peripheral bonding pads of the silicon substrate are connected with a flexible printed circuit for electrically connecting to a multi-layer printed circuit board of a probe card.

Owner:CHIPMOS TECH INC

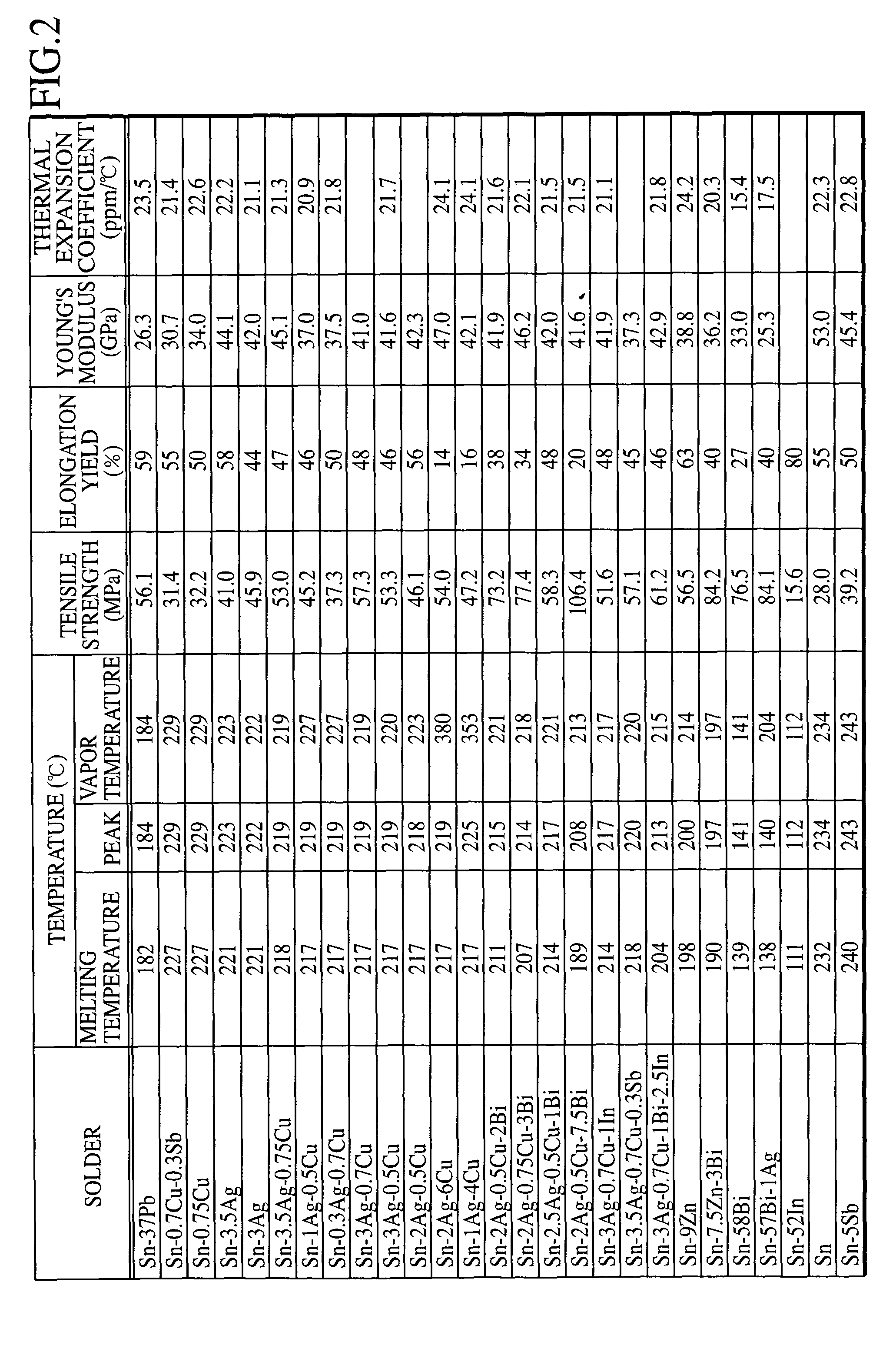

Solder material and electric or electronic device in which the same is used

InactiveUS20030015575A1Low melting pointIntensifies brittlenessPrinted circuit assemblingWelding/cutting media/materialsMetallurgyElectronic component

There is provided an improved lead-free solder material which is preferably used as a connecting material in a mounting process of an electronic component. The solder material according to the present invention contains 1.0 to 4.0% by weight of Ag, 1.0 to 20% by weight of Bi, 0.1 to 1.0% by weight of Ni, and 75 to 97.9% by weight of Sn.

Owner:PANASONIC CORP

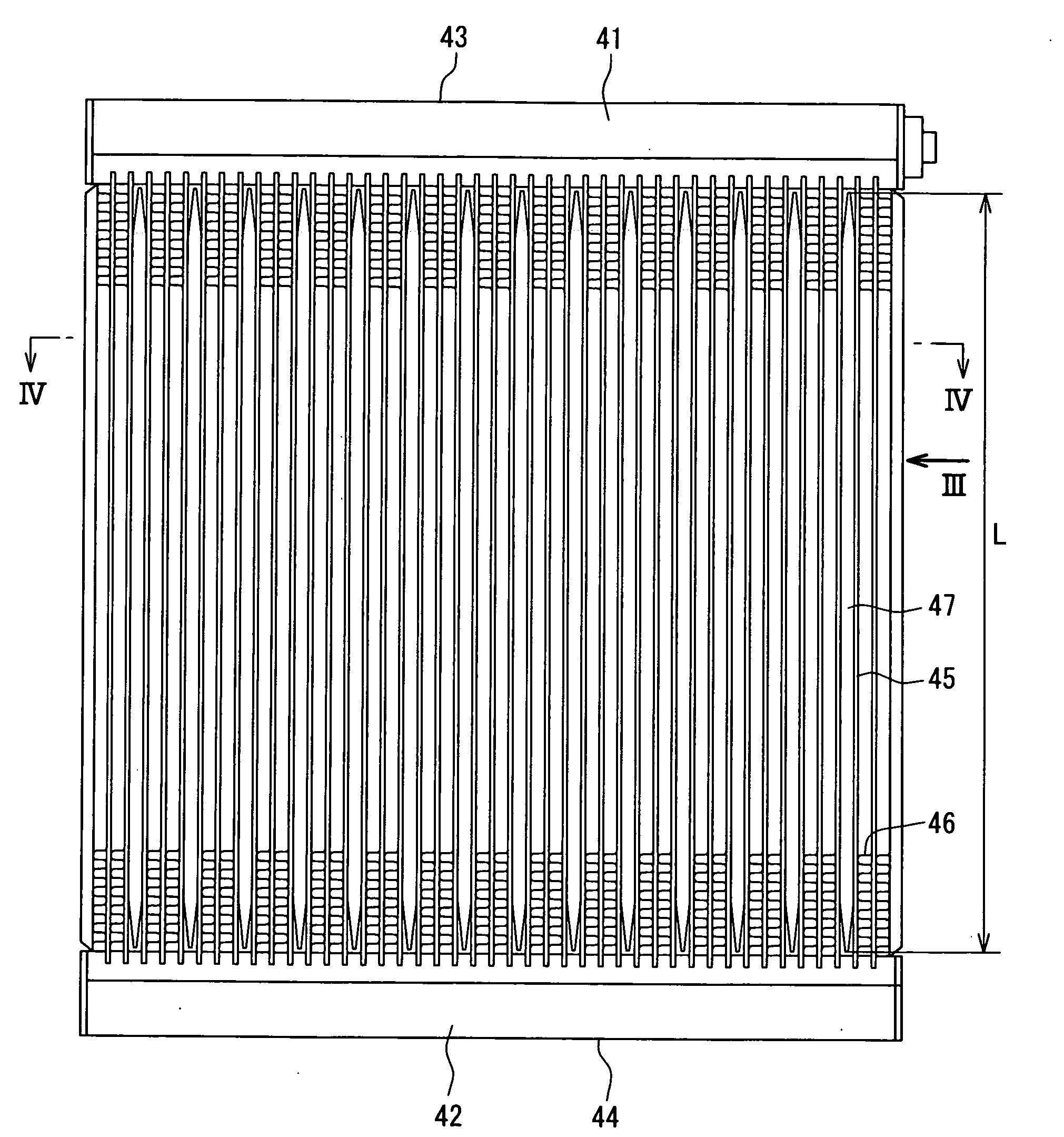

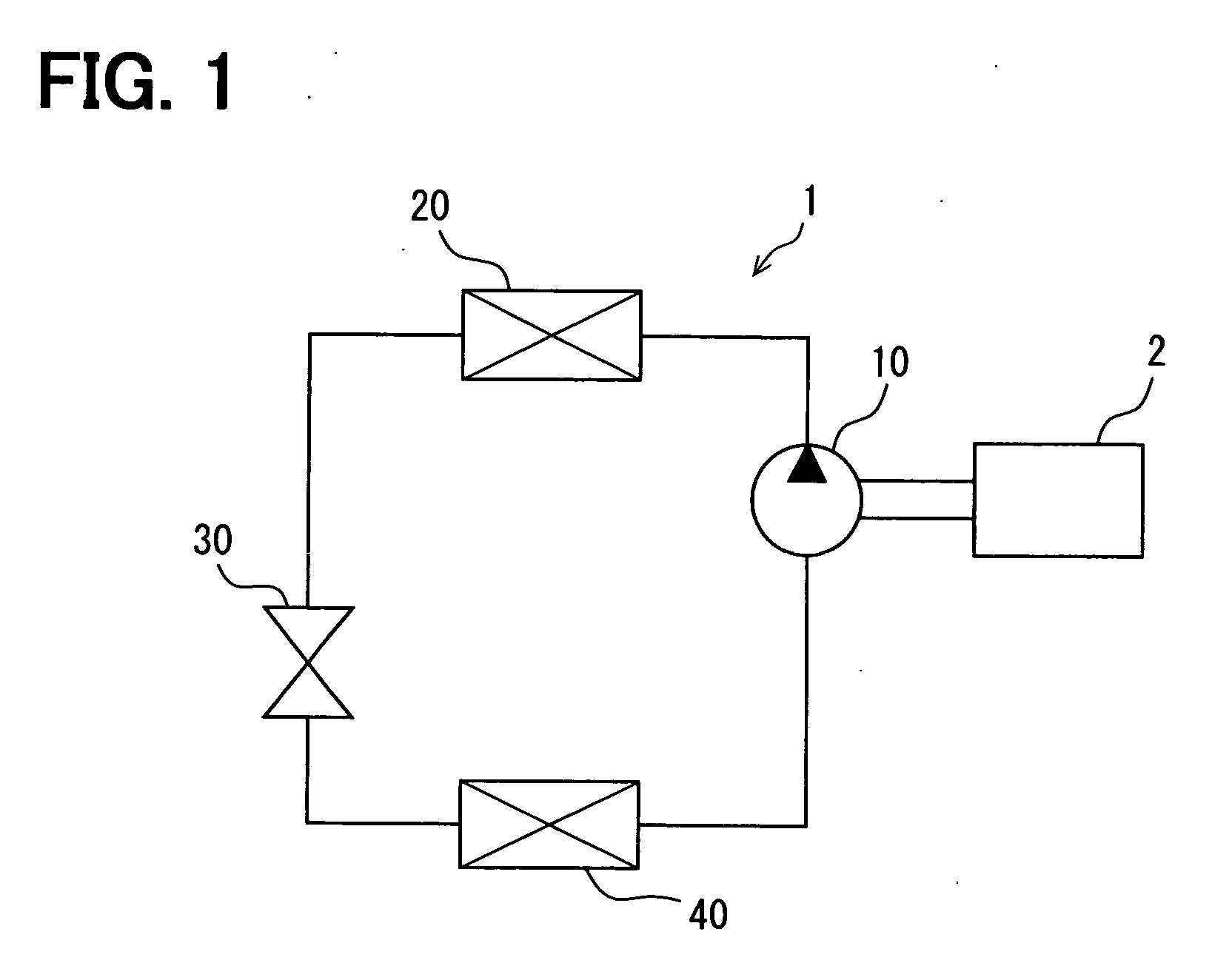

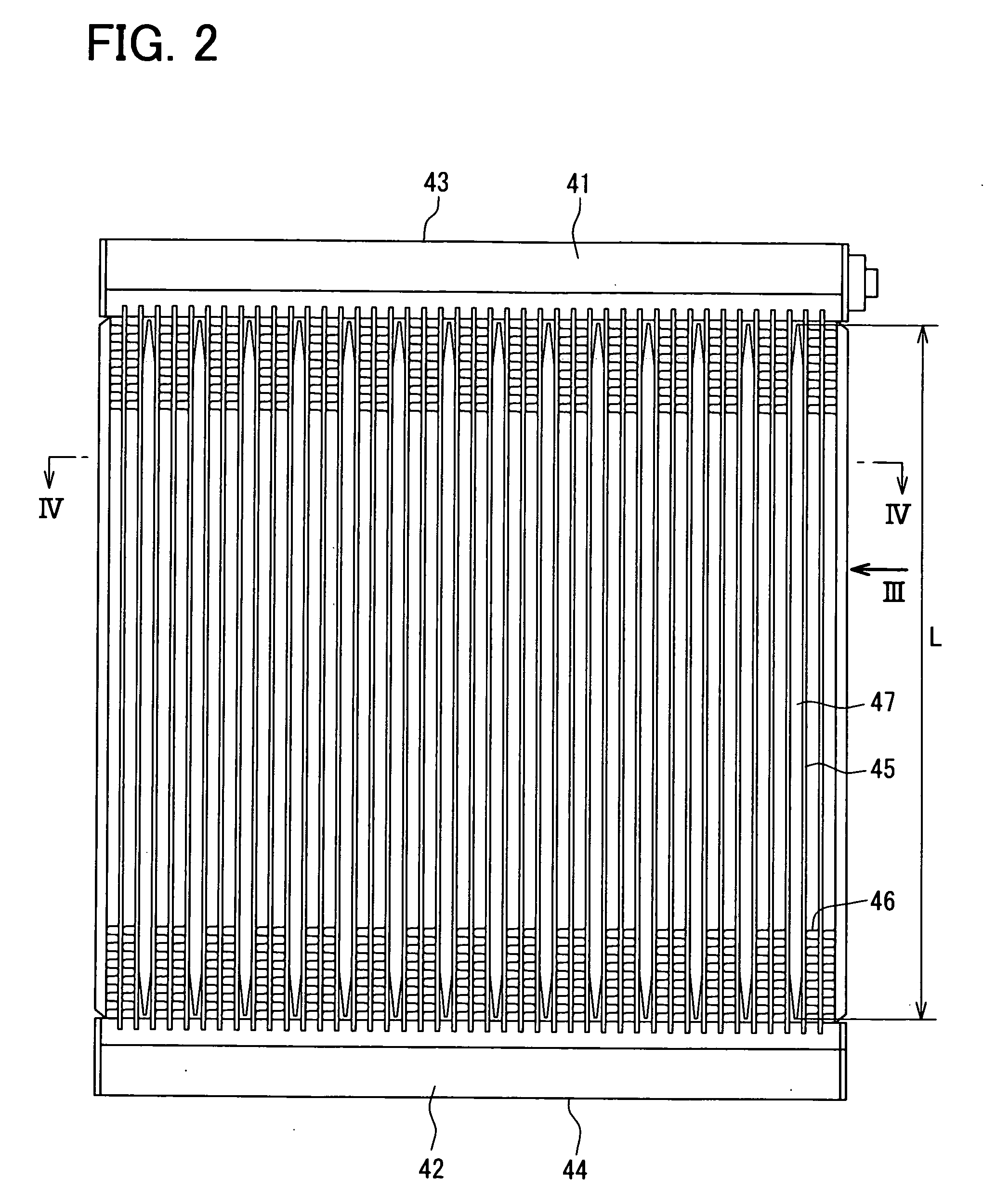

Cool-storage type heat exchanger

ActiveUS20100065244A1Efficient storageImprove productivityHeat storage plantsVehicle heating/cooling devicesProduction rateCool storage

An object of the invention is to provide an effective cooling-energy storing performance and a stable cooling-energy radiating performance and to realize a high productivity. An evaporator has a plurality of refrigerant tubes arranged at almost equal intervals to form therebetween accommodating spaces. A plurality of cooling-storage containers are arranged in some of the accommodating spaces and fins are arranged in the remaining accommodating spaces. A cooling-storage unit is formed by one cooling-storage container and two refrigerant tubes arranged at both sides of the cooling-storage container. Each of the cooling-storage container has projections extending from one wall portion to the other wall portion to form heat exchange portions. The cooling-storage container is connected to the refrigerant tubes by soldering material.

Owner:DENSO CORP

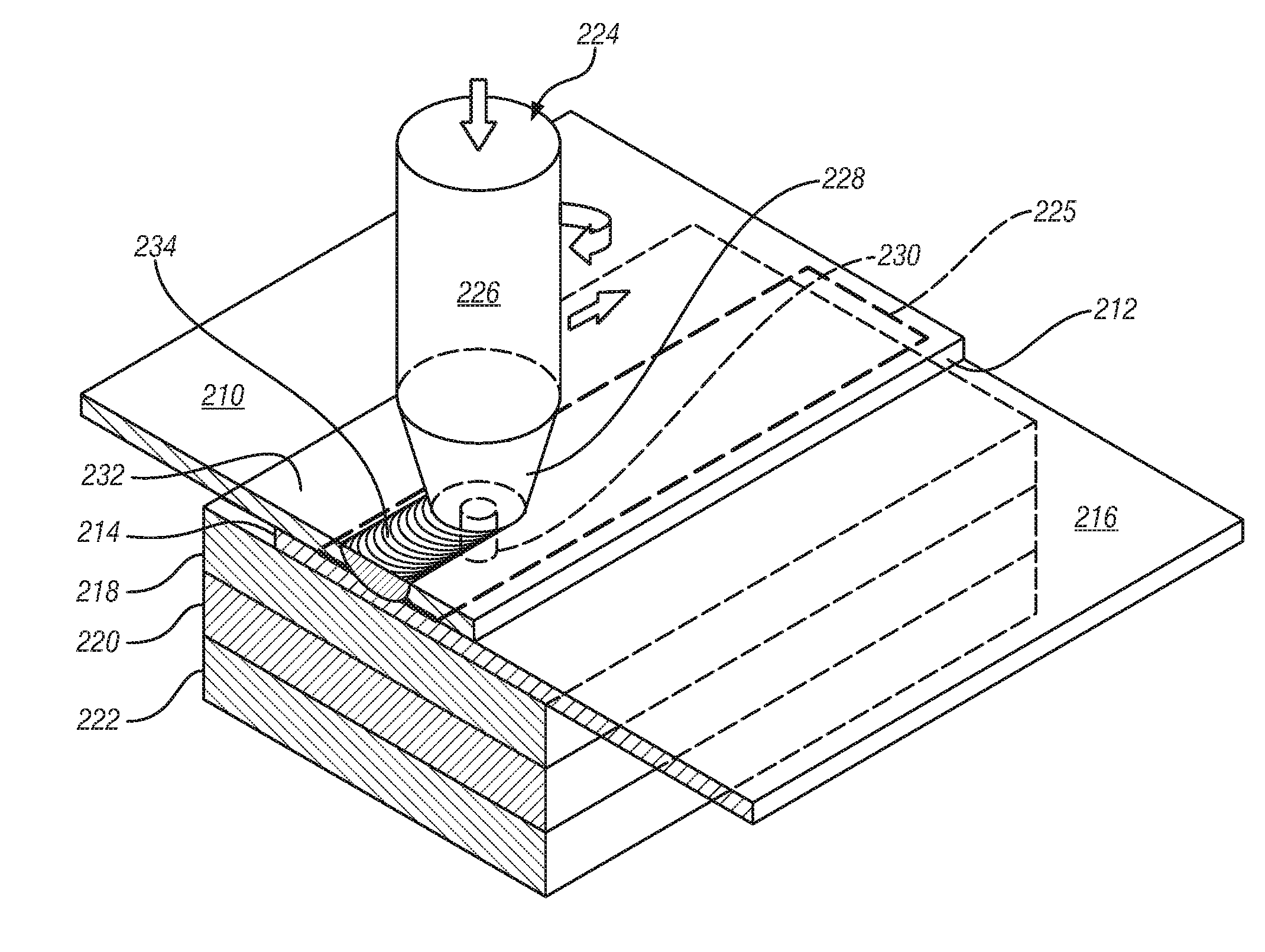

Friction stir welding of dissimilar metals

InactiveUS20100089976A1Improve adhesionImprove joint strengthWelding/cutting media/materialsWelding/soldering/cutting articlesAdhesiveMaterials science

When a friction stir weld tool penetrates the interface of two workpieces of dissimilar metal alloy materials, the resultant weld of the different alloy materials may produce a weak weld joint. Such weak joints are often experienced, for example, when attempting to form spot welds or other friction stir welds between a magnesium alloy sheet or strip and an aluminum alloy sheet or strip. It is discovered that suitable coating compositions including an adhesive placed at the interface of assembled workpieces can alter the composition of the friction stir weld material and strengthen the resulting bond. In the example of friction stir welds between magnesium alloy and aluminum alloy workpieces, it is found that combinations of an adhesive with copper, tin, zinc, and / or other powders can strengthen the magnesium-containing and aluminum-containing friction stir weld material.

Owner:GM GLOBAL TECH OPERATIONS LLC

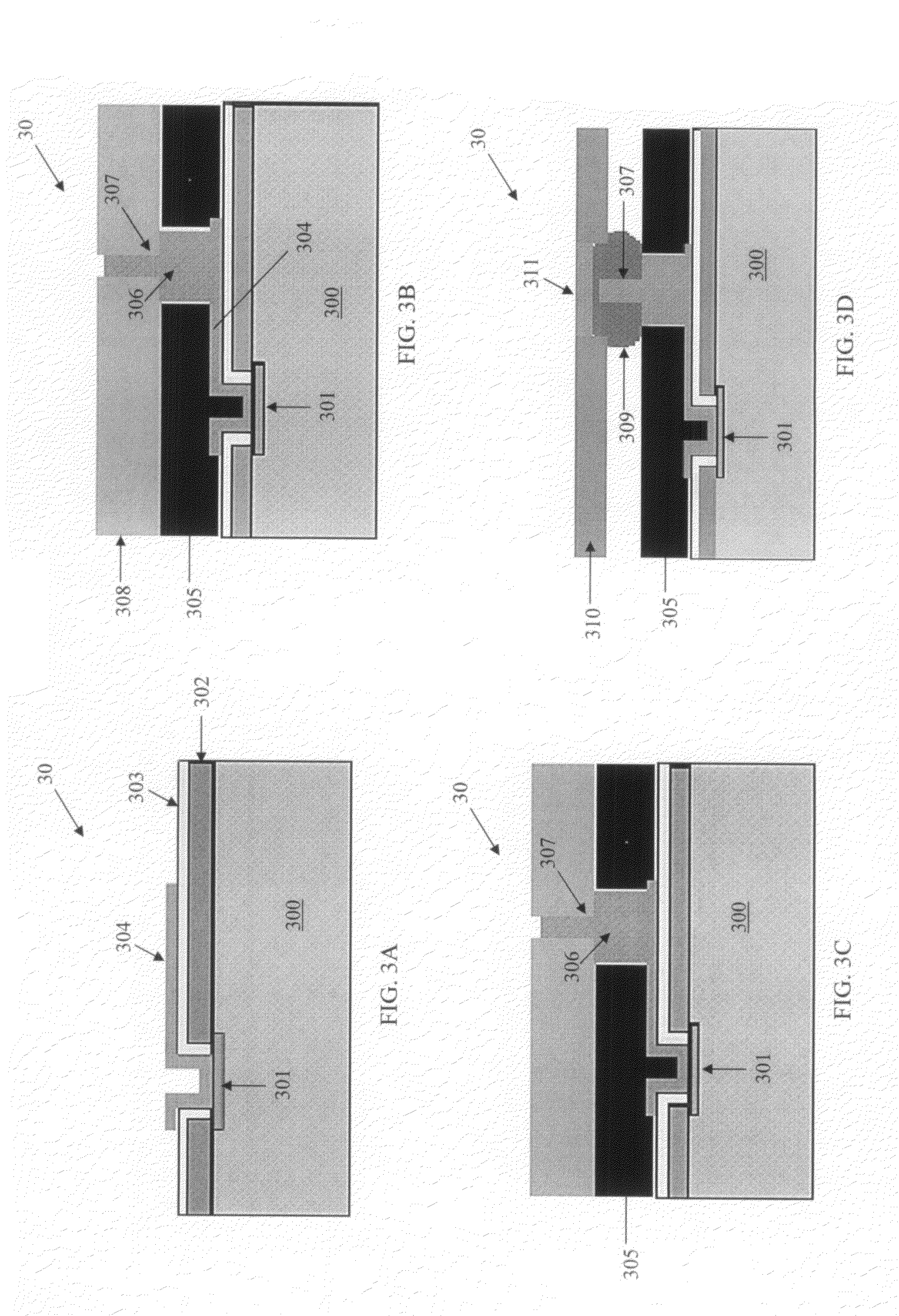

Method for forming improved bump structure

InactiveUS20070087544A1Semiconductor/solid-state device detailsSolid-state devicesContact padEngineering

Methods for forming an improved bump structure on a semiconductor device are provided. In one embodiment, a substrate is provided having at least one contact pad formed thereon. A first passivation layer is formed over the substrate, the first passivation layer having at least one opening therein exposing a portion of the contact pad. A first patterned and etched conductive metal layer is formed on the contact pad and above a portion of the first passivation layer. A second patterned and etched passivation layer is formed above the first passivation layer and a portion of the first conductive metal layer, wherein a portion of the ends of the first conductive metal layer is wedged between the first and second passivation layers. A second conductive metal layer is formed above the second passivation layer and the first conductive metal layer. A patterned and etched photoresist layer is then formed over a portion of the second passivation layer, the photoresist layer having an opening overlying the contact pad, and a solder material is deposited in the opening to form a solder column. The photoresist layer is thereafter removed and the second conductive metal layer is etched to the second passivation layer by using the solder column as an etching mask. The solder column is then reflown to create a solder bump.

Owner:TAIWAN SEMICON MFG CO LTD

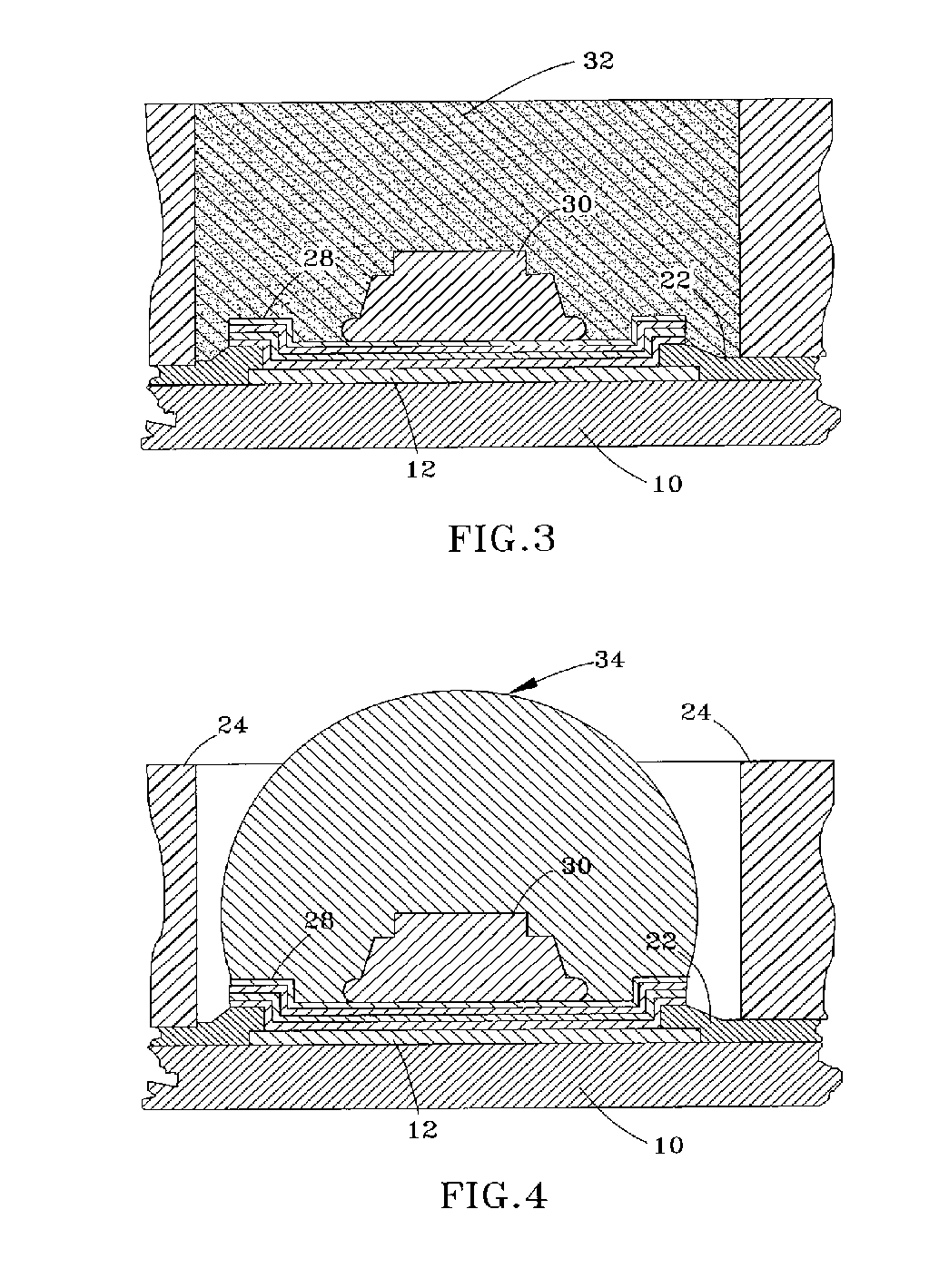

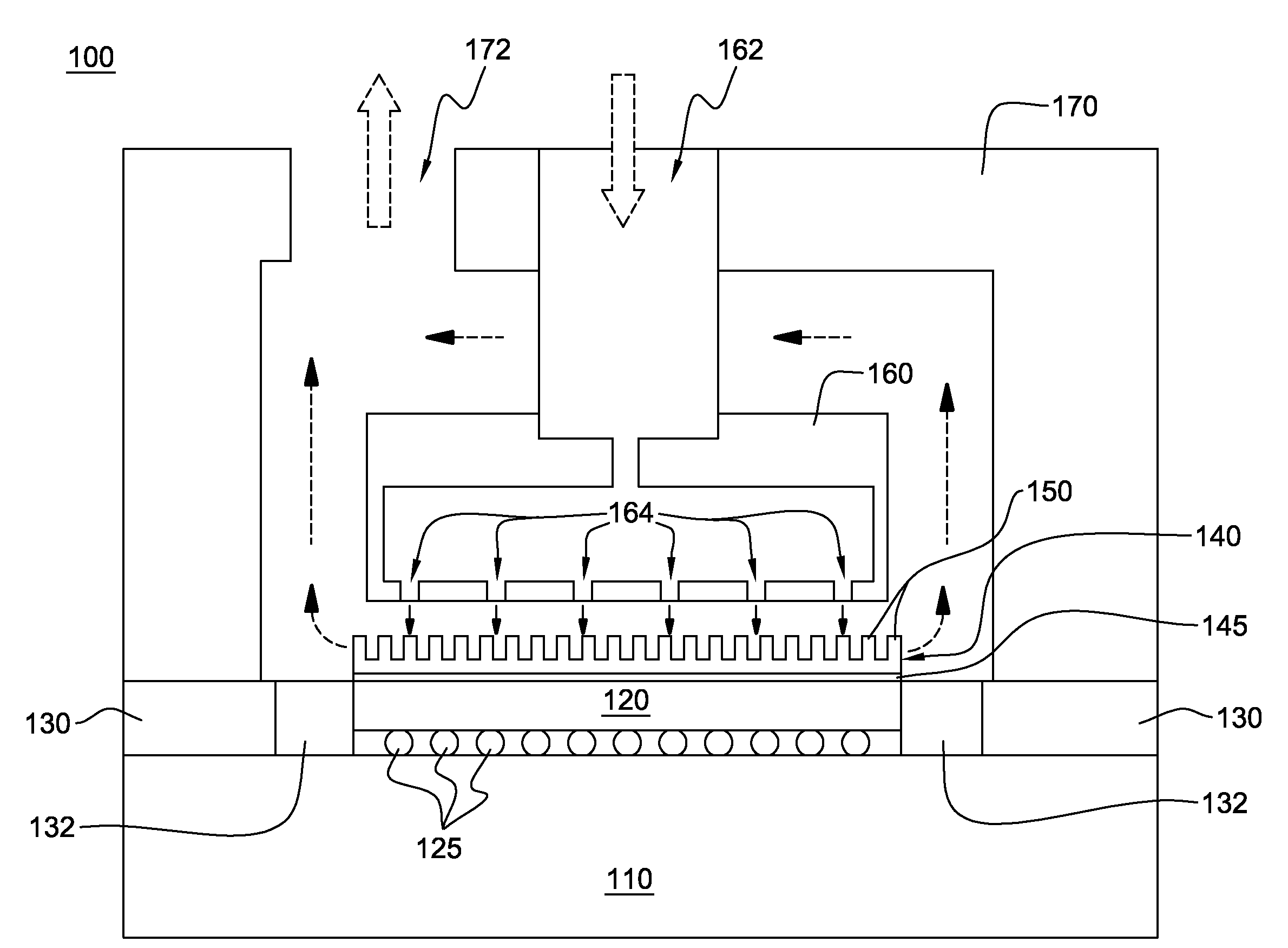

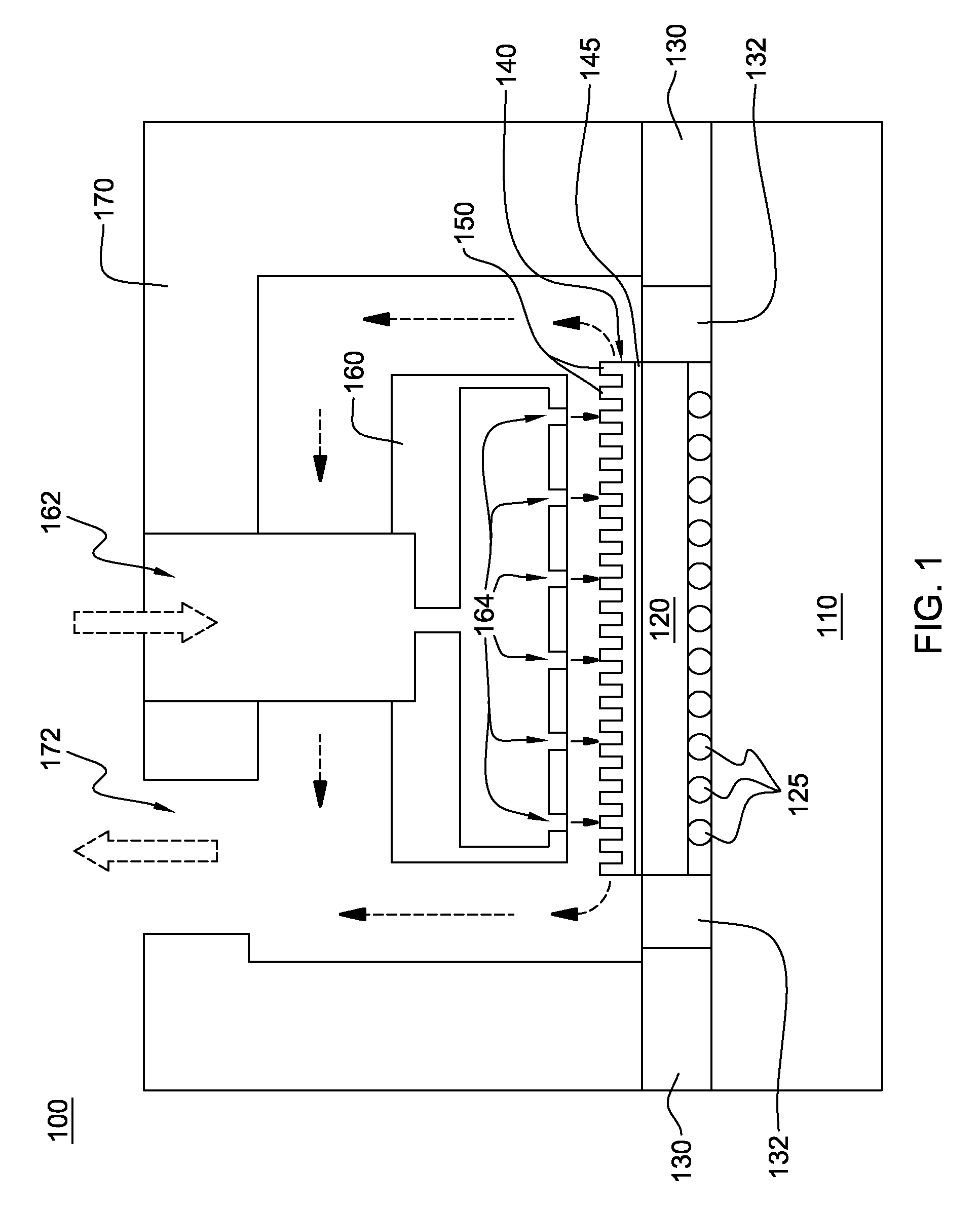

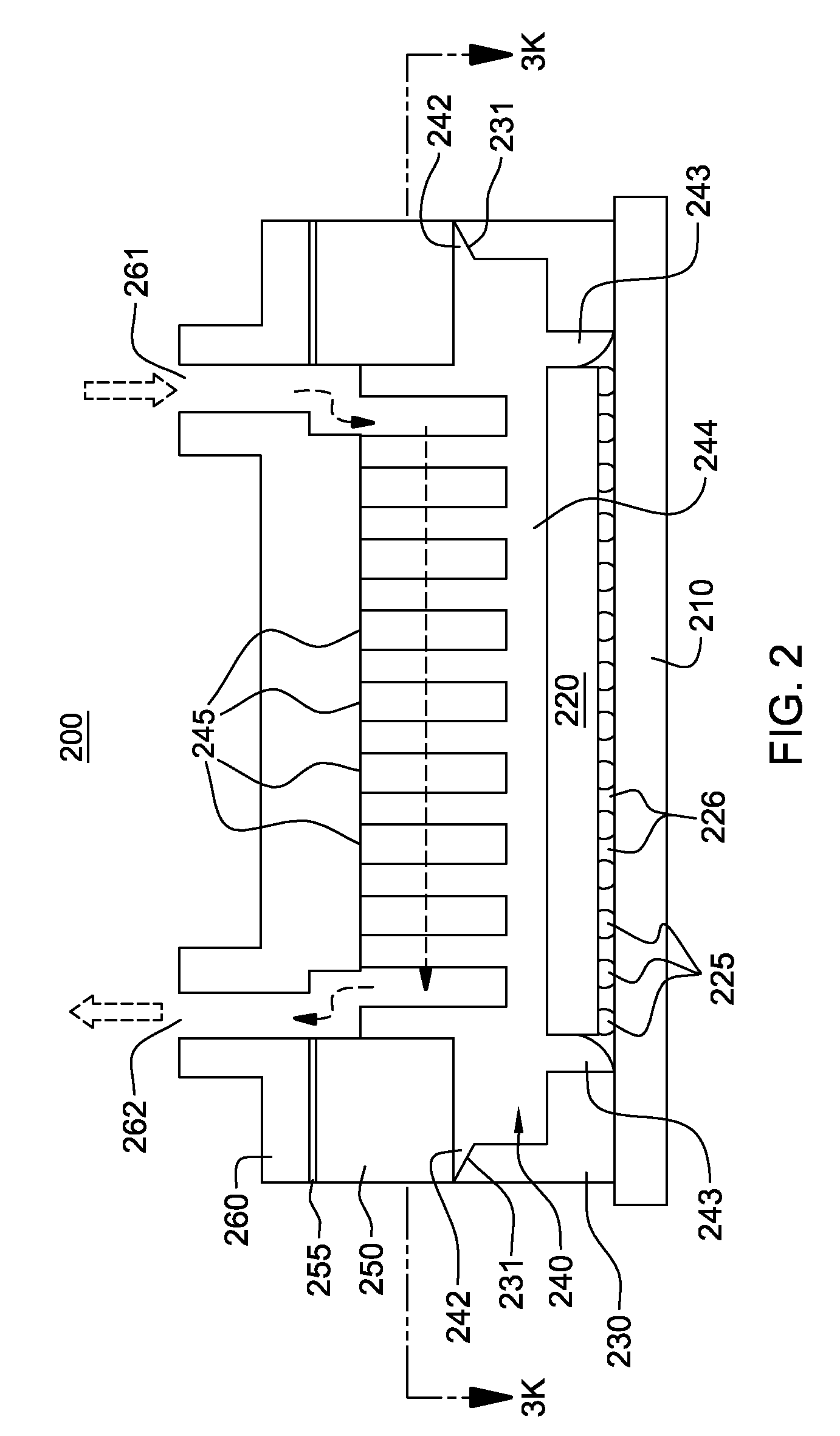

Cooling apparatus and method of fabrication thereof with a cold plate formed in situ on a surface to be cooled

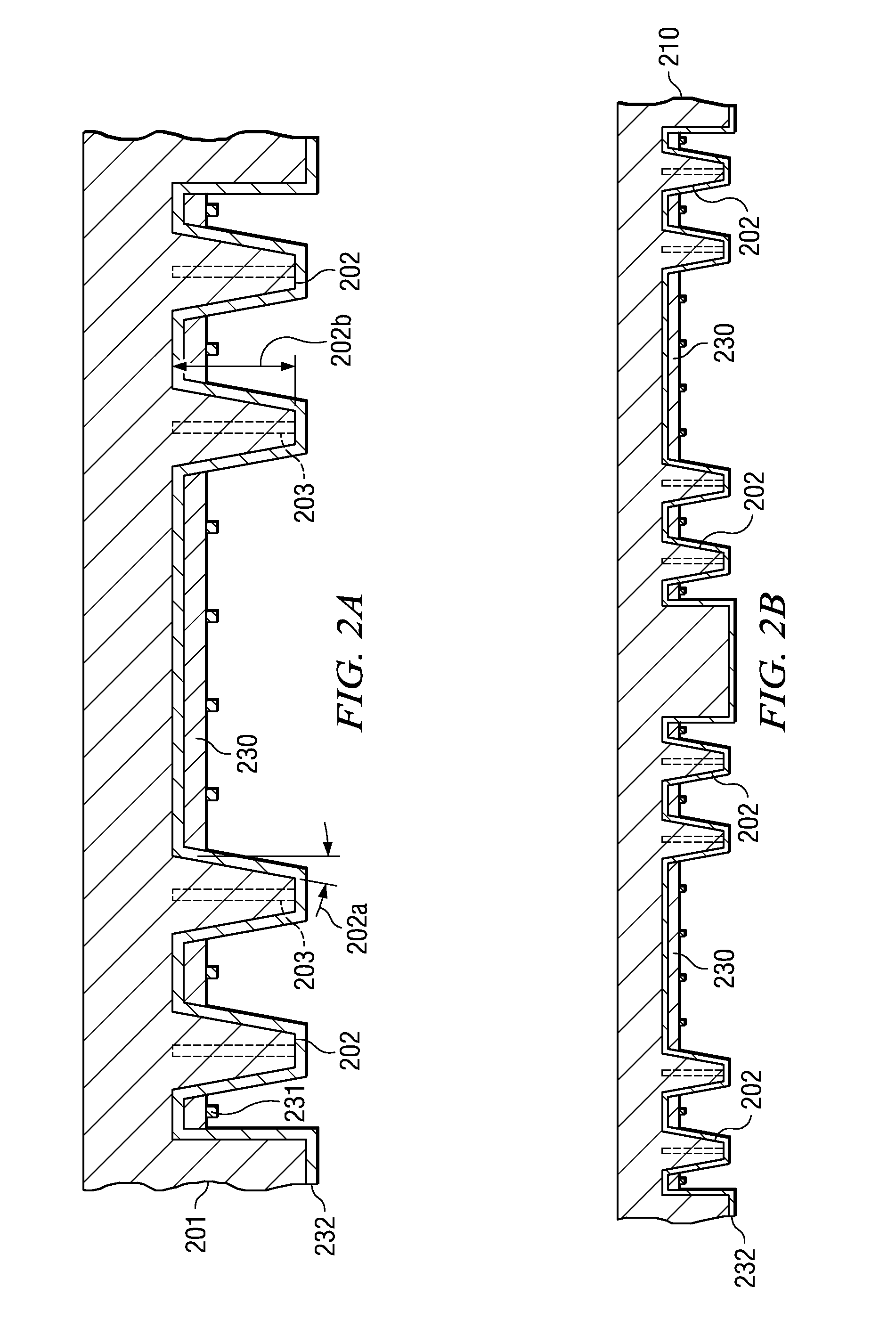

InactiveUS20090316360A1Semiconductor/solid-state device detailsSolid-state devicesMetallurgyCold plate

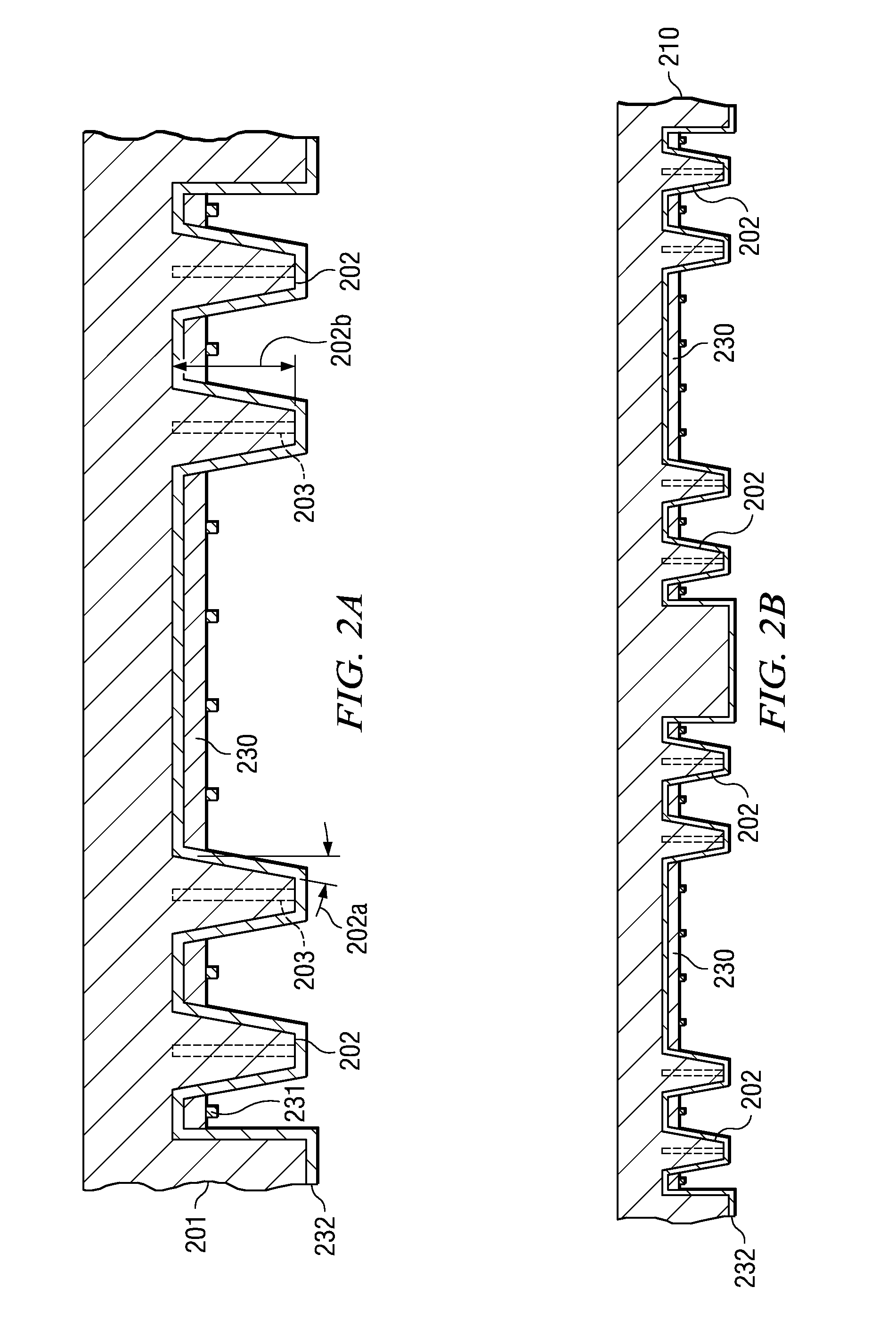

A cooling apparatus and method of fabrication are provided for facilitating removal of heat from a heat-generating electronic device. The method of fabrication includes: obtaining a solder material; disposing the solder material on a surface to be cooled; and reflowing and shaping the solder material disposed on the surface to be cooled to configure the solder material as a base with a plurality of fins extending therefrom. In addition to being in situ-configured on the surface to be cooled, the base is simultaneously metallurgically bonded to the surface to be cooled. The solder material, configured as the base with a plurality of fins extending therefrom, is a single, monolithic structure thermally attached to the surface to be cooled via the metallurgical bonding thereof to the surface to be cooled.

Owner:GLOBALFOUNDRIES INC

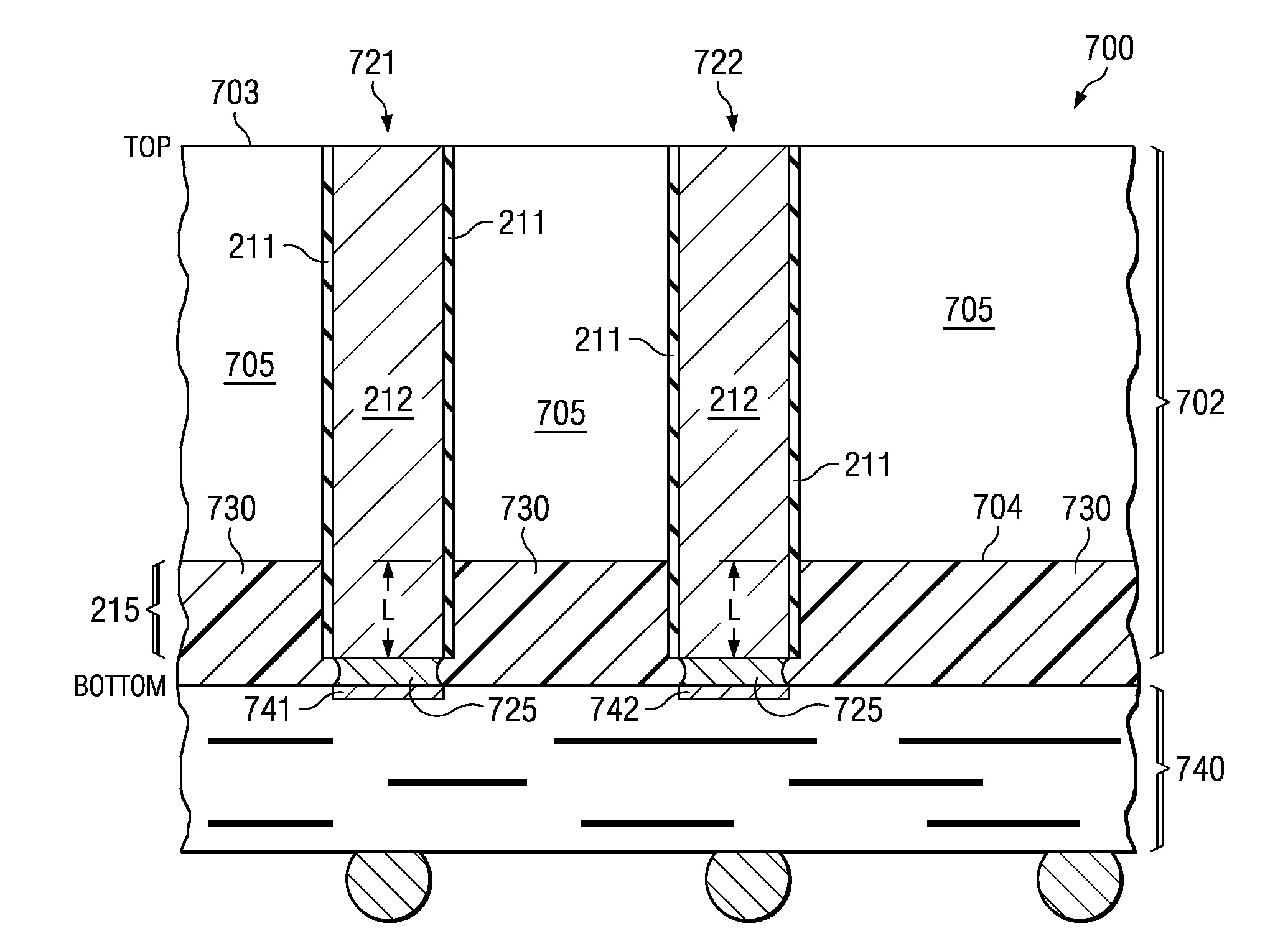

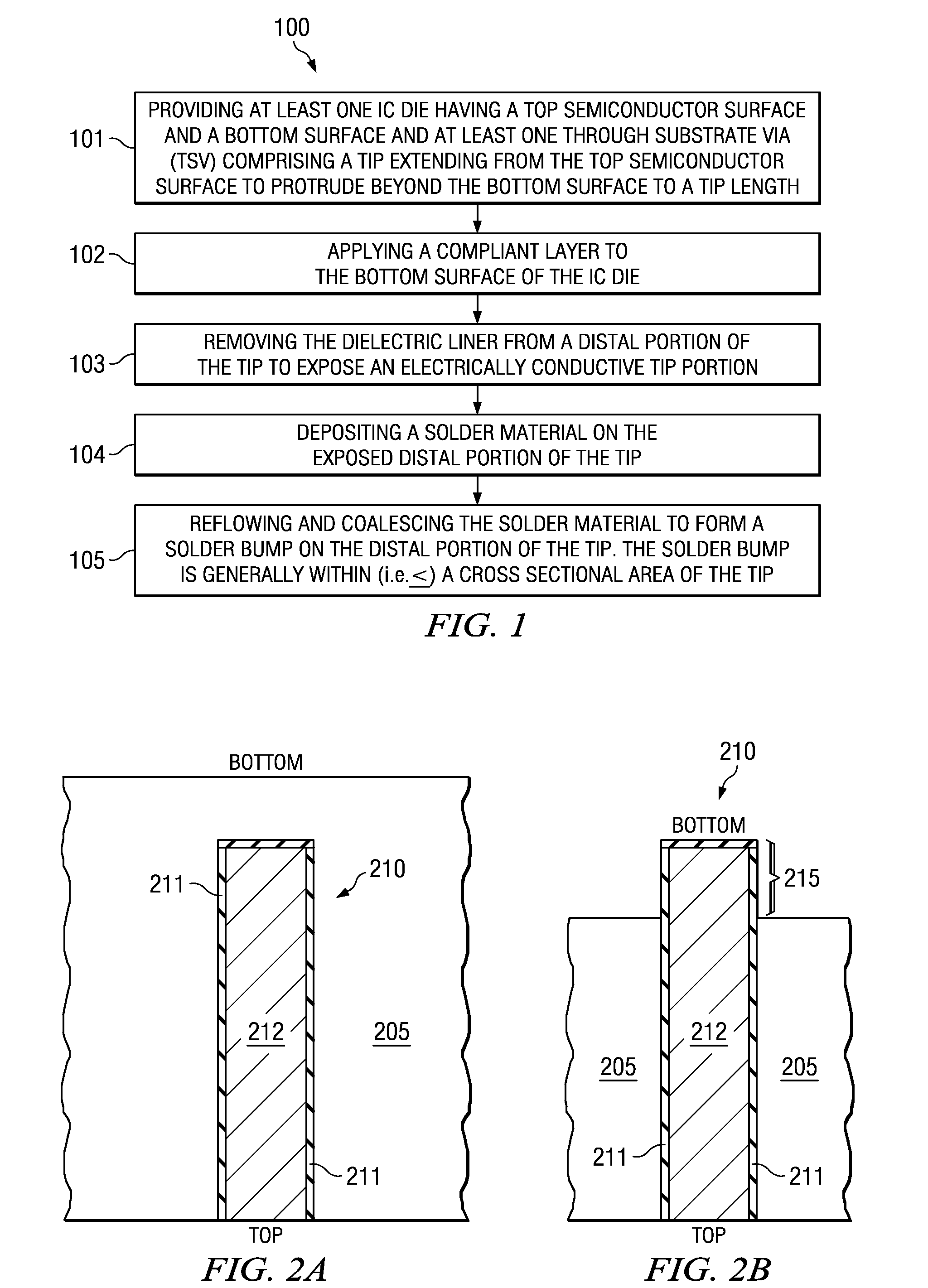

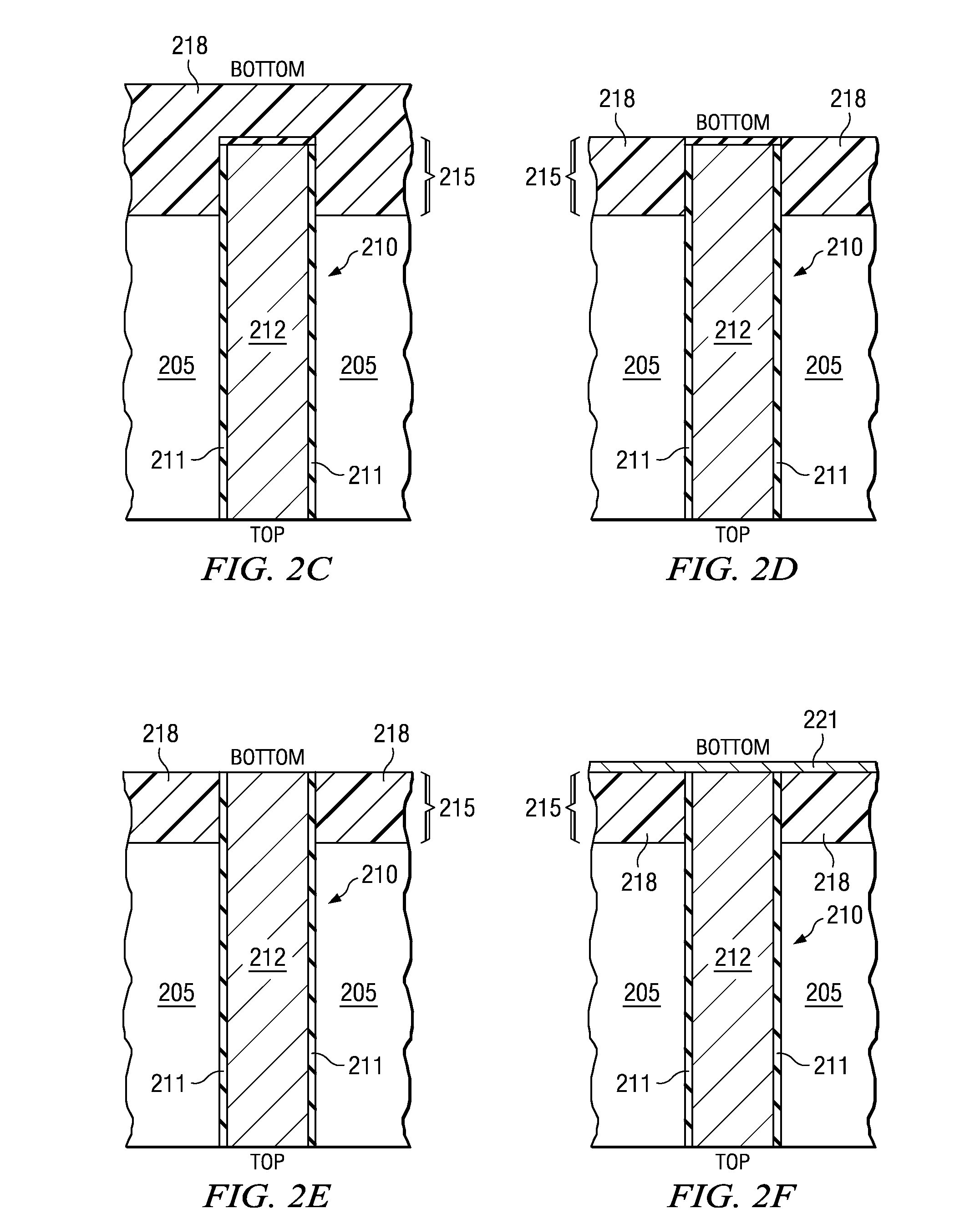

IC die having TSV and wafer level underfill and stacked IC devices comprising a workpiece solder connected to the TSV

ActiveUS20100096738A1Shorten assembly timeReduce throughputSemiconductor/solid-state device detailsSolid-state devicesIc devicesSemiconductor

A method of forming integrated circuit (IC) die configured for attachment to another die or a package substrate, and stacked IC devices therefrom. At least one IC die having a top semiconductor surface and a bottom surface and at least one through substrate via (TSV) including a tip protruding beyond the bottom surface to a tip length is provided. The tip has an outer dielectric tip liner, and an electrically conductive portion within the outer dielectric tip liner. A compliant layer is applied to the bottom surface of the IC die. The dielectric tip liner is removed from a distal portion of the tip to expose an electrically conductive tip portion. A solder material is deposited on the exposed distal portion of the tip. The solder material is reflowed and coalesced to form a solder bump on the distal portion of the tip.

Owner:TEXAS INSTR INC

Array molded package-on-package having redistribution lines

ActiveUS7944034B2Shorten the time to marketSimple methodLiquid surface applicatorsSemiconductor/solid-state device detailsContact padCoupling

A semiconductor device with a sheet-like insulating substrate (101) integral with two or more patterned layers of conductive lines and vias, a chip attached to an assembly site, and contact pads (103) in pad locations has an encapsulated region on the top surface of the substrate, extending to the edge of the substrate, enclosing the chip, and having contact apertures (703) at the pad locations for external communication with the pad metal surfaces. The apertures may have not-smooth sidewall surfaces and may be filled with solder material (704) to contact the pads. Metal-filled surface grooves (710) in the encapsulated region, with smooth groove bottom and sidewalls, are selected to serve as customized routing interconnections, or redistribution lines, between selected apertures and thus to facilitate the coupling with another semiconductor device to form a package-on-package assembly.

Owner:TEXAS INSTR INC

Method to form solder deposits on substrates

ActiveUS20110189848A1Uniform layersHigh aspect ratioPrinted circuit assemblingSemiconductor/solid-state device detailsSolder maskAlloy

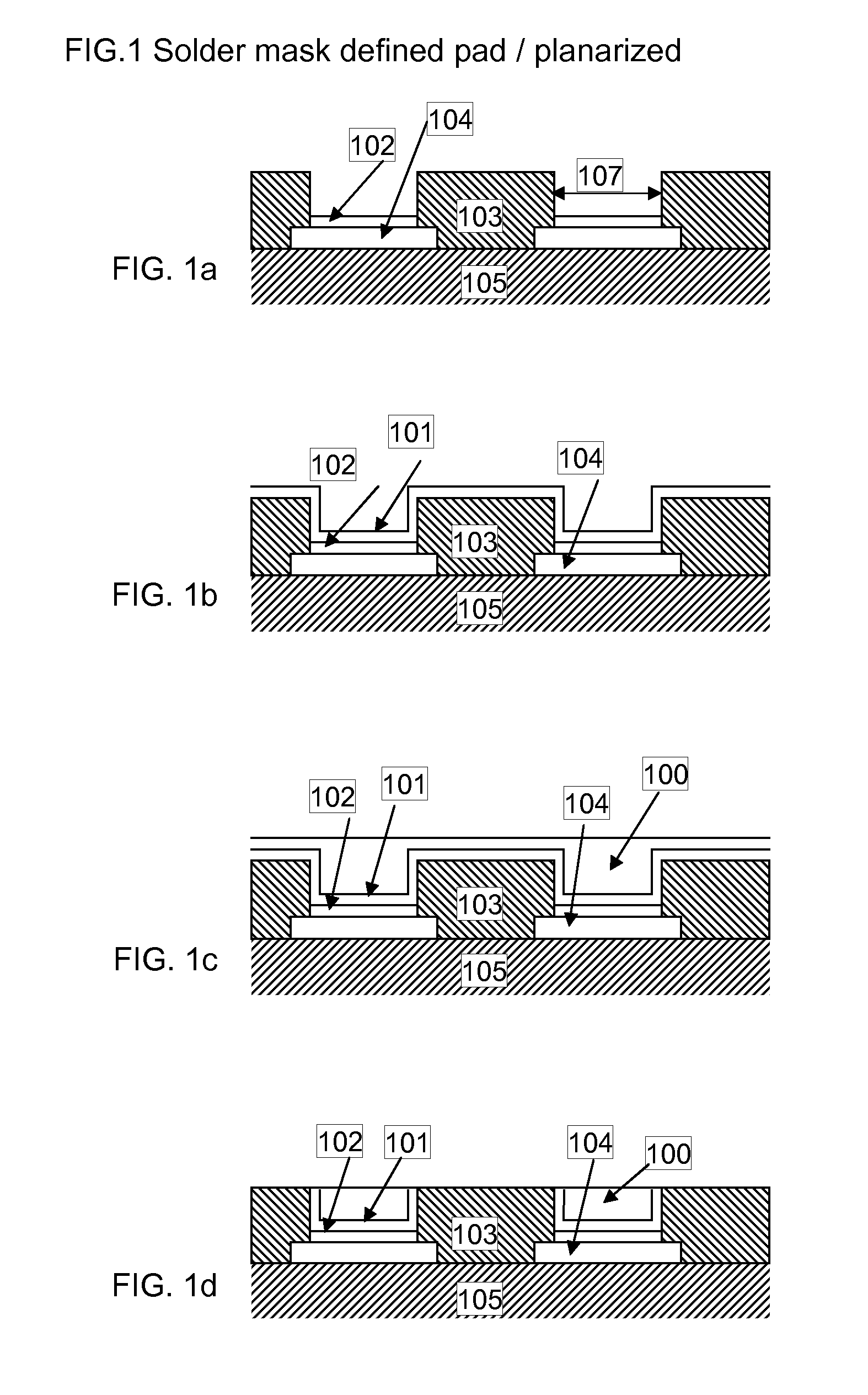

Described is a method of forming a solder deposit on a substrate comprising the following steps i) provide a substrate including a surface bearing electrical circuitry that includes at least one contact area, ii) form a solder mask layer that is placed on the substrate surface and patterned to expose the at least one contact area, iii) contact the entire substrate area including the solder mask layer and the at least one contact area with a solution suitable to provide a conductive layer on the substrate surface, iv) electroplate a solder deposit layer containing a tin or tin alloy onto the conductive layer and v) etch away an amount of the solder deposit layer containing tin or tin alloy sufficient to remove the solder deposit layer from the solder mask layer area leaving a solder material layer on the at least one contact area.

Owner:ATOTECH DEUT GMBH

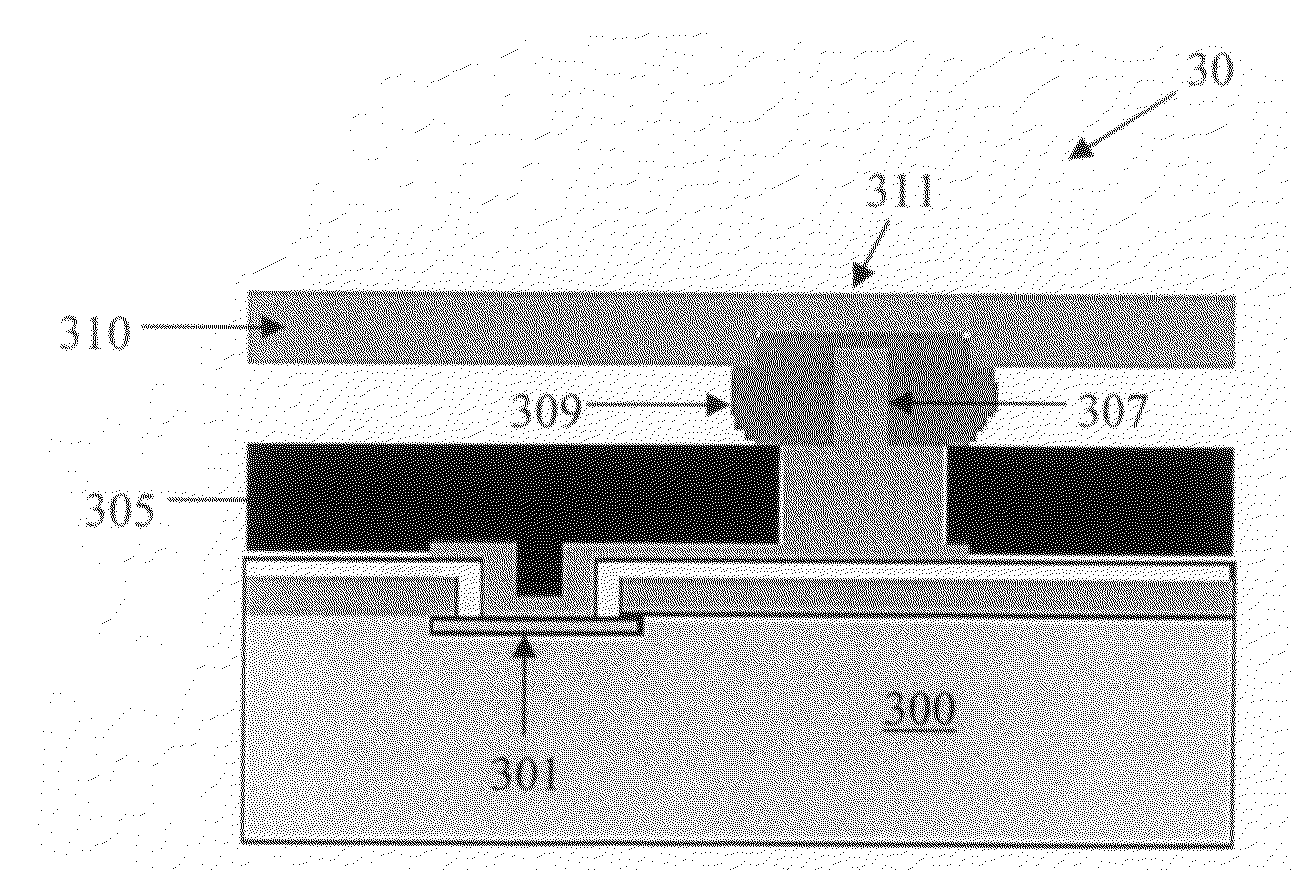

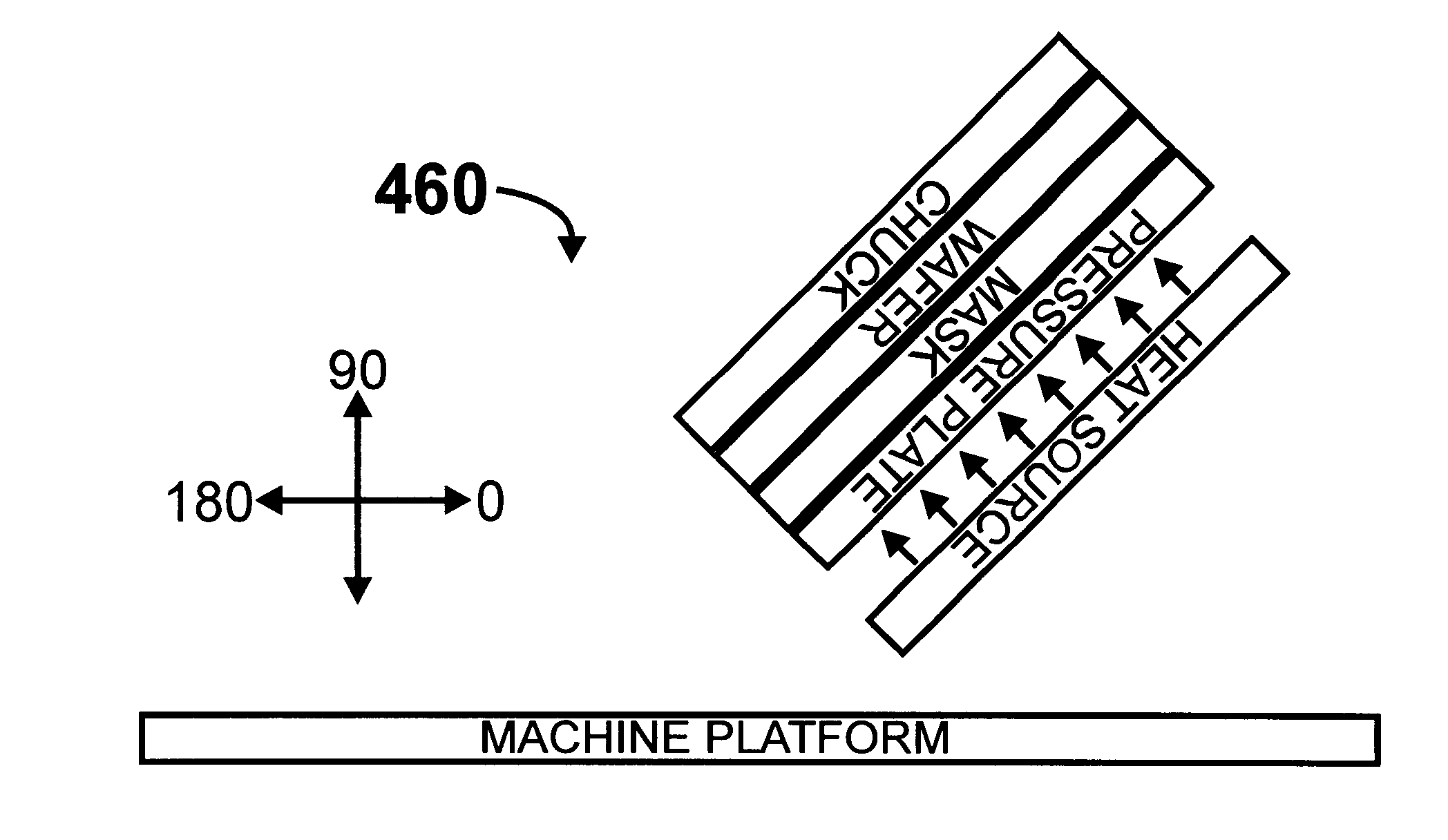

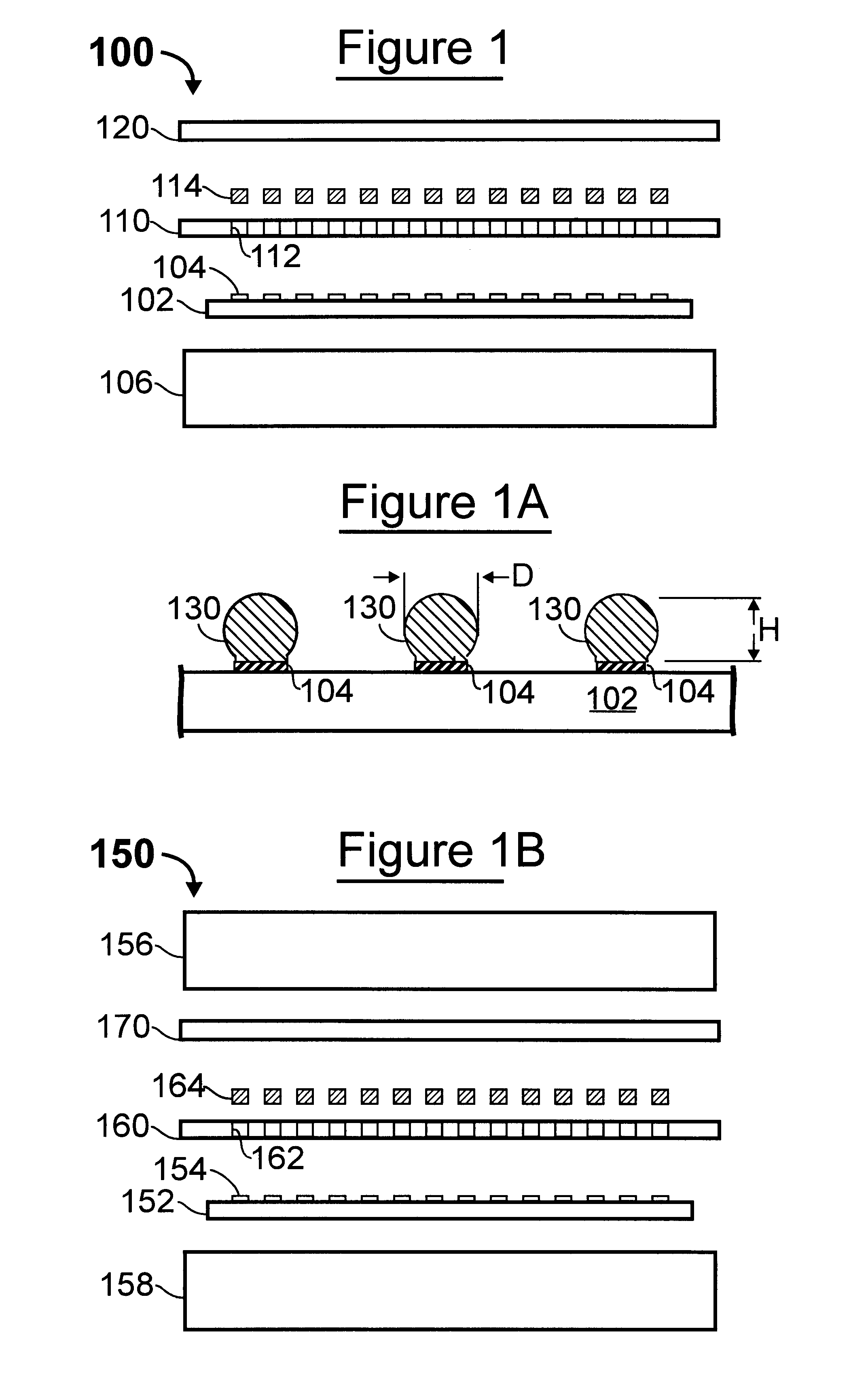

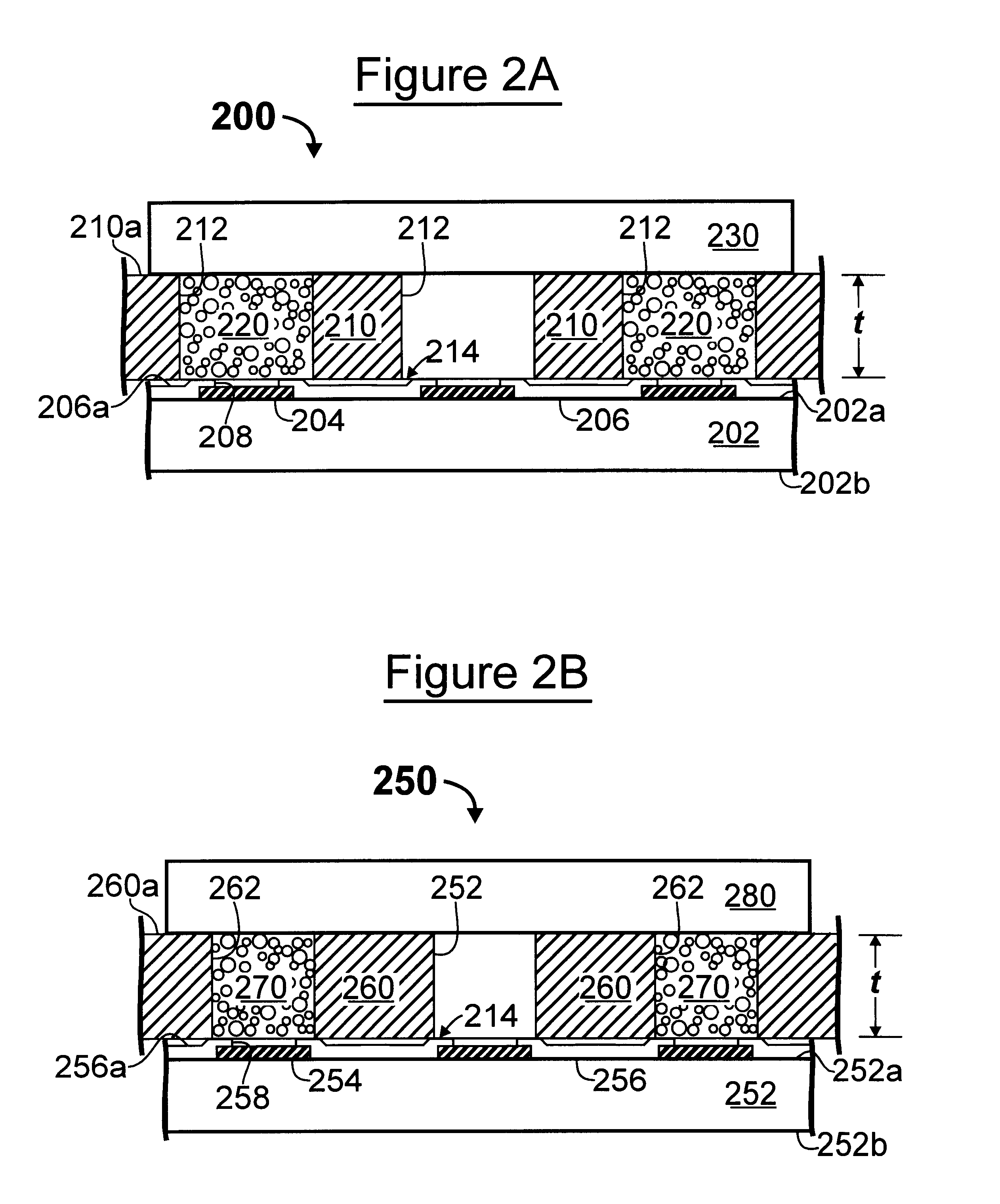

Methods for forming solder balls on substrates

InactiveUS6293456B1Reduce effective thermal massPromote wettingPrinted circuit assemblingPrinted circuit aspectsSolder ballMechanical engineering

A mask (110; see also 160, 210, 260, 310, 408, 500, 702, 802, 904) having a plurality of openings (cells) is disposed on, or nearly on, the surface of a substrate (102), the openings (112) of the mask being aligned over a corresponding plurality of pads (104) on the substrate. The openings in the mask are filled with solder material (114). A pressure plate (120) is disposed over the mask to capture the solder material in the cells. Heat is directed at the mask (through the pressure plate) to reflow the solder. This is done in an inverted or partially inverted orientation. The stackup (assembly) of substrate / mask / pressure plate may be un-inverted prior to cooling. Mask configurations, methods of mounting the masks, and solder material compositions are described. The methods are robust, and are well suited to fine pitch as well as coarse pitch ball bumping of substrates.

Owner:SEMIPAC INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com