Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2369 results about "Solder mask" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Solder mask or solder stop mask or solder resist is a thin lacquer-like layer of polymer that is usually applied to the copper traces of a printed circuit board (PCB) for protection against oxidation and to prevent solder bridges from forming between closely spaced solder pads. A solder bridge is an unintended electrical connection between two conductors by means of a small blob of solder. PCBs use solder masks to prevent this from happening. Solder mask is not always used for hand soldered assemblies, but is essential for mass-produced boards that are soldered automatically using reflow or solder bath techniques. Once applied, openings must be made in the solder mask wherever components are soldered, which is accomplished using photolithography. Solder mask is traditionally green but is now available in many colors.

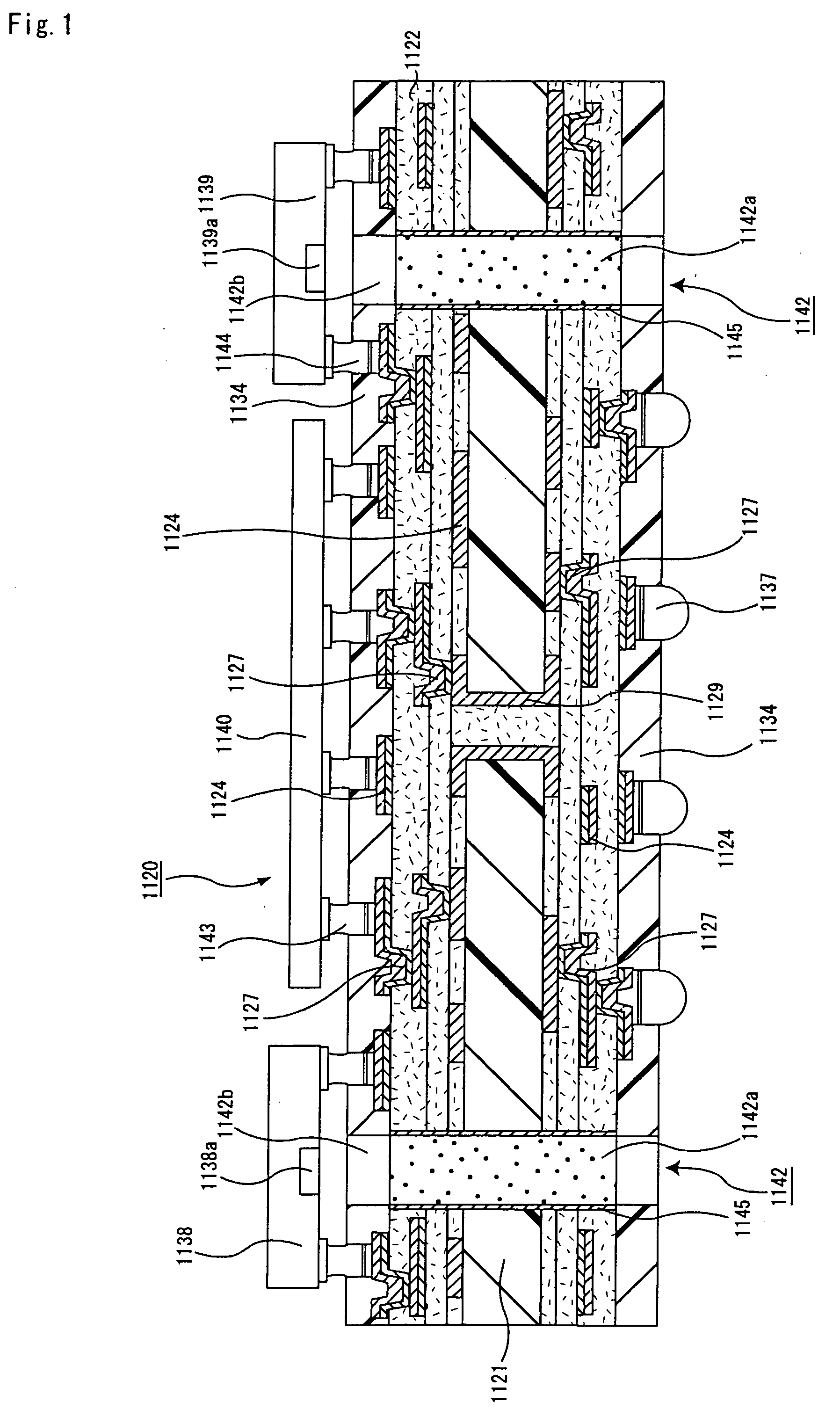

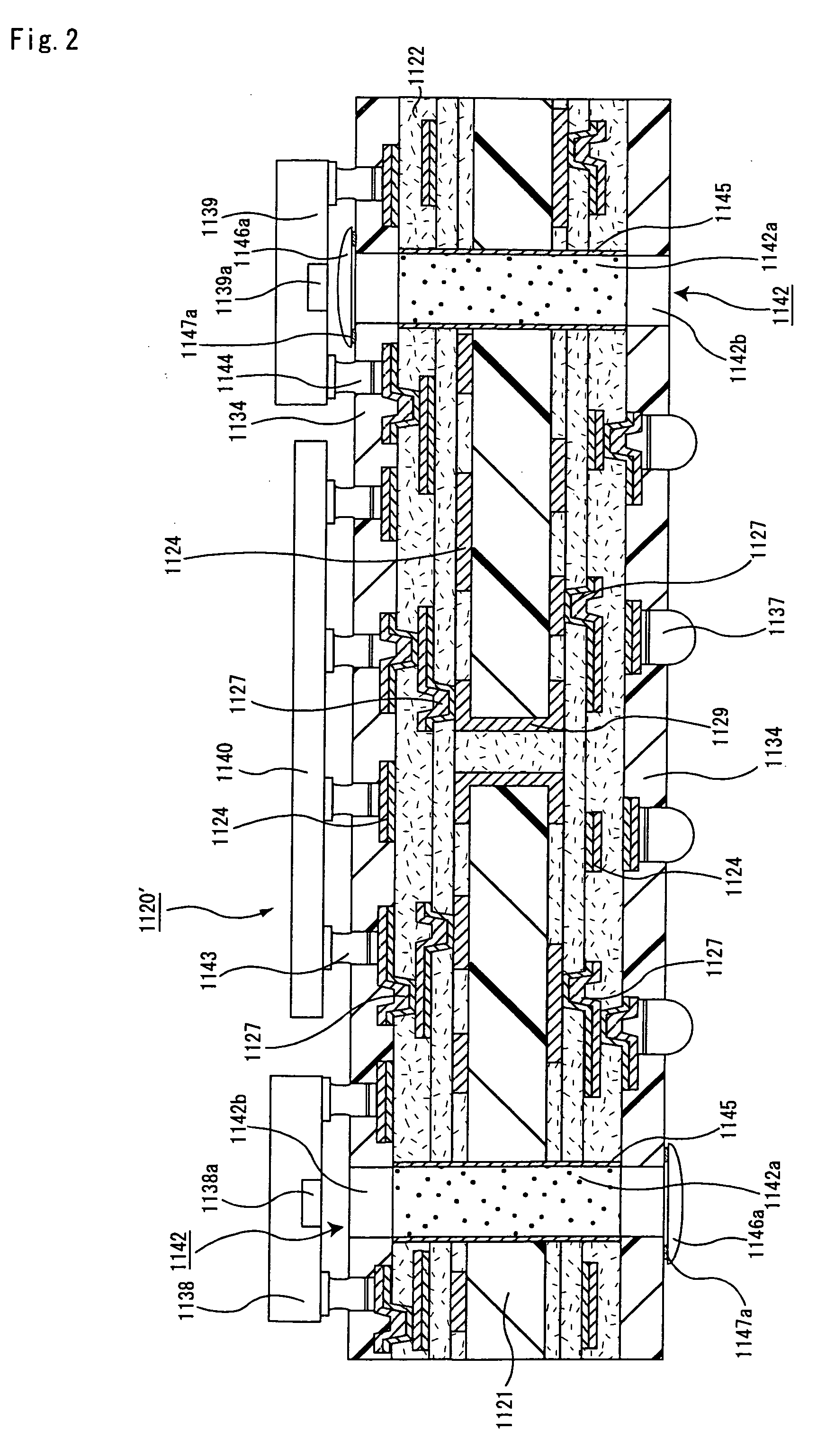

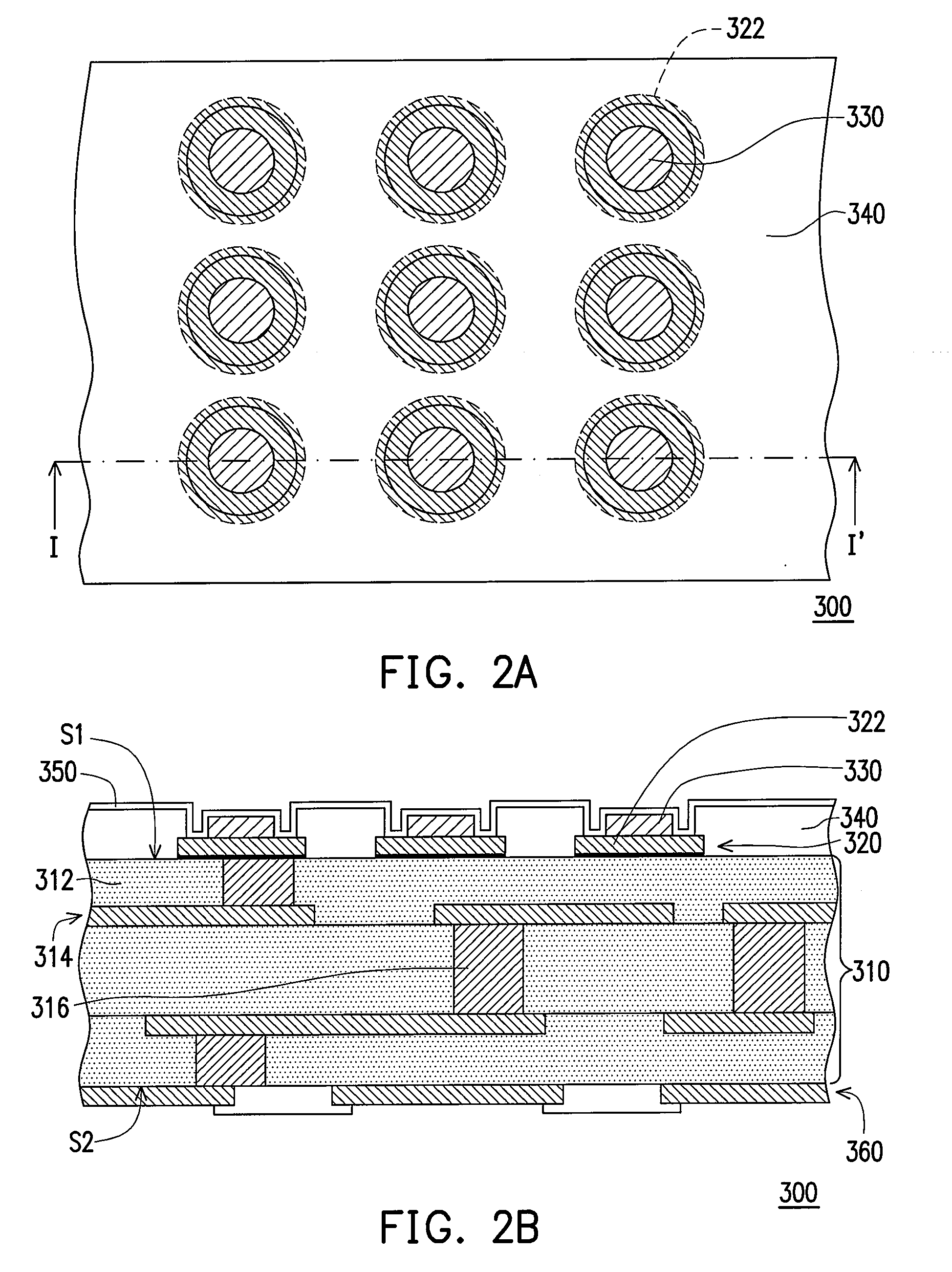

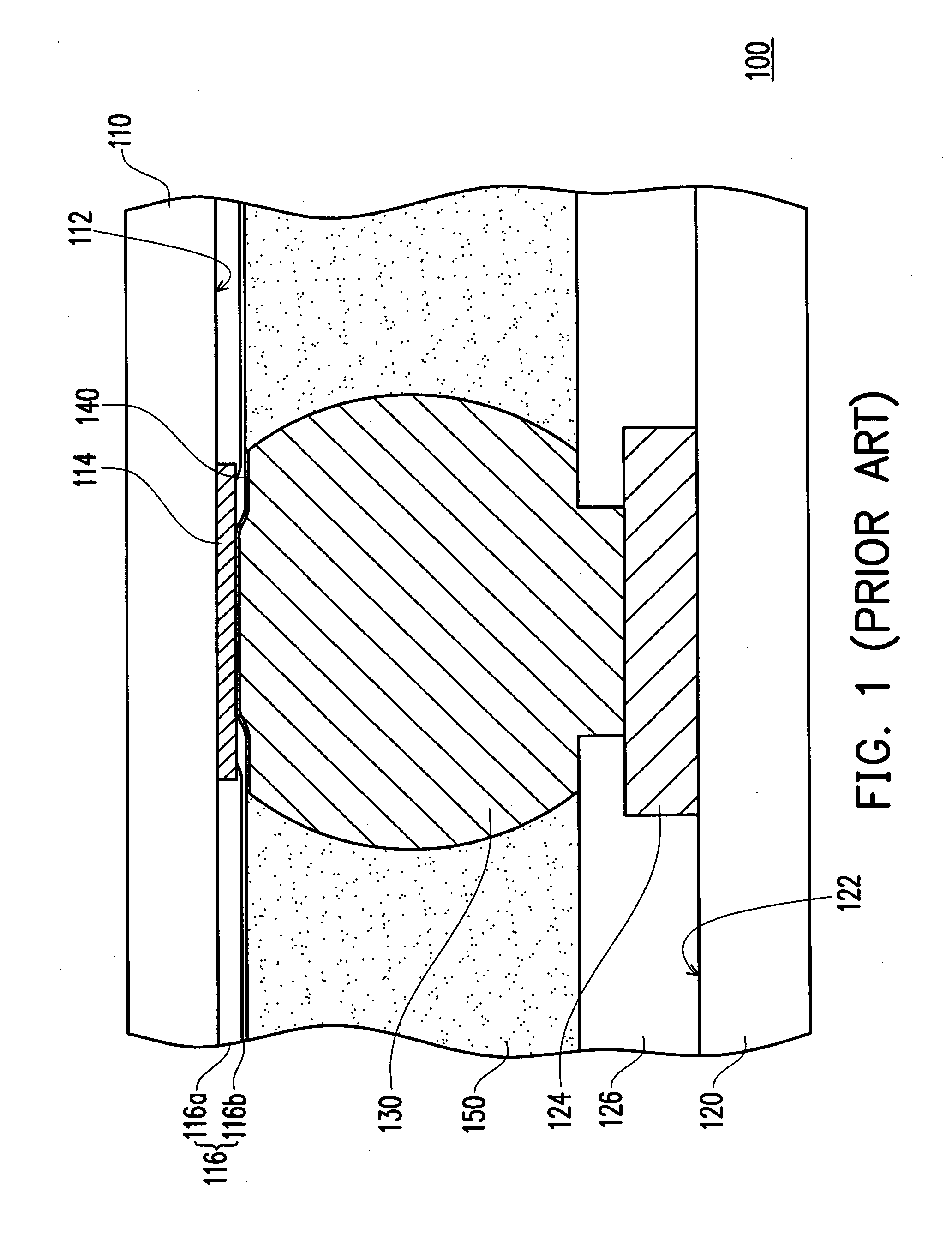

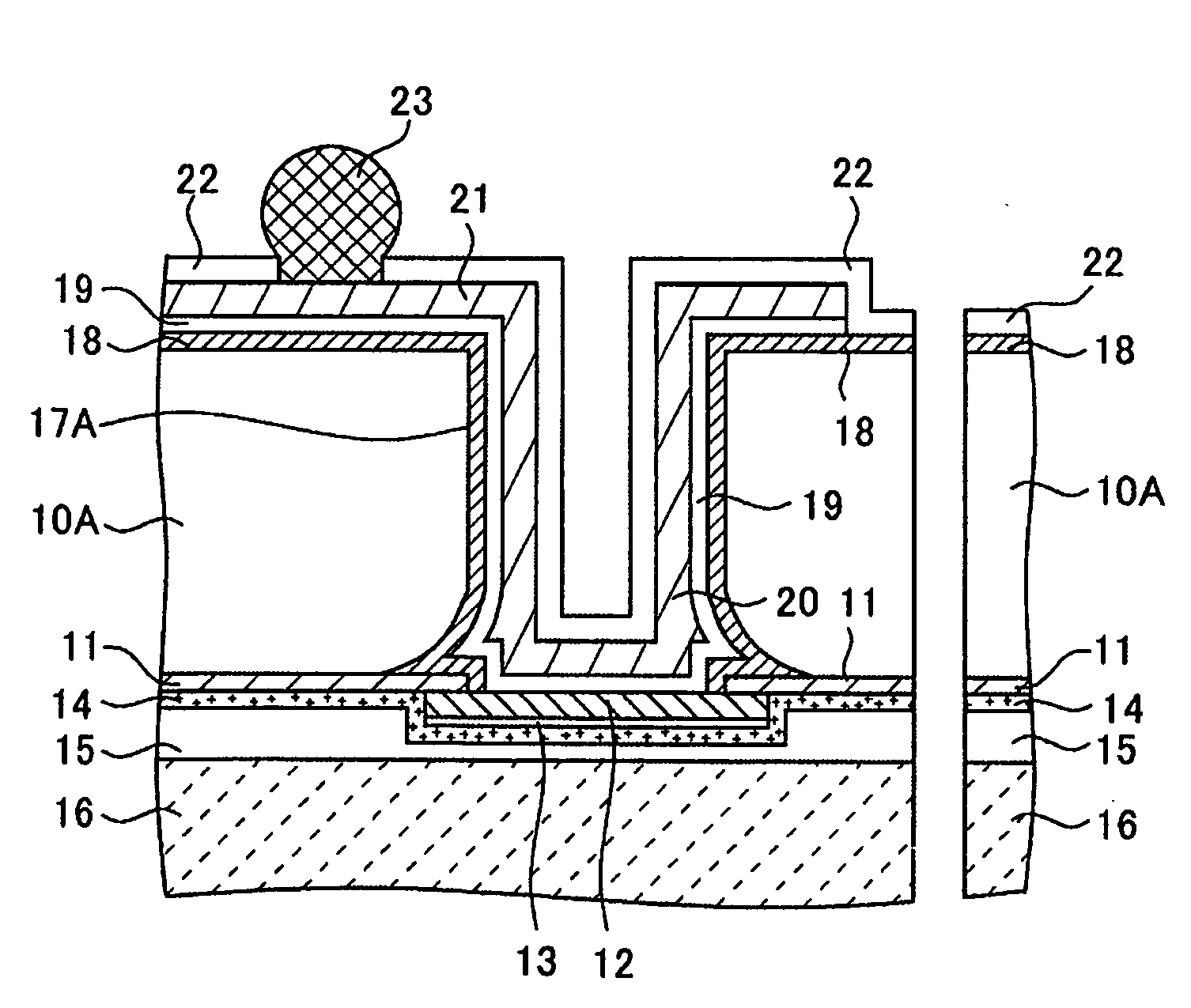

Ic chip mounting substrate, ic chip mounting substrate manufacturing method, optical communication device, and optical communication device manufacturing method

InactiveUS20060012967A1Improve connection reliabilitySmall sizeCircuit optical detailsSolid-state devicesResistElectrical conductor

An object of the present invention is to provide a substrate for mounting an IC chip which is a component for optical communication having an IC chip and an optical component integrally provided thereon, which can ensure a short distance between the IC chip and the optical component, which is excellent in electric signal transmission reliability and which can transmit optical signal through an optical path for transmitting optical signal. The substrate for mounting an IC chip of the present invention is a substrate for mounting an IC chip comprising: a substrate and, as serially built up on both faces thereof, a conductor circuit and an interlaminar insulating layer in an alternate fashion and in repetition; a solder resist layer formed as an outermost layer; and an optical element mounted thereto, wherein an optical path for transmitting optical signal, which penetrates the substrate for mounting an IC chip, is disposed.

Owner:IBIDEN CO LTD

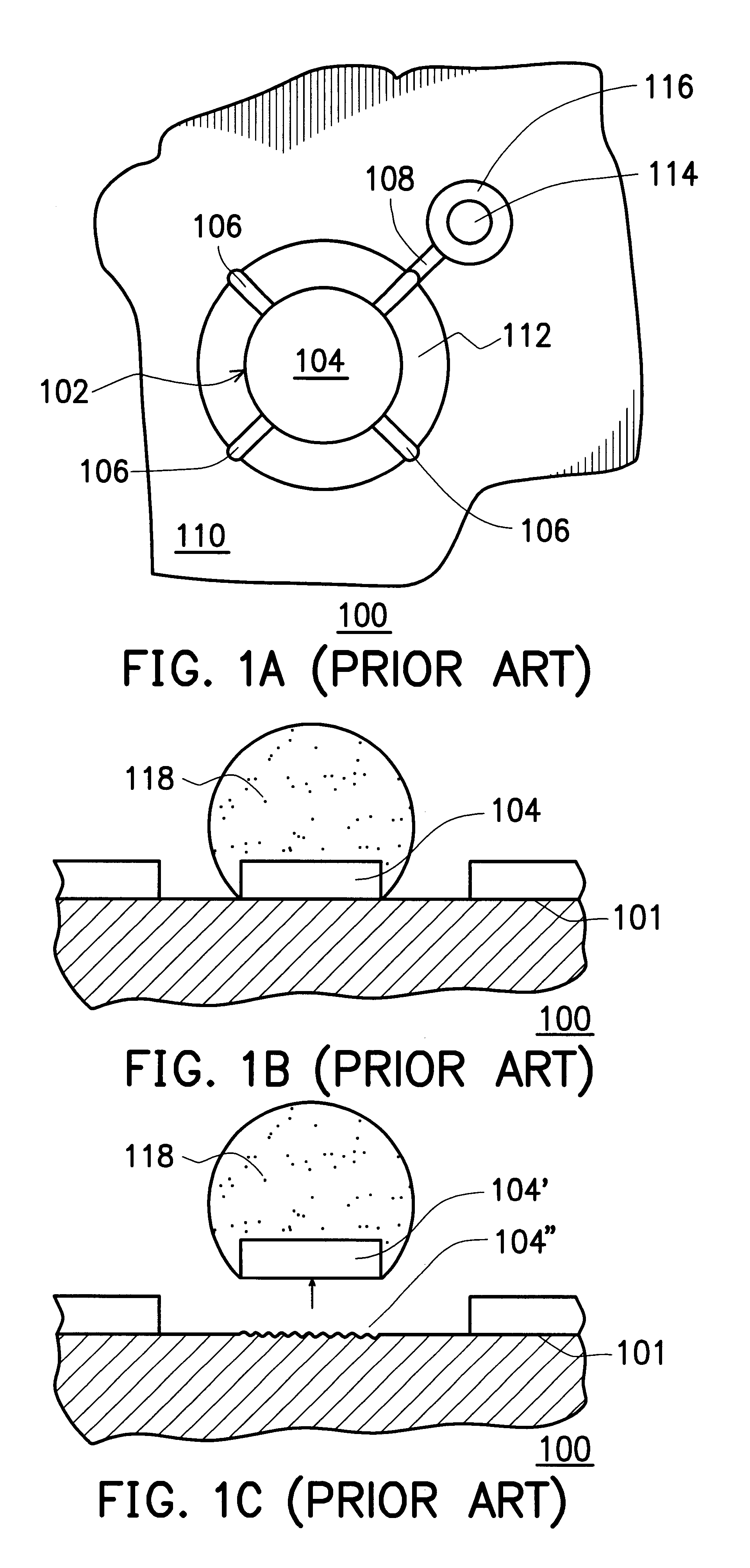

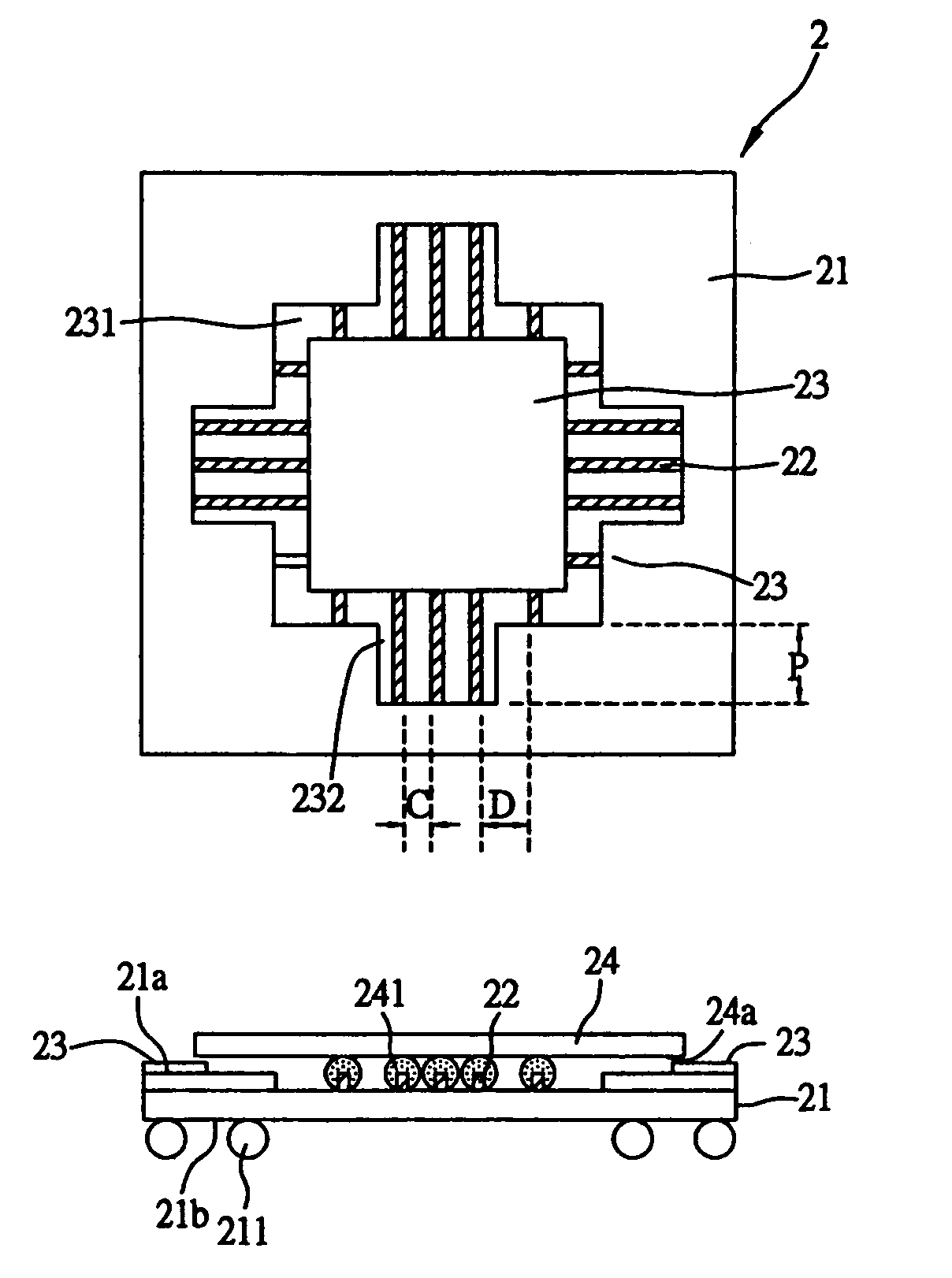

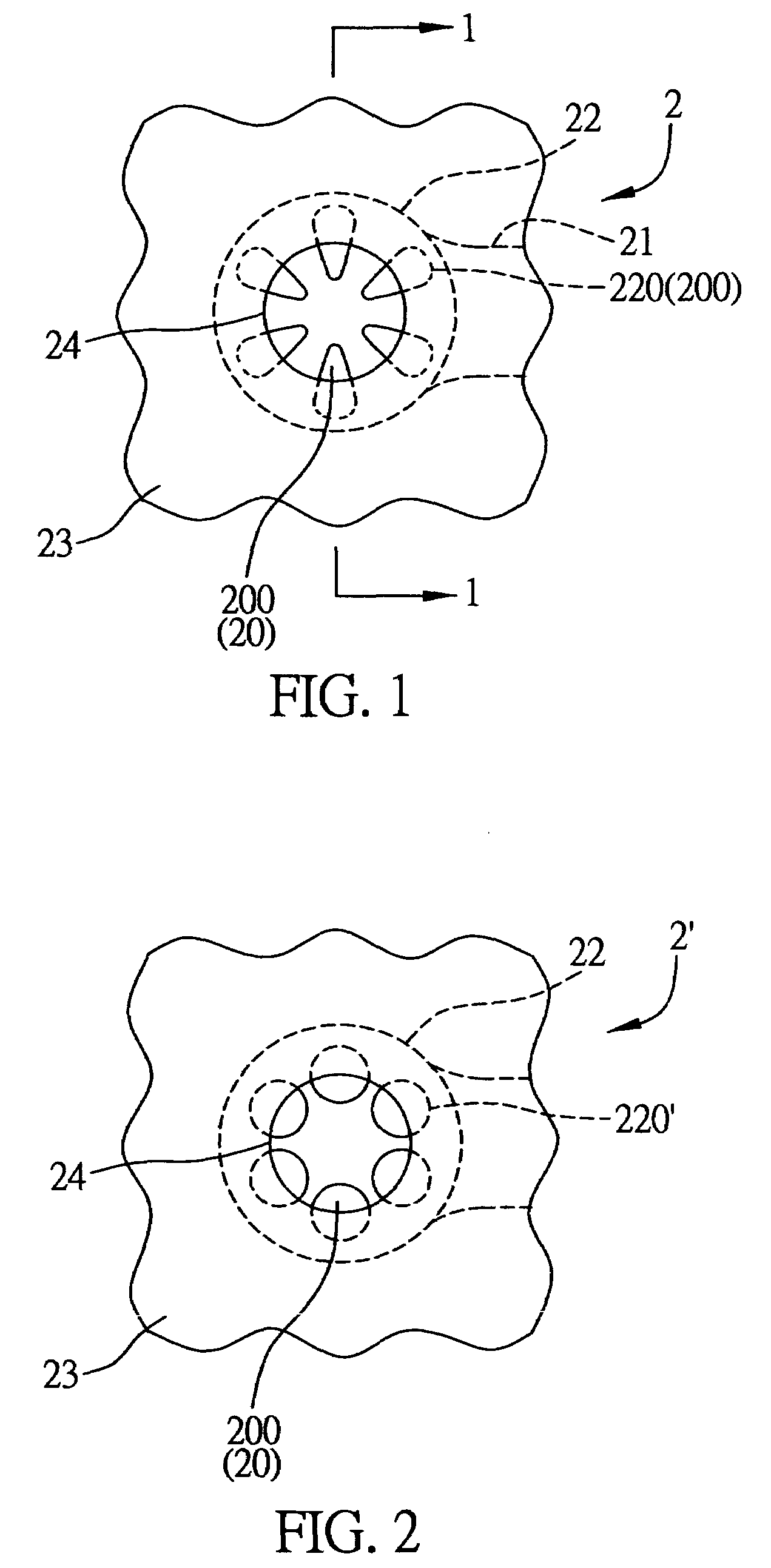

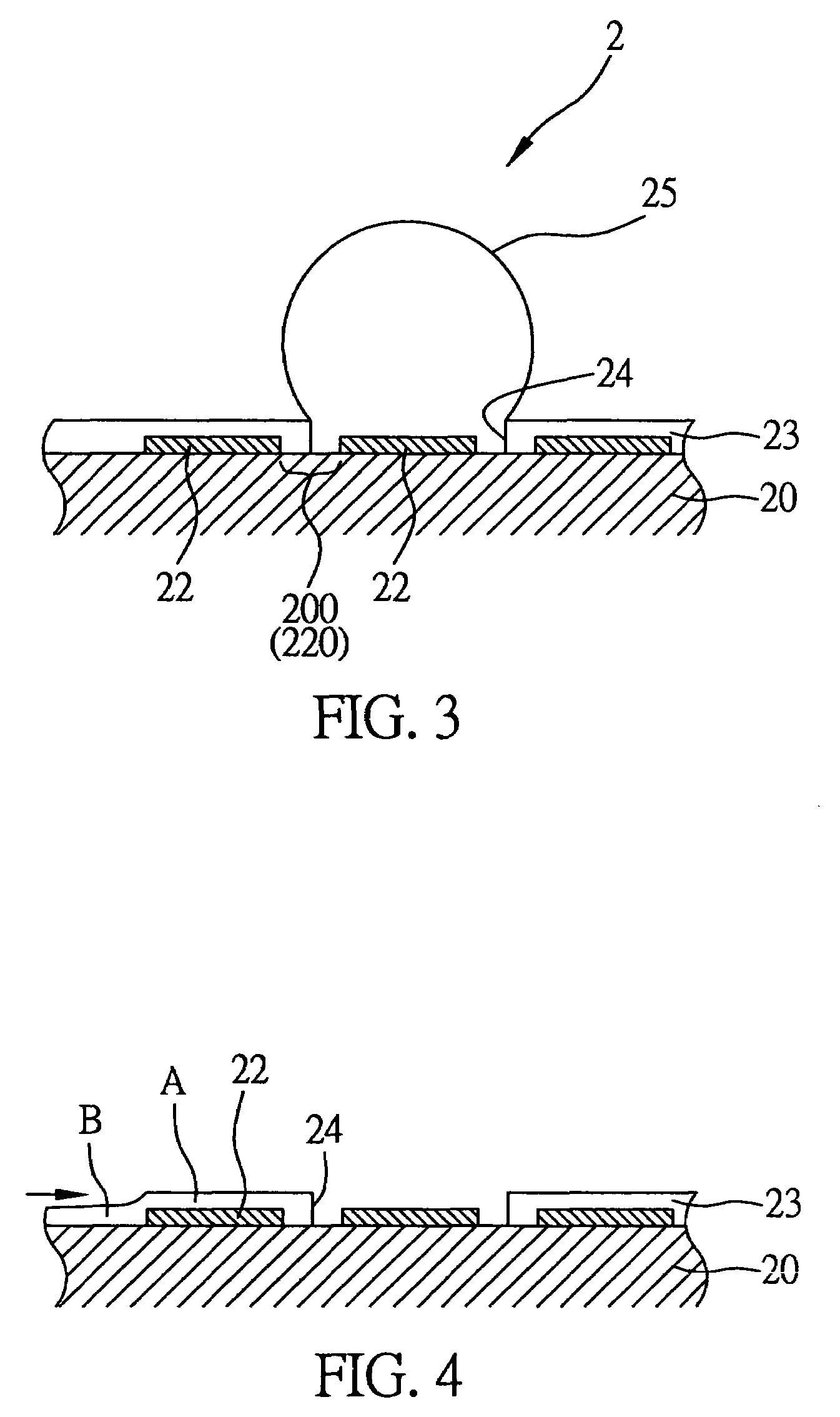

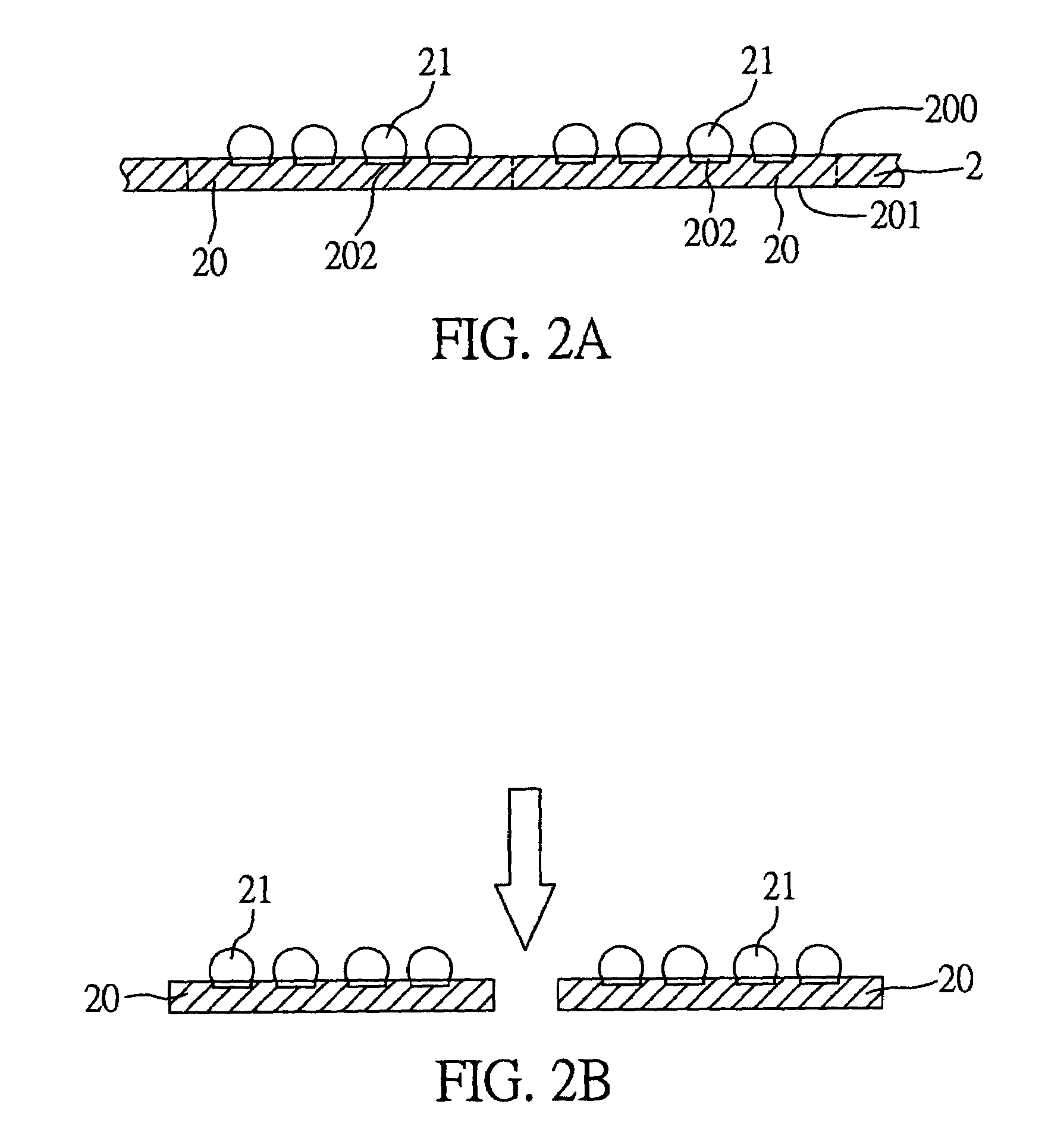

Substrate with reinforced contact pad structure

ActiveUS7005750B2Improve positional stabilitySimple structurePrinted circuit assemblingFinal product manufactureSolder maskContact pad

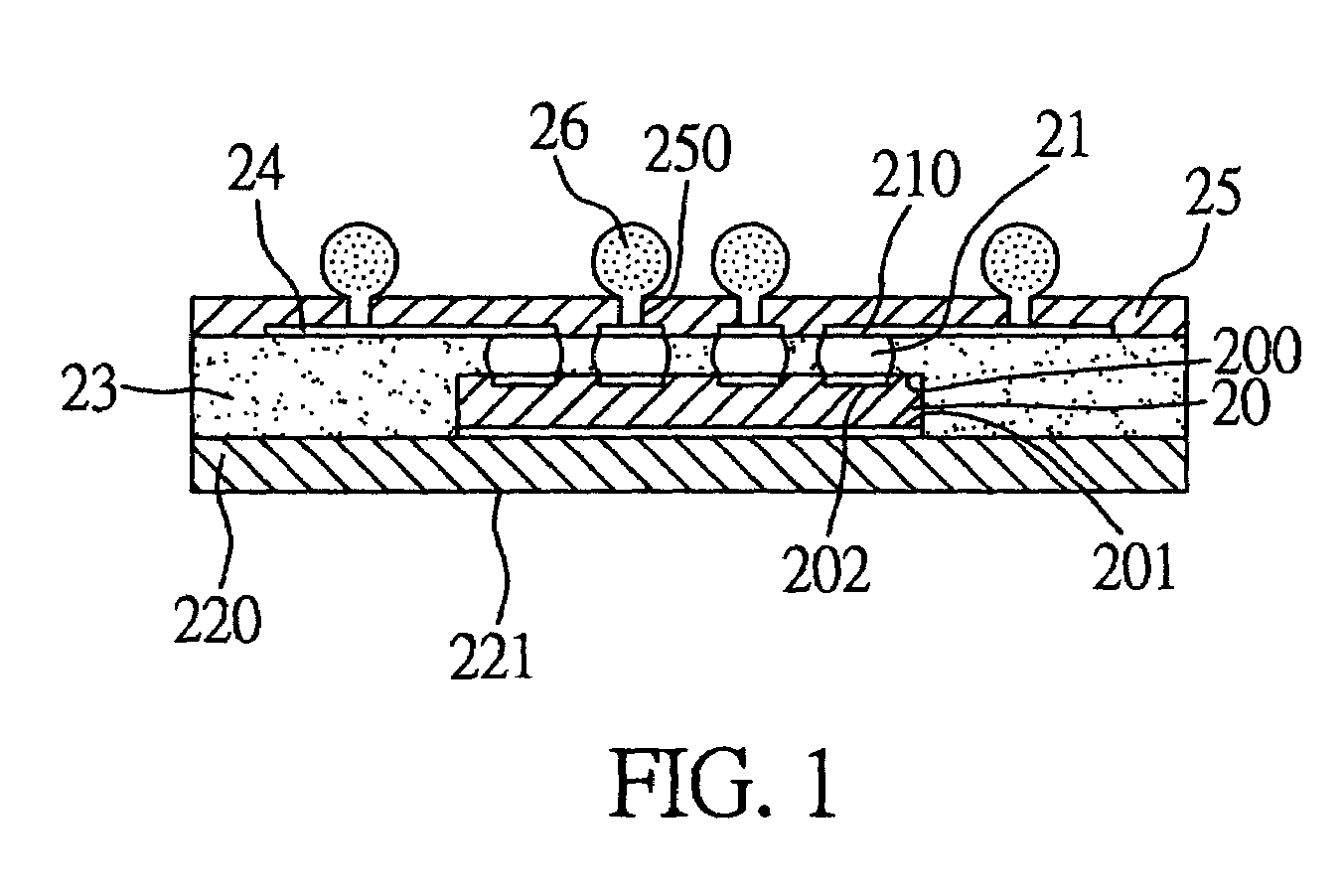

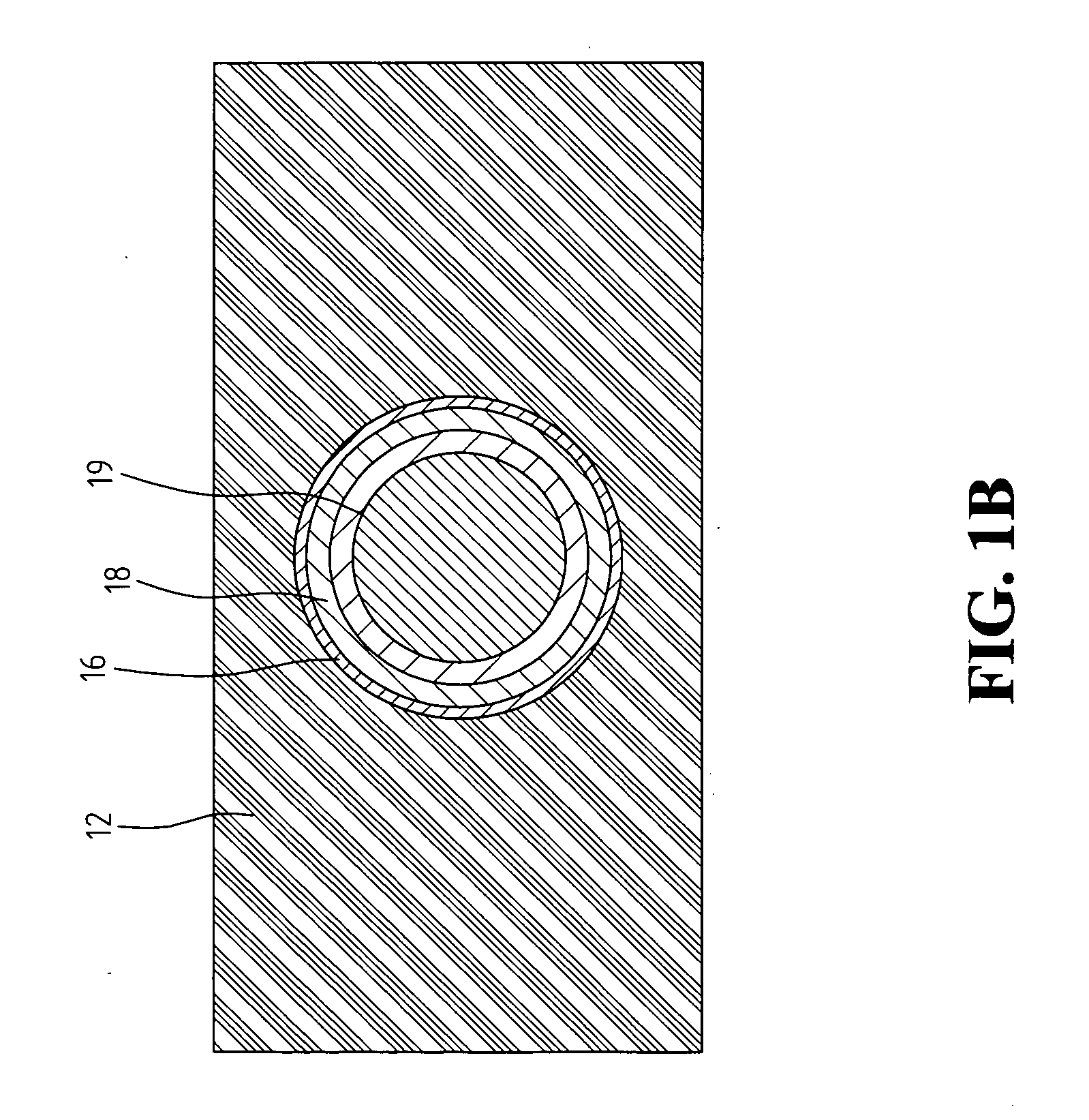

A substrate with reinforced contact pad structure includes a metal wiring layer and a solder mask formed over its surface. The metal wiring layer includes at least a NSMD (Non-Solder Mask Defined) type contact pad, a trace and an extension. The extension connects the contact pad and the trace, and has an upper surface which is covered by the solder mask so as to enhance the connecting strength between the trace and the contact pad and to improve the position stability of the NSMD type contact pad on the substrate. In an embodiment, the contact pad is circular for bonding a bump or a solder ball. The first extension is fan-shaped. The extension also has a sidewall exposed out of the solder mask.

Owner:ASE SHANGHAI

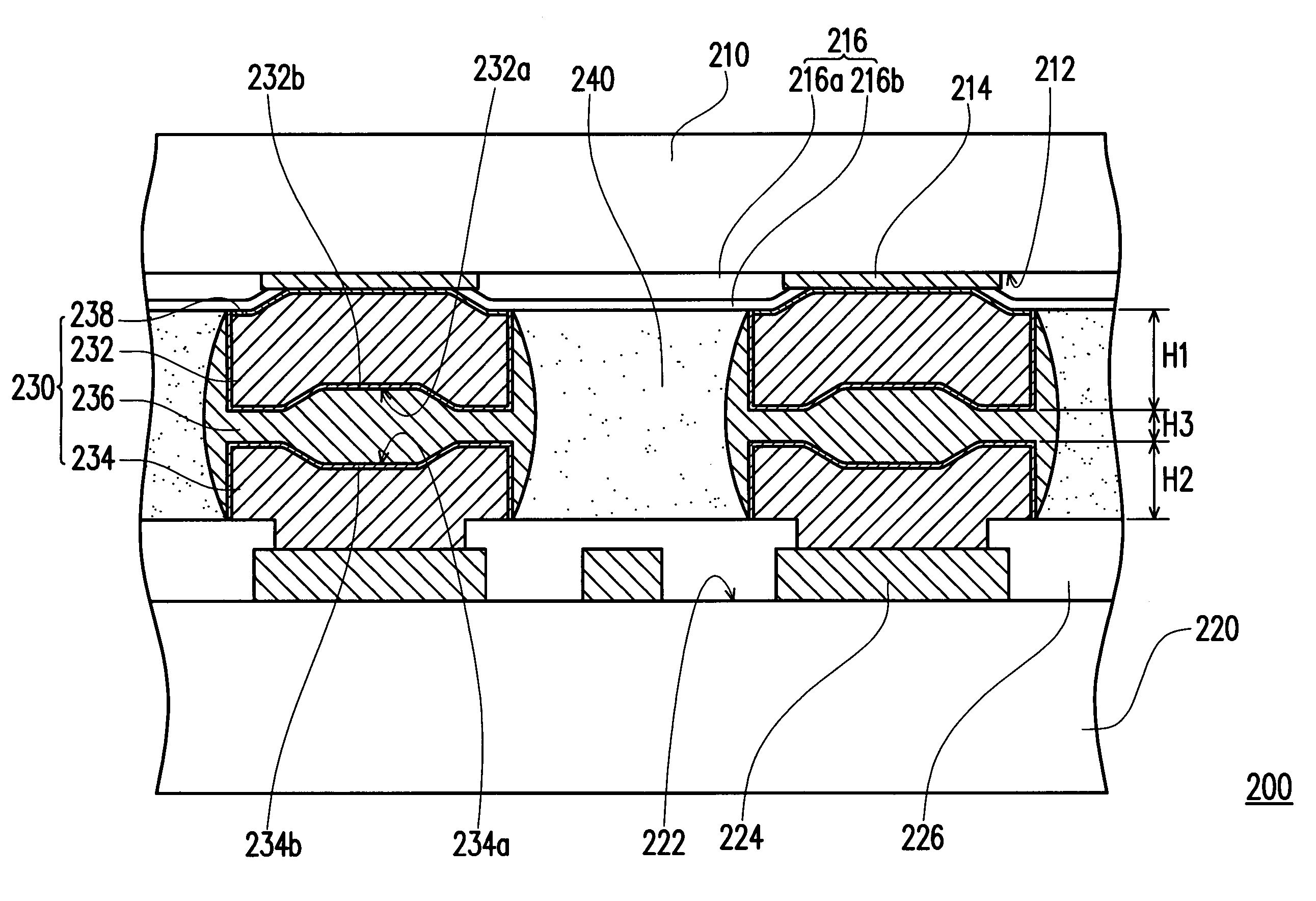

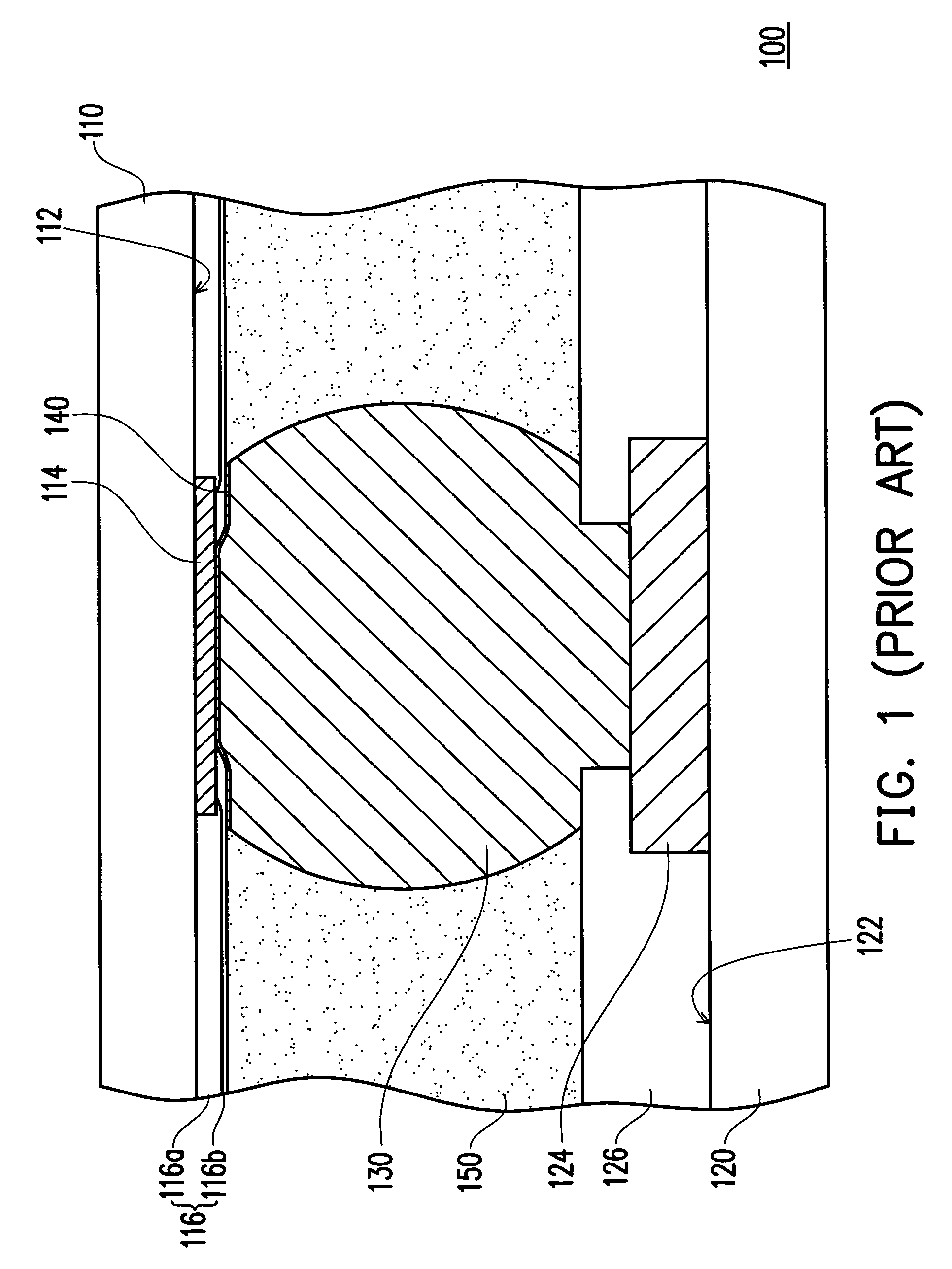

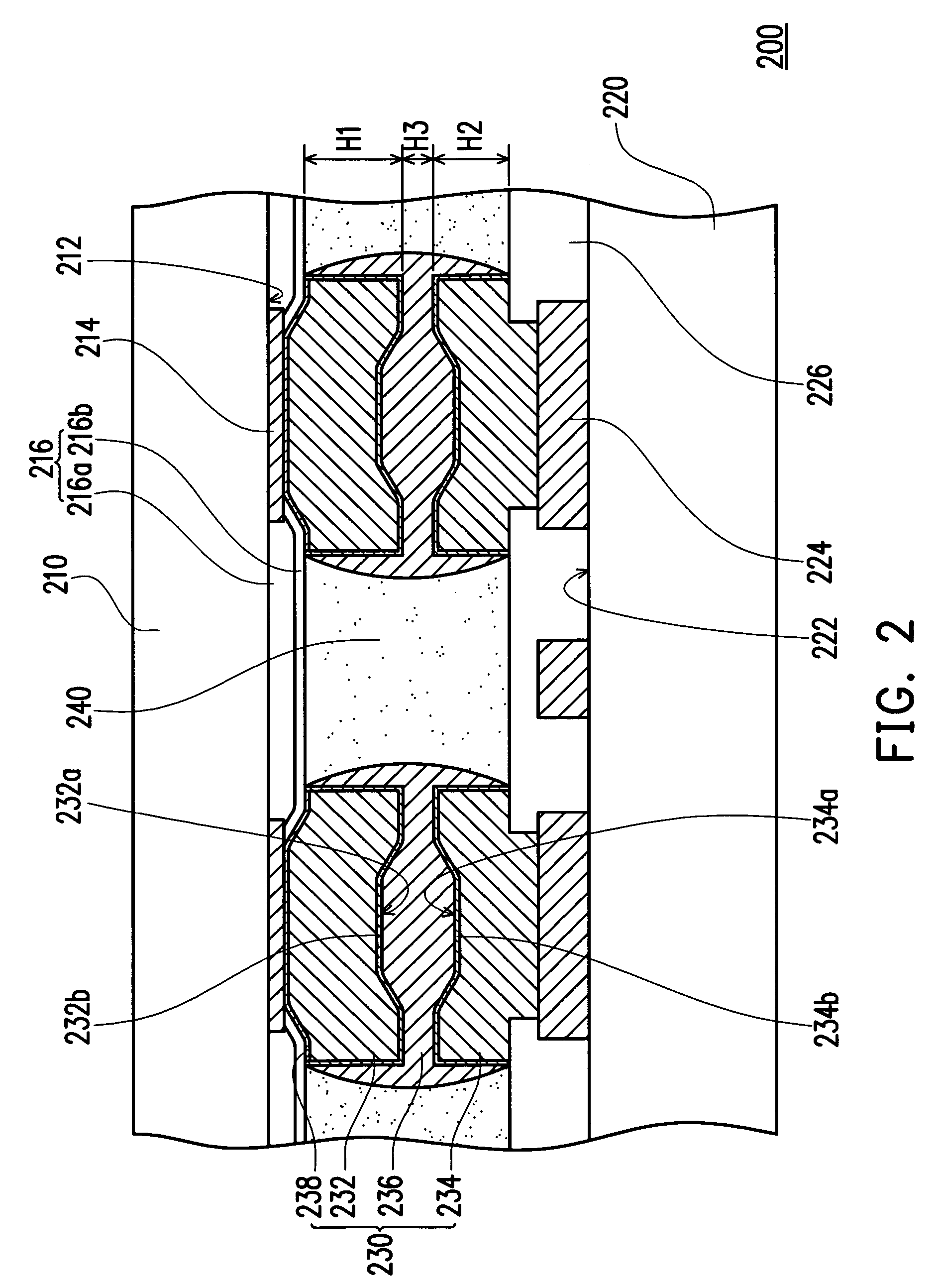

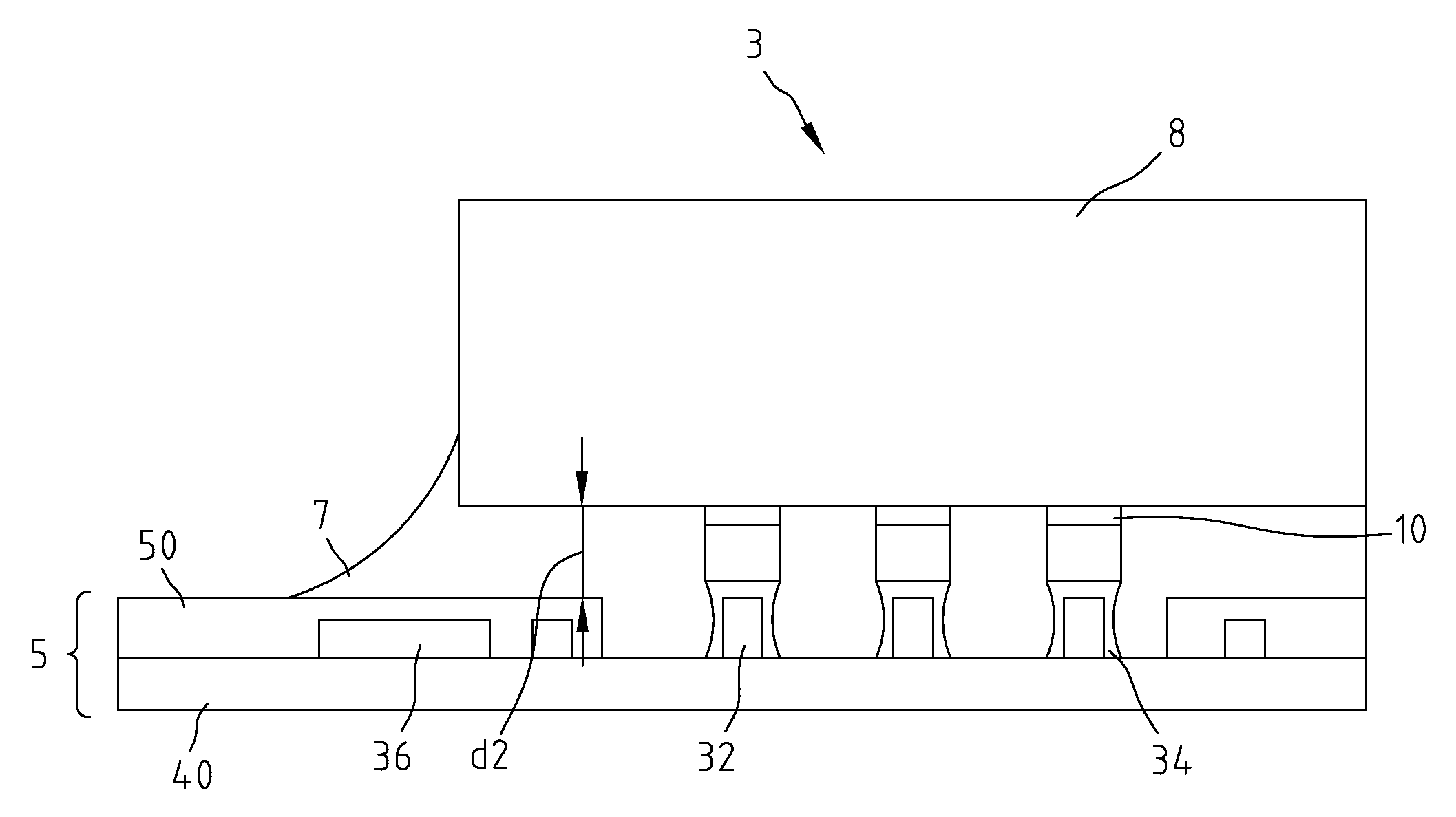

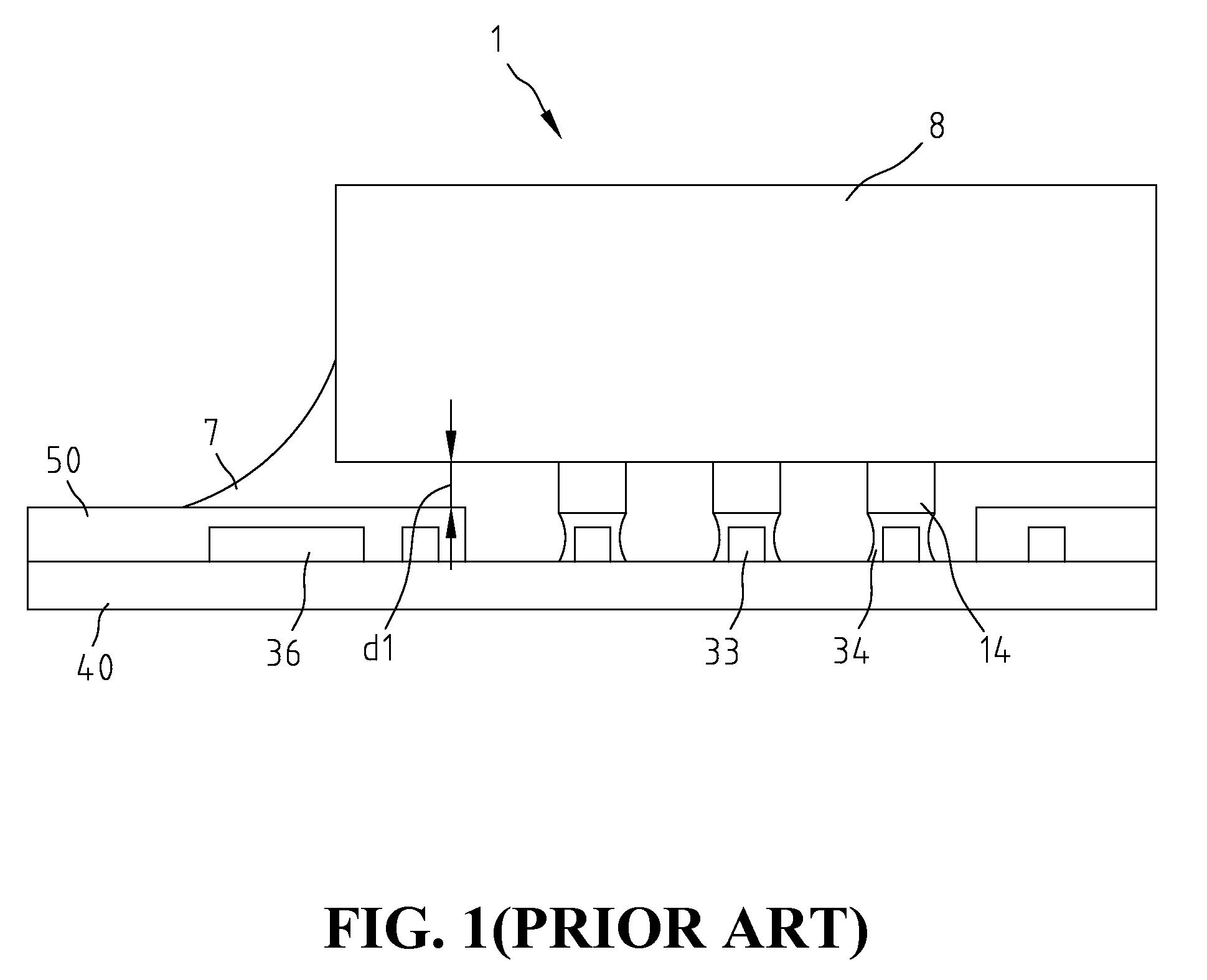

Pillar-to-pillar flip-chip assembly

ActiveUS7569935B1Reduce thermal stressPrevent peelingFinal product manufactureSemiconductor/solid-state device detailsSolder maskSolder ball

A pillar-to-pillar flip-chip assembly primarily comprises a substrate, a chip disposed on the substrate, a plurality of first copper pillars on the bonding pads of the chip, a plurality of second copper pillars on the bump pads of the substrate, and a soldering material. A first height of the first copper pillars protruding from the active surface of the chip is the same as a second height of the second copper pillars from the solder mask on the substrate. When the soldering material electrically and mechanically connects the first copper pillars to the second copper pillars, a plurality of central points of the soldering material are formed on an equal-dividing plane between the chip and the substrate to reduce the direct stresses exerted at the soldering material to avoid peeling or breaks from the bump pads. Moreover, each of conventional solder balls is replaced with two soldered copper pillars to meet the lead-free requirements with higher reliability and lower costs.

Owner:POWERTECH TECHNOLOGY

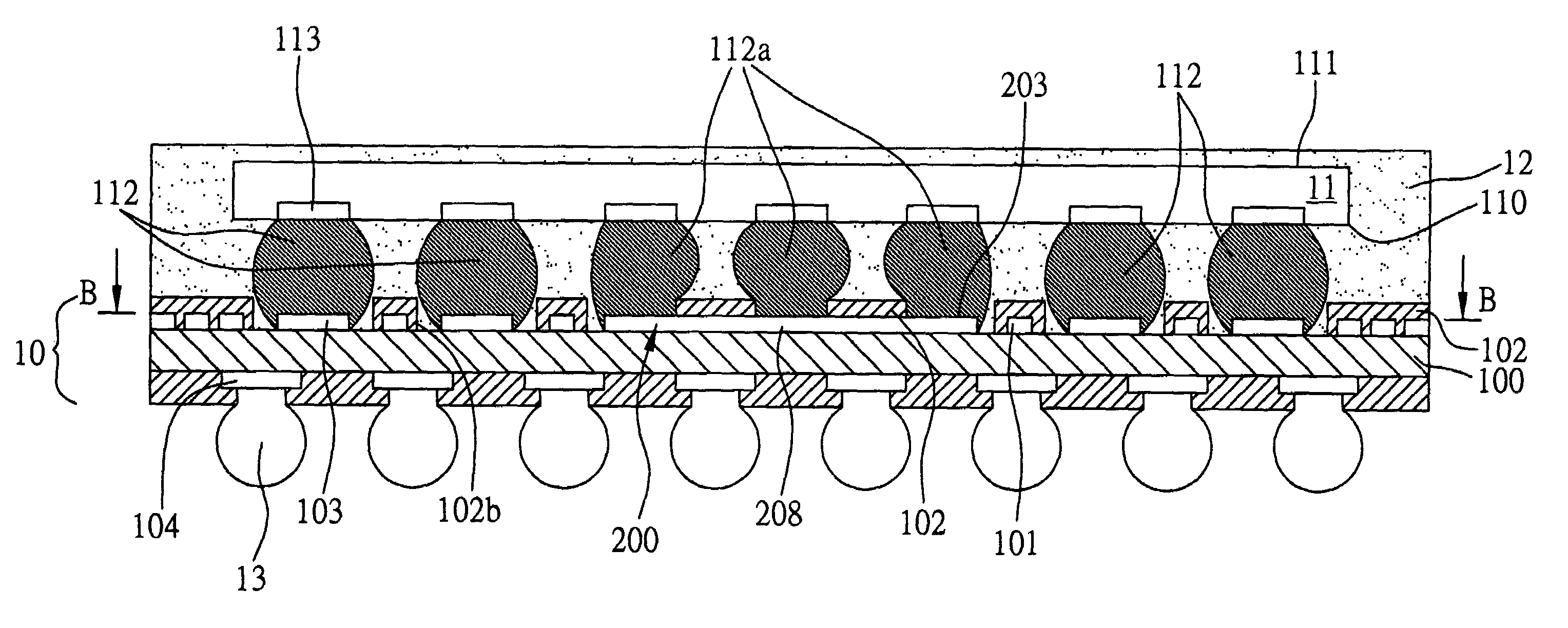

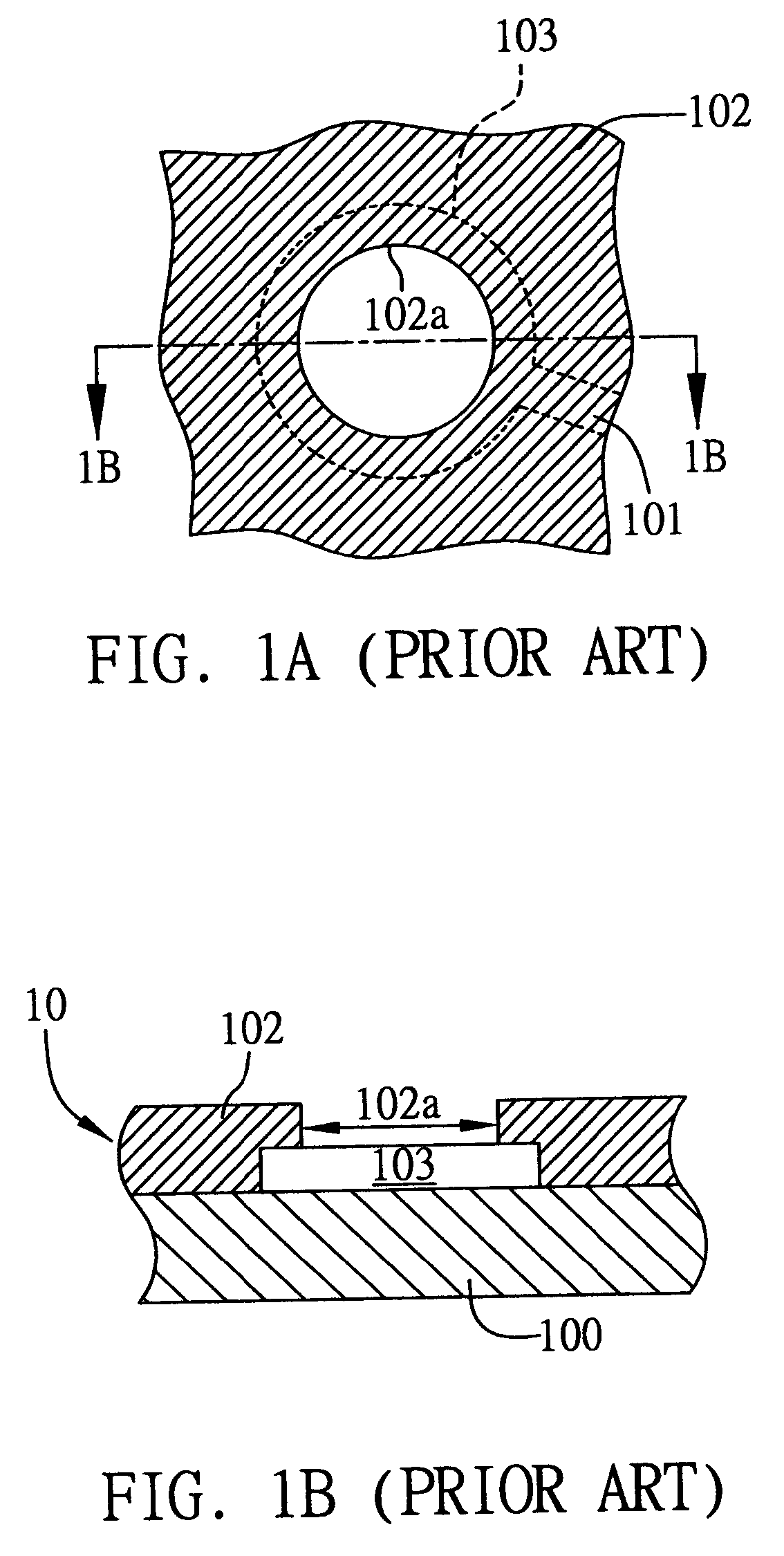

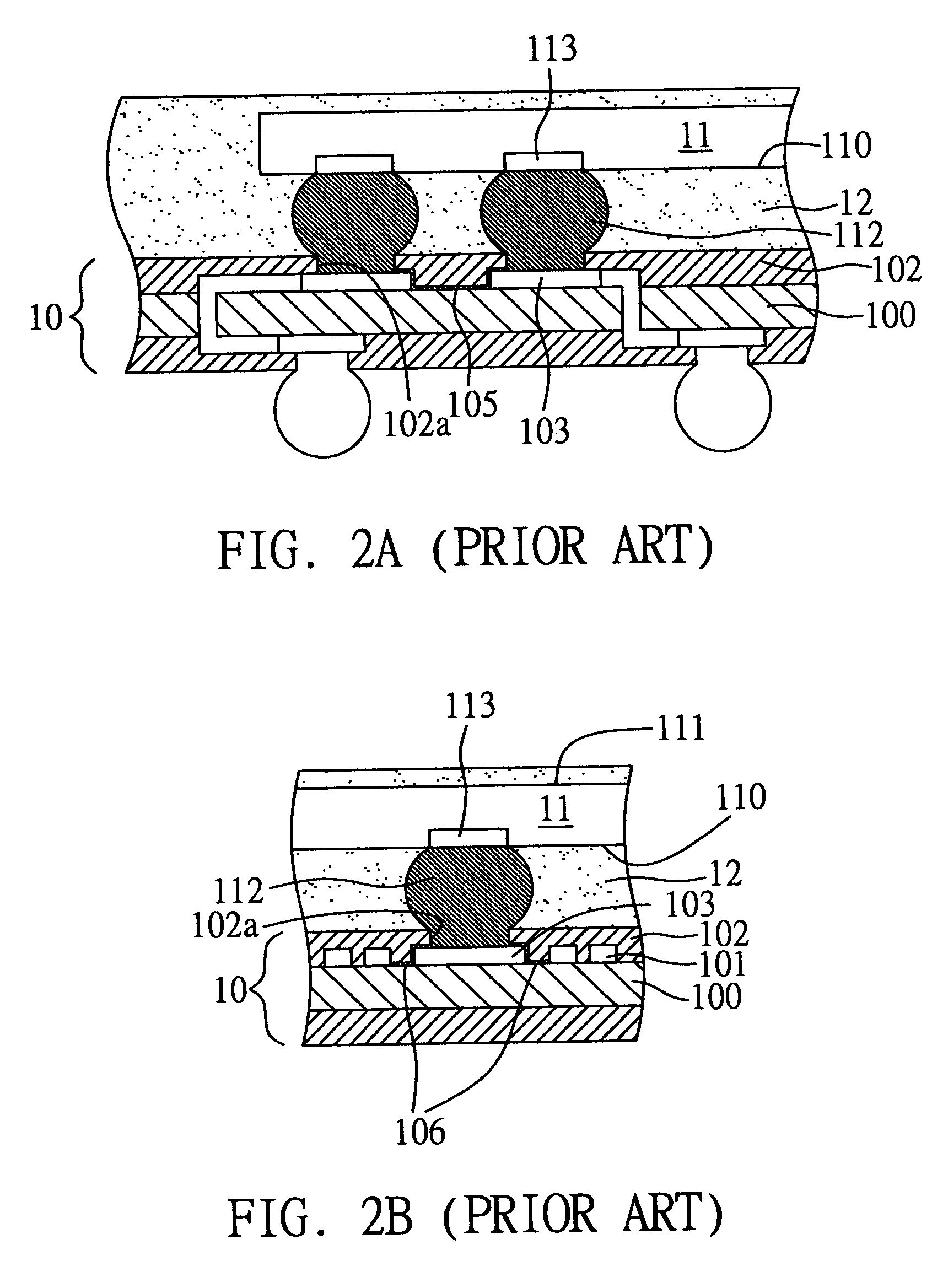

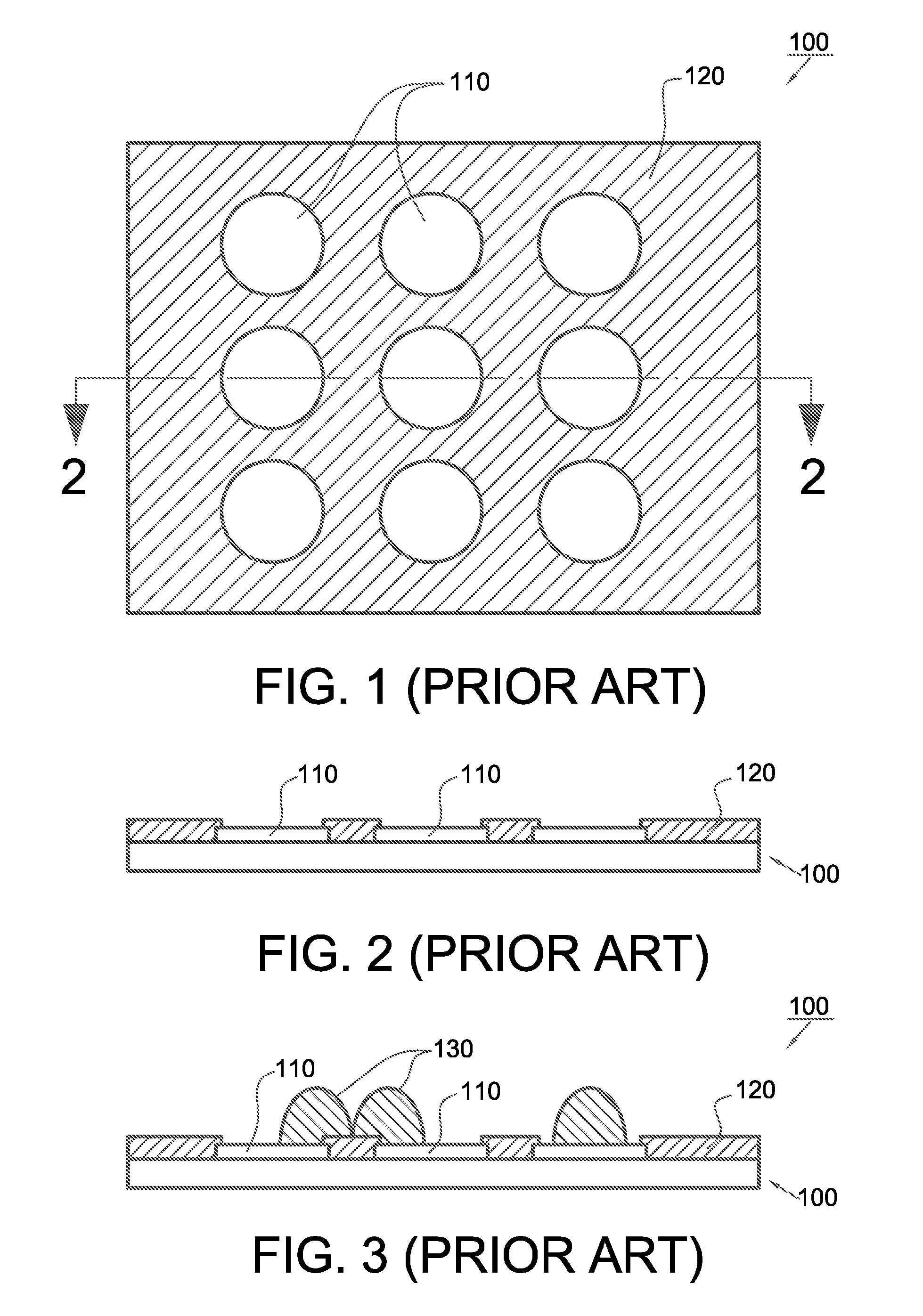

Ball grid array package

InactiveUS6396707B1Printed circuit assemblingSemiconductor/solid-state device detailsSolder maskSolder ball

A ball grid array package comprises a substrate having a first surface and a second surface, a chip, an insulating material, and a solder ball. The surface of the substrate comprises ball pads, conducting traces, and solder masks wherein the conducting traces are disposed in between the adjacent ball pads, and are covered by the solder mask, in addition, a portion of each of the ball pads is also covered by the solder mask. The solder mask includes an opening positioned in the area corresponding to the ball pads wherein the opening exposes a portion of the surface the ball pad and a portion of the side wall of the ball pad. The chip is disposed on the second surface of the substrate, and is sealed and encapsulated by the insulated material. The solder balls are disposed on the first surface of the substrate, and are positioned at the openings of the ball pads. Additionally, the solder balls are electrically connected to a portion of the surface of the ball pads and a portion of the side wall of the ball pads disposed at the ball pad openings.

Owner:SILICONWARE PRECISION IND CO LTD

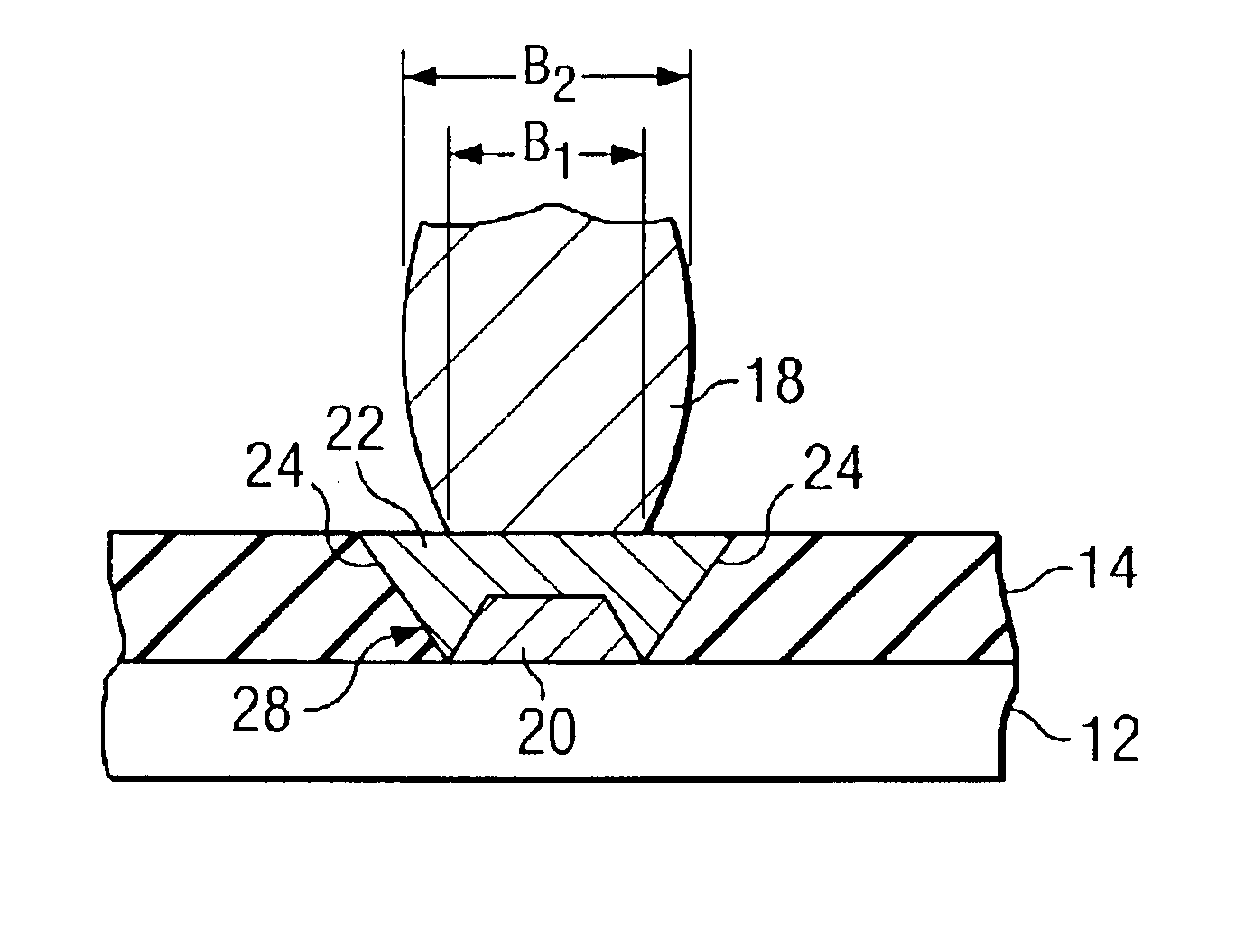

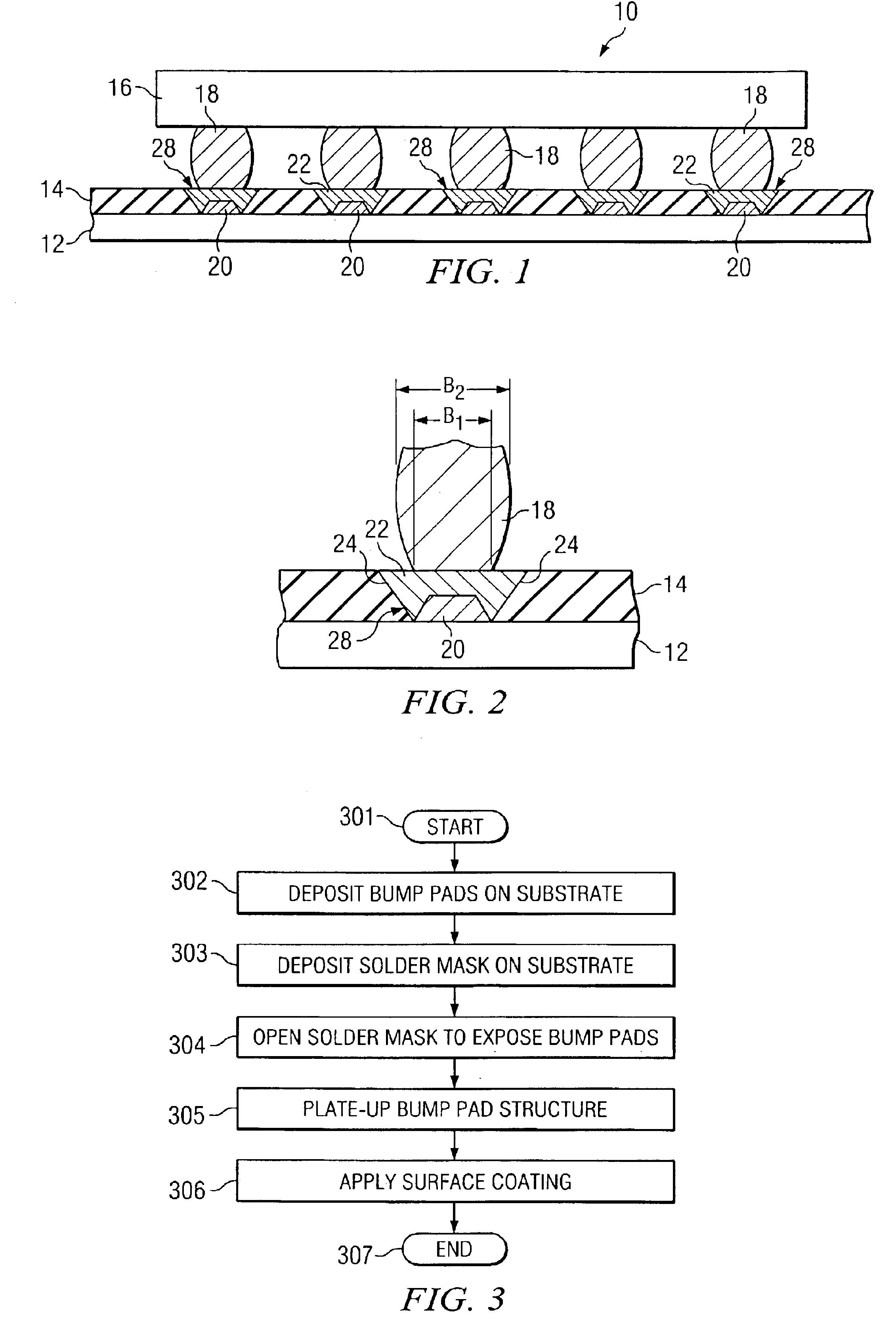

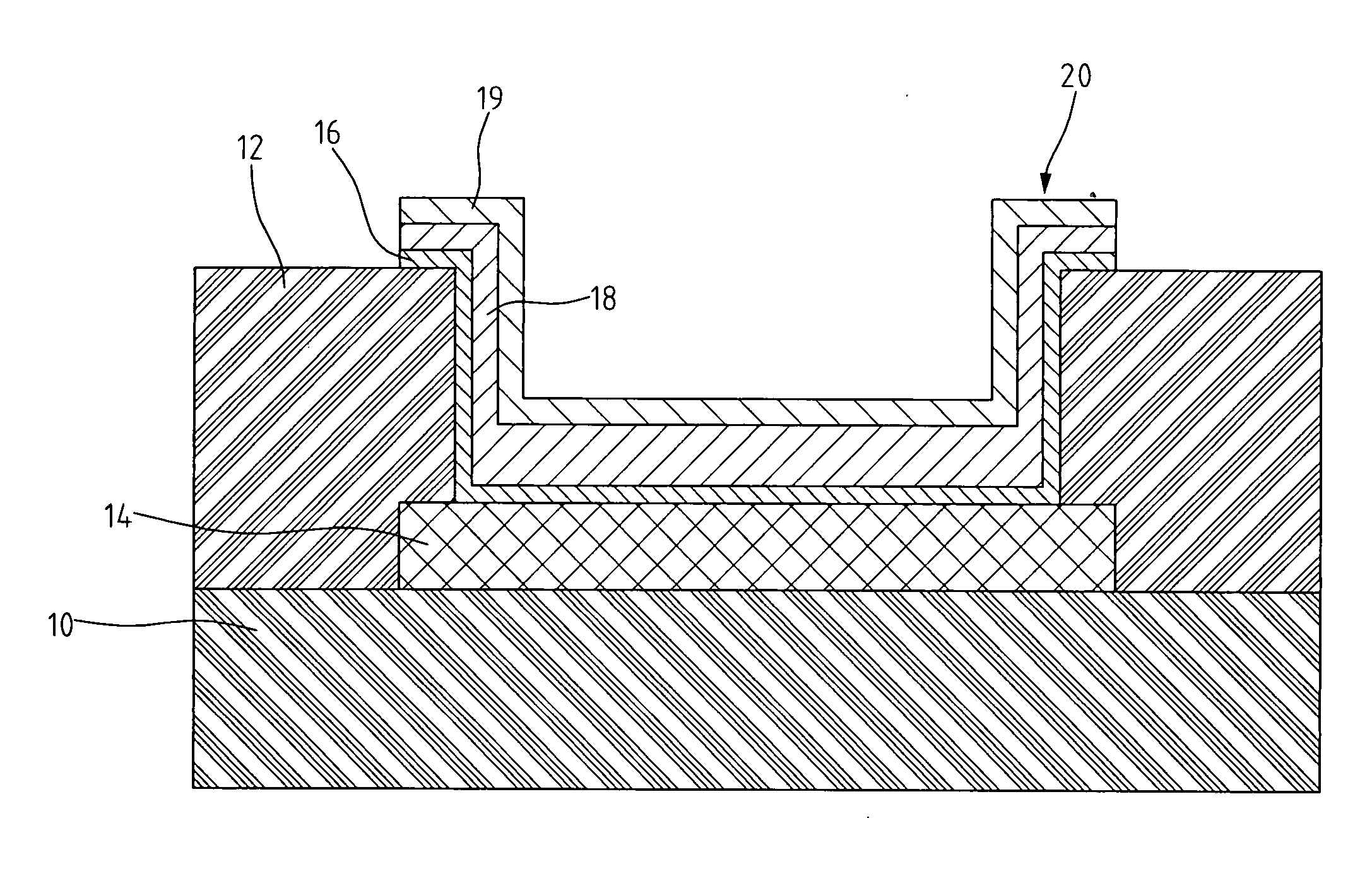

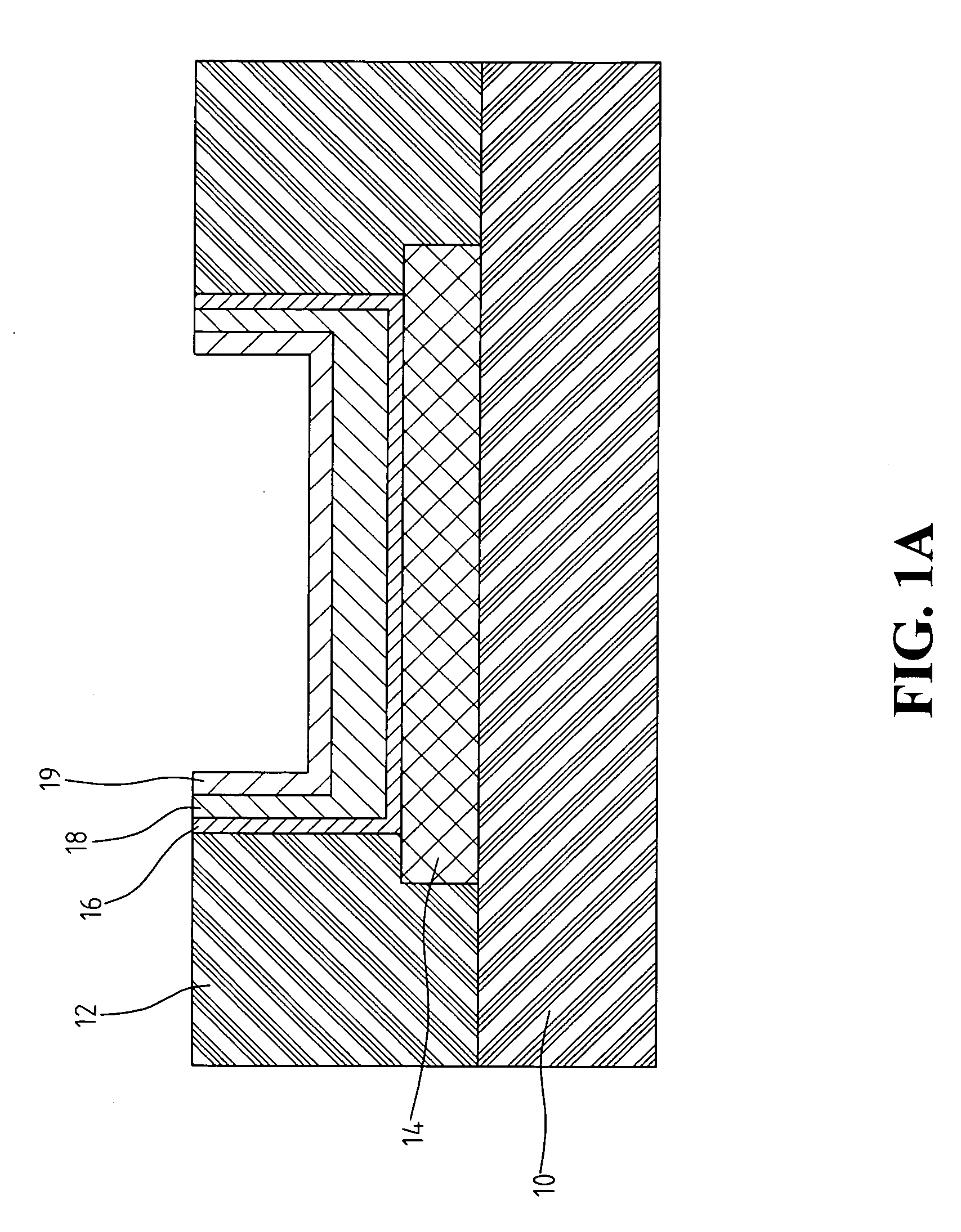

Built-up bump pad structure and method for same

InactiveUS6888255B2Reduce thicknessLess sensitivePrinted circuit assemblingFinal product manufactureSolder maskConductive materials

In accordance with the present invention, a built-up bump pad structure and method for the same are provided. The bump pad structure includes a substrate, a bump pad disposed upon the substrate, a solder mask disposed upon the substrate defining an opening around the bump pad, and a conductive material deposited upon the bump pad such that the conductive material at least partially fills the opening around the bump pad.

Owner:TEXAS INSTR INC

Substrate structure of flip chip package

InactiveUS6787918B1Printed circuit assemblingSemiconductor/solid-state device detailsSolder maskEngineering

A substrate structure of Flip Chip package includes a plurality of patterned circuit layers alternately stacking up with at least an insulative layer for isolating the patterned circuit layers. The patterned circuit layers are electrically connected each other wherein one of the patterned circuit layers is positioned on the surface of the substrate. The patterned circuit layer includes a plurality of first mounting pads and a plurality of second mounting pads. The solder mask layer covers the patterned circuit layer on the surface of the substrate, and a portion of the surface of the outer edge of the mounting pads while exposes a portion of the surface of the first mounting pads and the whole surface of the second mounting pads.

Owner:SILICONWARE PRECISION IND CO LTD

Semiconductor die package including carrier with mask and semiconductor die

InactiveUS7157799B2Semiconductor/solid-state device detailsSolid-state devicesSolder maskEngineering

A carrier for use in a semiconductor die package is disclosed. In one embodiment, the carrier includes a die attach region and an edge region. A solder mask is on the edge region.

Owner:FAIRCHILD SEMICON CORP +1

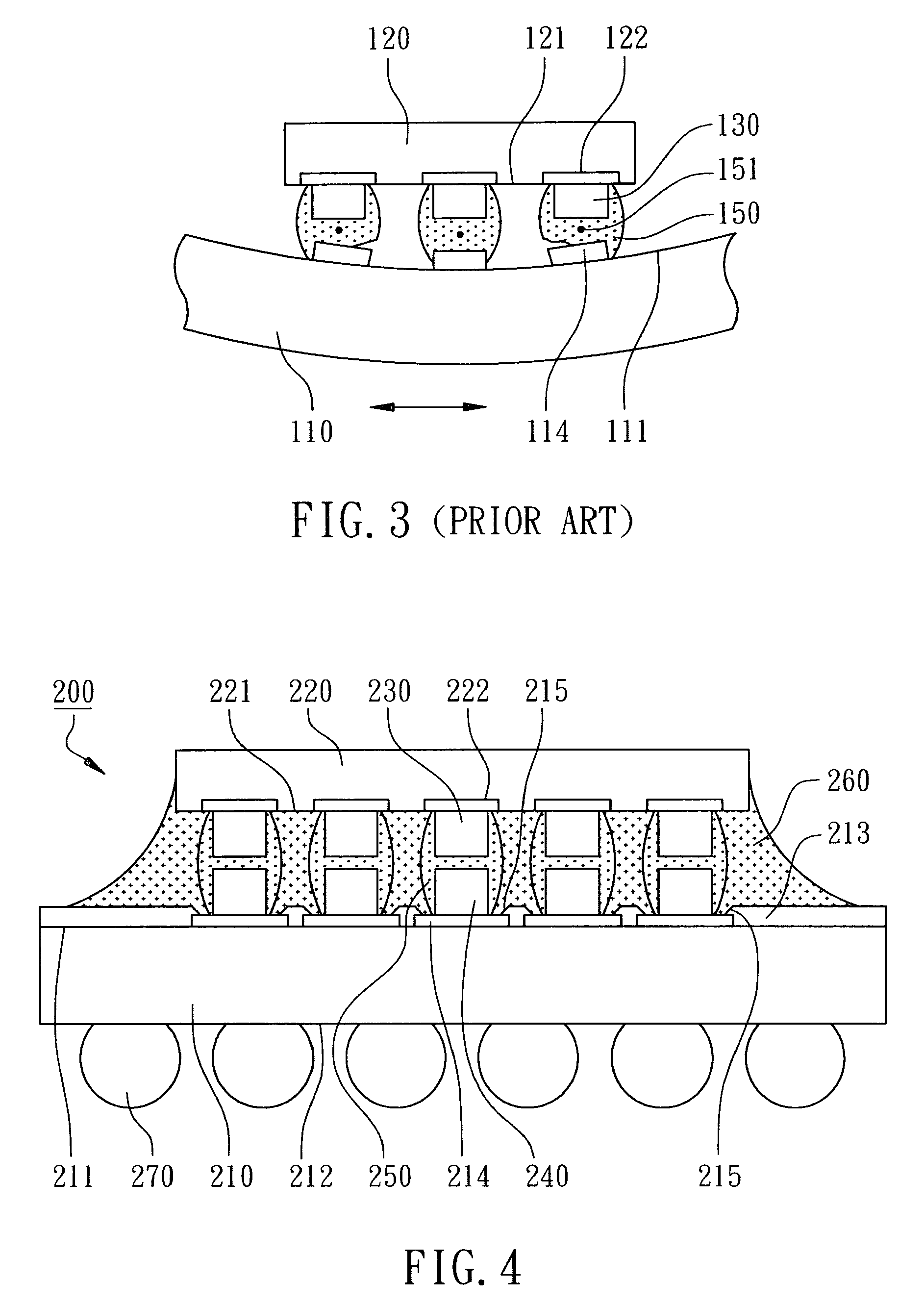

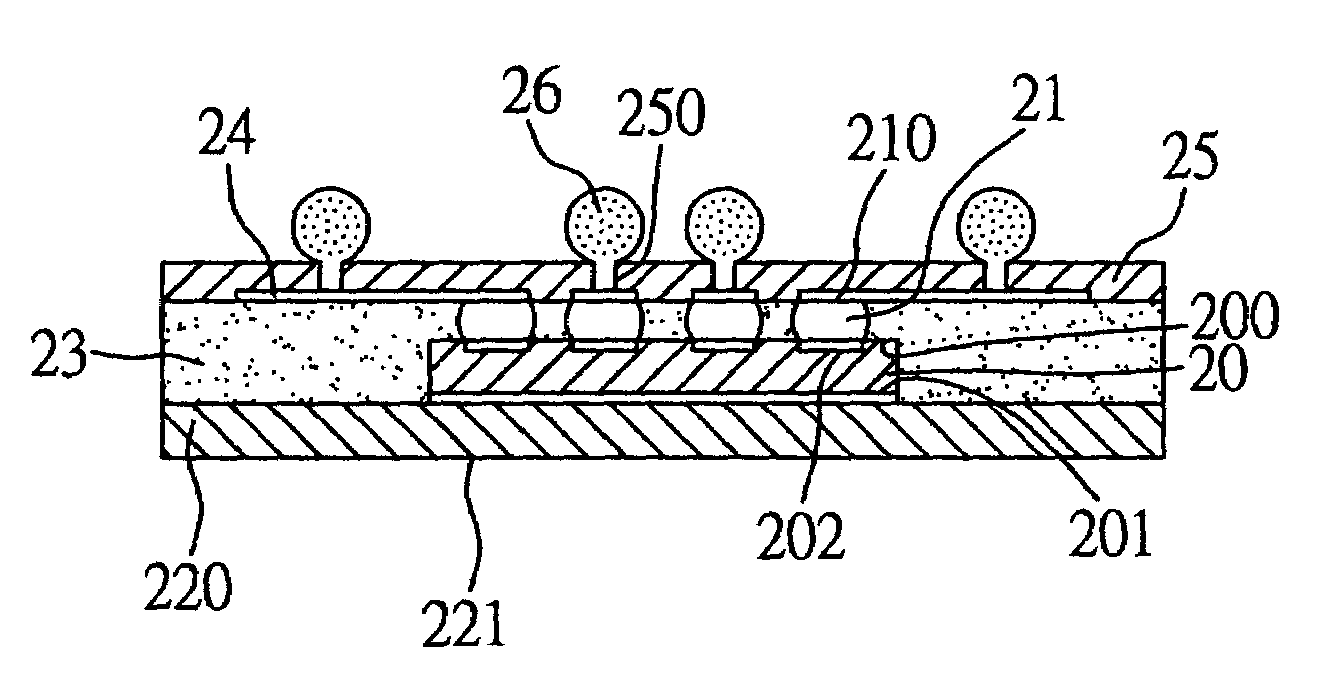

Package substrate, method of fabricating the same and chip package

InactiveUS20080179740A1Improve chip reliabilityIncrease distribution densitySemiconductor/solid-state device detailsStacked resist layersSolder maskEngineering

A package substrate, including a base layer, a surface circuit layer, a plurality of conductive bumps, and a patterned solder mask layer, is provided. The surface circuit layer having a plurality of bonding pads is disposed on a surface of the base layer. The conductive bumps are disposed on the bonding pads individually. The patterned solder mask layer is disposed on the surface of the base layer and outside a corresponding region occupied by the conductive bumps, so as to expose the conductive bumps. In addition, a method of fabricating the package substrate and a chip package structure employing the package substrate are also provided.

Owner:ADVANCED SEMICON ENG INC

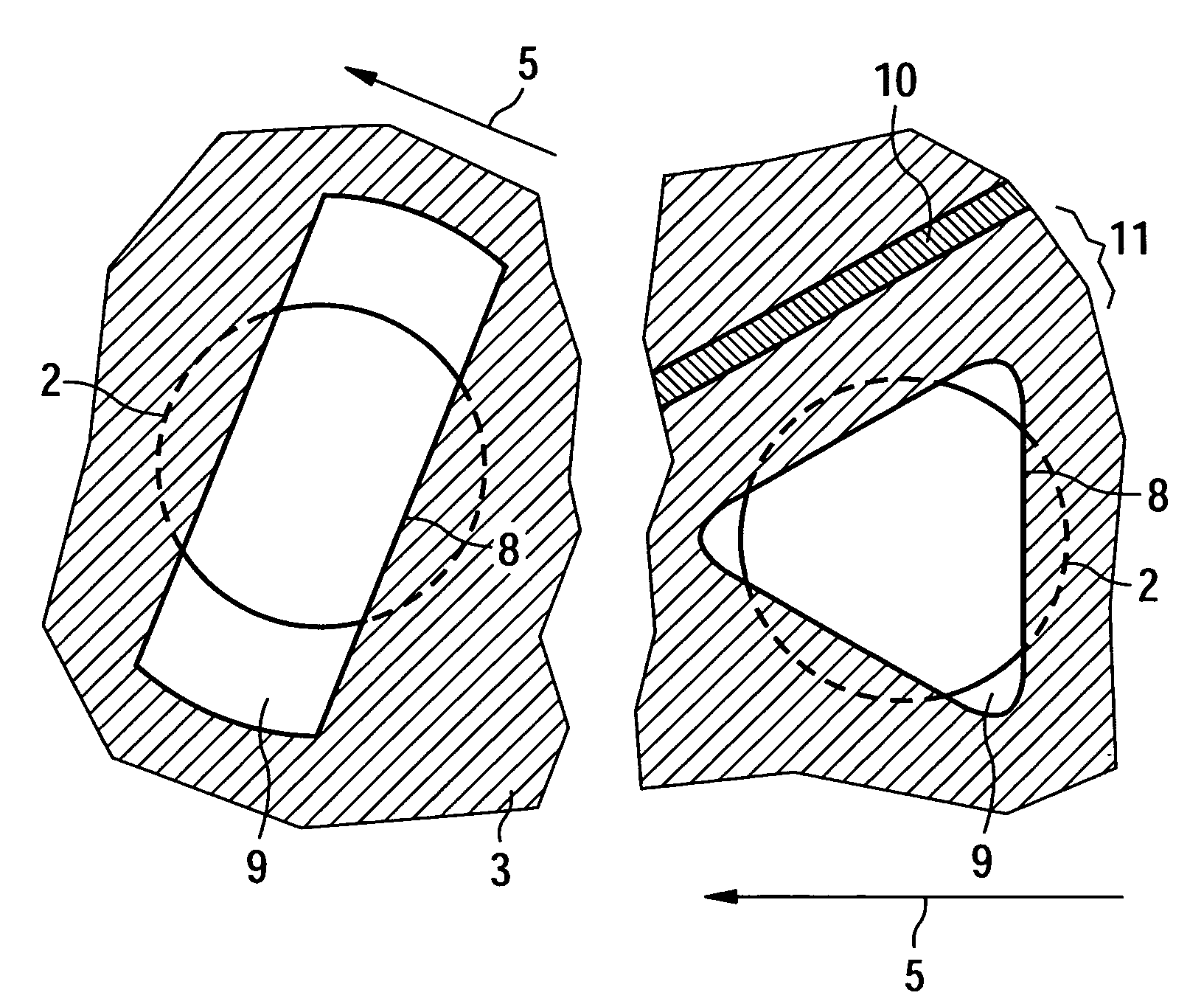

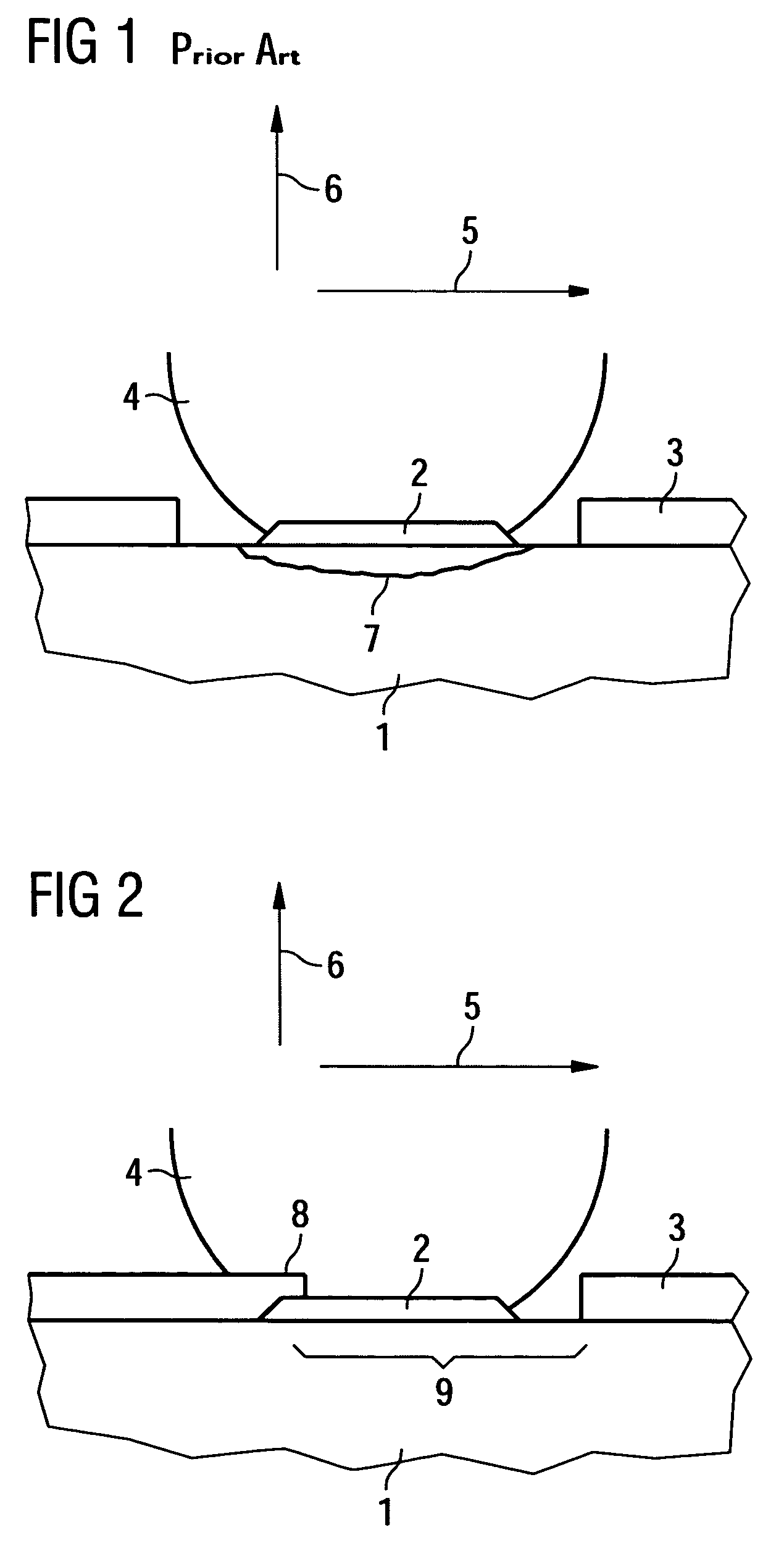

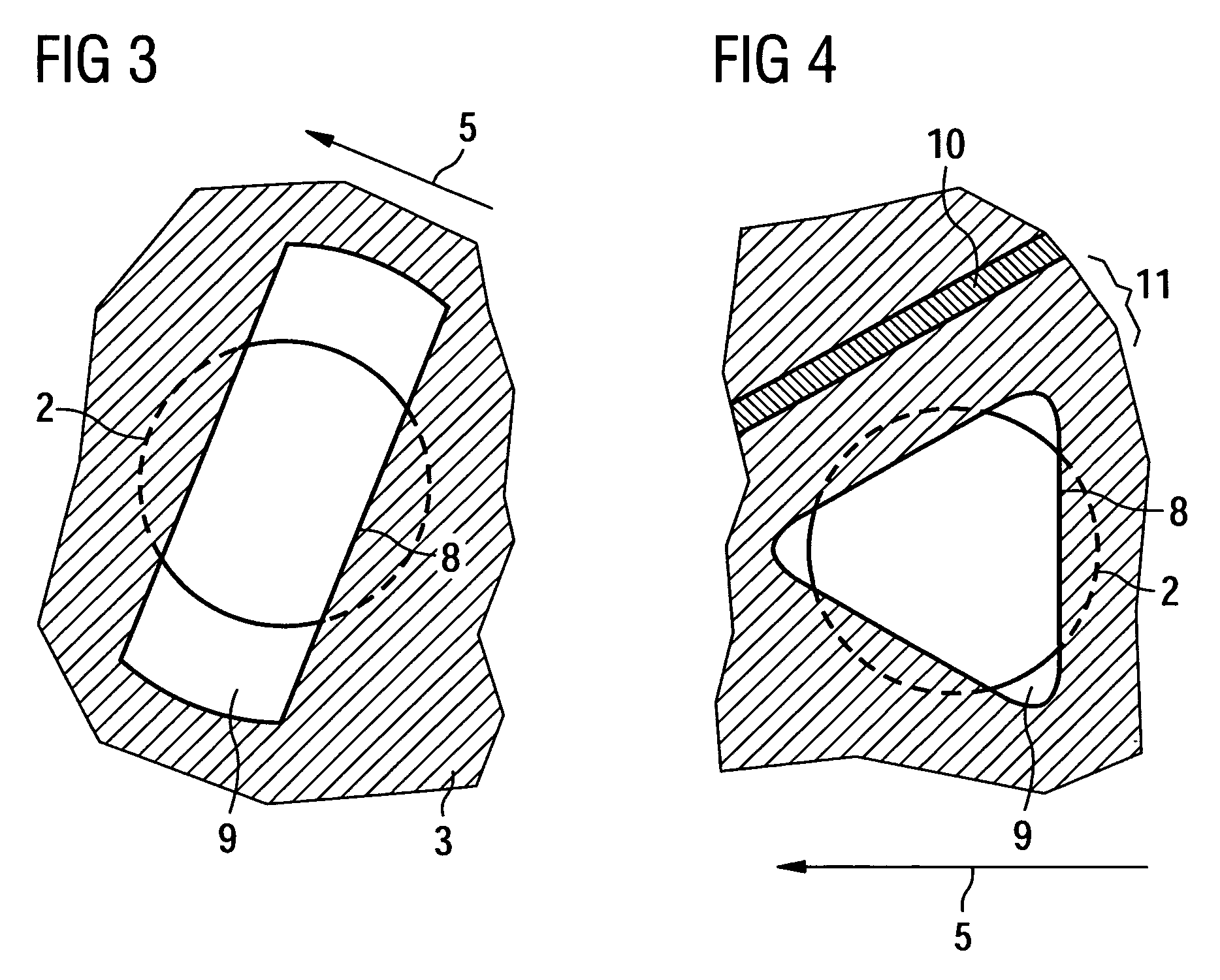

Substrate for producing a soldering connection

InactiveUS7271484B2Improve reliabilityReducing in fashionPrinted circuit assemblingSemiconductor/solid-state device detailsSolder maskEngineering

A solderable device includes a substrate and a soldering pad overlying the substrate. A solder mask overlies the substrate and portions of the soldering pad. The solder mask has an opening that exposes a portion of the soldering pad. The opening has at least two edges that symmetrically overlie portions of the soldering pad.

Owner:POLARIS INNOVATIONS LTD

Ground pad structure for preventing solder extrusion and semiconductor package having the ground pad structure

ActiveUS7173828B2Reduce generationQuality improvementPrinted circuit assemblingFinal product manufactureSolder maskSemiconductor package

A ground pad structure for preventing solder extrusion and a semiconductor package having the ground pad structure are disclosed, wherein the ground pad structure has the ground pads located along the circumference of its ground plane be formed in a non-solder mask defined manner. Accordingly, a good grounding quality is maintained, and the occurrence of the electrical bridging among the adjacent conductive traces can be avoided as the extrusion of the molten solder bumps from the ground pads located along the ground pad structure's circumference toward their adjacent conductive traces is effectively prevented.

Owner:SILICONWARE PRECISION IND CO LTD

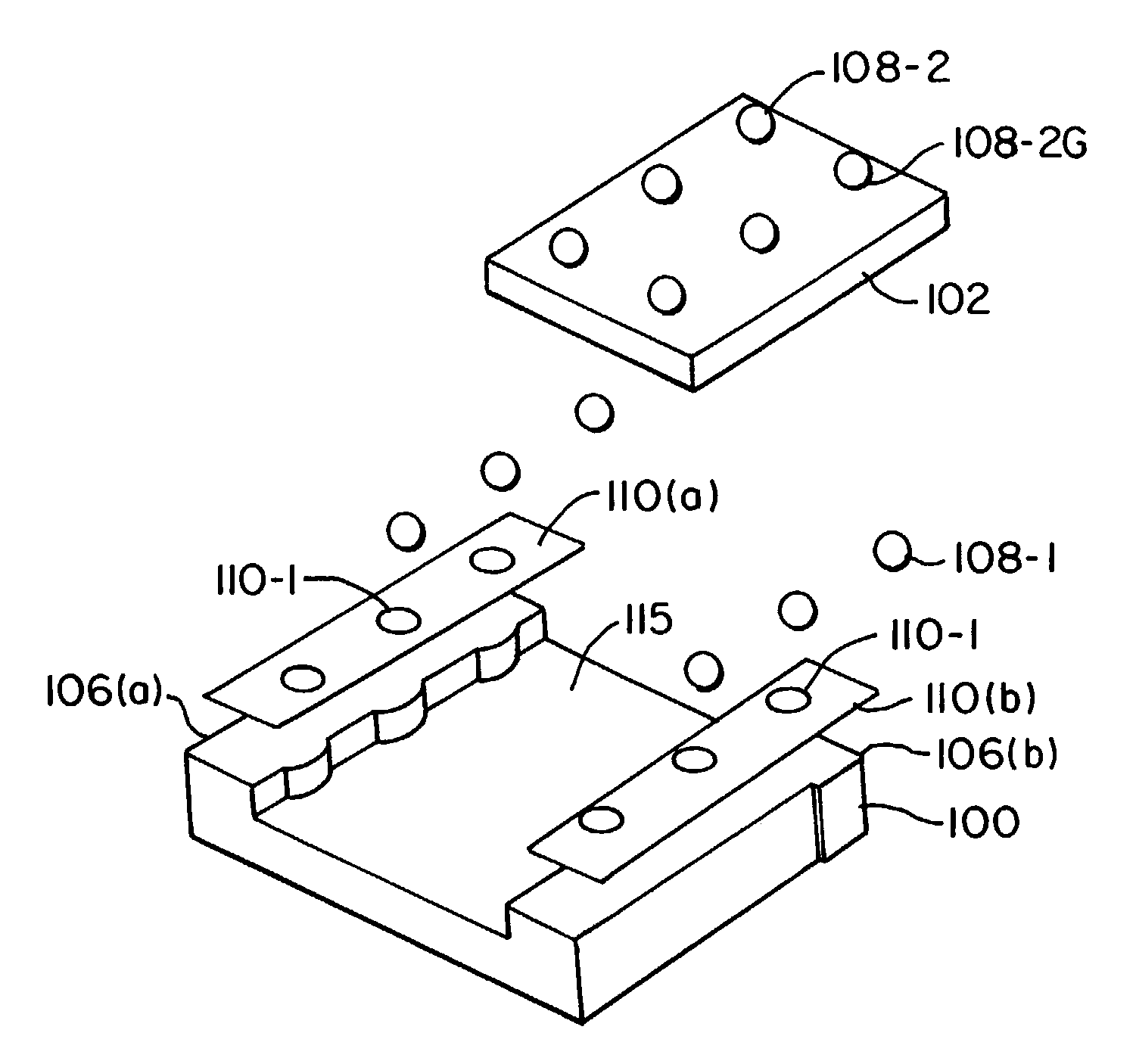

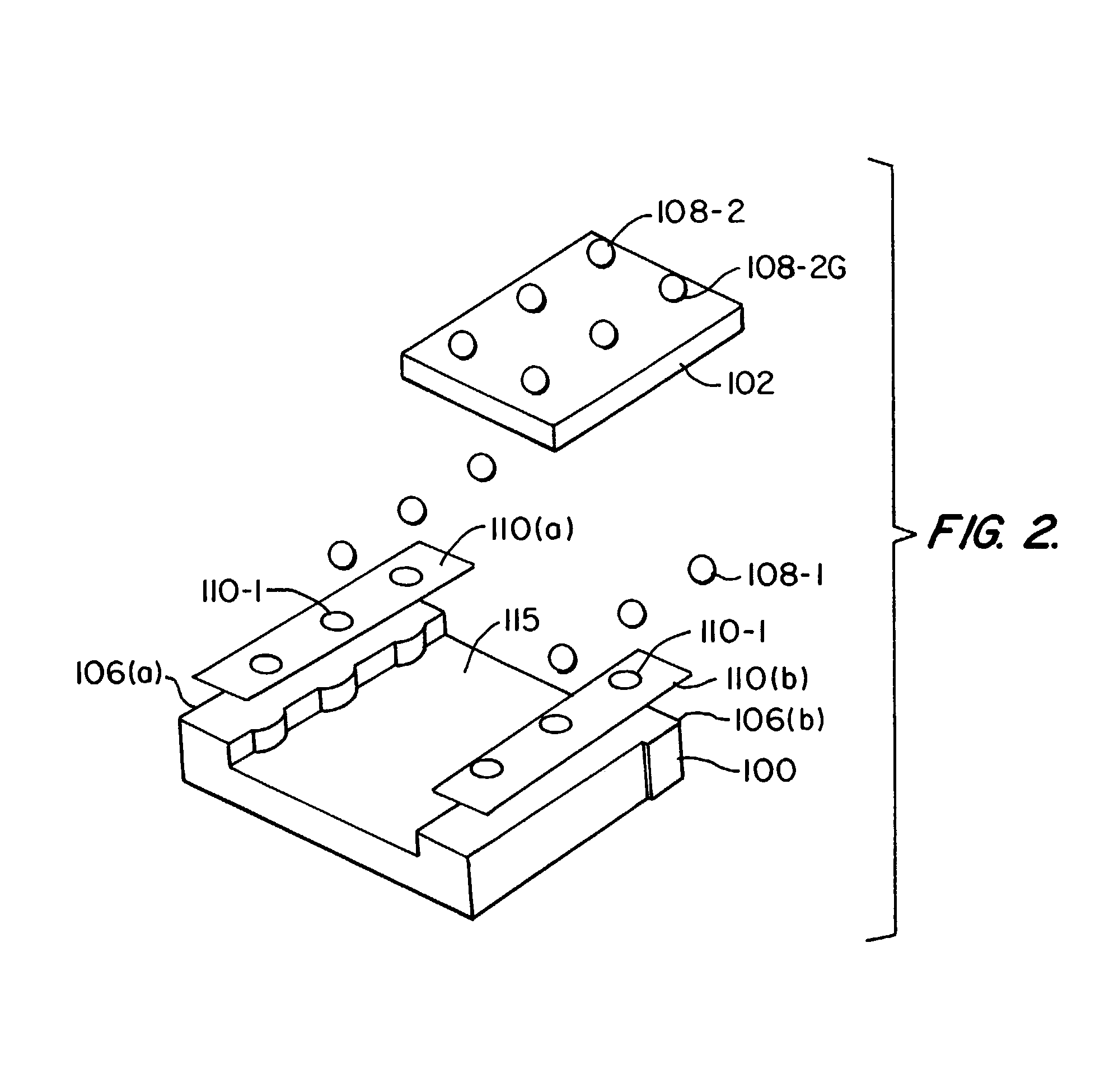

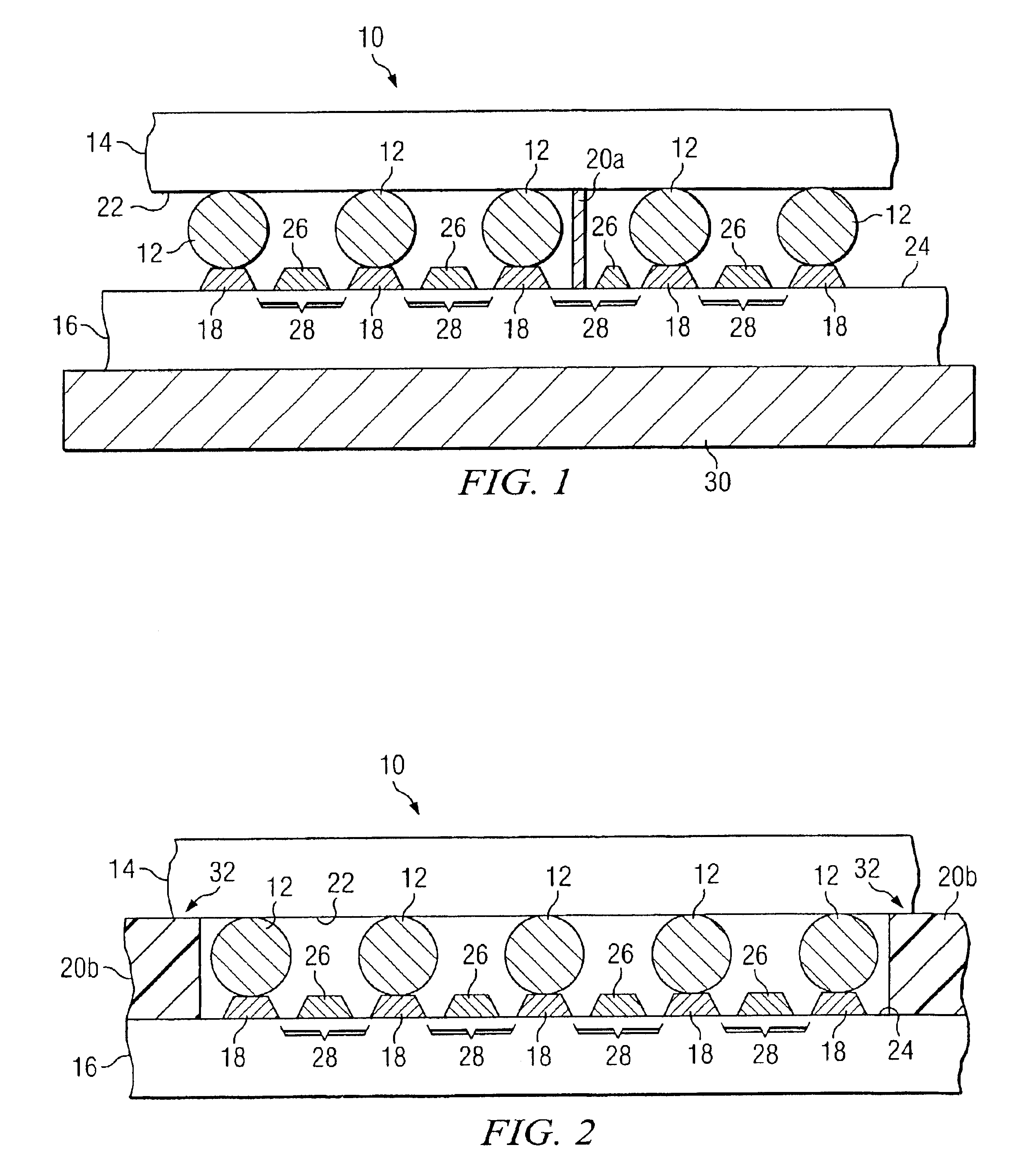

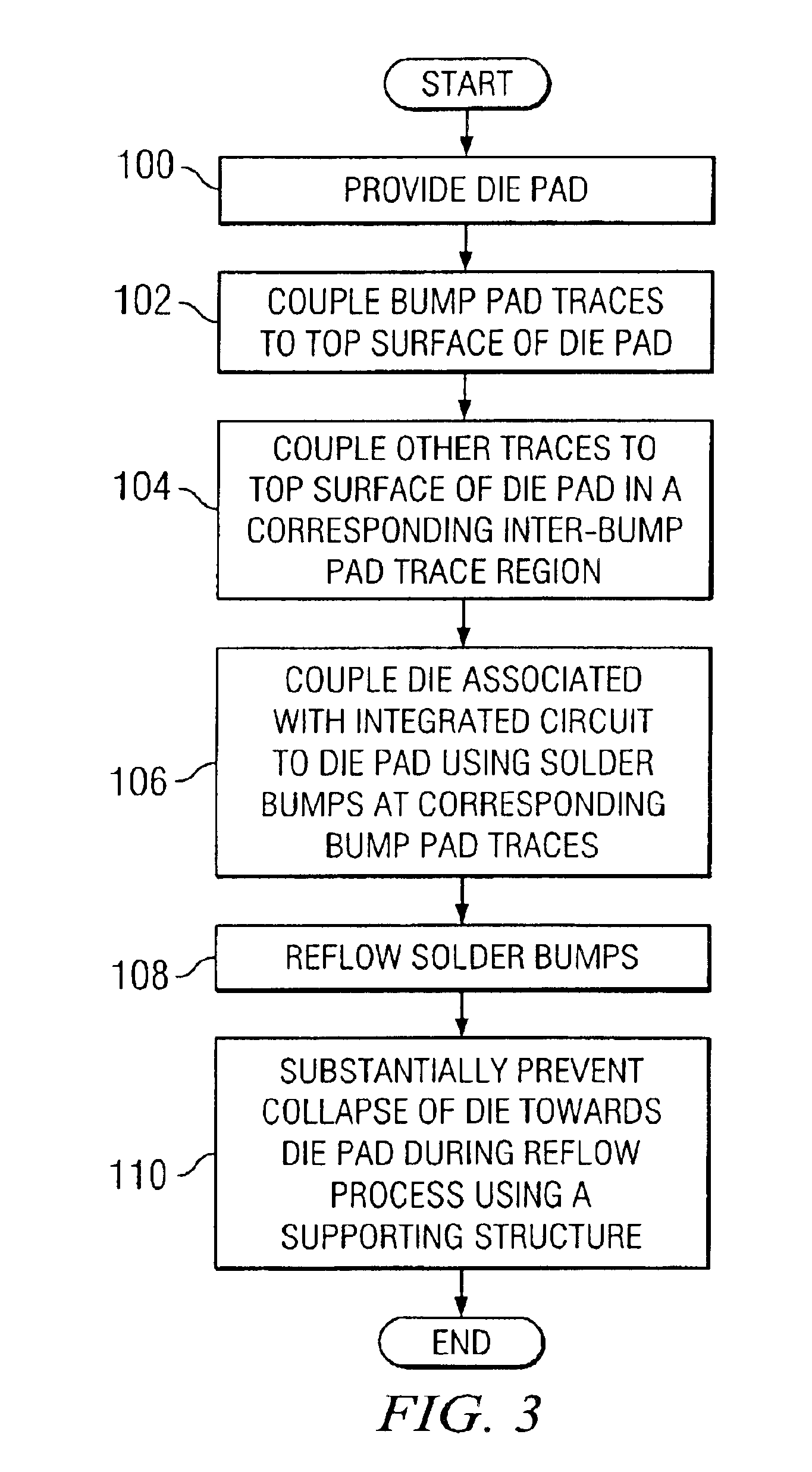

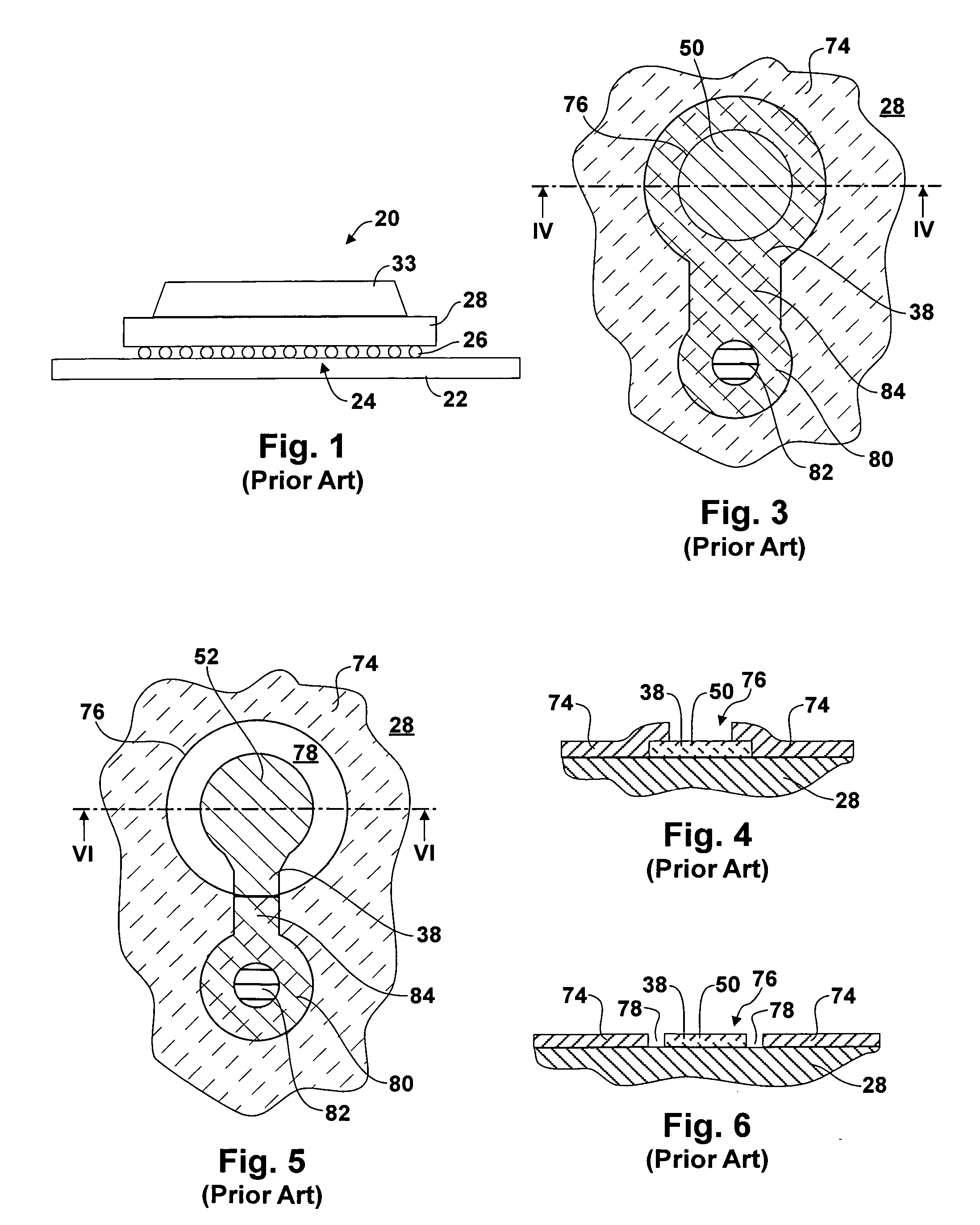

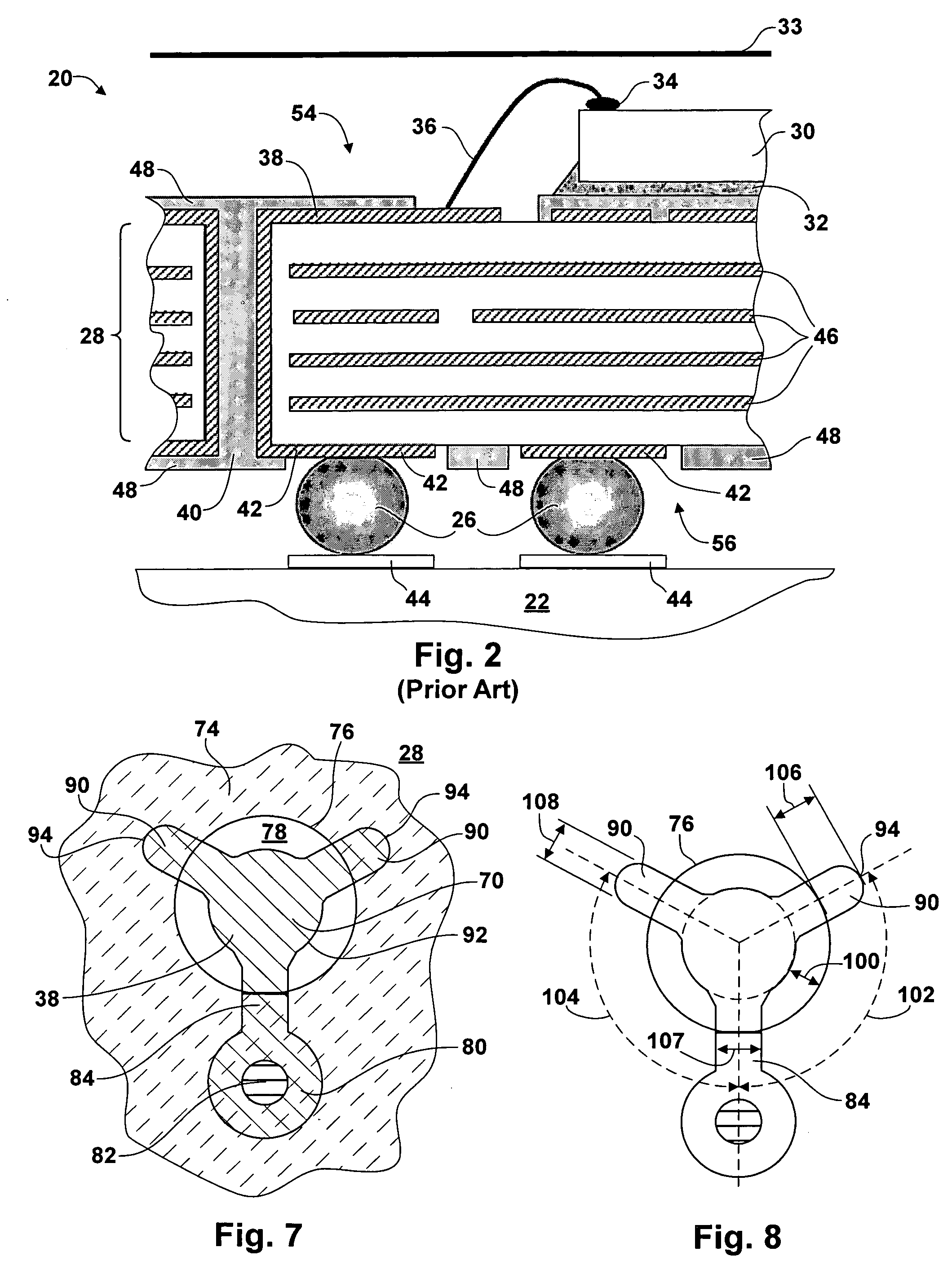

Using a supporting structure to control collapse of a die towards a die pad during a reflow process for coupling the die to the die pad

InactiveUS6849944B2Prevent crashReduce eliminatePrinted circuit assemblingFinal product manufactureSolder maskEngineering

In one embodiment, an integrated circuit package includes a die associated with an integrated circuit and a die pad. The die has a bottom surface, and the pad has a top surface opposite the bottom surface of the die. Two or more bump pad traces are each coupled to the top surface of the pad, and one or more other traces are each coupled to the top surface of the pad in a corresponding inter-bump pad region between adjacent bump pad traces. A number of solder bumps each couple the die to the pad at a corresponding bump pad trace to provide electrical connectivity between circuitry associated with the die and circuitry associated with the die pad. Each inter-bump pad region is free from any solder mask material deposited to control collapse of the die towards the pad during a reflow process for bonding the die to the pad using the bumps, a supporting structure that contacts the die during the reflow process having been used instead.

Owner:TEXAS INSTR INC +1

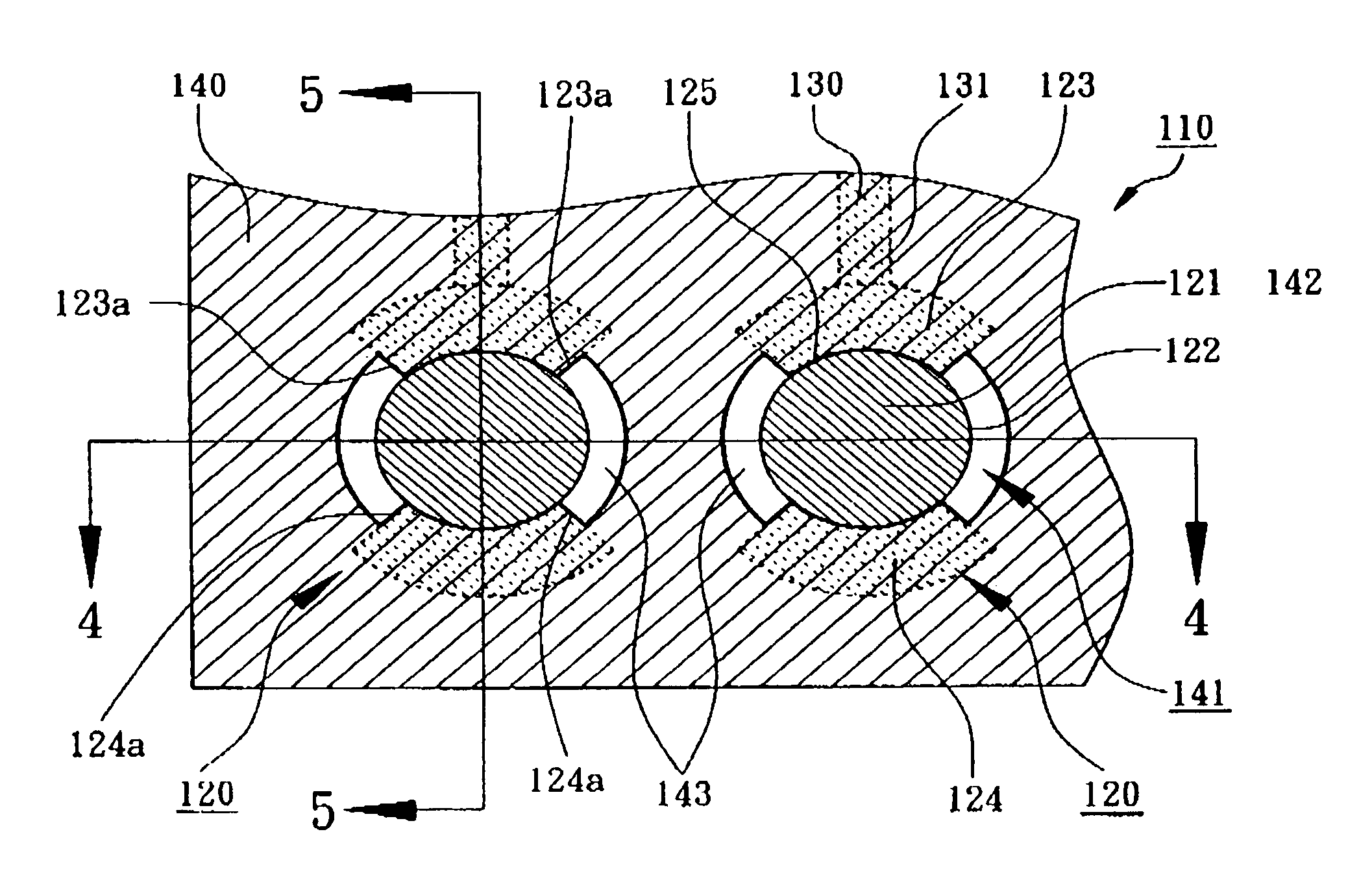

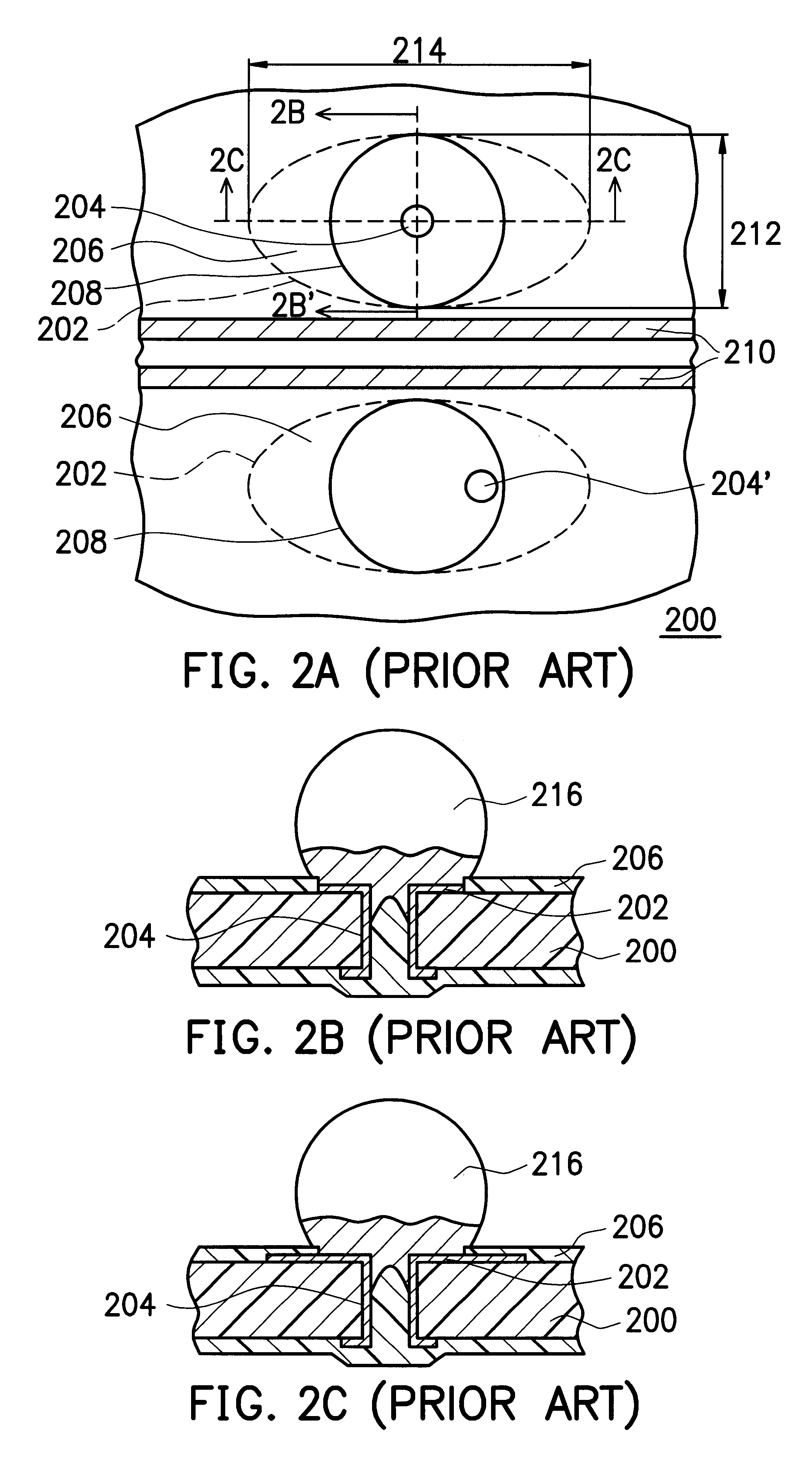

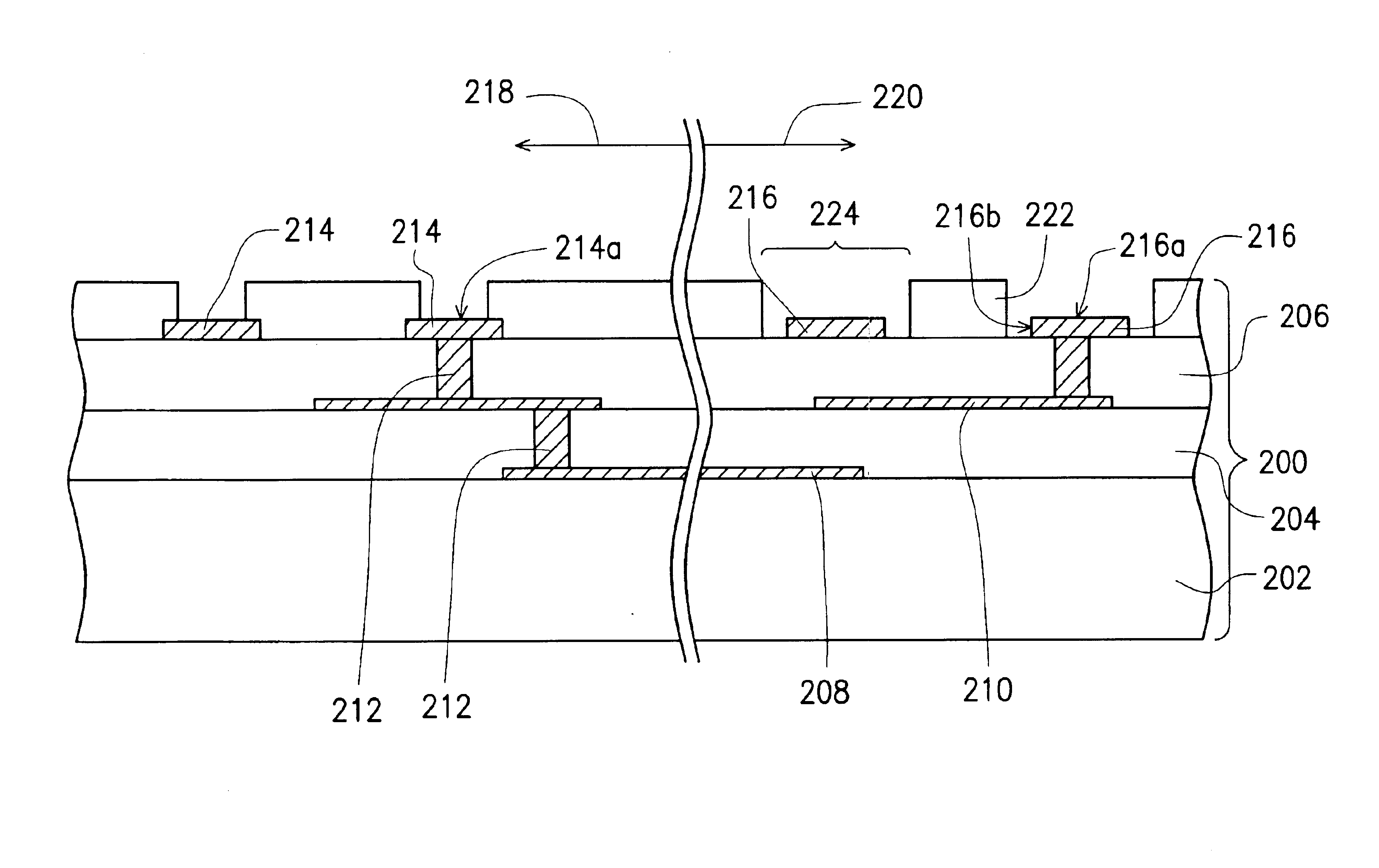

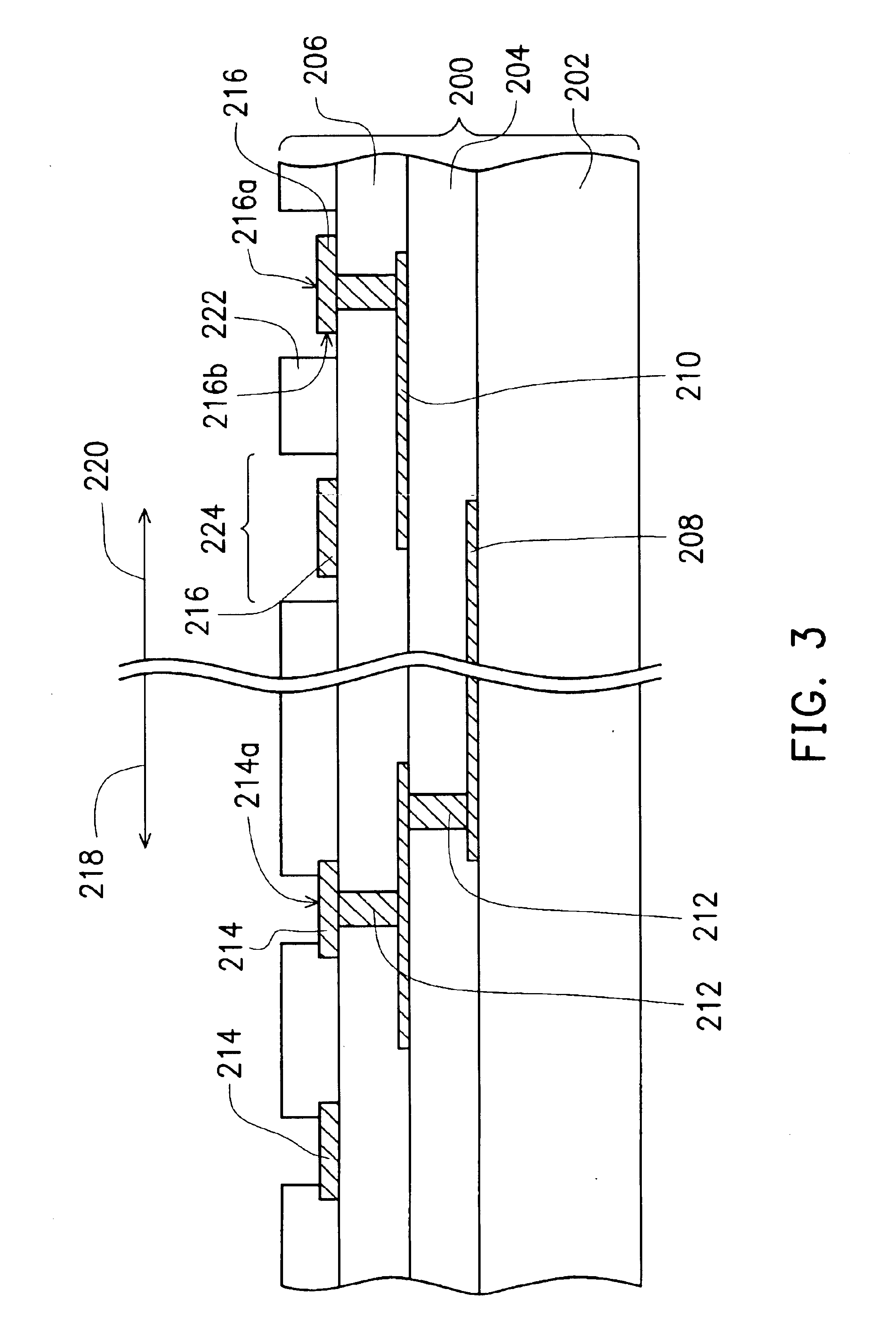

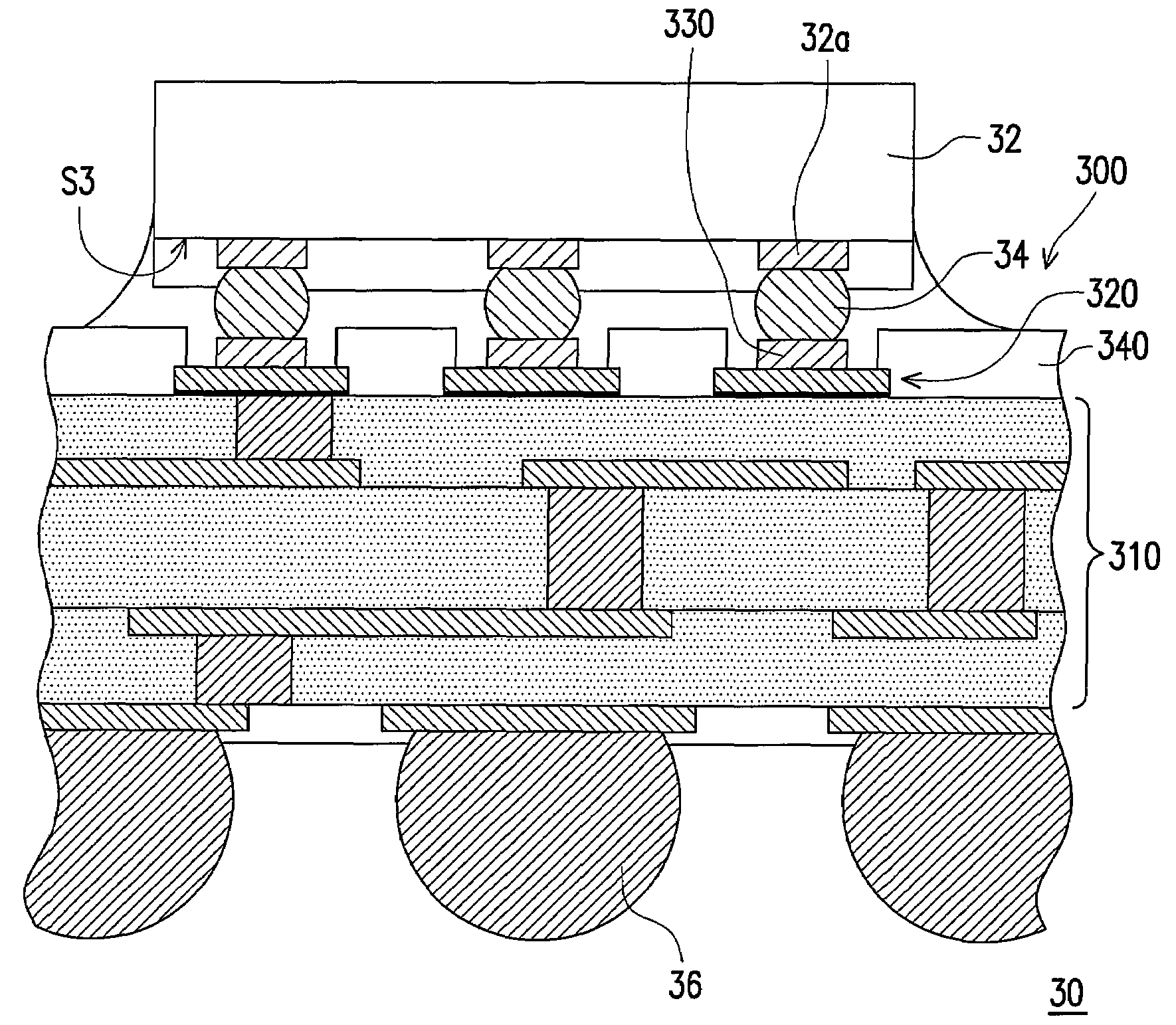

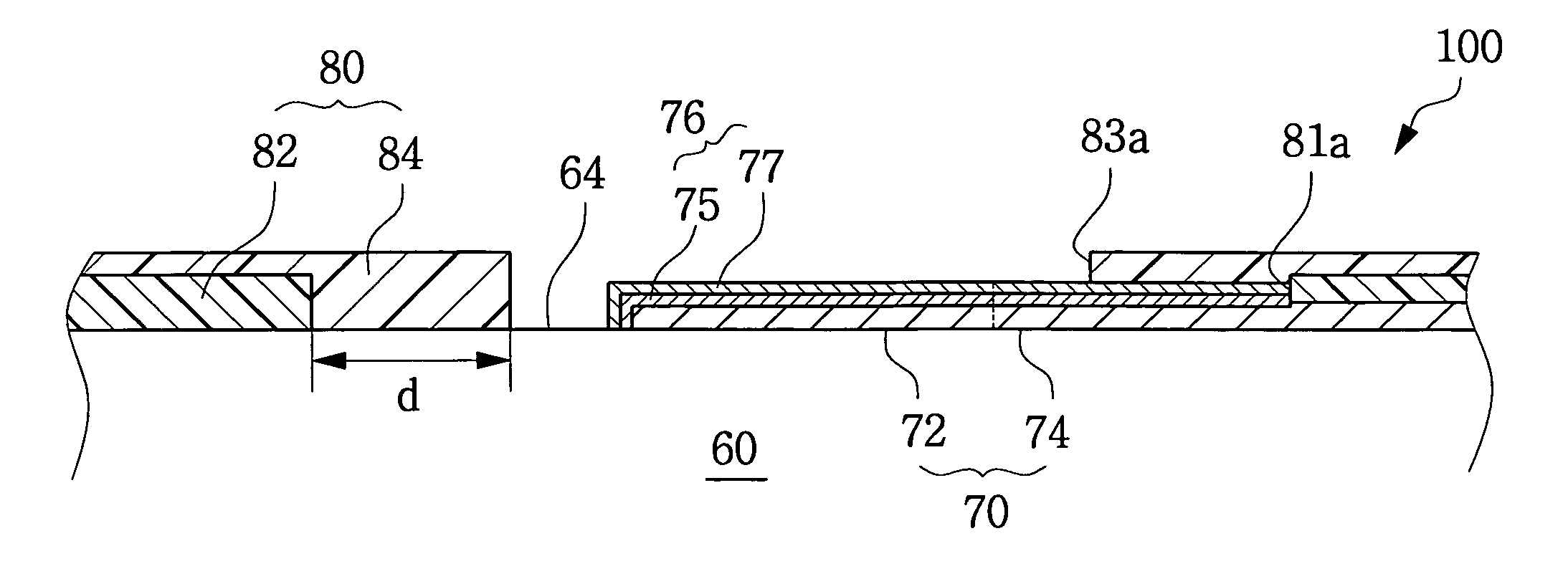

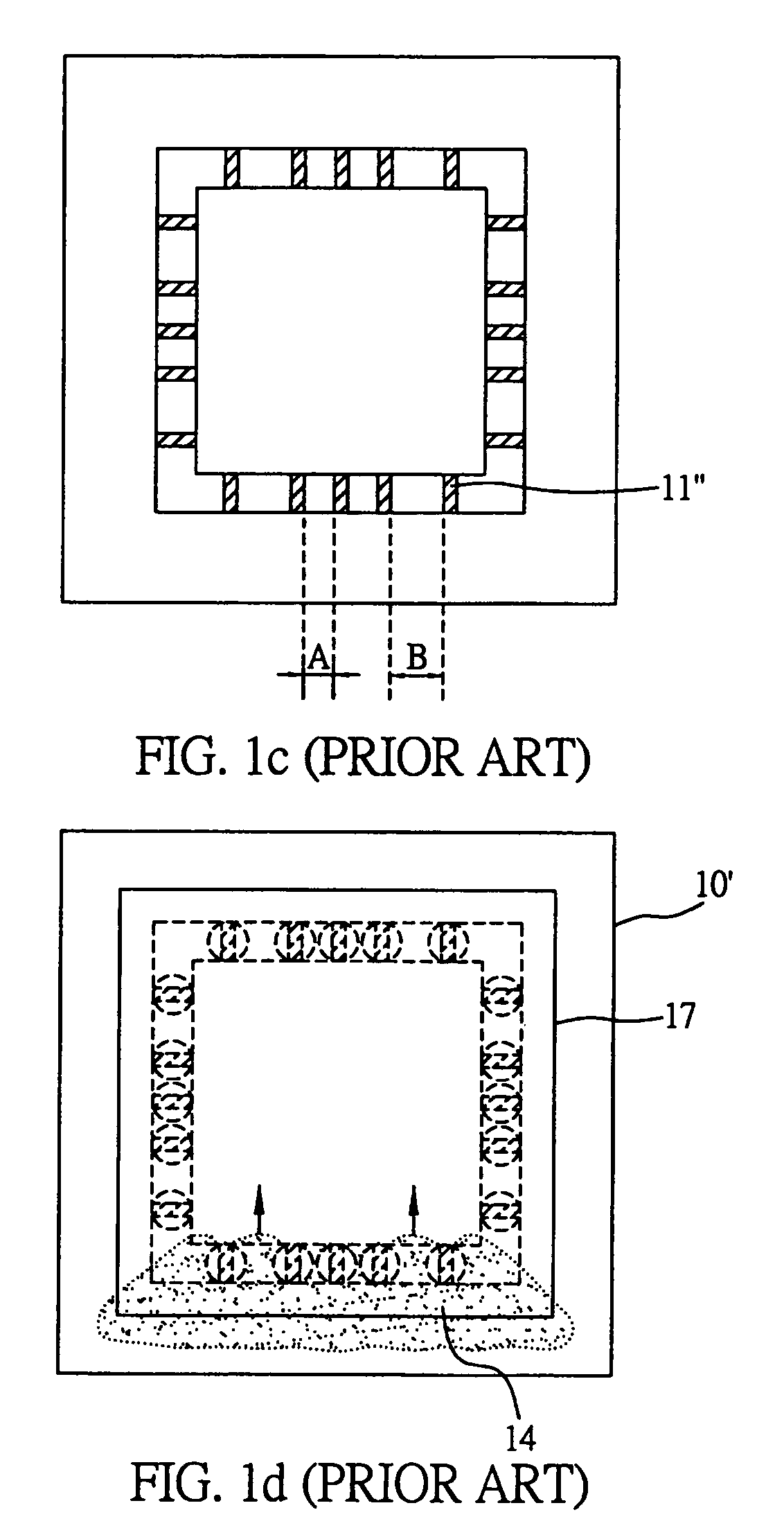

Non-solder mask defined (NSMD) type wiring substrate for ball grid array (BGA) package and method for manufacturing such a wiring substrate

ActiveUS7098407B2Reduce crackingReduce stress concentrationPrinted circuit assemblingSemiconductor/solid-state device detailsStress concentrationSolder mask

In one embodiment, a pad is formed on a substrate surface. The pad is connected with a connecting pattern. A first mask is formed on the substrate. The first mask has a first opening exposing at least a portion of the pad and a portion of the connecting pattern. A second mask is formed on the first mask. The second mask has a second opening exposing at least a portion of the pad and a portion of the connecting pattern. A boundary surface or sidewall of the first opening is not coplanar with a boundary surface or sidewall of the second opening. Therefore, stresses may be prevented from concentrating on the boundary surface of the first opening, thereby allowing dispersion of the stresses and restraining pattern cracks.

Owner:SAMSUNG ELECTRONICS CO LTD

Chip carrier for semiconductor chip

ActiveUS7102239B2Reduce formationInhibition effectSemiconductor/solid-state device detailsSolid-state devicesSolder maskSemiconductor chip

A chip carrier for a semiconductor chip is provided. A plurality of solder pads for bump soldering are formed on a chip mounting surface of the chip carrier, to allow a flip chip to be mounted and electrically connected to the chip carrier. A solder mask layer is formed on the chip carrier, wherein a plurality of openings are provided in the solder mask layer to expose the solder pads, and an outwardly opening extended portion is formed respectively from the openings corresponding to the solder pads having a relatively narrower pitch therebetween, so as to prevent formation of voids during an underfill process for filing a gap between the flip chip and the chip carrier.

Owner:SILICONWARE PRECISION IND CO LTD

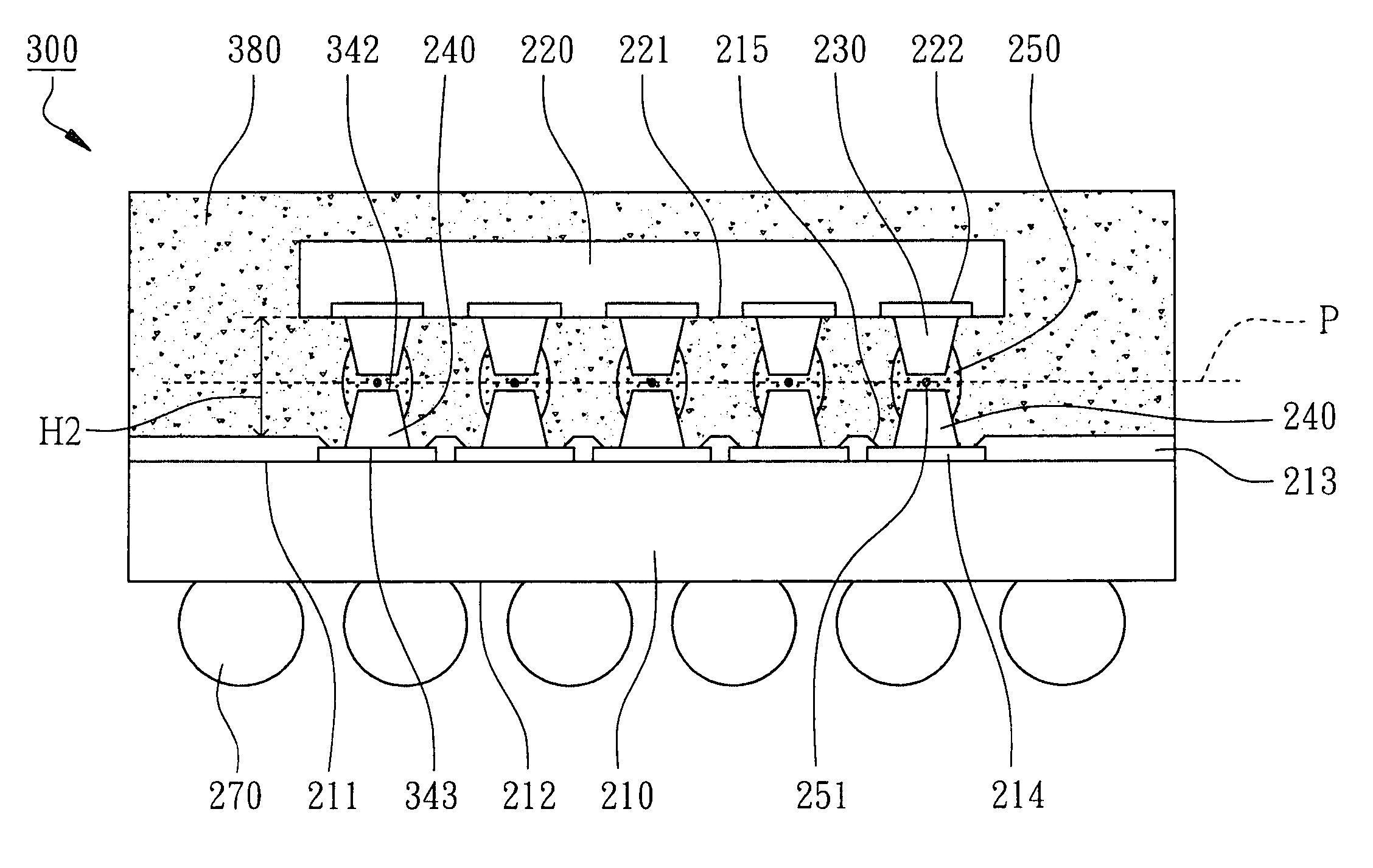

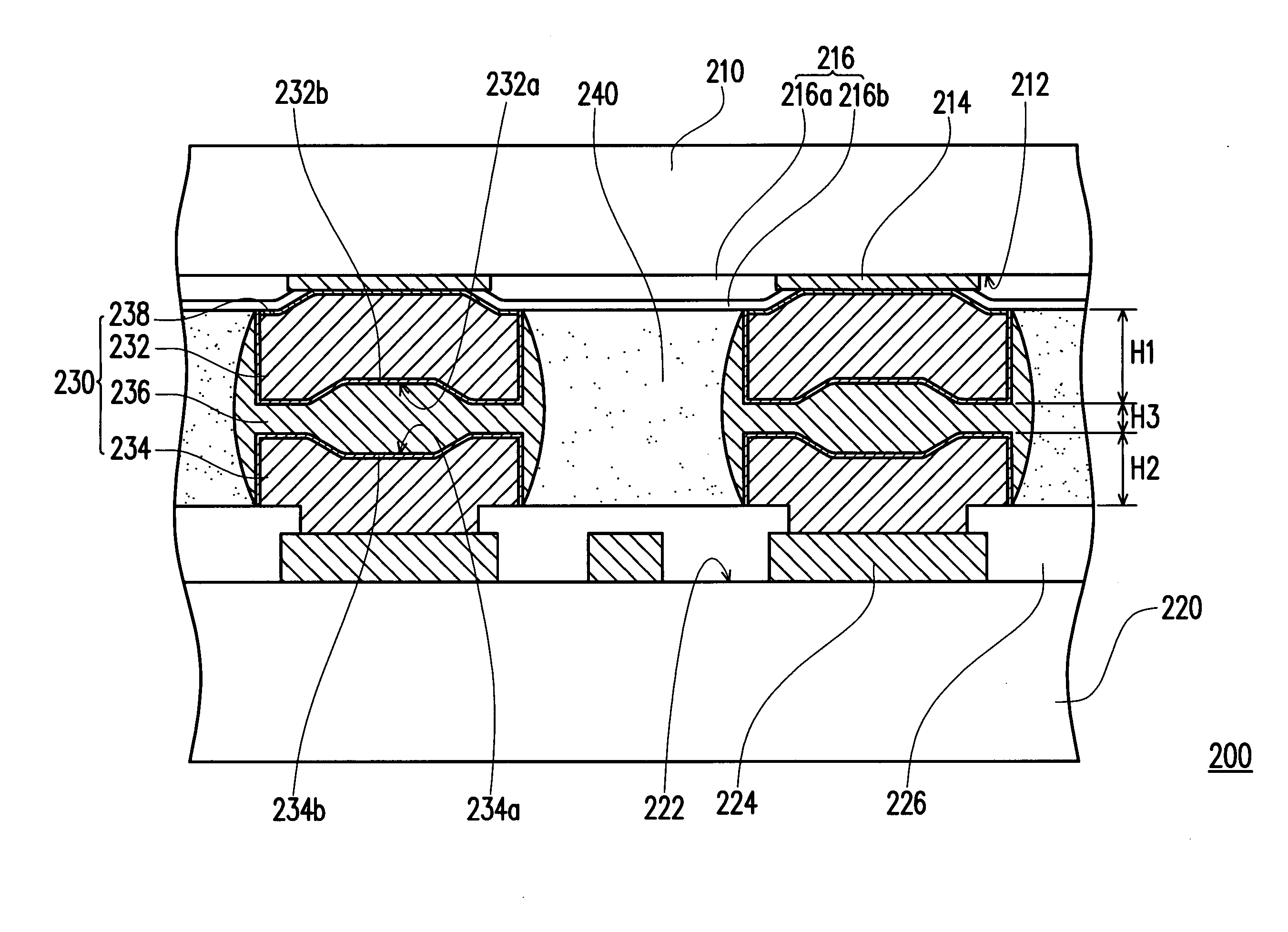

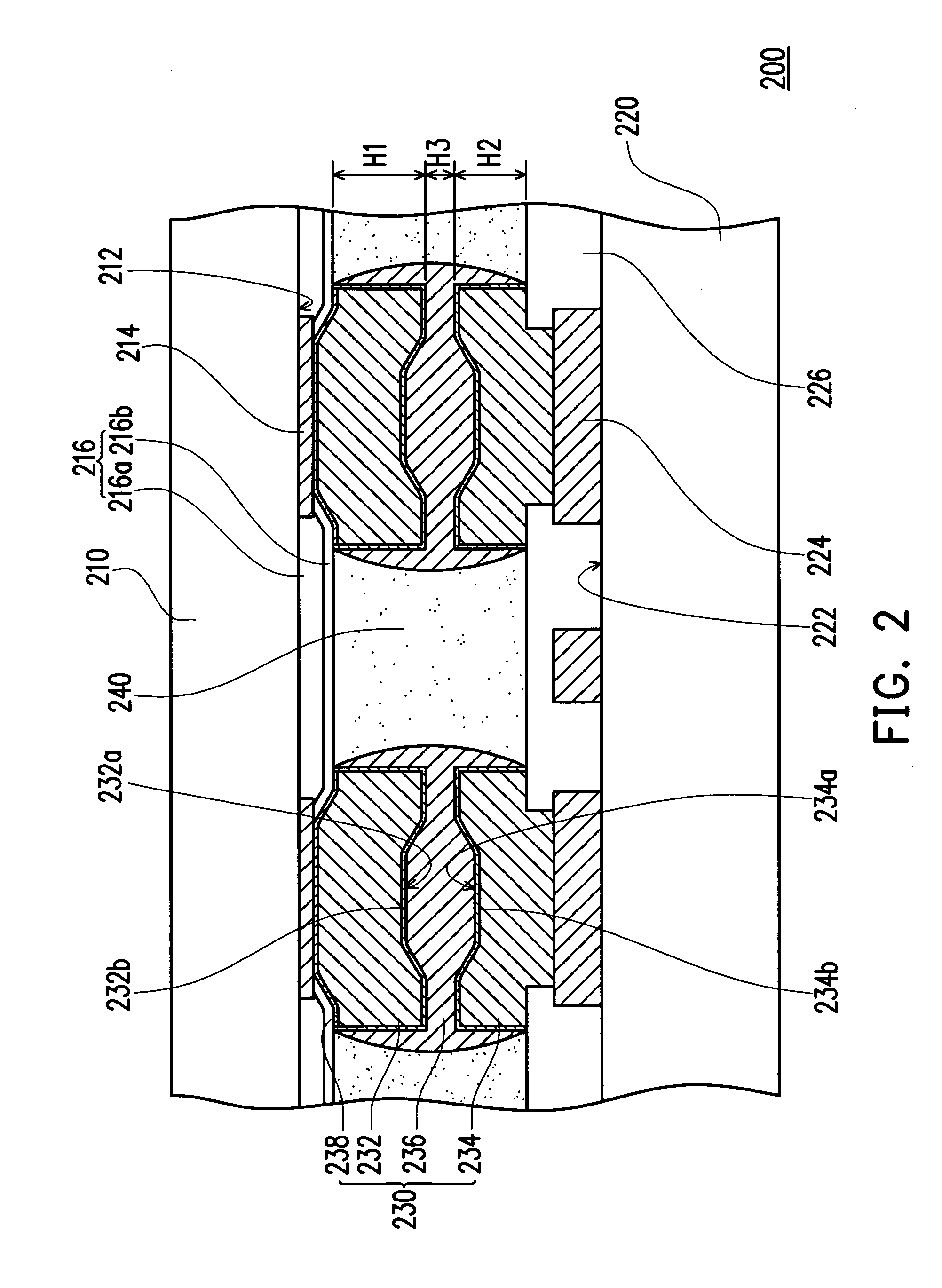

Chip package and bump connecting structure thereof

ActiveUS7382049B2Final product manufactureSemiconductor/solid-state device detailsSolder maskMicrometer

A chip package includes a chip, a carrier, and at least a bump connecting structure for connecting the chip to the carrier. The bump connecting structure includes a first metal bump disposed on a chip pad of the chip and has a first height relative to a passivation layer of the chip, a second metal bump disposed on a carrier pad of the carrier and has a second height relative to a solder mask layer of the carrier, and a middle metal part disposed between the first and the second metal bumps. The sum of the minimum distance between the first and the second metal bumps, the first height of the first metal bump, and the second height of the second metal bump is less than 60 micrometers. The melting point of the middle metal part is lower than that of the first and the second metal bumps.

Owner:VIA TECH INC

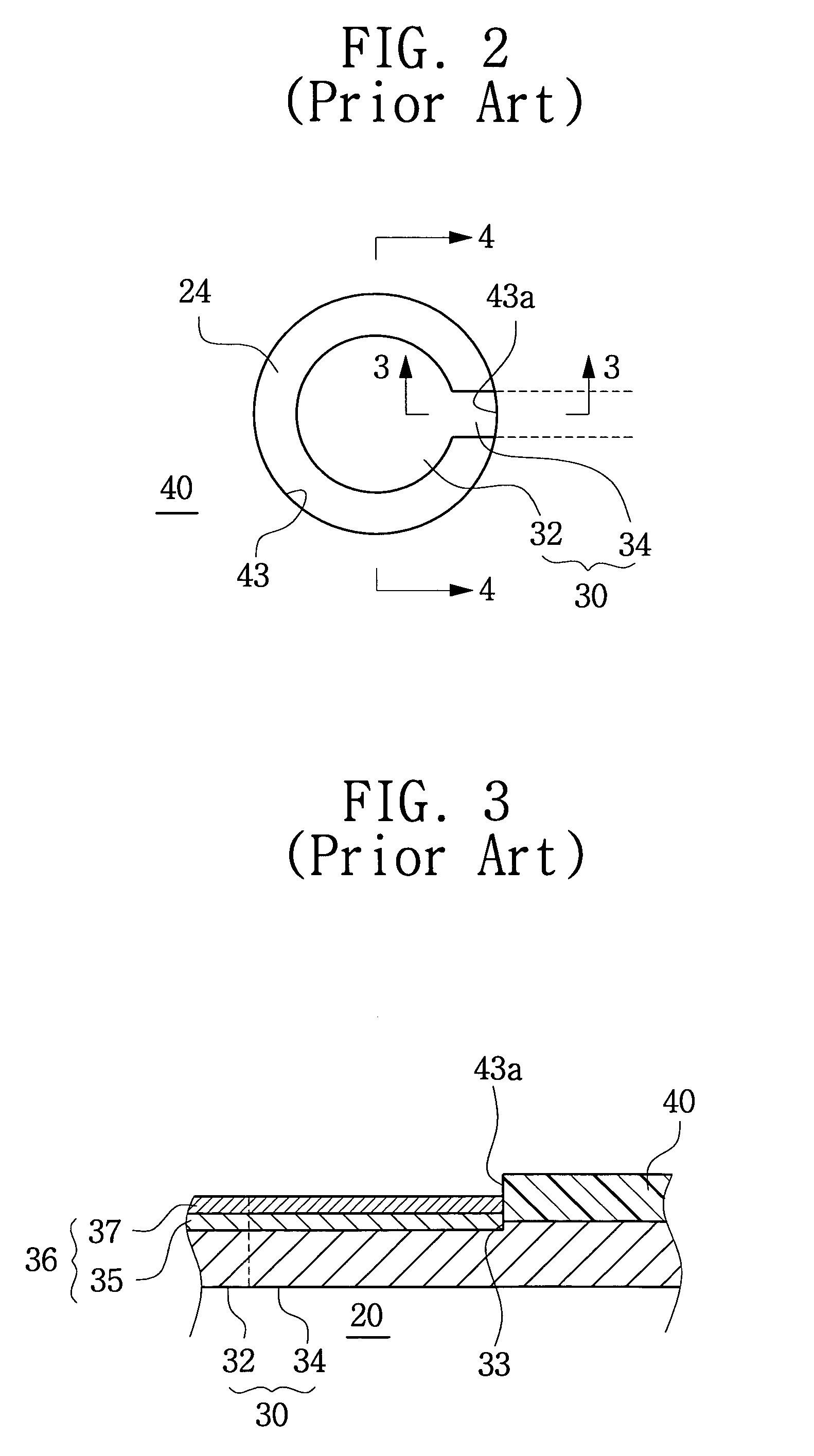

Substrate for solder joint

InactiveUS7224073B2Avoid pollutionPerformed easily and accuratelyPrinted circuit assemblingFinal product manufactureSolder maskEngineering

A substrate for solder joint is provided, including: a core layer; at least one conductive trace formed on the core layer and having a circular terminal as a pad through which a plurality of hollow portions are formed and expose predetermined portions of the core layer underneath the pad, wherein the hollow portions are arranged at equal intervals and spaced from a periphery of the circular pad; and a solder mask for covering the conductive trace and having at least one opening bordered across each of the hollow portions of the pad, such that part of the pad and part of each of the predetermined portions of the core layer are exposed via the opening, to allow a conductive element to be bonded to the exposed part of the pad and the exposed part of the predetermined portions of the core layer in the opening of the solder mask.

Owner:UTAC HEADQUARTERS PTE LTD

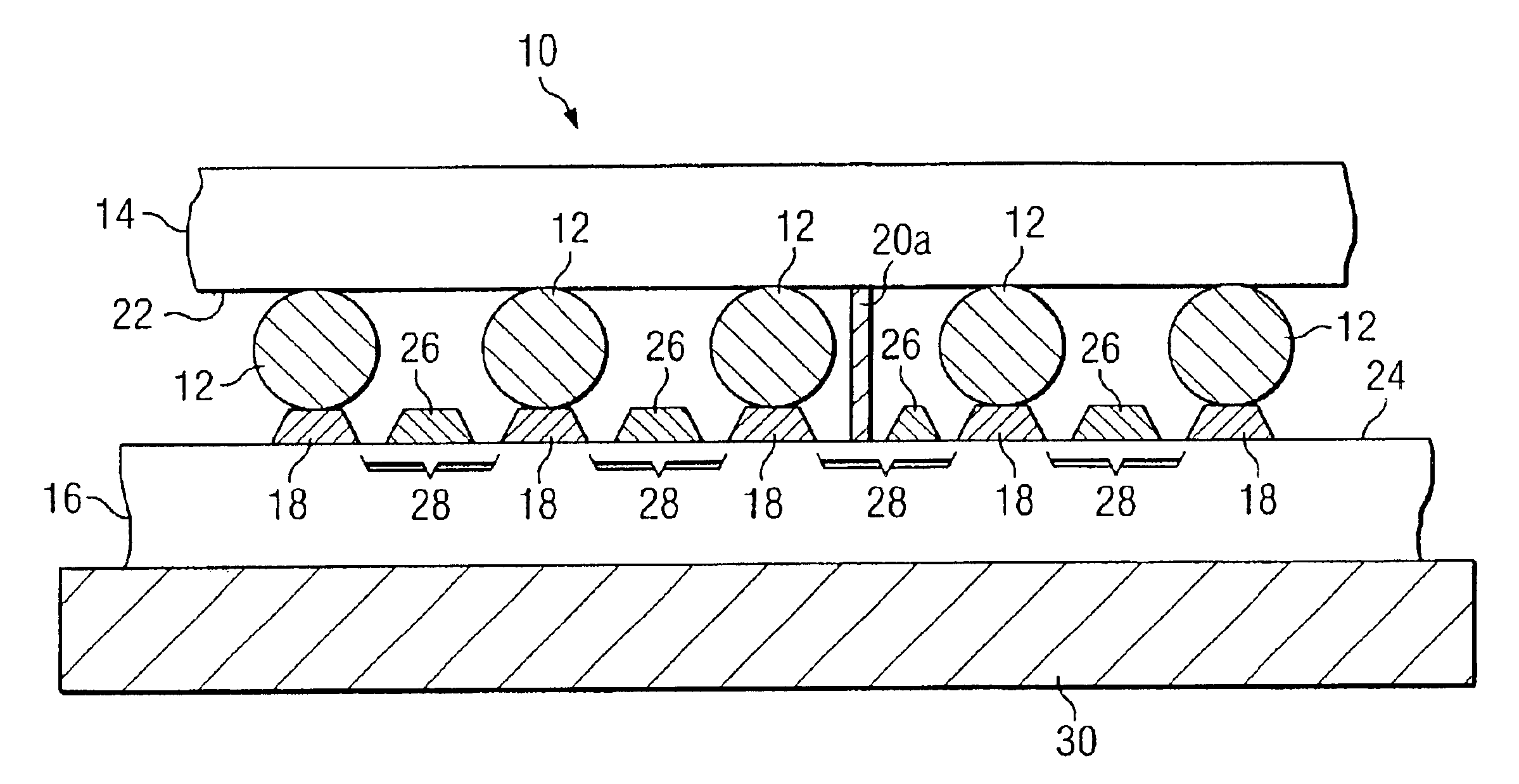

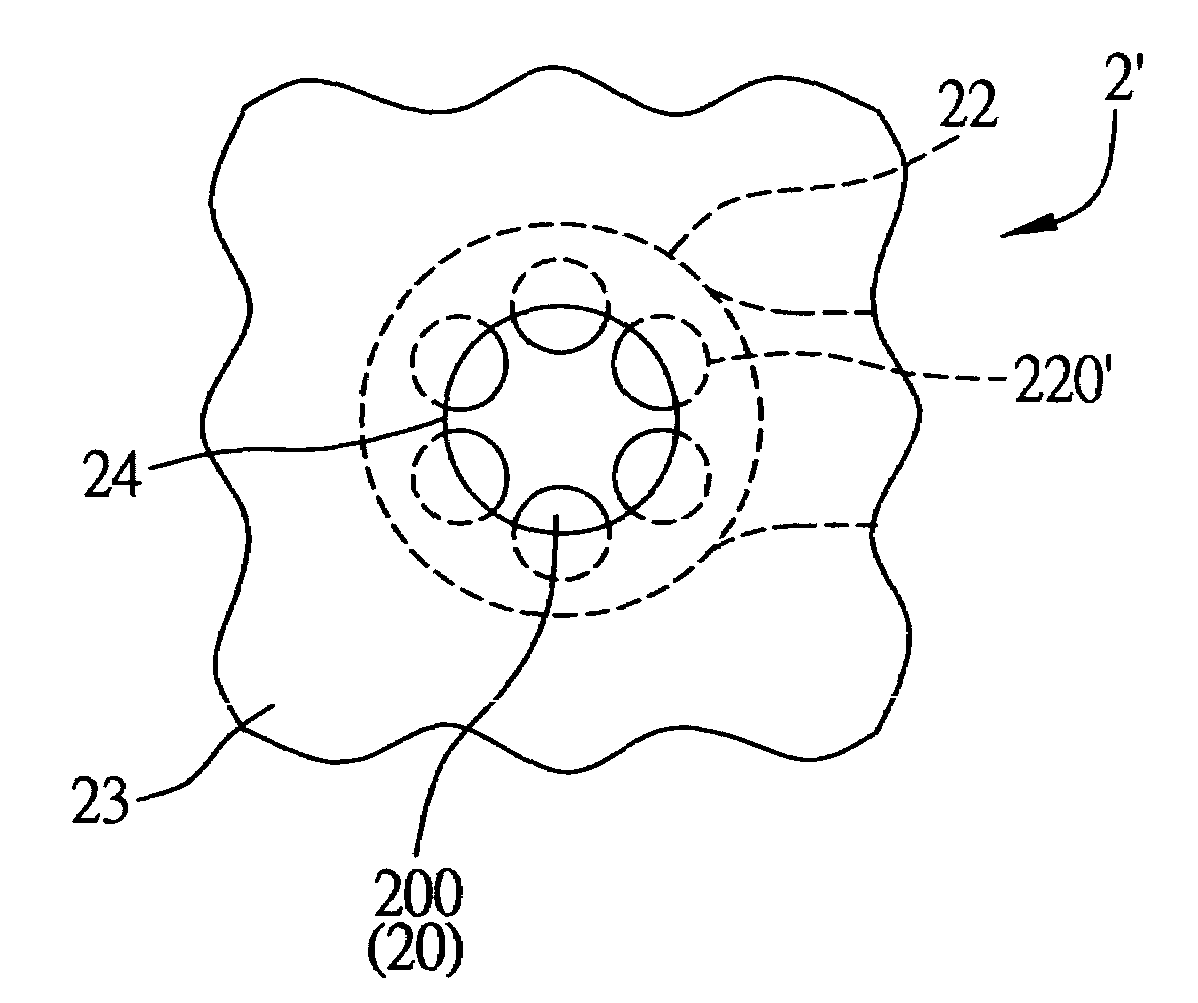

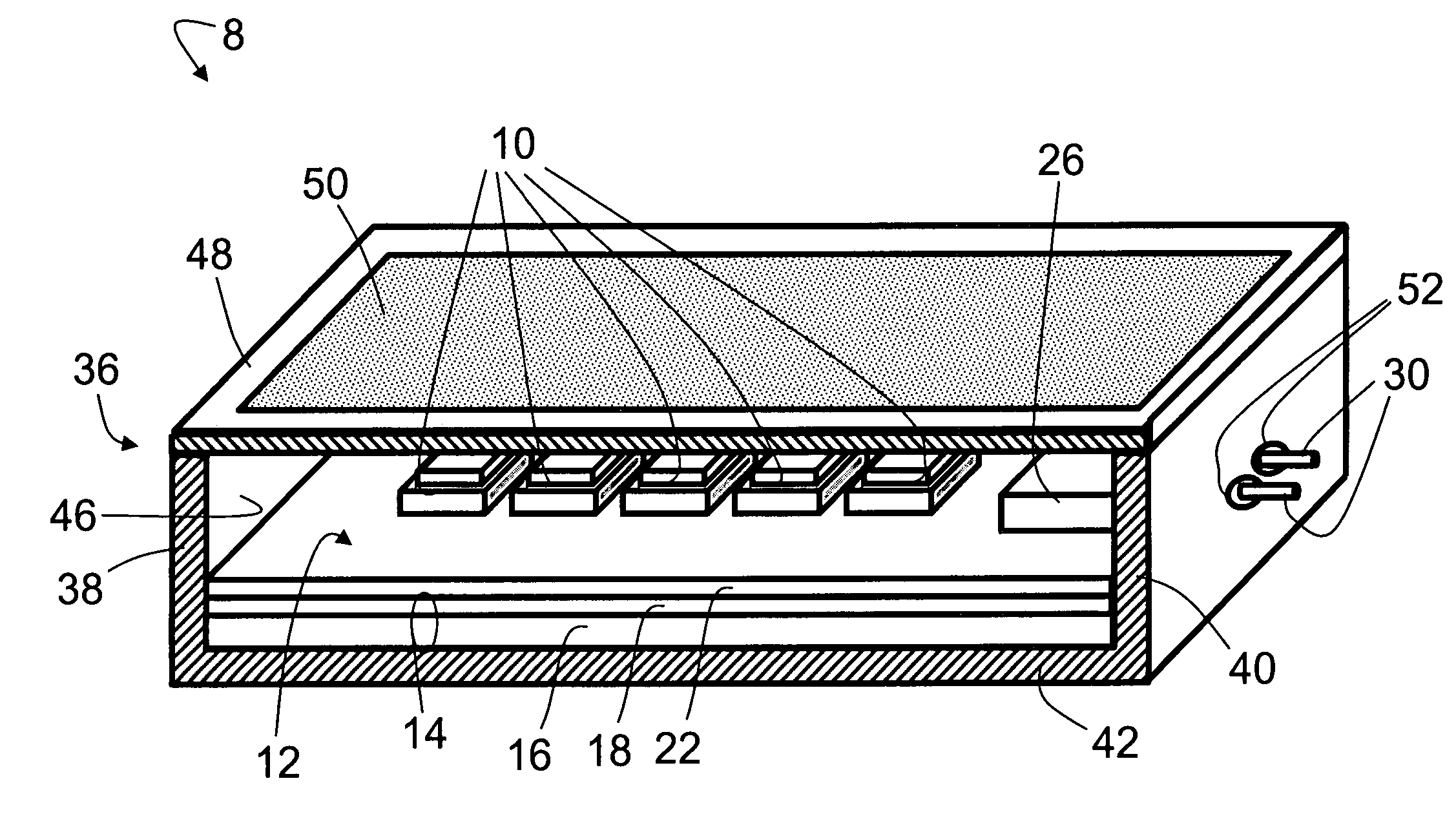

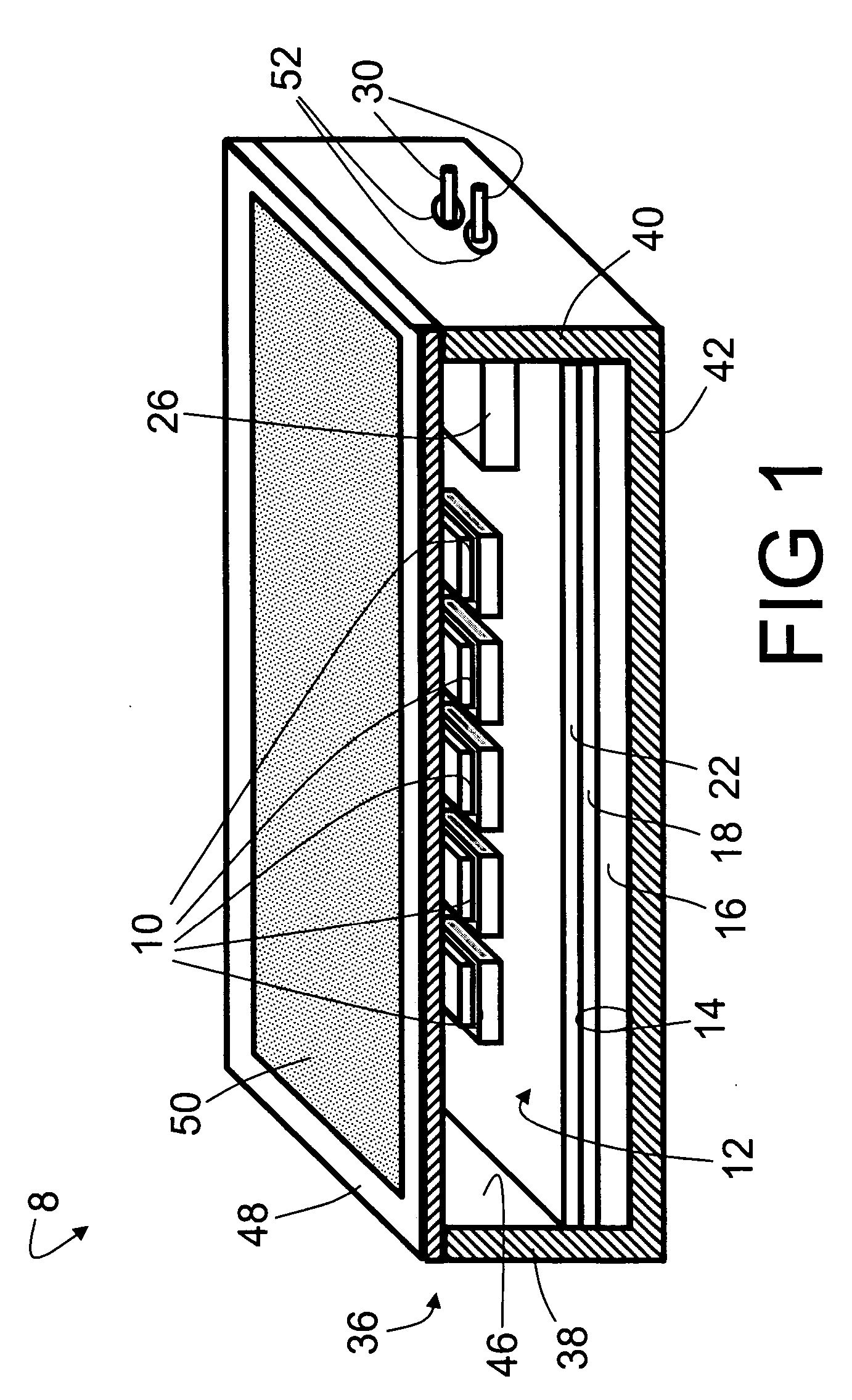

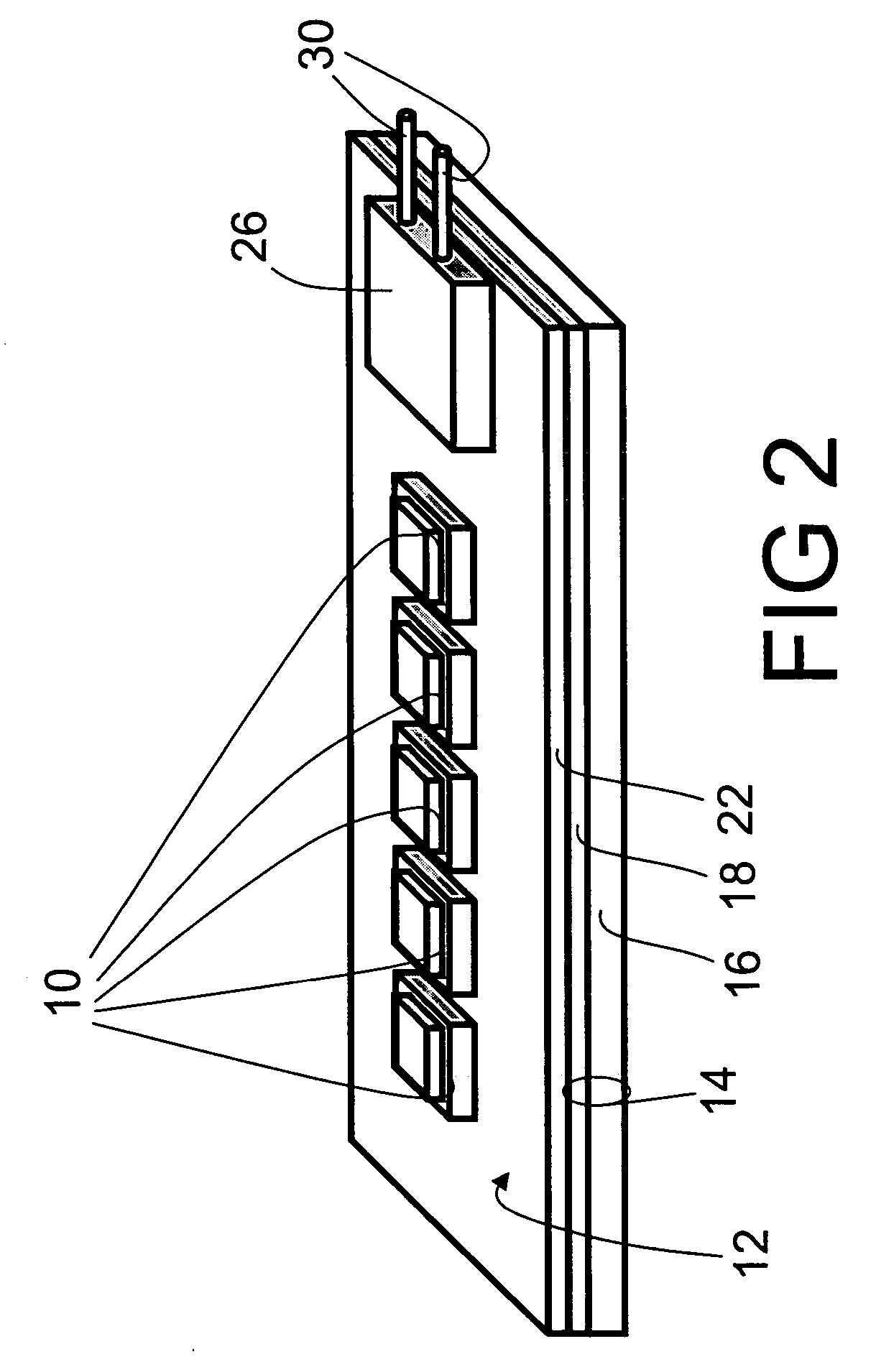

Led lighting system with reflective board

A light emitting apparatus (8) includes one or more light emitting chips (10) that are disposed on a printed circuit board (12) and emit light predominantly in a wavelength range between about 400 nanometers and about 470 nanometers. The printed circuit board includes: (i) an electrically insulating board (14); (ii) electrically conductive printed circuitry (20); and (iii) an electrically insulating solder mask (22) having vias (24) through which the one or more light emitting chips electrically contact the printed circuitry. The solder mask (22) has a reflectance of greater than 60% at least between about 400 nanometers and about 470 nanometers.

Owner:SONY COMPUTER ENTERTAINMENT INC +1

Flip-Chip Package Structure

InactiveUS20110049703A1Save substrate areaMade smallSemiconductor/solid-state device detailsSolid-state devicesSolder maskLead bonding

A flip-chip (FC) package structure is provided. The FC package structure includes a substrate, a chip, a plurality of copper platforms, a plurality of copper bumps, a plating layer, a circuit layer and a solder mask layer. The copper bumps are disposed on the substrate. The copper platforms are stacked on the copper bumps. The plating layer covers the copper bumps and the copper platforms, for contacting with chip foot pads configured at a bottom of the chip. The FC package structure does not need to reserve a space for wire bonding, thus saving the area of the substrate. The copper platforms are stacked on the copper bumps, and are higher than the circuit pattern layer. Therefore, the chip is blocked up, and the gap between the chip and the substrate is enlarged, thus preventing the risk of configuring voids when filling the cladding material and improving the packaging yield.

Owner:KINSUS INTERCONNECT TECH

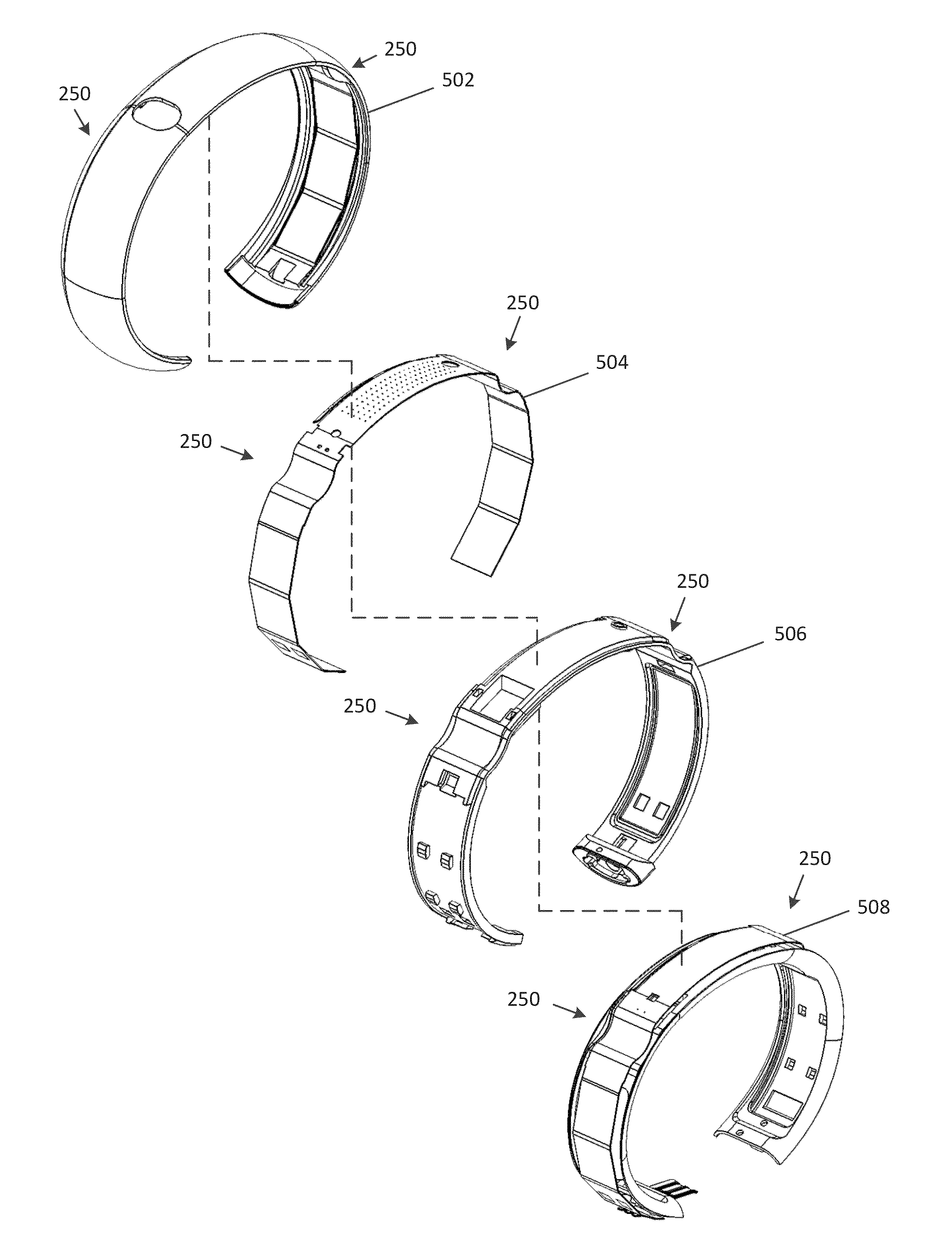

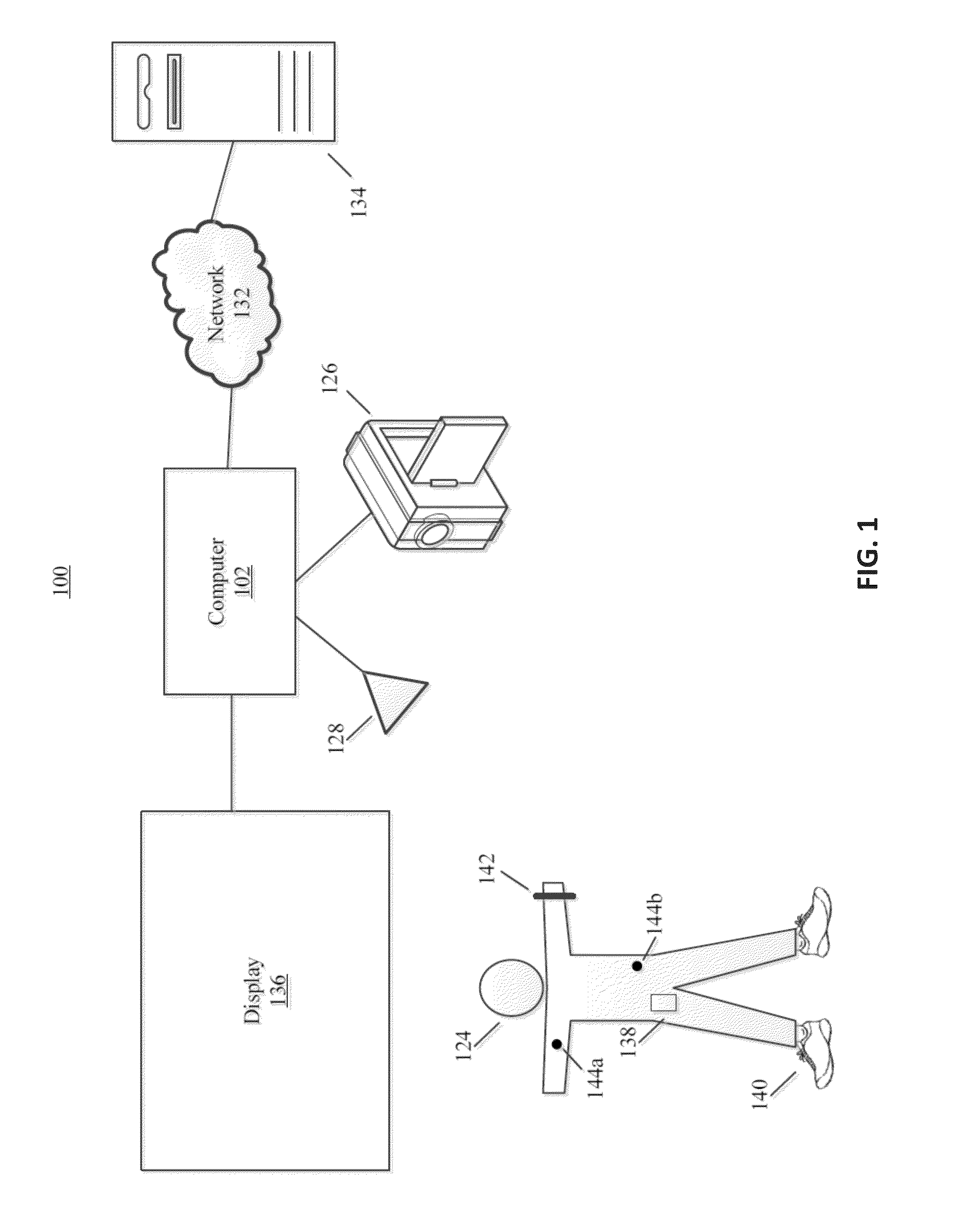

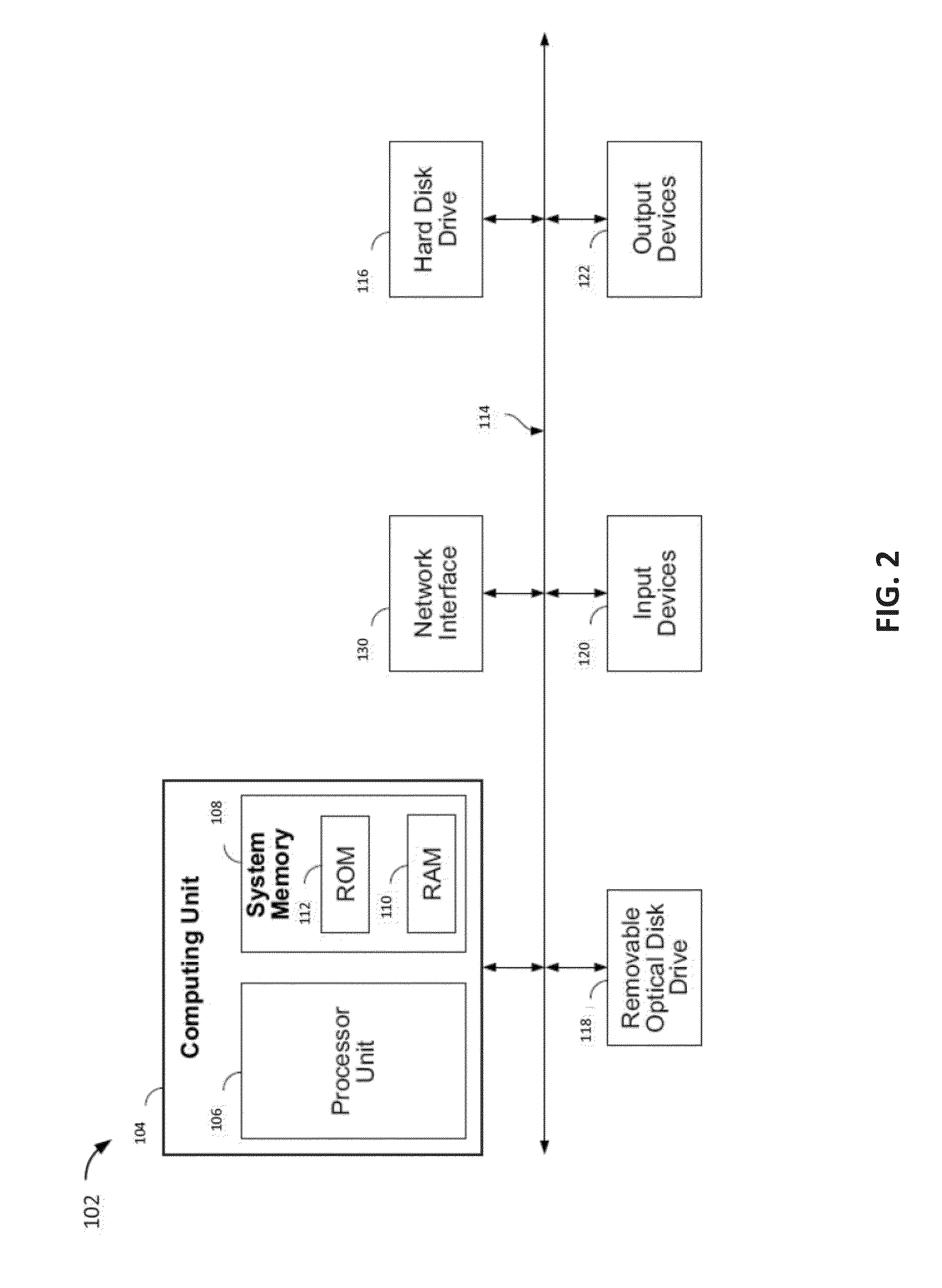

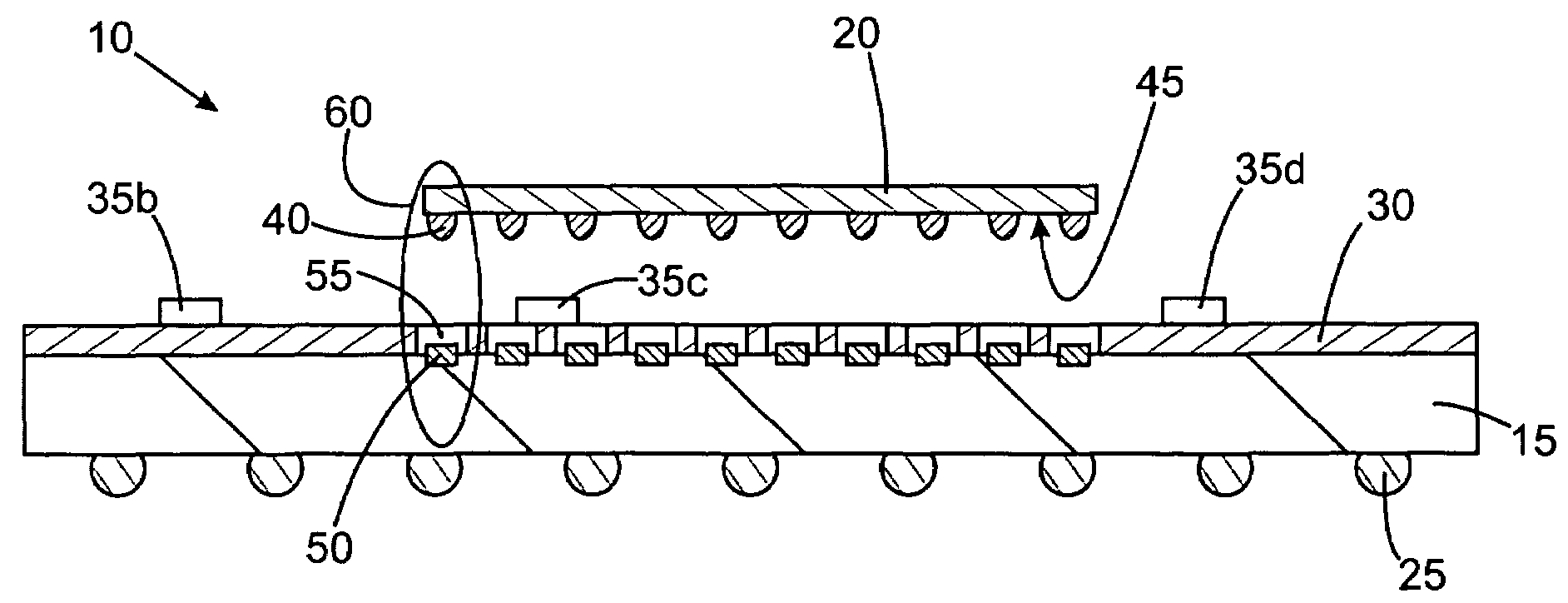

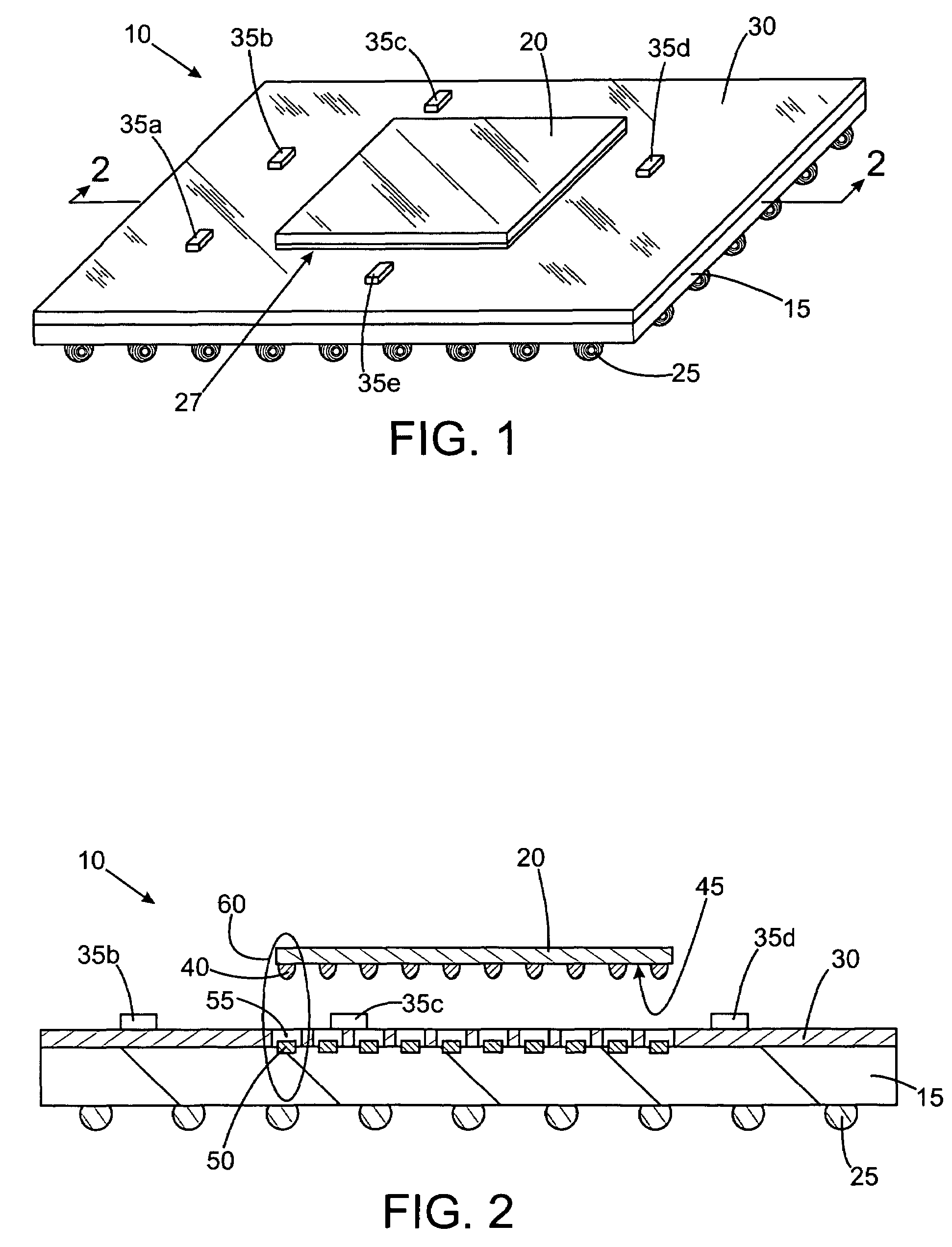

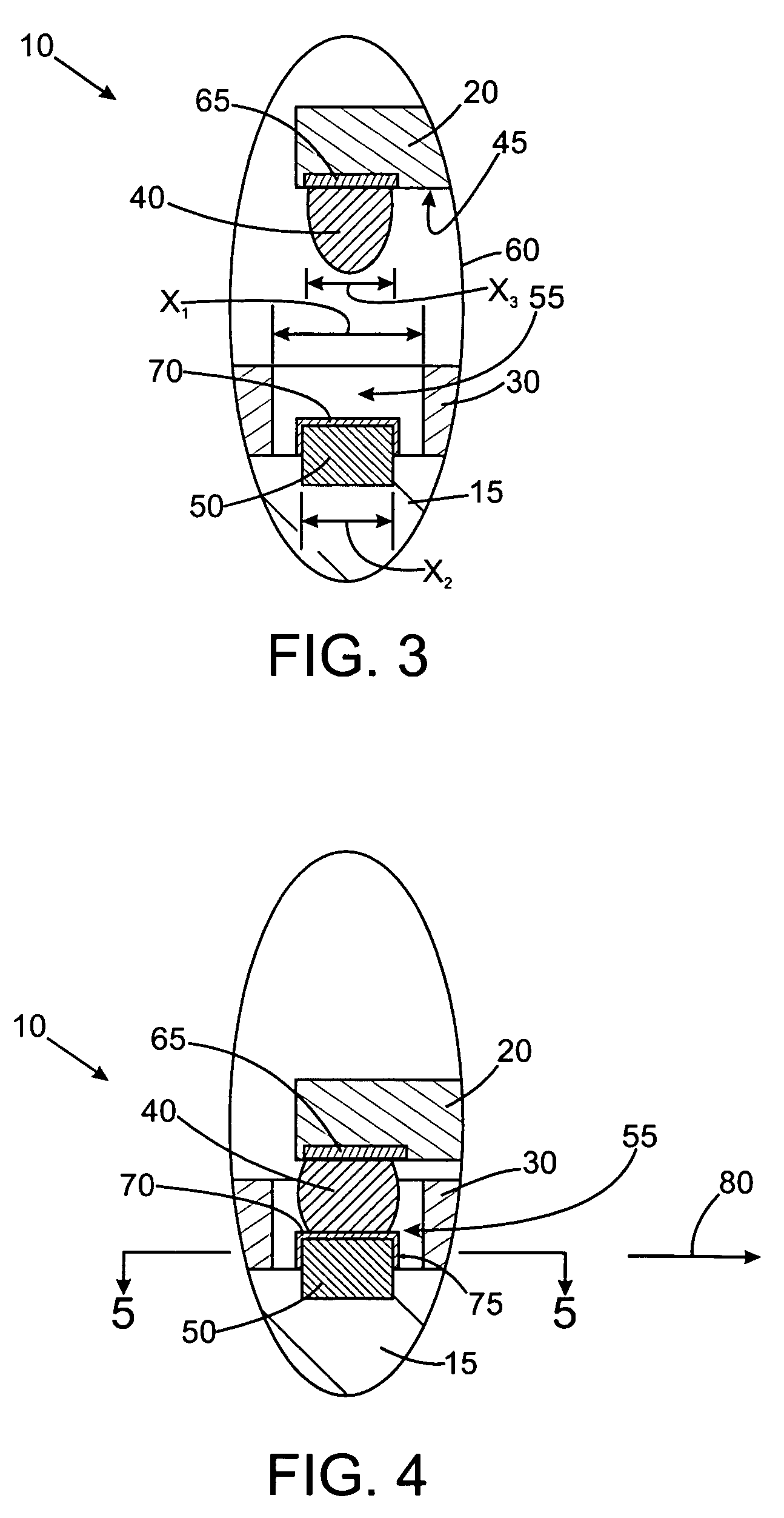

Wearable device assembly having solder mask

ActiveUS20130188322A1Distribute pressureCircuit bendability/stretchabilityElectric signal transmission systemsSolder maskFlexible circuits

A wrist-worn device monitors movements of a user. A curvilinear body of the wrist-worn device includes a plurality of flex areas, and an internal spine member of the wrist-worn device extends through the curvilinear body. A flexible circuit member is wrapped around and connected to the spine member. The flexible circuit member interconnects a controller and one or more sensors of a sensor assembly within the body. A solder mask applied to the flexible circuit member includes a curvilinear edge that distributes stress caused by flexing of the flexible circuit member.

Owner:NIKE INC

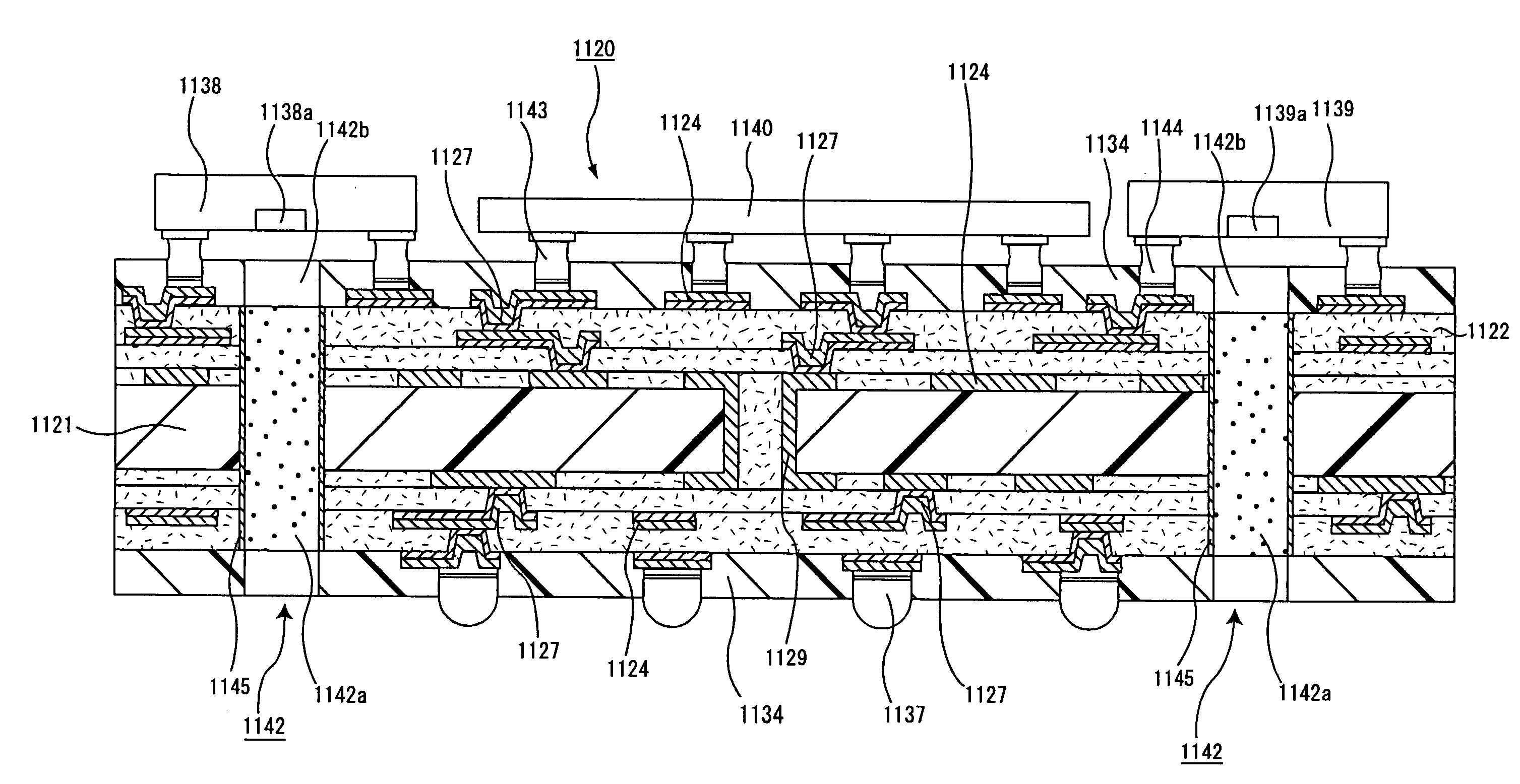

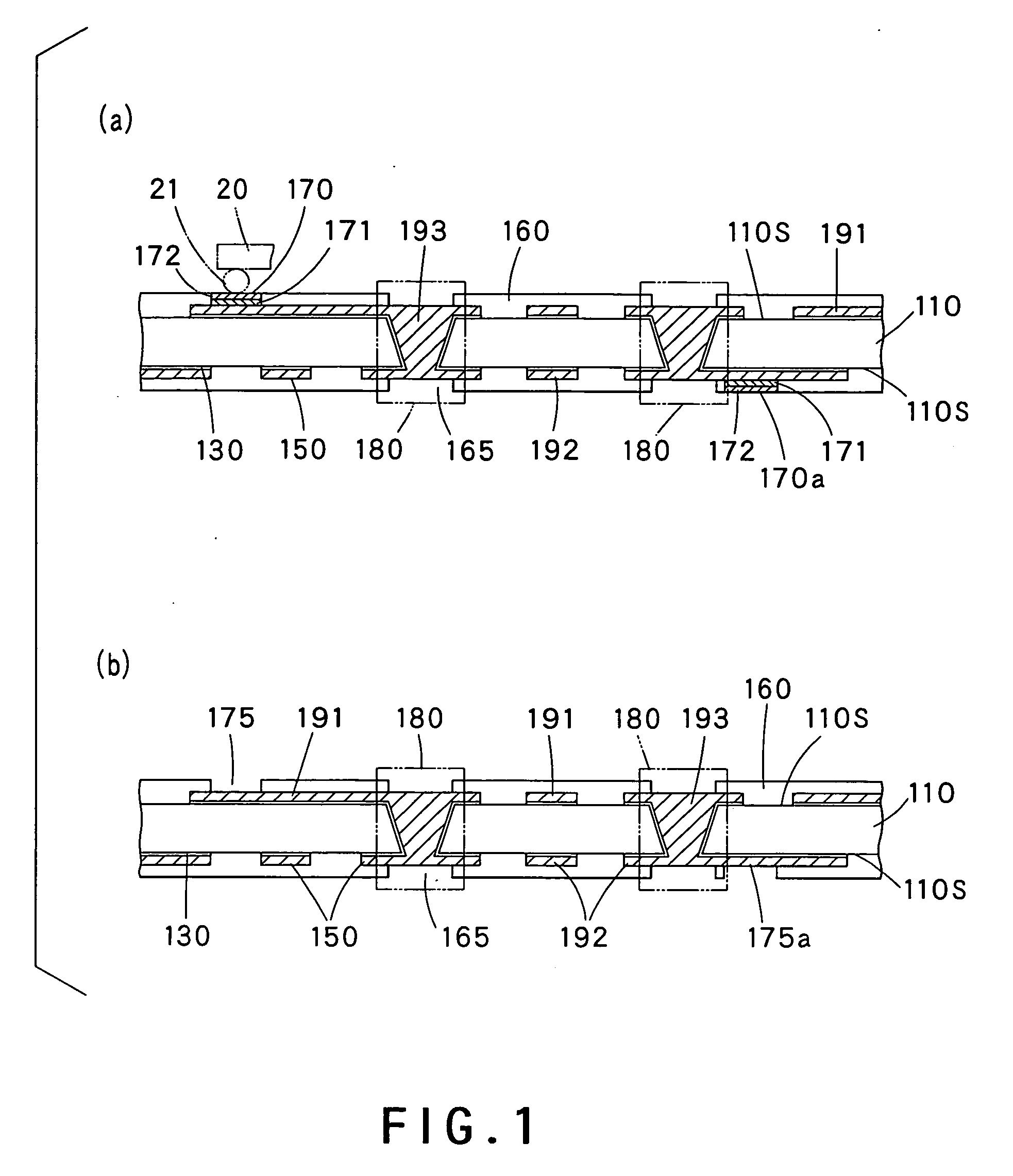

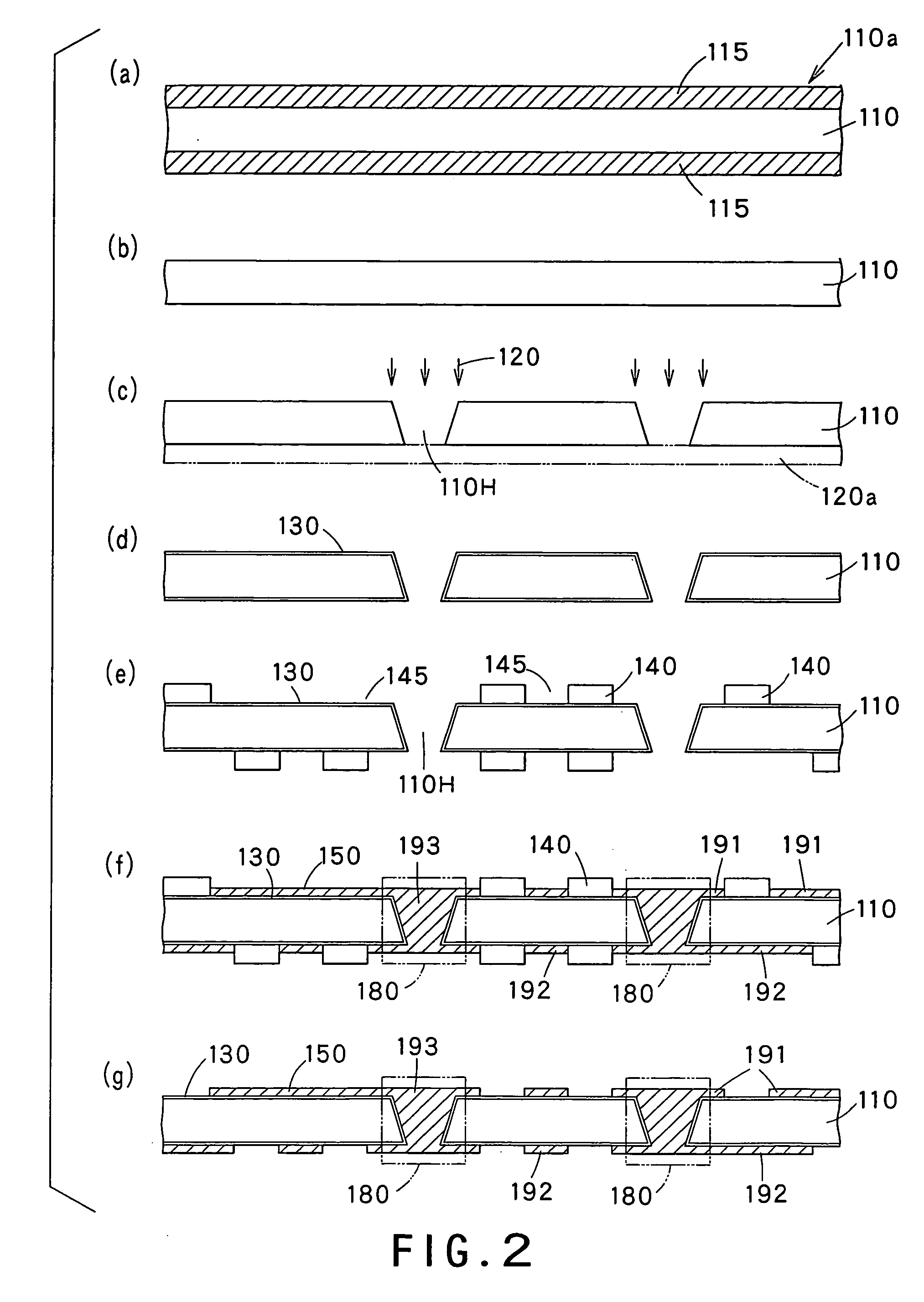

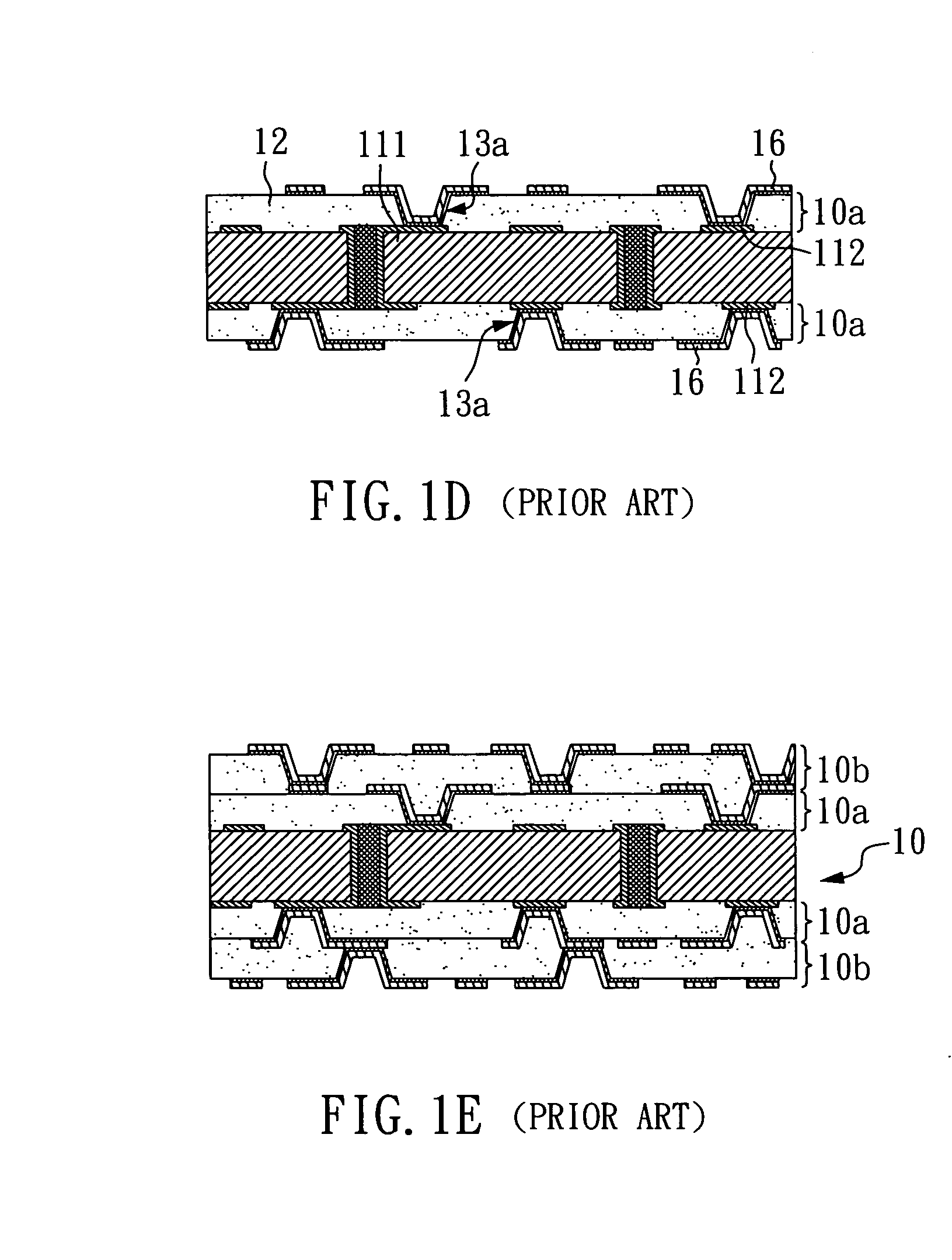

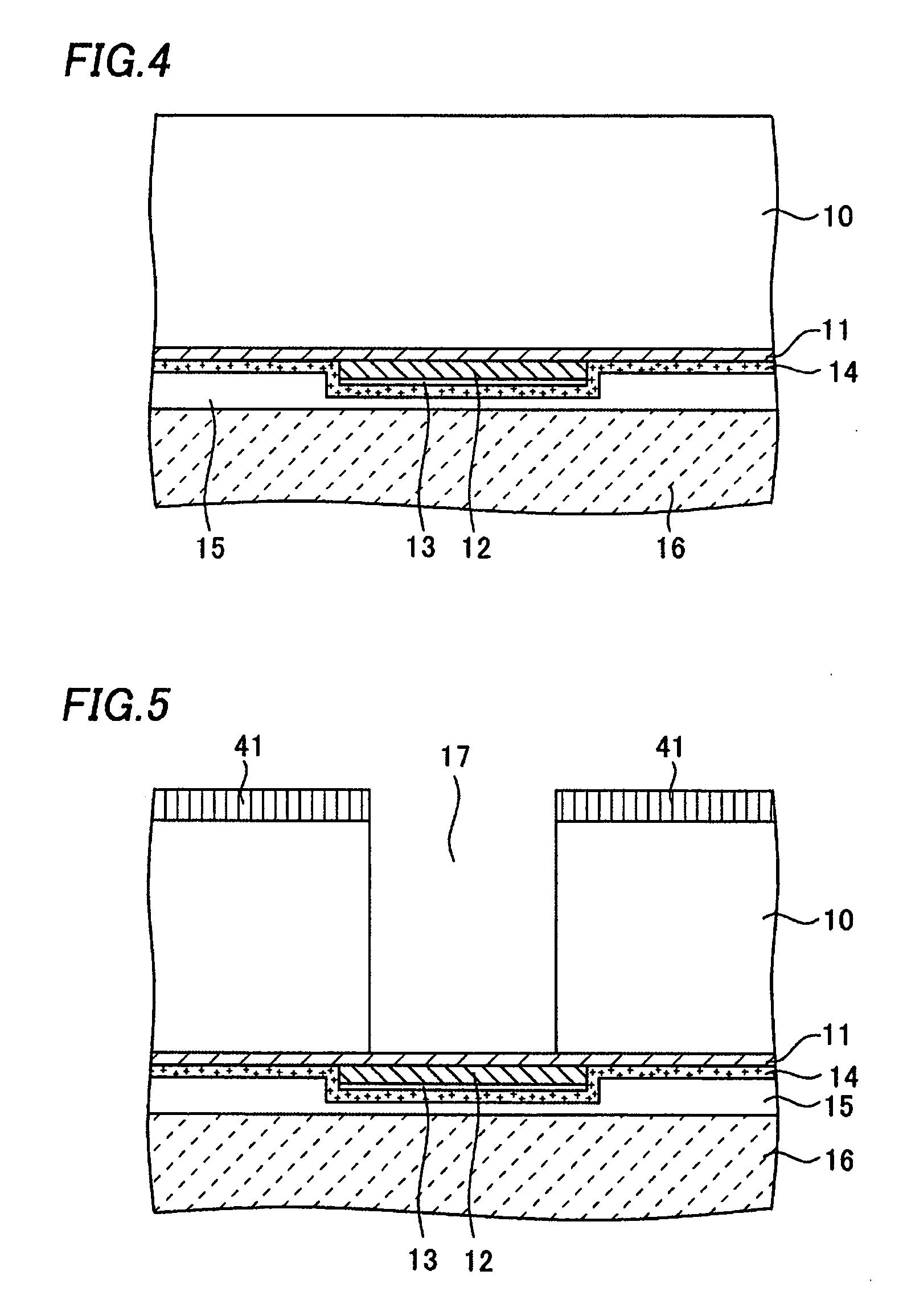

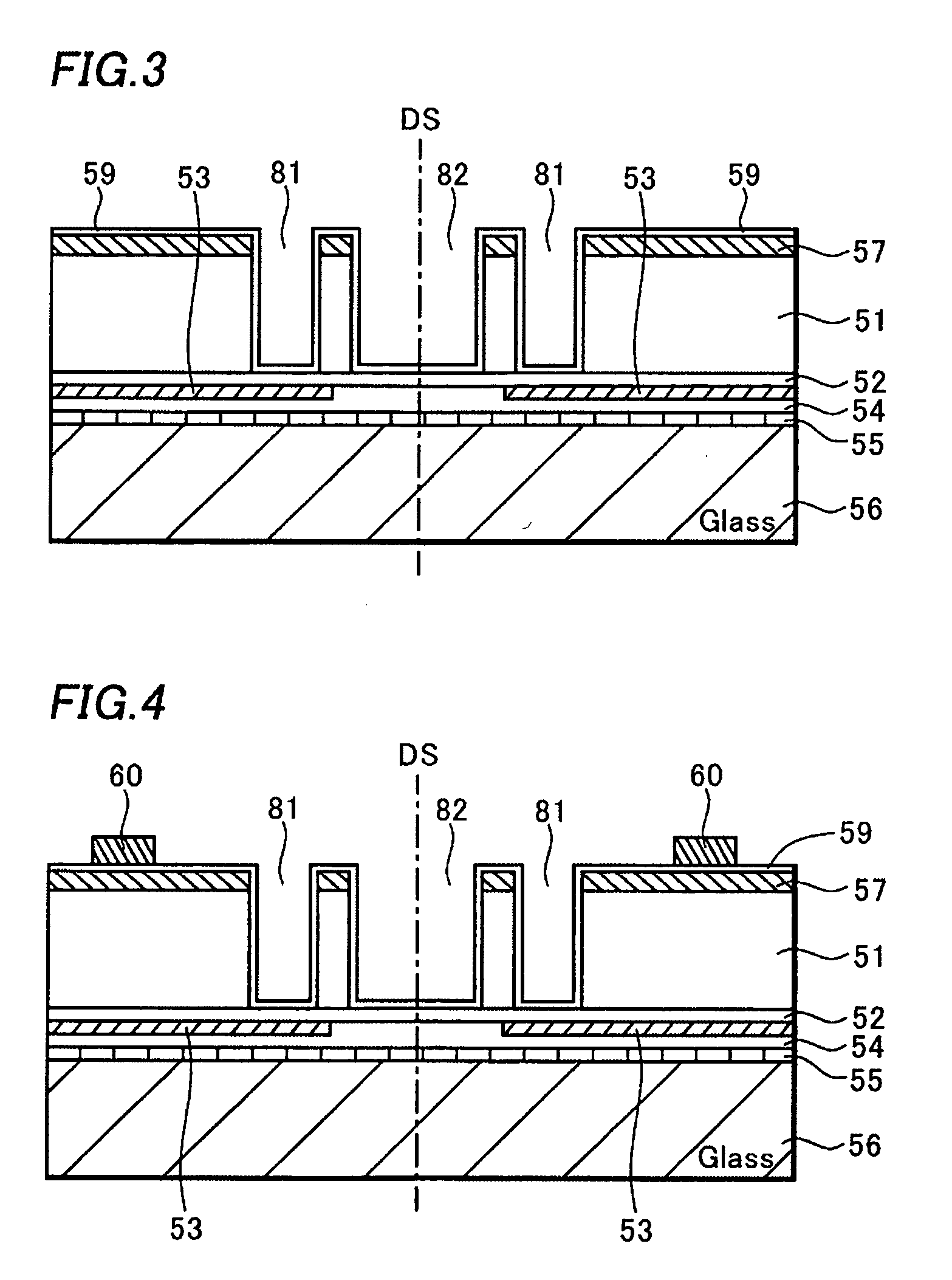

Double-sided wiring board, double sided wiring board manufacturing method, and multilayer wiring board

InactiveUS20060289203A1Improve productivitySemiconductor/solid-state device detailsPrinted circuit aspectsResistSolder mask

A single wiring layer is formed on each of both the roughened surfaces of a core substrate by a semiadditive method. The wiring layers formed on the surfaces of the core substrate are electrically connected through a through hole formed in the core substrate. The through hole is formed in the core substrate by laser machining. The through hole is filled up with conductive a plug. Both the surfaces of the core substrate are coated with solder resist layers, respectively, with predetermined terminal parts of the wiring layers exposed through openings formed in the solder resist layers. End surfaces of the conductive plug filling up the through holes, and the surfaces of the wiring layers are planarized by mechanical or chemical-mechanical polishing.

Owner:DAI NIPPON PRINTING CO LTD

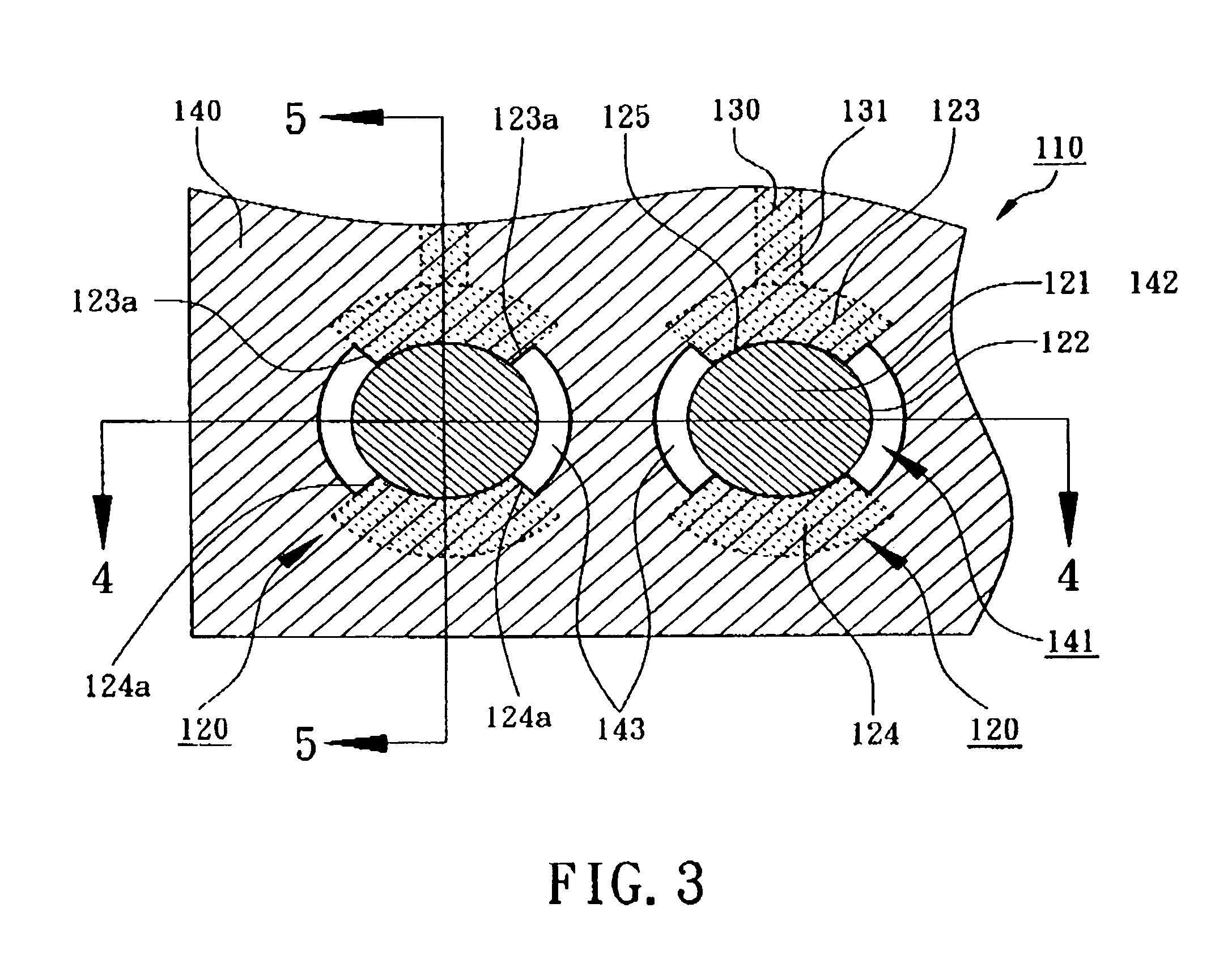

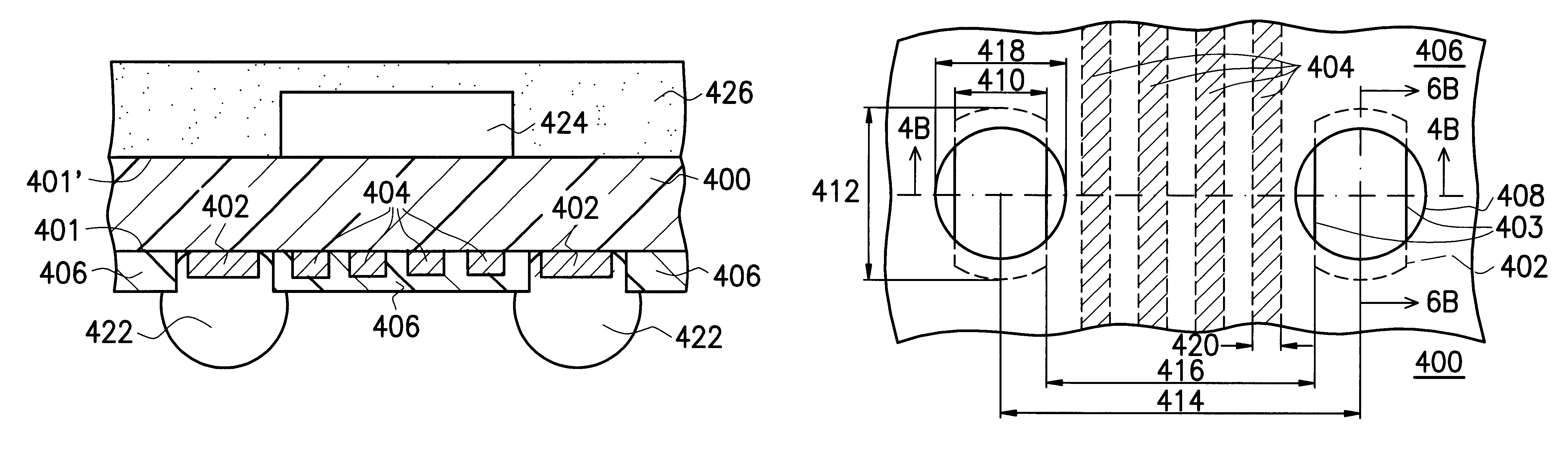

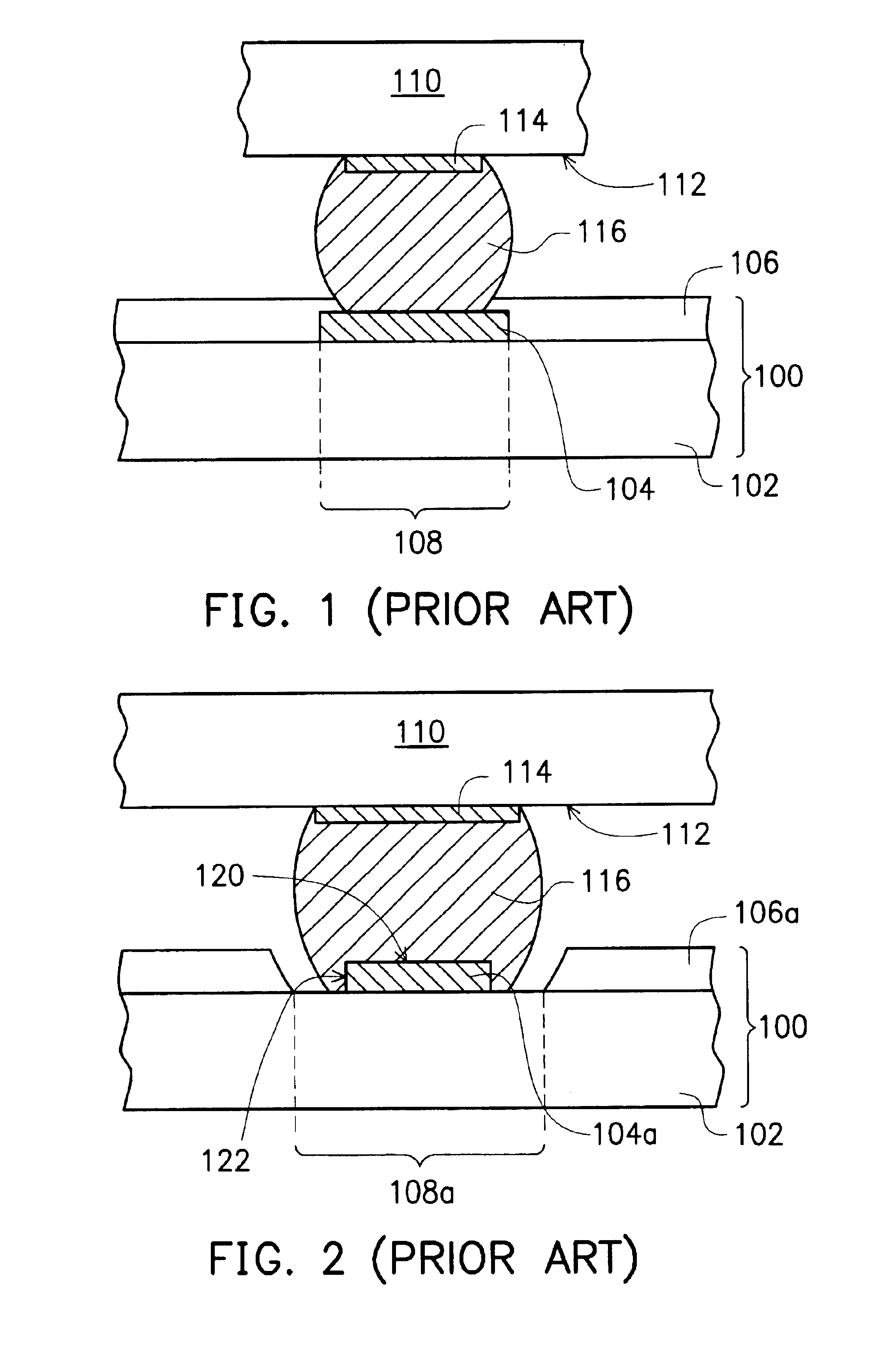

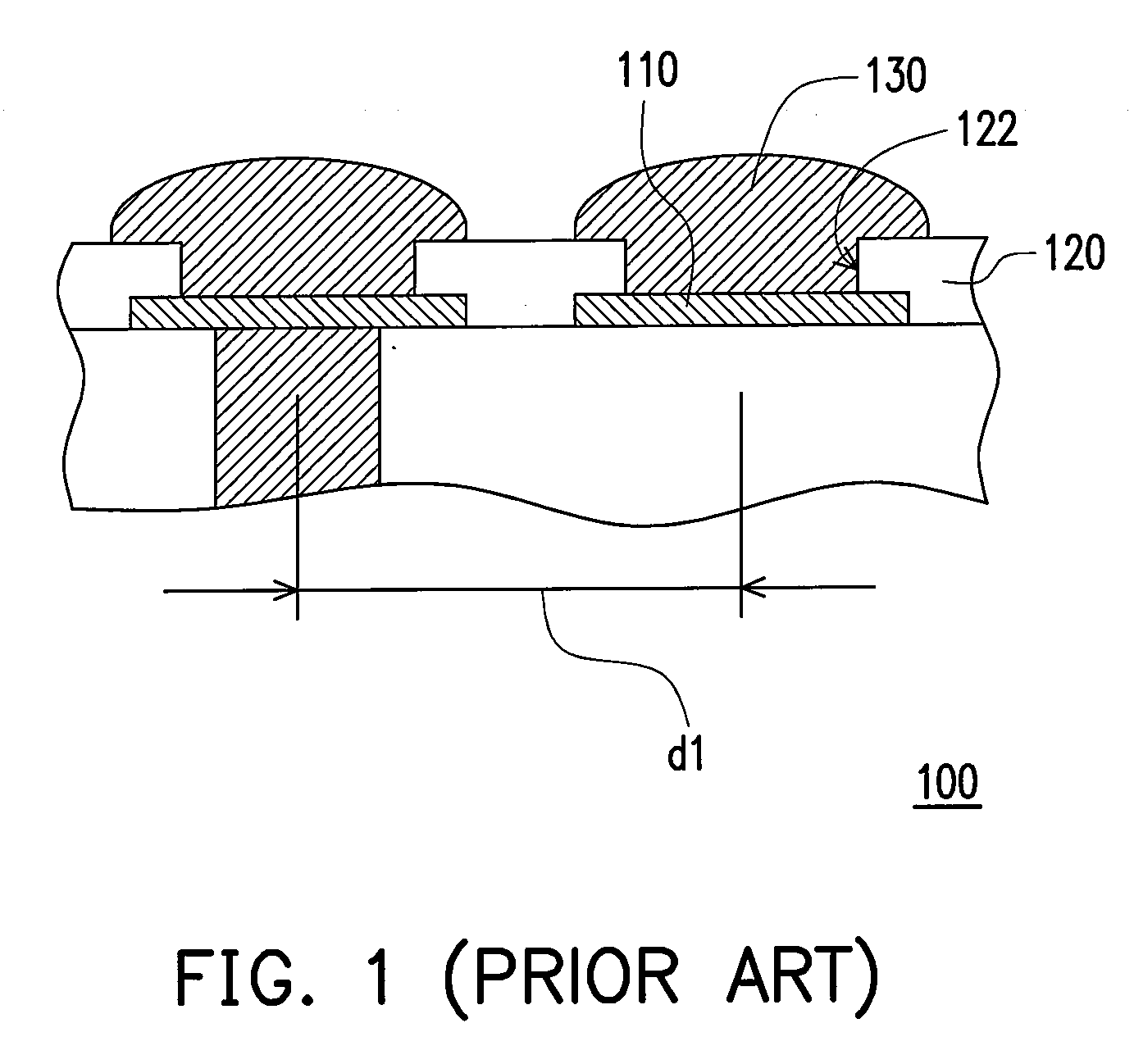

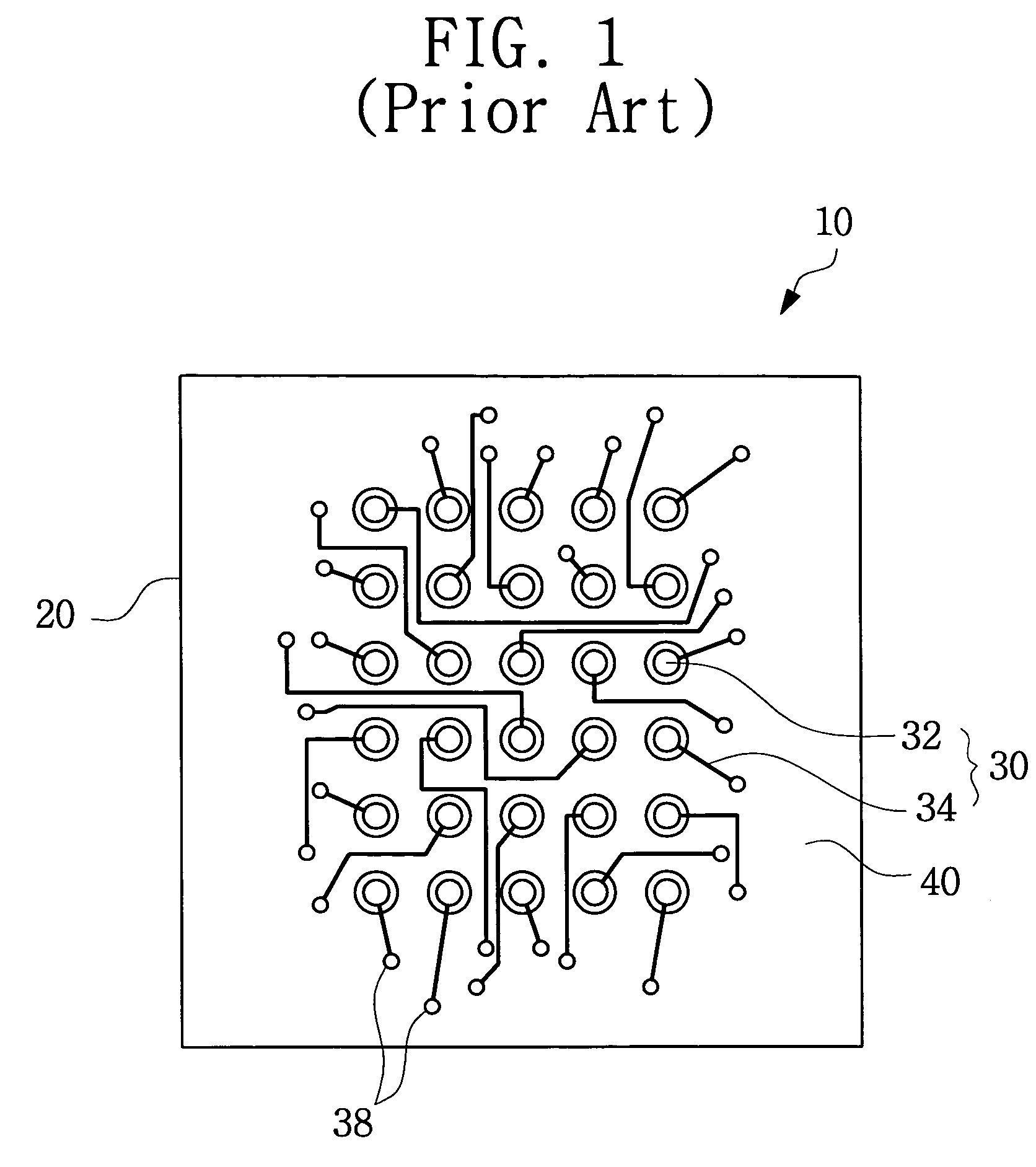

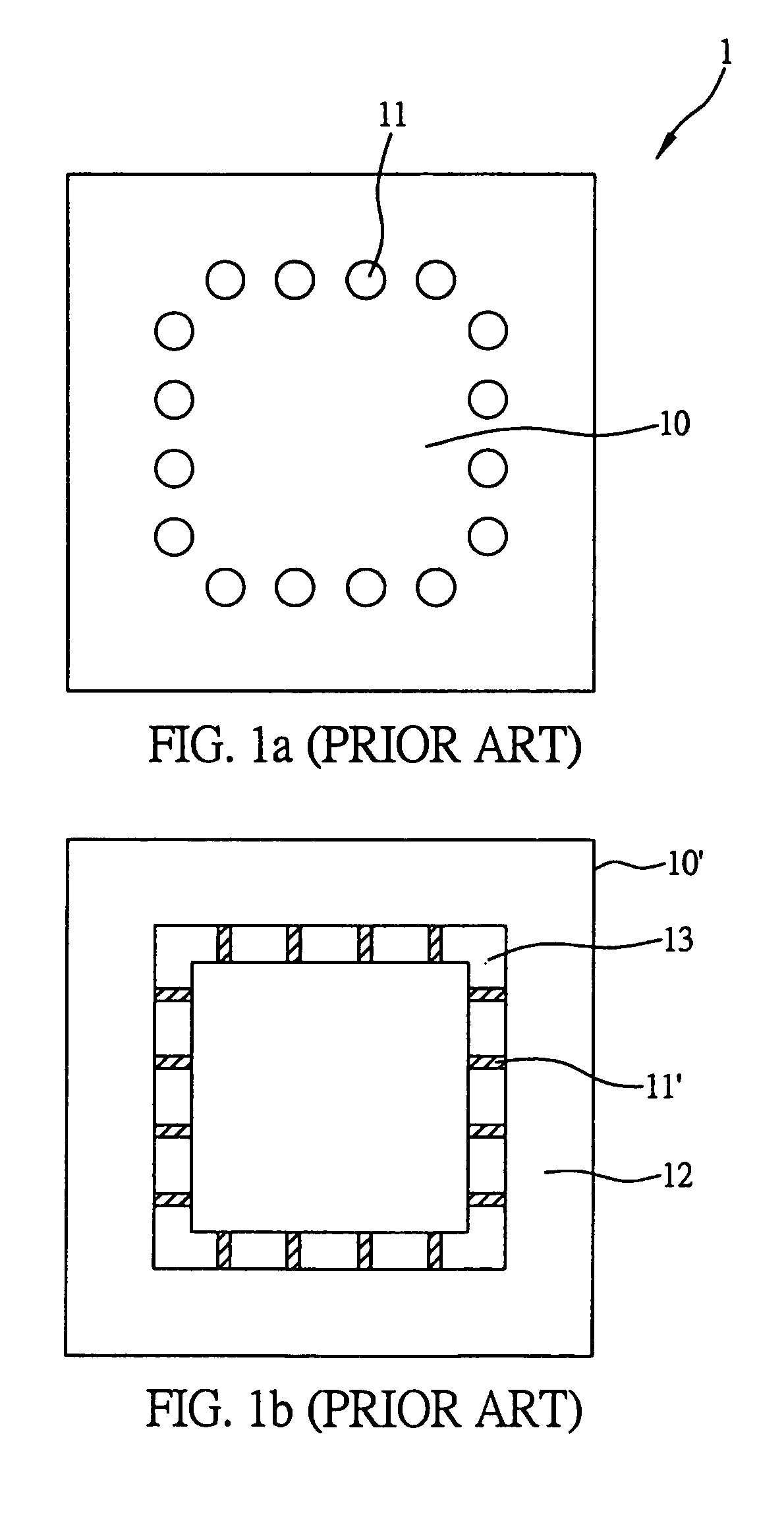

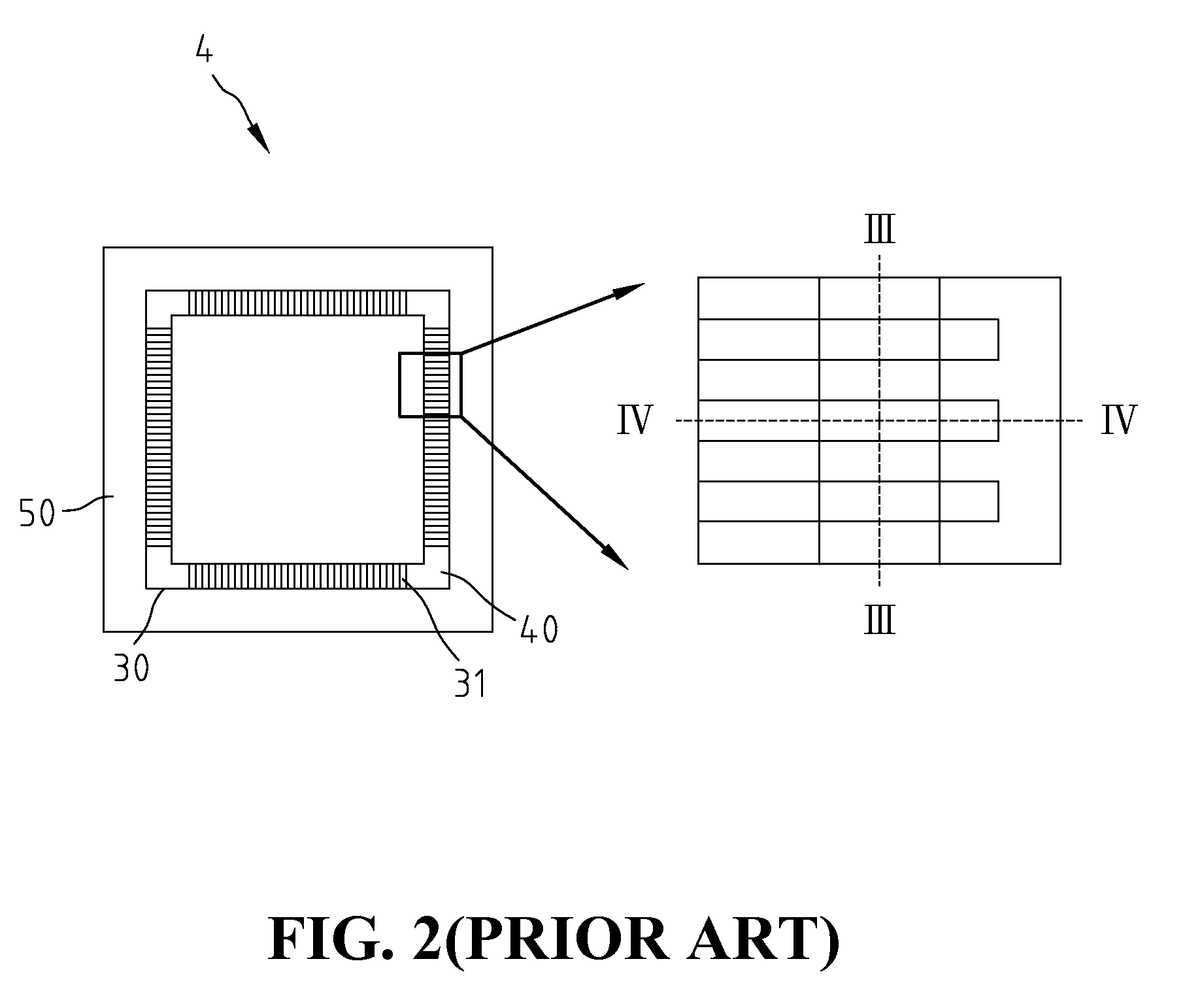

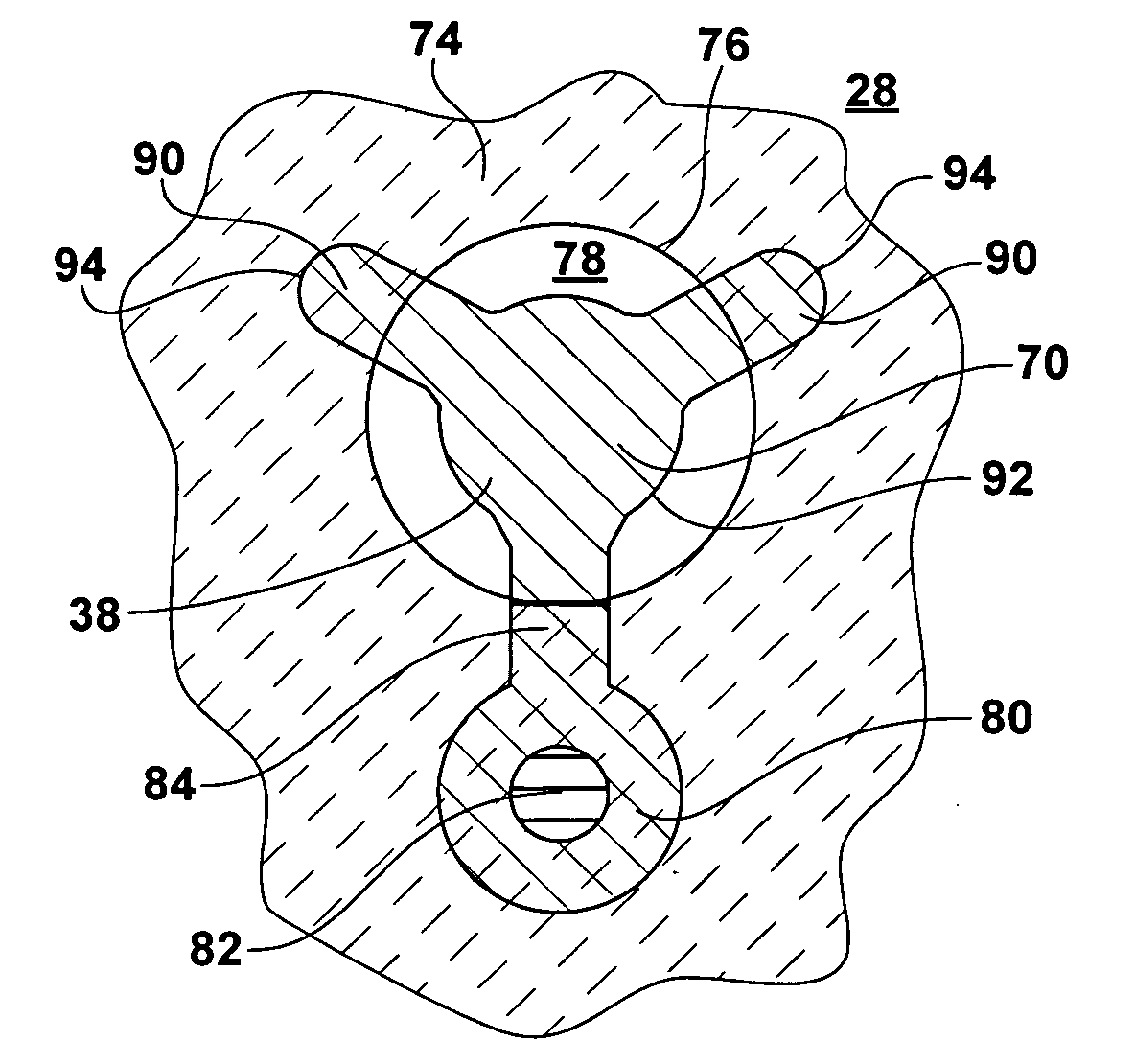

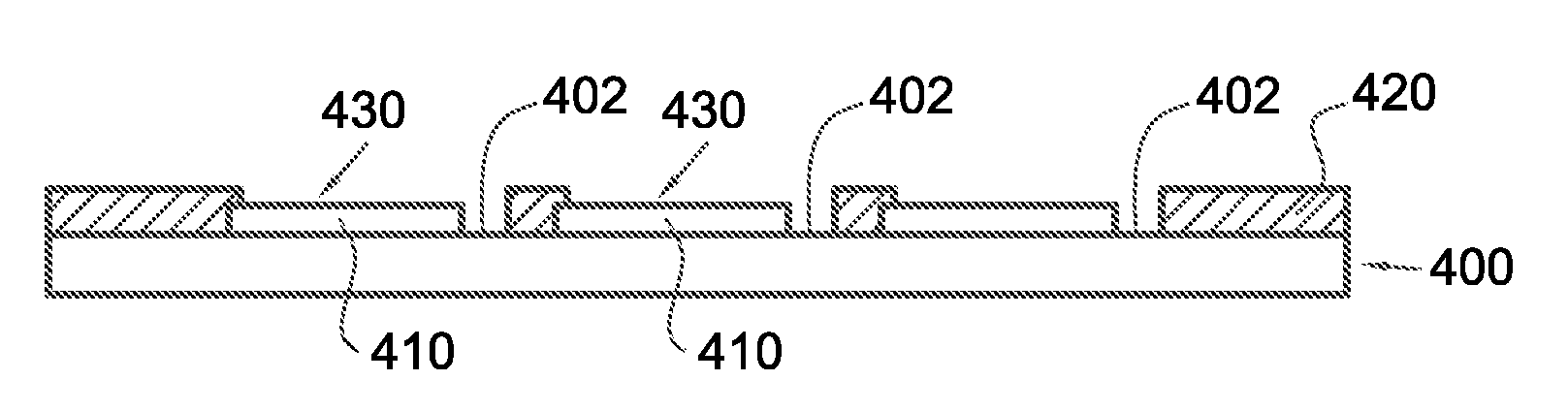

Anchored non-solder mask defined ball pad

InactiveUS20060131758A1Semiconductor/solid-state device detailsPrinted circuit aspectsElectrical conductorSolder mask

A ball grid pad for connecting a ball grid array package to a printed circuit board includes a circular pad area adhered on a ball grid connection surface. A solder mask on the ball grid connection surface has an opening surrounding and spaced apart from the circular pad area. The ball pad includes an anchor trace on the ball grid connection surface wherein the ball pad conductor material extends radially from the edge of the circular pad area to a terminating point beyond the opening of the solder mask so that a portion of the anchor trace is covered by the solder mask. The ball grid connection surface may be an integrated circuit package substrate or a printed circuit board surface.

Owner:STMICROELECTRONICS SRL

Chip package and bump connecting structure thereof

ActiveUS20070045869A1Final product manufactureSemiconductor/solid-state device detailsSolder maskMicrometer

A chip package includes a chip, a carrier, and at least a bump connecting structure for connecting the chip to the carrier. The bump connecting structure includes a first metal bump disposed on a chip pad of the chip and has a first height relative to a passivation layer of the chip, a second metal bump disposed on a carrier pad of the carrier and has a second height relative to a solder mask layer of the carrier, and a middle metal part disposed between the first and the second metal bumps. The sum of the minimum distance between the first and the second metal bumps, the first height of the first metal bump, and the second height of the second metal bump is less than 60 micrometers. The melting point of the middle metal part is lower than that of the first and the second metal bumps.

Owner:VIA TECH INC

Thermally enhanced semiconductor package

InactiveUS7019406B2Effective coolingImprove cooling efficiencySemiconductor/solid-state device detailsSolid-state devicesSolder maskSolder ball

A thermally enhanced semiconductor package and a fabrication method thereof are provided. A plurality of conductive bumps are formed on bond pads on an active surface of a chip. A heat sink is attached to an inactive surface of the chip and has a surface area larger than that of the chip. An encapsulation body encapsulates the heat sink, chip and conductive bumps, while exposing a bottom or surfaces, not for attaching the chip, of the heat sink and ends of the conductive bumps outside. A plurality of conductive traces are formed on the encapsulation body and electrically connected to the ends of the conductive bumps. A solder mask layer is applied over the conductive traces and formed with a plurality of openings for exposing predetermined portions of the conductive traces. A solder ball is implanted on each exposed portion of the conductive traces.

Owner:SILICONWARE PRECISION IND CO LTD

Bonding pad with high bonding strength to solder ball and bump

InactiveUS20070108619A1High bonding strengthBonding strengthSemiconductor/solid-state device detailsPrinted circuit aspectsSolder maskSolder ball

A bonding pad with high bonding strength to a solder ball and a bump includes a carrier, a wiring layer formed on the carrier, a protection layer formed on top of the wiring layer and a solder mask layer surrounded around the protection layer and the wiring layer to form a bonding pad opening. The protection layer is extended outside the bonding pad opening such that when solder are extended into the bonding pad opening, the solder balls engage with side faces defining the bump pad opening as well as the protection layer outside the bump pad opening and a bonding strength between the bonding pad and the solder performance is increased.

Owner:KINSUS INTERCONNECT TECH

Flip chip substrate structure and the method for manufacturing the same

InactiveUS20080060838A1Reduce substrate thicknessReduce thicknessSemiconductor/solid-state device detailsPrinted circuit aspectsSolder maskElectrical contacts

A flip chip substrate structure and a method to fabricate thereof are disclosed. The structure comprises a build up structure, a first solder mask and a second solder mask. Plural first and second electrical contact pads are formed on the first and second surface of the build up structure, respectively. A first solder mask having plural openings is formed on the first surface of the build up structure, and the openings expose the first electrical contact pads, wherein the aperture of the openings of the first solder mask are equal to the outer diameter of the first electrical contact pads. A second solder mask having plural openings is formed on the second surface of the build up structure, and the openings expose the second electrical contact pads, wherein the aperture of the openings of the second solder mask are smaller than the outer diameter of the second electrical contact pads.

Owner:PHOENIX PRECISION TECH CORP

Semiconductor device and manufacturing method of the same

ActiveUS20060087042A1Improve reliabilityHigh yieldSemiconductor/solid-state device detailsSolid-state devicesResistSolder mask

The invention is directed to a semiconductor device having a penetrating electrode and a manufacturing method thereof in which reliability and a yield of the semiconductor device are enhanced. A refractory metal layer is formed on a pad electrode formed on a semiconductor substrate with a first insulation film therebetween. Next, a passivation layer is formed on a front surface of the semiconductor substrate including on the pad electrode and on the refractory metal layer, and a supporting body is further formed with a resin layer therebetween. Next the semiconductor substrate is etched to form a via hole from a back surface of the semiconductor substrate to the pad electrode. Next, a penetrating electrode electrically connected with the pad electrode exposed at a bottom of the via hole and a wiring layer 21 are formed with a second insulation film therebetween. Furthermore, a solder resist layer and a conductive terminal are formed. Finally, the semiconductor substrate is cut and separated into semiconductor dies by dicing.

Owner:SEMICON COMPONENTS IND LLC

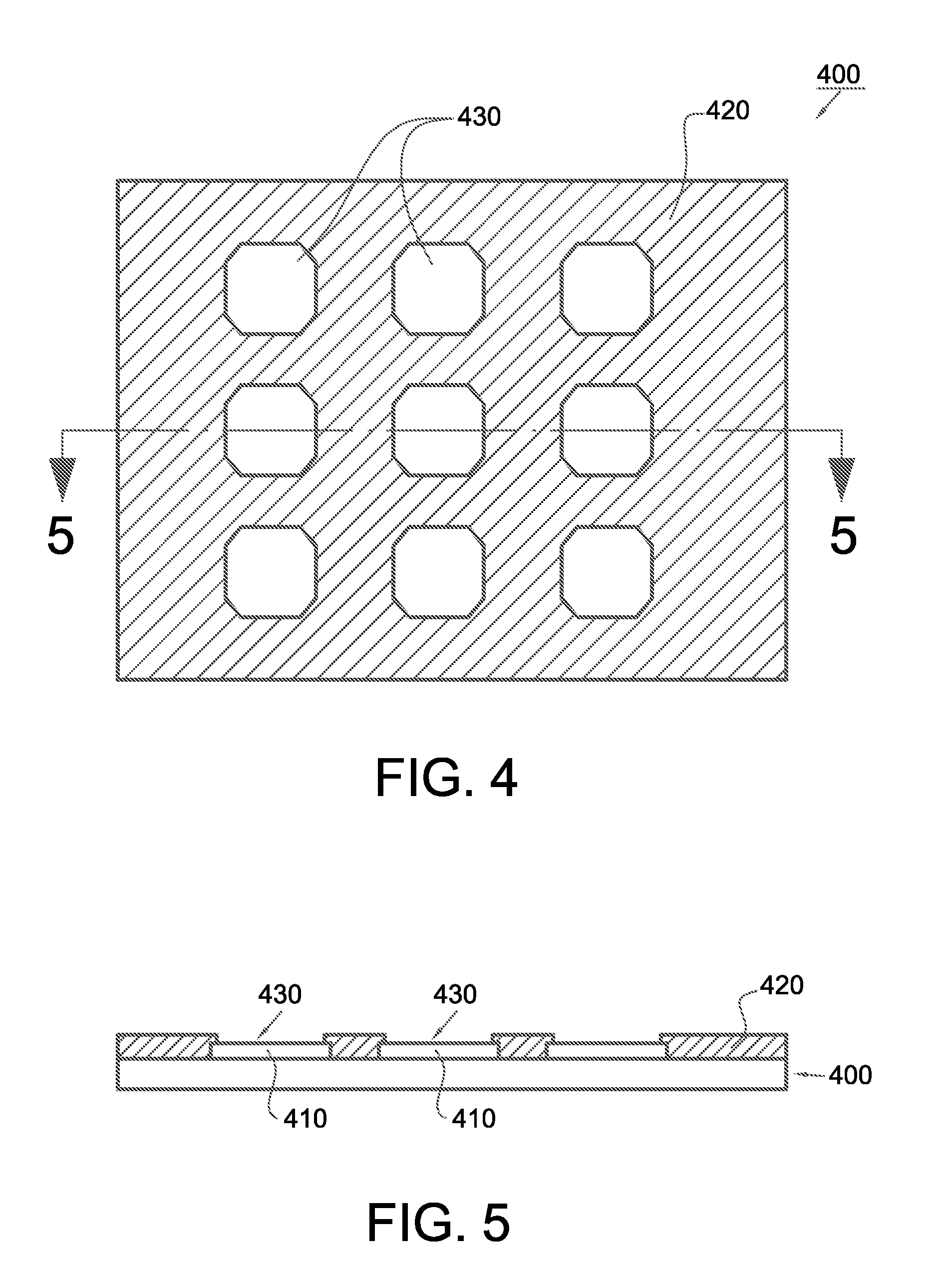

Substrate structure

InactiveUS20090114436A1Improve bindingUnique shapeSemiconductor/solid-state device detailsPrinted circuit aspectsSolder maskEngineering

A substrate structure is provided. A plurality of solder pads is positioned on a substrate. A solder mask covers the substrate and has a plurality of openings to respectively expose portions of the solder pads, wherein the openings have the shape of a polygon of at least five sides.

Owner:ADVANCED SEMICON ENG INC

Semiconductor chip bump connection apparatus and method

ActiveUS7670939B2Semiconductor/solid-state device detailsPrinted circuit aspectsSolder maskElectrical conductor

Various semiconductor chip packages and methods of making the same are disclosed. In one aspect, a method of manufacturing is provided that includes coupling a solder bump to a side of a semiconductor chip and bringing the solder bump into contact with a conductor pad coupled to a substrate and positioned in an opening of a solder mask on the substrate. The conductor pad has a first lateral dimension and the opening has a second lateral dimension that is larger than the first lateral dimension. A metallurgical bond is established between the solder bump and the conductor pad.

Owner:ATI TECH INC

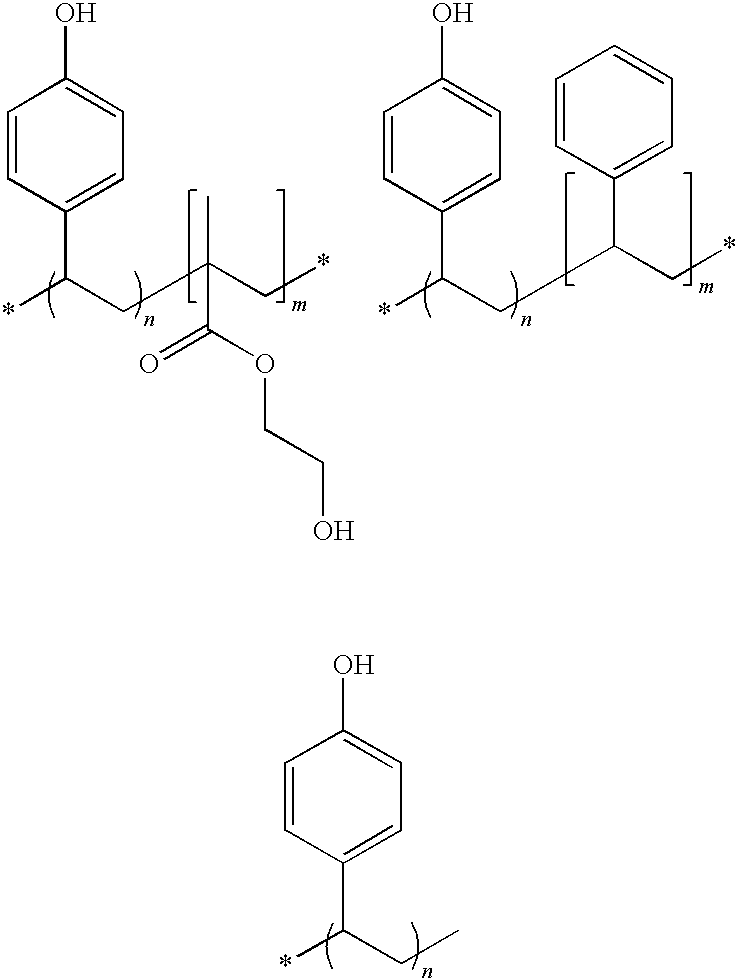

Uv curable hybridcuring ink jet ink composition and solder mask using the same

InactiveUS20090163615A1Improve adhesionImprove impact resistanceImpression capsInksCross-linkSolder mask

The present application provides a latent ink-jet ink formulation suitable as solder mask. The composition generally comprises: (a) at least one compound capable of self cross-linking (USM); (b) at least one phenolic resin; (c) at least one solvent; (d) at least one mineral filler; (e) at least one polyol; and (f) at least one photoinitiator.

Owner:CAMTEK LTD

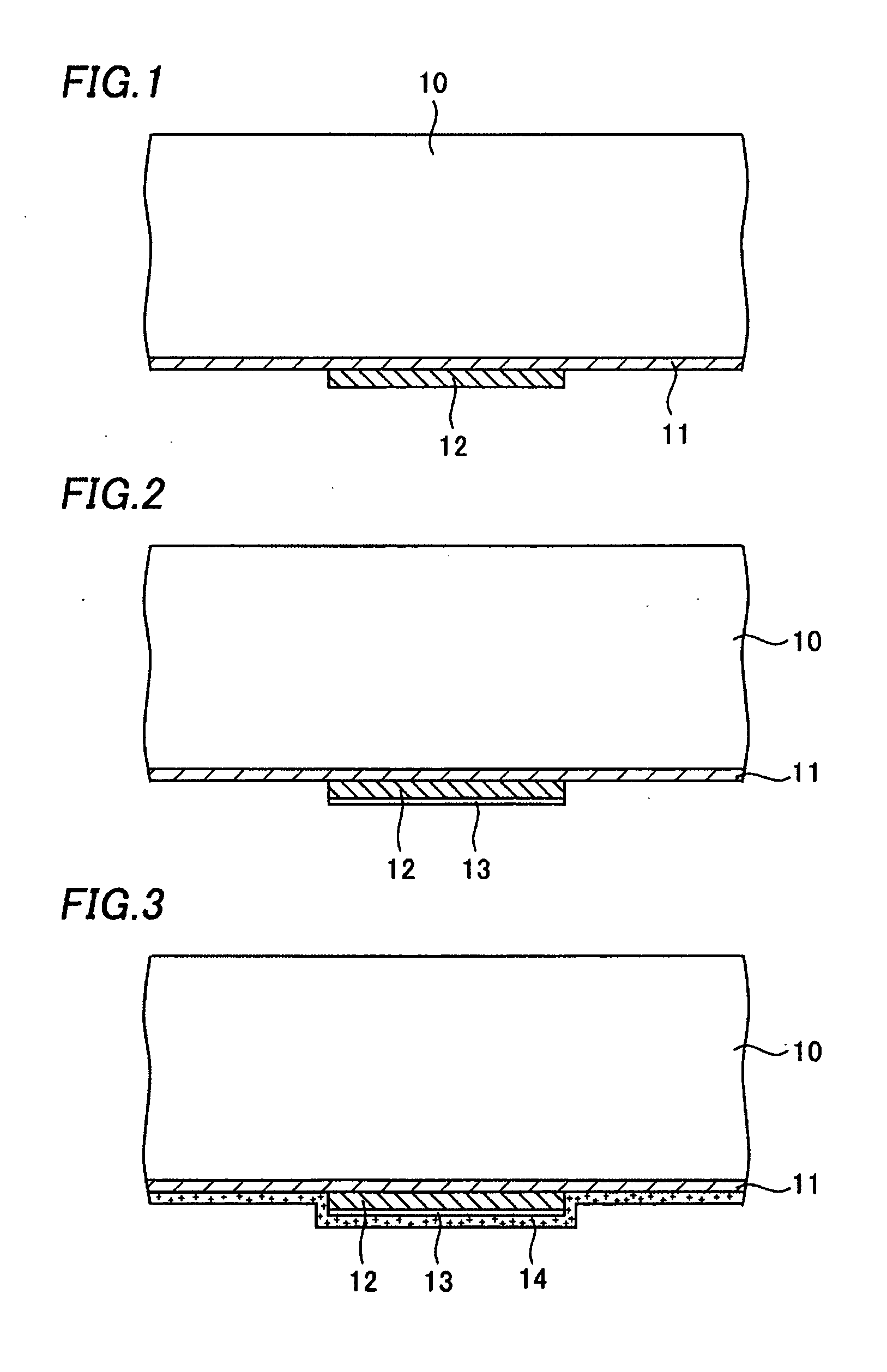

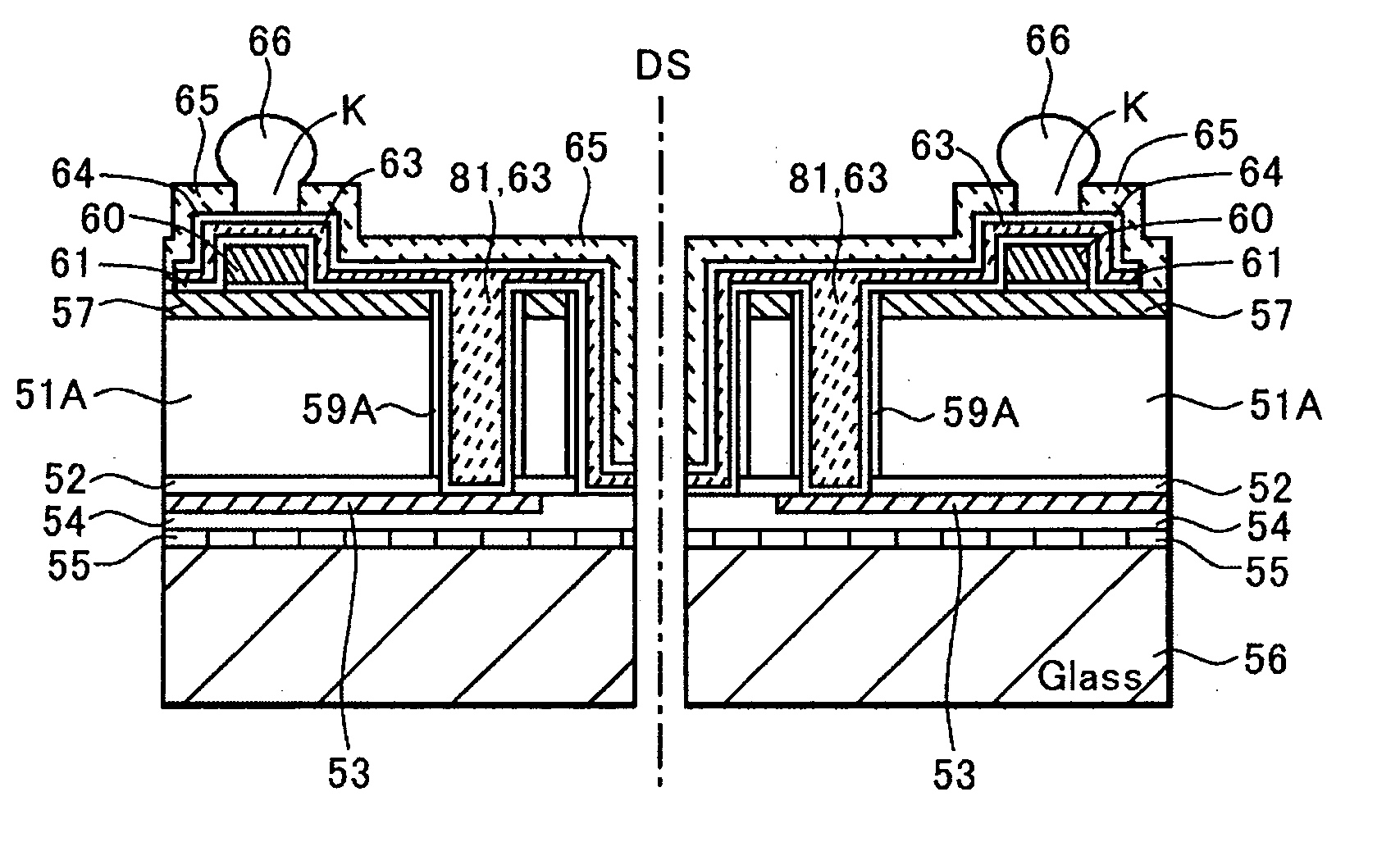

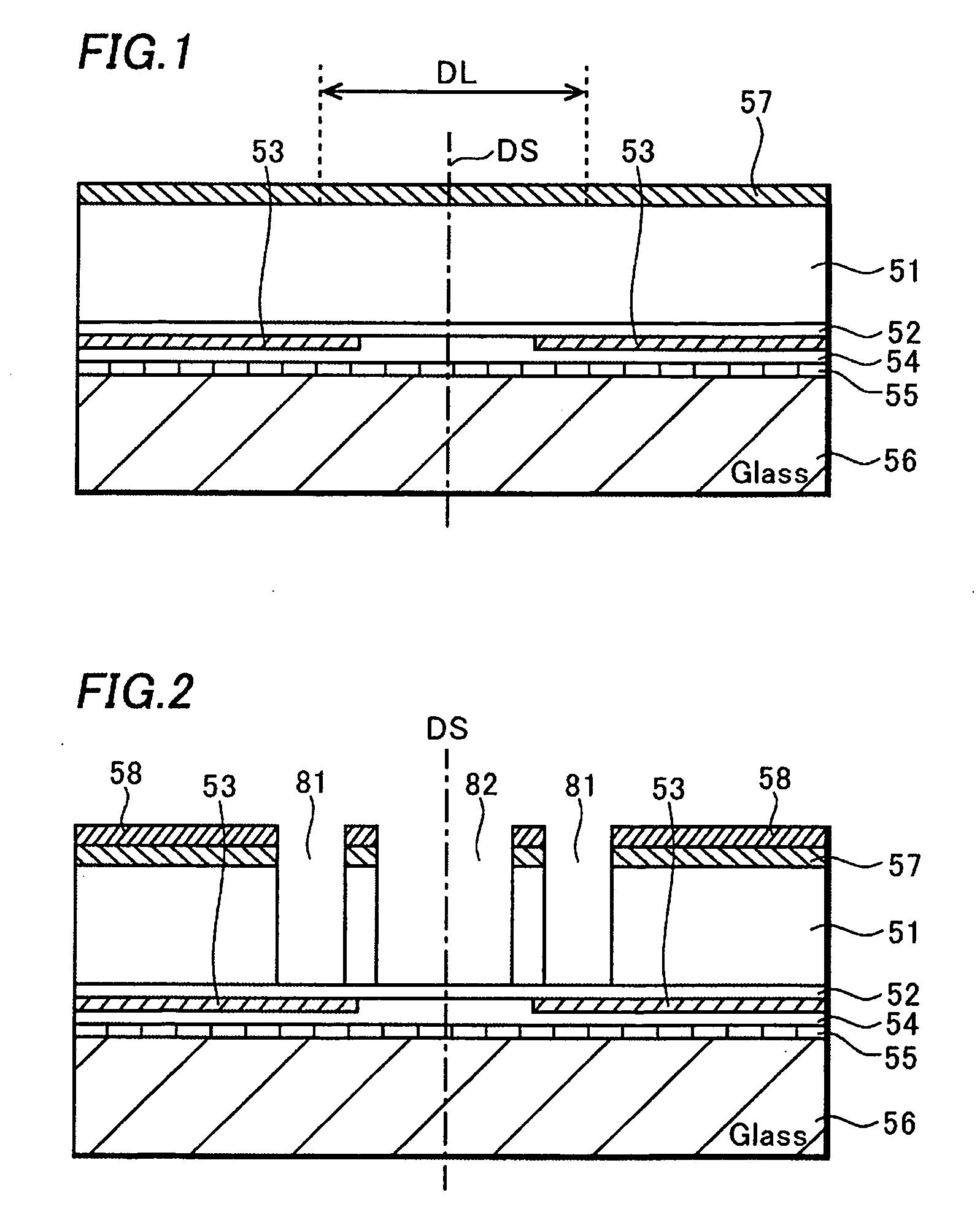

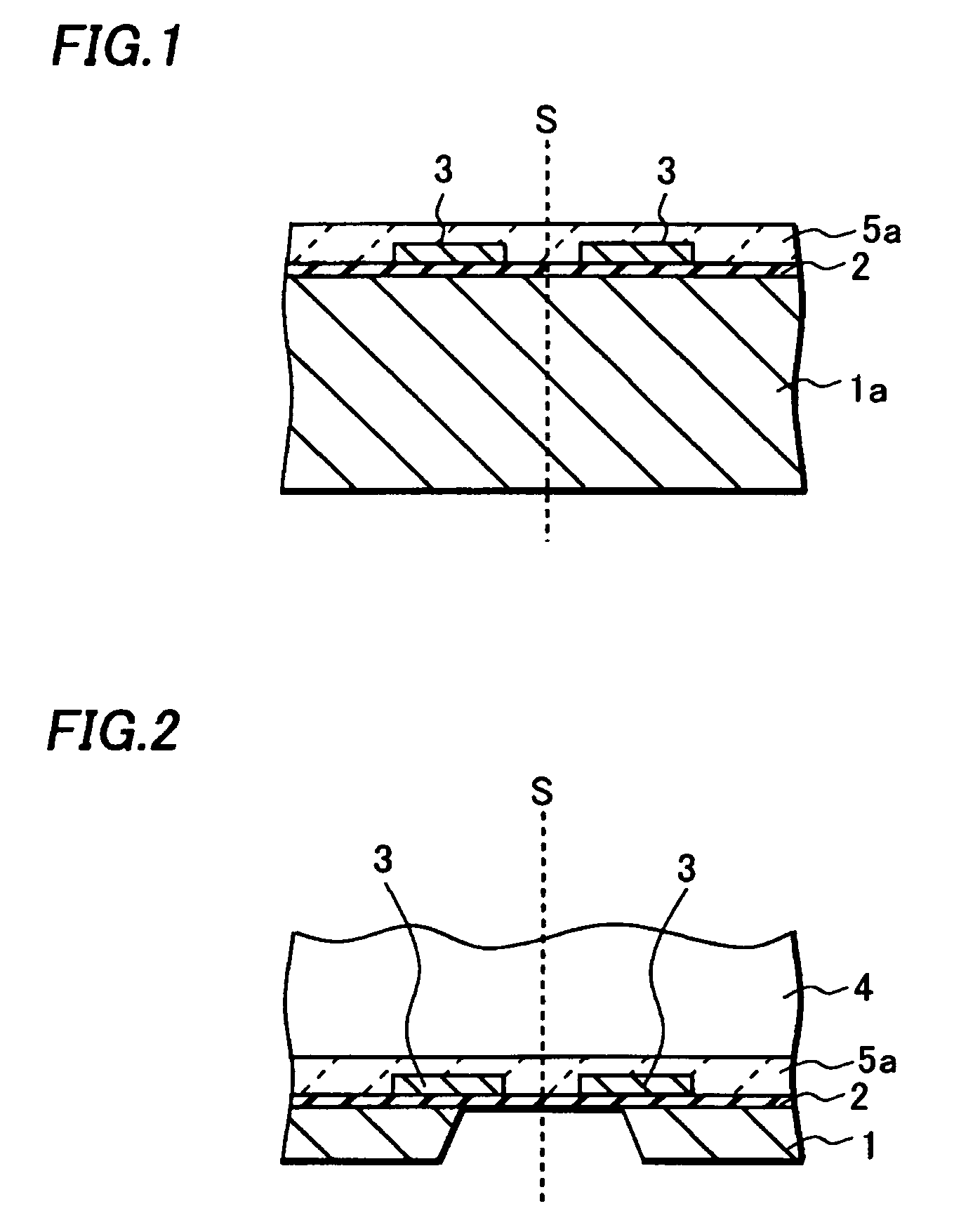

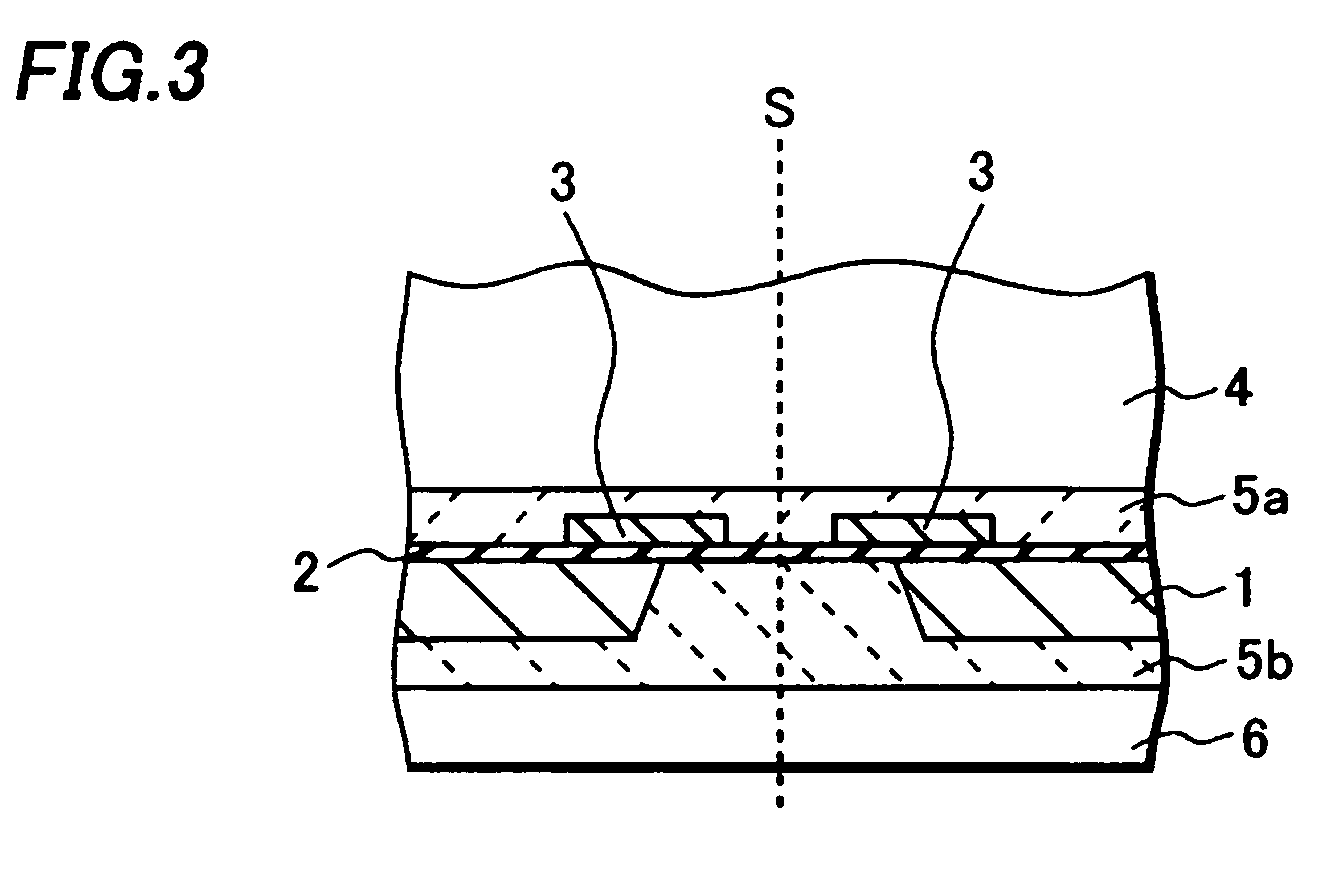

Semiconductor device and manufacturing method of the same

ActiveUS20050194670A1Semiconductor/solid-state device detailsSolid-state devicesSolder maskDevice material

This invention improves reliability of a semiconductor device and a manufacturing method thereof. A glass substrate is bonded on a surface of a silicon wafer formed with pad electrodes. Next, via holes are formed from a back surface of the silicon wafer to pad electrodes, and a groove is formed extending along a center line of a dicing line and penetrating the silicon wafer from its back surface. After then, in processes including heating treatment, cushioning pads, wirings, a solder mask, and solder balls are formed on the back surface of the silicon wafer. Finally, the silicon wafer bolstered by the glass substrate is separated into individual silicon dice by dicing.

Owner:SANYO ELECTRIC CO LTD

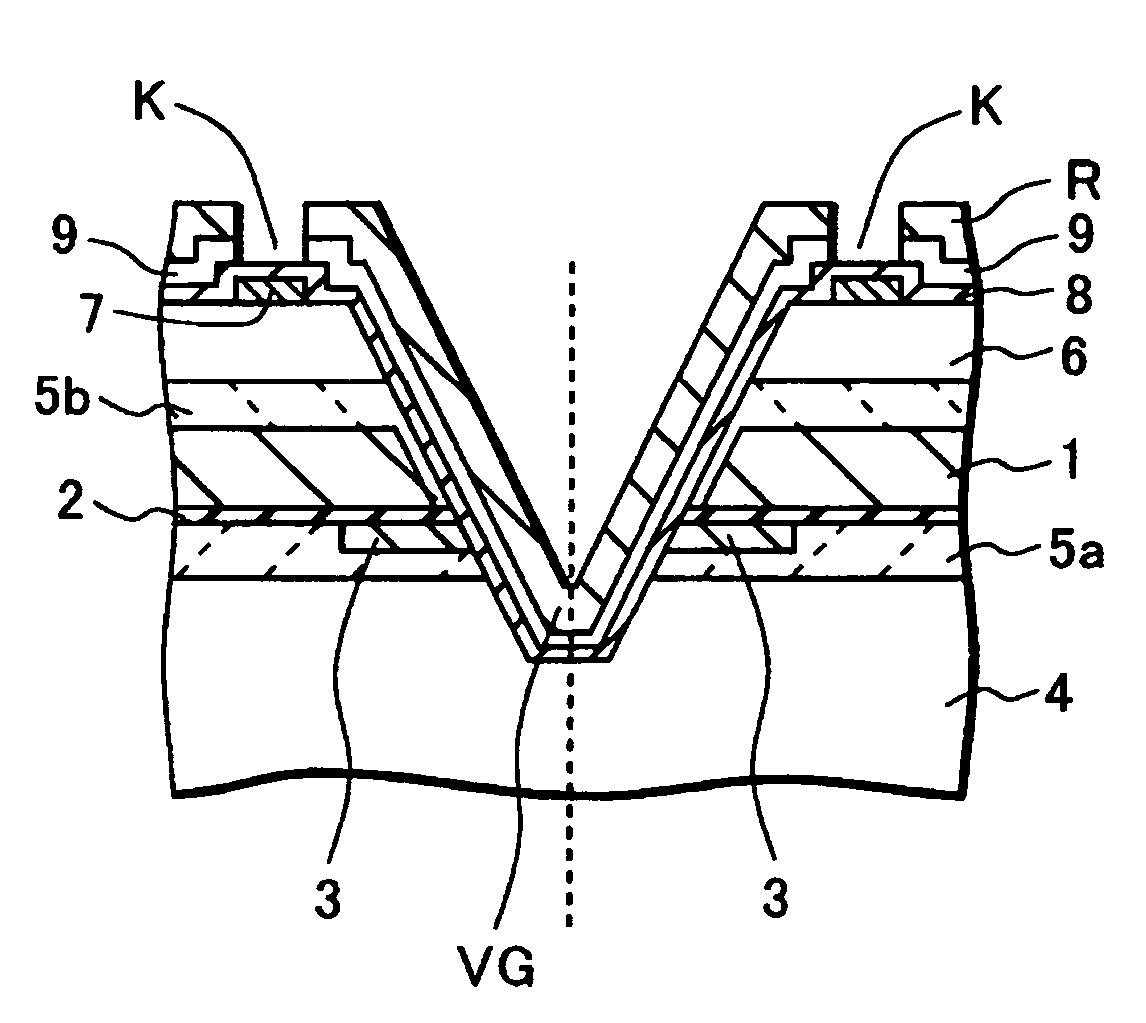

Manufacturing method of semiconductor device

ActiveUS7101735B2High yieldImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesCushioningScreen printing

A first glass substrate is bonded through a resin to a top surface of a semiconductor wafer on which a first wiring is formed. A second glass substrate is bonded to a back surface of the semiconductor wafer through a resin. A V-shaped groove is formed by notching from a surface of the second glass substrate through a part of the first glass substrate. A second wiring connected with the first wiring and extending to the surface of the second glass substrate is formed. A protection film composed of an organic resin and a photoresist layer to provide the protection film with an opening are formed on the second wiring by spray coating. A conductive terminal is formed by screen printing using the protection film as a solder mask. A cushioning material may be formed on the second glass substrate by spray coating.

Owner:SEMICON COMPONENTS IND LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com