Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

53results about How to "Improve chip reliability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

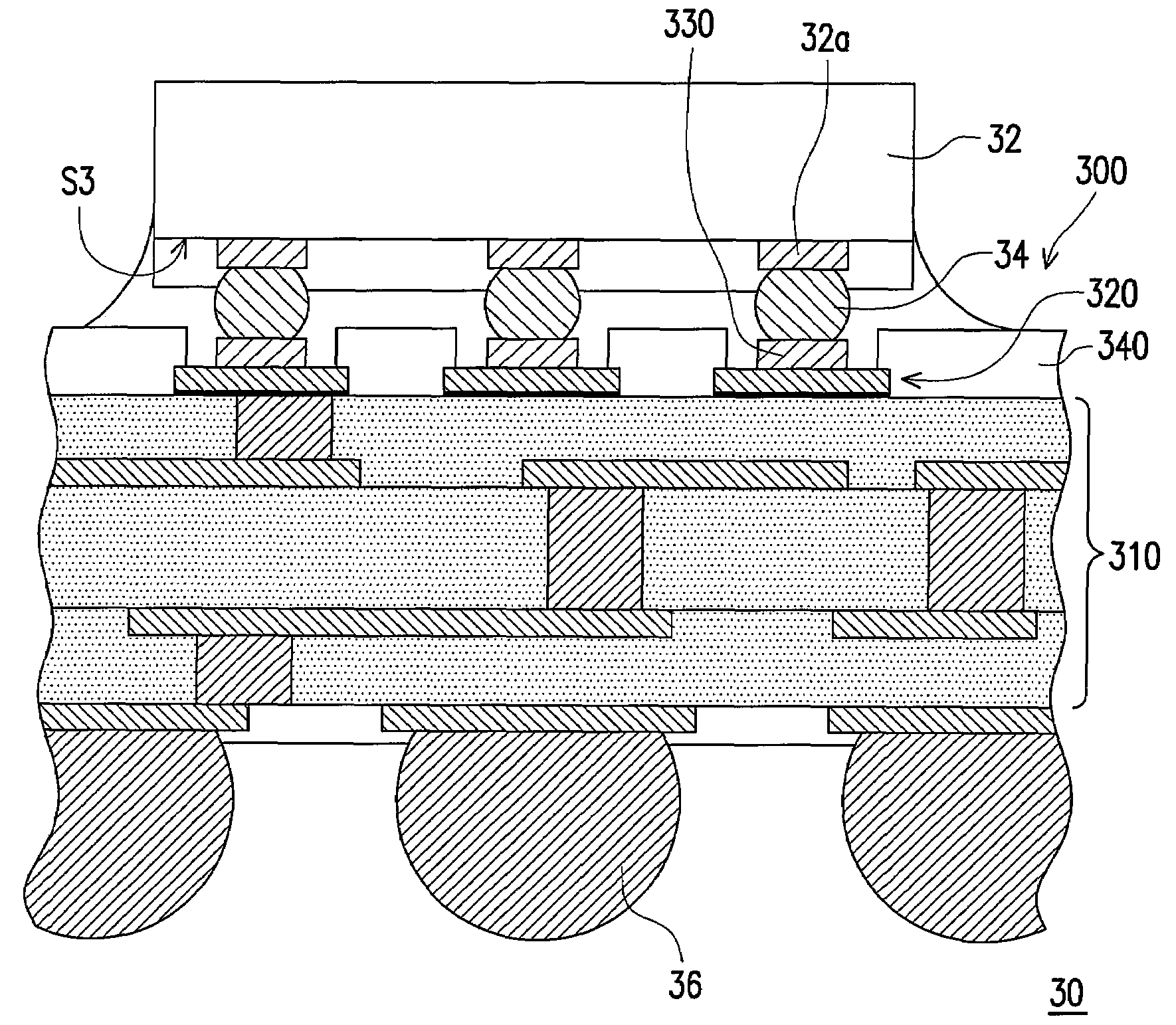

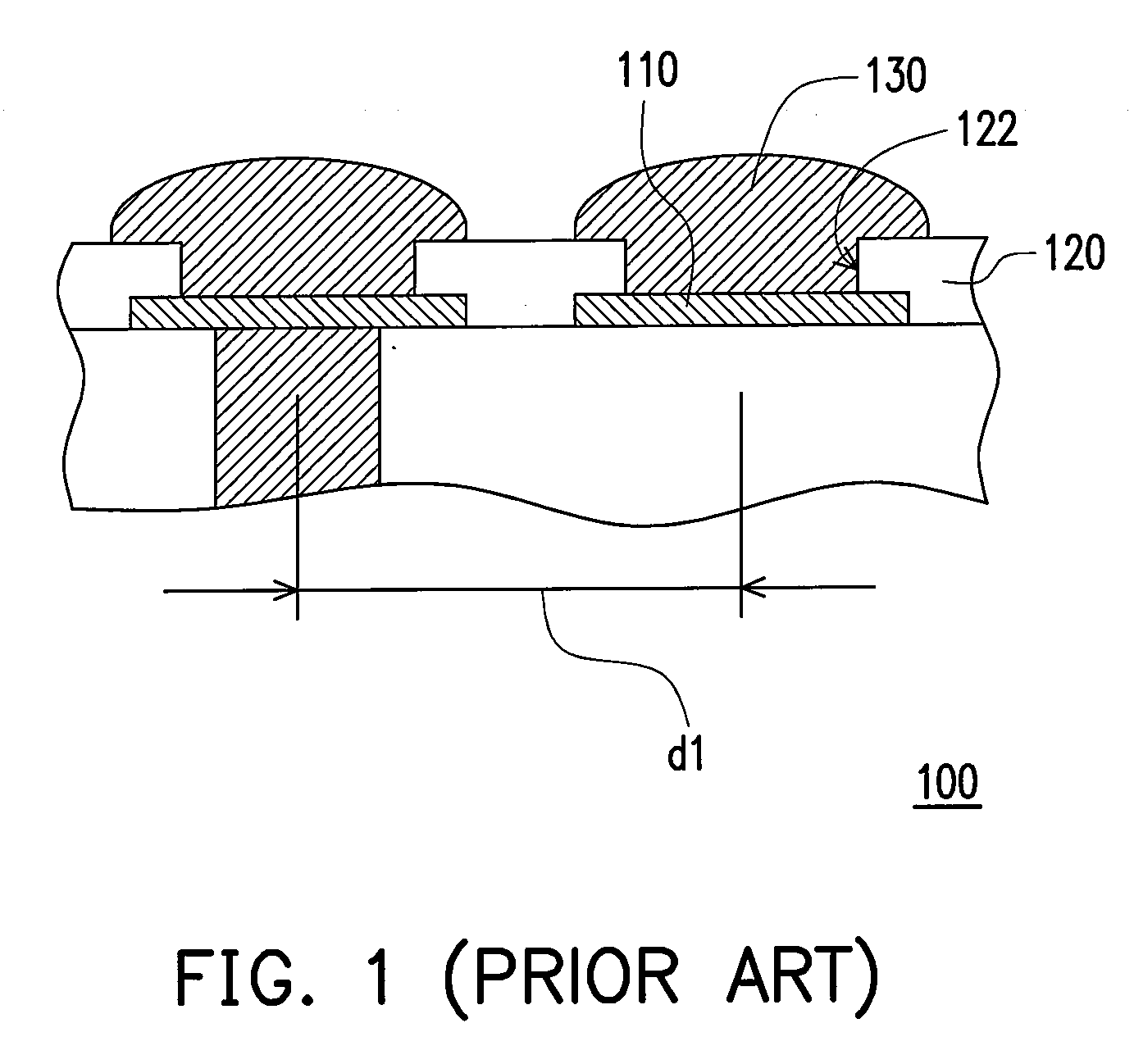

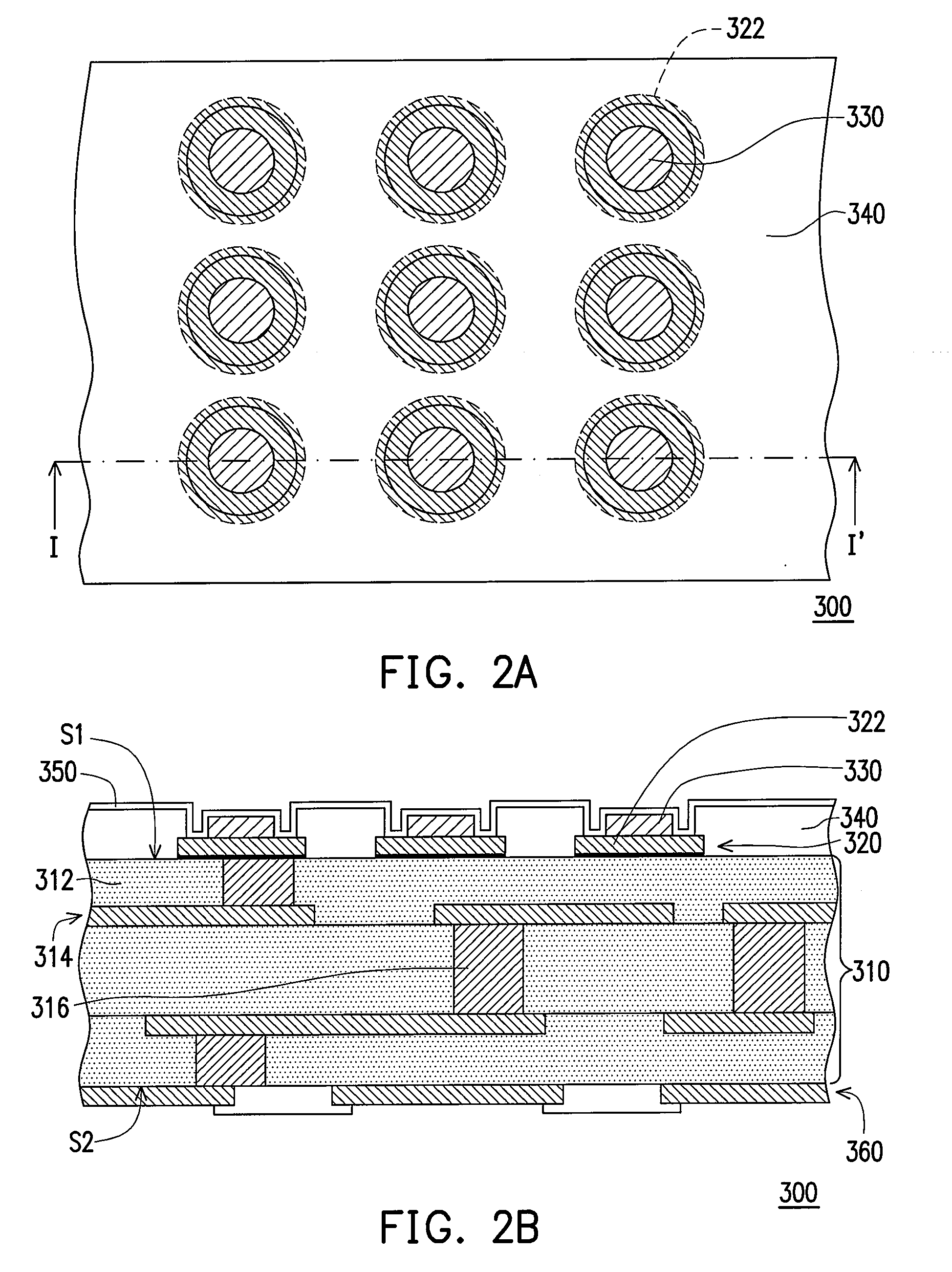

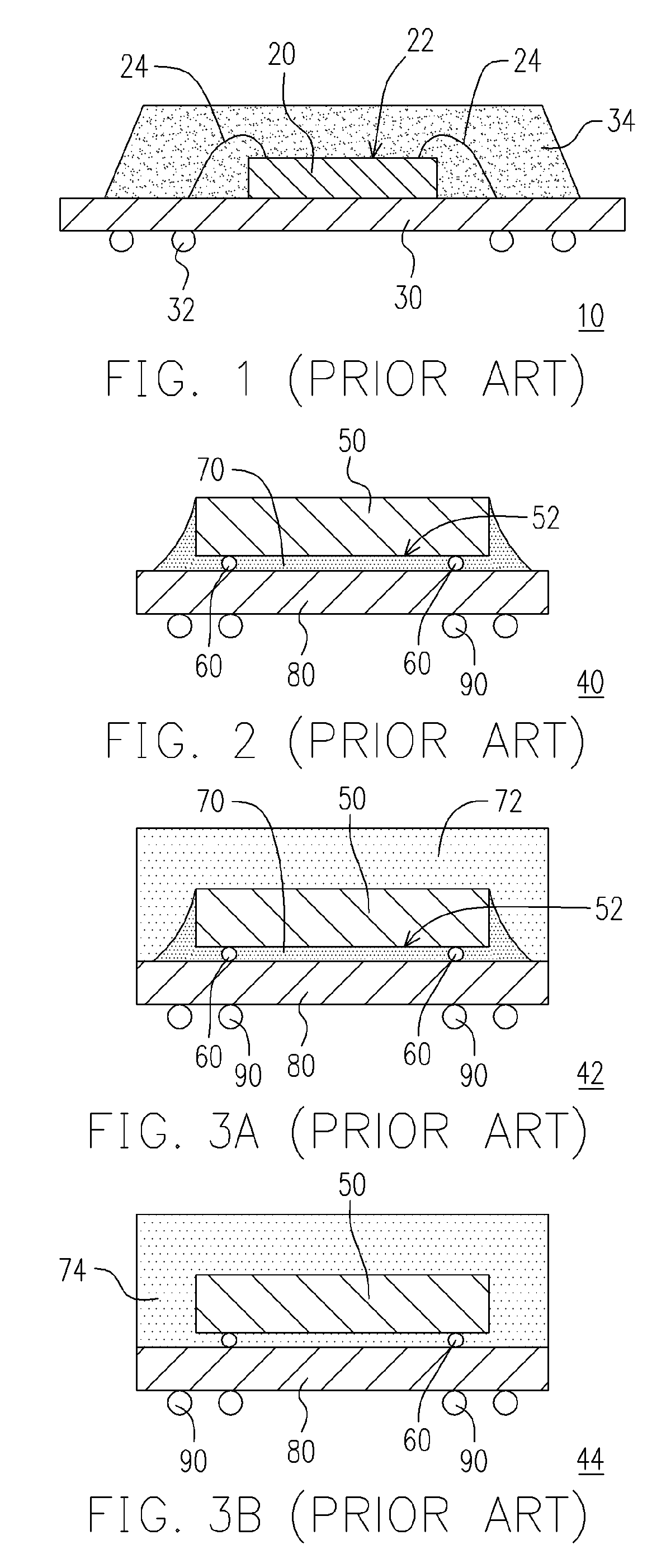

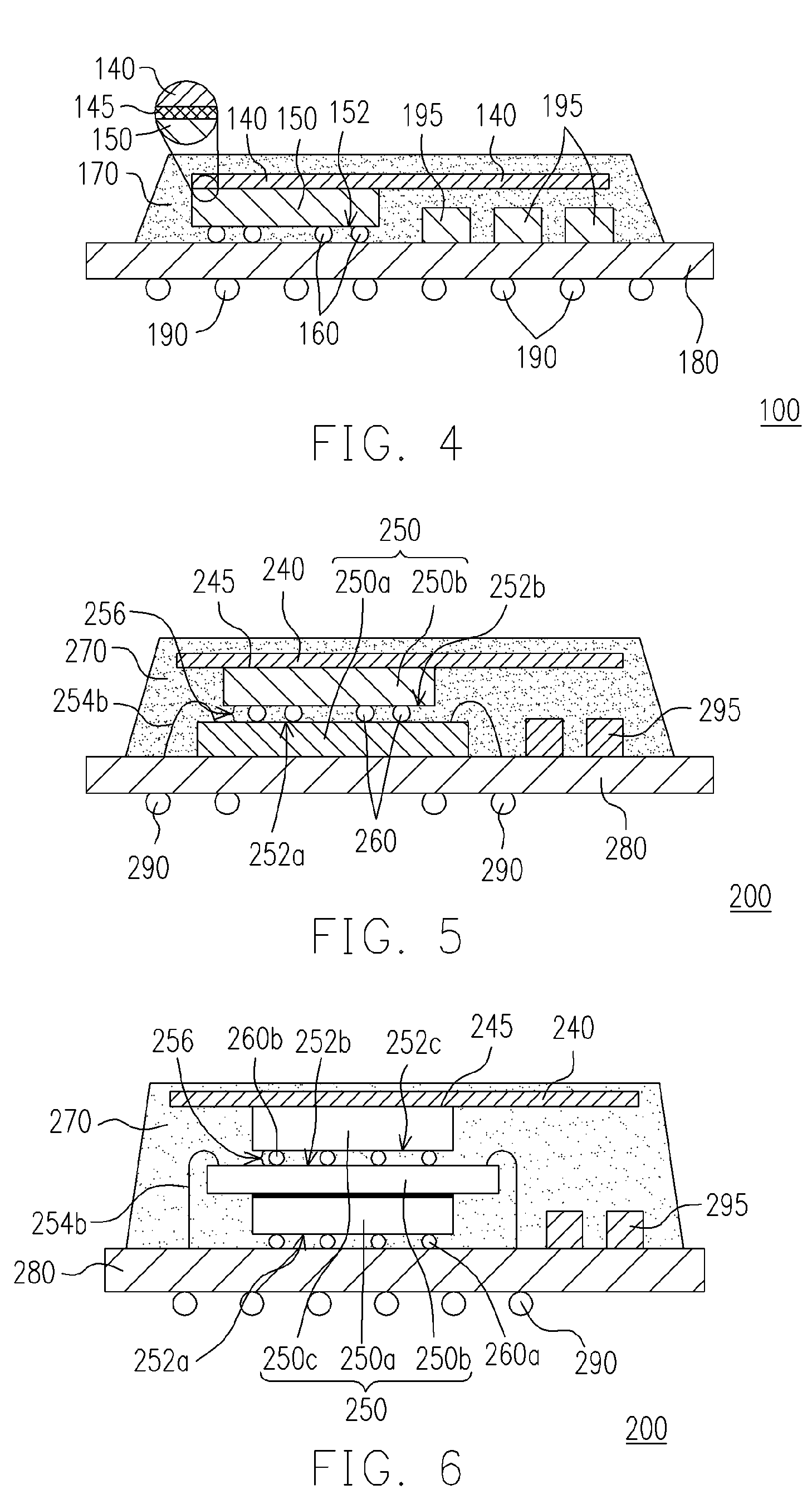

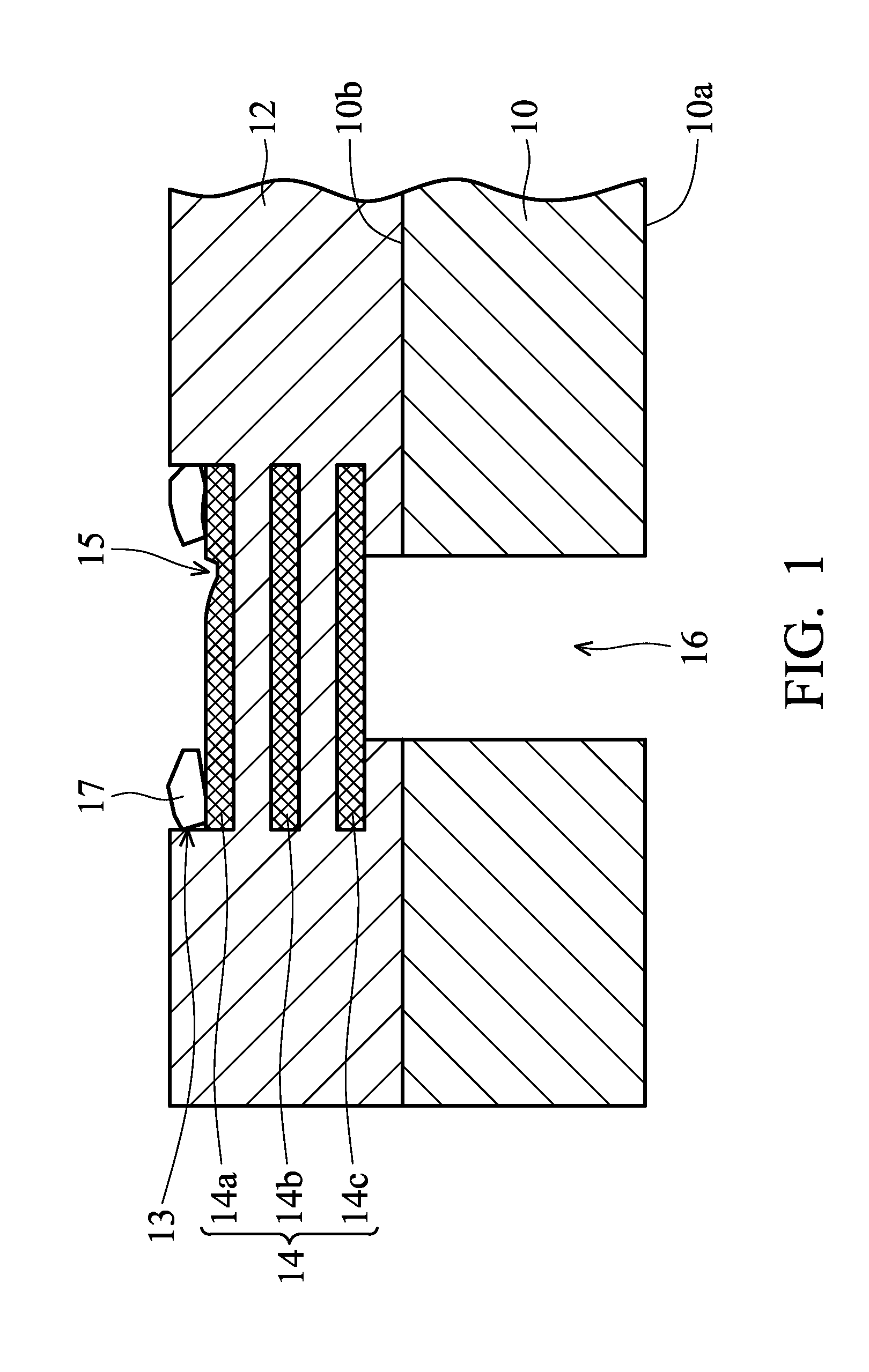

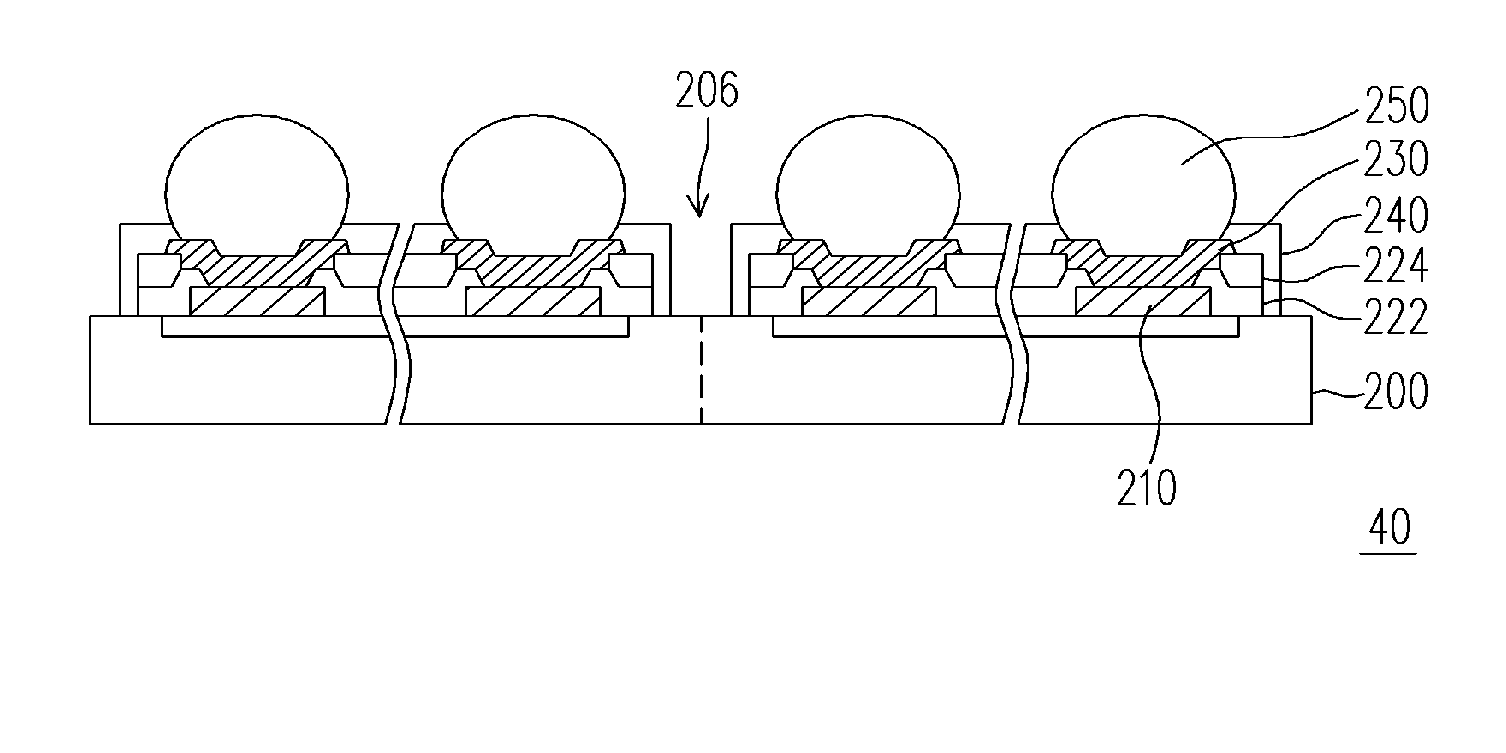

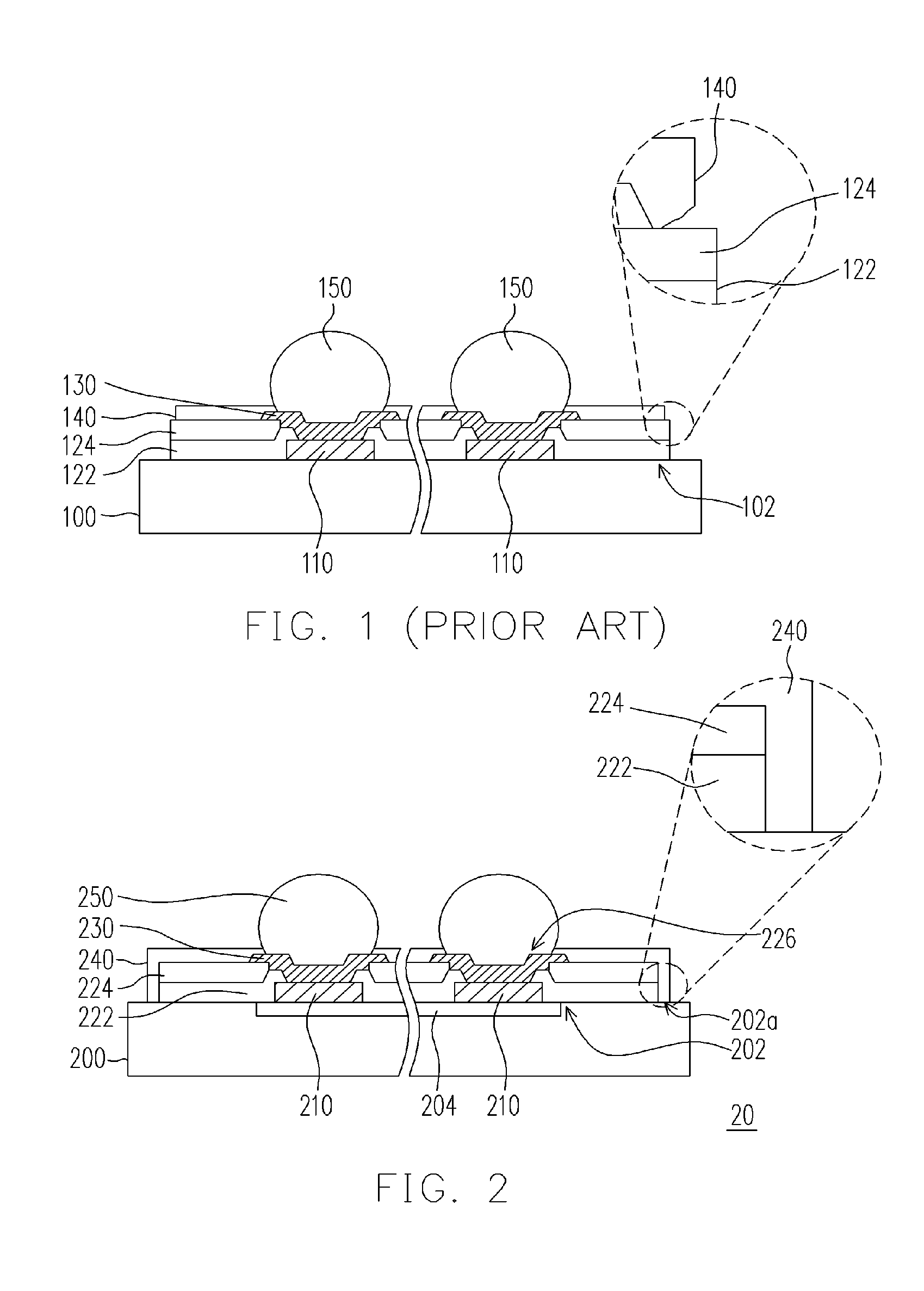

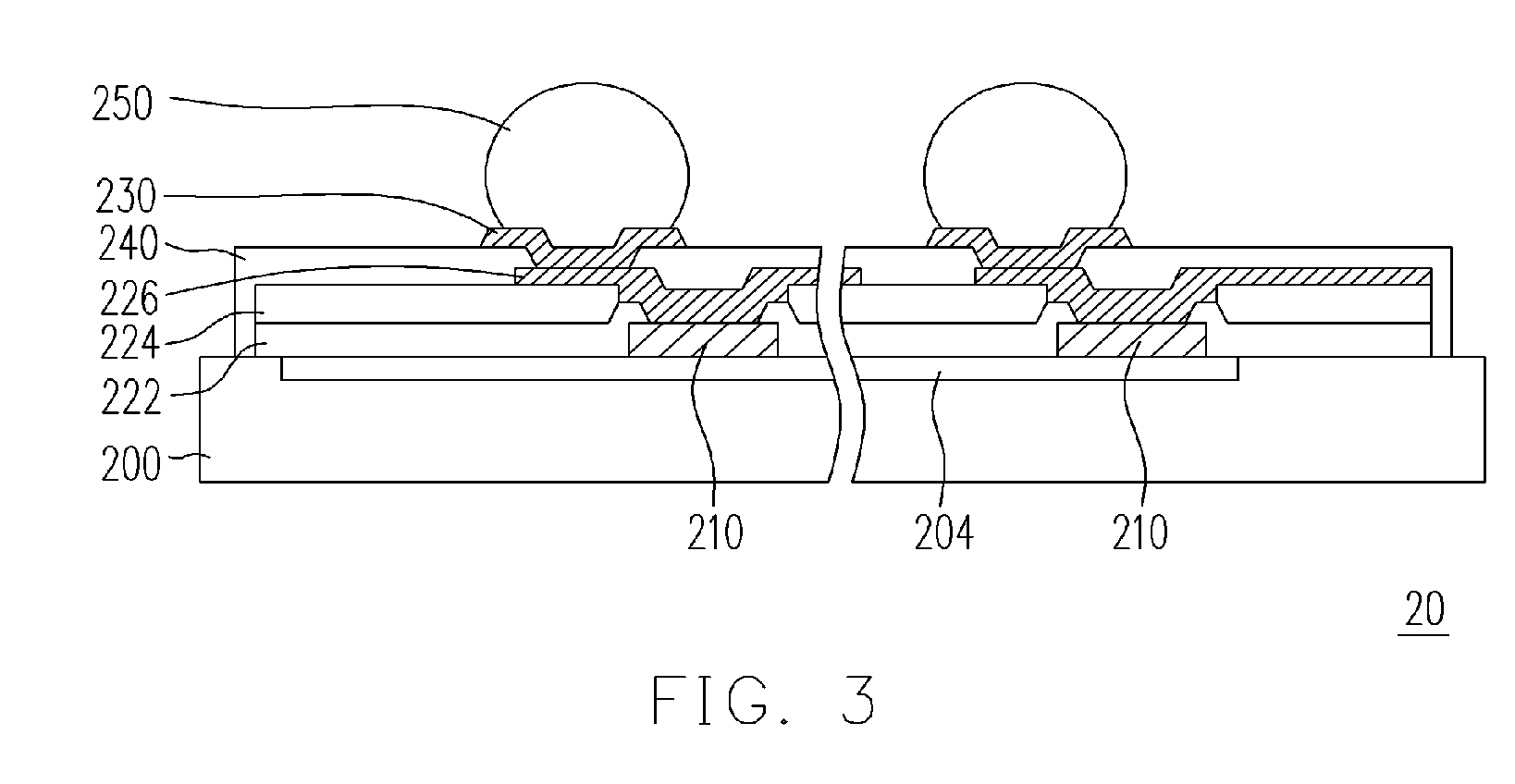

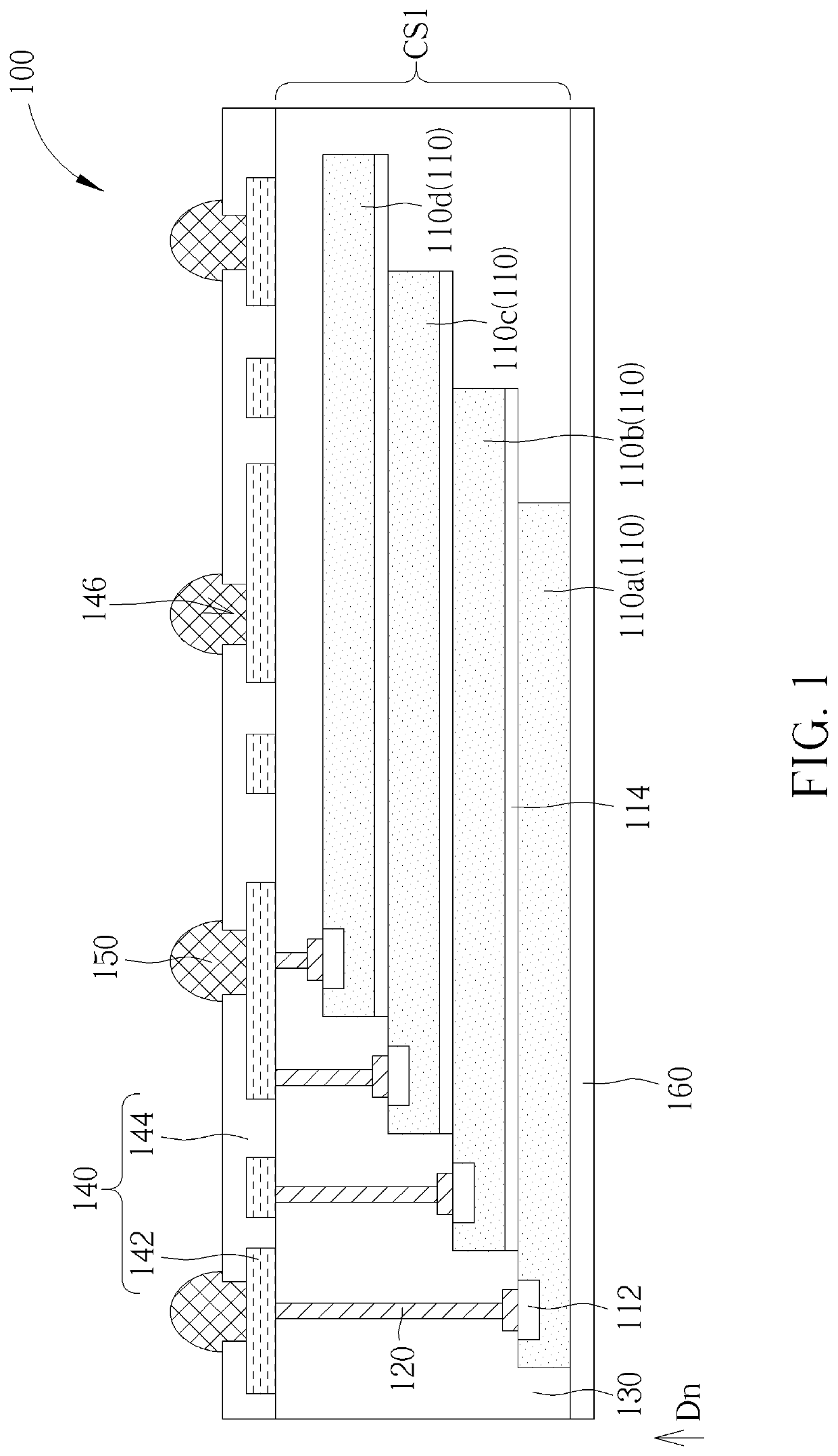

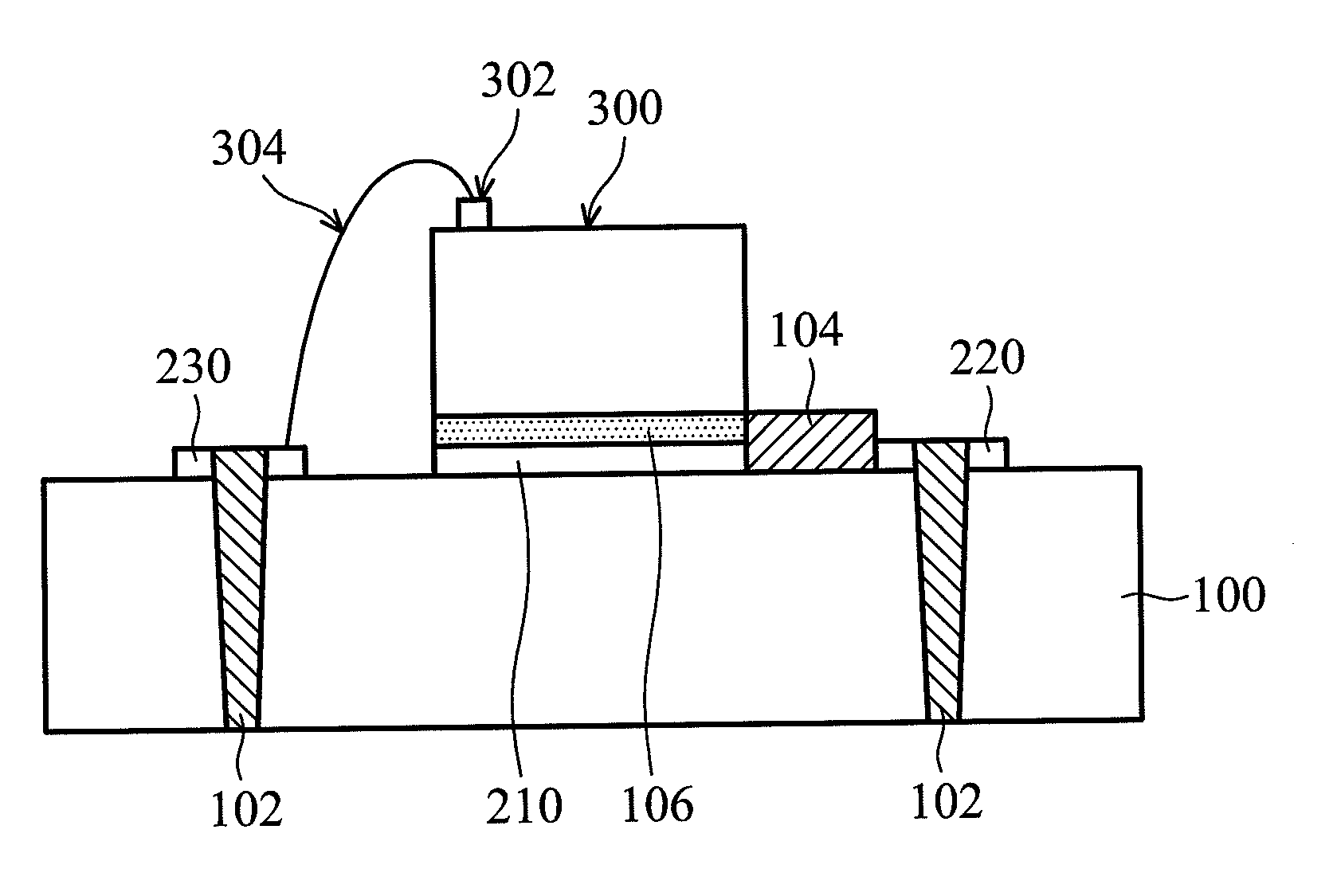

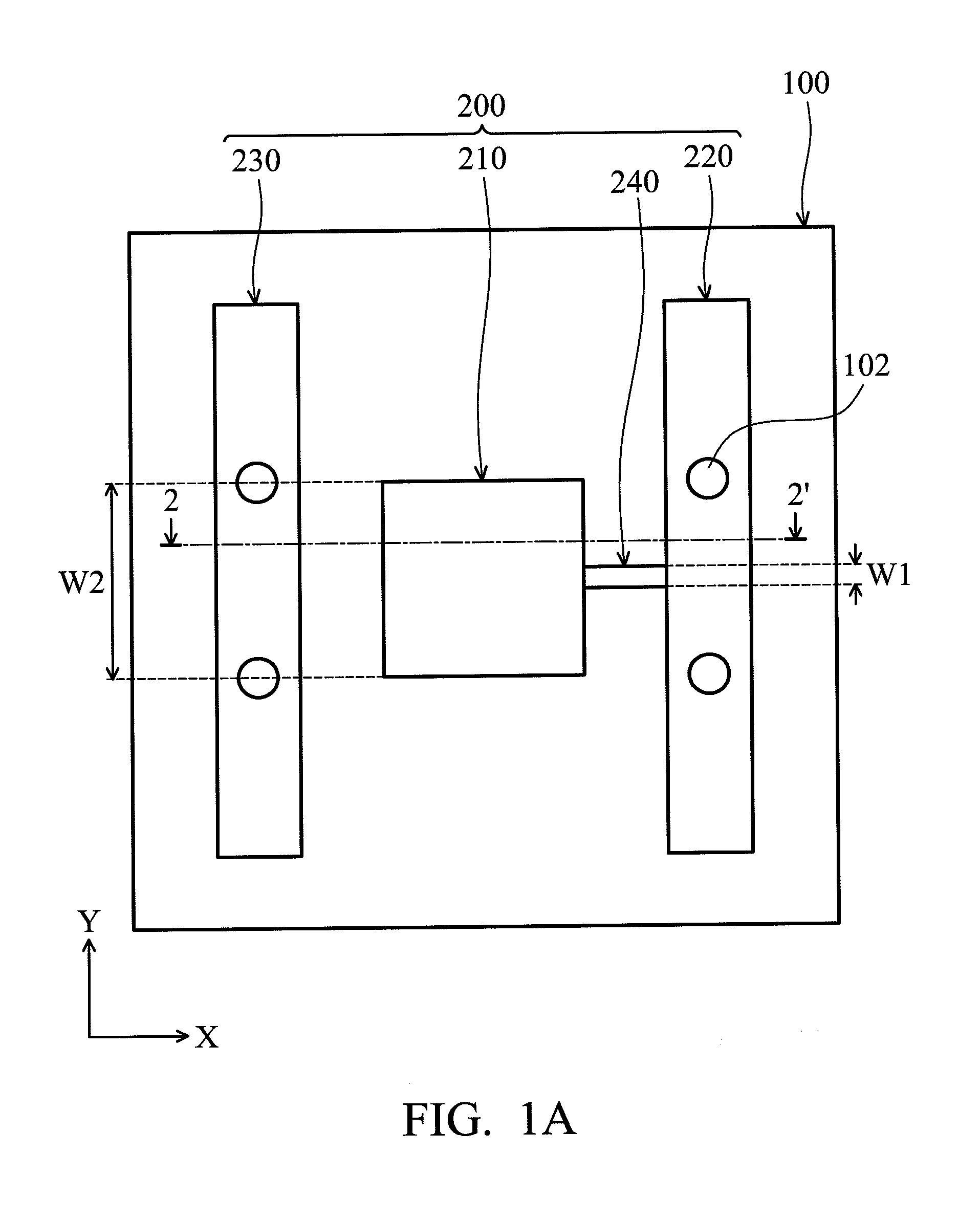

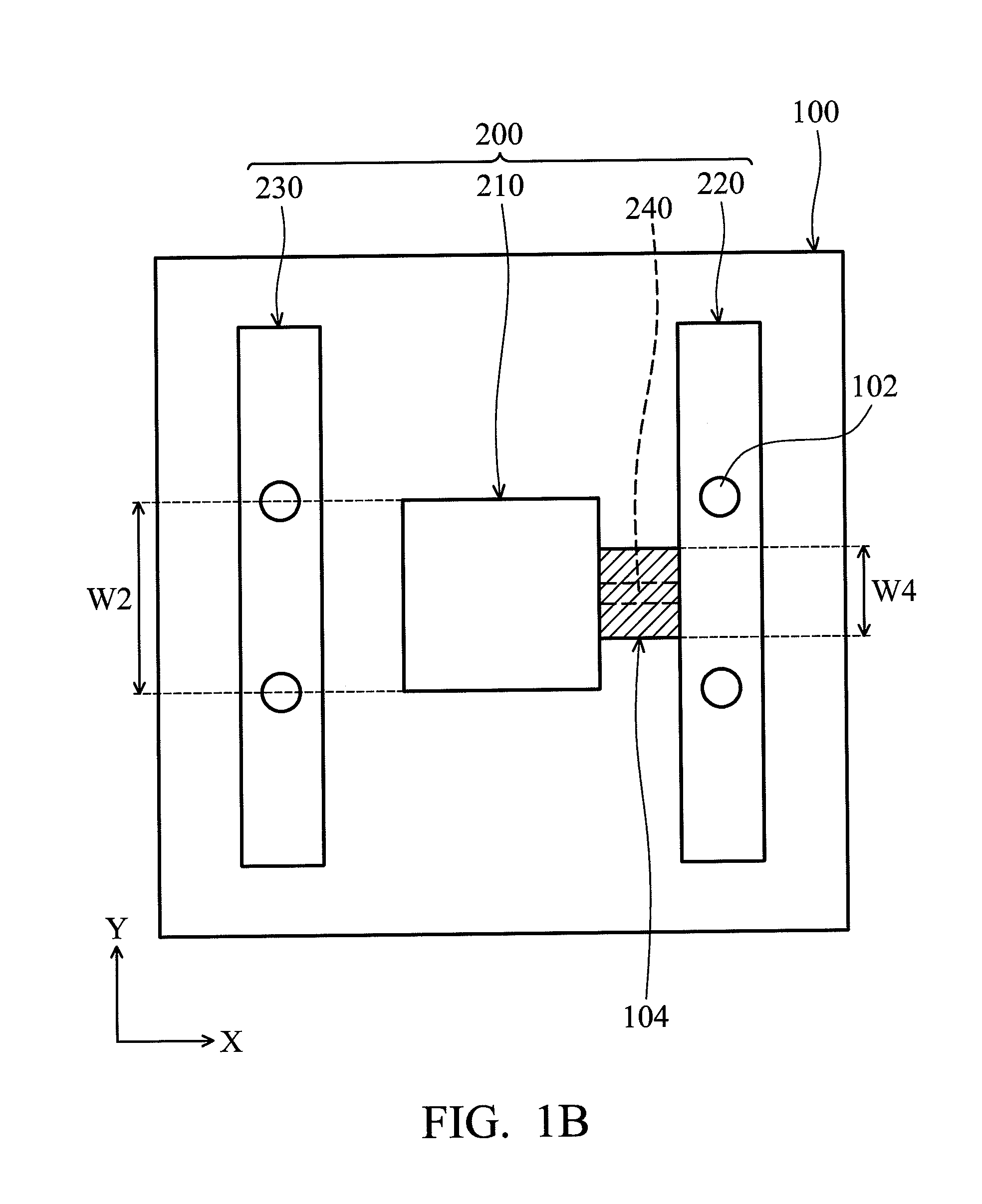

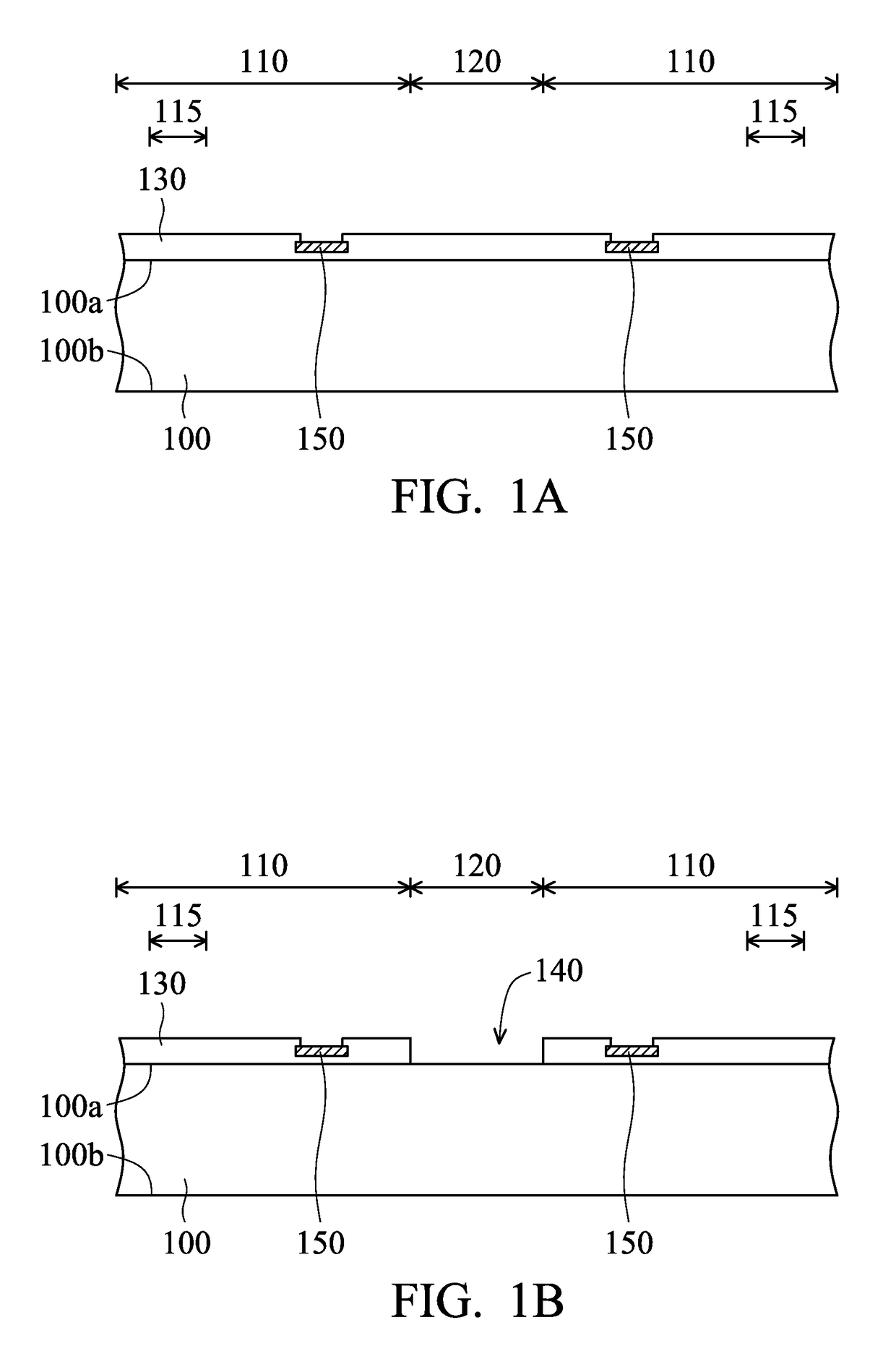

Package substrate, method of fabricating the same and chip package

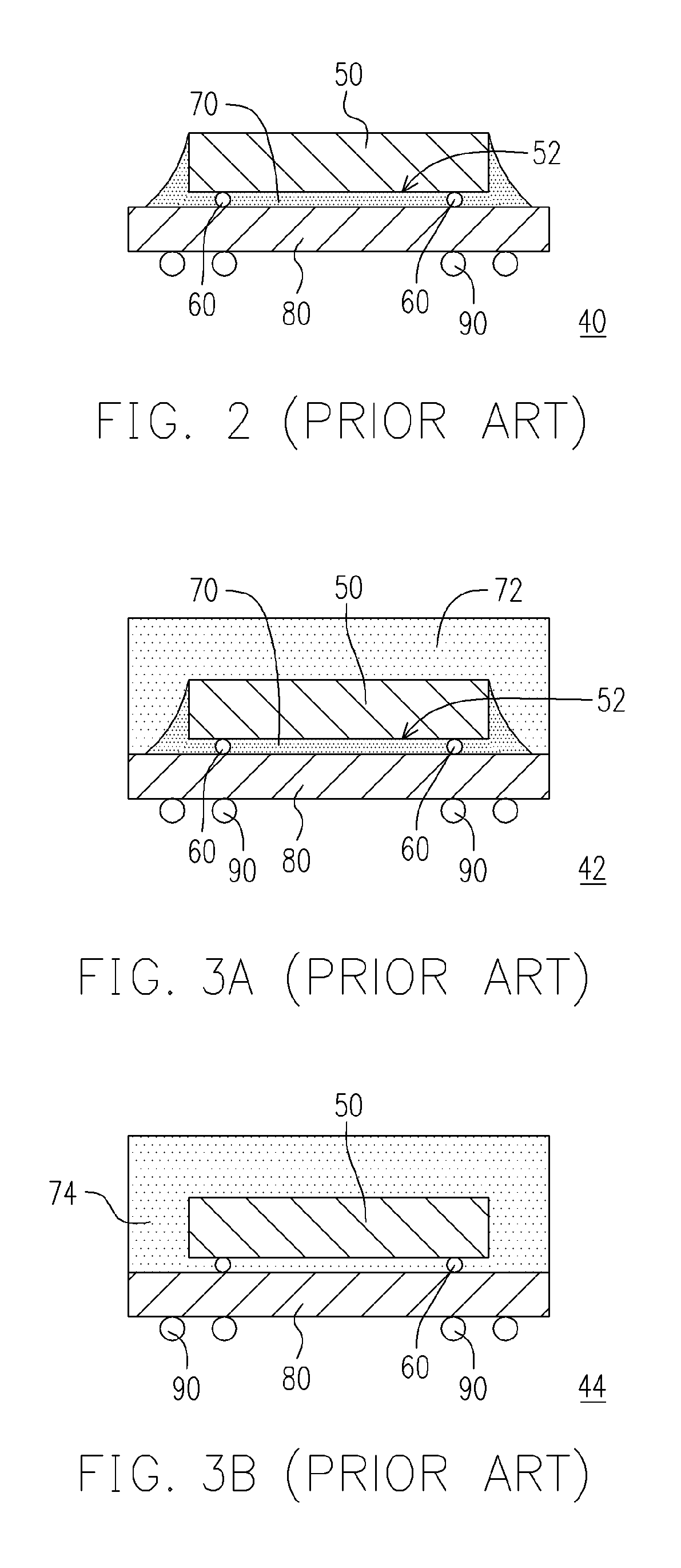

InactiveUS20080179740A1Improve chip reliabilityIncrease distribution densitySemiconductor/solid-state device detailsStacked resist layersSolder maskEngineering

A package substrate, including a base layer, a surface circuit layer, a plurality of conductive bumps, and a patterned solder mask layer, is provided. The surface circuit layer having a plurality of bonding pads is disposed on a surface of the base layer. The conductive bumps are disposed on the bonding pads individually. The patterned solder mask layer is disposed on the surface of the base layer and outside a corresponding region occupied by the conductive bumps, so as to expose the conductive bumps. In addition, a method of fabricating the package substrate and a chip package structure employing the package substrate are also provided.

Owner:ADVANCED SEMICON ENG INC

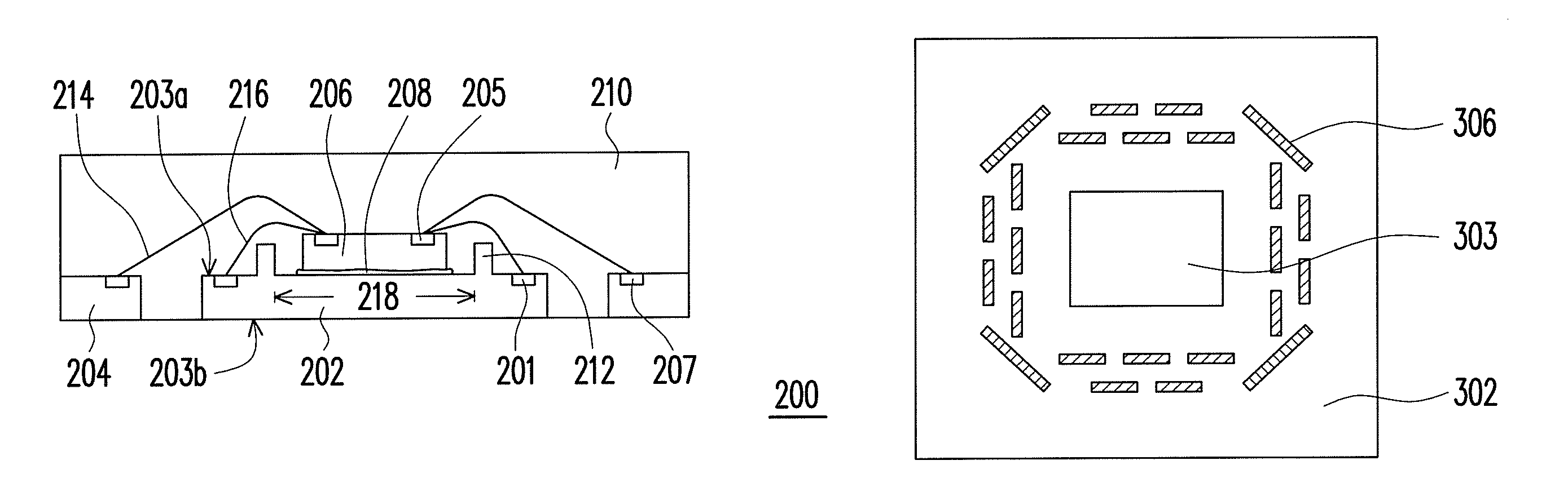

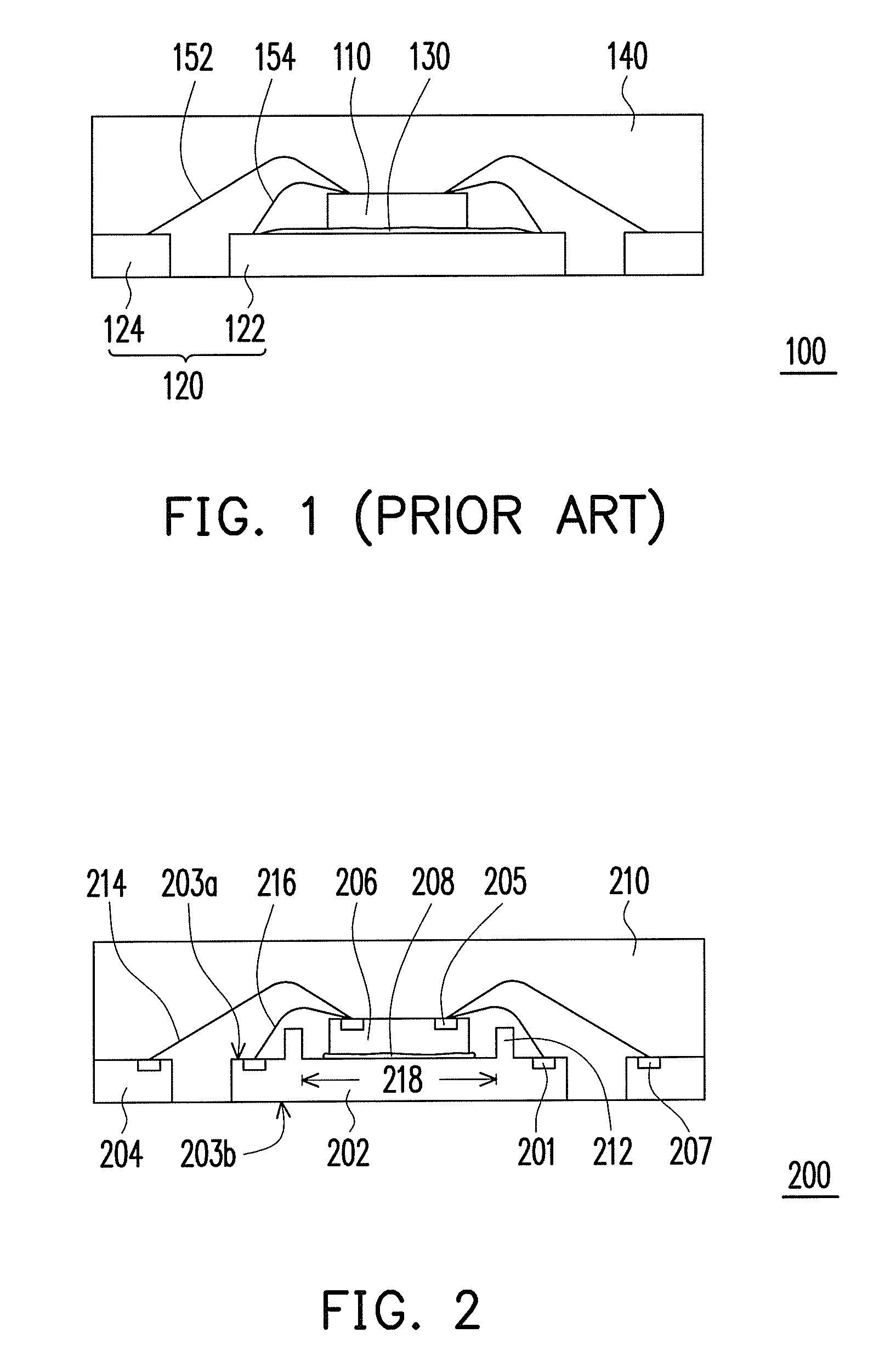

Chip package structure

ActiveUS7057277B2Improve electrical performanceImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesHeat sinkThermal conductivity

A chip package structure is disclosed. The chip package structure essentially comprises a carrier, one or more chips, a heat sink and an encapsulating material layer. At least one of the chips is bonded and electrically connected to the carrier or another chip using a flip-chip bonding technique. A flip-chip bonding gap is set up between the chip and he carrier or other chips. The heat sink is set up over the top chip. The heat sink has an area bigger than the chip. The encapsulating material layer fills up the flip-chip bonding gap and covers the carrier as well as the heat sink. The encapsulating material layer is formed in a simultaneous molding process and has a thermal conductivity more than 1.2 W / m.K. Furthermore, a plurality of standoff components may be selectively positioned on the heat sink.

Owner:IND TECH RES INST +1

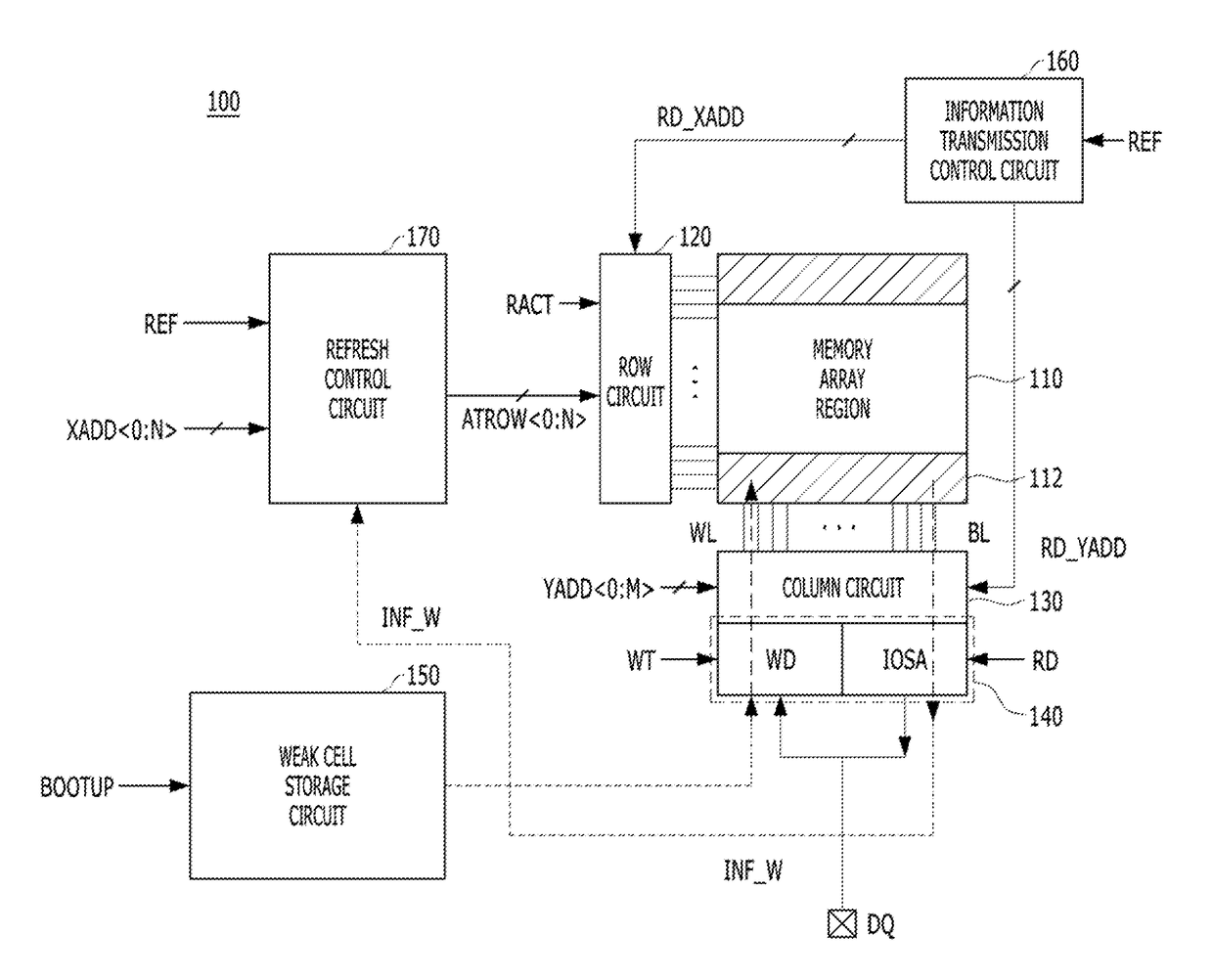

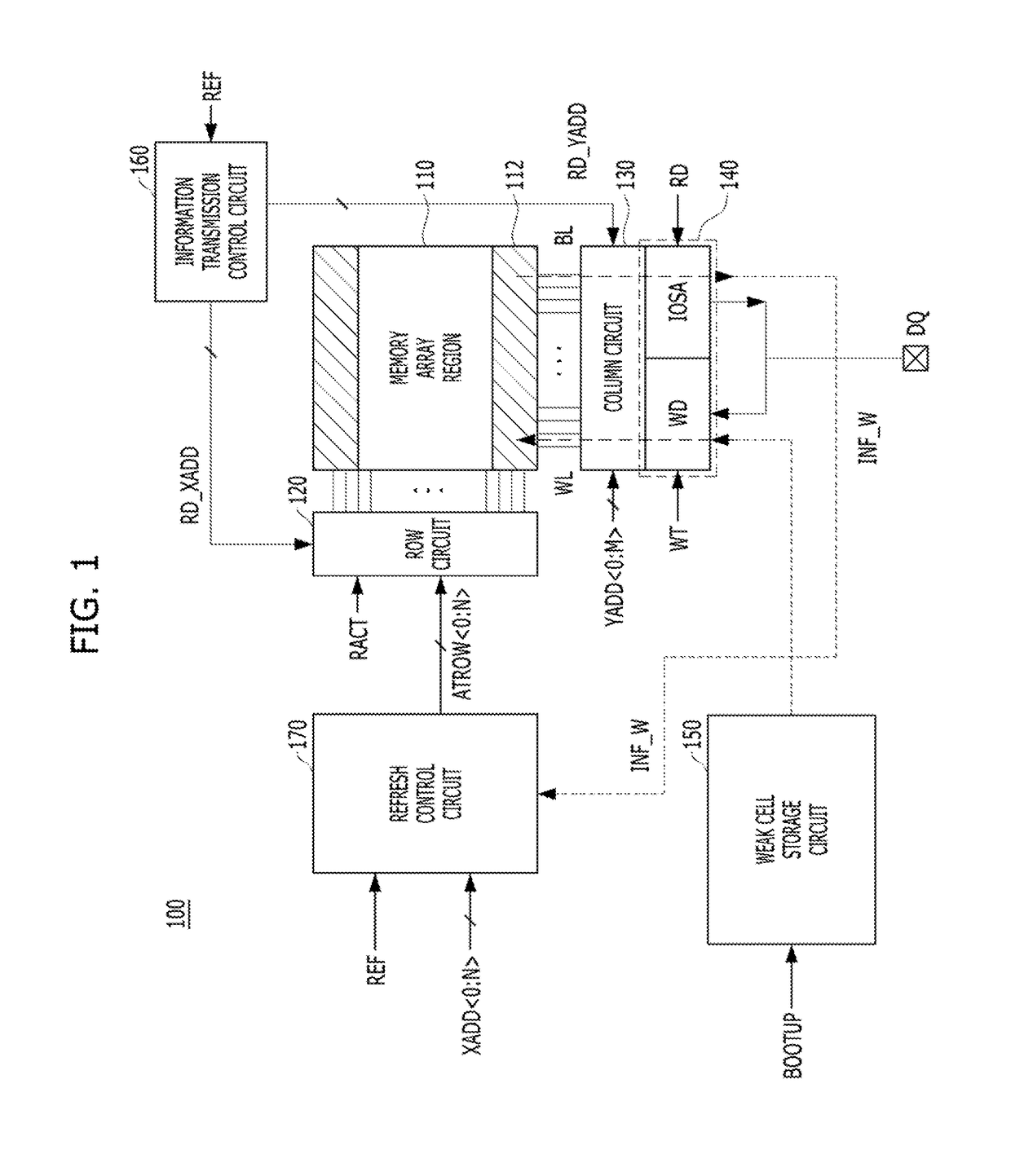

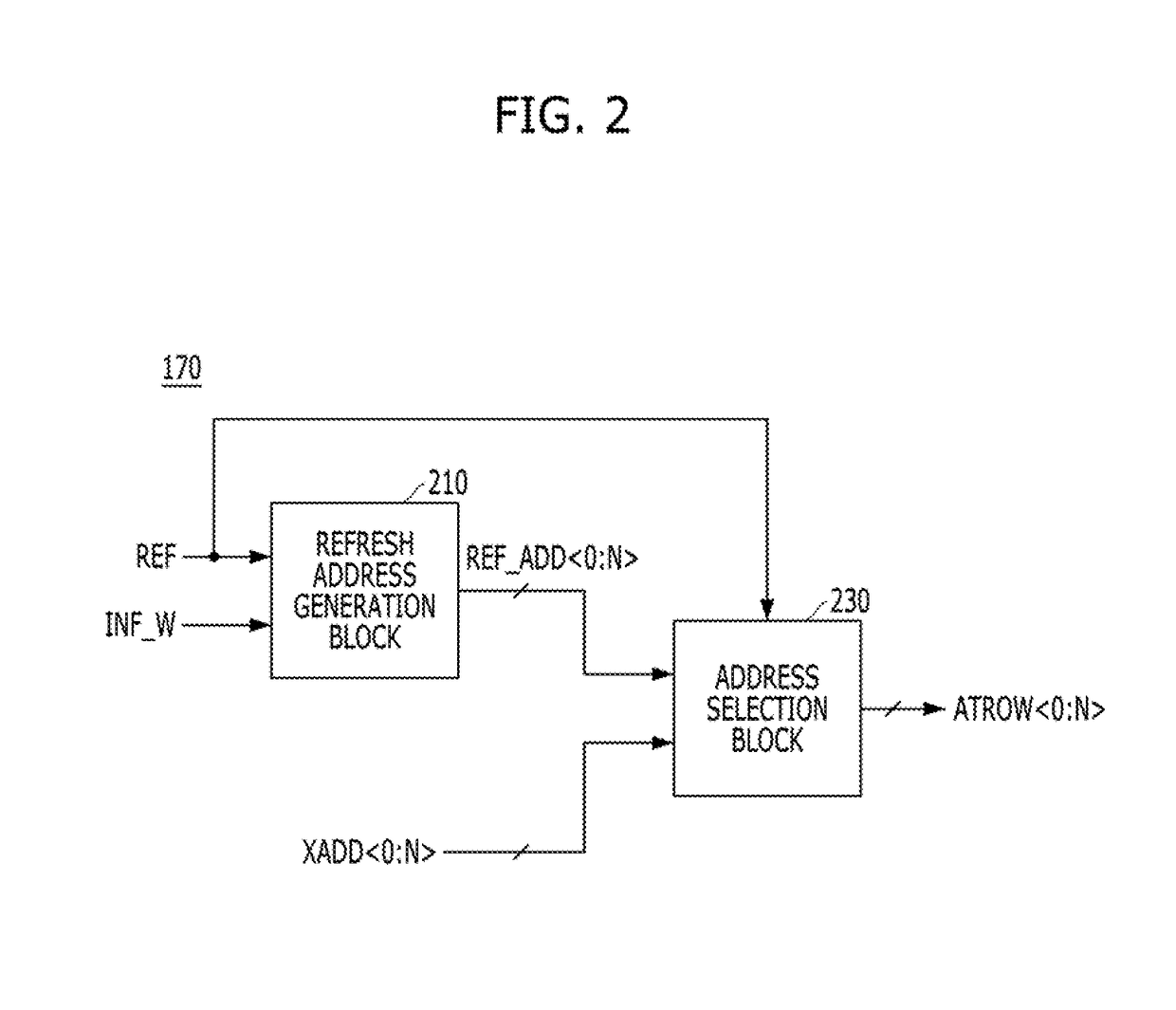

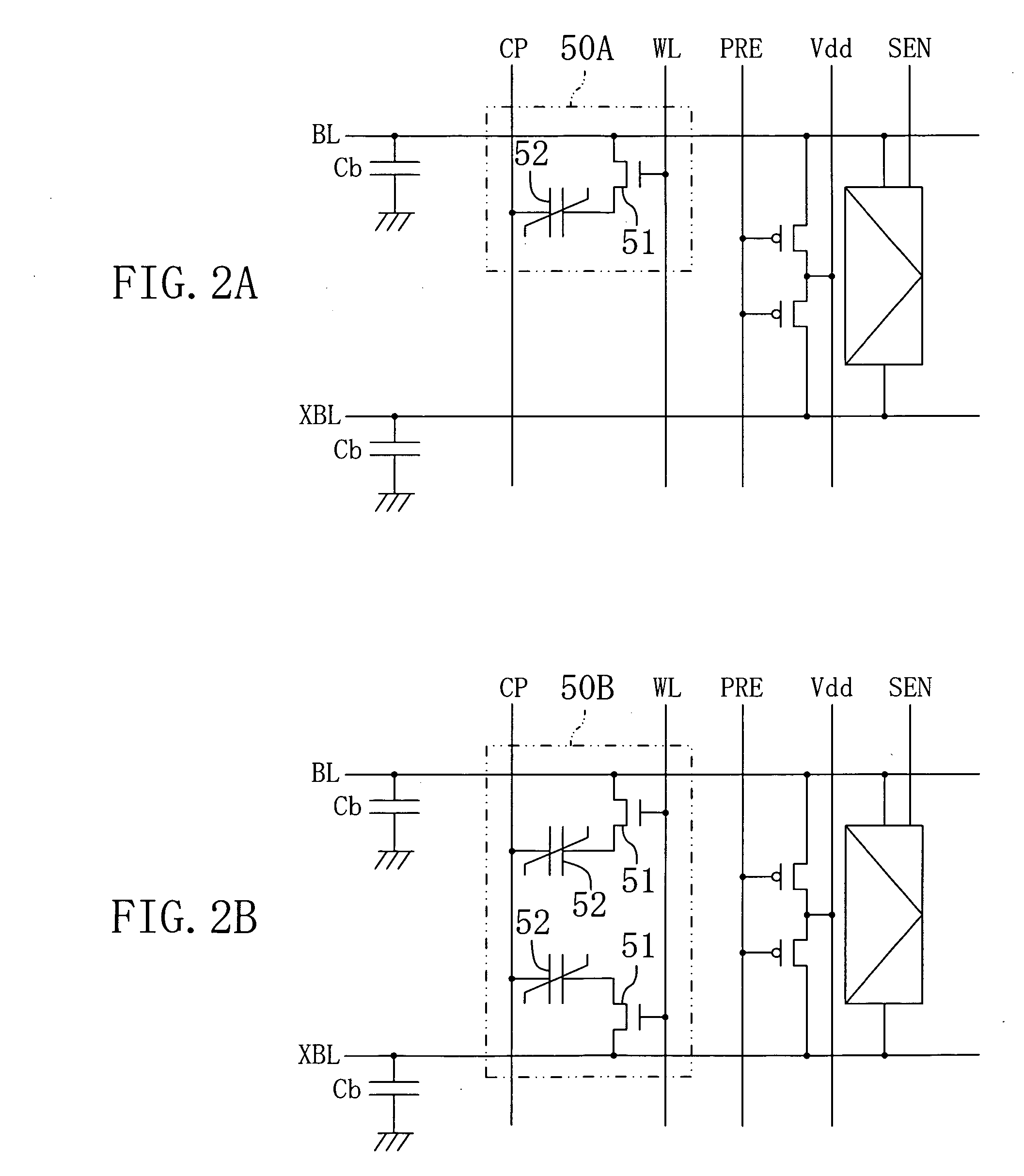

Semiconductor memory device and operating method thereof

A semiconductor memory device including a weak cell storage circuit suitable for programming therein weak cell information, and outputting the weak cell information in an initialization operation; a cell array region including a first cell region which stores the weak cell information received from the weak cell storage circuit, in the initialization operation; a refresh address generation block suitable for generating a refresh address by counting a refresh signal, and outputting a weak cell address corresponding to the weak cell information outputted from the first cell region, as the refresh address, with a predetermined cycle; and a refresh circuit suitable for performing a refresh operation for a word line corresponding to the refresh address, among a plurality of word lines.

Owner:SK HYNIX INC

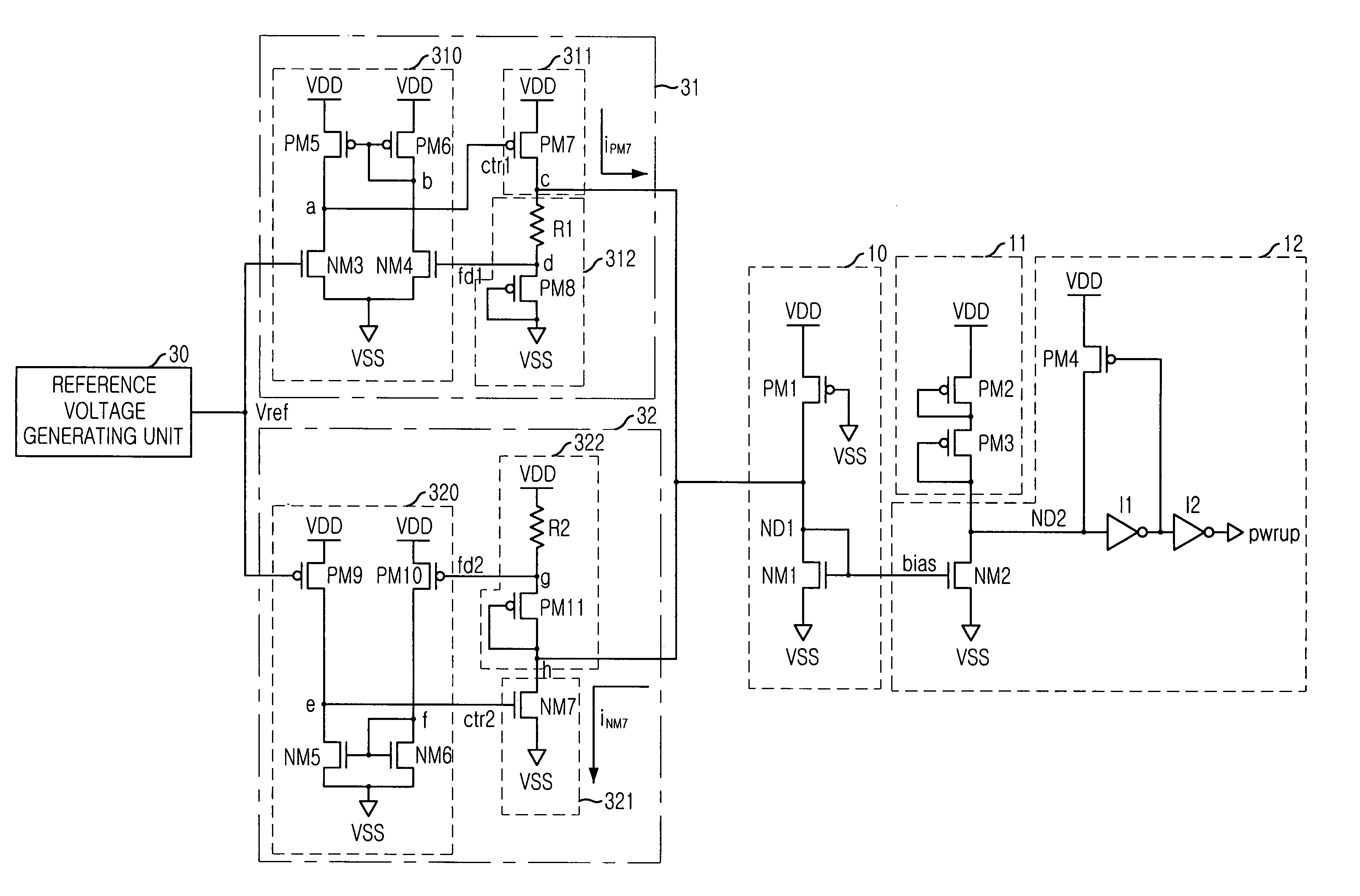

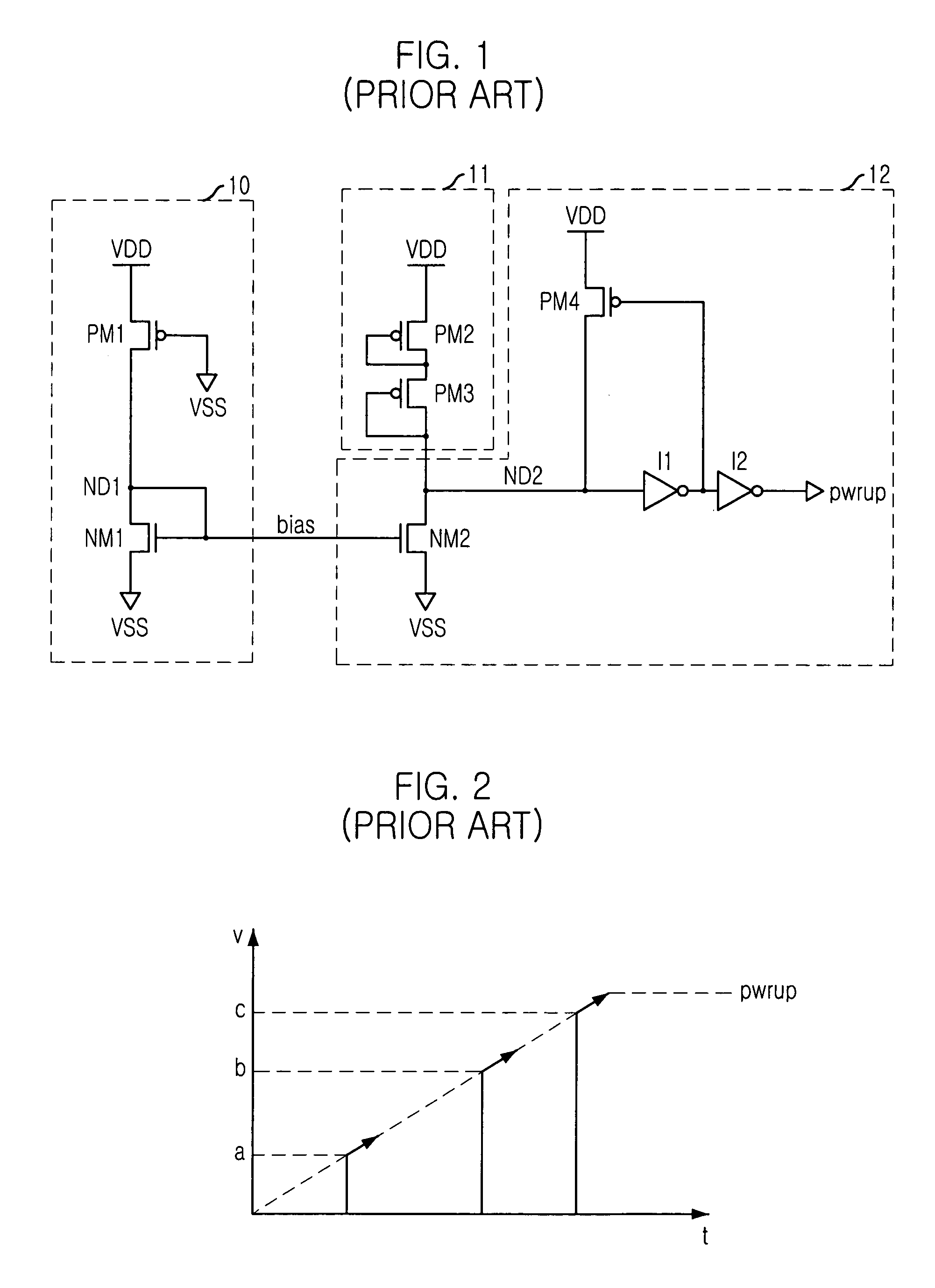

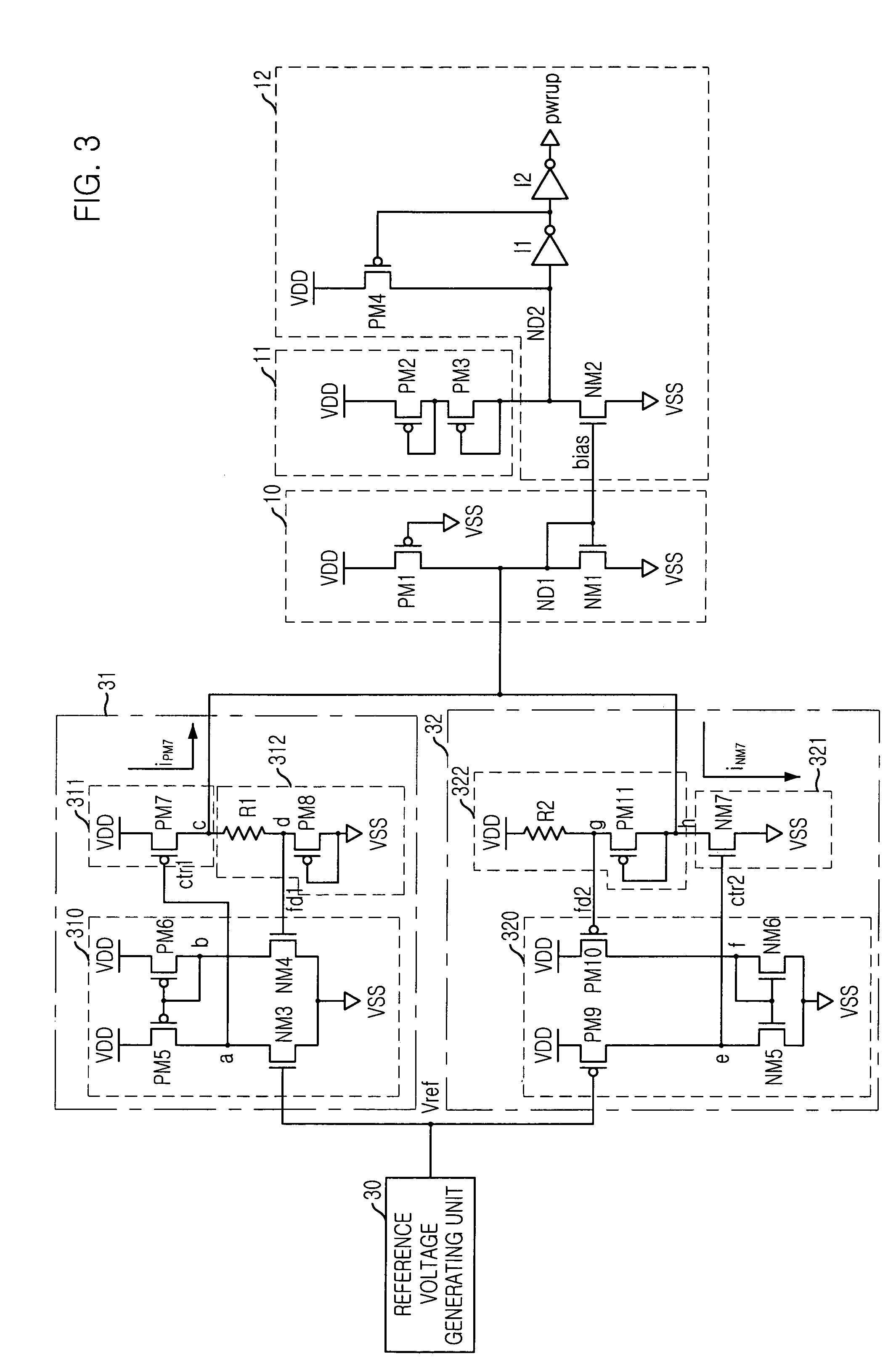

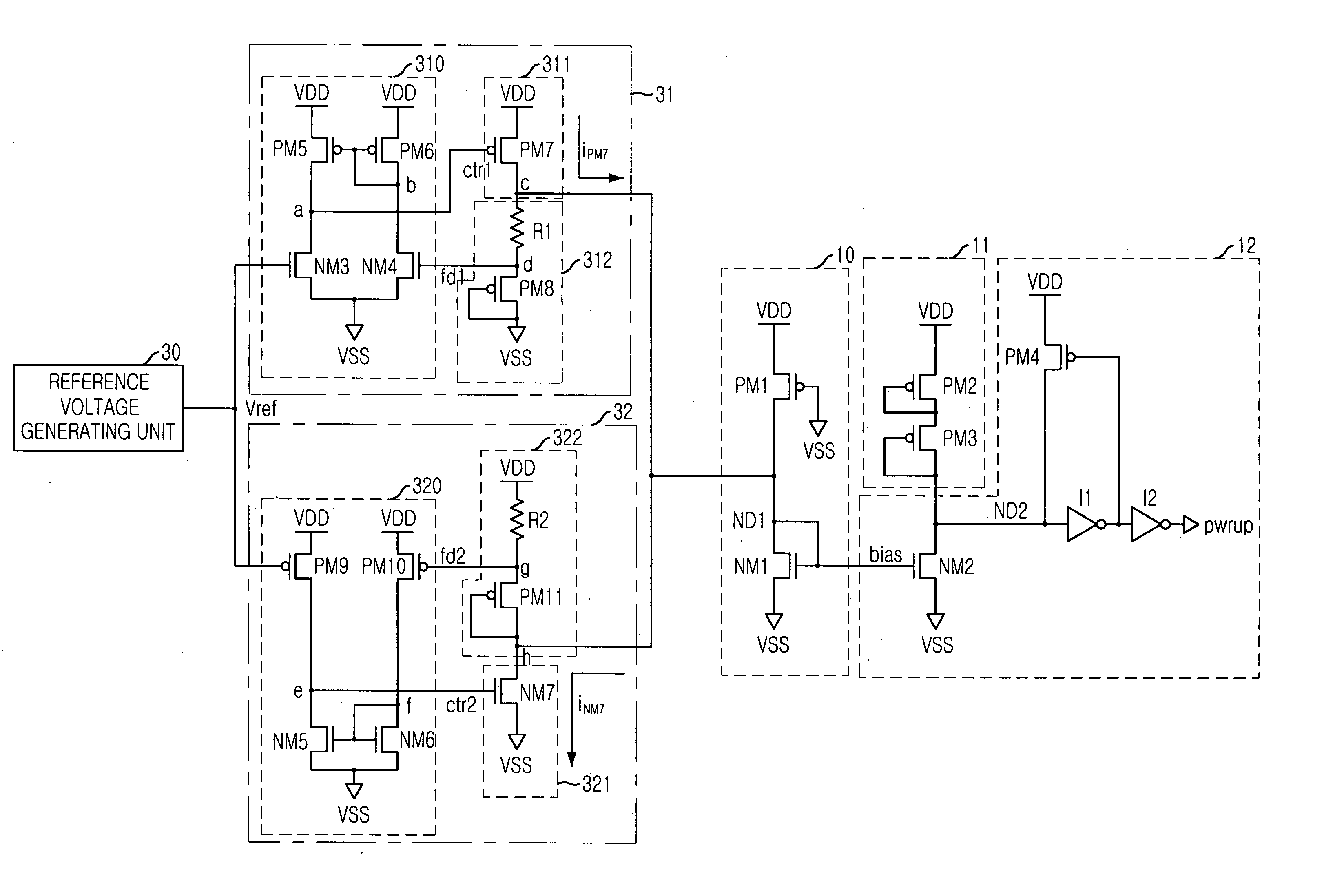

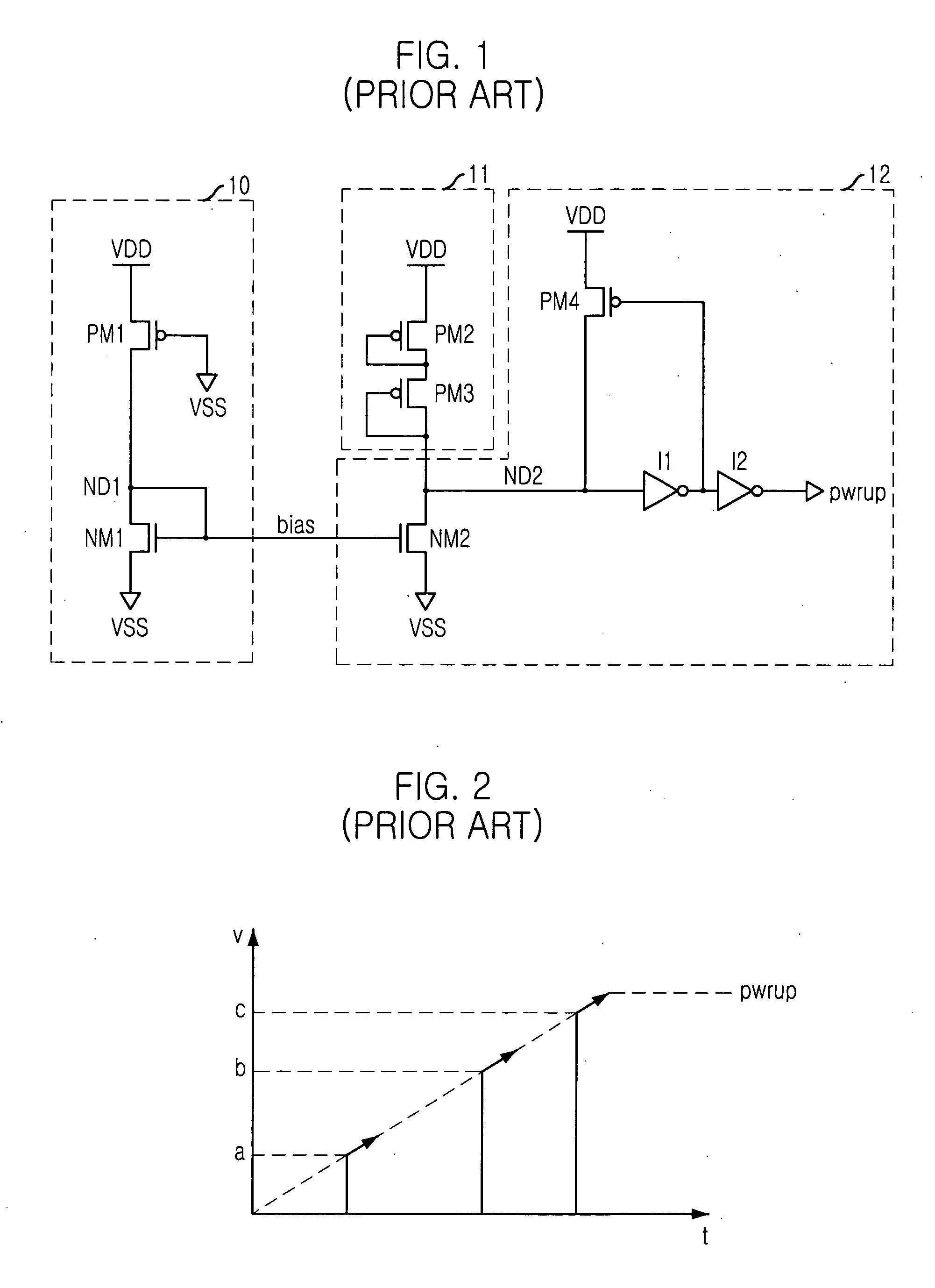

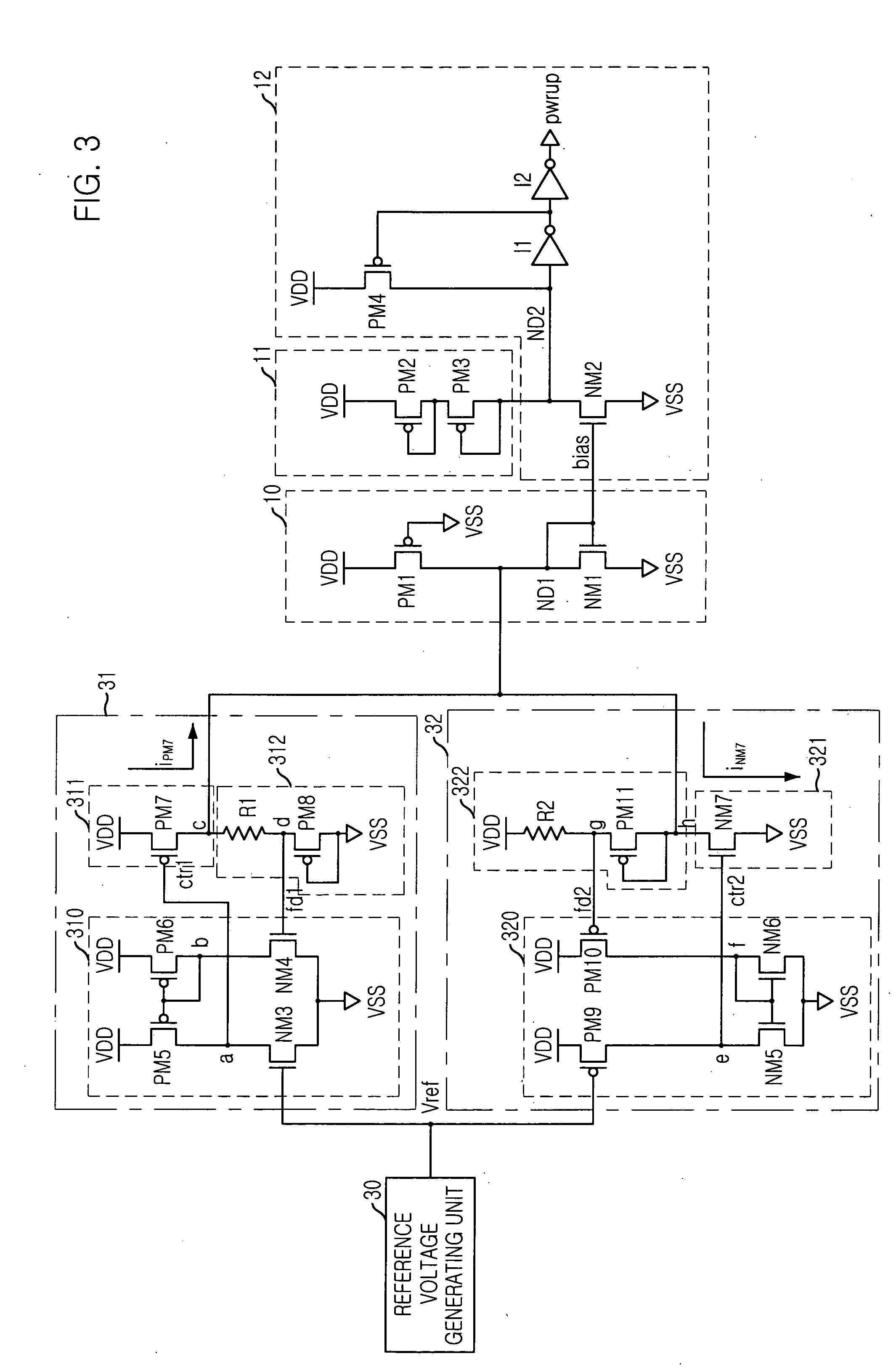

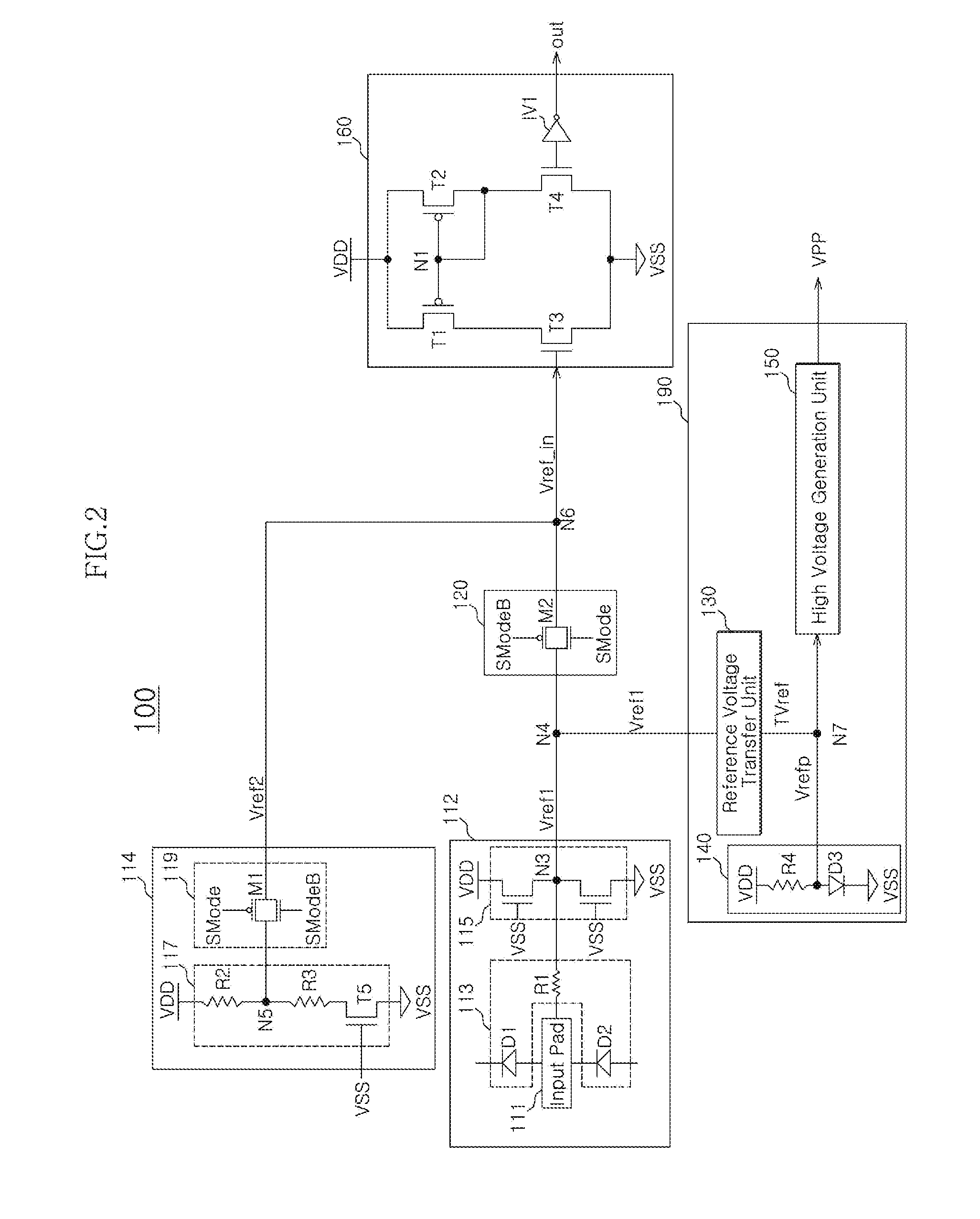

Power-up signal generating apparatus

InactiveUS7212046B2Improve chip reliabilityPulse automatic controlElectric lighting sourcesElectricityEngineering

In a power-up signal generating device, a power-up signal is activated at a certain level of the power supply voltage VDD by adjusting the turn-on resistance value of the MOS transistor so that the chip reliability can be improved. The power-up signal generating device comprises a reference voltage generating unit, a bias level adjusting unit, a bias signal generating unit and a signal outputting unit. The reference voltage generating unit generates a reference voltage. The bias level adjusting unit receives the reference voltage as an input for controlling a voltage level of a bias signal in a constant level. The bias signal generating unit generates the bias signal under control of the bias level adjusting unit. The signal outputting unit outputs a power-up signal depending on the voltage level of the bias signal.

Owner:SK HYNIX INC

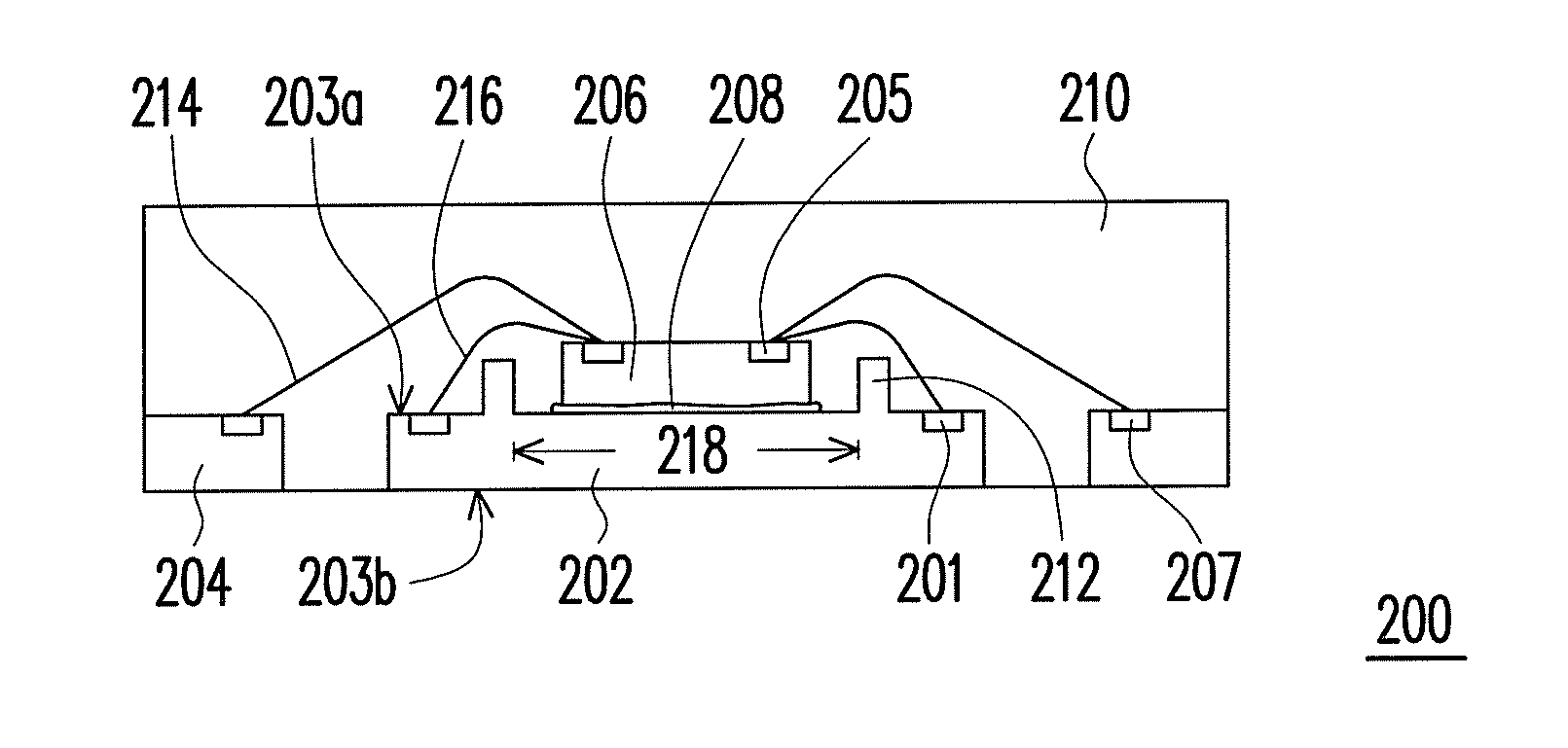

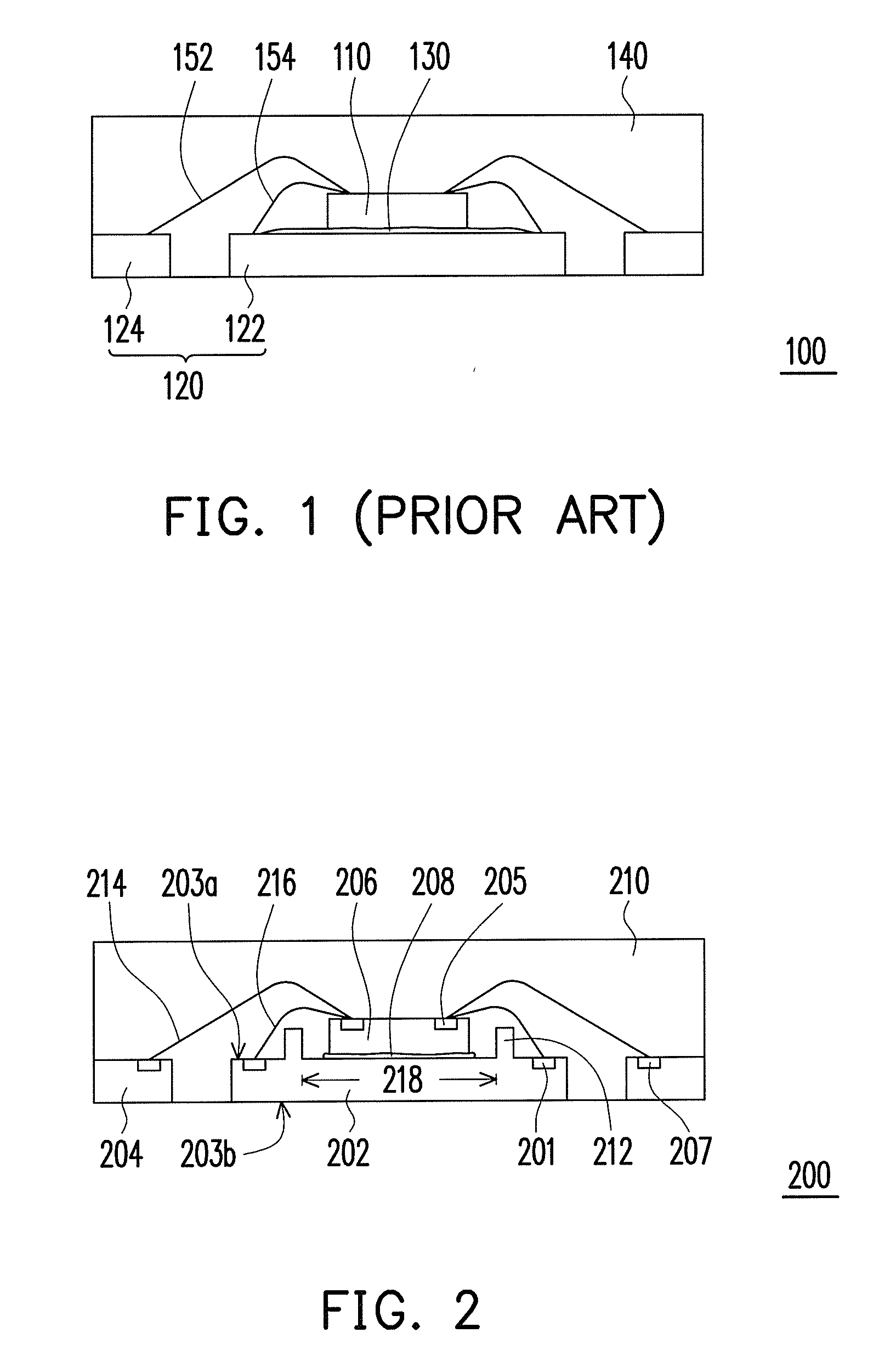

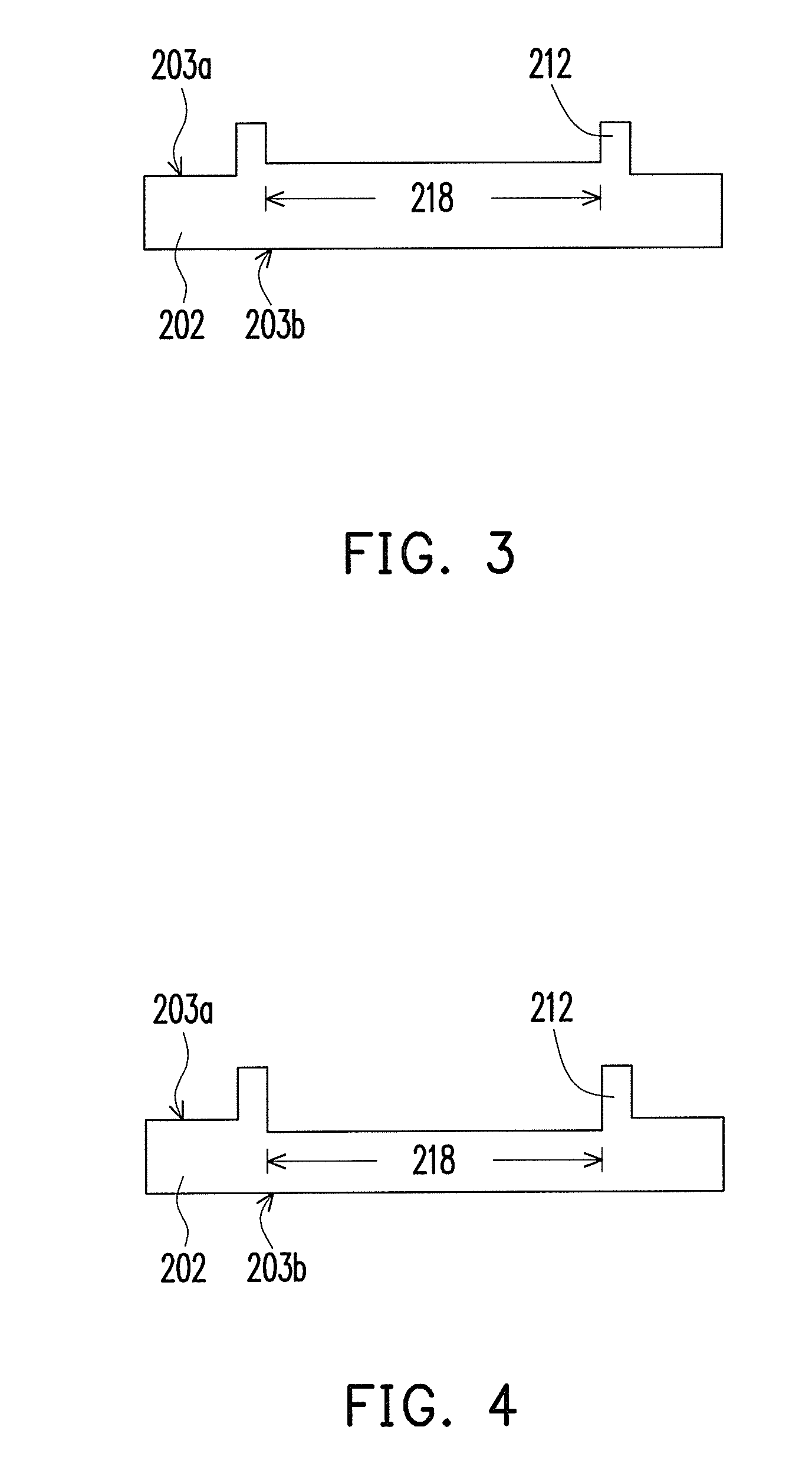

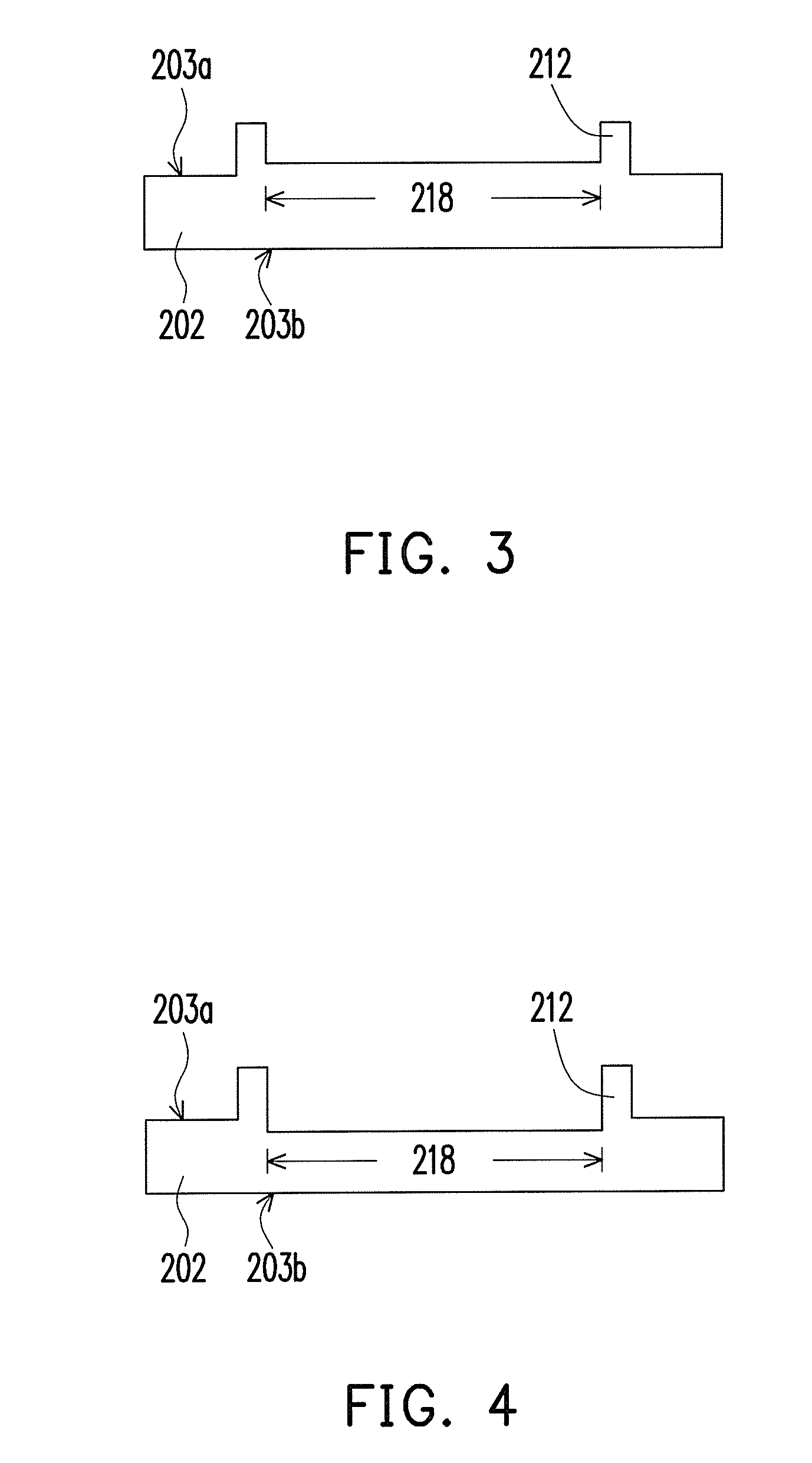

Chip package

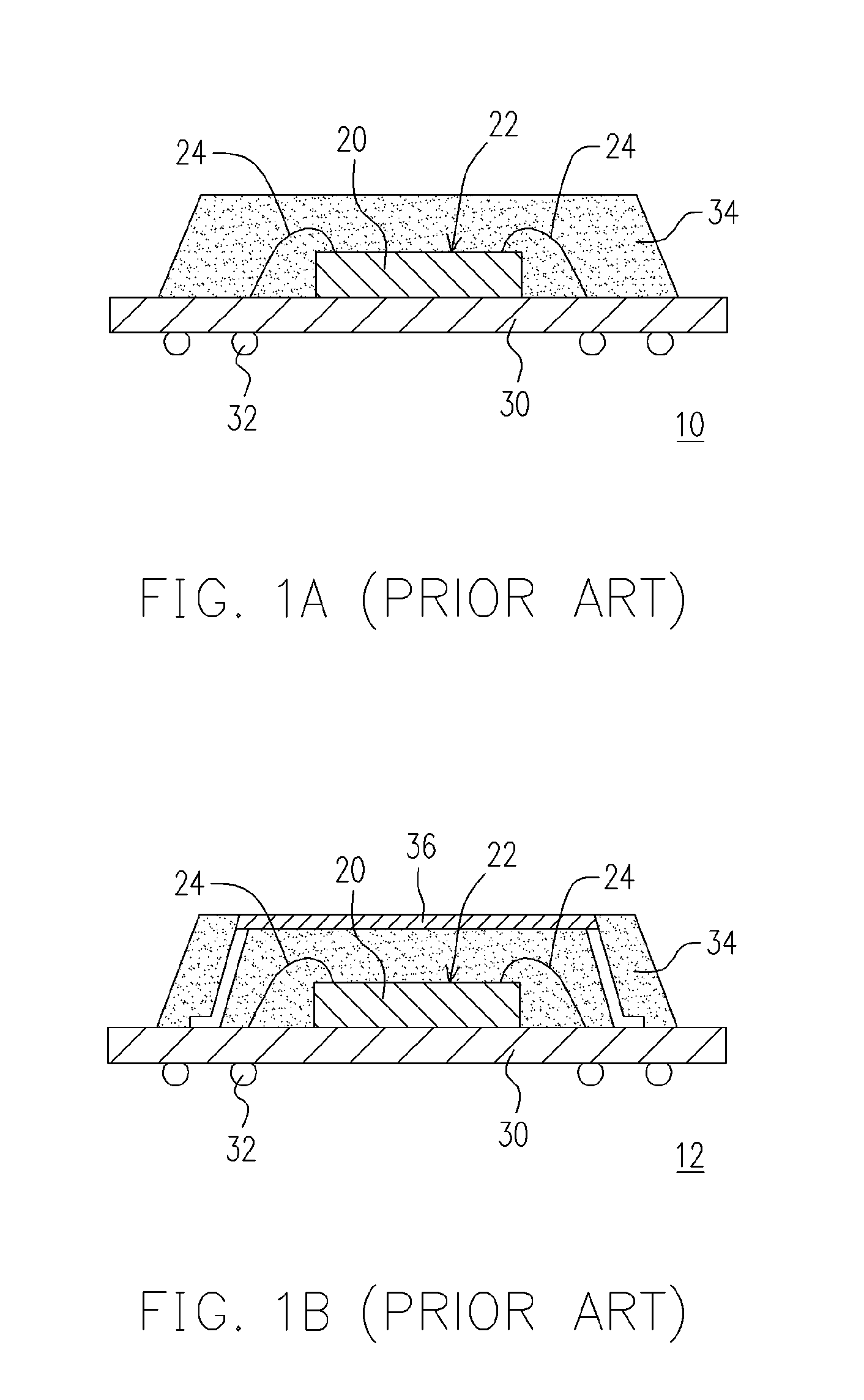

InactiveUS20090224384A1Improve chip reliabilityImprove reliabilityElectrically conductive connectionsSemiconductor/solid-state device detailsAdhesiveElectrical and Electronics engineering

A chip package including a die pad, a plurality of leads, a chip, an adhesive, and a molding compound is provided. The die pad has a top surface and a bottom surface opposite to the top surface, wherein the die pad has a blocking portion disposed on the top surface, and the leads are disposed around the die pad. The chip is disposed on the top surface of the die pad surrounded by the blocking portion and is electrically connected to the leads. A top surface of the blocking portion is higher than the top surface of the die pad surrounded by the blocking portion. The adhesive is disposed between the chip and the die pad. The molding compound encapsulates the chip, a portion of the leads, and the die pad.

Owner:CHIPMOS TECH INC

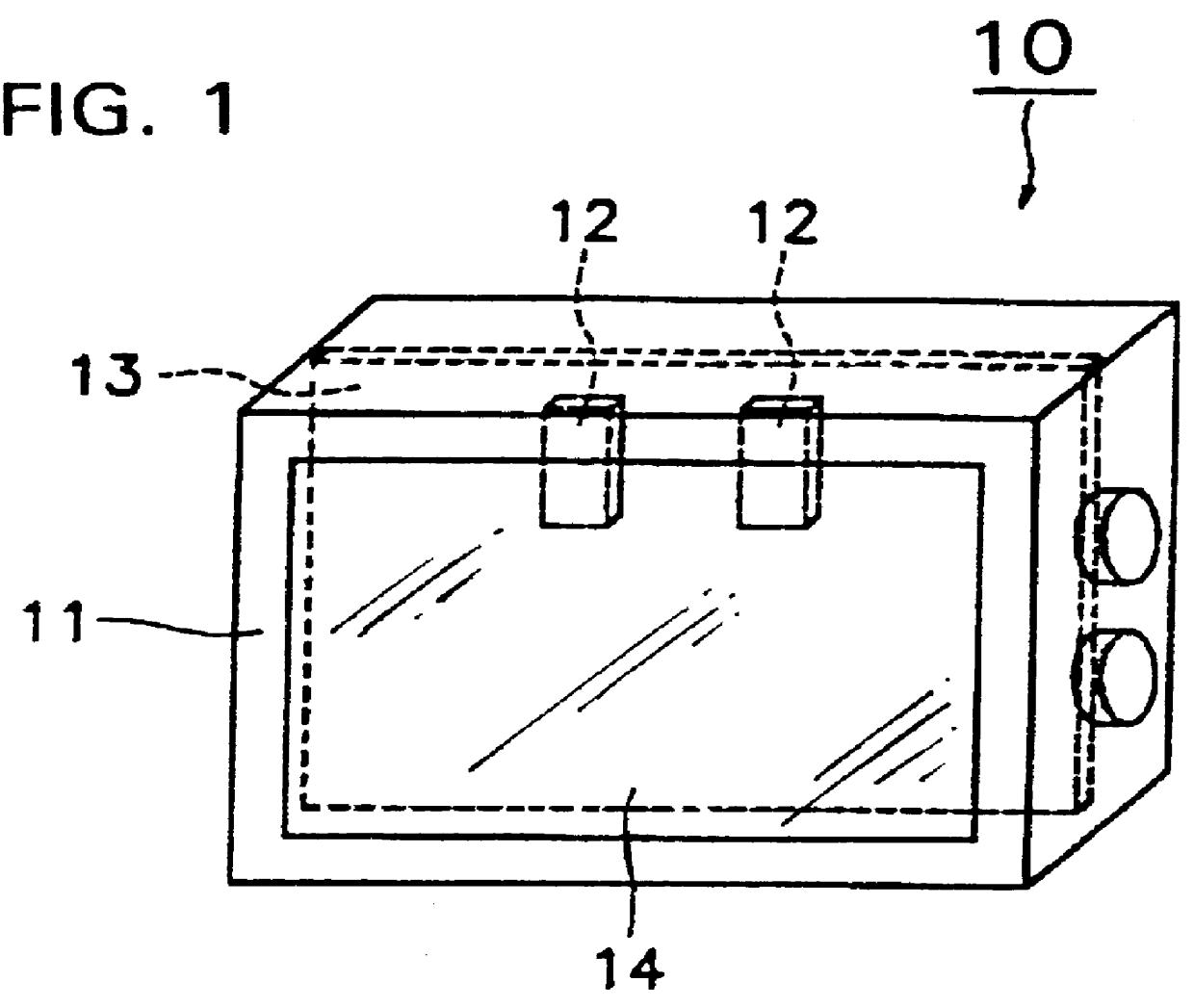

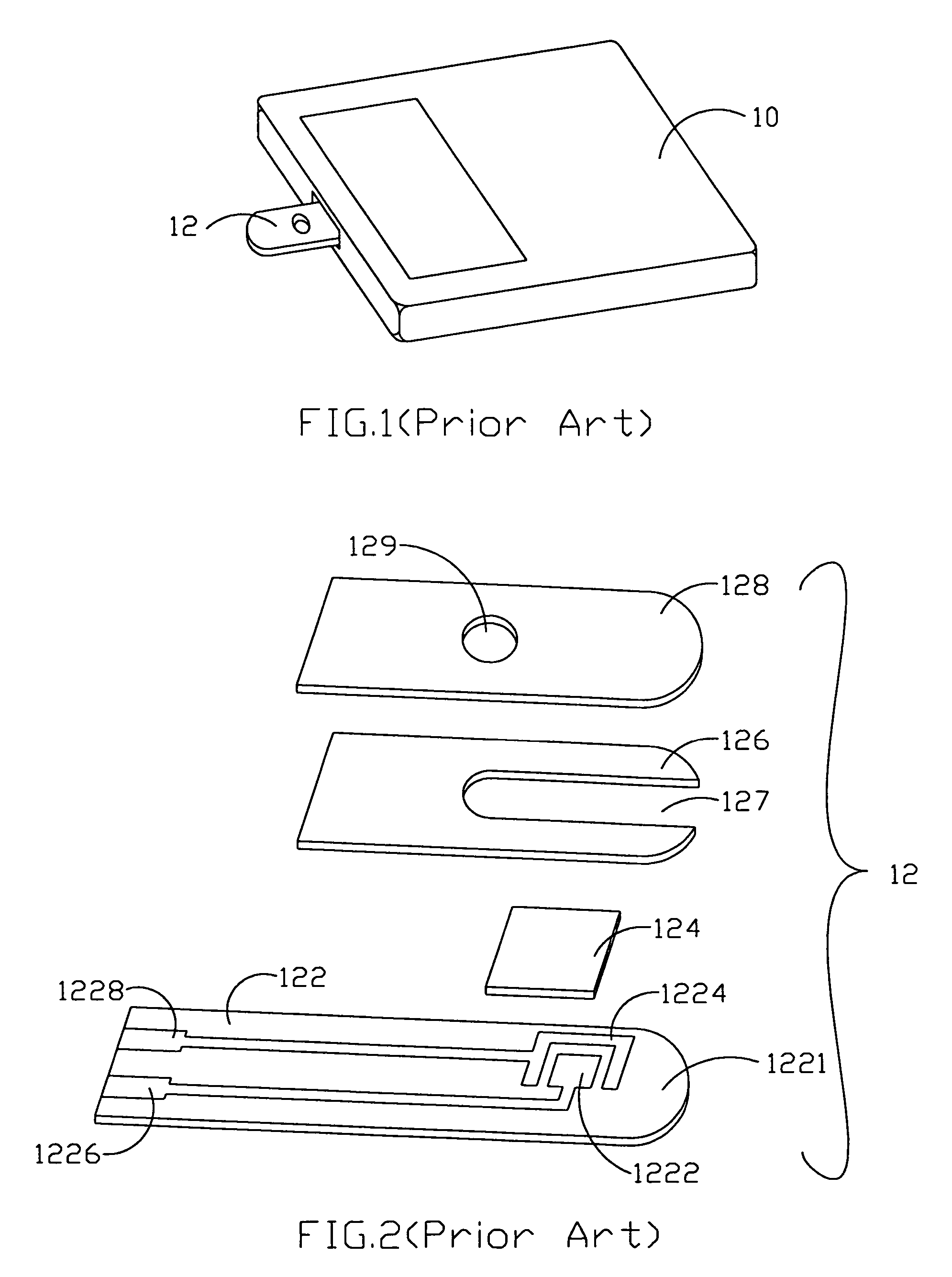

Mobile image apparatus and an antenna apparatus used for the mobile image apparatus

InactiveUS6028554AIncrease the lengthHigh sensitivitySimultaneous aerial operationsAntenna supports/mountingsElectrical conductorEngineering

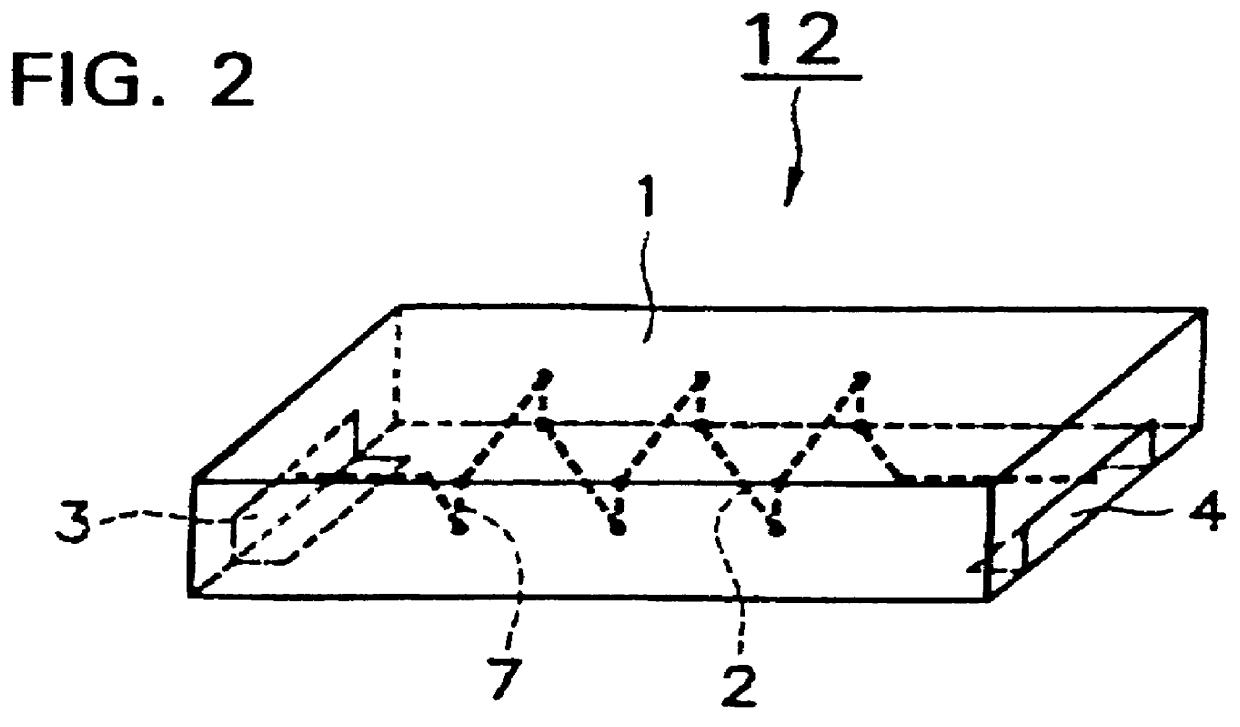

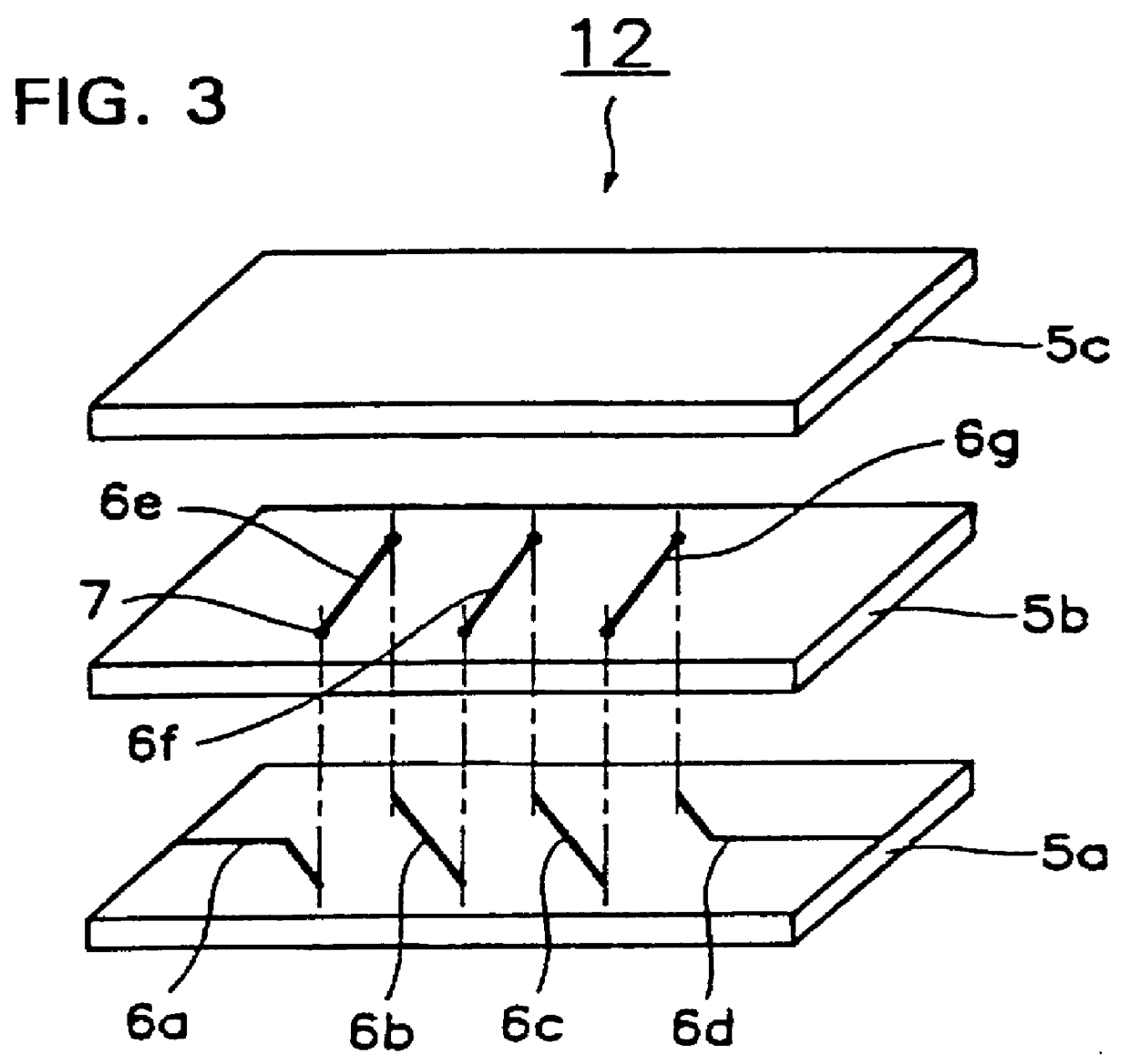

The invention provides a mobile image apparatus (10), comprising: a case unit (11); at least one antenna (12) disposed at least one of within said case unit (11) and outside said case unit (11); wherein said chip antenna (12) comprises; a substrate (1) made of at least one of a dielectric material and a magnetic material; at least one conductor (2) disposed at least one of within said substrate (1) and on a surface of said substrate (1); at least one power feeding terminal (3) disposed on a surface of said substrate (1) and connected to one end of said conductor (2) for applying a voltage to said conductor (2).

Owner:MURATA MFG CO LTD

Chip package structure

ActiveUS7061103B2Improve electrical performanceImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesEngineeringDie bonding

A chip package structure is disclosed. The chip package structure essentially comprises a carrier, one or more chips, a heat sink and an encapsulating material layer. At least one of the chips is flip-chip bonded and electrically connected to the carrier or another chip. There is a flip-chip bonding gap between the chip and the carrier or other chips. A heat sink is positioned on the uppermost chip. The encapsulating material layer fills the flip-chip bonding gap as well as a gap between the uppermost chip and the heat sink. A part of the surface of the heat sink away from the upper-most chip is exposed. Furthermore, the encapsulating material layer is formed in a simultaneous molding process. For example, the chip is separated from the heat sink by a distance between 0.03˜0.2 mm, and the encapsulating material has a thermal conductivity greater than 1.2 W / m.K.

Owner:IND TECH RES INST +1

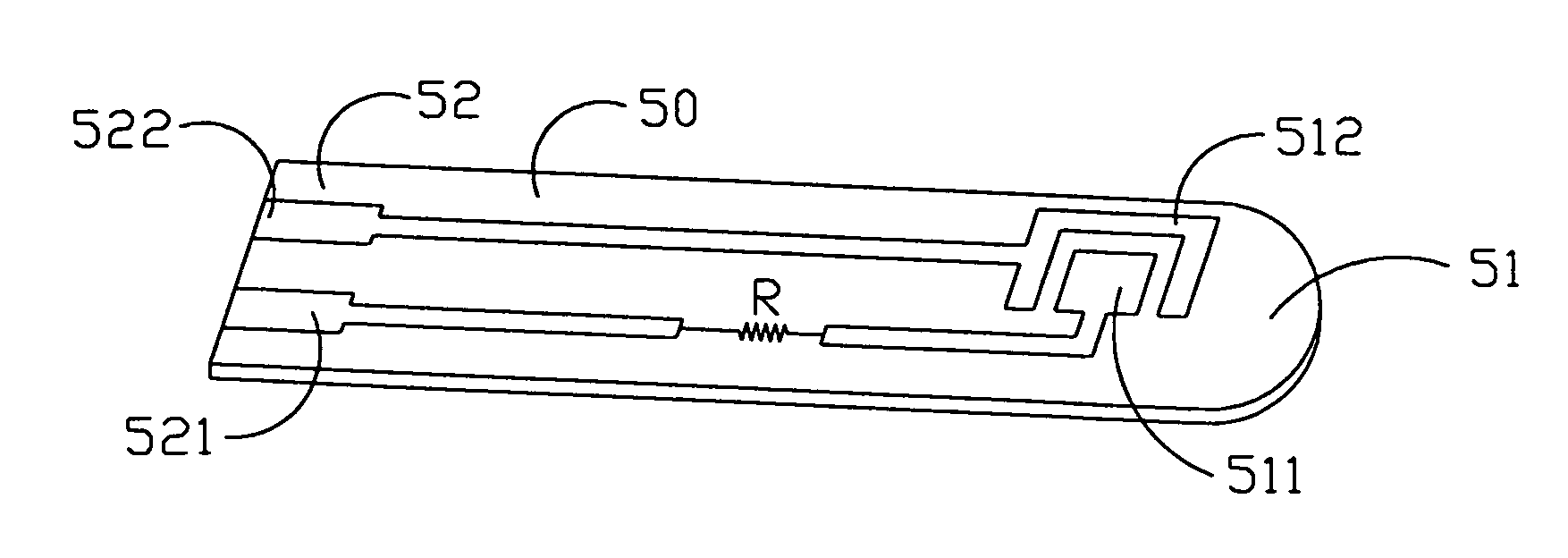

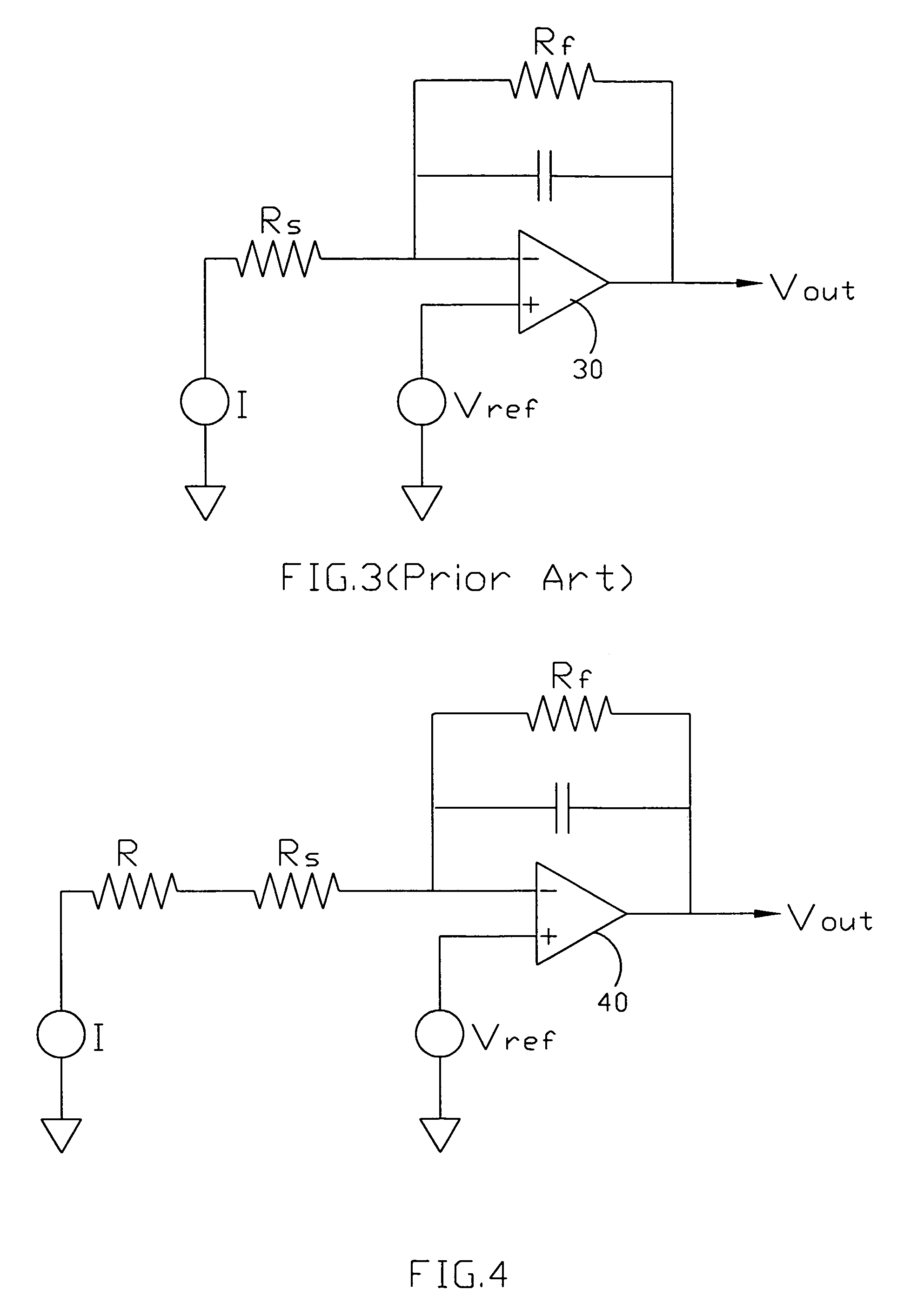

Chip with measuring reliability and a method thereof

ActiveUS7374721B2Improve chip reliabilityImprove measurement reliabilityImmobilised enzymesBioreactor/fermenter combinationsElectrical resistance and conductanceResistor

A chip with measuring reliability and a method thereof are provided. The present invention serially connects a resistor having a resistance equal to or a little more than a maximum resistance of the chip itself to the resistor Rs of the chip so as to compensate the resistance differences among chips. A noise to signal (N / S) ratio of the chip is decreased, and a measuring reliability of the chip is improved.

Owner:INTELLECTUAL VENTURES I LLC

Chip package with a dam structure on a die pad

InactiveUS7812432B2Improve chip reliabilityImprove reliabilityElectrically conductive connectionsSemiconductor/solid-state device detailsAdhesiveElectrical and Electronics engineering

Owner:CHIPMOS TECH INC

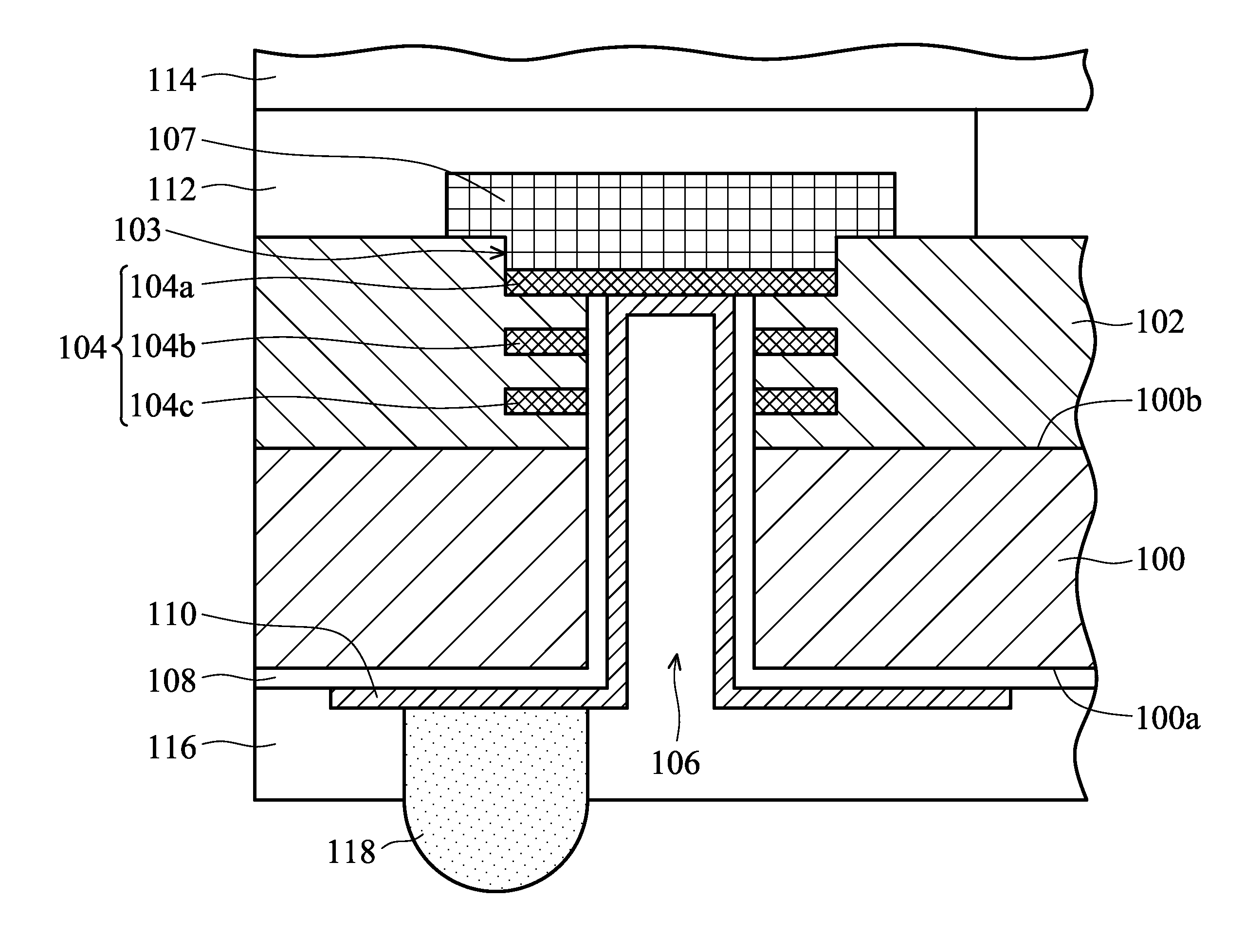

Chip package and method for forming the same

ActiveUS20120181672A1Improve chip reliabilityImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringDielectric layer

An embodiment of the invention provides a chip package which includes a substrate having a first surface and a second surface; a conducting pad structure located on the first surface; a dielectric layer located on the first surface of the substrate and the conducting pad structure, wherein the dielectric layer has an opening exposing a portion of the conducting pad structure; and a cap layer located on the dielectric layer and filled into the opening.

Owner:XINTEC INC

Power-up signal generating apparatus

InactiveUS20050093529A1Improve chip reliabilityPulse automatic controlElectric lighting sourcesVoltage generatorElectricity

In a power-up signal generating device, a power-up signal is activated at a certain level of the power supply voltage VDD by adjusting the turn-on resistance value of the MOS transistor so that the chip reliability can be improved. The power-up signal generating device comprises a reference voltage generating unit, a bias level adjusting unit, a bias signal generating unit and a signal outputting unit. The reference voltage generating unit generates a reference voltage. The bias level adjusting unit receives the reference voltage as an input for controlling a voltage level of a bias signal in a constant level. The bias signal generating unit generates the bias signal under control of the bias level adjusting unit. The signal outputting unit outputs a power-up signal depending on the voltage level of the bias signal.

Owner:SK HYNIX INC

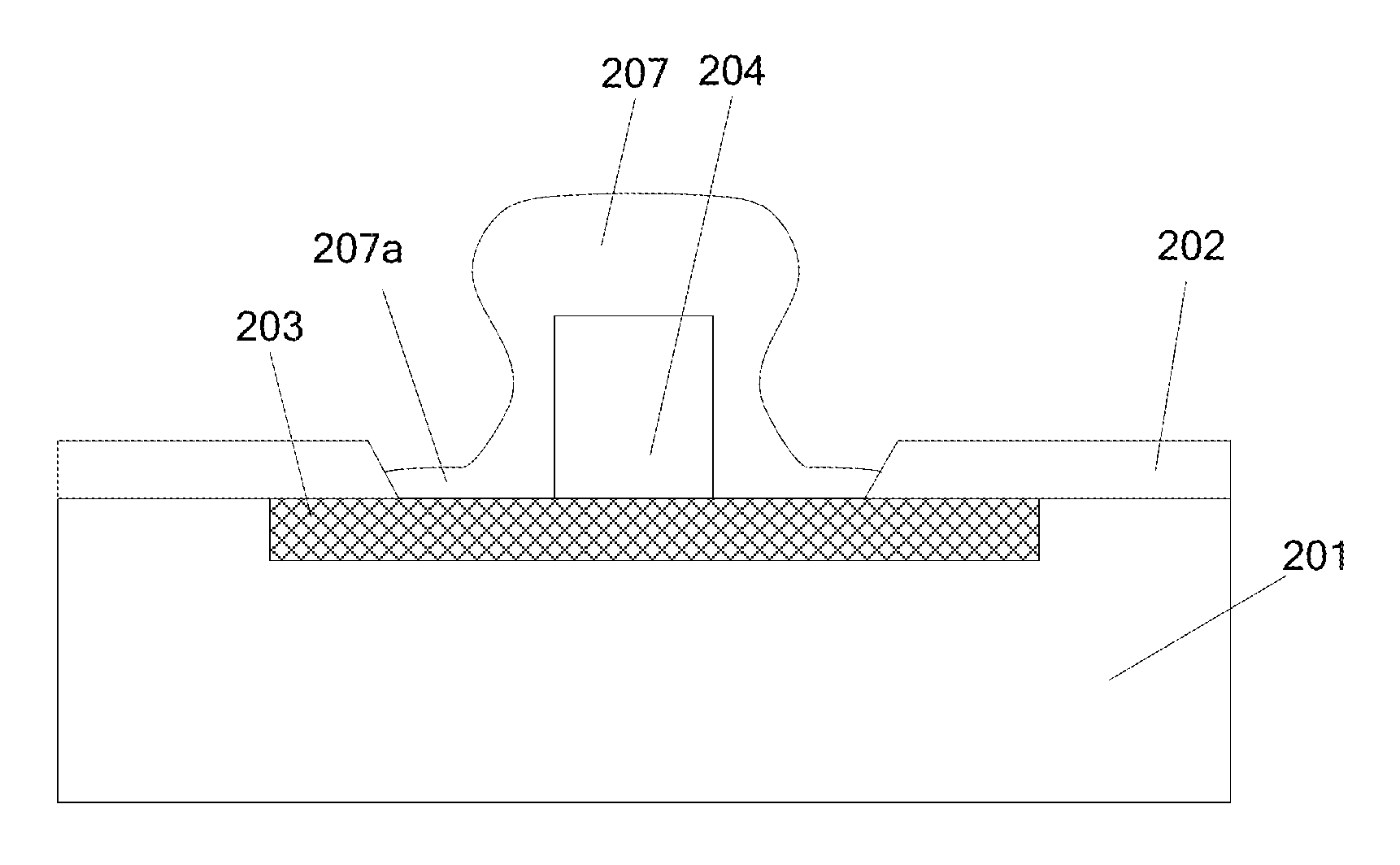

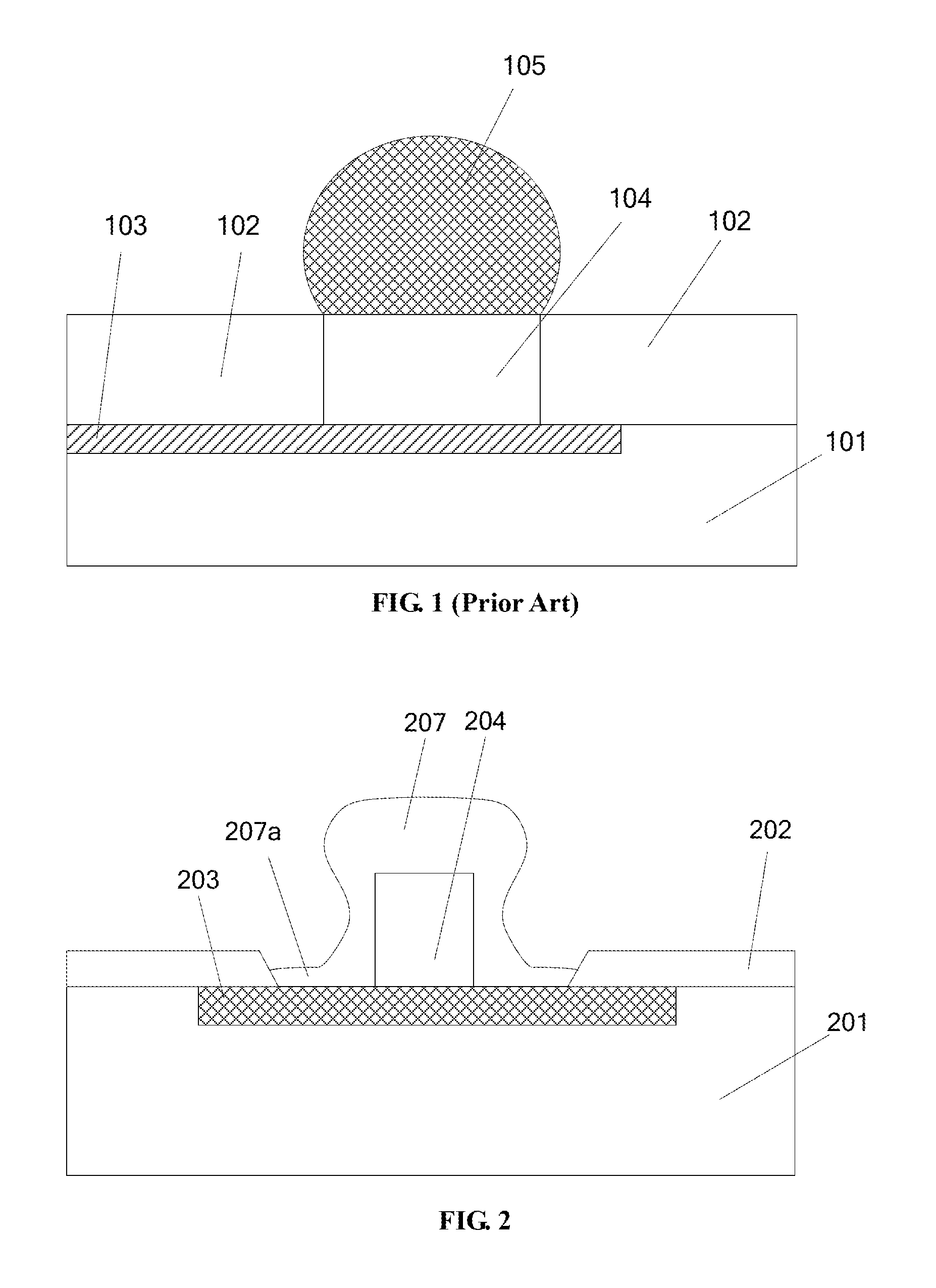

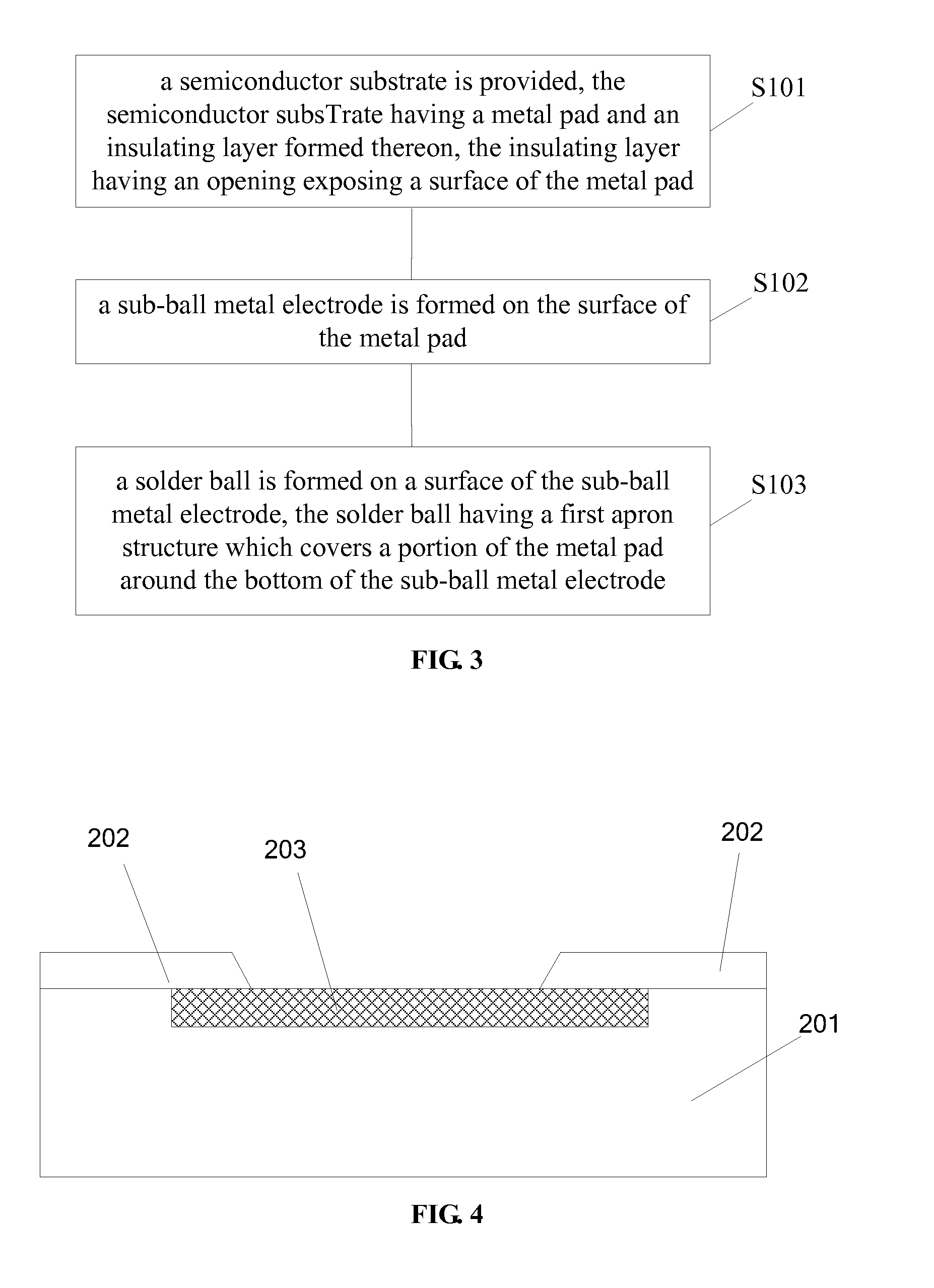

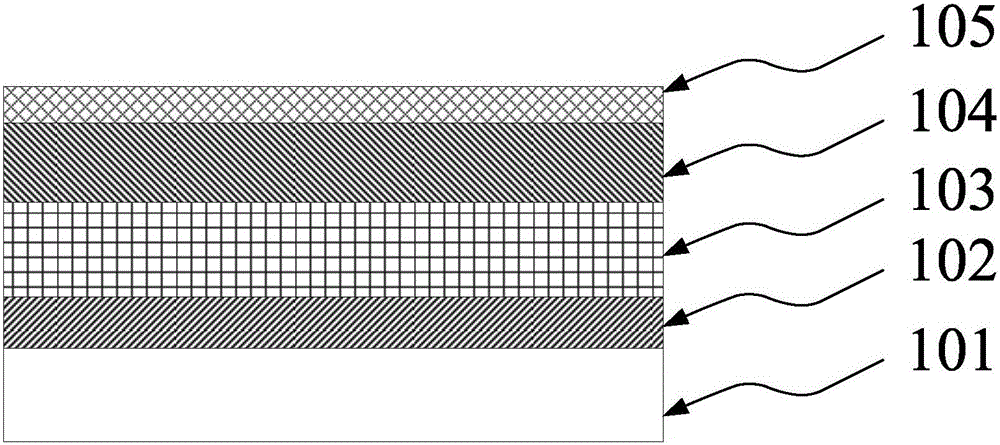

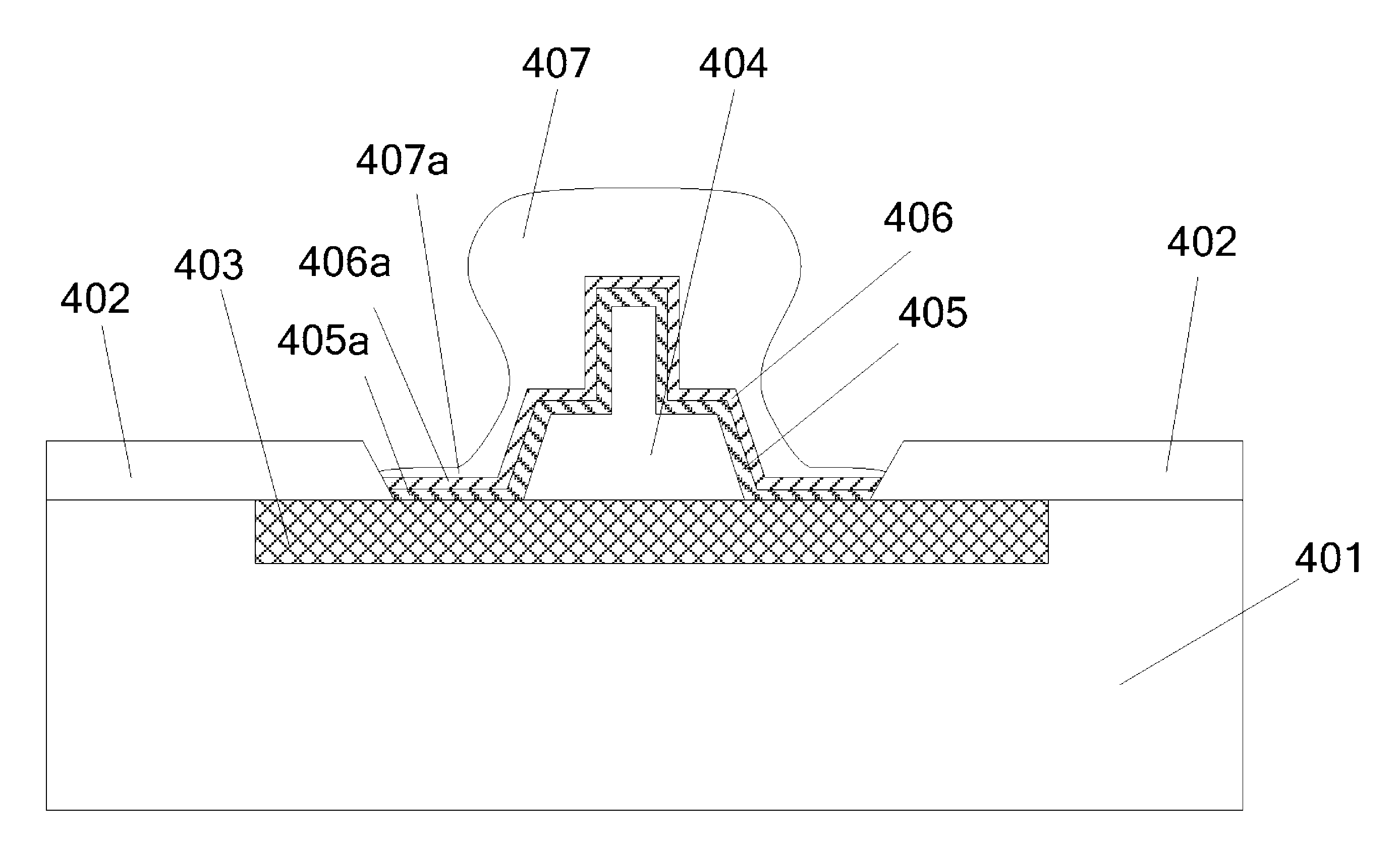

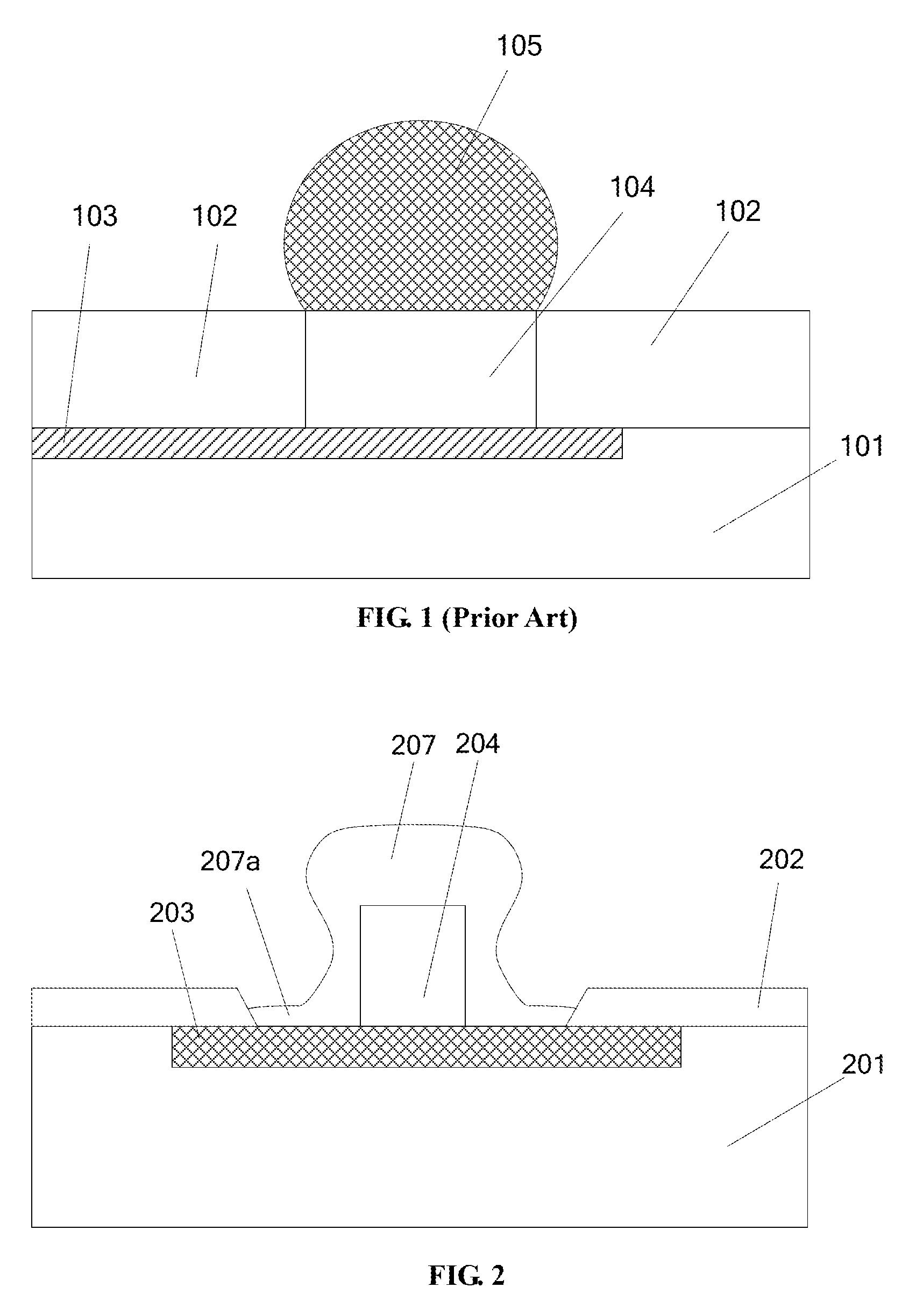

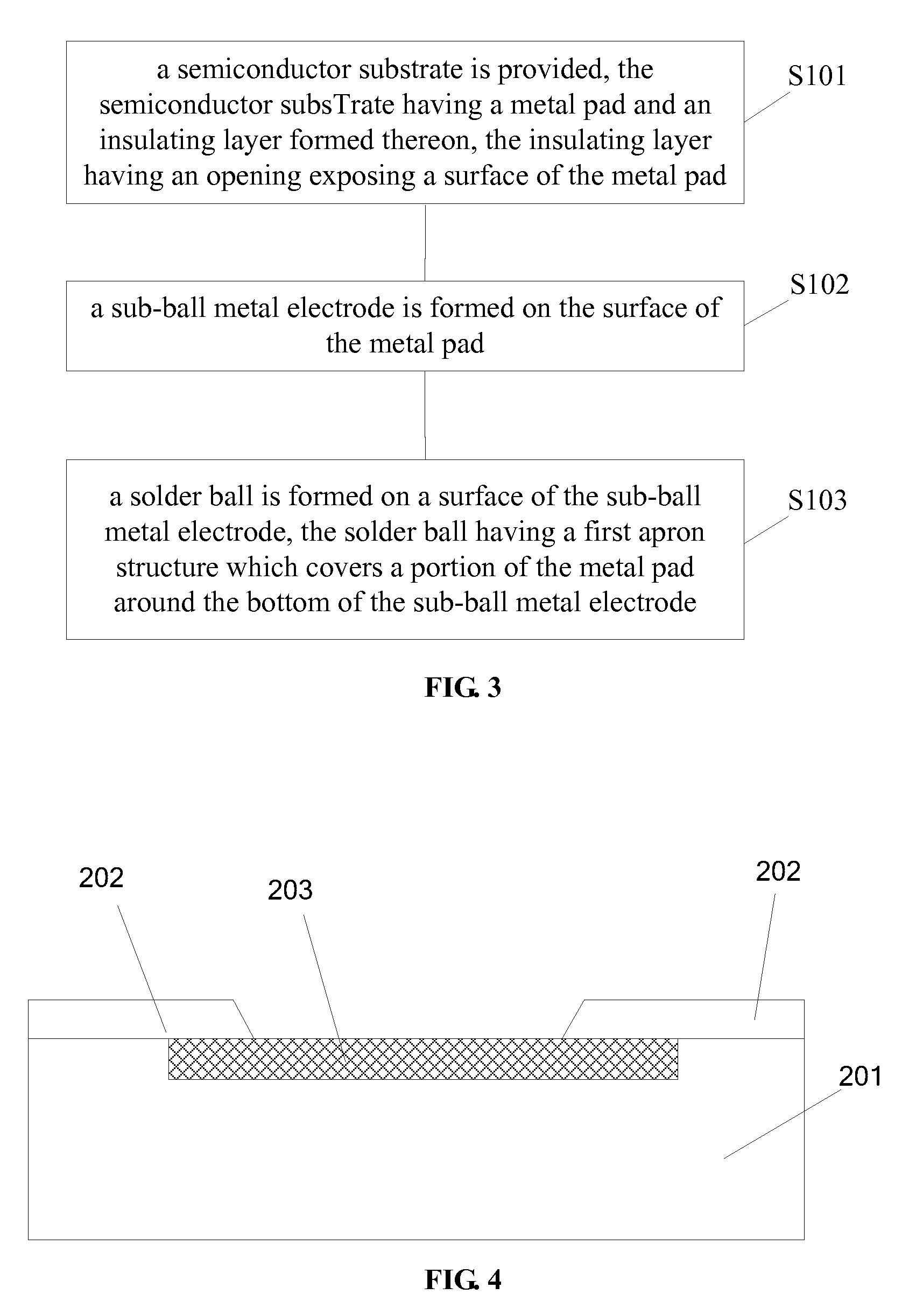

Chip packaging structure and packaging method

ActiveUS20150294949A1Increase contact areaEnhance adhesionSemiconductor/solid-state device detailsSolid-state devicesSolder ballSemiconductor

A chip packaging structure and packaging method. The packaging structure comprises: a semiconductor substrate; a metal pad provided inside the semiconductor substrate; an insulating layer provided on the semiconductor substrate, the insulating layer having an opening for exposing the metal pad; a sub-ball metal electrode provided on the metal pad; a solder ball provided on the surface of the sub-ball metal electrode, the solder ball having a first apron structure and the first apron structure covering partial metal pad on the periphery of the bottom of the under-ball metal electrode. The chip packaging structure of the present invention enhances the adhesion between the solder ball and the metal pad, and improves the reliability in chip packaging.

Owner:NANTONG FUJITSU MICROELECTRONICS

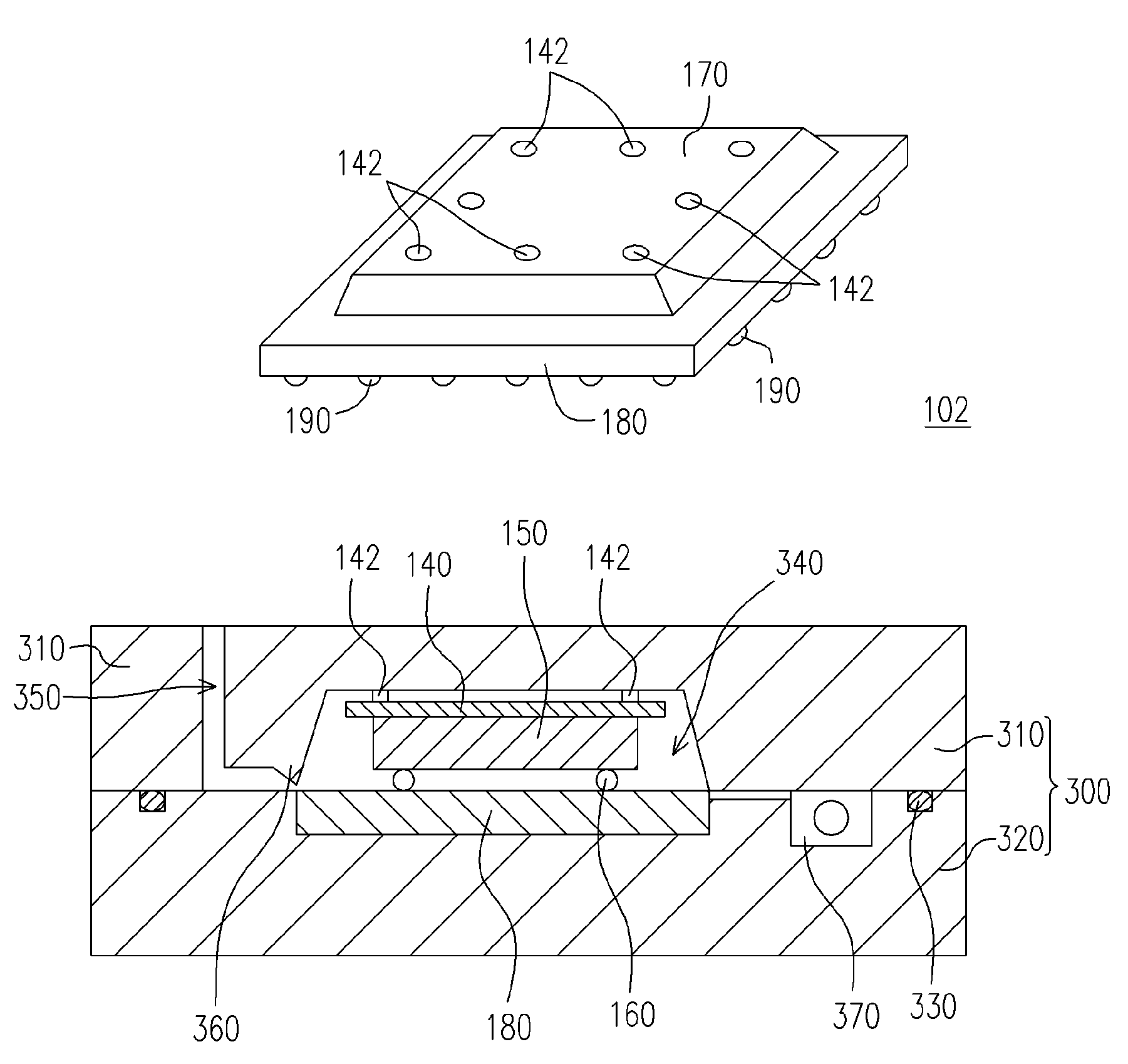

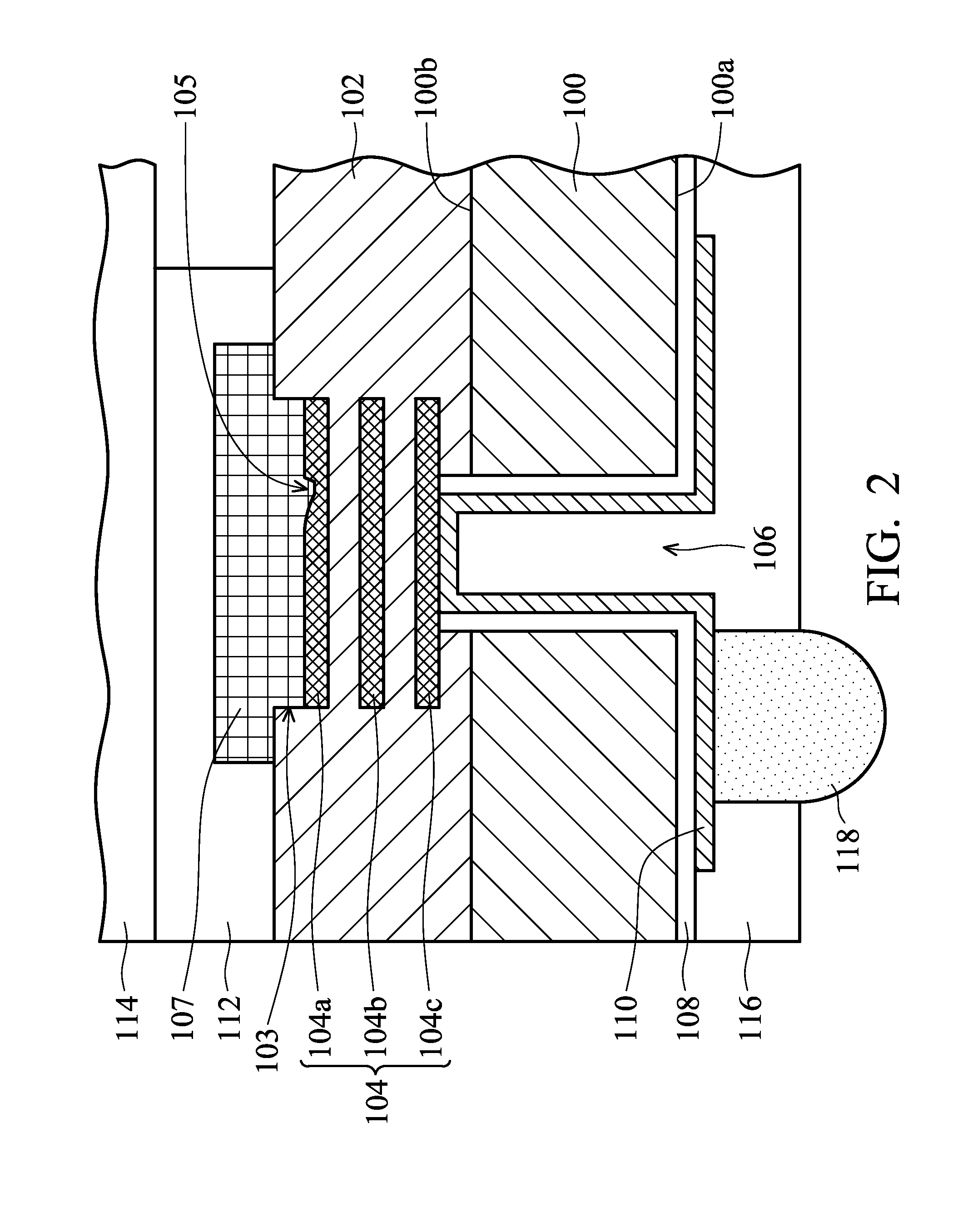

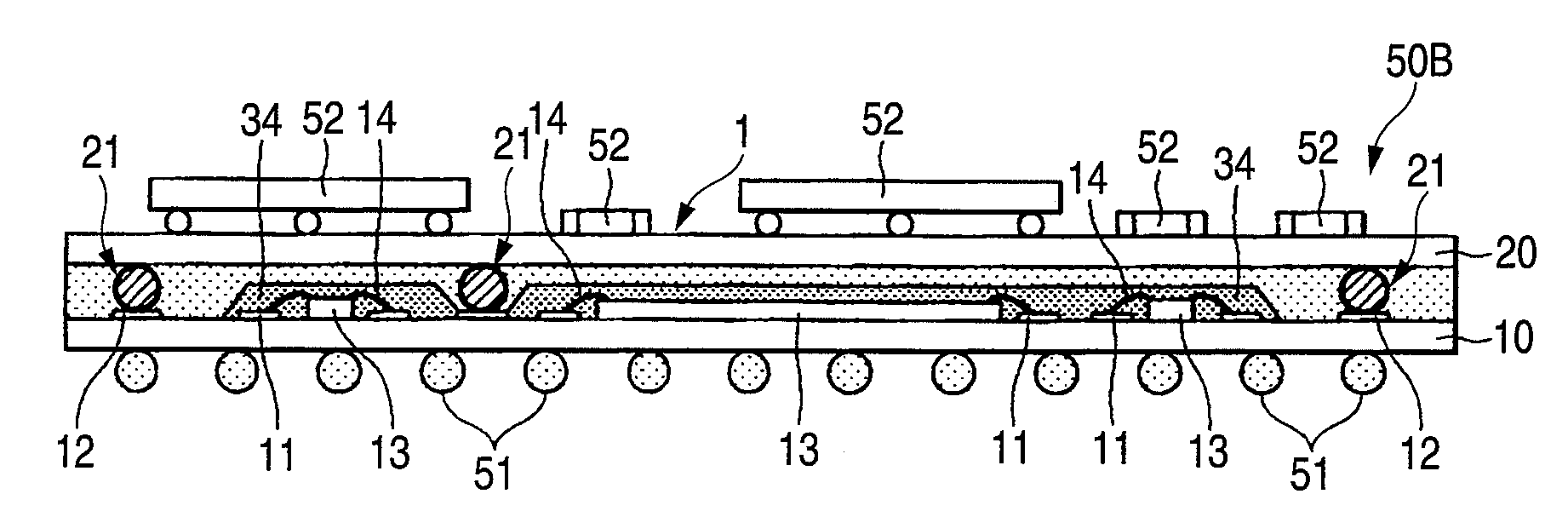

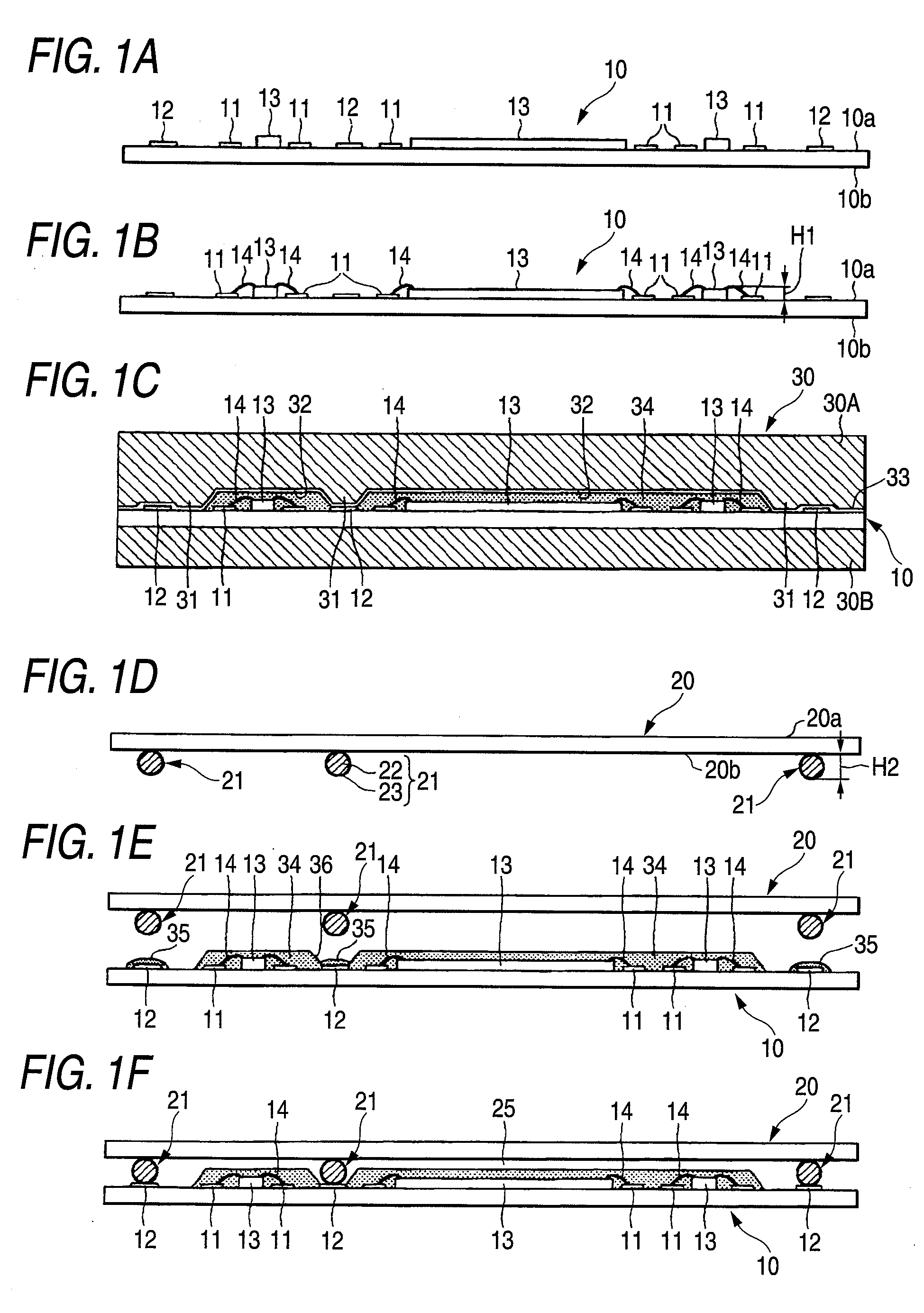

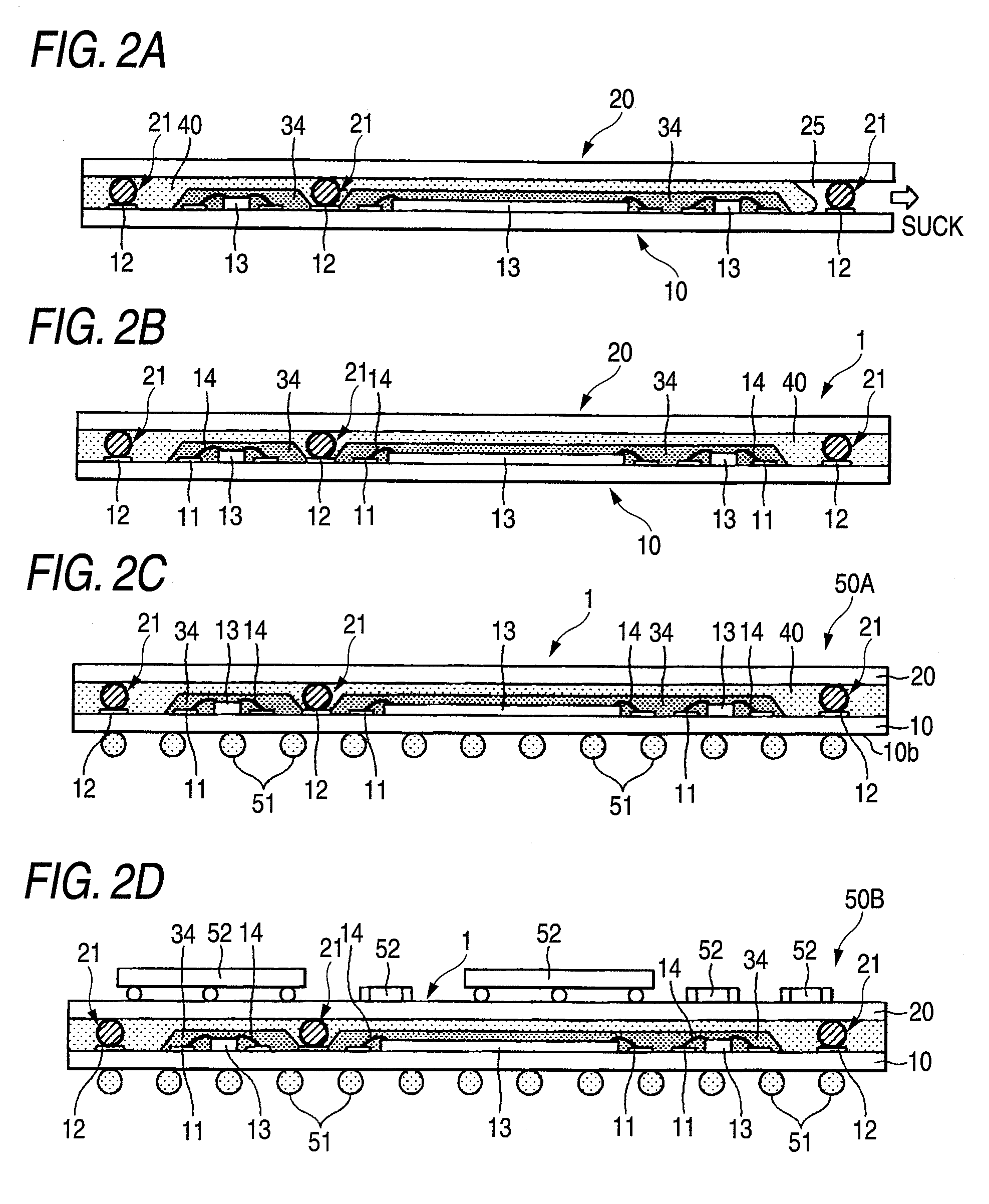

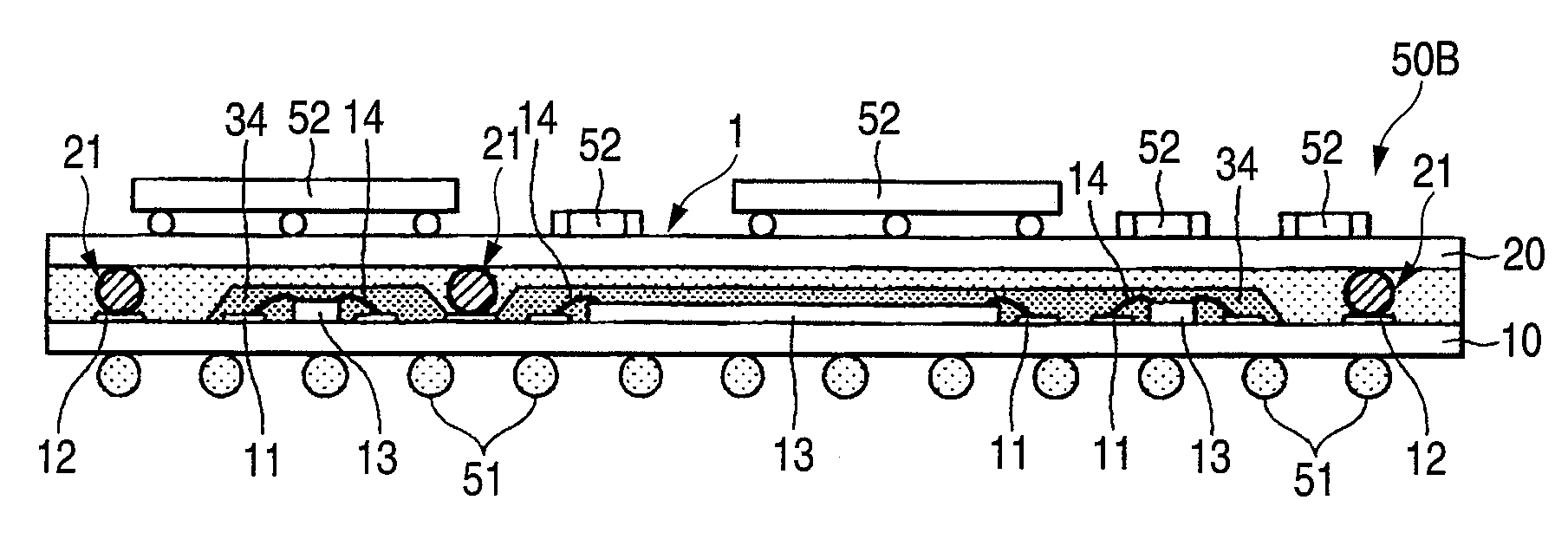

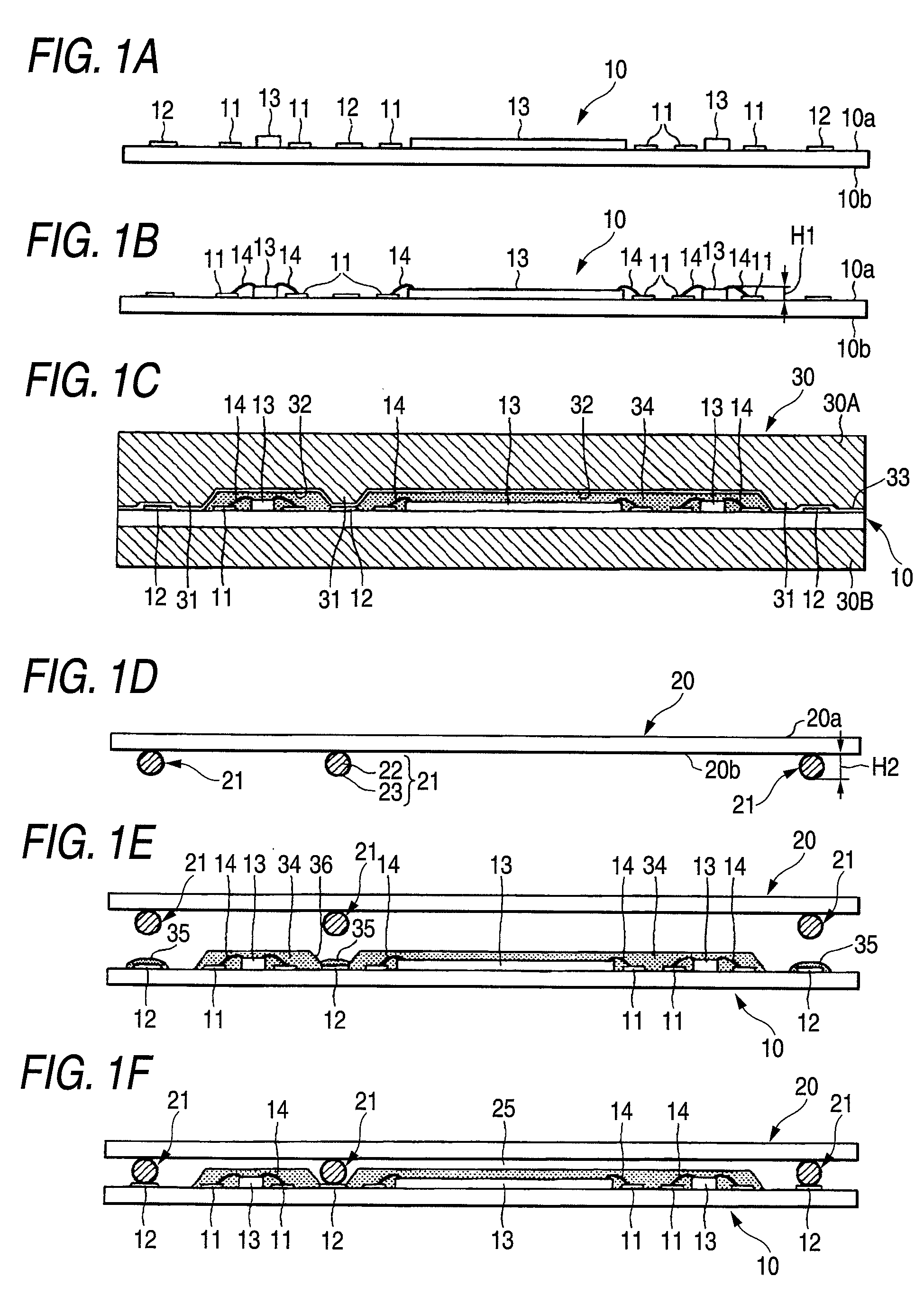

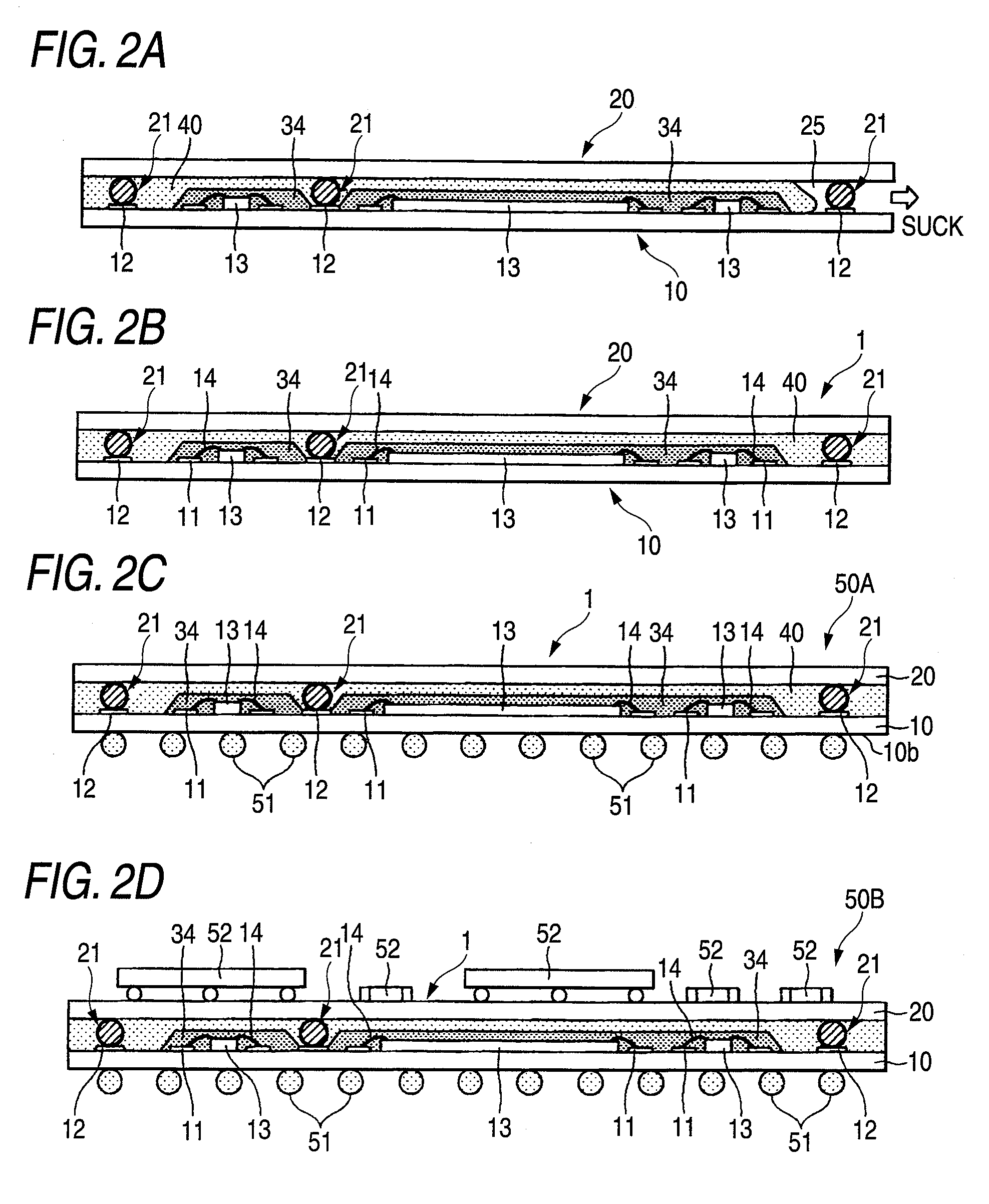

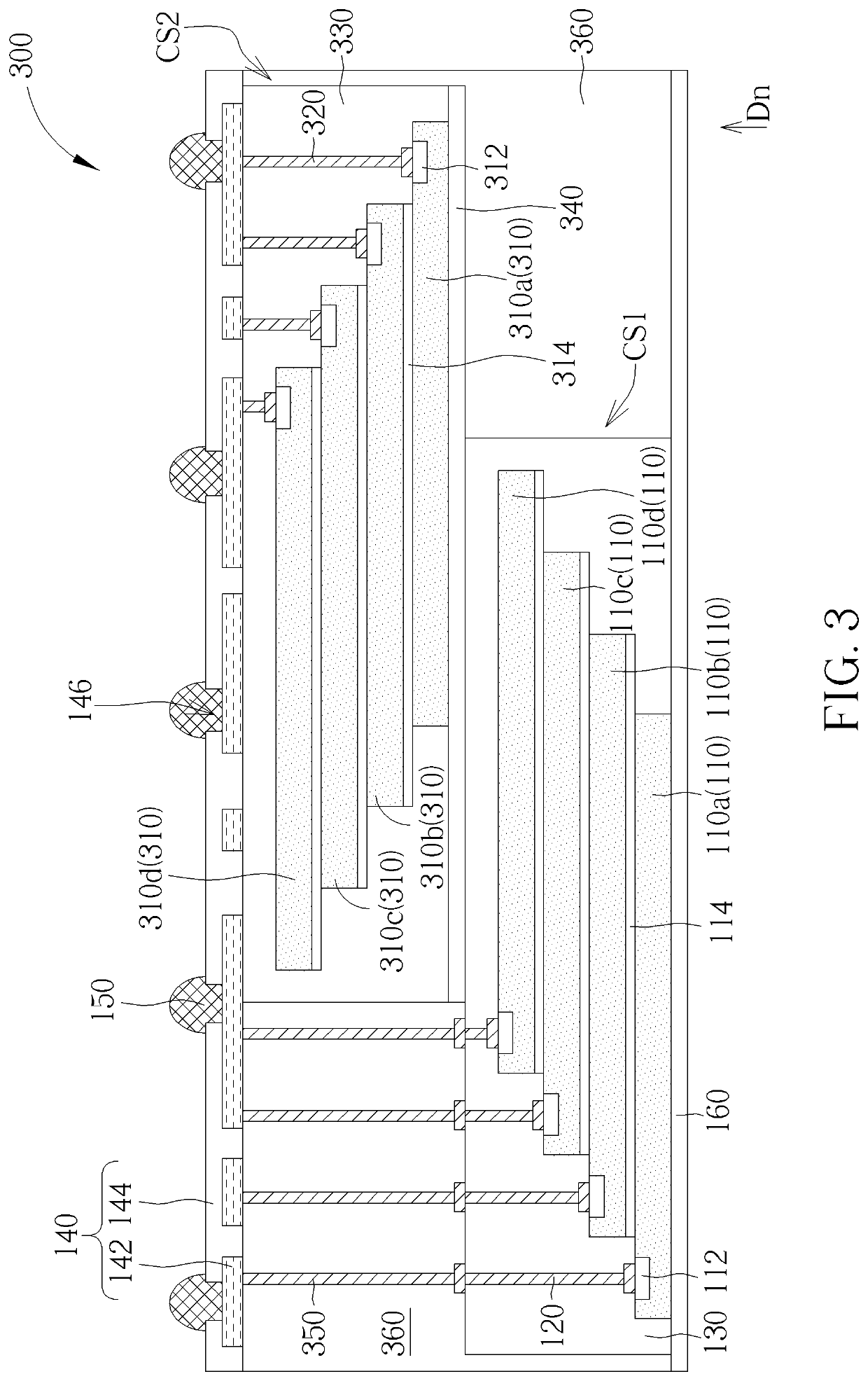

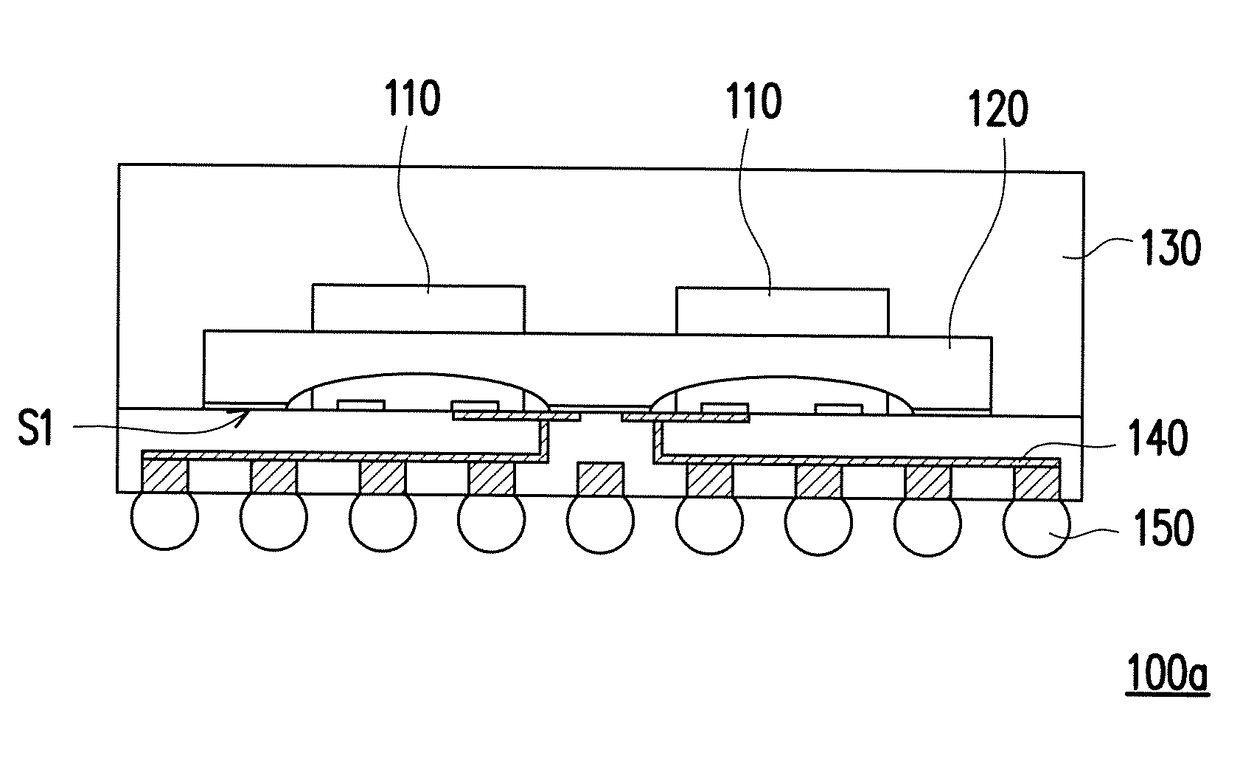

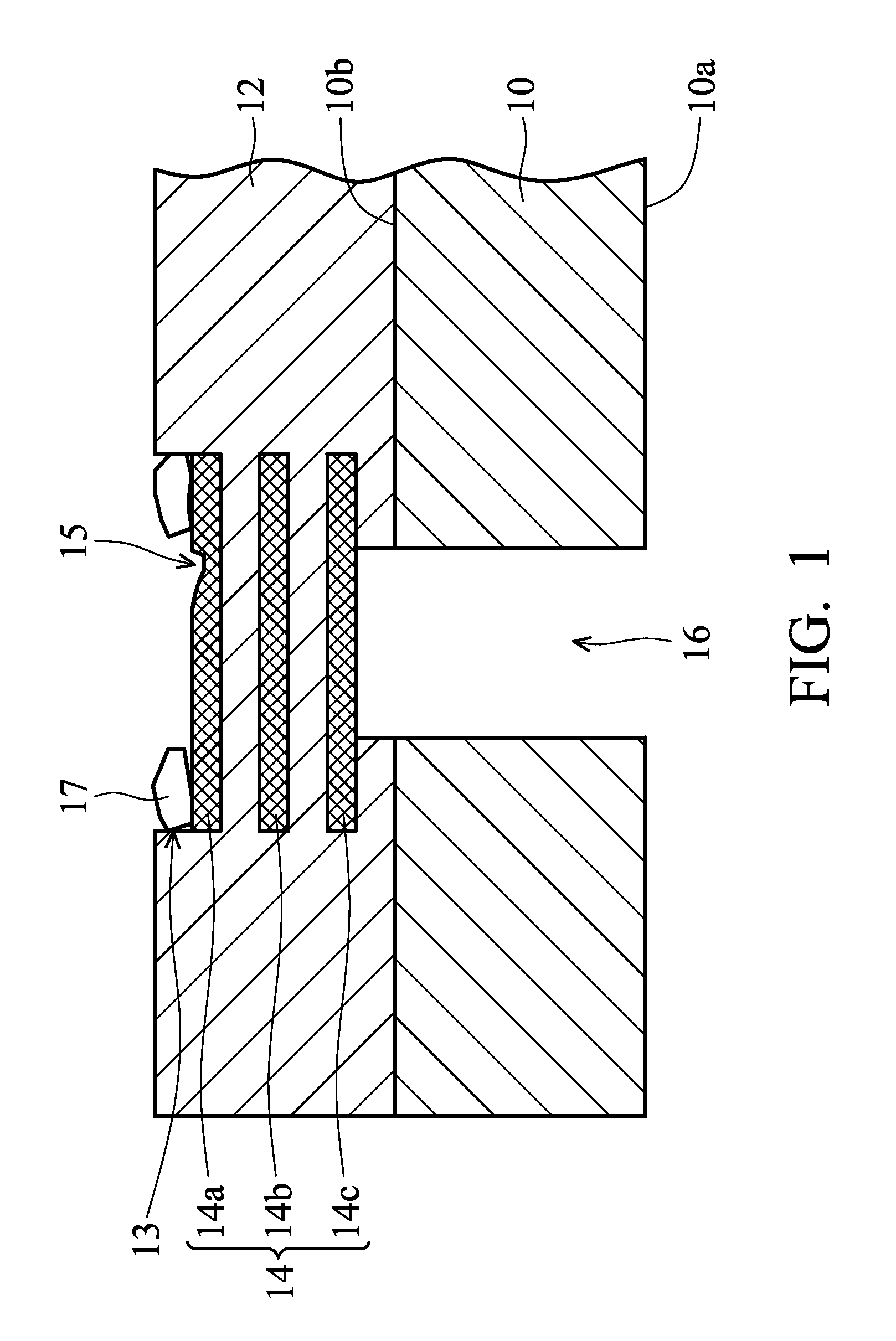

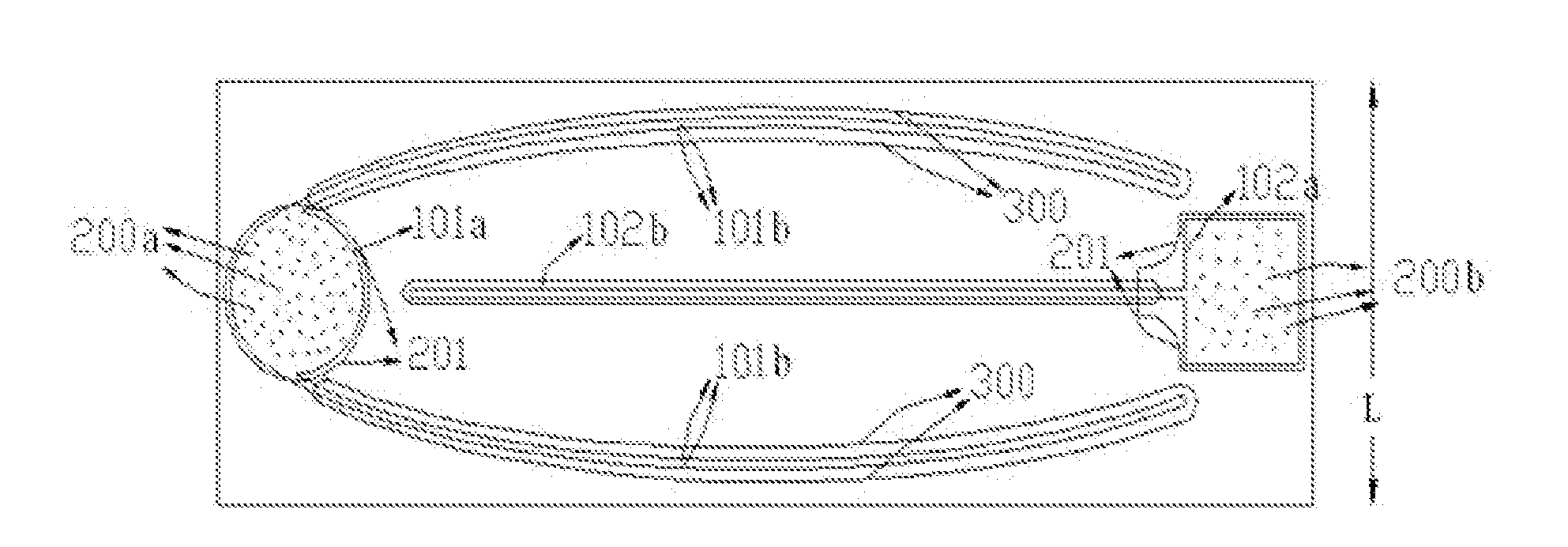

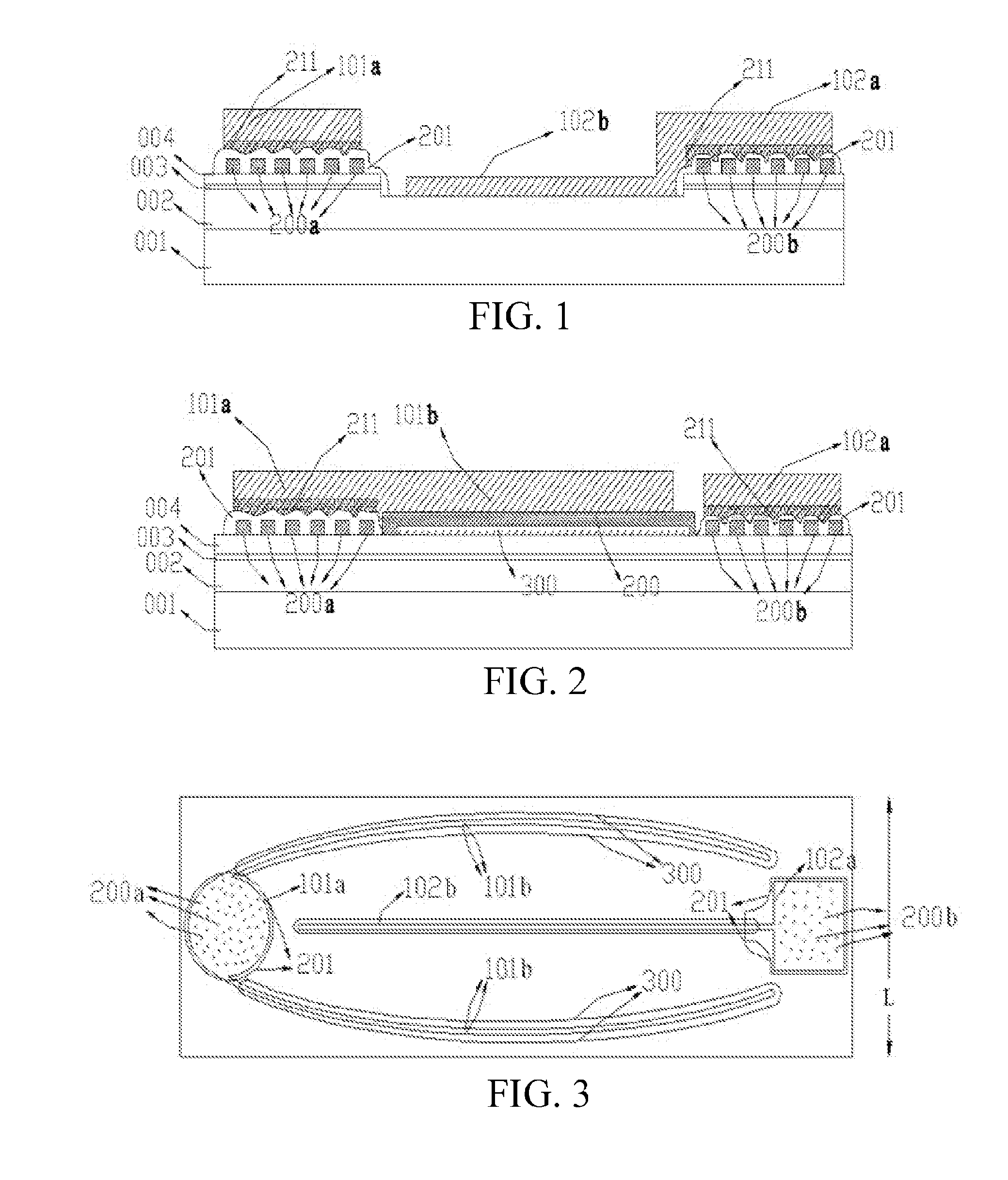

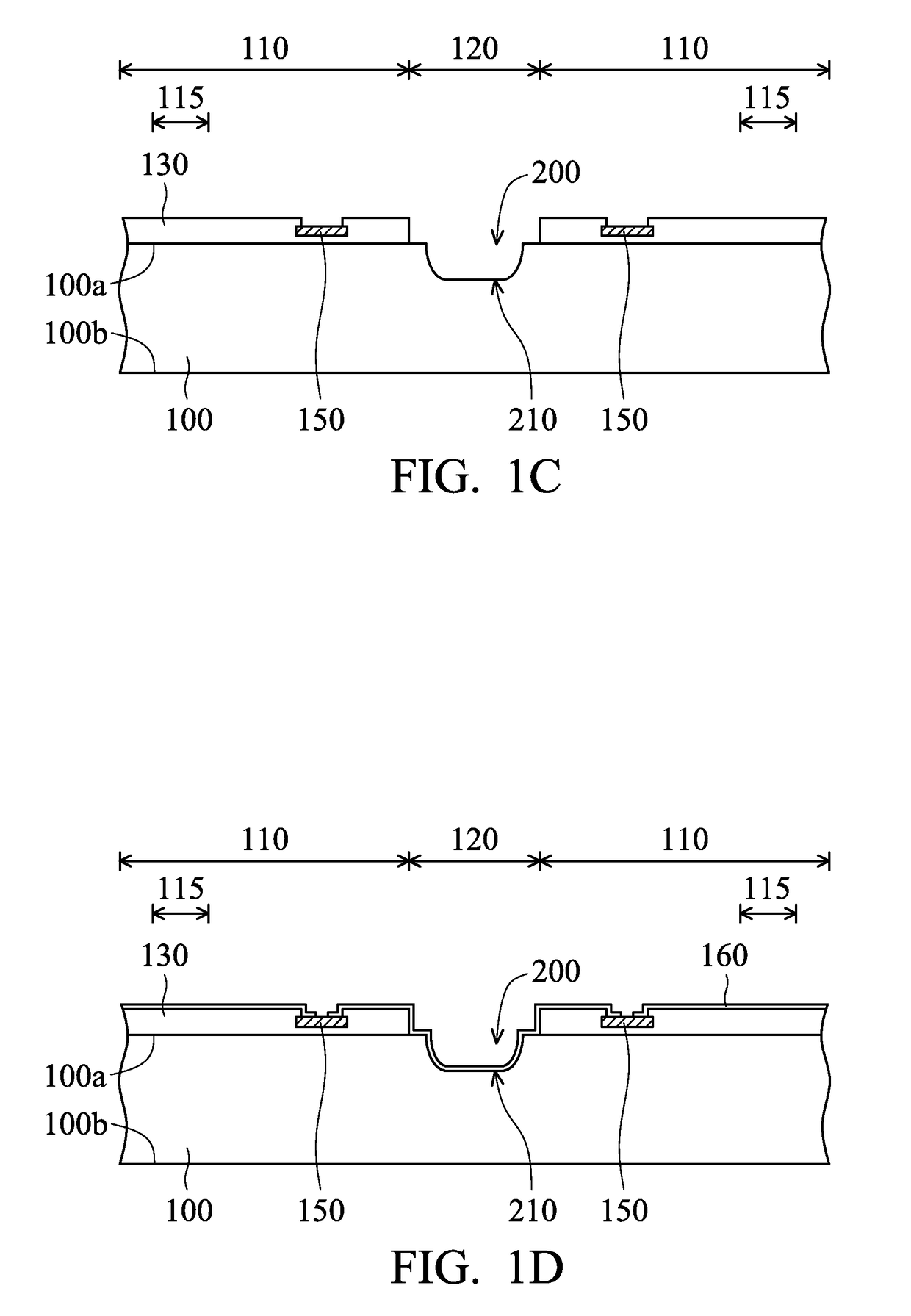

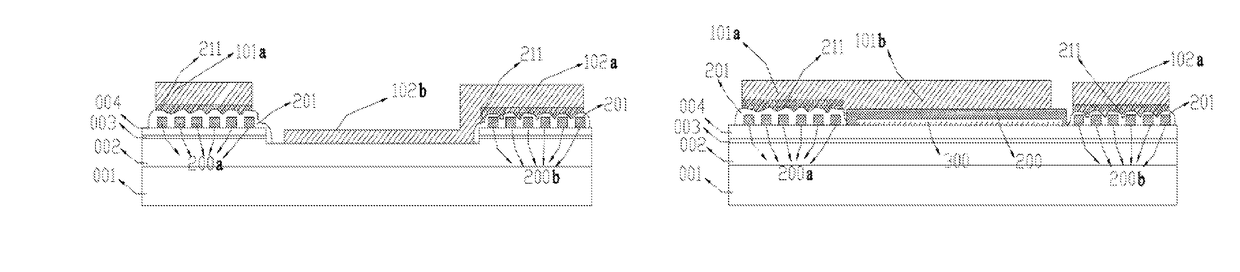

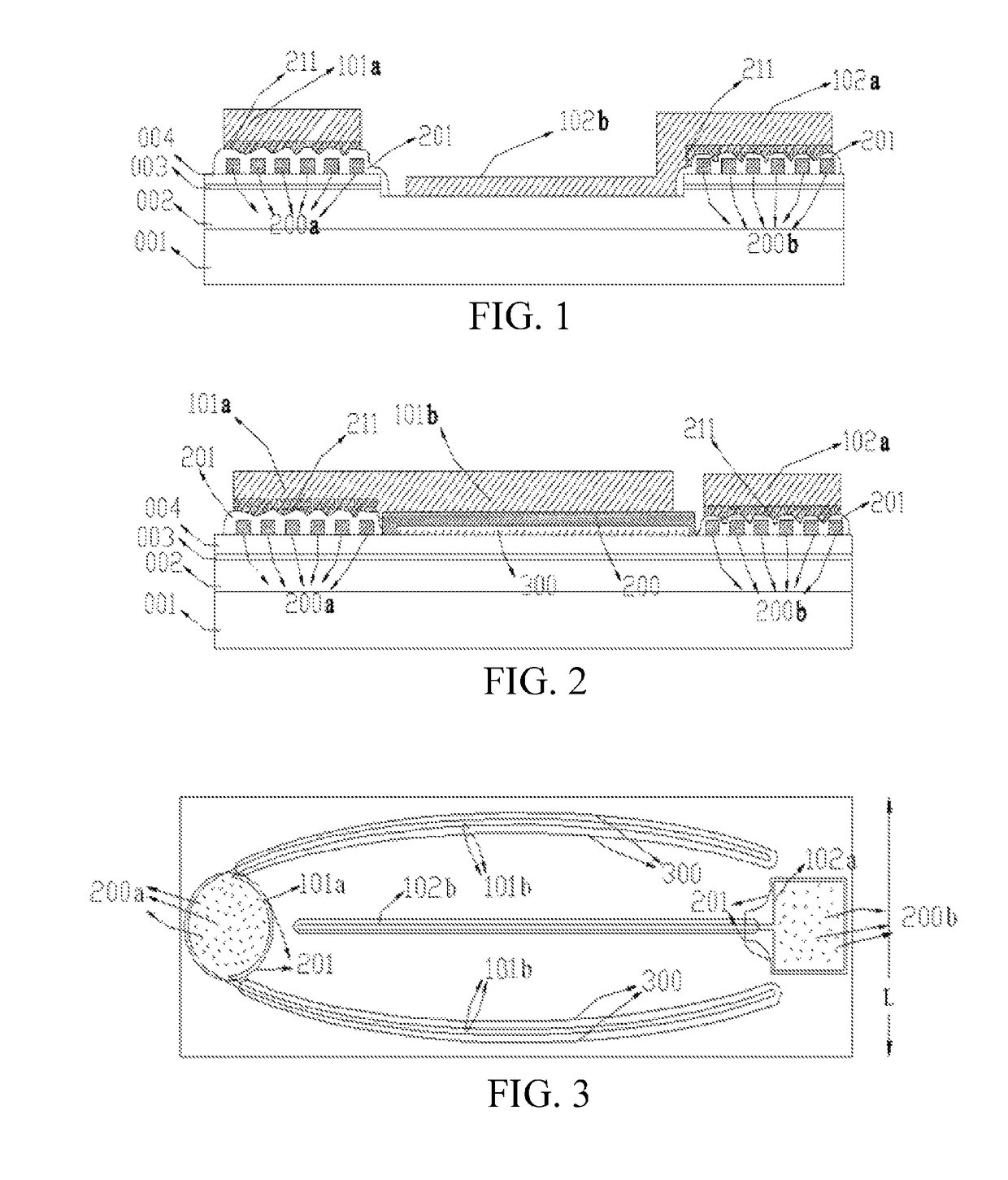

Method of manufacturing chip integrated substrate

ActiveUS20080293189A1Improve reliabilityPrevent breakage and short circuitSemiconductor/solid-state device detailsPrinted circuit aspectsElectrical and Electronics engineering

There are provided the steps of connecting a chip component 13 to a first substrate 10 through a wire 14, providing an electrode 21 on a second substrate 20, attaching, to the first substrate 10, a molding tool 30 having a protruded portion 31 formed corresponding to an array of a bump connecting pad 12 of the first substrate 10 and a cavity 32 formed corresponding to a region in which the chip component 13 is mounted, thereby forming a first sealing resin 34 for sealing the chip component 13 and the wire 14, bonding the electrode 21 to the bump connecting pad 12 through a solder, thereby bonding the first substrate 10 to the second substrate 20, and filling a second filling resin 40 in a clearance portion between the first substrate 10 and the second substrate 20.

Owner:SHINKO ELECTRIC IND CO LTD

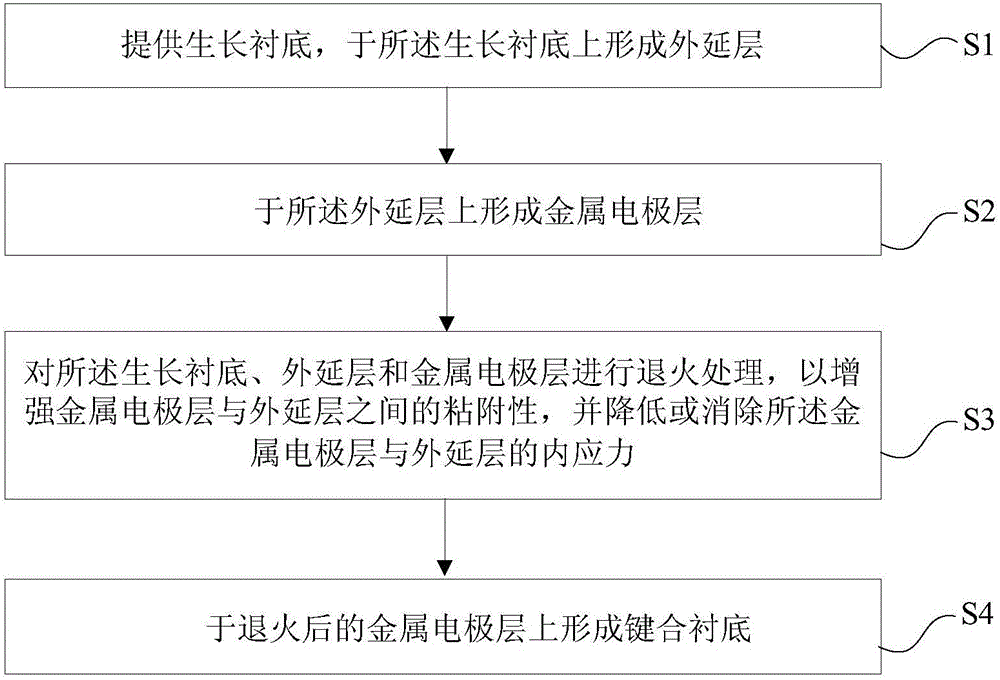

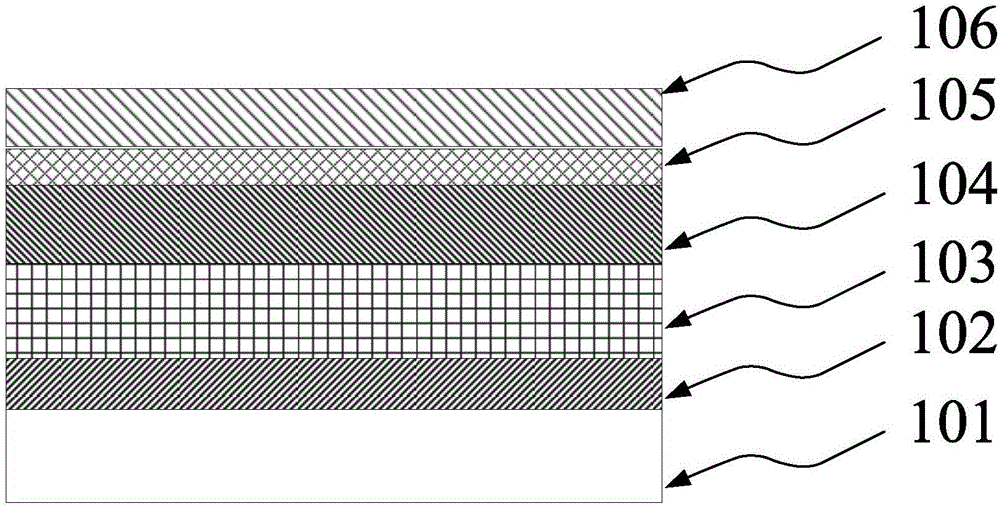

Vertical light emitting diode (LED) chip structure and fabrication method thereof

InactiveCN105742445AImprove chip reliabilityInterlaminar Stress ReliefSolid-state devicesSemiconductor/solid-state device manufacturingInternal stressDiode

The invention provides a vertical light emitting diode (LED) chip structure and a fabrication method thereof. The fabrication method comprises the following steps of 1) providing a growth substrate, and forming an epitaxial layer on the growth substrate; 2) forming a metal electrode layer on the epitaxial layer; 3) carrying out annealing processing on the growth substrate, the epitaxial layer and the metal electrode layer so as to improve the adhesion between the metal electrode layer and the epitaxial layer and reduce or eliminate the internal stress between the metal electrode layer and the epitaxial layer; and 4) forming a bonding substrate on the annealed metal electrode layer. By the fabrication method, the problems that a bonding substrate is easy to break or seriously deform and microscopic influence is generated on the epitaxial layer structure and the performance to directly cause serious electric leakage and extremely poor finished rate due to large internal stress of a wafer after bonding during vertical fabrication of a large-sized LED chip in the prior art are solved.

Owner:ENRAYTEK OPTOELECTRONICS

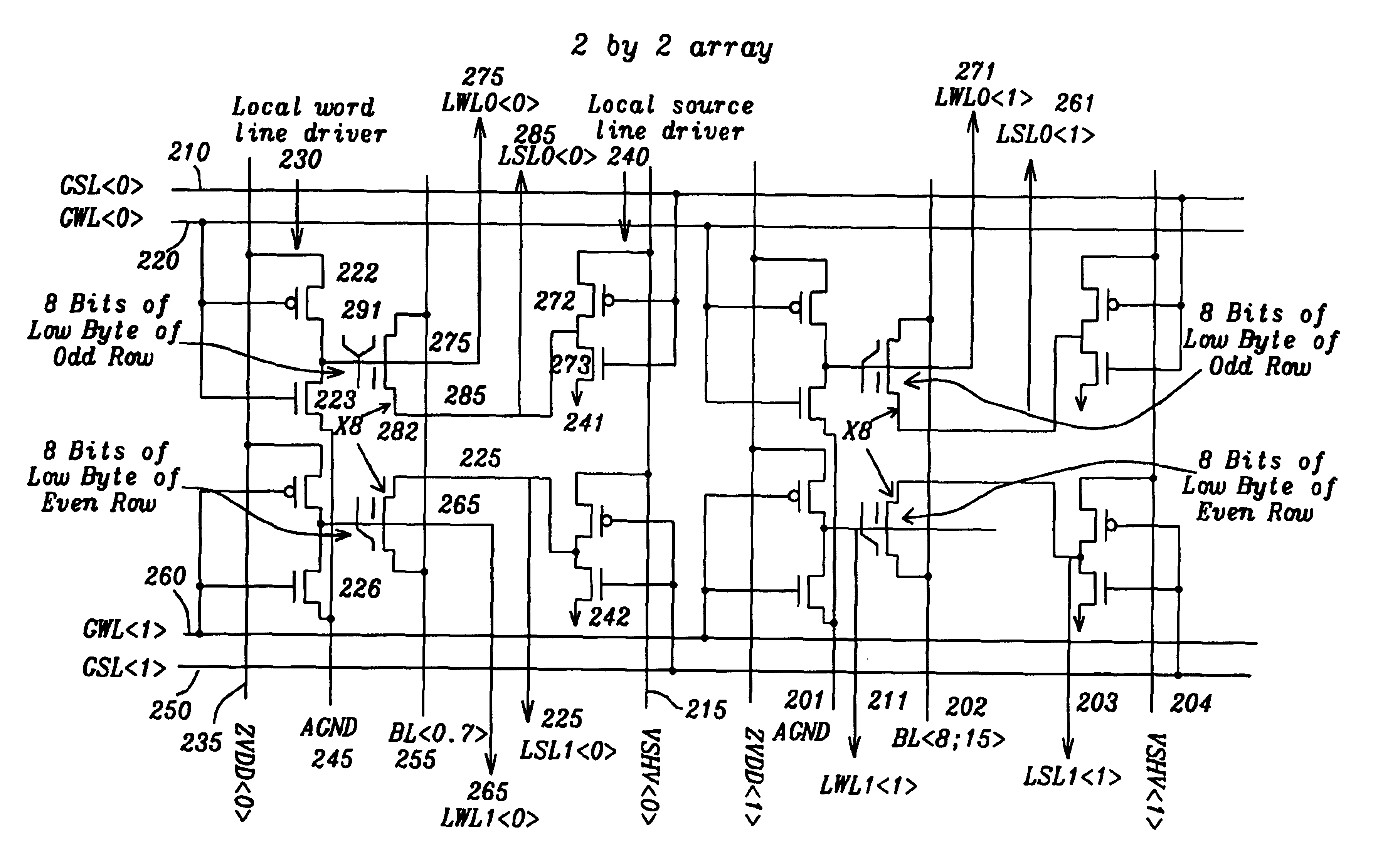

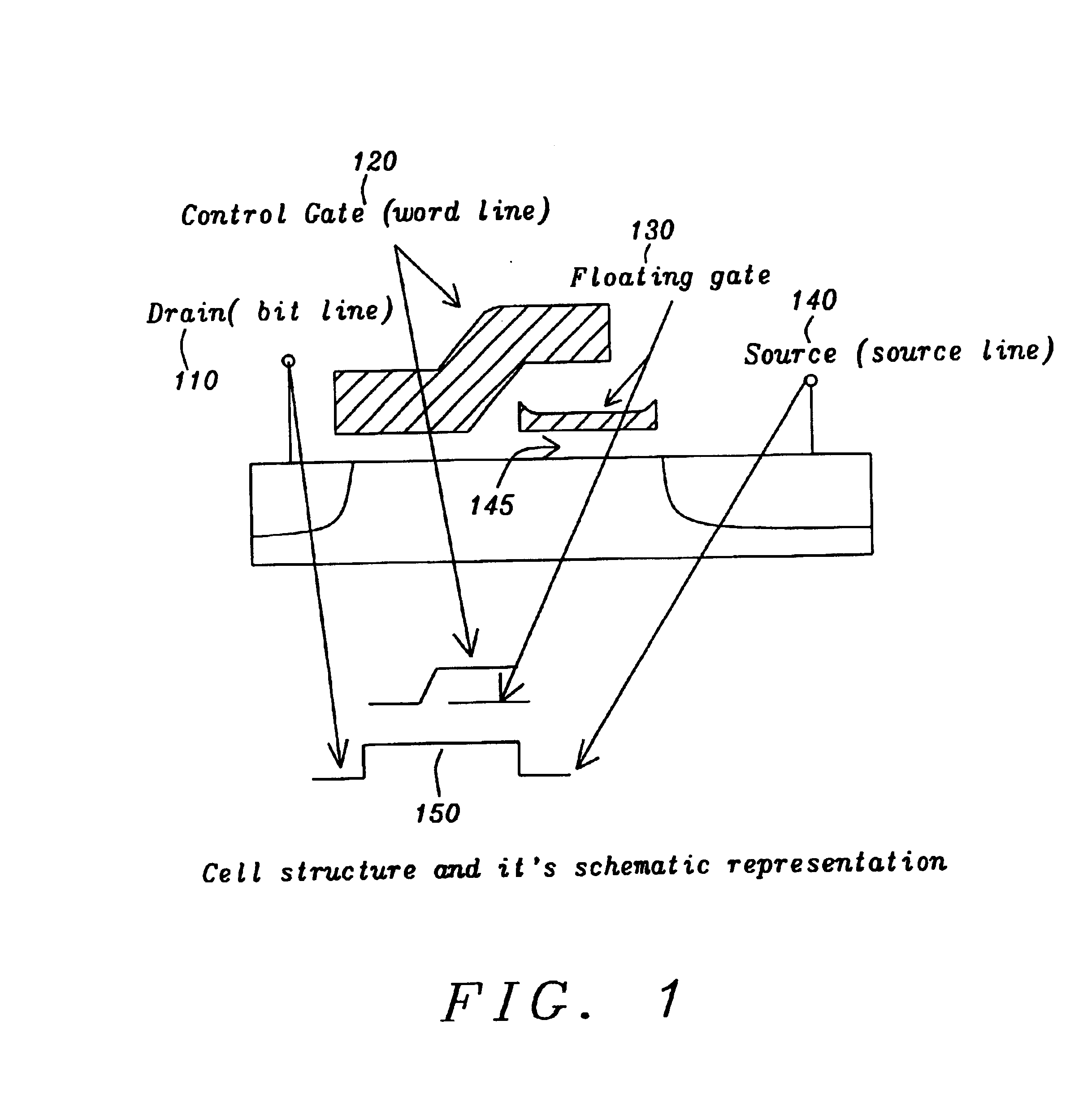

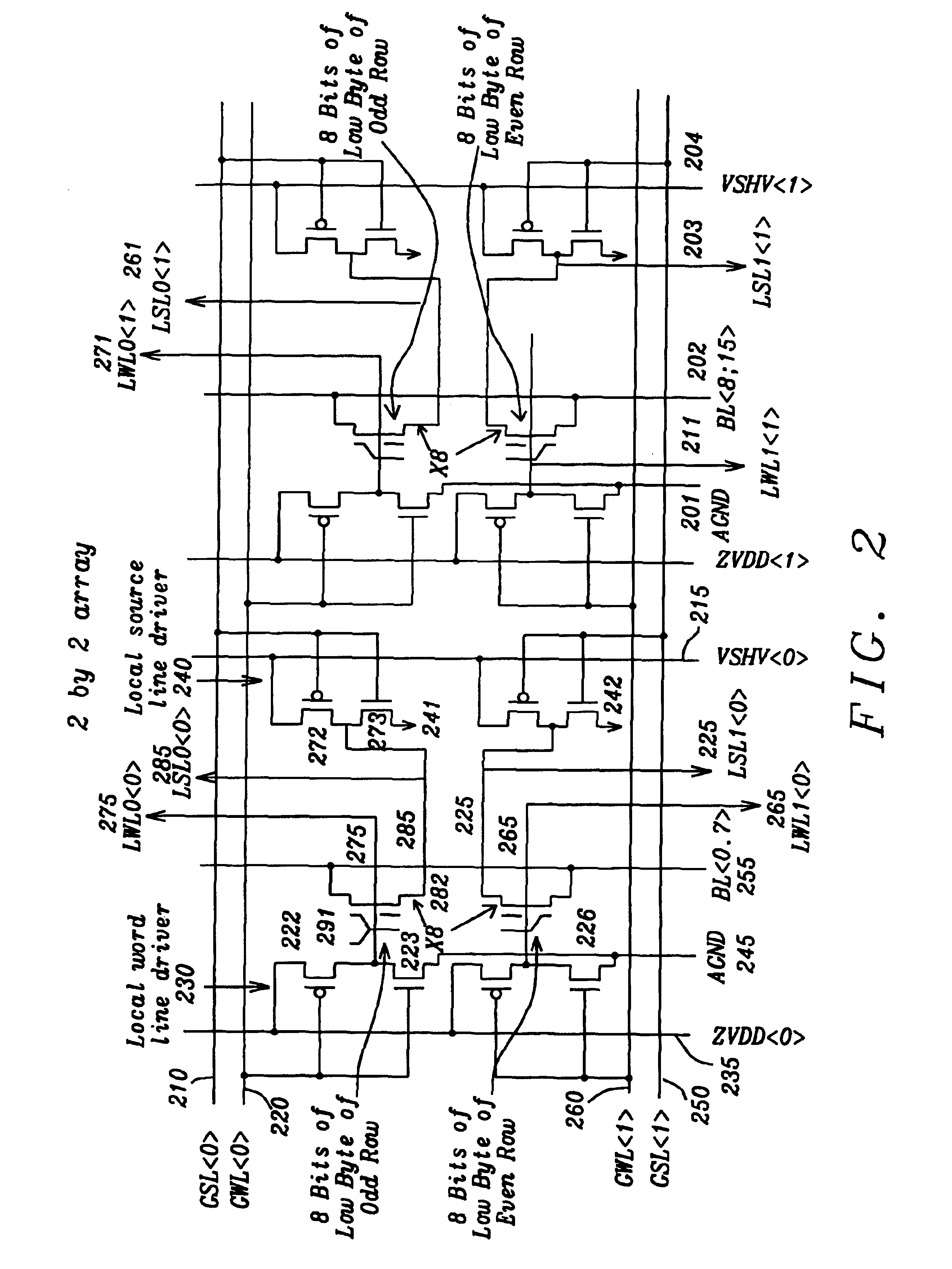

Nonvolatile semiconductor memory array with byte-program, byte-erase, and byte-read capabilities

InactiveUS6888754B2Reduce the amount requiredReduce high voltage stressRead-only memoriesDigital storageDriver circuitHigh pressure

This invention provides a memory array and its peripheral circuit with byte-erase capability. The advantage of this invention is the ability to access bytes for program, erase, and read operations. This invention allows this access with the addition of one word line switch and one source line switch for each byte to be accessed for program, erase, and read operations. Also, this invention utilizes a new bias condition to lessen the voltage stress on the high voltage device. In addition, this invention utilizes separate and dedicated power supplies for the local word line driver circuits and for the local source line driver circuits. This is coupled with the partitioning of the main memory array into sub-arrays of 8 columns. This allows the placing of high voltage only on the selected 8 column (byte) subarray. This also substantially lessens the voltage stress on the memory cells and enhances long-term reliability.

Owner:TAIWAN SEMICON MFG CO LTD

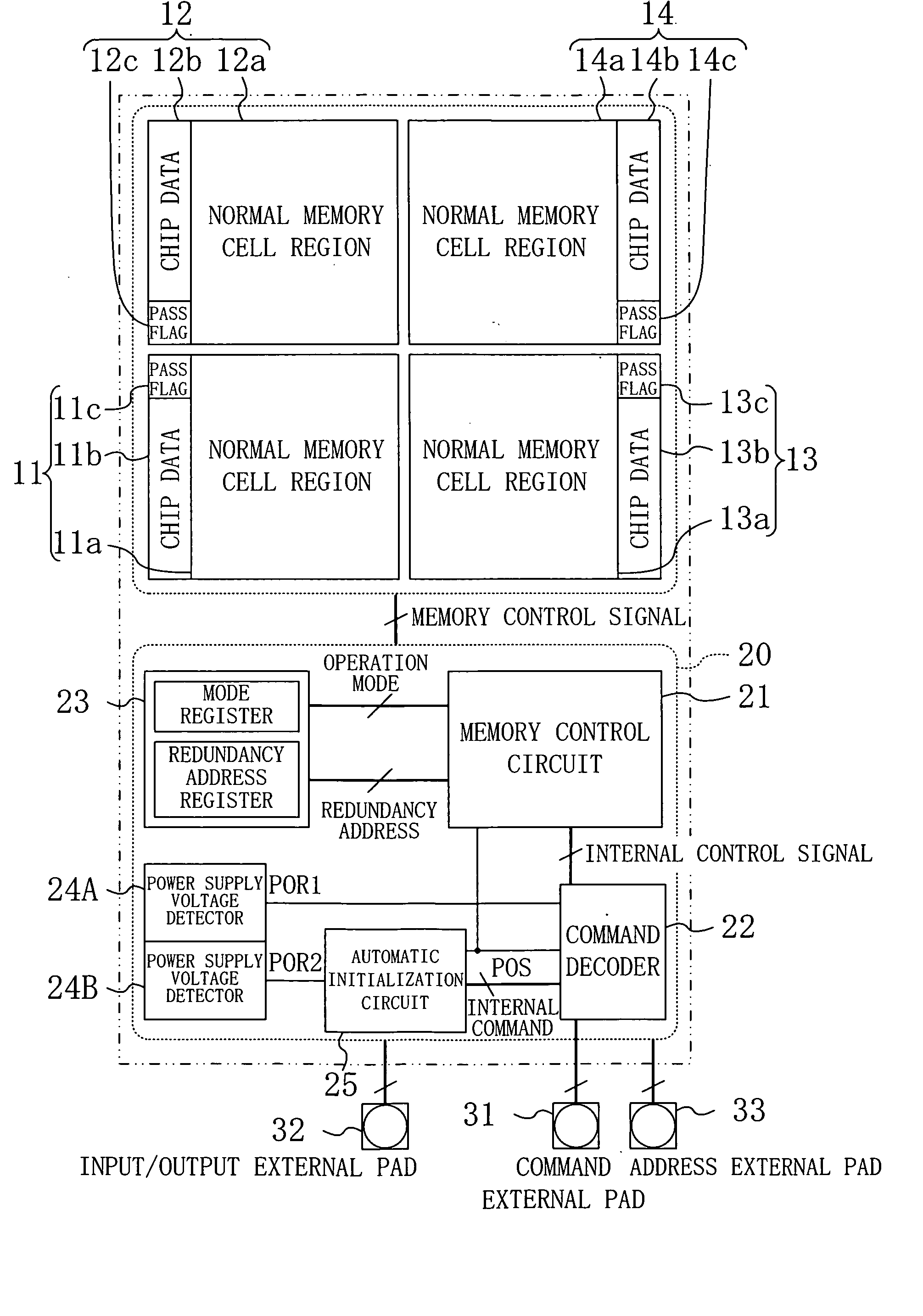

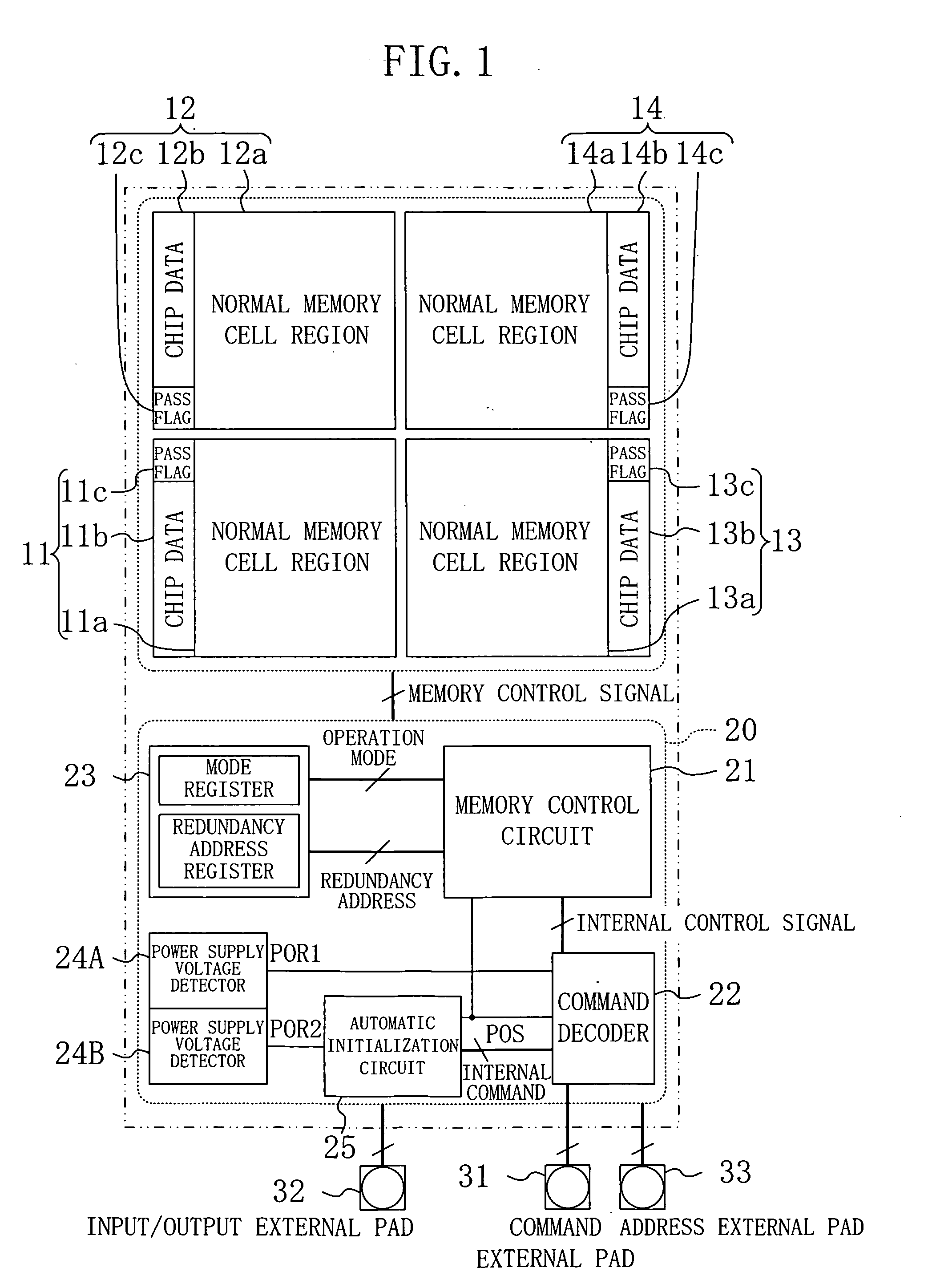

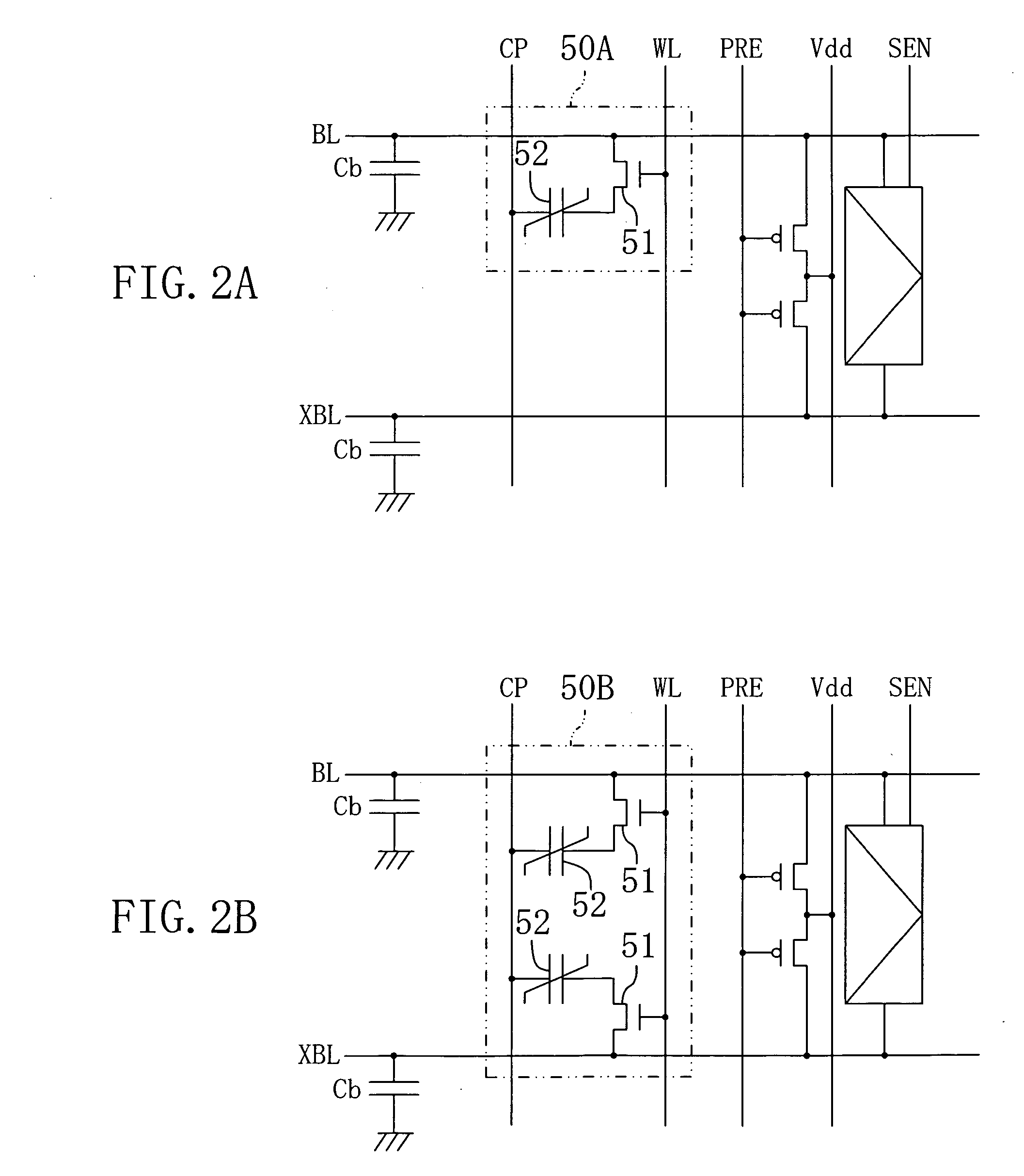

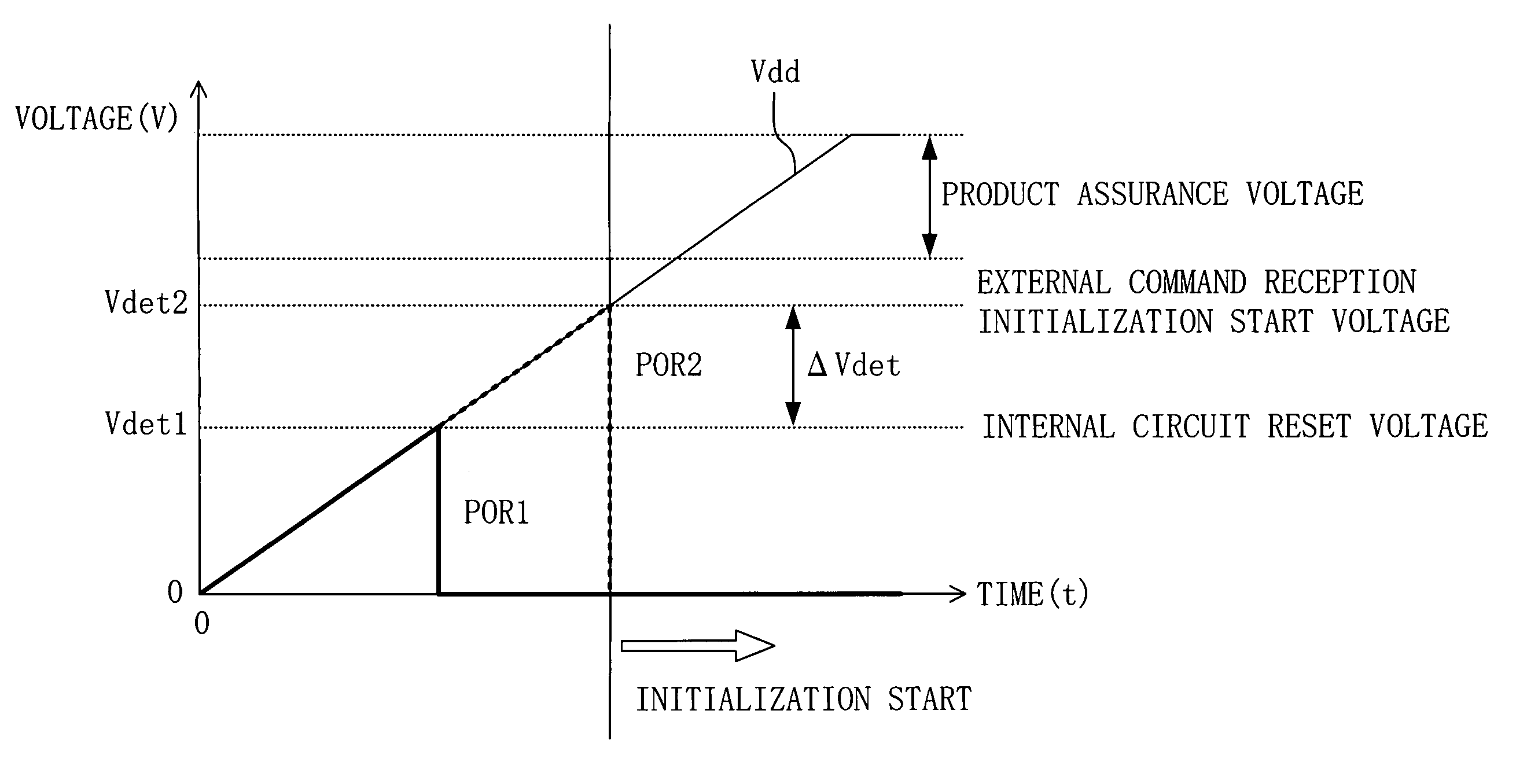

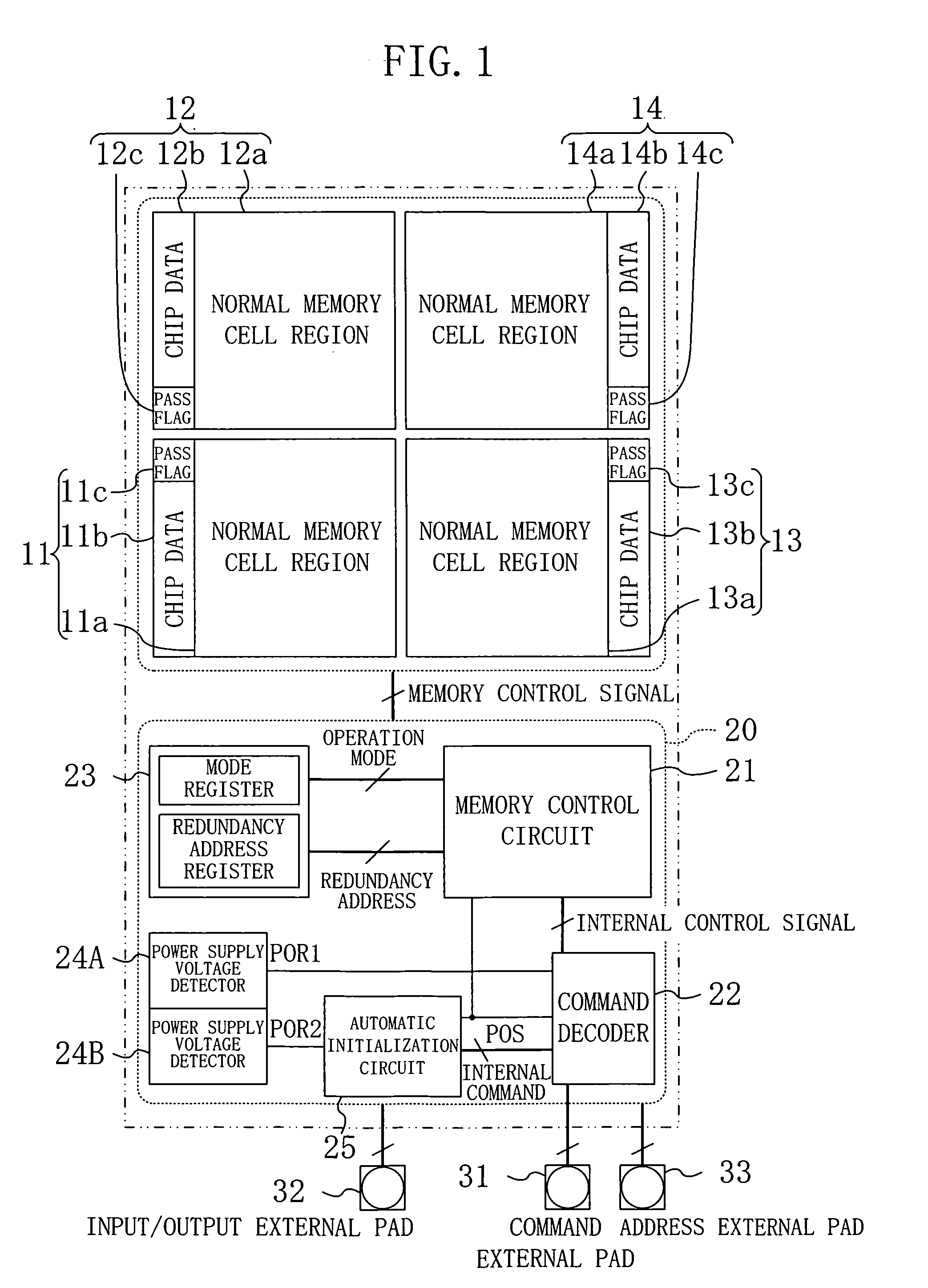

Semiconductor memory device and method for initializing the same

ActiveUS20050181554A1Prevent malfunction and data destructionImprove chip reliabilitySemiconductor/solid-state device manufacturingDigital storageSemiconductor memorySemiconductor

A semiconductor memory device includes memory cell blocks (11) through (14) including a nonvolatile memory cell. The memory cell blocks (11) through (14) include chip-data storing regions (11b) through (14b) for storing chip data containing operation parameters of the semiconductor memory device and pass-flag storing regions (11c) through (14c) for storing pass flags which correspond to the respective chip-data storing regions and show the validity of the stored chip data. The chip-data storing regions store the same chip data.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

Metal contact for chip packaging structure

ActiveUS9293432B2Improve chip reliabilityImprove adhesionSemiconductor/solid-state device detailsSolid-state devicesSolder ballMetal electrodes

A chip packaging structure and packaging method. The packaging structure comprises: a semiconductor substrate; a metal pad provided inside the semiconductor substrate; an insulating layer provided on the semiconductor substrate, the insulating layer having an opening for exposing the metal pad; a sub-ball metal electrode provided on the metal pad; a solder ball provided on the surface of the sub-ball metal electrode, the solder ball having a first apron structure and the first apron structure covering partial metal pad on the periphery of the bottom of the under-ball metal electrode. The chip packaging structure of the present invention enhances the adhesion between the solder ball and the metal pad, and improves the reliability in chip packaging.

Owner:NANTONG FUJITSU MICROELECTRONICS

Method of manufacturing chip integrated substrate

ActiveUS7807510B2Improve reliabilityPrevent breakage and short circuitSemiconductor/solid-state device detailsPrinted circuit aspectsElectrical and Electronics engineeringEngineering

There are provided the steps of connecting a chip component 13 to a first substrate 10 through a wire 14, providing an electrode 21 on a second substrate 20, attaching, to the first substrate 10, a molding tool 30 having a protruded portion 31 formed corresponding to an array of a bump connecting pad 12 of the first substrate 10 and a cavity 32 formed corresponding to a region in which the chip component 13 is mounted, thereby forming a first sealing resin 34 for sealing the chip component 13 and the wire 14, bonding the electrode 21 to the bump connecting pad 12 through a solder, thereby bonding the first substrate 10 to the second substrate 20, and filling a second filling resin 40 in a clearance portion between the first substrate 10 and the second substrate 20.

Owner:SHINKO ELECTRIC IND CO LTD

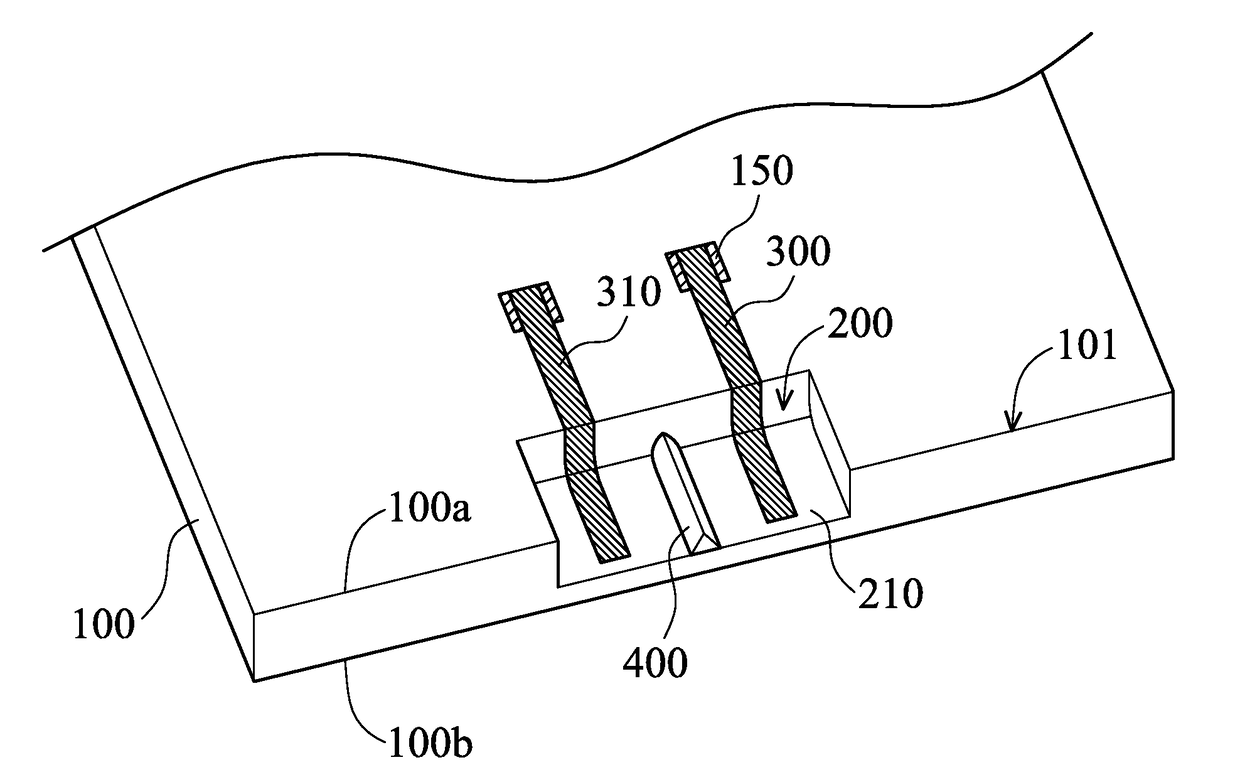

Chip structure and manufacturing process thereof

InactiveUS20060199306A1Improve reliabilityAvoid structureSemiconductor/solid-state device detailsSolid-state devicesEngineeringMoisture

A chip structure and the manufacturing process thereof are provided. The feature of the present application is that the chip structure has a first passivation layer covering a substrate of the chip and exposing each of bonding pads and a portion of the substrate surface, and a second passivation layer covering the sidewalls of the first passivation layer and the portion of substrate surface exposed by the first passivation layer, to prevent moisture infiltration from the edge of the substrate. Therefore, the reliability of the chip structure is enhanced.

Owner:ADVANCED SEMICON ENG INC

Semiconductor memory device and method for initializing the same

InactiveUS7110314B2Improve chip reliabilityImprove reliabilitySemiconductor/solid-state device manufacturingDigital storageData storingSemiconductor

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

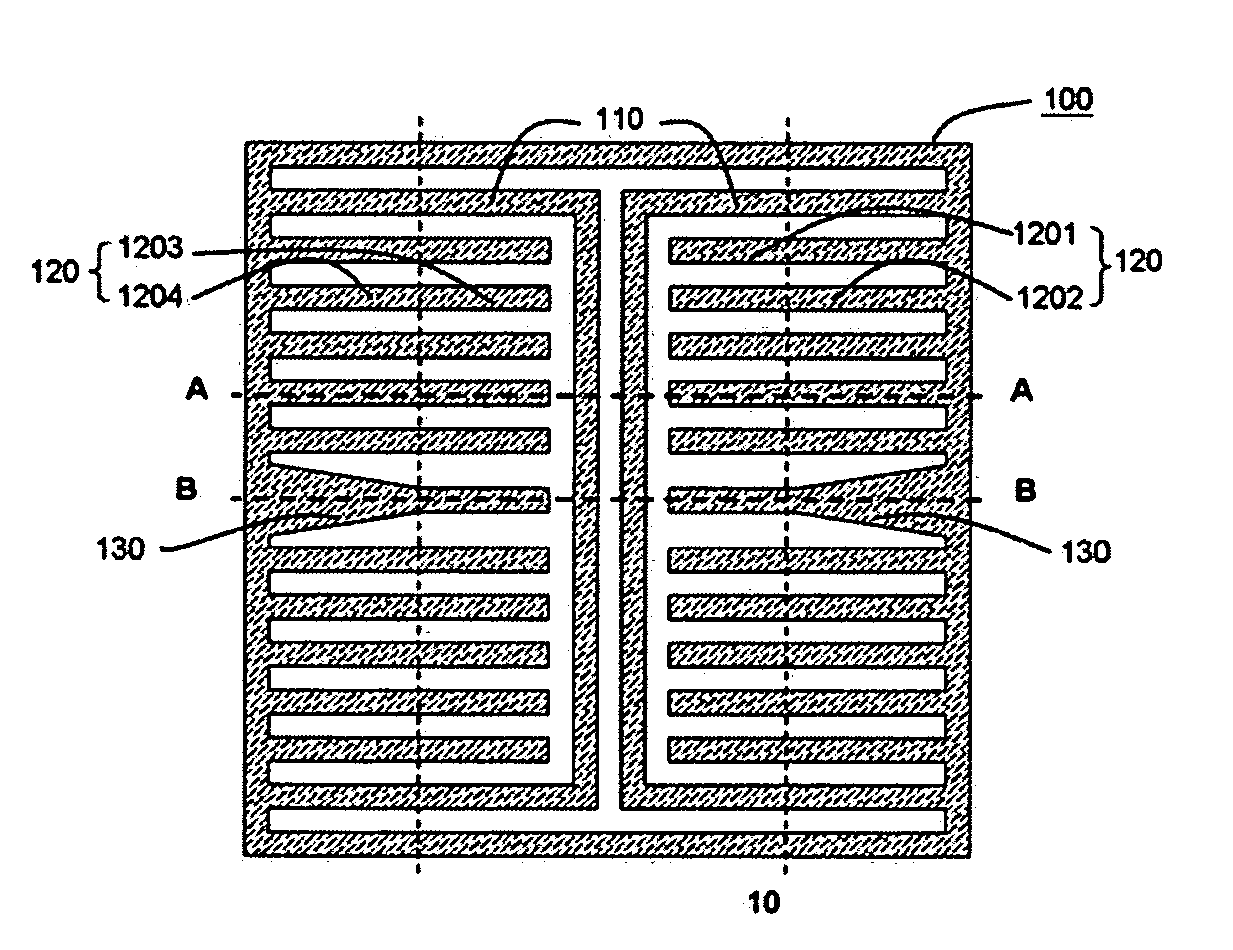

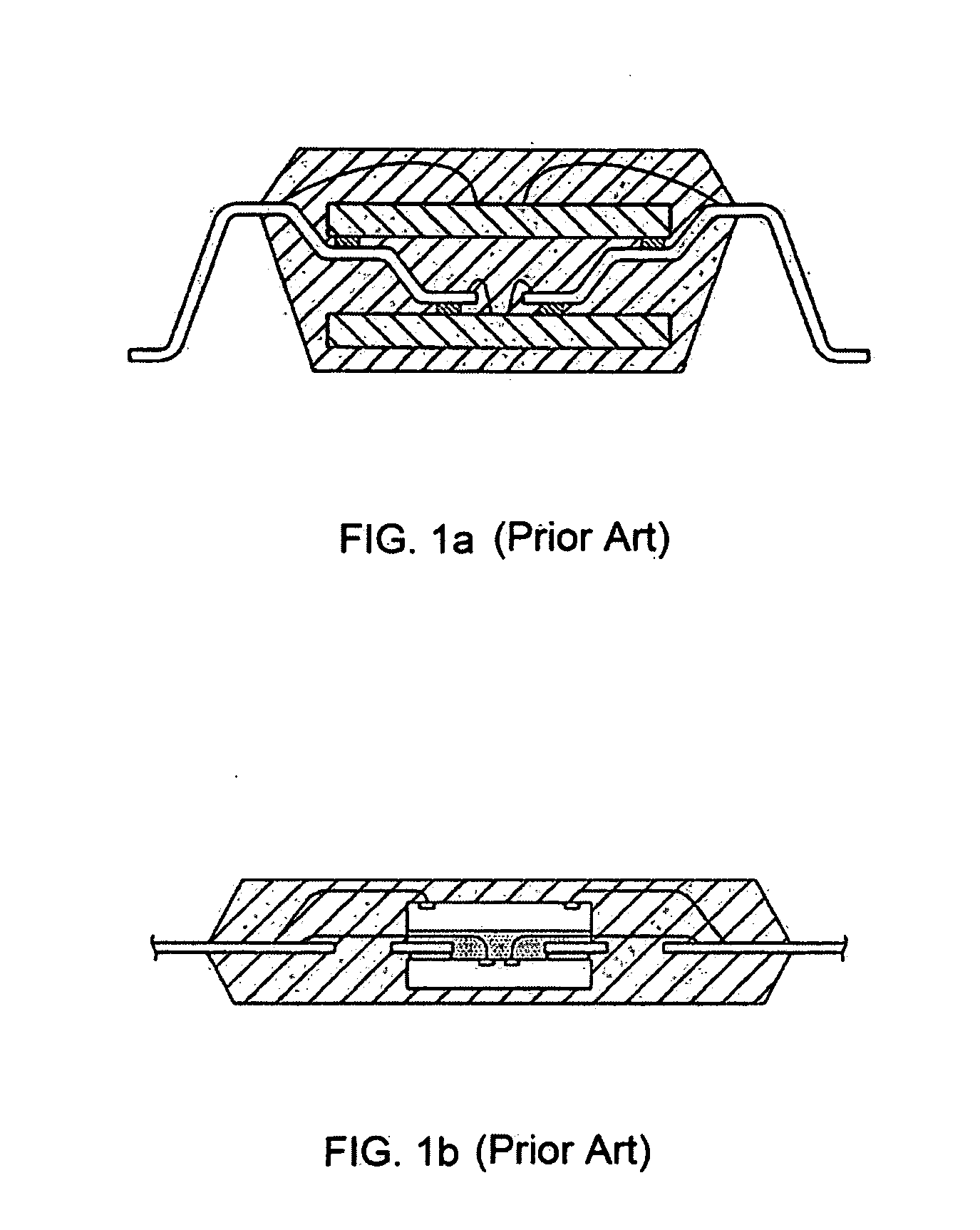

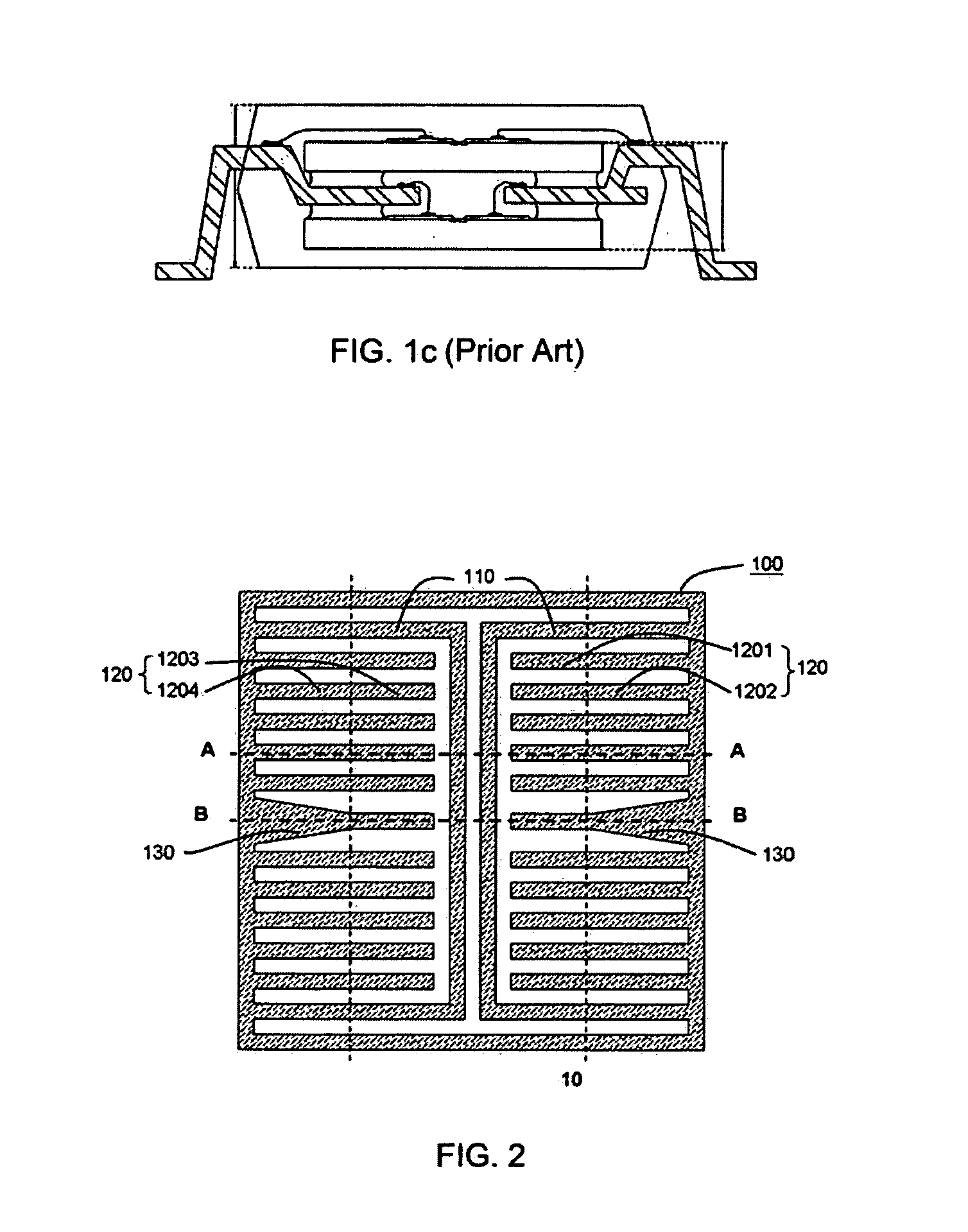

Multi-Chip Stacked Package Structure

InactiveUS20090072361A1Improve chip reliabilityImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringLead frame

A multi-chip stacked package structure, comprising: a lead-frame having a top surface a back surface, the inner leads comprising a plurality of first inner leads and a plurality of second inner leads in parallel; a first chip fixedly connected to the back surface of the lead-frame, and the first chip having an active surface and a plurality of first pads adjacent to the central area of the active surface; a plurality of first metal wires electrically connected the first inner leads and the second inner leads and the first pads on the active surface of the first chip; a second chip fixedly connected to the top surface of the lead-frame, and the second chip having an active surface and a plurality of second pads adjacent to the central area of the active surface; a pair of the spacers provided on the thermal fin of the lead-frame; a plurality of second metal wires electrically connected to the top surface of first inner leads and the second inner leads and the second pads on the active surface of the second chip; and a package body encapsulated the first chip, the plurality of metal wires the second chip, the plurality of pads, the first inner leads and the second inner leads and to expose the outer leads.

Owner:CHIPMOS TECH INC

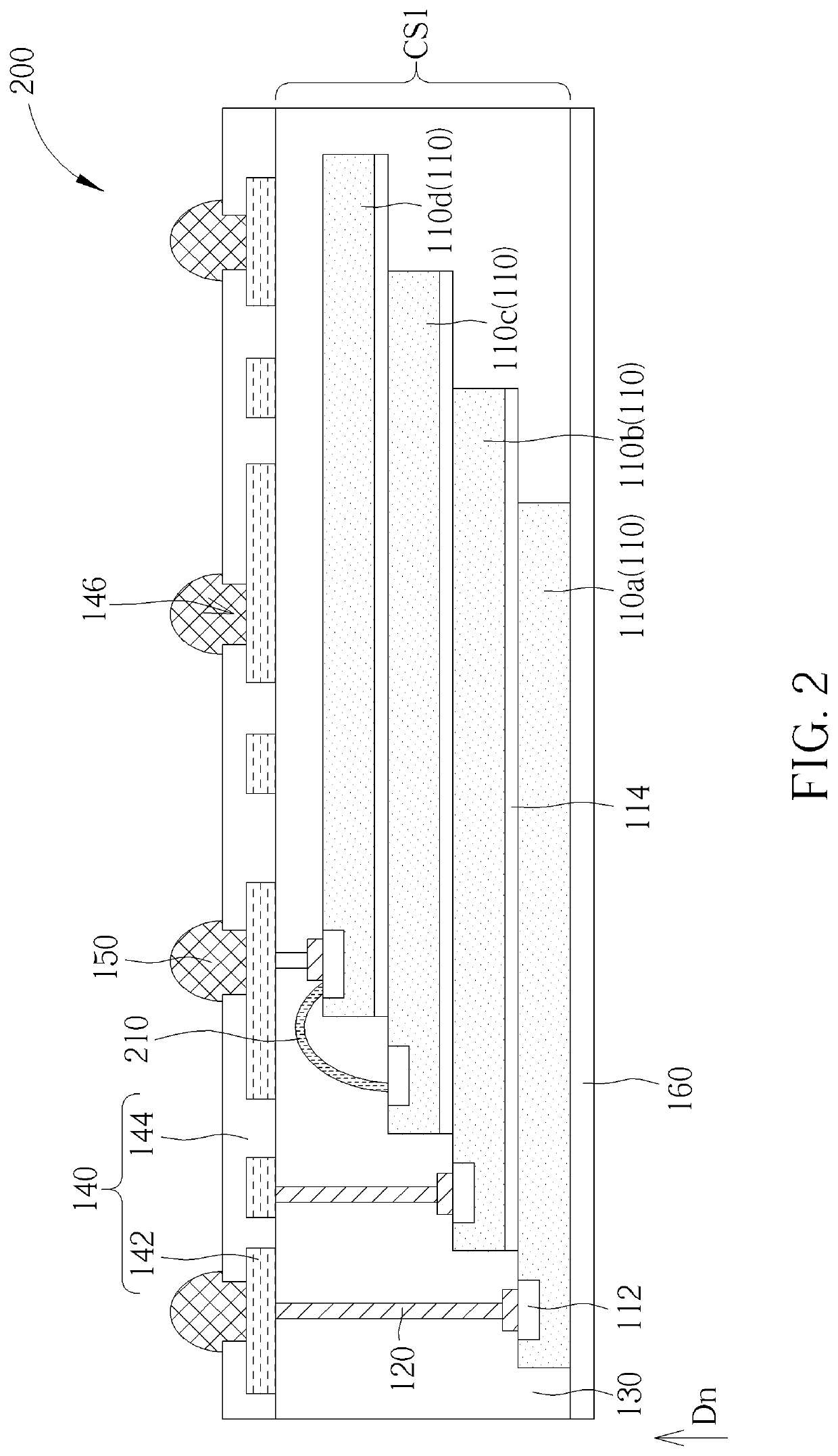

Chip package structure with stacked chips and manufacturing method thereof

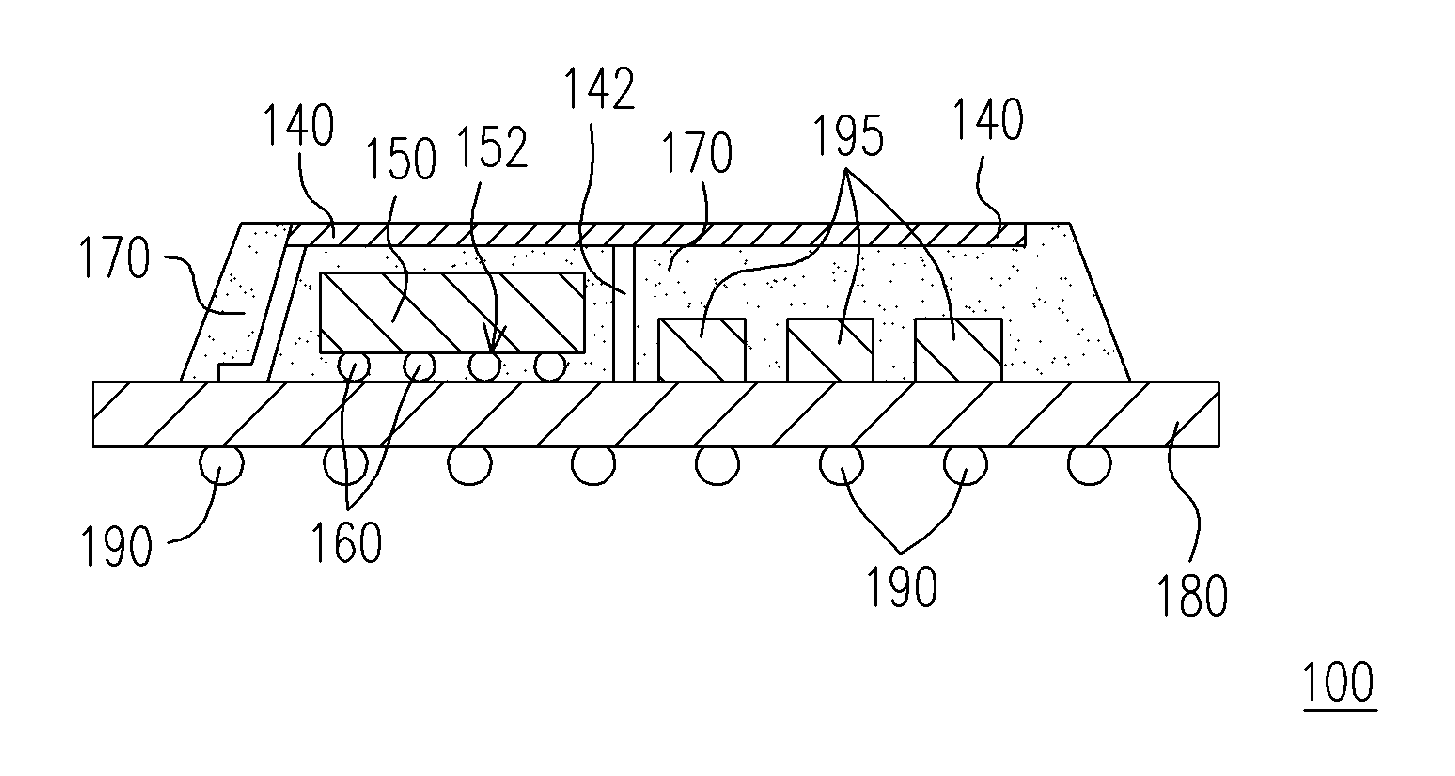

ActiveUS11133290B2Reduce horizontal sizeExternal device may beSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerElectrical connection

Owner:YANGTZE MEMORY TECH CO LTD

Chip package structure and manufacturing method thereof

ActiveUS20180114734A1Increase stiffnessHigh strengthSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerSolder ball

A chip package structure includes a redistribution layer, at least one chip, a reinforcing frame, an encapsulant and a plurality of solder balls. The redistribution layer includes a first surface and a second surface opposite to each other. The chip is disposed on the first surface and electrically connected to the redistribution layer. The reinforcing frame is disposed on the first surface and includes at least one through cavity. The chip is disposed in the through cavity and a stiffness of the reinforcing frame is greater than a stiffness of the redistribution layer. The encapsulant encapsulates the chip, the reinforcing frame and covering the first surface. The solder balls are disposed on the second surface and electrically connected to the redistribution layer.

Owner:POWERTECH TECHNOLOGY

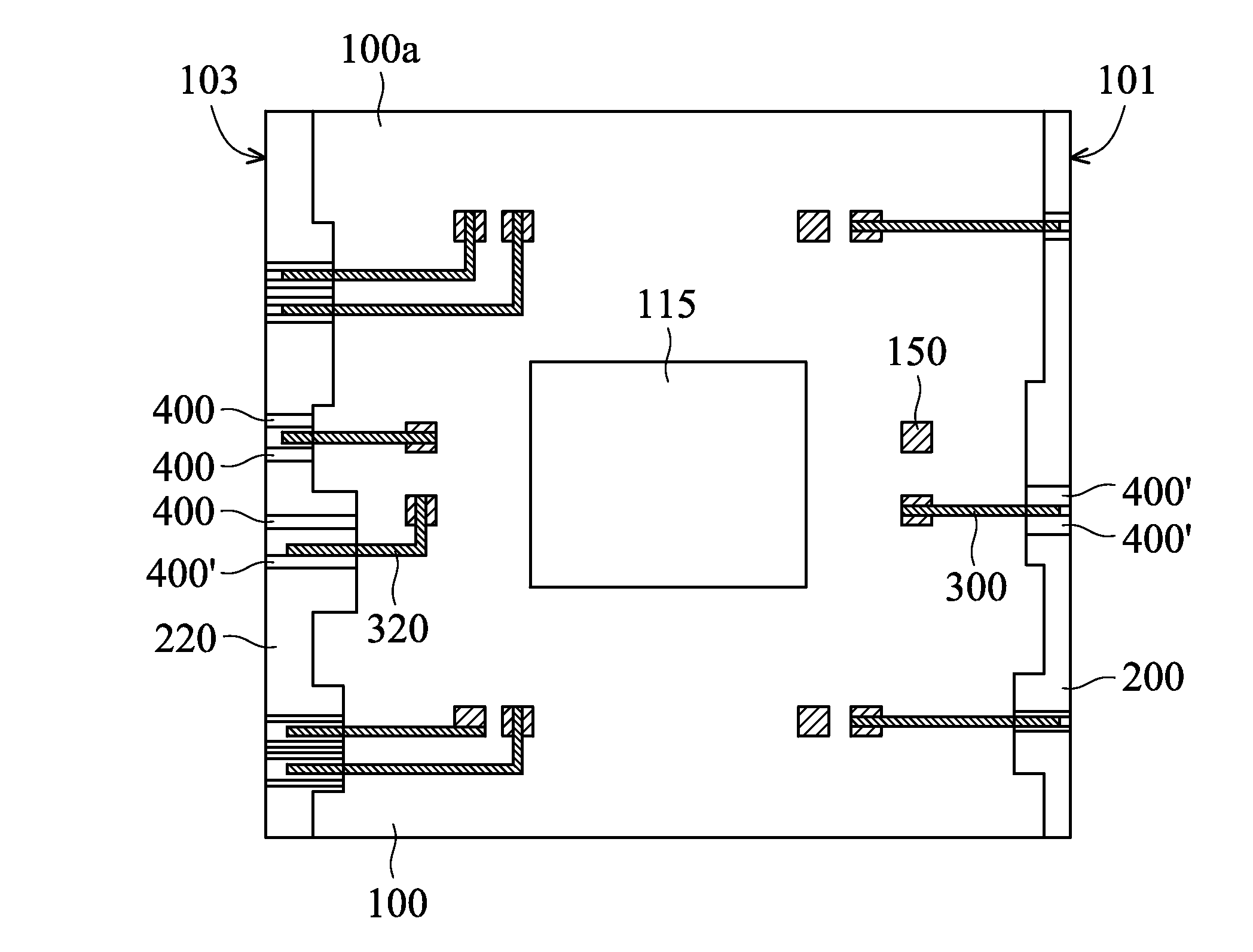

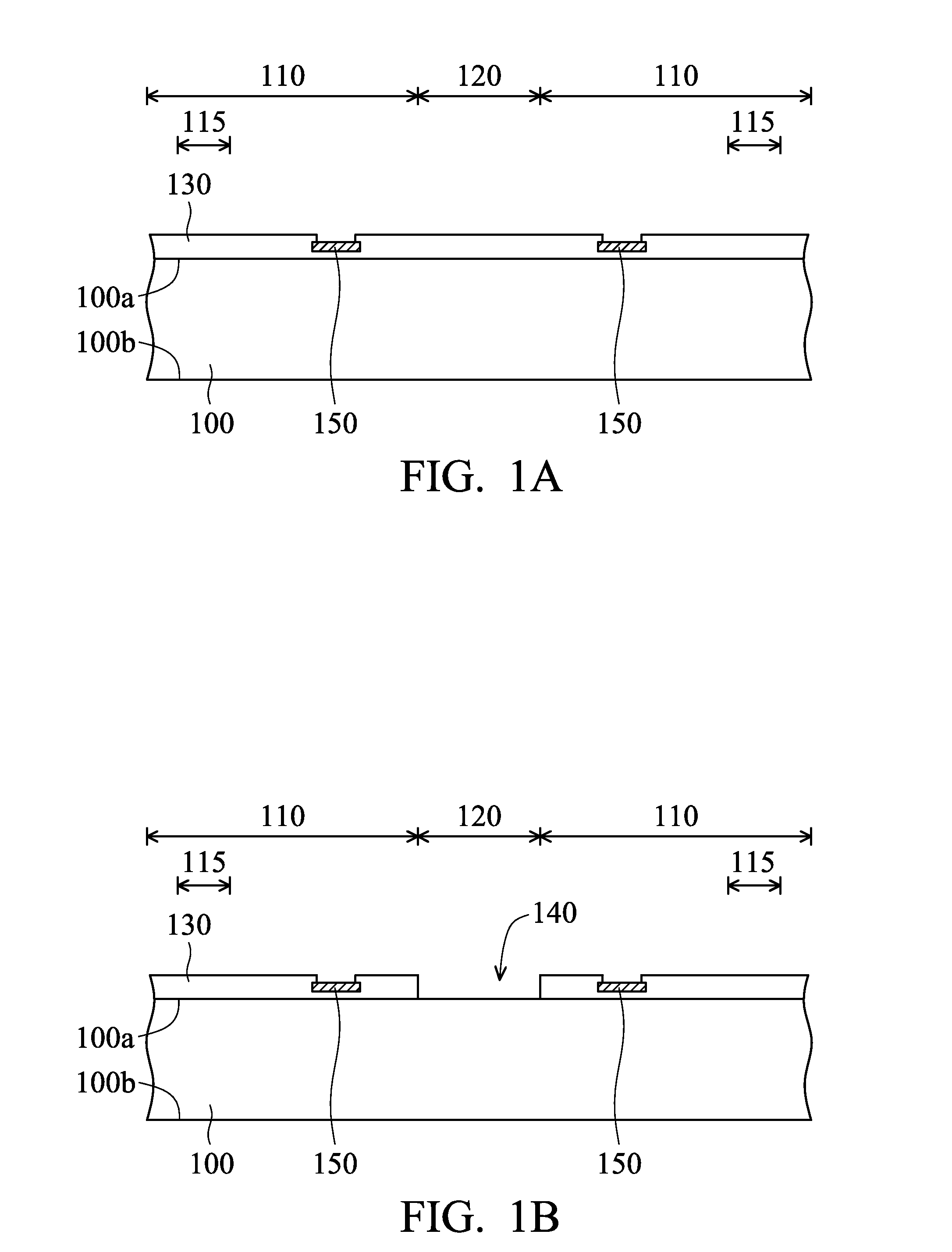

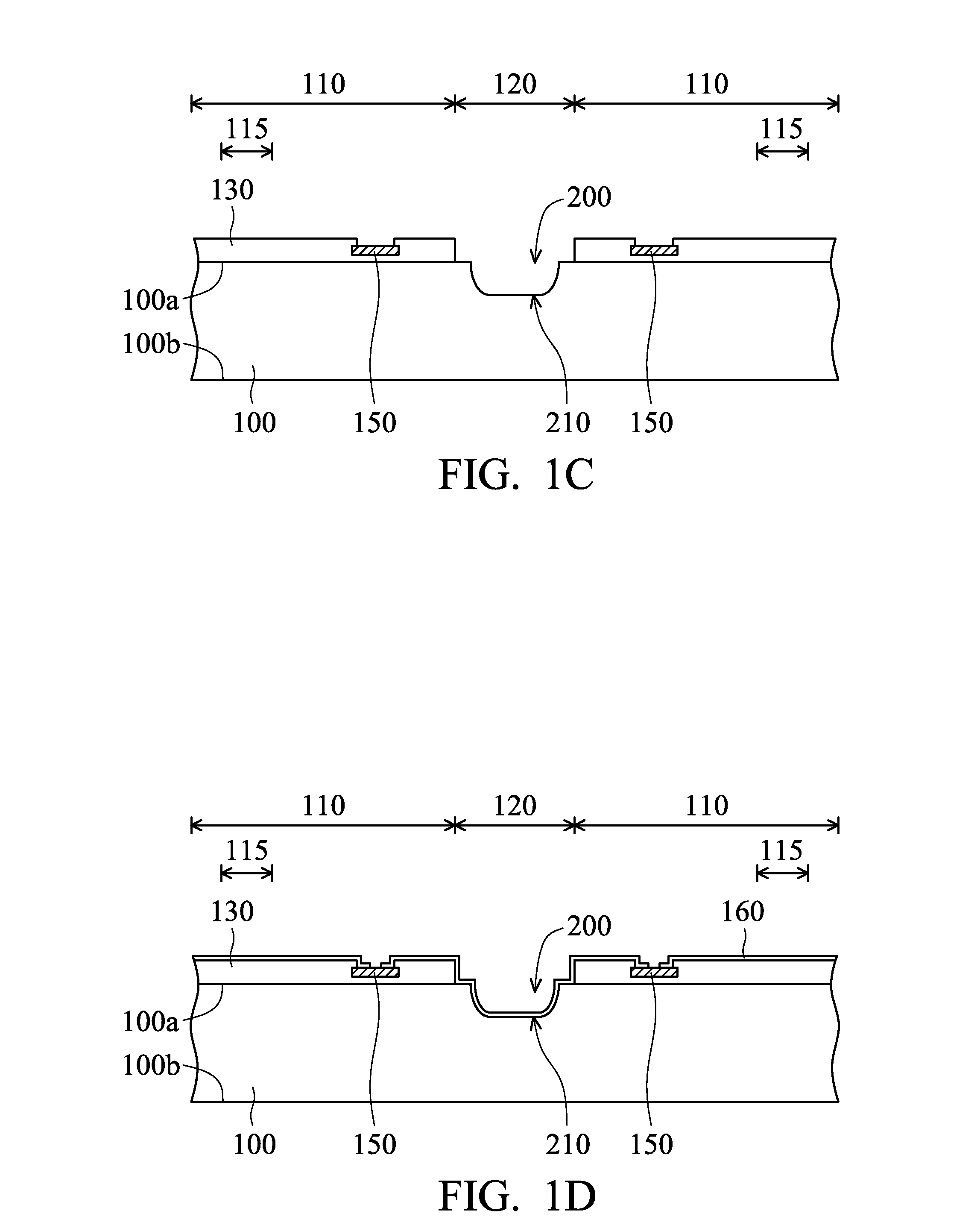

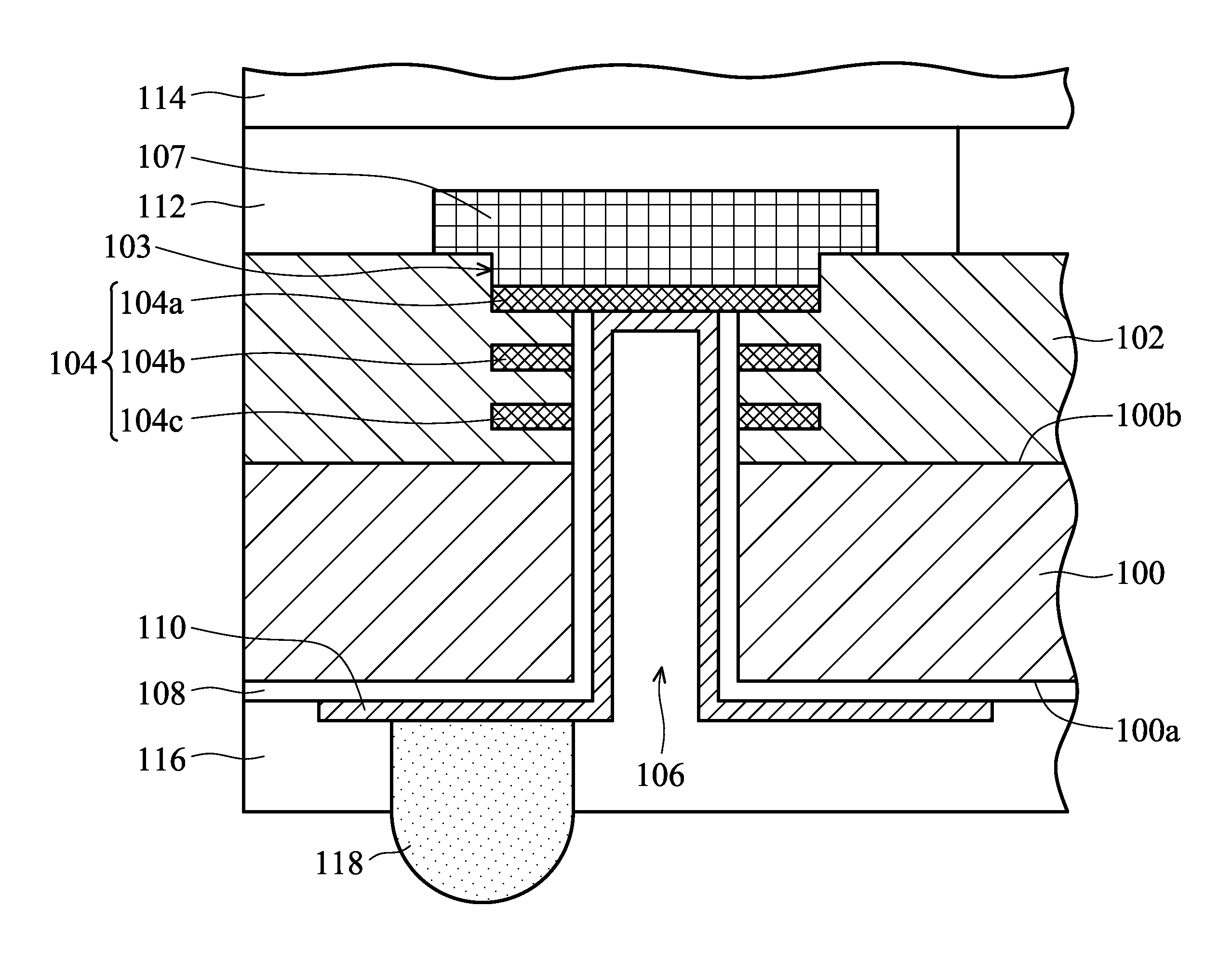

Chip package and method for forming the same

ActiveUS20150228536A1Avoid crackingImprove layout flexibilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A chip package including a semiconductor substrate is provided. A recess is in the semiconductor substrate and adjoins a side edge of the semiconductor substrate, wherein the semiconductor substrate has at least one spacer protruding from the bottom of the recess. A conducting layer is disposed on the semiconductor substrate and extends into the recess.

Owner:XINTEC INC

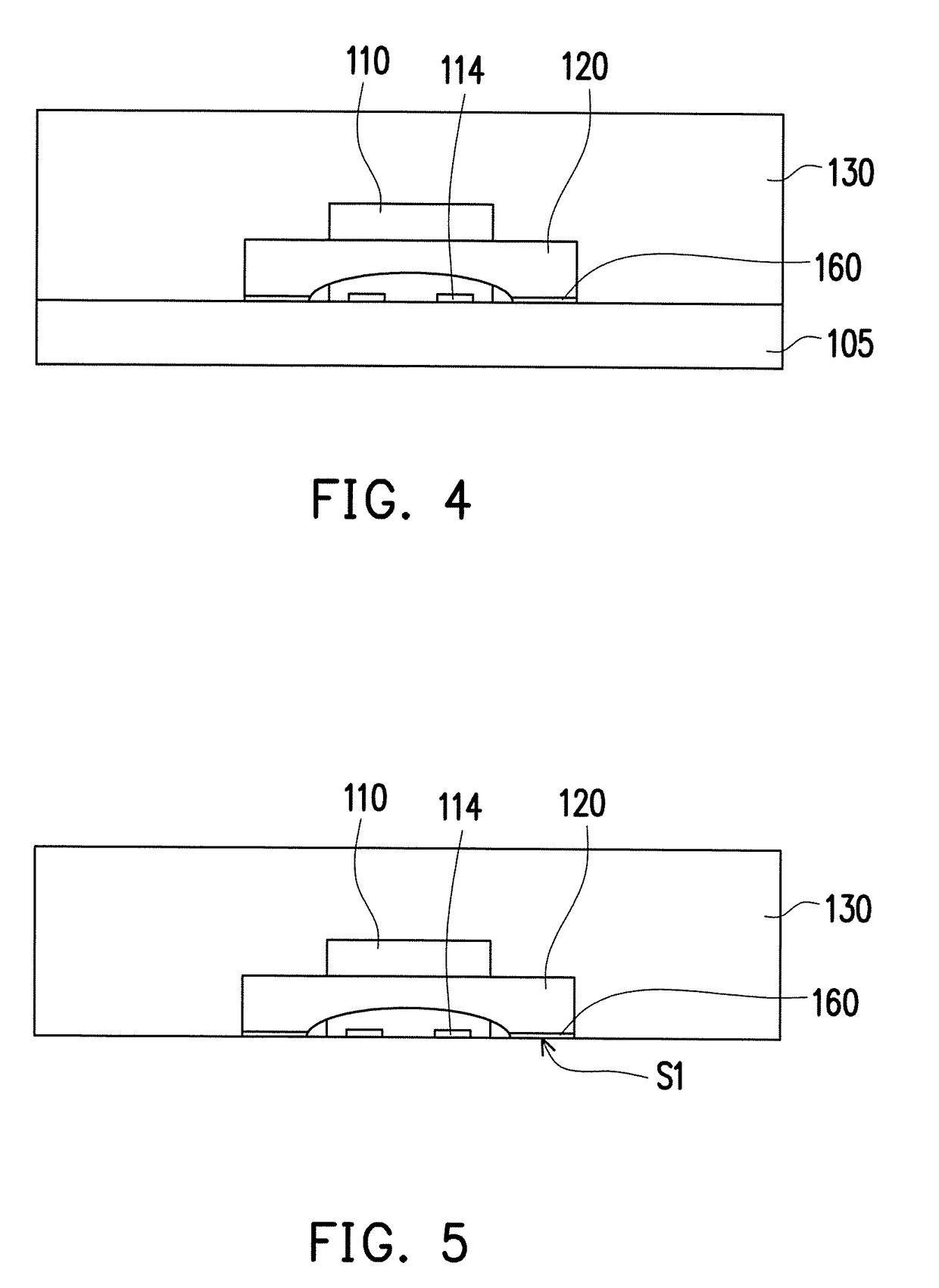

Chip package and fabricating method thereof

InactiveUS20120025387A1Improve reliabilityPrevent overflowSemiconductor/solid-state device detailsSolid-state devicesEngineeringElectrical and Electronics engineering

A chip package and a fabrication method thereof are provided. The chip package includes a substrate and a chip disposed over the substrate. A solder layer is disposed between the chip and the substrate. A conductive pad is disposed between the solder layer and the substrate, wherein the conductive pad includes a first portion disposed under the solder layer, a second portion disposed away from the first portion and a connective portion disposed between the first portion and the second portion. The connective portion has a width which is narrower than a width of the first portion along a first direction perpendicular to a second direction extending from the first portion to the connective portion.

Owner:SEMILEDS OPTOELECTRONICS CO LTD +1

Chip package and method for forming the same

ActiveUS8742564B2Improve chip reliabilityImprove reliabilityTransistorSemiconductor/solid-state device detailsEngineeringDielectric layer

An embodiment of the invention provides a chip package which includes a substrate having a first surface and a second surface; a conducting pad structure located on the first surface; a dielectric layer located on the first surface of the substrate and the conducting pad structure, wherein the dielectric layer has an opening exposing a portion of the conducting pad structure; and a cap layer located on the dielectric layer and filled into the opening.

Owner:XINTEC INC

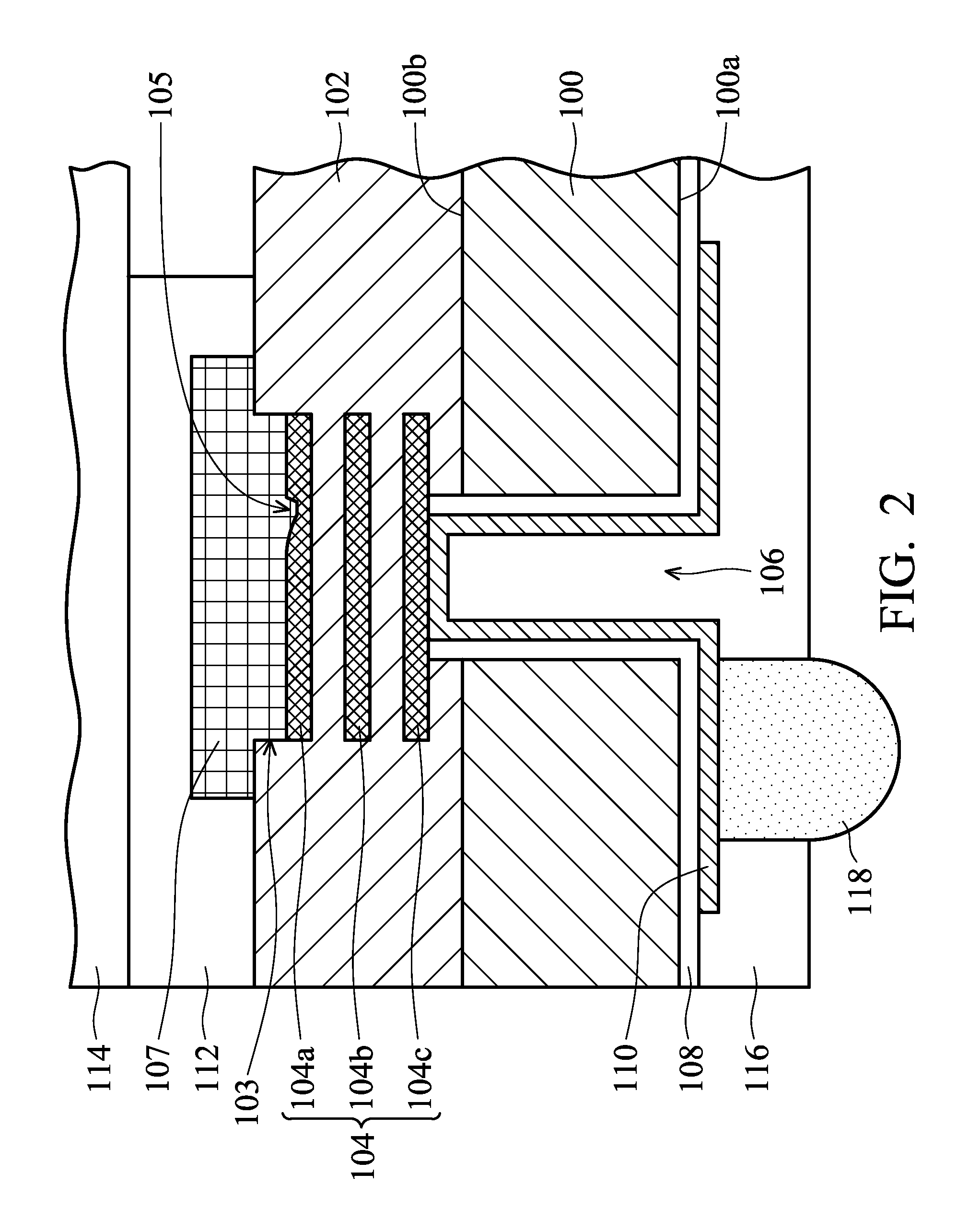

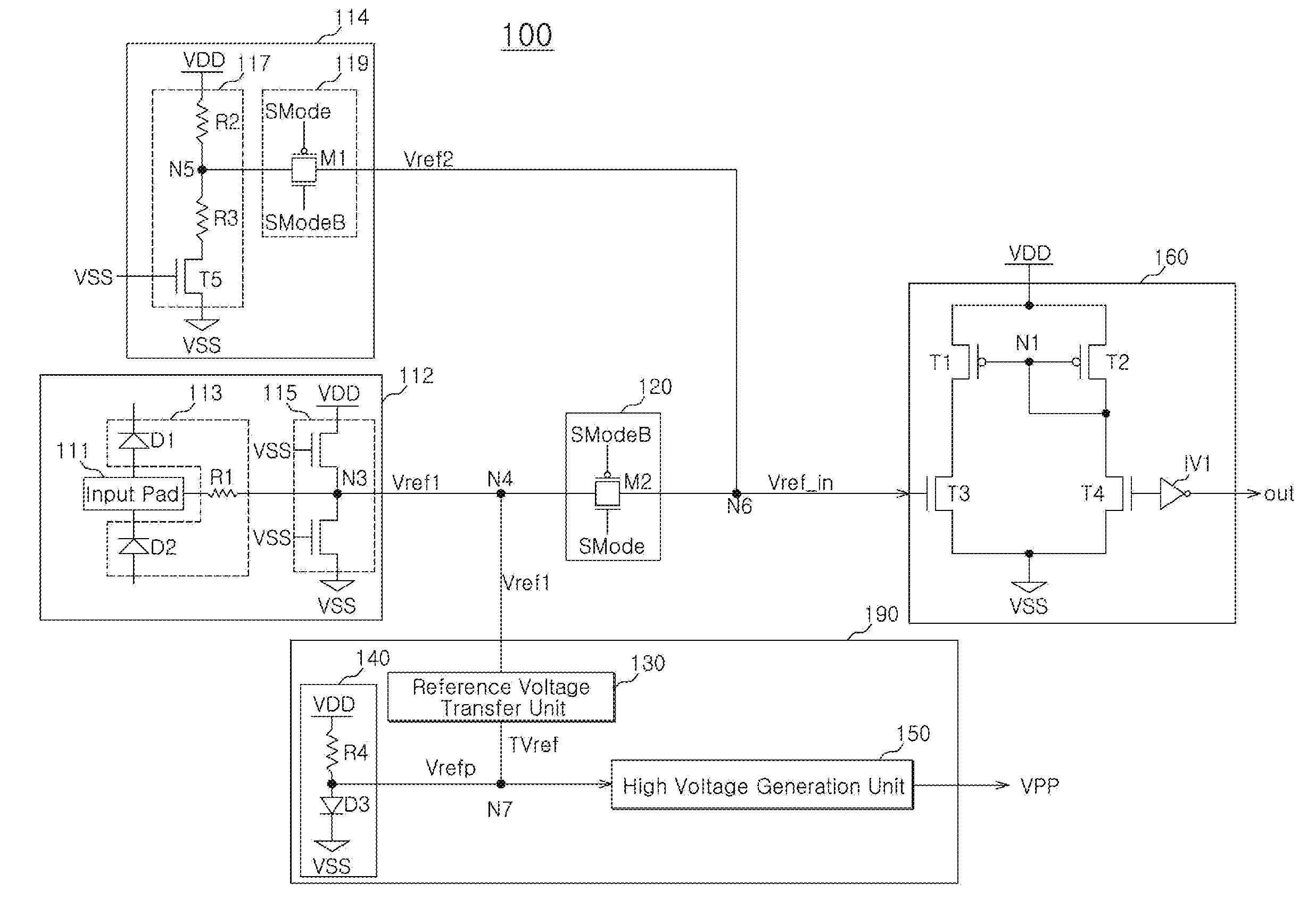

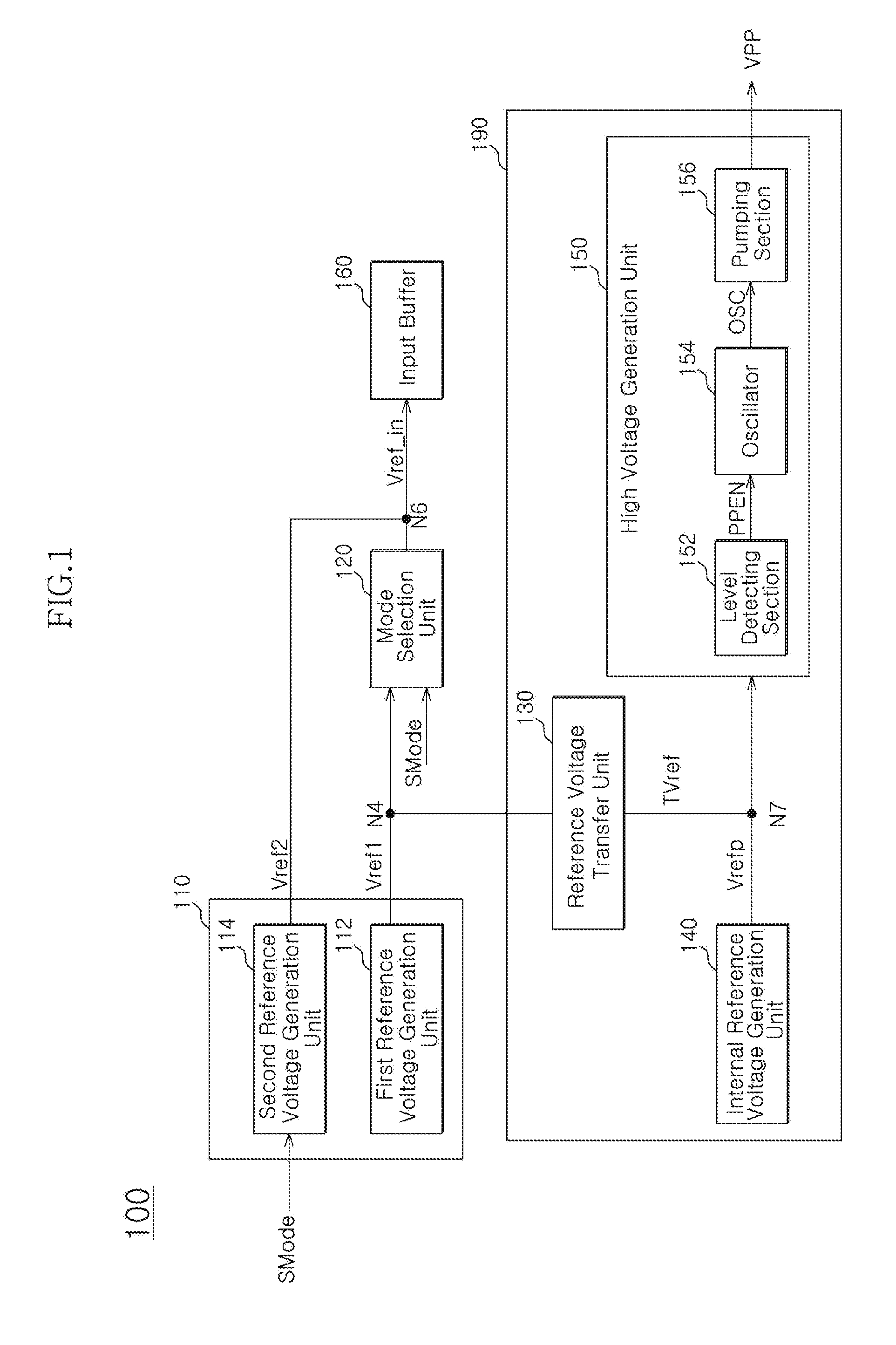

Semiconductor integrated circuit

ActiveUS20110291639A1Improve reliabilityImprove chip reliabilityStatic storageLogic circuitsIntegrated circuitVoltage reference

A semiconductor integrated circuit includes an internal reference voltage generation unit configured to generate an internal reference voltage; a high voltage generation unit configured to pump an external driving voltage based on the internal reference voltage applied from the internal reference voltage generation unit, and generate a high voltage having a specified level; and a reference voltage transfer unit configured to generate a test reference voltage from a reference voltage in a package test mode to correspond to a change in a driving operation of the external driving voltage applied from outside, and monitor and force the internal reference voltage.

Owner:SK HYNIX INC

Semiconductor Light Emitting Diode Chip

ActiveUS20160247989A1Increase the light areaFine surfaceSemiconductor devicesManufacturing technologyCurrent distribution

A semiconductor light emitting diode chip relates to the field of production technologies of a light emitting diode. In the present invention, corresponding graphical current extension layers are respectively disposed below an N pad and a P pad, and in all light emitting compound areas, there is electronic compound light emitting. Compared with the prior art, an area of a light emitting compound area is increased, which can effectively improve current distribution and light emitting brightness of a chip. In addition, graphical current extension can effectively increase an adhesion of a pad on a surface and improve the reliability of a chip.

Owner:YANGZHOU ZHONGKE SEMICON LIGHTING

Chip package including recess in side edge

ActiveUS9601460B2Avoid crackingImprove layout flexibilitySemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A chip package including a semiconductor substrate is provided. A recess is in the semiconductor substrate and adjoins a side edge of the semiconductor substrate, wherein the semiconductor substrate has at least one spacer protruding from the bottom of the recess. A conducting layer is disposed on the semiconductor substrate and extends into the recess.

Owner:XINTEC INC

Semiconductor light emitting diode chip with current extension layer and graphical current extension layers

ActiveUS9666779B2Light brightnessDistribution lightSemiconductor devicesManufacturing technologyCurrent distribution

A semiconductor light emitting diode chip relates to the field of production technologies of a light emitting diode. In the present invention, corresponding graphical current extension layers are respectively disposed below an N pad and a P pad, and in all light emitting compound areas, there is electronic compound light emitting. Compared with the prior art, an area of a light emitting compound area is increased, which can effectively improve current distribution and light emitting brightness of a chip. In addition, graphical current extension can effectively increase an adhesion of a pad on a surface and improve the reliability of a chip.

Owner:YANGZHOU ZHONGKE SEMICON LIGHTING

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com