Vertical light emitting diode (LED) chip structure and fabrication method thereof

A technology of LED chips and epitaxial layers, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems affecting the yield rate of subsequent processes, lowering the yield rate of finished products, and low yield rate of bonding process, etc. Improve overall product yield, reduce internal stress, and improve chip reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

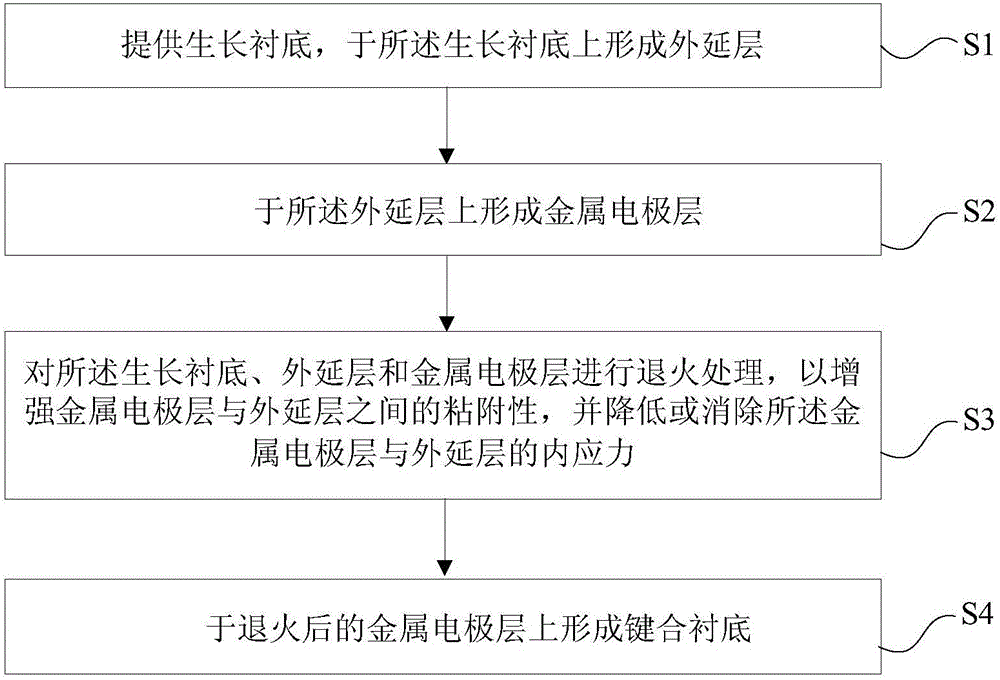

[0036] see Figure 1 to Figure 2 , the invention provides a method for manufacturing a vertical LED chip structure comprising the following steps:

[0037] S1: providing a growth substrate 101, and forming an epitaxial layer on the upper surface of the growth substrate 101;

[0038] S2: forming a metal electrode layer 106 on the surface of the epitaxial layer;

[0039] S3: Perform annealing treatment on the growth substrate 101, the epitaxial layer and the metal electrode layer 106 to enhance the adhesion between the metal electrode layer 106 and the epitaxial layer, and reduce or eliminate the connection between the metal electrode layer 106 and the epitaxial layer. internal stress;

[0040] S4: forming a bonding substrate 107 on the annealed metal electrode layer 106 .

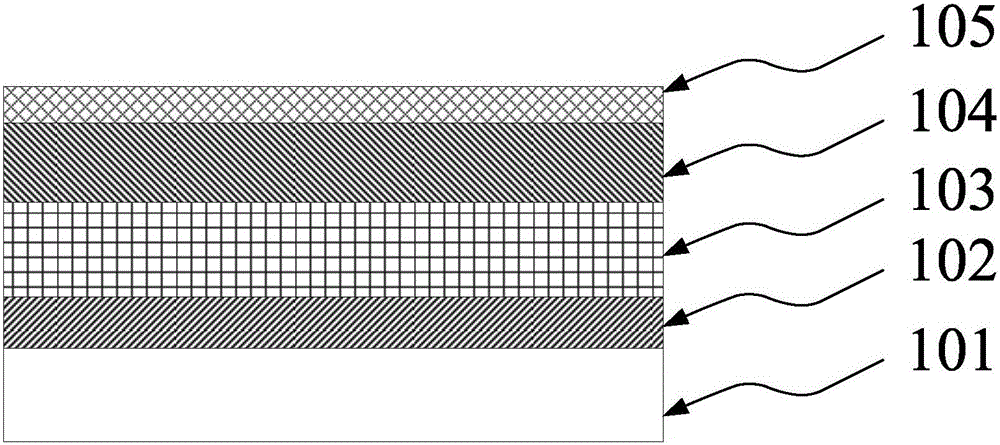

[0041] In step S1, see figure 1 Step S1 in and figure 2 , providing a growth substrate 101 , and forming an epitaxial layer on the growth substrate 101 . Wherein, the epitaxial layer includes an undop...

Embodiment 2

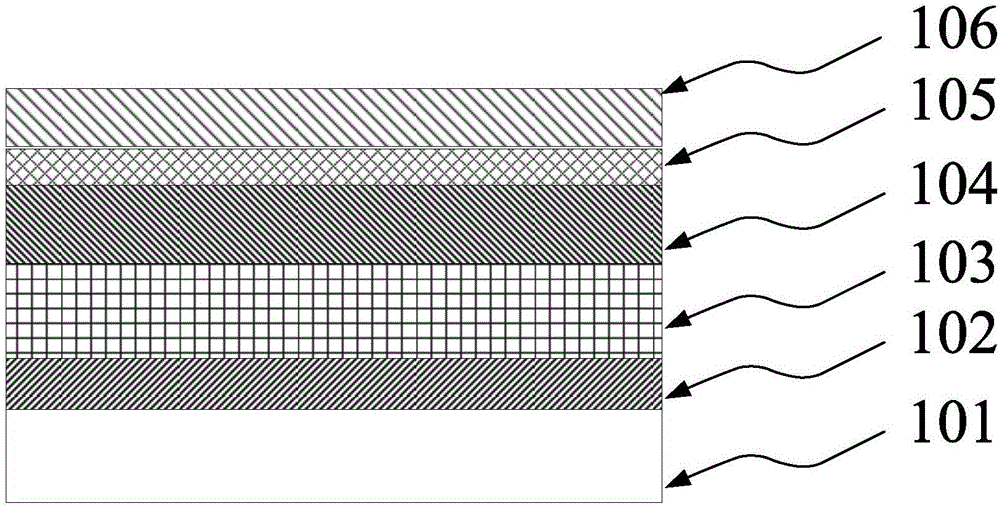

[0054] The present invention provides a vertical LED chip structure, please refer to Figure 4 , the vertical LED chip includes: a growth substrate 101; an epitaxial layer located on the growth substrate 101, the epitaxial layer includes an undoped GaN layer 102, an N- GaN layer 103, multi-quantum well layer 104, and P-GaN layer 105; a metal electrode layer 106 located on the epitaxial layer, the metal electrode layer 106 comprising patterned layers sequentially formed on the P-GaN layer 105 A current spreading layer, a patterned reflective layer and a metal bonding layer, wherein the metal bonding layer is in contact with the epitaxial layer through the patterned current spreading layer and the reflective layer; the bond on the metal electrode layer 106 shown Composite substrate 107. In other embodiments, an N electrode may also be included. The vertical LED chip structure in this embodiment can be obtained by using the preparation method in Embodiment 1.

[0055] Specific...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com