Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1844 results about "Redistribution layer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A redistribution layer (RDL) is an extra metal layer on a chip that makes the IO pads of an integrated circuit available in other locations of the chip, for better access to the pads where necessary. When an integrated circuit is manufactured, it usually has a set of IO pads that are wirebonded to the pins of the package. A redistribution layer is an extra layer of wiring on the chip that enables you to bond out from different locations on the chip, making chip-to-chip bonding simpler. Another example of the use for RDL is for spreading the contact points around the die so that solder balls can be applied, and the thermal stress of mounting can be spread.

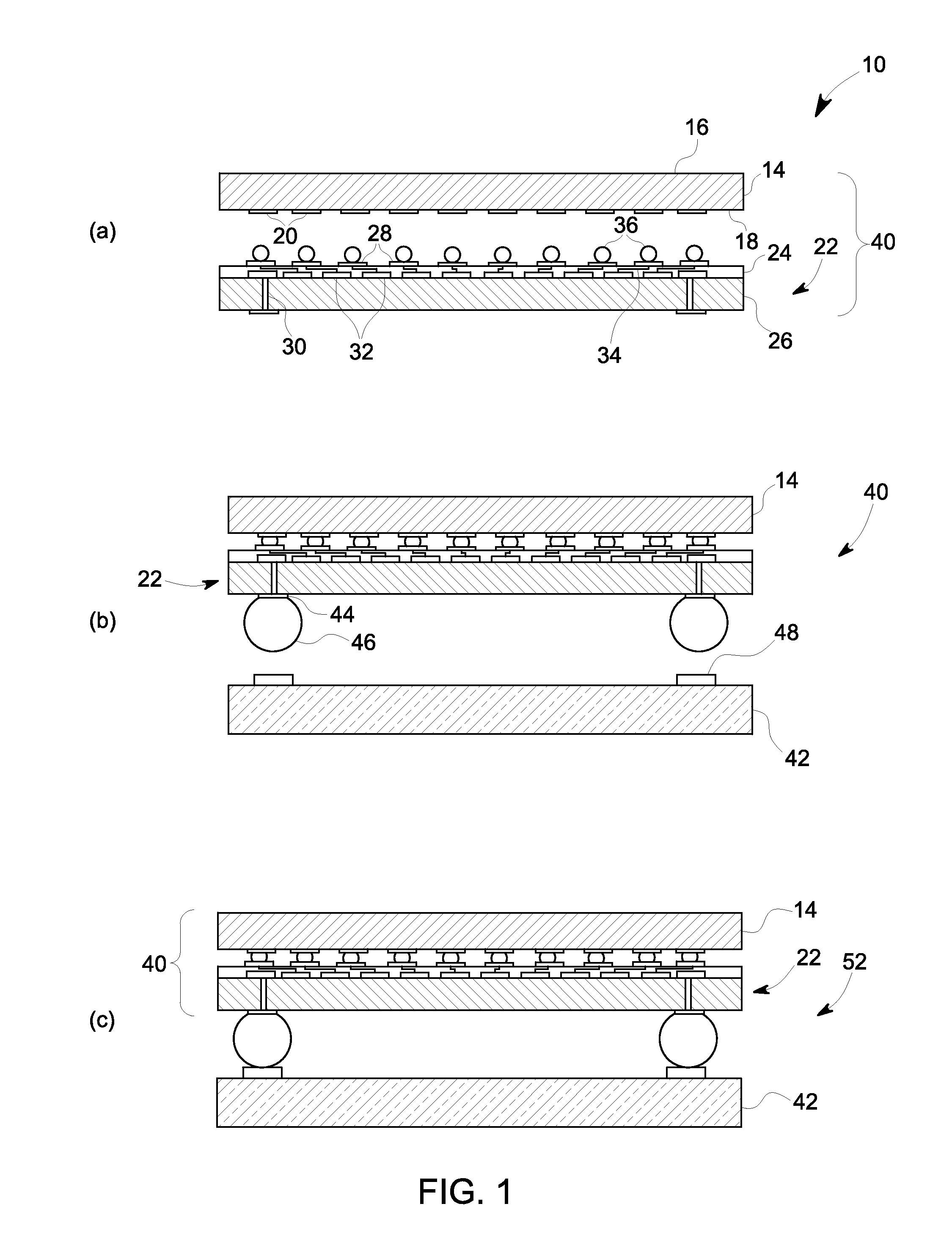

Integrated structures and fabrication methods thereof implementing a cell phone or other electronic system

ActiveUS7619901B2Semiconductor/solid-state device detailsSolid-state devicesElectronic systemsContact pad

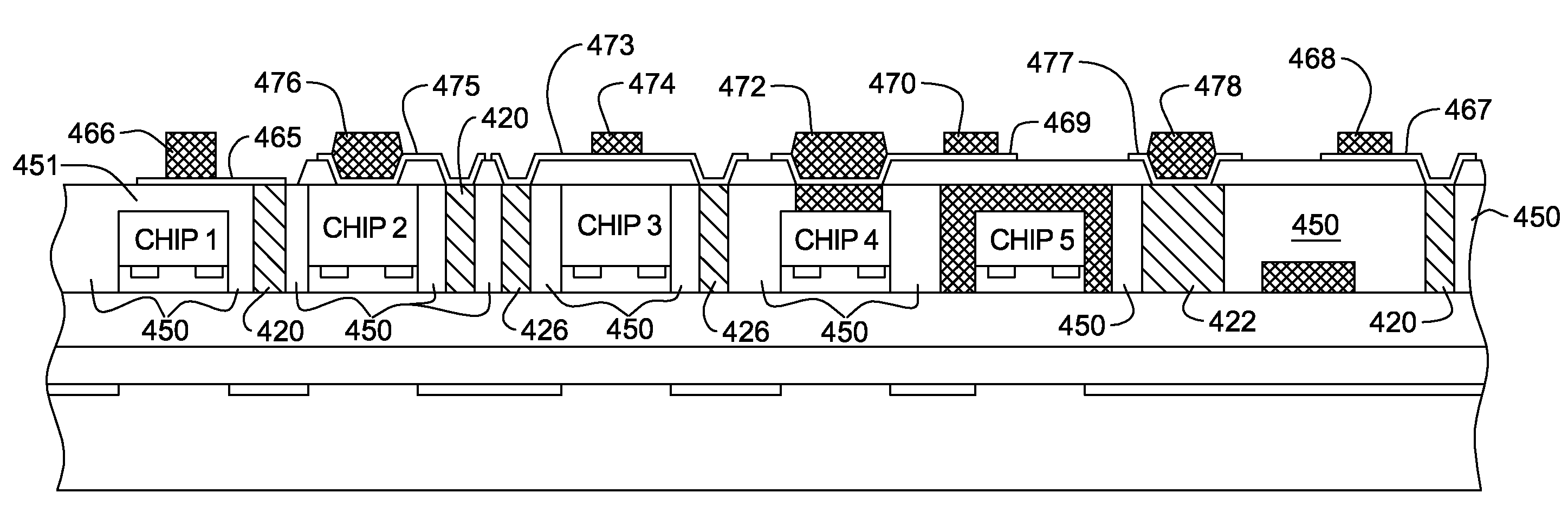

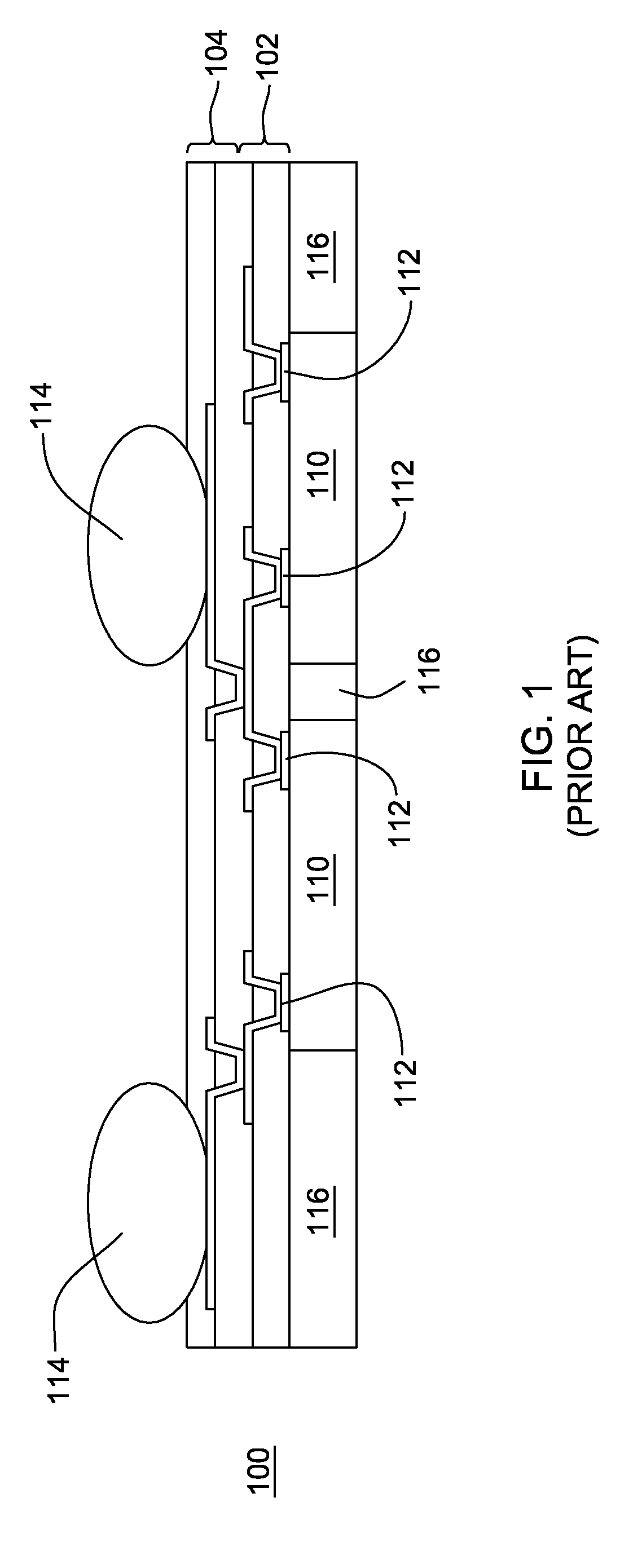

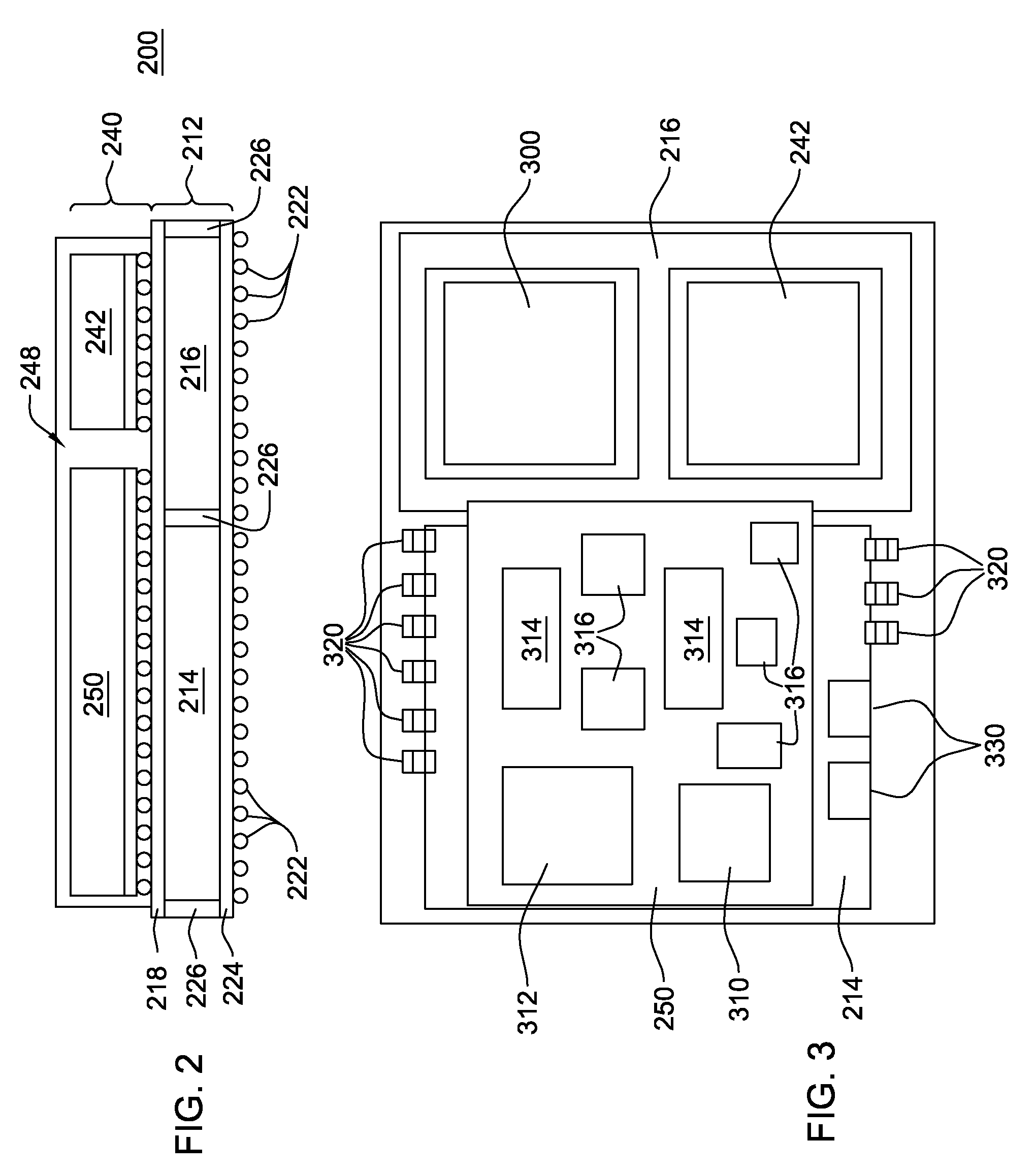

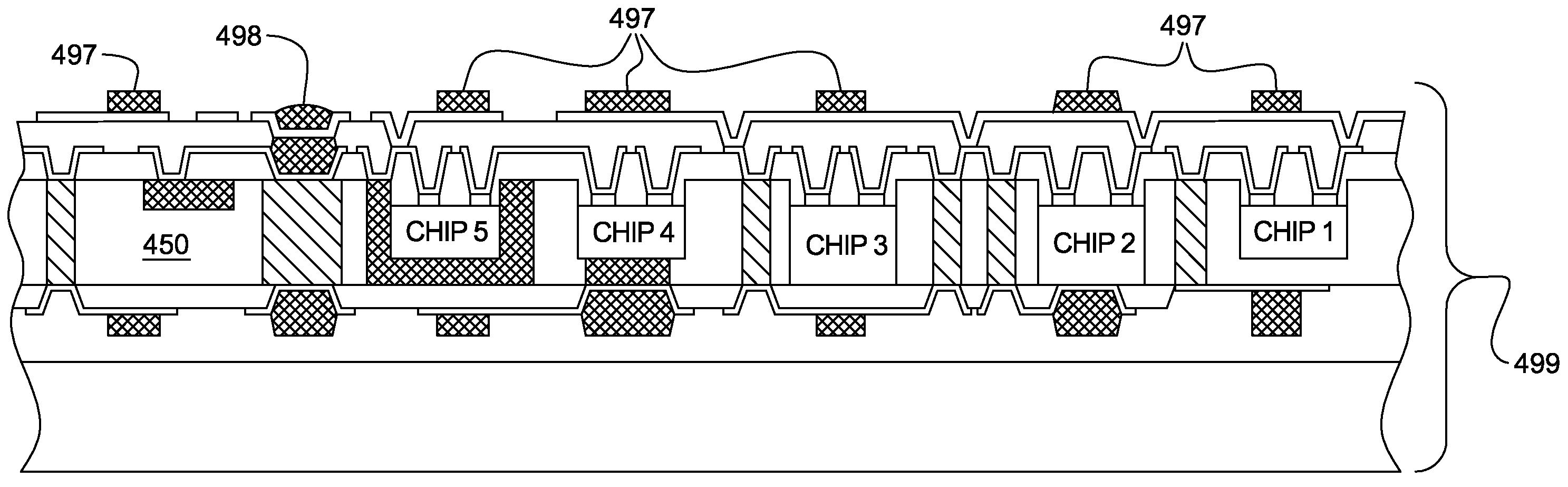

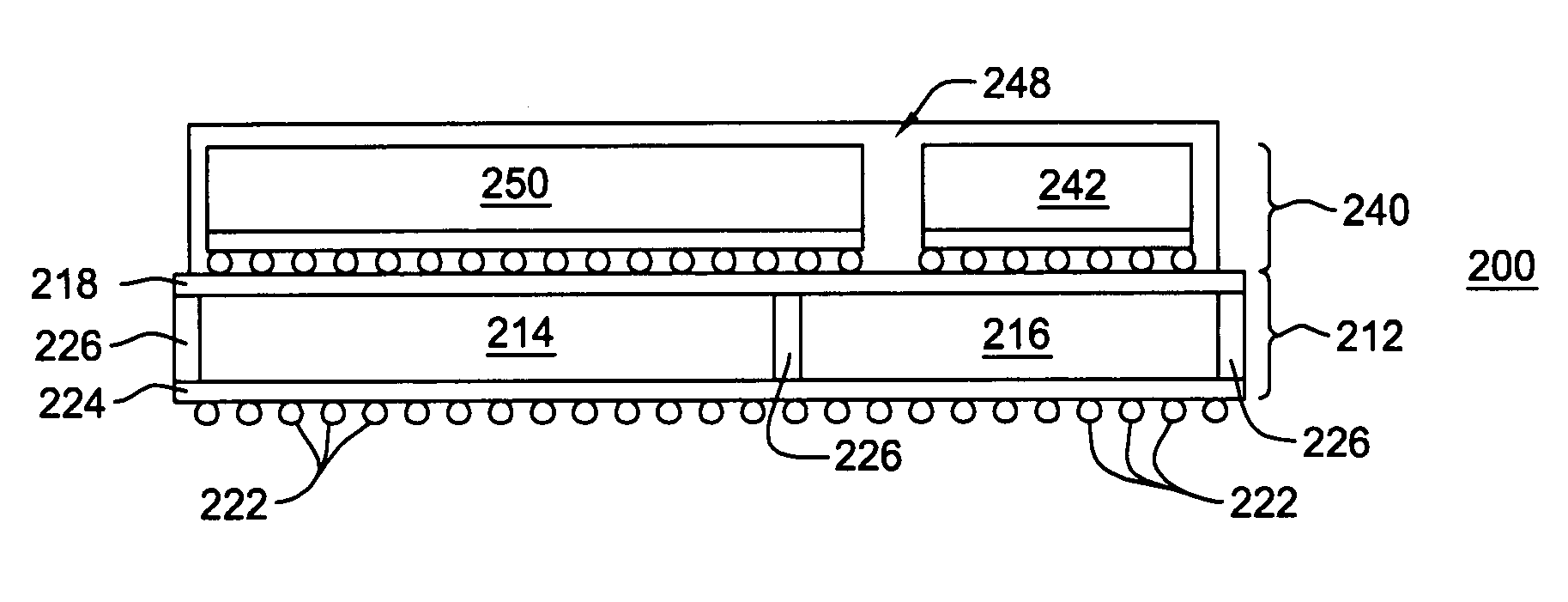

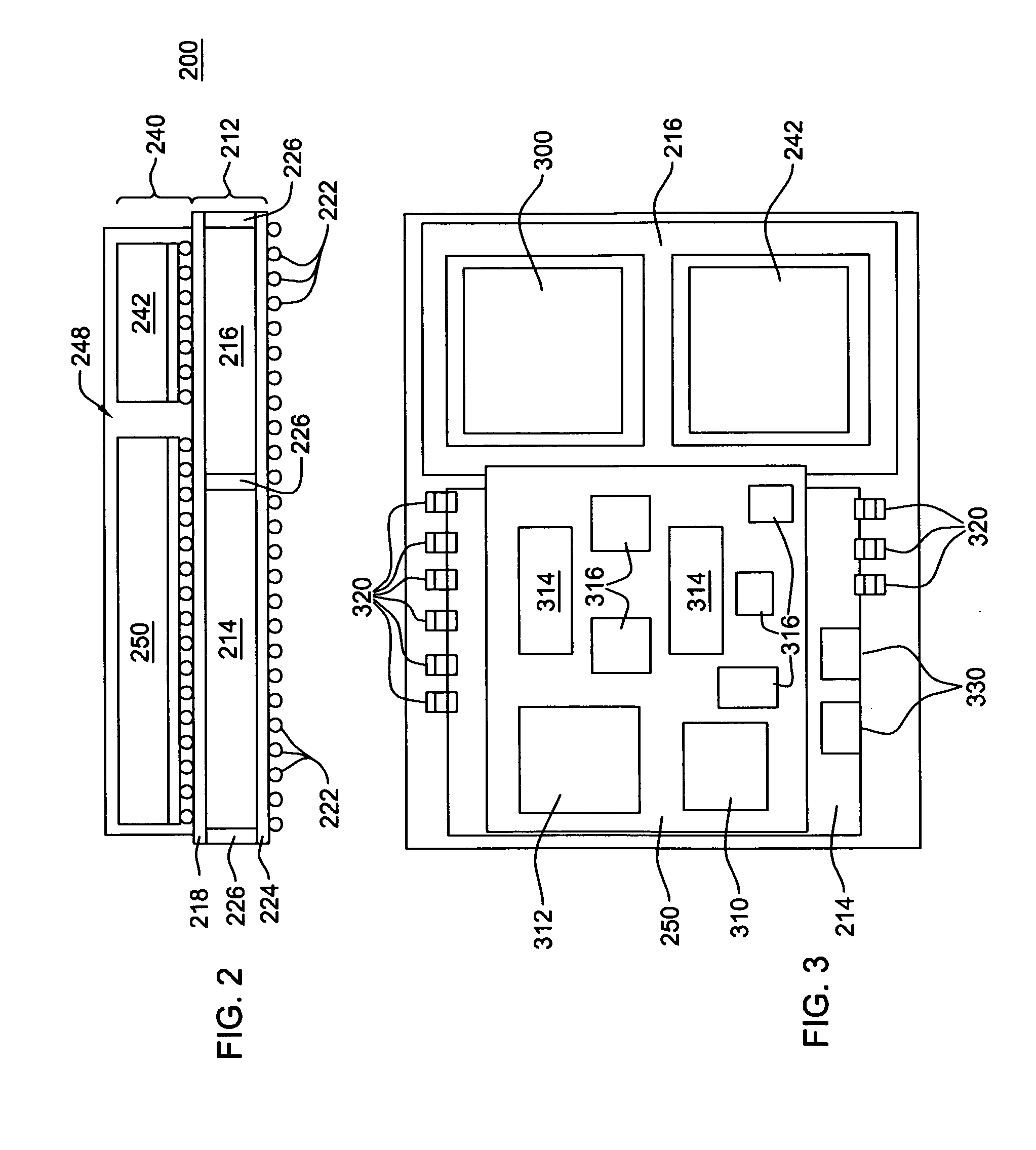

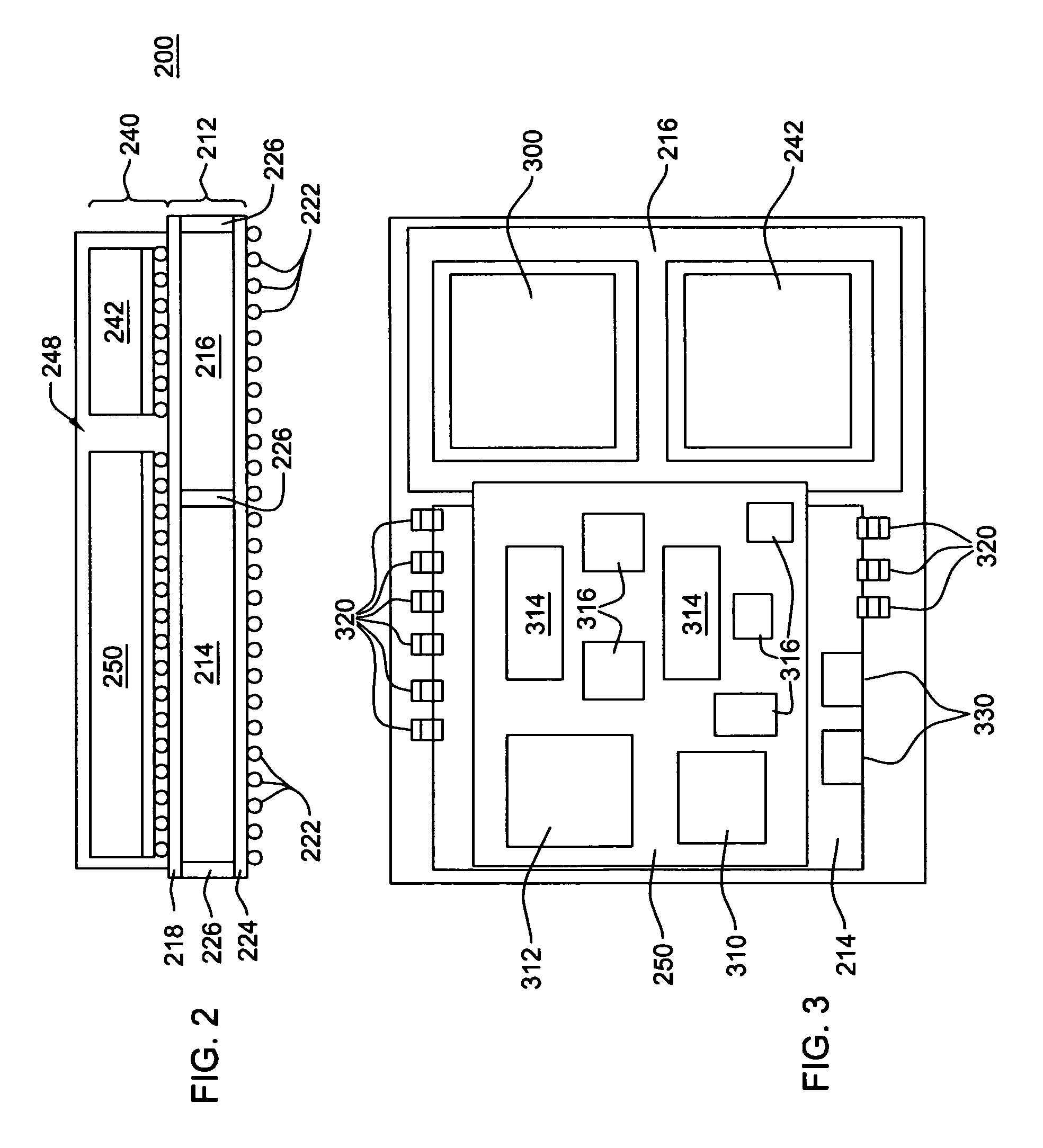

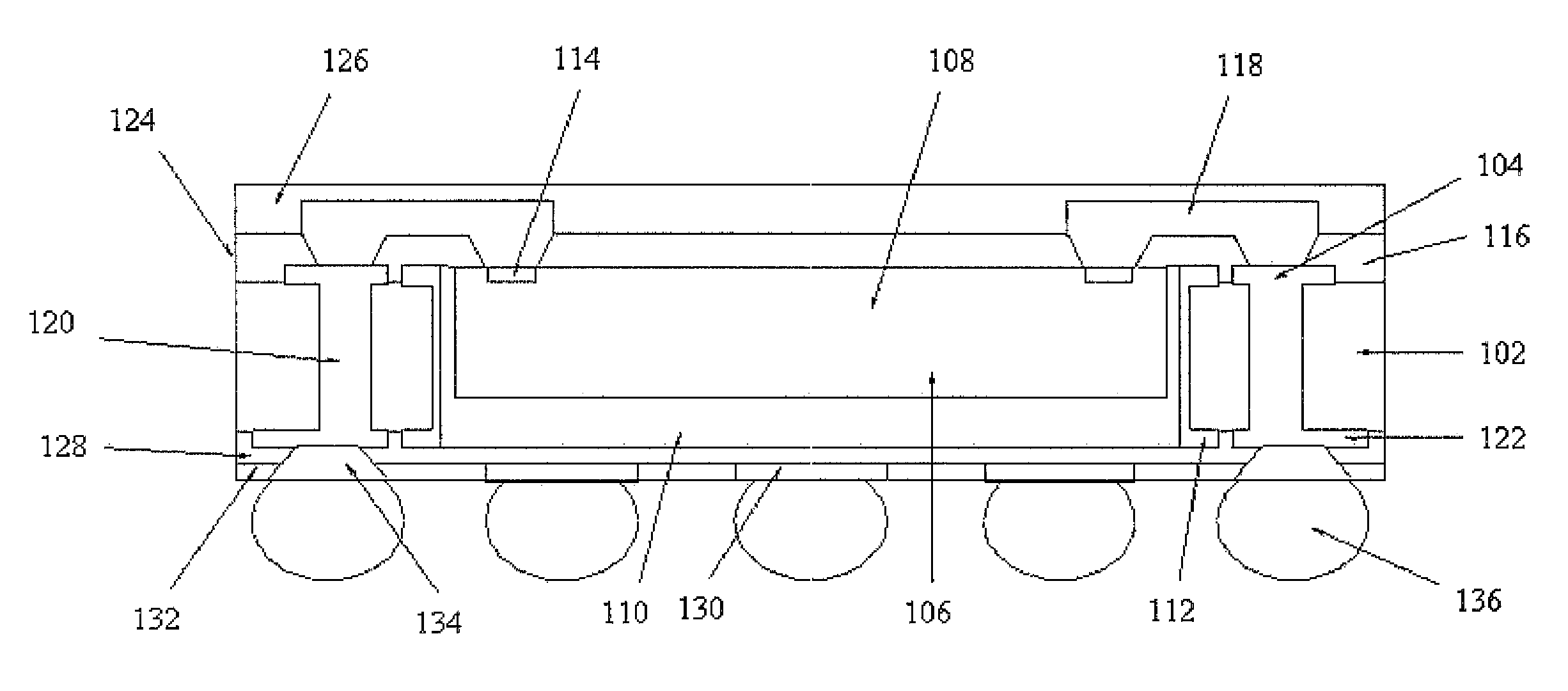

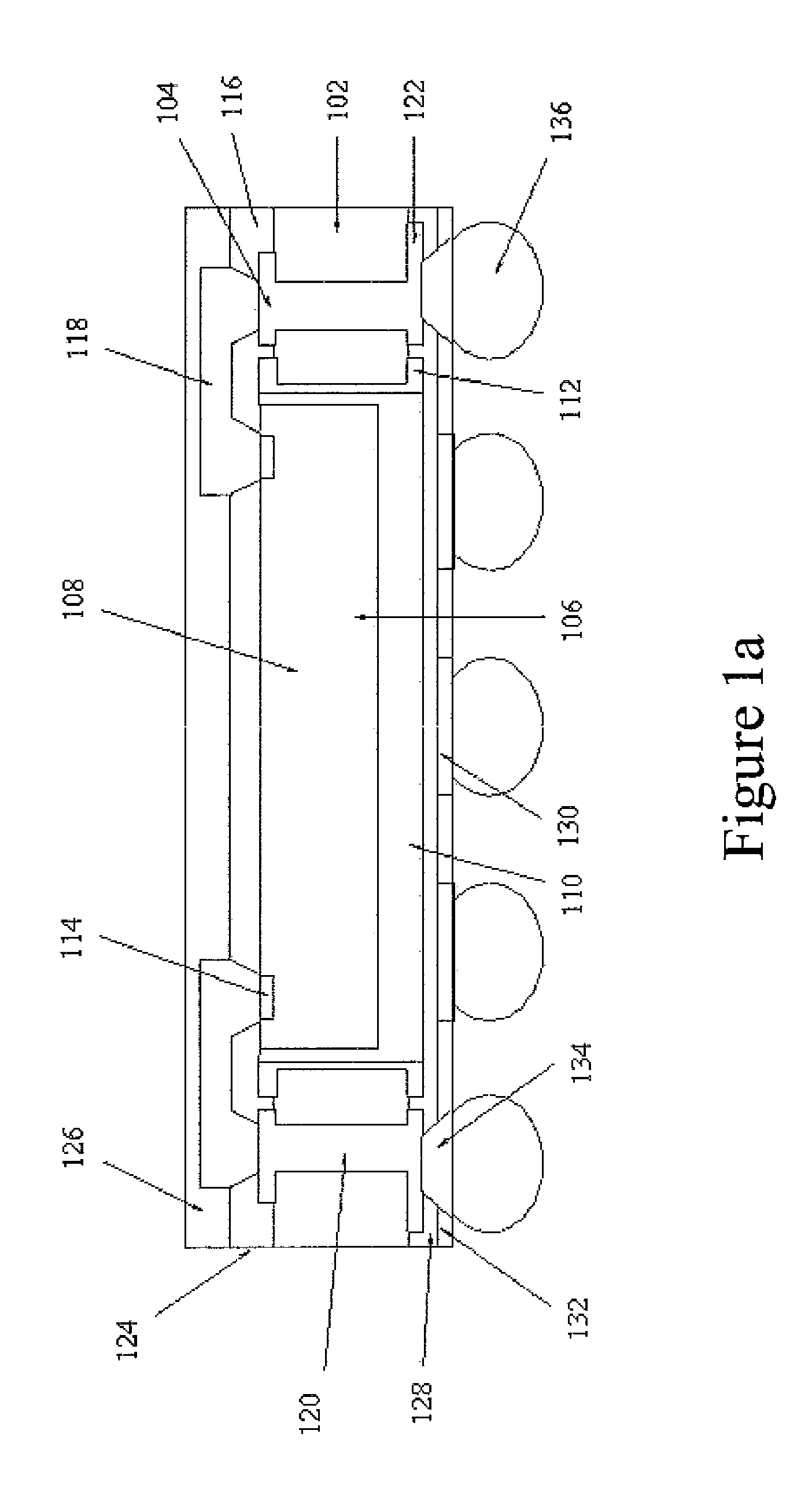

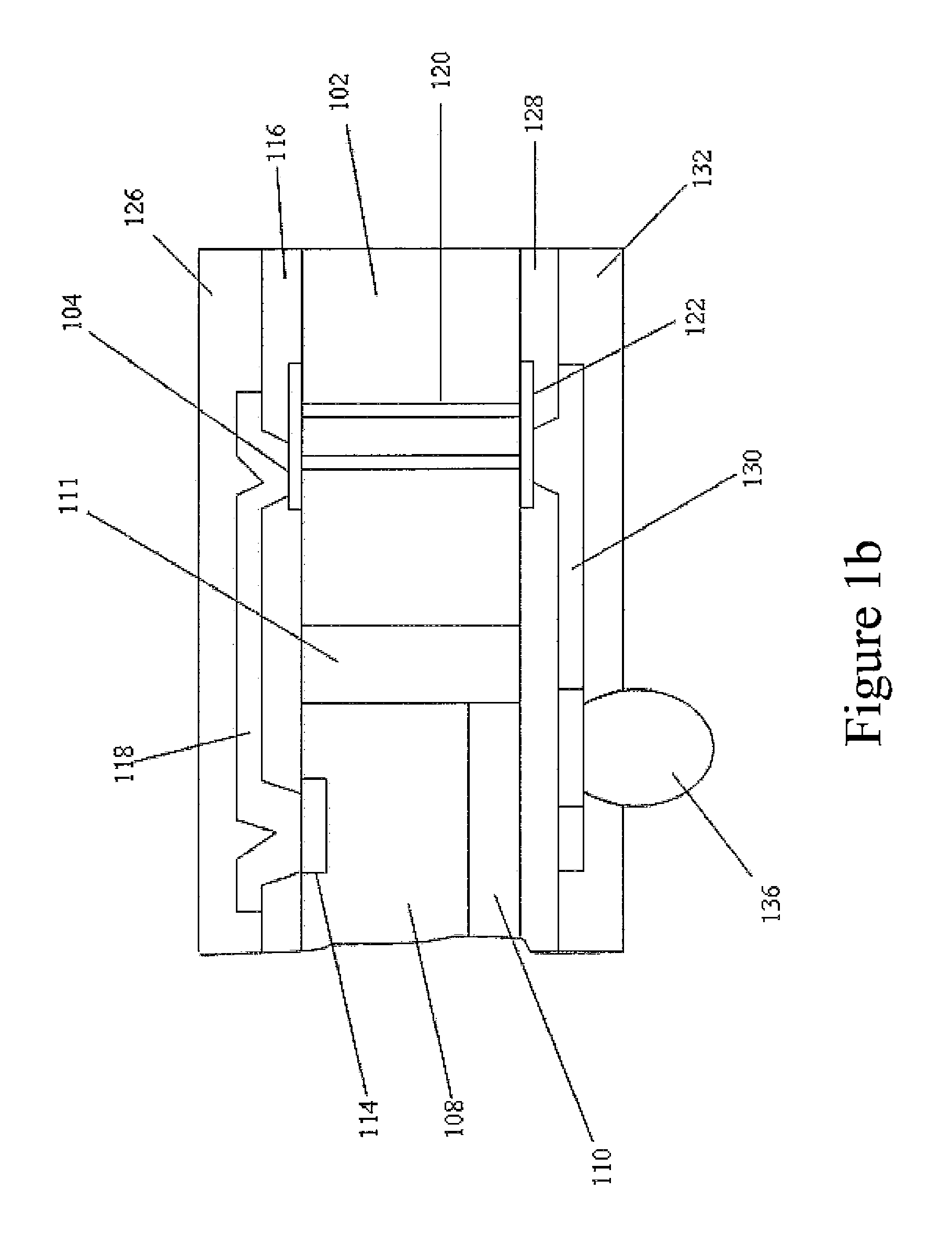

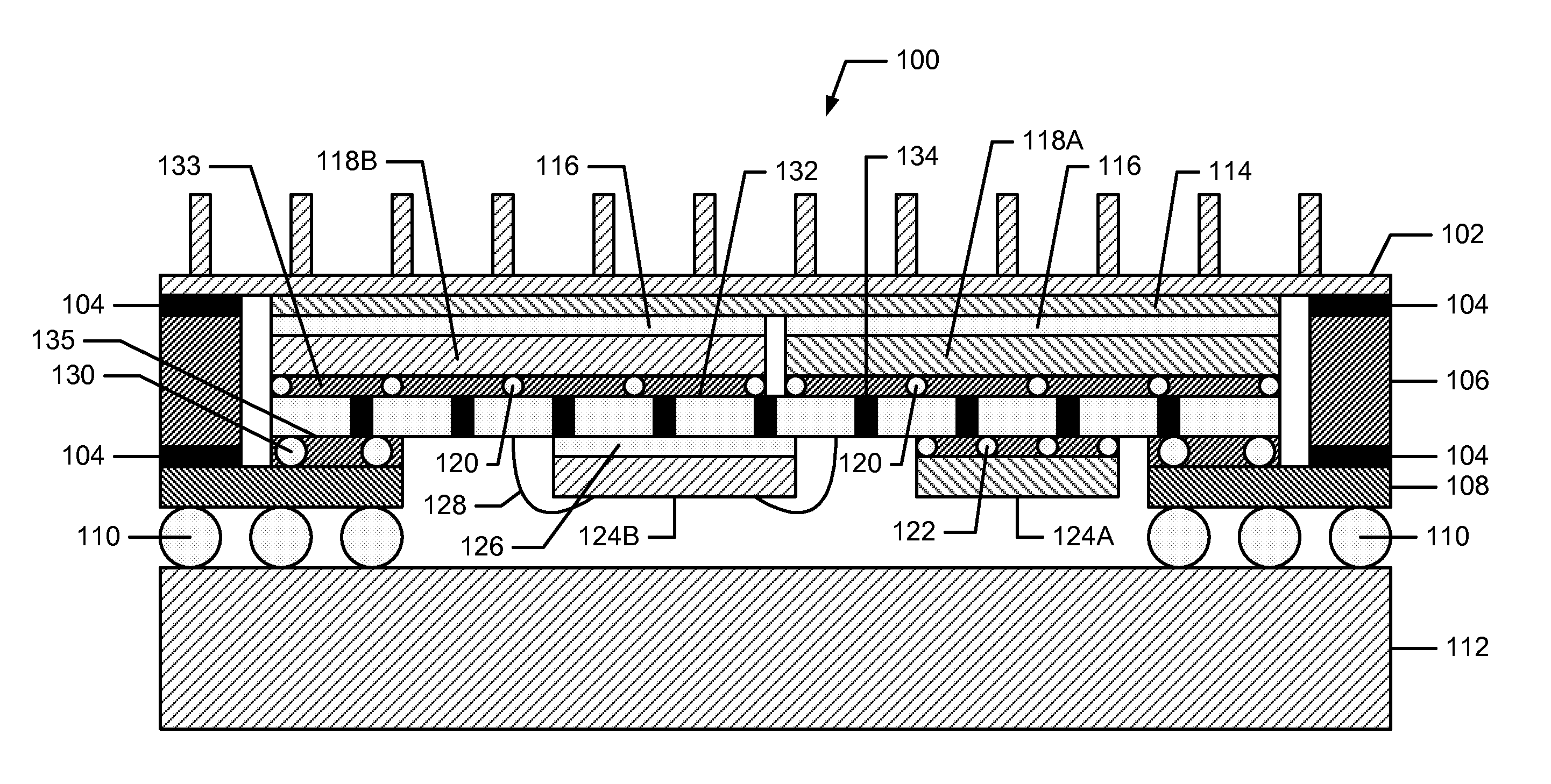

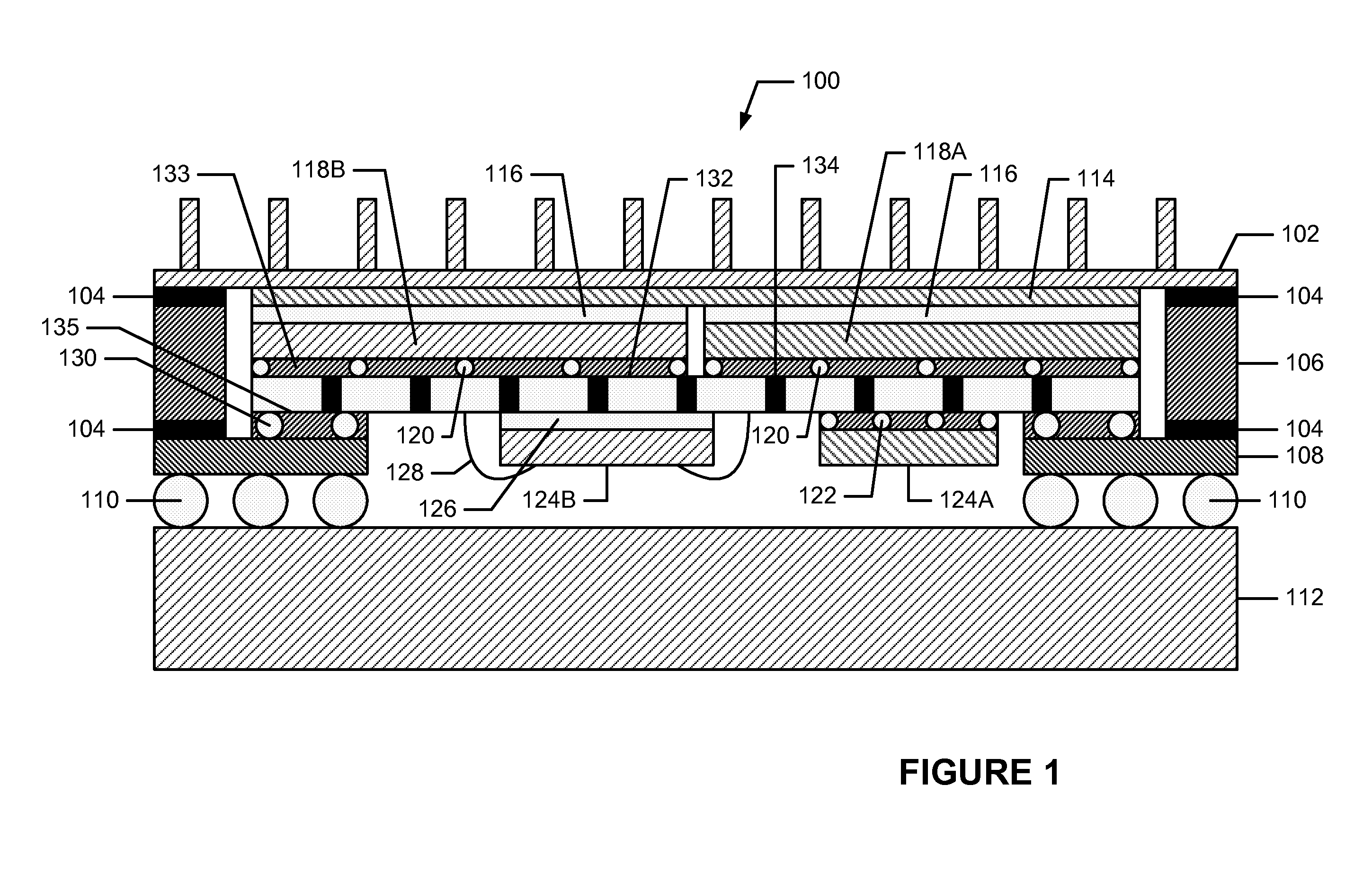

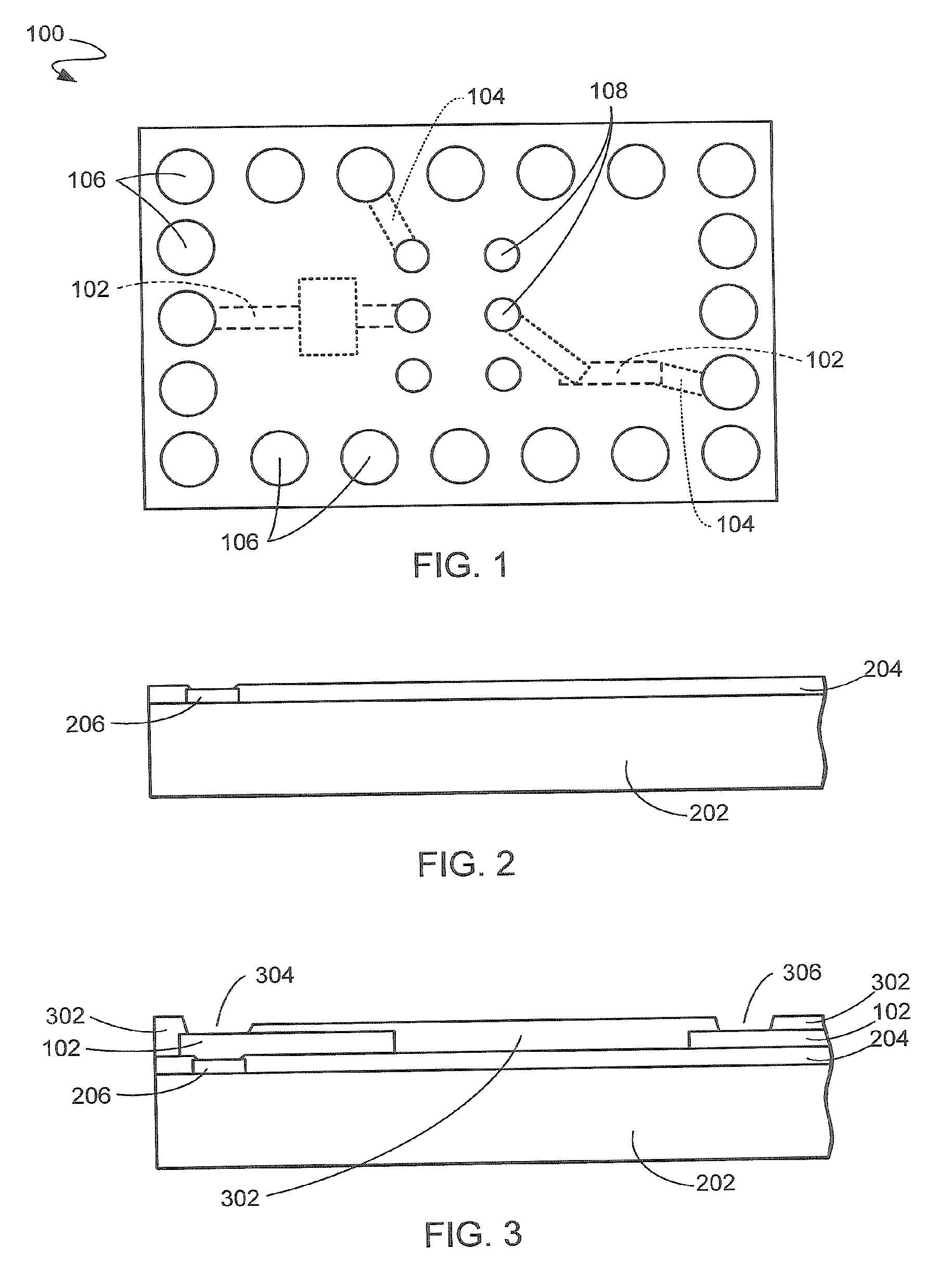

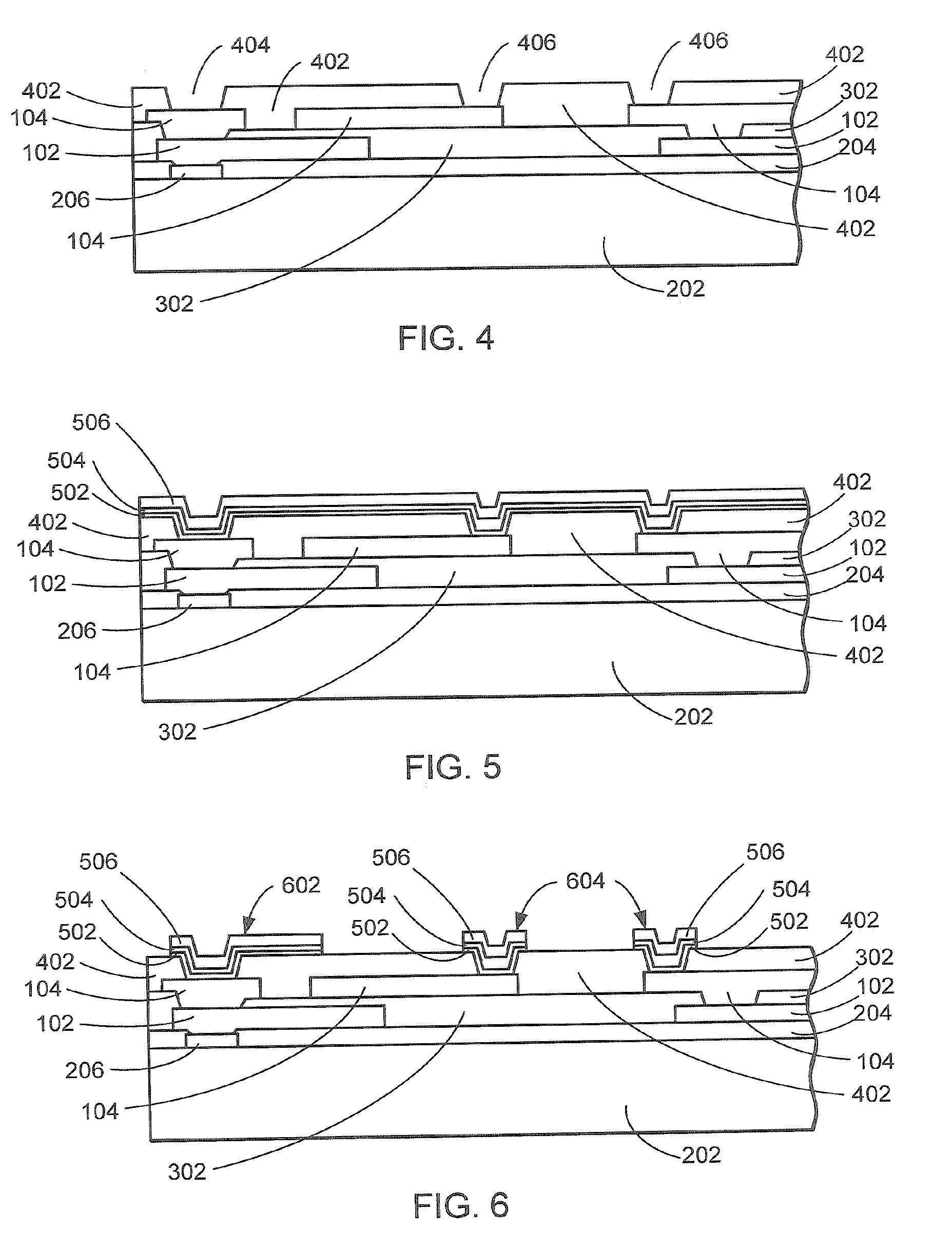

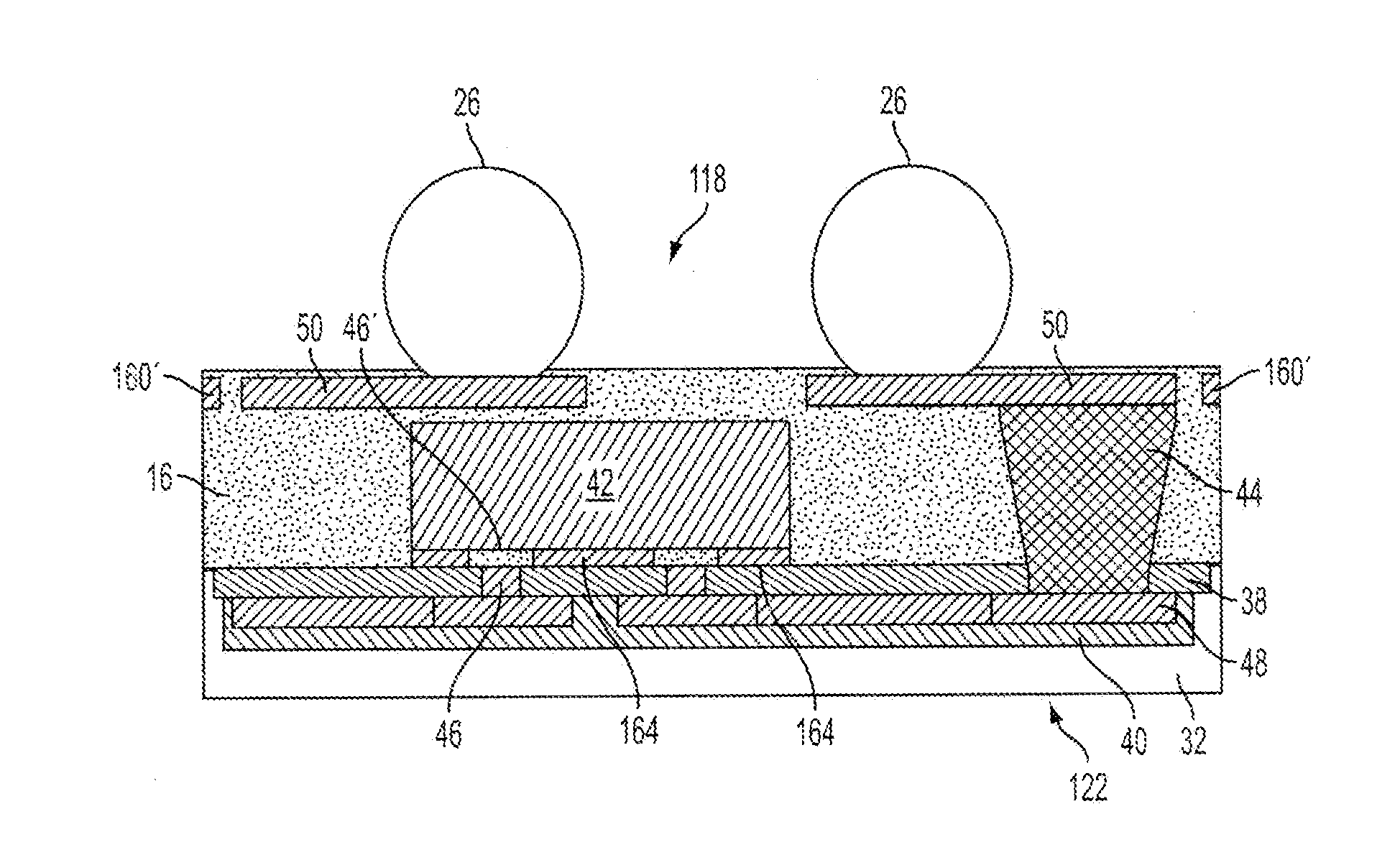

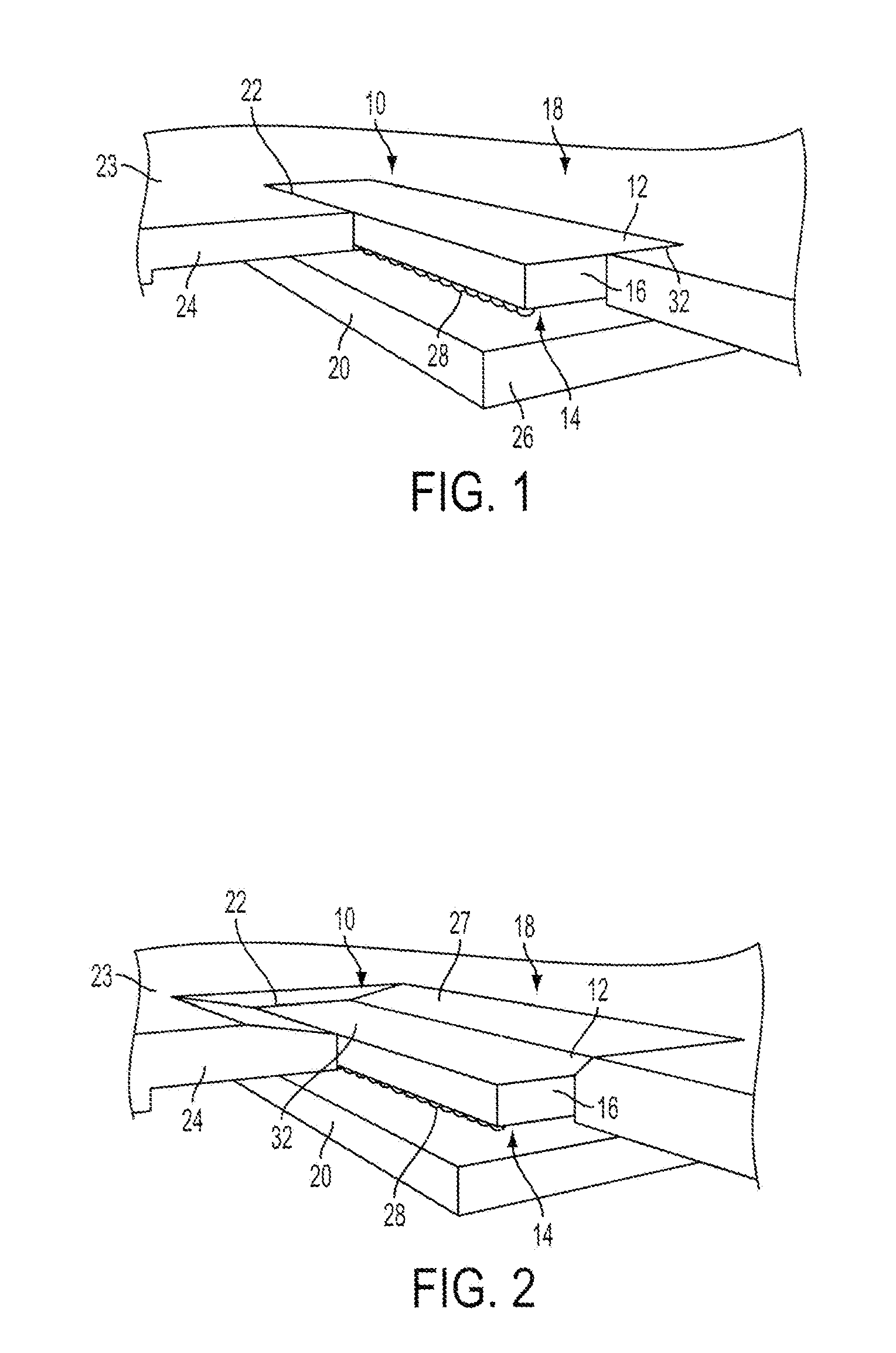

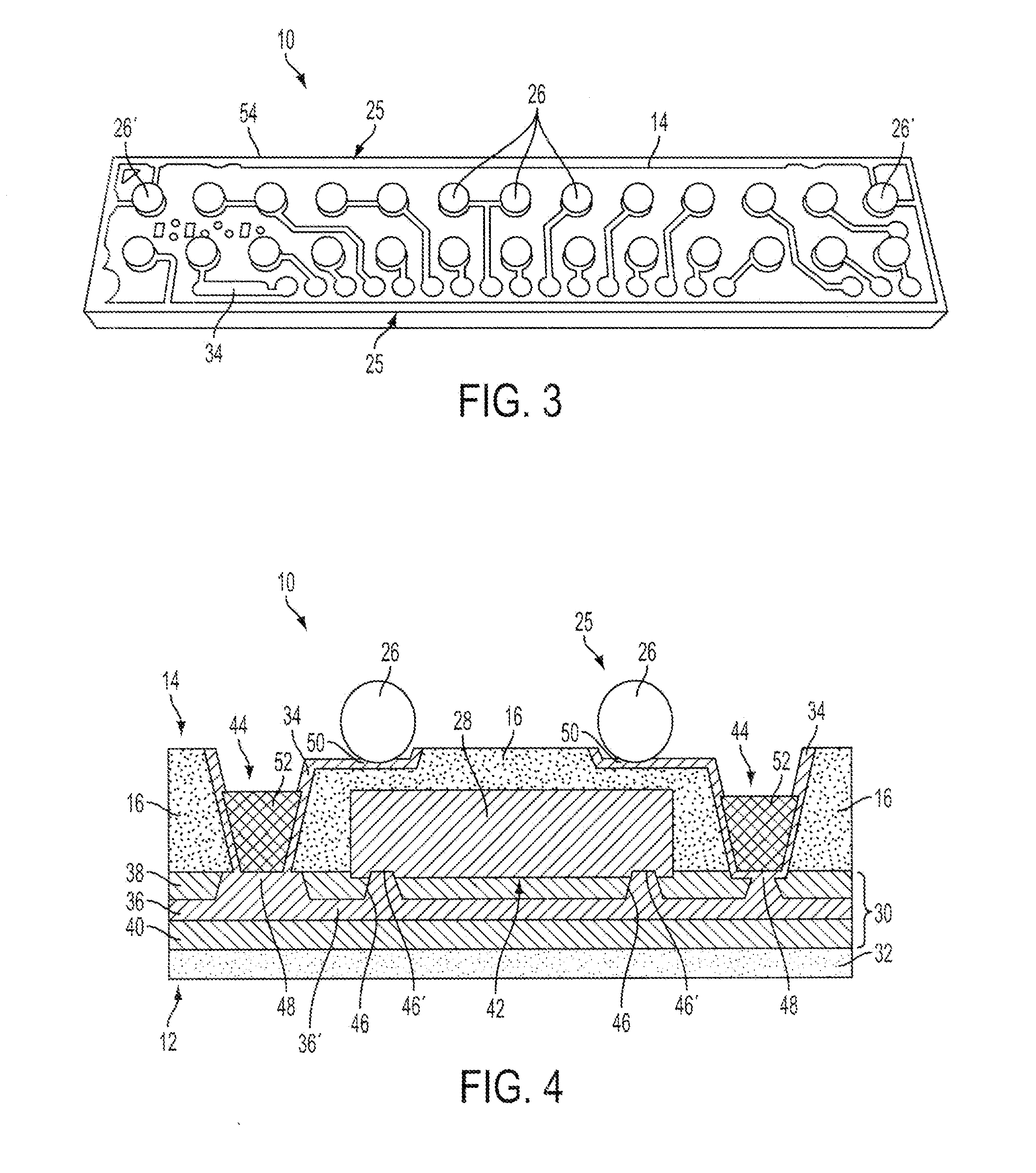

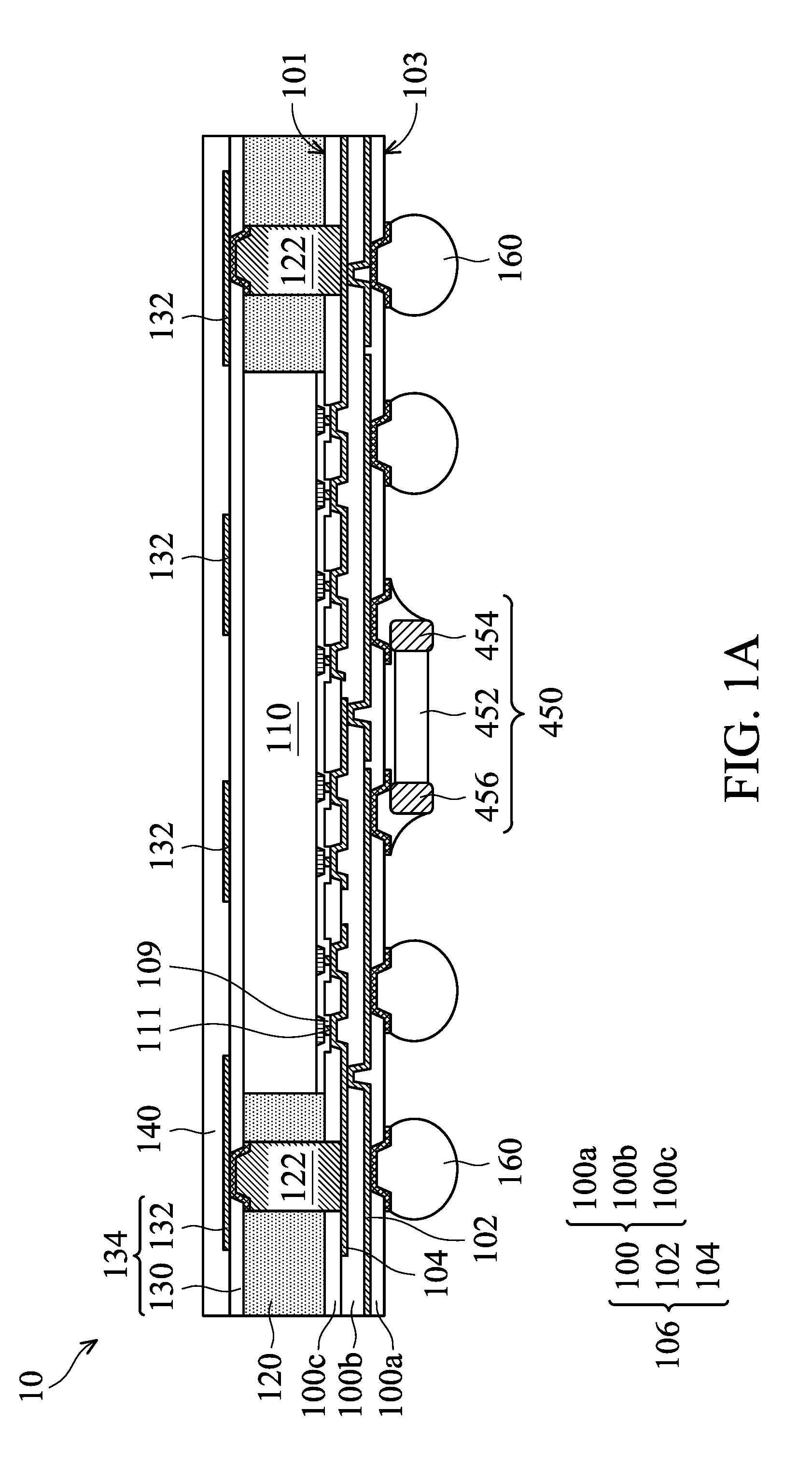

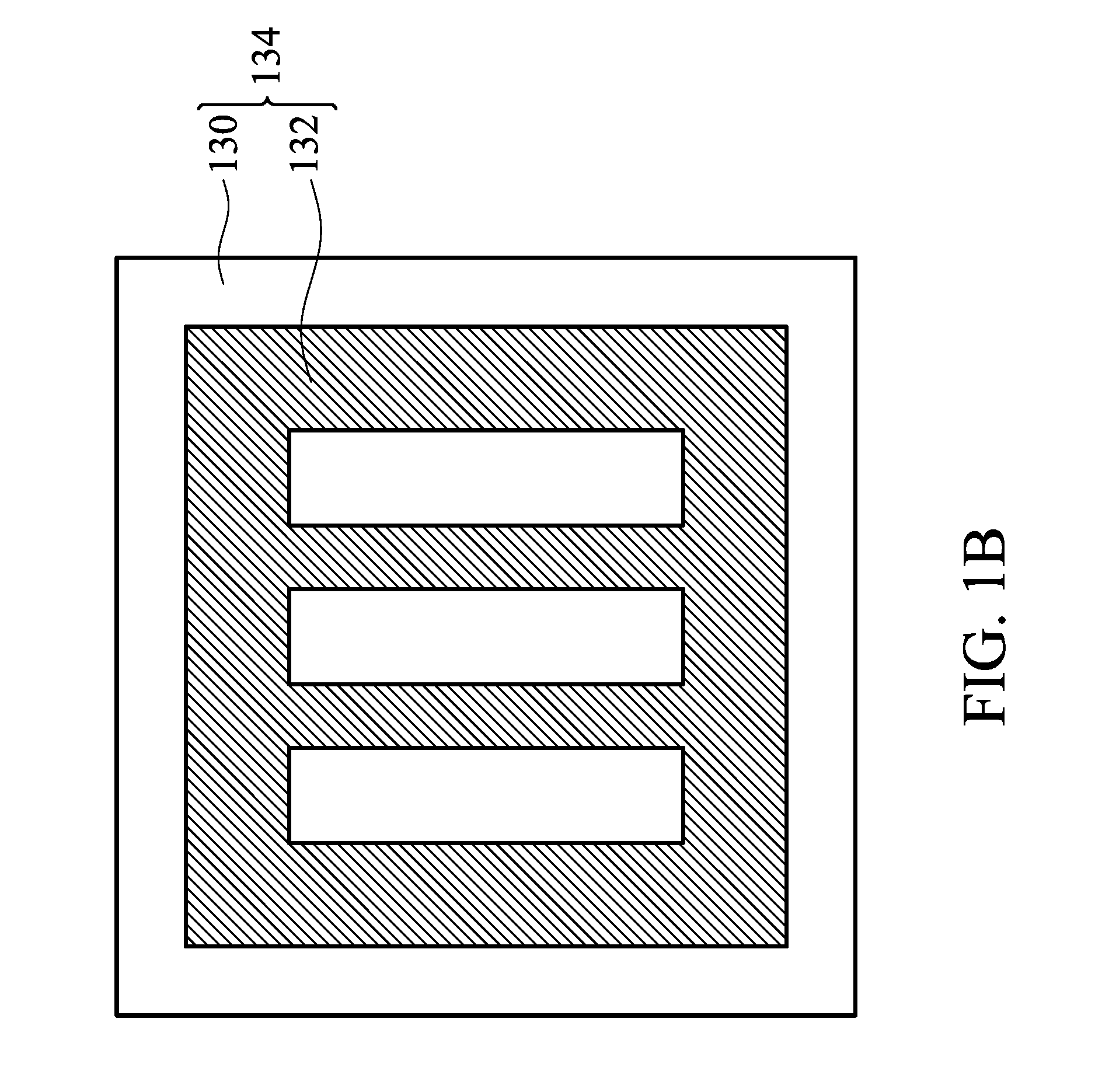

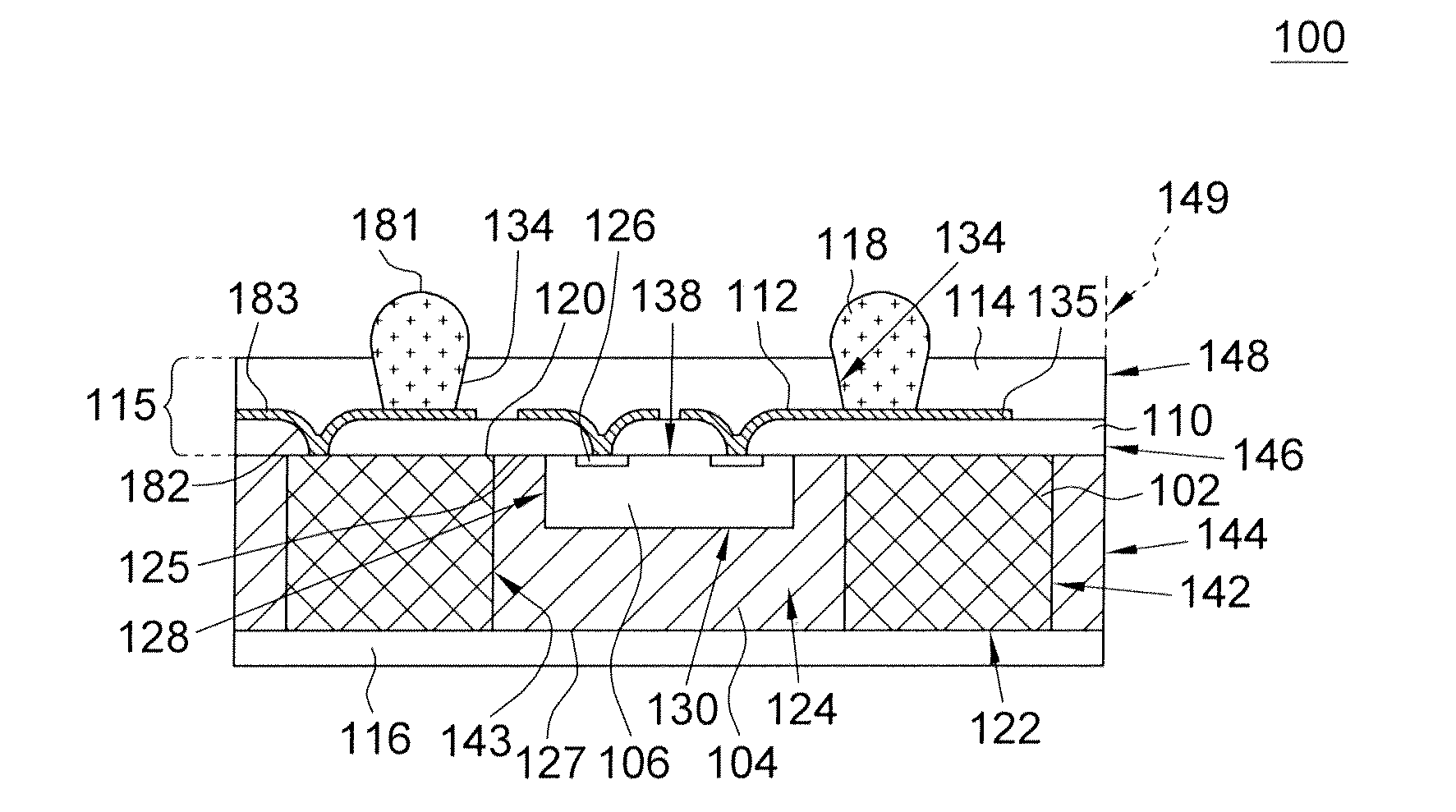

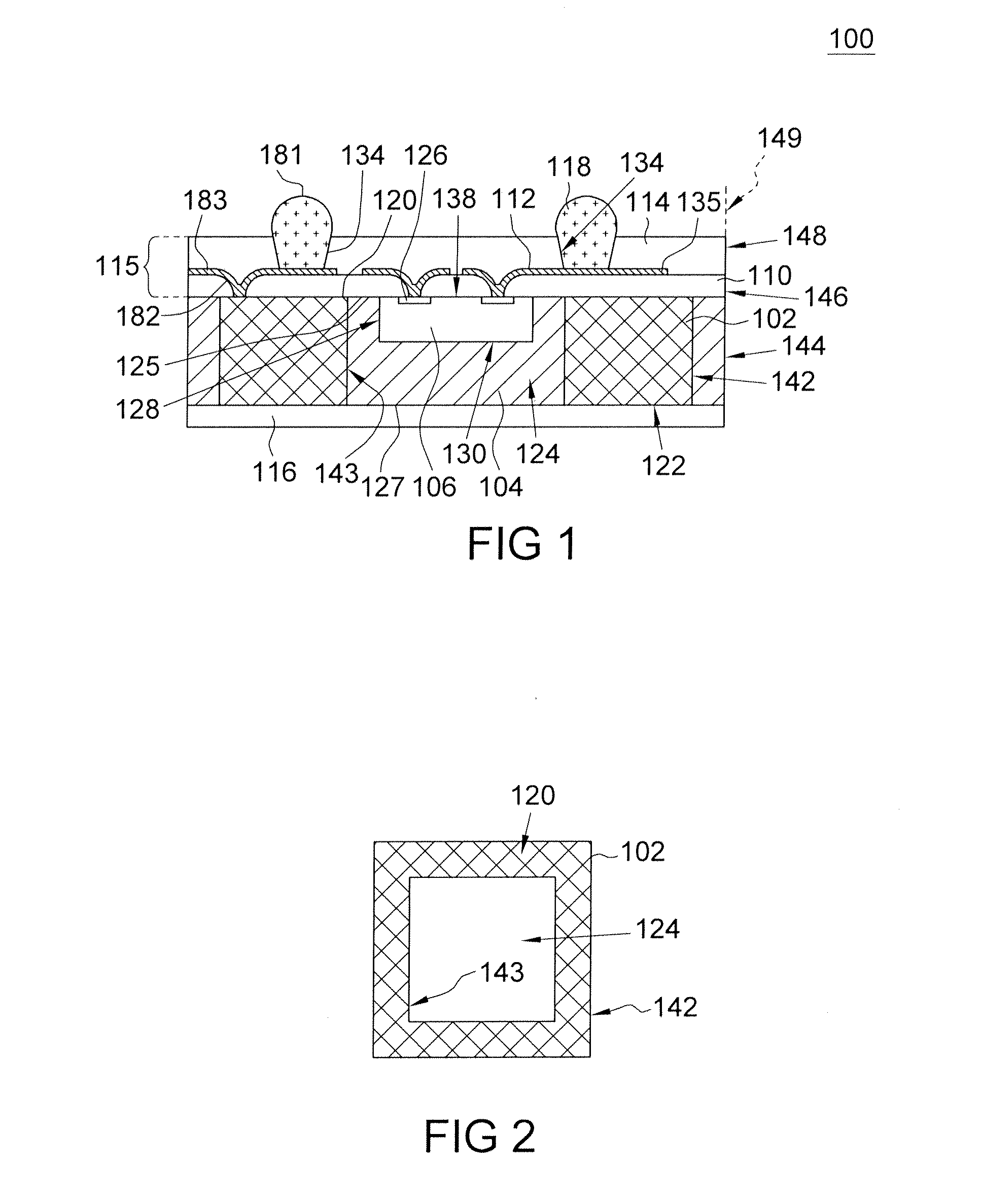

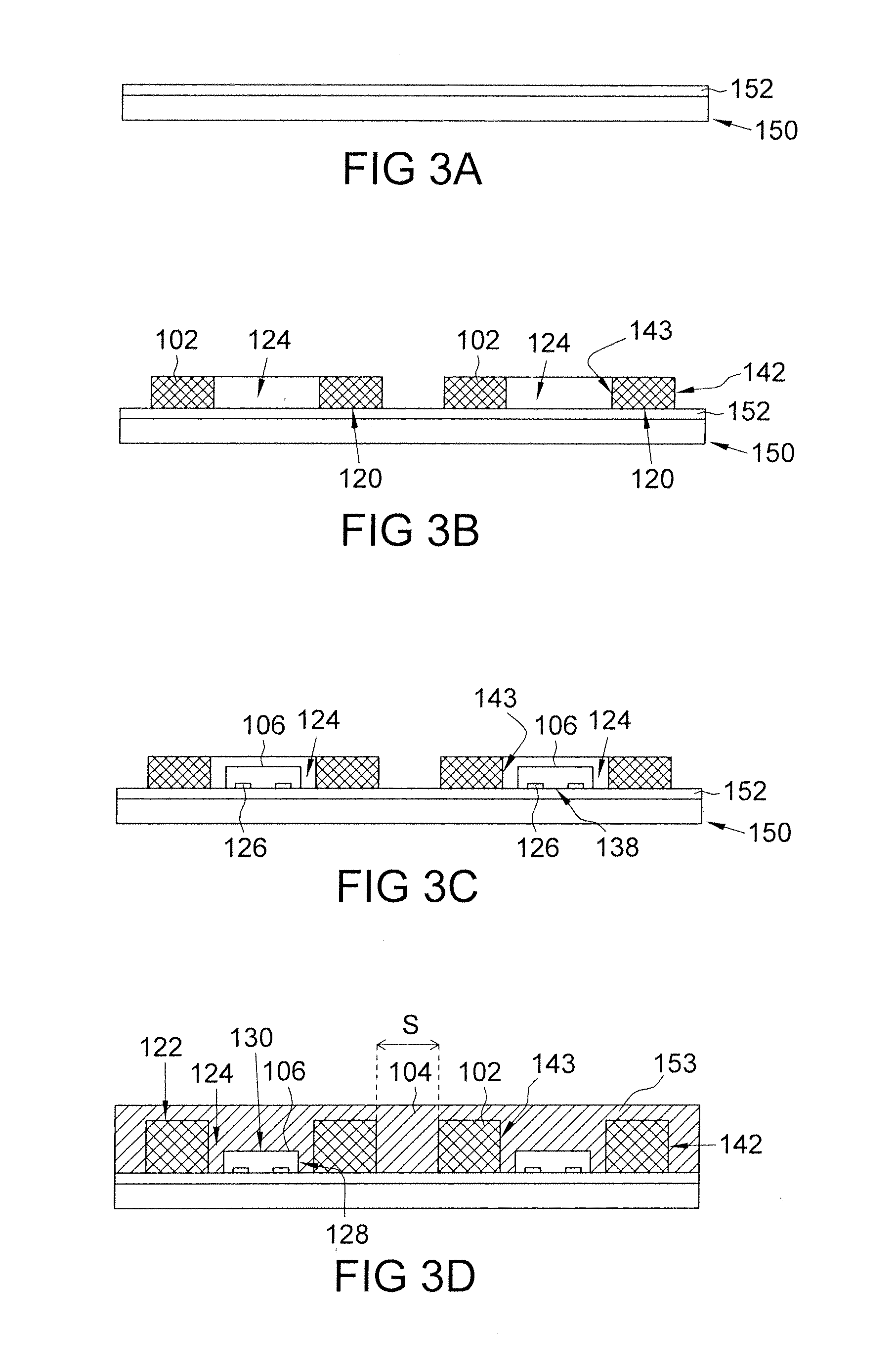

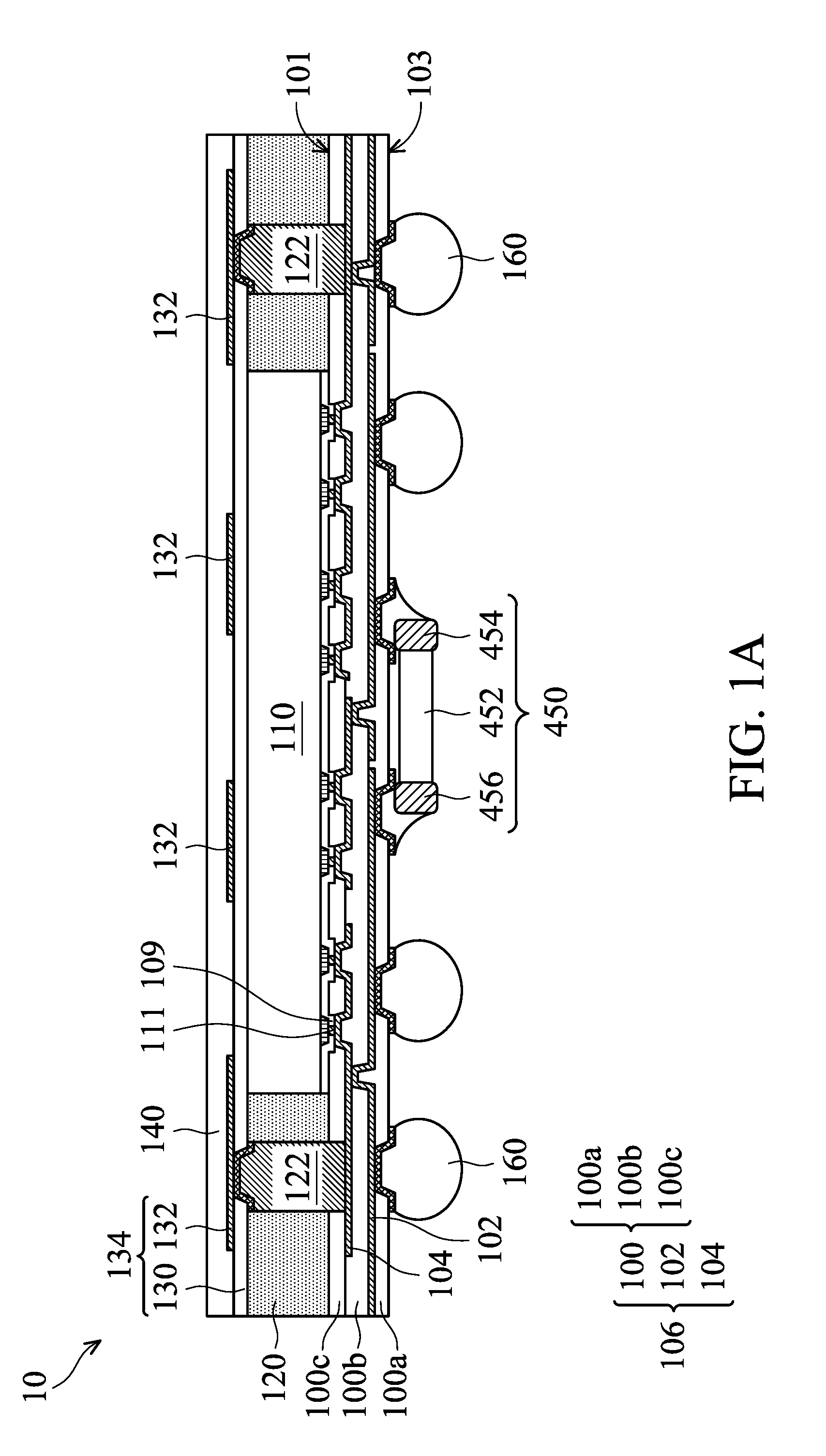

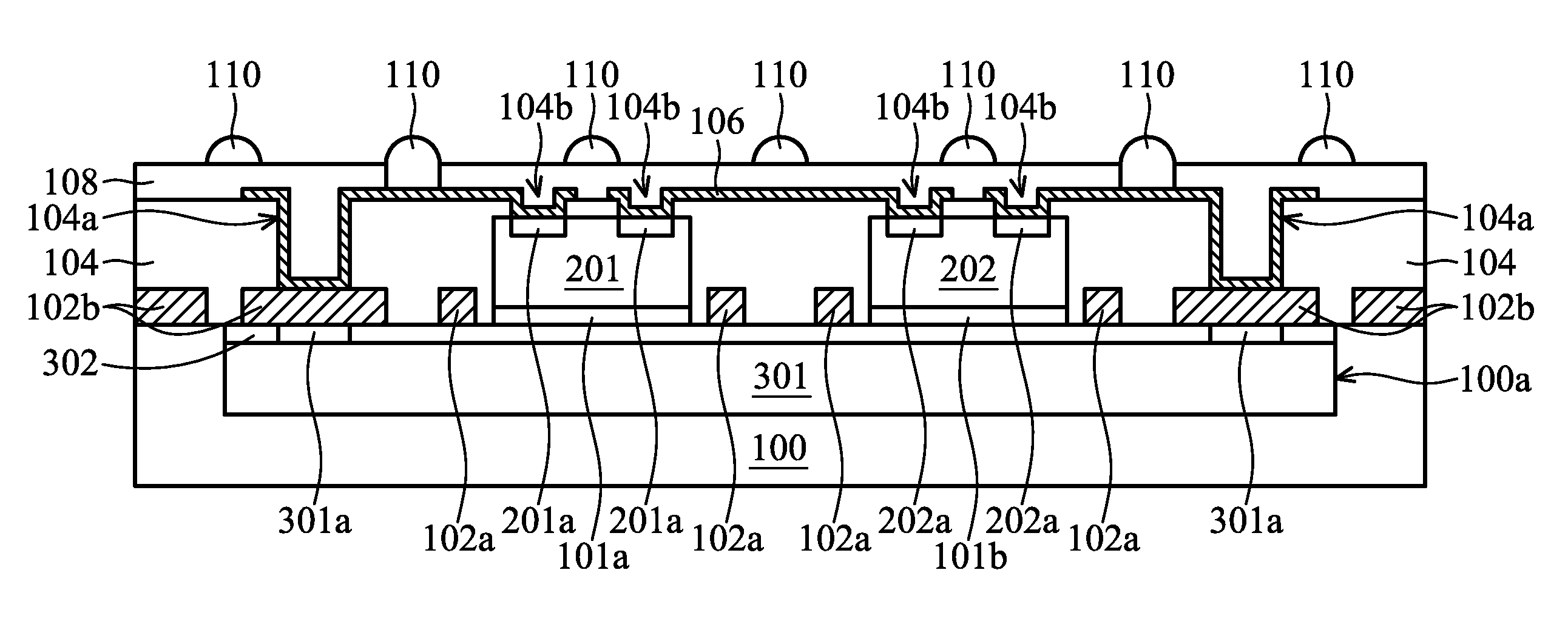

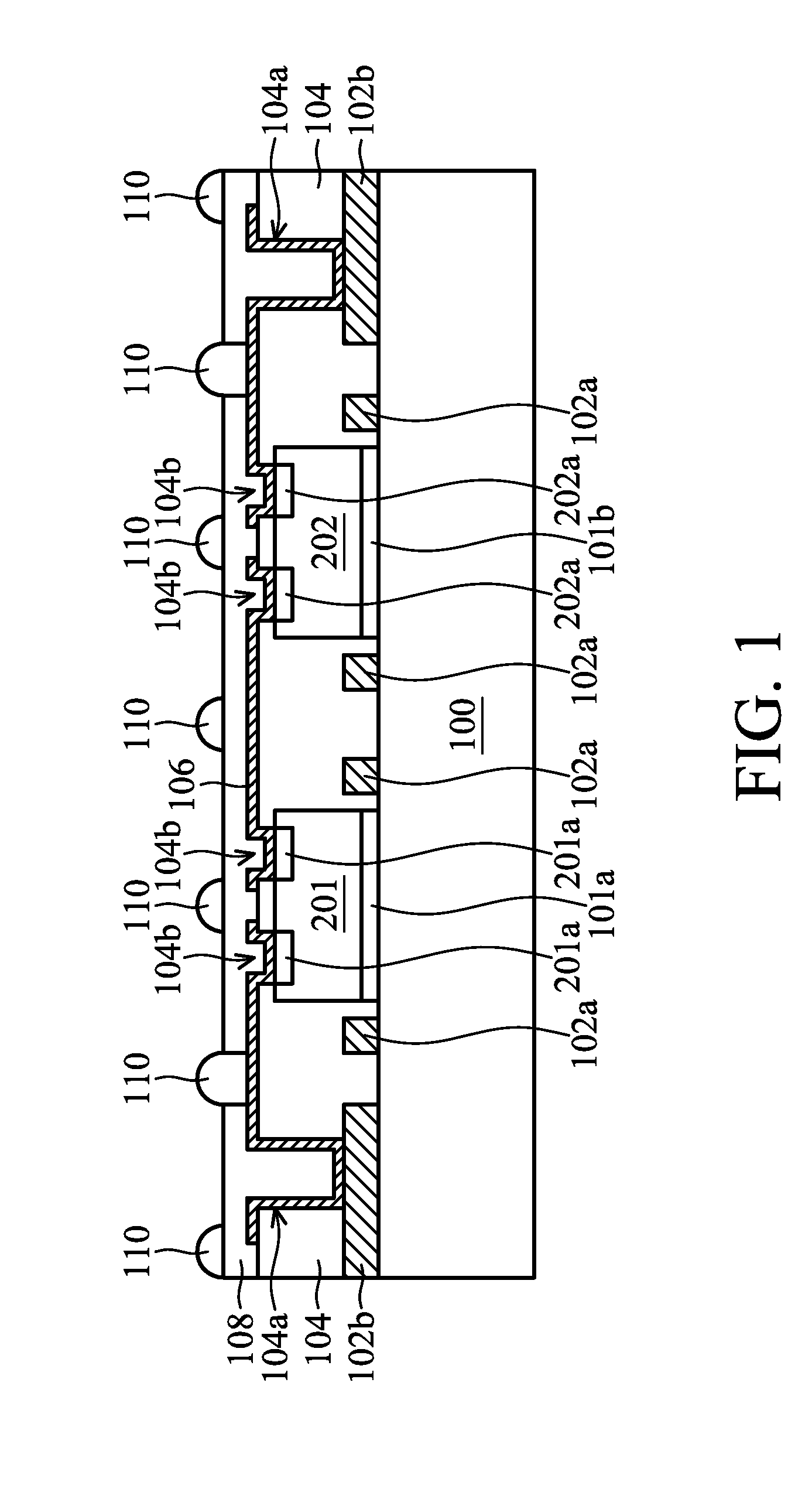

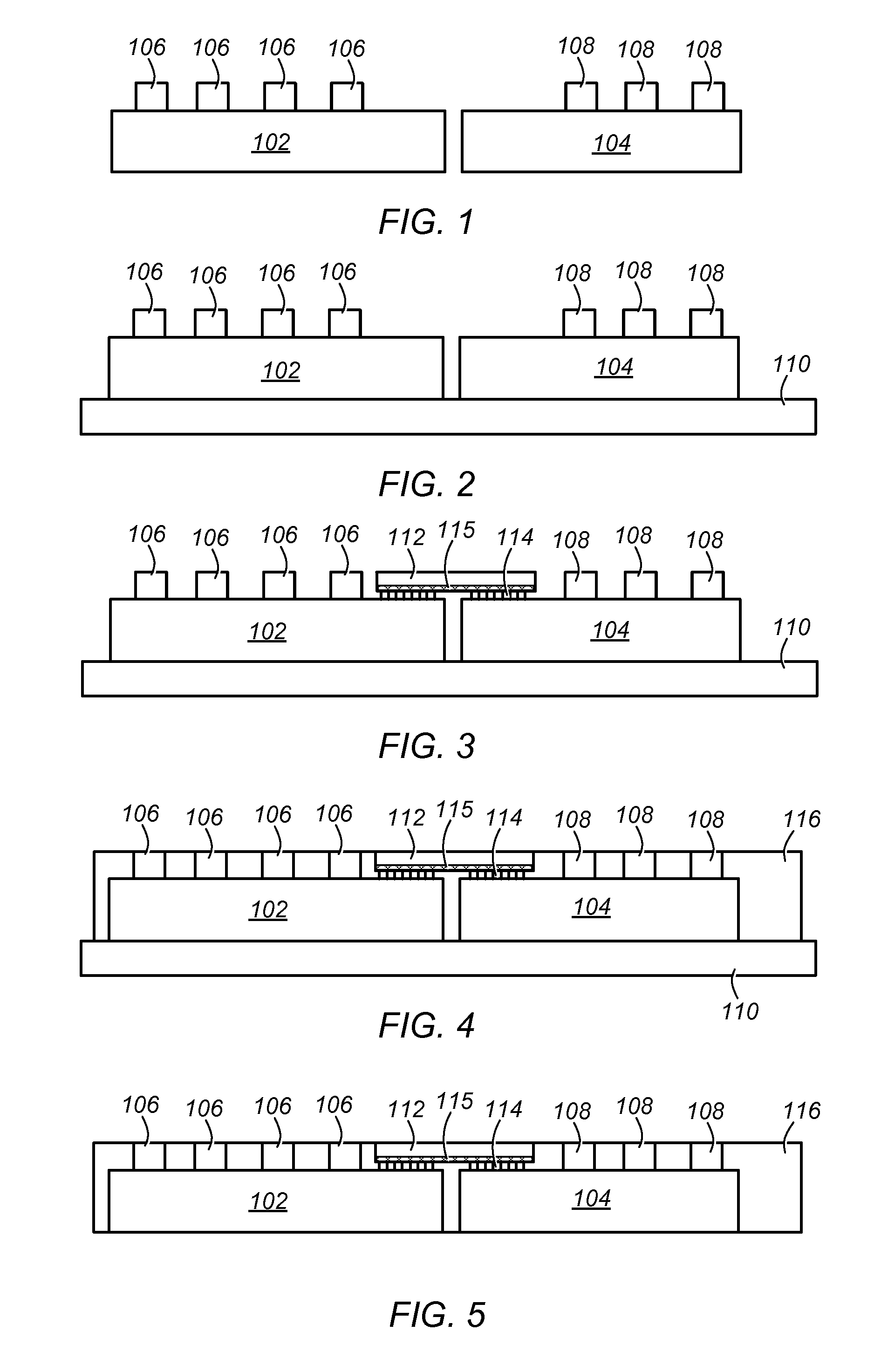

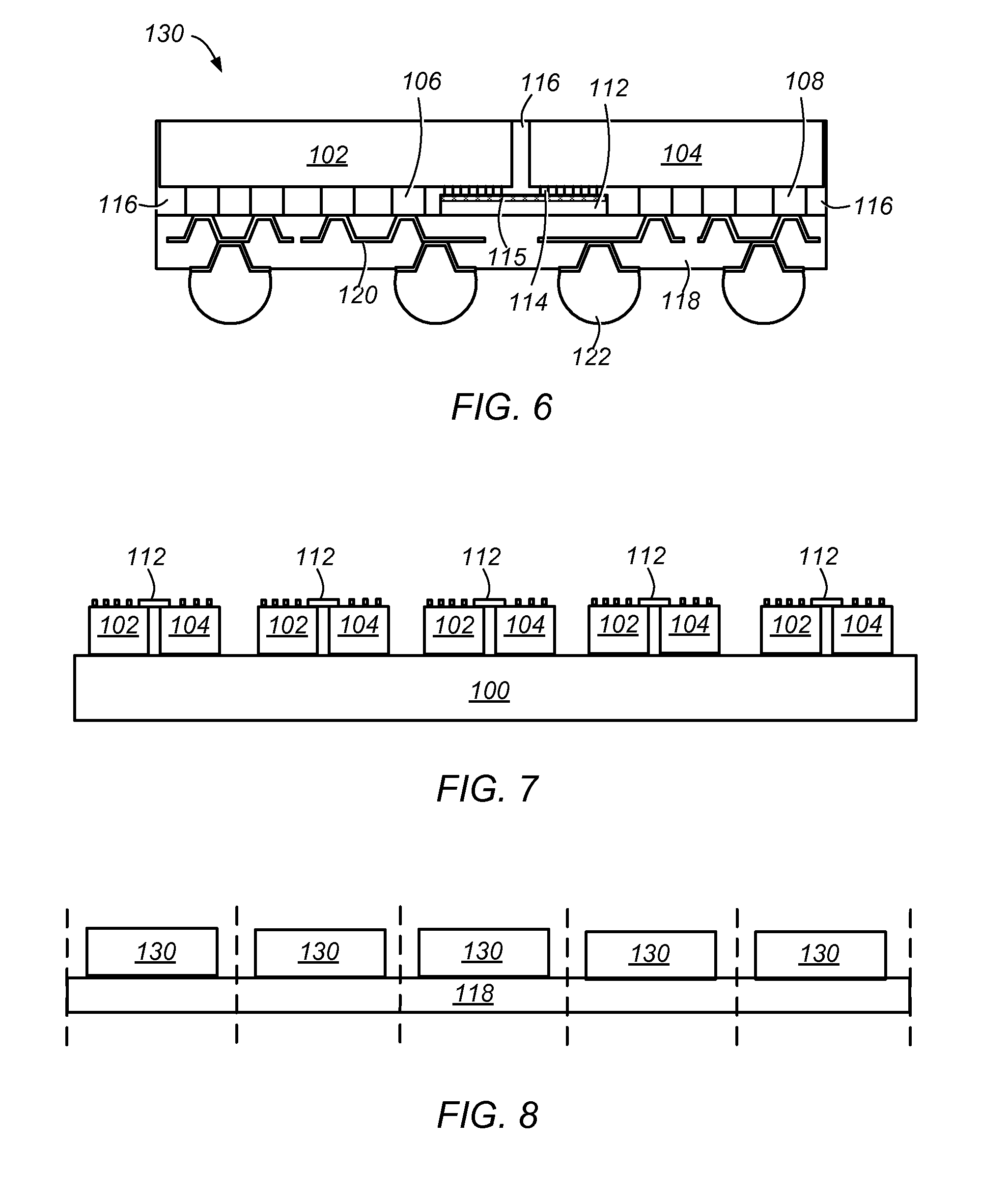

Circuit structures and methods of fabrication are provided for facilitating implementing a complete electronic system in a compact package. The circuit structure includes, in one embodiment, a chips-first multichip base layer with conductive structures extending therethrough. An interconnect layer is disposed over the front surface of the multichip layer and includes interconnect metallization electrically connected to contact pads of the chips and to conductive structures extending through the structural material. A redistribution layer, disposed over the back surface of the multichip layer, includes a redistribution metallization also electrically connected to conductive structures extending through the structural material. Input / output contacts are arrayed over the redistribution layer, including over the lower surfaces of at least some integrated circuit chips within the multichip layer, and are electrically connected through the redistribution metallization, conductive structures, and interconnect metallization to contact pads of the integrated circuit chips of the multichip layer.

Owner:EPIC TECH INC

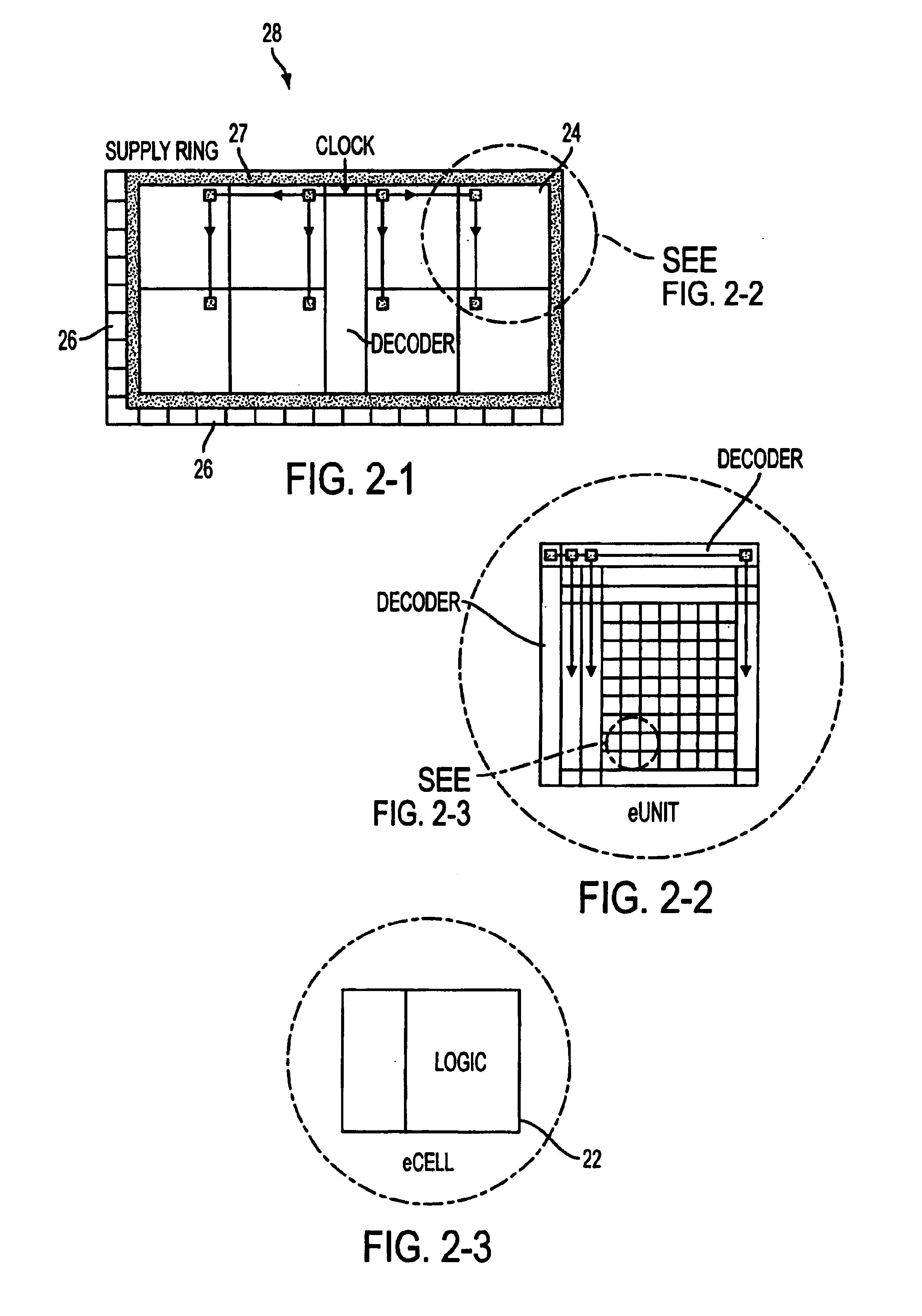

Semiconductor device having borderless logic array and flexible I/O

InactiveUS6953956B2Reduces high cost of manufacturingReduced flexibilitySemiconductor/solid-state device detailsSolid-state devicesRedistribution layerDevice material

Owner:INTEL CORP

Integrated structures and fabrication methods thereof implementing a cell phone or other electronic system

ActiveUS20080316714A1Semiconductor/solid-state device detailsSolid-state devicesElectronic systemsContact pad

Circuit structures and methods of fabrication are provided for facilitating implementing a complete electronic system in a compact package. The circuit structure includes, in one embodiment, a chips-first multichip base layer with conductive structures extending therethrough. An interconnect layer is disposed over the front surface of the multichip layer and includes interconnect metallization electrically connected to contact pads of the chips and to conductive structures extending through the structural material. A redistribution layer, disposed over the back surface of the multichip layer, includes a redistribution metallization also electrically connected to conductive structures extending through the structural material. Input / output contacts are arrayed over the redistribution layer, including over the lower surfaces of at least some integrated circuit chips within the multichip layer, and are electrically connected through the redistribution metallization, conductive structures, and interconnect metallization to contact pads of the integrated circuit chips of the multichip layer.

Owner:EPIC TECH INC

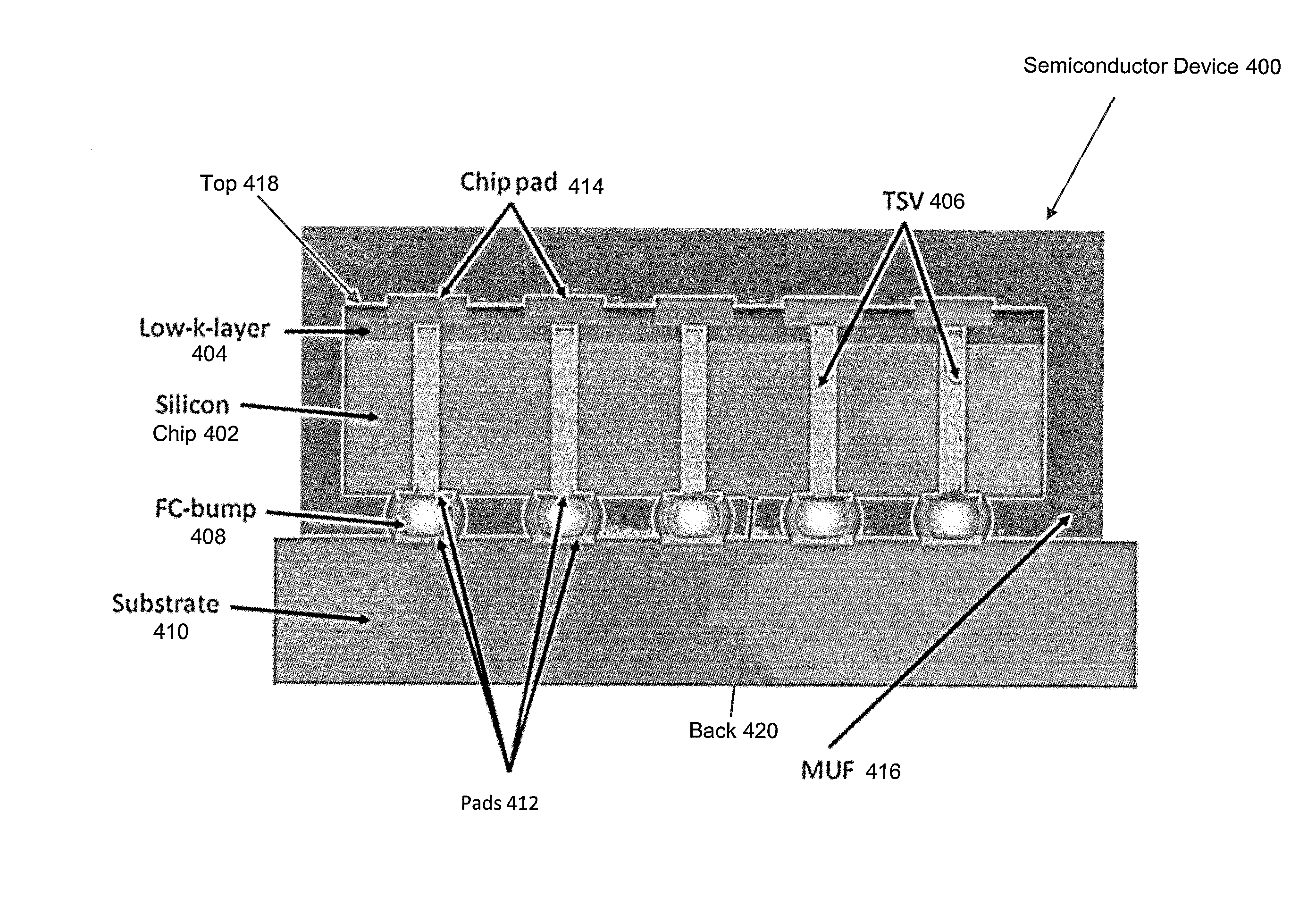

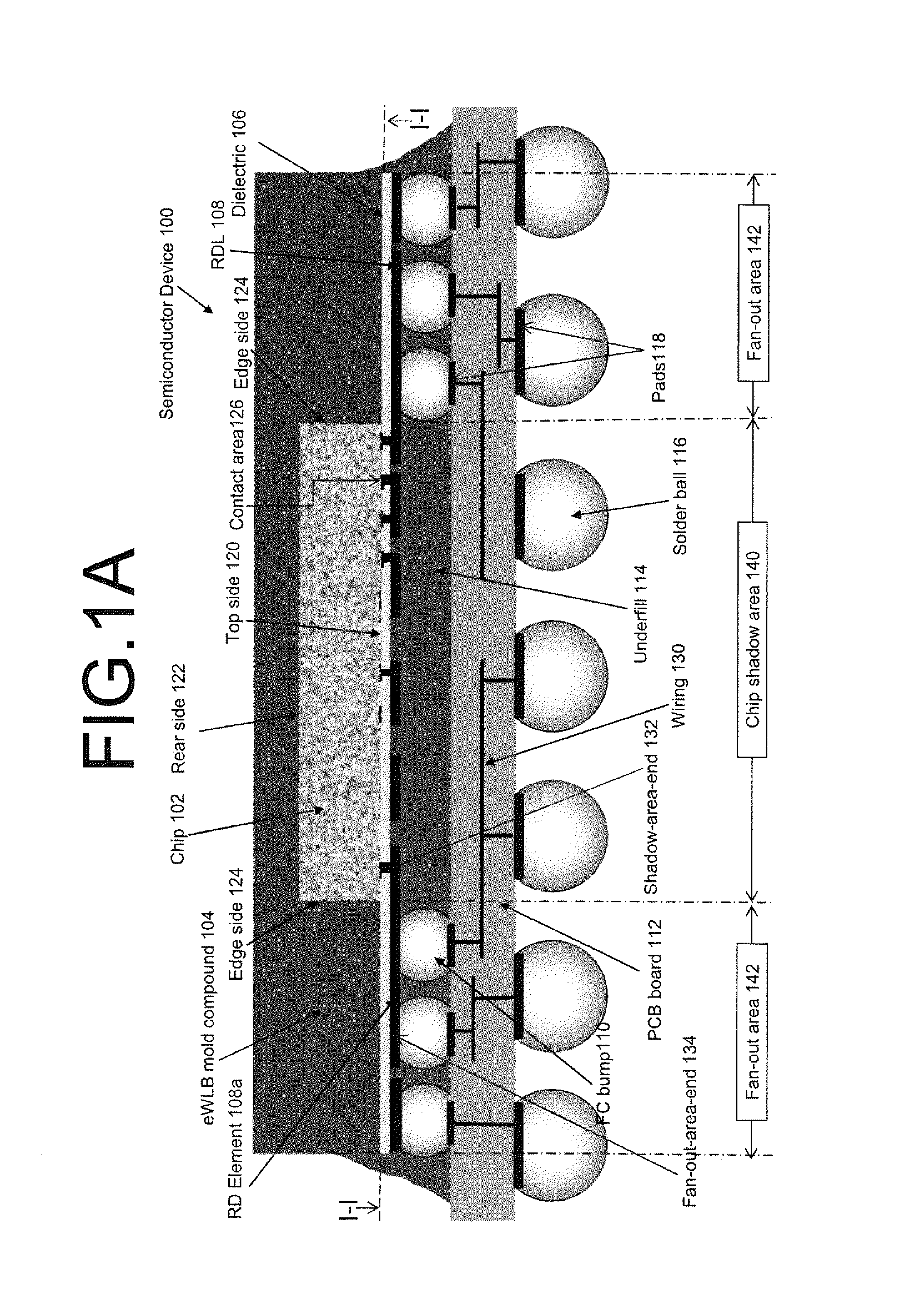

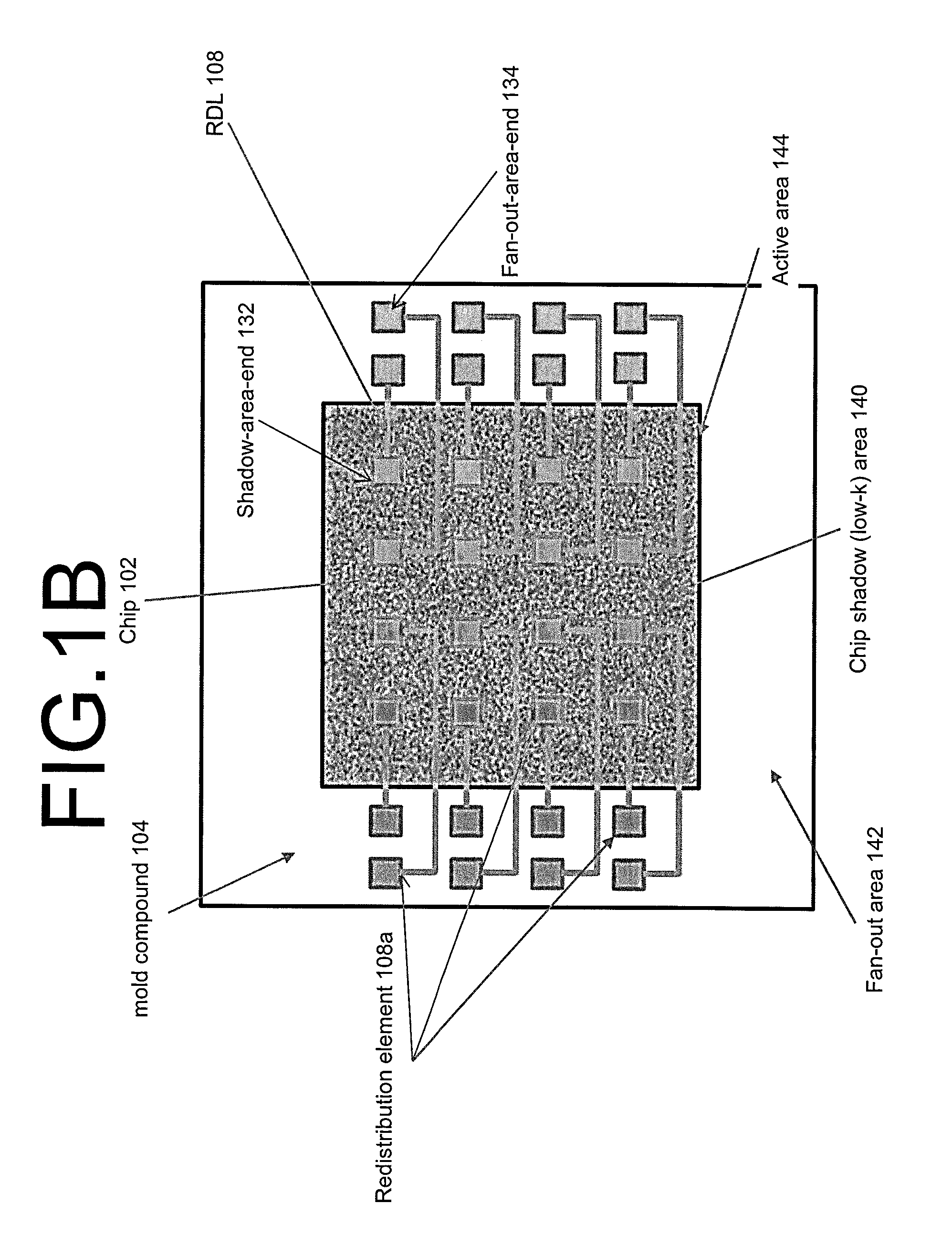

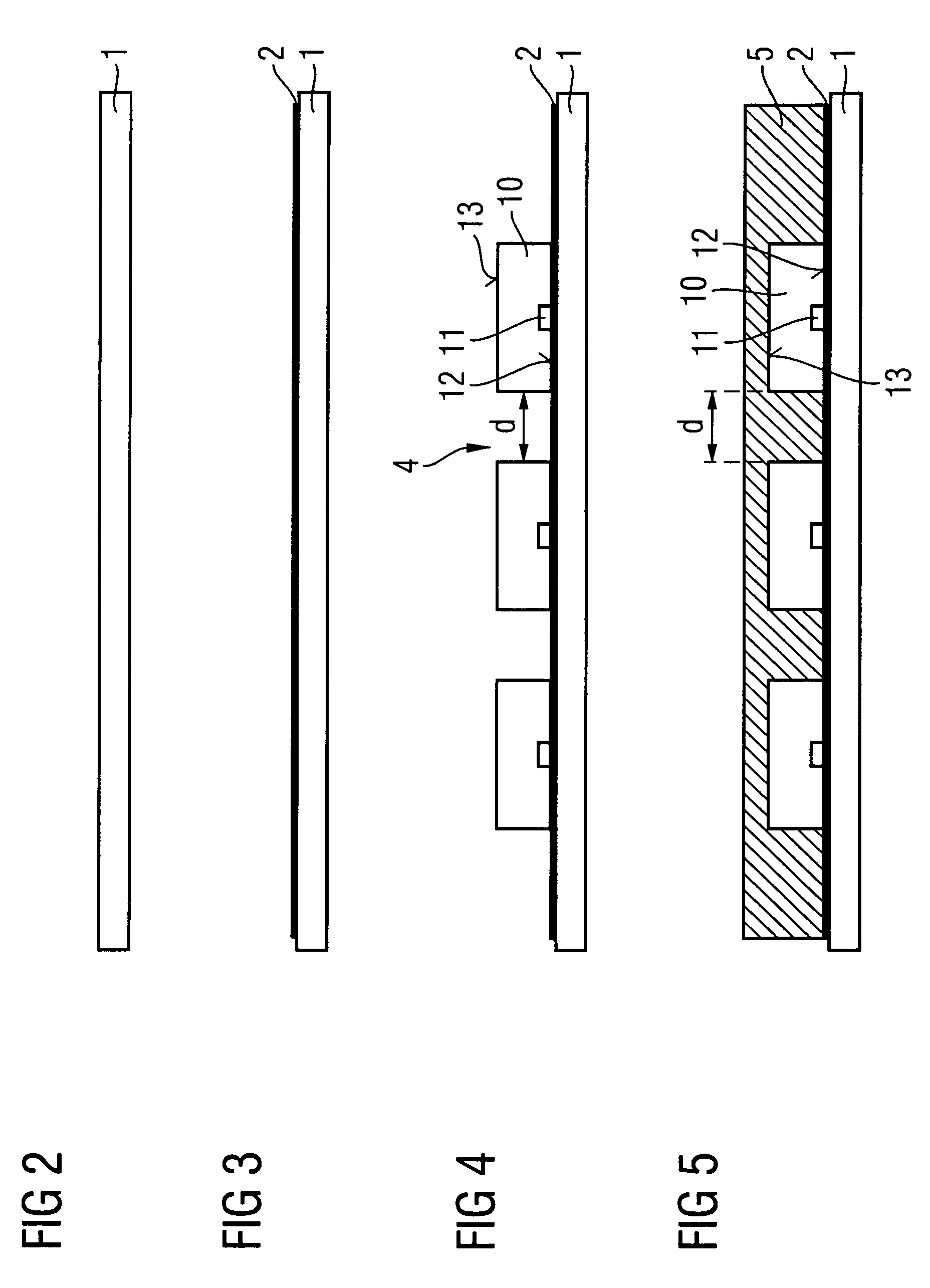

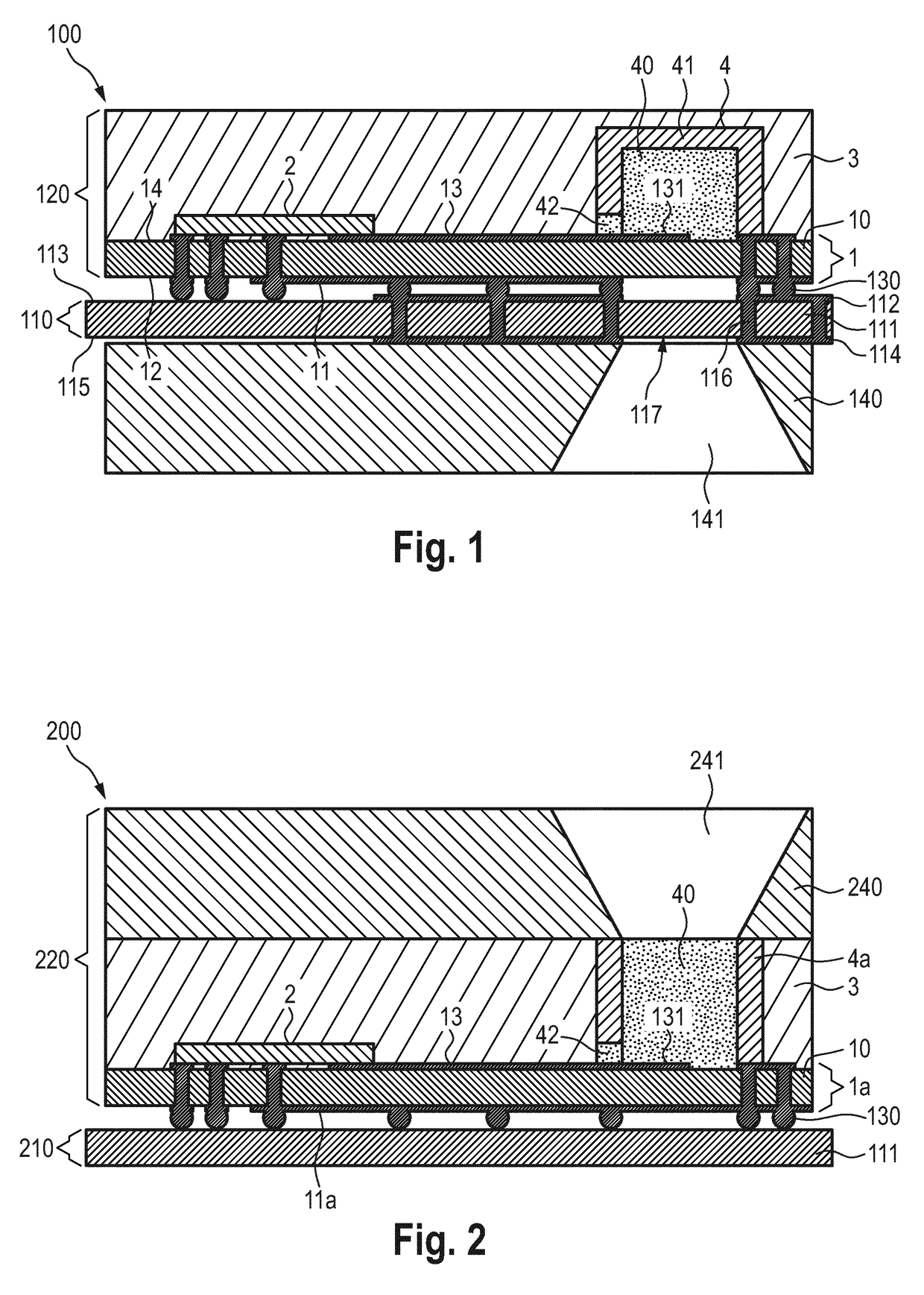

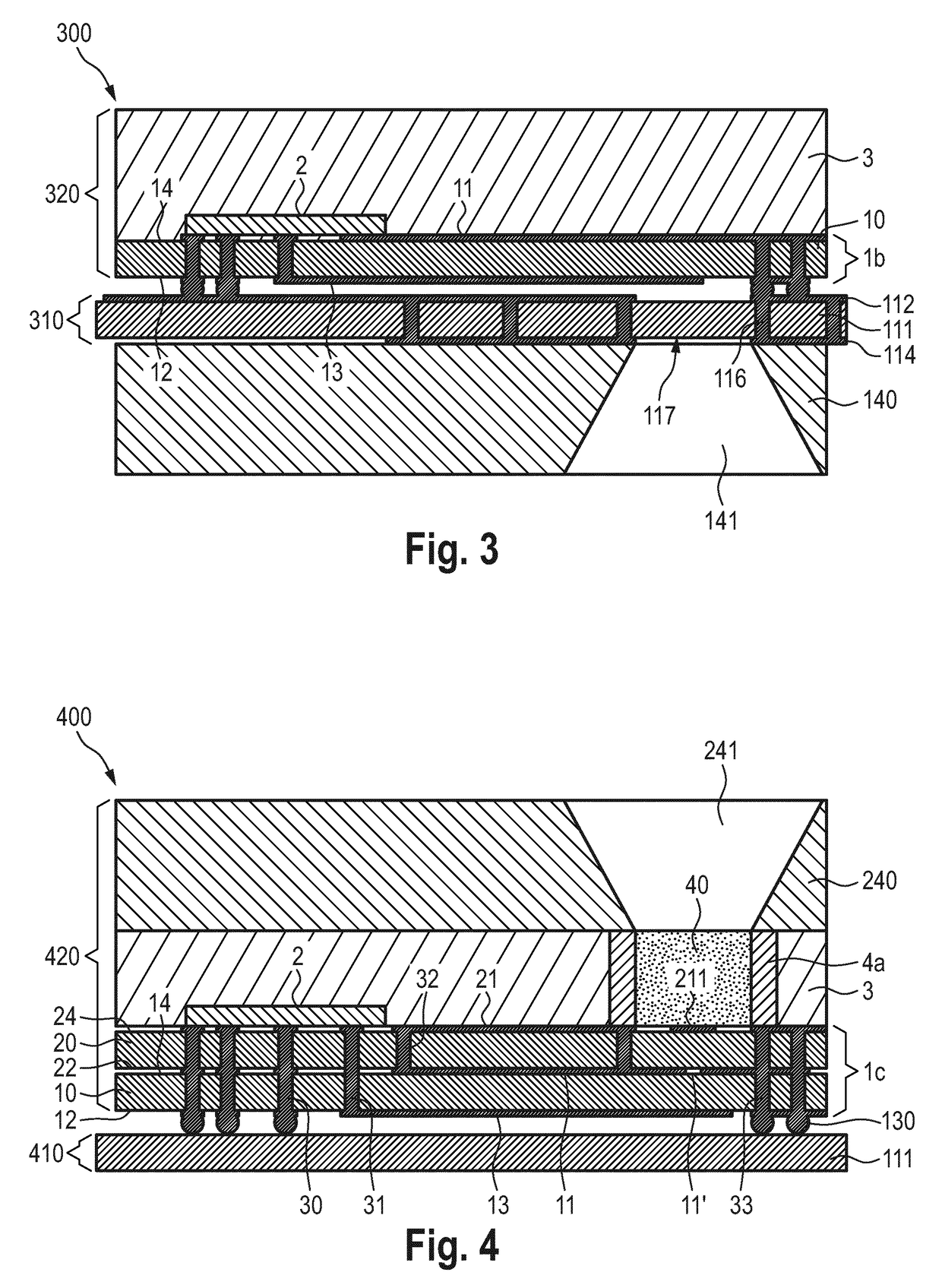

Semiconductor device with chip having low-k-layers

ActiveUS20140197530A1Firm packagingSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerSemiconductor chip

A semiconductor device is described having at least one semiconductor chip, the chip having an active area on a top side thereof, the active area formed at least in part of low-k material, said low-k material defining a low-k subarea of said active area; an embedding material, in which said at least one semiconductor chip is embedded, at least part of the embedding material forming a coplanar area with said active area; at least one contact area within the low-k subarea; a redistribution layer on the coplanar area, the redistribution layer connected to said contact areas; at least one first-level interconnect, located outside said low-k subarea, the first-level interconnect electrically connected to at least one of said contact areas via the redistribution layer.

Owner:INTEL CORP

Integrated conductive structures and fabrication methods thereof facilitating implementing a cell phone or other electronic system

ActiveUS20080315375A1Printed circuit assemblingCross-talk/noise/interference reductionContact padElectronic systems

Circuit structures and methods of fabrication are provided for facilitating implementing a complete electronic system in a compact package. The circuit structure includes, in one embodiment, a chips-first multichip base layer with conductive structures extending therethrough. An interconnect layer is disposed over the front surface of the multichip layer and includes interconnect metallization electrically connected to contact pads of the chips and to conductive structures extending through the structural material. A redistribution layer, disposed over the back surface of the multichip layer, includes a redistribution metallization also electrically connected to conductive structures extending through the structural material. Input / output contacts are arrayed over the redistribution layer, including over the lower surfaces of at least some integrated circuit chips within the multichip layer, and are electrically connected through the redistribution metallization, conductive structures, and interconnect metallization to contact pads of the integrated circuit chips of the multichip layer.

Owner:EPIC TECH INC

Semiconductor Device Package Structure and Method for the Same

InactiveUS20100301474A1Shrink wellShrinkage sizeSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerPunching

The present invention discloses a semiconductor device package and the method for the same. The method includes preparing a first substrate and a second substrate; opening a die opening window through the second substrate by using laser or punching; preparing an adhesion material; attaching the first substrate to the second substrate by the adhesion material; aligning a die by using the aligning mark of the die metal pad and attaching the die onto the die metal pad with force by the adhesion material; forming a first dielectric layer on top surfaces of the second substrate and the die and pushing the first dielectric layer into gap between the side wall of the die and the side wall of the die opening window under vacuum condition; opening a plurality of via openings in the first dielectric layer; and forming a redistribution layer in the plurality of via openings and on the first dielectric layer.

Owner:KING DRAGON INT

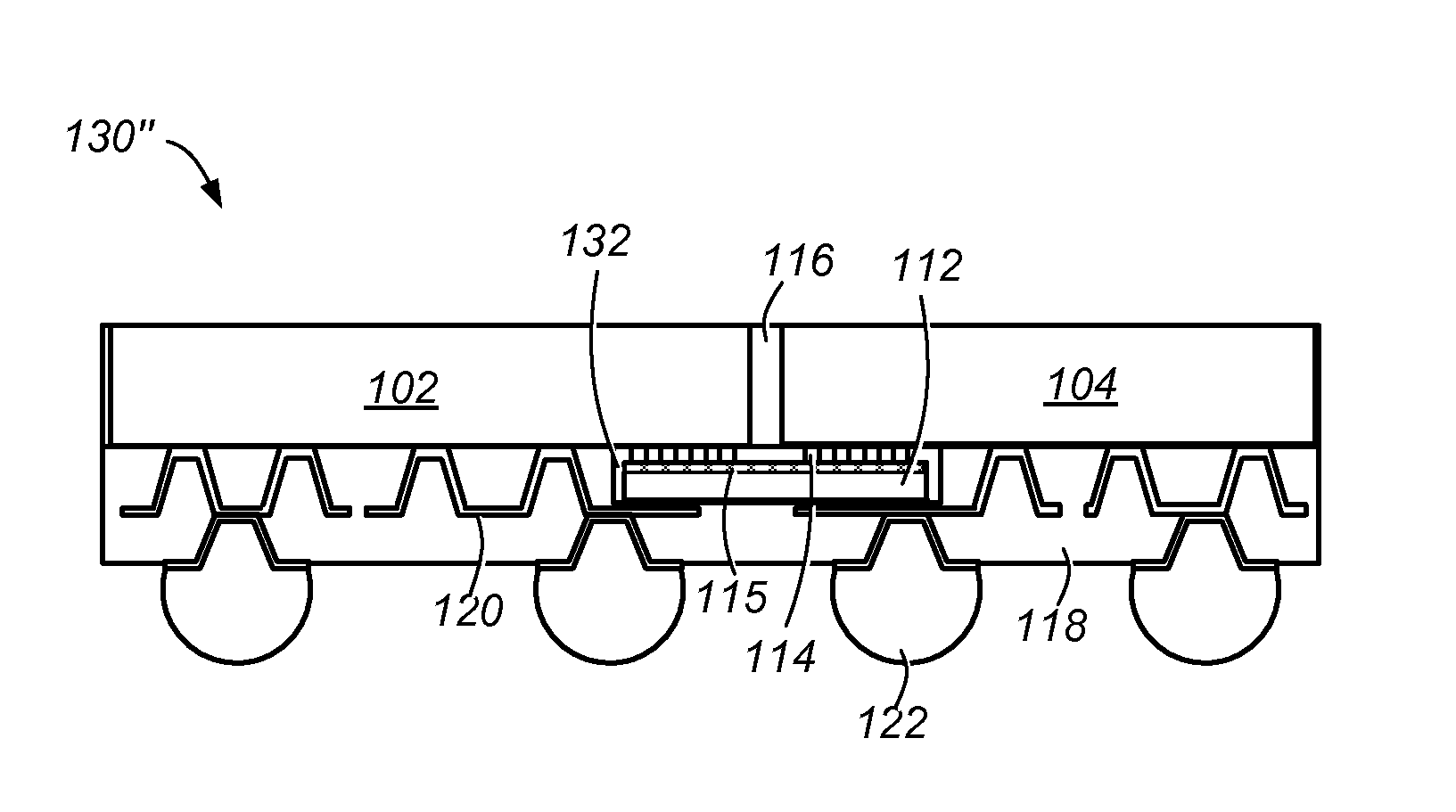

Packaged electronic modules and fabrication methods thereof implementing a cell phone or other electronic system

InactiveUS20080315377A1Printed circuit assemblingCross-talk/noise/interference reductionContact padRedistribution layer

Circuit structures and methods of fabrication are provided for facilitating implementing a complete electronic system in a compact package. The circuit structure includes, in one embodiment, a chips-first multichip base layer with conductive structures extending therethrough. An interconnect layer is disposed over the front surface of the multichip layer and includes interconnect metallization electrically connected to contact pads of the chips and to conductive structures extending through the structural material. A redistribution layer, disposed over the back surface of the multichip layer, includes a redistribution metallization also electrically connected to conductive structures extending through the structural material. Input / output contacts are arrayed over the redistribution layer, including over the lower surfaces of at least some integrated circuit chips within the multichip layer, and are electrically connected through the redistribution metallization, conductive structures, and interconnect metallization to contact pads of the integrated circuit chips of the multichip layer.

Owner:EPIC TECH INC

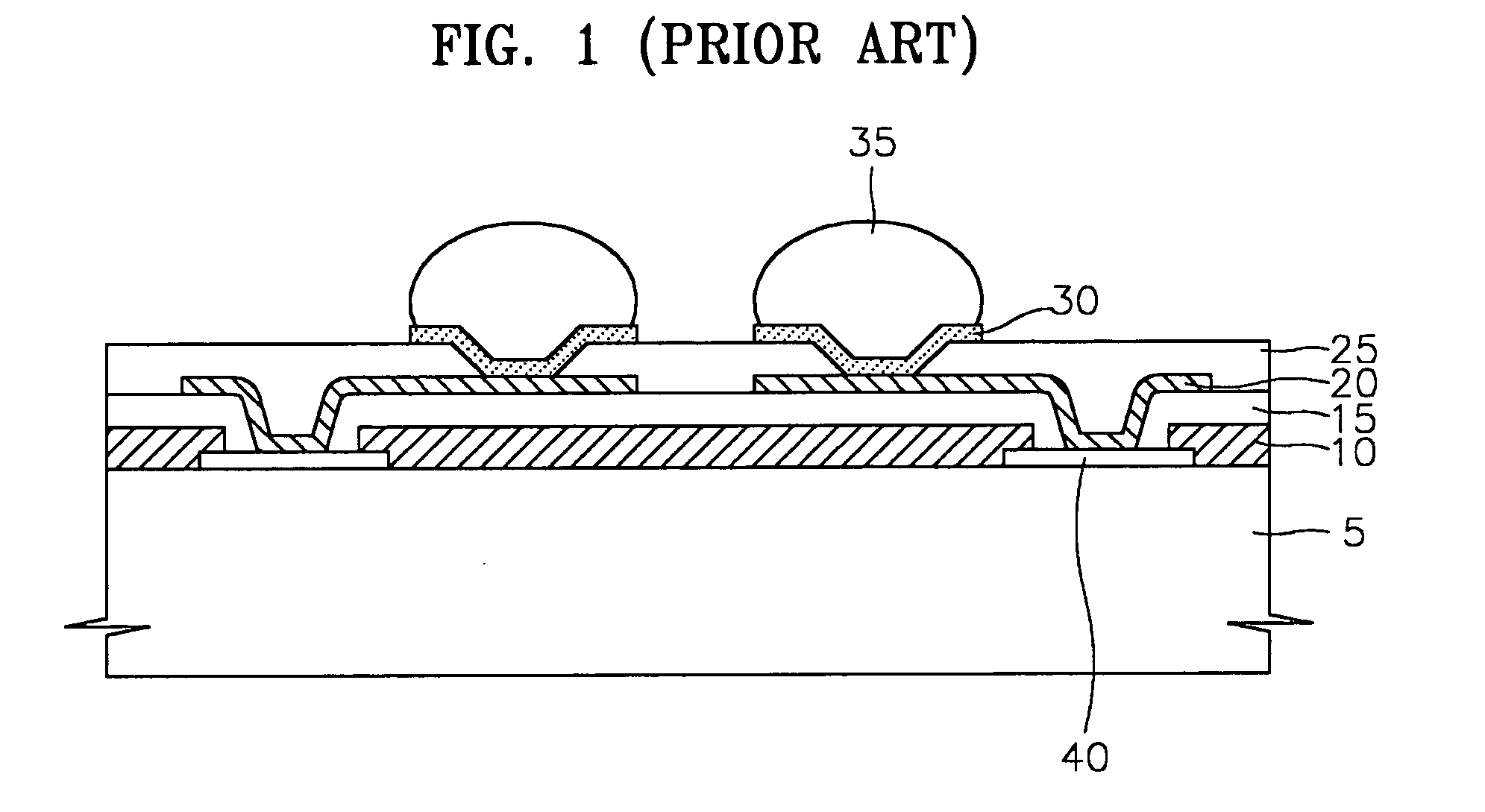

Wafer level chip size package having redistribution layers

ActiveUS7977783B1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerChip size

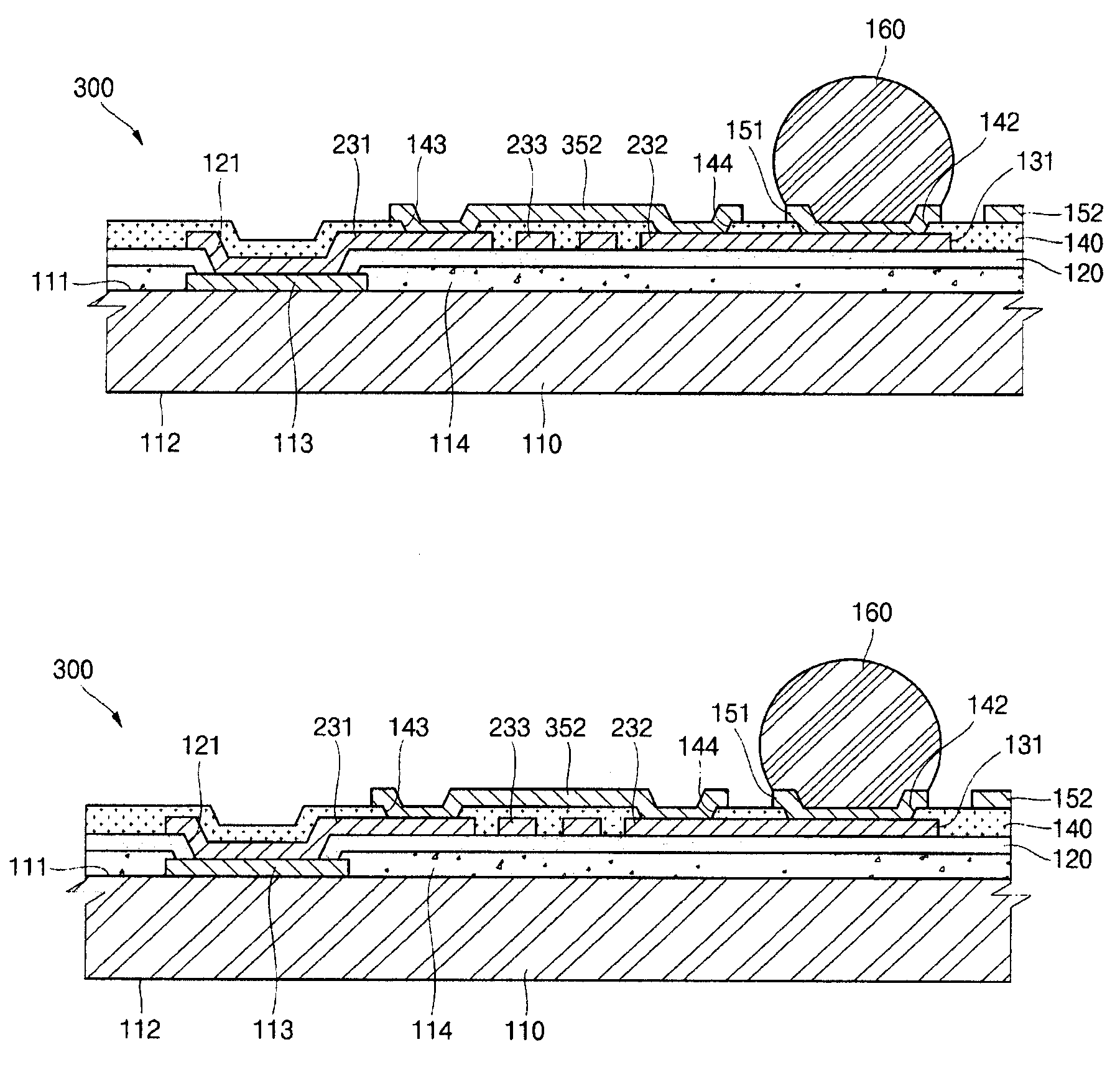

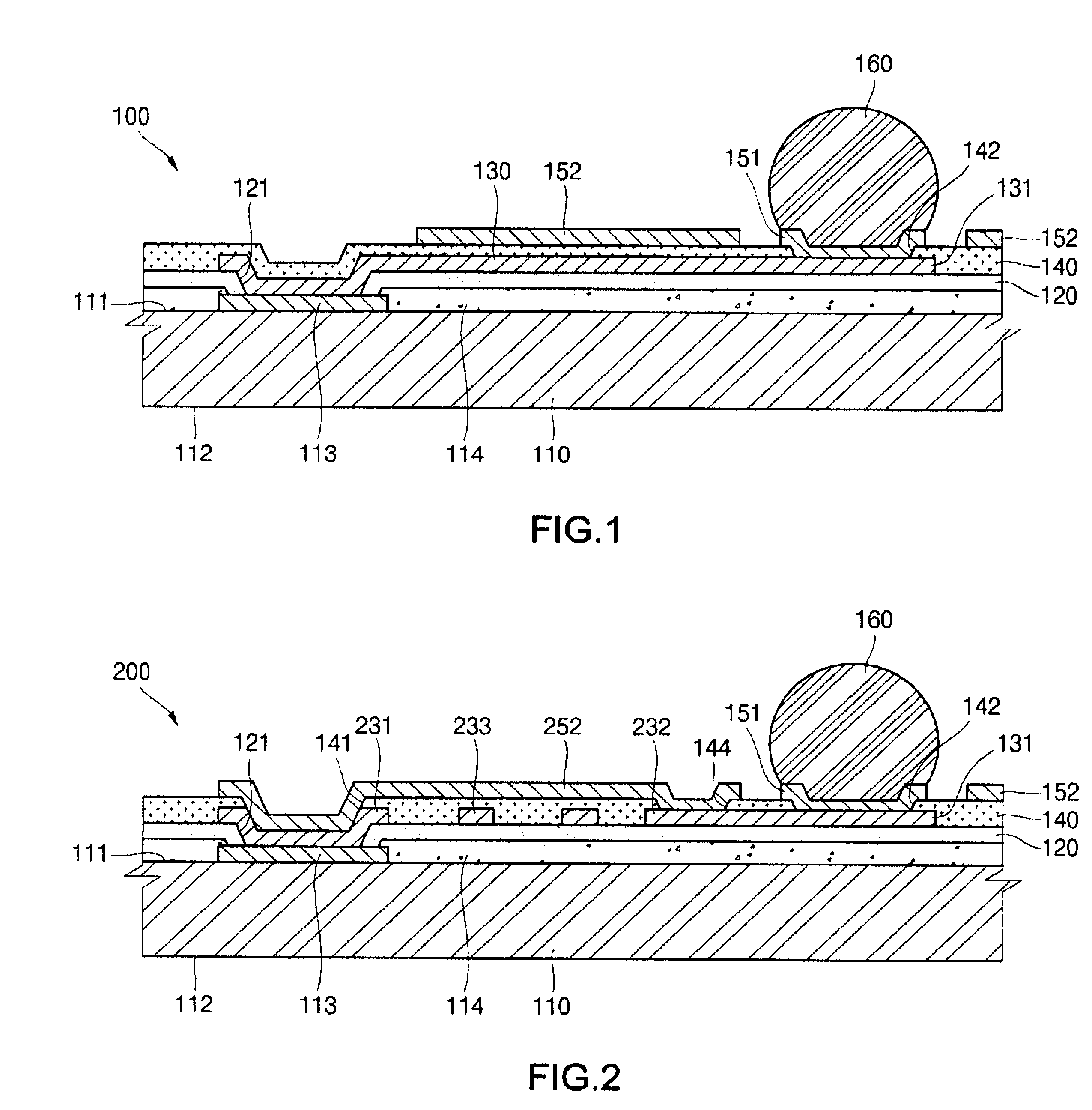

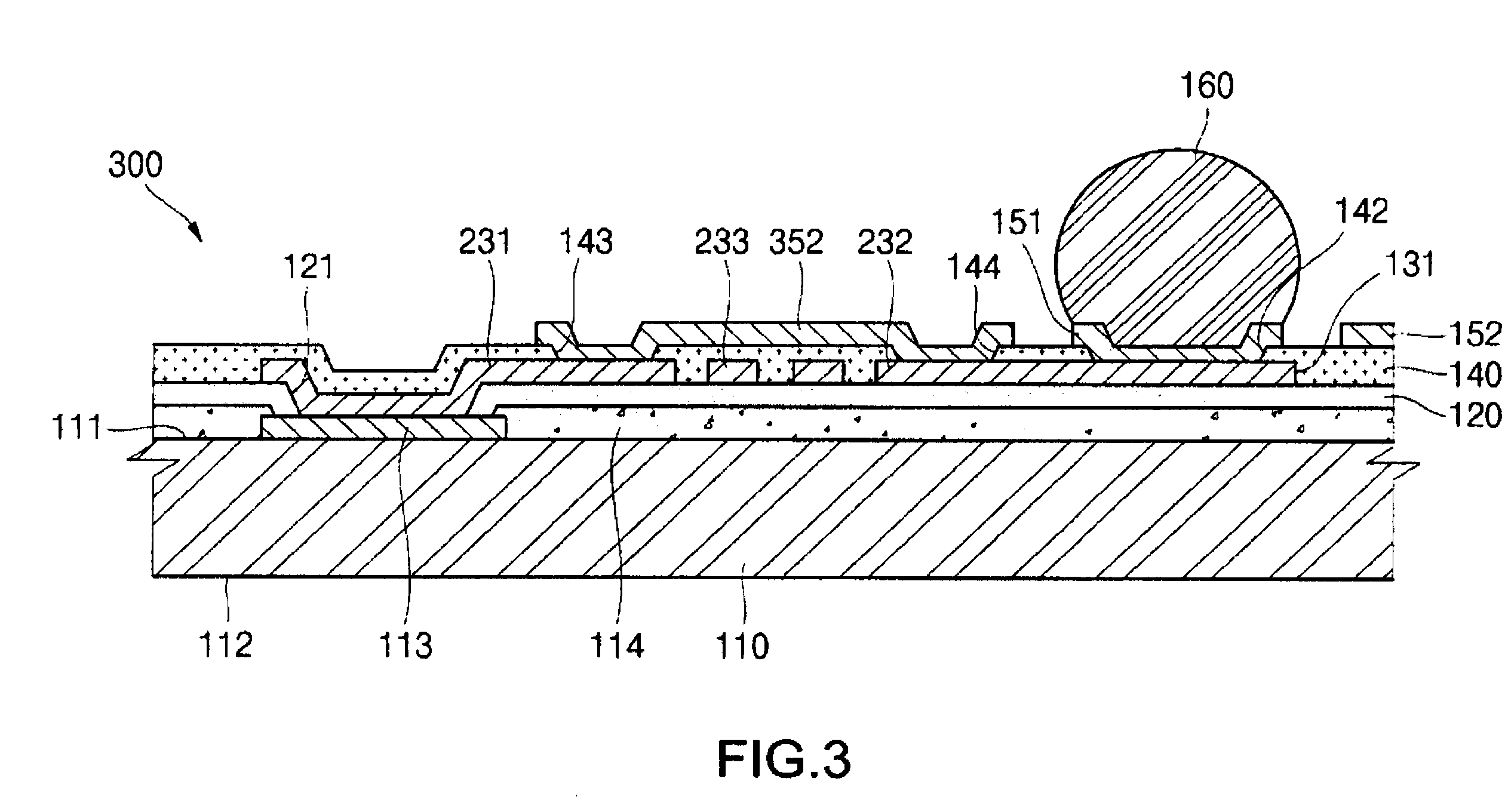

A wafer level chip size package (WLCSP) and a method of manufacturing the same are disclosed. Lands are formed at the ends of redistribution layers. The redistribution layers excluding the lands and a first dielectric layer are covered with a second dielectric layer. After forming a first under bump metallurgy (UBM) layer on the land, a solder ball is reflowed to the first UBM layer. A second UBM layer is widely formed on the entire second dielectric layer that is the outer circumference of the first UBM layer and is connected to the redistribution layer through a via-hole. Therefore, the second UBM layer having a large area can be used as a ground plane or a power plane. In addition, the second UBM layer can electrically connect the redistribution layers physically separated from each other. Therefore, the plurality of redistribution layers can cross each other without being electrically shorted with each other.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

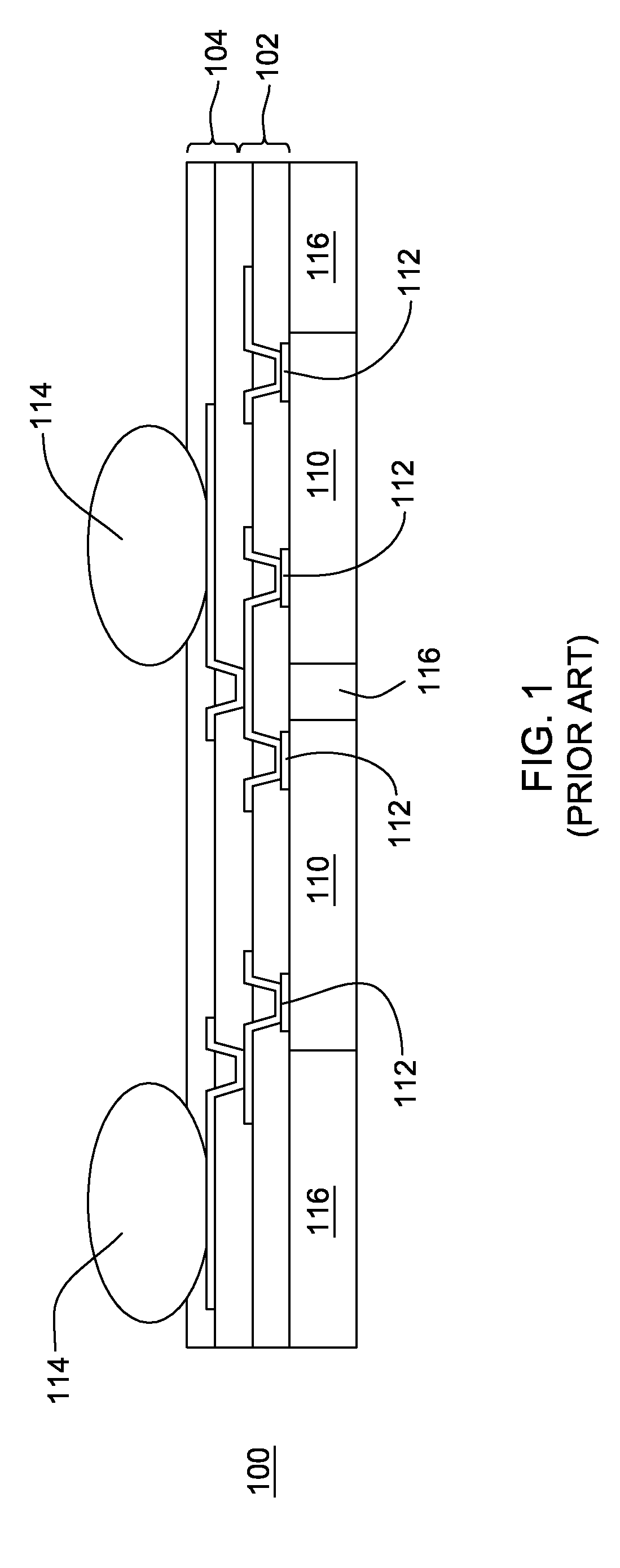

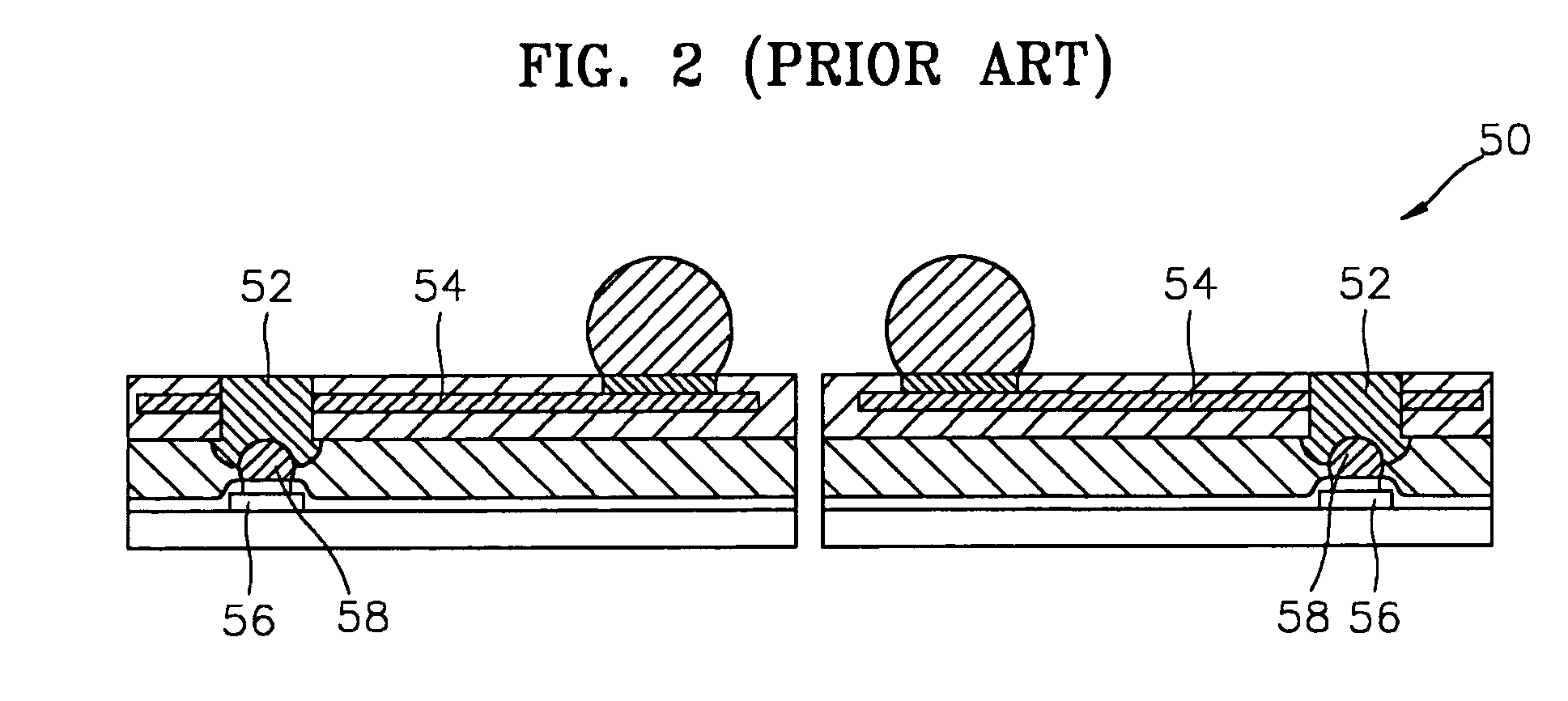

Semiconductor device package with die receiving through-hole and dual build-up layers over both side-surfaces for wlp and method of the same

InactiveUS20080237828A1Board level reliabilityImprove matchSemiconductor/solid-state device detailsSolid-state devicesContact padRedistribution layer

The present invention discloses a structure of package comprising a substrate with at least one die receiving through holes, a conductive connecting through holes structure and a contact pads on both side of substrate. At least one die is disposed within the die receiving through holes. A first material is formed under the die and second material is formed filled in the gap between the die and sidewall of the die receiving though holes. Dielectric layers are formed on the surface of both side of the die and the substrate. Redistribution layers (RDL) are formed on the both sides and coupled to the contact pads. A protection bases are formed over the RDLs.

Owner:ADVANCED CHIP ENG TECH

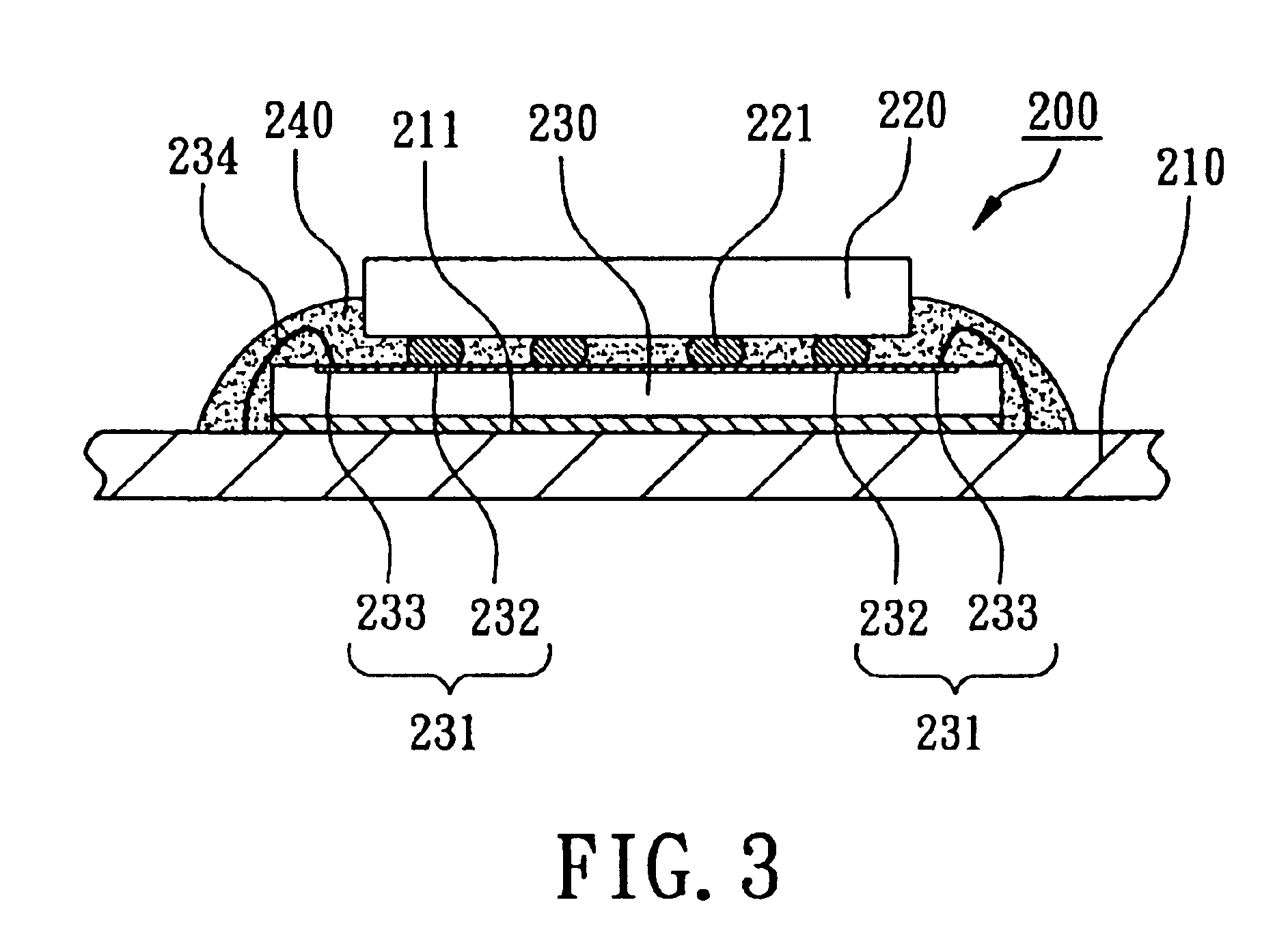

Wafer-level chip scale package and method for fabricating and using the same

InactiveUS20050012225A1Address rising pricesSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerChip size

A packaged semiconductor device (a wafer-level chip scale package) containing a conductive adhesive material as an electrical interconnect route between the semiconductor die and a patterned conductive substrate is described. The patterned conductive substrate acts not only as a substrate, but also as a redistribution layer that converts the dense pad layout of the die to a larger array configuration of the solder balls in the circuit board. Using the invention allows the formation of a lower priced chip scale package that also overcomes the restriction of the die size used in die-sized chip packages and the input-output pattern that can be required by the printed circuit board. Thus, the invention can provide a familiar pitch (i.e.,interface) to the printed circuit board for any small die.

Owner:SEMICON COMPONENTS IND LLC

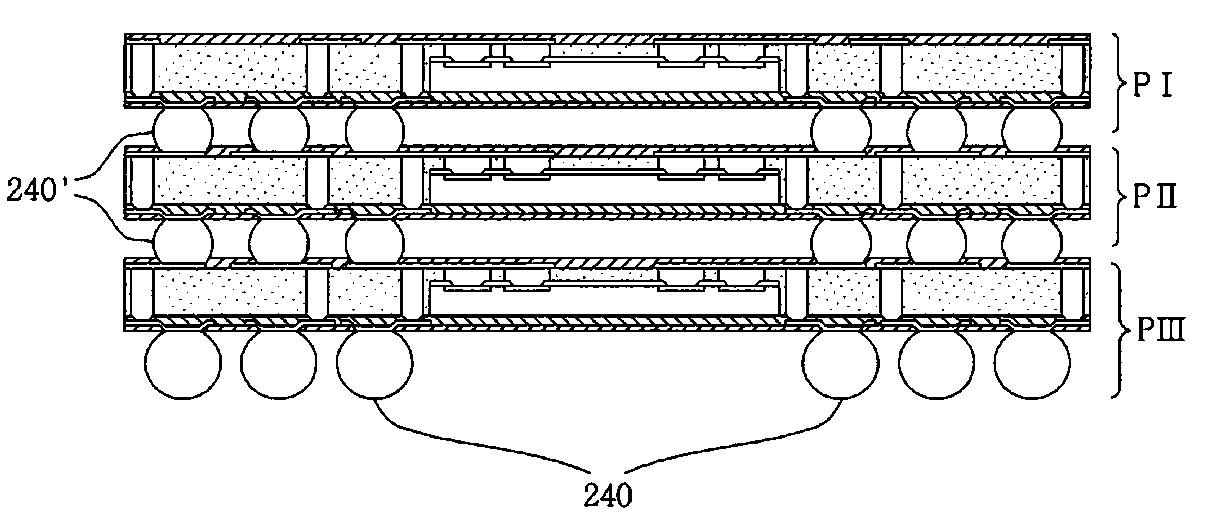

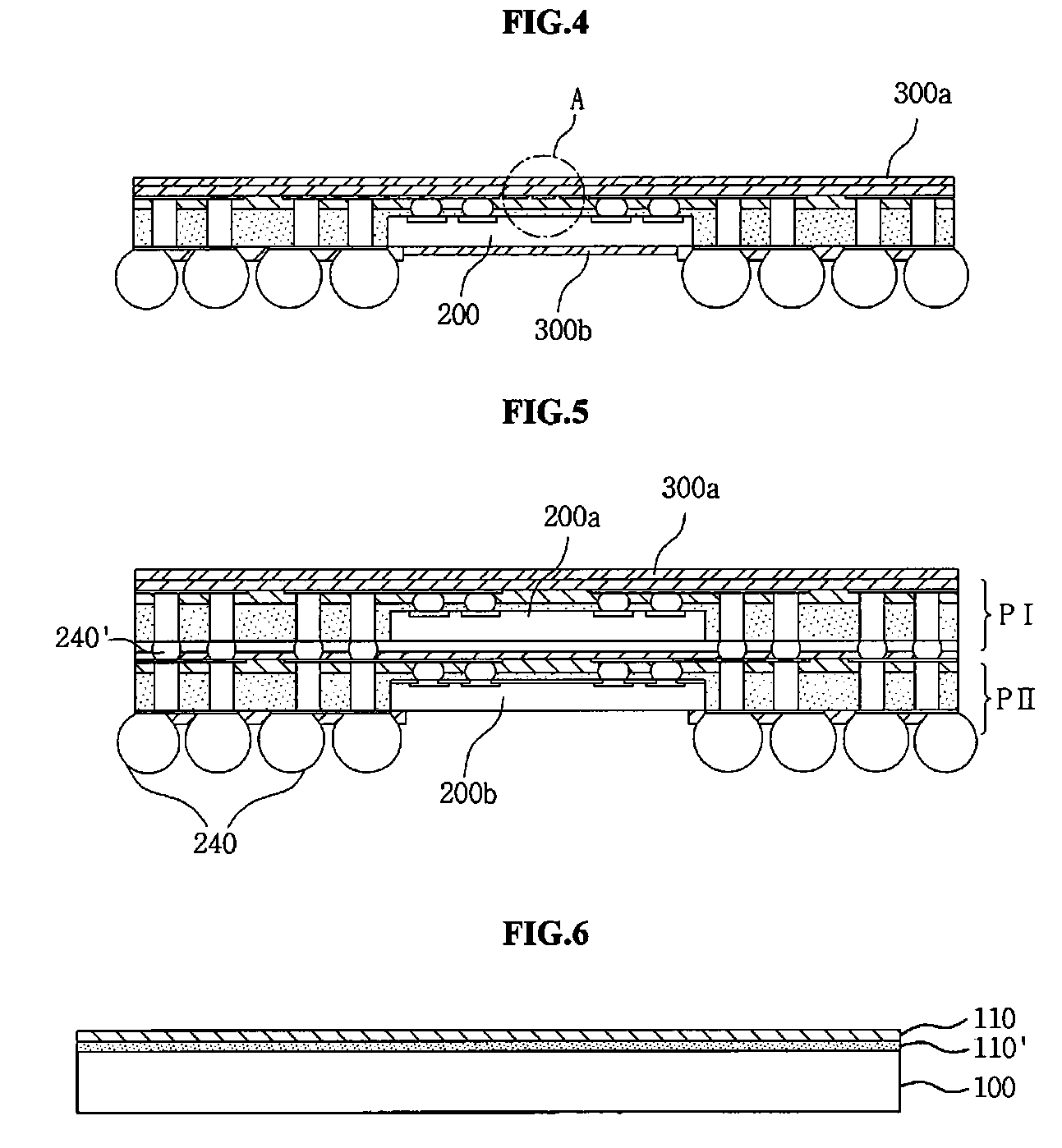

Ultra slim semiconductor package and method of fabricating the same

ActiveUS20090008762A1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerSemiconductor chip

There is provided an ultra slim semiconductor package comprising: a multilayer thin film layer including at least one or more dielectric layers and at least one or more redistribution layers; at least one semiconductor chip electrically connected to the redistribution layer and mounted on the multilayer thin film layer; conductive structures electrically connected to the redistribution layer and each formed in a post shape at one side of the multilayer thin film layer; a molding part formed on the multilayer thin film layer and at least partially covering the conductive structures and the semiconductor chip; and bumps for external connection formed on the molding part and electrically connected to the conductive structures. The semiconductor package according to the present invention enables mass production at wafer level, is easily stacked between the packages, and has an excellent electrical characteristic. Further, since the package thickness is very thin, the semiconductor package contributes to the slimming of diverse electronic products.

Owner:NEPES CO LTD

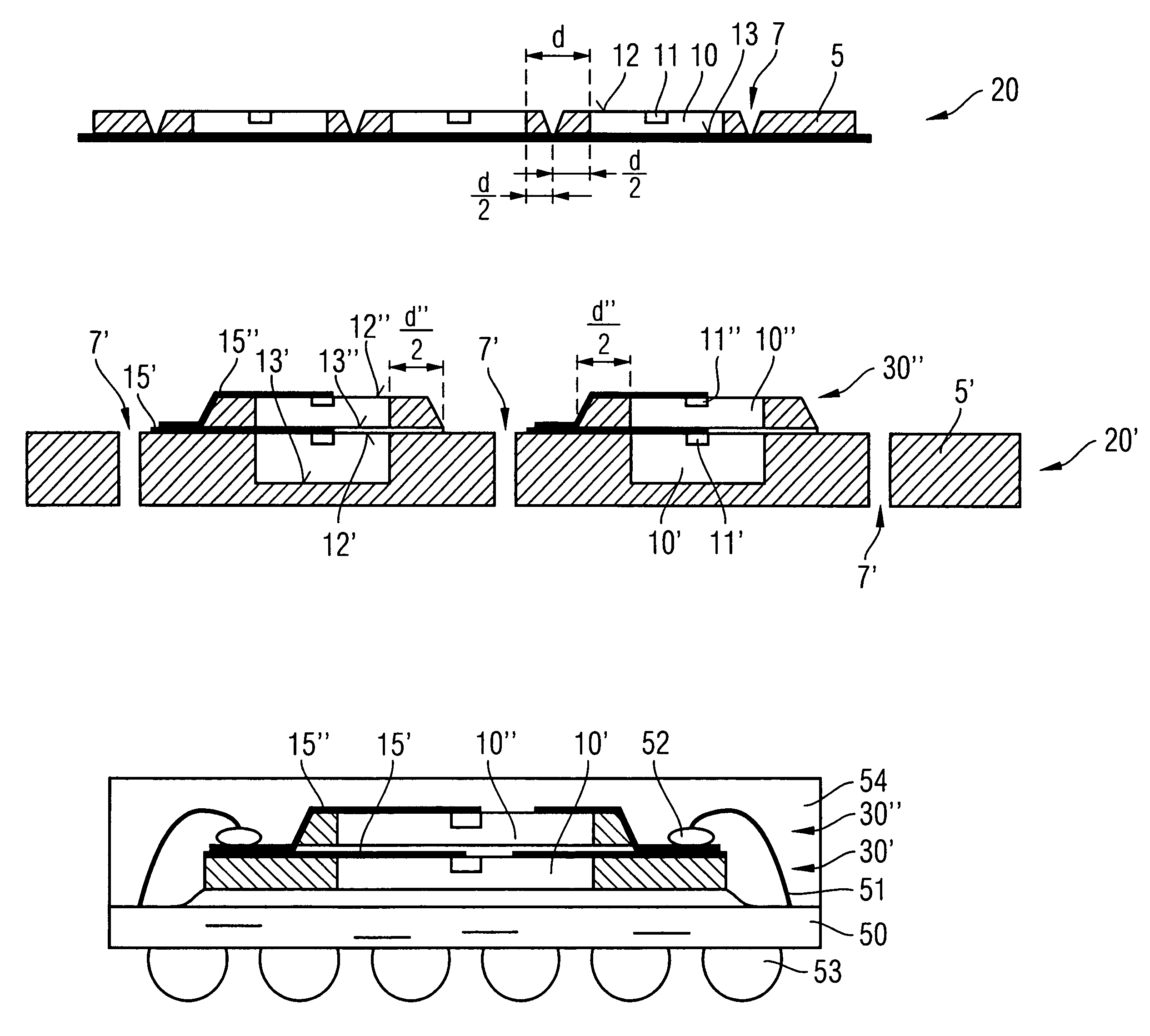

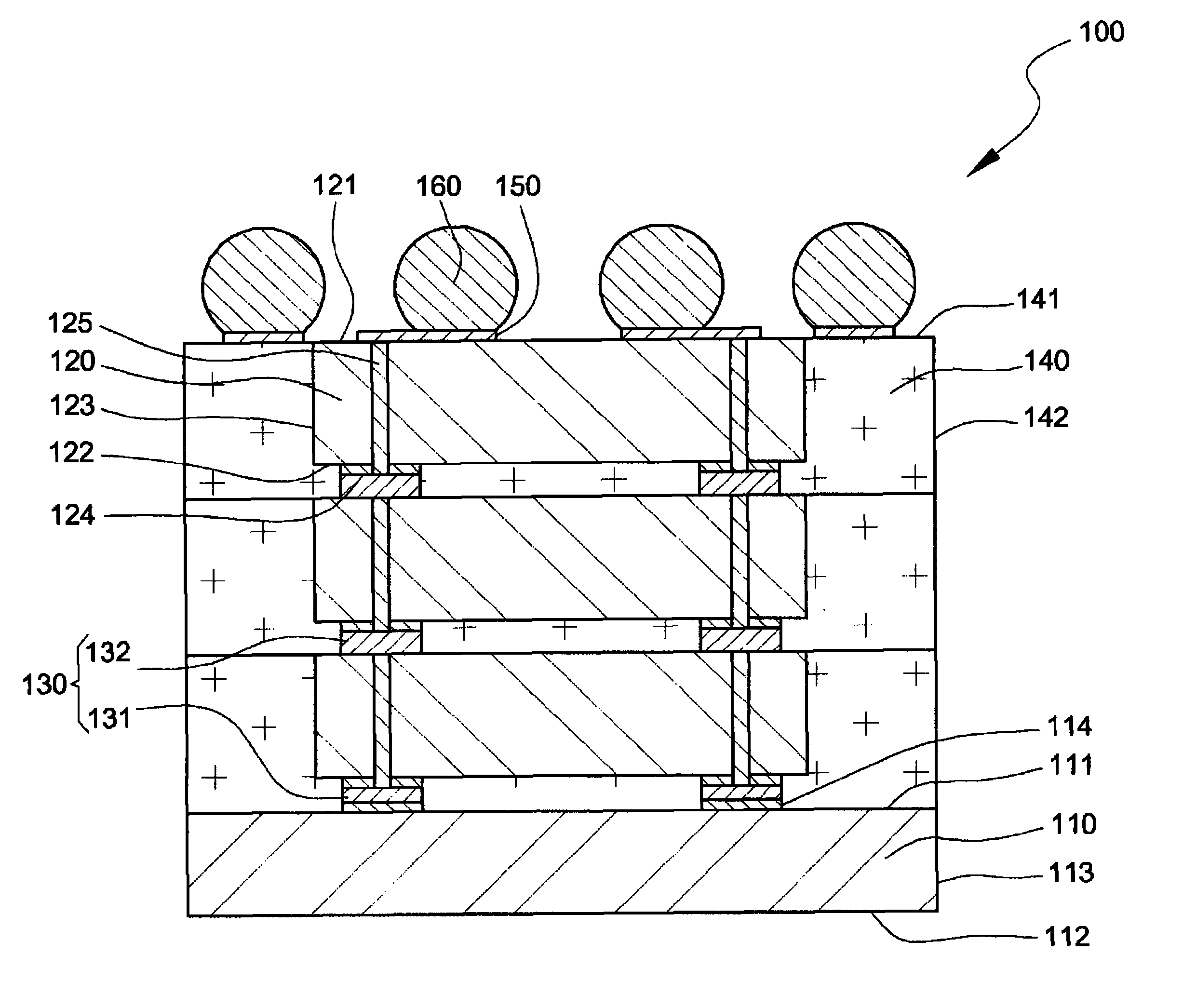

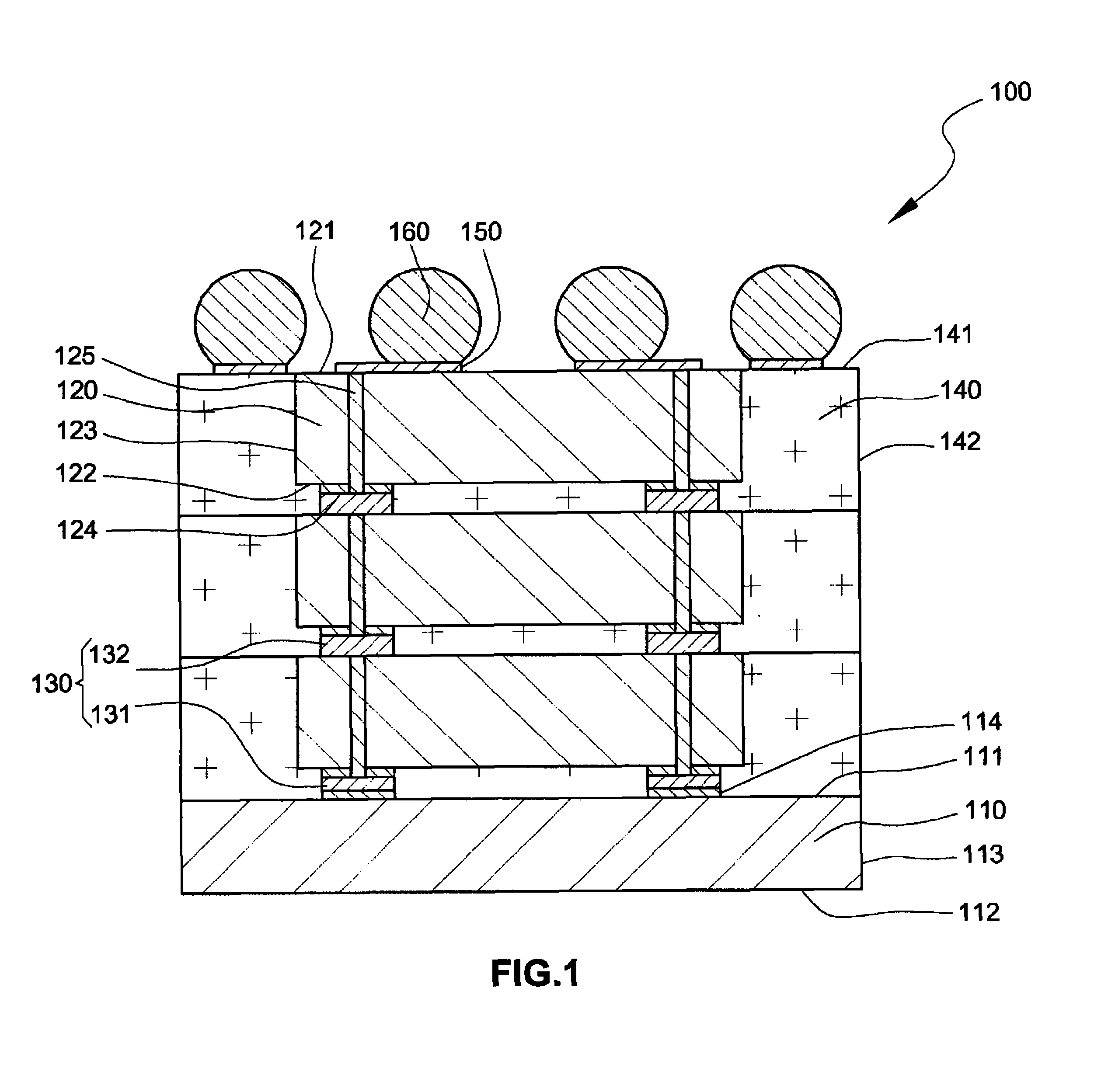

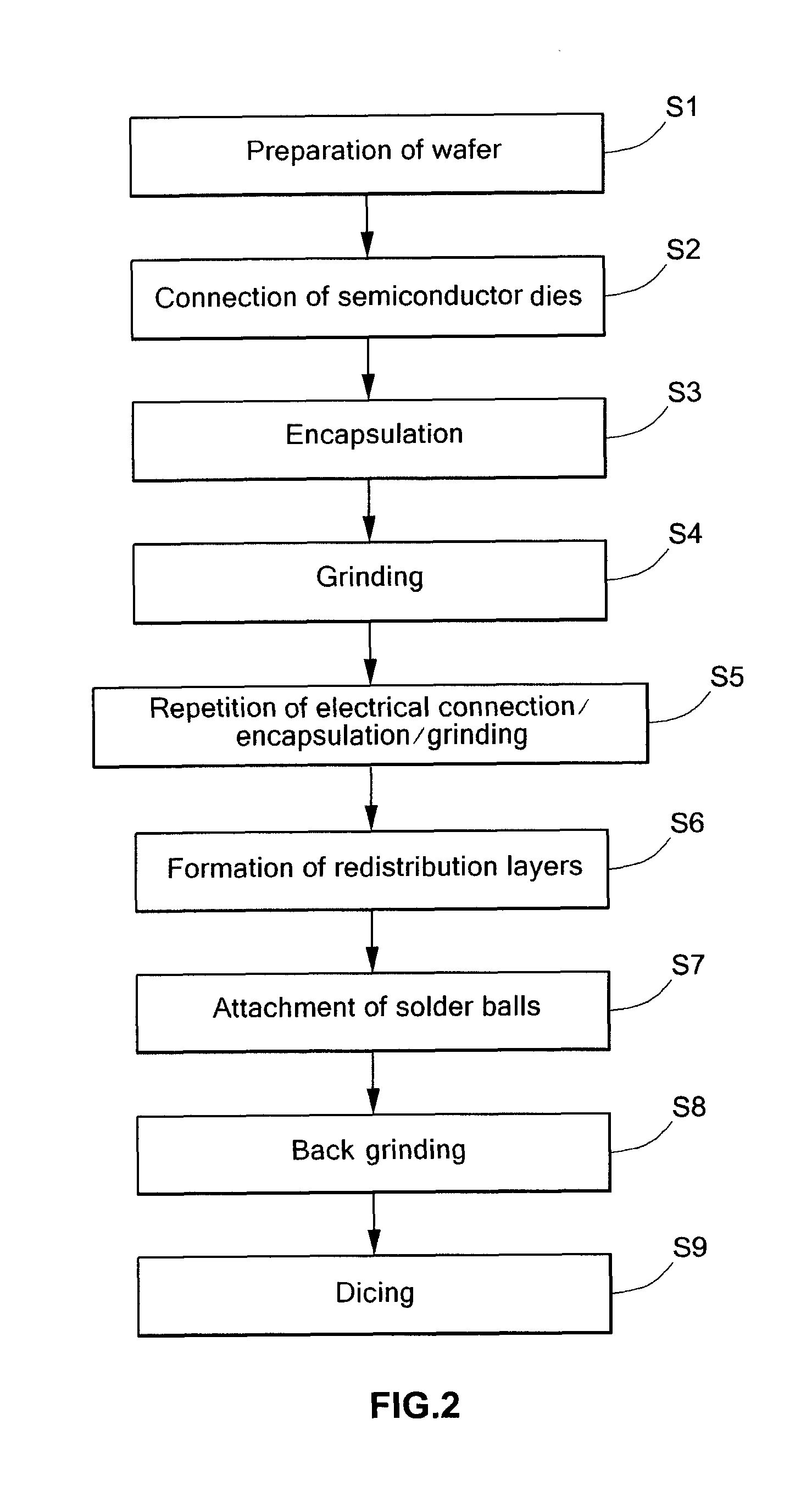

Method of manufacturing a semiconductor device comprising stacked chips and a corresponding semiconductor device

ActiveUS7208345B2Reduce stack heightReduce the overall heightSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerContact pad

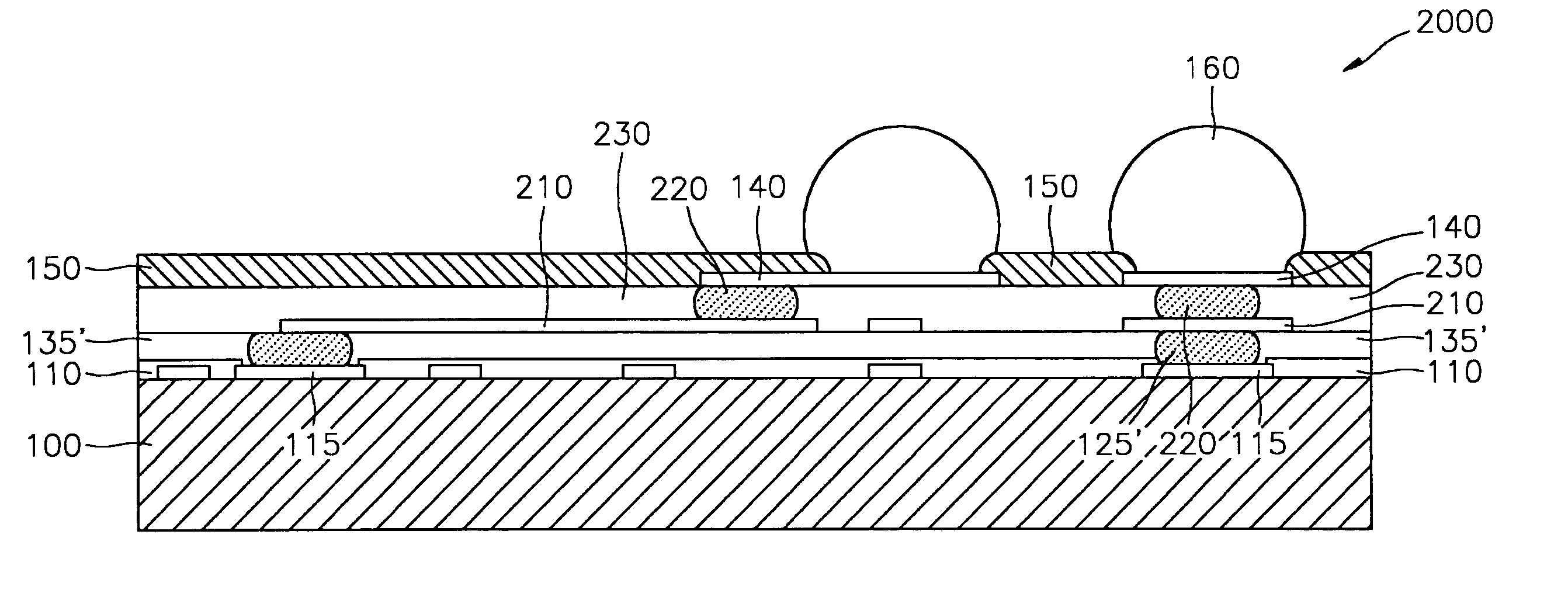

A first reconstituted wafer is formed, followed by a first redistribution layer. In parallel, a second reconstituted wafer is formed. The second reconstituted wafer is diced along a gap such that individualized embedded chips are formed having tilted sidewalls defining an angle of more than 90 degrees with respect to the active surface of the reconstituted wafer. The embedded chips are placed with the backside on an active surface of the first reconstituted wafer on the first redistribution layer. Afterwards, a second redistribution layer is formed on the active surface of the embedded chips and tilted sidewalls wherein the second redistribution layer connects contact pads of the second chips with the first redistribution layer.

Owner:POLARIS INNOVATIONS

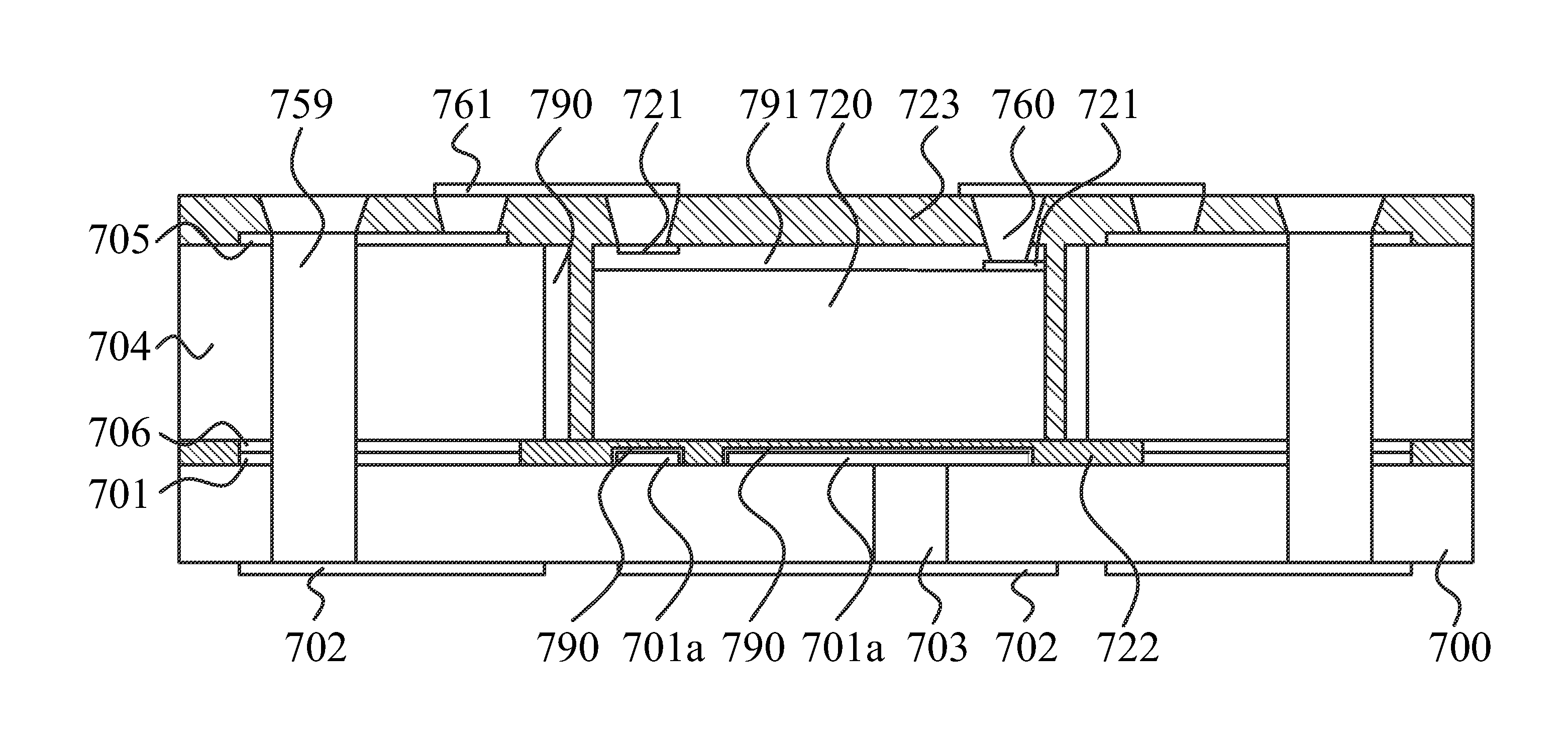

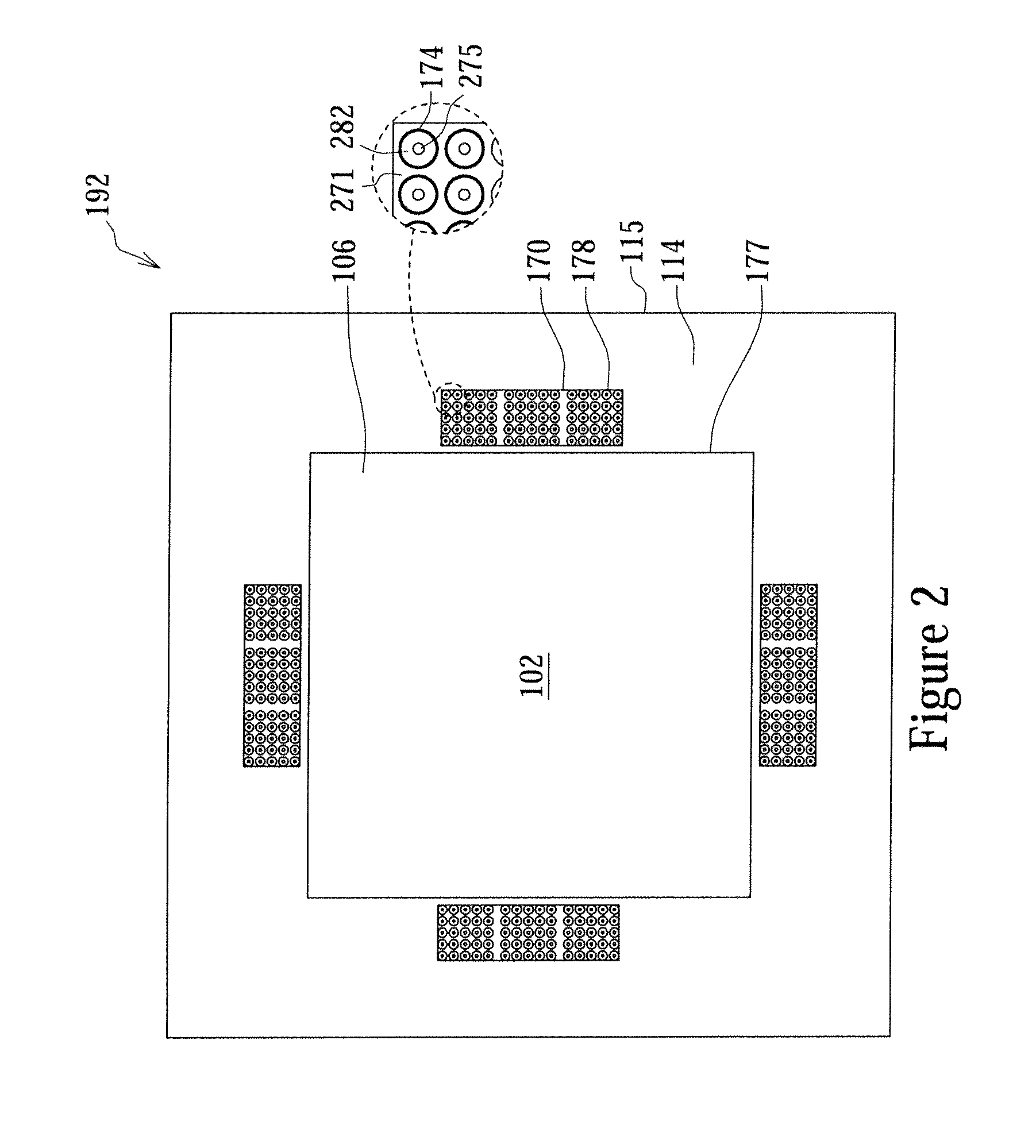

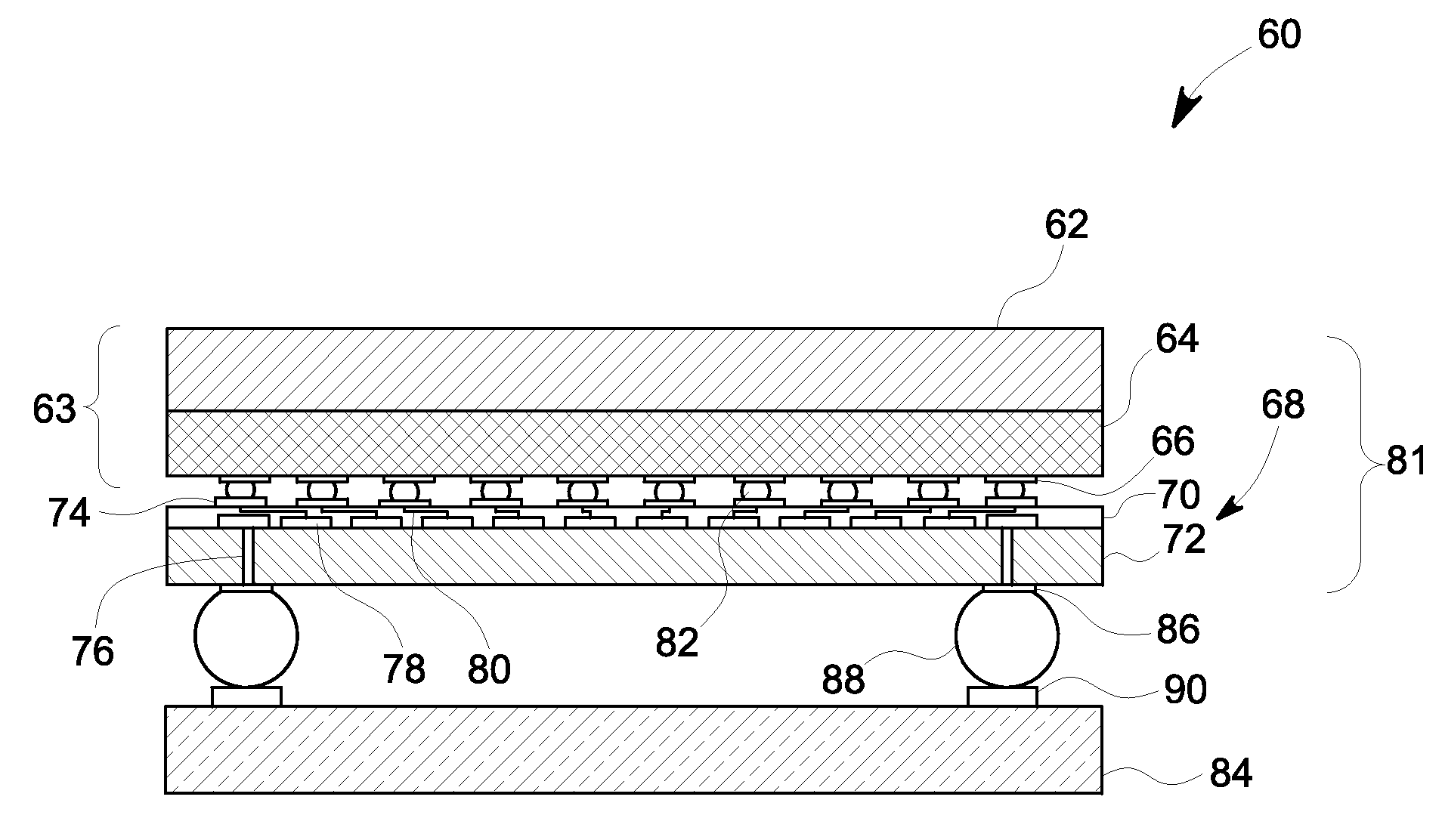

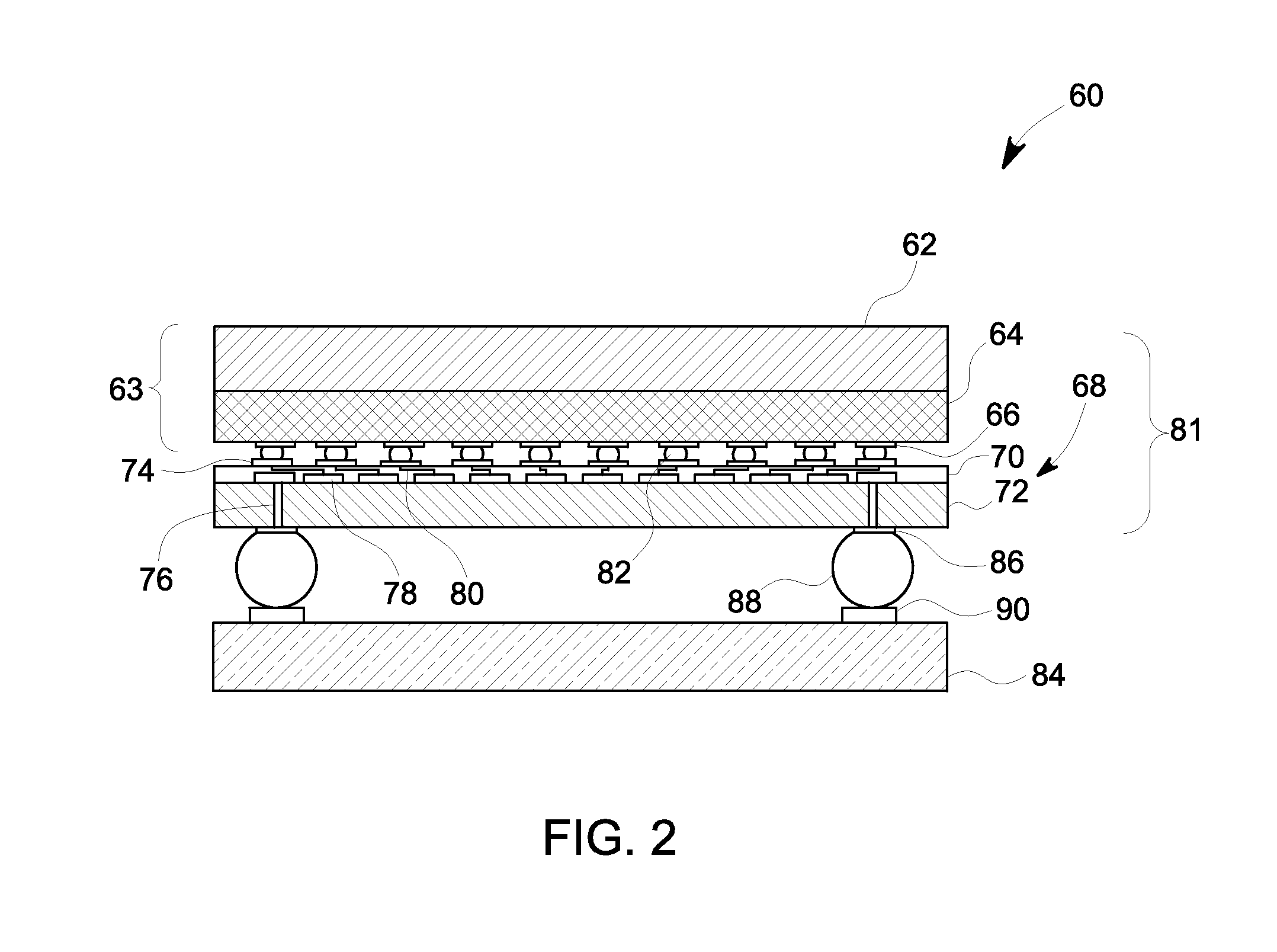

Apparatus having thermal-enhanced and cost-effective 3D IC integration structure with through silicon via interposers

ActiveUS20100213600A1Improved thermal managementImprove thermal performanceSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerInterposer

An apparatus having a three-dimensional integrated circuit structure is described herein. The apparatus include an interposer for carrying a plurality of high and low-power chips. The high-power chips are attached and connected to one side of the interposer, while the low-power chips are attached and connected to the other side of the interposer. In generally, the high-power chips produce more heat than does the low-power chip during their operations. The interposer further include through silicon vias and redistribution layers for connecting the chips on both surfaces. In addition, the interposer assembly is attached and connected to a substrate layer, which is in turn attached and connected to a printed circuit board. In order to provide improve thermal management, the interposer surface carrying the high-power chips are oriented away from the circuit board. A heat spreader is attached to the back sides of the high-power chips for dissipating the heat.

Owner:THE HONG KONG UNIV OF SCI & TECH

Integrated circuit solder bumping system

ActiveUS20070069346A1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerInsulation layer

An integrated circuit solder bumping system provides a substrate and forms a redistribution layer on the substrate. An insulation layer is formed on the redistribution layer. The insulation layer has a plurality of openings therethrough. A first UBM layer of titanium is deposited on the insulation layer and in the openings therethrough. A second UBM layer of chromium / copper alloy is deposited on the first UBM layer. A third UBM layer of copper is deposited on the second UBM layer. UBM pads of at least two different sizes are formed from the UBM layers. Solder paste is printed over at least some of the UBM pads. The solder paste is reflowed to form at least smaller solder bumps on at least some of the UBM pads. Bigger solder bumps are formed on at least some of the UBM pads.

Owner:JCET SEMICON (SHAOXING) CO LTD

Wafer level semiconductor package and manufacturing methods thereof

ActiveUS20120119373A1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerSemiconductor package

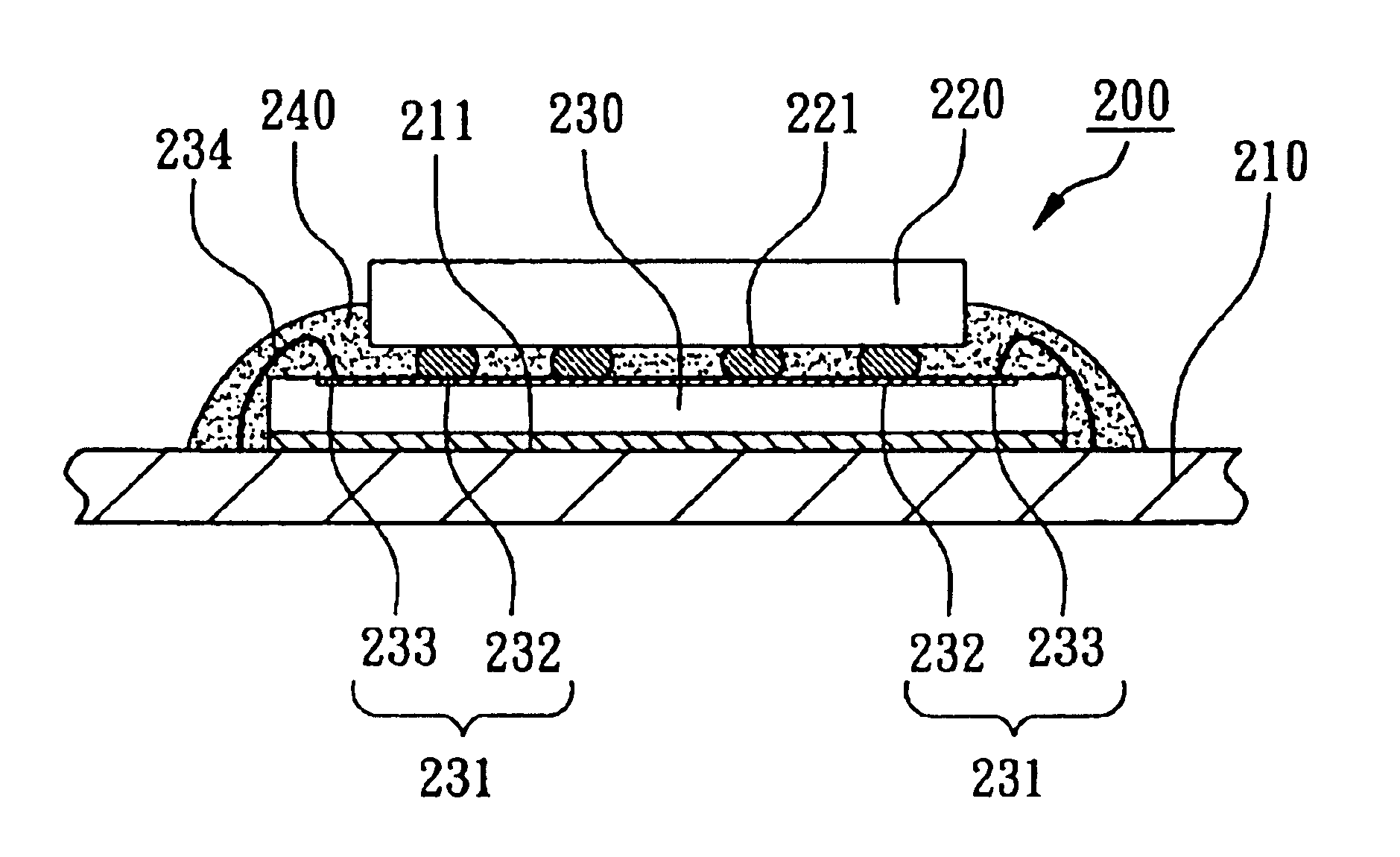

A semiconductor package includes at least one semiconductor die having an active surface, an interposer element having an upper surface and a lower surface, a package body, and a lower redistribution layer. The interposer element has at least one conductive via extending between the upper surface and the lower surface. The package body encapsulates portions of the semiconductor die and portions of the interposer element. The lower redistribution layer electrically connects the interposer element to the active surface of the semiconductor die.

Owner:ADVANCED SEMICON ENG INC

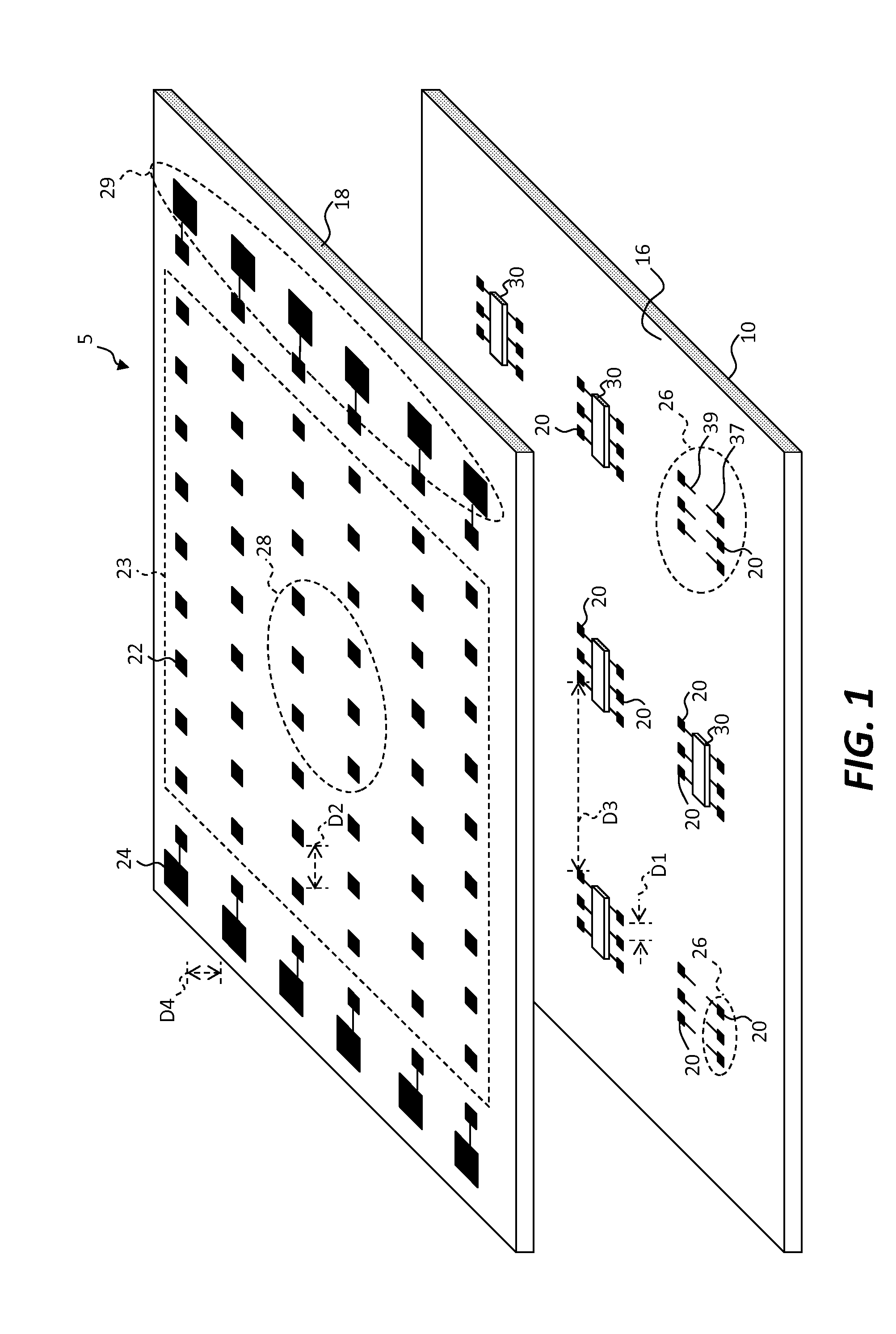

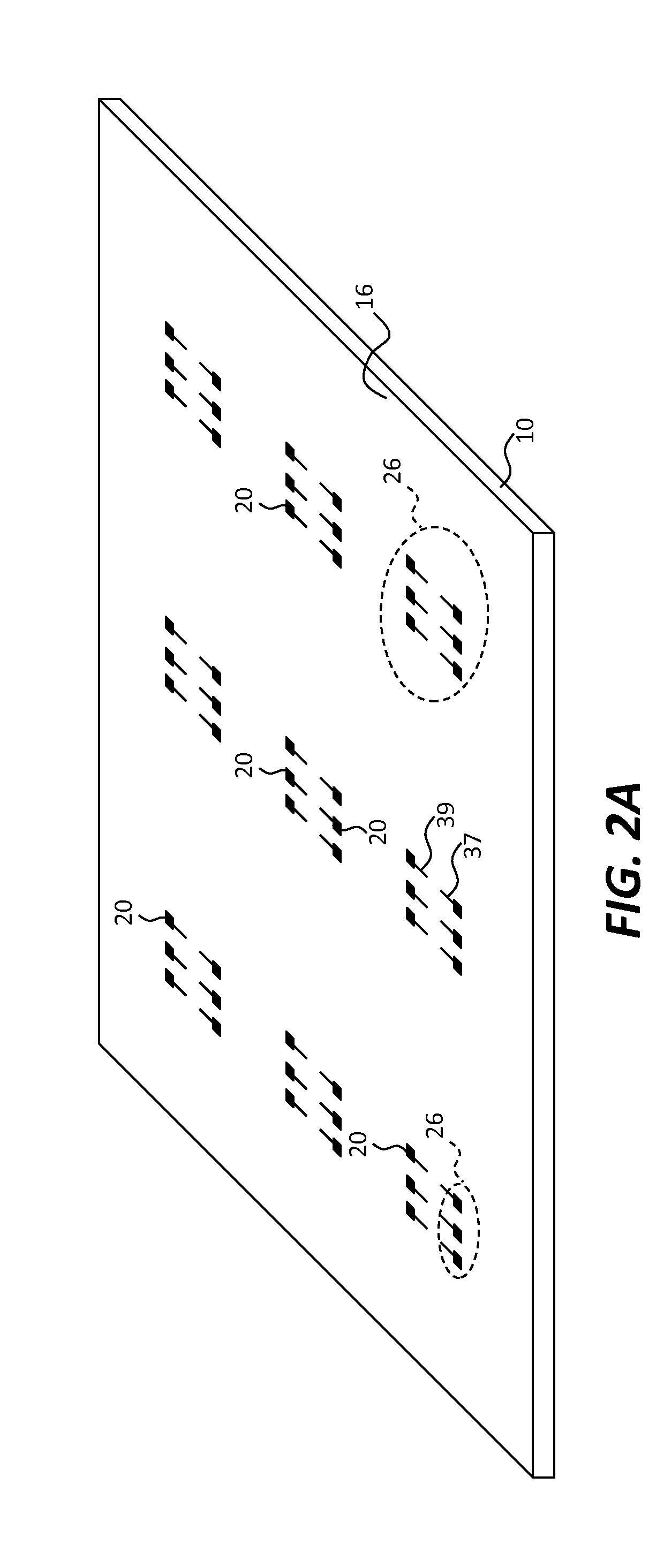

Redistribution layer for substrate contacts

ActiveUS20170025593A1High resolutionEfficient preparationSolid-state devicesInput/output processes for data processingRedistribution layerElectrical connection

A structure with an interconnection layer for redistribution of electrical connections includes a plurality of first electrical connections disposed on a substrate in a first arrangement. An insulating layer is disposed on the substrate over the first electrical connections. A plurality of second electrical connections is disposed on the insulating layer on a side of the insulating layer opposite the plurality of first electrical connections in a second arrangement. Each second electrical connection is electrically connected to a respective first electrical connection. An integrated circuit is disposed on the substrate and is electrically connected to the first electrical connections. The first electrical connections in the first arrangement have a greater spatial density than the second electrical connections in the second arrangement.

Owner:X DISPLAY CO TECH LTD

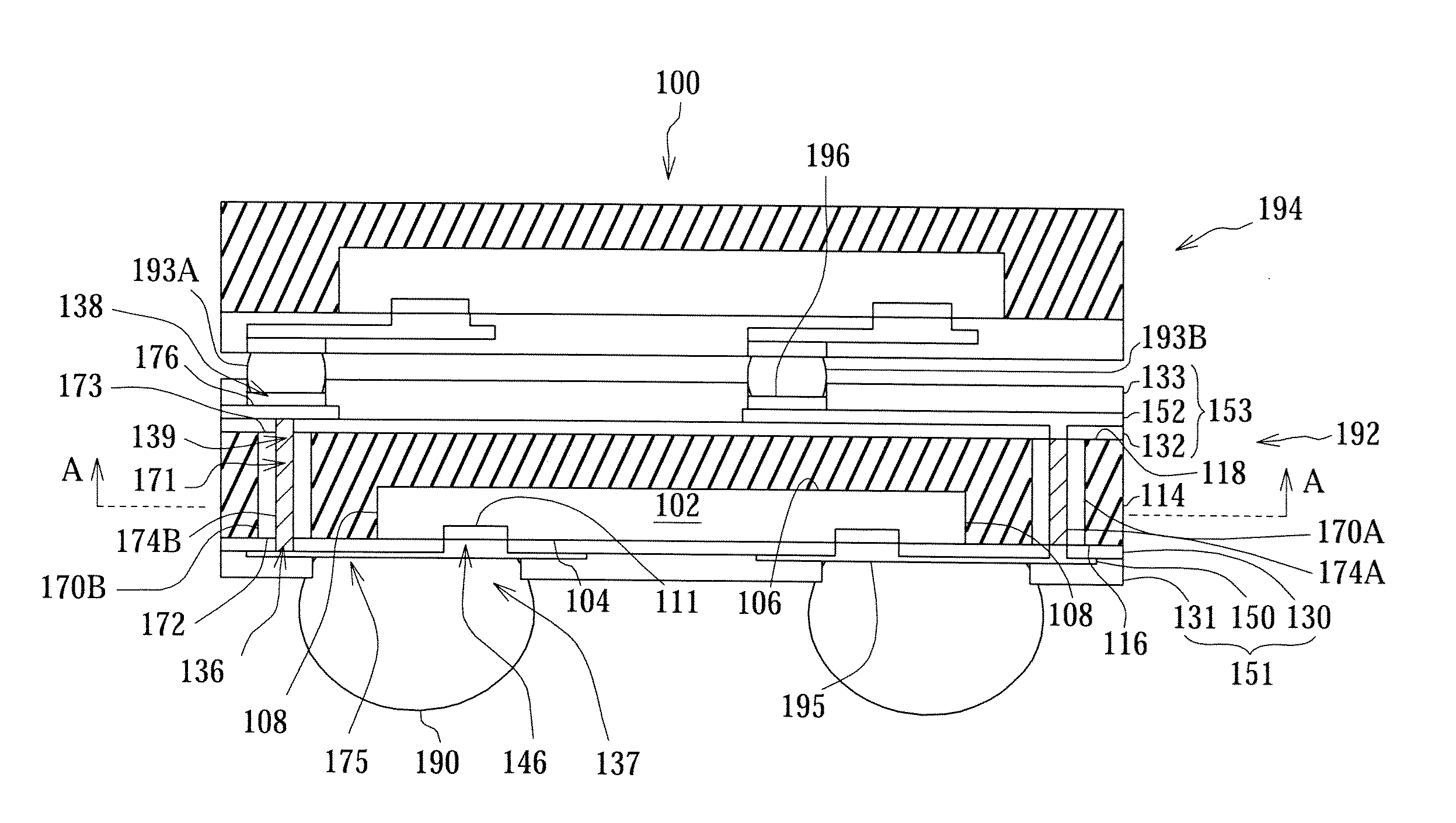

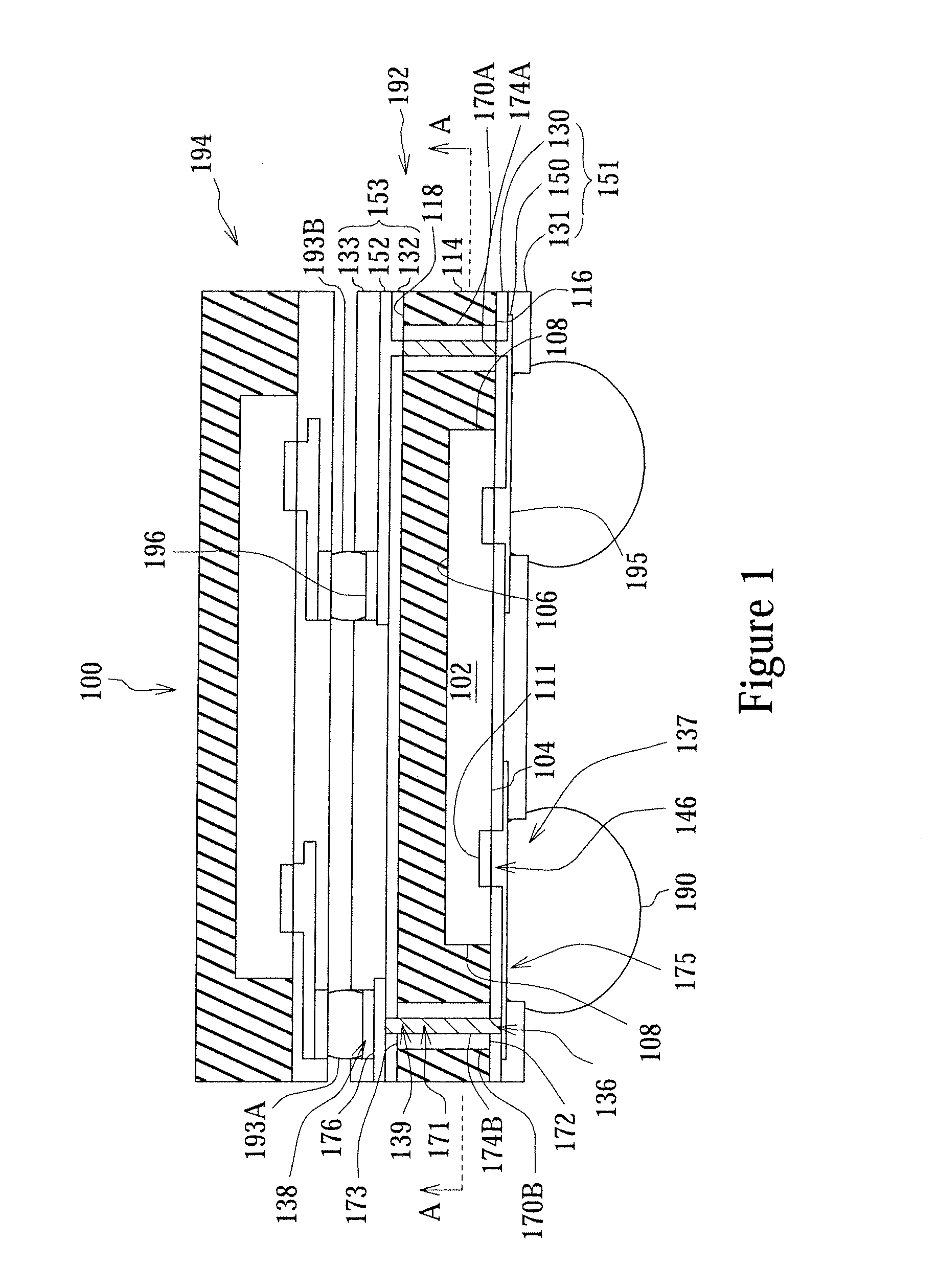

Packaging for fingerprint sensors and methods of manufacture

ActiveUS20120256280A1Semiconductor/solid-state device detailsSolid-state devicesElectricityRedistribution layer

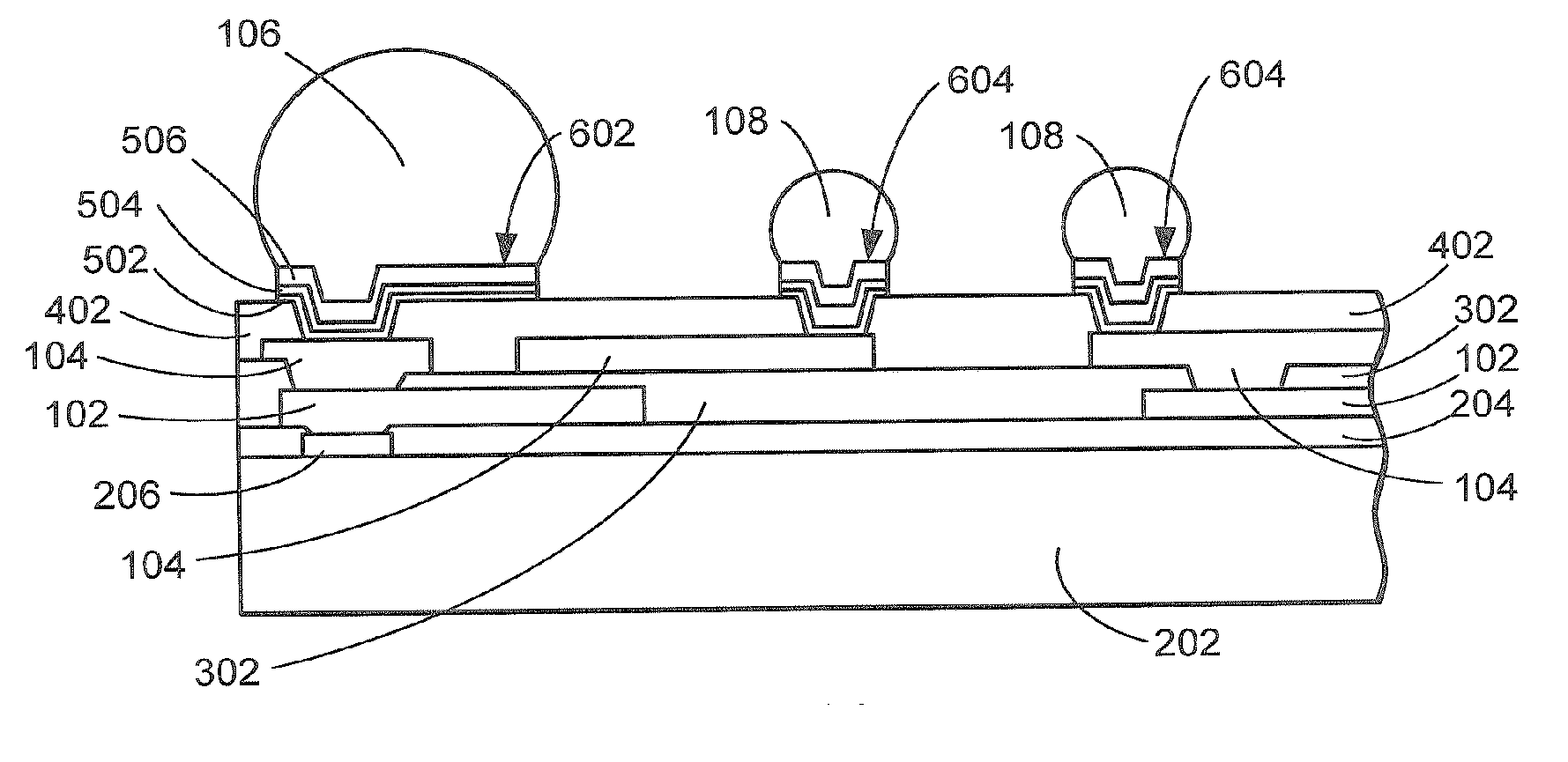

A fingerprint sensor package, including a sensing side for sensing fingerprint information and a separate connection side for electrically connecting the fingerprint sensor package to a host device, is disclosed. The fingerprint sensor package can also include a sensor integrated circuit facing the sensing side and substantially surrounded by a fill material. The fill material includes vias at peripheral locations around the sensor integrated circuit. The fingerprint sensor package can further include a redistribution layer on the sensing side which redistributes connections of the sensor integrated circuit to the vias. The connections can further be directed through the vias to a ball grid array on the connection side. Some aspects also include electrostatic discharge traces positioned at least partially around a perimeter of the connection side. Methods of manufacturing arc also disclosed.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

Fan-out package structure including antenna

InactiveUS20170040266A1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerSemiconductor package

The invention provides a semiconductor package assembly. The semiconductor package assembly includes a first semiconductor package including a first redistribution layer (RDL) structure having a first surface and a second surface opposite to the first substrate. The first RDL structure includes a plurality of first conductive traces close to the first surface of the first RDL structure. An antenna pattern is disposed close to the second surface of the first RDL structure. A first semiconductor die is disposed on the first surface of the first RDL structure and electrically coupled to the first RDL structure. A plurality of conductive structures is disposed on the first surface of the first RDL structure and electrically coupled to the first RDL structure. The plurality of conductive structures is spaced apart from the antenna pattern through the plurality of first conductive traces of the first RDL structure.

Owner:MEDIATEK INC

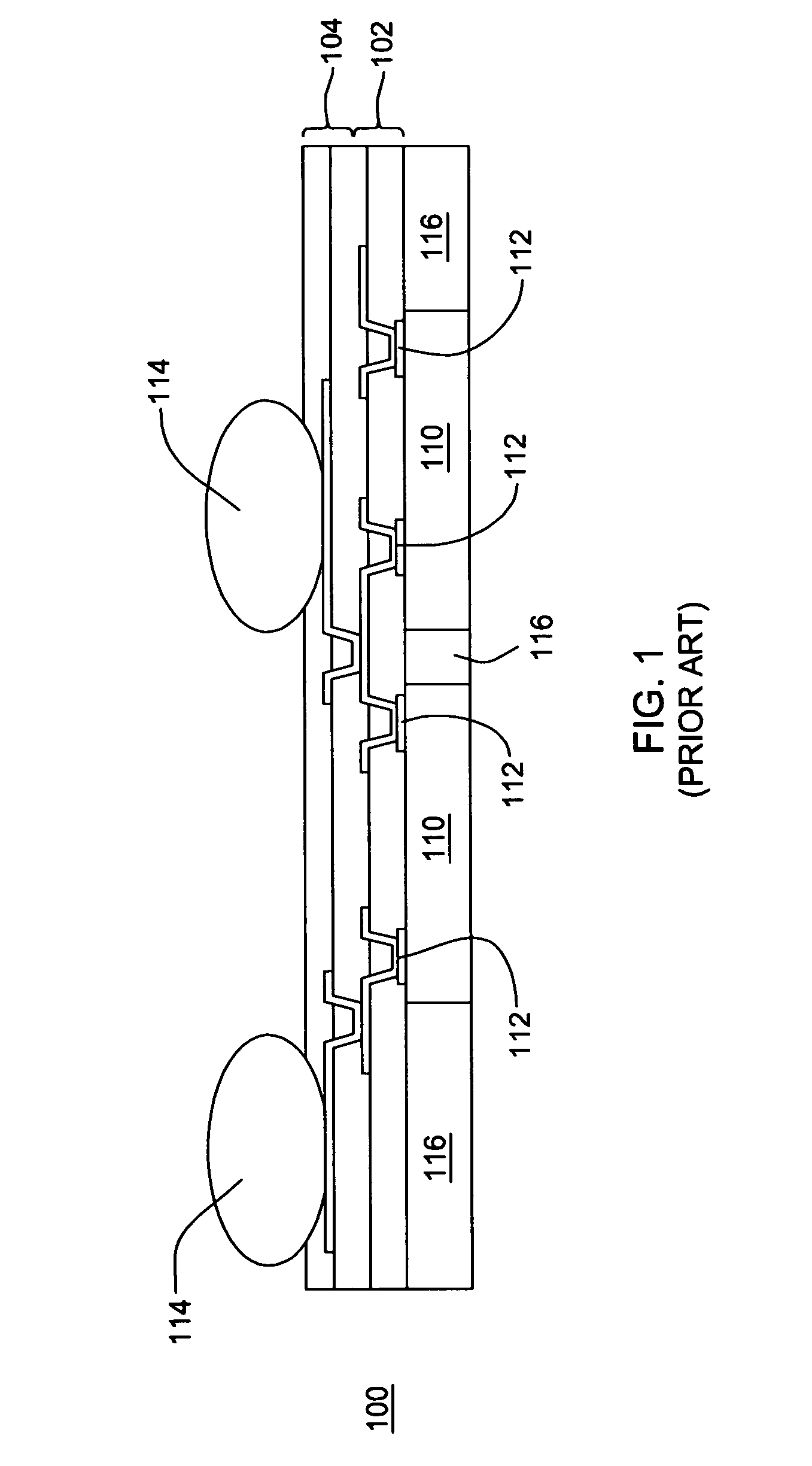

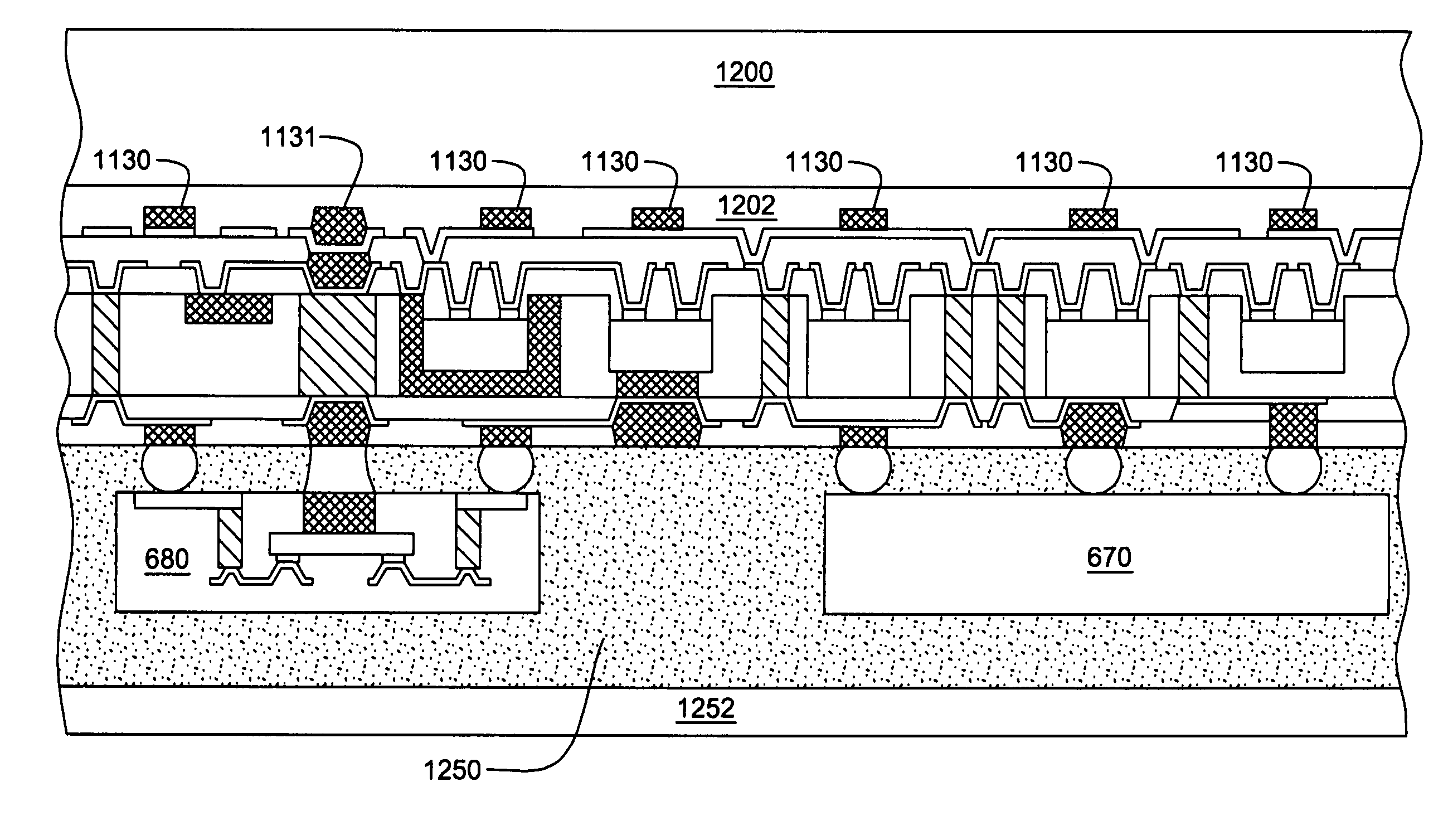

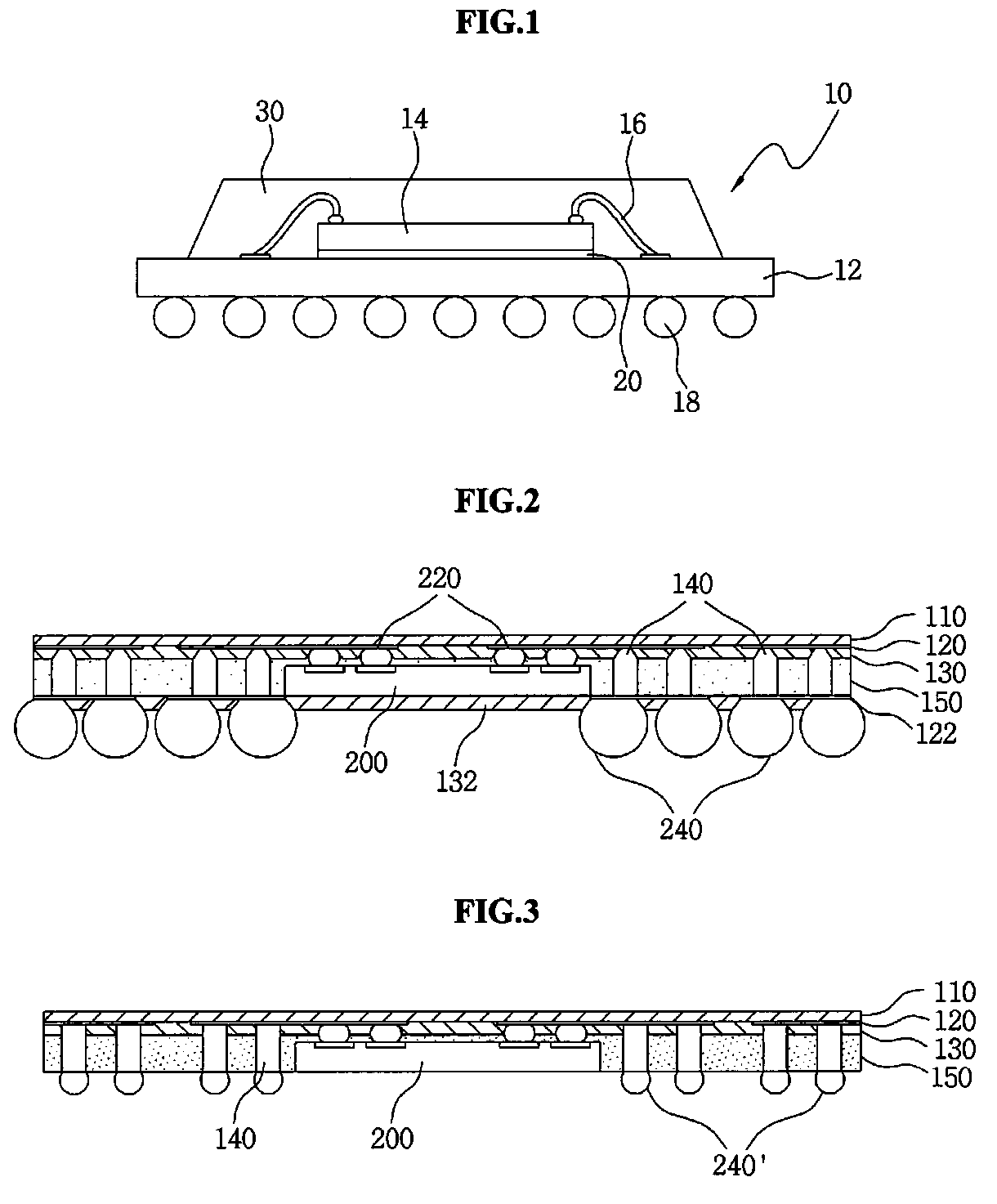

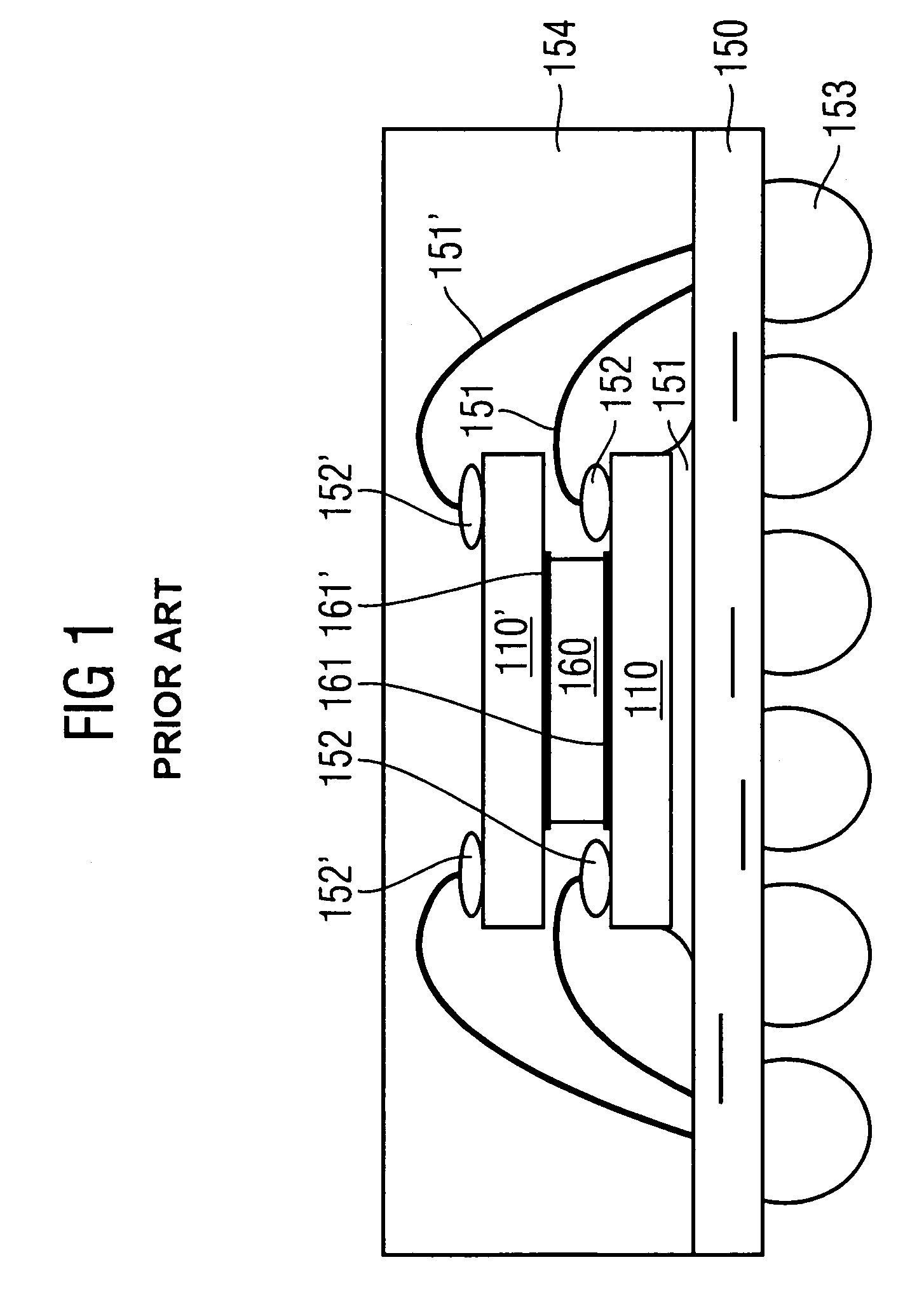

Elimination of RDL using tape base flip chip on flex for die stacking

InactiveUS7189593B2Strengthen interconnectionReduce assembly heightSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerFlexible circuits

A flexible film interposer for stacking a flip chip semiconductor die onto a second (bottom) semiconductor die, semiconductor devices and stacked die assemblies that incorporate the flexible film interposer, and methods of fabricating the devices and assemblies are provided. The incorporation of the flexible film interposer achieves densely packaged semiconductor devices, without the need for a redistribution layer (RDL).

Owner:MICRON TECH INC

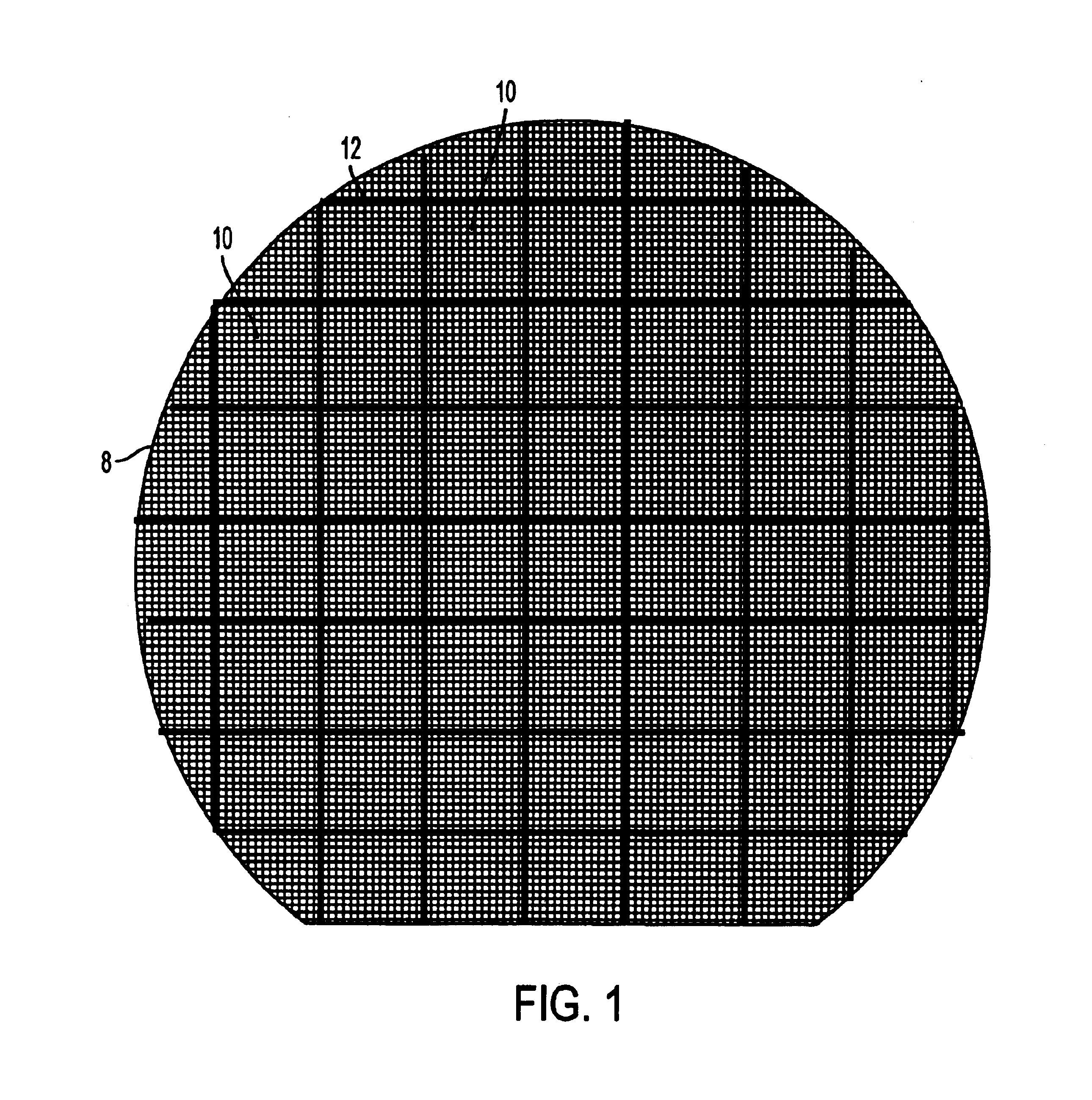

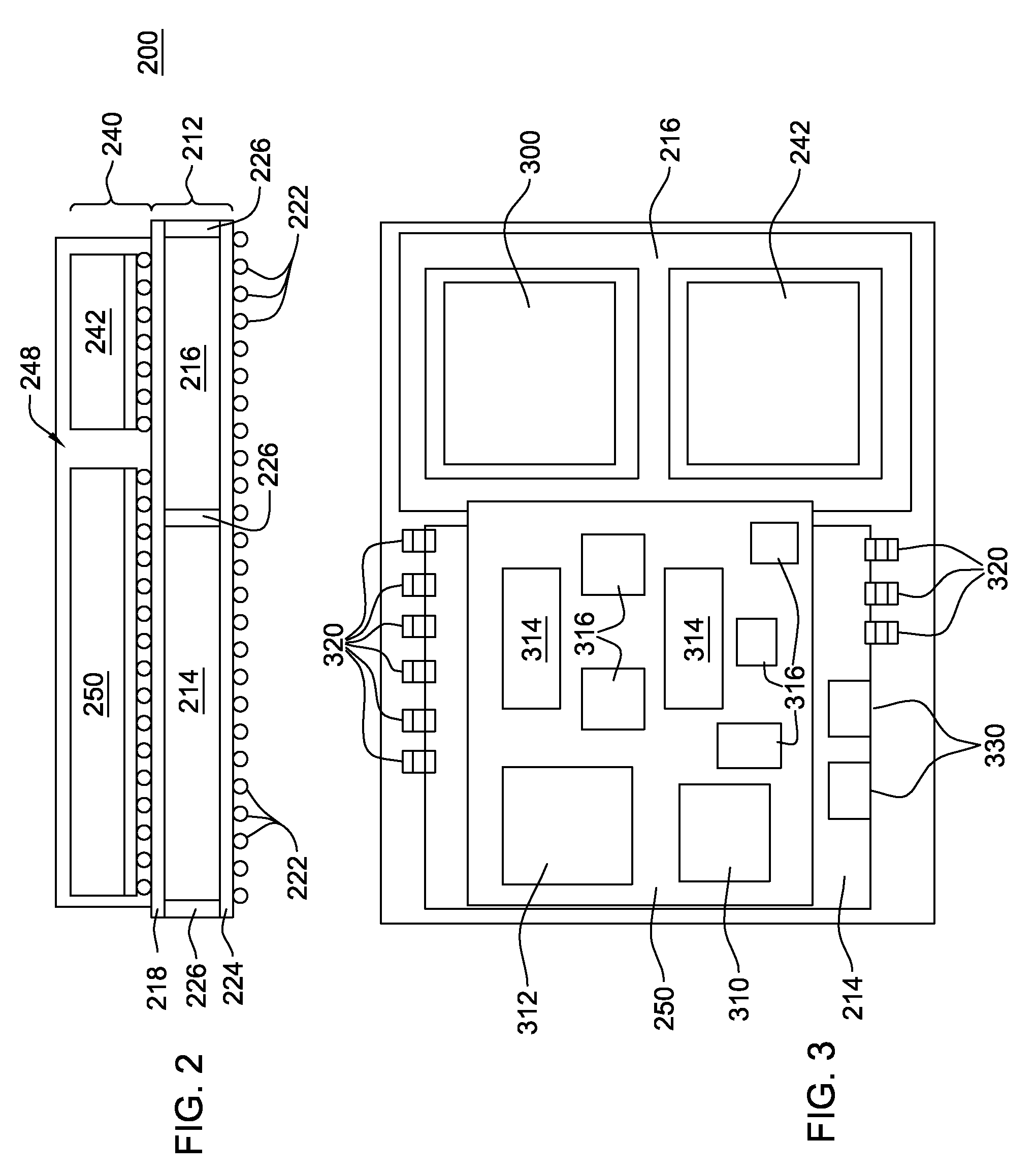

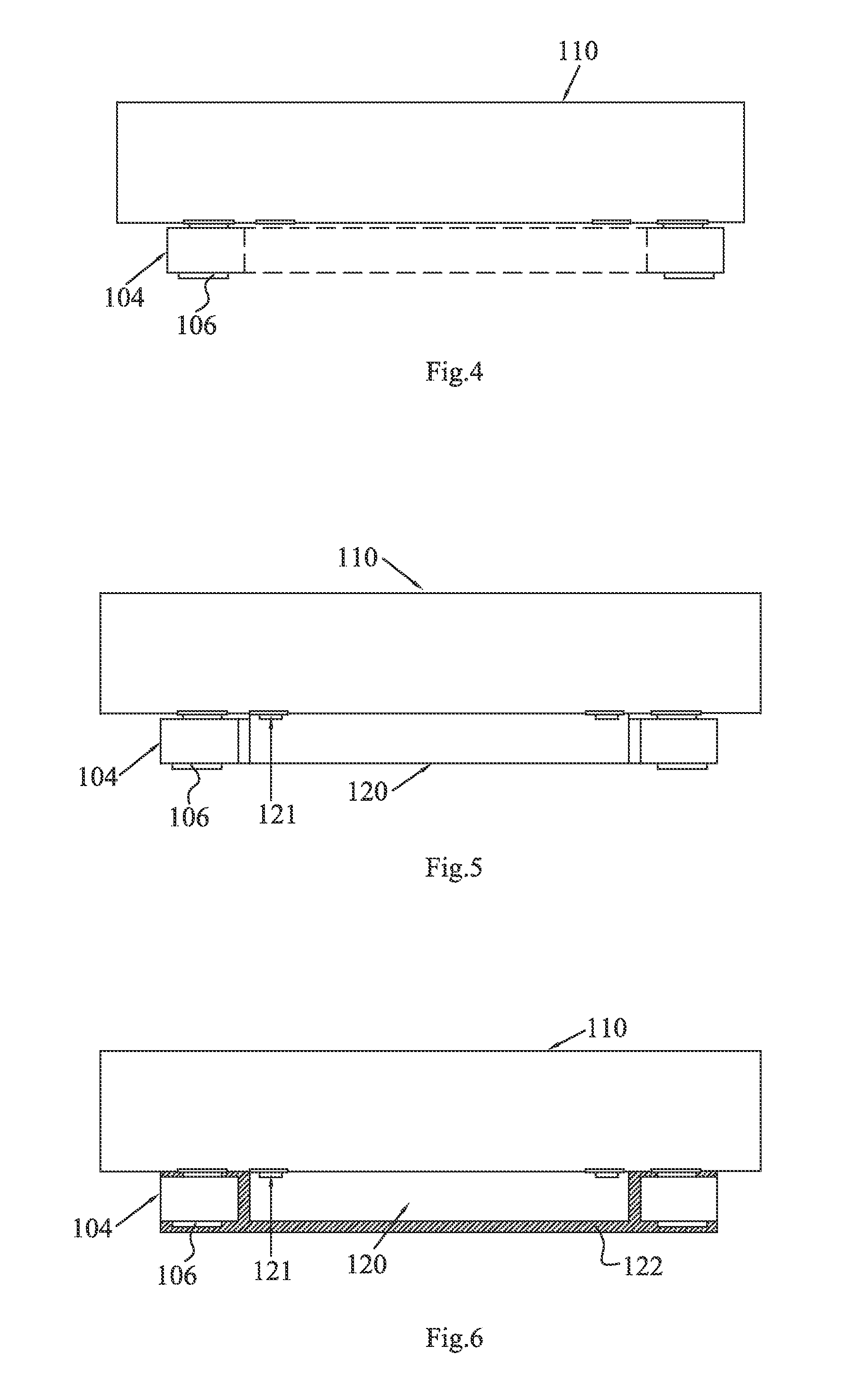

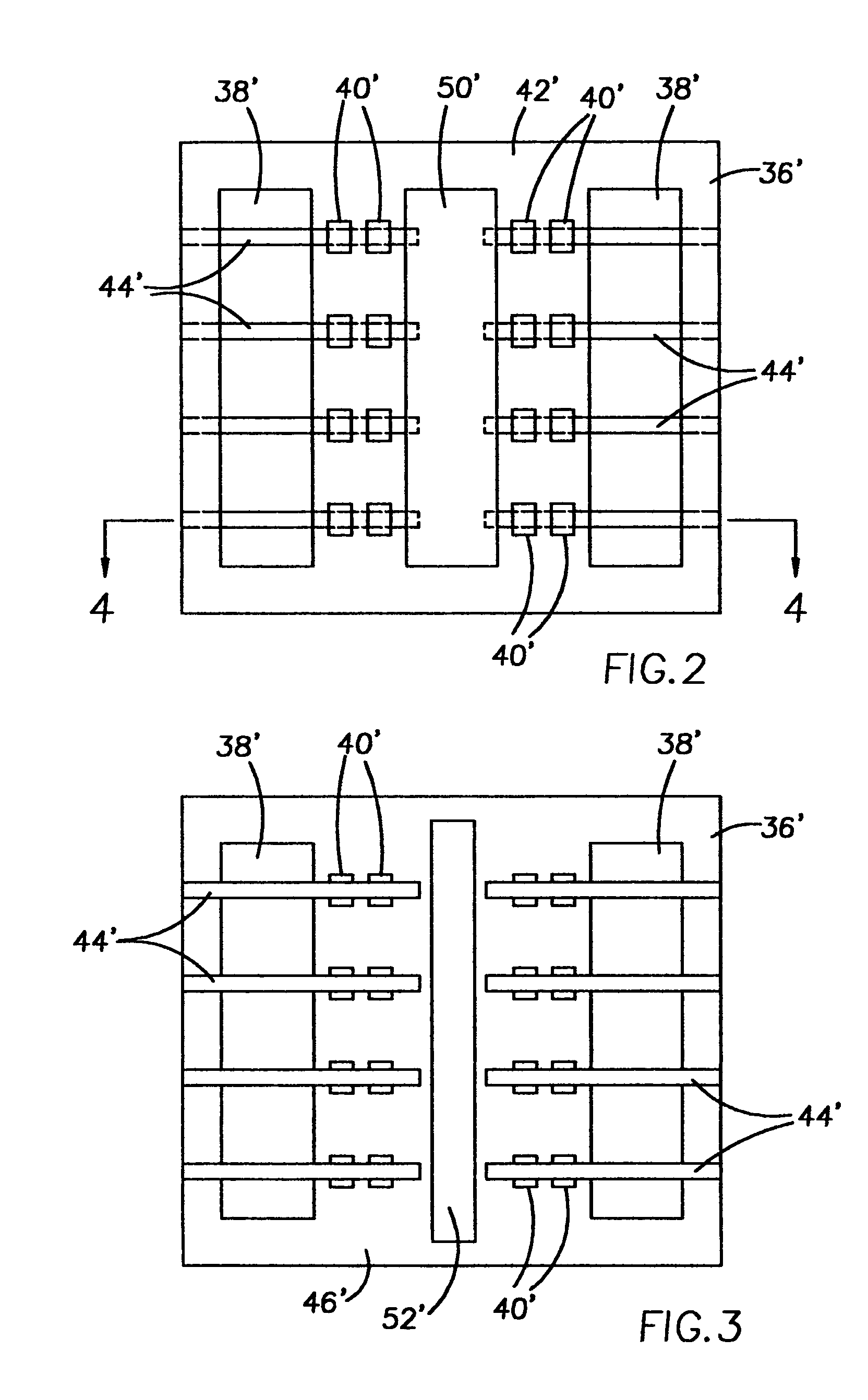

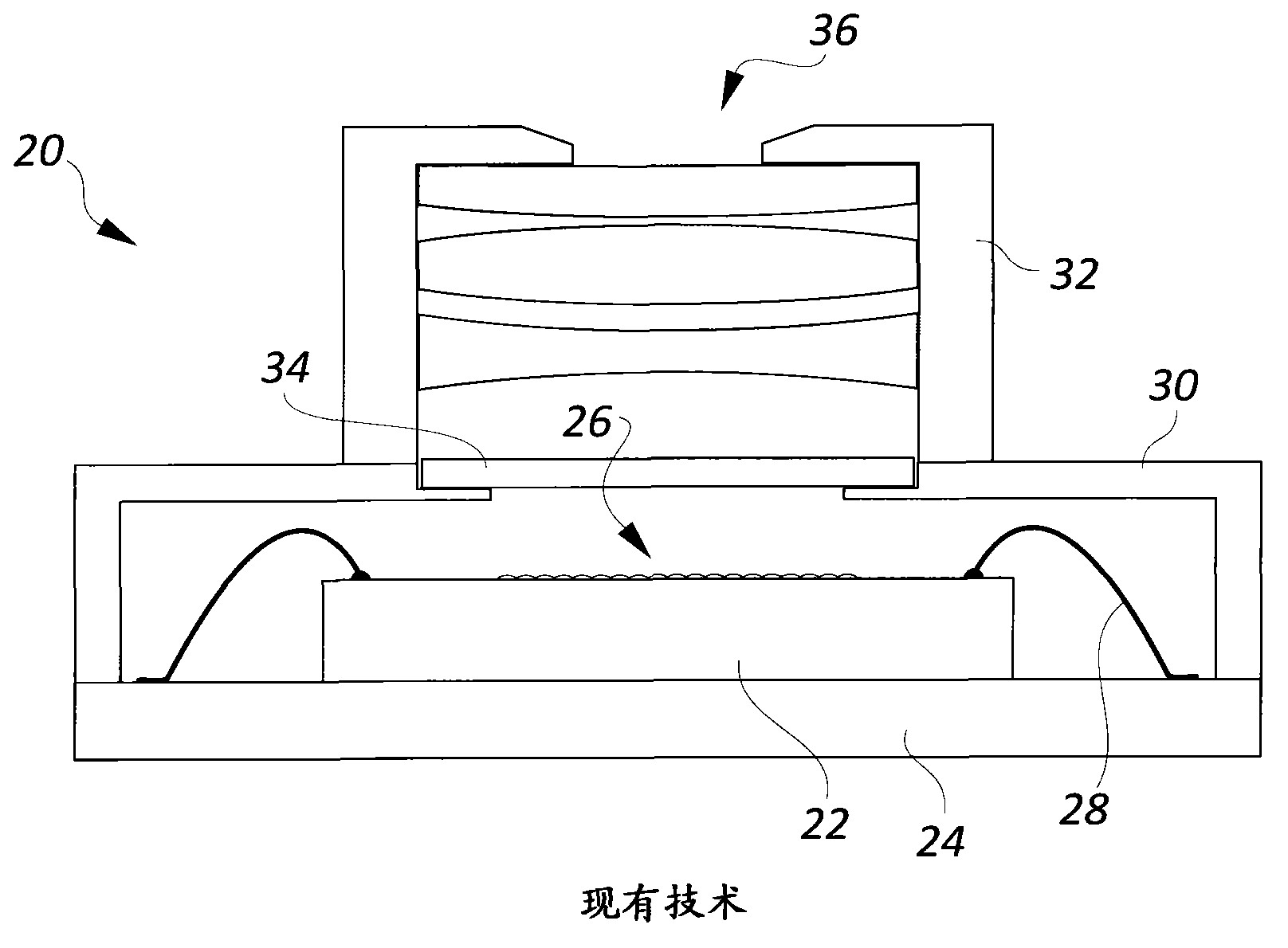

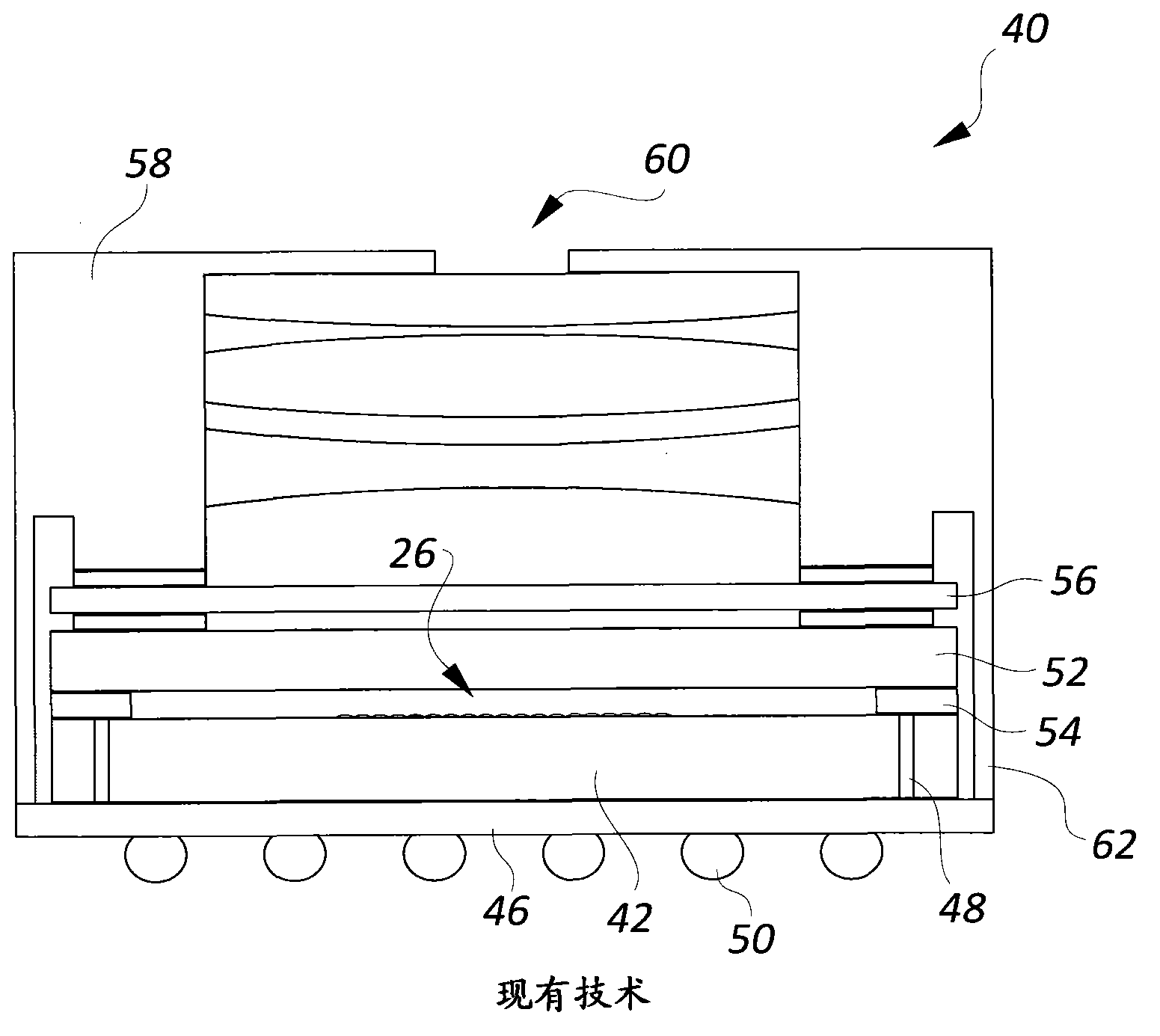

Tileable sensor array

ActiveUS20120133001A1Ultrasonic/sonic/infrasonic diagnosticsSolid-state devicesSensor arrayContact pad

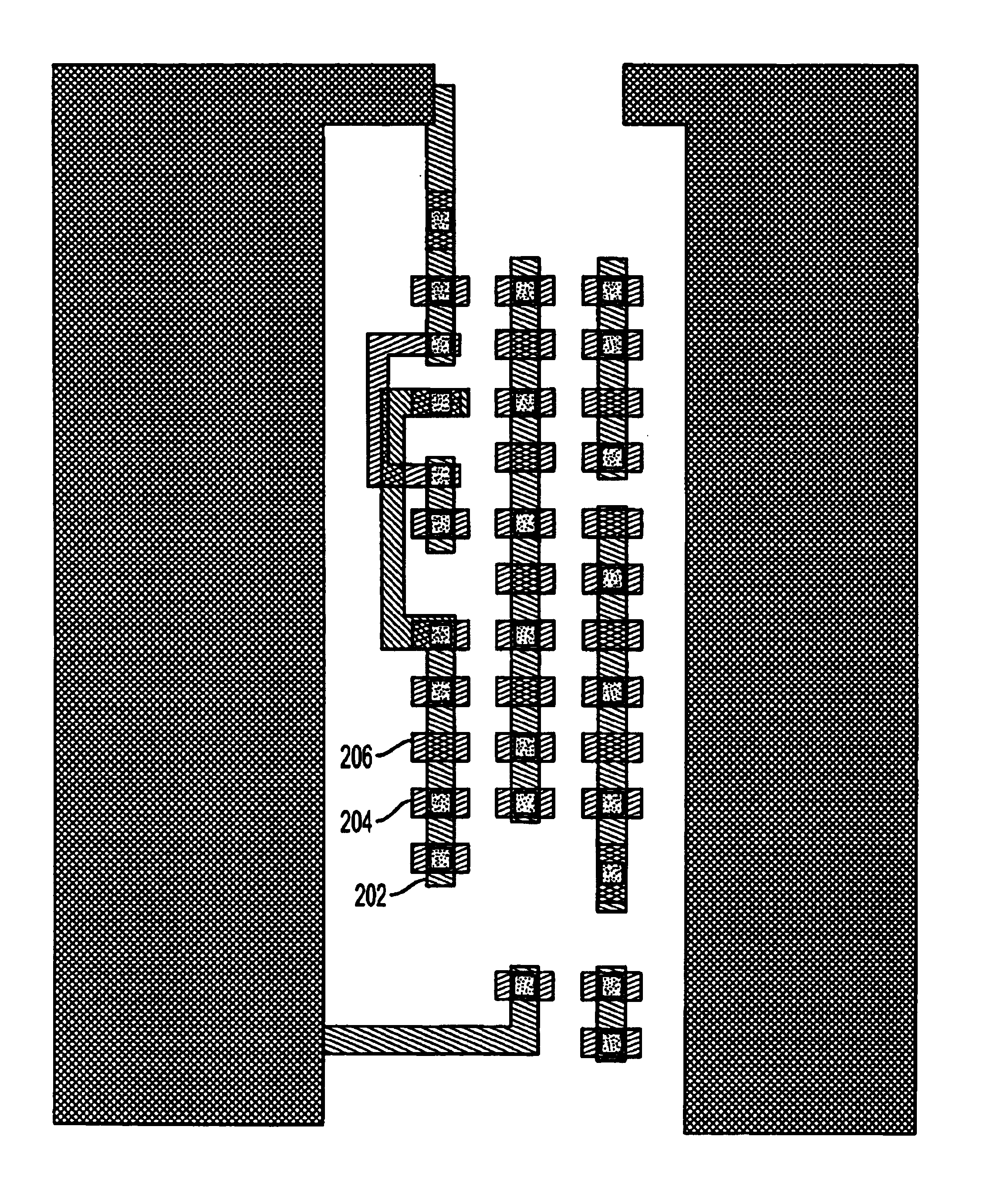

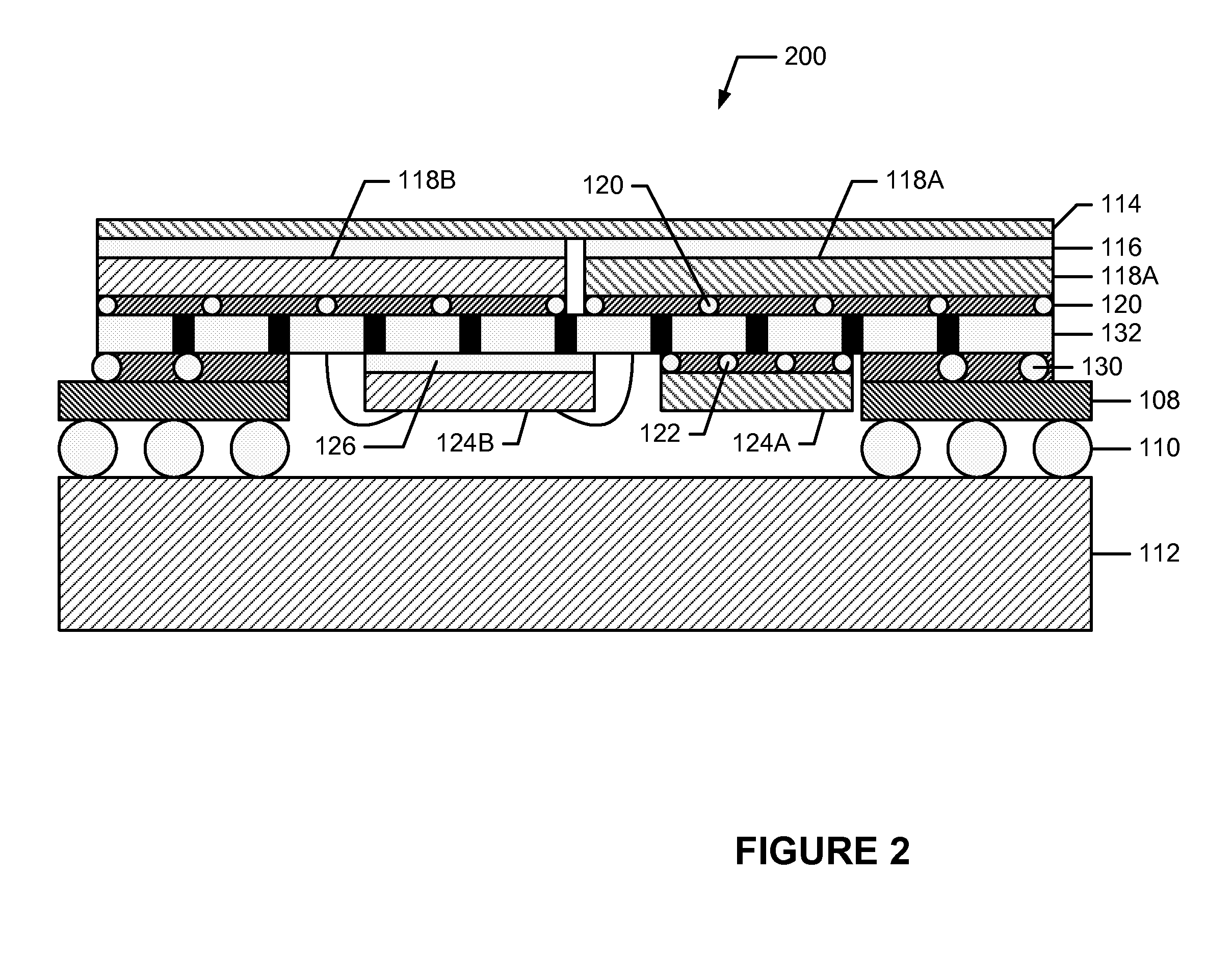

A method for forming a tileable detector array is presented. The method includes forming a detector module, where forming the detector module includes providing a sensor array having a first side and a second side, where the sensor array includes a first plurality of contact pads disposed on the second side of the sensor array, disposing the sensor array on an interconnect layer, where the interconnect layer includes a redistribution layer having a first side and a second side, where the redistribution layer includes a second plurality of contact pads disposed on the first side, an integrated circuit having a plurality of through vias disposed therethrough, where a first side of the integrated circuit is operationally coupled to the second side of the redistribution layer, where the sensor array is disposed on the interconnect layer such that the first plurality of contact pads on the second side of the sensor array are aligned with the second plurality of contact pads on the first side of the redistribution layer, operationally coupling the first plurality of contact pads on the second side of the sensor array to the second plurality of contact pads on the redistribution layer to form a sensor stack, coupling the sensor stack to a substrate to form the detector module, and tiling a plurality of detector modules on a second substrate to form the tileable detector array.

Owner:GENERAL ELECTRIC CO

Semiconductor Package and Manufacturing Methods Thereof

InactiveUS20110127654A1Semiconductor/solid-state device detailsSolid-state devicesEffective surfaceRedistribution layer

A semiconductor package and manufacturing methods thereof are provided. In one embodiment, the semiconductor package includes a die, a shield, a package body, and a redistribution layer. The die has an active surface and an inactive surface. The shield is disposed over the inactive surface of the die. The package body encapsulates the die and a first portion of the shield, where a first surface of the package body is substantially coplanar with the active surface of the die. The redistribution layer is disposed on the active surface of the die and on portions of the first surface of the package body.

Owner:ADVANCED SEMICON ENG INC

Fan-out package structure including antenna

InactiveUS20160329299A1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerSemiconductor package

A semiconductor package structure including a first semiconductor package is provided. The first semiconductor package includes a first semiconductor package including a first redistribution layer (RDL) structure having a first surface and a second surface opposite thereto. A first semiconductor die and a first molding compound that surrounds the first semiconductor die are disposed on the first surface of the first RDL structure. An IMD structure having a conductive layer with an antenna pattern or a conductive shielding layer is disposed on the first molding compound and the first semiconductor die.

Owner:MEDIATEK INC

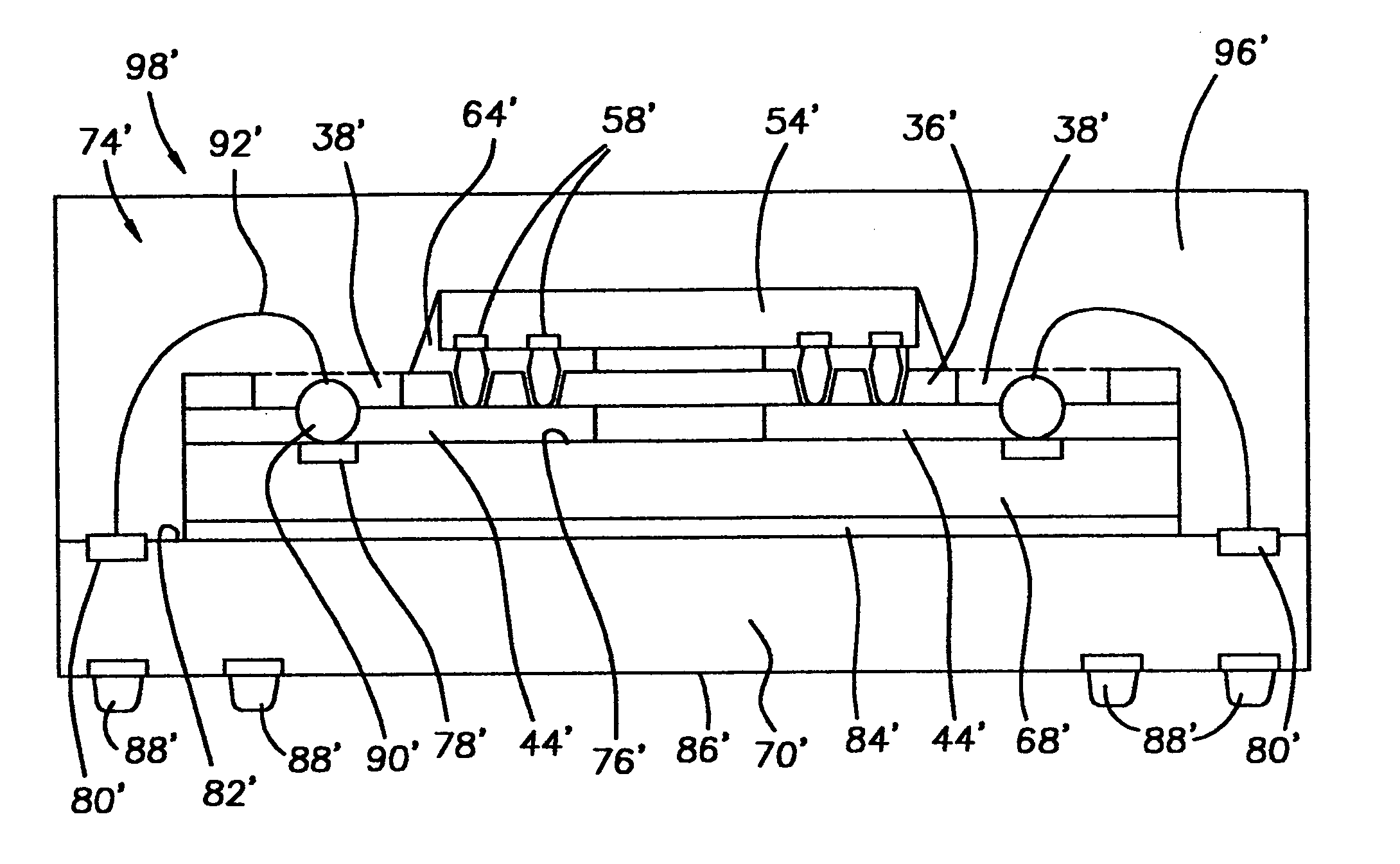

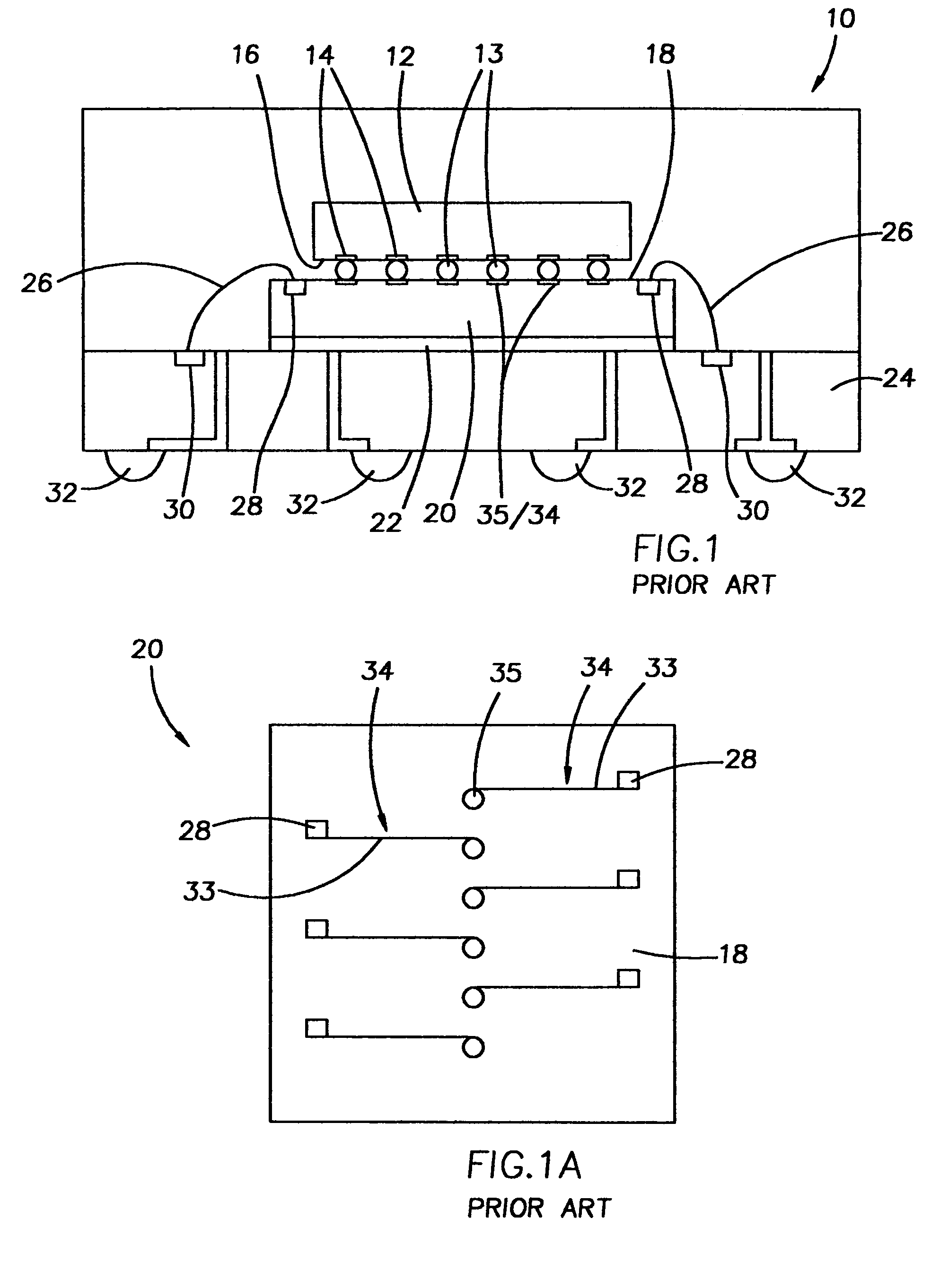

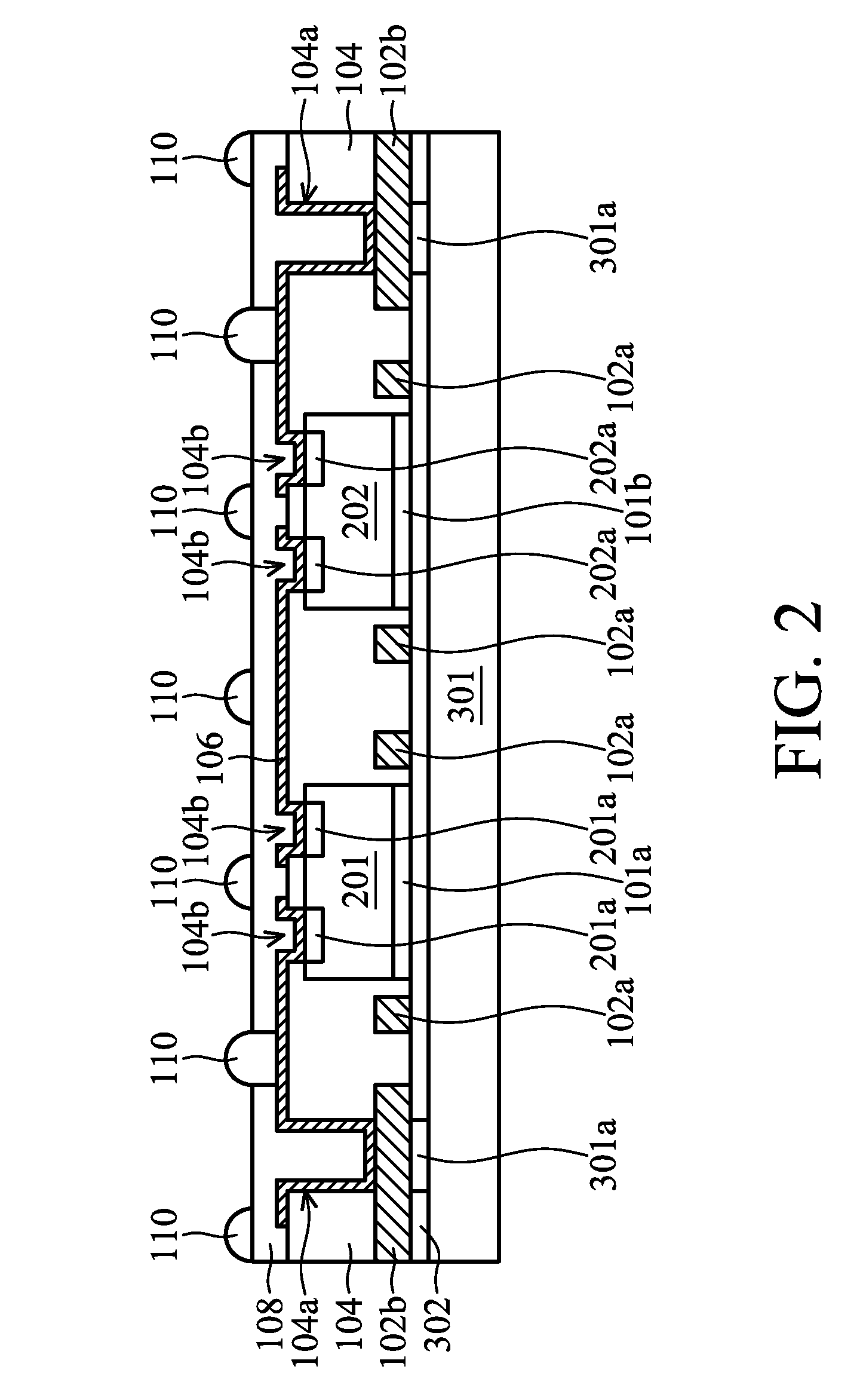

Multi-chip stack flip-chip package

ActiveUS6861761B2Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerEngineering

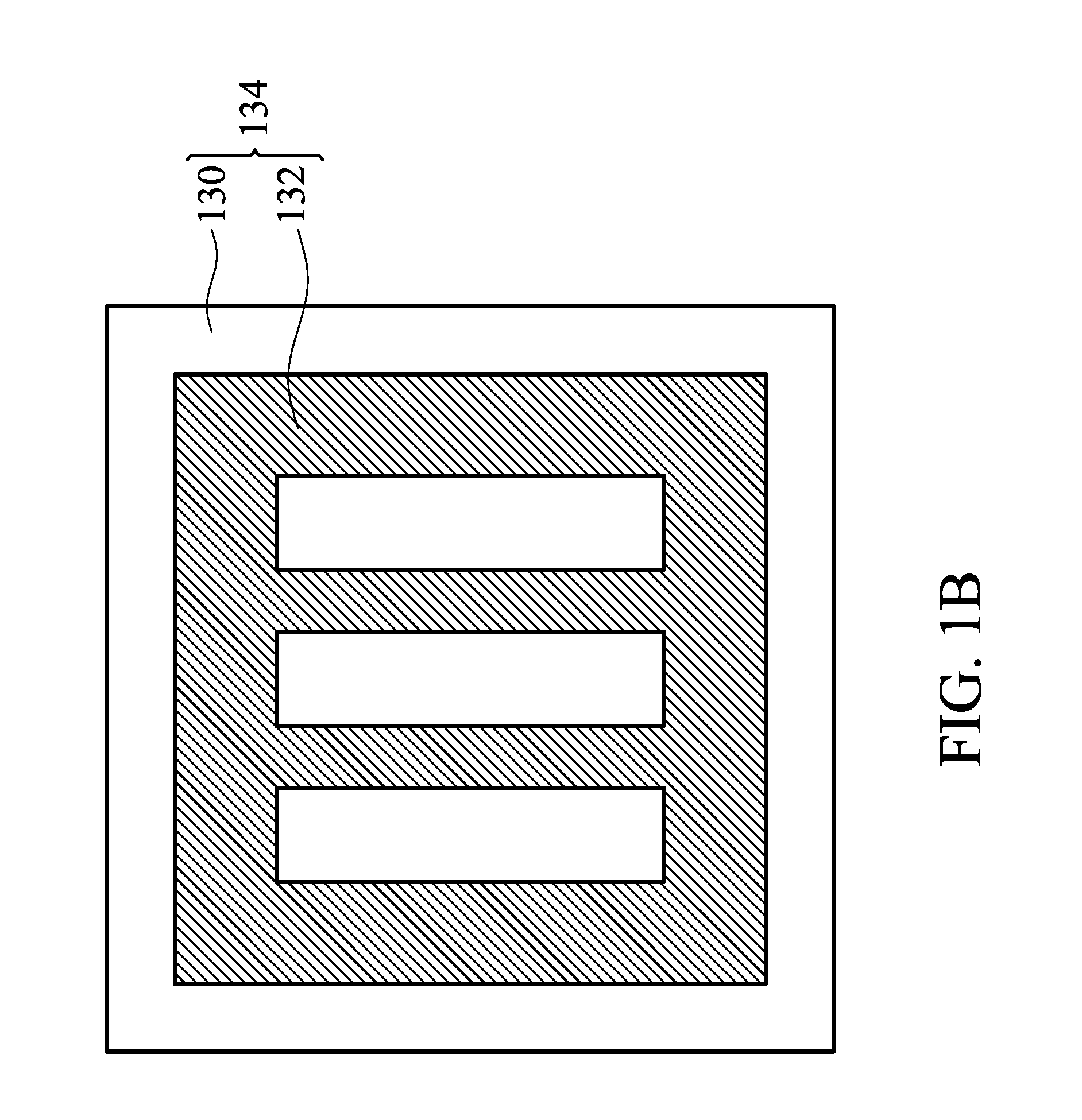

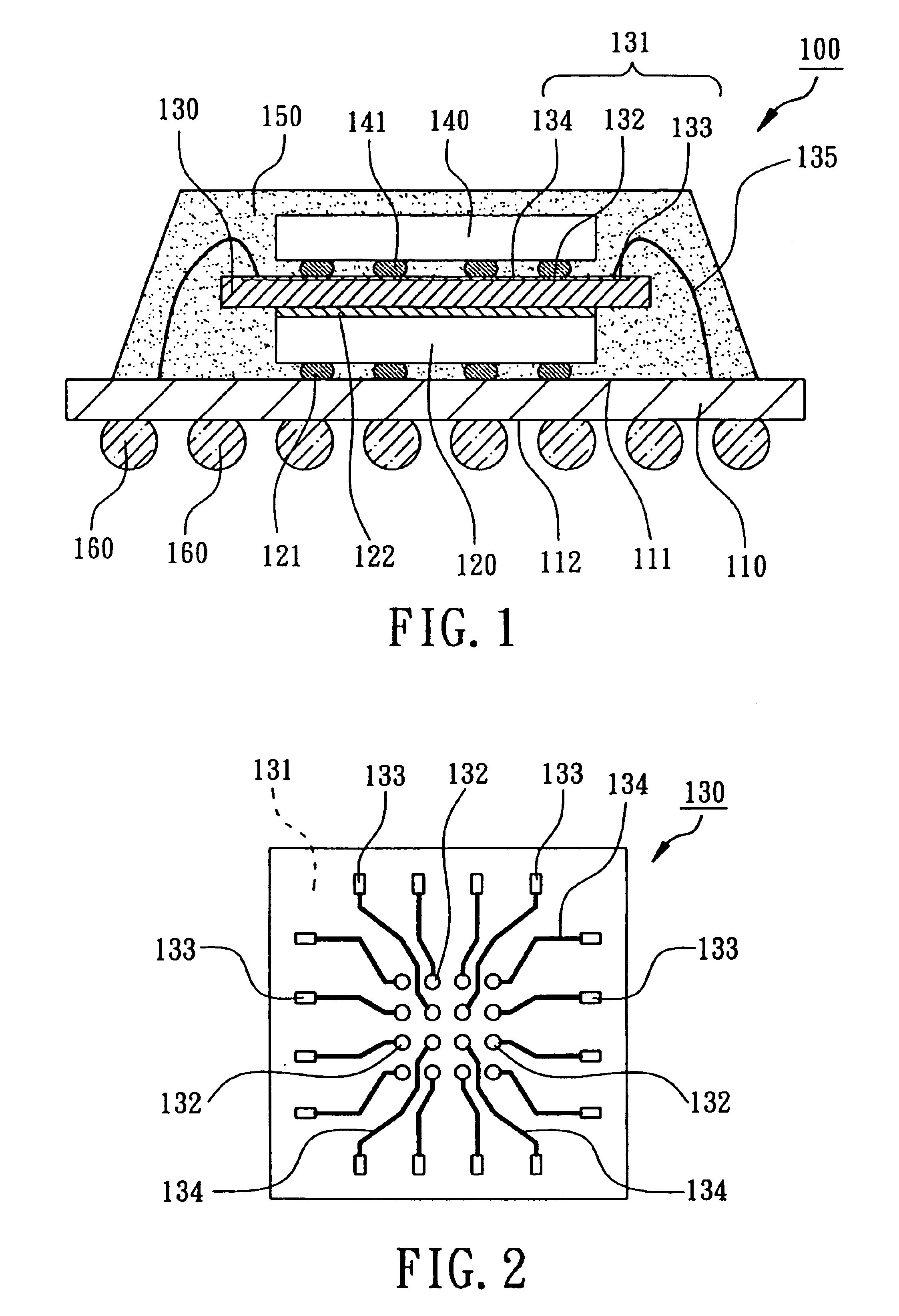

A multi-chip stack flip-chip package comprises a substrate and a chip assembly on the substrate. The chip assembly includes a dummy chip and a flip chip. The dummy chip has a redistribution layer that has a plurality of bump pads for mounting the flip chip, a plurality of peripheral pads for electrically connecting to the substrate, and a plurality of integrated circuit traces connecting the bump pads with the peripheral pads. The dummy chip is disposed between the flip chip and the substrate as an electrically connecting interface between the flip chip and the substrate for multi-chip flip-chip stack and fine pitch flip-chip mounting.

Owner:ADVANCED SEMICON ENG INC

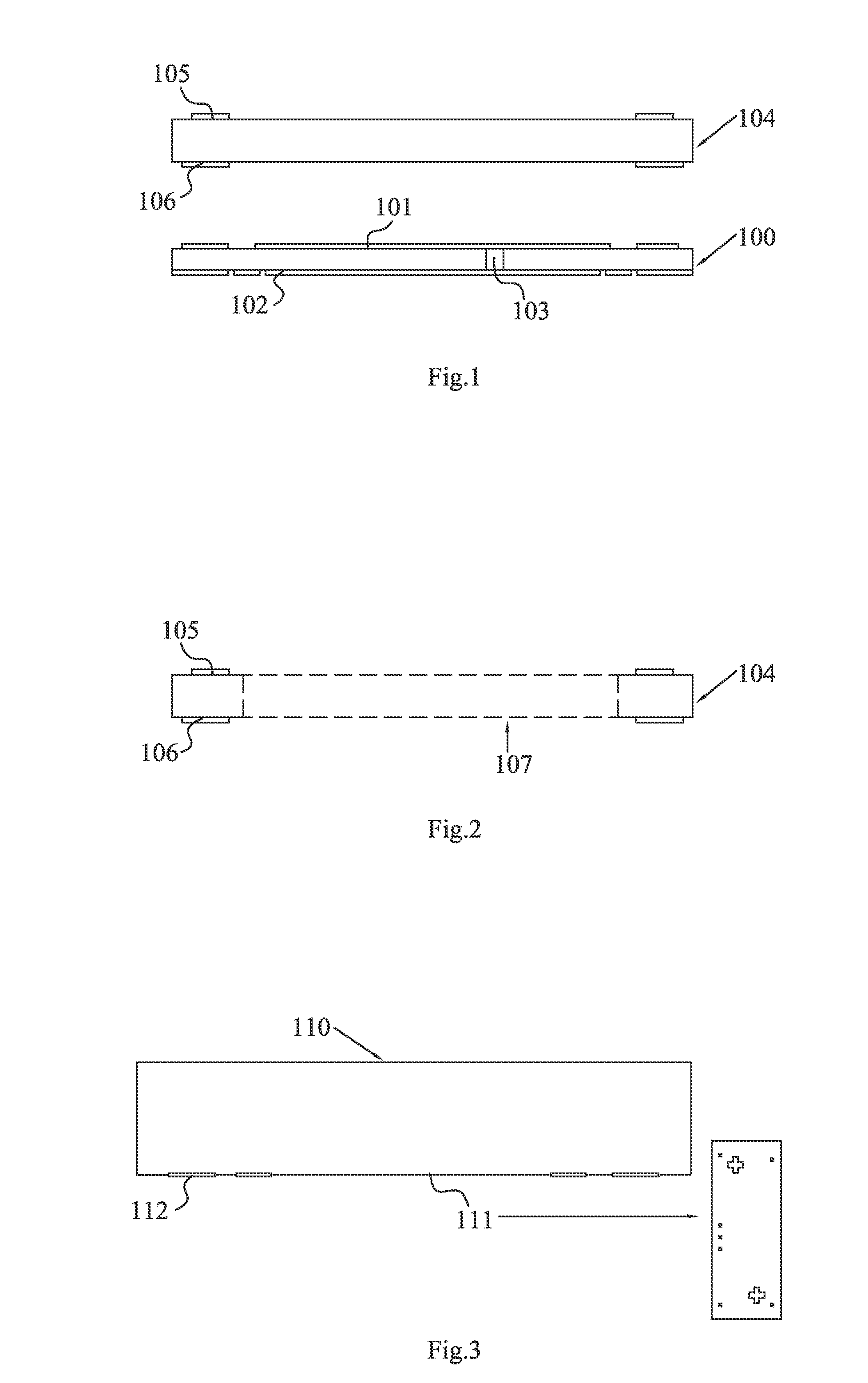

Chip package and fabrication method thereof

ActiveUS20110084382A1Semiconductor/solid-state device detailsSolid-state devicesFilling materialsRedistribution layer

A chip package is disclosed. The package includes a carrier substrate and at least two semiconductor chips thereon. Each semiconductor chip includes a plurality of conductive pads. A position structure is disposed on the carrier substrate to fix locations of the semiconductor chips at the carrier substrate. A fill material layer is formed on the carrier substrate, covers the semiconductor chips and the position structure, and has a plurality of openings correspondingly exposing the conductive pads. A redistribution layer (RDL) is disposed on the fill material layer and is connected to the conductive pads through the plurality of openings. A protective layer covers the fill material layer and the RDL. A plurality of conductive bumps is disposed on the protective layer and is electrically connected to the RDL. A fabrication method of the chip package is also disclosed.

Owner:XINTEC INC

Semiconductor devices and fabrication methods thereof

ActiveUS7843052B1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerSolder ball

Semiconductor devices are disclosed. In an embodiment, a plurality of second semiconductor dies formed with through-silicon vias are stacked on a first semiconductor die. The stack of the second semiconductor dies is encapsulated by an encapsulant. Redistribution layers are formed on one surface of the stack and are connected to the through-silicon vias. Solder balls are attached to the respective redistribution layers. In another embodiment, a plurality of second semiconductor dies formed with through-silicon vias are stacked on a first semiconductor die formed with through-silicon vias. Redistribution layers are formed on the back surface of the first semiconductor die. Solder balls are attached to the respective redistribution layers. Further disclosed are methods for fabricating the semiconductor devices.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

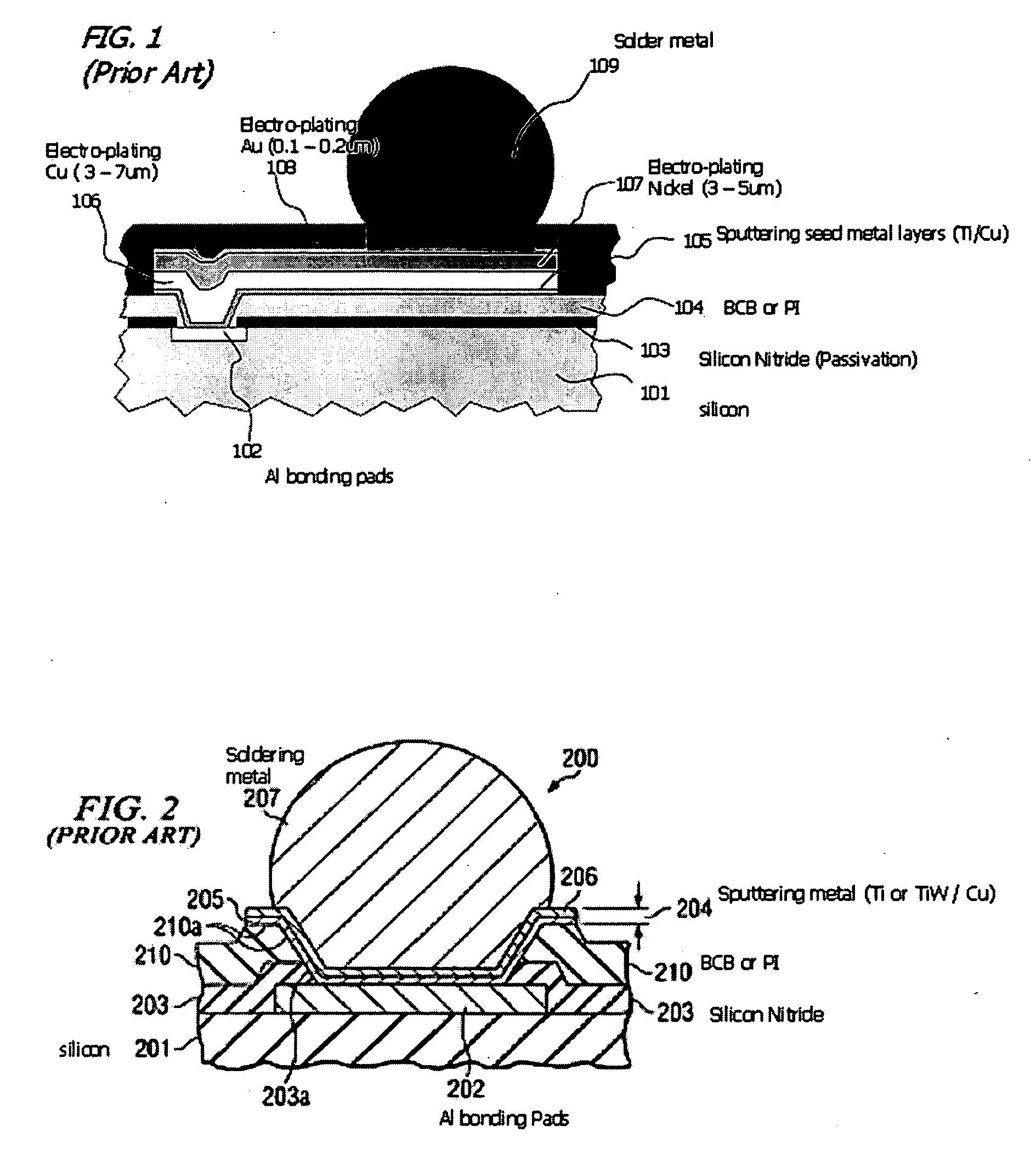

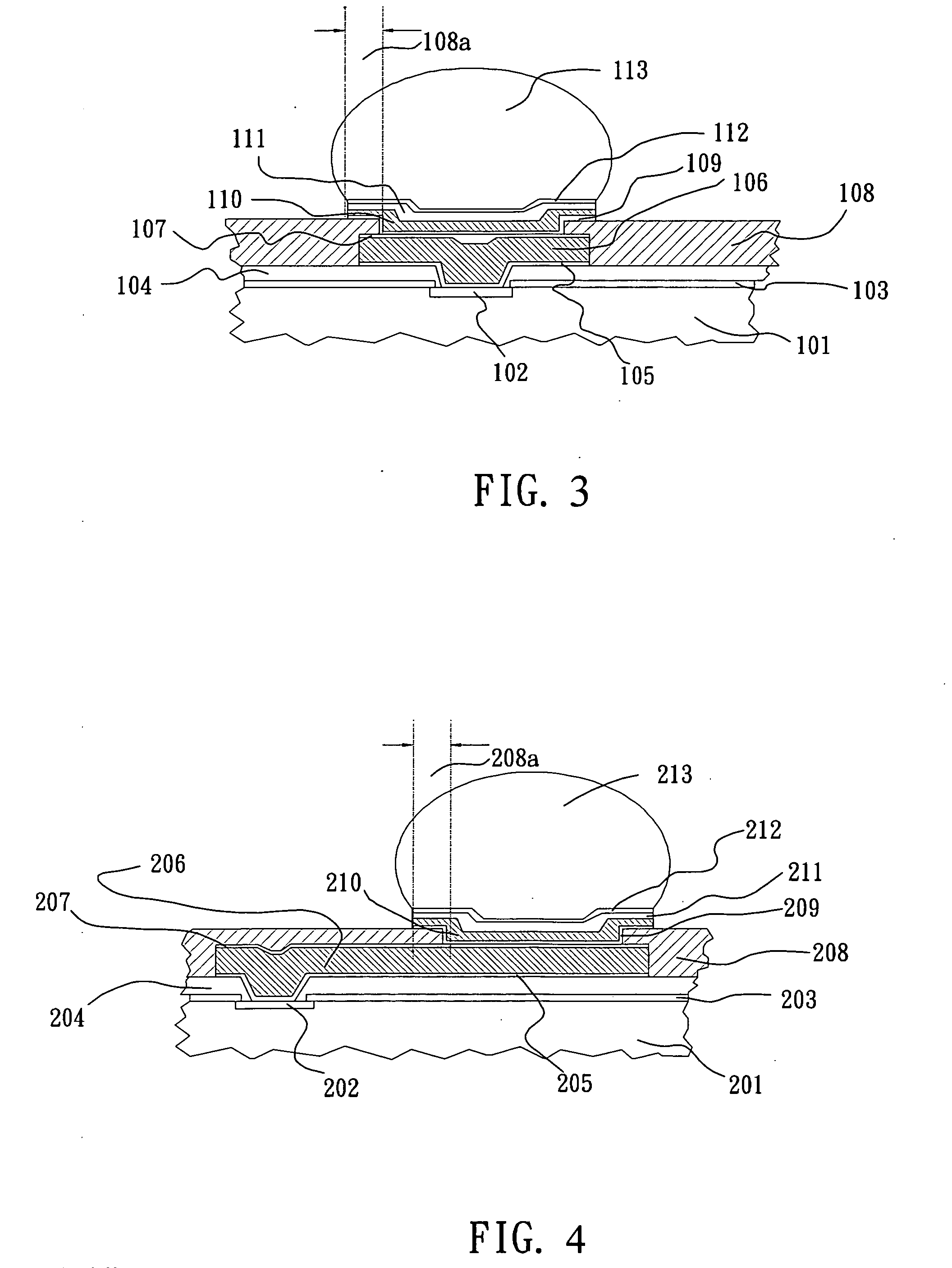

Under bump metallurgy structure of a package and method of making same

InactiveUS20080169539A1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerSolder ball

A package for a semiconductor integrated circuit die comprises a redistributed layer formed over a first barrier layer electrically connected to a bonding pad of a die. A second barrier layer is formed over the redistributed layer. A multi-metal layer is formed over the second barrier layer for coupling to a solder ball, wherein the multi-metal layer has an extending part that extends outside a second opening over the upper of the second dielectric layer to prevent tin infiltration from the solder ball to the redistribution layer.

Owner:ADVANCED CHIP ENG TECH +1

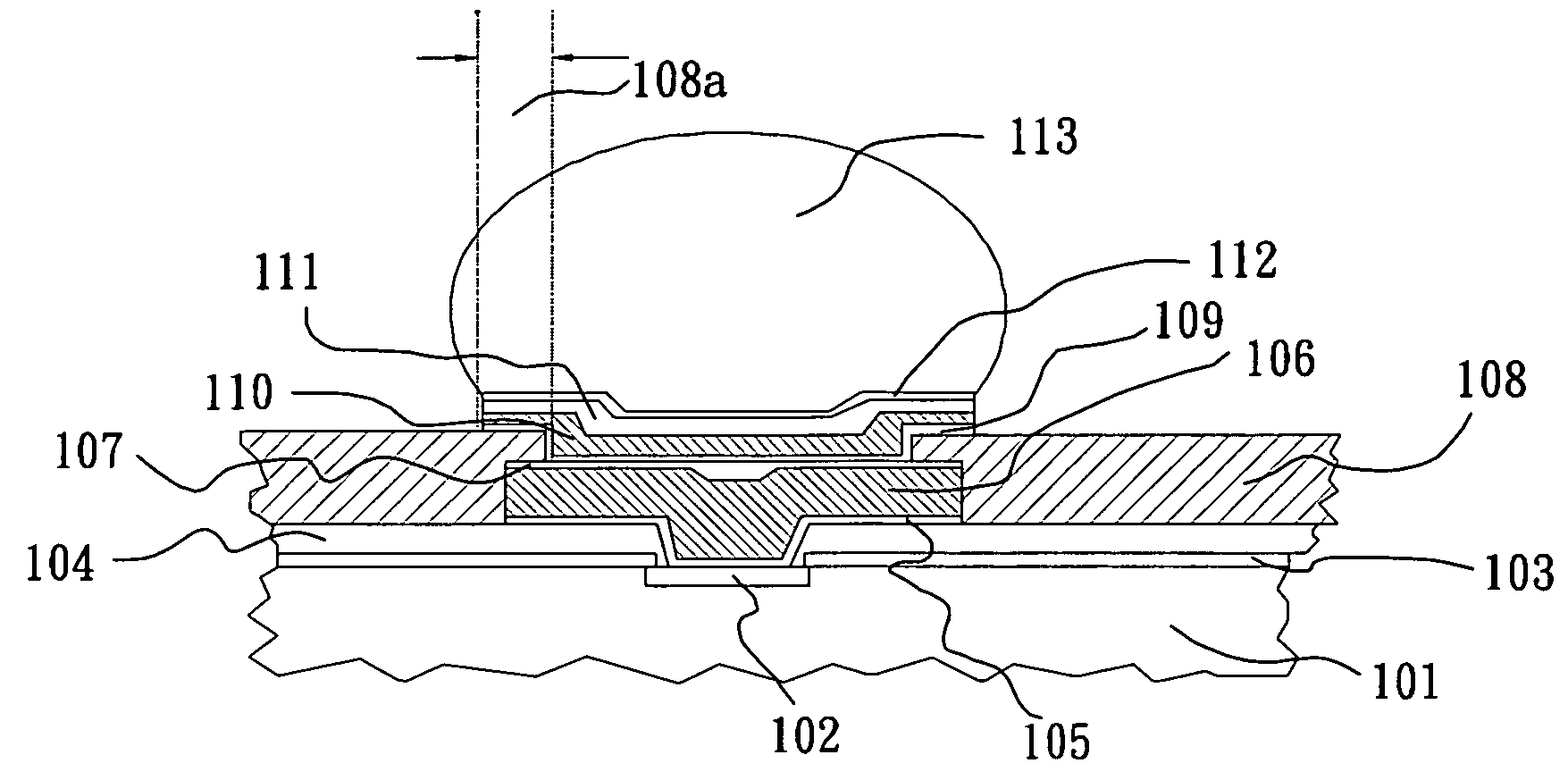

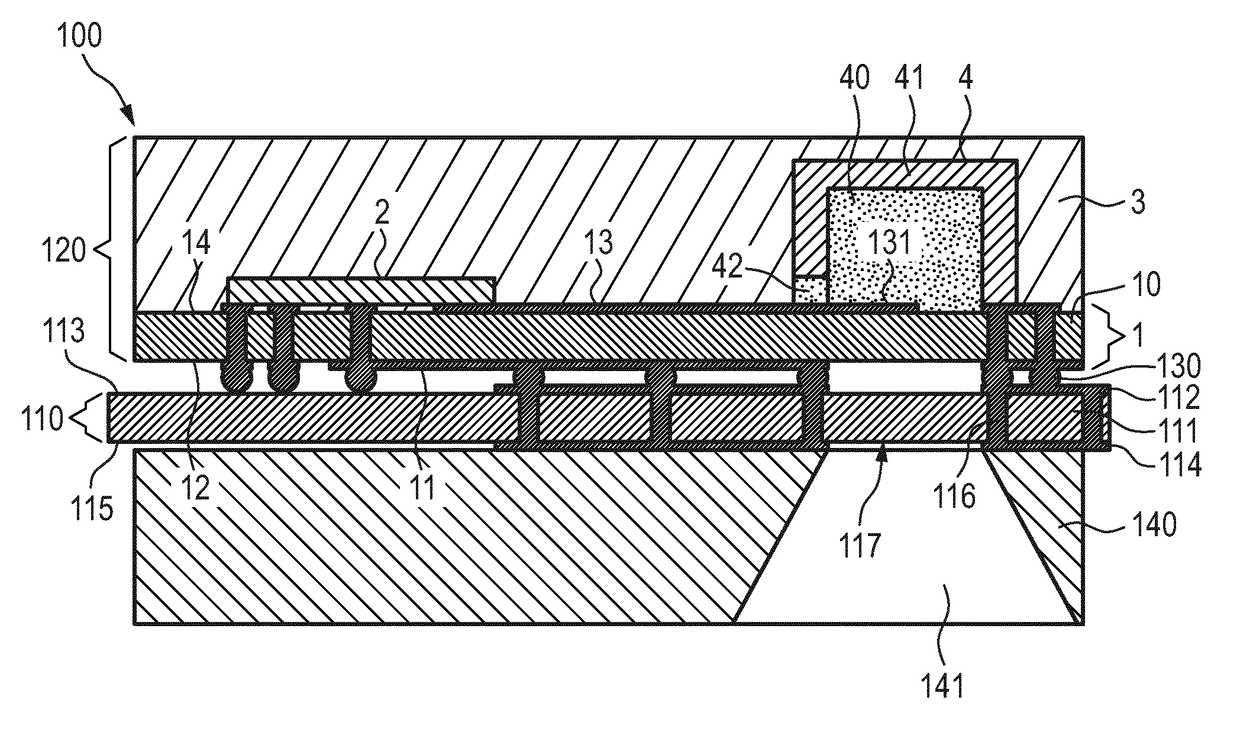

Wafer level optical sensor package and low profile camera module, and method of manufacture

The invention provides a wafer lever optical sensor package and low profile camera module and a method of manufacture. The wafer-level camera sensor package includes a semiconductor substrate with an optical sensor on a front surface. Through-silicon-vias (TSV) extend through the substrate and provide I / O contact with the sensor from the back side of the substrate. A glass cover is positioned over the front surface, and the cover and substrate are embedded in a molding compound layer (MCL), the front surface of the MCL lying coplanar with the front of the cover, and the back surface lying coplanar with the back of the substrate. Surface-mount devices, electromagnetic shielding, and through-wafer-connectors can be embedded in the MCL. A redistribution layer on the back surface of the MCL includes bottom contact pads for mounting the package, and conductive traces interconnecting the contact pads, TSVs, surface-mount devices, shielding, and through-wafer-connectors. Anisotropic conductive adhesive is positioned on the front of the MCL for physically and electrically attaching a lens array.

Owner:STMICROELECTRONICS SRL

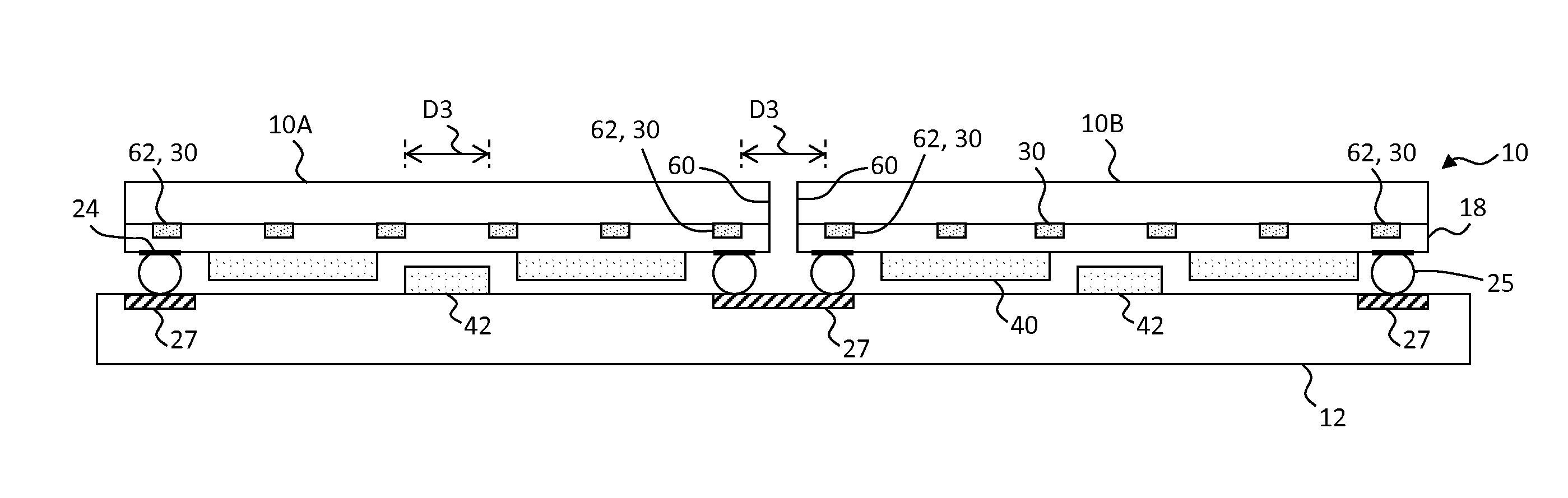

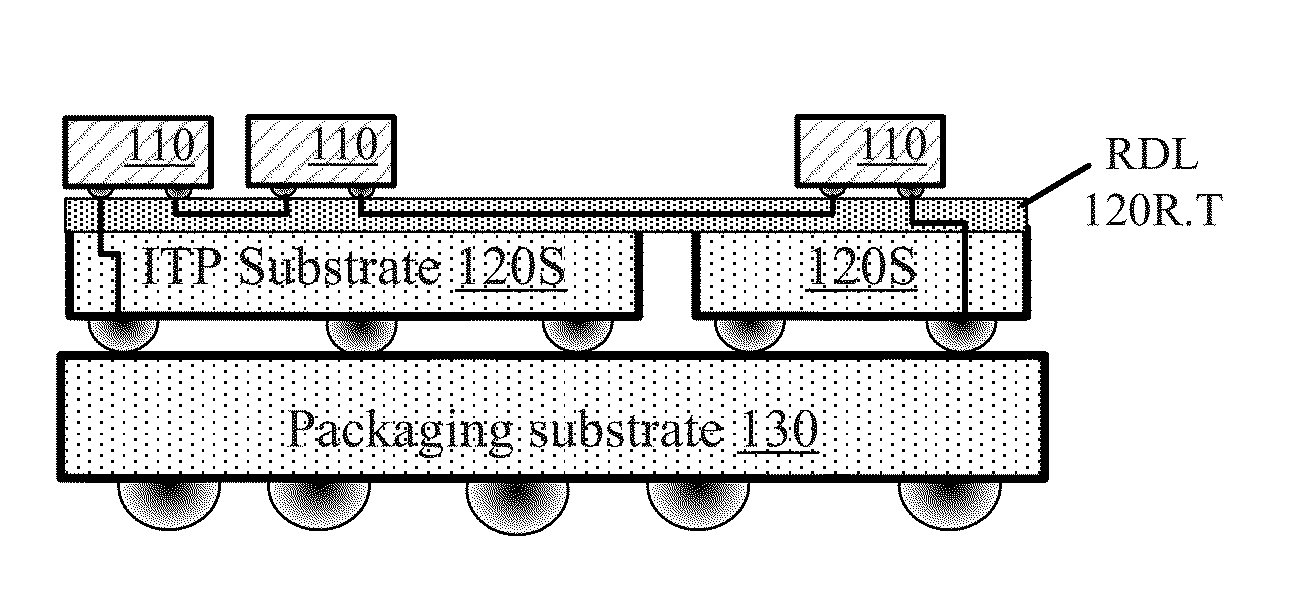

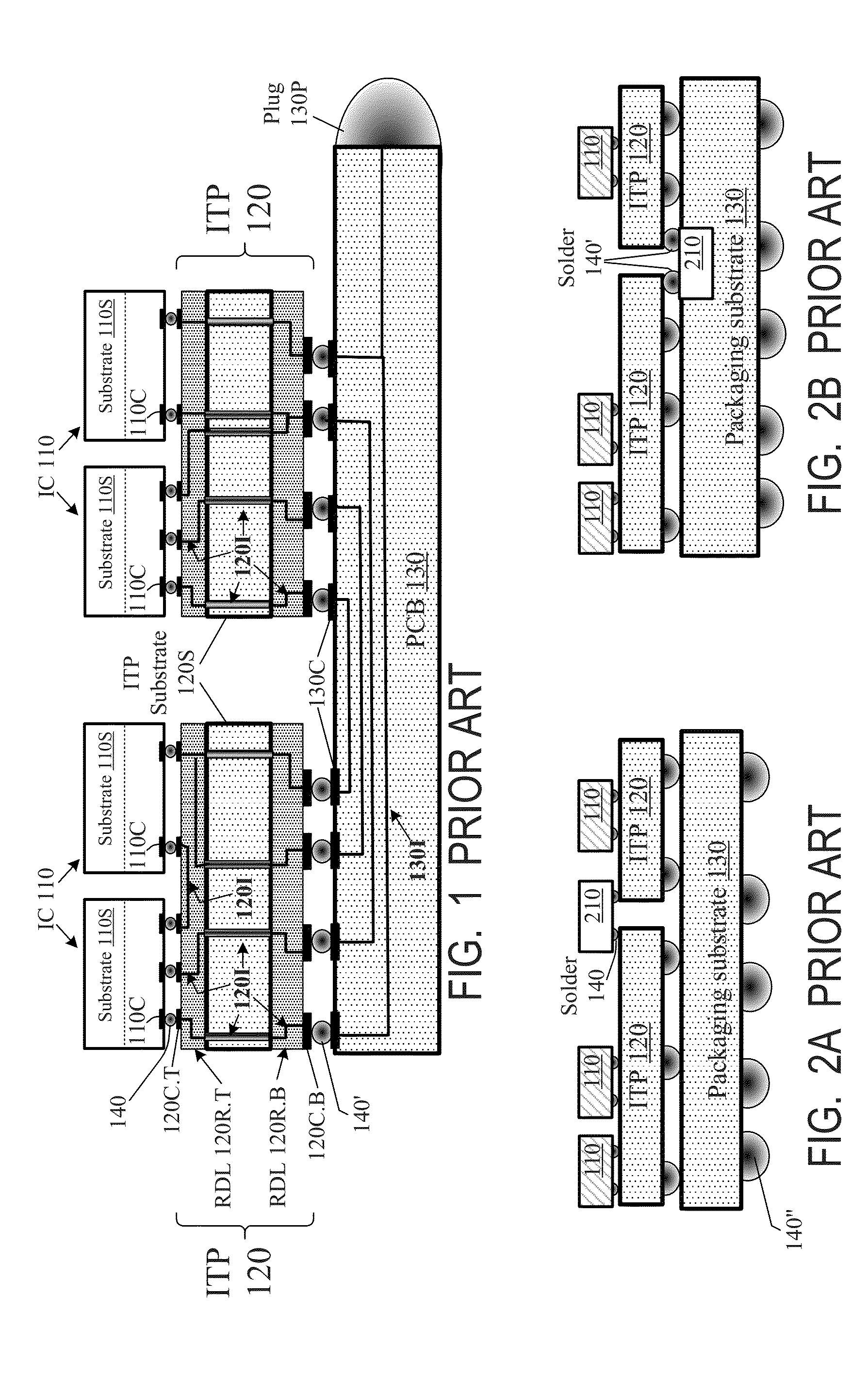

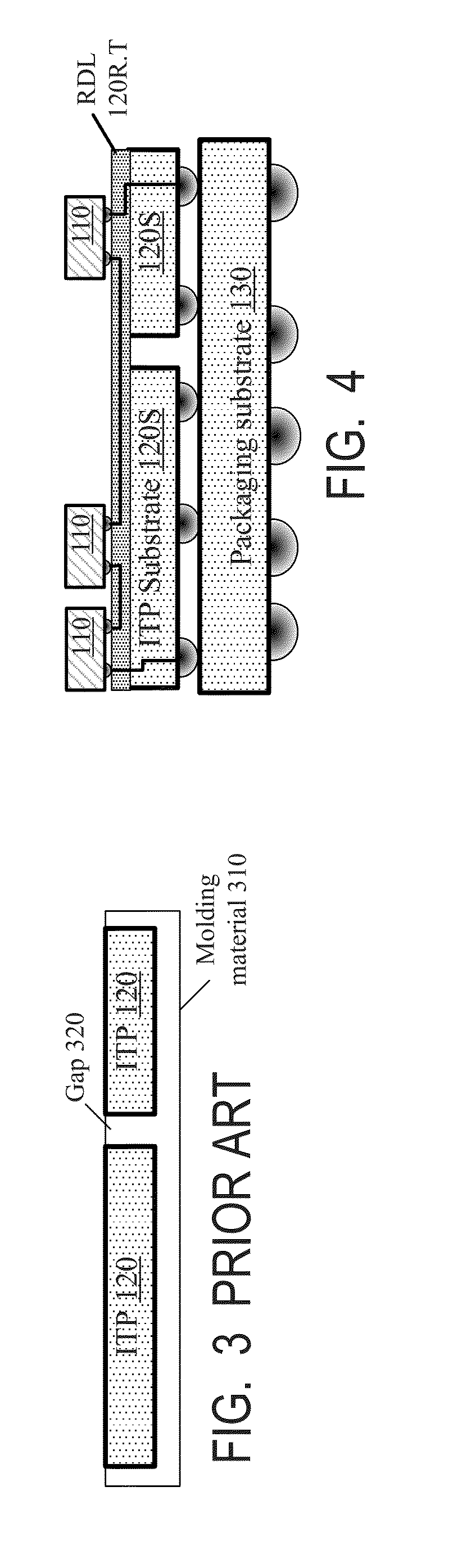

Circuit assemblies with multiple interposer substrates, and methods of fabrication

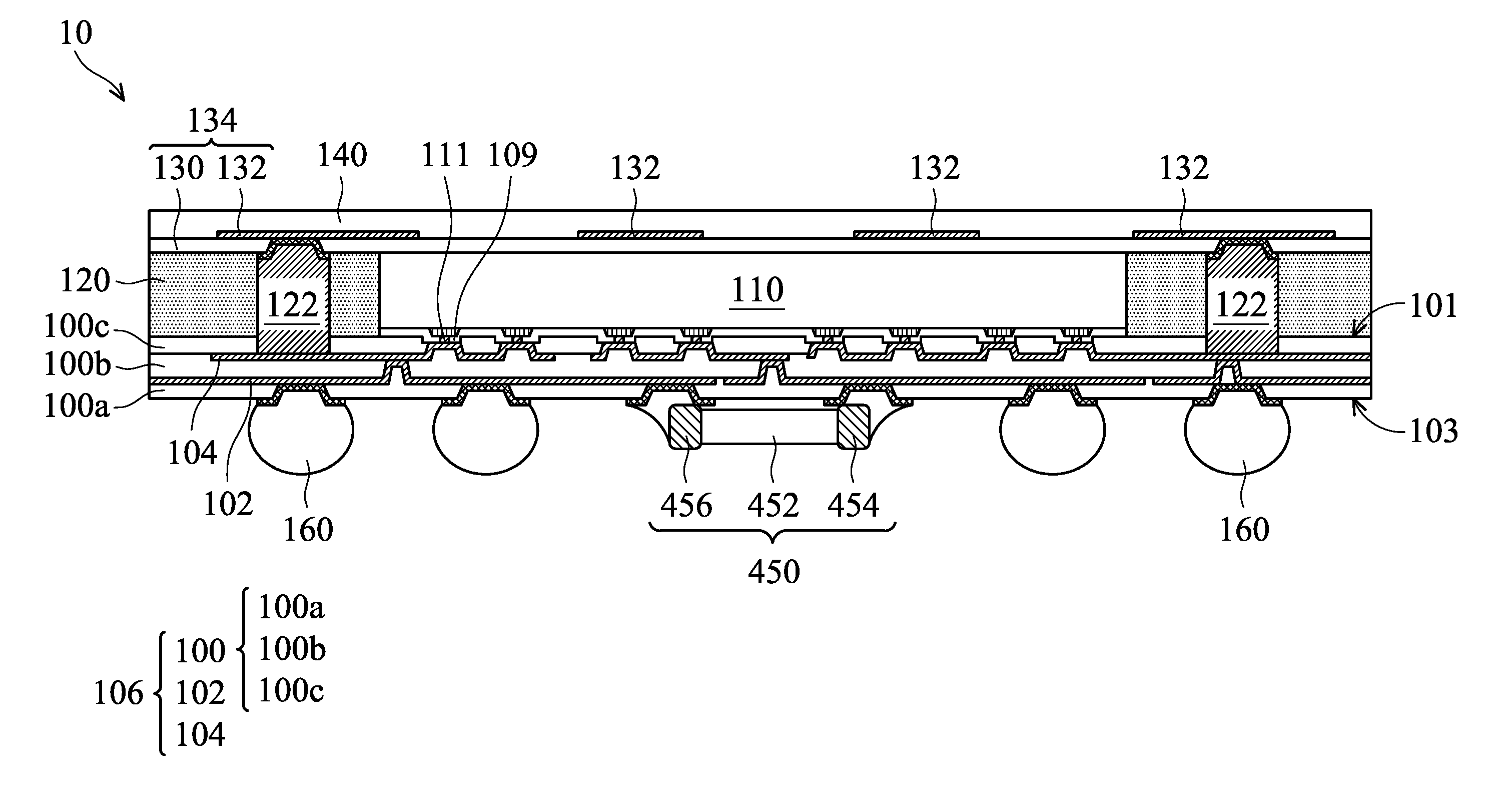

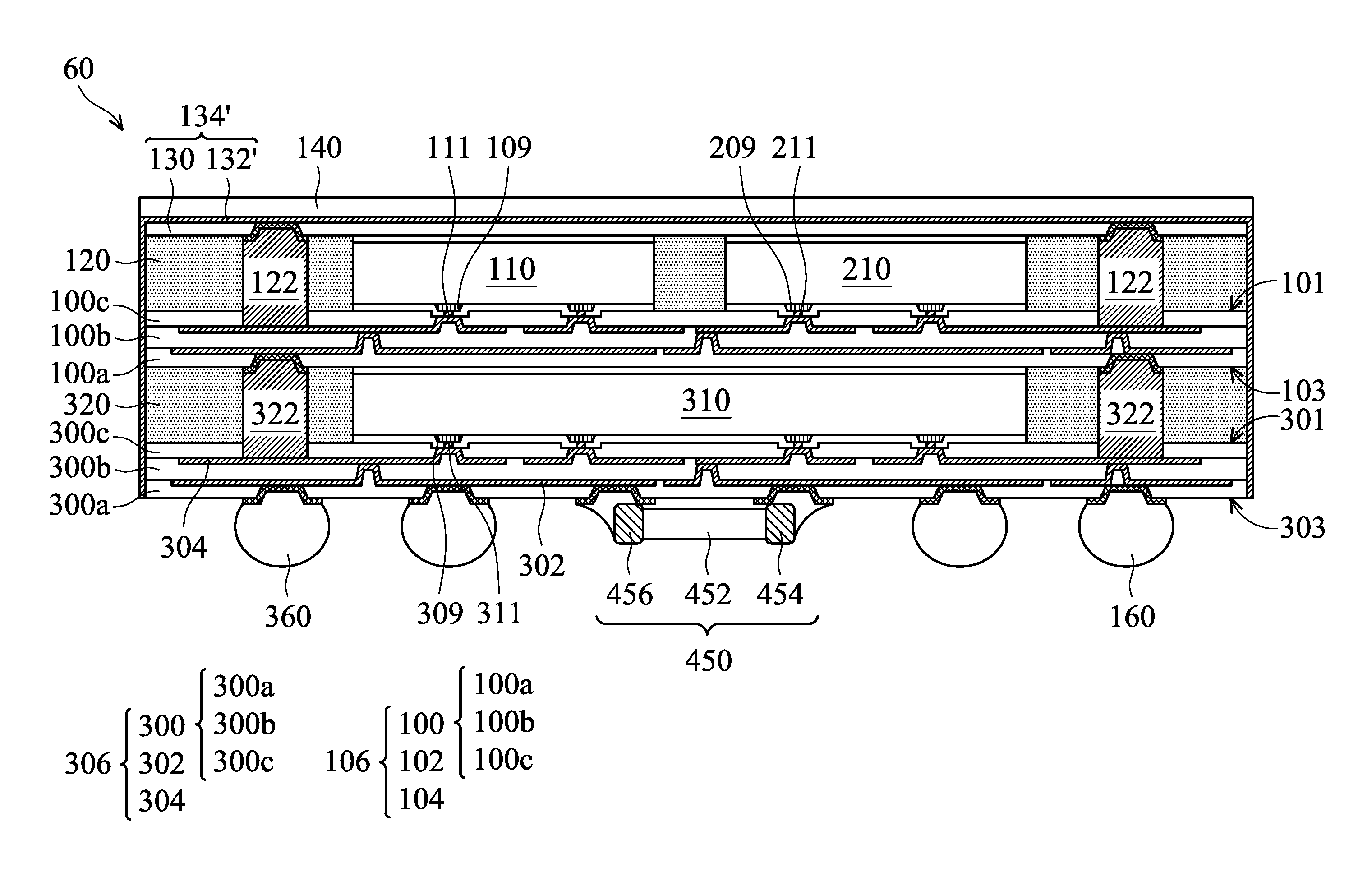

ActiveUS20150327367A1High strengthImproves heat dissipation propertySemiconductor/solid-state device detailsSolid-state devicesRedistribution layerInterposer

A combined interposer (120) includes multiple constituent interposers (120.i), each with its own substrate (120.iS) and with a circuit layer (e.g. redistribution layer) on top and / or bottom of the substrate. The top circuit layers can be part of a common circuit layer (120R.T) which can interconnect different interposers. Likewise, the bottom circuit layers can be part of a common circuit layer (120R.B). The constituent interposer substrates (120.iS) are initially part of a common wafer, and the common top circuit layer is fabricated before separation of the constituent interposer substrates from the wafer. Use of separated substrates reduces stress compared to use of a single large substrate. Other features are also provided.

Owner:INVENSAS CORP

Fan out wafer level package using silicon bridge

InactiveUS20150364422A1Semiconductor/solid-state device detailsSolid-state devicesRedistribution layerEngineering

A semiconductor device package includes a logic die coupled to a memory die in a side-by-side configuration on a redistribution layer (e.g., the logic die and the memory die are substantially adjacent). A silicon bridge may be used to interconnect the logic die and the memory die. The silicon bridge may be positioned between the die and the redistribution layer. The silicon bridge and the redistribution layer may be coupled to the lower (active) surfaces of the logic die and the memory die. The package may be formed using a wafer level process that forms a plurality of packages simultaneously.

Owner:APPLE INC

Microwave antenna apparatus, packing and manufacturing method

ActiveUS20170324135A1Relatively large bandwidthImproved radiation patternWaveguide hornsSolid-state devicesRedistribution layerMicrowave

A microwave antenna apparatus includes: a redistribution layer including a carrier layer, a ground plane arranged on a first or second surface of the carrier layer, and a microstrip line arranged on the other one of the first or second surface of the carrier layer; a semiconductor element mounted on the first surface of the carrier layer and coupled to the ground plane and the microstrip line; a mold layer that covers the semiconductor element and the first surface of the carrier layer; and a waveguide arranged within the mold layer and on the first surface of the carrier layer and coupled to the semiconductor element by the microstrip line, wherein a solid state filling material is arranged within the waveguide. Further, integrated antennas and transitions are presented within eWLB packages.

Owner:SONY CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com