Fan-out package structure including antenna

a technology of semiconductor package and antenna, which is applied in the direction of semiconductor device details, semiconductor/solid-state devices, electrical devices, etc., can solve the problems of poor smt process control, delamination between the antenna component and the underlying package, and the difficulty of reducing the package size, etc., to achieve the effect of reducing reliability, yield and throughput of the semiconductor package structur

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030]The following description is of the best-contemplated mode of carrying out the invention. This description is made for the purpose of illustrating the general principles of the invention and should not be taken in a limiting sense. The scope of the invention is determined by reference to the appended claims.

[0031]The present invention will be described with respect to particular embodiments and with reference to certain drawings, but the invention is not limited thereto and is only limited by the claims. The drawings described are only schematic and are non-limiting. In the drawings, the size of some of the elements may be exaggerated for illustrative purposes and not drawn to scale. The dimensions and the relative dimensions do not correspond to actual dimensions in the practice of the invention.

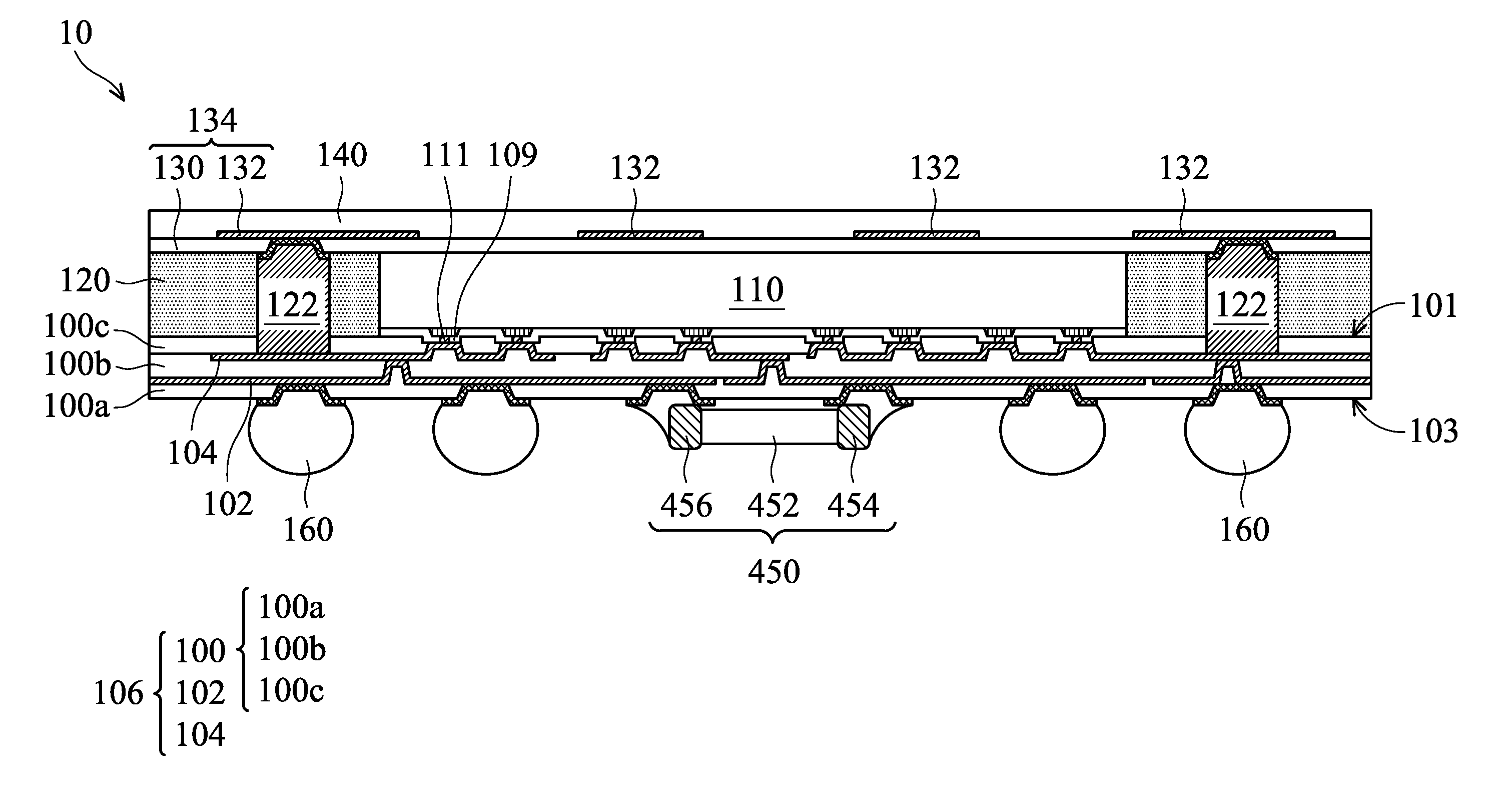

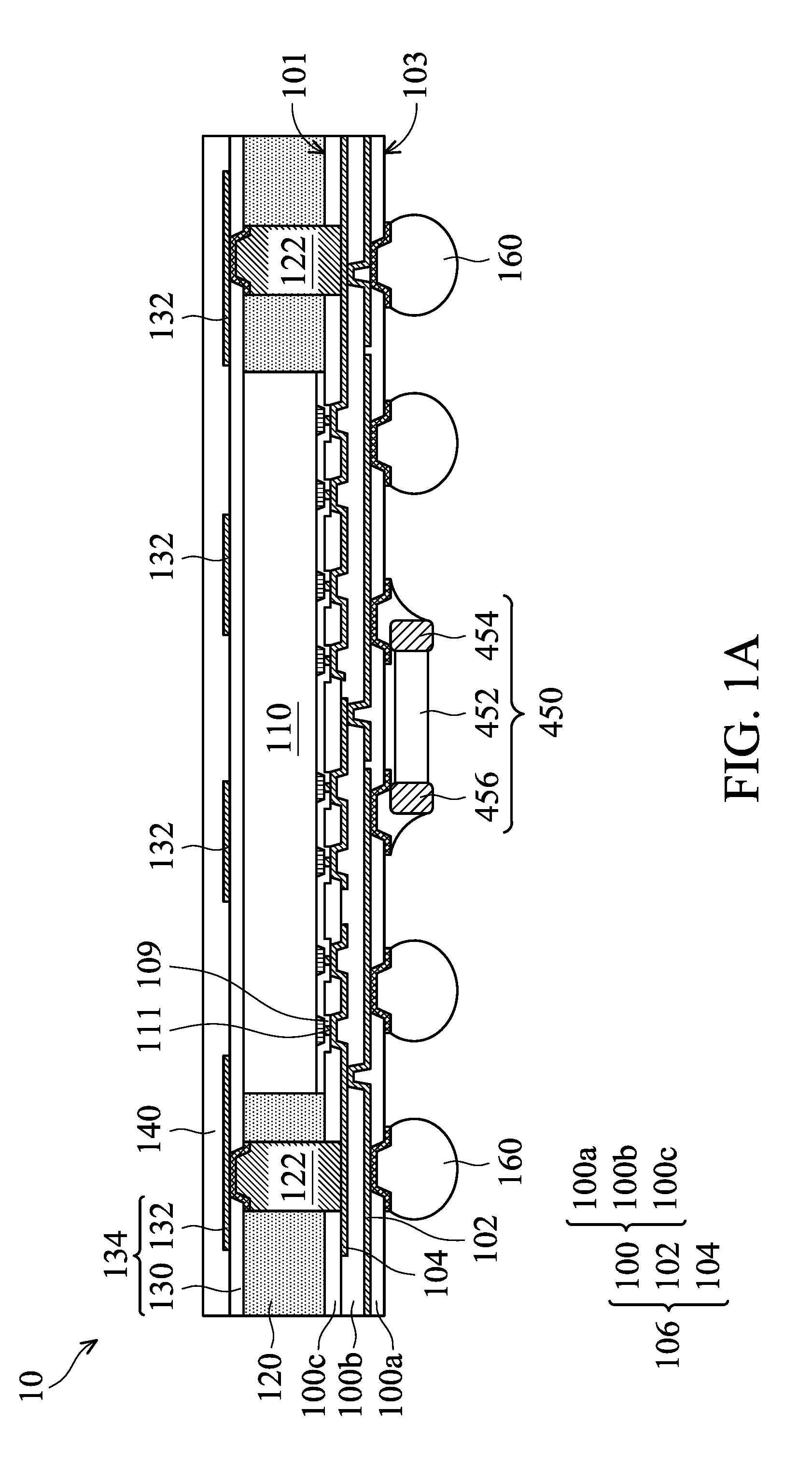

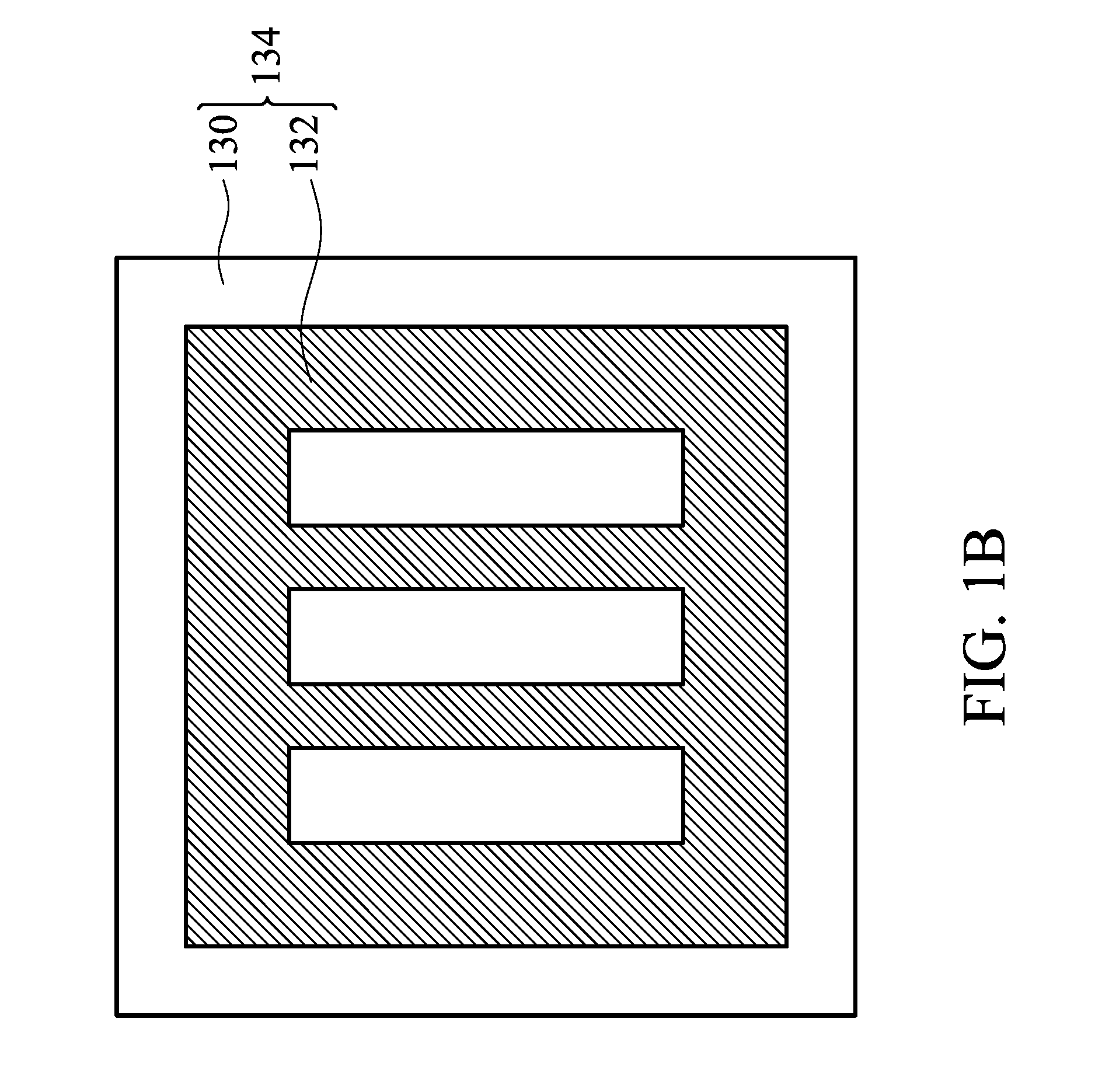

[0032]FIG. 1A is a cross-sectional view of a semiconductor package structure 10 in accordance with some embodiments of the disclosure. FIG. 1B is a plan view of an IMD structure 134 o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com