Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1397 results about "Cell region" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

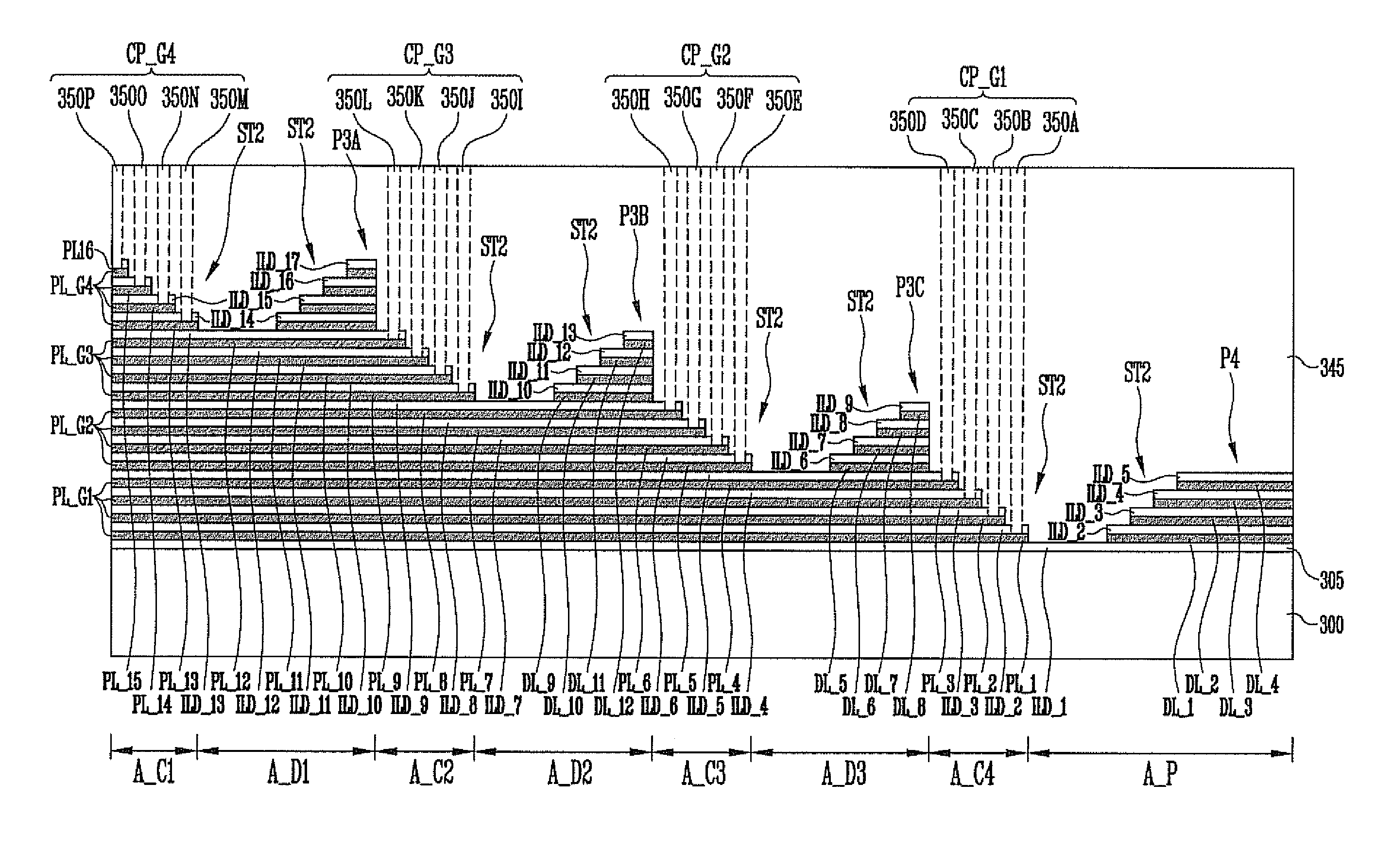

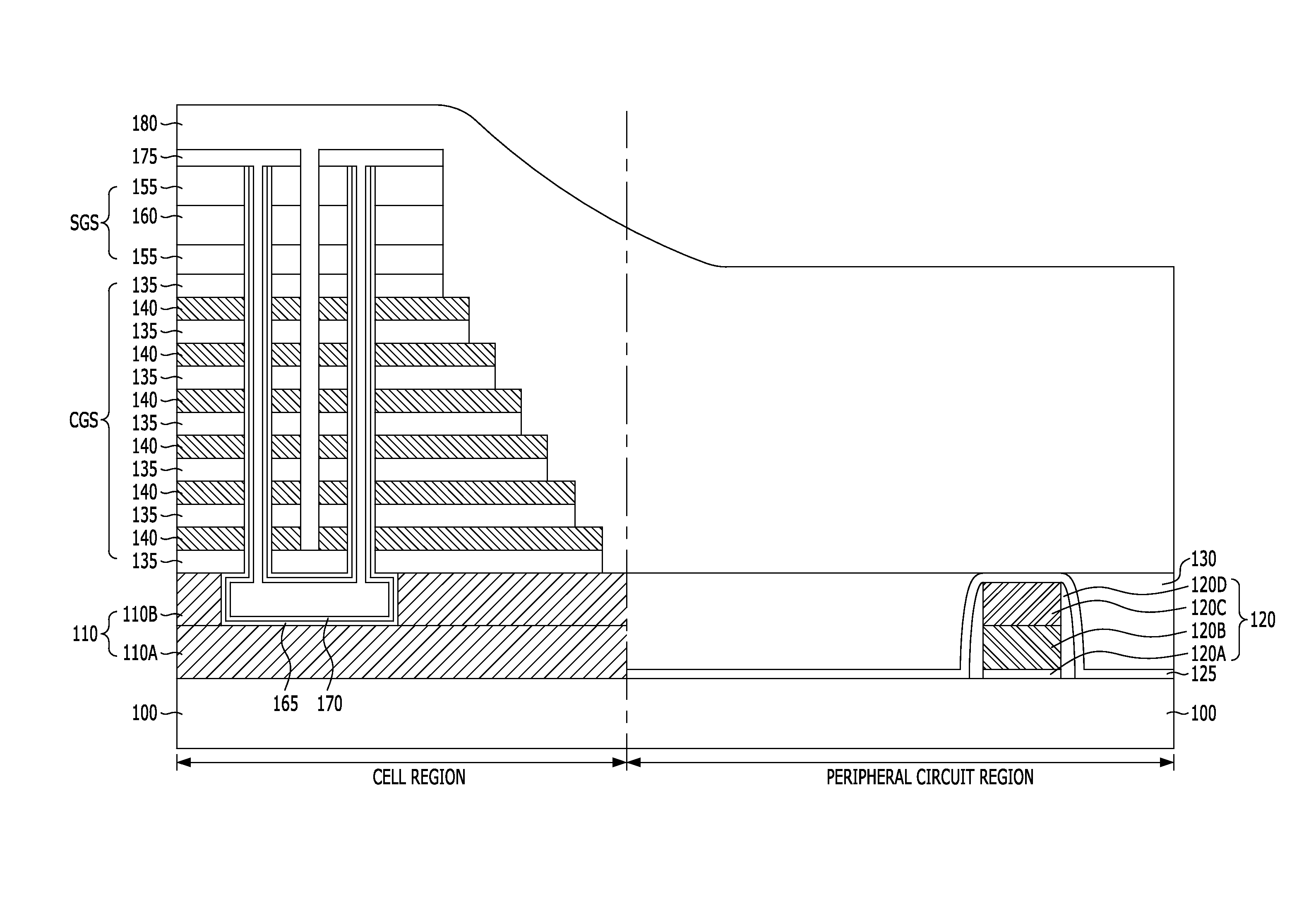

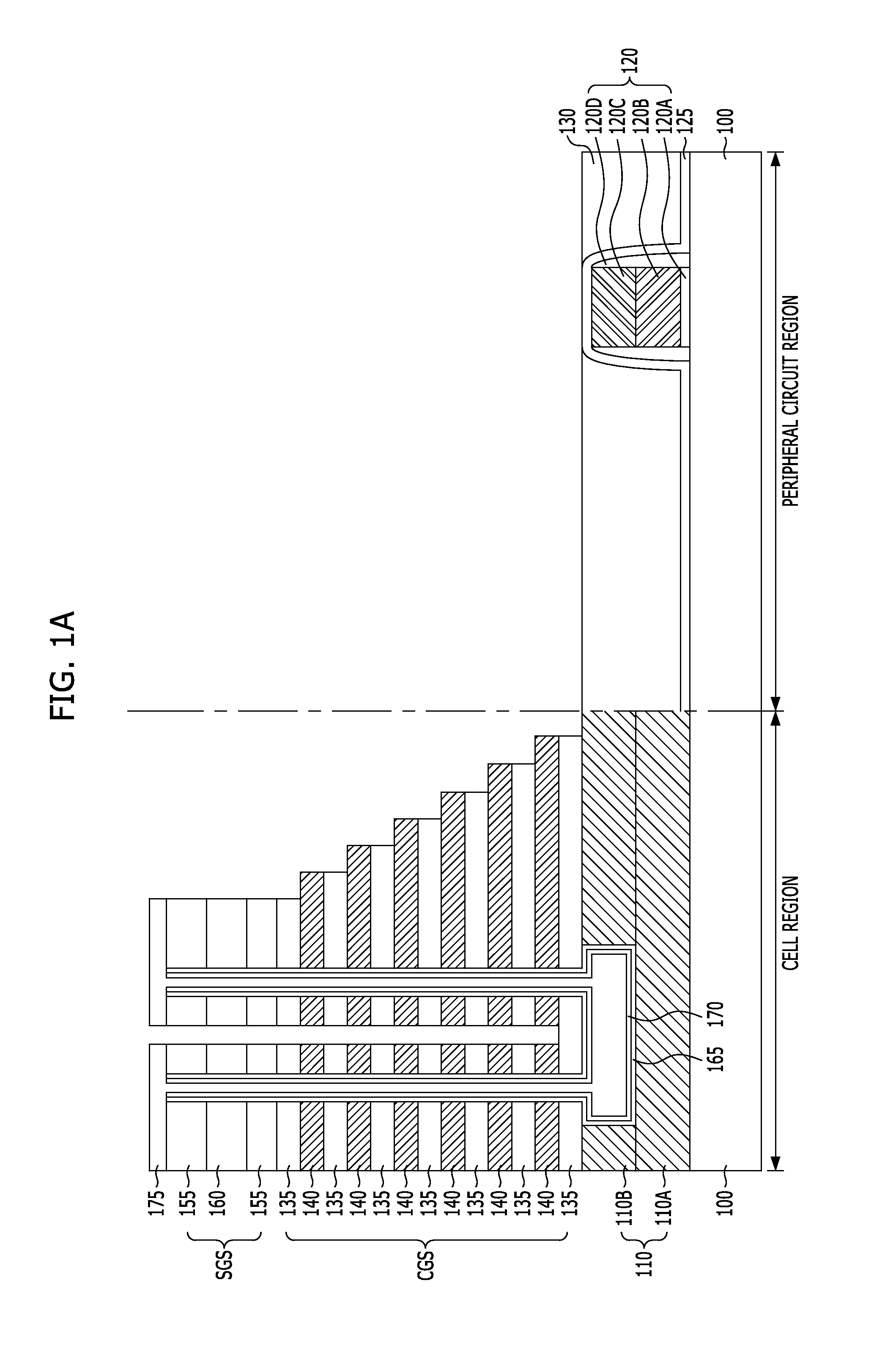

Semiconductor devices having conductive pads and methods of fabricating the same

ActiveUS20150287710A1Improve reliabilitySemiconductor/solid-state device detailsSolid-state devicesDevice materialCell region

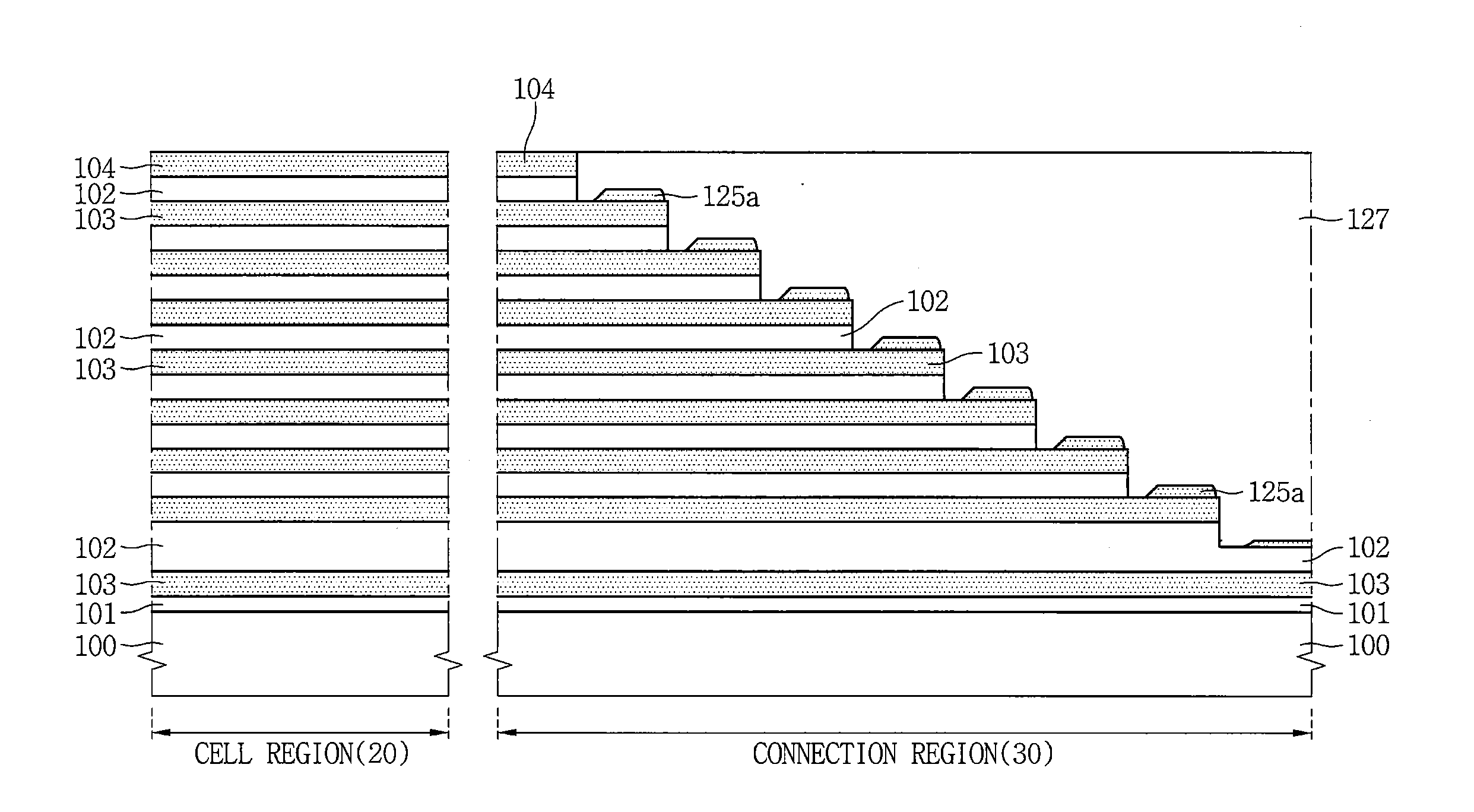

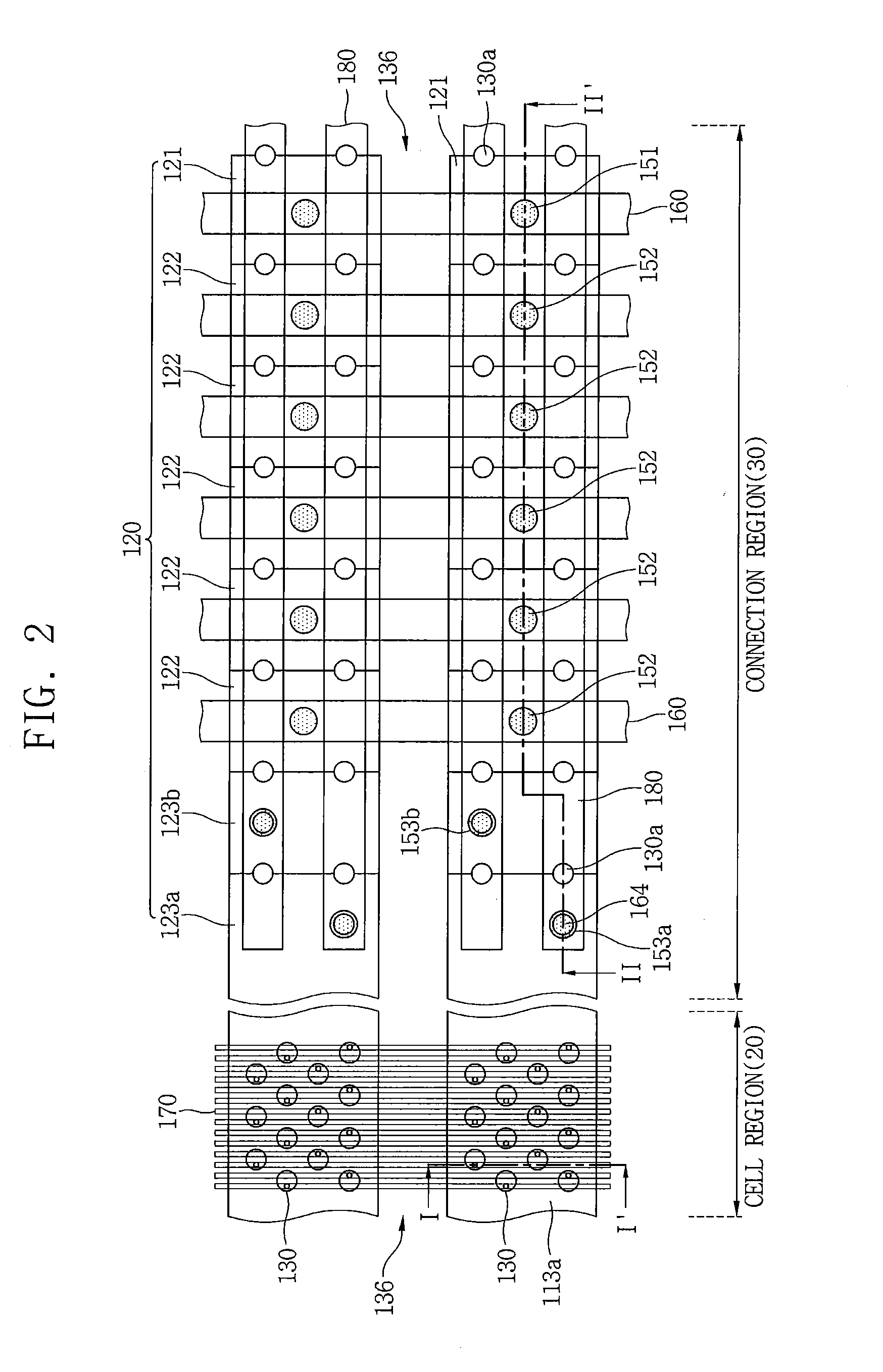

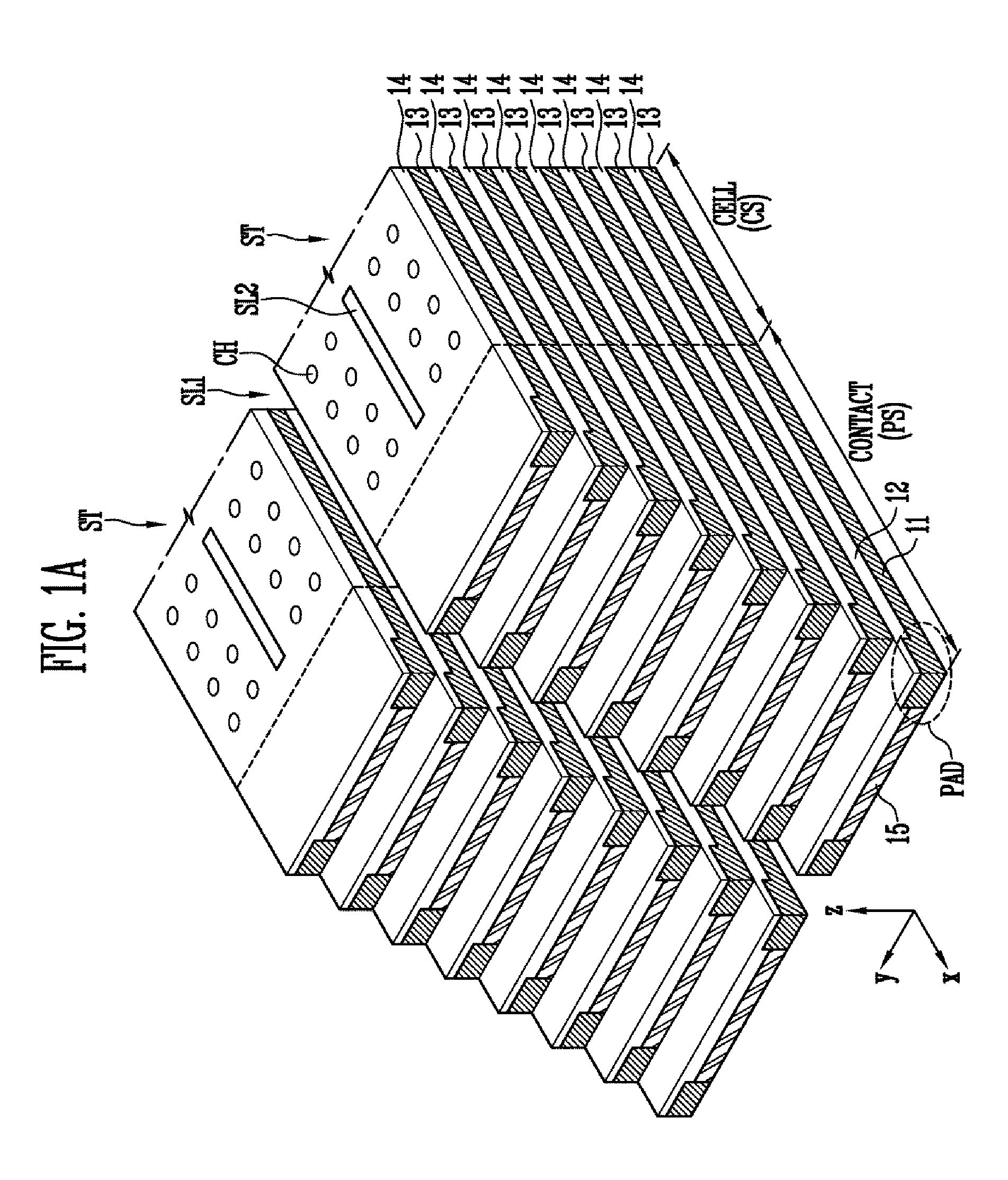

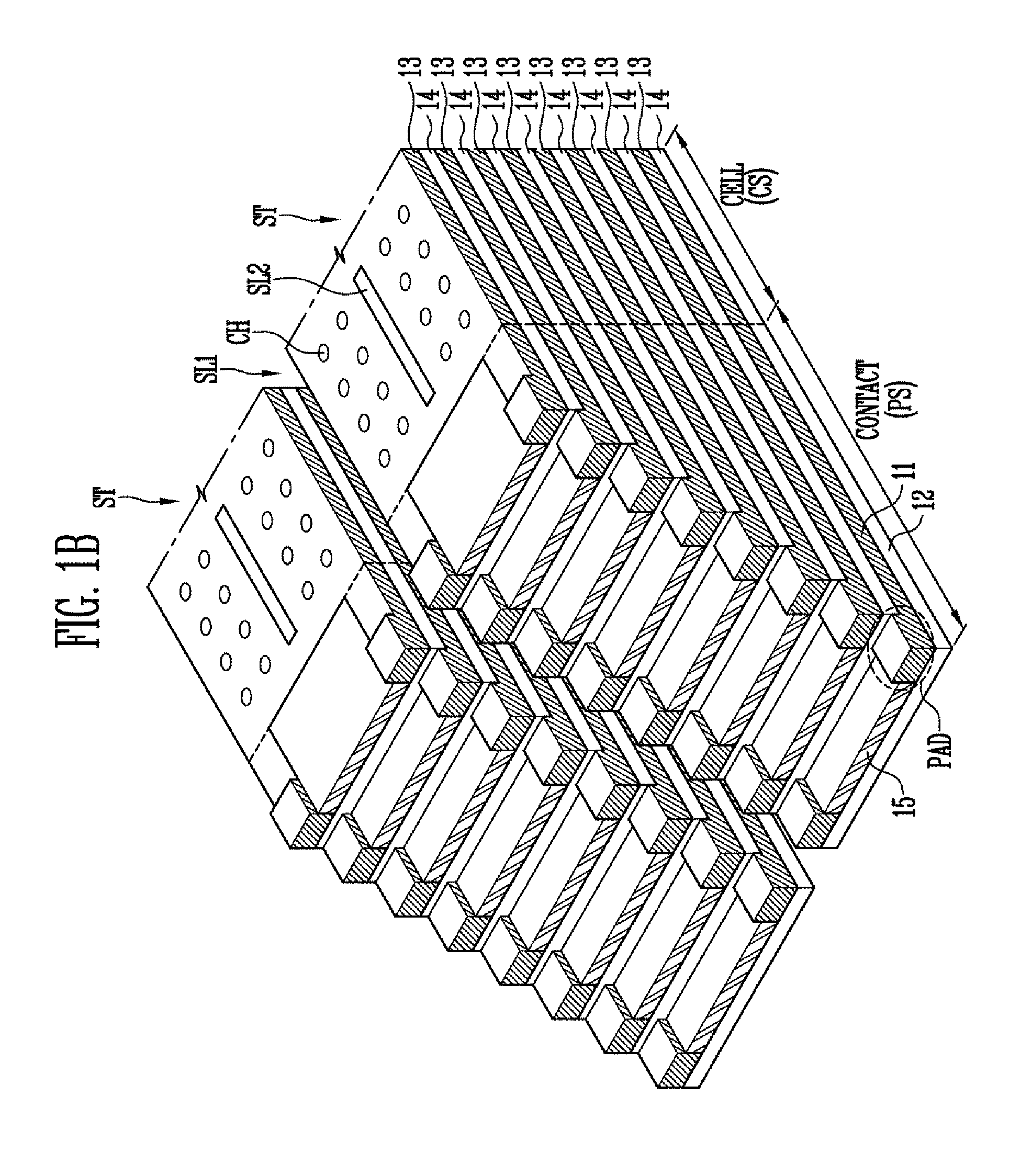

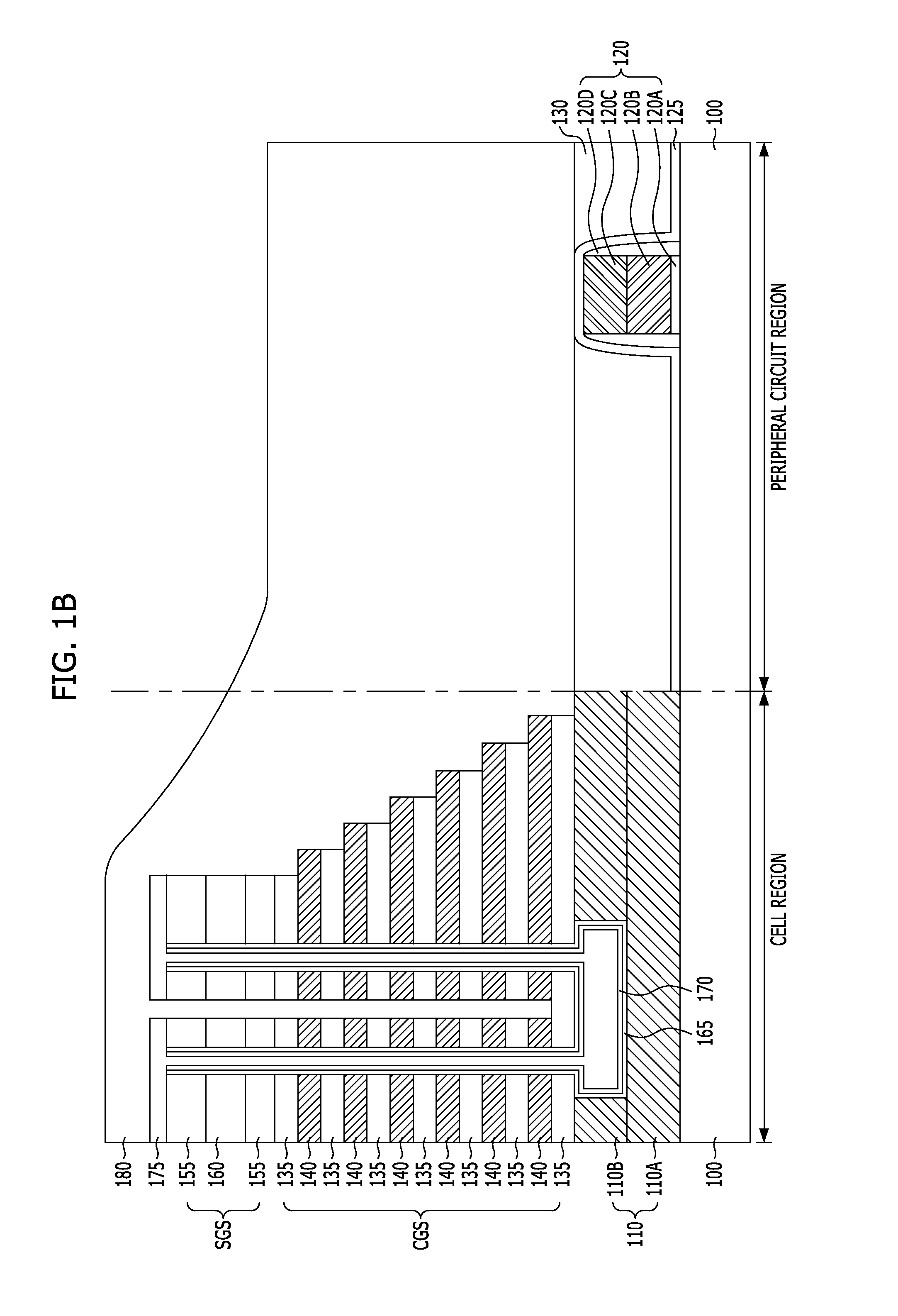

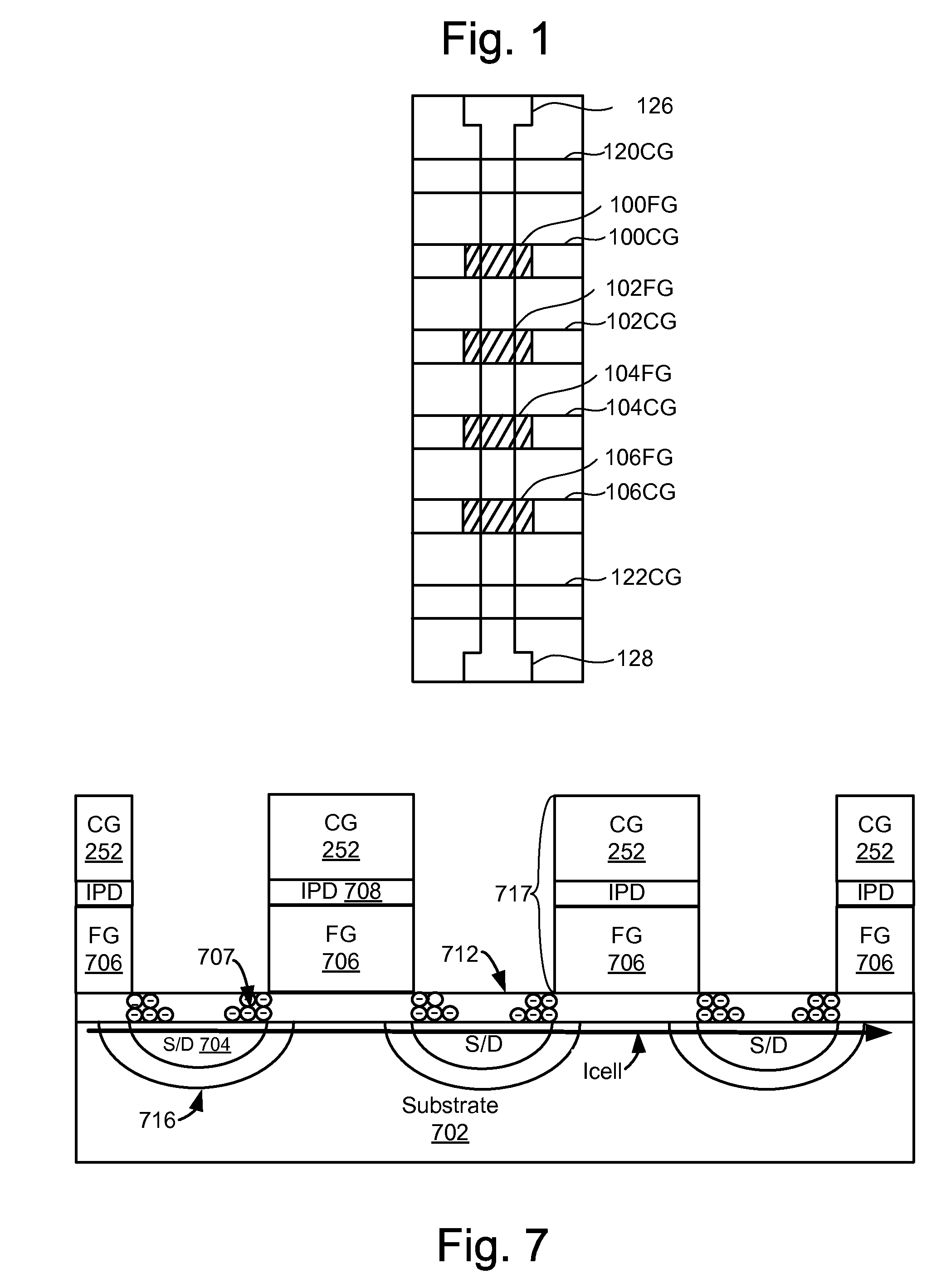

A semiconductor device includes a substrate having a cell region and a connection region. A plurality of gate electrodes is stacked in a vertical direction in the cell region of the substrate. Conductive pads that are electrically connected to a peripheral circuit extend horizontally from the gate electrodes to the connection region. The conductive pads form a cascade structure in the connection region. Contact plugs that have different vertical lengths are electrically connected to respective ones of the conductive pads. The conductive pads have contact portions that are thicker in the vertical direction than the gate electrodes.

Owner:SAMSUNG ELECTRONICS CO LTD

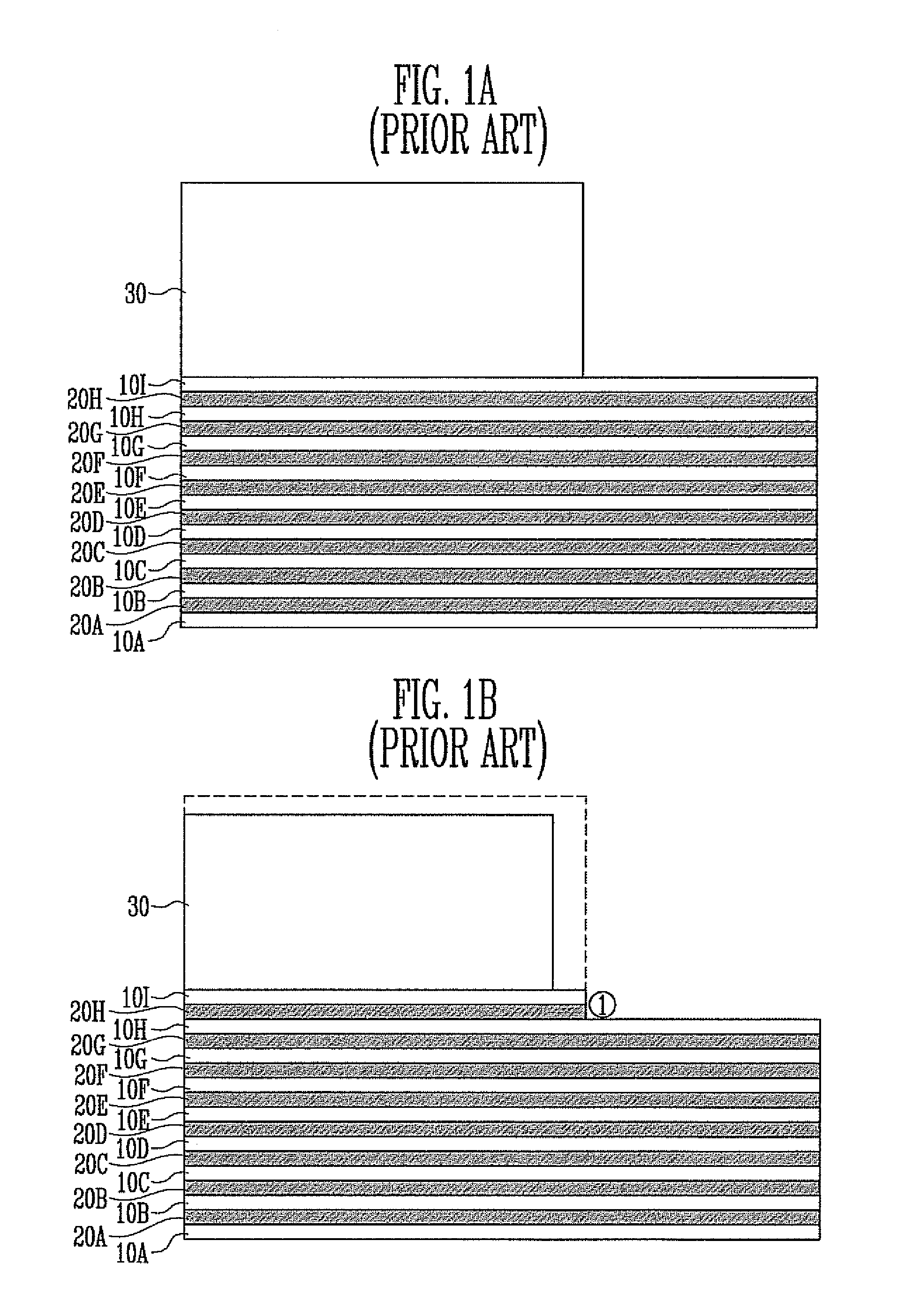

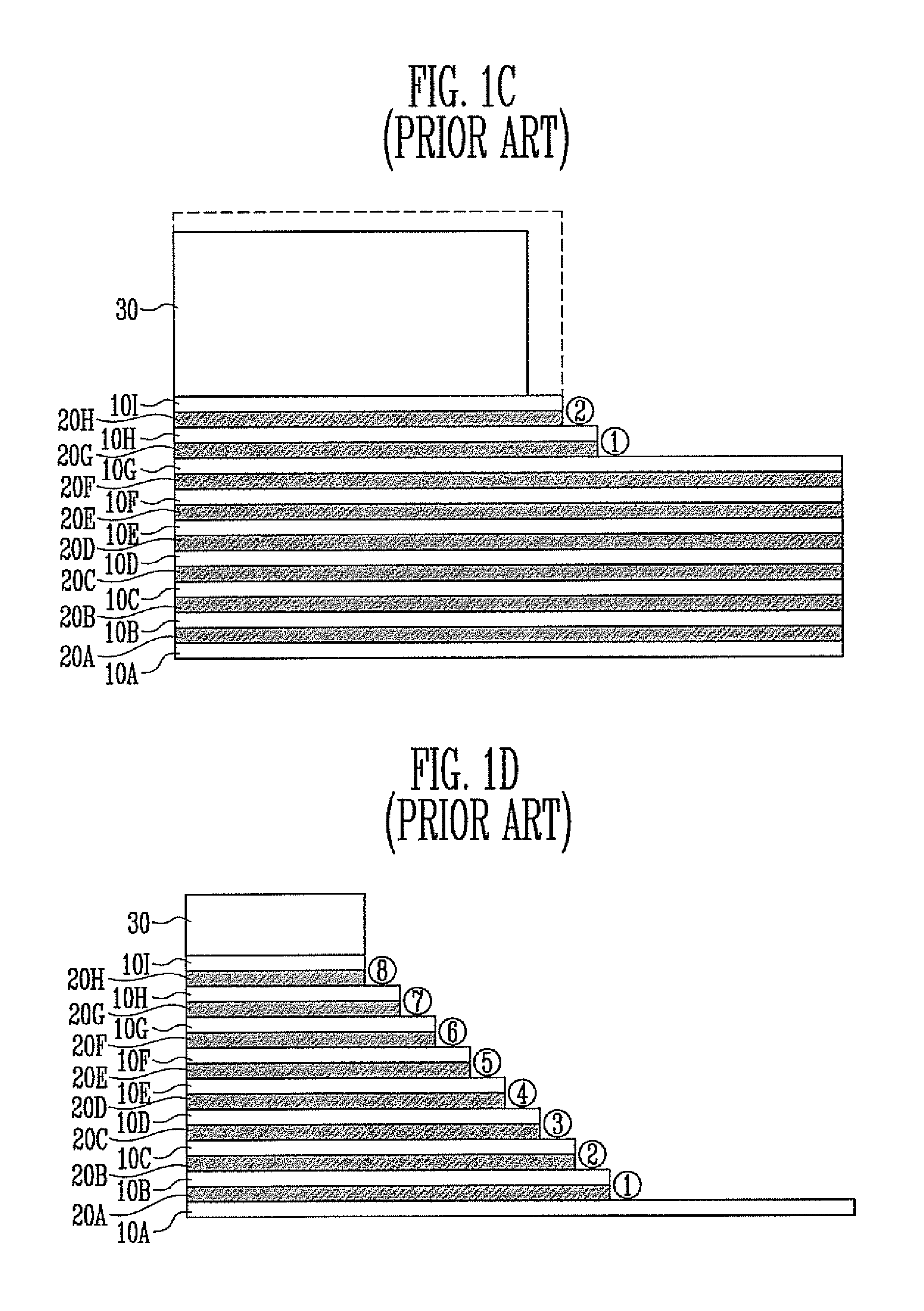

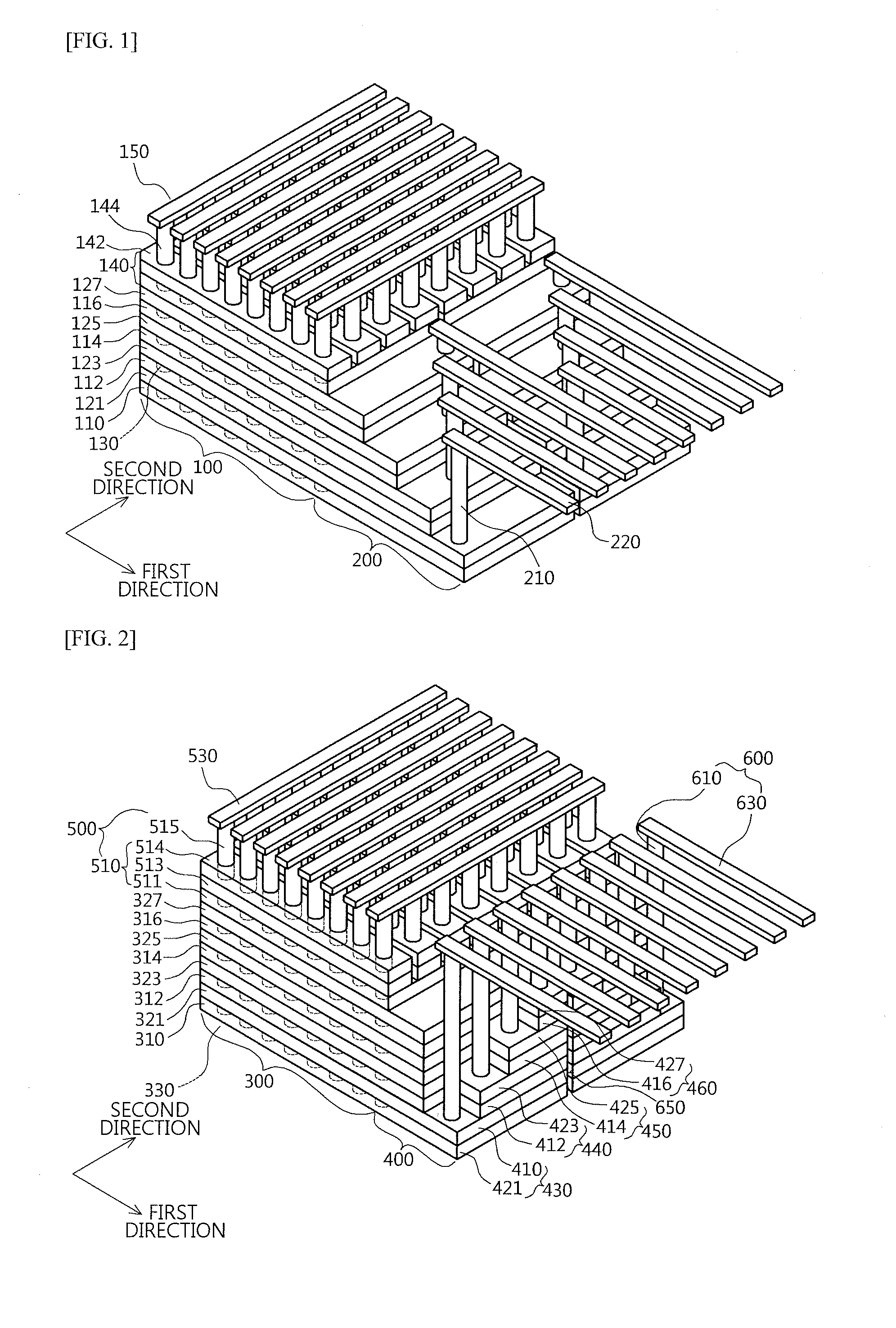

Semiconductor device and method of manufacturing the same

ActiveUS20140191389A1Well formedSemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceCell region

A semiconductor device includes a substrate in which a cell region and a contact region are defined, a pad structure including a plurality of first conductive layers and a plurality of first insulating layers formed alternately with each other in the contact region of the substrate, wherein an end of the pad structure is patterned stepwise, portions of the first conductive layers exposed at the end of the pad structure are defined as a plurality of pad portions, and the plurality of pad portions have a greater thickness than unexposed portions of the plurality of first conductive layers.

Owner:SK HYNIX INC

Method and Apparatus of Transmitting, Receiving, Displaying and Playing Weather Data

ActiveUS20090316671A1Low costReception problemWeather condition predictionWireless commuication servicesData synchronizationTransceiver

A transmitter transmits time synchronized data via a pager / WiMax / 802.x access to a receiver system, wherein the receiver system is programmed to receive data for specific geographic locations. The geographic locations may be specified by the user or by the receiver system, and includes state, zip codes, towns, counties, towns, or cardinal regions. The receiver is able to find its location when outside its cell region and is able to synchronize to the data transmitted in the new cell region. Further, the receiver system is able to remotely monitor weather data and other information at a different location via wireless Internet or voice over IP. A transceiver may also be used to receive weather or alert data. In response to receiving data, the transceiver transmits the data to low powered devices in a house using a different frequency band than the frequency band it received the data.

Owner:LA CROSSE TECH

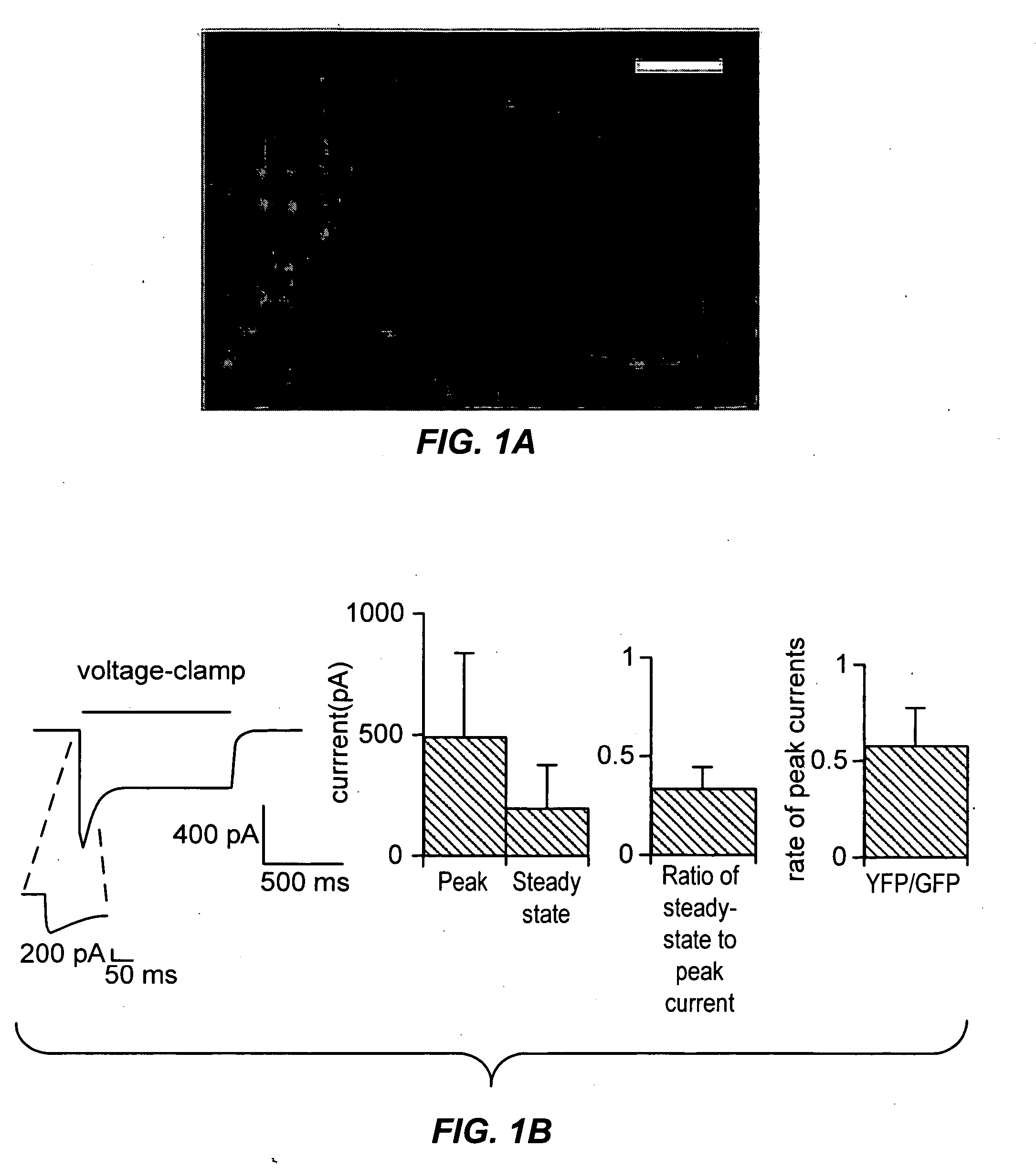

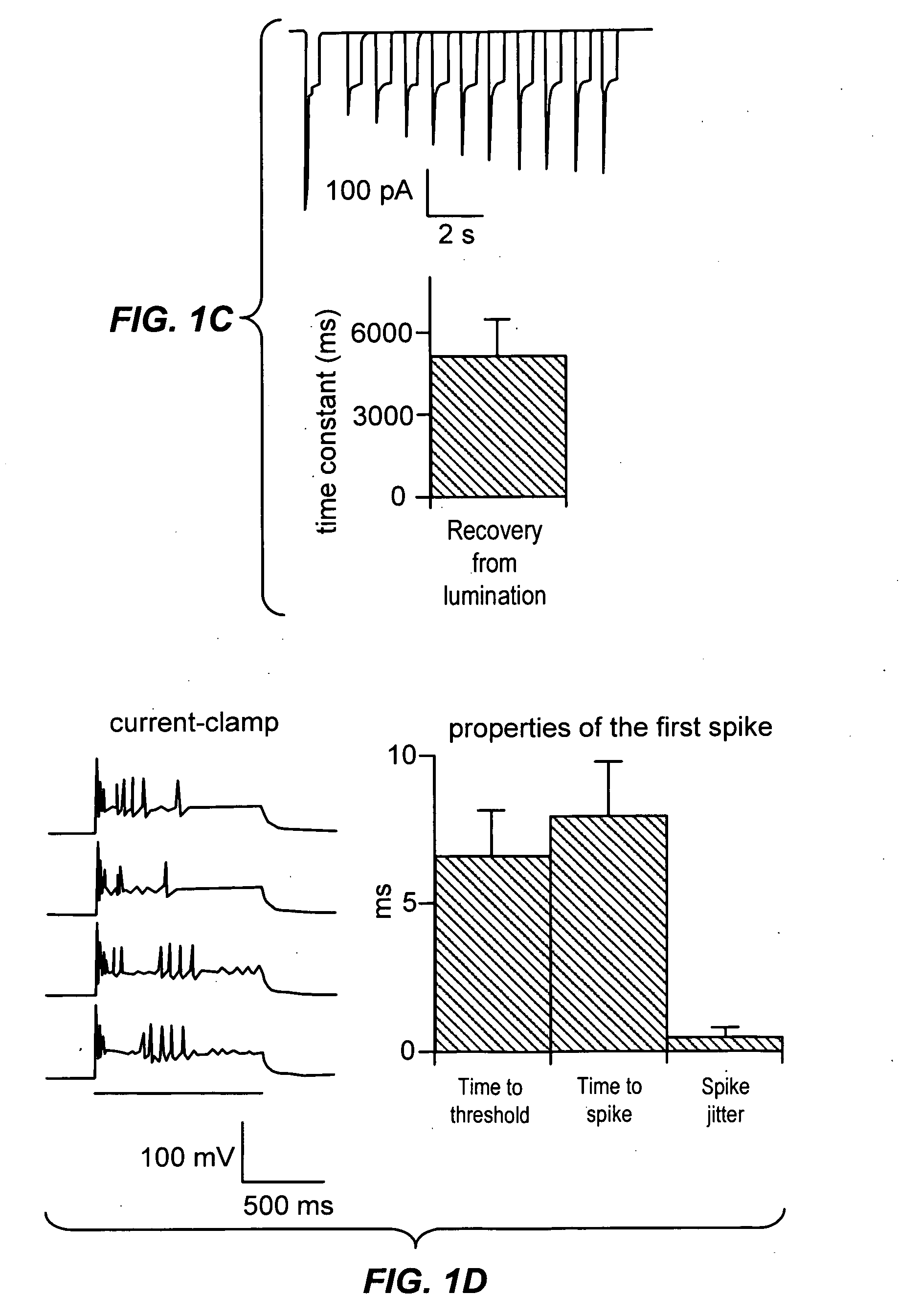

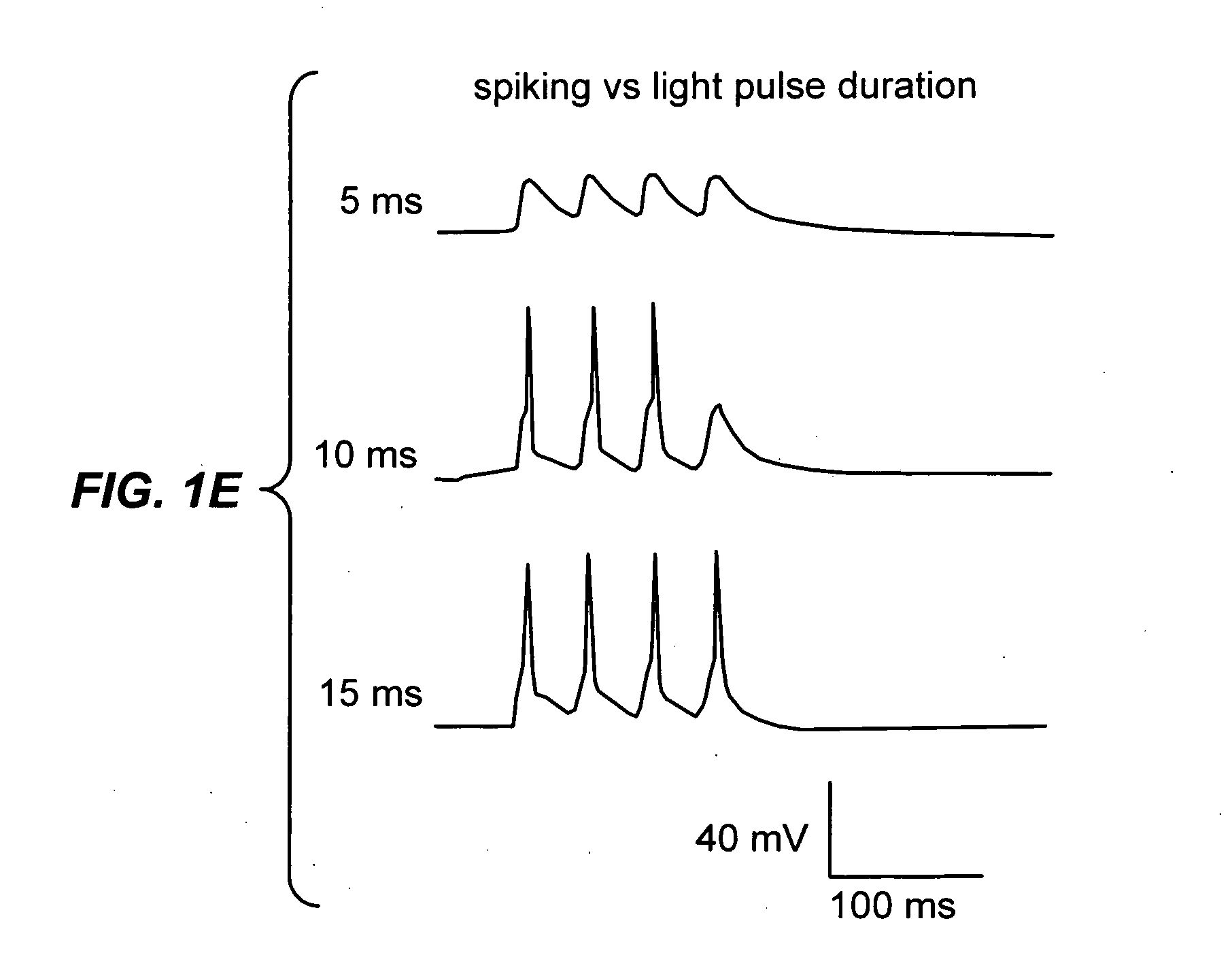

Light-activated cation channel and uses thereof

ActiveUS20070054319A1Improve abilitiesOrganic active ingredientsSenses disorderCell membraneExcitable cell

The present invention provides compositions and methods for light-activated cation channel proteins and their uses within cell membranes and subcellular regions. The invention provides for proteins, nucleic acids, vectors and methods for genetically targeted expression of light-activated cation channels to specific cells or defined cell populations. In particular the invention provides millisecond-timescale temporal control of cation channels using moderate light intensities in cells, cell lines, transgenic animals, and humans. The invention provides for optically generating electrical spikes in nerve cells and other excitable cells useful for driving neuronal networks, drug screening, and therapy.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

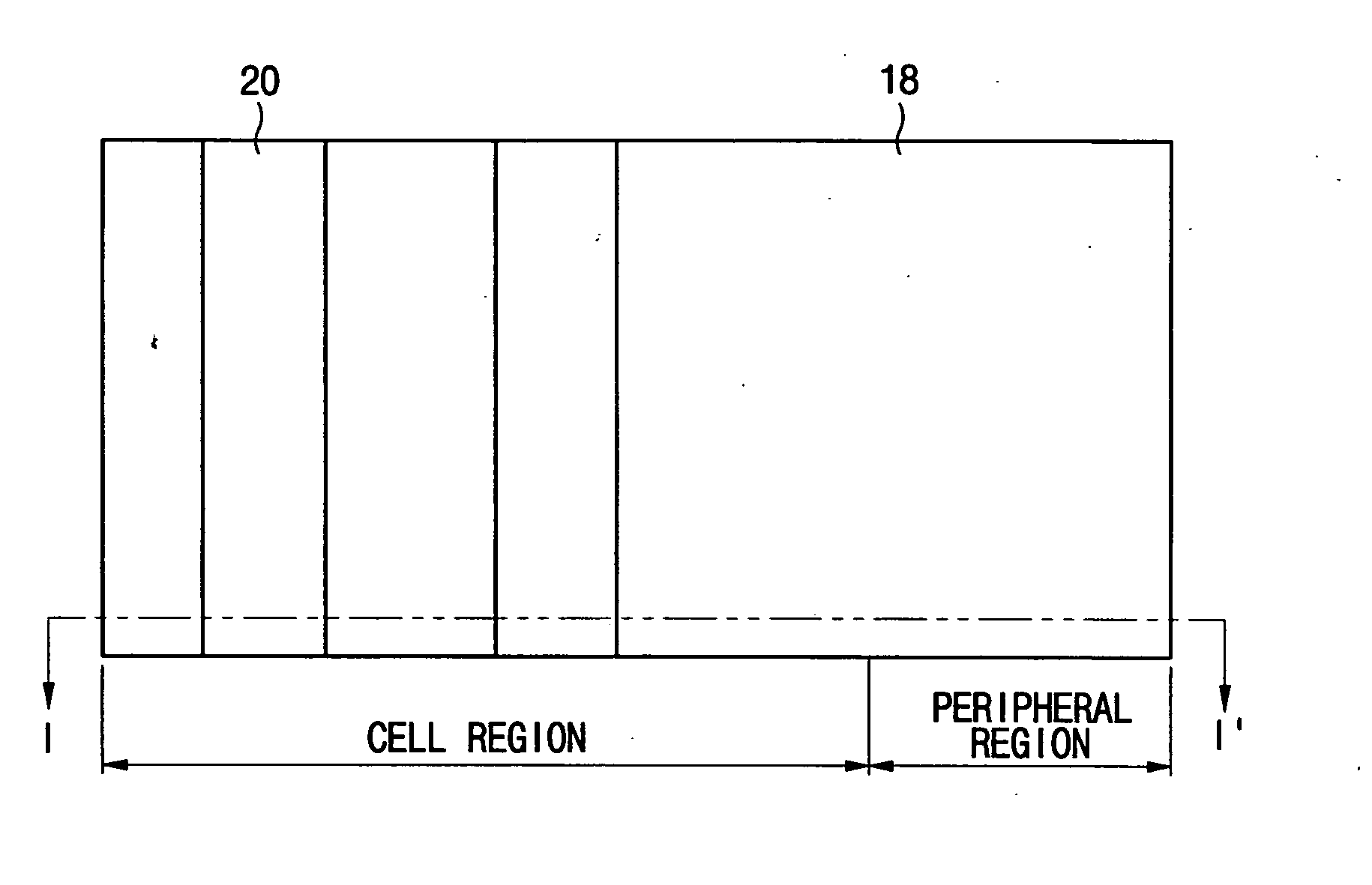

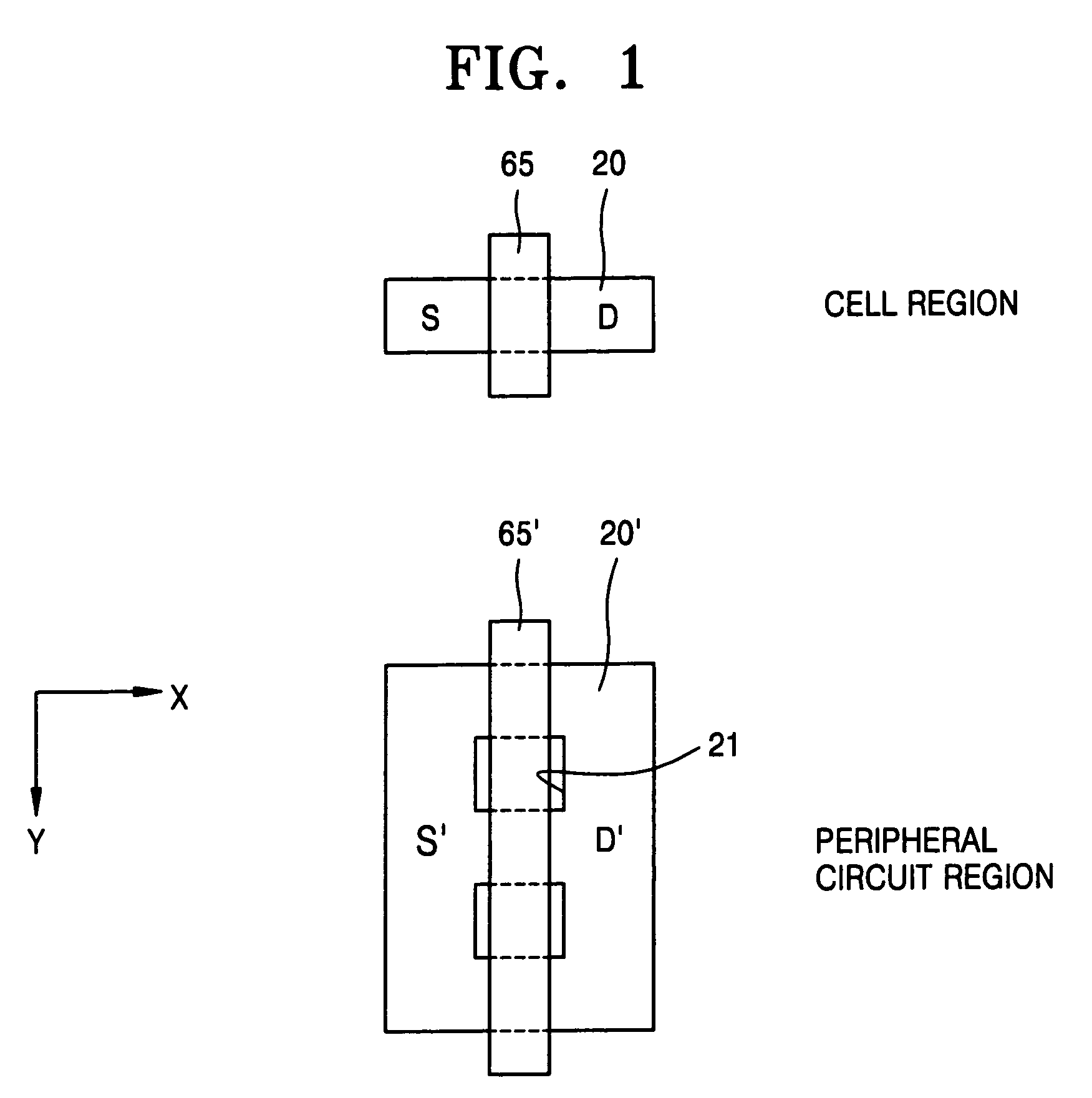

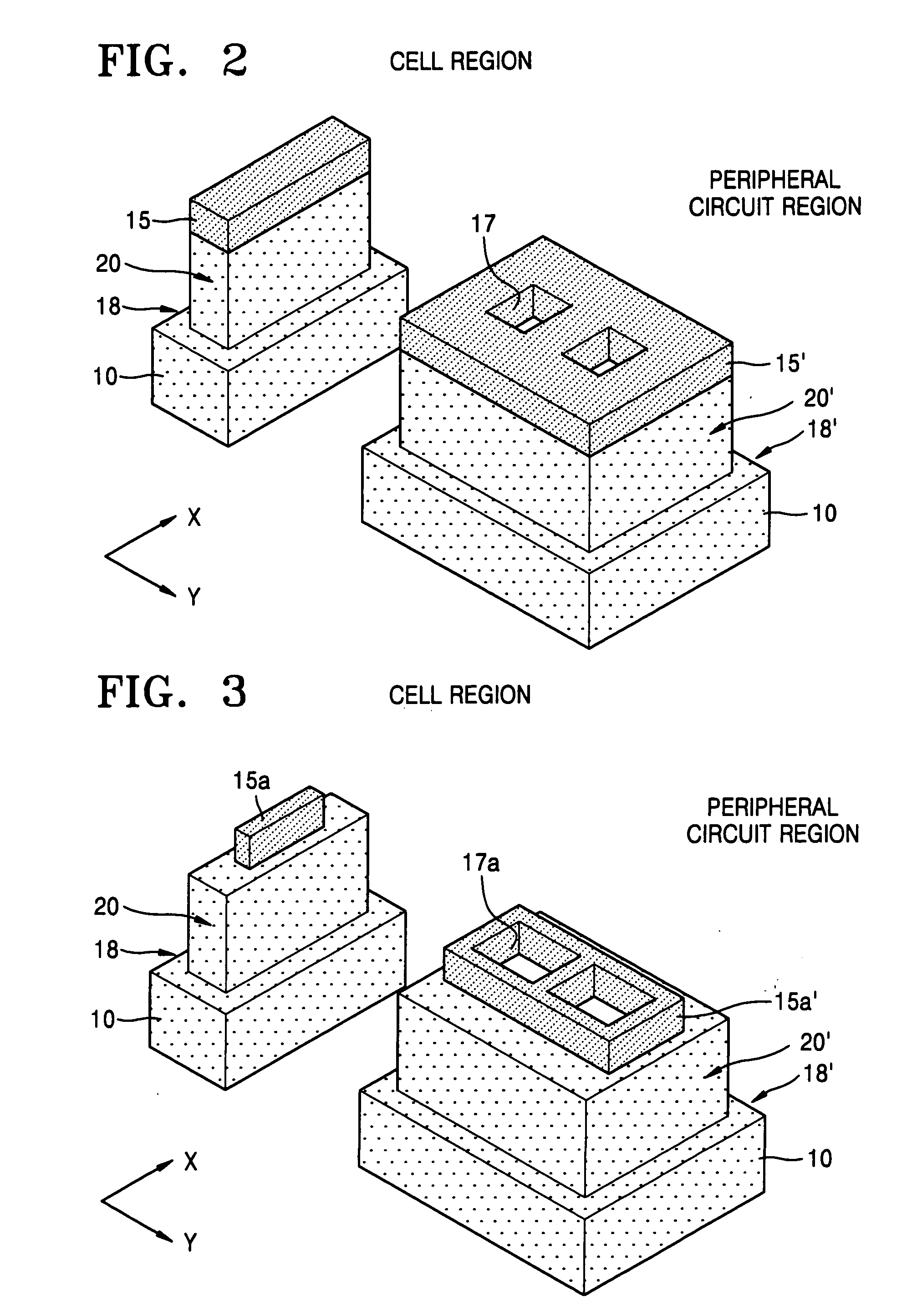

Method of forming a pattern in a semiconductor device and method of forming a gate using the same

InactiveUS20050142497A1Small line widthLine width variationPhotomechanical apparatusSemiconductor/solid-state device manufacturingDevice materialCell region

A method of forming a pattern in a semiconductor device is described. A substrate divided into cell and peripheral regions is provided, and an object layer is formed on a substrate. A buffer pattern is formed on the object layer in the cell region along a first direction. A spacer is formed along a sidewall of the buffer pattern in the cell region, and a hard mask layer remains on the object layer in the peripheral region. The buffer layer is removed, and the spacer is separated along a second direction different from the first direction, thereby forming a cell hard mask pattern. A peripheral hard mask pattern is formed in the peripheral region. A minute pattern is formed using the cell and peripheral hard mask patterns in the substrate. Therefore, a line width variation or an edge line roughness due to the photolithography process is minimized.

Owner:SAMSUNG ELECTRONICS CO LTD

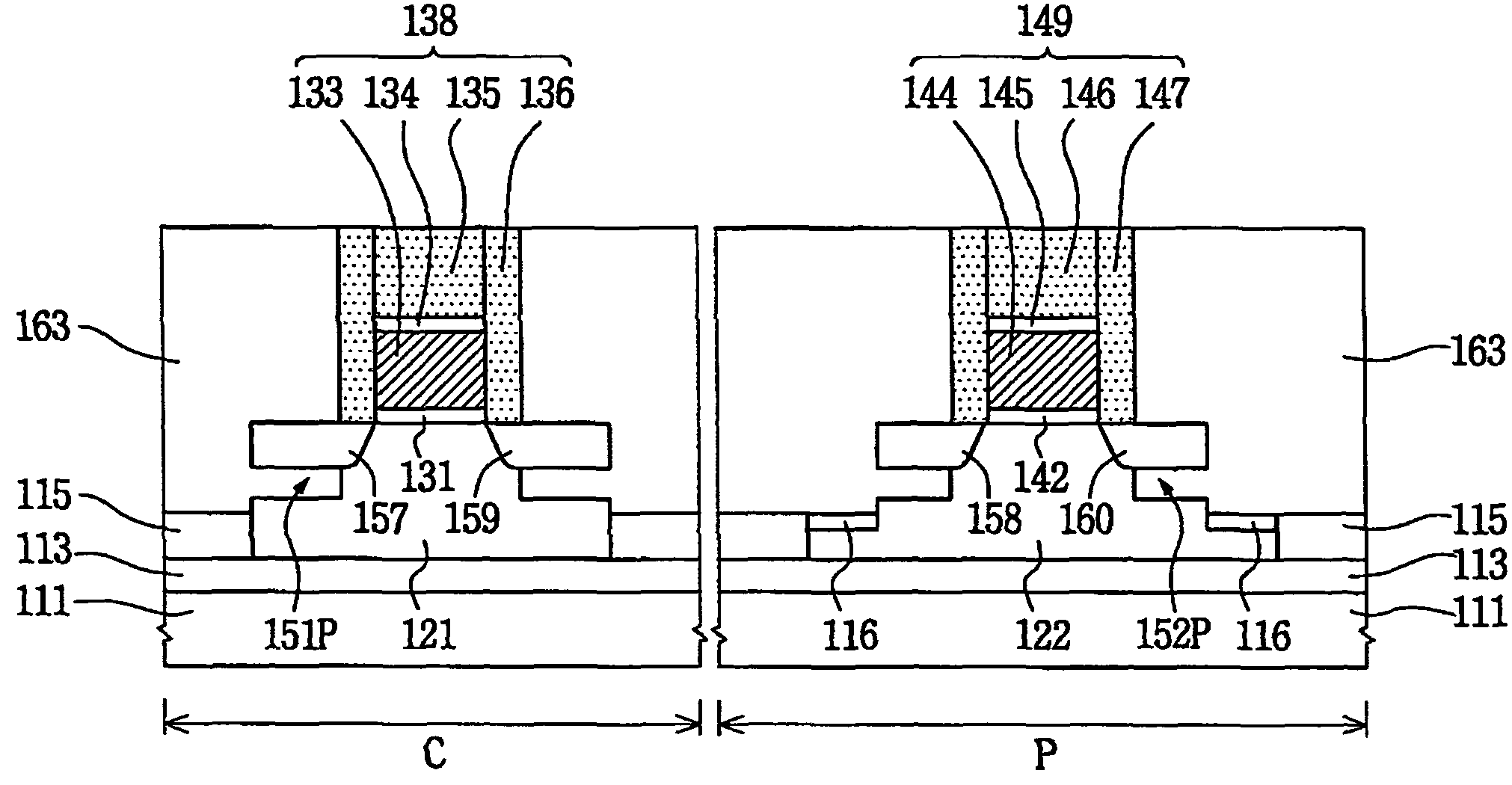

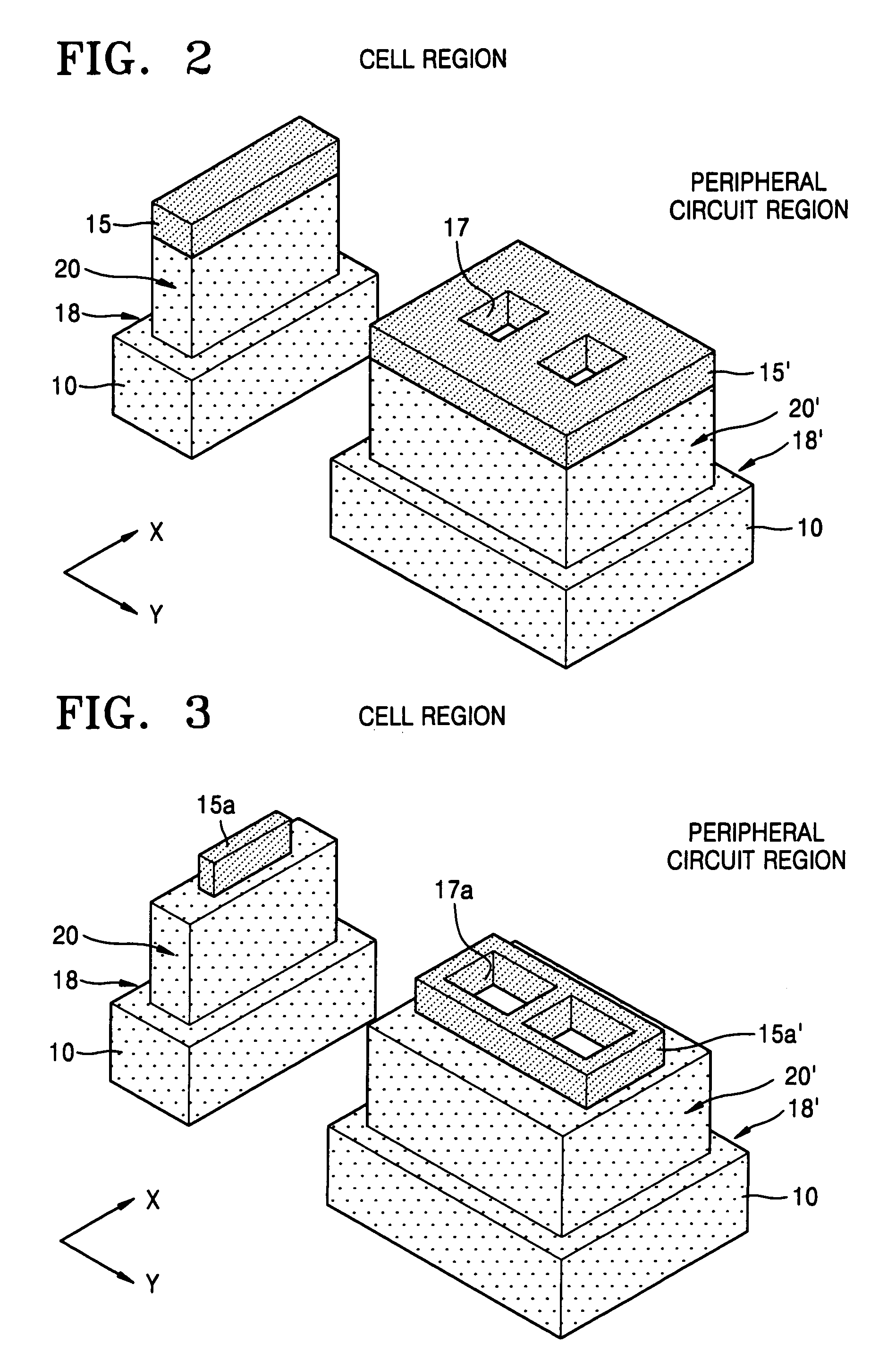

Floating body memory and method of fabricating the same

A floating body memory includes a semiconductor substrate having a cell region and a peripheral circuit region. A floating body cell is located in the cell region and a first floating body is located in the peripheral circuit region of the semiconductor substrate. A peripheral gate pattern is positioned on the first floating body. First source and drain regions are positioned at both sides of the peripheral gate pattern. First leakage shielding patterns are positioned between the first floating body and the first source and drain regions, the first source and drain regions contacting the first floating body. The first leakage shielding patterns may be positioned outside outer edges of the peripheral gate pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

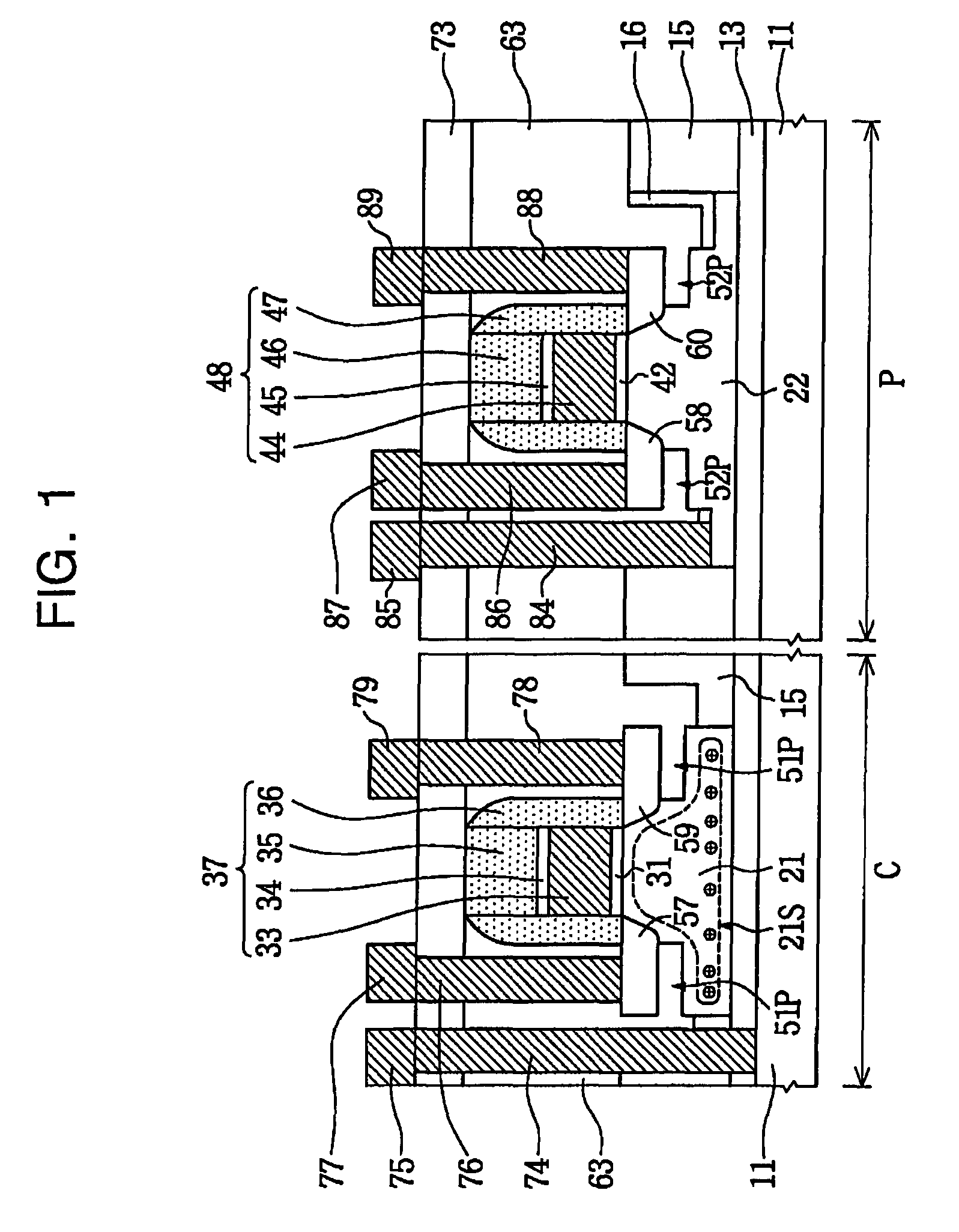

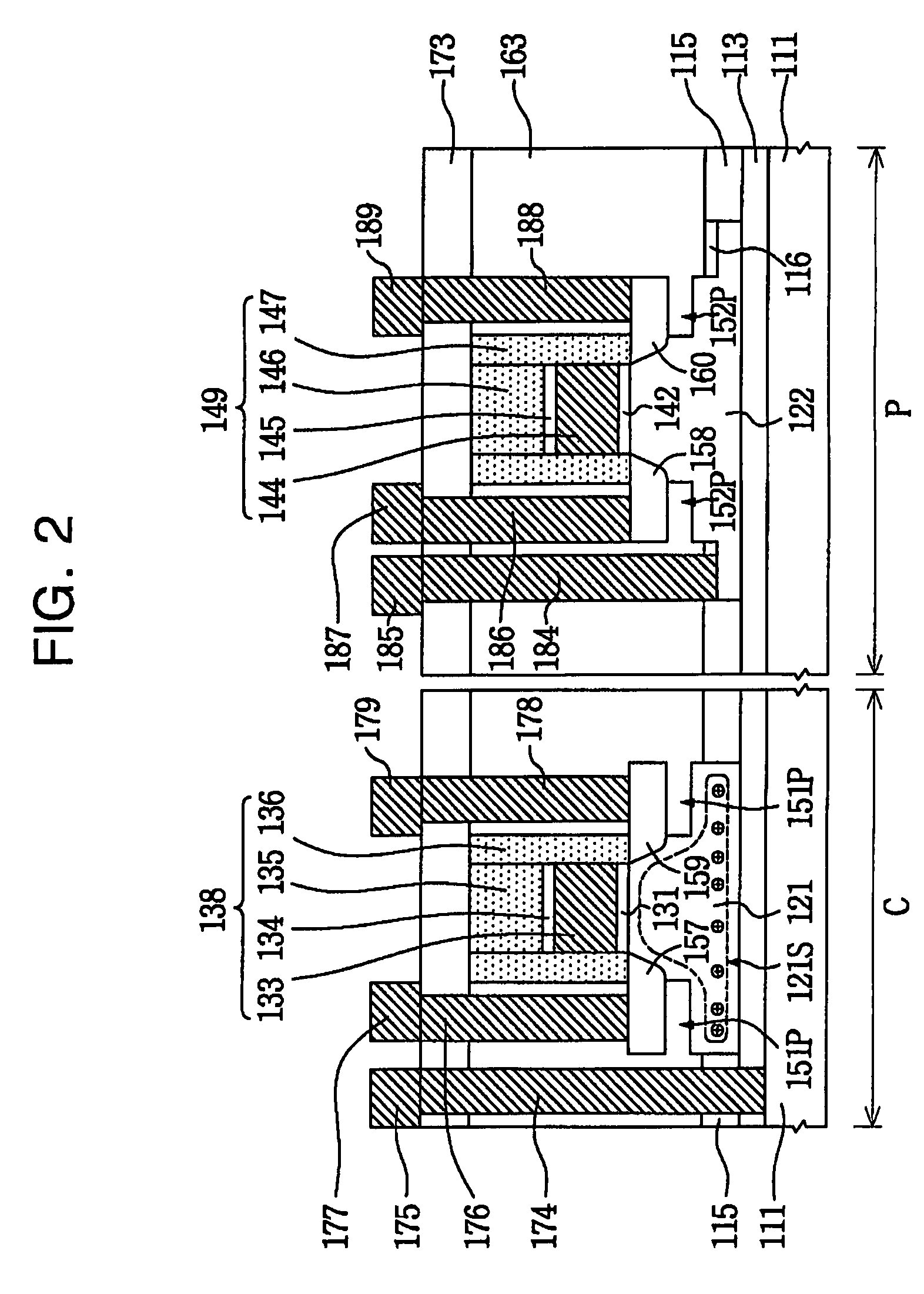

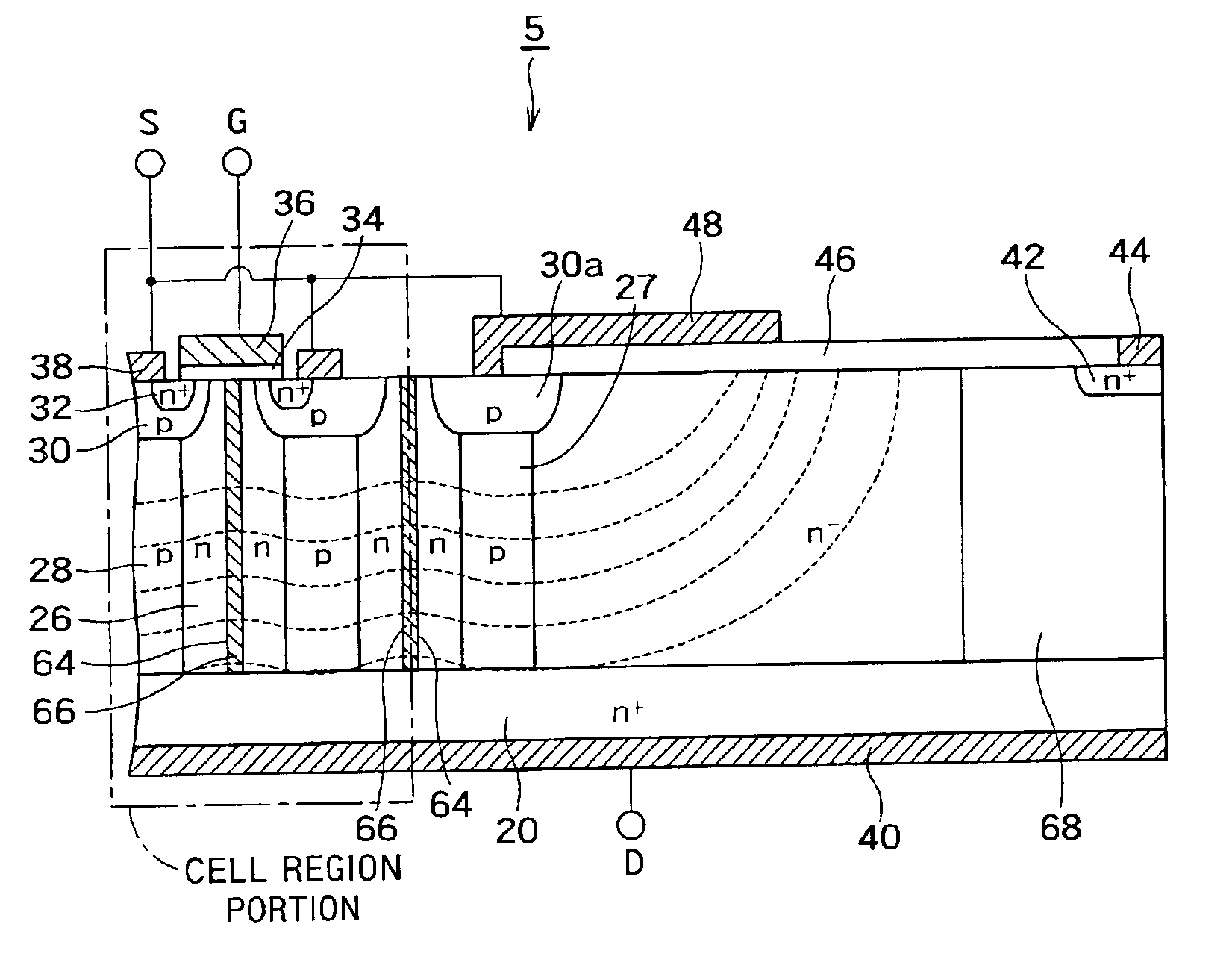

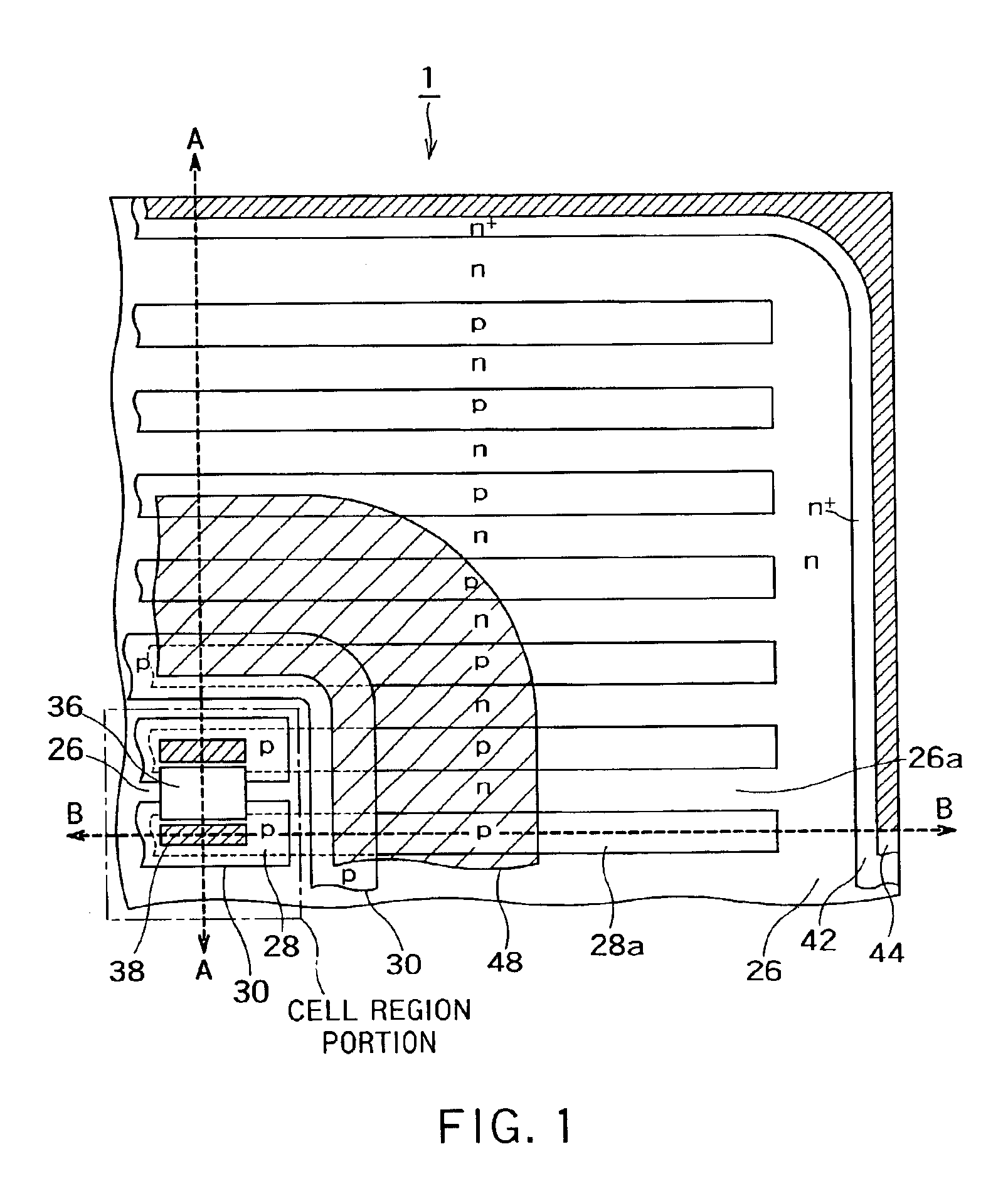

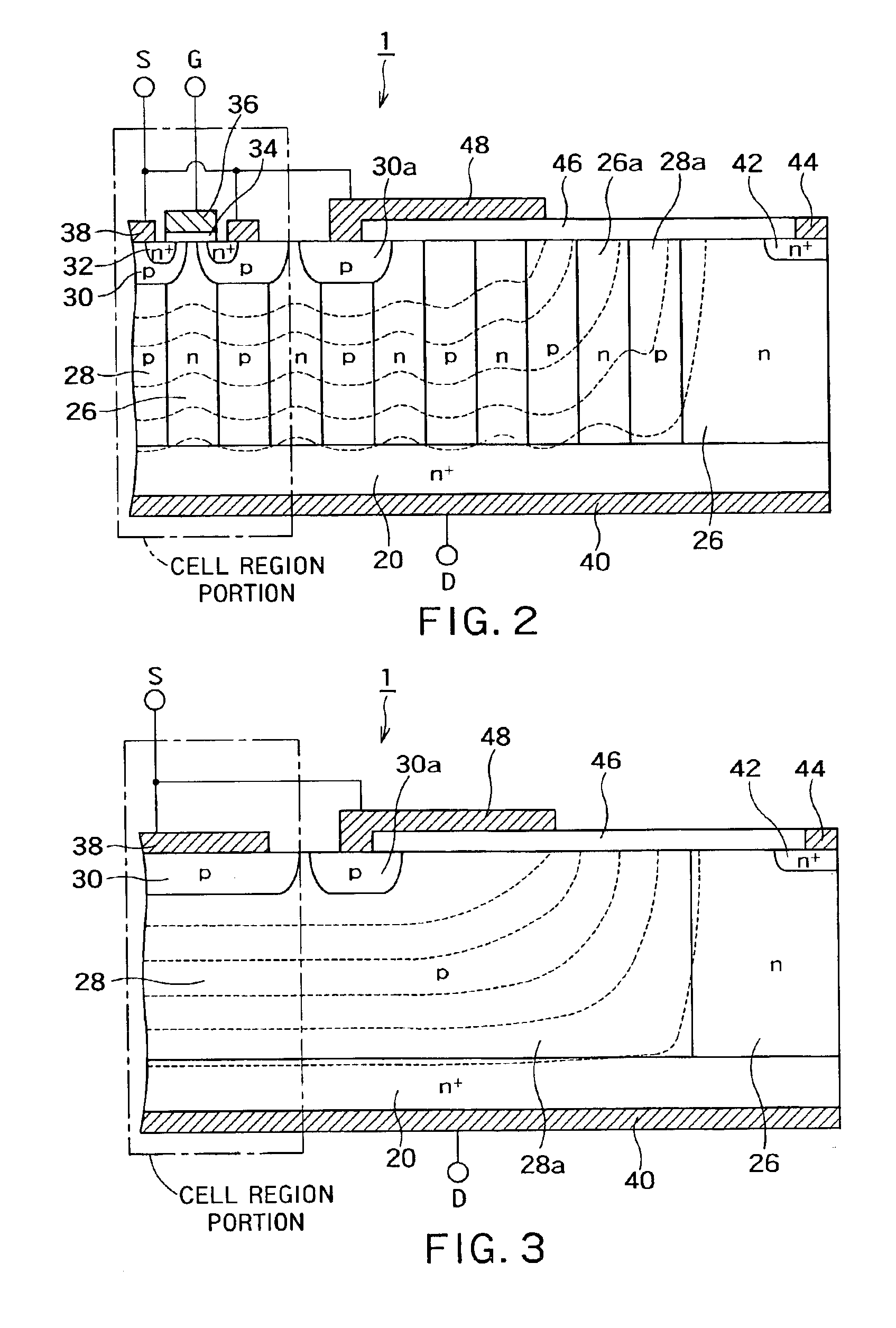

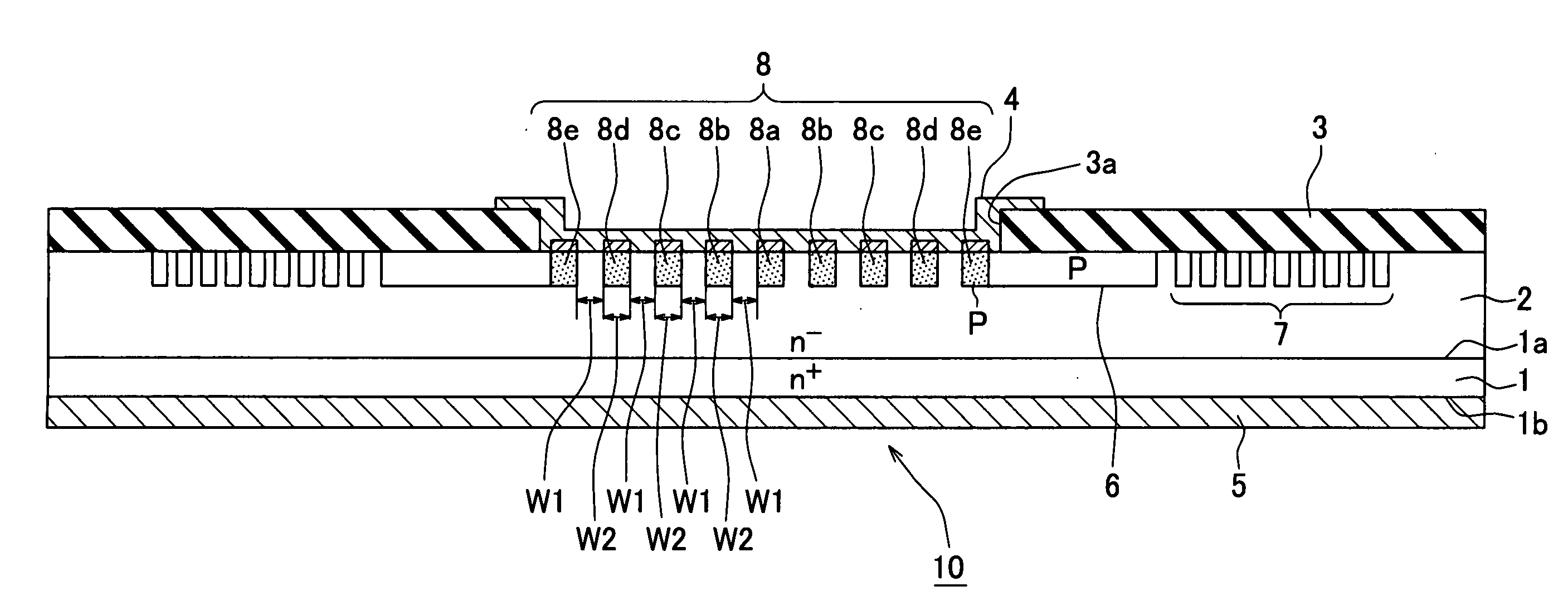

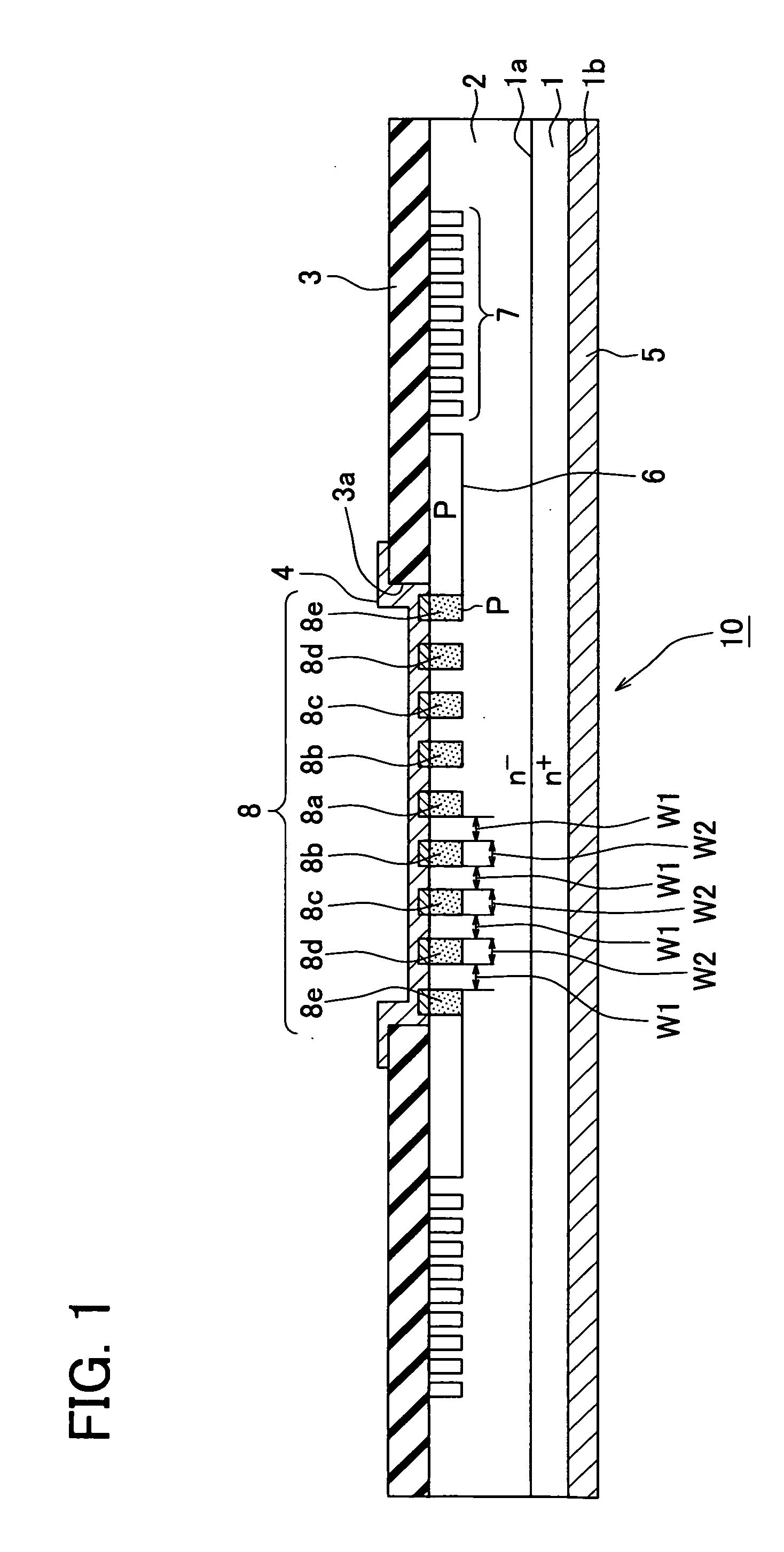

Semiconductor device with super junction region

InactiveUS6844592B2Improve breakdown voltageEfficiently obtainedSemiconductor/solid-state device manufacturingSemiconductor devicesCell regionSemiconductor

A semiconductor device includes a first-conductivity-type semiconductor layer which includes a cell region portion and a junction terminating region portion. The junction terminating region portion is a region portion which is positioned in an outer periphery of the cell region portion to maintain a breakdown voltage by extending a depletion layer to attenuate an electric field.

Owner:KK TOSHIBA

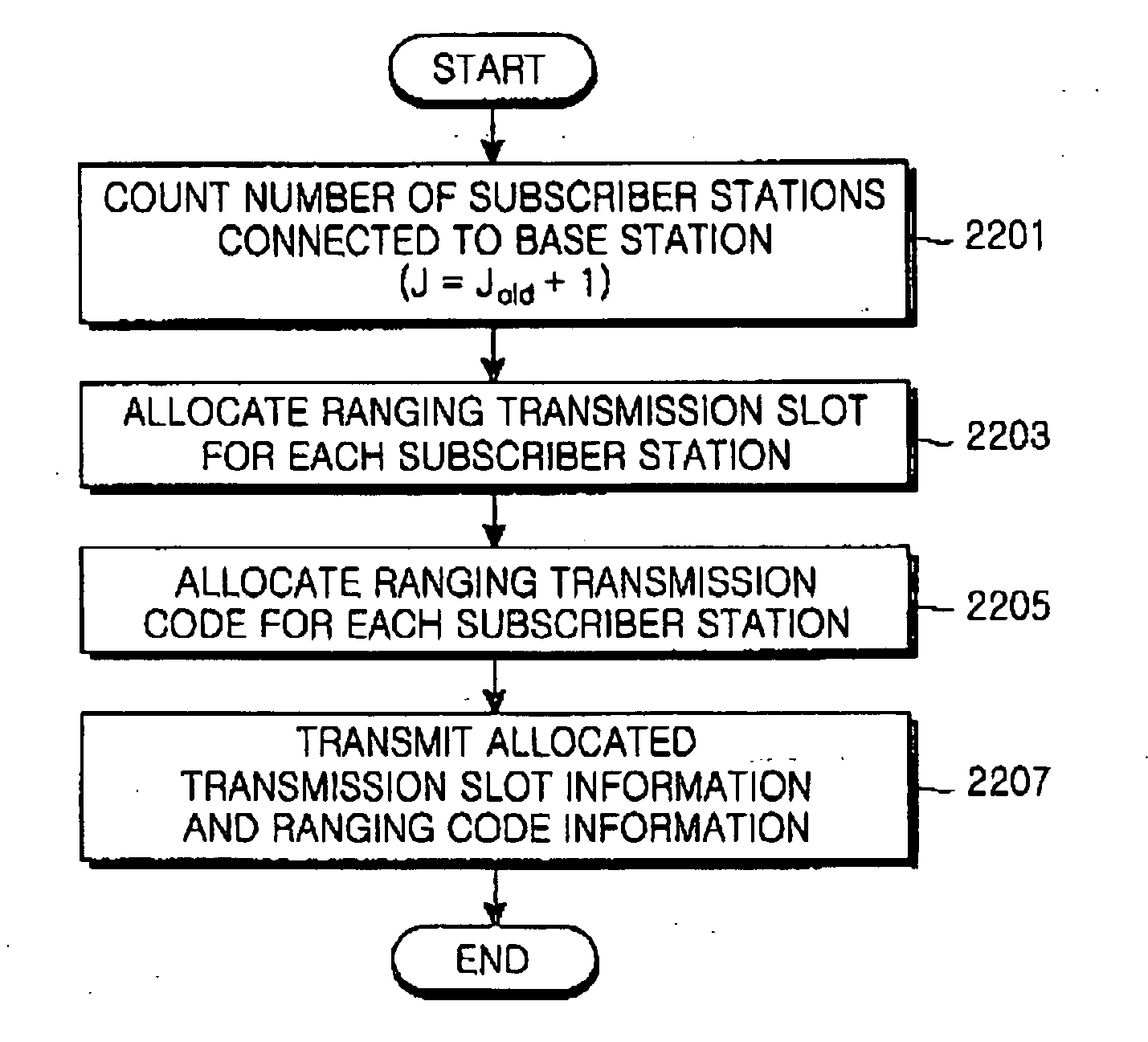

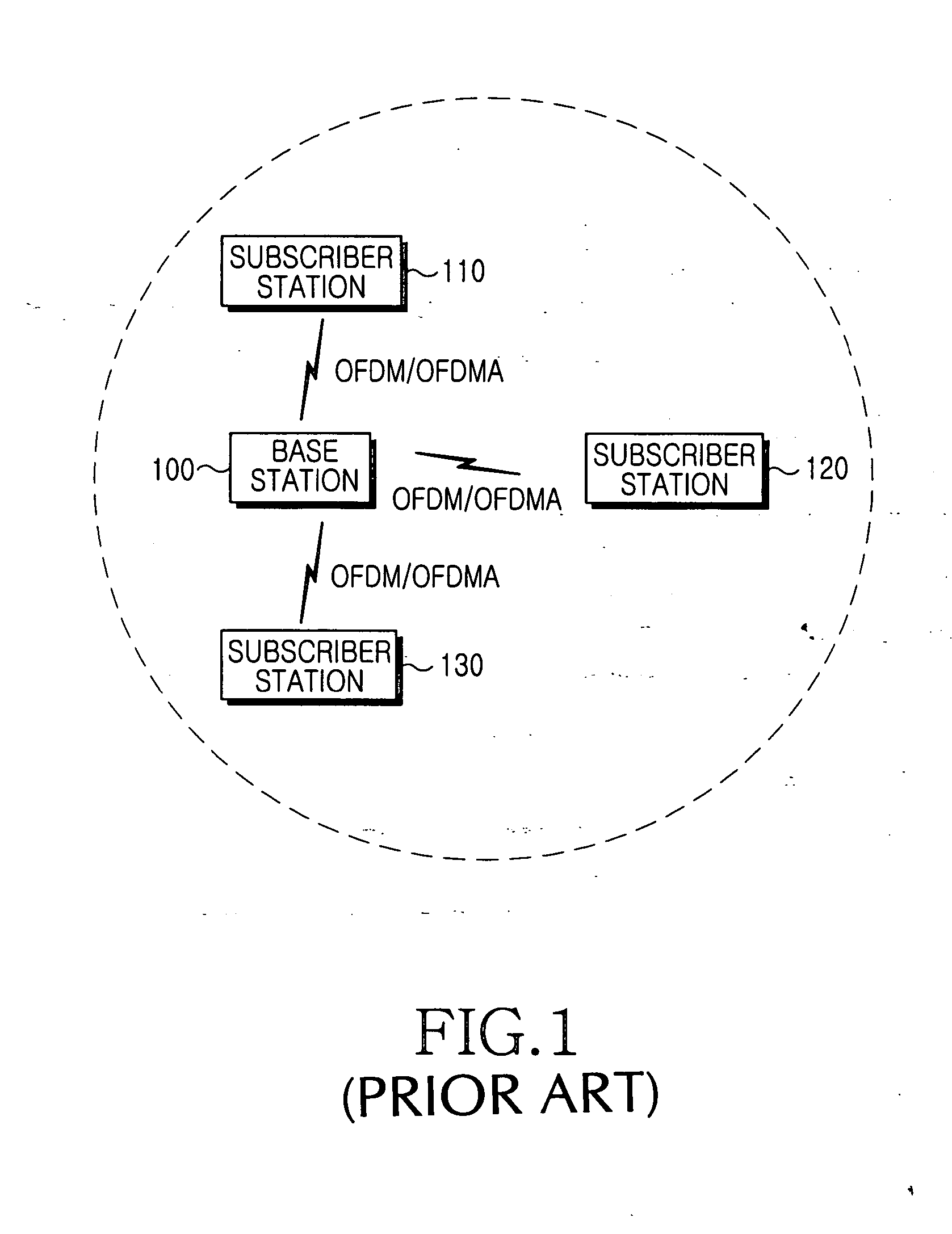

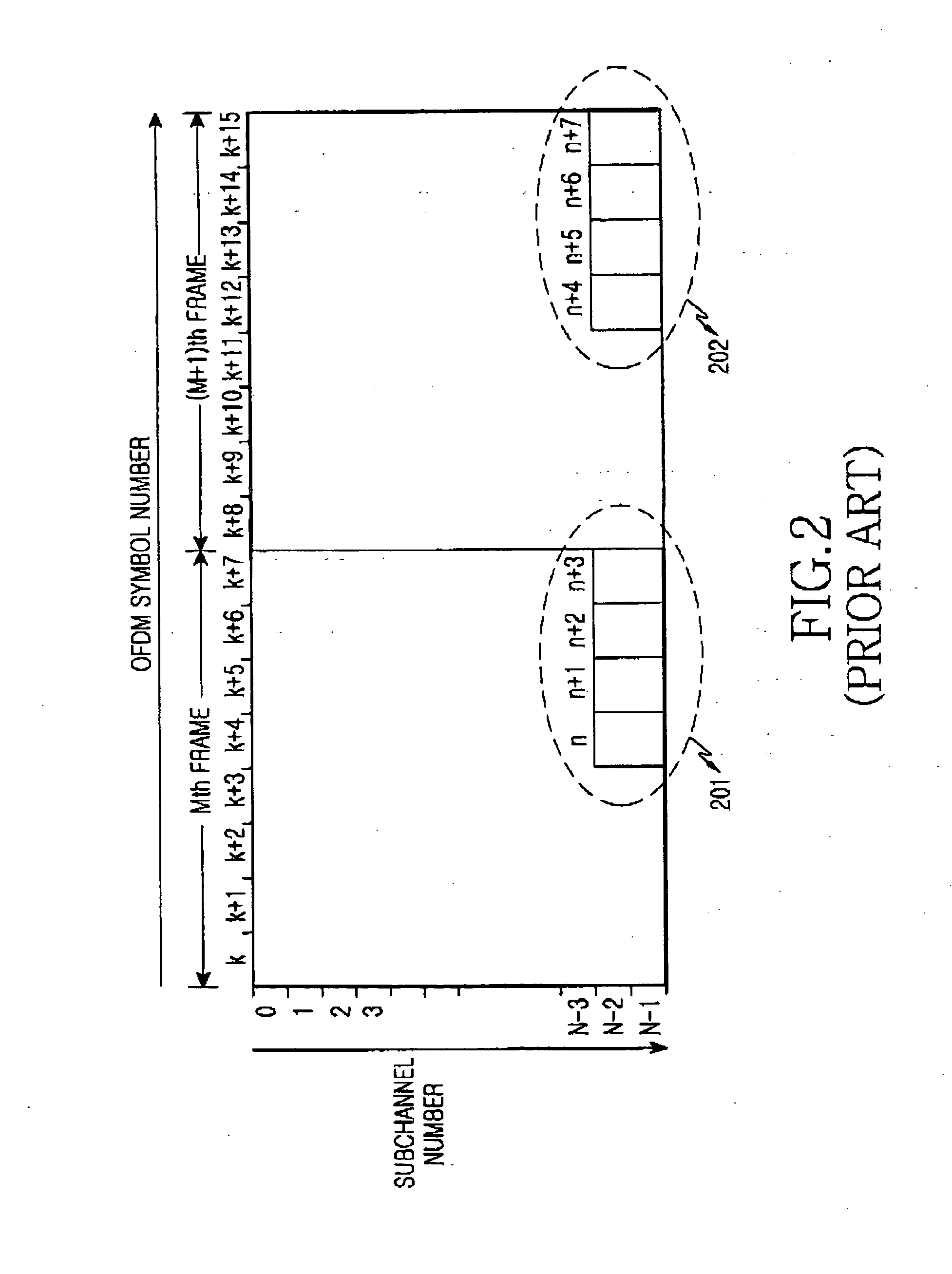

Apparatus and method for modulating ranging signals in a broadband wireless access communication system

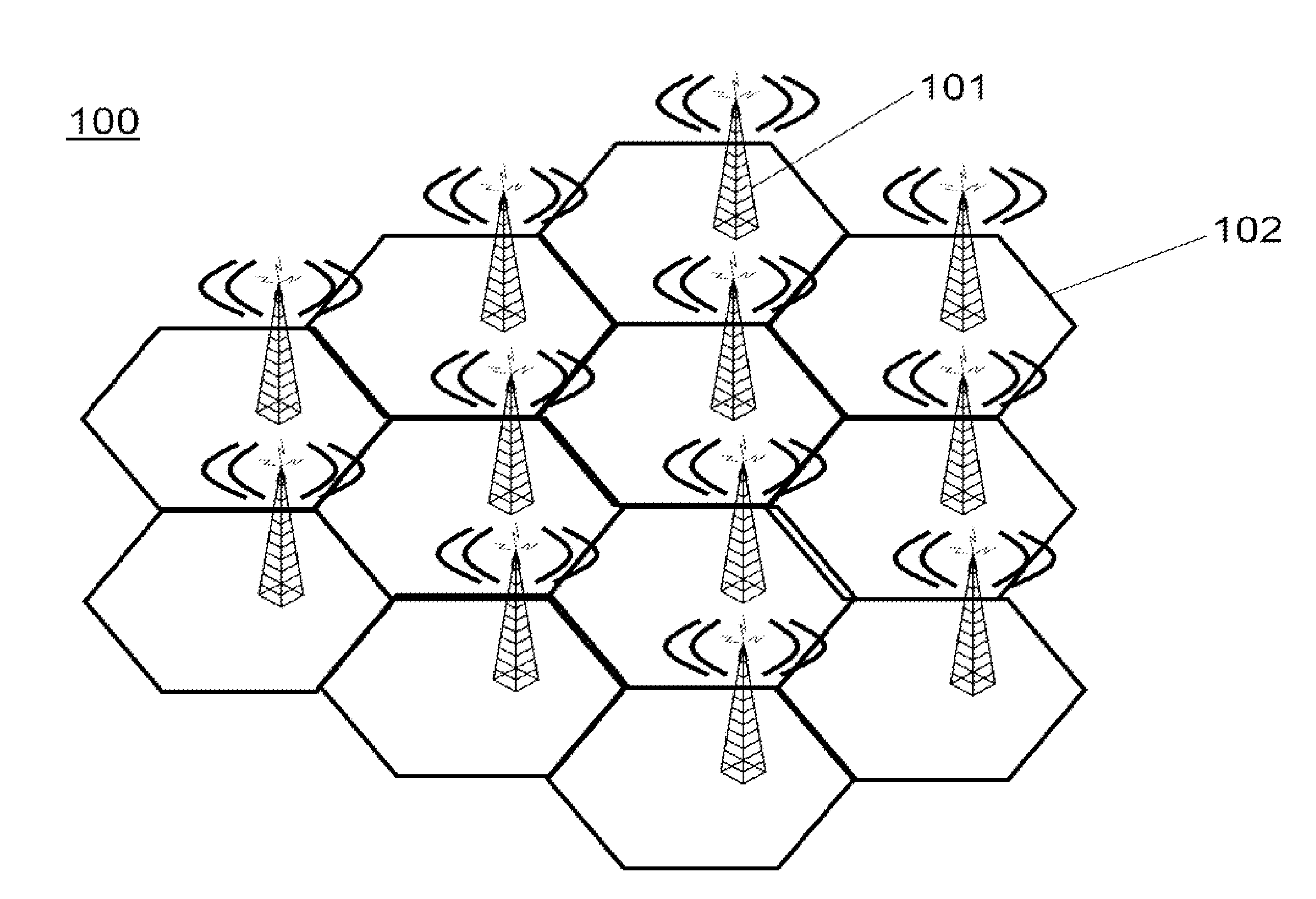

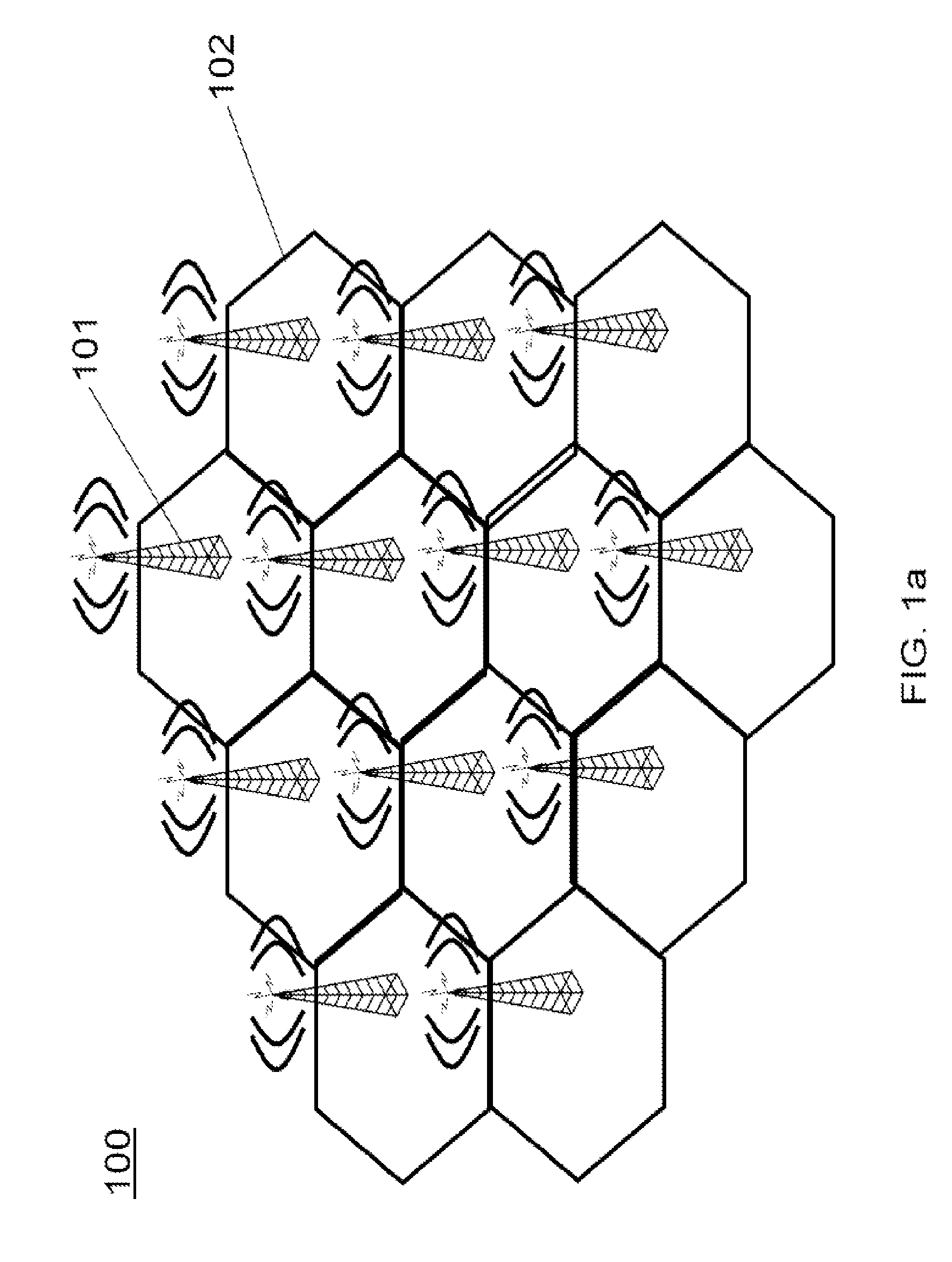

InactiveUS20050030931A1Avoid signal interferenceEasy searchTime-division multiplexRadio transmissionCommunications systemCell region

An method and apparatus for transmitting ranging information from at least one base station to subscriber stations and generating a ranging signal by the subscriber station using received ranging information in a Broadband Wireless Access (BWA) communication system including a plurality of neighbor cells and a plurality of the subscriber stations located in each cell region. A first code generator generates a first code using different first code information received from the base stations in the neighbor cells allocated the first code information. A second code generator generates a second code using second code information received by each of the subscriber stations existing in cell regions of the neighbor cells. A ranging signal generator generates a new ranging signal by combining the first code with the second code.

Owner:SAMSUNG ELECTRONICS CO LTD

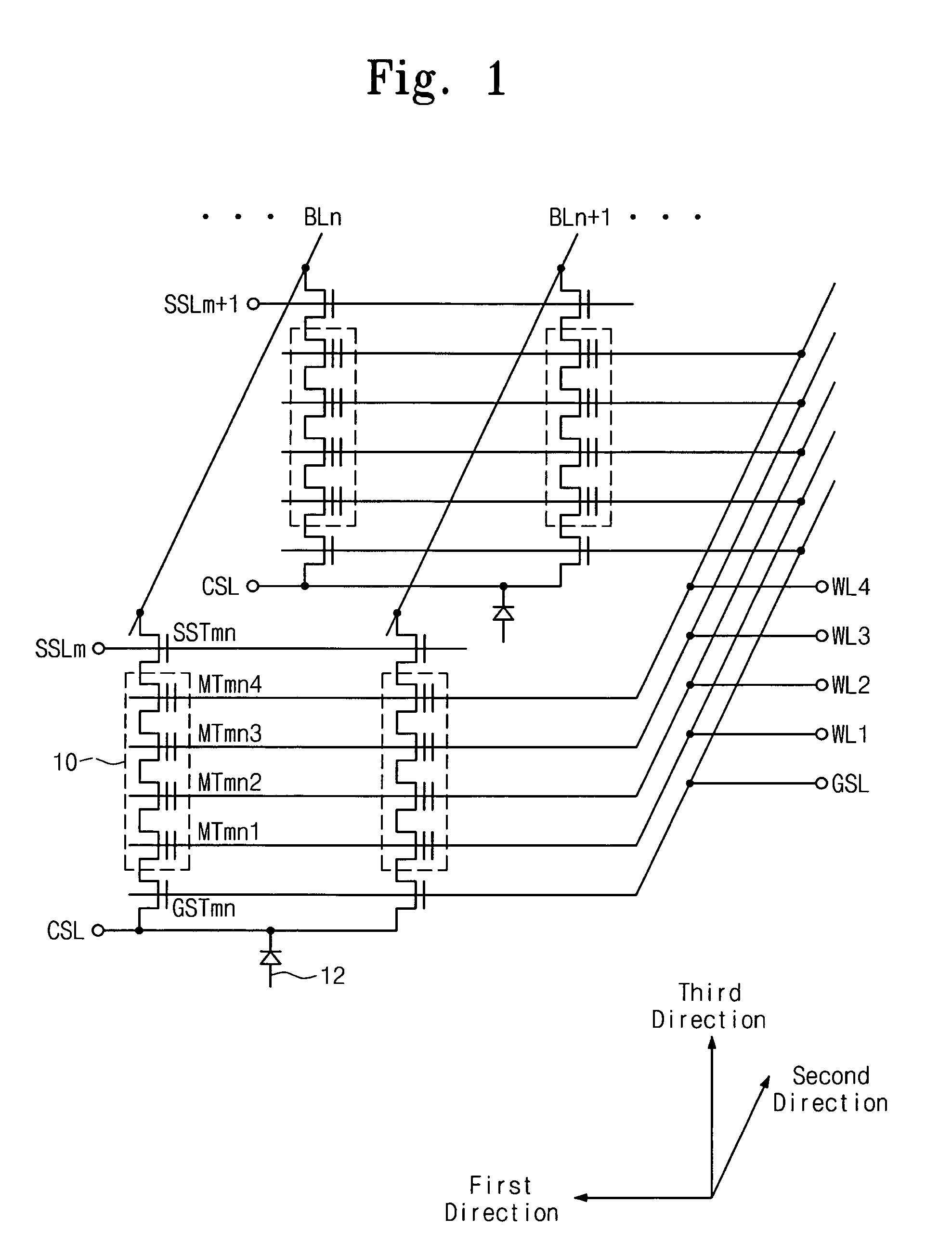

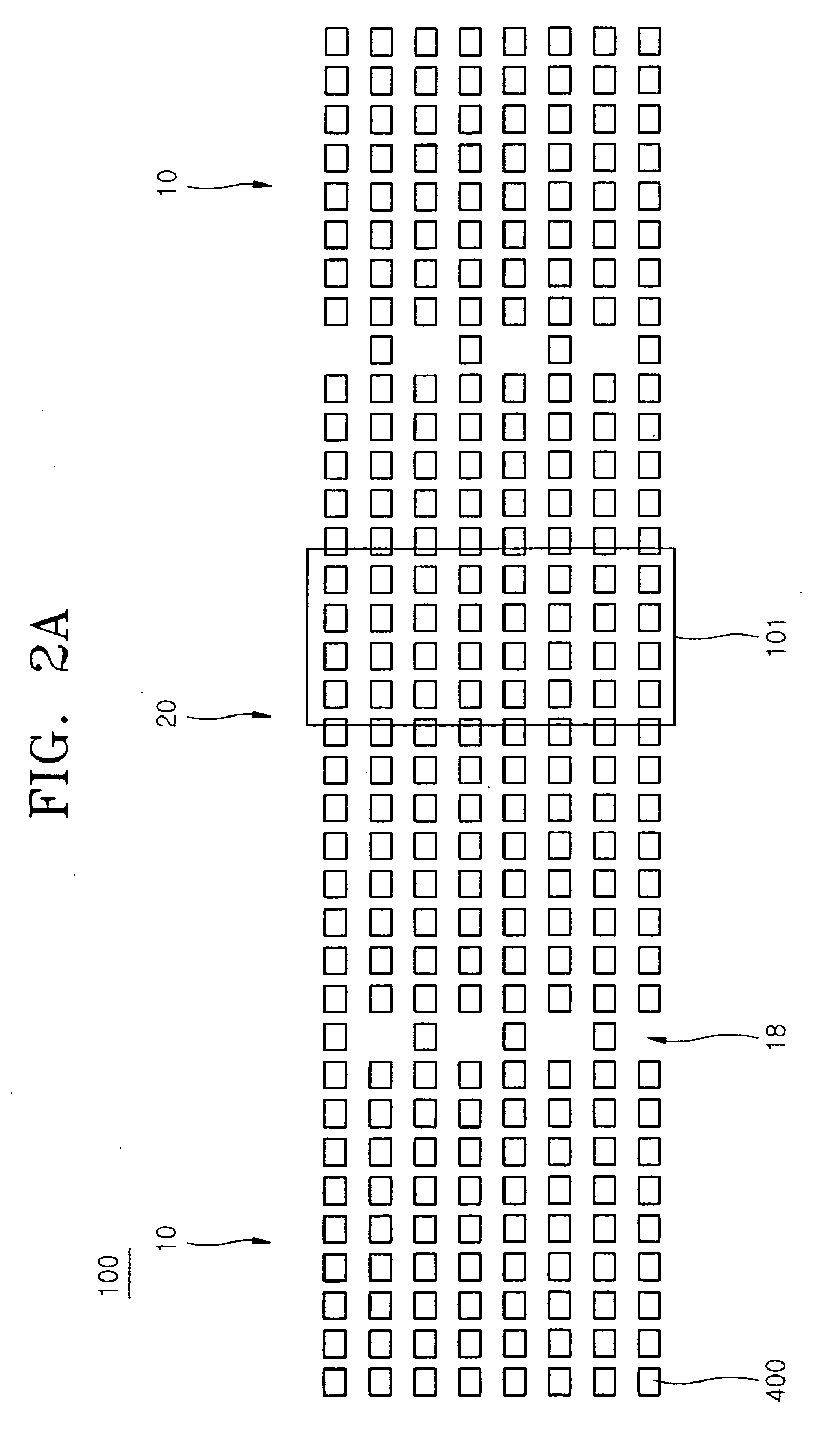

Semiconductor Memory Device and Method for Arranging and Manufacturing the Same

A semiconductor memory device and method of manufacturing the same are disclosed. The semiconductor memory device includes a semiconductor substrate having a cell region and a peripheral circuit region, first transistors provided on the semiconductor substrate, a first semiconductor layer provided on the first transistors, and bonded by a bonding technique, and second transistors provided on the first semiconductor layer, wherein the first and second transistors are provided in the peripheral circuit regions of the semiconductor substrate and the first semiconductor layer, respectively, and a metal layer is formed on gates of the first and second transistors respectively provided in the peripheral circuit regions of the semiconductor substrate and the first semiconductor layer. As a result, the transistors in the peripheral circuit region requiring high performance can be formed on an upper layer and a lower layer.

Owner:SAMSUNG ELECTRONICS CO LTD

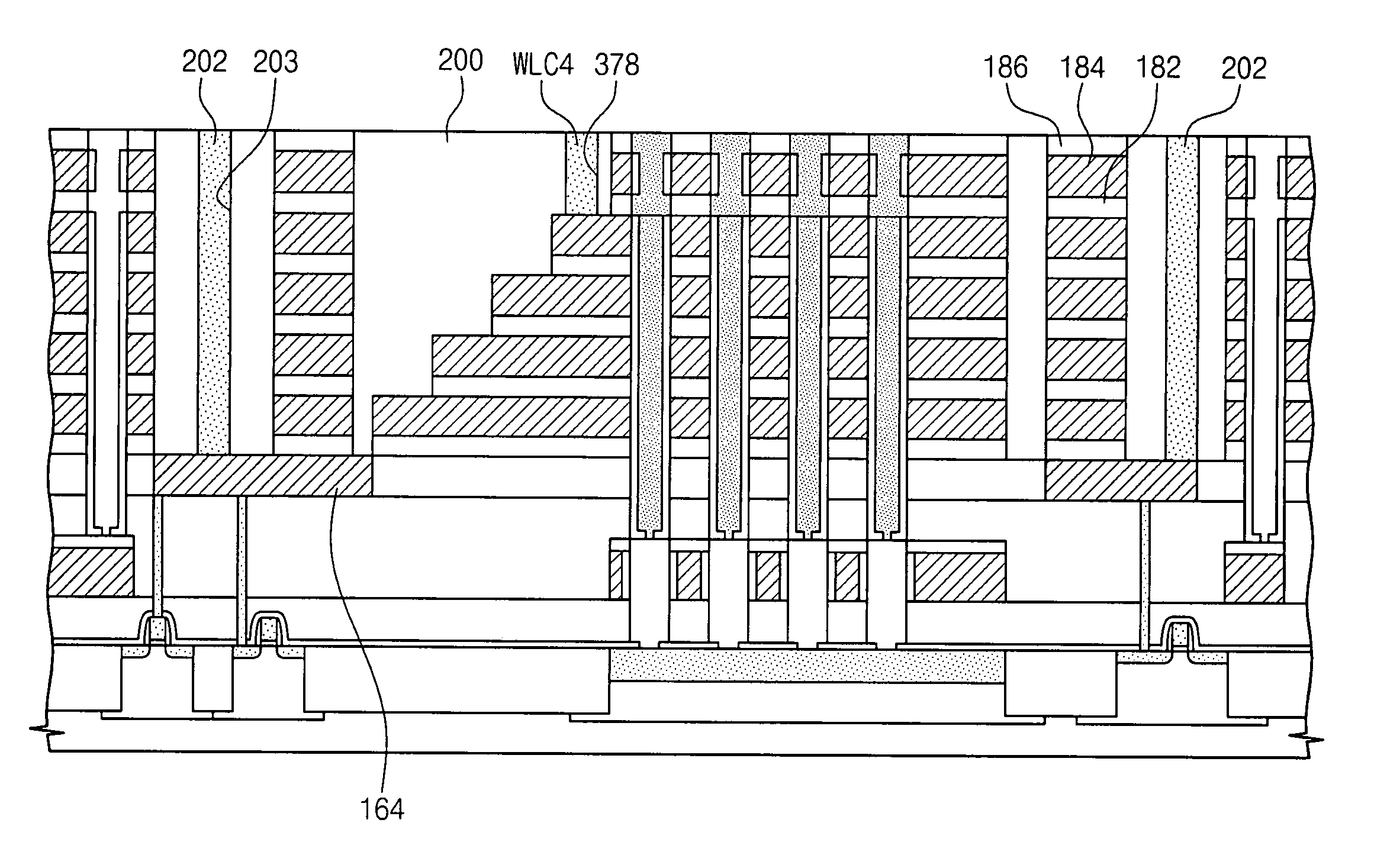

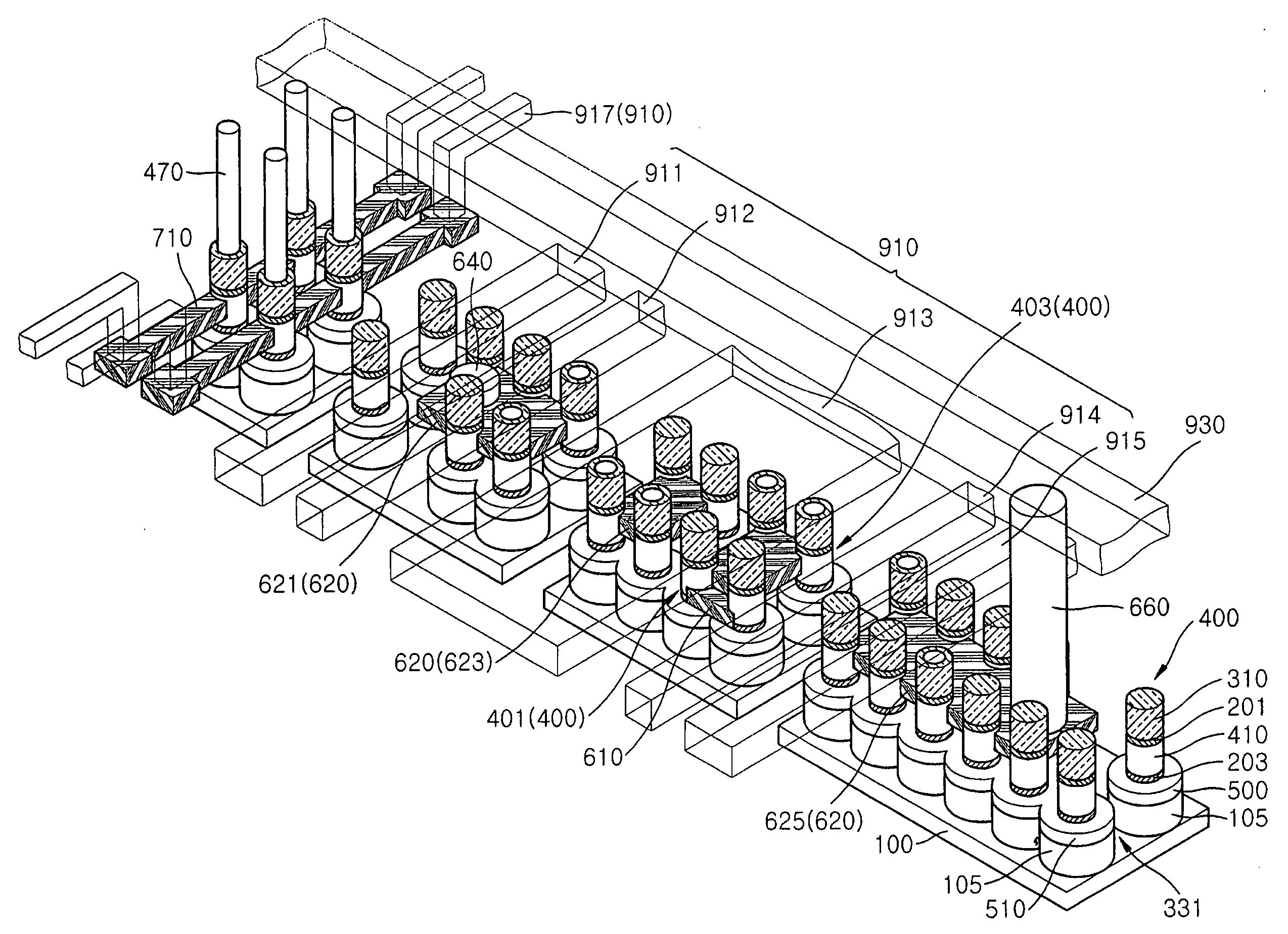

Vertical-type semiconductor device and method of manufacturing the same

ActiveUS20100090286A1Minimize moistureMinimize contaminationSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricSemiconductor structure

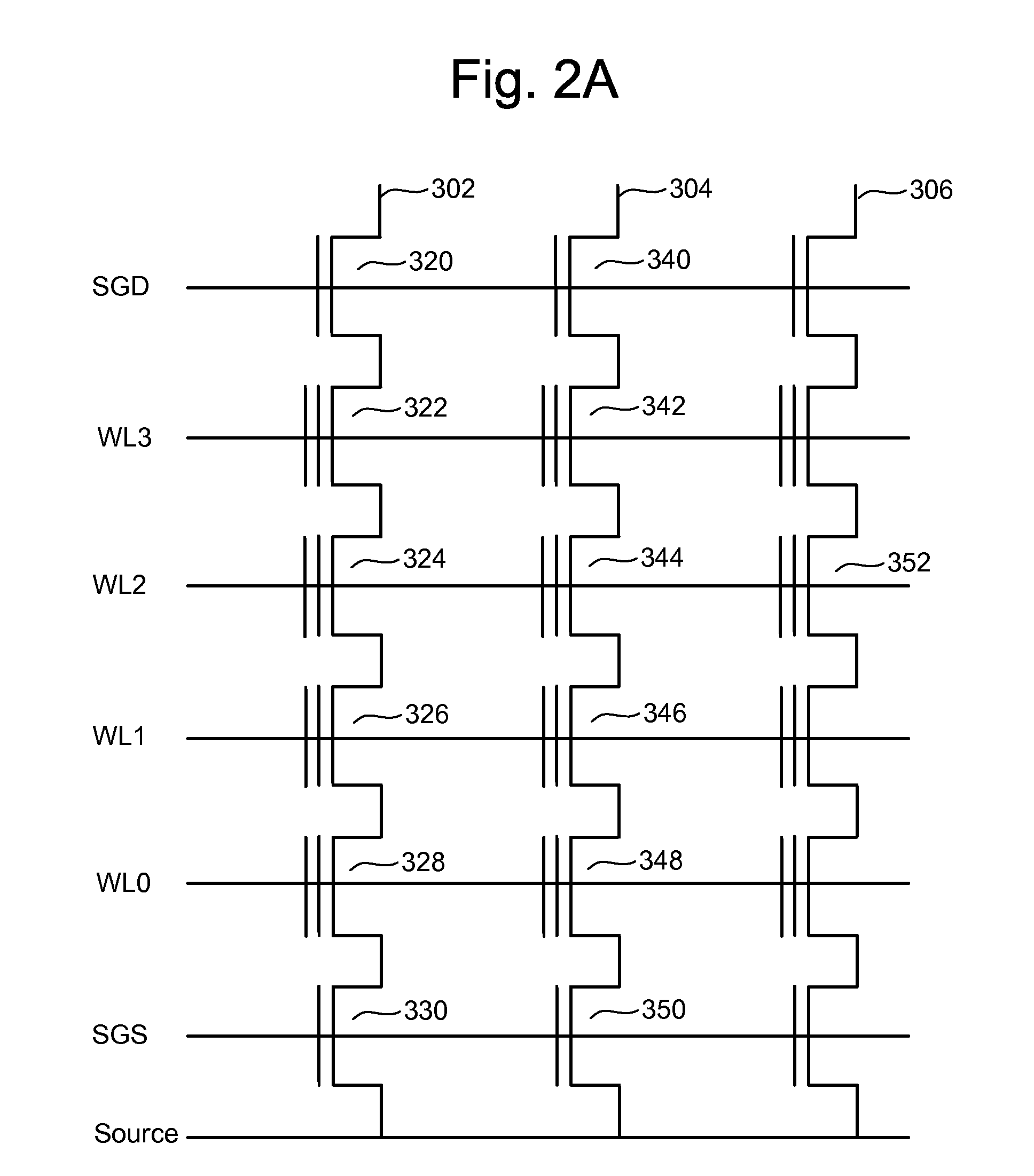

A vertical-type semiconductor device includes a semiconductor substrate having a cell region and a peripheral circuit region, a wordline structure on the cell region of the semiconductor substrate, the wordline structure including a plurality of wordlines stacked on top of each other, a semiconductor structure through the wordline structure, a gate dielectric between the wordline structure and the semiconductor structure, and a dummy wordline structure on the peripheral circuit region, the dummy wordline structure having a vertical structure and including same components as the wordline structure.

Owner:SAMSUNG ELECTRONICS CO LTD

Circuit device including vertical transistors connected to buried bitlines and method of manufacturing the same

ActiveUS20070075359A1Reduce areaConfiguring the peripheral circuitSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricCell region

In a circuit device including vertical transistors connected to buried bitlines and a method of manufacturing the circuit device, the circuit device includes a semiconductor substrate including a peripheral circuit region and left and right cell regions at both sides of the peripheral circuit region; bottom active regions arranged on the semiconductor substrate to be spaced apart from one another in a column direction and to extend from the peripheral circuit region alternately to the left cell region and the right cell region in a row direction; channel pillars protruding from the bottom active regions in a vertical direction and arranged to be aligned in the row direction and spaced apart from one another; gate electrodes provided with a gate dielectric layer and attached to surround side surfaces of the channel pillars; buried bitlines extending along the bottom active regions, the bottom active regions including a bottom source / drain region; local interconnection lines contacting side surfaces of the gate electrodes in the peripheral circuit region and extending between the gate electrodes to commonly interconnect the gate electrodes in the peripheral circuit region, thereby configuring a peripheral circuit; signal lines electrically connected to upper surfaces of the channel pillars or to at least one of the local interconnection lines; and interconnection contacts electrically connecting the local interconnection line to the buried bitline of a different row from that of the commonly-connected gate electrodes or electrically connecting the local interconnection lines to the signal lines, thereby configuring the peripheral circuit.

Owner:SAMSUNG ELECTRONICS CO LTD

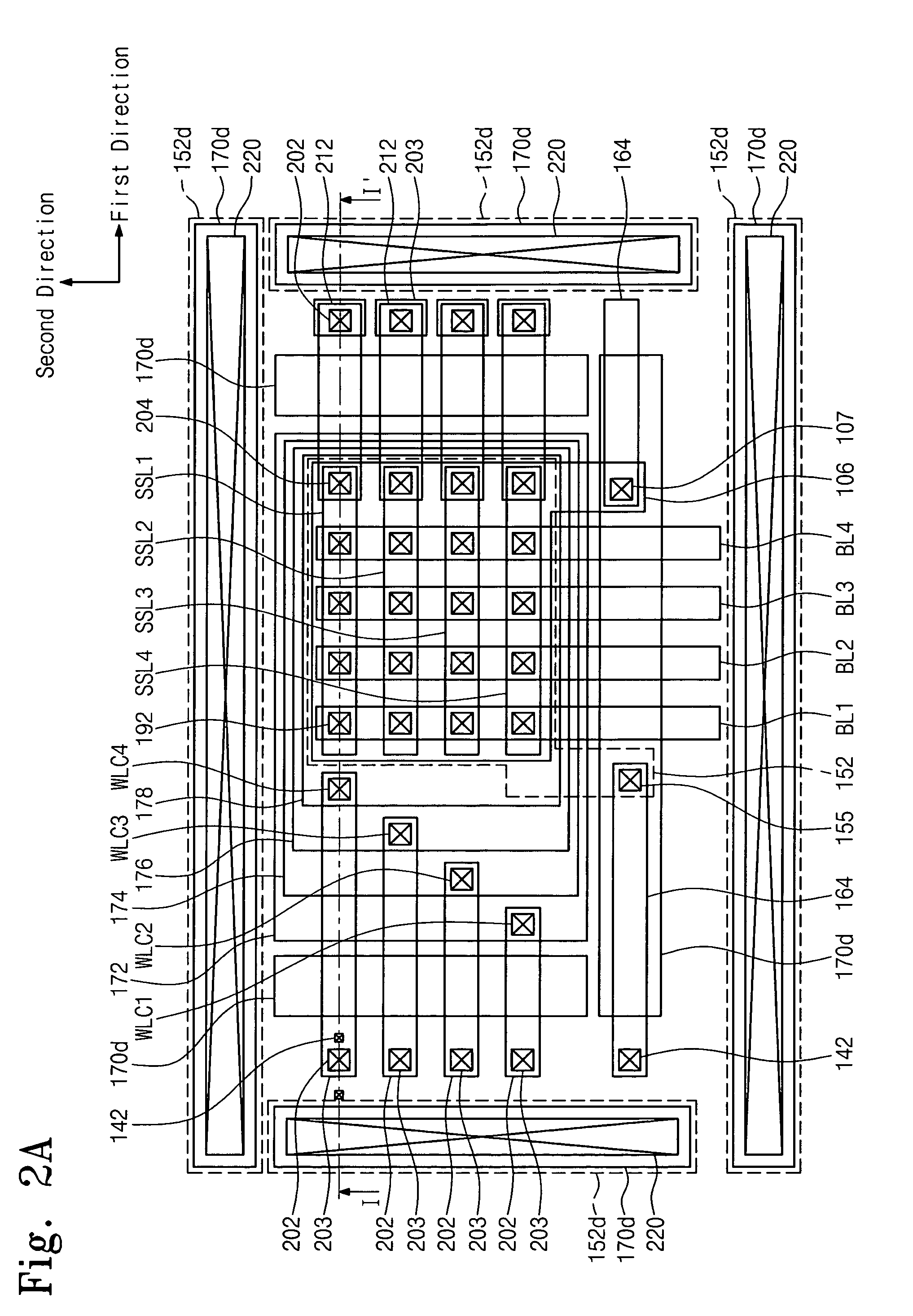

Nonvolatile memory device and method of manufacturing the same

ActiveUS20130161821A1Semiconductor/solid-state device detailsSolid-state devicesCell regionEngineering

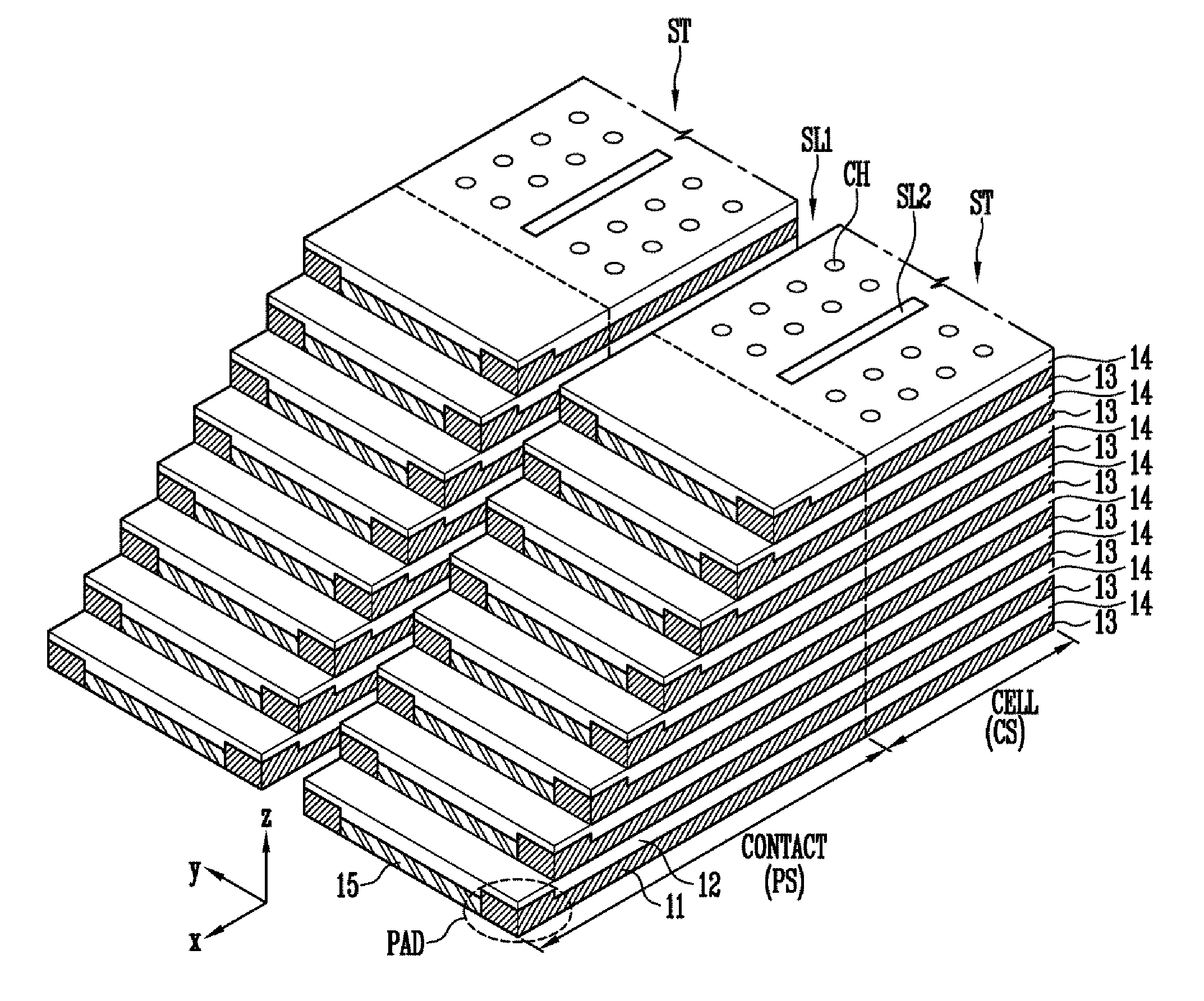

A nonvolatile memory device includes a substrate including a cell region, contact regions and dummy contact regions. The contact regions and the dummy contact regions alternately are disposed. A plurality of word lines stacked at the cell region of the substrate and contact groups stacked at the contact regions and the dummy contact regions of the substrate. The contact groups include a plurality of pad layers being coupled to the word lines, and each of the contact groups has stepped structure disposed at a corresponding contact region.

Owner:SK HYNIX INC

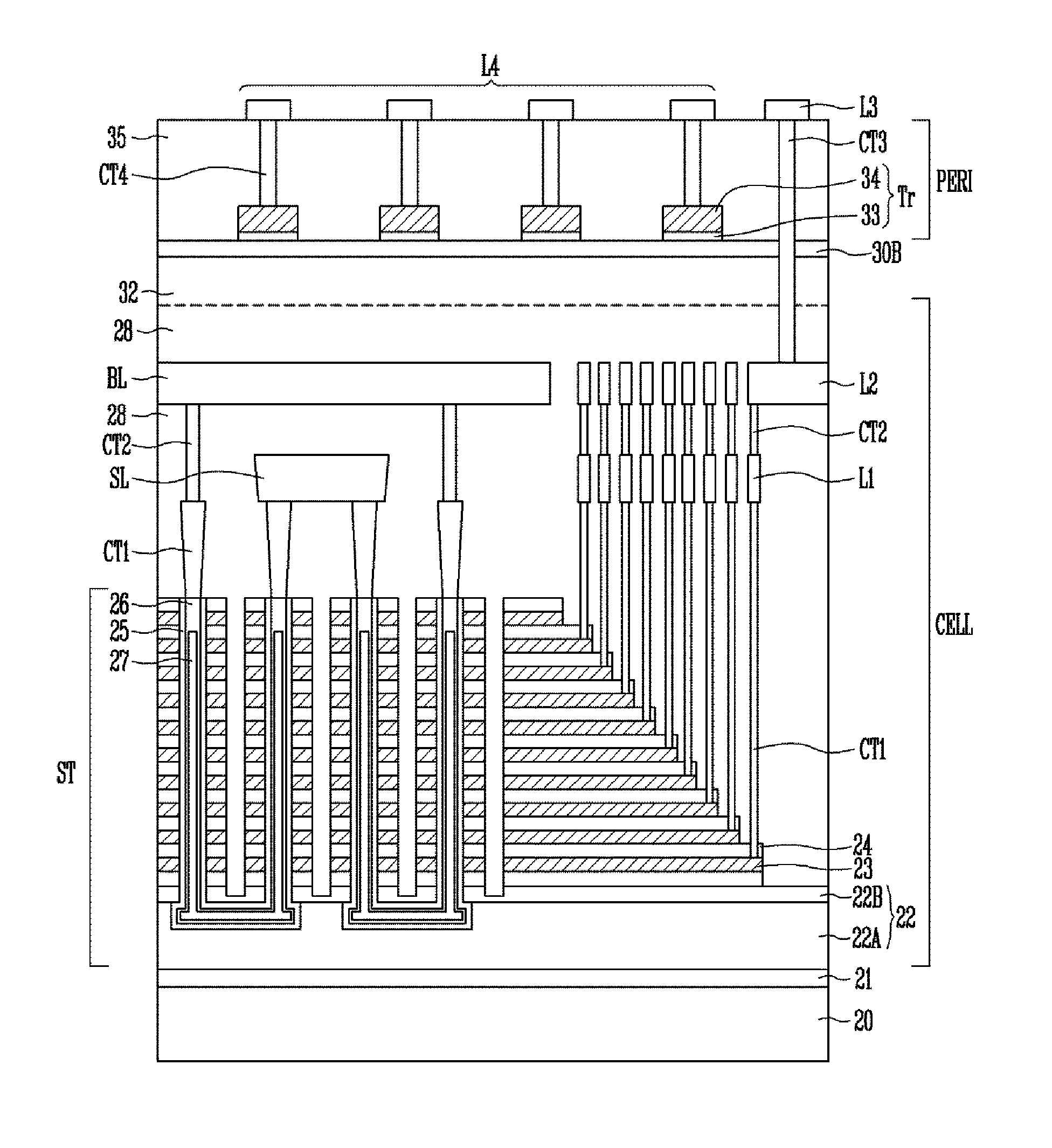

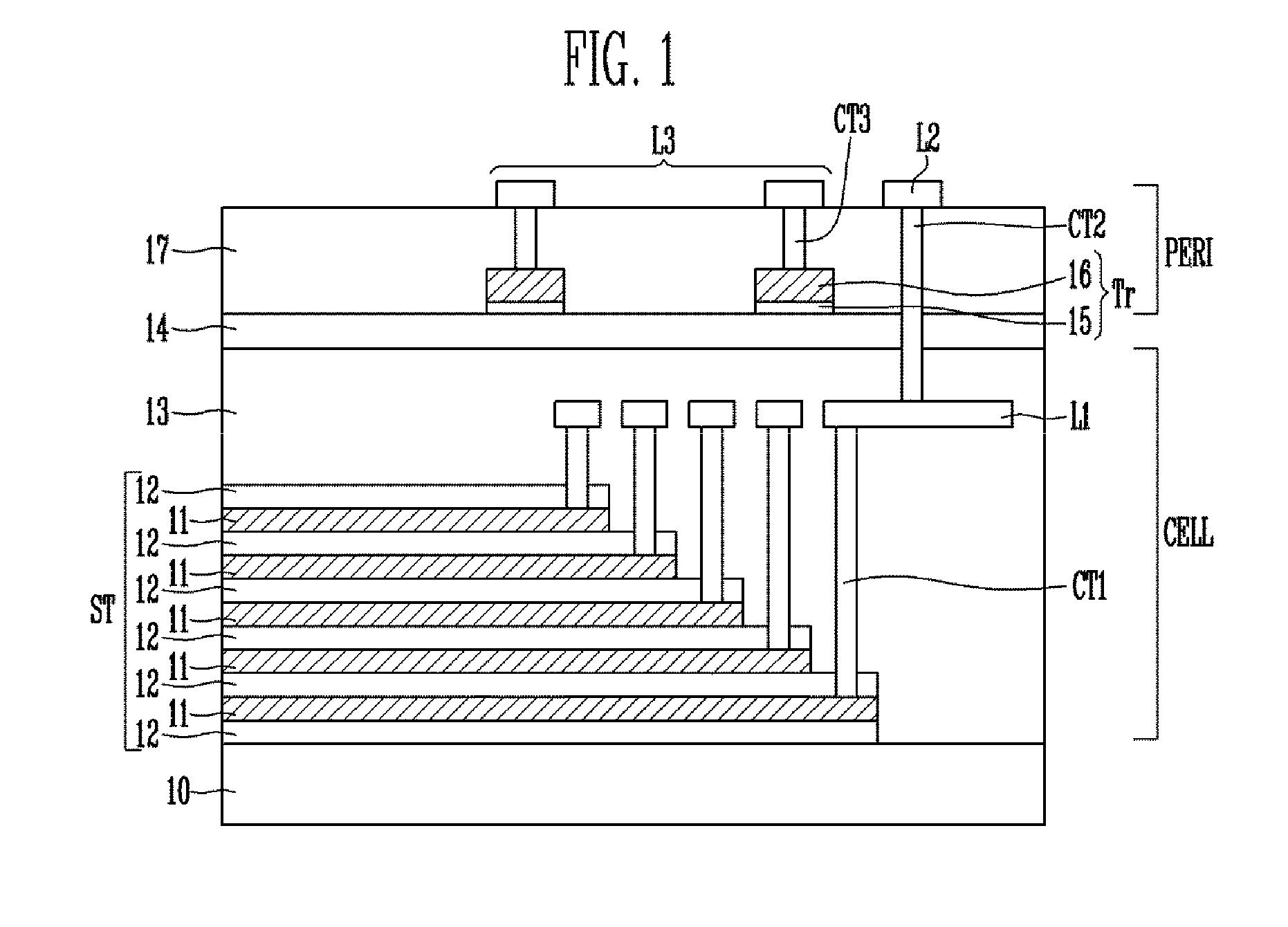

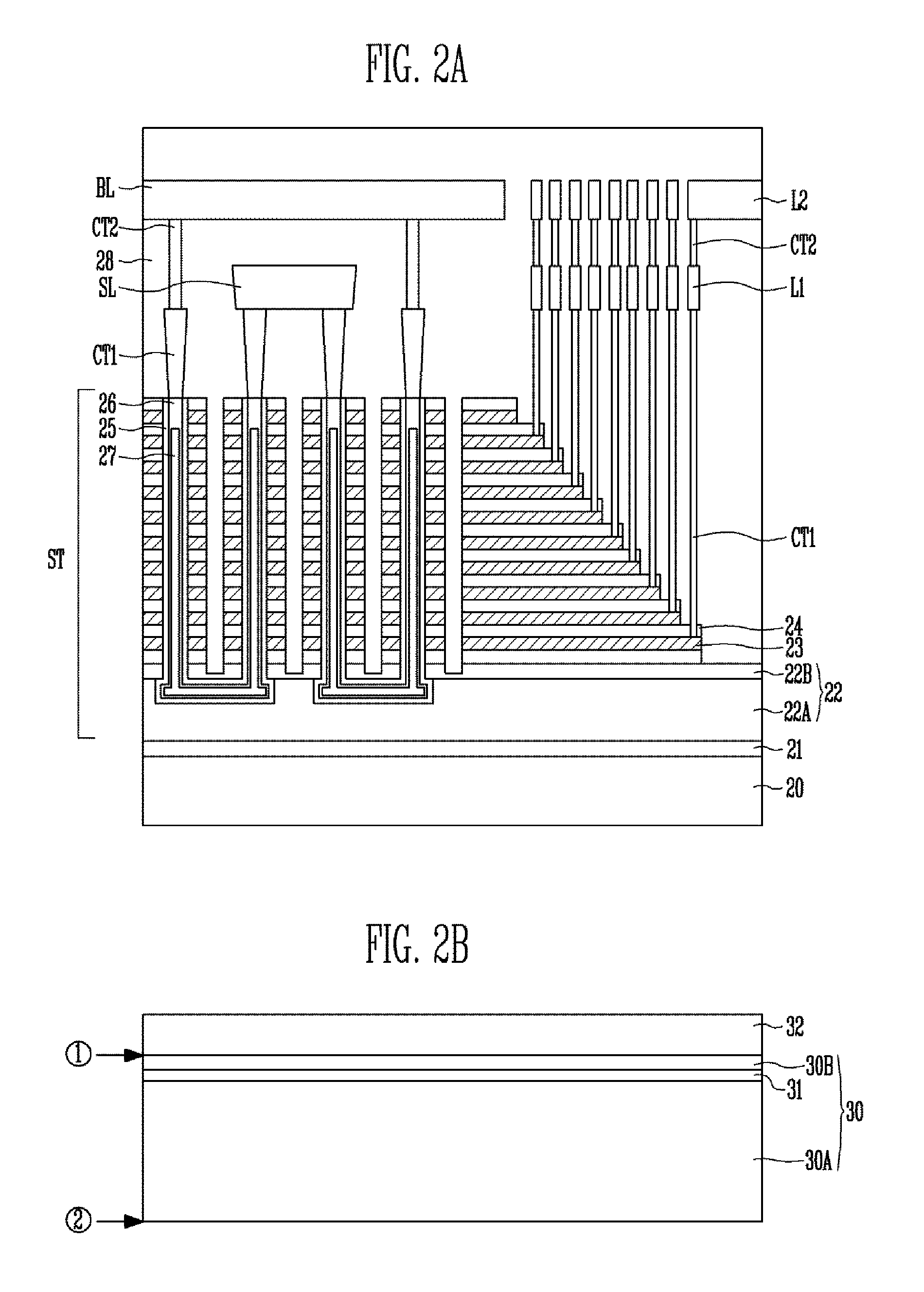

Semiconductor device and method of manufacturing the same

ActiveUS20140061750A1Highly integratedSolid-state devicesSemiconductor/solid-state device manufacturingCell regionEngineering

A semiconductor memory device includes a first substrate on which a cell region is defined. In the cell region, memory cells are stacked. A second substrate is located above the first substrate, and a peripheral region is defined on the second substrate. One or more conductive lines are located in the peripheral region. The one or more lines extend through the second substrate and couple to the cell region.

Owner:SK HYNIX INC

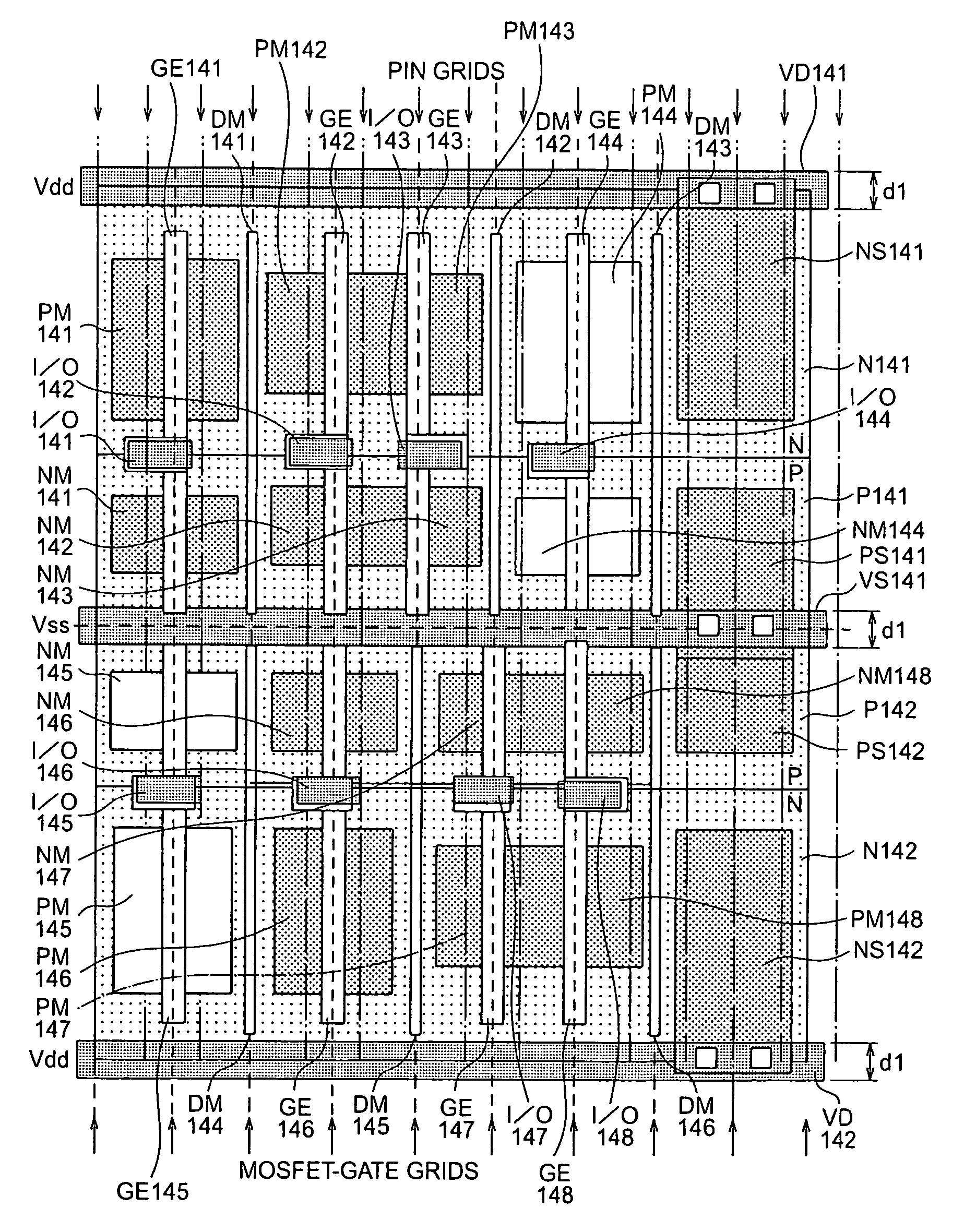

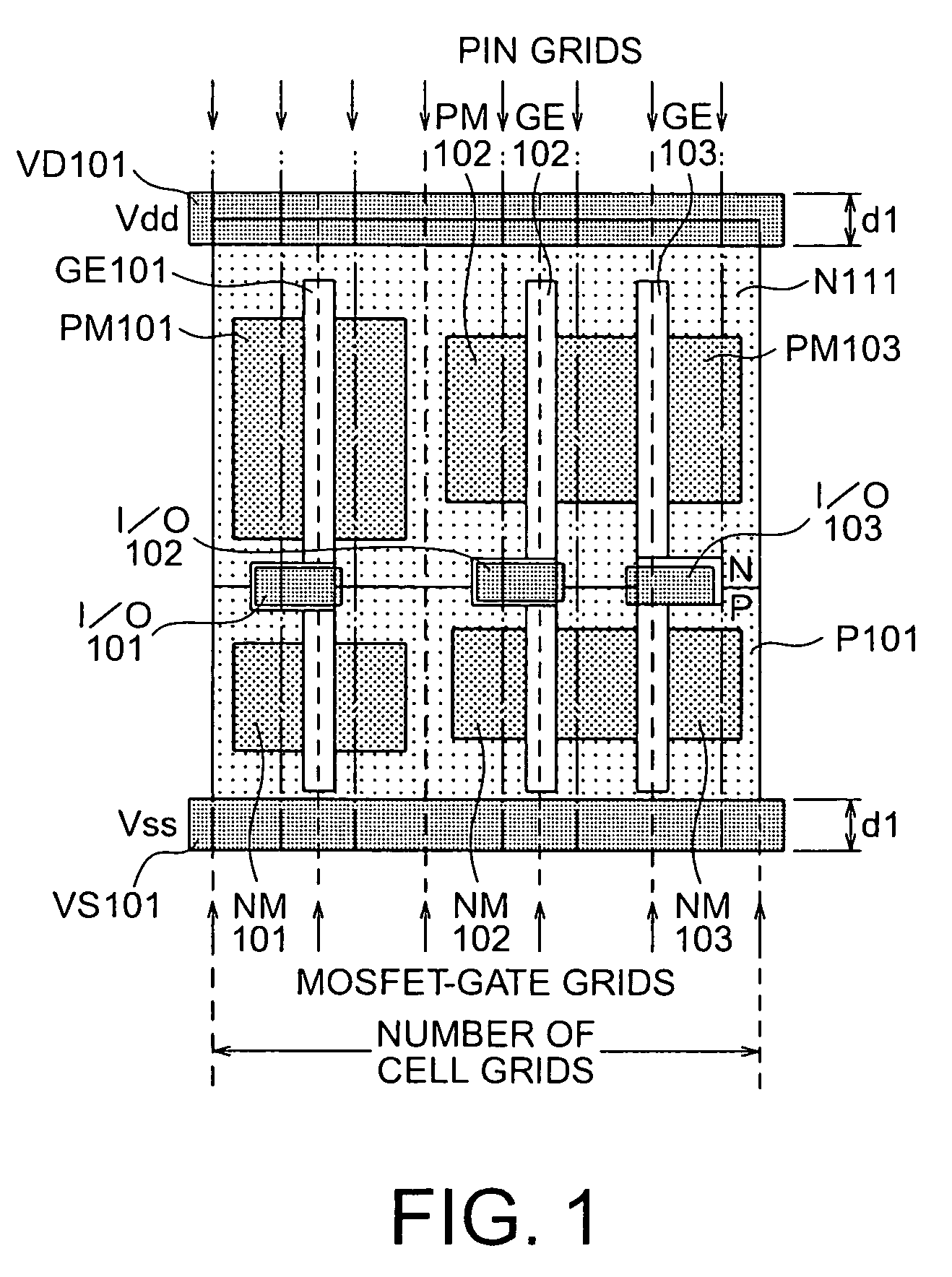

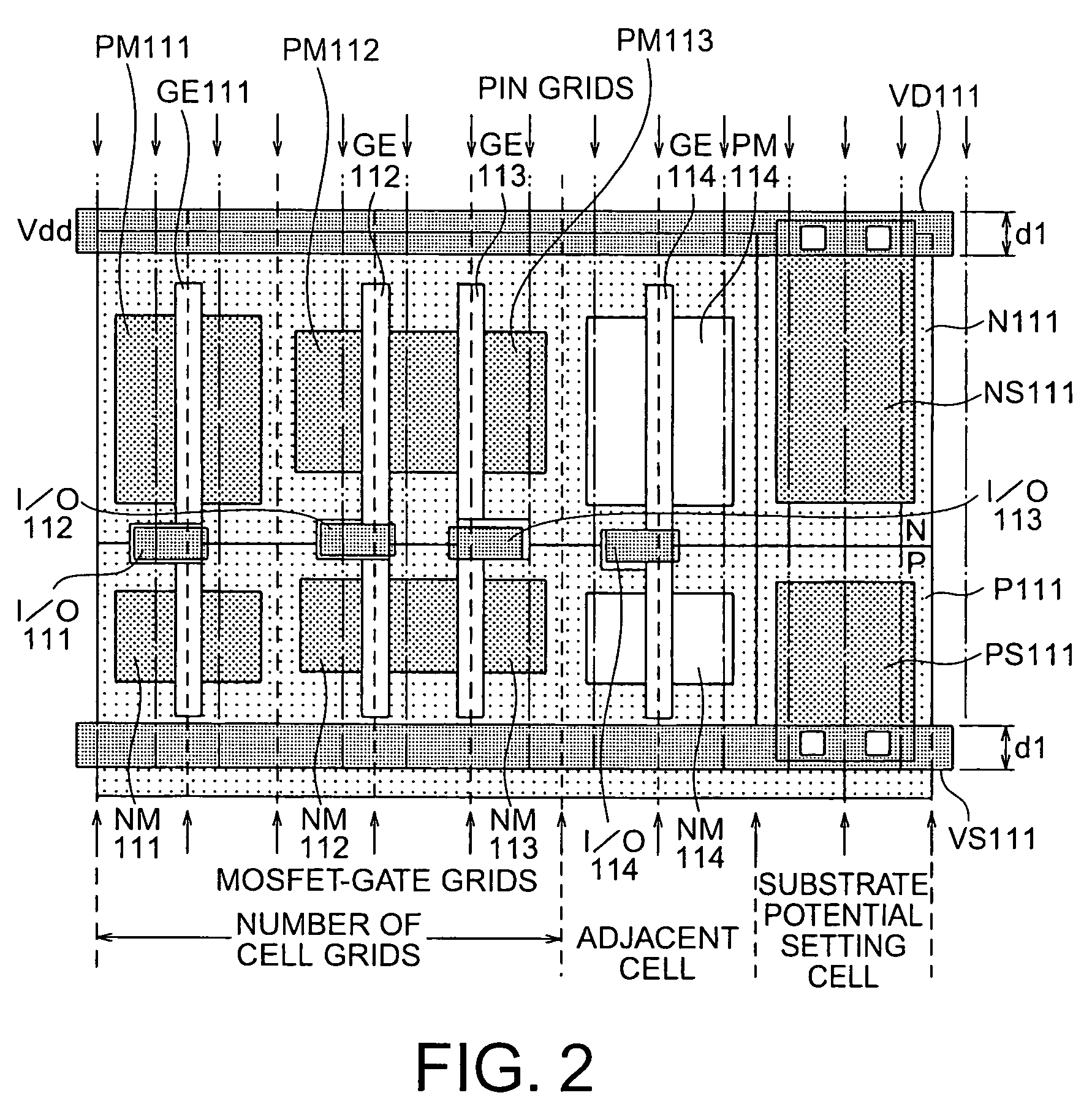

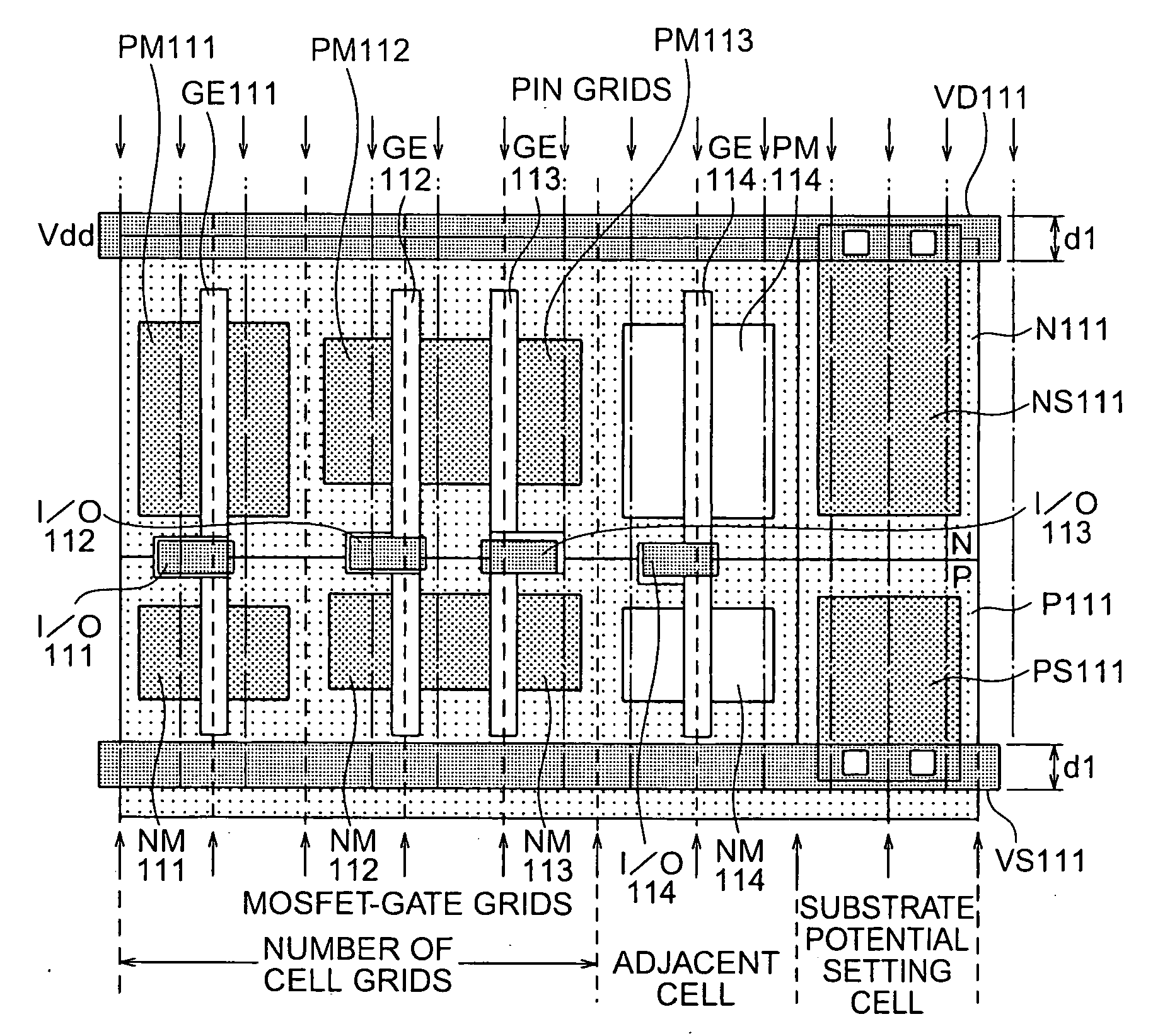

Semiconductor integrated circuit and method of designing the same

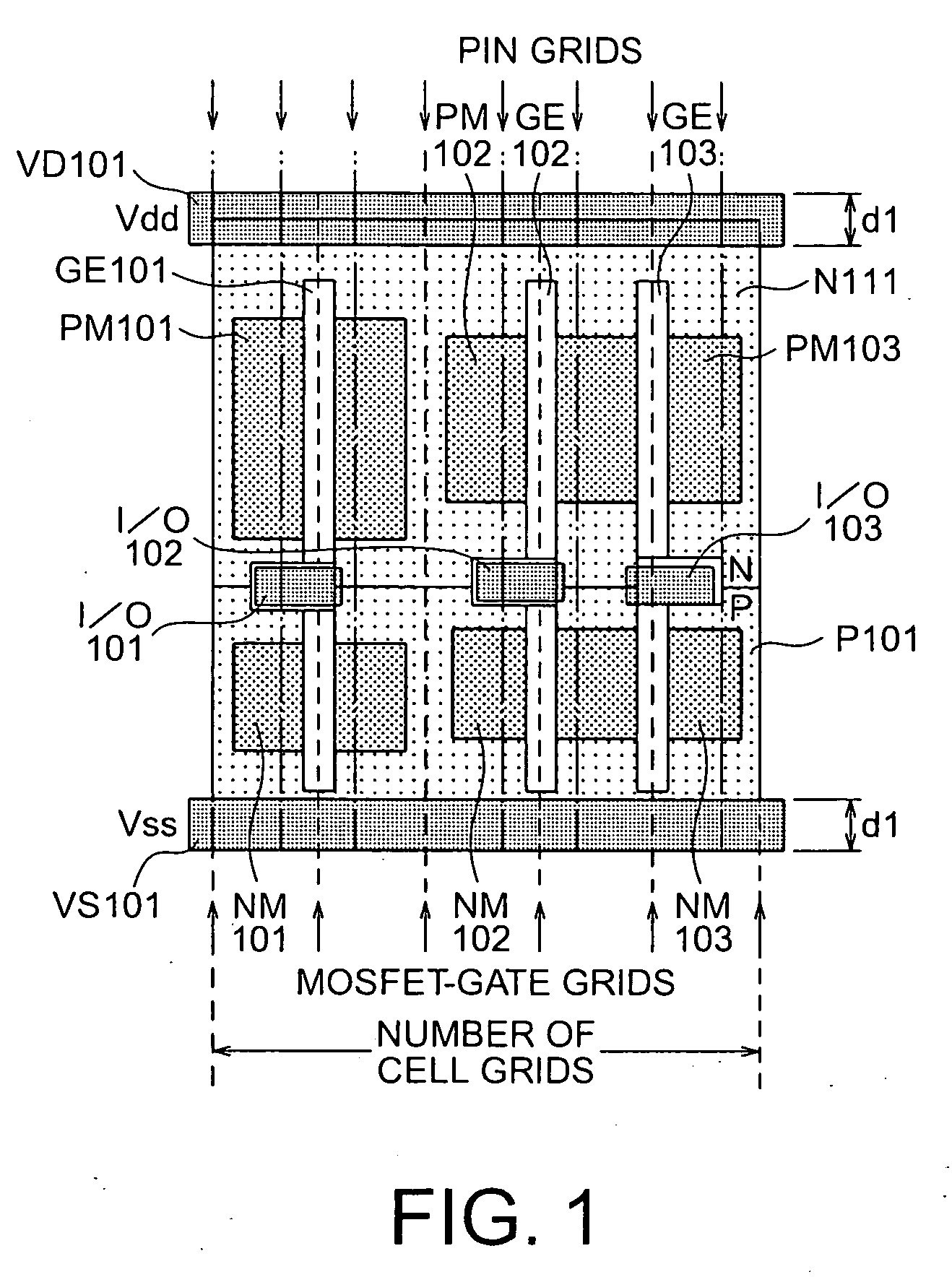

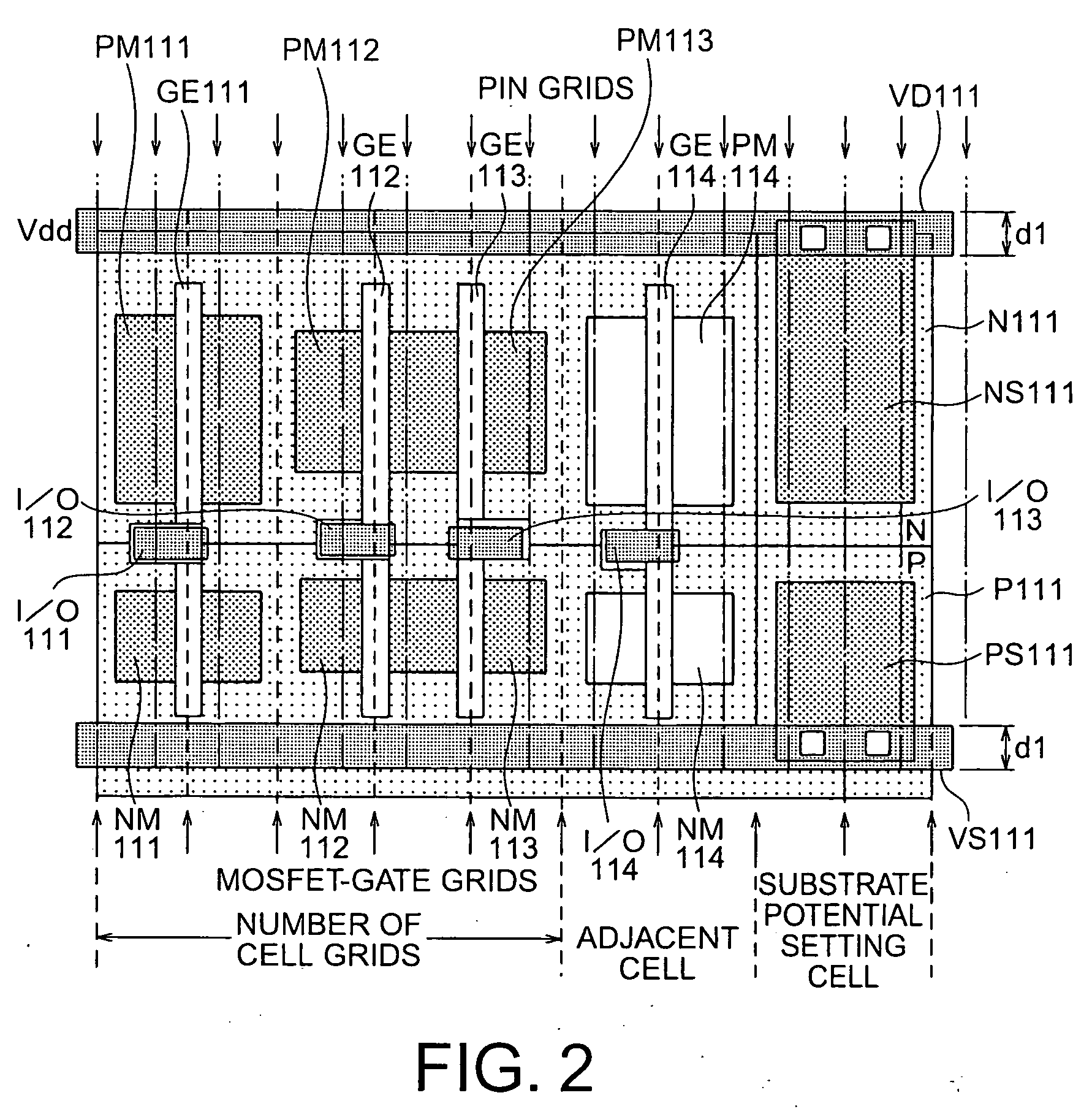

InactiveUS7205191B2Semiconductor/solid-state device detailsSolid-state devicesCell regionInterconnection

According to the present invention, a semiconductor integrated circuit having a cell region in which a plurality of MOS transistors forming at least one cell are placed; and first and second power lines placed along one direction in a peripheral portion of the cell region, wherein in the cell region, gate grids for defining a first pitch in the one direction and pin grids for defining a second pitch in the one direction are set, gate electrodes of the MOS transistors are placed in accordance with the gate grids, and an interconnection layer is placed in accordance with the pin grids.

Owner:KK TOSHIBA

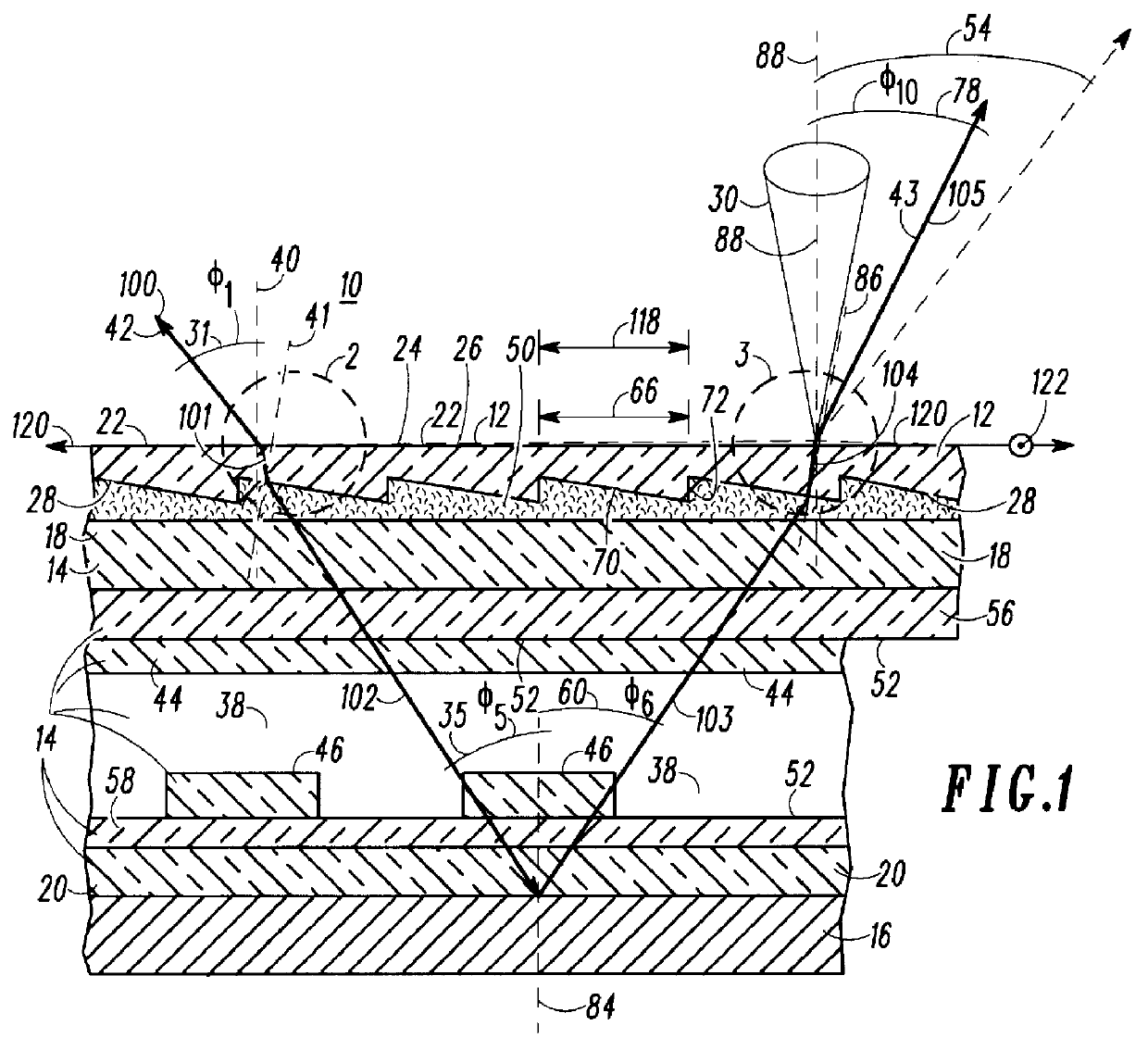

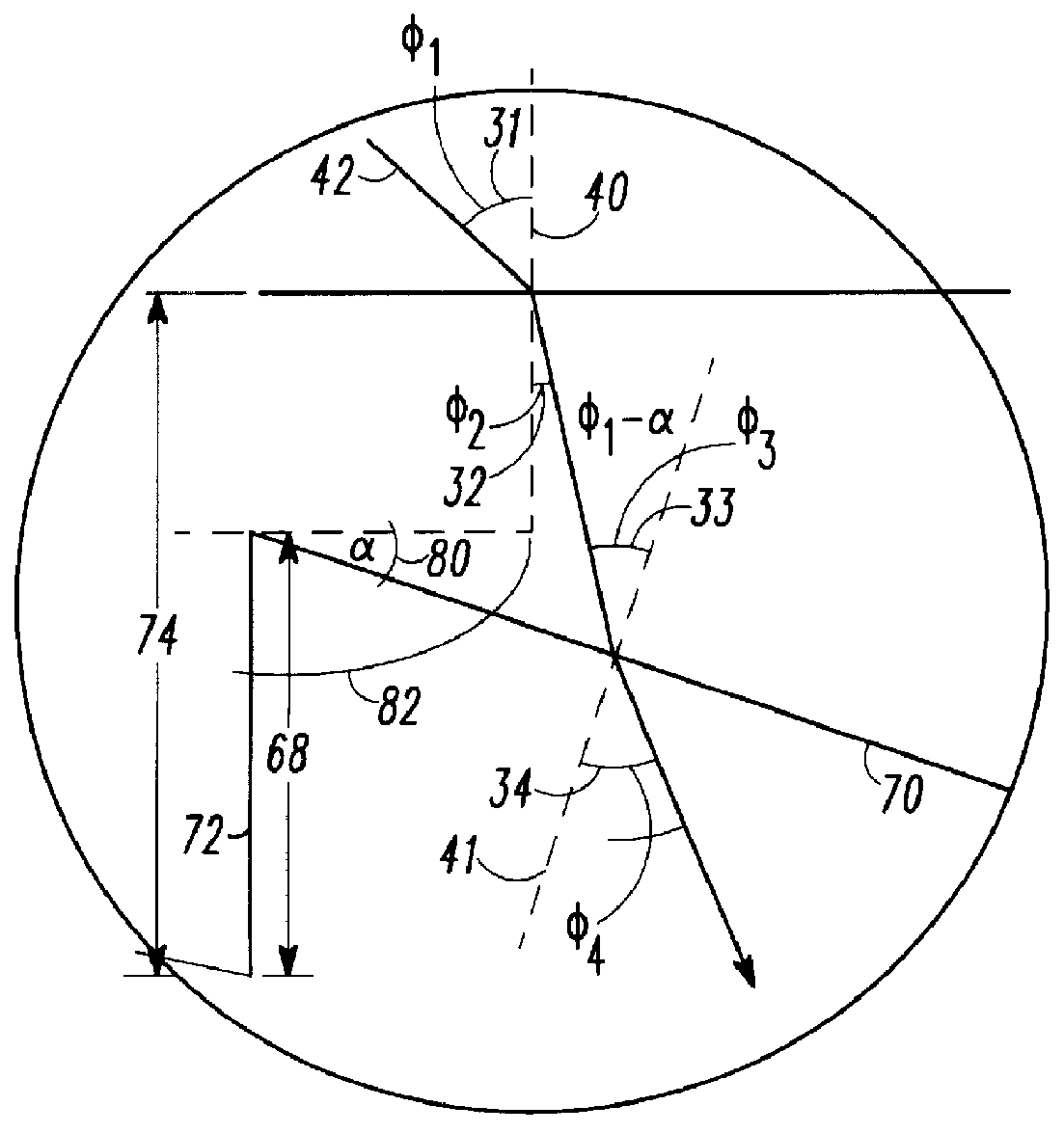

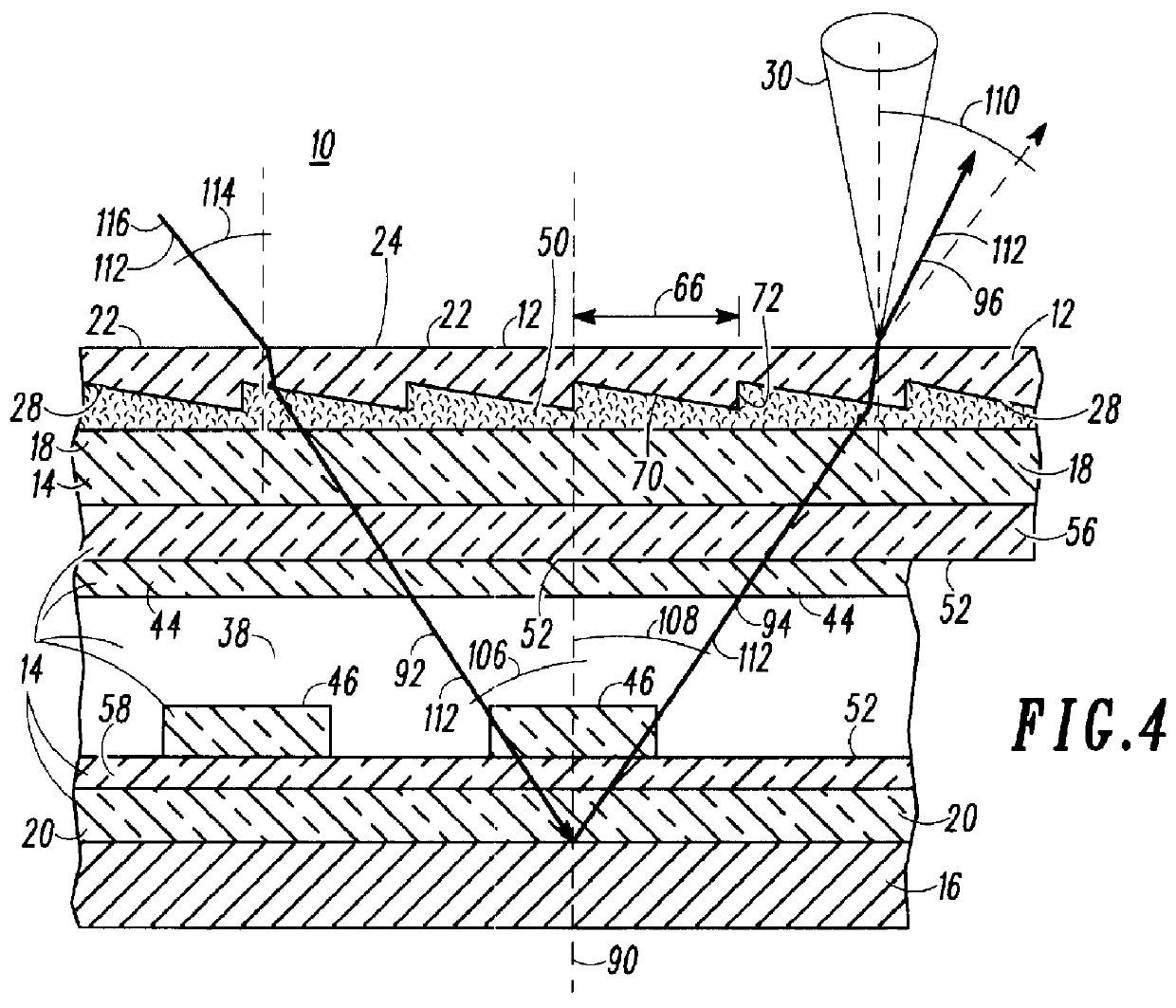

Optical display device having prismatic film for enhanced viewing

InactiveUS6166787AImprove visibilityImprove legibilityPrismsLaser detailsOptical propertyOptical interaction

The display device includes an optical cell having a cell front with at least one cell region being capable of an optically transmissive mode and an optically nontransmissive mode with reference to the cell front. The optical cell contains an optically active material responsive to an applied electrical field such that optical properties of the material are controllably changeable. A reflector may be optically coupled to the cell. A prismatic film including a prismatic surface is optically coupled to the optical cell. The prismatic surface preferably comprises a series of prisms. The prisms have first faces and second faces intersecting the first faces. The first faces are oriented to refract light obliquely intercepting the first faces and the second faces are oriented to minimize refractive, reflective, and optical interactions of the light with the second faces. The prismatic film, the cell, and the reflector optically cooperate such that light entering a display at an incident angle is emitted from the display at an exiting angle distinct from the incident angle for viewing of the display.

Owner:GOOGLE TECH HLDG LLC

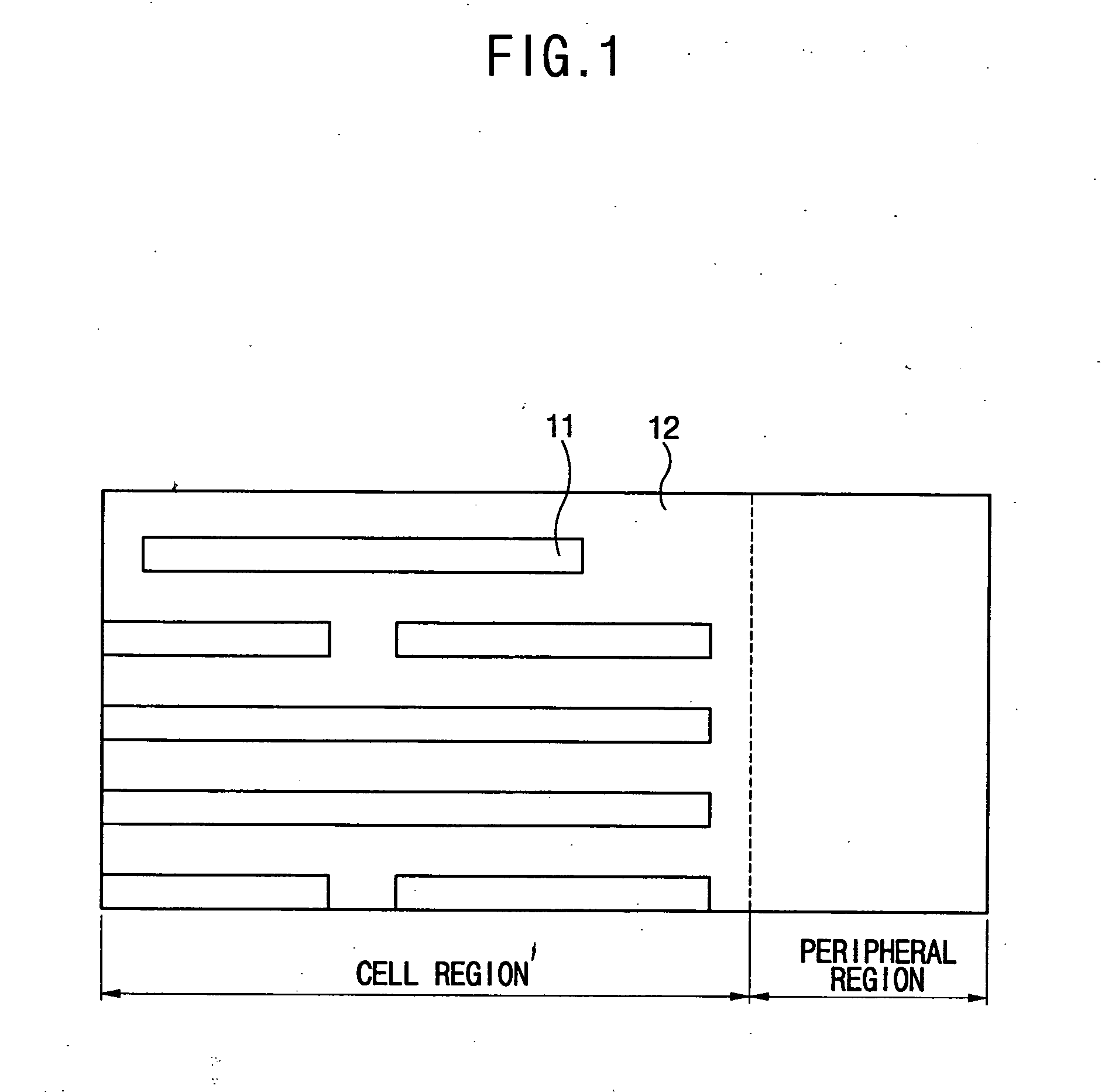

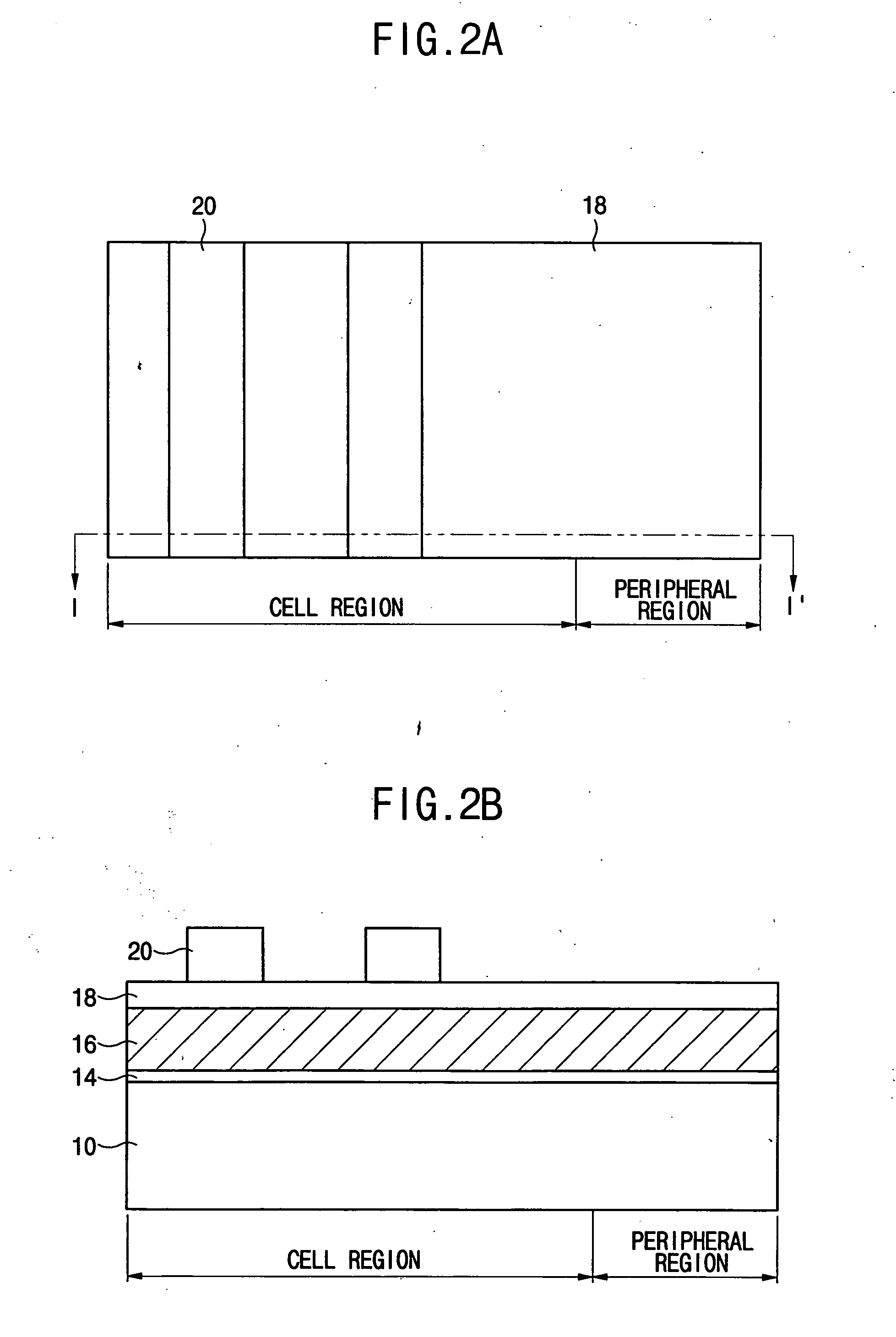

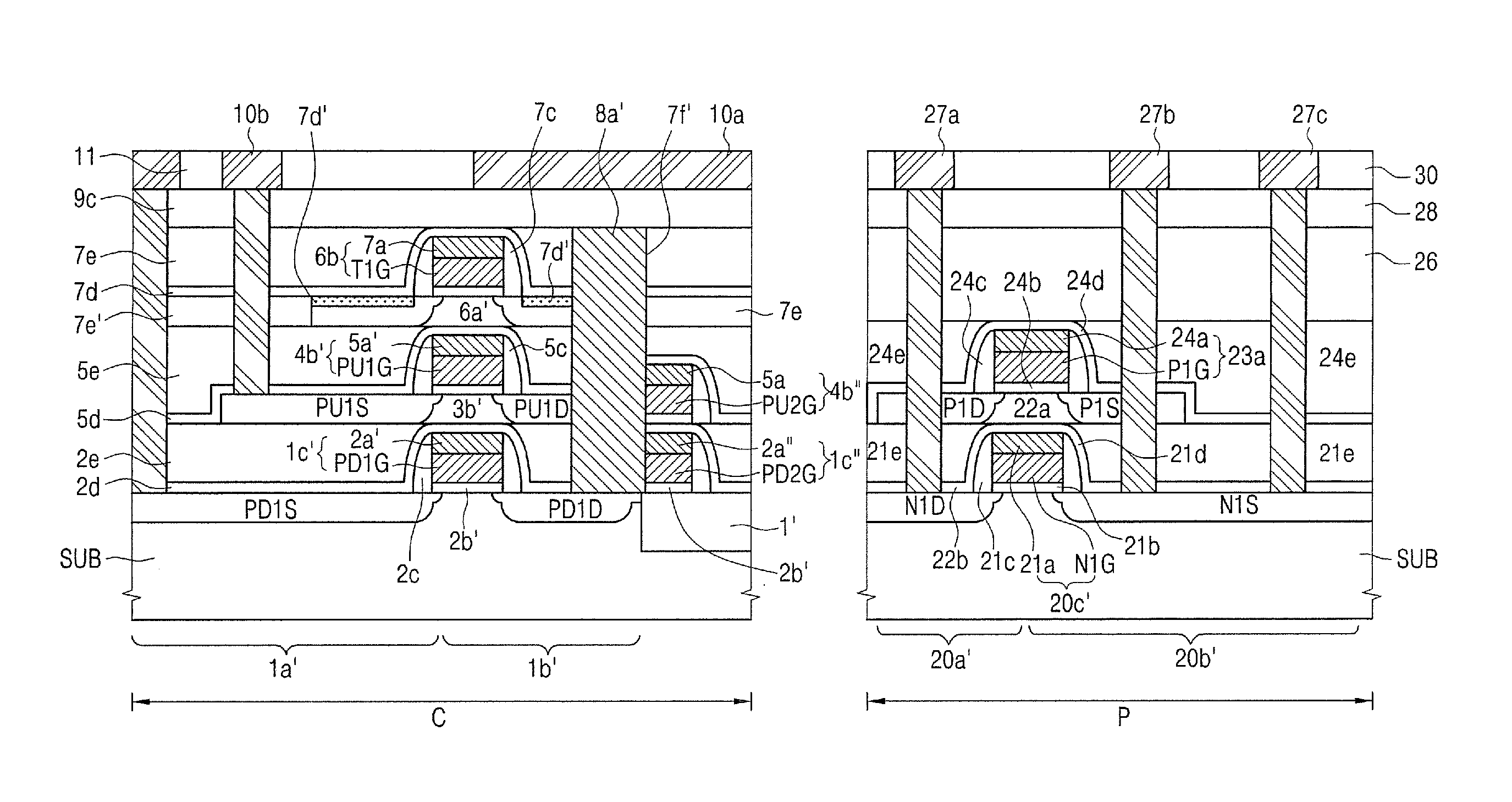

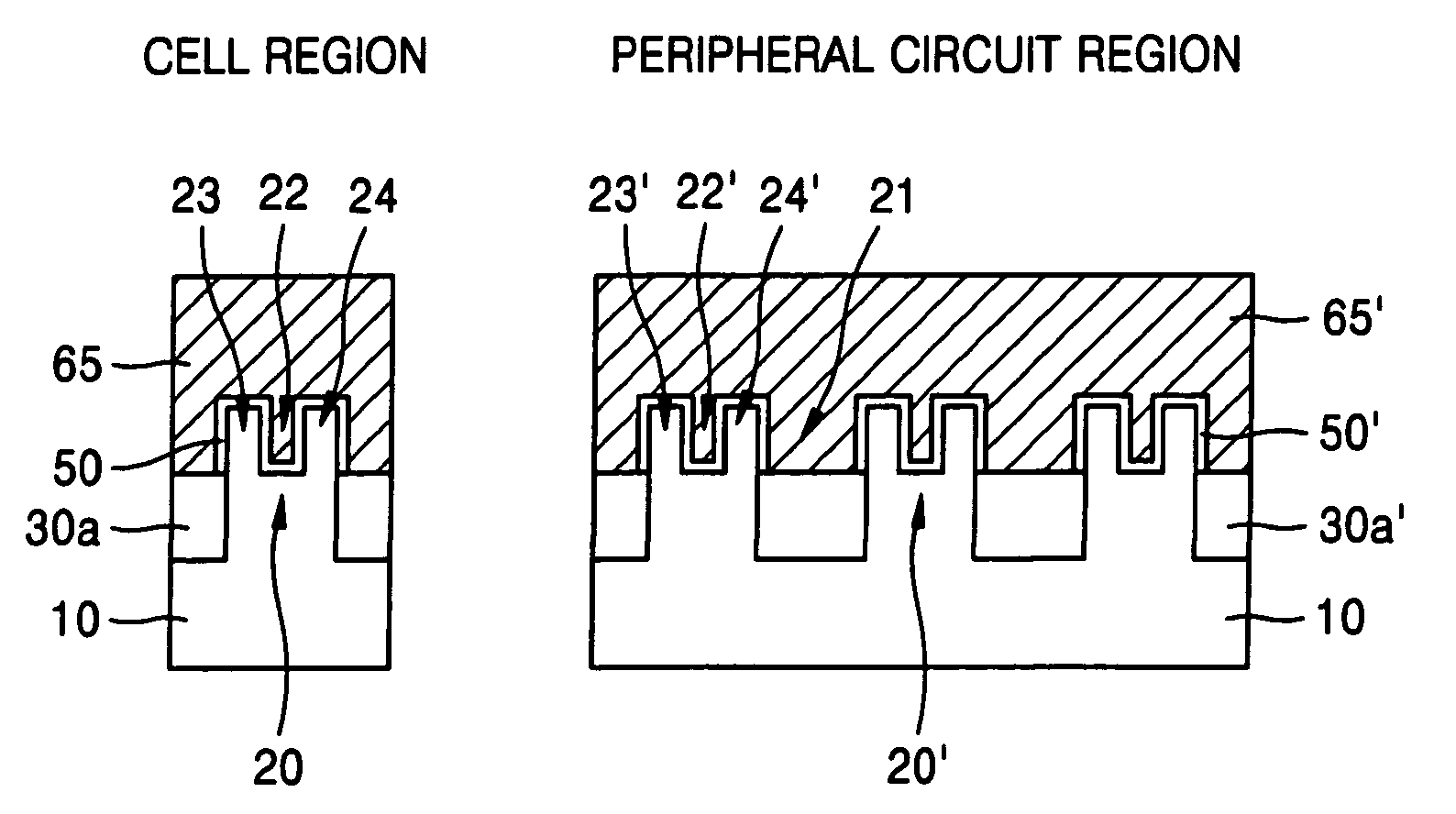

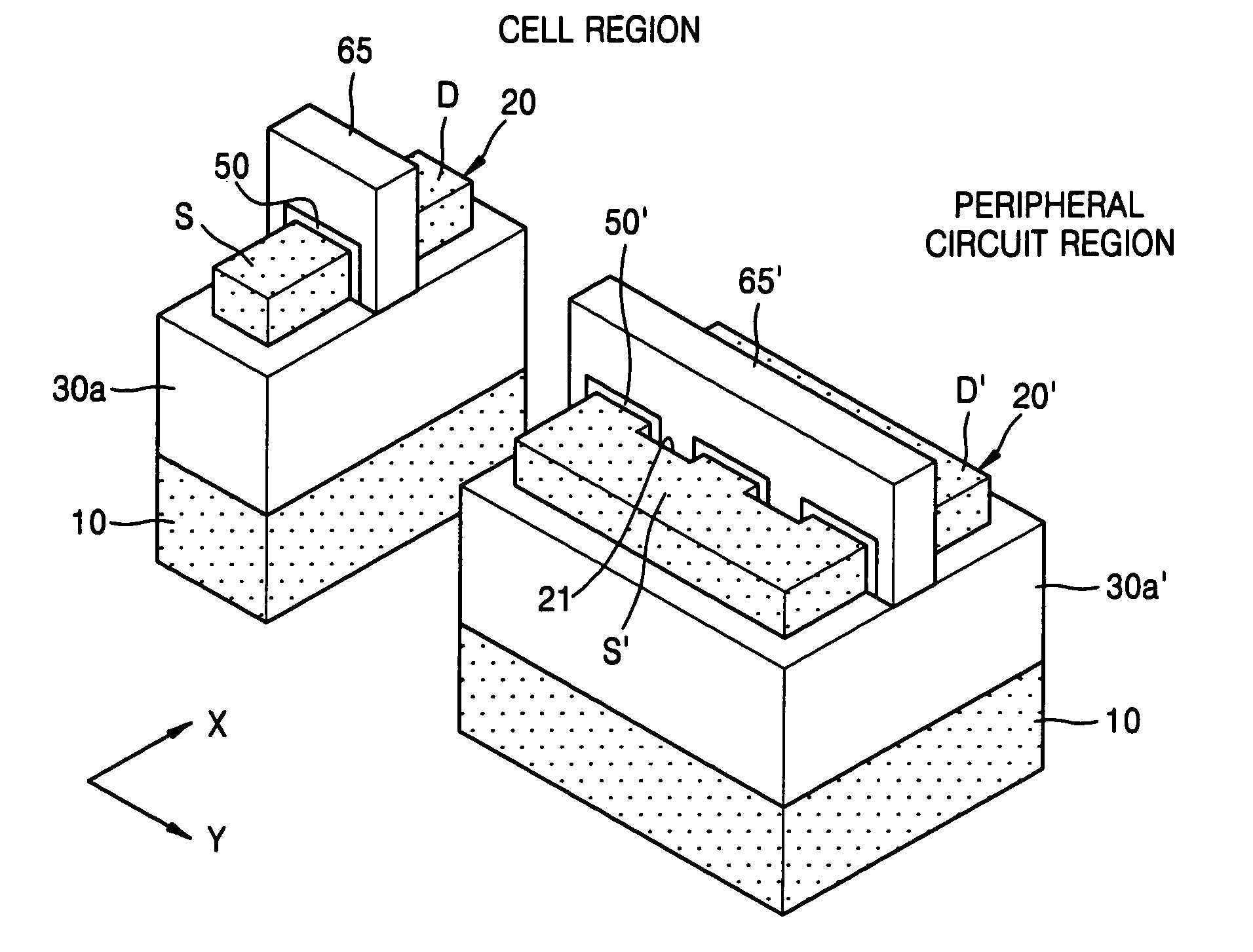

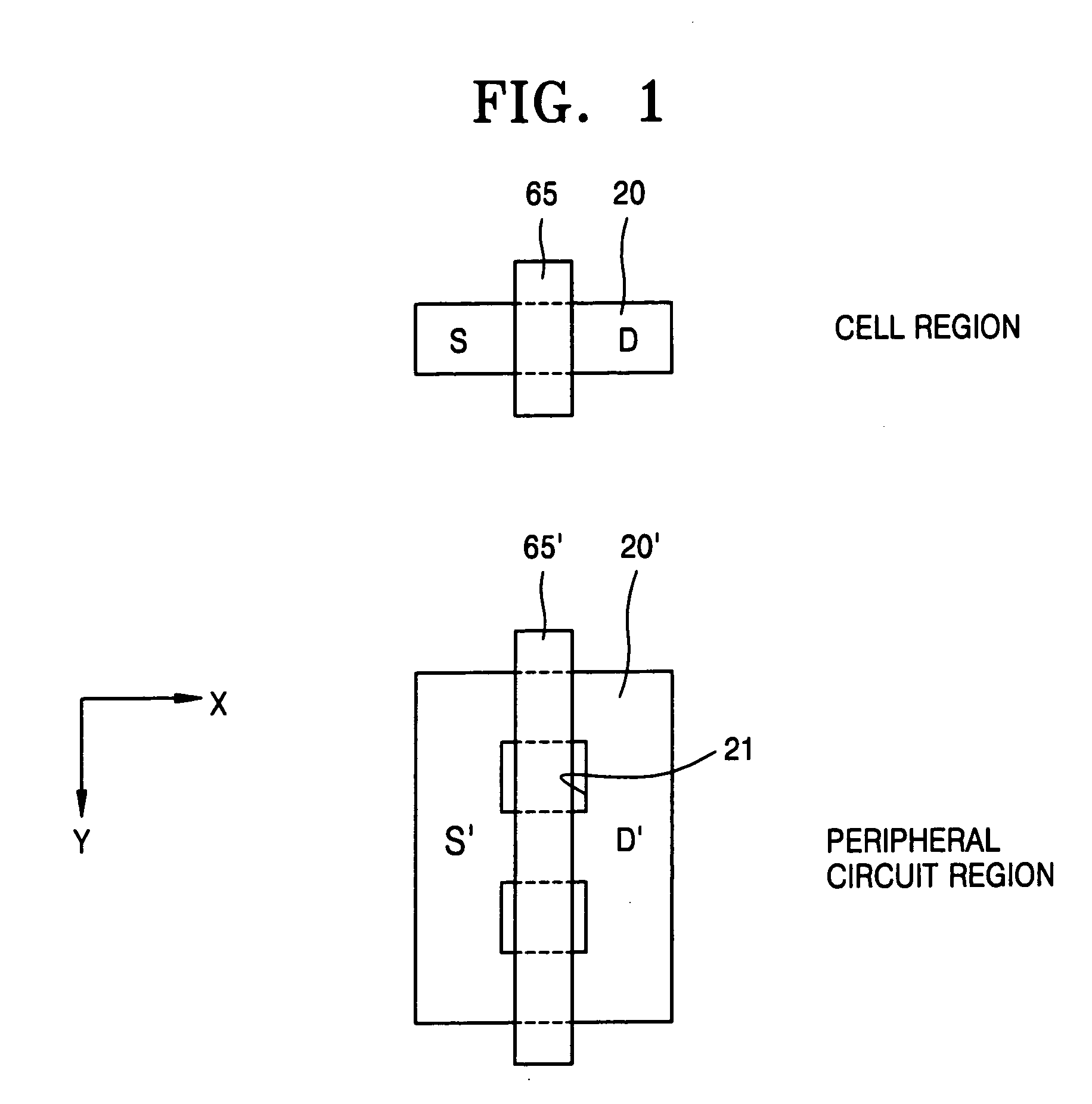

Semiconductor device including a multi-channel fin field effect transistor including protruding active portions and method of fabricating the same

ActiveUS7394116B2Increase the effective channel lengthIncrease the current levelTransistorSolid-state devicesGate dielectricDevice material

In a semiconductor device, and a method of fabricating the same, the semiconductor device includes a semiconductor substrate having a cell region and a peripheral circuit region, a portion of the semiconductor substrate in the cell region and in the peripheral circuit region including an isolation region defining an active region, a portion of the active region protruding above an upper surface of the isolation region to define at least two active channels, a gate dielectric layer formed over the active region of the semiconductor substrate including the at least two protruding active channels, a gate electrode formed over the gate dielectric layer and the isolation region of the semiconductor substrate, and a source / drain region formed in the active region of the semiconductor substrate on either side of the gate electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

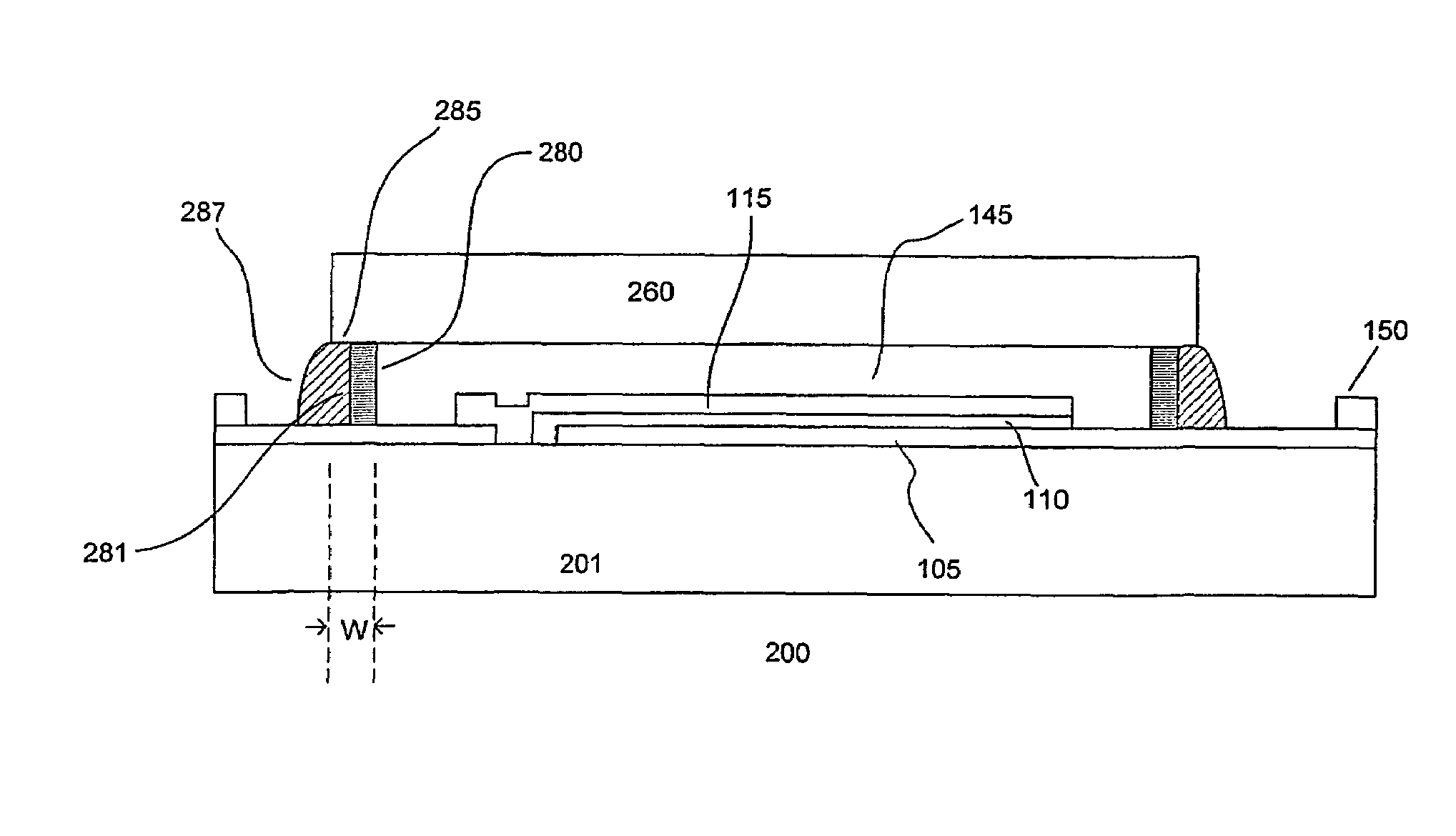

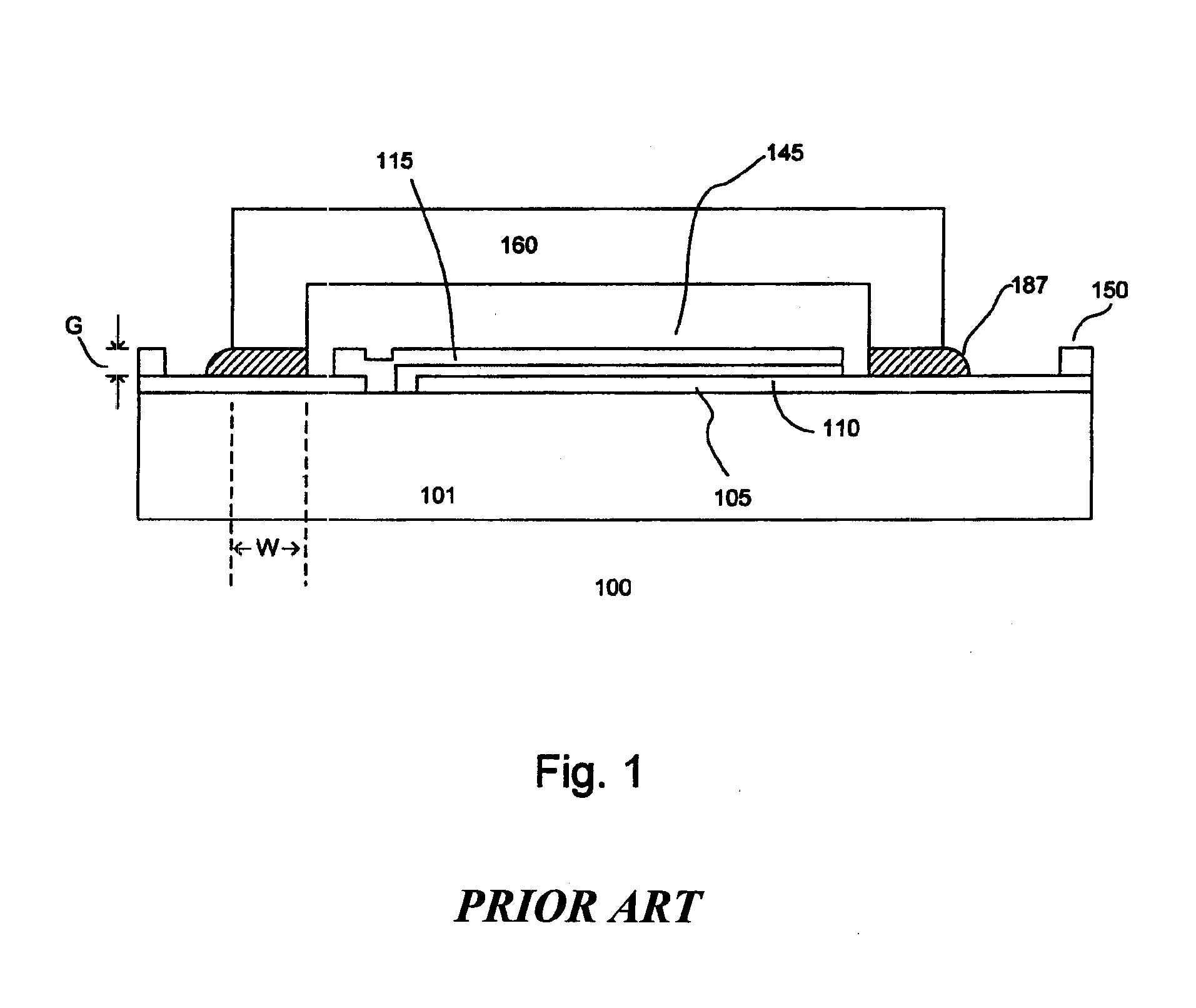

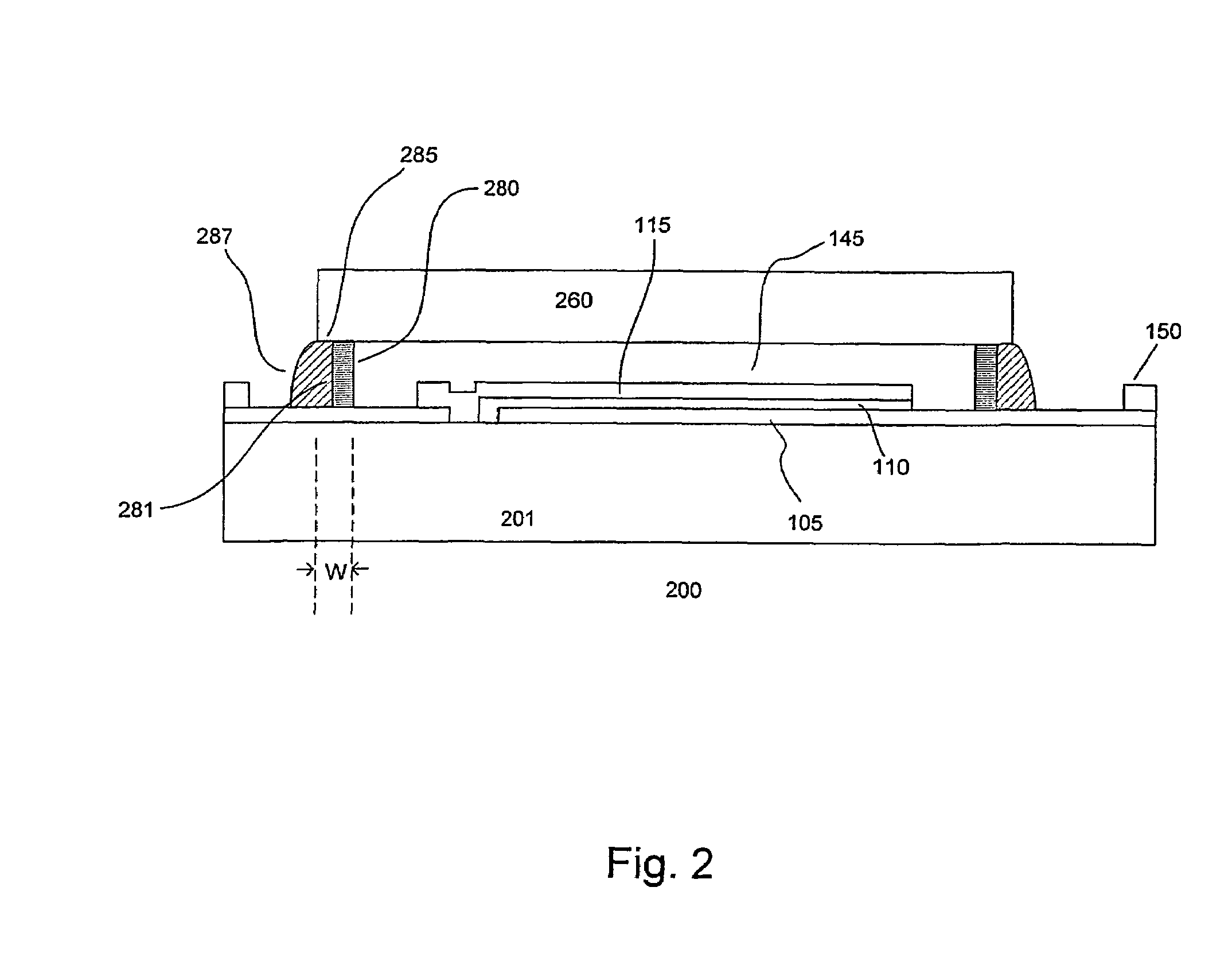

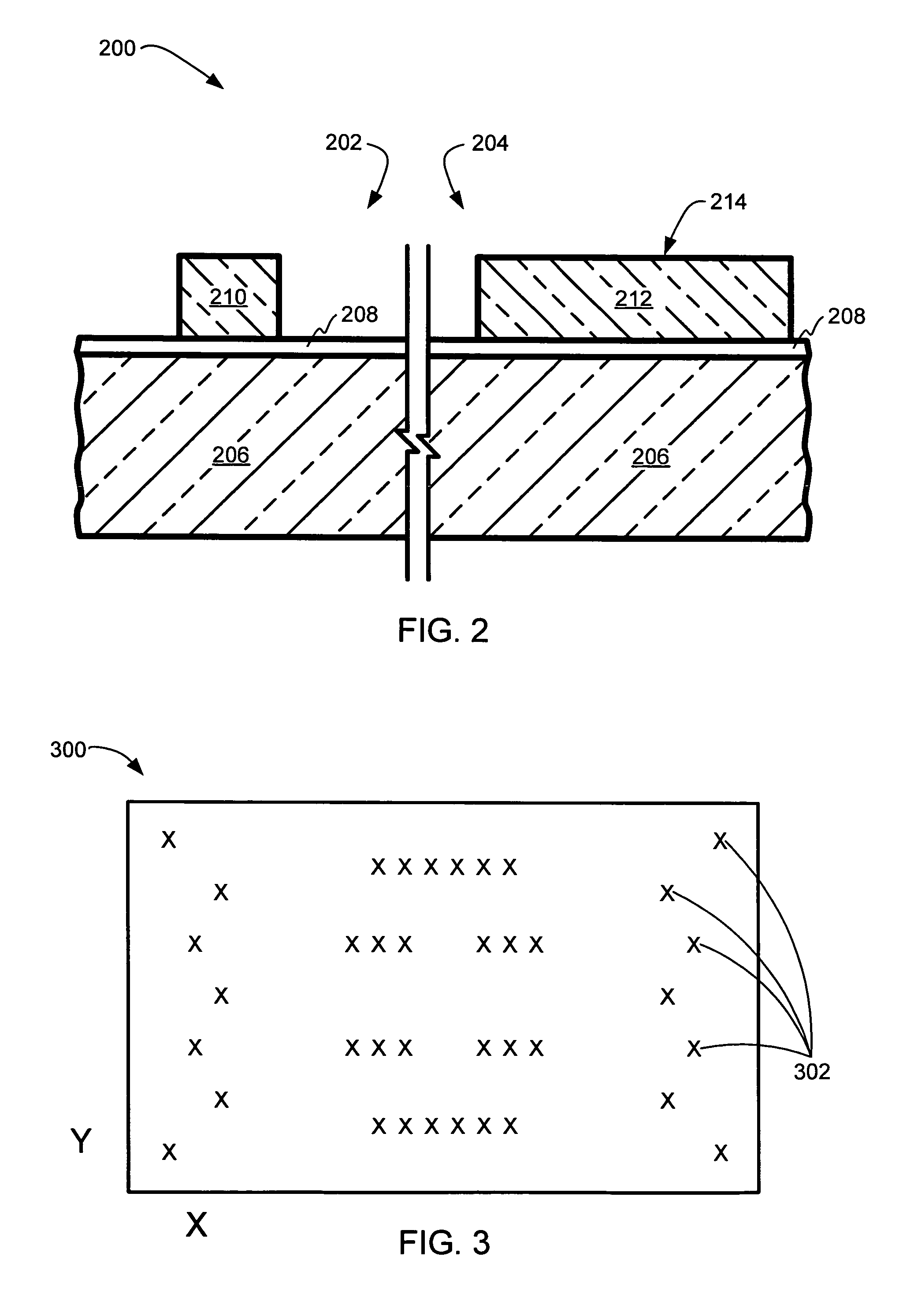

Encapsulation for oled devices

An encapsulation for an organic light emitting diode (OLED) (201) device is disclosed. The encapsulation includes a sealing dam (280) surrounding the cell region of the OLED device to support a cap. The sealing dam provides a sealing region between the edge of the cap and dam in which an adhesive is applied to seal the OLED device. The use of the sealing dam advantageously enables devices to be formed with narrower sealing widths.

Owner:OSRAM OPTO SEMICONDUCTORS GMBH +1

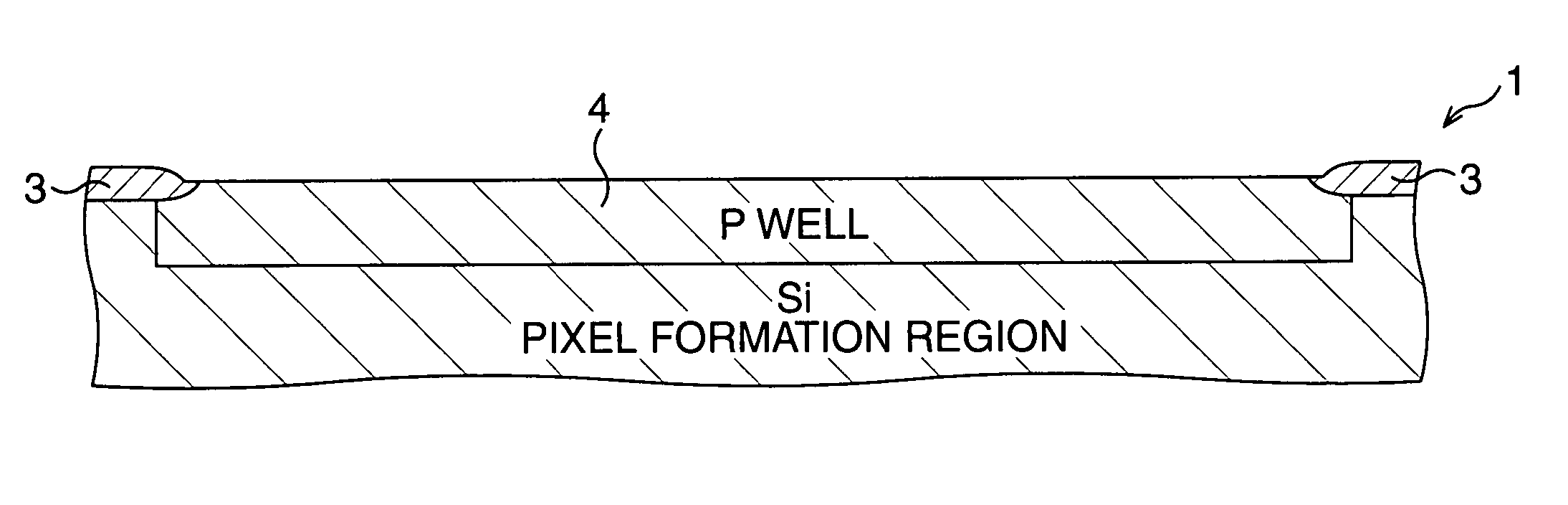

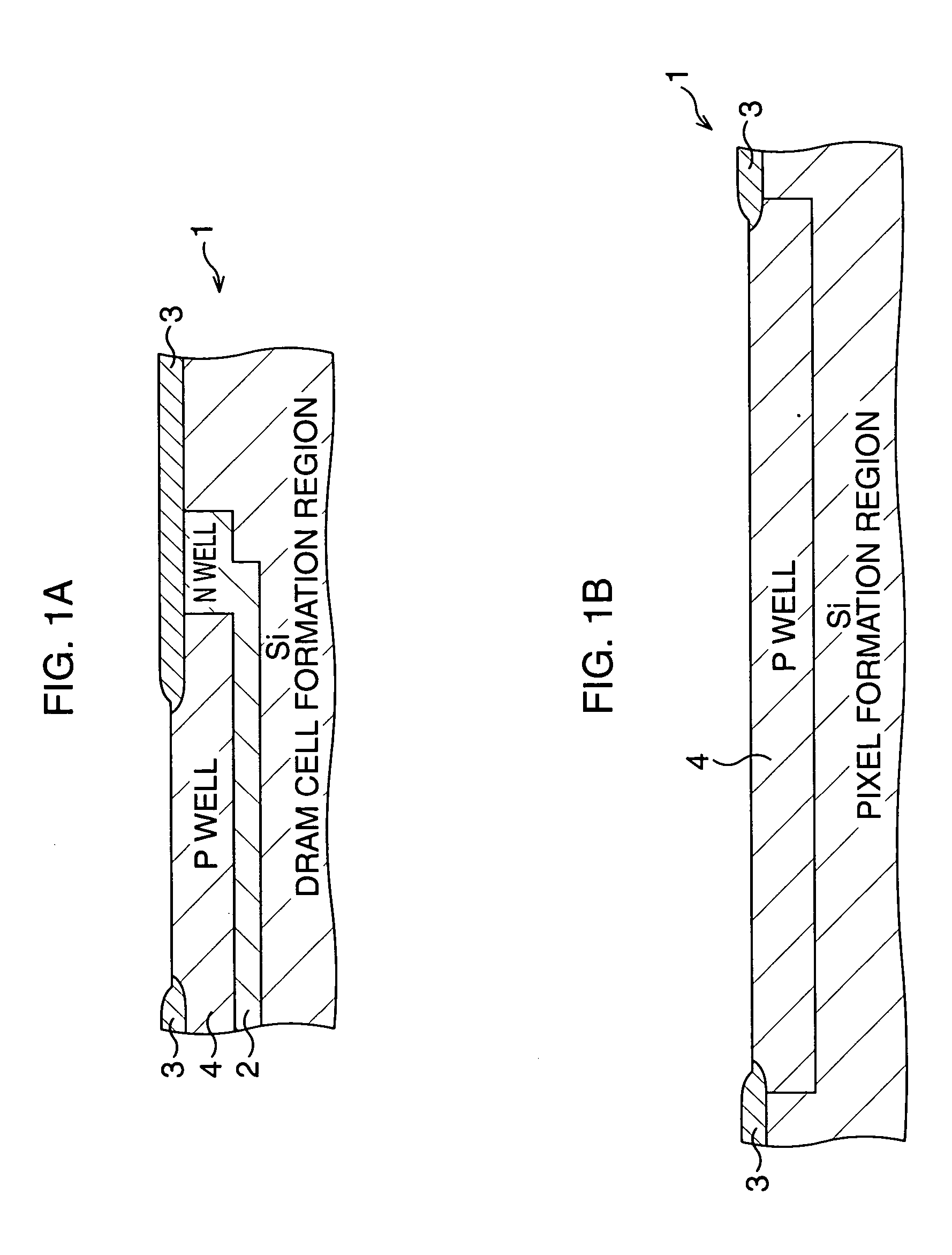

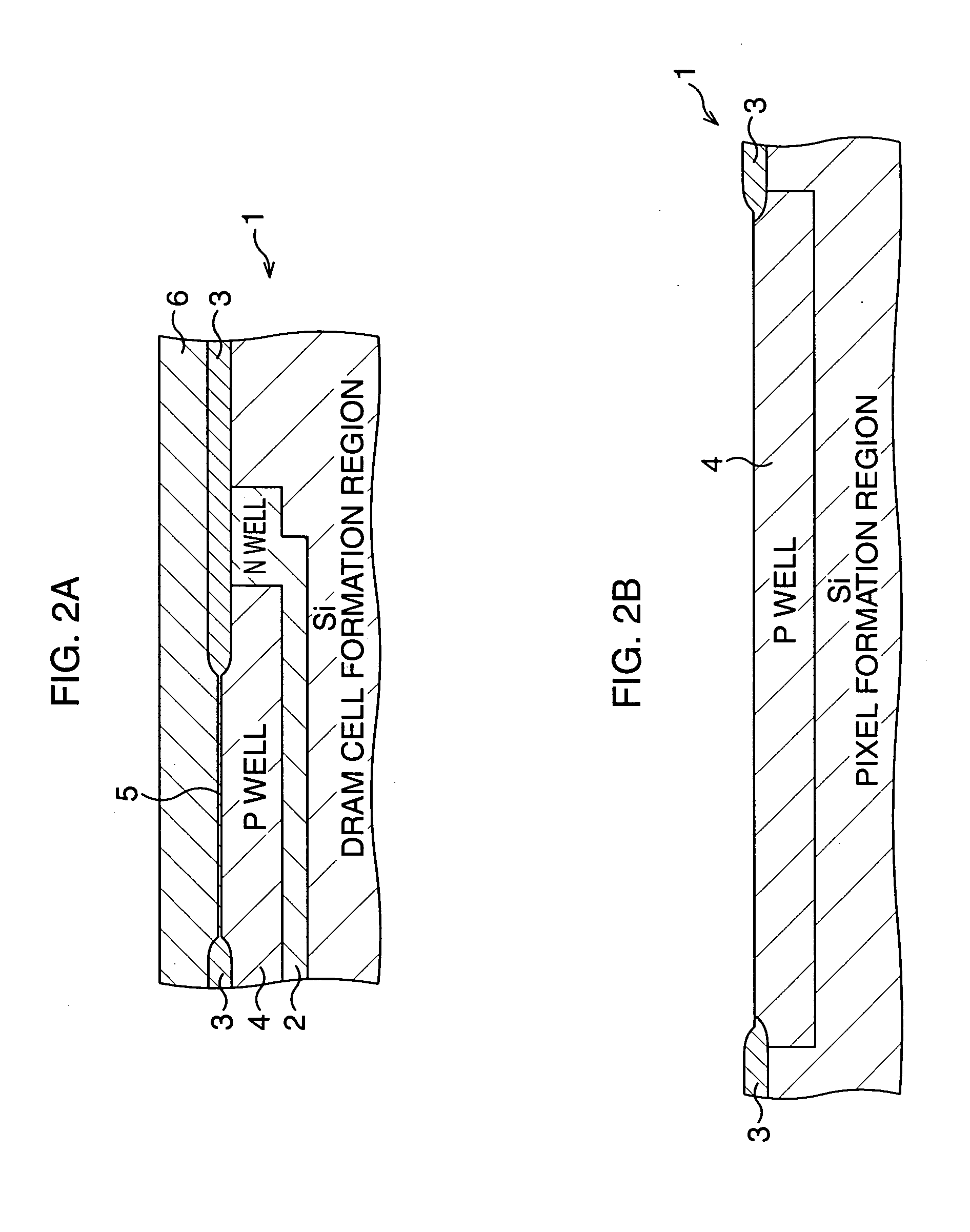

Semiconductor device, manufacturing process thereof and imaging device

InactiveUS20050224853A1Avoid desensitizationTransistorTelevision system detailsManufacturing technologyDevice material

A semiconductor device including a pixel region in which one or more pixels are formed and a DRAM cell region in which one or more DRAM cells for storing output signals from the pixels are formed, characterized in that the layers constituting the pixel region and the DRAM cell region are formed in the same semiconductor process.

Owner:FUJITSU SEMICON LTD

Non-volatile memory device and method of fabricating the same

InactiveUS20120168858A1Reduce step heightSolid-state devicesSemiconductor/solid-state device manufacturingContact formationInter layer

A method of fabricating a non-volatile memory device includes providing a substrate with a cell region where a plurality of memory cells that are stacked vertically are to be formed and a peripheral circuit region where a peripheral circuit device is to be formed. Forming a gate structure where an inter-layer dielectric layer and a gate electrode layer are alternately stacked over the substrate of the cell region and the peripheral circuit region. Forming a first trench that isolates the gate electrode layers in one direction by selectively etching the gate structure of the cell region and forming a trench by selectively etching the gate structure corresponding to a contact formation region of the peripheral circuit region.

Owner:SK HYNIX INC

Semiconductor device including a multi-channel fin field effect transistor and method of fabricating the same

ActiveUS20050285204A1Increase the effective channel lengthIncrease the current levelTransistorSolid-state devicesGate dielectricDevice material

In a semiconductor device, and a method of fabricating the same, the semiconductor device includes a semiconductor substrate having a cell region and a peripheral circuit region, a portion of the semiconductor substrate in the cell region and in the peripheral circuit region including an isolation region defining an active region, a portion of the active region protruding above an upper surface of the isolation region to define at least two active channels, a gate dielectric layer formed over the active region of the semiconductor substrate including the at least two protruding active channels, a gate electrode formed over the gate dielectric layer and the isolation region of the semiconductor substrate, and a source / drain region formed in the active region of the semiconductor substrate on either side of the gate electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

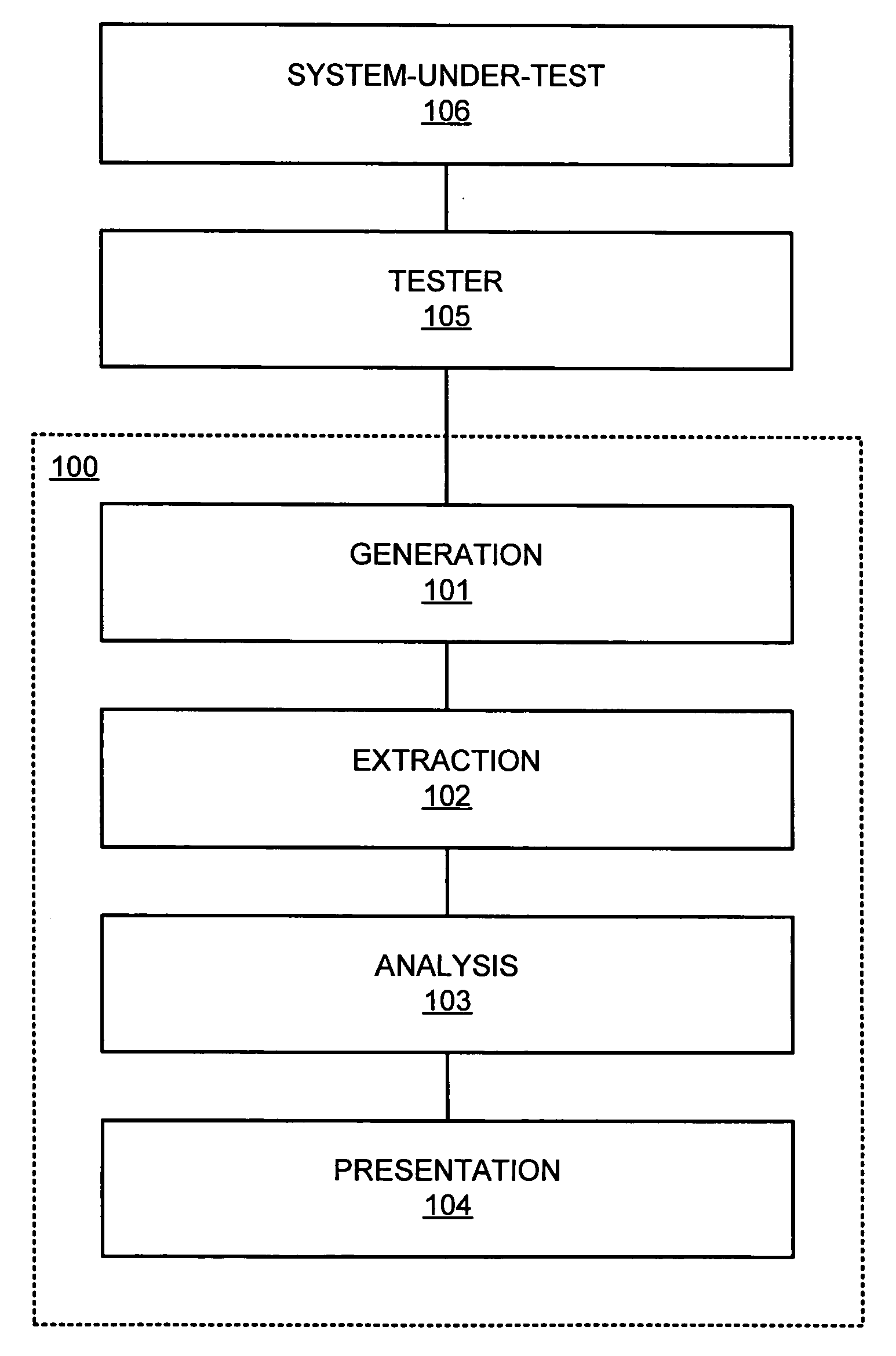

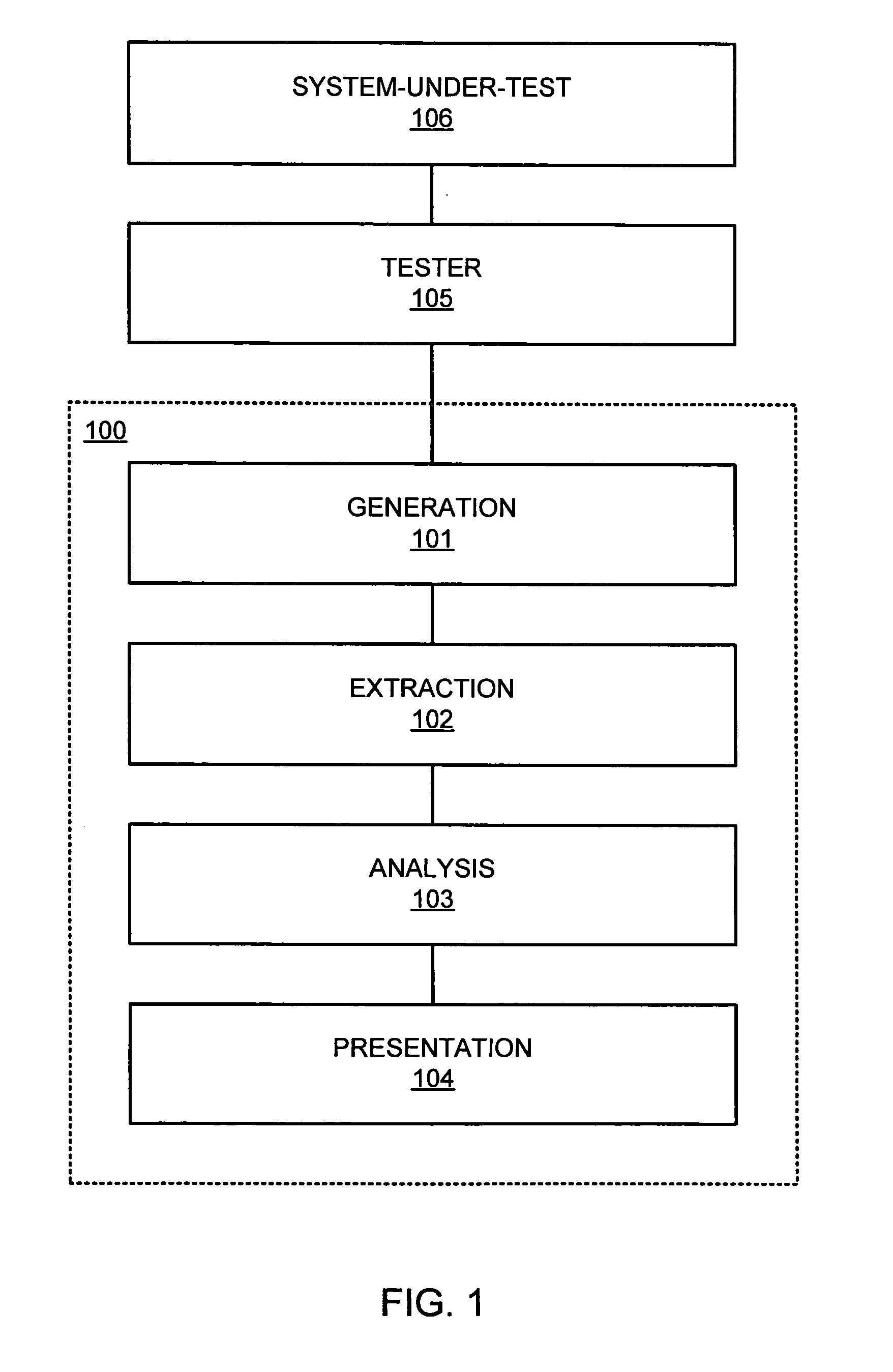

In-line voltage contrast determination of tunnel oxide weakness in integrated circuit technology development

InactiveUS7101722B1Semiconductor/solid-state device testing/measurementRead-only memoriesTechnology developmentCell region

A method for determination of tunnel oxide weakness is provided. A tunnel oxide layer is formed on a semiconductor wafer. At least one poly gate is formed on the tunnel oxide layer in a flash memory region of the semiconductor wafer. At least one poly island, which is substantially larger than the poly gate, is formed on the tunnel oxide layer in a voltage contrast cell region of the semiconductor wafer. The poly island and the tunnel oxide layer therebeneath form a voltage contrast tunnel oxide cell. A voltage contrast measurement is performed on the voltage contrast tunnel oxide cell. The voltage contrast measurement is then compared with prior such voltage contrast measurements on other such voltage contrast tunnel oxide cells. The tunnel oxide weakness of the tunnel oxide layer is then determined from the voltage contrast measurement comparisons.

Owner:ADVANCED MICRO DEVICES INC

Semiconductor integrated circuit and method of designing the same

InactiveUS20050001271A1Semiconductor/solid-state device detailsSolid-state devicesCell regionEngineering

According to the present invention, a semiconductor integrated circuit having: a cell region in which a plurality of MOS transistors forming at least one cell are placed; and first and second power lines placed along one direction in a peripheral portion of the cell region, wherein in the cell region, gate grids for defining a first pitch in the one direction and pin grids for defining a second pitch in the one direction are set, gate electrodes of the MOS transistors are placed in accordance with the gate grids, and an interconnection layer is placed in accordance with the pin grids.

Owner:KK TOSHIBA

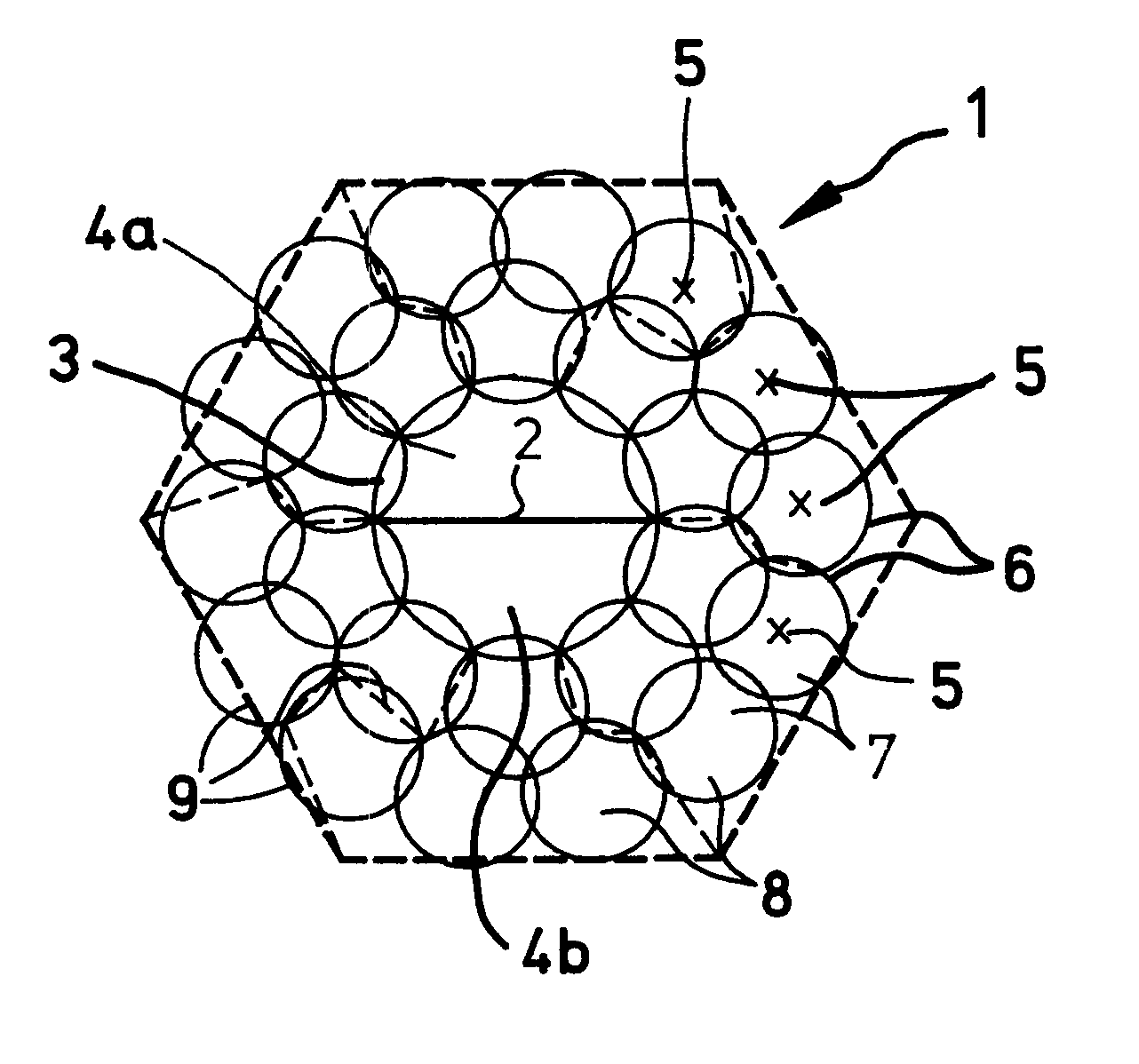

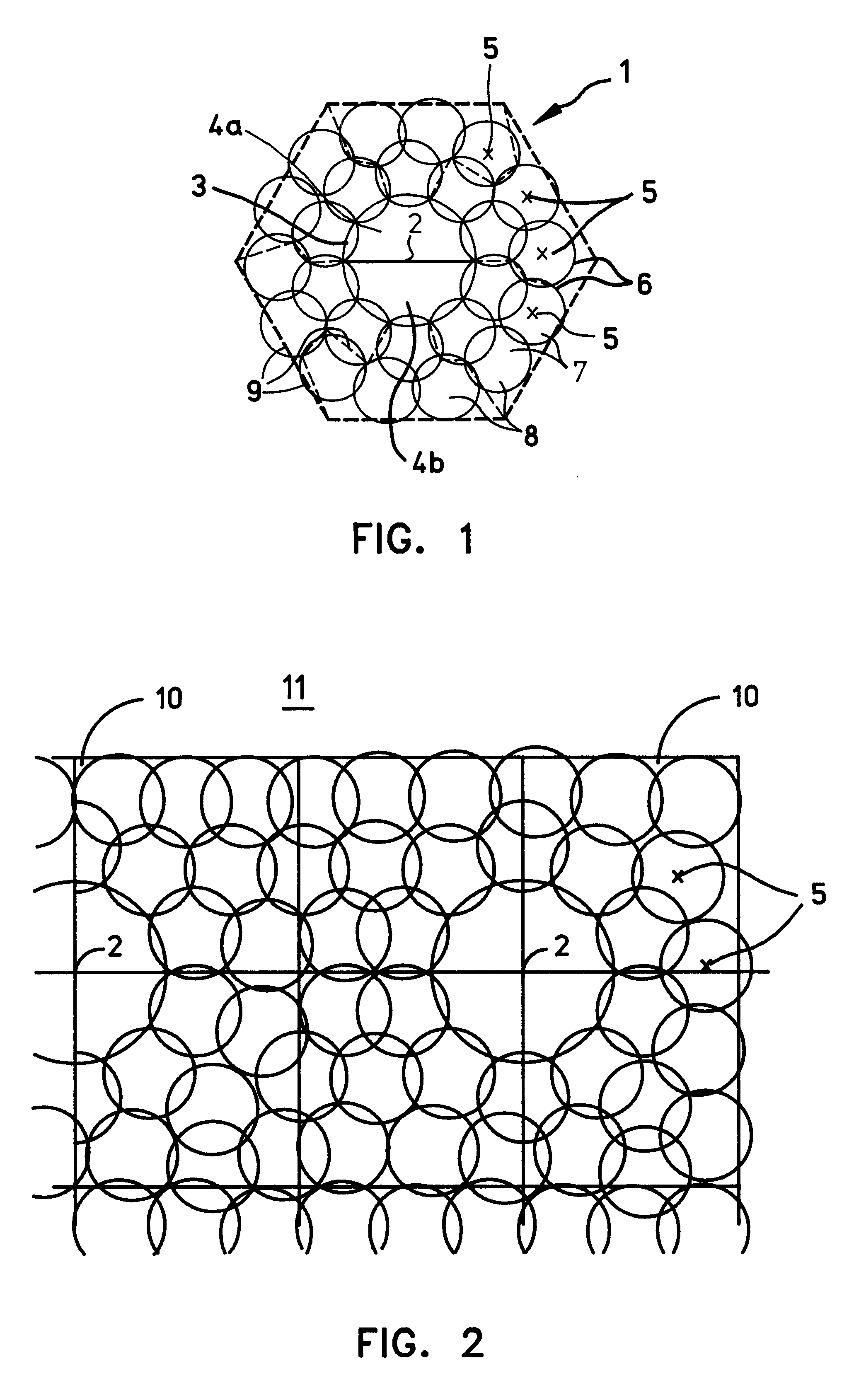

Methods of operating arrangements of base transceiver stations in an area-covering network

InactiveUS6459900B1Reduce in quantityGuaranteed uptimeRadio/inductive link selection arrangementsSubstation equipmentCellular radioTransceiver

Owner:LITTLEFEET

GPS correction methods, apparatus and signals

InactiveUS6862526B2Compensating for such errorRoad vehicles traffic controlPosition fixationCell regionGps receiver

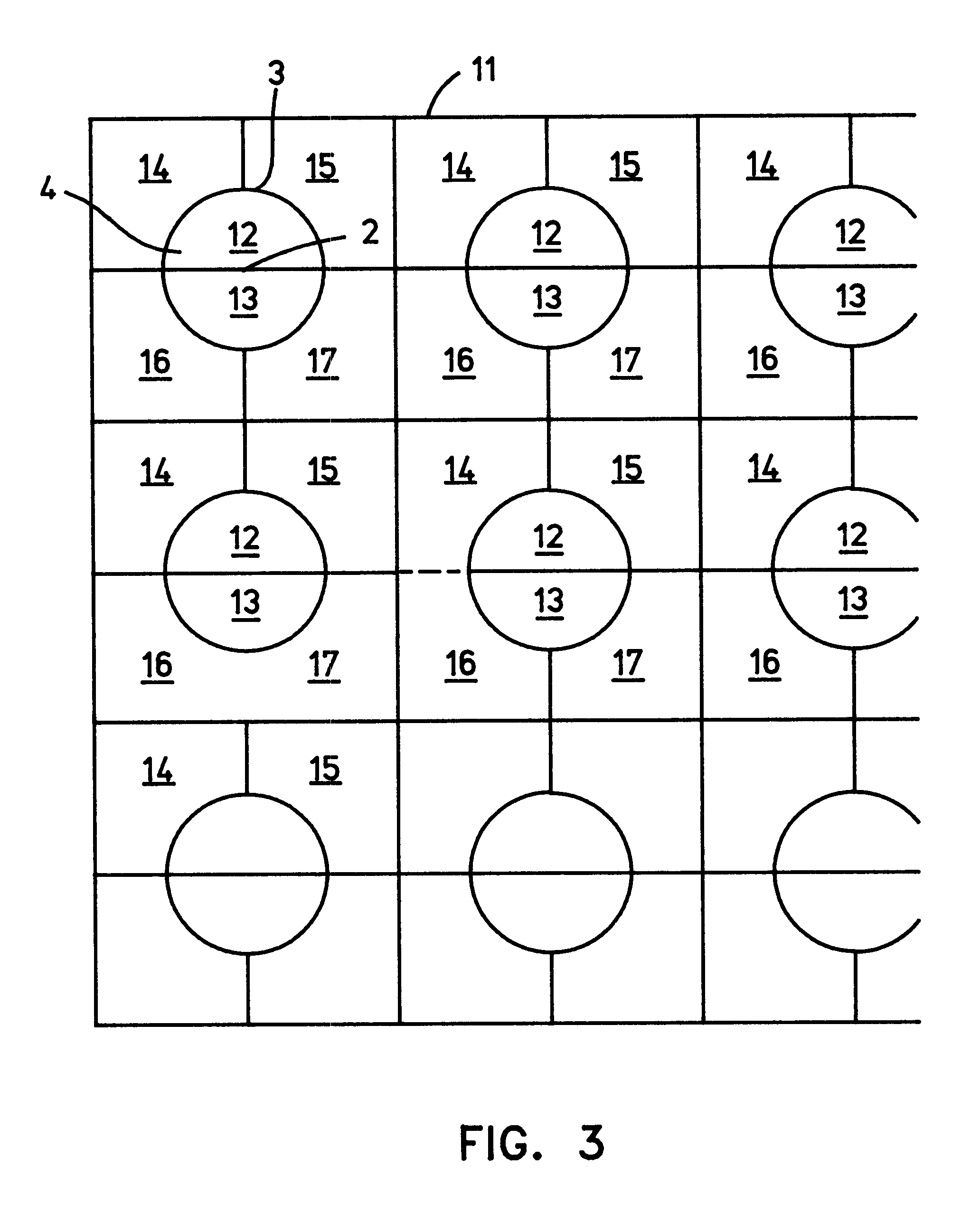

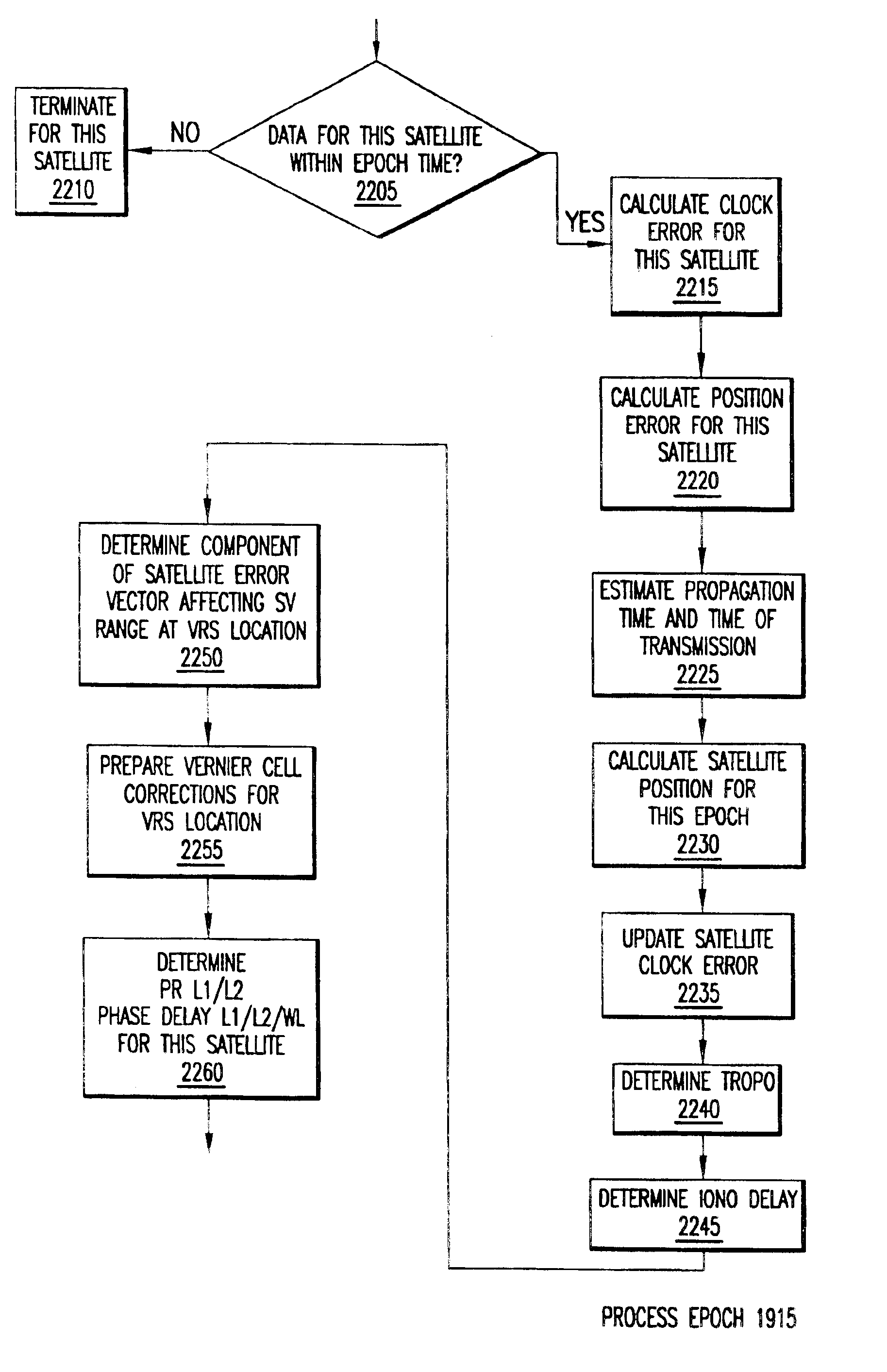

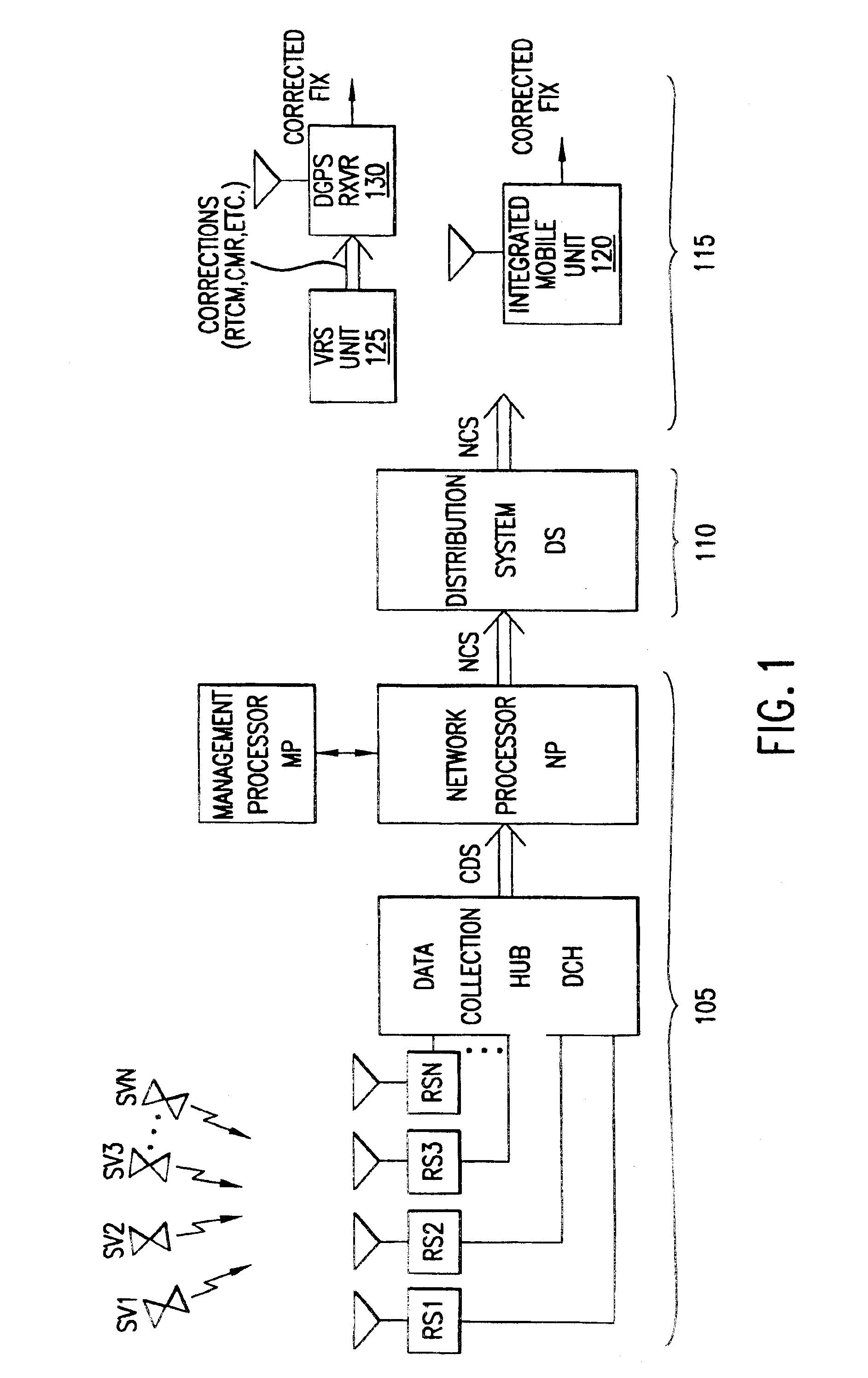

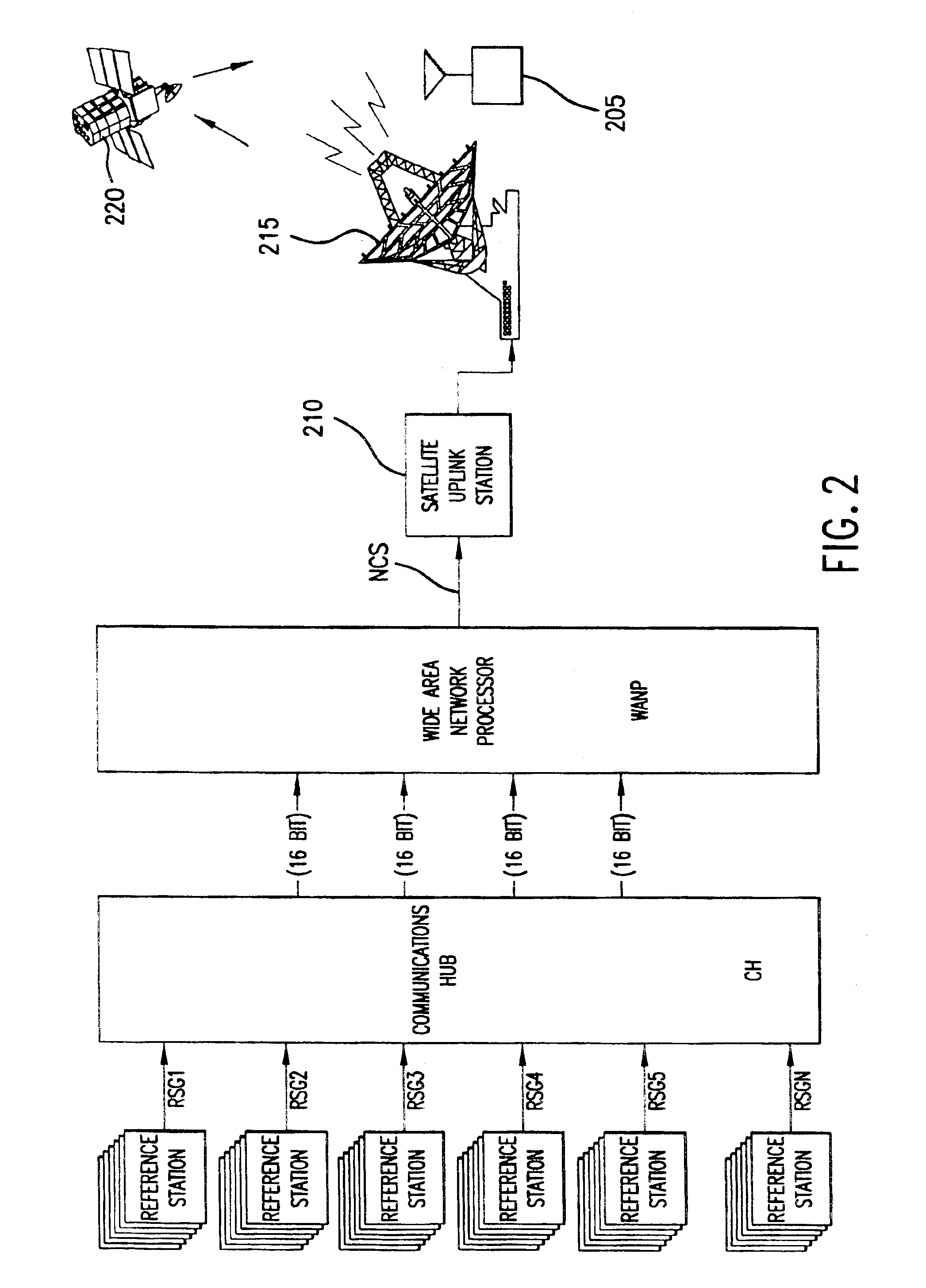

Methods and apparatus are described and illustrated for producing GPS corrections, comprising: collecting measurements from a plurality of network reference stations; determining network corrections from the measurements; determining residual errors at one or more vernier-cell reference stations; and preparing vernier-cell corrections to compensate the residual errors within a vernier-cell region. Network correction streams are described and illustrated which contain network corrections derived from a plurality of network reference stations and residual error corrections derived from one or more vernier-cell reference stations. Methods and apparatus are described for employing such network correction streams in a virtual reference station to produce corrections and / or virtual measurements for use in a GPS receiver.

Owner:TRIMBLE NAVIGATION LTD

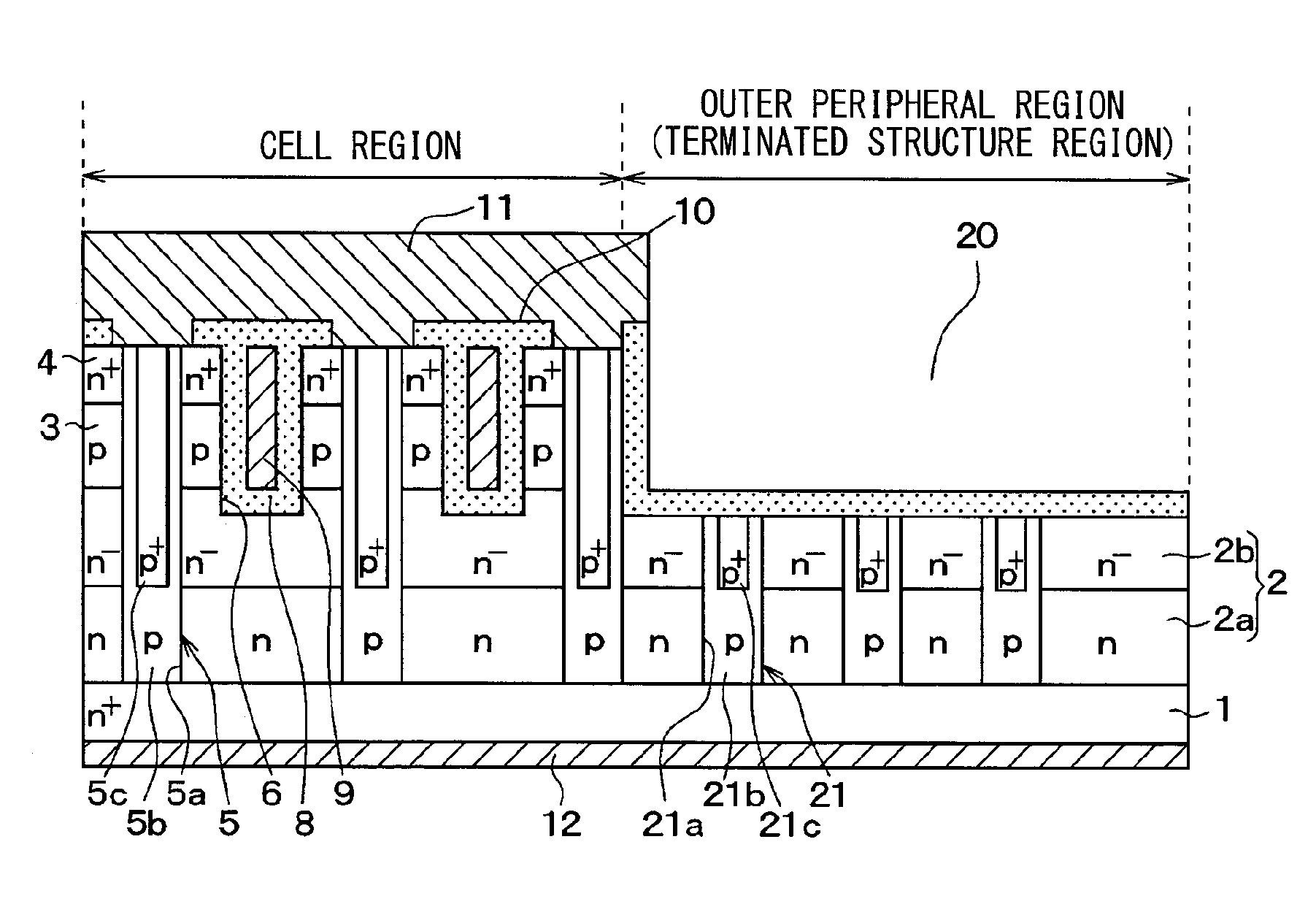

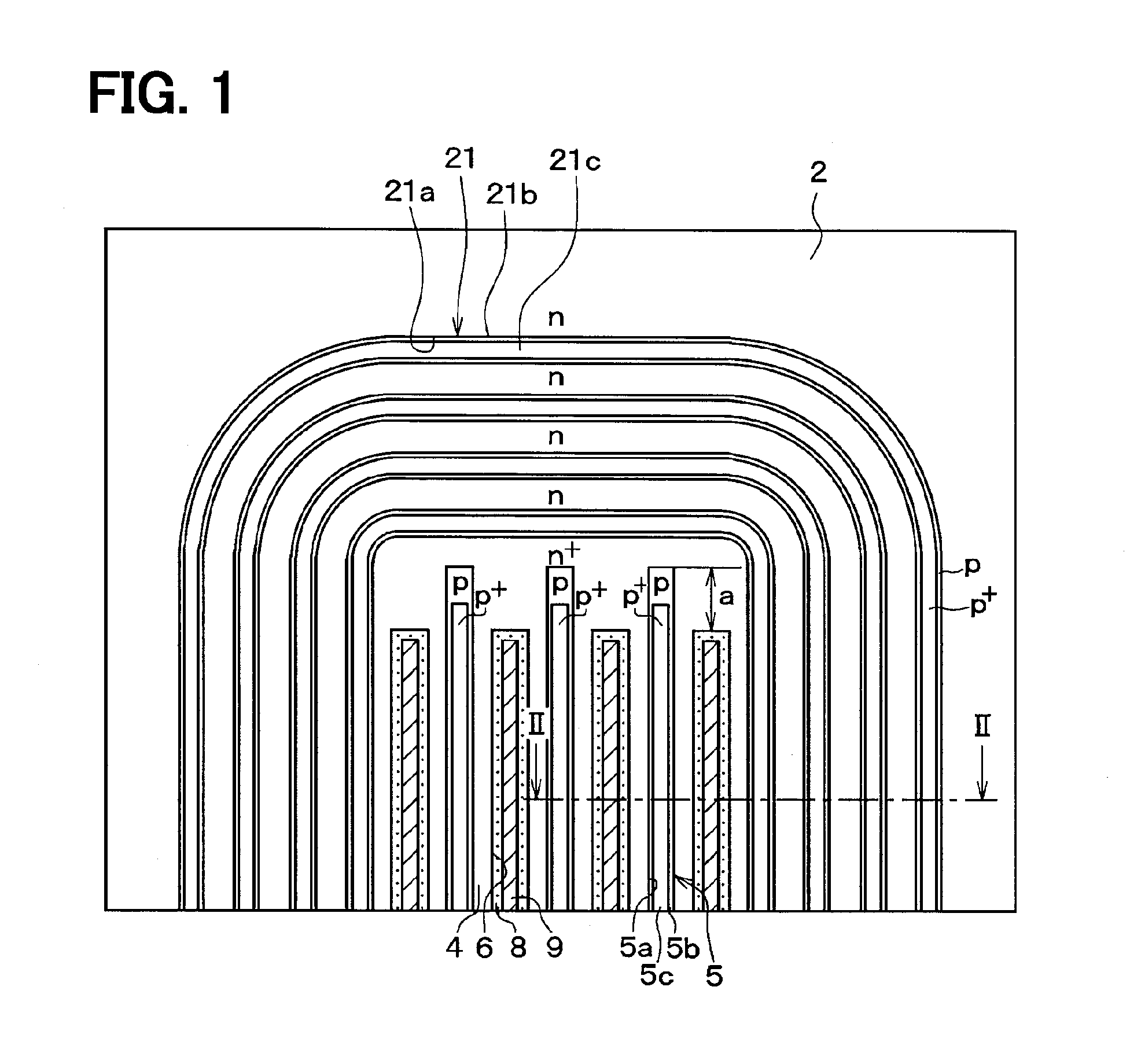

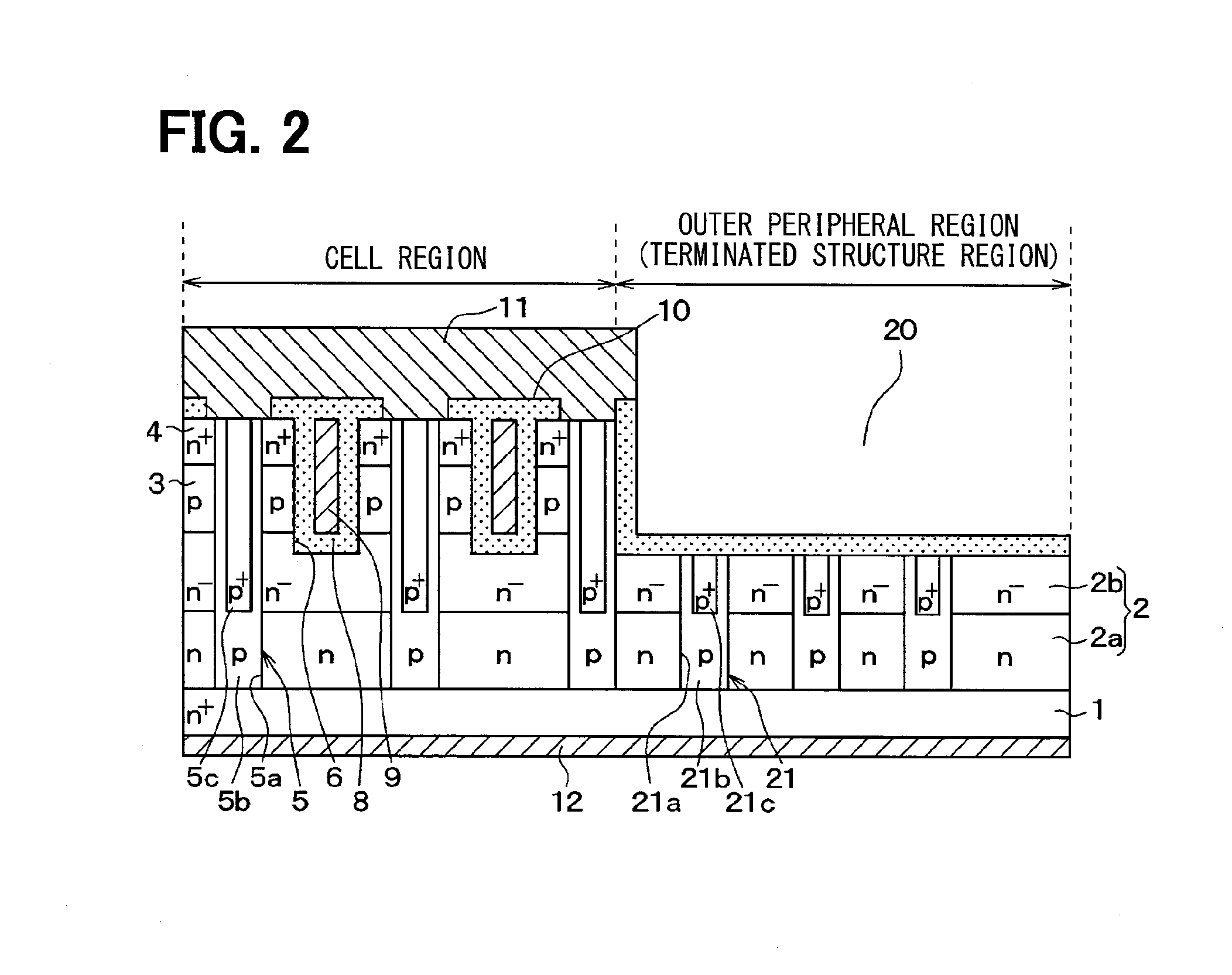

Silicon carbide semiconductor device and method for producing the same

ActiveUS20150115286A1Simple processLower on-state resistanceSemiconductor/solid-state device manufacturingDiodeHigh concentrationCell region

An SiC semiconductor device has a p type region including a low concentration region and a high concentration region filled in a trench formed in a cell region. A p type column is provided by the low concentration region, and a p+ type deep layer is provided by the high concentration region. Thus, since a SJ structure can be made by the p type column and the n type column provided by the n type drift layer, an on-state resistance can be reduced. As a drain potential can be blocked by the p+ type deep layer, at turnoff, an electric field applied to the gate insulation film can be alleviated and thus breakage of the gate insulation film can be restricted. Therefore, the SiC semiconductor device can realize the reduction of the on-state resistance and the restriction of breakage of the gate insulation film.

Owner:DENSO CORP +1

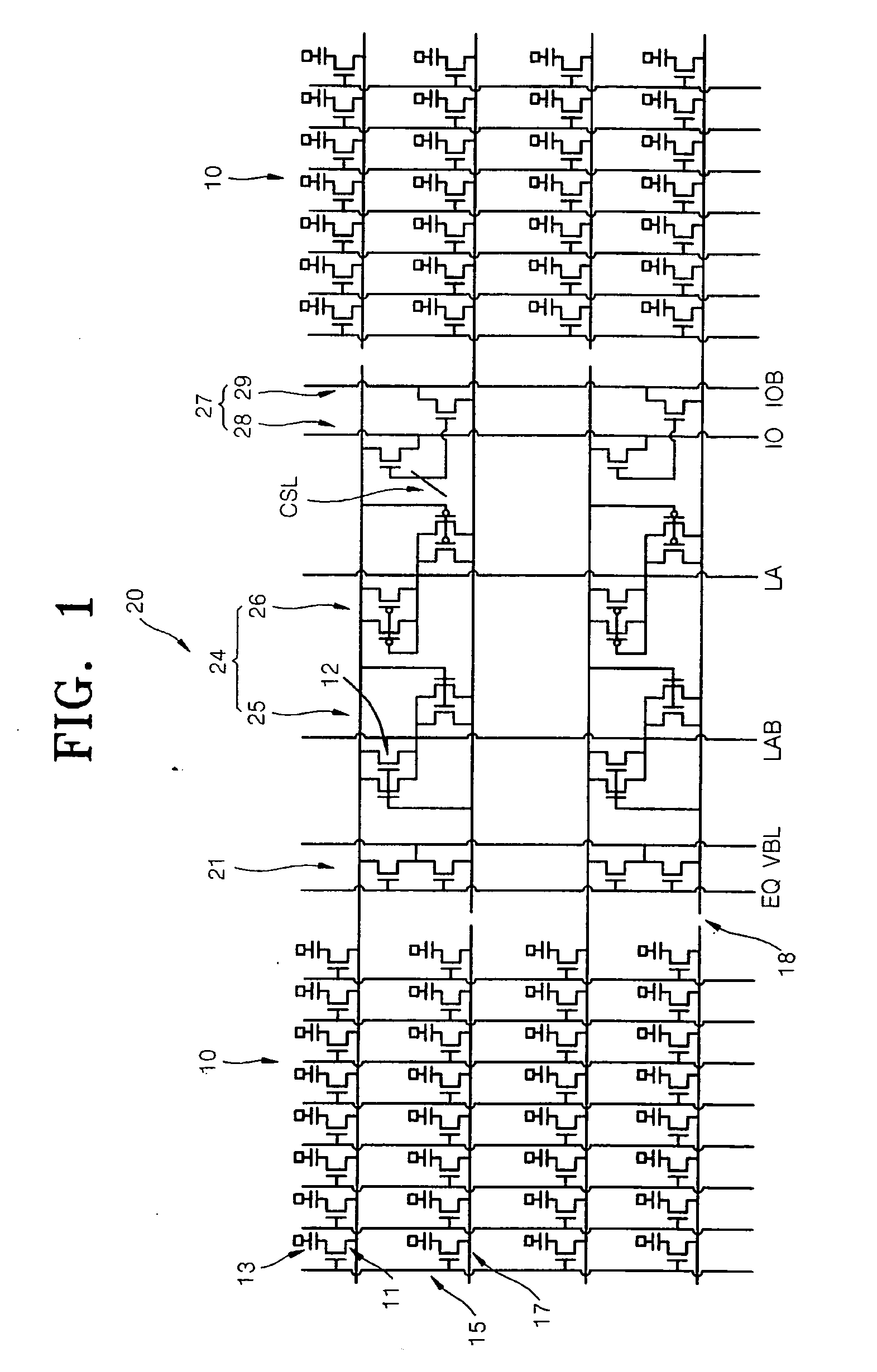

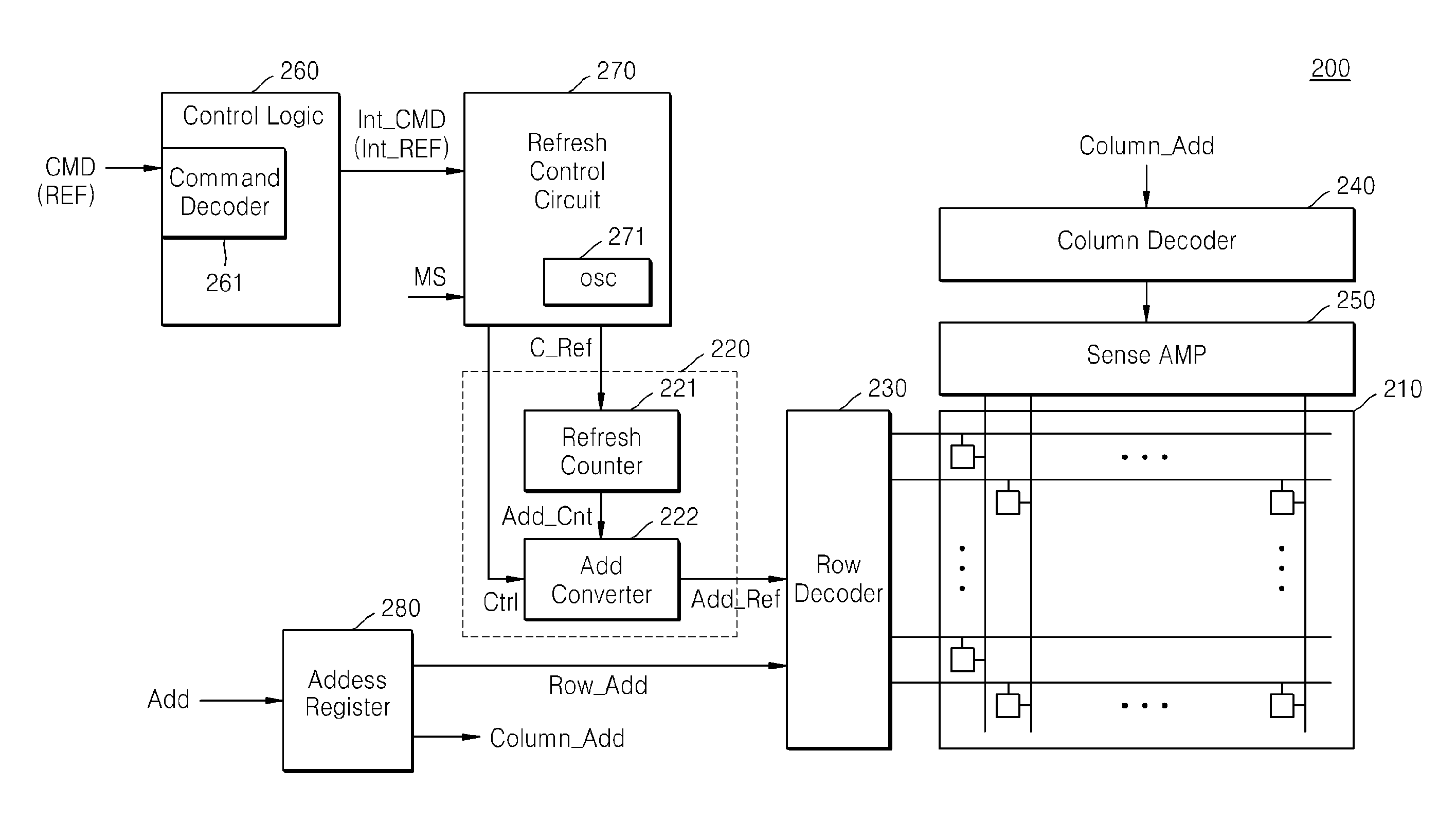

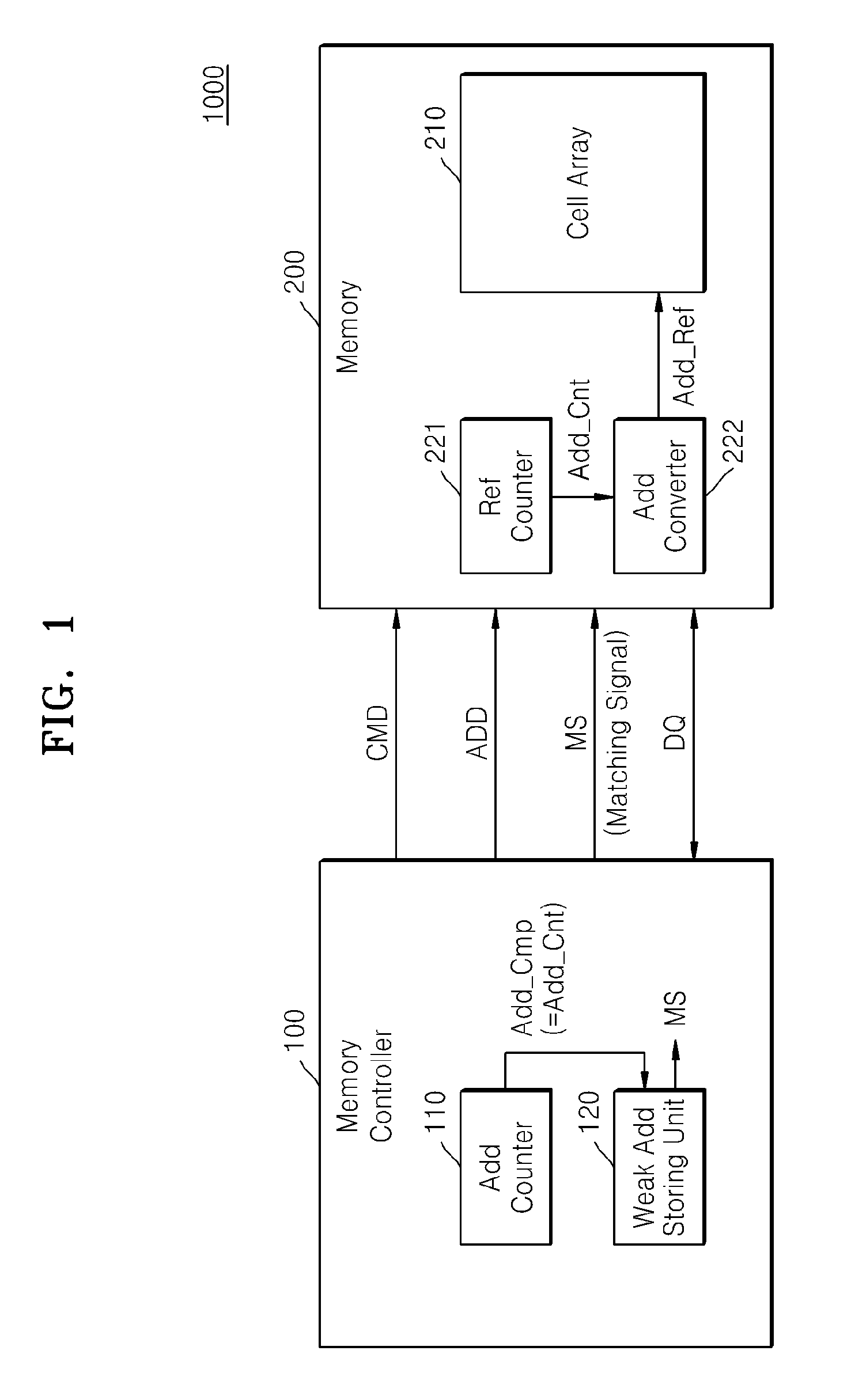

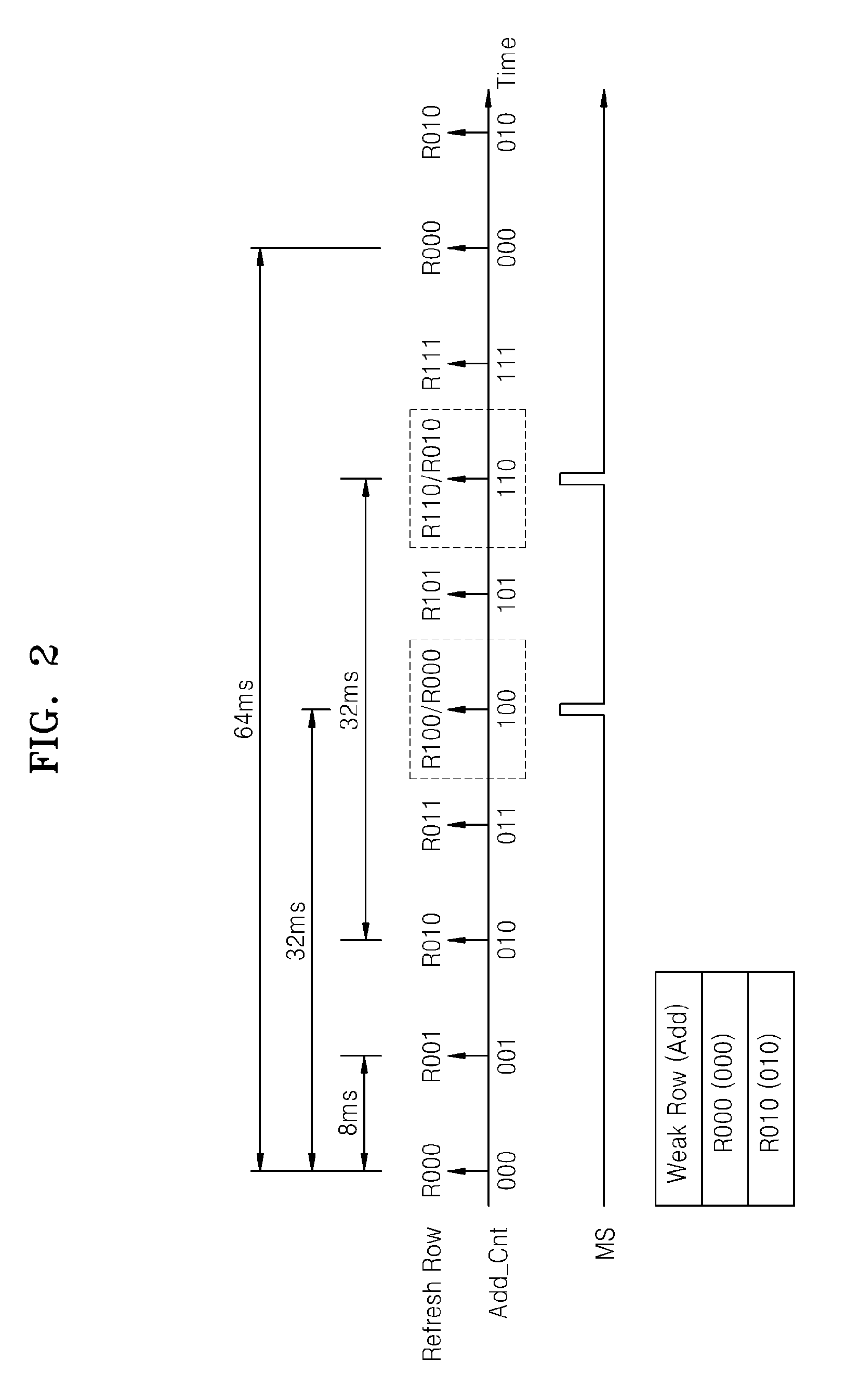

Semiconductor memory device having adjustable refresh period, memory system comprising same, and method of operating same

ActiveUS9153294B2Increase consumptionImprove reliabilityDigital storageMemory systemsControl signalCell region

A semiconductor memory device includes a cell array including a plurality of cell regions, a row decoder configured to drive rows corresponding to cell regions in which a refresh operation is to be performed, based on a counting address, and a refresh address generator configured to generate the counting address and a modified address in response to a control signal, wherein the modified address is generated by inverting at least one bit of the counting address, and wherein the semiconductor memory device performs concurrent refresh operations on a first cell region corresponding to the counting address and a second cell region corresponding to the modified address where the second cell region is determined to have weak cells.

Owner:SAMSUNG ELECTRONICS CO LTD

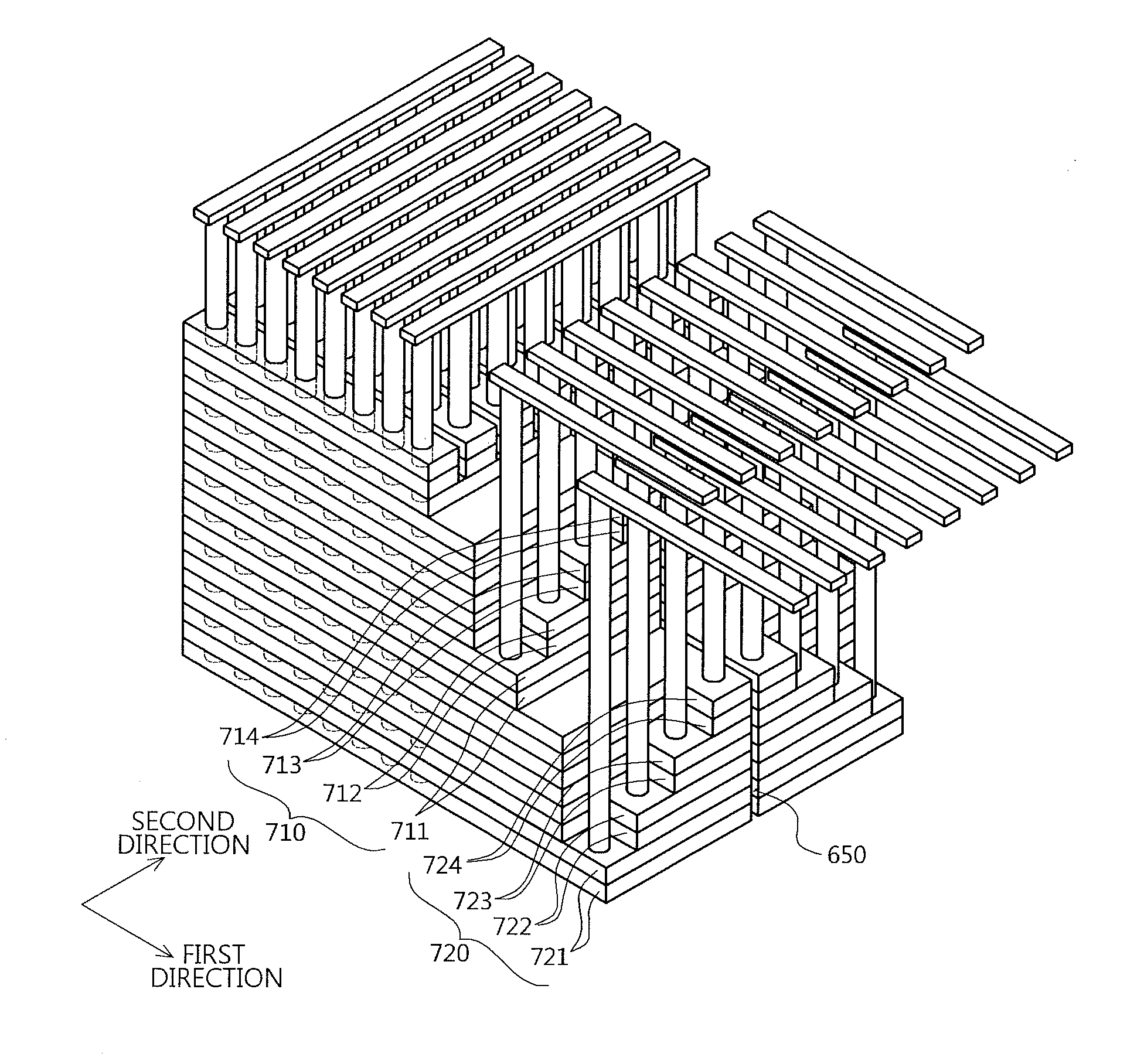

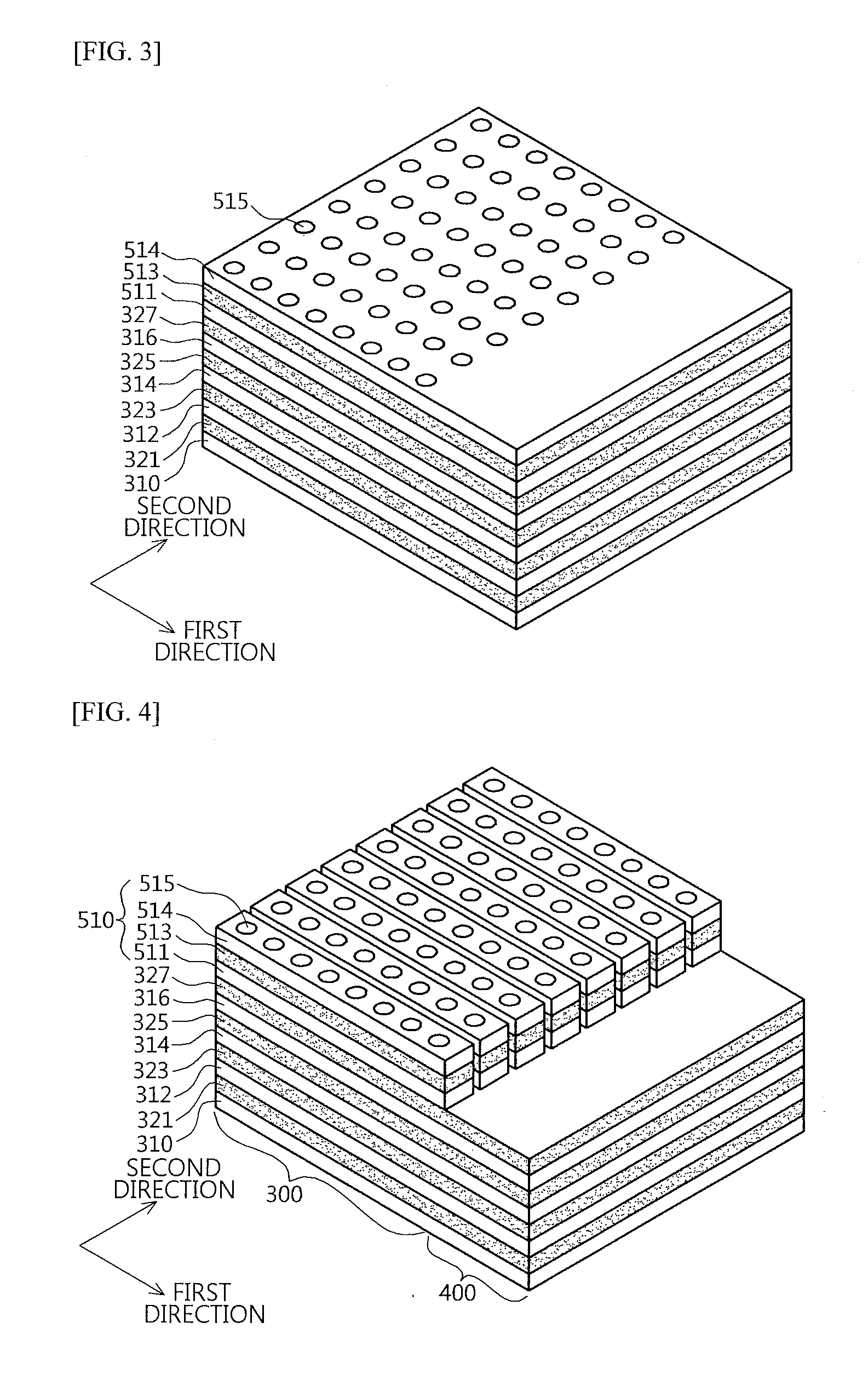

Memory having three-dimensional structure and manufacturing method thereof

InactiveUS20130009274A1Easy to integrateThe solution function is relatively simpleSolid-state devicesSemiconductor/solid-state device manufacturingEtchingCell region

Provided are a memory having a 3-dimensional structure and a method of fabricating the same, by which high integration density can be obtained. A contact region connected to a word line is formed to extend from a cell region in a first direction. A plurality of step difference layers constituting the contact region are formed to have step differences in a second direction different from the first direction. Also, provided is a method of fabricating a nonvolatile memory by which step differences are formed in a direction substantially perpendicular to a direction in which active regions are aligned. An insulating layer and etching layers are sequentially formed. By performing a selective etching process and pattern transfer, step differences are formed in a direction perpendicular to a direction in which multilayered active layers are disposed. Furthermore, the etching layers are removed using a wet etching process, and an oxide-nitride-oxide (ONO) layer and conductive layers are provided on the multilayered active layers having exposed side surfaces to form cell transistors. Thus, a memory having a high integration density is fabricated.

Owner:IUCF HYU (IND UNIV COOP FOUND HANYANG UNIV)

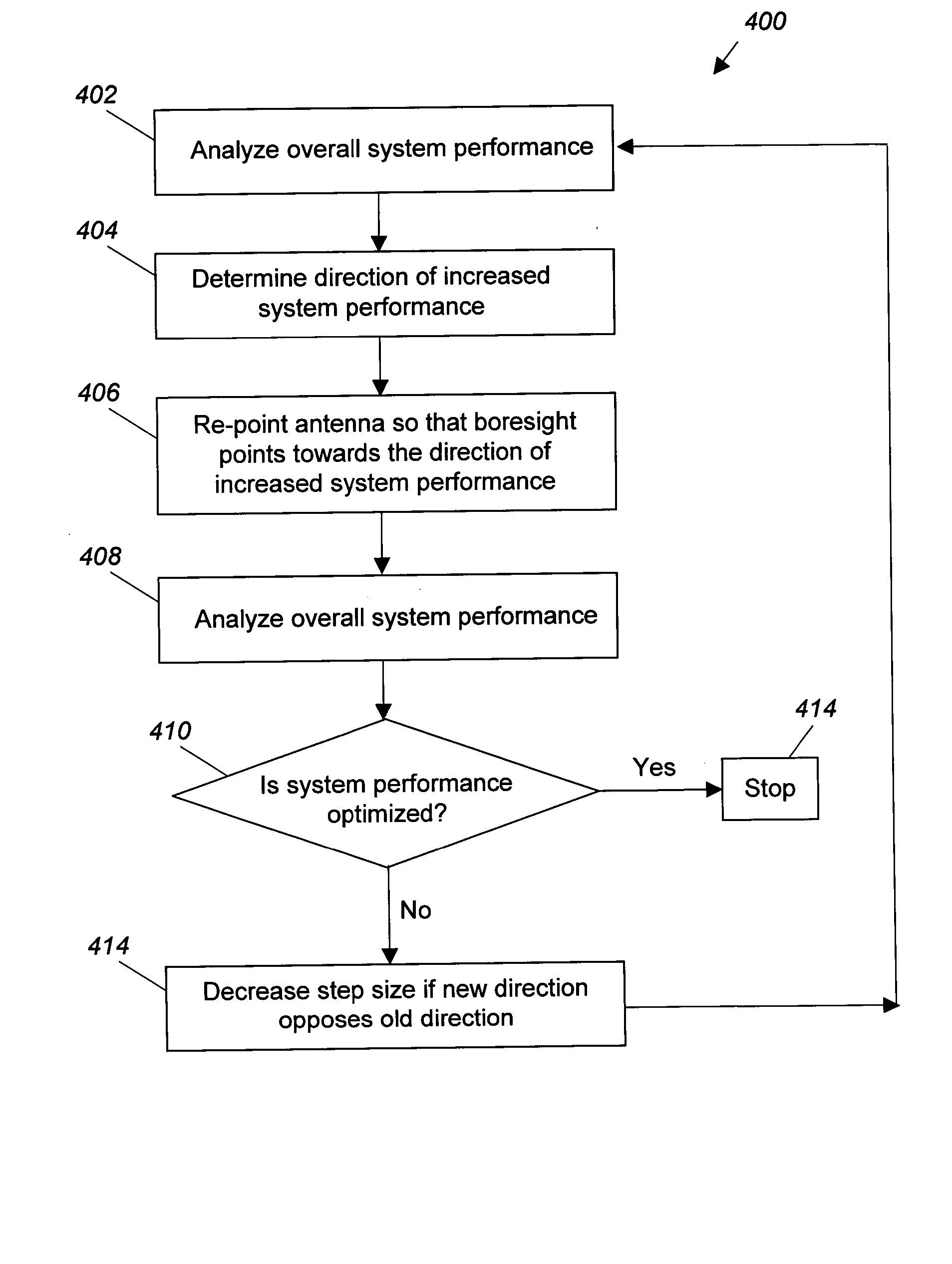

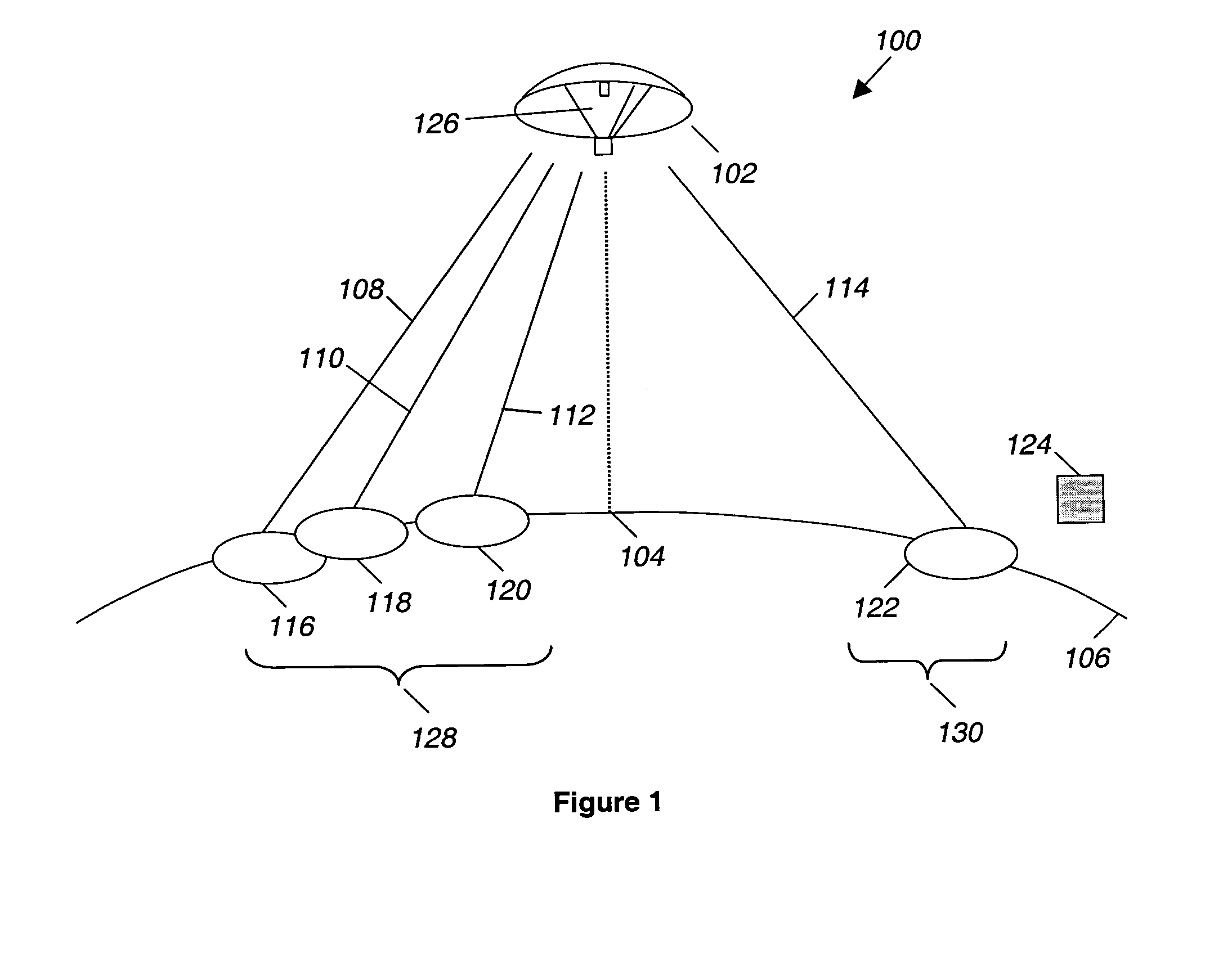

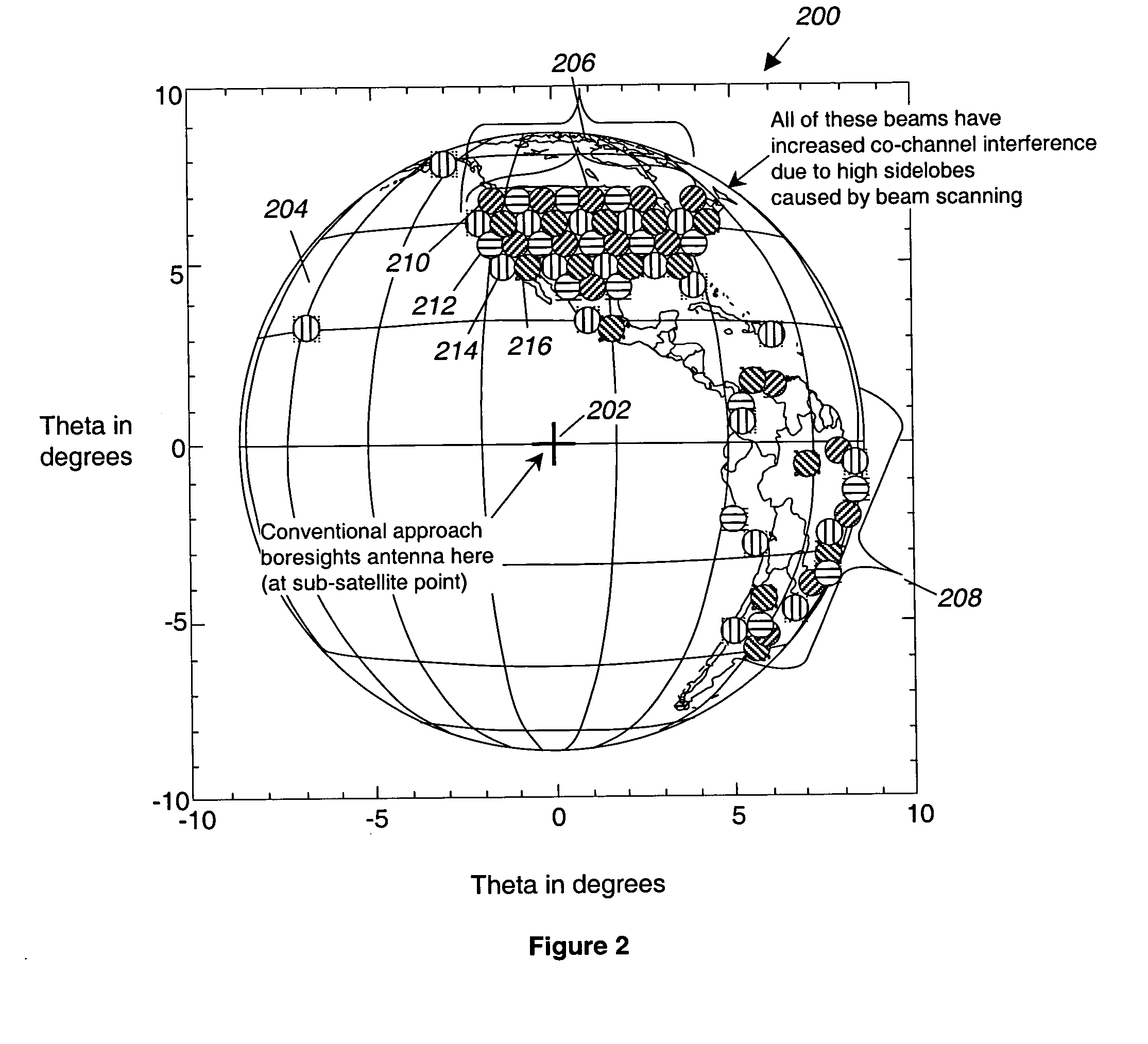

Reducing co-channel interference in satellite communications systems by antenna re-pointing

ActiveUS20050068230A1Improve performanceMinimizes CCIAntenna adaptation in movable bodiesRadio transmissionCommunications systemHigh density

A system and method for increasing the performance of a satellite communication system by using a multivariate analysis approach to optimize the pointing of the boresight of a satellite-mounted antenna. Optimizing the pointing of the boresight of the antenna minimizes sidelobe generation, and thus Co-Channel Interference (CCI) in geographic areas served by the system. By minimizing CCI, the overall system performance of the communication system is optimized. To optimize the pointing of the boresight of the antenna, the overall performance of the satellite communication system is determined, and the boresight of the antenna is iteratively repointed in the direction of increasing system performance until the optimized boresight pointing is determined. Alternatively, the frequency re-use plan of the satellite communication system may be analyzed to determine a high density cell region and the boresight may be pointed to the high density cell region.

Owner:NORTHROP GRUMMAN SYST CORP

SIS semiconductor having junction barrier schottky device

A semiconductor device having a junction barrier Schottky diode includes: a SiC substrate; a drift layer on the substrate; an insulation film on the drift layer having an opening in a cell region; a Schottky barrier diode having a Schottky electrode contacting the drift layer through the opening of the insulation film and an ohmic electrode on the substrate; a terminal structure having a RESURF layer surrounding the cell region; and multiple second conductive type layers on an inner side of the RESURF layer. The second conductive type layers and the drift layer provide a PN diode. The Schottky electrode includes a first Schottky electrode contacting the second conductive type layers with ohmic contact and a second Schottky electrode contacting the drift layer with Schottky contact.

Owner:DENSO CORP

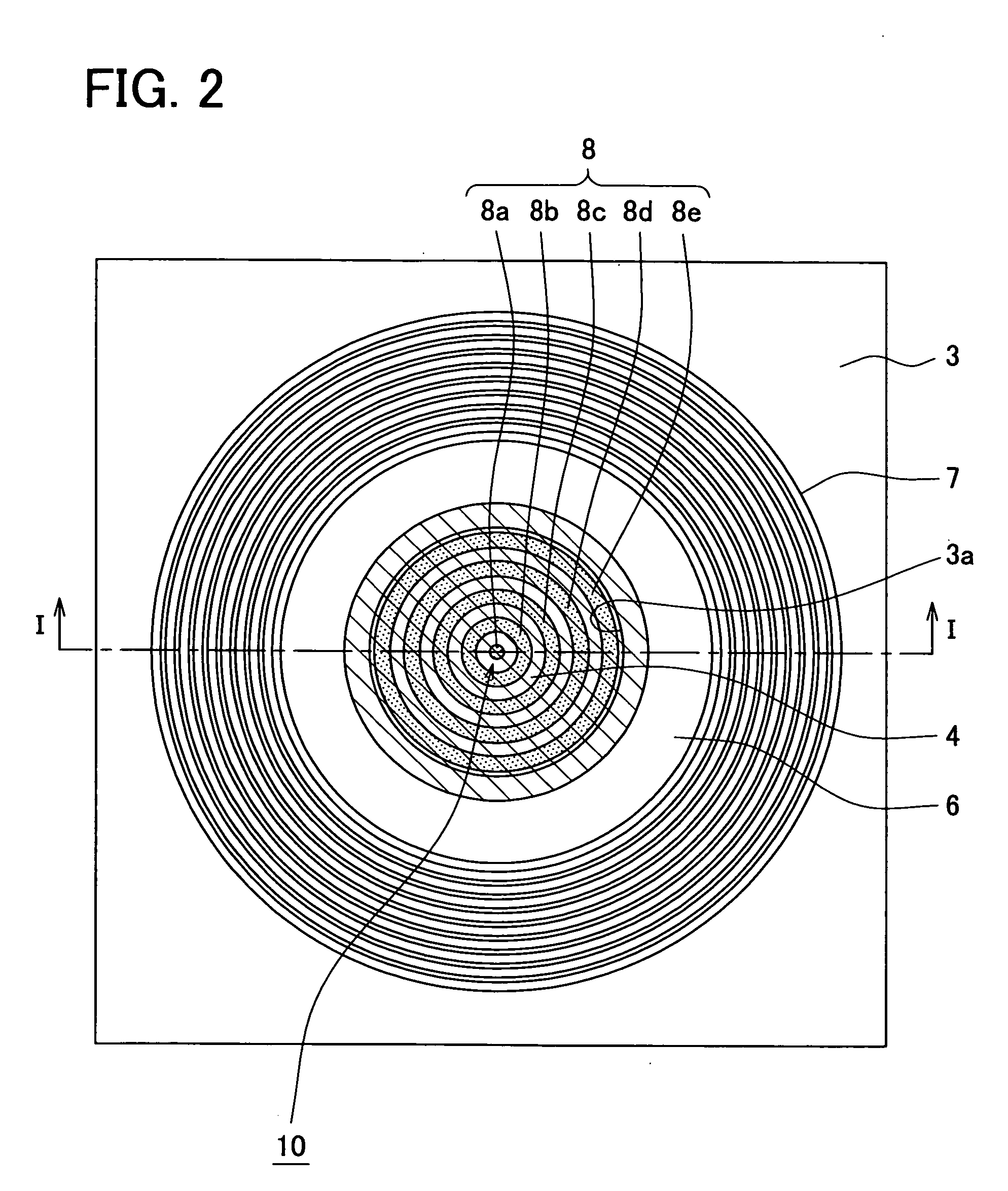

Fabricating and operating a memory array having a multi-level cell region and a single-level cell region

ActiveUS20100246257A1Improve staminaImprove reliabilityTransistorRead-only memoriesCell regionSingle level

Techniques are disclosed herein for applying different process steps to single-level cell (SLC) blocks in a memory array than to multi-level cell (MLC) blocks such that the SLC blocks will have high endurance and the MLC blocks will have high reliability. In some aspects, different doping is used in the MLC blocks than the SLC blocks. In some aspects, different isolation is used in the MLC blocks than the SLC blocks. Techniques are disclosed that apply different read parameters depending on how many times a block has been programmed / erased. Therefore, blocks that have been cycled many times are read using different parameters than blocks that have been cycled fewer times.

Owner:SANDISK TECH LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com