Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1165 results about "Sic substrate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

SiC substrates also have a low coefficient for thermal expansion. Thermal expansion is the amount and direction a material expands or contracts as it is heats up or cools down. The most common explanation is ice, although it behaves opposite of most metals, expanding as it cools and shrinking as it heats up.

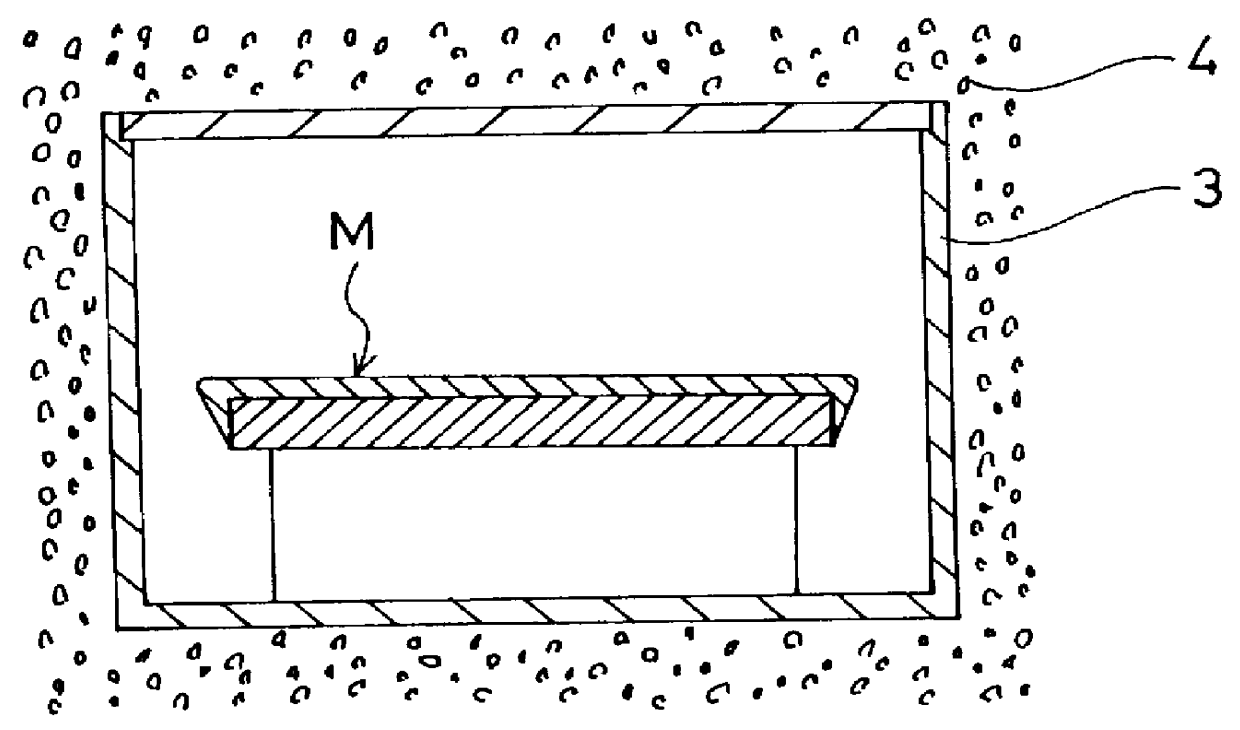

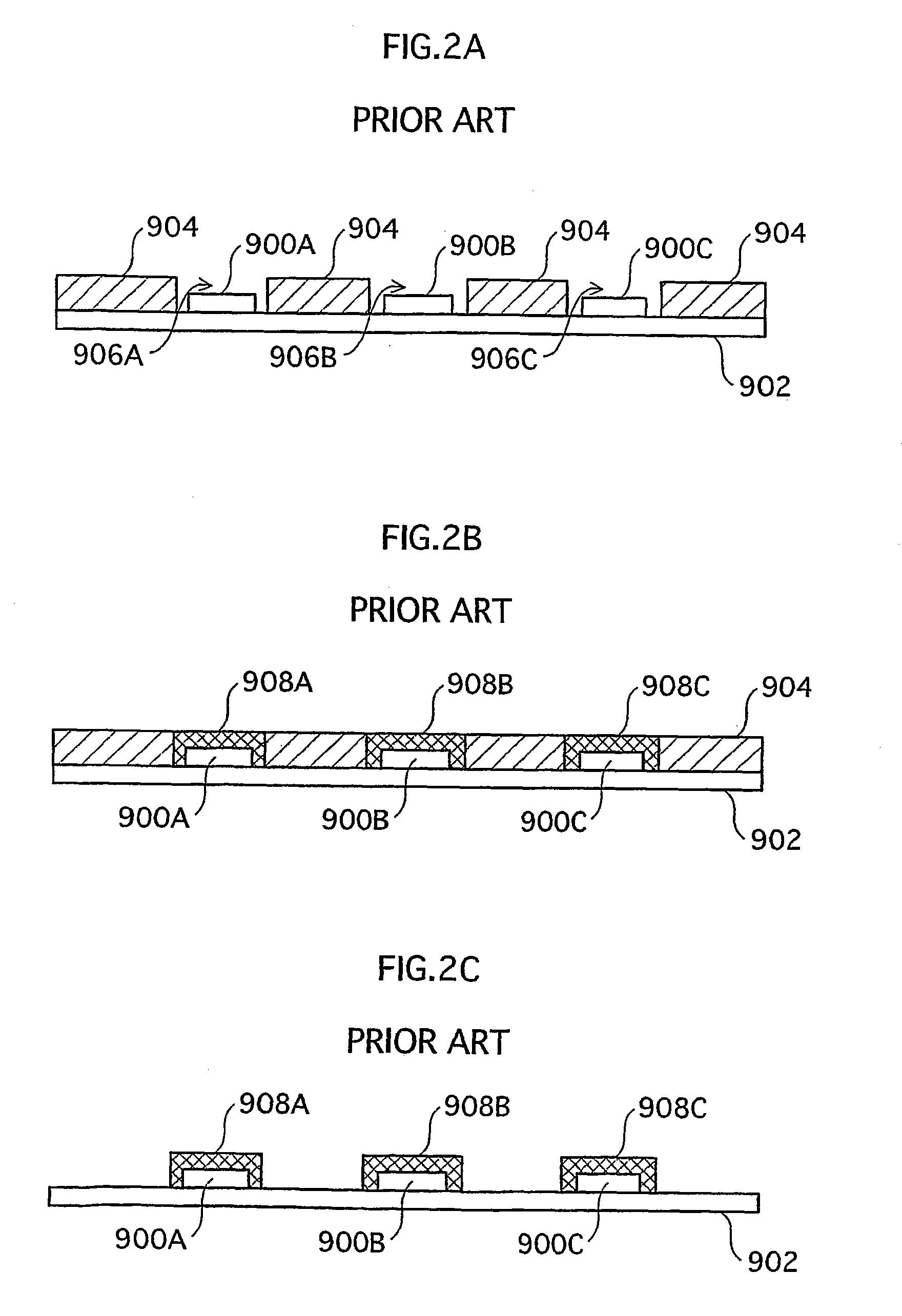

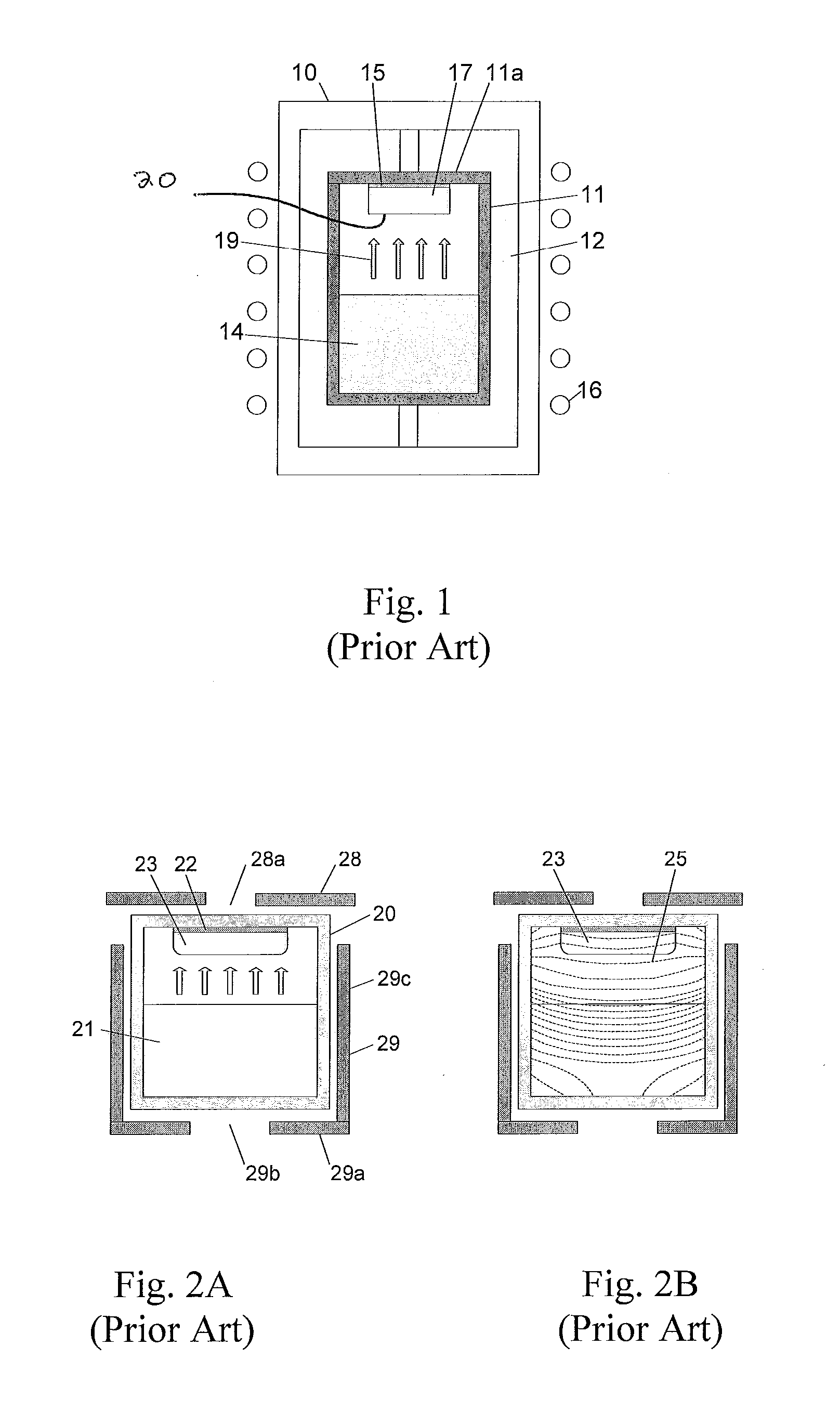

Method for manufacturing susceptor

ActiveUS20100163524A1Decorative surface effectsSemiconductor/solid-state device manufacturingSusceptorMetallurgy

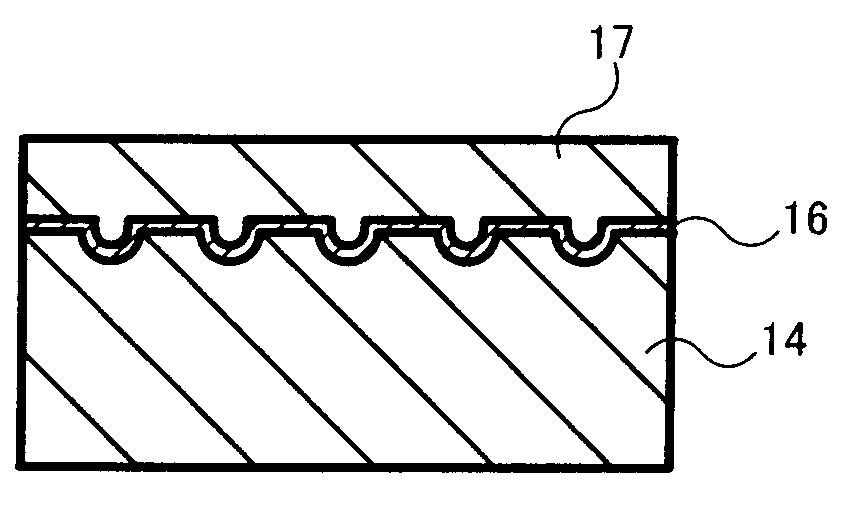

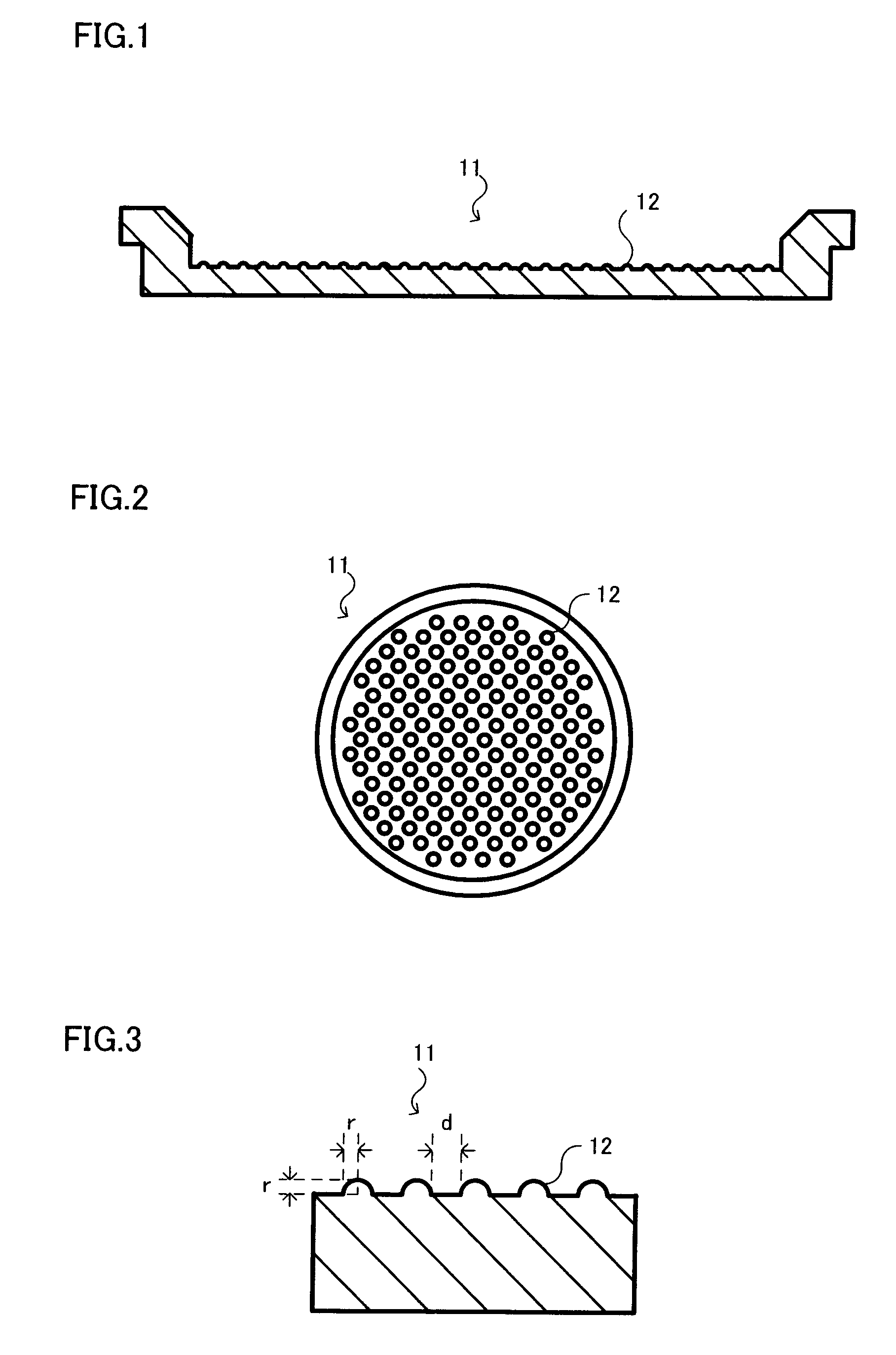

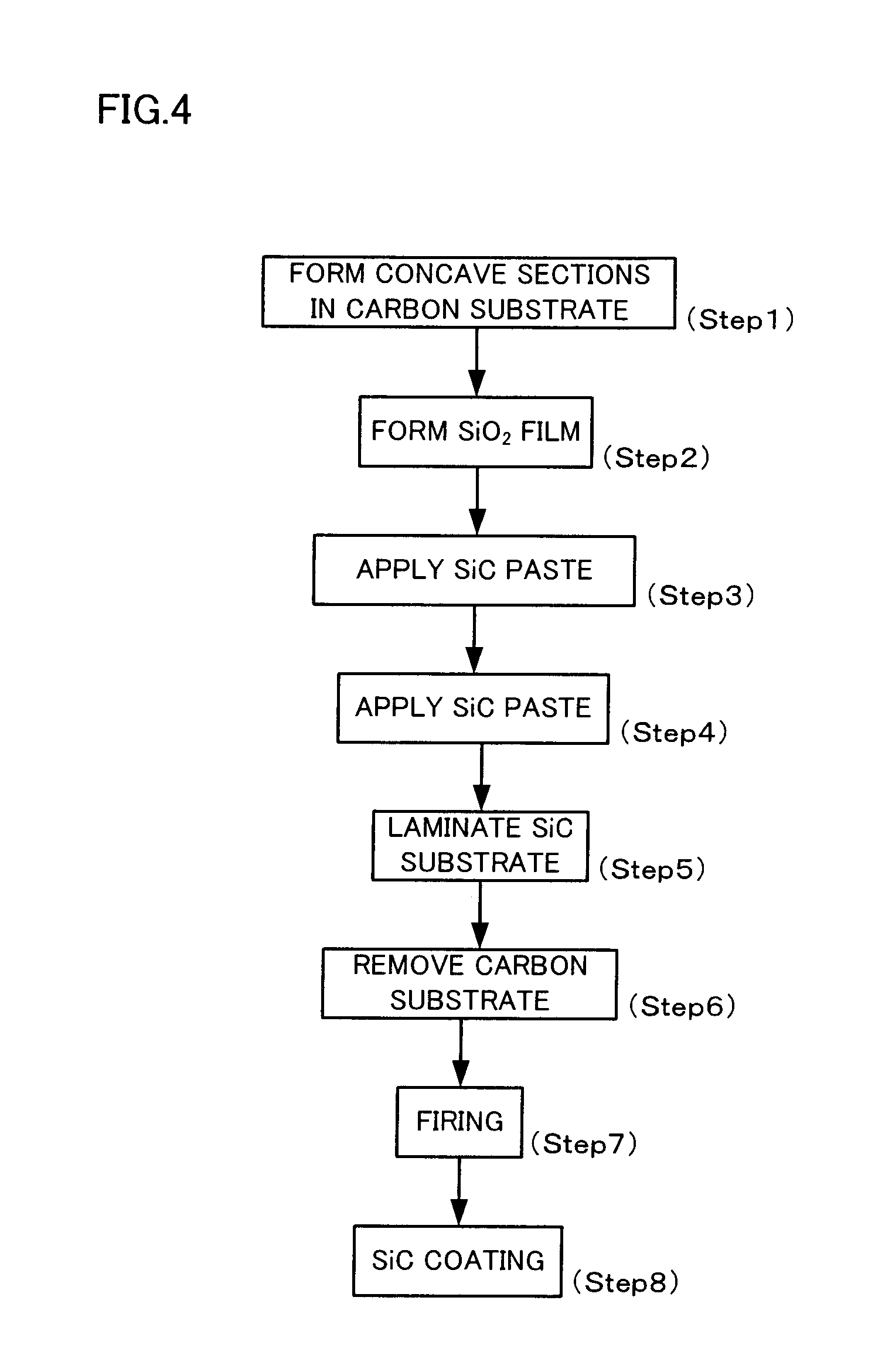

A method for manufacturing a susceptor includes: forming a concave pattern in a surface of a substrate to be processed; applying a SiC paste containing a SiC powder and a sintering agent to the surface of the substrate to be processed to fill the concave pattern to form a SiC coating layer; laminating a SiC substrate on the SiC coating layer; and firing the SiC coating layer to form a SiC layer having at least one convex section on the surface of the SiC substrate.

Owner:NUFLARE TECH INC

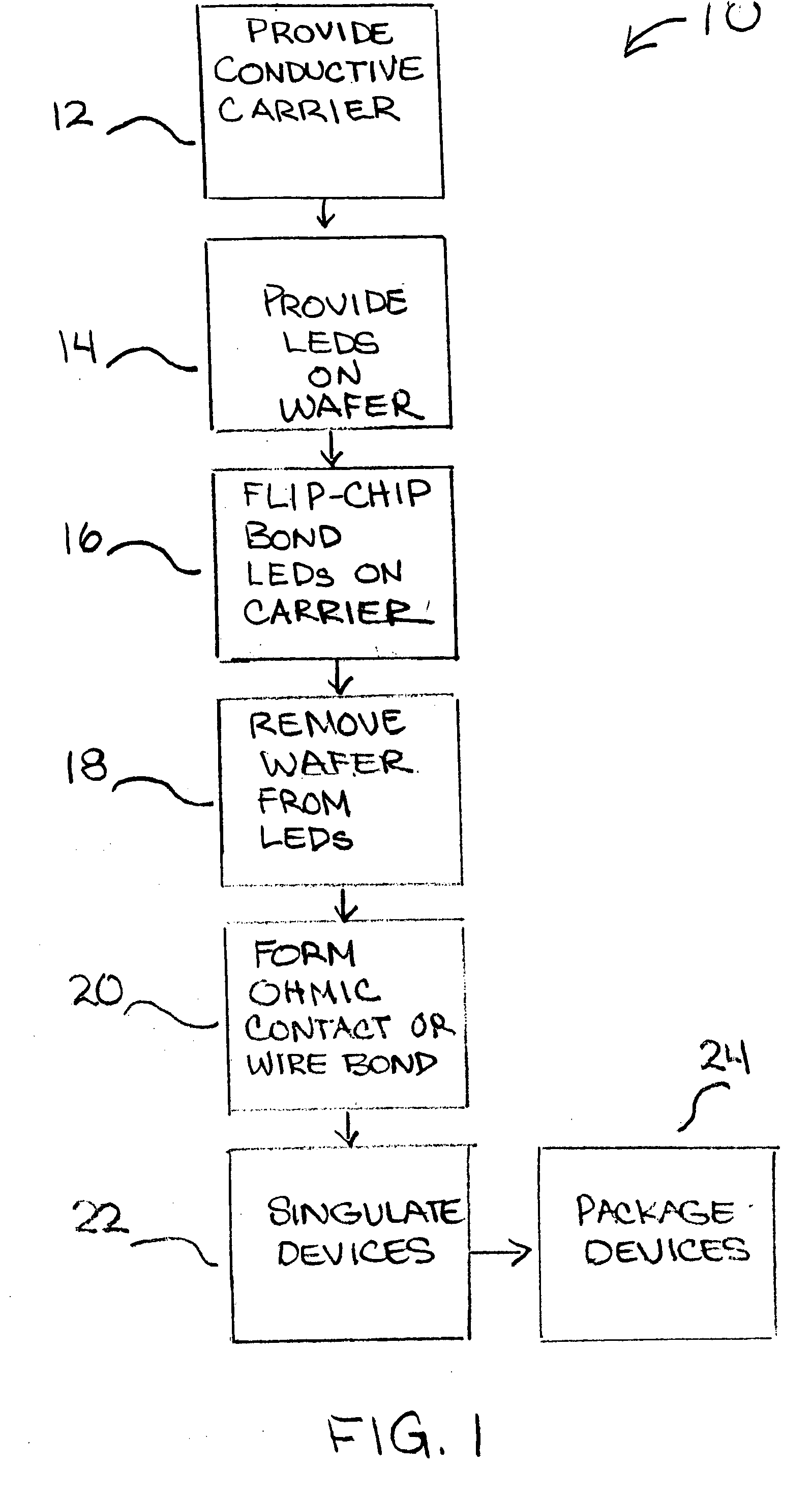

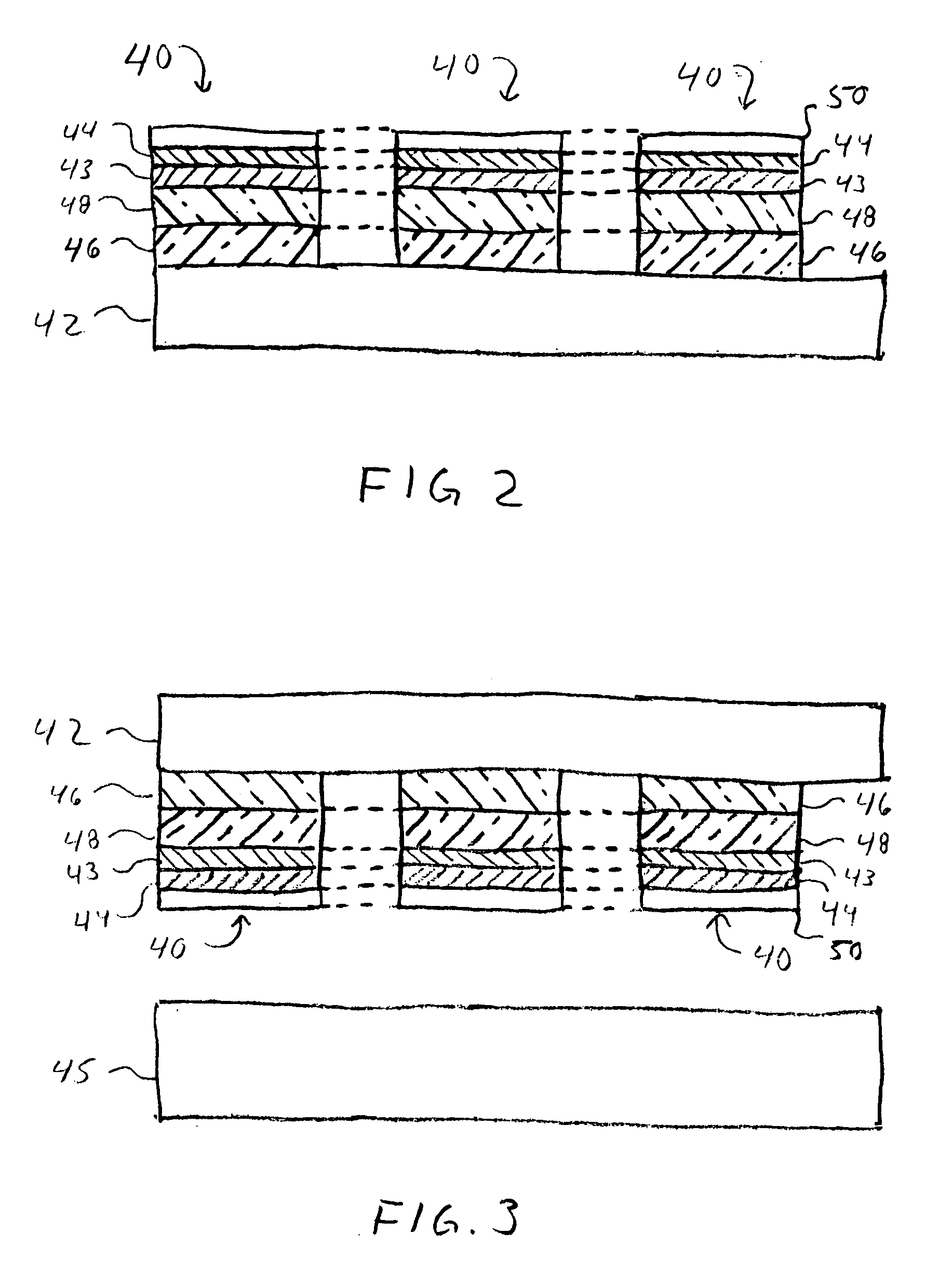

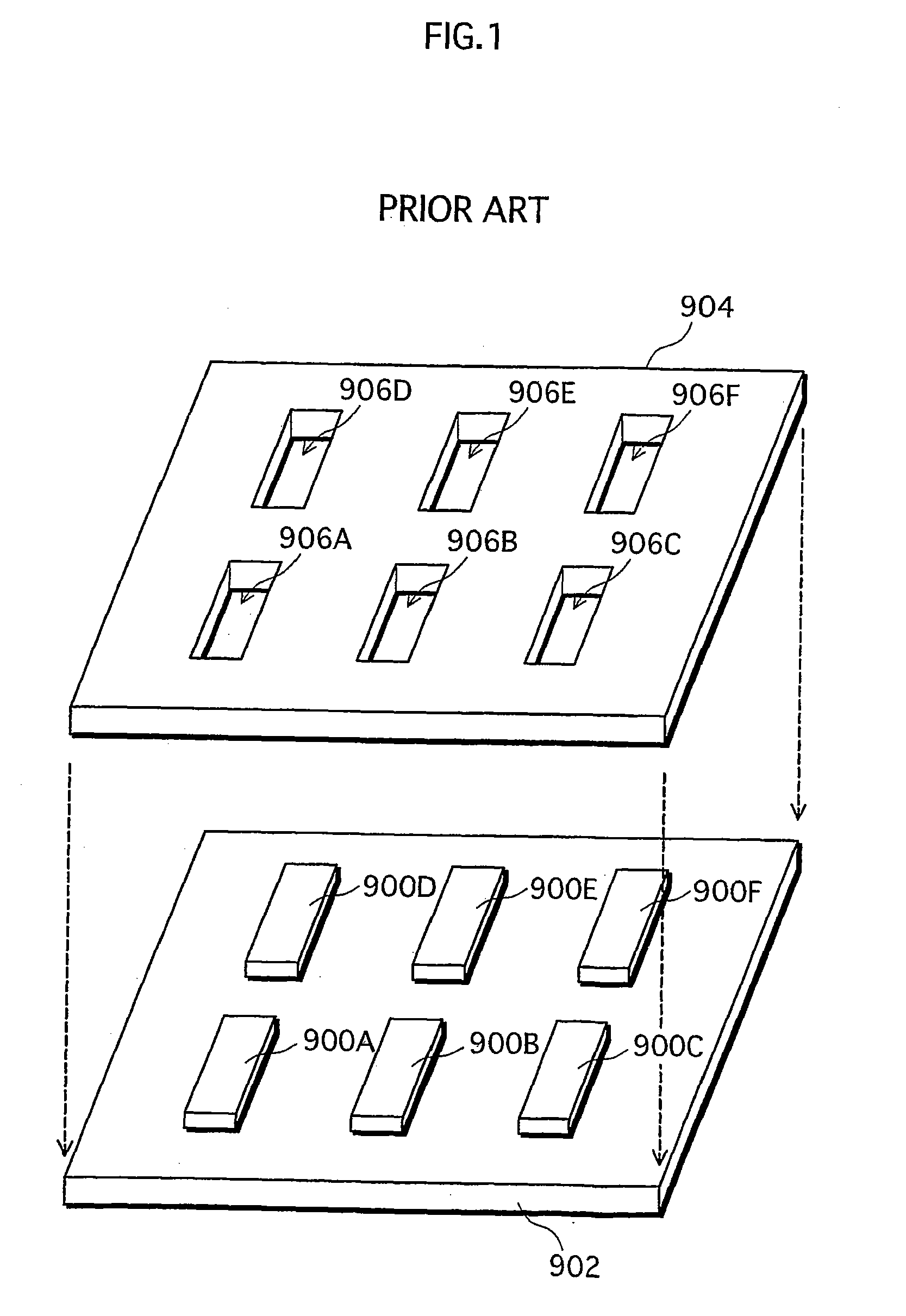

Substrate removal process for high light extraction LEDs

ActiveUS20060189098A1Index matchingImprove light extractionSemiconductor/solid-state device manufacturingSemiconductor devicesNitrideLight-emitting diode

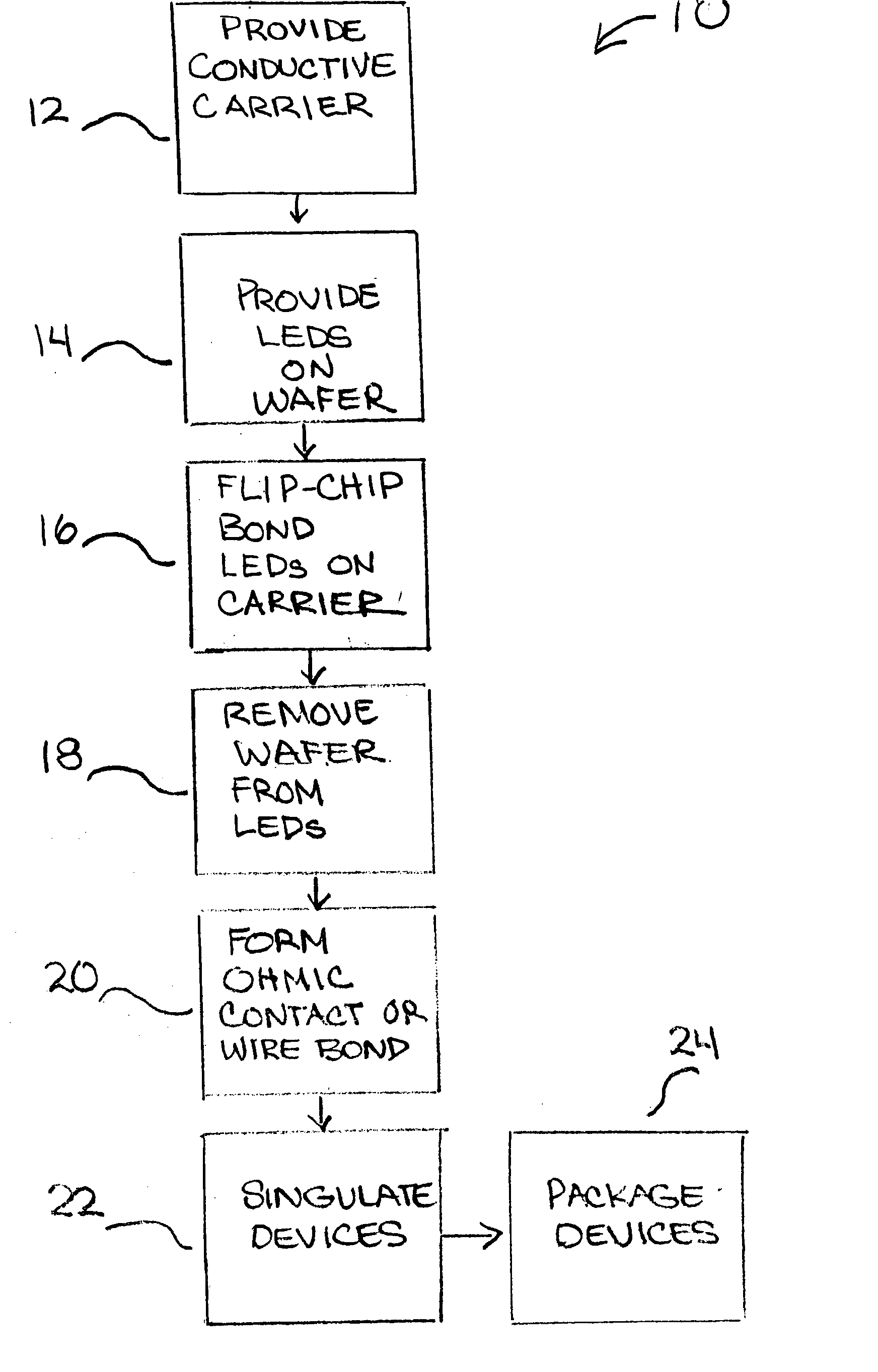

A method for fabricating light emitting diode (LEDs) comprises providing a plurality of LEDs on a substrate wafer, each of which has an n-type and p-type layer of Group-III nitride material formed on a SiC substrate with the n-type layer sandwiched between the substrate and p-type layer. A conductive carrier is provided having a lateral surface to hold the LEDs. The LEDs are flip-chip mounted on the lateral surface of the conductive carrier. The SiC substrate is removed from the LEDs such that the n-type layer is the top-most layer. A respective contact is deposited on the n-type layer of each of the LEDs and the carrier is separated into portions such that each of the LEDs is separated from the others, with each of the LEDs mounted to a respective portion of said carrier.

Owner:CREELED INC

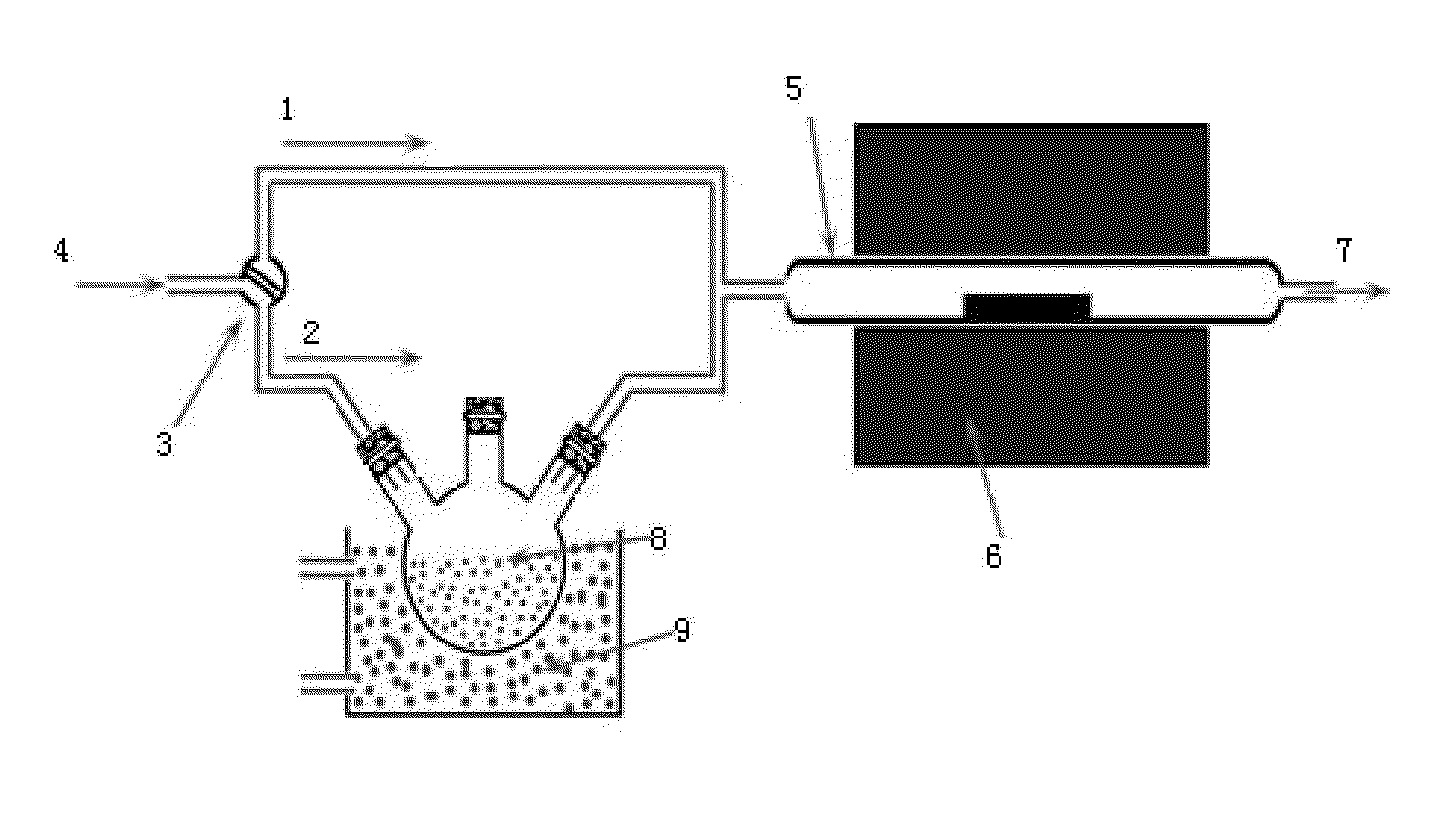

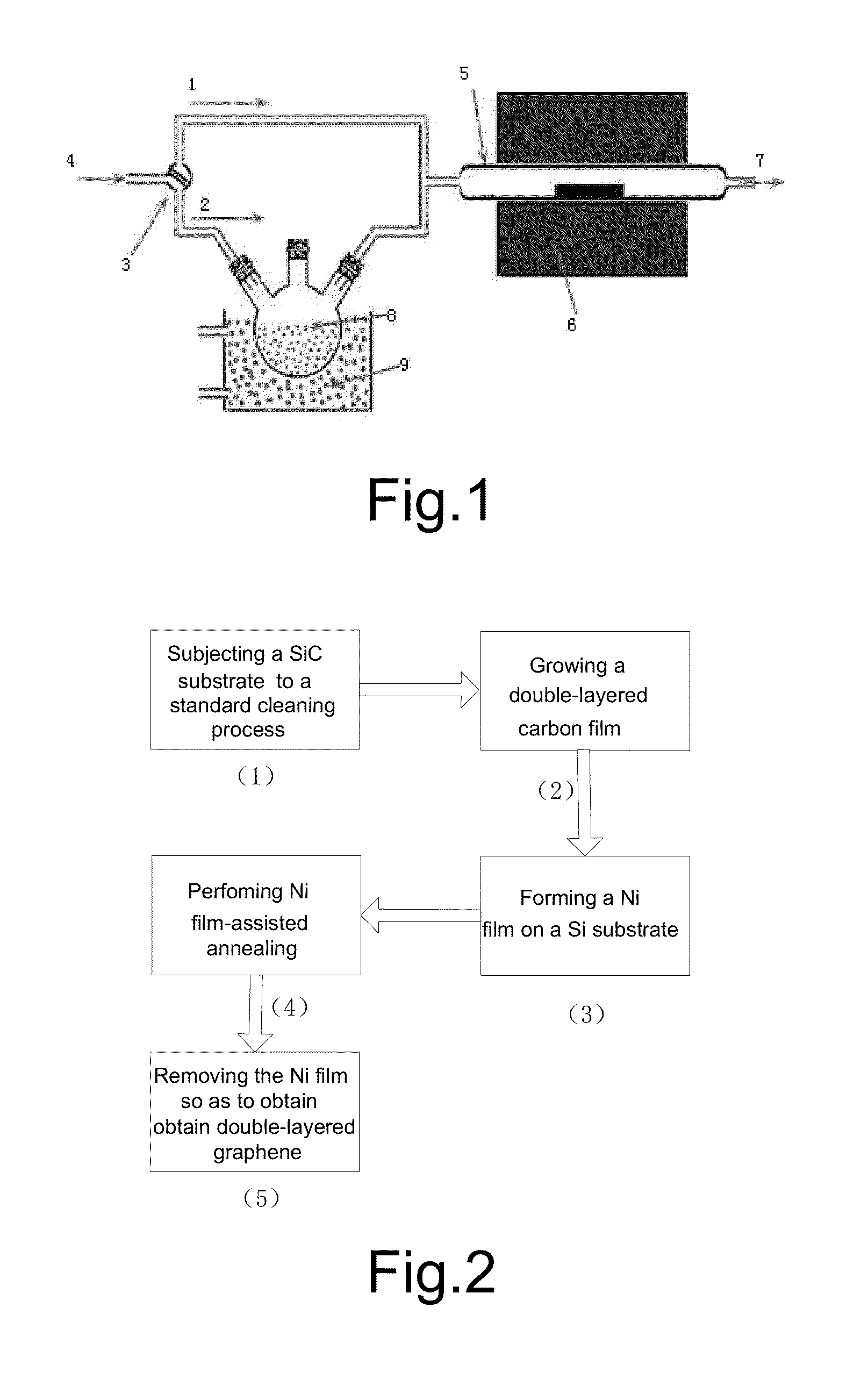

Process for Preparing Graphene on a SiC Substrate Based on Metal Film-Assisted Annealing

ActiveUS20140367642A1Simply and energy-efficientFlat surfaceMaterial nanotechnologyVacuum evaporation coatingCarbon filmElectron beam deposition

Provided is a process for preparing graphene on a SiC substrate, based on metal film-assisted annealing, comprising the following steps: subjecting a SiC substrate to a standard cleaning process; placing the cleaned SiC substrate into a quartz tube and heating the quartz tube up to a temperature of 750 to 1150° C.; introducing CCl4vapor into the quartz tube to react with SiC for a period of 20 to 100 minutes so as to generate a double-layered carbon film, wherein the CCl4 vapor is carried by Ar gas; forming a metal film with a thickness of 350 to 600 nm on a Si substrate by electron beam deposition; placing the obtained double-layered carbon film sample onto the metal film; subsequently annealing them in an Ar atmosphere at a temperature of 900 to 1100° C. for 10-30 minutes so as to reconstitute the double-layered carbon film into double-layered graphene; and removing the metal film from the double-layered graphene, thereby obtaining double-layered graphene. Also provided is double-layered graphene prepared by said process.

Owner:XIDIAN UNIV

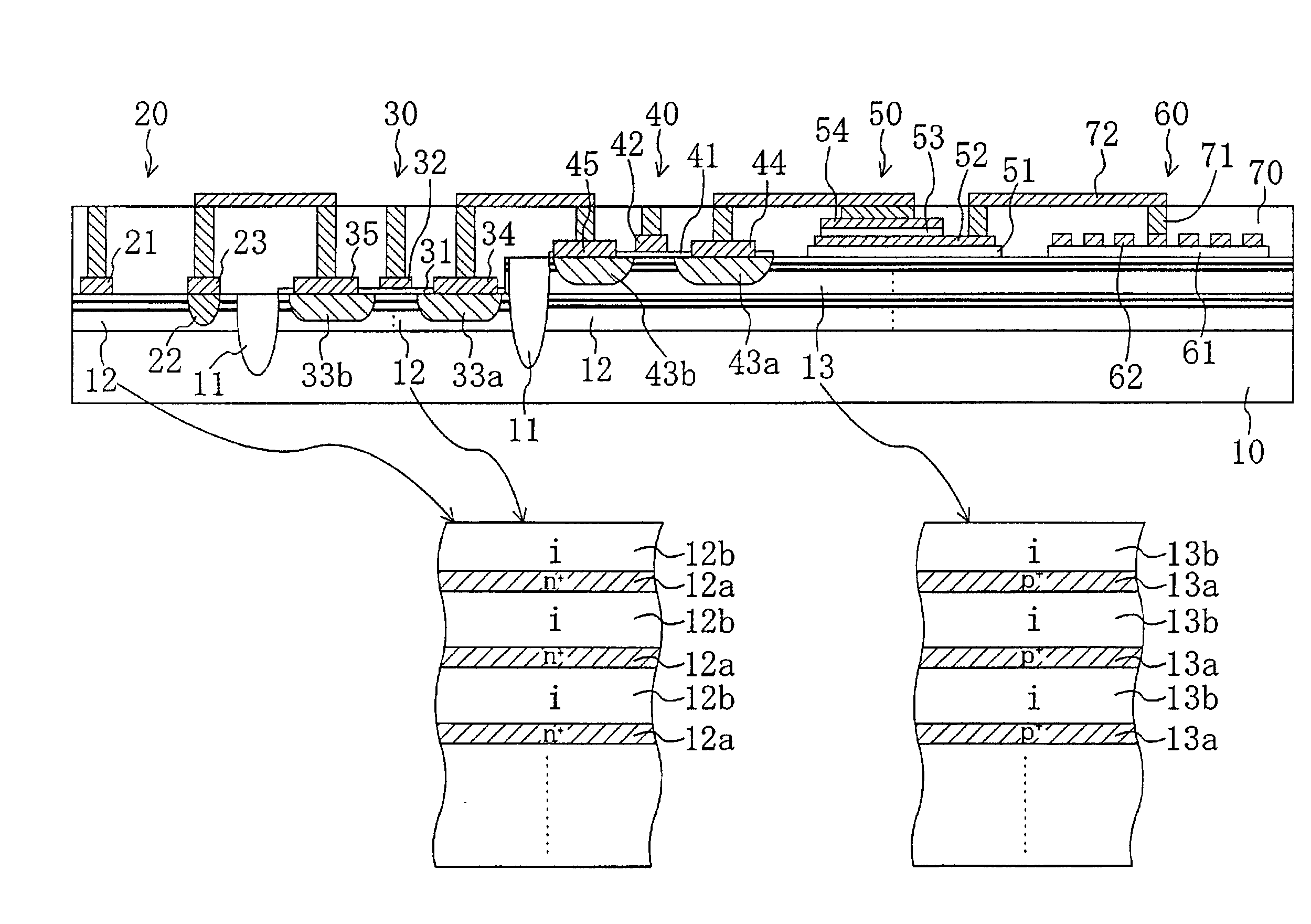

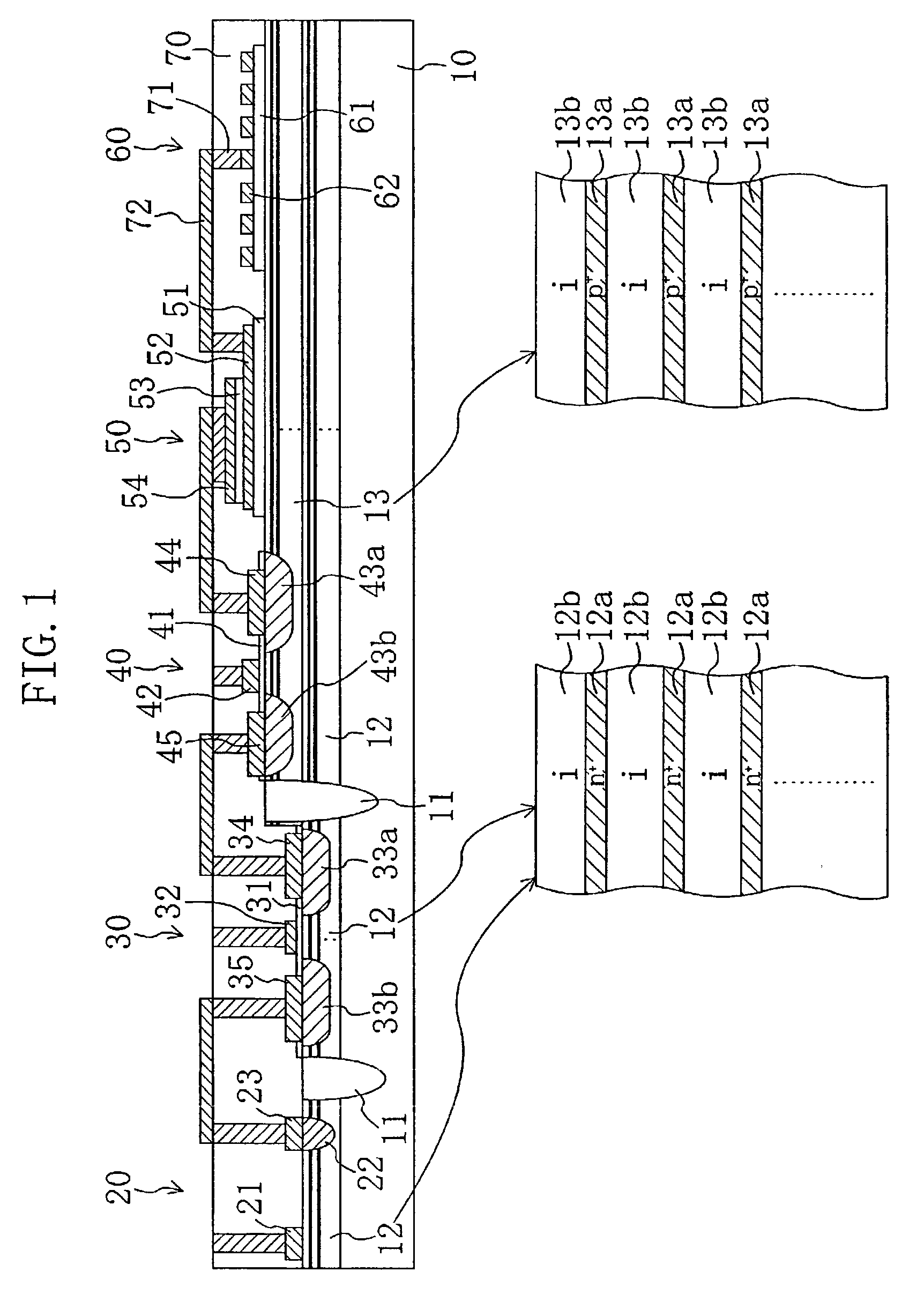

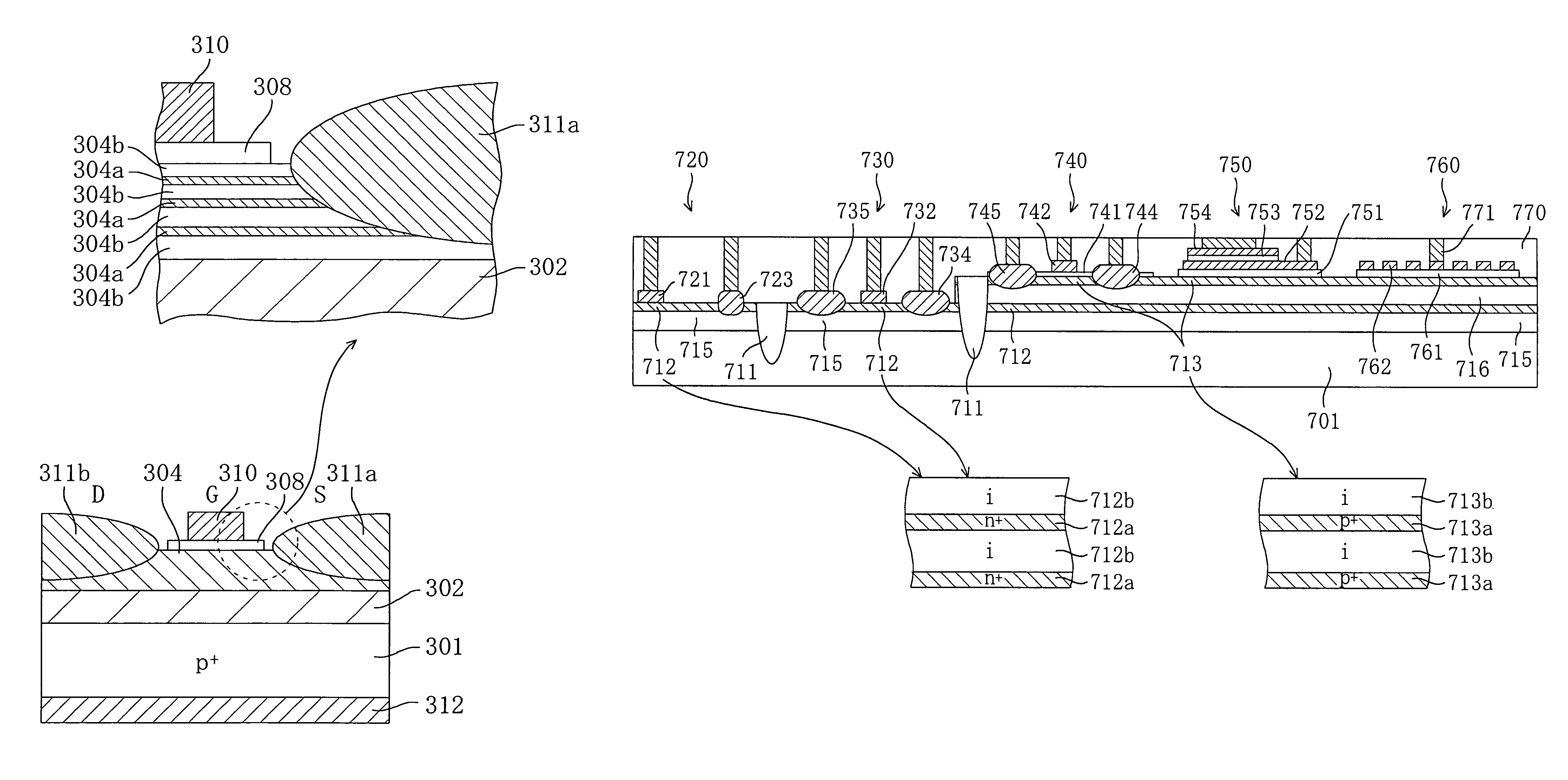

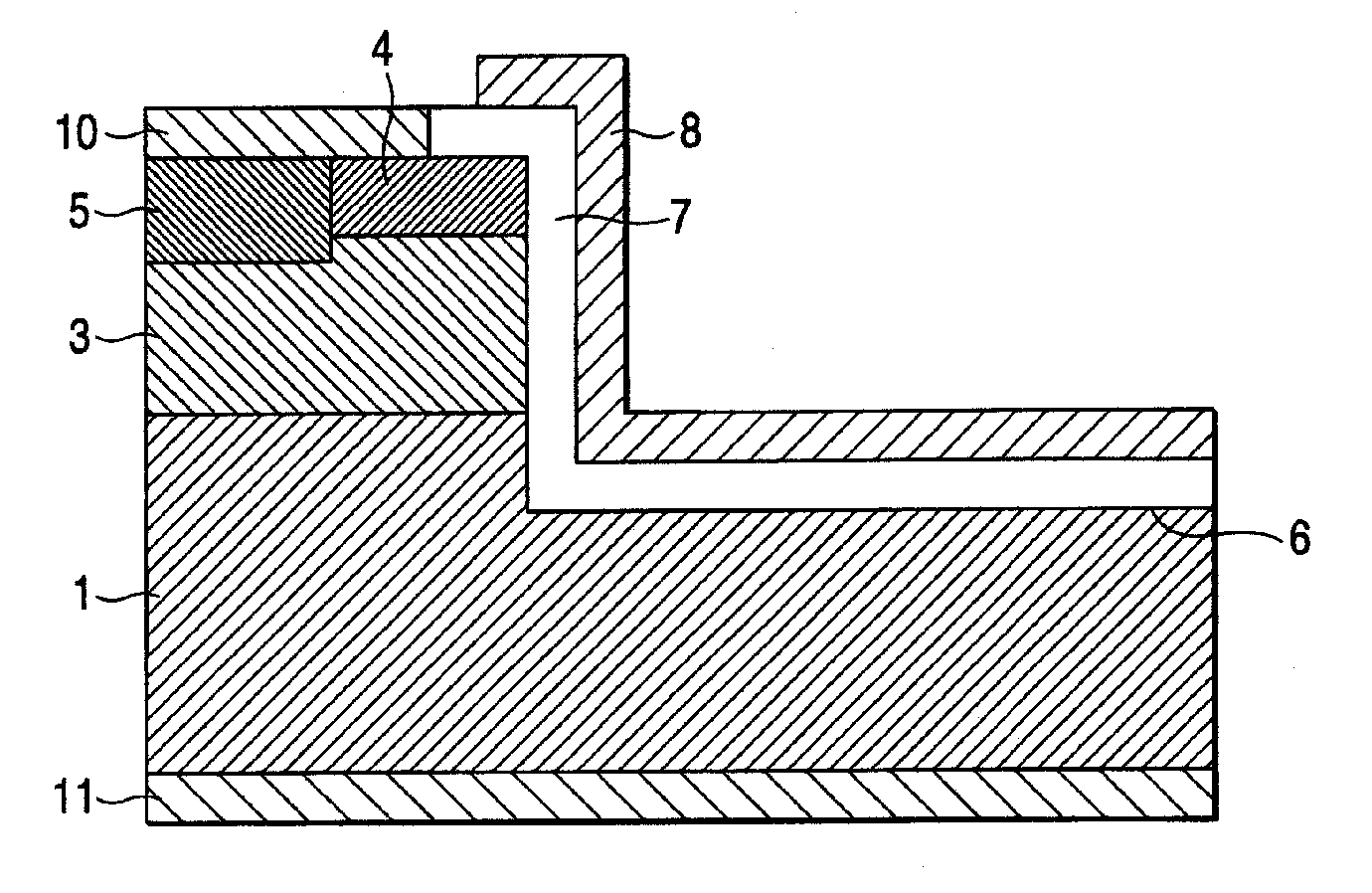

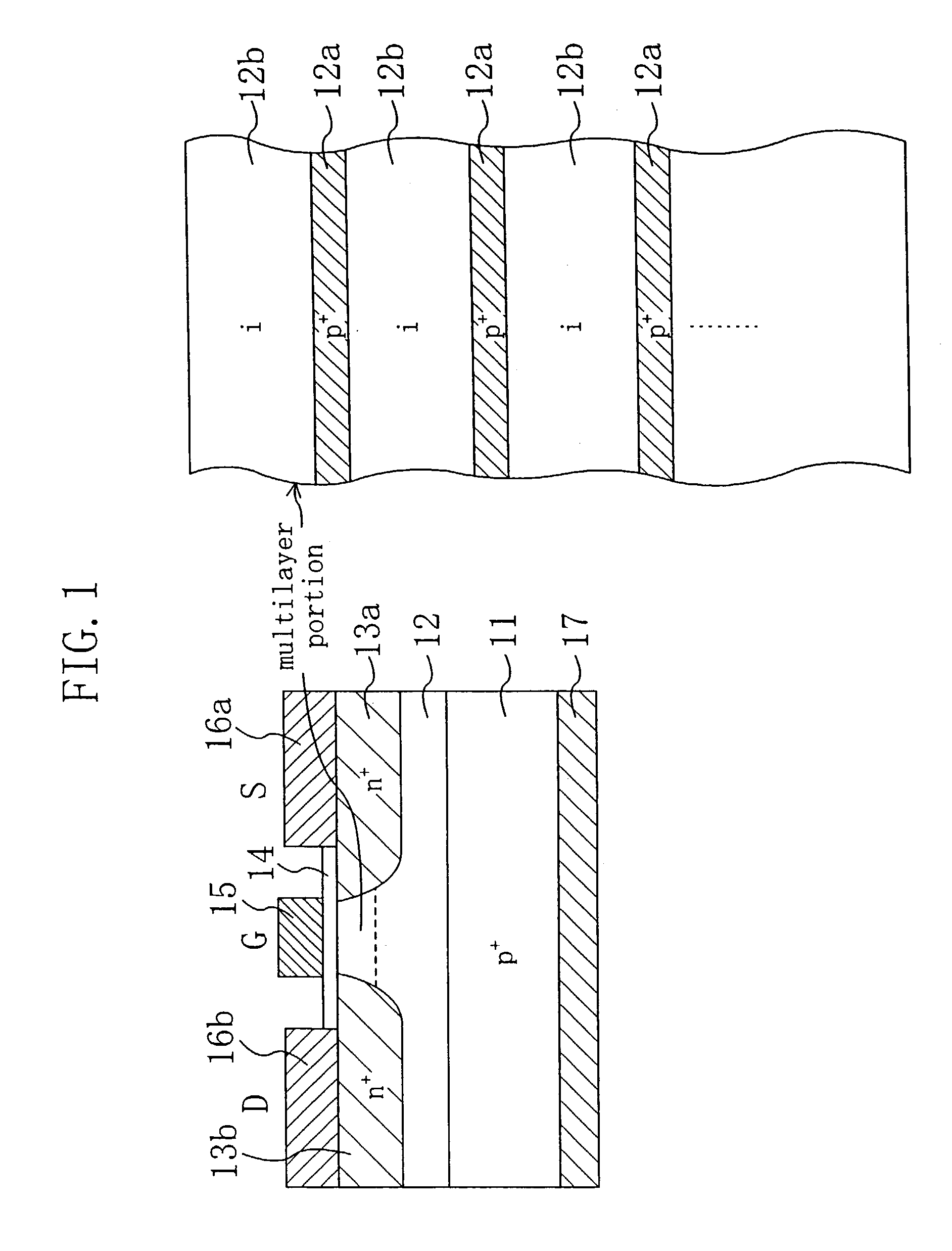

Semiconductor device

InactiveUS20030006415A1Increase flexibilityReduce in quantityTransistorSolid-state devicesMOSFETInductor

In a SiC substrate (10), a first active region (12) composed of n-type heavily doped layers (12a) and undoped layers (12b), which are alternately stacked, and a second active region (13) composed of p-type heavily doped layers (13a) and undoped layers (13b), which are alternately stacked, are provided upwardly in this order. A Schottky diode (20) and a pMOSFET (30) are provided on the first active region (12). An nMOSFET (40), a capacitor (50), and an inductor (60) are provided on the second active region (13). The Schottky diode (20) and the MOSFETs (30, 40) have a breakdown voltage characteristic and a carrier flow characteristic due to a multilayer structure composed of delta-doped layers and undoped layers and are integrated in a common substrate.

Owner:PANASONIC CORP

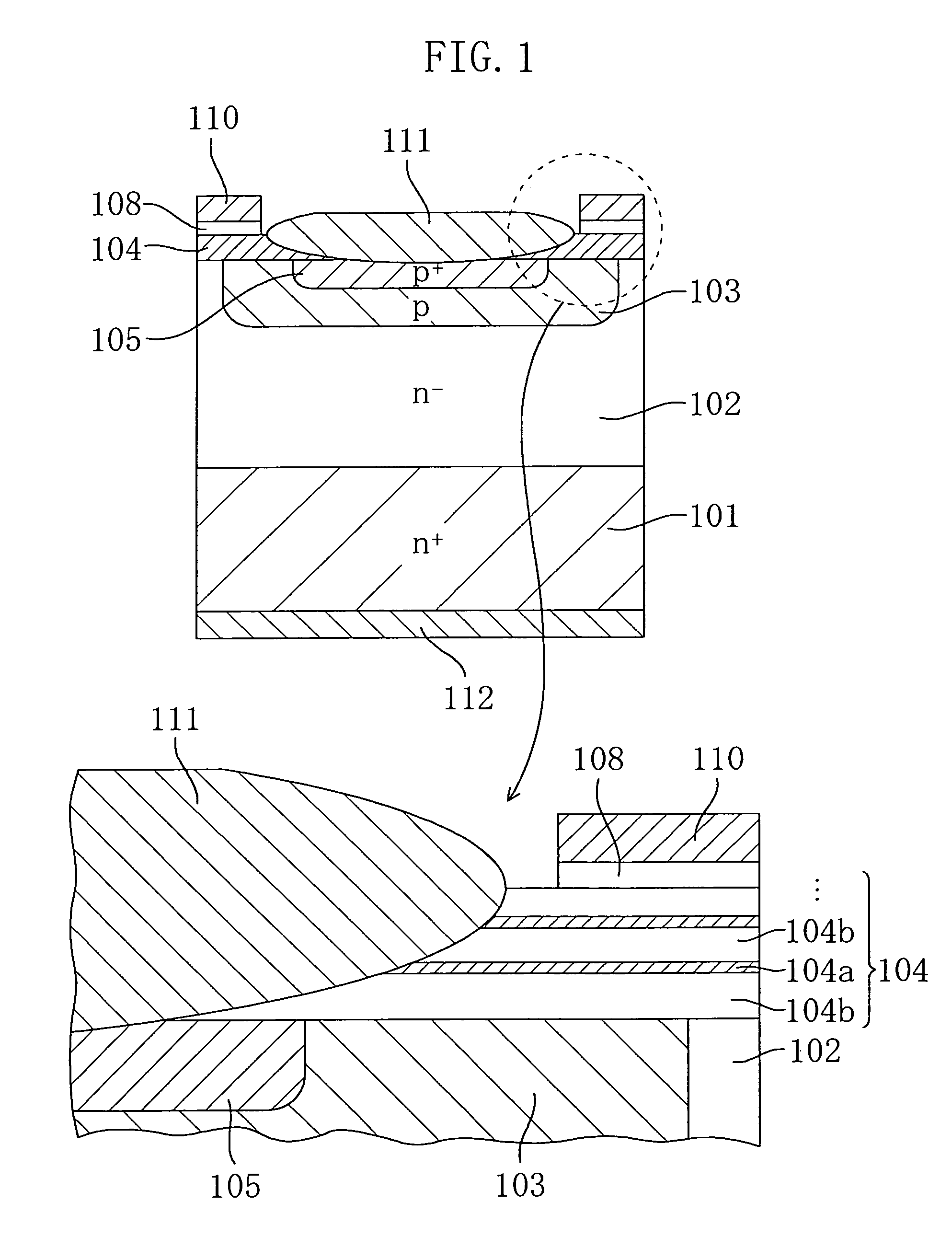

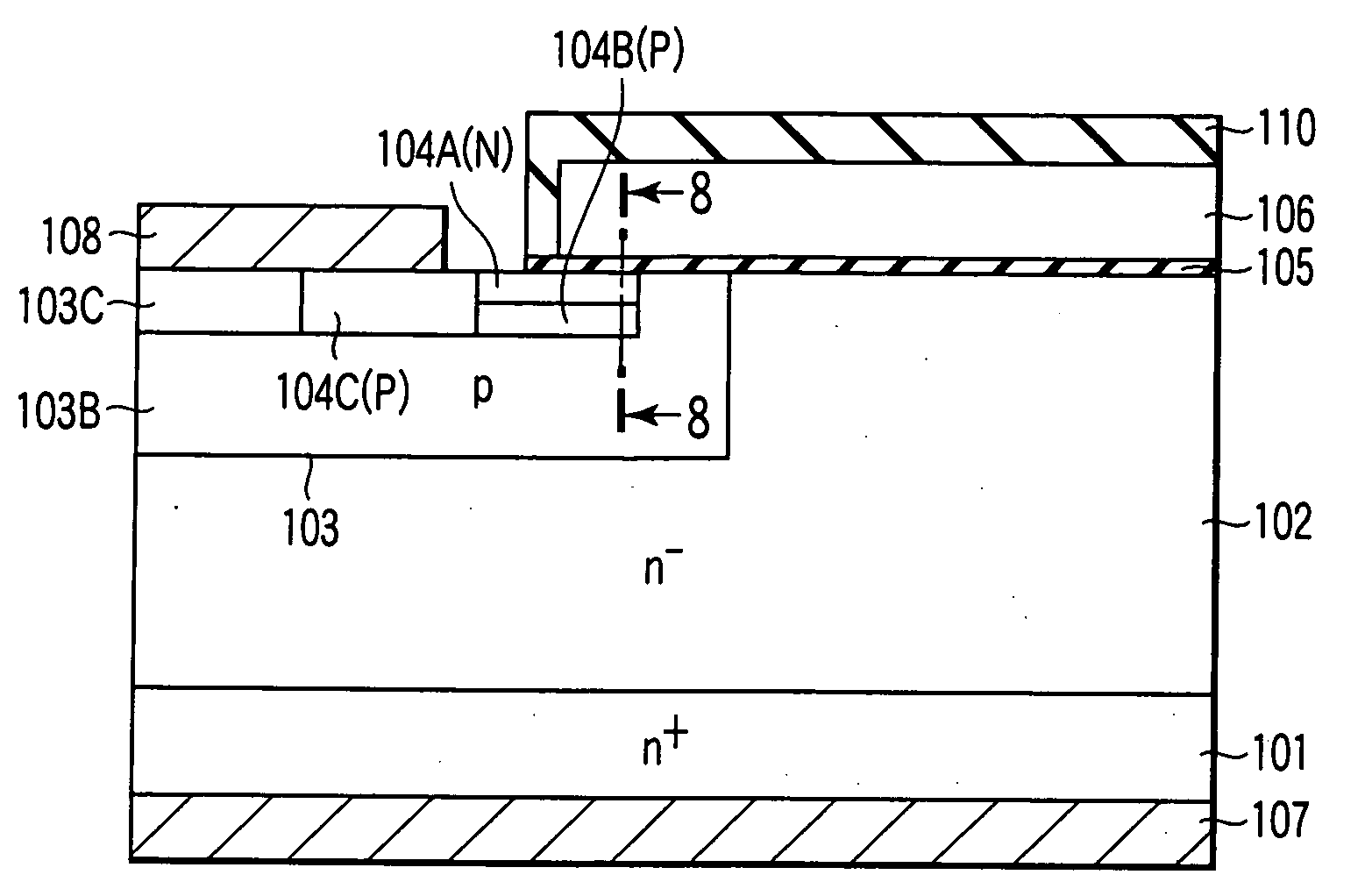

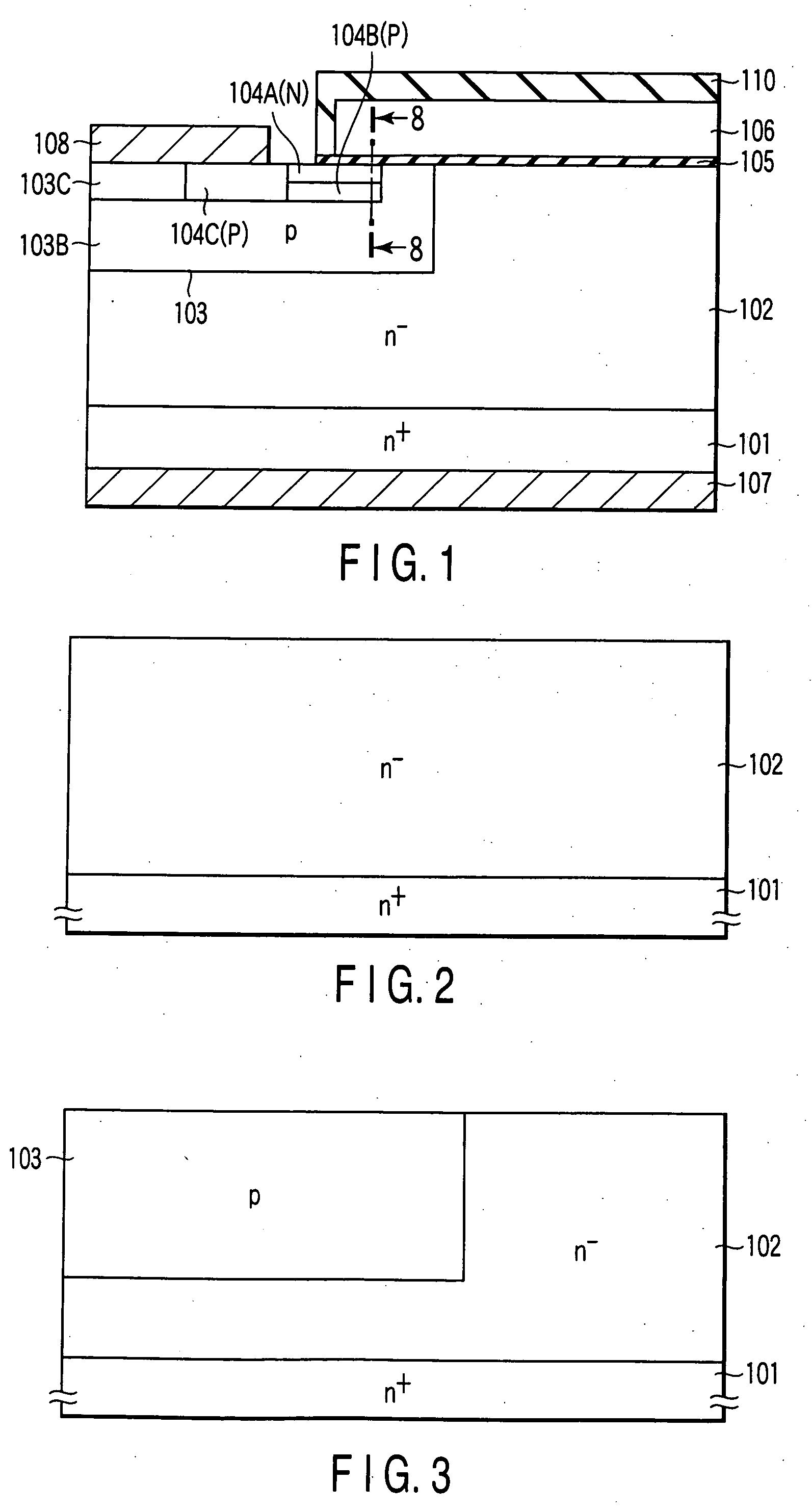

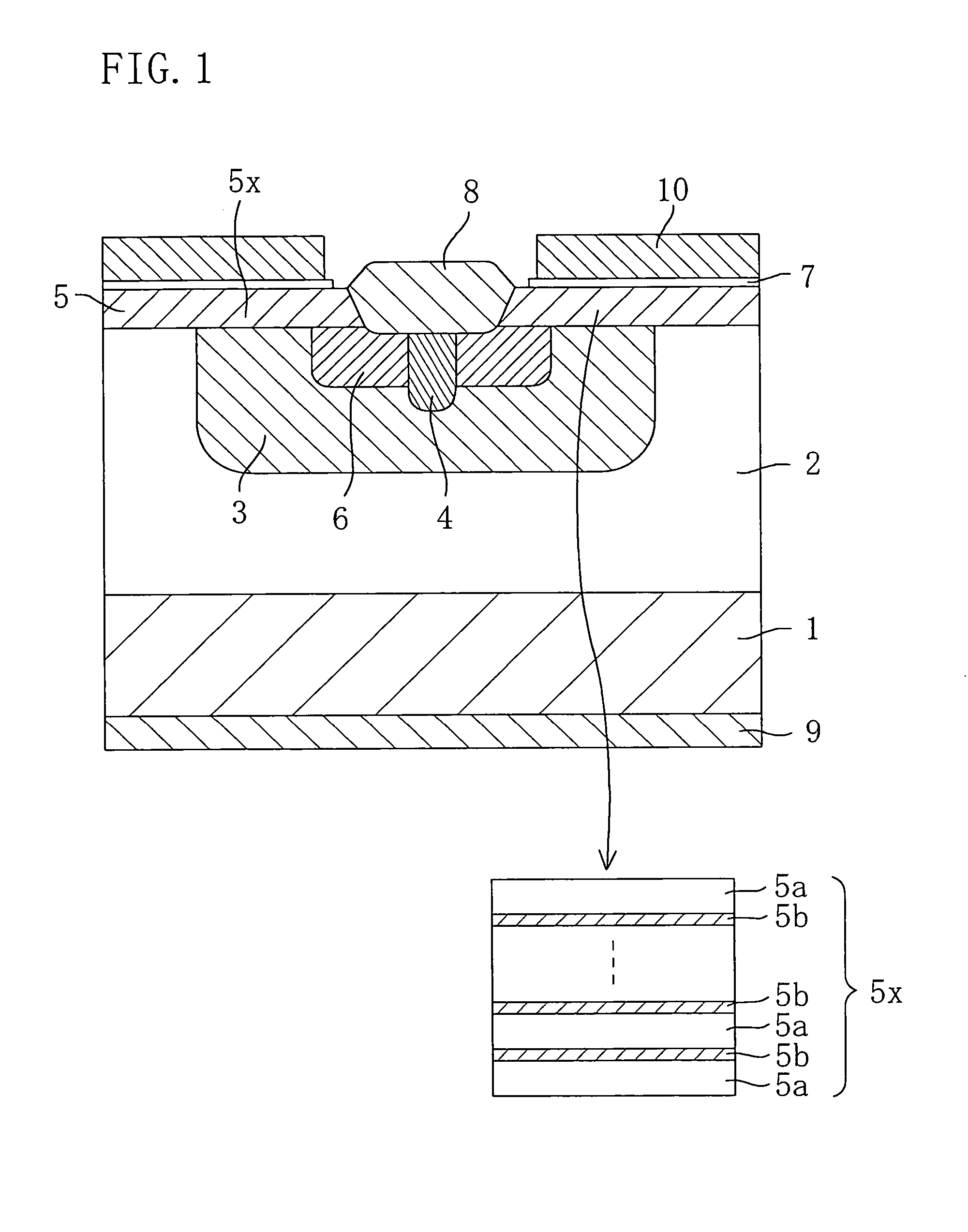

Semiconductor device and method for manufacturing same

InactiveUS7507999B2Improve breakdown voltageReduce lossTransistorSolid-state devicesHigh resistanceSic substrate

An accumulation-mode MISFET comprises: a high-resistance SiC layer 102 epitaxially grown on a SiC substrate 101; a well region 103; an accumulation channel layer 104 having a multiple δ-doped layer formed on the surface region of the well region 103; a contact region 105; a gate insulating film 108; and a gate electrode 110. The accumulation channel layer 104 has a structure in which undoped layers 104b and δ-doped layers 104a allowing spreading movement of carriers to the undoped layers 104b under a quantum effect are alternately stacked. A source electrode 111 is provided which enters into the accumulation channel layer 104 and the contact region 105 to come into direct contact with the contact region 105. It becomes unnecessary that a source region is formed by ion implantation, leading to reduction in fabrication cost.

Owner:PANASONIC CORP

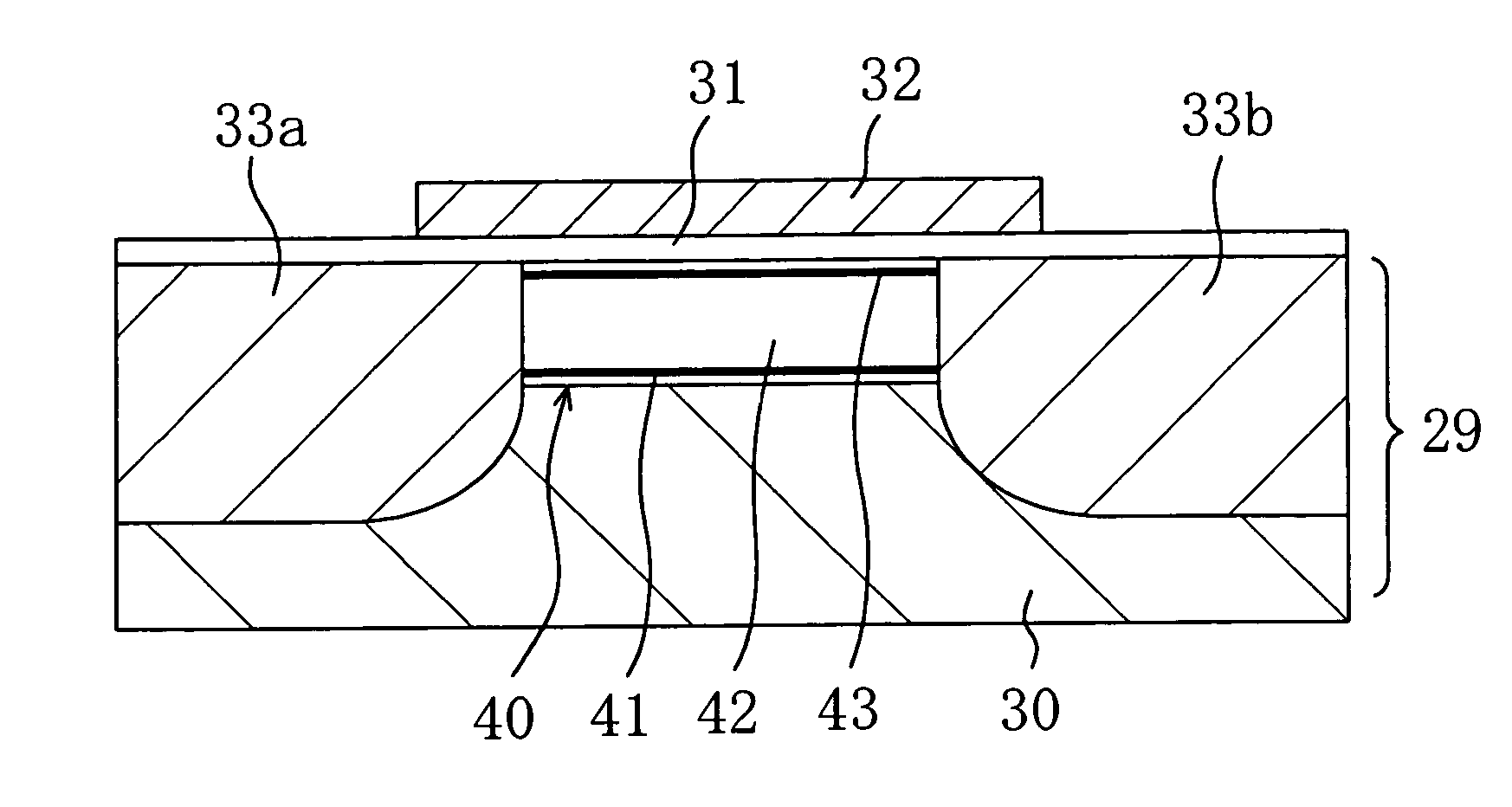

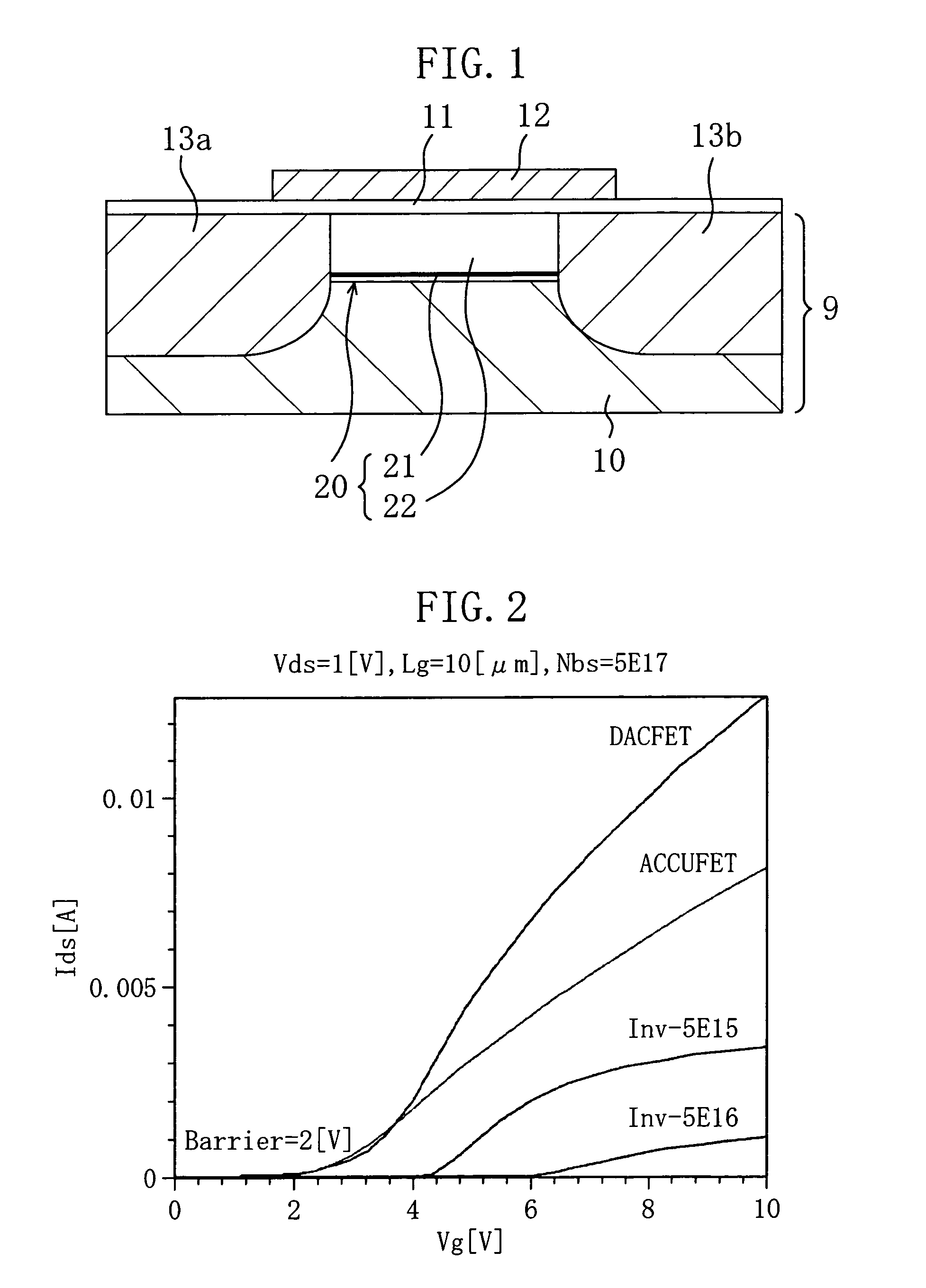

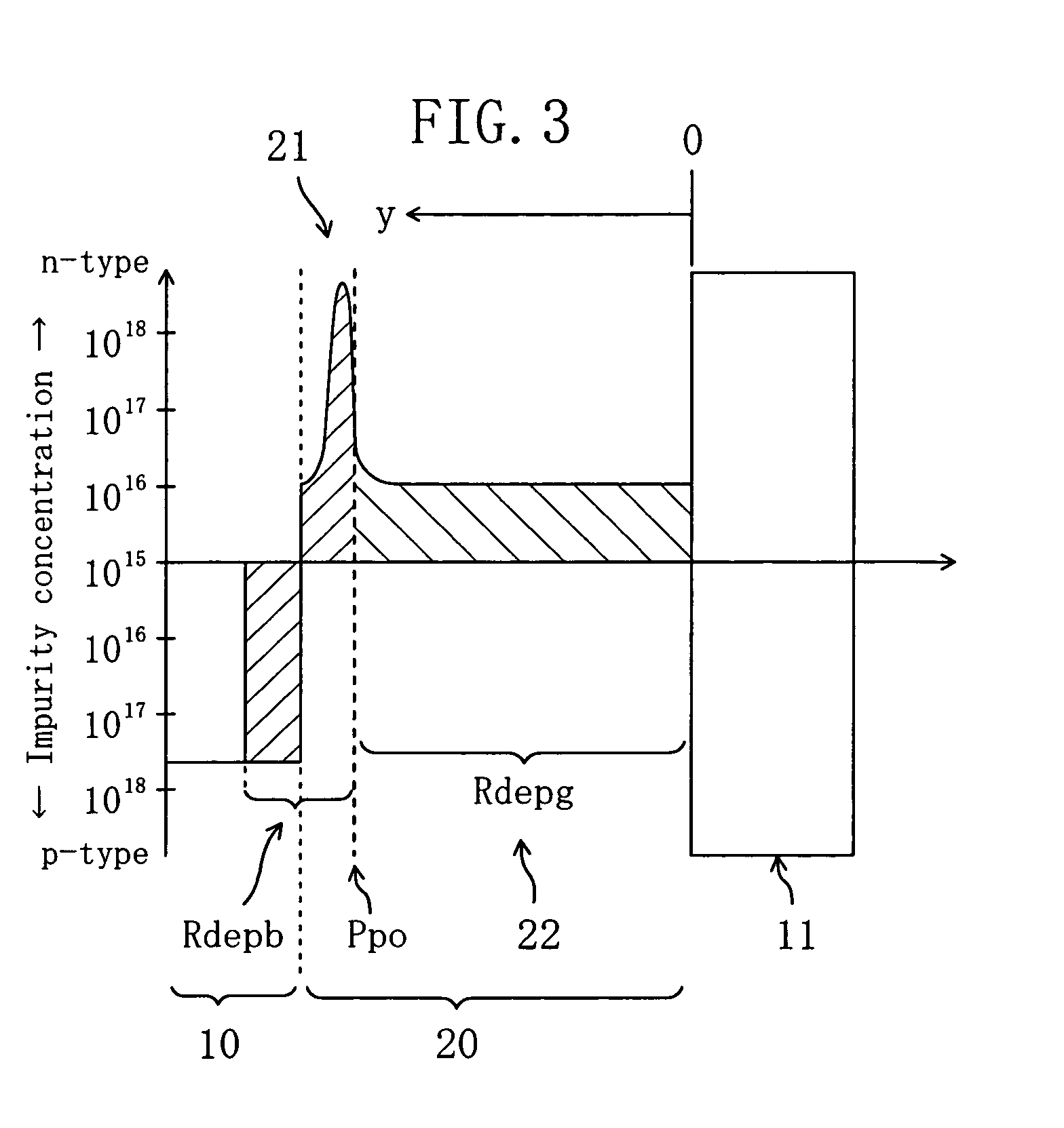

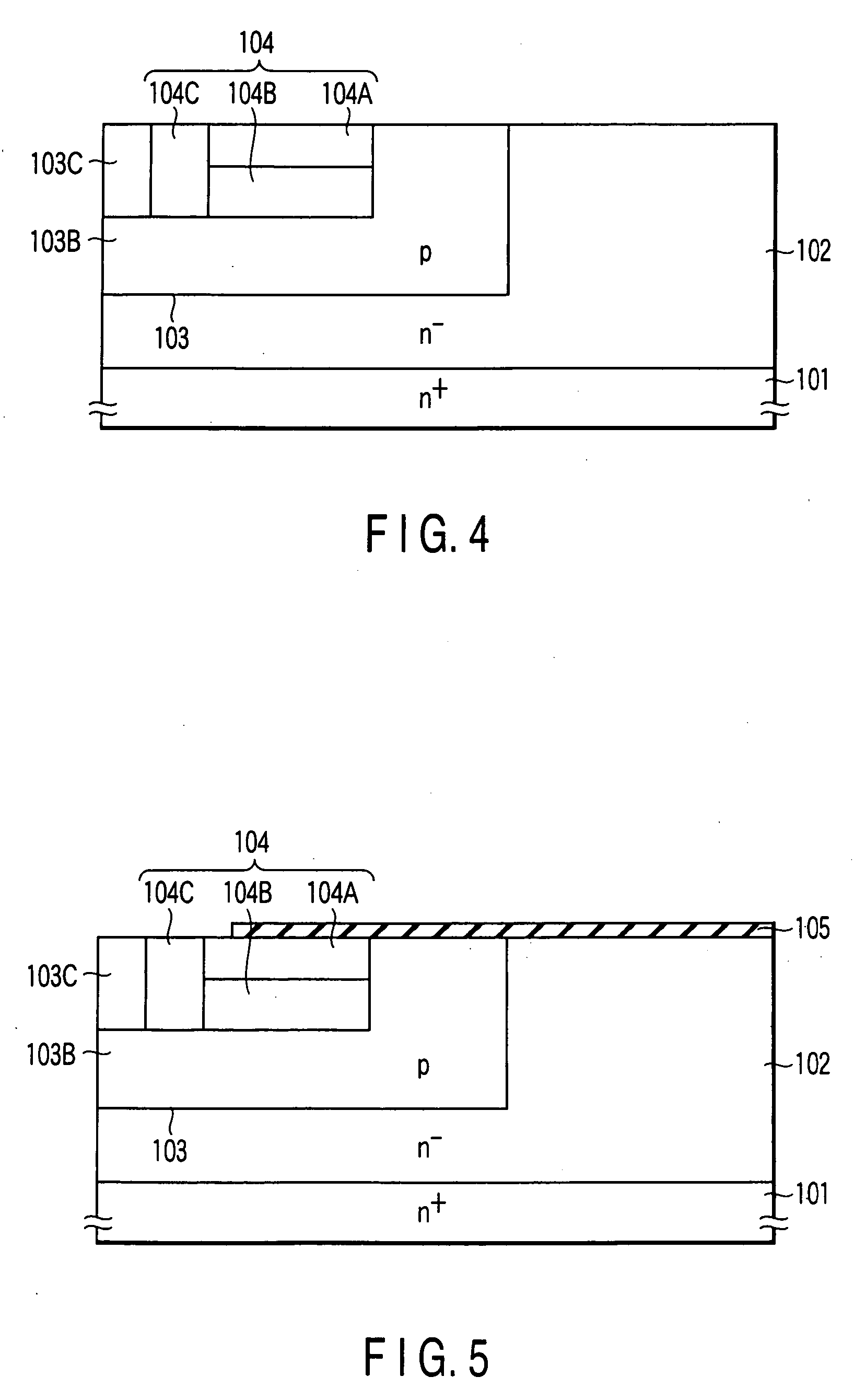

Semiconductor device

InactiveUS6995397B2Improve mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationSic substrate

A semiconductor device having an accumulation channel SiC-MISFET structure includes a p-type SiC layer 10 formed on an SiC substrate, an n-type channel layer 20, a gate insulating film 11, a gate electrode 12, and n-type source and drain layers 13a and 13b. The channel layer 20 includes an undoped layer 22 and a δ doped layer 21 which is formed in the vicinity of the lower end of the undoped layer 22. Since the channel layer 20 includes the high-concentration δ doped layer 21 in its deeper portion, the electric field in the surface region of the channel layer is weakened, thereby allowing the current driving force to increase.

Owner:PANASONIC CORP

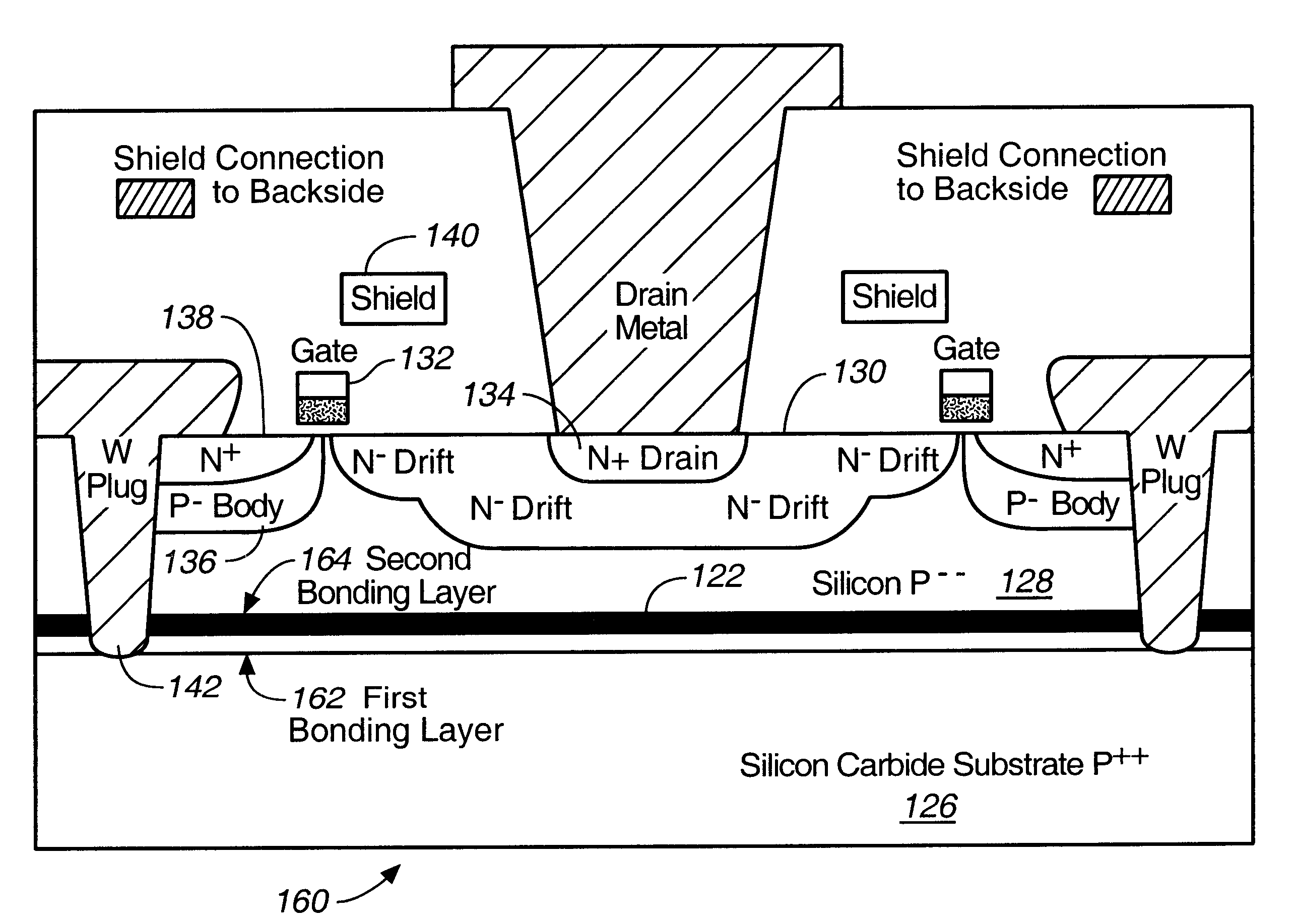

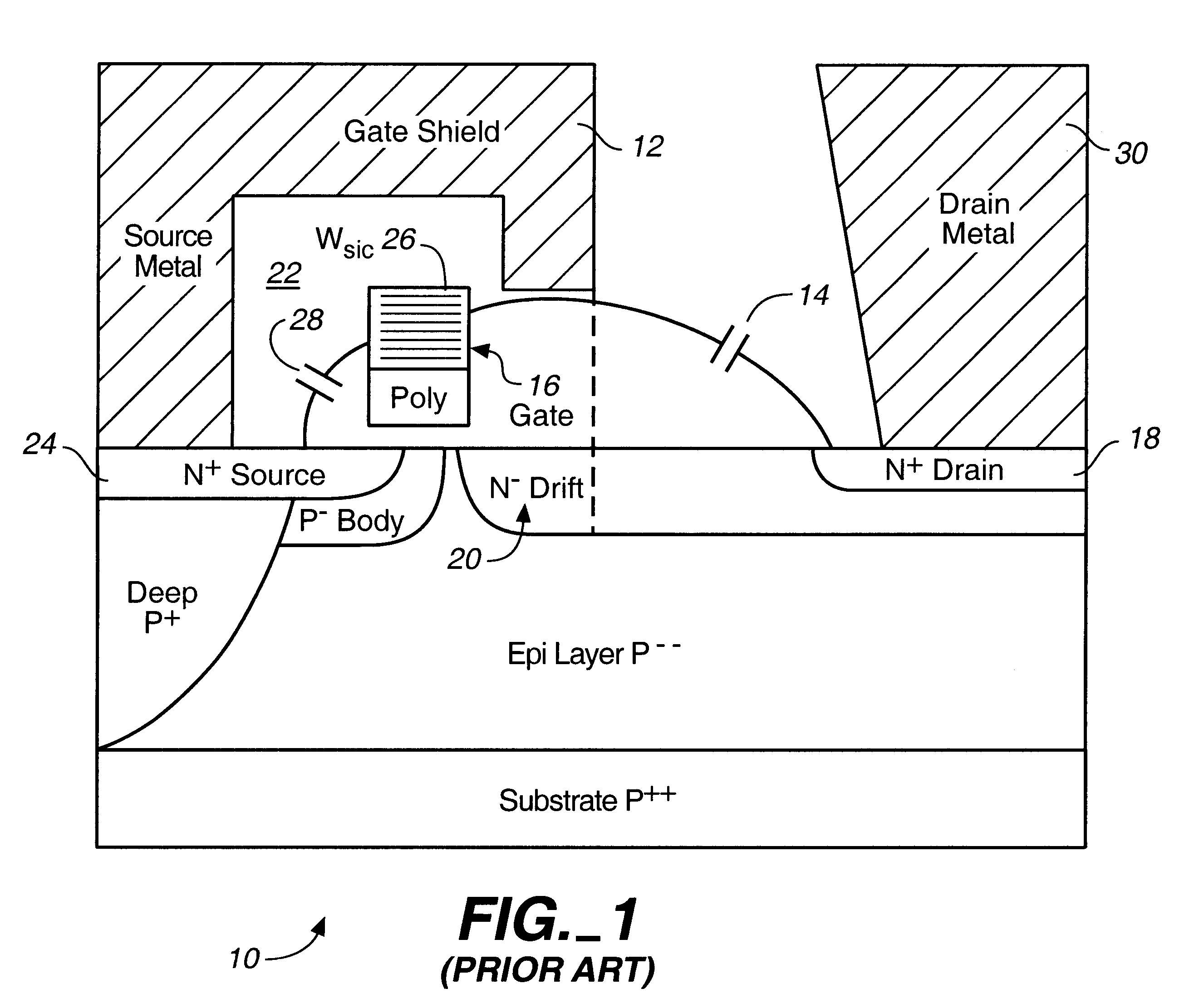

Microwave field effect transistor structure on silicon carbide substrate

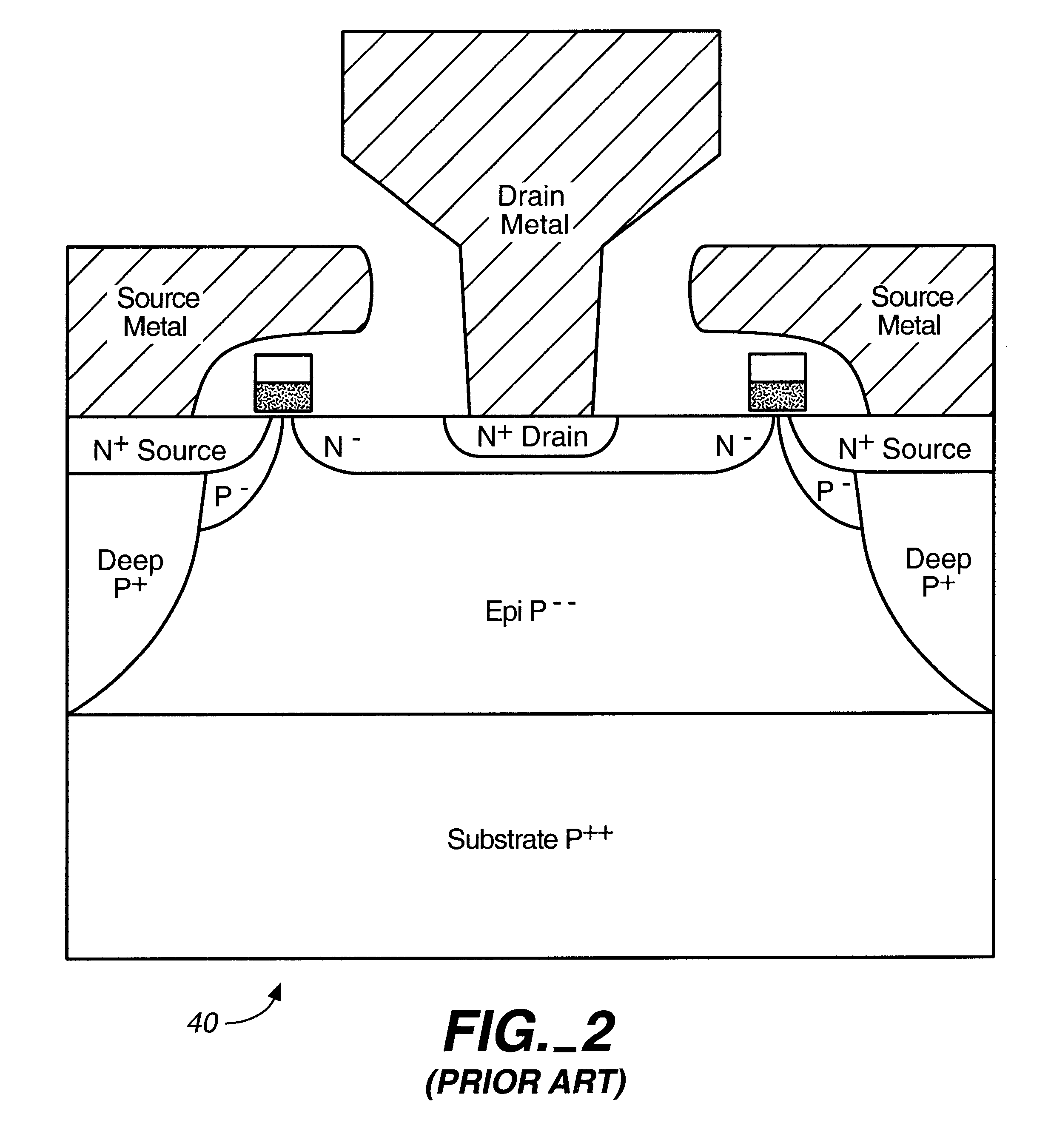

InactiveUS6521923B1Semiconductor/solid-state device detailsSolid-state devicesDopantSemiconductor materials

A microwave transistor structure comprising: (a) a SiC substrate having a top surface; (b) a silicon semiconductor material of a first conductivity type overlaying the top surface of the semiconductor substrate and having a top surface; (c) a conductive gate overlying and insulated from the top surface of the silicon semiconductor material; (d) a channel region of the first conductivity type formed completely within the silicon semiconductor material including a channel dopant concentration; (e) a drain region of the second conductivity type formed in the silicon semiconductor material and contacting the channel region; (f) a body region of the first conductivity type and having a body region dopant concentration formed in the silicon semiconductor material under the conductive gate region; (g) a source region of the second conductivity type and having a source region dopant concentration formed in the silicon semiconductor material within the body region; (h) a shield plate region being adjacent and being parallel to the drain region formed on the top surface of the silicon semiconductor material over a portion of the channel region; wherein the shield plate region is adjacent and parallel to the conductive gate region; and wherein the shield plate extends above the top surface of the silicon semiconductor material to a shield plate height level, and is insulated from the top-surface of the silicon semiconductor material; and (i) a conductive plug region formed in the body region of the silicon semiconductor material to connect a lateral surface of the body region to the top surface of the substrate.

Owner:QORVO US INC

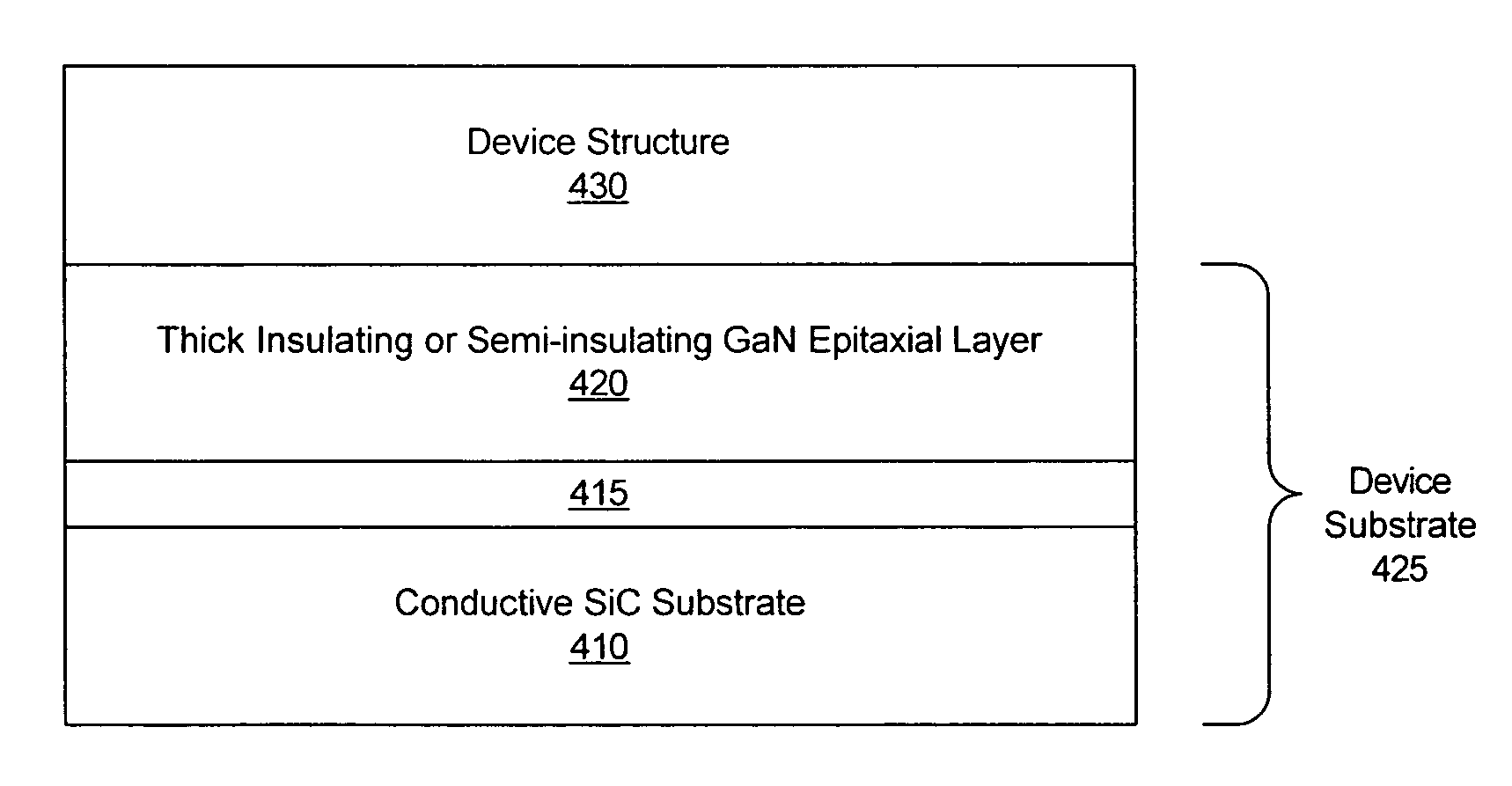

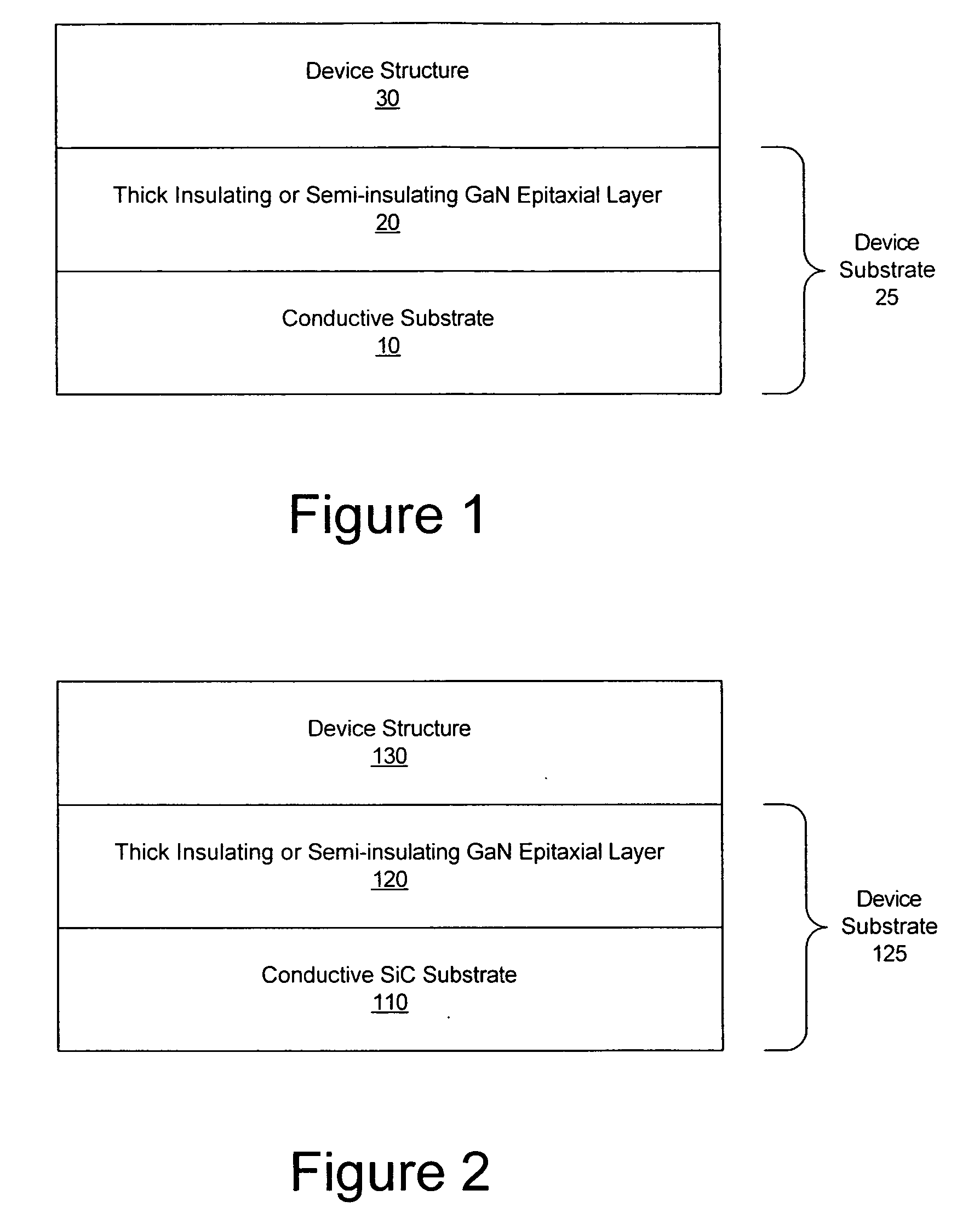

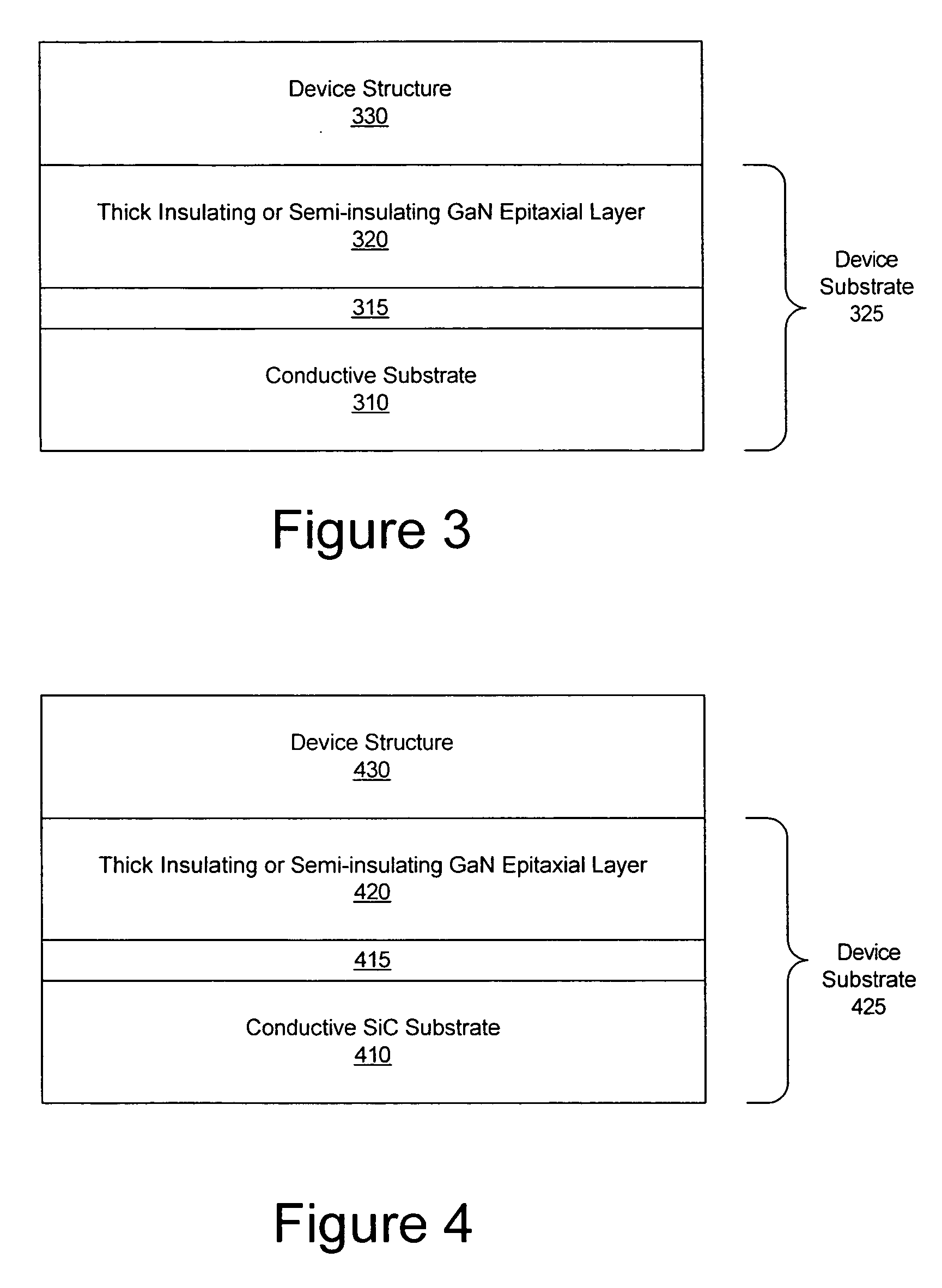

Thick semi-insulating or insulating epitaxial gallium nitride layers and devices incorporating same

ActiveUS20060226412A1High electron mobilityHigh dopingSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialGallium nitride

Semiconductor device structures and methods of fabricating semiconductor devices structures are provided that include a semi-insulating or insulating GaN epitaxial layer on a conductive semiconductor substrate and / or a conductive layer. The semi-insulating or insulating GaN epitaxial layer has a thickness of at least about 4 μm. GaN semiconductor device structures and methods of fabricating GaN semiconductor device structures are also provided that include an electrically conductive SiC substrate and an insulating or semi-insulating GaN epitaxial layer on the conductive SiC substrate. The GaN epitaxial layer has a thickness of at least about 4 μm. GaN semiconductor device structures and methods of fabricating GaN semiconductor device structures are also provided that include an electrically conductive GaN substrate, an insulating or semi-insulating GaN epitaxial layer on the conductive GaN substrate, a GaN based semiconductor device on the GaN epitaxial layer and a via hole and corresponding via metal in the via hole that extends through layers of the GaN based semiconductor device and the GaN epitaxial layer.

Owner:CREE INC

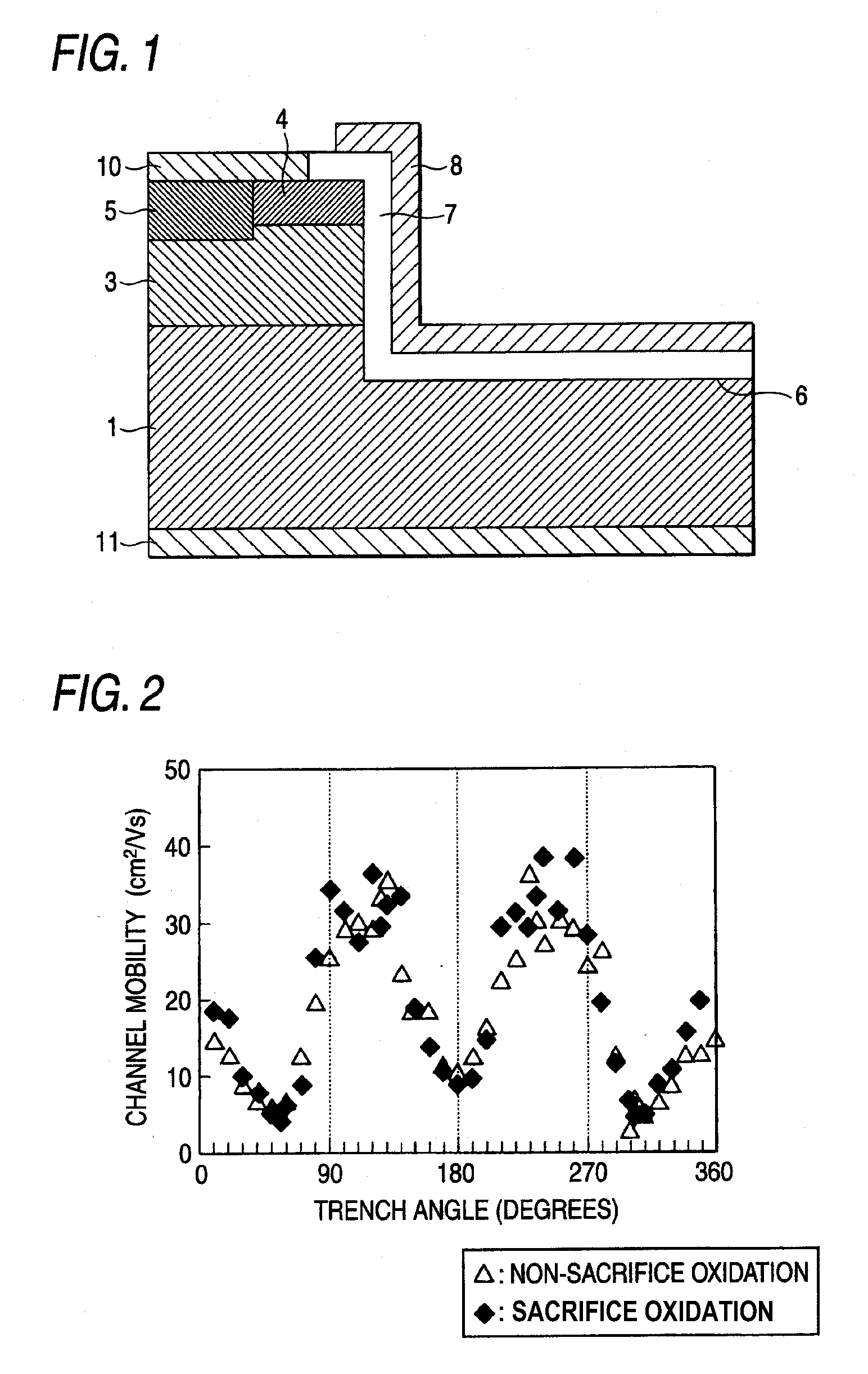

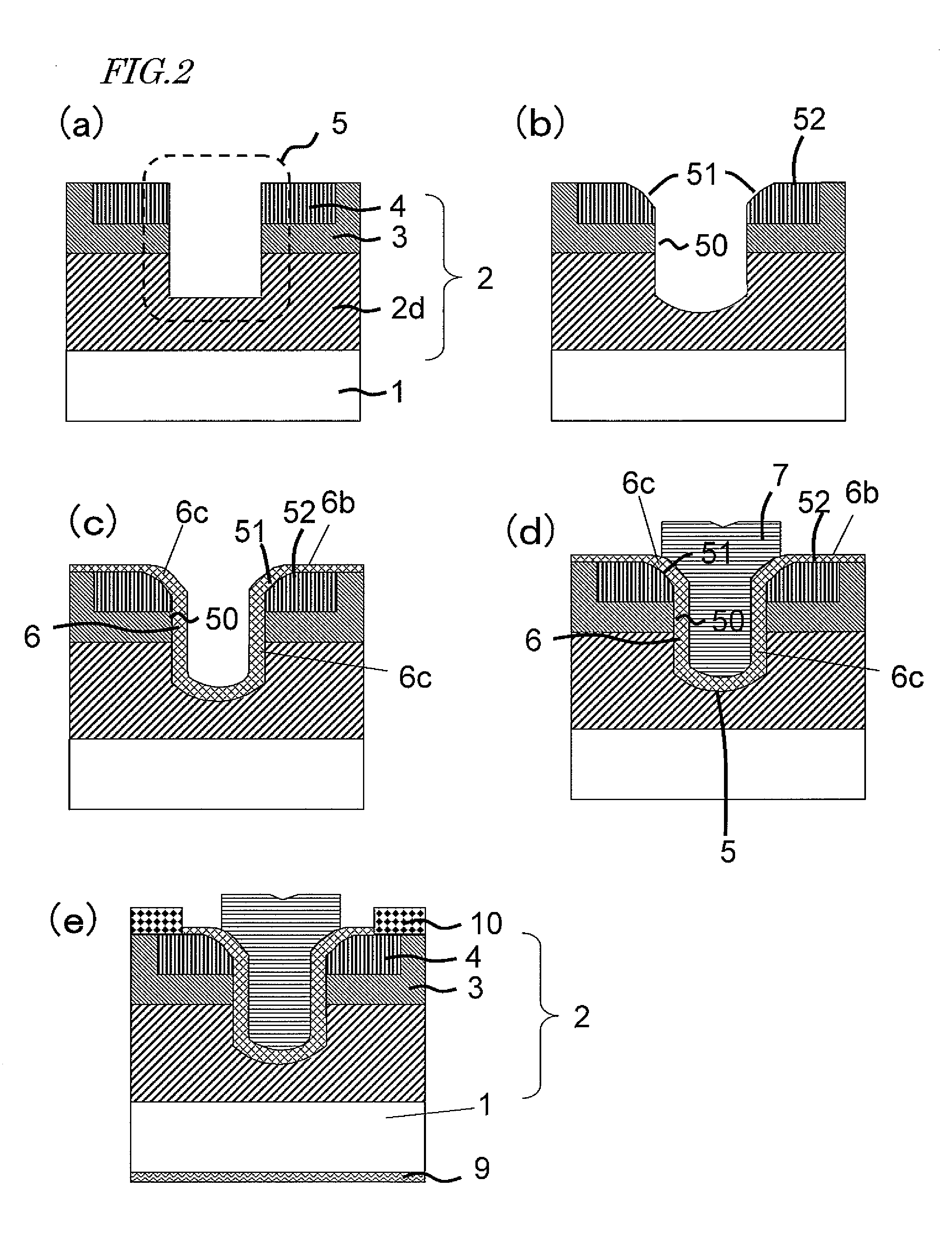

Semicoductor device and manufacturing method thereof

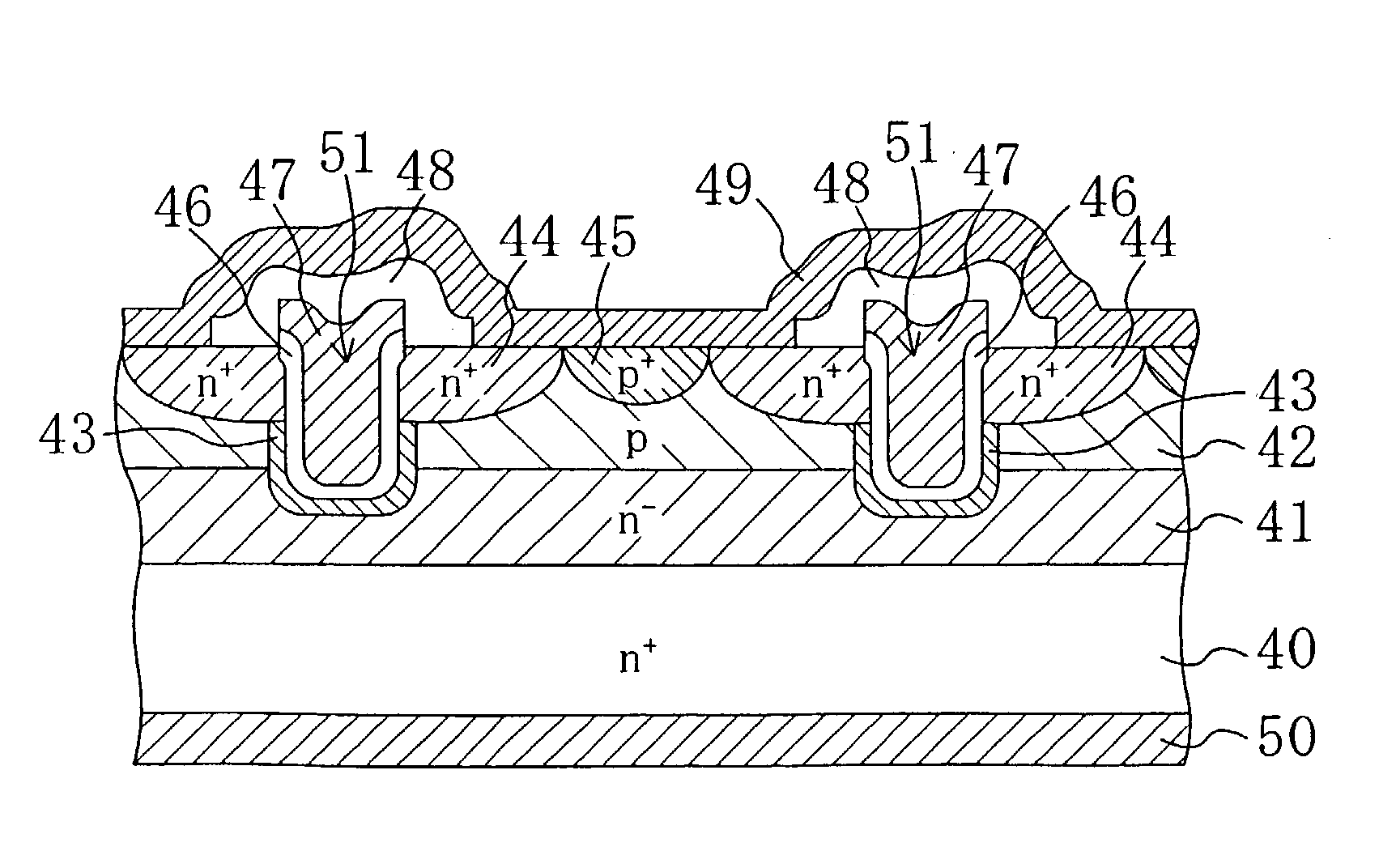

InactiveUS20070057262A1Semiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetSic substrate

In a semiconductor device having SiC vertical trench MOSFETs, it is aimed to prevent the generation of large scattering in the channel resistance without largely increasing the average value of channel resistance. A 4H-SiC substrate having a major face thereof that is generally a {0001} face and having an off angle α. The trench is formed with the standard deviation σ in scattering of the angle formed by a trench side wall face and a substrate major face within a wafer face. By setting the designed value of the angle formed by the trench side wall face and the substrate major face at an any angle ranging from [(60 degrees)+2σ] to [(90 degrees)−tan−1 (0.87×tan α)−2σ] in forming the trench in the SiC substrate, a semiconductor device in which the angle formed by the trench side wall face and the substrate major face is 60 degrees or more but not more than [(90 degrees)−tan−1 (0.87×tan α)] can be obtained.

Owner:FUJI ELECTRIC HLDG CO LTD

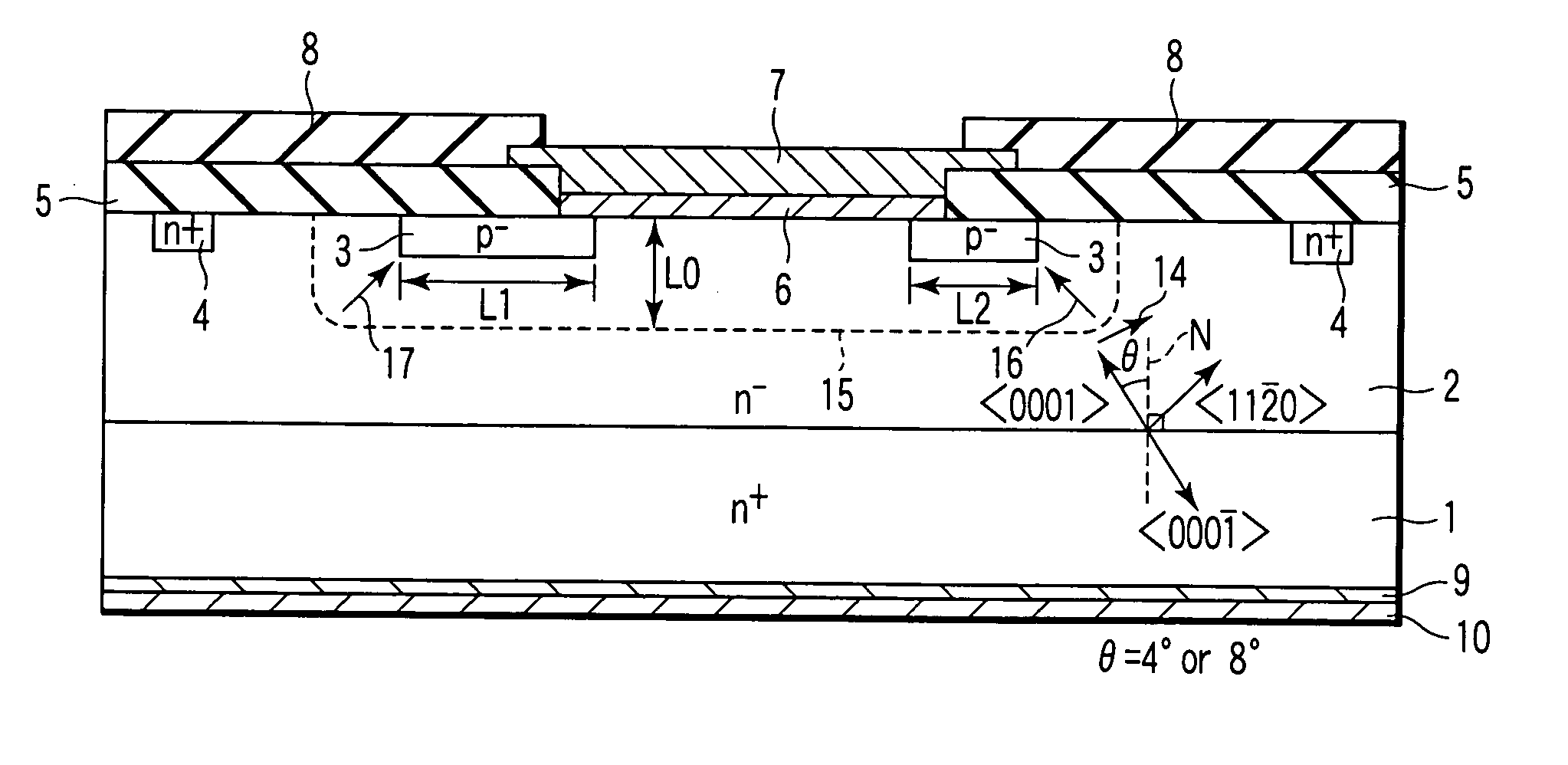

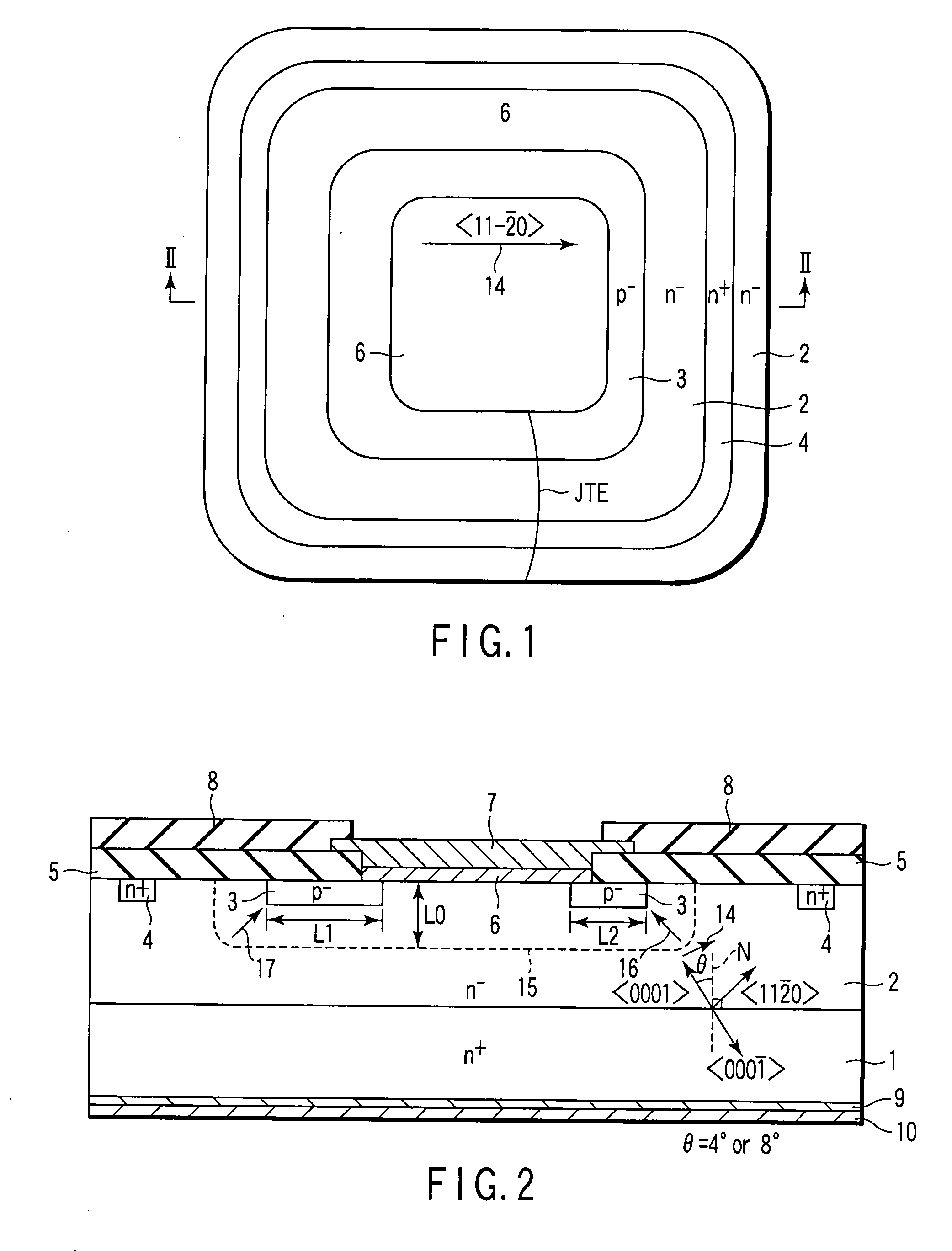

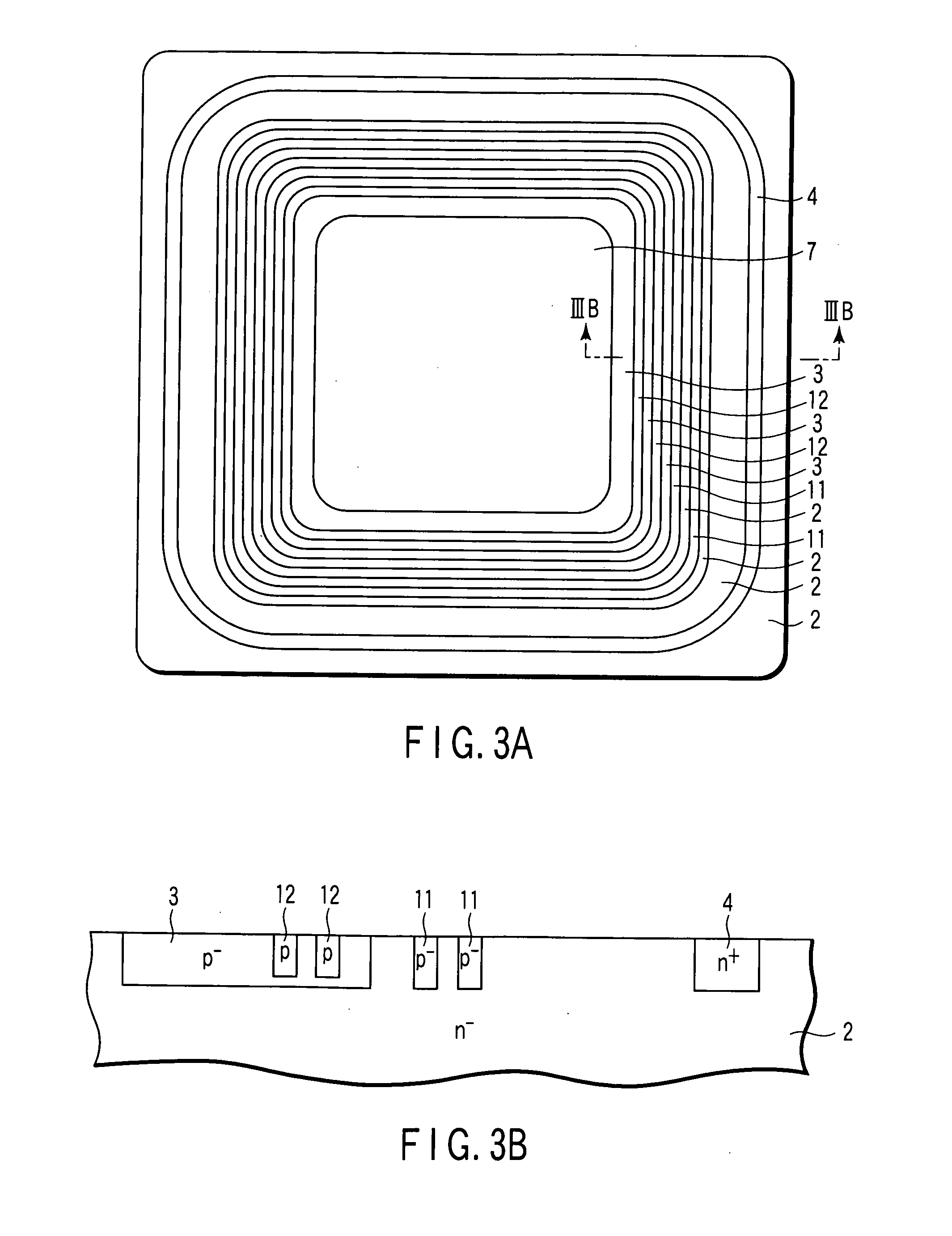

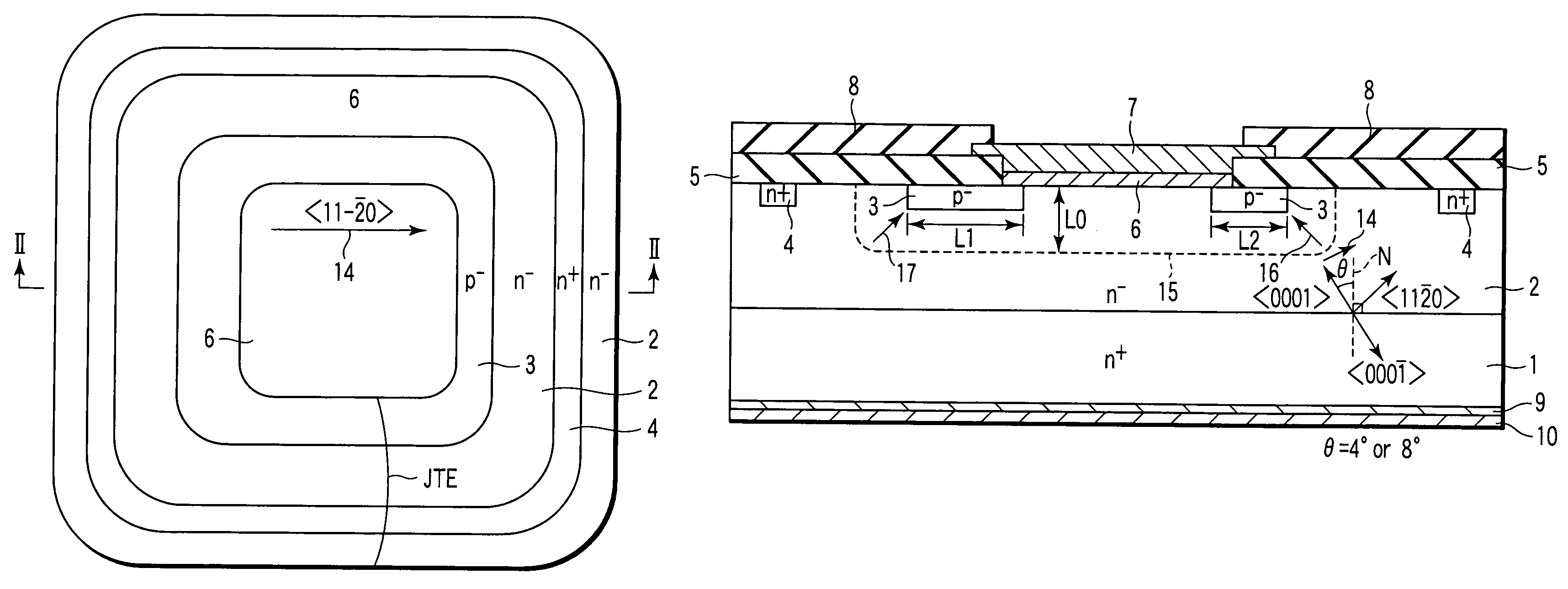

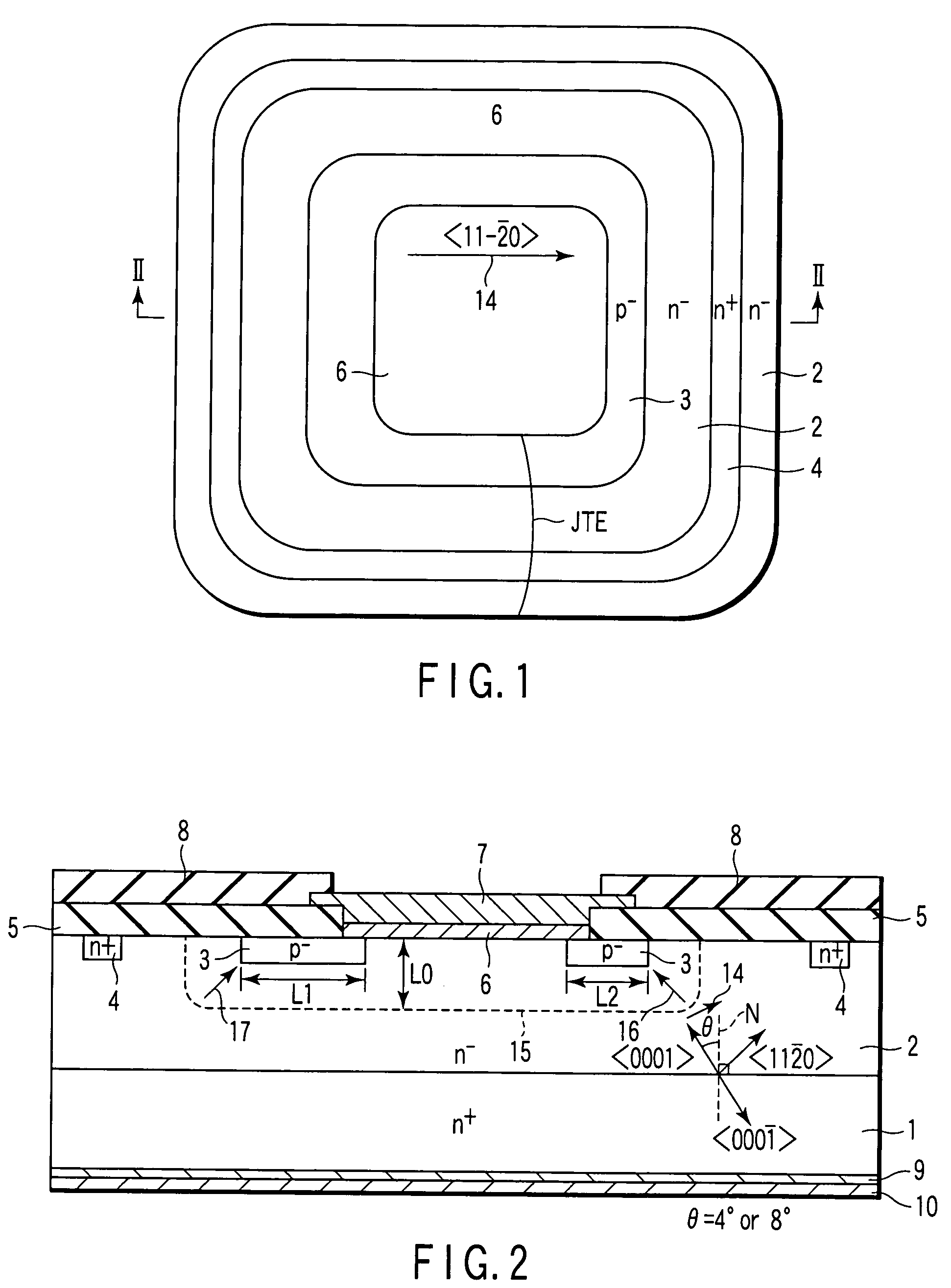

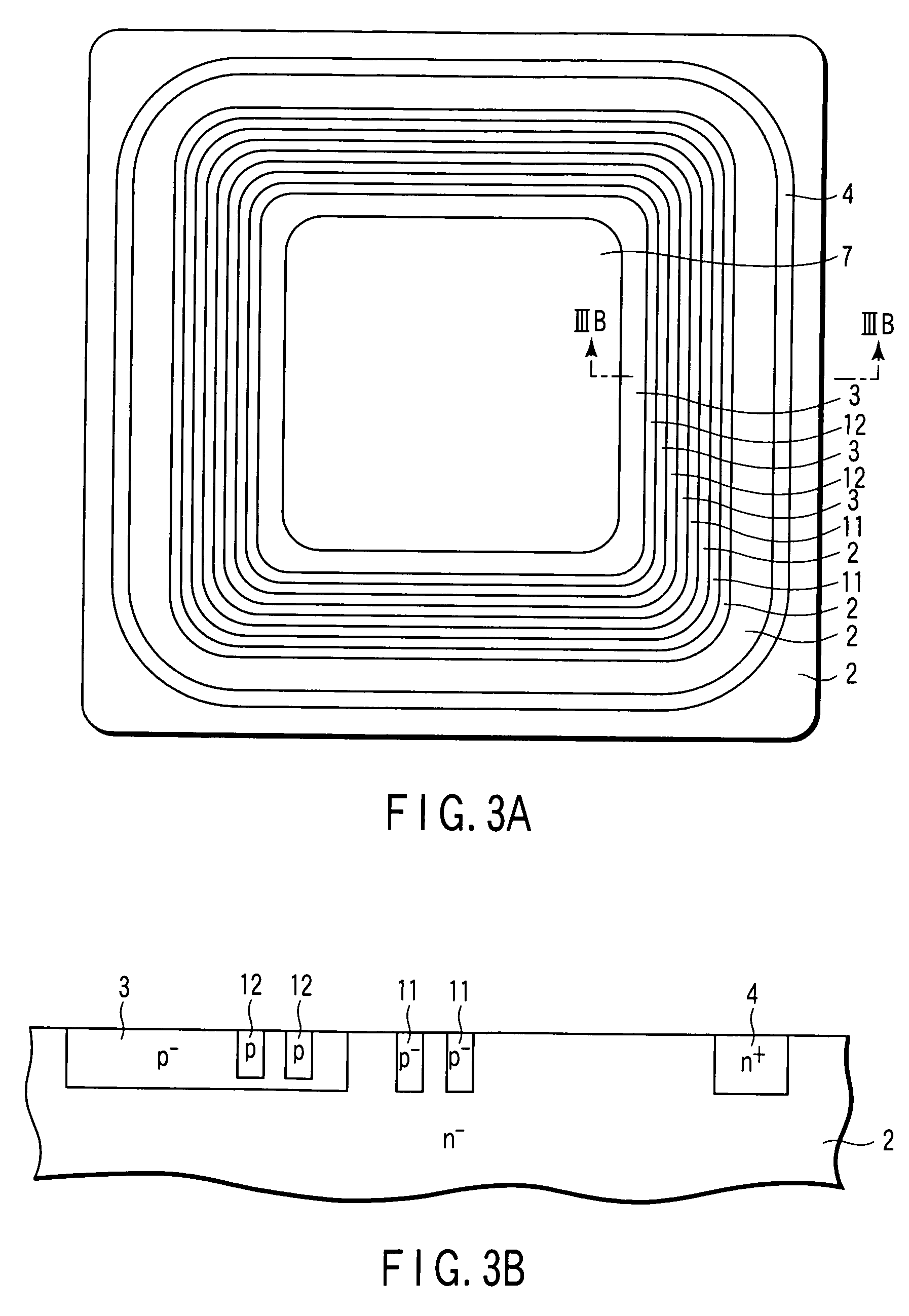

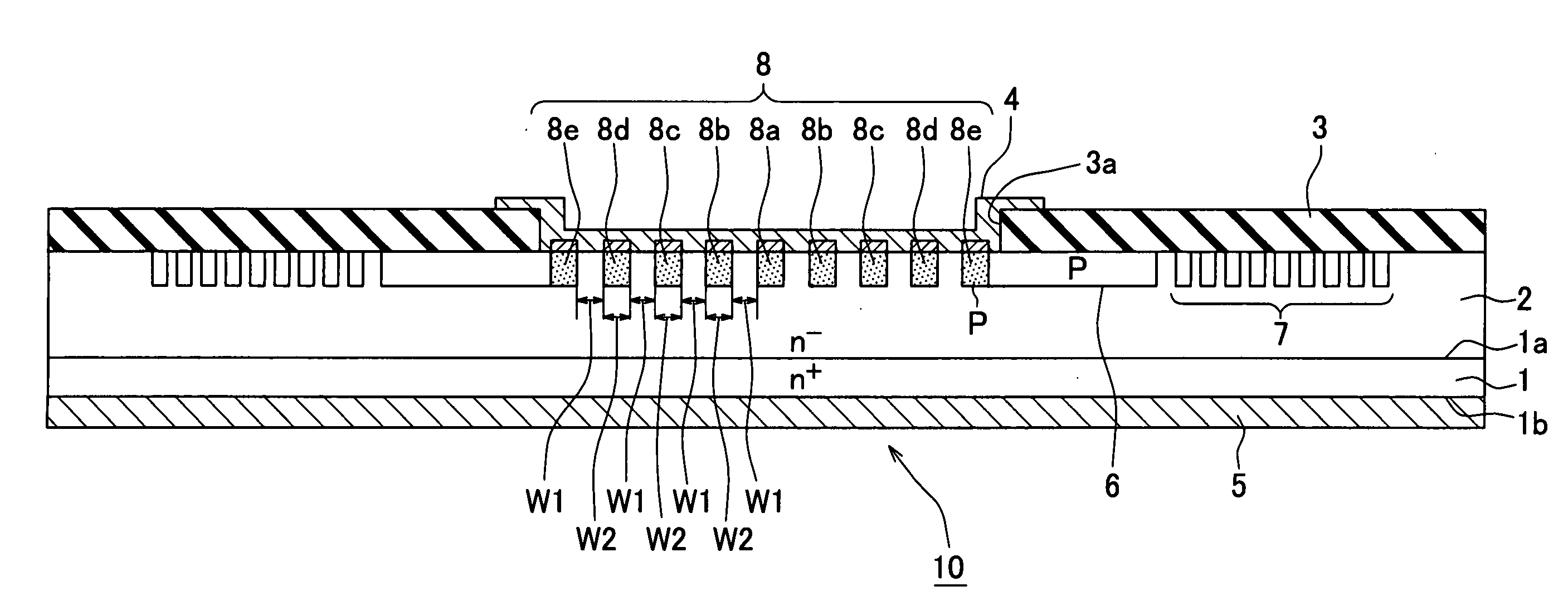

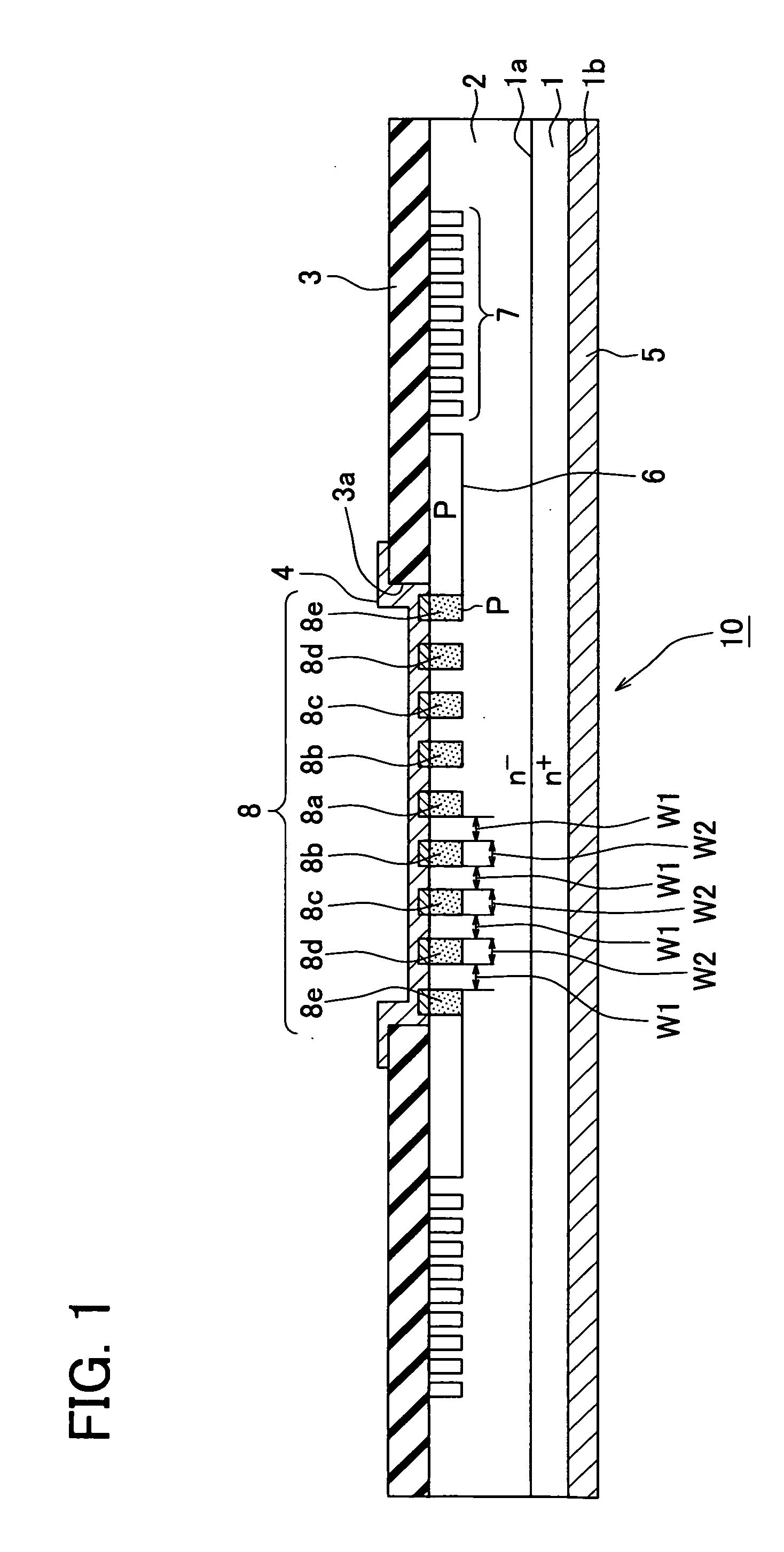

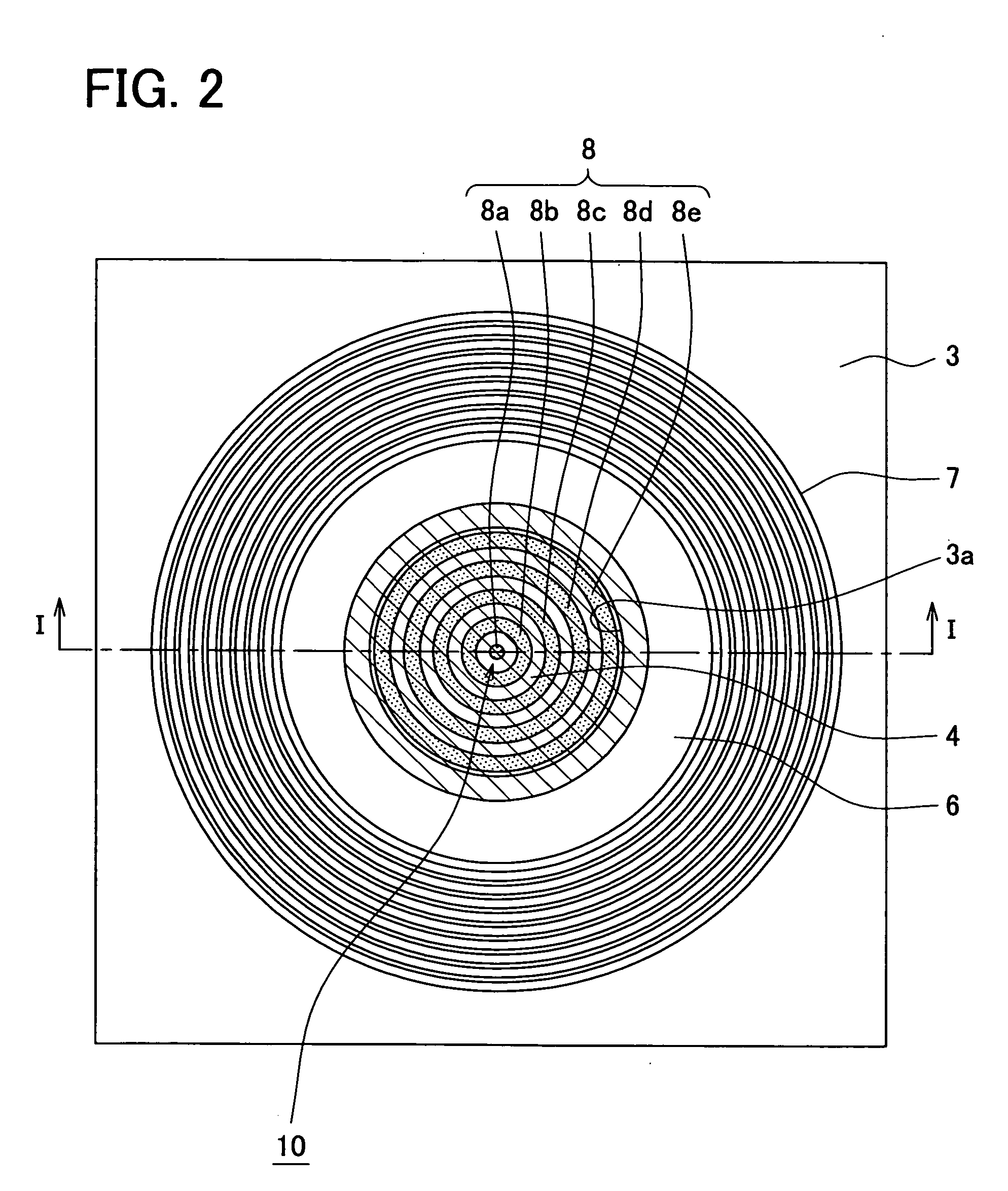

Semiconductor device

A semiconductor device includes an SiC substrate, a normal direction of the substrate surface being off from a <0001> or <000-1> direction in an off direction, an SiC layer formed on the SiC substrate, a junction forming region formed in a substantially central portion of the SiC layer, a junction termination region formed to surround the junction forming region, and including a semiconductor region of a conductivity type different from the SiC layer formed as a substantially quadrangular doughnut ring, having two edges facing each other, each crossing a projection direction, which is obtained when the off direction is projected on the upper surface of the SiC layer, at a right angle, wherein a width of one of the two edges on an upper stream side of the off direction is L1, that of the other edge on a down stream side is L2, and a relation L1>L2 is satisfied.

Owner:KK TOSHIBA

Semiconductor device

A semiconductor device includes an SiC substrate, a normal direction of the substrate surface being off from a <0001> or <000-1> direction in an off direction, an SiC layer formed on the SiC substrate, a junction forming region formed in a substantially central portion of the SiC layer, a junction termination region formed to surround the junction forming region, and including a semiconductor region of a conductivity type different from the SiC layer formed as a substantially quadrangular doughnut ring, having two edges facing each other, each crossing a projection direction, which is obtained when the off direction is projected on the upper surface of the SiC layer, at a right angle, wherein a width of one of the two edges on an upper stream side of the off direction is L1, that of the other edge on a down stream side is L2, and a relation L1>L2 is satisfied.

Owner:KK TOSHIBA

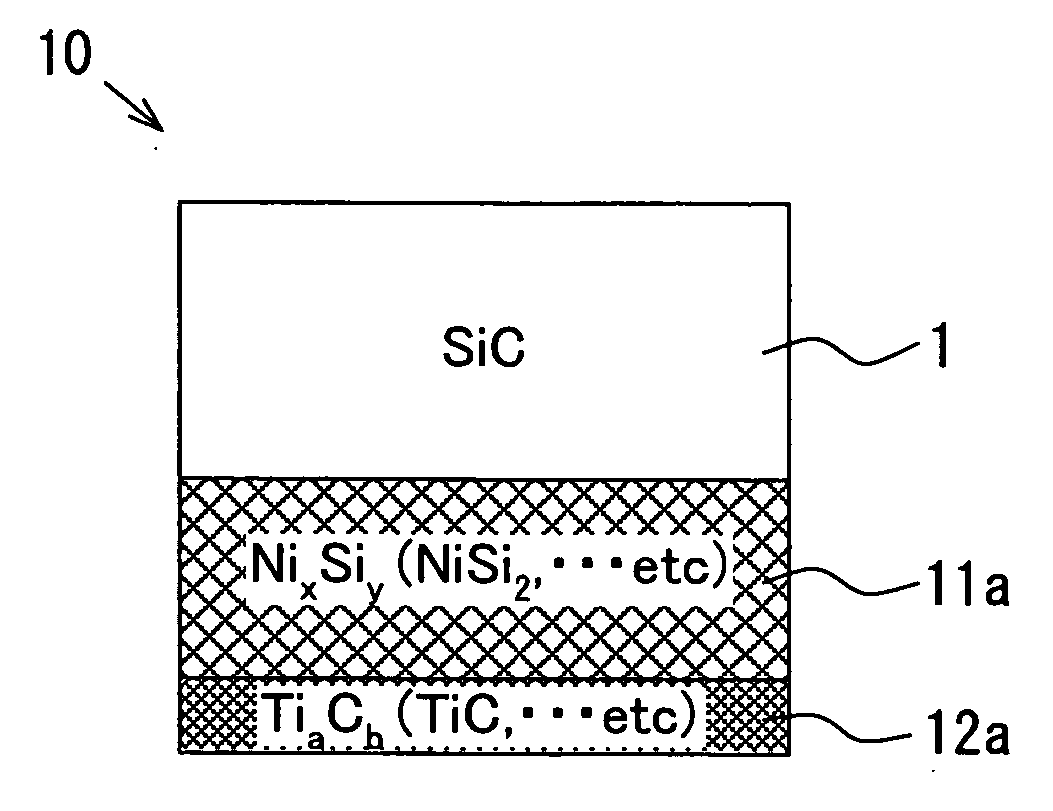

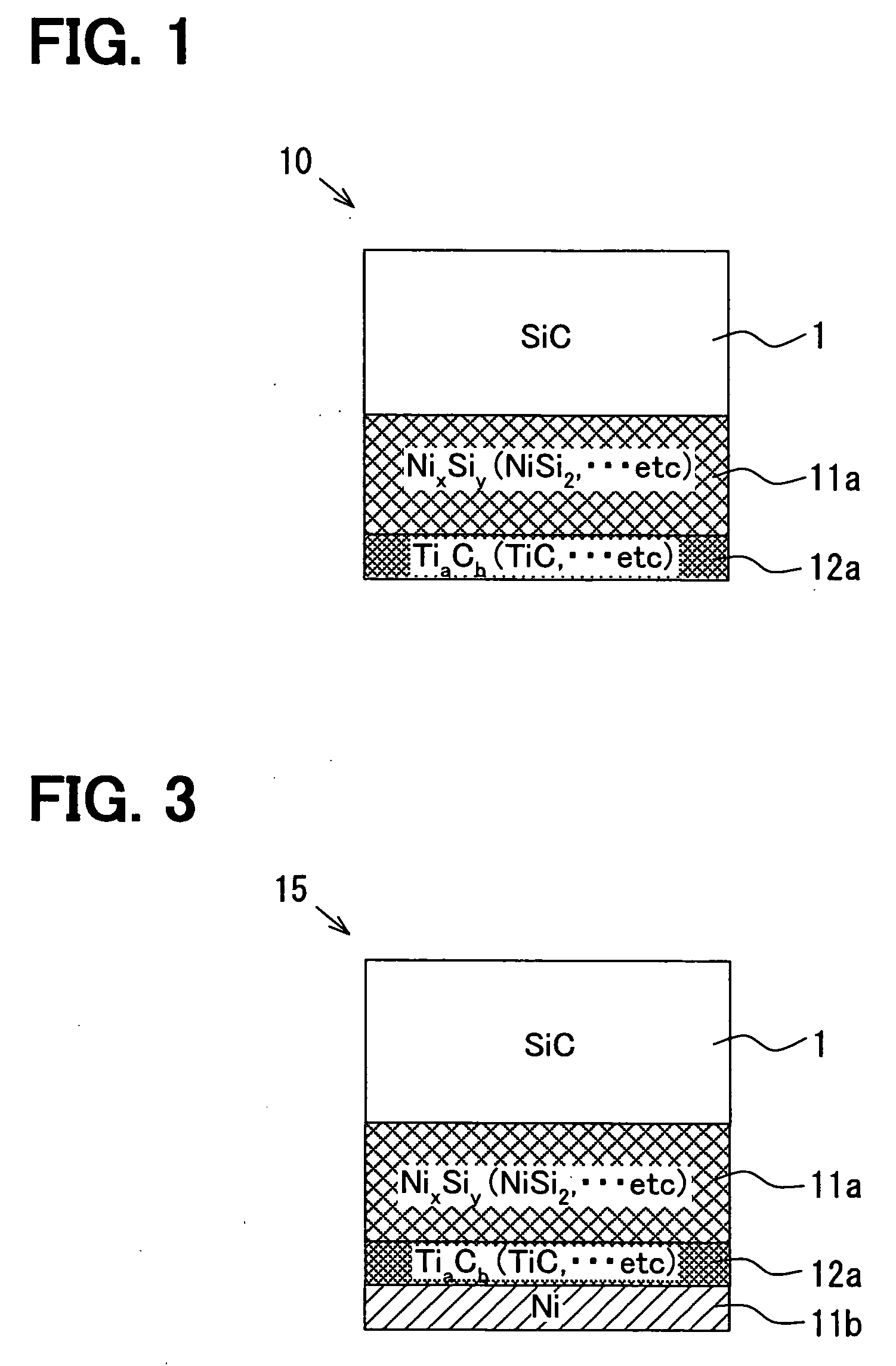

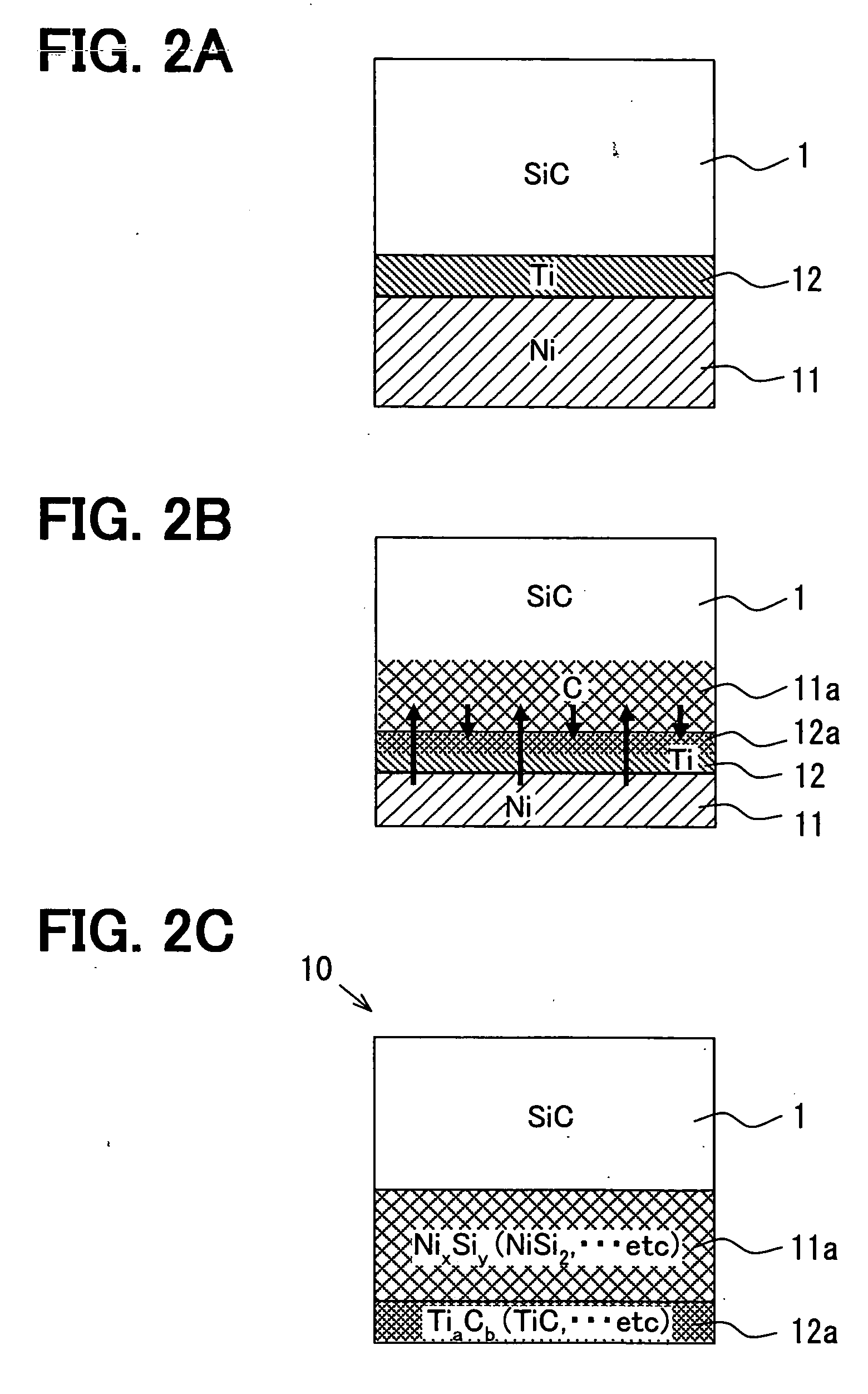

Semiconductor device having SiC substrate and method for manufacturing the same

InactiveUS20060273323A1Good ohmic contactHigh quality surface metallizationSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialOhmic contact

A semiconductor device includes: a SiC substrate; a silicide layer disposed on the SiC substrate; and a carbide layer disposed on the silicide layer. The silicide layer includes a first metal, and the carbide layer includes a second metal. The first metal is Ni or Ni alloy, and the second metal is Ti, Ta or W. The device provides excellent ohmic contact and high quality surface metallization construction.

Owner:DENSO CORP +1

SIS semiconductor having junction barrier schottky device

A semiconductor device having a junction barrier Schottky diode includes: a SiC substrate; a drift layer on the substrate; an insulation film on the drift layer having an opening in a cell region; a Schottky barrier diode having a Schottky electrode contacting the drift layer through the opening of the insulation film and an ohmic electrode on the substrate; a terminal structure having a RESURF layer surrounding the cell region; and multiple second conductive type layers on an inner side of the RESURF layer. The second conductive type layers and the drift layer provide a PN diode. The Schottky electrode includes a first Schottky electrode contacting the second conductive type layers with ohmic contact and a second Schottky electrode contacting the drift layer with Schottky contact.

Owner:DENSO CORP

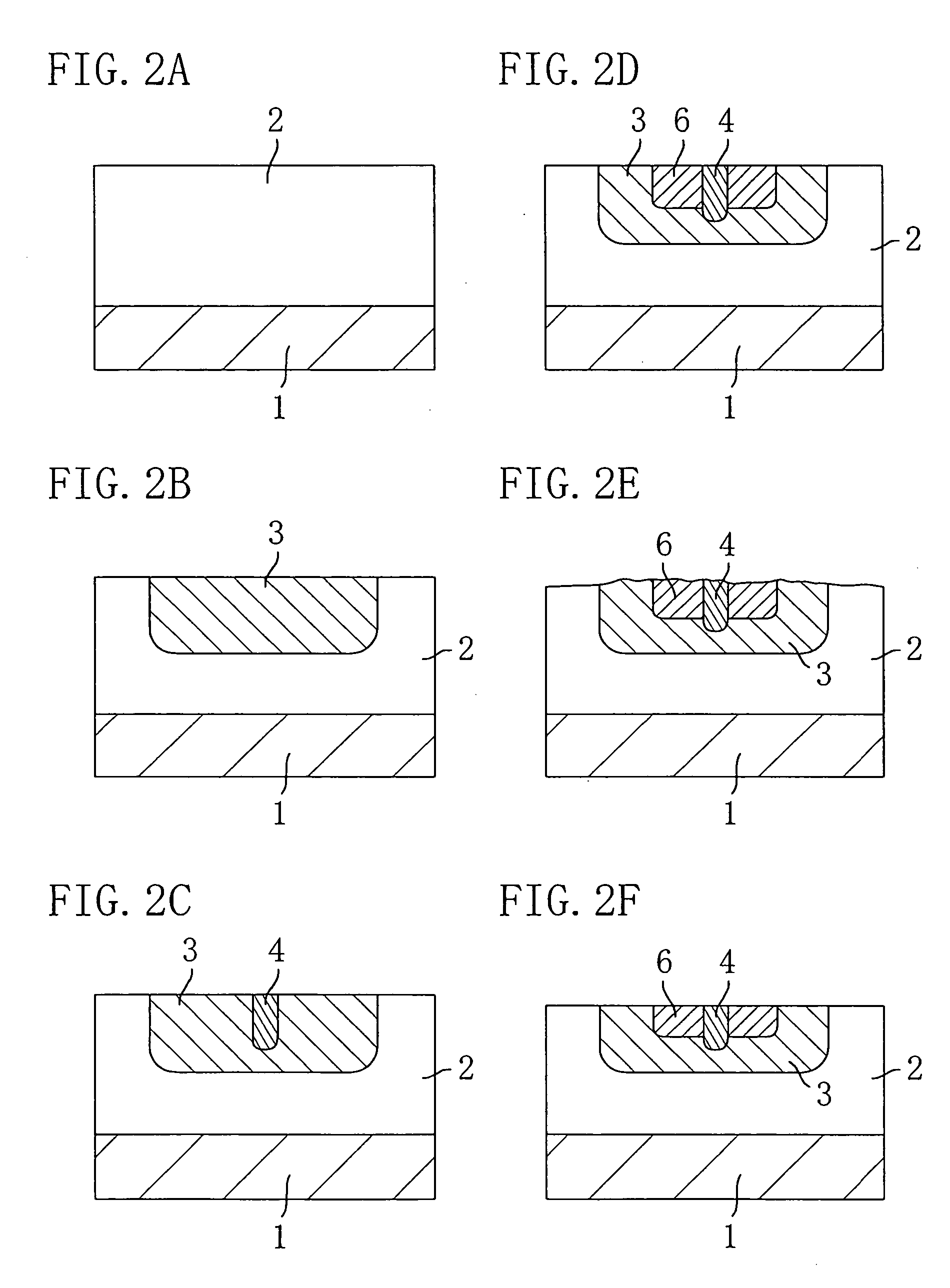

Method of manufacturing silicon carbide semiconductor device

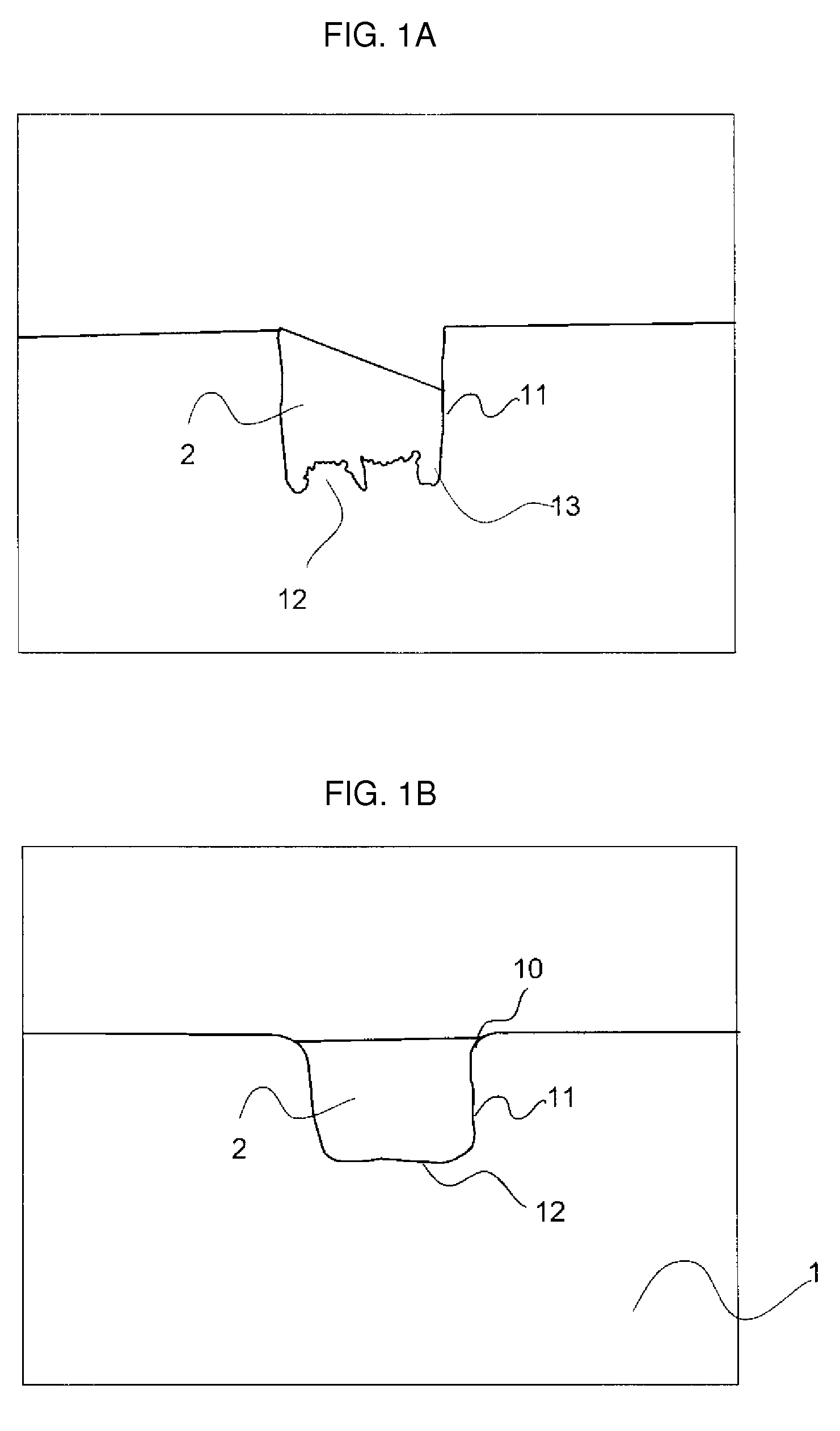

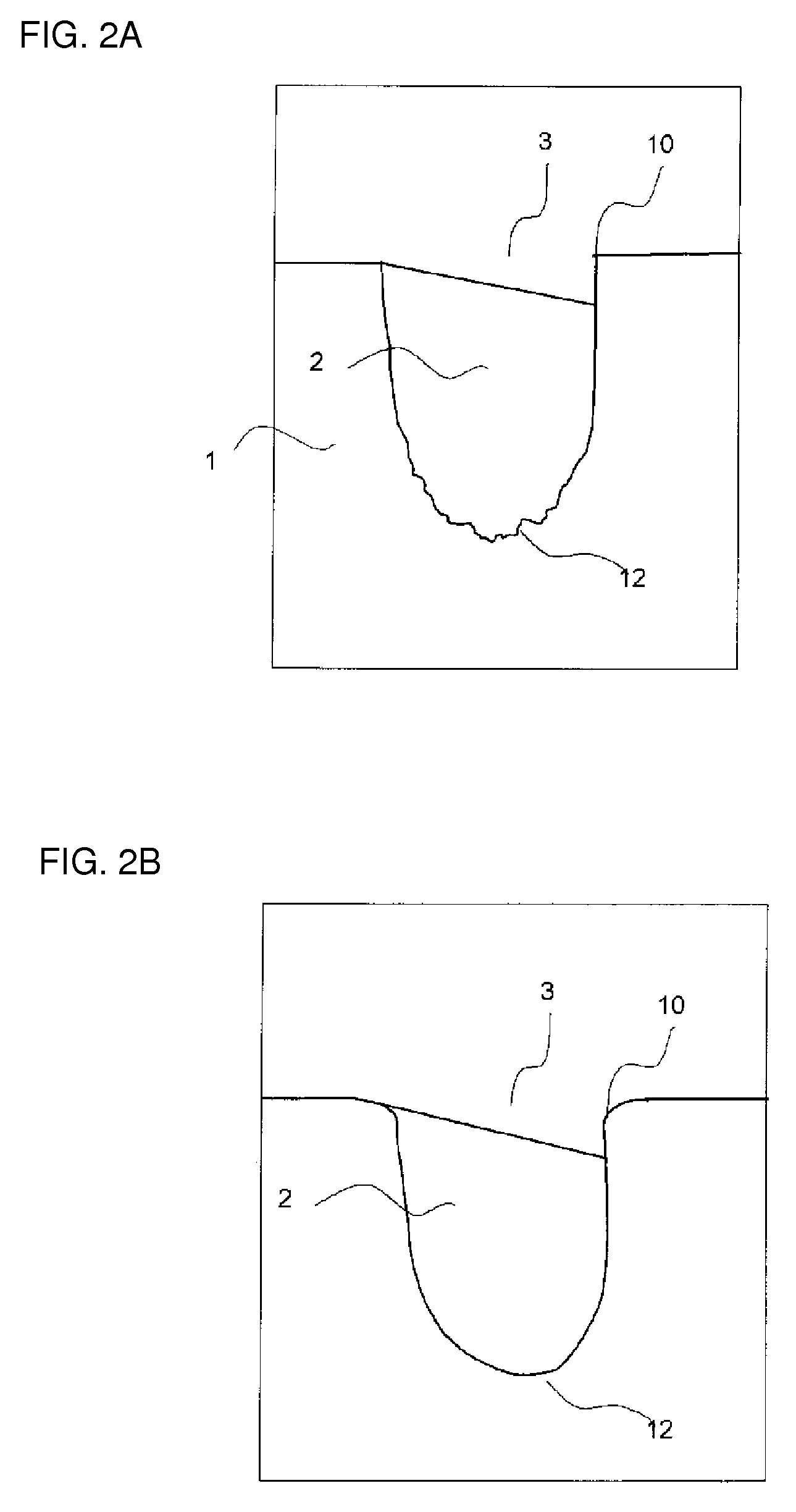

InactiveUS20080220620A1Improve corner shapeImprove inner surface propertySemiconductor/solid-state device manufacturingSemiconductor devicesHydrogenDry etching

A method of manufacturing a silicon carbide semiconductor device includes forming a trench for a MOS gate in an SiC substrate by dry etching. Thereafter, the substrate with the trench is heat treated. The heat treatment includes heating the substrate in an Ar gas atmosphere or in a mixed gas atmosphere containing SiH4 and Ar at a temperature between 1600° C. and 1800° C., and thereafter in a hydrogen gas atmosphere at a temperature between 1400° C. and 1500° C. The present manufacturing method smoothens the trench inner surface and rounds the corners in the trench to prevent the electric field from localizing thereto.

Owner:FUJI ELECTRIC CO LTD

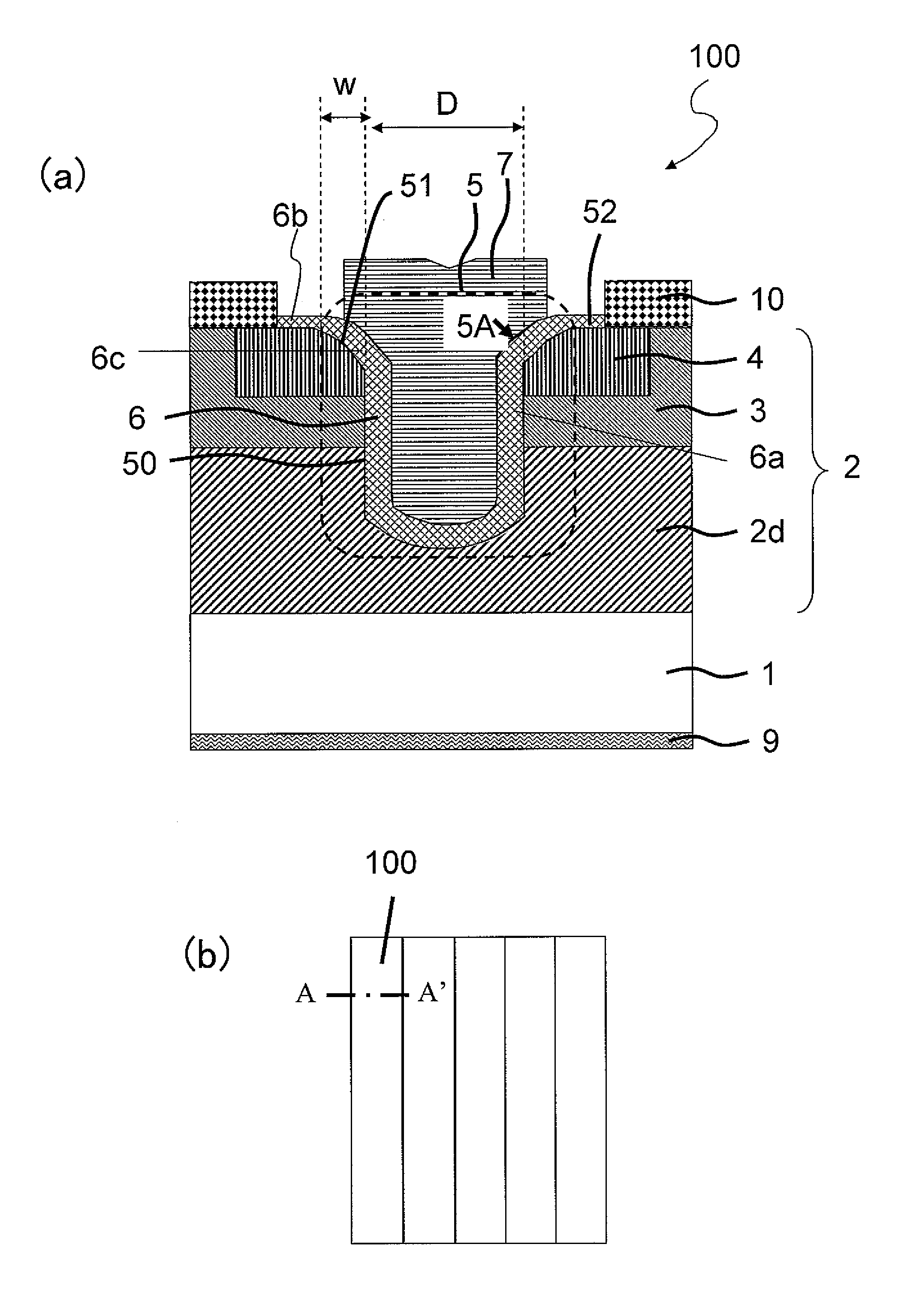

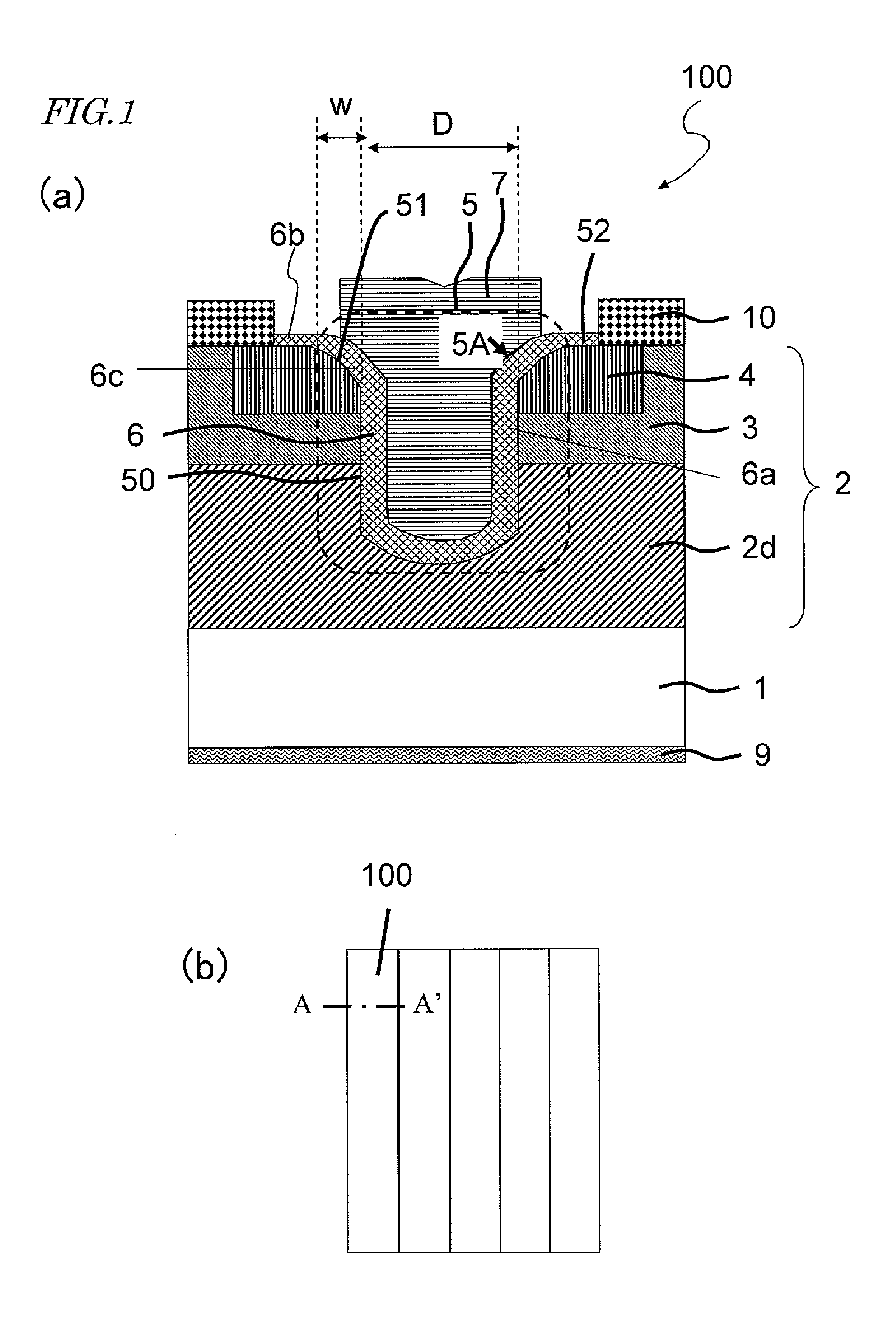

Silicon carbide semiconductor element and method for fabricating the same

ActiveUS20130168701A1Prevent intensity of electric fieldGate breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesElectrode ContactSemiconductor

A SiC semiconductor element includes: a SiC substrate which has a principal surface tilted with respect to a (0001) Si plane; a SiC layer arranged on the principal surface of the substrate; a trench arranged in the SiC layer and having a bottom, a sidewall, and an upper corner region located between the sidewall and the upper surface of the SiC layer; a gate insulating film arranged on at least a part of the sidewall and on at least a part of the upper corner region of the trench and on at least a part of the upper surface of the SiC layer; and a gate electrode arranged on the gate insulating film. The upper corner region has a different surface from the upper surface of the SiC layer and from a surface that defines the sidewall. The gate electrode contacts with both of a first portion of the gate insulating film located on the upper corner region and a second portion of the gate insulating film located on the sidewall. The first portion of the gate insulating film is thicker than a third portion of the gate insulating film located on the upper surface of the SiC layer. And an end portion of the gate electrode is located on the upper corner region.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

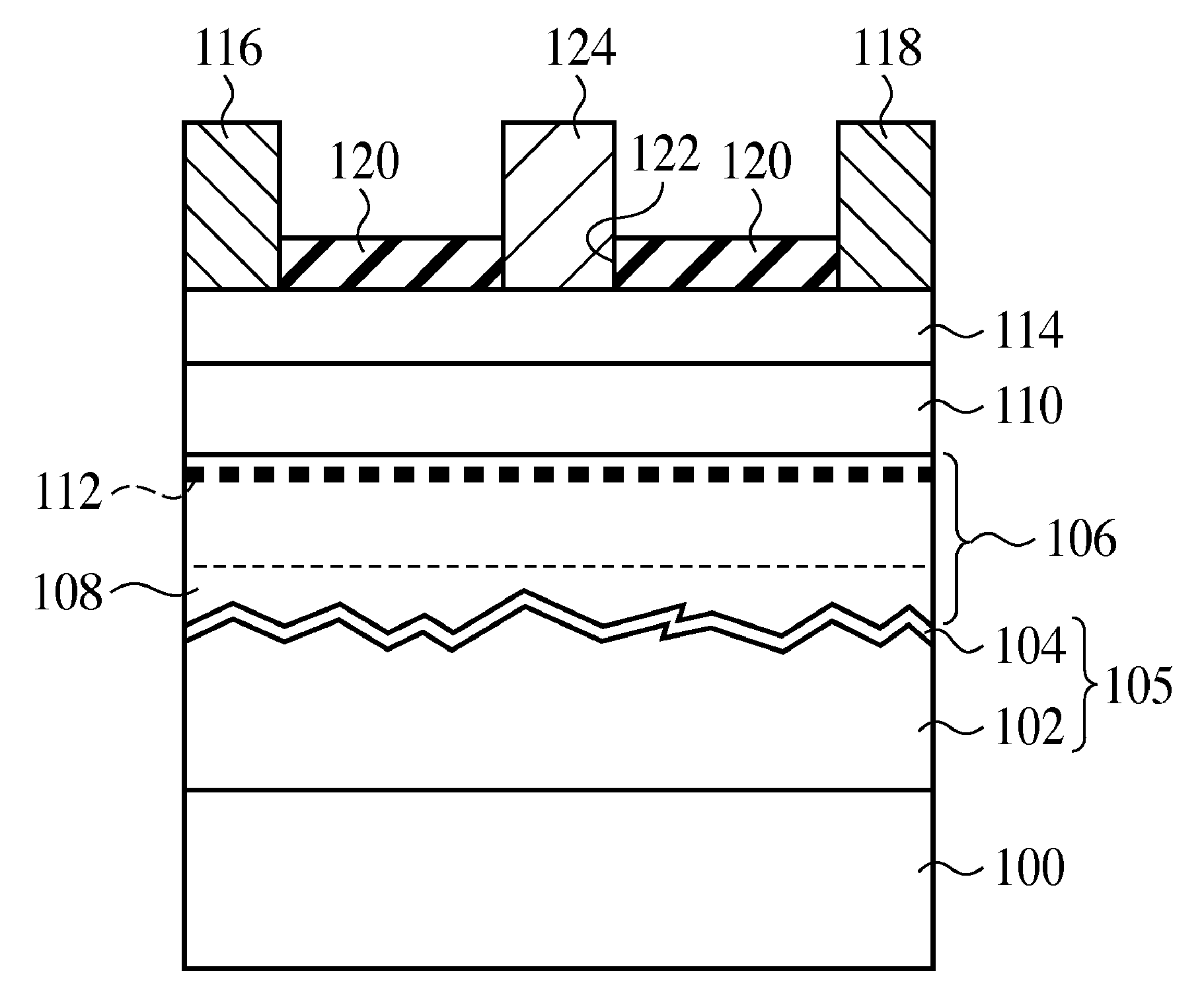

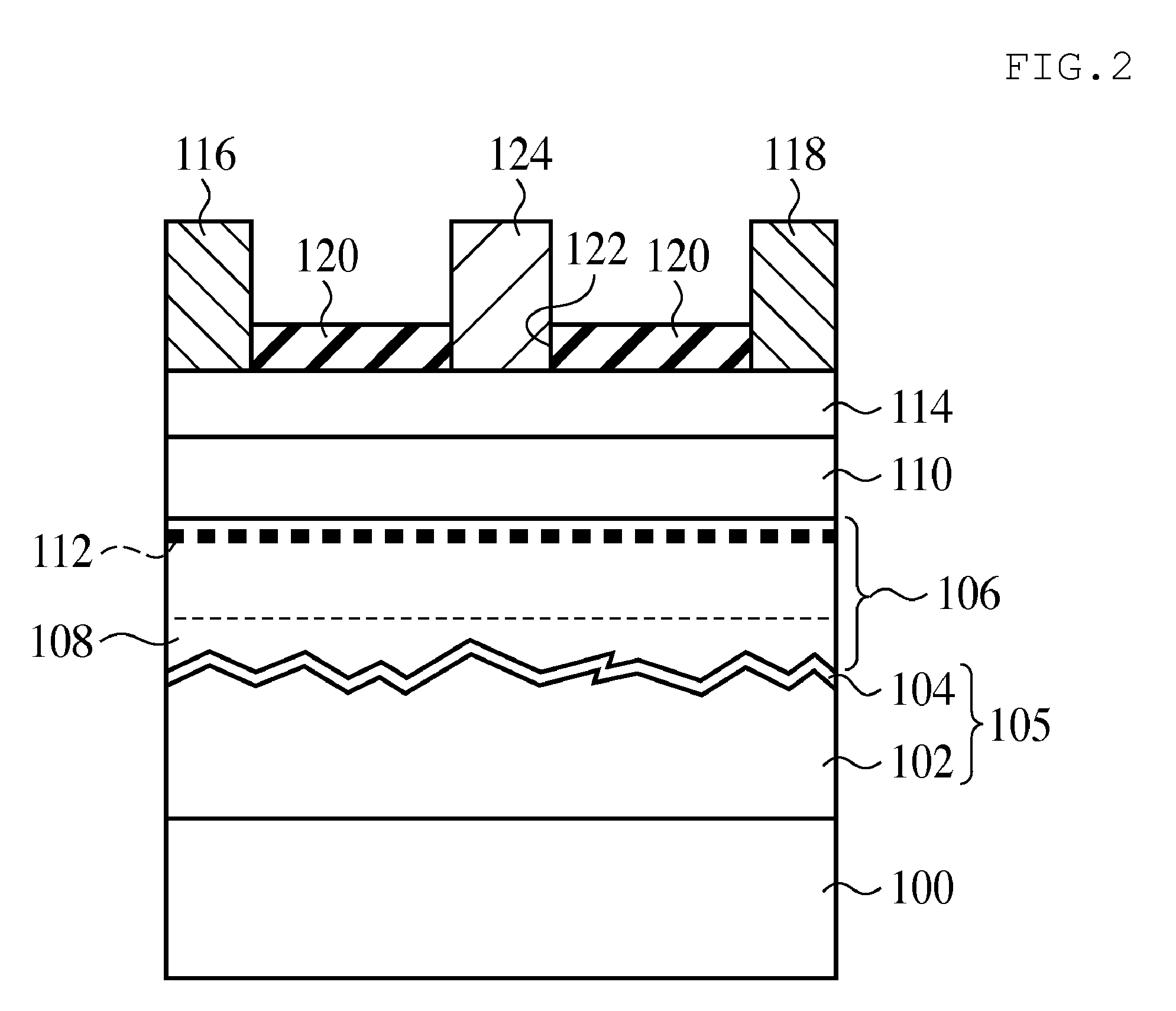

Compound semiconductor device and method of manufacturing the same

ActiveUS20080197359A1Reduce carrier concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesCompound (substance)Engineering

A compound semiconductor device has a buffer layer formed on a conductive SiC substrate, an AlxGa1-xN layer formed on the buffer layer in which an impurity for reducing carrier concentration from an unintentionally doped donor impurity is added and in which the Al composition x is 0<x<1, a GaN-based carrier transit layer formed on the AlxGa1-xN layer, a carrier supply layer formed on the carrier transit layer, a source electrode and a drain electrode formed on the carrier supply layer, and a gate electrode formed on the carrier supply layer between the source electrode and the drain electrode. Therefore, a GaN-HEMT that is superior in device characteristics can be realized in the case of using a relatively less expensive conductive SiC substrate compared with a semi-insulating SiC substrate.

Owner:FUJITSU LTD

Semiconductor device

A semiconductor device includes an SiC substrate, an SiC layer of a first conductivity type disposed on the upper surface of the SiC substrate, a first SiC region of a second conductivity type disposed on the SiC layer, a second SiC region of the first conductivity type disposed on a surface region of the first SiC region, including a nitrogen-added first sub-region and a phosphorus-added second sub-region disposed in contact with the first sub-region, a gate insulating film disposed to extend over the SiC layer, first SiC region, and first sub-region of the second SiC region, a gate electrode formed on the gate insulating film, a first electrode formed on the second sub-region of the second SiC region and the first SiC region, and a second electrode formed on the lower surface of the SiC substrate.

Owner:KK TOSHIBA

Semiconductor device and method for fabricating the same

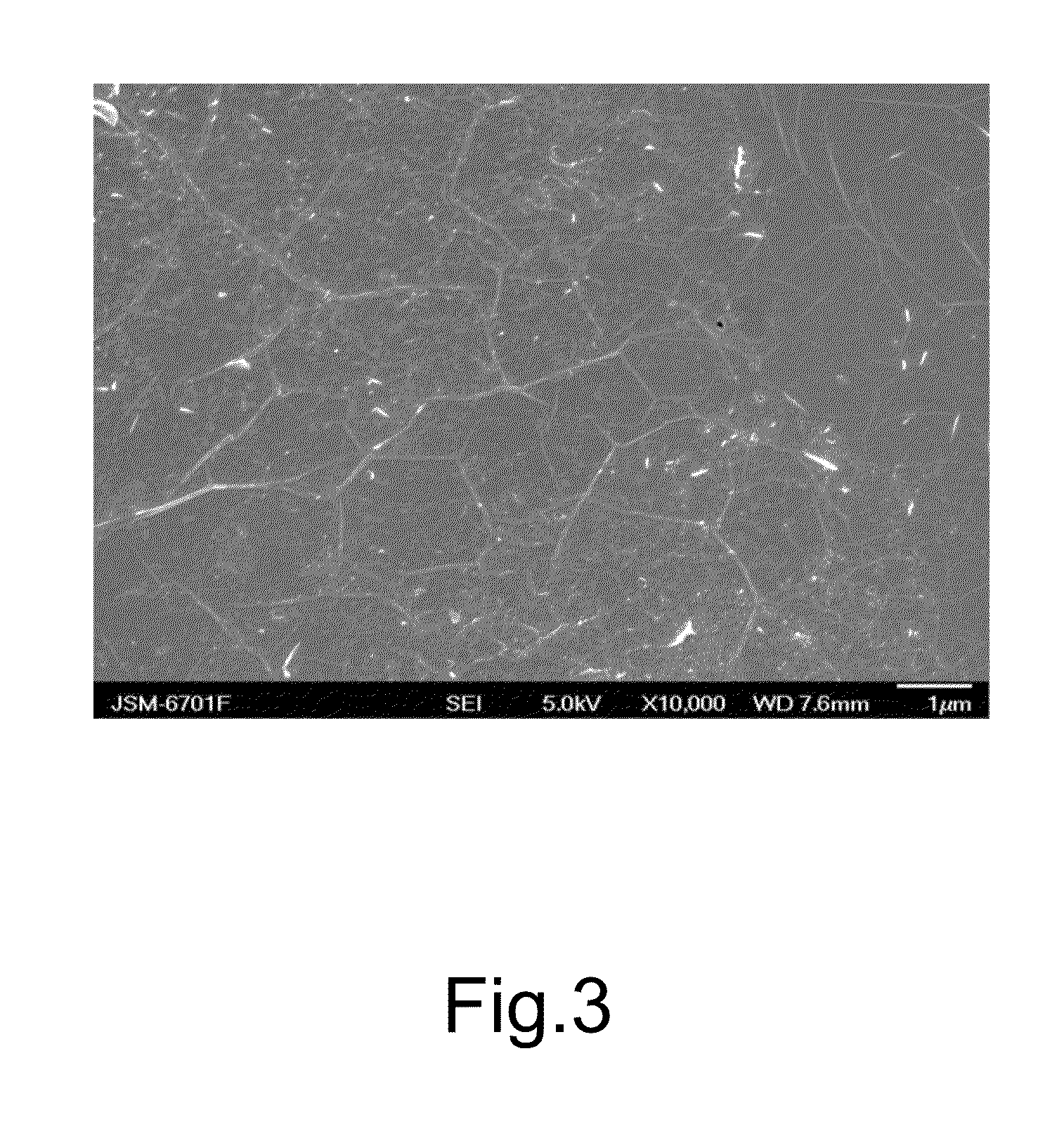

ActiveUS20050001217A1Reduced carrier mobilityHigh carrier mobilityTransistorSemiconductor/solid-state device manufacturingHigh resistanceCarbon film

Ion implantation is carried out to form a p-well region and a source region in parts of a high resistance SiC layer on a SiC substrate, and a carbon film is deposited over the substrate. With the carbon film deposited over the substrate, annealing for activating the implanted dopant ions is performed, and then the carbon film is removed. Thus, a smooth surface having hardly any surface roughness caused by the annealing is obtained. Furthermore, if a channel layer is epitaxially grown, the surface roughness of the channel layer is smaller than that of the underlying layer. Since the channel layer having a smooth surface is provided, it is possible to obtain a MISFET with a high current drive capability.

Owner:PANASONIC CORP

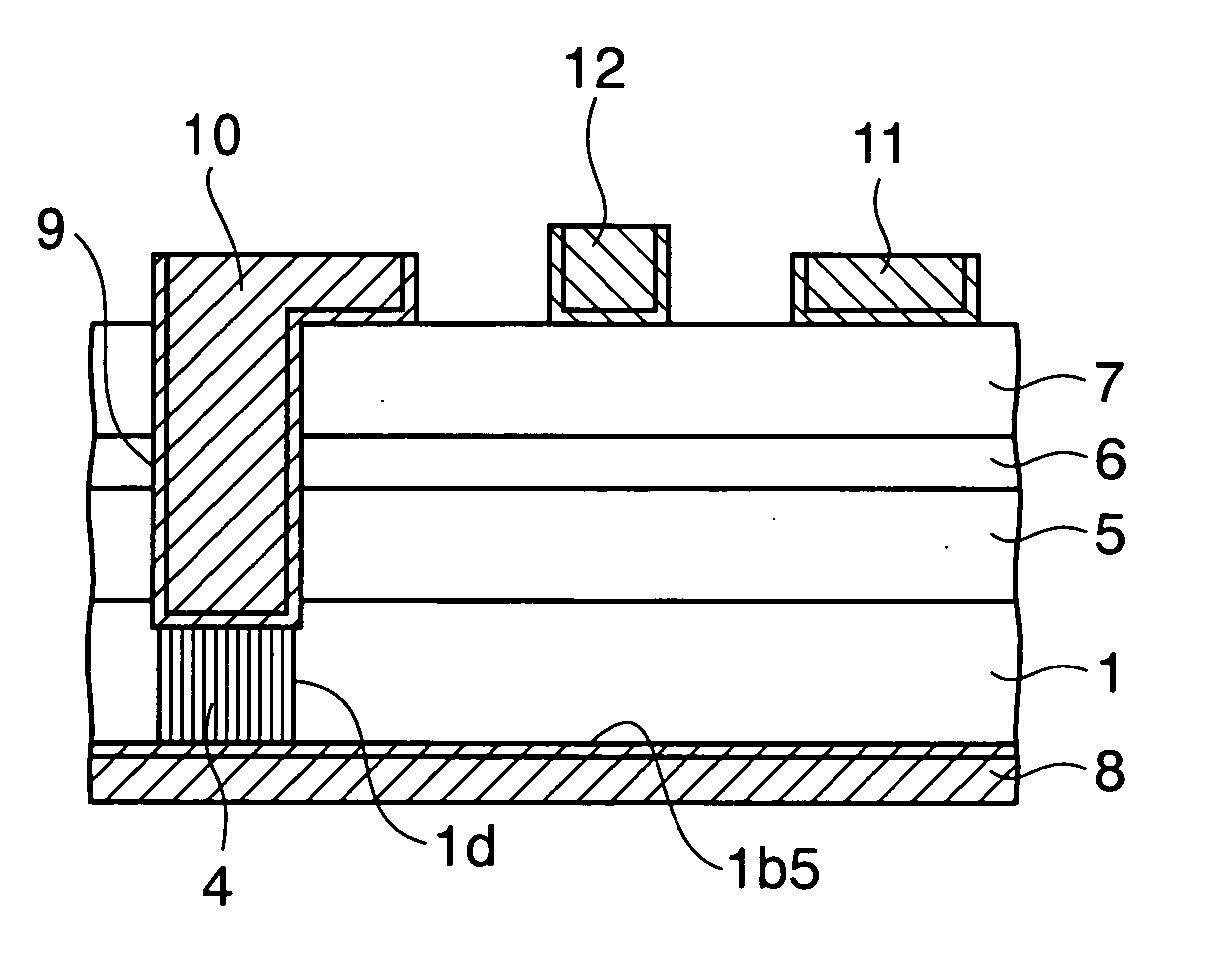

Semiconductor device and manufacturing method thereof

InactiveUS20050067693A1Improve thermal conductivityAvoid temperature riseMaterial nanotechnologySemiconductor/solid-state device detailsElectrical conductorSic substrate

Disclosed is a semiconductor device including a SiC substrate and a heat conductor formed in a hole in the SiC substrate and made of a linear structure of carbon elements.

Owner:FUJITSU LTD

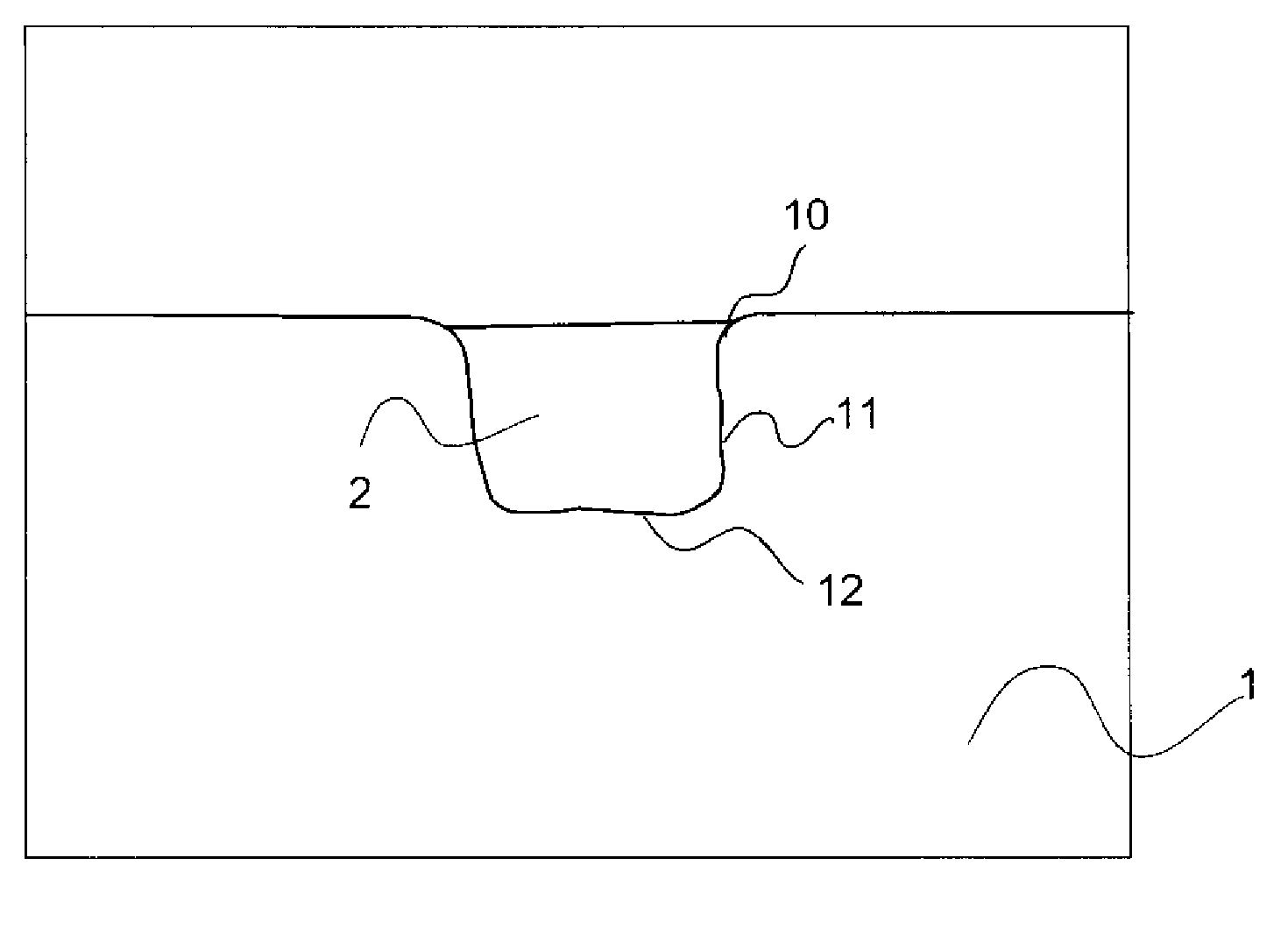

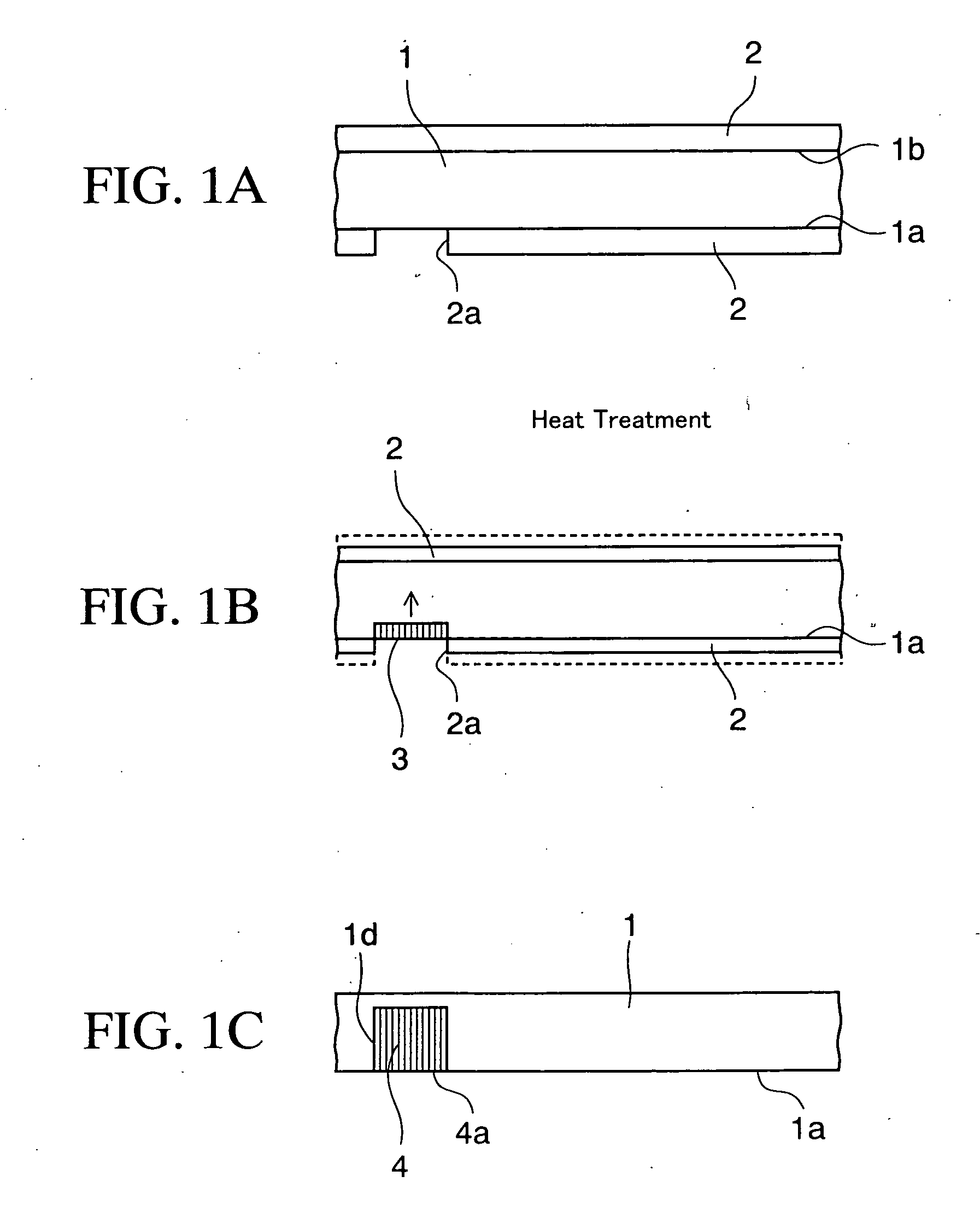

Single crystal SiC and a method of producing the same

InactiveUS6053973AEasily eliminate mismatchStably and efficiently obtainFrom gel statePolycrystalline material growthPorous carbonSurface roughness

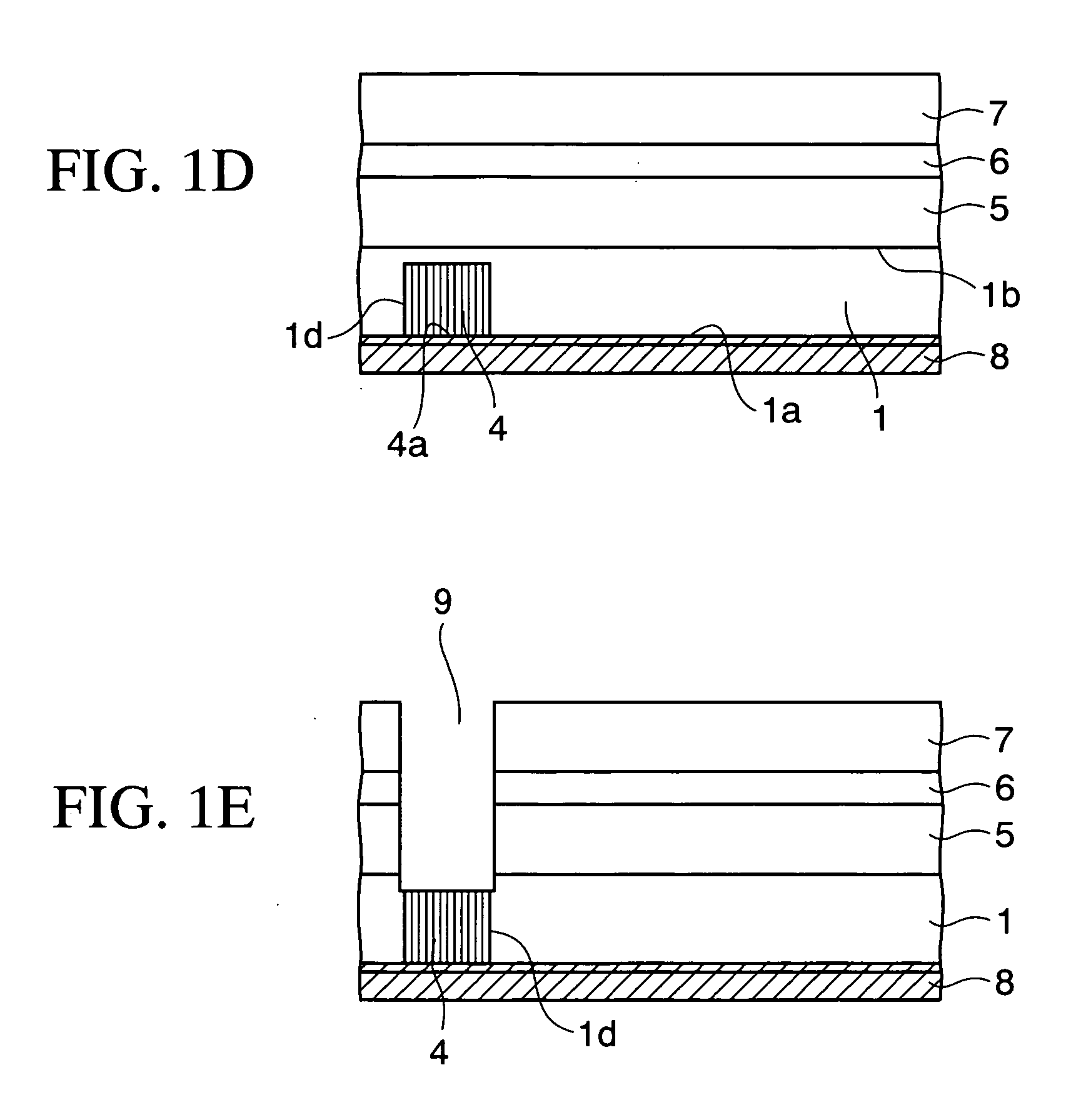

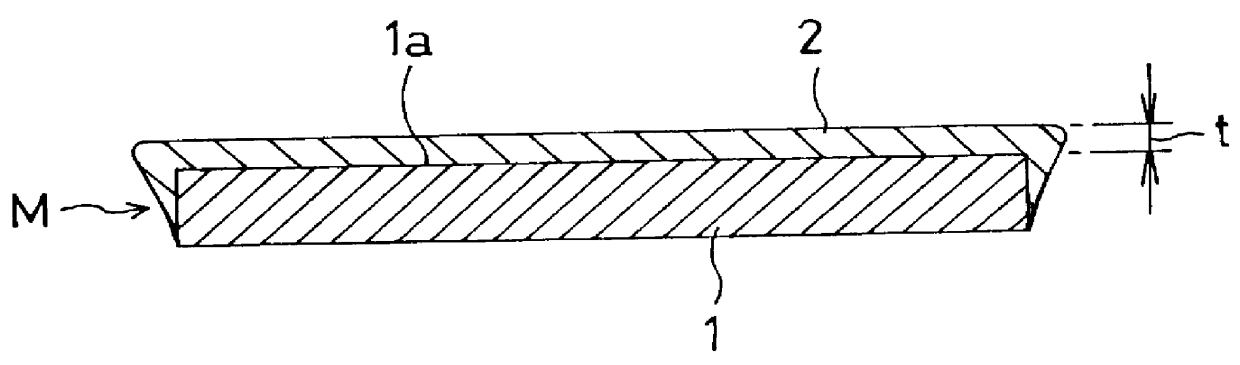

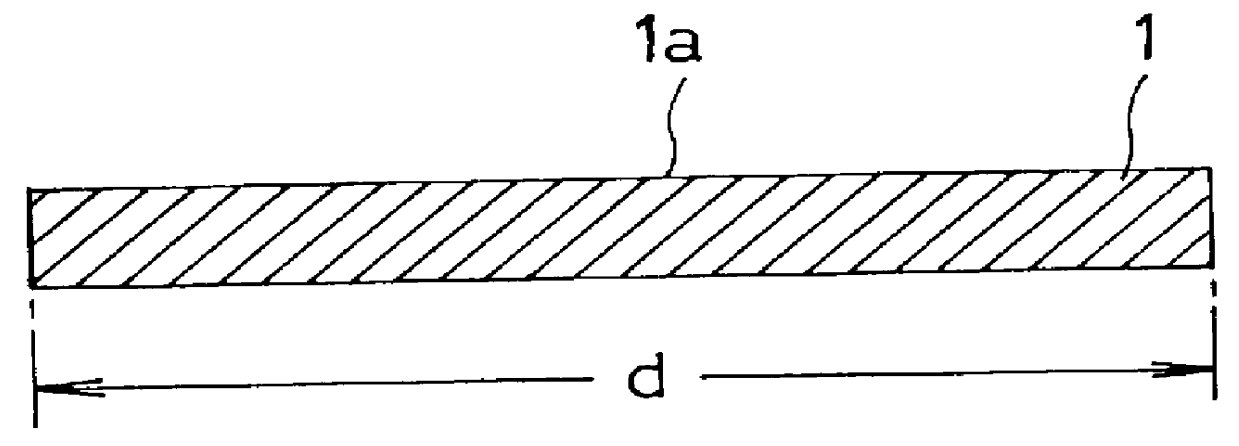

The surface 1a of a single crystal alpha -SiC substrate 1 is adjusted so as to have a surface roughness equal to or lower than 2,000 angstroms RMS, and preferably equal to or lower than 1,000 angstroms RMS. On the surface 1a of the single crystal alpha -SiC substrate 1, a polycrystalline alpha -SiC film 2 is grown by thermal CVD to form a complex is placed in a porous carbon container and the carbon container is covered with alpha -SiC powder. The complex is subjected to a heat treatment at a temperature equal to or higher than a film growing temperature, i.e., in the range of 1,900 to 2,400 DEG C. in an argon gas flow, whereby single crystal alpha -SiC is integrally grown on the single crystal alpha -SiC substrate 1 by crystal growth and recrystallization of the polycrystalline alpha -SiC film 2. It is possible to stably and efficiently produce single crystal SiC of a large size which has a high quality and in which any crystal nucleus is not generated.

Owner:NISSIN ELECTRIC CO LTD

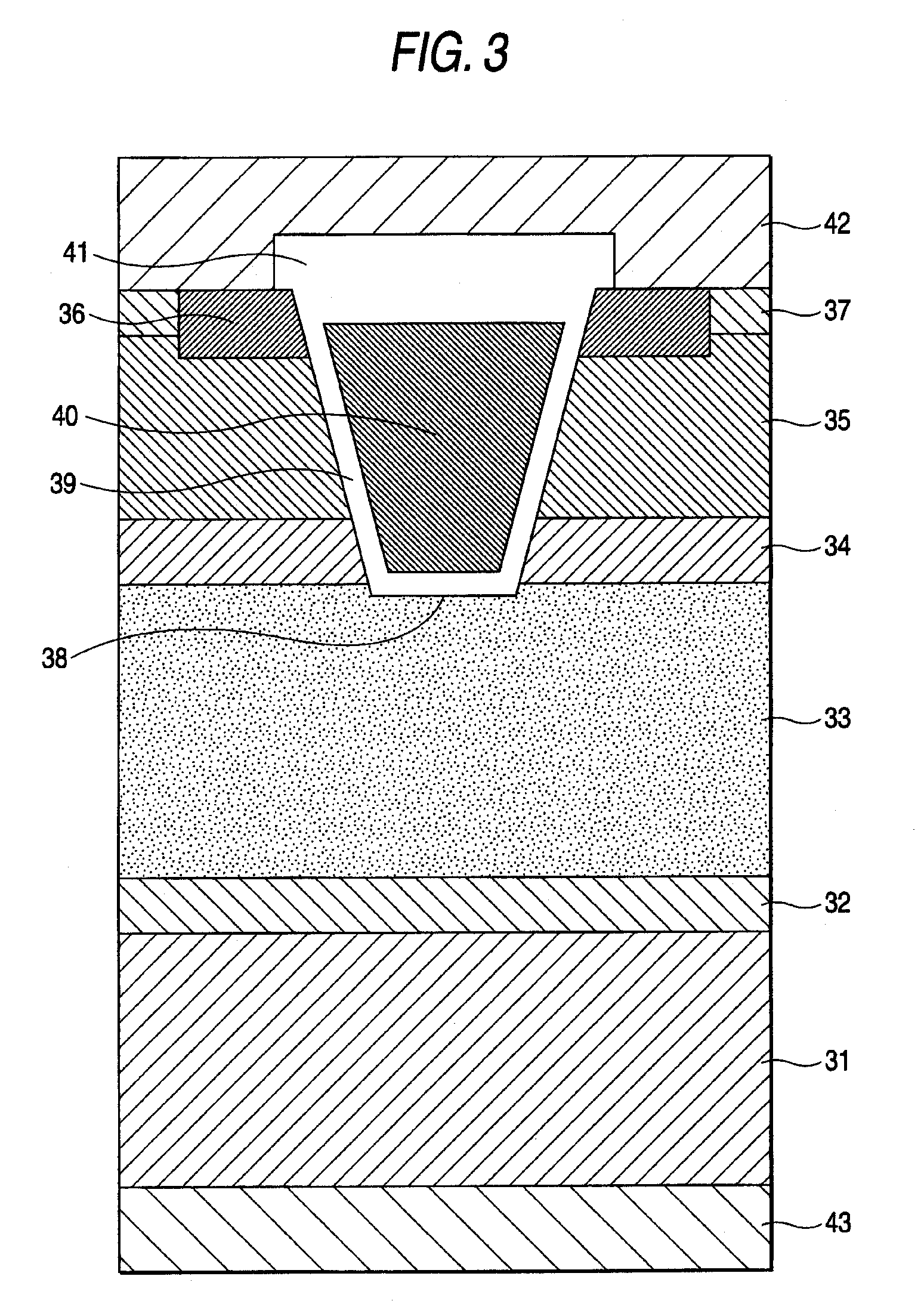

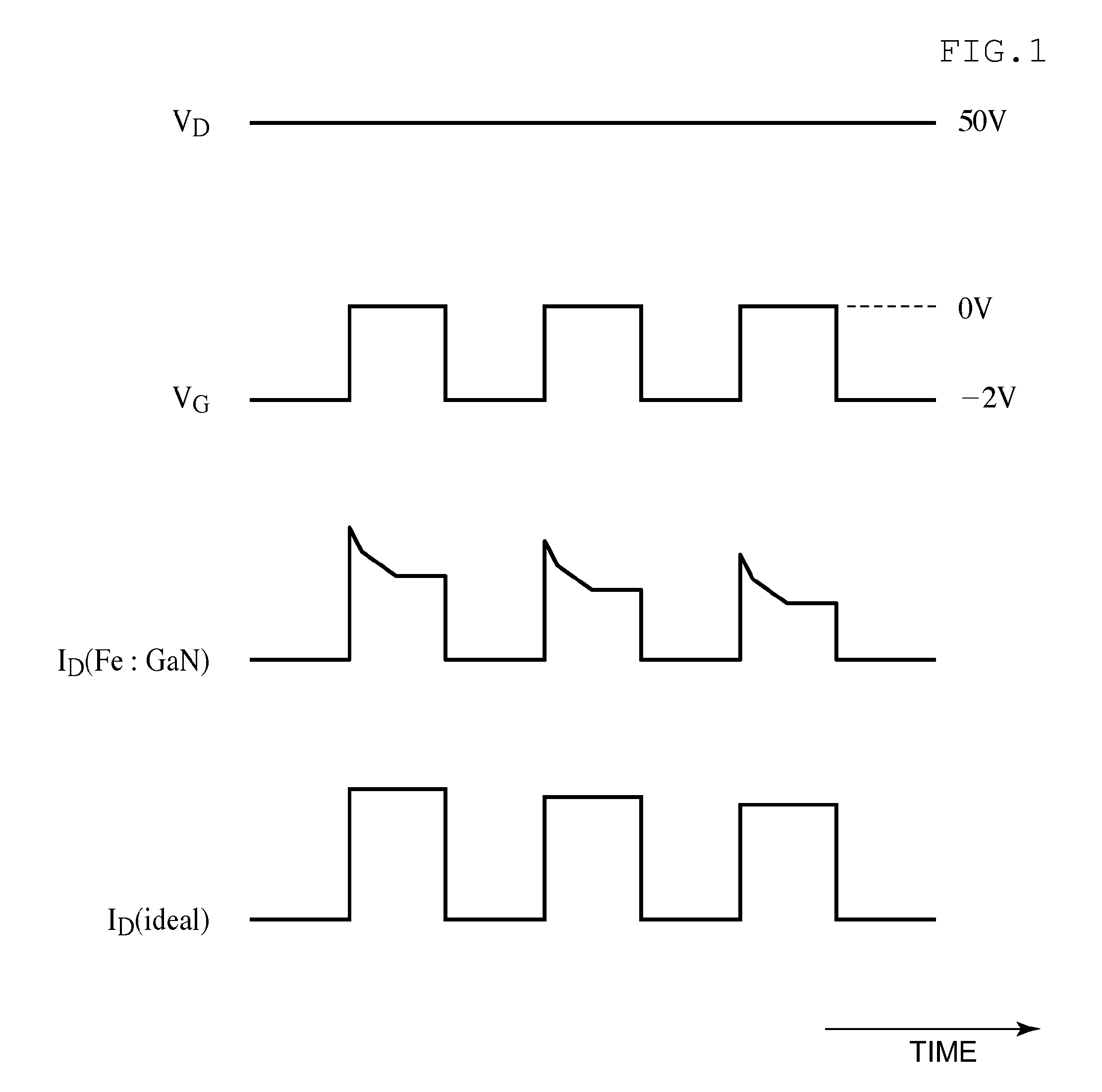

Semiconductor device and electrical circuit device using thereof

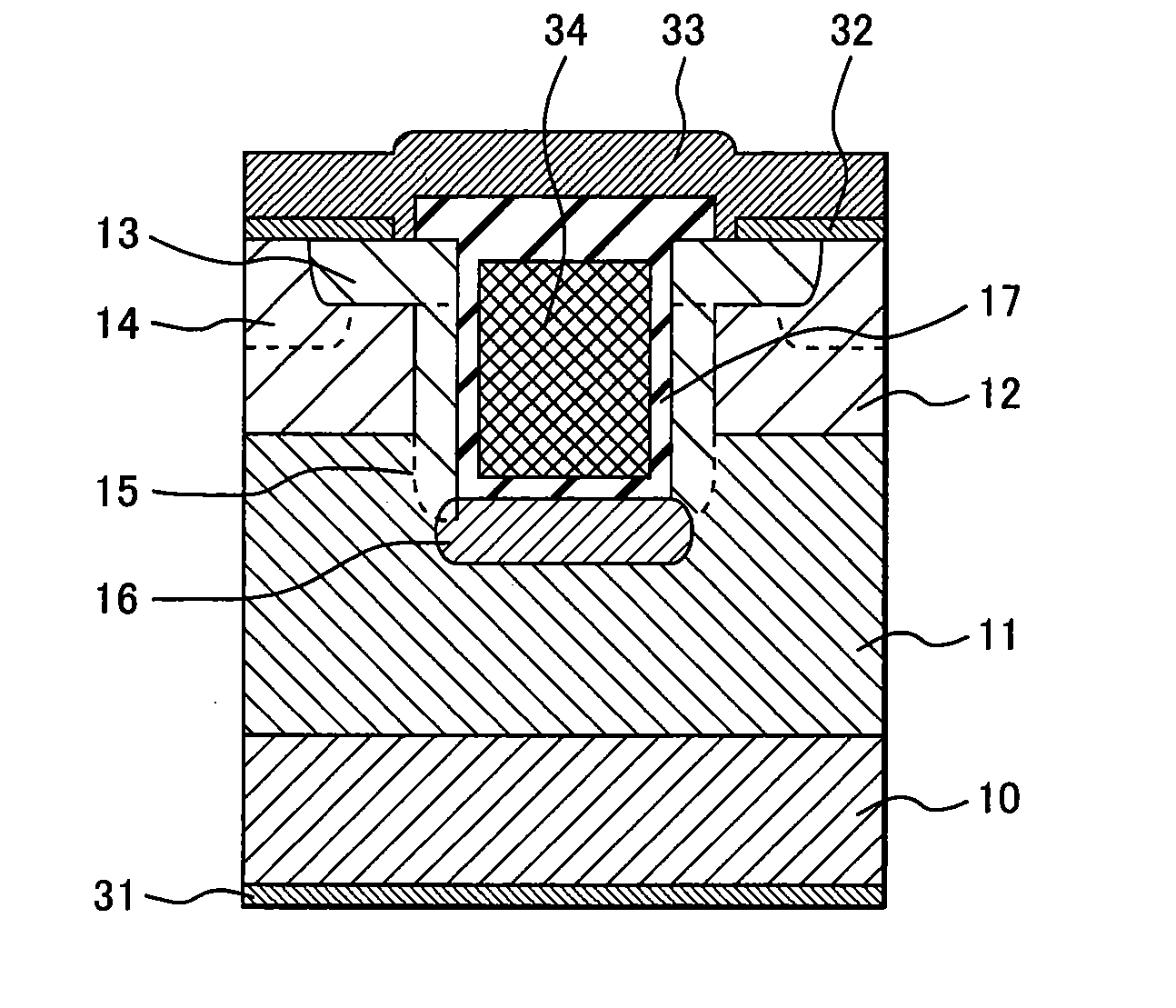

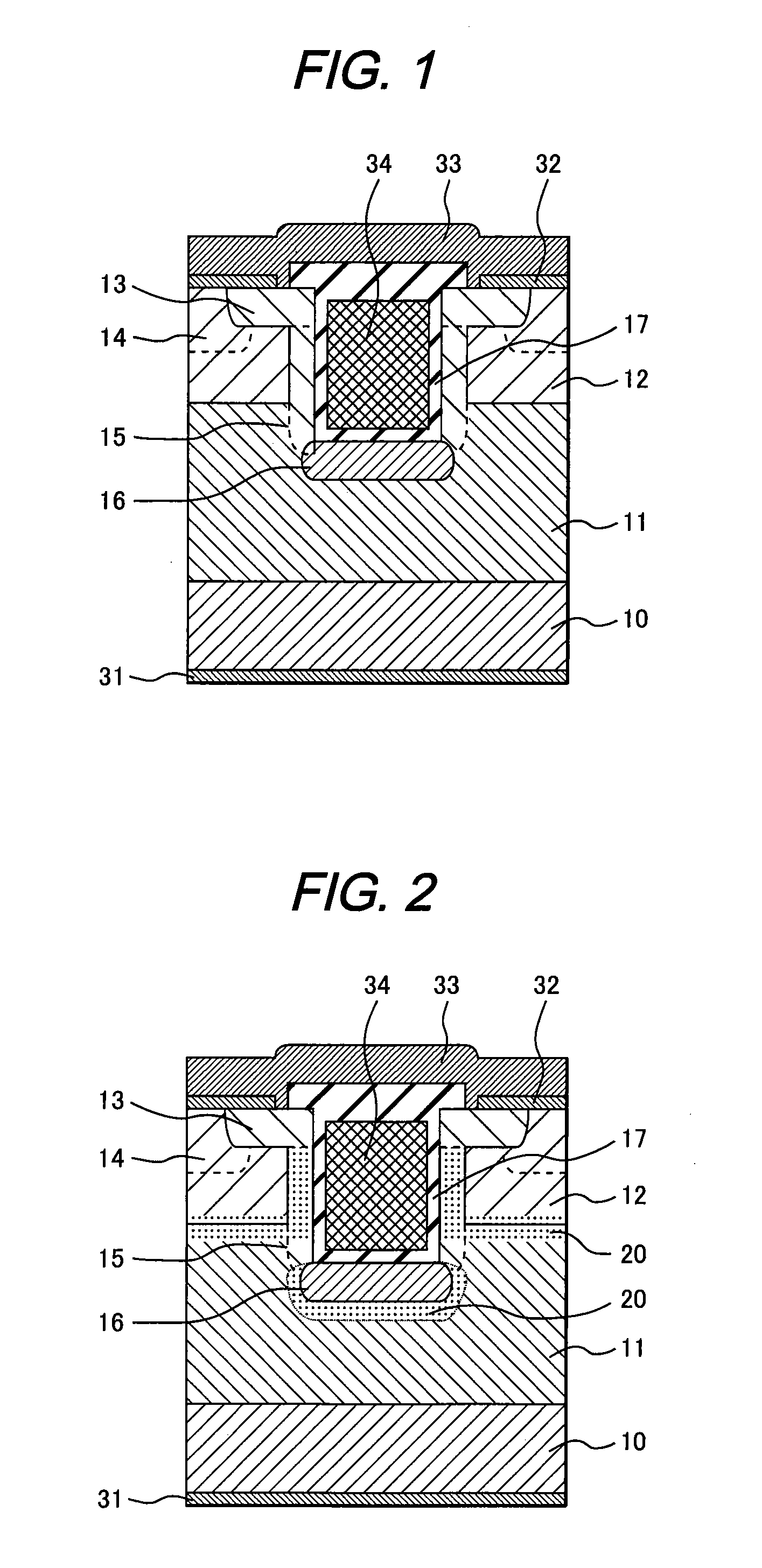

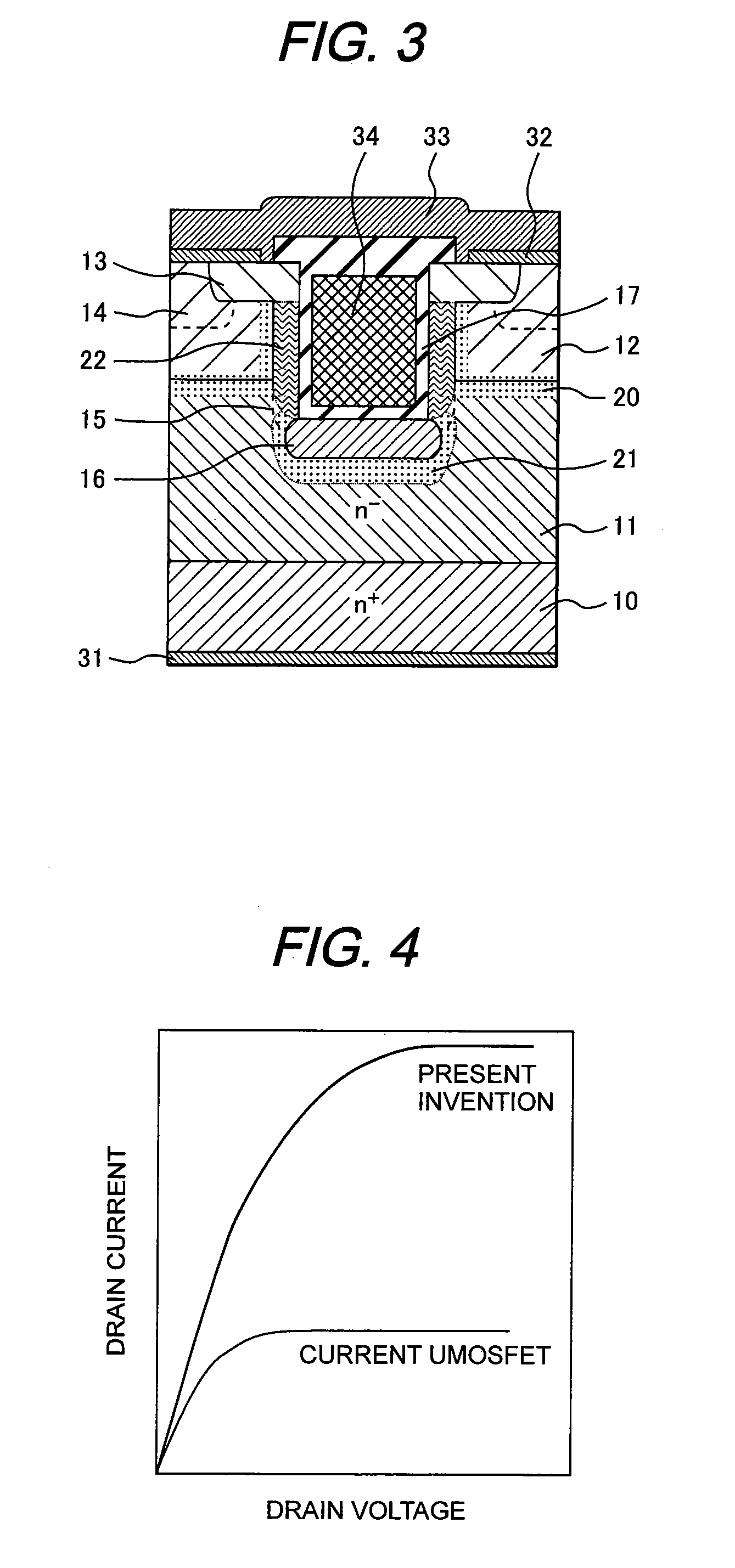

ActiveUS20090032821A1Large saturation currentLower threshold voltageSolid-state devicesSemiconductor devicesEngineeringImpurity

A UMOSFET is capable of reducing a threshold voltage and producing a large saturation current. A typical UMOSFET according to the present invention includes: an N+ type SiC substrate constituting a drain layer; an N− type SiC layer that is in contact with the drain layer and constitutes a drift layer; a P type body layer formed on the drift layer and being a semiconductor layer; an N+ type SiC layer constituting a source layer; a trench extending from the source layer to a predetermined location placed in the drift layer; a P type electric field relaxation region provided around and outside a bottom portion of the trench; and a channel region extending from the N+ type source layer to the P type electric field relaxation region and having an impurity concentration higher than that of the N− type drift layer and lower than that of the P type body layer.

Owner:HITACHI POWER SEMICON DEVICE

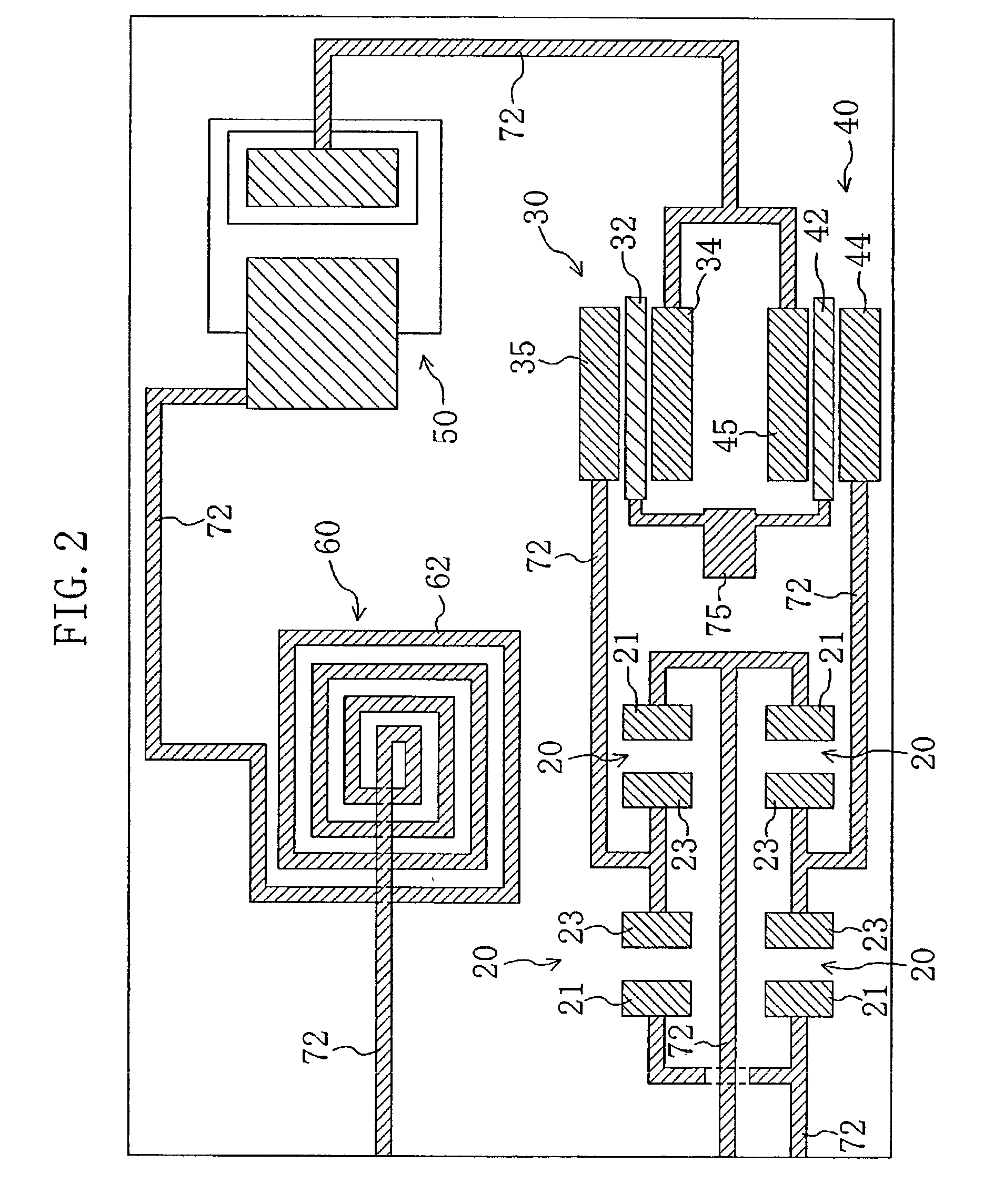

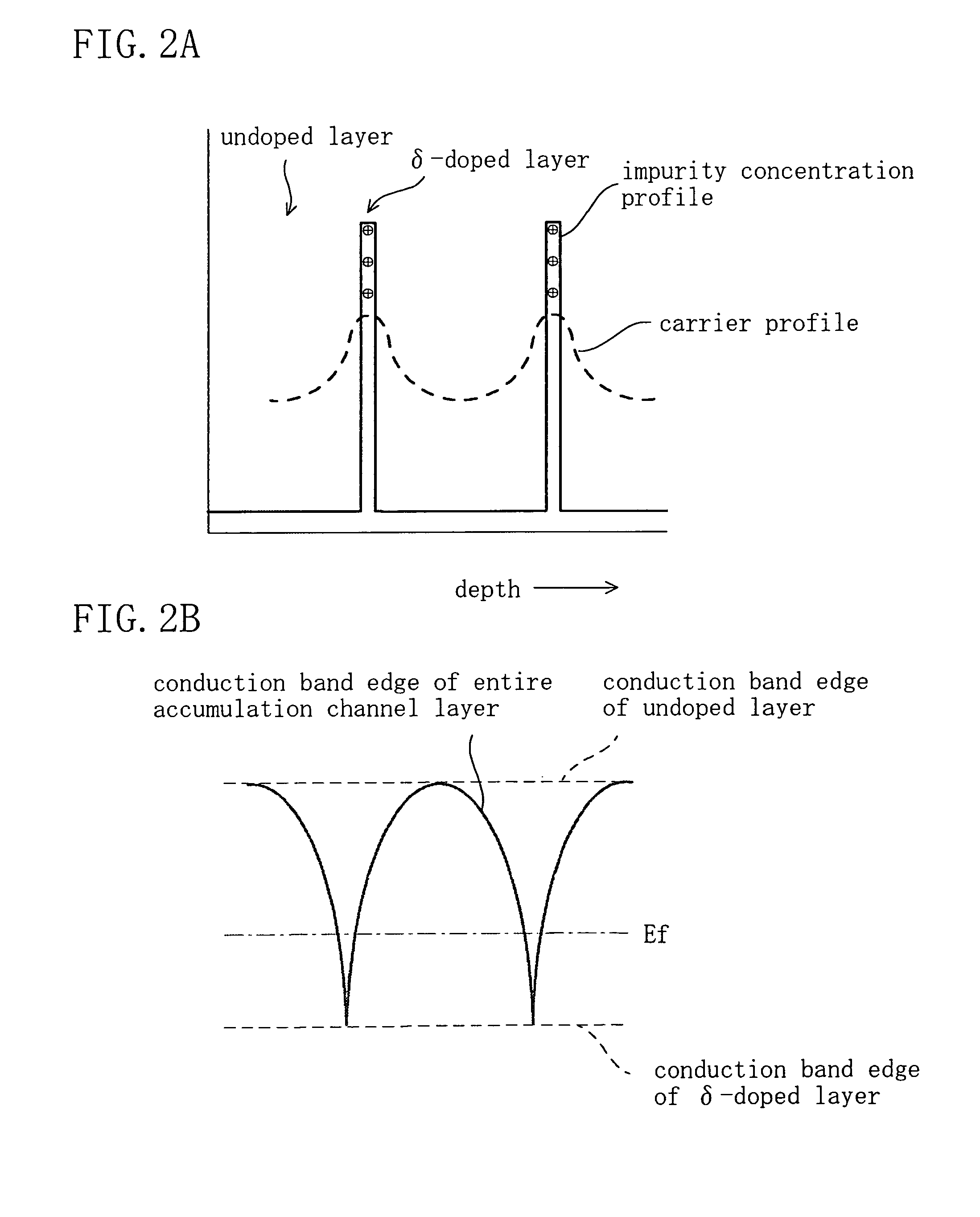

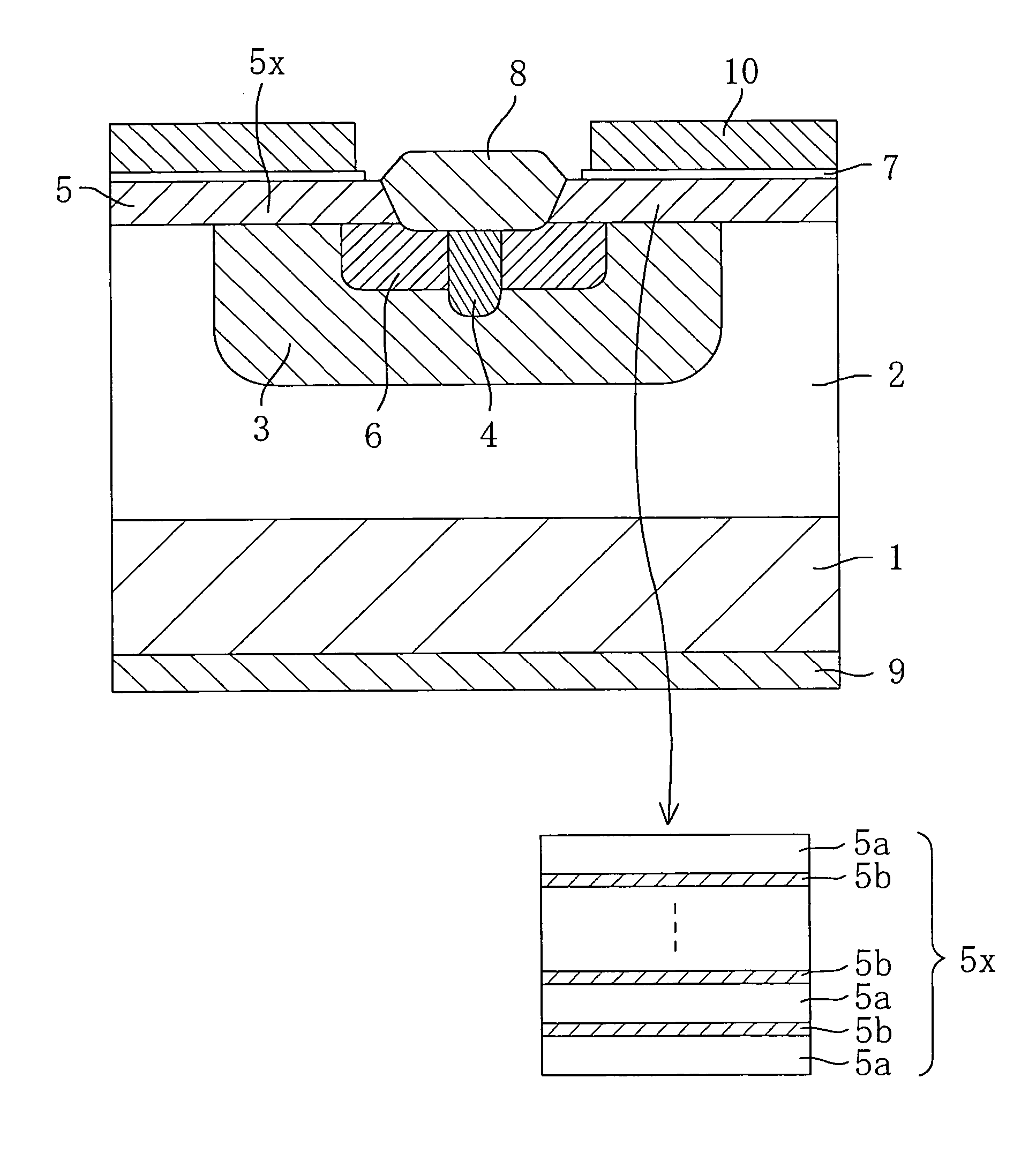

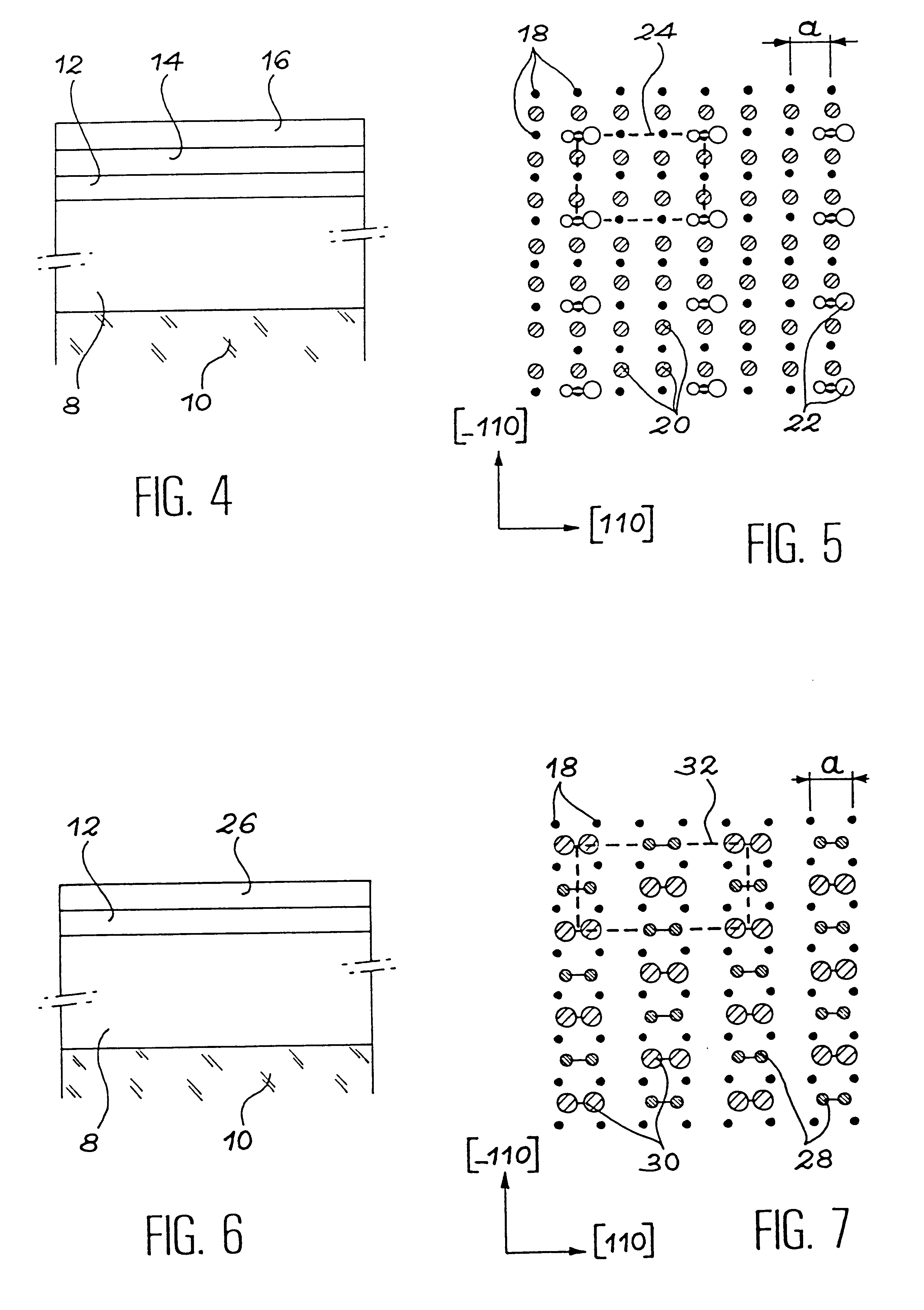

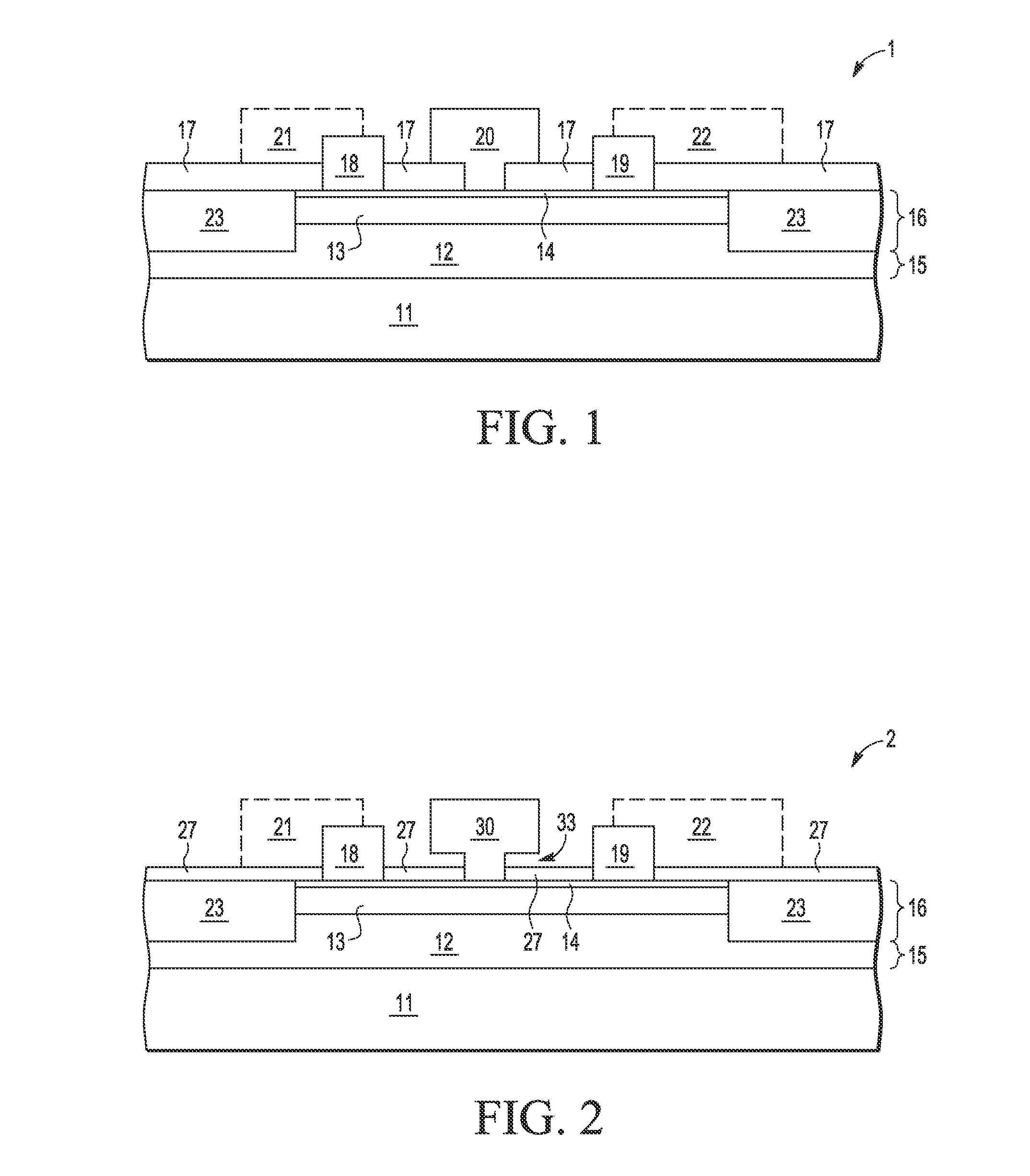

Misfet

InactiveUS20030227061A1Improve electronic propertiesAvoid harmful effectsSolid-state devicesSemiconductor/solid-state device manufacturingImpurity ionsSic substrate

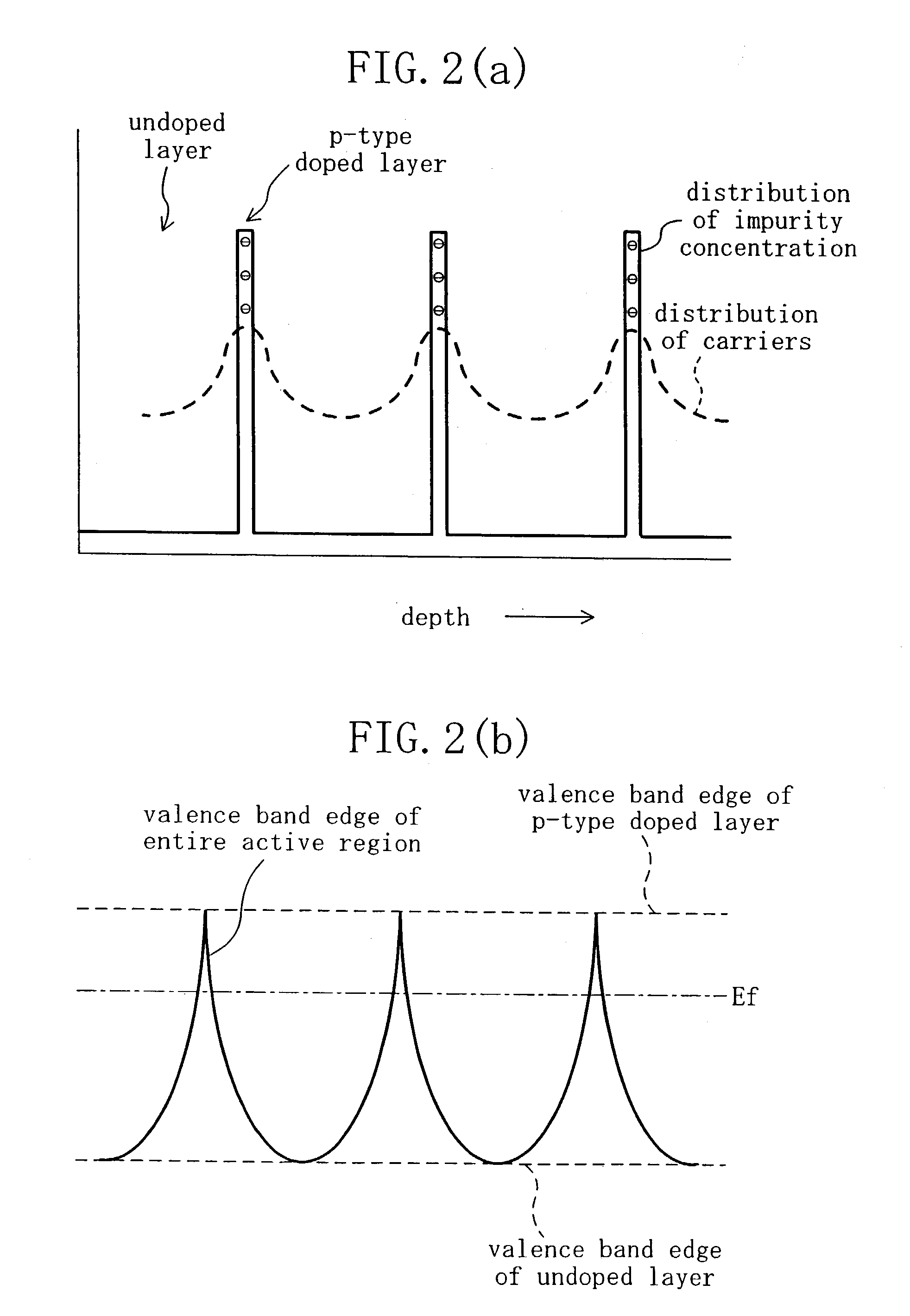

P-type active region 12; n-type source / drain regions 13a and 13b; gate insulating film 14 made of a thermal oxide film; gate electrode 15; source / drain electrodes 16a and 16b, are provided over a p-type SiC substrate 11. In the active region 12, p-type heavily doped layers 12a, which are thin enough to create a quantum effect, and thick undoped layers 12b are alternately stacked. When carriers flow, scattering of impurity ions in the active region is reduced, and the channel mobility increases. In the OFF state, a depletion layer expands throughout the active region, and the breakdown voltage increases. As a result of reduction in charges trapped in the gate insulating film or near the interface between the gate insulating film and the active region, the channel mobility further increases.

Owner:PANASONIC CORP

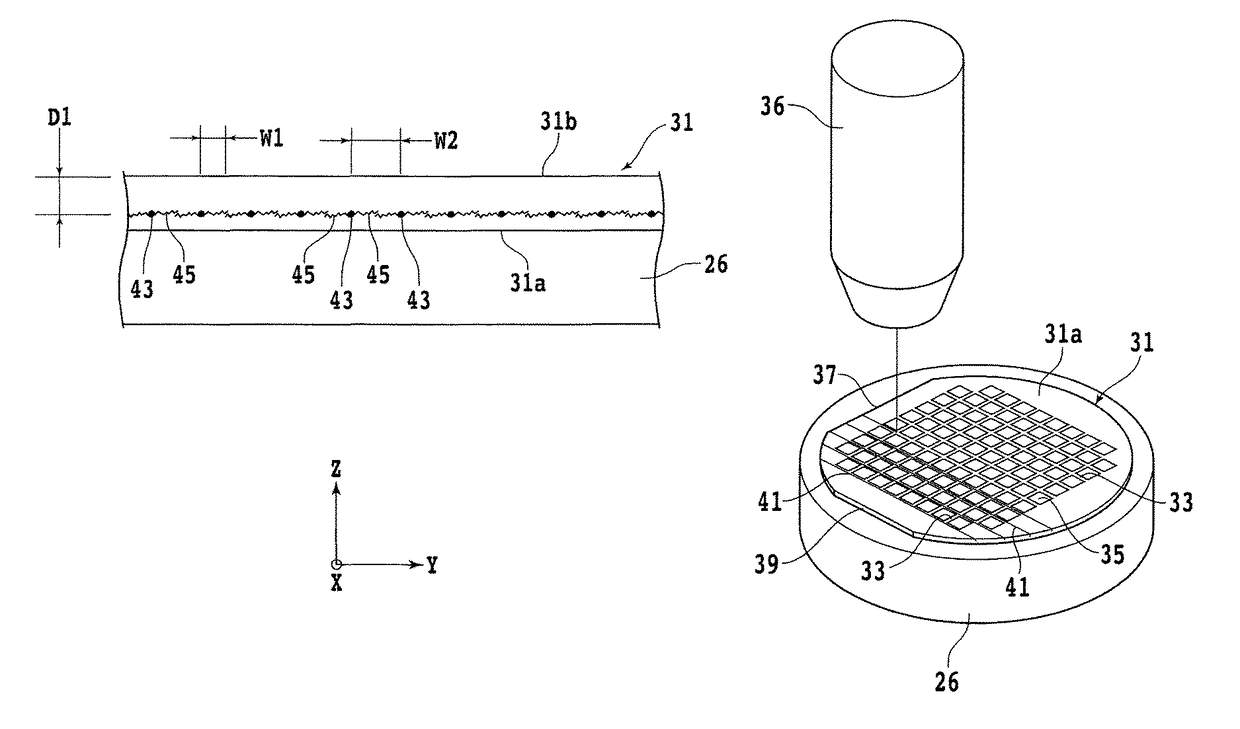

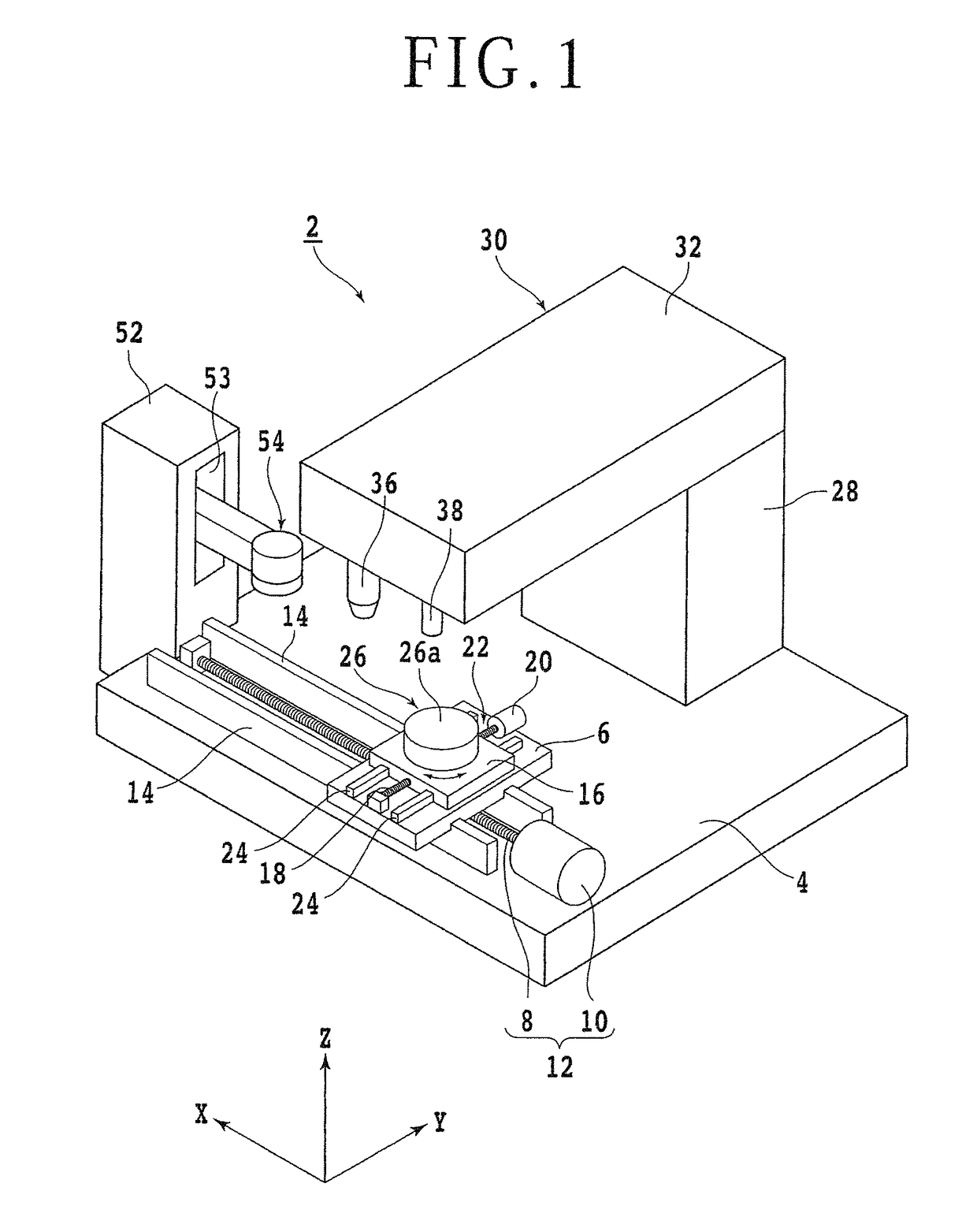

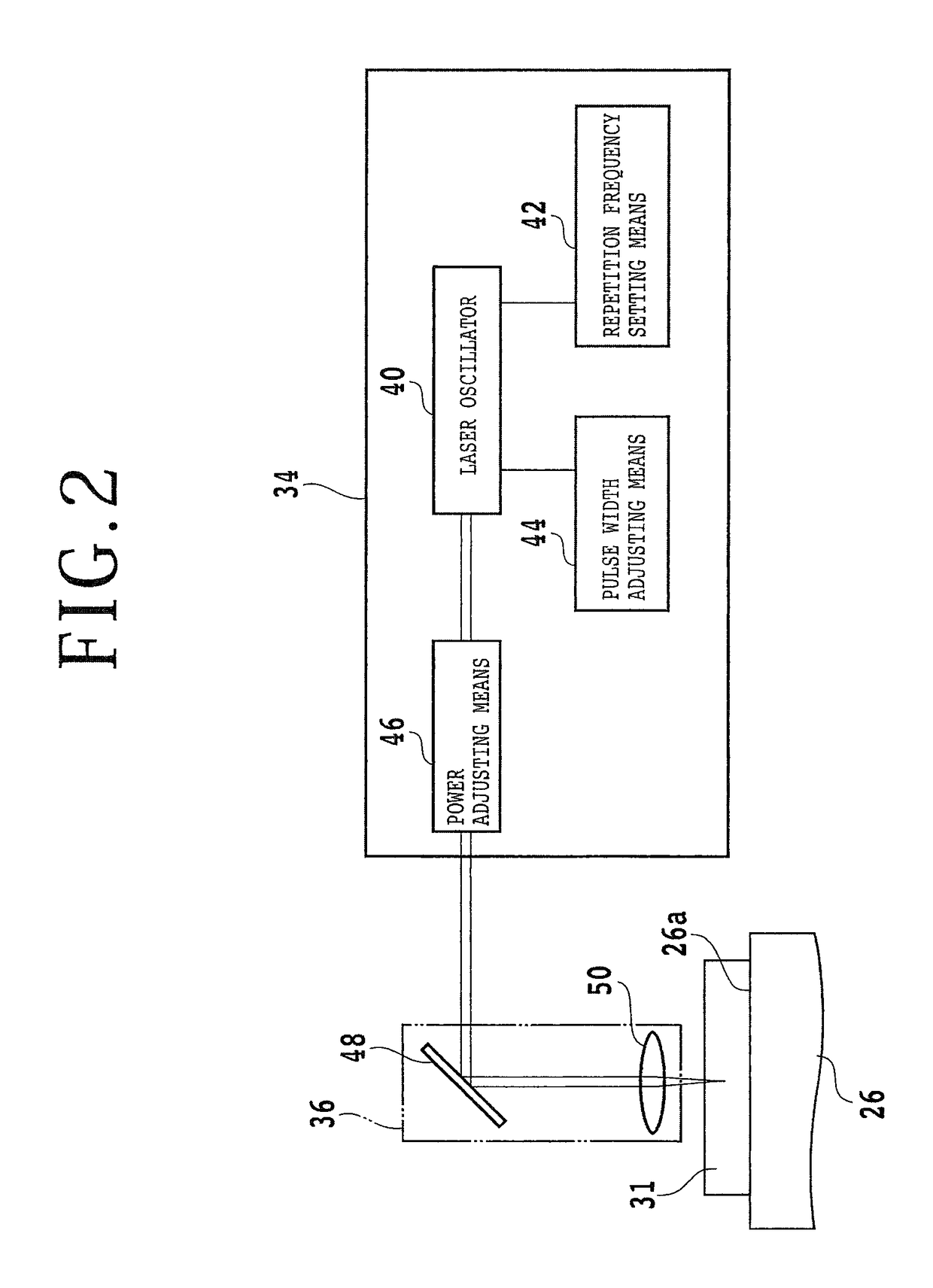

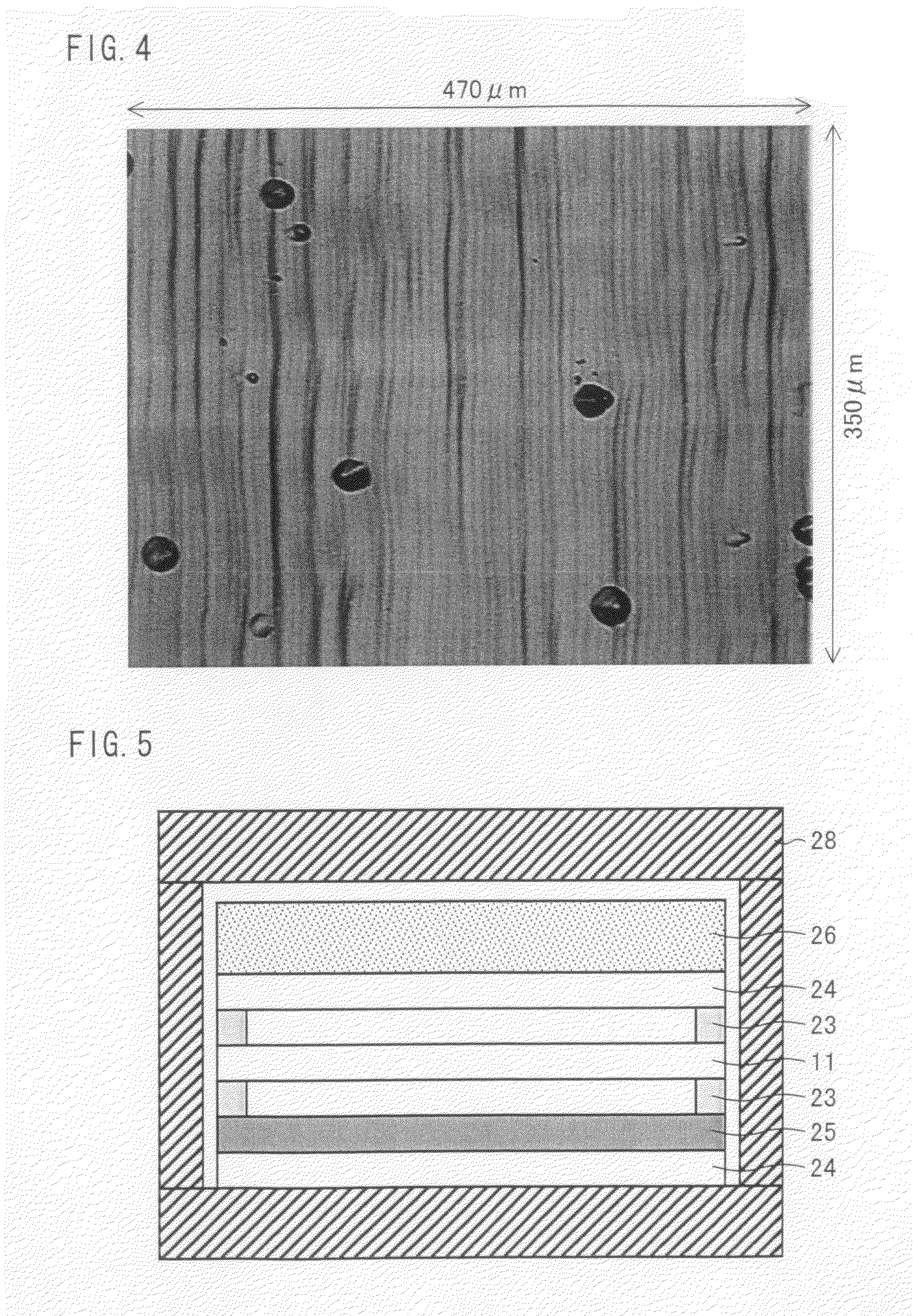

Wafer processing method

ActiveUS9620415B2Semiconductor/solid-state device detailsSolid-state devicesSplit linesOptoelectronics

A wafer formed from an SiC substrate having a first surface and a second surface is divided into individual device chips. A division start point formed by a cutting blade has a depth corresponding to the finished thickness of each device chip along division lines formed on the first surface. A separation start point is formed by a laser beam having a focal point set inside the SiC substrate at a predetermined depth from the second surface, and the laser beam is applied to the second surface while relatively moving the focal point and the SiC substrate to thereby form a modified layer parallel to the first surface and cracks extending from the modified layer along a c-plane. An external force is applied to the wafer, thereby separating the wafer into a first wafer having the first surface and a second wafer having the second surface.

Owner:DISCO CORP

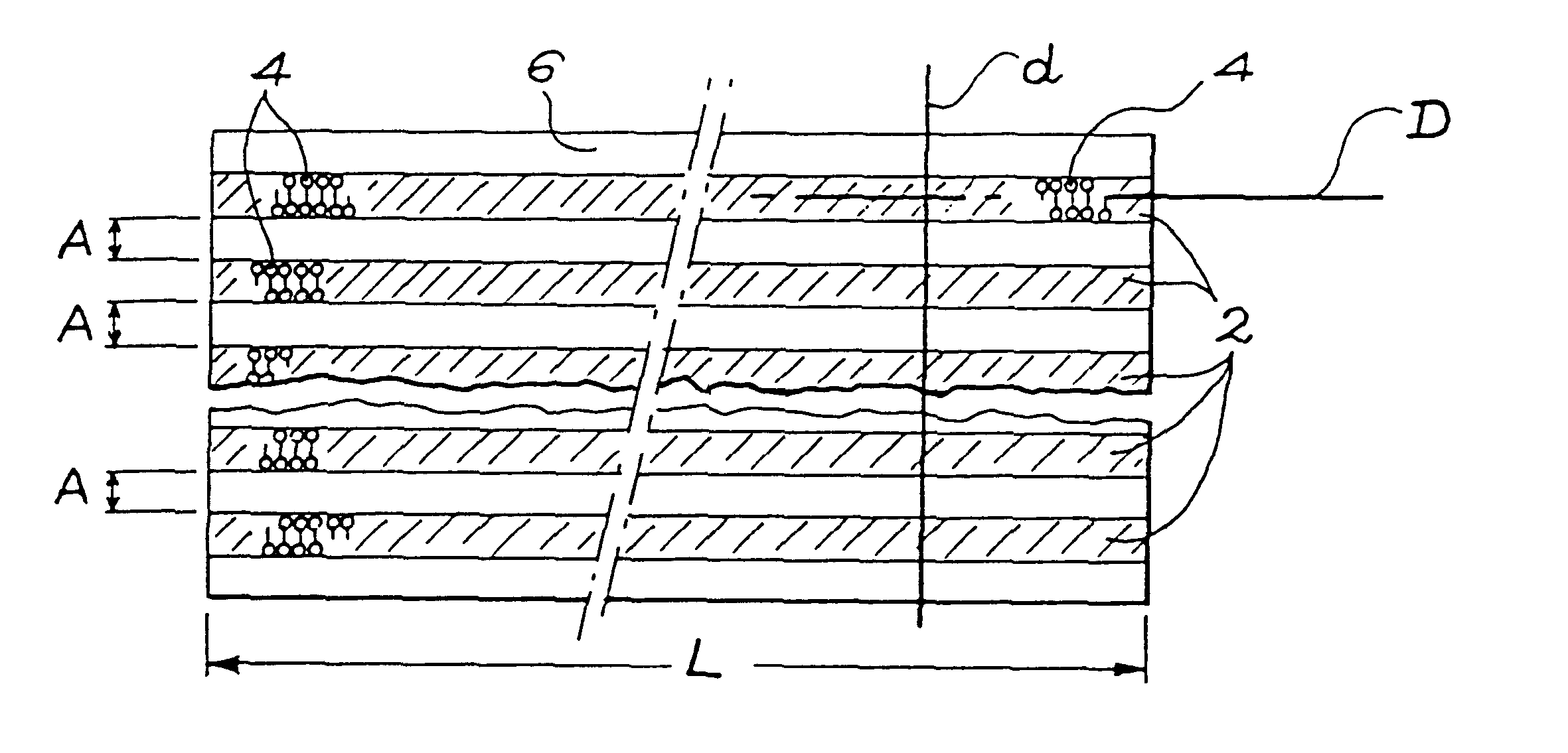

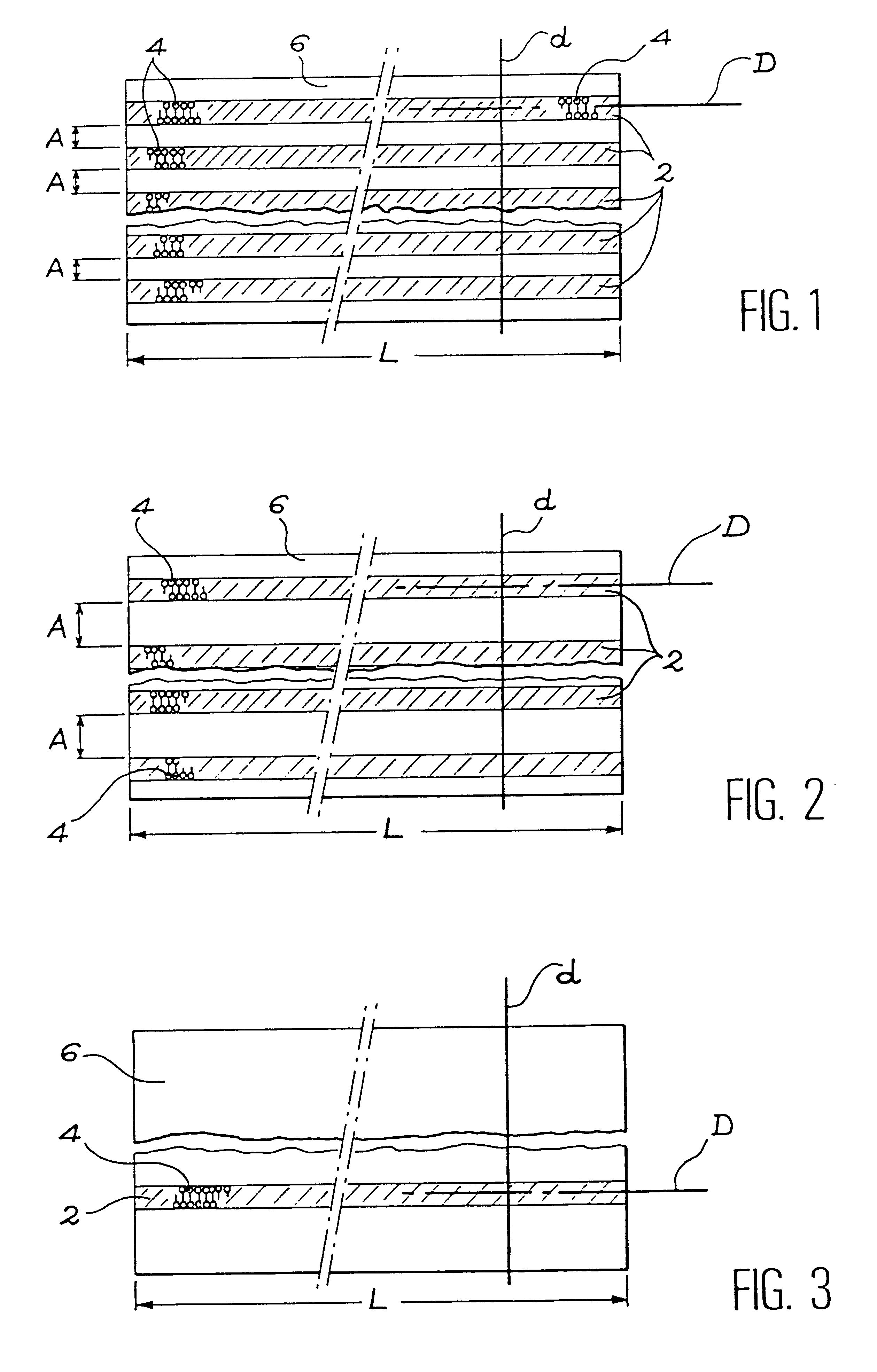

Very long and highly stable atomic wires, method for making these wires, application in nano-electronics

InactiveUS6274234B1Convenient lengthImprove stabilityNanoinformaticsSolid-state devicesEngineeringSic substrate

Atomic wires of great length and great stability are formed on the surface of a SiC substrate as straight chains of dimers of an element chosen from amongst SiC and C. In order to produce same, layers of the element are formed on the surface and the assembly is constructed by means of annealings of the surface provided with the layers. The resulting wires have application to nanoelectronics.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES +1

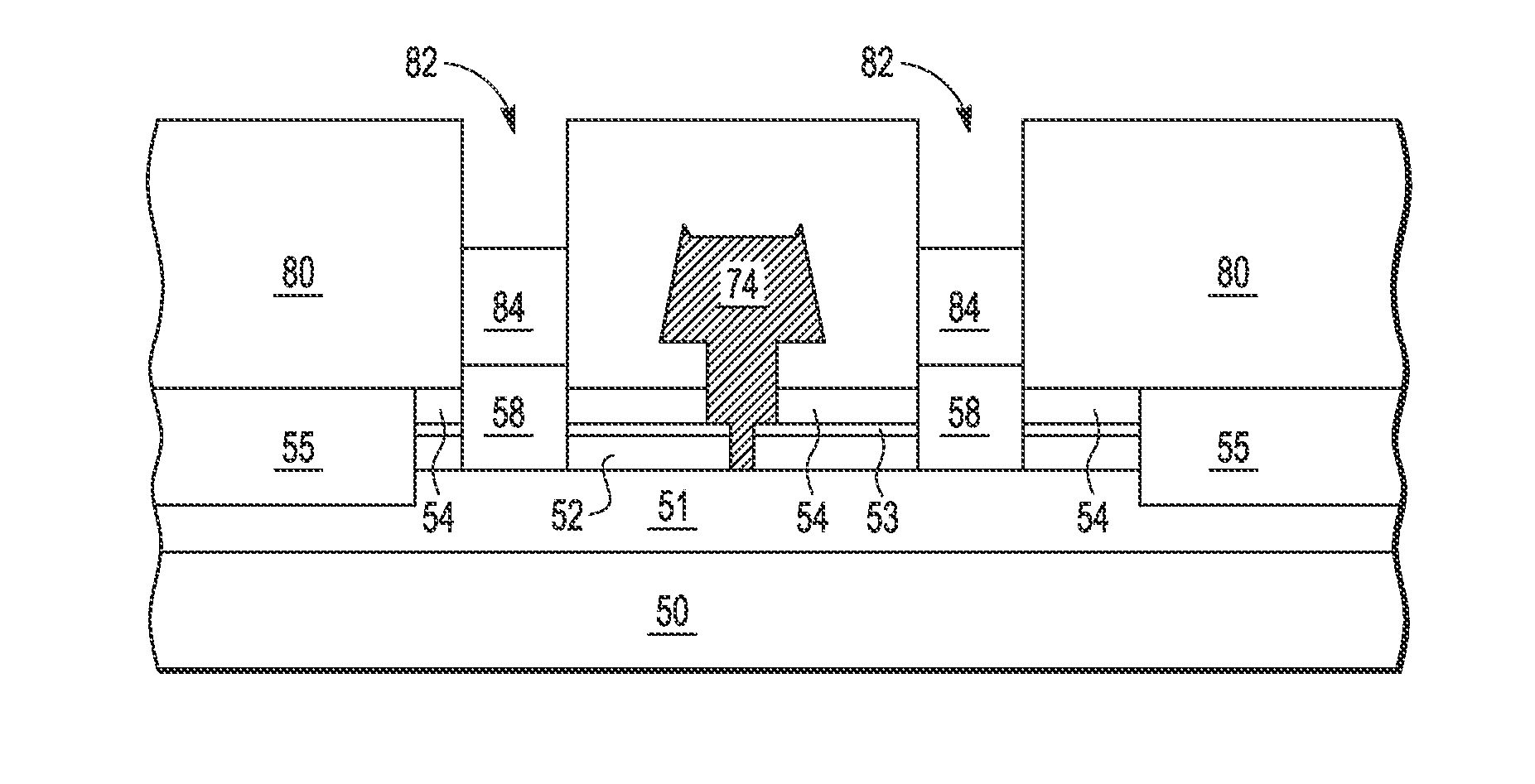

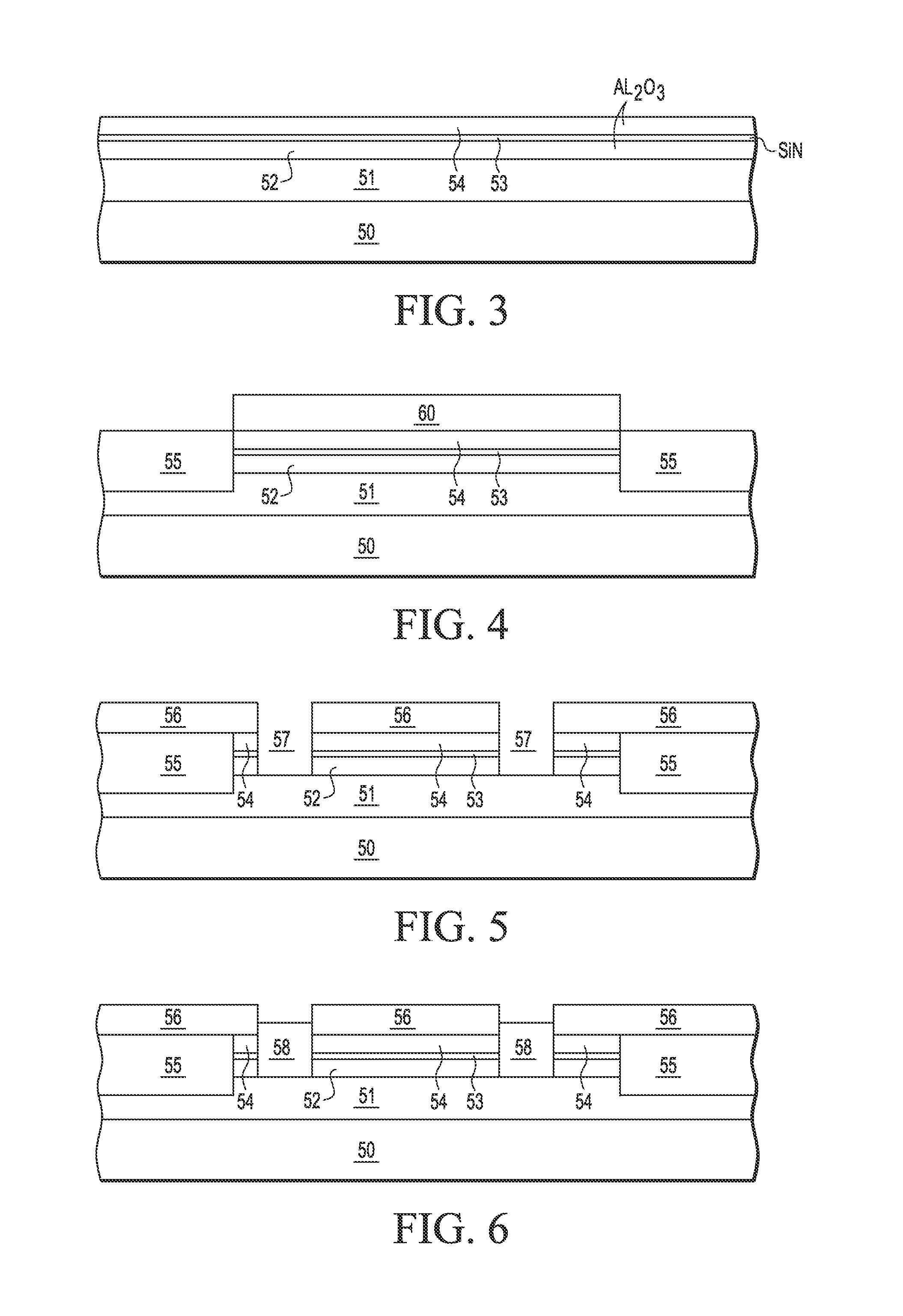

Method for Improving E-Beam Lithography Gate Metal Profile for Enhanced Field Control

ActiveUS20150311084A1Semiconductor/solid-state device manufacturingSemiconductor devicesSic substrateSemiconductor

A semiconductor device is provided which includes a GaN-on-SiC substrate (50-51) and a multi-layer passivation stack (52-54) in which patterned step openings (76) are defined and filled with gate metal layers using a lift-off gate metal process to form a T-gate electrode (74) as a stepped gate electrode having sidewall extensions and a contact base portion with one or more gate ledges.

Owner:NXP USA INC

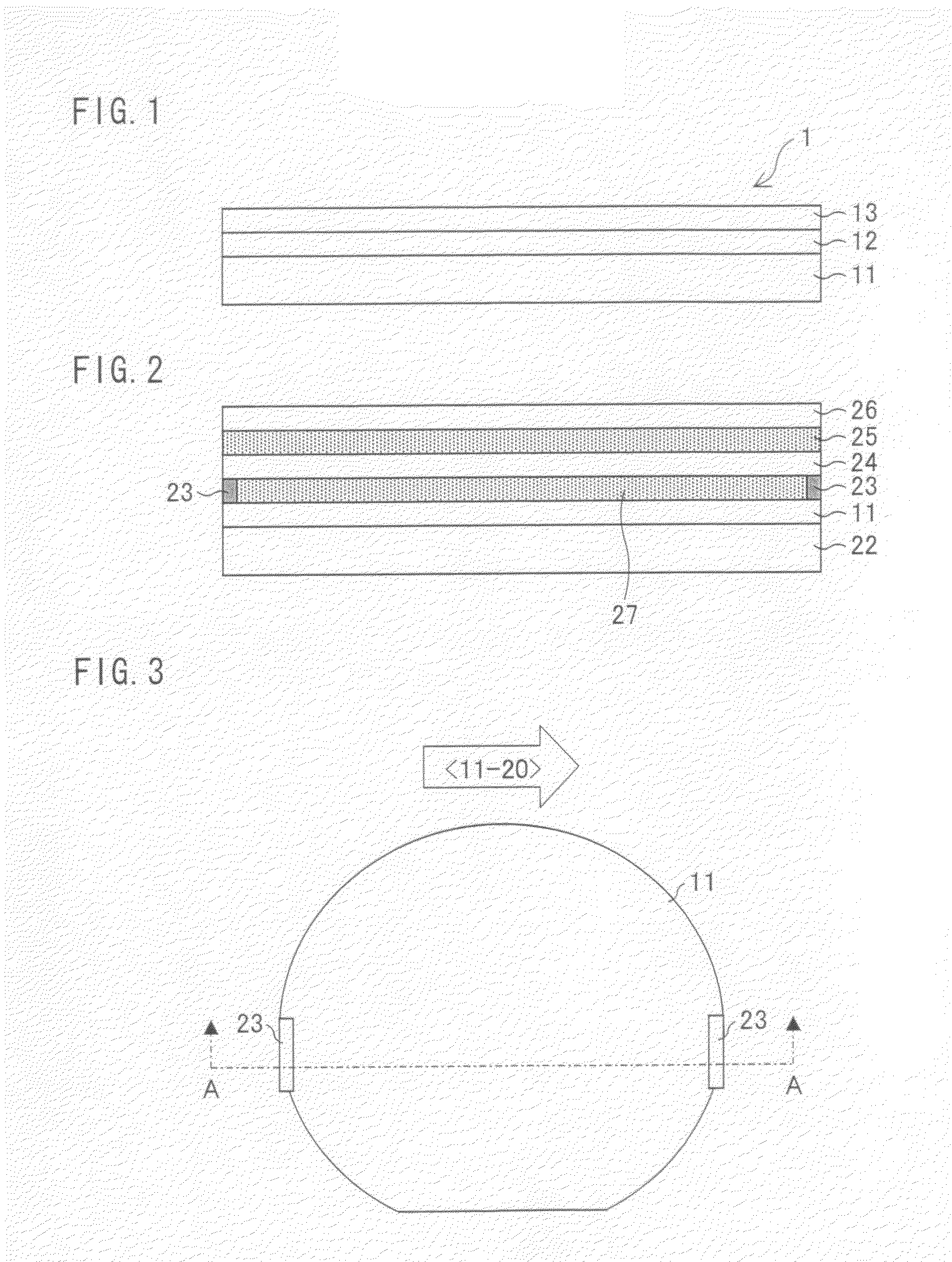

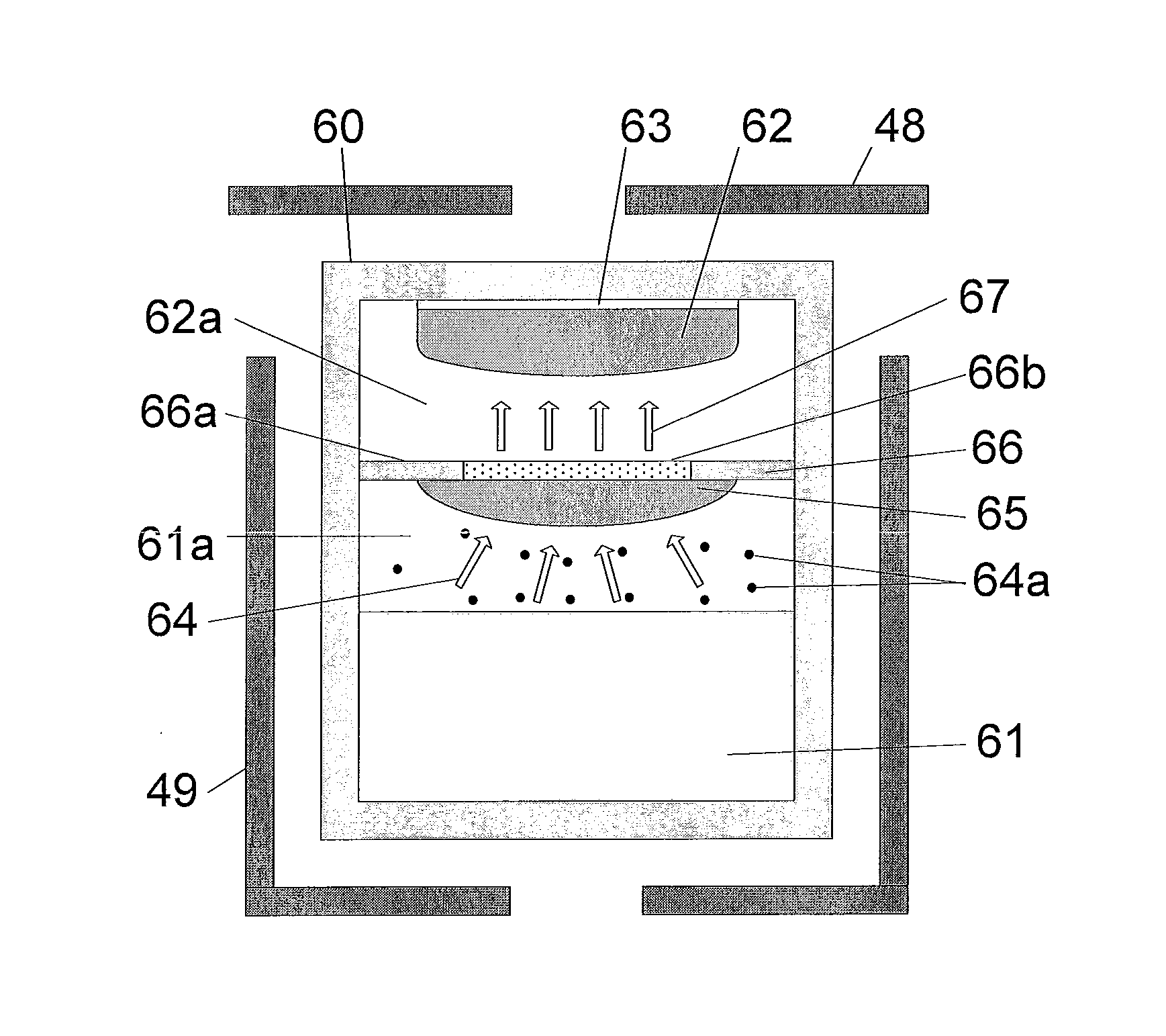

Sic epitaxial substrate and method for producing the same

InactiveUS20100119849A1High film thicknessReduce in quantityPolycrystalline material growthBy zone-melting liquidsSingle crystalOptoelectronics

In one embodiment of the present invention, a monocrystal SiC epitaxial substrate is produced which includes a monocrystal SiC substrate; a buffer layer made of a first SiC epitaxial film formed on the monocrystal SiC substrate; and an active layer made of a second SiC epitaxial film formed on the buffer layer. The buffer layer is grown by heat-treating a set of the monocrystal SiC substrate, a carbon source plate, and a metal Si melt layer having a predetermined thickness and interposed between the monocrystal SiC substrate and the metal Si melt layer, so as to epitaxially grow monocrystal SiC on the monocrystal SiC substrate. The active layer is grown by epitaxially growing monocrystal SiC on the buffer layer by vapor phase growth method. This allows for production of a monocrystal SiC epitaxial substrate including a high-quality monocrystal SiC active layer being low in defects.

Owner:RES INST OF INNOVATIVE TECH FOR THE EARTH +1

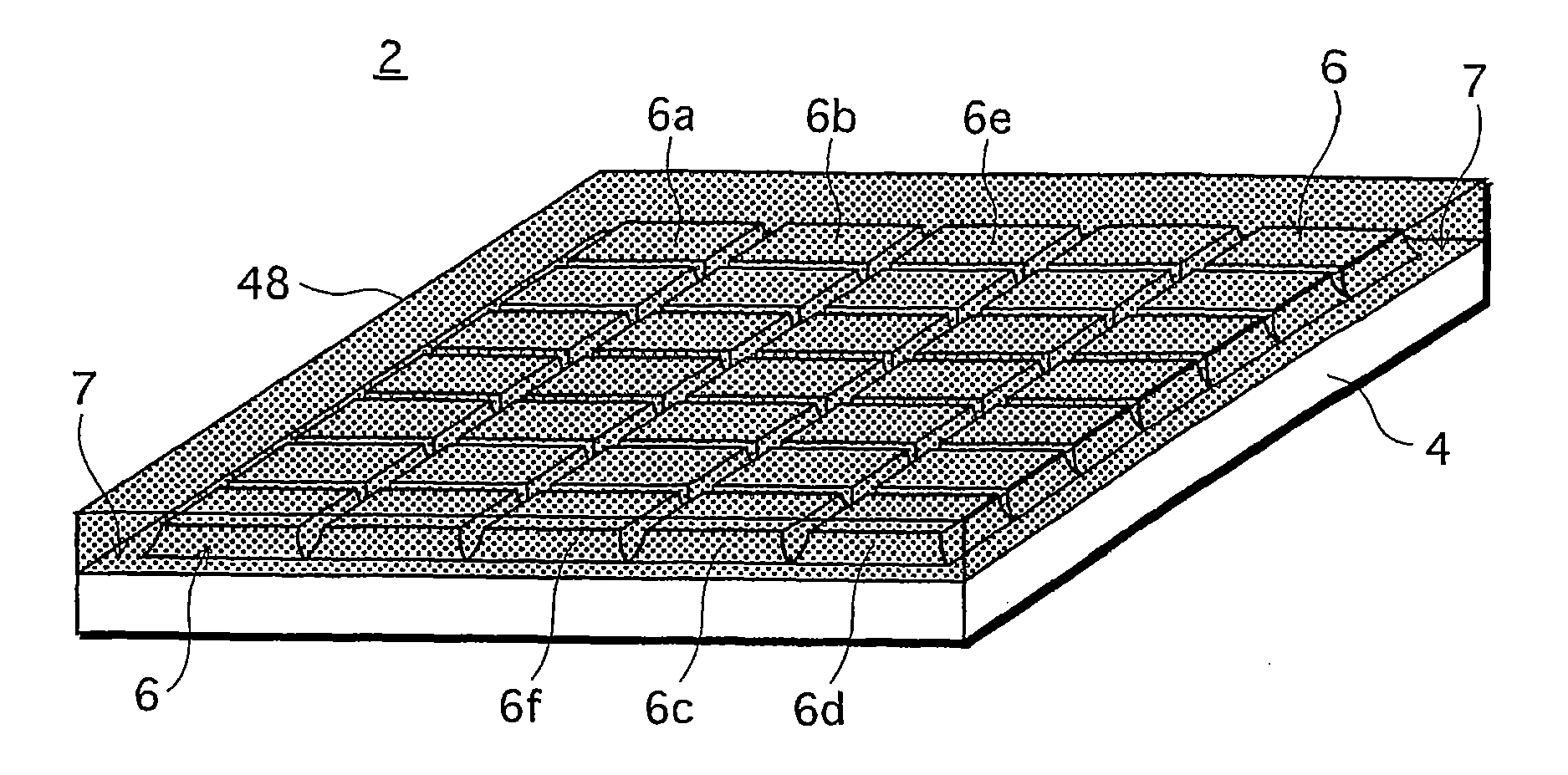

Semiconductor light emitting device, lighting module, lighting apparatus, display element, and manufacturing method for semiconductor light emitting device

ActiveUS20090134420A1Efficient collectionDischarge tube luminescnet screensLamp detailsPhosphorLed array

In an LED array chip (2), LEDs (6) are connected together in series by a bridging wire (30). The LEDs (6) each have a semiconductor multilayer structure (8-18) including a light emitting layer (14). Here, the semiconductor multilayer structure (8-18) is epitaxially grown on a front surface of an SiC substrate (4). A phosphor film (48) covers the LEDs (6). Two power supply terminals (36 and 38), which are electrically independent from each other, are formed on a back surface of the SiC substrate (4). The power supply terminal (36) is connected to a cathode electrode (32) of an LED (6a) at a lower potential end by a bridging wire (40) and a plated-through hole (42). The power supply terminal (38) is connected to an anode electrode (34) of an LED (6d) at a higher potential end by a bridging wire (44) and a plated-through hole (46).

Owner:SATCO PRODS

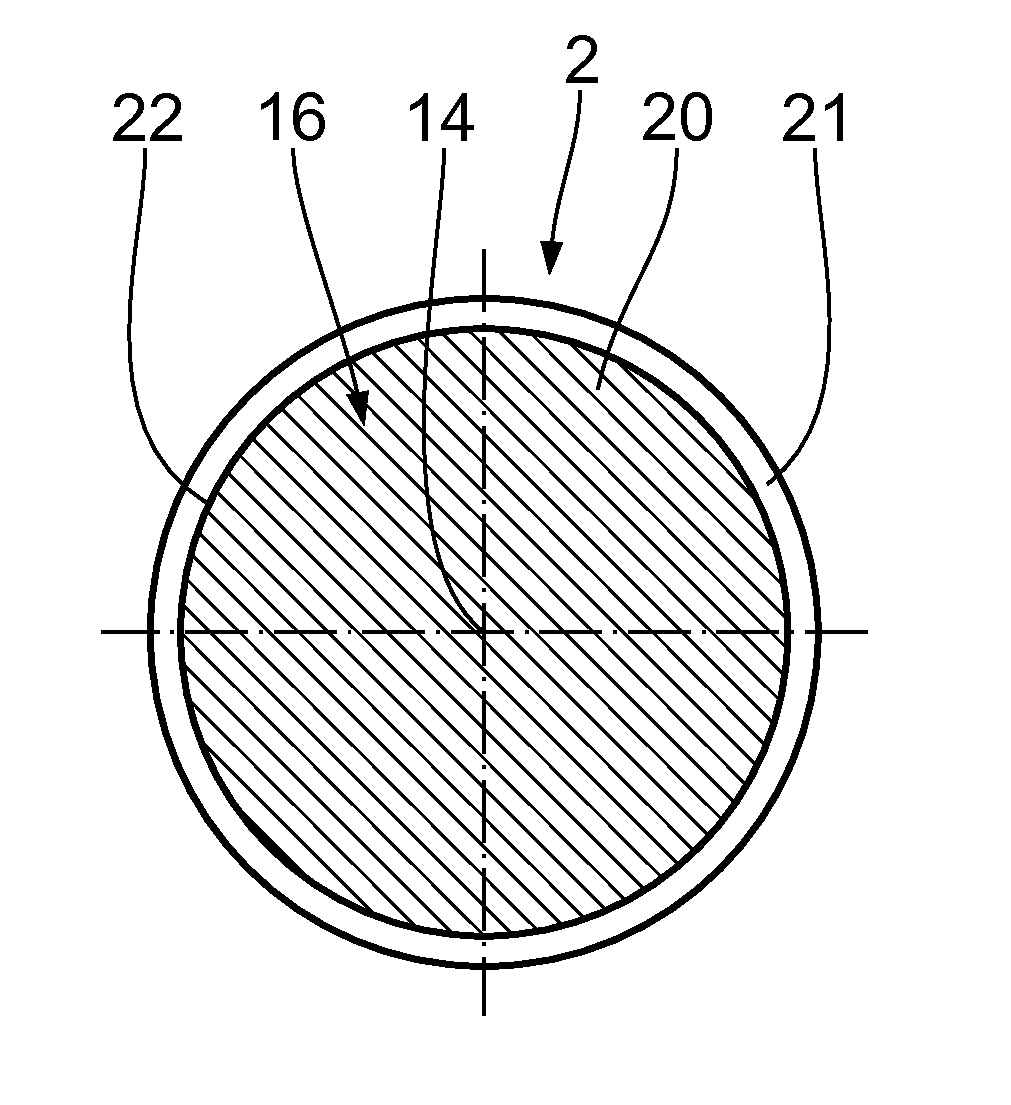

Production method for a bulk SiC single crystal with a large facet and monocrystalline SiC substrate with homogeneous resistance distribution

ActiveUS8865324B2Improve adaptabilityPolycrystalline material growthGlass/slag layered productsDopantSource material

A method is used to produce a bulk SiC single crystal. A seed crystal is arranged in a crystal growth region of a growing crucible. An SiC growth gas phase is produced in the crystal growth region. The bulk SiC single crystal having a central longitudinal mid-axis grows by deposition from the SiC growth gas phase, the deposition taking place on a growth interface of the growing bulk SiC single crystal. The SiC growth gas phase is at least partially fed from an SiC source material and contains at least one dopant from the group of nitrogen, aluminum, vanadium and boron. At least in a central main growth region of the growth interface arranged about the longitudinal mid-axis, a lateral temperature gradient of at most 2 K / cm measured perpendicular to the longitudinal mid-axis is adjusted and maintained in this range. The bulk SiC single crystal has a large facet region.

Owner:SICRYSTAL GMBH

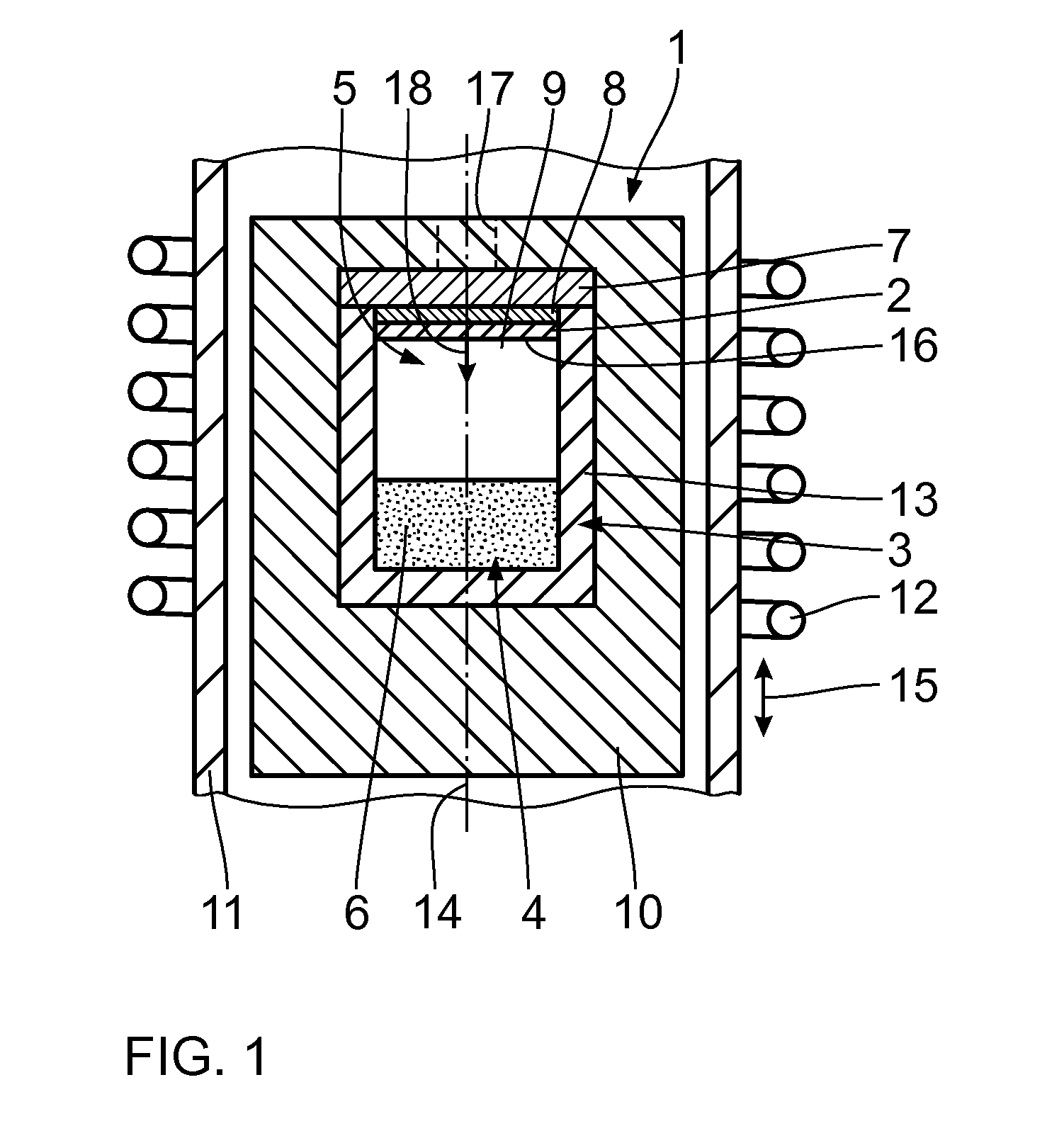

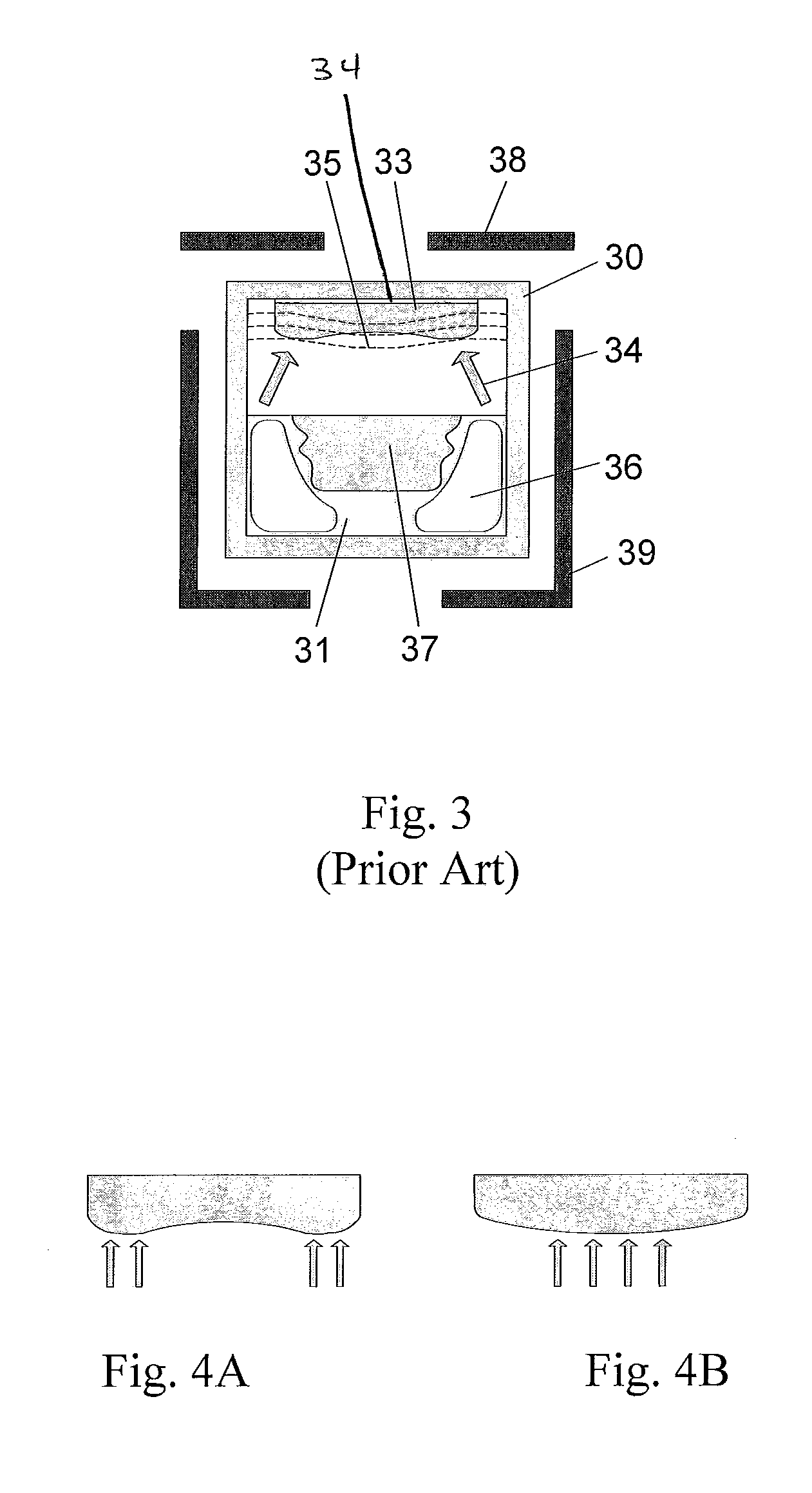

Large Diameter, High Quality SiC Single Crystals, Method and Apparatus

ActiveUS20130280466A1Increase temperaturePolycrystalline material growthLayered productsParticulatesStacking fault

A method and system of forming large-diameter SiC single crystals suitable for fabricating high crystal quality SiC substrates of 100, 125, 150 and 200 mm in diameter are described. The SiC single crystals are grown by a seeded sublimation technique in the presence of a shallow radial temperature gradient. During SiC sublimation growth, a flux of SiC bearing vapors filtered from carbon particulates is substantially restricted to a central area of the surface of the seed crystal by a separation plate disposed between the seed crystal and a source of the SiC bearing vapors. The separation plate includes a first, substantially vapor-permeable part surrounded by a second, substantially non vapor-permeable part. The grown crystals have a flat or slightly convex growth interface. Large-diameter SiC wafers fabricated from the grown crystals exhibit low lattice curvature and low densities of crystal defects, such as stacking faults, inclusions, micropipes and dislocations.

Owner:II VI DELAWARE INC

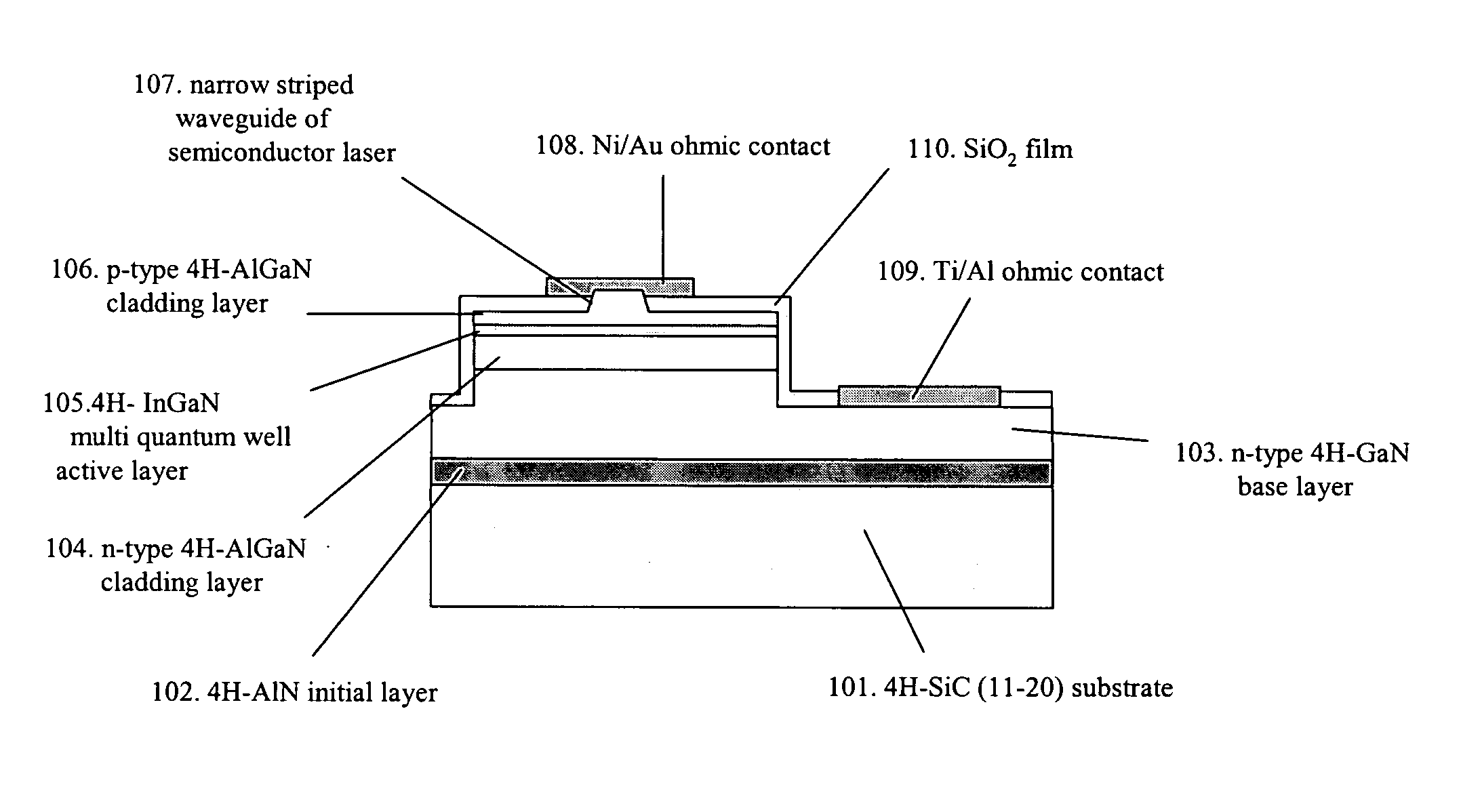

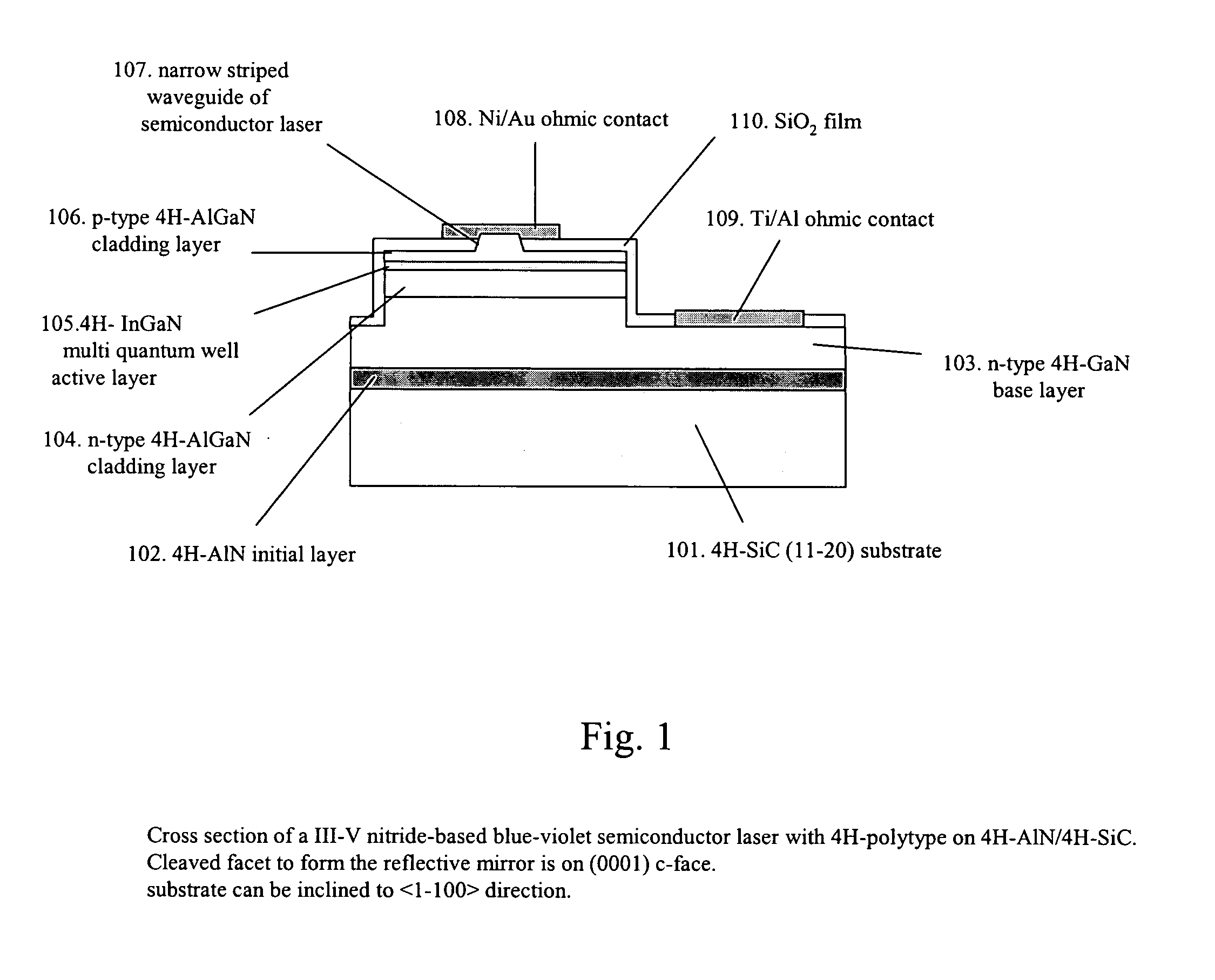

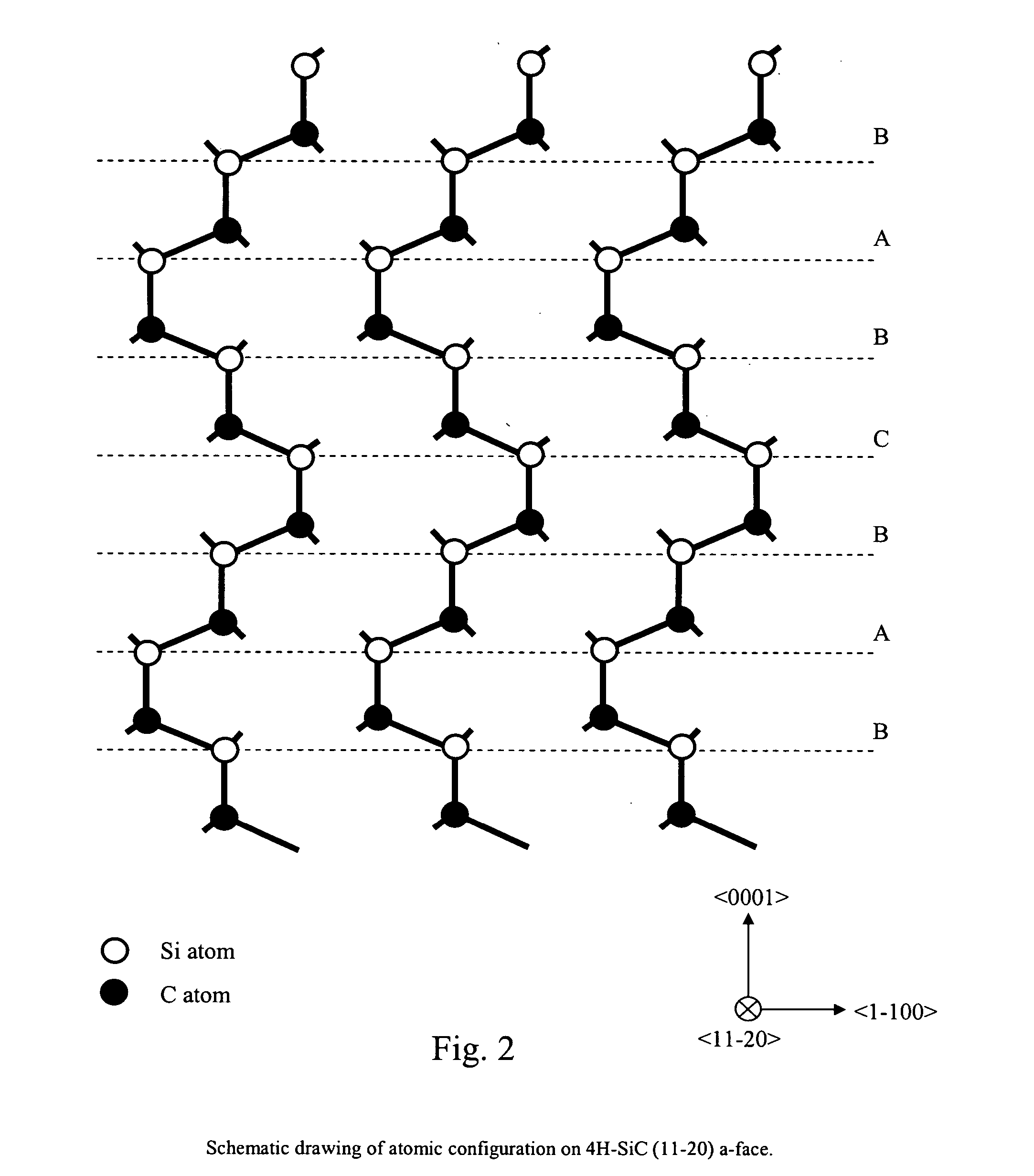

4H-polytype gallium nitride-based semiconductor device on a 4H-polytype substrate

InactiveUS20050218414A1Laser detailsSemiconductor/solid-state device manufacturingDevice materialAlloy

4H-InGaAlN alloy based optoelectronic and electronic devices on non-polar face are formed on 4H-AlN or 4H-AlGaN on (11-20) a-face 4H-SiC substrates. Typically, non polar 4H-AlN is grown on 4H-SiC (11-20) by molecular beam epitaxy (MBE). Subsequently, III-V nitride device layers are grown by metal organic chemical vapor deposition (MOCVD) with 4H-polytype for all of the layers. The non-polar device does not contain any built-in electric field due to the spontaneous and piezoelectric polarization. The optoelectonic devices on the non-polar face exhibits higher emission efficiency with shorter emission wavelength because the electrons and holes are not spatially separated in the quantum well. Vertical device configuration for lasers and light emitting diodes(LEDs) using conductive 4H-AlGaN interlayer on conductive 4H-SiC substrates makes the chip size and series resistance smaller. The elimination of such electric field also improves the performance of high speed and high power transistors. The details of the epitaxial growth s and the processing procedures for the non-polar III-V nitride devices on the non-polar SiC substrates are also disclosed.

Owner:PANASONIC CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com