Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

95results about How to "Reduce carrier concentration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

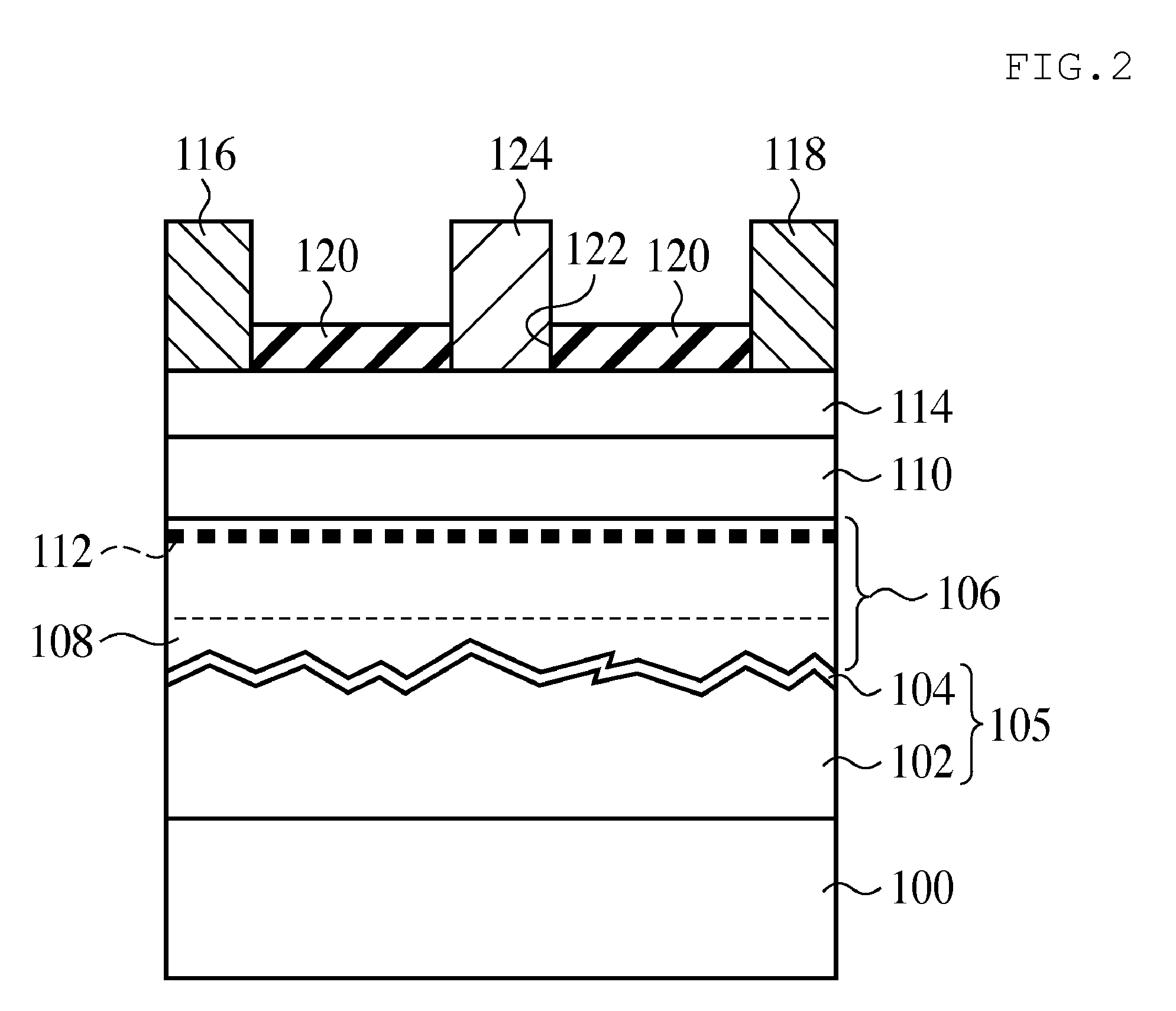

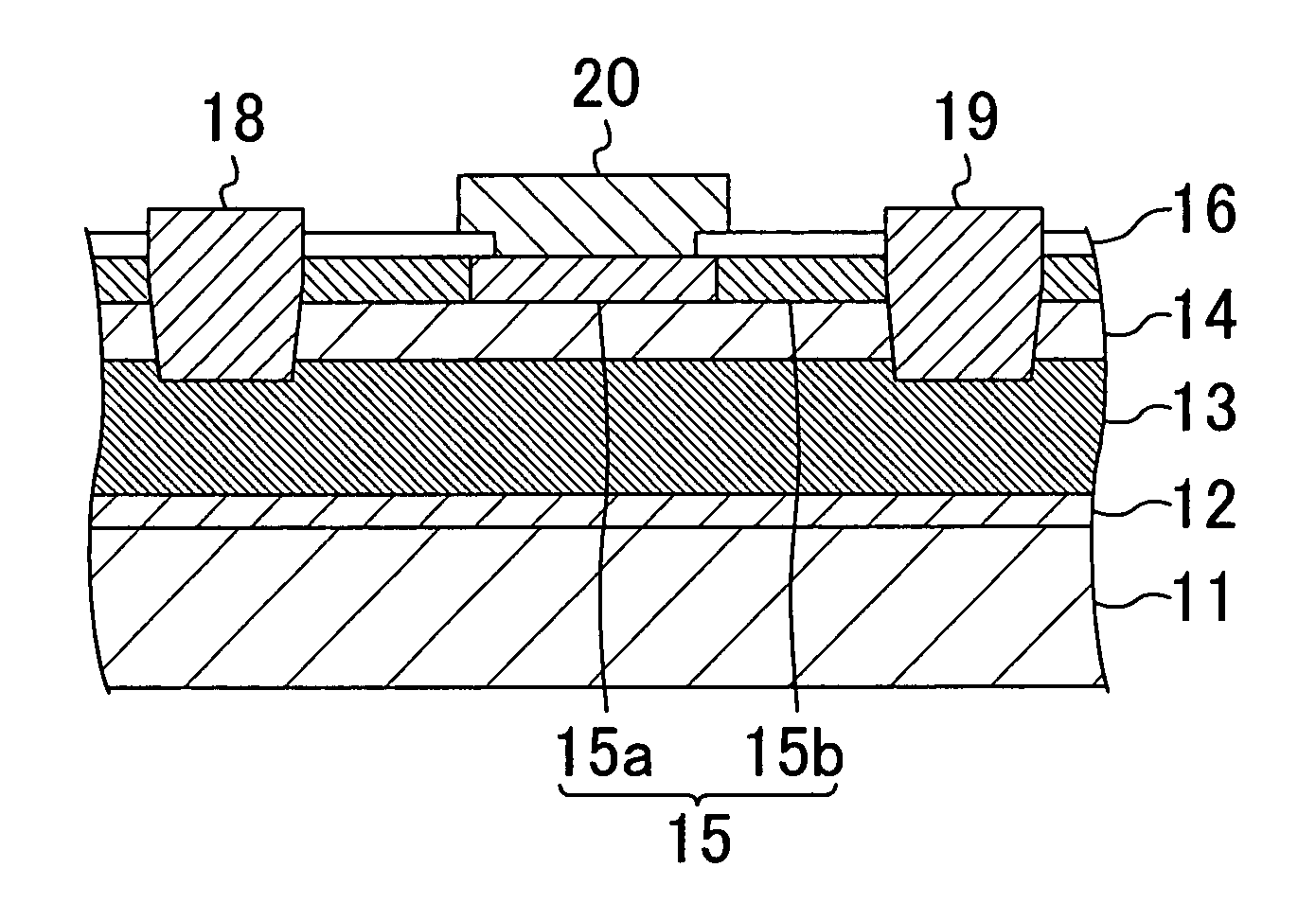

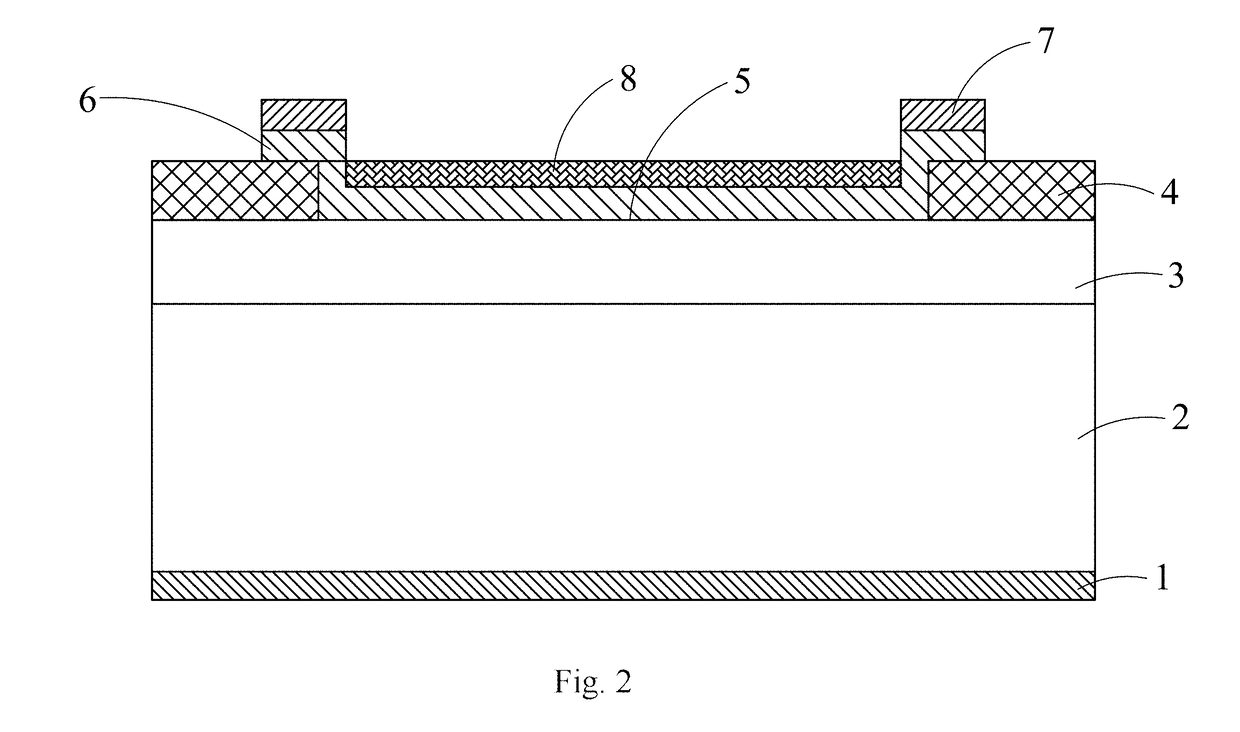

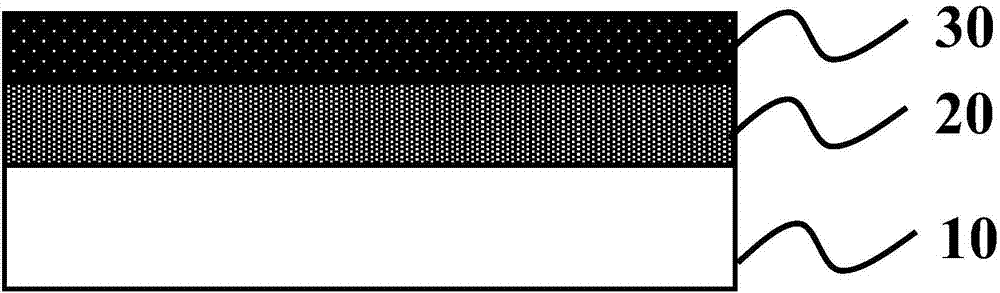

METHOD OF MANUFACTURING ZnO-BASED THIN FILM TRANSISTOR

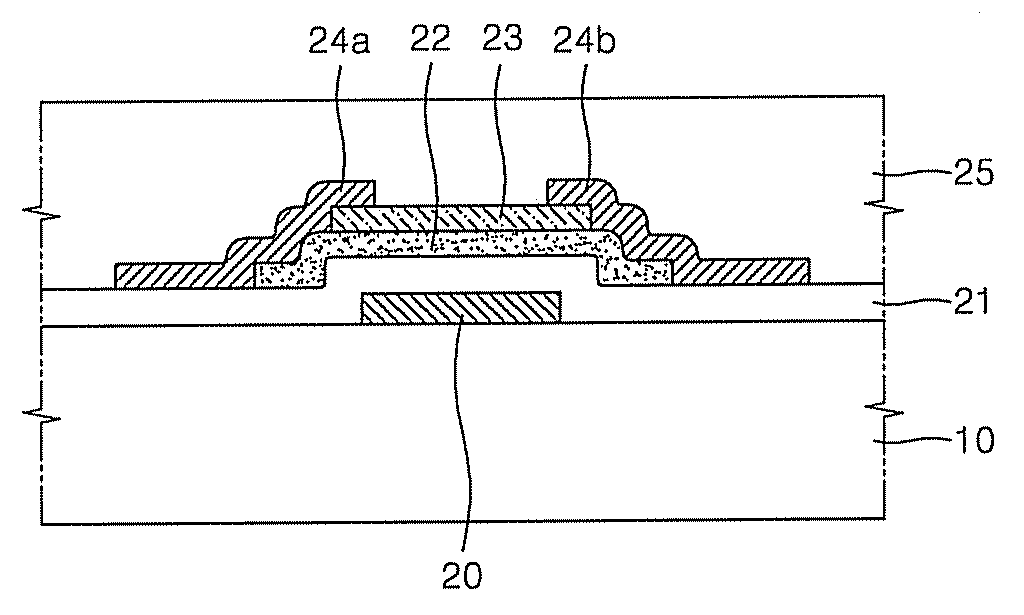

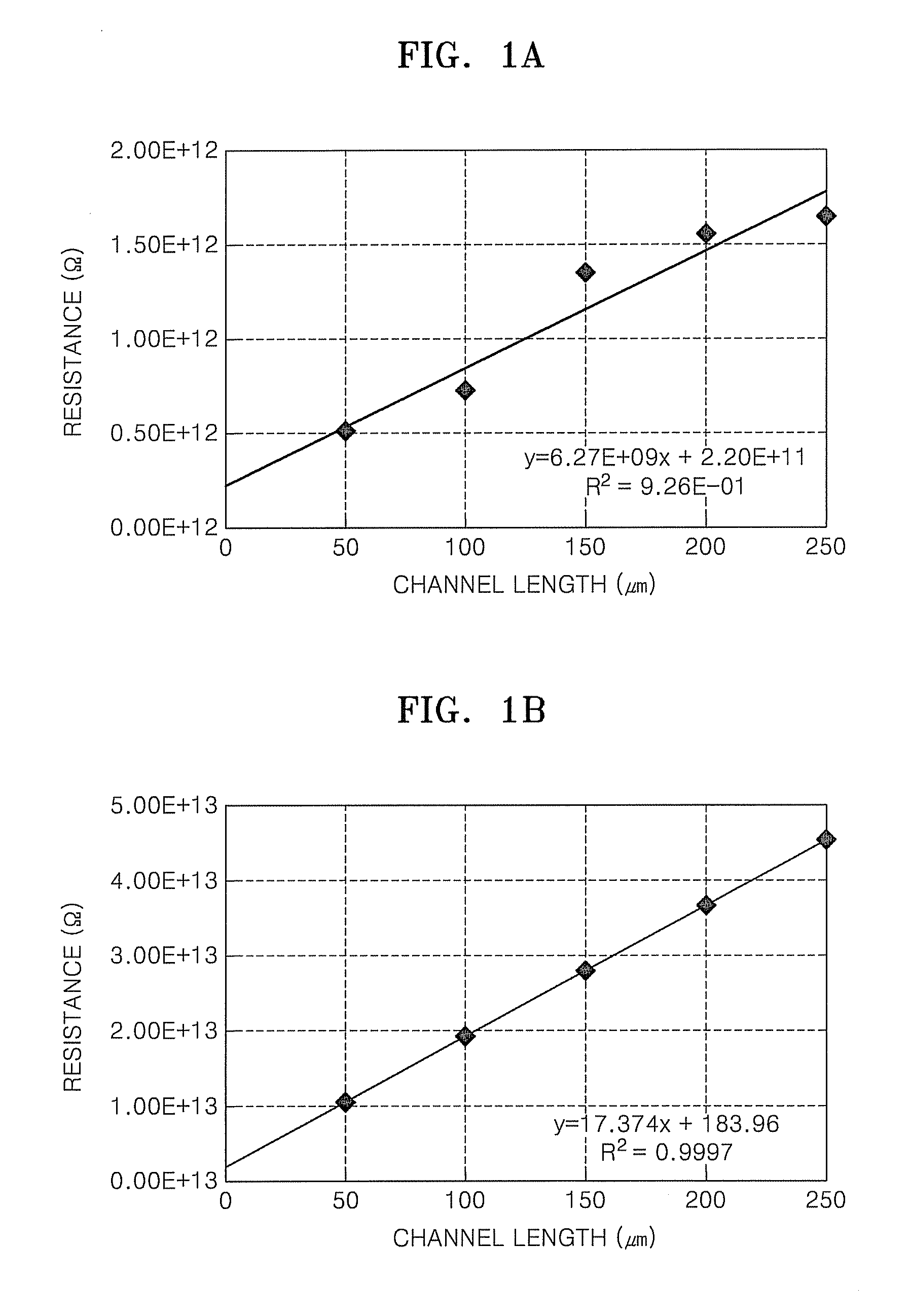

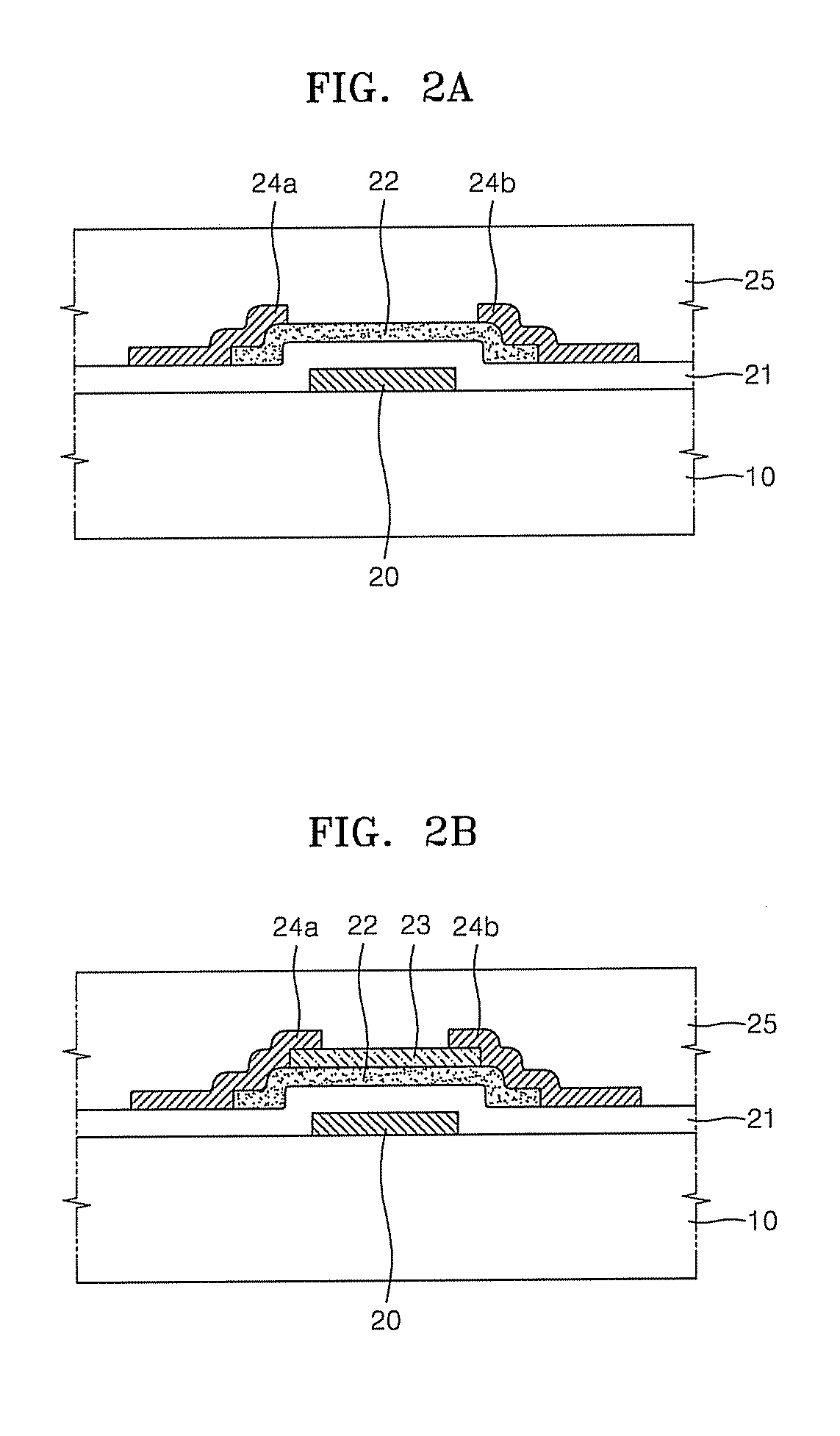

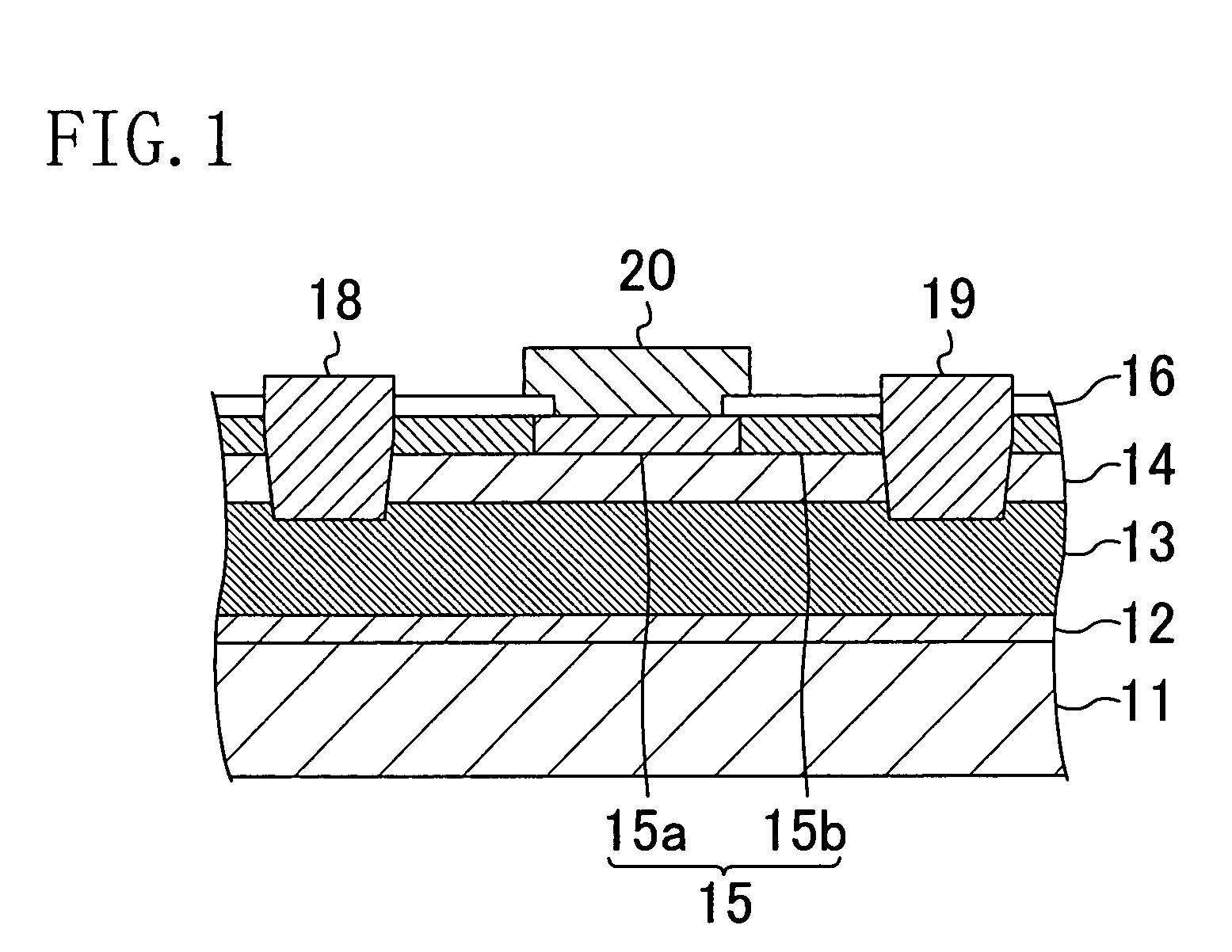

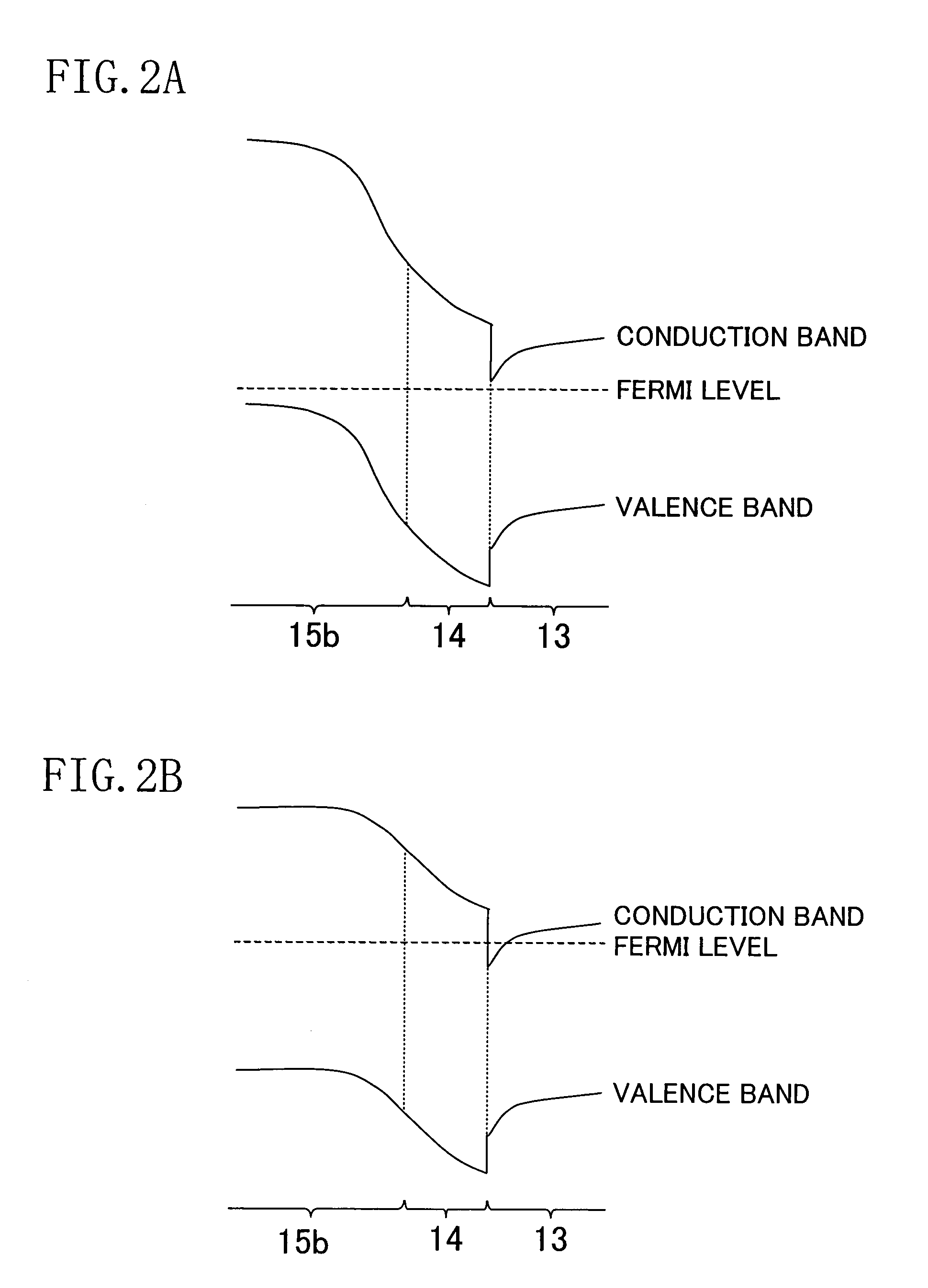

InactiveUS20080299702A1Reduce carrier concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesInterfacial reactionBottom gate

A ZnO-based thin film transistor (TFT) is provided herein. Also provided is a method for manufacturing the TFT. The ZnO-based TFT is very sensitive to the oxygen concentration present in a channel layer. In order to prevent damage to a channel layer of a bottom gate TFT, and to avoid a deep negative threshold voltage resulting from damage to the channel layer, the method for manufacturing the ZnO-based TFT comprises formation of an etch stop layer or a passivation layer comprising unstable or incompletely bonded oxygen, and annealing the layers to induce an interfacial reaction between the oxide layer and the channel layer and to reduce the carrier concentration.

Owner:SAMSUNG ELECTRONICS CO LTD

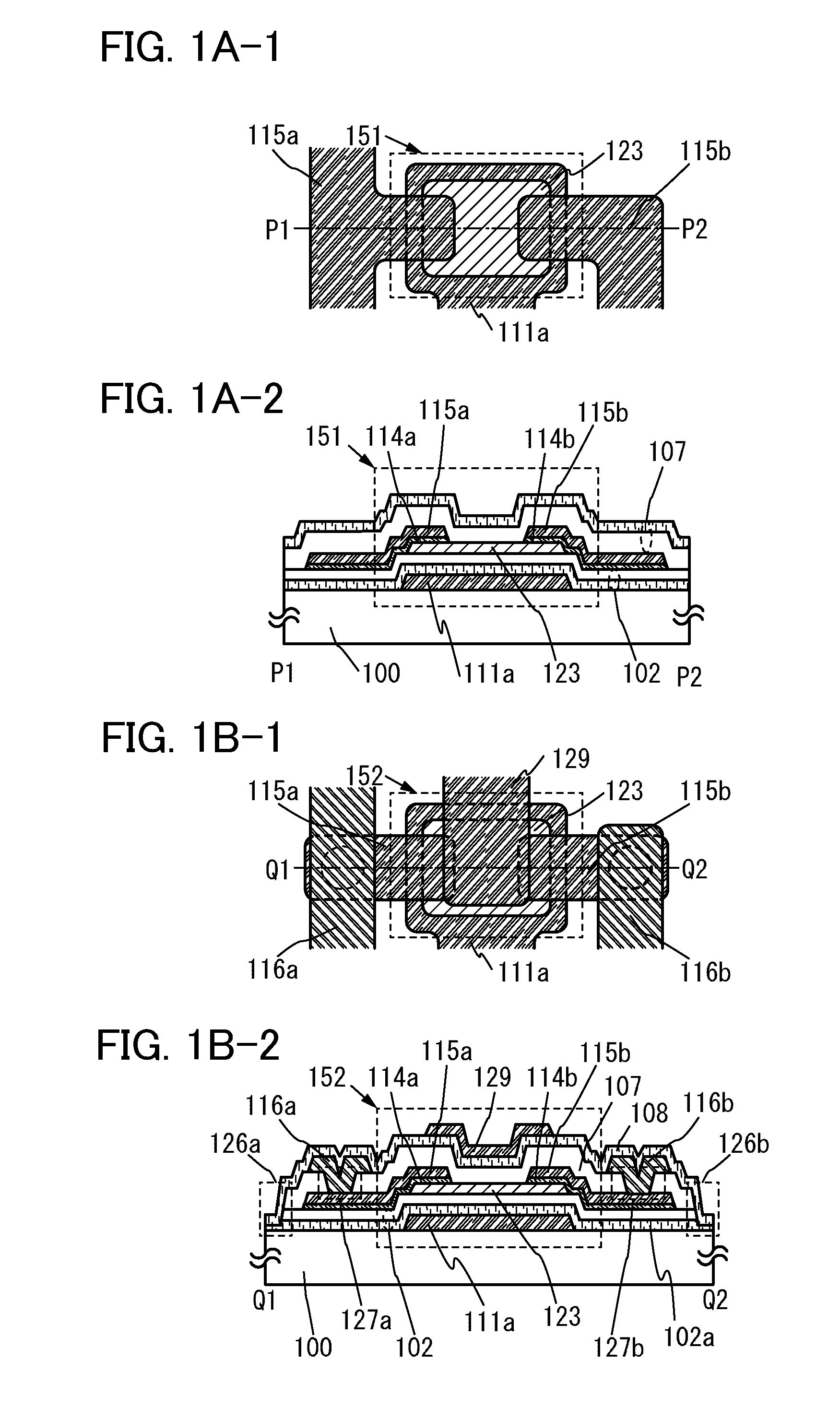

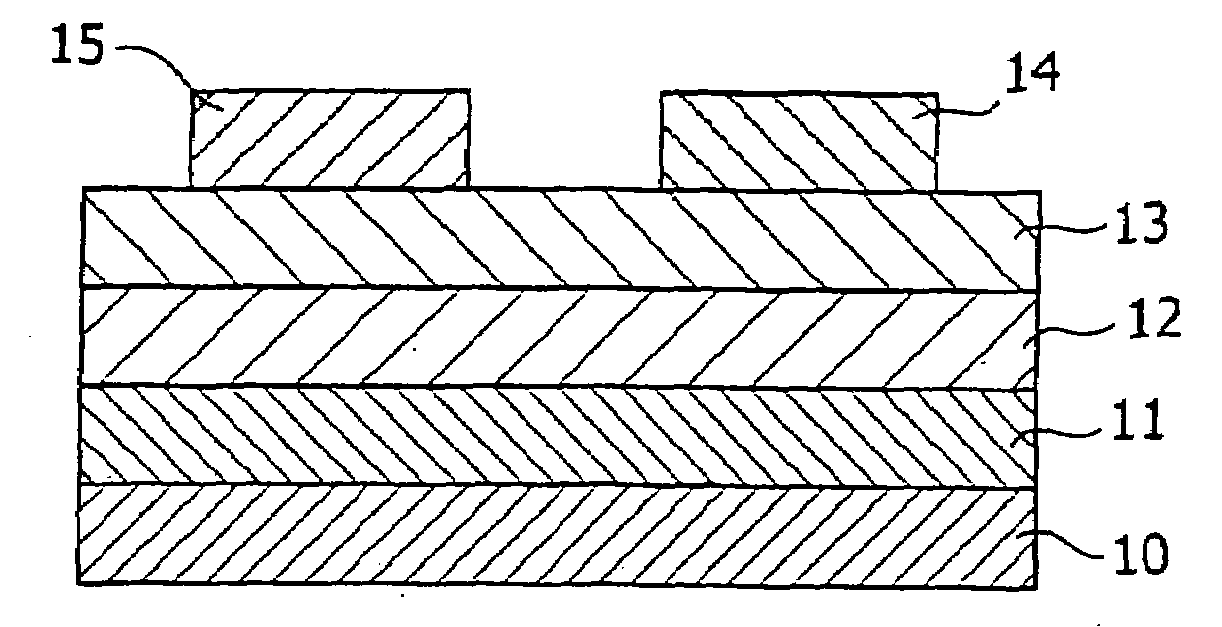

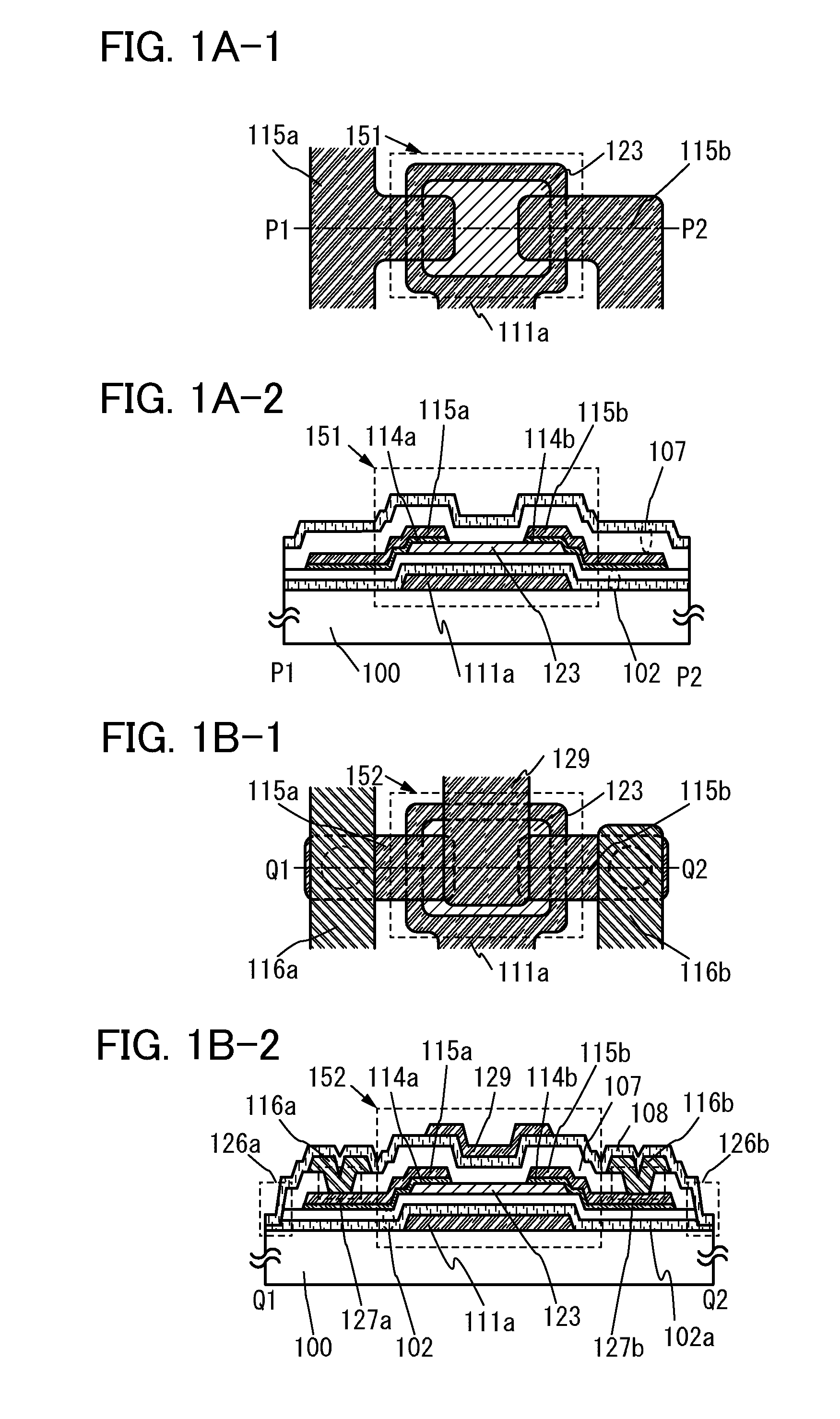

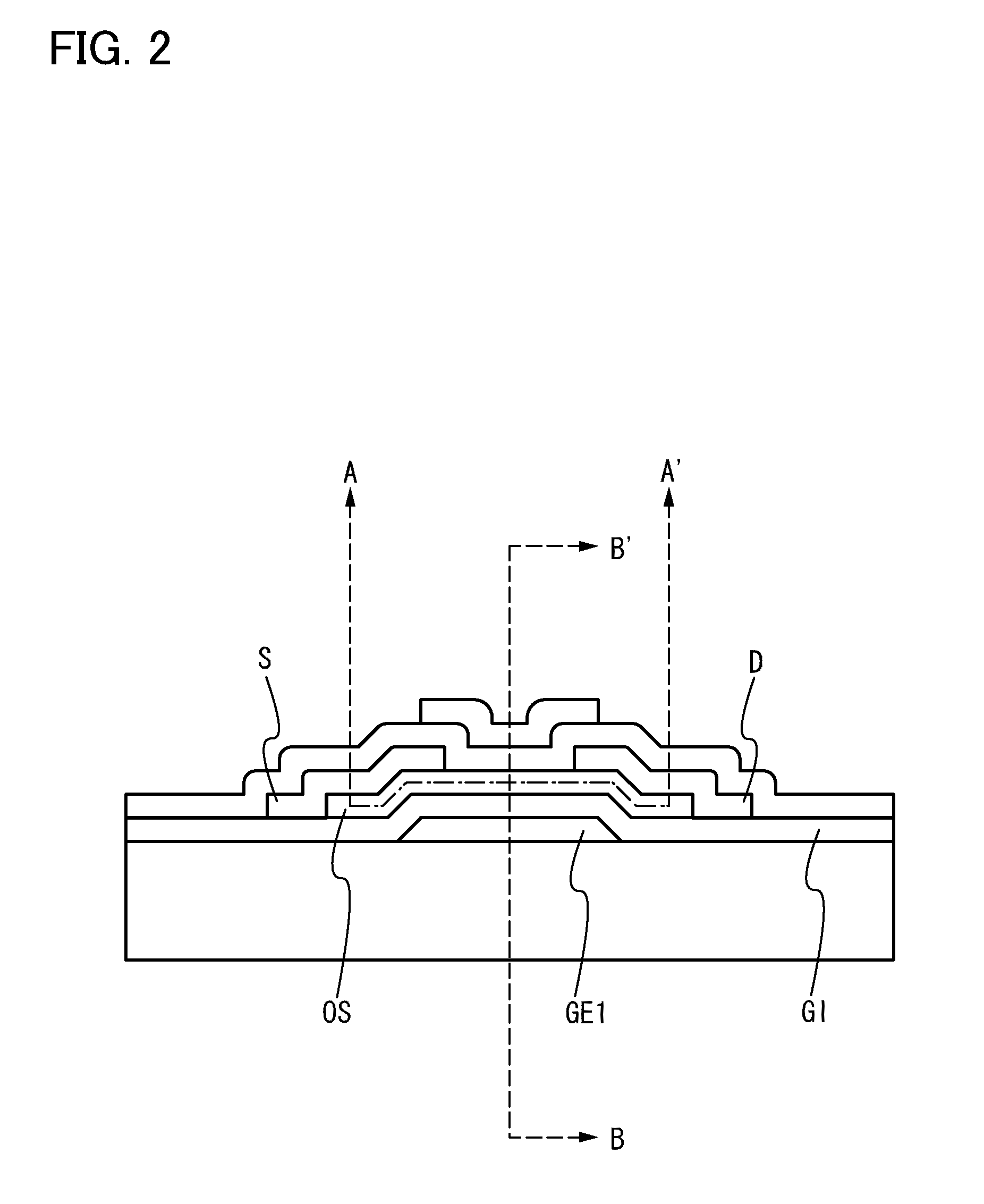

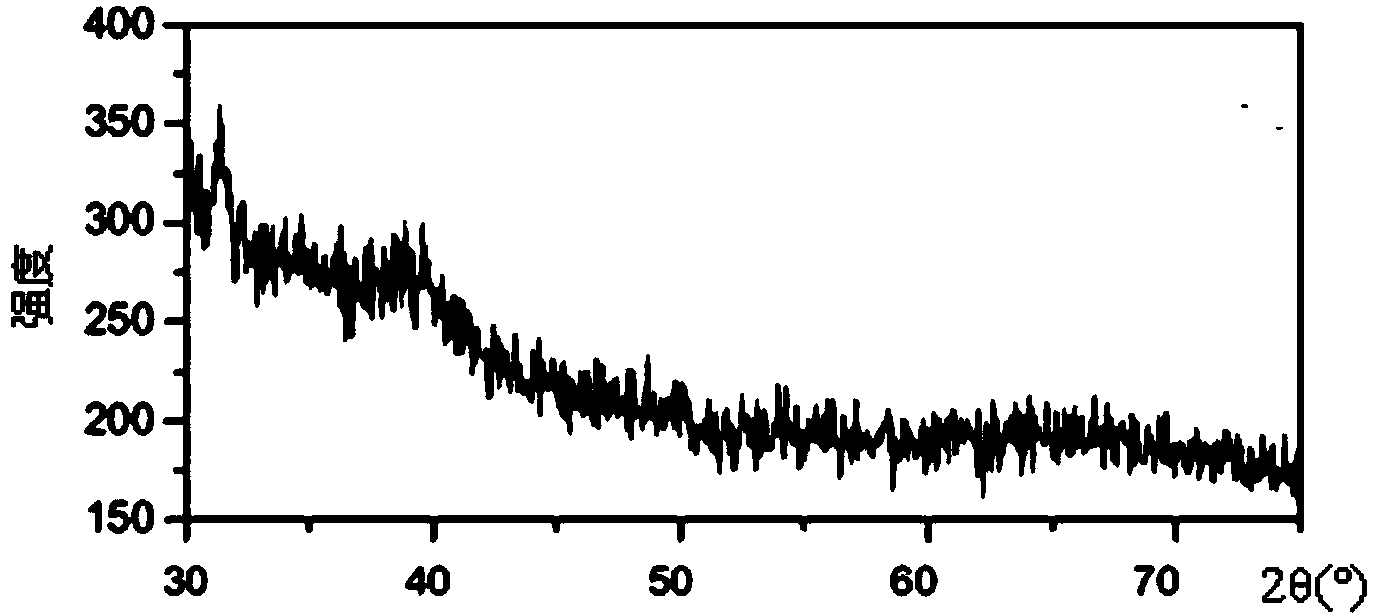

Oxide semiconductor, thin film transistor, and display device

ActiveUS20100102312A1Reduce defectsReduce carrier concentrationTransistorSolid-state devicesHydrogenDisplay device

An object is to control composition and a defect of an oxide semiconductor. Another object is to increase field effect mobility of a thin film transistor and to obtain a sufficient on-off ratio with off current suppressed. The oxide semiconductor is represented by InMO3(ZnO)n (M is one or a plurality of elements selected from Ga, Fe, Ni, Mn, Co, and Al, and n is a non-integer number of greater than or equal to 1 and less than 50) and further contains hydrogen. In this case, the concentration of Zn is made to be lower than the concentrations of In and M (M is one or a plurality of elements selected from Ga, Fe, Ni, Mn, Co, and Al). In addition, the oxide semiconductor has an amorphous structure. Here, n is preferably a non-integer number of greater than or equal to 50, more preferably less than 10.

Owner:SEMICON ENERGY LAB CO LTD

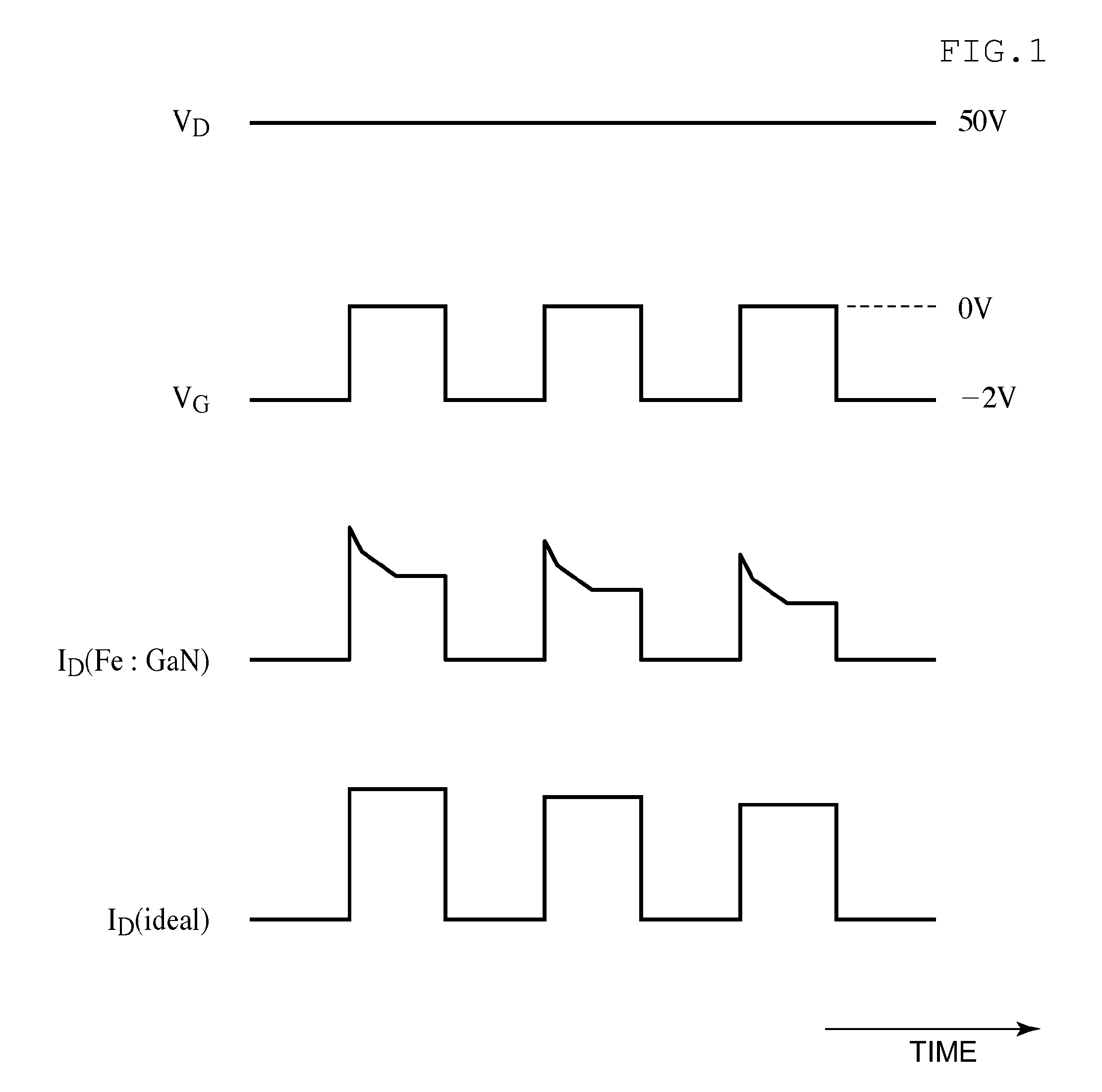

Nitride semiconductor device and method for fabricating the same

ActiveUS20080087915A1Large operating currentImprove switching characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesHigh resistanceWide band

A nitride semiconductor device includes: a first nitride semiconductor layer; a second nitride semiconductor layer formed on the first nitride semiconductor layer and having a wider band gap than the first nitride semiconductor layer; and a third nitride semiconductor layer formed on the second nitride semiconductor layer. A region of the third nitride semiconductor layer located below the gate electrode is formed with a control region having a p-type conductivity, and a region of the third nitride semiconductor layer located between the gate electrode and each of the source electrode and the drain electrode is formed with a high resistive region having a higher resistance than the that of the control region.

Owner:PANASONIC CORP

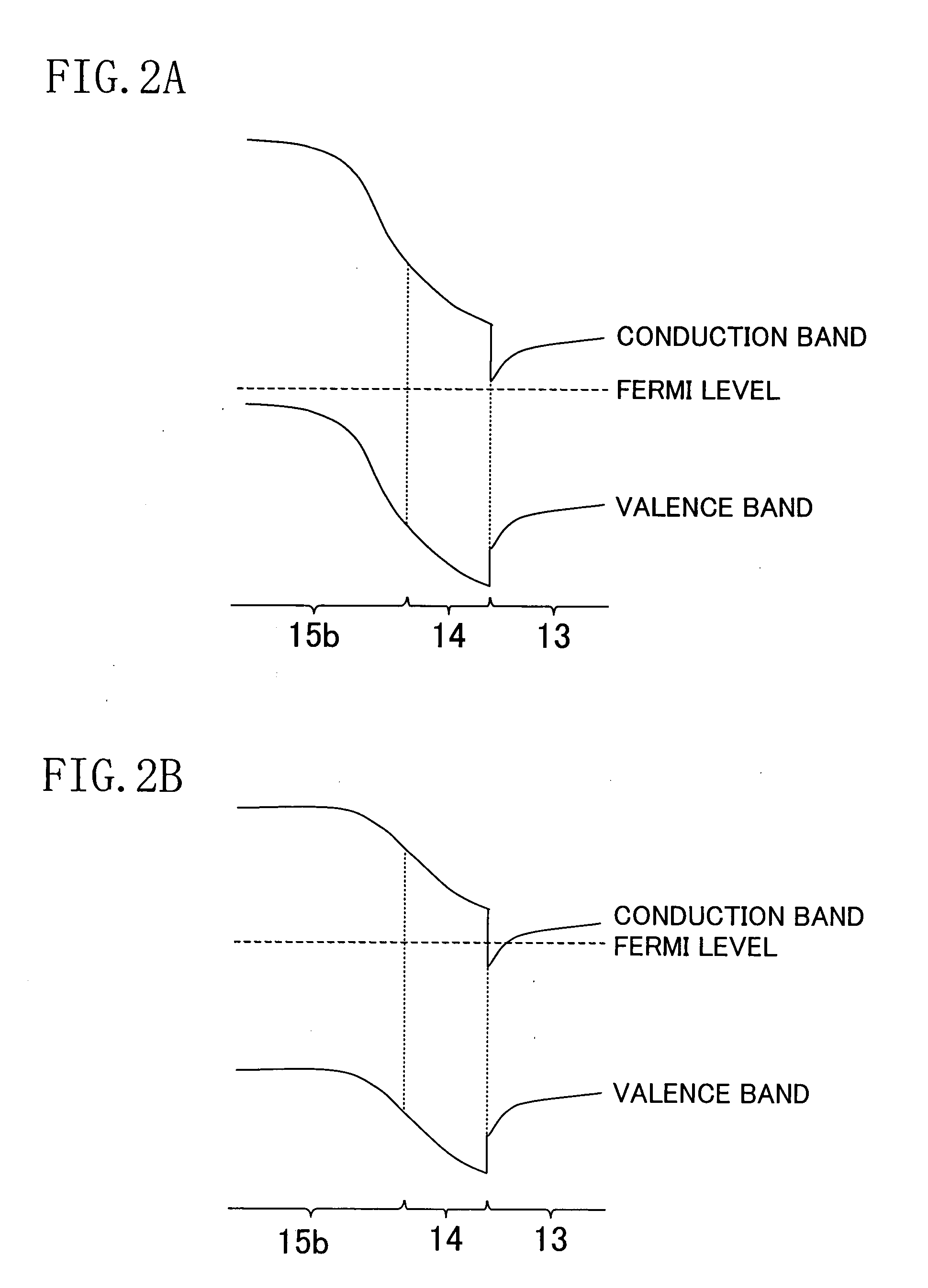

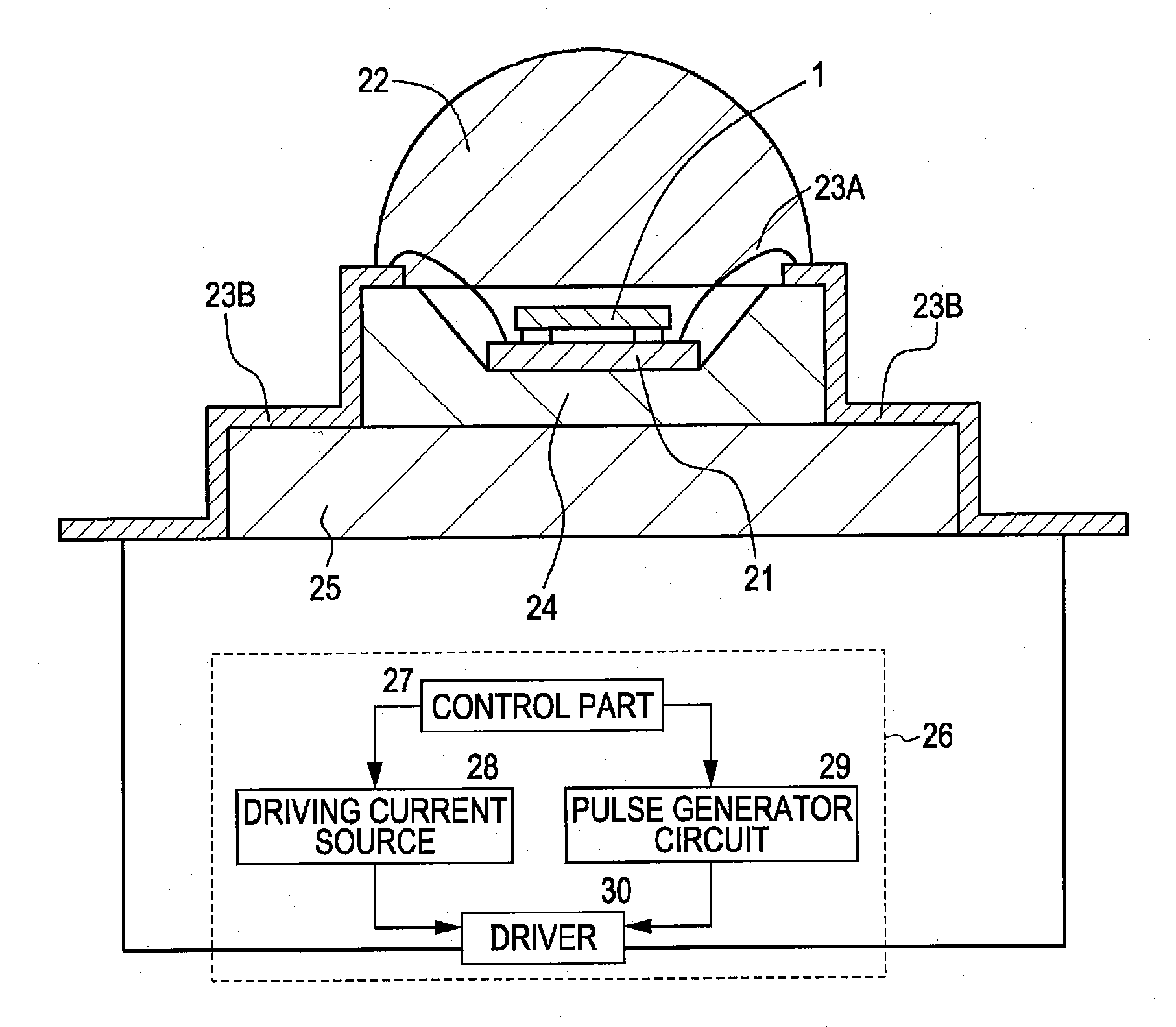

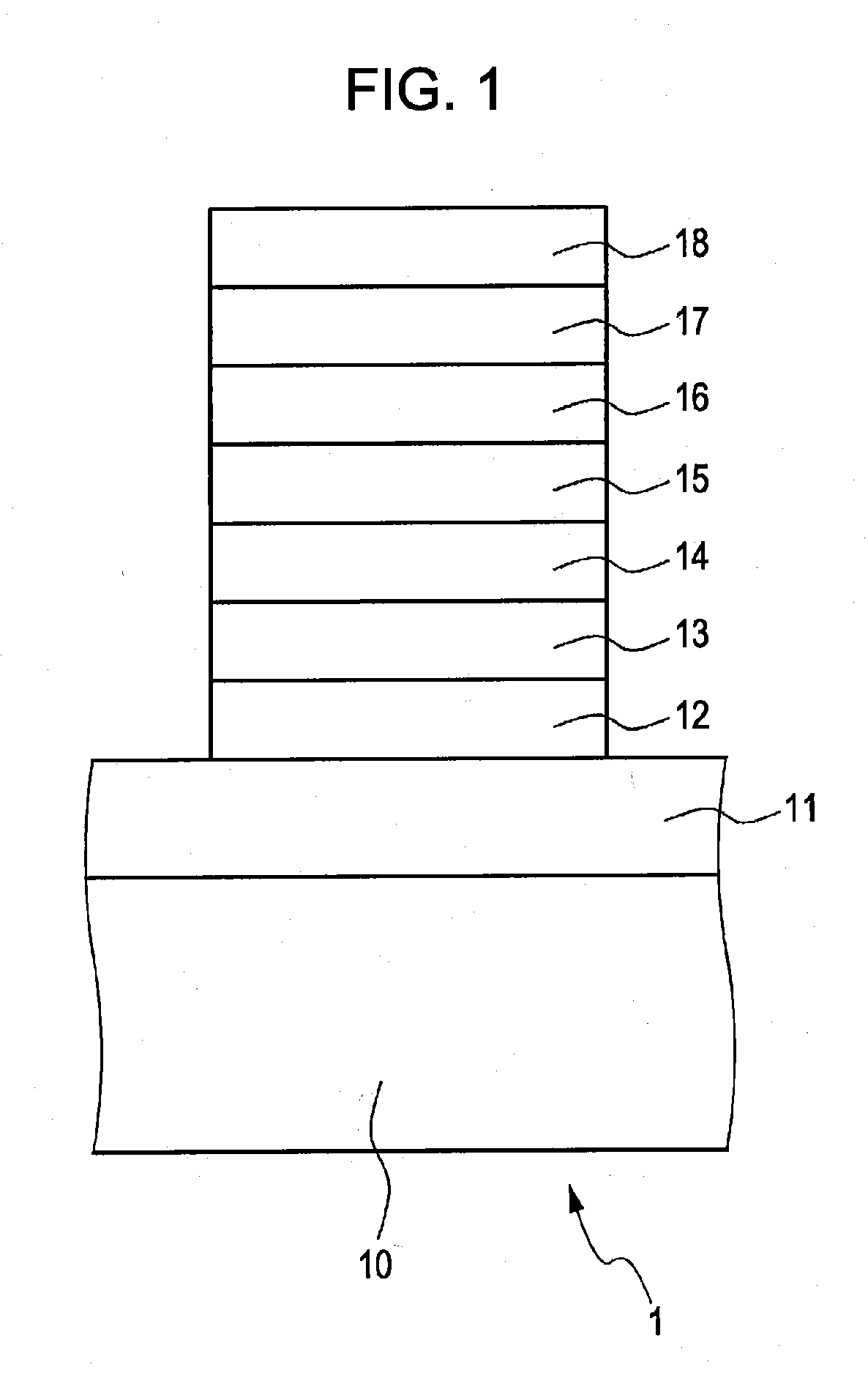

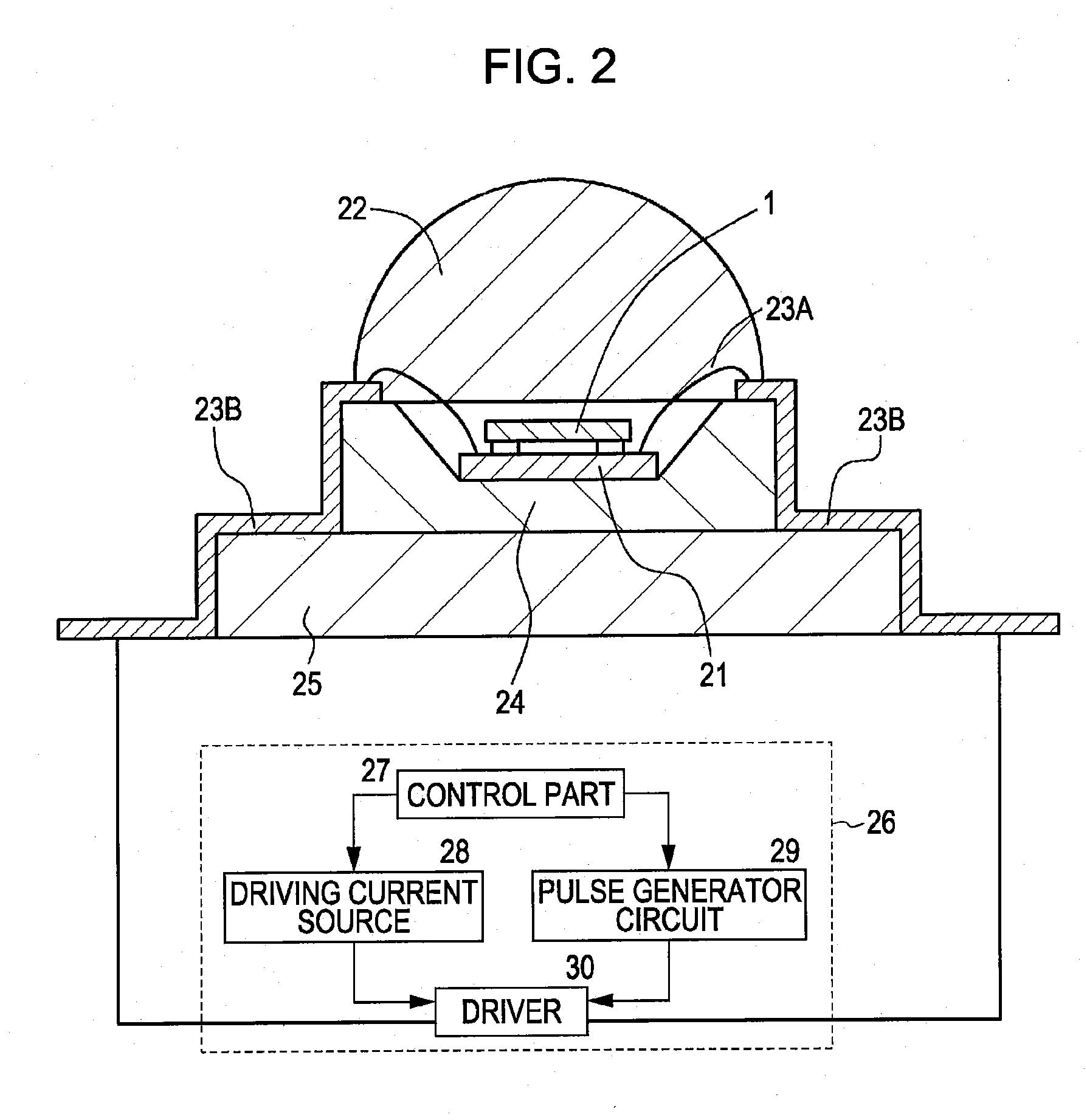

Gan-Based Semiconductor Light-Emitting Device, Light Illuminator, Image Display Planar Light Source Device, and Liquid Crystal Display Assembly

ActiveUS20070284564A1Suppress large shift of emission wavelengthIncrease in operating current densitySolid-state devicesNanoopticsLiquid-crystal displayQuantum well

A GaN-based semiconductor light-emitting device includes (A) a first GaN-based compound semiconductor layer 13 having n-type conductivity, (B) an active layer 15 having a multi-quantum well structure including well layers and barrier layers for separating between the well layers, and (C) a second GaN-based compound semiconductor layer 17 having p-type conductivity. The well layers are disposed in the active layer 15 so as to satisfy the relation d1<d2 wherein d1 is the well layer density on the first GaN-based compound semiconductor layer side in the active layer and d2 is the well layer density on the second GaN-based compound semiconductor layer side.

Owner:SONY SEMICON SOLUTIONS CORP

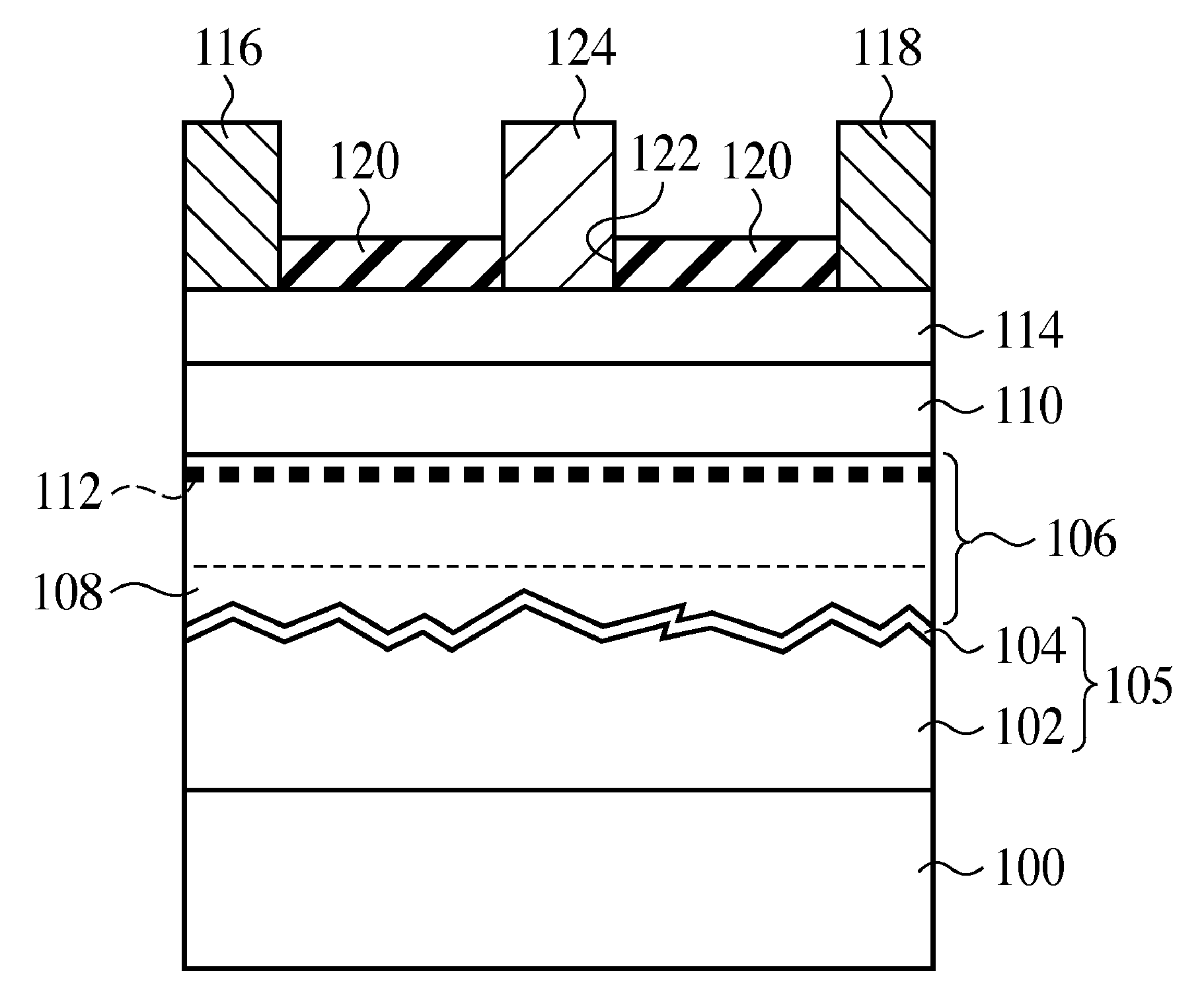

Compound semiconductor device and method of manufacturing the same

ActiveUS20080197359A1Reduce carrier concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesCompound (substance)Engineering

A compound semiconductor device has a buffer layer formed on a conductive SiC substrate, an AlxGa1-xN layer formed on the buffer layer in which an impurity for reducing carrier concentration from an unintentionally doped donor impurity is added and in which the Al composition x is 0<x<1, a GaN-based carrier transit layer formed on the AlxGa1-xN layer, a carrier supply layer formed on the carrier transit layer, a source electrode and a drain electrode formed on the carrier supply layer, and a gate electrode formed on the carrier supply layer between the source electrode and the drain electrode. Therefore, a GaN-HEMT that is superior in device characteristics can be realized in the case of using a relatively less expensive conductive SiC substrate compared with a semi-insulating SiC substrate.

Owner:FUJITSU LTD

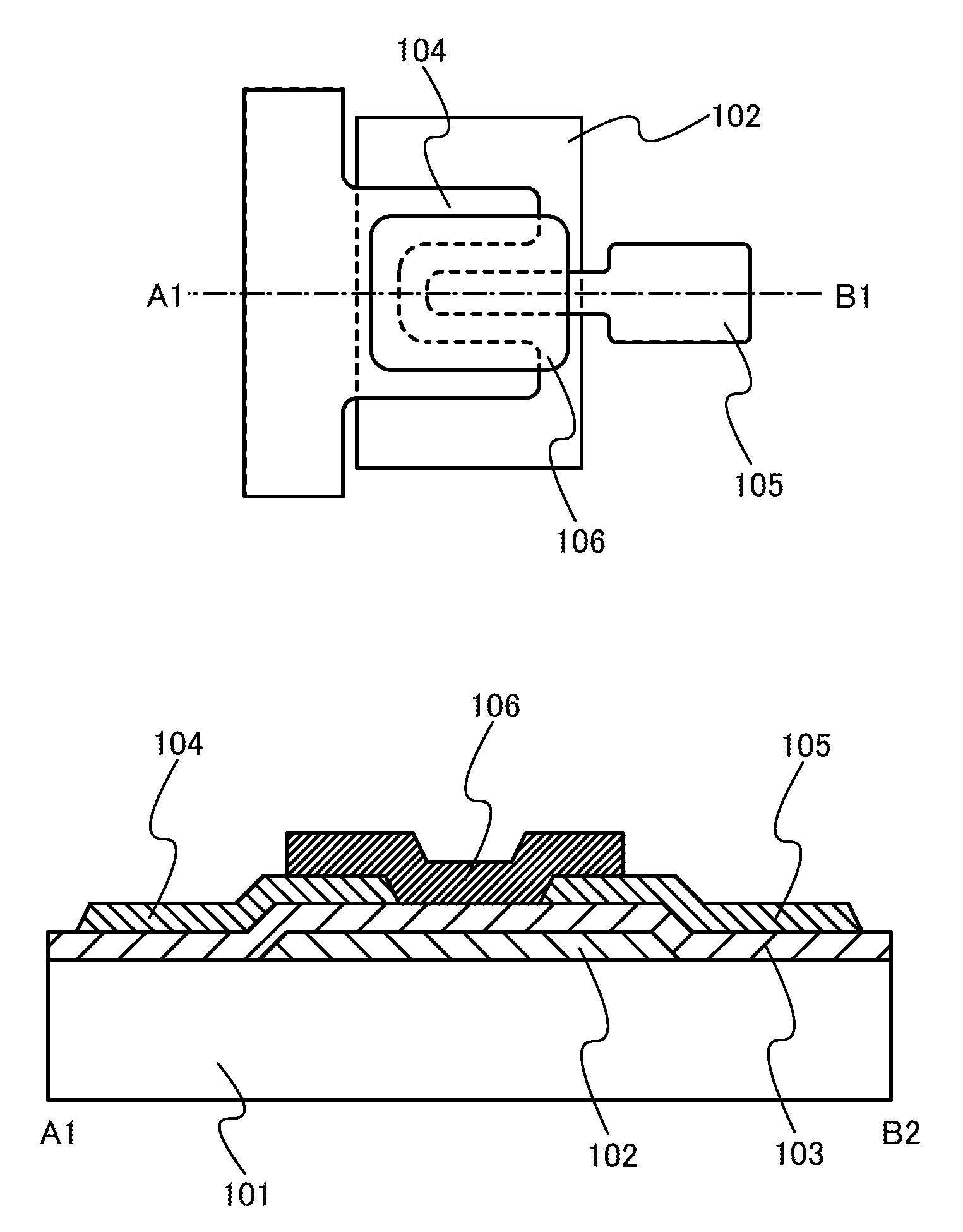

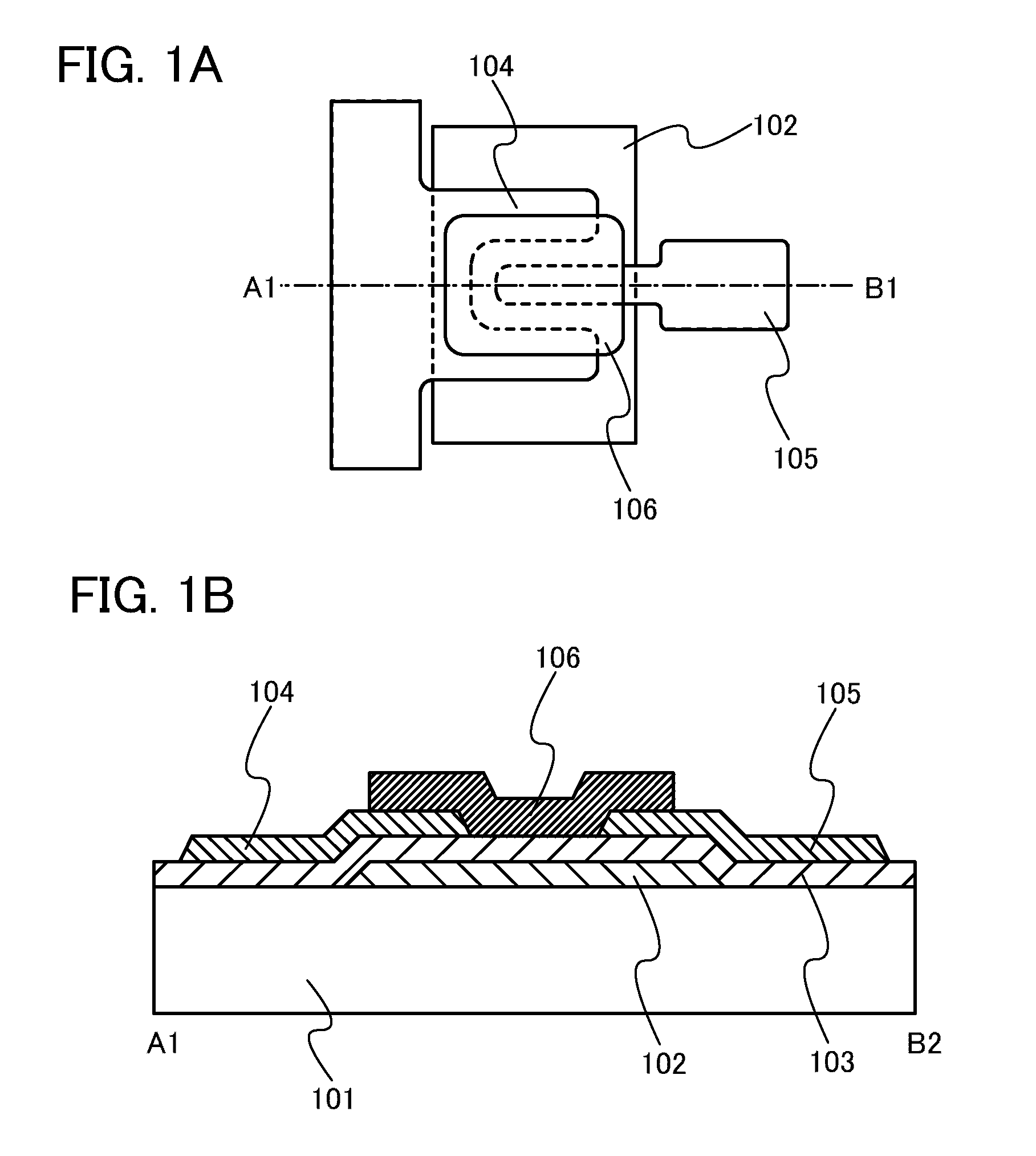

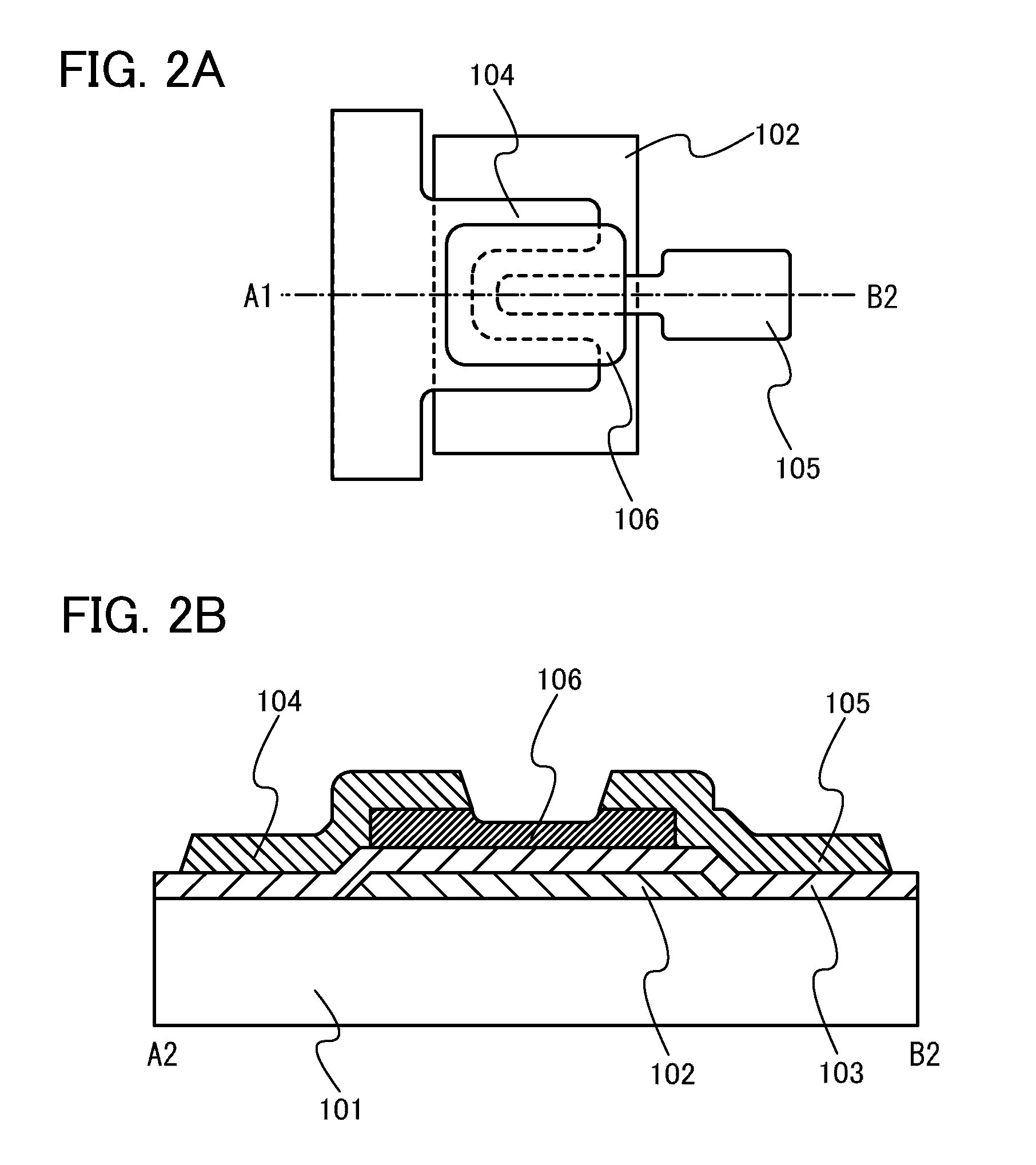

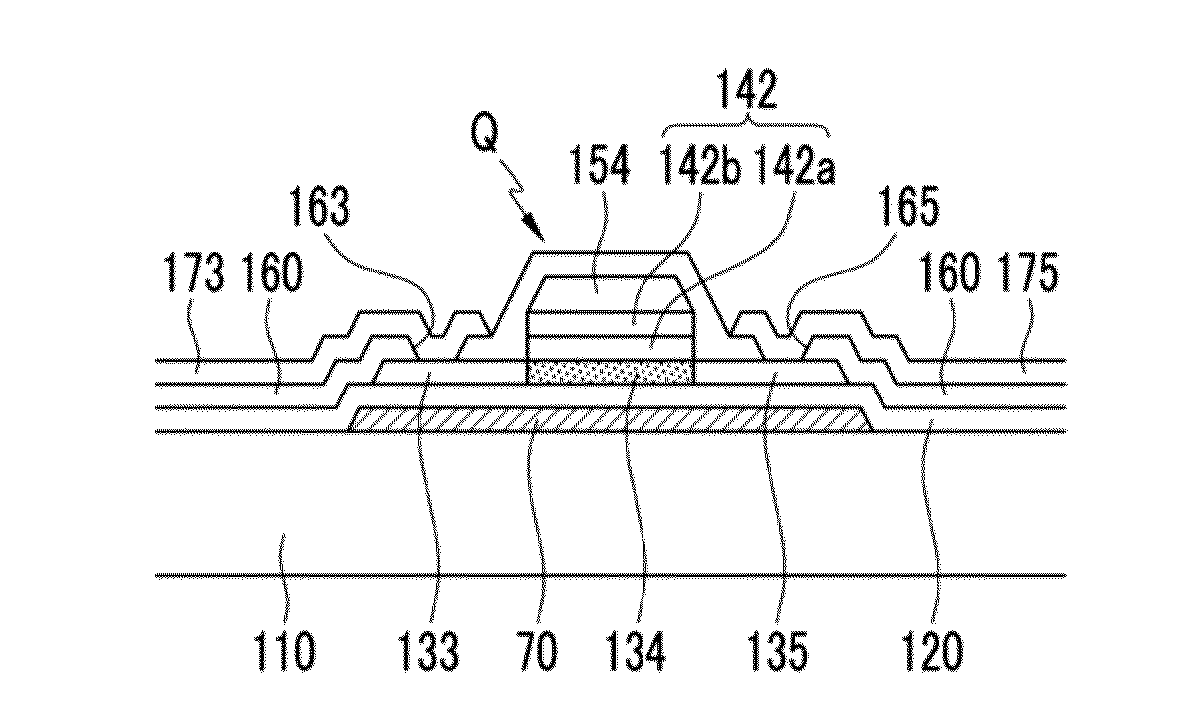

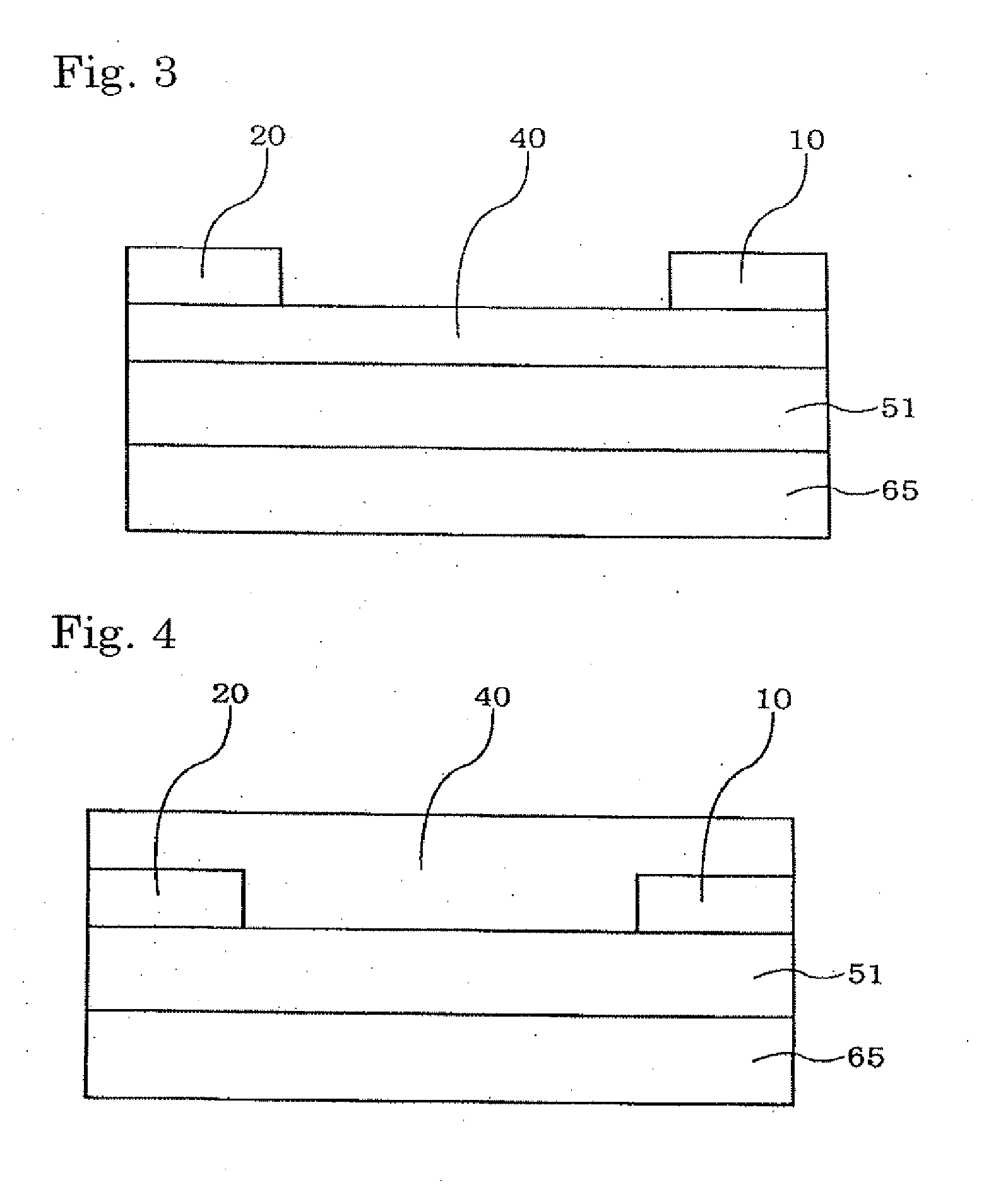

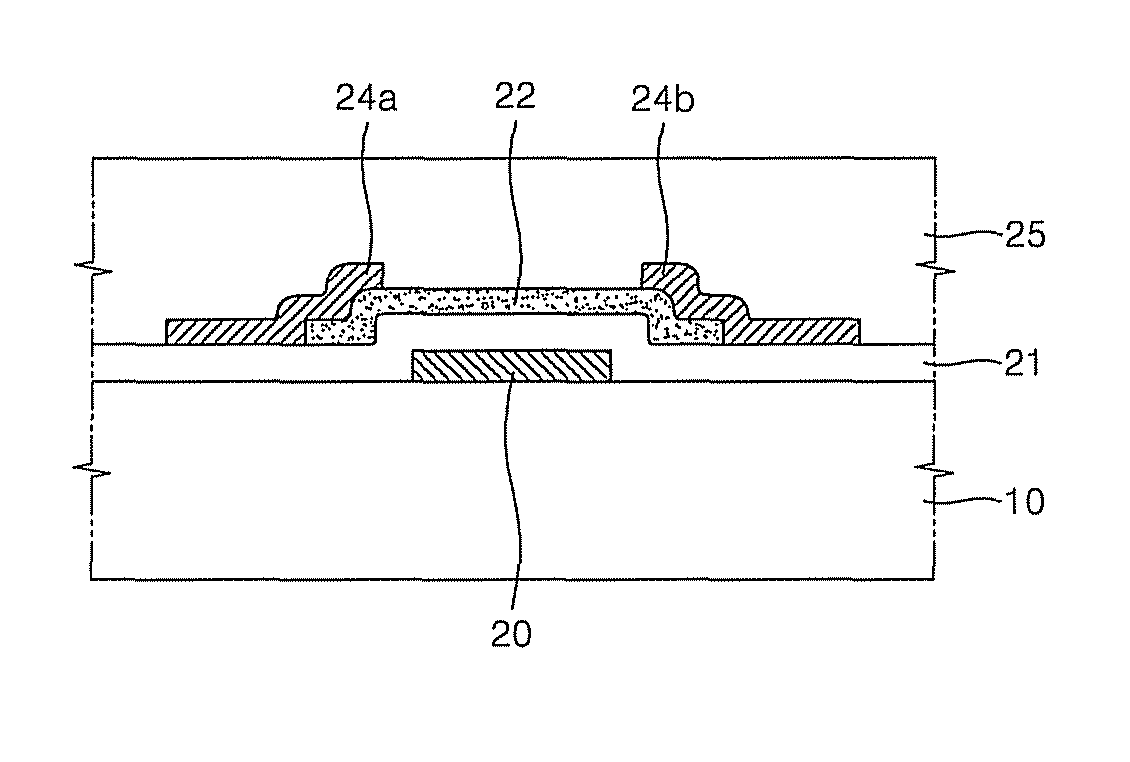

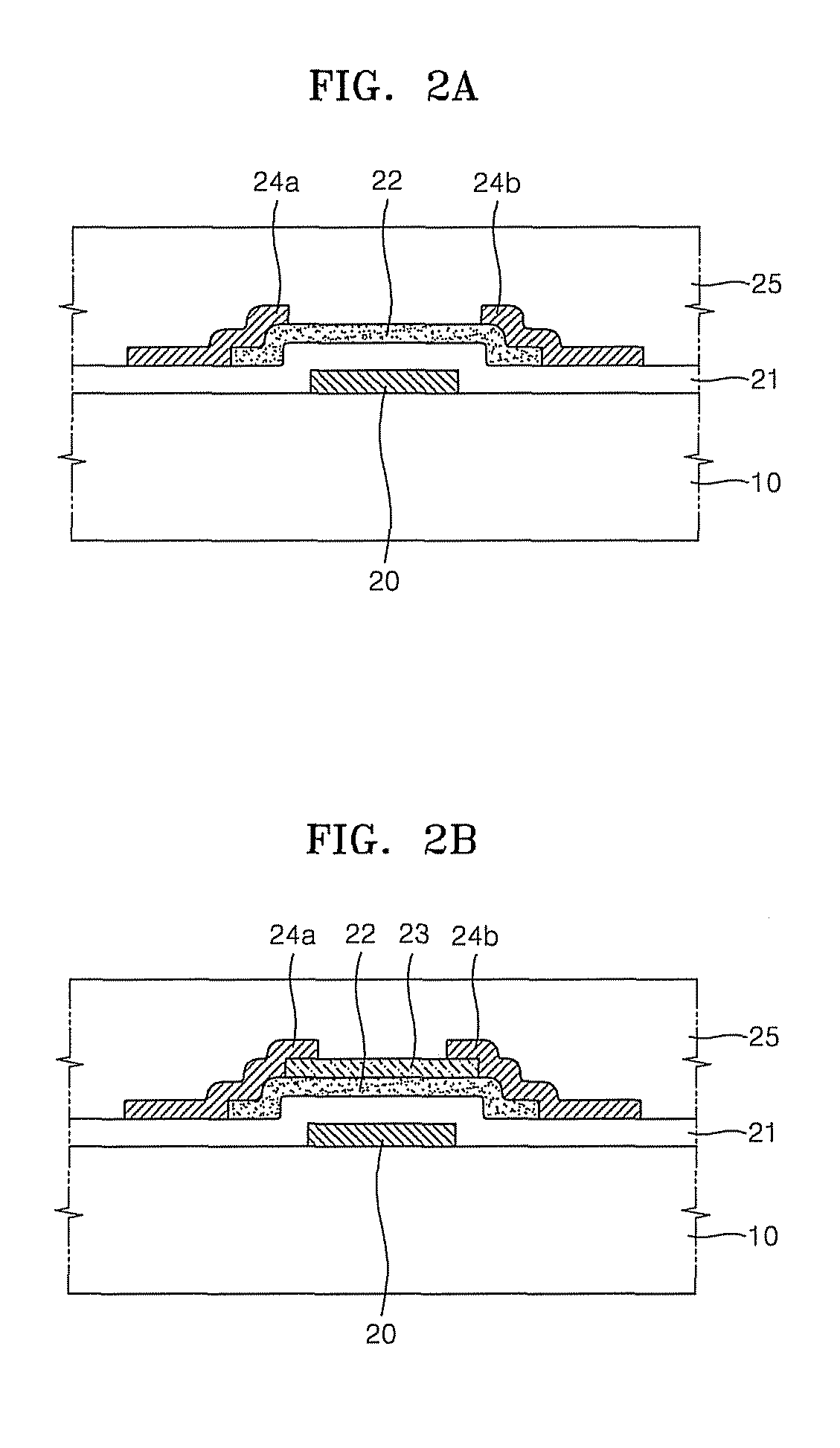

Thin film transistor, thin film transistor array panel including the same, and method of manufacturing the same

ActiveUS20140167040A1Reduce carrier concentrationTransistorSolid-state devicesEngineeringSemiconductor

A thin film transistor according to an exemplary embodiment of the present invention includes an oxide semiconductor. A source electrode and a drain electrode face each other. The source electrode and the drain electrode are positioned at two opposite sides, respectively, of the oxide semiconductor. A low conductive region is positioned between the source electrode or the drain electrode and the oxide semiconductor. An insulating layer is positioned on the oxide semiconductor and the low conductive region. A gate electrode is positioned on the insulating layer. The insulating layer covers the oxide semiconductor and the low conductive region. A carrier concentration of the low conductive region is lower than a carrier concentration of the source electrode or the drain electrode.

Owner:SAMSUNG DISPLAY CO LTD

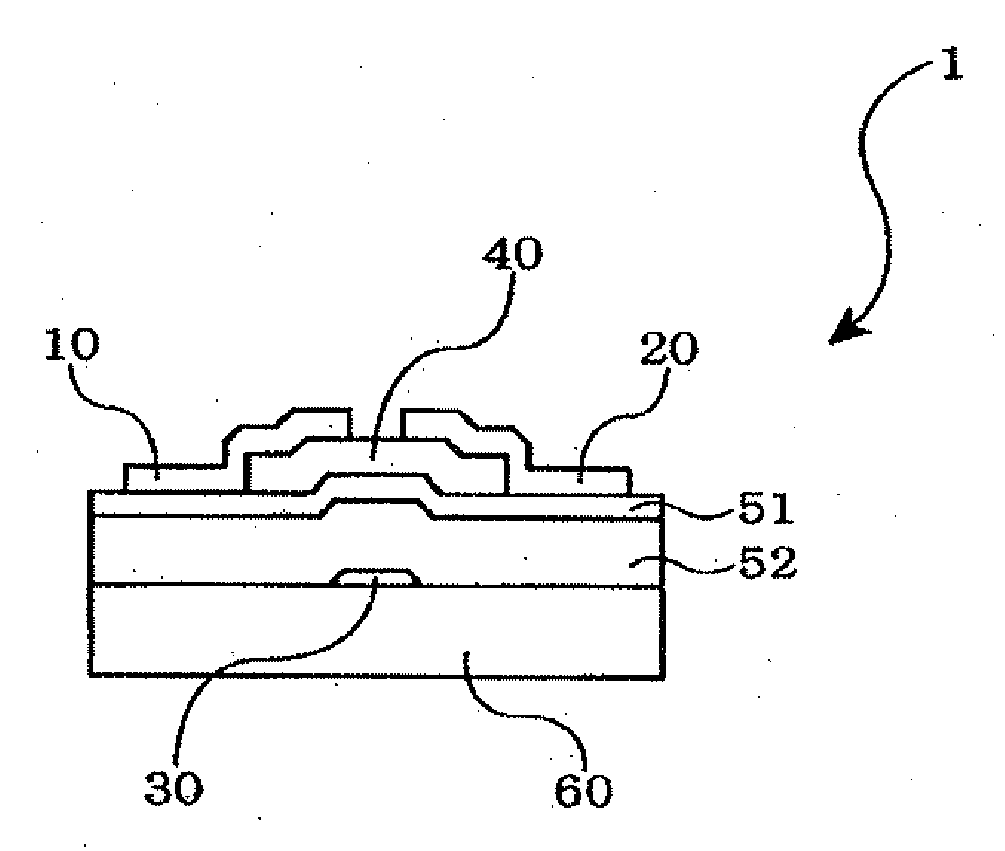

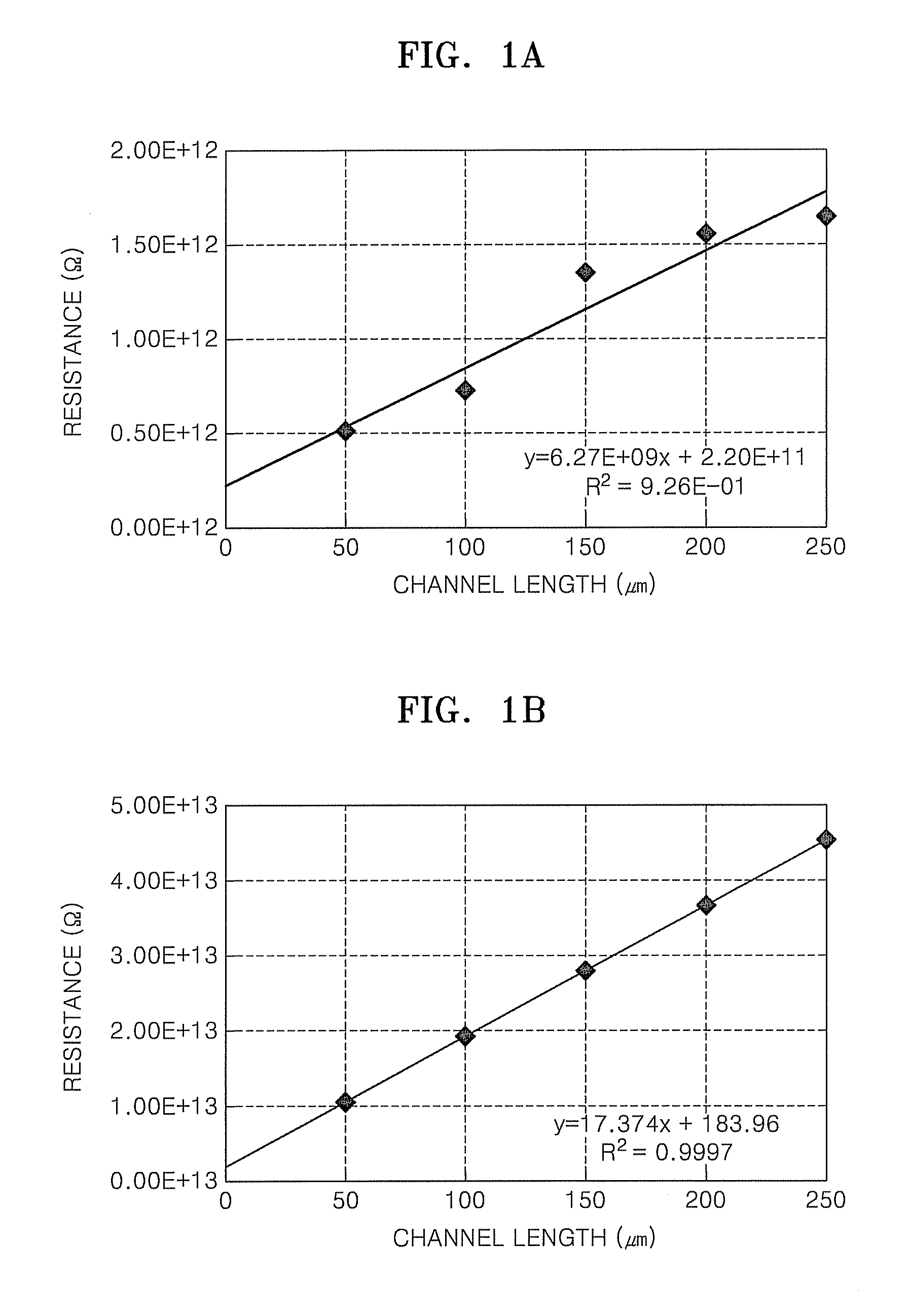

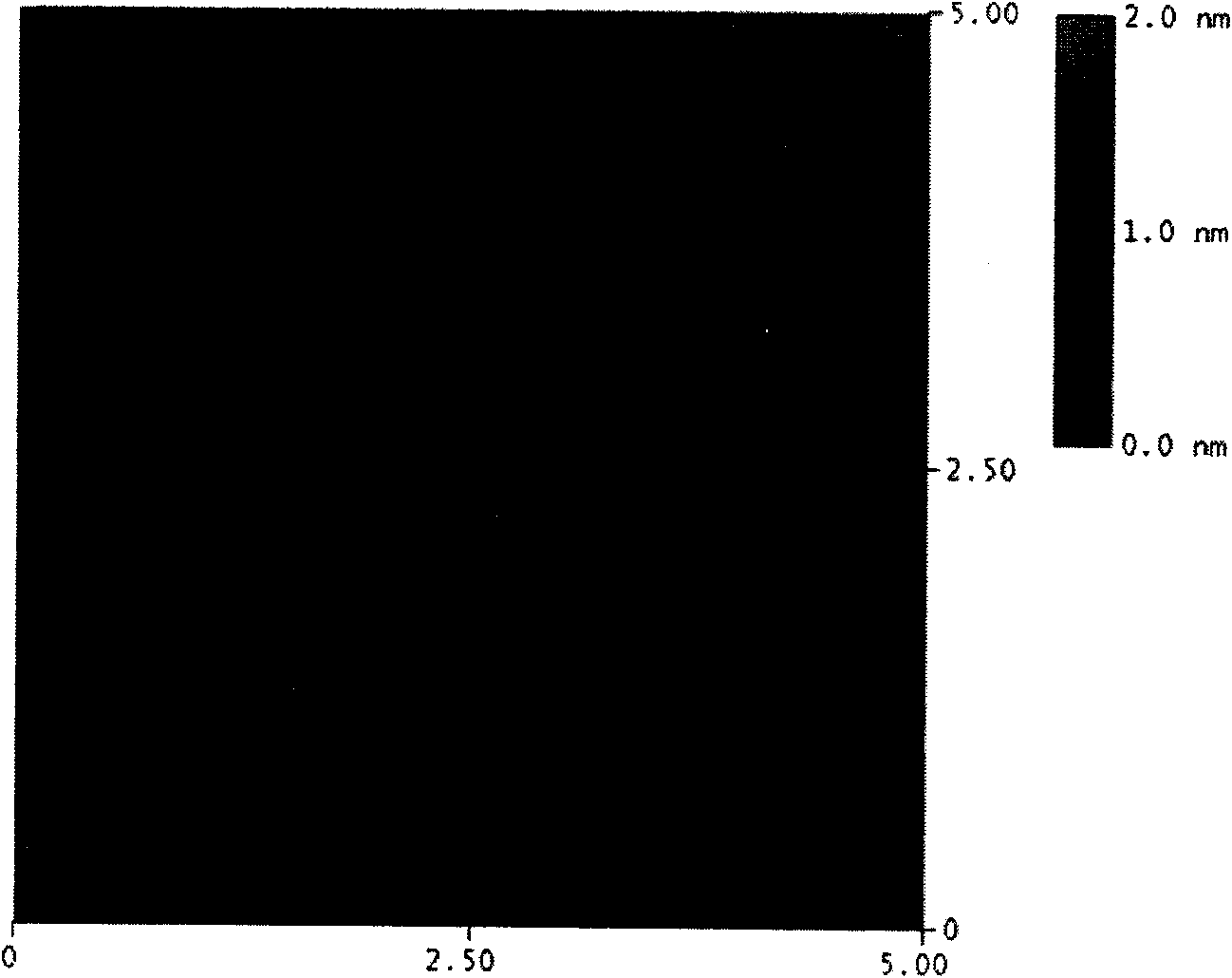

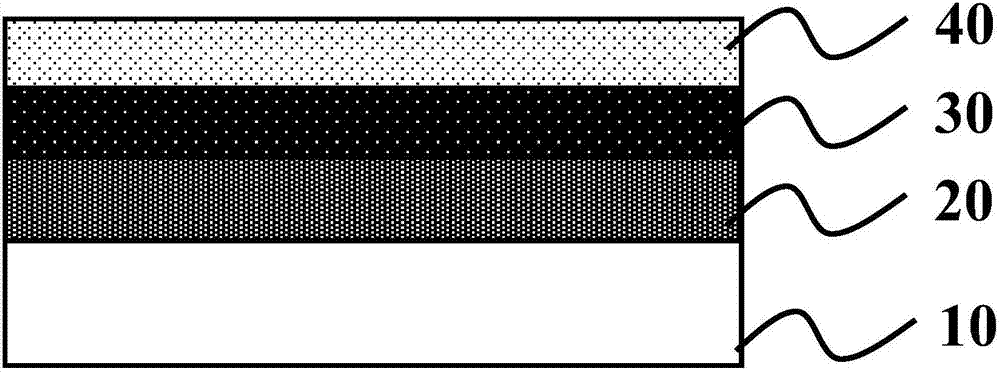

Semiconductor thin film, method for producing the same, and thin film transistor

InactiveUS20130221348A1Improve mobilityReduce carrier concentrationTransistorTin compoundsIndiumSemiconductor

Owner:IDEMITSU KOSAN CO LTD

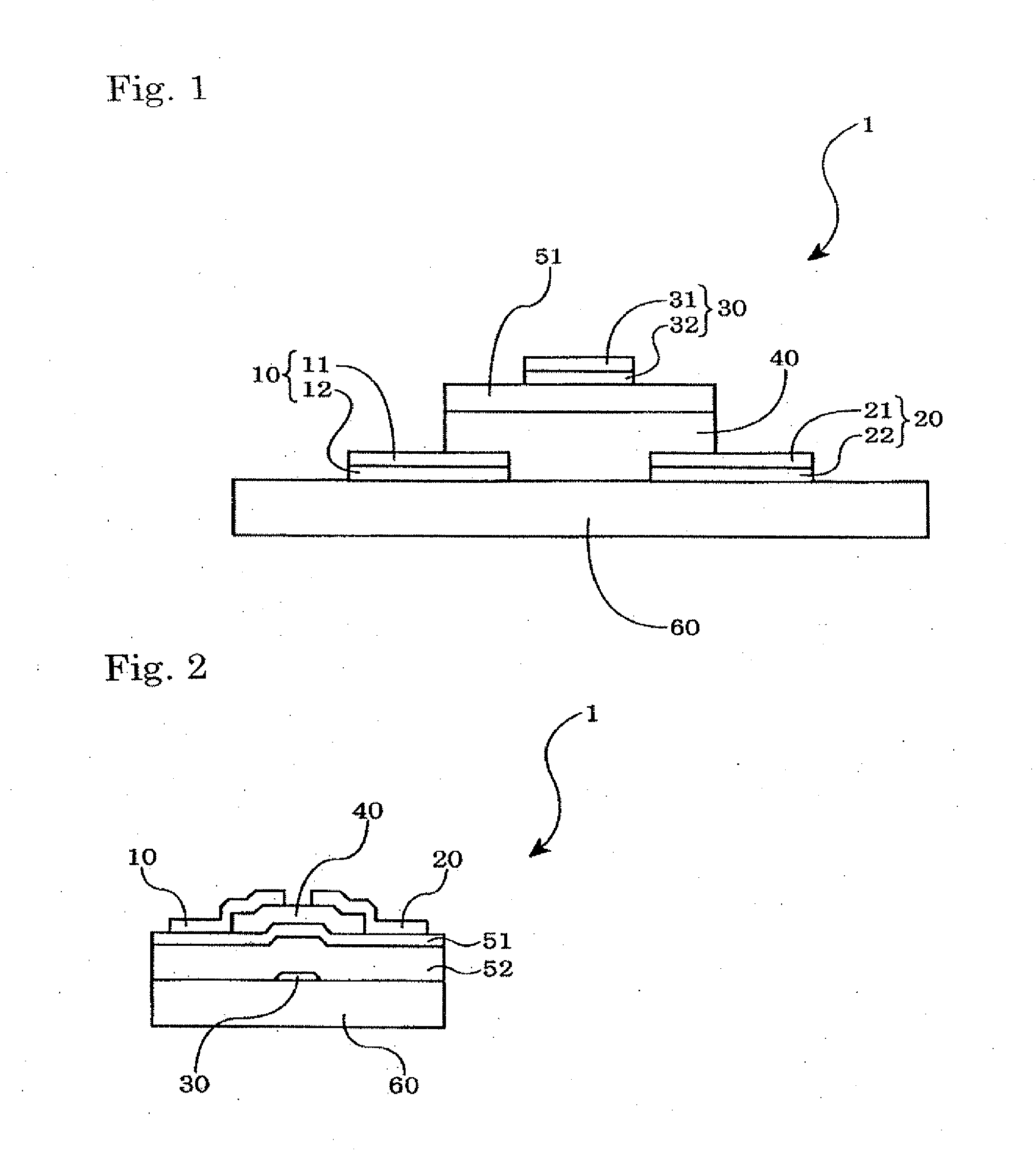

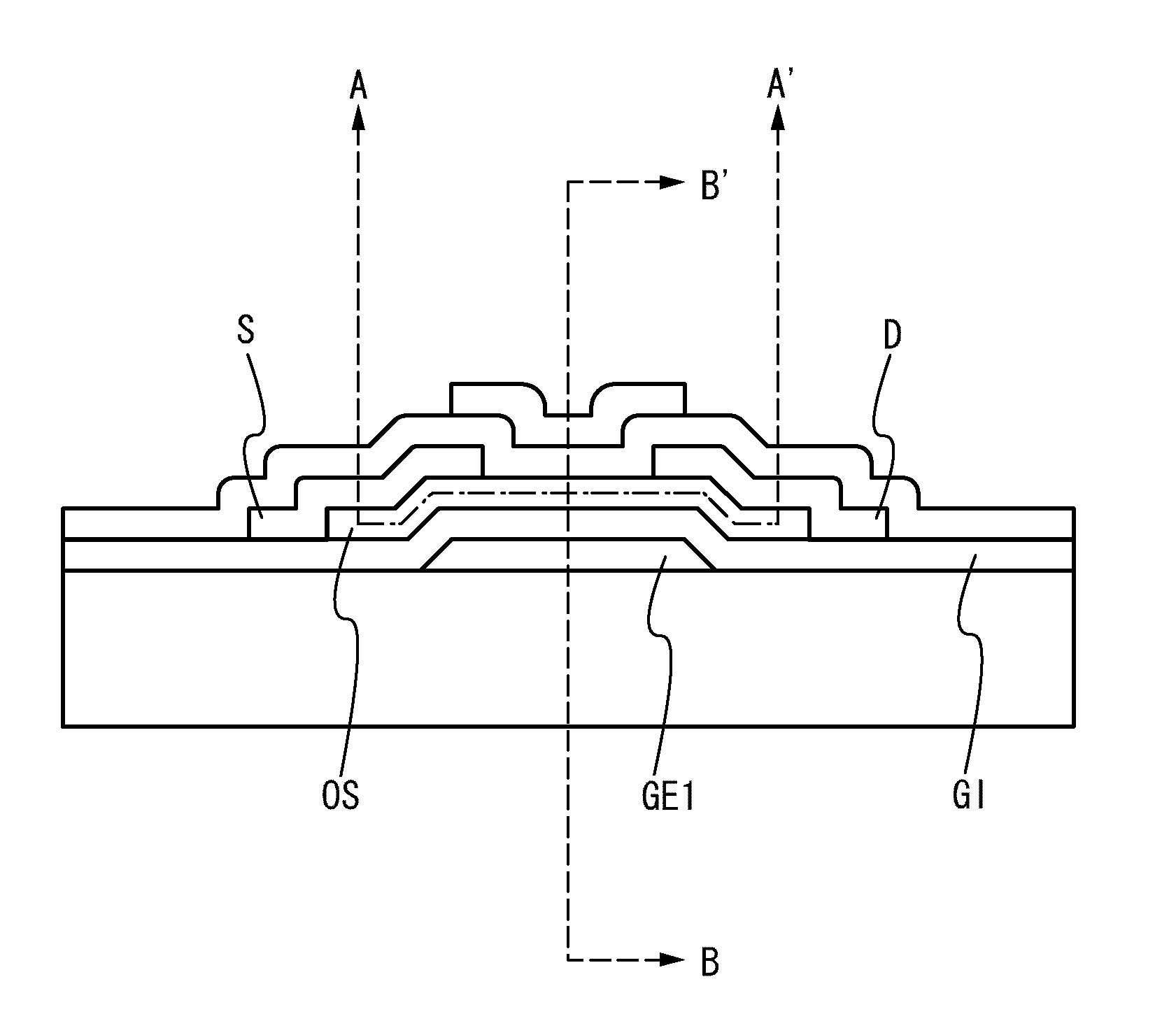

Semiconductor device and manufacturing method thereof

ActiveUS20110140109A1Small off-currentImprove reliabilityTransistorSolid-state devicesElectrical conductorHydrogen

A semiconductor device includes an oxide semiconductor layer including a channel formation region which includes an oxide semiconductor having a wide band gap and a carrier concentration which is as low as possible, and a source electrode and a drain electrode which include an oxide conductor containing hydrogen and oxygen vacancy, and a barrier layer which prevents diffusion of hydrogen and oxygen between an oxide conductive layer and the oxide semiconductor layer. The oxide conductive layer and the oxide semiconductor layer are electrically connected to each other through the barrier layer.

Owner:SEMICON ENERGY LAB CO LTD

Nitride semiconductor device and method for fabricating the same

ActiveUS8129748B2Large operating currentImprove switching characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceHigh resistance

A nitride semiconductor device includes: a first nitride semiconductor layer; a second nitride semiconductor layer formed on the first nitride semiconductor layer and having a wider band gap than the first nitride semiconductor layer; and a third nitride semiconductor layer formed on the second nitride semiconductor layer. A region of the third nitride semiconductor layer located below the gate electrode is formed with a control region having a p-type conductivity, and a region of the third nitride semiconductor layer located between the gate electrode and each of the source electrode and the drain electrode is formed with a high resistive region having a higher resistance than the that of the control region.

Owner:PANASONIC CORP

Method of manufacturing ZnO-based thin film transistor

InactiveUS8735229B2Reduce carrier concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesInterfacial reactionBottom gate

A ZnO-based thin film transistor (TFT) is provided herein. Also provided is a method for manufacturing the TFT. The ZnO-based TFT is very sensitive to the oxygen concentration present in a channel layer. In order to prevent damage to a channel layer of a bottom gate TFT, and to avoid a deep negative threshold voltage resulting from damage to the channel layer, the method for manufacturing the ZnO-based TFT comprises formation of an etch stop layer or a passivation layer comprising unstable or incompletely bonded oxygen, and annealing the layers to induce an interfacial reaction between the oxide layer and the channel layer and to reduce the carrier concentration.

Owner:SAMSUNG ELECTRONICS CO LTD

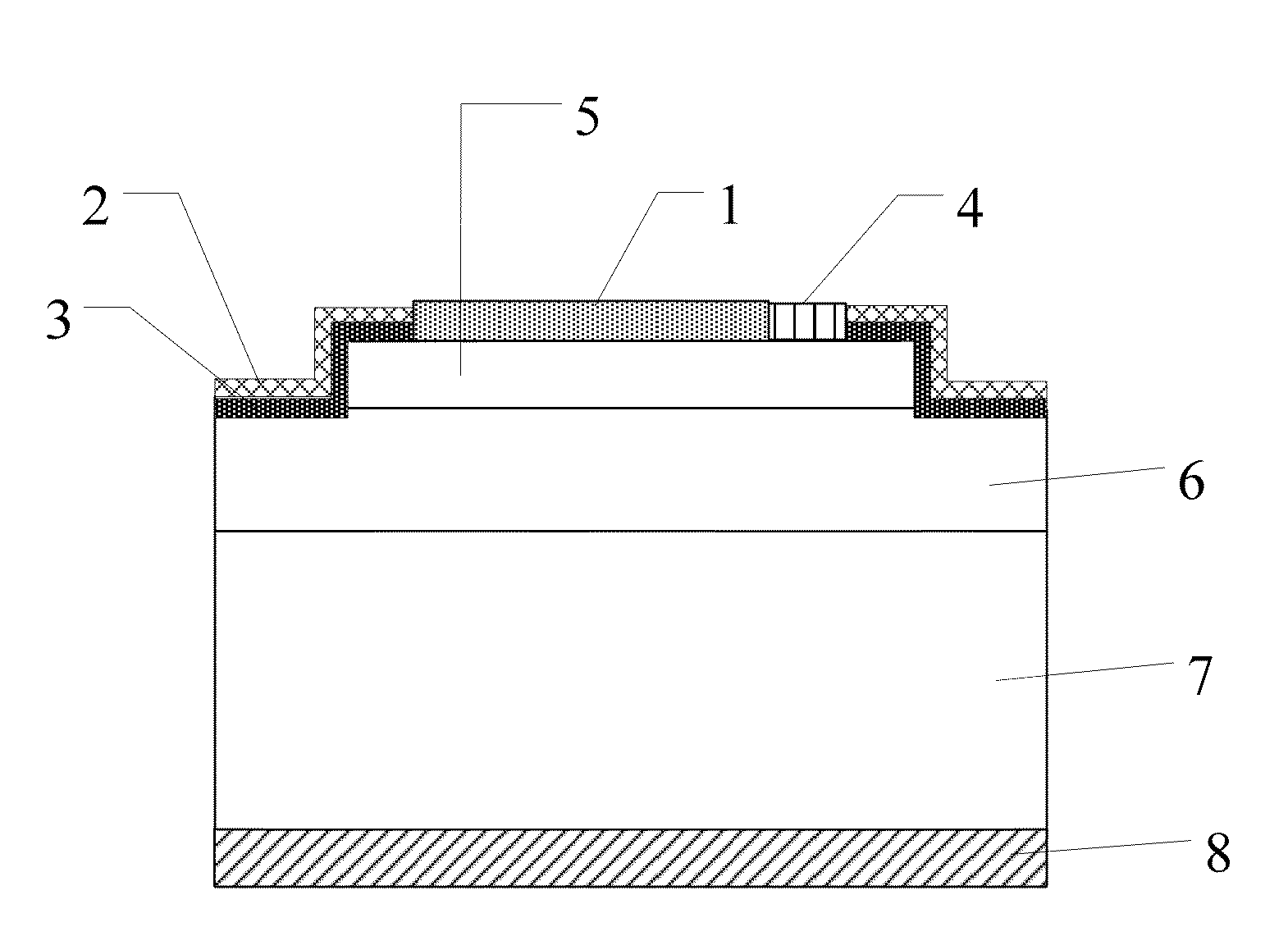

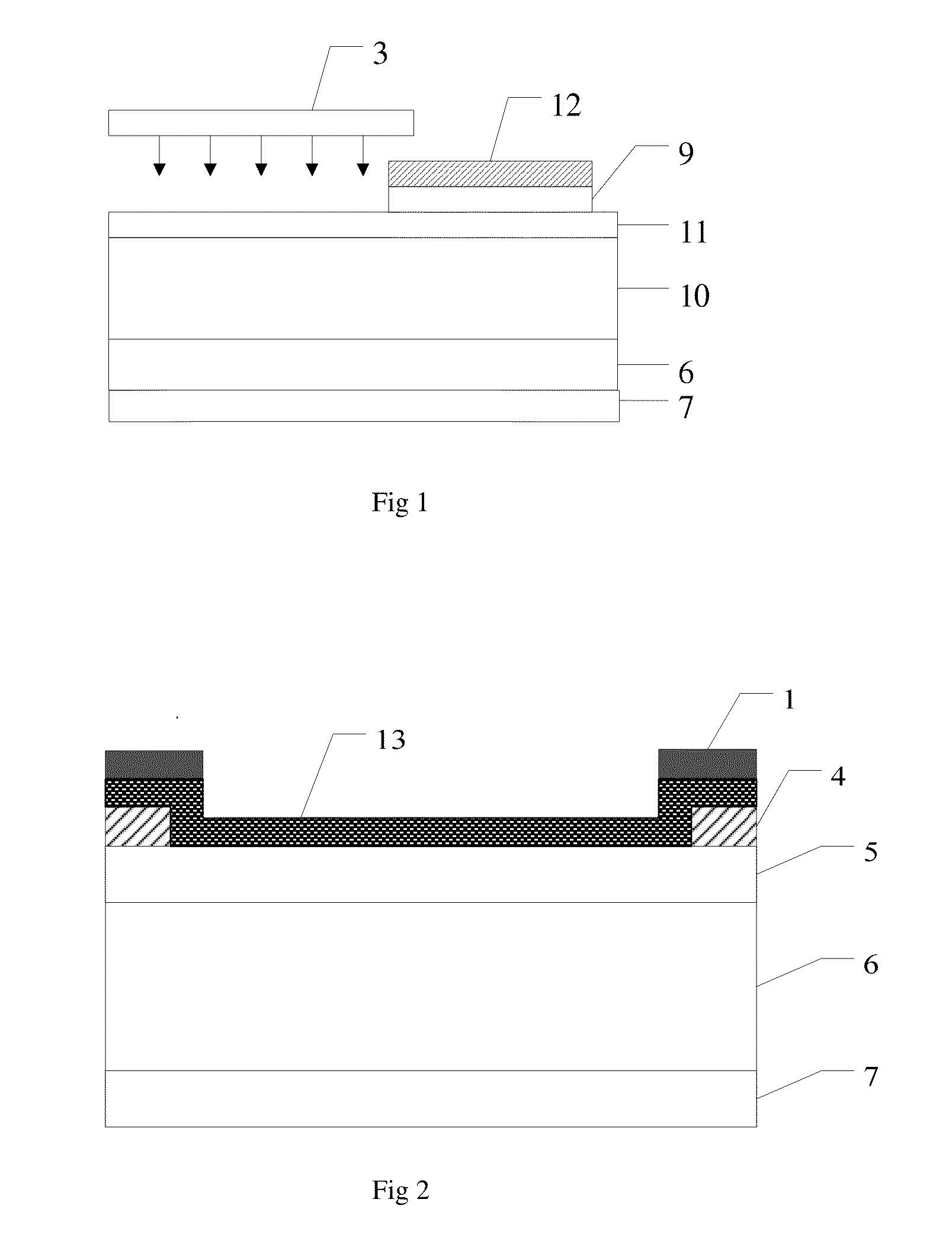

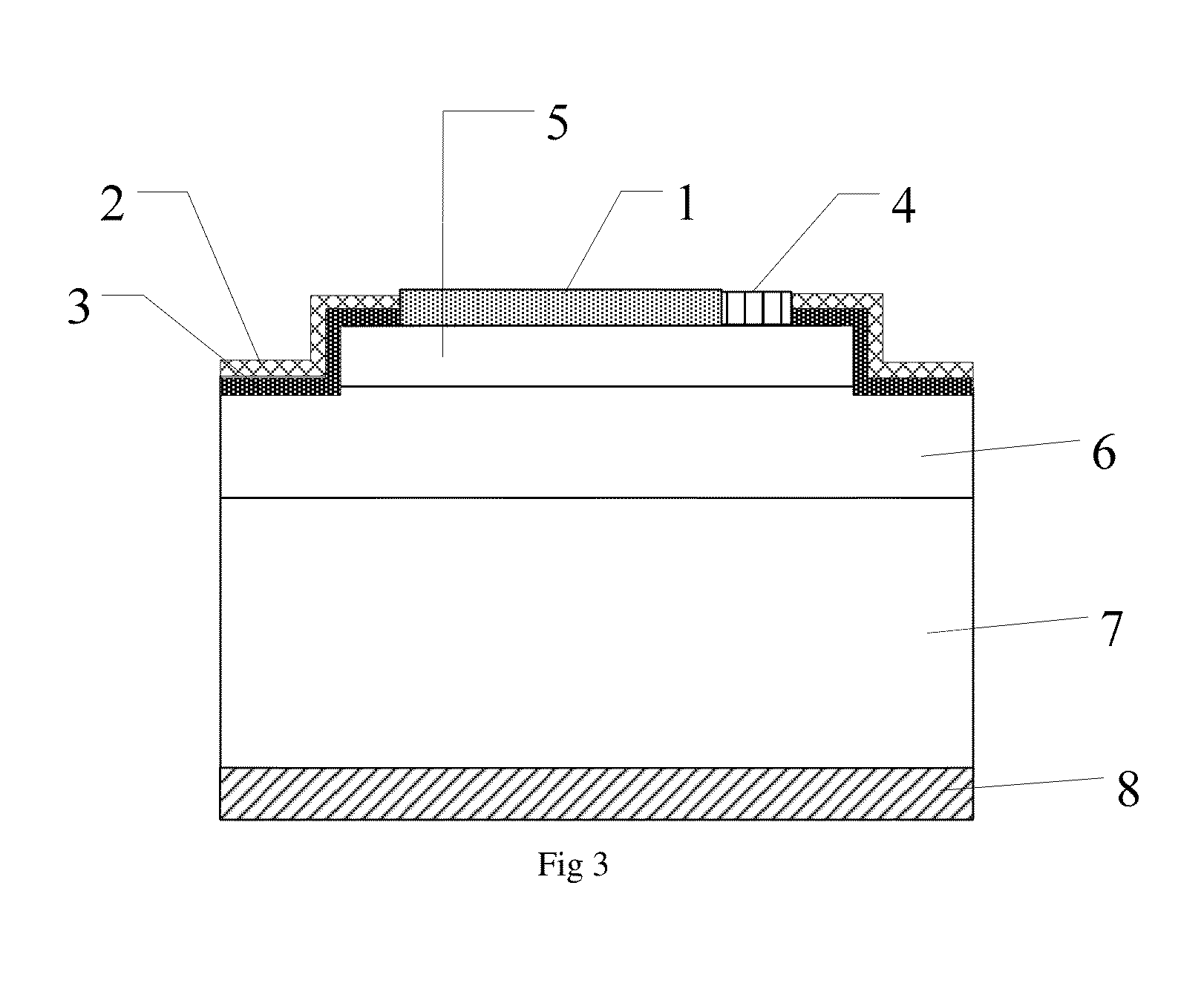

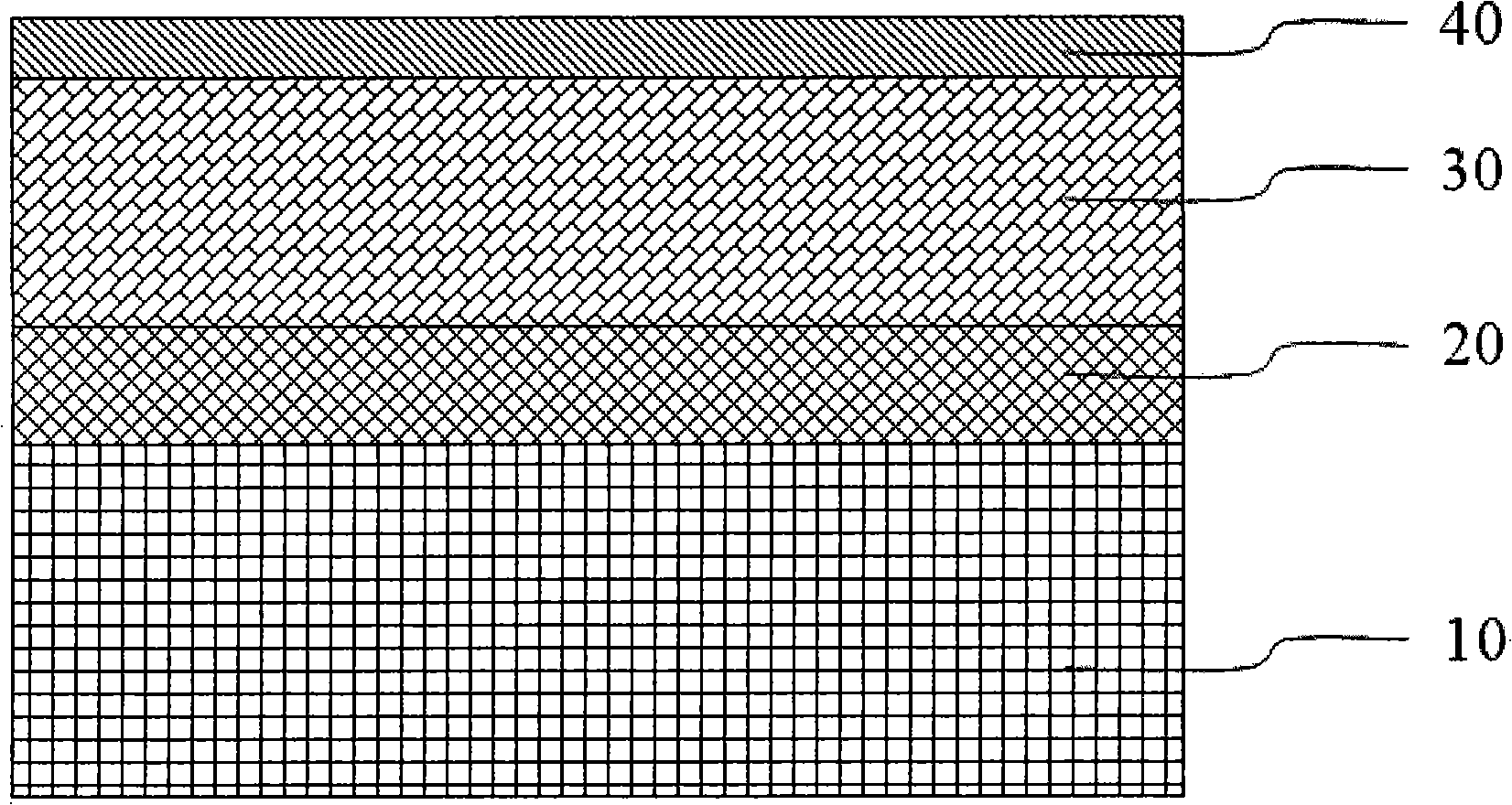

I-Layer Vanadium-Doped Pin Type Nuclear Battery and the Preparation Process Thereof

ActiveUS20140225472A1Increase widthIncrease collection rateSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerVanadium doping

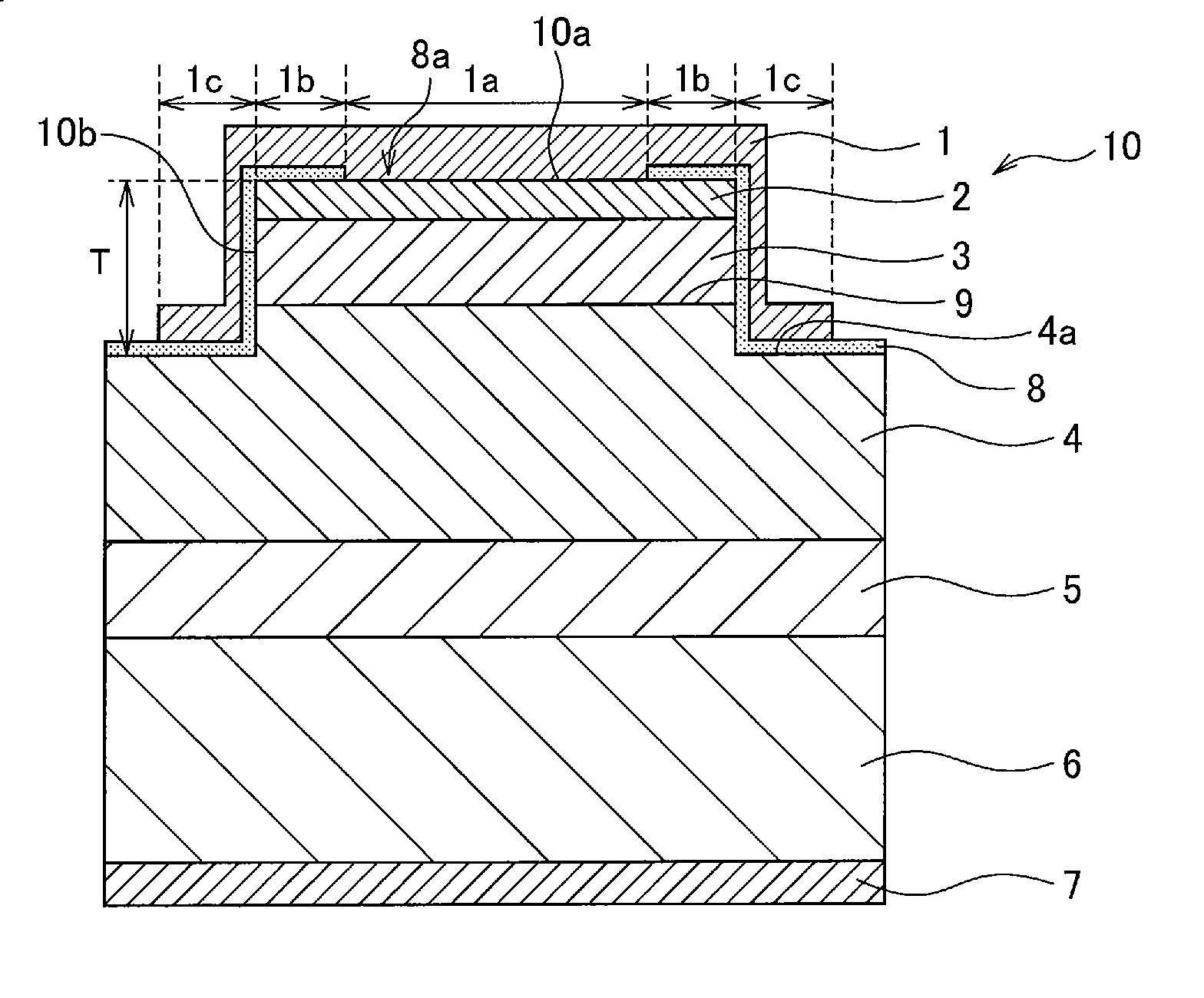

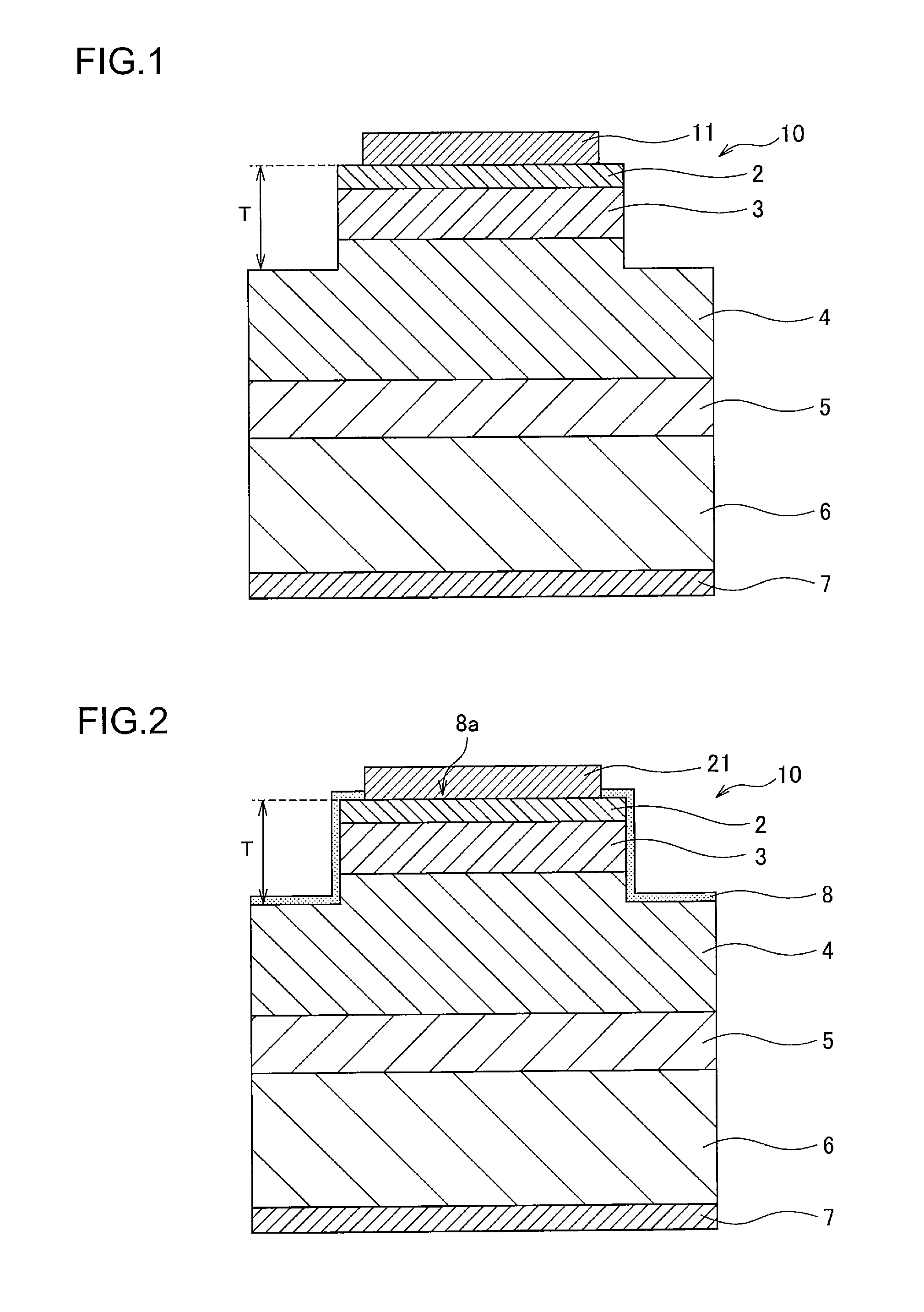

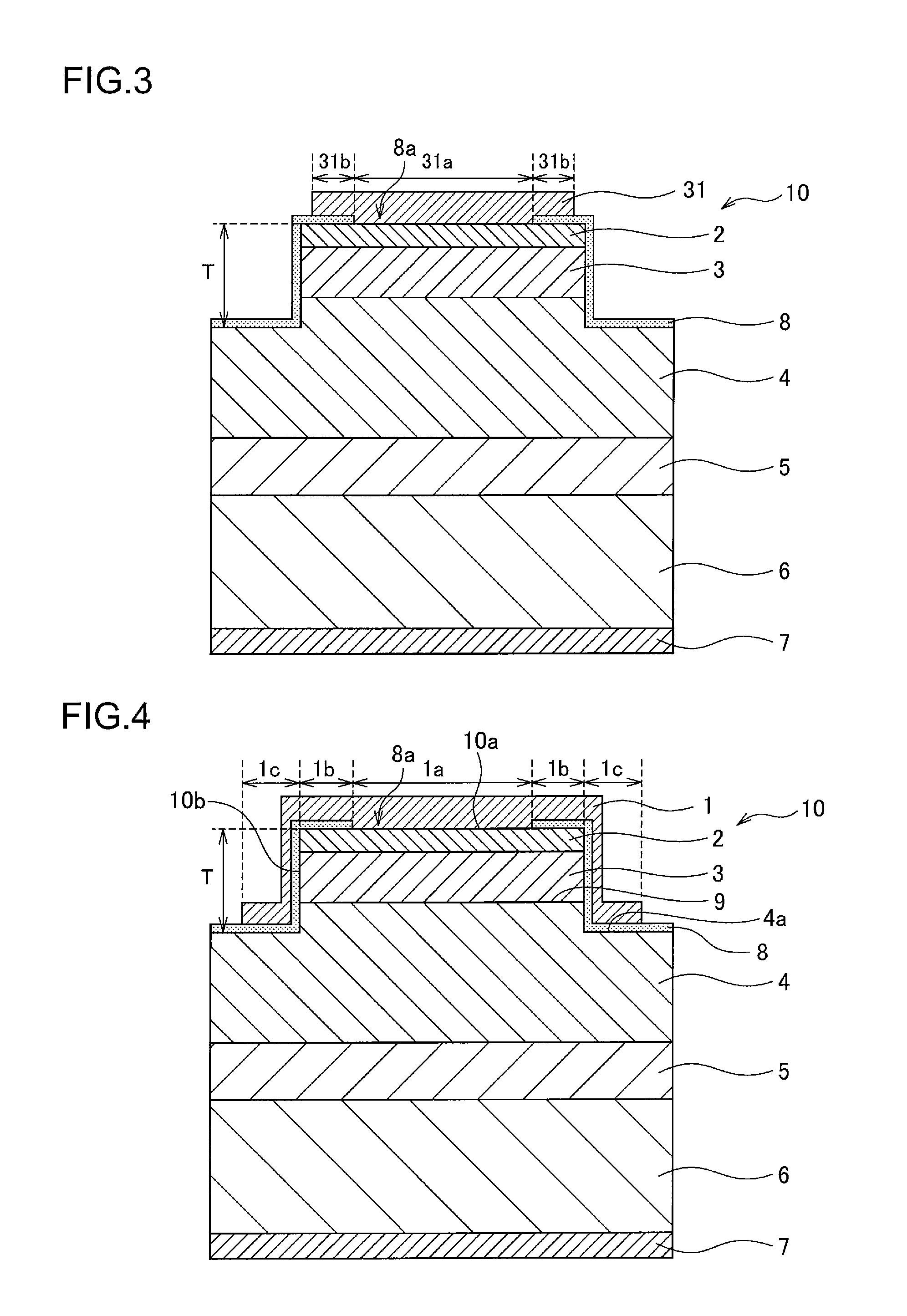

A layer I vanadium-doped PIN-type nuclear battery, including from top to bottom a radioisotope source layer(1), a p-type ohm contact electrode(4), a SiO2 passivation layer(2), a SiO2 compact insulation layer(3), a p-type SiC epitaxial layer(5), an n-type SiC epitaxial layer(6), an n-type SiC substrate(7) and an n-type ohm contact electrode(8). The doping density of the p-type SiC epitaxial layer(5) is 1×1019 to 5×1019 cm3, the doping density of the n-type SiC substrate(7) is 1×1018 to 7×1018 cm3. The n-type SiC epitaxial layer(6) is a low-doped layer I formed by injecting vanadium ions, with the doping density thereof being 1×1013 to 5×1014 cm3. Also provided is a preparation method for a layer I vanadium-doped PIN-type nuclear battery. The present invention solves the problem that the doping density of layer I of the exiting SiC PIN-type nuclear battery is high.

Owner:XIDIAN UNIV

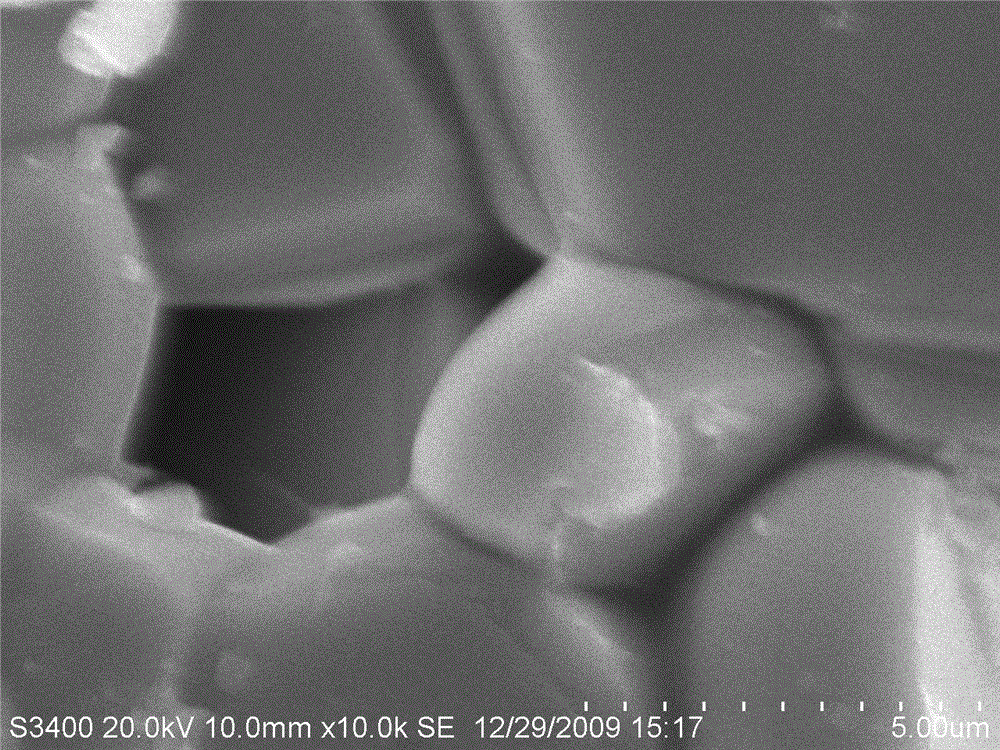

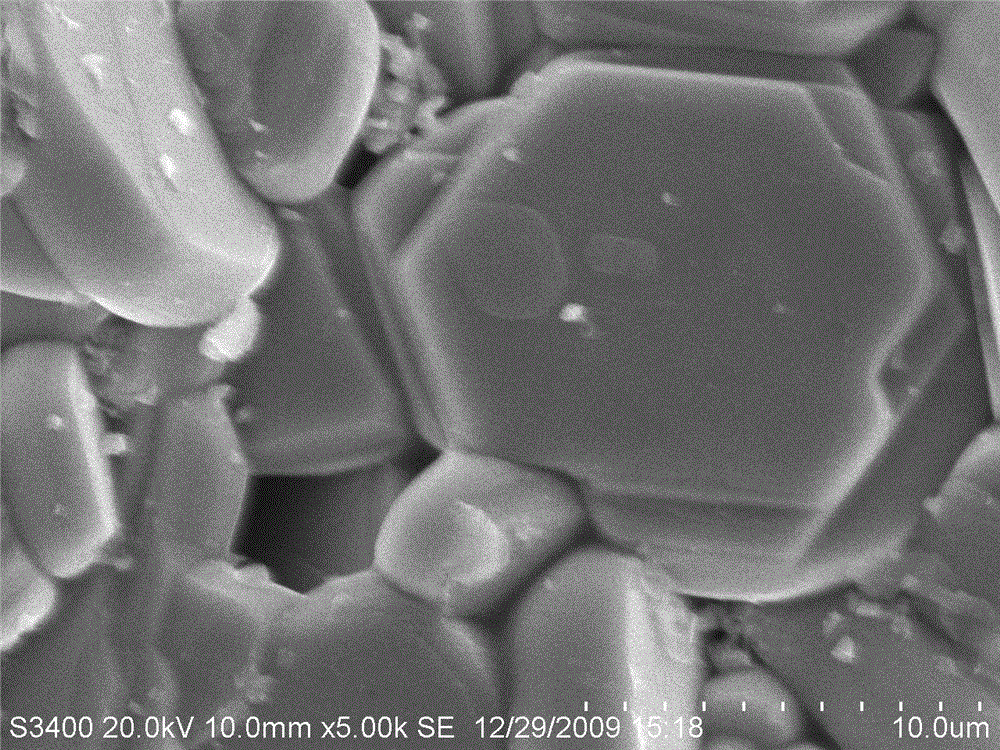

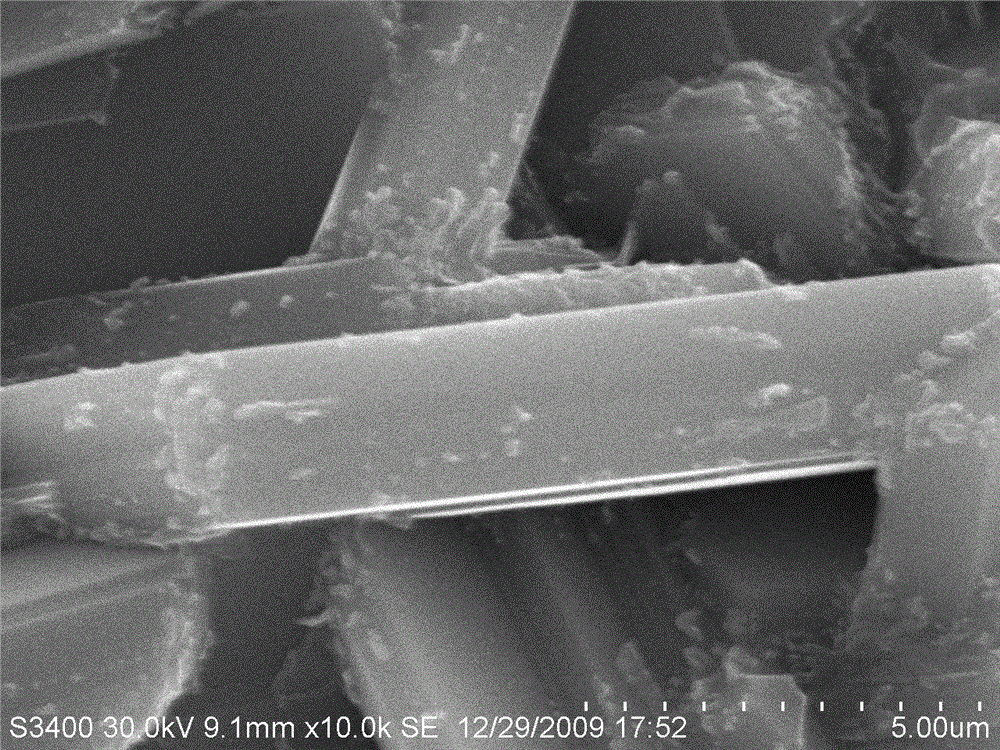

Method for producing a coated item by means of texture etching

ActiveCN102473743AImprove conduction abilityImprove permeabilityConductive layers on insulating-supportsApparatus for manufacturing conducting/semi-conducting layersEtchingMetal

The invention relates to a method for producing a coated item (2) by depositing at least one transparent conductive metal oxide layer (3) on a substrate (5), comprising the deposition (I) and preferably a subsequent temperature treatment (II) of the coating (3). After the optional temperature treatment (II), the surface texture (8) of the coating (3) is statistically adjusted by means of an etching method.

Owner:INTERPANE ENTWICKLUNGS UND BERATUNGSGESELLSCHAFT MBH & CO KG

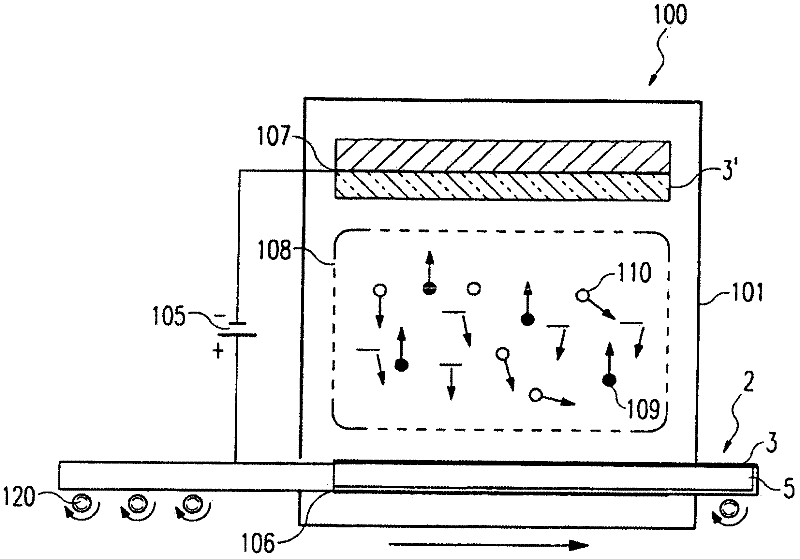

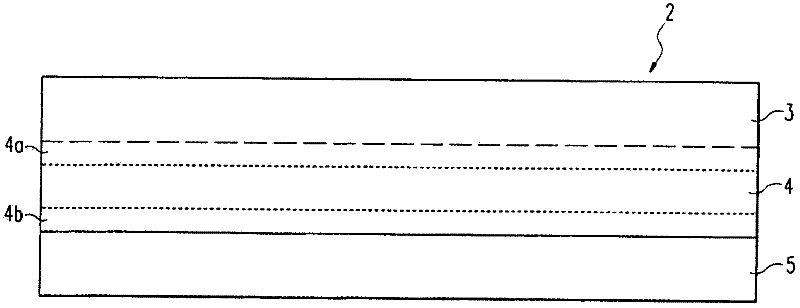

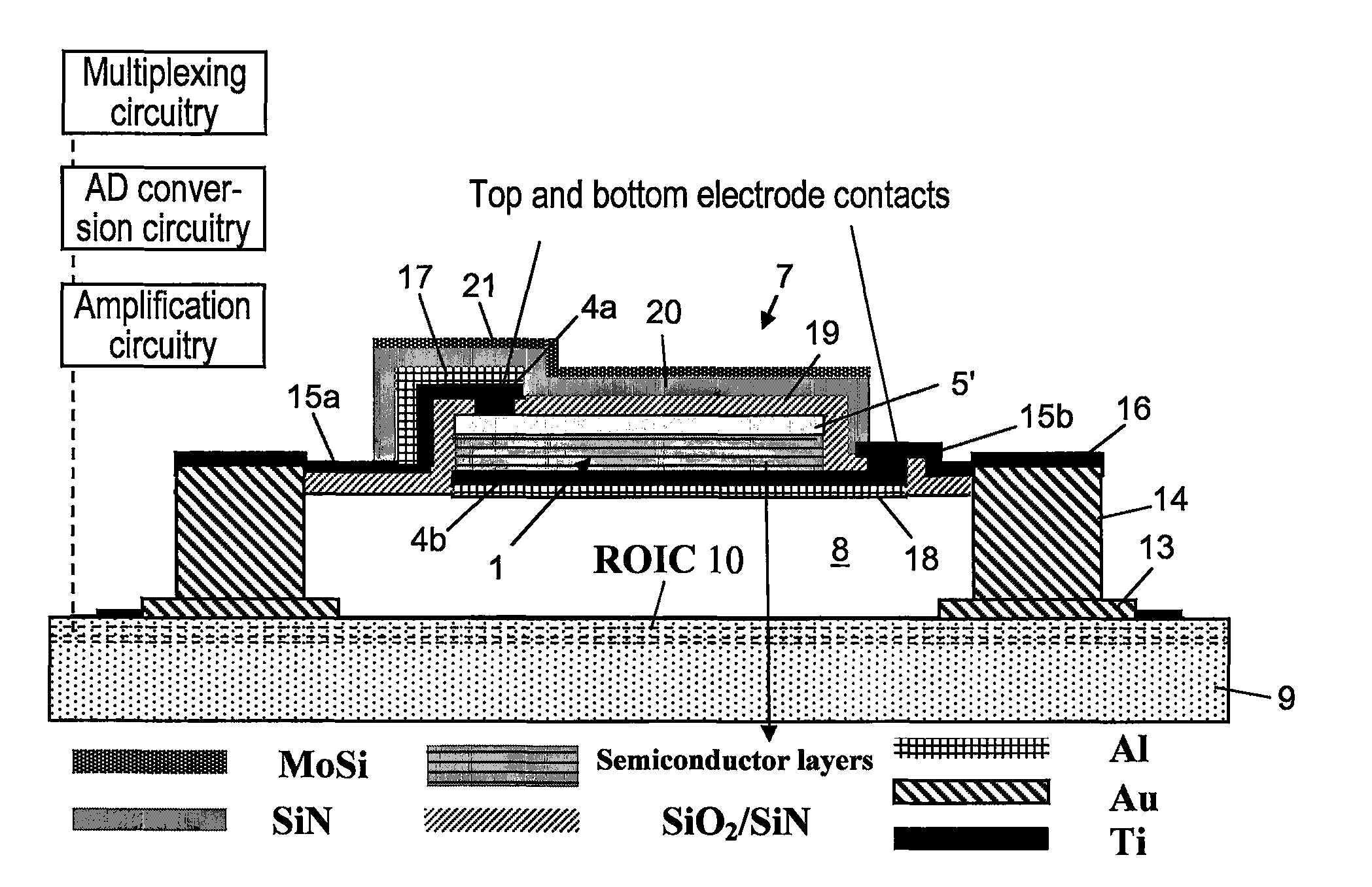

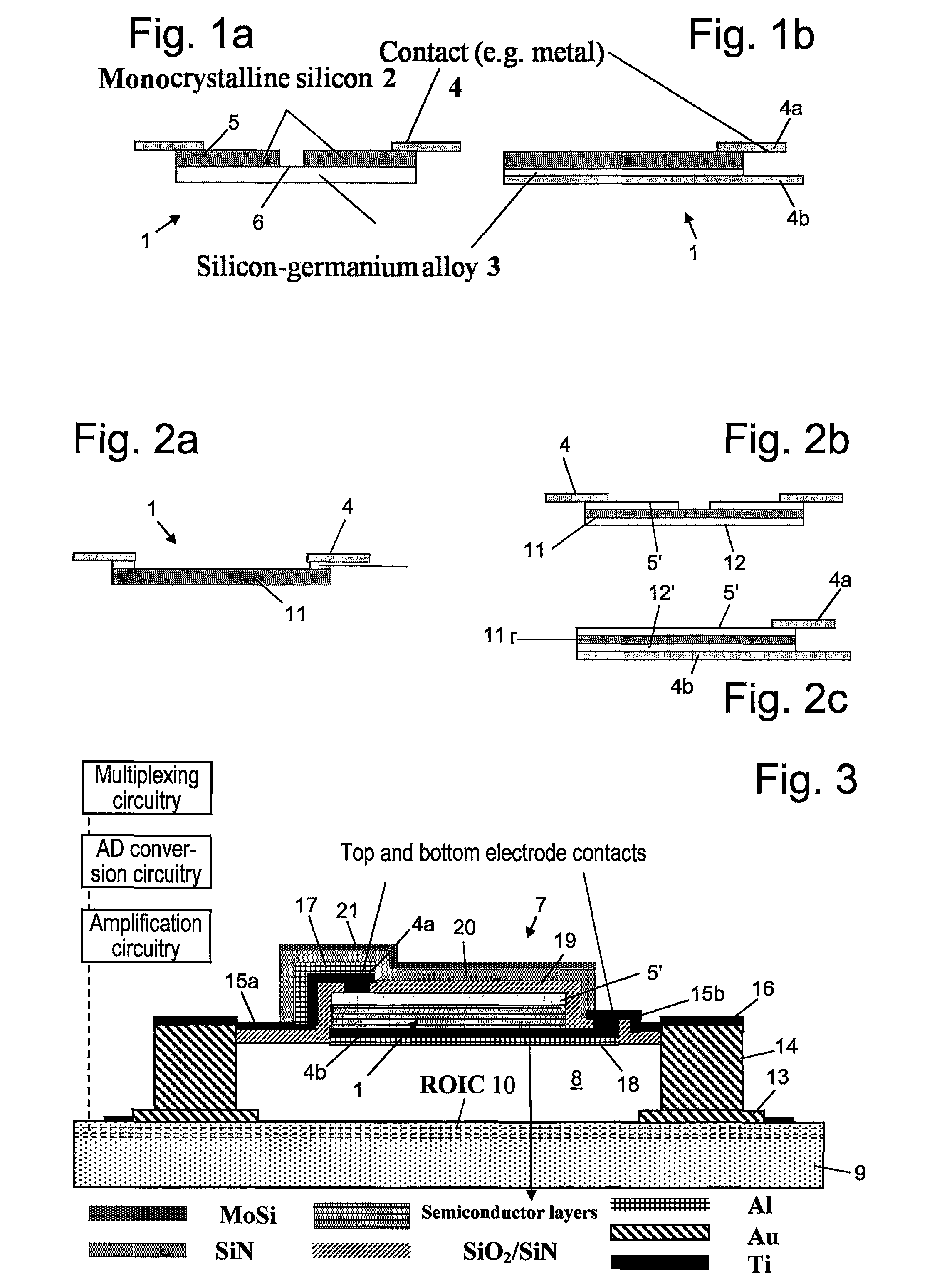

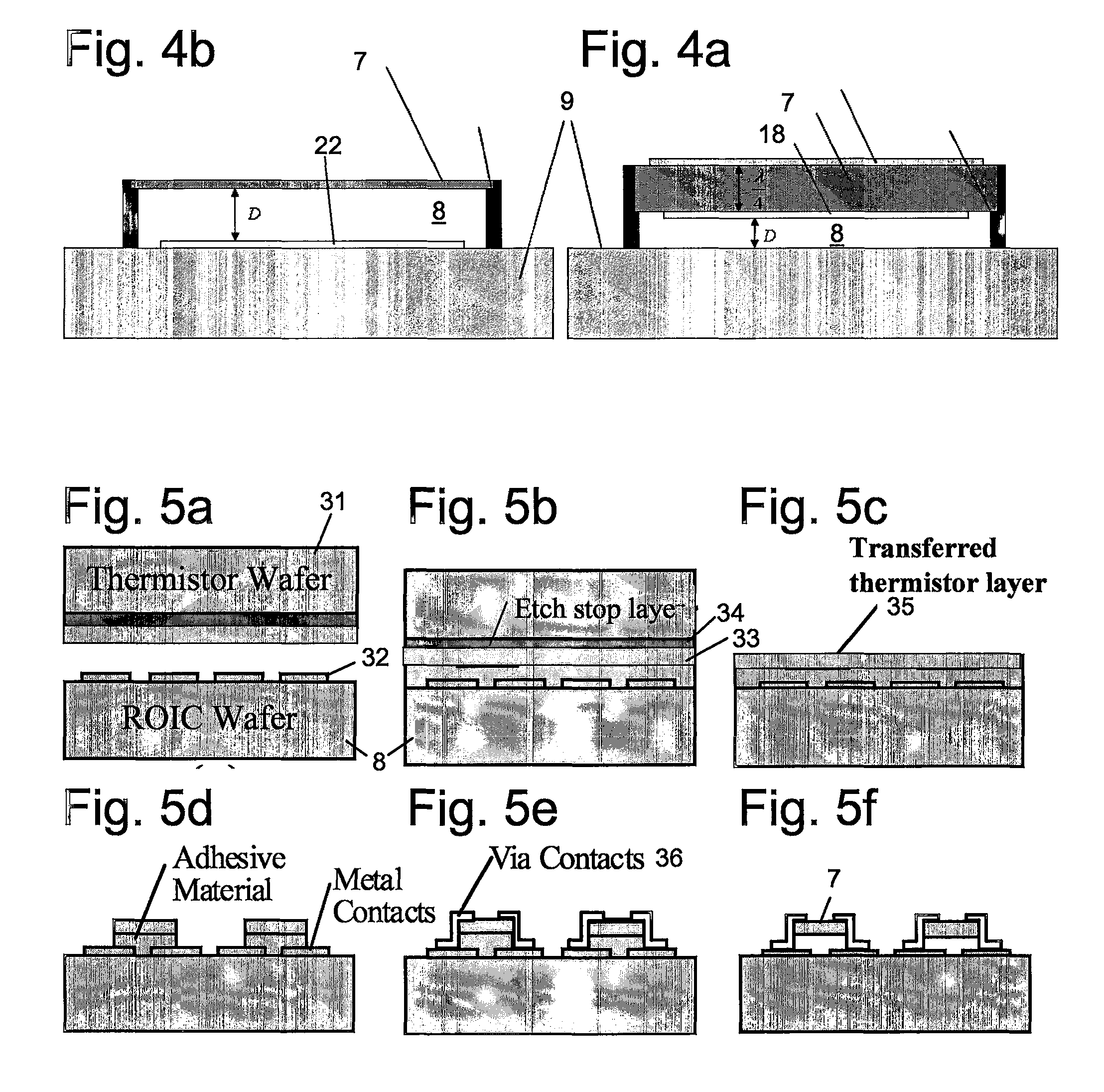

Microbolometer Semiconductor Material

ActiveUS20120139078A1High sensitivityReduce noiseFinal product manufactureSolid-state devicesHeterojunctionIndium

A sensor for detecting intensity of radiation such as of infrared radiation includes an ROIC substrate (9) and a resistance element (1) arranged at a distance of the surface of the ROIC substrate. The resistance element comprises one more semiconducting layers such as a silicon semiconducting layer and a semiconducting layer of a silicon-germanium alloy forming a heterojunction. The semiconducting layer or layers can be doped with one or more impurity dopants, the doping level or levels selected so that the layer retains the basic crystallographic properties of the respective material such as those of monosilicon or a monocrystalline silicon-germanium alloy. The impurity dopants are selected from the elements in groups IE, IV, and V, in particular among boron, aluminium, indium, arsenic, phosphorous, antimony, germanium, carbon and tin. The doping can be abrupt so that there is an interior layer inside said semiconducting layer or layers having a significantly higher doping level.

Owner:SENSIRION HLDG

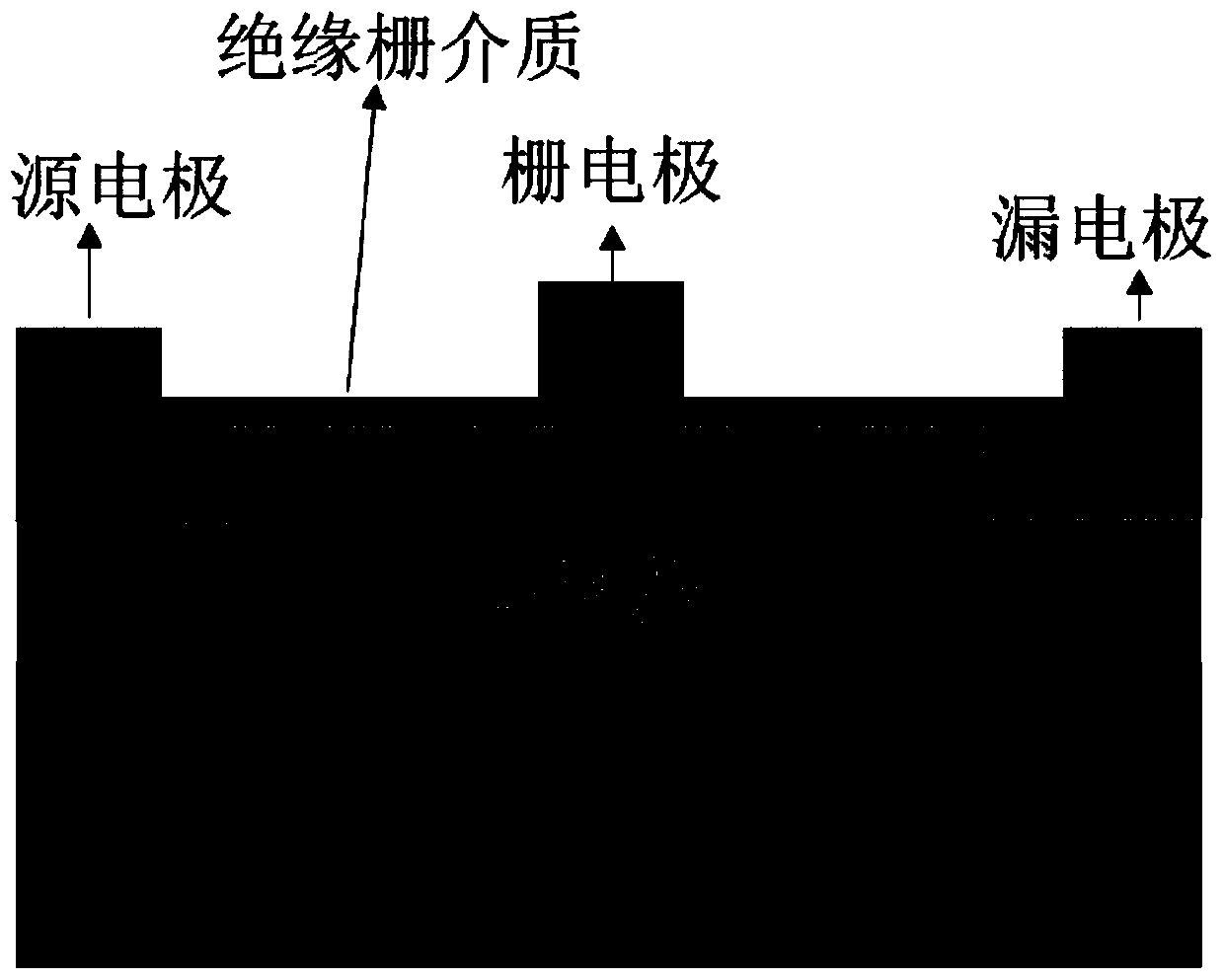

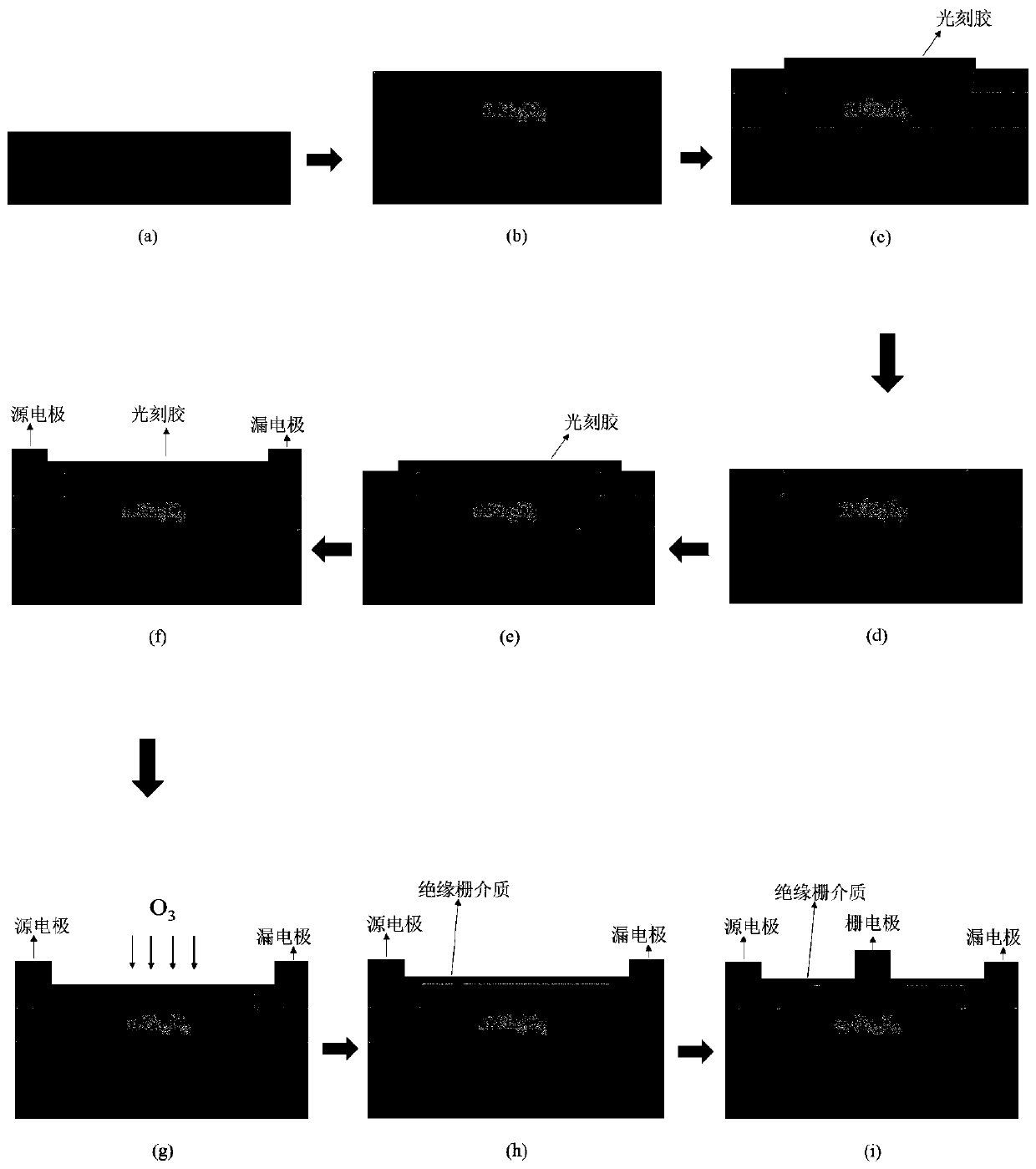

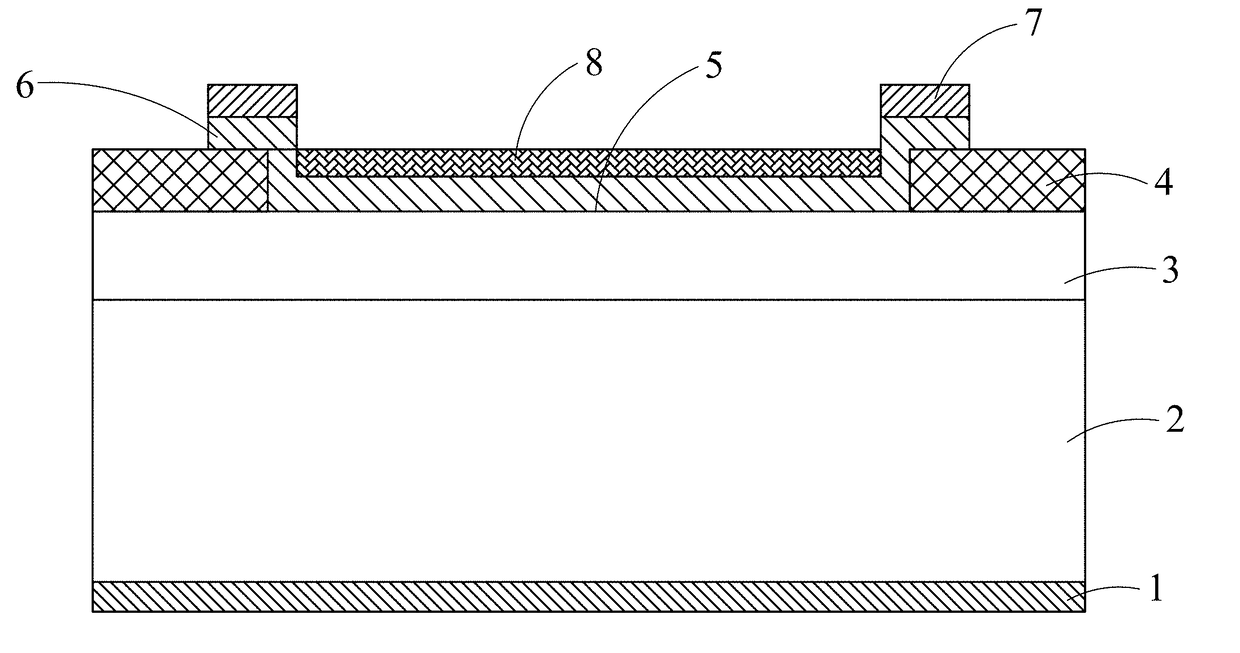

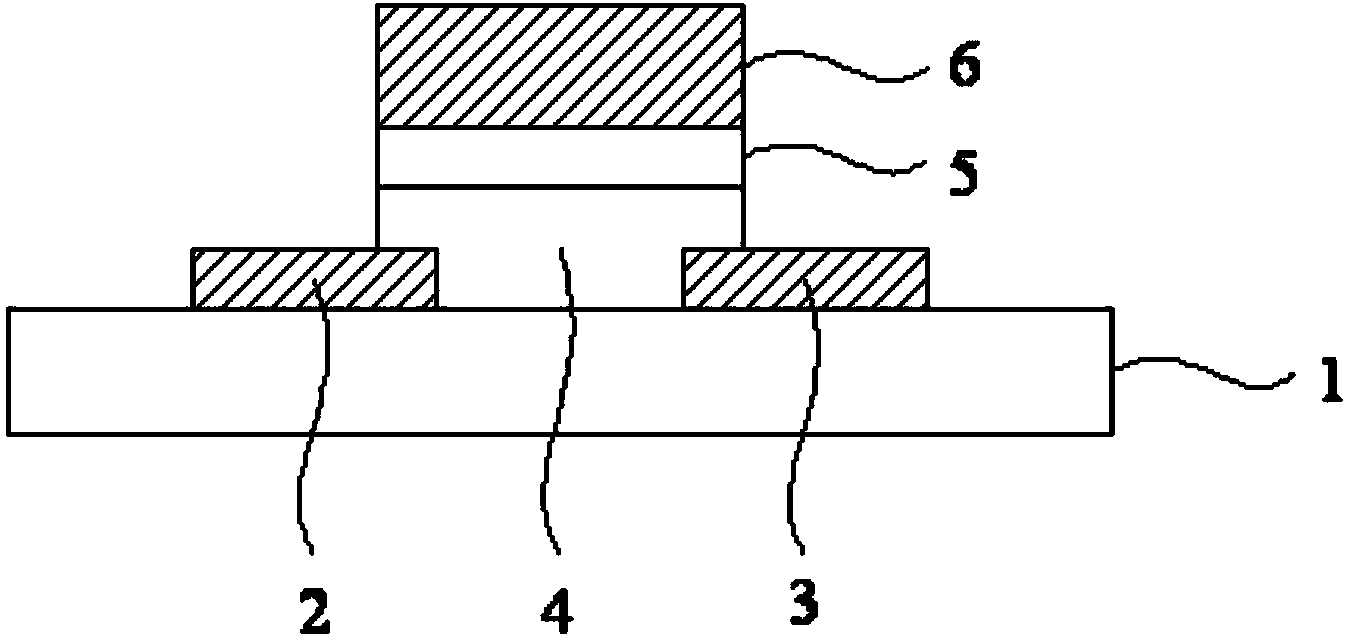

Enhanced Ga2O3 metal oxide semiconductor field effect transistor and manufacturing method thereof

InactiveCN110690291AReduce static power consumptionReduce point defectsVacuum evaporation coatingSputtering coatingGate dielectricField effect

The invention discloses an enhanced Ga2O3 metal oxide semiconductor field effect transistor and a manufacturing method thereof, which mainly solve the problem of complex manufacturing of similar devices in the prior art. The enhanced Ga2O3 metal oxide semiconductor field effect transistor comprises a substrate, an epitaxial layer and an insulated gate dielectric layer from bottom to top; a sourceelectrode and a drain electrode are arranged on the epitaxial layer, and a gate electrode is arranged on the insulated gate dielectric layer. The thickness of the insulated gate dielectric layer is 10-30 nm; the epitaxial layer is an n-type Ga2O3 epitaxial layer, the thickness being 150-300 nm, and the electron concentration being 2.0 * 10 < 16 >-1.0 * 10 < 18 > cm <-3 >. The manufacturing key ofthe device is that before an insulated gate dielectric layer is deposited, the temperature of a cavity is set to be 200-500 DEG C, and O3 is introduced into an ALD reaction cavity to treat the surfaceof an n-type Ga2O3 channel layer for 5-15 min. The interface state density and static power consumption of the device are reduced, the threshold voltage is increased, the manufacturing cost and difficulty are reduced, and the method can be used for power devices and high-voltage switching devices.

Owner:XIDIAN UNIV

Pi-orbital semiconductor quantum cell

ActiveUS20180211738A1Enhance nuclear energy to electric energy conversion efficiencyReduce carrier concentrationSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsCarbon–carbon bond

Herein is disclosed a quantum cell from top to down including: an N-type ohmic contact electrode, an N-type π-orbital semiconductor substrate, an N-type π-orbital semiconductor epitaxy layer, a SiO2 passivation layer, a graphite contact layer, a Schottky contact electrode, a binding layer, and a radioisotope layer. The N-type π-orbital semiconductor substrate includes an organic semiconductor material with an aromatic group or a semiconductor material with a carbon-carbon bond. The N-type π-orbital semiconductor epitaxy layer has a doping concentration of 1×1013-5×1014 cm−3 and is formed by injection of a cationic complex in a dose of 6×1013-1×1015 cm−3.

Owner:CHEN BOR RUEY

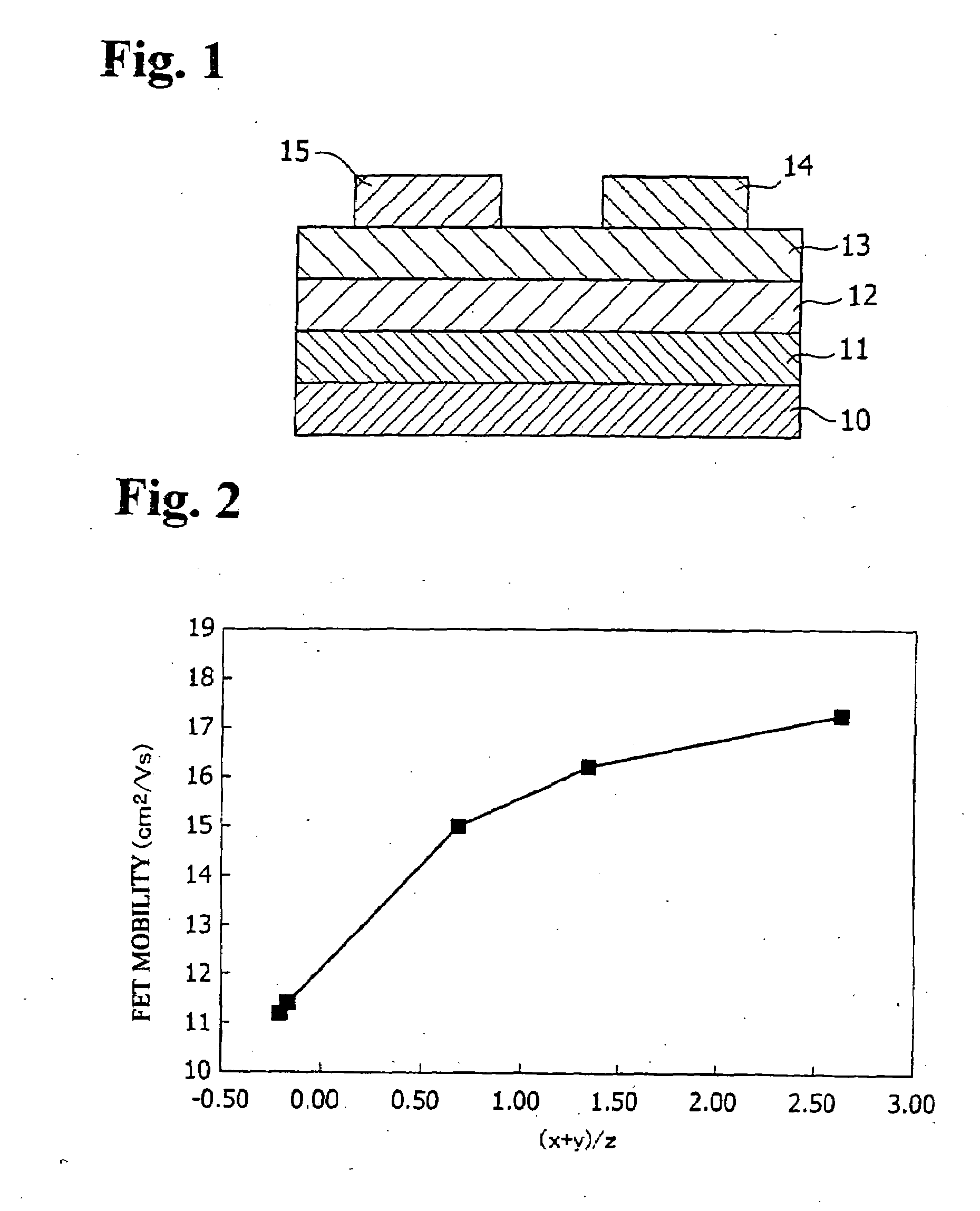

Oxide Semiconductor, Thin-Film Transistor and Method for Producing the Same

InactiveUS20090289249A1Off-current can be reducedMaintain mobilityTin compoundsSemiconductor/solid-state device manufacturingSemiconductorHeat treated

Disclosed is an oxide semiconductor having an amorphous structure, wherein higher mobility and reduced carrier concentration are achieved. Also disclosed are a thin film transistor, a method for producing the oxide semiconductor, and a method for producing the thin film transistor. Specifically disclosed is an oxide semiconductor which is characterized by being composed of an amorphous oxide represented by the following a general formula: Inx+1MZny+1SnzO(4+1.5x+y+2z) (wherein M is Ga or Al, 0≦x≦1, −0.2≦y≦1.2, z≧0.4 and 0.5≦(x+y) / z≦3). This oxide semiconductor is preferably subjected to a heat treatment in an oxidizing gas atmosphere after film formation. Also specifically disclosed is a thin film transistor which is characterized by comprising the oxide semiconductor.

Owner:FUJI ELECTRIC CO LTD

Semiconductor device and manufacturing method thereof

ActiveUS8563976B2Small loss of on currentAvoid changeSolid-state devicesSemiconductor devicesElectrical conductorHydrogen

A semiconductor device includes an oxide semiconductor layer including a channel formation region which includes an oxide semiconductor having a wide band gap and a carrier concentration which is as low as possible, and a source electrode and a drain electrode which include an oxide conductor containing hydrogen and oxygen vacancy, and a barrier layer which prevents diffusion of hydrogen and oxygen between an oxide conductive layer and the oxide semiconductor layer. The oxide conductive layer and the oxide semiconductor layer are electrically connected to each other through the barrier layer.

Owner:SEMICON ENERGY LAB CO LTD

Silicon carbide consubstantial PIN (Personal Identification Number) microstructure material and preparation method thereof

InactiveCN102064187ABright surfaceUniform resistivitySemiconductor/solid-state device manufacturingSemiconductor devicesElectric devicesElectric power

The invention discloses a silicon carbide consubstantial PIN (Personal Identification Number) microstructure material which comprises an N type silicon carbide substrate, an N-variable concentration buffer layer arranged on the N type silicon carbide substrate, an intrinsic layer arranged on the N-variable concentration buffer layer, and a P+ cap layer arranged on the intrinsic layer. The invention simultaneously discloses a preparation method of the silicon carbide consubstantial PIN microstructure material. The invention can prepare an extension SiC epitaxial material with the advantages ofbright surface and uniform resistivity, the background carrier concentration of the intrinsic epitaxial layer can be reduced to the 1015 order of magnitude, and the microstructure material provided by the invention is suitable for high-power electronic and electric devices of semiconductors.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

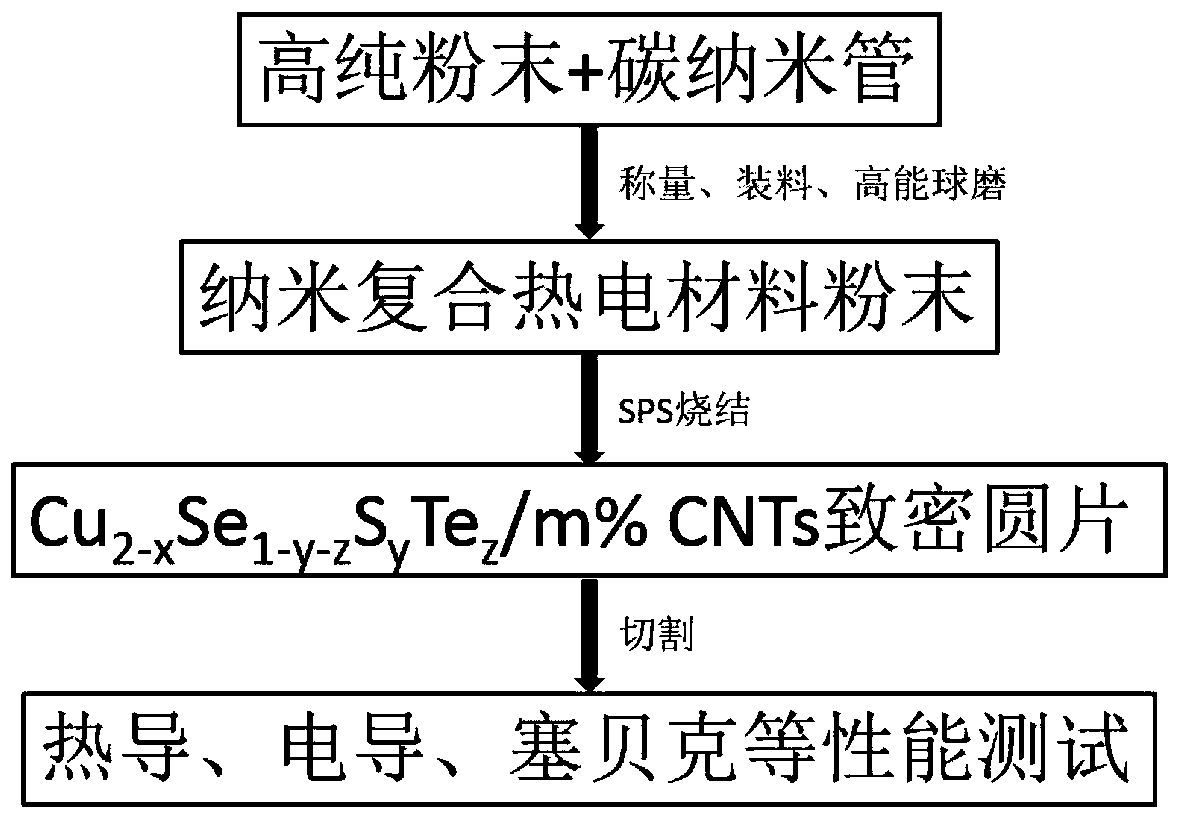

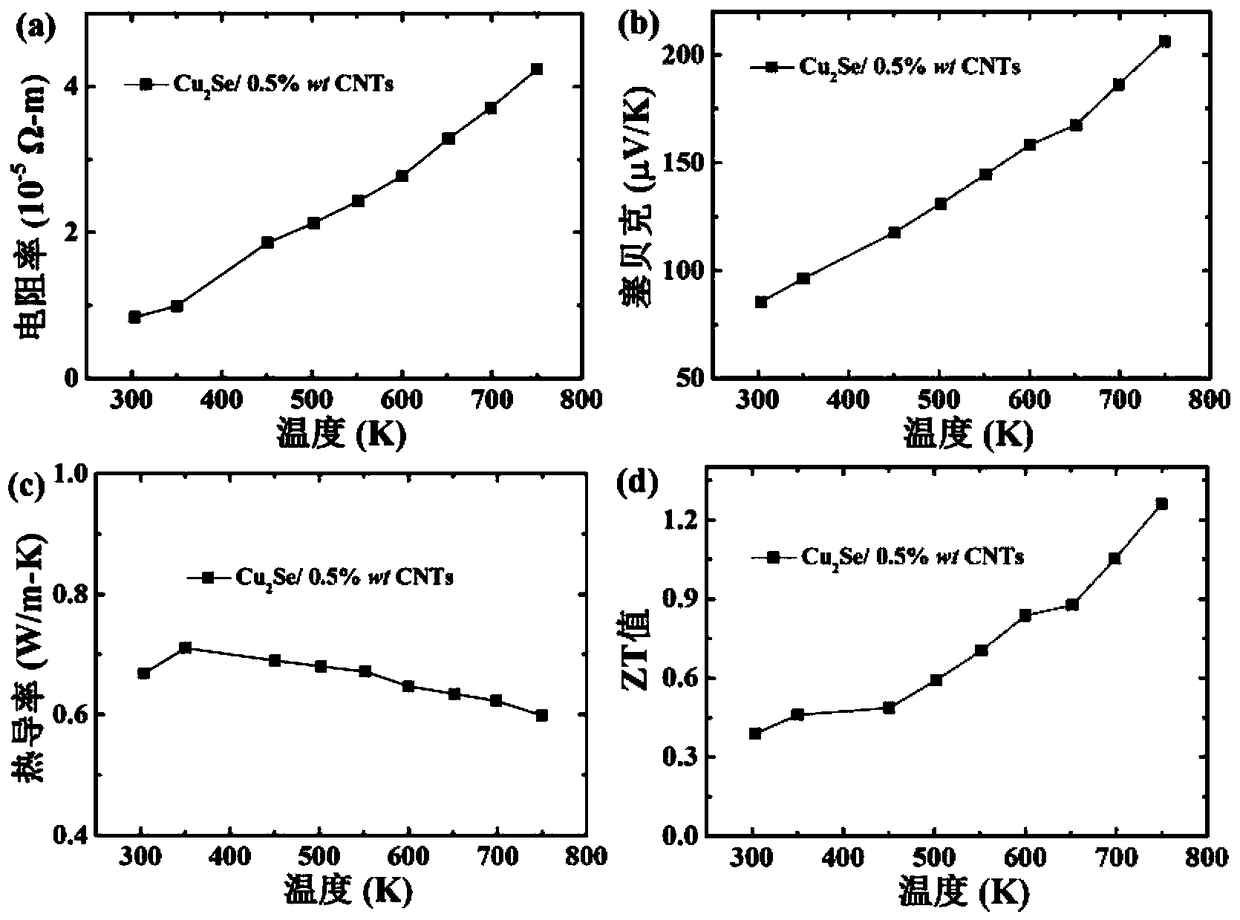

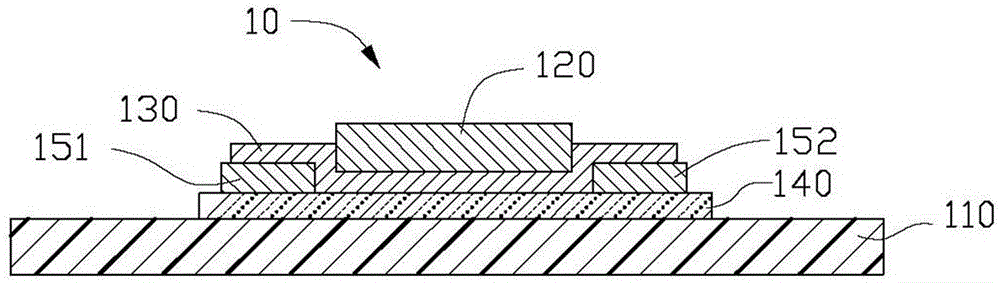

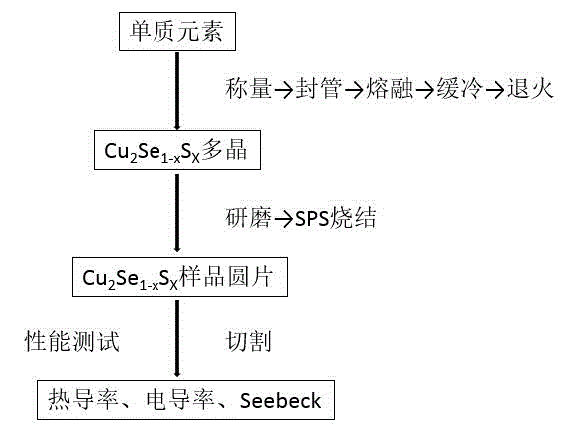

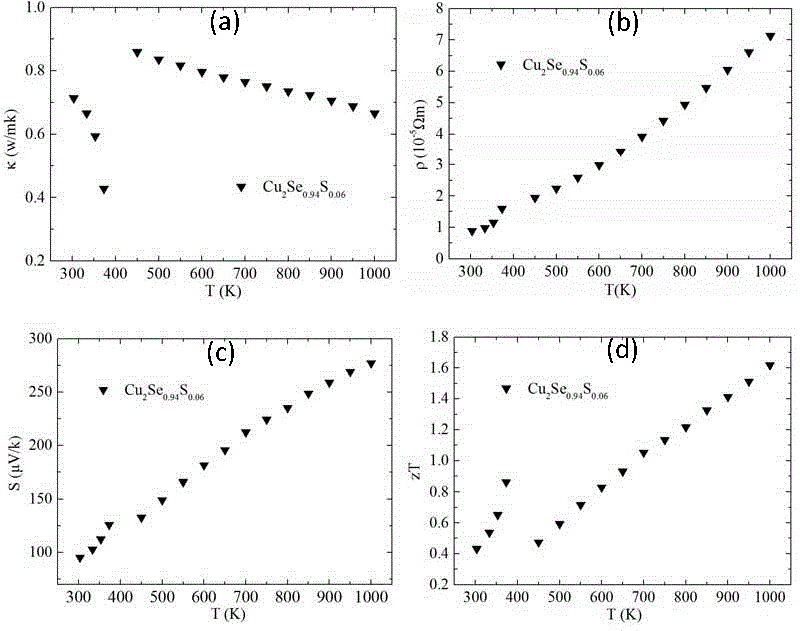

Copper-selenium-based nano-composite thermoelectric material and preparation method thereof

ActiveCN108242500AEfficient use ofAchieve the goal of energy saving and emission reductionMaterial nanotechnologyThermoelectric device manufacture/treatmentThermoelectric materialsCarbon nanotube

The invention relates to a copper-selenium-based nano-composite thermoelectric material and a preparation method thereof. The p-type nano-composite thermoelectric material comprises Cu2 xSe1 y zSyTezand carbon nano-tubes distributed in the Cu2 xSe1 y zSyTez, 0<=x<=0.15, 0<=y<=1, 0<=z<=1, y+z<=1, and mass percentage of the carbon nanotubes <=2%. The raw materials used in the preparation method areabundant in source and low in cost; production process and production equipment are simple; and controllability and repeatability are good.

Owner:SHANGHAI INST OF CERAMIC CHEM & TECH CHINESE ACAD OF SCI

Sputtering target, oxide semiconductor film, preparing method of sputtering target and preparing method of oxide semiconductor film

ActiveCN106435490AReduce carrier concentrationImprove mobilityElectric discharge tubesVacuum evaporation coatingIndiumCharge carrier mobility

The invention relates to an oxide semiconductor film. The oxide semiconductor film comprises the element In, the element Ce, the element Zn, the metal-doped element M and the element O, and the molar ratio of the In to the Ce to the Zn is 2: (0.5-2):1. The oxide semiconductor film is an n type semiconductor, the carrier concentration ranges from 10<12>cm<-3> to 10<20>cm<-3>, and the carrier mobility ranges from 5.0 cm<2>V<-1>s<-1> to 46.3 cm<2>V<-1>s<-1>. The invention further relates to a preparing method of the oxide semiconductor film, a sputtering target and a preparing method of the sputtering target.

Owner:TSINGHUA UNIV +1

Semiconductor diode

InactiveUS20120313108A1Improve reverse withstand voltage capabilityIncreasing on-resistance of the pn-junction diodeSemiconductor devicesOhmic contactSemiconductor

To provide a semiconductor diode with a part of a semiconductor lamination portion having a mesa structure portion, which is the part where a pn-junction is formed by lamination of an n-type semiconductor layer and a p-type semiconductor layer on a substrate, comprising: a protective insulating film formed by coating a main surface of the mesa structure portion, a side face of the mesa structure portion in which an interface of the pn-junction is exposed, and an etched and exposed surface of the n-type semiconductor layer; and an anode electrode formed in ohmic-contact with the p-type semiconductor layer exposed from an opening formed on a part of the main surface of the mesa structure portion of the protective insulating film, extending from the main surface, through the side face of the mesa structure portion, to the surface of the n-type semiconductor layer.

Owner:HITACHI METALS LTD

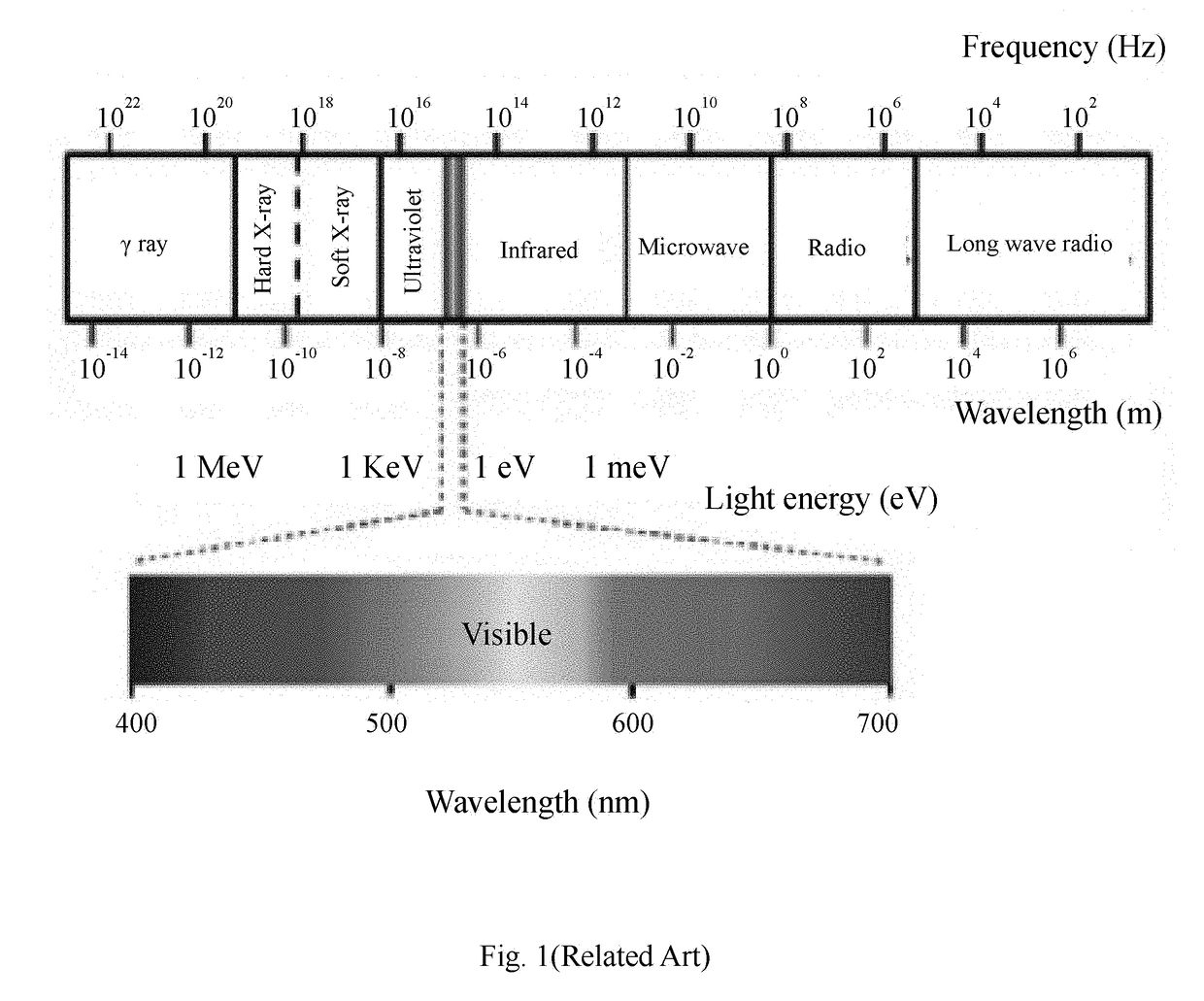

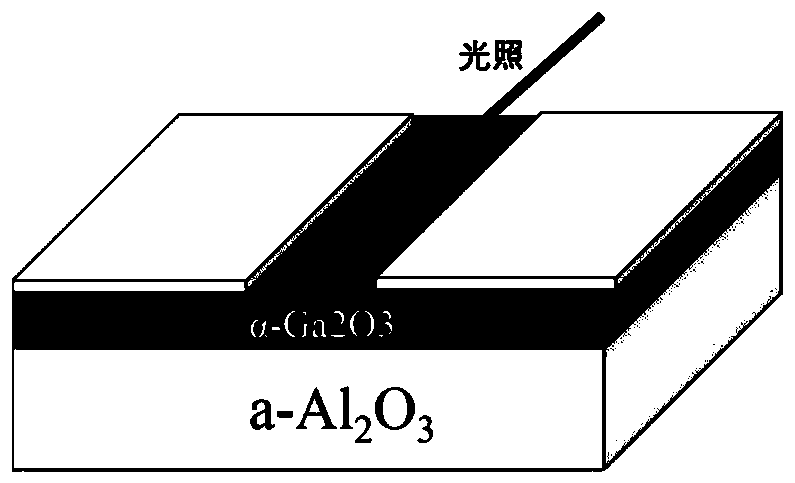

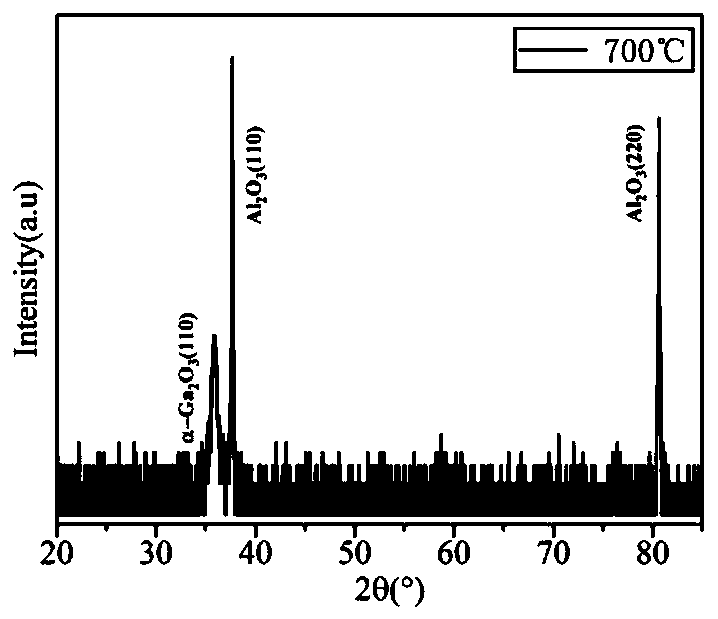

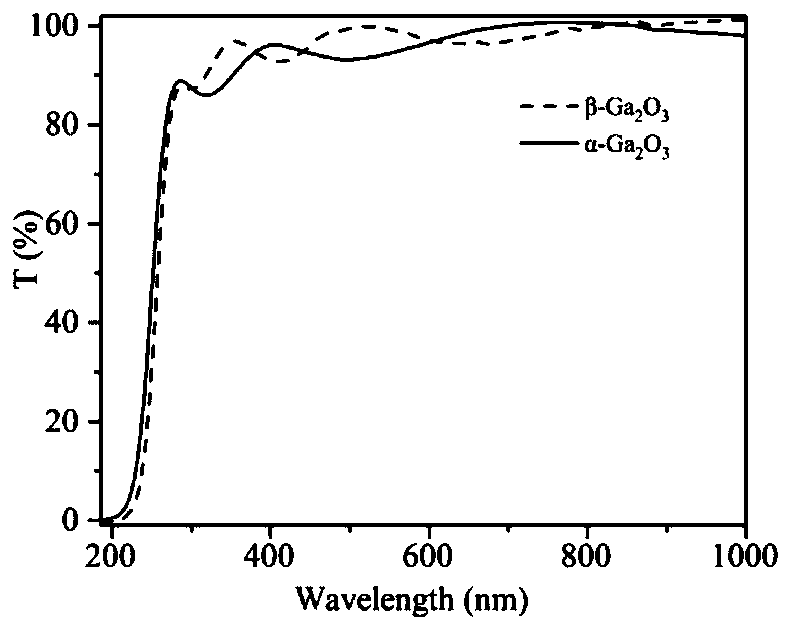

MSM type alpha-Ga2O3 based solar blind ultraviolet light detector

ActiveCN111293181AEasy to manufactureReduce carrier concentrationFinal product manufactureSemiconductor devicesMetallic electrodeLattice mismatch

The invention discloses an MSM type alpha-Ga2O3-based solar blind ultraviolet light detector and a preparation method thereof. The detector sequentially comprises an a-surface sapphire substrate, an active layer and a pair of parallel metal electrodes from bottom to top, wherein the active layer is a (110) oriented alpha-Ga2O3 film. According to the invention, the alpha-Ga2O3 and the sapphire havethe same crystal form and low lattice mismatch rate, the (110) oriented alpha-Ga2O3 film with better crystallization quality grows on the a-surface sapphire, and the film has high electron mobility,so that the gain of the device is large, and the light-dark current ratio of the device is large, and the responsivity is high. Besides, the solar blind ultraviolet light detector with the MSM structure prepared by the invention is simple in structure and manufacturing process, and the detector prepared by the invention has good detection capability on deep ultraviolet light with the wavelength of245nm, and is small in dark current, large in light-dark current ratio, high in responsivity and stable in performance.

Owner:HUBEI UNIV +1

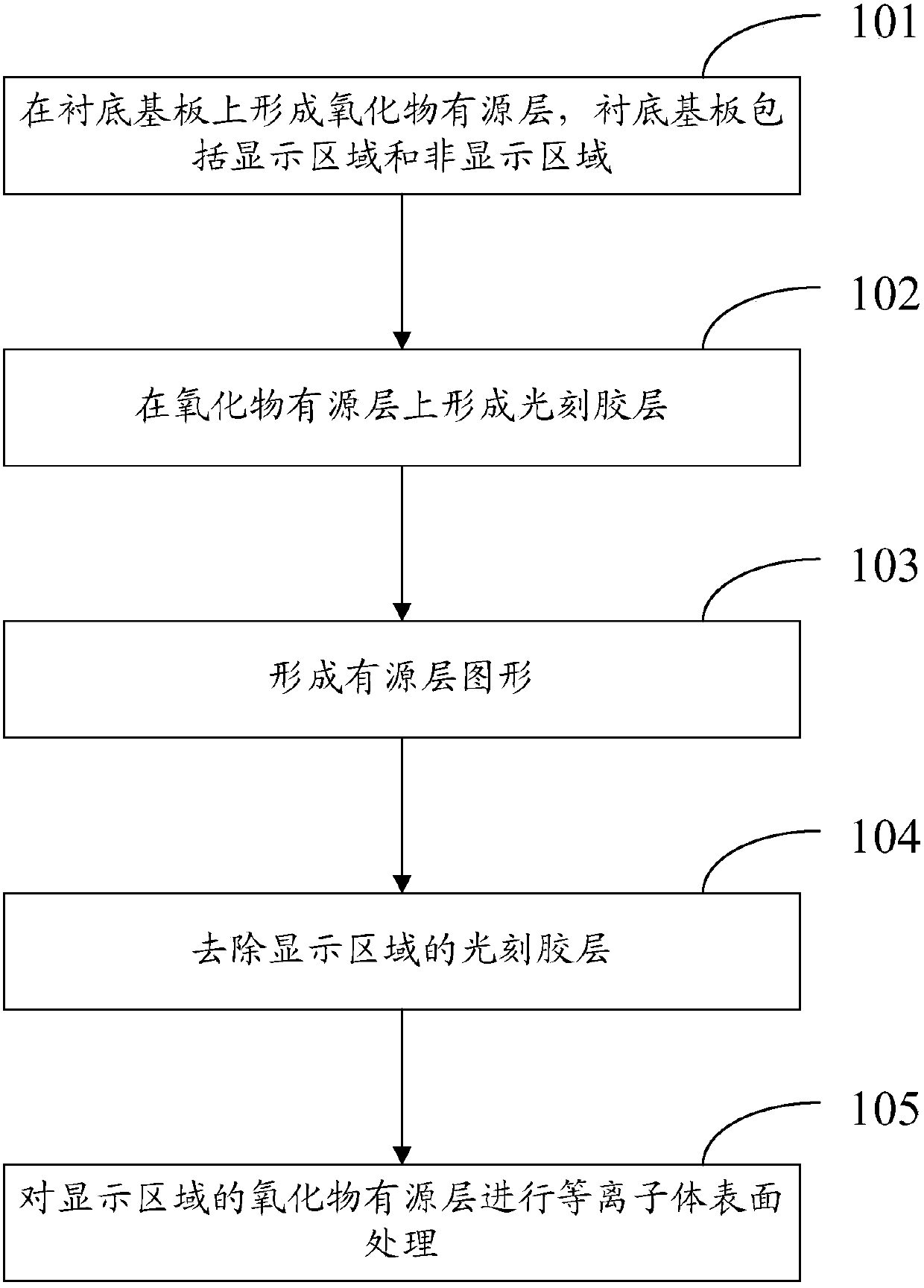

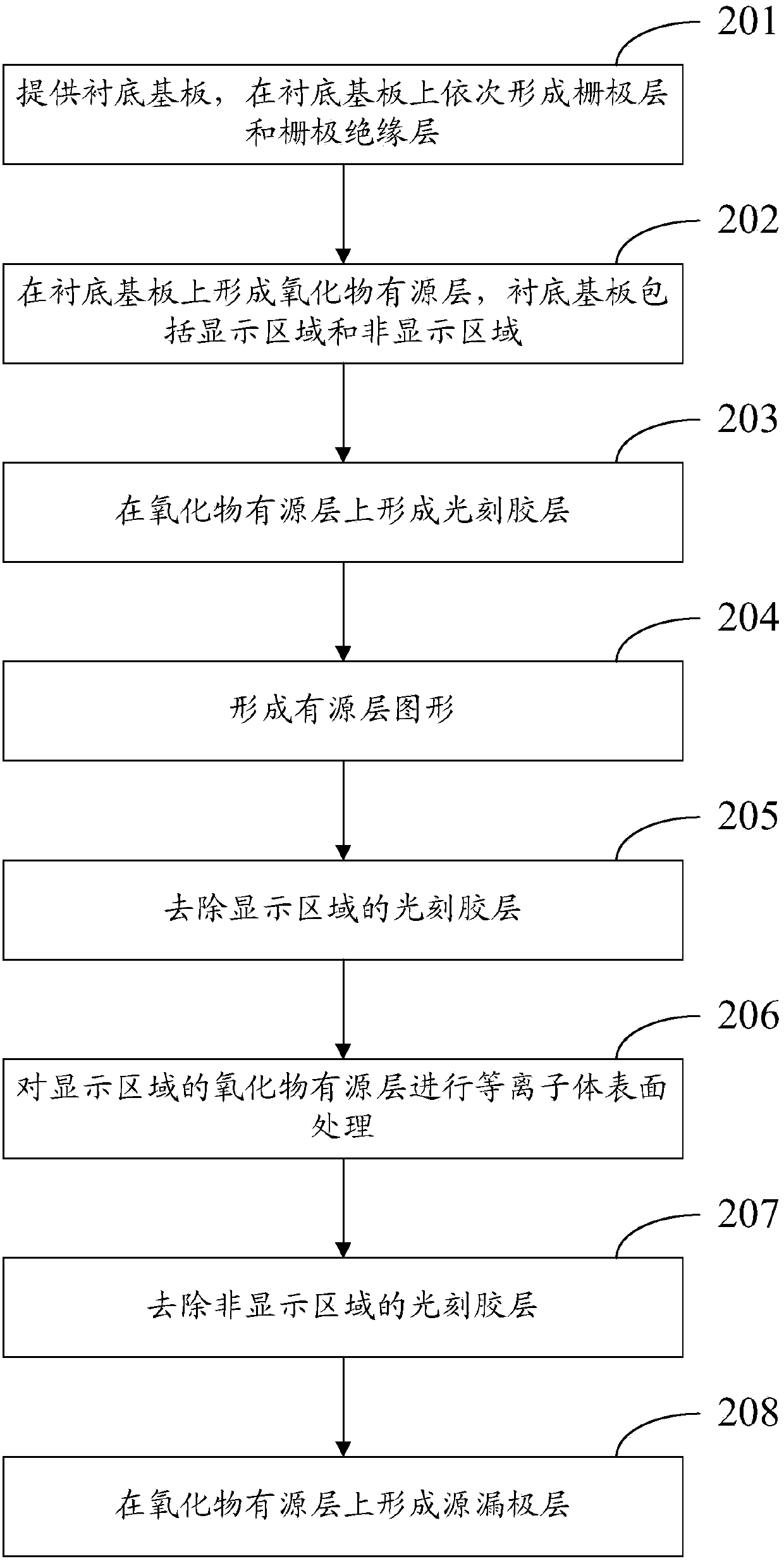

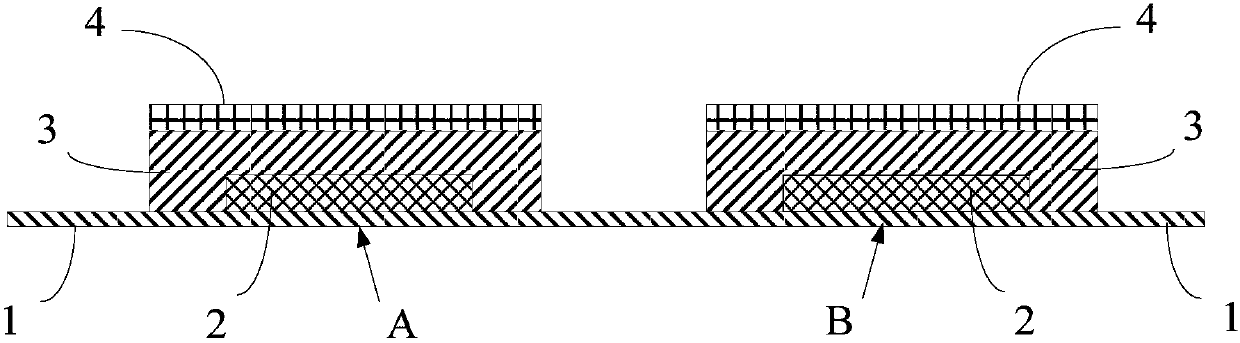

Active layer manufacturing method, oxide thin film transistor and manufacturing method thereof

InactiveCN106856173AOxygen point concentration decreasedReduce carrier concentrationTransistorSemiconductor/solid-state device manufacturingOxide thin-film transistorOptoelectronics

The invention discloses an active layer manufacturing method, an oxide thin film transistor and a manufacturing method thereof. The active layer manufacturing method comprises the following steps that an oxide thin film is deposited on a substrate and the oxide thin film is patterned so as to obtain an oxide layer; a photoresist layer covering the oxide layer is manufactured on the substrate, and the photoresist layer is patterned so that the oxide layer is enabled to be exposed out of a channel region; the substrate is arranged in electrolyte, the substrate acts as an anode, metal Pt acts as a cathode, anodic oxidation is performed on the substrate, and anodic oxidation is performed on the oxide layer on the channel region and then an active layer is formed; and the substrate is taken out and the photoresist layer is removed. The carrier concentration of the active layer is reduced by the anodic oxidation method so that positive shifting of device threshold voltage can be realized, the device is enabled to be in the "normally-off" state and thus the device of high stability and low power consumption can be obtained.

Owner:FOSHAN UNIVERSITY

Method for preparing nitrogen oxygen zinc thin film

ActiveCN103474356AImprove mobilityLow resistivitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingZinc nitrideRadio frequency magnetron sputtering

The invention discloses a method for preparing a nitrogen oxygen zinc thin film. Radio frequency magnetron sputtering is used, a zinc nitride target which is 99.9-99.999% in volume percentage is taken as sputtering target materials, and the distance between the target materials and a substrate is 20-150mm; under certain radio frequency, argon which is 99.9-99.999% in volume percentage is taken as sputtering gas, sputtering is carried out at the substrate temperature of 25-150DEG C and at power density of 0.5-5W / cm2, and the background vacuum of a sputtering room is smaller than 1*10-7torr; pre-sputtering is carried out for a period of time through the argon, and then oxygen which is 99.9-99.999% in volume percentage is taken as reaction gas to obtain the nitrogen zinc oxide thin film with oxygen flow of 0.1-60sccm and argon flow of 5-100sccm and at sputtering pressure of 0.1-10.0Pa, wherein the atomic number of Zn accounts for 51-66%, and N:O=1:3-2:1. The method for preparing the nitrogen zinc oxide thin film solves the problem that the nitrogen is low in solid solubility in zinc oxide, and the prepared n-type nitrogen zinc oxide thin film is high in carrier mobility and low in specific resistance.

Owner:SHENZHEN DANBANG INVESTMENT GROUP

Ni-doped CuCrO2-based oxide thermoelectric material and preparation method thereof

InactiveCN106006738AImprove conductivityReduce carrier concentrationThermoelectric device manufacture/treatmentChromates/bichromatesThermoelectric materialsChromium sesquioxide

The invention provides a Ni-doped CuCrO2-based oxide thermoelectric material. A chemical combination formula of the Ni-doped CuCrO2-based oxide thermoelectric material is CuCr1-xNixO2, and x is 0.001-0.08. A preparation method comprises the following steps: taking copper oxide, chromium sesquioxide and nickel oxide as starting materials; mixing, pre-sintering, carrying out tablet compressing and sintering to obtain the Ni-doped CuCrO2-based oxide thermoelectric material. The prepared nickel-doped CuCrO2 metal oxide thermoelectric material is excellent in thermoelectric property, the power factor of the thermoelectric material can reach up to 100 (mu)W / (mK<2>) to a maximum extent when the working temperature is 300 DEG C; meanwhile, by a solid-phase reaction mode, a preparation technology is simple in technological process, easy to control and suitable for large-scale production.

Owner:NORTH CHINA UNIV OF WATER RESOURCES & ELECTRIC POWER

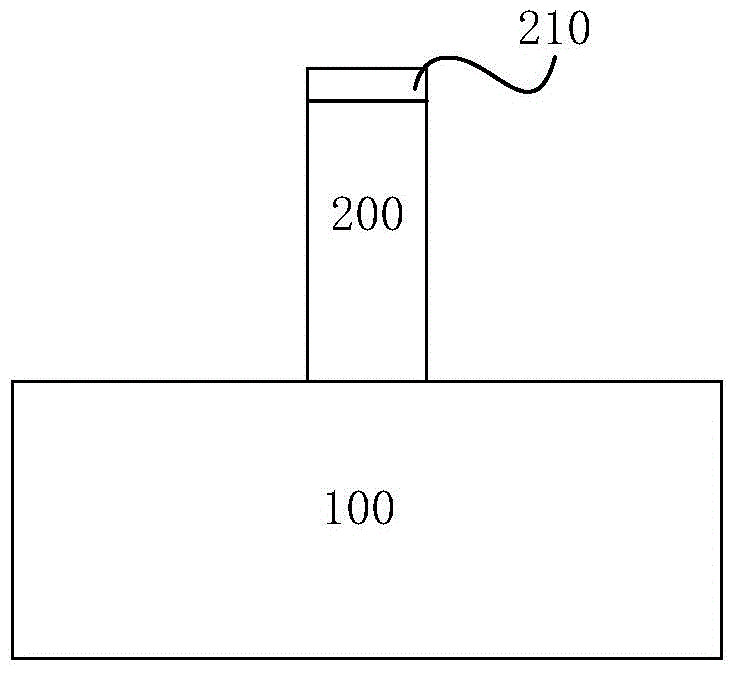

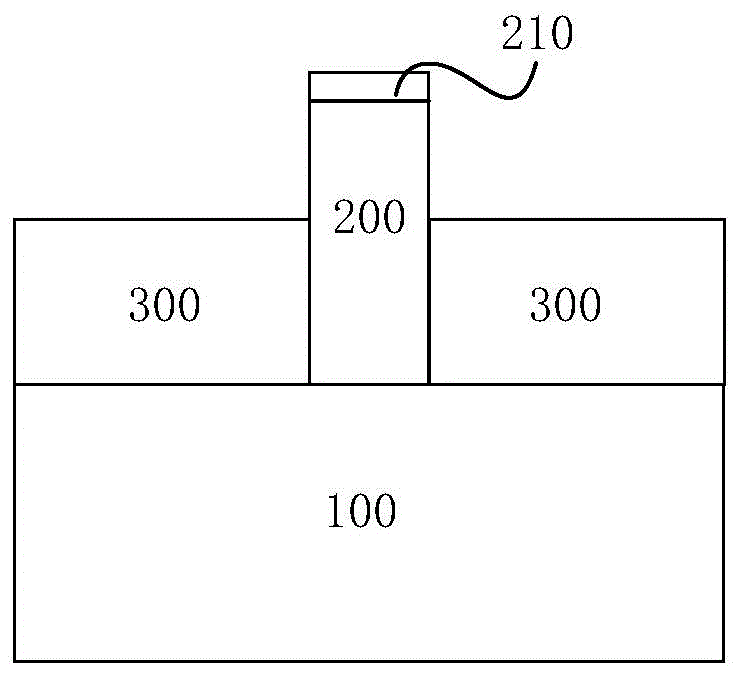

FinFET device and manufacturing method thereof

InactiveCN105632930AReduce carrier concentrationSuppression of punch-through currentSemiconductor/solid-state device manufacturingSemiconductor devicesIsolation layerEngineering

The invention provides an FinFET device and a manufacturing method thereof. The manufacturing method comprises the steps of a. providing a substrate on which a fin is disposed; b. forming shallow trench isolation on the substrate and at two sides of the fin; c. forming a protective mask at the two sides of the fin; d. thinning the shallow trench isolation to expose the fin partially; e. forming an isolation oxide layer on the fin that is not covered by the shallow trench isolation and the protective mask; f. removing the protective mask, and thickening the shallow trench isolation so as to be level with the isolation oxide layer; and g. forming a source and drain region, a gate structure and an interlayer dielectric layer in sequence on the thickened shallow trench isolation. According to the invention, the method of forming the oxide isolation layer in a region below a device trench allows a bulk silicon device have similar performance to an SOI device, and the punch-through current can be effectively suppressed without affecting other parameters of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

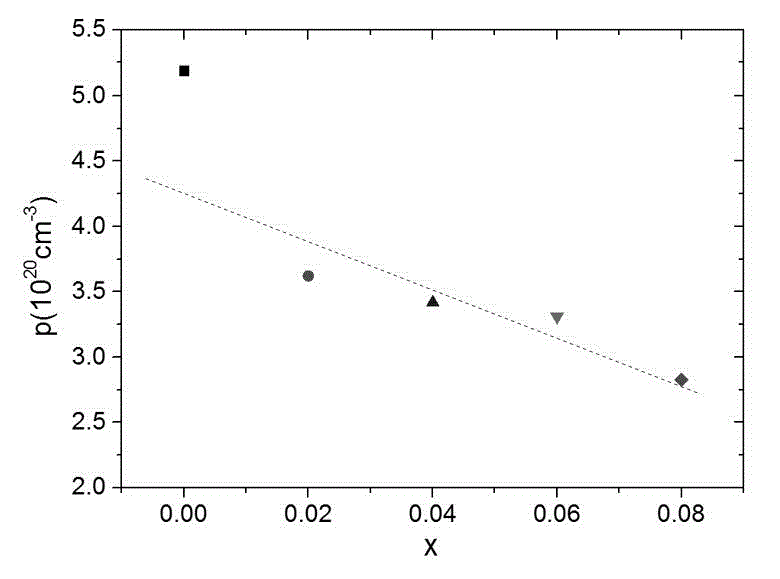

Copper-selenium based high performance thermoelectric material and preparation method of the same

ActiveCN105990510APromote precipitationPrevent precipitationThermoelectric device manufacture/treatmentThermoelectric device junction materialsThermoelectric materialsCopper

The invention relates to copper-selenium based high performance thermoelectric material and a preparation method of the same. The composition chemical formula of the copper-selenium based high performance thermoelectric material is Cu2Se1-xSX, wherein 0<x<=0.16. The copper-selenium based high performance thermoelectric material can restrain precipitation of copper to some extent so as to reduce the carrier concentration of a system.

Owner:SHANGHAI INST OF CERAMIC CHEM & TECH CHINESE ACAD OF SCI

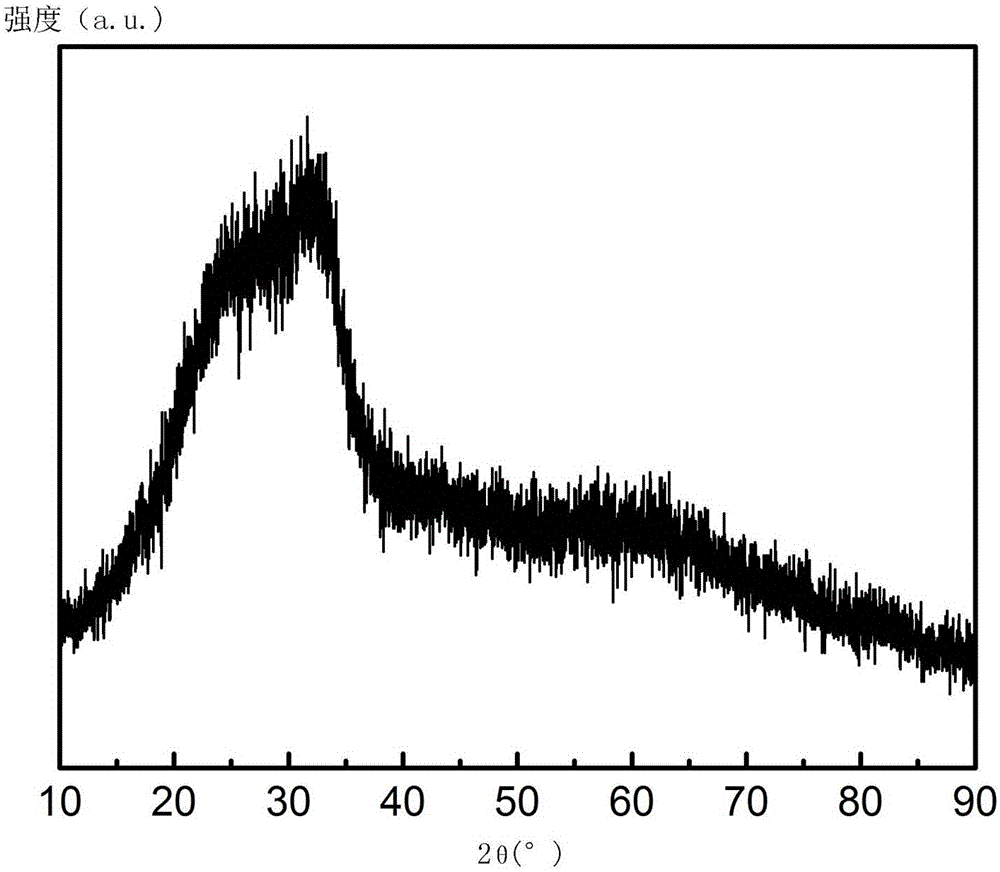

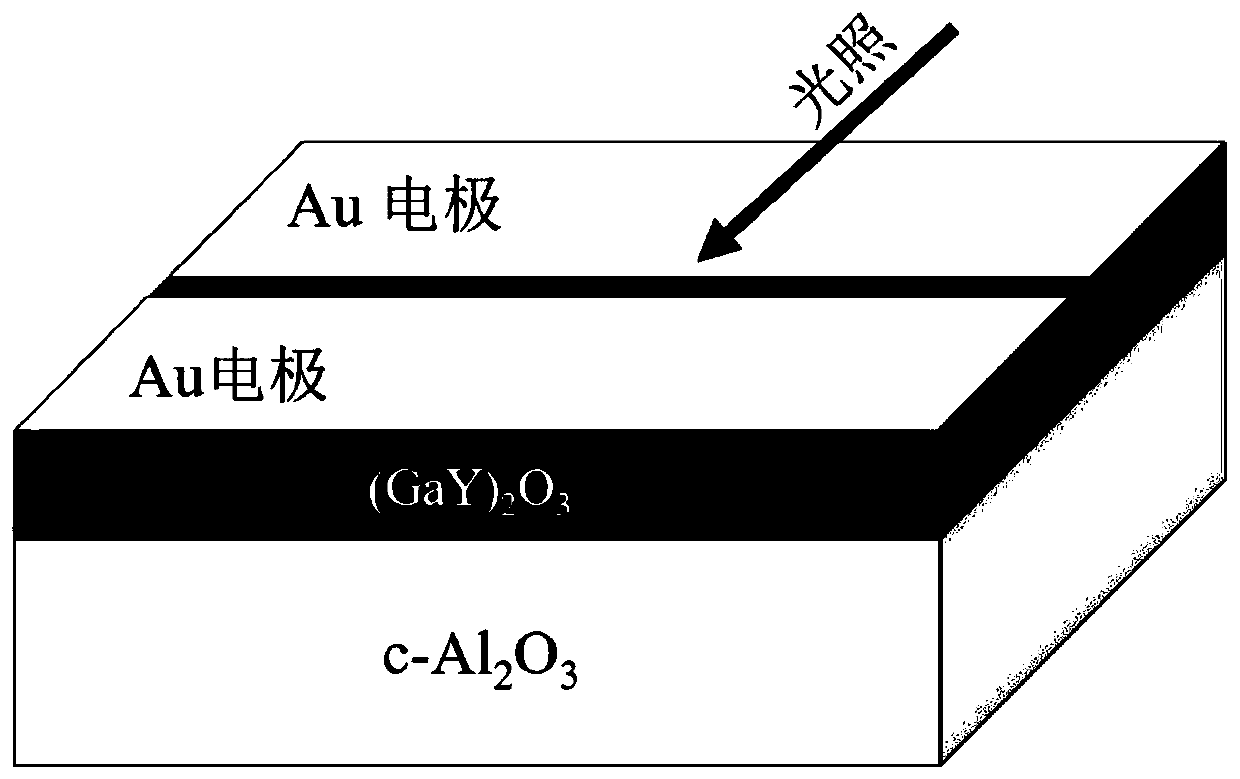

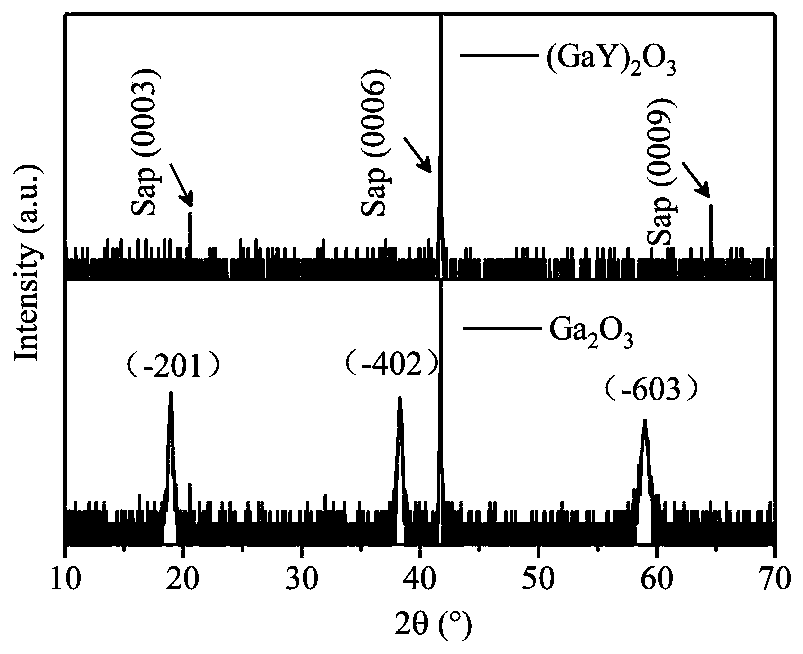

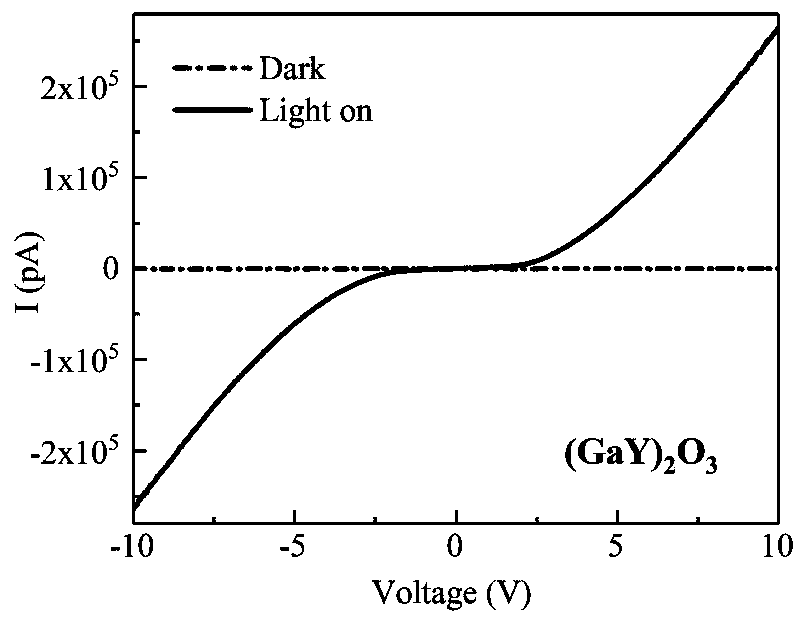

High-gain solar blind ultraviolet light detector based on (GaY)2O3 amorphous film and preparation method of high-gain solar blind ultraviolet light detector

ActiveCN110323291AReduce dark currentIncrease defect concentrationFinal product manufacturePhotovoltaic energy generationResponsivityUltraviolet lights

The invention discloses a high-gain solar blind ultraviolet light detector based on a (GaY)2O3 amorphous film and a preparation method of the high-gain solar blind ultraviolet light detector. The detector sequentially comprises a c-plane sapphire, an active layer and a pair of parallel electrodes from bottom to top, wherein the active layer is the amorphous (GaY)2O3 film. According to the invention, Y3+ ions are used for partially replacing Ga3+ ions in Ga2O3, so that the band gap of Ga2O3 is increased, and the thin film is converted into amorphous from single crystal. The amorphous (GaY)2O3 film with a higher band gap can effectively reduce the dark current of the device, and enables the cut-off wavelength to be blue-shifted to be within 280nm. Meanwhile, the amorphous (GaY)2O3 film has higher defect concentration, and the defects not only can improve the gain, but also can be used as a recombination center to promote carrier recombination, so that compared with a pure Ga2O3 device, an amorphous (GaY)2O3 device has the advantages that the responsivity is obviously improved, the relaxation time is obviously shortened, and the detection capability on deep ultraviolet light is greatly improved.

Owner:HUBEI UNIV +1

Array substrate manufacturing method, array substrate and display device

InactiveCN105957872AImproved negative bias stress toleranceReduced positive bias stress toleranceSolid-state devicesSemiconductor/solid-state device manufacturingOxideOptoelectronics

The invention discloses an array substrate manufacturing method, an array substrate and a display device, belonging to the technical field of display. The manufacturing method comprises steps: forming an oxide active layer on an underlayment substrate, wherein the underlayment substrate comprises a display region and a non-display region; forming a photoresist layer on the oxide active layer; forming an active layer pattern; removing the photoresist layer of the display region; performing plasma surface treatment for the oxide active layer of the display region to increase oxygen content of the oxide active layer of the display region. According to the invention, reliability of thin film transistors of the display region and the non-display region can be guaranteed at the same time.

Owner:BOE TECH GRP CO LTD

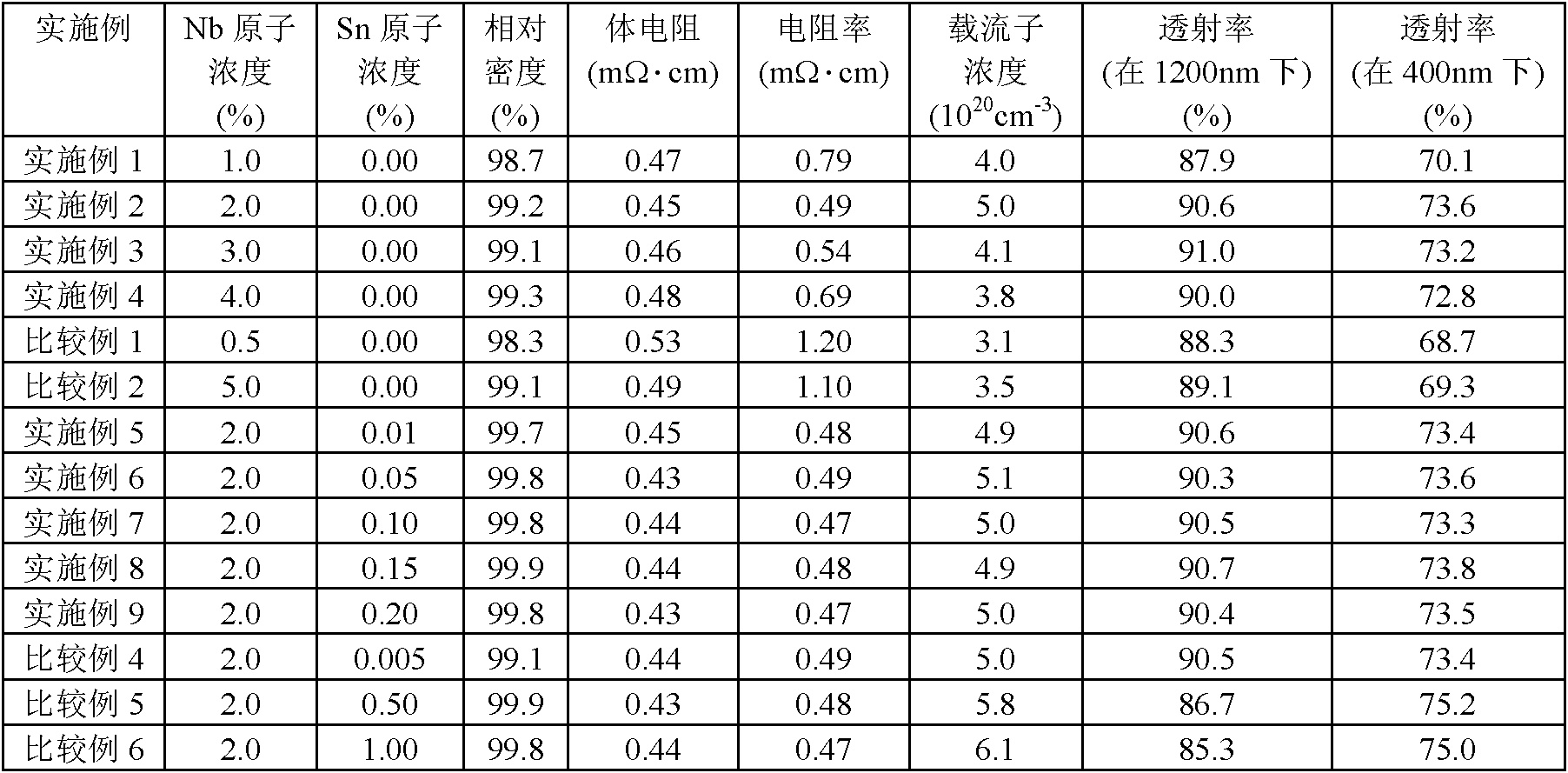

Indium oxide sintered body and indium oxide transparent conductive film

ActiveCN102666429AImprove transmittanceImprove conversion efficiencyConductive layers on insulating-supportsVacuum evaporation coatingIndiumNiobium

Disclosed is an indium oxide sintered body which contains niobium as an additive. The indium oxide sintered body is characterized in that: the ratio of the number of niobium atoms relative to the total number of atoms of all the metal elements contained in the sintered body is within the range of 1-4%; the relative density thereof is not less than 98%; and the bulk resistivity thereof is not more than 0.9 m[omega]cm. The indium oxide sintered body has high transmittances in short wavelength and long wavelength ranges, since the carrier concentration thereof is not too high although the resistivity thereof is low. Also disclosed is an indium oxide transparent conductive film.

Owner:JX NIPPON MINING & METALS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com