Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

72results about How to "Uniform resistivity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Silicon Single Crystal Doped with Gallium, Indium, or Aluminum

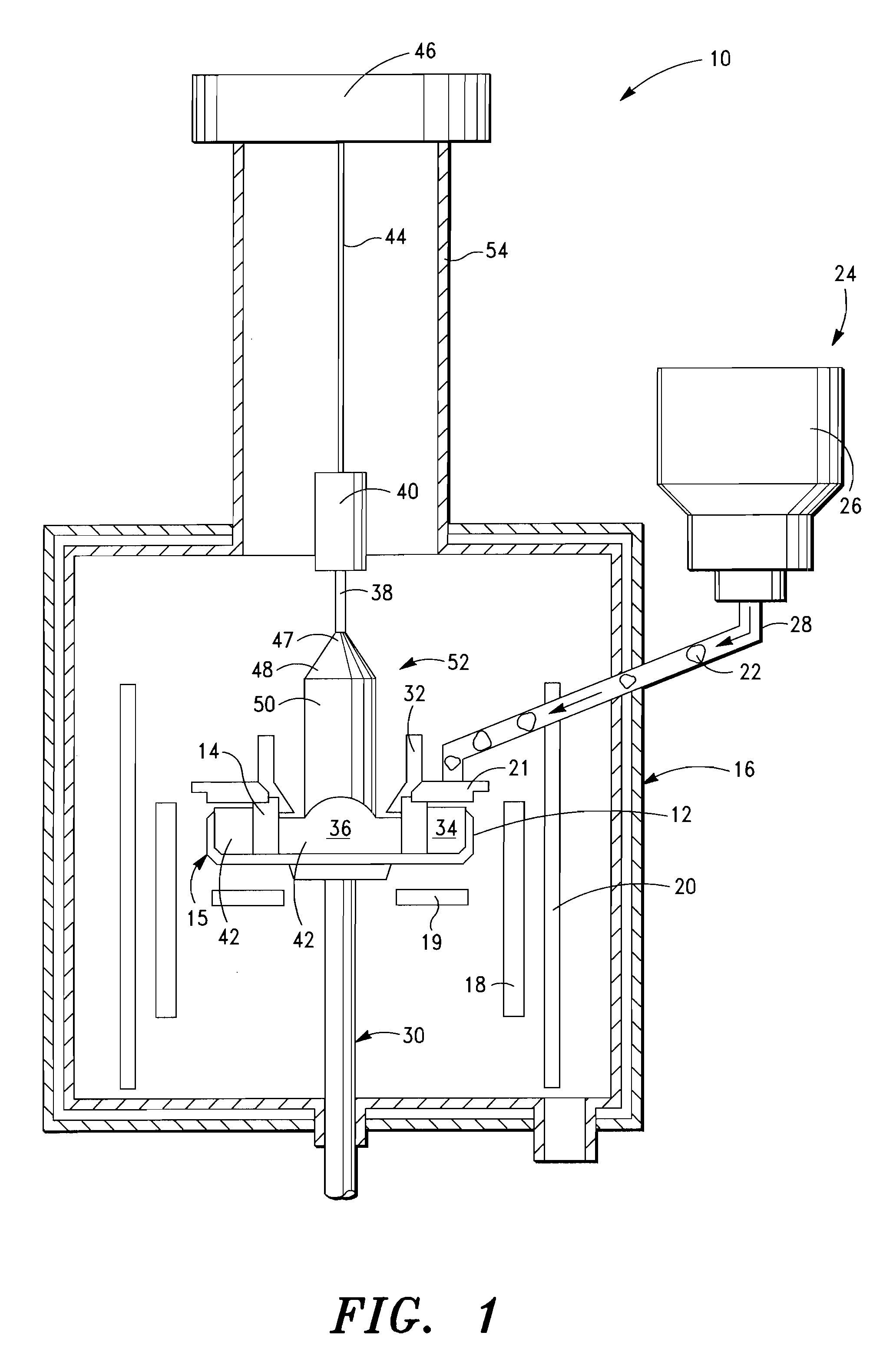

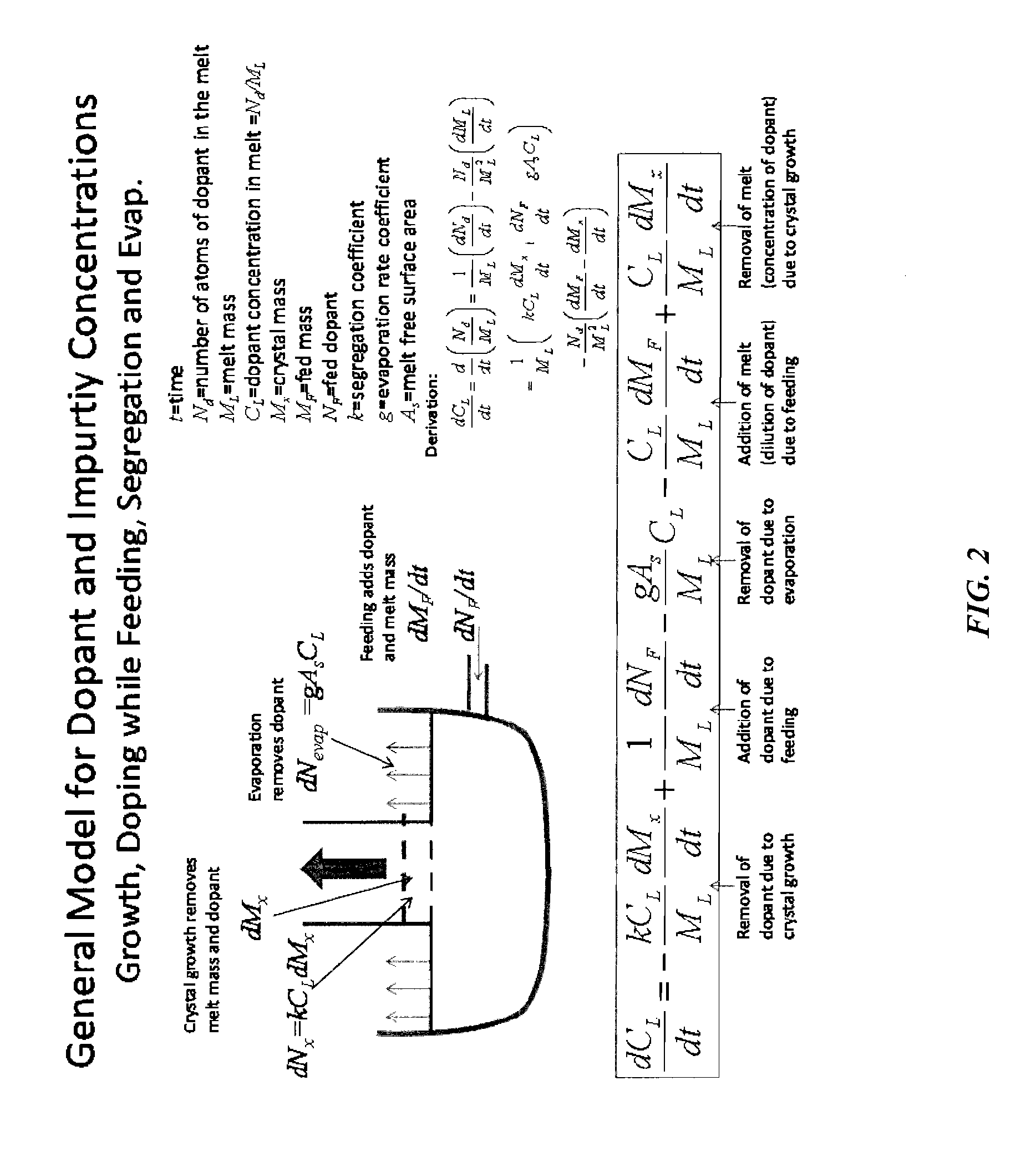

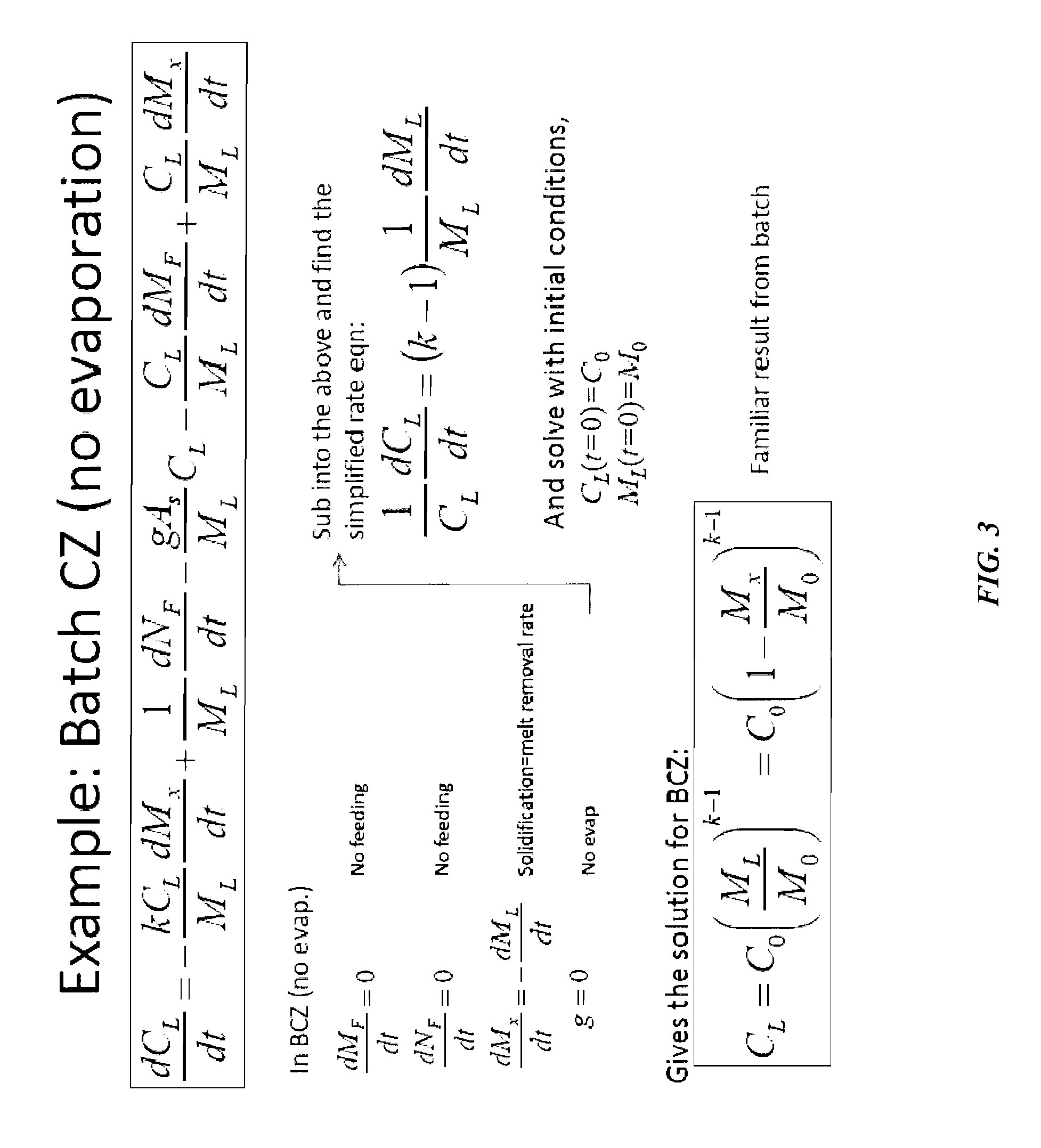

ActiveUS20120056135A1Reduces downtimeUniform resistivityPolycrystalline material growthConductive materialSeed crystalIndium

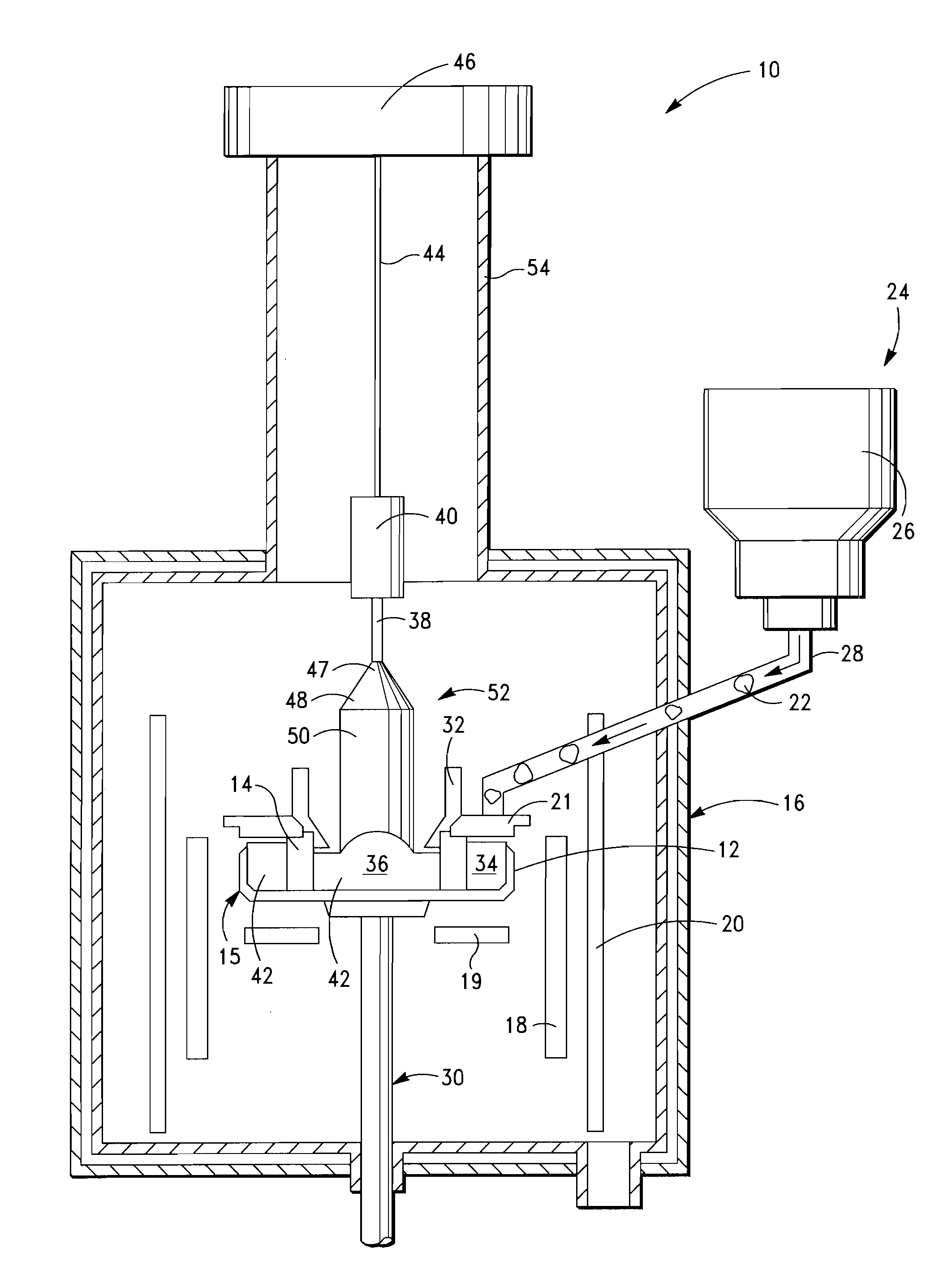

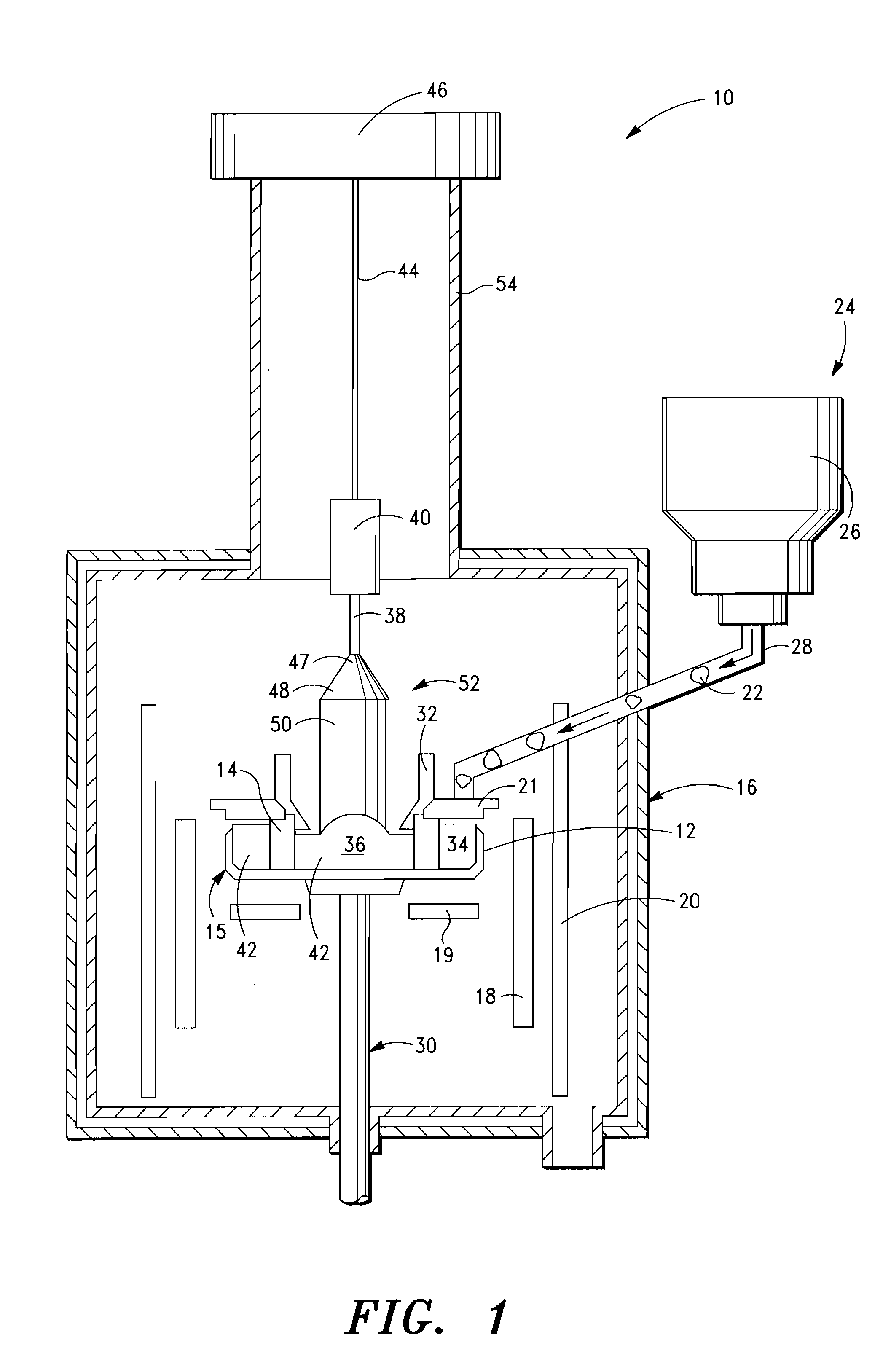

A doped silicon single crystal having a resistivity variation along a longitudinal and / or radial axis of less than 10% and a method of preparing one or a sequential series of doped silicon crystals is disclosed. The method includes providing a melt material comprising silicon into a continuous Czochralski crystal growth apparatus, delivering a dopant, such as gallium, indium, or aluminum, to the melt material, providing a seed crystal into the melt material when the melt material is in molten form, and growing a doped silicon single crystal by withdrawing the seed crystal from the melt material. Additional melt material is provided to the apparatus during the growing step. A doping model for calculating the amount of dopant to be delivered into the melt material during one or more doping events, methods for delivering the dopant, and vessels and containers used to deliver the dopant are also disclosed.

Owner:GTAT IP HLDG

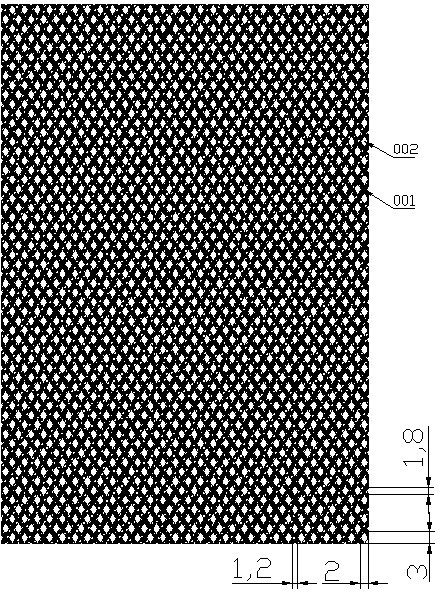

Electrothermic purifying filter element for treating high-air-quantity VOCs (volatile organic chemicals) waste gas

ActiveCN102600697AReduce wind resistanceRealize processingDispersed particle separationActivated carbonFiber

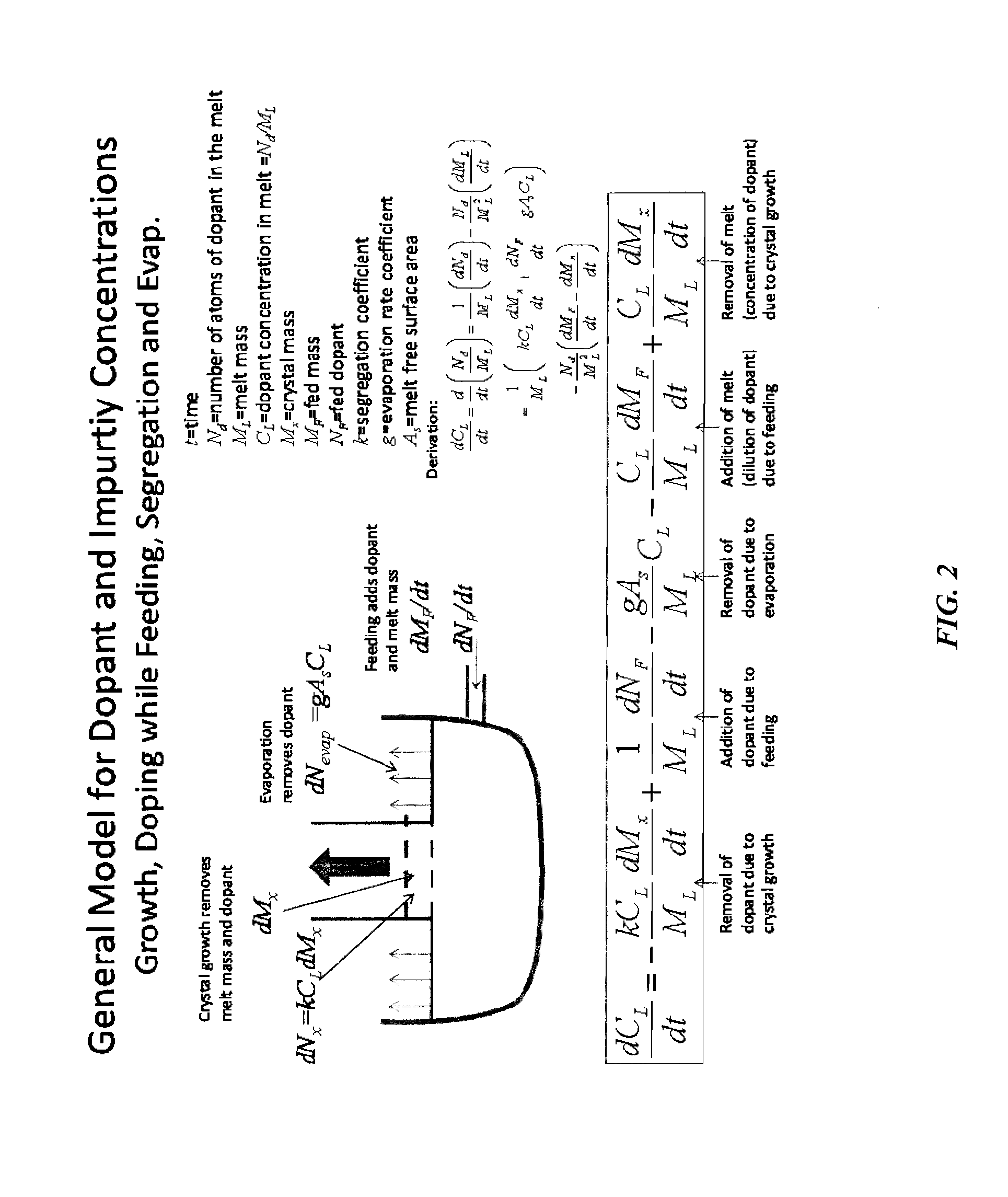

An electrothermic purifying filter element for treating high-air-quantity VOCs (volatile organic chemicals) waste gas comprises a containment structure and an adsorption bed layer filled in the containment structure, and is characterized in that activated carbon eyelet fabrics or / and porous activated carbon fiber cloth (felt) are overlapped to form the adsorption bed layer, an electrode A and an electrode B are arranged on two optional opposite end surfaces or positions close to the end surfaces of the adsorption bed layer, current can be led into the adsorption bed layer via the two electrodes, a couple is arranged in the adsorption bed layer, the temperature of the adsorption bed layer is tested in an electrothermic temperature rising process, the containment structure comprises a sealing portion, an air inlet surface and an air outlet surface, and each of the air inlet surface and the air outlet surface is made of one layer or multiple layers of mesh or porous materials. The air resistance of the electrothermic purifying filter element for treating the high-air-quantity VOCs waste gas is reduced, the high-air-quantity organic waste gas is treated by small equipment, filling quantities of adsorption materials in units of the adsorption bed layer are increased, adsorption period is long, energy consumption caused by frequent desorption and adsorption switching of the equipment due to low filling quantities of the adsorption materials is avoided, the adsorption materials are filled compactly, resistivity of the adsorption bed layer is uniform and identical, and potential safety hazards caused by local over heat are avoided.

Owner:李鑫焱

Method for processing silicon polished section with low-roughness concentration

ActiveCN101352829AIncrease roughnessReduce defectsPolishing machinesSemiconductor/solid-state device manufacturingSurface roughnessSingle crystal

The invention relates to a processing method of low roughness silicon polished wafers, which comprises a process during which polishing treatment is carried out for silicon single crystal wafers by utilizing a polisher, and the process sequentially comprises a rough polishing process, a moderate polishing process and a fine polishing process. In the fine polishing process, the polish finish is carried out for the silicon single crystal wafers by utilizing polishing cloth and fine polishing slurries are introduced between the polishing cloth and the silicon single crystal wafer surface, and the fine polishing slurry consists of pure water and activators. The surface roughness of the silicon wafer processed by the processing method can be raised to 3 to 5 degree, the performance is steady and the resistivity is uniform.

Owner:无锡光炜电子材料有限公司

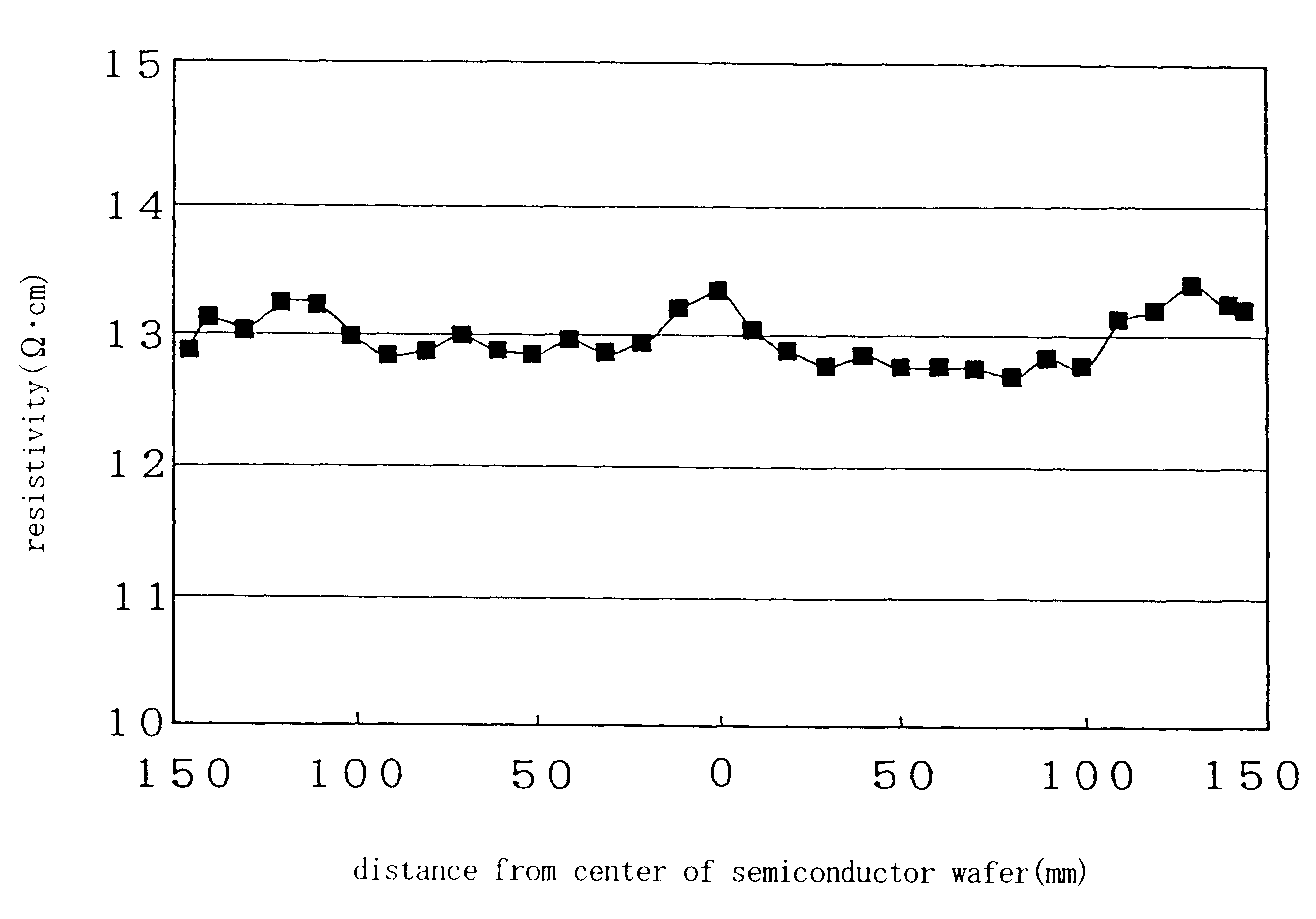

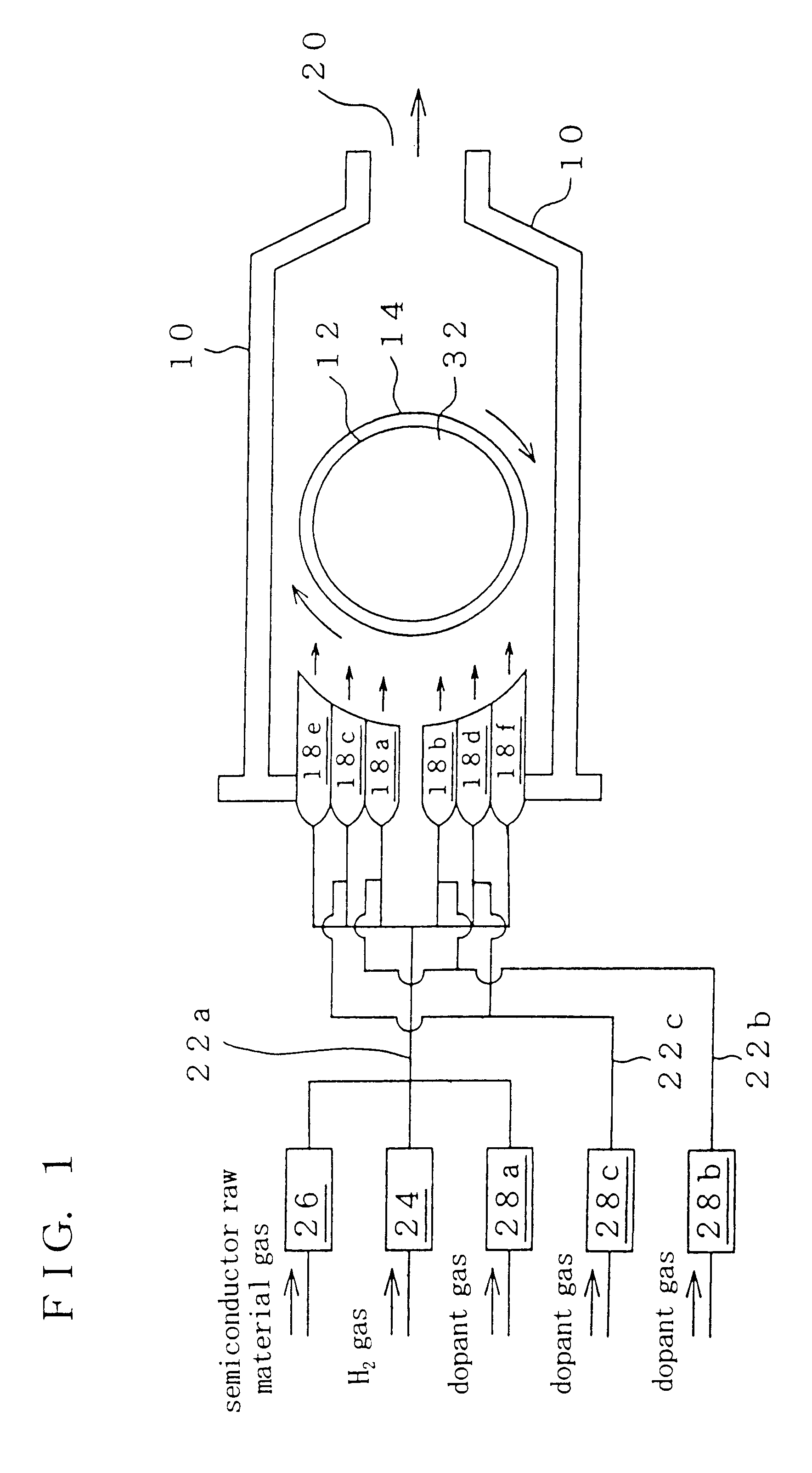

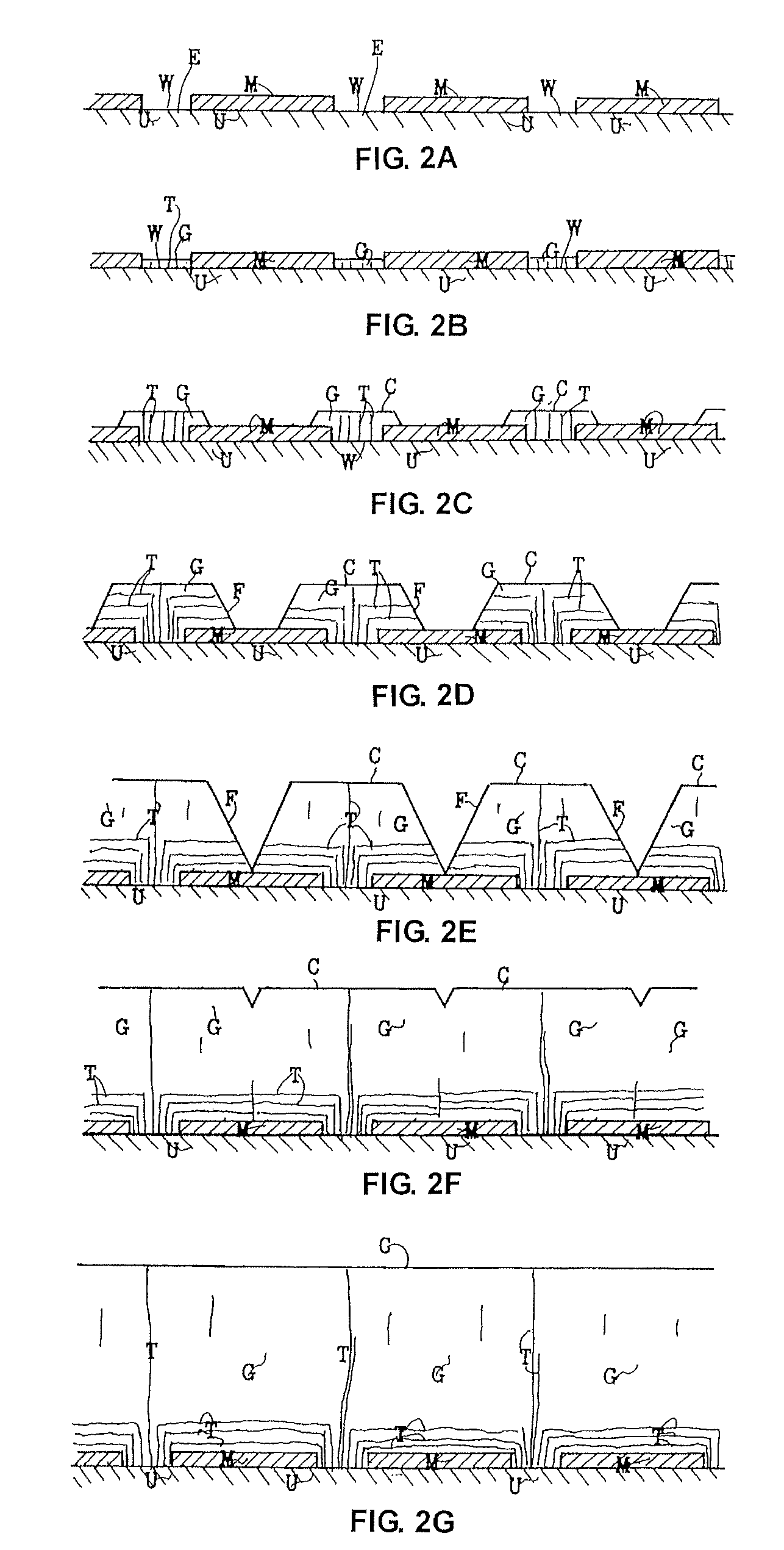

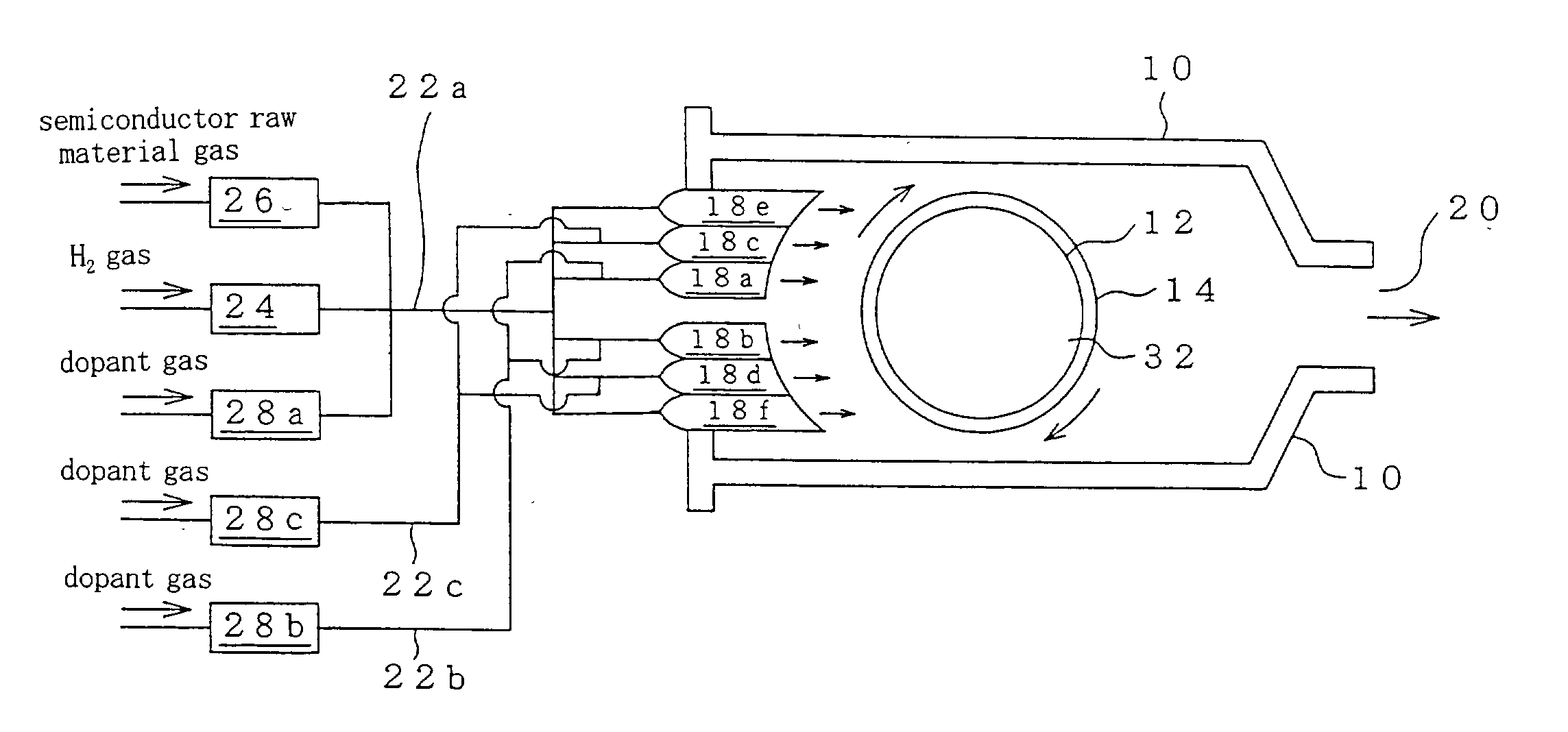

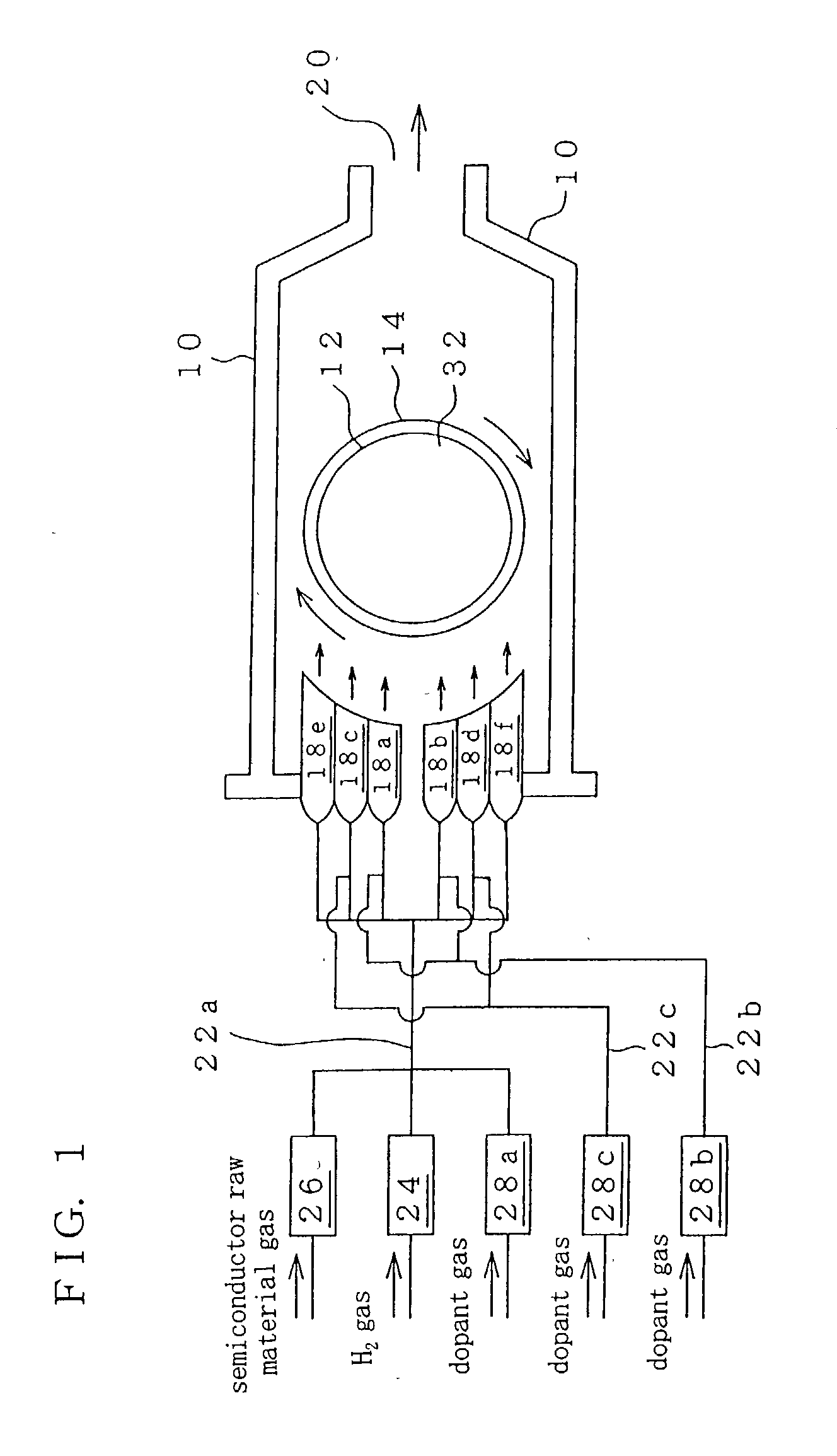

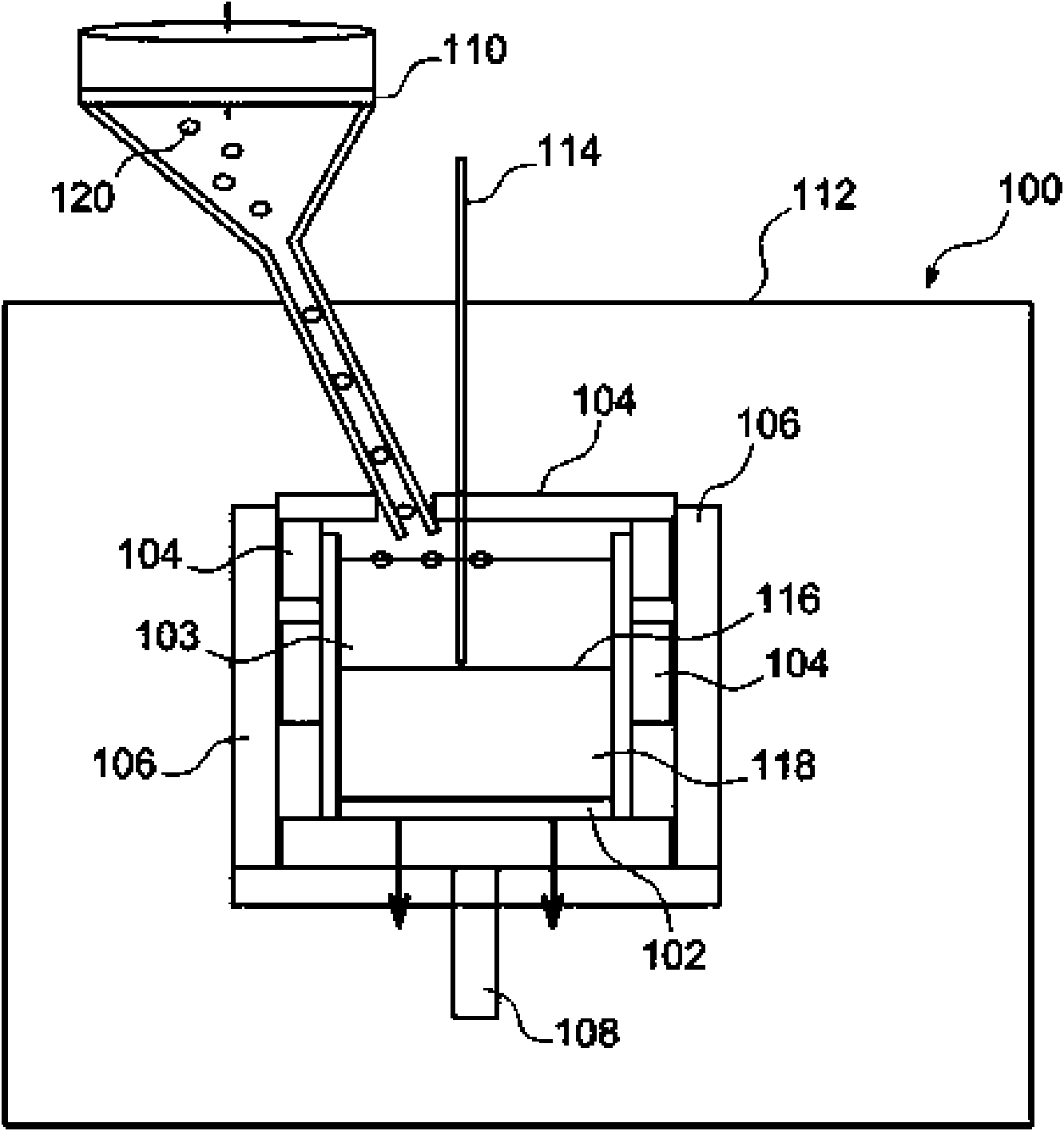

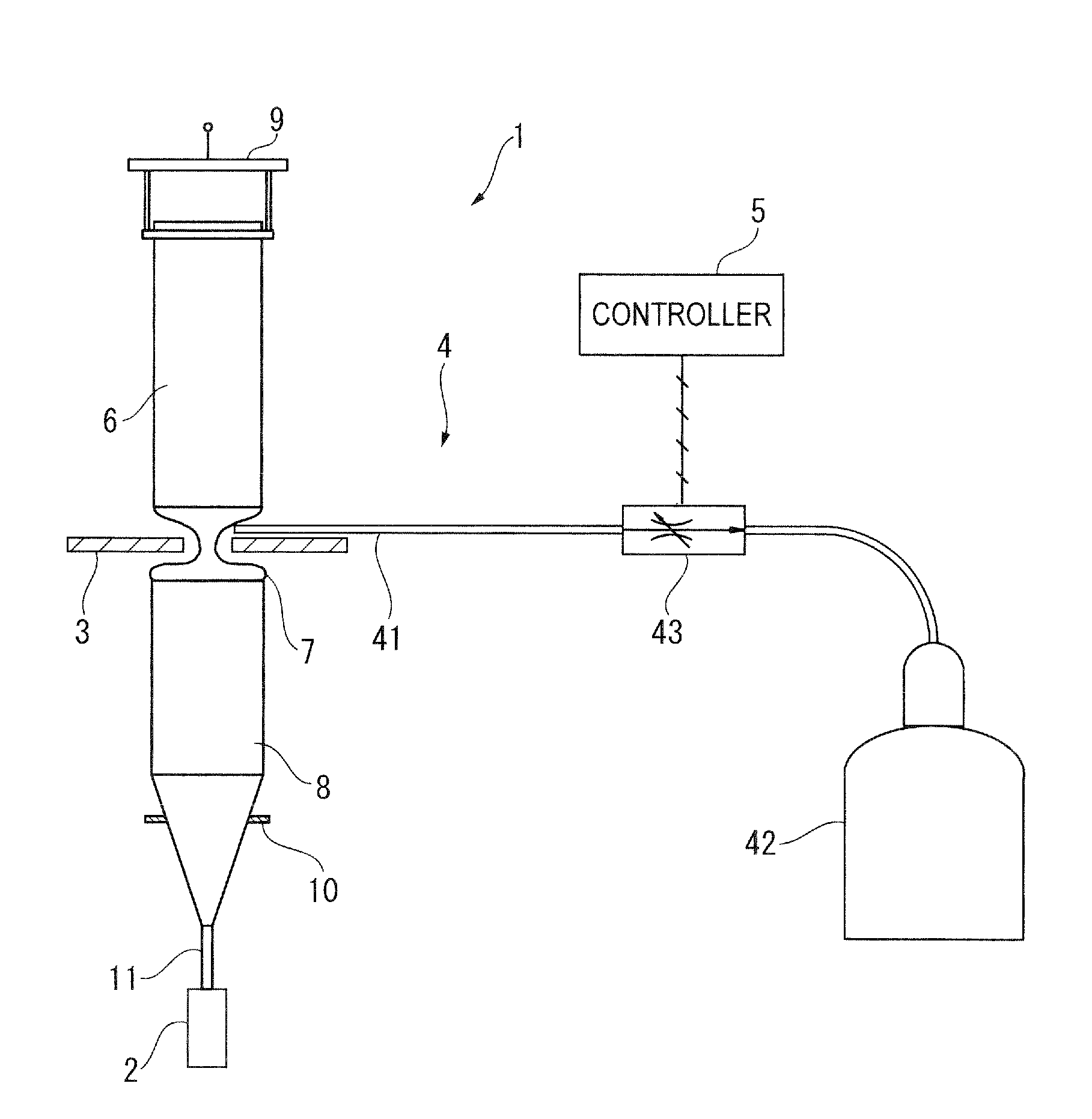

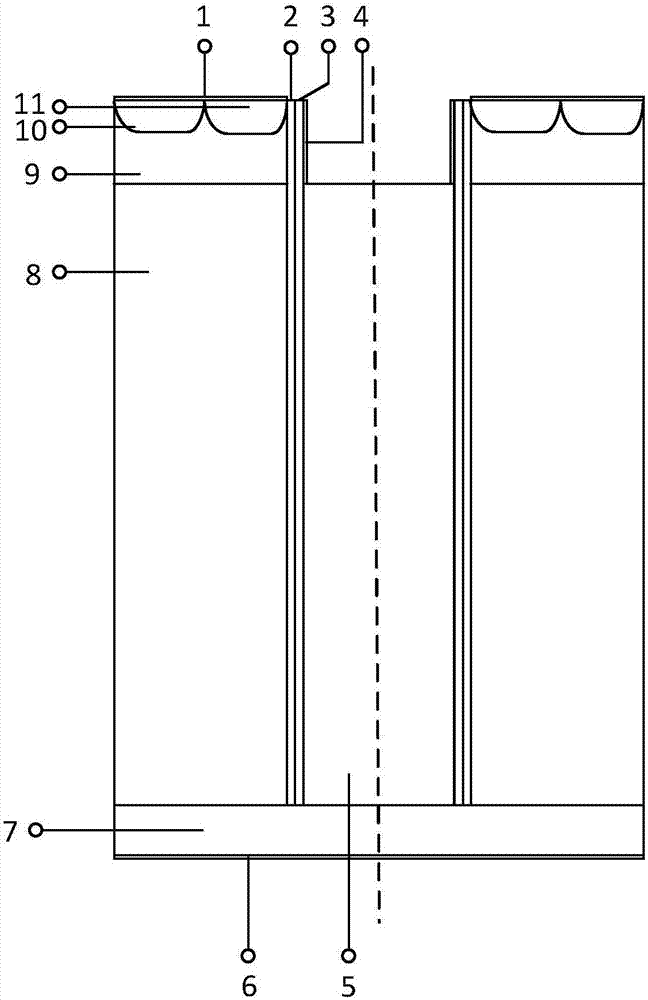

Semiconductor wafer and vapor growth apparatus

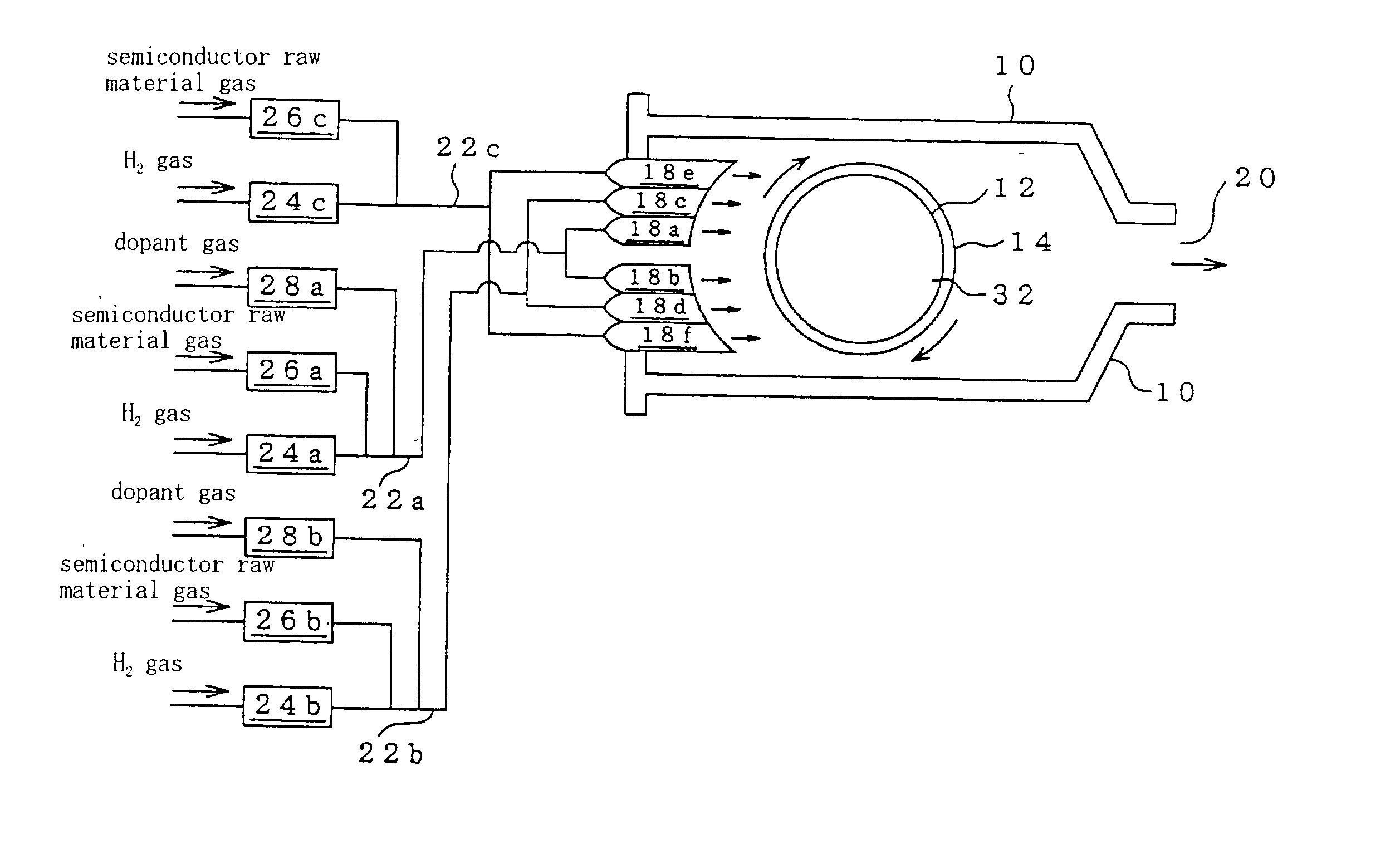

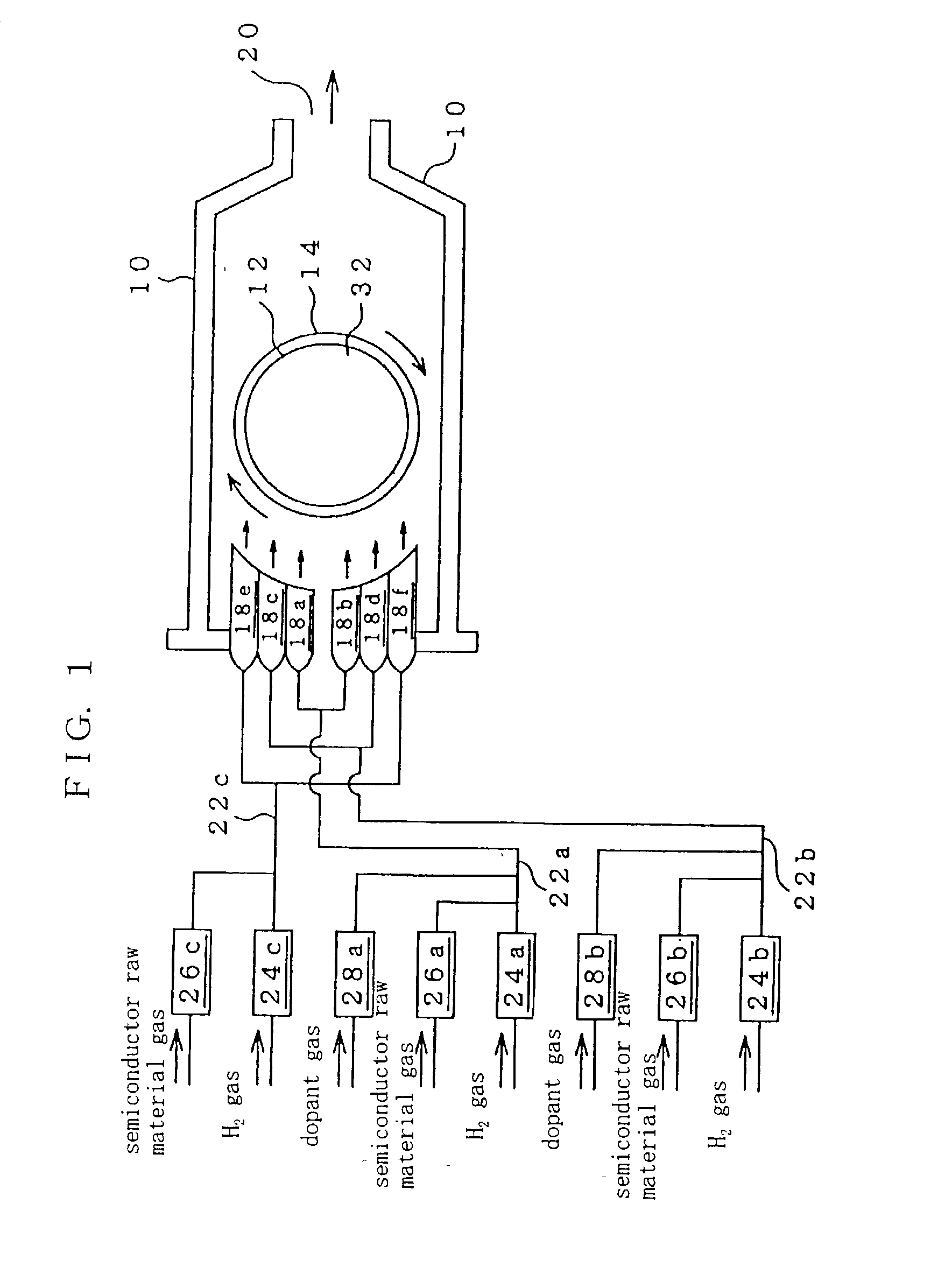

InactiveUS6475627B1Uniform resistivityImprove throughputPolycrystalline material growthSemiconductor/solid-state device manufacturingDislocationVapor phase

It is the object of the present invention to provide not only a semiconductor wafer obtained by forming a semiconductor thin film with uniform resistivity and substantially no slip dislocation on a main surface of a semiconductor single crystal substrate having a relatively low dopant concentration, as large as 300 mm or more in diameter but also a vapor phase growth apparatus by means of which such a semiconductor wafer can be produced. A dopant gas is supplied into a reaction chamber 10 through all of the inlet ports 18a to 18f disposed in a width direction of the reaction chamber 10 from a common gas pipe 22a functioning as a main dopant gas pipe. Further, the dopant gas is additionally supplied through inner inlet ports 18a and 18b, and middle inlet ports 18c and 18d, as specific gas inlet ports, into the reaction chamber 10 from first and second auxiliary dopant gas pipes 22b and 22c.

Owner:SHIN-ETSU HANDOTAI CO LTD

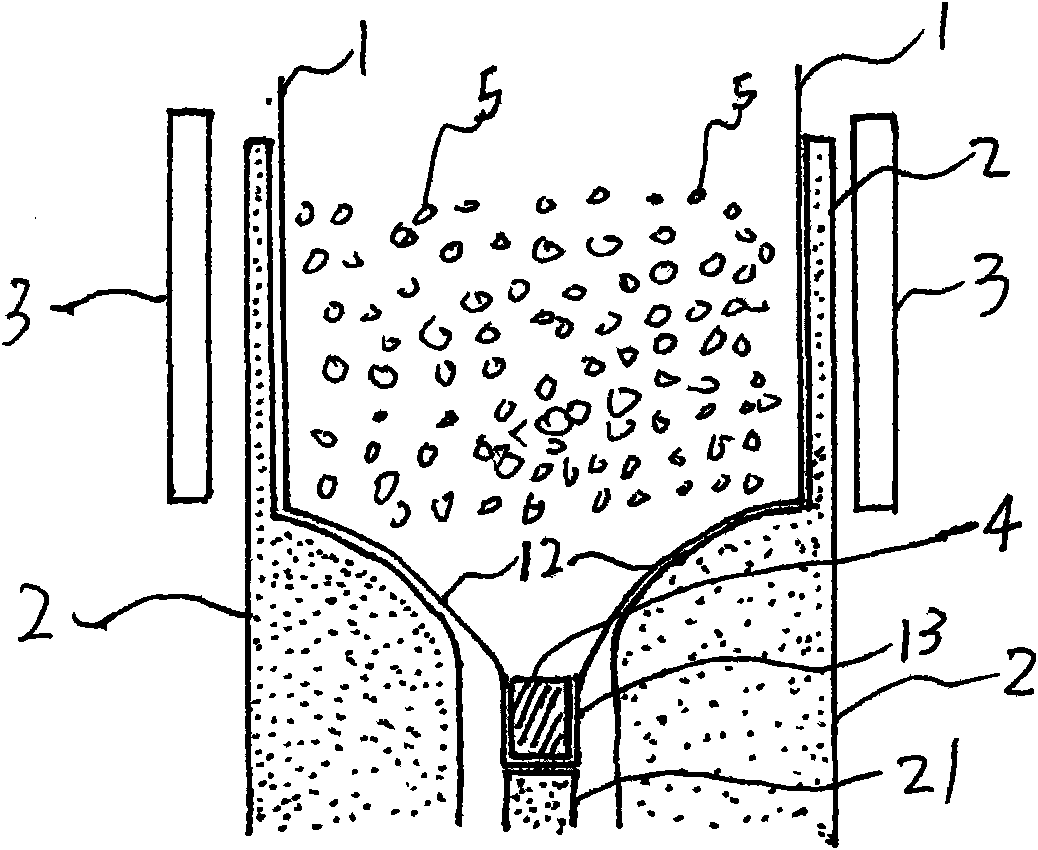

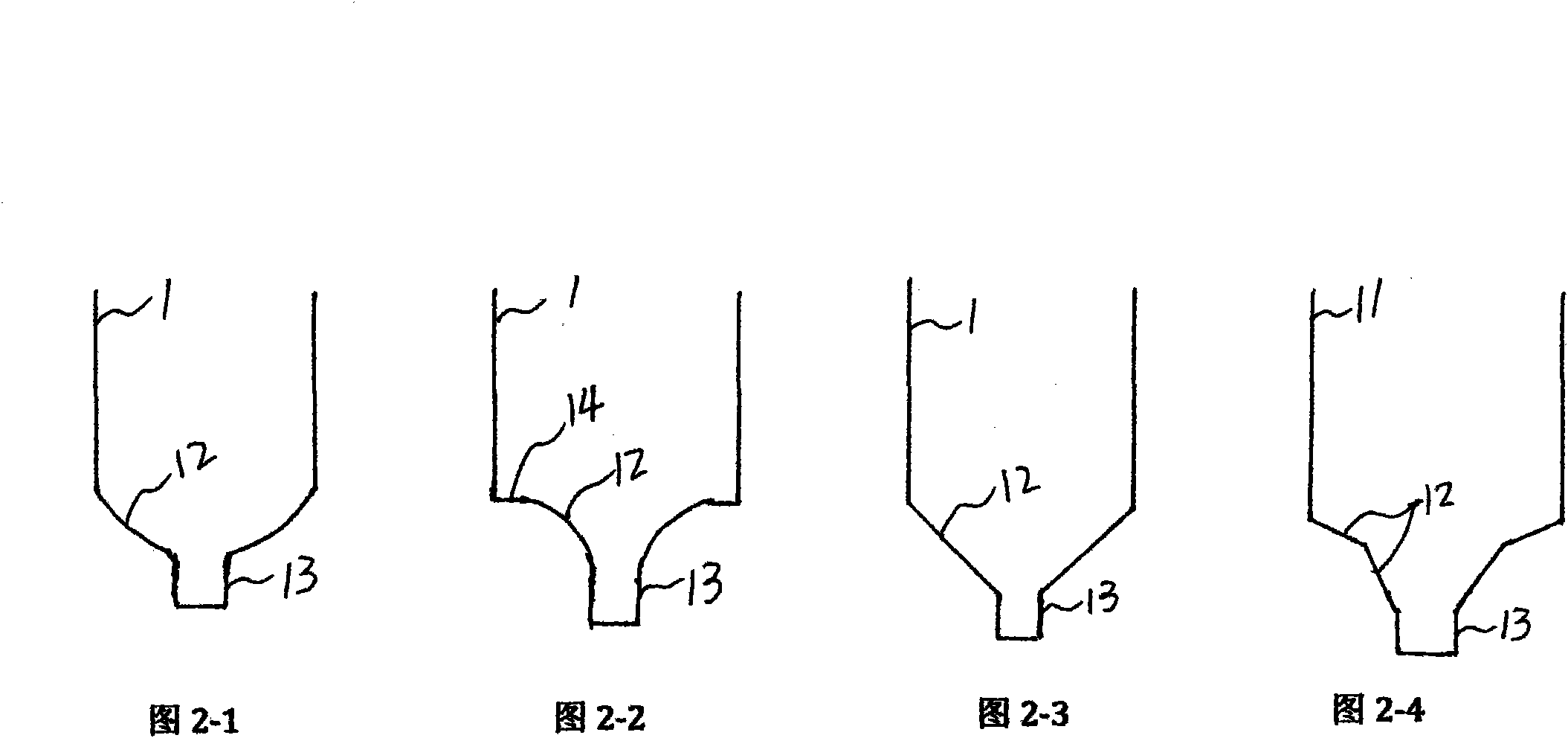

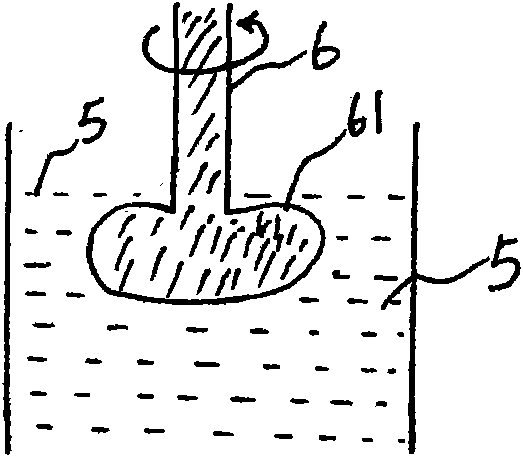

Method for casting crystal by seed crystal induction

InactiveCN102312279AImprove photoelectric efficiencyLow costFrom frozen solutionsSeed crystalDirectional solidification

The invention relates to a crystal material with a bigger size, which is manufactured by using a seed crystal induction vertical directional solidification casting method, in particular to a polycrystal or monocrystal material suitable for photoelectric application, such as silicon or silicon germanium. A traditional seed crystal used for casting a silicon crystal has a bigger size and higher consumption, thus, the invention provides a seed crystal with a smaller size and lower consumption, a method of casting a polycrystal or a monocrystal with the bigger size by using the seed crystal and the directional solidification method, the crystal material obtained by adopting the method, including a semiconductor crystal, and an application of the seed crystal in manufacturing semiconductor devices.

Owner:赵钧永

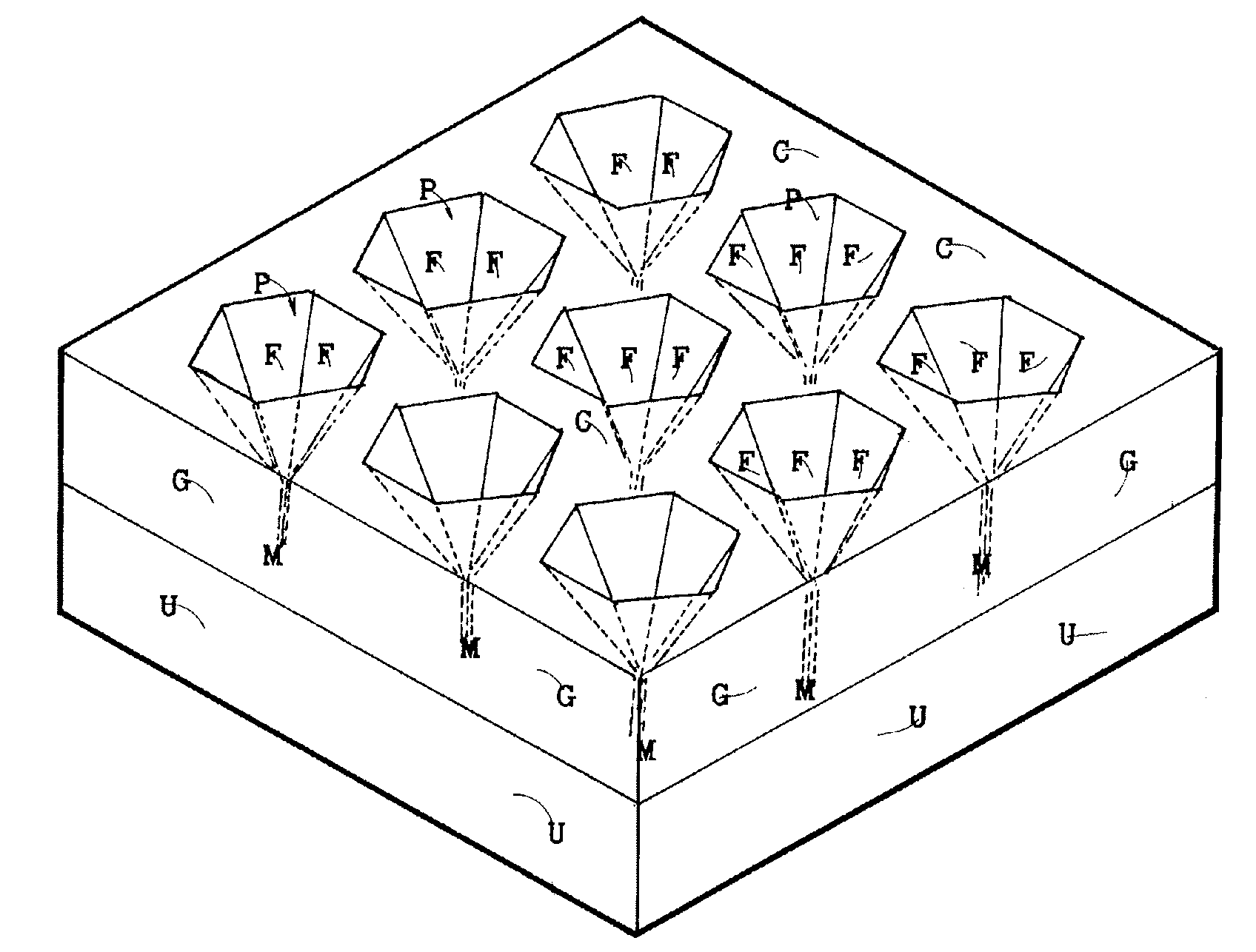

Crystal material containing seed crystal and manufacturing method and manufacturing device thereof

InactiveCN102312281ALow costImprove photoelectric efficiencyFrom frozen solutionsCrystal orientationDirectional solidification

The invention generally relates to a vertical directional solidification casting method using seed crystal induction, which is used for manufacturing a crystal material with a reserved crystal orientation and comprises a polycrystal material and a monocrystal material. When a traditional method for casting the crystal by using the seed crystal induction is used for producing the crystal with a bigger size, the problems that the seed crystal consumption is high, a mixed crystal is easy to generate, the internal stress is high, the monocrystal material is hard to obtain or the expected quality requirement is hard to reach and the like exist. The problems are solved by the invention through providing a gradually-changed crystal growth area of which the horizontal cross section is gradually increased, thereby, a good crystal growth effect is obtained, and the obtained cast monocrystal or polycrystal material, such as silicon or silicon germanium, has fewer defects, high quality and a good performance, and is especially suitable for the application of the semiconductor field and the photovoltaic field.

Owner:赵钧永

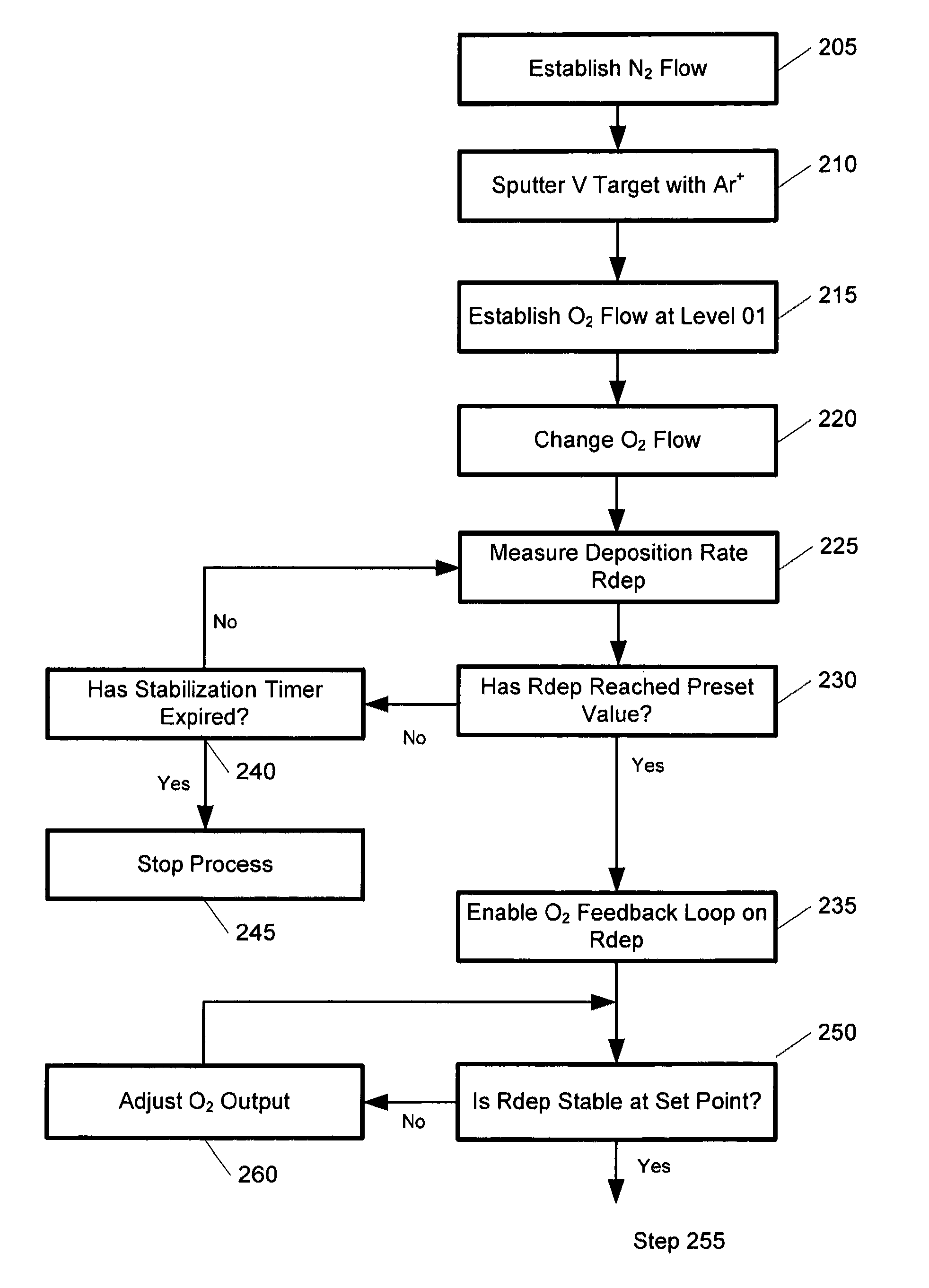

Thin films and methods and machines for forming the thin films

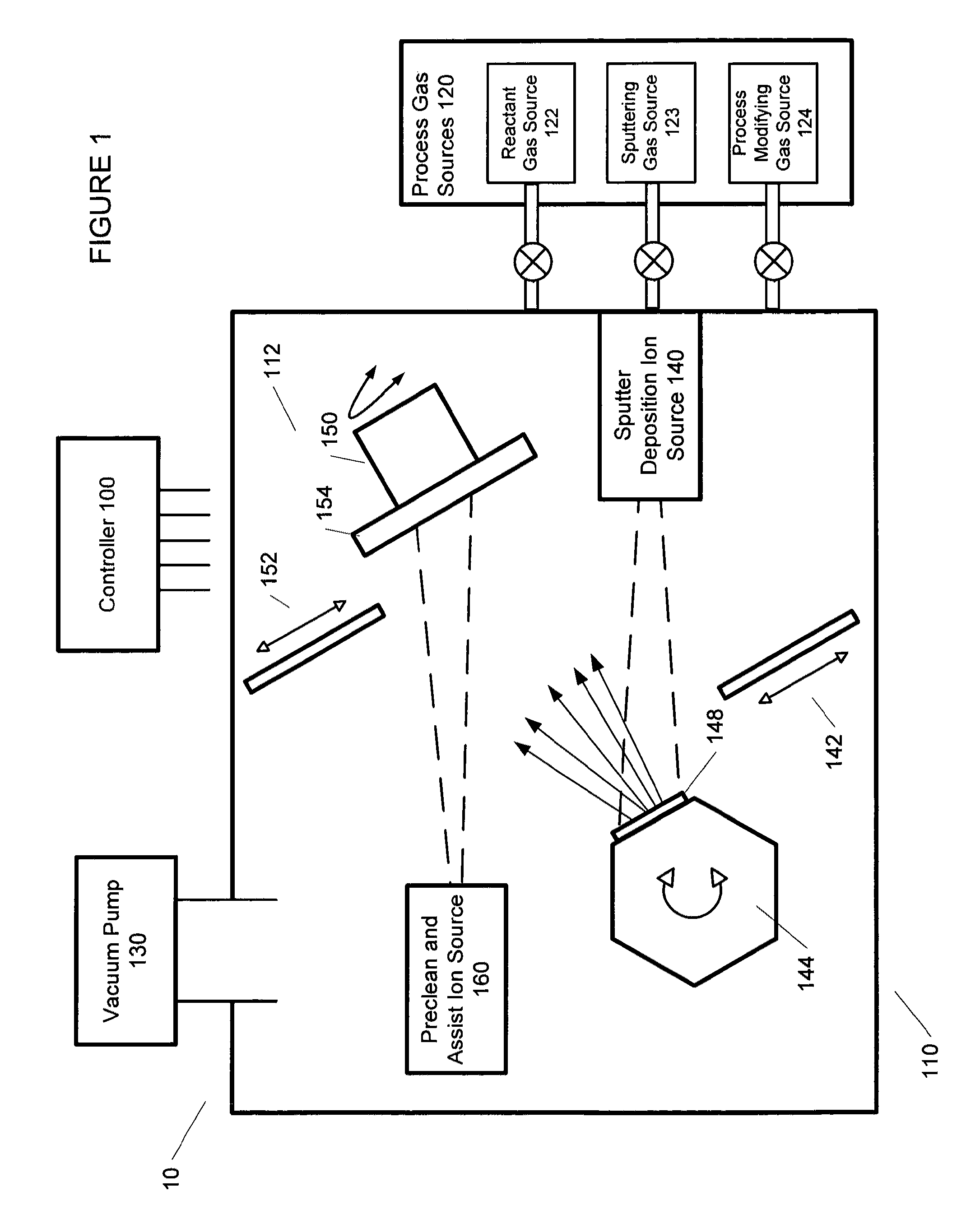

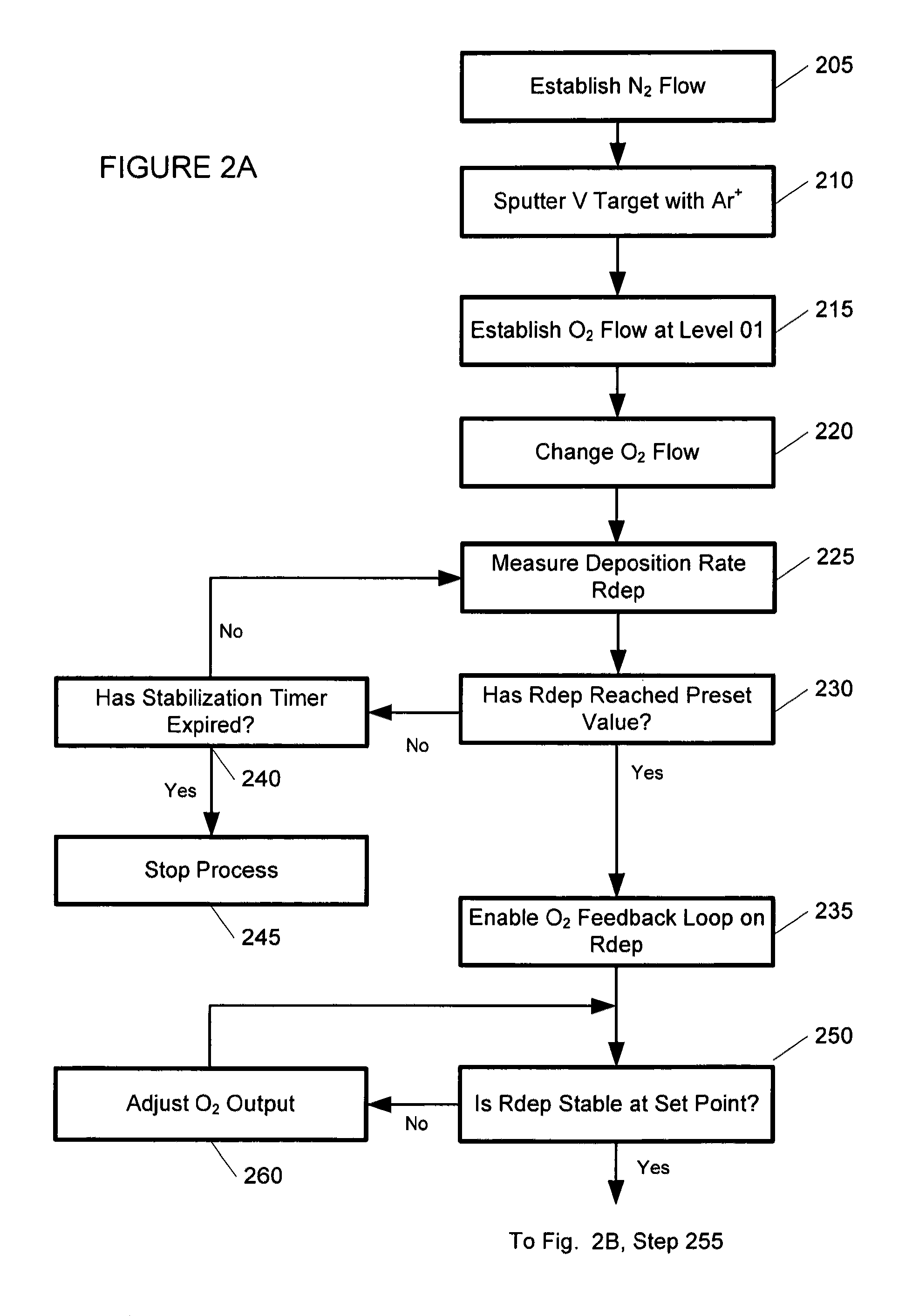

ActiveUS8329002B1Easy to optimizeImprove stabilityVacuum evaporation coatingSputtering coatingNitrogenBolometer

Methods for depositing an amorphous vanadium oxide (VOx) film include vaporizing vanadium from a vanadium source while the a gas containing an oxygen species and a process modifying additive are in the chamber so as to deposit an amorphous VOx film on the substrate, where x>0. The process modifying additive includes a gas flowing into the chamber or vaporized material from a target source. The additive may stabilize the deposition rate of VOx, reduce resistivity, improve thickness control, and improve uniformity of thickness and resistivity. The thin film may be a nitrogen-enhanced, amorphous vanadium oxide (VOxNy) film formed on a substrate, where x>y>0, and the film contains at least 0.2 atomic % nitrogen. The film may be used in a device, such as a thermal or infrared sensor, or more particularly a bolometer.

Owner:4WAVE

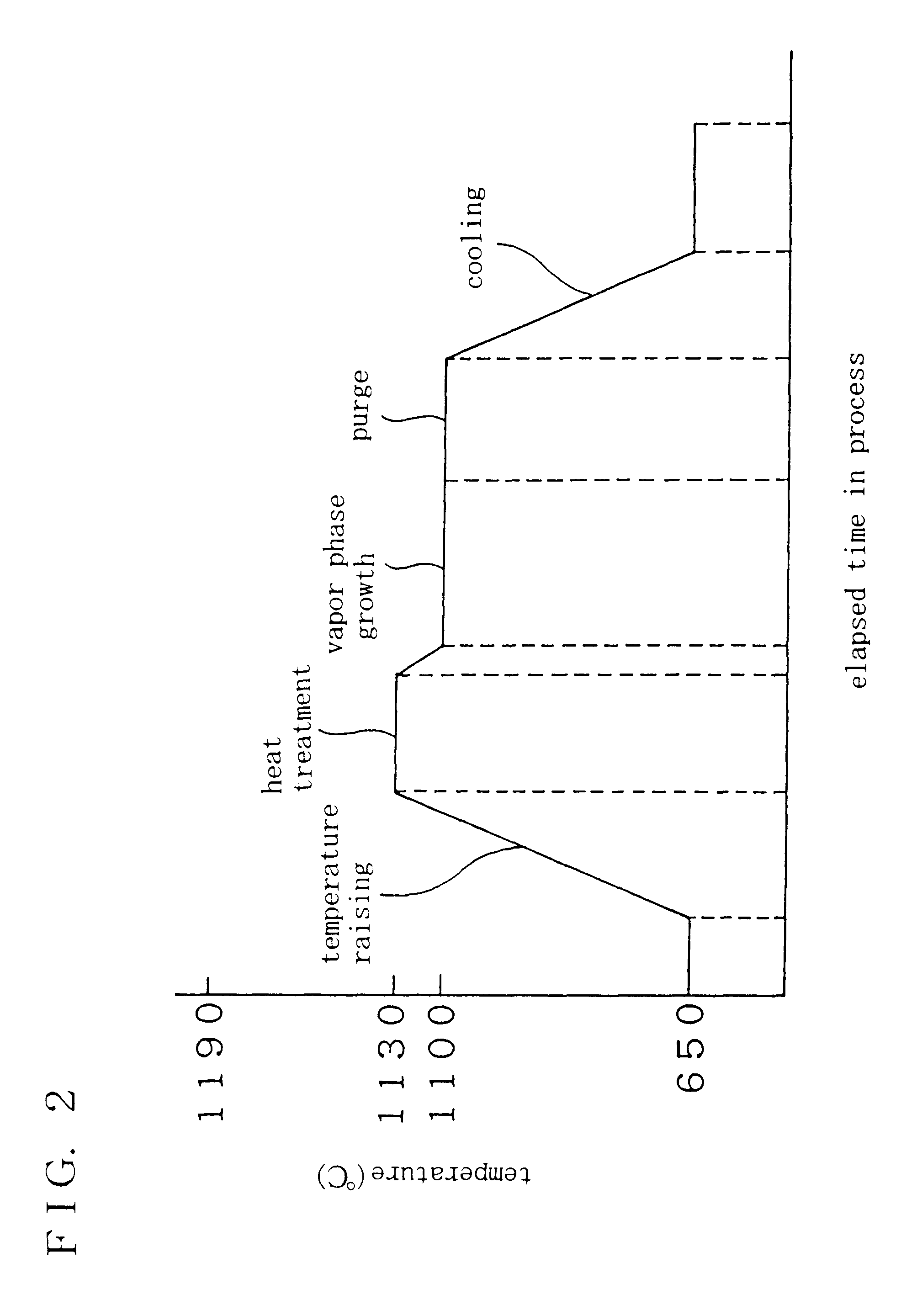

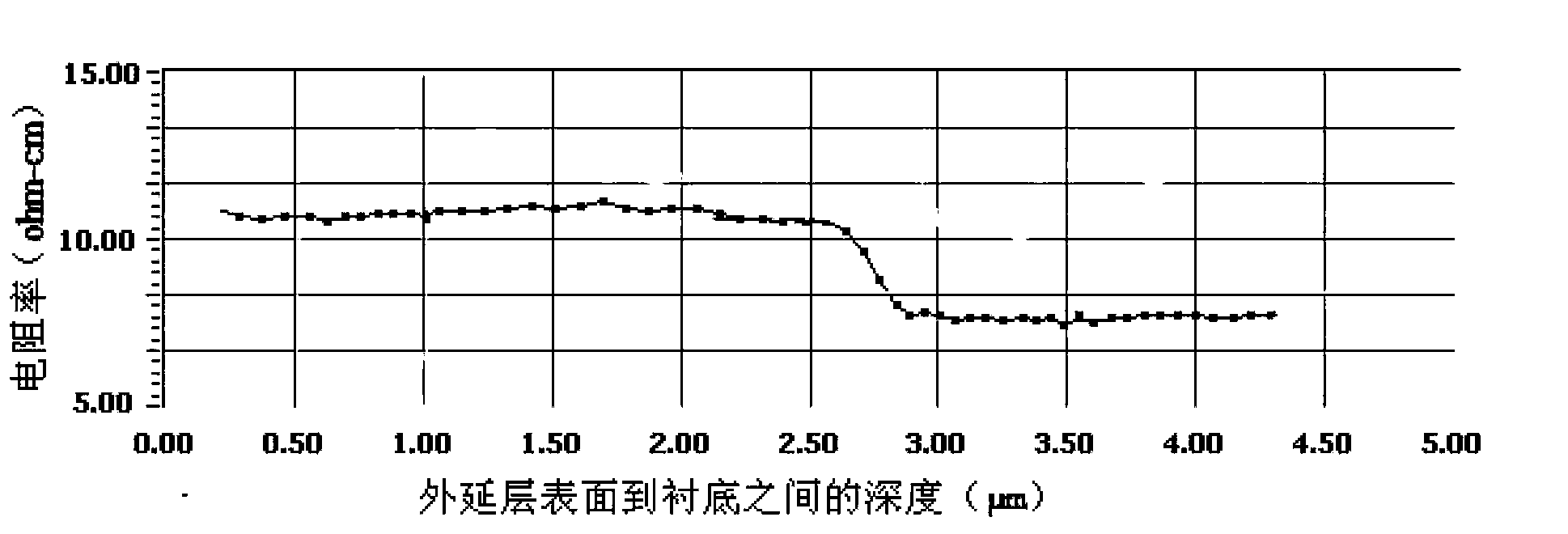

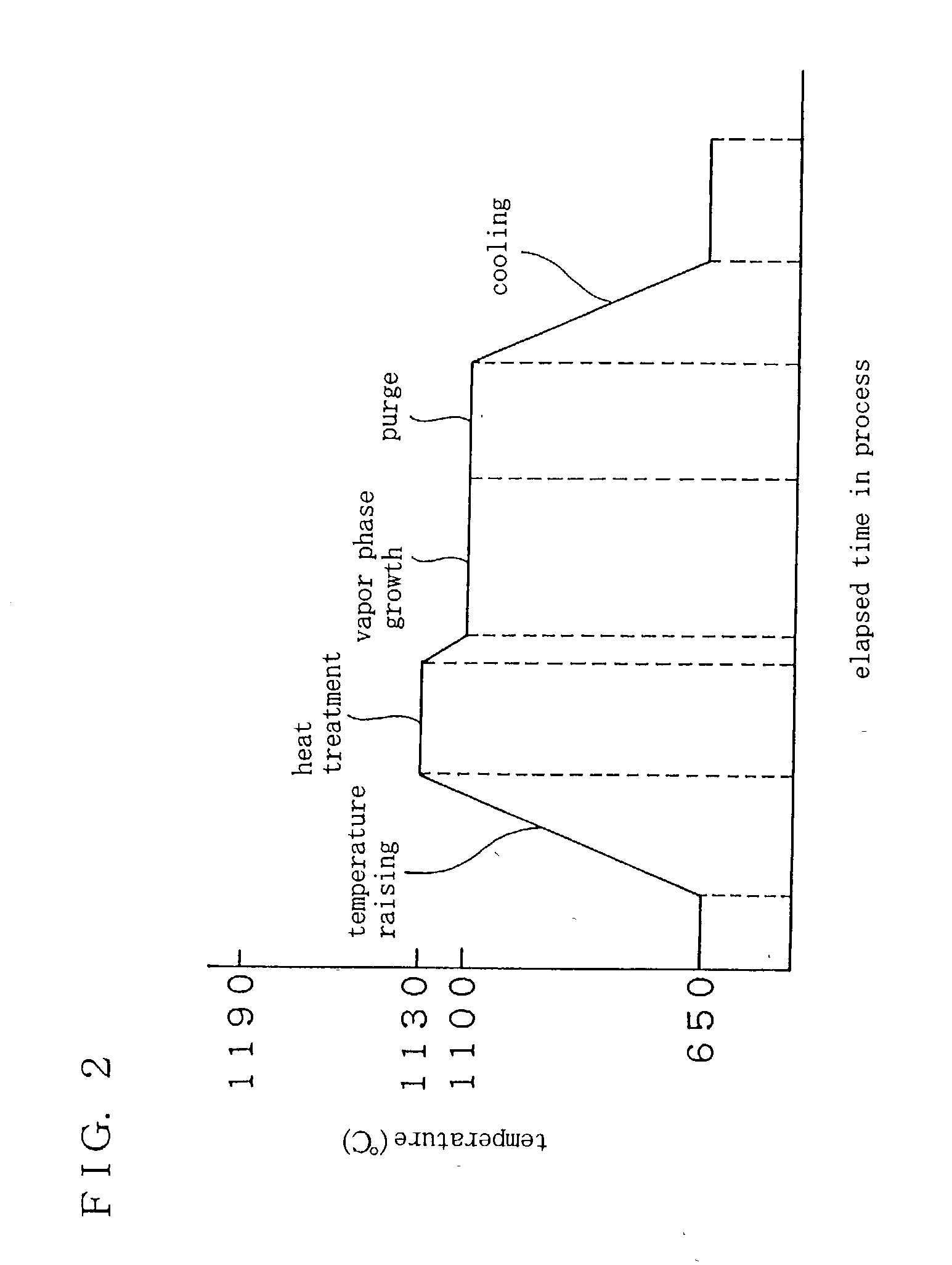

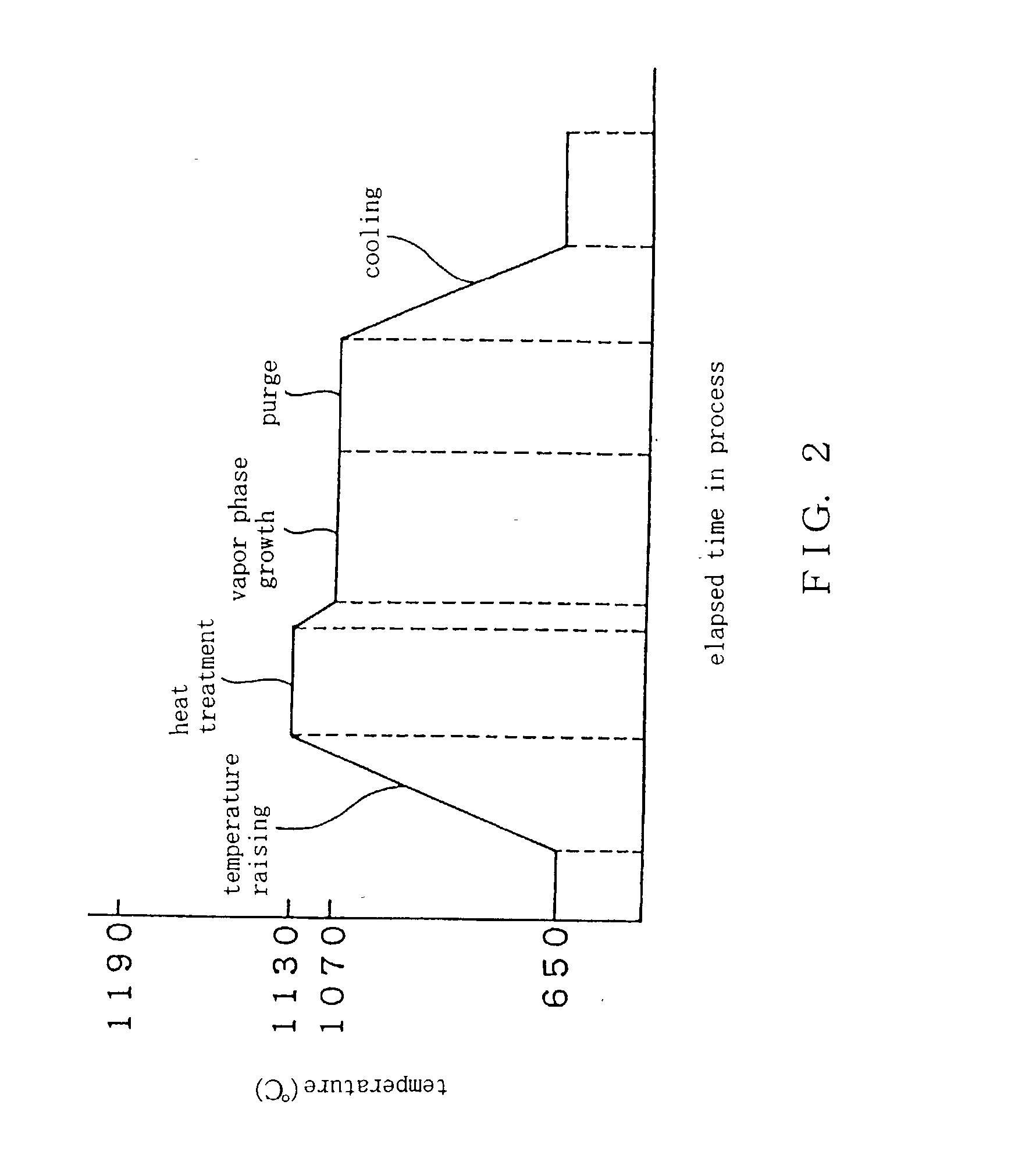

Technology for producing 12-inch monocrystalline silicon epitaxial wafers through pressure reduction

ActiveCN103820849AUniform resistivityPolycrystalline material growthSemiconductor/solid-state device manufacturingDopantPressure reduction

The invention provides a technology for producing 12-inch monocrystalline silicon epitaxial wafers through pressure reduction. The technology comprises the following steps: (1) cleaning a reaction cavity with high-purity HCl gas at 1150-1190 DEG C; (2) introducing high-purity H2 to purge the HCl gas and reaction products remaining in the reaction cavity; (3) lowering the temperature inside the reaction cavity to 700-900 DEG C, loading 12-inch monocrystalline silicon wafers onto a slide glass base; (4) reducing the pressure intensity inside the reaction cavity to 20-200 Torr, then heating to 1000-1050 DEG C, wherein the flow rate of the carrier gas high-purity H2 is 40-160 SLM; (5) pre-flowing reaction gas, and adjusting the process and the time that DCS and doping agent are introduced into the reaction cavity to grow an epitaxial layer; (6) cooling to 900 DEG C, and taking out the epitaxial wafers. Through the technology provided by the invention, the epitaxial wafers which have the advantages that electrical resistivity of the epitaxial layer is uniform and the epitaxial layer and substrate electrical resistivity transition areas are narrow can be prepared.

Owner:GRINM SEMICONDUCTOR MATERIALS CO LTD

Conductive nitride semiconductor substrate and method for producing the same

InactiveUS8110484B1Reduce dislocation densityReduce misalignmentPolycrystalline material growthSemiconductor/solid-state device manufacturingVapor phaseSilicon

A method for producing a conductive nitride semiconductor substrate circuit includes the steps of forming, on an underlying substrate, a mask including dot or stripe masking portions having a width or diameter of 10 to 100 μm and arranged at a spacing of 250 to 10,000 μm; growing a nitride semiconductor crystal on the underlying substrate by hydride vapor phase epitaxy (HVPE) at a growth temperature of 1,040° C. to 1,150° C. by supplying a group III source gas, a group V source gas, and a silicon-containing gas in a V / III ratio of 1 to 10; and removing the underlying substrate, thus forming a free-standing conductive nitride semiconductor crystal substrate having a resistivity r of 0.0015 Ωcm≦r≦0.01 Ωcm, a thickness of 100 μm or more, and a radius of bow curvature U of 3.5 m≦U≦8 m.

Owner:SUMITOMO ELECTRIC IND LTD

Semiconductor wafer and vapor phase growth apparatus

InactiveUS20030044616A1Improve throughputHigh yieldPolycrystalline material growthSemiconductor/solid-state device manufacturingDopantGas phase

It is an object of the present invention to provide not only a semiconductor wafer obtained by forming a semiconductor thin film with uniform resistivity and substantially no slip dislocation on a main surface of a semiconductor single crystal substrate having a relatively low dopant concentration, as large as 300 mm or more in diameter but also a vapor phase growth apparatus by means of which such a semiconductor wafer can be produced. A dopant gas is supplied into a reaction chamber 10 through all of the inlet ports 18a to 18f disposed in a width direction of the reaction chamber 10 from a common gas pipe 22a functioning as a main dopant gas pipe. Further, the dopant gas is additionally supplied through inner inlet ports 18a and 18b, and middle inlet ports 18c and 18d, as specific gas inlet ports, into the reaction chamber 10 from first and second auxiliary dopant gas pipes 22b and 22c.

Owner:SHIN-ETSU HANDOTAI CO LTD

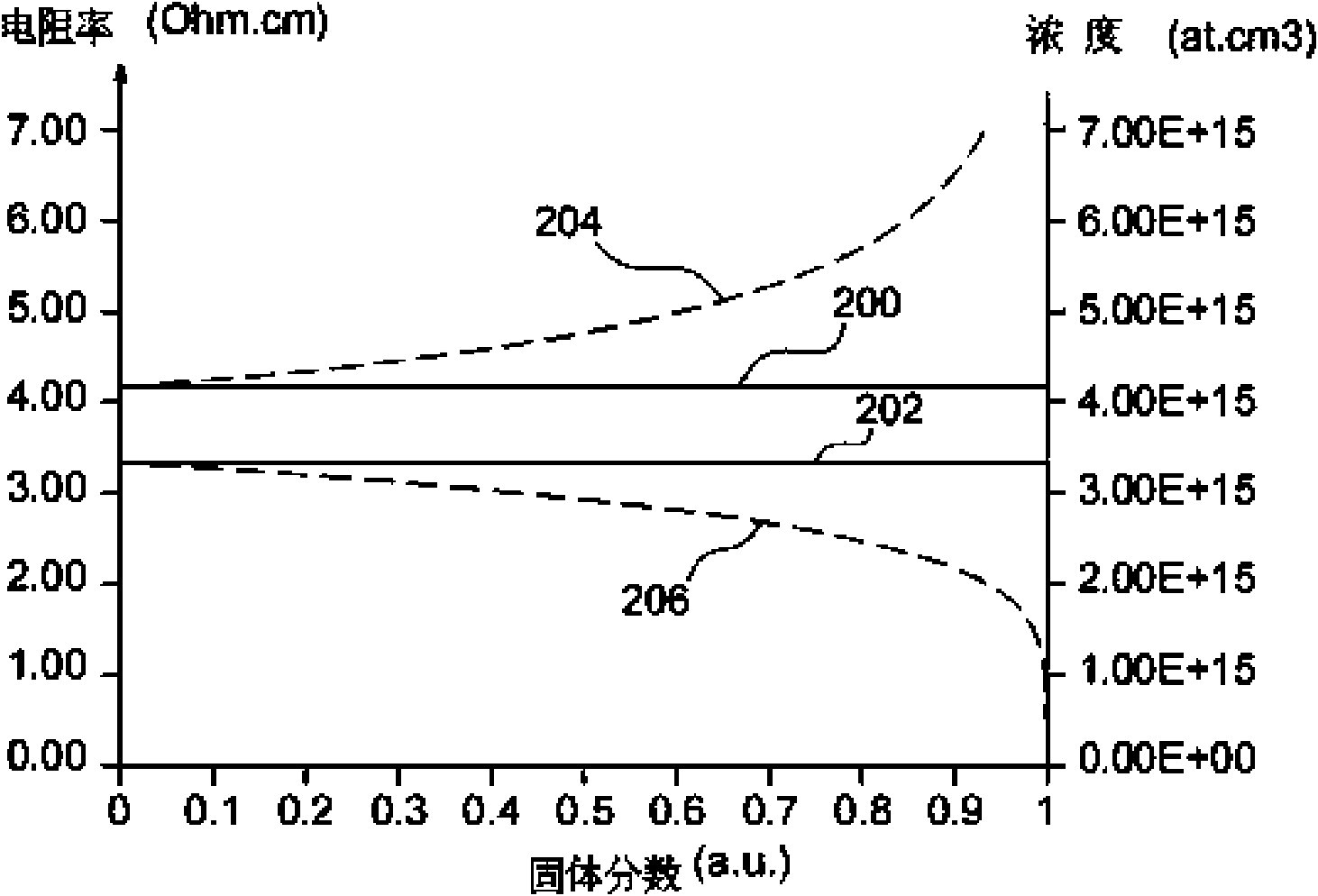

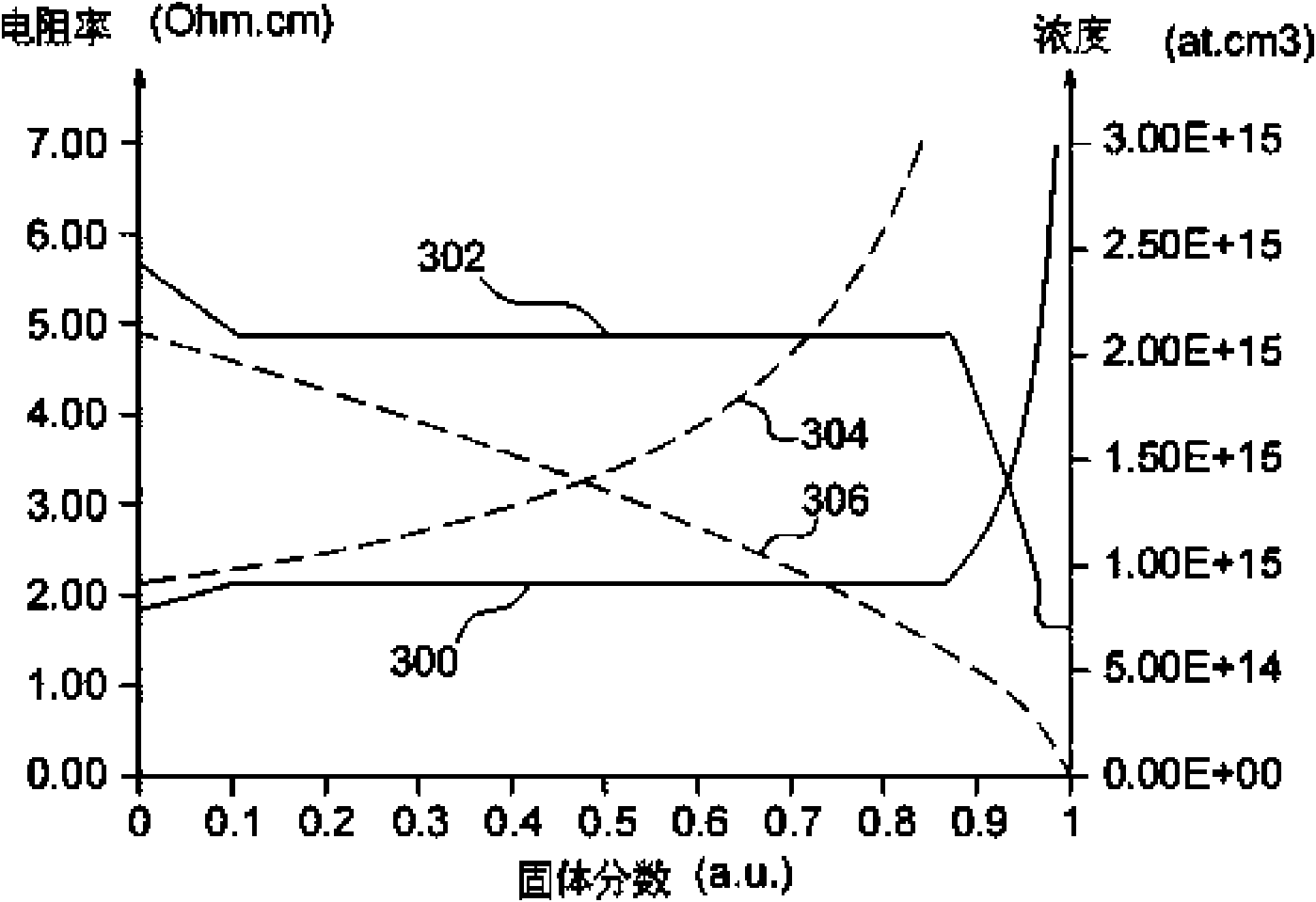

Method For Solidifying A Semiconductor With Adding Charges Of A Doped Semiconductor During The Crystallisation

InactiveCN103088407AUniform resistivityAvoid conductivity type changesPolycrystalline material growthBy zone-melting liquidsDopantSemiconductor materials

A method for semiconductor solidification which includes steps for: forming a bath of molten semiconductor from a first charge of semiconductor which includes dopants, solidification of the molten semiconductor, and which in addition includes, during solidification, the implementation of one or more steps for the addition of supplementary charges of semiconductor, which also contains dopants, to the molten semiconductor bath. The method has homogeneous resistivity throughout the solidified semiconductor, whilst preventing changes in the type of conductivity over the entire or a very large part of the semiconductor and which does not adversely effect the electrical properties of devices made from the semiconductor that is obtained.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

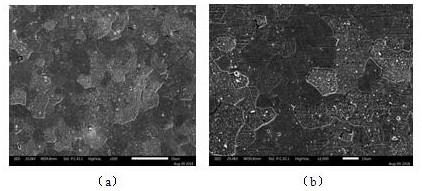

Manufacturing method for high-purity iron-chromium-aluminum alloy powder

ActiveCN110125383AReduce burning lossImprove performanceAdditive manufacturing apparatusTransportation and packagingOxygen contentNitride

The invention relates to the technical fields of metal smelting and powder preparation, and discloses a manufacturing method for a high-purity iron-chromium-aluminum alloy powder. The manufacturing method comprises the two phases of melting and gas atomization. Compared with the prior art, the manufacturing method is capable of effectively preventing powder oxidation and avoiding impurity elements; and meanwhile, a powder is adequately dispersed in a cooling process, and the generation of a satellite spherical powder in the powder is reduced, so that preparation for the spherical alloy power with a small particle size is realized. The prepared alloy powder is small in particle size, high in sphericity degree and flowability, low in oxygen content and satellite spherical powder content, good in atomization effect, and capable of effectively preventing the powder oxidation, realizing high purity of alloy, refining crystalline grains, reducing inclusions, reducing separation for the brittle phase of nitride, and providing raw materials with excellent performance for the subsequent powder metallurgy process.

Owner:JIANGSU UNIV +1

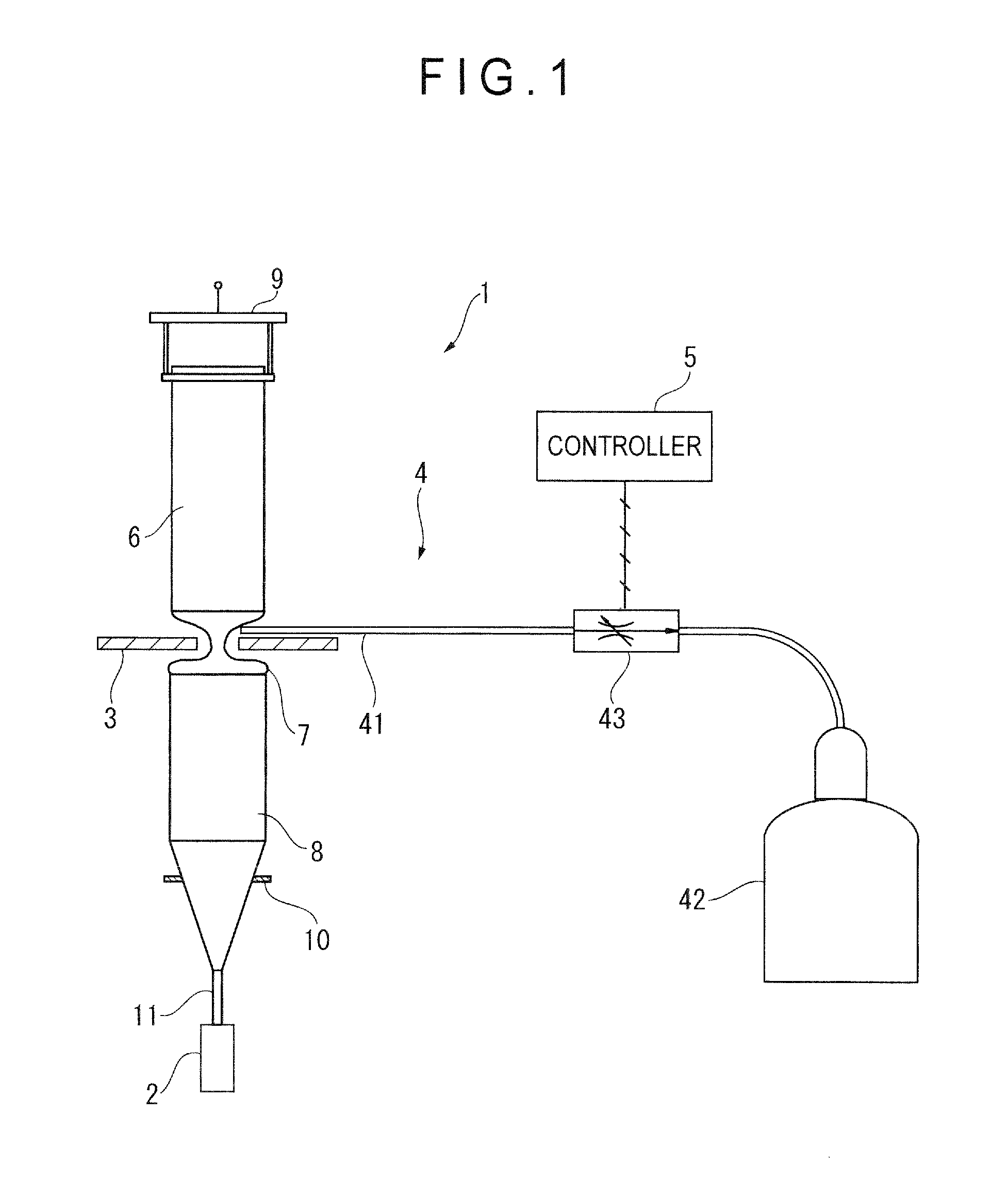

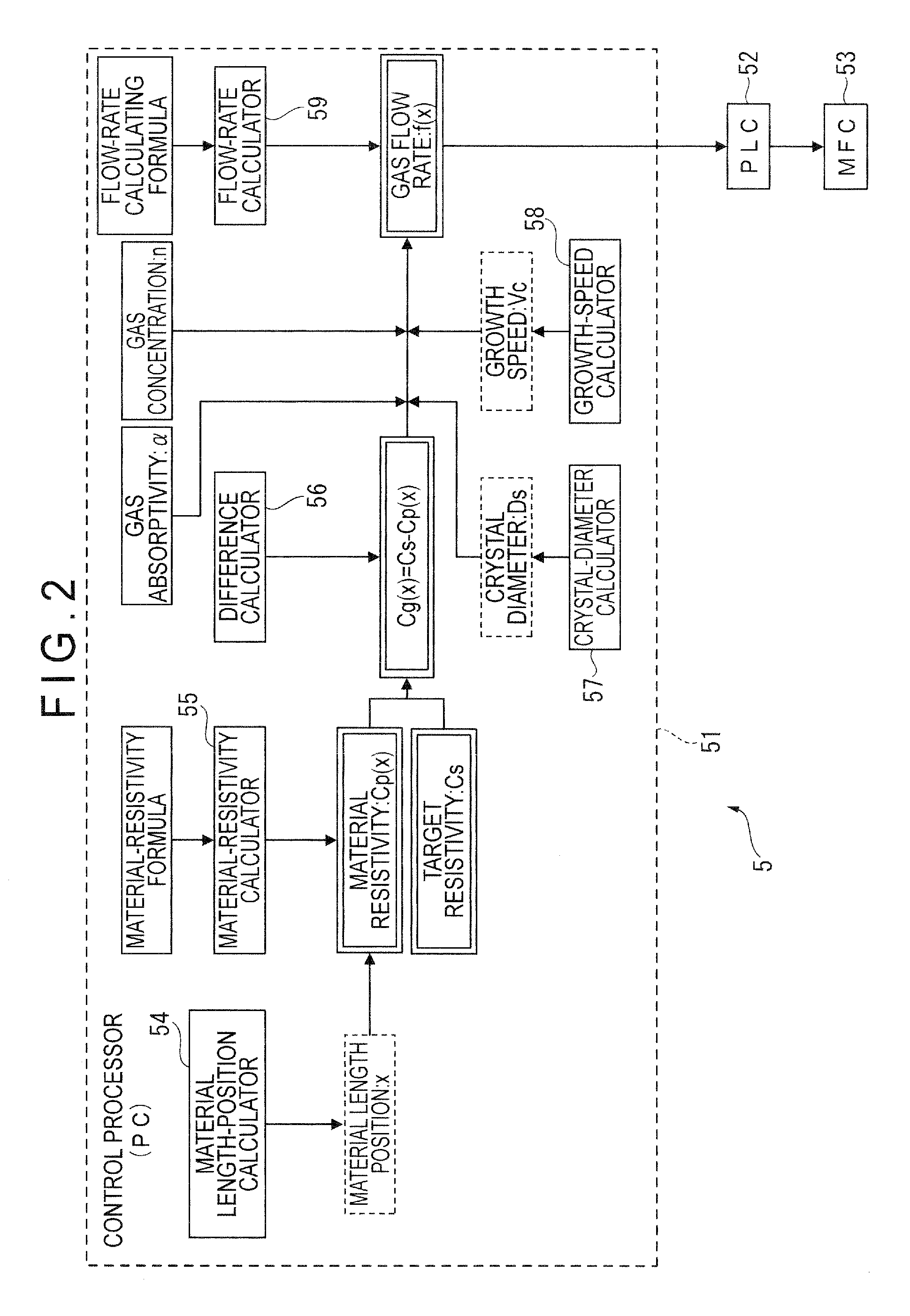

Silicon single crystal manufacturing method, silicon single crystal, silicon wafer, apparatus for controlling manufacture of silicon single crystal, and program

ActiveUS20090309069A1Uniform resistivitySuppressing raw material costPolycrystalline material growthBy zone-melting liquidsSingle crystalImpurity

A method of manufacturing a silicon monocrystal by FZ method, wherein a P-type or N-type silicon crystal having been pulled up by CZ method is used as a raw material. While impurities whose conductivity type is the same as that of the raw material are supplied by a gas doping method, the raw material is recrystallized by an induction-heating coil for obtaining a product-monocrystal.

Owner:SUMCO TECHXIV

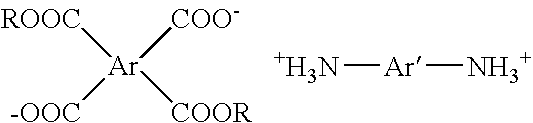

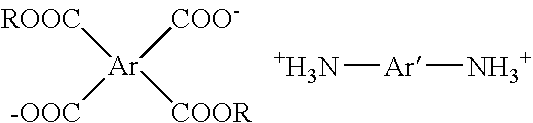

Endless tubular polyimide film

ActiveUS20070178264A1Simple and efficient and economicalImprove dispersion stabilityLayered productsSpecial tyresAcid derivativeCarboxylic acid

The present invention provides a method for producing a high-quality nonconductive or semi-conductive seamless (jointless) tubular polyimide film in a simple, efficient, and economical manner, and the like. More specifically, the invention relates to an electrically non-conductive or electrically semi-conductive seamless tubular polyimide film comprising polyimide having at least two aromatic tetracarboxylic acid derivatives comprising 15 to 55 mol % of asymmetric aromatic tetracarboxylic acid component and 85 to 45 mol % of symmetric aromatic tetracarboxylic acid component and at least one aromatic diamine component, in which, as required, a specific amount of carbon black is dispersed, and relates to a method for producing the same.

Owner:GUNZE LTD +1

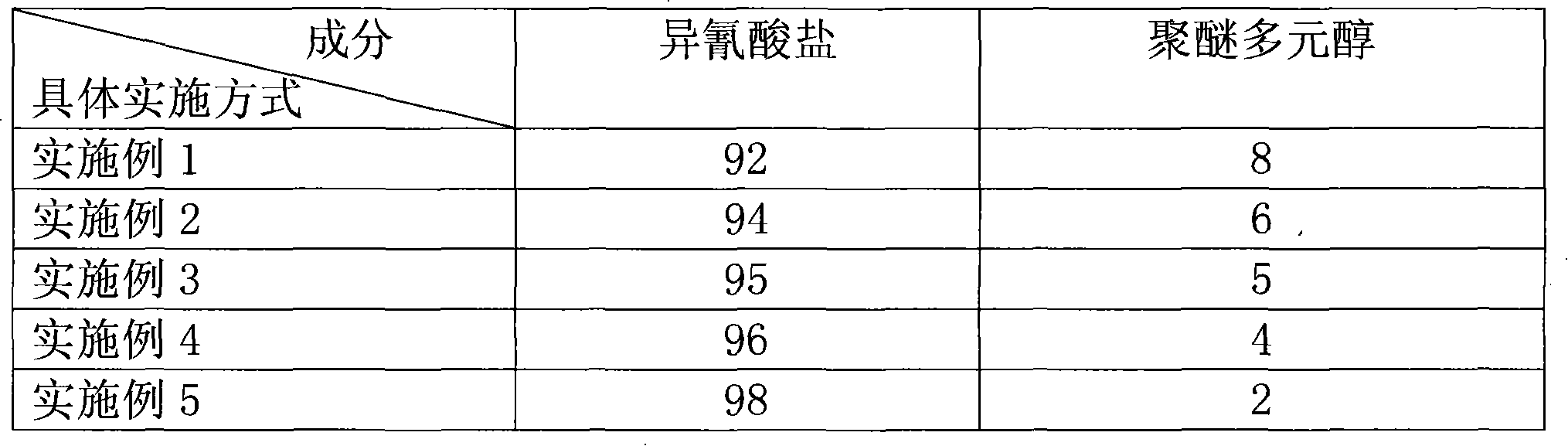

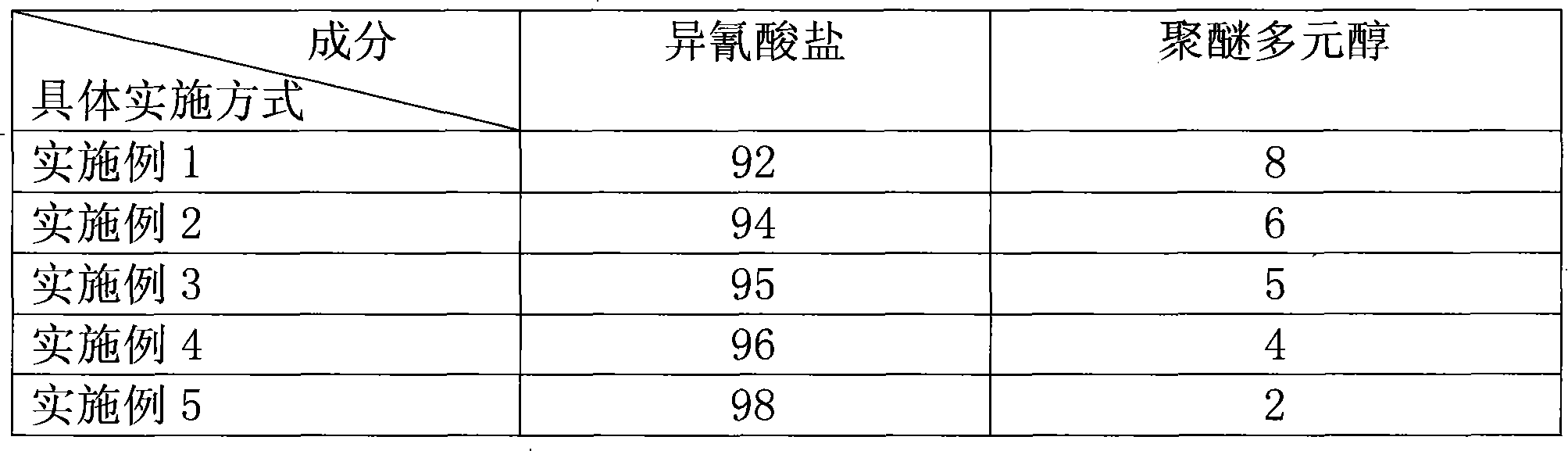

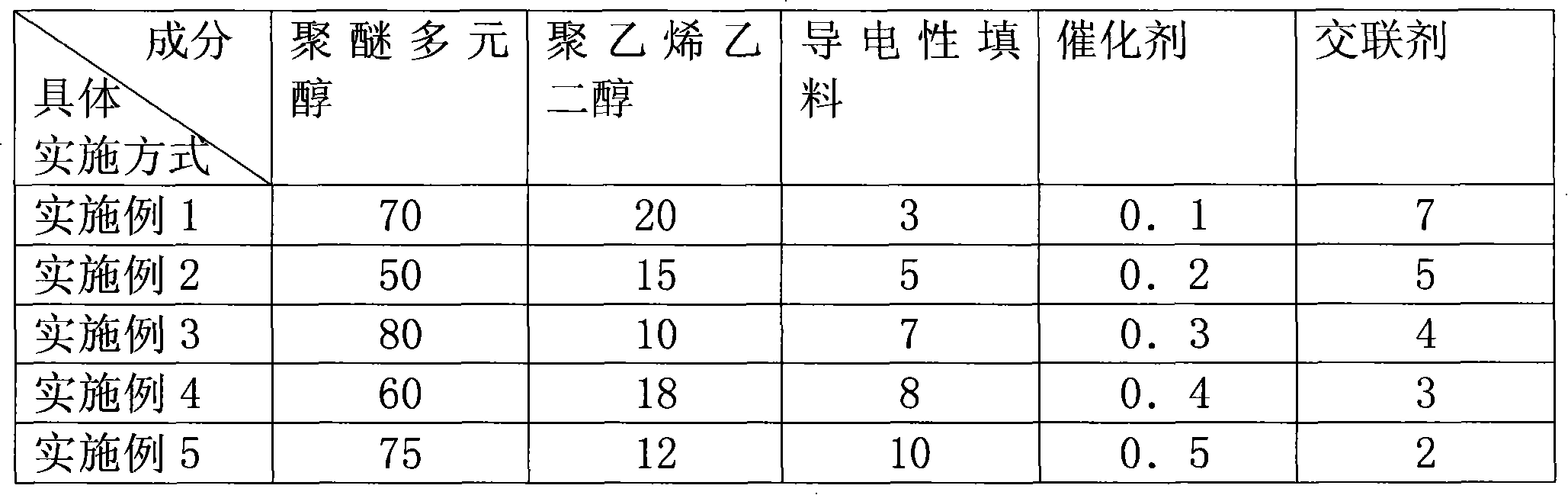

Charge roller and method of producing the same

InactiveCN101178559ASolve conductivity problemsSolve pollutionCoatingsSpecial surfacesPolyurethane elastomerHydrogen

The invention relates to a charging roller and a preparation method thereof. The charging roller comprises a metal shaft, on which a polyurethane elastomer is bonded, and a conductive surface layer with a thickness of 10-40 μm is sprayed on the surface of the polyurethane elastomer. , the polyurethane elastomer is made of a prepolymer-R liquid and a prepolymer-P liquid, and the prepolymer-R liquid includes a conductive substance with a weight percentage of 2 to 8%; the prepolymer Polymer-P liquid includes isocyanate of 50-70% by weight; the charging roller of the present invention is made of polyurethane material, which has proper elasticity, good wear resistance, good heat resistance, and good chemical stability. It is not easy to produce photosensitive drum contamination, and the compression deformation rate is low.

Owner:ZHEJIANG DONGYANG CHENGJI ELECTRO MECHANICS CO LTD

Preparation method of self-compensation back-sealing semiconductor substrate

ActiveCN104112653AQuality improvementImprove efficiencySemiconductor/solid-state device manufacturingSelf compensationProduct demand

The invention discloses a preparation method of a self-compensation back-sealing semiconductor substrate. The preparation method comprises a technical method of growing an opposite type lightly doped epitaxial layer on a heavily doped substrate. By adopting a mean of producing a self-compensation back sealing layer before the epitaxial growth in the substrate processing stage, the method for growing lightly doped epitaxial layer in opposite conduction type in batches on the heavily doped substrate is provided to solve a problem of same-type epitaxial growth on the inner edge of a chip or the whole chip caused by lightly doped epitaxial atmosphere transoid which is resulted from a backside self-doping effect and an edge effect. With the adoption of the self-compensation back sealing technology, that the epitaxial parameters meet with the product demands still can be guaranteed even full-furnace growth is performed by using a normal-pressure epitaxial furnace.

Owner:BEIJING YANDONG MICROELECTRONICS

Developer roll and method of producing the same

InactiveCN101178560ASolve conductivity problemsSolve pollutionShaft and bearingsElectrographic process apparatusPolyurethane elastomerSurface layer

The invention relate to a developing roller and a preparation method thereof. The developing roller comprises a metallic axle. The metallic axle is adhered with a polyurethane elastomer. The surface of the polyurethane elastomer is coated with a developing surface layer the thickness of which is 10 to 40Mum. The polyurethane elastomer is made of prepolymer-R solution or prepolymer-P solution. The prepolymer-R solution comprises conductive substances the weight percentage of which is 2 to 8 percent. The prepolymer-P solution comprises TDI the weight percentage of which is 50 to 70 percent. The developing roller is made of prepolymer materials. Therefore, the invention has the advantages of proper elasticity, good wear resistance, good heat resistance, good chemical stability, and low compression deformation rate and is not likely to pollute the OPC drum.

Owner:ZHEJIANG DONGYANG CHENGJI ELECTRO MECHANICS CO LTD

Semiconductor wafer and production method therefor

InactiveUS20030001160A1Improve throughputHigh yieldPolycrystalline material growthSemiconductor/solid-state device manufacturingDopantSingle crystal substrate

It is an object of the invention to provide a semiconductor wafer obtained by forming a semiconductor thin film with uniform resistivity on a main surface of a semiconductor single crystal substrate of 300 mm or more in diameter. When a process gas is supplied to over a main surface of a silicon single crystal substrate 12 in rotation in almost parallel to the main surface thereof in one direction in a reaction chamber 10 through six inlet ports 18a to 18f disposed in width direction of the reaction chamber 10, H2 gas, a semiconductor raw material gas and a dopant gas are supplied onto an area in the vicinity of the center of the main surface of the silicon single crystal substrate 12 and an intermediate area thereof through the inner inlet ports 18a and 18b and the middle inlet ports 18c and 18d, and only H2 gas and the semiconductor raw material gas without the dopant gas are supplied onto an area in the vicinity of the outer periphery thereof from the outer inlet ports 18e and 18f. In such arrangement, a dopant gas produced by the auto-doping phenomenon is supplied onto the area in the vicinity of the outer periphery of the main surface of the silicon single crystal substrate 12. For this reason, the dopant gases from both sources are combined, thereby a concentration of the dopant gas supplied over all the main surface of the silicon single crystal substrate 12 is almost uniform.

Owner:SHIN-ETSU HANDOTAI CO LTD

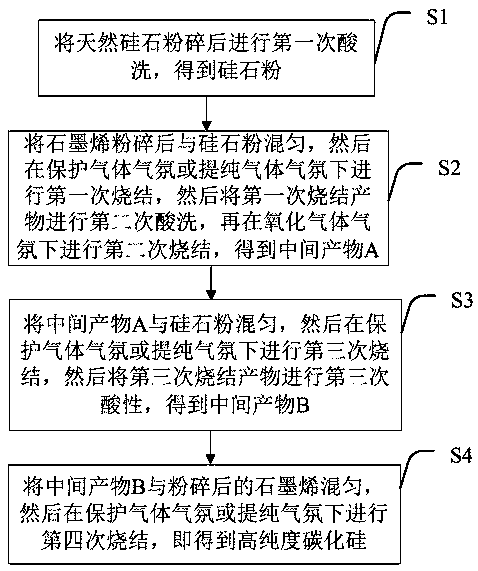

High-purity silicon carbide, silicon carbide wafer and preparation method of high-purity silicon carbide

ActiveCN110104651AImprove integrityUniform sizePolycrystalline material growthNanotechnologyShielding gasCvd graphene

The invention discloses high-purity silicon carbide, a silicon carbide wafer and a preparation method of high-purity silicon carbide. The preparation method of high-purity silicon carbide comprises the steps that natural silica is pulverized and subjected to first pickling to obtain silica powder; graphene is pulverized and uniformly mixed with the silica powder, the mixture is subjected to firstsintering under a protective gas atmosphere or a purified gas atmosphere, and a first sintering product is subjected to second pickling and then subjected to second sintering under an oxidizing gas atmosphere to obtain an intermediate product A; the intermediate product A is uniformly mixed with the silica powder and then subjected to third sintering under a protective gas atmosphere or a purification atmosphere, and a third sintering product is subjected to third pickling to obtain an intermediate product B; the intermediate product B is uniformly mixed with the pulverized graphene and then subjected to fourth sintering under a protective gas atmosphere or a purification atmosphere to obtain high-purity silicon carbide. The problems are solved that preparation processes of high-purity silicon carbide in the prior art are complicated and the cost is too high.

Owner:SHENZHEN EIGEN EQUATION GRAPHENE TECH CO LTD

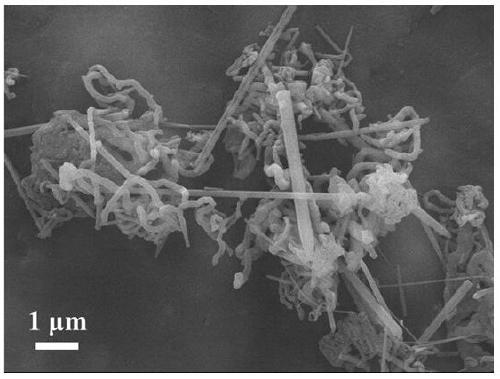

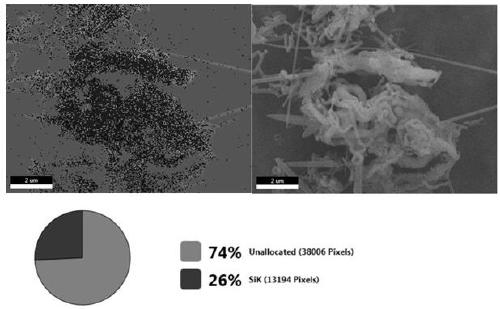

Silicon single crystal doped with gallium, indium, or aluminum

ActiveUS9051659B2Uniform radial and axial resistivityUniform resistivityPolycrystalline material growthConductive materialDopantIndium

A doped silicon single crystal having a resistivity variation along a longitudinal and / or radial axis of less than 10% and a method of preparing one or a sequential series of doped silicon crystals is disclosed. The method includes providing a melt material comprising silicon into a continuous Czochralski crystal growth apparatus, delivering a dopant, such as gallium, indium, or aluminum, to the melt material, providing a seed crystal into the melt material when the melt material is in molten form, and growing a doped silicon single crystal by withdrawing the seed crystal from the melt material. Additional melt material is provided to the apparatus during the growing step. A doping model for calculating the amount of dopant to be delivered into the melt material during one or more doping events, methods for delivering the dopant, and vessels and containers used to deliver the dopant are also disclosed.

Owner:GTAT IP HLDG

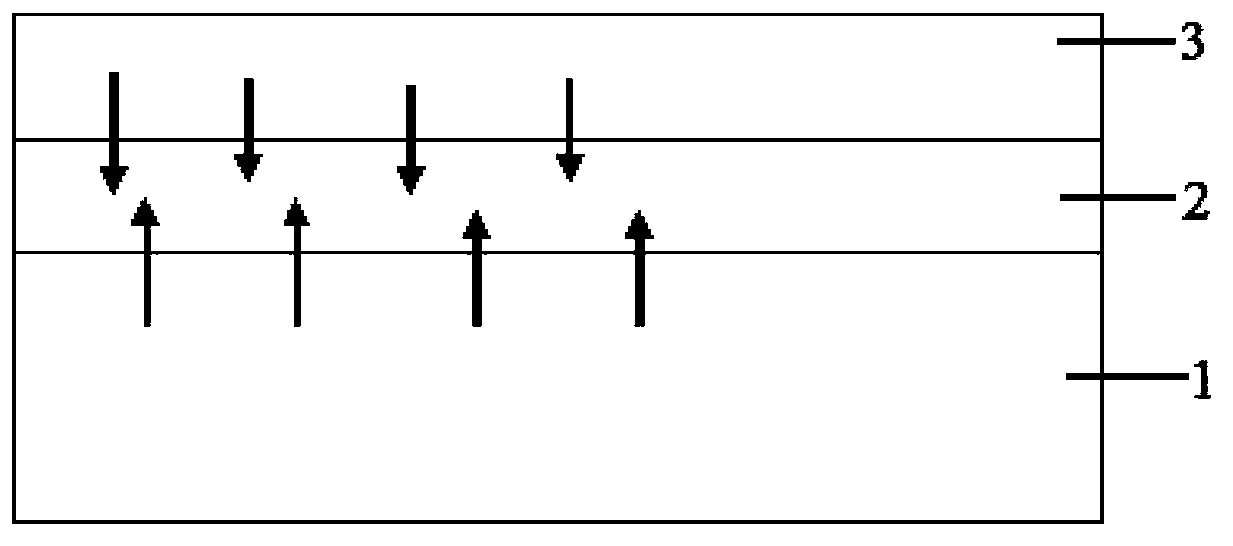

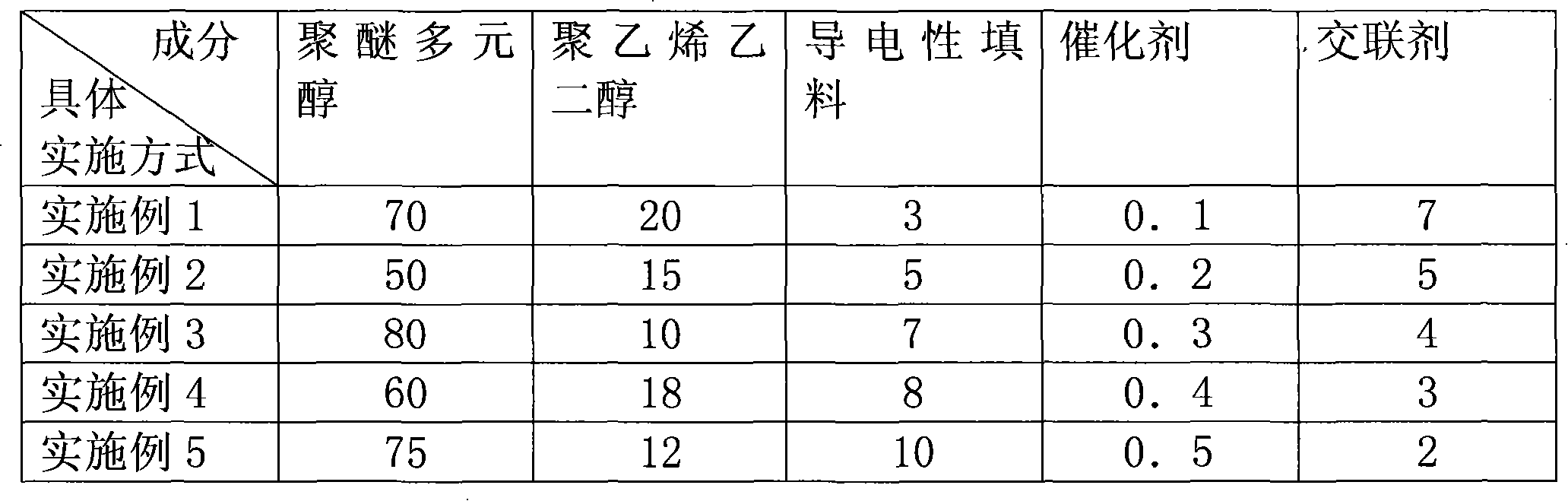

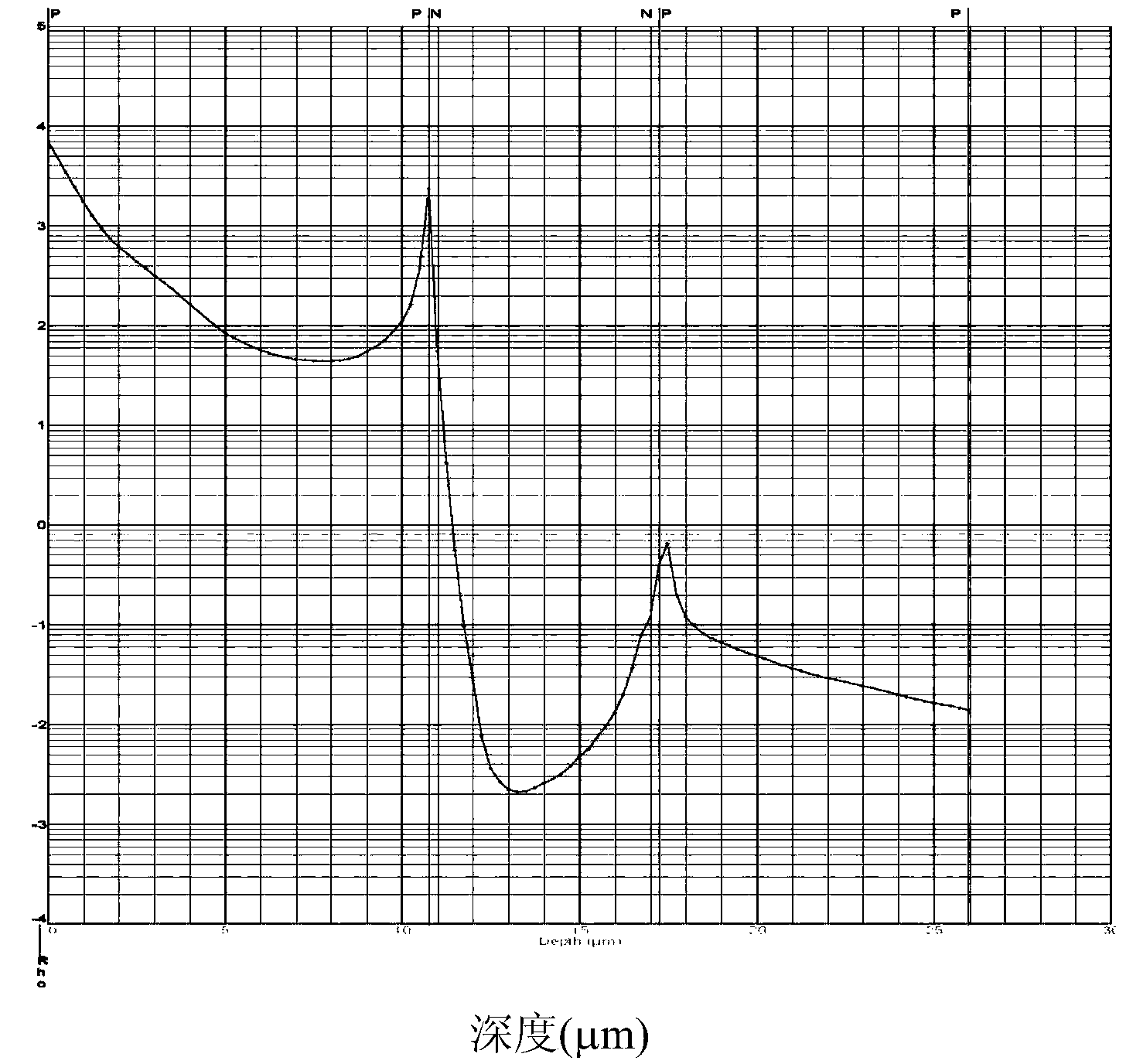

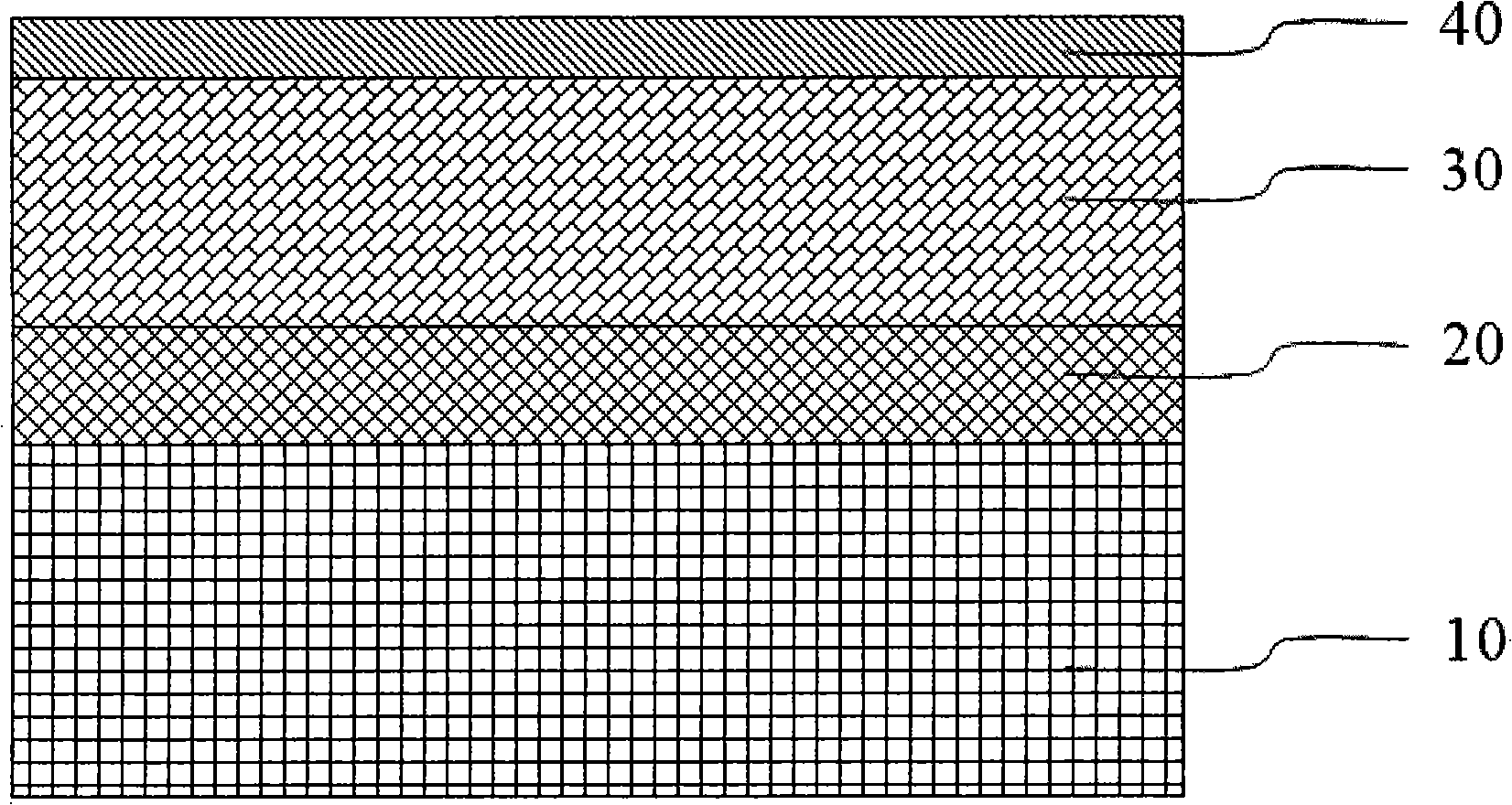

Silicon carbide consubstantial PIN (Personal Identification Number) microstructure material and preparation method thereof

InactiveCN102064187ABright surfaceUniform resistivitySemiconductor/solid-state device manufacturingSemiconductor devicesElectric devicesElectric power

The invention discloses a silicon carbide consubstantial PIN (Personal Identification Number) microstructure material which comprises an N type silicon carbide substrate, an N-variable concentration buffer layer arranged on the N type silicon carbide substrate, an intrinsic layer arranged on the N-variable concentration buffer layer, and a P+ cap layer arranged on the intrinsic layer. The invention simultaneously discloses a preparation method of the silicon carbide consubstantial PIN microstructure material. The invention can prepare an extension SiC epitaxial material with the advantages ofbright surface and uniform resistivity, the background carrier concentration of the intrinsic epitaxial layer can be reduced to the 1015 order of magnitude, and the microstructure material provided by the invention is suitable for high-power electronic and electric devices of semiconductors.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

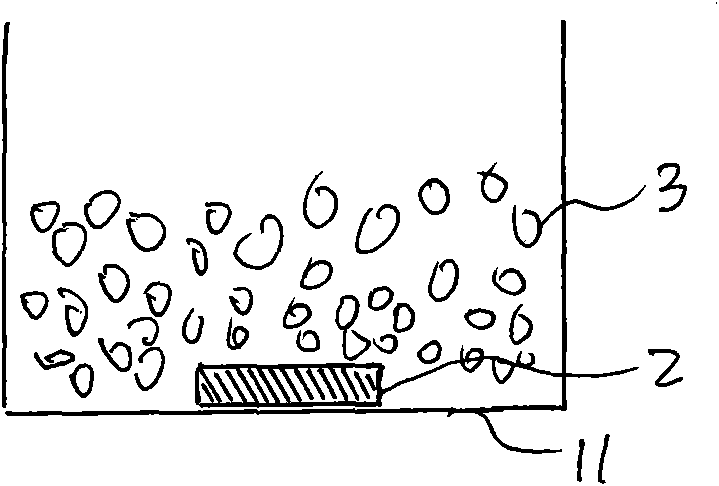

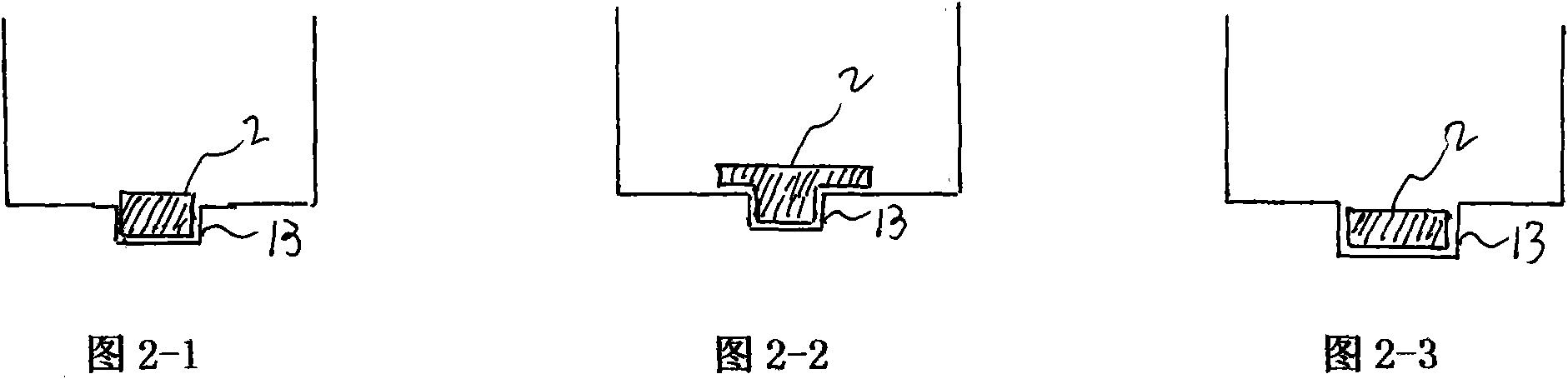

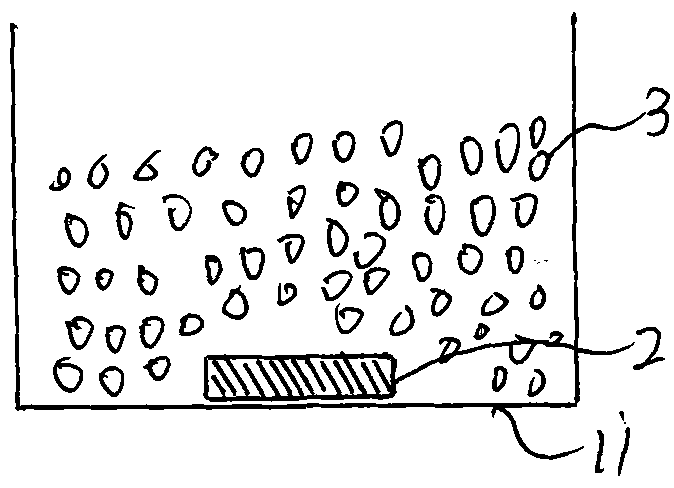

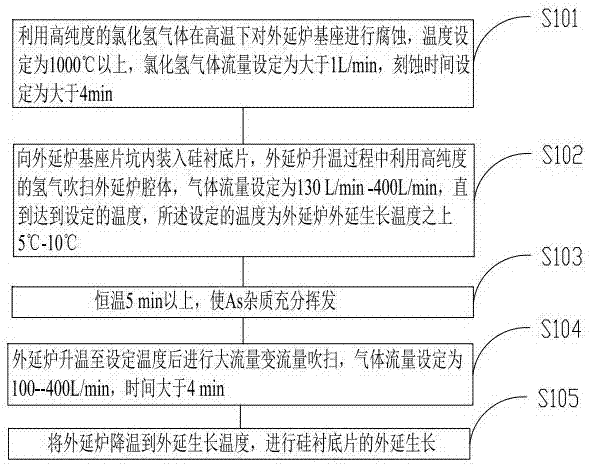

Method for improving on-chip resistivity uniformity of epitaxial wafer

InactiveCN106876246AUniform resistivityImprove Curve Profile ConsistencySemiconductor/solid-state device manufacturingHydrogenMetallurgy

The invention discloses a method for improving on-chip resistivity uniformity of an epitaxial wafer, and relates to the technical field of a fabrication method for a silicon substrate epitaxial layer. The method comprises the following steps of corroding an epitaxial furnace base under a high temperature by a high-purity hydrogen chloride gas; loading a silicon substrate sheet into a pit of the epitaxial furnace base, and blowing an epitaxial furnace cavity by high-purity hydrogen during the temperature rising process of an epitaxial furnace until a set temperature is reached; performing heat preservation for over 5 minutes; performing large-flow and variable-flow blowing when the temperature of the epitaxial furnace is risen to the set temperature, wherein the gas flow is set 100-(-400)L / min, and the time is more than 4 minutes; and reducing the temperature of the epitaxial furnace to an epitaxial growth temperature, and performing epitaxial growth of the silicon substrate sheet. By the method, the on-chip resistivity of the epitaxial wafer can be more uniform, the finished rate is greatly improved, and the profile consistency of SRP curve is greatly improved.

Owner:HEBEI POSHING ELECTRONICS TECH

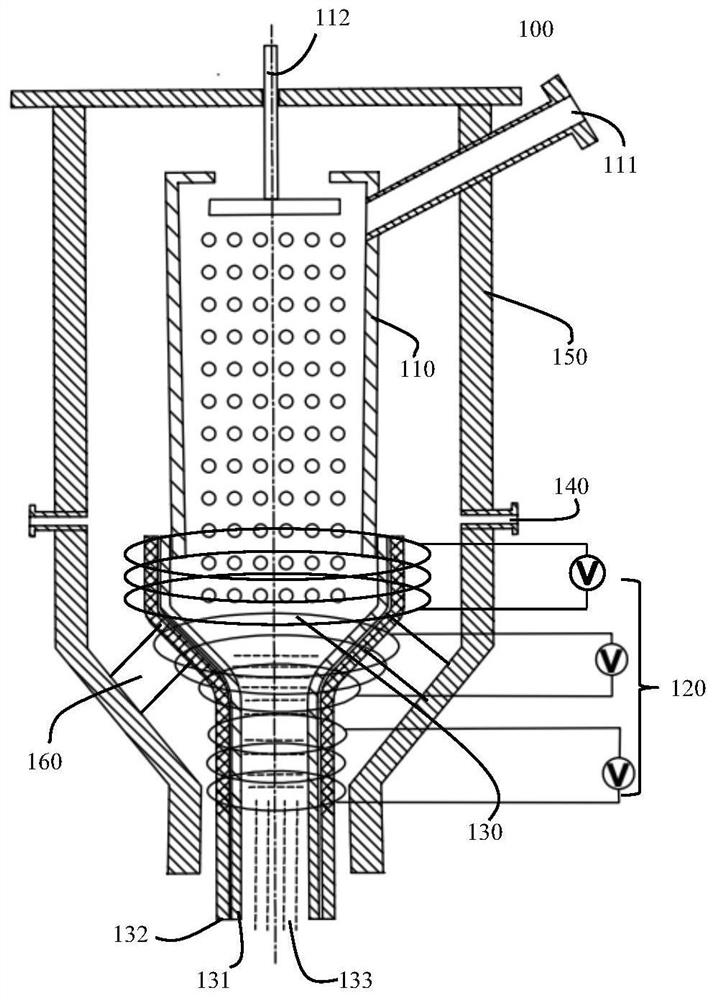

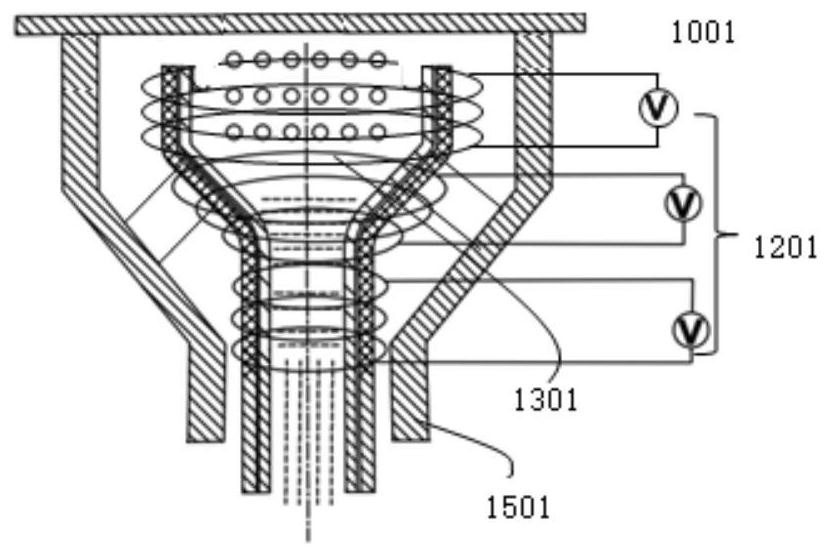

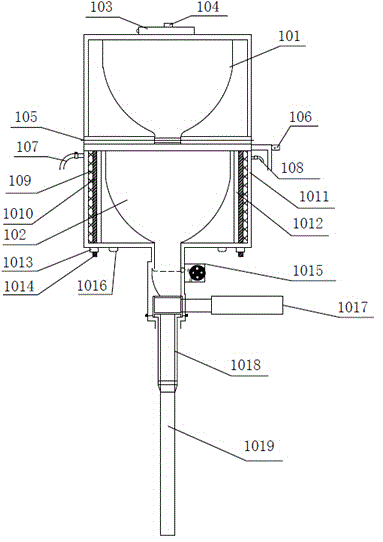

Continuous czochralski single crystal furnace and method capable of controlling oxygen content of monocrystalline silicon

PendingCN113061982AImprove qualityUniform resistivityPolycrystalline material growthBy pulling from meltSingle crystalOxygen content

The invention relates to the technical field of monocrystalline silicon czochralski and provides a continuous czochralski single crystal furnace for controlling oxygen content in monocrystalline silicon, which comprises a crucible, a crucible inner dam, asealing shell and a feeder, the feeder comprises a molten silicon feeder, the molten silicon feeder is arranged above the crucible and provides liquid silicon for the crucible according to a preset speed; and the sealing shell is used for carrying out surrounding and vacuum sealing on the whole structure of the continuous Czochralski single crystal furnace. The depth of the liquid level of the liquid molten silicon in the crucible is smaller than 1 / 2 of the diameter of the crucible, and the maximum amount of the molten silicon in the crucible is smaller than 2 / 3 of the total molten silicon demand quantity of single crystal pulling. The invention also provides a continuous Czochralski single crystal method for controlling the oxygen content and / or inhibiting the COP of the single crystal silicon. The method can inhibit the exchange of oxygen atoms inside and outside the dam, reduces impurities such as oxygen atoms to inhibit the COP of monocrystalline silicon, and is effective, simple and convenient.

Owner:SHANGHAI YINWAN OPTICAL ELECTRONICS CO LTD

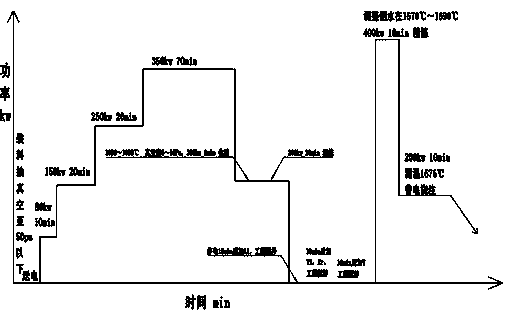

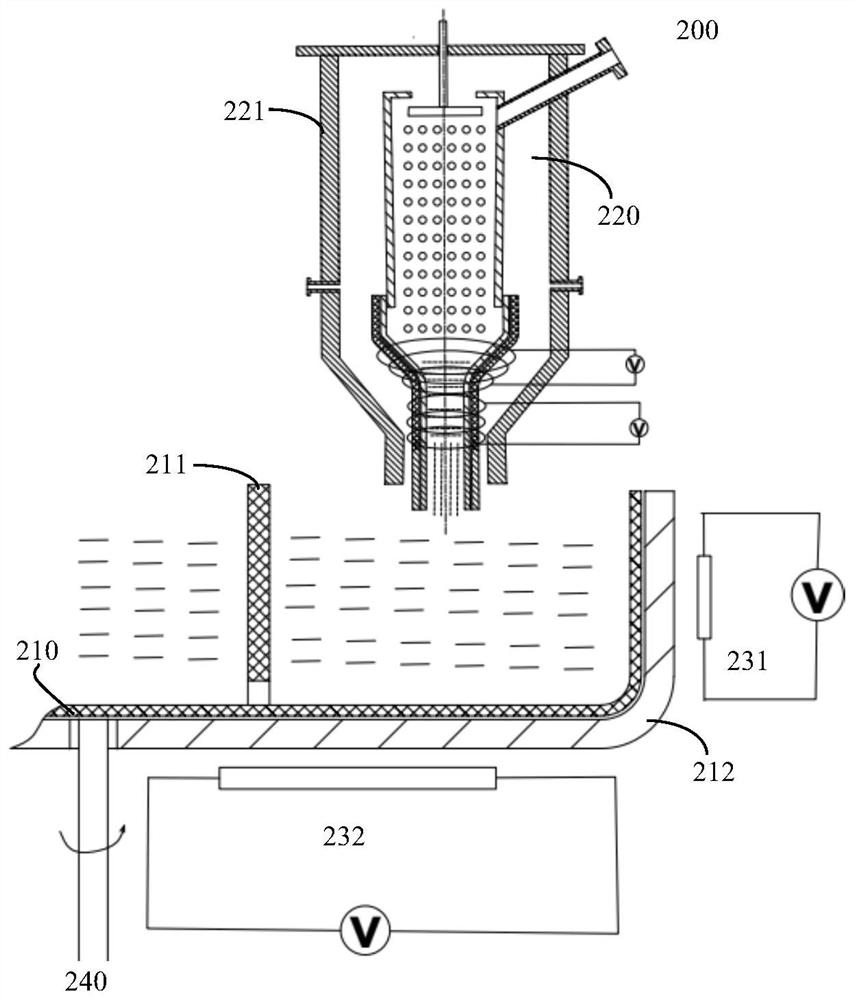

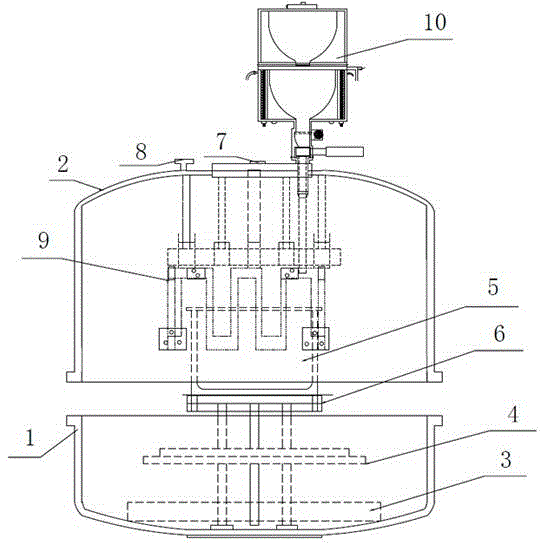

N type polycrystalline ingot casting equipment and process for preparing N type polycrystalline ingot

InactiveCN104805499AUniform resistivityImprove homogeneityPolycrystalline material growthSingle crystal growth detailsIngot castingMetallurgy

The invention provides N type polycrystalline ingot casting equipment and a process for preparing an N type polycrystalline ingot. According to the N type polycrystalline ingot casting equipment, an improvement, namely additionally arranging a set of secondary feeding devices, is made on original equipment for preparing a P type polycrystalline cast ingot, so that the N type polycrystalline ingot can be cast, no equipment needs to be changed, and thus the production cost is reduced. By the adoption of the process disclosed by the invention, the electrical resistivity of the N type polycrystalline ingot prepared by adopting the equipment provided by the invention is more uniform, and the homogeneity of a battery piece is improved.

Owner:王进

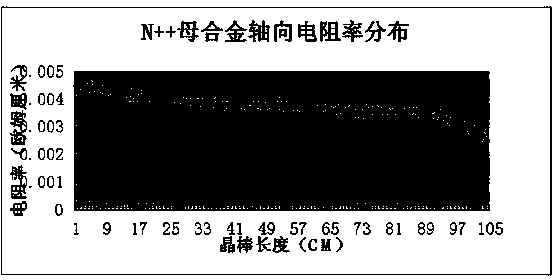

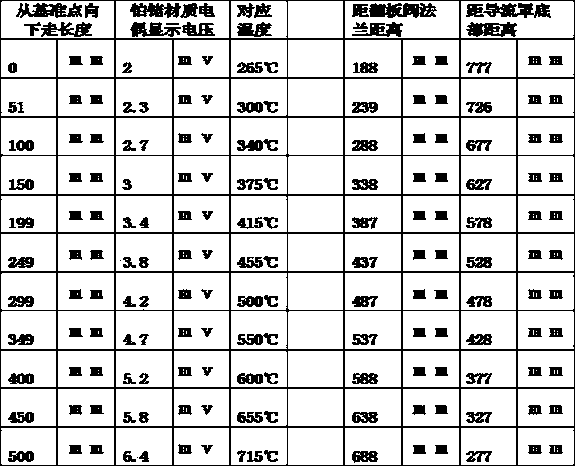

Preparation process of N-type heavily-doped phosphorus master alloy silicon rod

The invention discloses a preparation process of an N-type heavily-doped phosphorus master alloy silicon rod. The preparation process comprises the following steps of: selecting a single crystal furnace, a 20 graphite thermal field and a 20 quartz crucible, and heating to melt 70kg of polycrystalline silicon; placing 520g of N high-purity red phosphorus into a quartz doper; installing an adapting doper at a seed crystal bayonet, ascending the adapting doper into an auxiliary chamber of the single crystal furnace to guide air, then, opening a flap valve, descending the quartz doper to a tested 390-mm position, enabling the air to be sublimated and automatically guided into a silicon melt, and pulling crystals under the conditions that the rotating speed of a crystal rod is 12r / min, the rotating speed of the crucible is 8r / min, the pulling speed of the head of the crystal rod is 1.1mm / min, and the pressure of the furnace is 2000-2500Pa; and cutting the pulled crystal rod into cakes with the thickness of 2cm, grading according to the electrical resistivity, then, treating by using a water quenching technology, pickling, then, preparing fragments with the size of 5-20mm by using a silicon briquette mutual-collision method, packaging according to different grades, and labeling for self use or sell. The safety in preparing the N-type heavily-doped phosphorus master alloy silicon rod is ensured, and the electrical resistivity of the crystal rod is uniform and ranges from 0.001 to 0.005ohm.cm.

Owner:JIANGXI SORNID HI TECH

Vertical double-diffused metal oxide semiconductor field effect transistor having semi-insulating polysilicon layer

ActiveCN107046062ALower on-resistanceIncrease the doping concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesPotential differenceField-effect transistor

The invention provides a vertical double-diffused metal oxide semiconductor field effect transistor (VDMOS) having a semi-insulating polysilicon layer (SIPOS). The VDMOS is mainly characterized in that an SIPOS filling layer is formed on the side wall of a device drift region, and two ends of the SIPOS filling layer are connected with a gate end and a drain end of the VDMOS. On one hand, since the SIPOS has uniform resistivity, the SIPOS has a uniform electric field when the VDMOS is turned off. According to an electric displacement continuity equation, an electric field on the device drift region is modulated by means of the uniform electric field on the SIPOS and becomes more uniform, and the SIPOS layer enhances the depletion of the device drift region of the VDMOS, thus doping concentration of the device drift region is increased, and the VDMOS has low on-resistance when being turned on; on the other hand, since a potential difference exists between the surfaces of the SIPOS layer and the device drift region, the device drift region has majority carrier accumulation, thereby further decreasing the on-resistance of the VDMOS.

Owner:XIDIAN UNIV

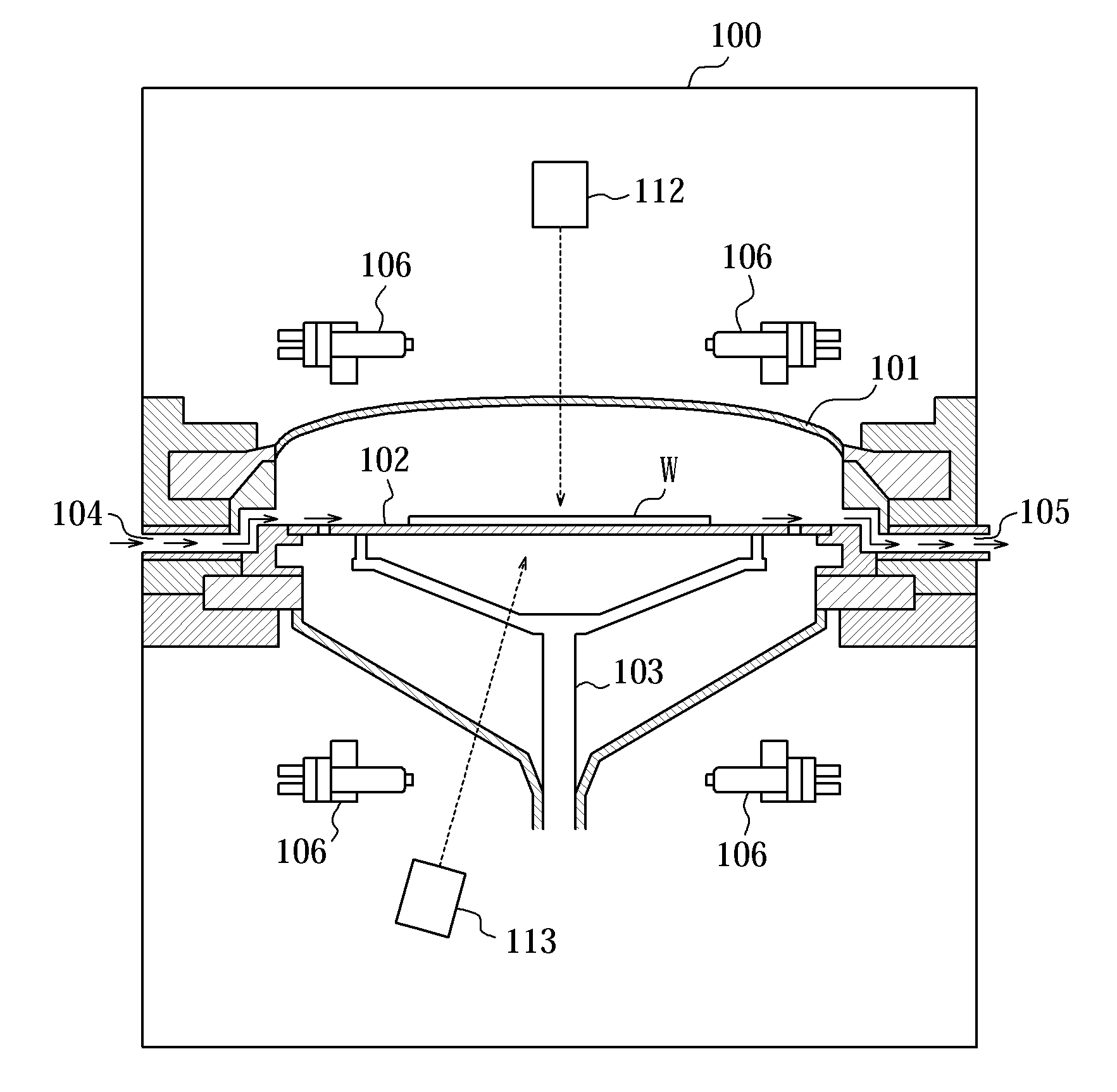

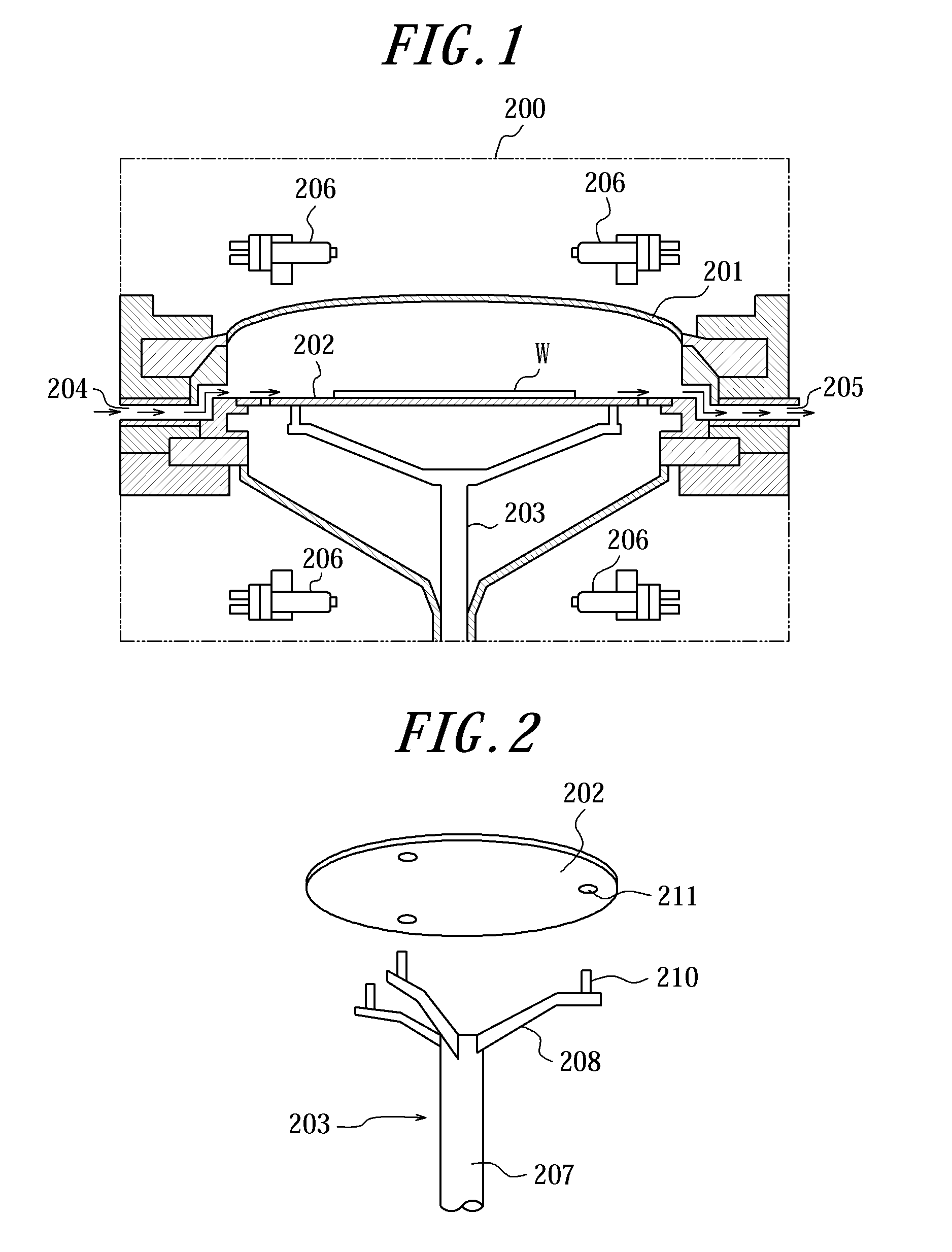

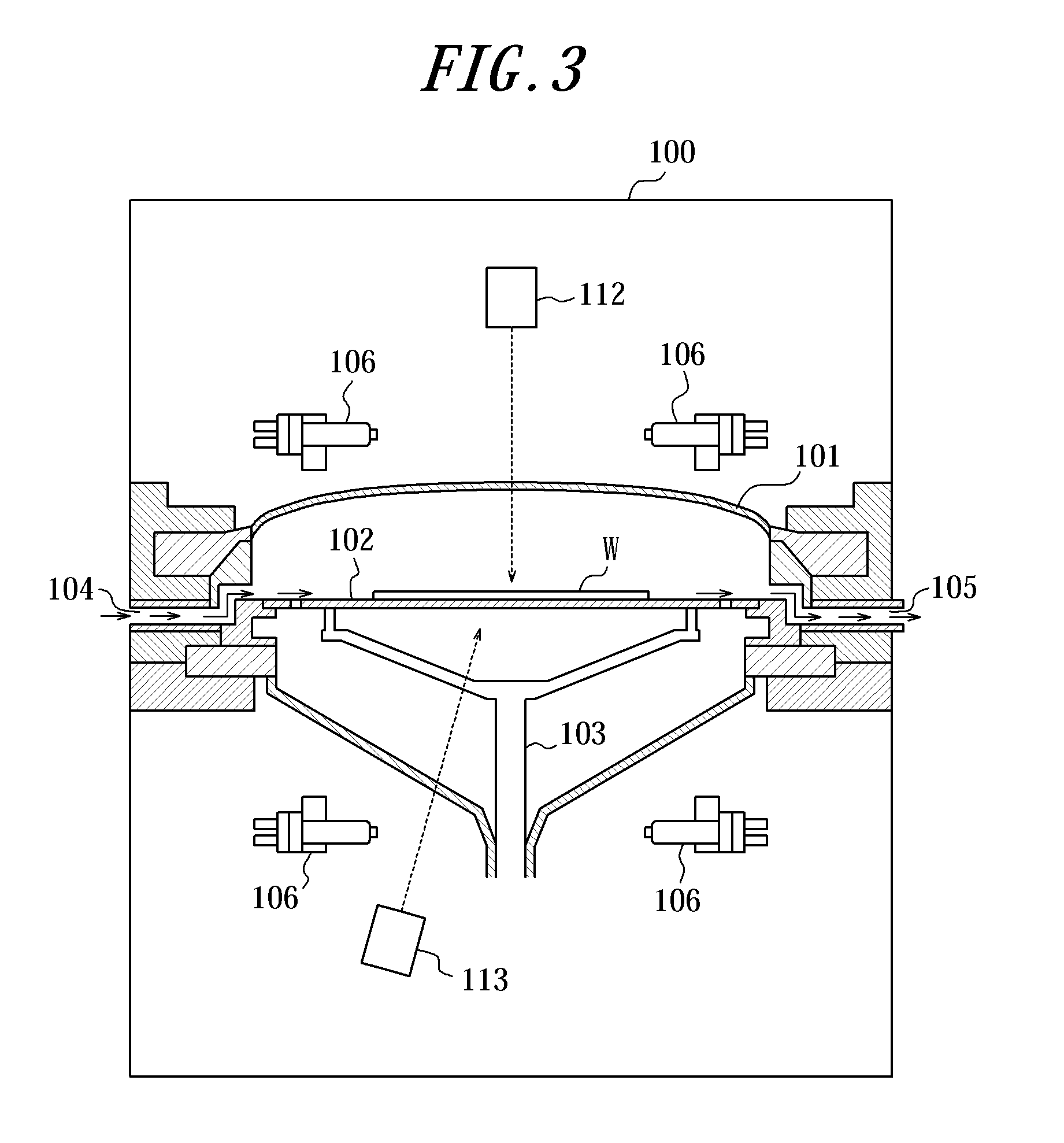

Epitaxial growth apparatus and epitaxial growth method

ActiveUS20120285382A1Suppresses resistance changesEnsuring in detectingSemiconductor/solid-state device manufacturingFrom chemically reactive gasesIn planeEngineering

A susceptor support shaft for an epitaxial growth apparatus capable of forming a high quality epitaxial film by suppressing in-plane resistance variation of the epitaxial film due to deflection of a susceptor, wherein the susceptor support shaft supports a susceptor at an underneath portion of the susceptor in an epitaxial growth apparatus. The susceptor support shaft includes a support column located substantially coaxial with a center of the susceptor; a plurality of arms extending radially from the support column to positions under a peripheral portion of the susceptor; an arm connecting member connecting tips of the arms next to each other; and support pins extending from the arm connecting member, thereby supporting the susceptor.

Owner:SUMCO CORP

Preparation process of high-uniformity conductive silicon target material

InactiveCN111074191AImprove conductivityUniform doping contentMolten spray coatingSpray GranulationLow vacuum

The invention relates to a preparation process of a high-uniformity conductive silicon target material. The preparation process comprises the following steps of 1, preparing materials, specifically, high-purity silicon powder and boron powder are added according to the proportion that the boron concentration content is 20-200 ppm; 2, grinding, specifically, ball milling is carried out on the mixture obtained in step 1 by using a mechanical ball mill; 3, spray granulating, specifically, the powder, with the particle size of 1-10 micros, ground in the step 2 is introduced into a spray granulation dryer for granulating, and spherical ground powder with the particle size of 40-160 micros is obtained; and 4, vacuum spraying, specifically, the spherical powder obtained in the step 3 is sprayed on the surface of a target material base material in a low vacuum environment by means of a plasma spraying mode. According to the preparation process of the high-uniformity conductive silicon target material, the quality of the target material is effectively improved, and the cost is reduced.

Owner:SOLERAS ADVANCED COATINGS (JIANGYIN) CO LTD

Endless tubular polyimide film

ActiveUS8097693B2Simple and efficient and economicalImprove dispersion stabilityLayered productsSpecial tyresAcid derivativeCarboxylic acid

The present invention provides a method for producing a high-quality nonconductive or semi-conductive seamless (jointless) tubular polyimide film in a simple, efficient, and economical manner, and the like. More specifically, the invention relates to an electrically non-conductive or electrically semi-conductive seamless tubular polyimide film comprising polyimide having at least two aromatic tetracarboxylic acid derivatives comprising 15 to 55 mol % of asymmetric aromatic tetracarboxylic acid component and 85 to 45 mol % of symmetric aromatic tetracarboxylic acid component and at least one aromatic diamine component, in which, as required, a specific amount of carbon black is dispersed, and relates to a method for producing the same.

Owner:GUNZE LTD +1

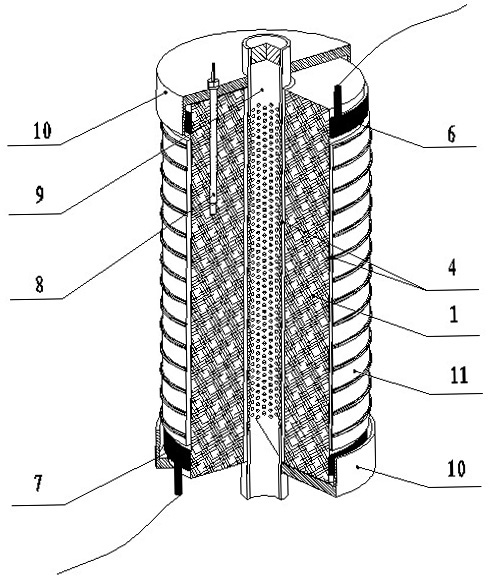

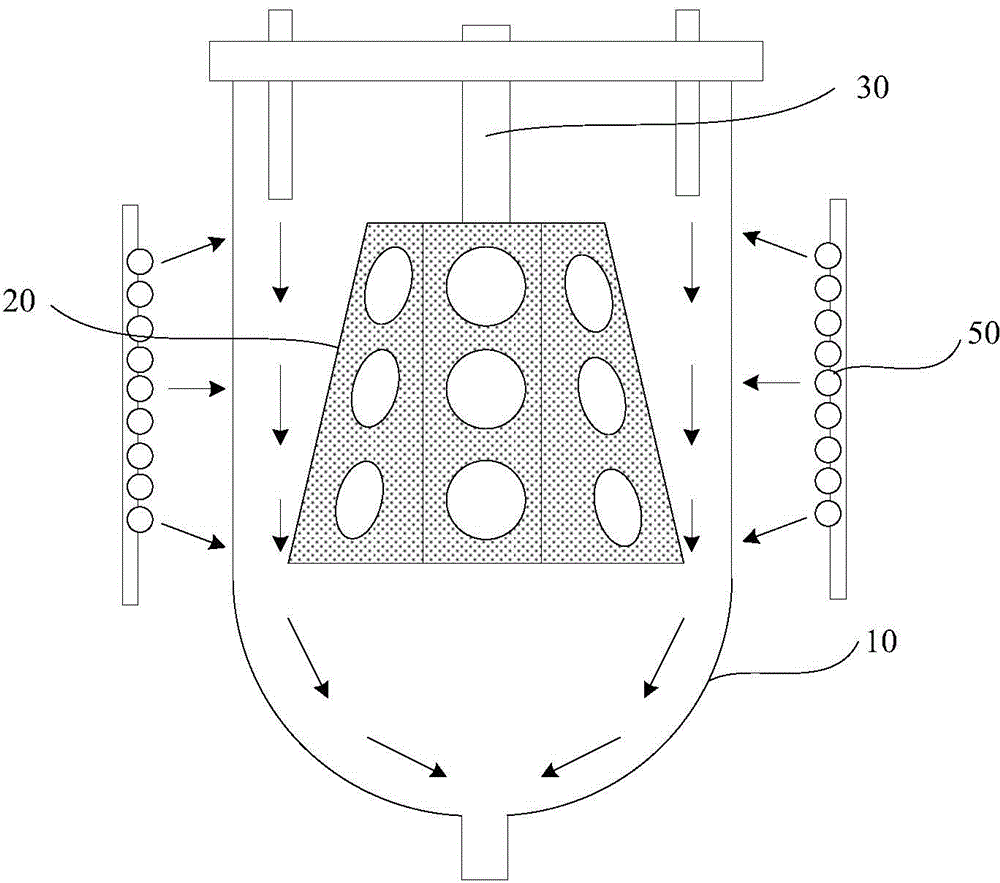

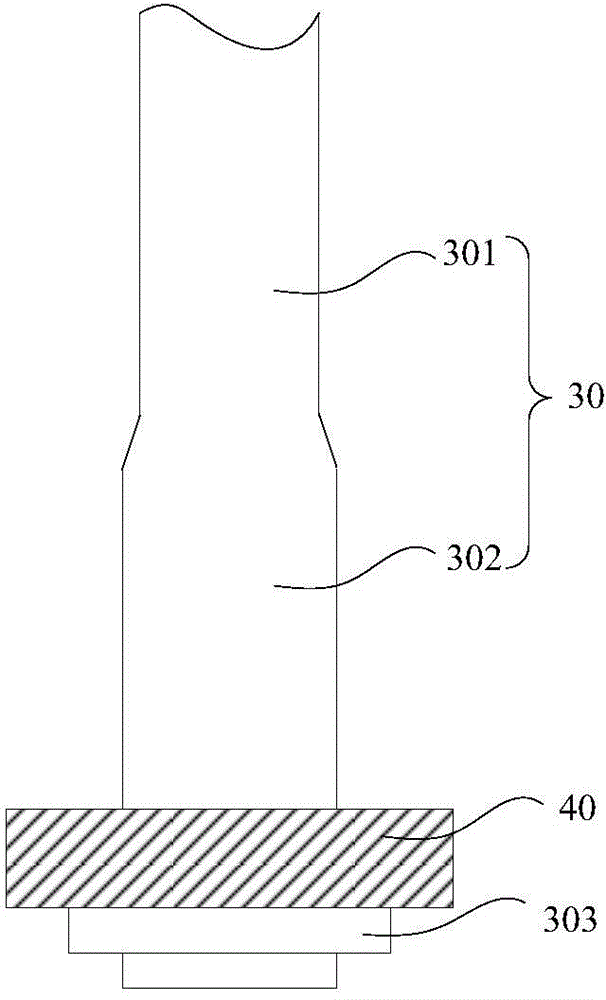

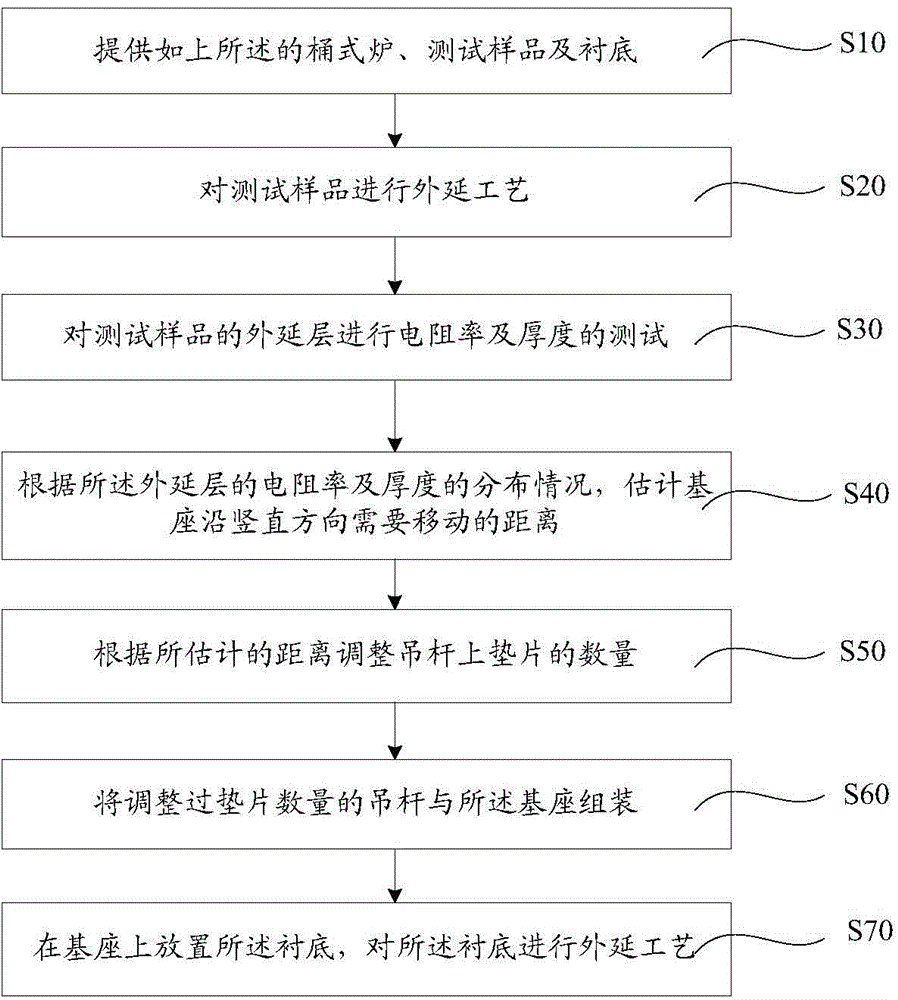

Barrel type furnace and method for manufacturing semiconductor

InactiveCN103985657AUniform thicknessUniform resistivitySemiconductor/solid-state device manufacturingTemperature controlEngineering

The invention provides a barrel type furnace and a method for manufacturing a semiconductor. The barrel type furnace is suitable for the epitaxy technique, the length of a suspender is set to be 300 mm to 350 mm, the suspender is used in cooperation with detachable gaskets, the number of the gaskets on the suspender is increased or reduced according to actual needs, the vertical position of a base in the vertical direction can be adjusted, substrates borne by an upper area and a lower area are located in a good temperature control area when the epitaxy technique is carried out, and therefore after the epitaxy technique is carried out, epitaxial layers on the substrates are even in thickness and electrical resistivity, and the product yield is improved.

Owner:ADVANCED SEMICON MFG CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com