Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1333 results about "Mixed crystal" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

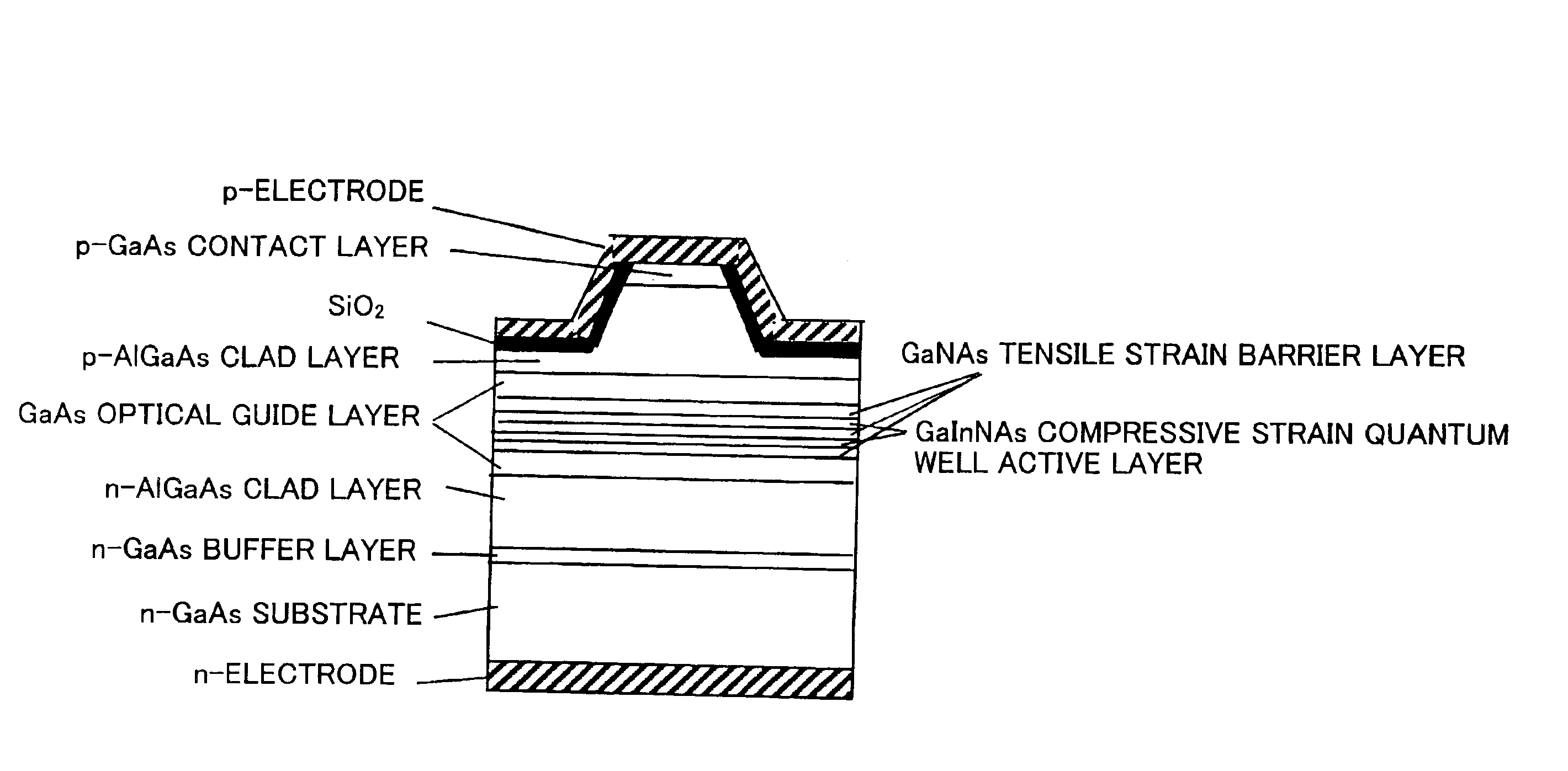

Semiconductor light-emitting device and semiconductor light-emitting device

InactiveUS7087932B2Well formedSolid-state devicesSemiconductor/solid-state device manufacturingCrystal planeCrystallinity

Owner:SAMSUNG ELECTRONICS CO LTD

Method of manufacturing semiconductor device, and semiconductor device

ActiveUS20070254414A1Sufficient carrier mobilityImpurity will diffuseSemiconductor/solid-state device manufacturingSemiconductor devicesSurface layerConcentration gradient

A method of manufacturing a semiconductor device includes: the first step of forming a gate electrode over a silicon substrate, with a gate insulating film; and the second step of digging down a surface layer of the silicon substrate by etching conducted with the gate electrode as a mask. The method of manufacturing the semiconductor device further includes the third step of epitaxially growing, on the surface of the dug-down portion of the silicon substrate, a mixed crystal layer including silicon and atoms different in lattice constant from silicon so that the mixed crystal layer contains an impurity with such a concentration gradient that the impurity concentration increases along the direction from the silicon substrate side toward the surface of the mixed crystal layer.

Owner:SONY CORP

Flat float glass

InactiveUS6846760B2High degreeLess sensitiveGlass furnace apparatusGlass rolling apparatusArsenic oxideTransmittance

This invention relates to a flat float glass that can be prestressed or transformed into a glass ceramic with high quartz mixed crystals or keatite mixed crystals. To eliminate undesirable surface defects during floating and to achieve superior characteristics of the glass or of he glass ceramic, in particular with regard to a low coefficient of thermal expansion and high light transmittance, the glass has a concentration of less than 300 ppb Pt, less than 30 ppb Rh, less than 1.5 wt. % ZnO and less than 1 wt. % SnO2, and is refined during melting without the use of the conventional fining agents arsenic oxide and / or antimony oxide.

Owner:SCHOTT AG

Flat float glass

InactiveUS20020023463A1High degreeLess sensitiveGlass furnace apparatusGlass rolling apparatusArsenic oxideThermal expansion

This invention relates to a flat float glass that can be prestressed or transformed into a glass ceramic with high quartz mixed crystals or keatite mixed crystals. To eliminate undesirable surface defects during floating and to achieve superior characteristics of the glass or of he glass ceramic, in particular with regard to a low coefficient of thermal expansion and high light transmittance, the glass has a concentration of less than 300 ppb Pt, less than 30 ppb Rh, less than 1.5 wt. % ZnO and less than 1 wt. % SnO2, and is refined during melting without the use of the conventional fining agents arsenic oxide and / or antimony oxide.

Owner:SCHOTT AG

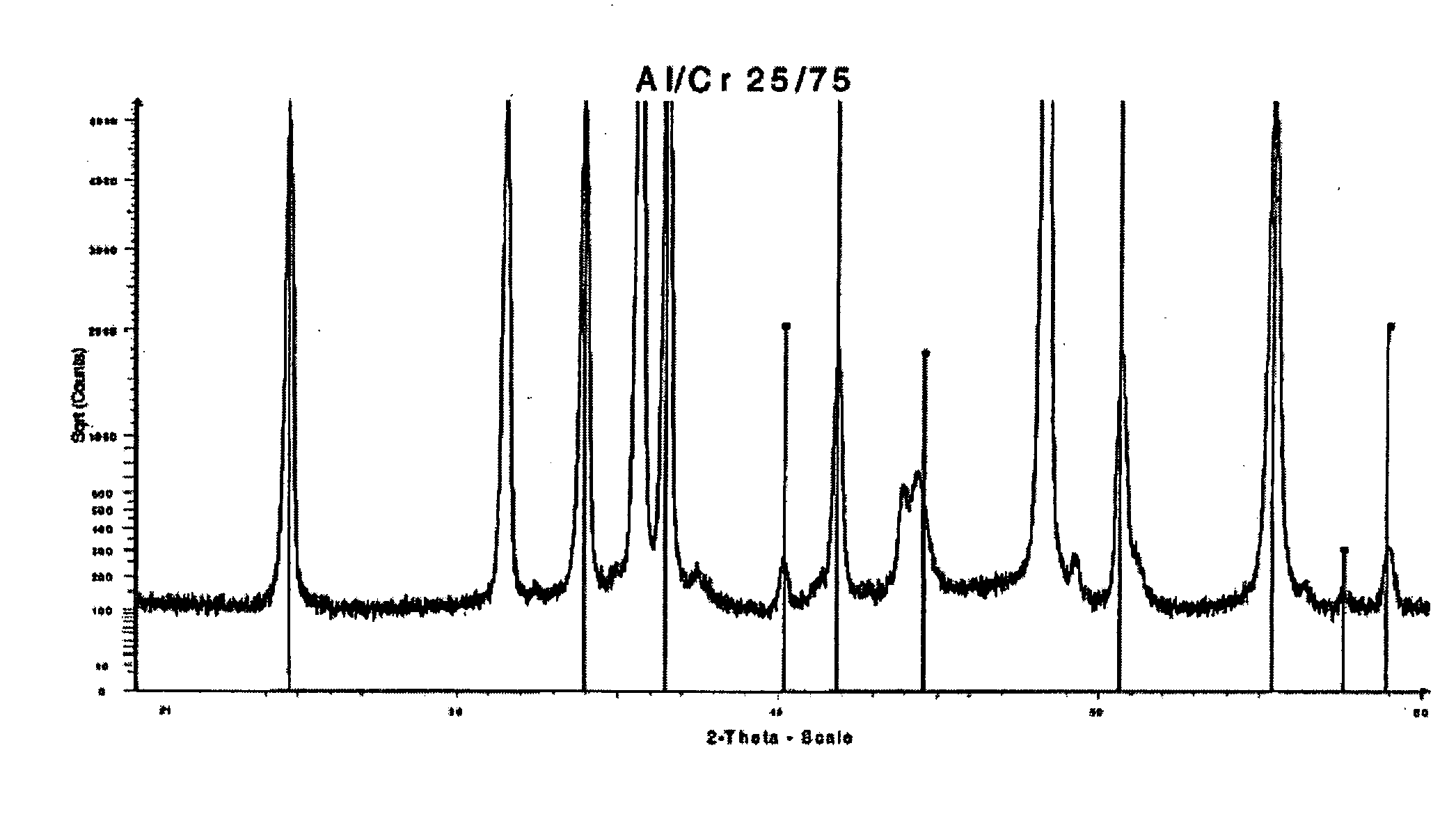

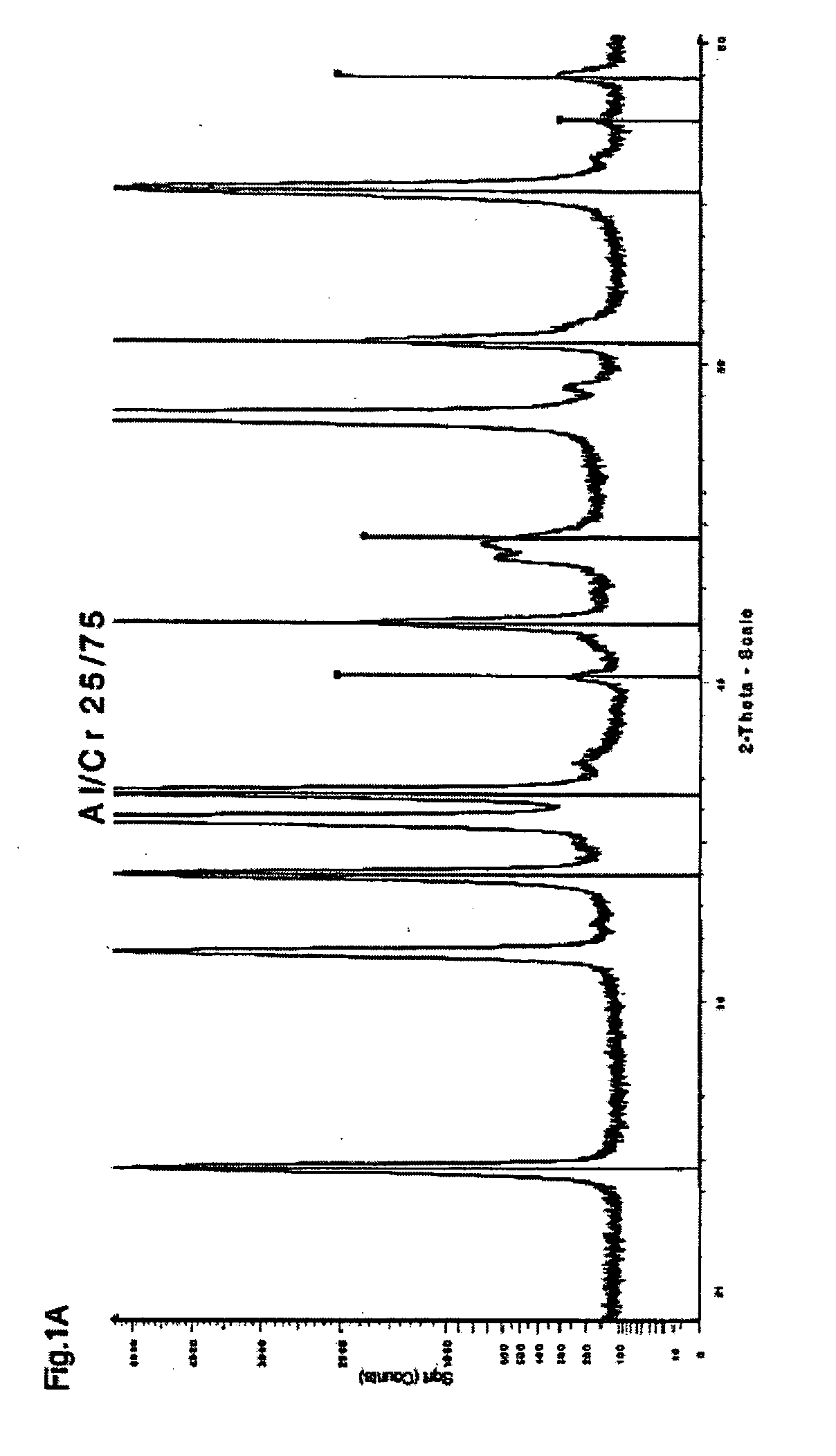

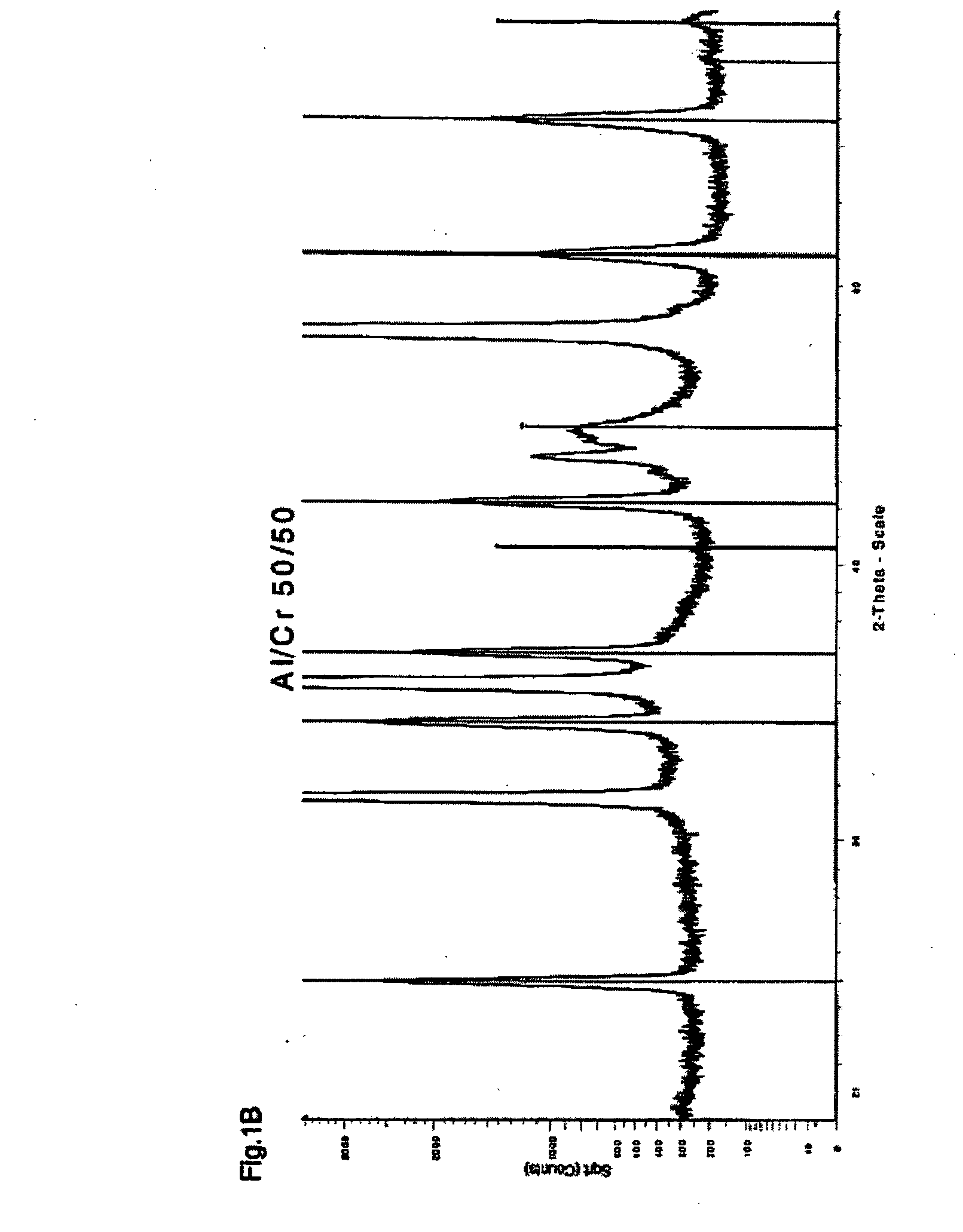

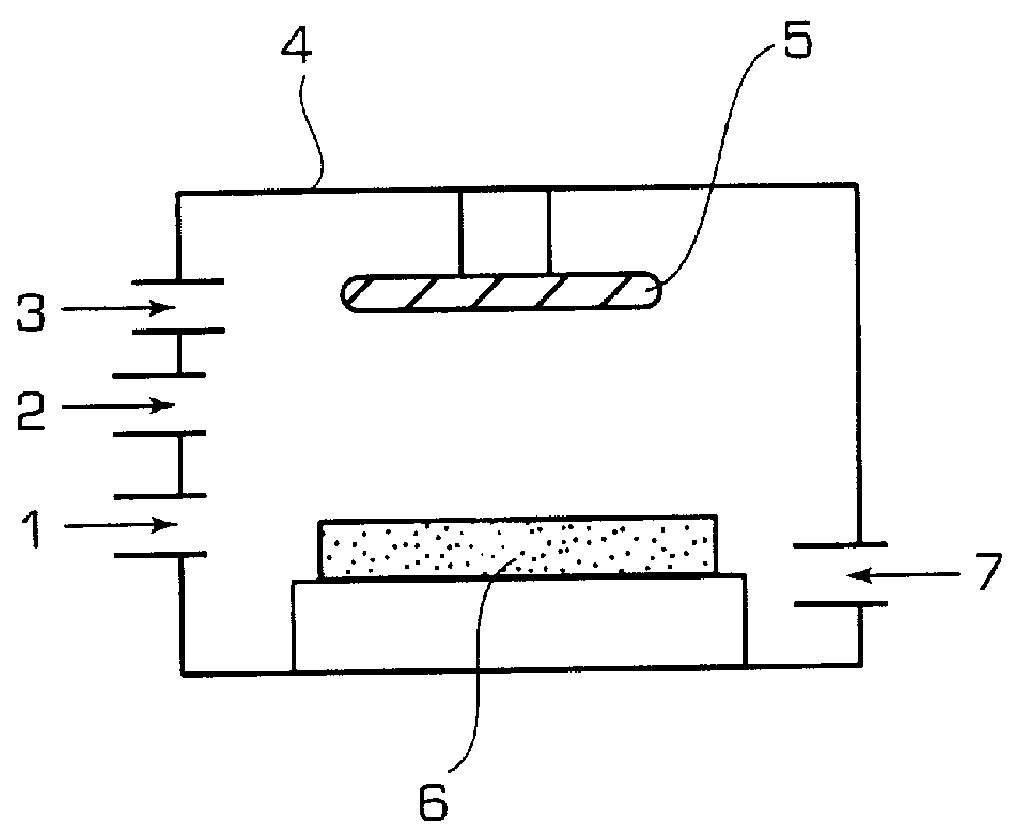

Layer system with at least one mixed crystal layer of a multi-oxide

A PVD layer system for the coating of workpieces encompasses at least one mixed-crystal layer of a multi-oxide having the following composition: (Me11-xMe2x)2O3, where Me1 and Me2 each represent at least one of the elements Al, Cr, Fe, Li, Mg, Mn, Nb, Ti, Sb or V. The elements of Me1 and Me2 differ from one another. The crystal lattice of the mixed-crystal layer in the PVD layer system has a corundum structure which in an x-ray diffractometrically analyzed spectrum of the mixed-crystal layer is characterized by at least three of the lines associated with the corundum structure. Also disclosed is a vacuum coating method for producing a mixed-crystal layer of a multi-oxide, as well as correspondingly coated tools and components.

Owner:OERLIKON SURFACE SOLUTIONS AG PFAFFIKON

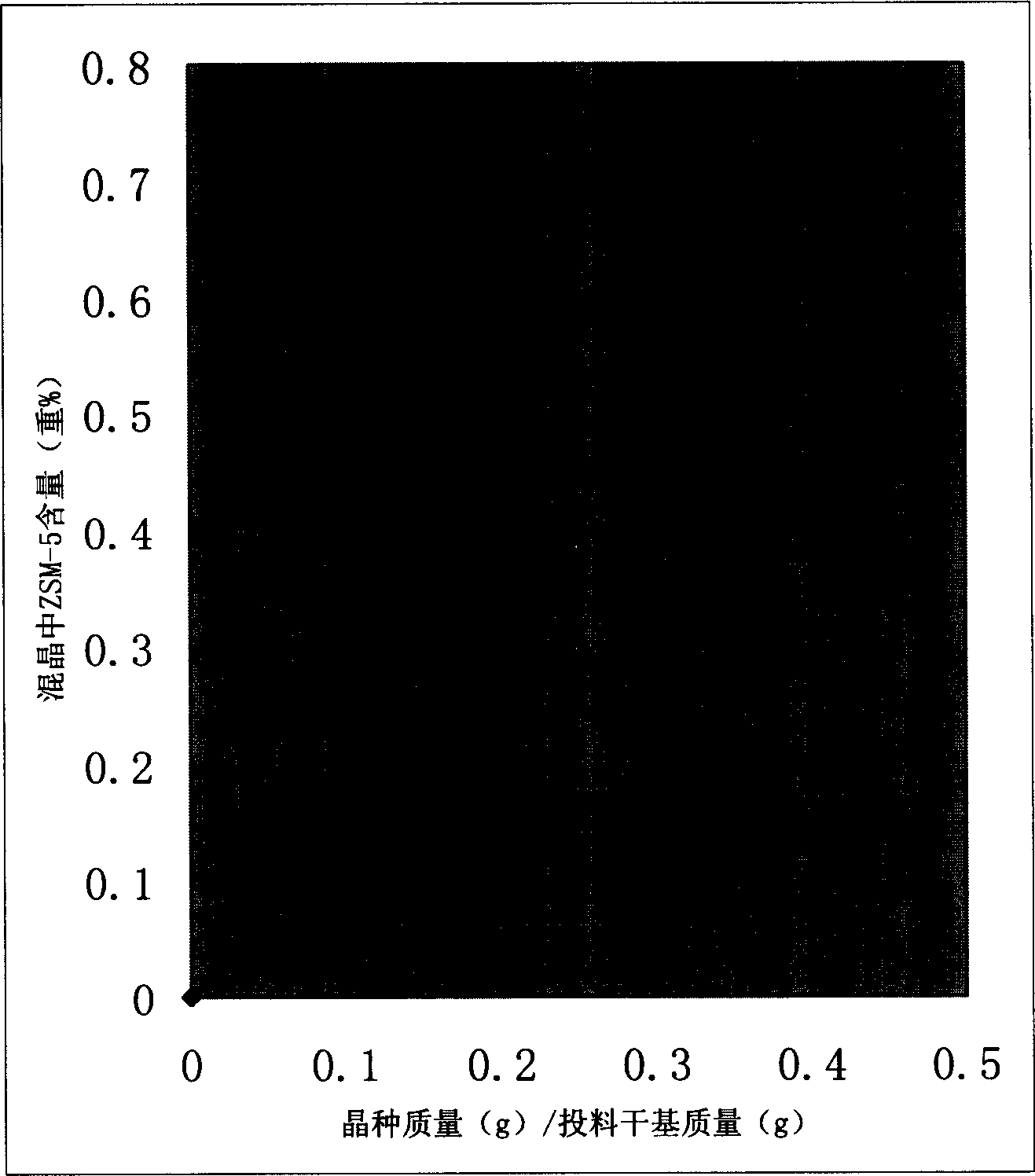

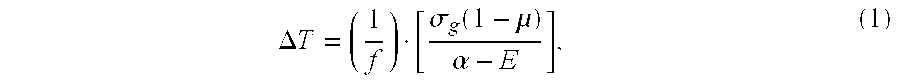

Synthetic method for ZSM-5/mordenite mixed crystal material

InactiveCN1565970ALower synthesis costEasy to adjustMolecular sieve catalystsMordenite aluminosilicate zeoliteMordeniteThermal crystallization

The invention discloses a synthetic method for ZSM-5 / mordenite mixed crystal material, wherein ZSM-5 molecular sieve is charged into the synthesized reaction mixture of mordenite as seed crystal, and said material is prepared through water thermal crystallization. The invention realizes low making cost and more ideal catalyzing performance.

Owner:CHINA PETROLEUM & CHEM CORP +2

Semiconductor light emitter

A semiconductor light emitter includes a quantum well active layer which includes nitrogen and at least one other Group-V element, and barrier layers which are provided alongside the quantum well active layer, wherein the quantum well active layer and the barrier layers together constitute an active layer, wherein the barrier layers are formed of a Group-III-V mixed-crystal semiconductor that includes nitrogen and at least one other Group-V element, a nitrogen composition thereof being smaller than that of the quantum well active layer.

Owner:RICOH KK

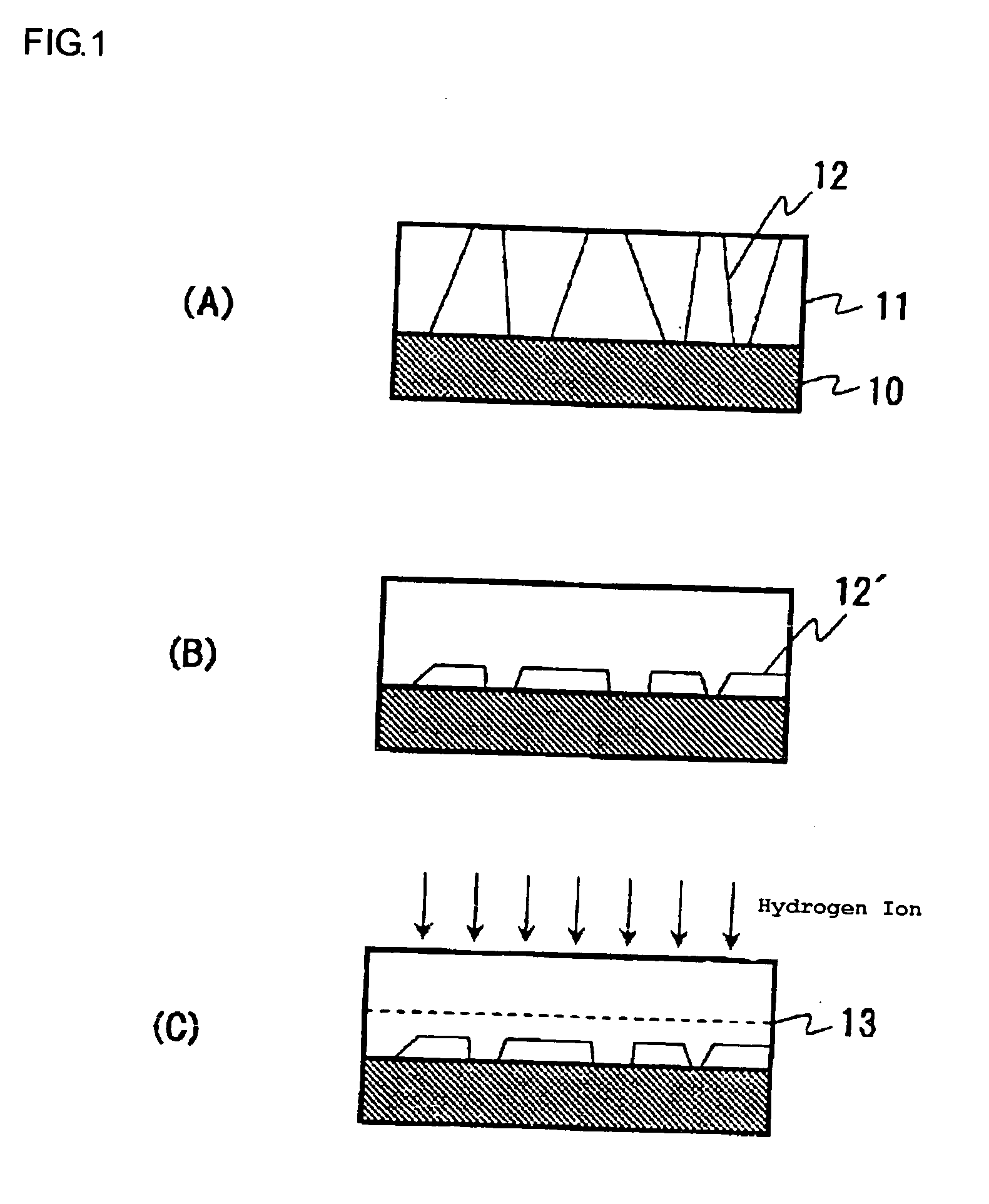

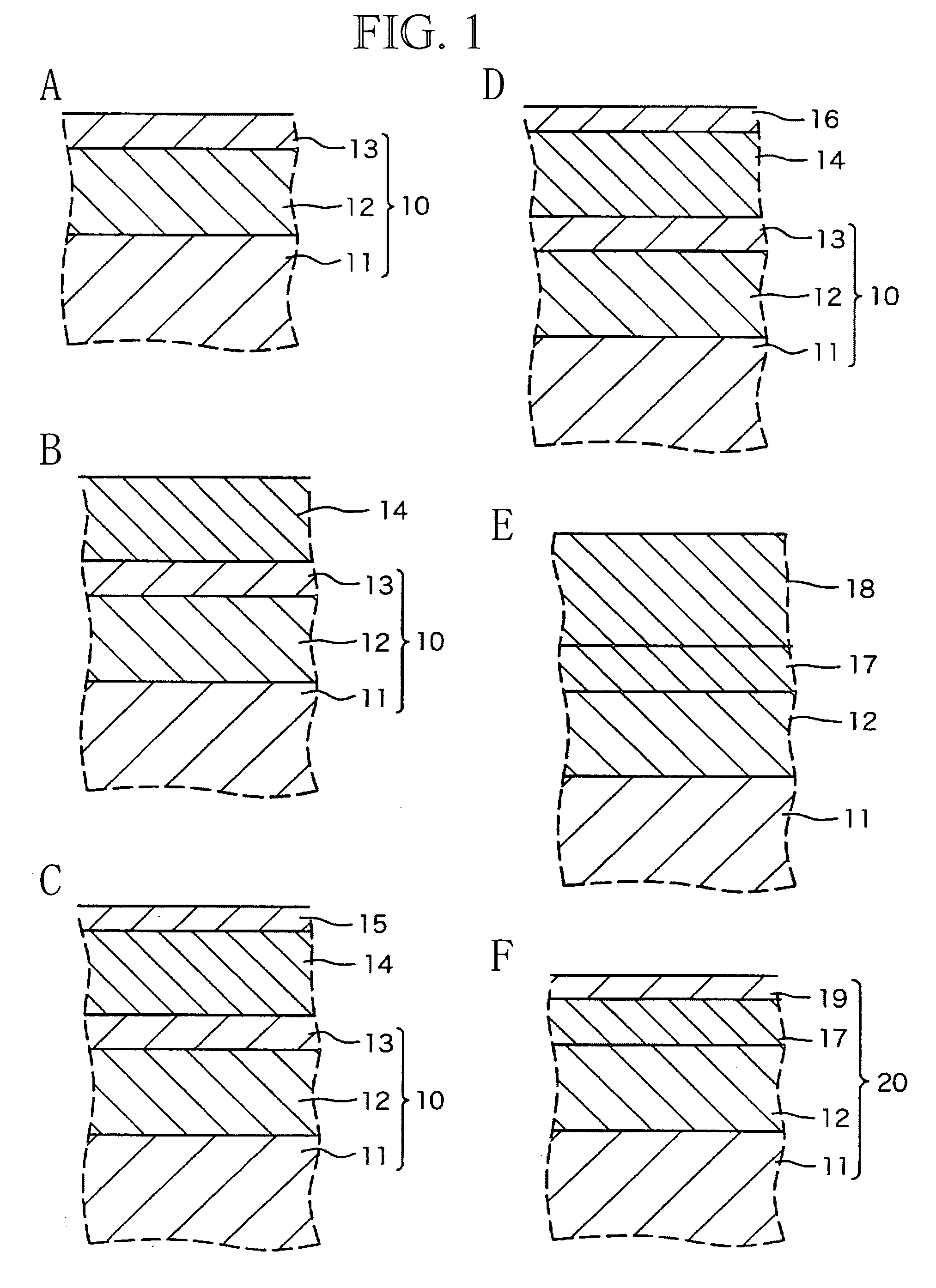

Method for manufacturing semiconductor substrate

ActiveUS20080194078A1Simple technologyQuality improvementSemiconductor/solid-state device manufacturingSemiconductor devicesThreading dislocationsHigh density

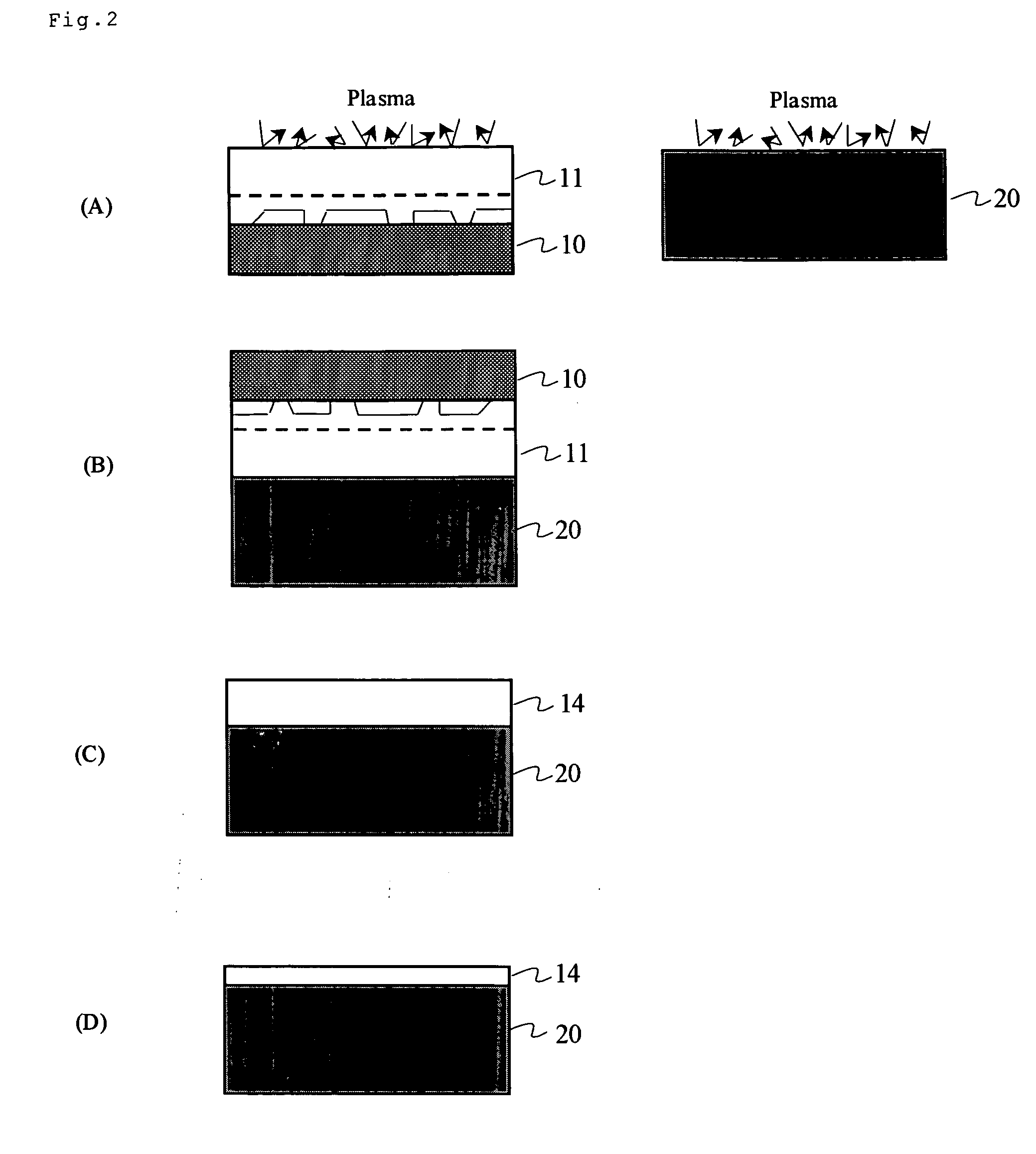

To obtain a semiconductor substrate having a high-quality Ge-based epitaxial film in a large area, a SiGe mixed crystal buffer layer and a Ge epitaxial film is grown on a main surface of a Si substrate 10. Although high-density defects are introduced in the Ge epitaxial film 11 from an interface between the Ge epitaxial film 11 and the Si substrate 10, the Ge epitaxial film is subjected to a heat treatment at a temperature of not less than 700° C. and not more than 900° C. to cause threading dislocations 12 to change into dislocation-loop defects 12′ near the interface between the Ge epitaxial film 11 and the Si substrate. A main surface of at least one of the Ge epitaxial film 11 with an ion implanted layer and a support substrate 20 is then subjected to a plasma treatment or ozone treatment for the purpose of surface cleaning, surface activation, and the like, after which the main surfaces of the Ge epitaxial film 11 and the support substrate 20 are appressed against and bonded to each other with their surfaces being determined as the joint surfaces. An external impact is then applied to the bonding interface, causing the Ge epitaxial film to be delaminated along a hydrogen ion implanted interface 13, thus obtaining a Ge thin film 14. A surface of the Ge thin film 14 is subsequently subjected to a final surface treatment (for example, CMP) to remove the damage caused by the hydrogen ion implantation, thus resulting in a GeOI substrate having the Ge thin film 14 on the surface thereof.

Owner:SHIN ETSU CHEM IND CO LTD

Light emitting device

ActiveUS20090134413A1Easy to provideImprove luminous performanceElectroluminescent light sourcesSolid-state devicesAlkaline earth metalPhosphor

The present invention relates to a light emitting device comprising at least one light emitting diode which emits light in a predetermined wavelength region, copper-alkaline earth metal based inorganic mixed crystals activated by rare earths, which include copper-alkaline earth silicate phosphors which are disposed around the light emitting diode and absorb a portion of the light emitted from the light emitting diode and to emit light different in wavelength from the absorbed light.

Owner:SEOUL SEMICONDUCTOR

Translucent or opaque colored glass-ceramic article providing a cooking surface and its use

InactiveUS20050252503A1Minimizing contentEasy resistanceCooking-vessel materialsStoves/ranges foundationsChemical reactionAdditive ingredient

The translucent or opaque colored glass-ceramic article provides a cooking surface and has an adjustable light transmission in a visible range under 15%, as measured for a 4 mm sample thickness; a flaw-free upper surface with an impact resistance of greater than 18 cm breaking height, as tested with a 200 g steel ball in a falling ball test; a temperature difference resistance of greater than 500° C.; a high crystallinity with keatite mixed crystals as principal crystal phase in an interior of the glass-ceramic article and with a residual glass phase fraction of less than 8% by weight; a glassy upper surface layer of from 0.5 to 2.5 μm thick, which is substantially free of high quartz mixed crystals and which inhibits chemical reactions, and a content of enriched ingredients in the residual glass phase in the interior of the glass-ceramic and in the glassy surface layer of ΣNa2O+K2O+CaO+SrO+BaO+F+refining agents of from 0.2 to 1.6% by weight.

Owner:SCHOTT AG

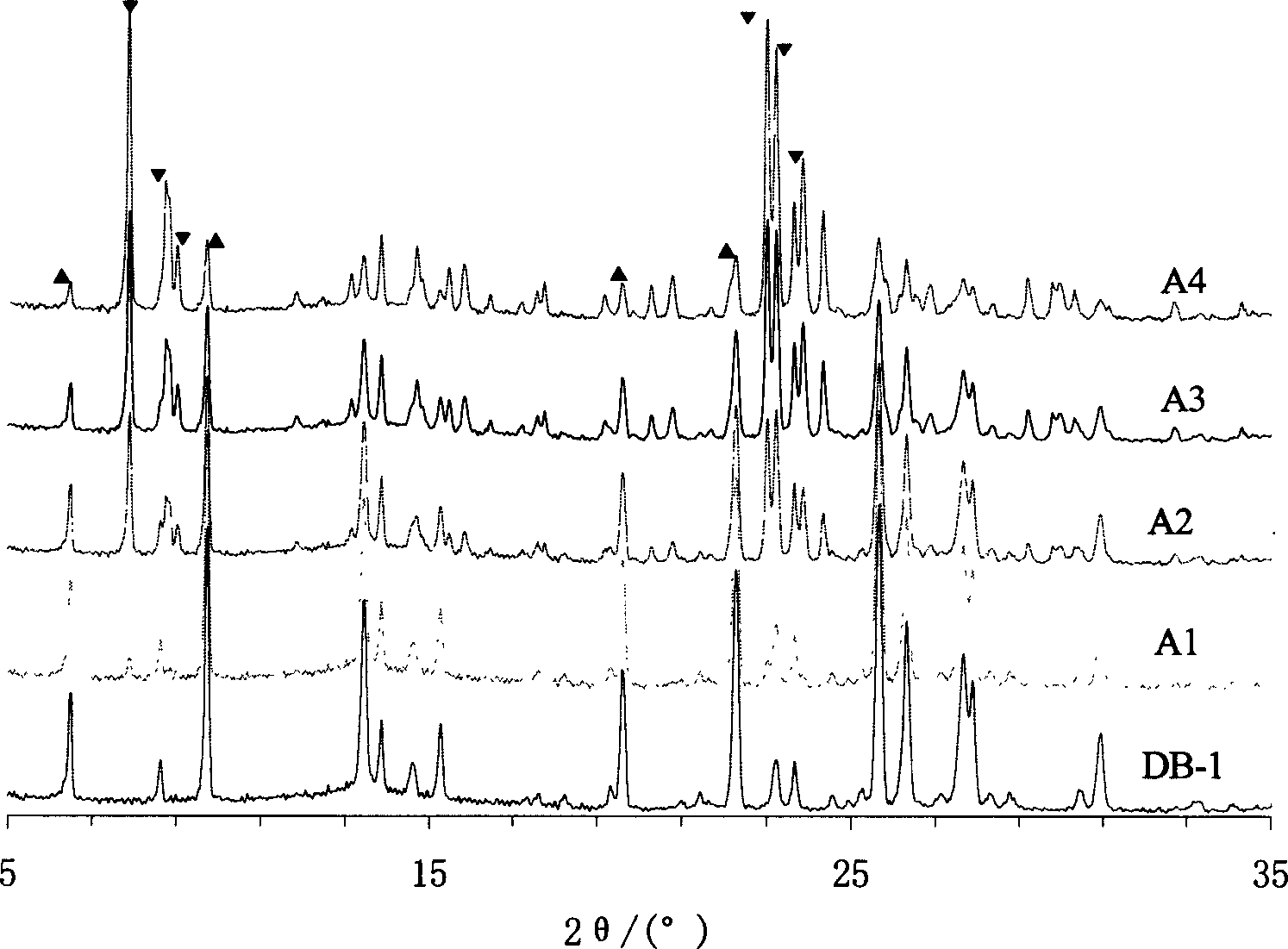

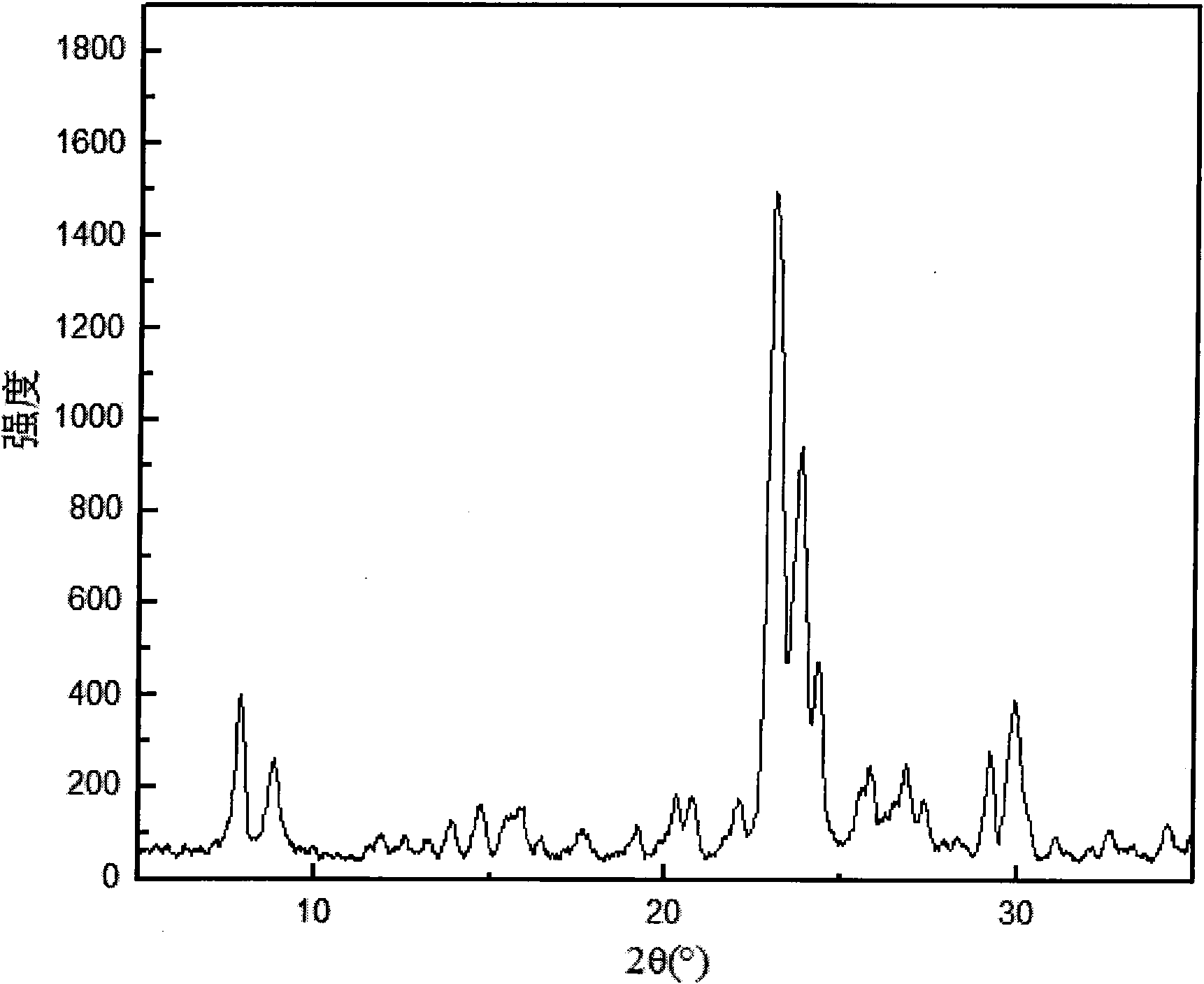

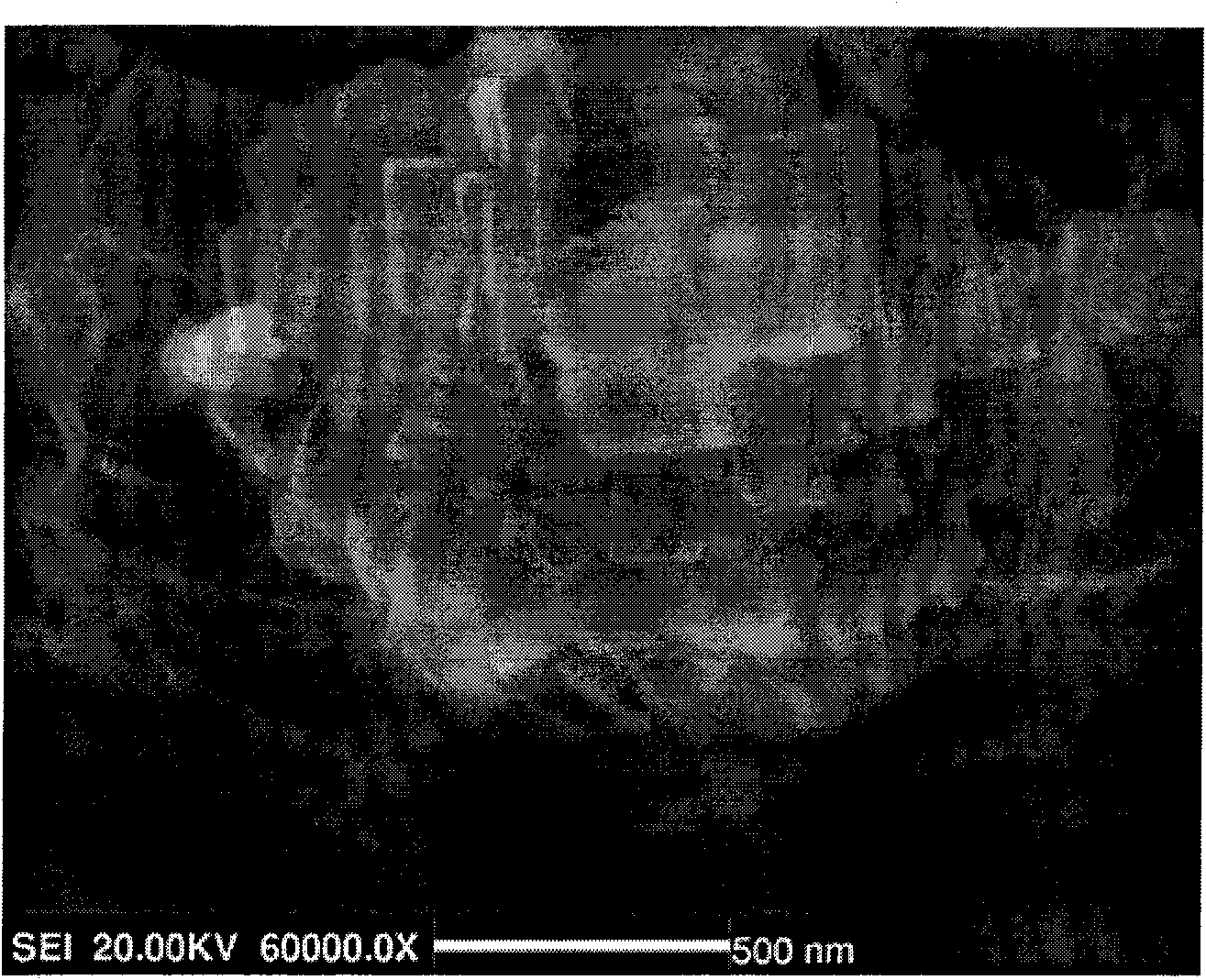

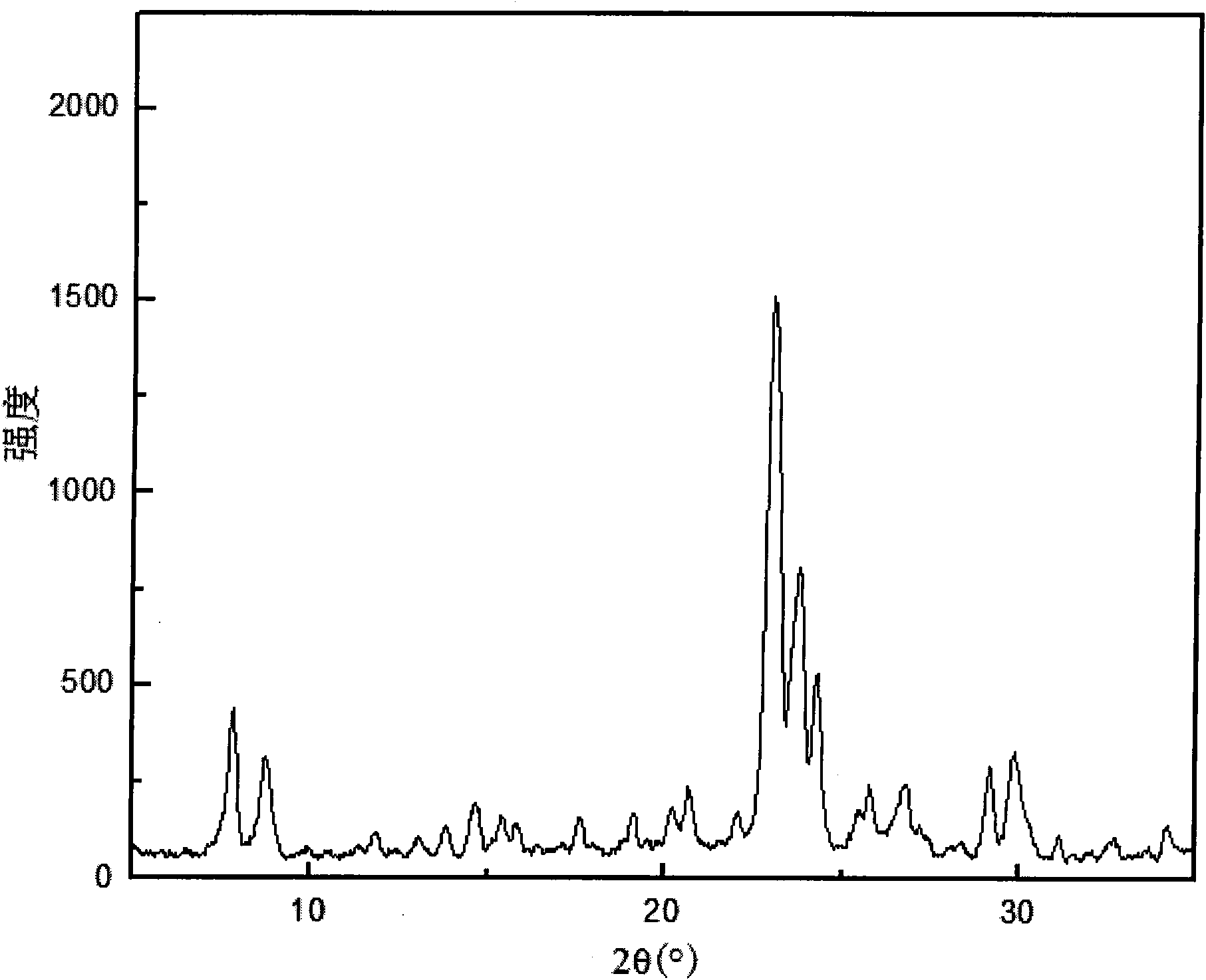

Preparation method of nano-ZSM-5 molecular sieve

InactiveCN101643219ASolve the costSolve pollutionPentasil aluminosilicate zeoliteRoom temperatureNanoscopic scale

The invention relates to a preparation method of a nano-ZSM-5 molecular sieve, which belongs to the field of preparation of zeolite molecular sieve catalysts. The preparation method can solve the problem that the existing synthesis technology has the defects of easy emergence of mixed crystal phase, high cost, environmental pollution and easy loss of features of nanomaterials. The method is as follows: adding pre-crystallized crystal seeds into a gel system of the template-free synthetic nano-ZSM-5 molecular sieve, carrying out crystallization for 24 hours at the temperature of 160-180 DEG C,cooling to room temperature, carrying out centrifugal filtration on products, washing, drying and baking. The prepared nano-ZSM-5 molecular sieve is highly concentrated nanoscale crystals without themixed crystal phase; and the method has the advantages of low cost and environmental protection.

Owner:HEILONGJIANG UNIV

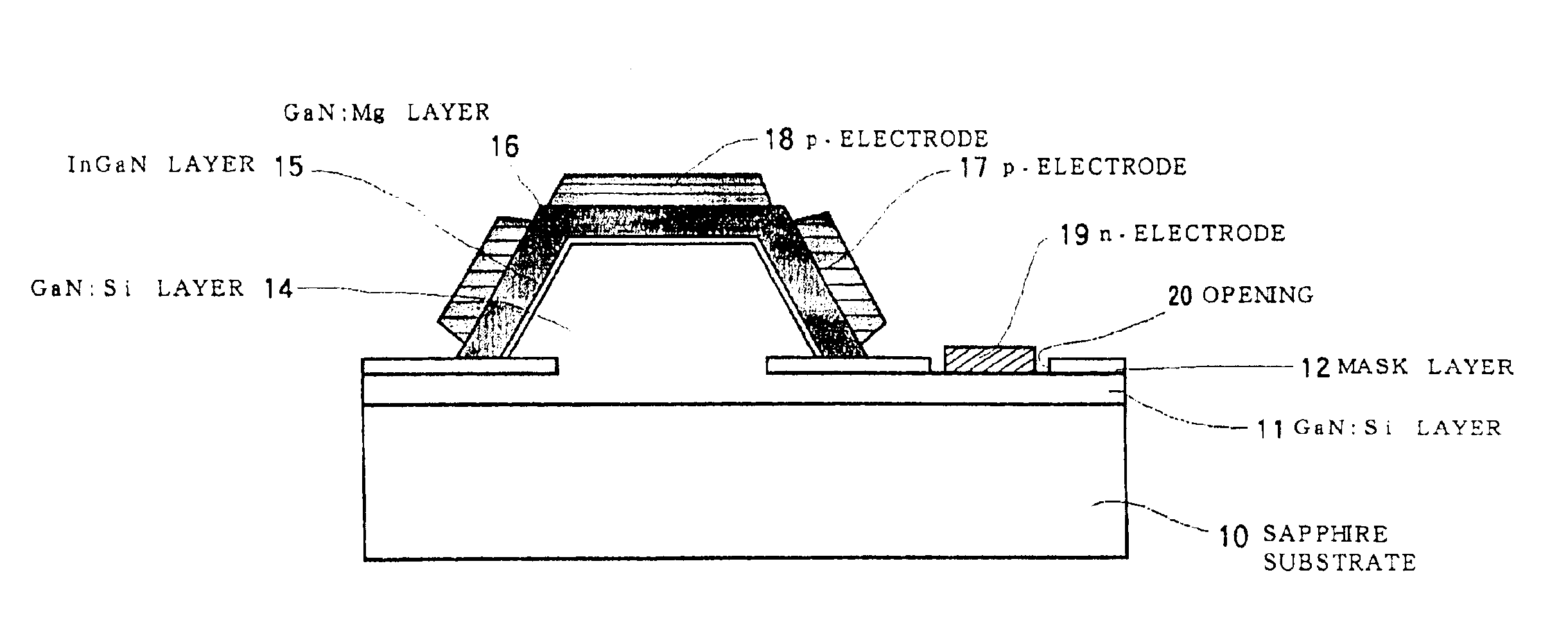

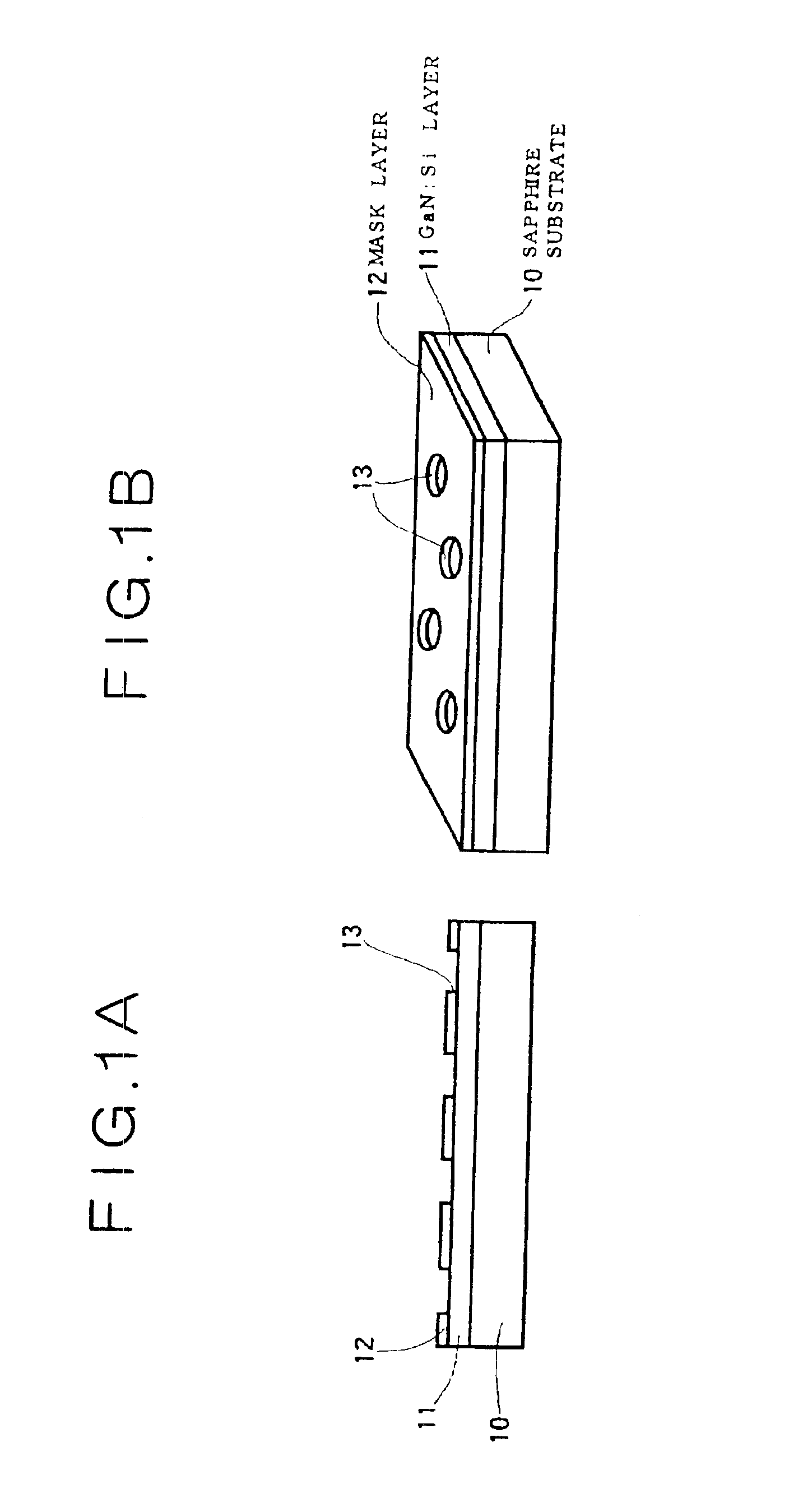

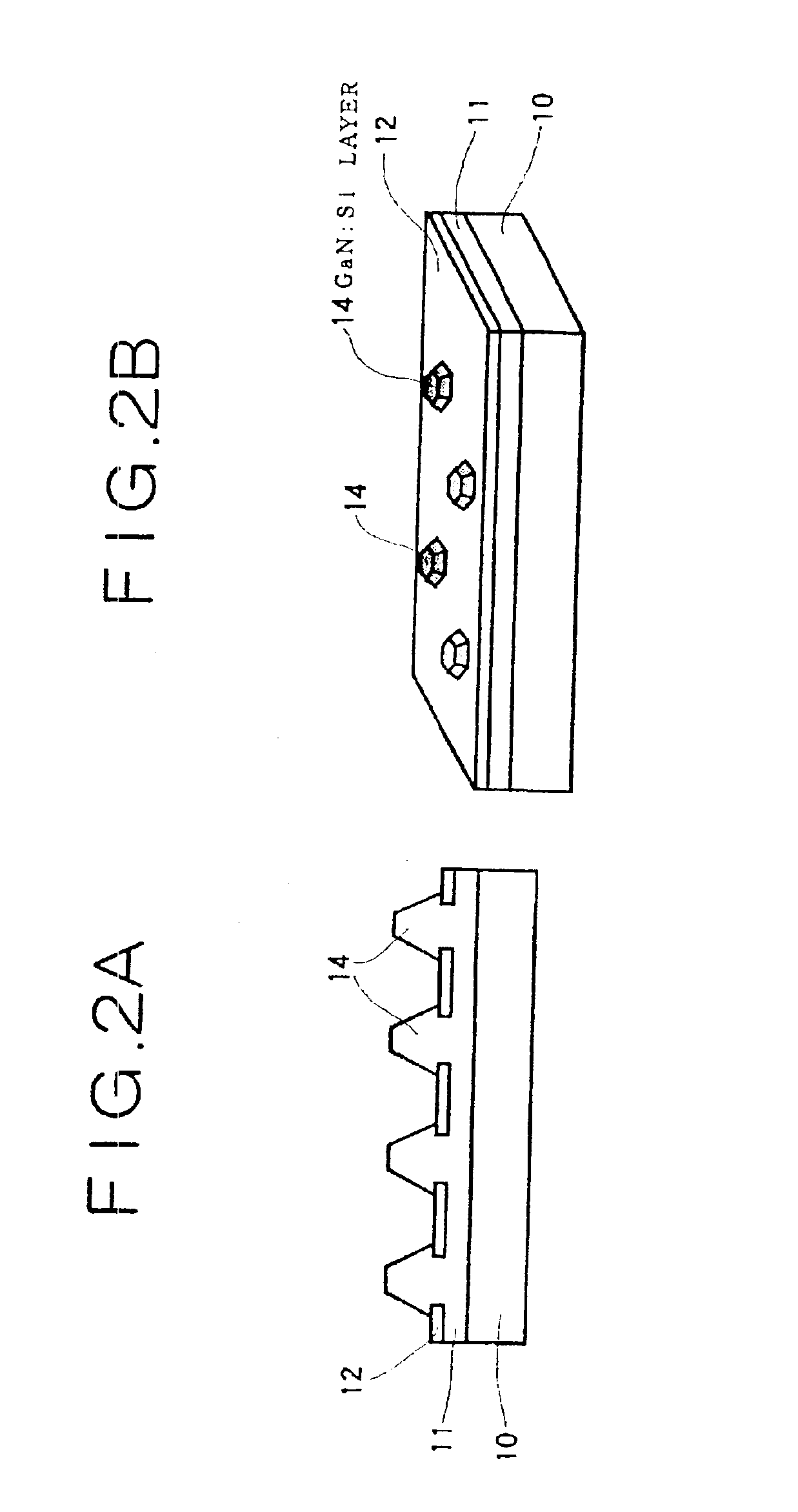

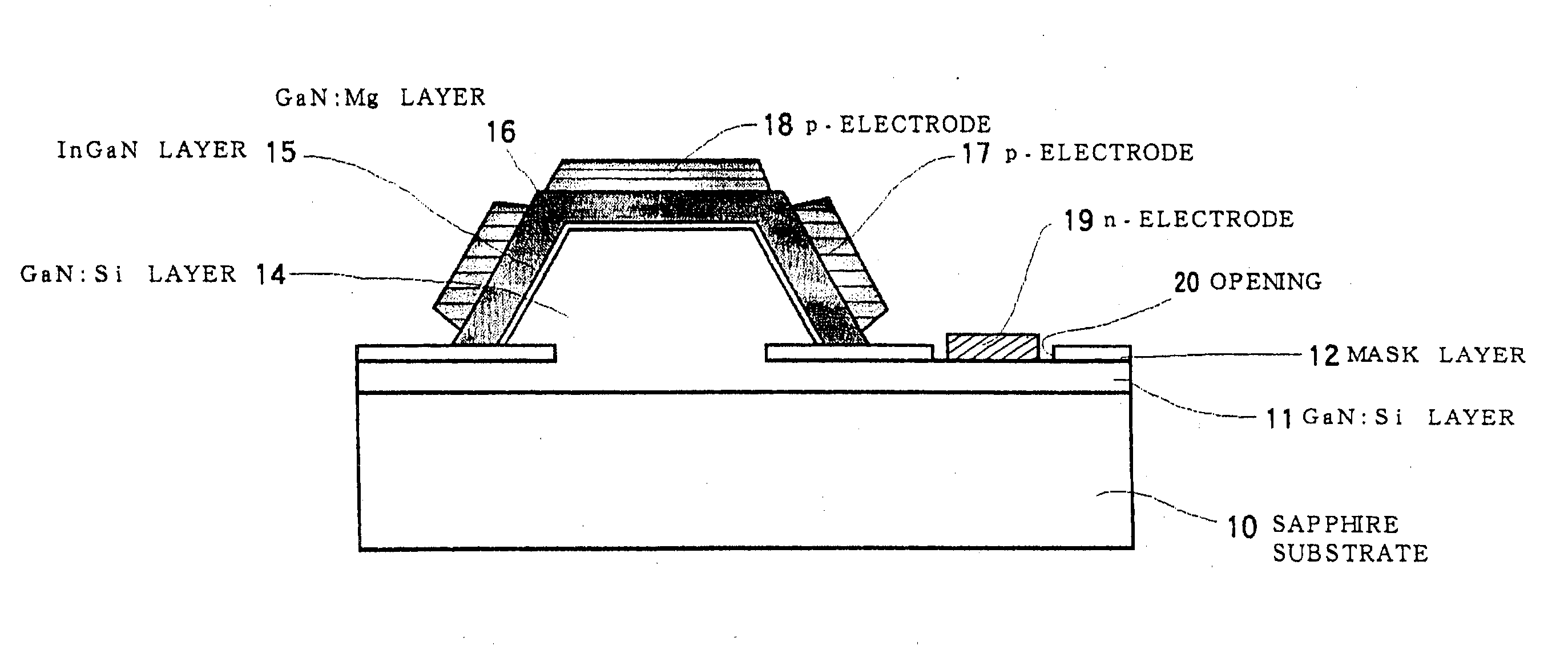

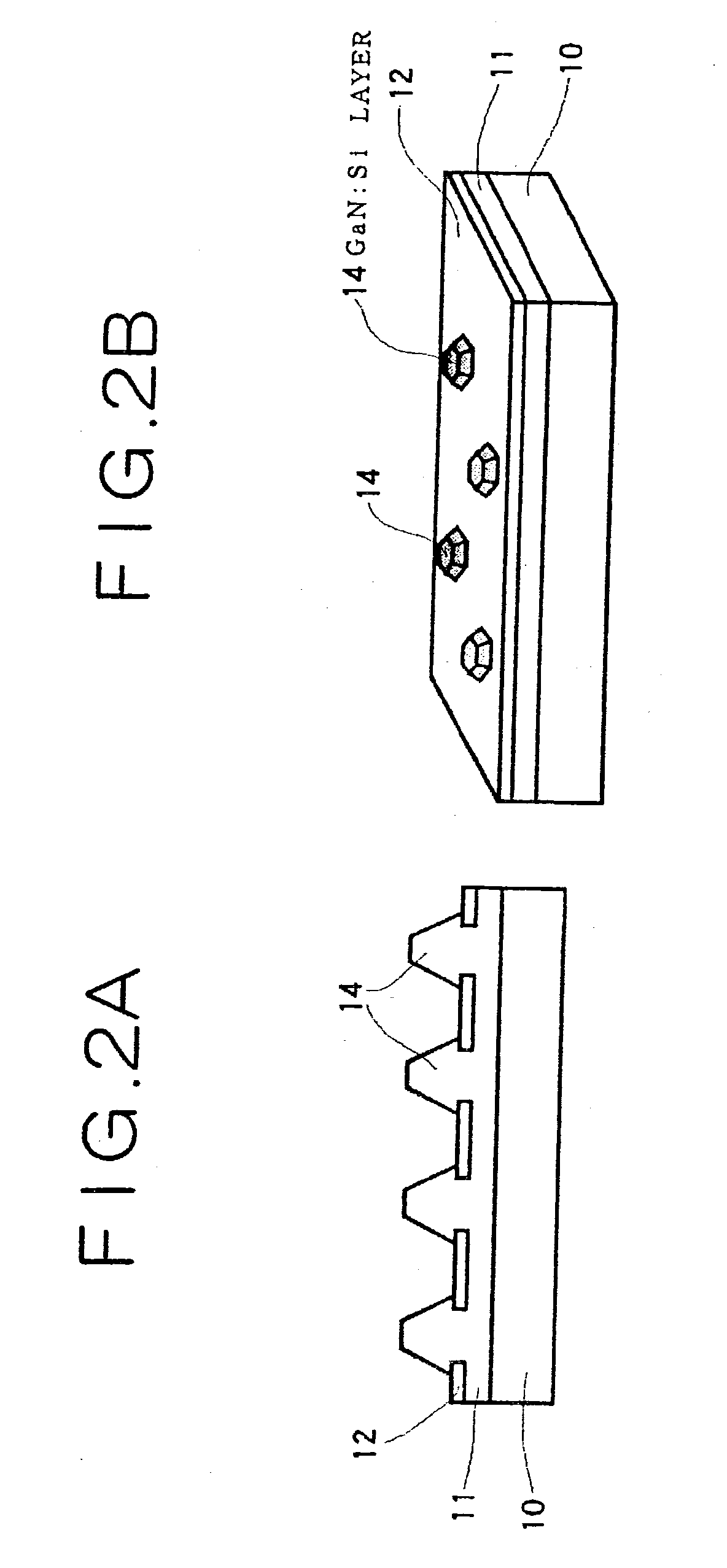

Semiconductor light-emitting device and semiconductor light-emitting apparatus

InactiveUS20030107047A1Easily feasibleReduce lightSolid-state devicesSemiconductor/solid-state device manufacturingManufacturing technologyCrystal plane

A semiconductor light-emitting element having a structure that does not complicate a fabrication process, can be formed in high precision and does not invite any degradation of crystallinity is provided. A light-emitting element is formed, which includes a selective crystal growth layer formed by selectively growing a compound semiconductor of a Wurtzite type, and a clad layer of a first conduction type, an active layer and a clad layer of a second conduction type, which are formed on the selective crystal growth layer wherein the active layer is formed so that the active layer extends in parallel to different crystal planes, the active layer is larger in size than a diffusion length of a constituent atom of a mixed crystal, or the active layer has a difference in at least one of a composition and a thickness thereof, thereby forming the active layer having a plurality of light-emitting wavelength region whose emission wavelengths differ from one another. The element is so arranged that an electric current or currents are chargeable into the plurality of light-emitting wavelength regions. Because of the structure based on the selective growth, it is realized that the band gap energy varies within the same active layer, thereby forming an element or device in high precision without complicating a fabrication process.

Owner:SAMSUNG ELECTRONICS CO LTD

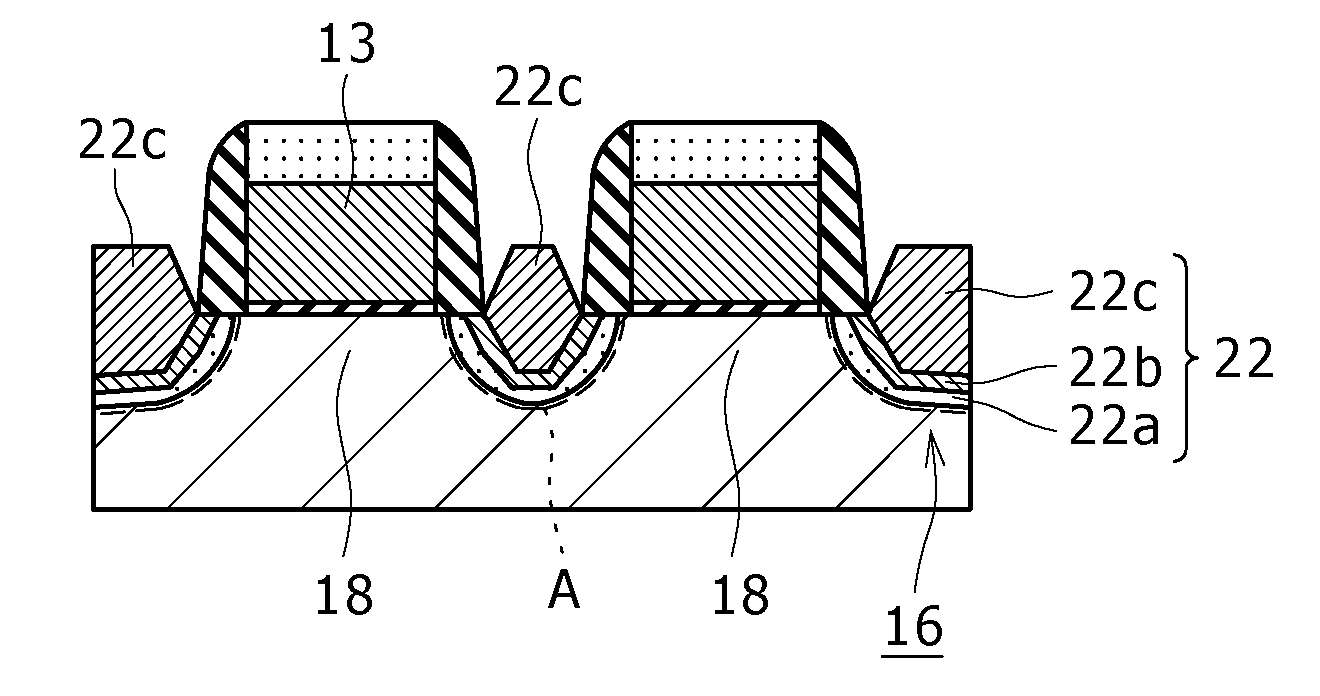

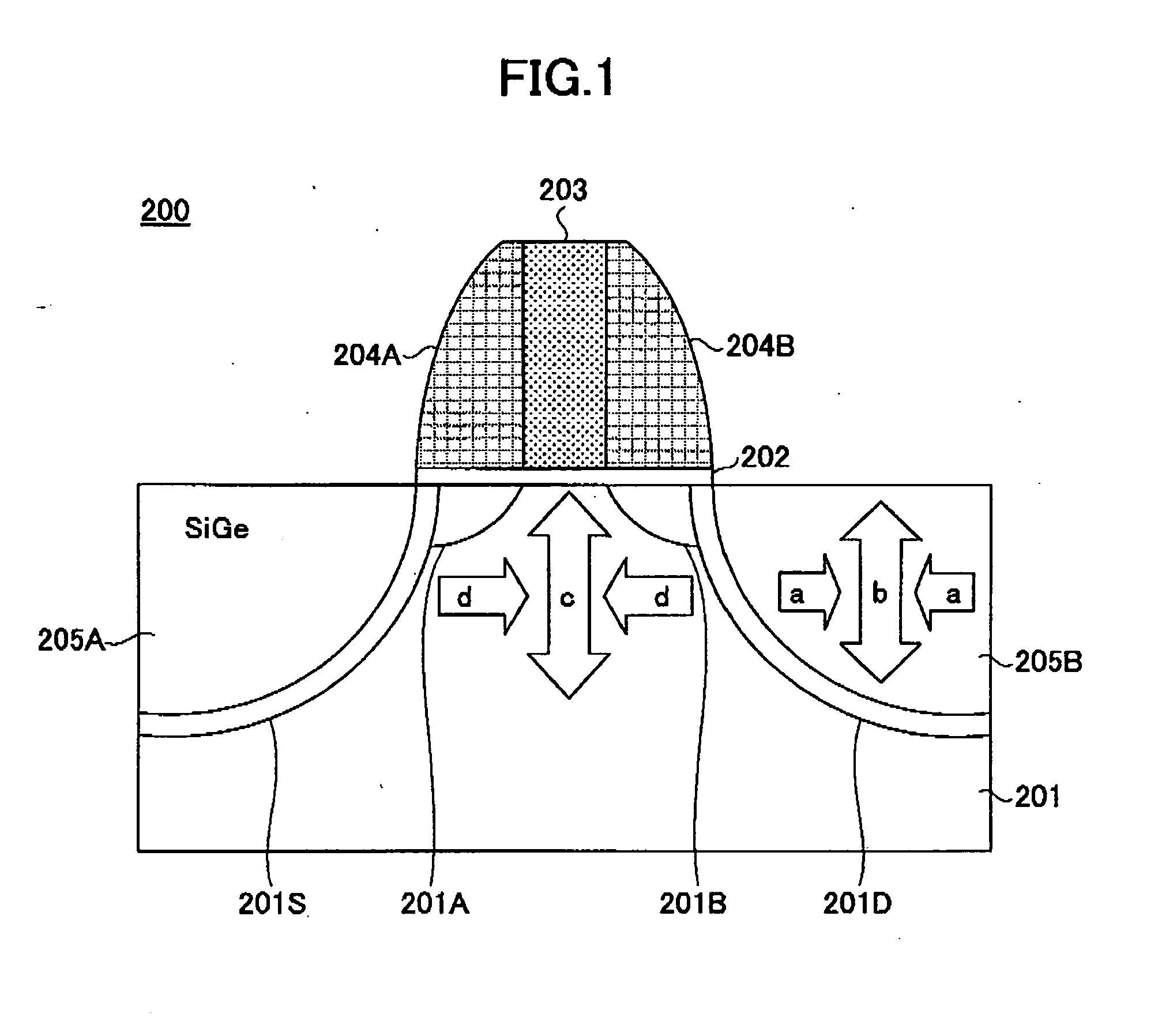

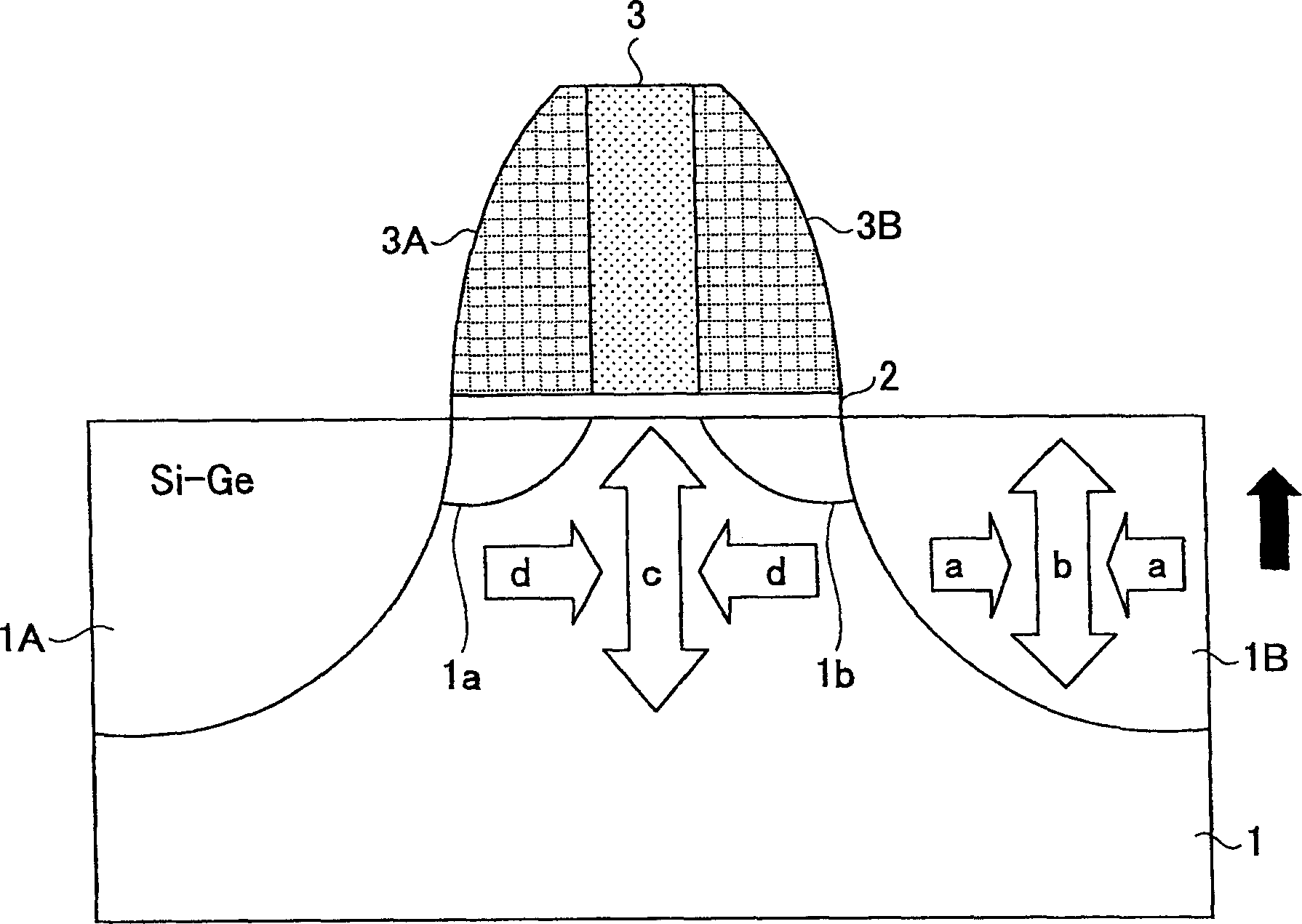

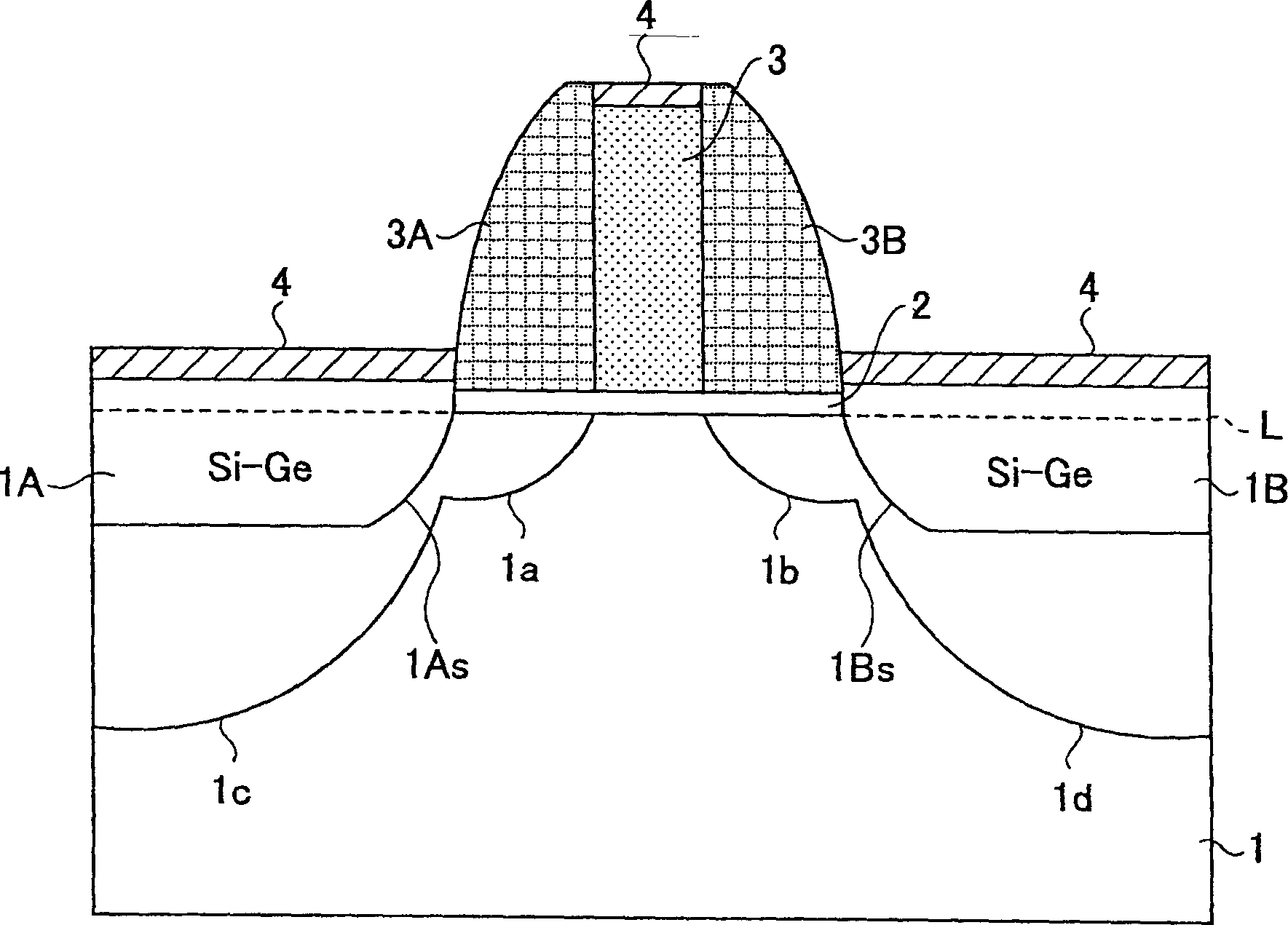

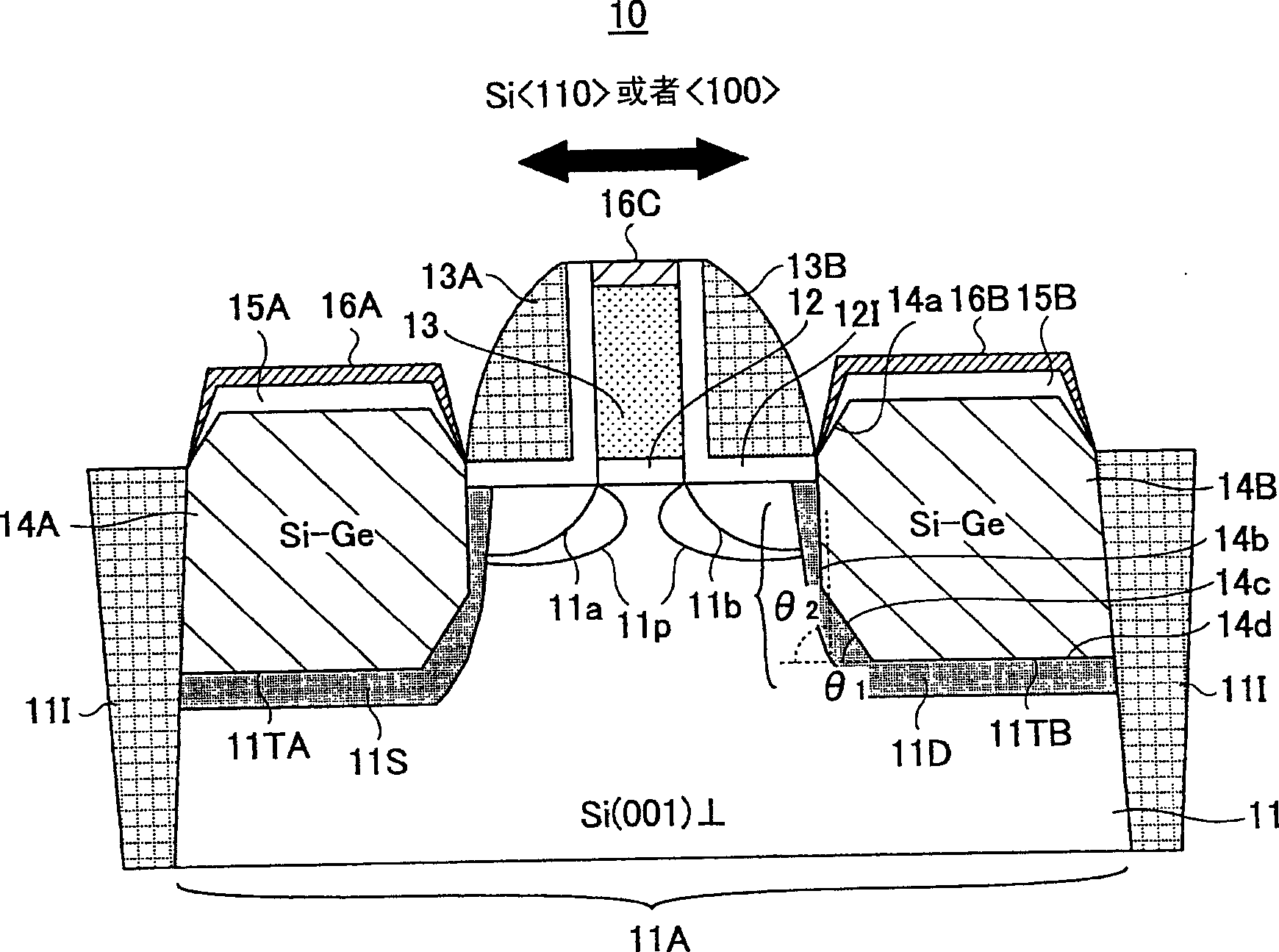

Semiconductor device and production method thereof

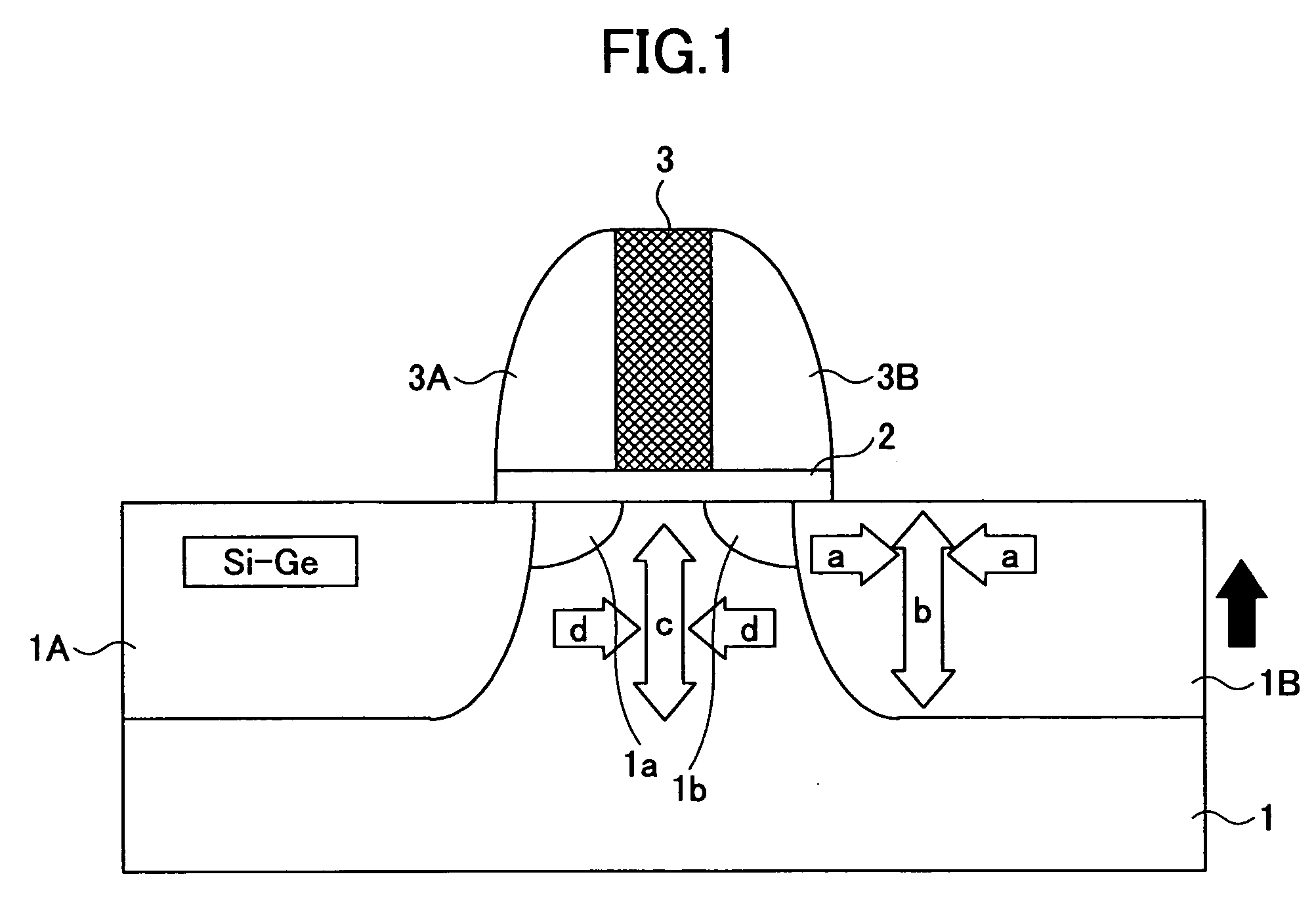

ActiveUS20070012913A1Avoid layeringSuppression of short channel effectsSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialCharge carrier mobility

A method of fabricating a semiconductor device is disclosed that is able to suppress a short channel effect and improve carrier mobility. In the method, trenches are formed in a silicon substrate corresponding to a source region and a drain region. When epitaxially growing p-type semiconductor mixed crystal layers to fill up the trenches, the surfaces of the trenches are demarcated by facets, and extended portions of the semiconductor mixed crystal layers are formed between bottom surfaces of second side wall insulating films and a surface of the silicon substrate, and extended portion are in contact with a source extension region and a drain extension region.

Owner:FUJITSU LTD

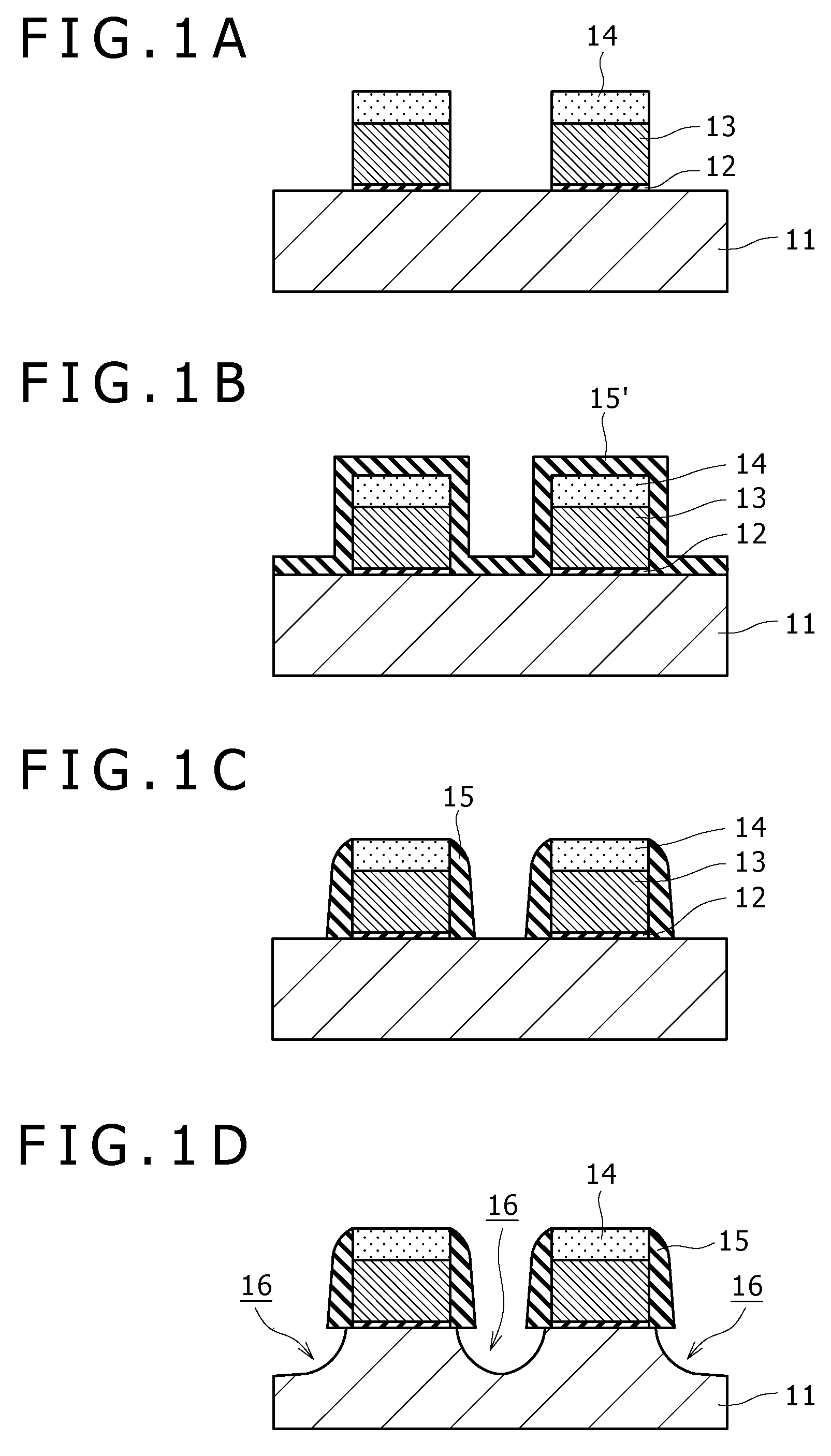

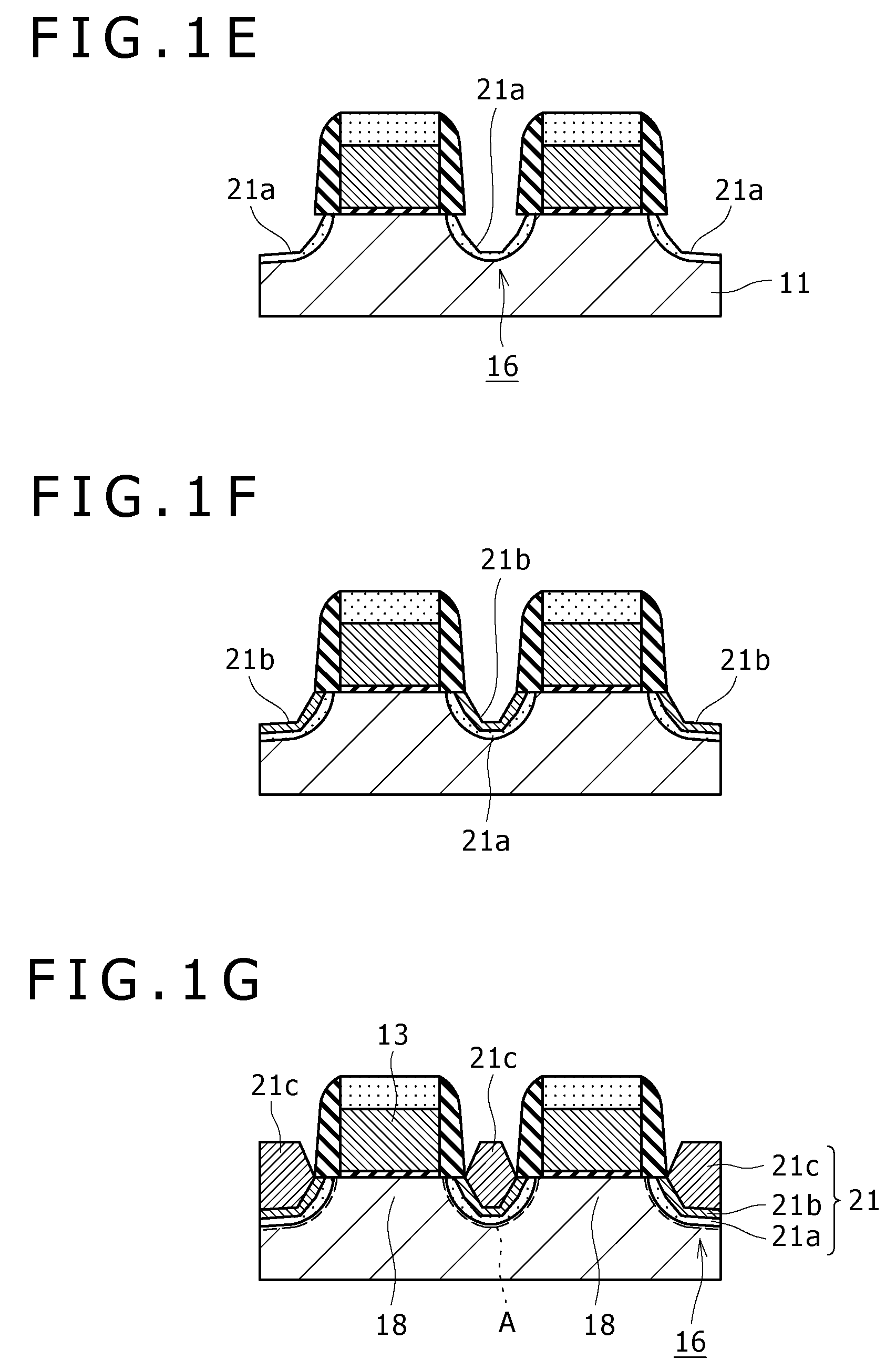

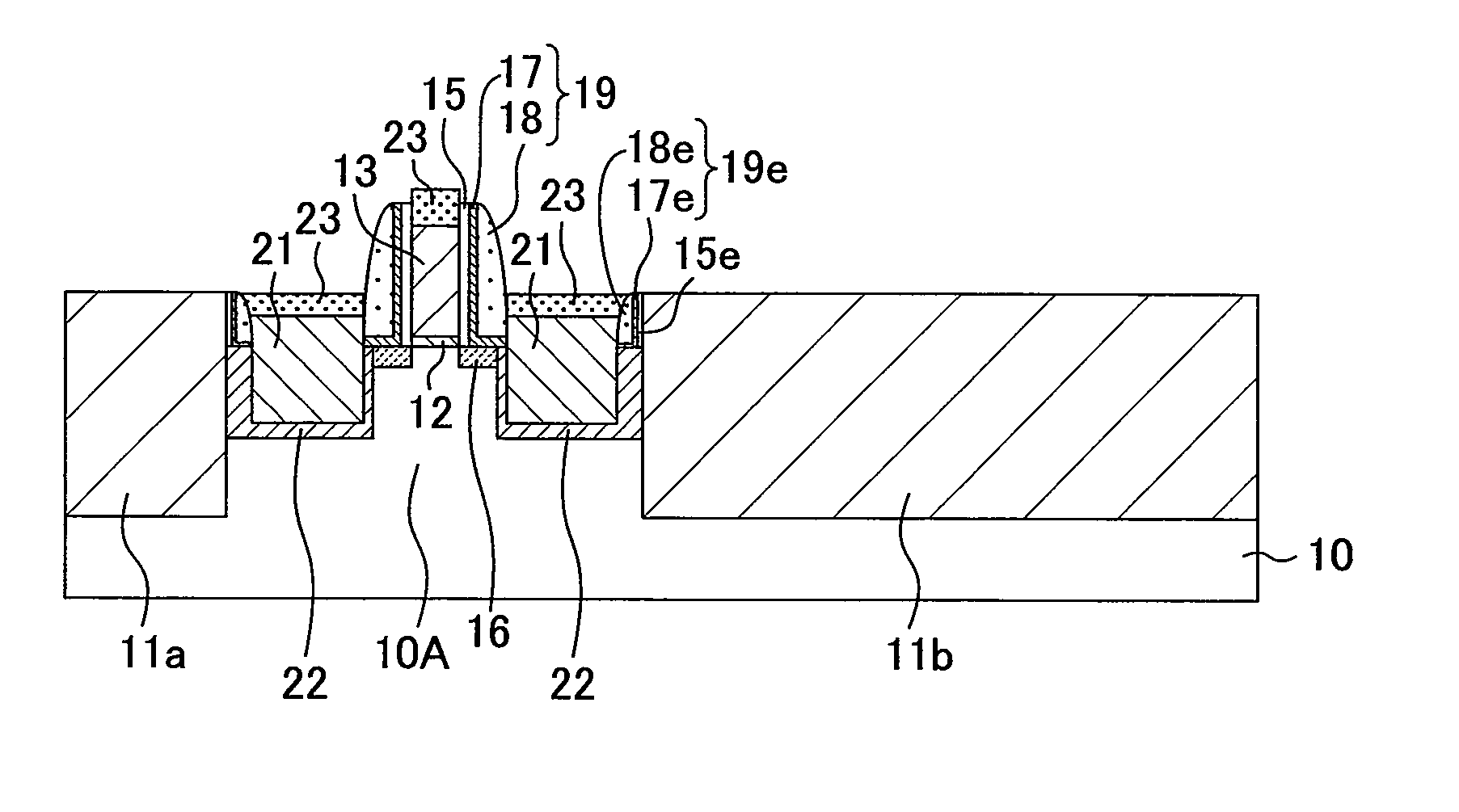

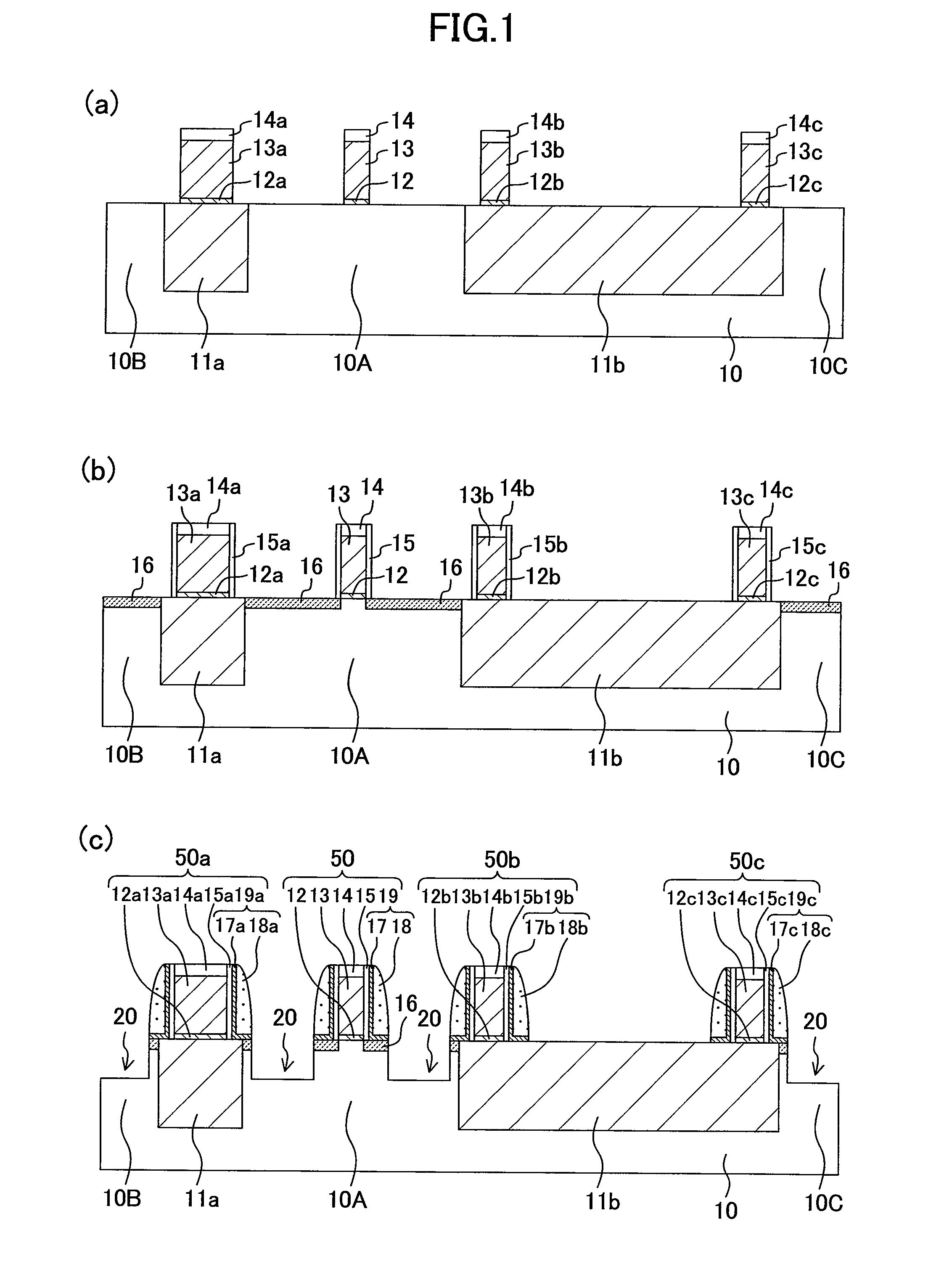

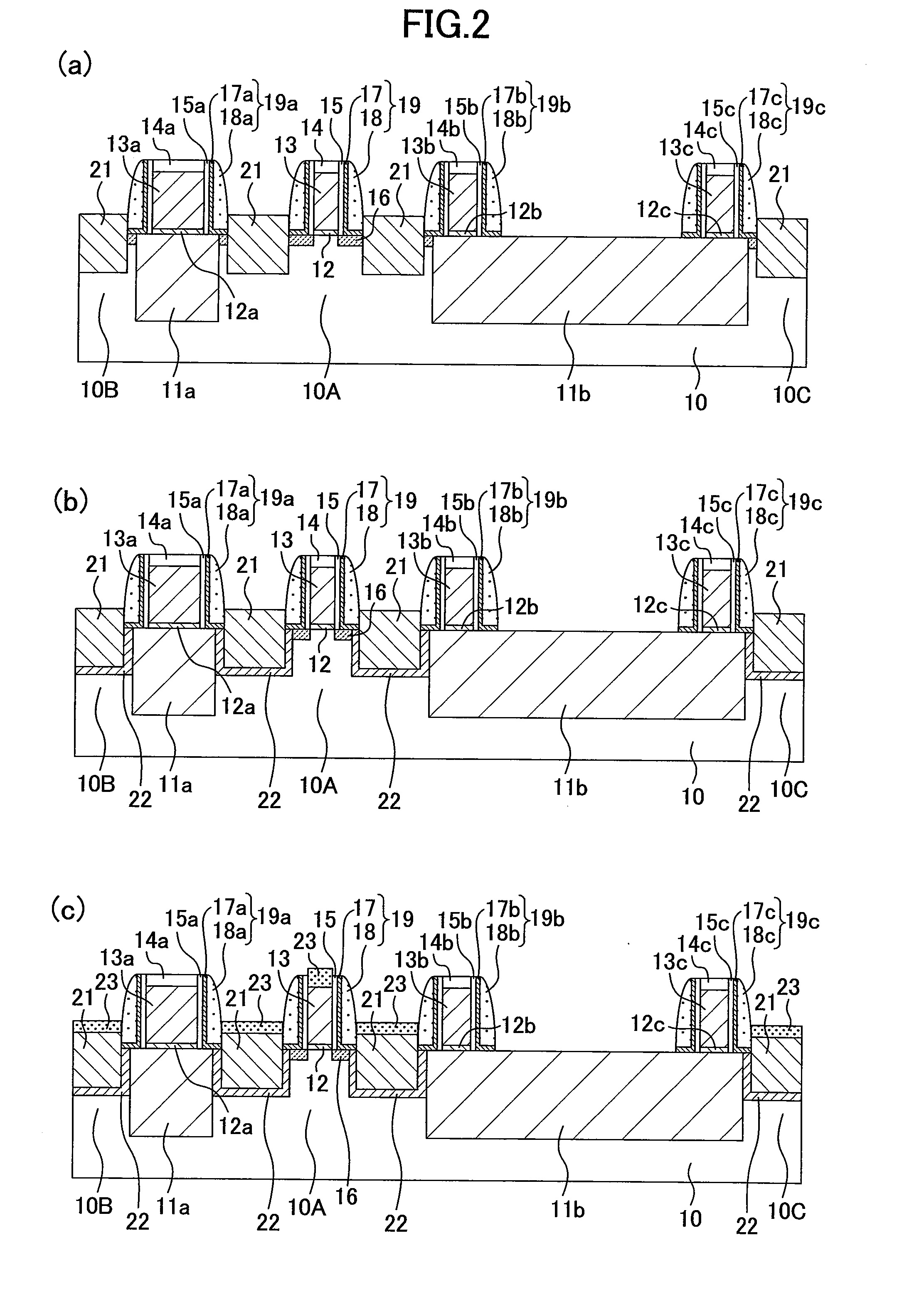

Semiconductor device and method for fabricating the same

ActiveUS20090242995A1Drive capability can be improvedImprove rendering capabilitiesSemiconductor/solid-state device manufacturingSemiconductor devicesSiliconSemiconductor

A semiconductor device includes an isolation region (11a) formed in a semiconductor substrate (10), an active region made of the semiconductor substrate (10) surrounded by the isolation region (11a) and having a trench portion, a MIS transistor of a first-conductivity type having a gate electrode (13) formed on the active region, a first sidewall (19) formed on a side surface of the gate electrode between the gate electrode (13) and the trench portion as viewed in the top, and a silicon mixed crystal layer (21) of the first-conductivity type, the trench portion being filled with the silicon mixed crystal layer (21) of the first-conductivity type, a substrate region provided between the trench portion and the isolation region (11a, 11b) and made of the semiconductor substrate (10), and an impurity region (22) of the first-conductivity type formed in the substrate region. The silicon mixed crystal layer (21) generates stress in a channel region of the active region.

Owner:PANNOVA SEMIC

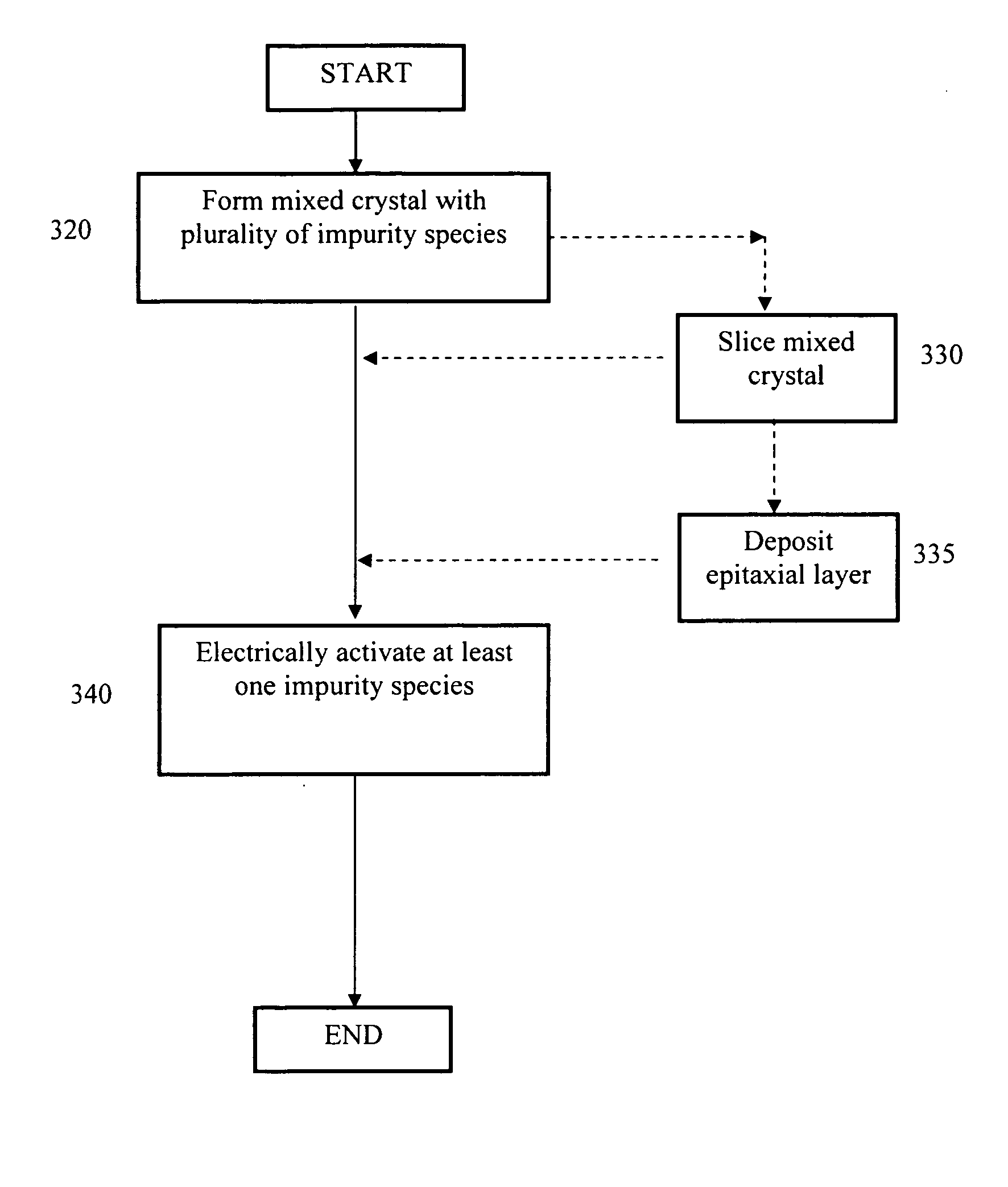

Doped aluminum nitride crystals and methods of making them

ActiveUS20070131160A1Promote formationSufficient conductivity and mobility characteristicPolycrystalline material growthSemiconductor/solid-state device manufacturingNitrideImpurity

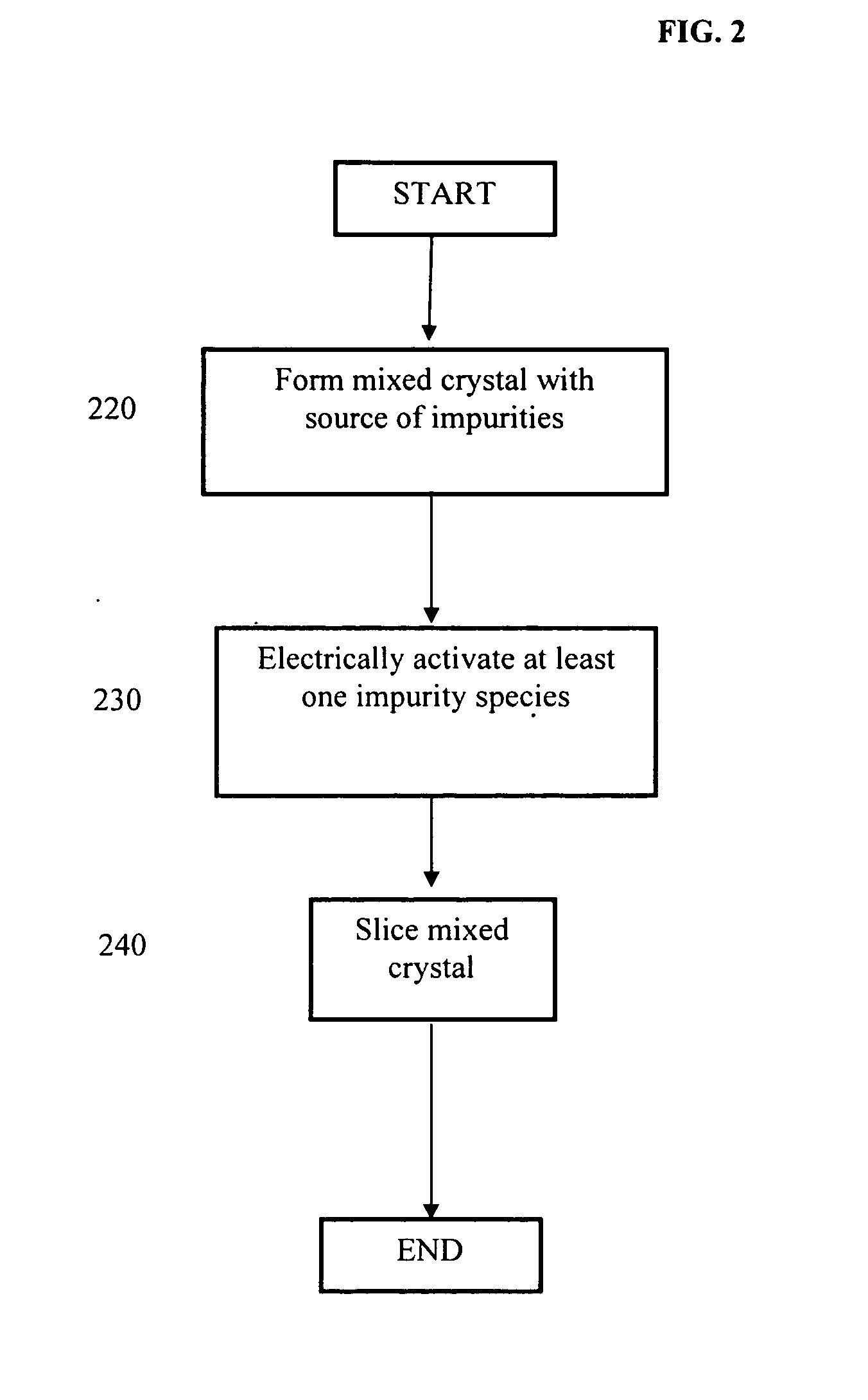

Fabrication of doped AlN crystals and / or AlGaN epitaxial layers with high conductivity and mobility is accomplished by, for example, forming mixed crystals including a plurality of impurity species and electrically activating at least a portion of the crystal.

Owner:CRYSTAL

Semiconductor integrated circuit and fabrication process thereof

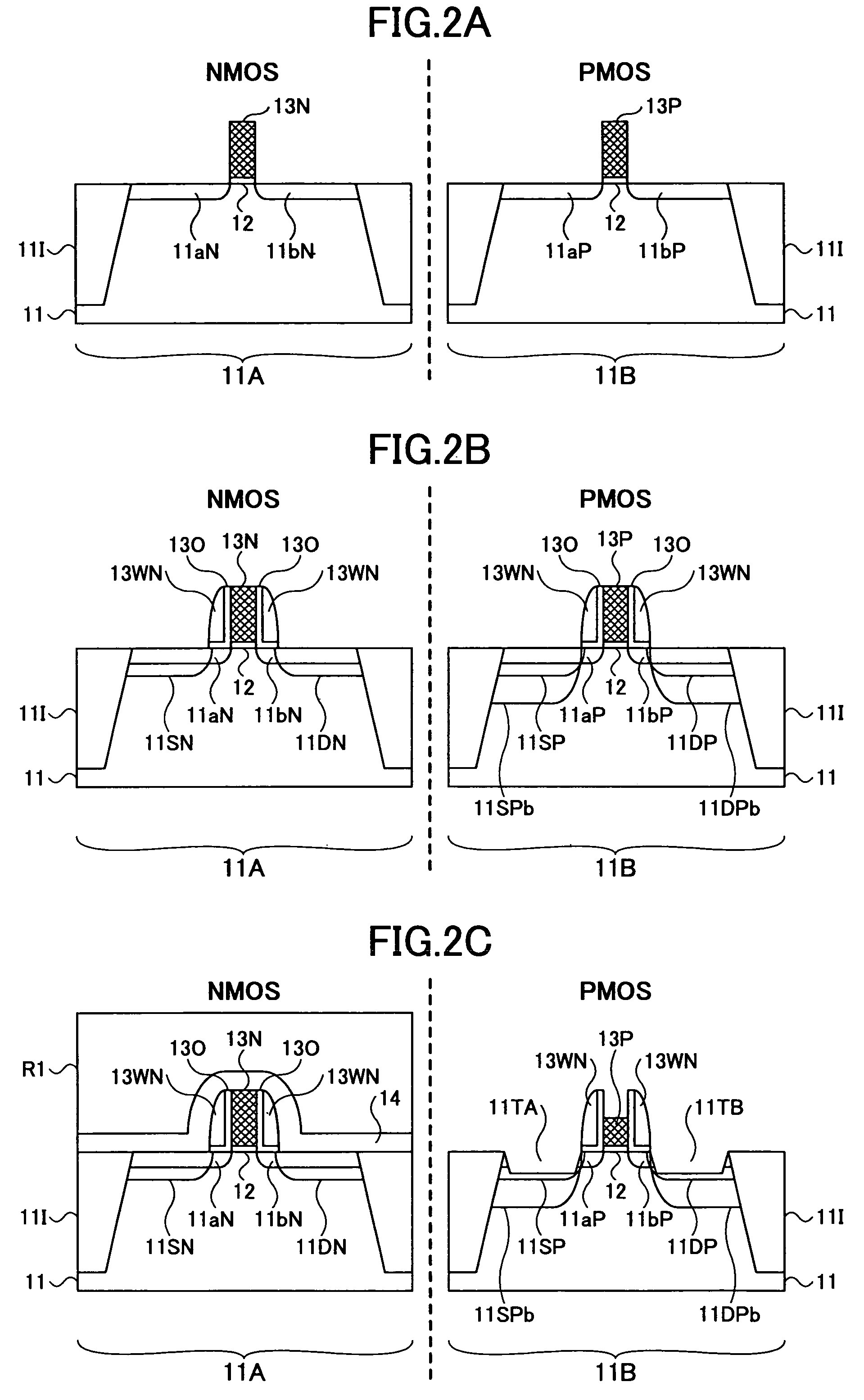

ActiveUS20060151776A1Suppress leakage currentSufficient distanceSemiconductor/solid-state device manufacturingSemiconductor devicesManufacturing technologyEngineering

A semiconductor integrated circuit device includes an n-channel MOS transistor formed on a first device region of a silicon substrate and a p-channel MOS transistor formed on a second device region of the silicon substrate, wherein the n-channel MOS transistor includes a first gate electrode carrying a pair of first sidewall insulation films formed on respective sidewall surfaces thereof, the p-channel MOS transistor includes a second gate electrode carrying a pair of second sidewall insulation films formed on respective sidewall surfaces thereof, first and second SiGe mixed crystal regions being formed in the second device region epitaxially so as to fill first and second trenches formed at respective, outer sides of the second sidewall insulation films so as to be included in source and drain diffusions of the p-channel MOS transistor, a distance between n-type source and drain diffusion region in the first device region being larger than a distance between the p-type source and drain diffusion regions in the second device region.

Owner:FUJITSU LTD

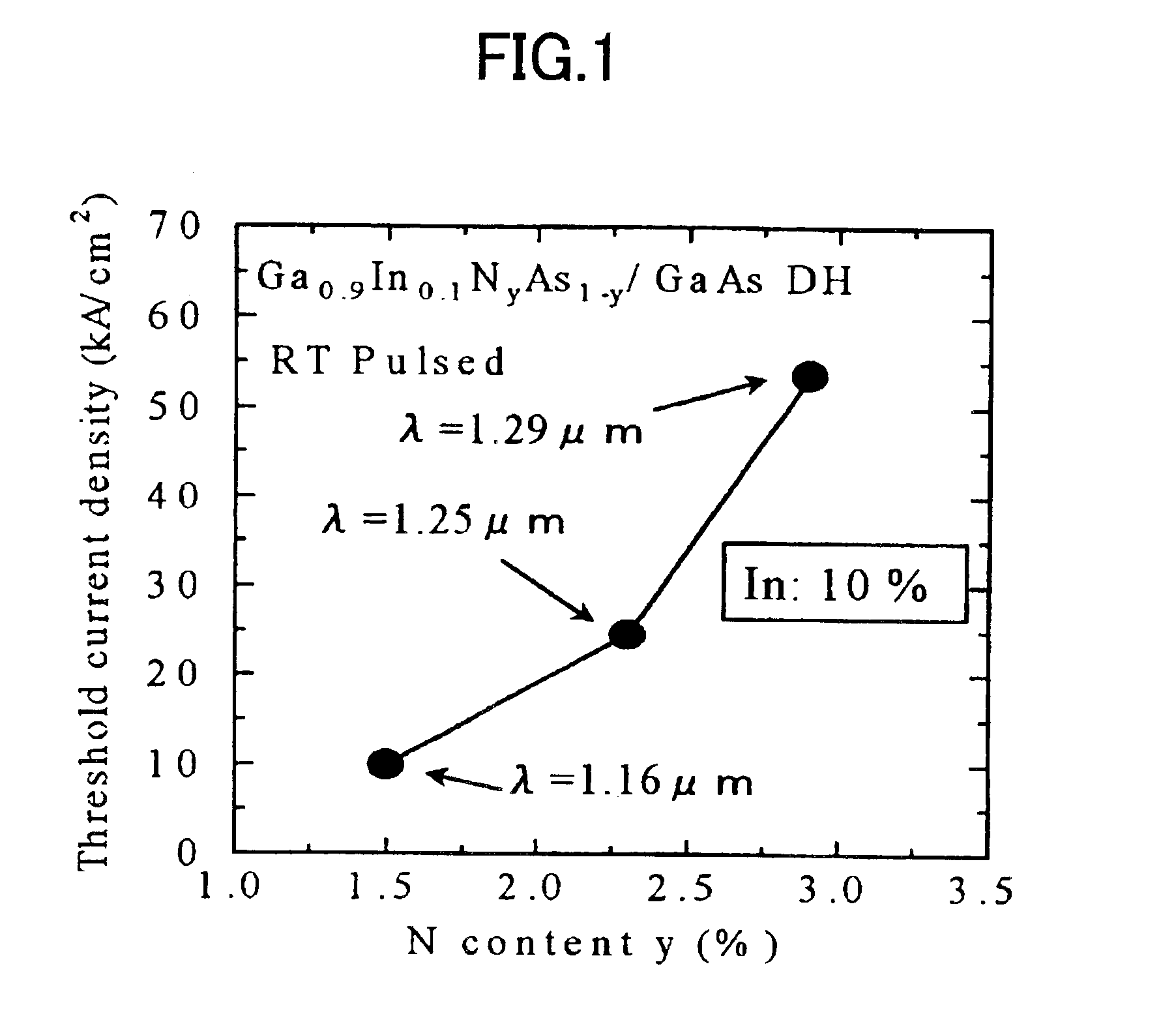

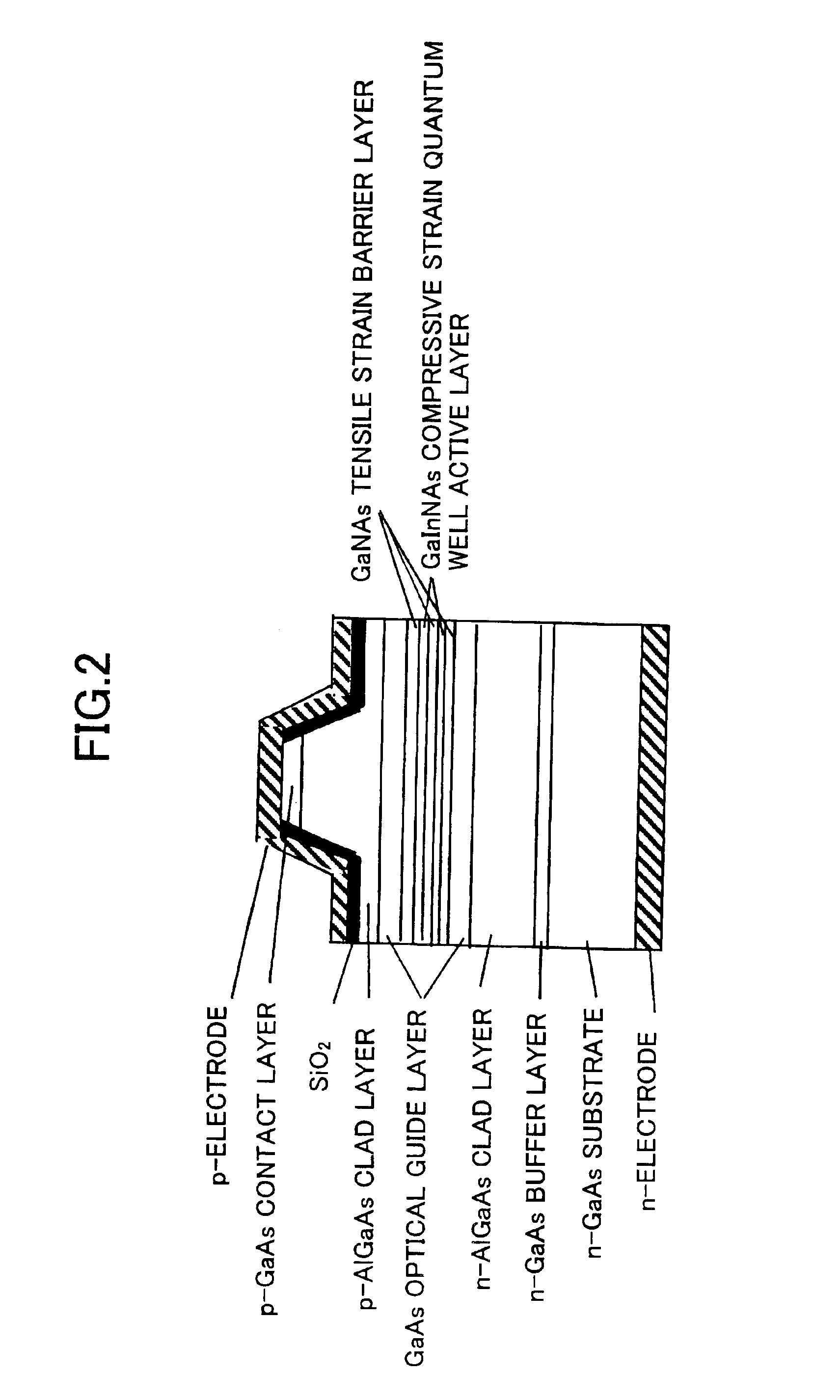

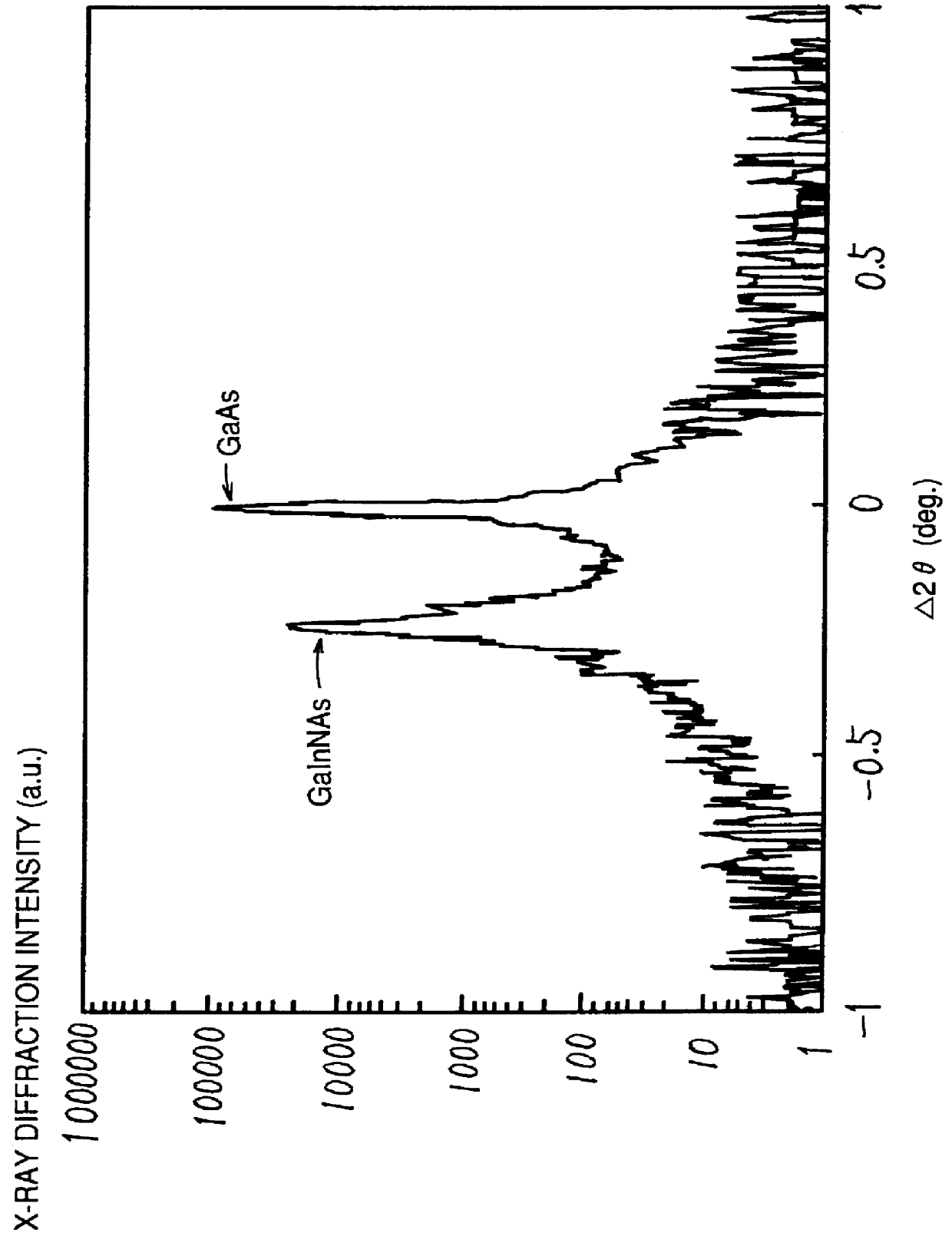

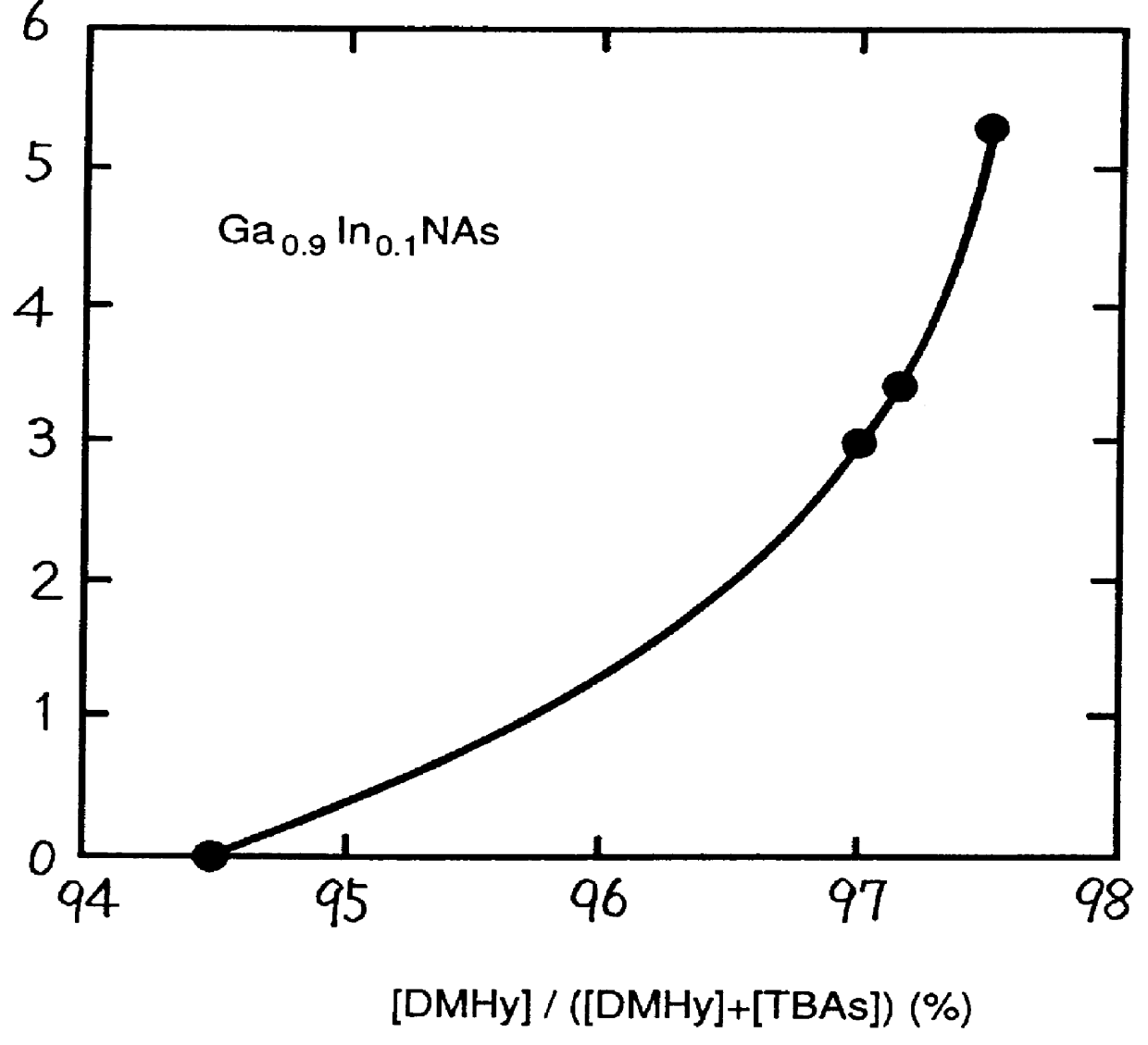

Method of crystal growth of compound semiconductor, compound semiconductor device and method of manufacturing the device

InactiveUS6150677ASemiconductor/solid-state device manufacturingBy pulling from meltHydrogen concentrationNitrogen

A semiconductor layer consisting of Ga1-xInx NyAs1-y and / or GaNyAs1-y and formed by incorporating nitrogen into a group III-V mixed crystal semiconductor is provided on a GaAs substrate. The hydrogen concentration in the semiconductor is kept at 5x1018 atoms / cm3 or below.

Owner:SUMITOMO ELECTRIC IND LTD

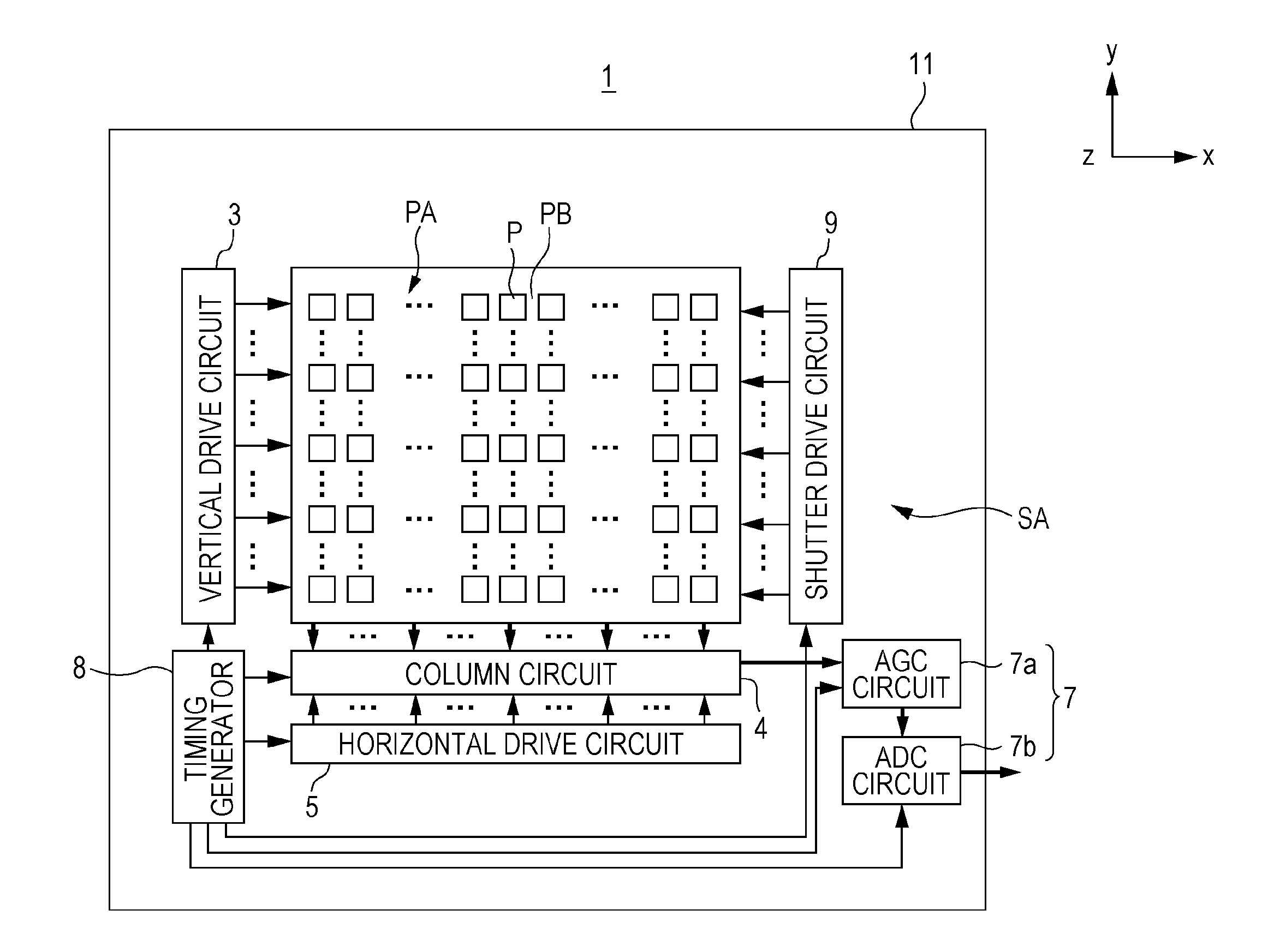

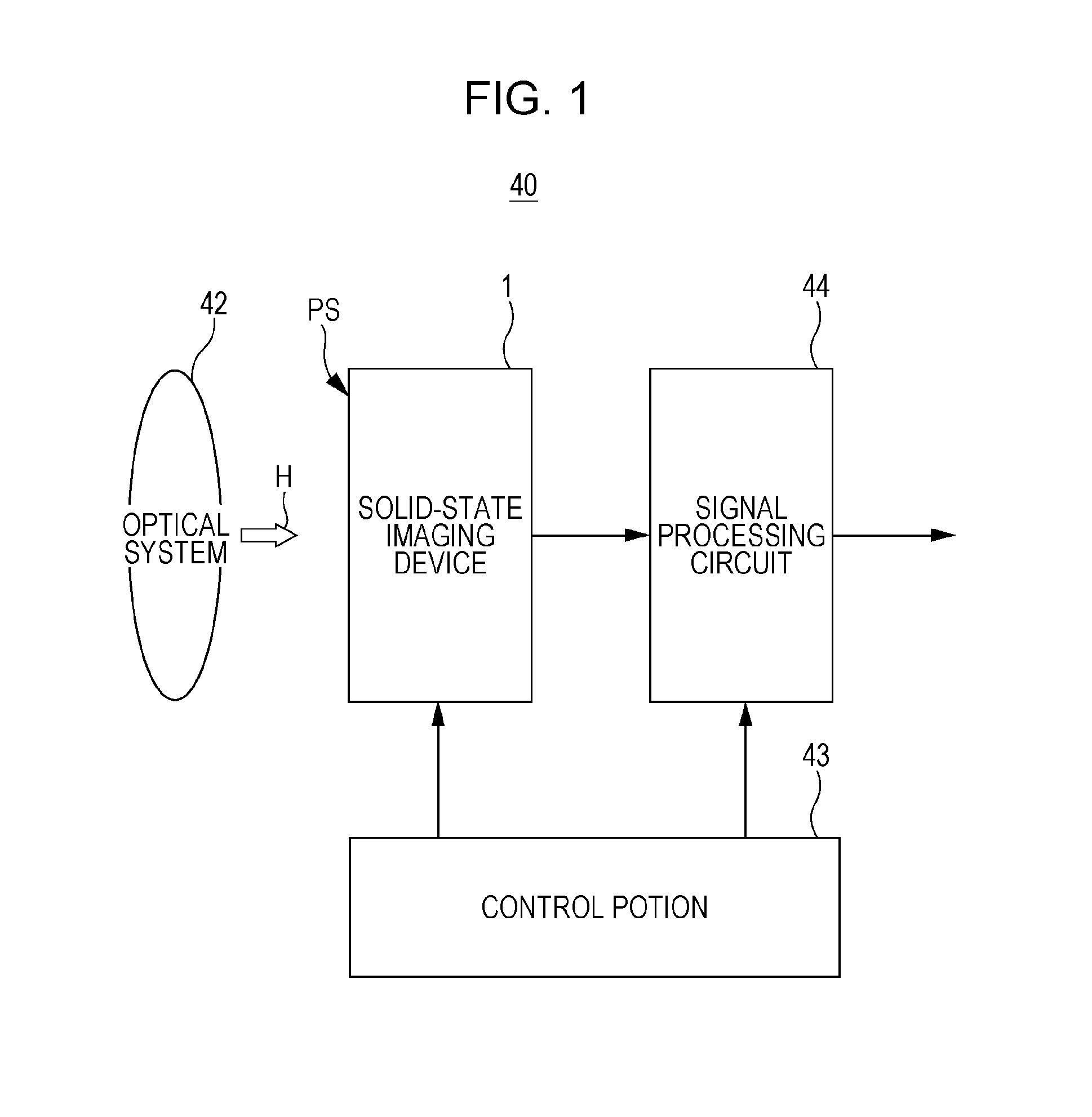

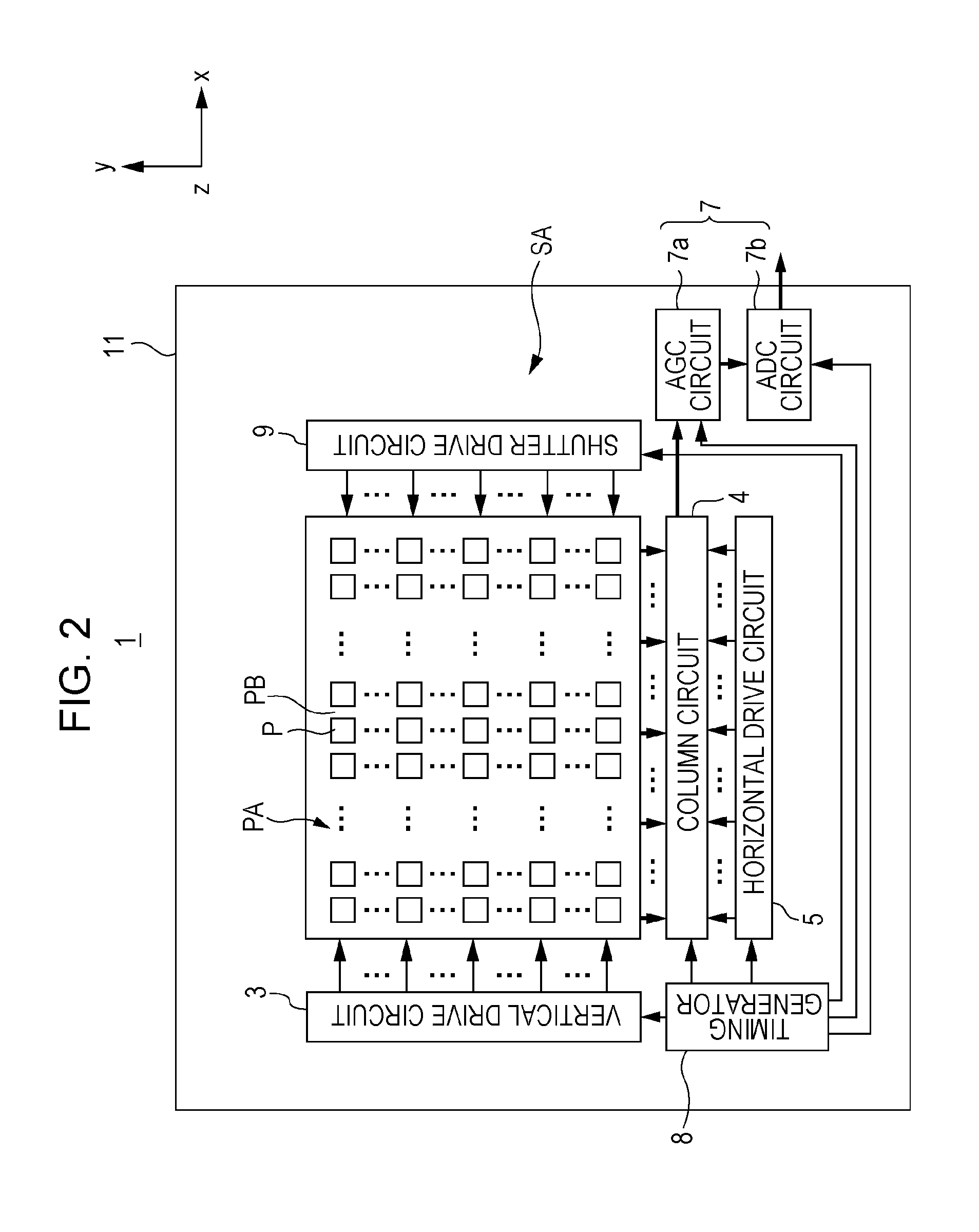

Solid-state imaging device, method for manufacturing solid-state imaging device, and electronic apparatus

InactiveUS20110227091A1Degradation can be suppressedAvoid it happening againFinal product manufactureSolid-state devicesIndiumGallium

A solid-state imaging device is provided with a pixel region in which a plurality of pixels including photoelectric conversion films are arrayed and pixel isolation portions are interposed between the plurality of pixels, wherein the photoelectric conversion film is a chalcopyrite-structure compound semiconductor composed of a copper-aluminum-gallium-indium-sulfur-selenium based mixed crystal or a copper-aluminum-gallium-indium-zinc-sulfur-selenium based mixed crystal and is disposed on a silicon substrate in such a way as to lattice-match the silicon substrate concerned, and the pixel isolation portion is formed from a compound semiconductor subjected to doping concentration control or composition control in such a way as to become a potential barrier between the photoelectric conversion films disposed in accordance with the plurality of pixels.

Owner:SONY CORP

Multi-layer plain bearing having an anti-fretting layer

The invention relates to a multi-layer plain bearing (1) that has a front side (4) that can face the element to be supported and a rear side (6) opposite the front side, comprising a supporting layer (2), a sliding layer (3) arranged on the front side (4), and an anti-fretting layer (5) arranged on the rear side (6), wherein the anti-fretting layer (5) is made of a copper-based alloy having copper mixed-crystal grains. The copper-based alloy of the anti-fretting layer (5) is formed by a binary alloy having an alloying element from the group comprising aluminum, zinc, indium, silicon, germanium, and antimony or by an at least ternary alloy having one alloying element from the group comprising aluminum, zinc, indium, silicon, germanium, tin, and antimony and at least one further element from said group and / or the further group comprising nickel, cobalt, iron, manganese, bismuth, lead, silver, and phosphorus, possibly with unavoidable impurities originating from production, wherein the total fraction of said alloying elements is at least 1 wt % and at most 30 wt %.

Owner:MIBA SINTER AUSTRIA

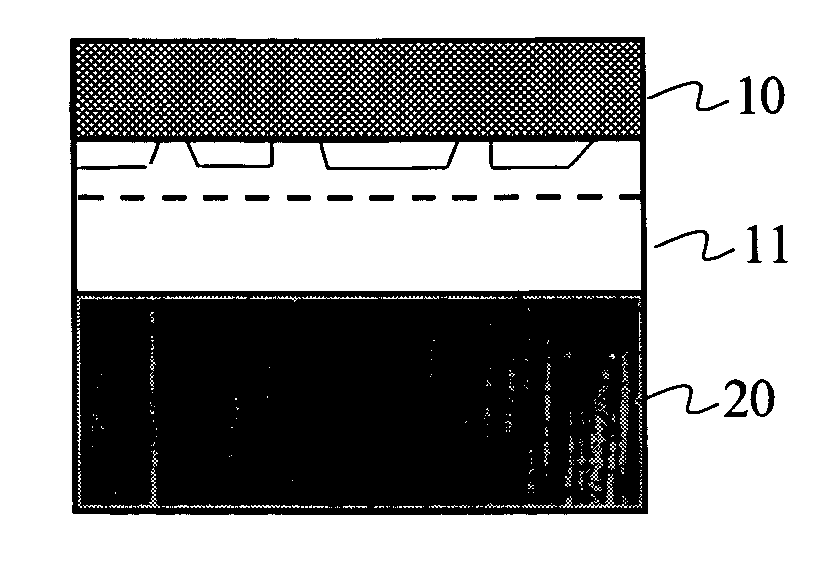

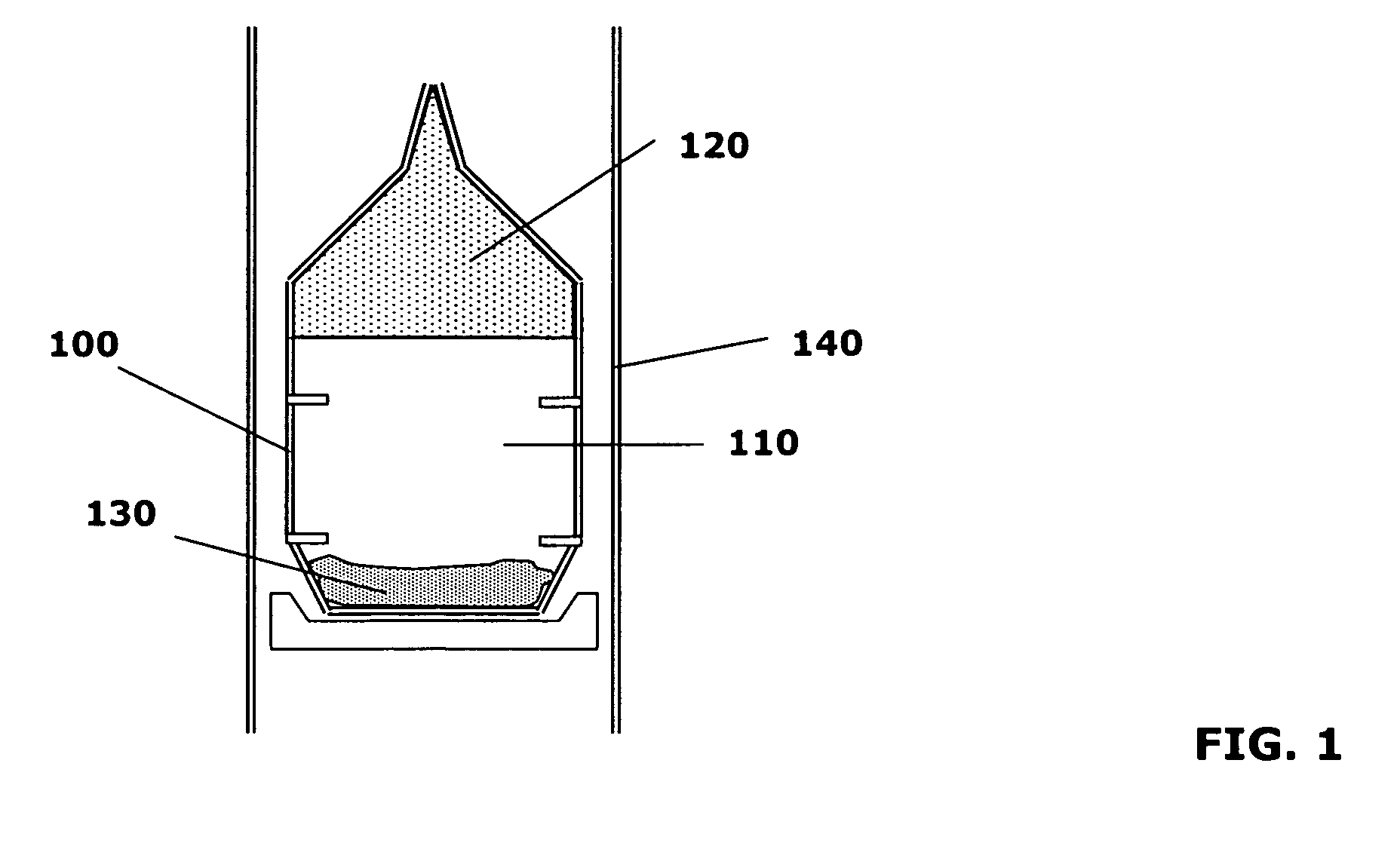

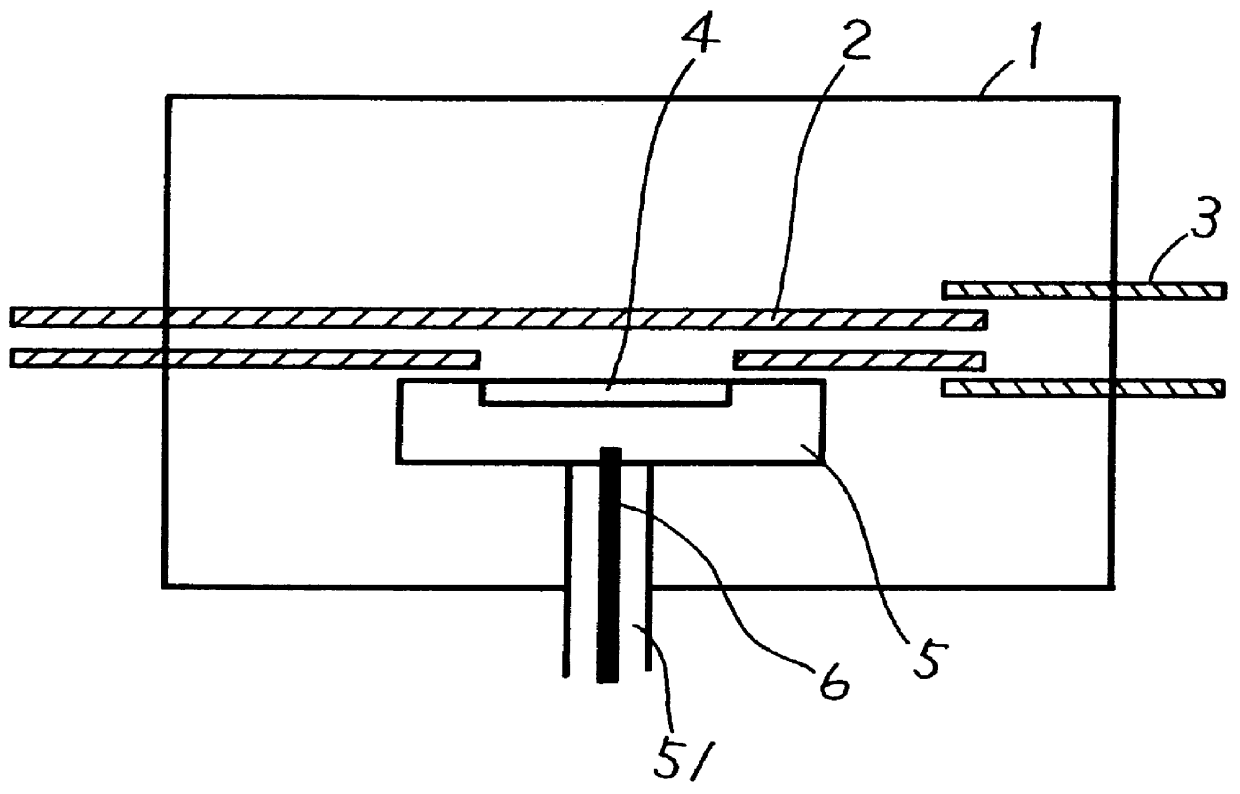

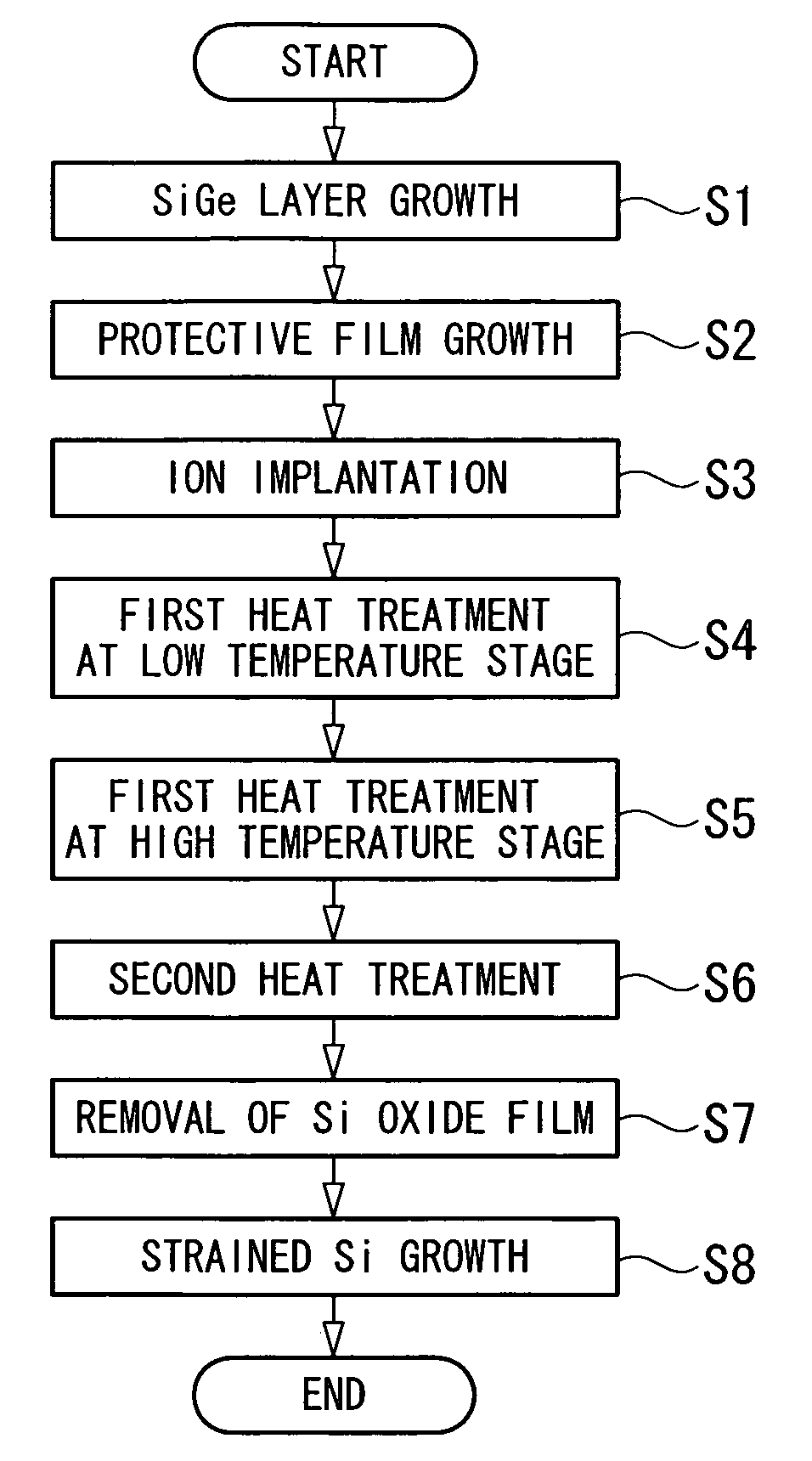

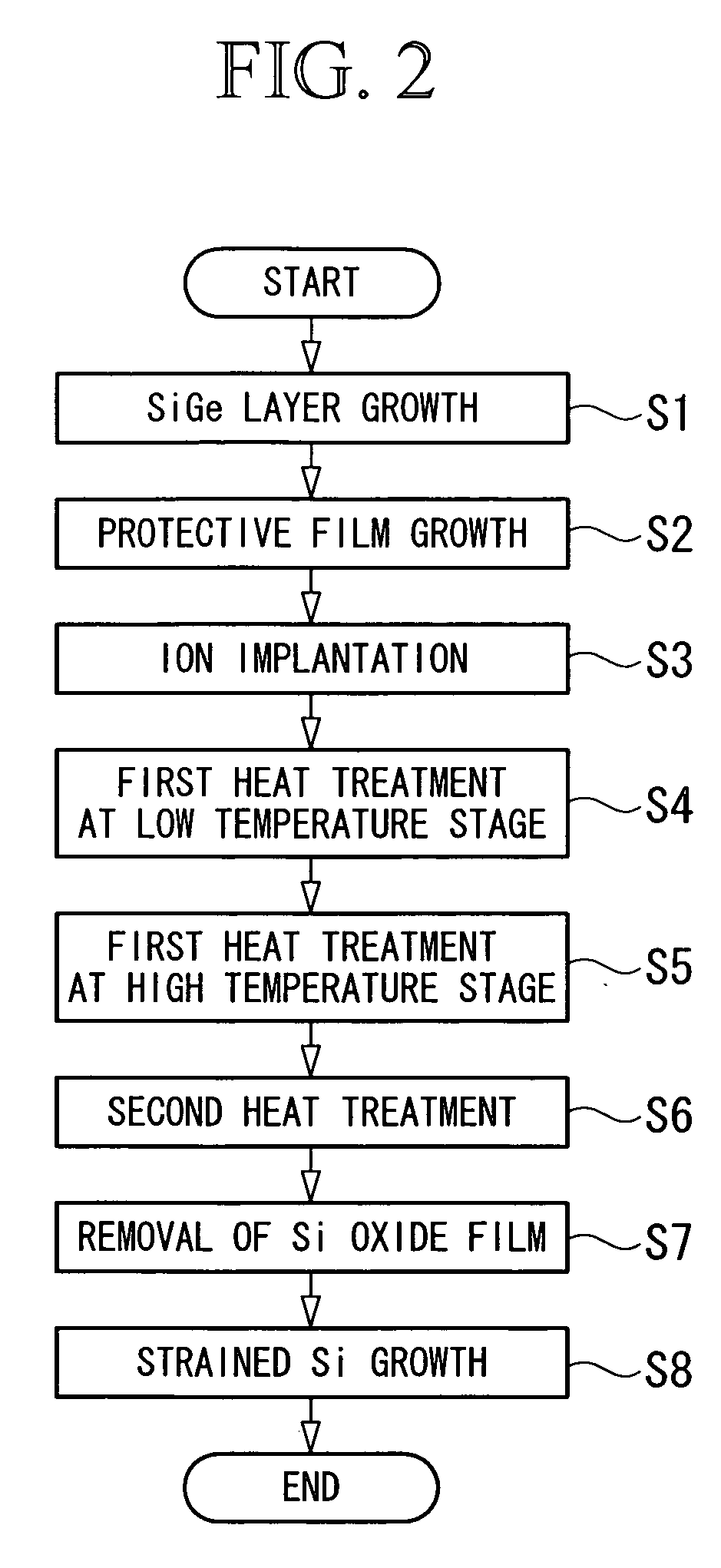

Production method of strained silicon-SOI substrate and strained silicon-SOI substrate produced by same

InactiveUS20060214257A1Reduce bond strengthEnhances strain relaxationSolid-state devicesSemiconductor/solid-state device manufacturingSoi substrateMixed crystal

A strained Si-SOI substrate is produced by a method comprising: growing a SiGe mixed crystal layer on an SOI substrate having a Si layer of not less than 5 nm in thickness and a buried oxide layer; forming a protective film on the SiGe mixed crystal layer; implanting light element ions into a vicinity of an interface between the silicon layer and the buried oxide layer; a first heat treatment for heat treating the substrate at a temperature of 400 to 1000° C. in an inert gas atmosphere; a second heat treatment for heat treating the substrate at a temperature not lower than 1050° C. in an oxidizing atmosphere containing chlorine; removing an oxide film from the surface of the substrate, and forming a strained silicon layer on the surface of the substrate.

Owner:SUMCO CORP +1

Copper-alkaline-earth-silicate mixed crystal phosphors

ActiveUS20090152496A1Improve luminous performanceImprove stabilityLuminescent compositionsRare-earth elementAlkaline earth metal

This invention relates to luminescent materials for ultraviolet light or visible light excitation comprising copper-alkaline-earth dominated inorganic mixed crystals activated by rare earth elements. The luminescent material is composed of one or more than one compounds of silicate type and / or germinate or germanate-silicate type. Accordingly, the present invention is a very good possibility to substitute earth alkaline ions by copper for a shifting of the emission bands to longer or shorter wavelength, respectively. Luminescent compounds containing Copper with improved luminescent properties and also with improved stability against water, humidity as well as other polar solvents are provided. The present invention is to provide copper containing luminescent compounds, which has high correlated color temperature range from about 2,000K to 8,000K or 10,000K and CRI up to over 90.

Owner:SEOUL SEMICONDUCTOR

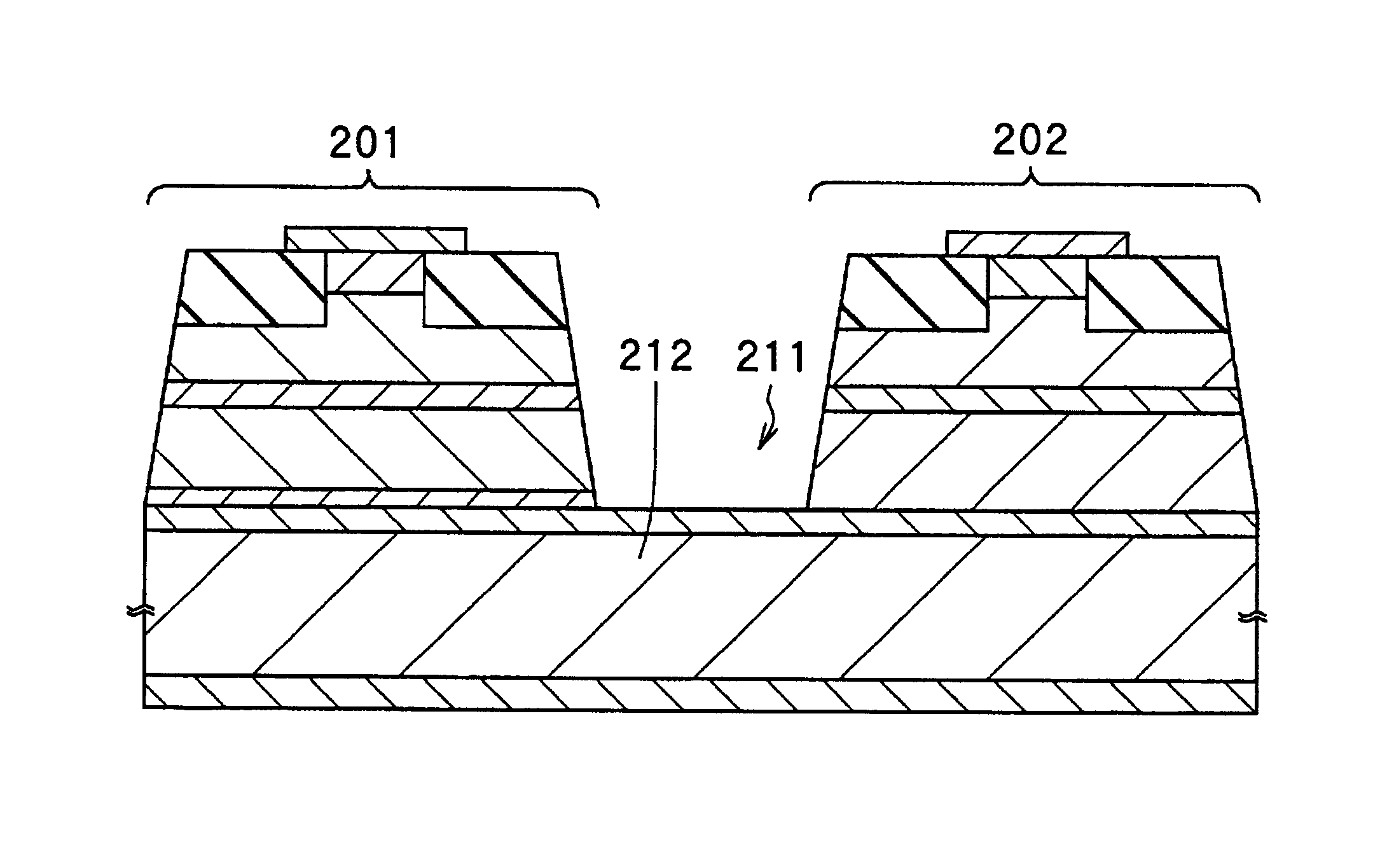

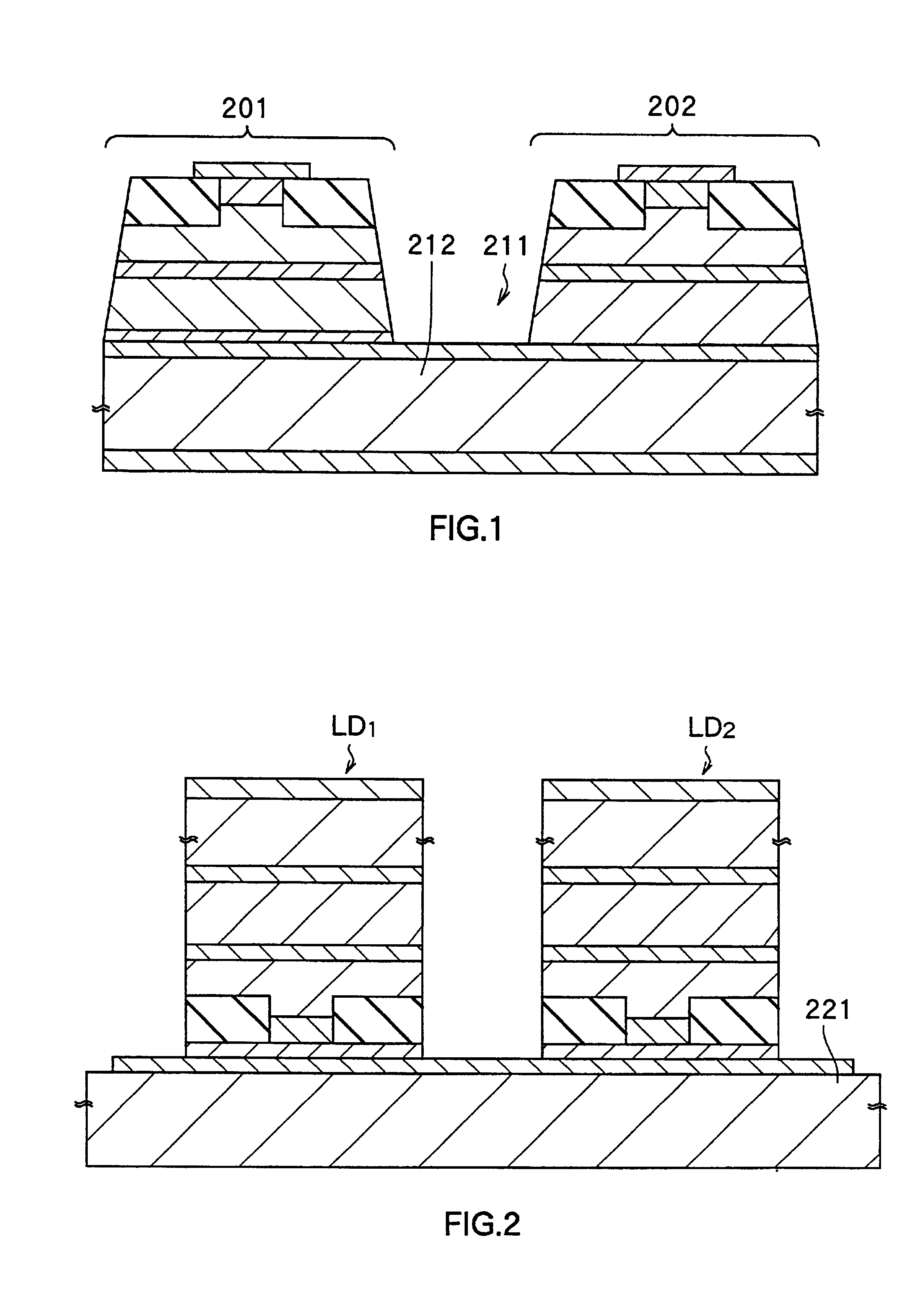

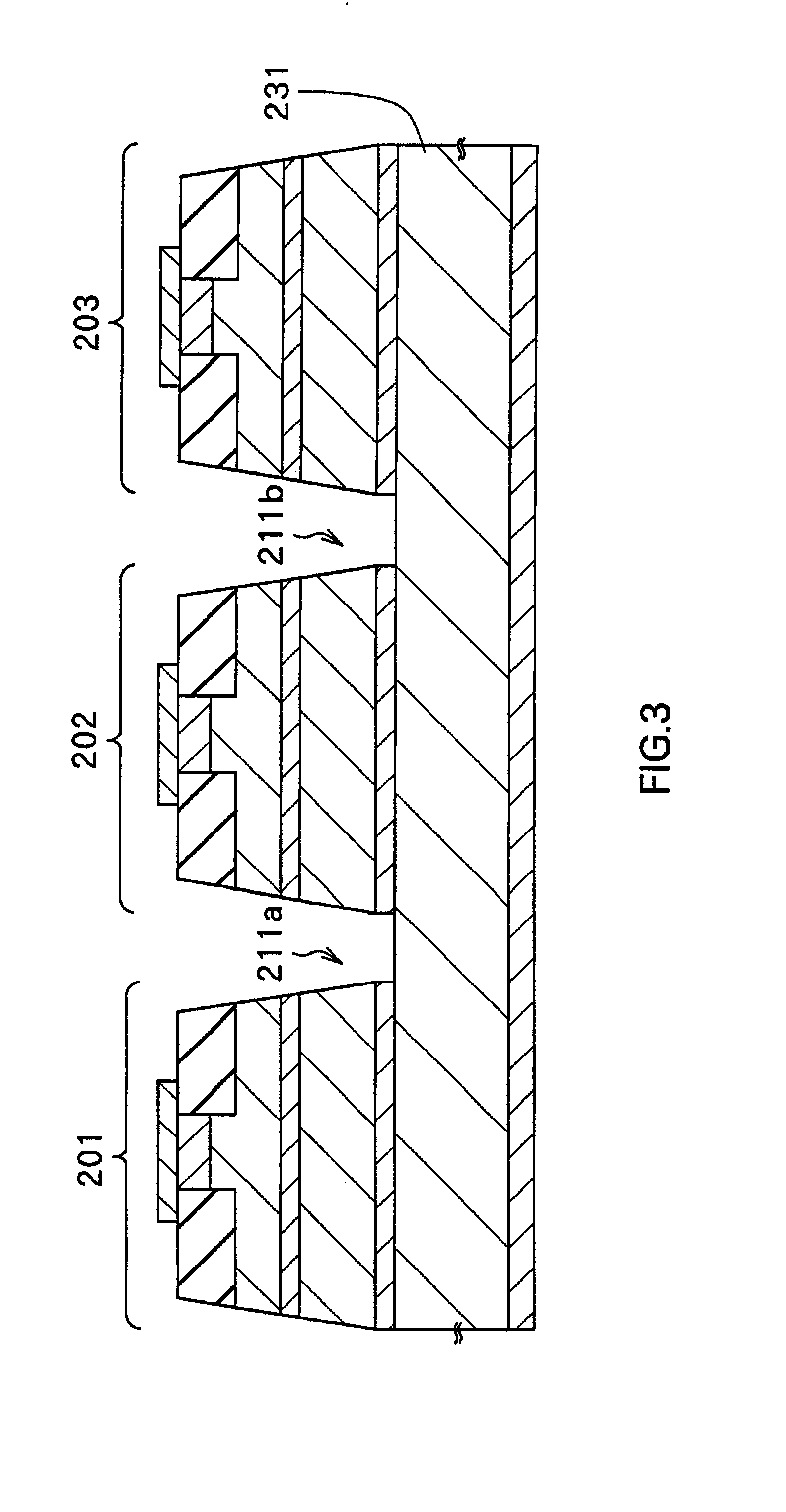

Semiconductor light emitting device with stacked light emitting elements

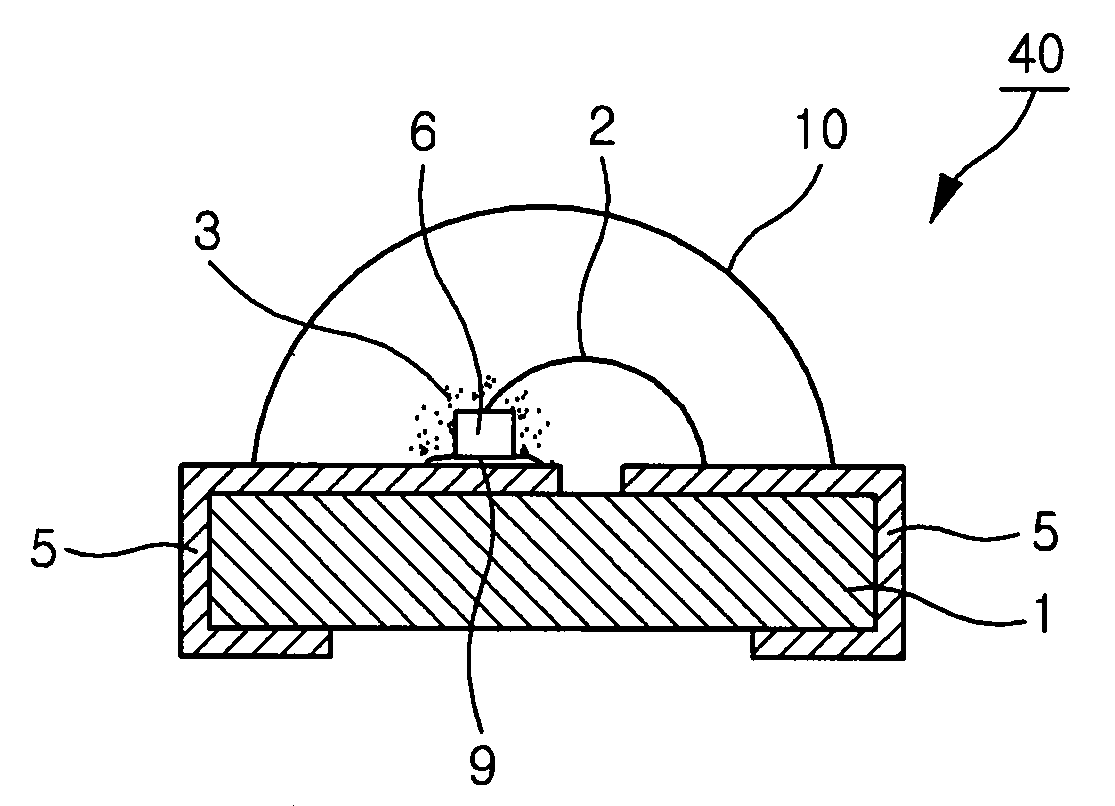

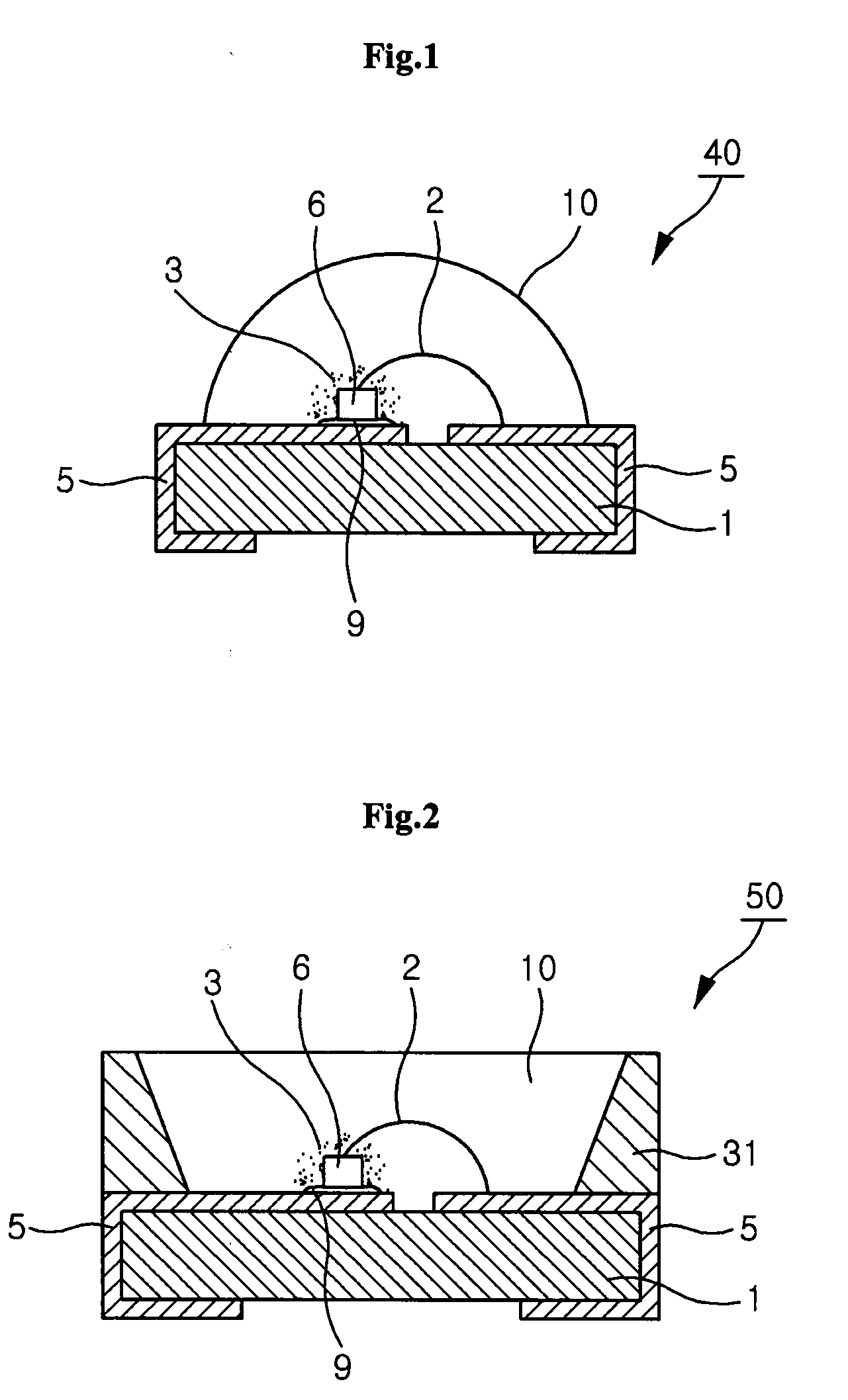

InactiveUS7119487B2Easy to manufactureImprove accuracySolid-state devicesSemiconductor/solid-state device manufacturingLithographic artistLength wave

A light emitting device which can be easily manufactured and can control the positions of light emission precisely, and an optical device. A first and second light emitting elements are formed on one face of a supporting base. The first light emitting element has an active layer made of GaInN mixed crystal on a GaN-made first substrate on the side thereof on which the supporting base is disposed. The second light emitting element has lasing portions on a GaAs-made second substrate on the side thereof on which the supporting base is disposed. Since the first and second light emitting elements are not grown on the same substrate, a multiple-wavelength laser having the output wavelength of around 400 nm can be easily obtained. Since the first substrate is transparent in the visible region, the positions of light emitting regions in the first and second light emitting elements can be precisely controlled by lithography.

Owner:SONY GRP CORP

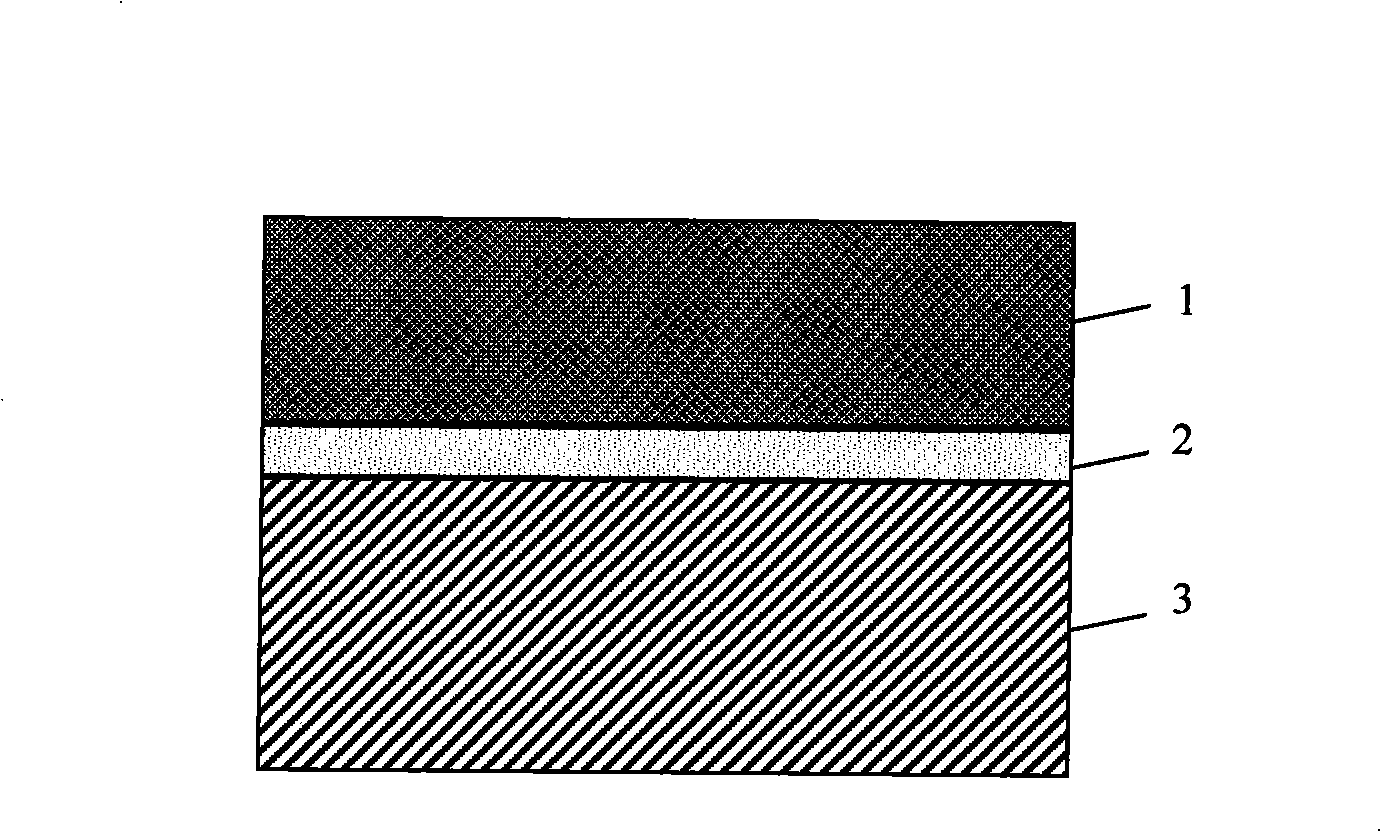

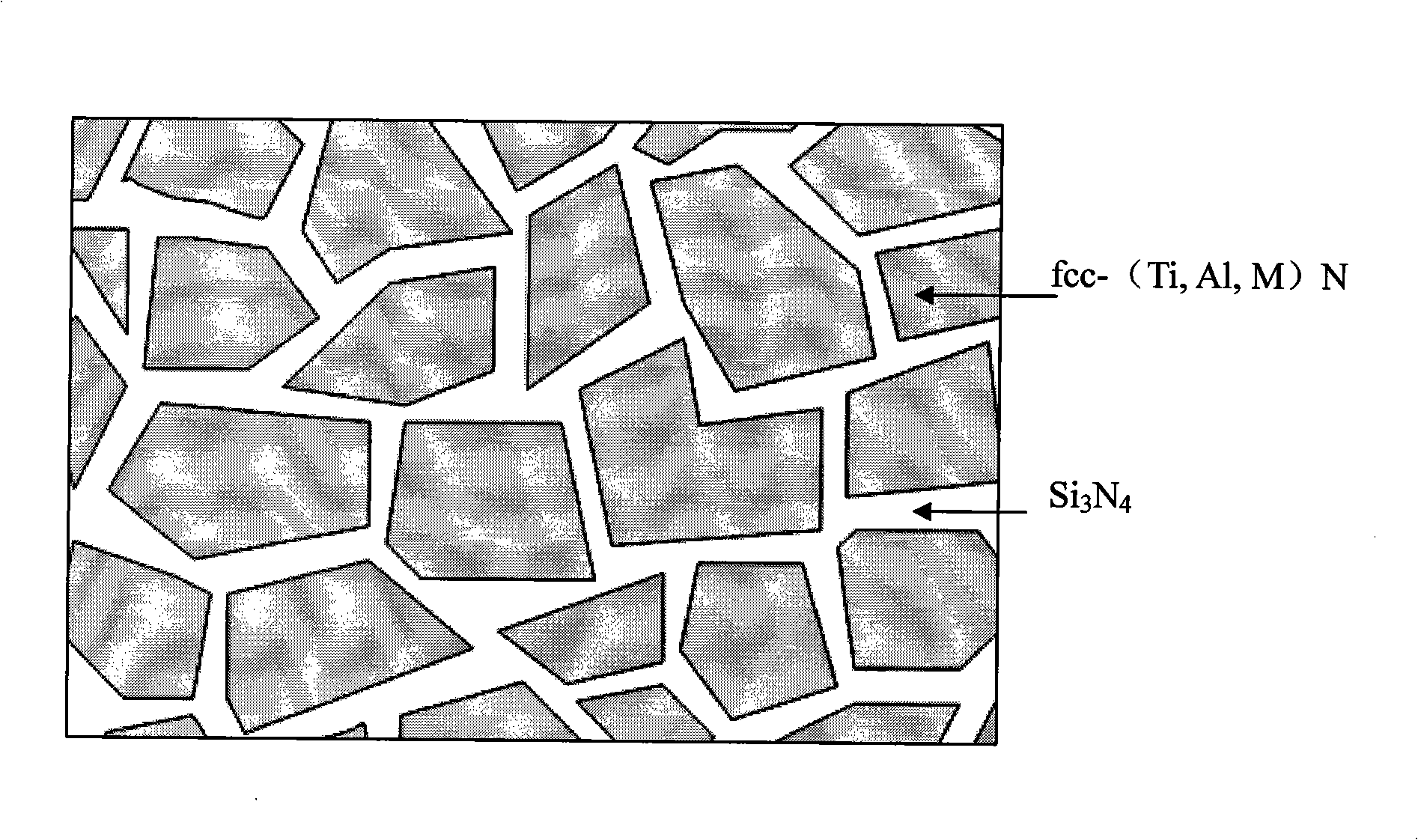

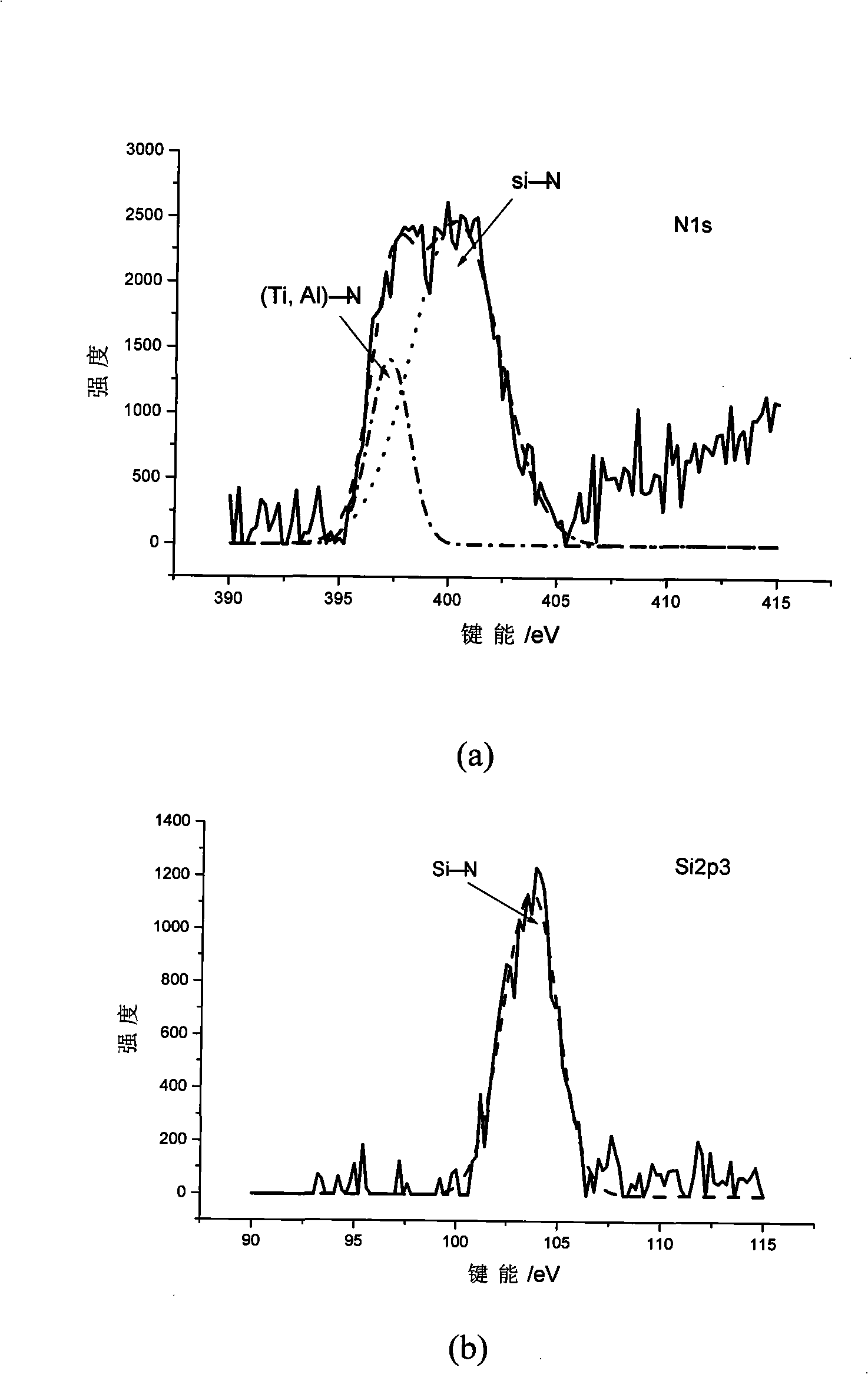

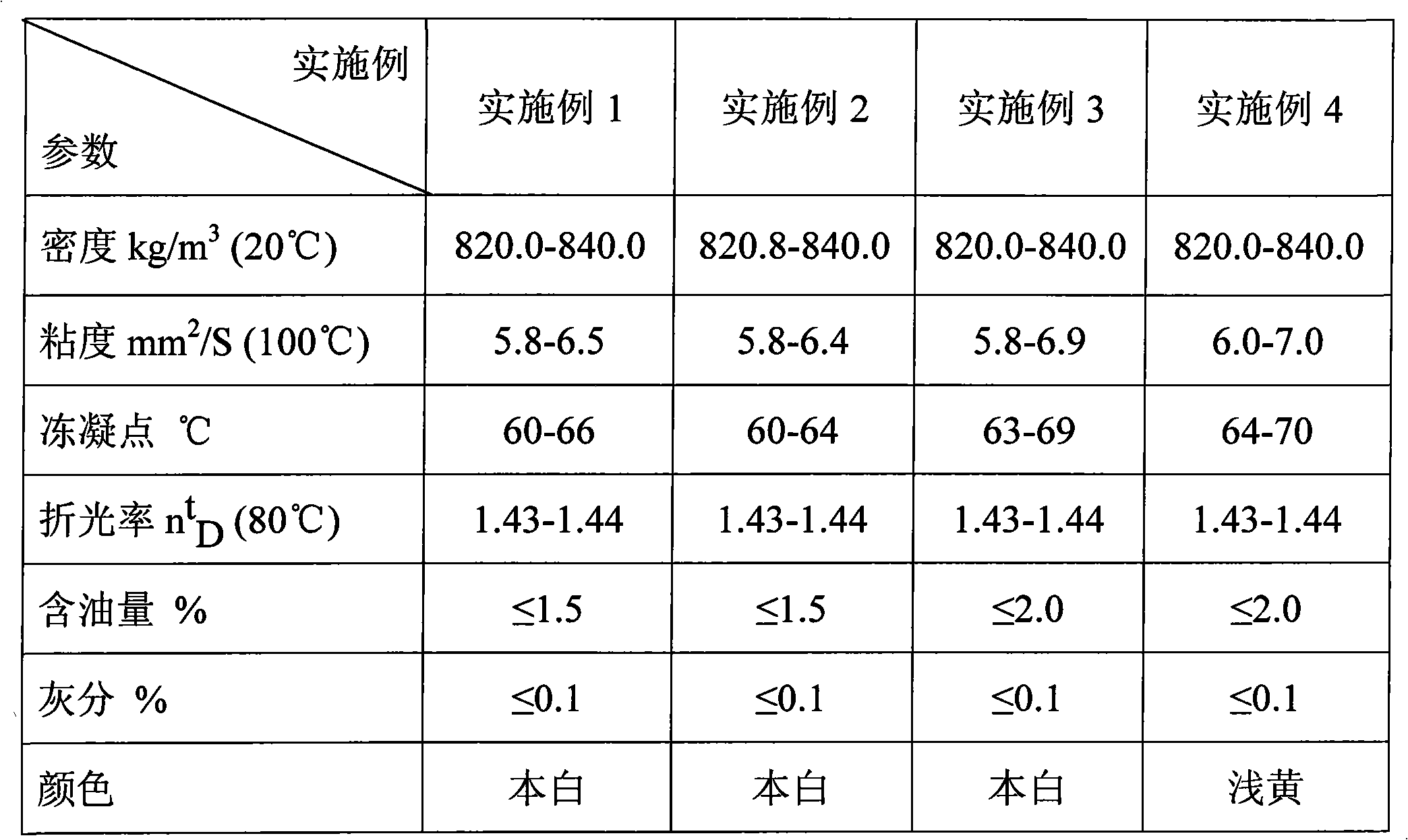

Cemented carbide cutting tool for multi-component coating

ActiveCN101407905AHigh coating hardnessImprove antioxidant capacityVacuum evaporation coatingSputtering coatingAlloyHigh intensity

The invention discloses a cemented carbide cutting tool of a multi-component coating, which comprises a matrix and a coating coated on the matrix by a PVD method; wherein, the coating comprises a matrix binding layer coated on the matrix and a composite mixed crystal structural layer which is coated on the matrix binding layer and contains nano crystalline / amorphous composition; the matrix binding layer comprises at least a Ti-based metal layer which comprises at least one of metal elements of Al, Si and groups of IVB, VB and VIB; the composite mixed crystal structural layer comprises elements of Ti1-a-b-cAlaMbSicN, wherein M is one or a plurality of metal elements of Ta, Nb, Zr, Cr, Hf and W. The cemented carbide cutting tool has the advantages of high wearing resistance, high intensity, high temperature resistance, impact resistance, good binding of the coating and matrix, etc.

Owner:ZHUZHOU CEMENTED CARBIDE CUTTING TOOLS CO LTD

Novel rubber protective wax

The invention discloses a novel rubber protective wax which comprises the following components in percentage by weight: 14-20 percent of paraffin, 55-60 percent of mixed crystal wax, 24-30 percent ofmicrocrystalline wax and 1-2 percent of polyethylene wax. The invention has favorable seal performance and can reinforce the ozone and ageing resistance of a rubber product and prolong the service life of the rubber product.

Owner:上海绿菱特种蜡制品厂

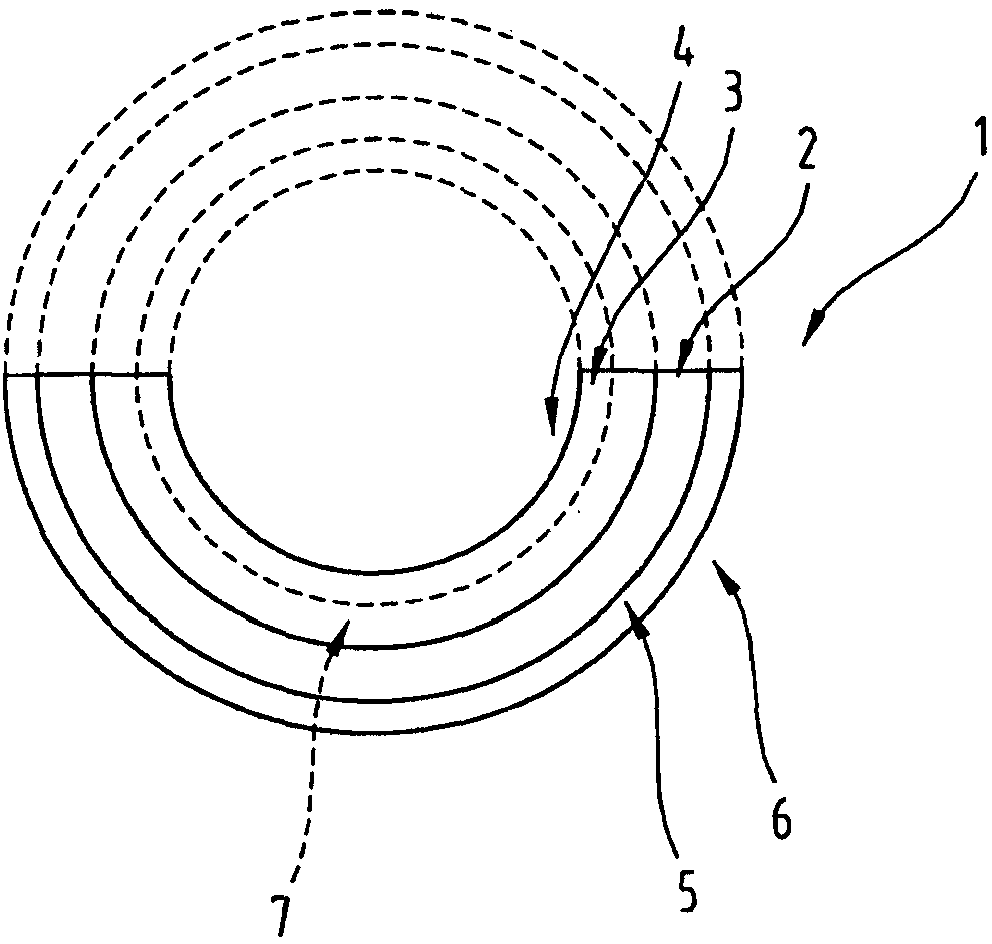

Semiconductor device and fabrication method thereof

ActiveCN1797783AUniaxial compressive stress maximizationMaximization effectSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSilicon

A semiconductor device includes a gate electrode formed on a silicon substrate via a gate insulation film in correspondence to a channel region, source and drain regions of a p-type diffusion region formed in the silicon substrate at respective outer sides of sidewall insulation films of the gate electrode, and a pair of SiGe mixed crystal regions formed in the silicon substrate at respective outer sides of the sidewall insulation films in epitaxial relationship to the silicon substrate, the SiGe mixed crystal regions being defined by respective sidewall surfaces facing with each other, wherein, in each of the SiGe mixed crystal regions, the sidewall surface is defined by a plurality of facets forming respective, mutually different angles with respect to a principal surface of the silicon substrate.

Owner:SOCIONEXT INC

Preparation method for wide-temperature blue-phase liquid crystal composite material

The invention provides a preparation method for a wide-temperature blue-phase liquid crystal composite material, comprising the following steps of: adding bent liquid crystal molecules such as oxadiazoles and thiophenes in a micro-molecular nematic mixed crystal according to a certain ratio, then adding one or more chiral compounds in a proper amount and having a helical twisting power (HTP) of 8-100 mum<-1>, so as to induce and broaden the temperature range of a blue-phase liquid crystal, wherein the temperature range can achieve 5-30 DEG C. The preparation method for a wide-temperature blue-phase liquid crystal composite material provided by the invention is simple in preparation and remarkable in effect; and the prepared system is good in stability, low in viscosity, and fast in the speed of a response to an electric field.

Owner:UNIV OF SCI & TECH BEIJING

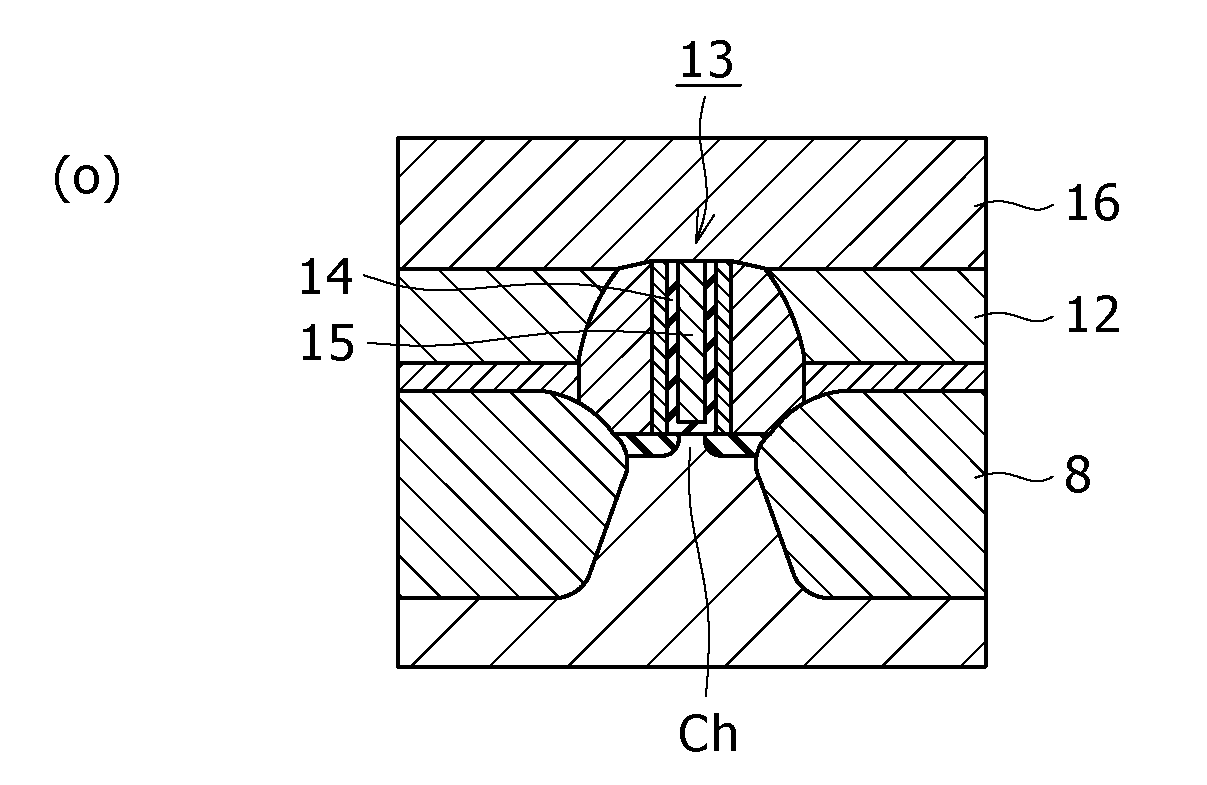

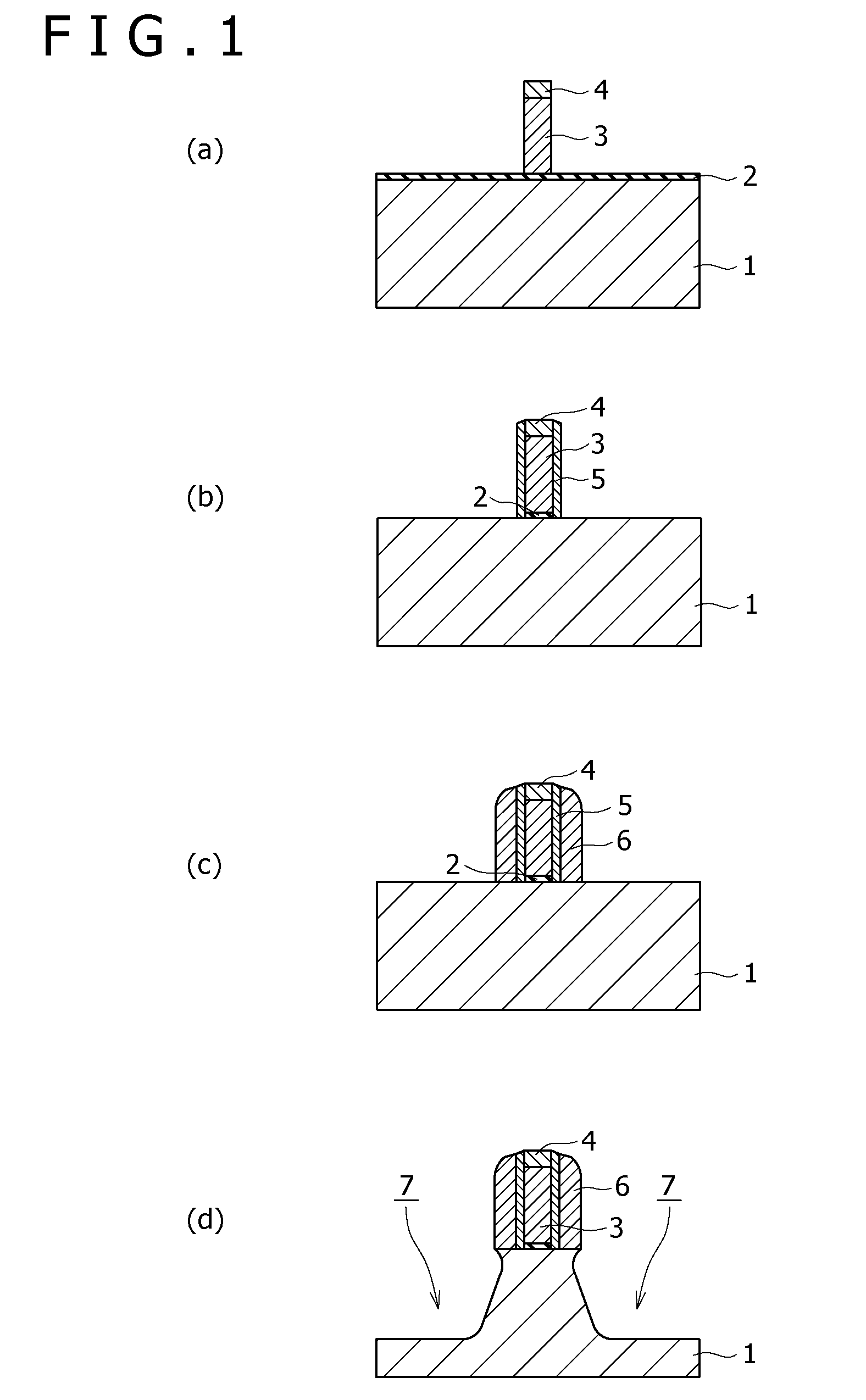

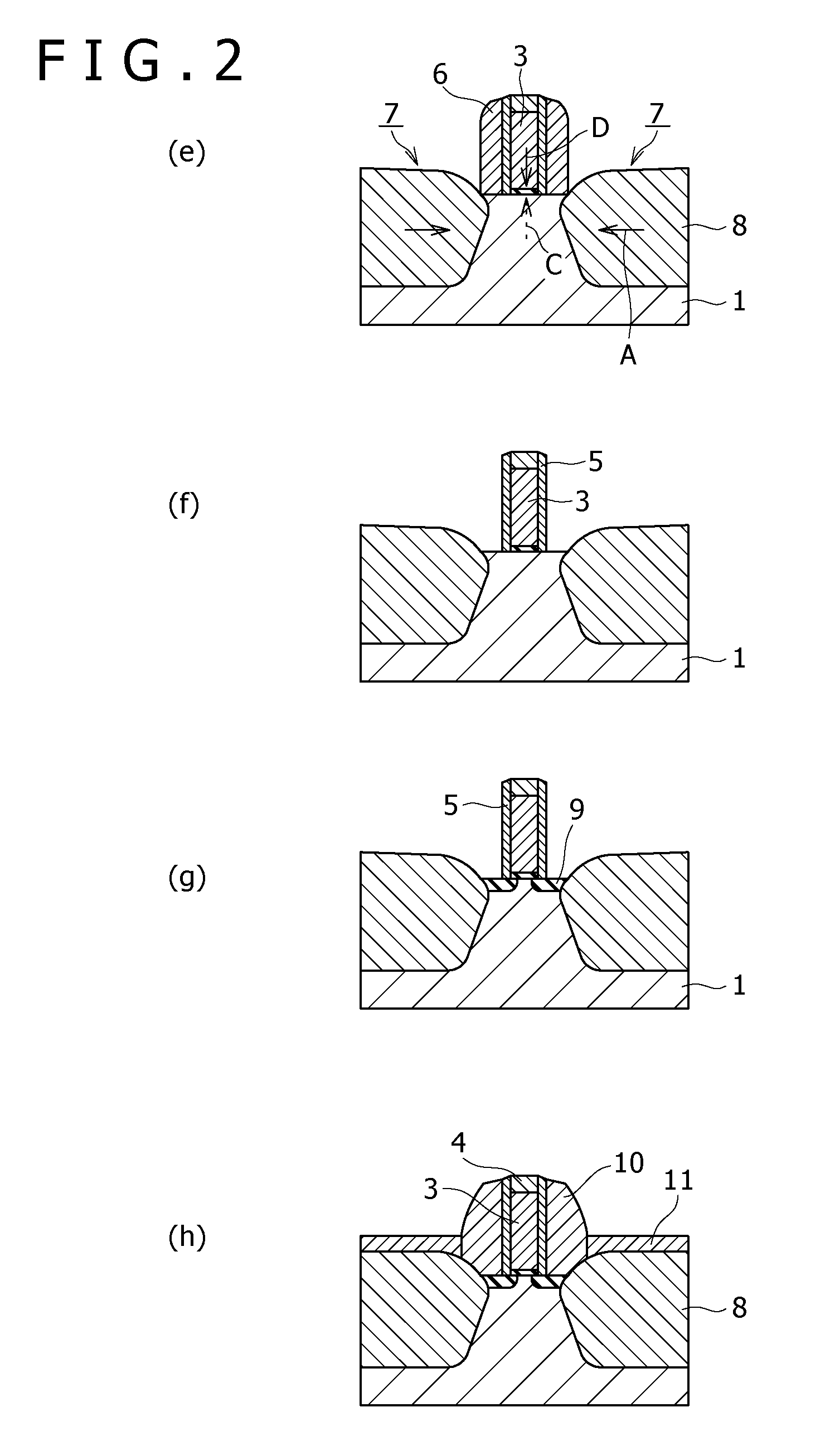

Method for manufacturing semiconductor device and semiconductor device

ActiveUS20100001323A1High carrier mobilityPrevent crystal defectTransistorSemiconductor/solid-state device manufacturingMixed crystalSemiconductor

Provided is a semiconductor device manufacturing method by which sufficient stress can be applied to a channel region within allowable ranges of concentrations of Ge and C in a mixed crystal layer. A semiconductor device is also provided. A dummy gate electrode 3 is formed on a Si substrate 1. Then, a recess region 7 is formed by recess etching by using the dummy gate electrode 3 as a mask. Next, on the surface of the recess region 7, a mixed crystal layer 8 composed of a SiGe layer is epitaxially grown. Subsequently, an interlayer insulating film 12 is formed on the mixed crystal layer 8 to cover the dummy gate electrode 3, and the interlayer insulating film 12 is removed until the surface of the dummy gate electrode 3 is exposed. A recess 13 is formed on the interlayer insulating film 12 to expose the Si substrate 1 by removing the dummy gate electrode 3. Then, a gate electrode 15 is formed in the recess 13 by having a gate insulating film 14 in between.

Owner:SONY CORP

Quasi-continuous laser metal 3D printing method capable of realizing regulation of nickel base alloy crystallographic texture

ActiveCN107790717AImprove consistencyImprove microstructureAdditive manufacturing apparatusIncreasing energy efficiencyMolten bathMatch rule

The invention discloses a quasi-continuous laser metal 3D printing method capable of realizing regulation of nickel base alloy crystallographic texture. Laser output is set as a quasi-continuous lasermode, and then a laser metal 3D printing technical window is preliminarily optimized. The temperature field of a molten bath under the preliminarily optimized parameter is calculated by using a finite element heat transfer model; the temperature gradient G and the cooling rate xi of the moving boundary of the molten bath during closing of laser in a single pulse period are extracted, and the growth length L of a single pulse internal columnar dendrite is worked out according to a structure growth theoretical model; the laser parameter is optimized according to the matching rule that the ratioof the scanning speed V to pulse frequency f is 0.5-0.8L, and finally 3D printing forming is conducted according to the optimized parameter, so that a formed part with the consistent crystallographicorientation height is obtained. By regulating the heat source output mode, an effective remelting mechanism for mixed crystal or isometric crystal is introduced in the scanning direction, all columnar dendrite growth is obtained, and the consistency of grain orientation is remarkably improved.

Owner:HUNAN UNIV

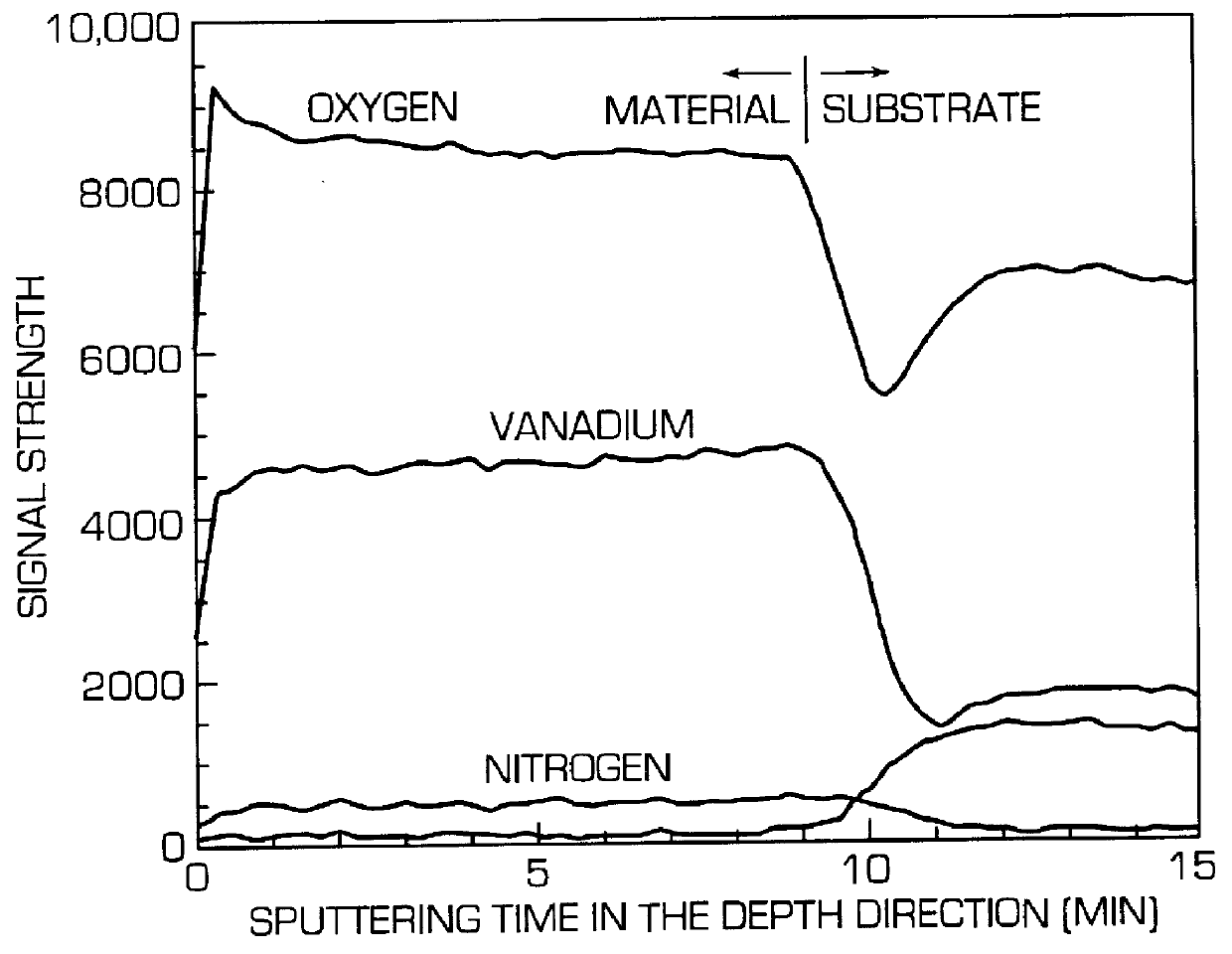

Thin-film temperature-sensitive resistor material and production process thereof

Described are a thin-film temperature-sensitive resistor material which comprises, at a temperature-sensitive resistor portion, a mixed crystal of a nitride and oxide of a transition metal such as vanadium preferably, that represented by the formula: MNxOy wherein 0<x<1, and 2< / =y< / =13 / 6, simultaneously exhibits a high temperature coefficient of resistance and a low specific resistance at about room temperature, and has excellent sensitivity at about room temperature; and a process for the production of a thin-film temperature-sensitive resistor material, which comprises forming its temperature-sensitive resistor portion by using a gas-atmosphere composed mainly of a nitrogen gas preferably, a mixed gas composed of nitrogen, argon and oxygen, and has a flow rate ratio of nitrogen to oxygen (nitrogen / oxygen) of 14 / 1 to 23 / 1.

Owner:NEC CORP

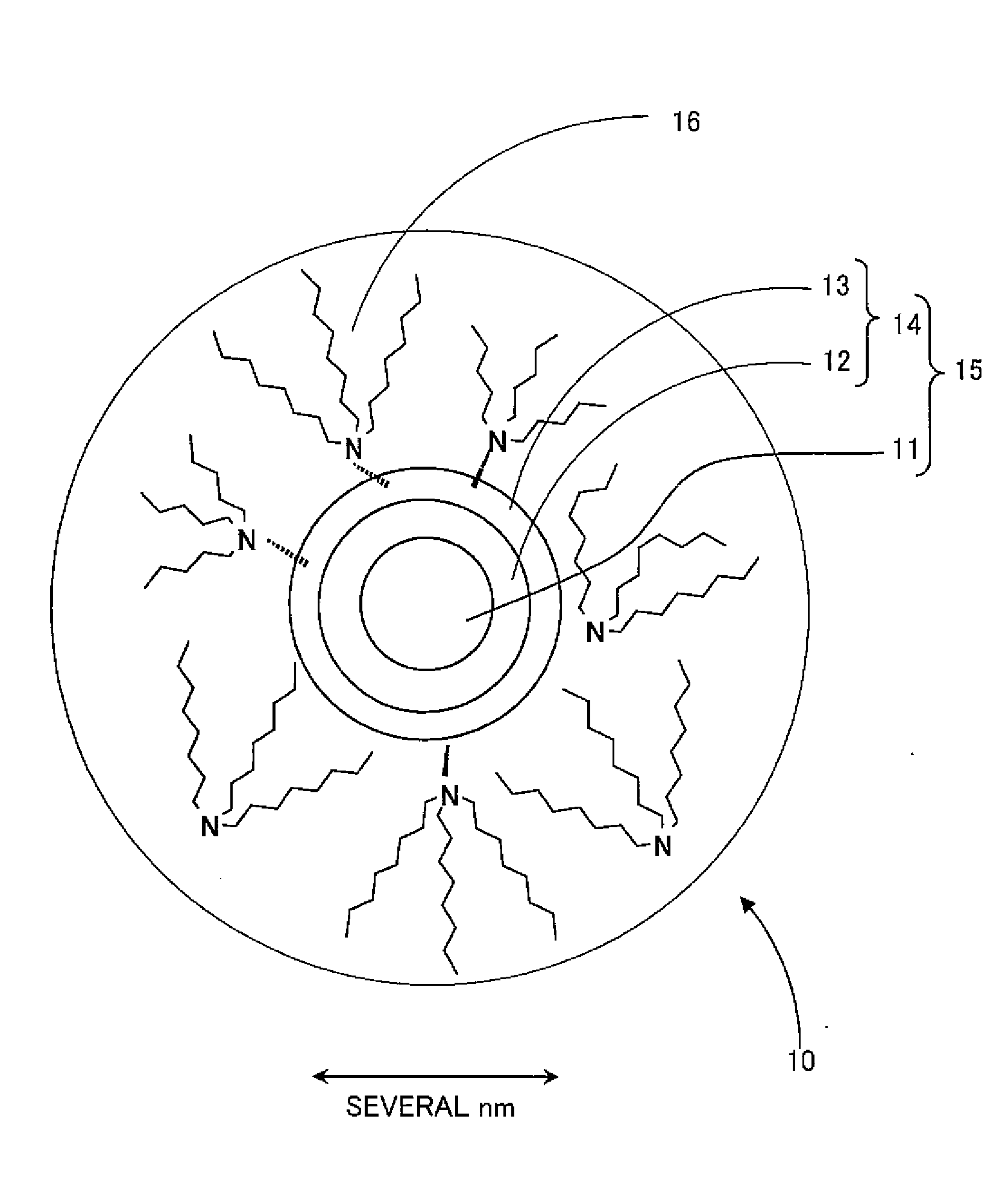

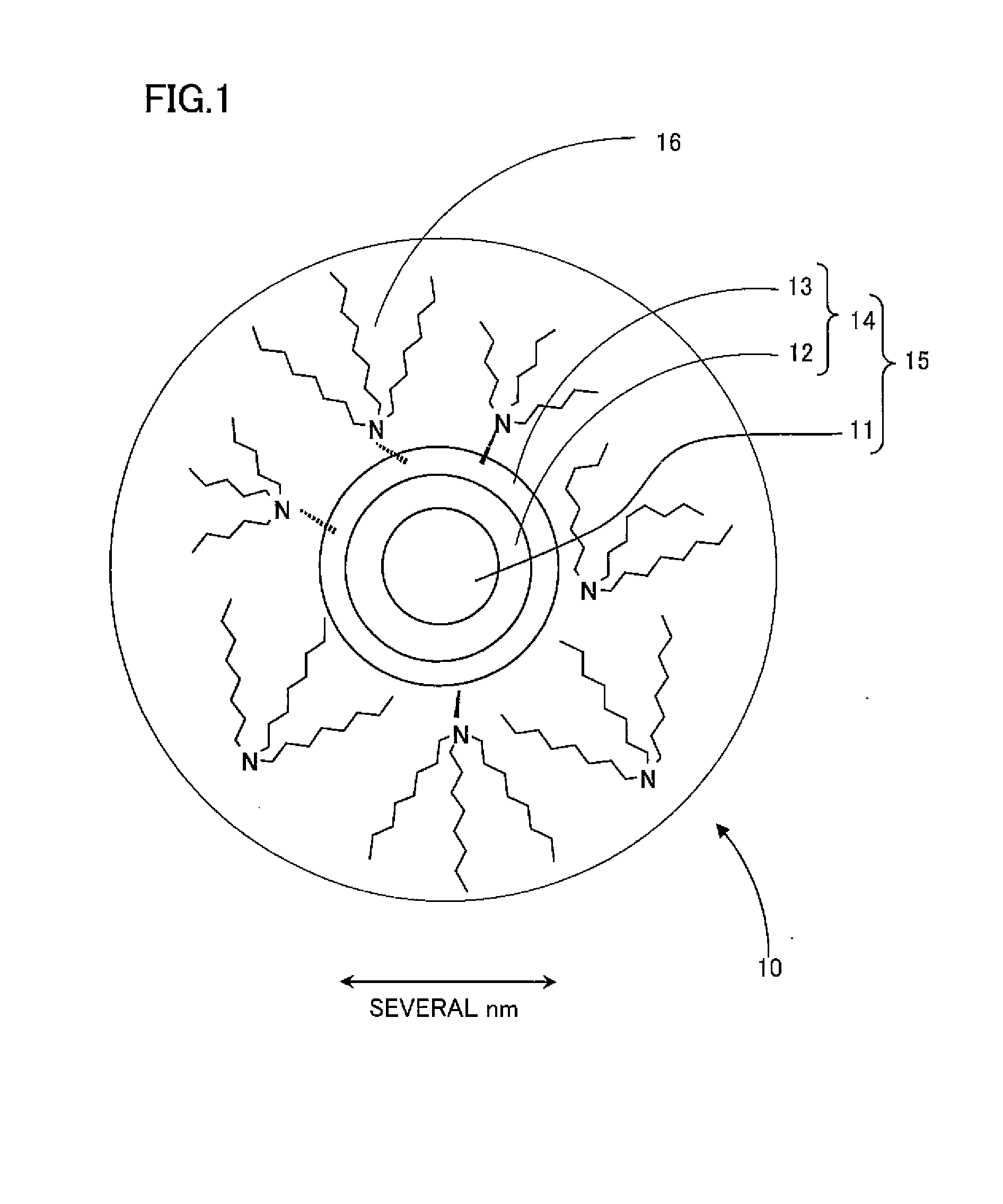

Nanocrystalline phosphor and coated nanocrystalline phosphor as well as method of preparing coated nanocrystalline phosphor

InactiveUS20080173845A1Solve low luminous efficiencyImprove reliabilityIndividual molecule manipulationSynthetic resin layered productsPhosphorNitrogen

Provided is a nanocrystalline phosphor having a core / shell structure formed by a core of a group 13 nitride semiconductor and a shell layer, covering the core, including a shell film of a group 13 nitride mixed crystal semiconductor. This nanocrystalline phosphor has high luminous efficiency, and is excellent in reliability. Also provided is a coated nanocrystalline phosphor prepared by bonding modified organic molecules to the nanocrystalline phosphor and / or coating the nanocrystalline phosphor with the modified organic molecules. This coated nanocrystalline phosphor has high dispersibility. Further provided is a method of preparing a coated nanocrystalline phosphor by heating a mixed solution containing a core of a group 13 nitride semiconductor, a nitrogen-containing compound, a group 13 element-containing compound and modified organic molecules.

Owner:SHARP KK

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com