Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

734results about How to "Suppress leakage current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

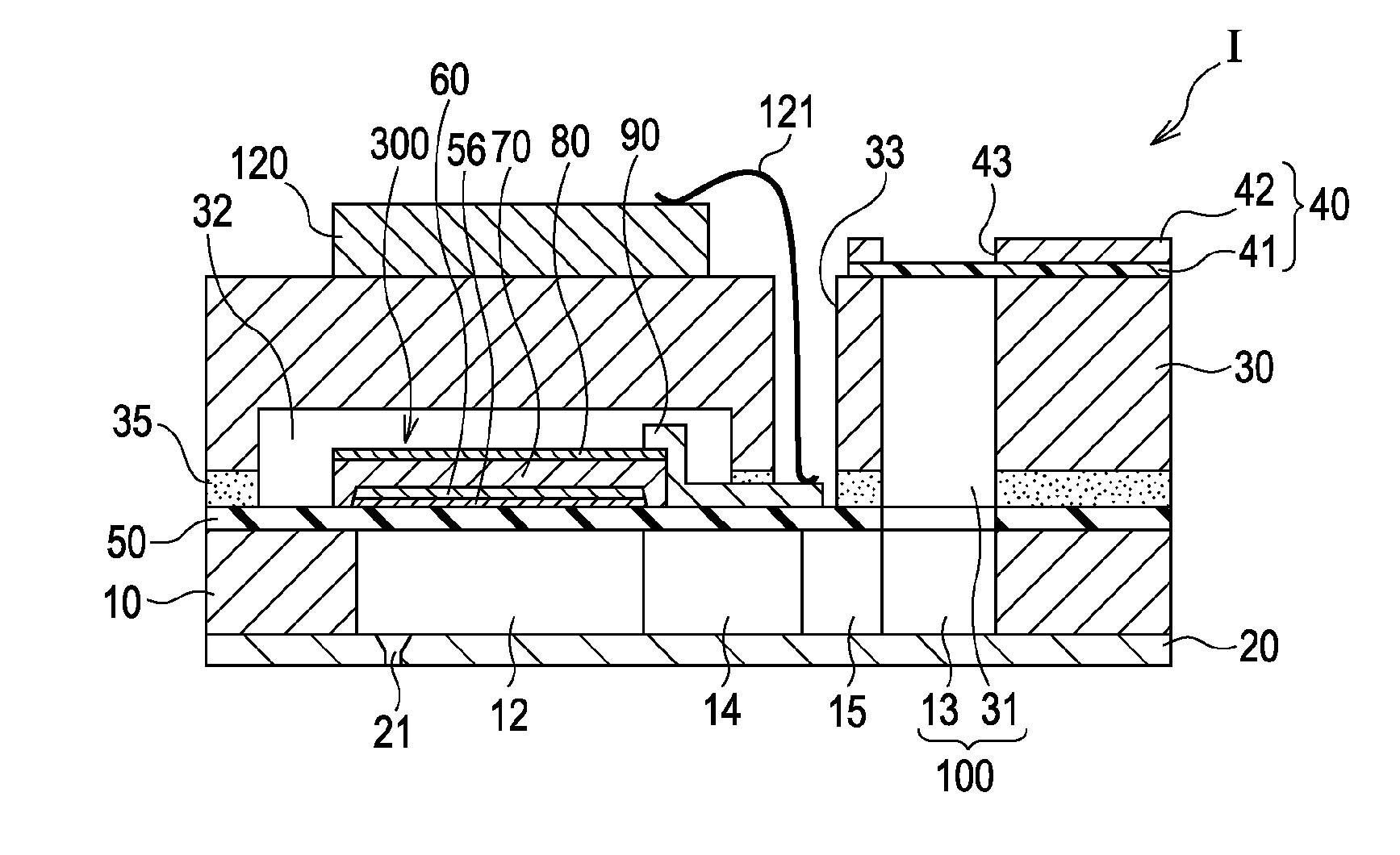

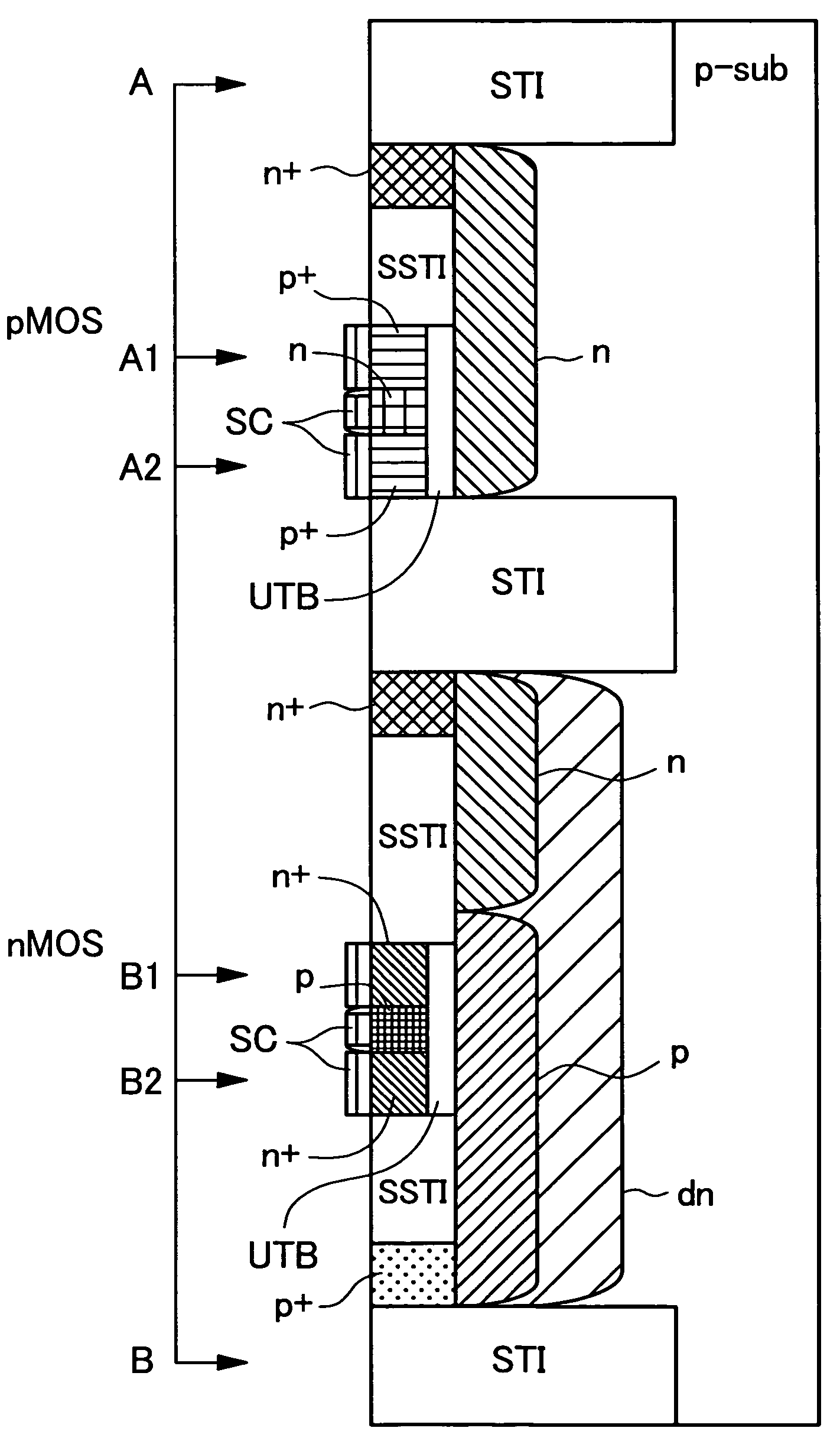

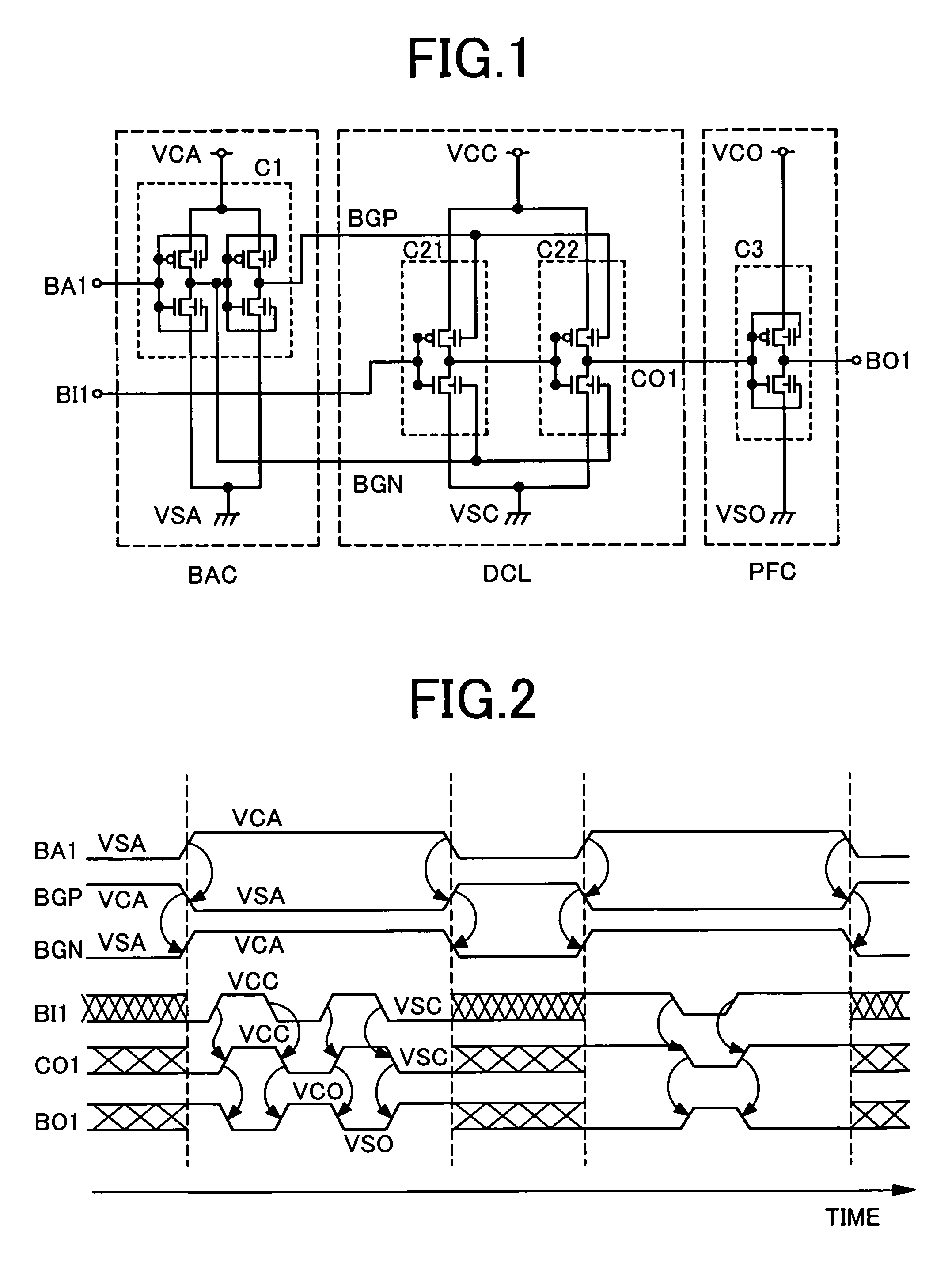

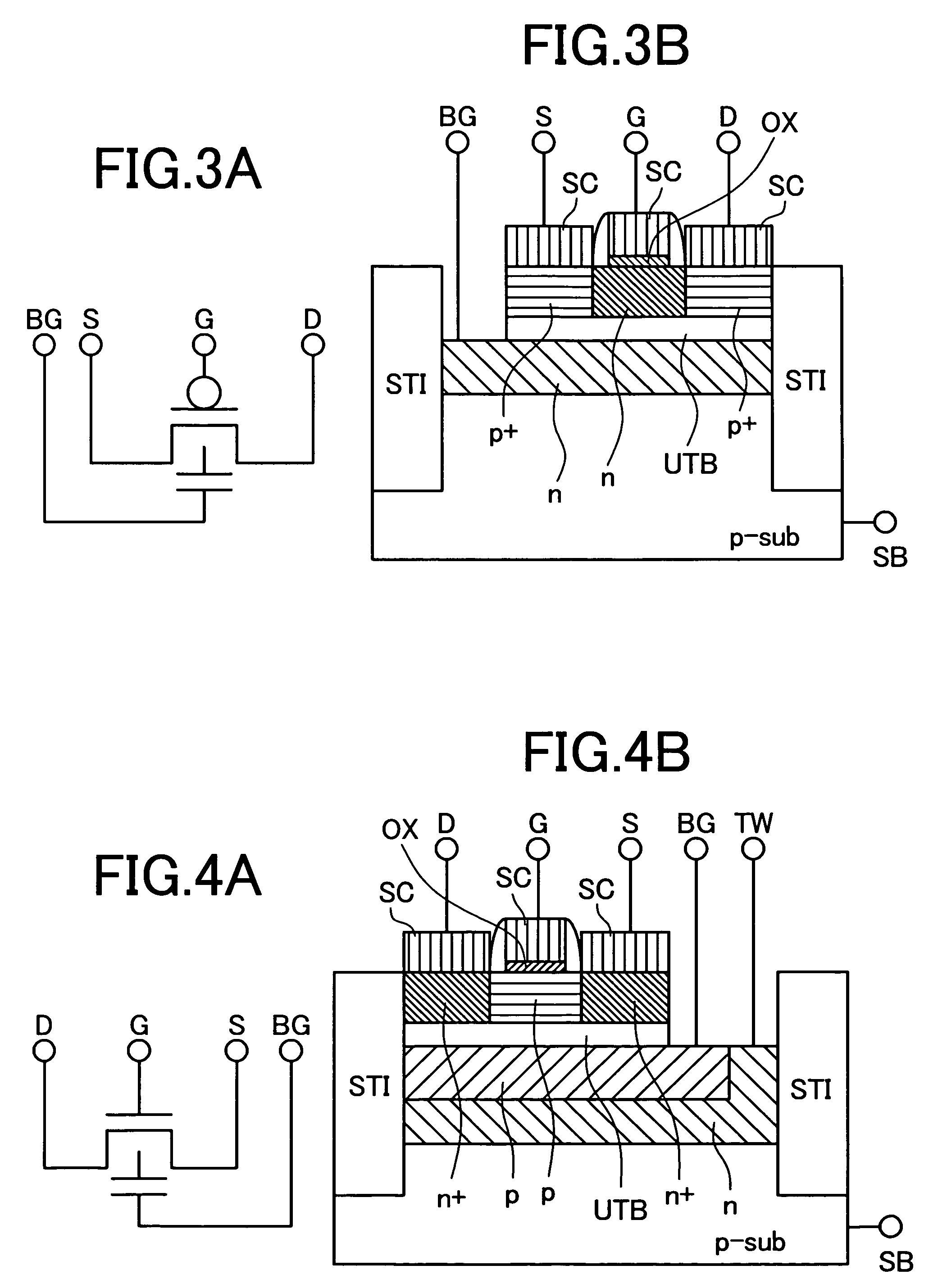

Semiconductor device and semiconductor integrated circuit using the same

InactiveUS20070063284A1Easy to processDrive capability can be improvedSolid-state devicesSemiconductor/solid-state device manufacturingHeavy loadHigh velocity

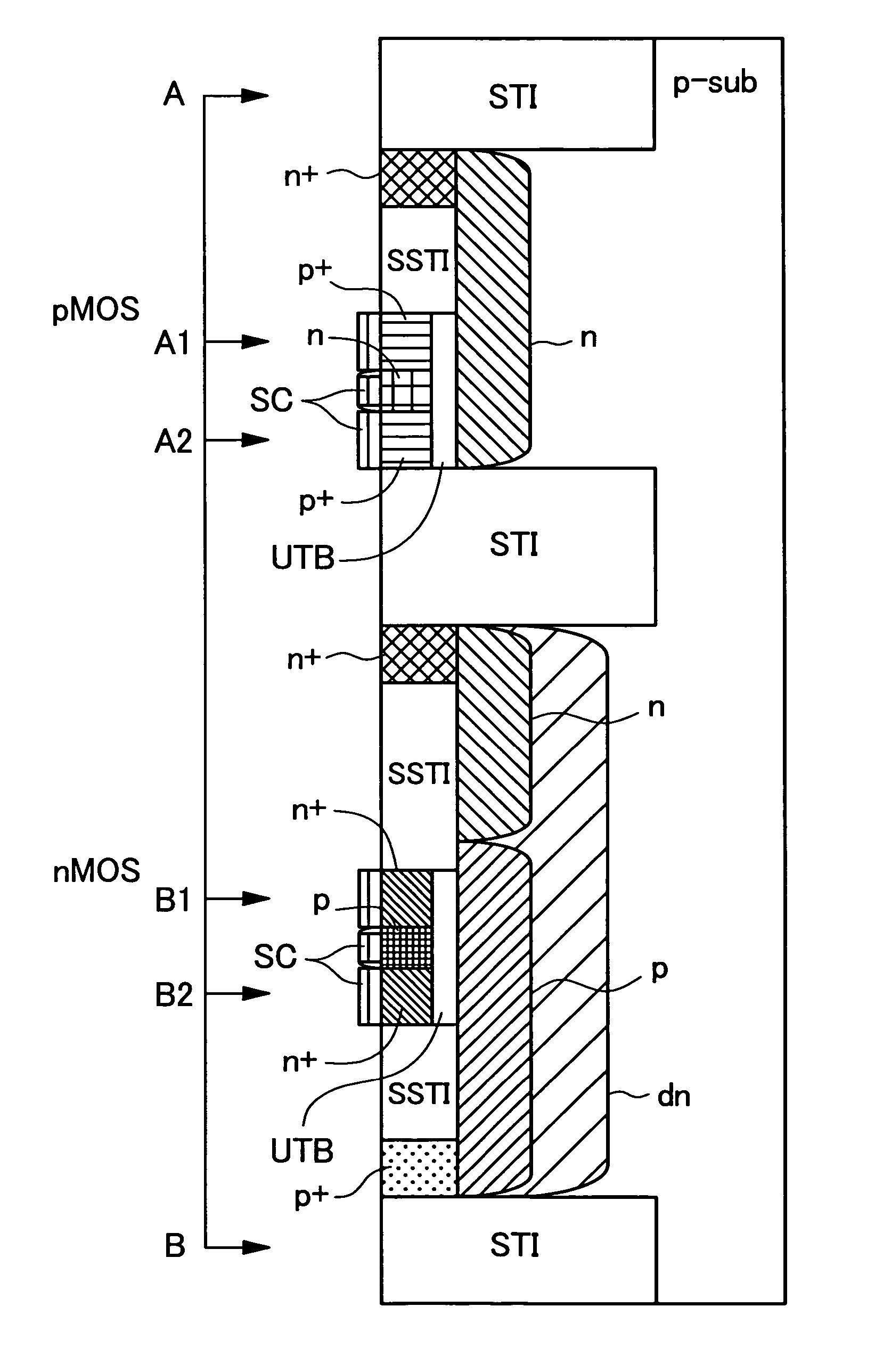

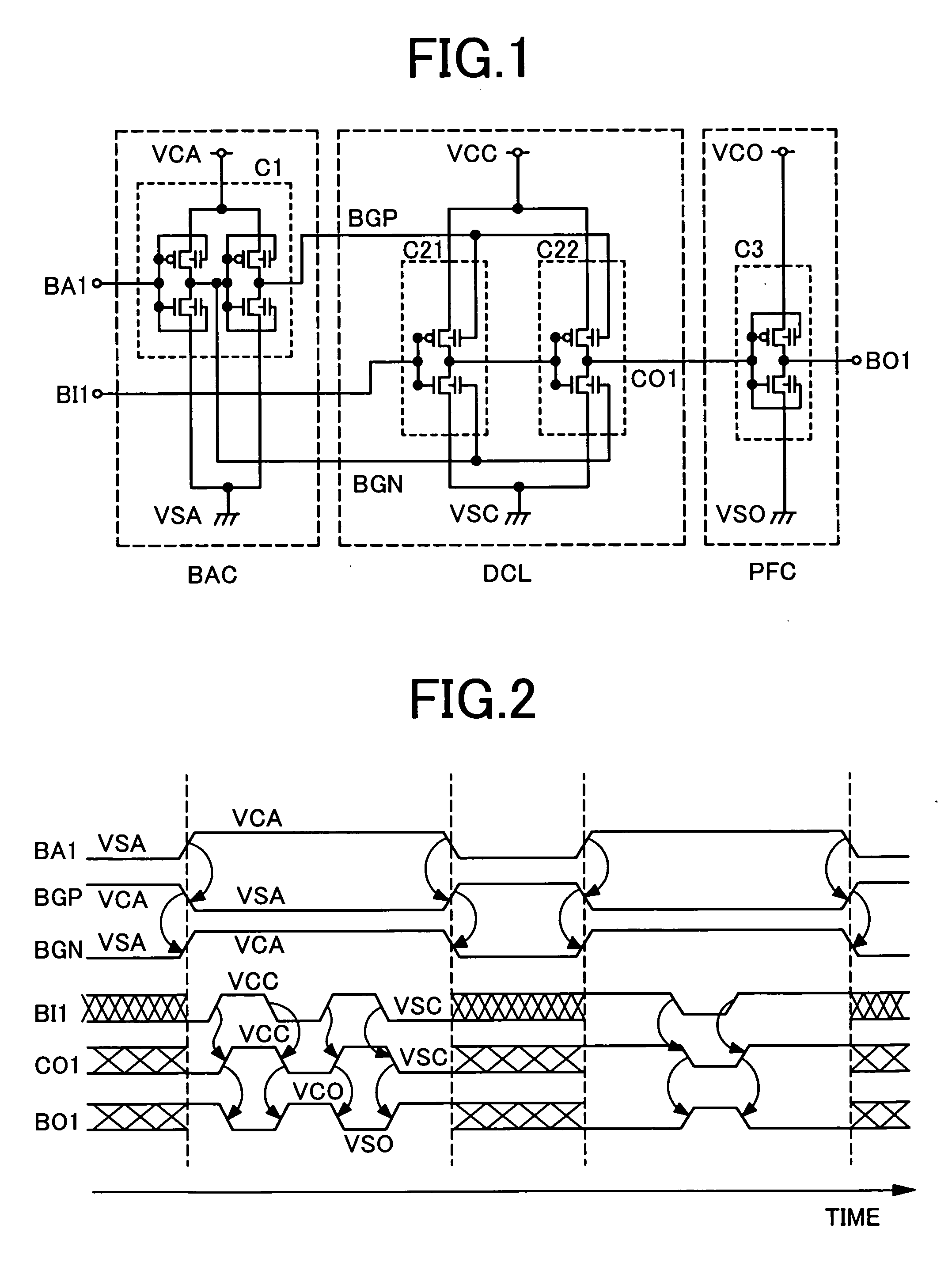

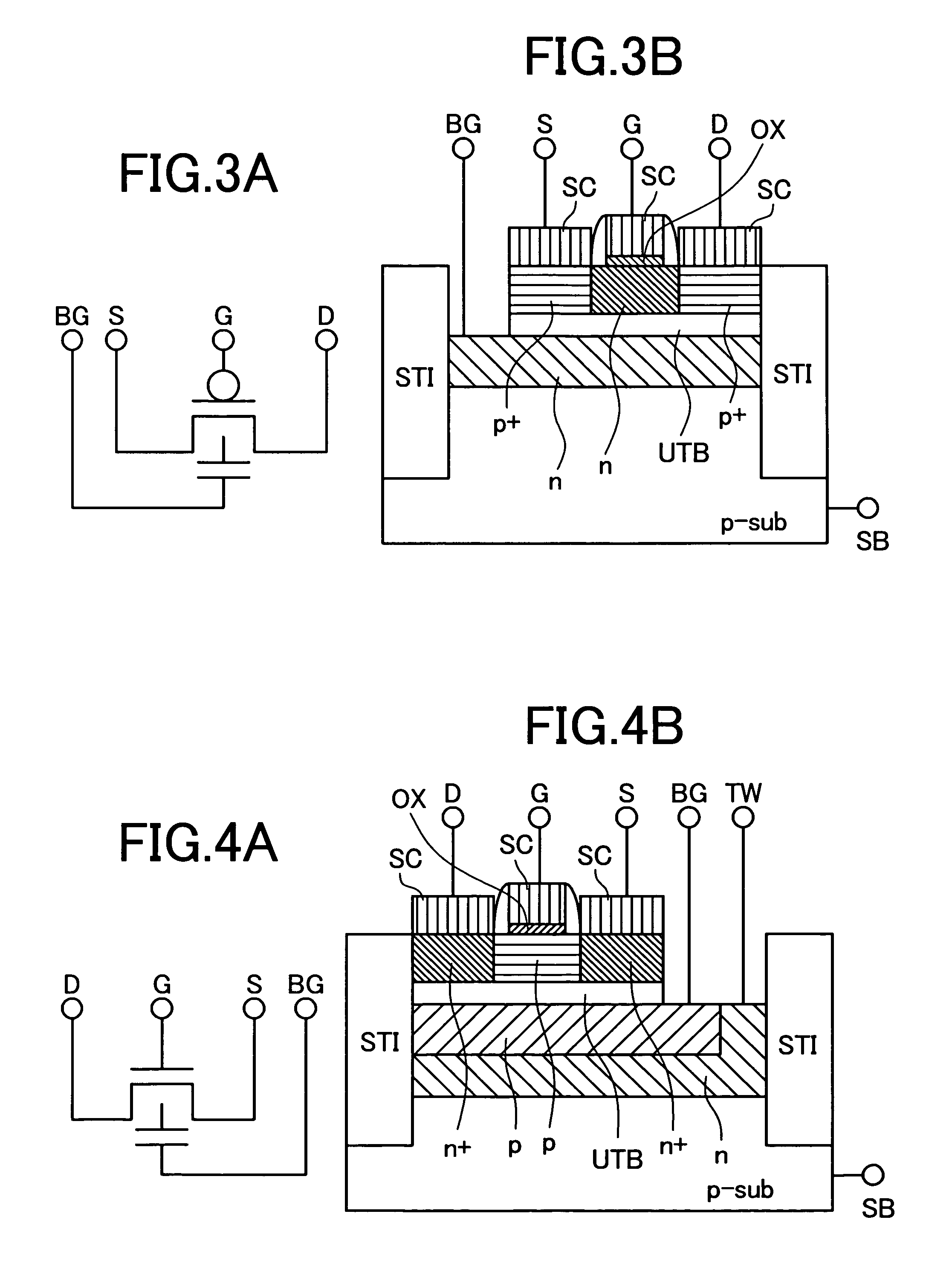

The present invention provides a high speed and low power consumption LSI operable in a wide temperature range in which a MOS transistor having back gates is used specifically according to operating characteristics of a circuit. In the LSI, an FD-SOI structure having an embedded oxide film layer is used and a lower semiconductor region of the embedded oxide film layer is used as a back gate. A voltage for back gates in the logic circuits having a small load in the logic circuit block is controlled in response to activation of the block from outside of the block. Transistors, in which the gate and the back gate are connected to each other, are used for the circuit generating the back gate driving signal, and logic circuits having a heavy load such as circuit block output section, and the back gates are directly controlled according to the gate input signal.

Owner:RENESAS ELECTRONICS CORP

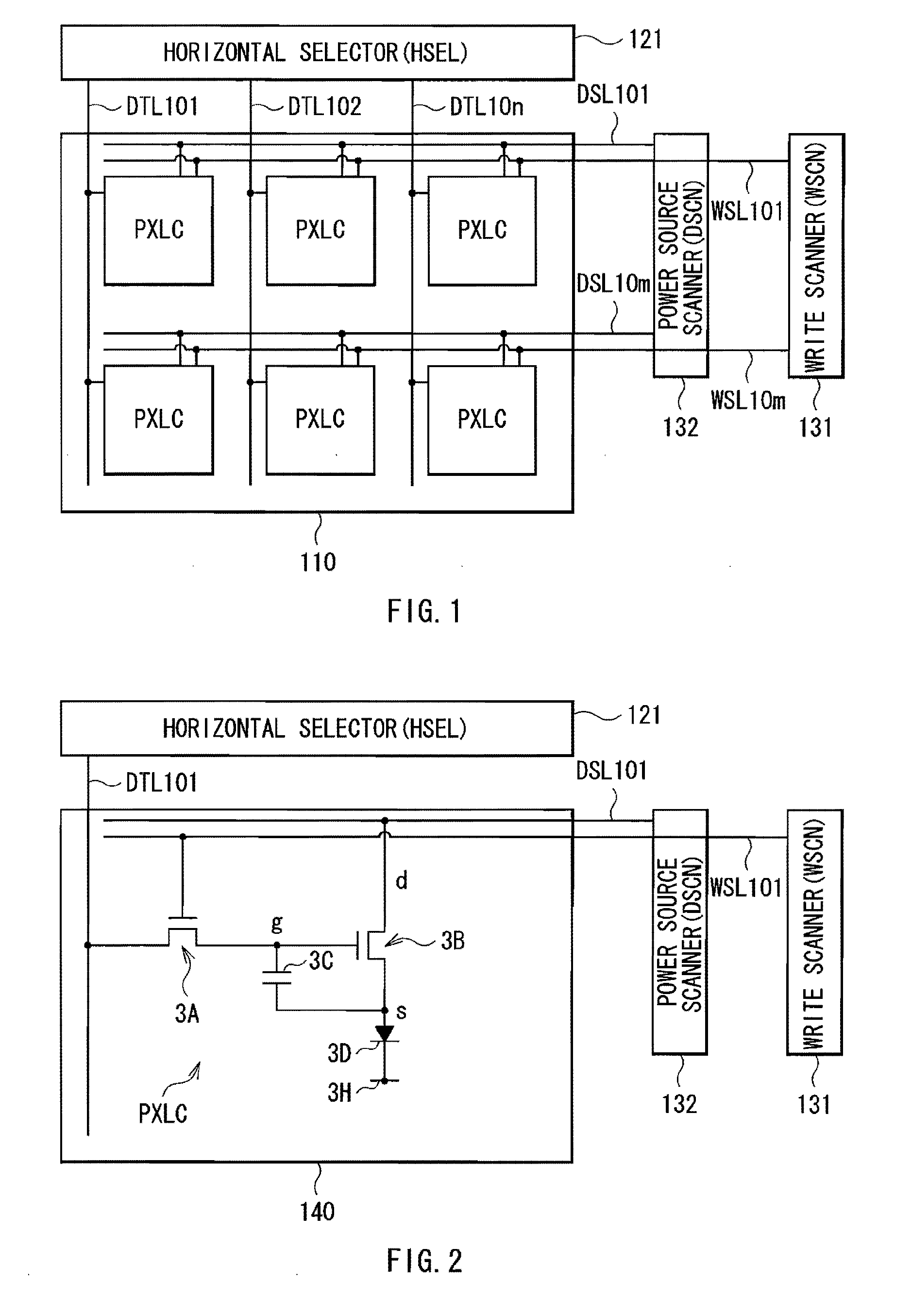

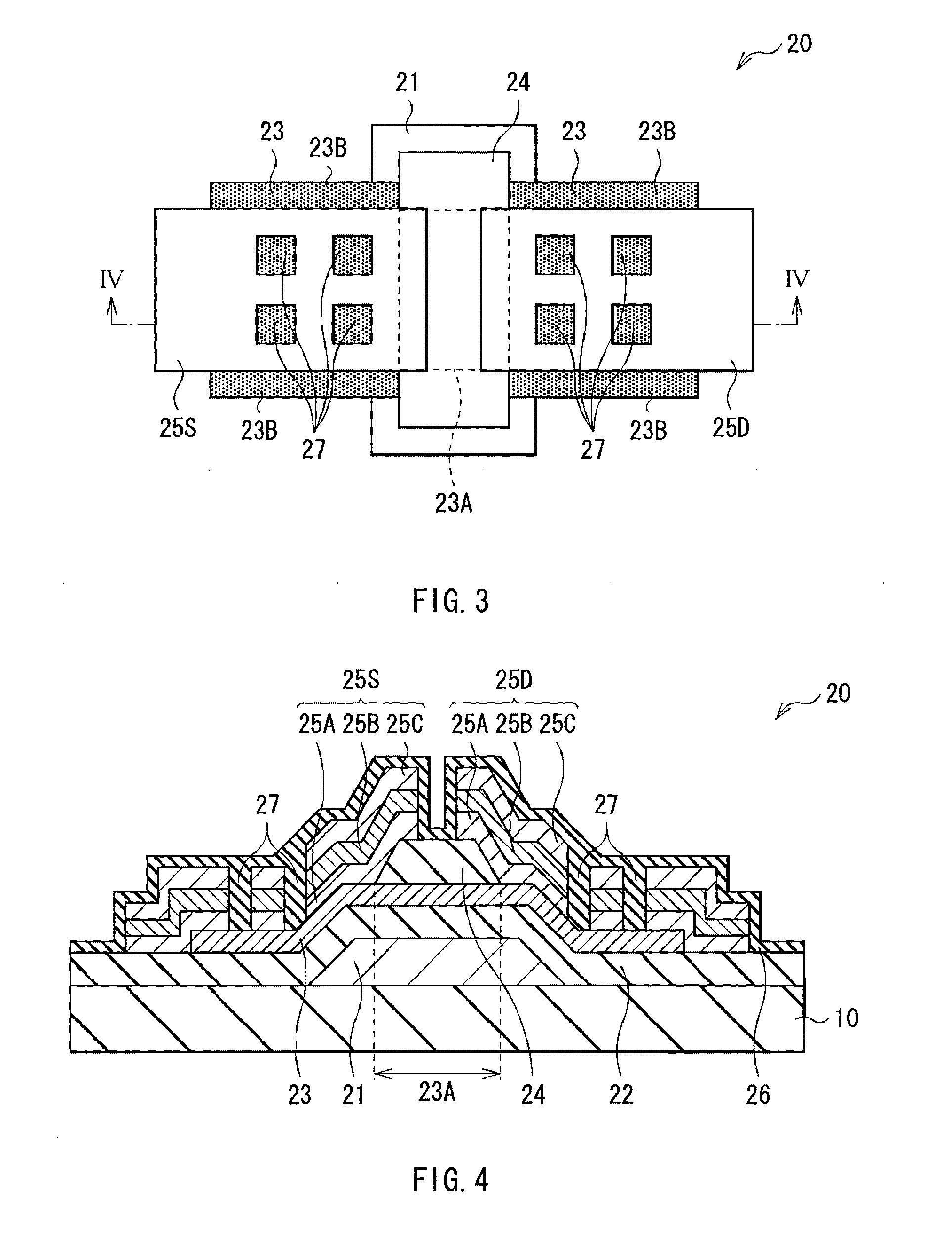

Thin film transistor and display unit

A thin film transistor with which oxygen is easily supplied to an oxide semiconductor layer and favorable transistor characteristics are able to be restored and a display unit including the same are provided. The thin film transistor includes sequentially over a substrate a gate electrode, a gate insulting film, an oxide semiconductor layer including a channel region, and a channel protective layer covering the channel region A source electrode and a drain electrode are formed on the oxide semiconductor layer located on both sides of the channel protective layer, and at least one of the source electrode and the drain electrode has an aperture to expose the oxide semiconductor layer.

Owner:JOLED INC

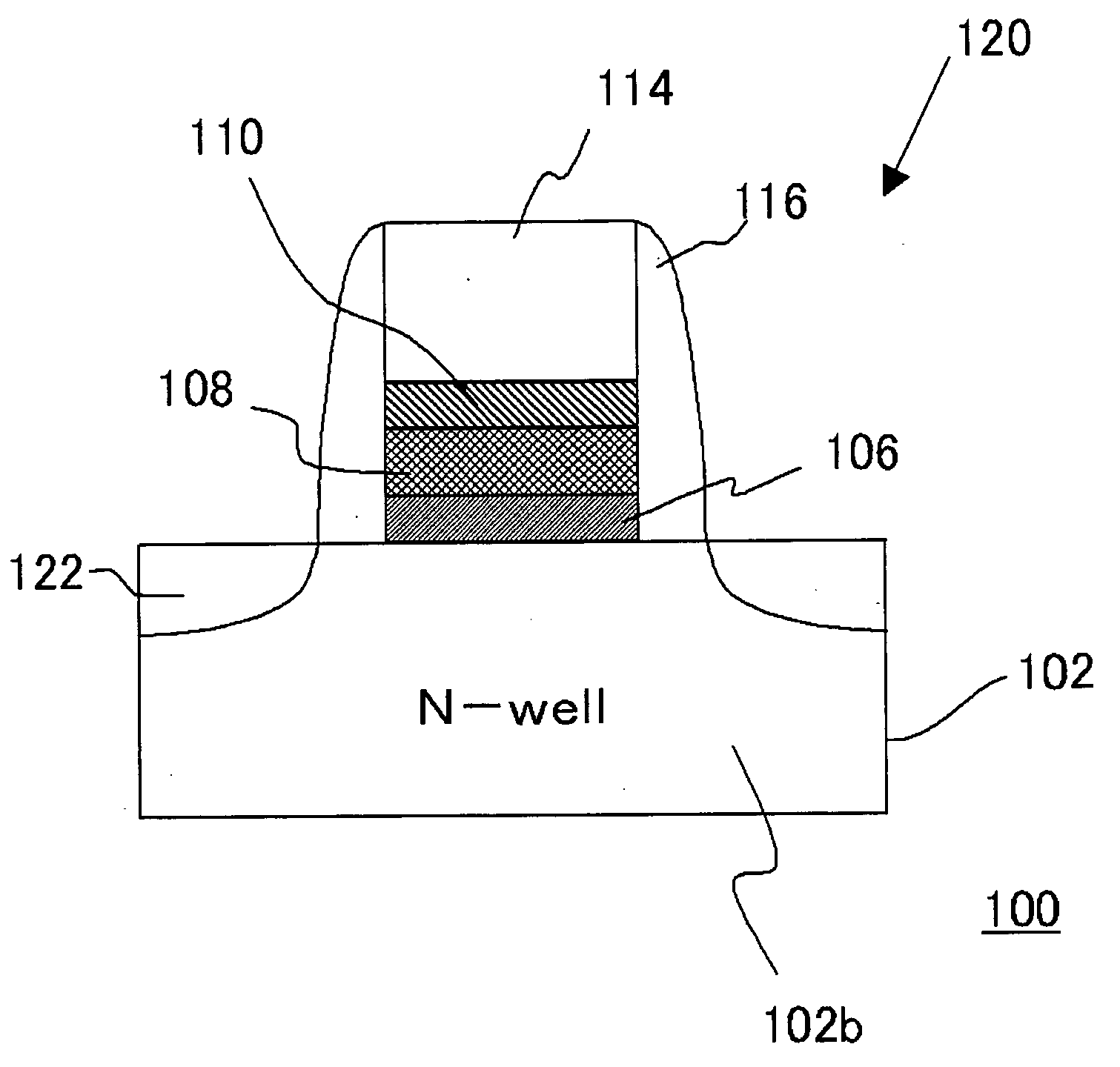

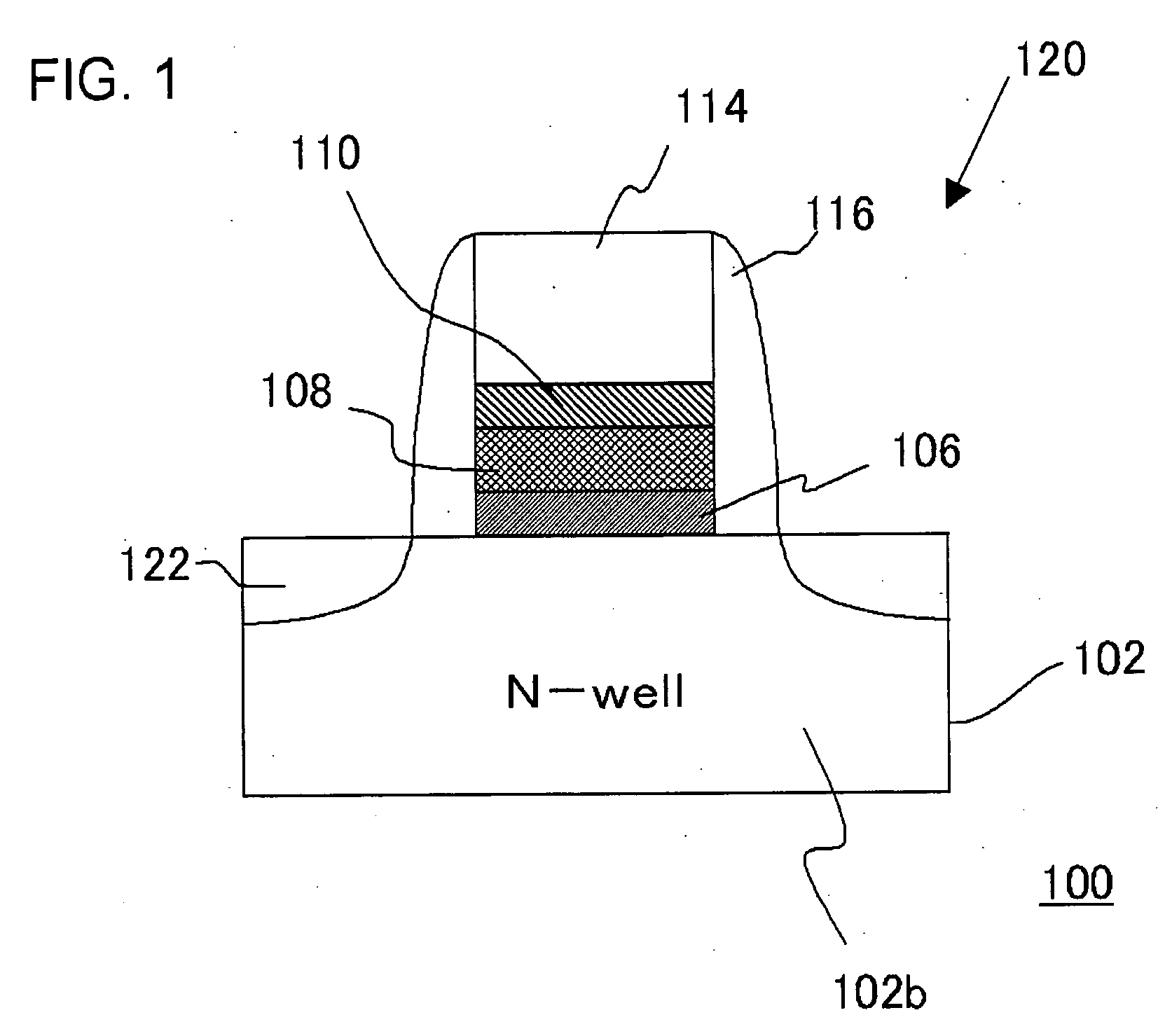

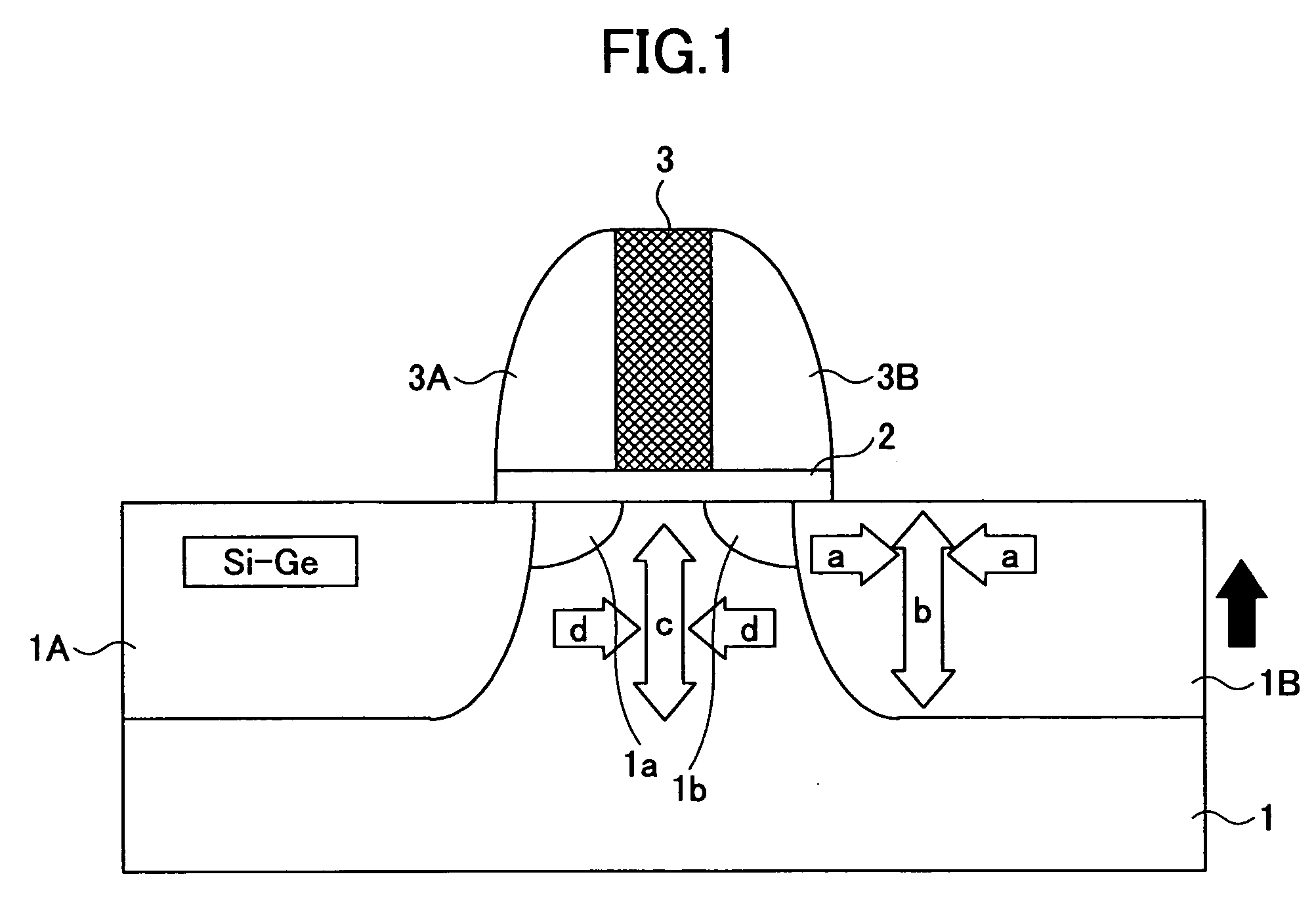

Semiconductor device

ActiveUS20060038236A1Improve heat resistanceSuppress leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETDevice material

A P-type MOSFET 120 includes a semiconductor substrate (N-well 102b); a gate insulating film formed on the semiconductor substrate, composed of a high-dielectric-constant film 108 which contains a silicate compound containing a first element selected from the group consisting of Hf, Zr and any of lanthanoids, together with N; a gate electrode formed on the gate insulating film, and is configured by a polysilicon film 114 containing a P-type impurity; and a blocking oxide film 110 formed between the gate insulating film and the gate electrode, blocking a reaction between the first element and the polysilicon film 114, and having a relative dielectric constant of 8 or above.

Owner:RENESAS ELECTRONICS CORP

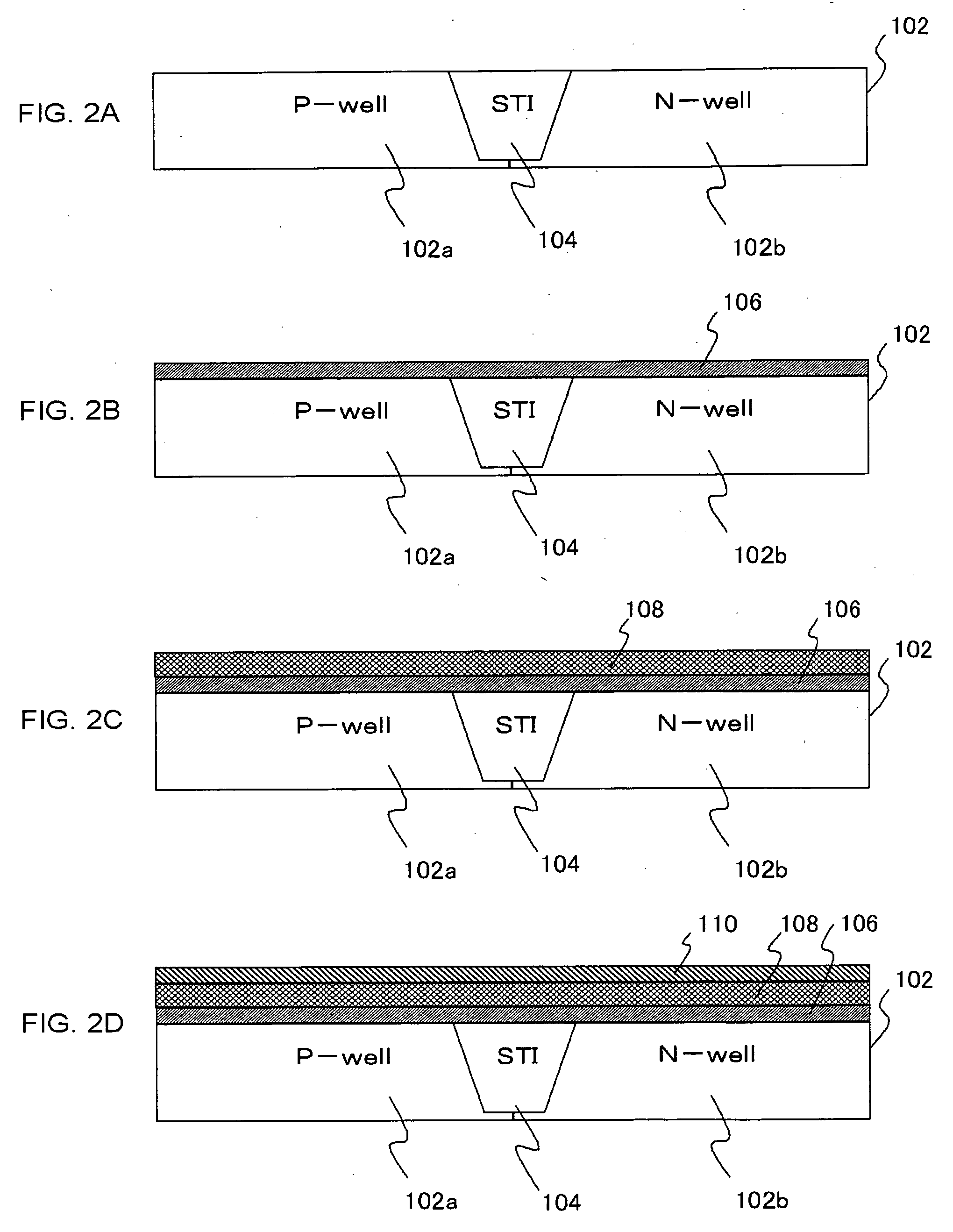

Semiconductor integrated circuit and fabrication process thereof

ActiveUS20060151776A1Suppress leakage currentSufficient distanceSemiconductor/solid-state device manufacturingSemiconductor devicesManufacturing technologyEngineering

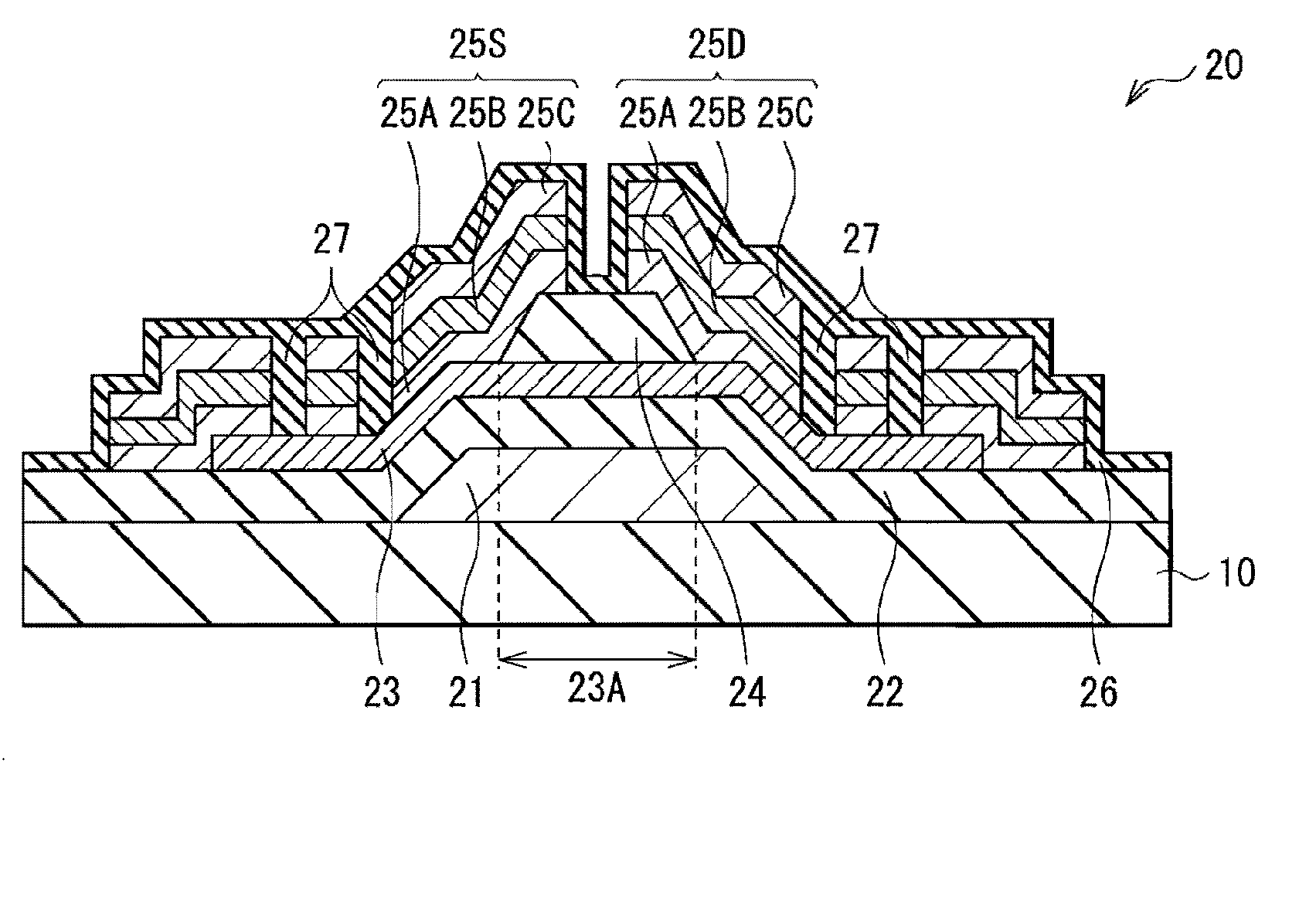

A semiconductor integrated circuit device includes an n-channel MOS transistor formed on a first device region of a silicon substrate and a p-channel MOS transistor formed on a second device region of the silicon substrate, wherein the n-channel MOS transistor includes a first gate electrode carrying a pair of first sidewall insulation films formed on respective sidewall surfaces thereof, the p-channel MOS transistor includes a second gate electrode carrying a pair of second sidewall insulation films formed on respective sidewall surfaces thereof, first and second SiGe mixed crystal regions being formed in the second device region epitaxially so as to fill first and second trenches formed at respective, outer sides of the second sidewall insulation films so as to be included in source and drain diffusions of the p-channel MOS transistor, a distance between n-type source and drain diffusion region in the first device region being larger than a distance between the p-type source and drain diffusion regions in the second device region.

Owner:FUJITSU LTD

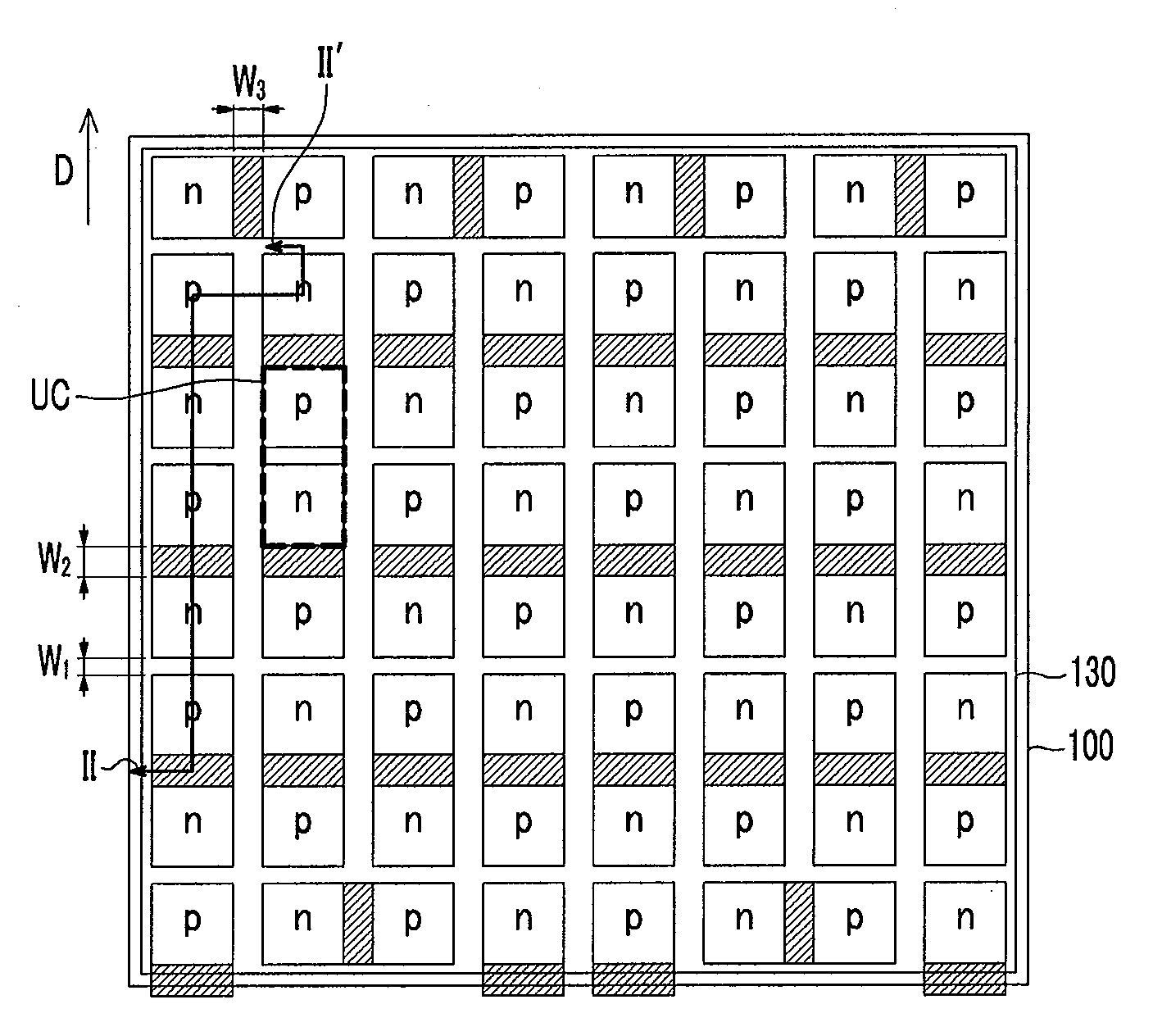

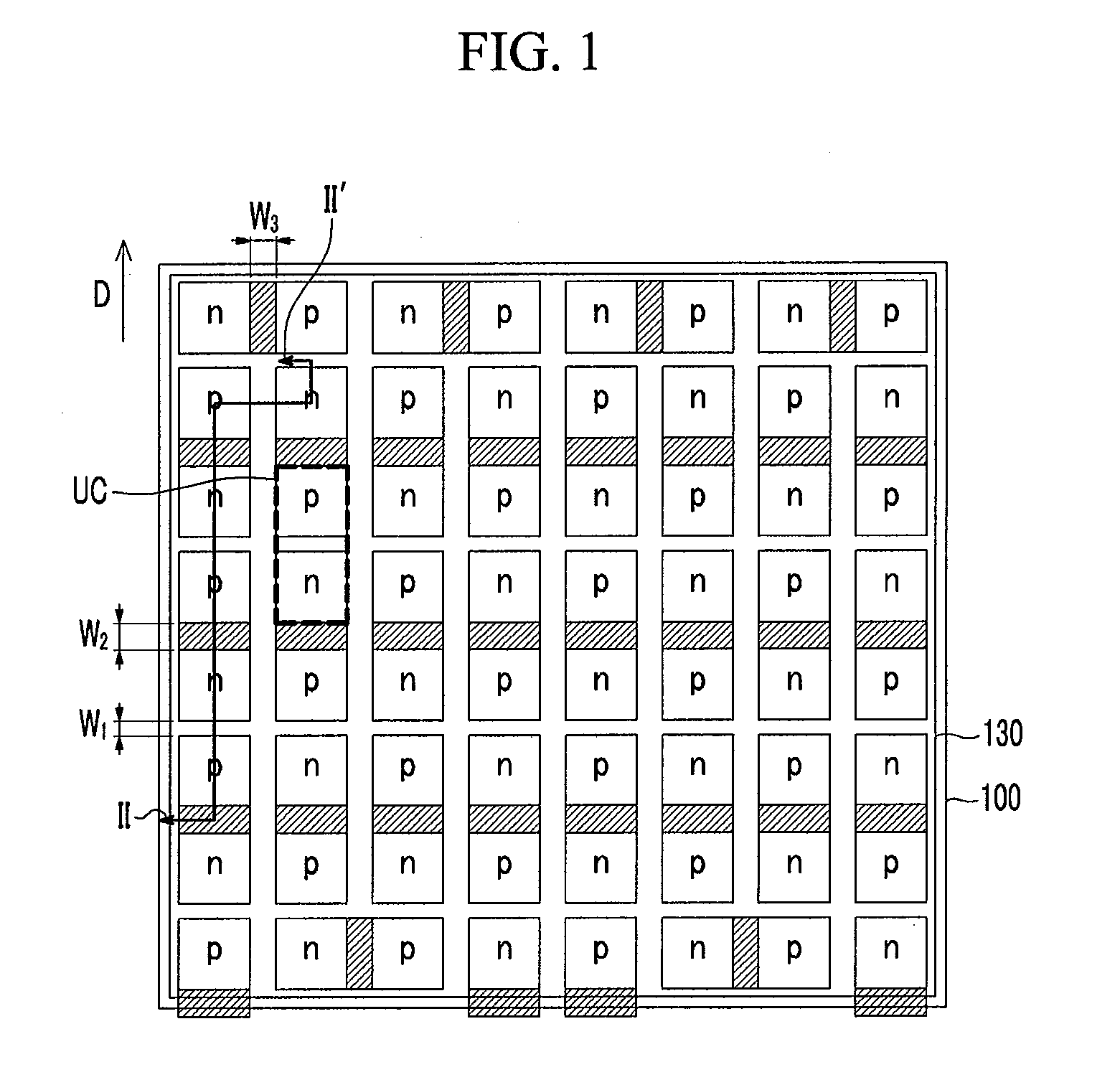

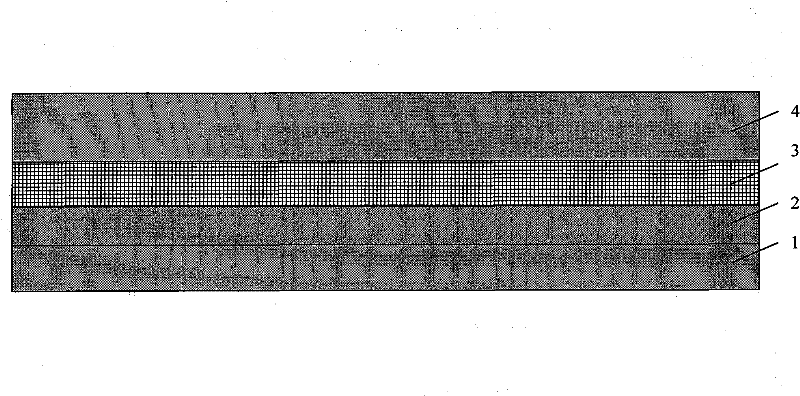

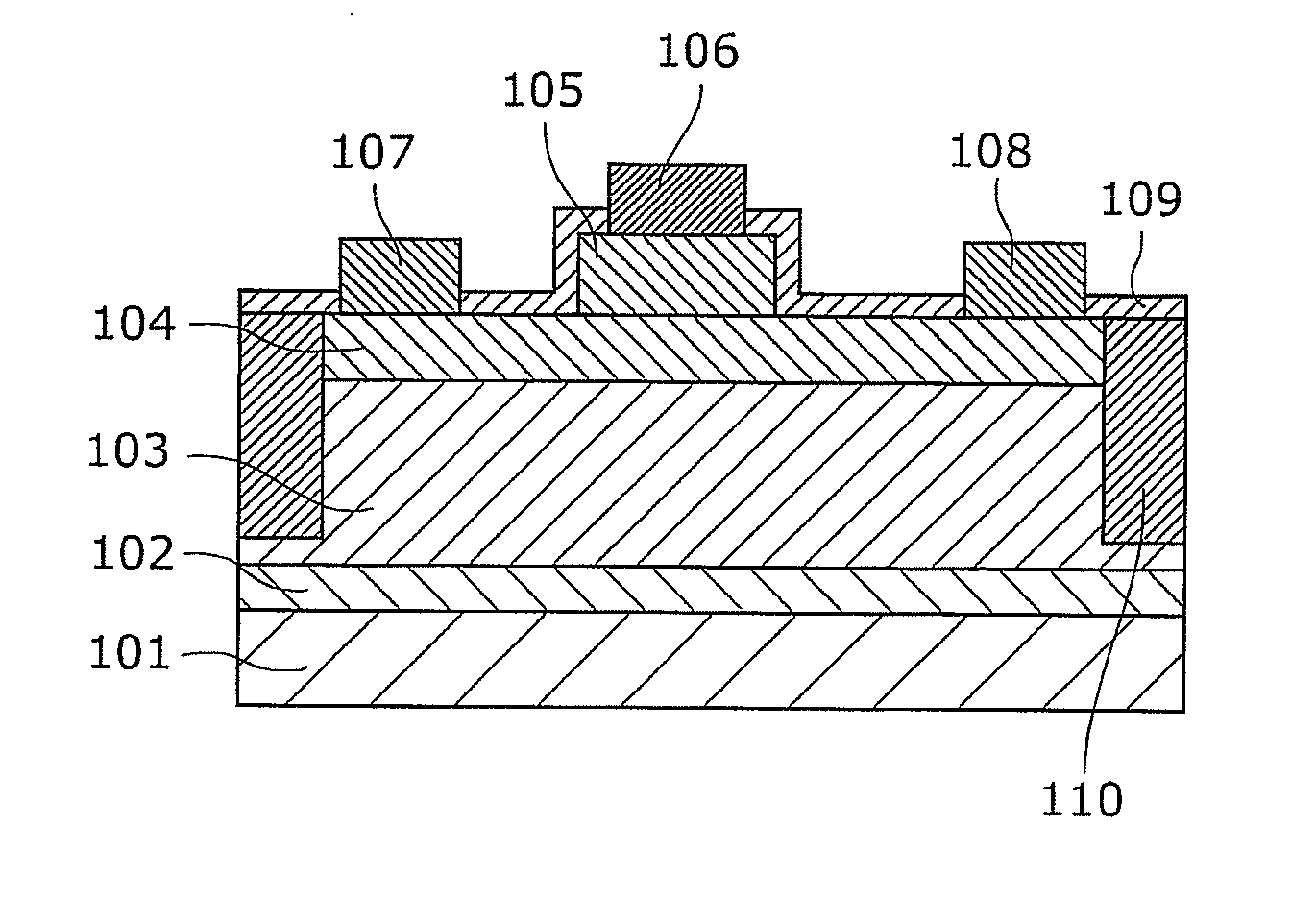

Photovoltaic device and method for manufacturing the same

InactiveUS20100101633A1Reduce manufacturing costImproving interface characteristicPV power plantsSemiconductor/solid-state device manufacturingMaterials sciencePhotovoltaics

A photovoltaic device and a manufacturing method thereof are provided. The photovoltaic device includes: a substrate; a first conductive layer formed on the substrate; P layers and N layers alternately formed along a first direction on the first conductive layer; and I layers covering the P layers and the N layers on the first conductive layer, wherein the P layers and the N layers are separated from each other by a first interval, the I layers are formed between the P layers and the N layers that are separated by the first interval, and the P layers, the I layers, and the N layers formed along the first direction form unit cells.

Owner:SAMSUNG DISPLAY CO LTD +1

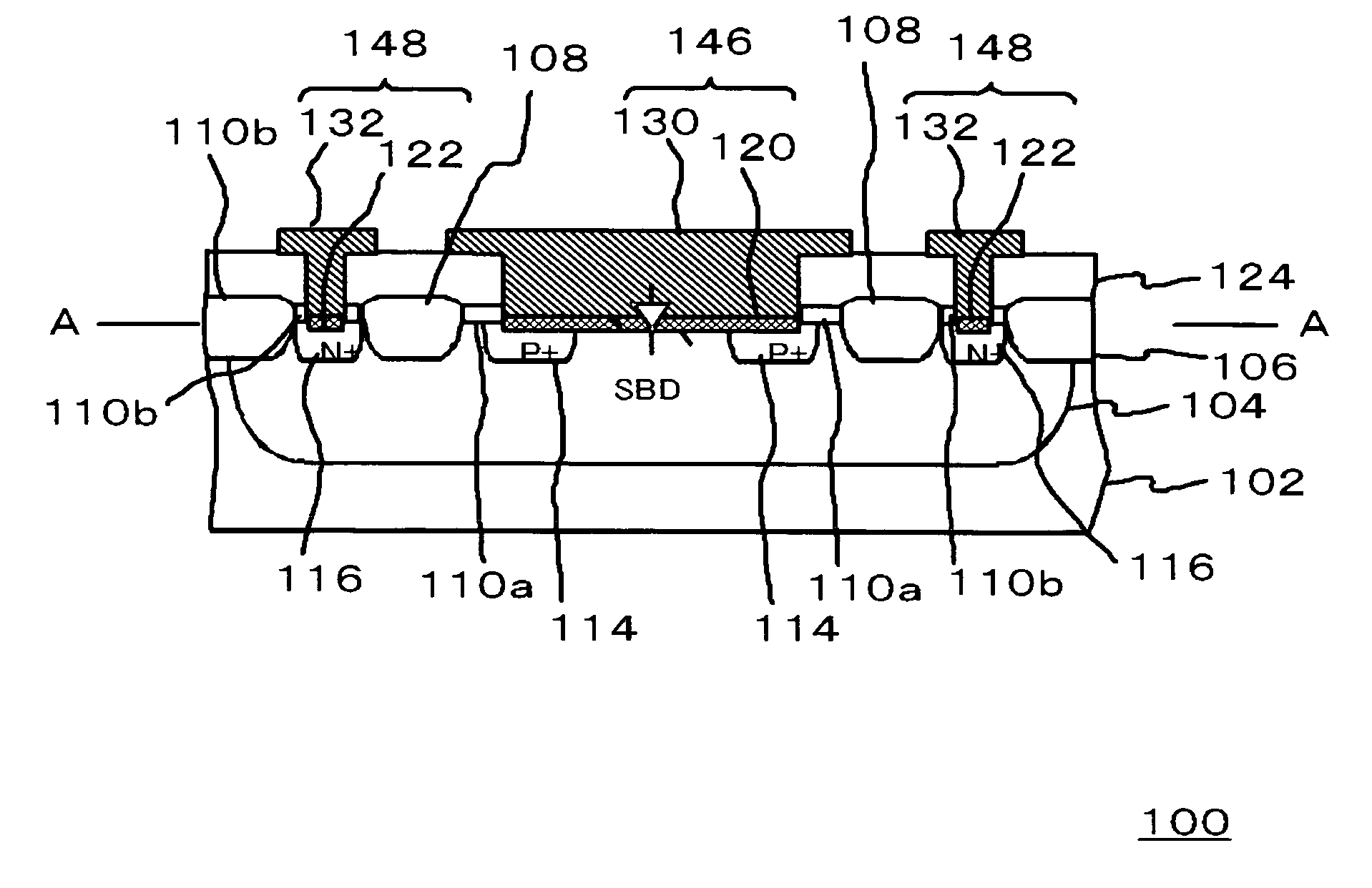

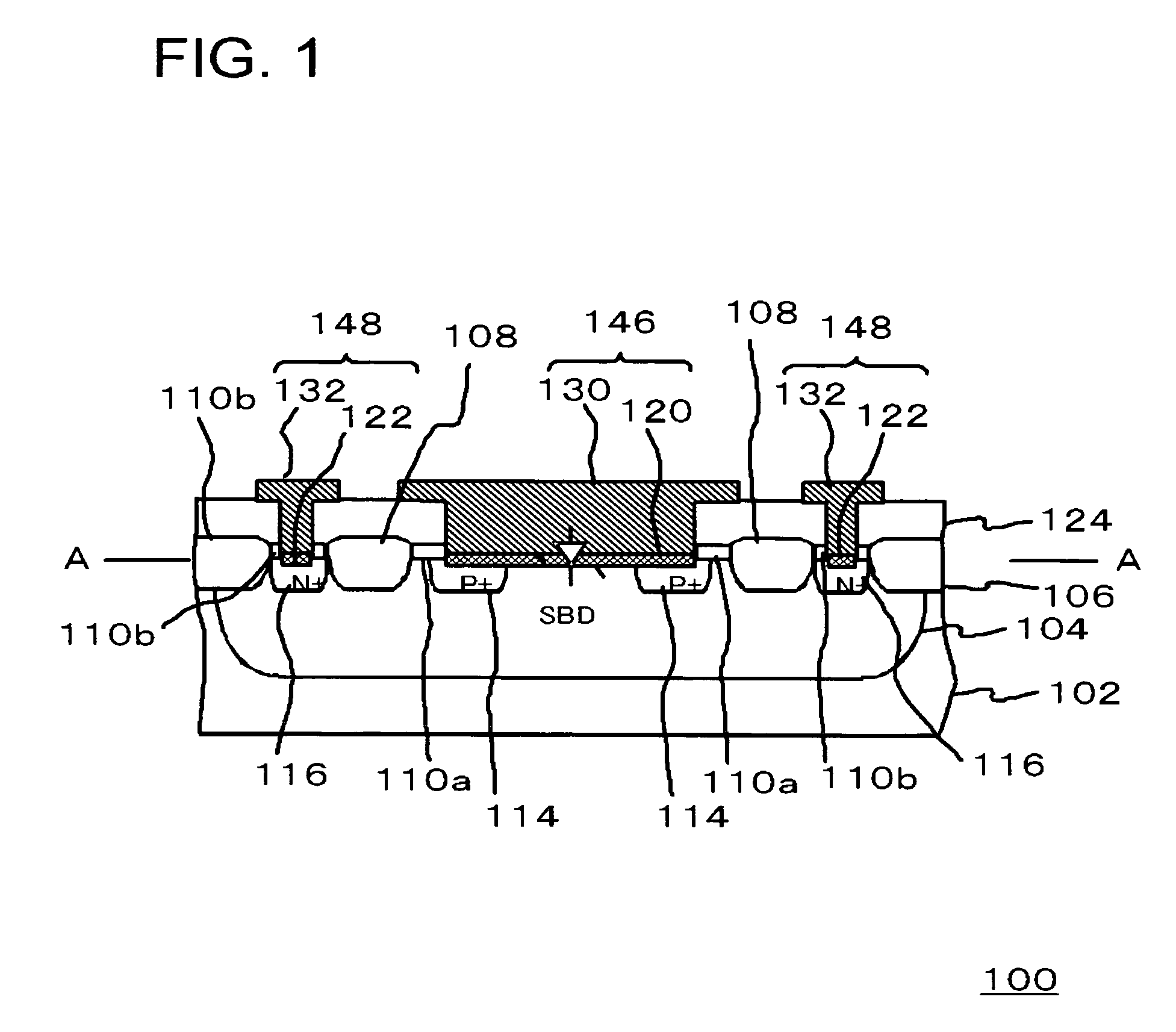

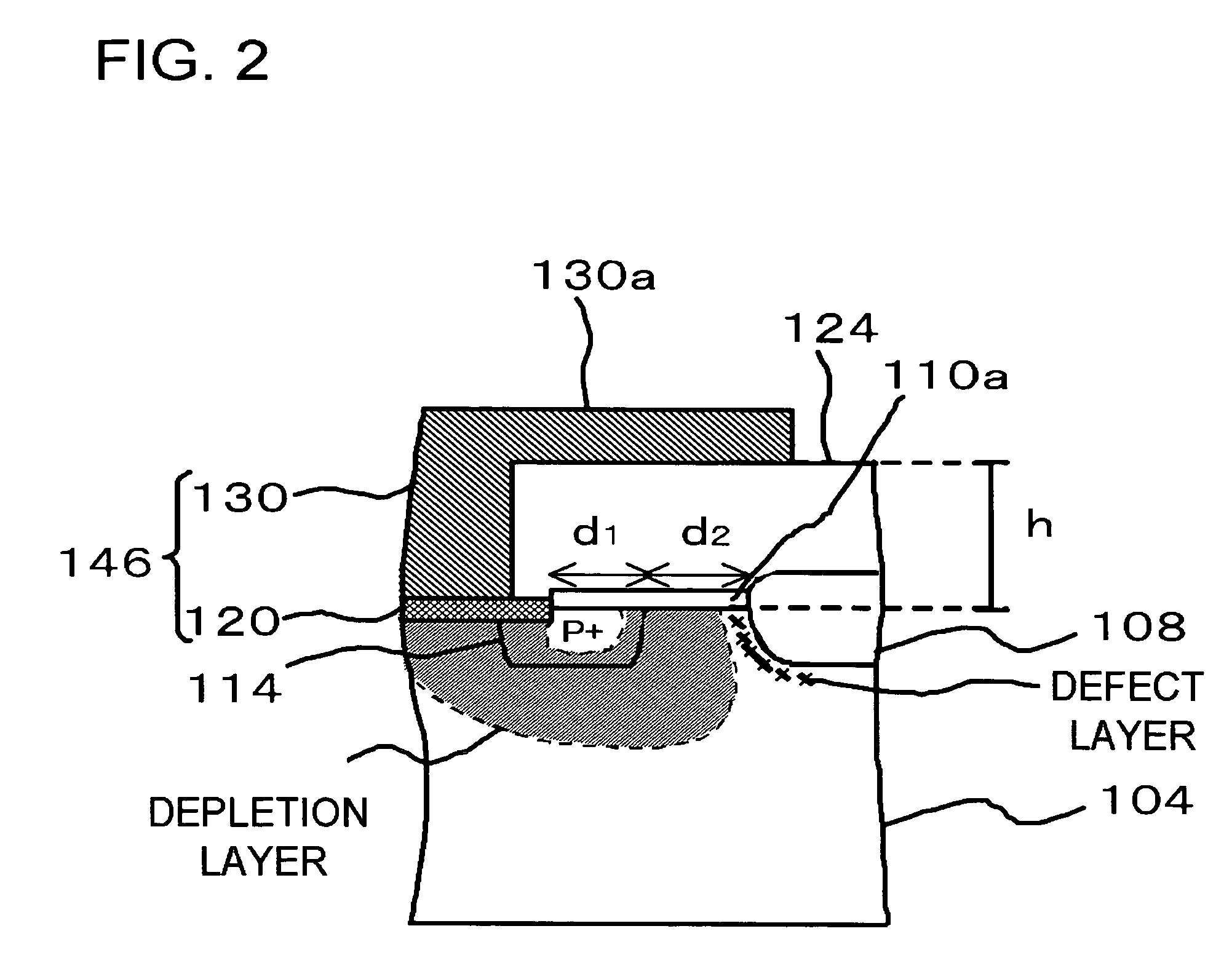

Semiconductor device and method of fabricating the same

InactiveUS20060244050A1Improve Schottky contactSuppress leakage currentSemiconductor devicesSchottky barrierSemiconductor

A semiconductor device 100 is configured as having a semiconductor substrate 102 having a first-conductivity-type semiconductor region 104 formed in its surficial portion; an anode 146 of a Schottky barrier diode formed on the first-conductivity-type semiconductor region 104; a second-conductivity-type guard ring 114 formed along the periphery of the anode 146 in the surficial portion of the first-conductivity-type semiconductor region; an isolation insulating film 108 formed along the periphery of, and being spaced from, the guard ring 114 in the surficial portion of the first-conductivity-type semiconductor region 104, so as to isolate the anode 146 from the other regions; and an anode-forming mask 110a covering the surface of the semiconductor substrate in a portion fallen between the anode 146 and the isolation insulating film 108, and being in contact with the end portion of the anode 146.

Owner:NEC ELECTRONICS CORP

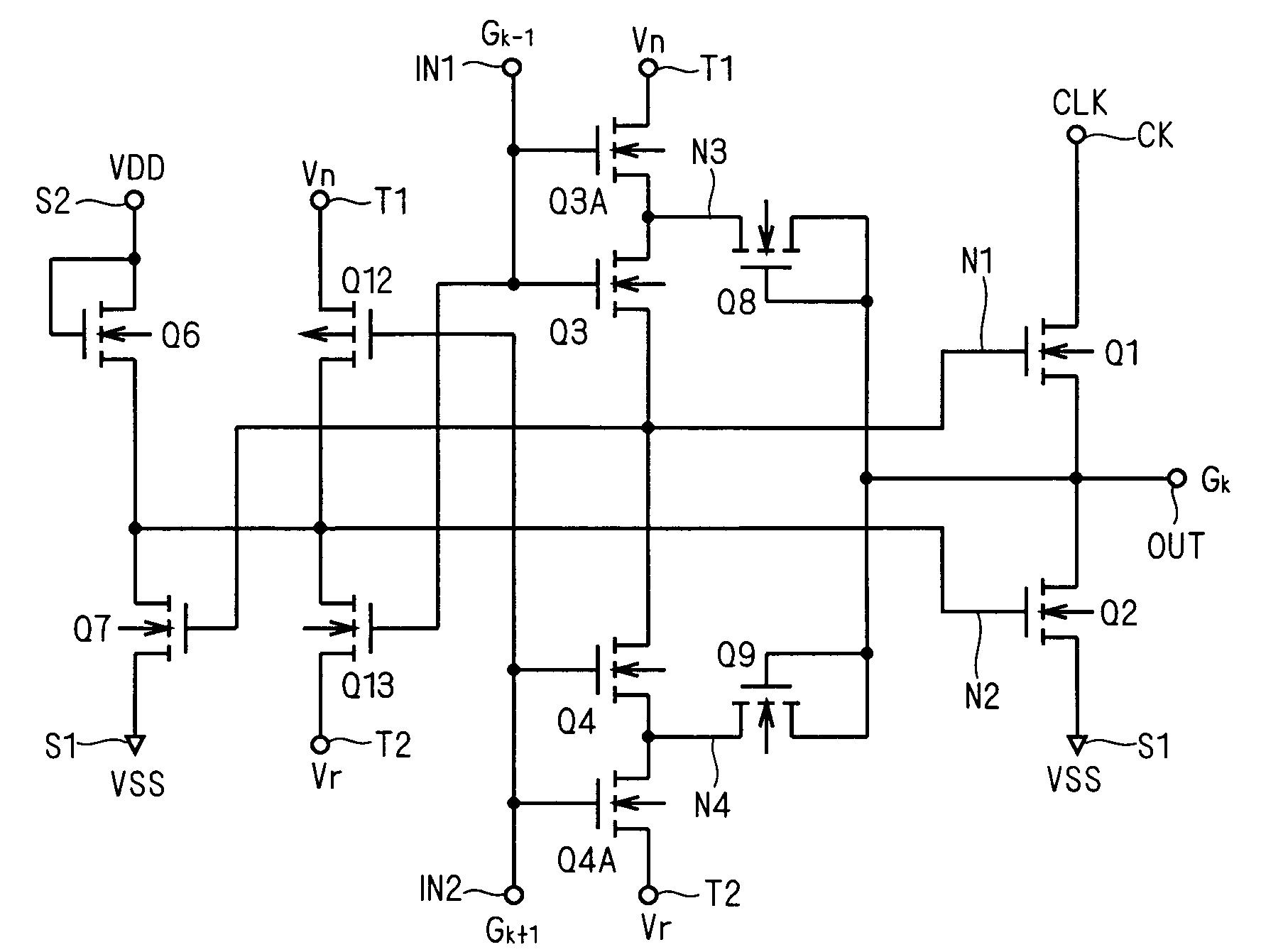

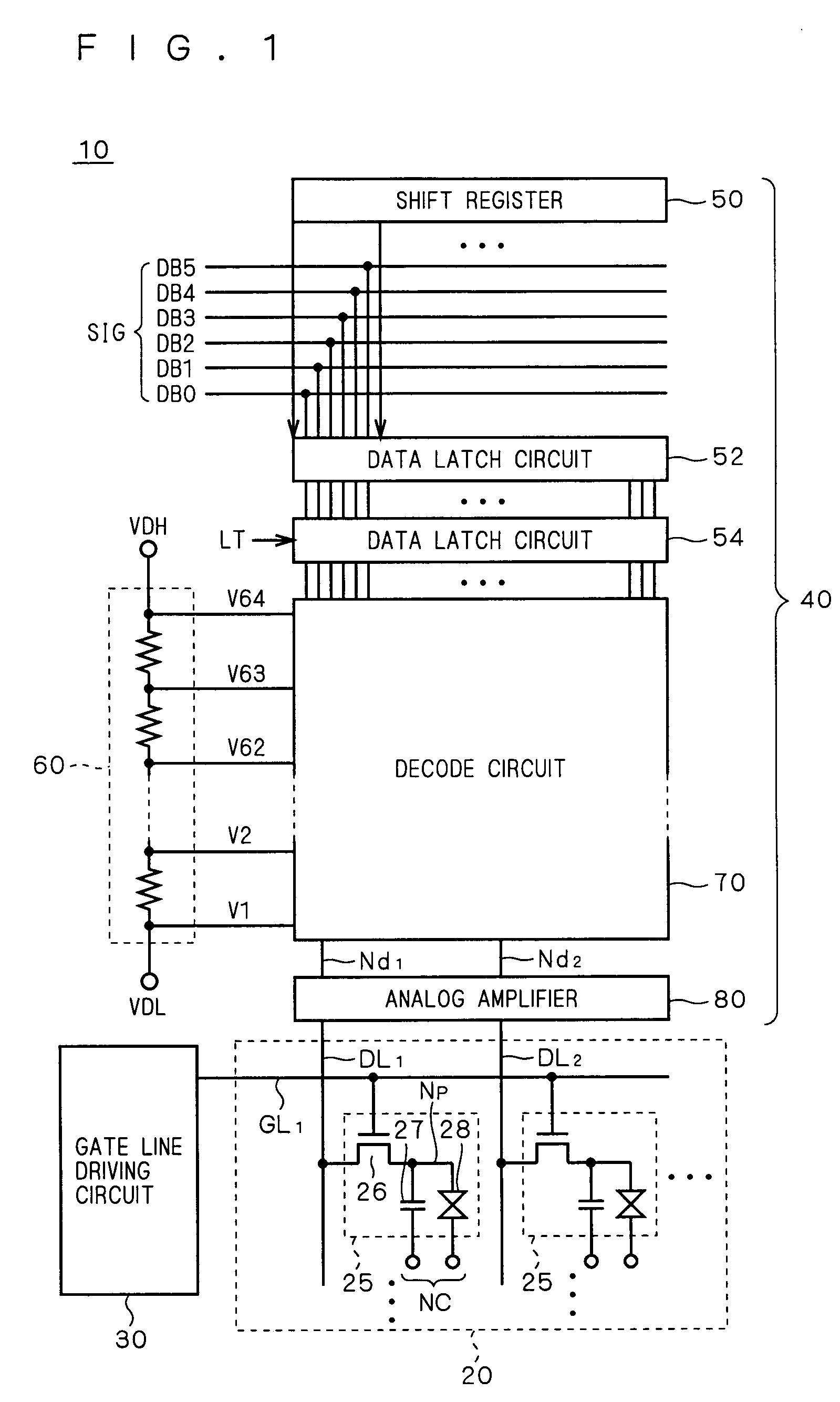

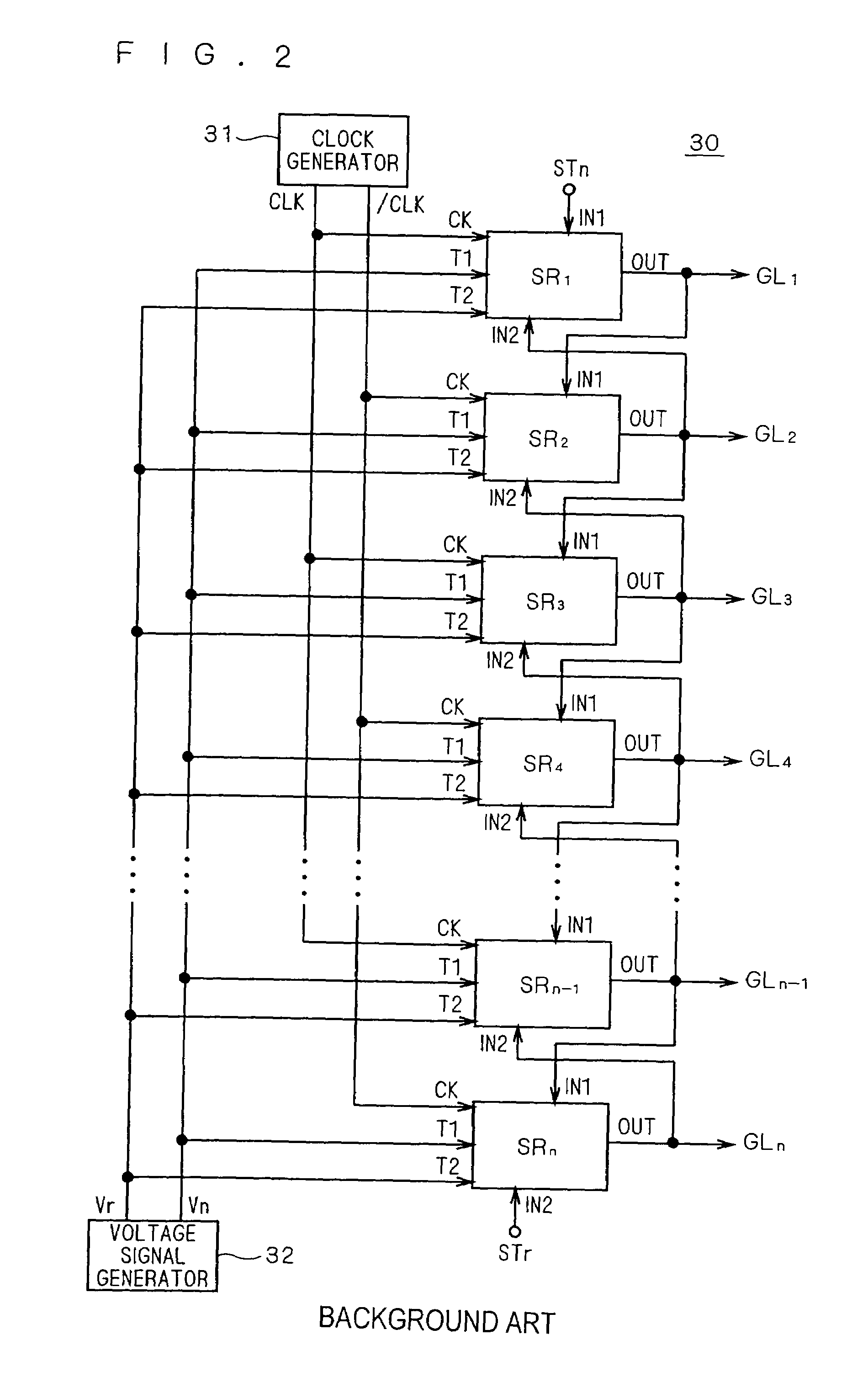

Shift register circuit and image display apparatus equipped with the same

ActiveUS7636412B2Reduce impactSuppress failureStatic indicating devicesDigital storageShift registerProcessor register

Malfunction caused by leakage current of the transistor is prevented in the shift register in which the signal can be shifted bi-directionally. The bi-directional unit shift register includes a transistor Q1 between a clock terminal CK and an output terminal OUT, a transistor Q2 for discharging the output terminal OUT, and transistors Q3, Q4 for providing first and second voltage signals Vn, Vr, which are complementary to each other, to the first node or a gate node of the transistor Q1. Furthermore, a transistor Q5, having a gate connected to a second node or a gate node of the transistor Q2, for discharging the first node is arranged.

Owner:TRIVALE TECH

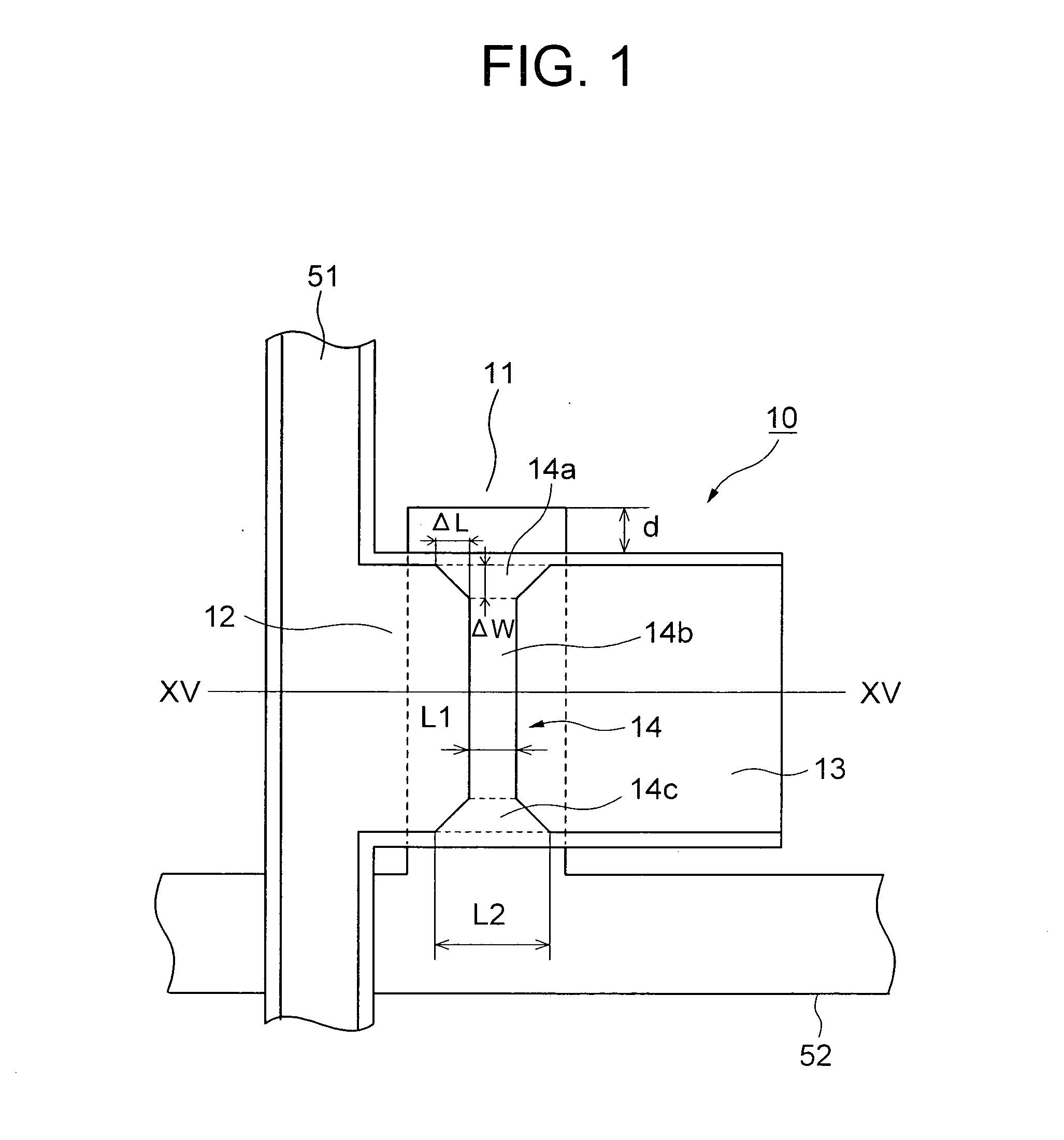

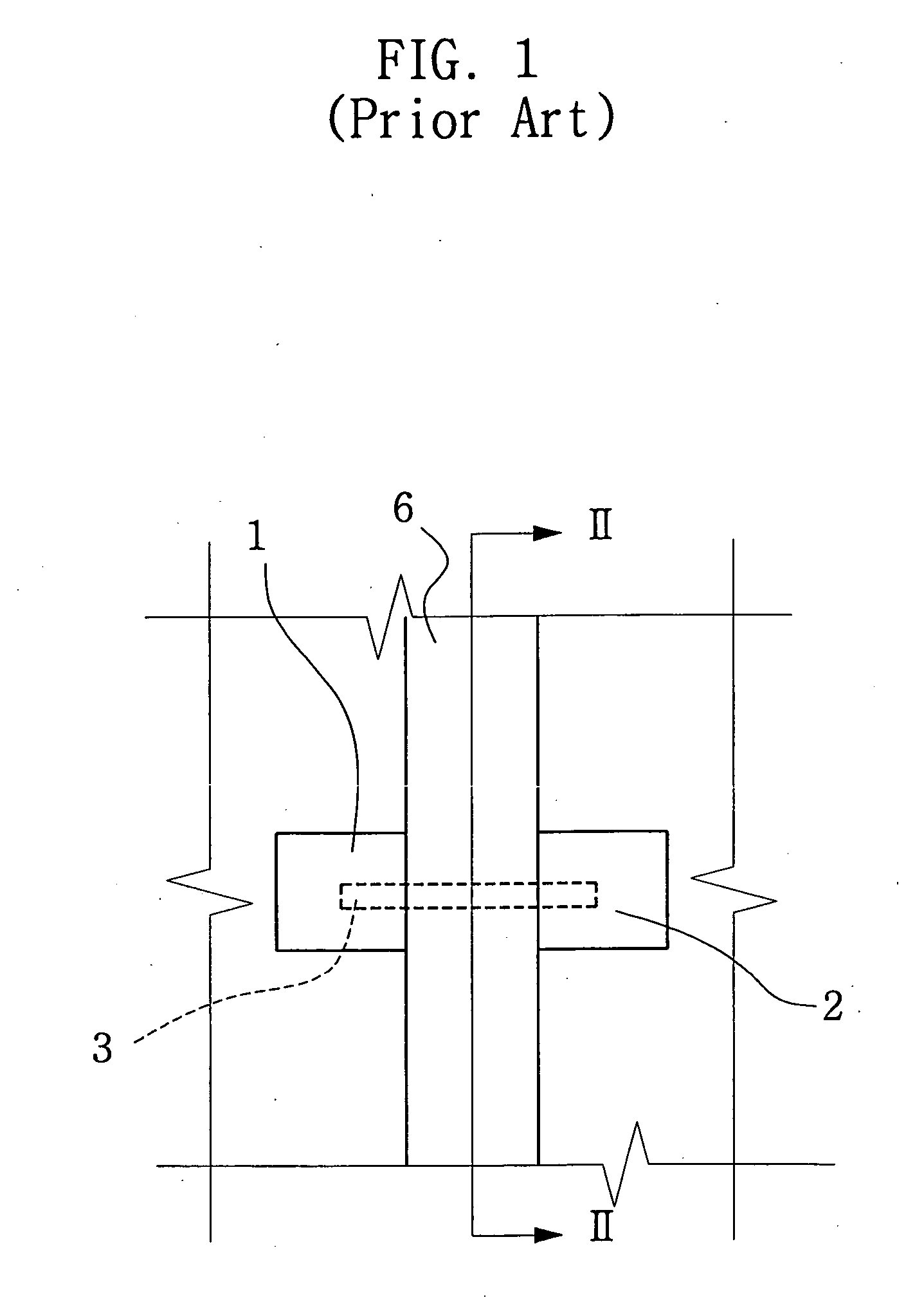

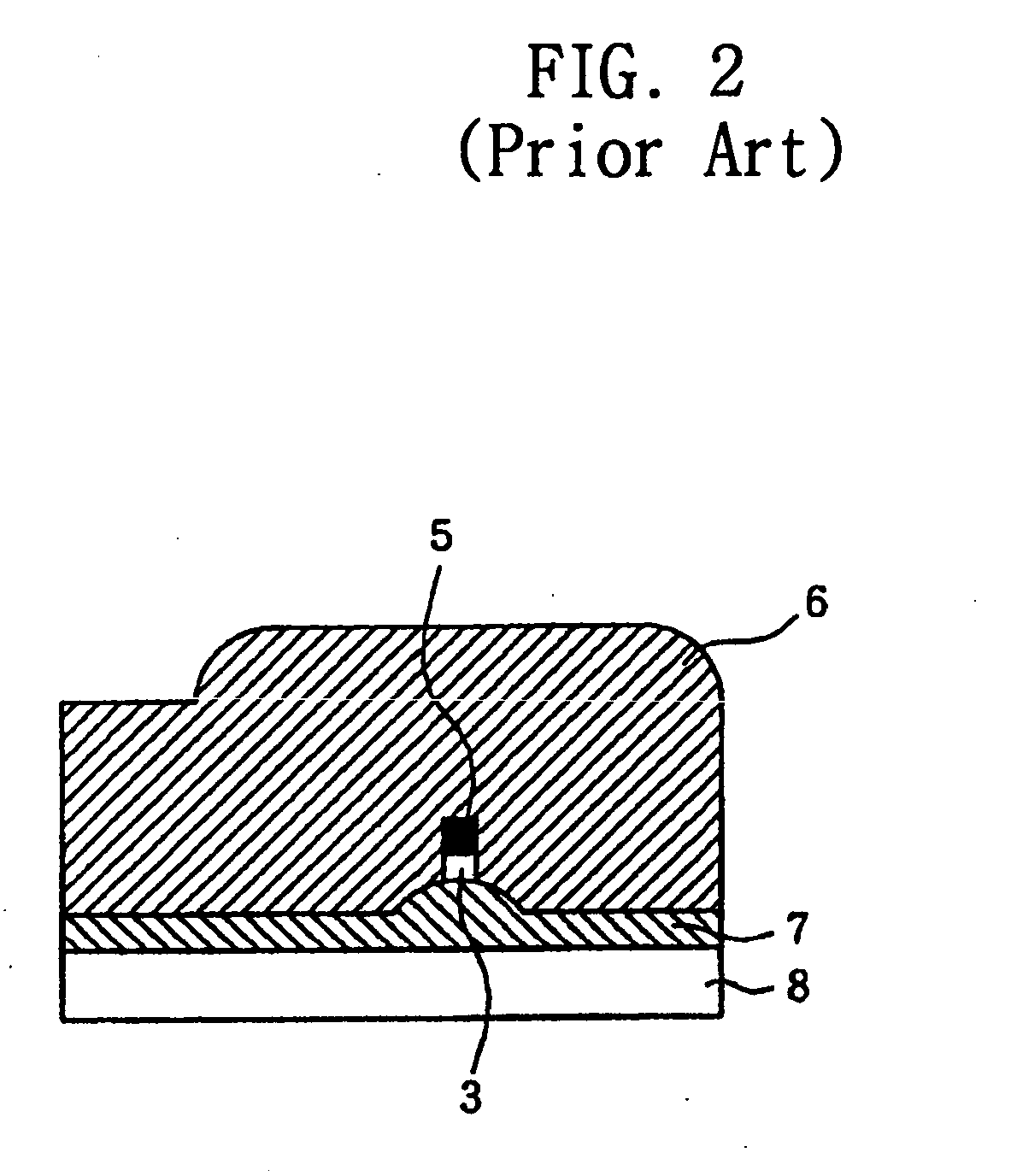

LCD device including a TFT for reducing leakage current

ActiveUS20050041169A1Reduce leakage currentSuppressing increase of TFT areaTransistorSemiconductor/solid-state device manufacturingAmorphous siliconEngineering

An amorphous-silicon TFT (thin-film-transistor) in an LCD device has a larger channel length at both the edge portions of the channel of the TFT compared to the central portion of the channel by forming chamfers at the corners of the source and drain electrodes. The larger channel length at both the edge portions reduces the leakage current caused by the turned-around light incident onto the channel.

Owner:HANNSTAR DISPLAY CORPORATION

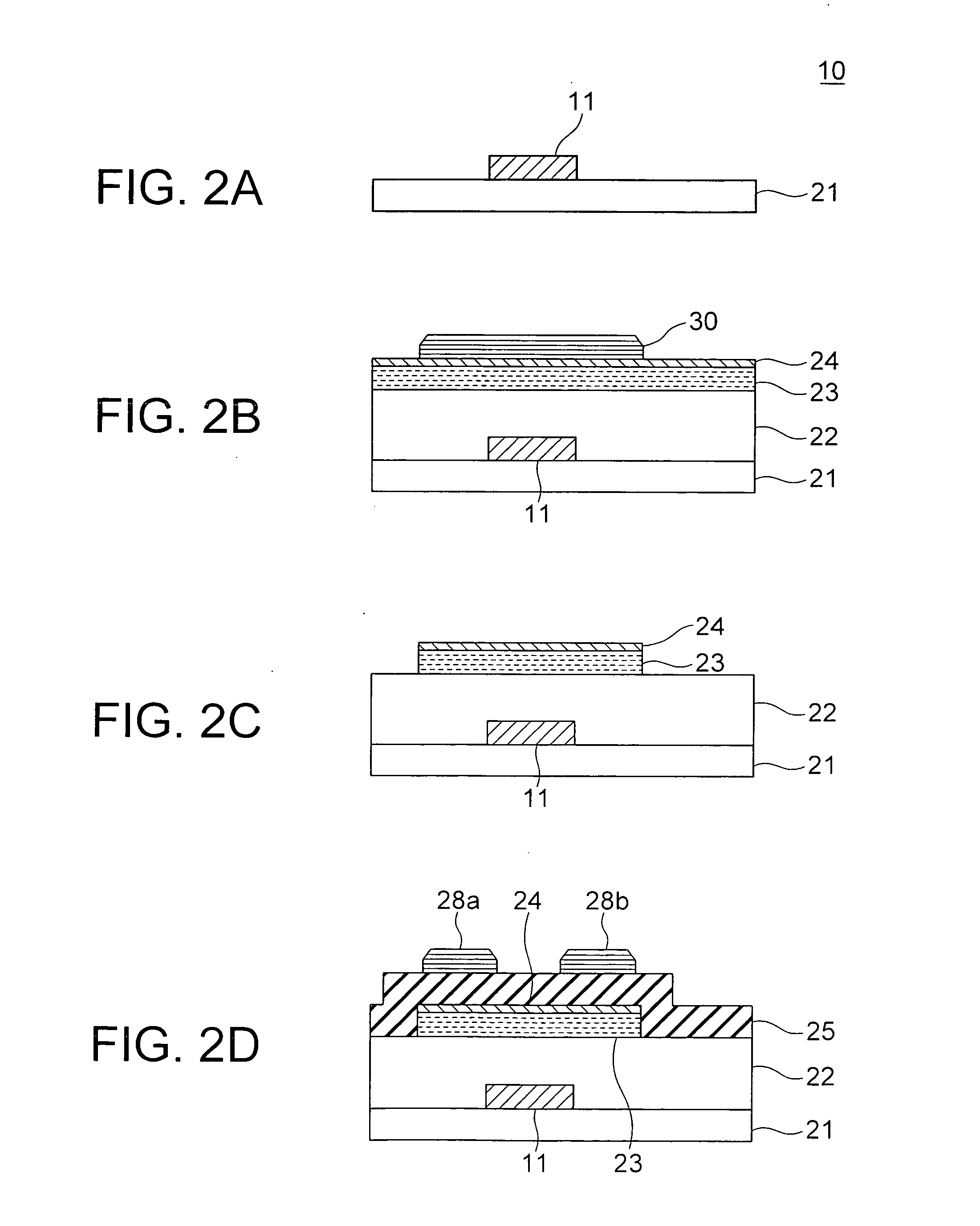

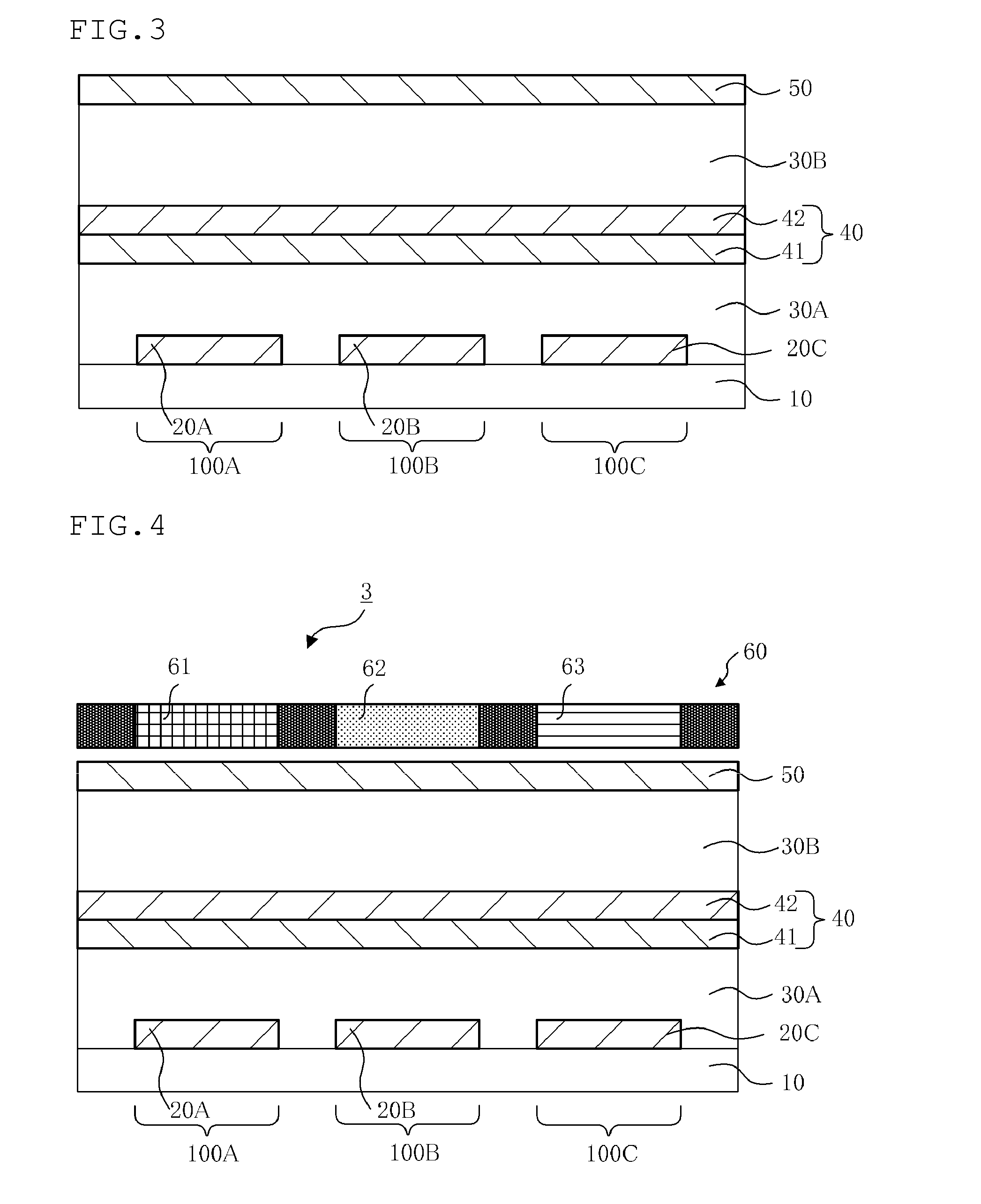

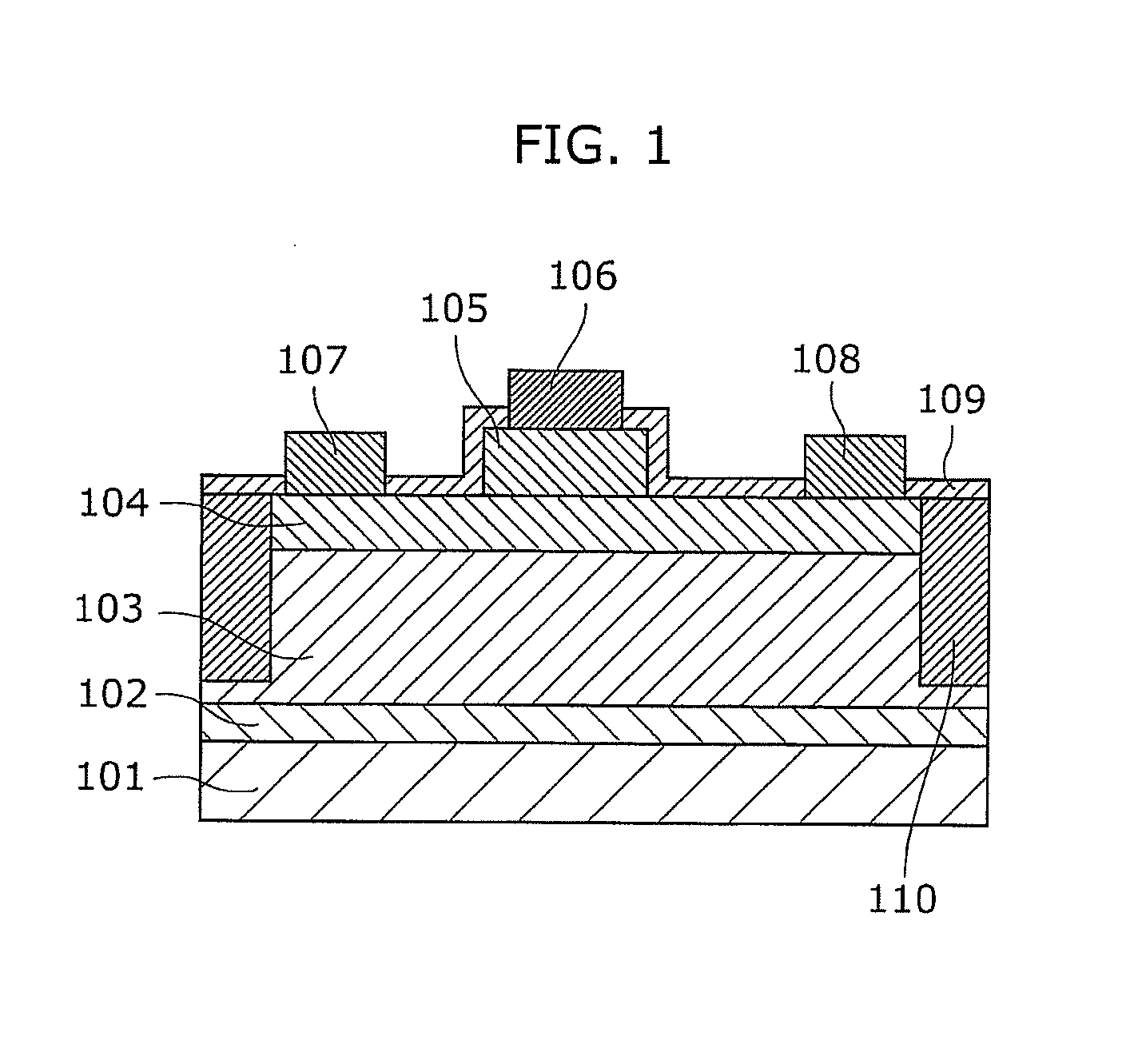

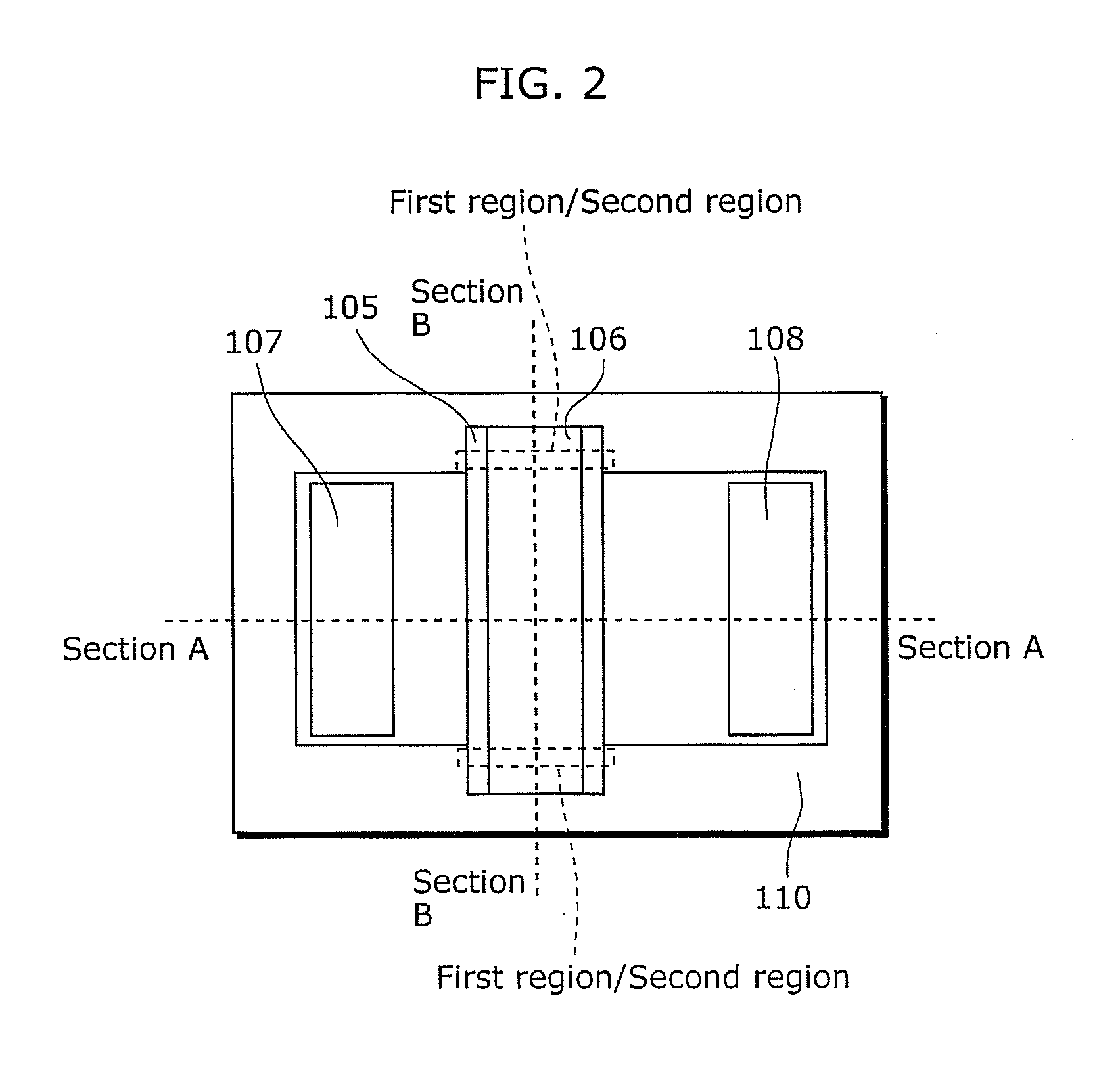

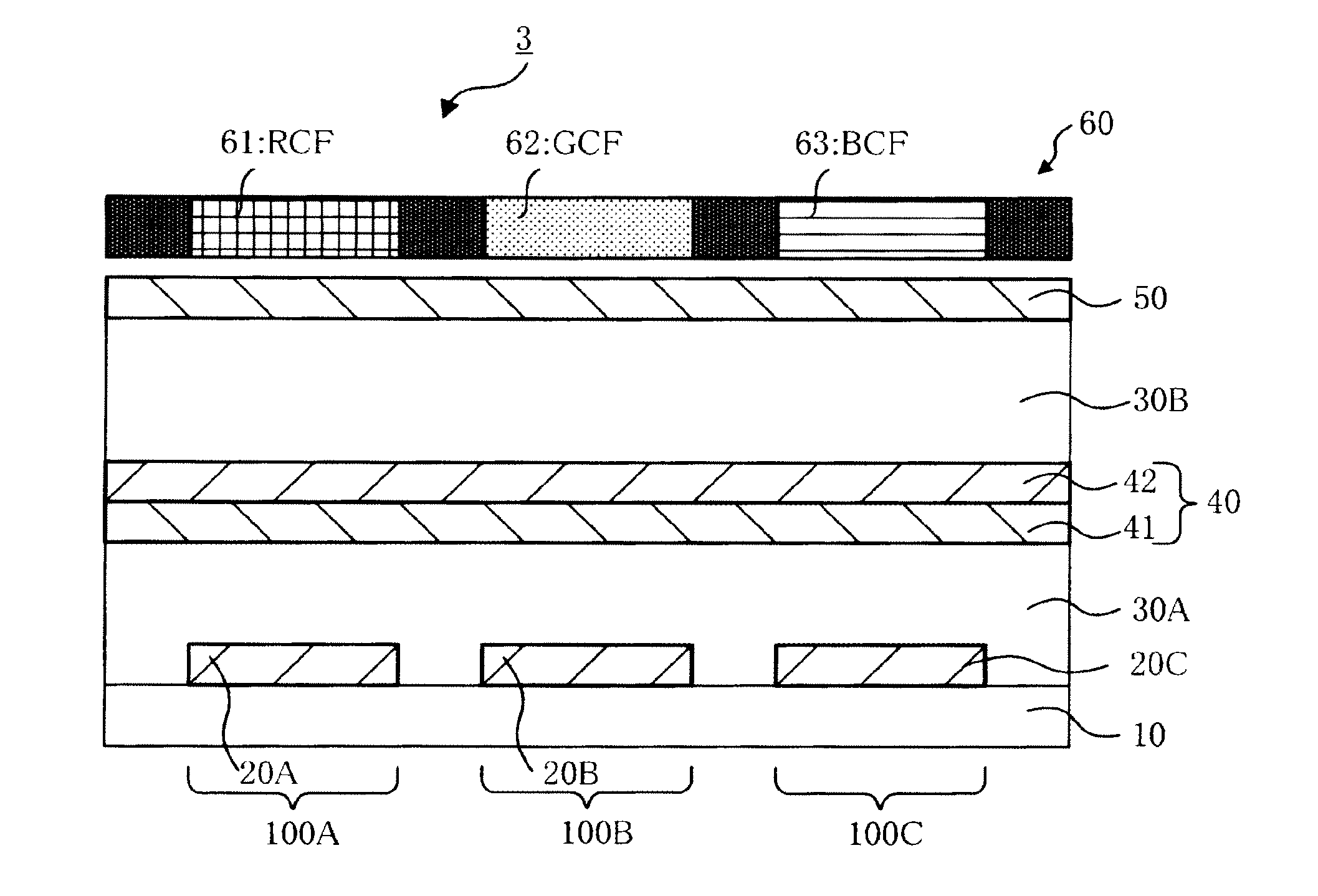

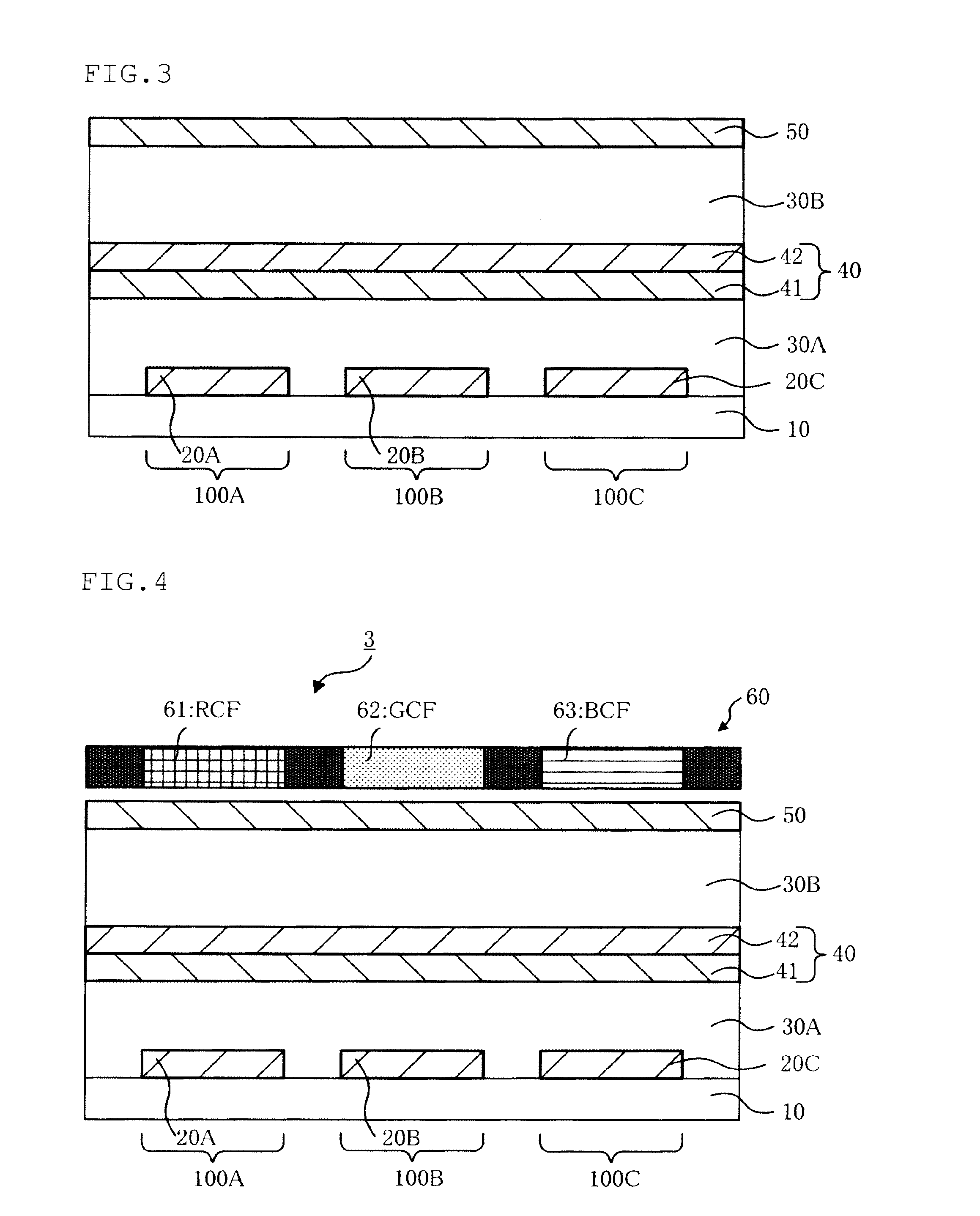

Photoelectric conversion device and method of manufacturing the same

ActiveUS20100059804A1Suppress leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingPhotoelectric conversionEngineering

A photoelectric conversion device includes a thin film transistor that is placed on a substrate, a photodiode that is connected to a drain electrode of the thin film transistor and includes an upper electrode, a lower electrode and a photoelectric conversion layer placed between the upper and lower electrodes, a first interlayer insulating film that covers at least the upper electrode, a second interlayer insulating film that is placed in an upper layer of the first interlayer insulating film and covers the thin film transistor and the photodiode, and a line that is connected to the upper electrode through a contact hole disposed in the first interlayer insulating film and the second interlayer insulating film.

Owner:TRIVALE TECH

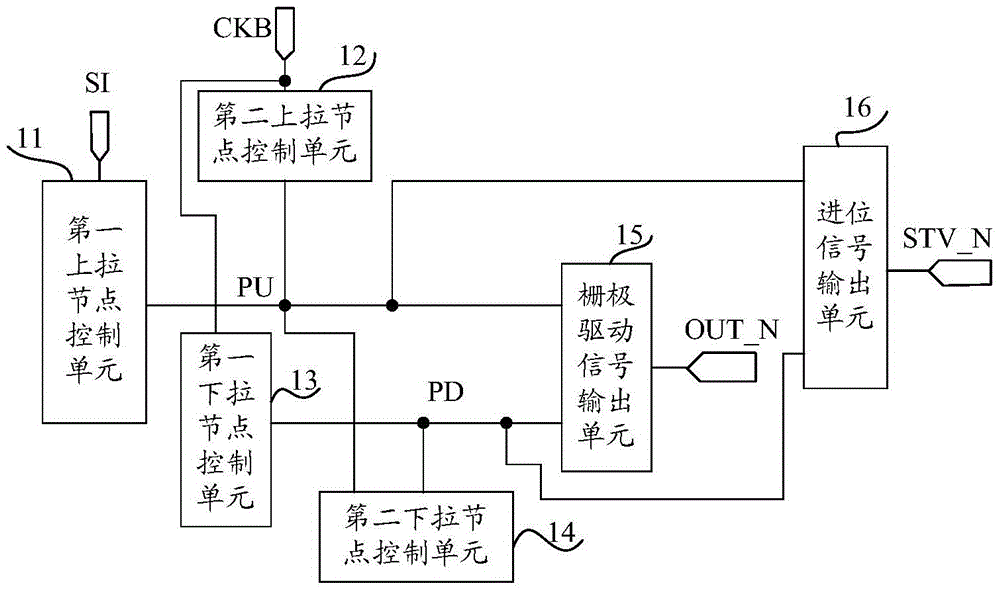

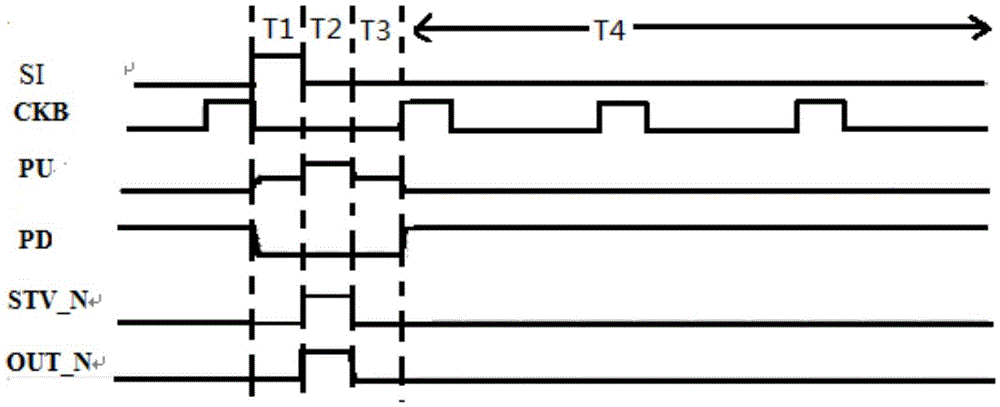

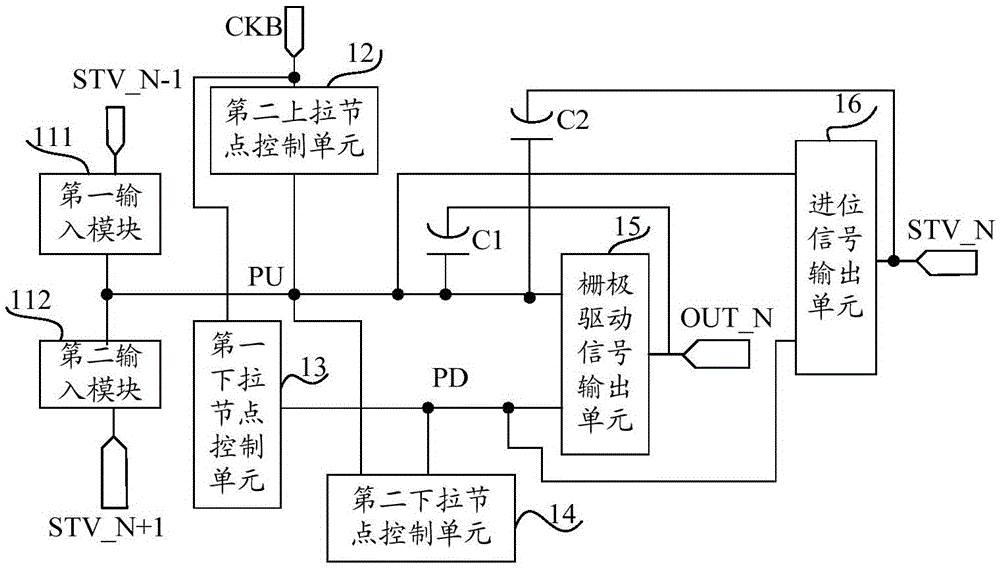

Shifting register unit, drive method thereof, grid drive circuit and display device

ActiveCN105609135ASuppress leakage currentAvoid the problem of large drift of threshold voltageStatic indicating devicesDigital storageShift registerDisplay device

The invention provides a shifting register unit, a drive method thereof, a grid drive circuit and a display device. The shifting register unit comprises a first pull-up node control unit, a second pull-up node control unit, a first pull-down node control unit, a second pull-down node control unit, a grid drive signal output unit and a carry signal output unit. The second pull-up node control unit is controlled by a first clock signal to control the potential of a pull-up node to be first potential at the pull-down keeping stage. The first pull-down node control unit is controlled by the first clock signal to control the potential of a pull-down node to be second potential at the pull-down keeping stage. The grid drive signal output unit is controlled by the pull-up node and the pull-down node to control a grid drive signal output end to output a grid drive signal. The carry signal output unit is controlled by the pull-up node and the pull-down node to control a carry signal output end to output a carry signal. The problems that under long-time or high-temperature reliability work conditions, the threshold voltage of a thin film transistor is greatly drifted and the response speed is low are solved.

Owner:BOE TECH GRP CO LTD

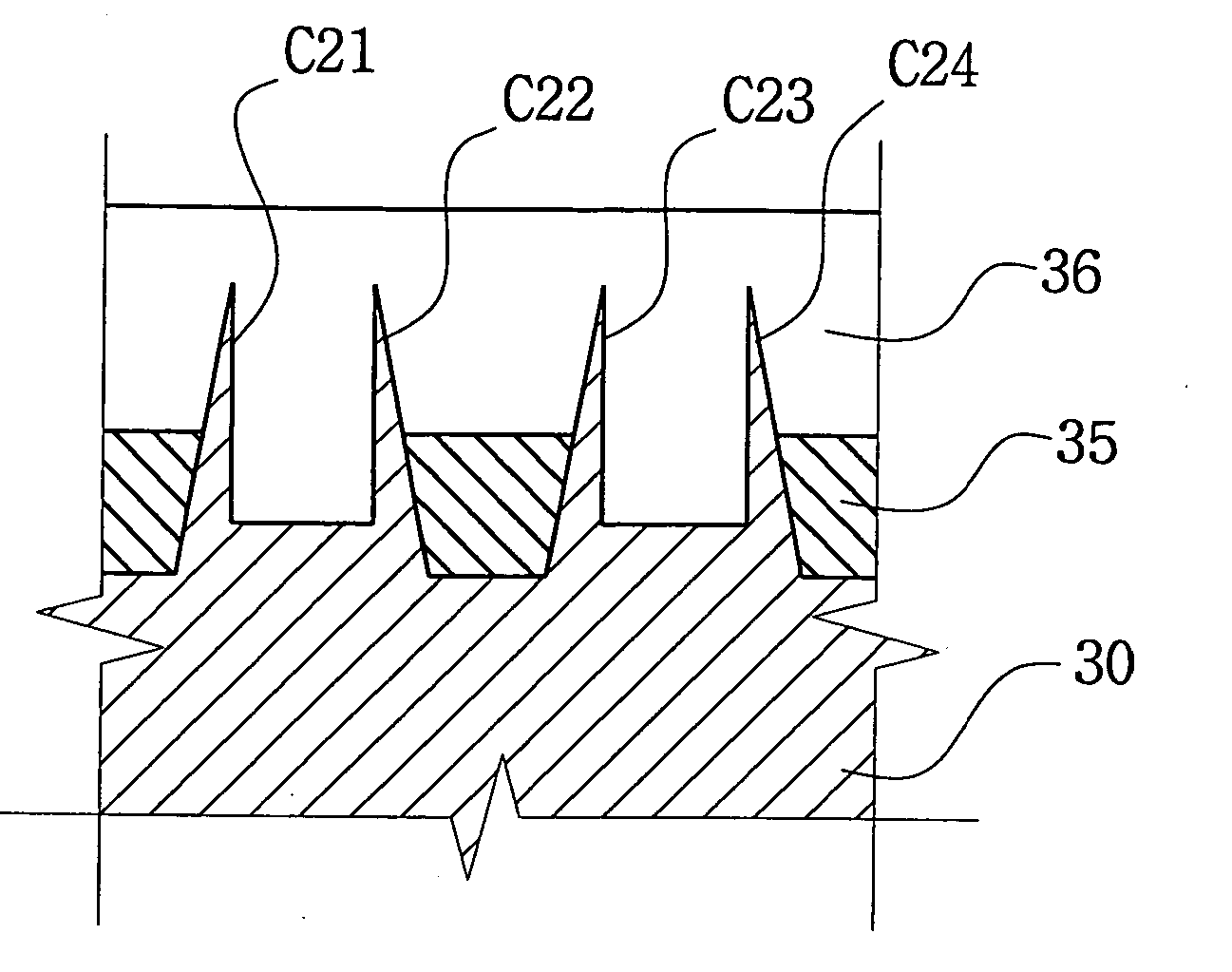

Field effect transistor device with channel fin structure and method of fabricating the same

InactiveUS20050179030A1Suppress leakage currentTransistorSemiconductor/solid-state device manufacturingField-effect transistorSemiconductor

A finFET device includes a semiconductor substrate having specific regions surrounded with a trench. The trench is filled with an insulating layer, and recess holes are formed within the specific regions such that channel fins are formed by raised portions of the semiconductor substrate on both sides of the recess holes. Gate lines are formed to overlie and extend across the channel fins. Source / drain regions are formed at both ends of the channel fins and connected by the channel fins. Other embodiments are described and claimed.

Owner:SAMSUNG ELECTRONICS CO LTD

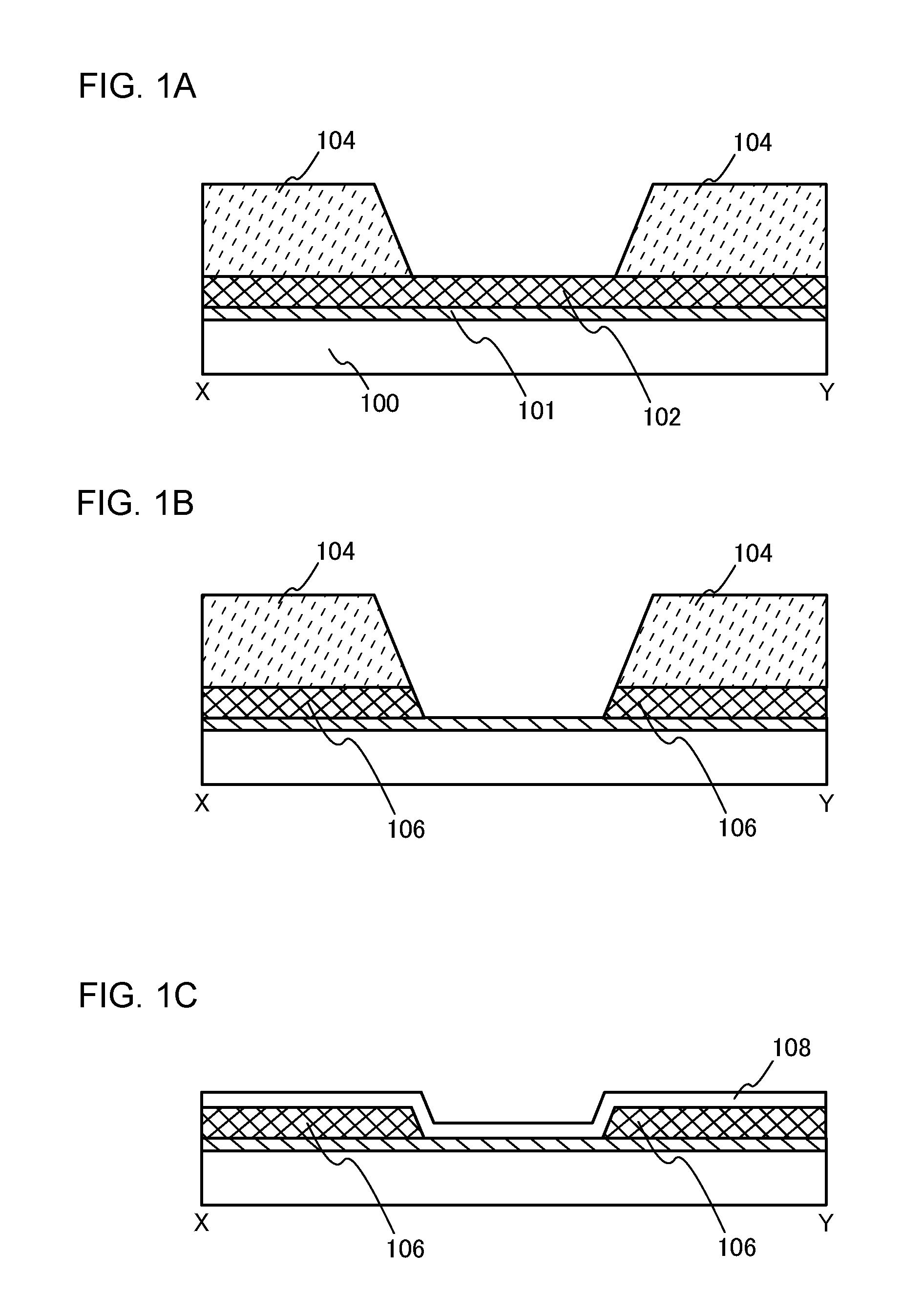

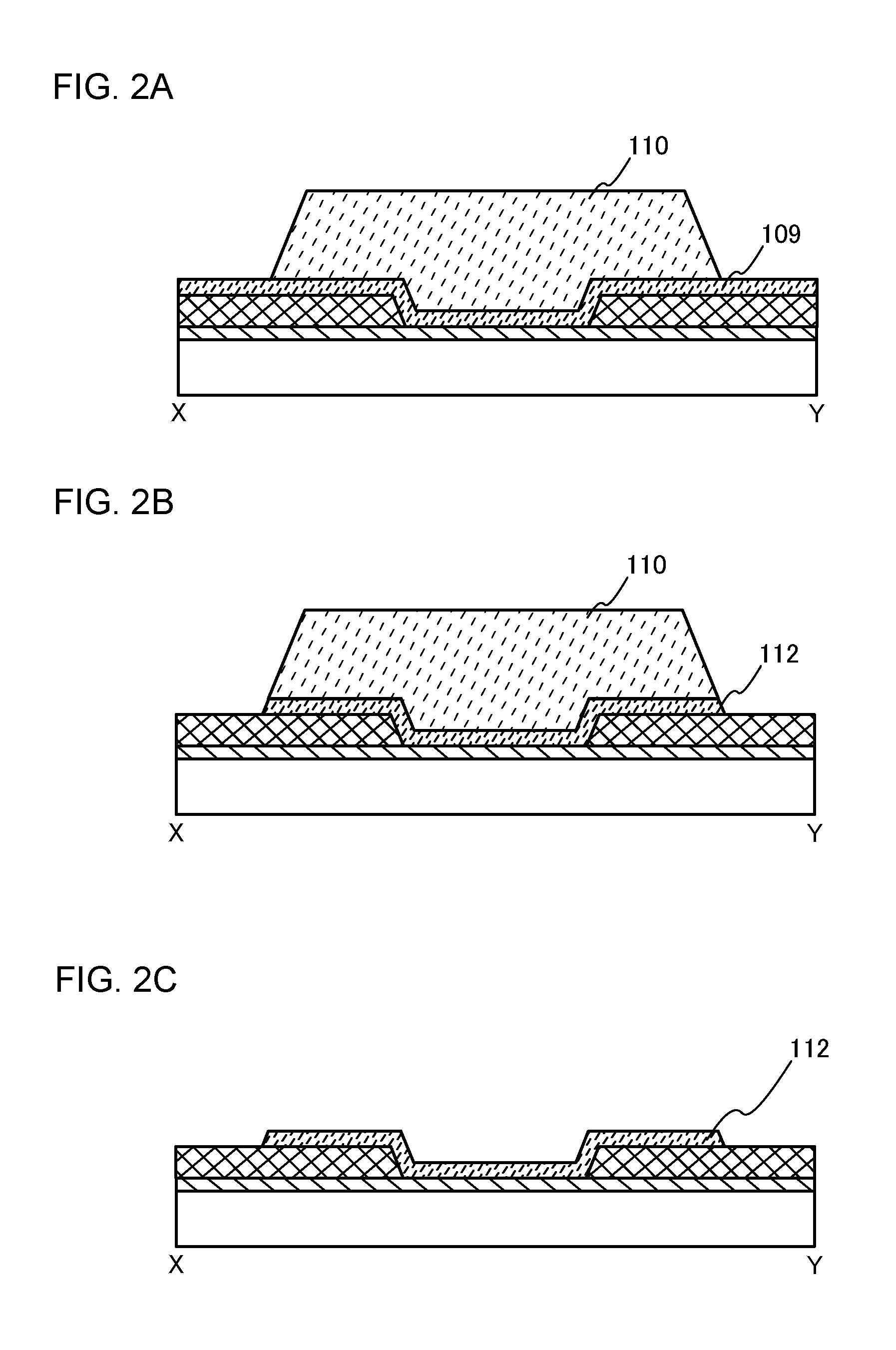

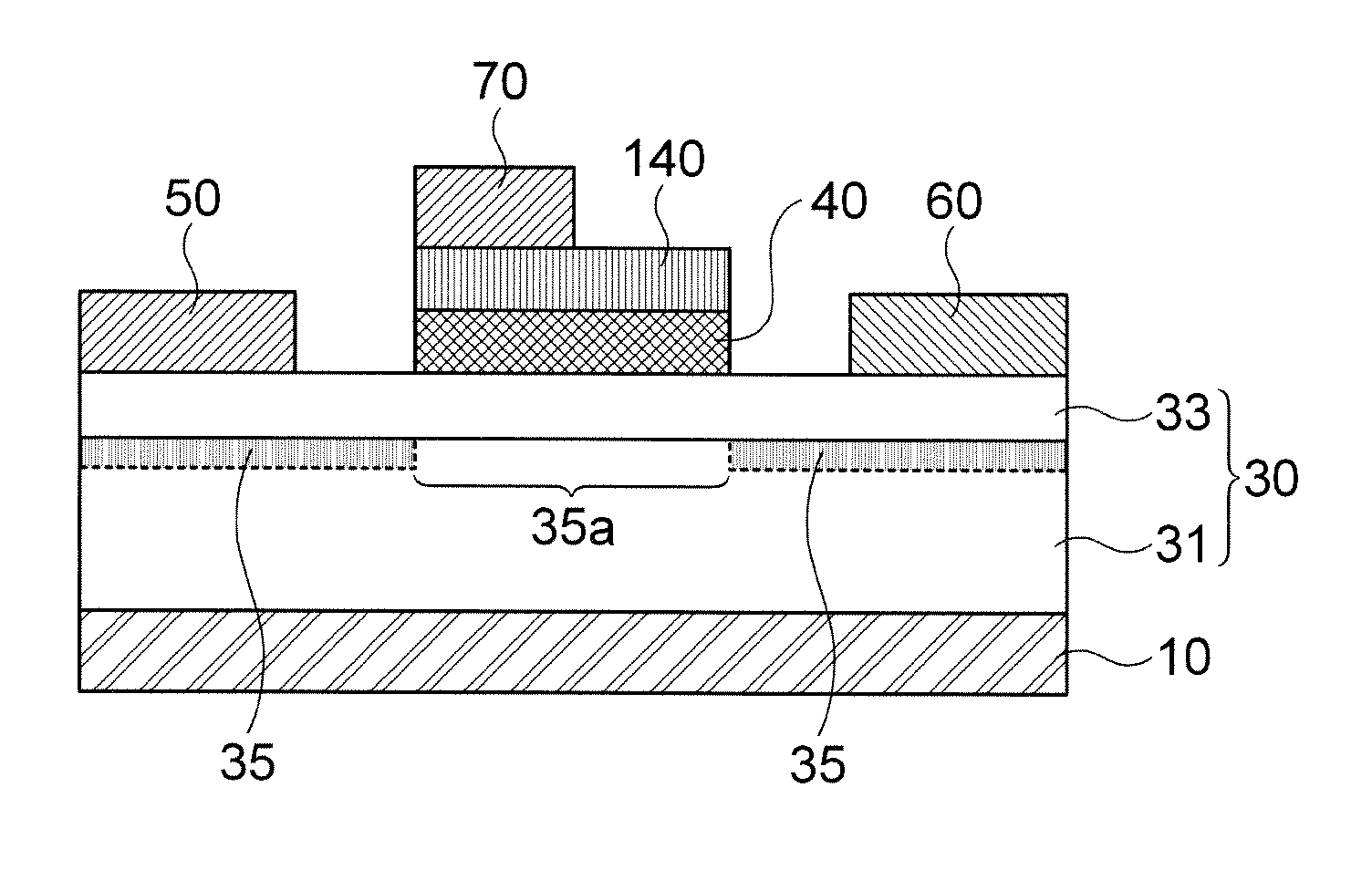

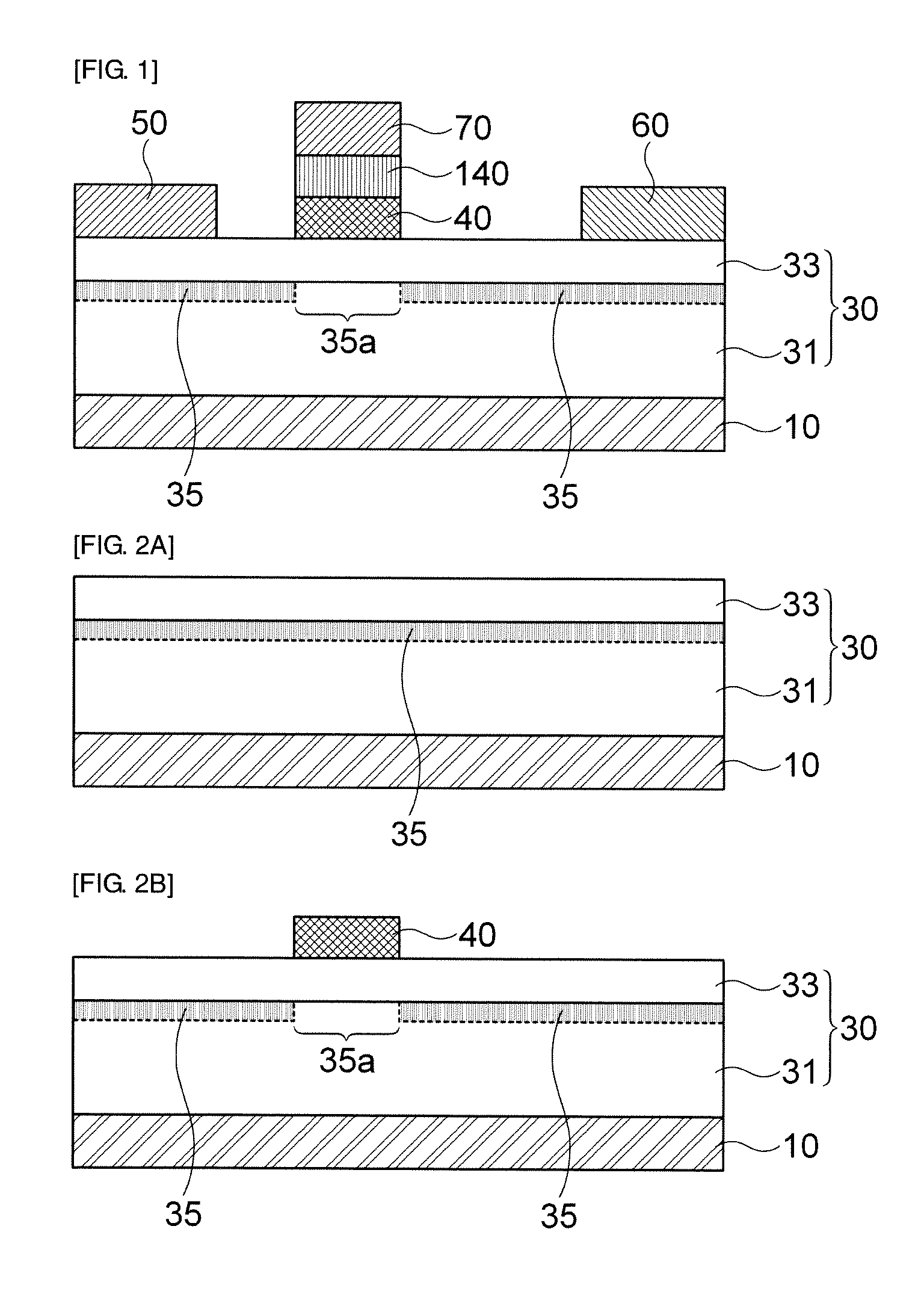

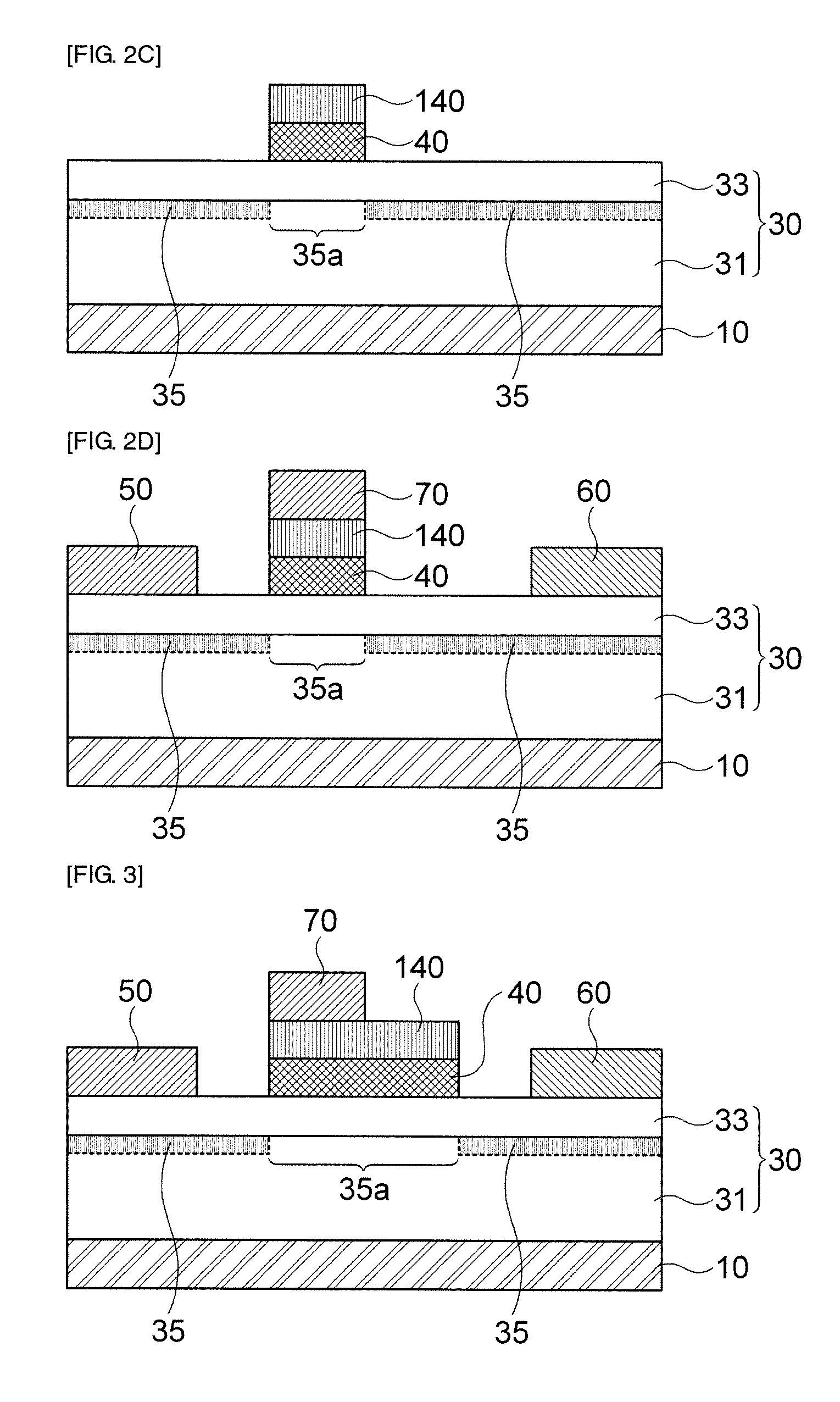

Method for manufacturing semiconductor device

InactiveUS20120178224A1Reduce resistanceSuppress leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesDesorptionOxygen deficiency

To provide a semiconductor device in which desorption of oxygen from side surfaces of an oxide semiconductor layer is prevented, defects (oxygen deficiency) in the oxide semiconductor layer are sufficiently reduced, and leakage current between a source and a drain is suppressed. The semiconductor device is manufactured through the following steps: after first heat treatment is performed on an oxide semiconductor film, the oxide semiconductor film is processed to form an oxide semiconductor layer; immediately after that, side walls of the oxide semiconductor layer are covered with an insulating oxide; and in second heat treatment, the side surfaces of the oxide semiconductor layer are prevented from being exposed to a vacuum and defects (oxygen deficiency) in the oxide semiconductor layer are reduced. Side walls of the oxide semiconductor layer are covered with sidewall insulating layers. The semiconductor device has a TGBC structure.

Owner:SEMICON ENERGY LAB CO LTD

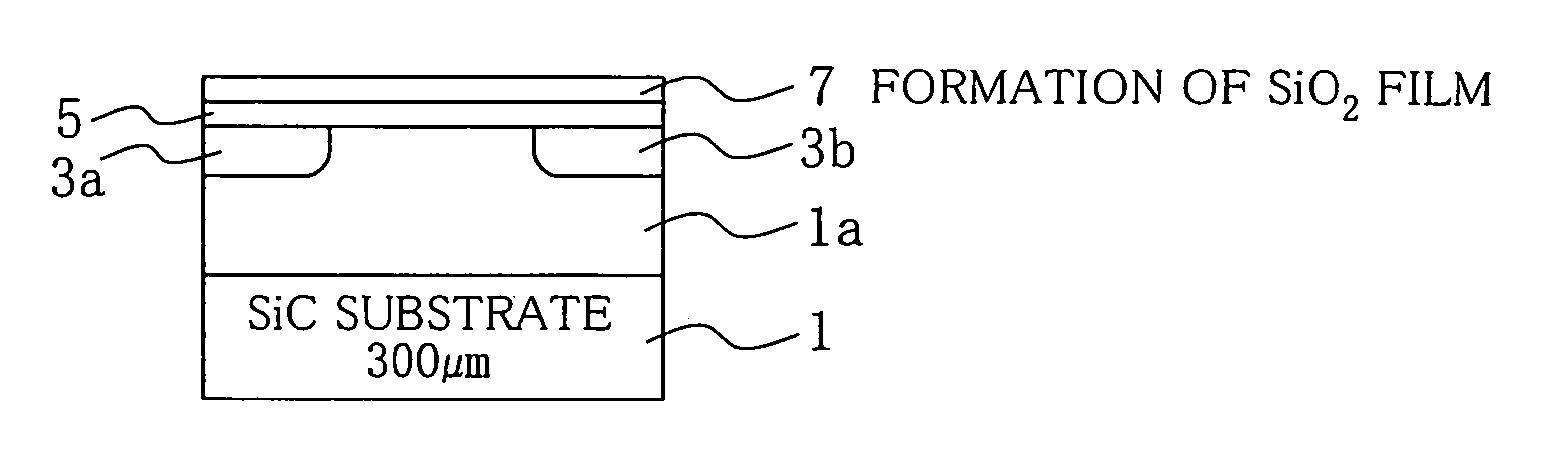

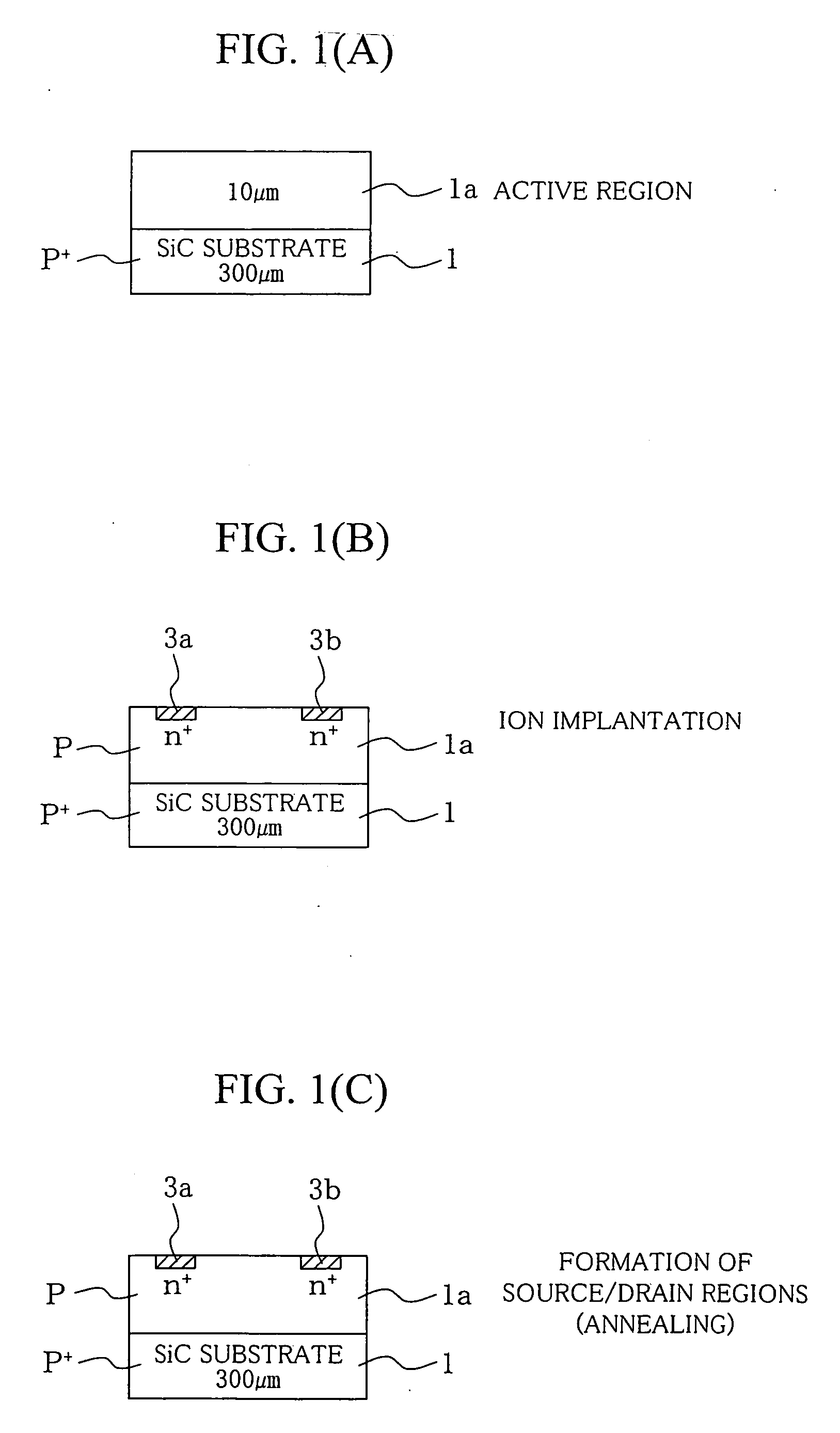

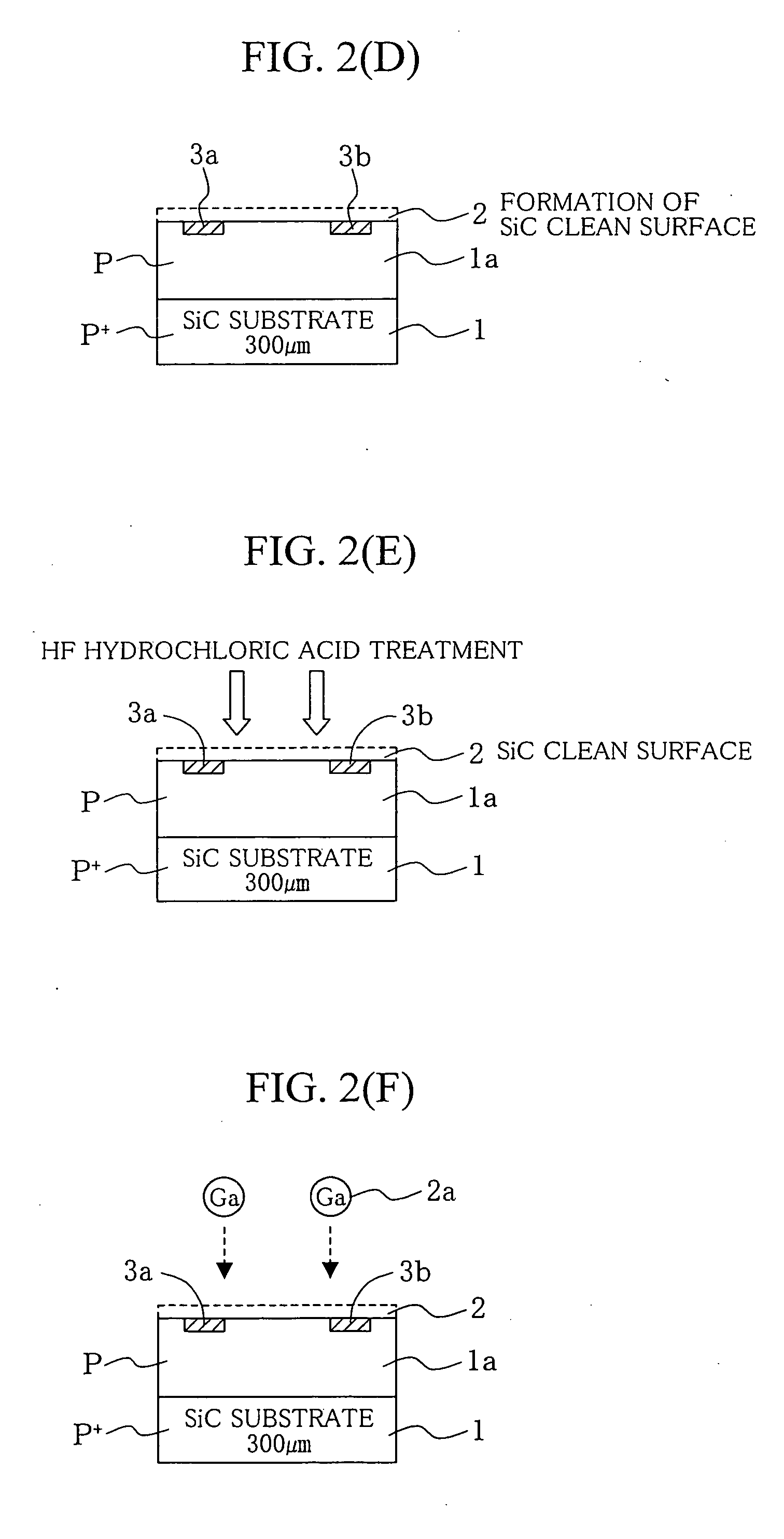

Field effect transistor and method for manufacturing same

InactiveUS20060194379A1Leakage currentFavorable condition of interfaceTransistorSemiconductor/solid-state device manufacturingField-effect transistorSic substrate

A field effect transistor comprises a SiC substrate 1, a source 3a and a drain 3b formed on the surface of the SiC substrate 1, an insulating structure comprising an AlN layer 5 formed in contact with the SiC surface and having a thickness of one molecule-layer or greater, and a SiO2 layer formed thereon, and a gate electrode 15 formed on the insulation structure. Leakage current can be controlled while the state of interface with SiC is maintained in a good condition.

Owner:JAPAN SCI & TECH CORP

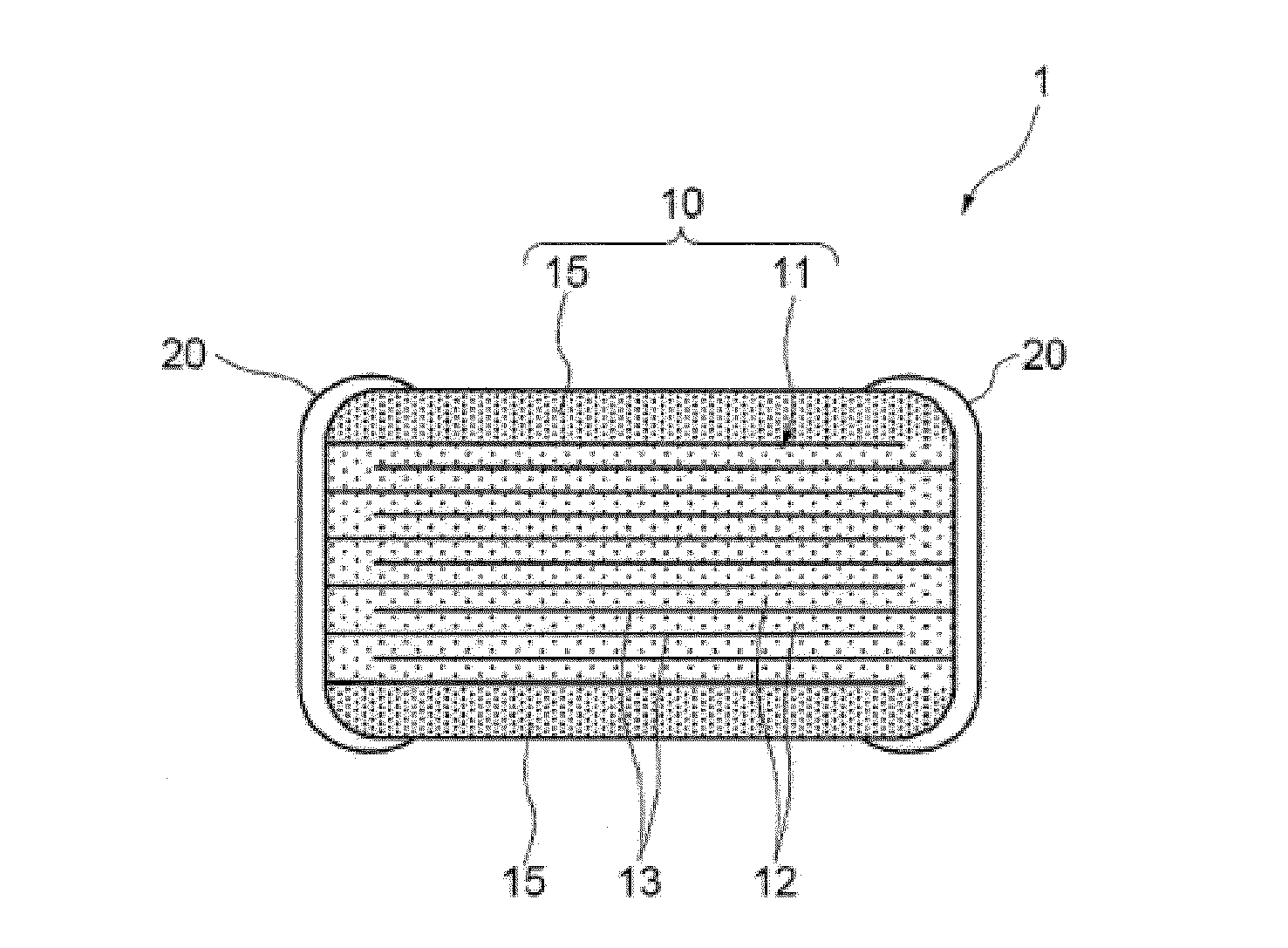

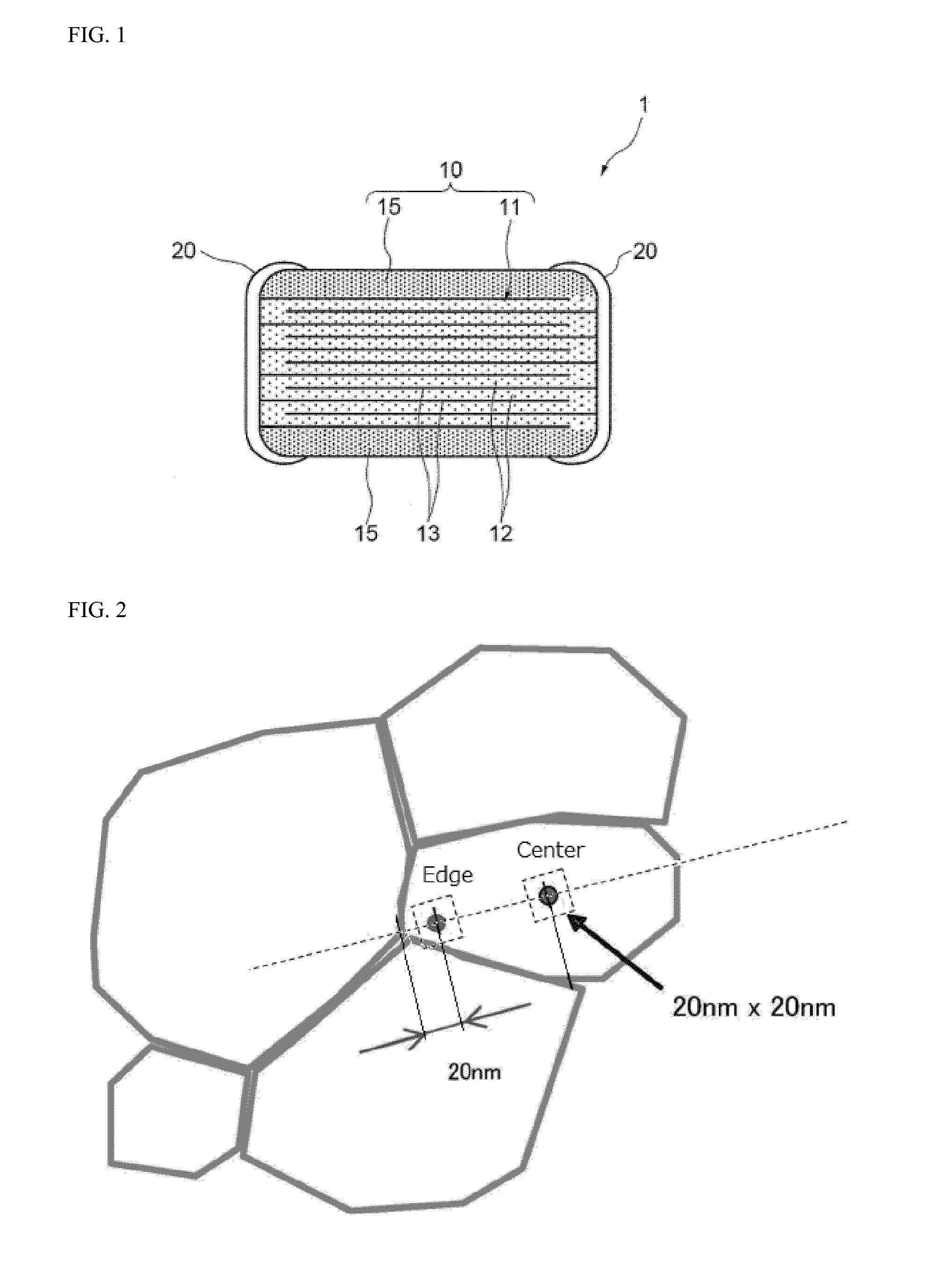

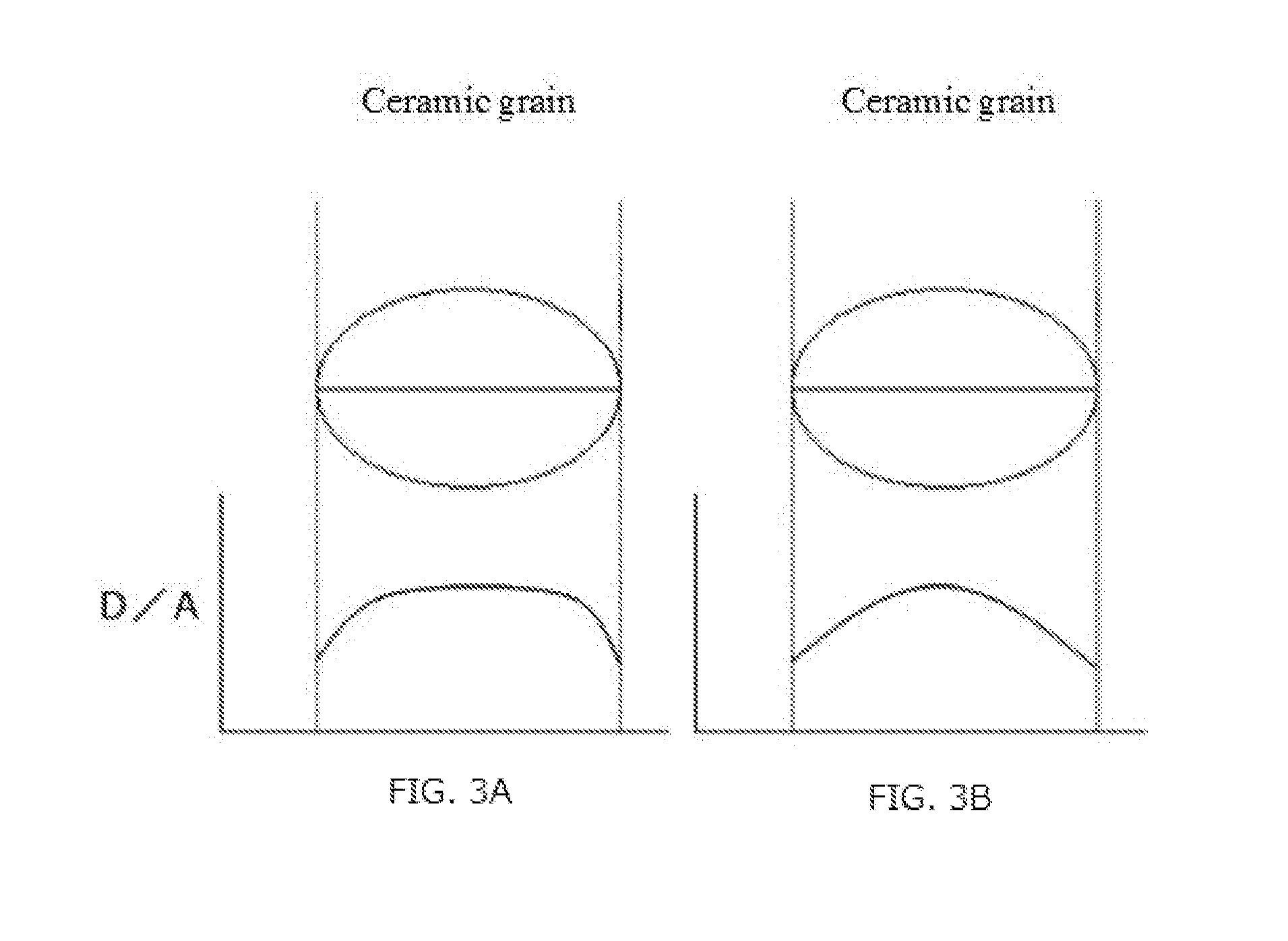

Multilayer ceramic capacitor

ActiveUS20160217924A1Improved life characteristicImprove life characteristicsFixed capacitor electrodesFixed capacitor dielectricPrimary componentMetallurgy

A multilayer ceramic capacitor has a laminate comprising dielectric layers stacked alternately with internal electrode layers of different polarities, wherein: the dielectric layers contain ceramic grains whose primary component is BaTiO3; the ceramic grains contain at least one type of donor element (D) selected from the group that includes Nb, Mo, Ta, and W, and at least one type of acceptor element (A) selected from the group that includes Mg and Mn; and the ratio of the concentration of the donor element (D) and that of the acceptor element (A) (D / A) is greater than 1 at the center parts of the ceramic grains, while the D / A ratio is less than 1 at the outer edge parts of the ceramic grains (if A=0, then D / A=∞ and D=A=0 never occurs).

Owner:TAIYO YUDEN KK

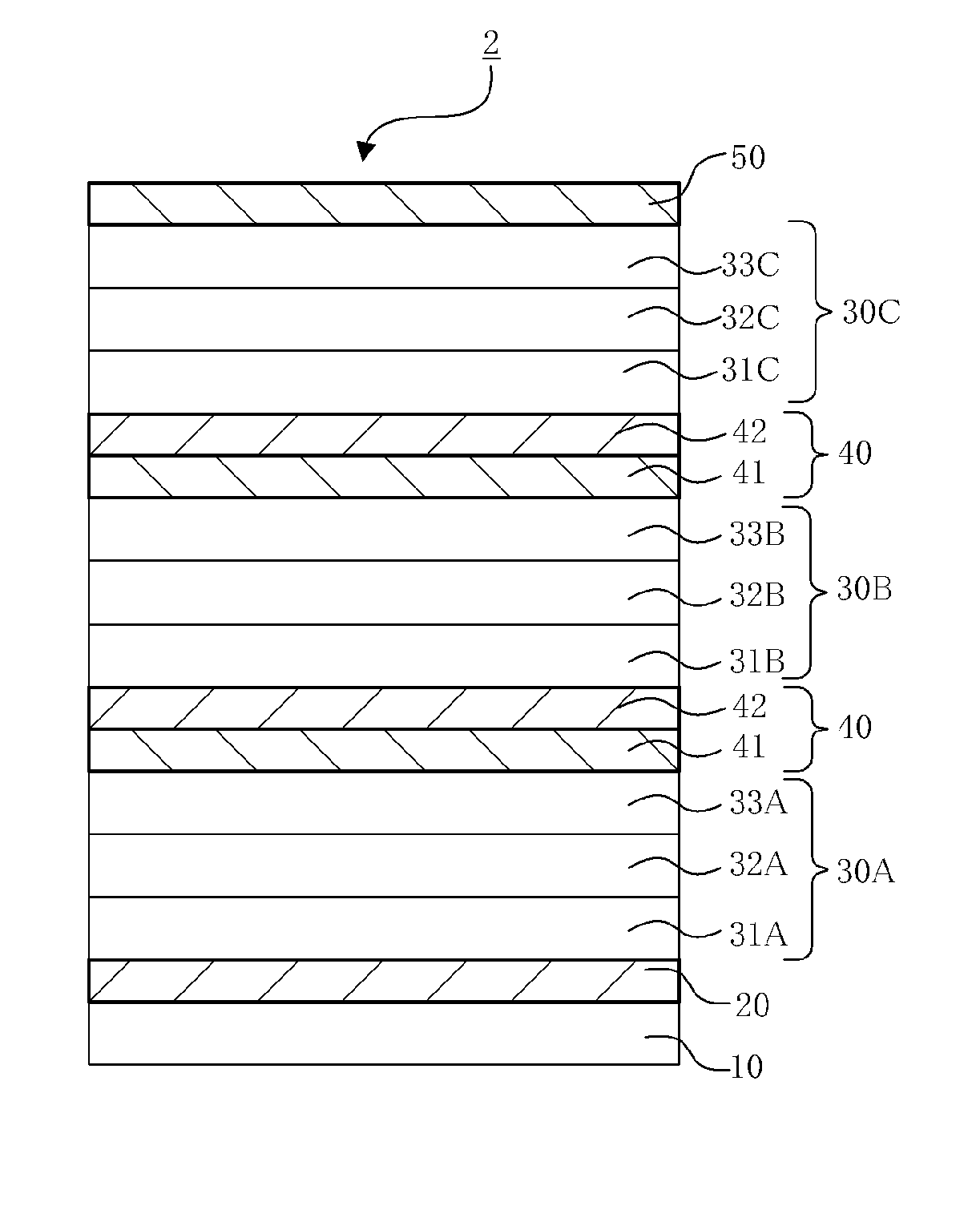

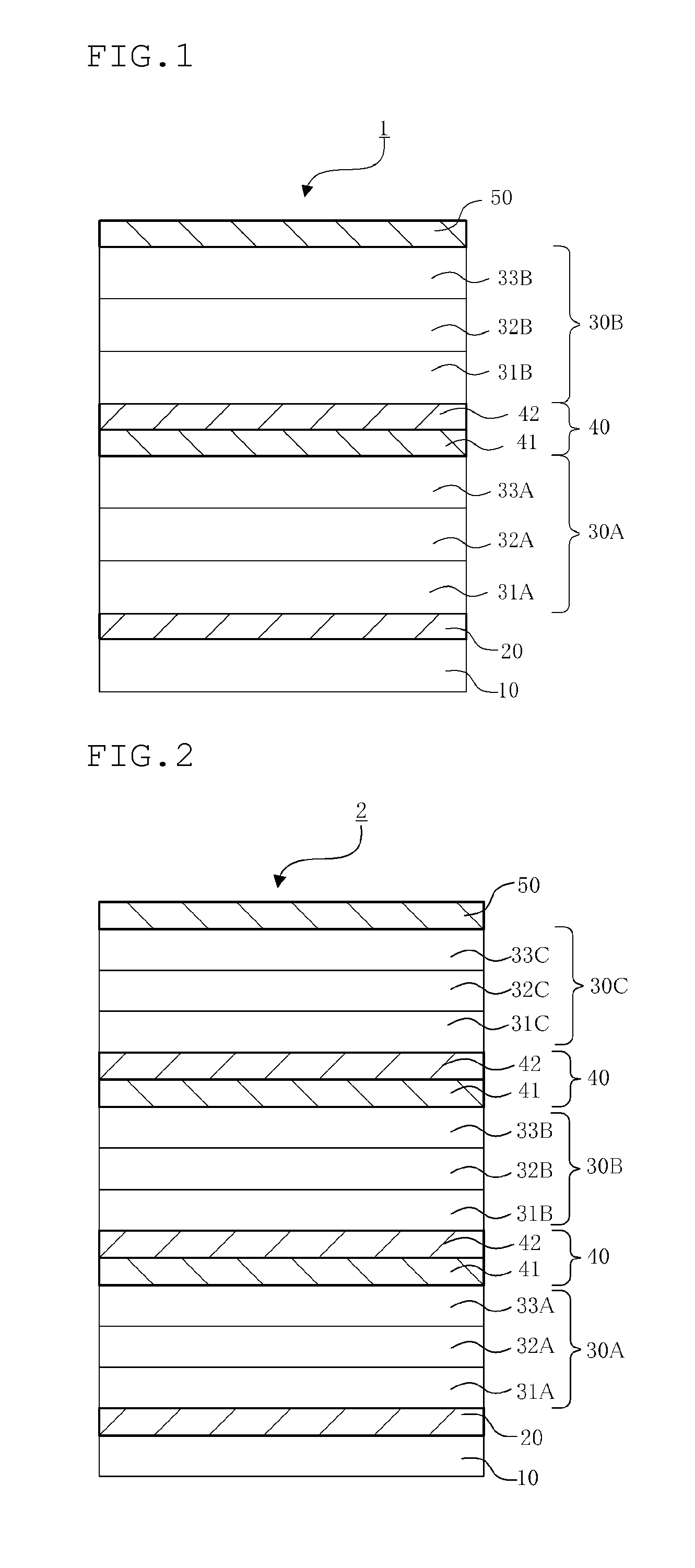

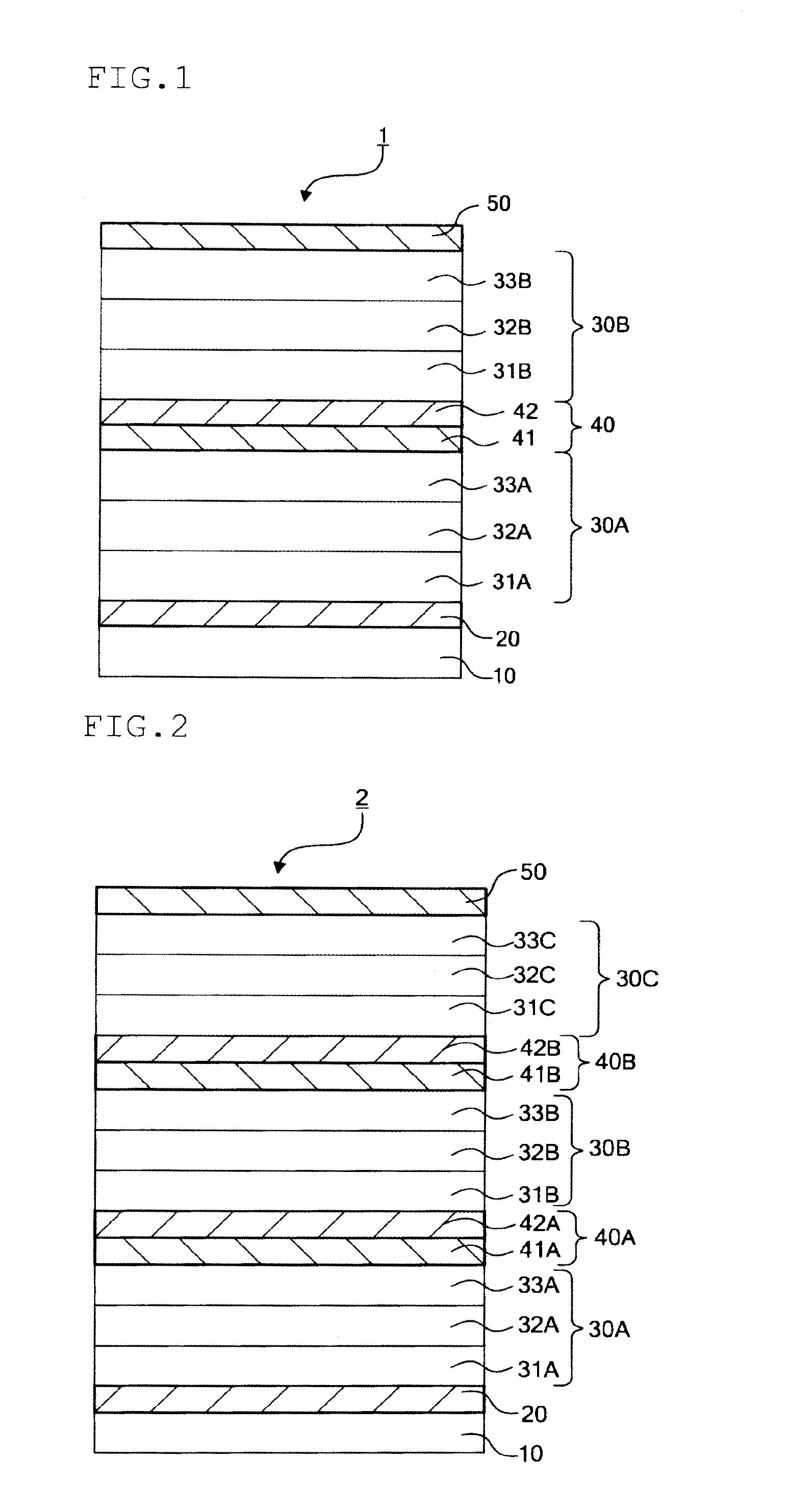

Organic electroluminescent element

ActiveUS20140246663A1High luminous efficiencyReduce the driving voltageOrganic chemistrySolid-state devicesOrganic electroluminescenceCharge generation

An organic electroluminescence device including: an anode; a cathode; two or more emitting units that are disposed between the anode and the cathode, each unit having an emitting layer; and a charge-generating layer that is disposed between the emitting units, wherein the charge-generating layer comprises an N layer nearer to the anode and a P layer nearer to the cathode, and the P layer comprises a compound represented by the following formula (I).

Owner:JOLED INC +1

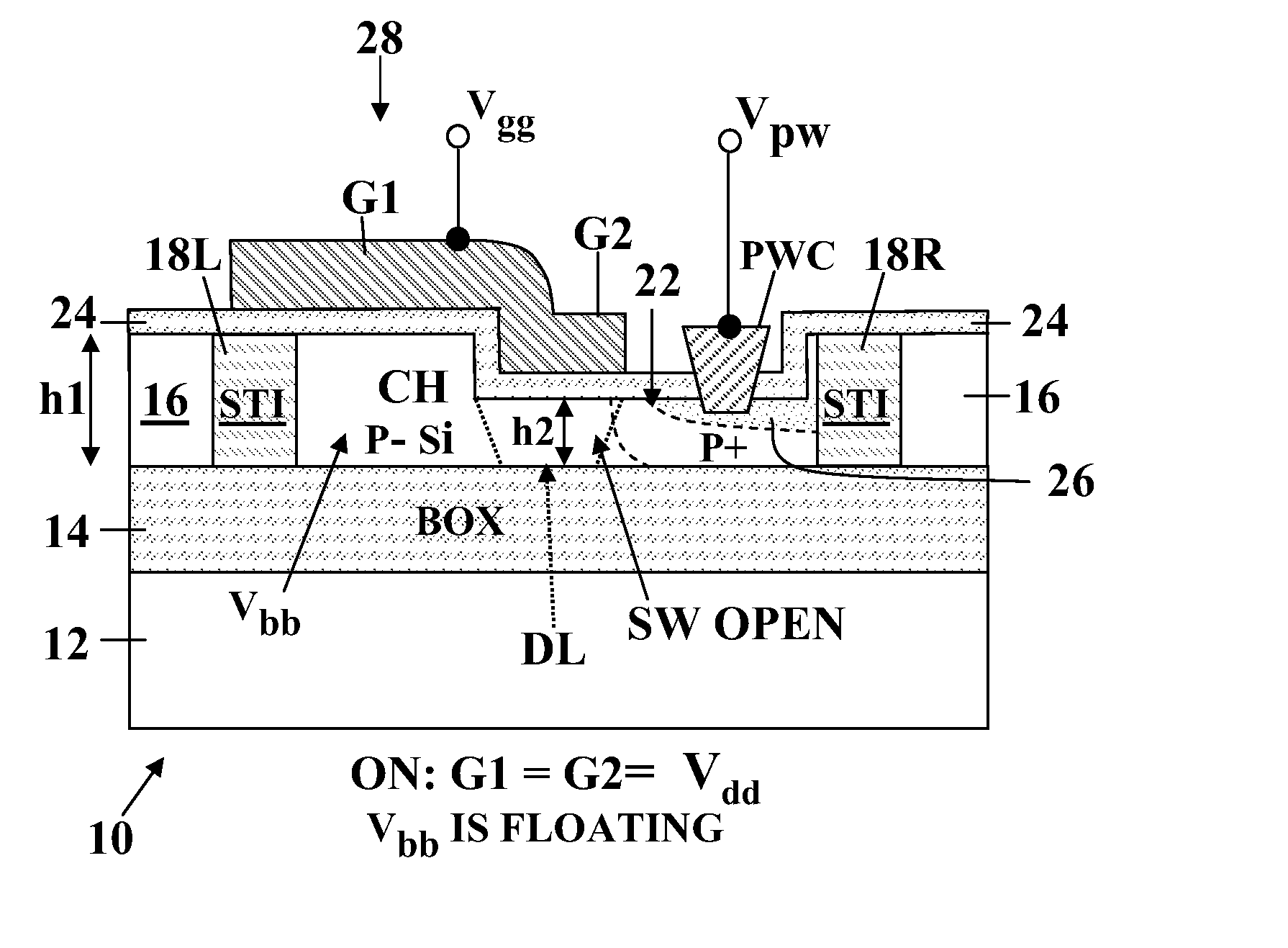

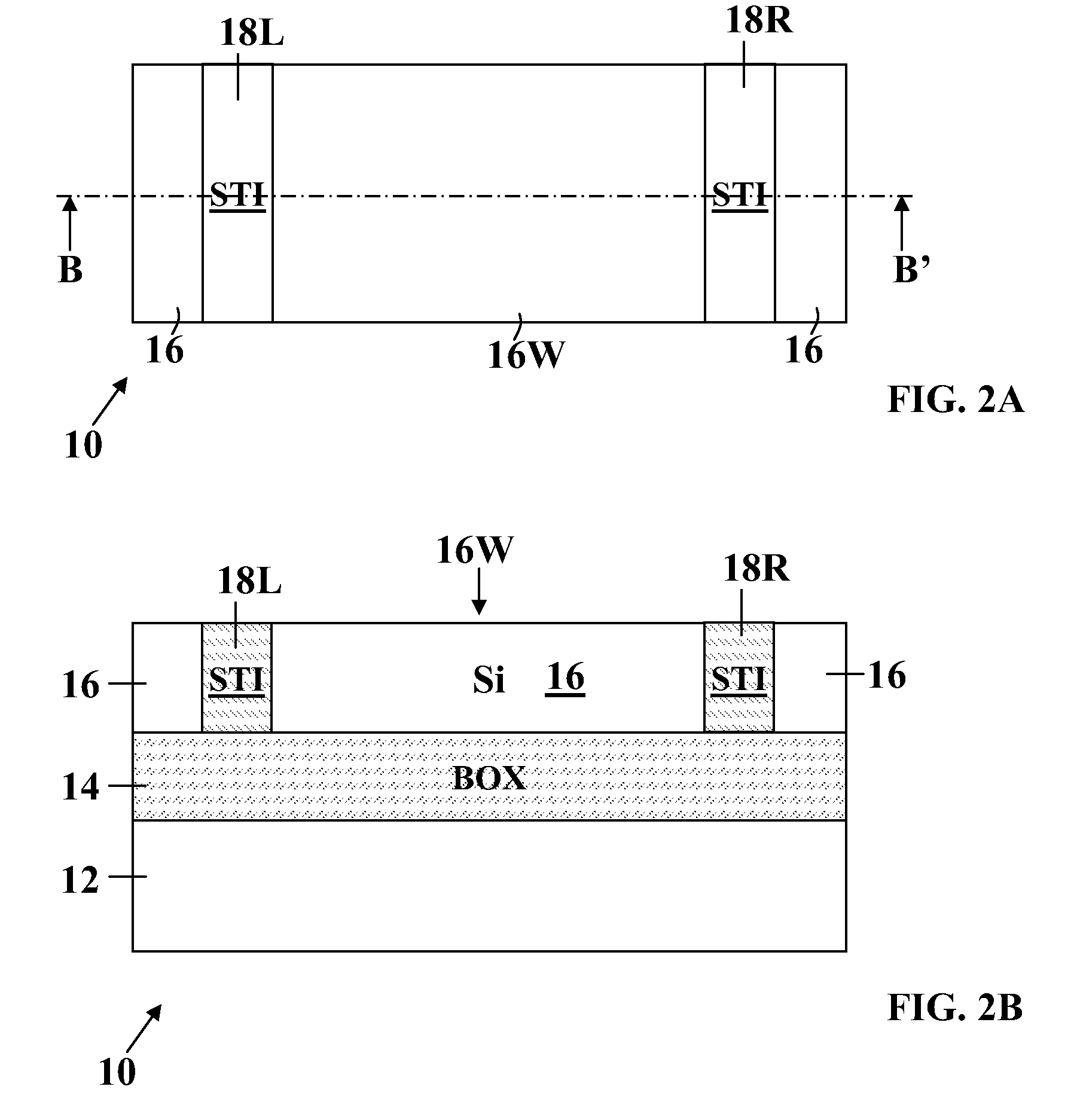

Soi mosfet device with adjustable threshold voltage

InactiveUS20080191788A1Increase circuit speedLimit leakage currentSemiconductor/solid-state device manufacturingElectric variable regulationMOSFETGate dielectric

An SOI semiconductor device includes a silicon semiconductor layer divided into an FET region with source, channel, and drain regions therein formed on a BOX layer, with a switch region next to the FET region; and a contact region next to the switch region distal from the FET region. The FET region has a greater thickness than the switch region. A conformal gate dielectric layer covers the FET region and the switch. A dual function gate electrode formed over the gate dielectric layer includes an FET portion above the FET region and an auxiliary gate portion extending therefrom above the switch region. A contact is formed reaching through the gate dielectric layer into electrical and mechanical contact with the contact region. The switch varies the depth of the depletion region to open and close current flow between the channel of the FET device and the contact region to suppress subthreshold leakage current.

Owner:IBM CORP

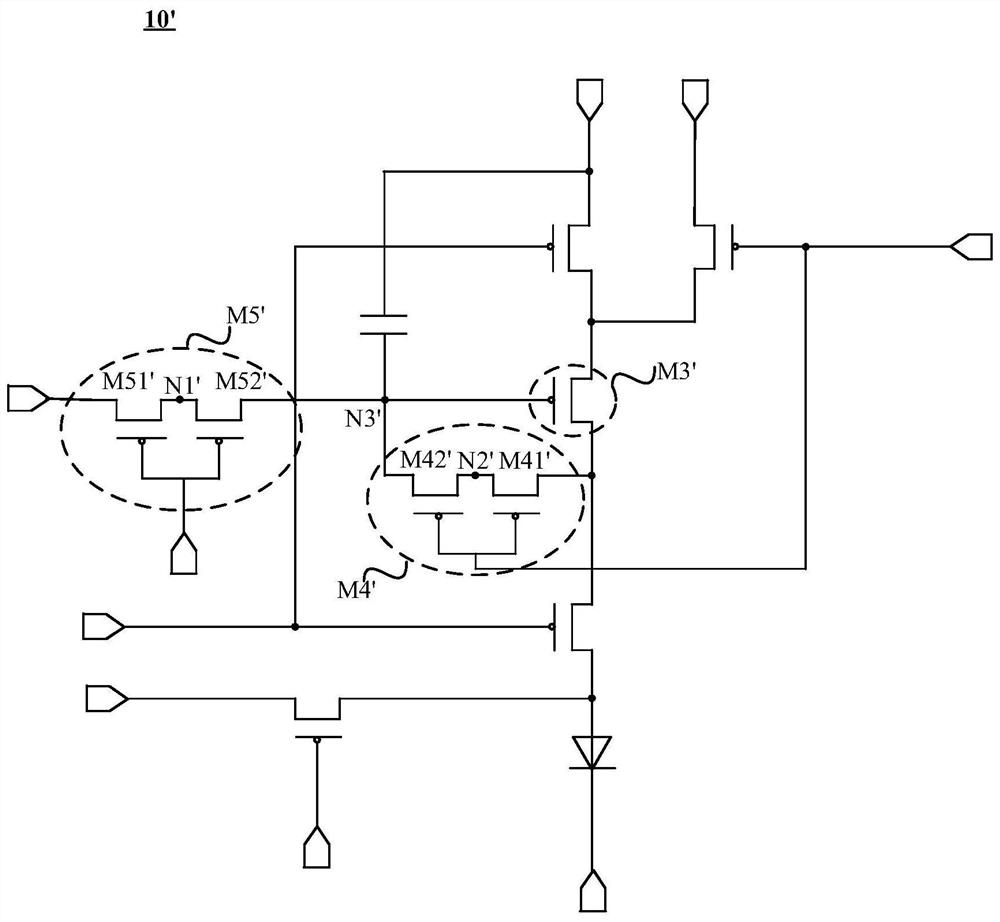

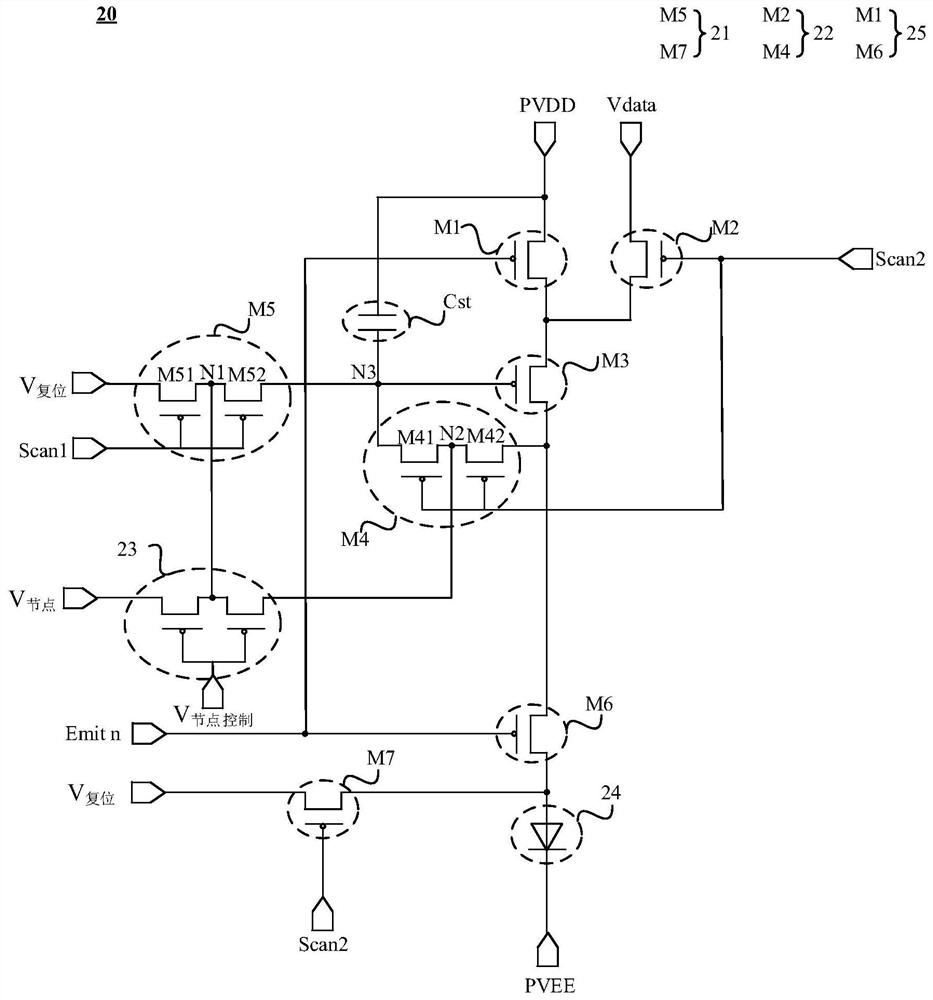

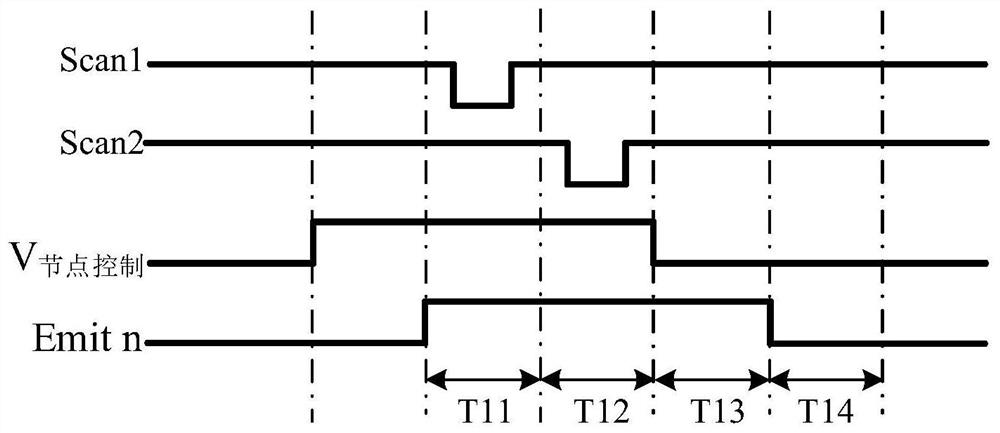

Pixel circuit and driving method thereof, display panel and display device

InactiveCN111613177AImprove the display effectSuppress leakage currentStatic indicating devicesComputer hardwareDriving current

The embodiment of the invention discloses a display panel, a driving method and a display device. The display panel comprises a substrate base plate; a plurality of sub-pixels positioned on one side of the substrate base plate; the plurality of sub-pixels being arranged in an array; each sub-pixel comprising a pixel driving circuit and a light-emitting element; a pixel driving circuit, comprisingan initialization transistor and a driving transistor, and the initialization transistor and the driving transistor each comprising a first electrode, a second electrode and a grid electrode; a firstelectrode of the initialization transistor being electrically connected with a grid electrode of the driving transistor, and the driving transistor being used for providing driving current for the light-emitting element; and at least one switch module. The second electrodes of the initialization transistors of the at least two sub-pixels are connected with the output end of the same switch module.The input end of the switch module is electrically connected with the initialization signal end. The switch module is used for transmitting an initialization signal to the second electrode of the initialization transistor. The problem that the gate voltage of a driving transistor is unstable due to electric leakage of an initialization transistor can be solved, and the display effect is improved.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

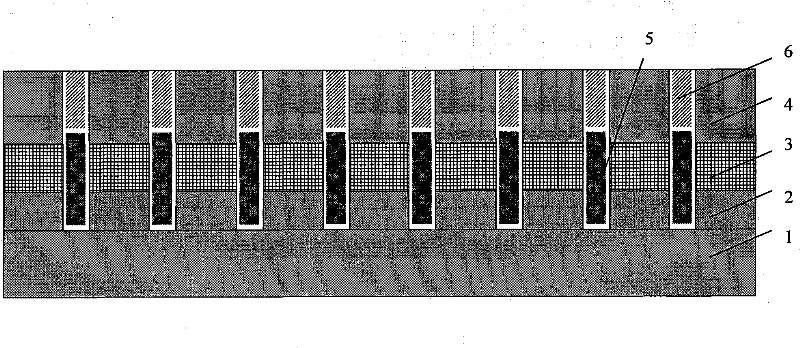

Preparation method for epitaxial diode array isolated by double shallow trenches

ActiveCN102412179ASuppress leakage currentWon't cause driftSemiconductor/solid-state device manufacturingDiodePhase-change memoryEtching

The invention discloses a preparation method for an epitaxial diode array isolated by double shallow trenches. The method includes the following steps: a heavily doped first conductivity type region and a highly doped second conductivity type region are first formed on a substrate, an epitaxial layer is grown, the isolation between work lines of the diode array is then formed by deep trench etching, the isolation between bit lines, which is perpendicular to the deep trench direction, is formed by shallow trench etching, and finally, independent diode array units are formed in regions defined by the deep trench isolation and the shallow trench isolation by the method of ion injection. The invention also provides an inhibition method for the crosstalk current between the neighboring word lines and bit lines, which is based on the epitaxial diode array isolated by the double shallow trenches. The invention is applicable to high-density, high-capacity memories driven by diodes, such as phase change memories, resistive memories, magnetic memories and ferroelectric memories; the method is fully compatible with the conventional CMOS (Complementary Metal-Oxide-Semiconductor Transistor) technique, the diode array is formed before a peripheral circuit is formed, so that the thermal process of the diode array cannot cause the drift of the peripheral circuit, and the invention solves the technical problem on how to achieve a high-density, high-capacity embedded phase change memory.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

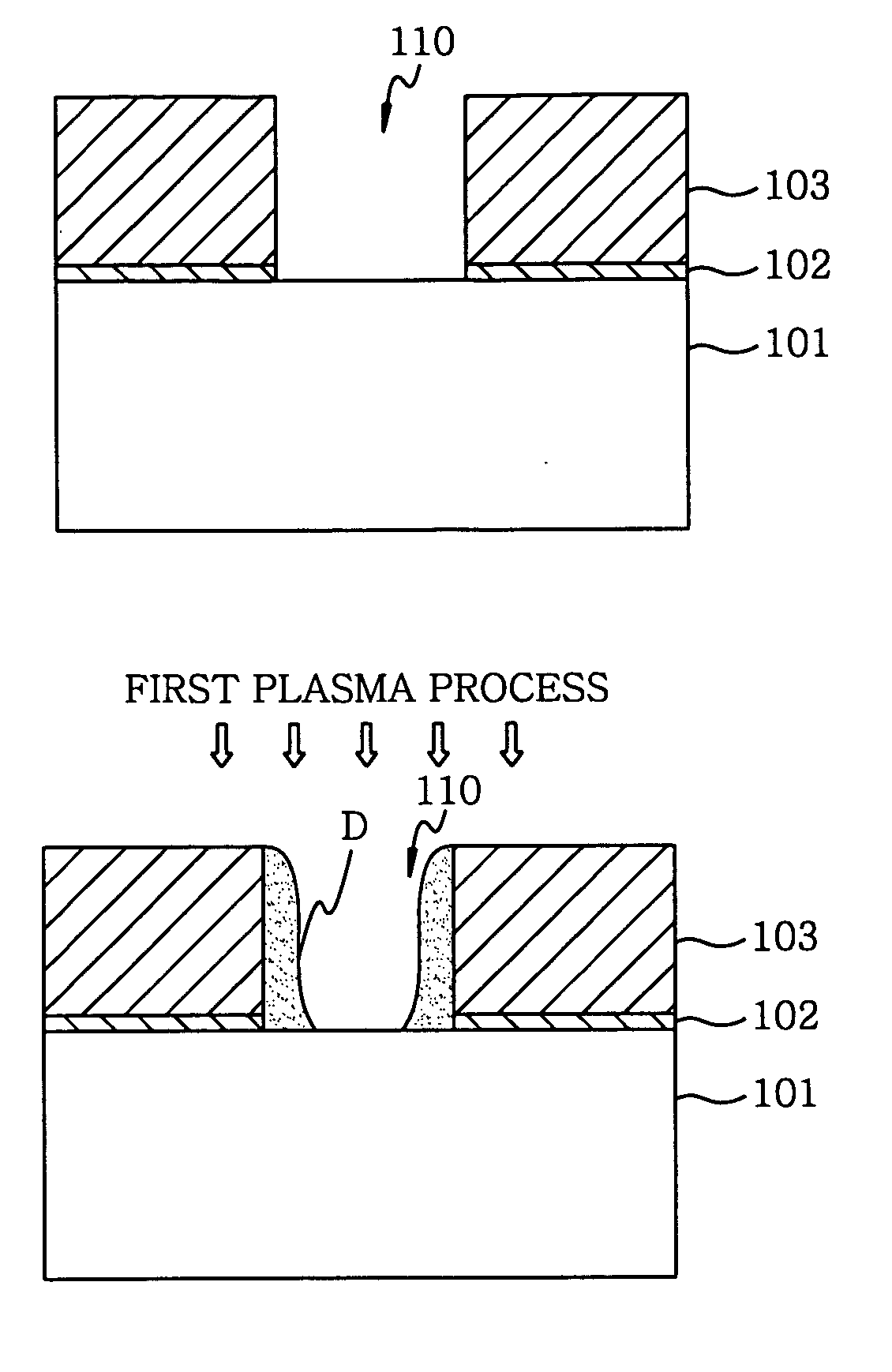

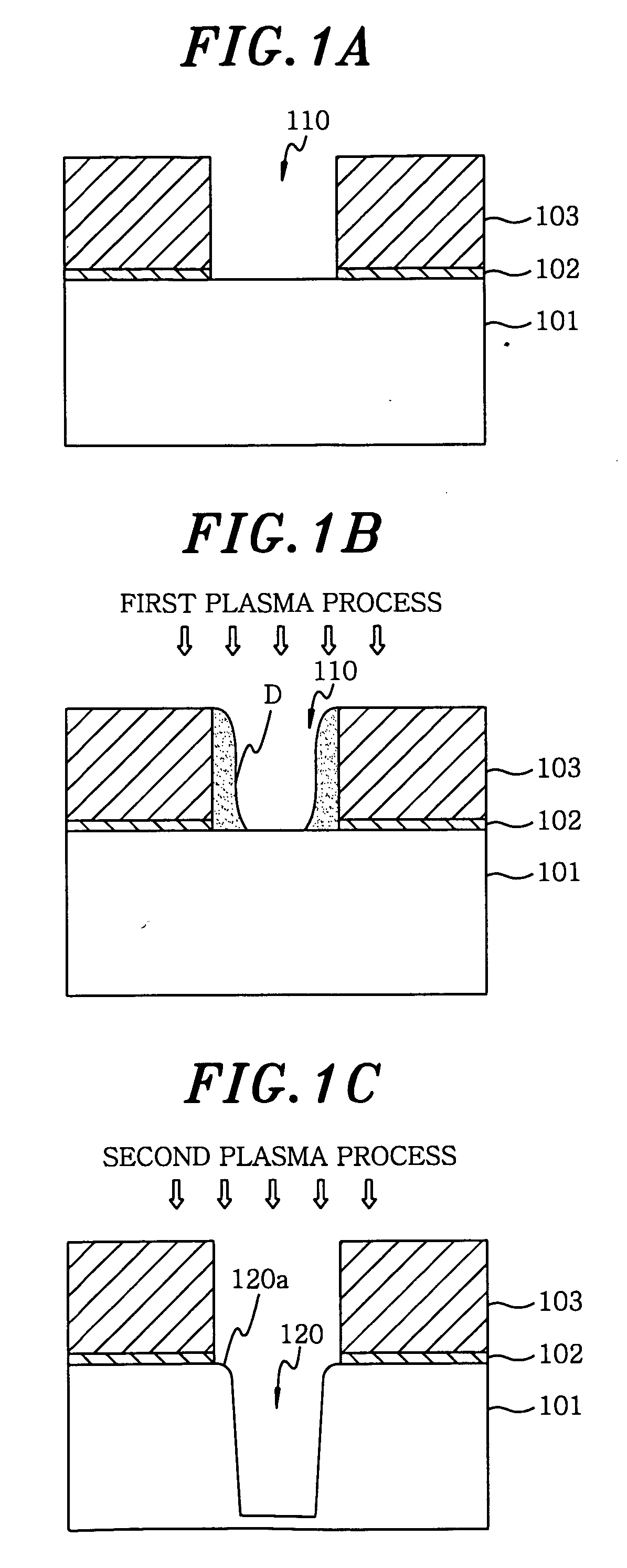

Plasma etching method

InactiveUS20060163202A1Fast processingForming accuratelyElectric discharge tubesDecorative surface effectsPlasma processingMask layer

A plasma etching method for etching an object to be processed, which has at least an etching target layer and a patterned mask layer formed on the etching target layer, to form a recess corresponding to a pattern of the mask layer in the etching target layer, includes a first plasma process of forming deposits on the etching target layer at least around a boundary between the etching target layer and the mask layer in an opening portion constituting the pattern of the mask layer, and a second plasma process of forming the recess by etching the etching target layer after the first plasma process. An edge portion of an upper sidewall constituting the recess is rounded off in the second plasma process.

Owner:TOKYO ELECTRON LTD

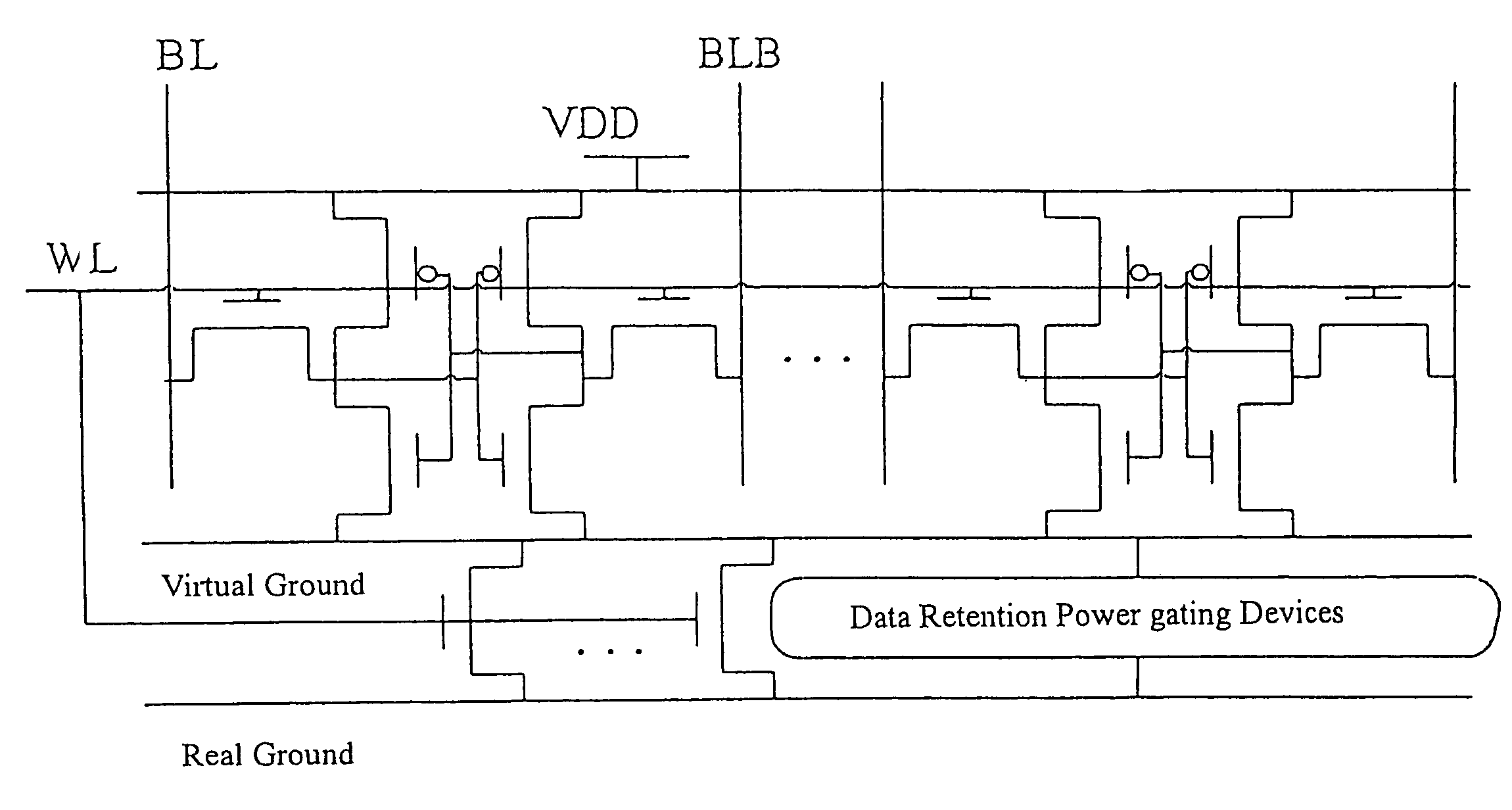

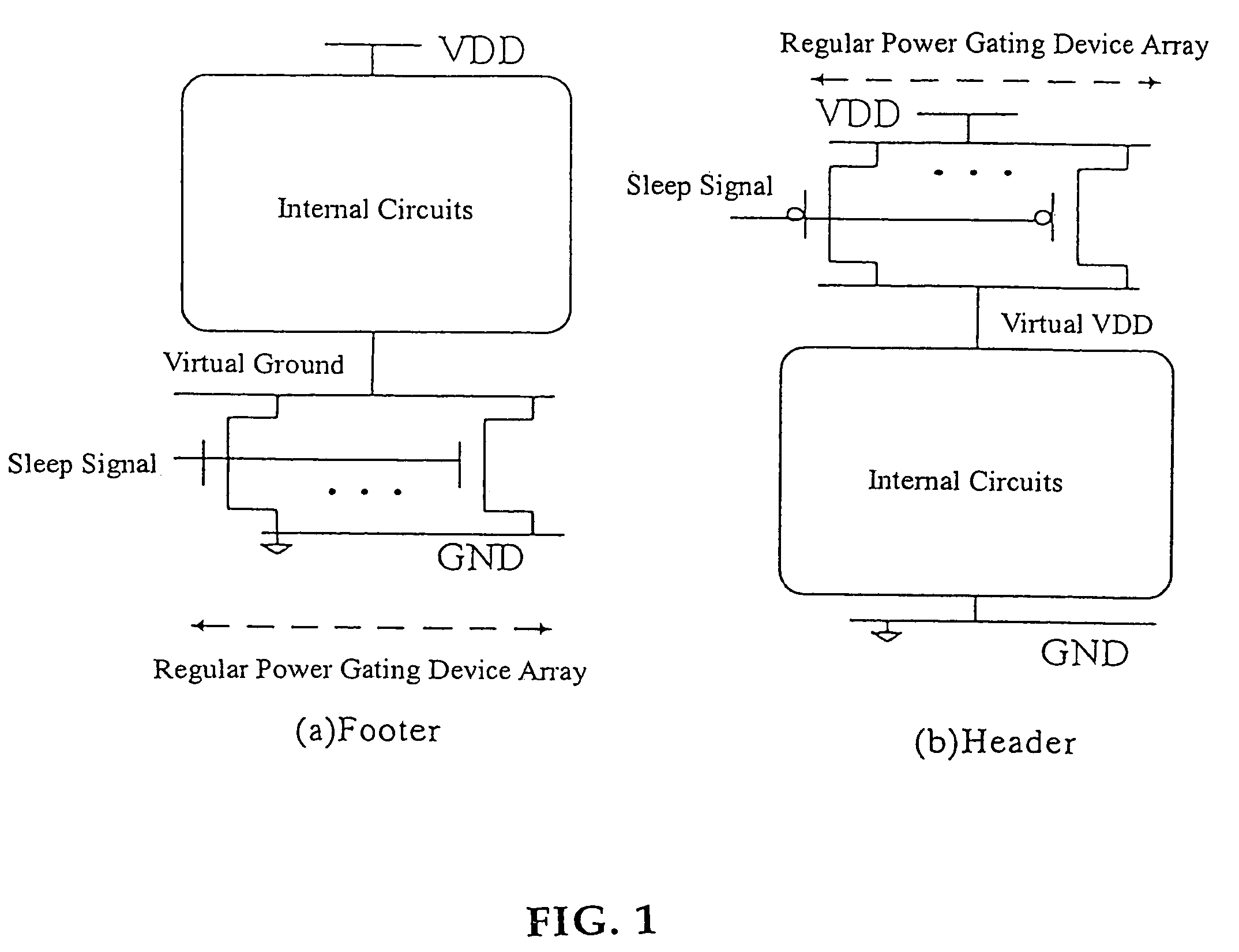

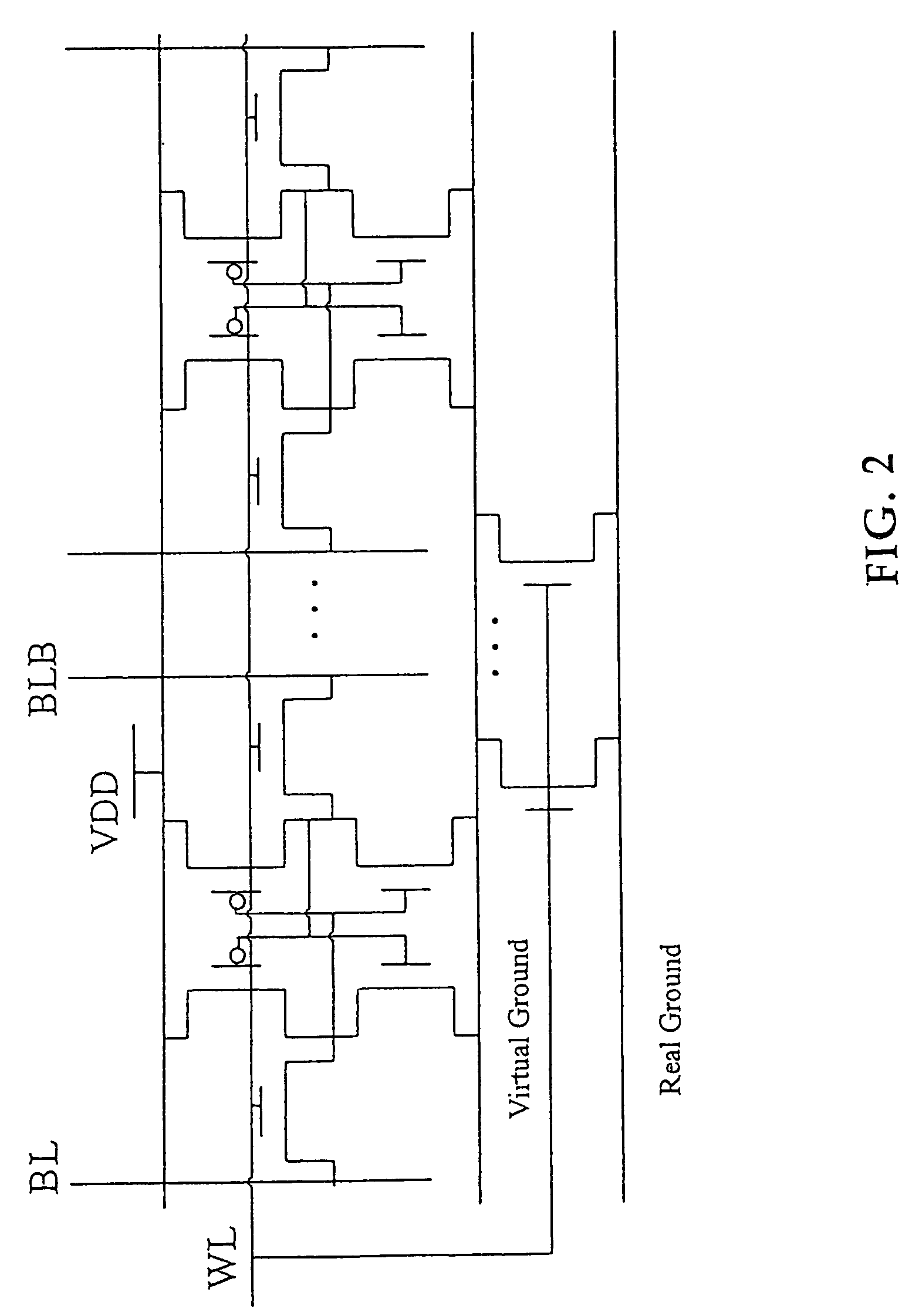

Power gating structure having data retention and intermediate modes

InactiveUS7190187B2Maintain efficiencyActive powerReliability increasing modificationsPower reduction by control/clock signalEngineeringOperation mode

The present invention provides a power gating structure having data retention and intermediate modes and able to operate under multiple modes. A conventional power gating structure has only turn-on and turn-off functions, and is used to suppress a leakage current problem which has become more and more serious in advance manufacture processes, under a turn-off mode. However, in a memory circuit, such as latch, register and SRAM, when the power gate is turned off, a new power gating structure is required for data retention. The power gating structure of the present invention can be set into one of 4 different operational modes: a data retention mode for maintaining the static noise margin of the memory, an intermediate mode for reducing the interference on ground and power levels, an active mode used when the circuit operates in normal condition, and a standby mode used when the circuit does not operate.

Owner:NAT CHIAO TUNG UNIV

Piezoelectric element, liquid ejecting head, and liquid ejecting apparatus

InactiveUS20120162320A1Leakage currentReduce the environmentInking apparatusPiezoelectric/electrostriction/magnetostriction machinesCeriumPotassium

A piezoelectric element comprises a piezoelectric layer and an electrode provided to the piezoelectric layer. The piezoelectric layer is made of complex oxide having a Perovskite-type structure containing bismuth and iron, and the complex oxide includes at least one kind of a first doping element selected from the group consisting of sodium, potassium, calcium, strontium and barium and a second doping element formed from cerium.

Owner:SEIKO EPSON CORP

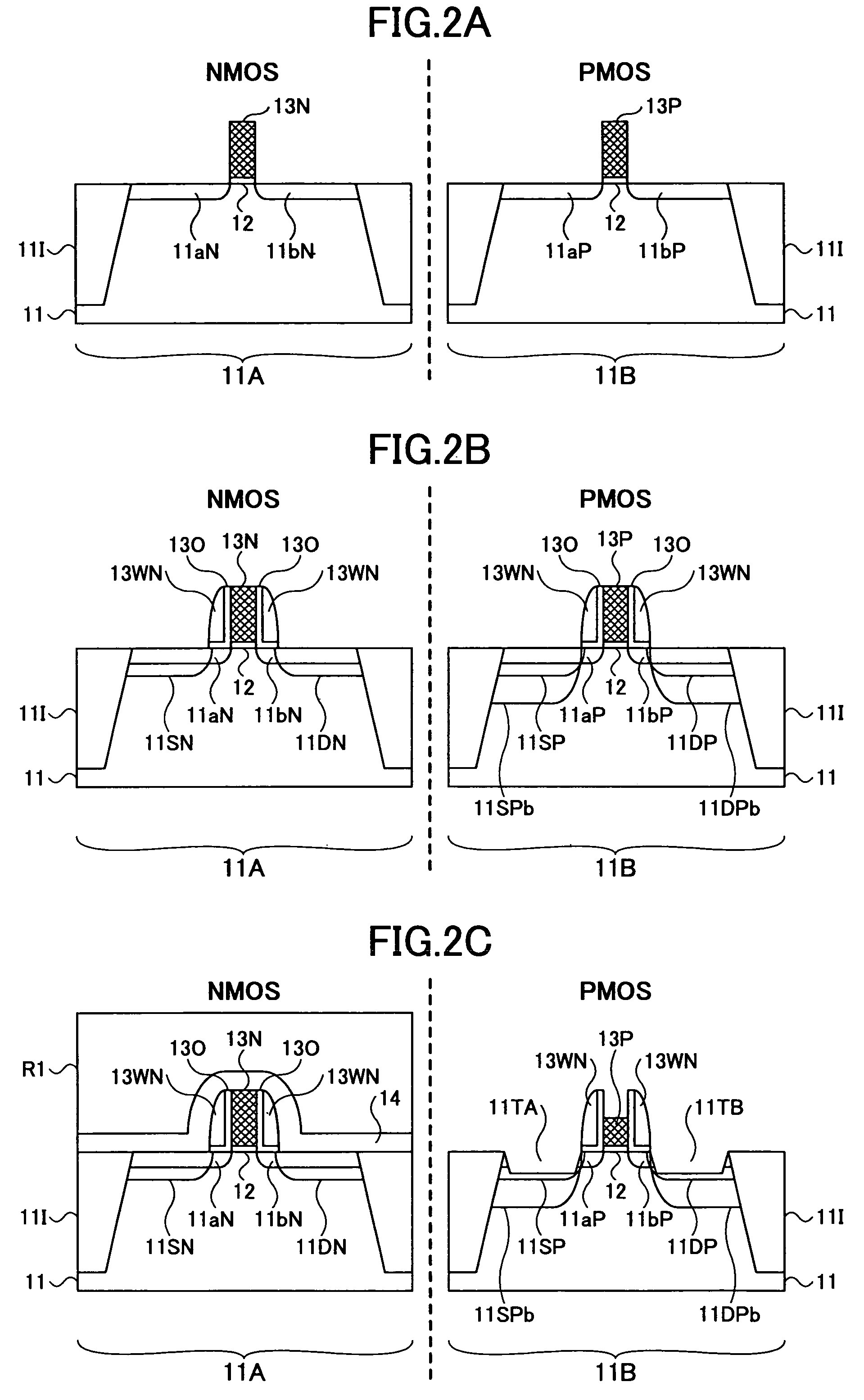

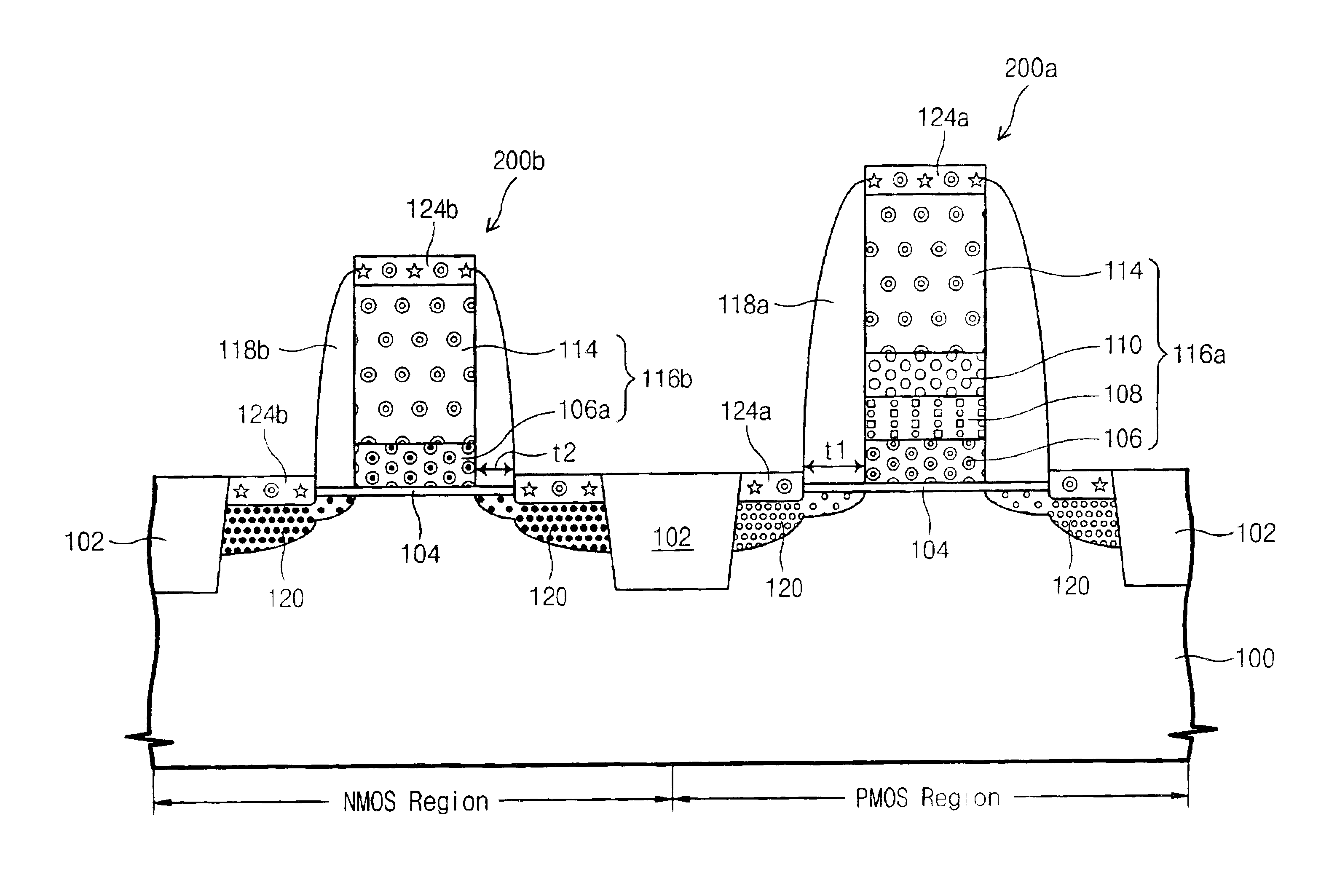

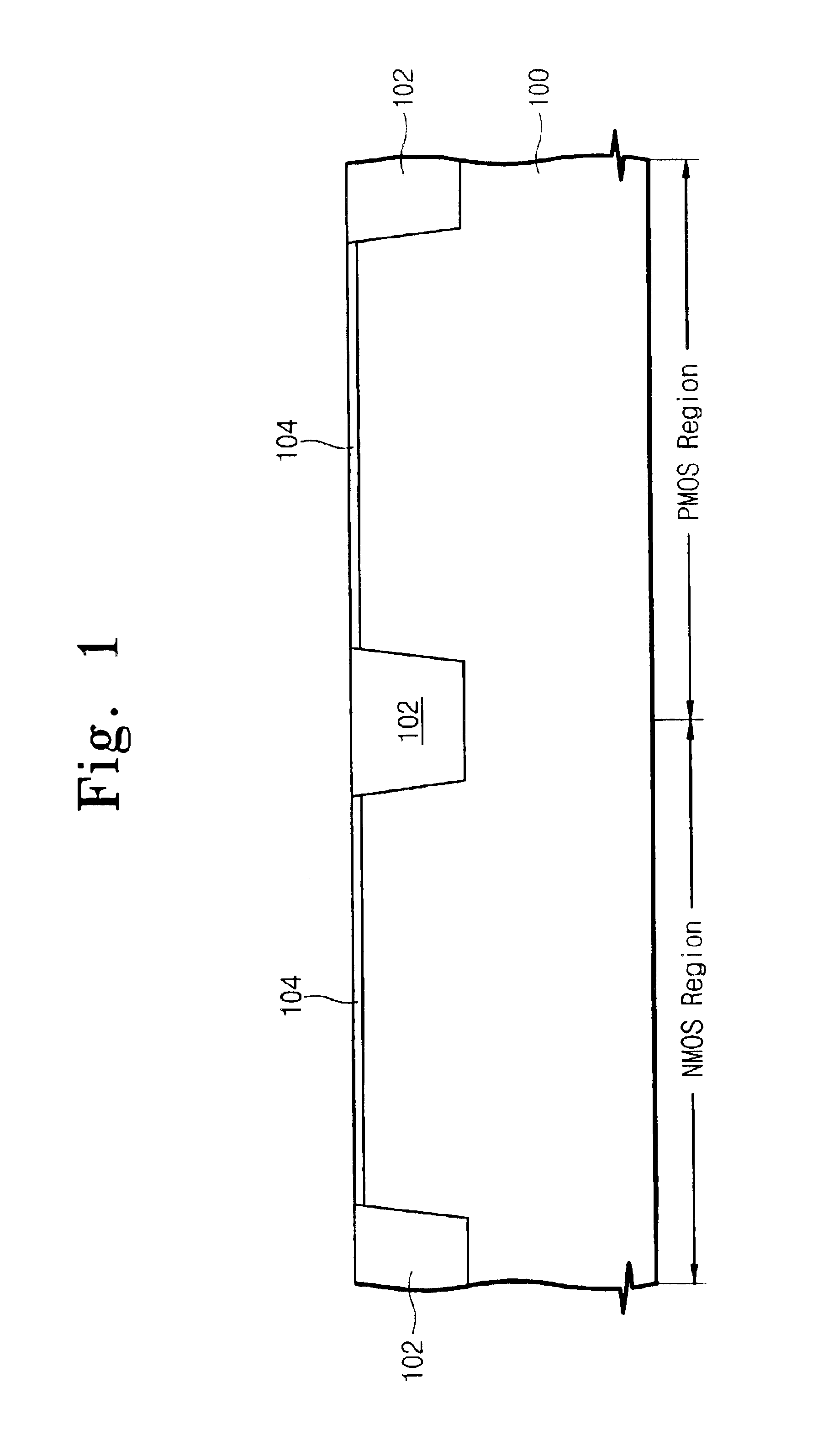

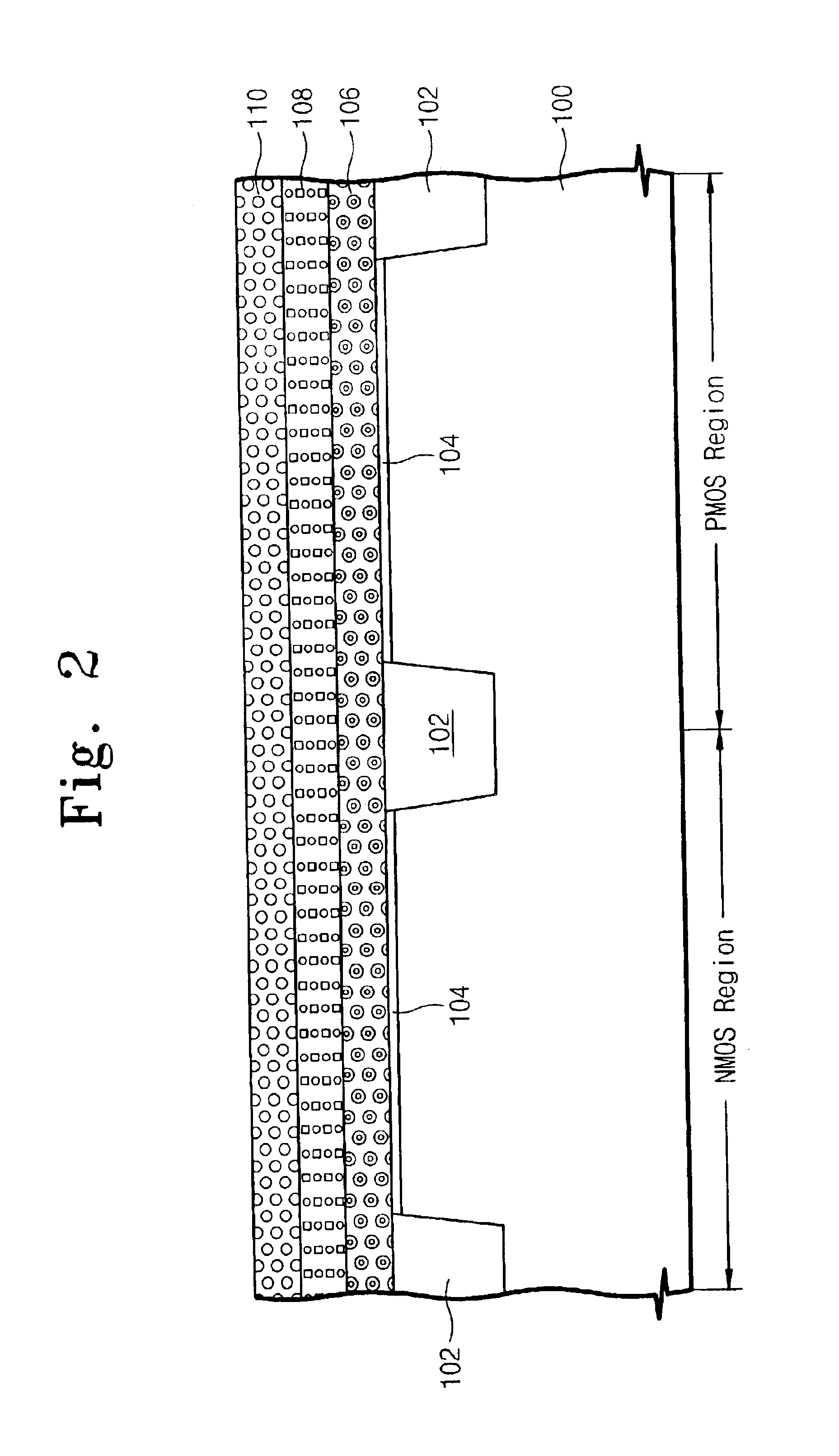

CMOS transistor having different PMOS and NMOS gate electrode structures and method of fabrication thereof

InactiveUS6855641B2Suppress leakage current and punchthroughEasy to spreadTransistorSemiconductor/solid-state device manufacturingCMOSAdemetionine

In a CMOS semiconductor device using a silicon germanium gate and a method of fabricating the same, a gate insulating layer, a conductive electrode layer that is a seed layer, a silicon germanium electrode layer, and an amorphous conductive electrode layer are sequentially formed on a semiconductor substrate. A photolithographic process is then carried out to remove the silicon germanium electrode layer in the NMOS region, so that the silicon germanium layer is formed only in the PMOS region and is not formed in the NMOS region.

Owner:SAMSUNG ELECTRONICS CO LTD

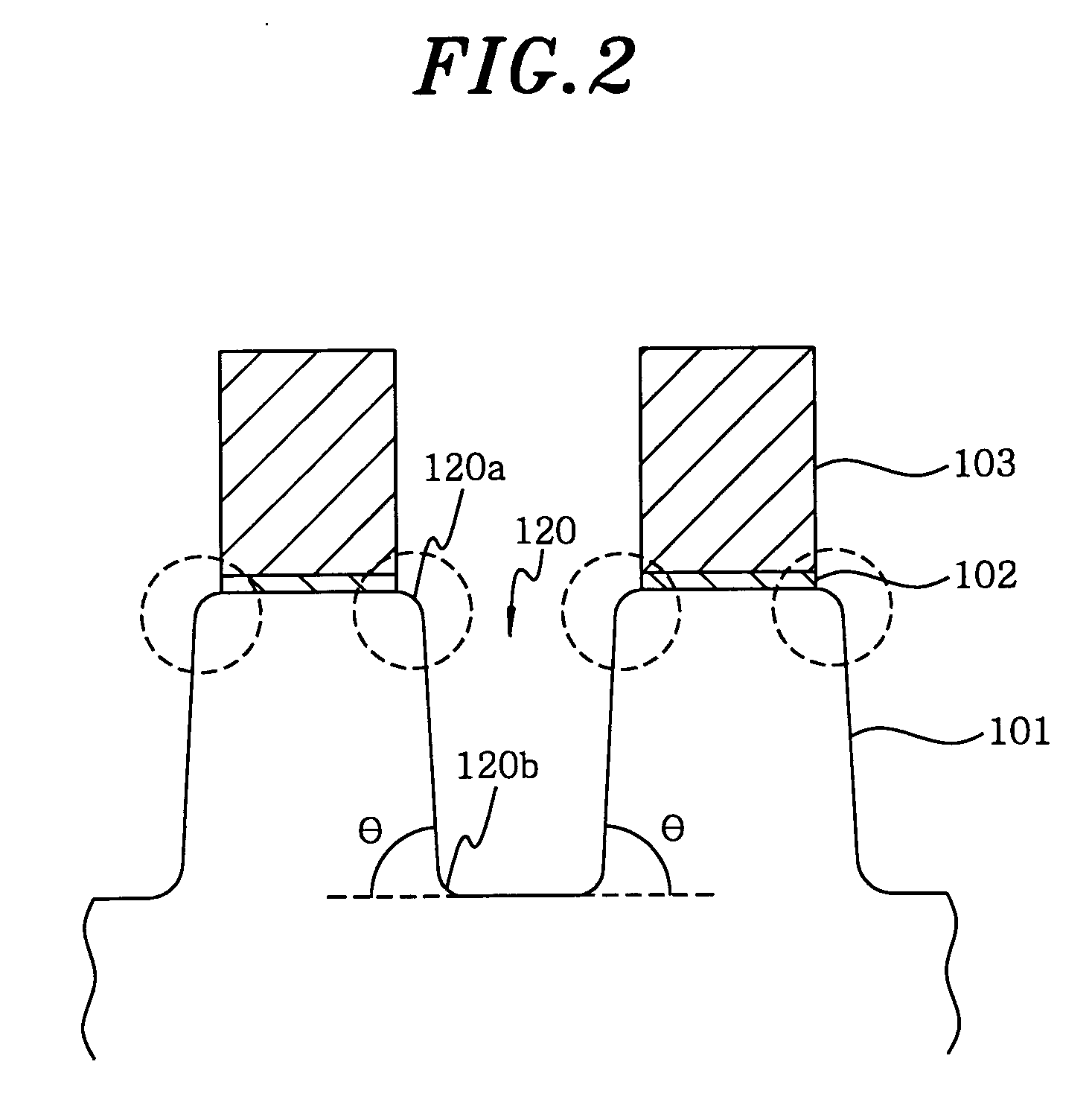

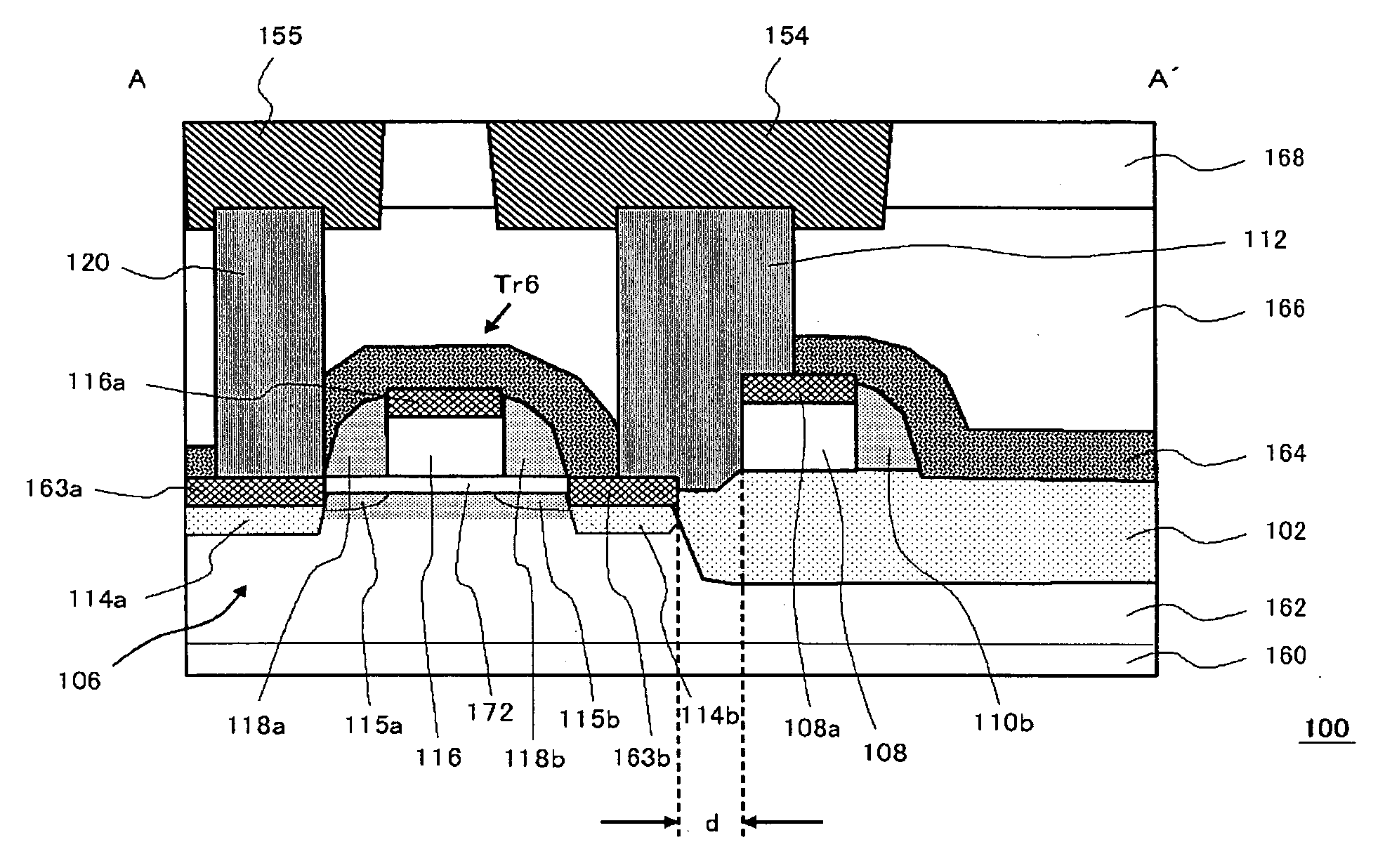

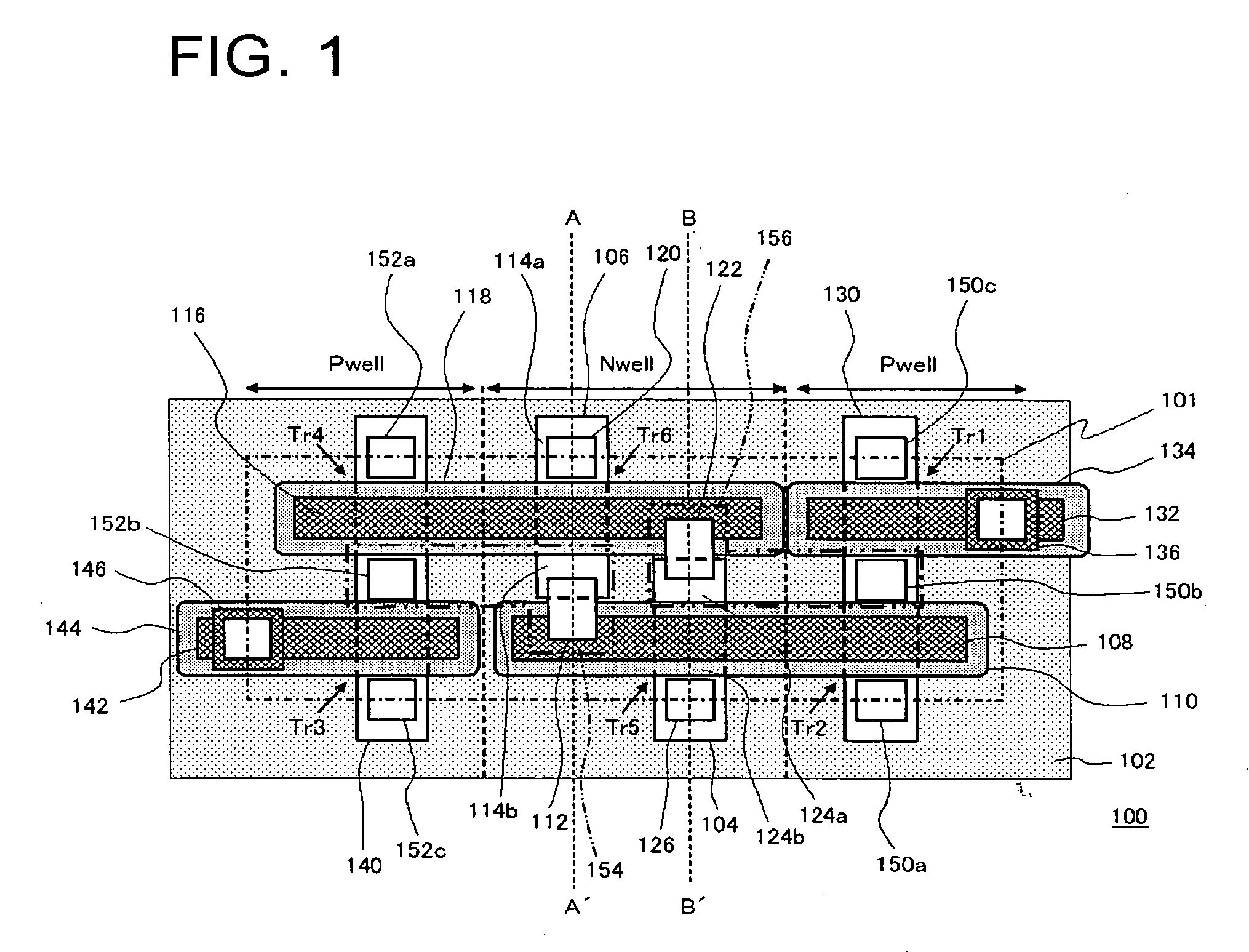

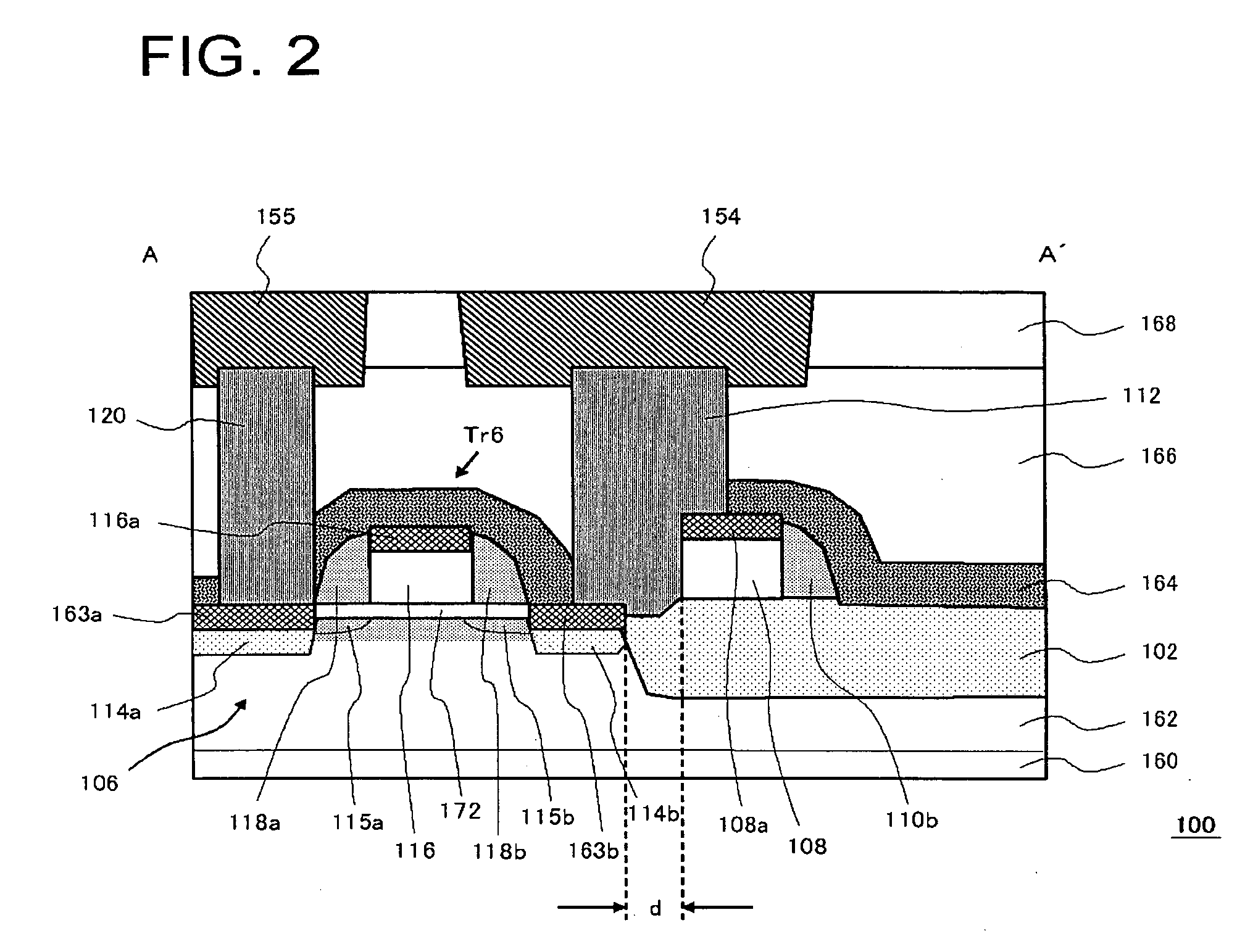

Semiconductor device and method of fabricating the same

ActiveUS20070023832A1Suppress leakage currentReduce distanceTransistorSolid-state devicesDevice materialEngineering

In view of micronizing semiconductor device and of suppressing current leakage in a shared contact allowing contact between a gate electrode and an impurity-diffused region, a semiconductor device 100 includes a first gate electrode 108, a fourth source / drain region 114b, and a shared contact electrically connecting the both, wherein in a section taken along the gate length direction, the first gate electrode 108 and the fourth source / drain region 114b are disposed as being apart from each other, an element-isolating insulating film 102 is formed over the entire surface of a semiconductor substrate 160 exposed therebetween, and the distance between the first gate electrode 108 and the fourth source / drain region 114b is made substantially equal to the width of the sidewall formed on the side face of the first gate electrode 108, when viewed in another section taken along the gate length direction.

Owner:RENESAS ELECTRONICS CORP

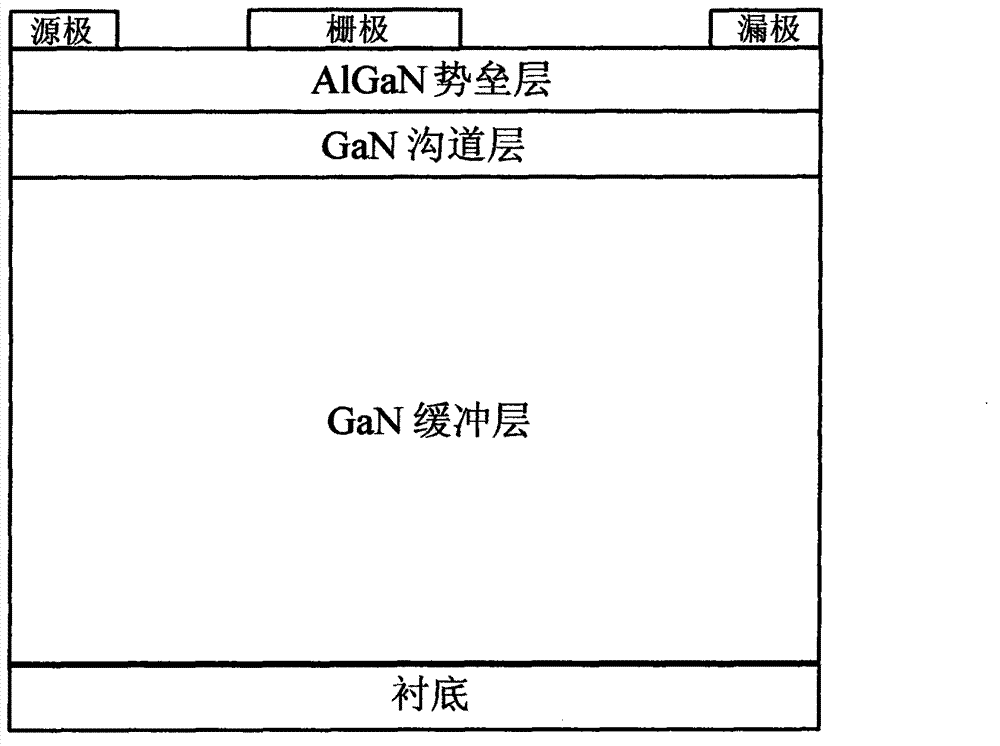

Field effect transistor and method of manufacturing the same

ActiveUS20110272740A1OFF-breakdown voltage is reducedOFF-breakdown voltage can be increasedTransistorSemiconductor/solid-state device manufacturingElectrical conductorField-effect transistor

A field-effect transistor includes a first semiconductor layer formed on a substrate, and a second semiconductor layer. The first semiconductor layer has a containing region provided as an isolation region which contains non-conductive impurities, and a non-containing region which contains no non-conductive impurities. A first region is defined by a vicinity of a portion of the interface between the containing region and the non-containing region, the portion of the interface being below a gate electrode, the vicinity including the portion of the interface and being included in the containing region. The second semiconductor layer includes a second region which is located directly above the first region. The concentration of the non-conductive impurities of the second region is lower than that of the first region.

Owner:PANASONIC CORP

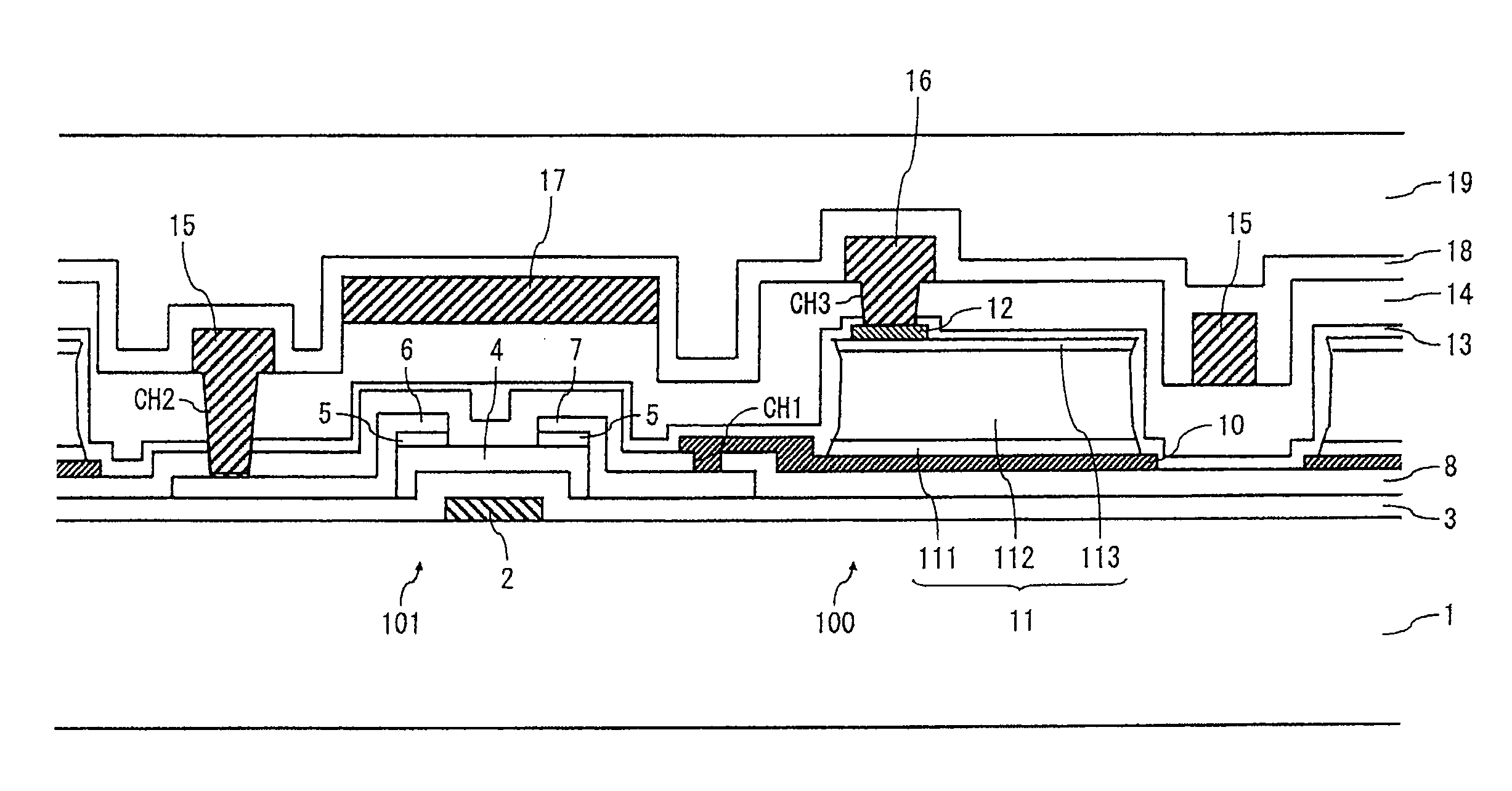

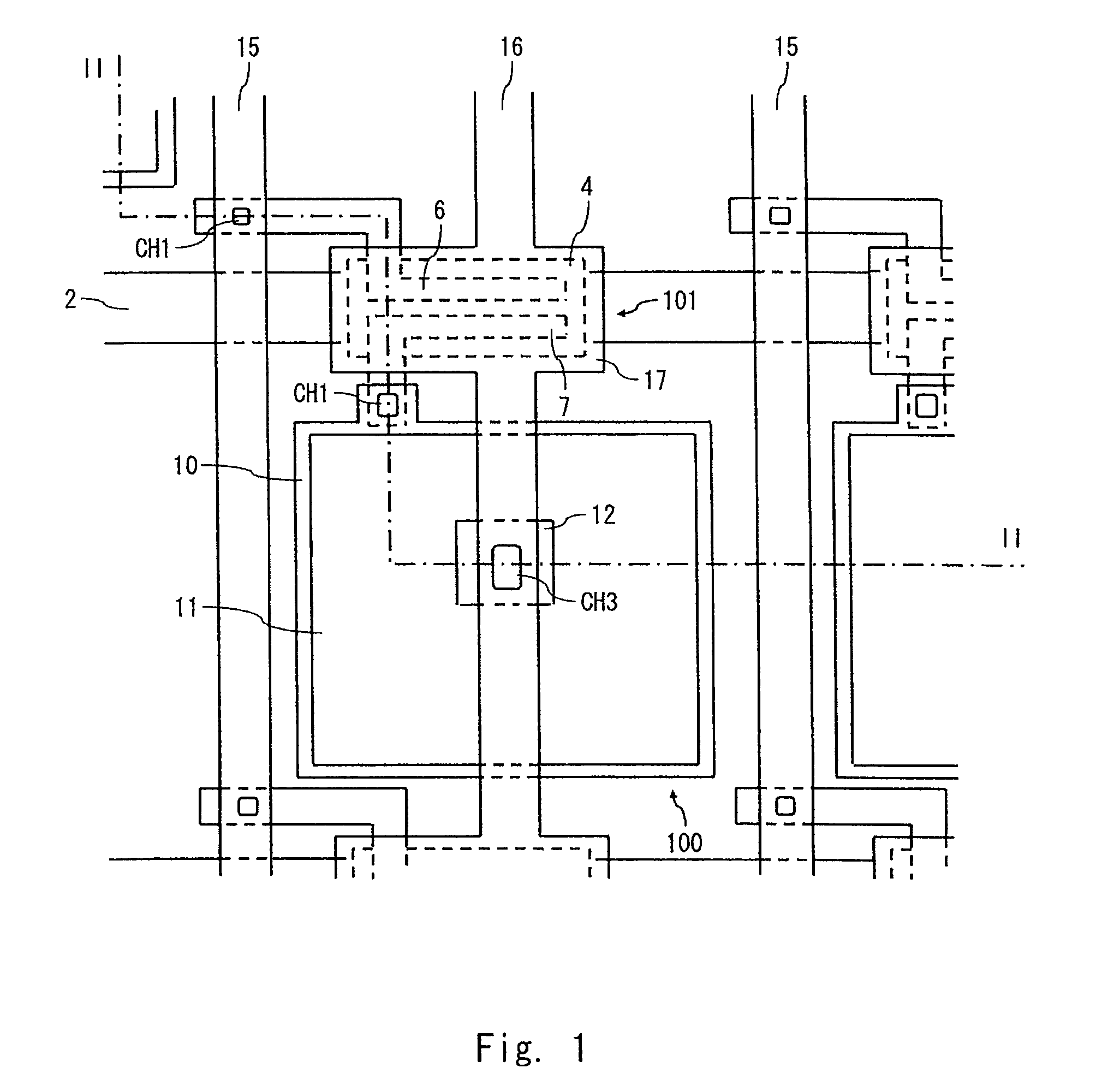

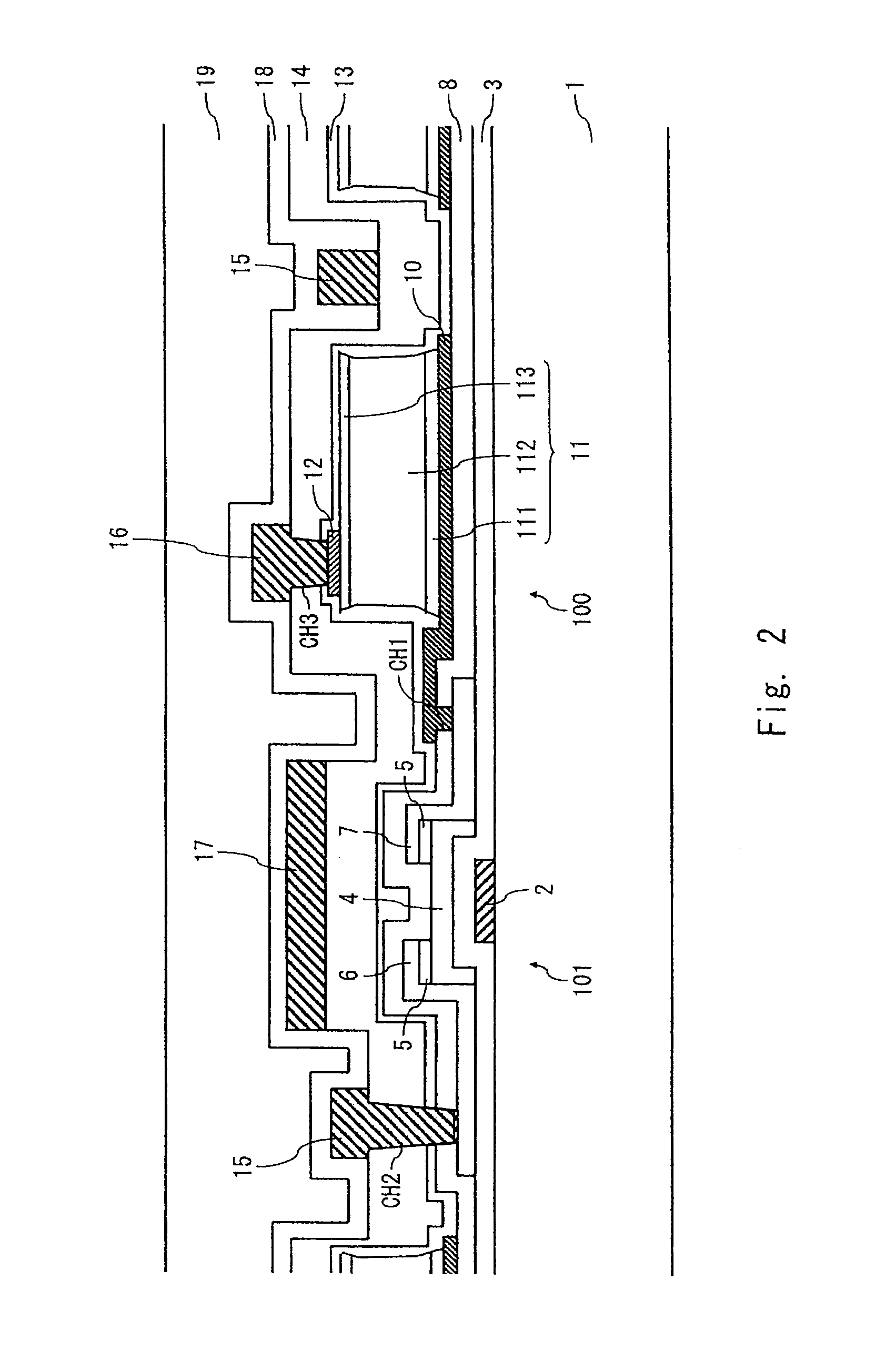

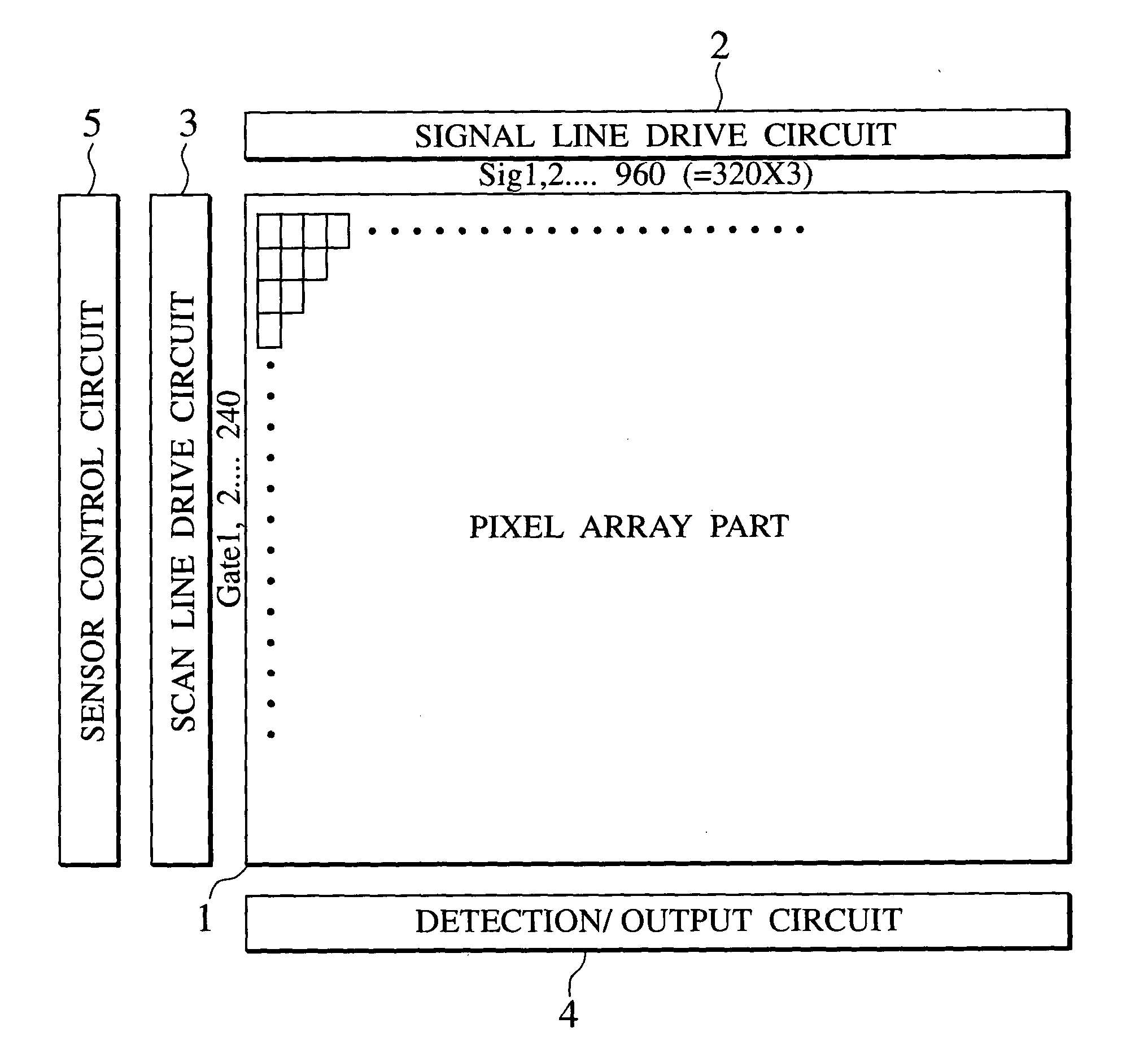

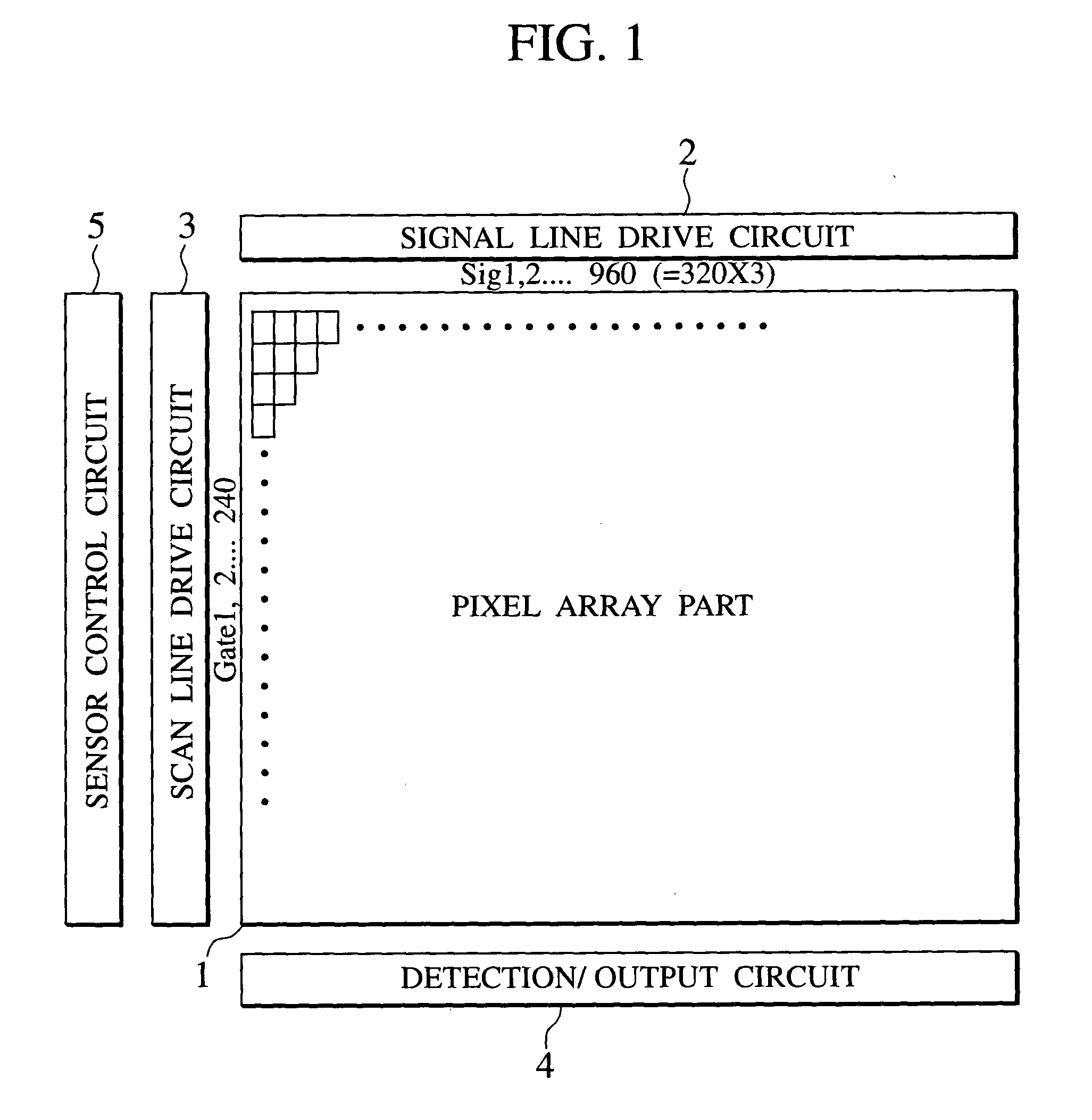

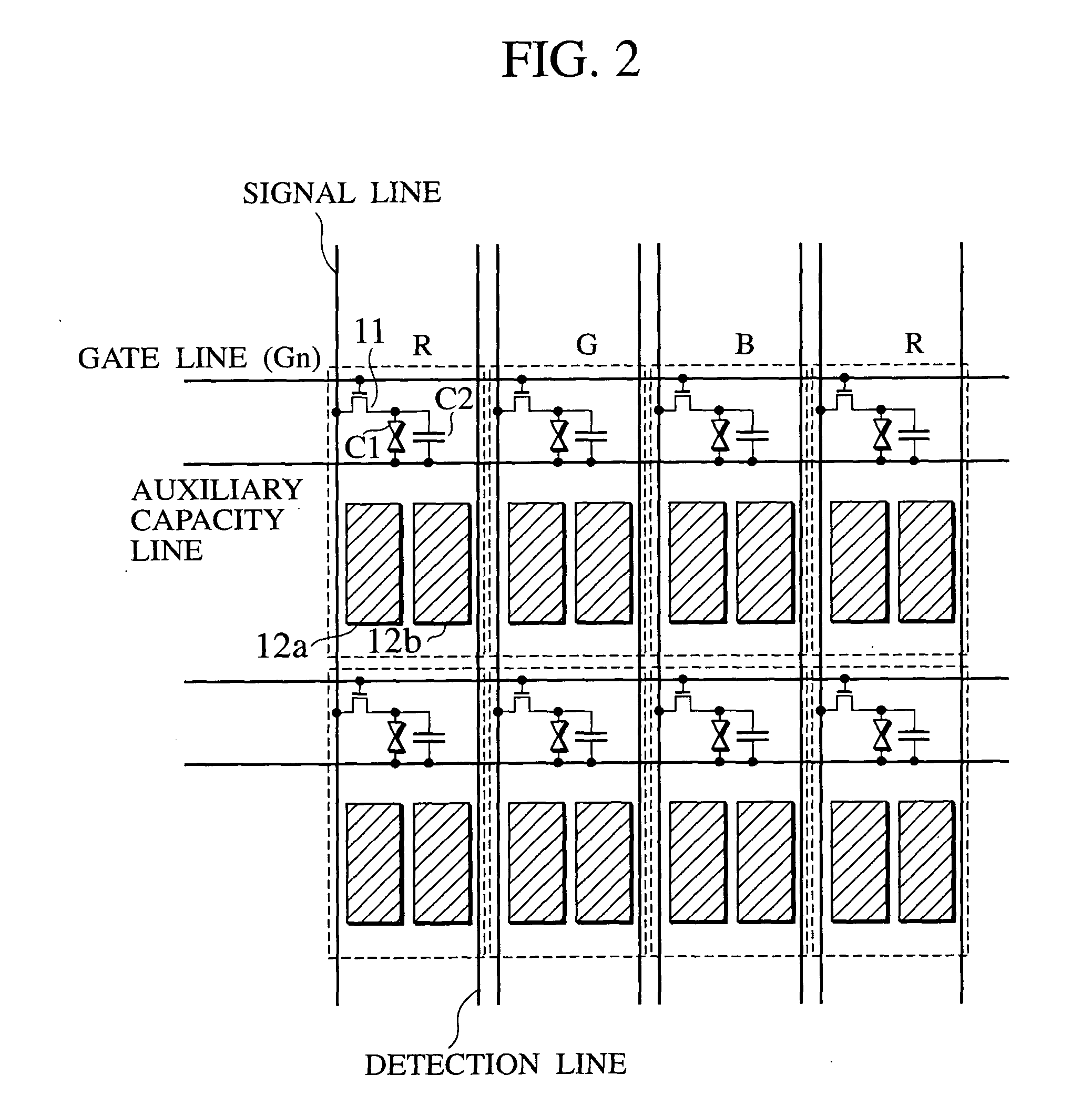

Suppression of leakage current in image acquisition

ActiveUS20040043676A1Current can be suppressedHigh sensitivityTransistorElectrically conductive connectionsDisplay deviceDangling bond

In a manufacturing process of a display device, hydrogenation in an I layer of photodiodes D1 and D2 is progressed less than that in a channel portion of a pixel TFT, and a defect density due to dangling bonds not terminated in the I layer of the photodiodes D1 and D2 is made higher than a defect density in the channel portion of the pixel TFT. Thus, while suppressing a leakage current of the pixel TFT, the sensitivity of the photodiodes D1 and D2 to light is improved. Moreover, a gate electrode is provided above an i region of a pin-type optical sensor diode with an insulating film interposed therebetween. Thus, a gate voltage can control a threshold of a bias voltage when a current starts to flow into the optical sensor diode and a leakage current is prevented from flowing into the optical sensor diode.

Owner:JAPAN DISPLAY CENT INC

Nitride semiconductor device and manufacturing method thereof

ActiveUS20130082276A1Suppresses Gate Leakage CurrentSuppress leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactNitride semiconductors

The present invention relates to a nitride semiconductor device and a manufacturing method thereof. According to one aspect of the present invention, a nitride semiconductor device including: a nitride semiconductor layer having a 2DEG channel; a source electrode in ohmic contact with the nitride semiconductor layer; a drain electrode in ohmic contact with the nitride semiconductor layer; a p-type nitride layer formed on the nitride semiconductor layer between the source and drain electrodes; an n-type nitride layer formed on the p-type nitride layer; and a gate electrode formed between the source and drain electrodes to be close to the source electrode and in contact with the n-type nitride layer so that a source-side sidewall thereof is aligned with source-side sidewalls of the p-type and n-type nitride layers is provided. Further, a method of manufacturing a nitride semiconductor device is provided.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Semiconductor device and semiconductor integrated circuit using the same

InactiveUS7732864B2Improve performanceReduce power consumptionSemiconductor/solid-state device detailsSolid-state devicesHeavy loadHigh velocity

Owner:RENESAS ELECTRONICS CORP

Organic electroluminescent device

ActiveUS20150303380A1Solve low luminous efficiencyReduce voltageOrganic chemistrySolid-state devicesOrganic electroluminescenceCharge generation

An organic electroluminescence device including: an anode; a cathode; two or more emitting units that are disposed between the anode and the cathode, each unit having an emitting layer; and a charge-generating layer that is disposed between the emitting units, wherein the charge-generating layer includes an N layer nearer to the anode and a P layer nearer to the cathode, and the N layer includes a compound represented by the following formula (I) or (II):

Owner:JOLED INC

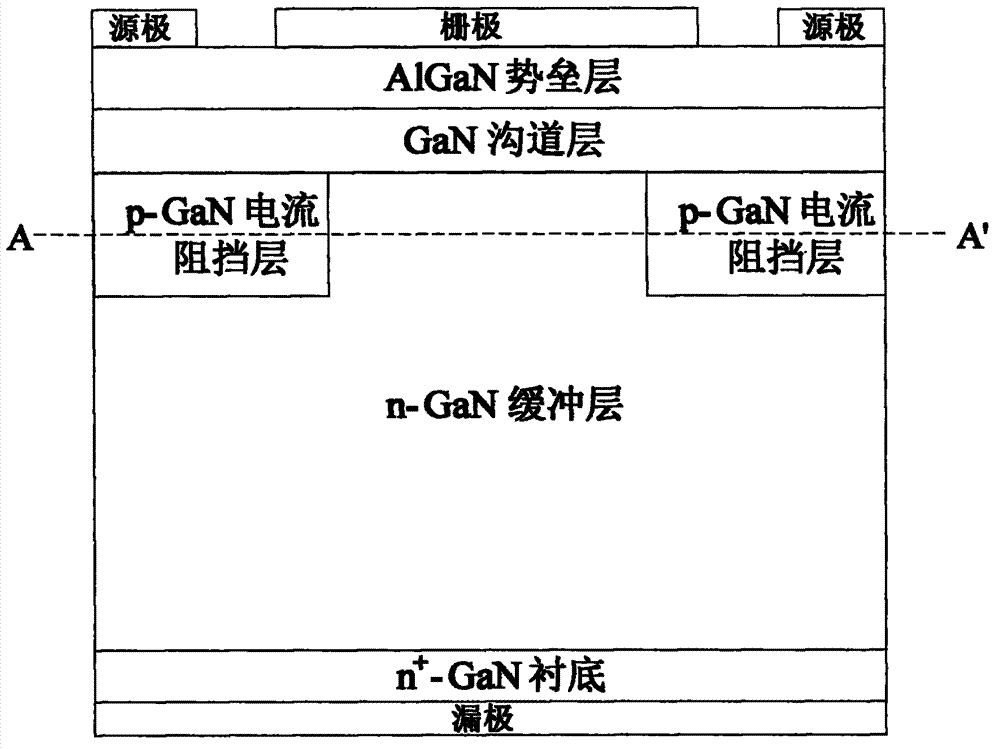

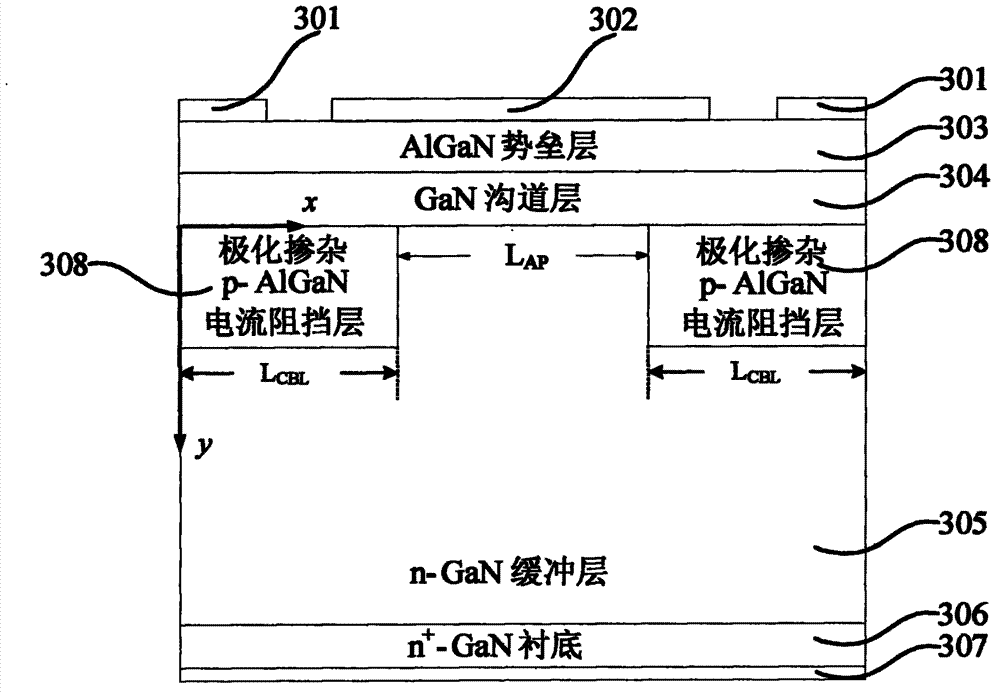

Vertical gallium nitride based nitride heterojunction field effect transistor with polarized doped current barrier layer

InactiveCN103035706AImprove thermal stabilityHigh activation rateSemiconductor devicesOhmic contactGallium nitride

The invention provides a vertical gallium nitride based nitride heterojunction field effect transistor with a polarized doped current barrier layer, which sequentially and mainly comprises a drain electrode, an n<+>-GaN substrate, an n-GaN buffer layer, a GaN channel layer, an AlGaN barrier layer, a source electrode on the AlGaN barrier layer and a grid electrode on the AlGaN barrier layer from bottom to top, wherein the source electrode and the drain electrode are both in ohmic contact, the grid electrode is in Schottky contact, the vertical gallium nitride based nitride heterojunction field effect transistor further comprises the polarized doped p-AlGaN current barrier layer between the n-GaN buffer layer and the GaN channel layer, and an Al component in the current barrier layer increases gradually in the y direction. According to the vertical gallium nitride based nitride heterojunction field effect transistor with the polarized doped current barrier layer, a polarized electric field, produced by the gradual change of the Al component in the current barrier layer, increases the activation rate of p-type impurities and the hole concentration of the current barrier layer, so that the breakdown voltage of an element is increased.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

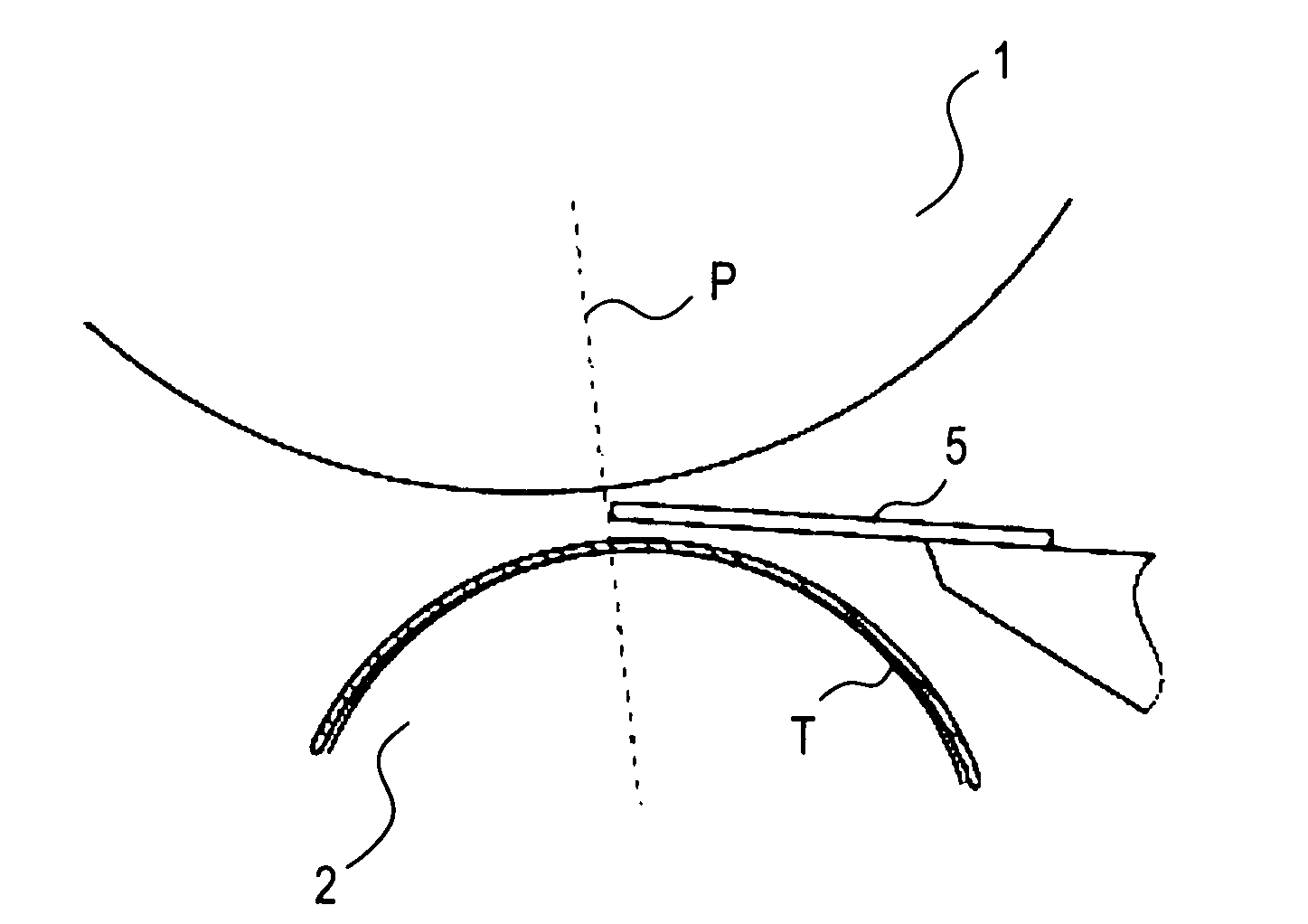

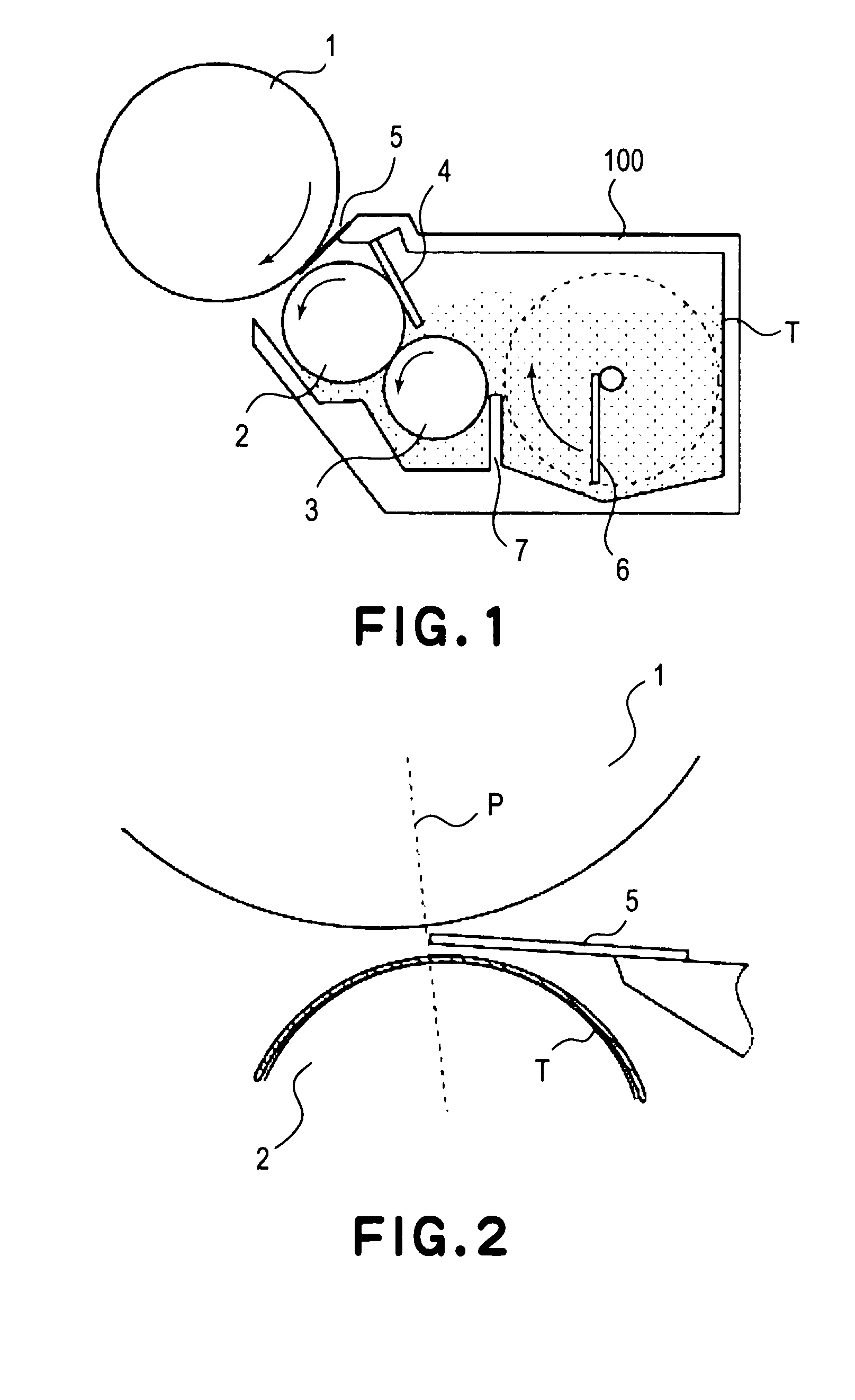

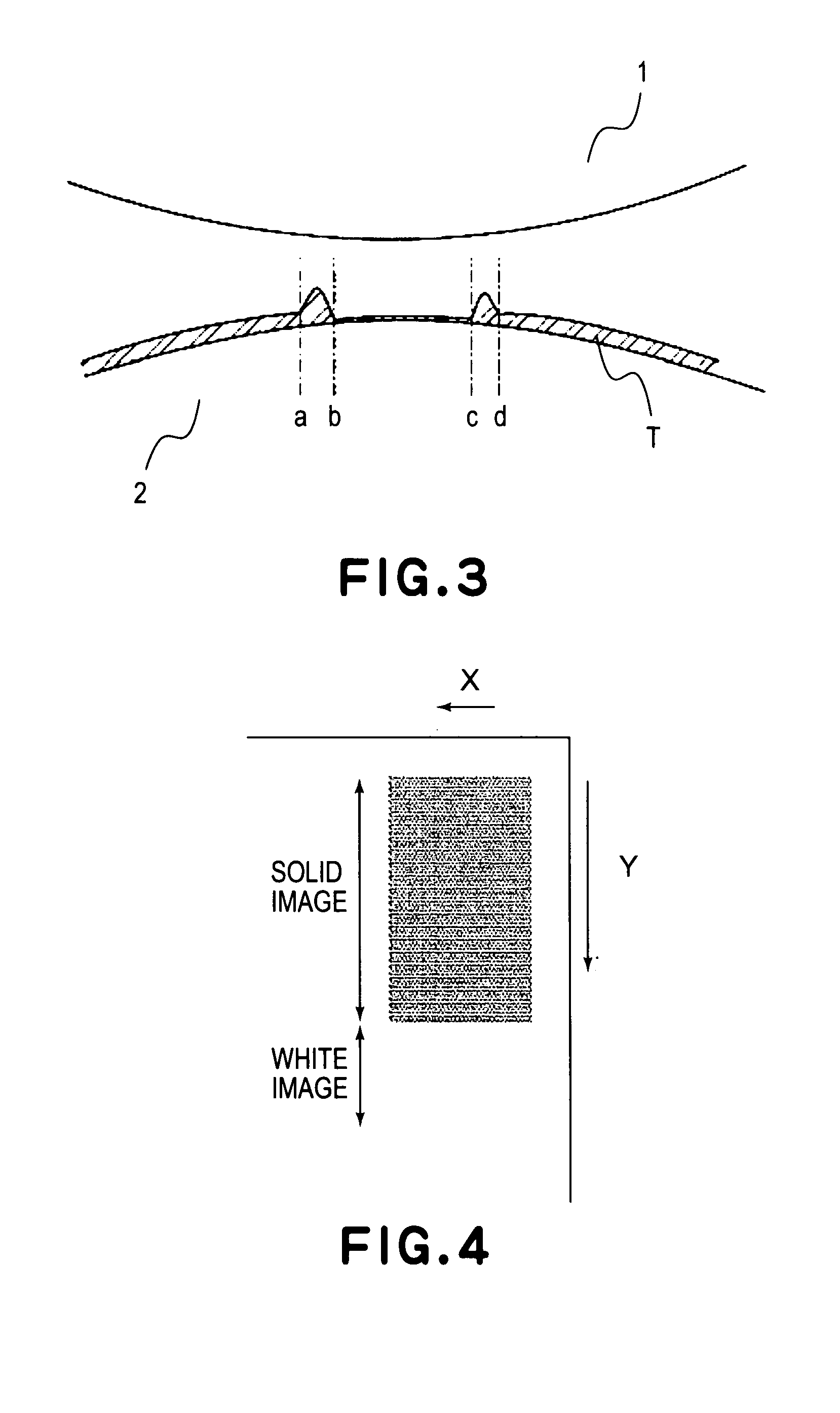

Developing apparatus

InactiveUS20050008401A1Simple processImprove environmental adaptabilityElectrographic process apparatusLatent imageMechanical engineering

A developing apparatus includes a developer carrying member, disposed opposite to an image bearing member, for carrying developer which is caused to jump from the developer carrying member to the image bearing member to develop an electrostatic latent image formed on said image bearing member by creating an oscillation electric field between the image bearing member and the developer carrying member at an opposing portion where the image bearing member and the developer carrying member are opposed to each other; and a jumping developer regulation member for regulating an area in which the developer is caused to jump in the opposing portion. The jumping developer regulation member is disposed apart from the developer carried by the developer carrying member and is an insulating member or an electrically floating member.

Owner:CANON KK

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com