Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

565results about How to "Suppress failure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

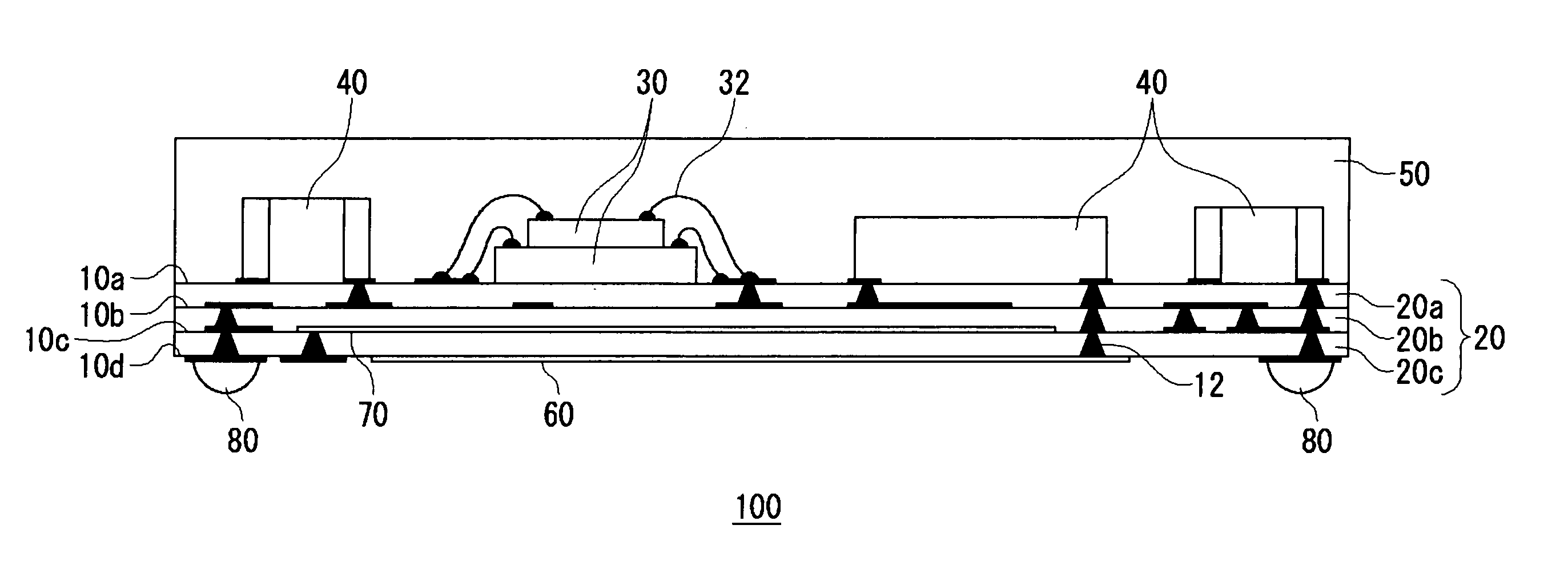

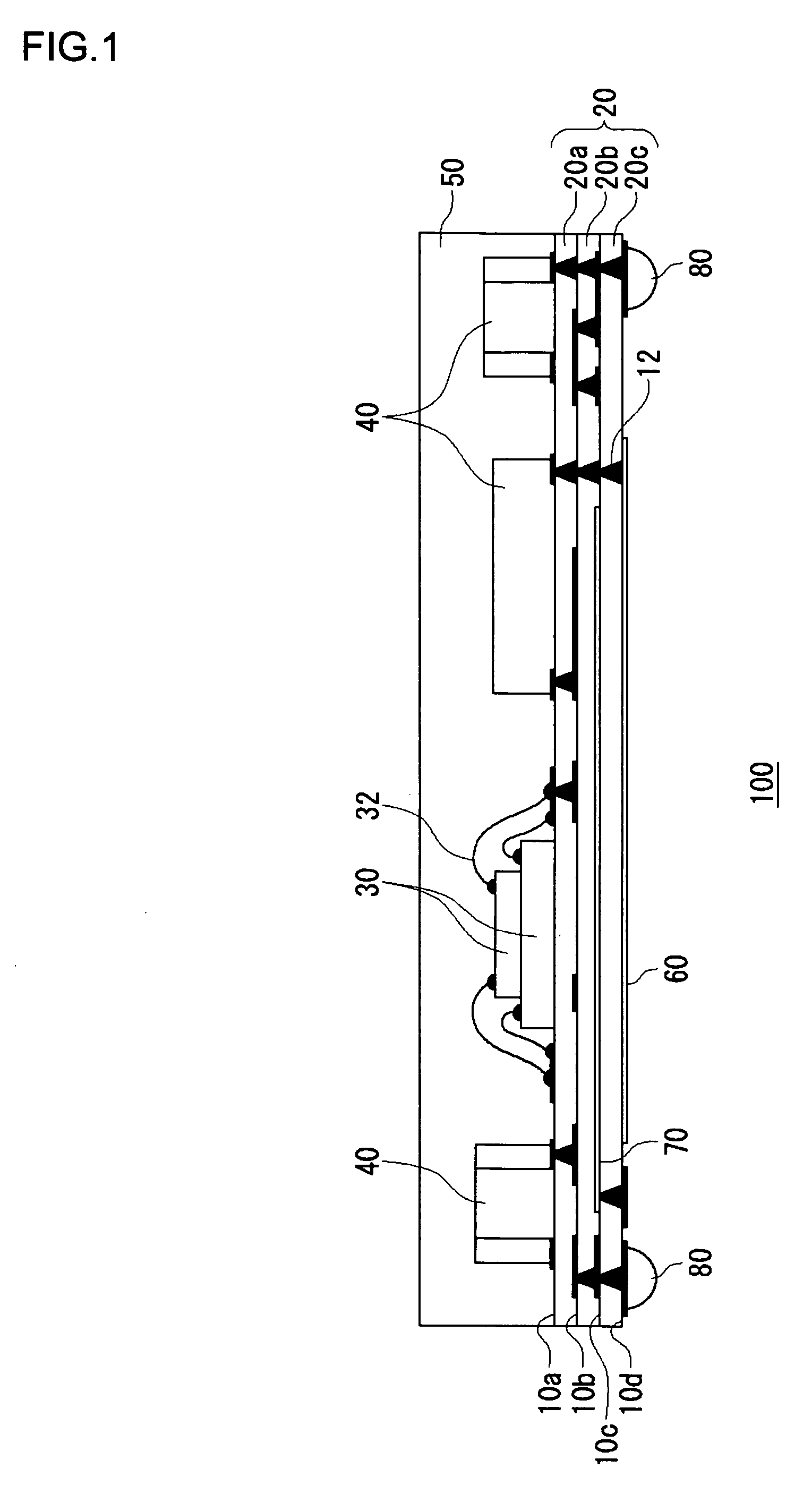

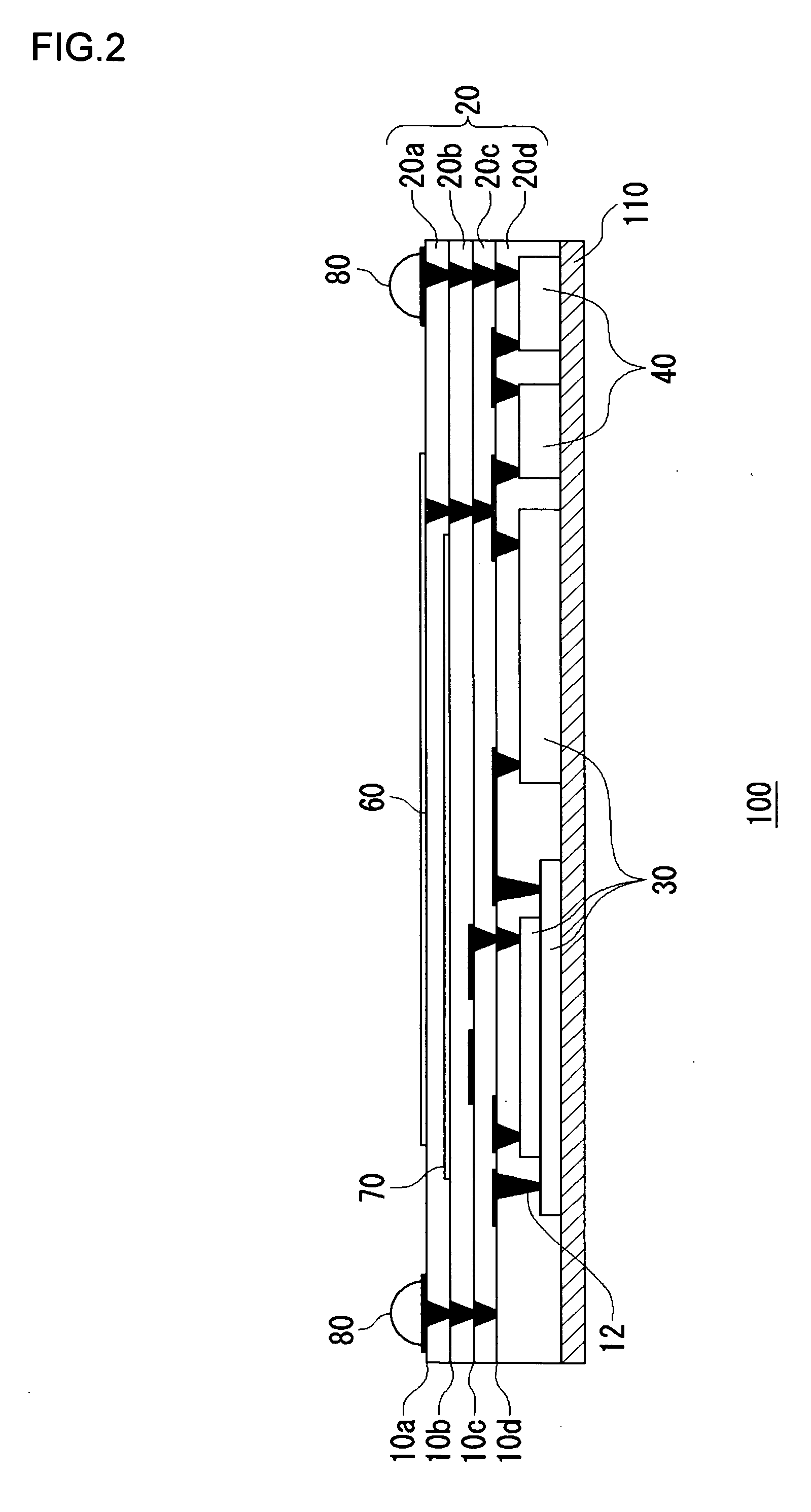

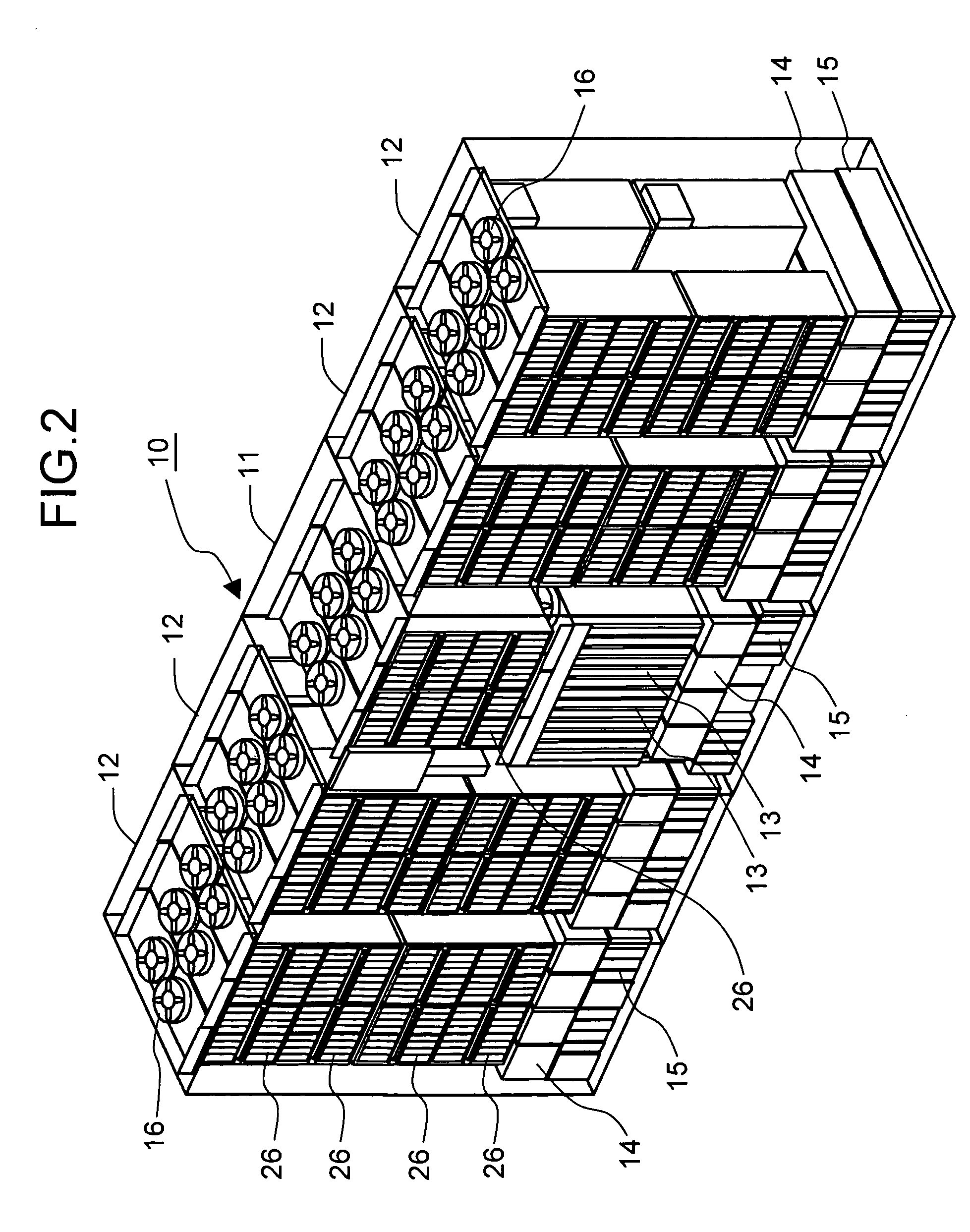

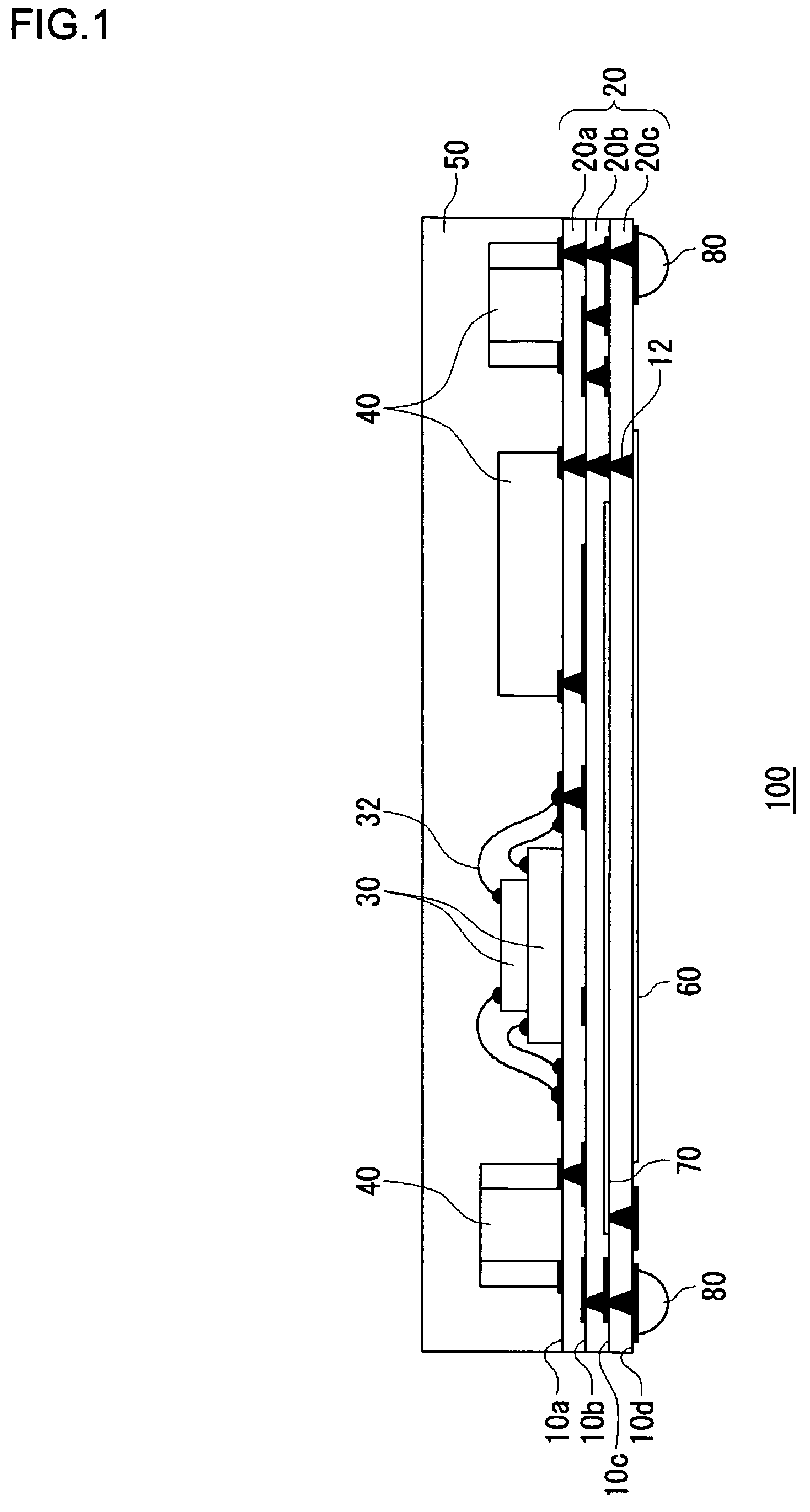

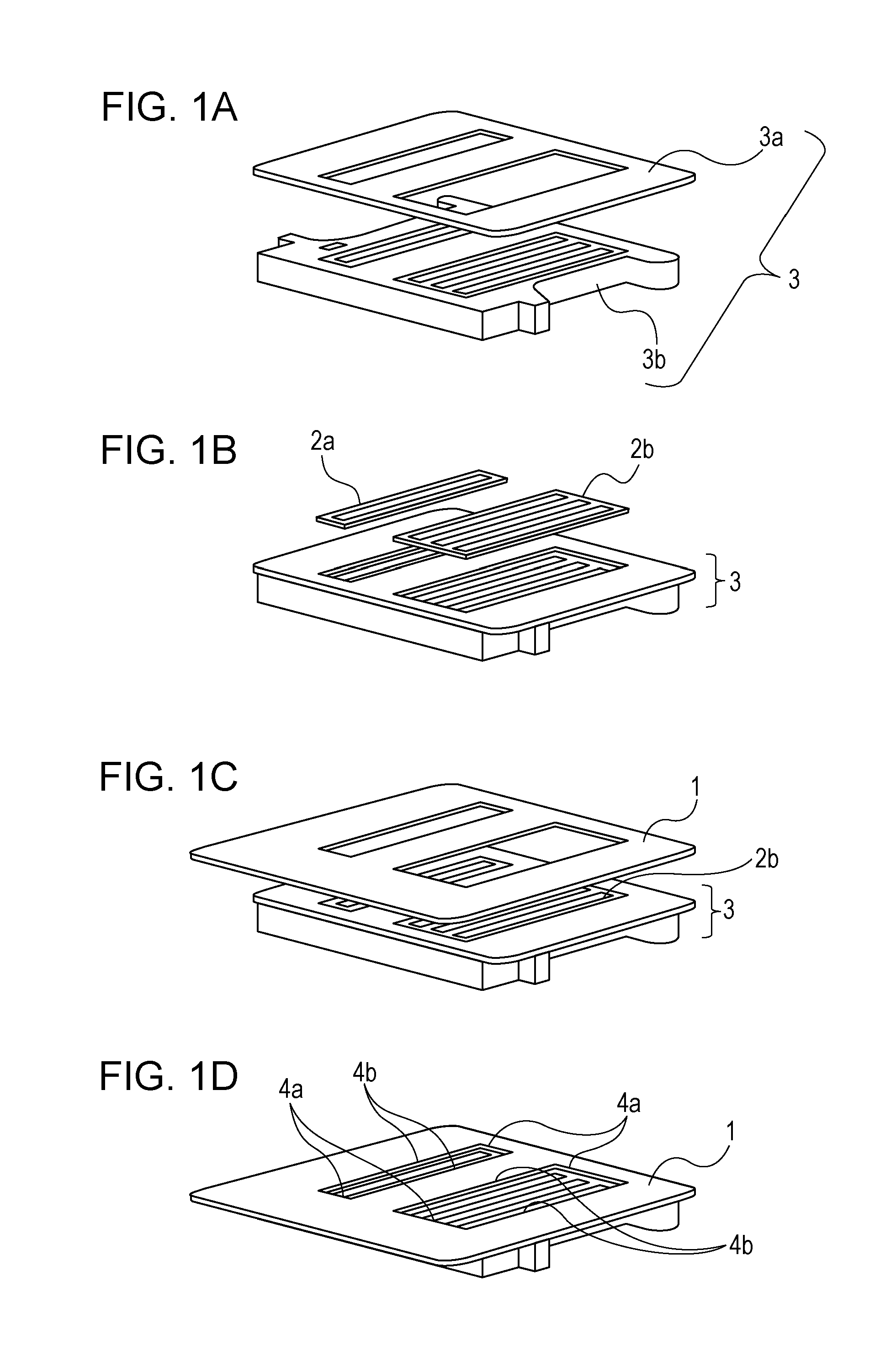

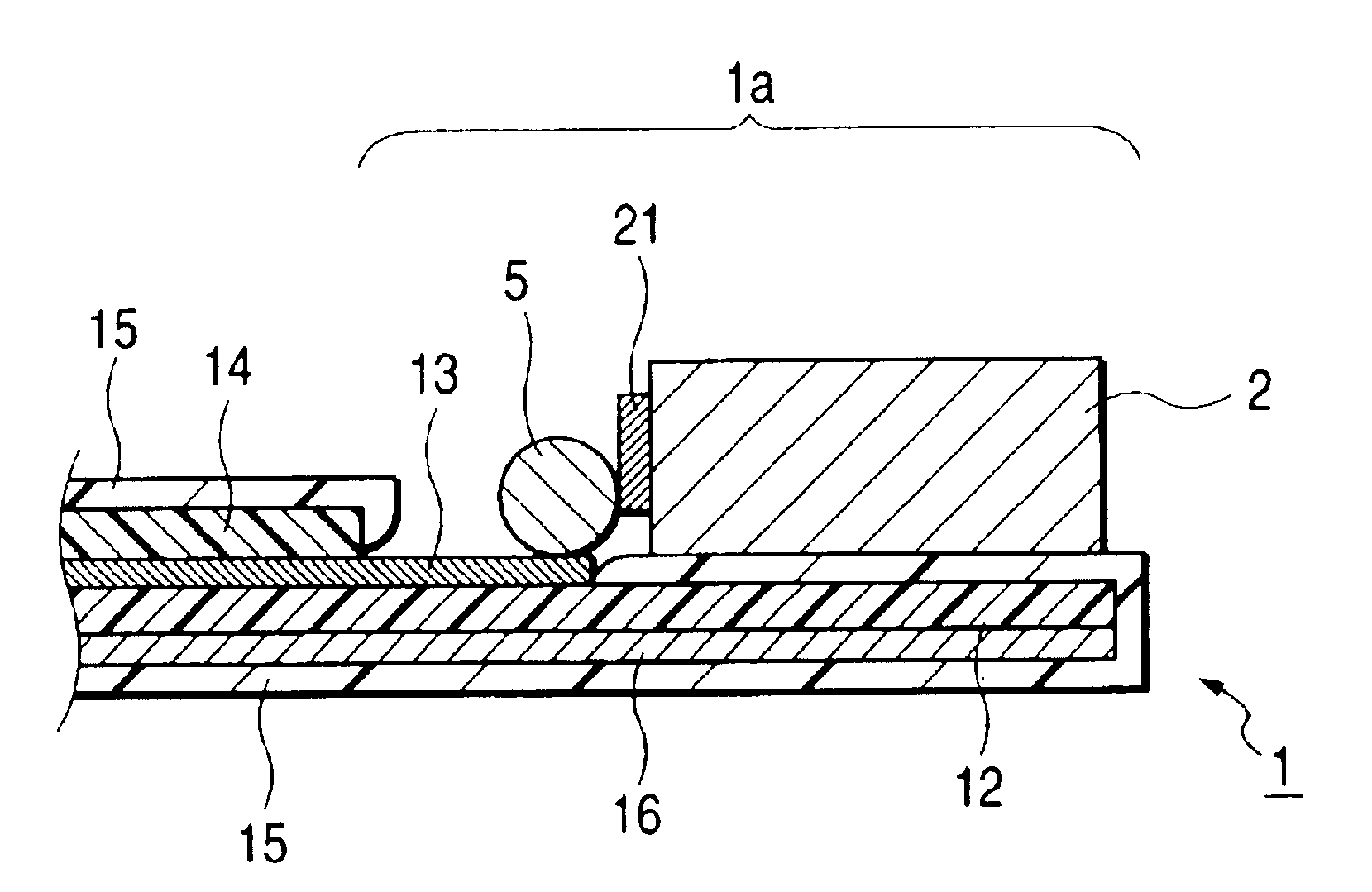

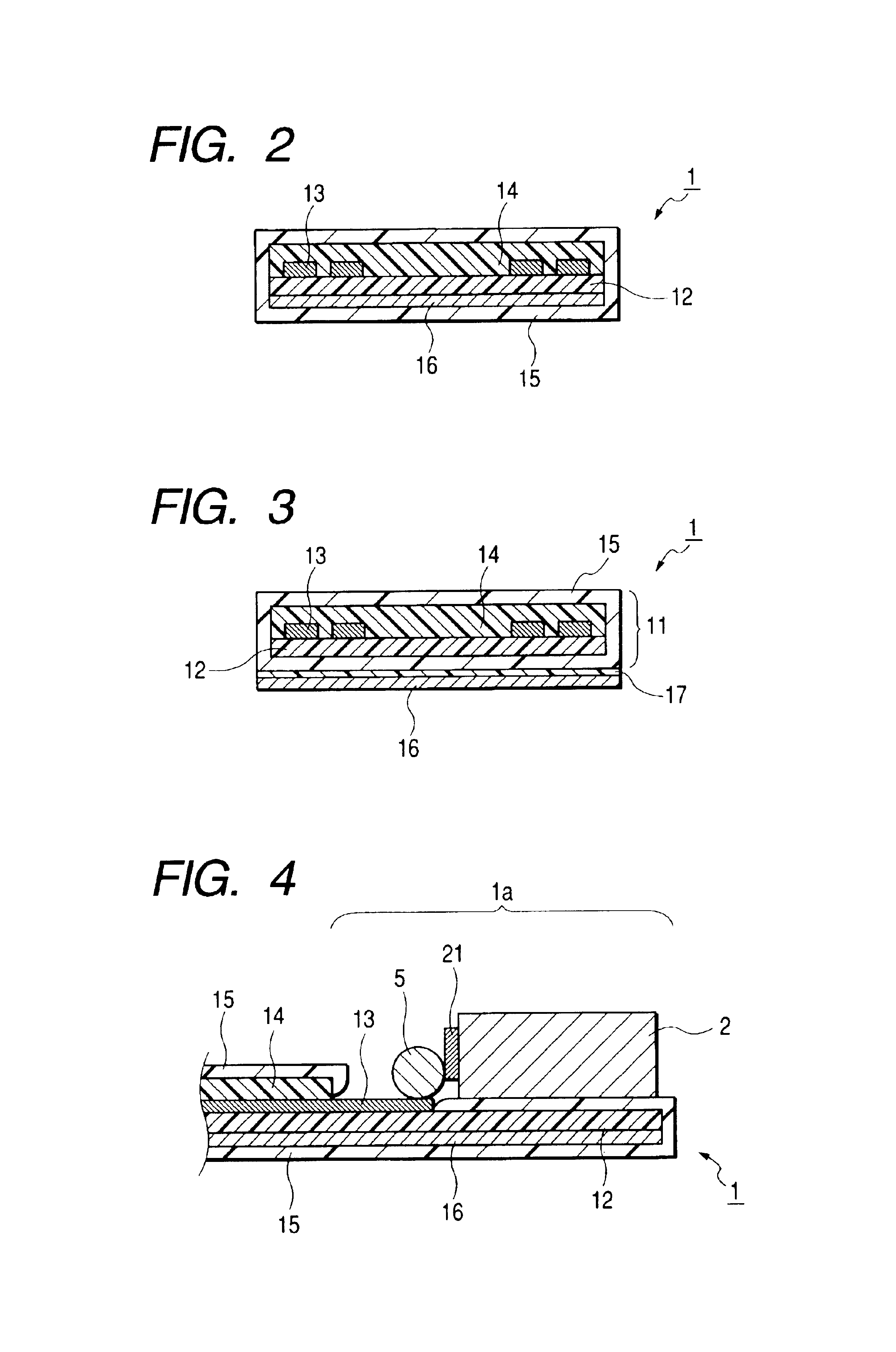

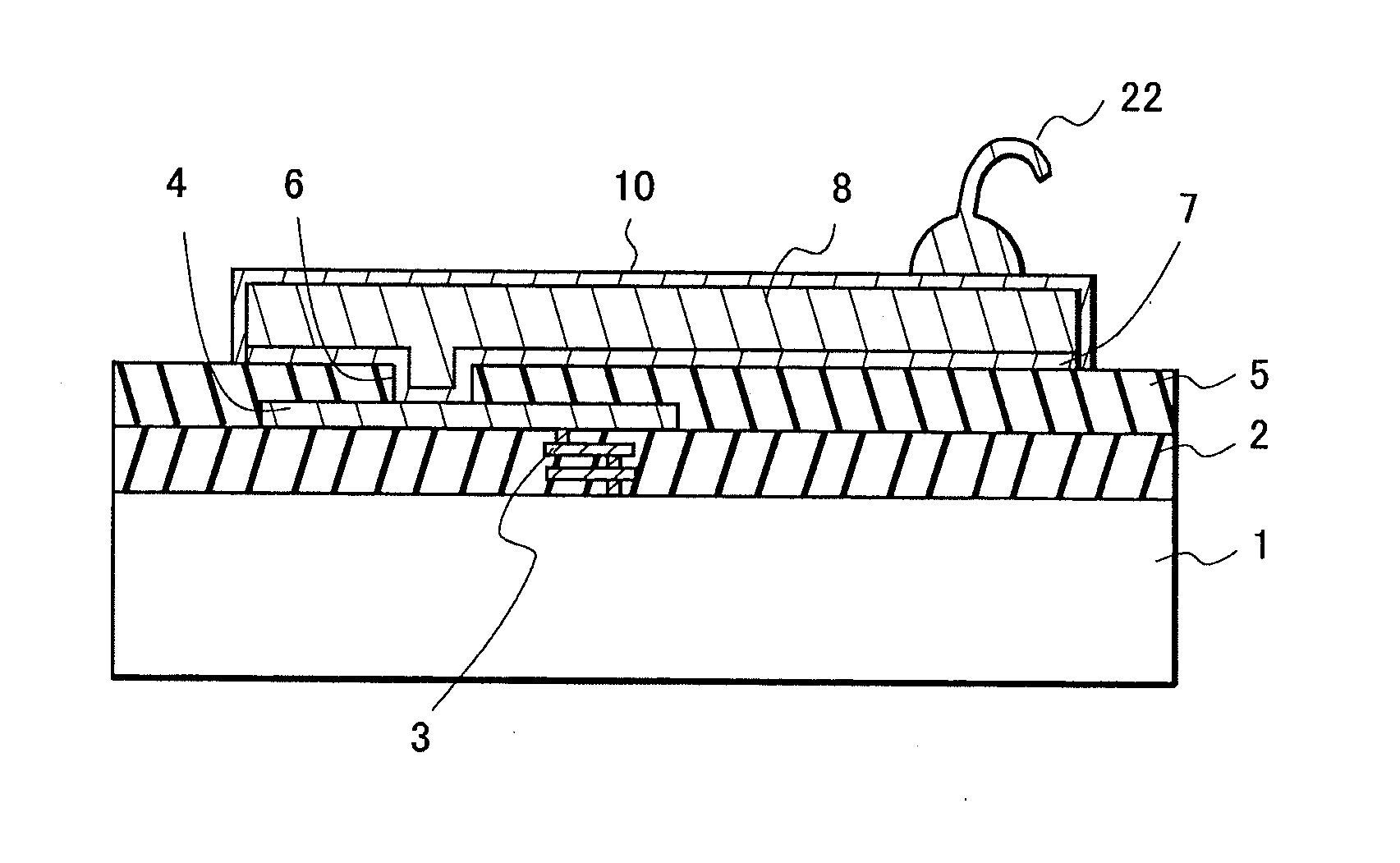

Integrated antenna type circuit apparatus

InactiveUS20060049995A1Reduce areaImprove emission efficiencyAntenna supports/mountingsPrinted electric component incorporationElectrical conductorIntegrated antenna

An integrated antenna type circuit apparatus which provides excellent circuit characteristics while suppressing an increase in packaging area. The integrated antenna type circuit apparatus includes an insulating base, a semiconductor circuit device, chip parts, a molding resin, an antenna conductor, a ground conductor, and external lead electrodes. The plurality of chip parts are mounted on the insulating base, and are soldered to electrodes of wiring conductors on the top of the insulating base for electric and physical connection. The insulating base has a multilayer structure, being formed by laminating a plurality of insulator layers. The antenna conductor is formed on the bottom of the insulating base. A wiring conductor adjacent to the antenna conductor is provided with the ground conductor so that it overlaps with the antenna conductor.

Owner:SANYO ELECTRIC CO LTD

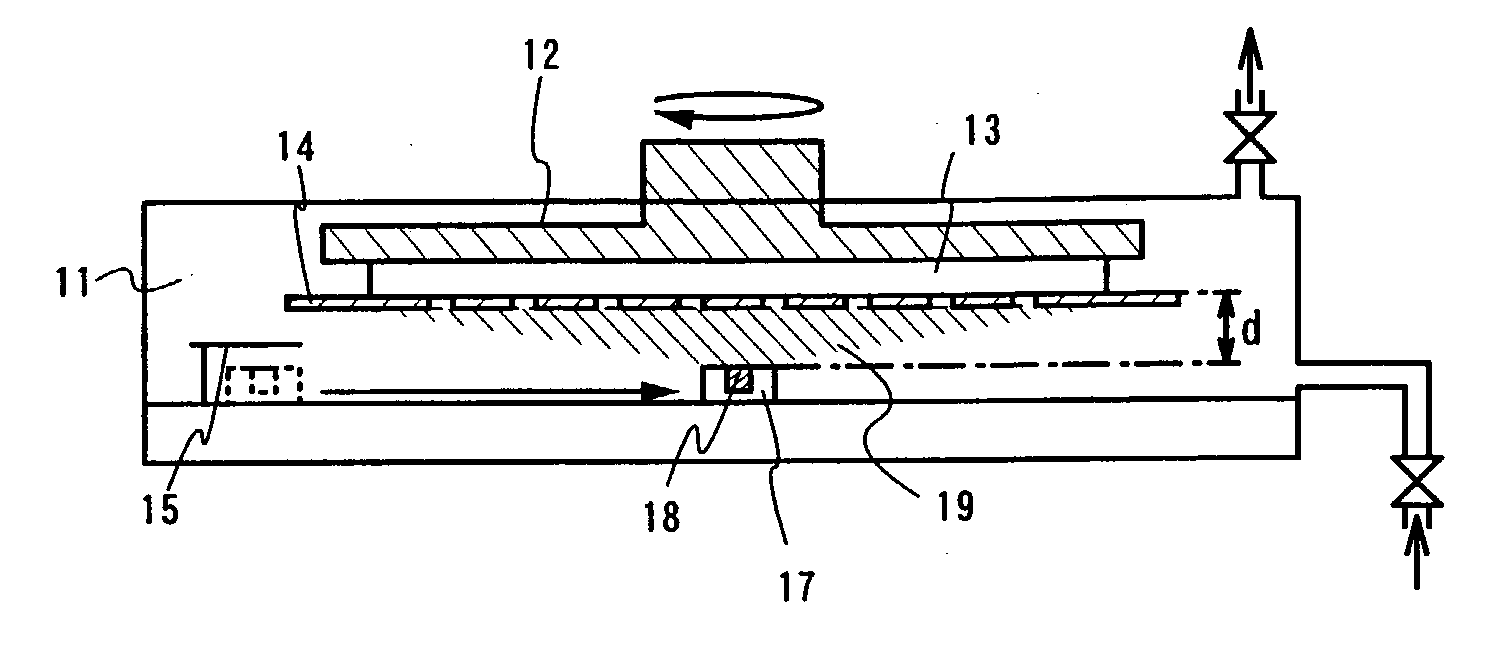

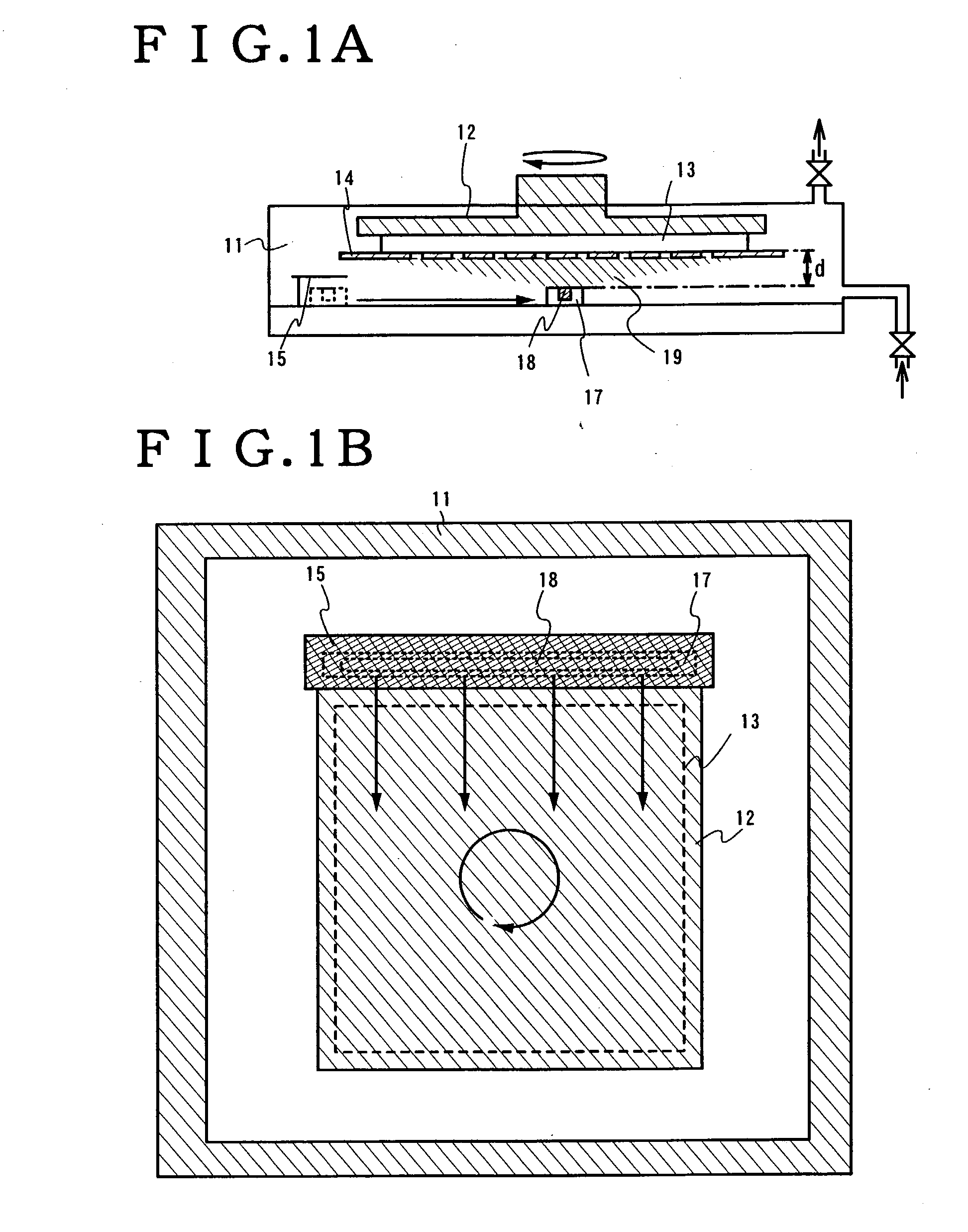

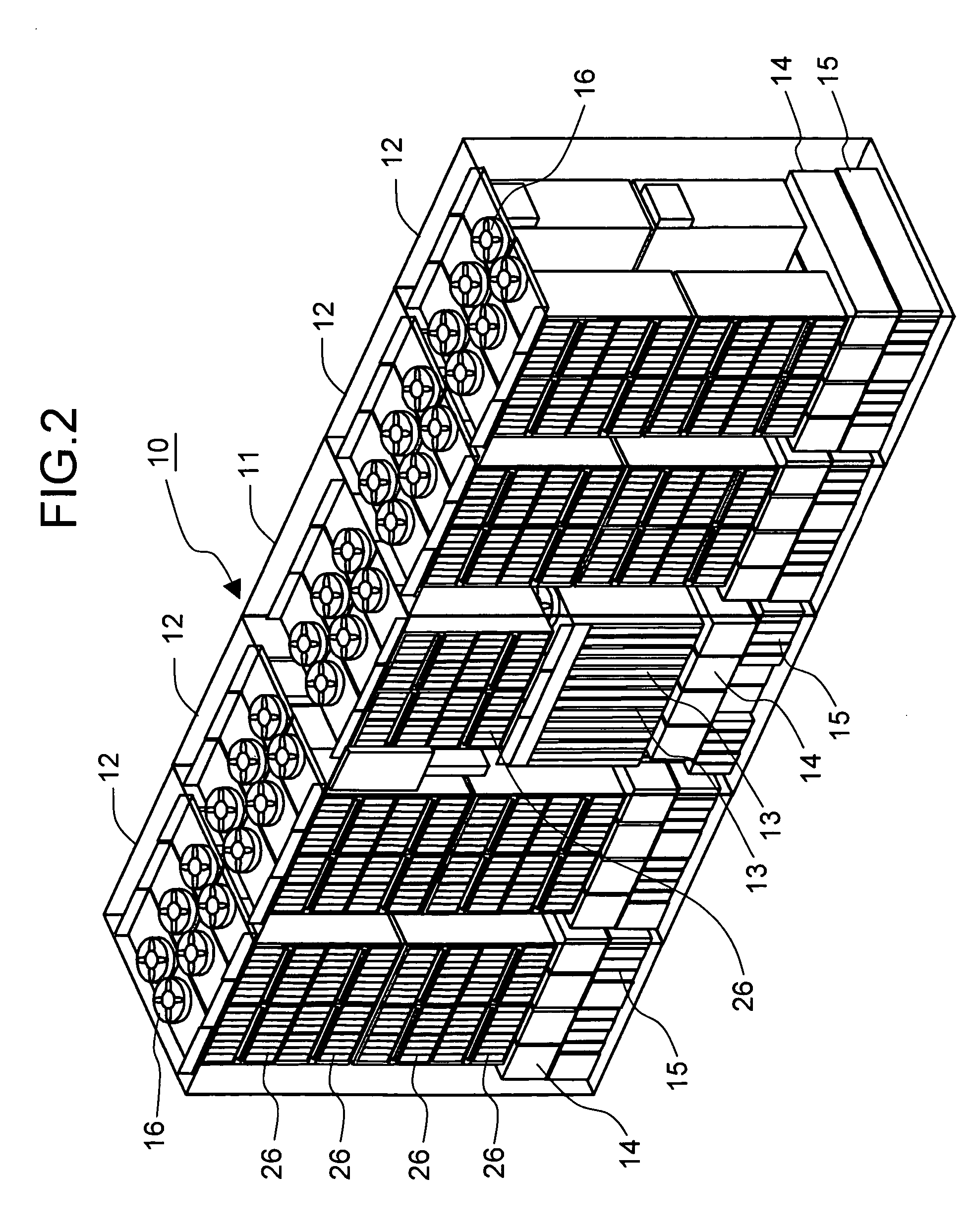

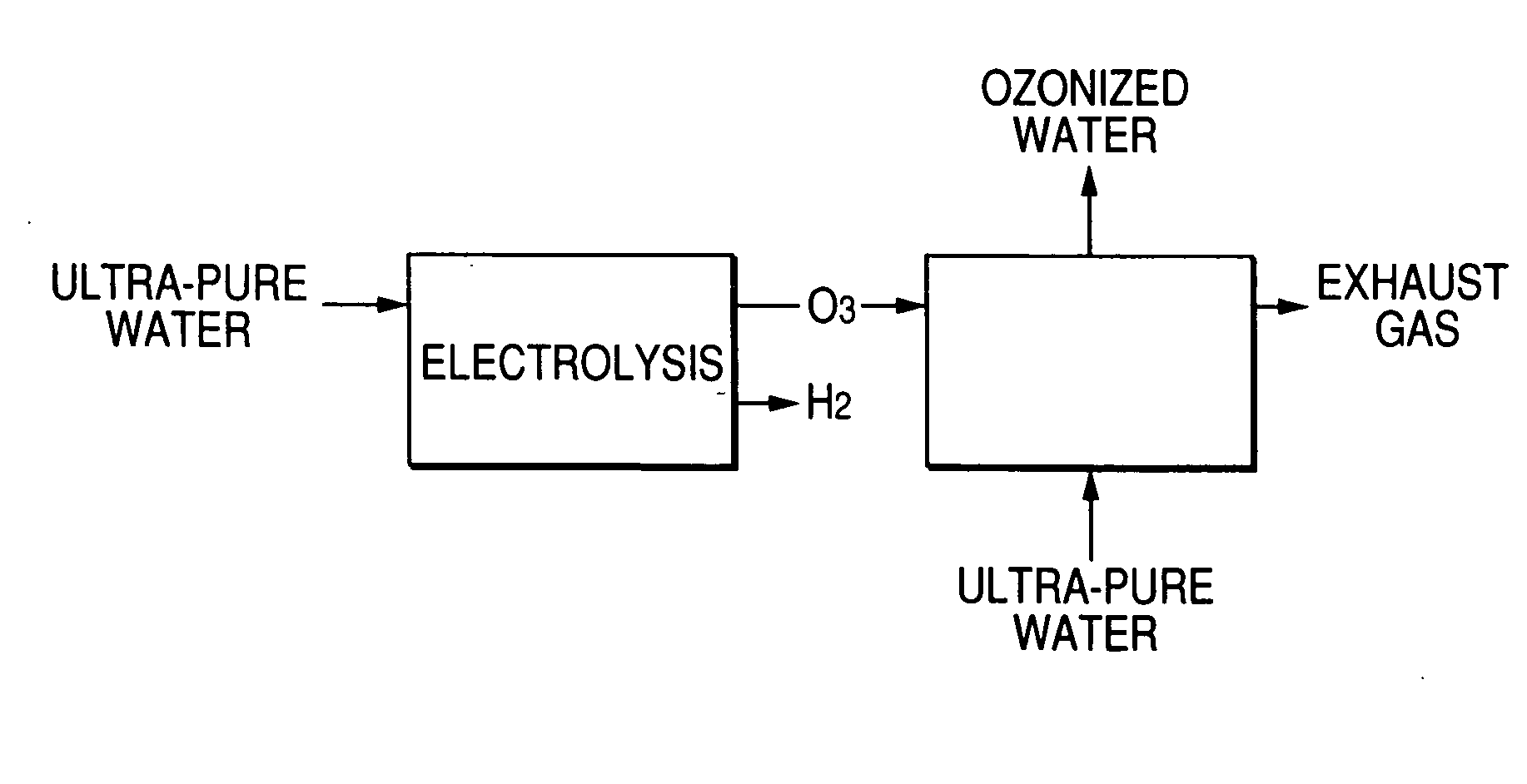

Fabrication system and a fabrication method of light emitting device

InactiveUS20030162314A1Improve utilization efficiencyReduce capacityLiquid surface applicatorsFrom solid stateEvaporationEngineering

An evaporation apparatus with high utilization efficiency for EL materials and excellent film uniformity is provided. The invention is an evaporation apparatus having a movable evaporation source and a substrate rotating unit, in which the space between an evaporation source holder and a workpiece (substrate) is narrowed to 30 cm or below, preferably 20 cm, more preferably 5 to 15 cm, to improve the utilization efficiency for EL materials. In evaporation, the evaporation source holder is moved in the X-direction or the Y-direction, and the workpiece (substrate) is rotated for deposition. Therefore, film uniformity is improved.

Owner:SEMICON ENERGY LAB CO LTD

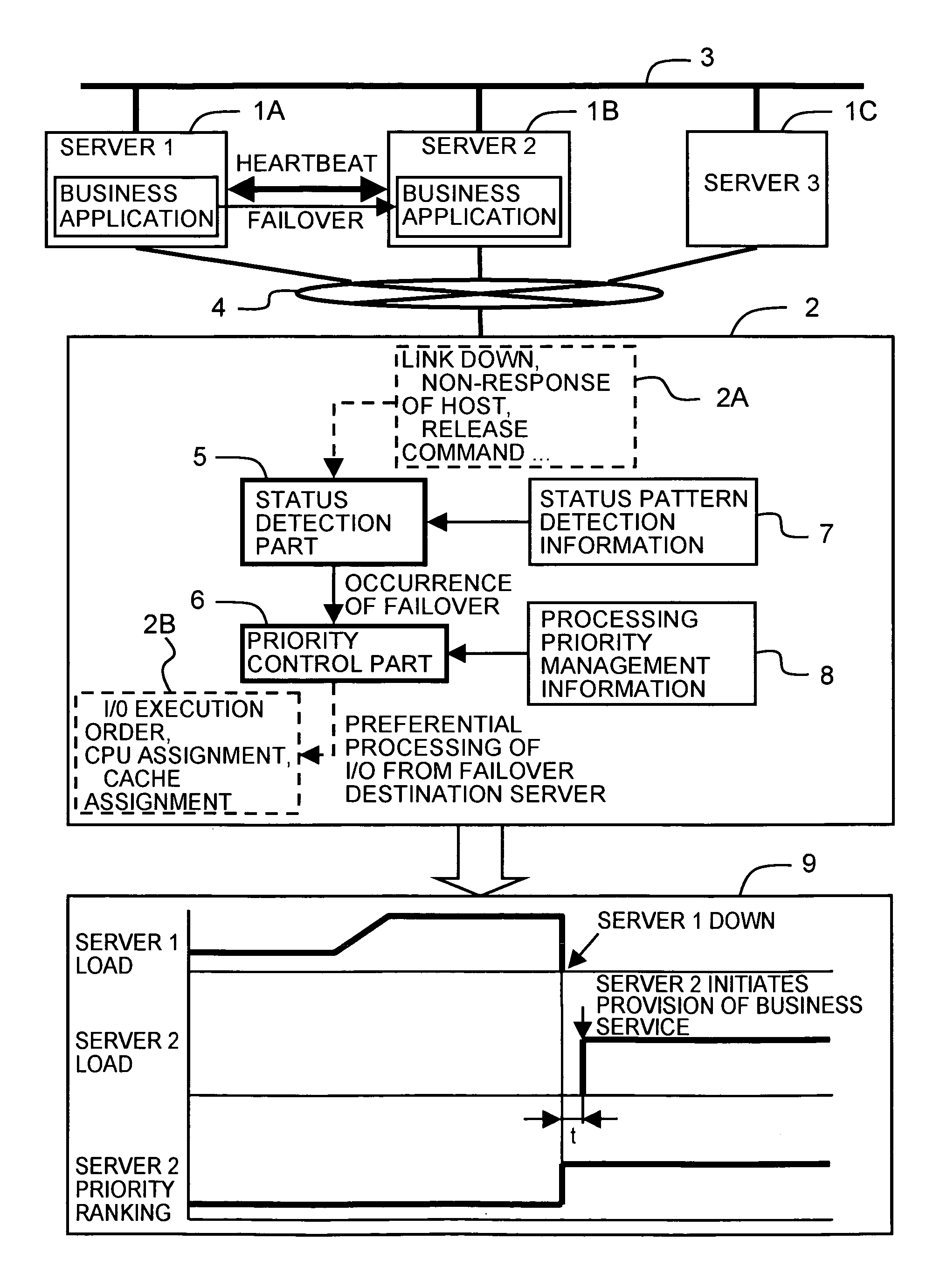

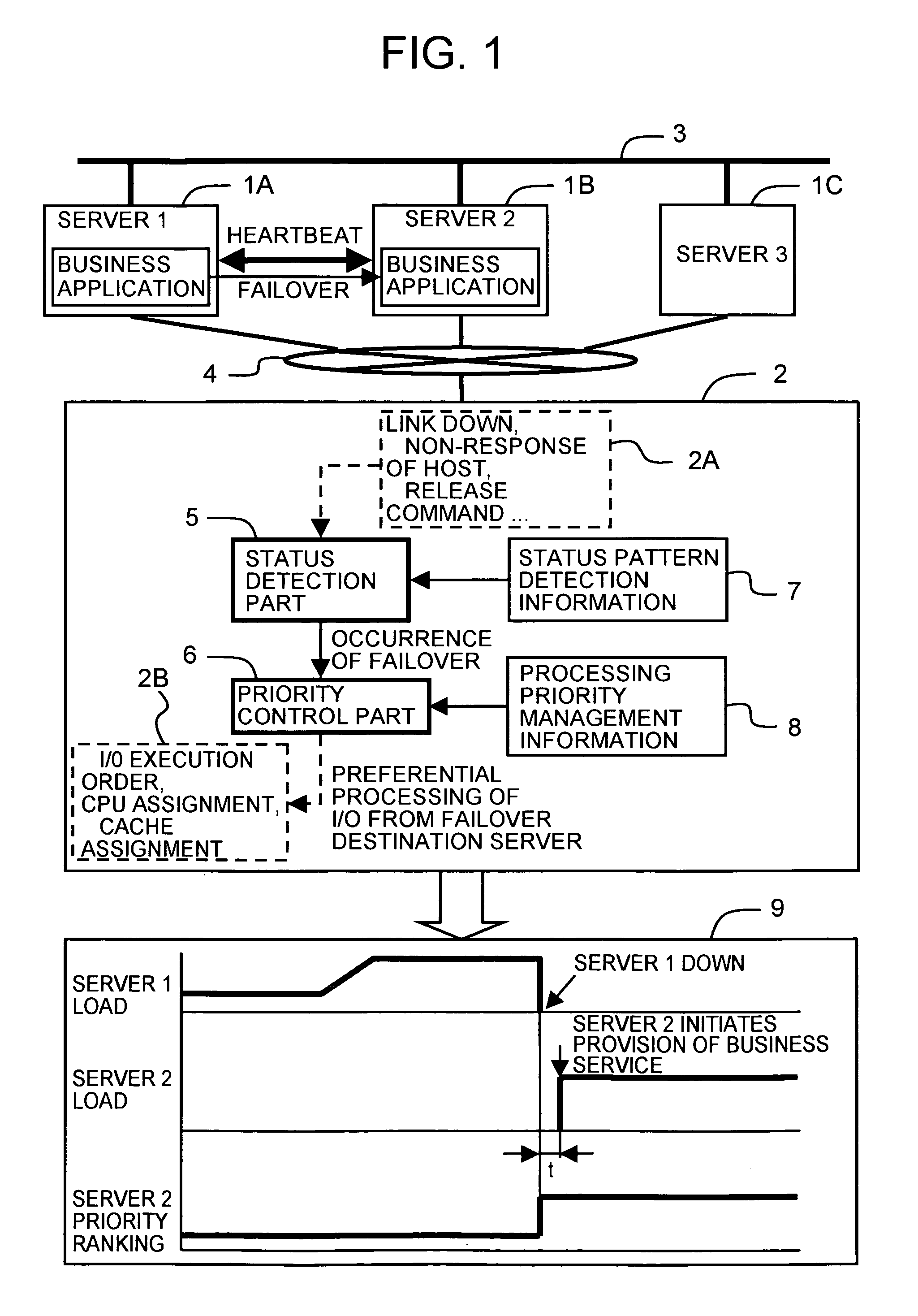

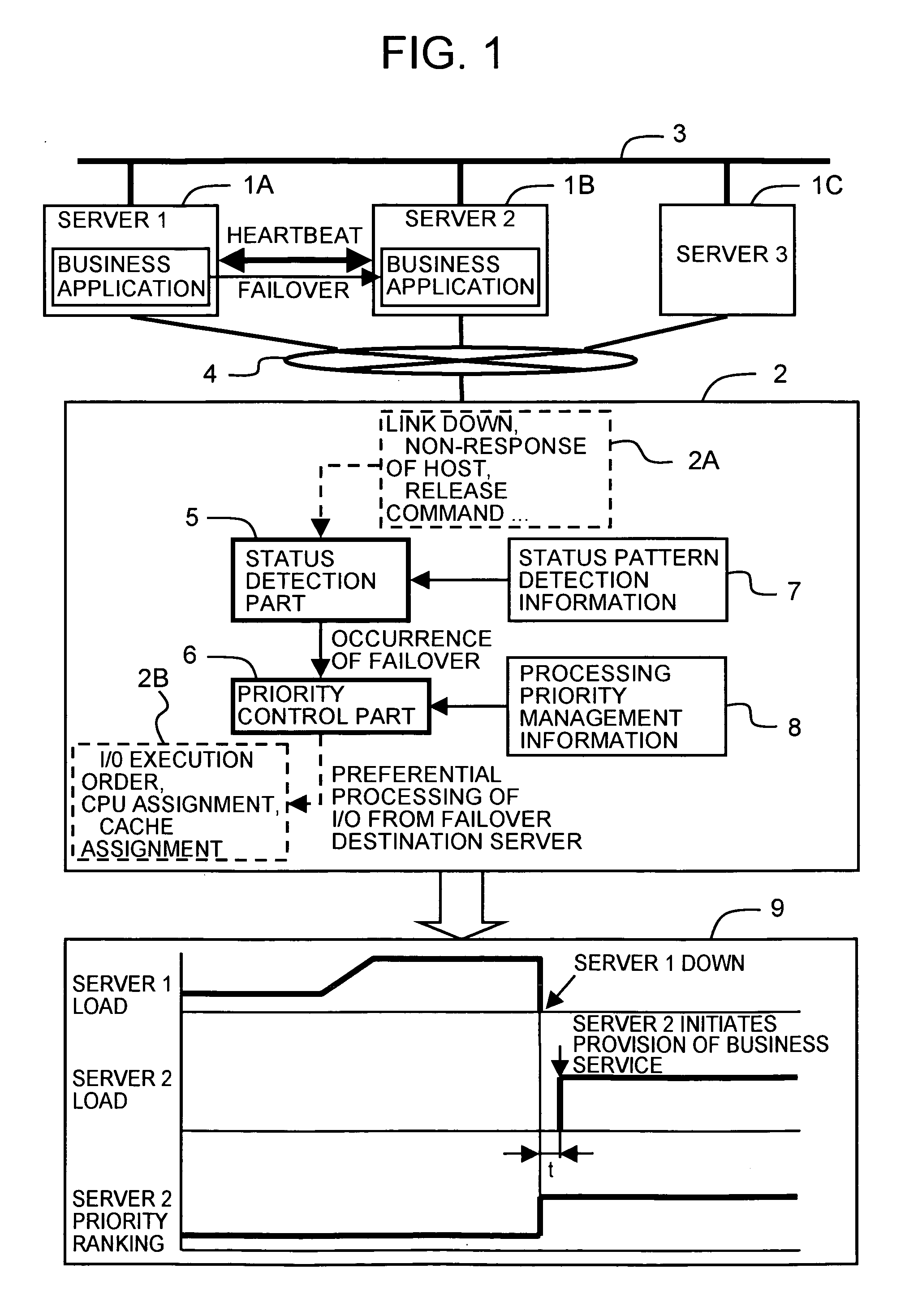

Storage device for monitoring the status of host devices and dynamically controlling priorities of the host devices based on the status

ActiveUS7240234B2Easy to handleSuppress failureInput/output to record carriersMemory systemsFailoverProcessing priority

Owner:GOOGLE LLC

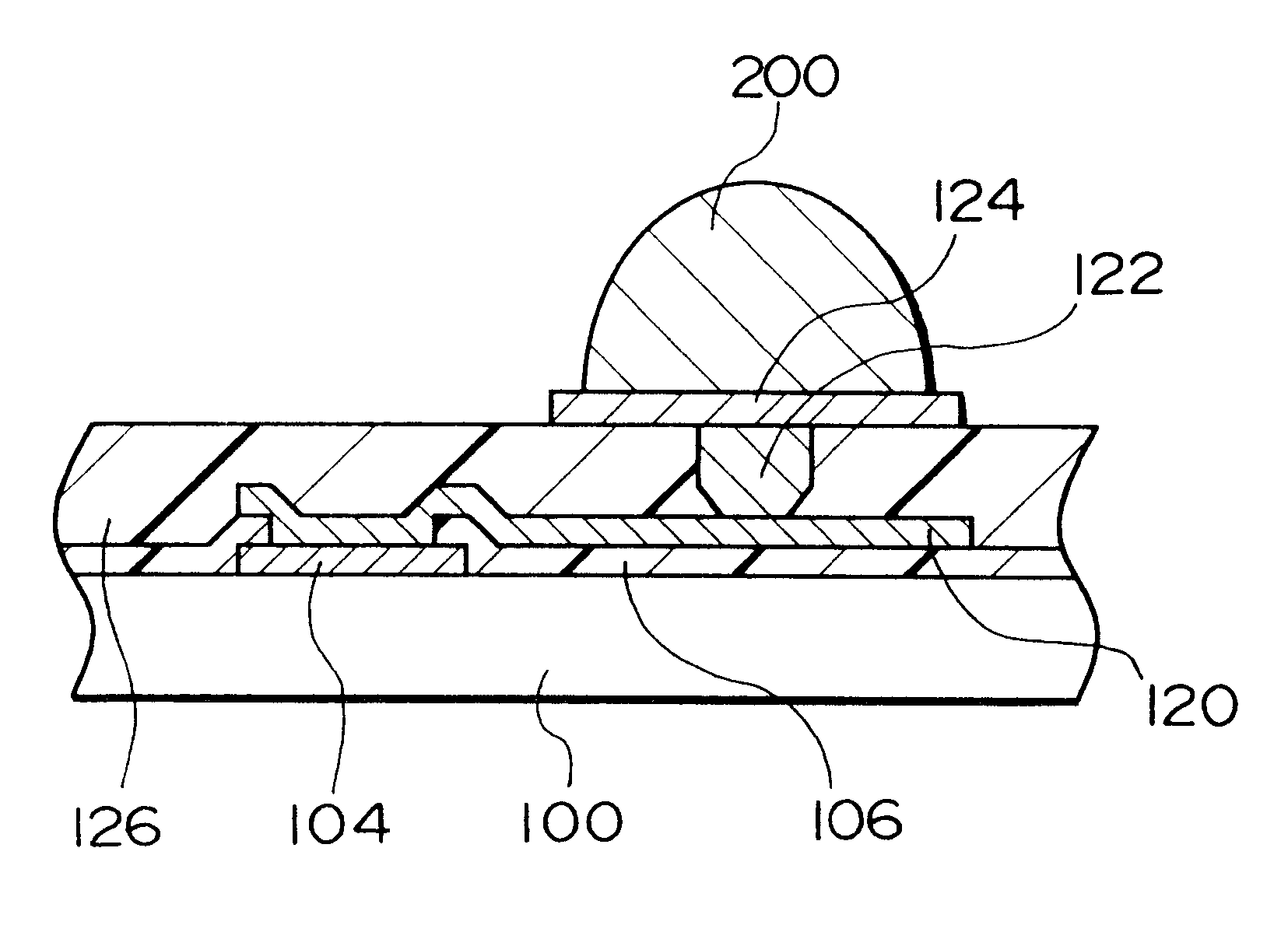

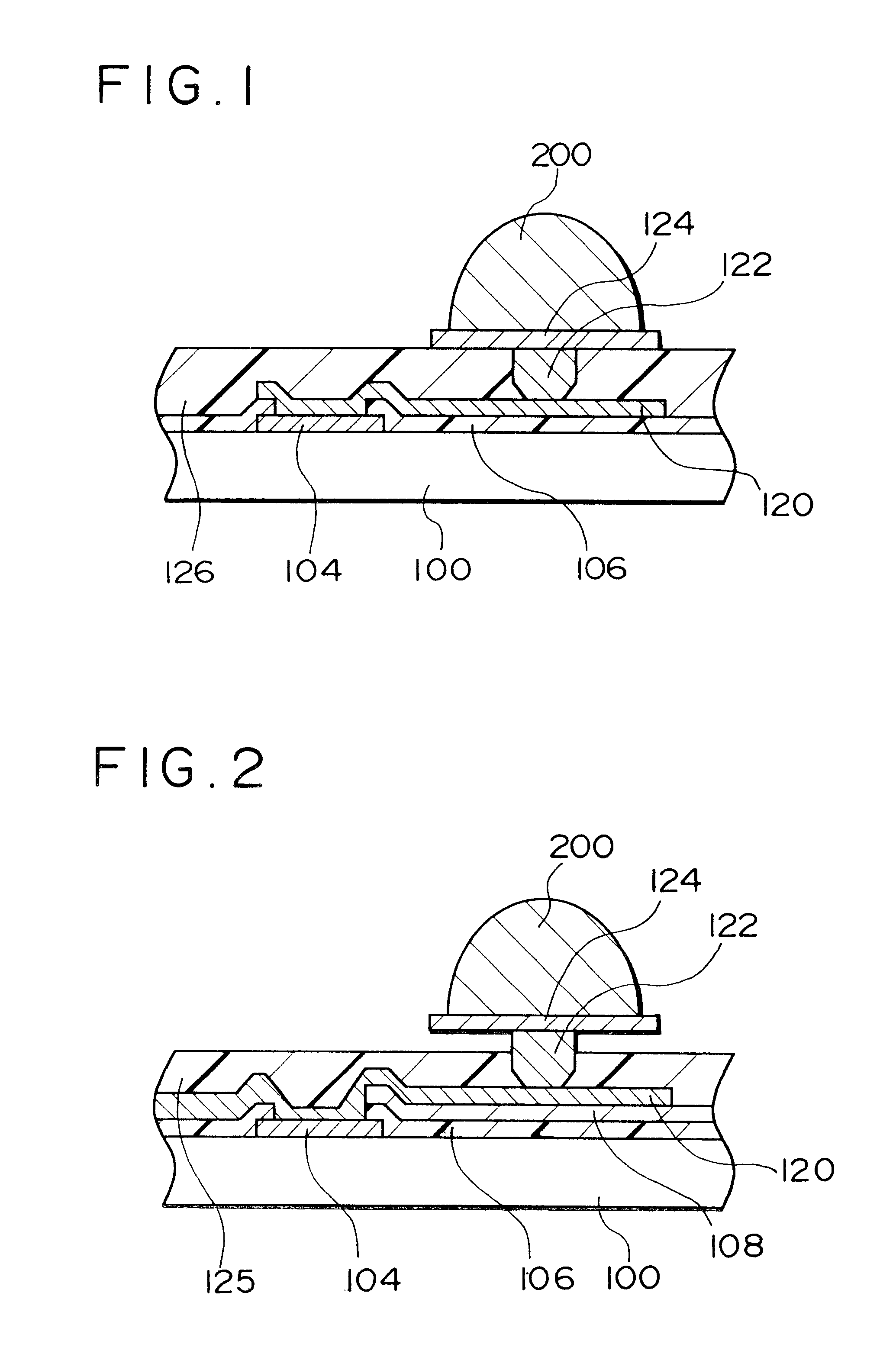

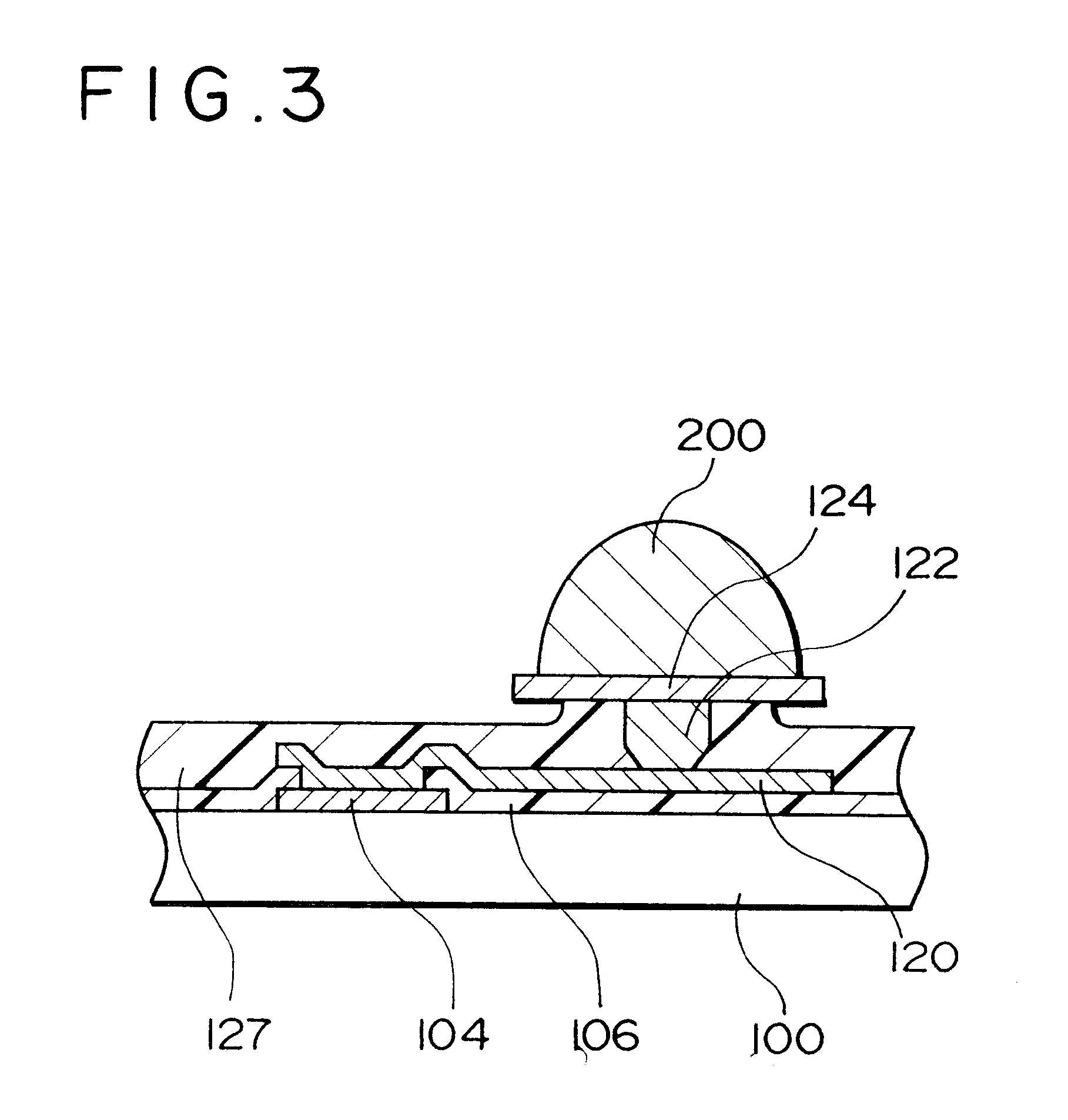

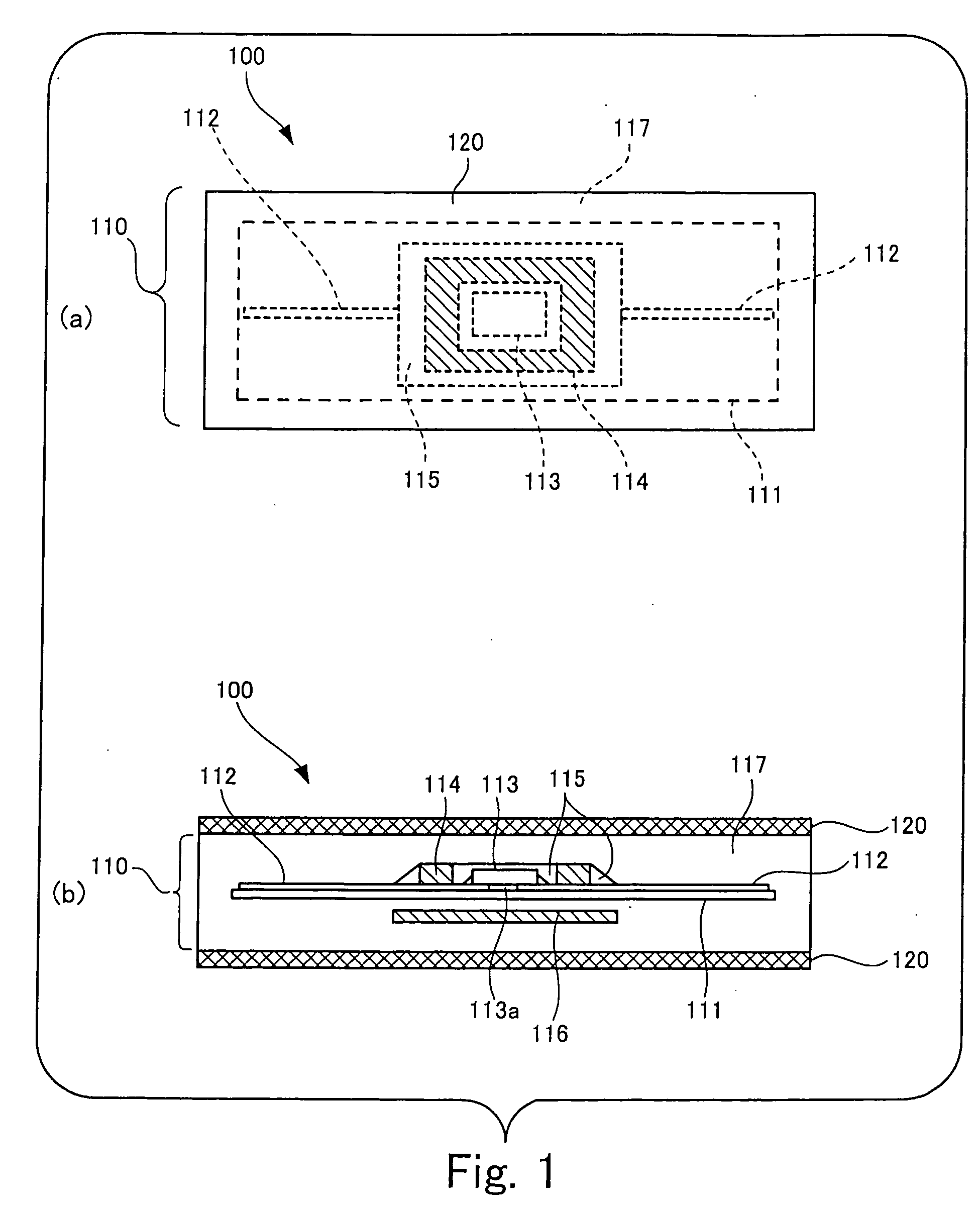

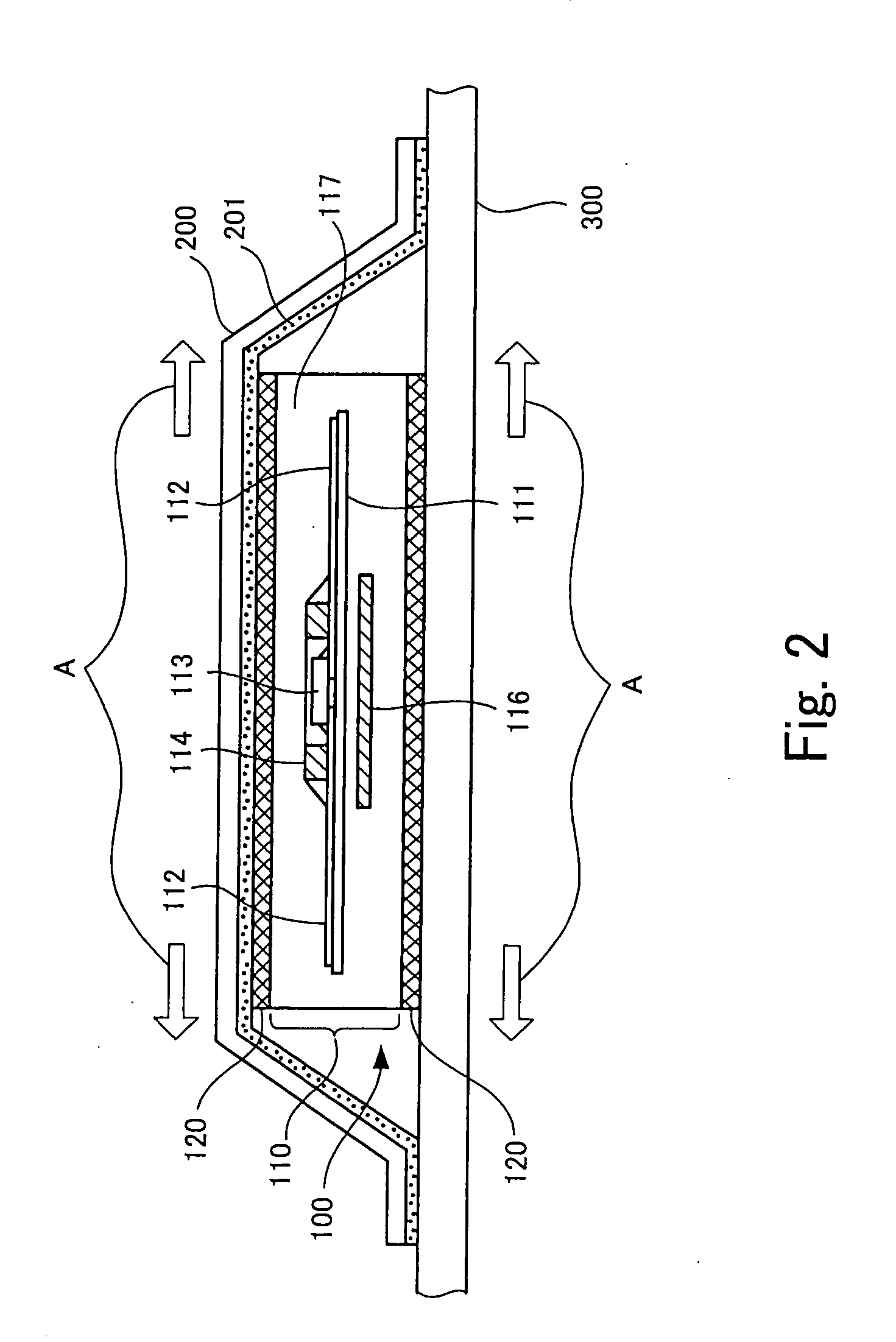

Semiconductor device and method of manufacturing the same, circuit board and electronic instrument

InactiveUS6181010B1Easy to transformEffective absorptionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipElectronic instrument

A semiconductor device and method of manufacturing the same, a circuit board and an electronic instrument are such that without substrate material selection or additional steps after connection, connection reliability can be assured, while direct connection to a substrate is possible, further allowing an electronic instrument to be made more compact and lightweight. The semiconductor device comprises a semiconductor chip (100) having electrodes (104), an interconnect layer (120) connected to the electrodes (104), a conducting layer (122) provided on the interconnect layer (120) avoiding the area of the electrodes (104), an underlying metal layer (124) having a size larger than the peripheral outline of the conducting layer (122) provided on the conducting layer (122) and easier to be deformed than the conducting layer (122), bumps (200) provided on the underlying metal layer (124), and a resin layer (126) provided on the periphery of the conducting layer (122).

Owner:SEIKO EPSON CORP

Storage device

ActiveUS20050228947A1Easy to handleSuppress failureInput/output to record carriersMemory systemsFailoverProcessing priority

The present invention observes the status on the server side from the storage device side, and controls the processing priority in accordance with the server status. The storage device 2 is utilized by numerous servers 1A through 1C. The server 1A and server 1B form a failover cluster. The status detection part 5 judges whether or not an event observed from the server 1A or 1B corresponds to a specified event (link down or the like). In cases where such a specified event is observed, the status detection part 5 detects the occurrence of failover. In accordance with the detection of the occurrence of failover, the priority control part 6 sets the processing priority of the failover destination server at a priority that is higher than the ordinary processing priority. When the preset failover time has elapsed, the priority during failover is returned to the ordinary priority.

Owner:GOOGLE LLC

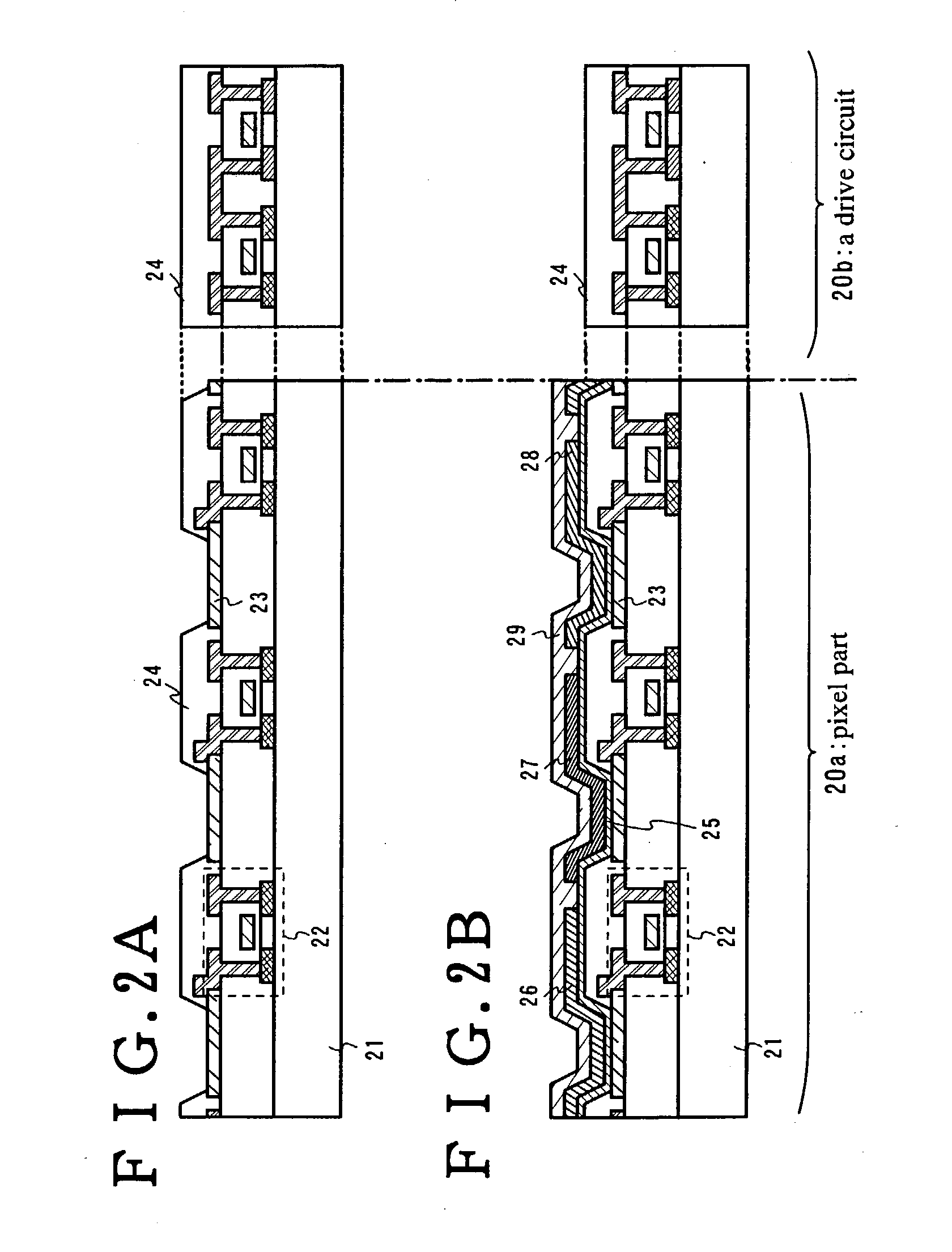

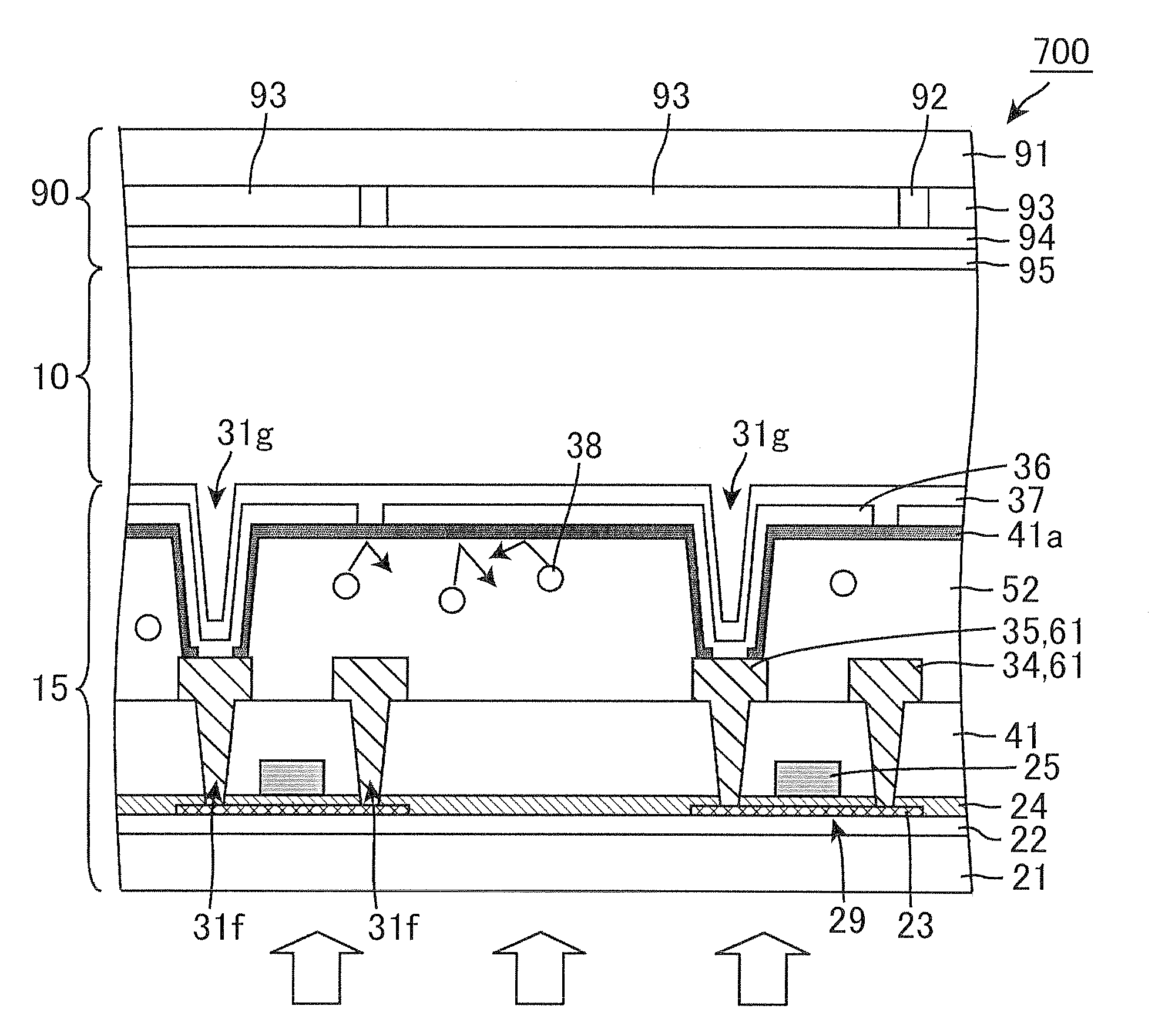

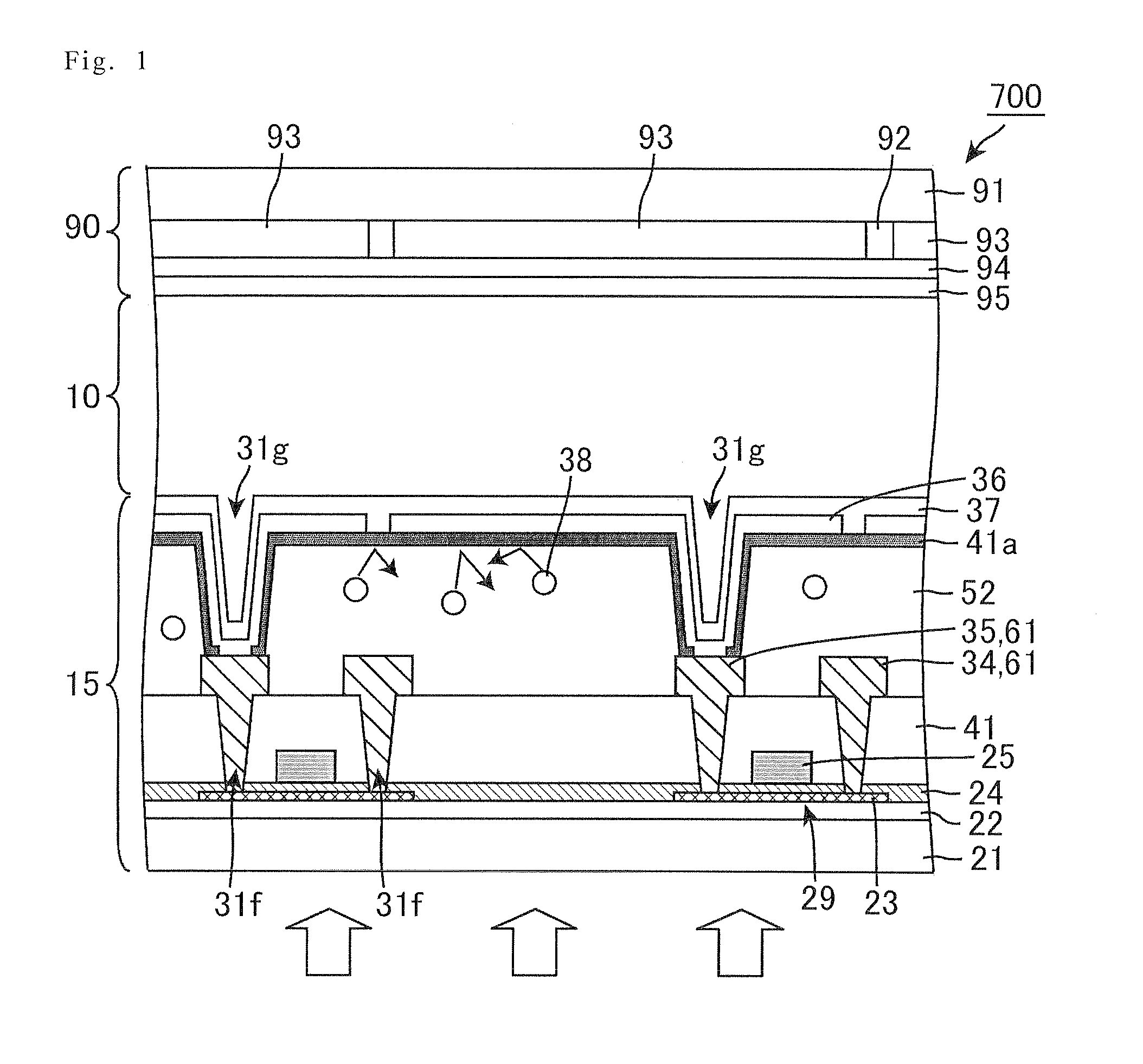

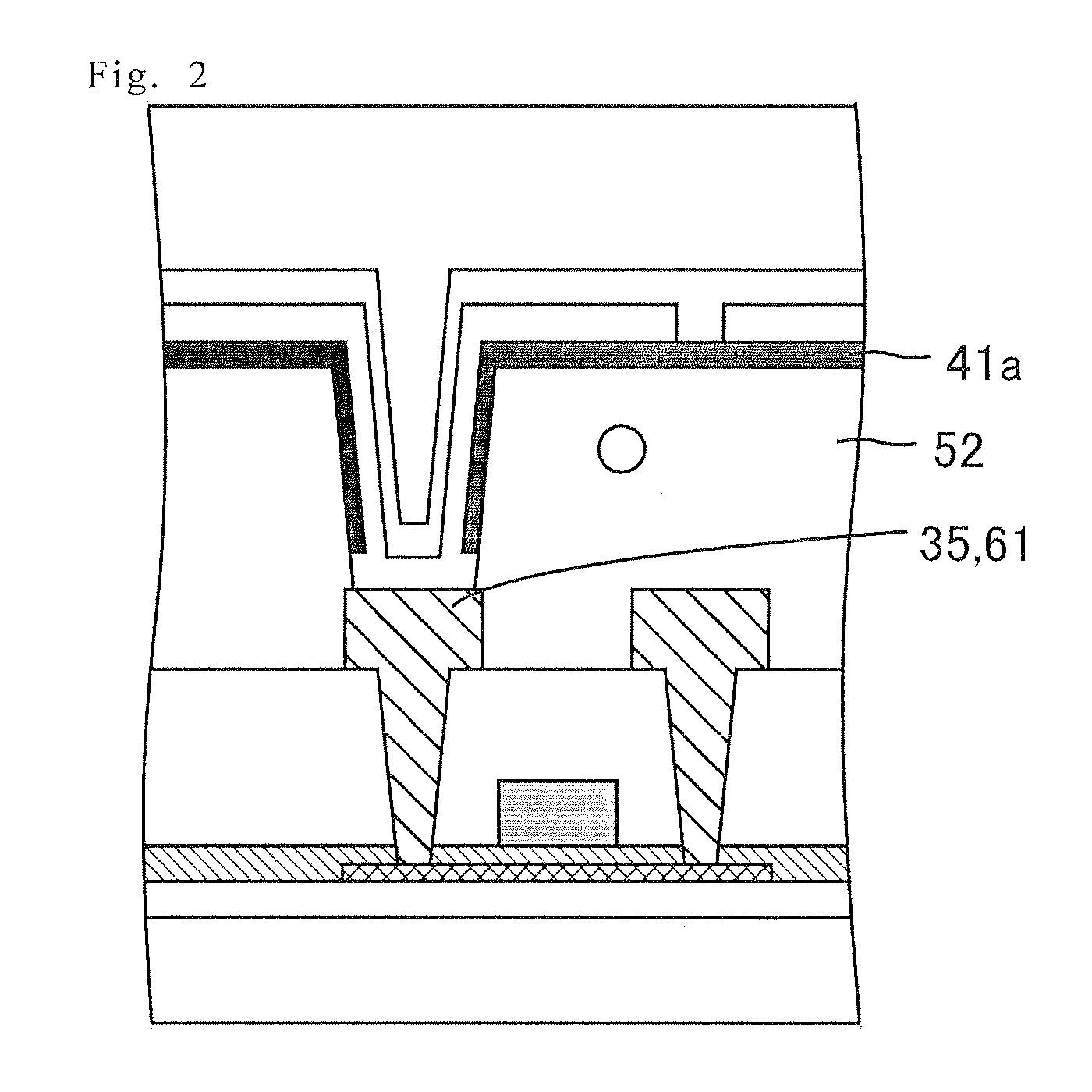

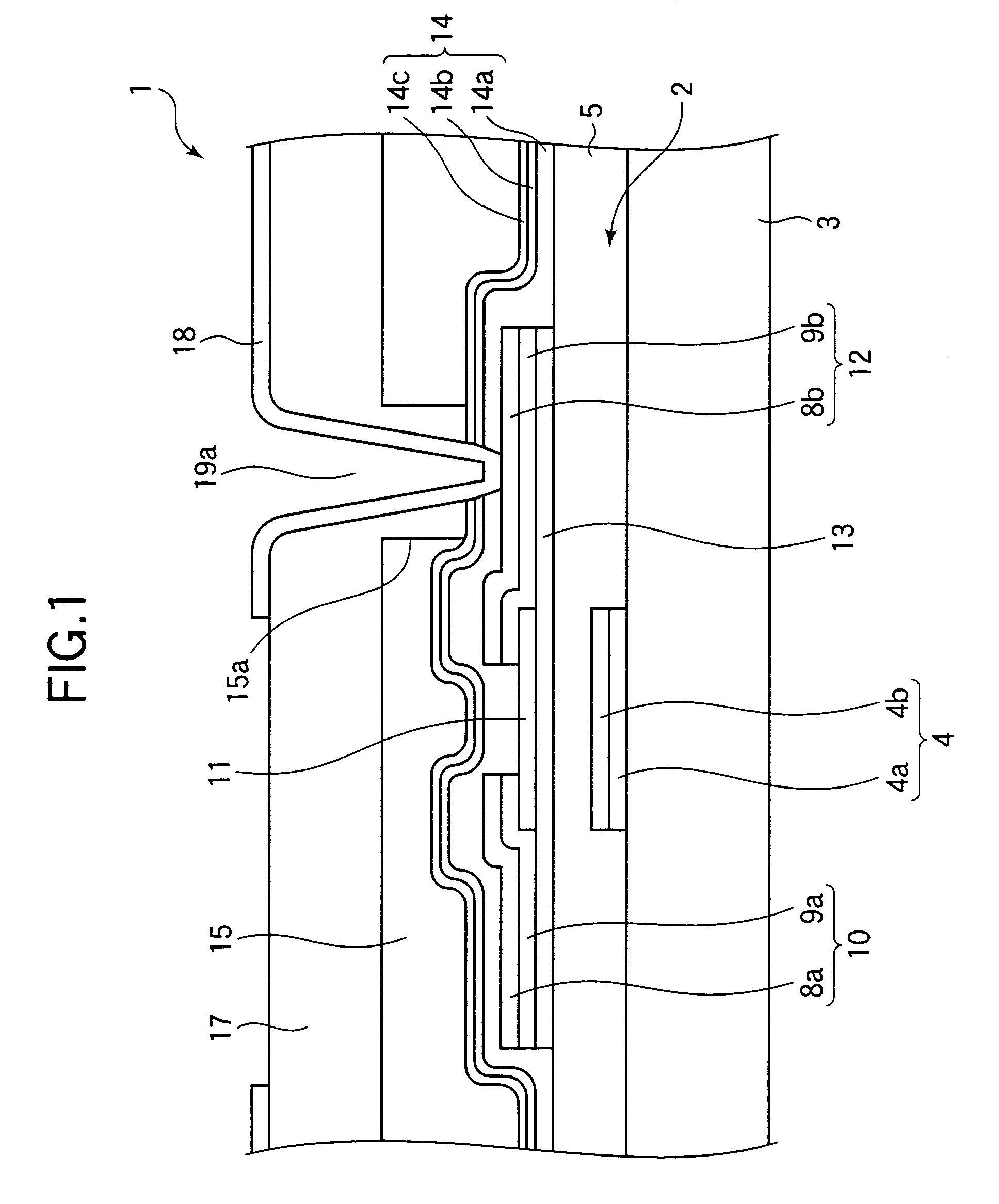

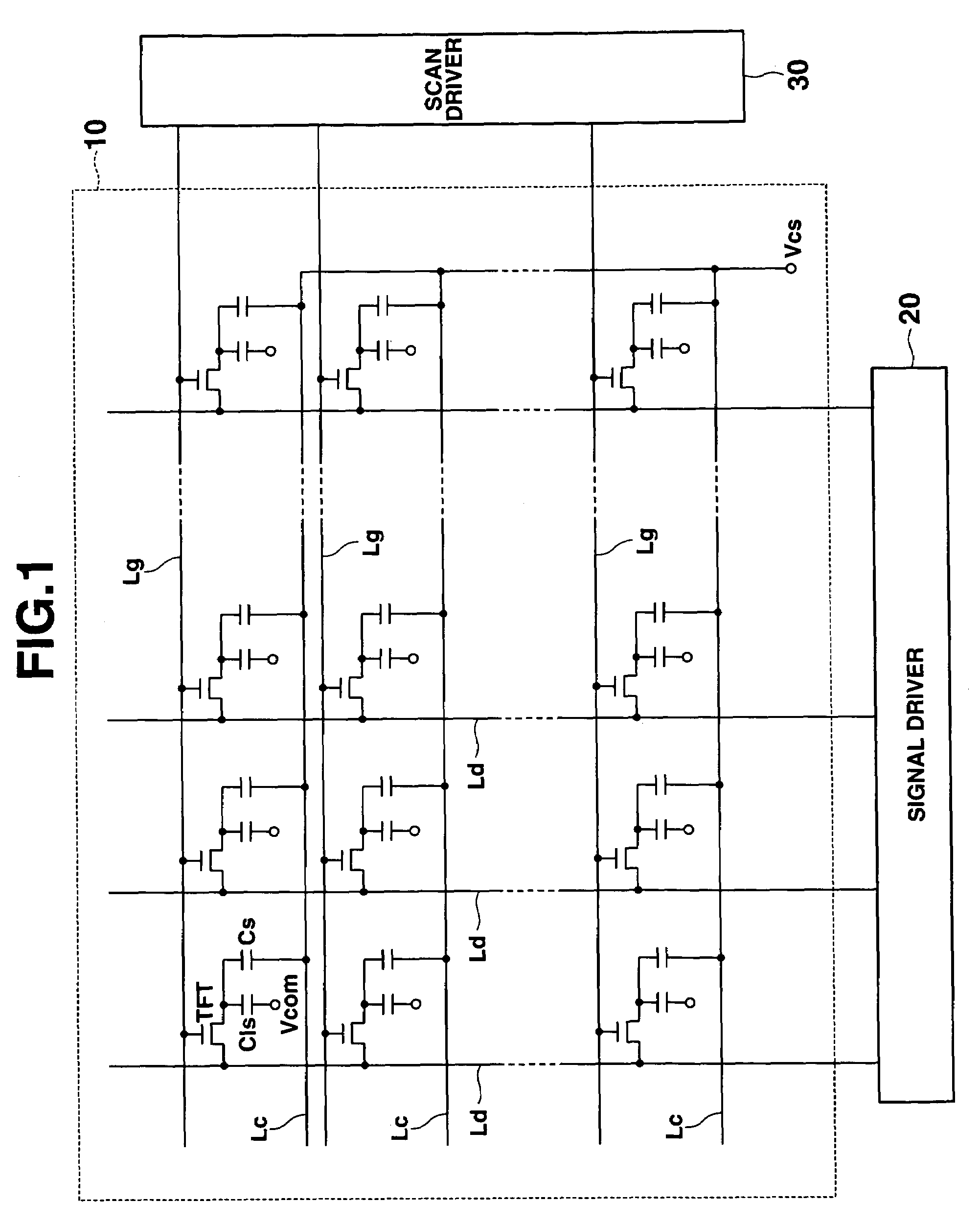

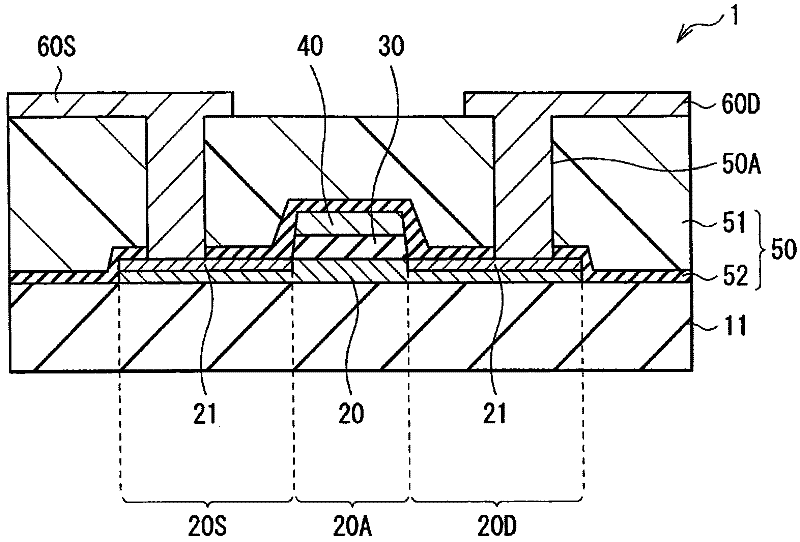

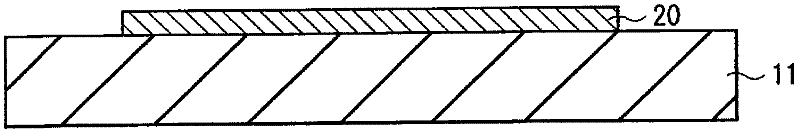

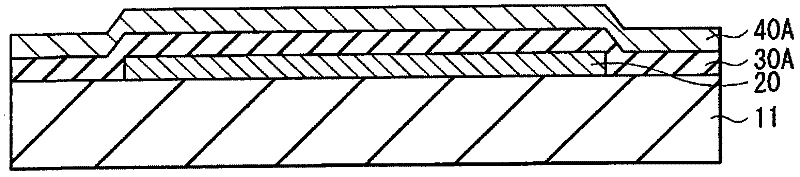

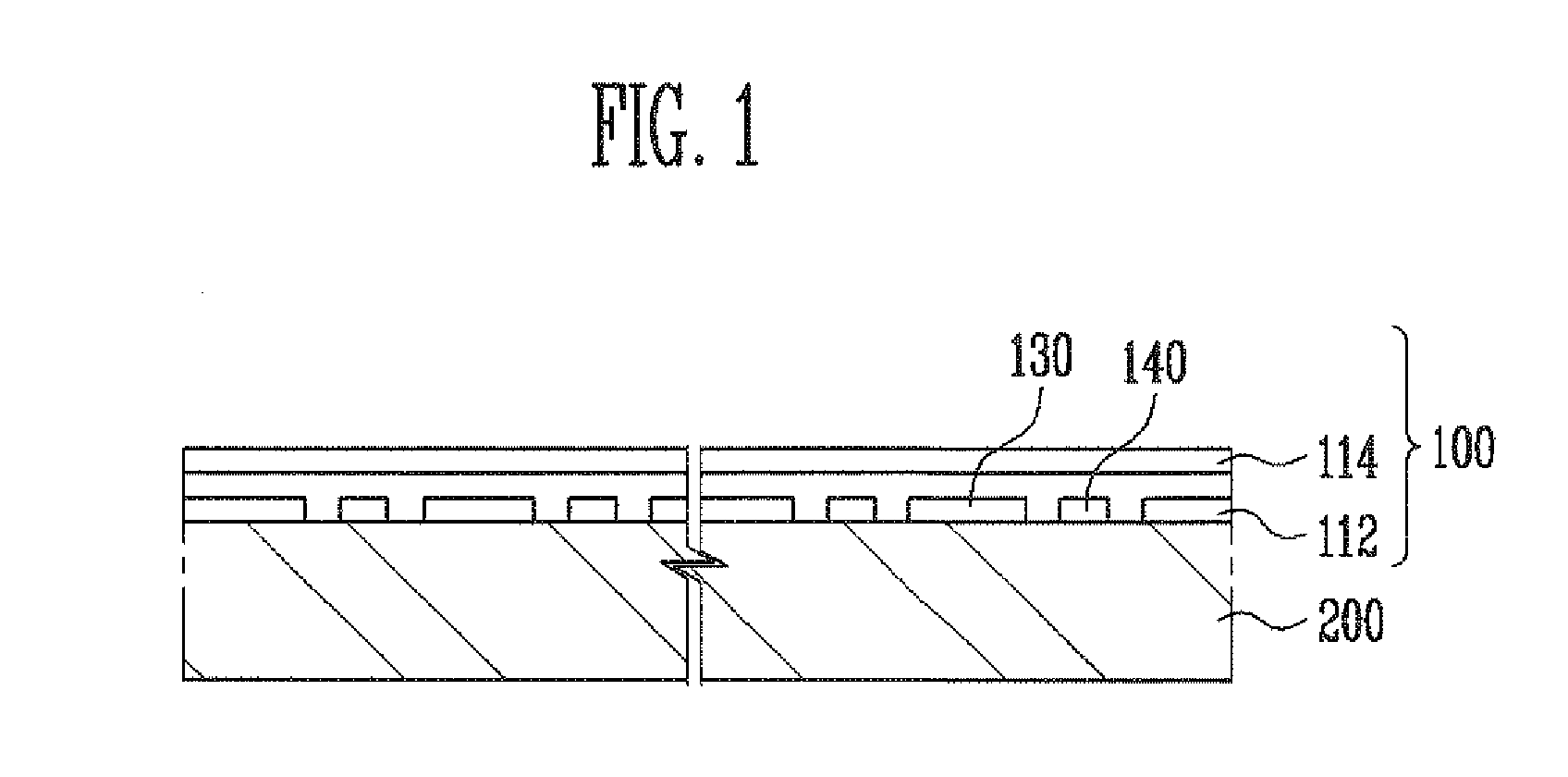

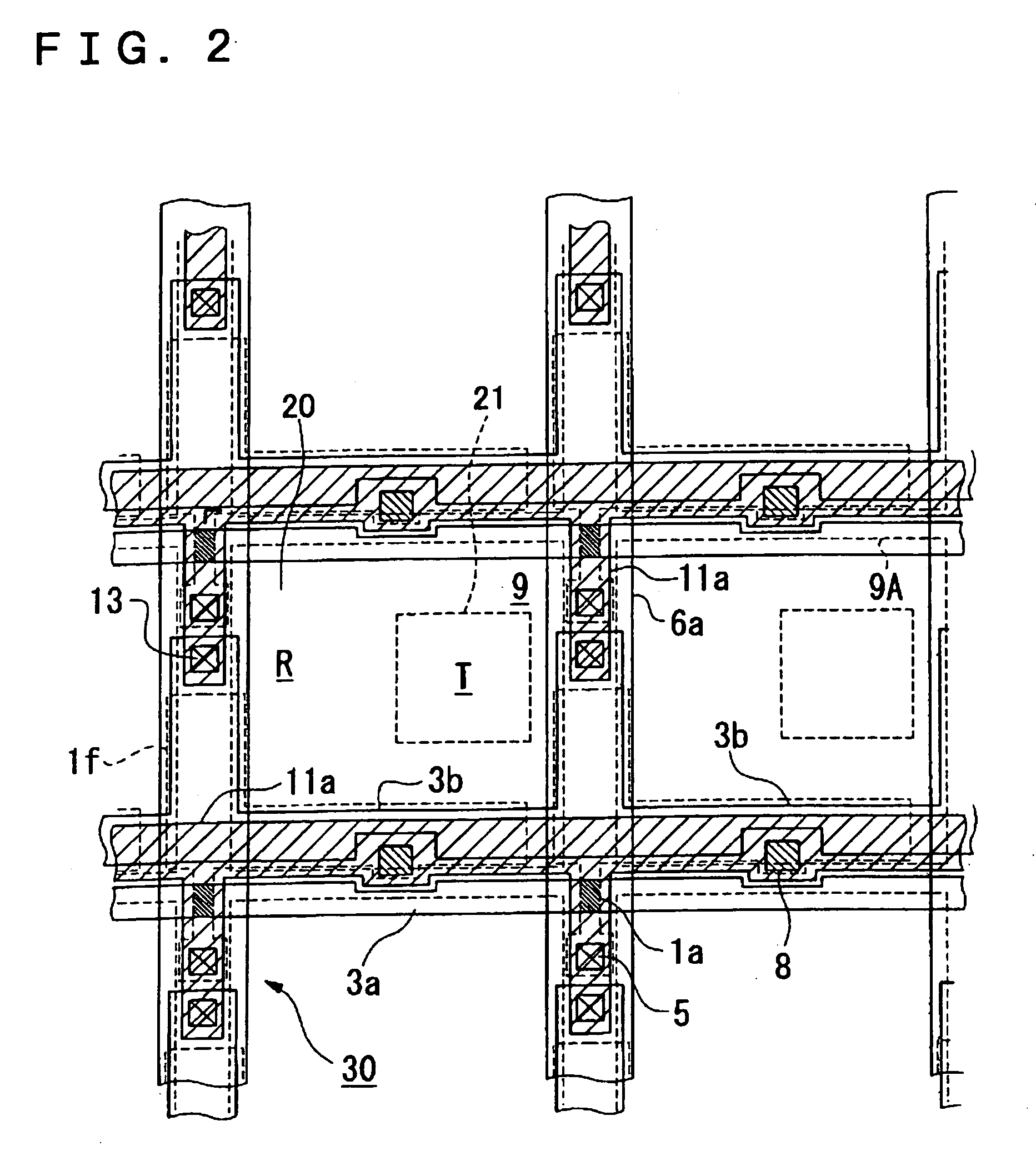

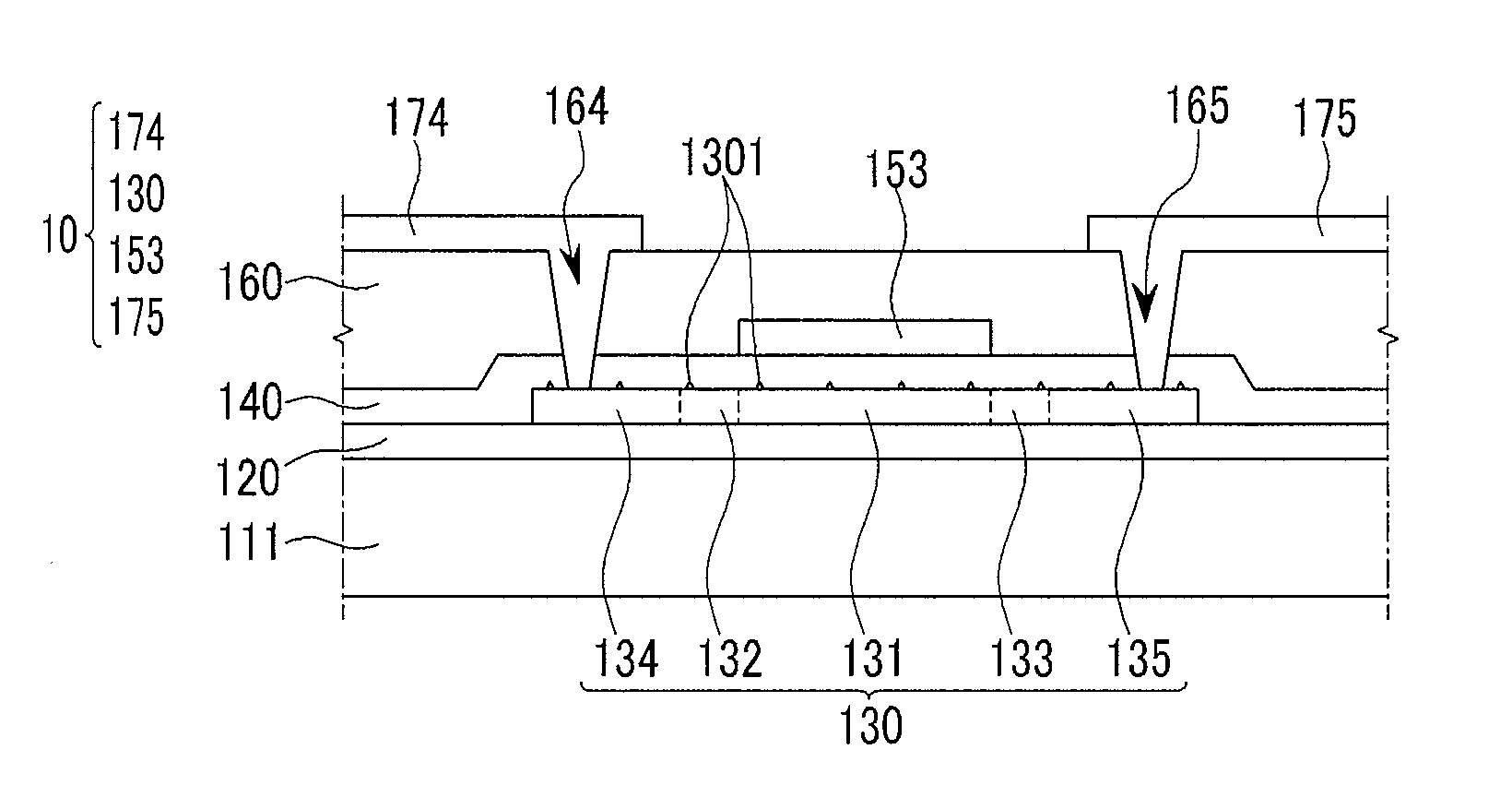

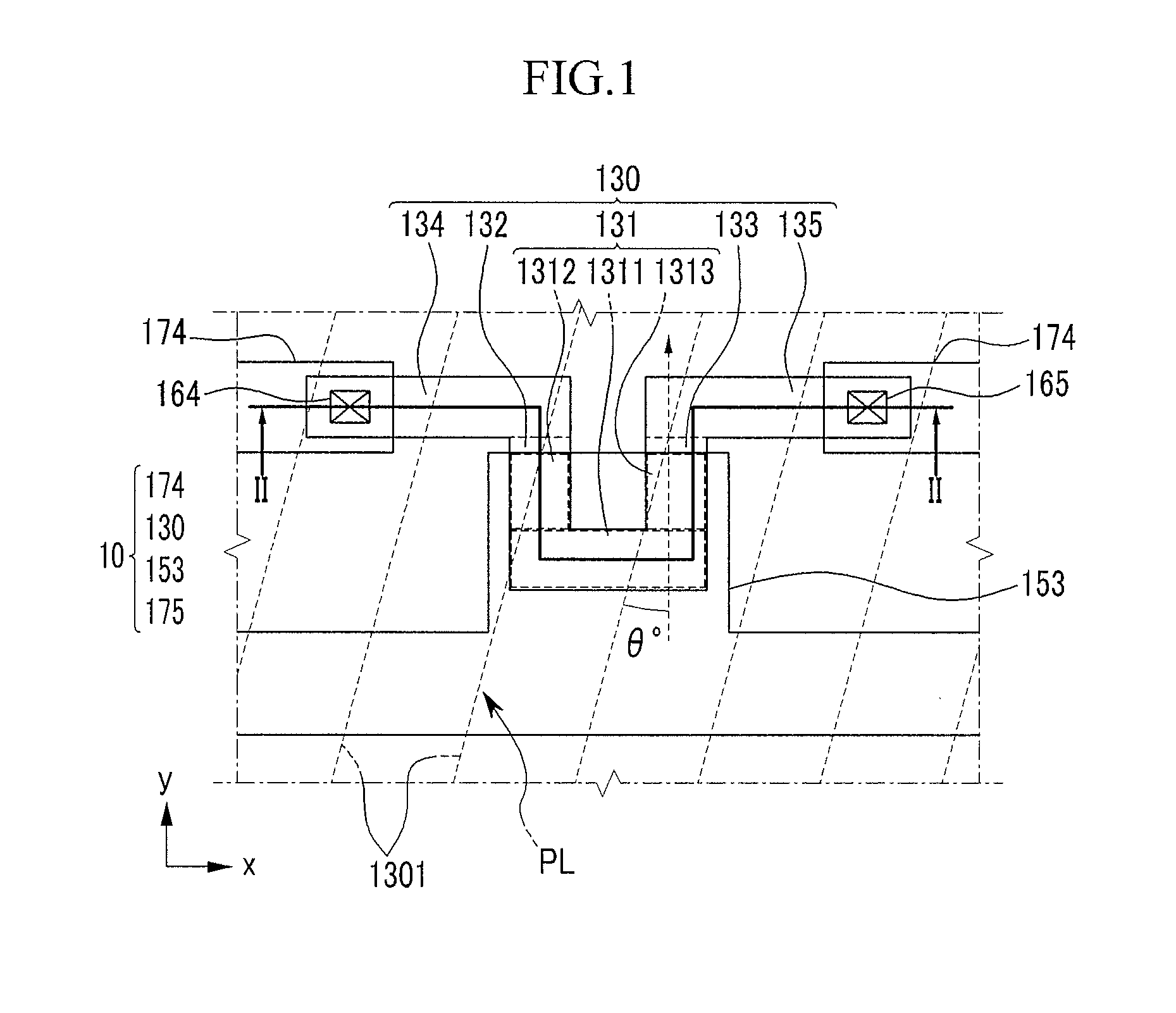

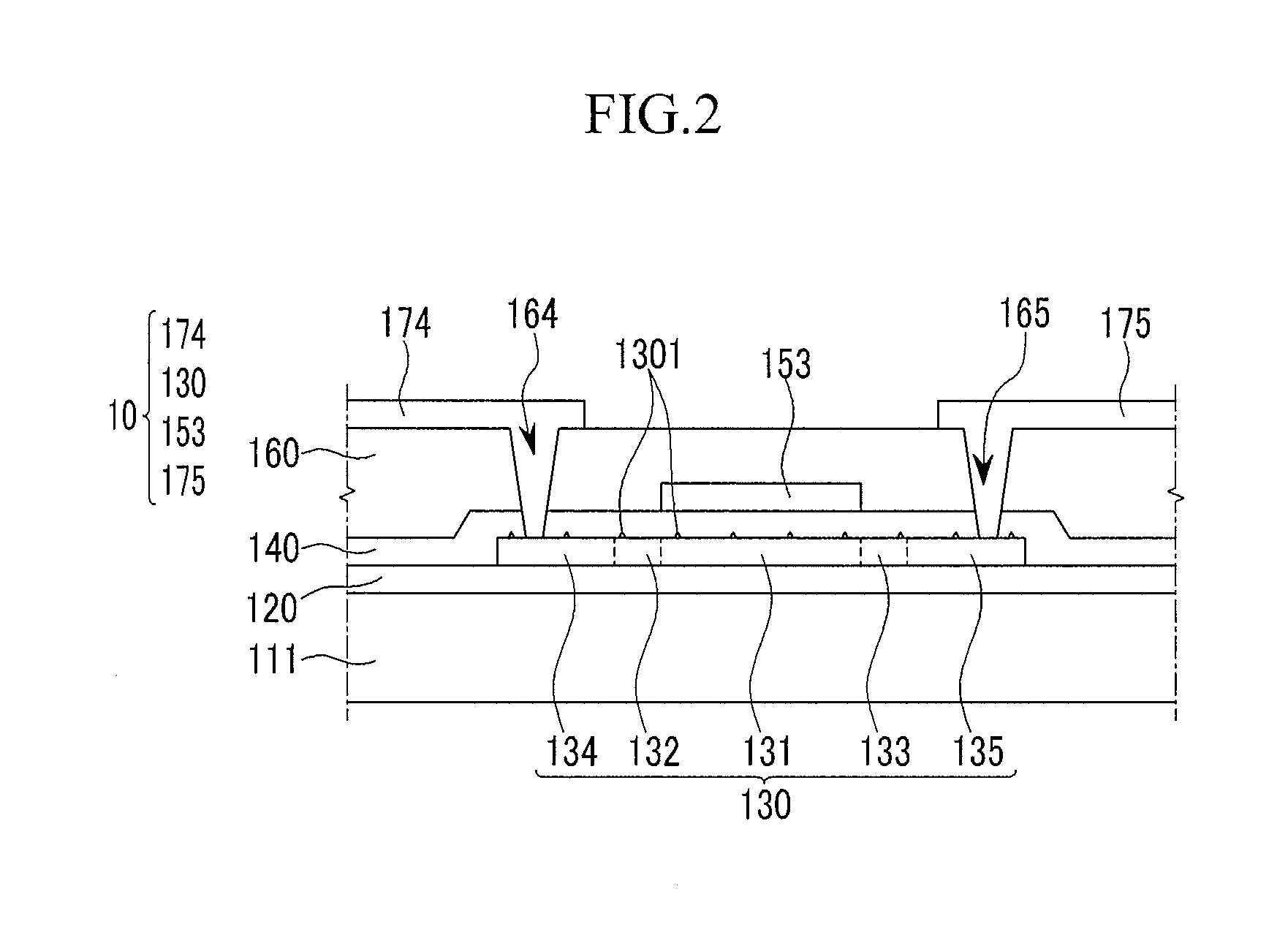

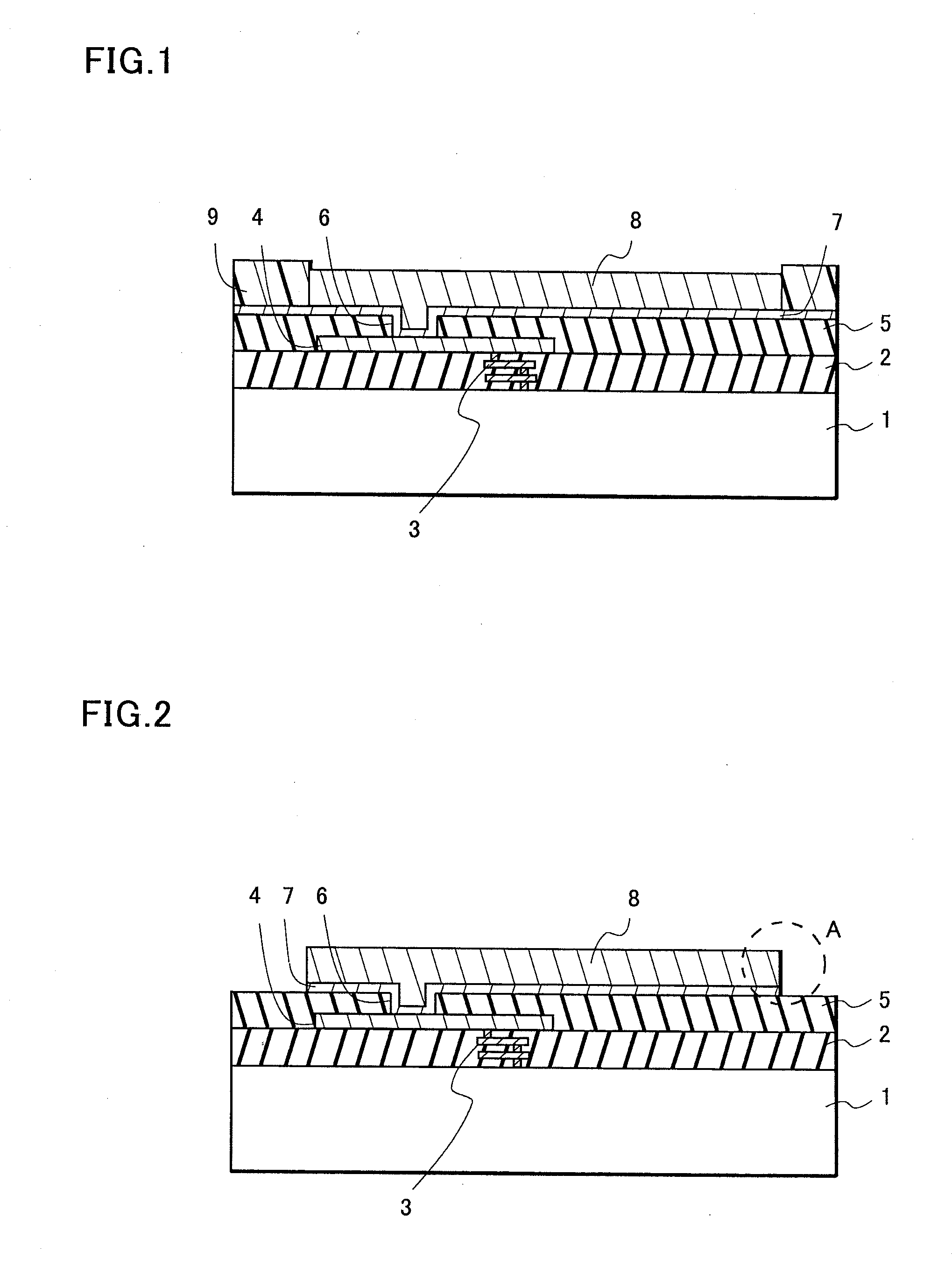

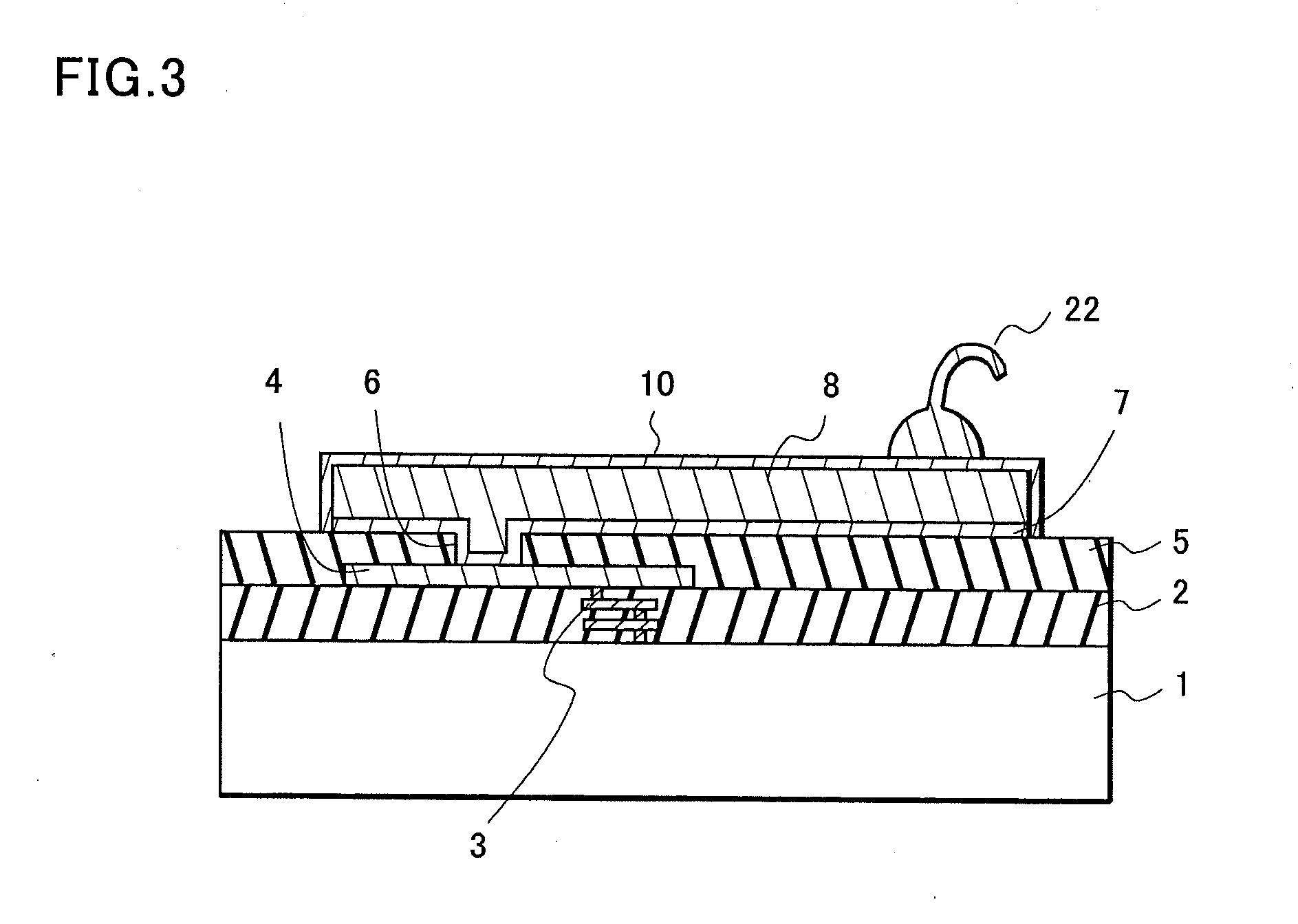

Display device substrate, display device substrate manufacturing method, display device, liquid crystal display device, liquid crystal display device manufacturing method and organic electroluminescent display device

ActiveUS20110199564A1Suppress failureSolid-state devicesOptical articlesLiquid-crystal displayEngineering

The present invention provides a display device substrate, a display device substrate manufacturing method, a display device, a liquid crystal display device, a liquid crystal display device manufacturing method and an organic electroluminescent display device that allow suppressing faults derived from occurrence of gas and / or bubbles in a pixel region. The present invention is a display device substrate that comprises: a photosensitive resin film; and a pixel electrode, in this order, from a side of an insulating substrate. The display device substrate has a gas-barrier insulating film, at a layer higher than the photosensitive resin film, for preventing advance of a gas generated from the photosensitive resin film, or has a gas-barrier insulating film, between the photosensitive resin film and the pixel electrode, for preventing advance of gas generated from the photosensitive resin film.

Owner:SHARP KK

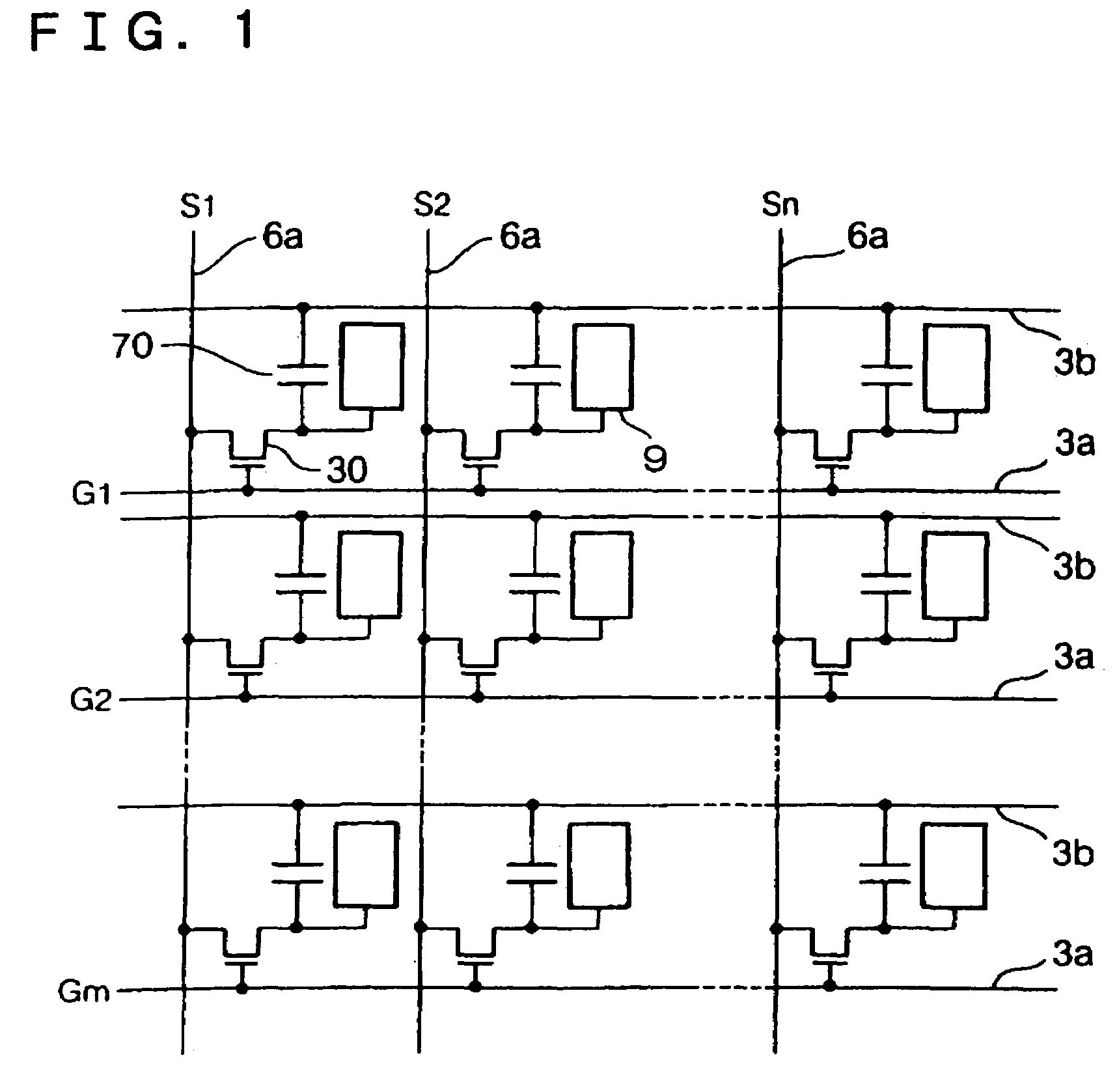

Liquid crystal panel, manufacturing method therefor, and electronic equipment

InactiveUS20030053022A1Reliable conductionEasy to manufactureNon-linear opticsLiquid-crystal displayEngineering

A liquid crystal panel 1 has a configuration in which an element substrate 10 including routing wiring 16 and a counter substrate 20 including scanning lines 25 are adhered with a sealing material 30 therebetween and, in addition, a liquid crystal is injected between both substrates through a liquid crystal injection hole 30a formed in the sealing material 30. The scanning lines 25 are brought into conduction with the routing wiring 16 through conducting particles 32 dispersed in the sealing material 30. However, the scanning lines 25, which have end portions reaching the neighborhood of the liquid crystal injection hole 30a, among the plurality of scanning lines 25, are brought into conduction with the routing wiring 16 through conducting particles 32 dispersed in a vertical conduction portion 37 or through the conducting particles 32 in both the sealing material 30 and the vertical conduction portion 37.

Owner:SEIKO EPSON CORP

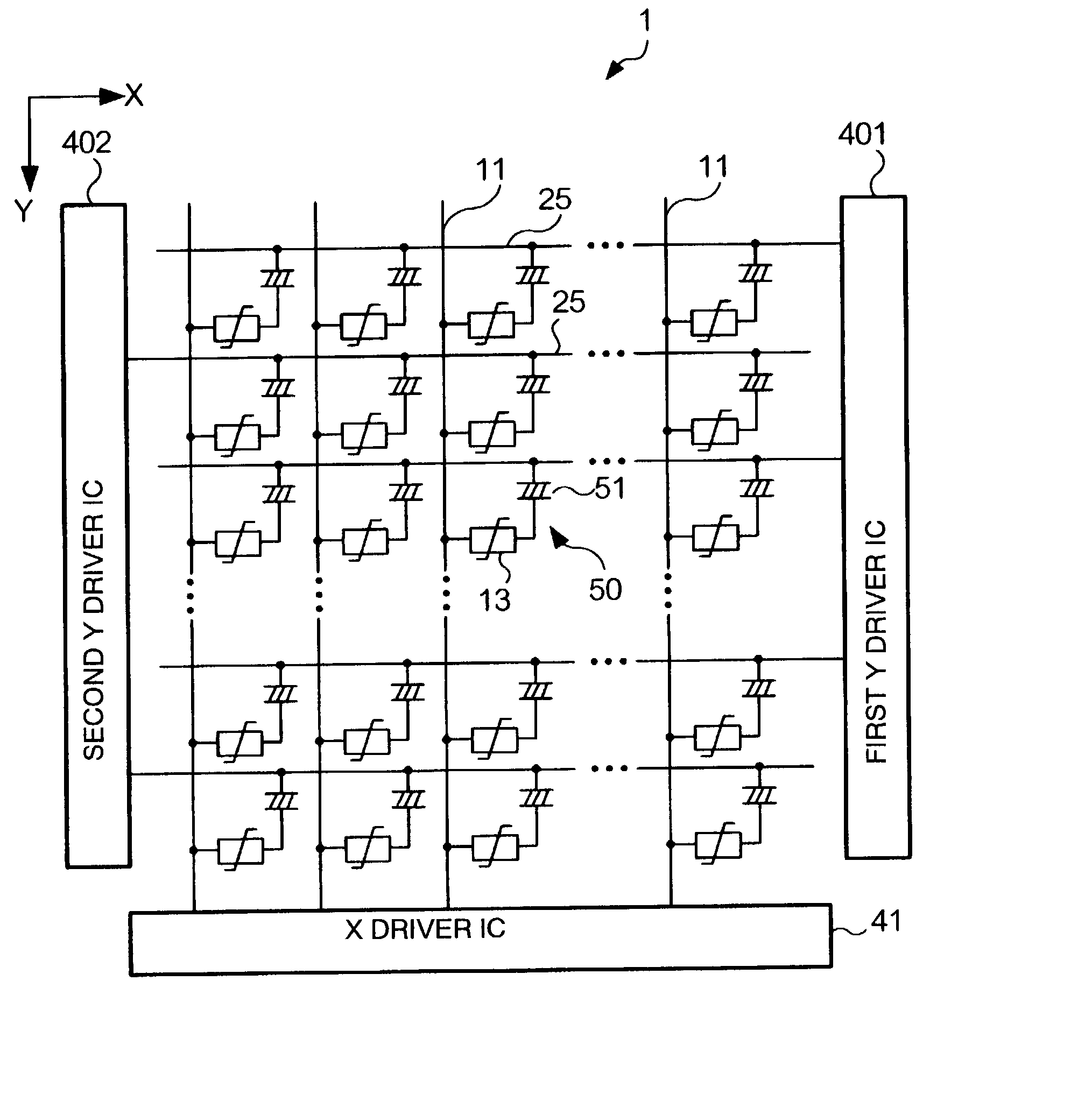

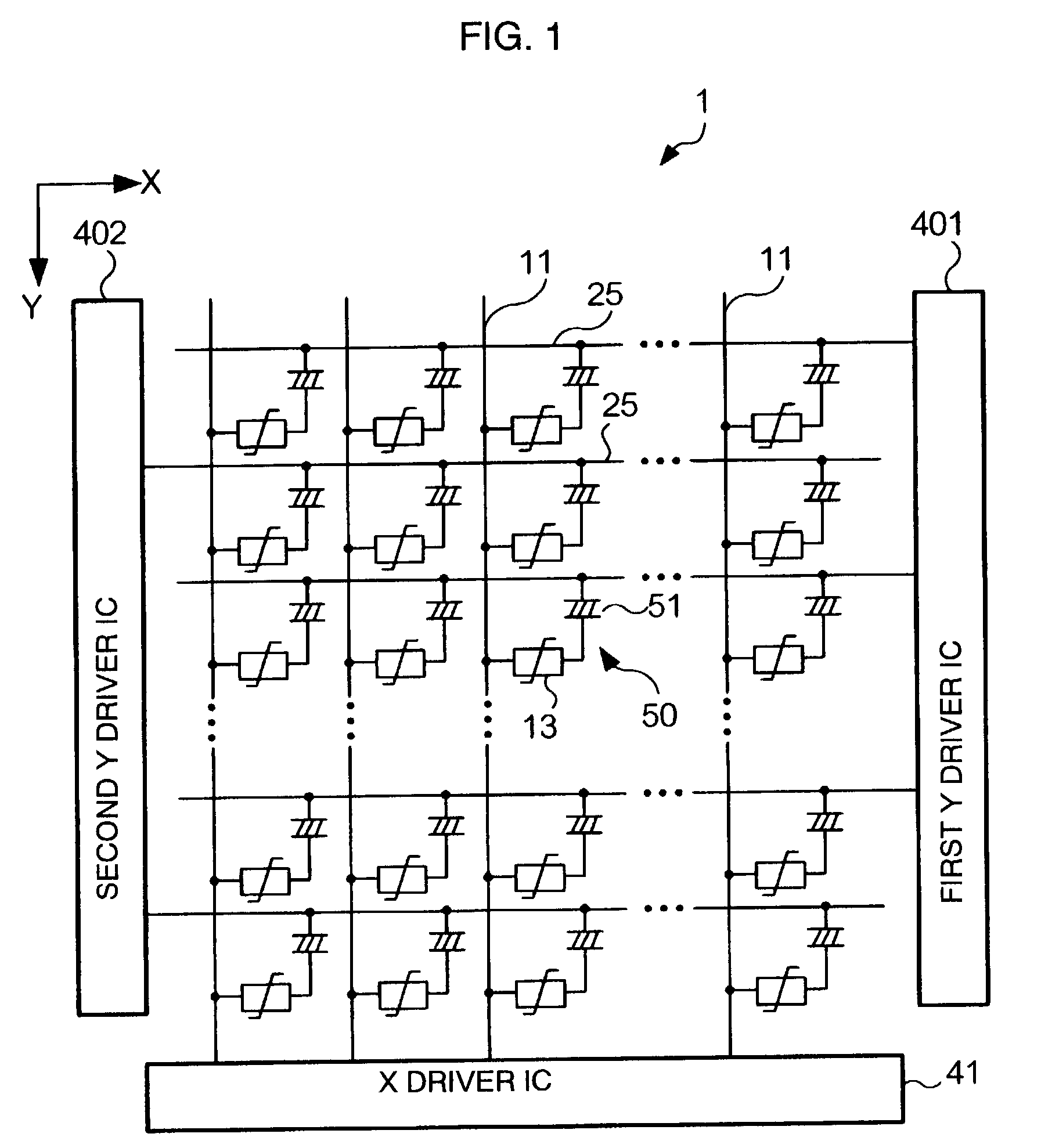

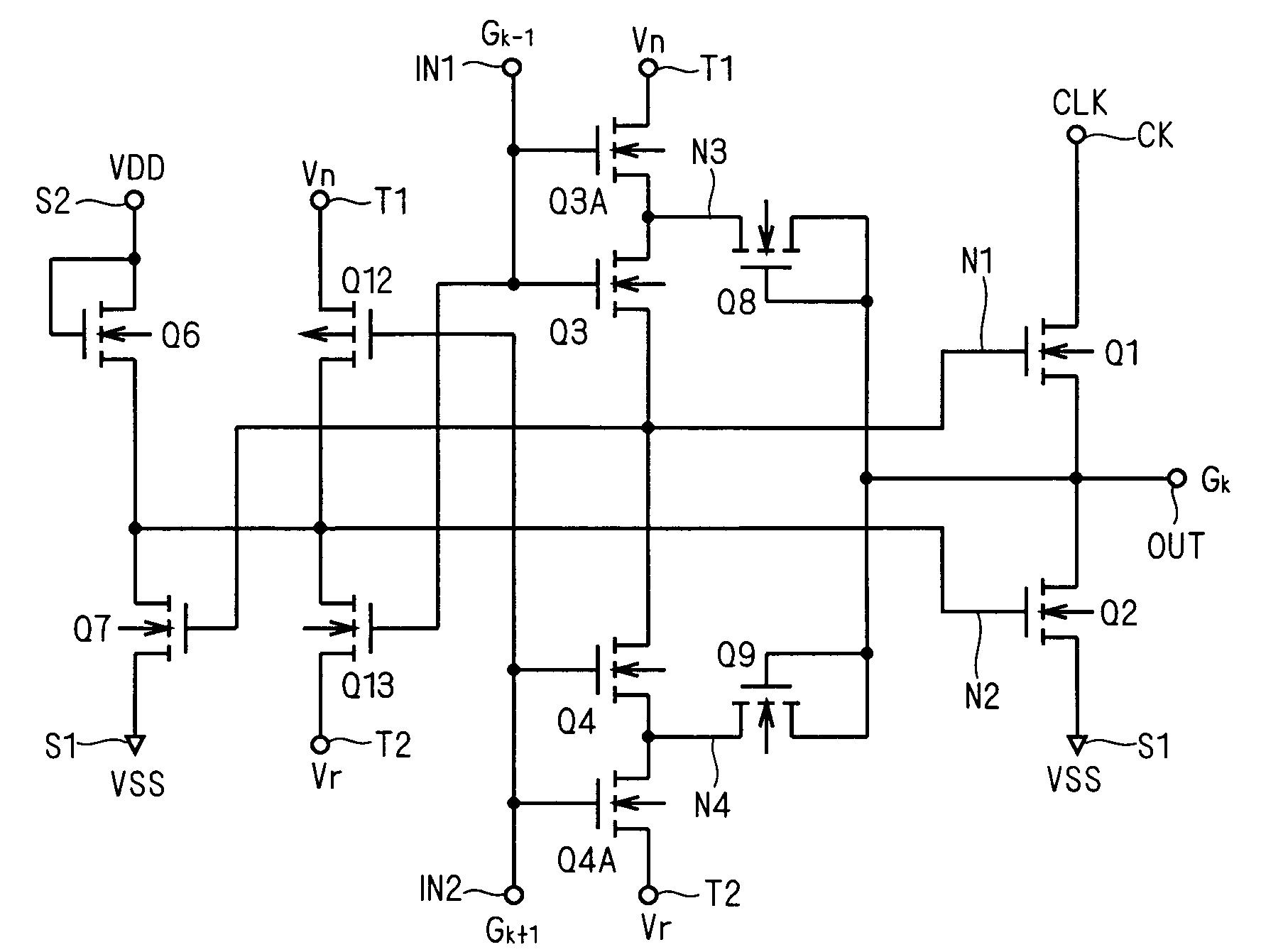

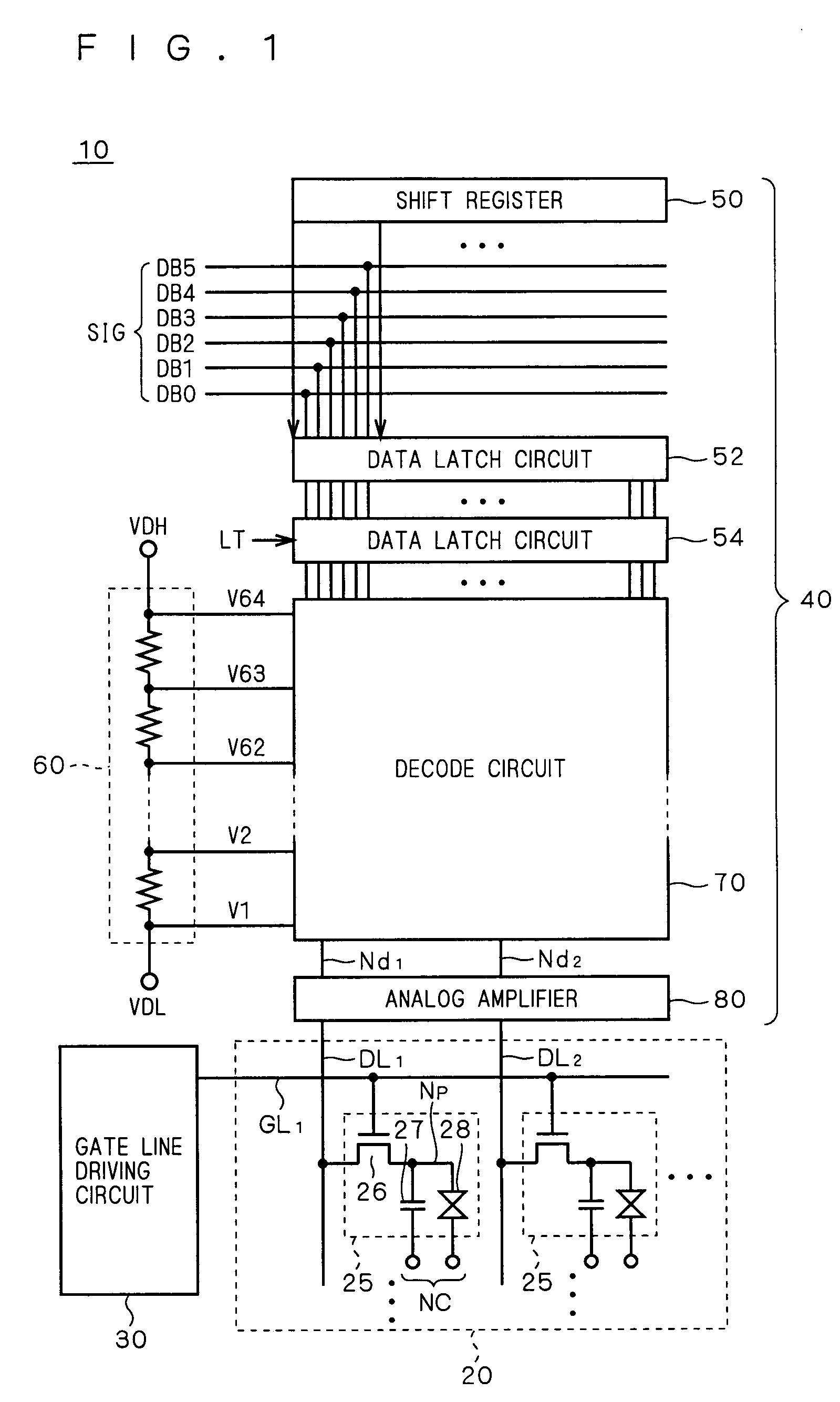

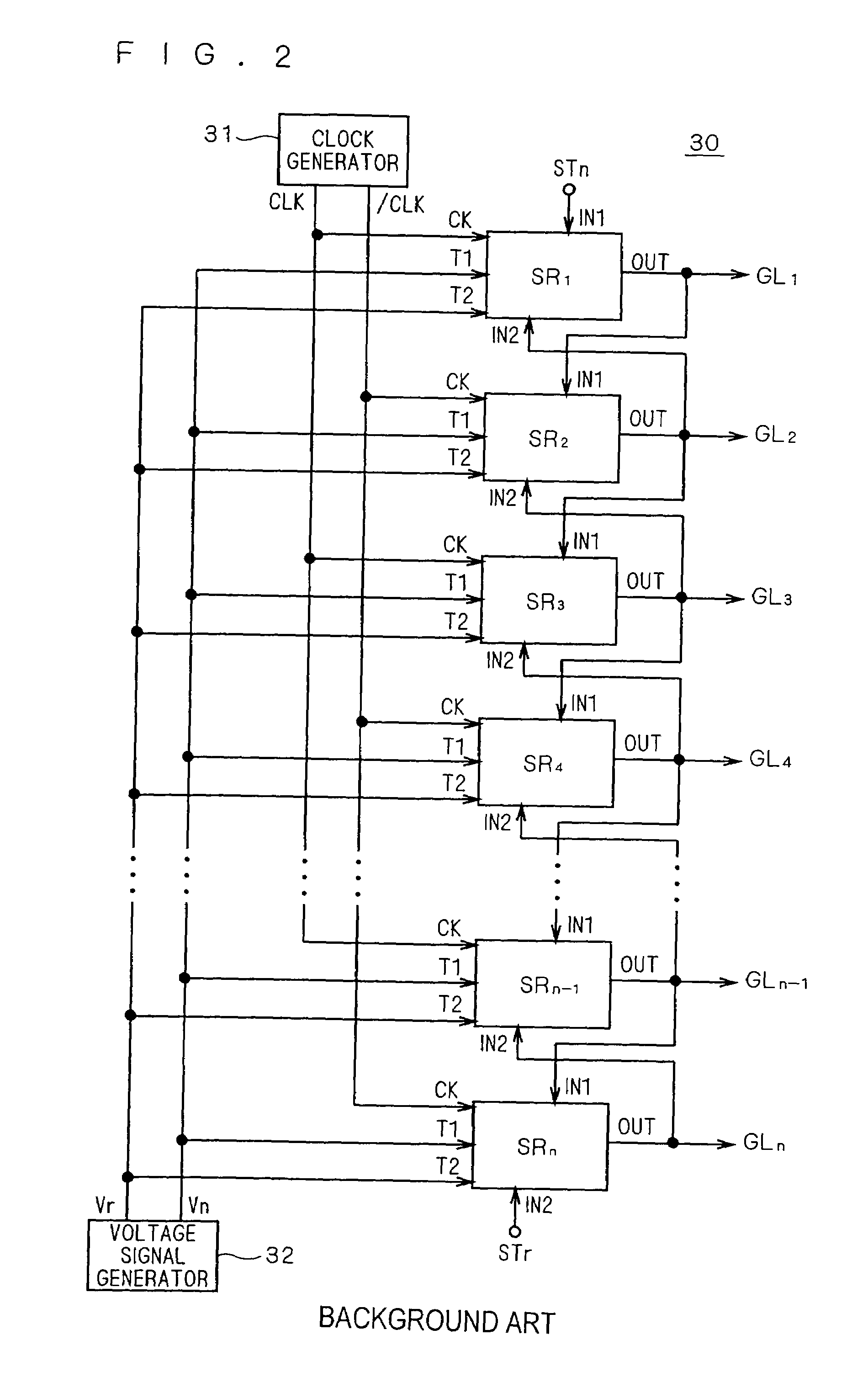

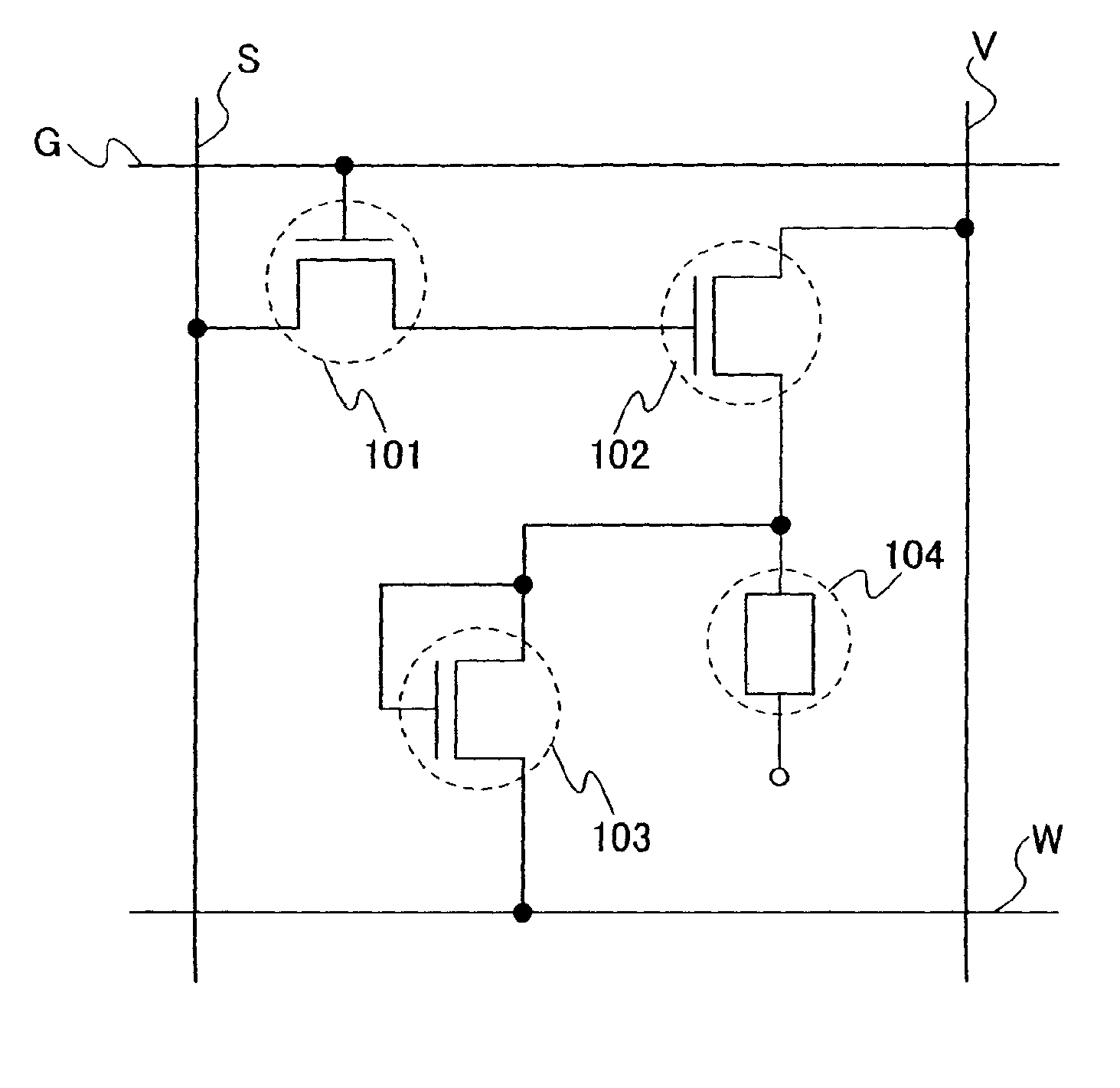

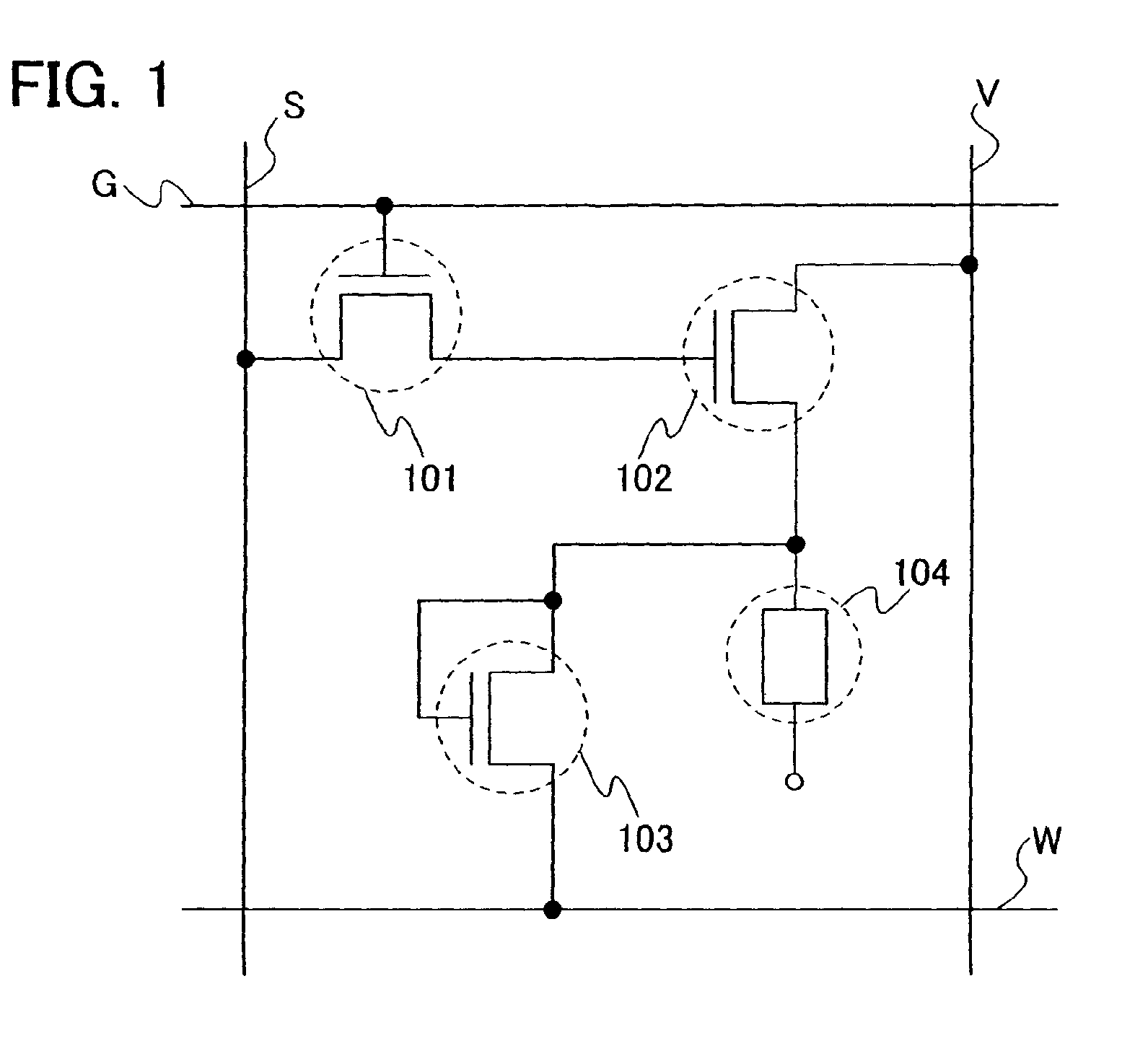

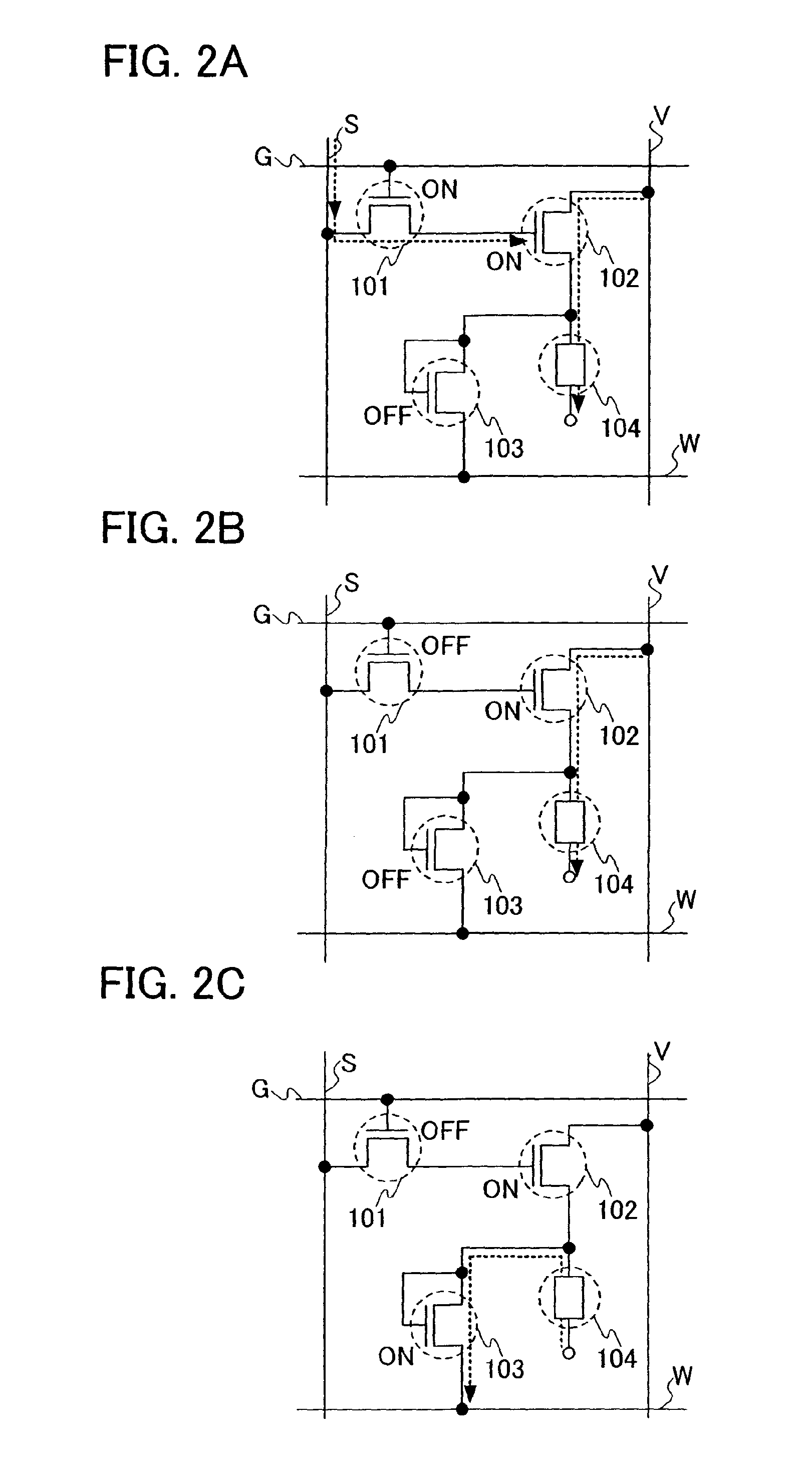

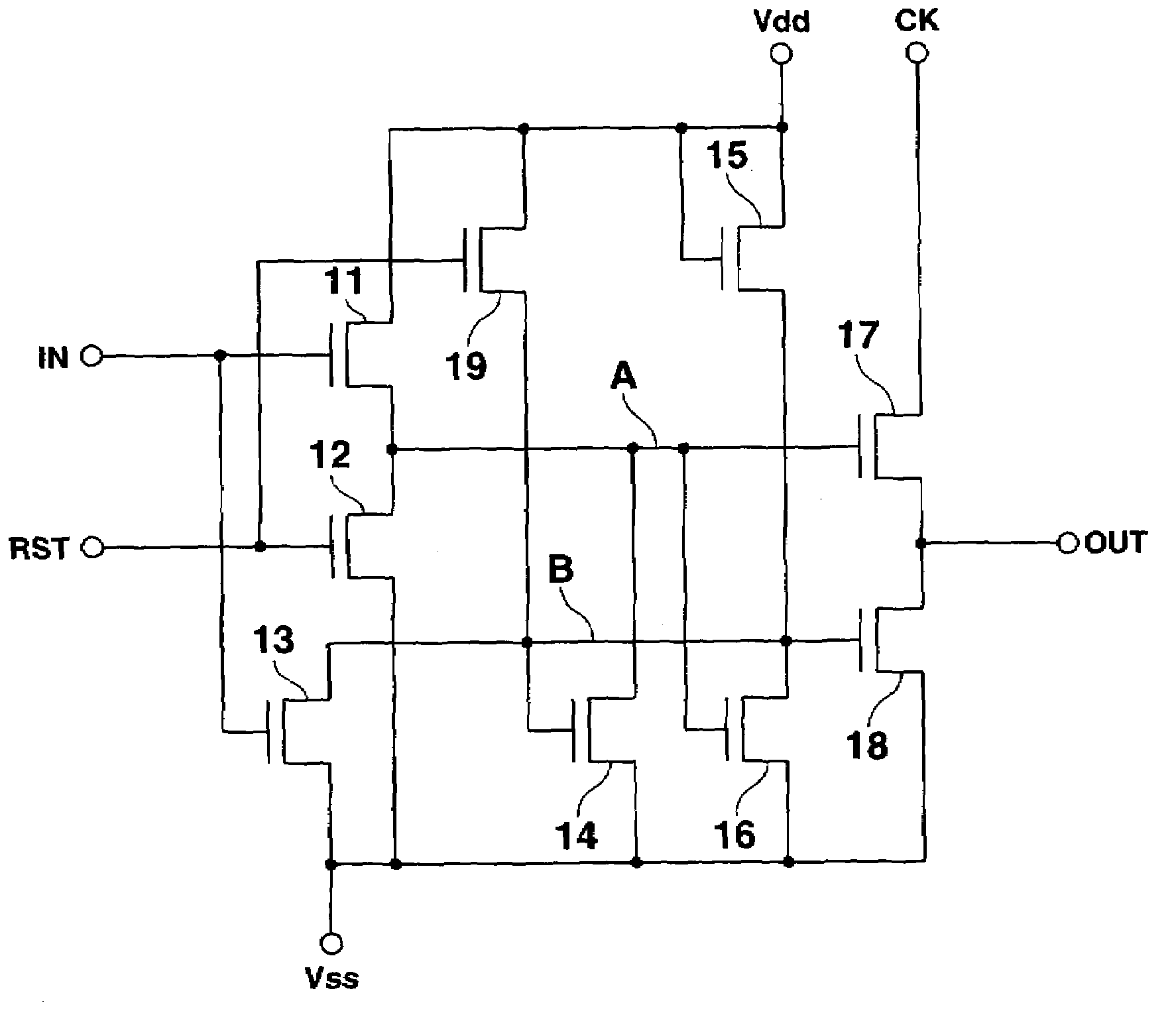

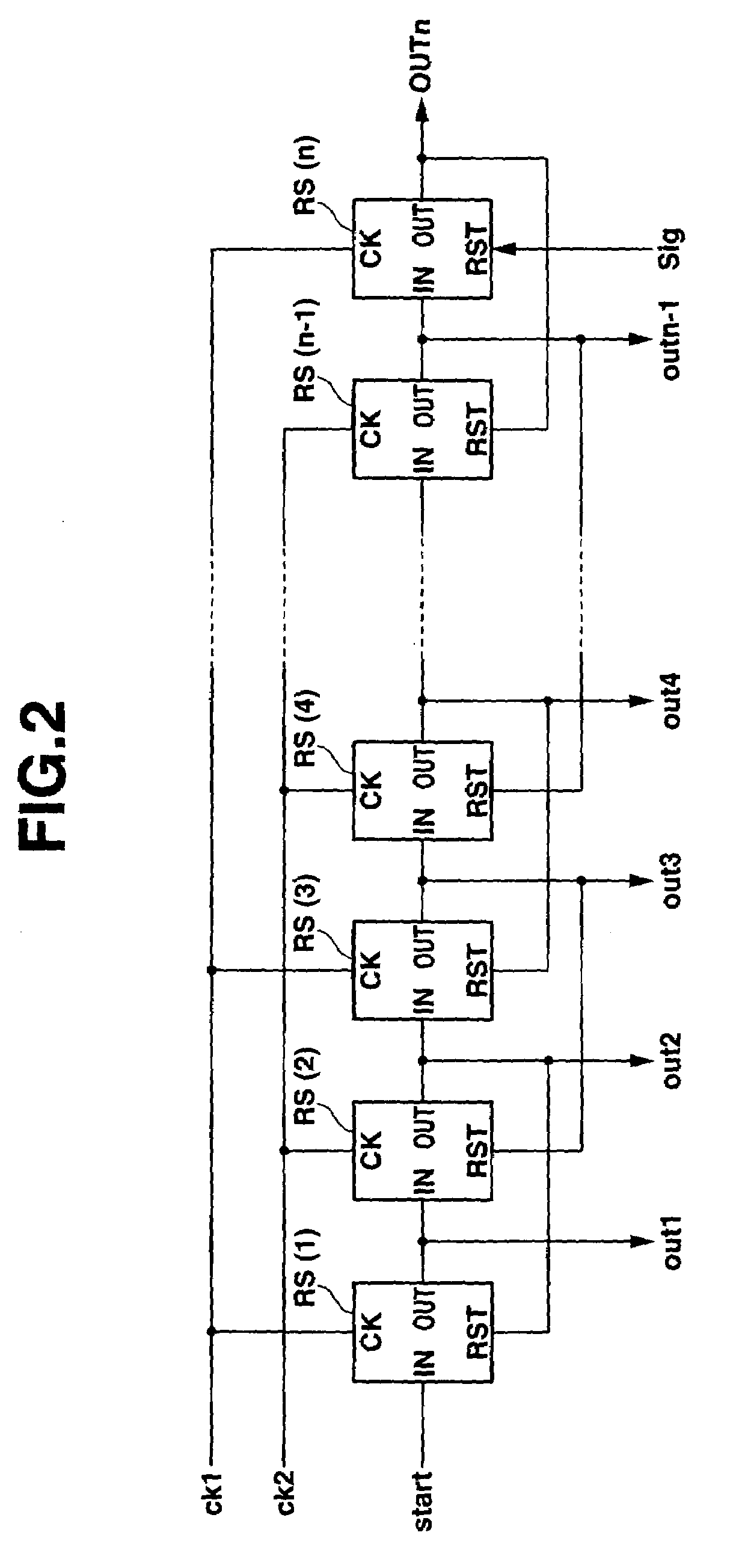

Shift register circuit and image display apparatus equipped with the same

ActiveUS7636412B2Reduce impactSuppress failureStatic indicating devicesDigital storageShift registerProcessor register

Malfunction caused by leakage current of the transistor is prevented in the shift register in which the signal can be shifted bi-directionally. The bi-directional unit shift register includes a transistor Q1 between a clock terminal CK and an output terminal OUT, a transistor Q2 for discharging the output terminal OUT, and transistors Q3, Q4 for providing first and second voltage signals Vn, Vr, which are complementary to each other, to the first node or a gate node of the transistor Q1. Furthermore, a transistor Q5, having a gate connected to a second node or a gate node of the transistor Q2, for discharging the first node is arranged.

Owner:TRIVALE TECH

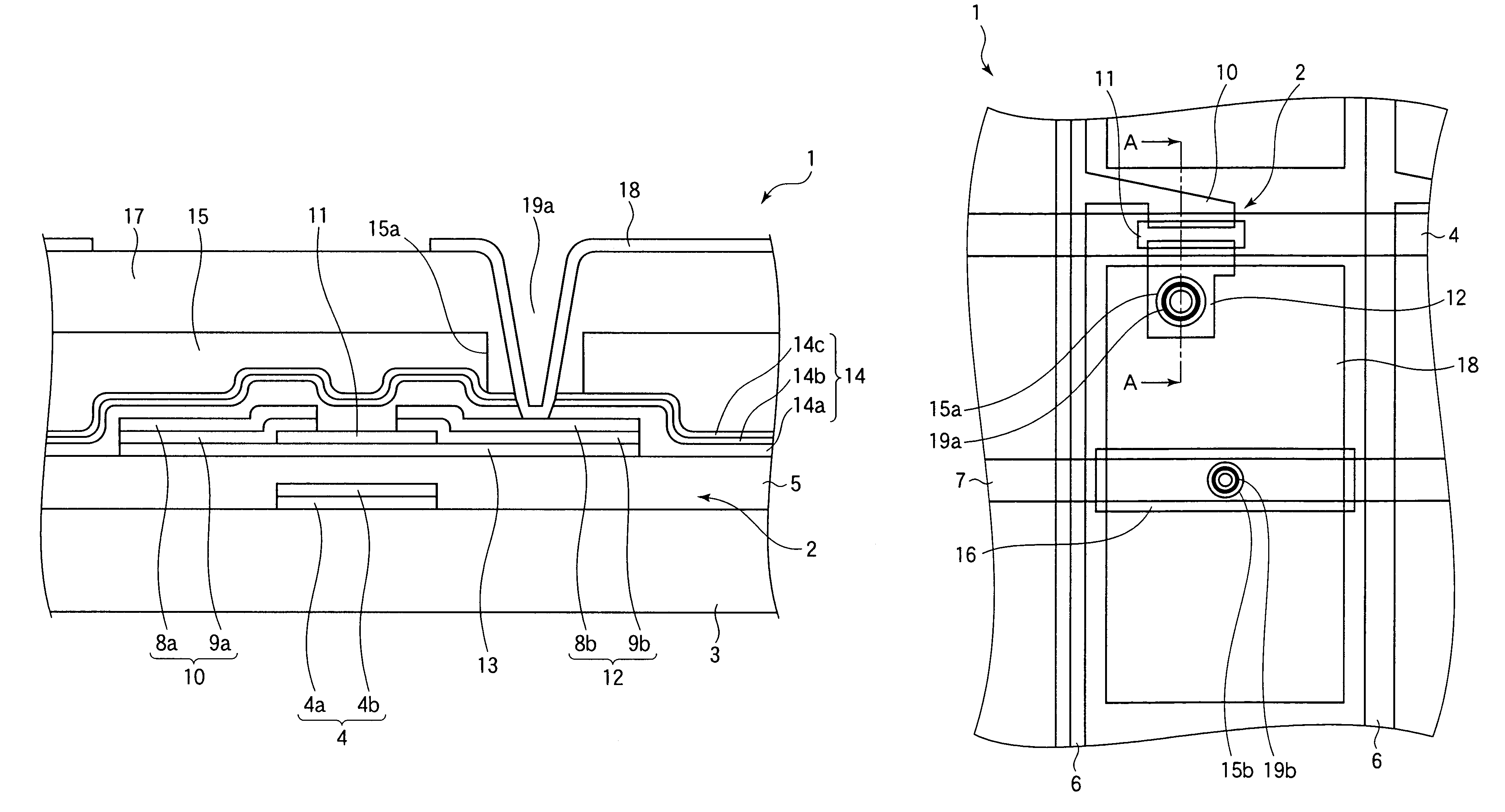

Substrate for liquid crystal display and liquid crystal display utilizing the same

ActiveUS7012658B2Occurrence of failureExcellent characteristicsTransistorOperating means/releasing devices for valvesLiquid-crystal displayPhysics

The generation of residues or flakes of a color filter is suppressed to eliminate conduction failures on an LCD substrate having a color filter on an array substrate. A passivation film formed between a pixel electrode formed in each of a plurality of pixel regions and a TFT for driving the pixel electrode has a multi-layer structure constituted by SiN layers and a SiO layers, and the SiO layer is located at the top of the film. A resin CF layer is formed on the passivation film having such a multi-layer structure. Since the resin CF layer is formed directly on the SiO layer, reduction of the adhesion of the same is suppressed. As a result, the color filter is unlikely to come off when the resin CF layer is formed, and residues of the color filter is unlikely to be generated when a contact hole is formed in the resin CF layer. This suppresses conduction failures and makes it possible to provide a reliable TFT substrate and LCD having high display characteristics.

Owner:UNIFIED INNOVATIVE TECH

Display device and electronic device

ActiveUS20070126666A1Extend lifeDecrease in luminanceElectrical apparatusStatic indicating devicesReverse currentEngineering

It is an object of the present invention to provide a display device in which a reverse current sufficient enough to insulate a short-circuited point flows and a transistor using amorphous silicon is used is applied. The display device includes a switching transistor that controls an input of a video signal, a driving transistor that controls a current flowing in a forward direction to a light emitting element, and an AC transistor that controls a current flowing in a reverse direction to the light emitting element; and a reverse bias current can be applied to the light emitting element. Furthermore, the above-described transistors are N-channel transistors.

Owner:SEMICON ENERGY LAB CO LTD

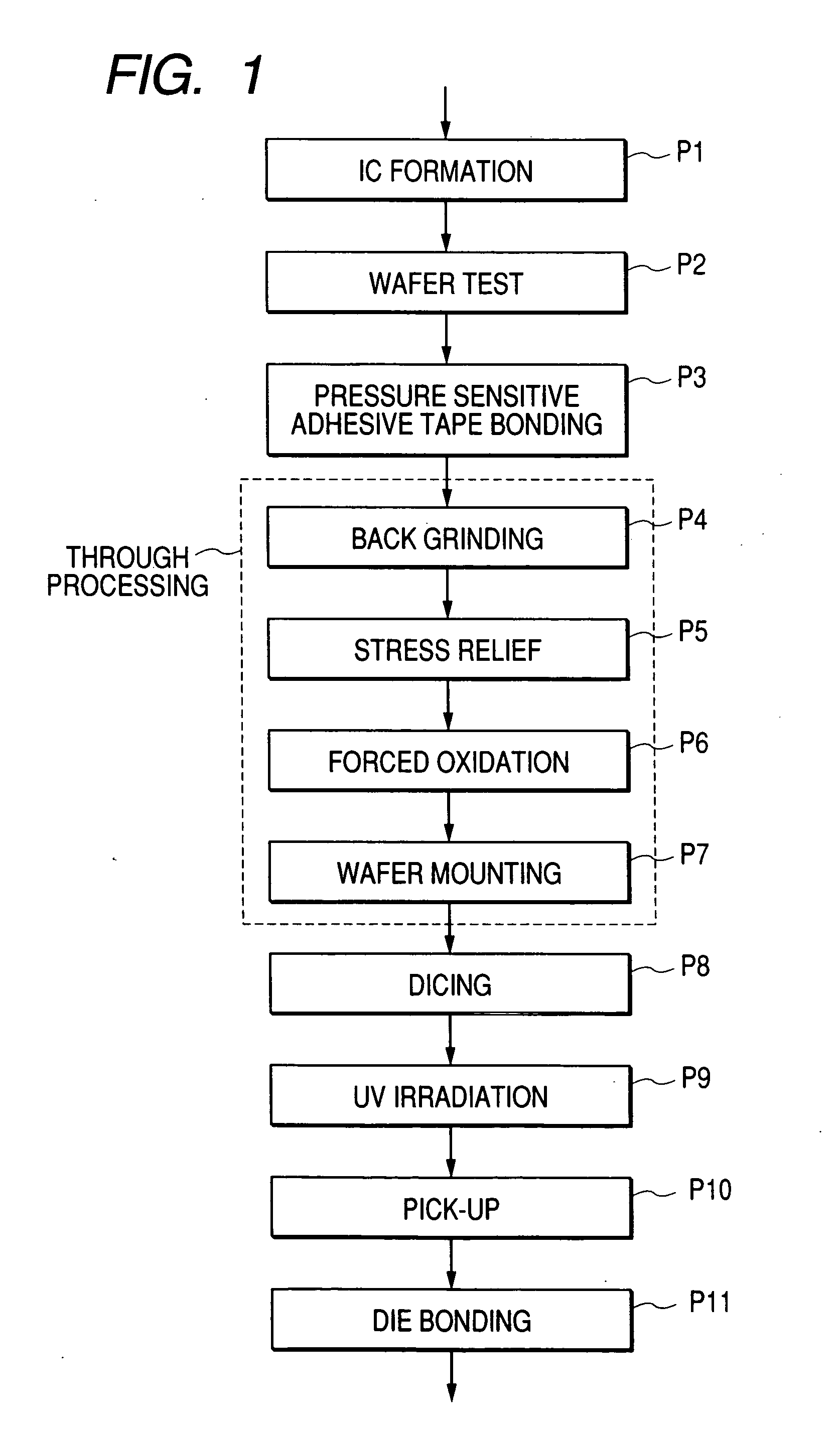

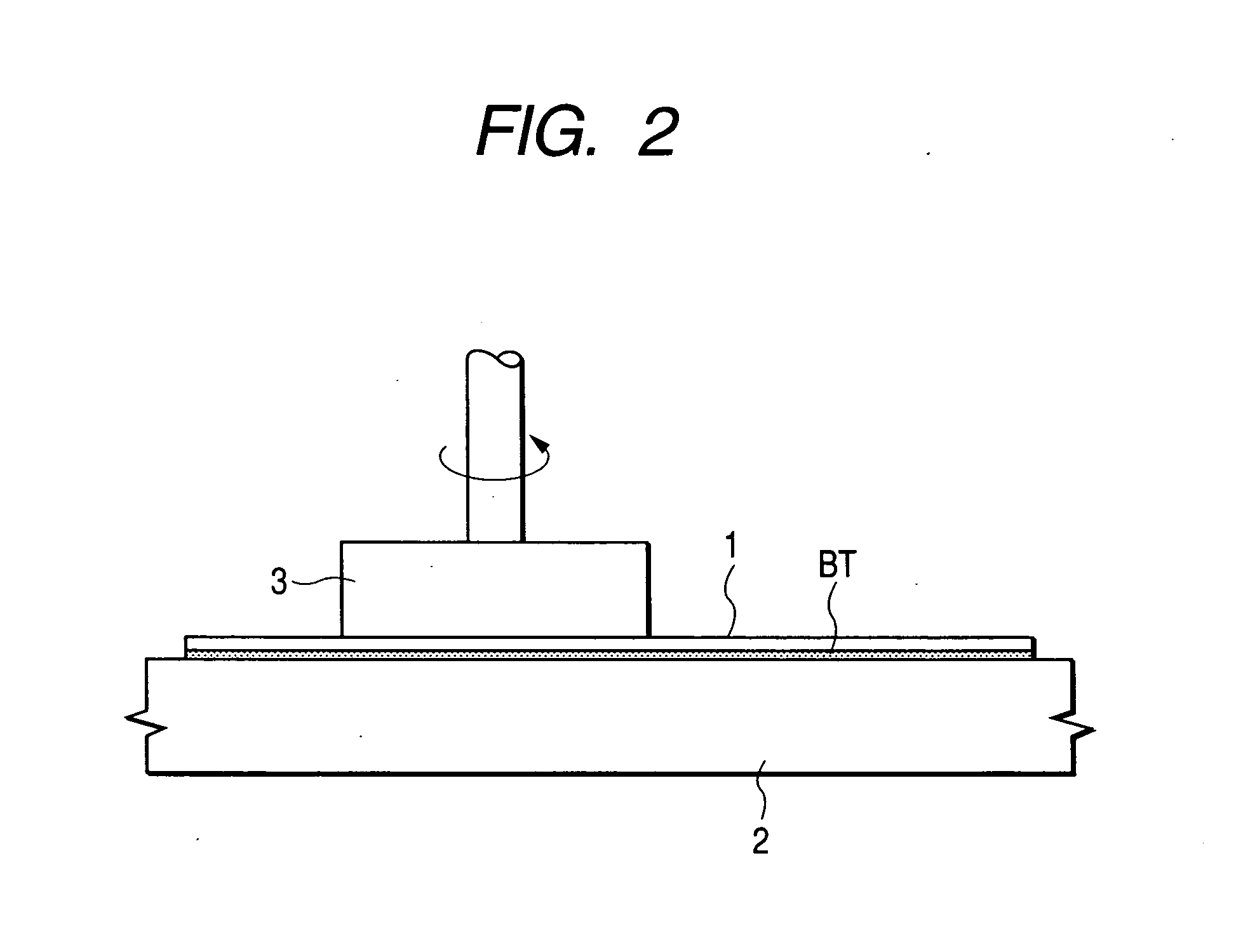

Fabrication method of semiconductor integrated circuit device

InactiveUS20050142815A1Wafer thickness reductionEasy to separateSolid-state devicesSemiconductor/solid-state device manufacturingWaferingDicing tape

A technique capable of stably releasing chips from a dicing tape, includes grinding a back surface of a semiconductor wafer, while adhering a pressure sensitive adhesive tape to a circuit forming surface of the semiconductor wafer formed with an integrated circuit, to achieve a predetermined thickness and forcibly oxidizing the back surface of the semiconductor wafer. Then, the pressure sensitive adhesive tape adhered to the circuit forming surface of the semiconductor wafer is released, and a dicing tape is adhered to the back surface of the semiconductor wafer. Further, the semiconductor wafer is divided by dicing it into individual chips, and then the back surface of the chip is pressed by way of the dicing tape, thereby releasing the chips from the dicing tape.

Owner:RENESAS ELECTRONICS CORP

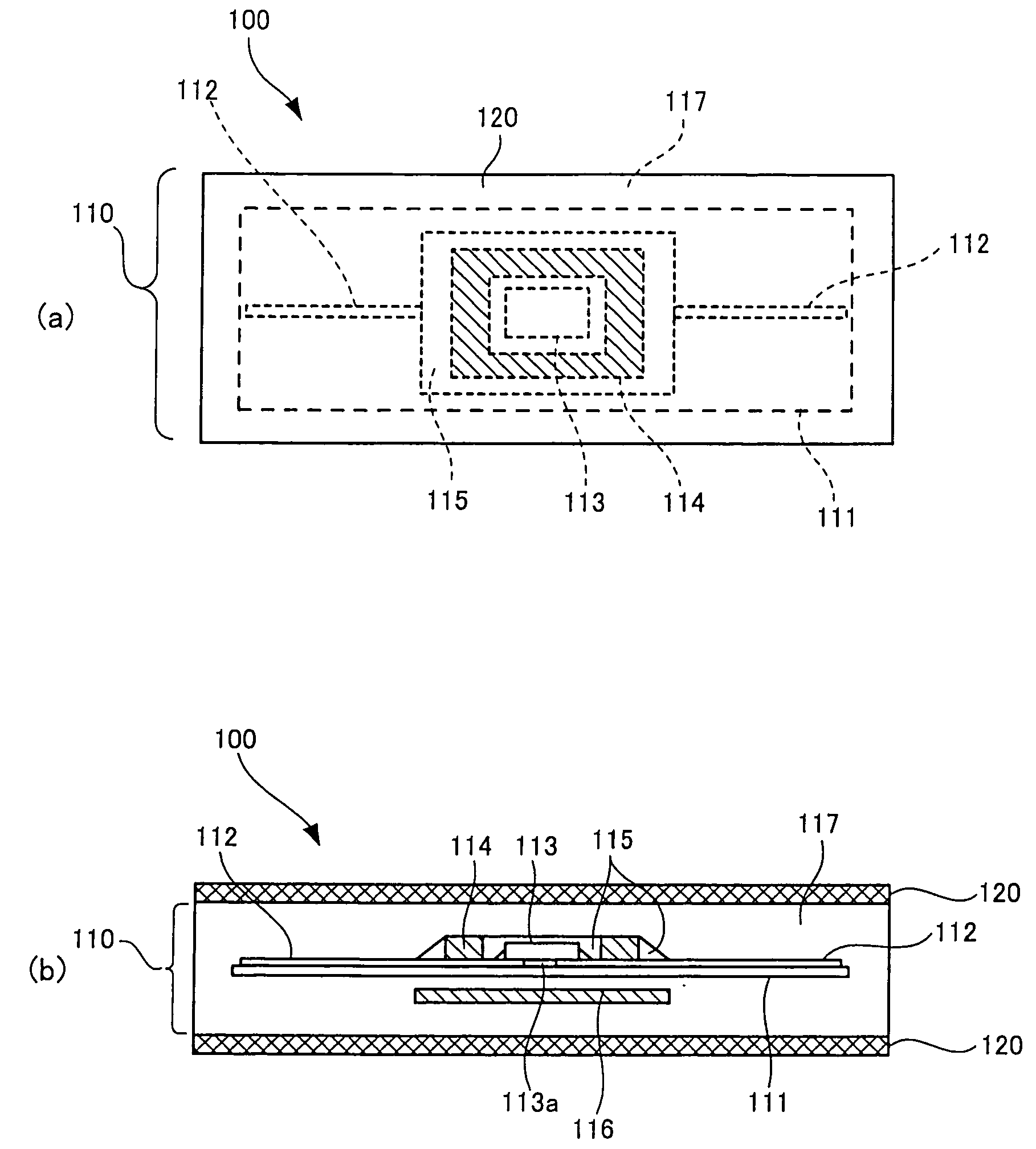

Integrated antenna type circuit apparatus

InactiveUS7615856B2Improve circuit characteristicsIncrease the areaAntenna supports/mountingsPrinted electric component incorporationElectrical conductorIntegrated antenna

An integrated antenna type circuit apparatus which provides excellent circuit characteristics while suppressing an increase in packaging area. The integrated antenna type circuit apparatus includes an insulating base, a semiconductor circuit device, chip parts, a molding resin, an antenna conductor, a ground conductor, and external lead electrodes. The plurality of chip parts are mounted on the insulating base, and are soldered to electrodes of wiring conductors on the top of the insulating base for electric and physical connection. The insulating base has a multilayer structure, being formed by laminating a plurality of insulator layers. The antenna conductor is formed on the bottom of the insulating base. A wiring conductor adjacent to the antenna conductor is provided with the ground conductor so that it overlaps with the antenna conductor.

Owner:SANYO ELECTRIC CO LTD

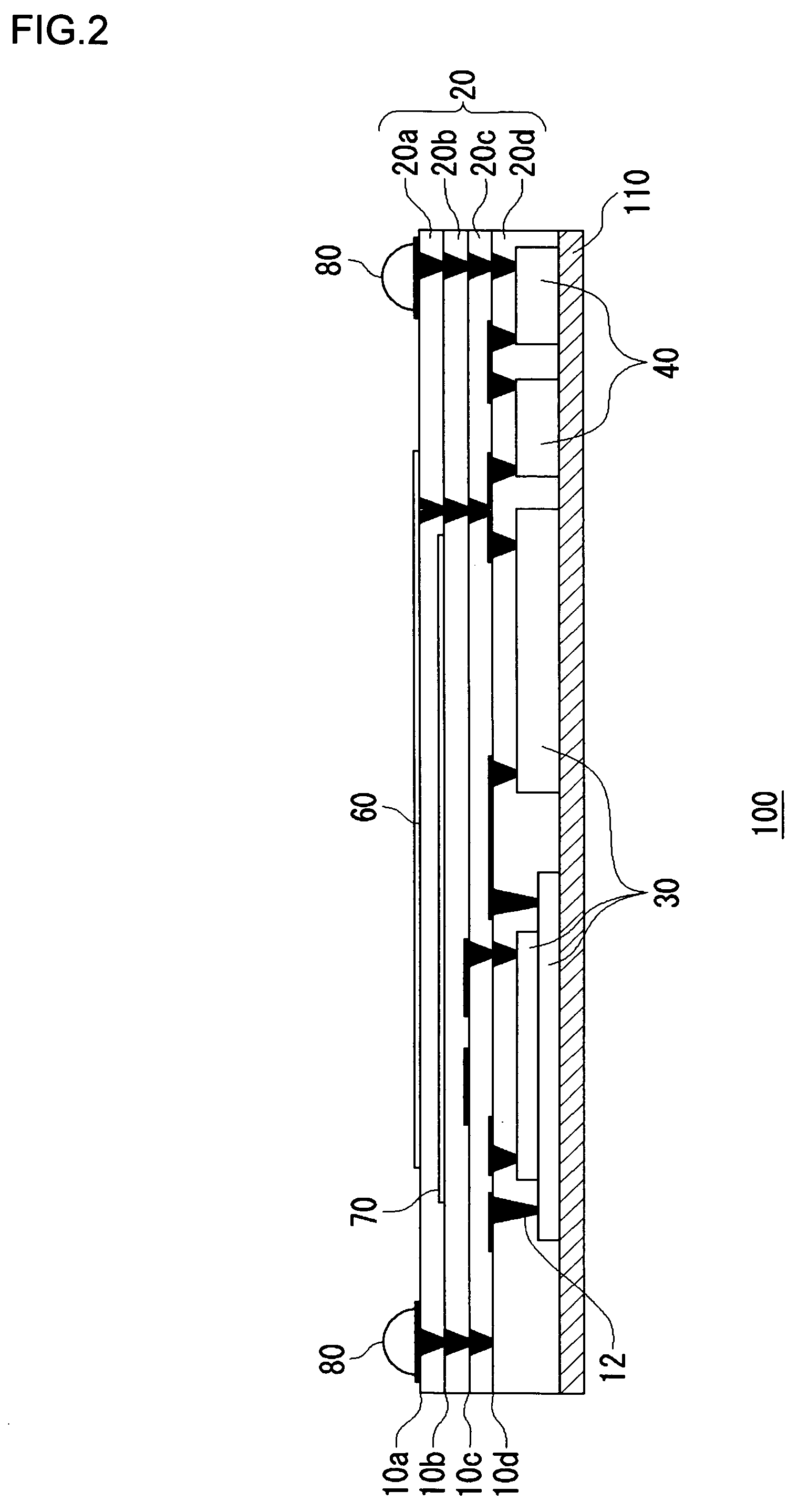

Shift register and display driving device comprising the same

ActiveUS7215315B2Stabilizing circuit operationSuppress failureStatic indicating devicesDigital storageShift registerVoltage

Owner:CASIO COMPUTER CO LTD

Thin film transistor and display device

InactiveCN102315277AIncreasing the thicknessSuppress failureTransistorElectroluminescent light sourcesOxide thin-film transistorDisplay device

A thin film transistor allowed to suppress a failure caused by an interlayer insulating film and improve reliability of a self-alignment structure, and a display device including this thin film transistor are provided. The thin film transistor includes: a gate electrode; an oxide semiconductor film having a channel region facing the gate electrode, and having a source region on one side of the channel region, and a drain region on the other side of the channel region; an interlayer insulating film provided in contact with the oxide semiconductor film as well as having a connection hole, and including an organic resin film; and a source electrode and a drain electrode connected to the source region and the drain region, respectively, via the connection hole.

Owner:JOLED INC

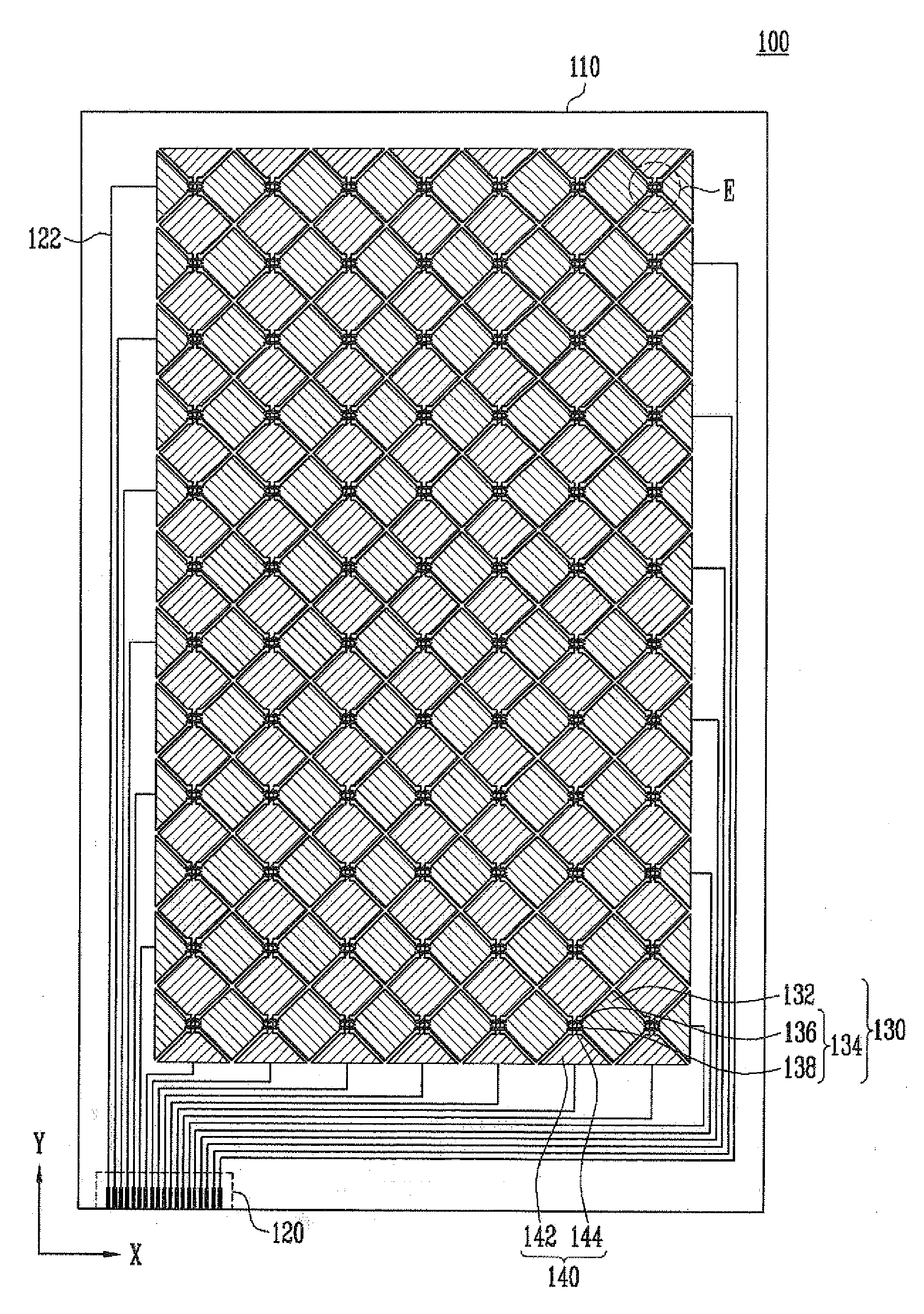

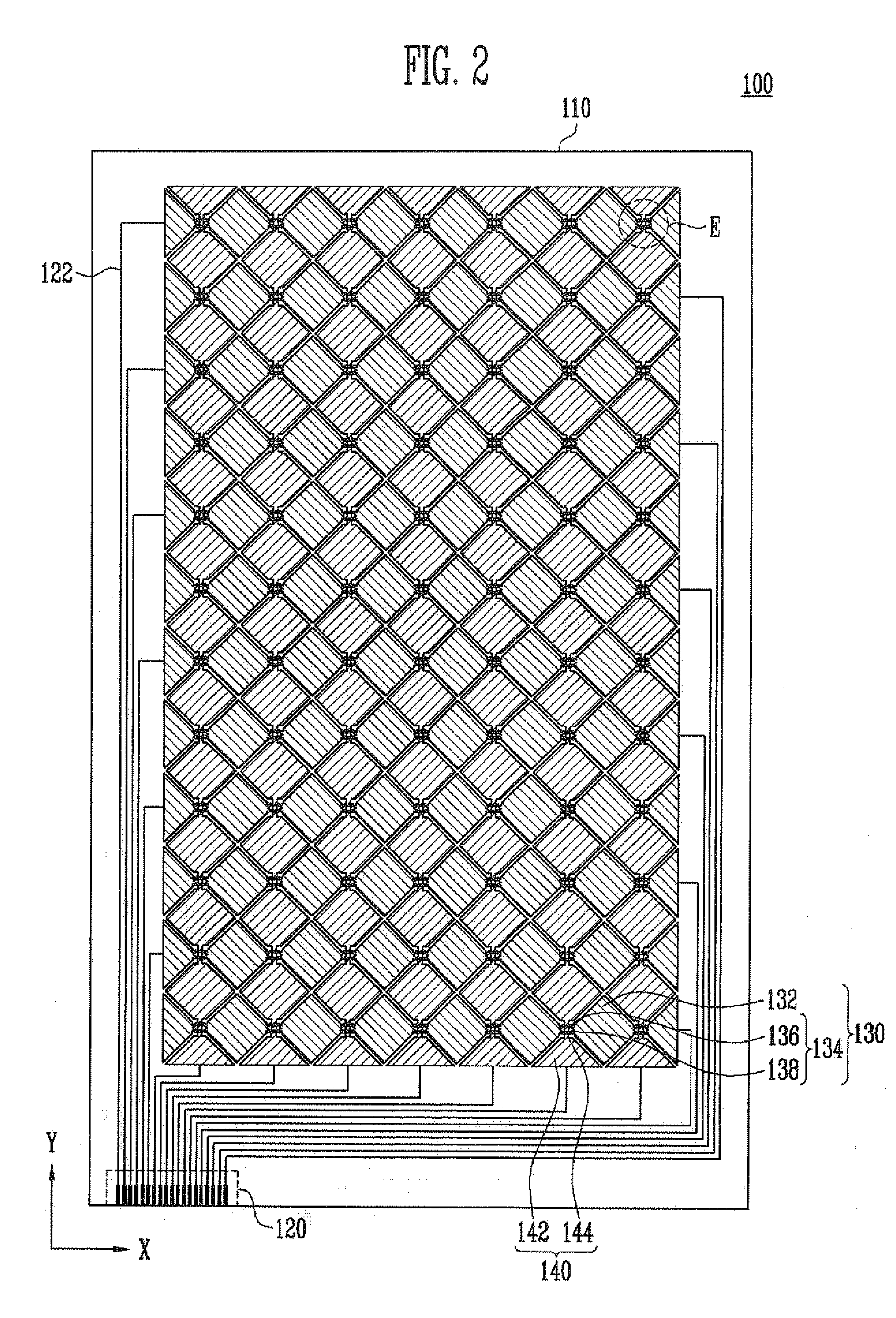

Touch Screen Panel and Display Device Having the Same

InactiveUS20120062487A1Improve weaknessAvoid failureNon-linear opticsInput/output processes for data processingVisibilityDisplay device

A touch screen panel and a display device having the same are capable of improving visibility and suppressing the occurrence of a failure caused by static electricity. In one embodiment, the touch screen panel includes a plurality of first sensing cells arranged along a first direction for each column on a transparent substrate. A first connection pattern electrically connects adjacent first sensing cells to each other. A plurality of second sensing cells are arranged along a second direction for each row while being spaced apart from the first sensing cells. A second connection pattern electrically connects adjacent second sensing cells to each other. In the touch screen panel, the first connection pattern comprises a pair of metal patterns and two pairs of dummy transparent patterns.

Owner:SAMSUNG DISPLAY CO LTD

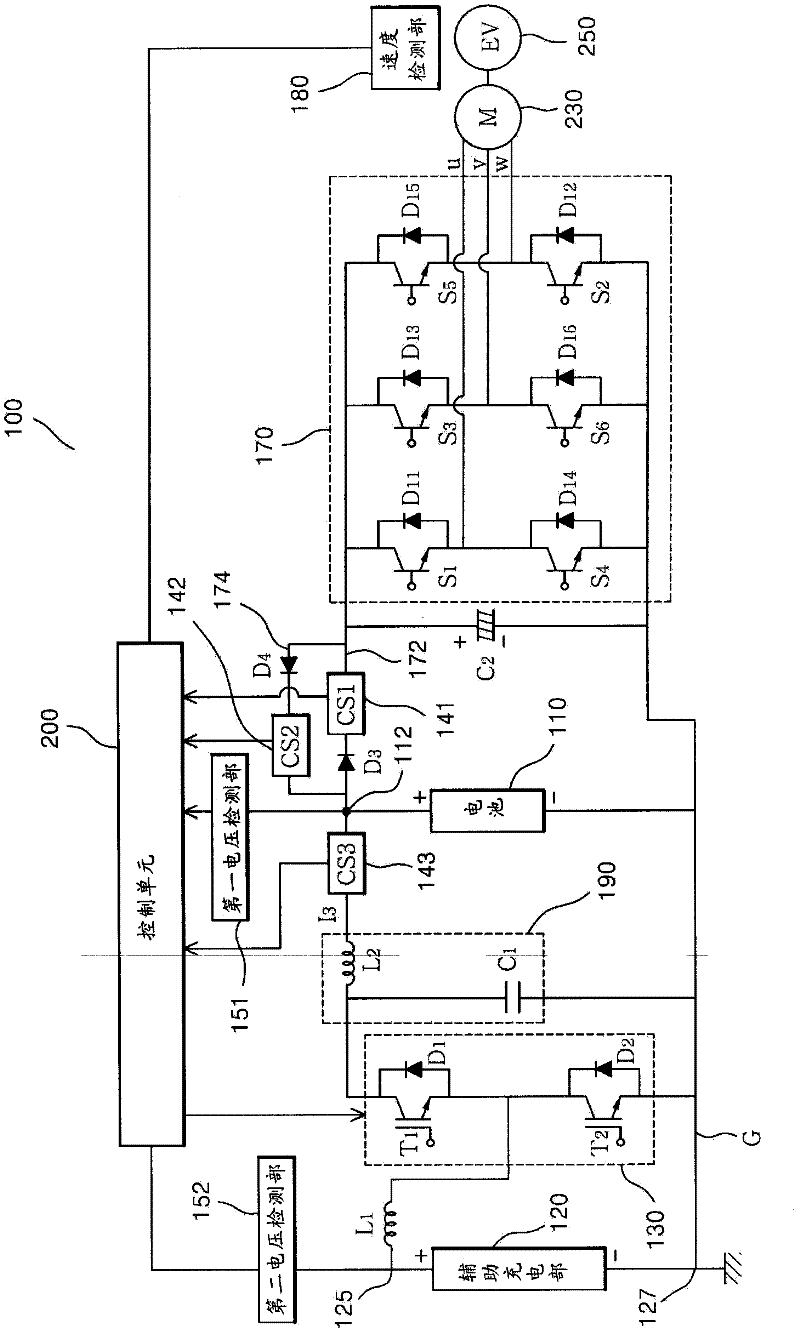

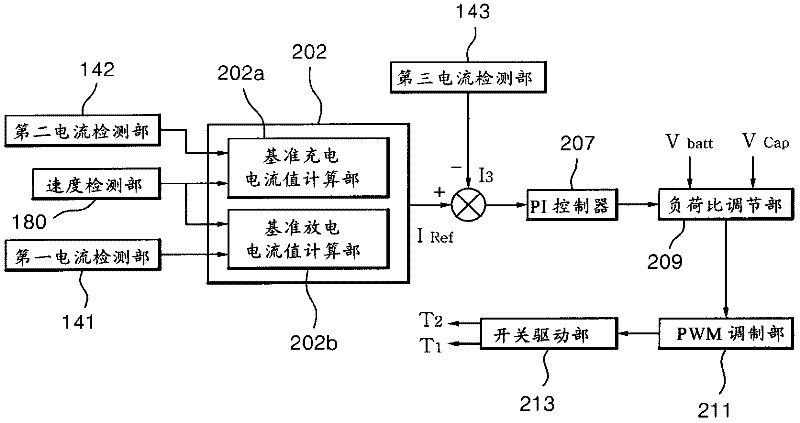

Electric energy charging and discharging apparatus and method using super capacitors for regenerative braking system of electric motorcycles

InactiveCN102570568AExtended driving distanceImprove storage efficiencyBatteries circuit arrangementsElectrodynamic brake systemsRegenerative brakeEngineering

An energy charging / discharging control apparatus of a regenerative braking apparatus of an electric vehicle and a method thereof are provided to improve electrical energy storage efficiency between a battery and a super capacitor, thereby increasing driving distance of the electric vehicle. Constitution A battery(110) is connected to both ends of an inverter(170). An auxiliary charging part(120) is connected to one or more super capacitors in series. A bidirectional converter(130) is connected between the battery and the auxiliary charging part. A current detector detects a charging / discharging current flowing between the battery and the bidirectional converter. A speed detector detects the speed of an electric vehicle.

Owner:IND ACADEMIC COOPERATION FOUND HONAM UNIV

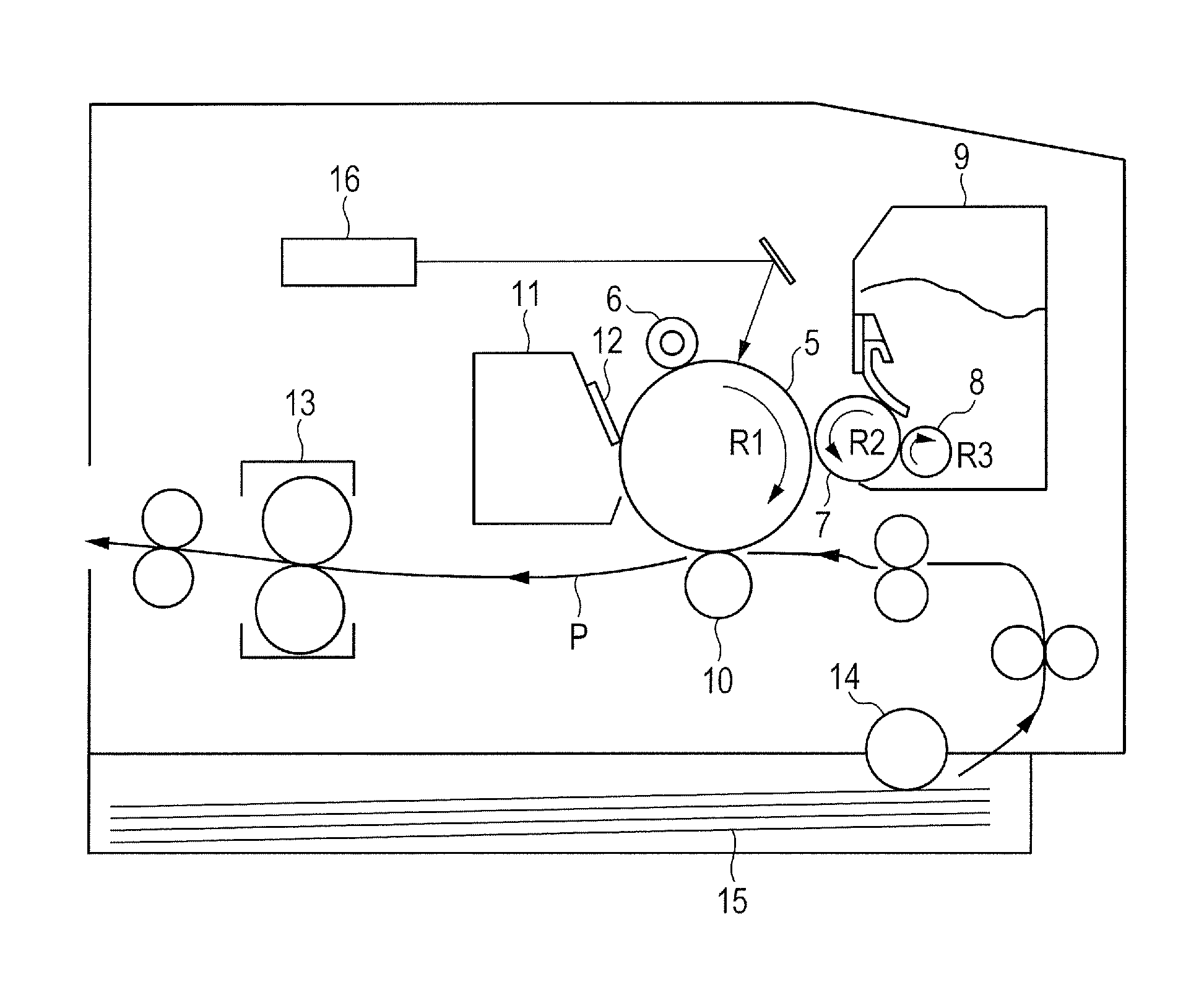

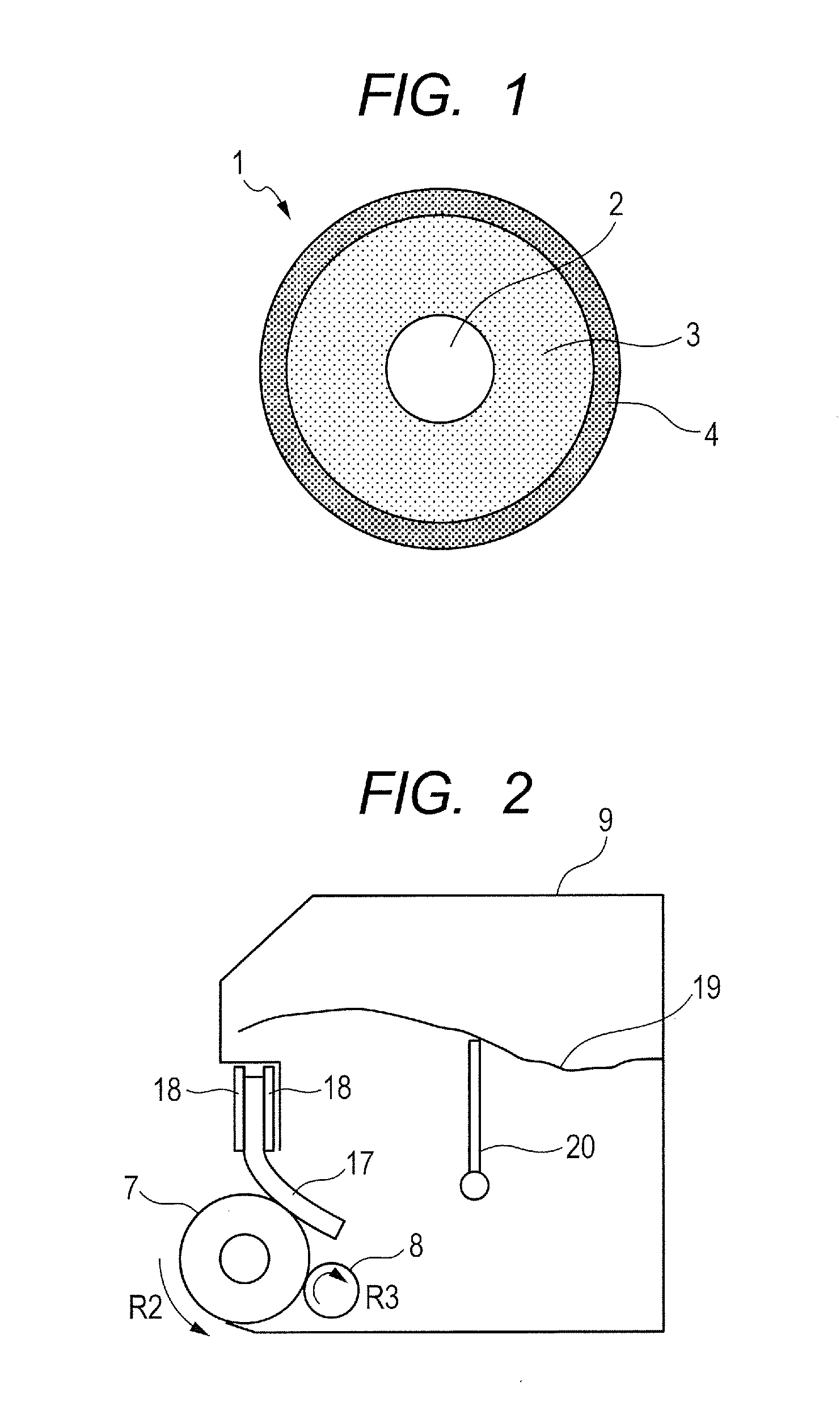

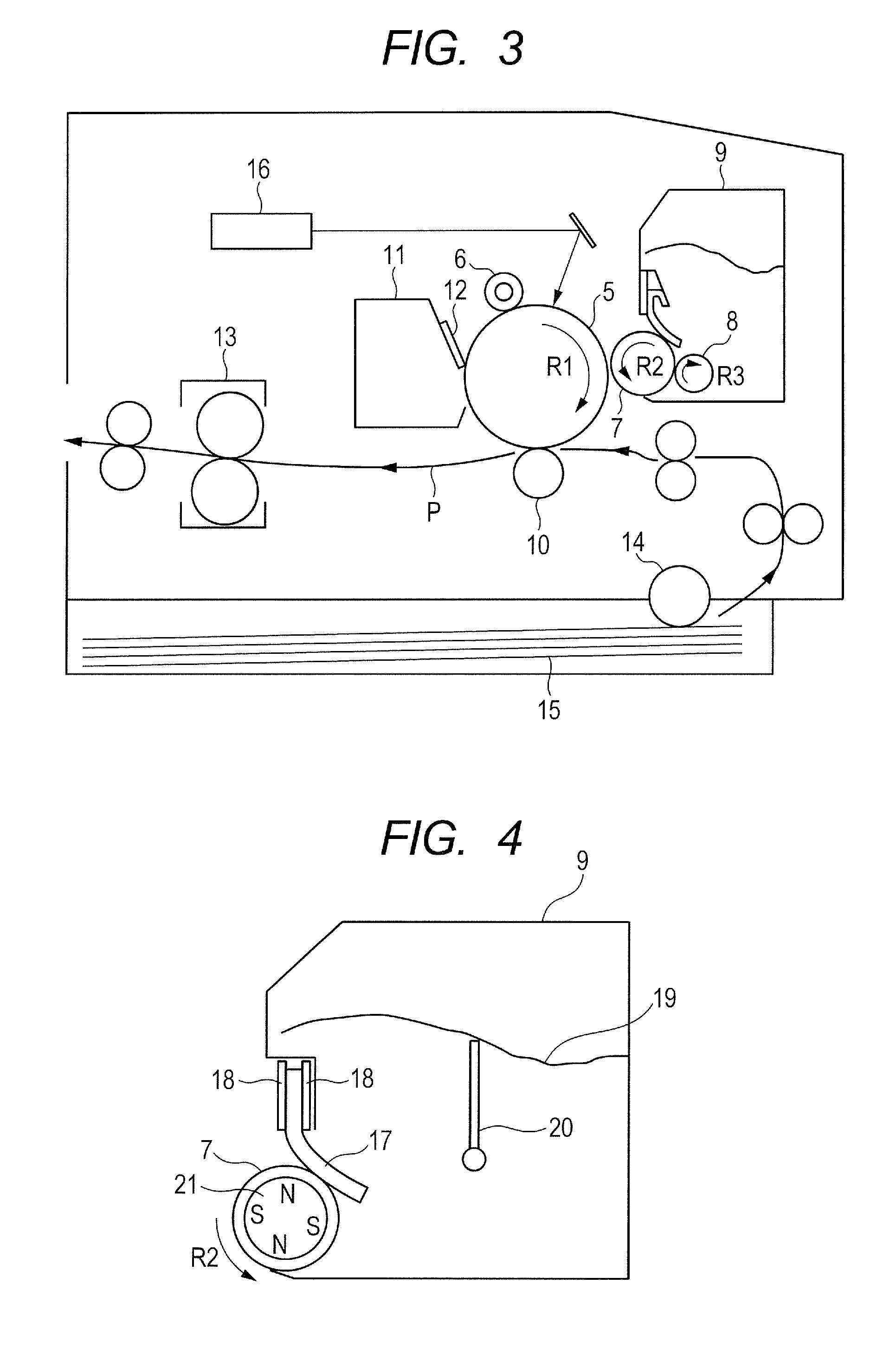

Developing apparatus, developing method, image forming apparatus and image forming method

ActiveUS9348246B2Fog suppressionSuppress failureDevelopersElectrographic process apparatusSilica particleSurface layer

The present invention provides a developing apparatus including a toner, a toner carrying member and a regulating member, wherein the toner is a magnetic toner including a toner particle, a first fine silica particle having a number average primary particle diameter of 5 to 20 nm and a second fine silica particle having a number average primary particle diameter of 40 to 200 nm, the second fine silica particle is a fine silica particle produced by a sol-gel method, the toner has a total energy of 270 to 355 mJ / (g / ml), the toner carrying member has a substrate, an elastic layer and a surface layer including a urethane resin, and the urethane resin has a partial structure derived from a reaction of a particular amine type compound with a polyisocyanate.

Owner:CANON KK

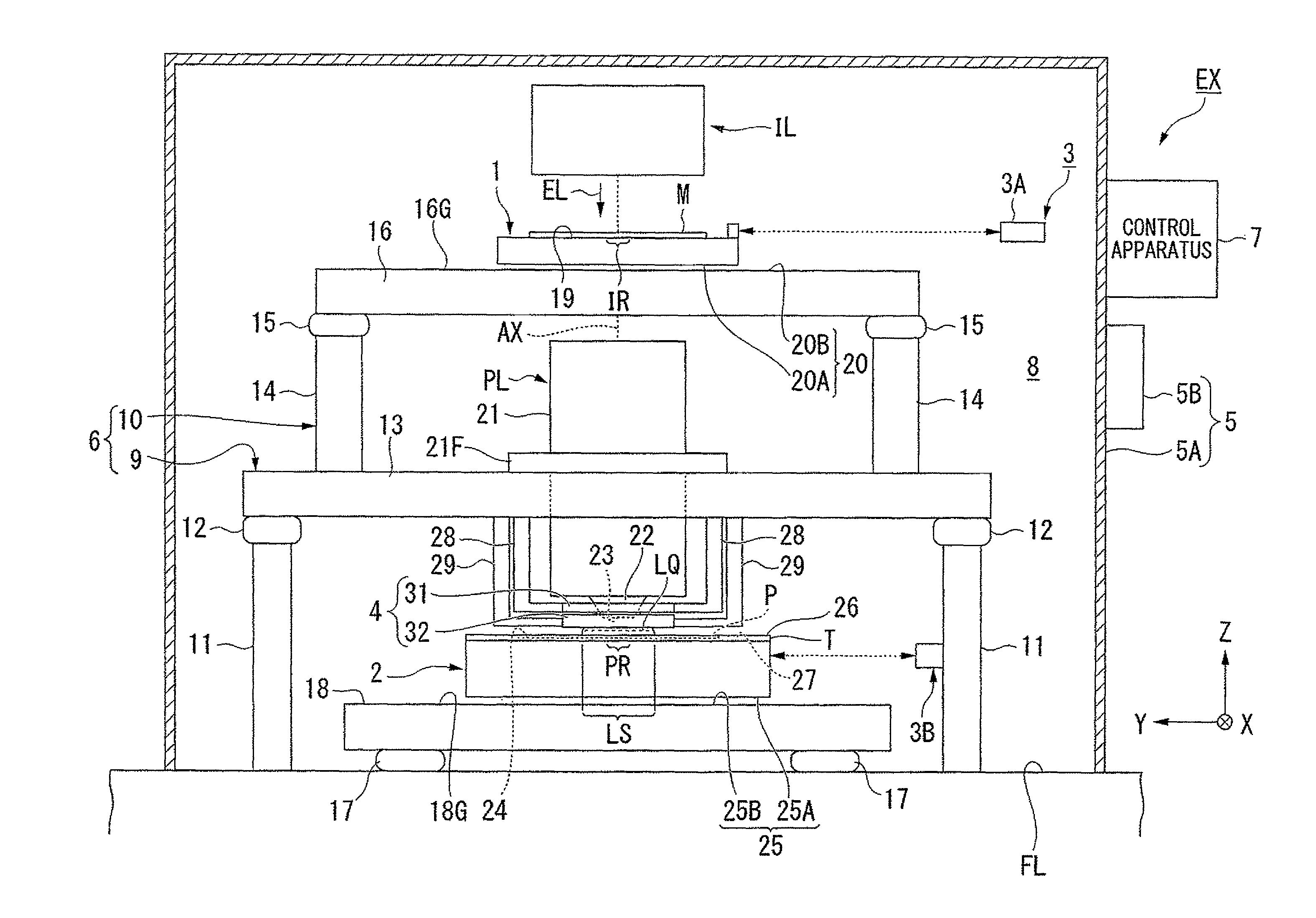

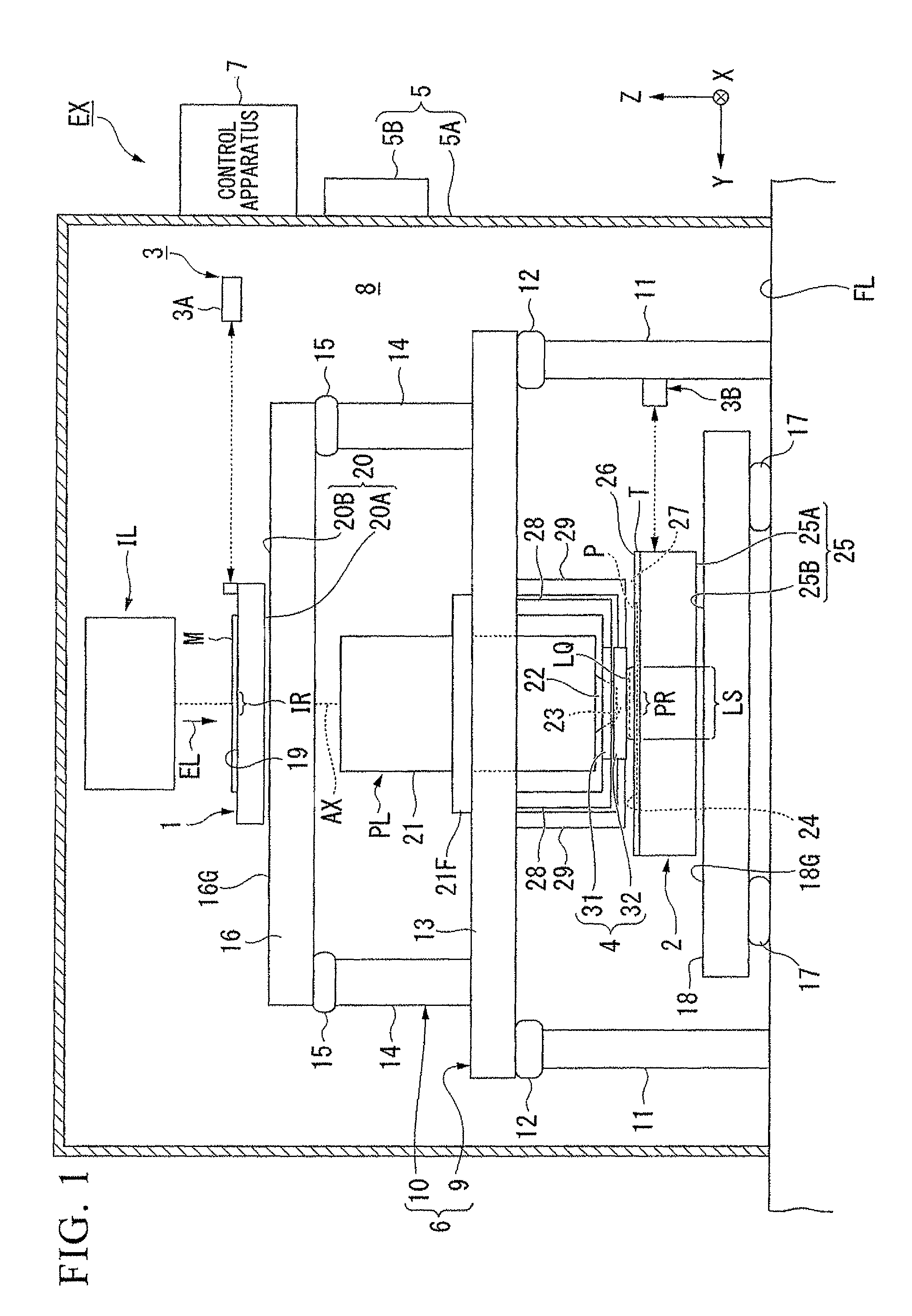

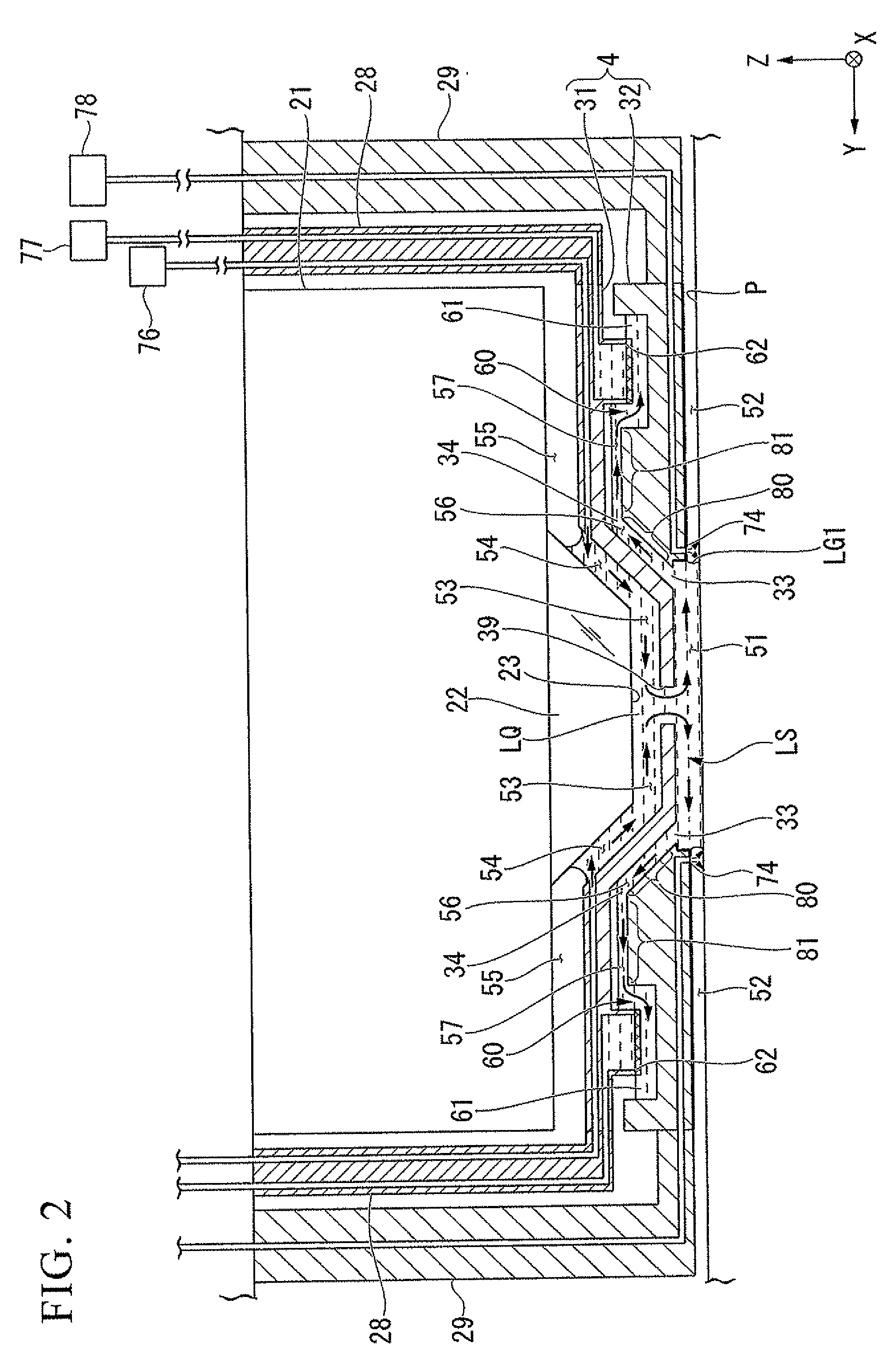

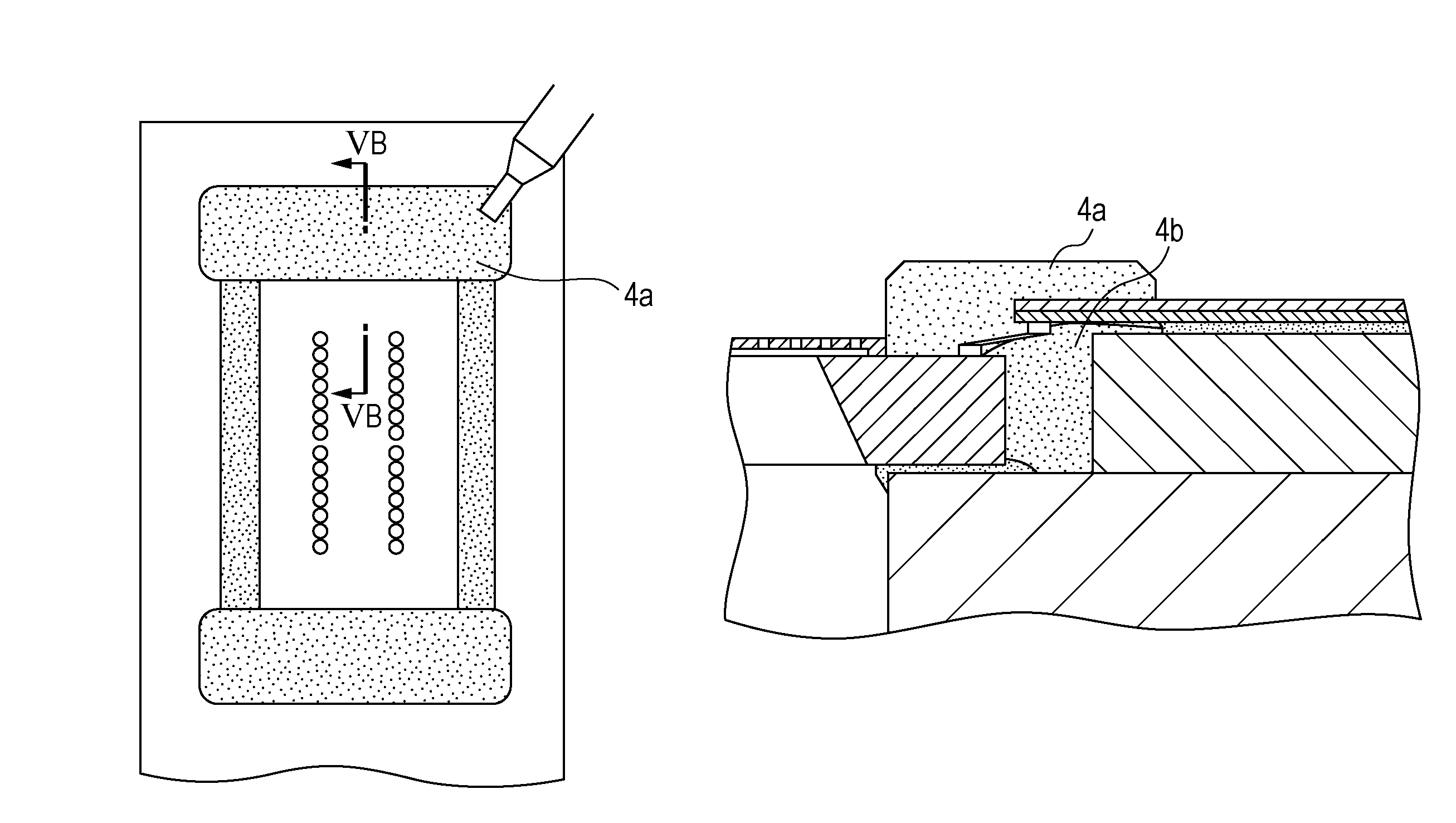

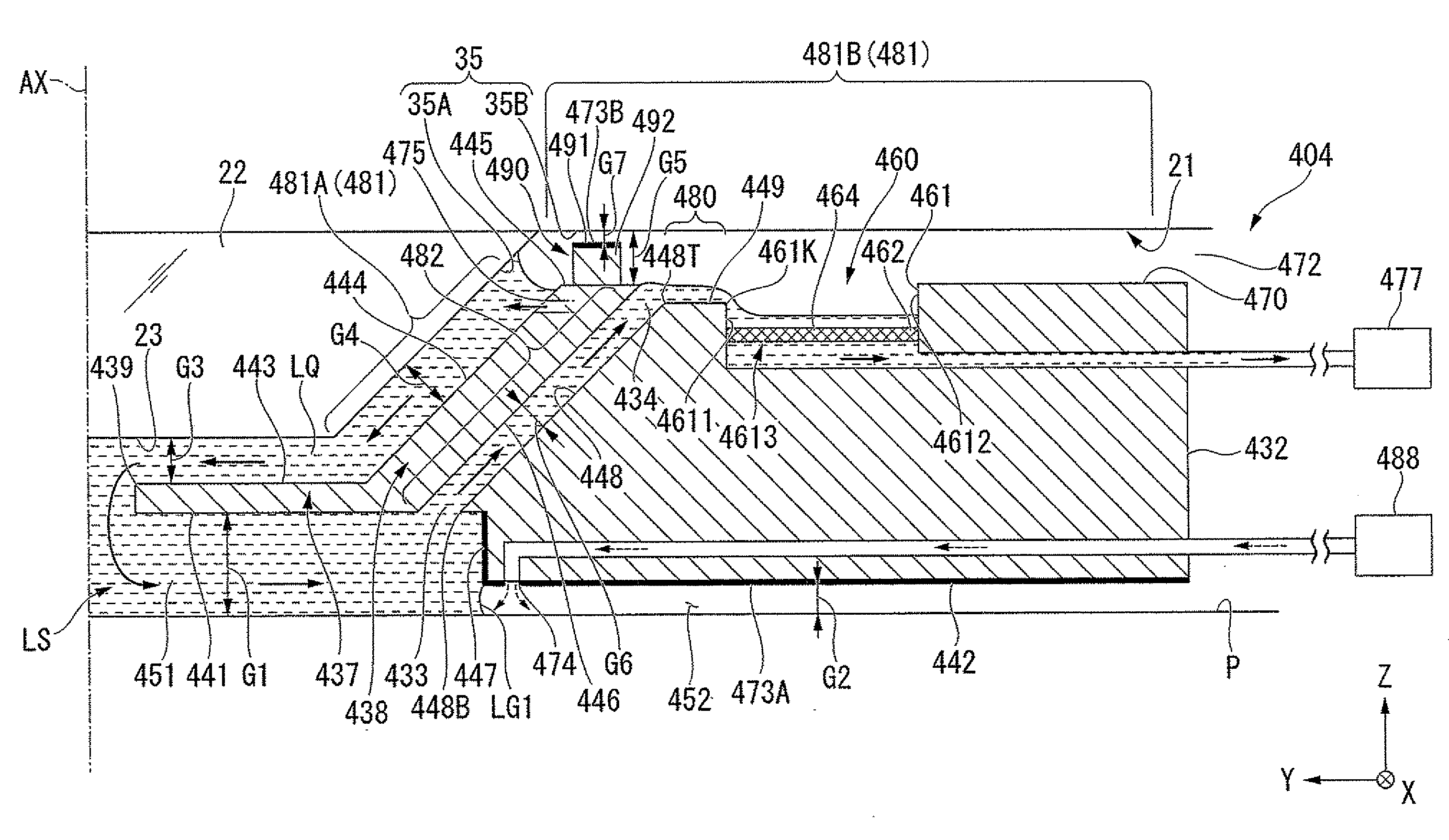

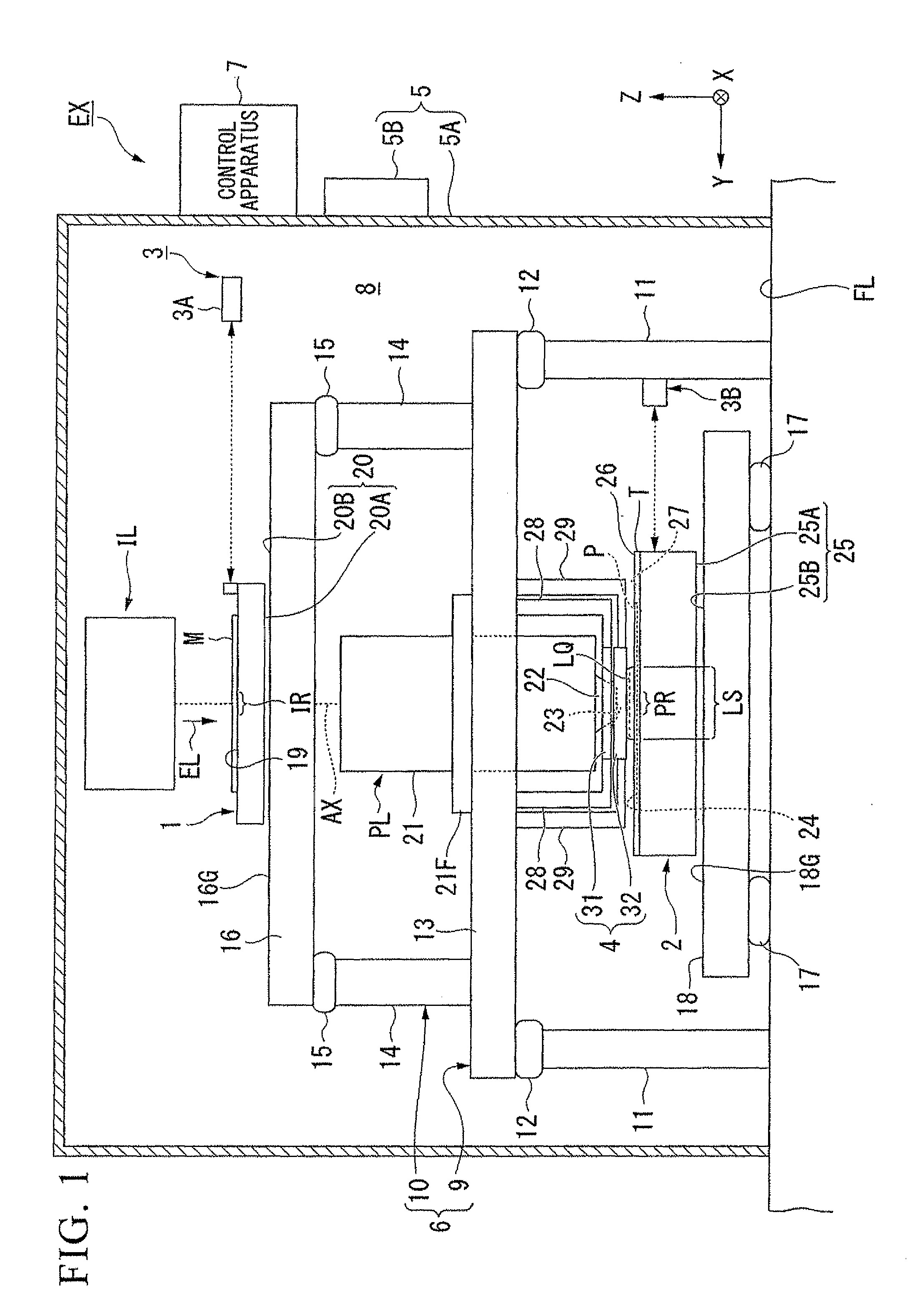

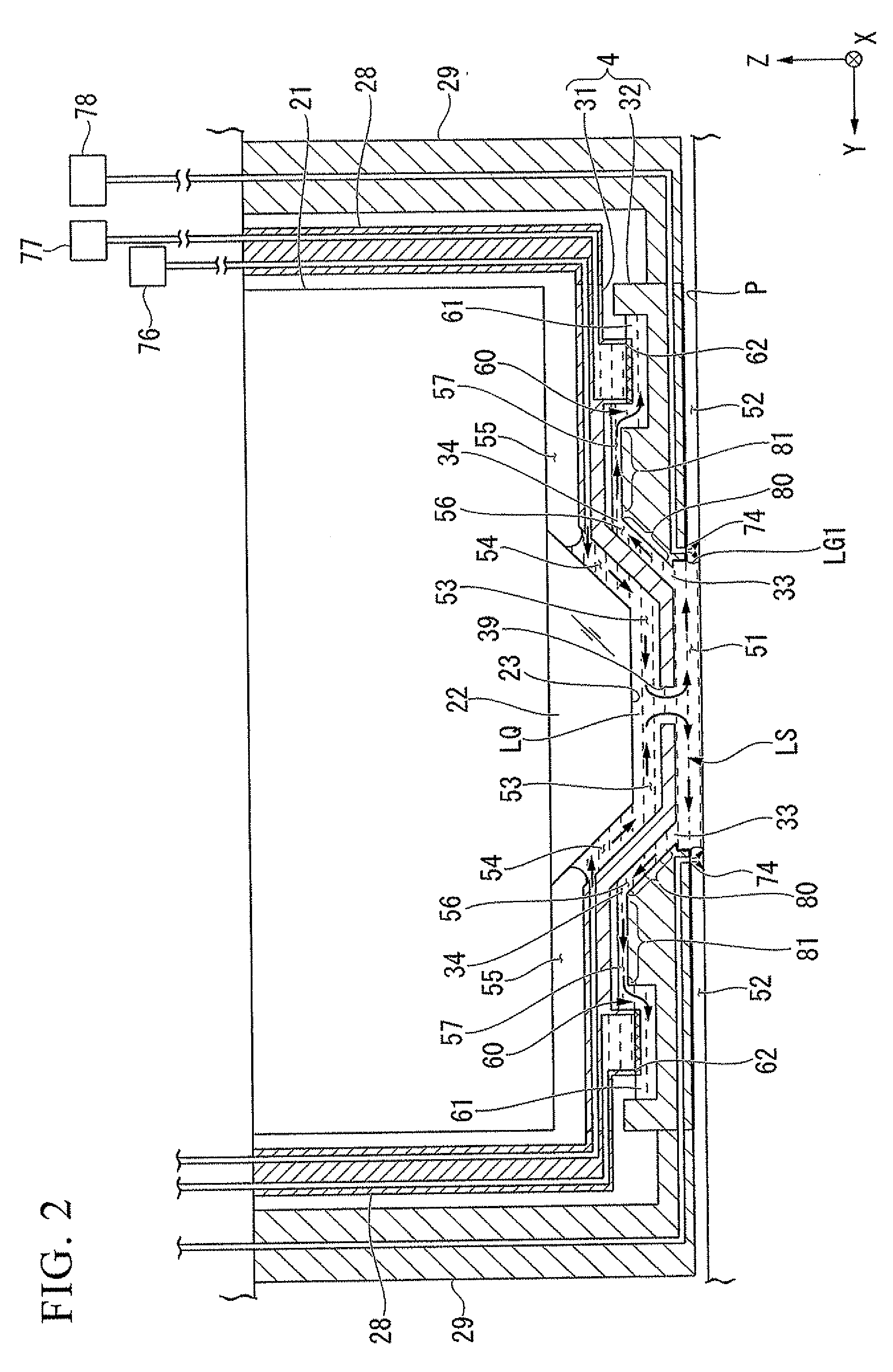

Exposure apparatus, exposure method, and device manufacturing method

ActiveUS8896806B2Suppression problemSuppress failurePhotomechanical apparatusOriginals for photomechanical treatmentAtmosphereOptical path

An exposure apparatus that exposes a substrate includes: an optical system that includes an emission surface from which an exposure light is emitted; a first surface that is disposed in at least a part of a surrounding of an optical path of the exposure light emitted from the emission surface; a second surface that is disposed in at least a part of a surrounding of the first surface and at a position lower than the first surface; a space portion into which a liquid can flow via a first aperture between the first surface and the second surface and which is opened to the atmosphere via a second aperture different from the first aperture; and a first recovery portion that recovers at least a part of the liquid flowing into the space portion. Here, the emission surface, the first surface, and the second surface are opposed to the surface of the substrate in at least a part of the exposure of the substrate, and the substrate is exposed with the exposure light from the emission surface via the liquid between the emission surface and the surface of the substrate.

Owner:NIKON CORP

Sealant, inkjet recording head using sealant, and method for manufacturing the same

ActiveUS8876257B2Adjustable viscositySuitable for useLine/current collector detailsPrintingCationic polymerizationSealant

A sealant contains a dicyclopentadiene type epoxy resin represented by formula 1 below, a hydrogenated bisphenol A epoxy resin, and a photo-induced cationic polymerization initiator, in which the content of the dicyclopentadiene type epoxy resin is 15 to 40 parts by mass relative to 100 parts by mass of the total mass of epoxy resins contained in the sealant.where n represents an integer of 0 to 2.

Owner:CANON KK

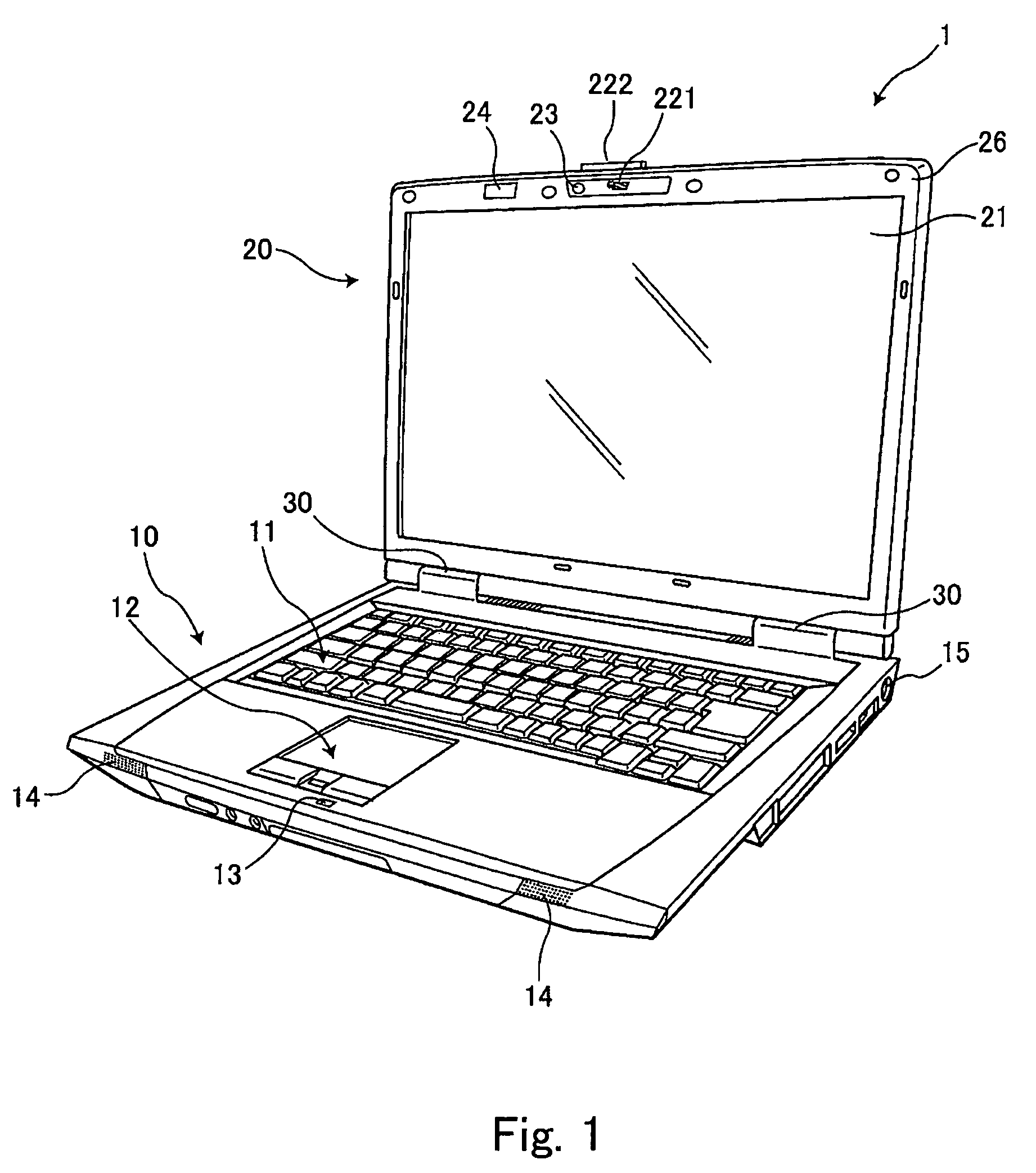

Electronic device

InactiveUS7948752B2Suppress failureHigh strengthTelevision system detailsColor television detailsSignal processing circuitsComputer module

An electronic device has a first cabinet and a second cabinet. The second cabinet has a locking module including a hook, an operation member and a linking mechanism. The hook is formed at a position near a top end of the second cabinet around the center in the lateral direction in opened state, and is engaged with the first cabinet to lock the second cabinet in the closed state. The operation member disengages the hook from the first cabinet in response to operation. The linking mechanism links the operation to movement of disengaging the hook. The second cabinet further has a board mounted with a camera module having an image taking lens and an imaging device and a signal processing circuit for the camera module. The board is disposed at such a position that a portion in which the signal processing circuit is mounted overlaps with the linking mechanism.

Owner:FUJITSU CLIENT COMPUTING LTD

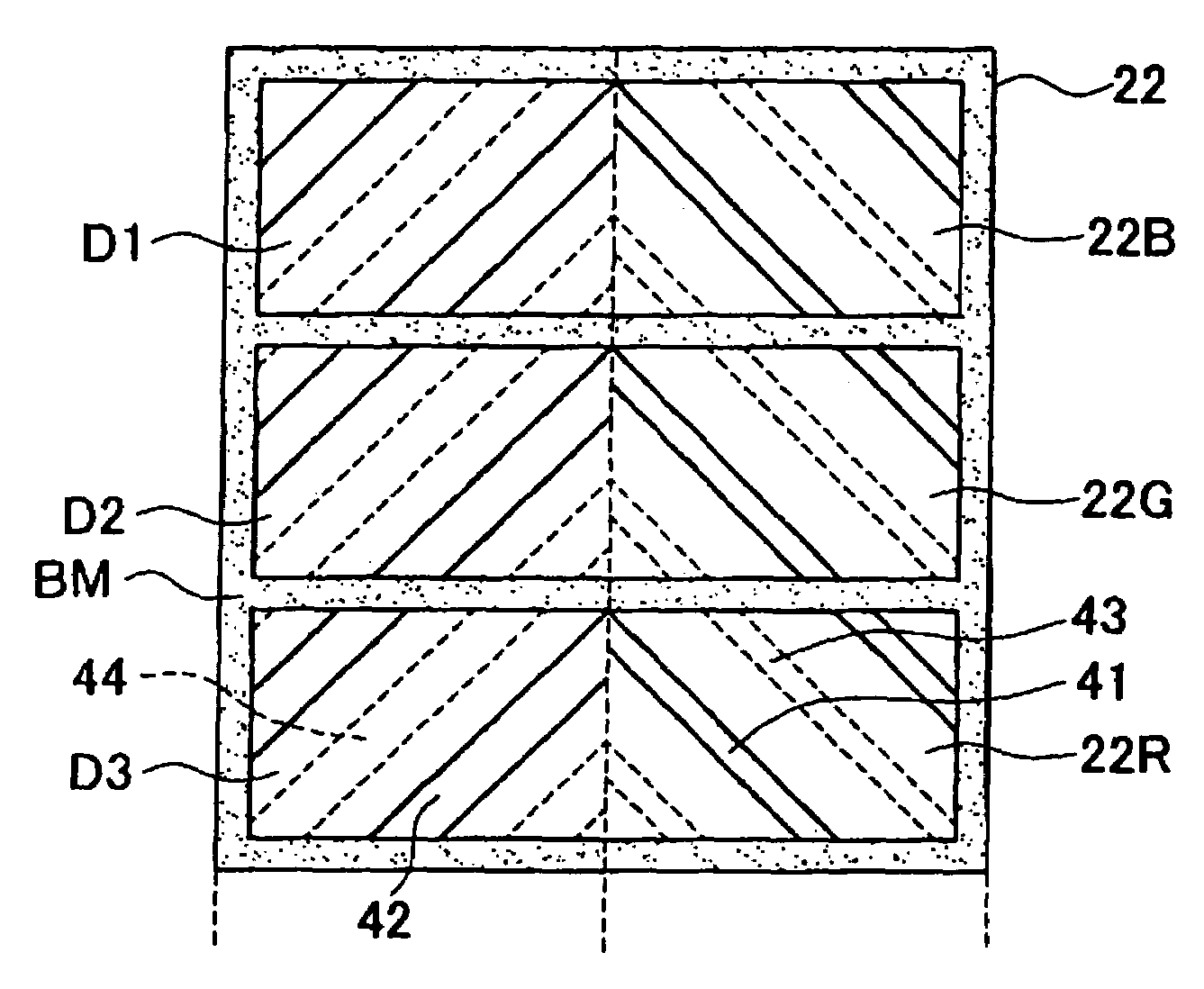

Liquid crystal display device having particular alignment controlling elements in transmissive and reflective pixel regions

ActiveUS7106405B2Wide viewing angleSuppress failureNon-linear opticsDielectric anisotropyDisplay device

To provide a transreflective liquid crystal display device that can produce a bright and high-contrast display with a wide viewing angle. A liquid crystal display device has a liquid crystal layer held between a pair of substrates and has a transmissive display region and a reflective display region in one dot region. The liquid crystal layer includes a liquid crystal being initially vertically aligned and having negative dielectric anisotropy. The pair of substrates have electrodes to drive the liquid crystal on sides facing the liquid crystal layer. The electrodes have openings and protrusions in the transmissive display region and the reflective display region, respectively. The opening areas of the openings and the in-plane occupying areas of the protrusions are larger in the reflective display region than in the transmissive display region.

Owner:BOE TECH GRP CO LTD

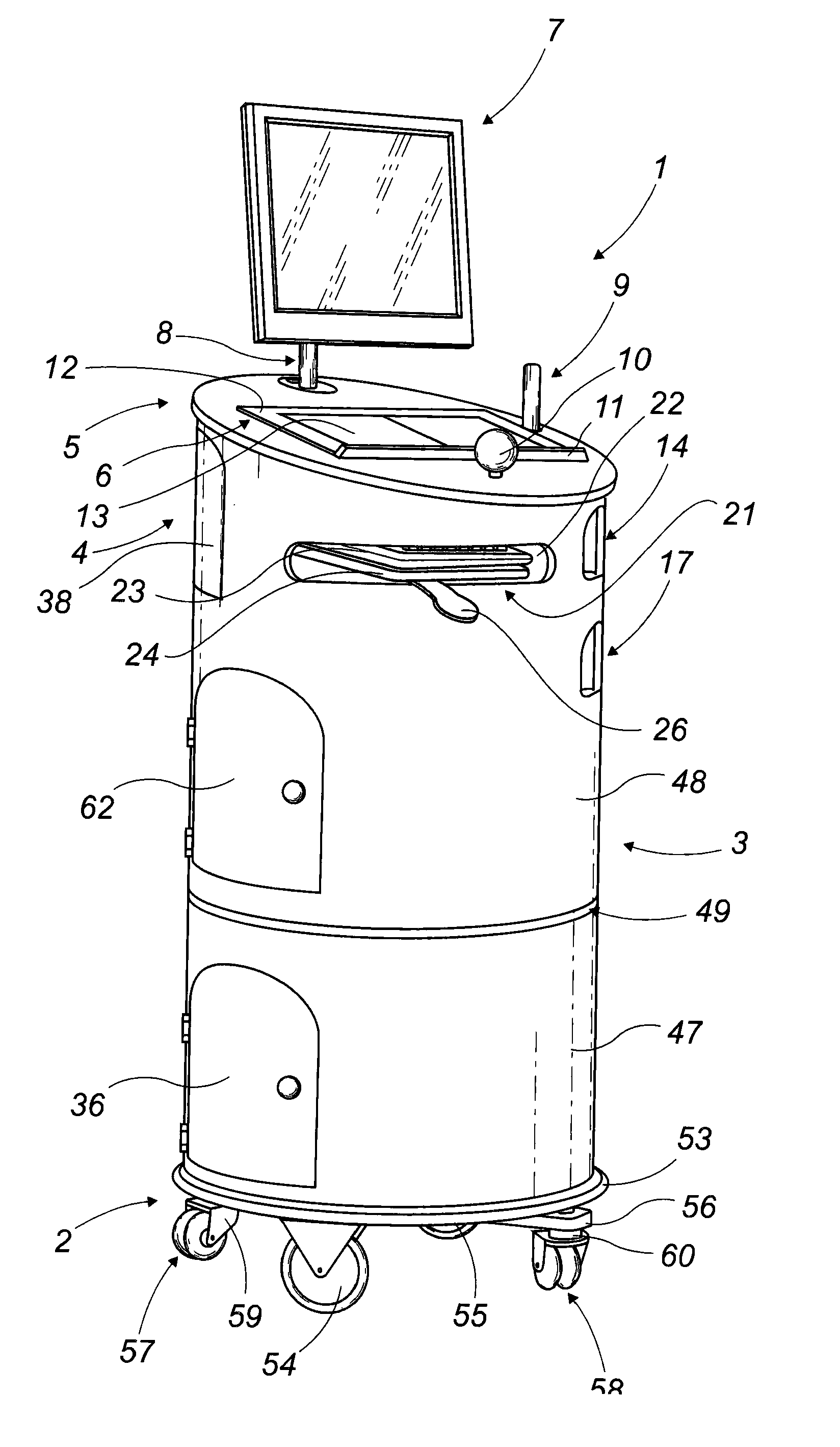

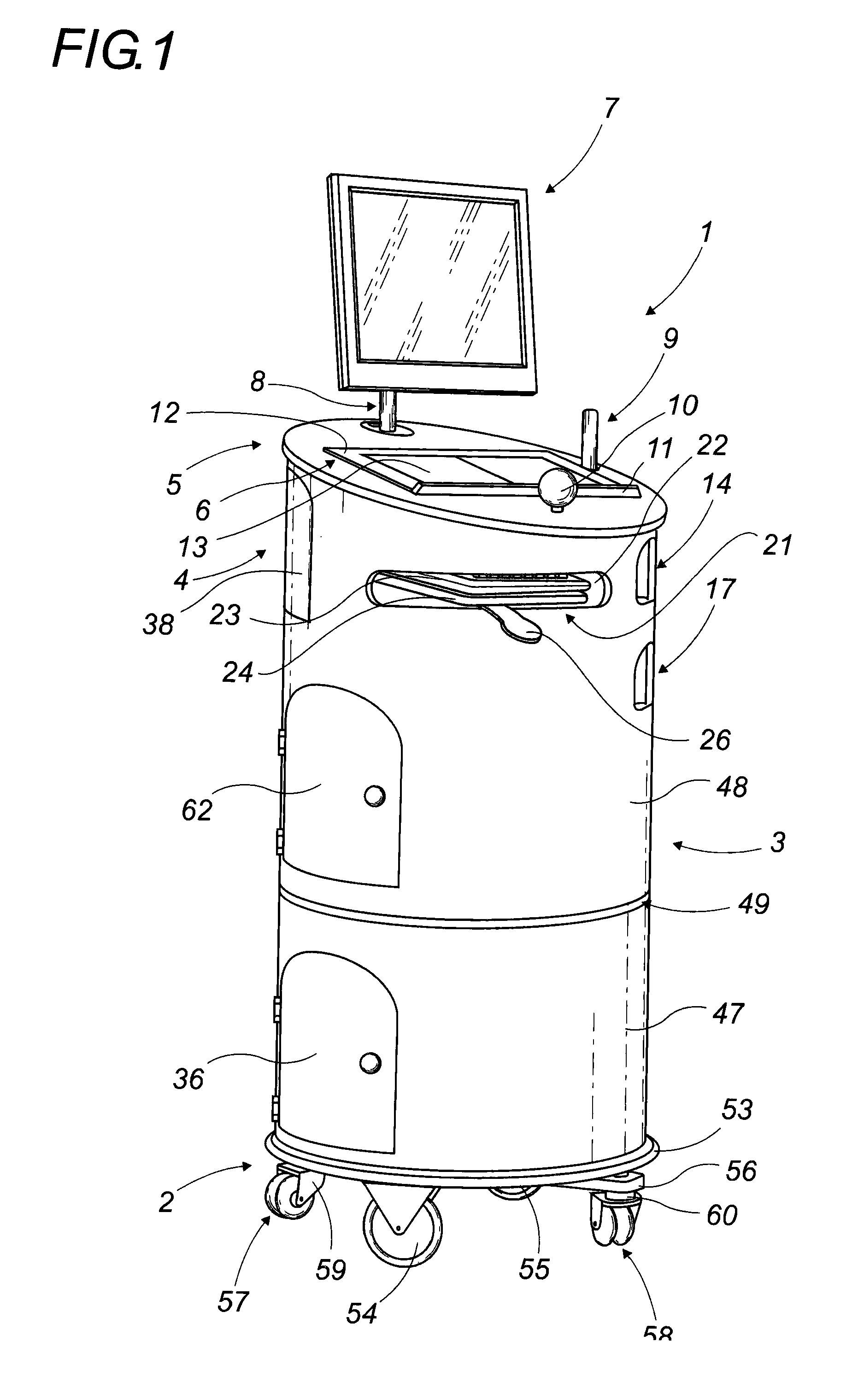

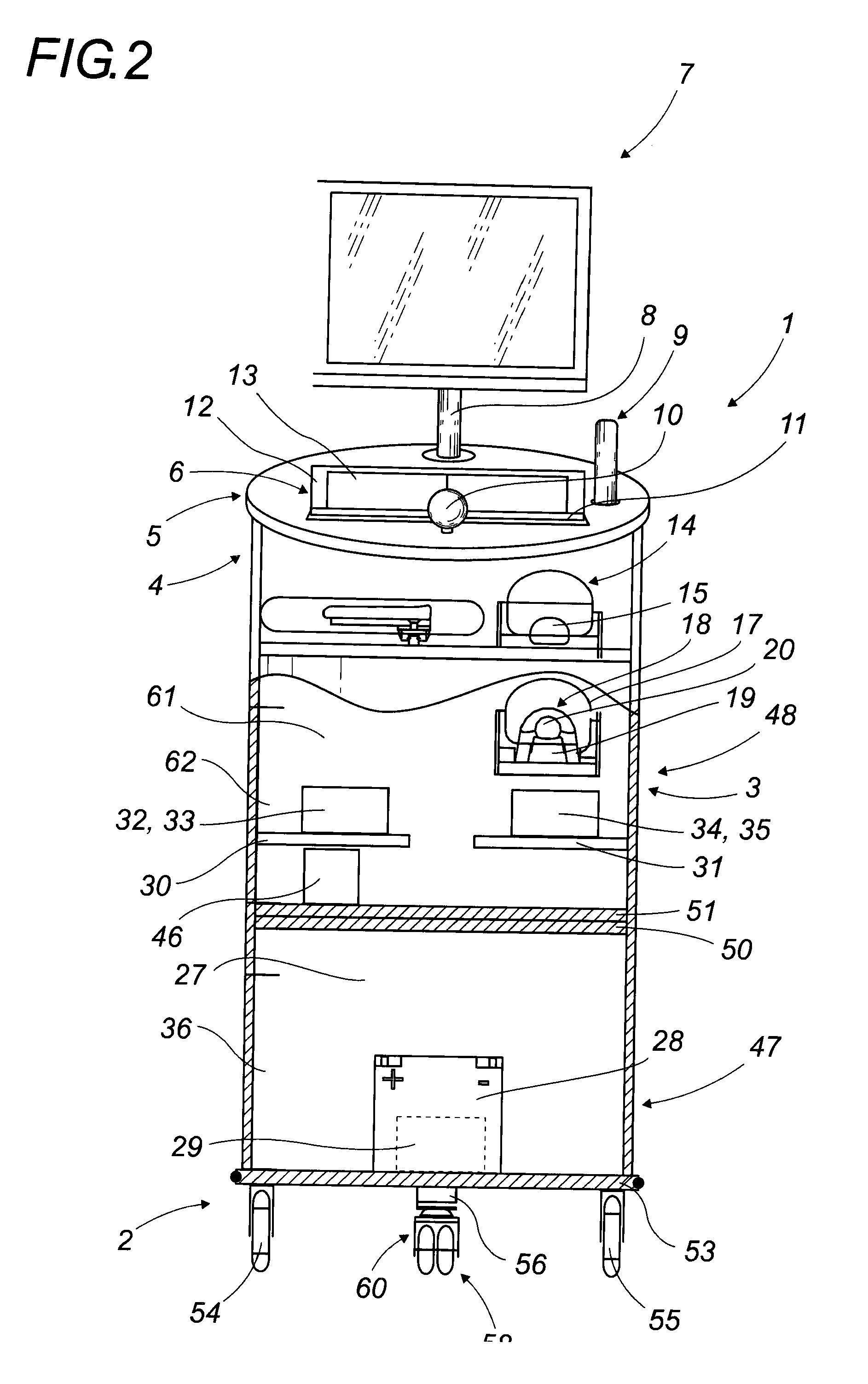

Multimedia, multiservice and connectable mobile assembly for diagnosis, prescriptions, medical checkups and nursing care

InactiveUS20100145160A1Suppressing re-writing uncertaintySuppression errorSurgical furnitureDiagnostic recording/measuringDocking stationNursing care

Connectable, multimedia and multiservice mobile assembly for diagnosis and medical checkups, characterized in that it is composed of a directional rolling base (2) and of a cylindrical hollow body (3) enclosing electrical power supply means (28, 29), identification means (18), computing means and multimedia communication means as well as a facility (39) for disinfecting the hands and in that it is predisposed for its reception and connection to a docking station. This invention is of particular interest to manufacturers of trolleys intended for hospitals and care units.

Owner:CINQUALBRE JACQUES +1

Thin film transistor and display device using the same

In a thin film transistor and a display device provided with the same, a thin film transistor according to an exemplary embodiment includes: a semiconductor layer including a channel region, a source region, a drain region, a light-doped source region, and a light-doped drain region; a gate electrode overlapping the channel region; a source electrode contacting the source region; and a drain electrode contacting the drain region. The channel region includes a main channel portion, a source channel portion, and a drain channel portion, and the source channel portion and the drain channel portion are extended from the main channel portion and separated from each other. The light-doped source region is disposed between the source channel portion and the source region and the light-doped drain region is disposed between the drain channel portion and the drain region.

Owner:SAMSUNG DISPLAY CO LTD

Exposure apparatus, exposure method, and device manufacturing method

ActiveUS20100304310A1Suppress exposure failureSuppression problemPhotomechanical exposure apparatusMicrolithography exposure apparatusOptic systemAtmosphere

An exposure apparatus that exposes a substrate includes: an optical system that includes an emission surface from which an exposure light is emitted; a first surface that is disposed in at least a part of a surrounding of an optical path of the exposure light emitted from the emission surface; a second surface that is disposed in at least a part of a surrounding of the first surface and at a position lower than the first surface; a space portion into which a liquid can flow via a first aperture between the first surface and the second surface and which is opened to the atmosphere via a second aperture different from the first aperture; and a first recovery portion that recovers at least a part of the liquid flowing into the space portion. Here, the emission surface, the first surface, and the second surface are opposed to the surface of the substrate in at least a part of the exposure of the substrate, and the substrate is exposed with the exposure light from the emission surface via the liquid between the emission surface and the surface of the substrate.

Owner:NIKON CORP

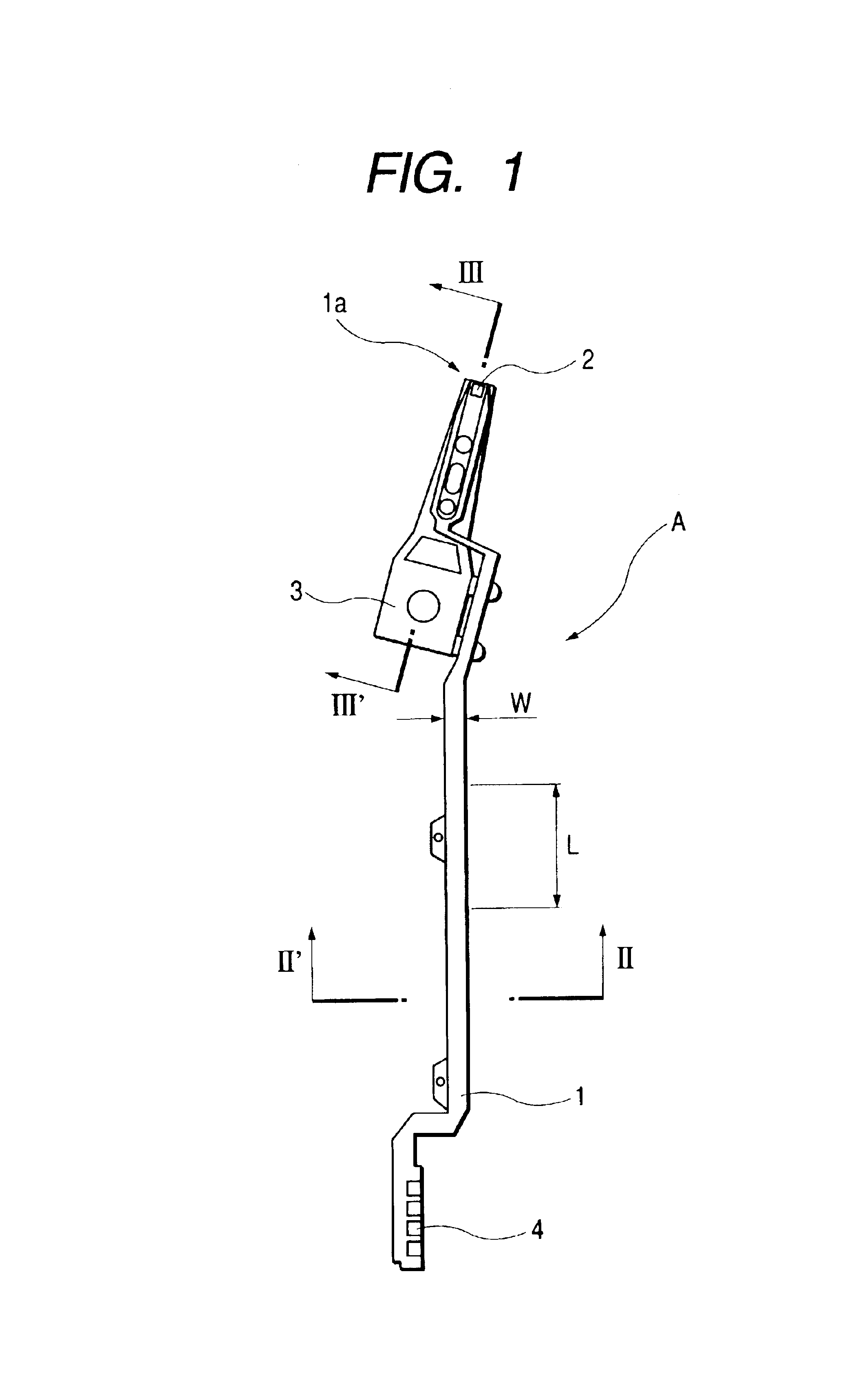

Flexible printed circuit board

InactiveUS6943302B2Prevent electrostatic dischargeSuppress failureElectrical connection between head and armRecord information storageMagnetic disksFlexible electronics

A flexible printed circuit board of the present invention directly relays connecting portions of a magnetic head placed on a suspension to connecting portions of a base end of a carriage arm in a head suspension assembly of a magnetic disk apparatus. The flexible printed circuit board includes a laminate composed of at least a base layer, a plurality of conductive circuits formed on the base layer, a cover layer covering the conductive circuits, and a conductive polymer layer formed in the insulating material portion in the surface of the laminate. The flexible printed circuit board includes a stainless layer below the base layer or on a lower side of the conductive polymer layer on the base layer side. More preferably, in the magnetic head connecting portion, the cover layer is not formed, and on the base layer in the magnetic head connecting portion, a conductive polymer layer is formed, whereas on the plurality of conductive circuits in the magnetic head connecting portion, the conductive polymer layer is not present or is substantially absent, if any, to such a degree as to allow the magnetic head to be electrically connected to the conductive circuits.

Owner:ACHILLES CORP

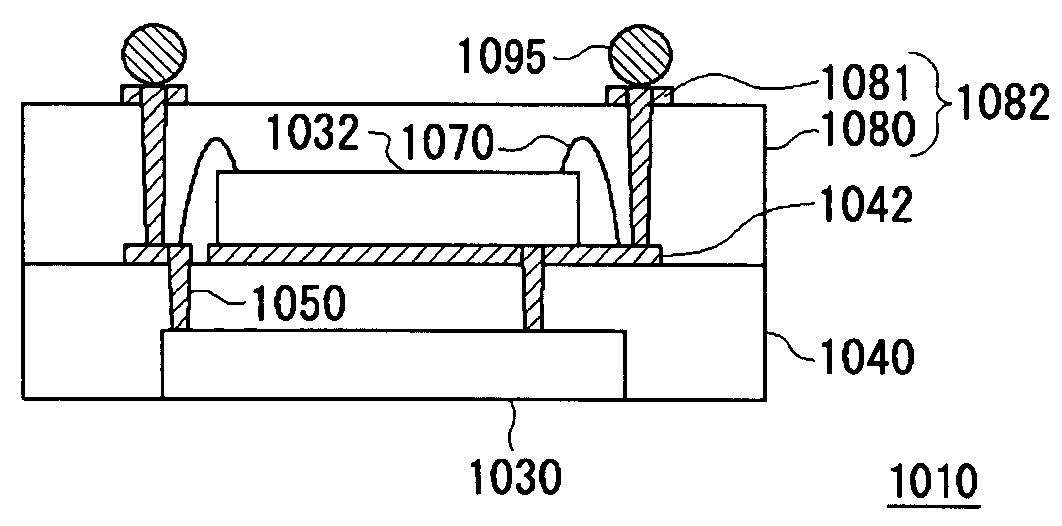

Semiconductor device and method of manufacturing the same

ActiveUS20100164105A1Suppress failureSemiconductor/solid-state device detailsSolid-state devicesCopper wireWire bonding

An object is to prevent a failure, such as a wiring separation or a crack, in an insulating film under a copper wire, in a semiconductor device formed by wire-bonding the copper wire on a portion above the copper wiring. A semiconductor device according to the present invention includes a copper wiring formed above a semiconductor substrate, a plated layer formed so as to cover a top surface and side surfaces of the copper wiring, and a copper wire which is wire-bonded on the plated layer above the copper wiring.

Owner:SEMICON COMPONENTS IND LLC

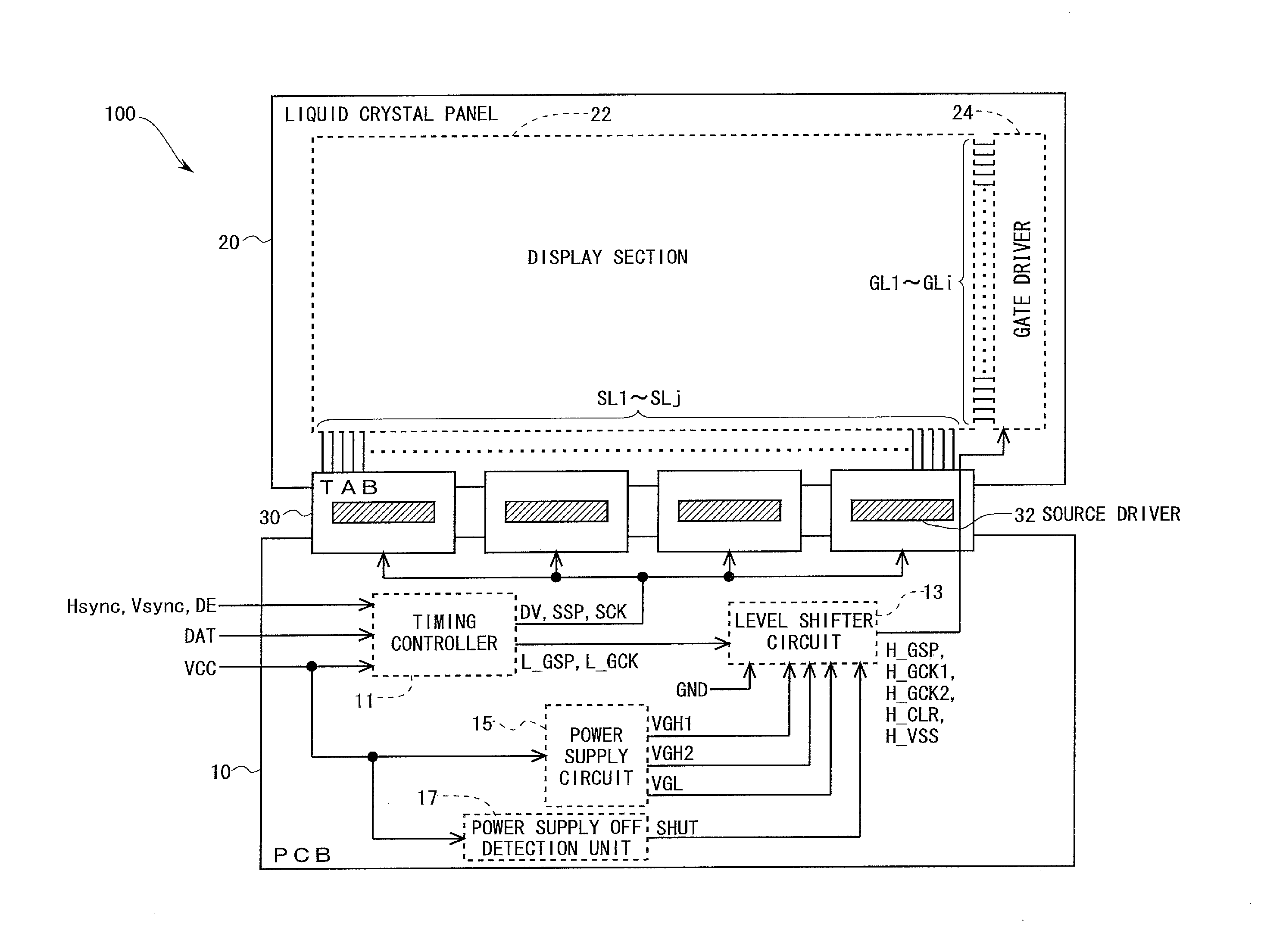

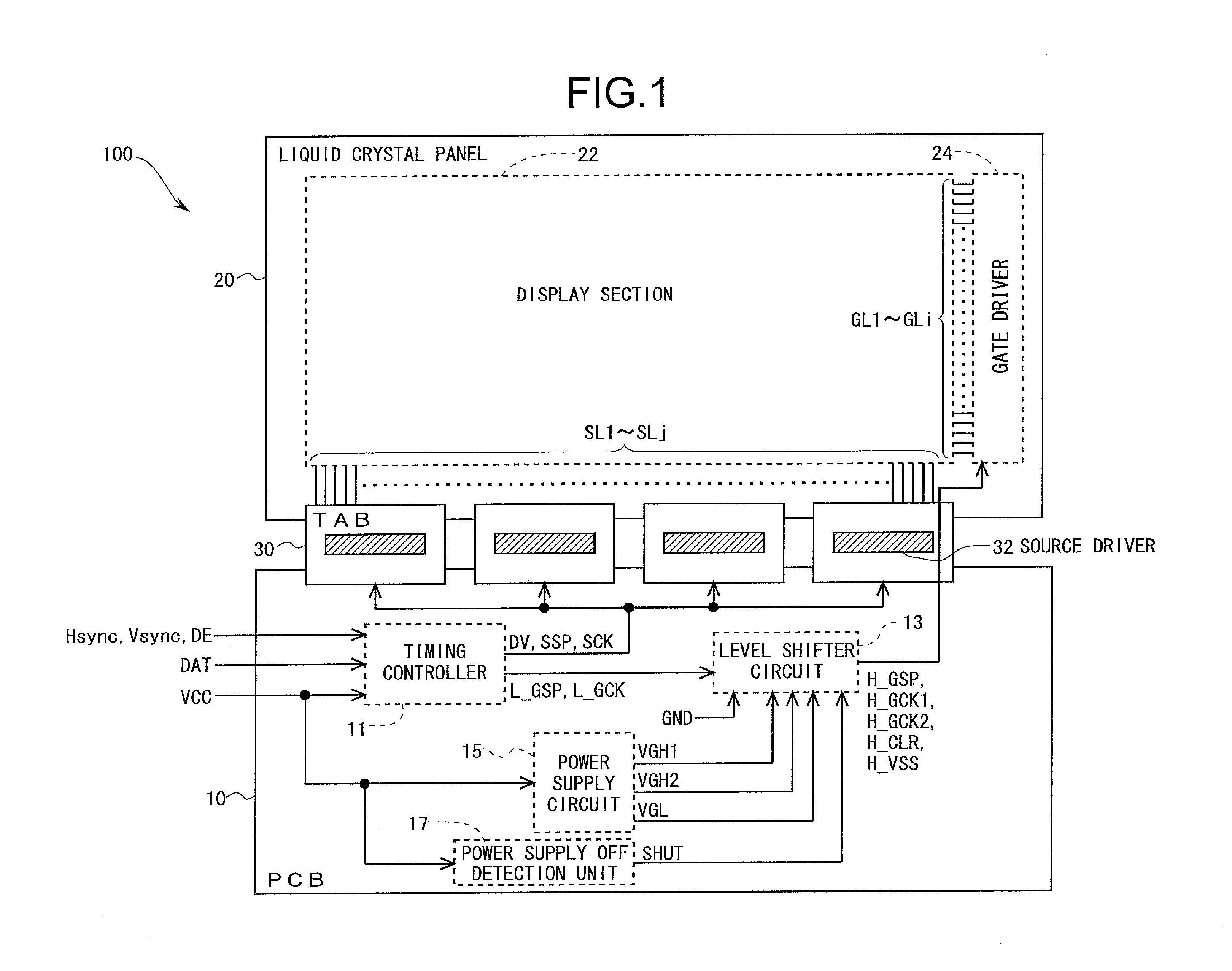

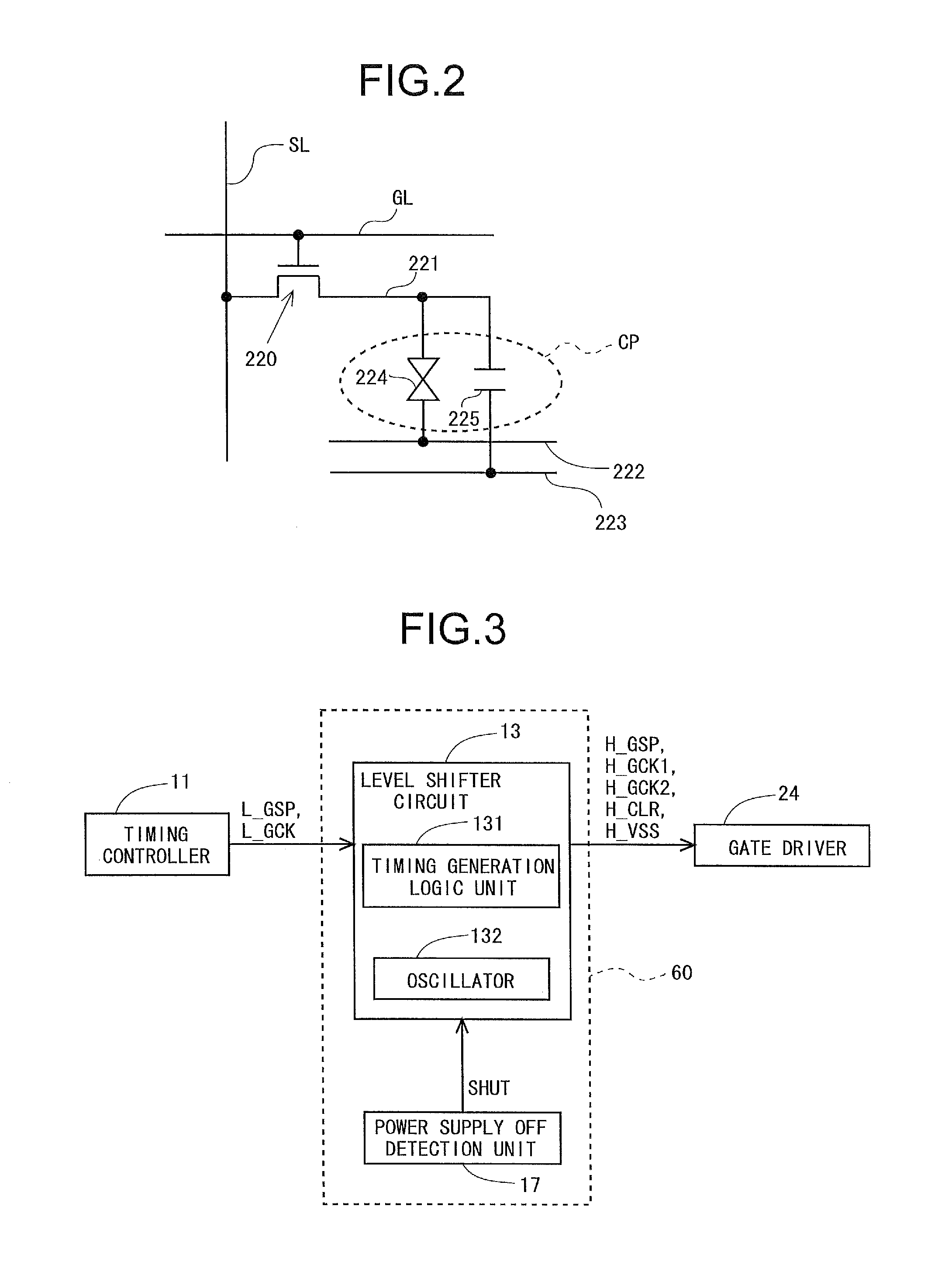

Display device and method of driving the same

ActiveUS20150269900A1Eliminate residual chargeReduce power consumptionStatic indicating devicesDigital storageDisplay deviceLimit value

A gate driver (24) which is provided by an IGZO-GDM and a level shifter circuit (13) are connected to each other via a first through a fifth wires (OL1 through OL5). Each wire (OL) is connected to a discharge unit (190). If an electric power supply to a first through a fifth output circuits (OC1 through OC5) in the level shifter circuit (13) becomes lower than a lower operation limit value during a power-off sequence which is supposed to remove a residual charge from inside a panel, outputs from the first through the fifth output circuits (OC1 through OC5) assume a high-impedance state, whereupon a potential on each wire (OL) is drawn by a discharge unit (190) into a ground potential. Therefore, residual charge inside the panel is removed quickly and stably when power supply is shut off.

Owner:SHARP KK

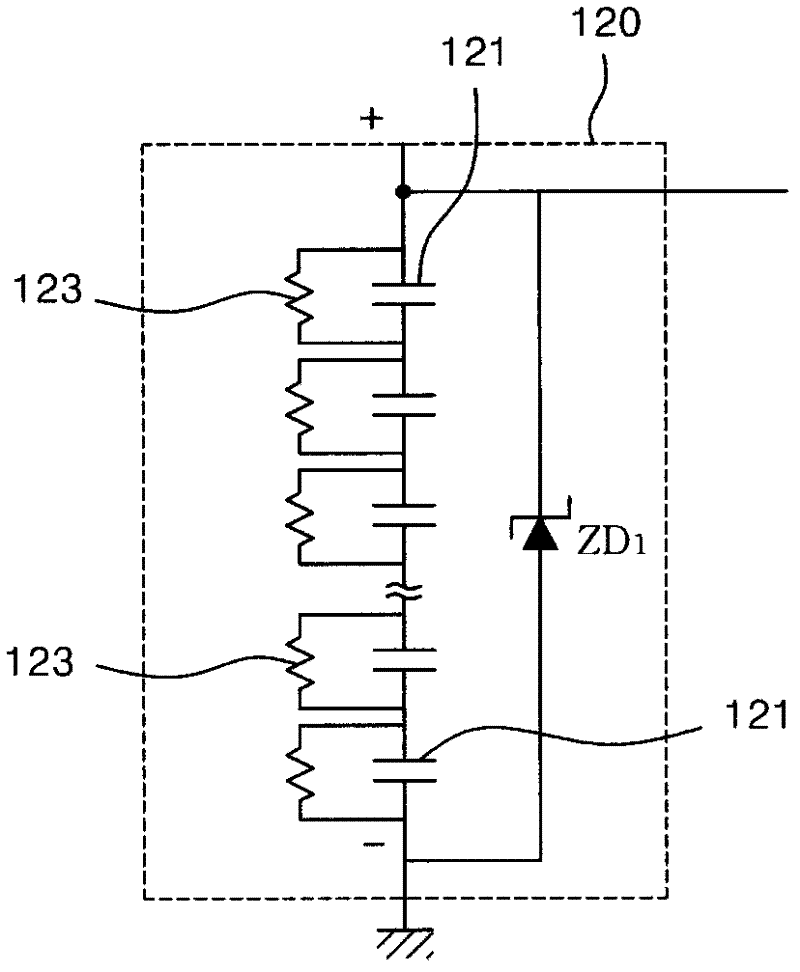

RFID tag and RFID tag production method

InactiveUS20080042851A1Suppress failureLamination ancillary operationsSemiconductor/solid-state device detailsEngineeringElectrical and Electronics engineering

The RFID tag includes: a main unit consisting of a base, a communication antenna that is wired on the base, a circuit chip that is electrically connected to the antenna and performs radio communication via the antenna, a chip reinforcing member covering the periphery of the circuit chip, an underside reinforcing member that is disposed at a position that sandwiches the base with respect to the chip reinforcing member, and a rubber cover member that covers these components; and protective layers that sandwich the main unit from the front and rear sides and have greater slipperiness than the slipperiness between the main unit and a contactant.

Owner:FUJITSU LTD +1

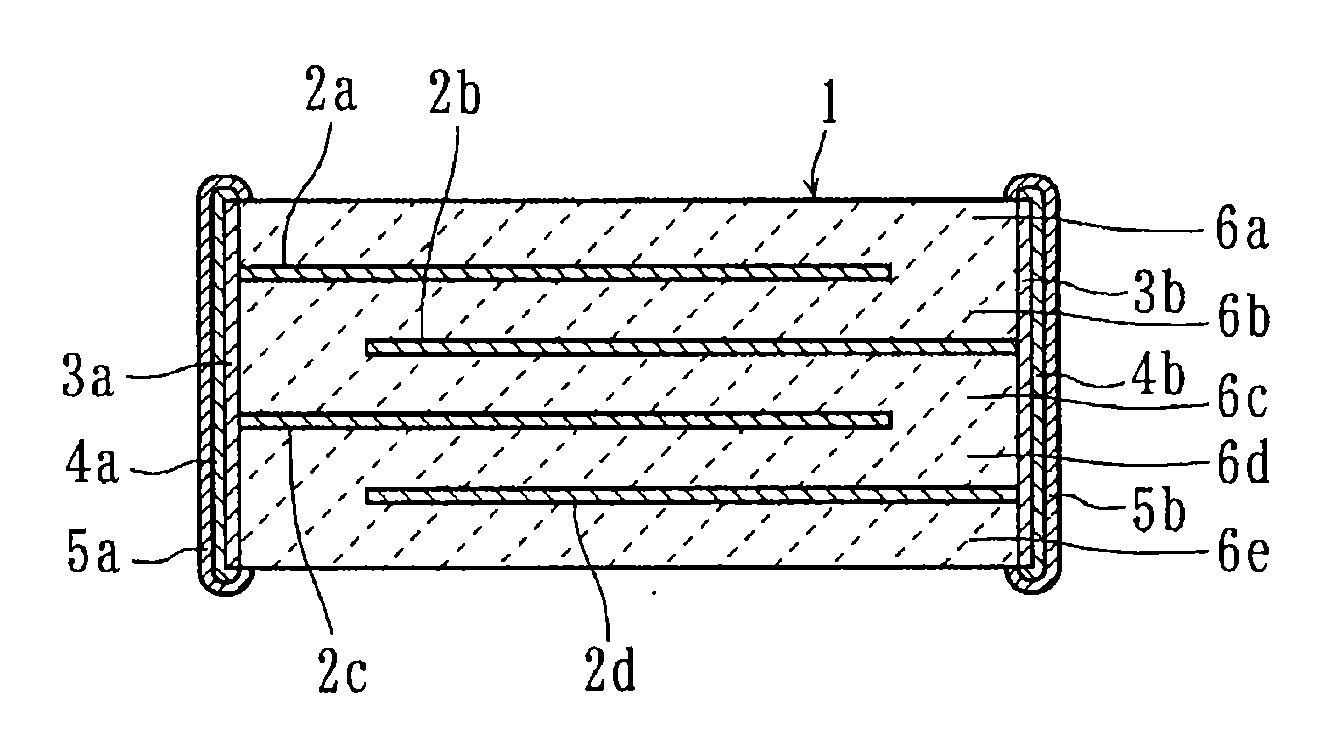

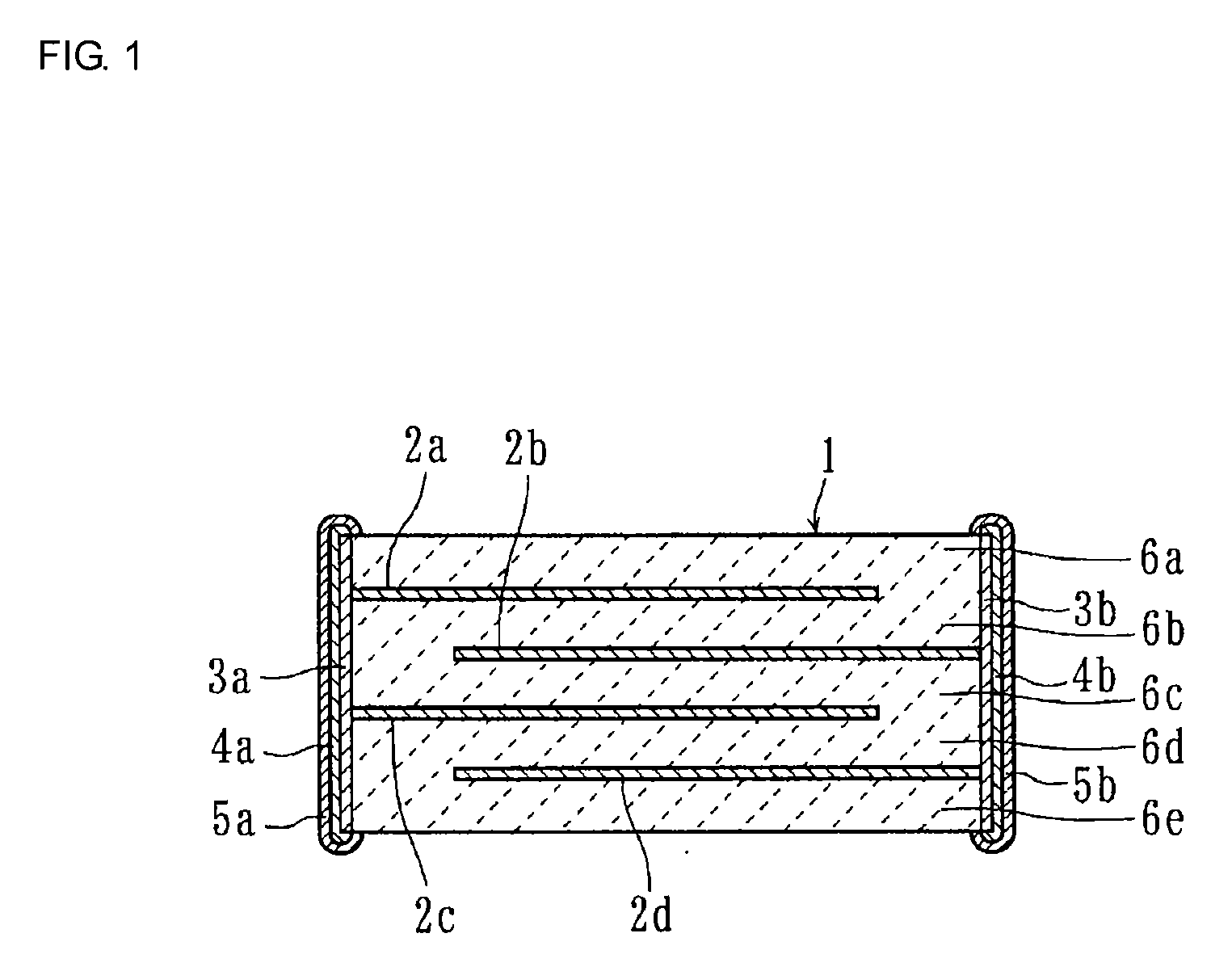

Dielectric ceramic, ceramic electronic element, and multilayer ceramic capacitor

ActiveUS20090128989A1Improve sintering performanceEasy to useFixed capacitor dielectricZirconium compoundsDielectricCeramic capacitor

A dielectric ceramic including a perovskite compound represented by the general formula {(Ba1-x-yCaxSny)m(Ti1-zZrz)O3} as a primary component in which the x, y, z, and m satisfy 0.02≦x≦0.20, 0.02≦y≦0.20, 0≦z≦0.05, and 0.99≦m≦1.1 and is processed by a thermal treatment at a low oxygen partial pressure of 1.0×10−10 to 1.0×10−12 MPa. Accordingly, there are provided a dielectric ceramic which can be stably used in a high-temperature atmosphere without degrading dielectric properties, properties of which can be easily adjusted, and which generates no electrode breakage even when ceramic layers and conductive films are co-fired, and a ceramic electronic element, such as a multilayer ceramic capacitor, which uses the above dielectric ceramic.

Owner:MURATA MFG CO LTD

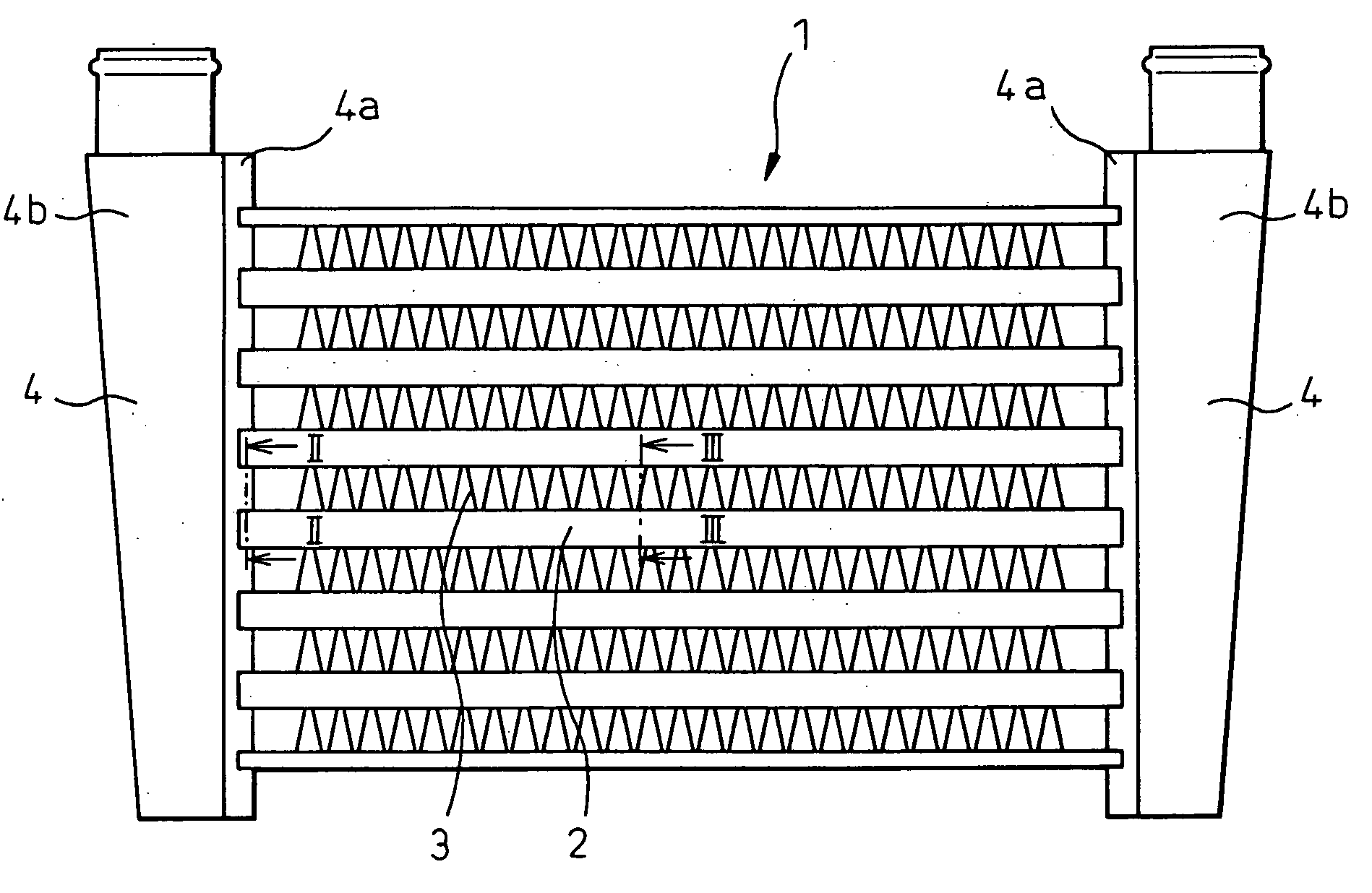

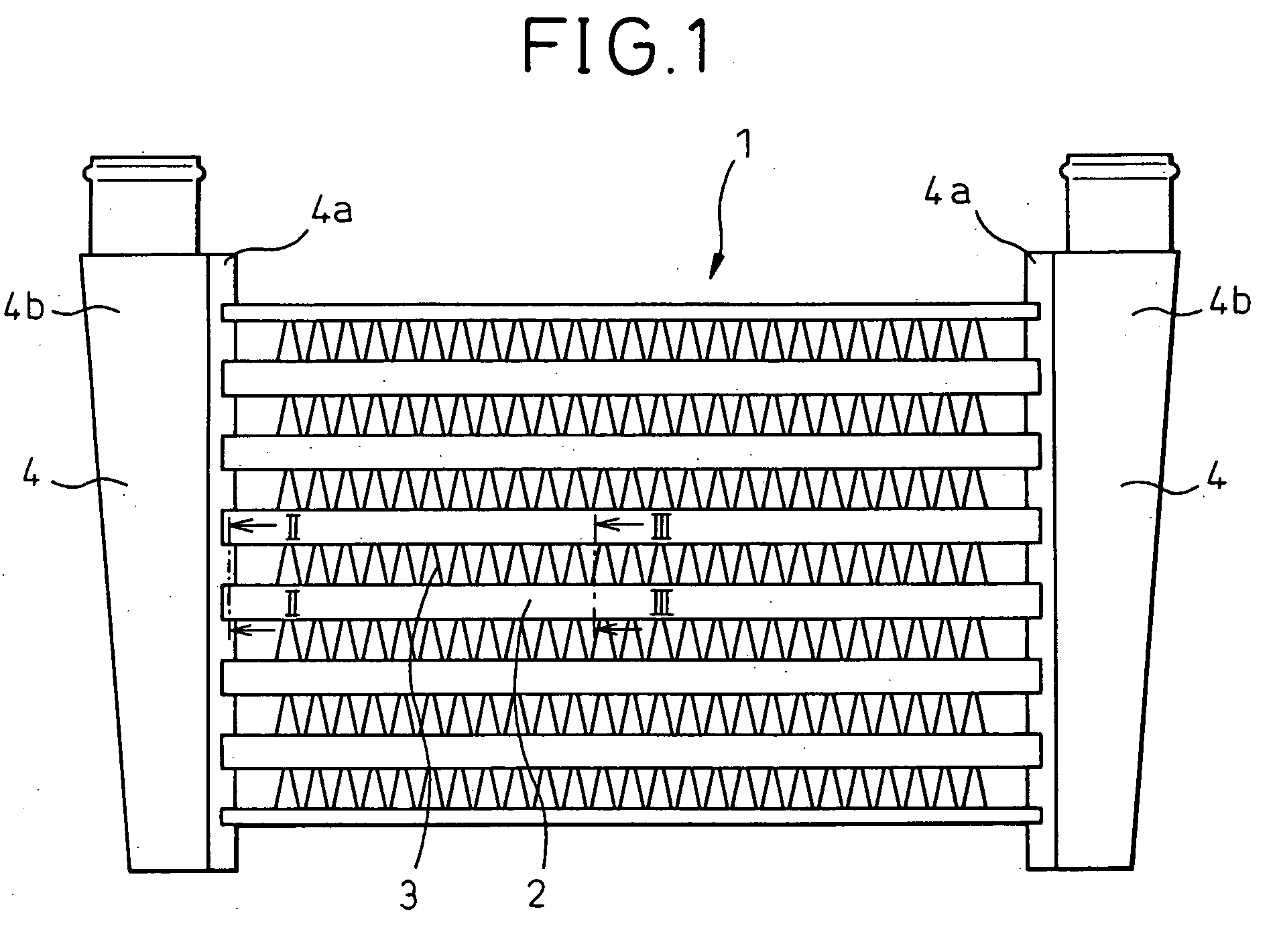

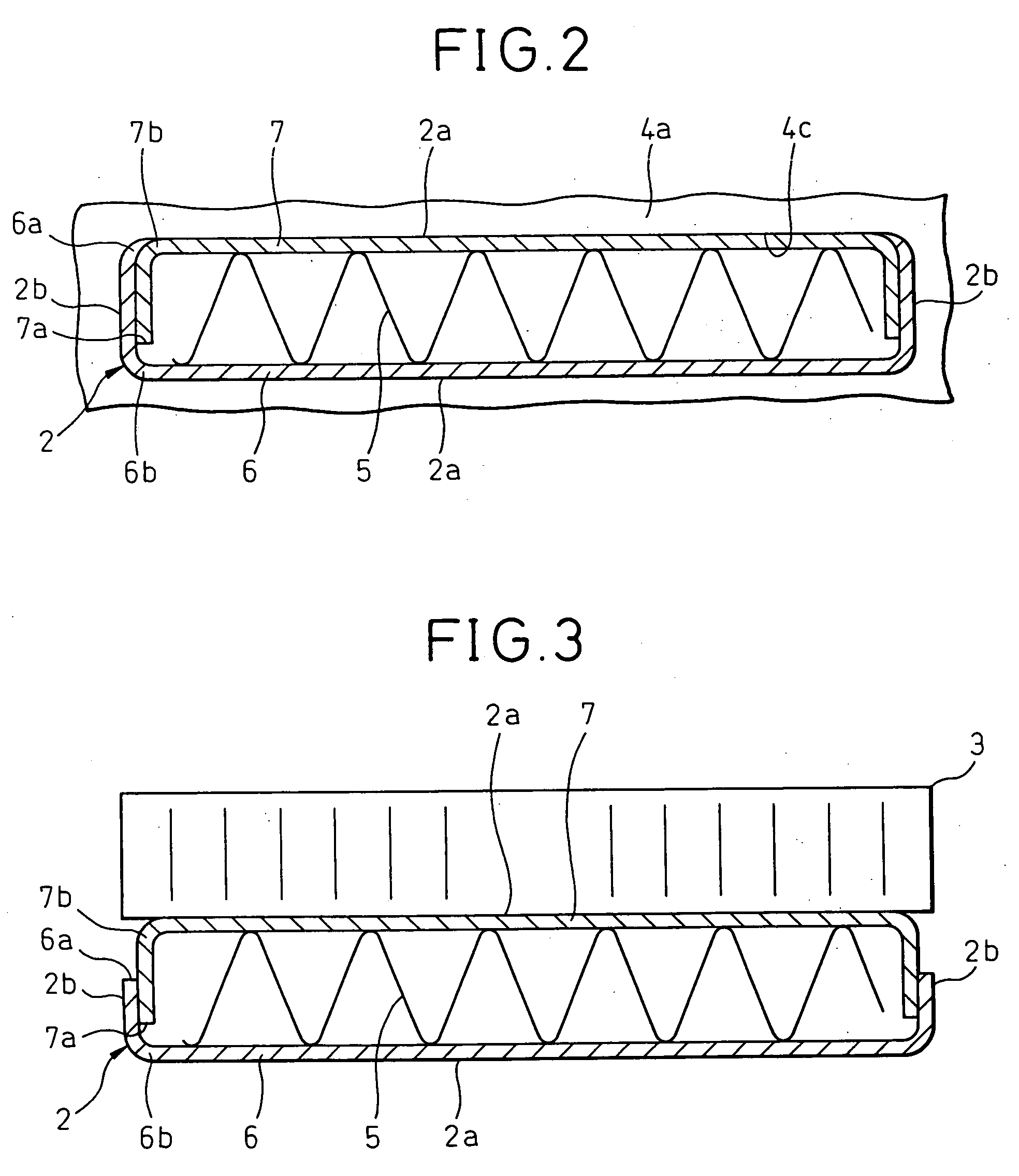

Heat exchanger

InactiveUS20070169926A1Simplify workImprove work performanceStationary conduit assembliesHeat exchanger casingsMechanical engineeringHeat exchanger

Owner:DENSO CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com