Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2512 results about "Wire bonding" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Wire bonding is the method of making interconnections (ATJ) between an integrated circuit (IC) or other semiconductor device and its packaging during semiconductor device fabrication. Although less common, wire bonding can be used to connect an IC to other electronics or to connect from one printed circuit board (PCB) to another. Wire bonding is generally considered the most cost-effective and flexible interconnect technology and is used to assemble the vast majority of semiconductor packages. Wire bonding can be used at frequencies above 100 GHz.

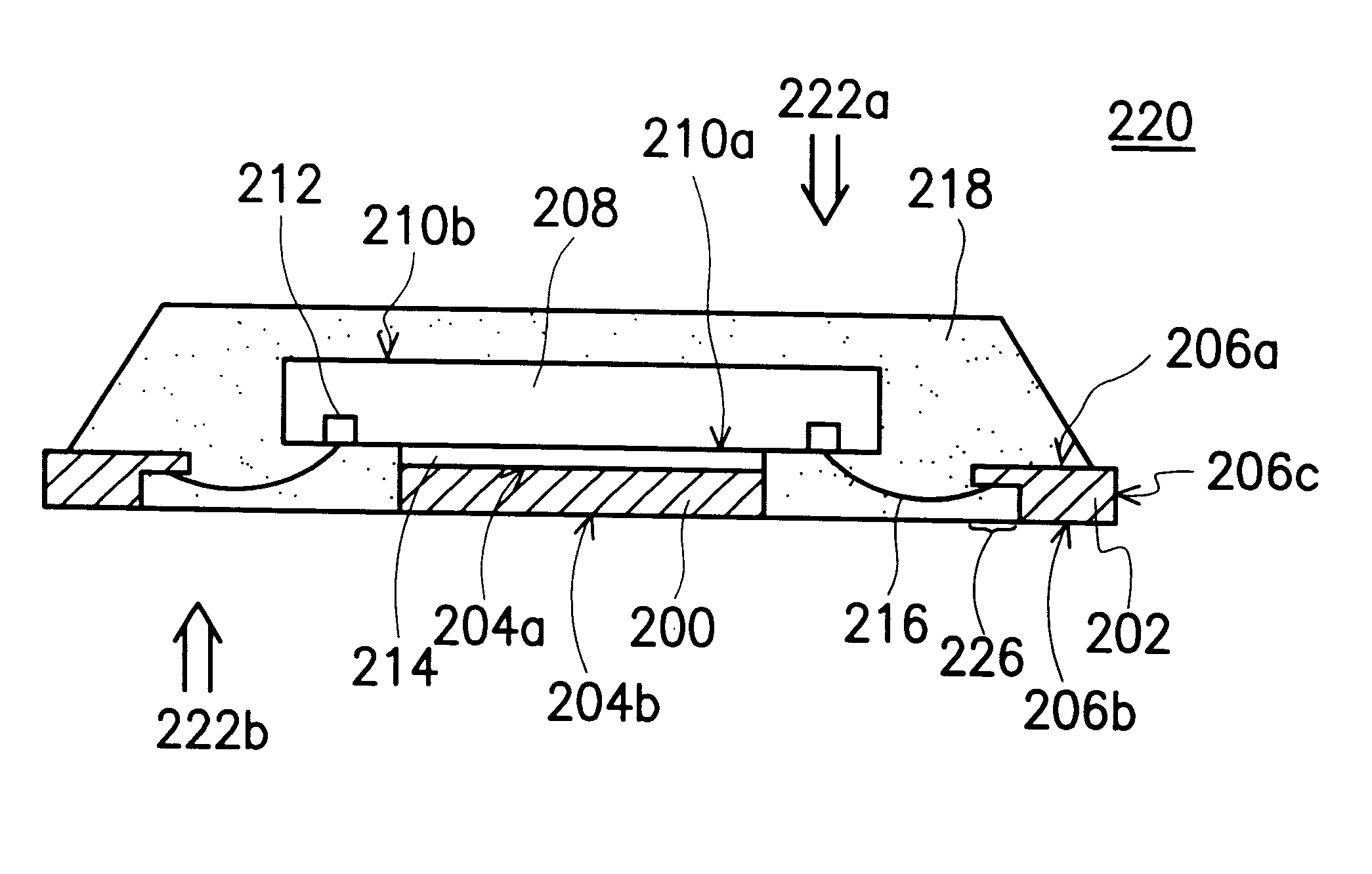

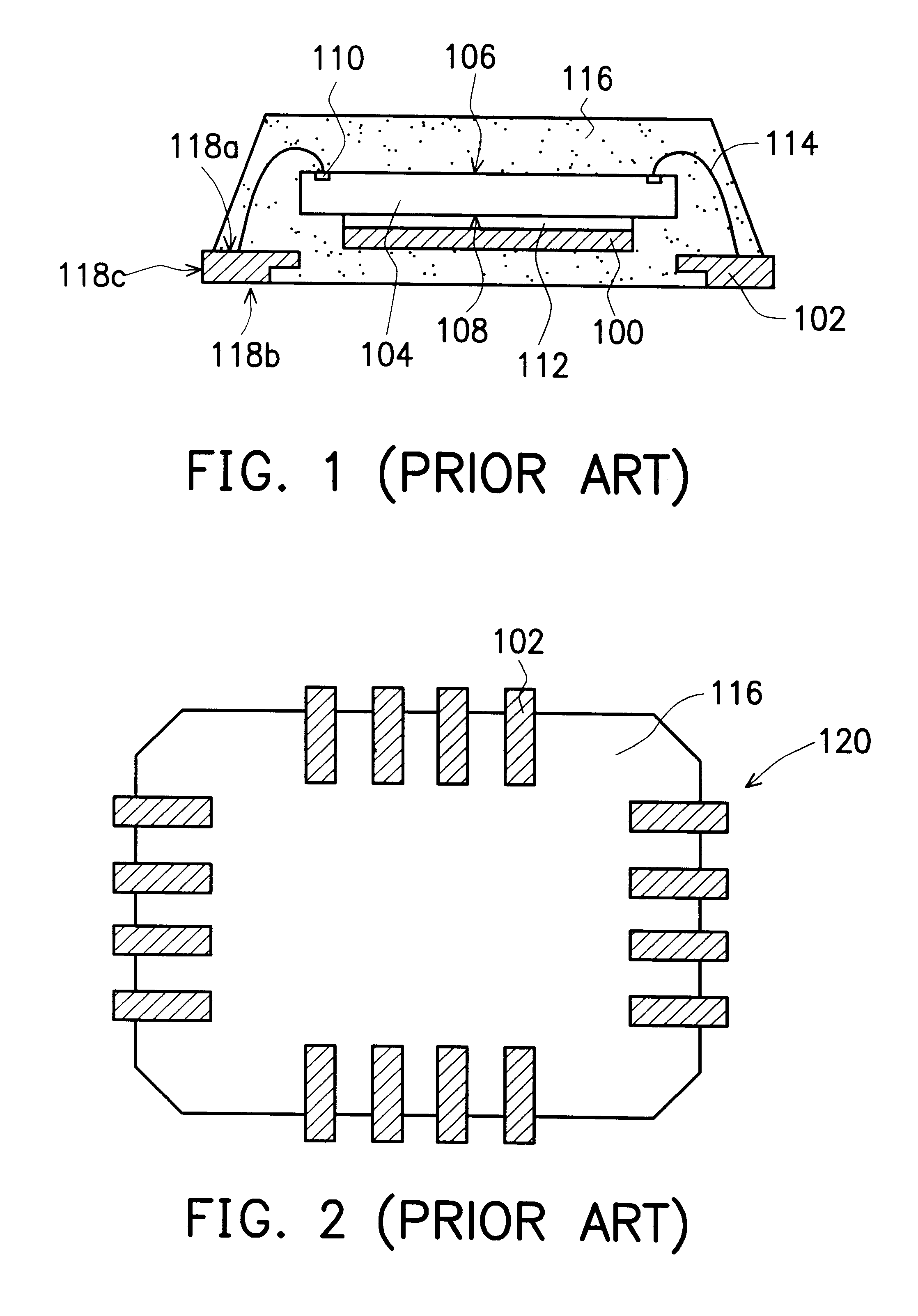

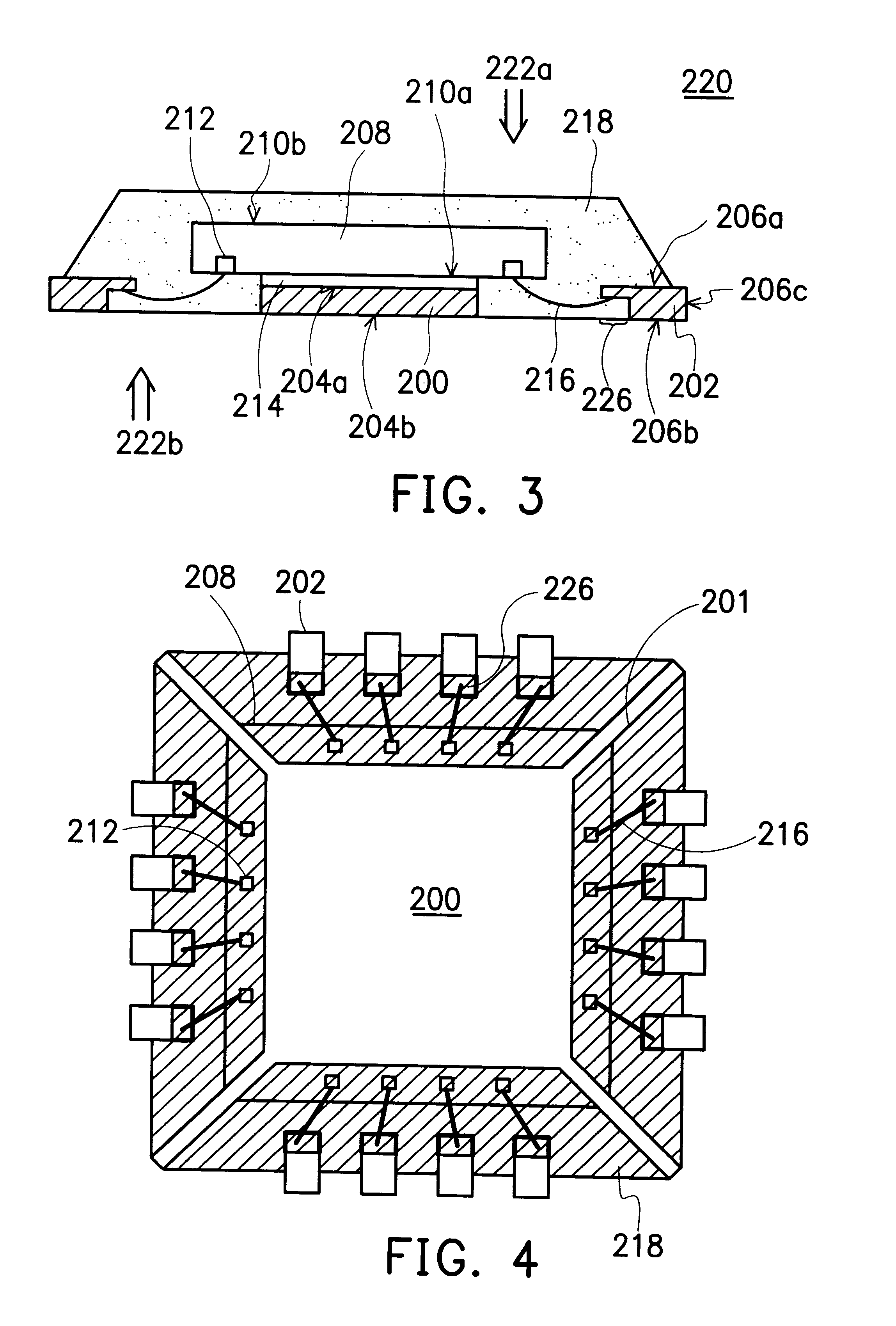

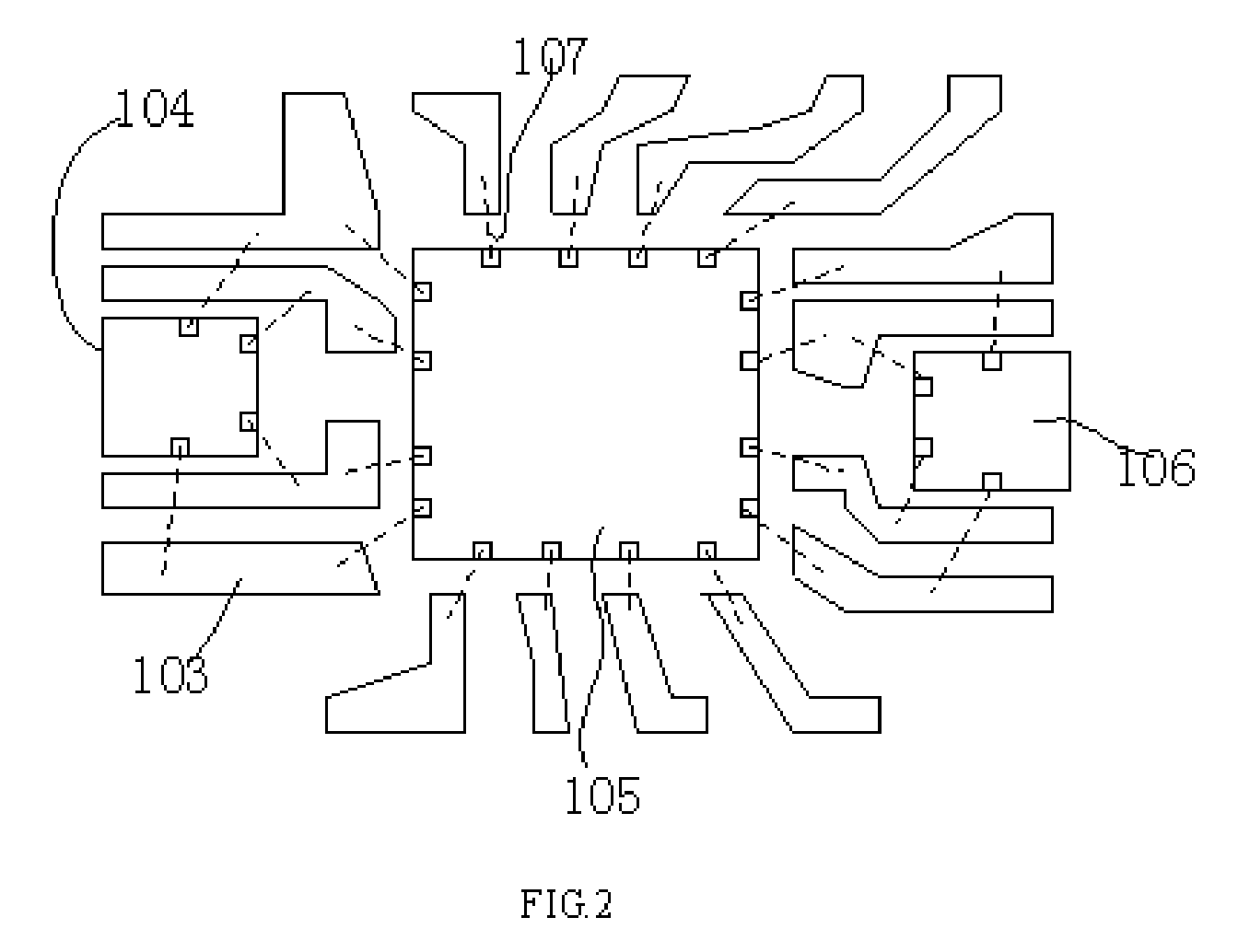

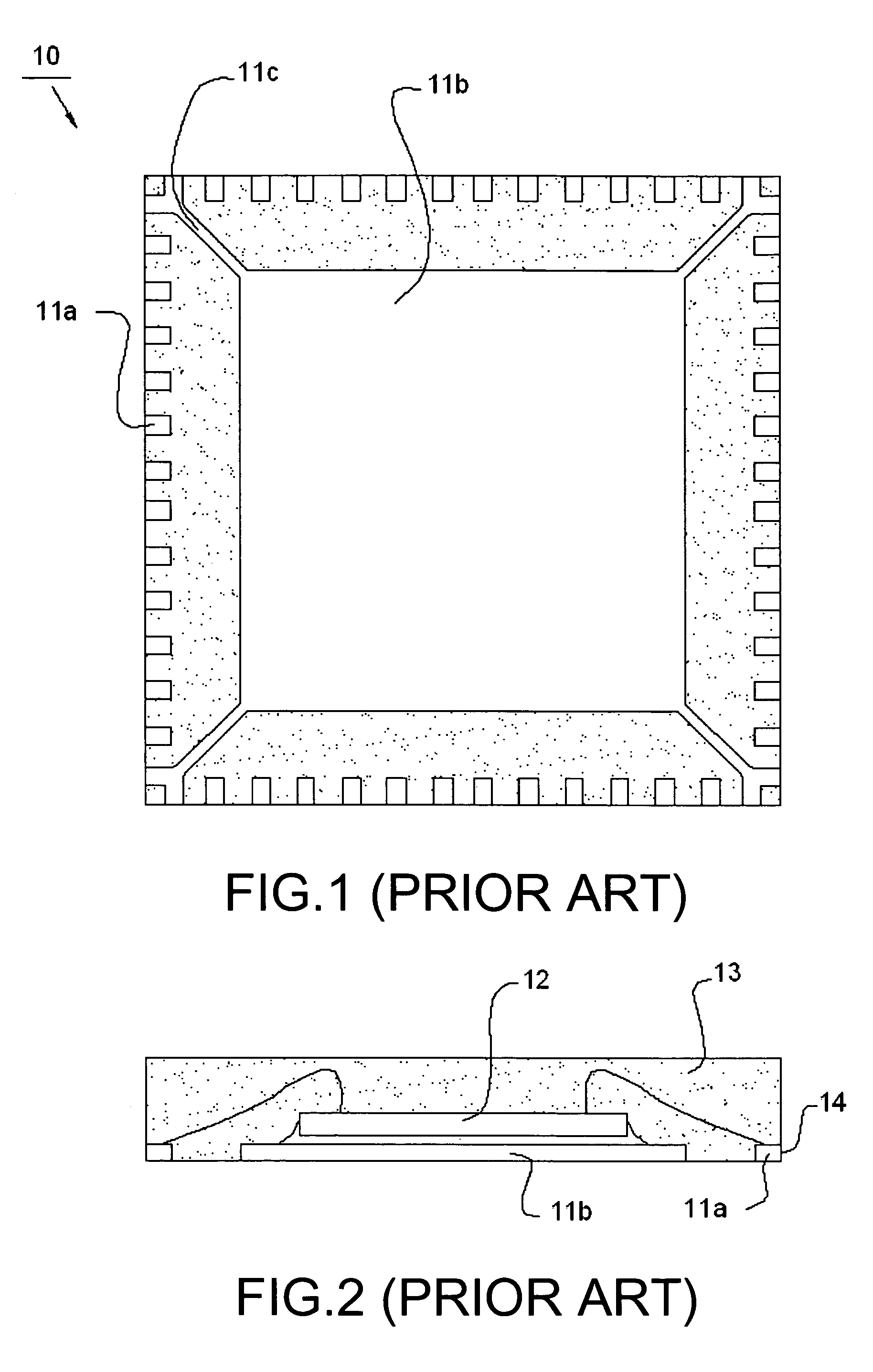

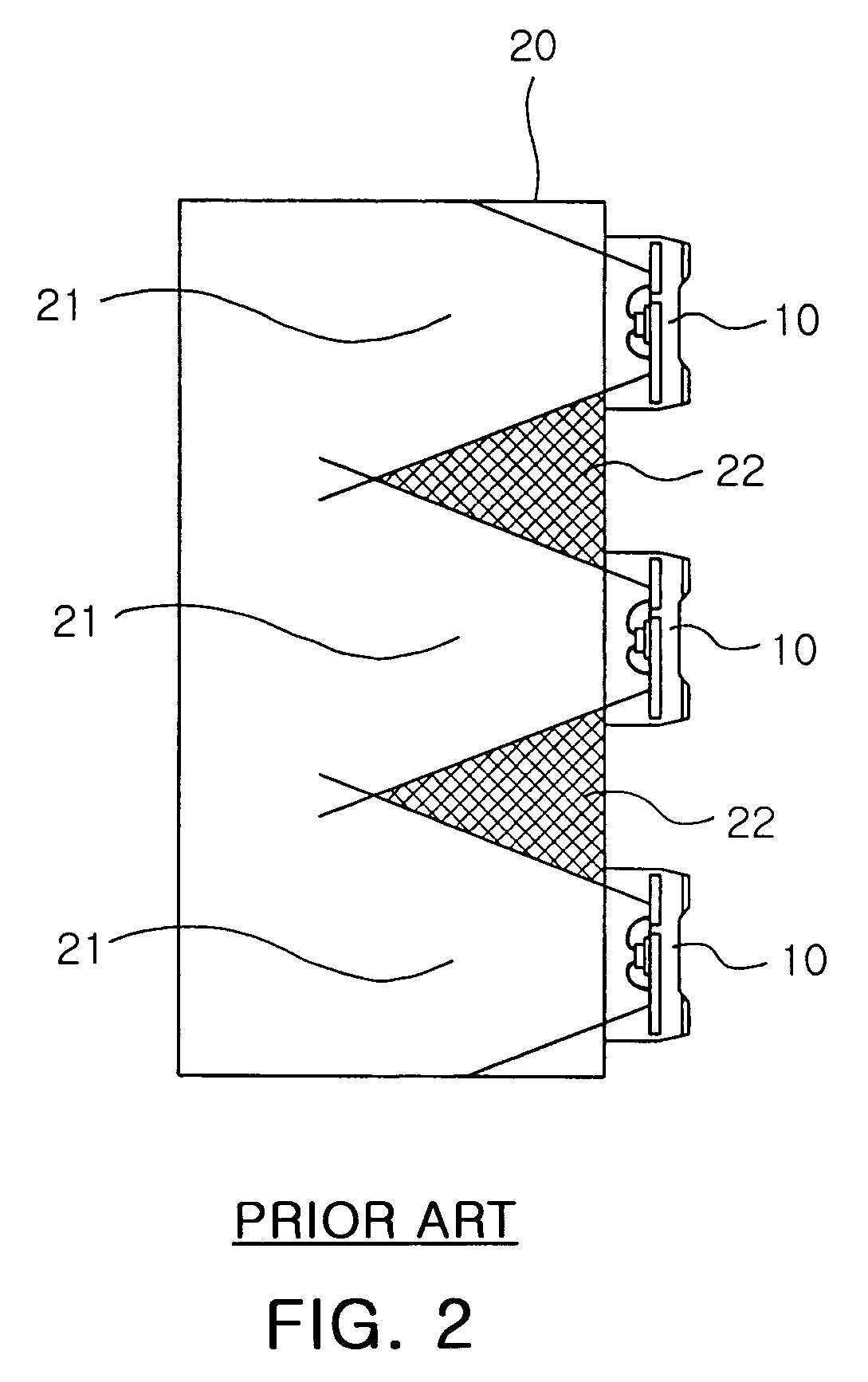

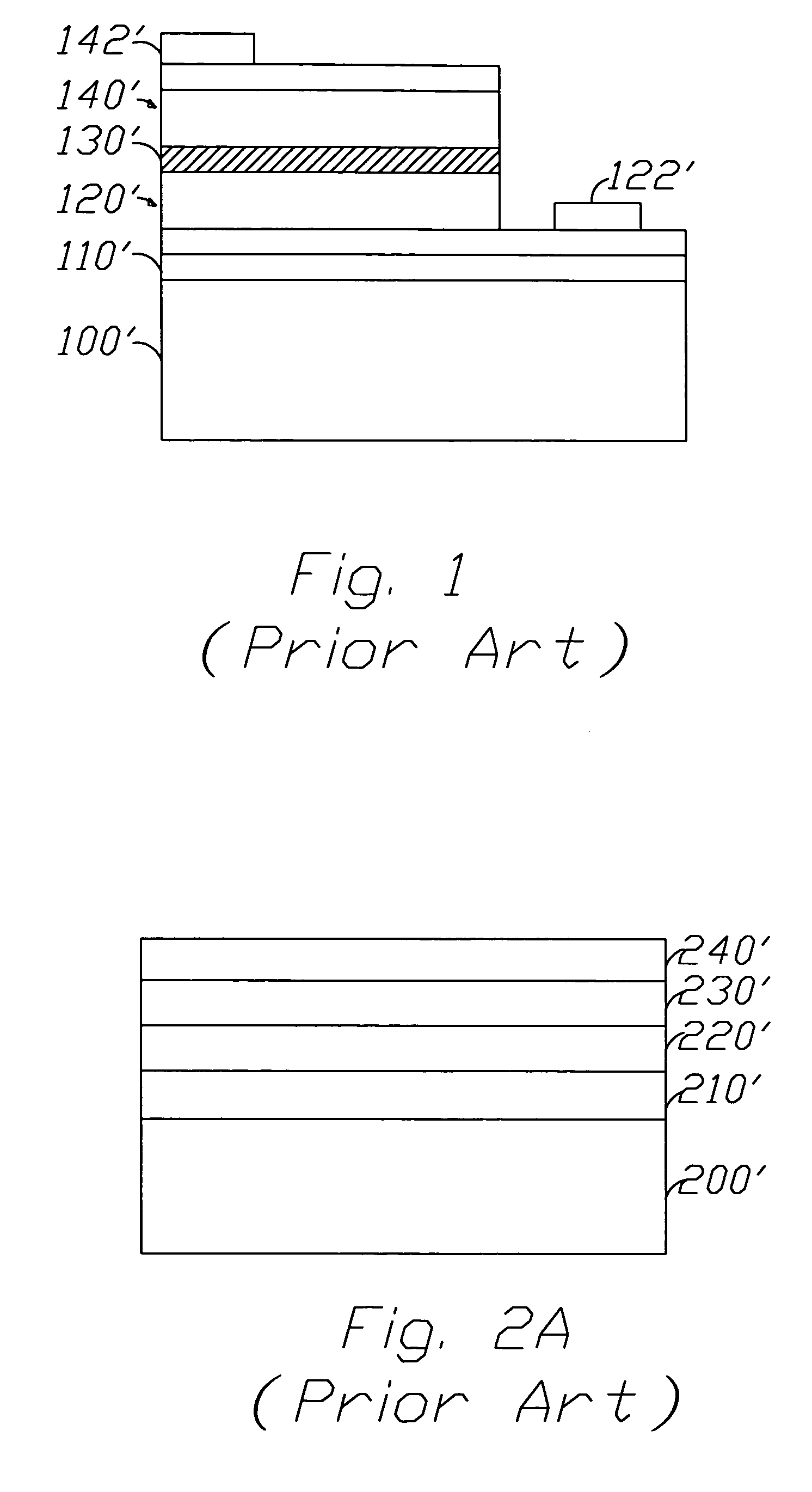

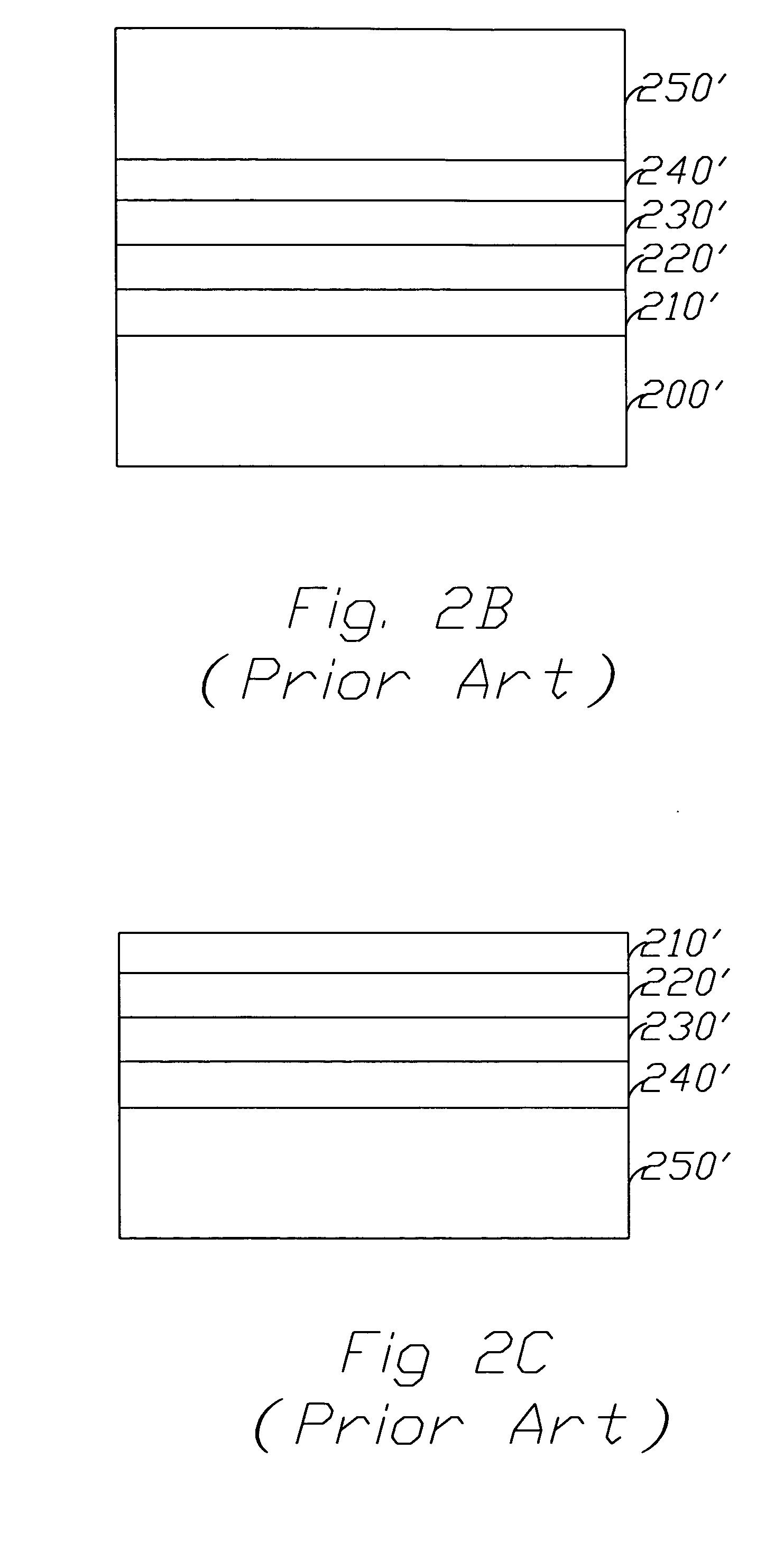

Thermally enhanced quad flat non-lead package of semiconductor

InactiveUS6198171B1Semiconductor/solid-state device detailsSolid-state devicesSemiconductorWire bonding

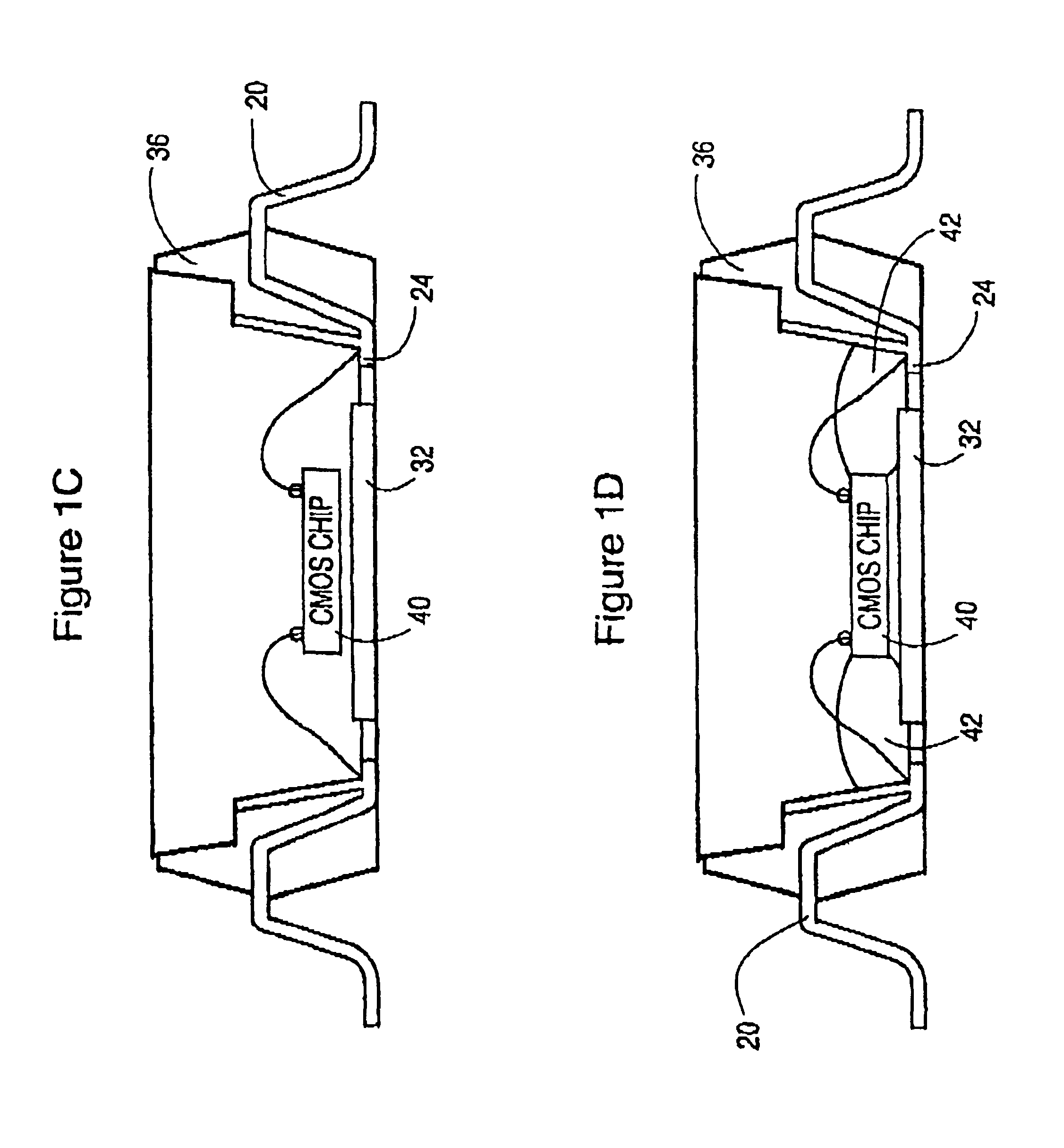

A thermally enhanced quad flat non-lead package of semiconductor comprises a chip a plurality of leads, and a molding compound. The chip has its active surface bonded to the top surface of the die pad, and the area of the die pad is smaller than that of the chip in order to expose the bonding pads on the active surface of the chip. The leads are disposed at the periphery of the die pad wherein the bottom surface of the lead has a stepped structure with a relatively thin portion to form a wire-bonding protruded zone. A plurality of bonding wires is used to electrically connect the wire-bonding protruded zone of the leads to the bonding pads of the chip. The molding compound encapsulates the chip, bonding wires, the die pad, and a portion of the surface of the leads, but exposes the bottom surface of the die pad. In this way, the encapsulating process makes the side surface of the lead, and the portion excluding the wire-bonding protruded zone of the bottom surface of the lead exposed in order to make the lead become the external connecting points of the package structure.

Owner:SILICONWARE PRECISION IND CO LTD

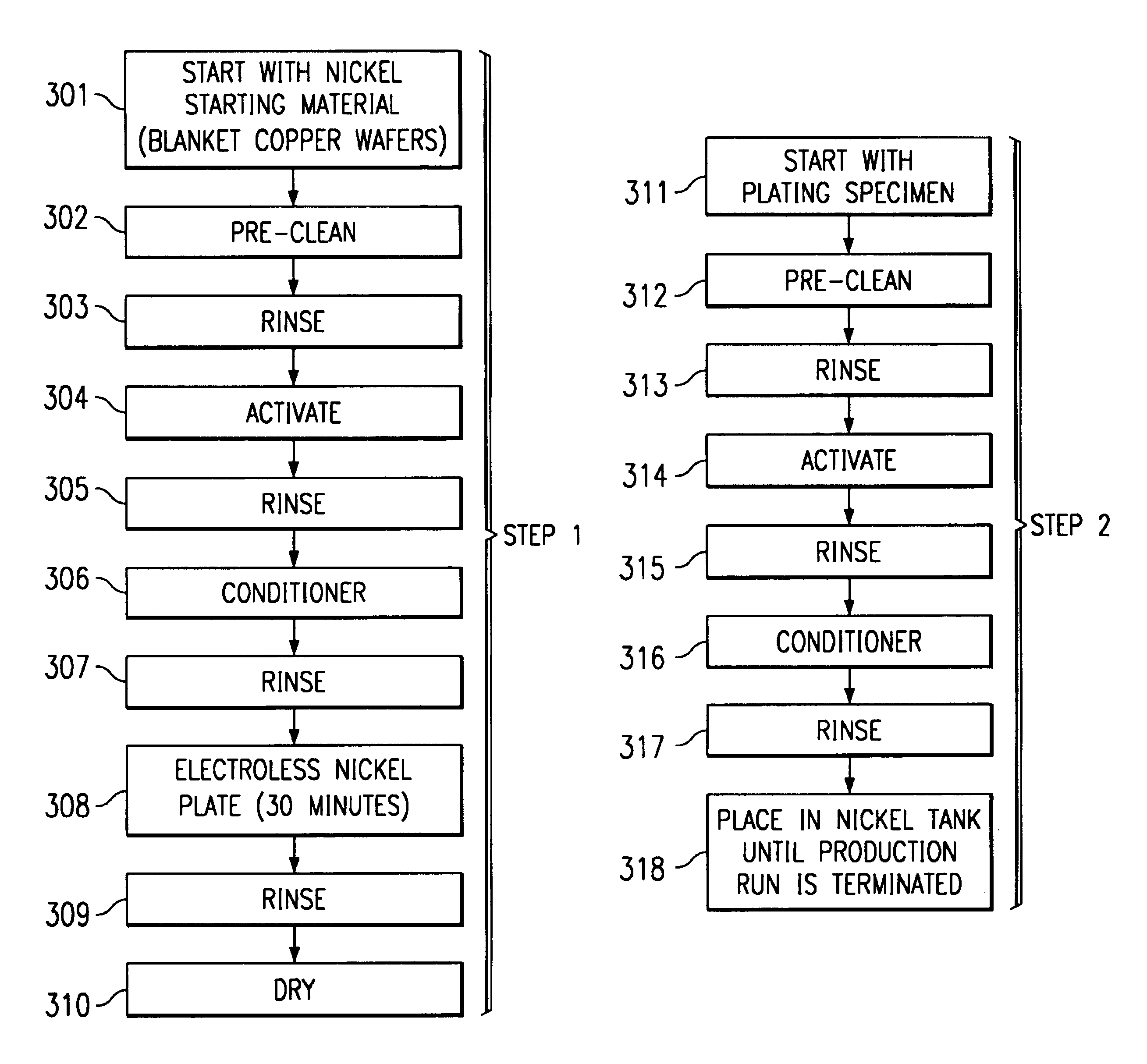

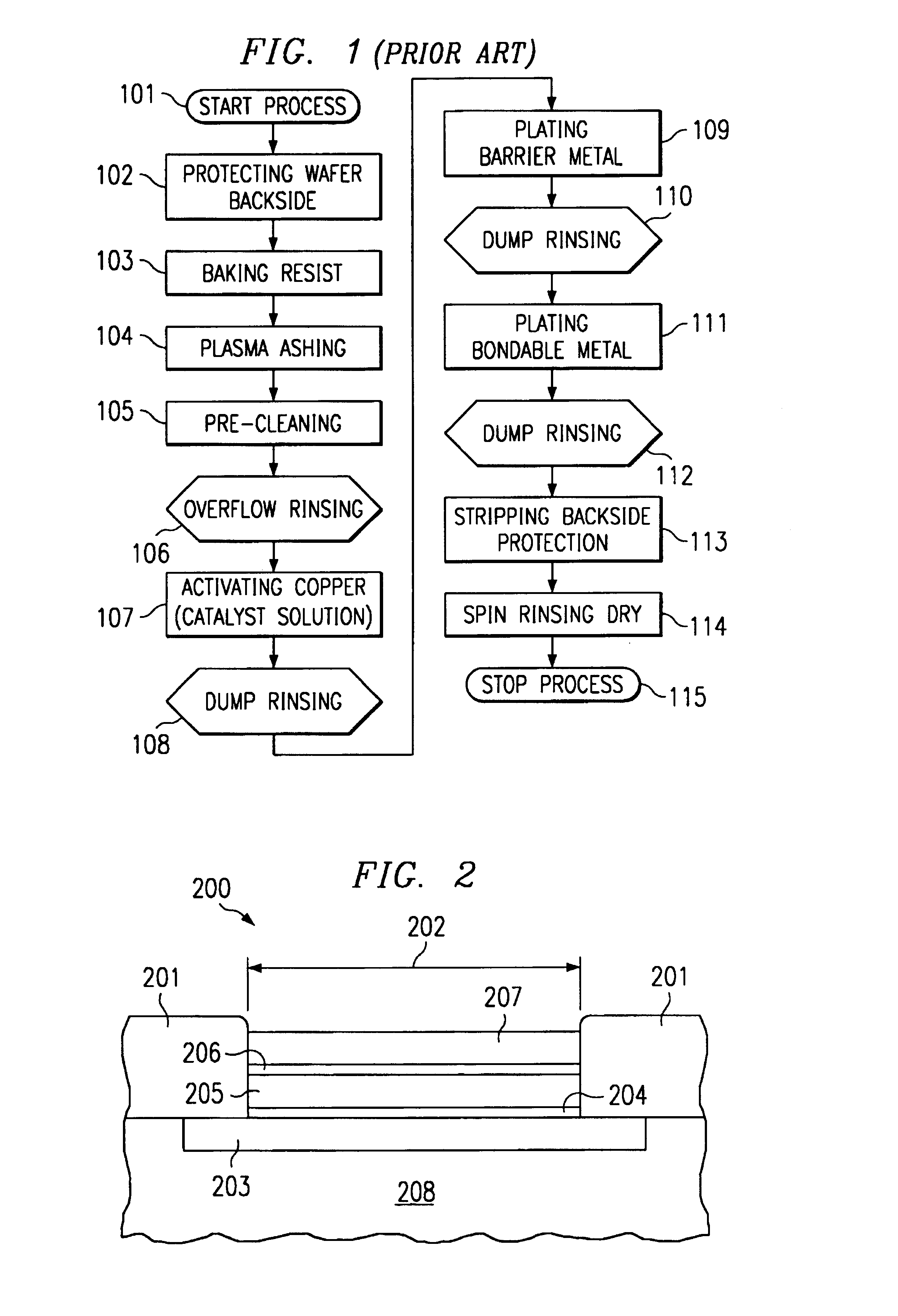

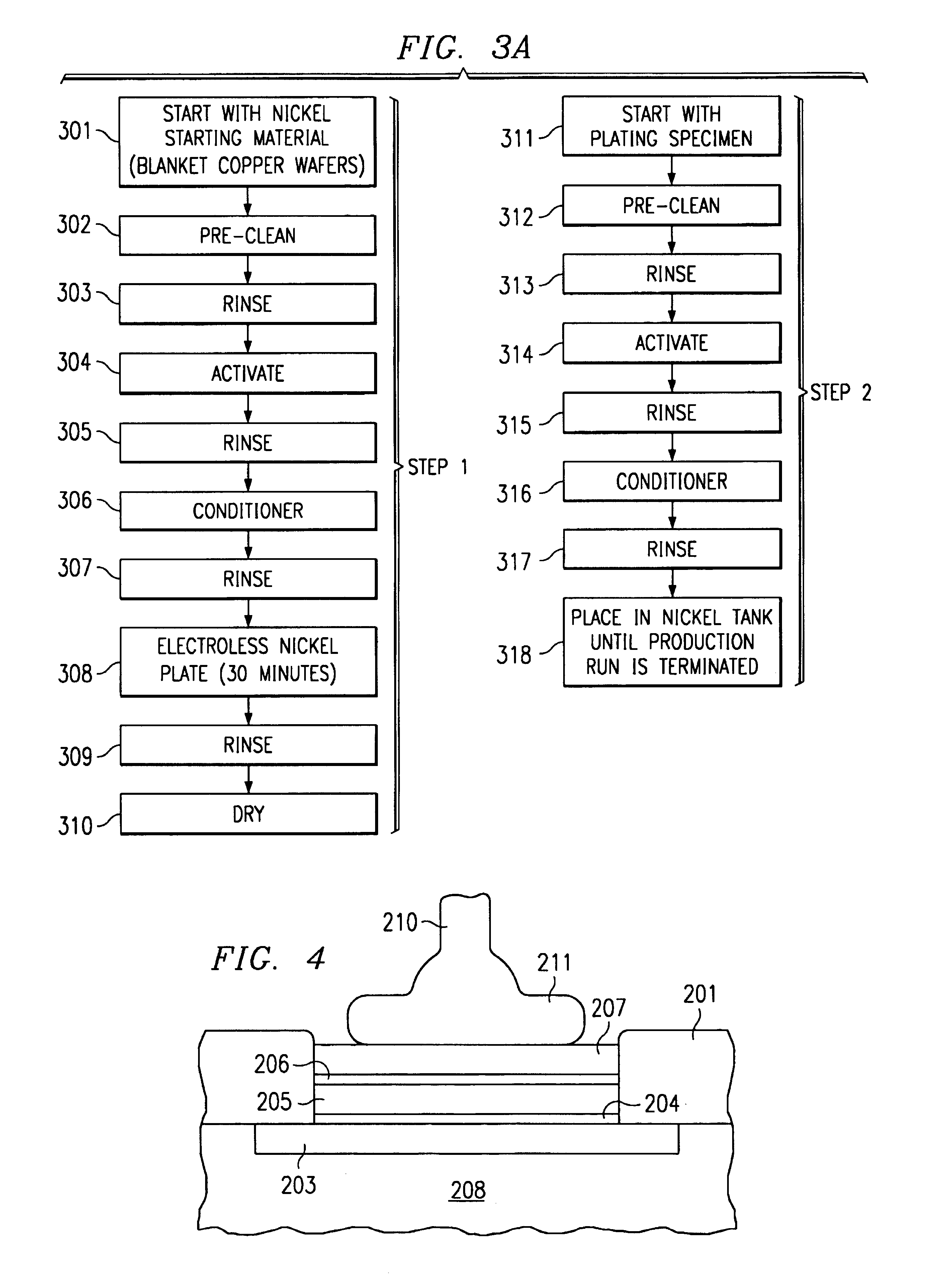

Method to achieve continuous hydrogen saturation in sparingly used electroless nickel plating process

InactiveUS6616967B1Maintain saturationSemiconductor/solid-state device detailsSolid-state devicesHydrogenCopper

An improved wire bonding process for copper-metallized integrated circuits is provided by a nickel layer that acts as a barrier against up-diffusing copper. In accordance with the present invention the nickel bath is placed and remains in hydrogen saturation by providing a piece of metal that remains in the nickel plating tank before and during the plating process.

Owner:TEXAS INSTR INC

Method of Forming Vias in Silicon Carbide and Resulting Devices and Circuits

InactiveUS20090104738A1Eliminate needSemiconductor/solid-state device manufacturingSemiconductor devicesInductanceSemiconductor

A method of fabricating an integrated circuit on a silicon carbide substrate is disclosed that eliminates wire bonding that can otherwise cause undesired inductance. The method includes fabricating a semiconductor device in epitaxial layers on a surface of a silicon carbide substrate and with at least one metal contact for the device on the uppermost surface of the epitaxial layer. The opposite surface of the substrate is then ground and polished until it is substantially transparent. The method then includes masking the polished surface of the silicon carbide substrate to define a predetermined location for at least one via that is opposite the device metal contact on the uppermost surface of the epitaxial layer and etching the desired via in steps. The first etching step etches through the silicon carbide substrate at the desired masked location until the etch reaches the epitaxial layer. The second etching step etches through the epitaxial layer to the device contacts. Finally, metallizing the via provides an electrical path from the first surface of the substrate to the metal contact and to the device on the second surface of the substrate.

Owner:WOLFSPEED INC

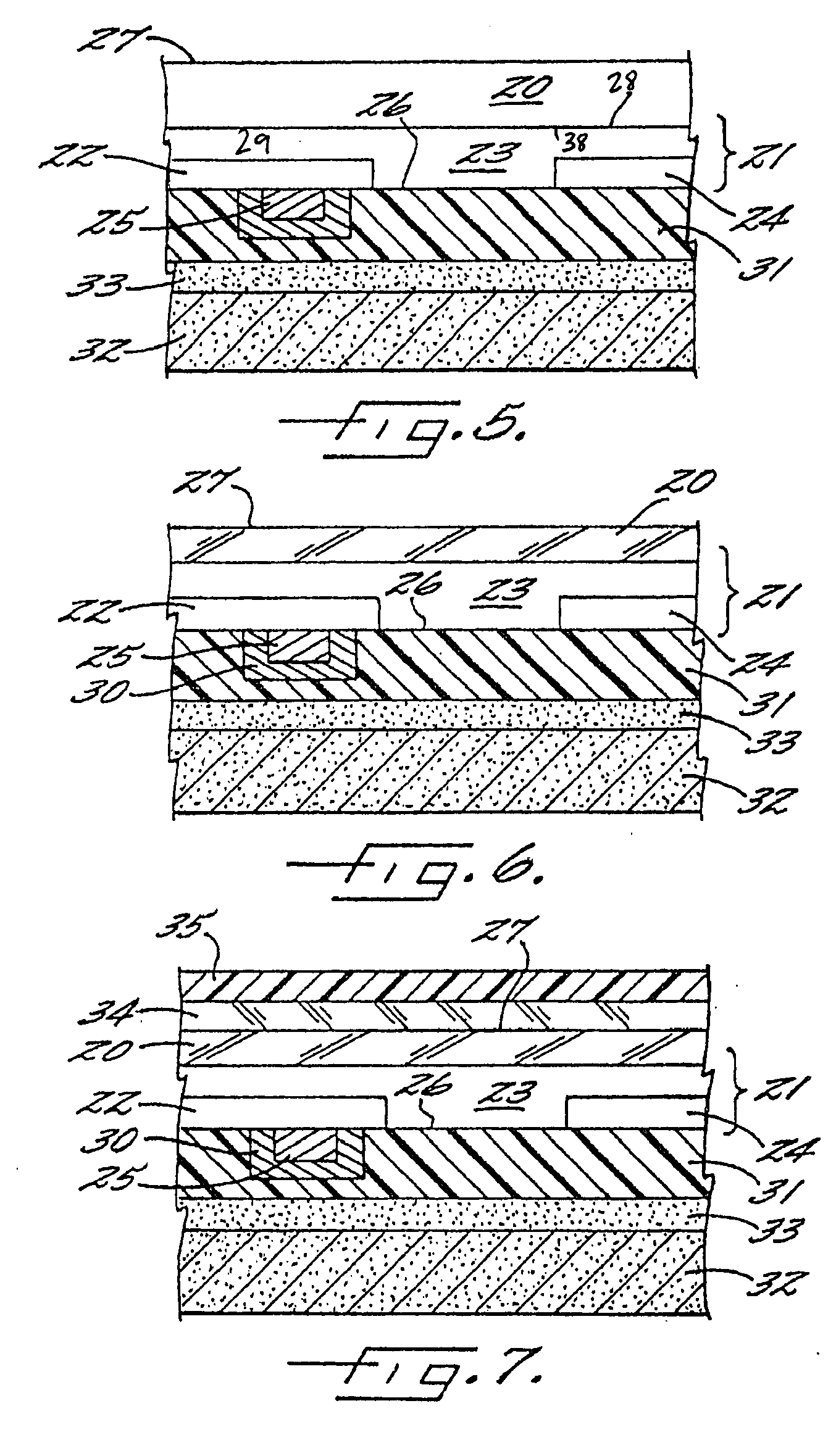

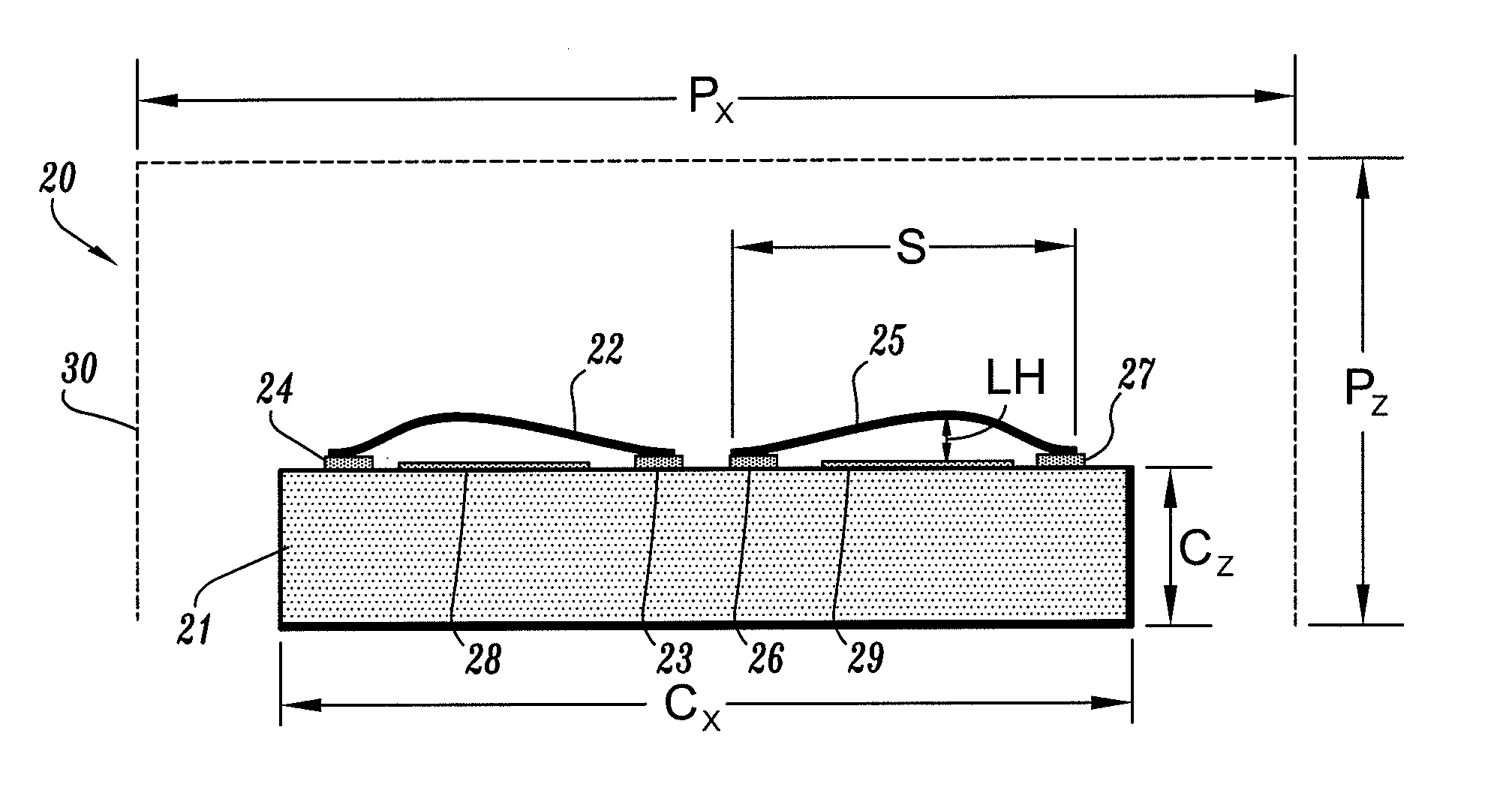

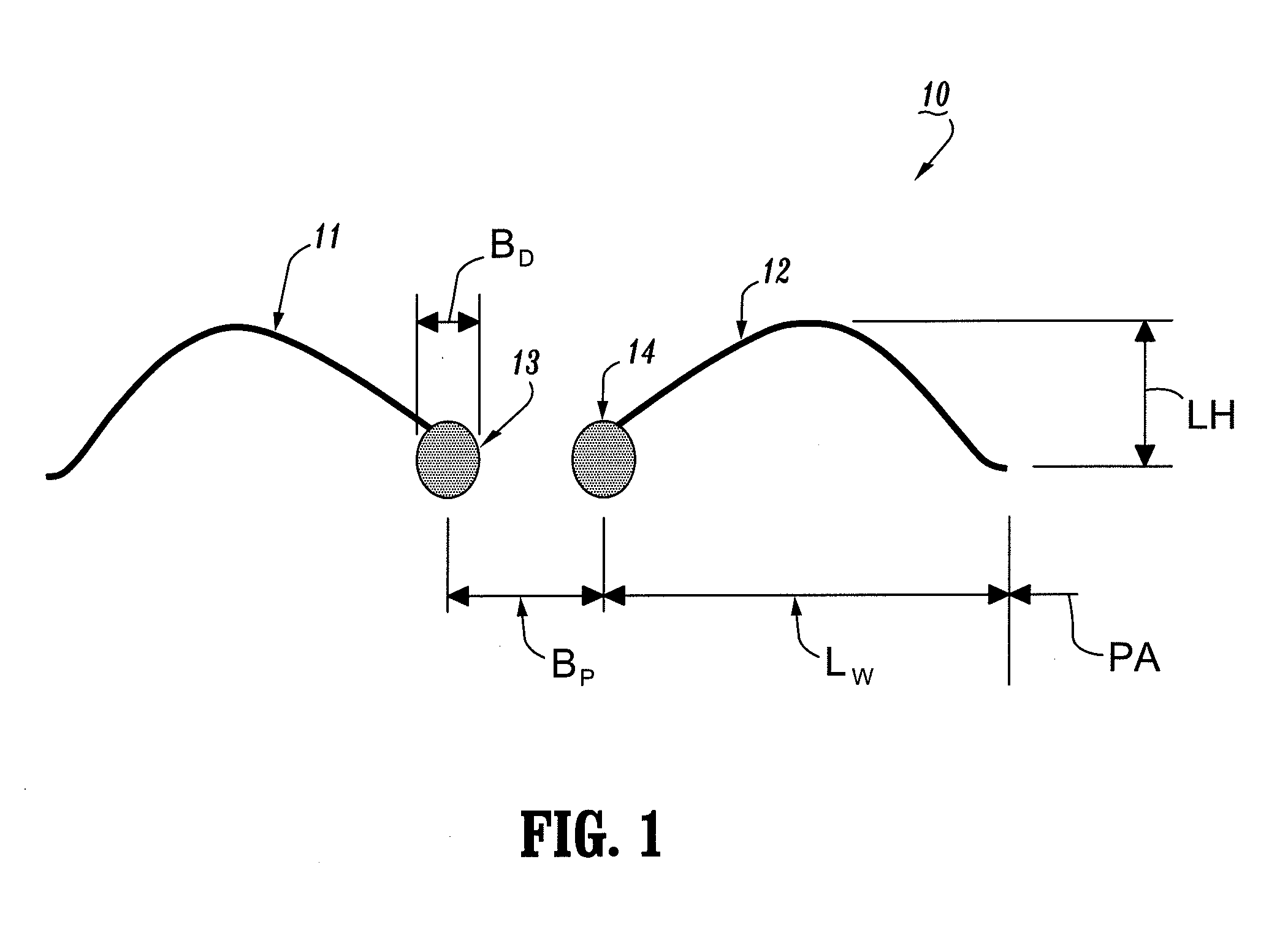

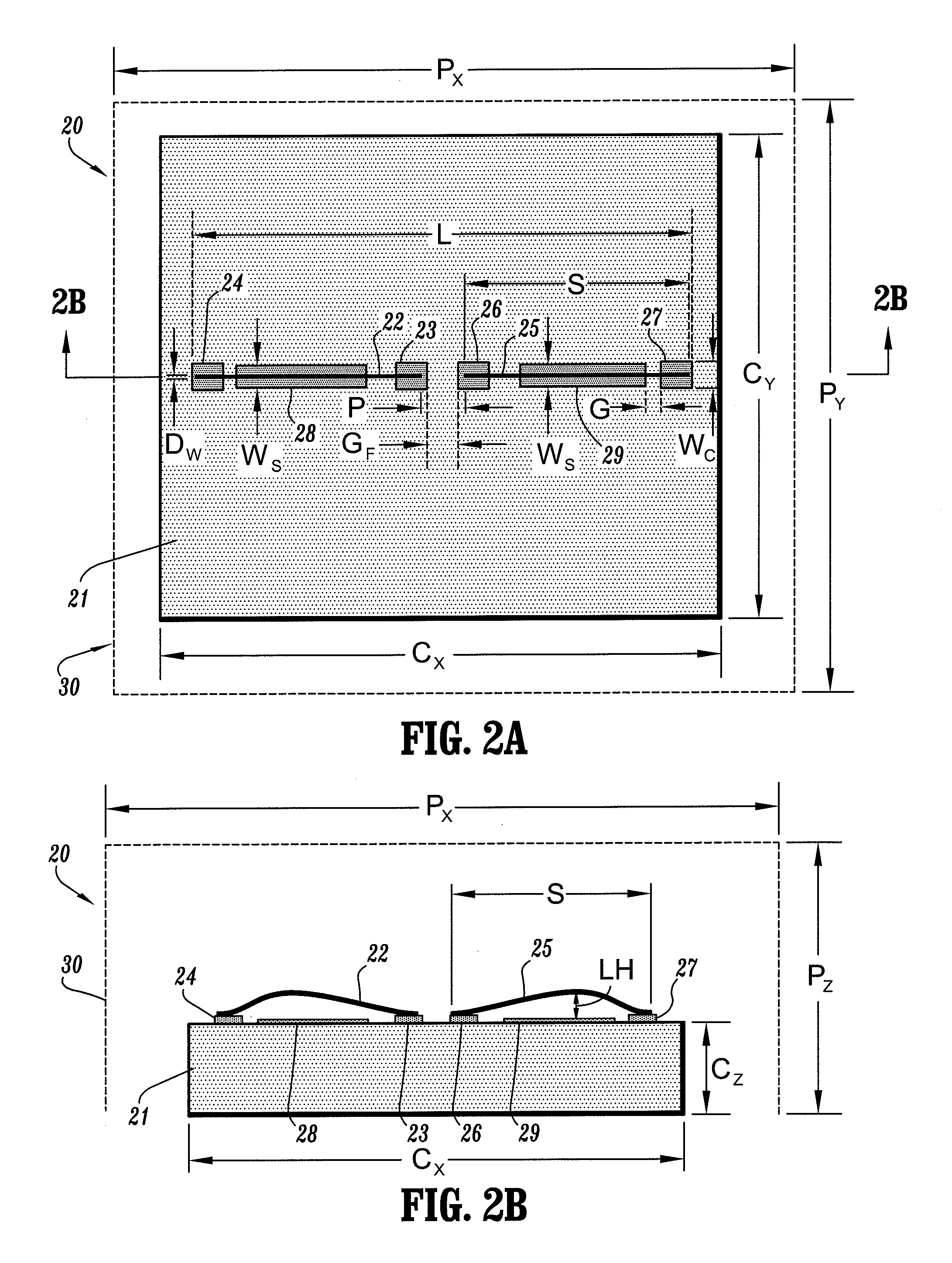

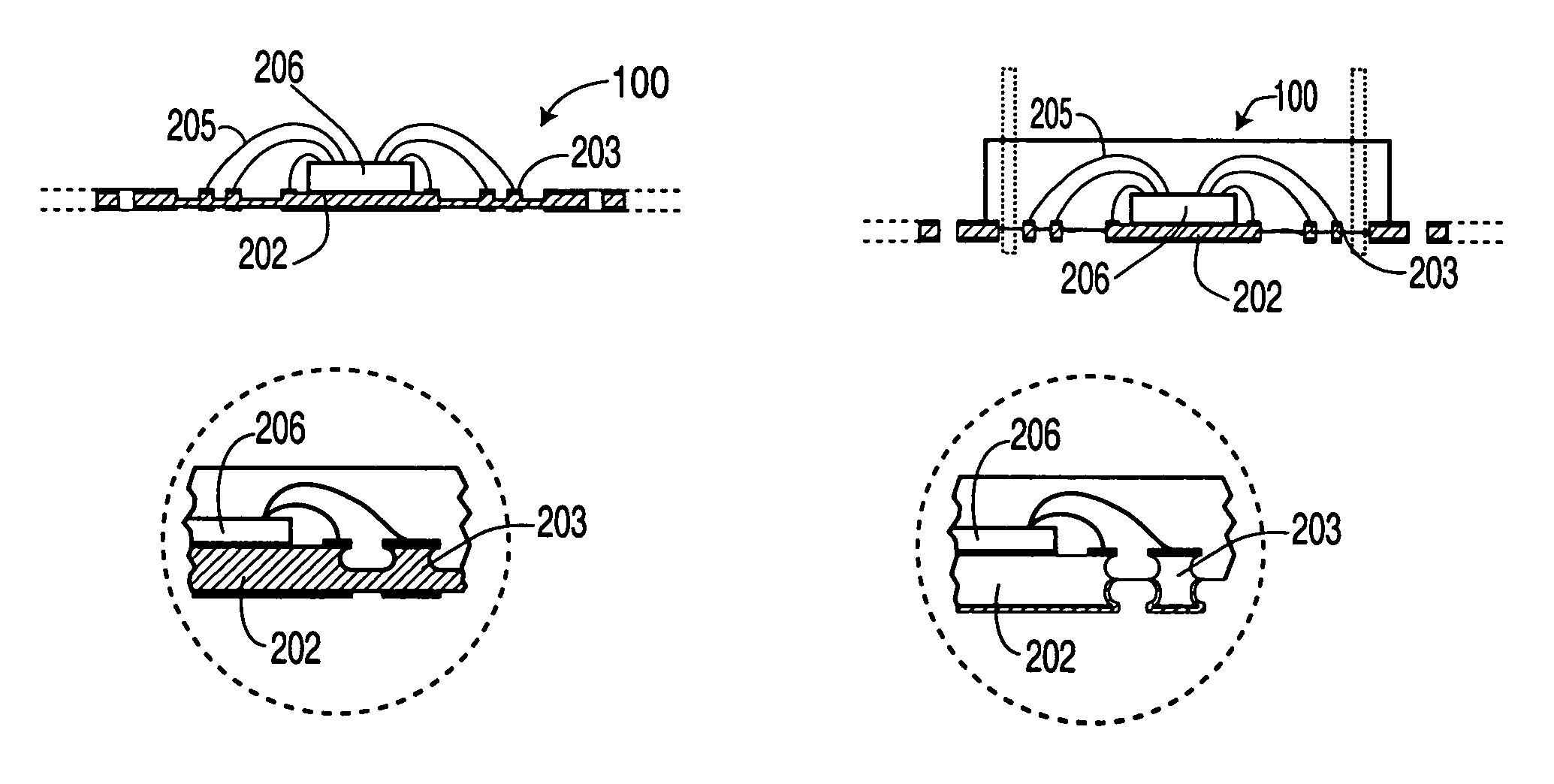

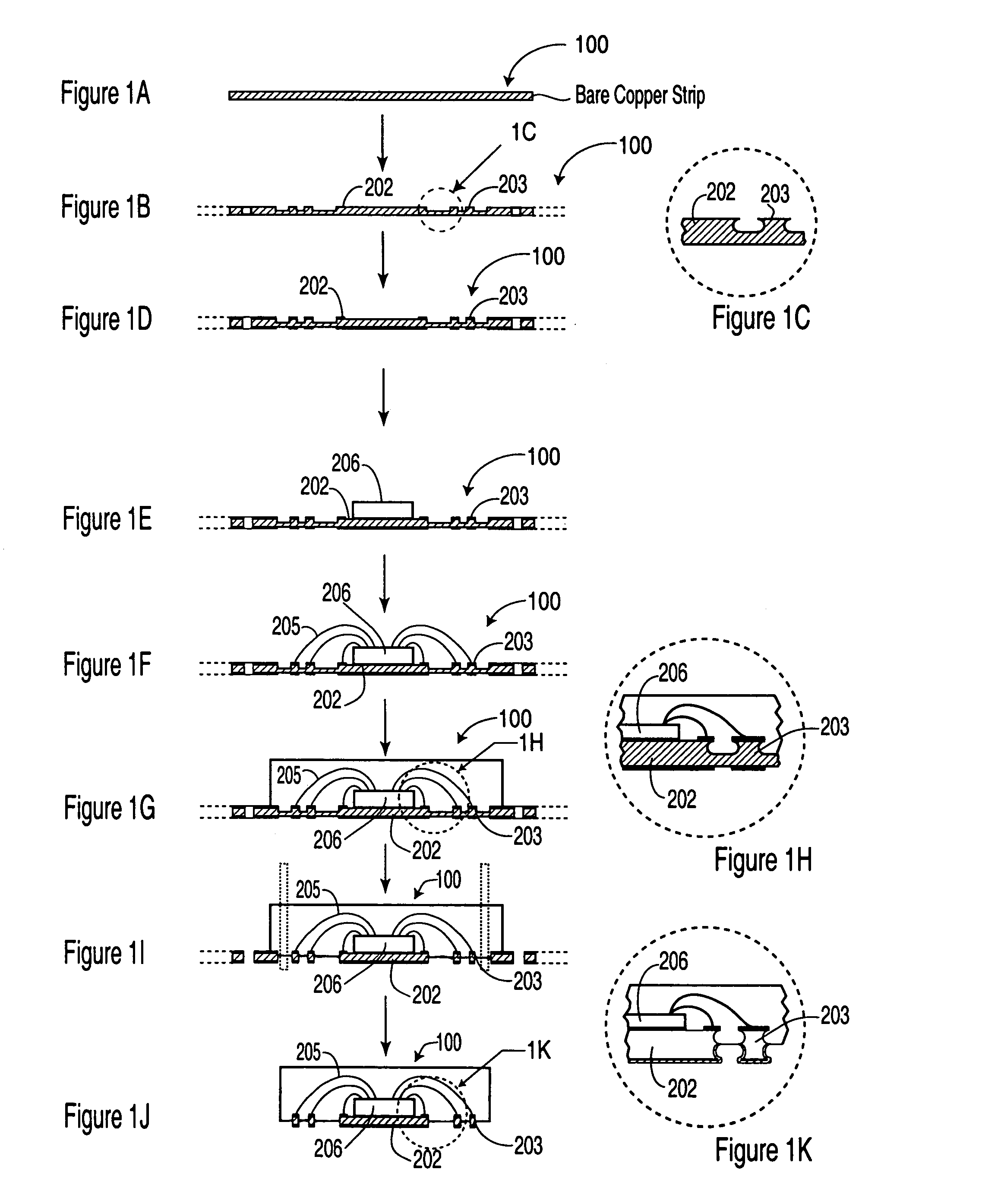

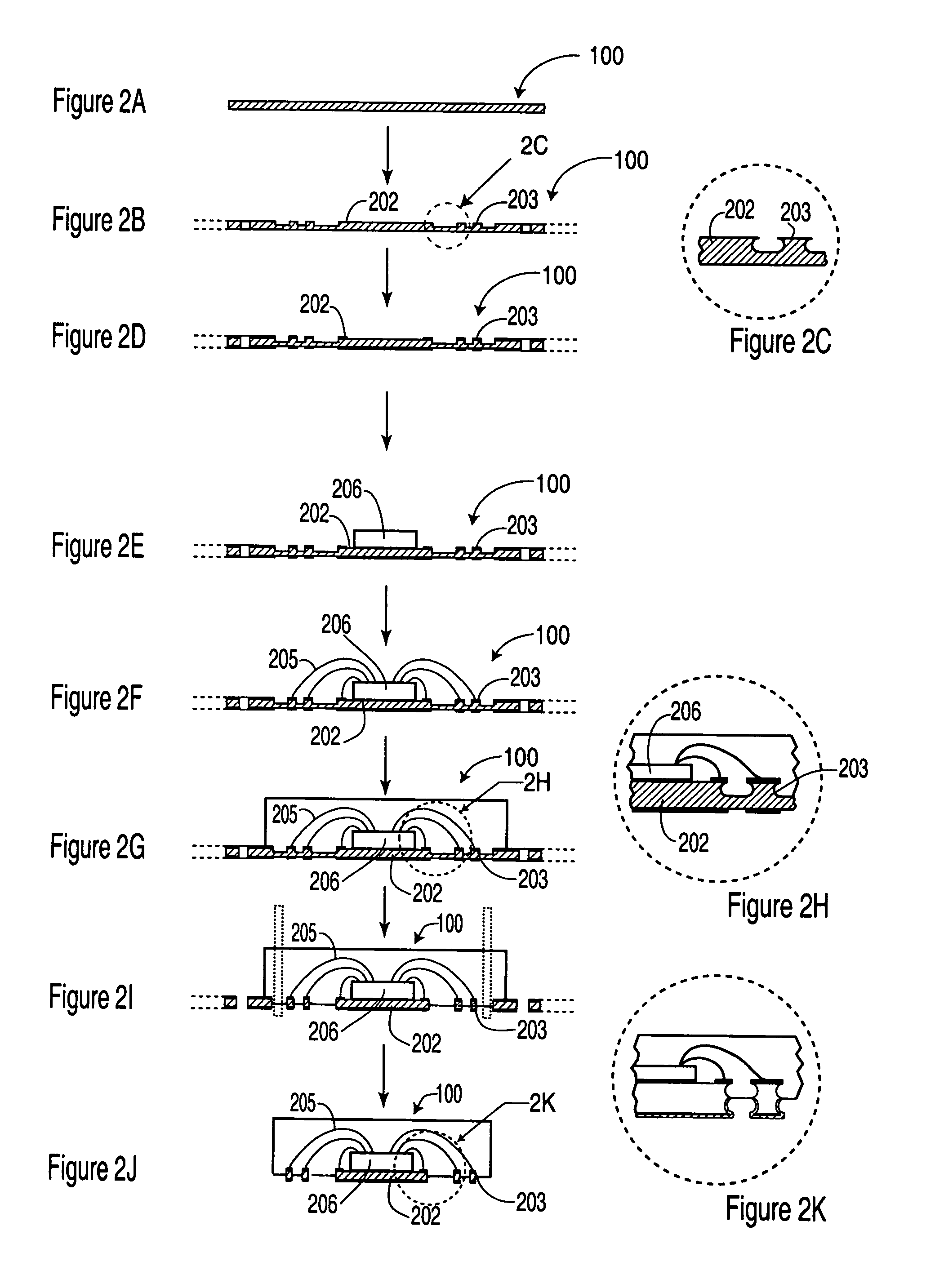

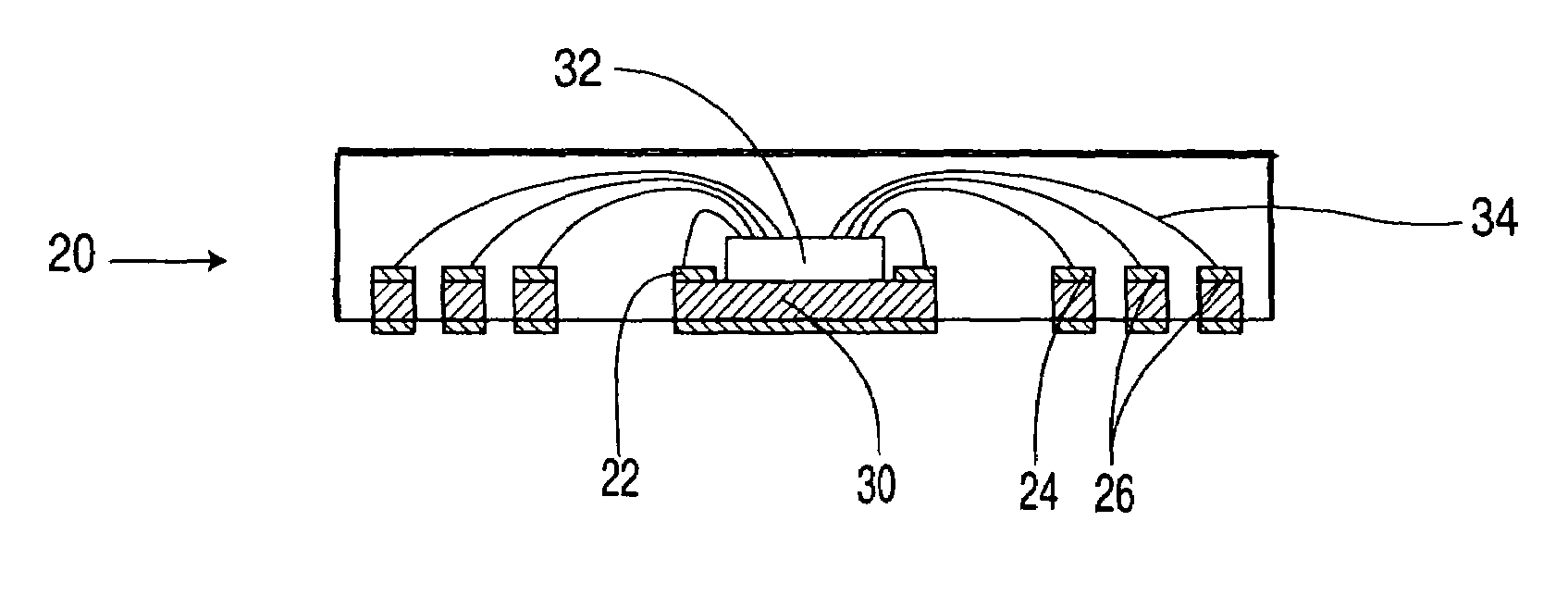

Apparatus and methods for constructing antennas using wire bonds as radiating elements

ActiveUS7295161B2Improve efficiencyWide bandwidthSimultaneous aerial operationsAntenna supports/mountingsCommunications systemTransceiver

Antennas are provided which are constructed using one or more wires as radiating elements attached to a substrate or chip, wherein wire bonding methods can be used to attach and form loop profiles for the wires. The antennas can be integrally packaged with IC chips (e.g., IC transceivers, receivers, transmitters, etc.) to build integrated wireless or RF (radio frequency) communications systems.

Owner:GLOBALFOUNDRIES US INC

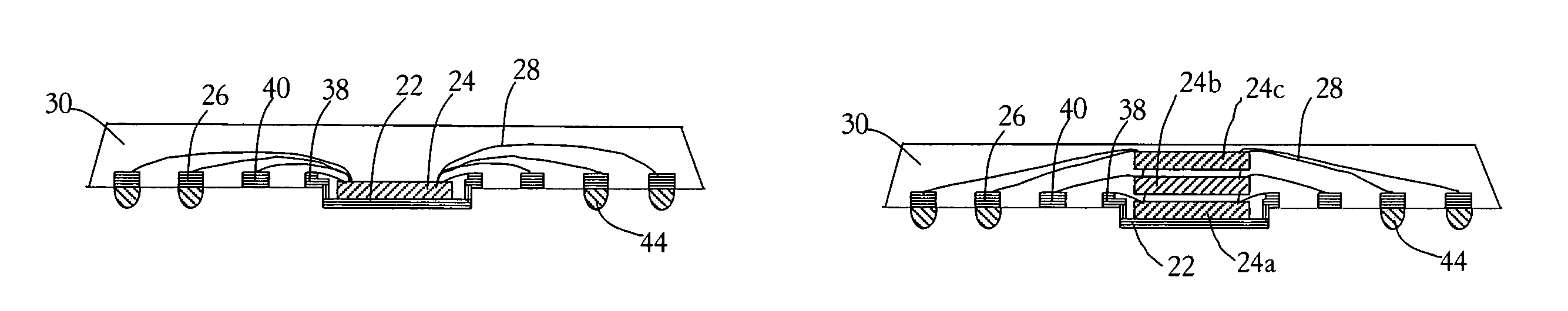

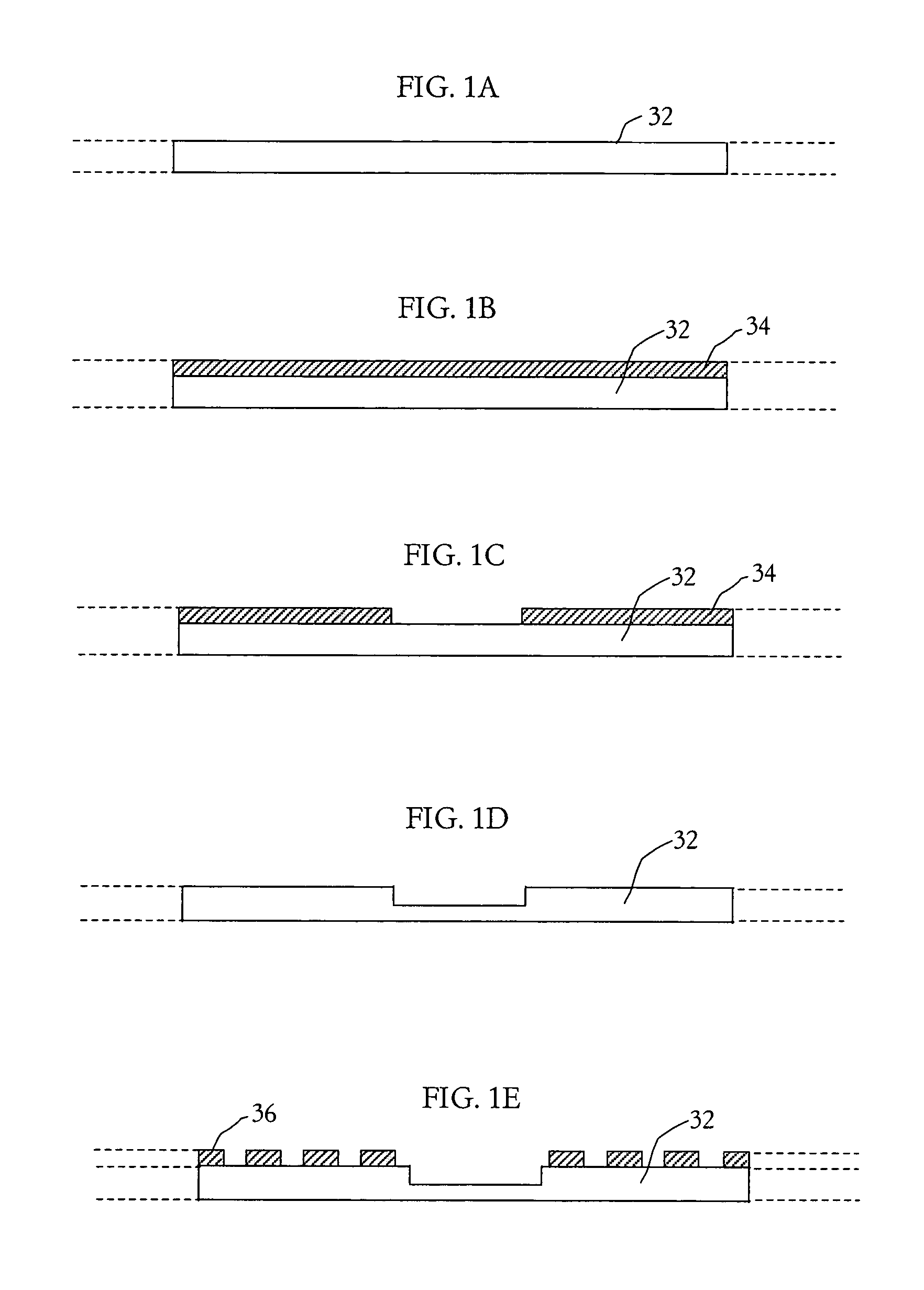

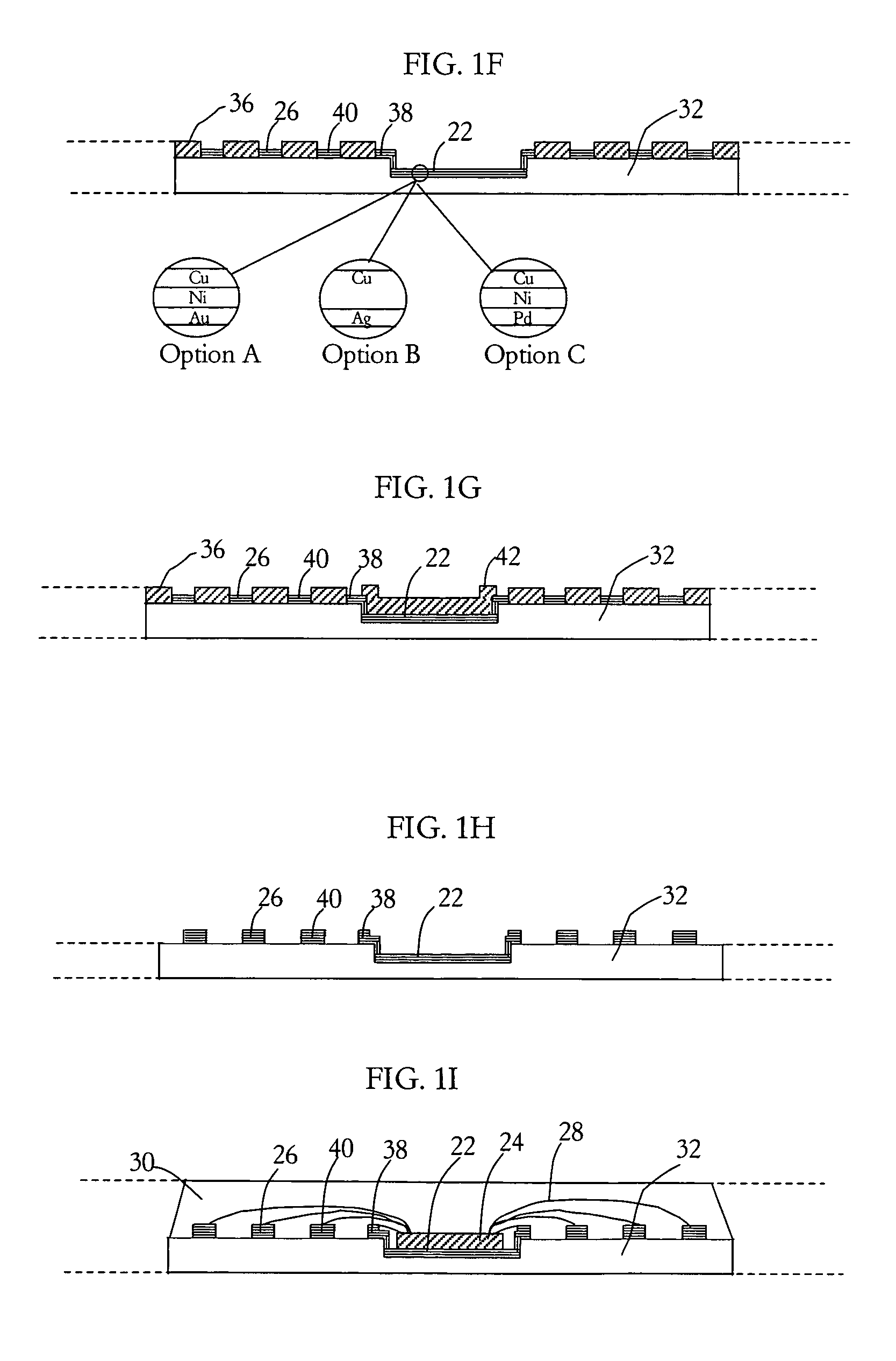

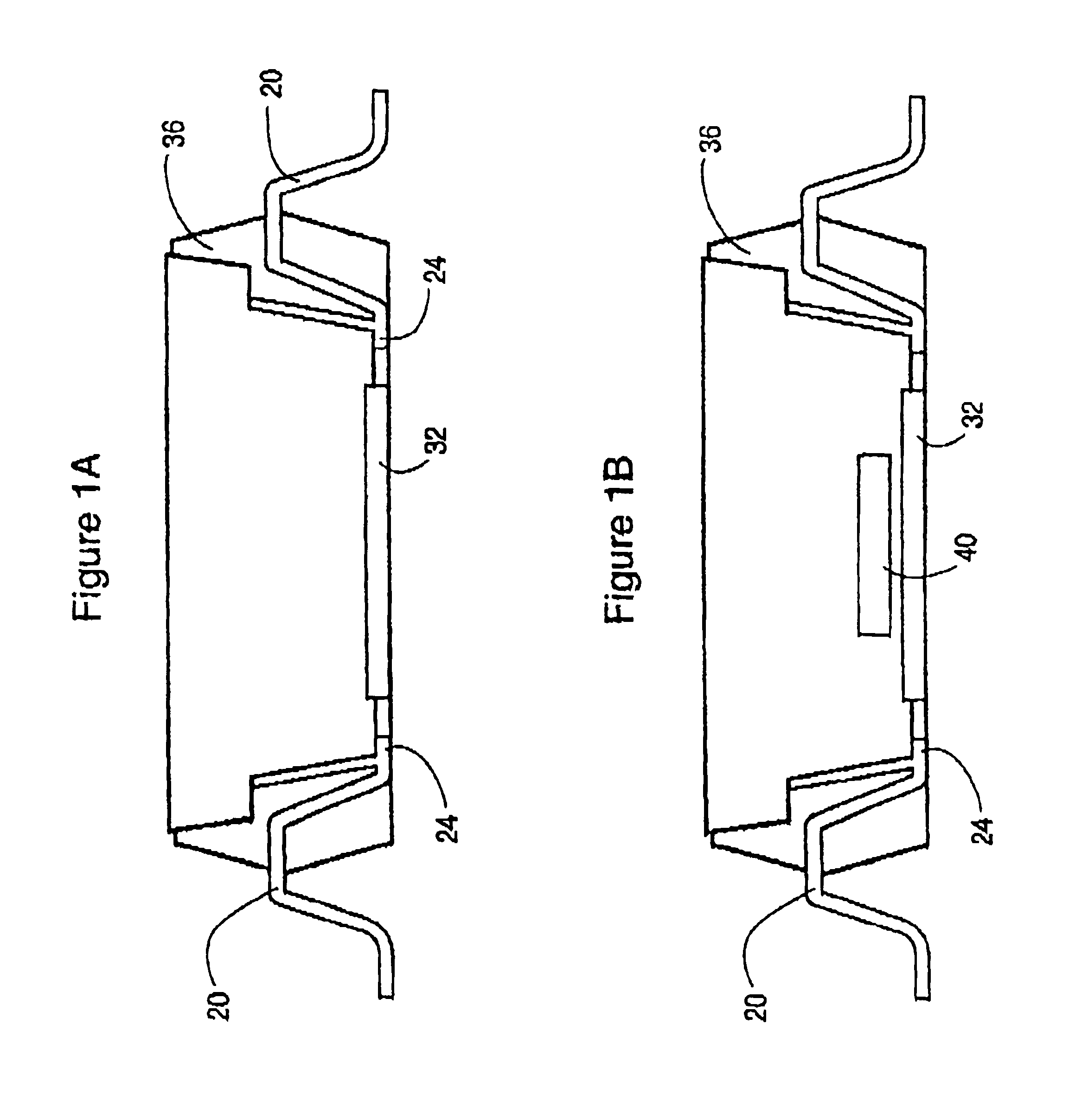

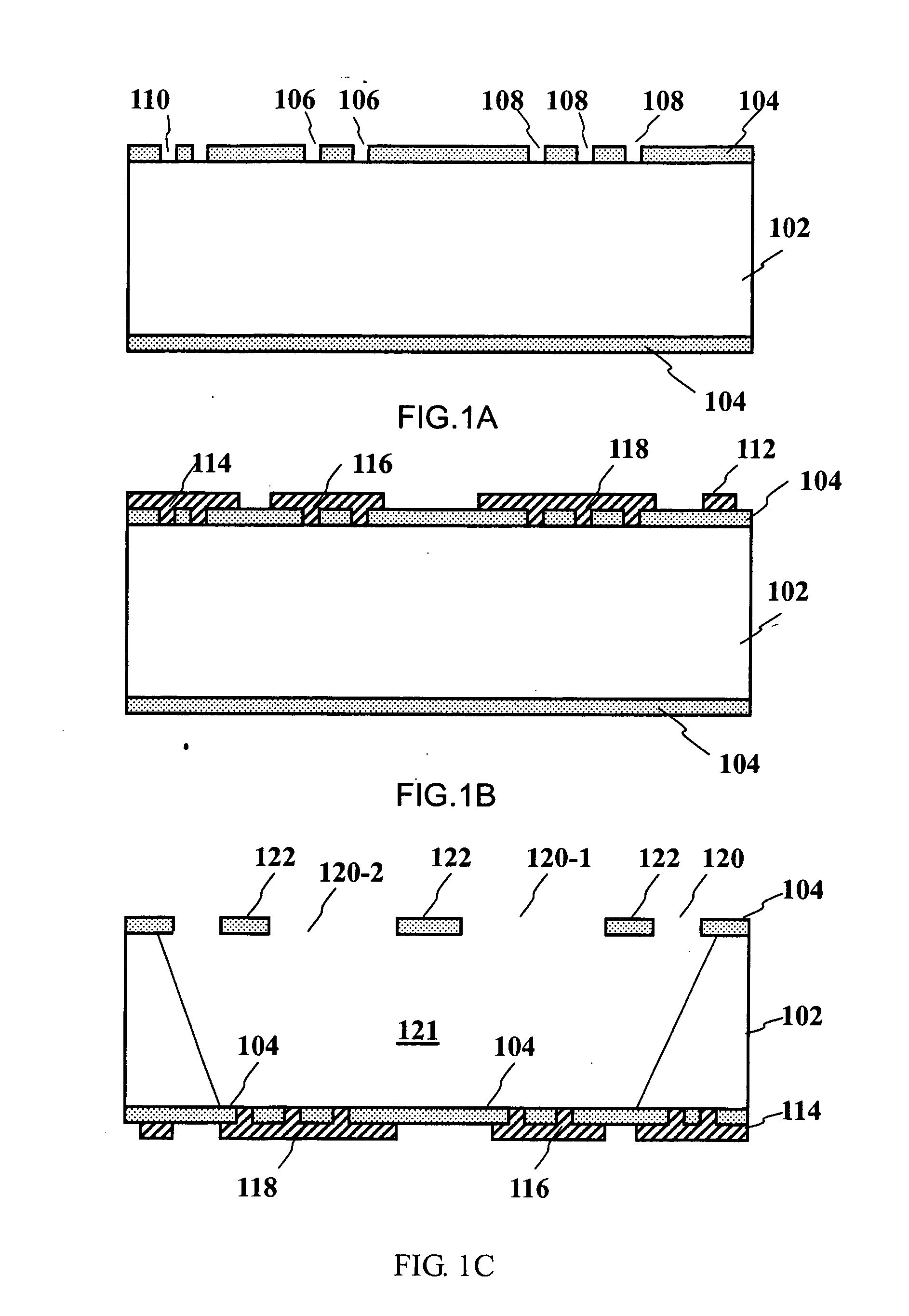

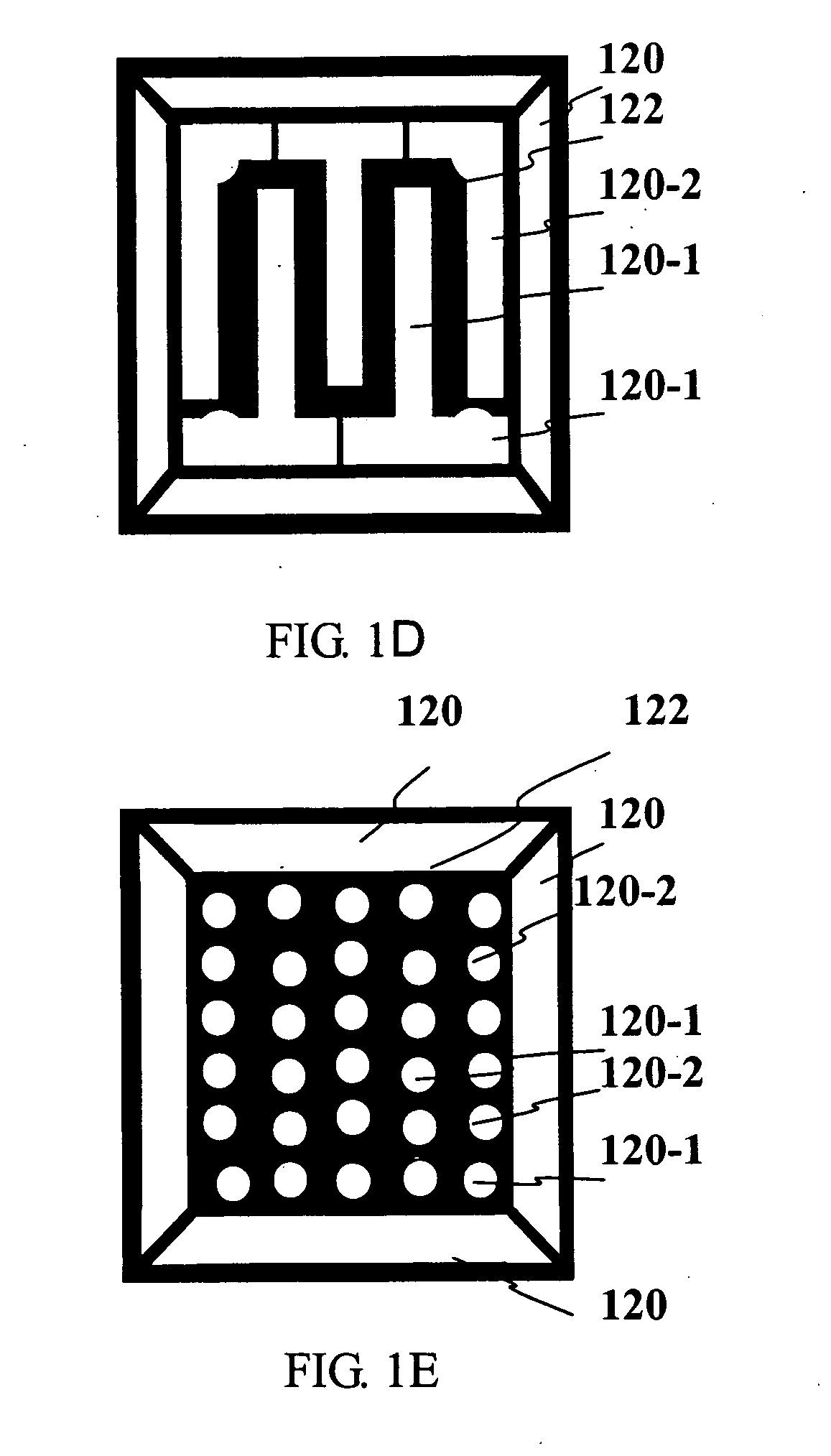

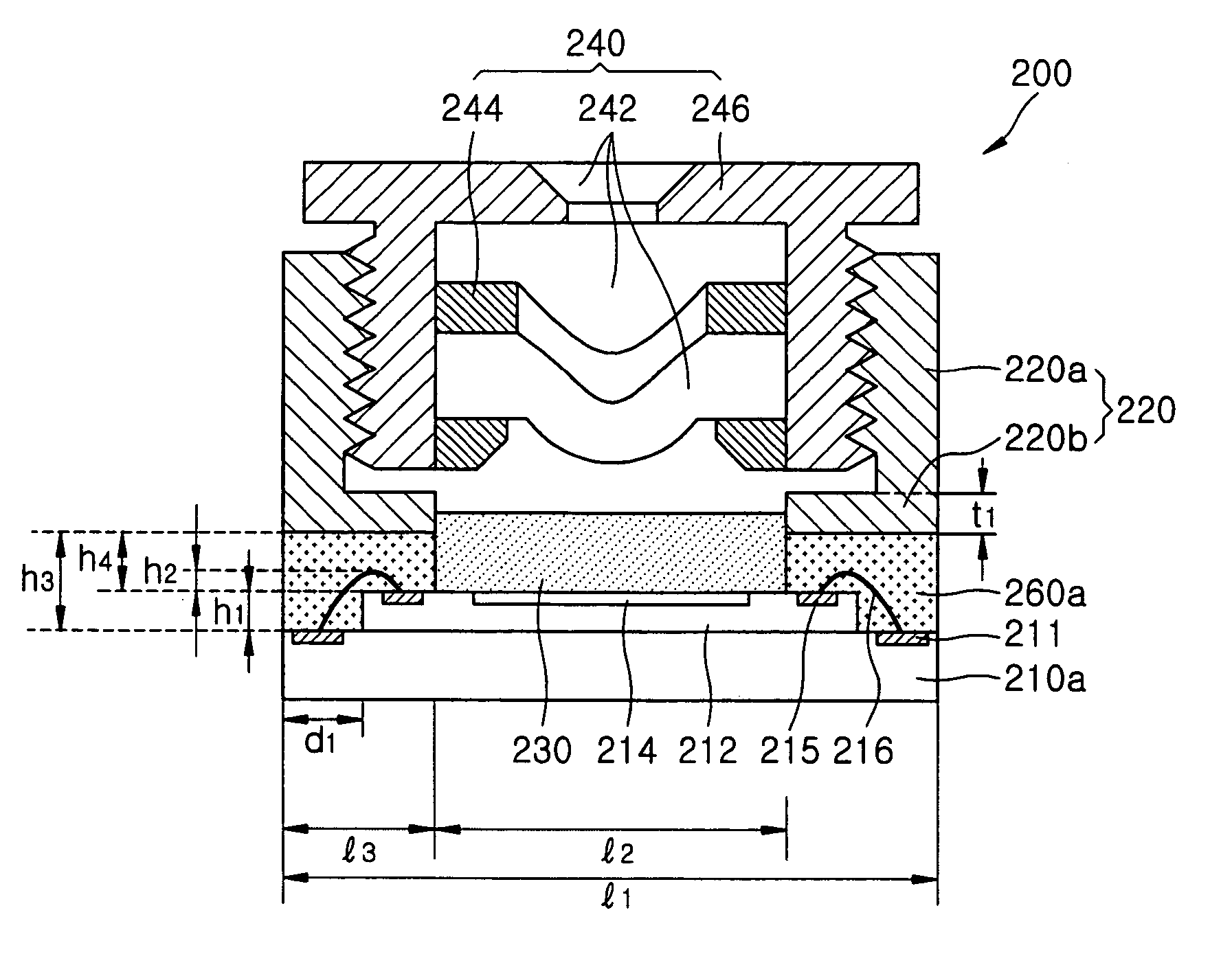

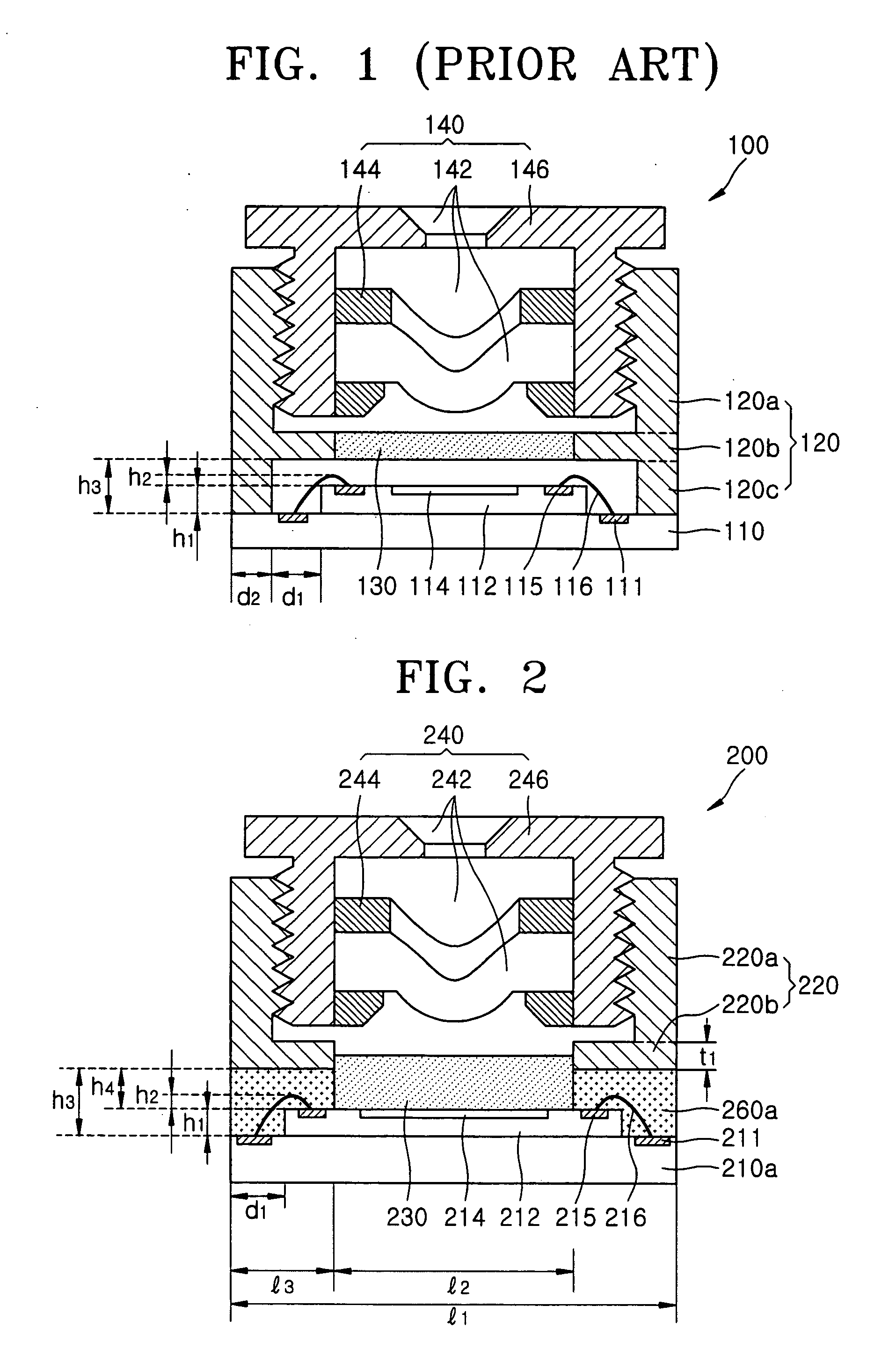

Leadless plastic chip carrier with standoff contacts and die attach pad

ActiveUS7049177B1Improve motherboard assemblyRelieve pressureSemiconductor/solid-state device detailsSolid-state devicesEtchingContact pad

A process for fabricating a leadless plastic chip carrier includes selectively etching at least a first surface of a leadframe strip to partially define at least a plurality of contact pads and a die attach pad; selectively plating at least one layer of metal on a second surface of the leadframe strip, on an undersurface of at least the plurality of contact pads and the die attach pad; mounting a semiconductor die on the first surface, on the partially defined die attach pad; wire bonding the semiconductor die to ones of the contact pads; encapsulating the wire bonds and the semiconductor die in a molding material such that the molding material covers a first portion of the die attach pad and first portions of the contact pads; selectively etching a second surface of the leadframe strip to define a second portion of the contact pads and a second portion of the die attach pad by etching the second surface with the at least one layer of metal resisting etching; and singulating the leadless plastic chip carrier from the leadframe strip.

Owner:UTAC HEADQUARTERS PTE LTD

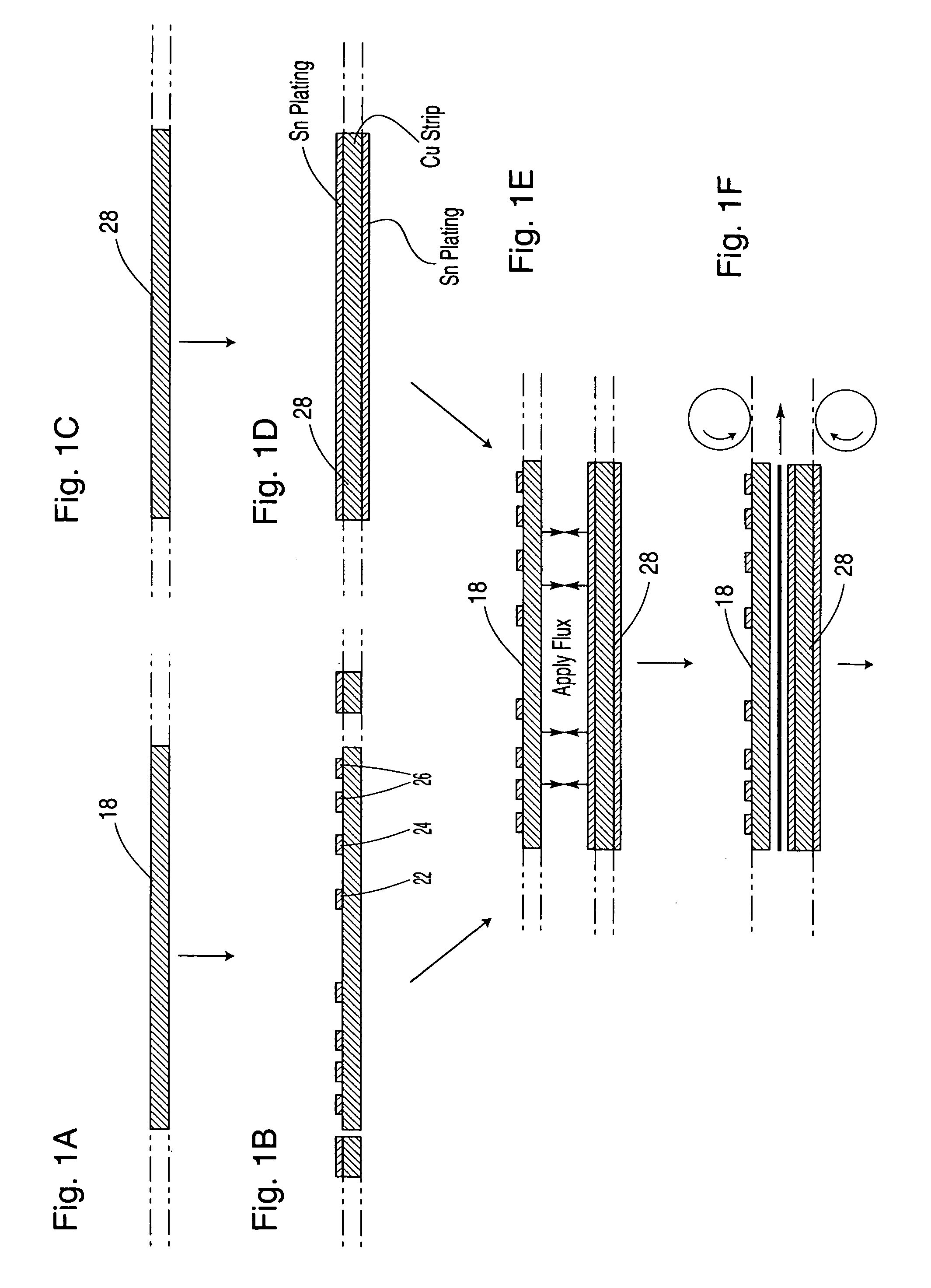

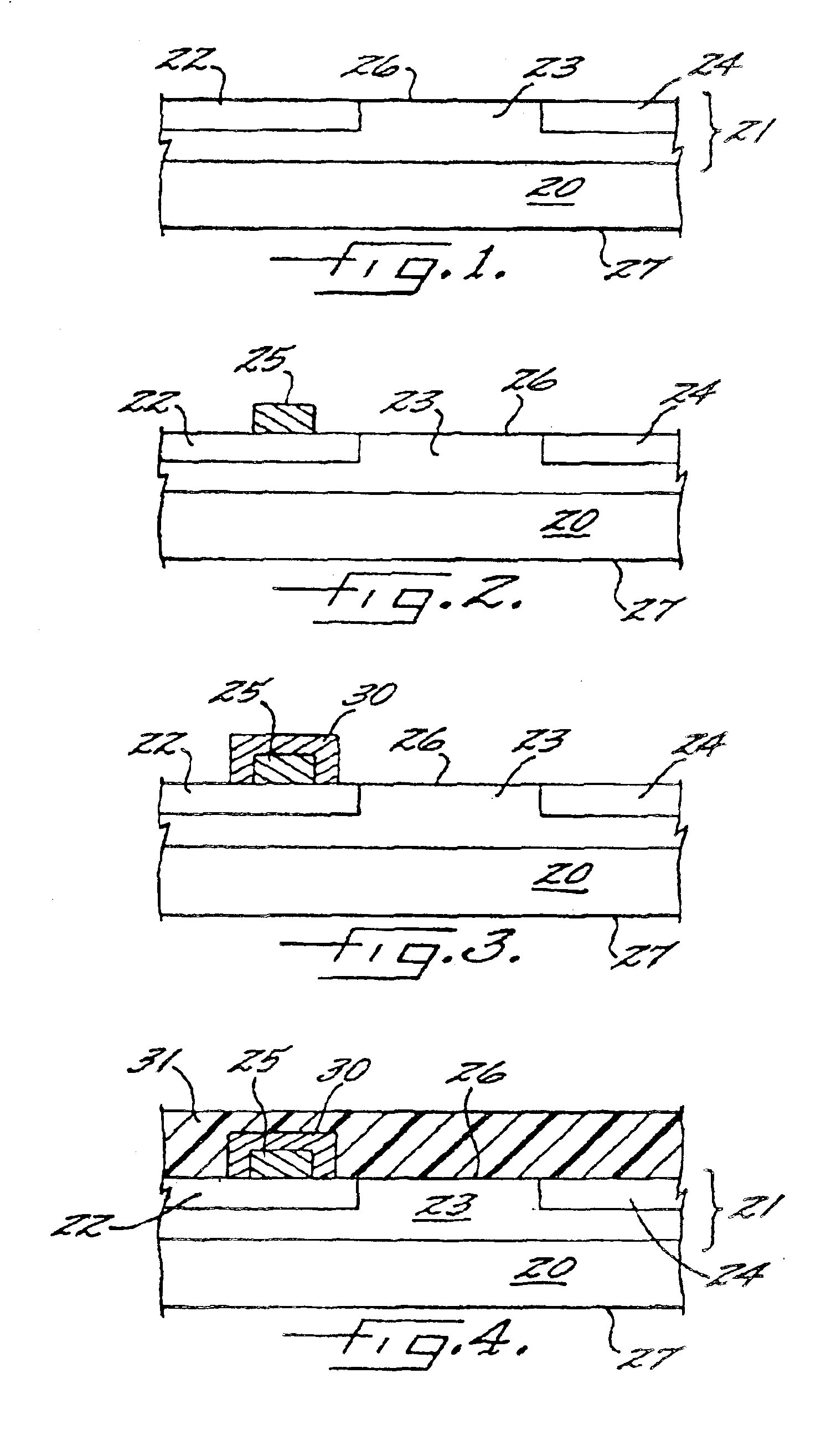

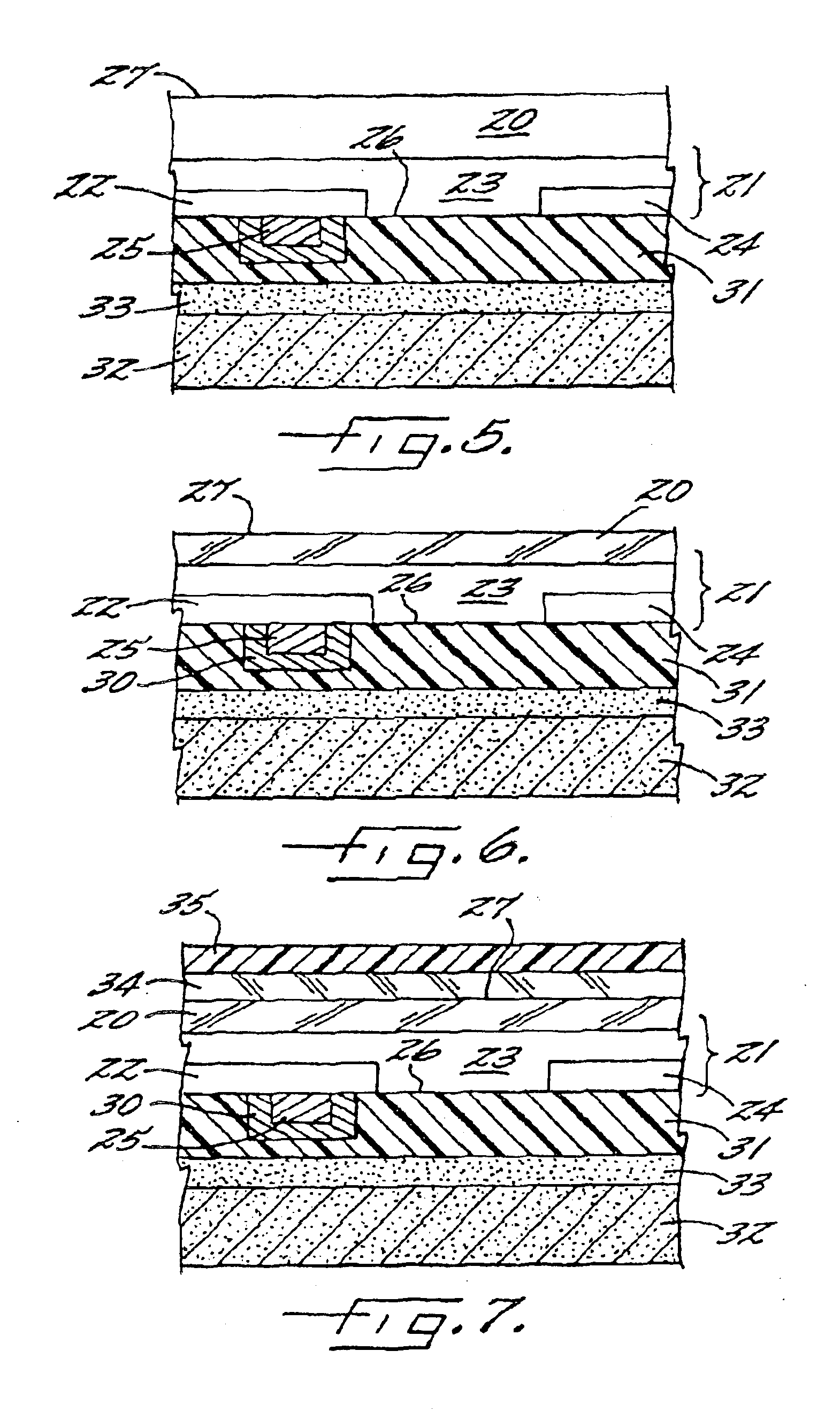

Process for fabricating a leadless plastic chip carrier

InactiveUS6946324B1Robust three dimensional structureReduce material costsSemiconductor/solid-state device detailsSolid-state devicesMetal stripsContact pad

A process for fabricating a leadless plastic chip carrier includes laminating a first metal strip to a second metal strip to form a leadframe strip, selectively etching the first metal strip to define at least a row of contact pads, mounting a semiconductor die to either a die attach pad or the second metal strip and wire bonding the semiconductor die to ones of the contact pads, encapsulating a top surface of the leadframe strip in a molding material, removing the second metal strip, thereby exposing the die attach pad and the at least one row of contact pads, and singulating the leadless plastic chip carrier from the leadframe strip.

Owner:UTAC HEADQUARTERS PTE LTD

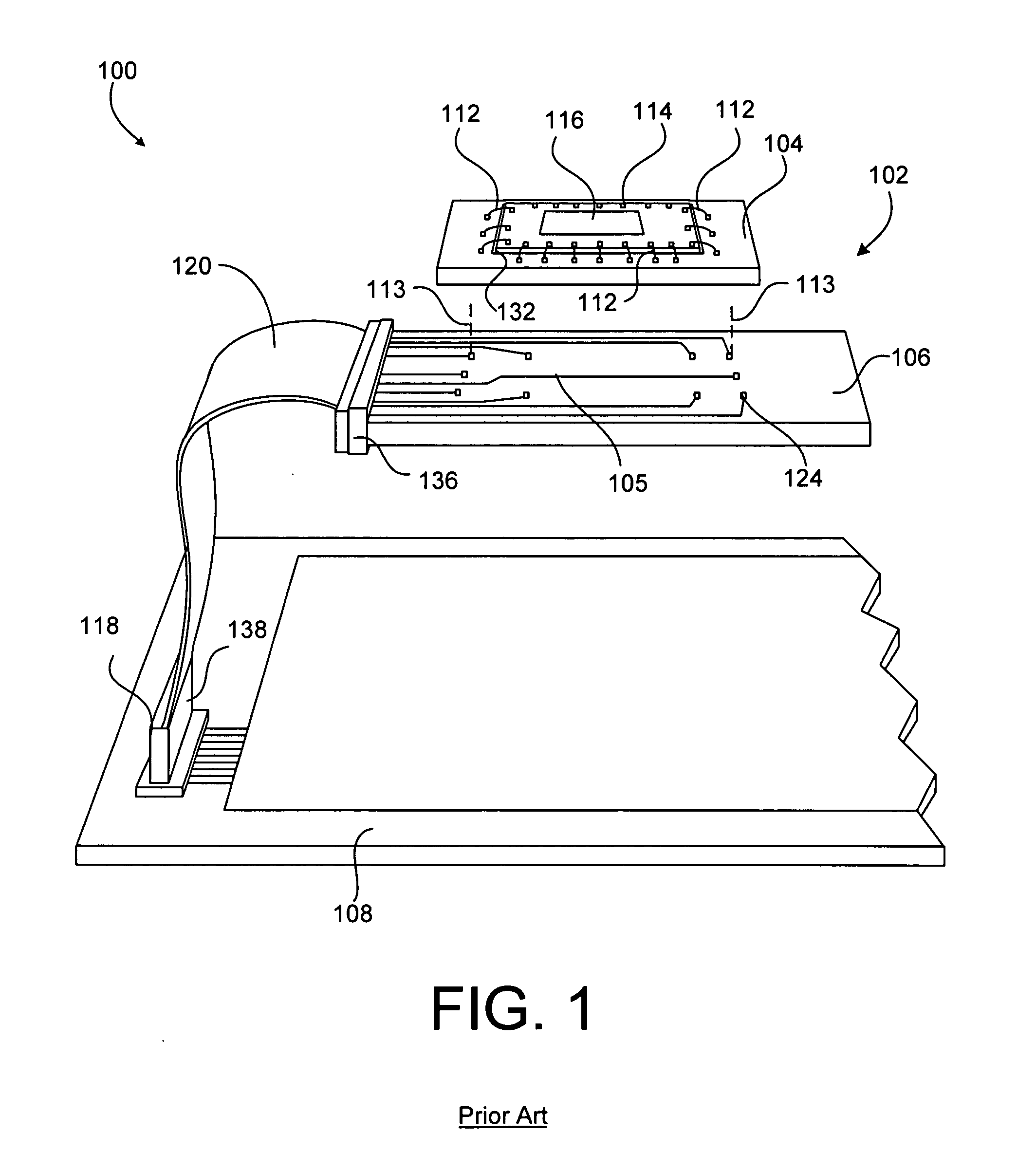

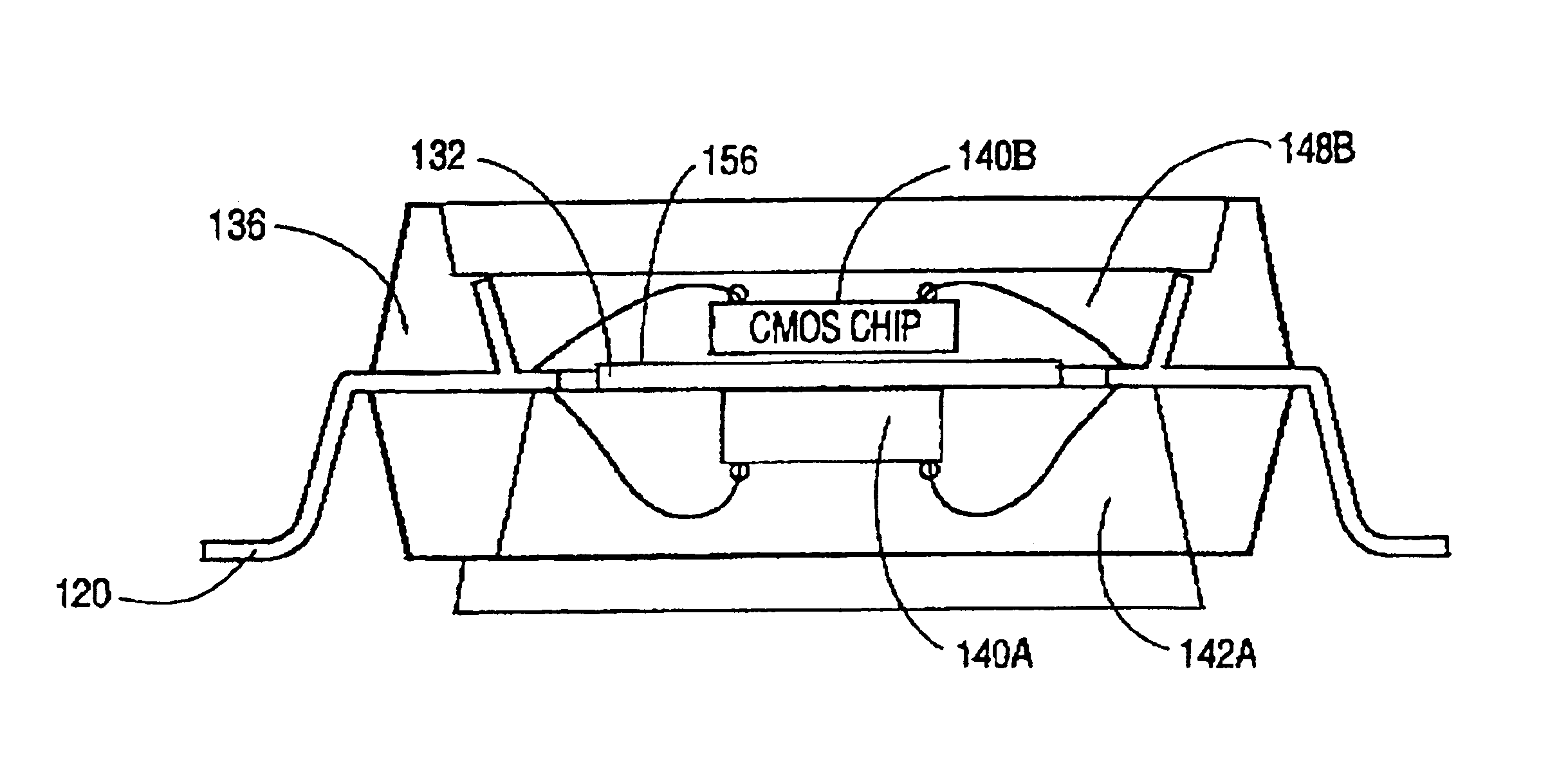

System and method for mounting an image capture device on a flexible substrate

ActiveUS20050285973A1Facilitates fastImprove assembly efficiencyTelevision system detailsSolid-state devicesAdhesiveFlexible circuits

A digital camera module includes an image capture device mounted on a flexible circuit substrate. In one embodiment of the digital camera module, the image capture device is mounted directly (e.g., by an adhesive) on the flexible circuit substrate. A stiffener (e.g., a piece of circuit board material) is mounted to the back of the flexible circuit substrate to support wire bonding of the image capture device onto the flexible circuit substrate and / or to support the mounting of additional components (e.g., a lens housing).

Owner:NANCHANG O FILM OPTICAL ELECTRONICS TECH CO LTD

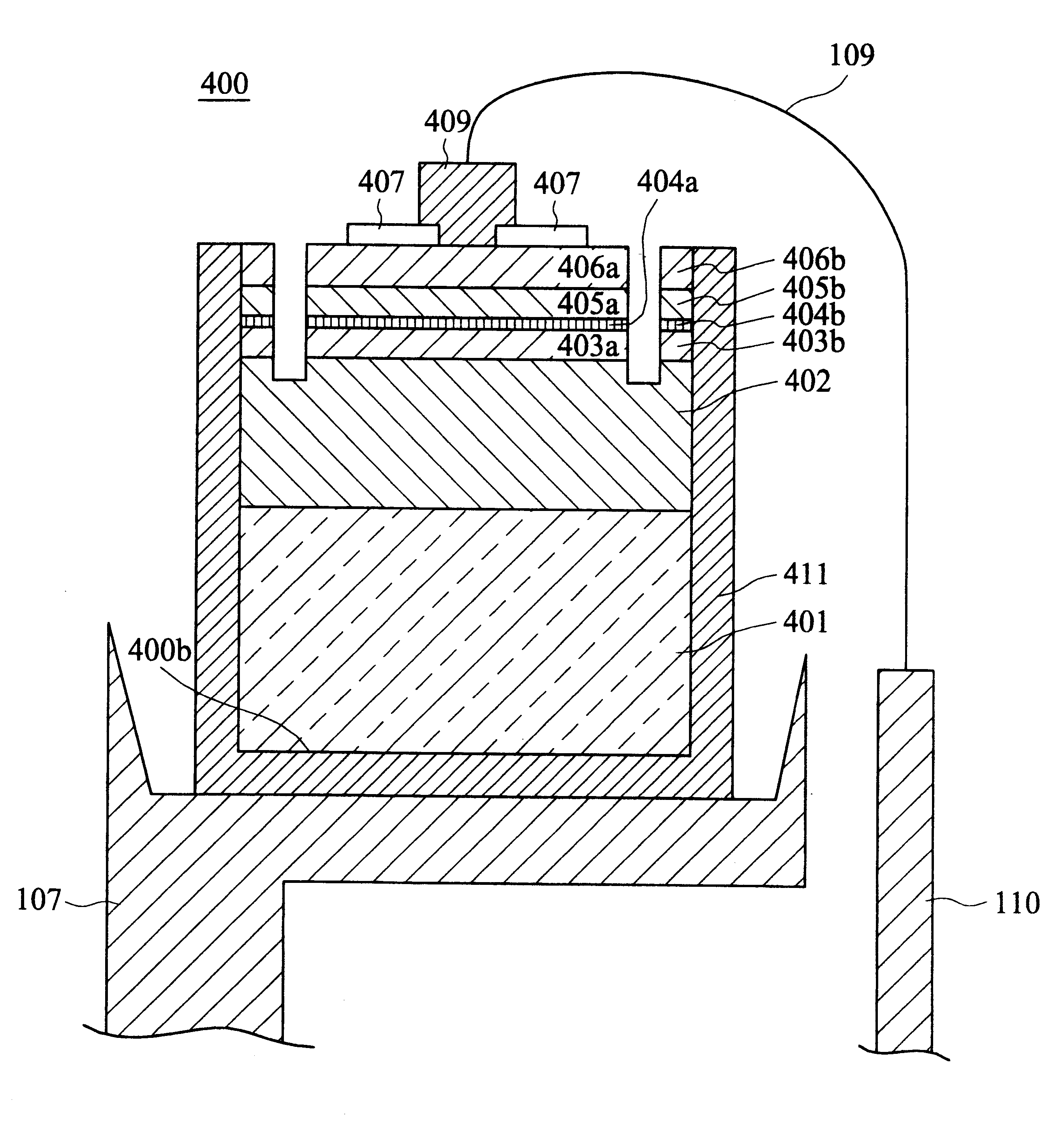

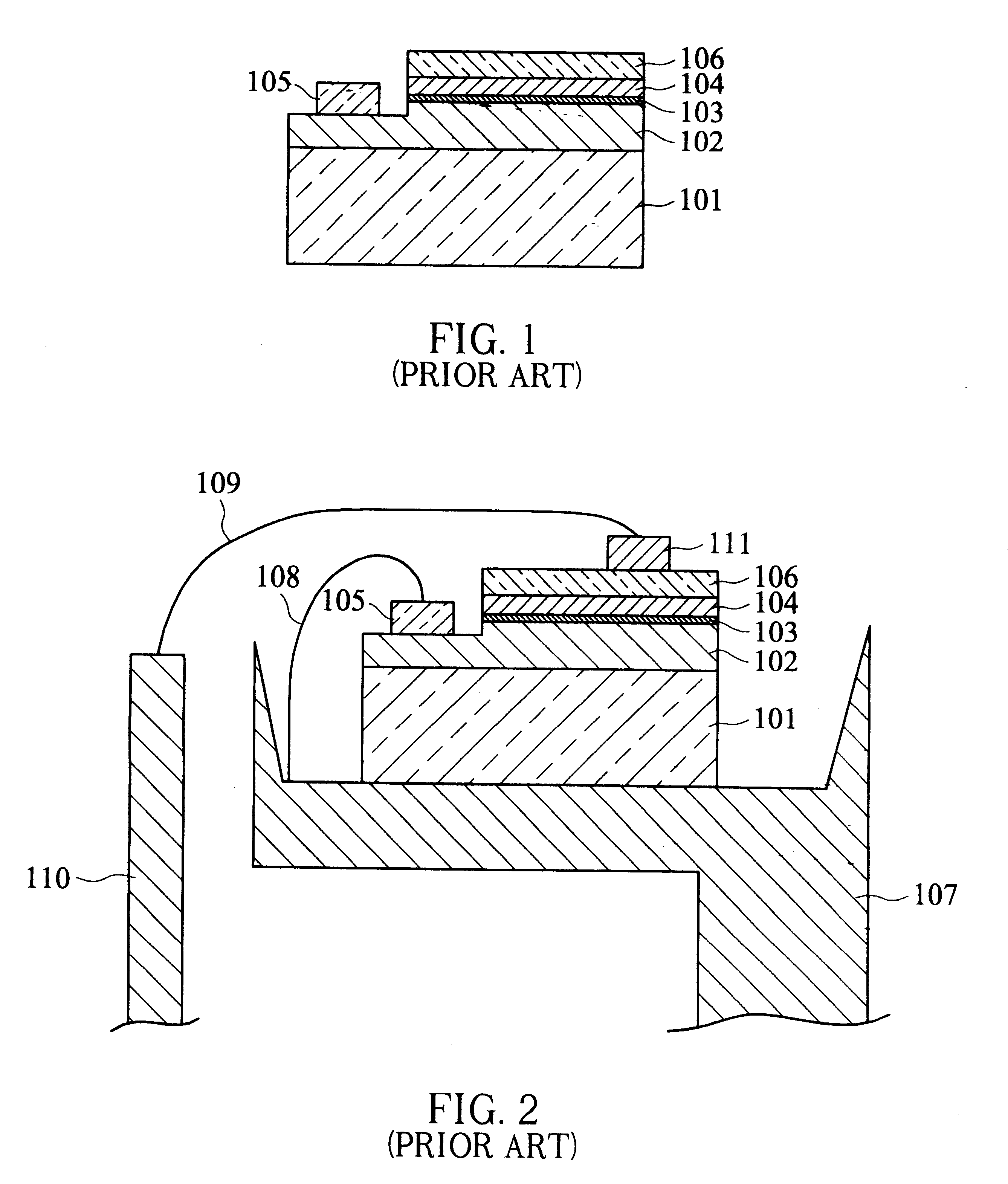

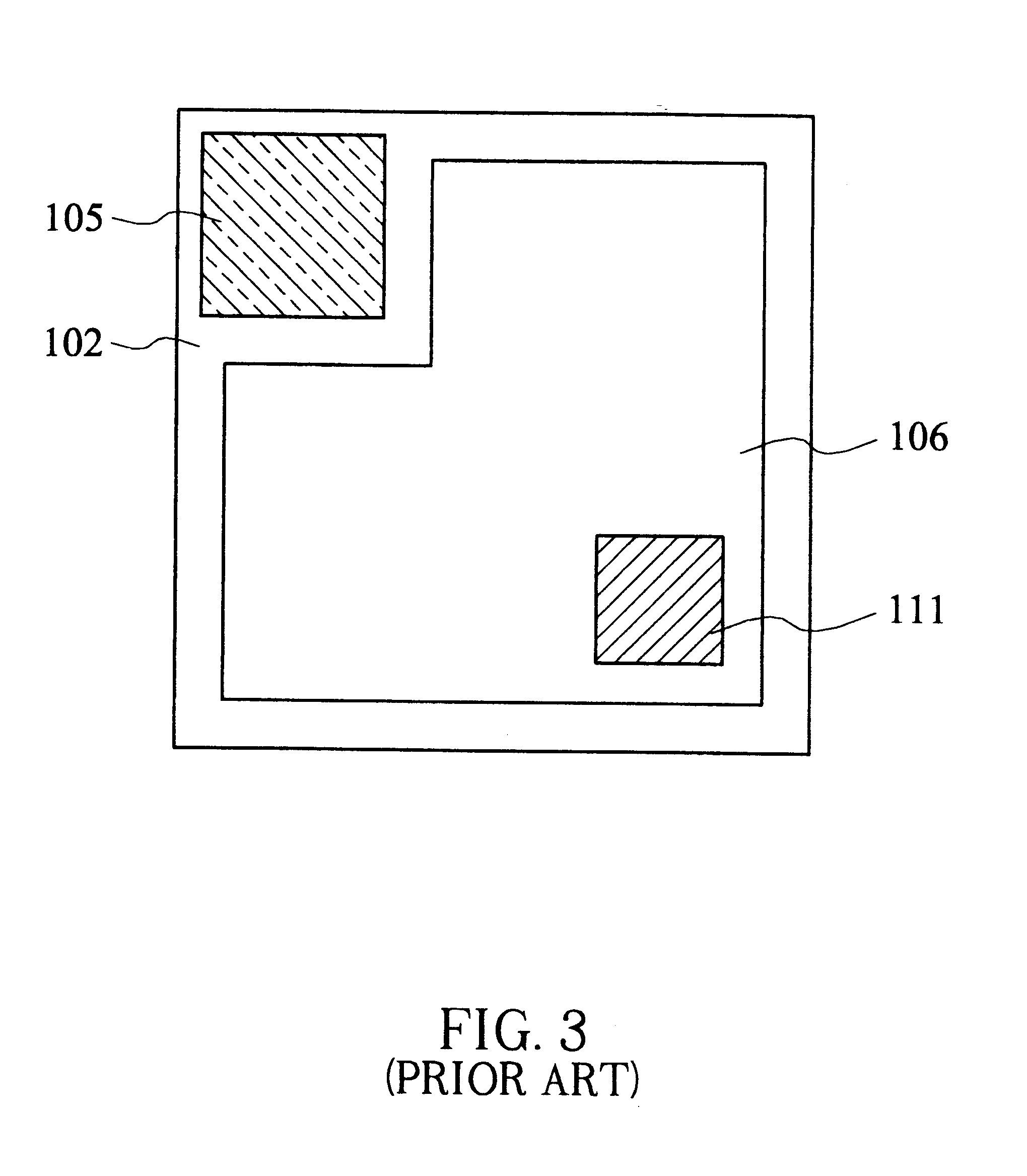

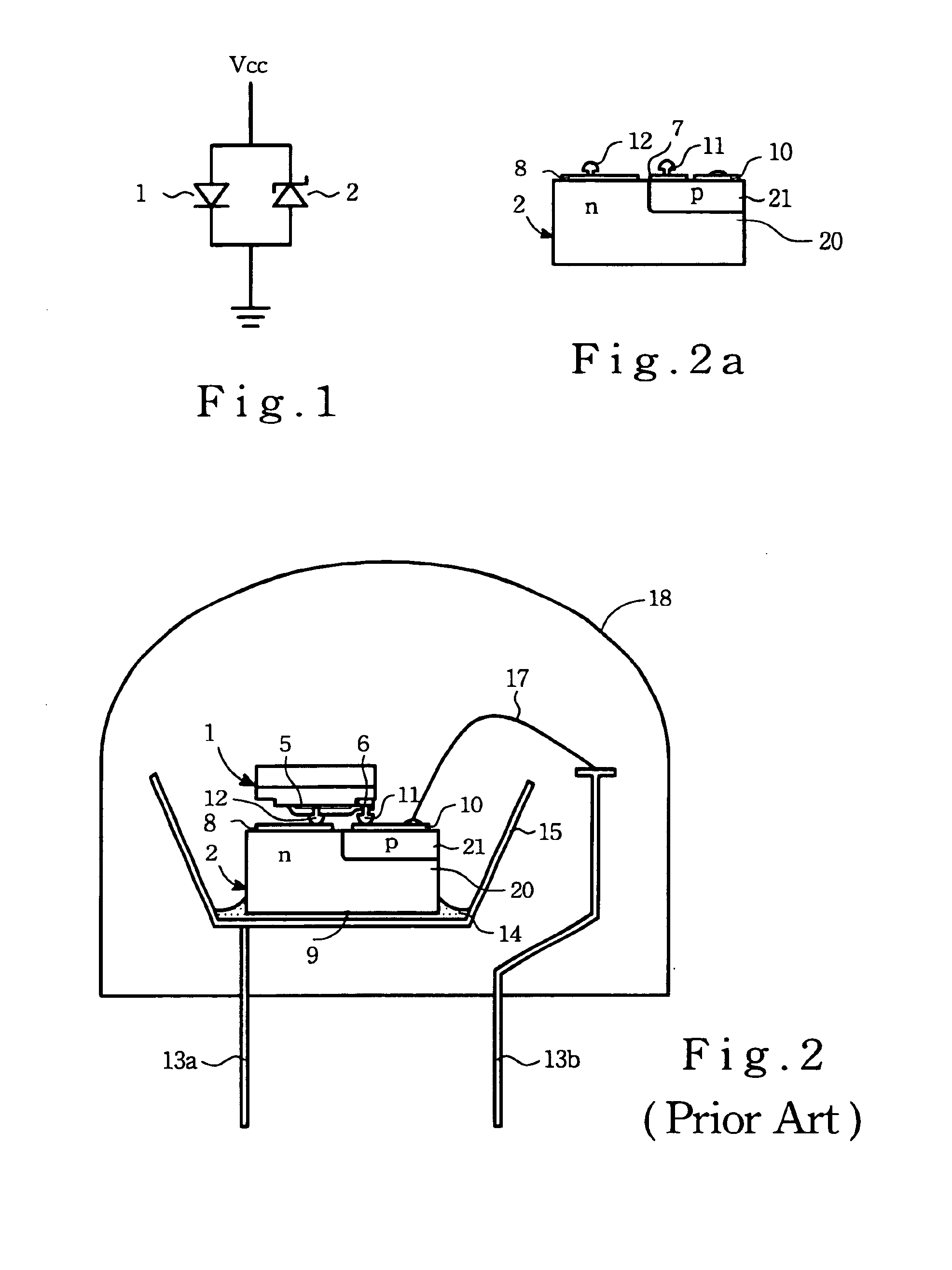

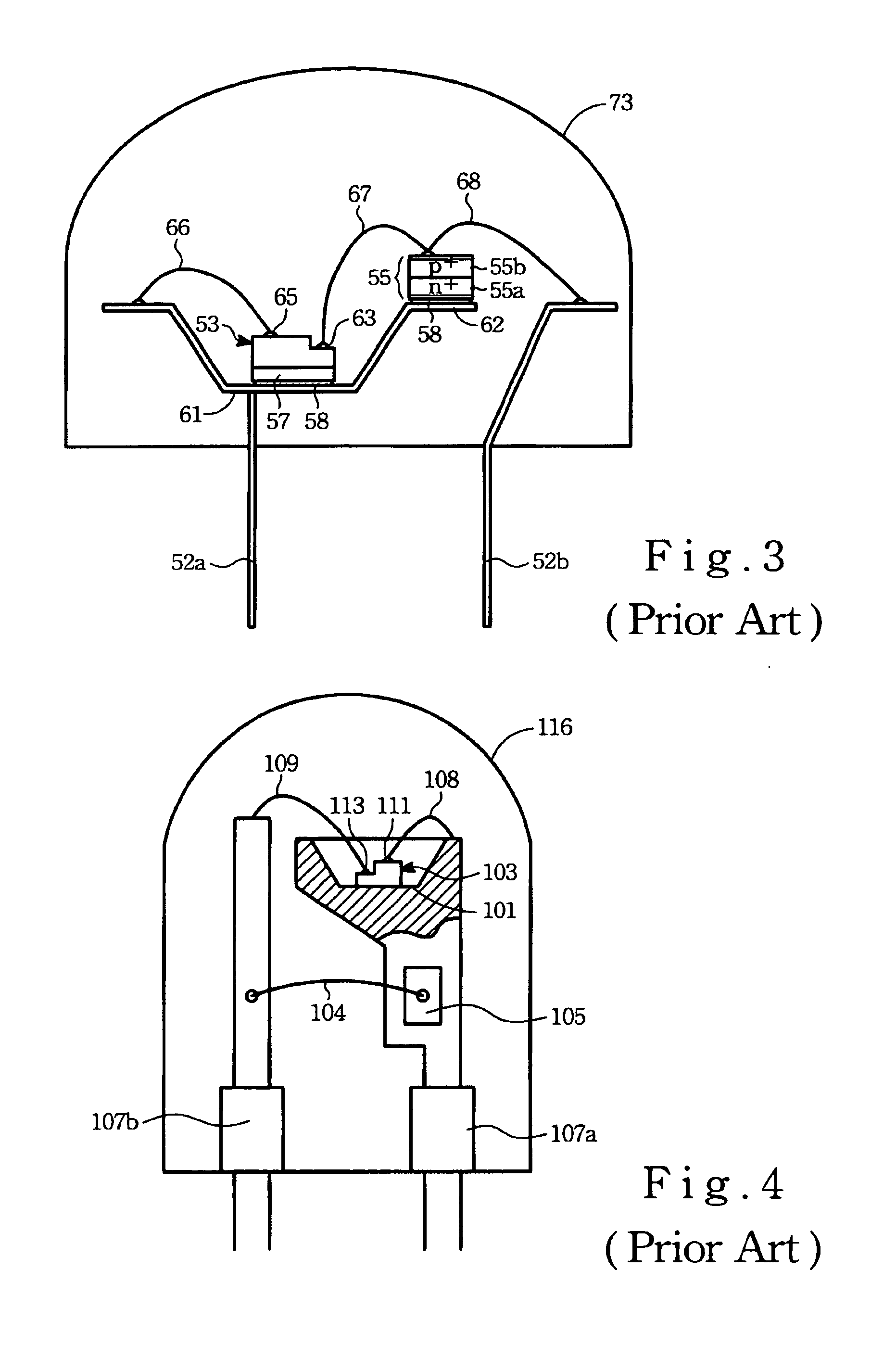

Light-emitting diode device and method of manufacturing the same

InactiveUS6255129B1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringHigh resistivity

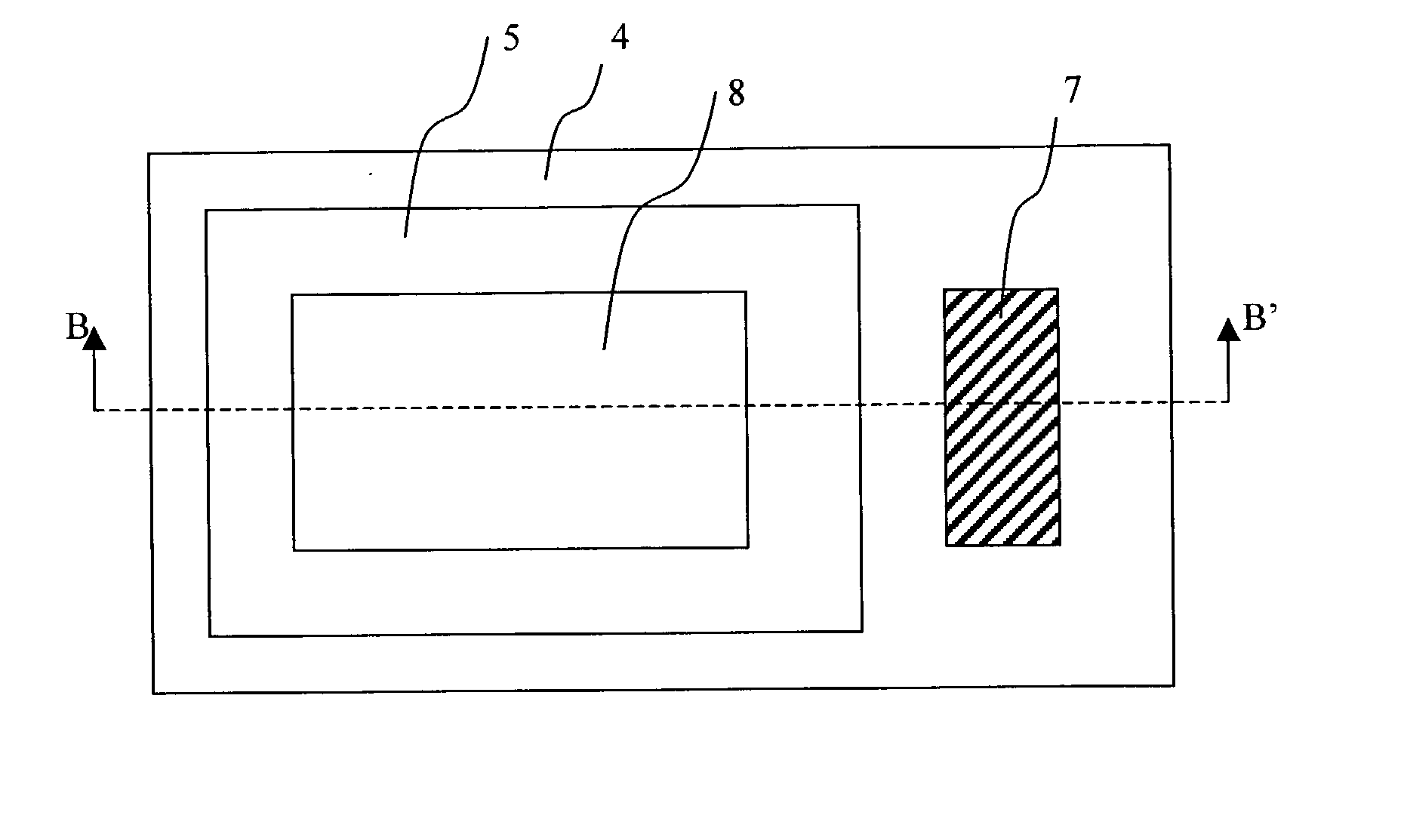

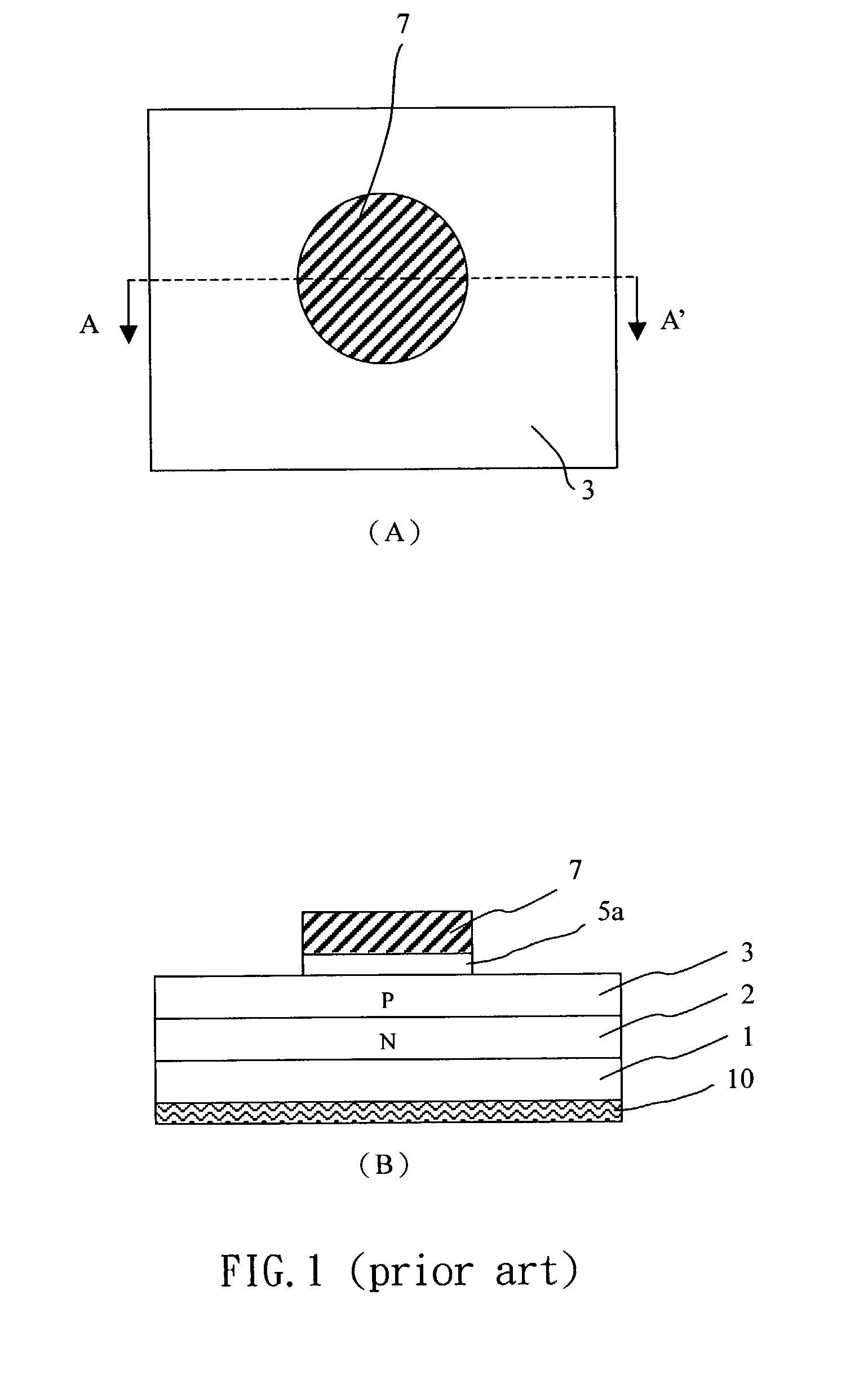

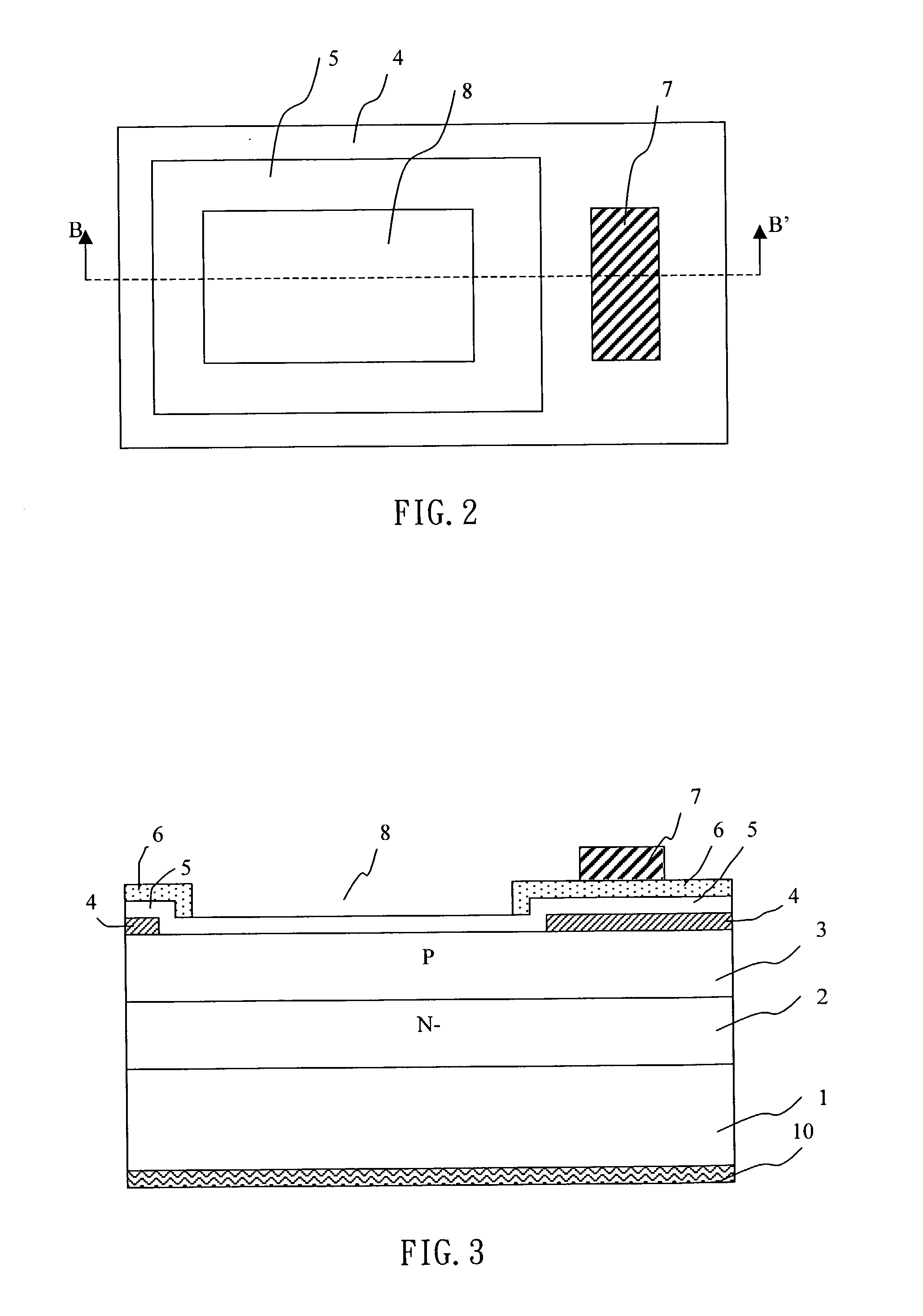

A light-emitting diode device, such as a blue, green, blue-green light-emitting diode, with a one-wire-bonding characteristic and the method of manufacturing the same have been disclosed. The light-emitting diode device has a GaN-based semiconductor laminated structure formed on an insulating substrate. The GaN-based semiconductor laminated structure includes an n-type layer on its bottom side, a p-type layer on its top side, and an active layer, for generating light, sandwiched between the n-type and p-type layers. An annular isolation portion such as a trench or a high resistivity portion formed by ion implantation is formed in the GaN-based semiconductor laminated structure to separate the p-type layer into a central p-type layer and a peripheral p-type layer and to separate the active layer into a central active layer and a peripheral active layer. A p-type electrode is formed on the central p-type layer without electrically connecting to the peripheral p-type layer. A conductive layer is coated to cover the sidewalls and the bottom surface of the insulating substrate and to ohmically contact with the n-type layer. Preferably, an adhesion layer is sandwiched between the sidewalls and the bottom surface of the insulating substrate and the conductive layer to enhance the adhesive property. According to the present invention, the conductive layer may be formed as a mirror-like reflector or a light-transmissive layer.

Owner:EPISTAR CORP

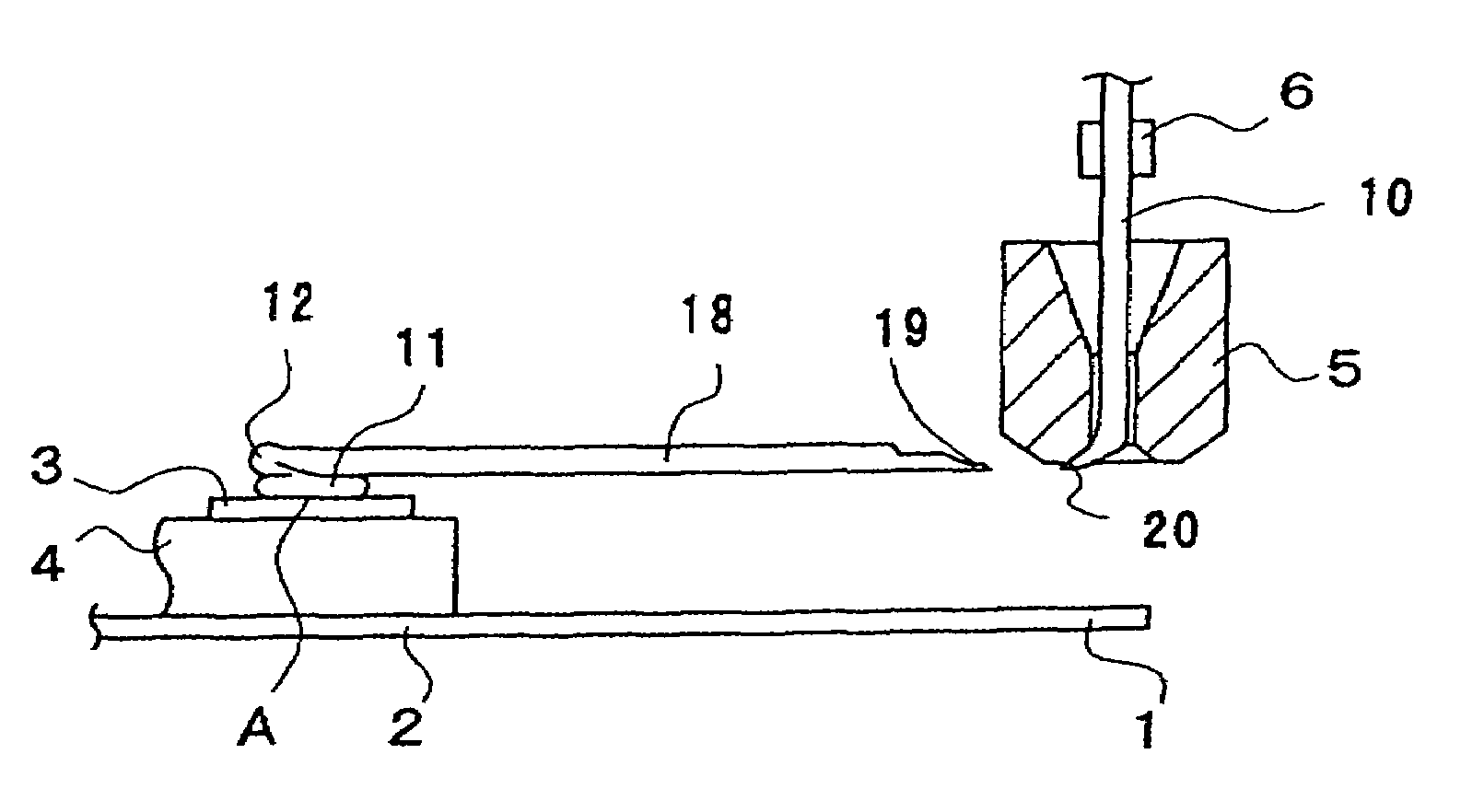

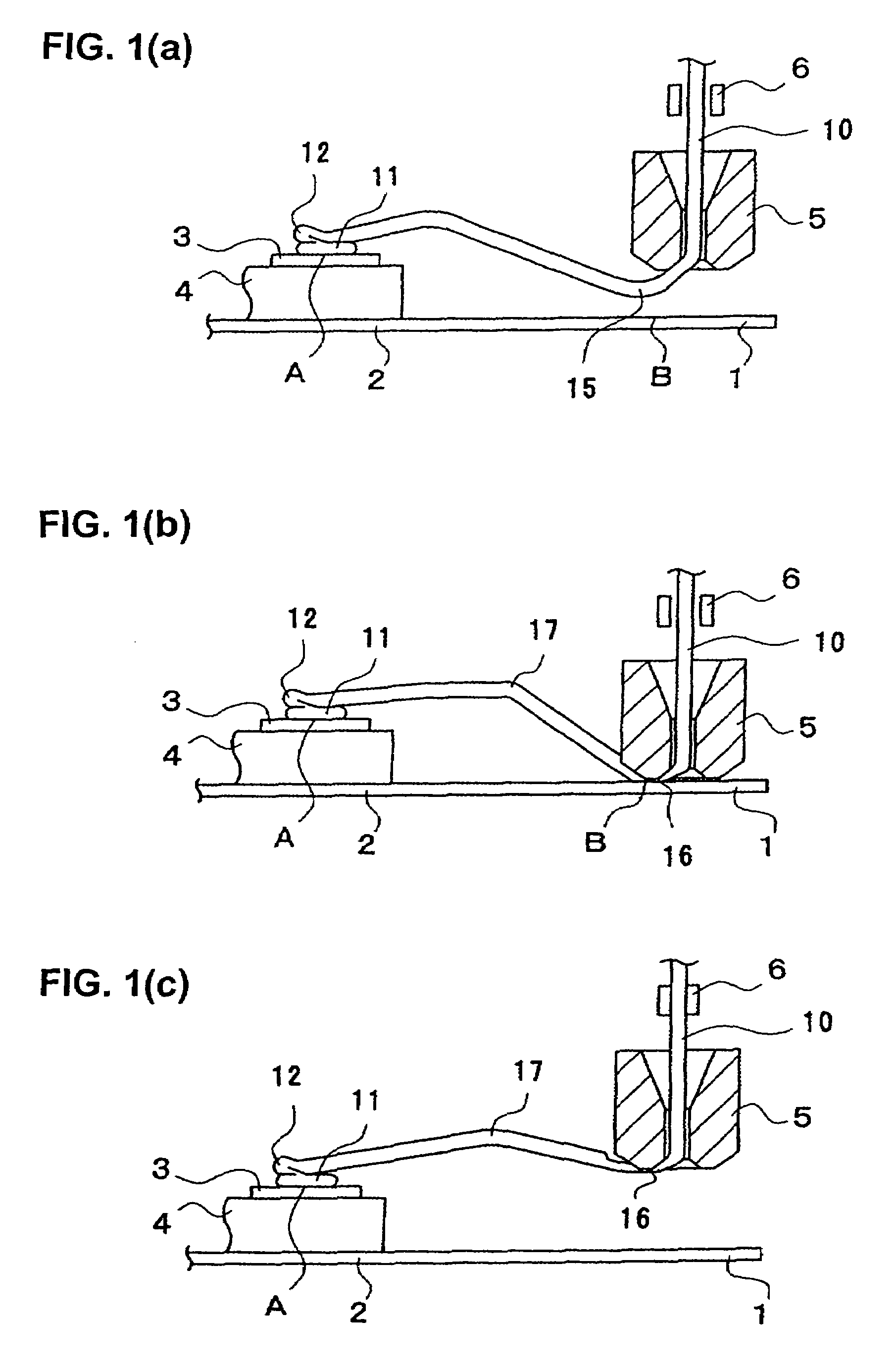

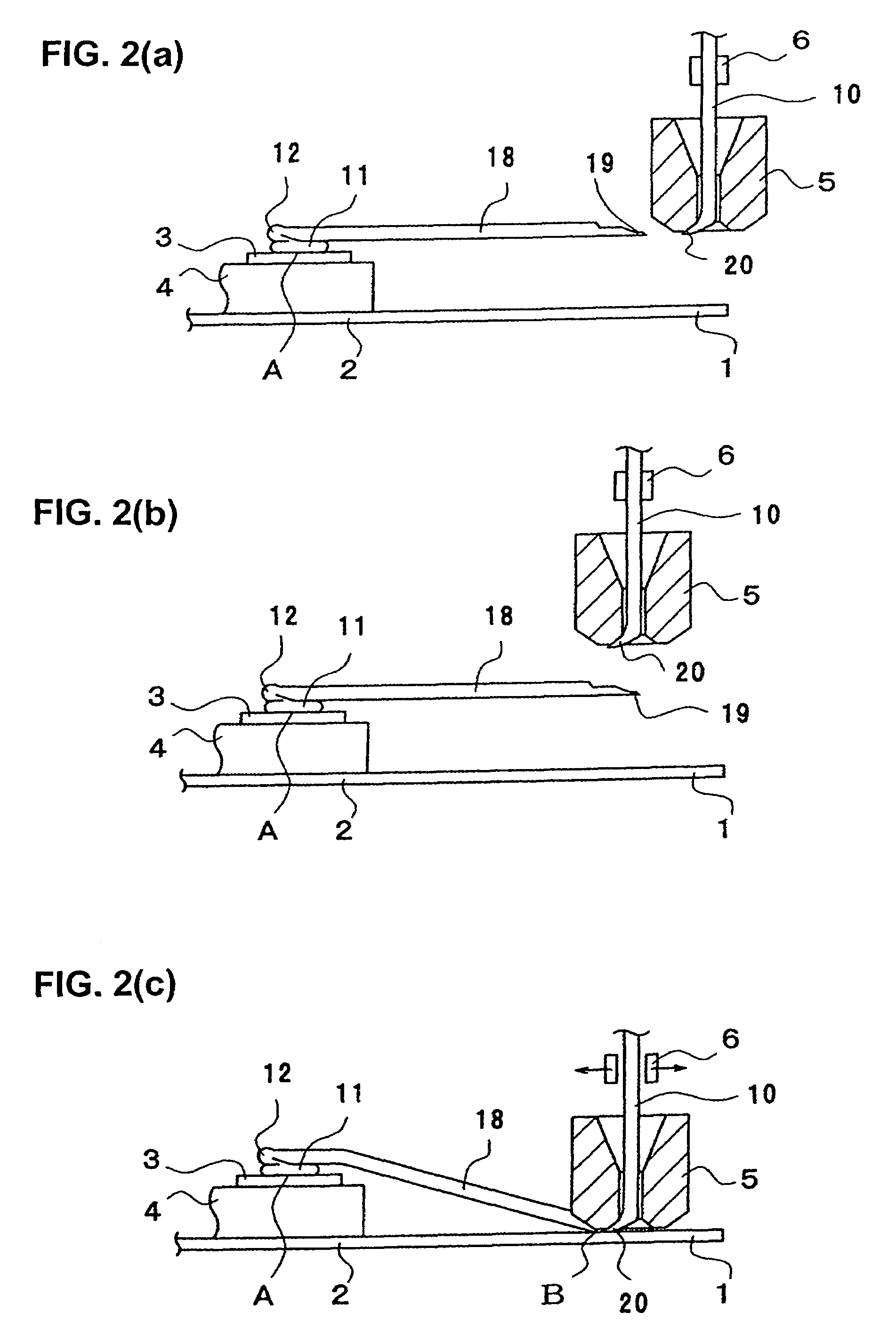

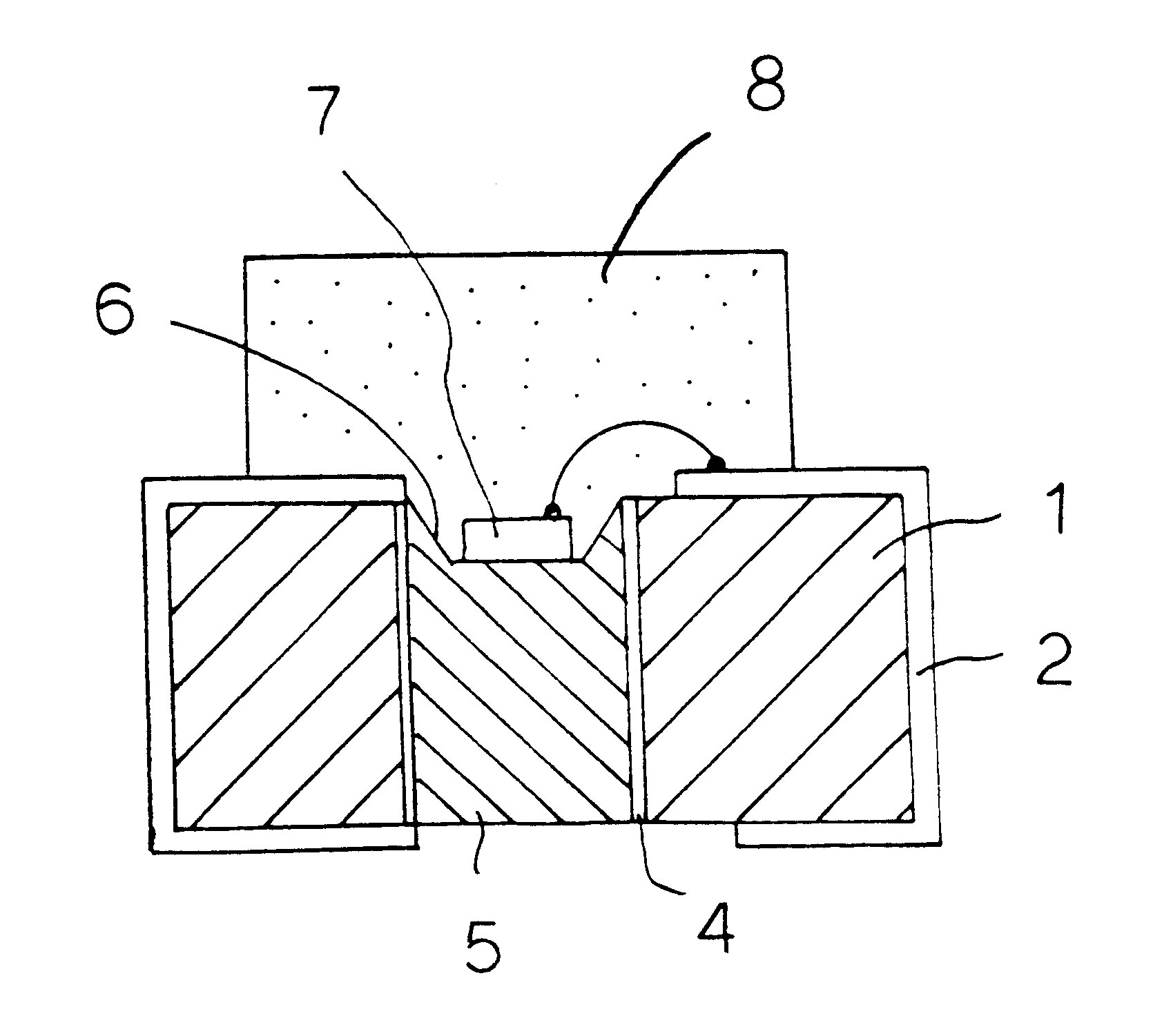

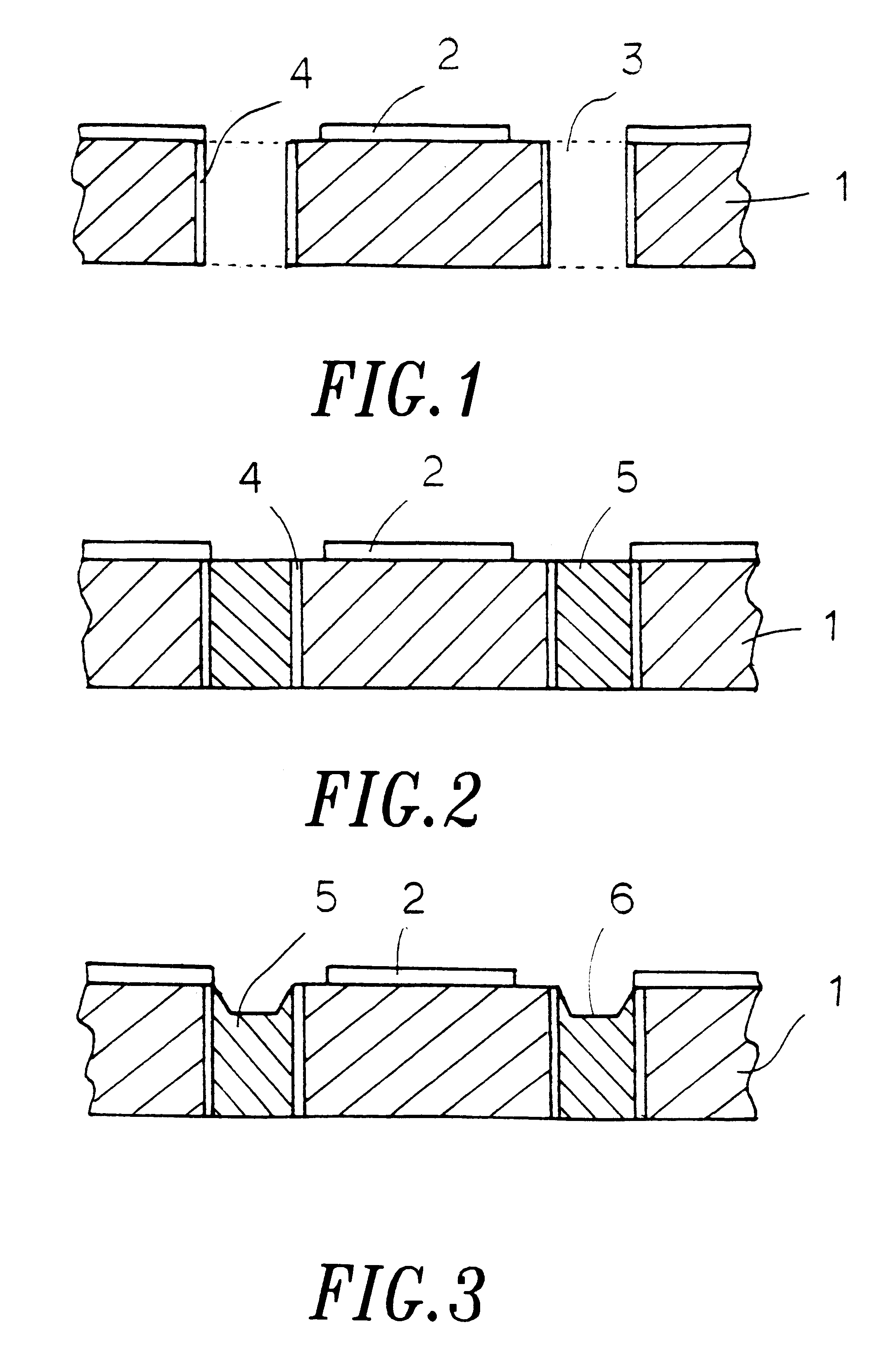

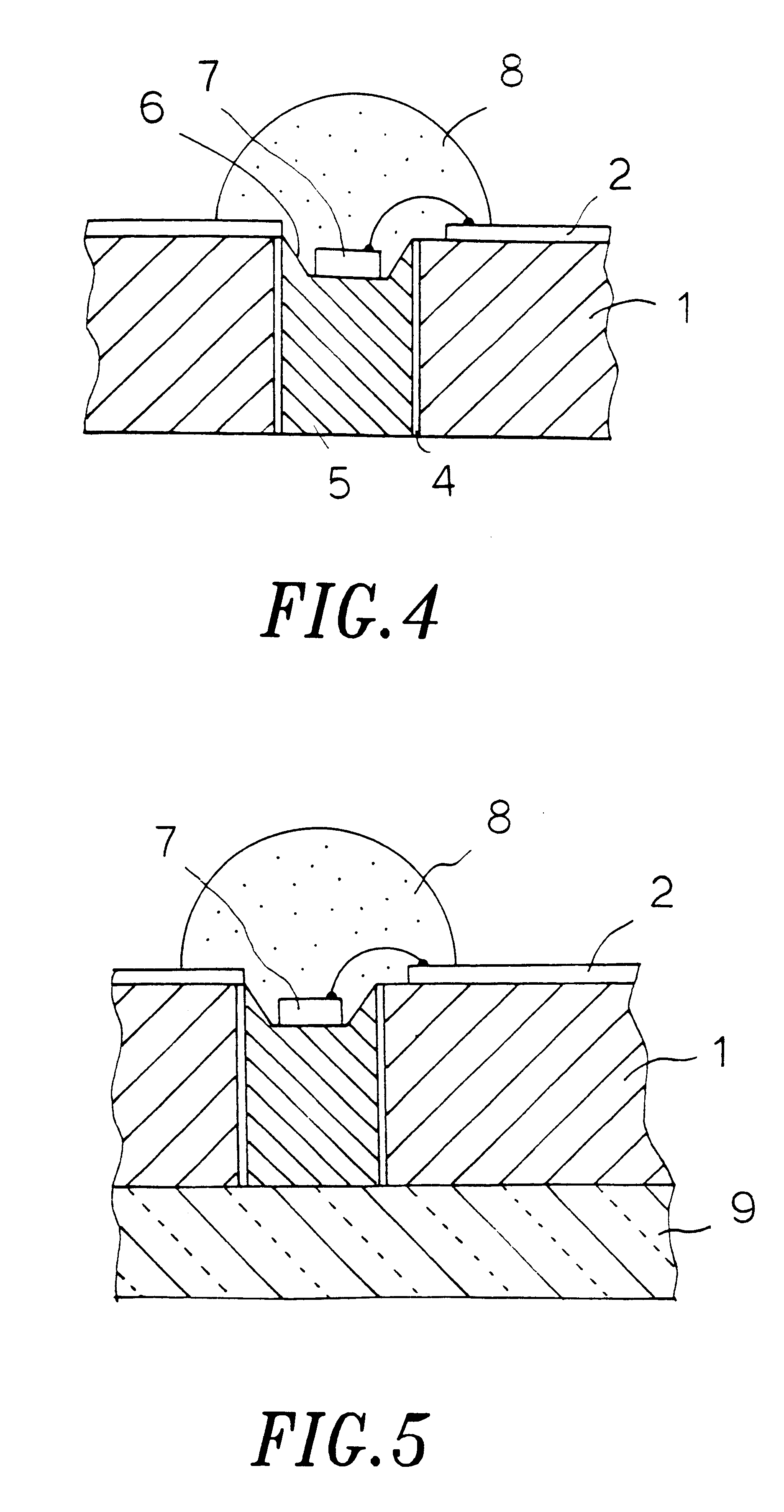

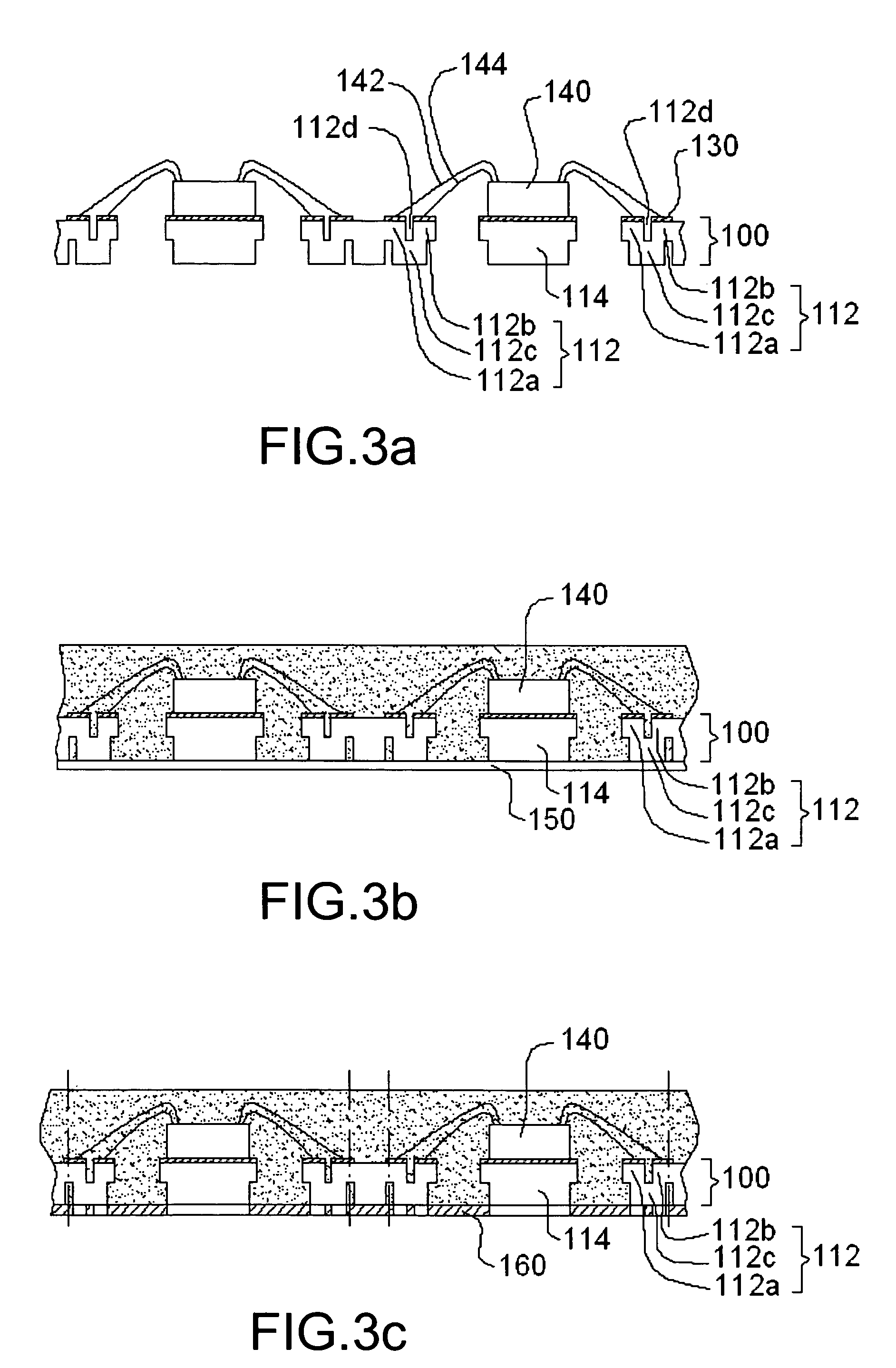

Wire bonding method

InactiveUS7621436B2Inhibit swellingImprove straightnessSolid-state devicesWelding/cutting auxillary devicesEngineeringWire bonding

A wire bonding method including the steps of: descending a capillary 5 from above an external lead 1 to press a wire 10 to such an extent that the wire is not completely connected to the external lead 1, thus forming a thin part 16 in the wire; next ascending the capillary 5 and the thin part 16 to substantially the same height as a first bonding point A, then moving the capillary 5 in a direction away from the first bonding point A, thus making a linear wire portion 18 and then cutting the wire at the thin part 16; then connecting the end 19 (thin part) of the linear wire portion 18 and the wire tip end 20 at the lower end of the capillary 5 are connected to the external lead 1; and then separating the wire tip end 20 from the external lead 1.

Owner:SHINKAWA CO LTD

An Intelligent Integrated Sensor Of Tire Pressure Monitoring System (TPMS)

InactiveUS20060185429A1Precise size controlAccurate identificationSolid-state devicesTyre measurementsAccelerometerEngineering

A single integrated sensing chip with multi-functions for tire pressure monitor system (TPMS) comprises: a pressure sensor, an accelerometer, a temperature sensor, and an ASIC (Applied Specific Integrated Circuit) that implements signal conditioning and digitalizes pressure output. The accelerometer incorporated for vehicle motion is used to determine centrifugal acceleration or three-axial acceleration of the rotating wheel, and used for the TPMS sensor wake-up from “power down” mode, or when the velocity of the vehicle is higher than certain speed threshold, which is more robust and lower in cost than the mechanical vibration switch and is naturally integrated with the electronic control unit. The accelerometer can be used for regular motion sensing to monitor the dynamic stability. The integrated sensor system can be packaged into one plastic package first, and then surface mounted to the printed circuit board, or the multi-function single chip can be wafer bonded on the wafer level first and diced into many individual chips, with each chip being directly attached on to the printed circuit board by wire bonding or flip-chip assembly.

Owner:WUHAN FINEMEMS

Thin leadless plastic chip carrier

ActiveUS7009286B1Thin package profileReduce electrical impedanceSemiconductor/solid-state device detailsSolid-state devicesContact padEngineering

A leadless plastic chip carrier is fabricated by selectively etching a leadframe strip to reduce a thickness of the strip at a portion thereof. Selectively masking the surface of the leadframe strip using a mask, follows selectively etching, to provide exposed areas of the surface at the portion and contact pad areas on leadframe the strip. At least one layer of metal is deposited on the exposed areas to define a die attach pad on the portion of the leadframe strip with reduced thickness and to define contact pads on the surface of the strip. At least one semiconductor die is mounted to the die attach pad, followed by wire bonding the at least one semiconductor die to ones of the contact pads. The at least one semiconductor die, the wire bonds, and the contact pads are covered with an overmold material and the leadframe strip is etched to thereby remove the leadframe strip. The leadless plastic chip carrier is singulated from the leadframe strip.

Owner:UTAC HEADQUARTERS PTE LTD

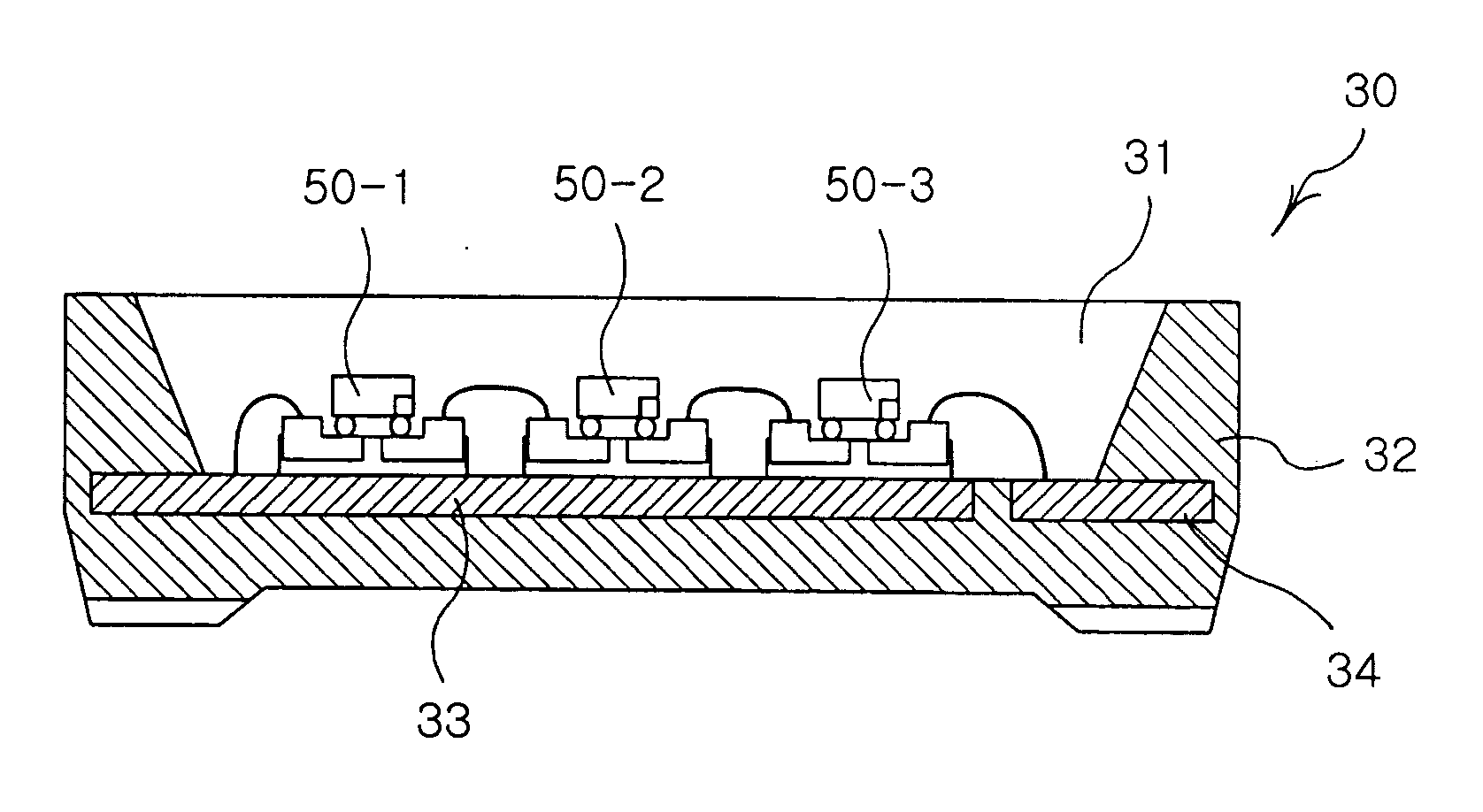

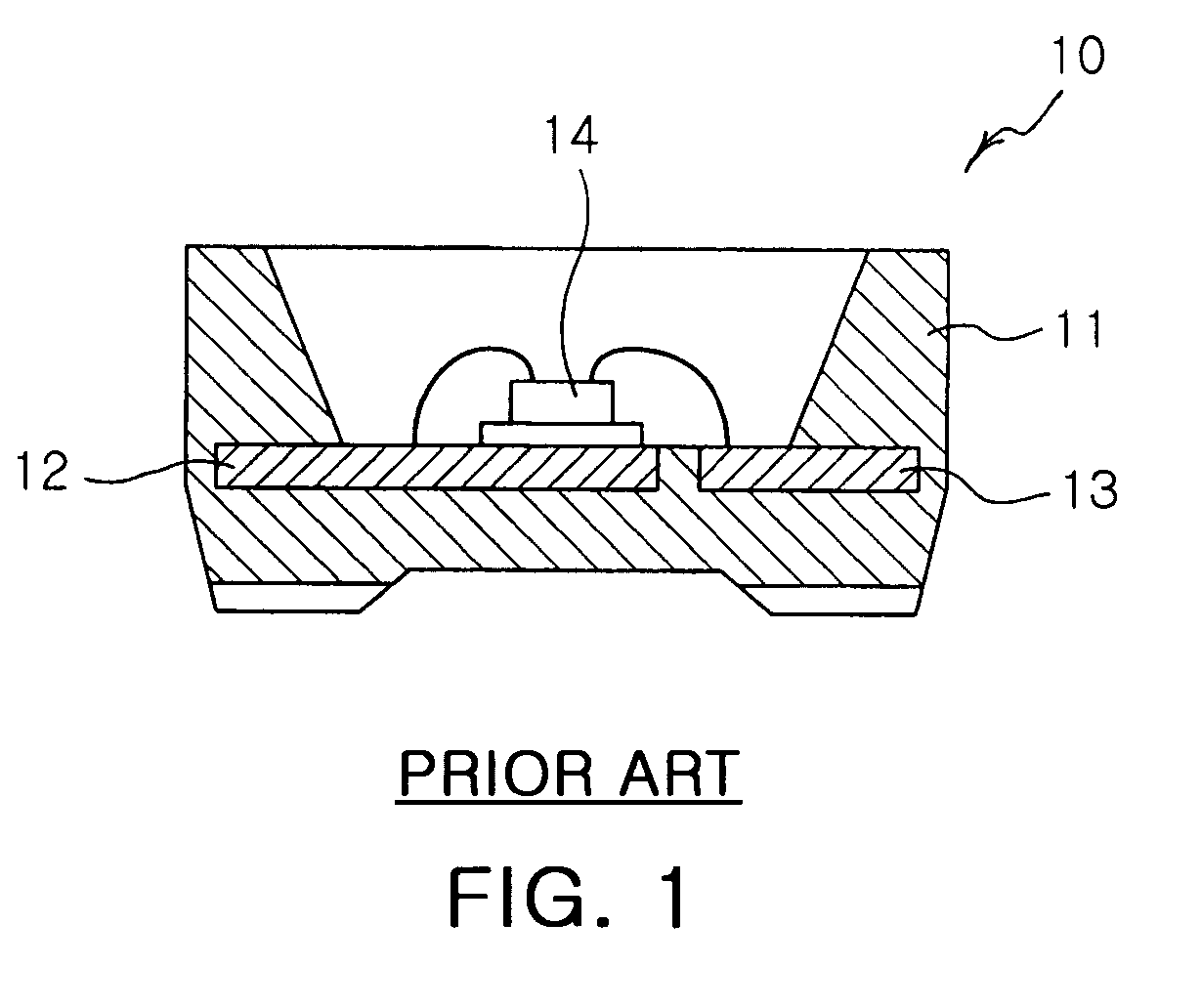

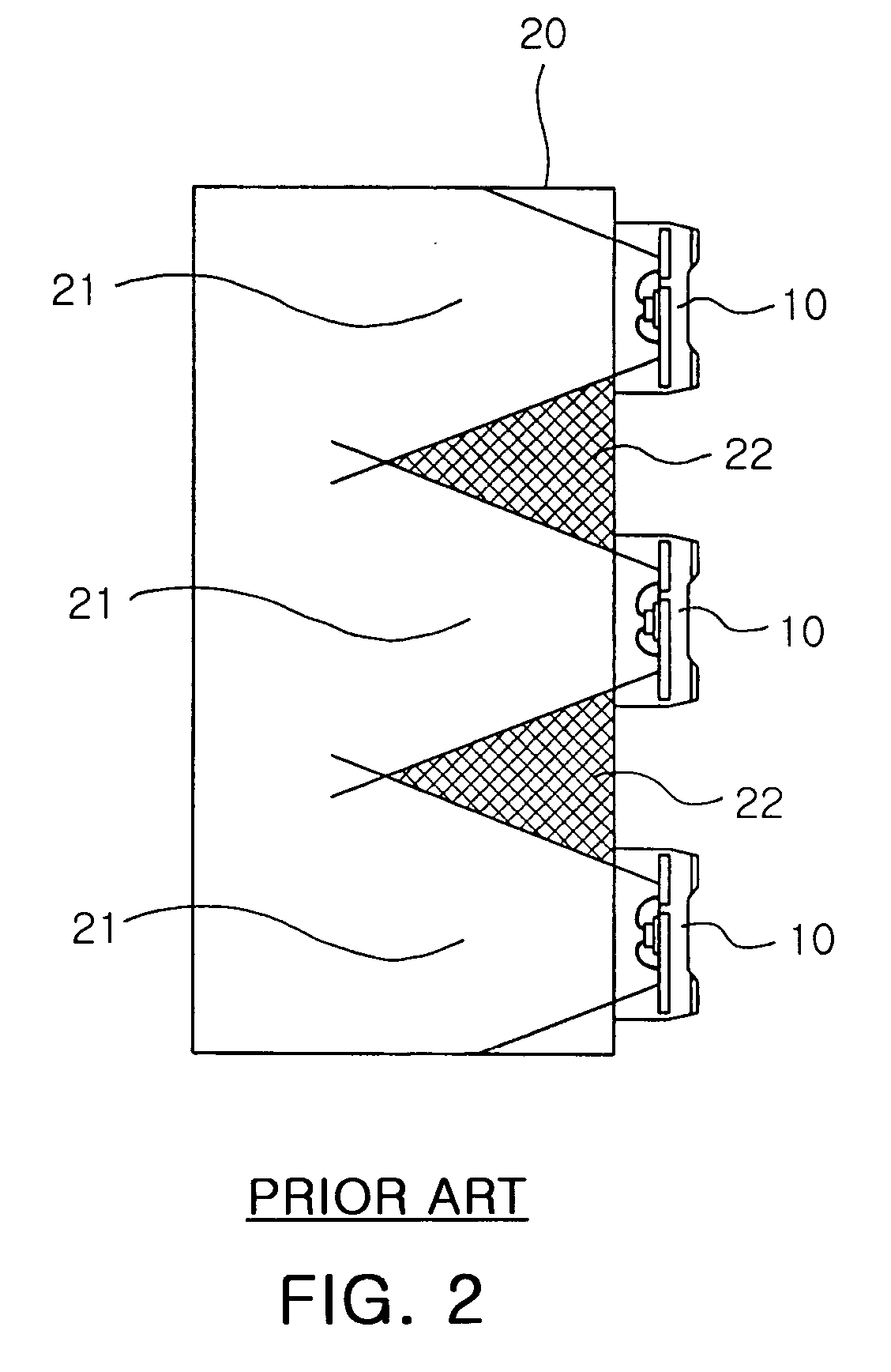

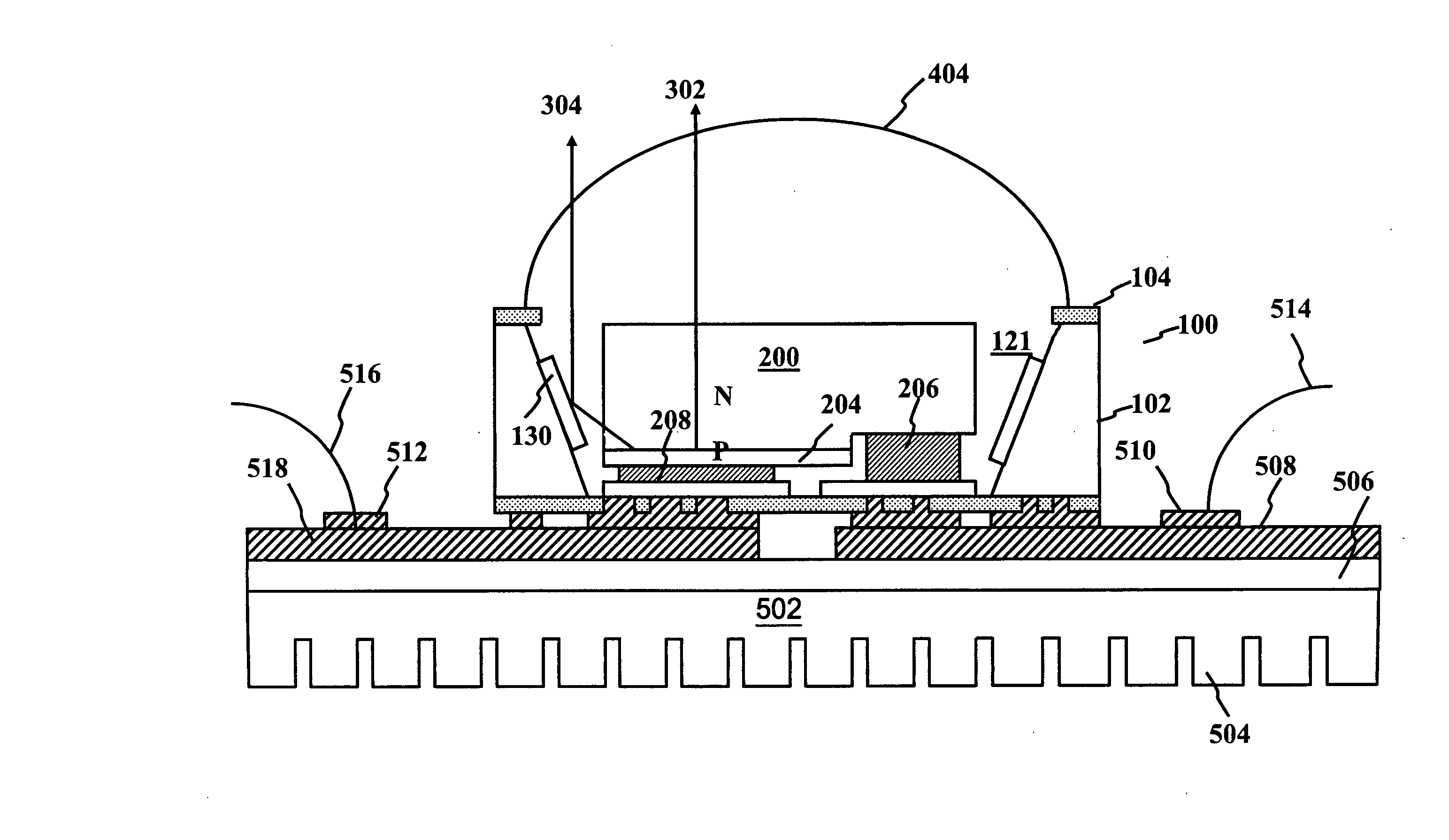

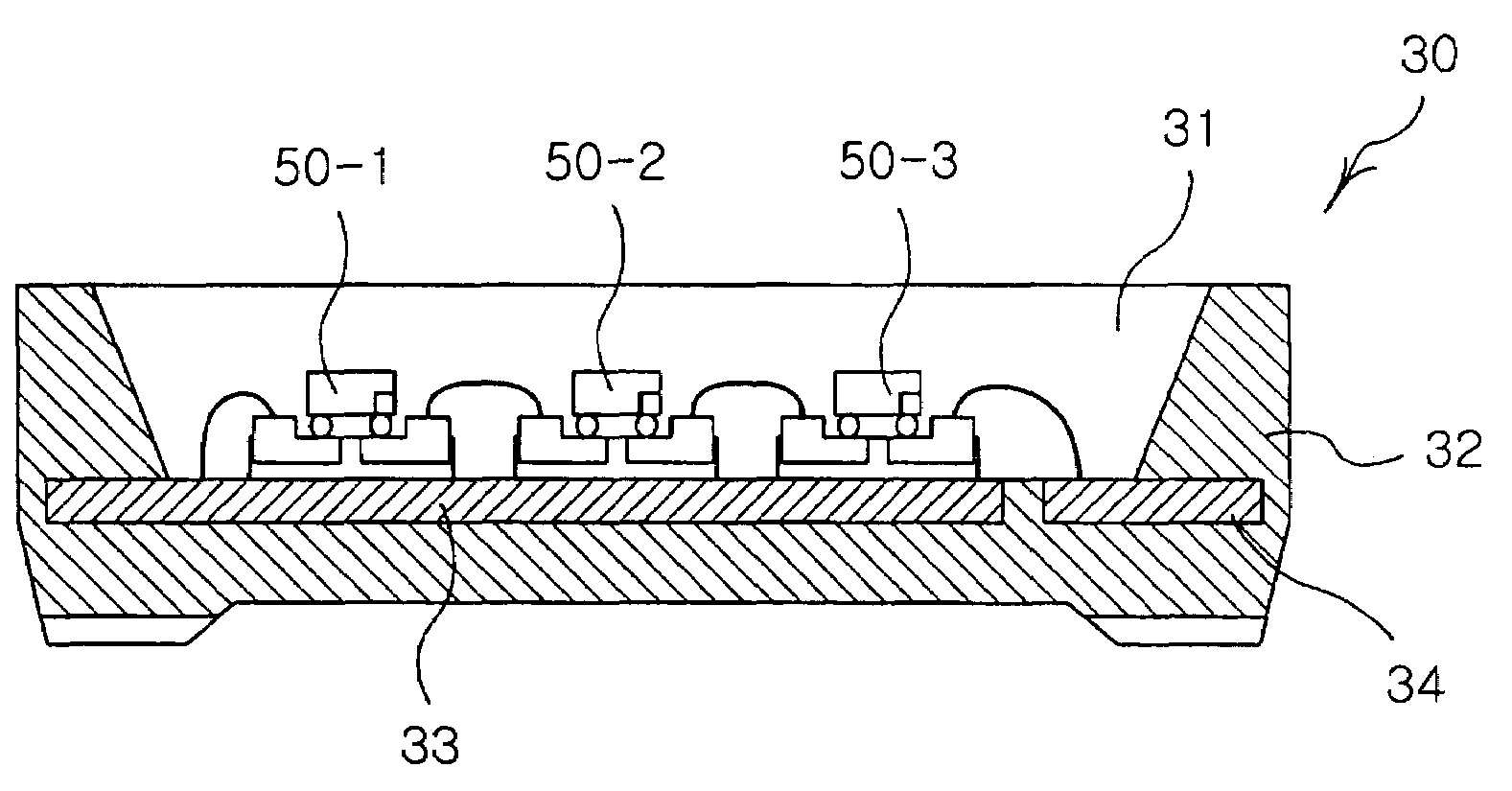

LED package for backlight unit

ActiveUS20060023451A1Avoid deformationImprove image qualityLighting support devicesGlass furnace apparatusEngineeringDie bonding

Disclosed herein is an LED package for a backlight unit. The LED package includes a plurality of LEDs, a die bonding part, a wire bonding part and a body. The die bonding part, on which the plurality of LEDs is arranged, allows the first electrodes of the LEDs to be electrically connected to an external circuit. The wire bonding part is spaced apart from the die bonding part by a predetermined distance to be insulated from the die bonding part and allows the second electrodes of the LEDs to be electrically connected to the external circuit so that the LEDs are operated. The body has a molding cup which is used to fill a space above the LEDs with transparent resin and a base on which the die bonding part and the wire bonding part are arranged.

Owner:SAMSUNG ELECTRONICS CO LTD

Layered semiconductor devices with conductive vias

InactiveUS6946739B2Promote differentiationReduce needSemiconductor/solid-state device detailsSolid-state devicesDevice materialInductance

A method of fabricating an integrated circuit on a silicon carbide substrate is disclosed that eliminates wire bonding that can otherwise cause undesired inductance. The method includes fabricating a semiconductor device on a first surface of a silicon carbide substrate and with at least one metal contact for the device on the first surface of the substrate. The opposite, second surface of the substrate is then ground and polished until it is substantially transparent. The method then includes masking the polished second surface of the silicon carbide substrate to define a predetermined location for a via that is opposite the device metal contact on the first surface; etching the desired via through the desired masked location until the etch reaches the metal contact on the first surface; and metallizing the via to provide an electrical contact from the second surface of the substrate to the metal contact and to the device on the first surface of the substrate.

Owner:WOLFSPEED INC

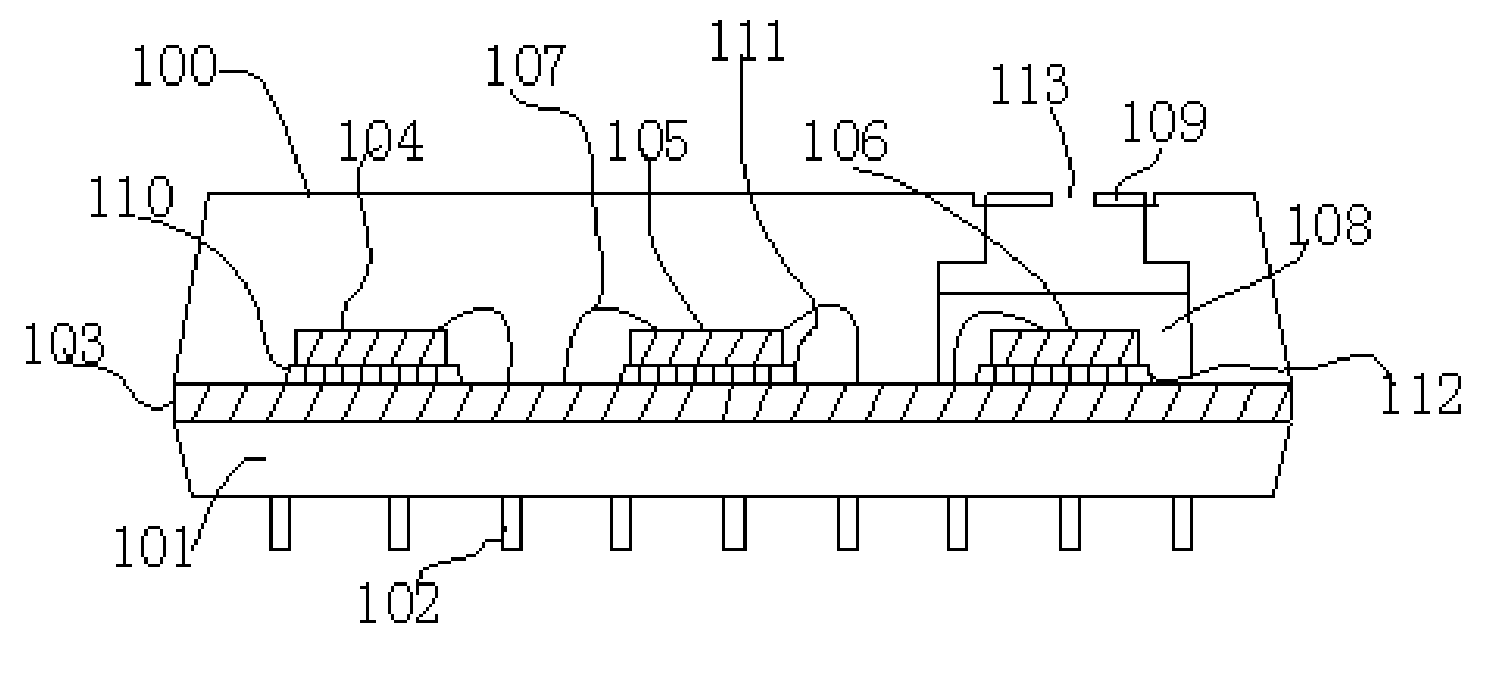

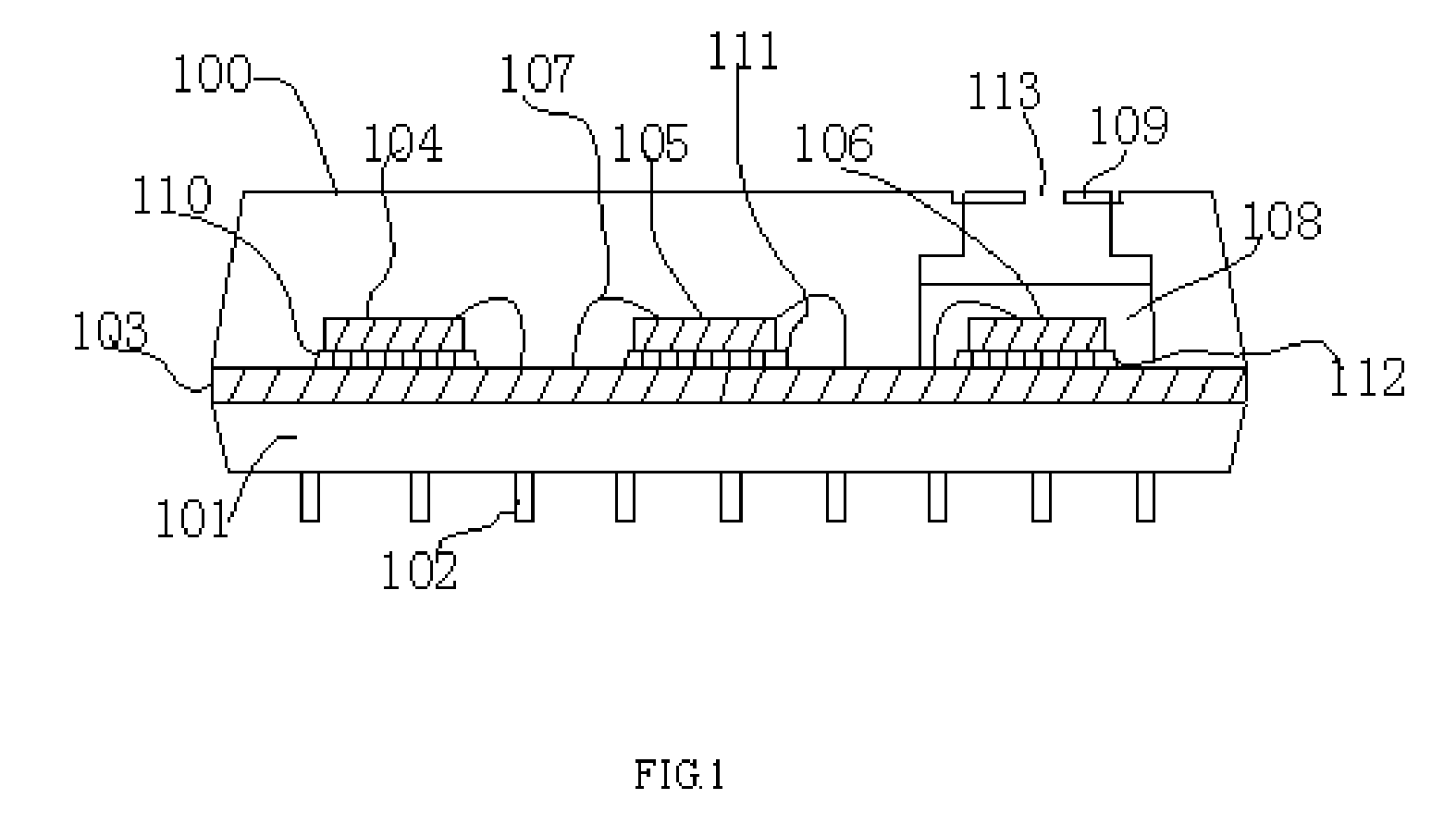

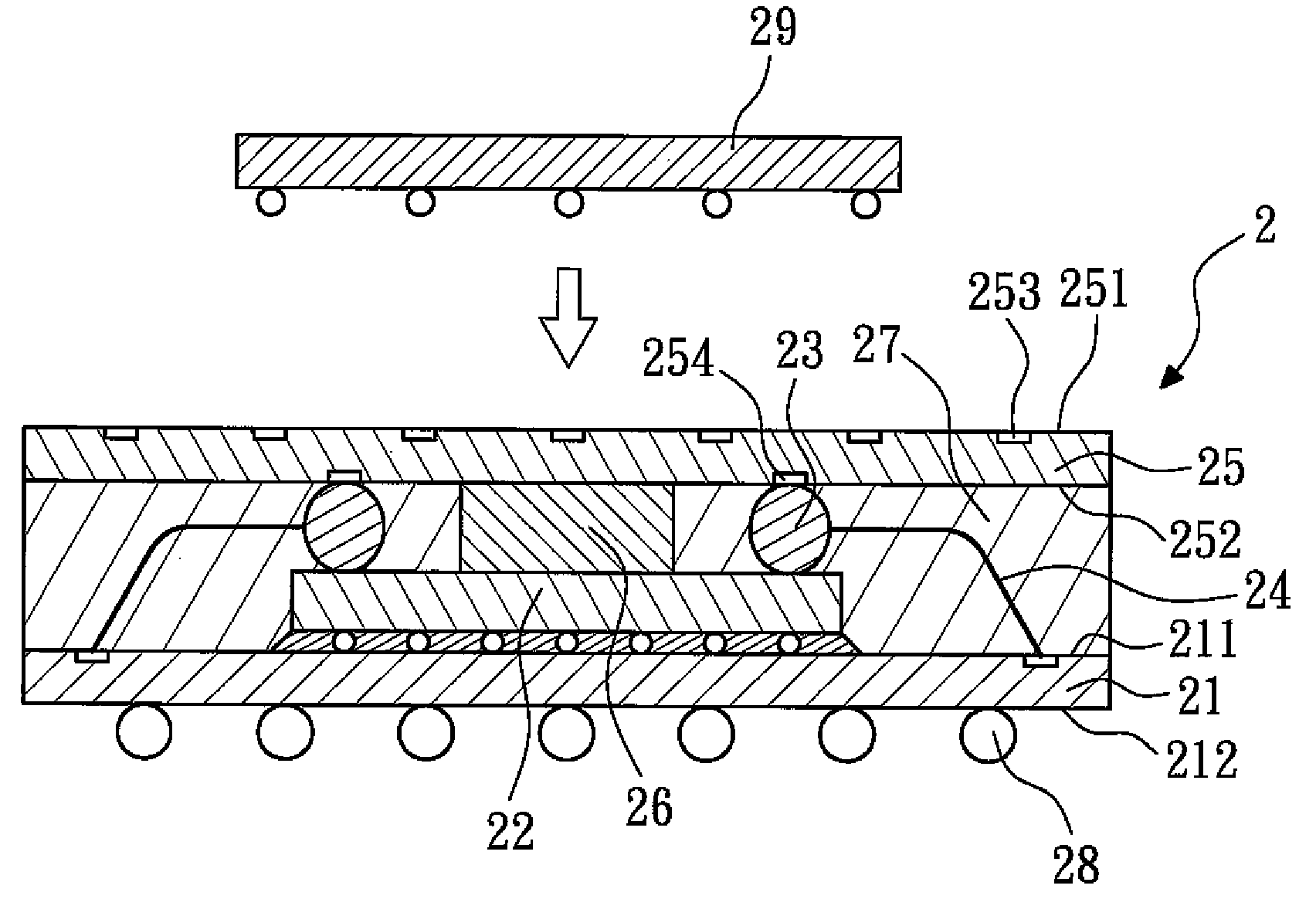

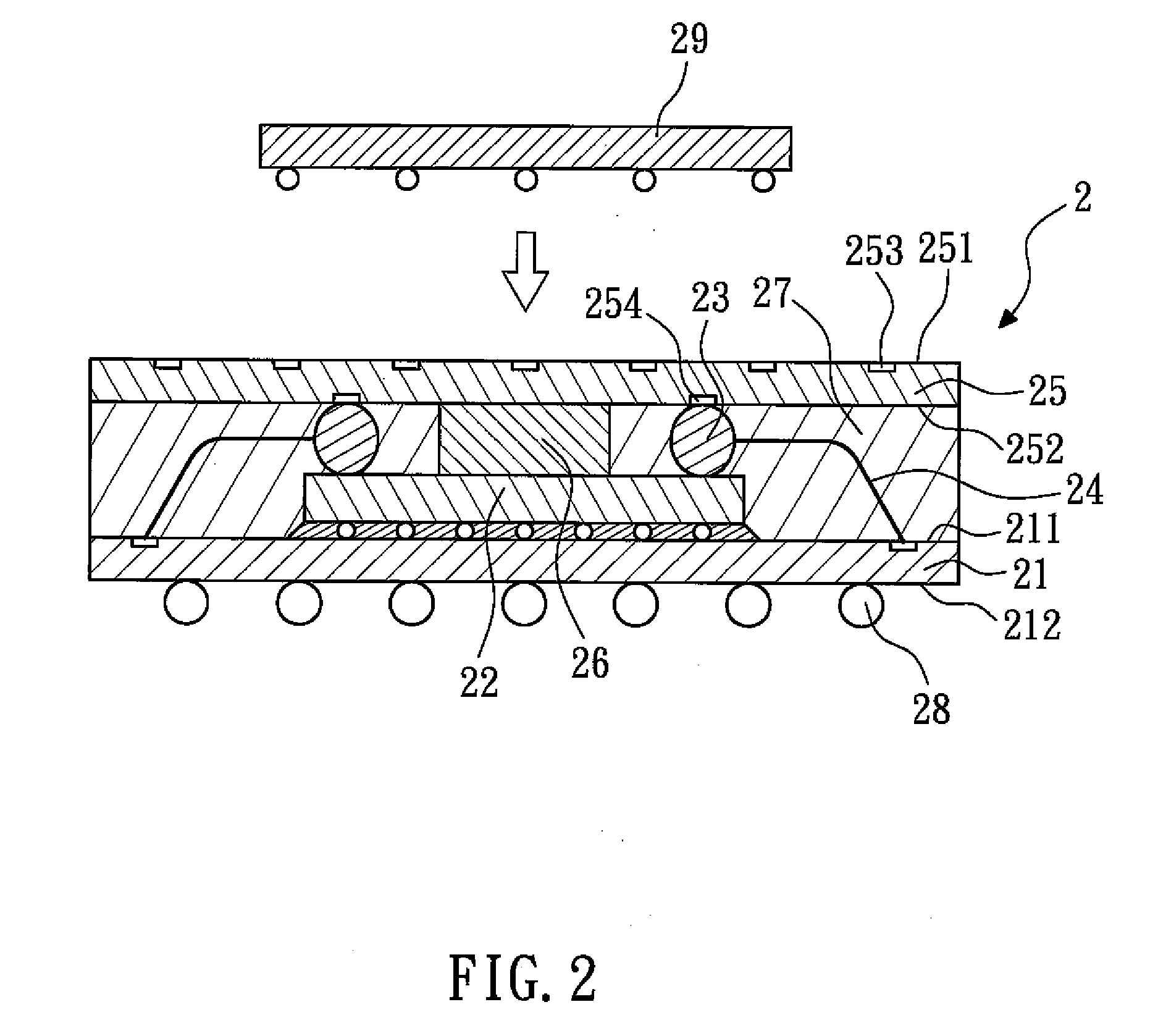

Stackable semiconductor package and the method for making the same

InactiveUS20080164595A1Avoid bondingSemiconductor/solid-state device detailsSolid-state devicesLead bondingSemiconductor package

The present invention relates to a stackable semiconductor package and the method for making the same. The stackable semiconductor package comprises a first substrate, a semiconductor device, a plurality of stud bumps, a plurality of first wires, a second substrate, and a molding compound. The semiconductor device is disposed on the first substrate and electrically connected to the first substrate. The stud bumps are above the semiconductor device. The first wires are used for electrically connecting the stud bumps and the first substrate. The stud bumps are in contact with the second substrate. The molding compound encapsulates the first substrate, the semiconductor device, the stud bumps, the first wires, and the second substrate, and thus, the second substrate will not undergo wire bonding, and will not be suspended and shake or sway, as present in a conventional stackable semiconductor package.

Owner:ADVANCED SEMICON ENG INC

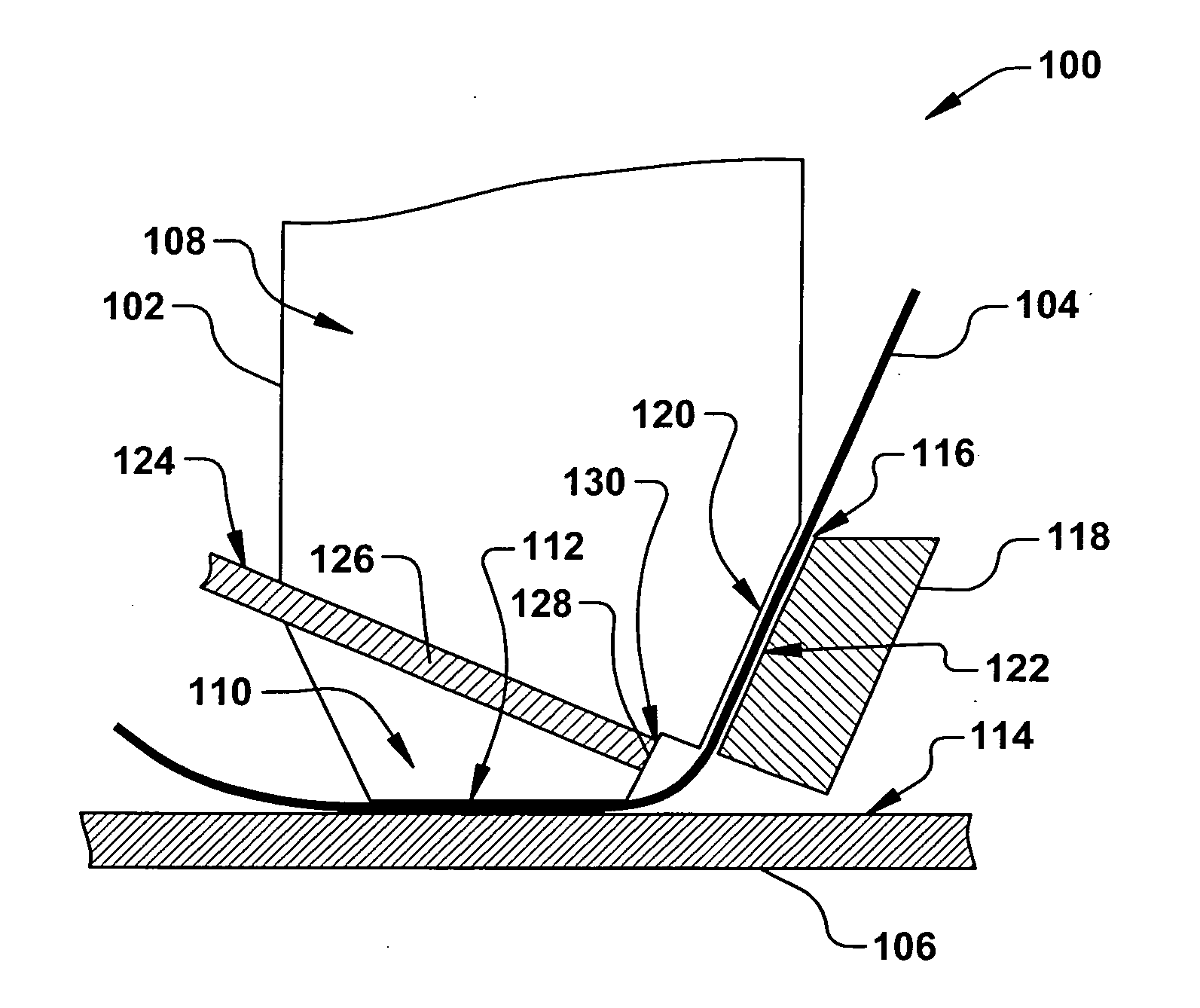

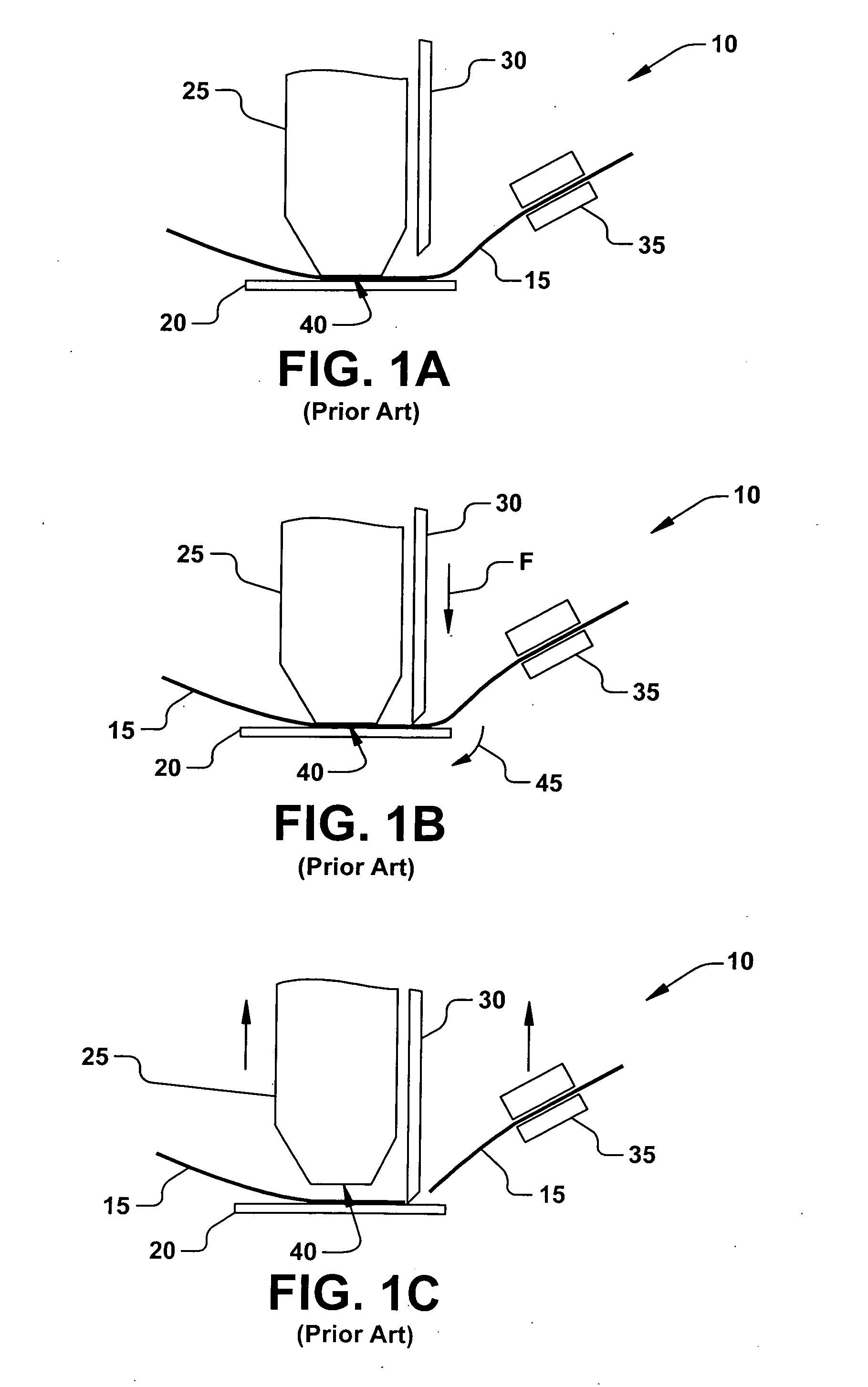

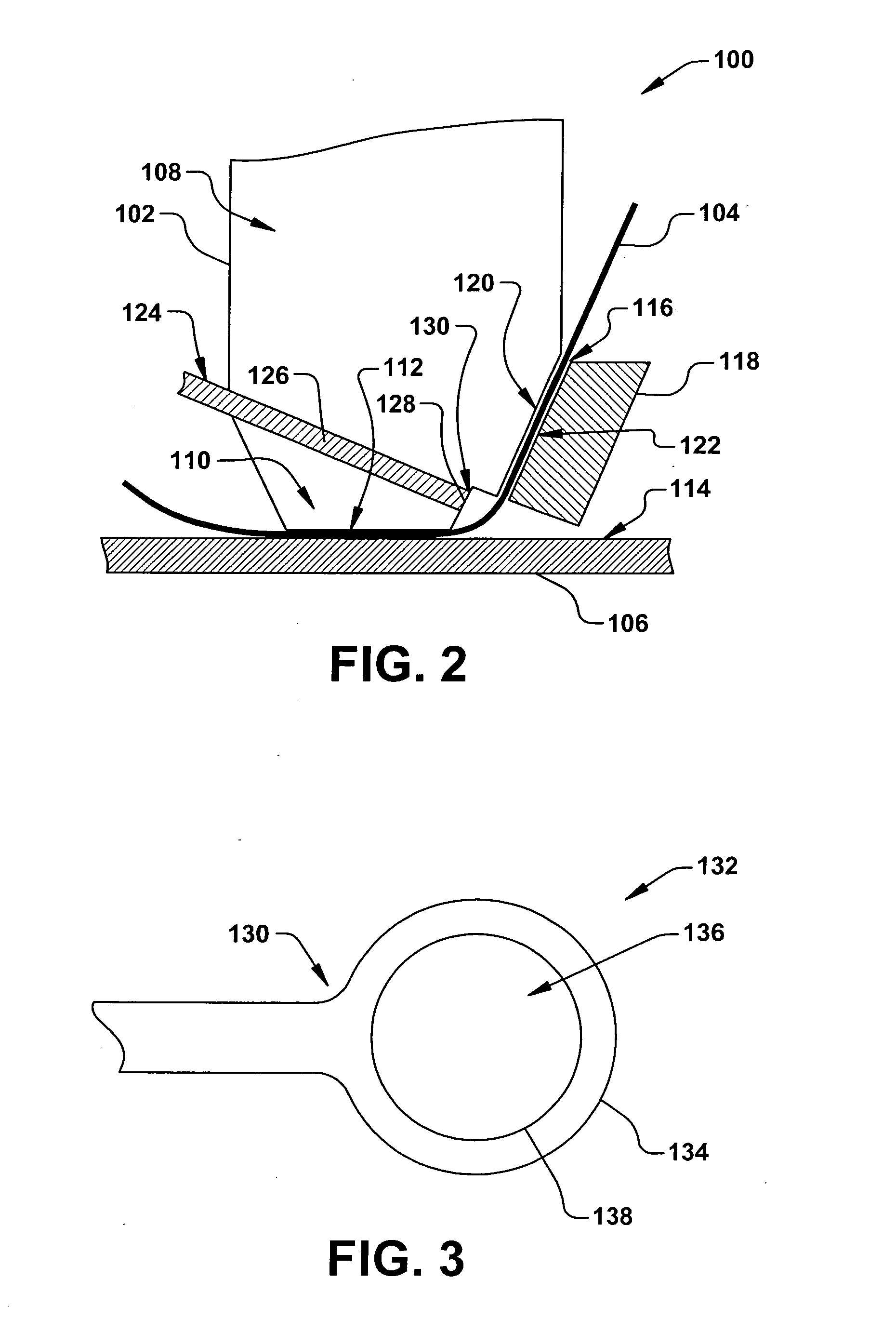

Bond capillary design for ribbon wire bonding

ActiveUS20060278682A1Overcome limitationsSolid-state devicesWelding/cutting auxillary devicesEngineeringWire bonding

A device (100) and method (200) for bonding a ribbon wire (104) to a workpiece (106) comprising feeding the ribbon wire through a passageway (116) of an ultrasonic bond capillary (102) and clamping the ribbon wire against an engagement surface (120) of the bond capillary via a clamping jaw (118) operably coupled to the bond capillary. The ribbon wire (104) is bonded to the workpiece (106) along a bonding surface (112) of the bond capillary (102) and penetrated, at least partially, between the bonding surface and the engagement surface (120) of the bond capillary by a cutting tool (124). The cutting tool (124) may comprise an elongate member (126) positioned between the bonding surface (112) and engagement surface (120), and may have a cutting blade (128) positioned at a distal end (130) thereof. The cutting tool (124) may further comprise a ring cutter (132), wherein the ribbon wire passes through a ring (134) having a cutting surface (138) defined about an inner diameter thereof.

Owner:TEXAS INSTR INC

Packaging types of light-emitting diode

InactiveUS6562643B2Affect performanceIncrease temperaturePrinted electric component incorporationSolid-state devicesElectrical conductorEngineering

A LED packaging process is to place LED chips at predetermined positions on the printed circuit board substrate, followed by drilling holes to penetrate the substrate, followed by passing the printed circuit board through the solder furnace to completely fill the through-hole position with solder points, followed by using molds to make the soldering points into a groove reflector, followed by placing LED chips in the groove reflector, followed by wire bonding and using encapsulation resin for packaging to form SMD LED with reflectors. In the present invention, the filling with metal conductor in electrode through holes on the printed circuit board to form the groove reflector can enhance the heat dissipation of LED and the brightness of LED, which has the advantageous effects that traditional SMD LED can not have.

Owner:SOLIDLITE CORP

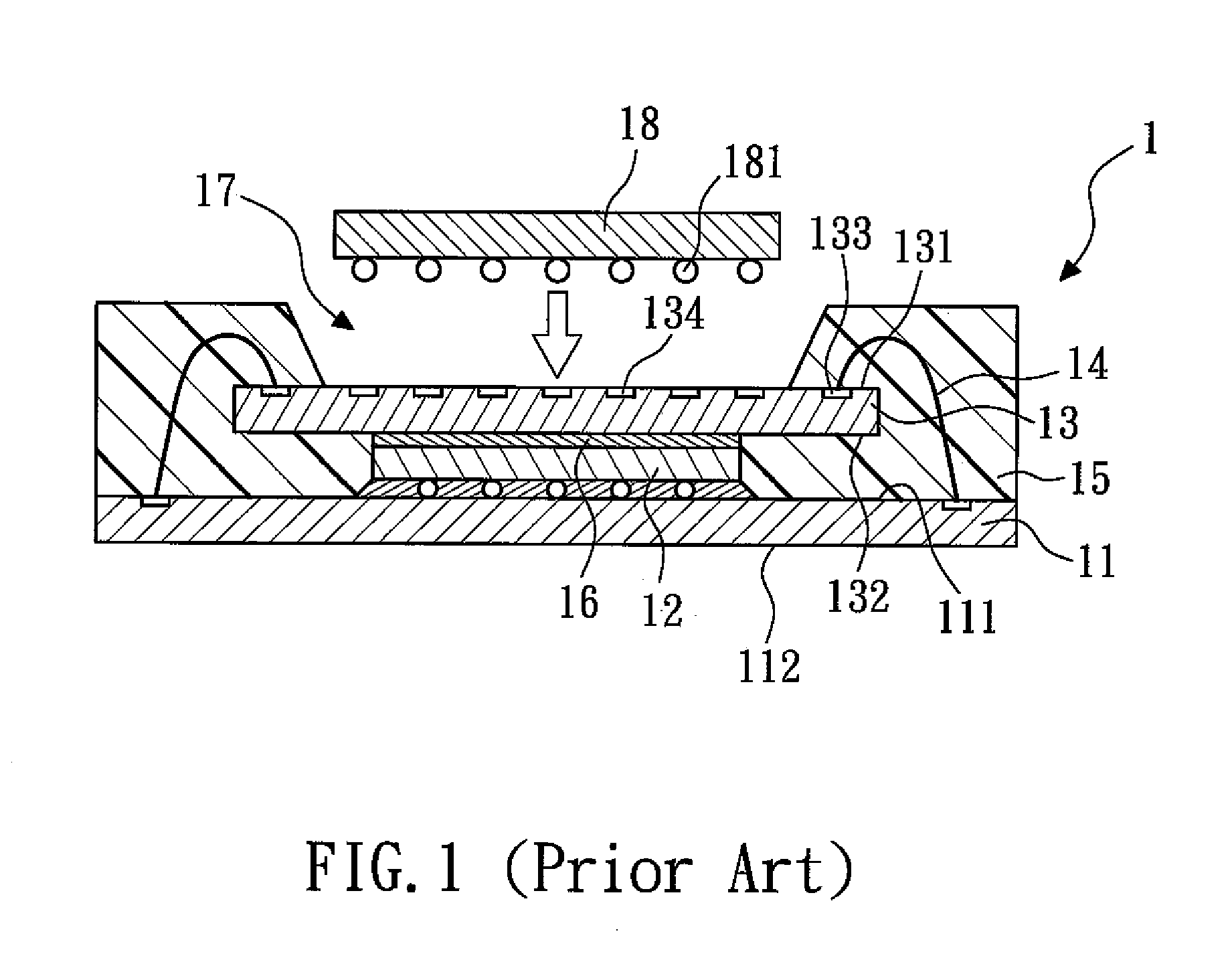

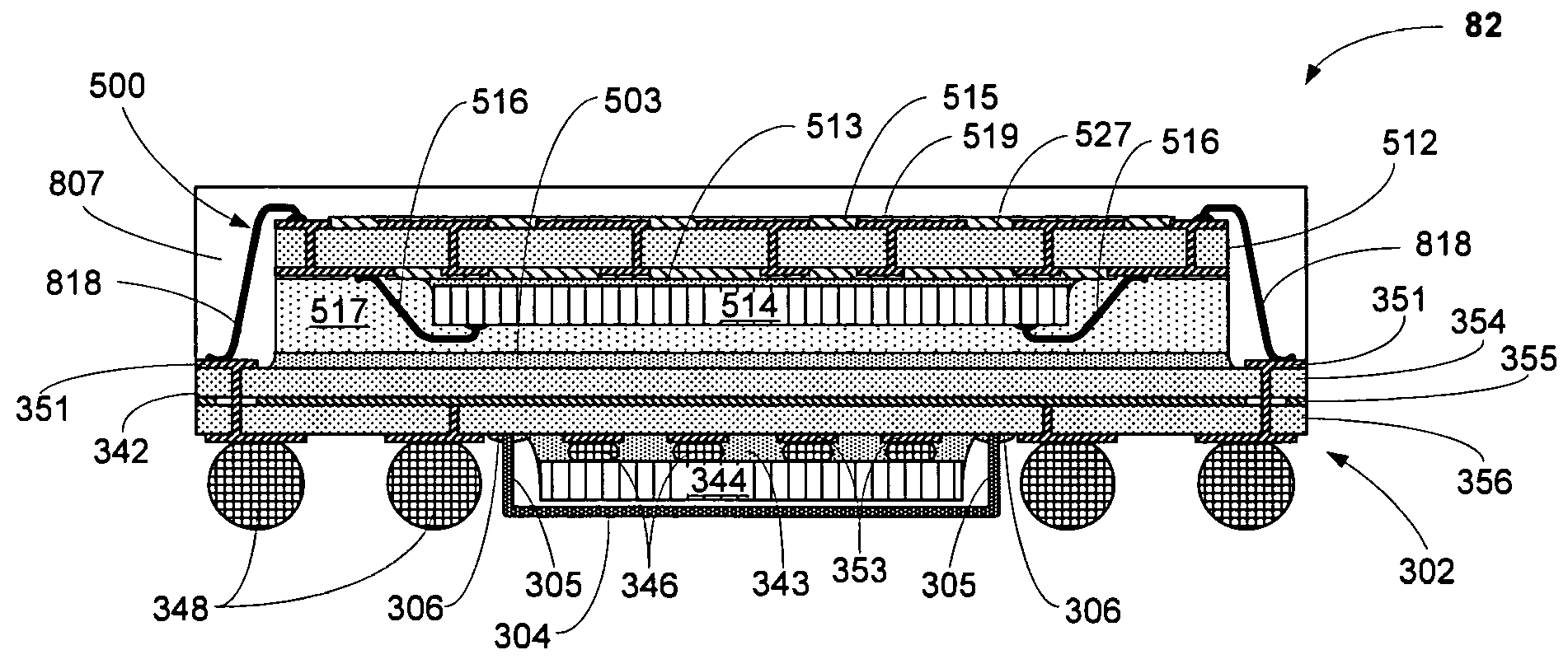

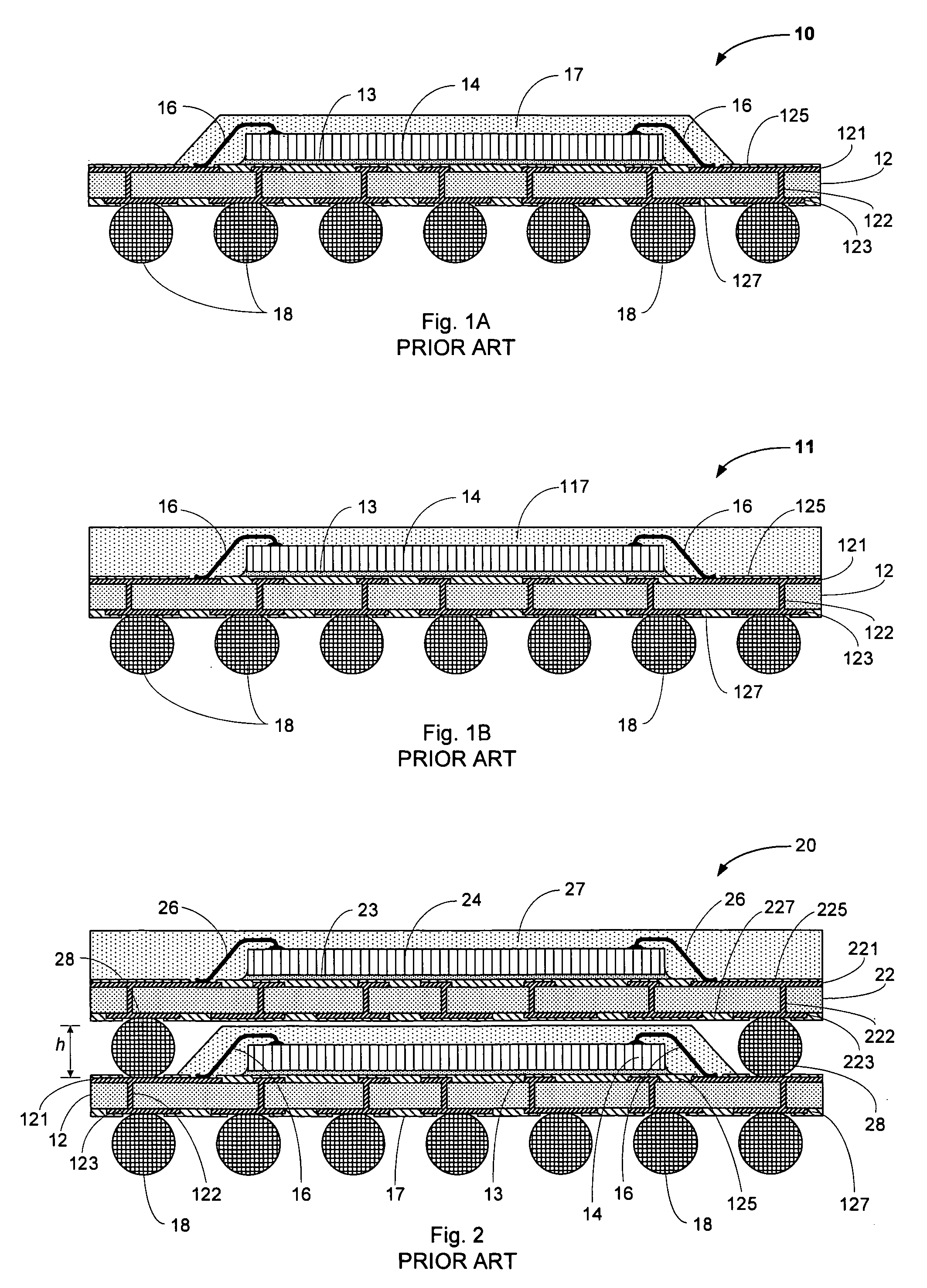

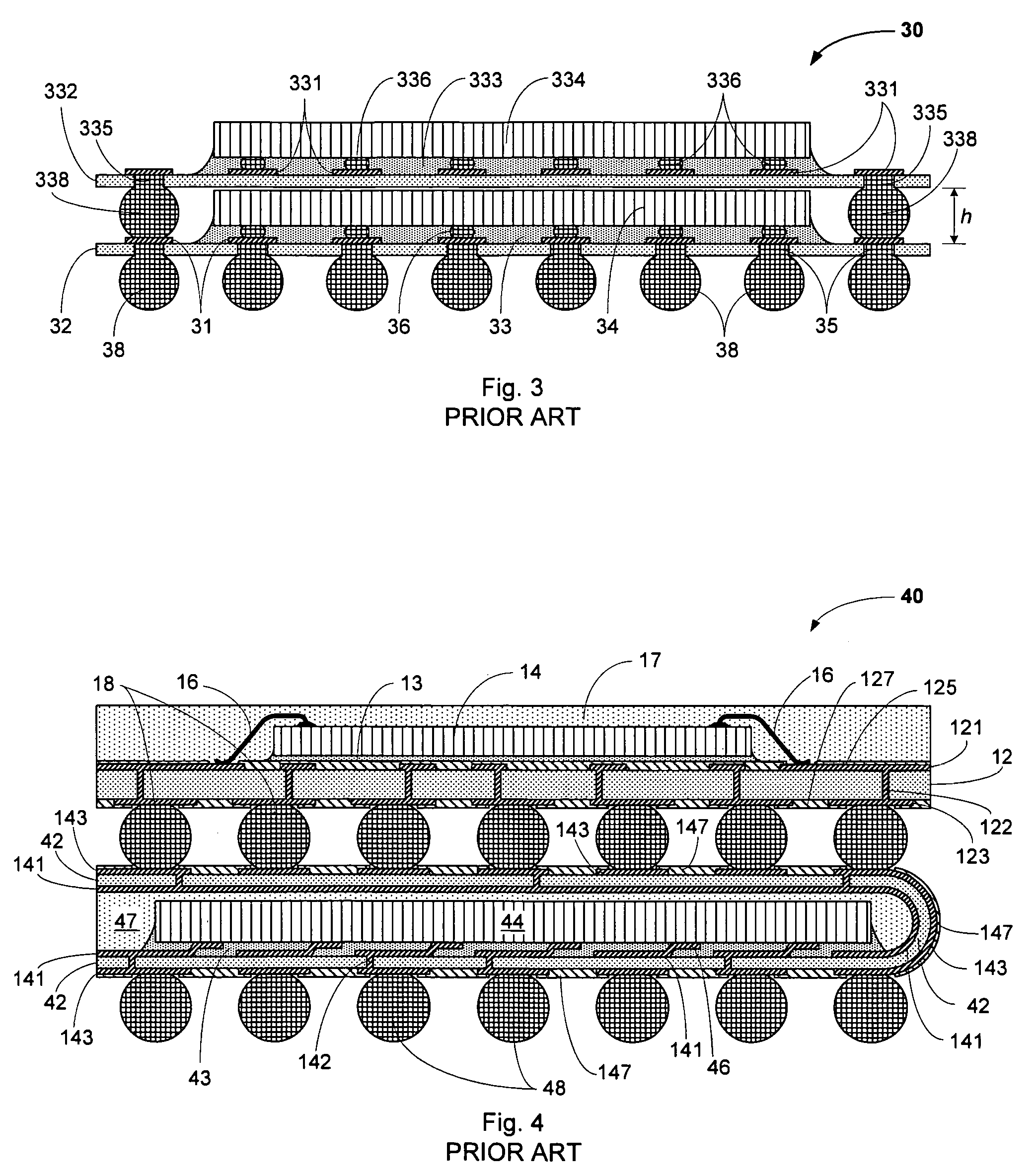

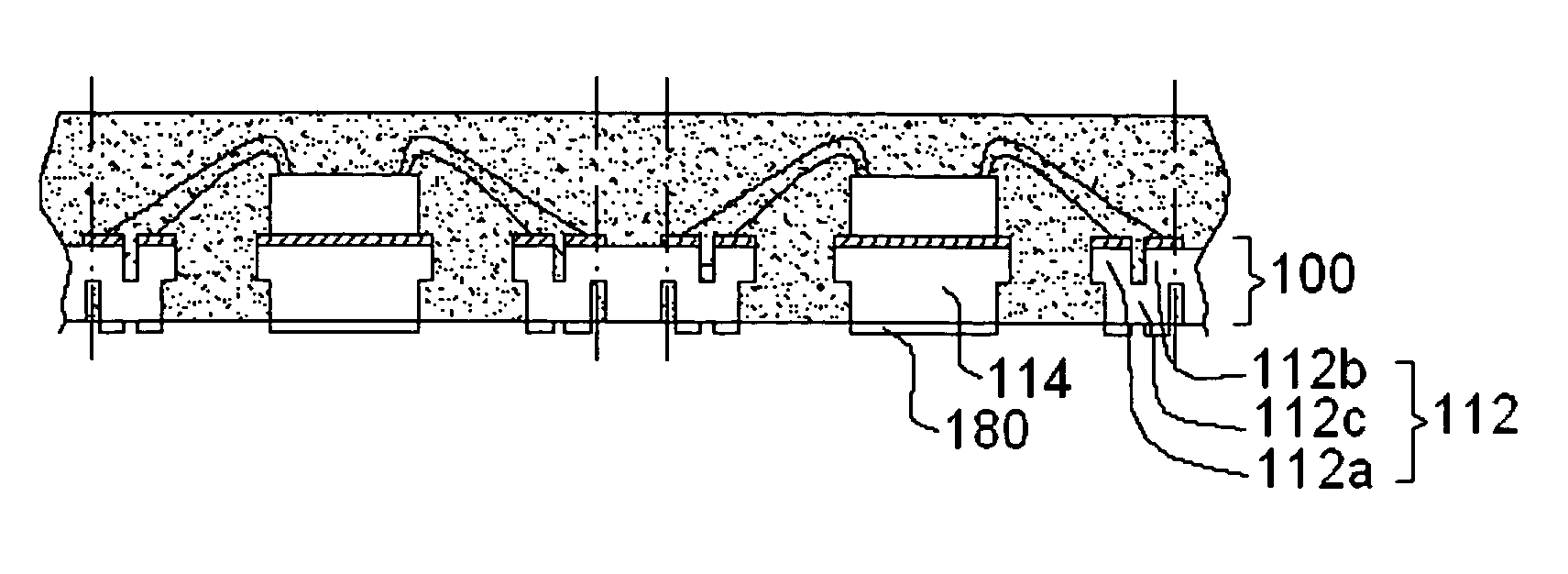

Semiconductor multi-package module having inverted second package stacked over die-up flip-chip ball grid array (BGA) package

ActiveUS7101731B2Low production costOverall design flexibilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

A semiconductor multi-package module has stacked lower and upper packages, each of which includes a die attached to a substrate, in which the second package is inverted, and in which the first and second substrates are interconnected by wire bonding, and in which the first package includes a flip-chip ball grid array package having a flip-chip in a die-down configuration. Also, a method for making a semiconductor multi-package module, by providing a lower molded package including a lower substrate and a flip-chip in a die-down configuration, affixing an upper molded package including an upper substrate in inverted orientation onto the upper surface of the lower package, and forming z-interconnects between the upper and lower substrates.

Owner:STATS CHIPPAC LTD

Premolded cavity IC package

InactiveUS6841859B1Avoid pollutionSemiconductor/solid-state device detailsSolid-state devicesFilling materialsEngineering

A process for fabricating a cavity-type integrated circuit package. The process includes: supporting an interior portion of each of a plurality of leads, in a mold; supporting a die attach pad in said mold; molding a package body in said mold such that said leads extend from an interior cavity of said package body to an exterior thereof; mounting a semiconductor die to said die attach pad; wire bonding various ones of said leads to said semiconductor die; adding a fill material for covering at least a surface of said interior portion of said leads; and mounting a lid on said package body for enclosing said die in said cavity of said package body.

Owner:UTAC HEADQUARTERS PTE LTD

Electrode structure of LED and manufacturing of the same

InactiveUS20030146445A1Improve luminous efficiencyEfficient emissionsSemiconductor devicesOhmic contactSemiconductor

The present invention discloses an electrode structure of a light emitted diode and manufacturing method of the electrodes. After formed a pn-junction 2, 3 of a light emitted diode on a substrate 1, a layer of SiO2 is deposited on the periphery of the LED die near the scribe line of the wafer, then a transparent conductive layer 5 is deposited, then a layer of gold or AuGe etc 6, is formed with an opening on the center of the die. After forming alloy with the semiconductor by heat treatment to form ohmic contact, a strip of aluminum (Al) 7 is formed on one side of the die on the front side for wire bonding and to be the positive electrode of the LED. The negative electrode 10 is formed on the substrate by metal contact. Another form of the electrode structure of the present invention is making both the positive electrode 7 and negative electrode 7a on the front side of the LED by etching the p-type semiconductor 3 of the pn-junction and forming a strip of negative electrode 7a on the n-type semiconductor area 2, the positive electrode is formed on the p-type semiconductor area.

Owner:HEN CHANG HSIU

Wire-bonding free packaging structure of light emitted diode

InactiveUS20070228386A1Improve heat transfer performanceIncrease light intensitySolid-state devicesSemiconductor devicesSurface mountingLead frame

A wire-bonding free packaging structure for light emitting diode (LED) is provided. Prepare a silicon sub-mount having a backside bulk micromachining reach-through U-shape cavity for accommodating a flip-chip LED. This stack-integrated packaging module with solder bumps on the surface is than bonded to an aluminum PC board with flip-chip surface mount packaging or bump technology. This gives very good heat conduction to the heat sink of the PC board and can endure more current to enhance light intensity of the LED. This stack-integrated packaging module can also be bonded on a lead frame with two leg packaging, which can also increase heat conduction.

Owner:INTEGRATED CRYSTAL TECH

Process and lead frame for making leadless semiconductor packages

ActiveUS7087461B2Increase the number ofPitch or spacing between adjacent leads is notSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

A process for making a plurality of leadless packages is disclosed. Firstly, chips are attached onto a lead frame with a first metal layer formed thereon. Each lead of the lead frame has a first portion, a second portion and a third portion connecting the first portion and the second portion, wherein the first metal layer is not provided on the third portion. After a wire bonding step and an encapsulating step are conducted, a second metal layer is selectively plated on the first portions and the second portions of the leads and the die pads exposed from the bottom of the molded product. Then, the third portion of each lead is selectively etched away such that the first portion and the second portion are electrically isolated from each other. Finally, a singulation step is conducted to complete the process. The present invention further provides a new lead frame design.

Owner:ADVANCED SEMICON ENG INC

LED package for backlight unit

ActiveUS7156538B2Improve image qualityImprove luminous efficiencyLighting support devicesGlass furnace apparatusEngineeringDie bonding

Owner:SAMSUNG ELECTRONICS CO LTD

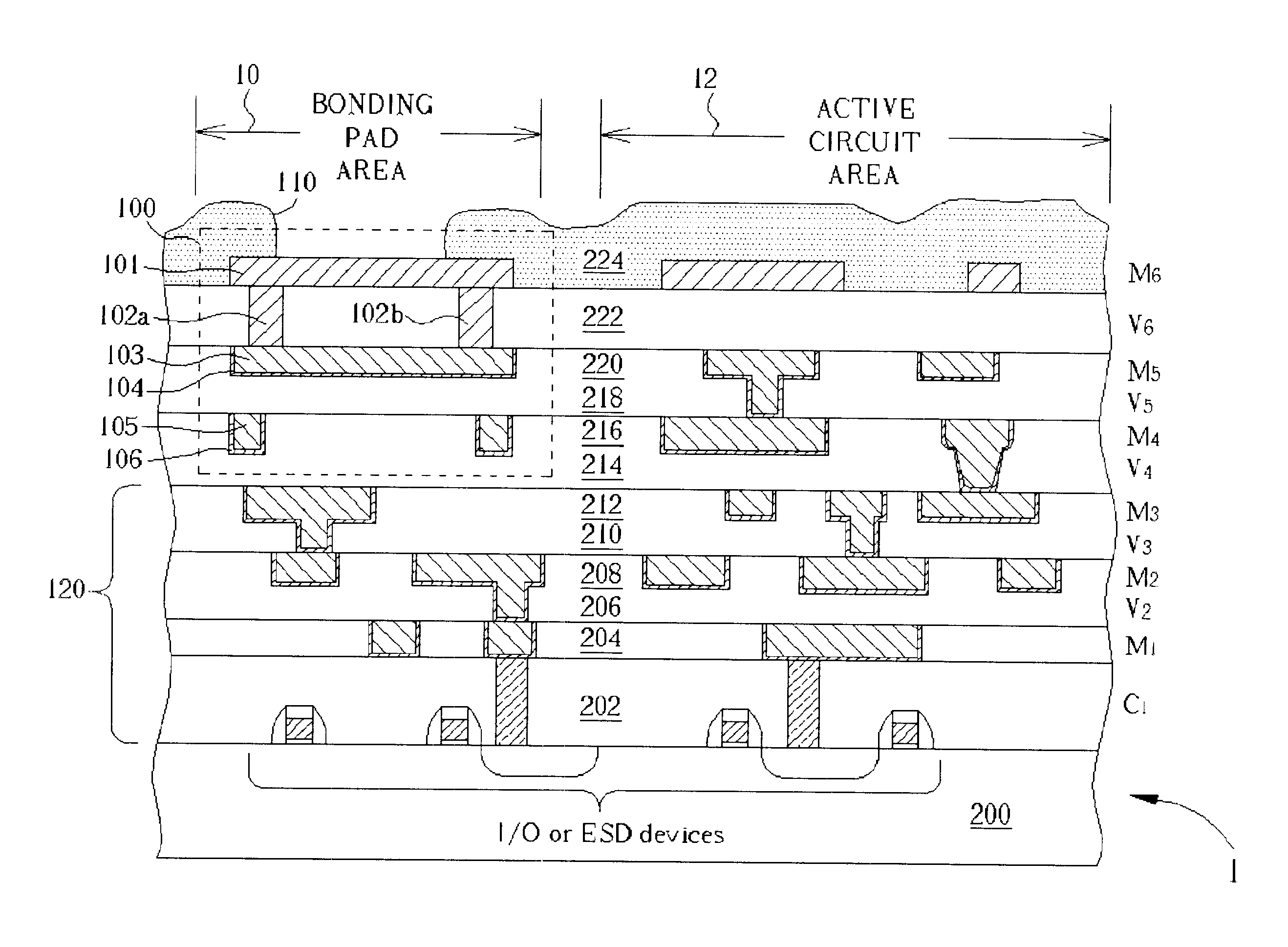

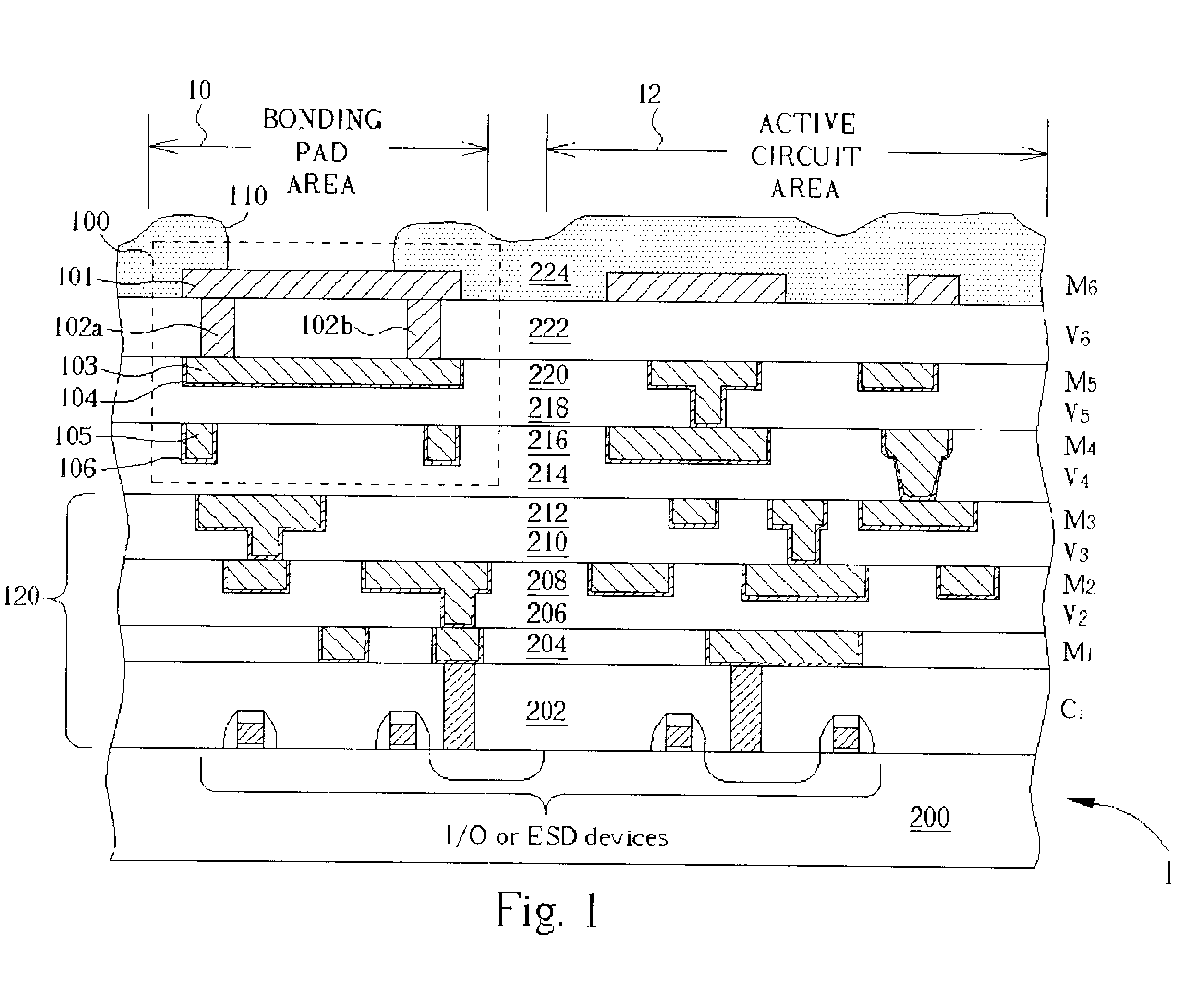

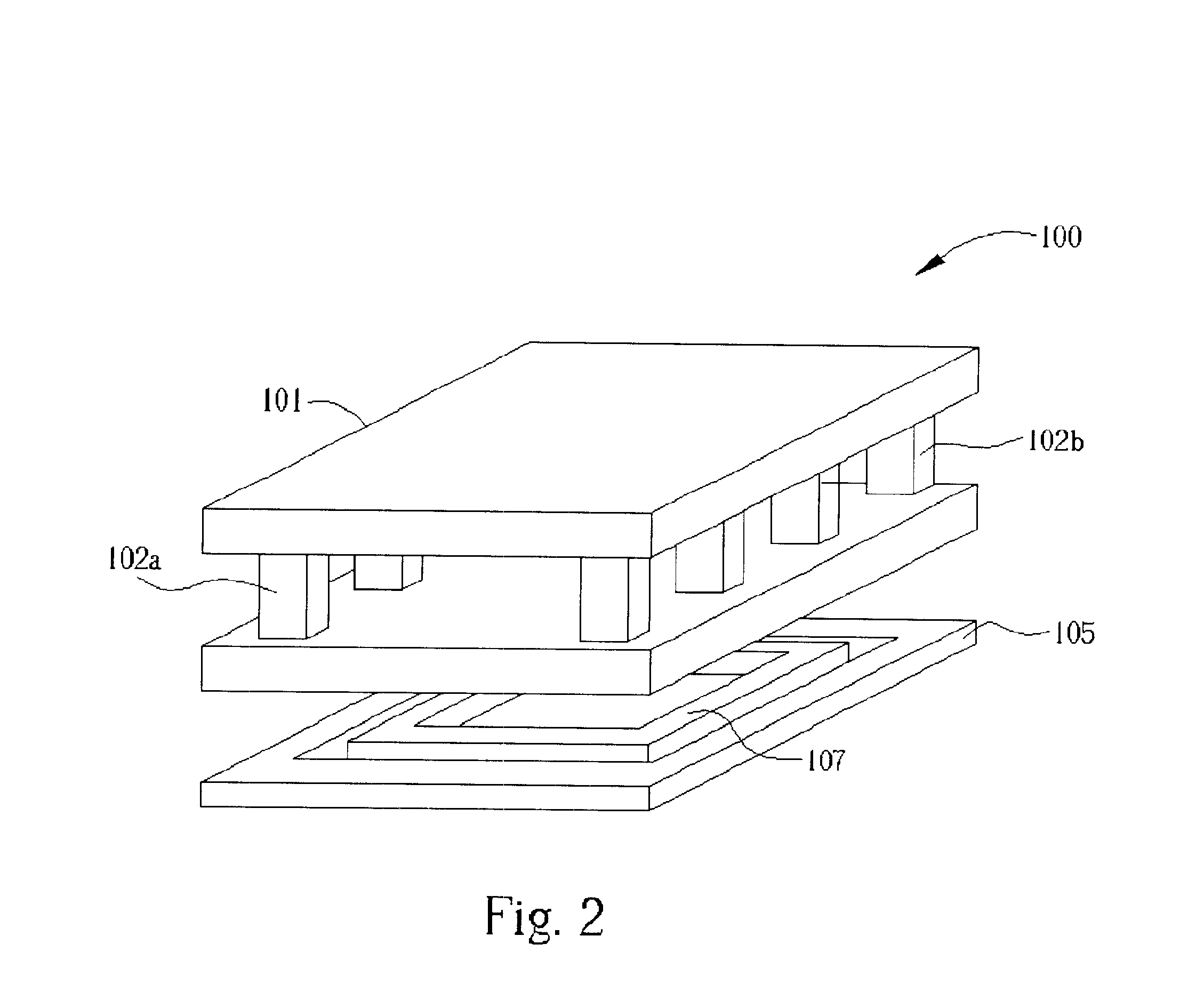

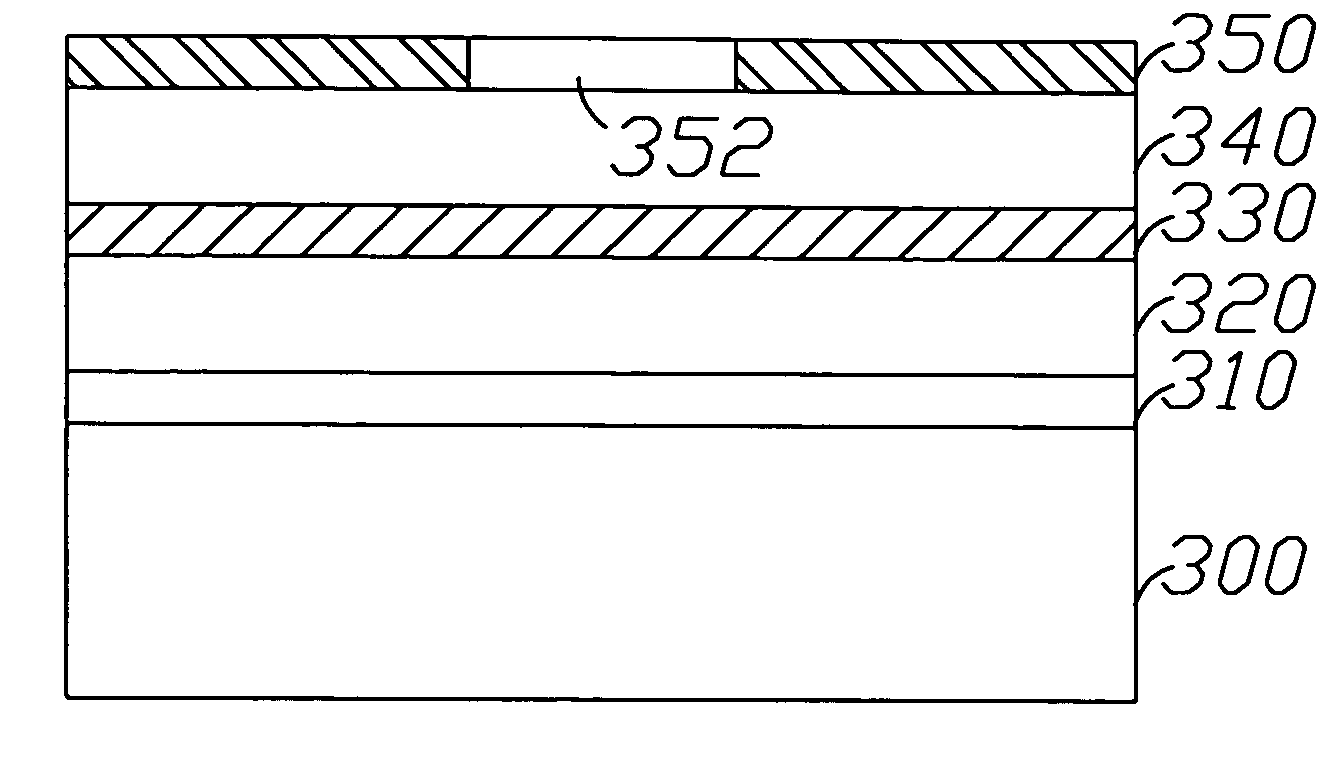

Semiconductor chip capable of implementing wire bonding over active circuits

ActiveUS6900541B1Save areaSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipDielectric layer

An integrated circuit including a reinforced bonding pad structure is disclosed. The reinforced bonding pad structure includes a bondable metal layer defined on a stress-buffering dielectric layer, and an intermediate metal layer damascened in a first inter-metal dielectric (IMD) layer disposed under the stress-buffering dielectric layer. The intermediate metal layer is situated directly under the bondable metal layer and is electrically connected to the bondable metal layer with a plurality of via plugs integrated with the bondable metal layer. At least one metal frame is damascened in a second IMD layer under the first IMD layer. The metal frame is situated directly under the intermediate metal layer for counteracting mechanical stress exerted on the bondable metal layer during bonding. An active circuit portion including active circuit components of the integrated circuit is situated directly under the metal frame of the reinforced bonding pad structure.

Owner:UNITED MICROELECTRONICS CORP

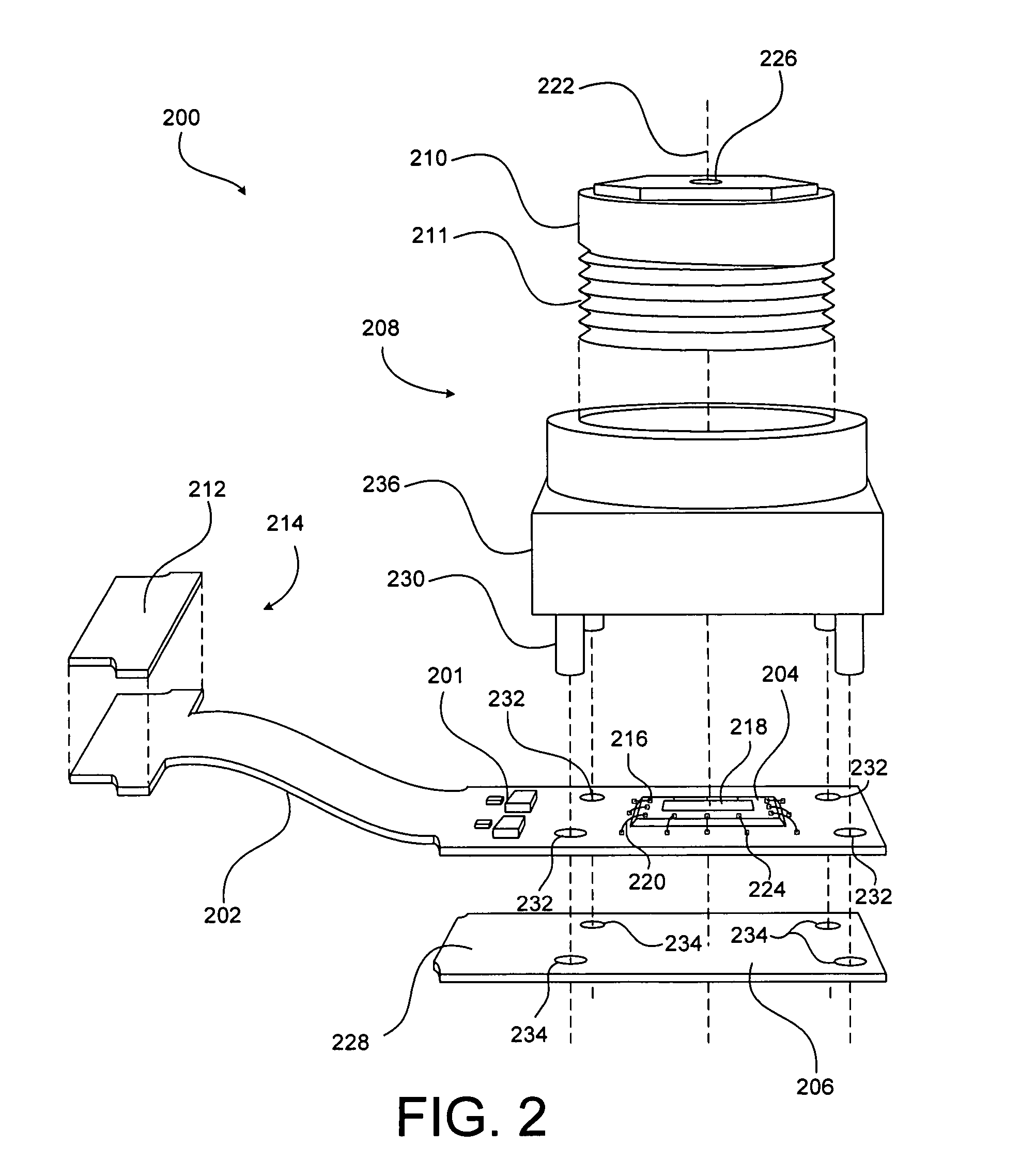

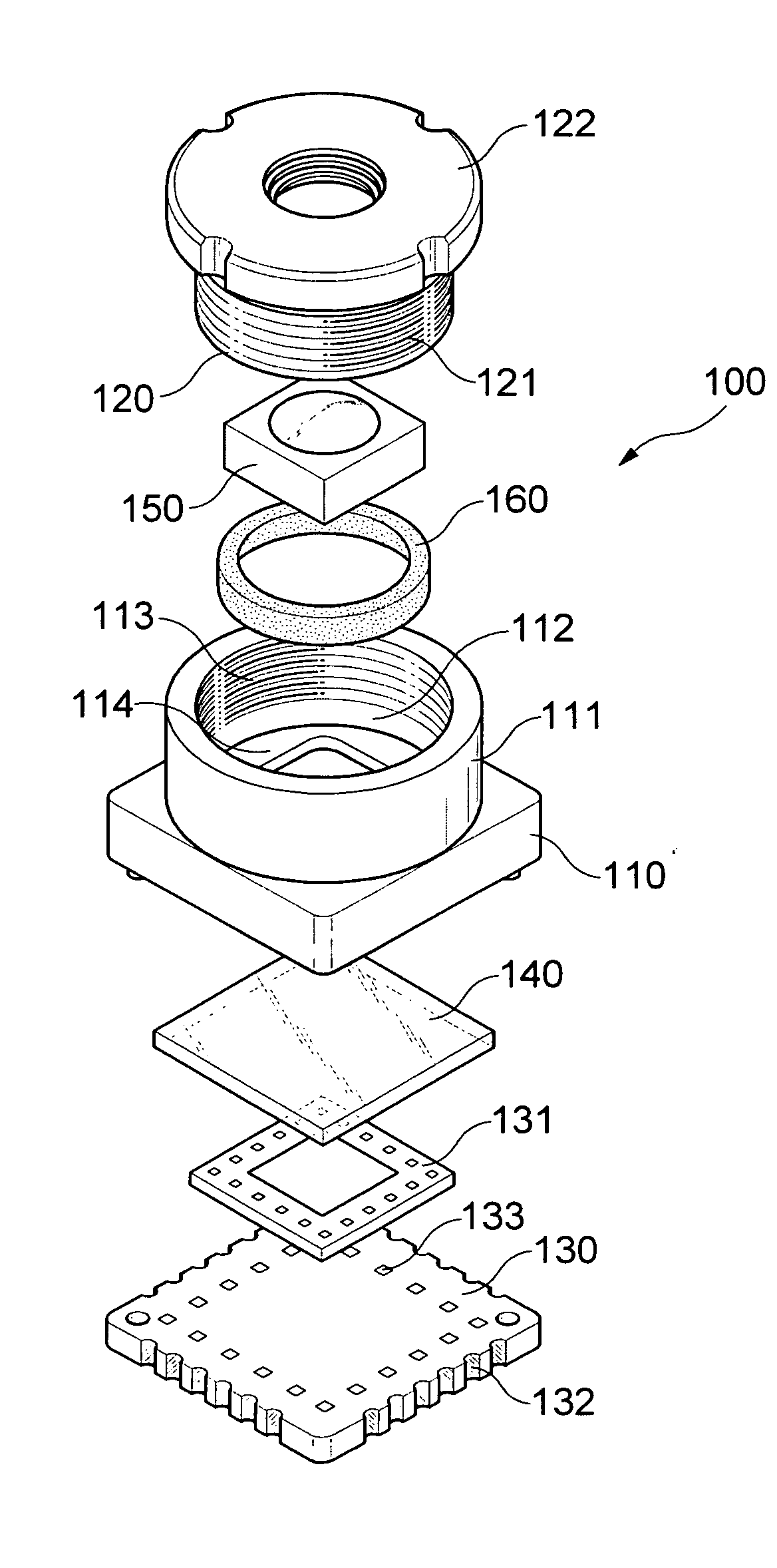

Camera module

InactiveUS20080278621A1Overcome disadvantagesOvercome problemsTelevision system detailsSolid-state devicesCouplingSurface mounting

The present invention relates to a camera module capable of being surface mounted (SMT) on a main substrate.In accordance with the present invention, the camera module includes a housing provided with a cylindrical barrel coupling unit extended upward from a central part of the housing, wherein a female screw unit is formed on an inner circumferential surface of the cylindrical barrel coupling unit and an opening unit is formed on a top portion of the cylindrical barrel coupling unit; a lens barrel provided with a male screw unit on an outer circumferential surface by being formed in a cylindrical shape to be conformally combined with the barrel coupling unit and screw-coupled to the female screw unit by being inserted through the opening unit of the barrel coupling unit; a wafer lens mounted in the lens barrel; and a substrate with an image sensor mounted on a top surface of the substrate by a wire bonding and closely coupled to a lower part of the housing by being provided with surface mounting pads on each lateral surface thereof and has advantages that the process for mounting the camera module onto the substrate is simplified and further a process cost is reduced by removing an additional connection device for electrically connecting the camera module to the main substrate.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Vertical electrode structure of gallium nitride based light emitting diode

InactiveUS20050236632A1Reduce reflectionImprove external luminous efficiencySemiconductor devicesAngle of incidenceReflection loss

A vertical electrode structure of GaN-based light emitting diode discloses an oxide window layer constructing the GaN-based light emitting diode of vertical electrode structure, which effectively decreases the Fresnel reflection loss and total reflection, and further advances the luminous efficiency. Moreover, the further included metal reflecting layer causes the reflection without the selective angle of incidence, thus increasing the coverage of the reflecting angles and further reflecting the light emitted from a light emitting layer effectively. In addition, the invented structure can also advance the function of heat elimination and the electrostatic discharge (ESD) so as to the increase the operating life of the component and to be applicable to the using under the high current driving. Moreover, the vertical electrode structure of the present invention is able to lower down the manufacturing square of the chip and facilitate the post stage of the conventional wire bonding process.

Owner:SUPERNOVA OPTOELECTRONICS

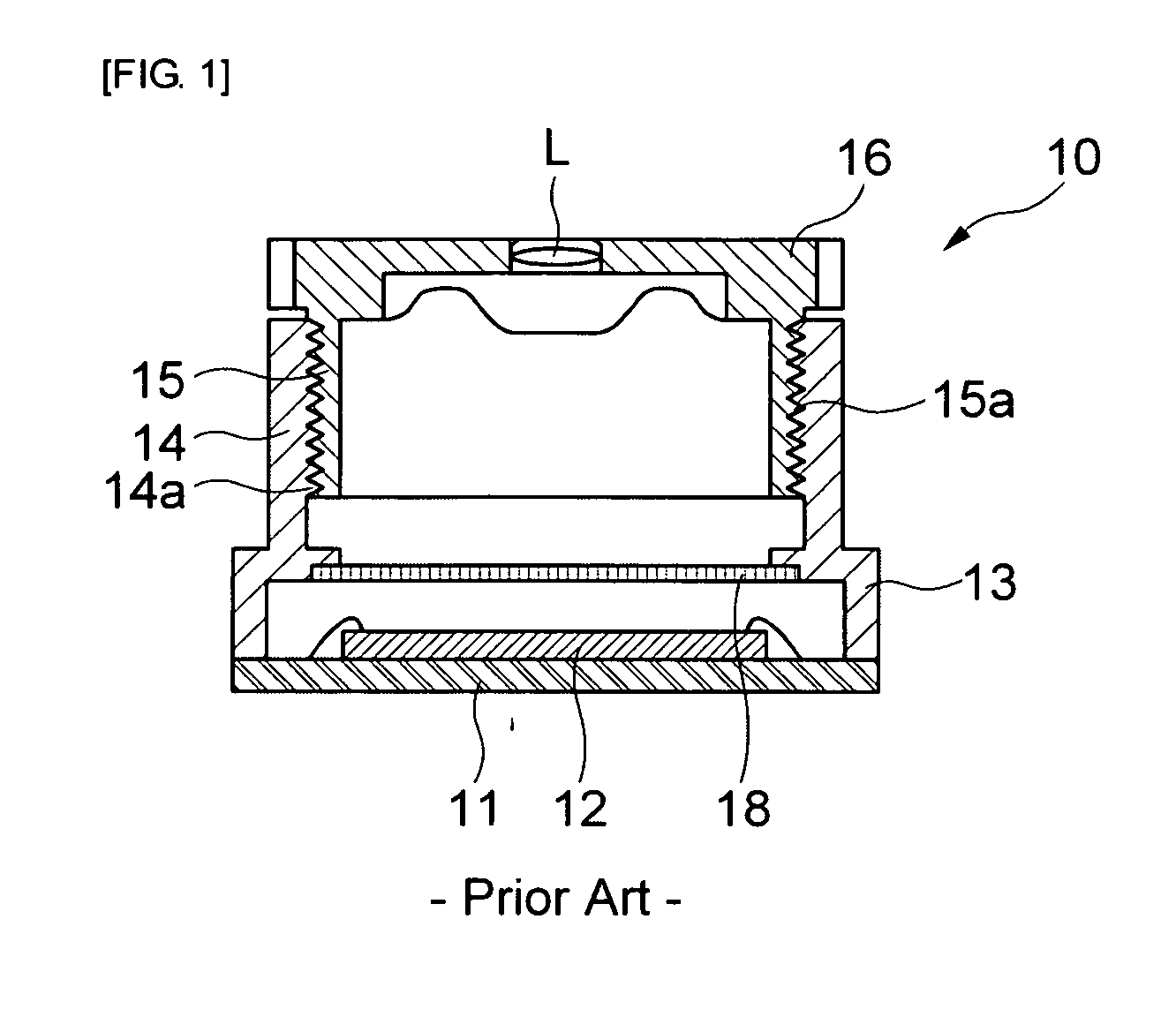

Image sensor module structure comprising wire bonding package and method of manufacturing the image sensor module structure

InactiveUS20050285016A1Reduce horizontal sizeReduce the possibilityTelevision system detailsSemiconductor/solid-state device detailsEngineeringInterconnection

An image sensor module structure includes an image sensor package, a housing, and an underfiller. The image sensor package includes a substrate having interconnection pads formed on an outermost edge. The housing includes a filter projecting from a bottom surface of a housing body. The projecting filter is attached on an image sensor chip using various adhesive patterns. Further, the underfiller is formed in a space between the housing body and the image sensor package.

Owner:SAMSUNG ELECTRONICS CO LTD

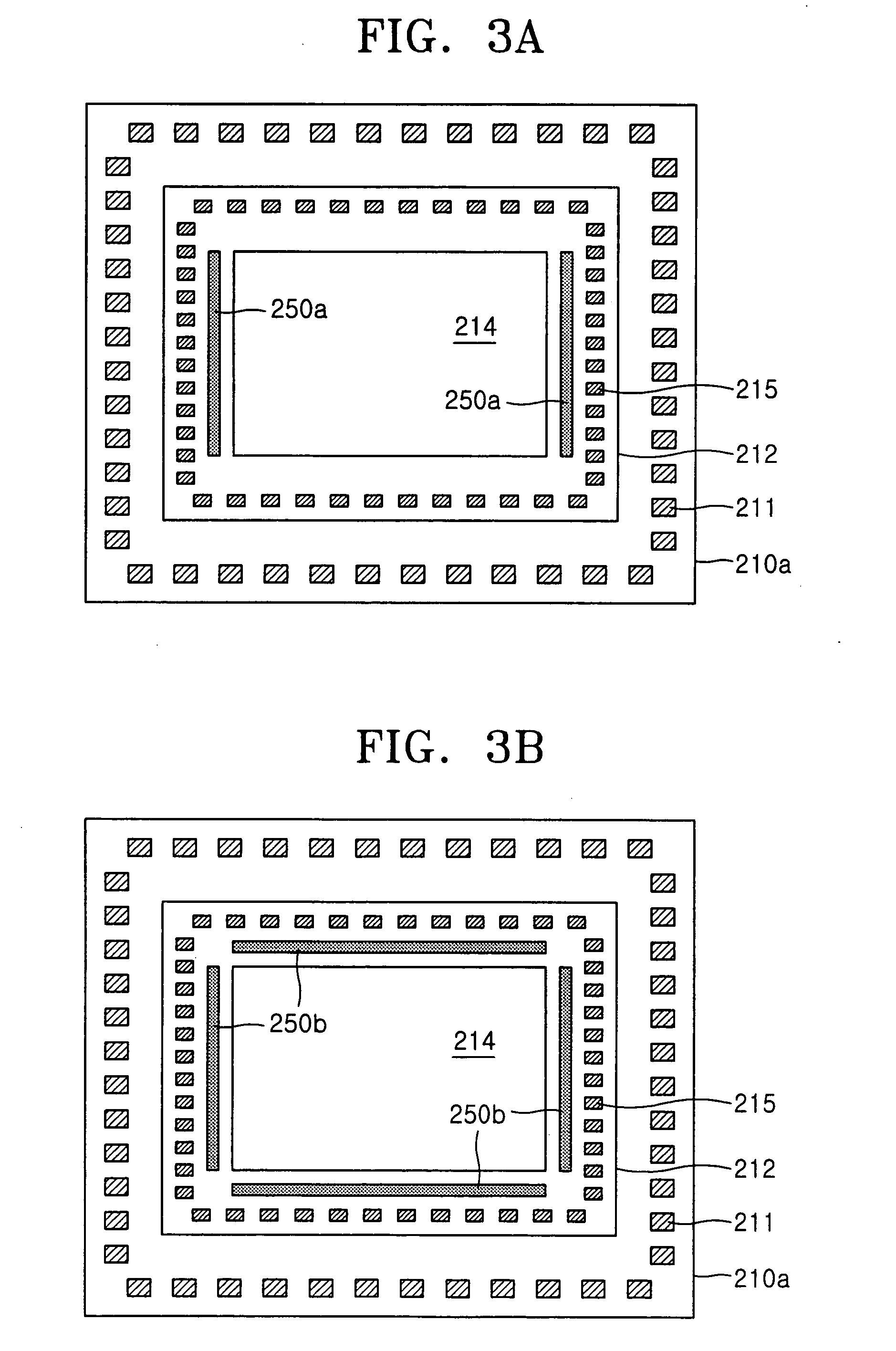

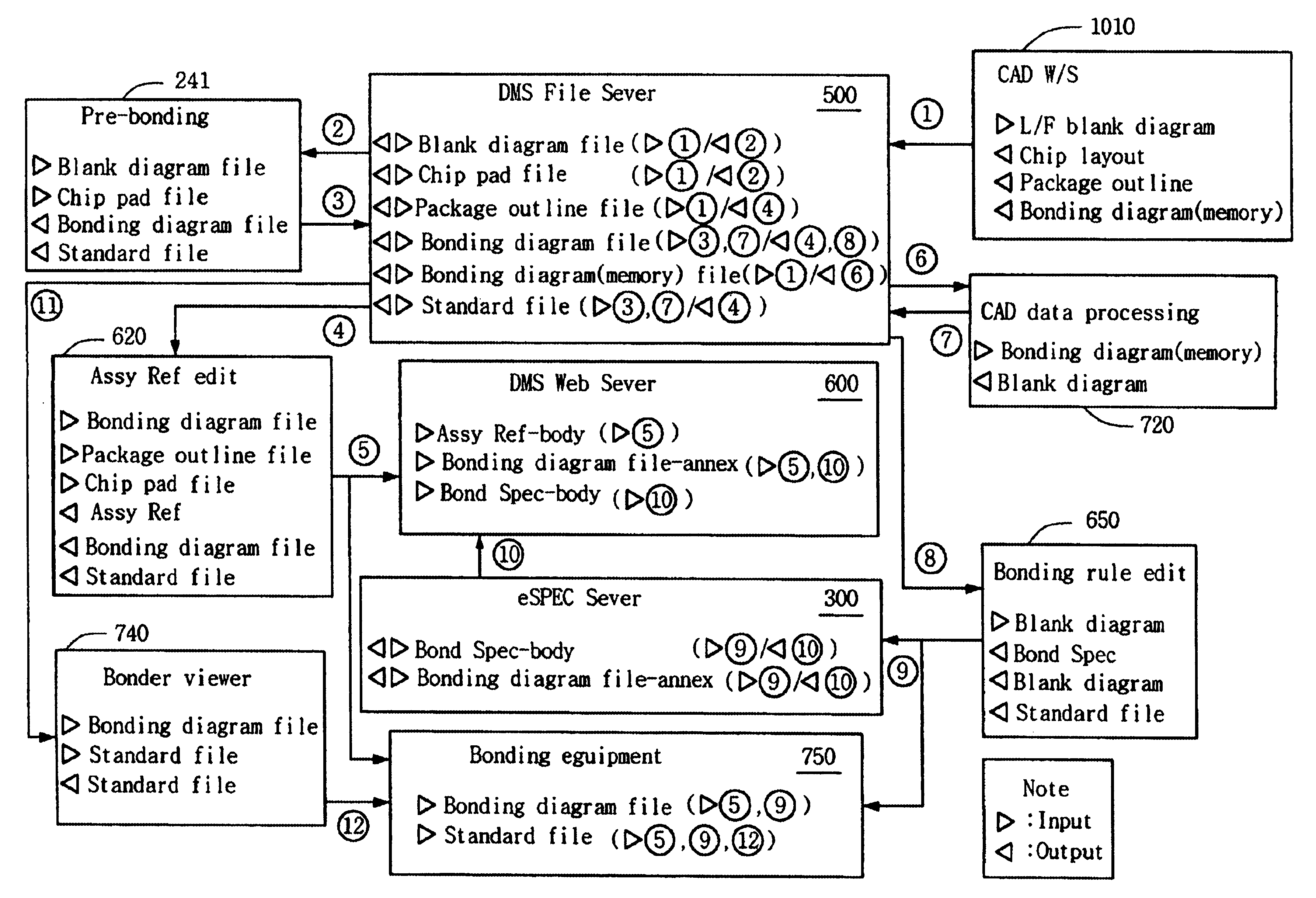

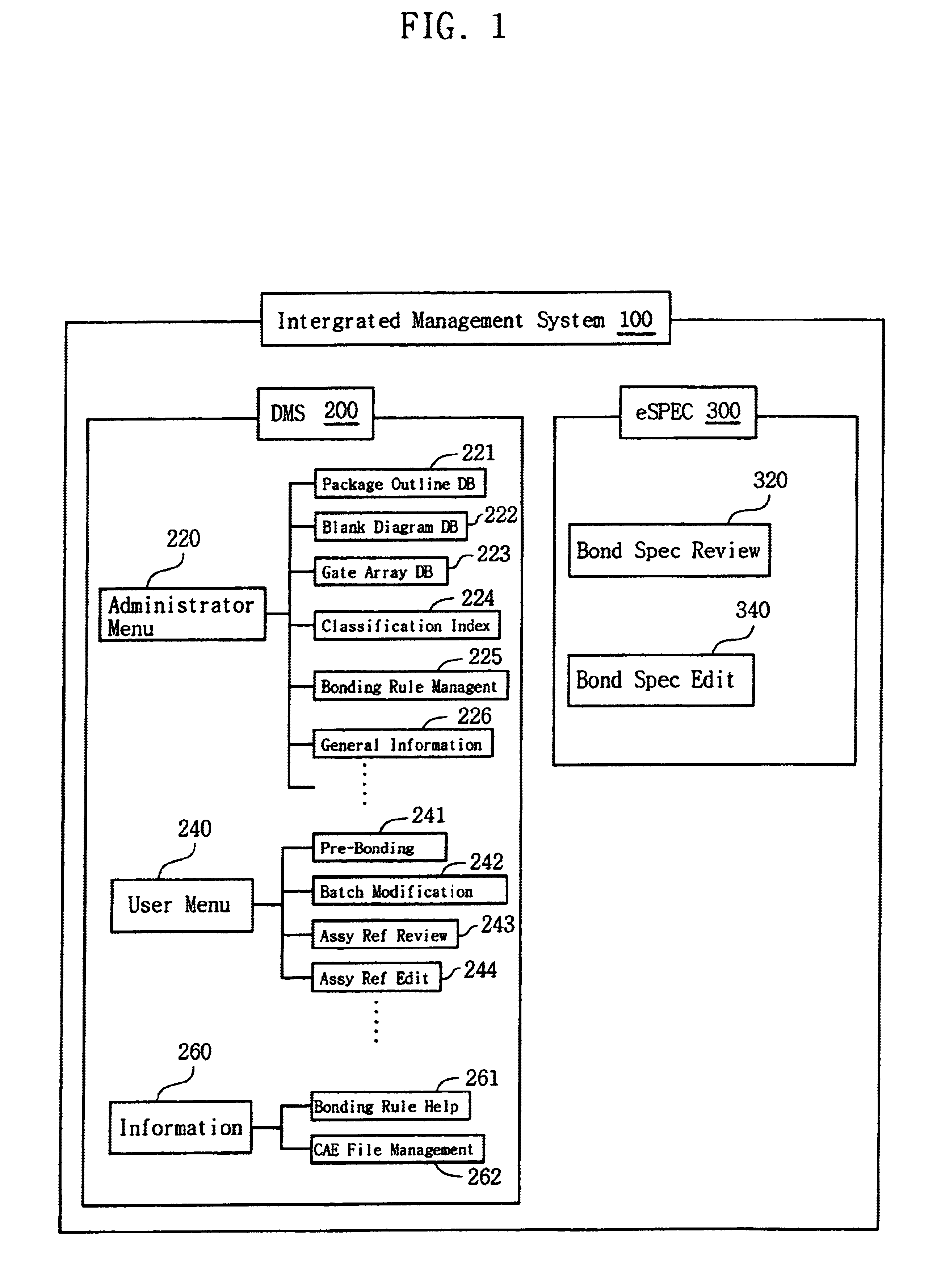

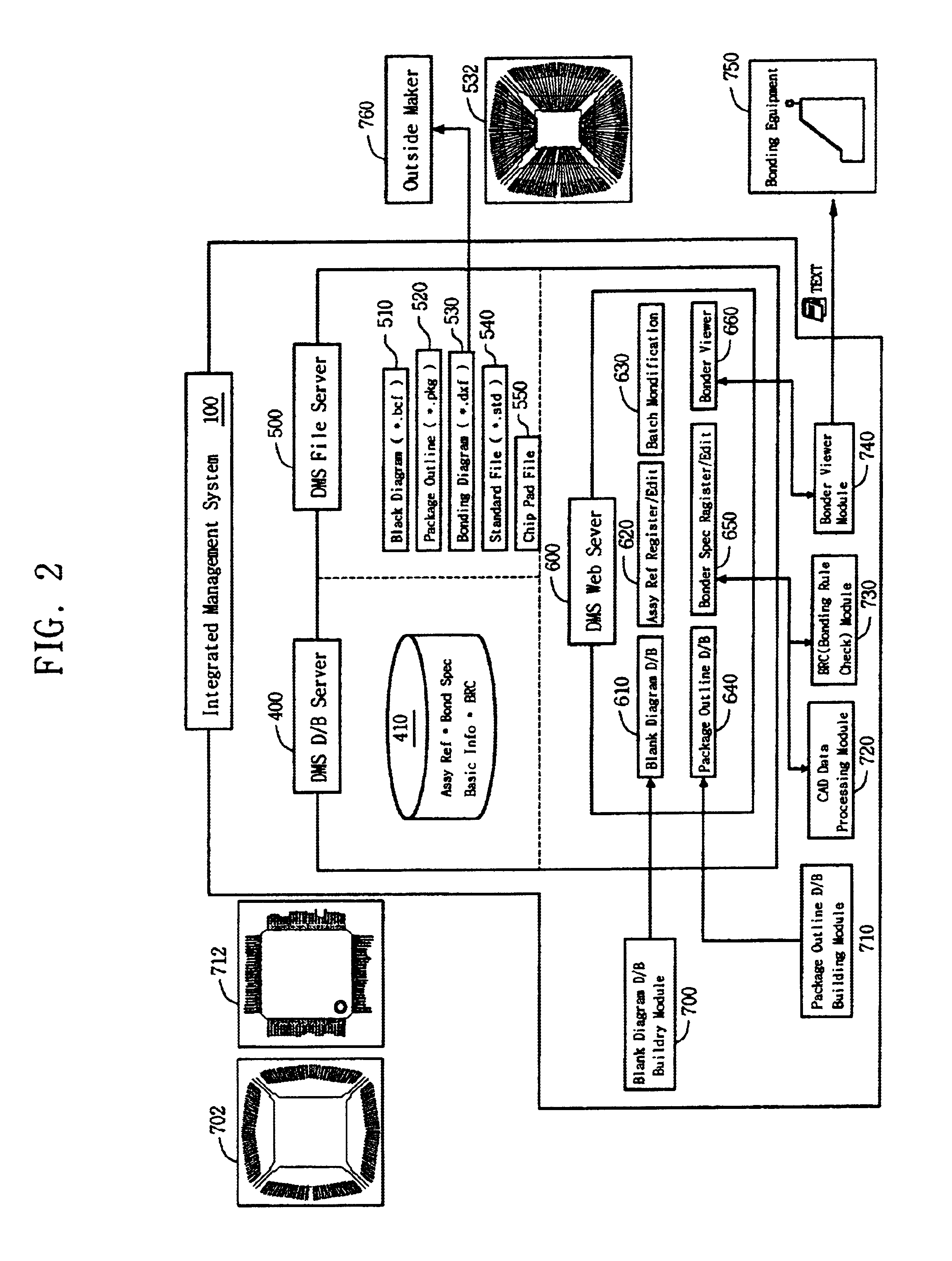

Management system for automated wire bonding process

InactiveUS6851100B1Solid-state devicesSemiconductor/solid-state device manufacturingWeb serviceDatabase server

An integrated management system is provided for automatically executing a procedure of reviewing and editing an assembly reference and a bonding specification used for manufacturing IC packages. The system includes a drawing management system (DMS) that creates the assembly reference, and a bonding specification drawing system that creates, based on the assembly reference, the bonding specification. The integrated management system further includes a DMS database server that stores and manages the assembly reference and the bonding specification, a DMS file server that manages a blank diagram, a package outline, a bonding diagram, and a standard file, and a DMS web server that provides a web interface to a user for permitting a remote access. In particular, the drawing management system has a bonding rule check module that verifies whether the bonding specification meets a bonding rule suitable for an automated wire bonding process. The drawing management system produces the standard file to be transmitted to bonding equipments.

Owner:SAMSUNG ELECTRONICS CO LTD

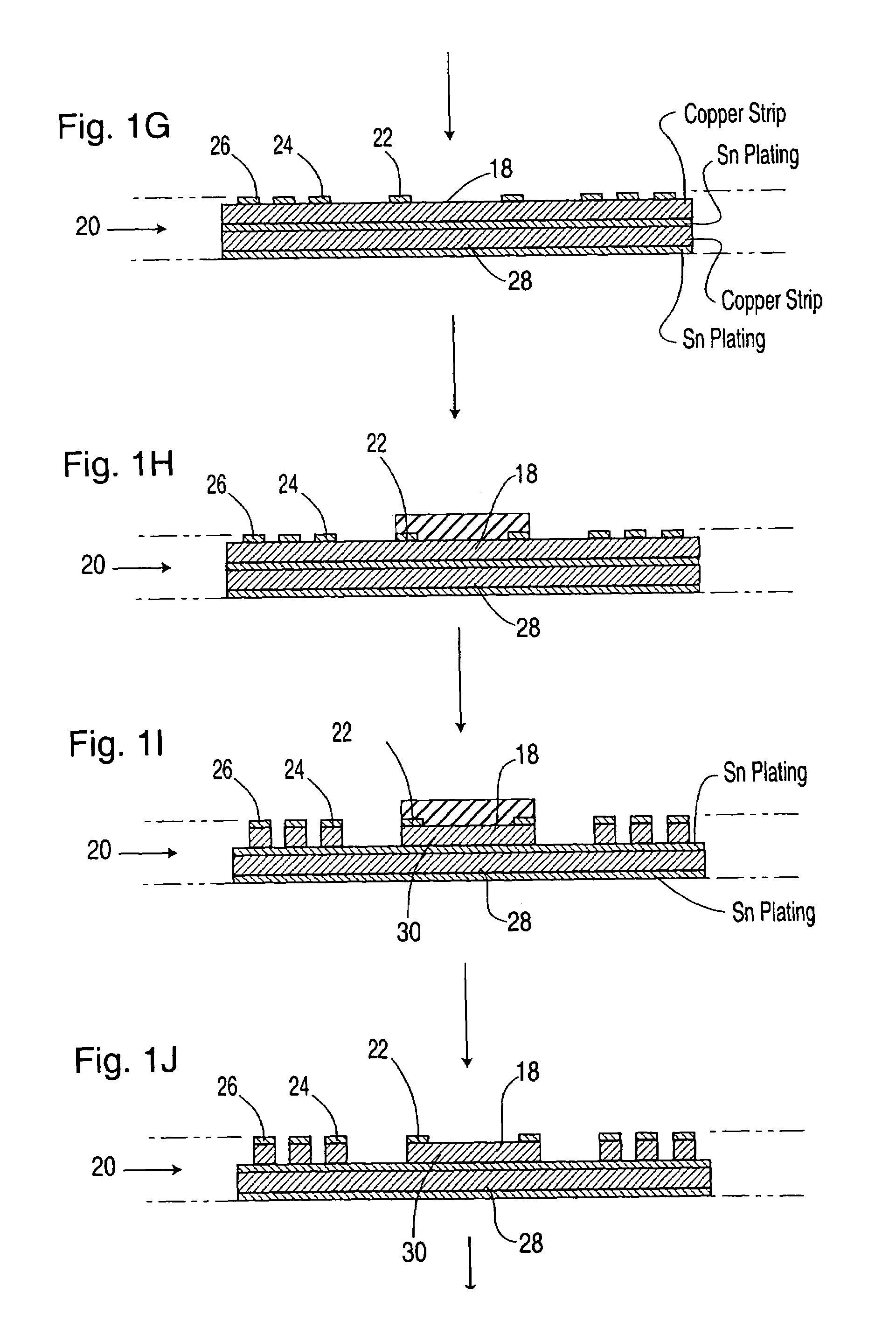

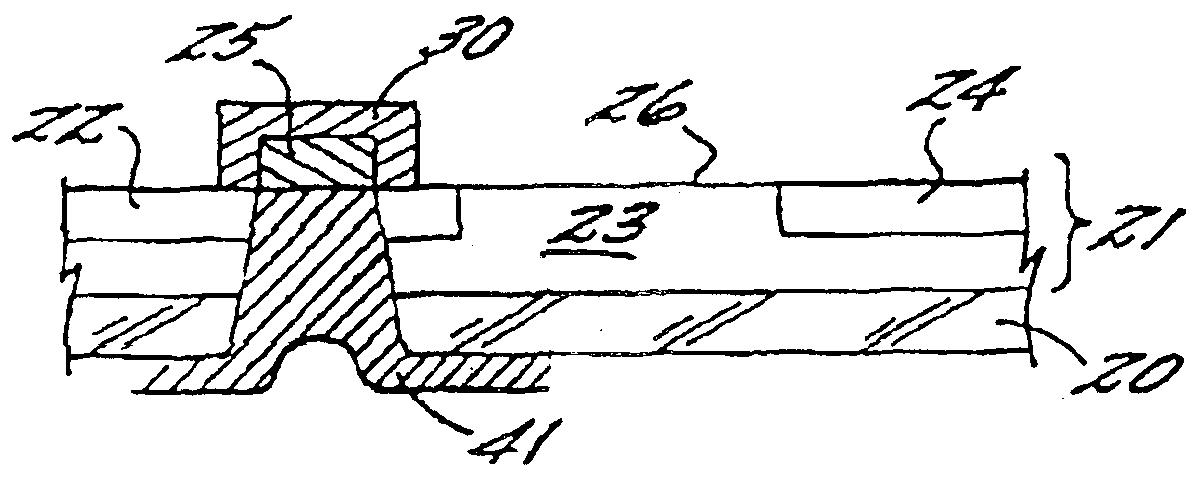

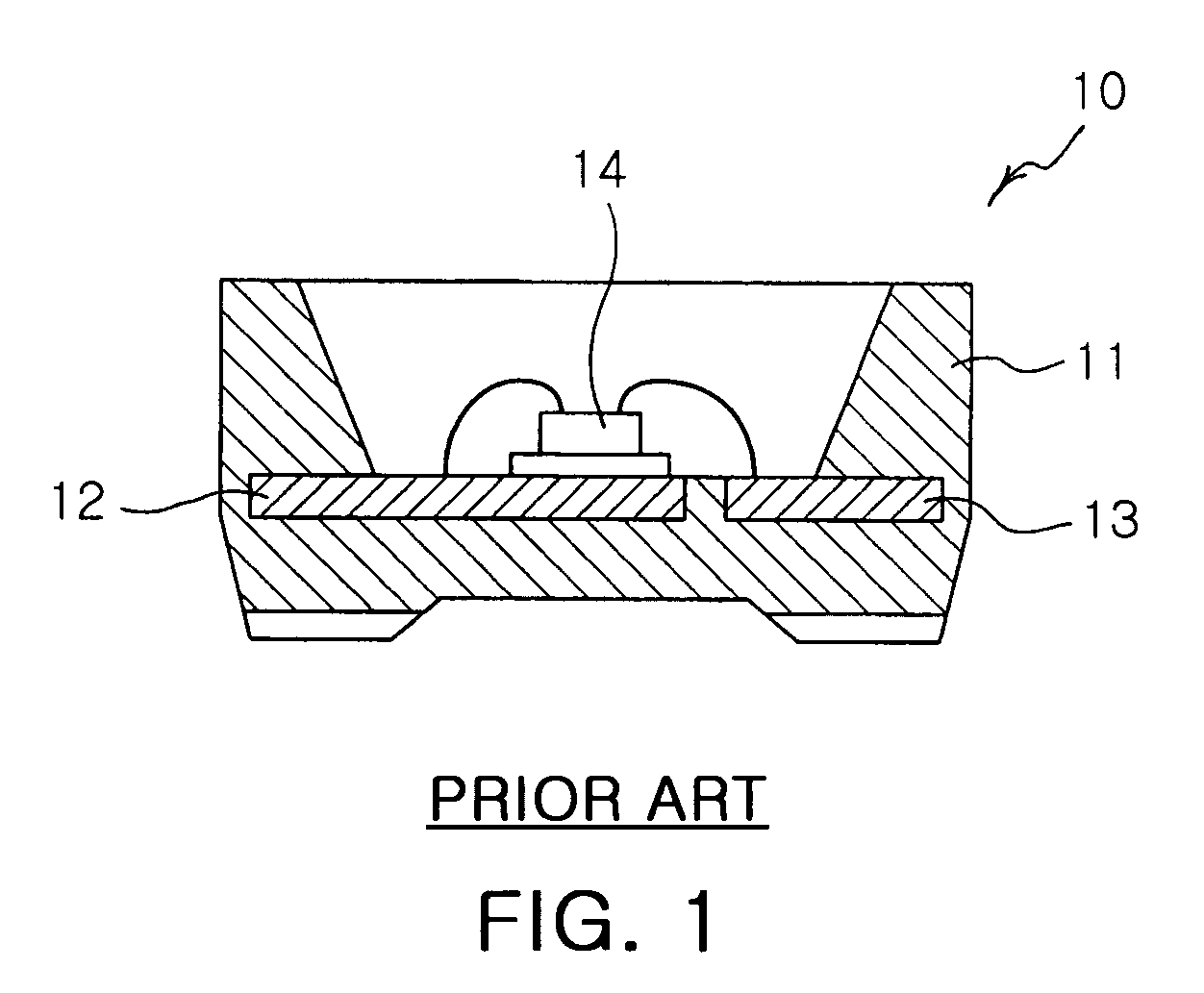

Semiconductor device

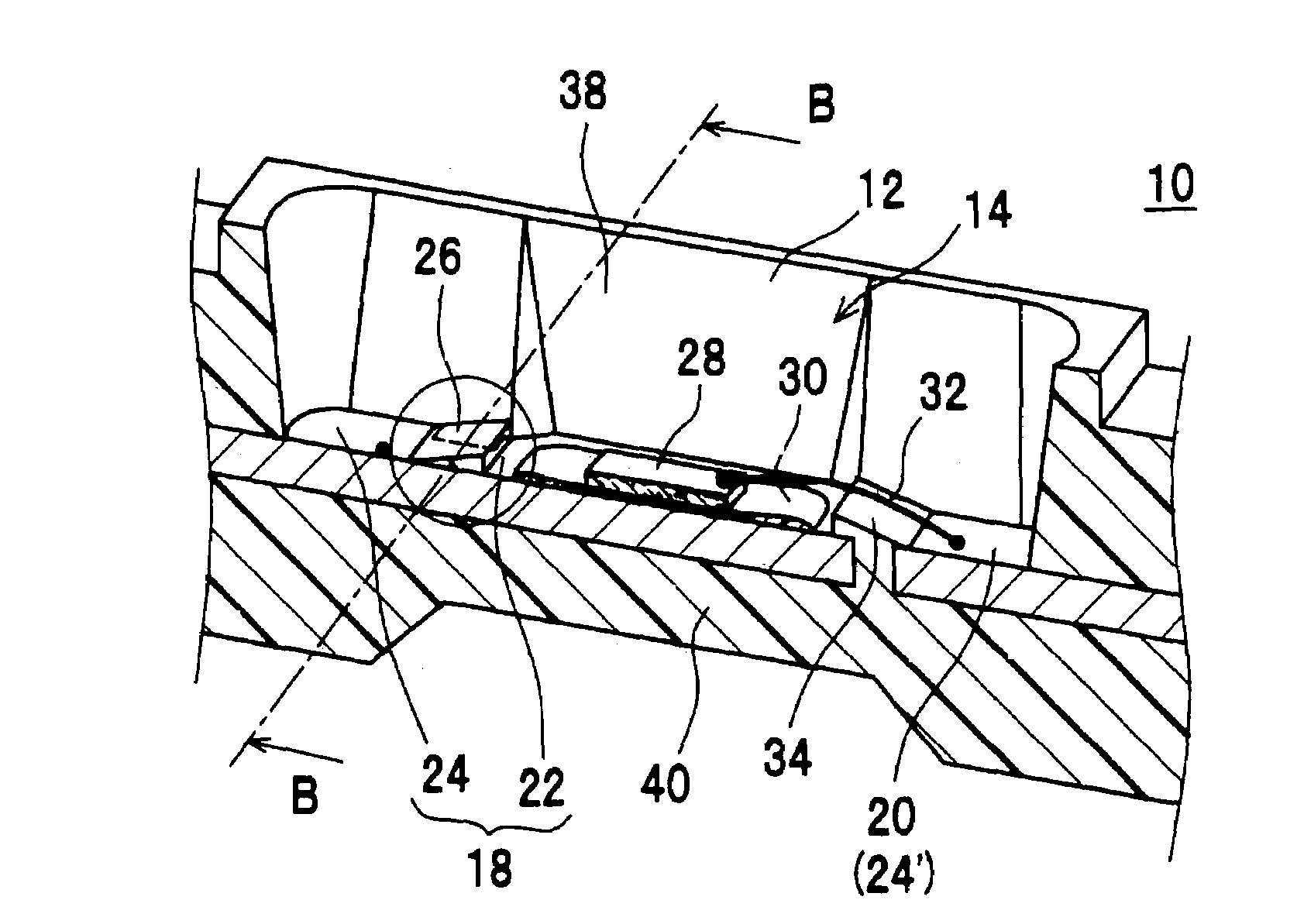

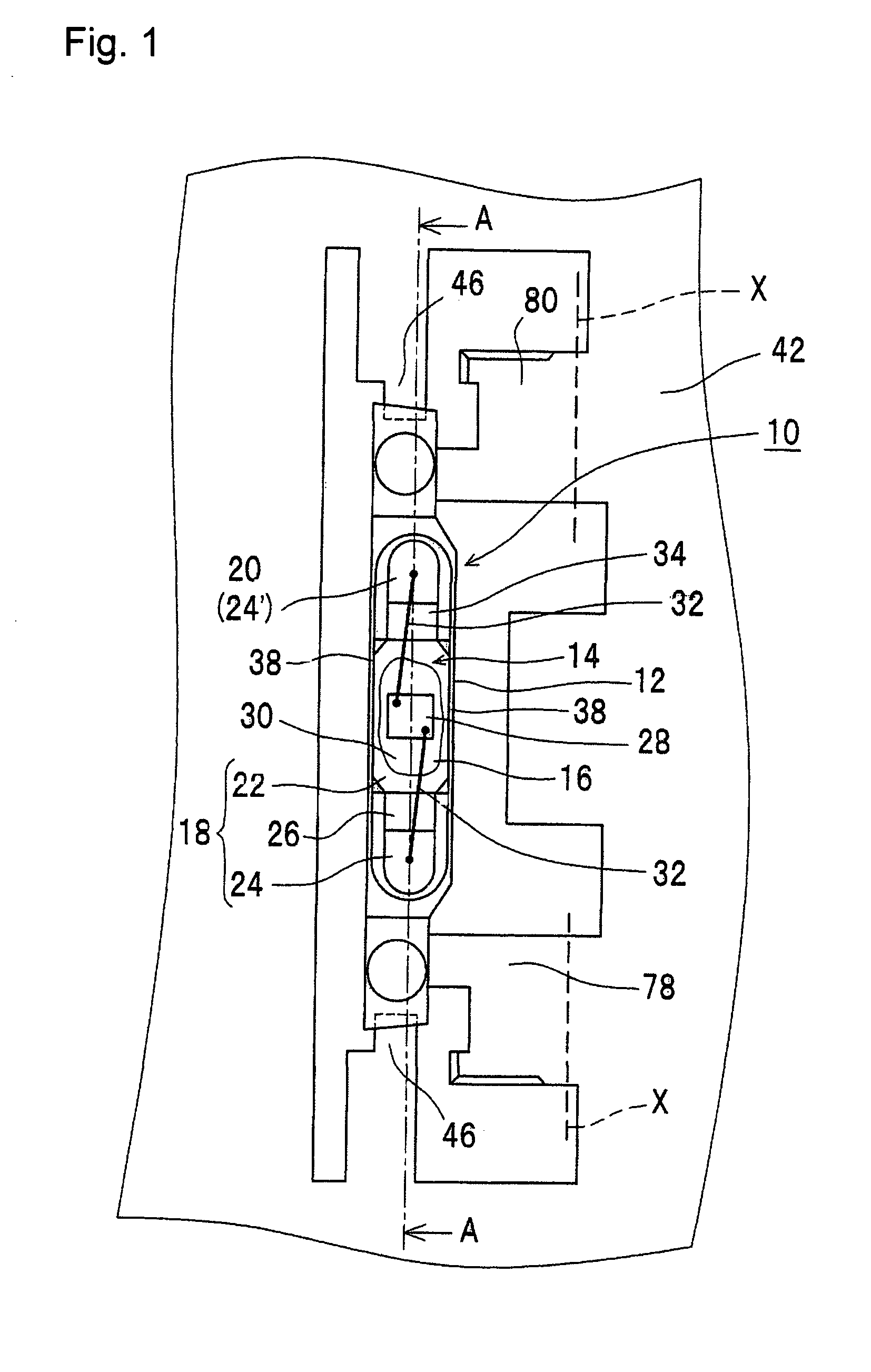

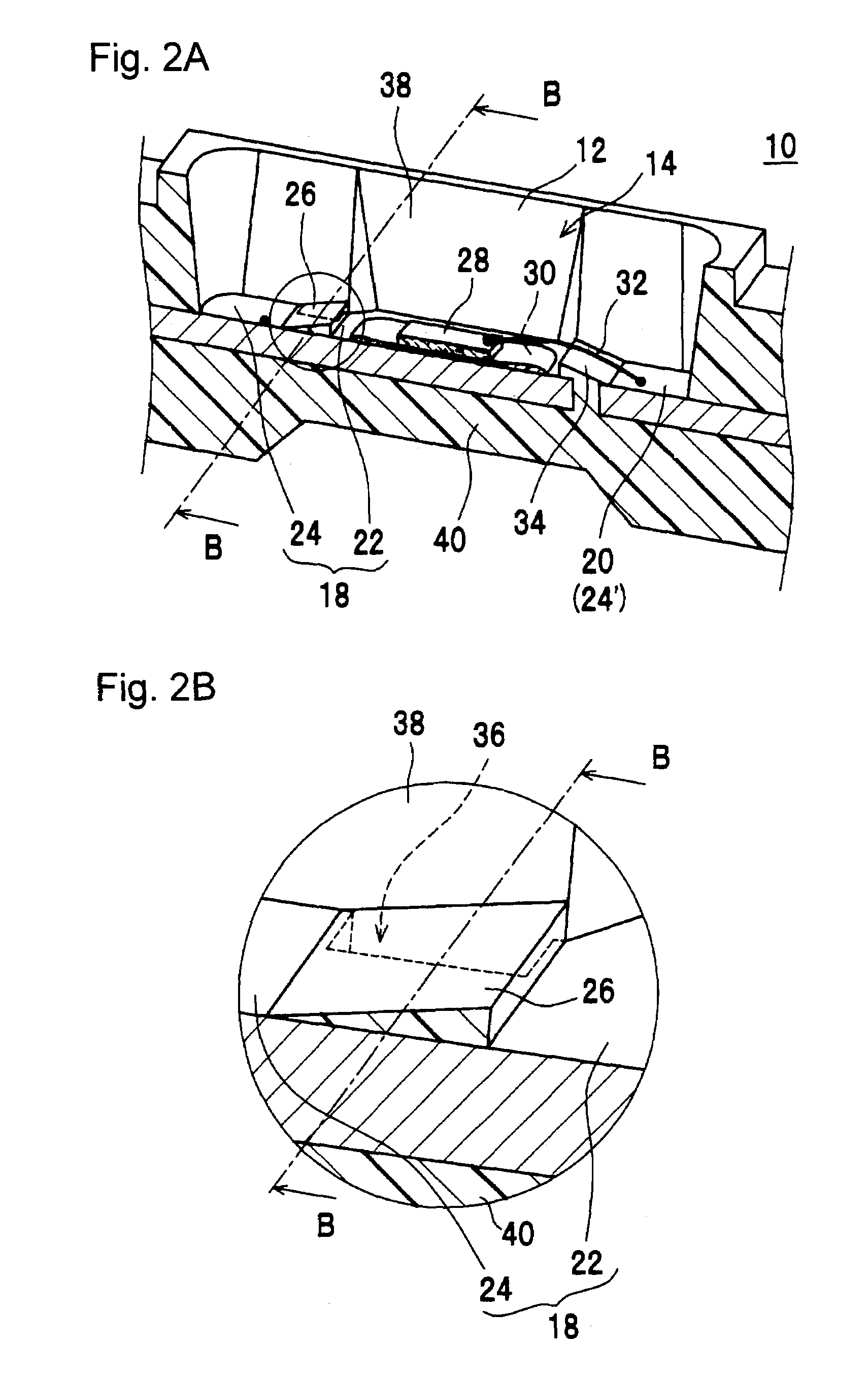

The present invention provides a semiconductor device capable of preventing an adhesive for die bonding from flowing to wire bonding area.The semiconductor device of the present invention comprises a semiconductor element 28 having a pair of electrodes, a housing 12 having the recess 14 for accommodating the semiconductor element 28, a first lead electrode 18 and the second lead electrode 20 which are exposed on the bottom of the recess 14, an adhesive layer 30 for die bonding between the semiconductor element 28 and the first lead electrode 18, and electrically conductive wires 32 for wire bonding between one electrode of the pair of electrodes of the semiconductor element and the first lead electrode 18 and between the other electrode and the second lead electrode 20, wherein the housing 12 has the wall 26 formed to extend across the bottom surface of the recess 14 so as to divide the surface of the first lead electrode 18 into a die bonding area 22 and a wire bonding area 24, and the first lead electrode 18 has the notch 36 which is formed by cutting off a portion of an edge of the first lead electrode 18 and located at least just below the wall 26, while the wall 26 and the bottom portion 40 of the housing 12 are connected to each other through the notch 36.

Owner:NICHIA CORP

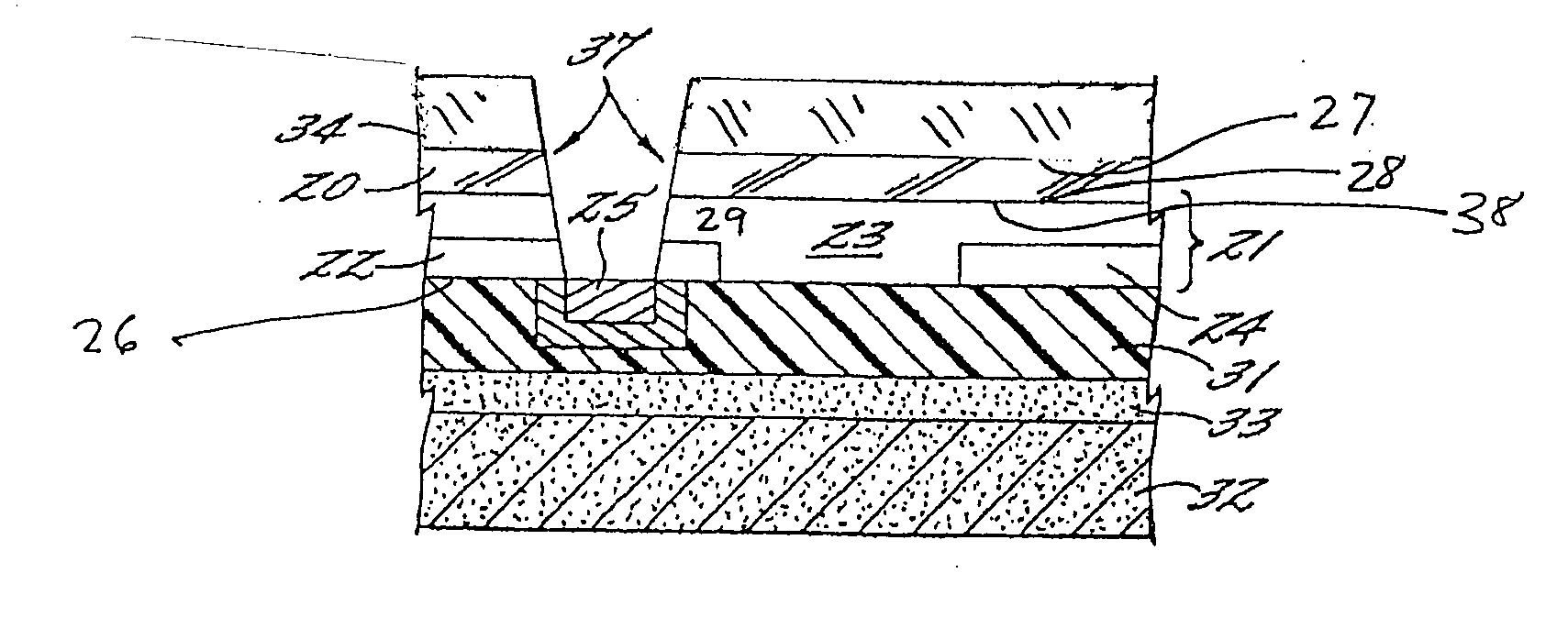

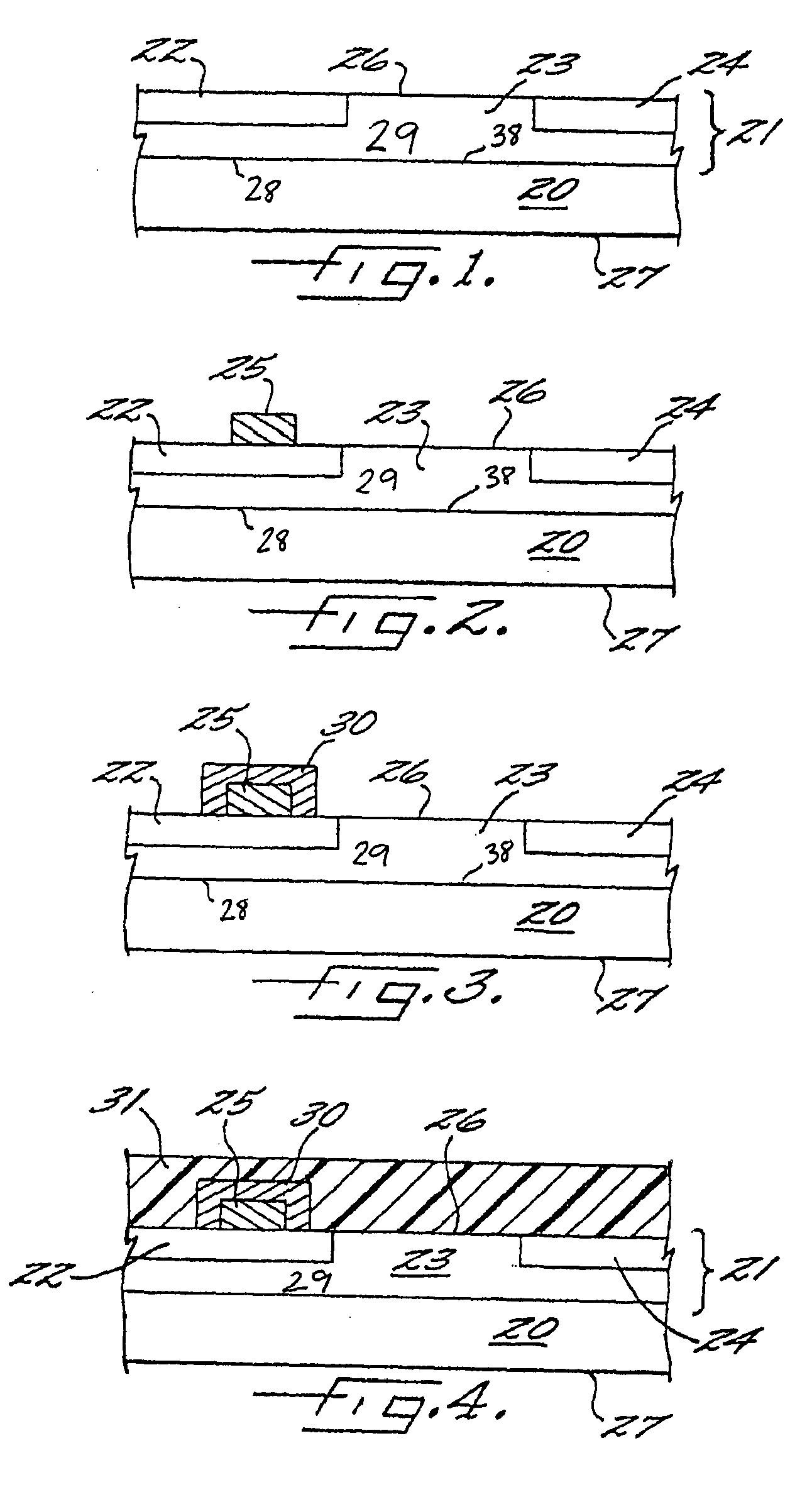

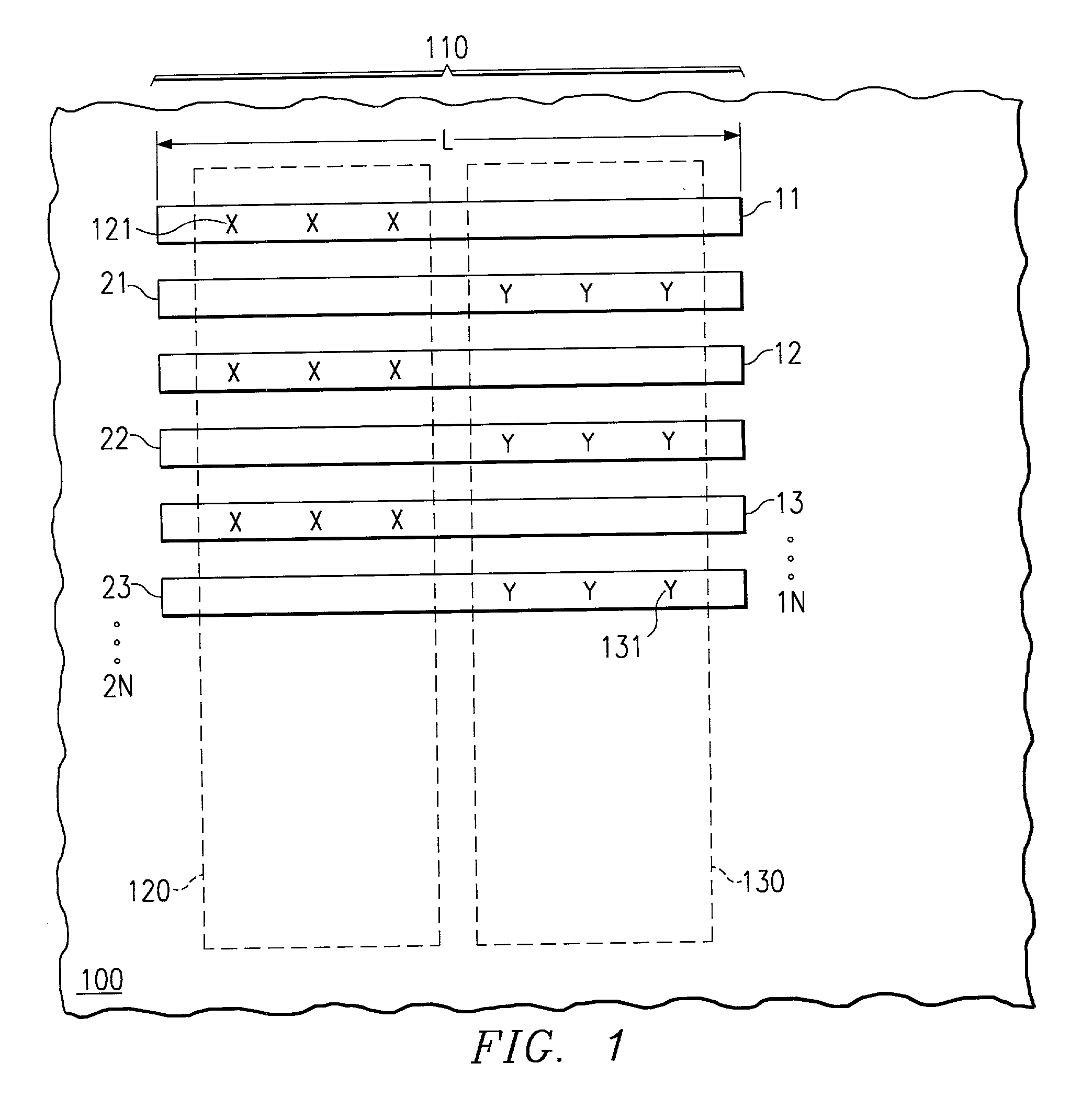

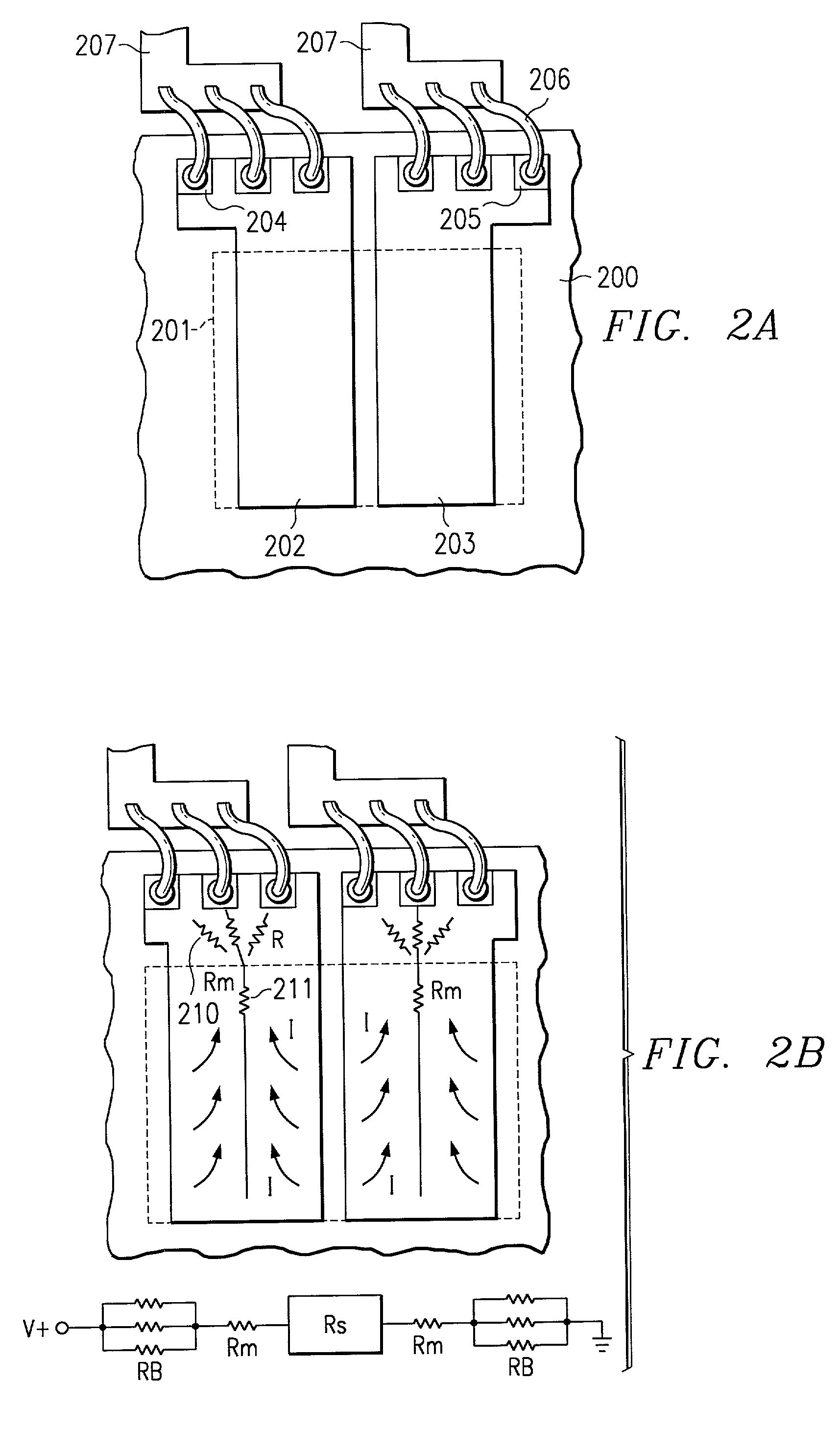

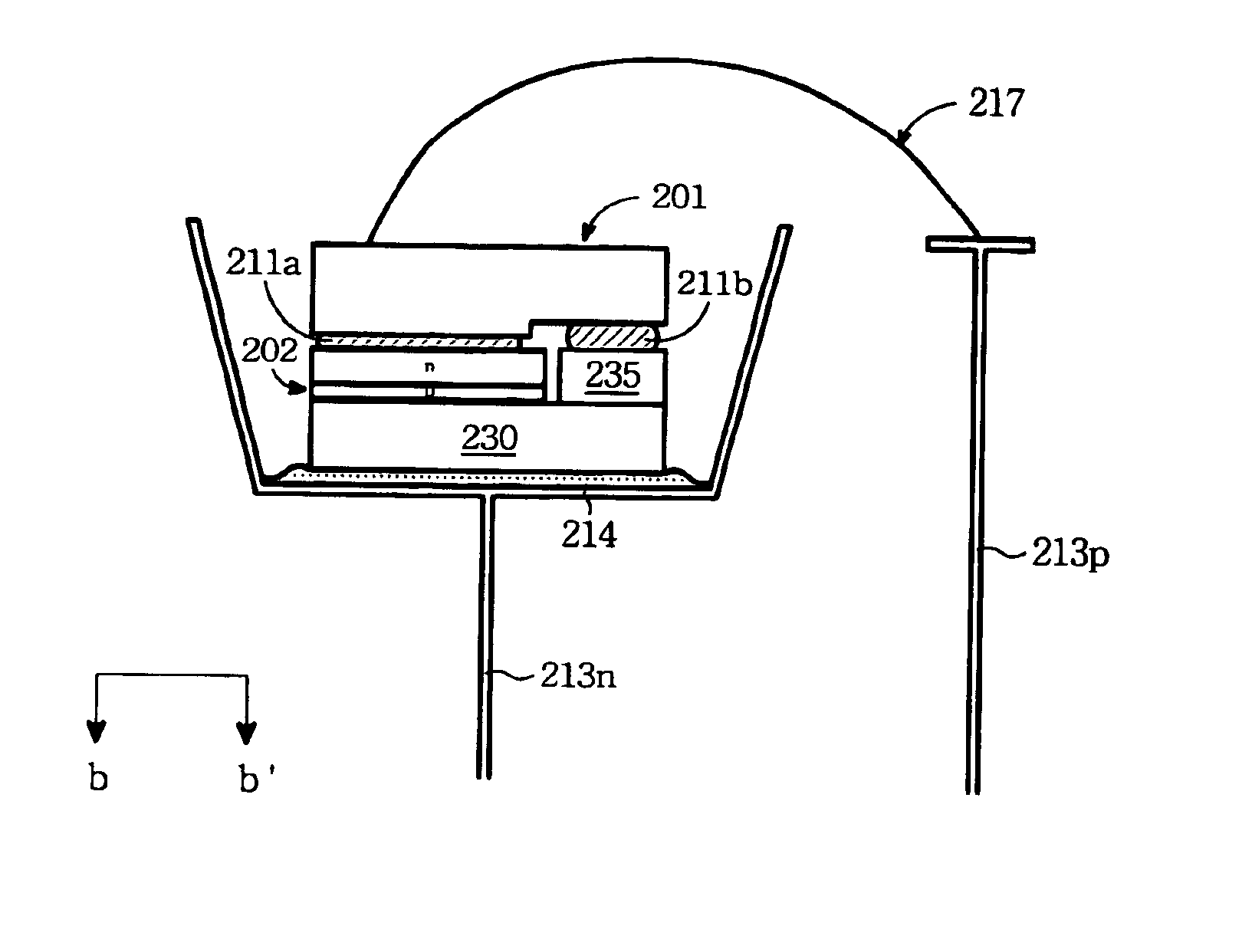

Integrated power circuits with distributed bonding and current flow

InactiveUS20020011674A1Increase speedLow costTransistorSemiconductor/solid-state device detailsThermal energyContact pad

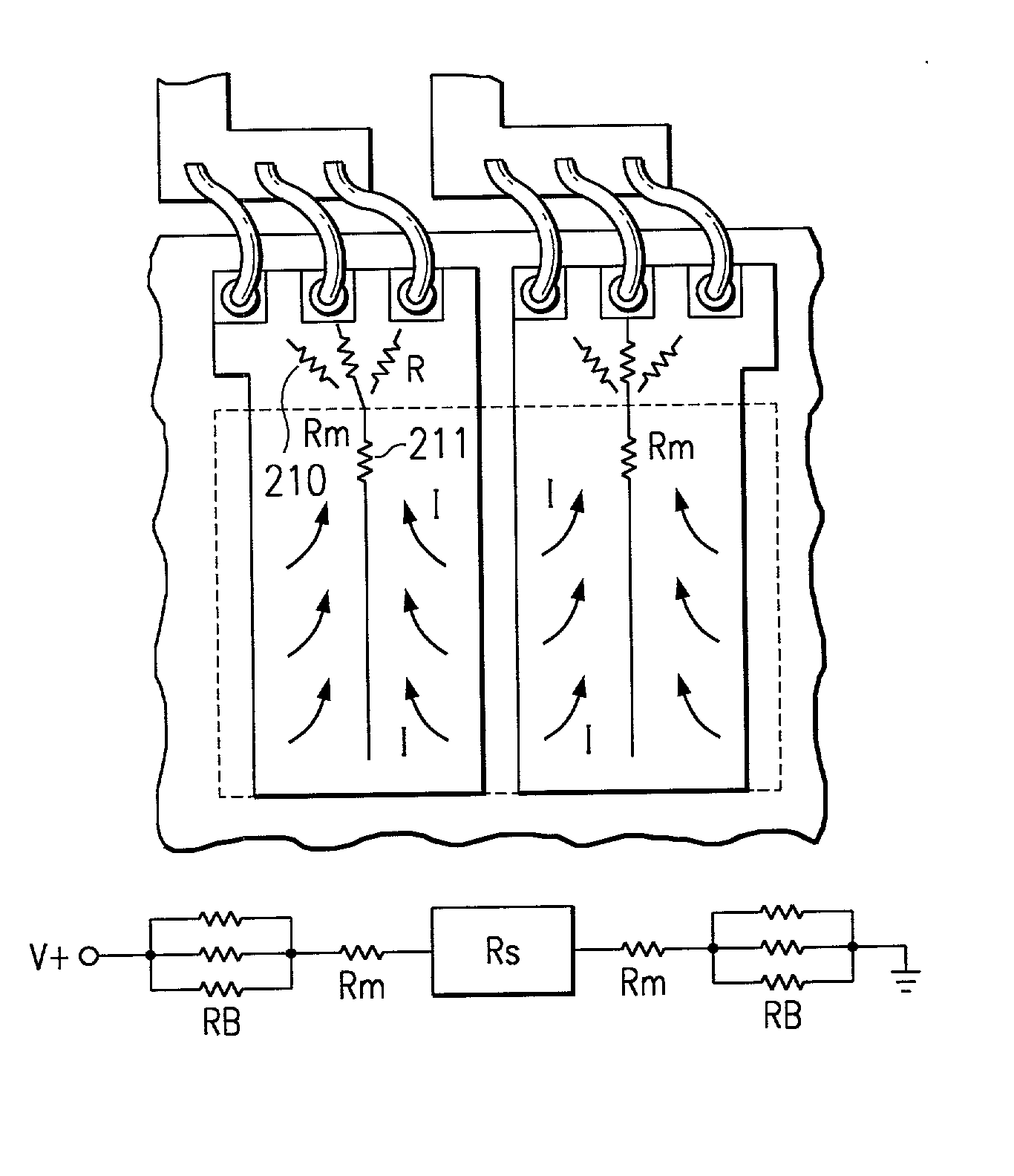

A semiconductor integrated circuit comprises contact pads located over active components, which are positioned to minimize the distance for power delivery between a selected pad and one or more corresponding active components, to which the power is to be delivered. This minimum distance further enhances dissipation of thermal energy released by the active components. More specifically, a semiconductor integrated circuit comprises a laterally organized power transistor, an array of power supply contact pads distributed over the transistor, means for providing a distributed, predominantly vertical current flow from the contact pads to the transistor, and means for connecting a power source to each of the contact pads. Positioning the power supply contact pads directly over the active power transistor further saves precious silicon real estate area. The means for vertical current flow include contact pads made of a stack of metal layers comprising refractory metals for adhesion, copper and nickel as stress-absorbing metals, and gold or palladium as bondable and solderable outermost metals. The means for connecting a power source include wire bonding and solder ball interconnection.

Owner:TEXAS INSTR INC

Package of lightemitting diode with protective element

InactiveUS6861677B2Increase light intensityDissipate quicklySolid-state devicesSemiconductor devicesInsulation layerElectrical connection

A package structure of light-emitting diode with an electrostatic protective diode is disclosed. The structure has a light-emitting diode, an electrostatic protective diode, an electrical & heat conductive pad, and an electrical & heat conductive base substrate. The light-emitting diode is flipped and with its p-electrode and n-electrode, respectively, mounted on the n-electrode of the electrostatic protective diode and the electrical & heat conductive pad by conductive bumps. The latter two are separated themselves by a gap or an insulation layer and both of them are mounted on and electrically connected to the electrical & heat conductive base substrate. The structure is then through a bonding wire bonding to a bonding pad and the electrical & heat conductive base structure, respectively, connected to a positive and a negative terminal of a DC power to implement the electrical connection. The foregoing bonding pad is located on the exposed portion of n-electrode of the electrostatic protective diode.

Owner:EPISTAR CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com