Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

64 results about "Quad Flat No-leads package" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

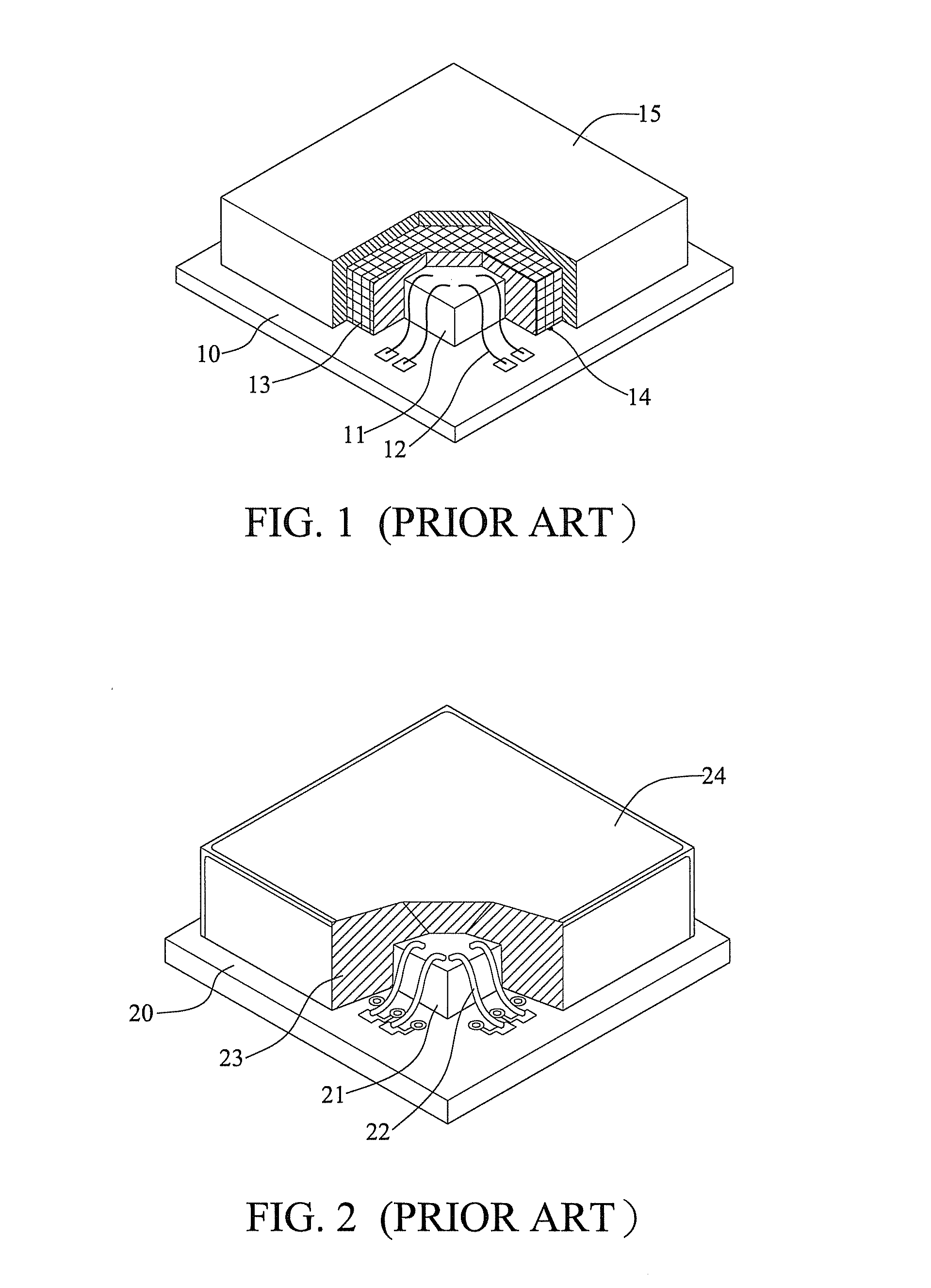

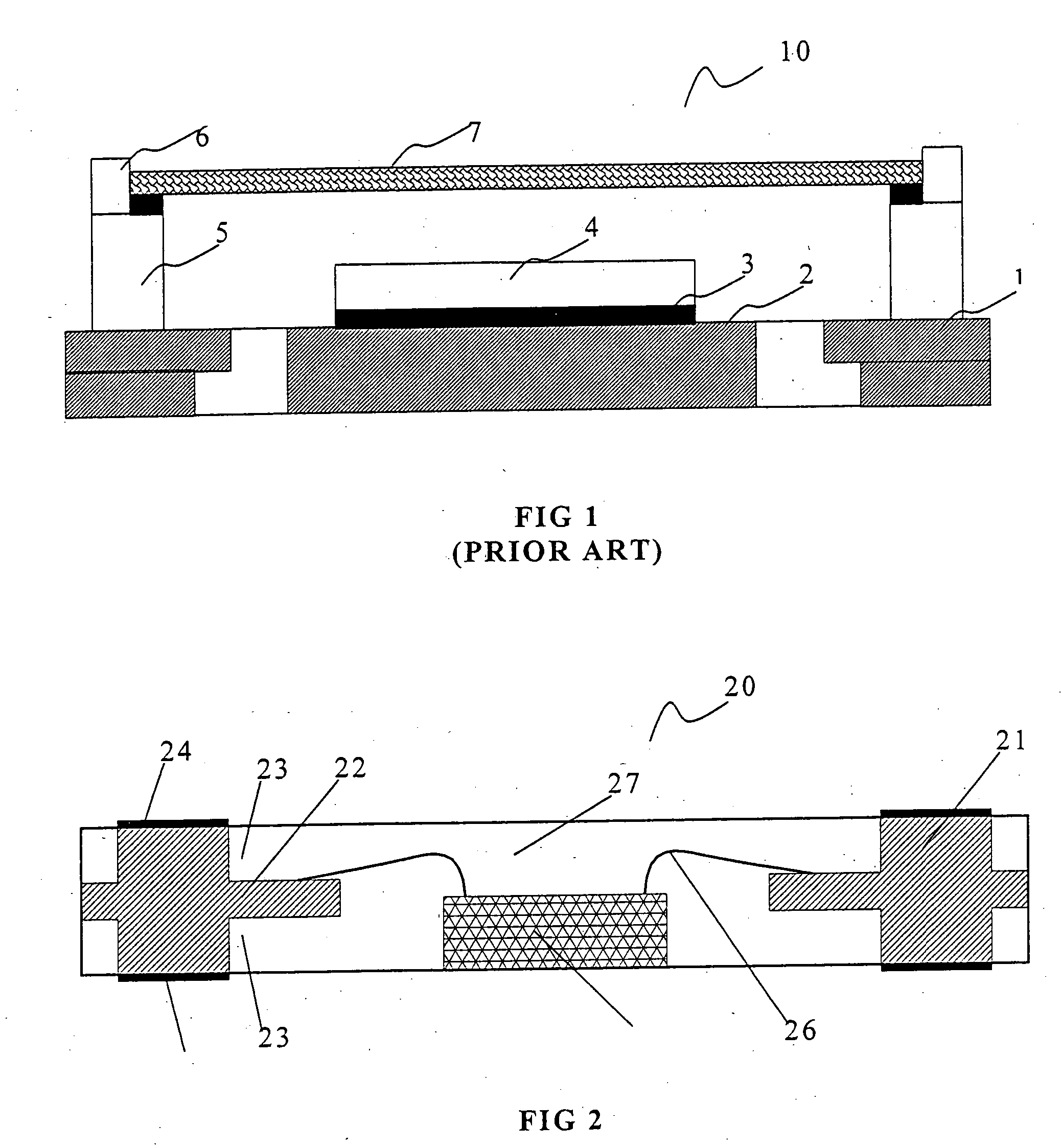

Flat no-leads packages such as quad-flat no-leads (QFN) and dual-flat no-leads (DFN) physically and electrically connect integrated circuits to printed circuit boards. Flat no-leads, also known as micro leadframe (MLF) and SON (small-outline no leads), is a surface-mount technology, one of several package technologies that connect ICs to the surfaces of PCBs without through-holes. Flat no-lead is a near chip scale plastic encapsulated package made with a planar copper lead frame substrate. Perimeter lands on the package bottom provide electrical connections to the PCB. Flat no-lead packages include an exposed thermal pad to improve heat transfer out of the IC (into the PCB). Heat transfer can be further facilitated by metal vias in the thermal pad. The QFN package is similar to the quad-flat package (QFP), and a ball grid array (BGA).

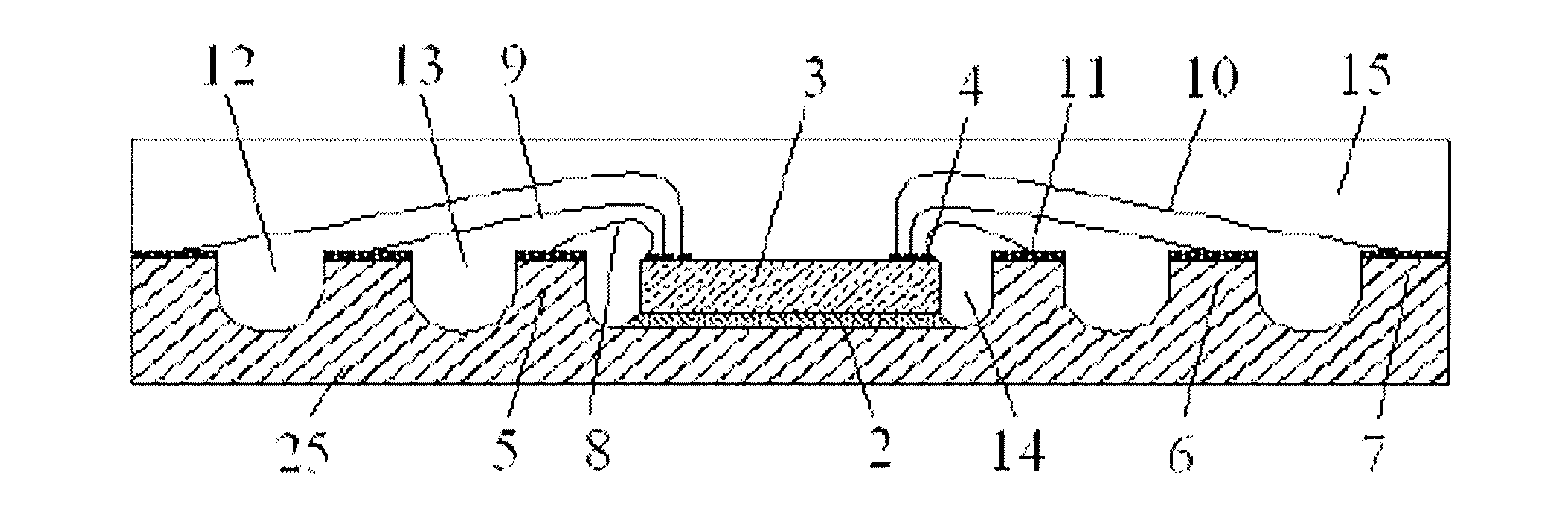

Thermally enhanced quad flat non-lead package of semiconductor

InactiveUS6198171B1Semiconductor/solid-state device detailsSolid-state devicesSemiconductorWire bonding

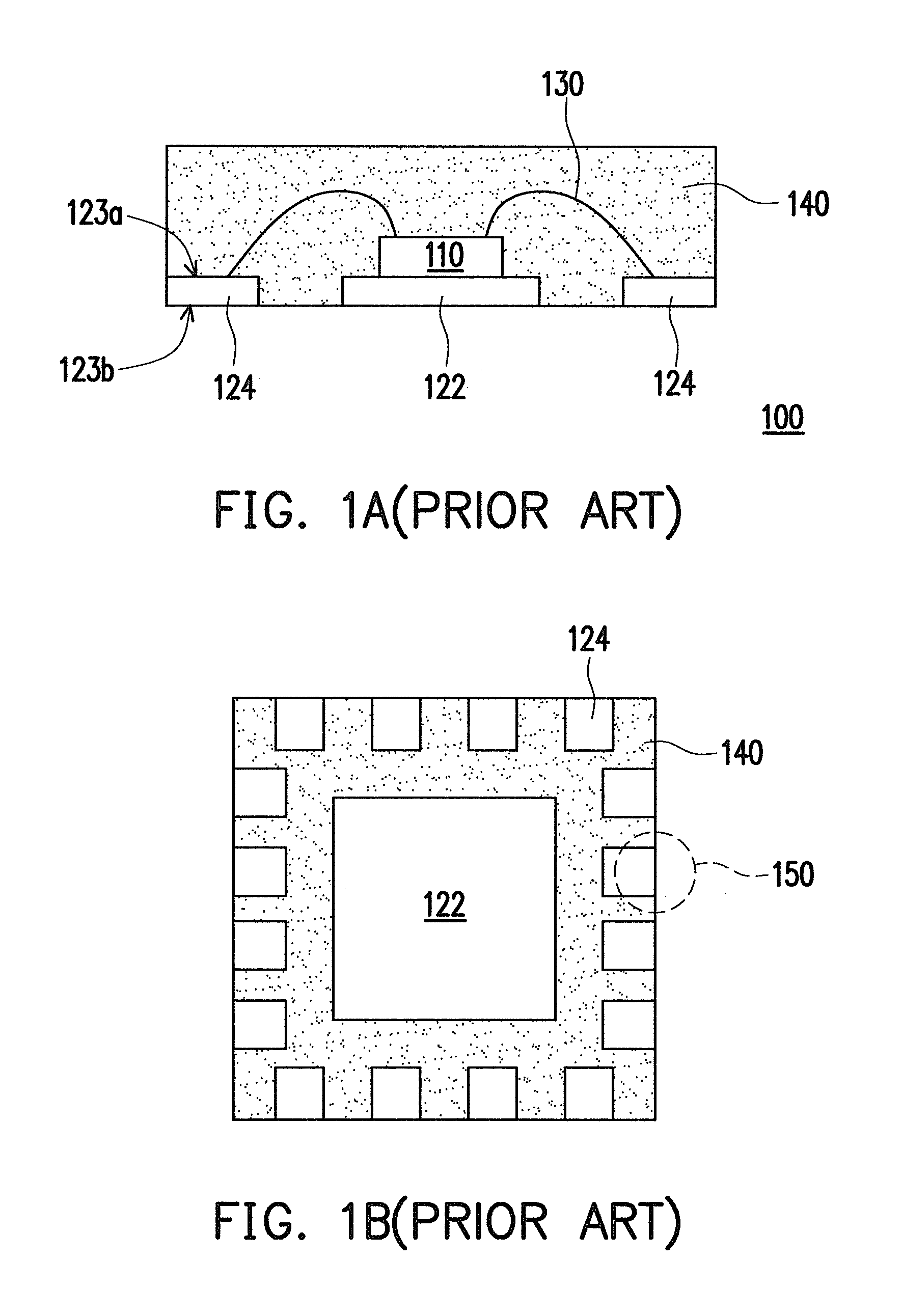

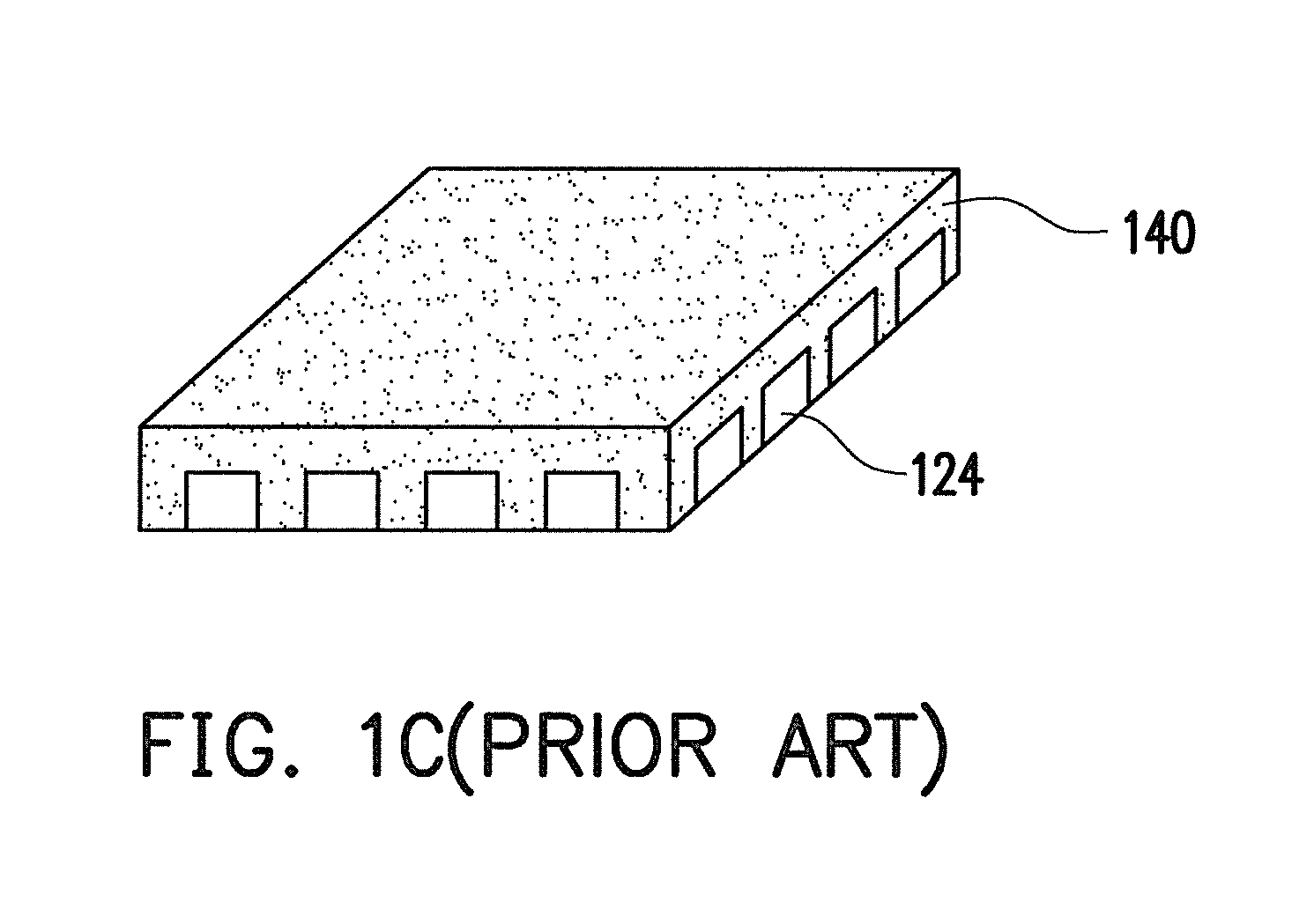

A thermally enhanced quad flat non-lead package of semiconductor comprises a chip a plurality of leads, and a molding compound. The chip has its active surface bonded to the top surface of the die pad, and the area of the die pad is smaller than that of the chip in order to expose the bonding pads on the active surface of the chip. The leads are disposed at the periphery of the die pad wherein the bottom surface of the lead has a stepped structure with a relatively thin portion to form a wire-bonding protruded zone. A plurality of bonding wires is used to electrically connect the wire-bonding protruded zone of the leads to the bonding pads of the chip. The molding compound encapsulates the chip, bonding wires, the die pad, and a portion of the surface of the leads, but exposes the bottom surface of the die pad. In this way, the encapsulating process makes the side surface of the lead, and the portion excluding the wire-bonding protruded zone of the bottom surface of the lead exposed in order to make the lead become the external connecting points of the package structure.

Owner:SILICONWARE PRECISION IND CO LTD

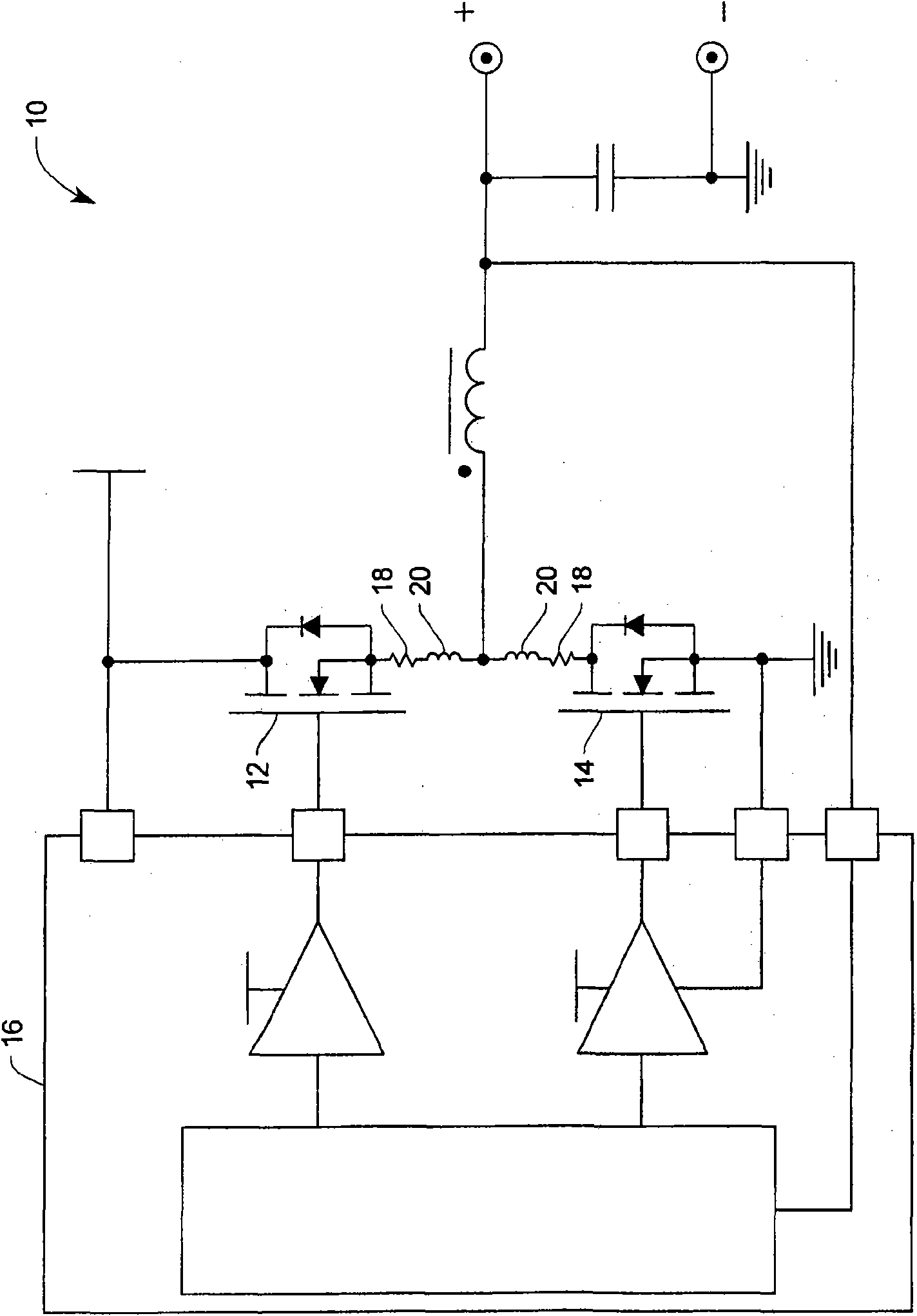

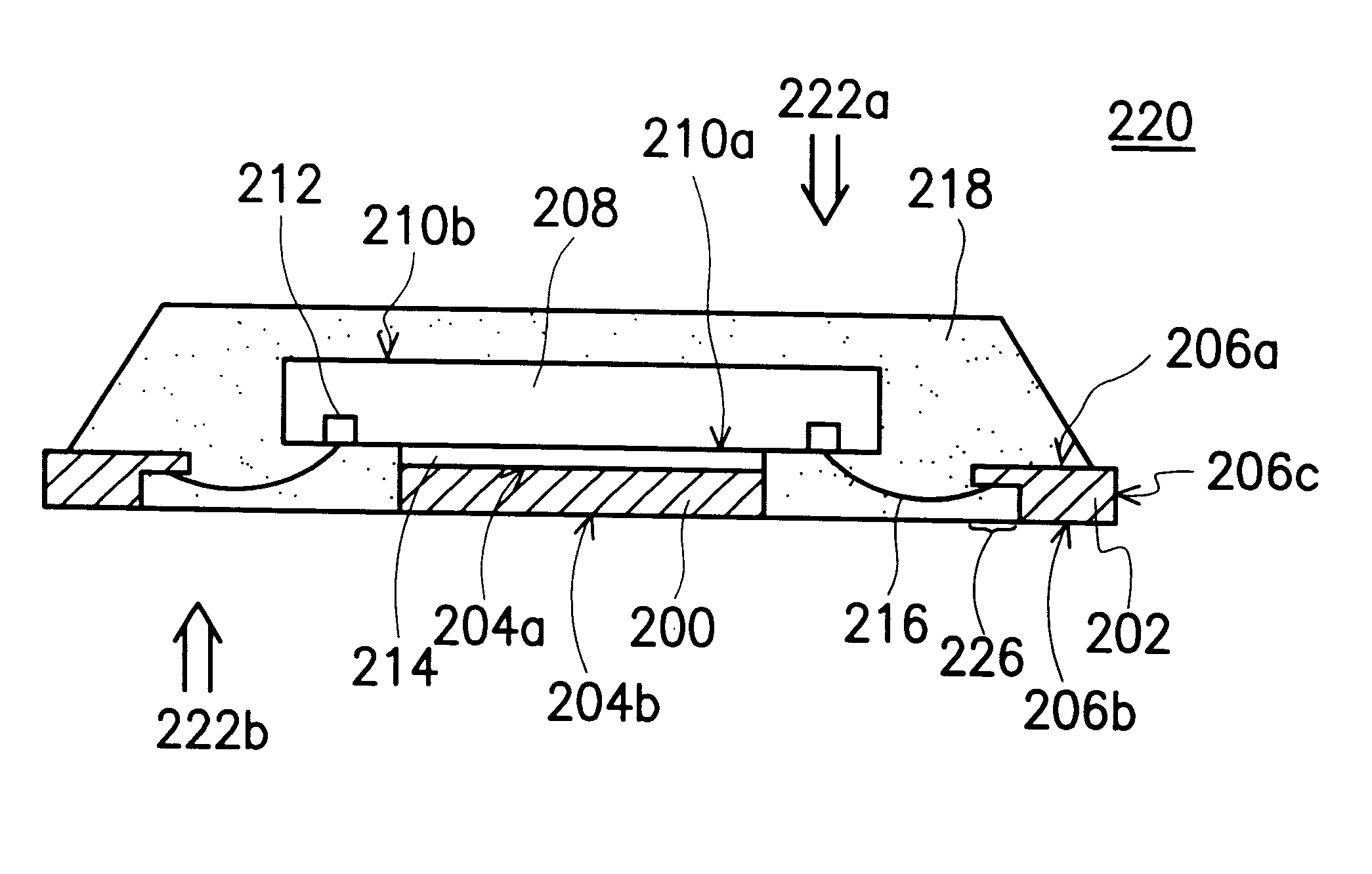

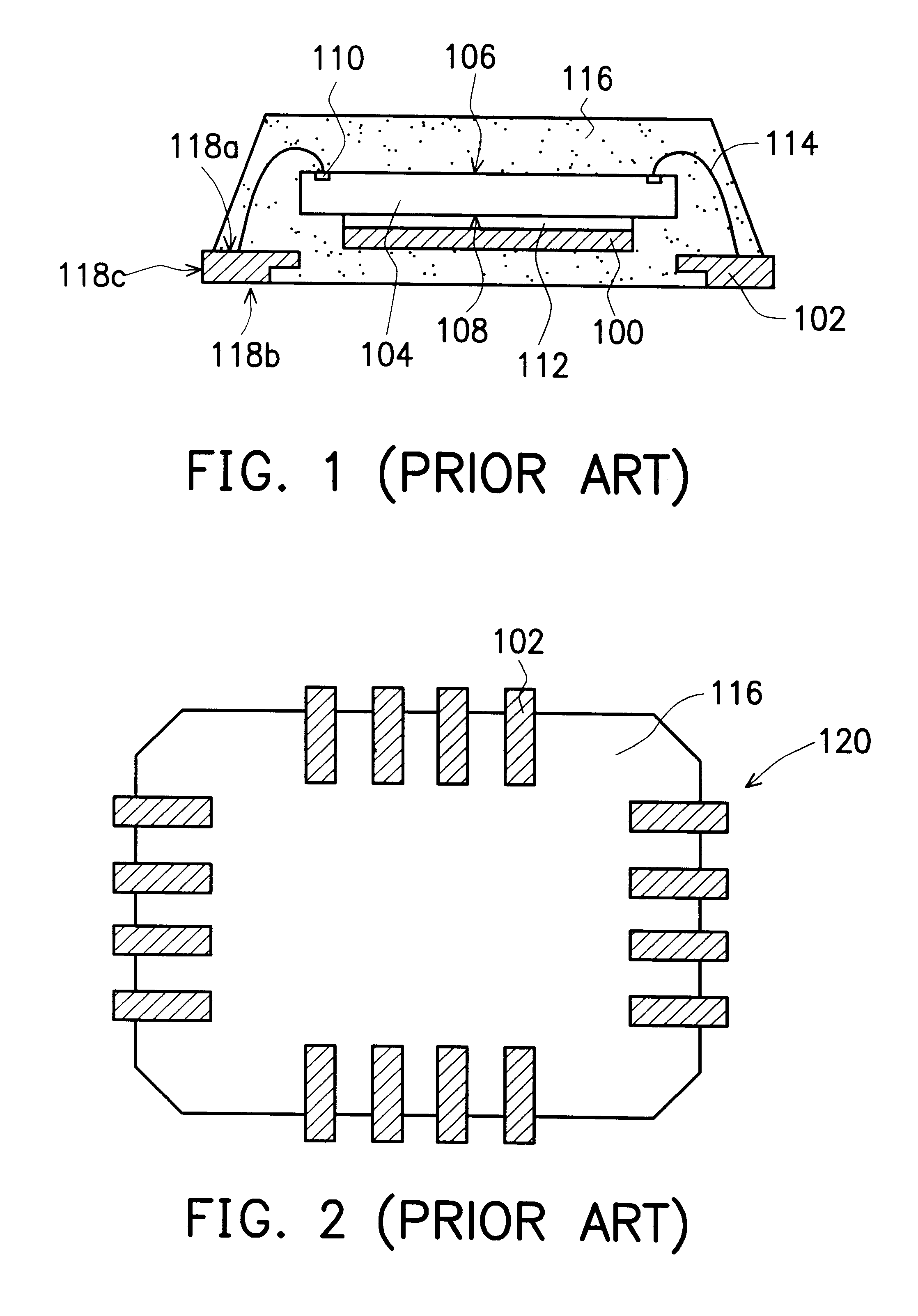

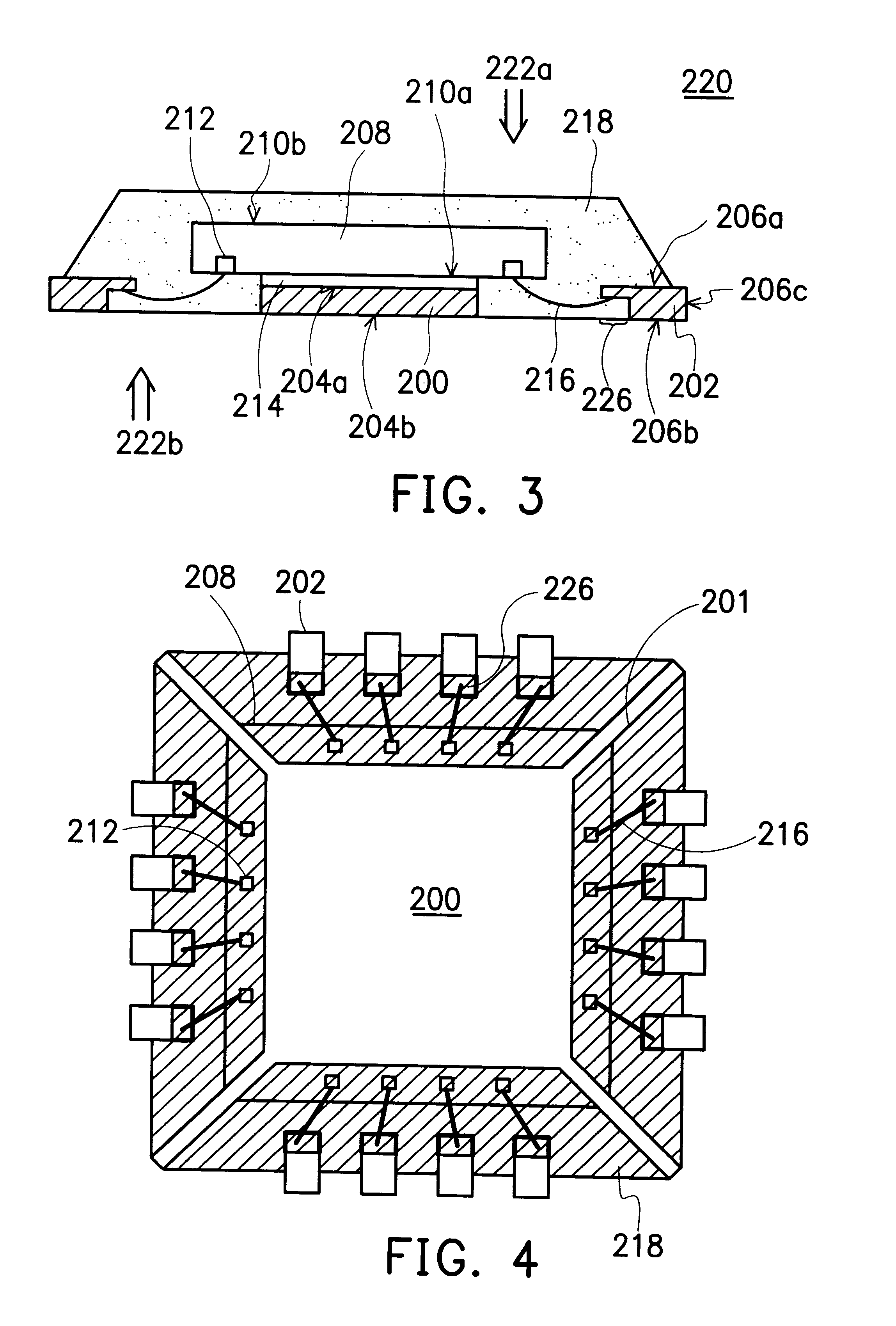

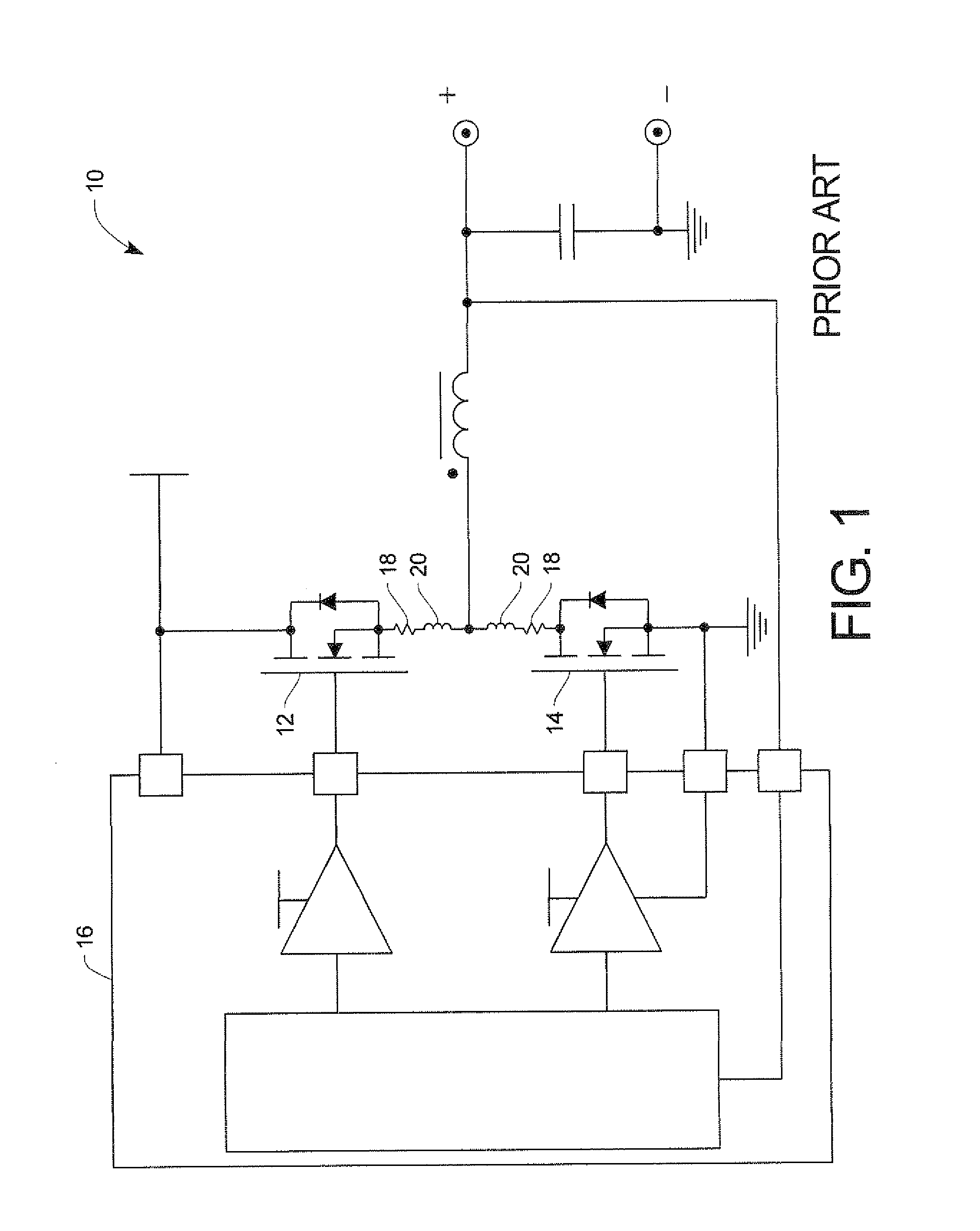

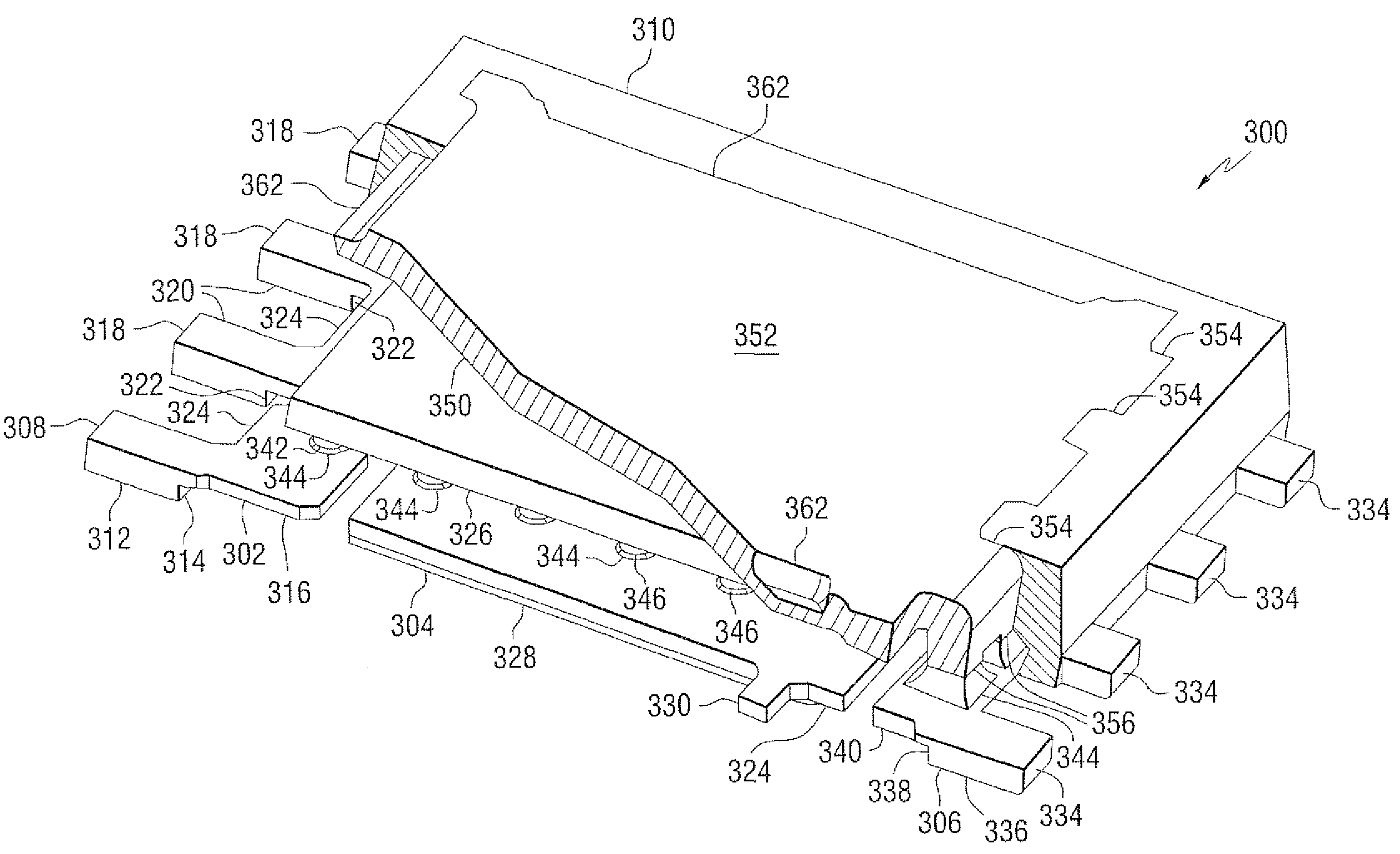

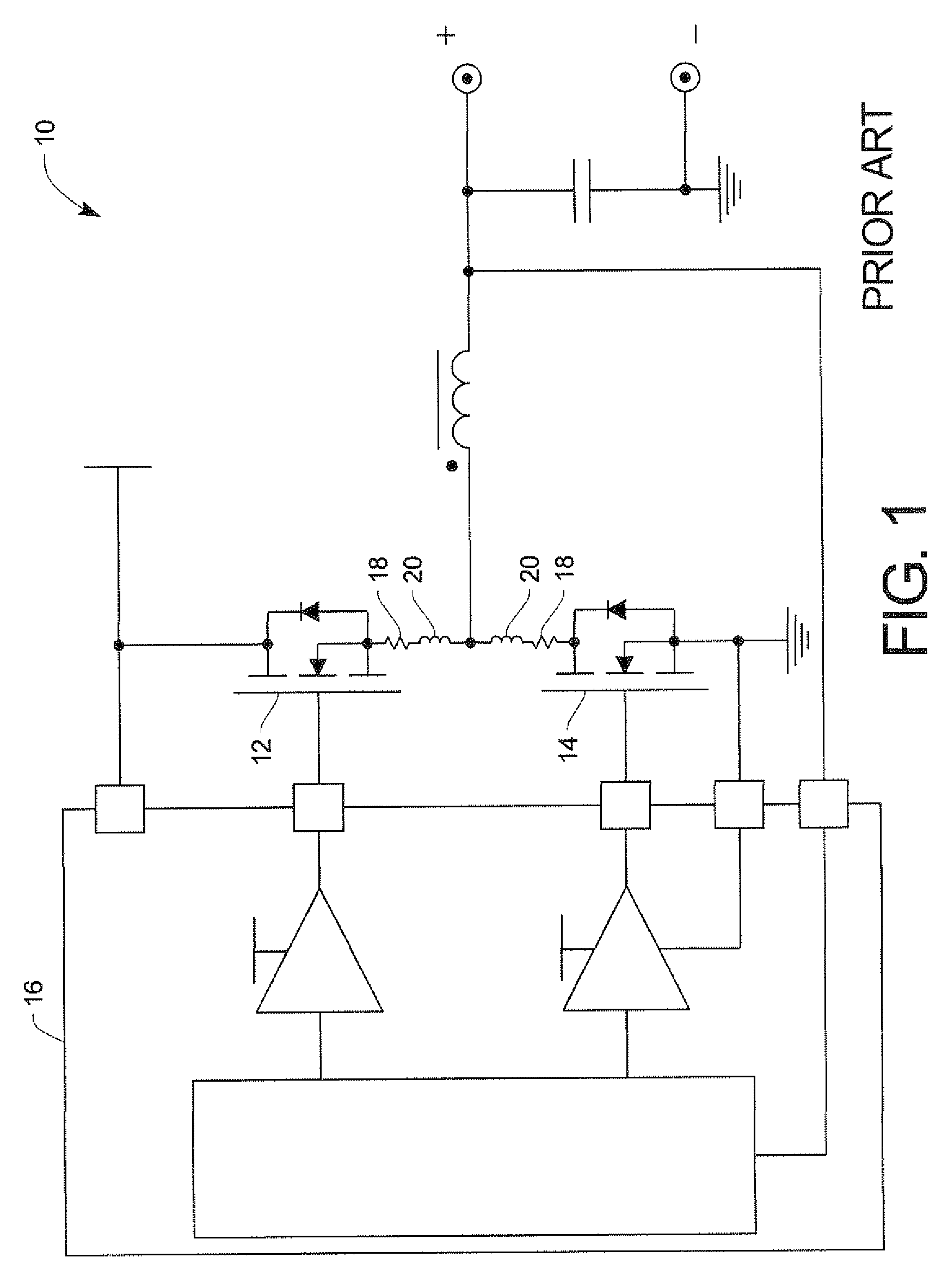

Dual side cooling integrated power device package and module and methods of manufacture

ActiveUS20080023807A1Semiconductor/solid-state device detailsSolid-state devicesEngineeringTransistor

An integrated power device module having a leadframe structure with first and second spaced pads and one or more common source-drain leads located between said first and second pads, first and second transistors flip chip attached respectively to said first and second pads, wherein the source of said second transistor is electrically connected to said one or more common source-drain leads, and a first clip attached to the drain of said first transistor and electrically connected to said one or more common source-drain leads. In another embodiment a partially encapsulated power quad flat no-lead package having an exposed top thermal drain clip which is substantially perpendicular to said with a folded stud exposed top thermal drain clip, and an exposed thermal source pad.

Owner:SEMICON COMPONENTS IND LLC

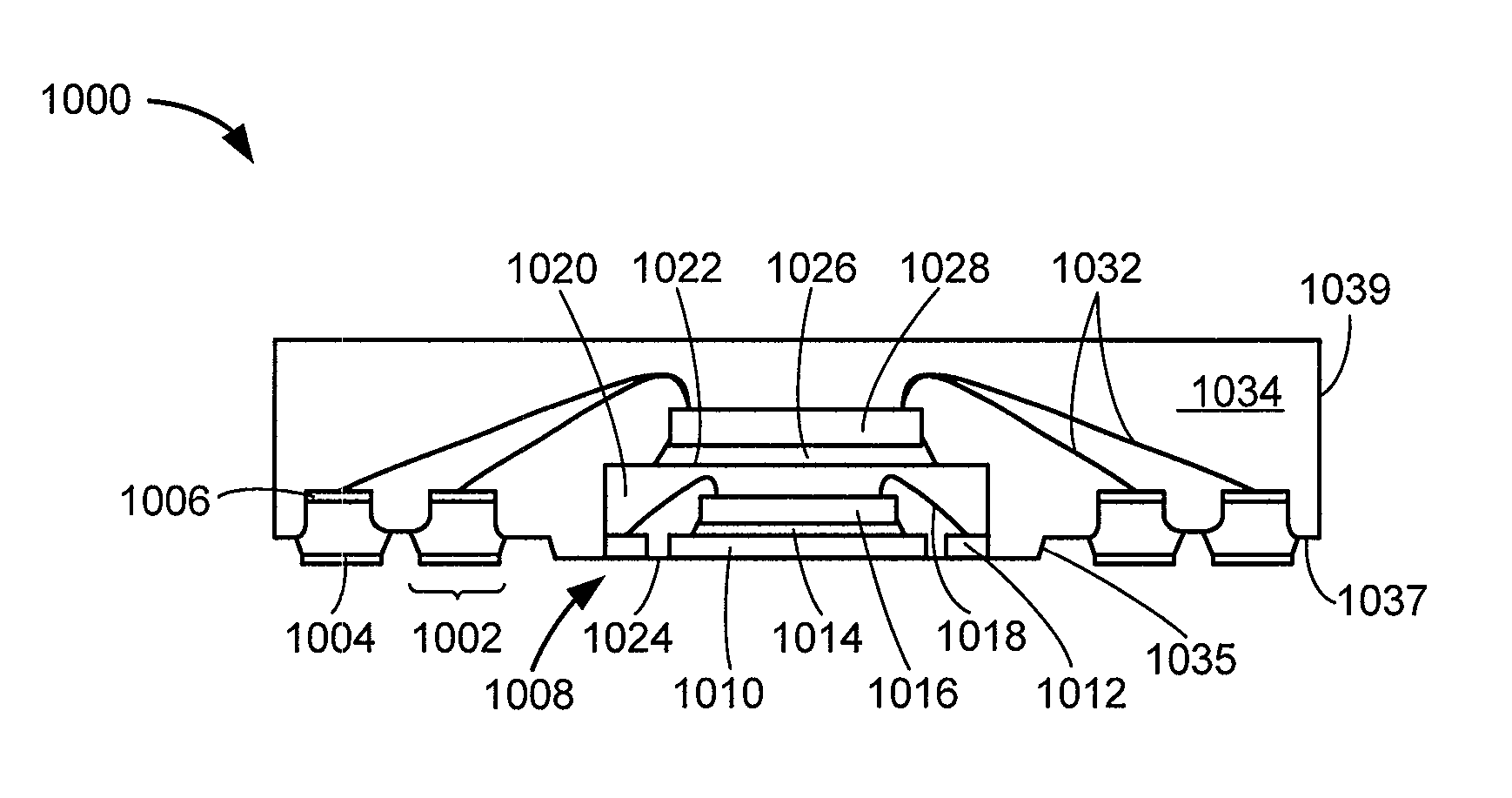

Dual side cooling integrated power device package and module with a clip attached to a leadframe in the package and the module and methods of manufacture

ActiveUS7663211B2Semiconductor/solid-state device detailsSolid-state devicesComputer moduleEngineering

An integrated power device module having a leadframe structure with first and second spaced pads and one or more common source-drain leads located between said first and second pads, first and second transistors flip chip attached respectively to said first and second pads, wherein the source of said second transistor is electrically connected to said one or more common source-drain leads, and a first clip attached to the drain of said first transistor and electrically connected to said one or more common source-drain leads. In another embodiment a partially encapsulated power quad flat no-lead package having an exposed top thermal drain clip which is substantially perpendicular to said with a folded stud exposed top thermal drain clip, and an exposed thermal source pad.

Owner:SEMICON COMPONENTS IND LLC

Ultra-thin quad flat no-lead (QFN) package

ActiveUS20070114641A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor packageSemiconductor chip

An ultra-thin Quad Flat No-Lead (QFN) semiconductor chip package having a leadframe with lead terminals formed by recesses from both the top and bottom surfaces and substantially aligned contact areas formed on either the top or bottom surfaces. A die is electrically connected to the plurality of lead terminals and a molding compound encapsulates the leadframe and die together so as to form the ultra-thin QFN package. Accordingly, the substantially aligned contact areas are exposed on both the top and bottom surfaces of the package. The present disclosure also provides an ultra-thin Optical Quad Flat No-Lead (OQFN) semiconductor chip package, a stacked semiconductor module comprising at least two QFN semiconductor chip packages, and a method for manufacturing an ultra-thin Quad Flat No-Lead (QFN) semiconductor packages.

Owner:STMICROELECTRONICS ASIA PACIFIC PTE

Packaged device adapter assembly with alignment structure and methods regarding same

InactiveUS6877993B2Semiconductor/solid-state device detailsSolid-state devicesQuad Flat No-leads packageHigh density

A packaged device adapter assembly for use with high density integrated circuit packages, e.g., micro lead frame packages, micro lead chip carriers, quad flat no lead packages, and micro ball grid array packages, etc., includes an alignment structure for aligning a packaged device therein.

Owner:IRONWOOD ELECTRONICS

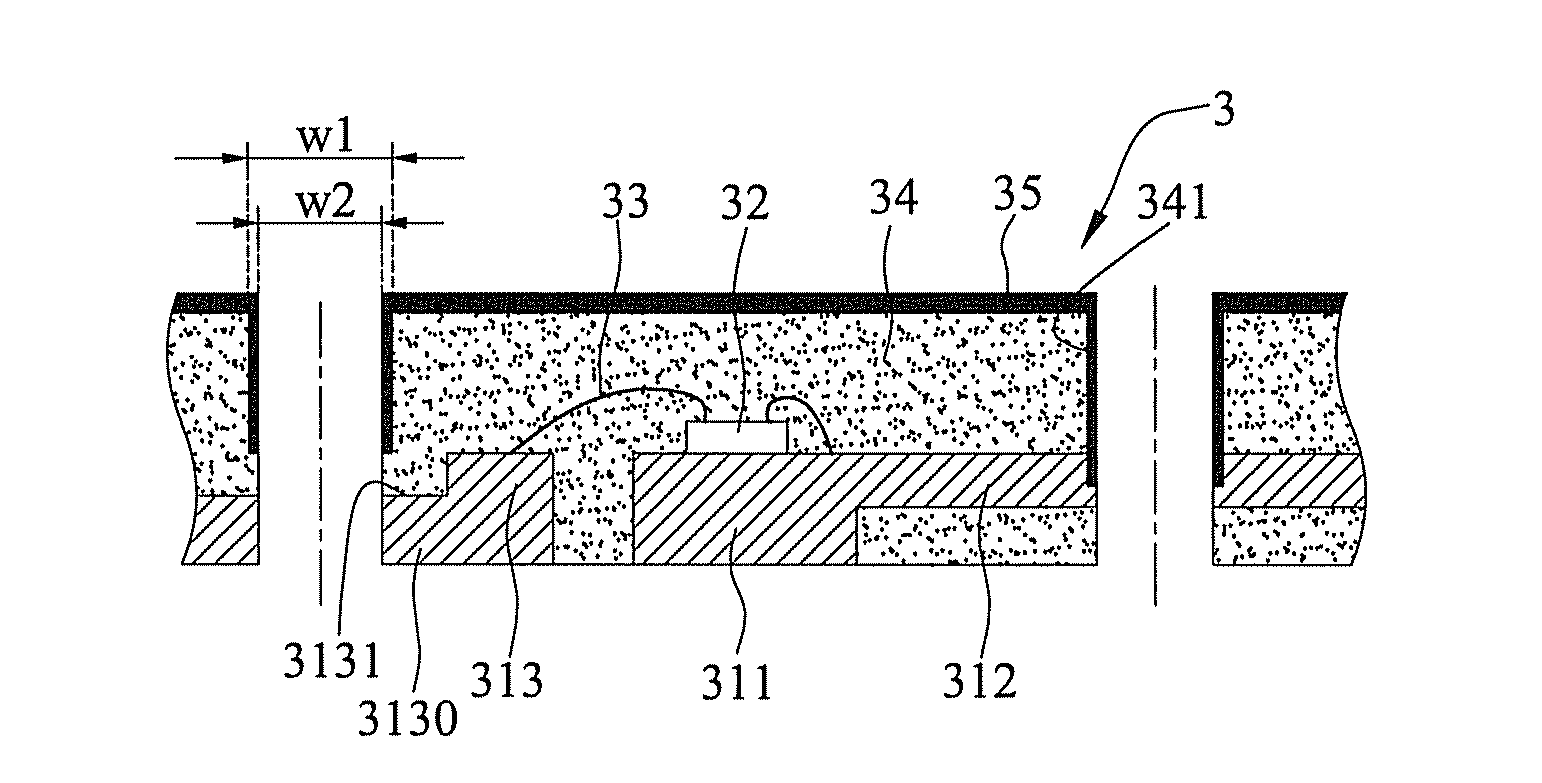

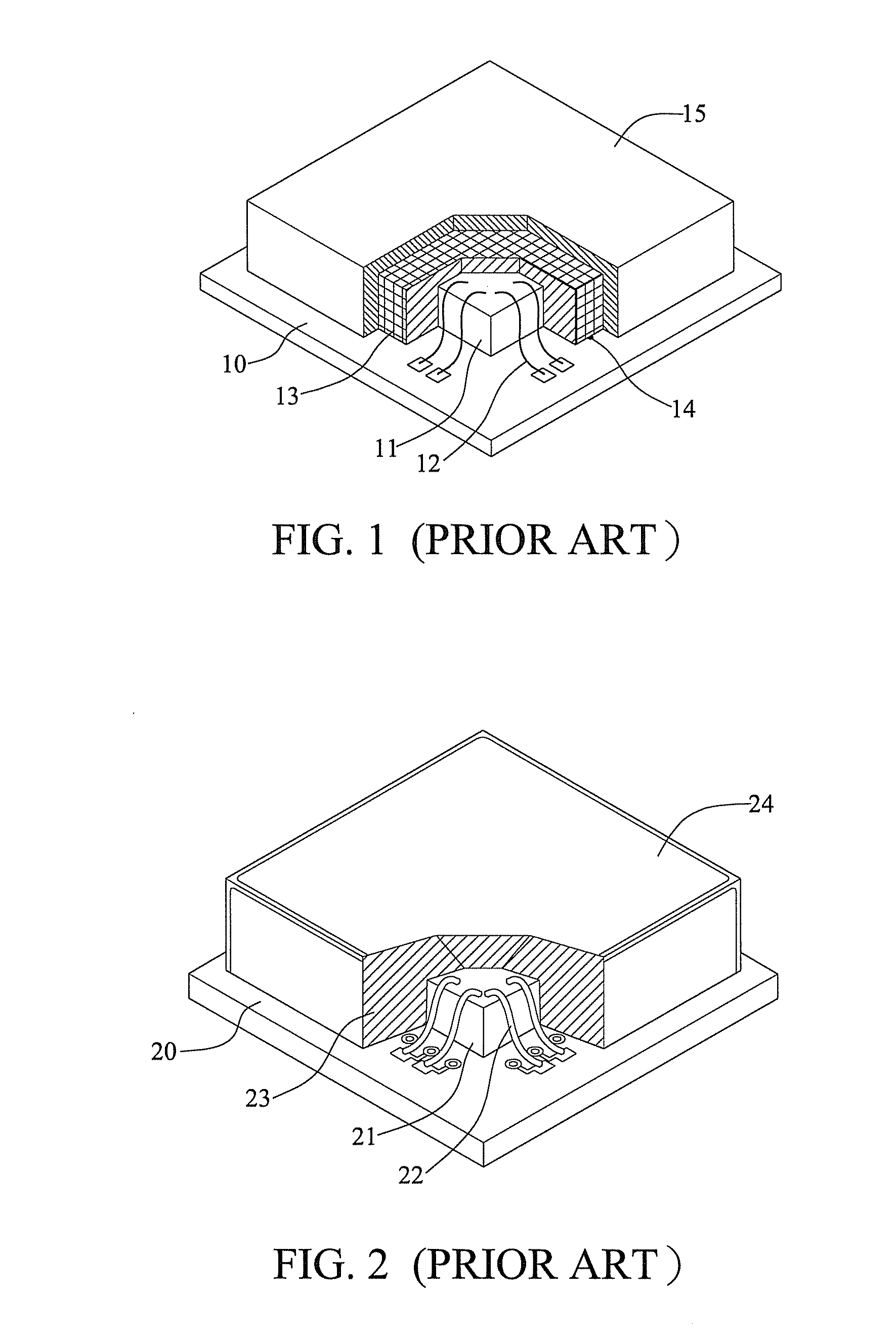

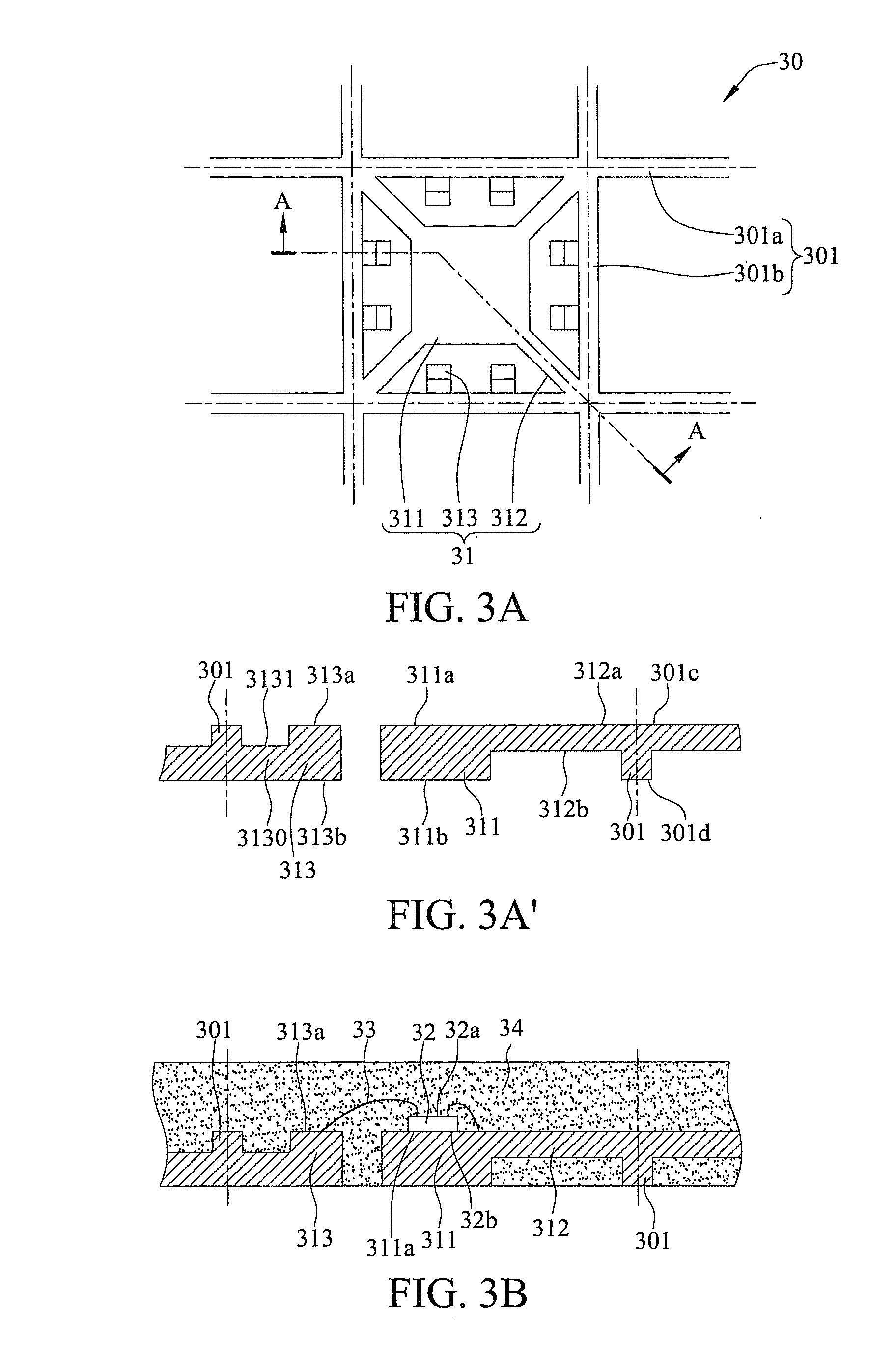

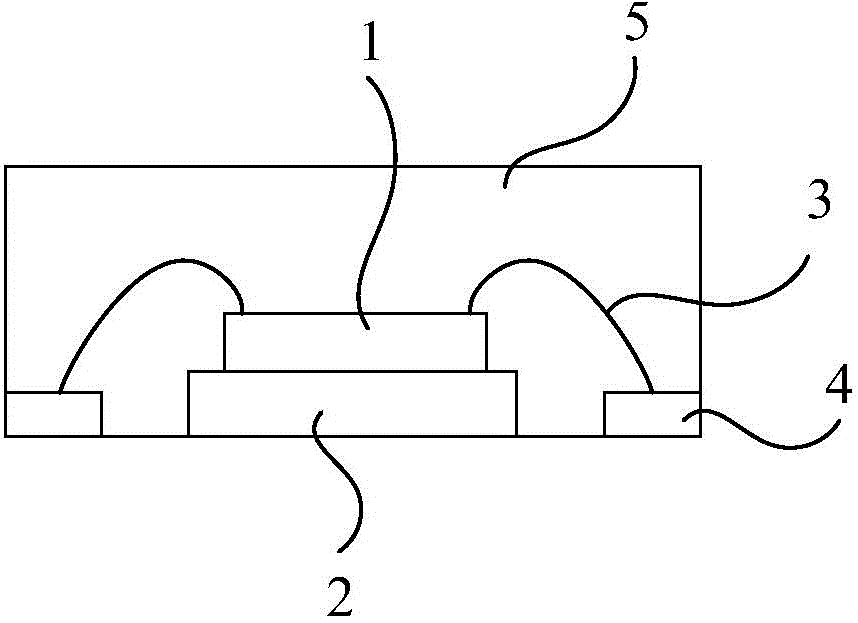

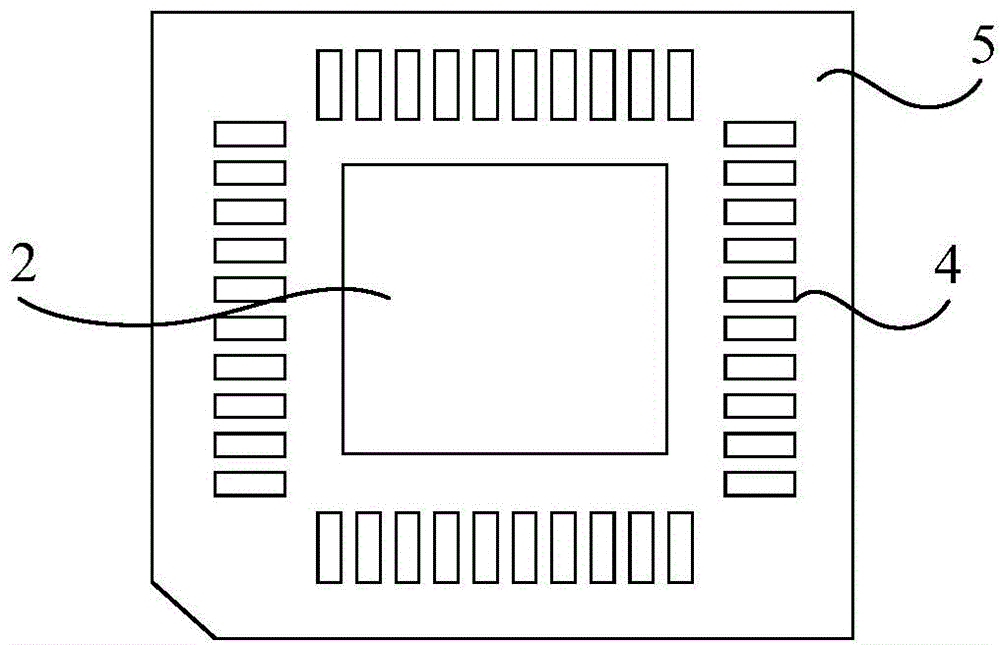

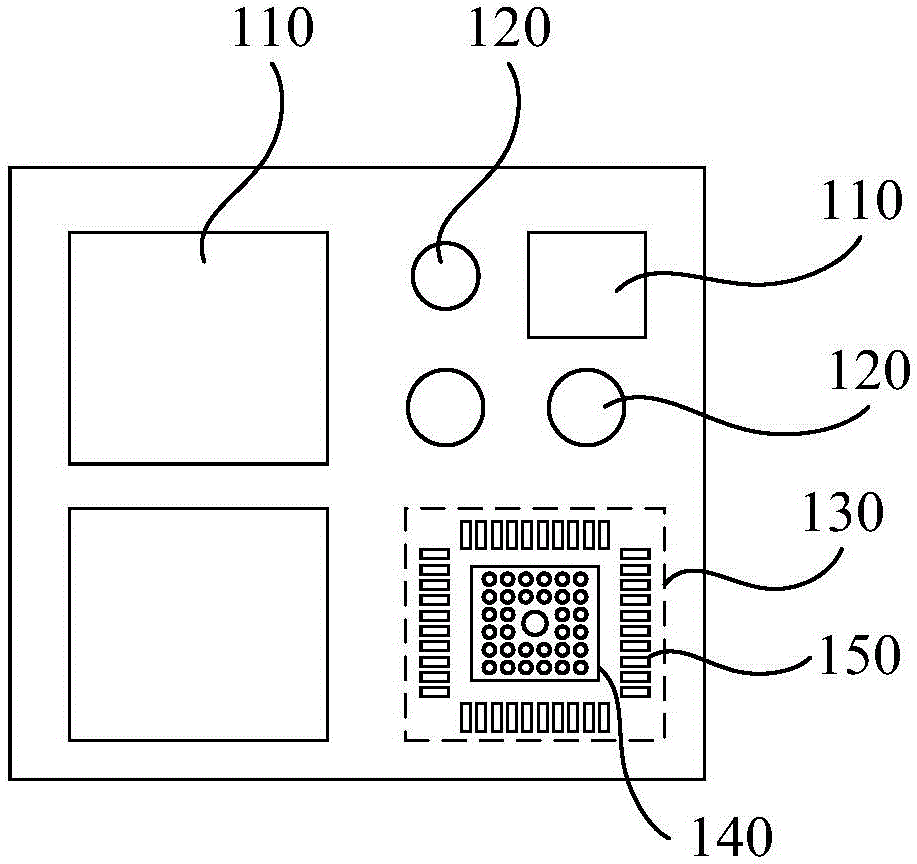

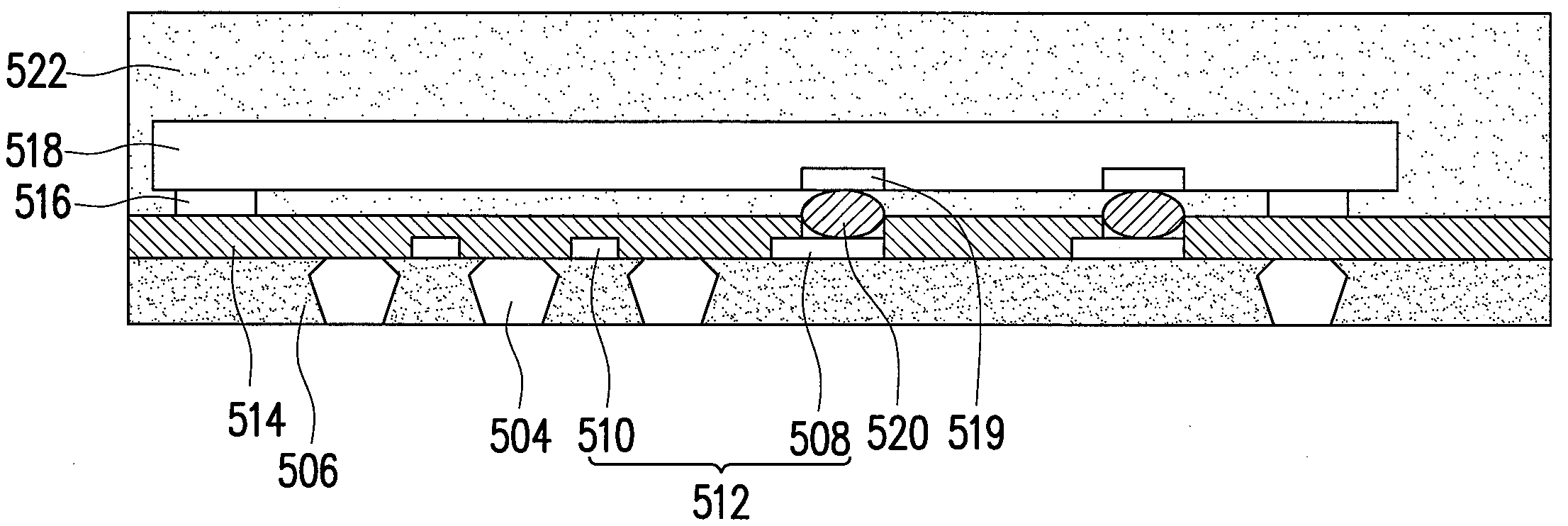

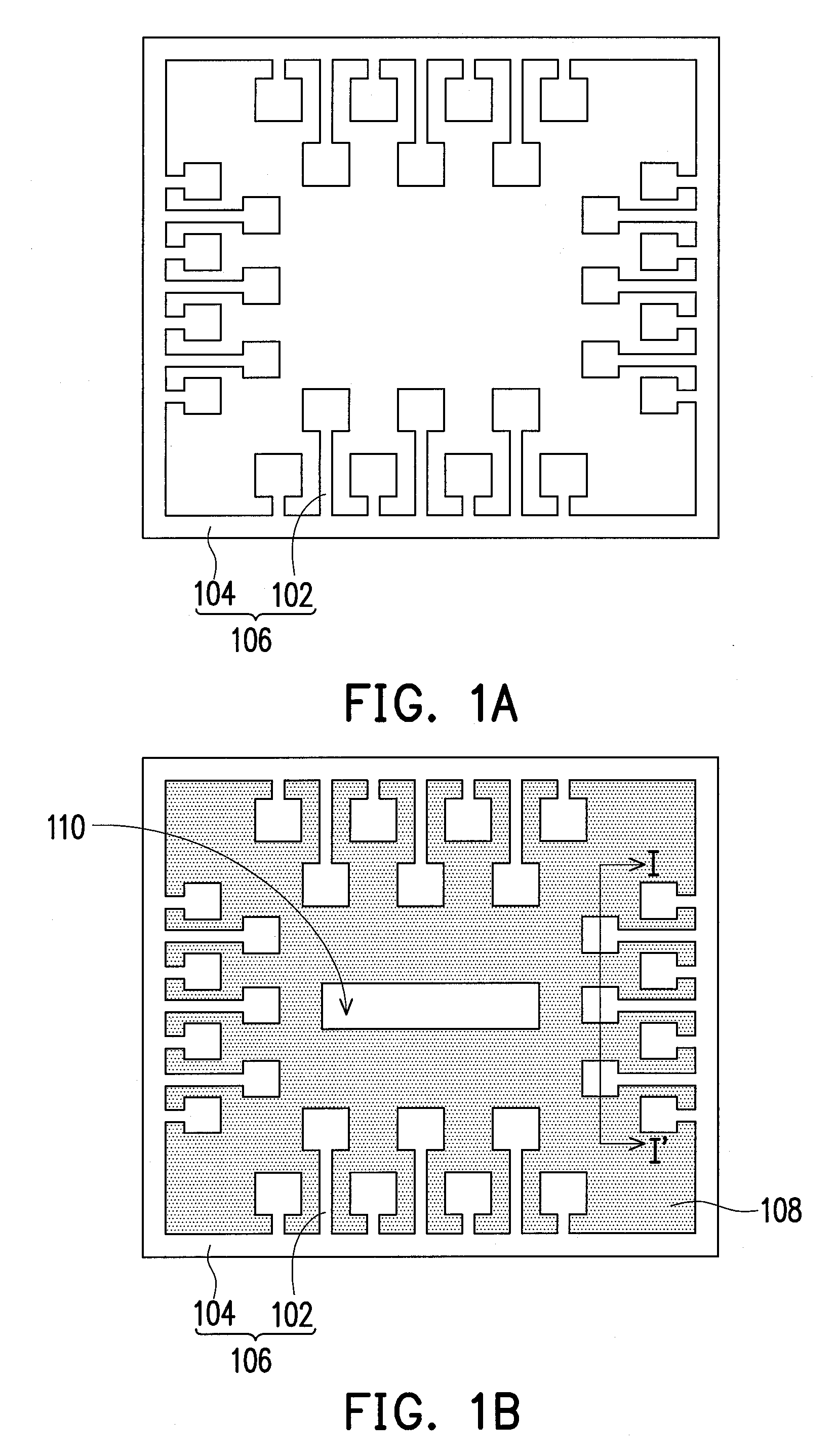

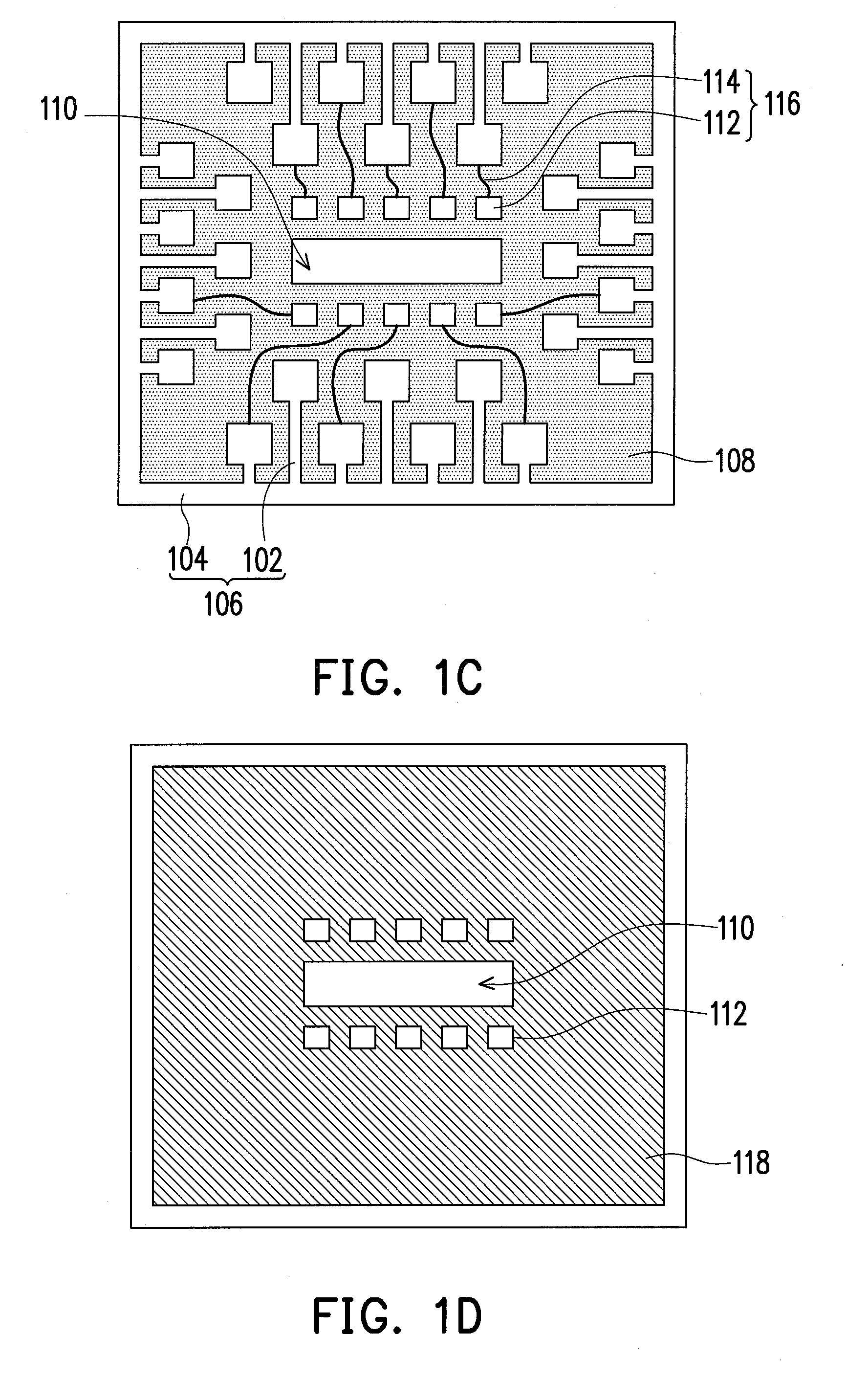

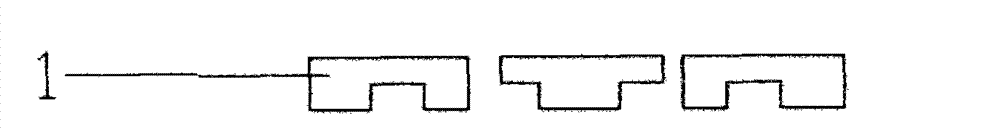

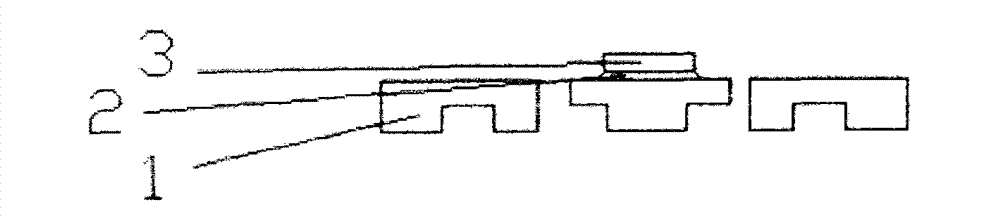

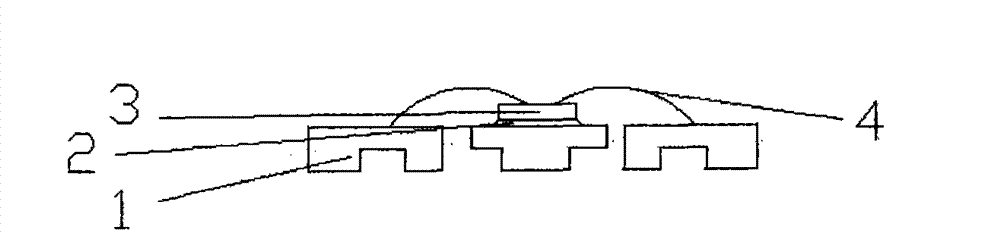

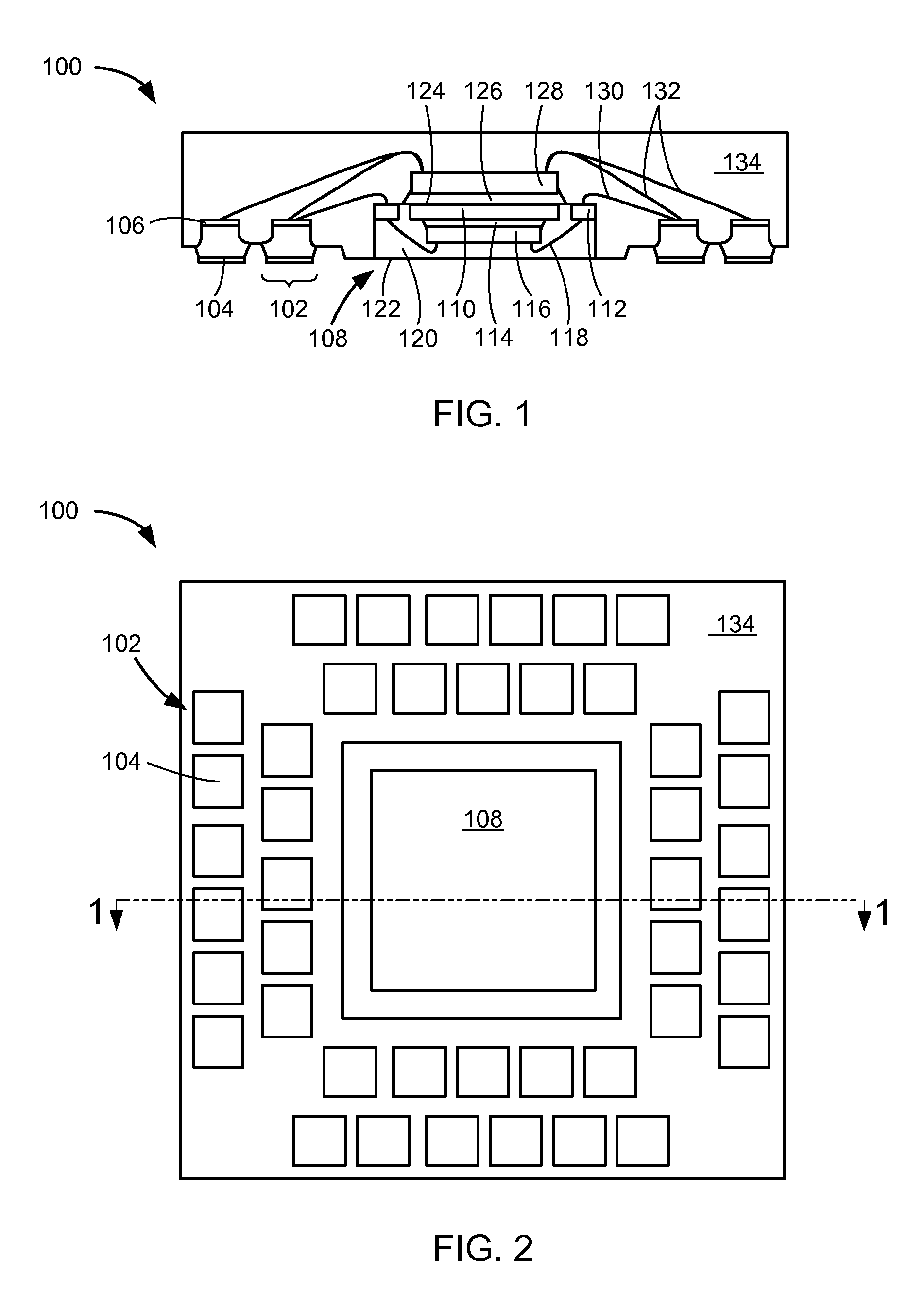

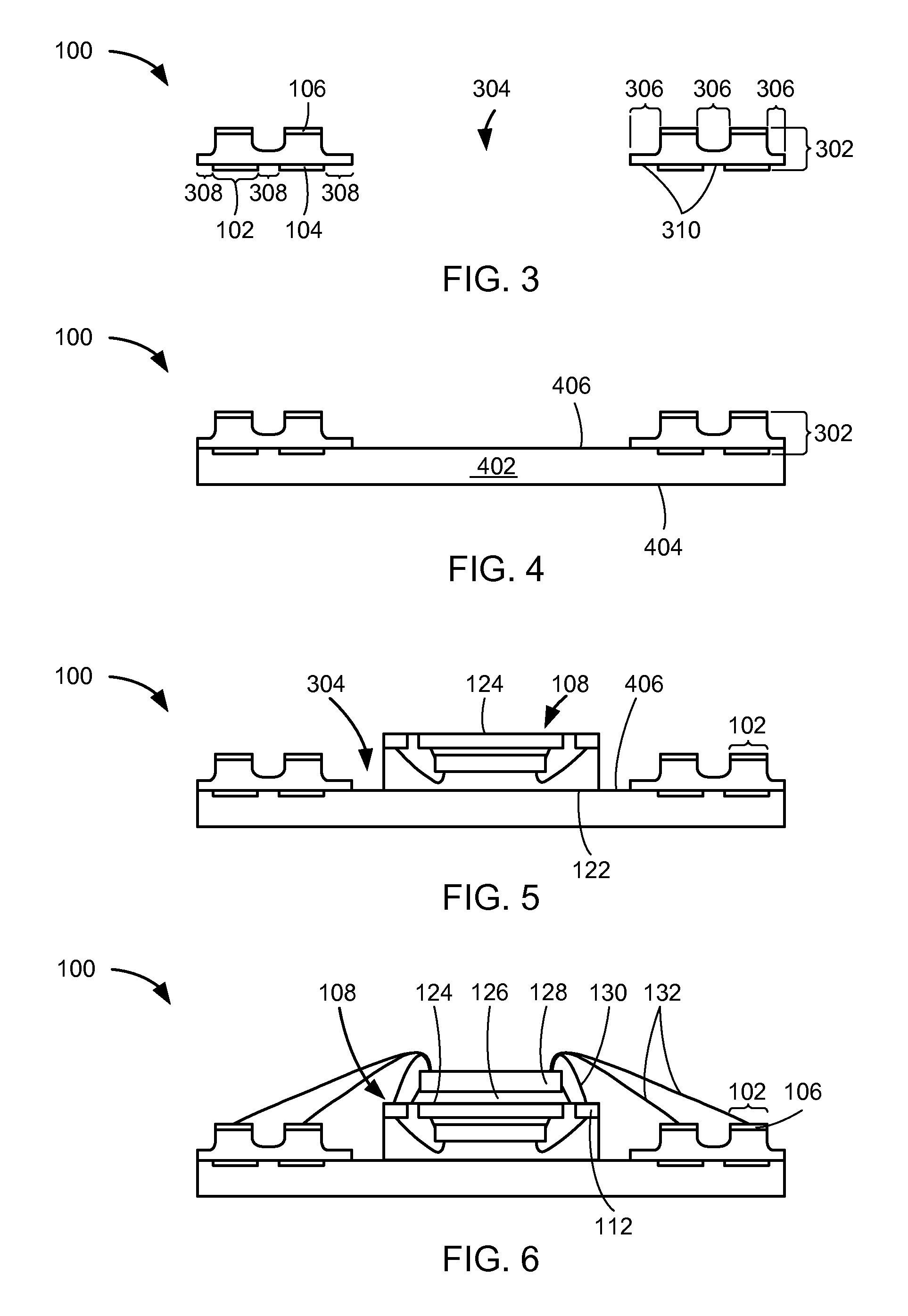

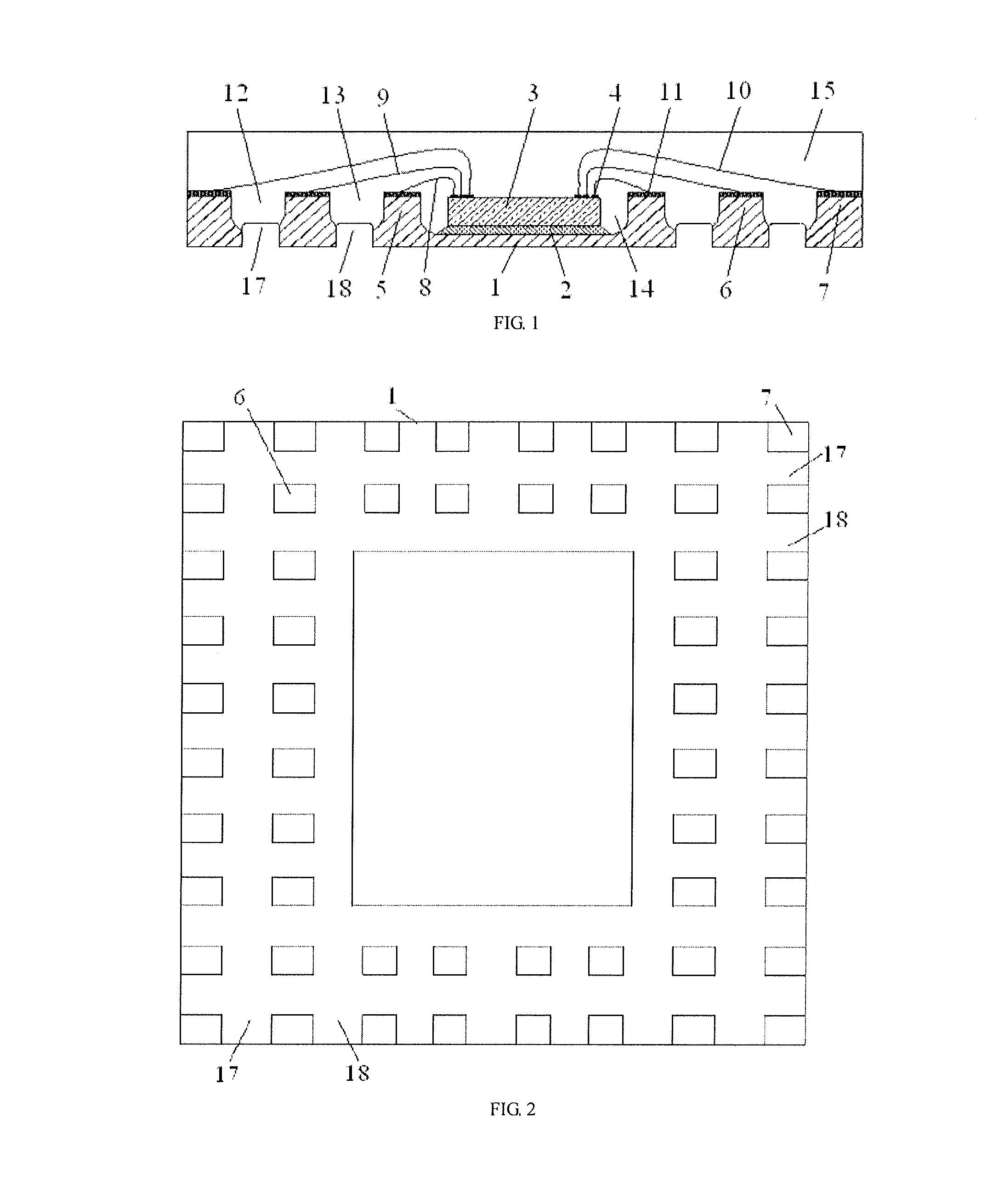

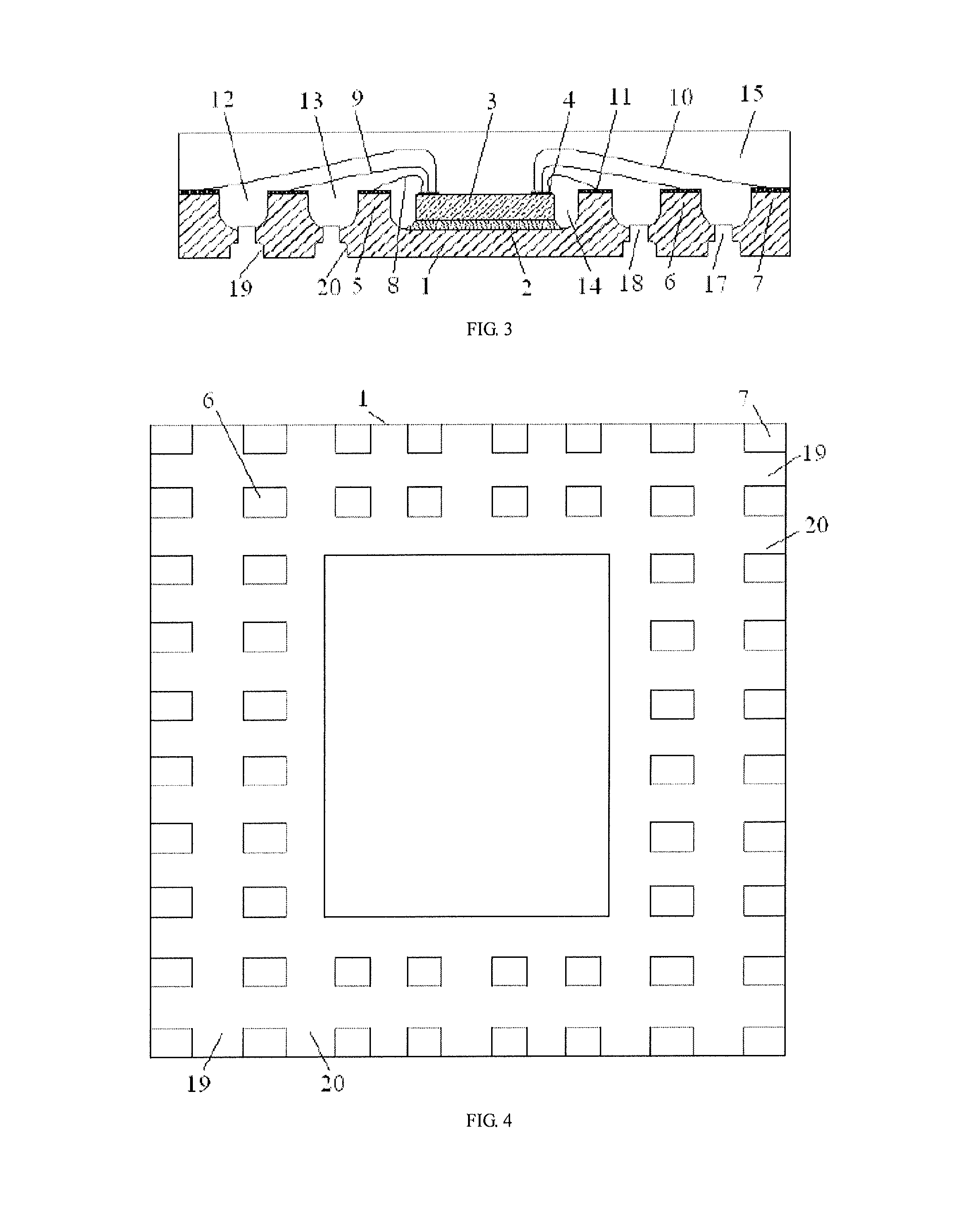

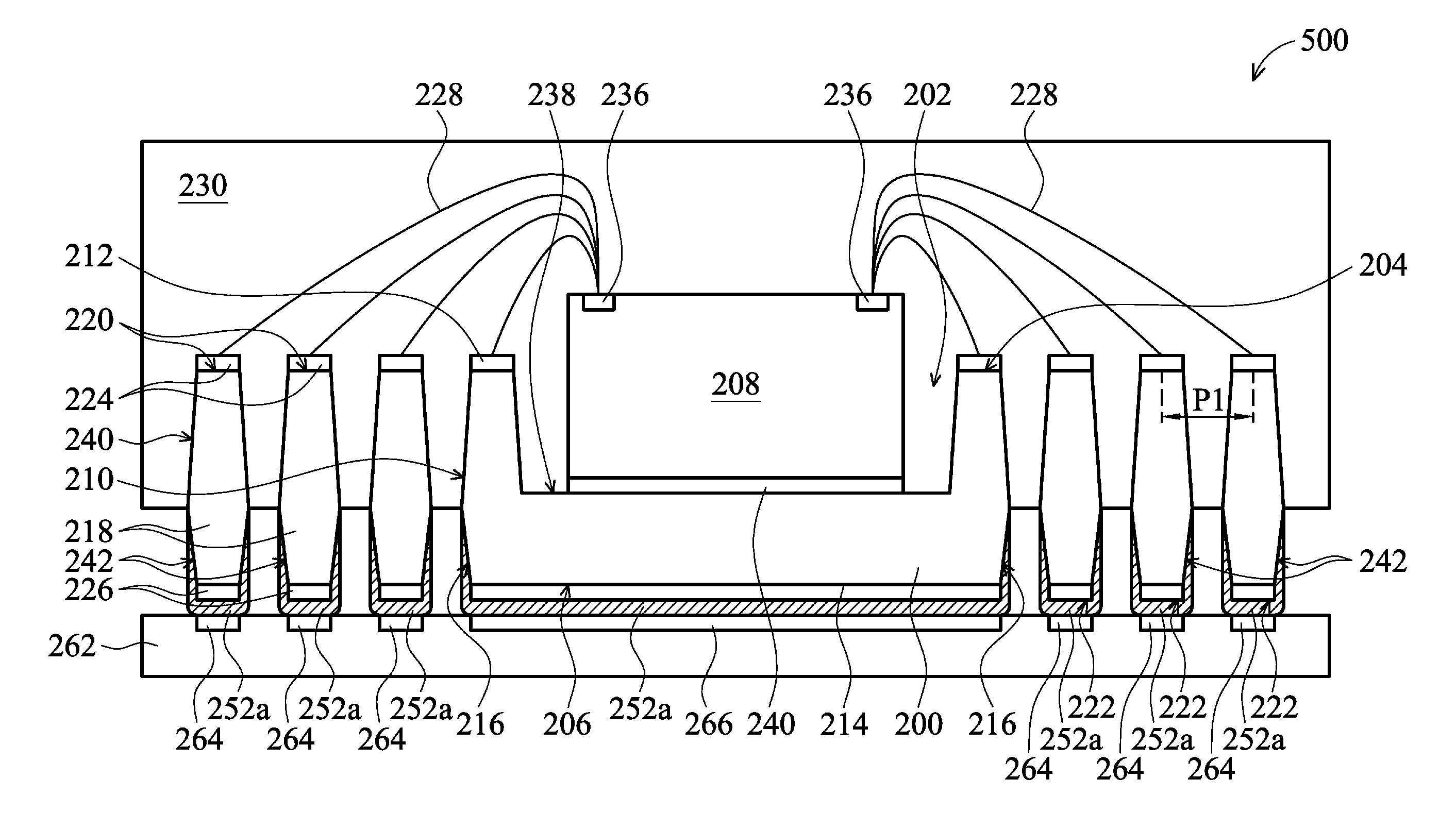

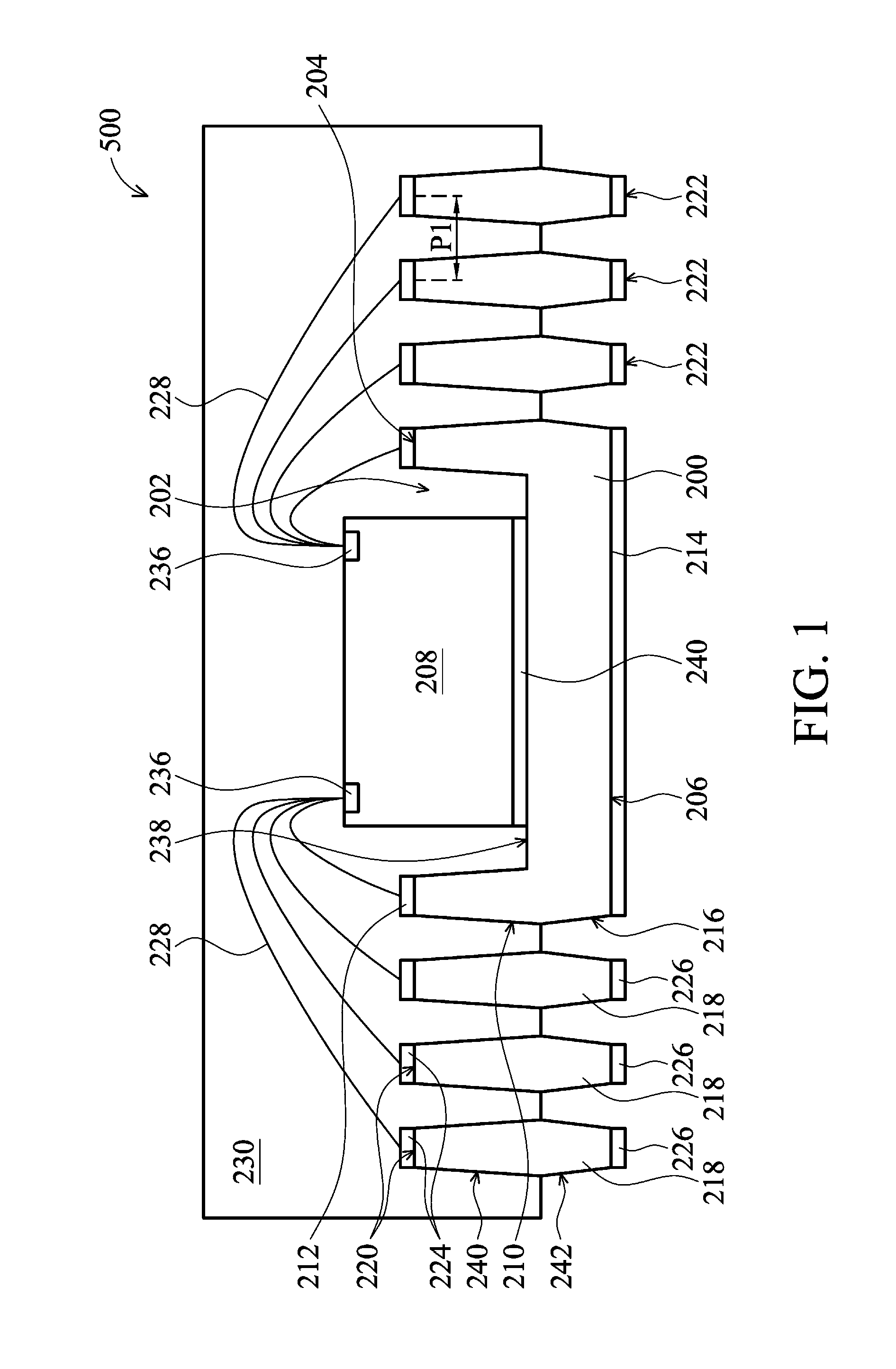

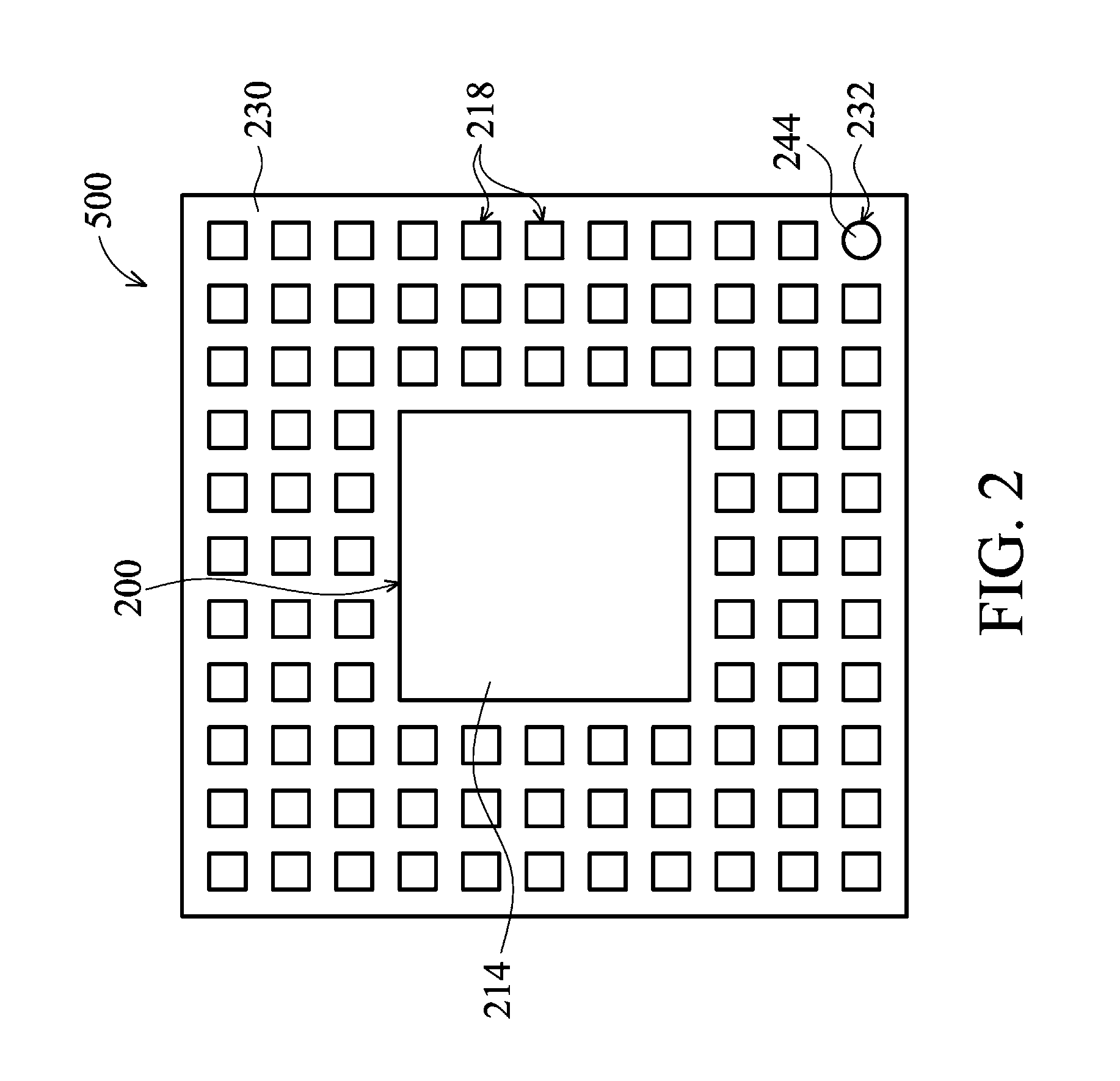

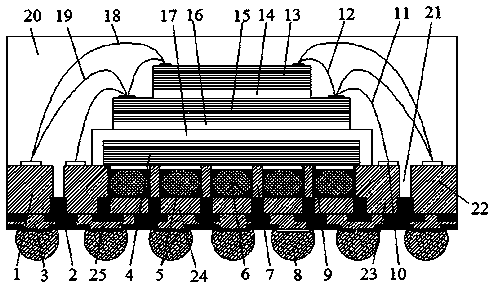

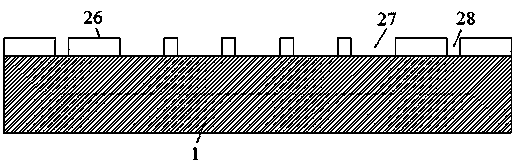

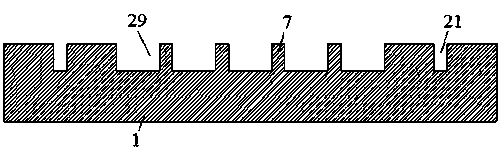

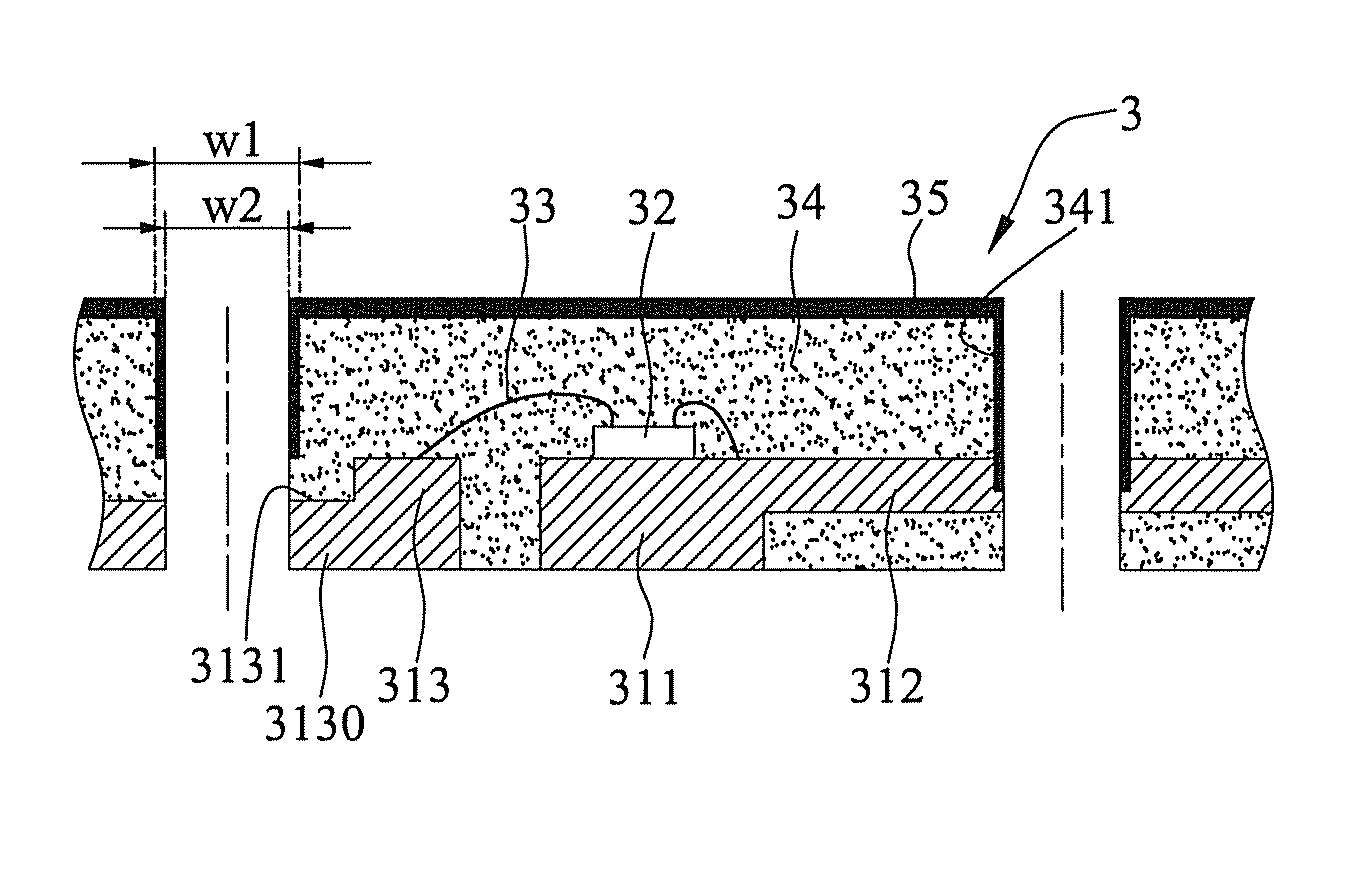

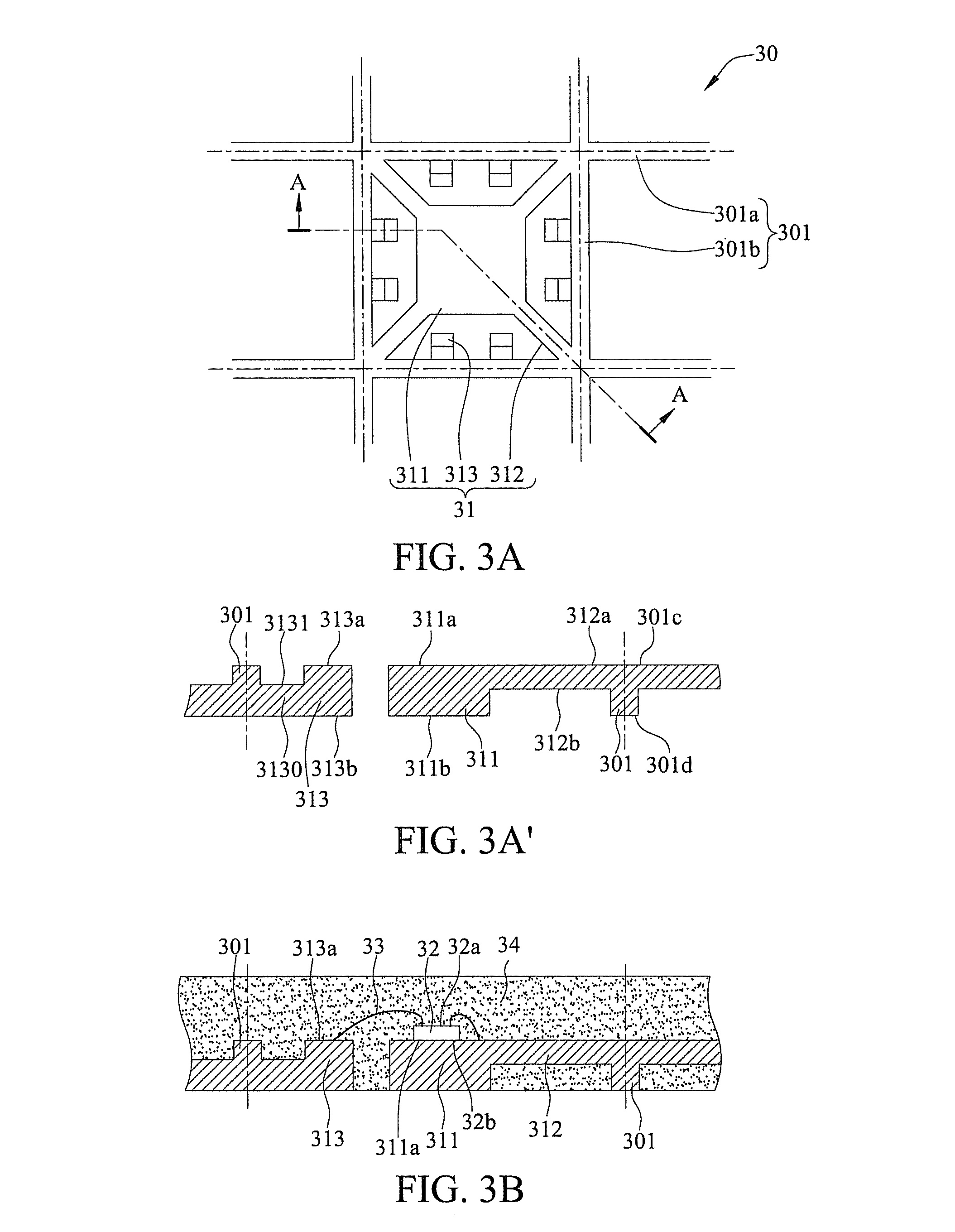

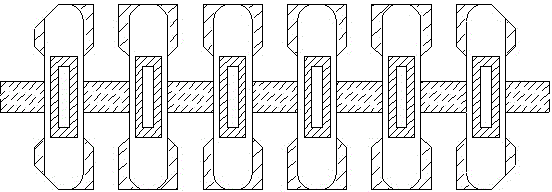

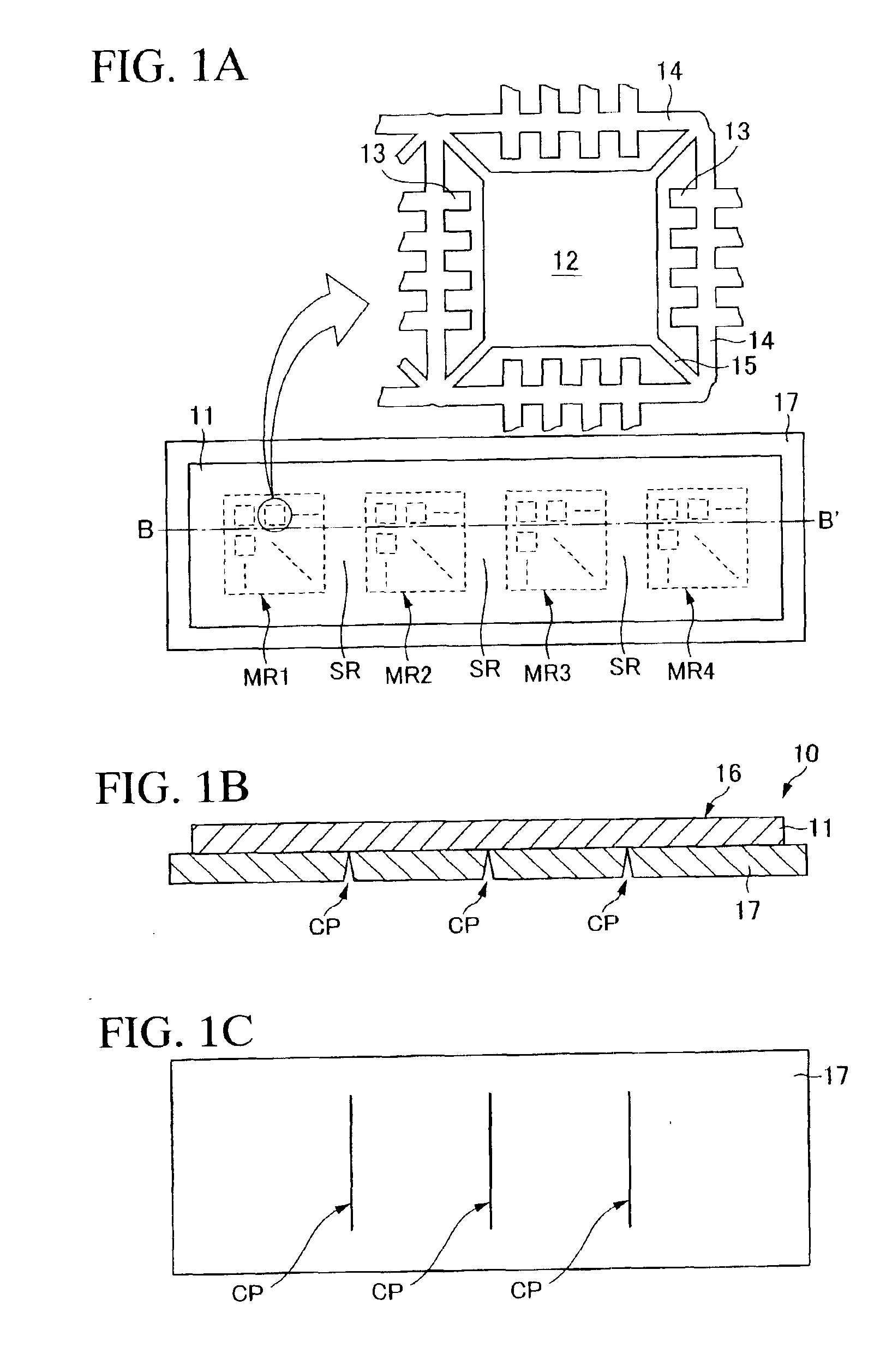

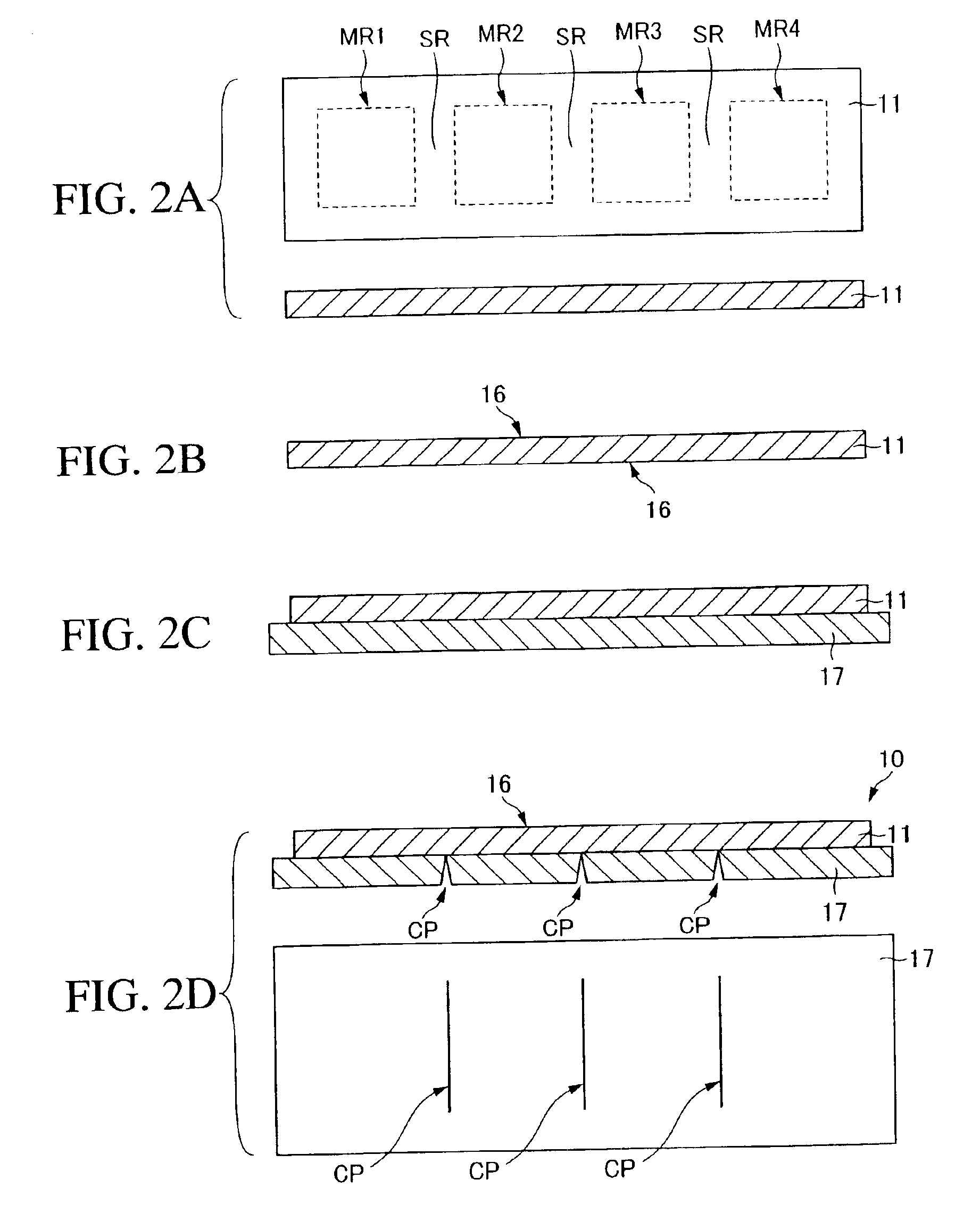

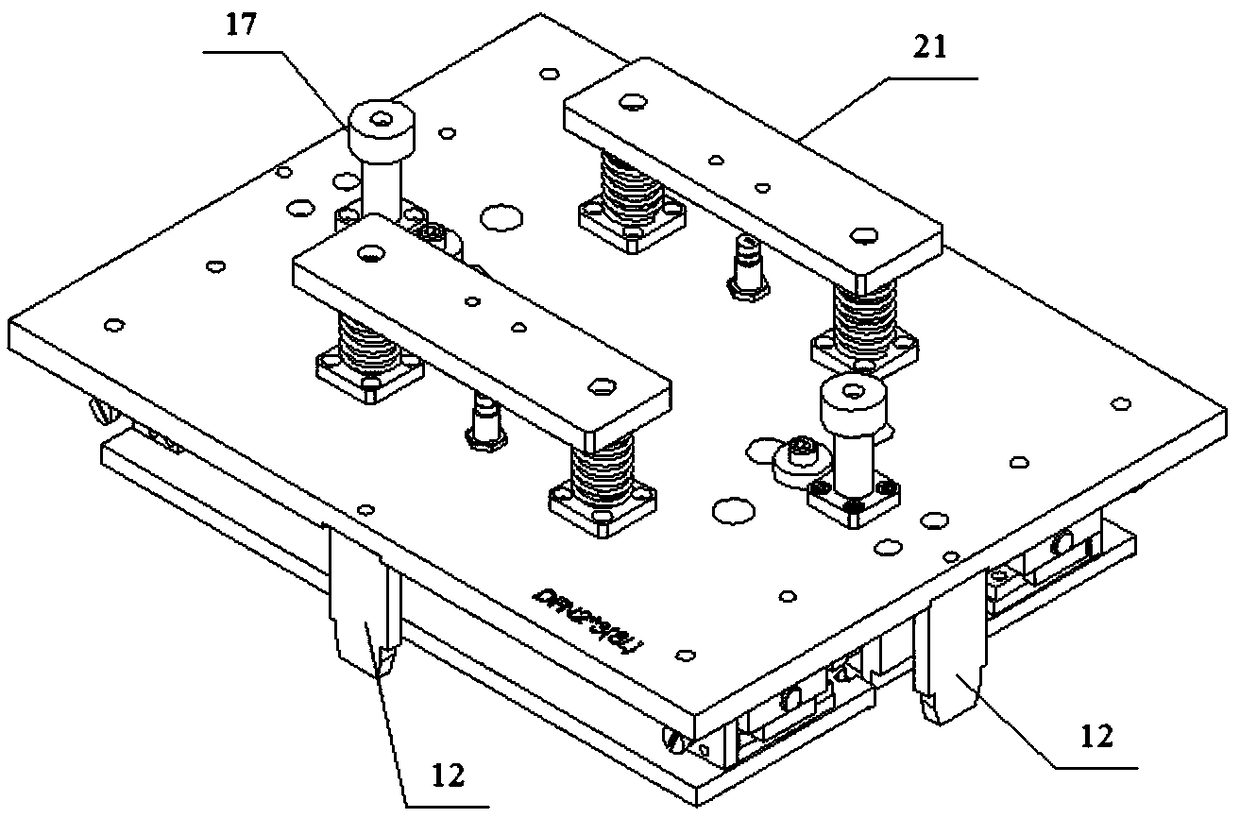

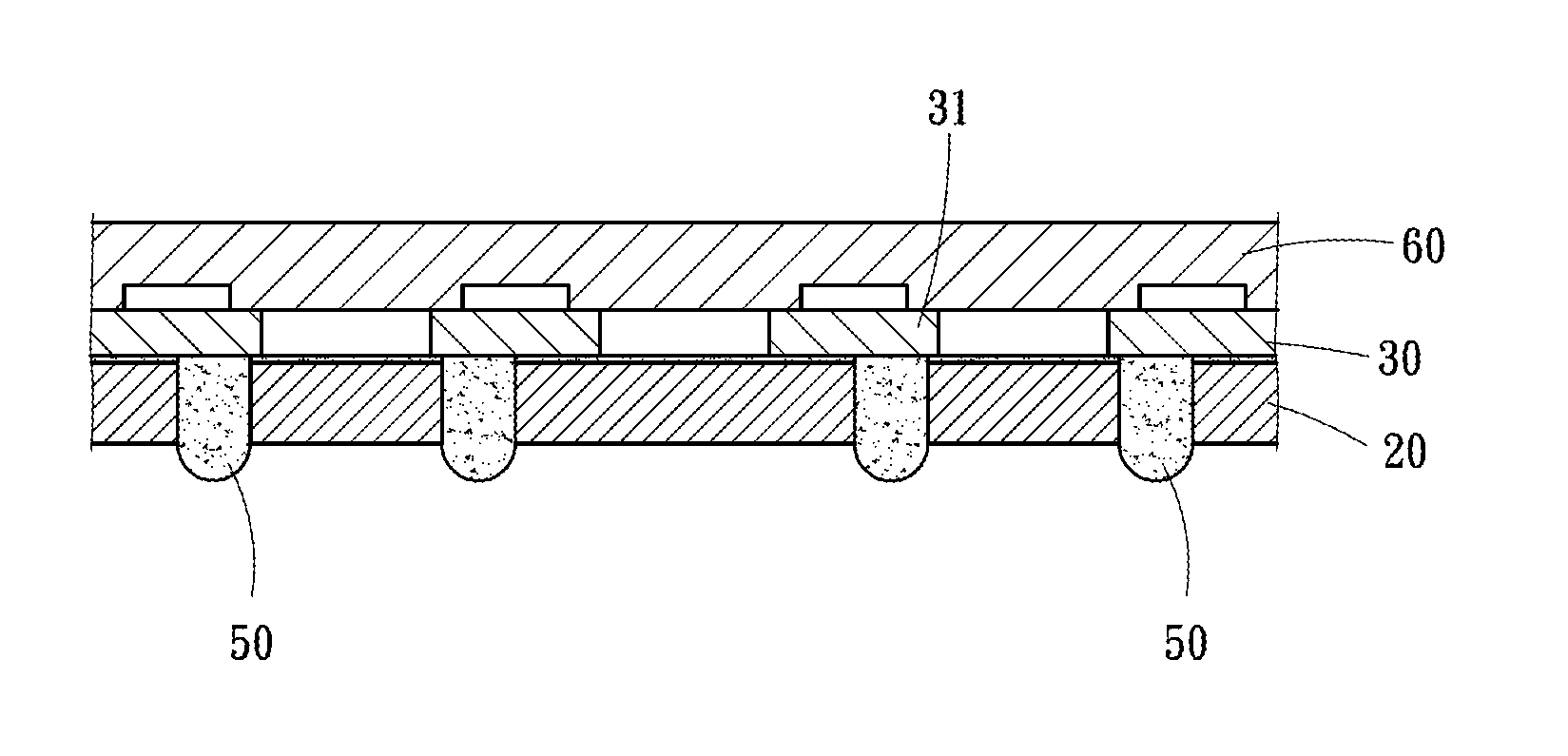

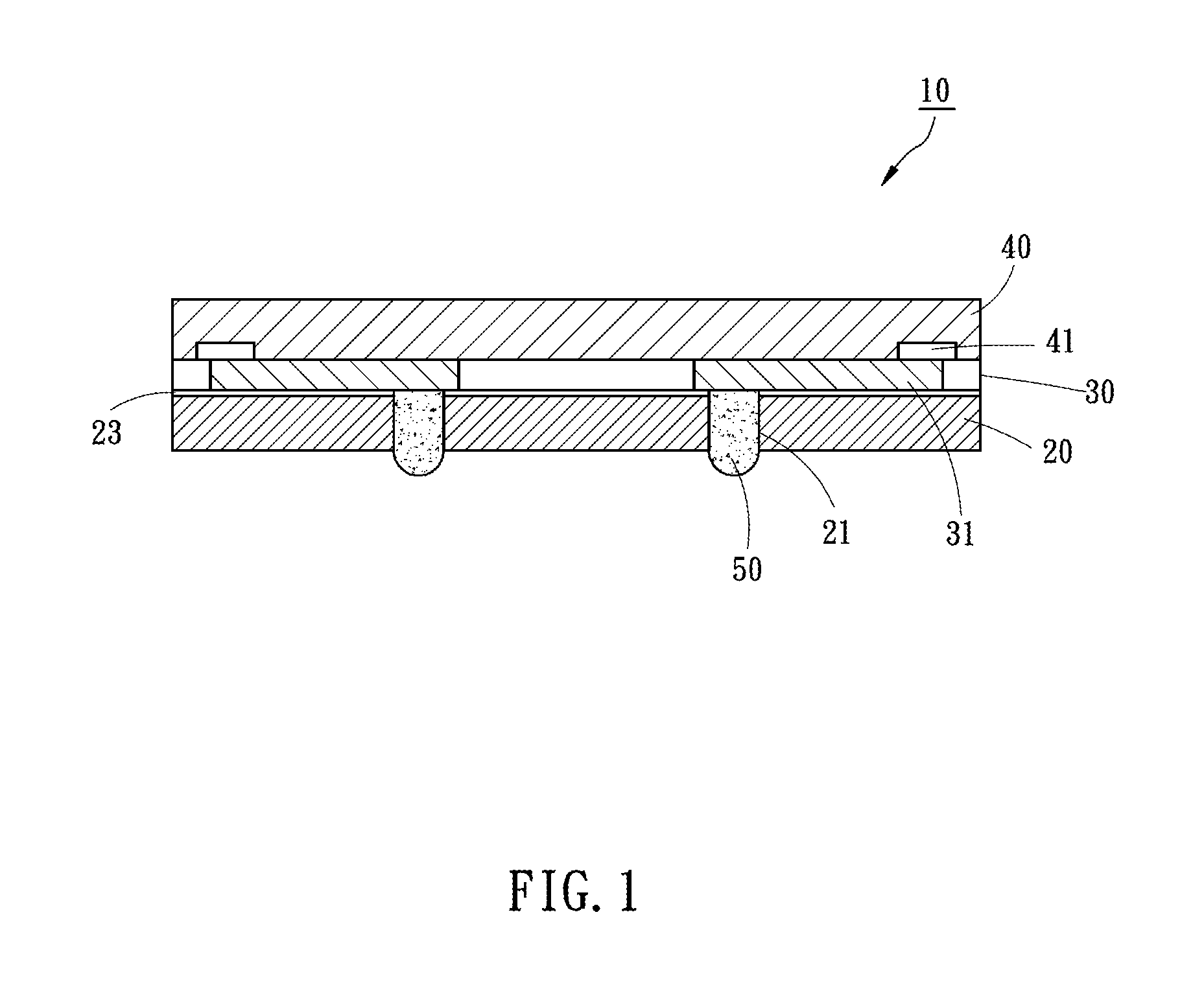

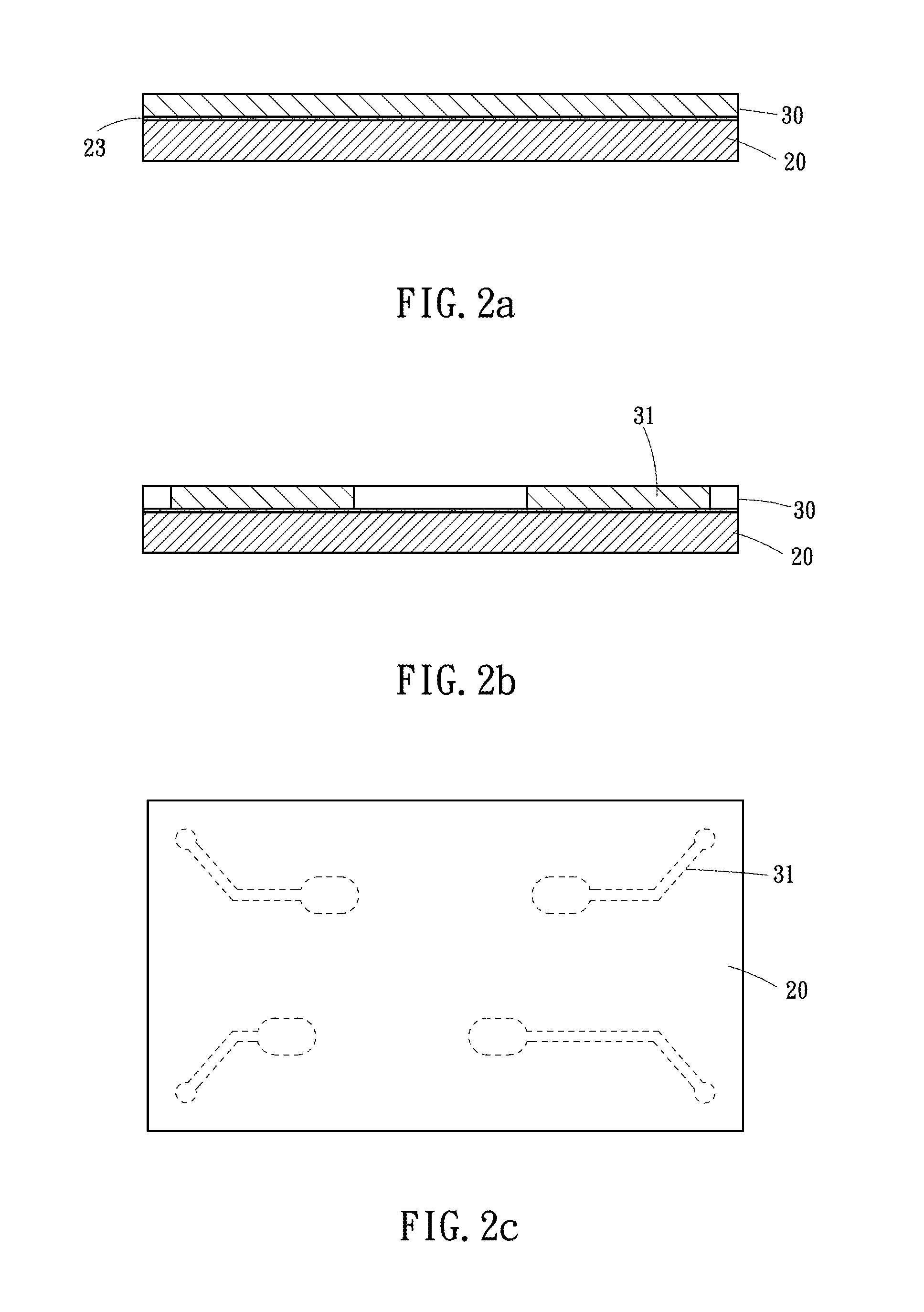

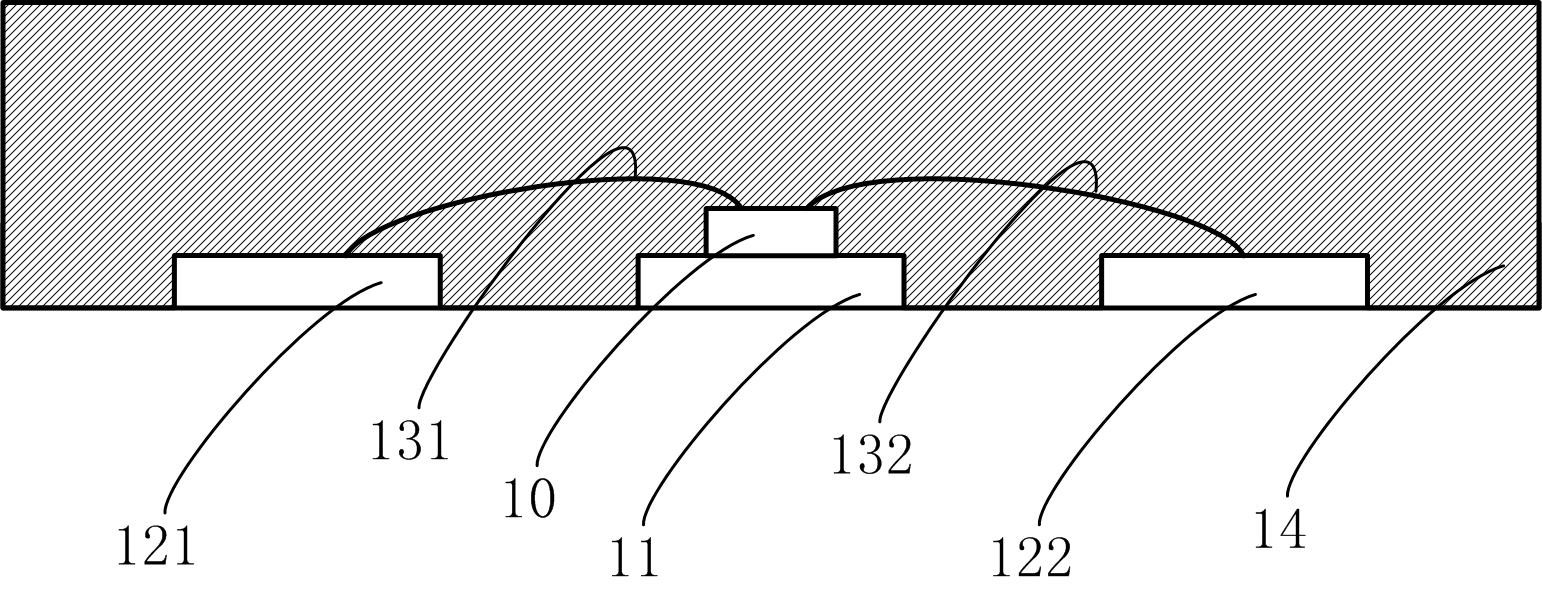

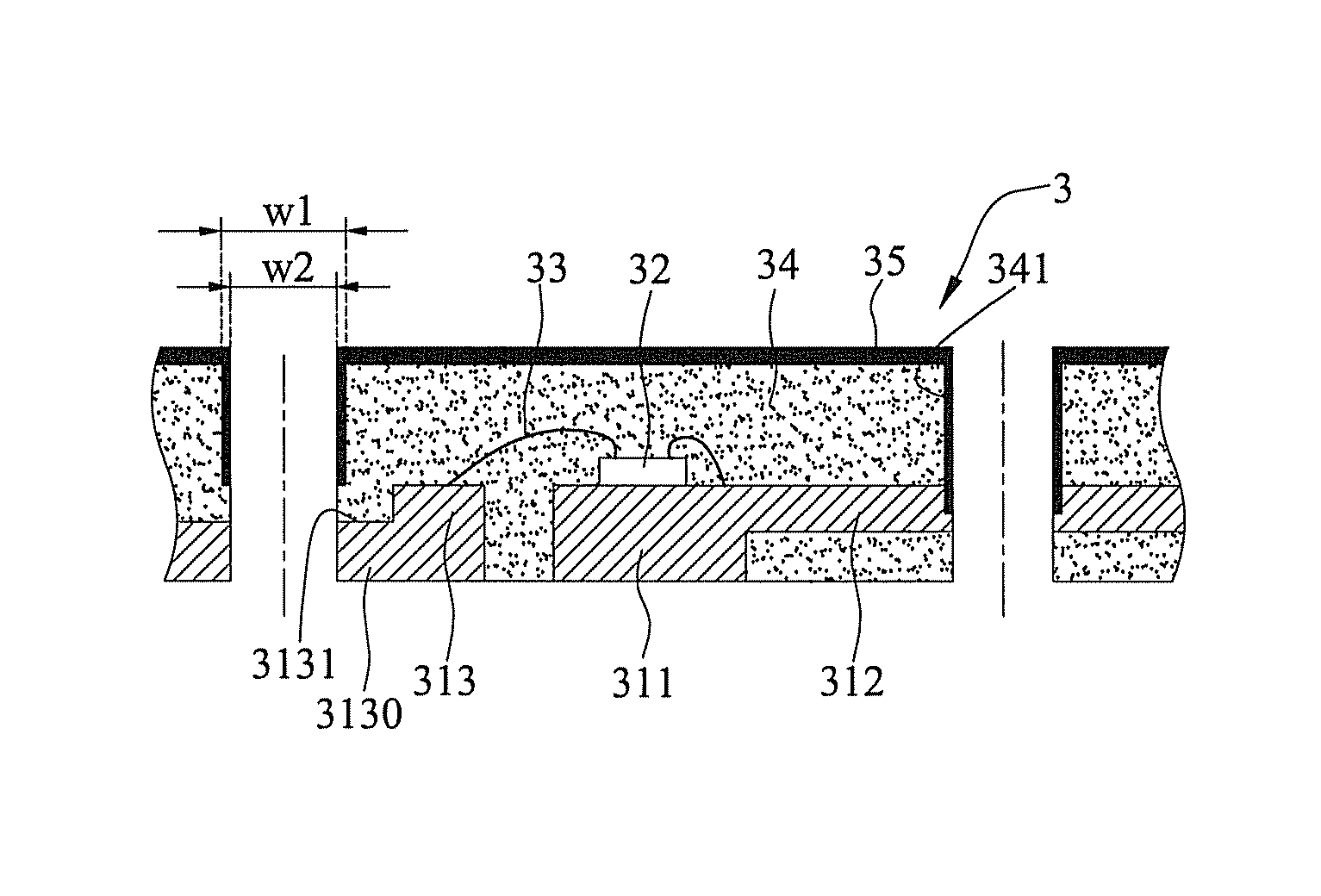

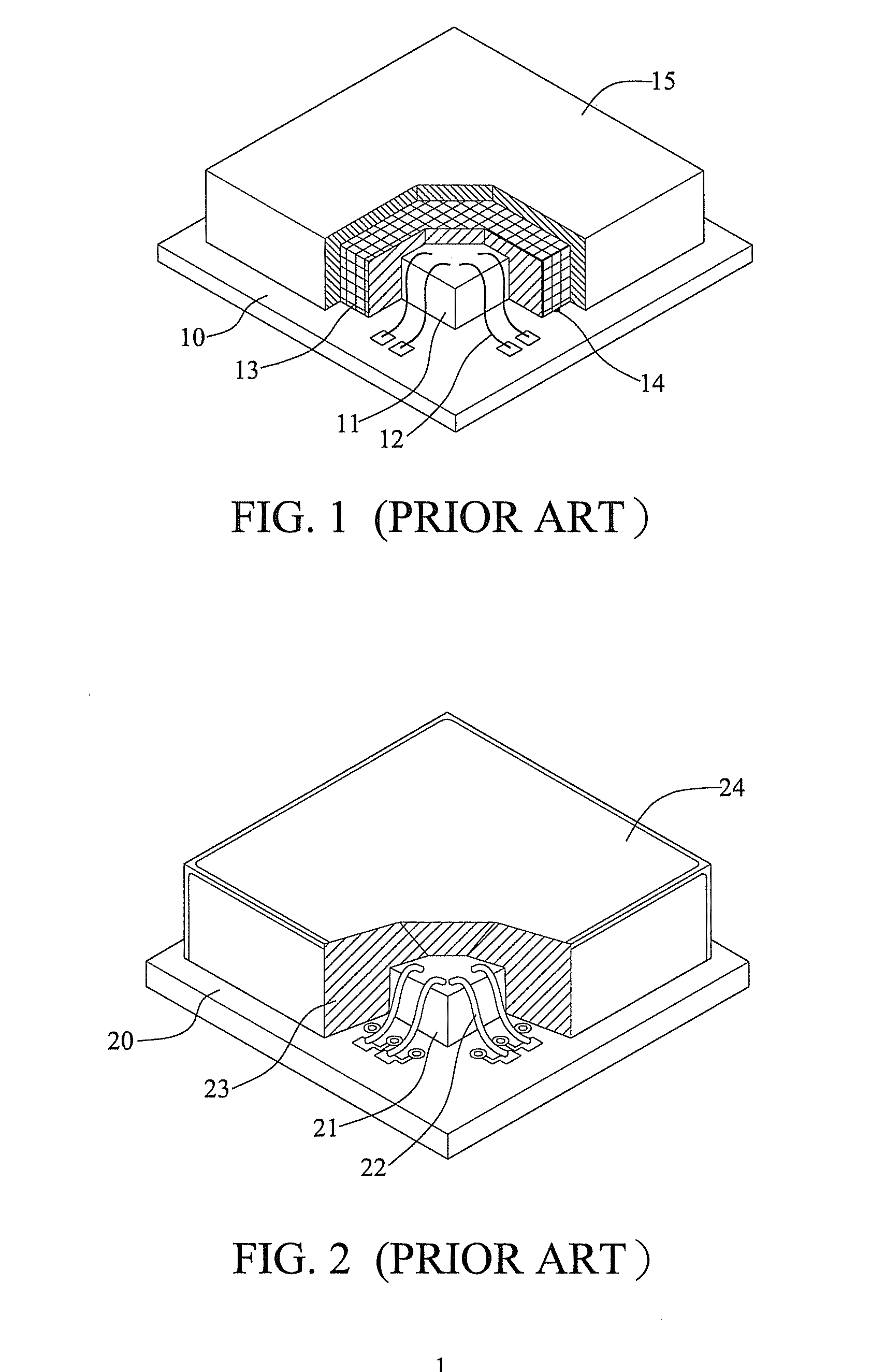

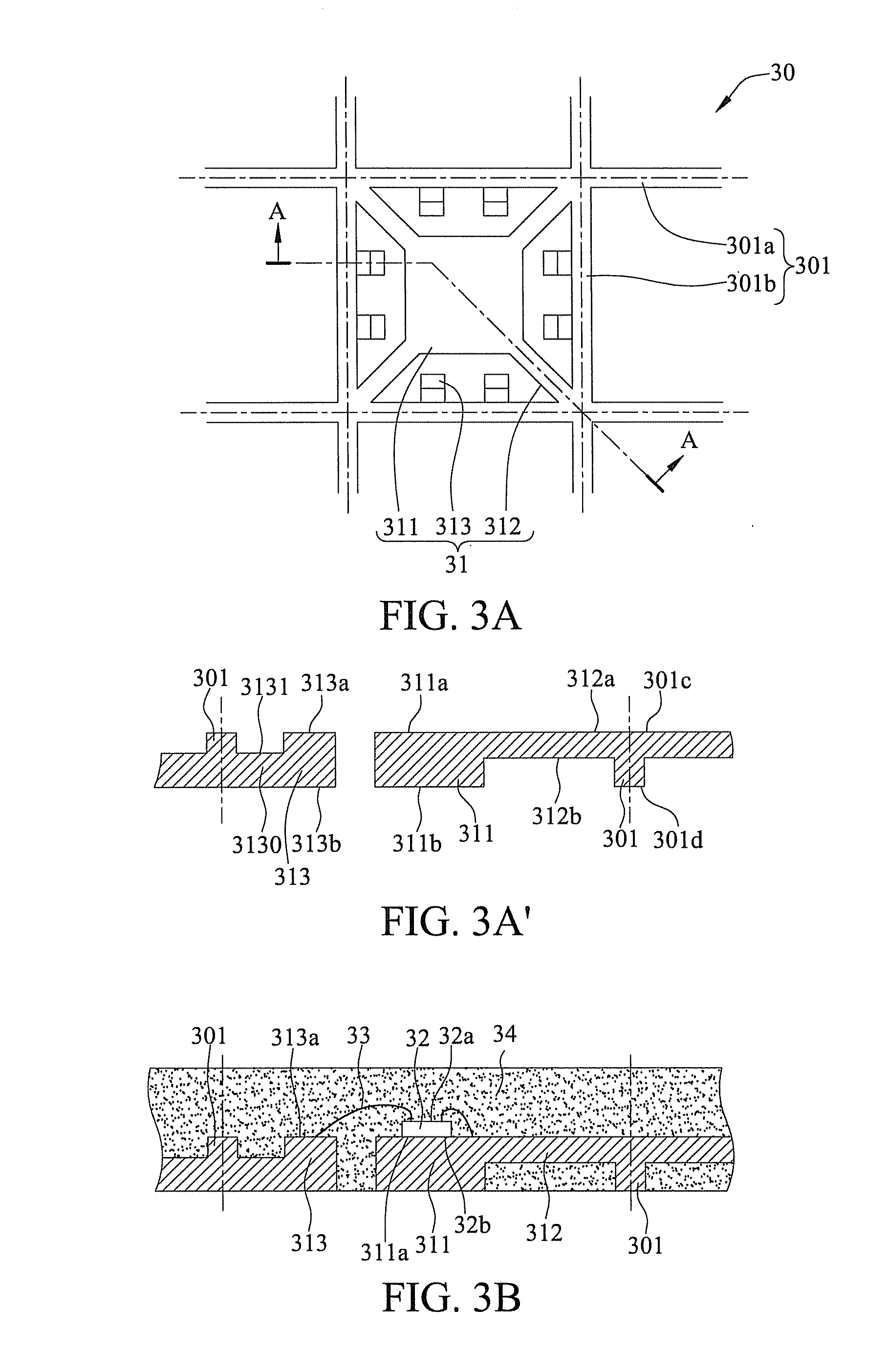

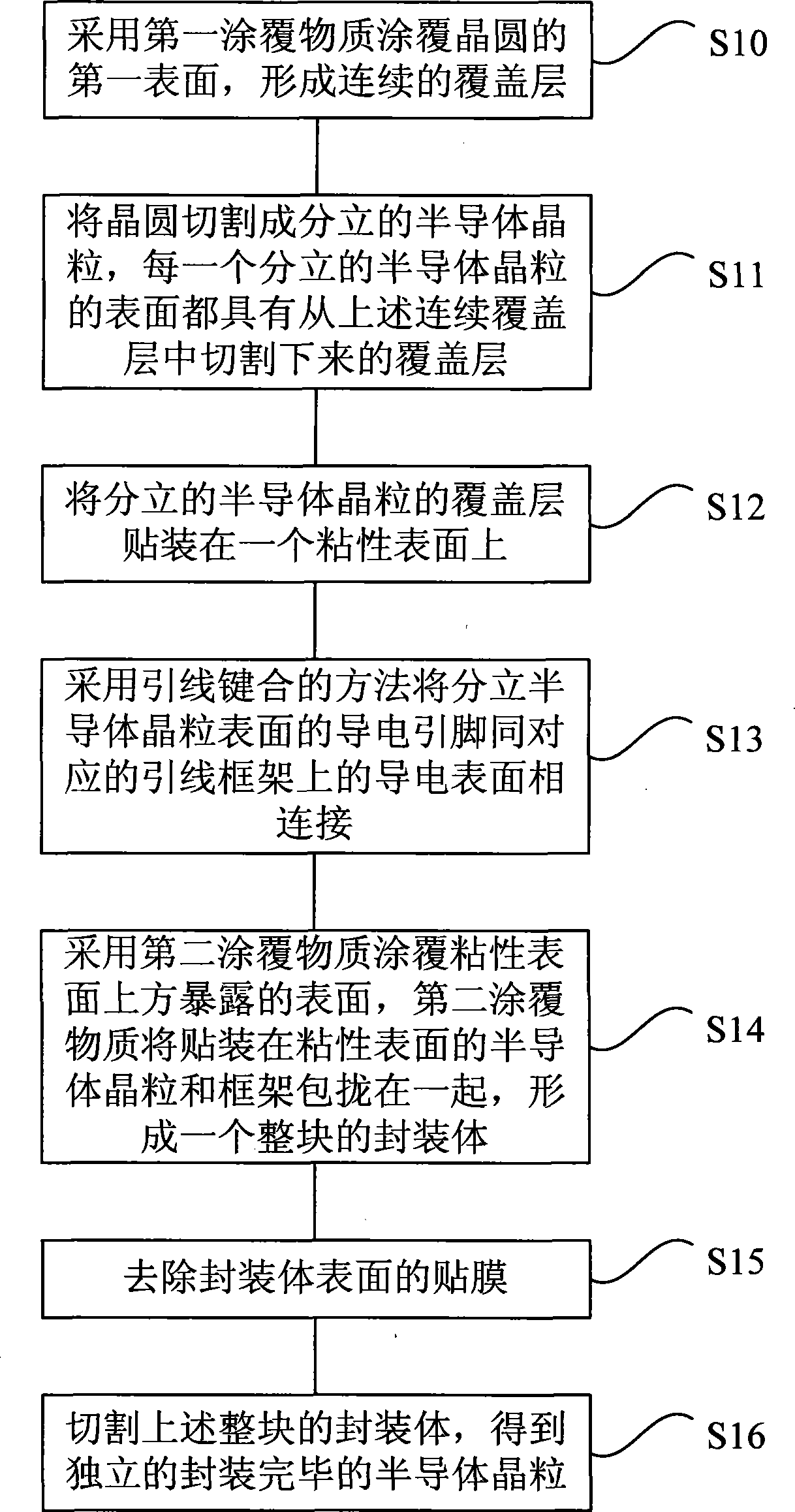

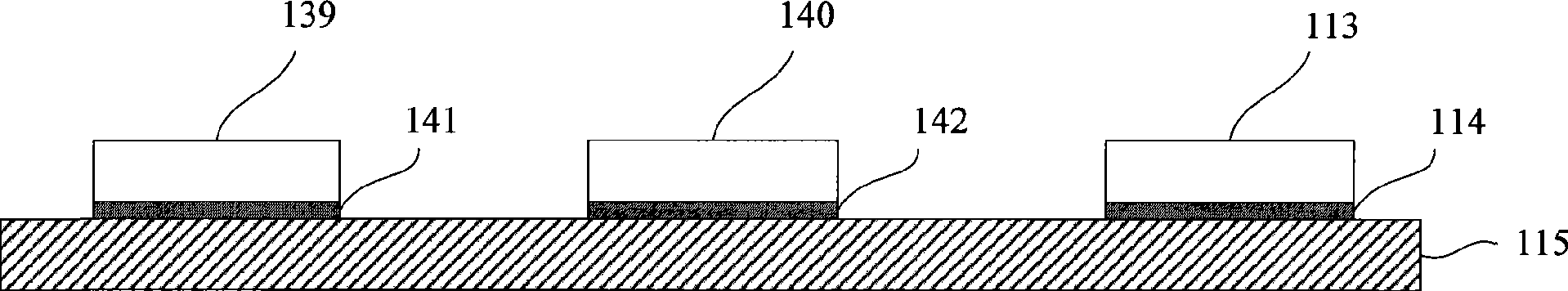

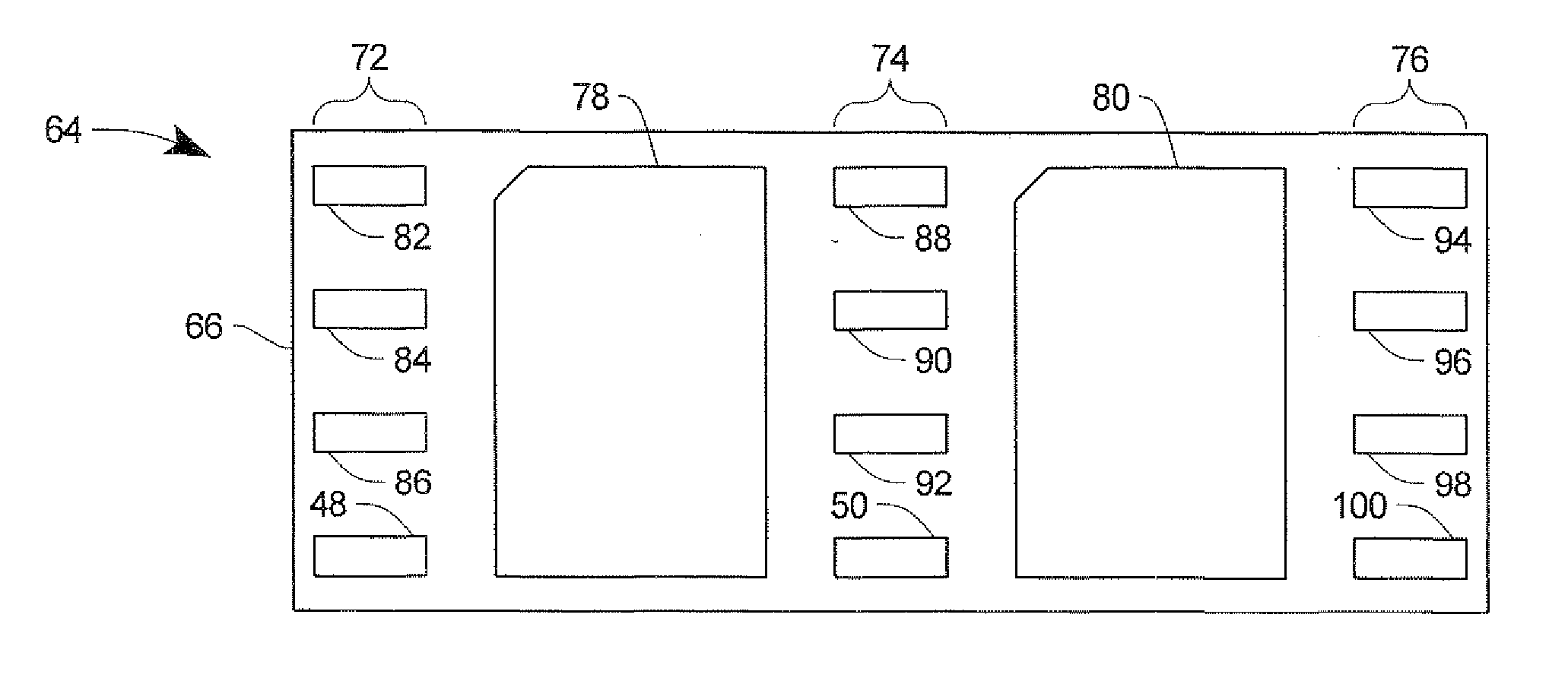

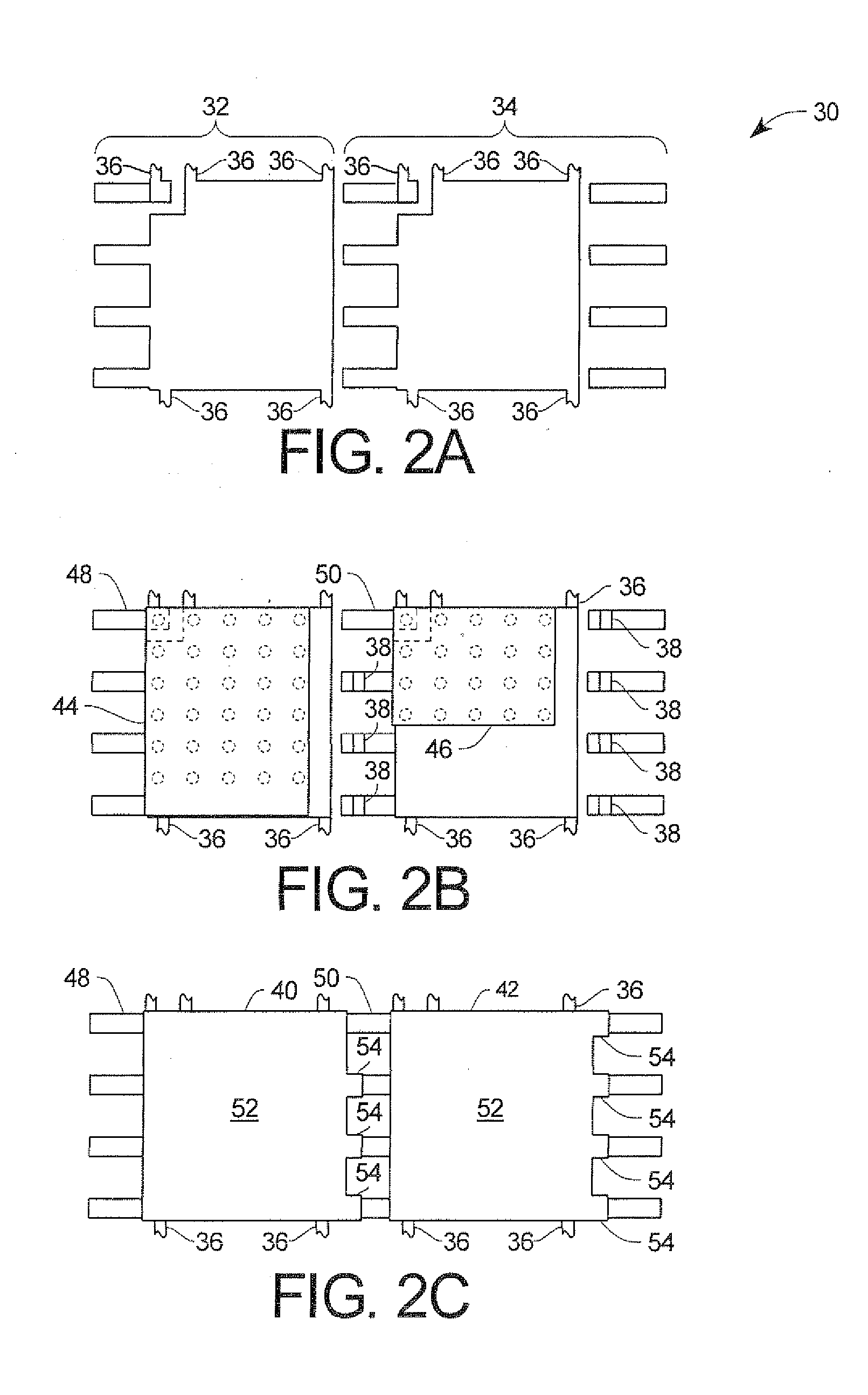

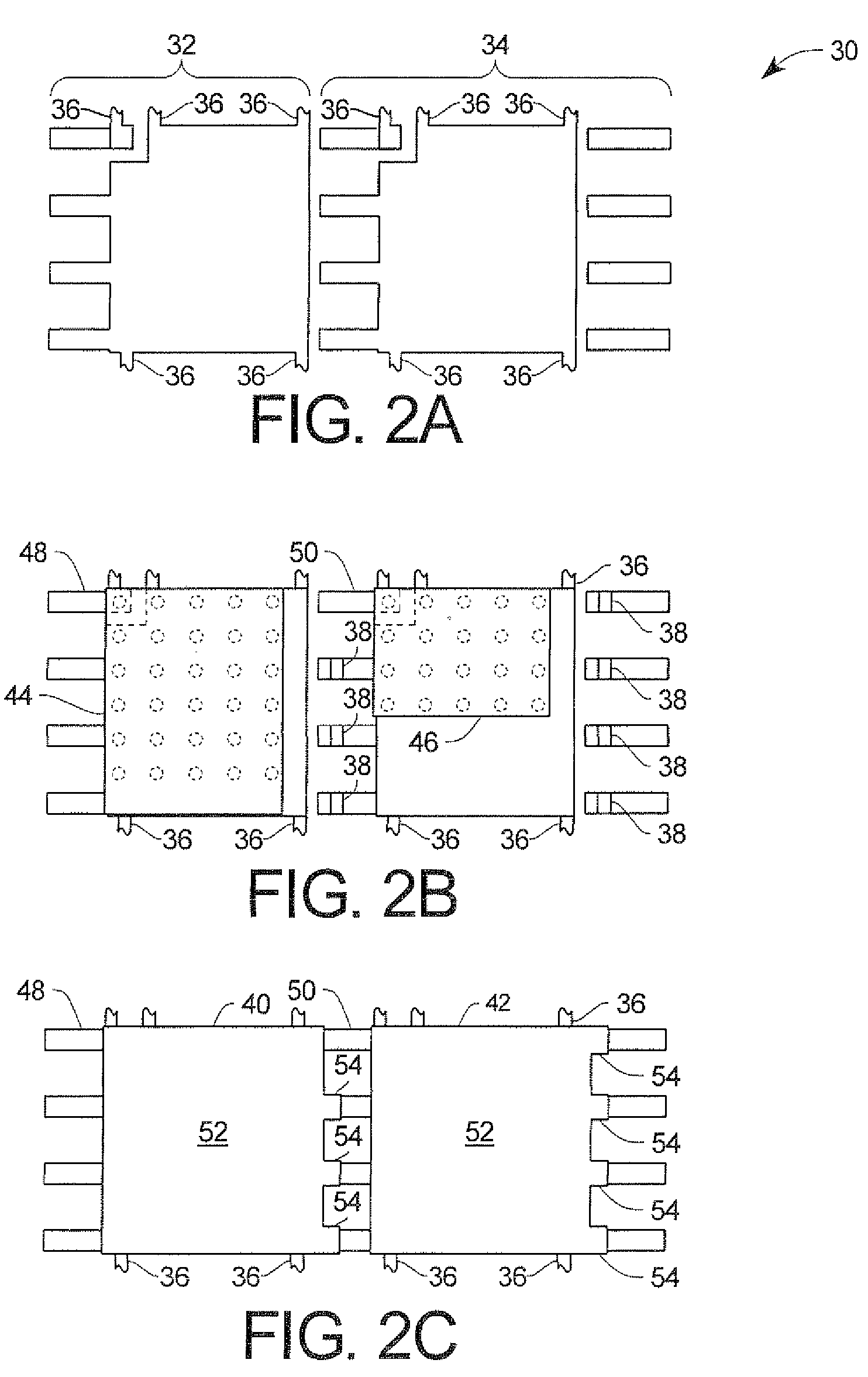

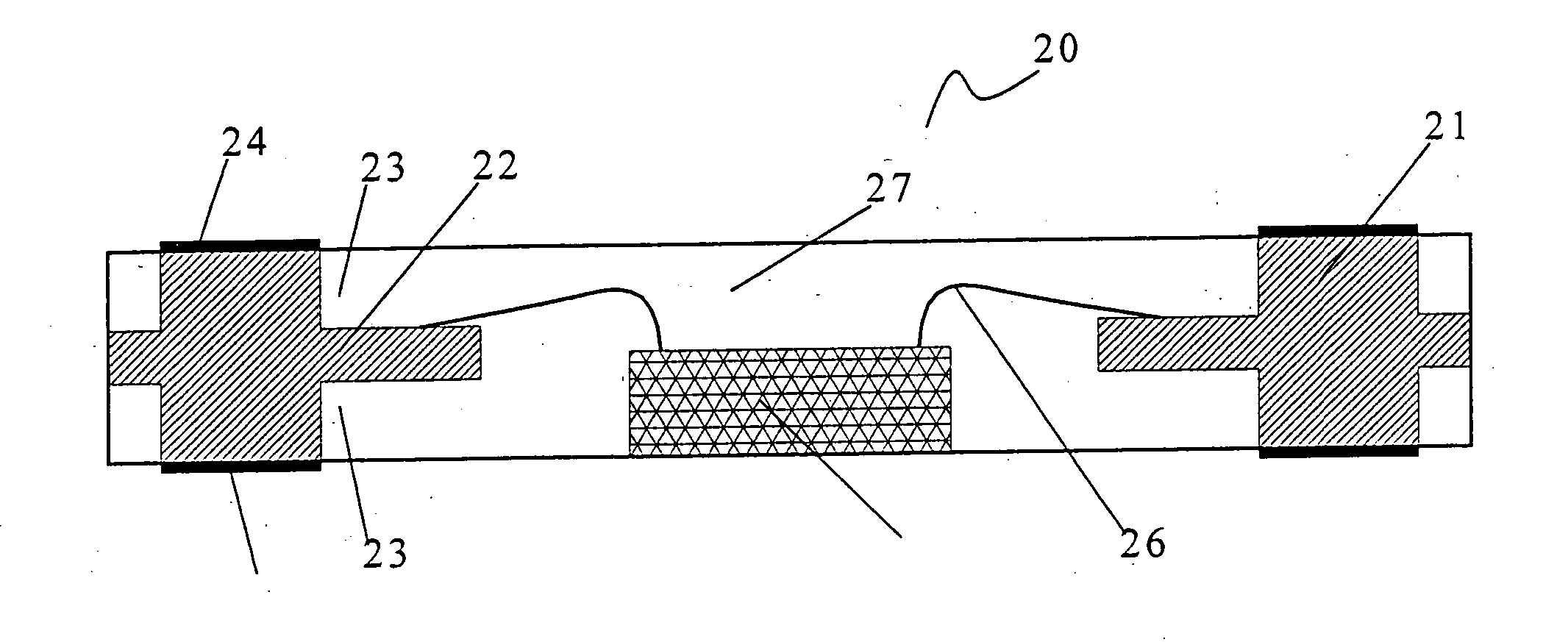

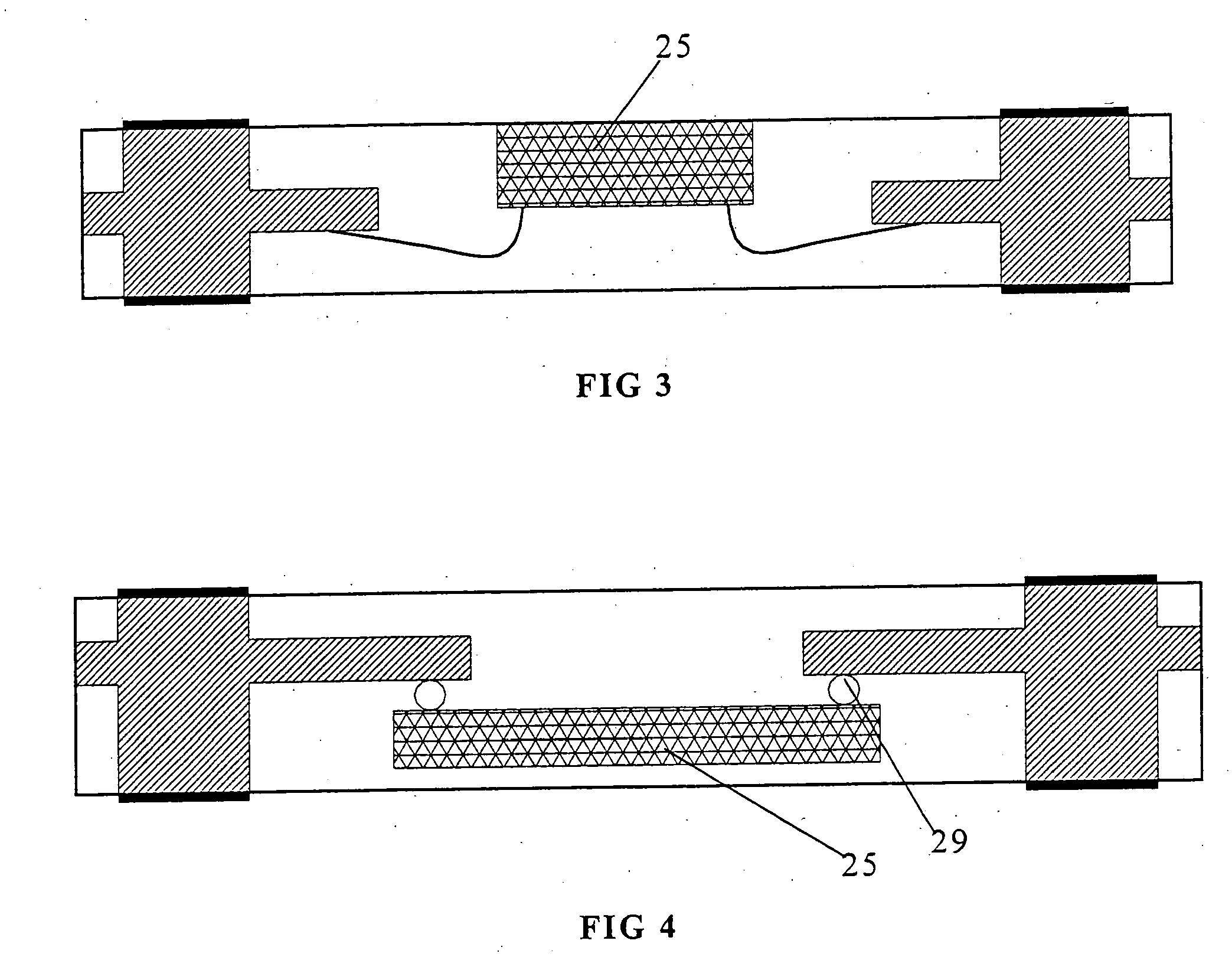

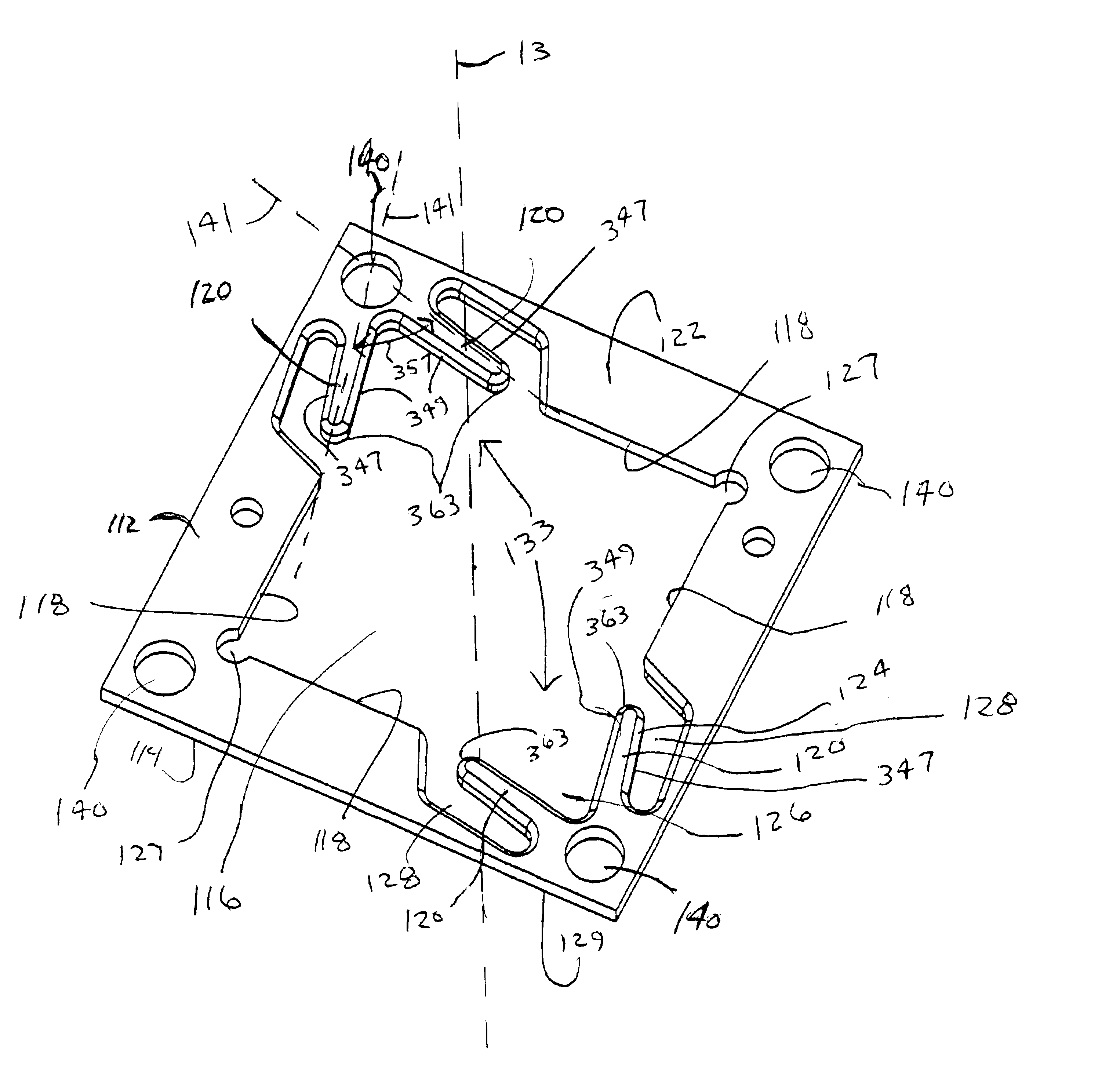

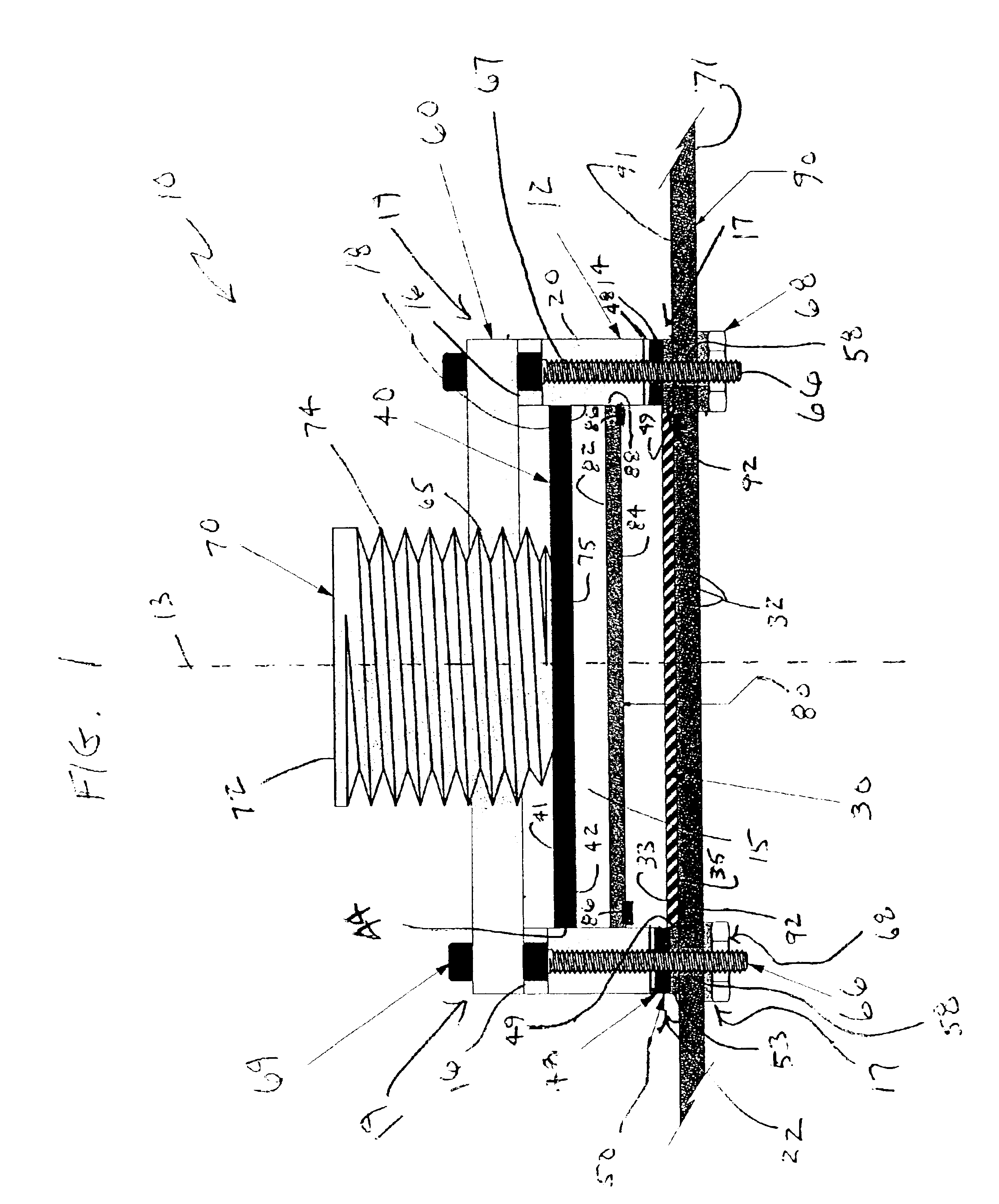

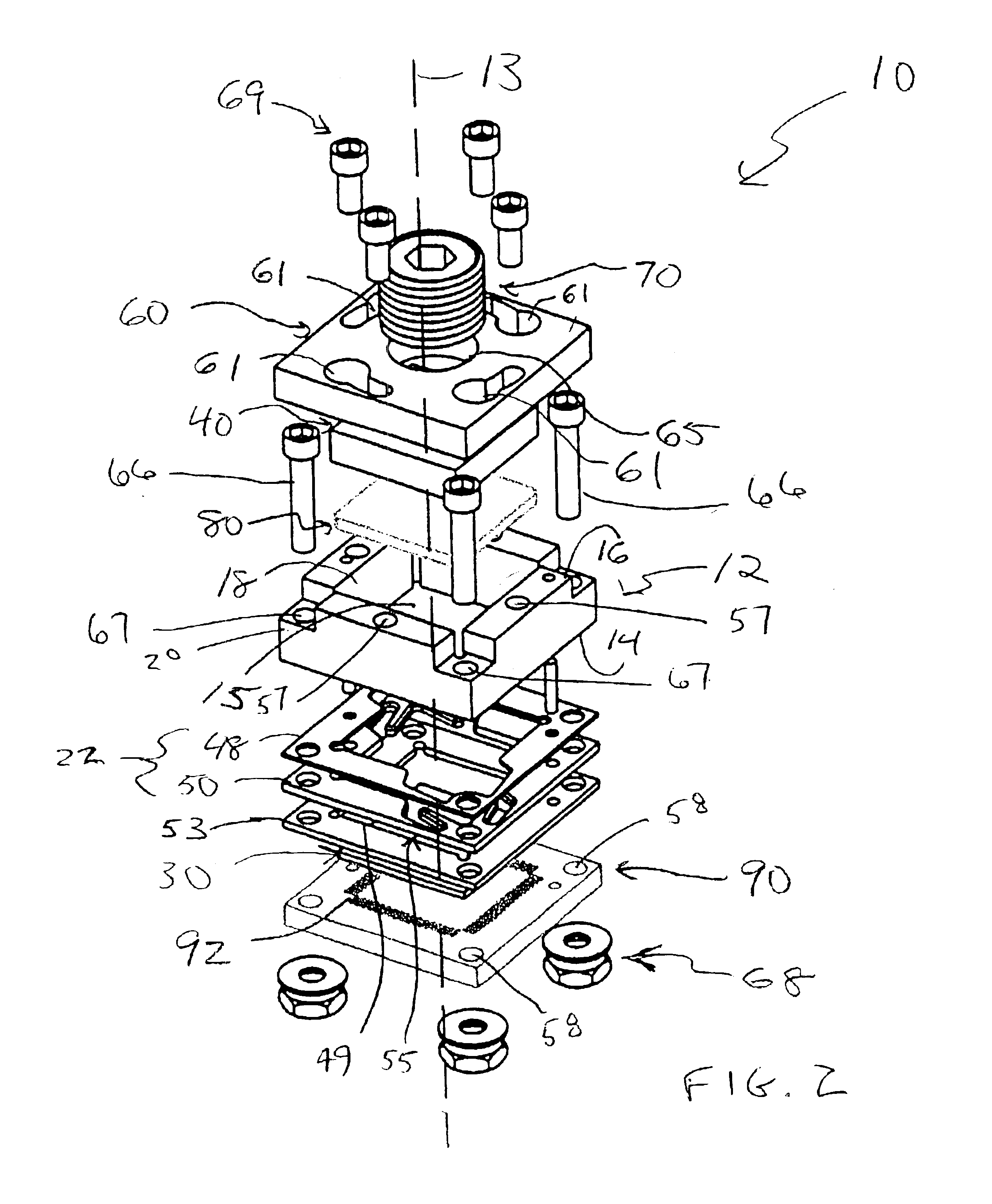

[quad flat no-lead package structure and manufacturing method thereof]

ActiveUS20050073055A1High I/O pad densityImprove packaging qualitySemiconductor/solid-state device detailsSolid-state devicesLead bondingEngineering

The present invention provides a QFN package structure, comprising a chip carrier and at least a chip. The chip is disposed on the top surface of the chip carrier, while the back surface of the chip carrier includes a plurality of flat no-lead conductive leads as I / O pads of the chip carrier for the external circuitry. A plurality of pads, corresponding to bonding pads of the chip, is disposed on the top surface of the chip carrier. The aforementioned package structure can employ wiring bonding technology, flip chip technology or surface mount technology to attach the chip to the chip carrier.

Owner:UNITED MICROELECTRONICS CORP

Quad flat non-leaded package structure with electromagnetic interference shielding function and method for fabricating the same

ActiveUS20110198737A1Ease of mass productionImprove electrical connection qualitySemiconductor/solid-state device detailsSolid-state devicesElectromagnetic interferenceEngineering

A quad flat non-leaded (QFN) package structure with an electromagnetic interference (EMI) shielding function is proposed, including: a lead frame having a die pad, a plurality of supporting portions connecting to the die pad and a plurality of leads disposed around the periphery of the die pad without connecting to the die pad; a chip mounted on the die pad; bonding wires electrically connecting the chip and the leads; an encapsulant for encapsulating the chip, the bonding wires and the lead frame and exposing the side and bottom surfaces of the leads and the bottom surface of the die pad; and a shielding film disposed on the top and side surfaces of the encapsulant and electrically connecting to the supporting portions for shielding from EMI. A method of fabricating the package structure as described above is further proposed.

Owner:SILICONWARE PRECISION IND CO LTD

PCB (printed circuit board) heat-radiation soldering pad used for QFN (quad flat no-lead package) chip, and QFN chip and PCB soldering method

ActiveCN104701291APrevent outflowGood welding performancePrinted circuit detailsSemiconductor/solid-state device detailsPrinting inkSoldering process

The invention discloses a PCB (printed circuit board) heat-radiation soldering pad used for a QFN (quad flat no-lead package) chip. The PCB heat-radiation soldering pad is provided with heat radiation via holes not larger than 0.3 mm in diameter and escape holes 0.8-1.2 mm in diameter. The invention further discloses a soldering method adopting the heat-radiation soldering pad. The soldering method includes printing ink used for plugging the heat radiation via holes on one side of a PCB which does not need soldering in correspondence to the heat-radiation soldering pad; painting tin paste on the heat-radiation soldering pad by a mesh plate without holes corresponding to the escape holes; attaching the QFN chip to the corresponding position of the PCB, so as to enable the QFN chip to expose to be flush with the PCB heat-radiation soldering pad and a pin area of the QFN chip with a PCB pin soldering pad; soldering the QFN chip on the PCB by reflow soldering. By the method, gas escape can be helped in the soldering process via the escape holes, soldering tin outflow can be prevented and good soldering effect is achieved.

Owner:SHENZHEN GONGJIN ELECTRONICS CO LTD

Flip chip quad flat non-leaded package structure and manufacturing method thereof and chip package structure

InactiveUS20090189296A1Reduce package thicknessImprove convenienceSemiconductor/solid-state device detailsSolid-state devicesResistRedistribution layer

A manufacturing method for a Flip Chip Quad Flat Non-leaded package structure is provided. A lead frame having a plurality of leads is provided at first in the manufacturing method. A dielectric layer is formed on the lead frame and exposes a top surface and a bottom surface of the leads. A redistribution layer including a plurality of pads and a plurality of conductive lines connected the pads and the top surface of the leads is formed on the dielectric layer. A solder resist layer is formed to cover the redistribution layer, the dielectric layer and the leads, and expose the surface of the pads. An adhesive layer is formed on the solder resist layer. A chip having a plurality of bumps is provided. The chip is adhered on the solder resist layer with the adhesive layer and each bump is electrically connected with one of the pads.

Owner:CHIPMOS TECH INC

Novel LED (Light Emitting Diode) packaging piece based on DFN (Double Flat No-lead package) and QFN (Quad Flat No-lead Package), and manufacturing method of packaging piece

InactiveCN102738365ASmall sizeLow costSolid-state devicesSemiconductor devicesManufacturing technologyPlastic packaging

The invention relates to a novel LED (Light Emitting Diode) packaging piece based on DFN (Double Flat No-lead package) and QFN (Quad Flat No-lead Package), and a manufacturing method of the packaging piece, belonging to the technical field of automatic electronic information components. The packaging piece comprises a lead frame carrier, a glue chip, an IC (Integrated Circuit) chip, a bonding line and a plastic packaging body, wherein the glue chip is fixed on the lead frame carrier; the IC chip is fixed on the glue chip; the PAD bonding line of the IC chip is connected with the lead frame carrier so as to form a current and signal channel of a circuit; and the plastic packaging body surrounds the lead frame carrier, the glue chip, the IC chip, the PAD on the IC chip and the bonding line connected with the lead frame carrier so as to form the overall circuit. The size of a product can be reduced effectively; and the packaging piece belongs to the high density packaging that the carrier is exposed, so that the cost is reduced, the application range of the product is expanded, and the packaging reliability is improved.

Owner:HUATIAN TECH XIAN

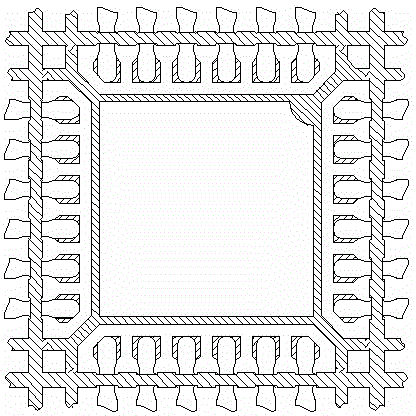

Integrated circuit packaging system with quad flat no-lead package and method of manufacture thereof

ActiveUS8334584B2Semiconductor/solid-state device detailsSolid-state devicesEngineeringQuad Flat No-leads package

A method of manufacture of an integrated circuit packaging system includes: providing a base array having terminals and an open region; attaching a coverlay layer directly on the base array; placing a component in the open region and directly on the coverlay layer; forming an encapsulation over the base array and the component; removing the coverlay layer to leave a plane of the terminals and a plane of the component partially exposed and substantially coplanar; and removing a portion of the base array between the terminals, the terminals electrically isolated.

Owner:STATS CHIPPAC LTD

Quad flat no lead package and production method thereof

ActiveUS20150102476A1More I/O numberSmall volumeSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsChemical platingPlastic packaging

The present invention discloses a quad flat no lead package and a production method thereof. The quad flat no lead package comprises a lead frame carrier consisting of a carrier pit and three circles of leads arranged around the carrier pit, wherein the three circles of leads respectively consist of a plurality of leads that are disconnected mutually; an IC chip is adhered in the carrier pit; and an inner lead chemical nickel and porpezite plated layer is plated on all the leads; the inner lead chemical nickel and porpezite plated layer is arranged in the same direction as the IC chip; the IC chip is connected with the inner lead chemical nickel and porpezite plated layer through a bonding wire; and the IC chip, the ends of all the leads plated with the inner lead chemical plating nickel and palladium metal layers and the bonding wire are all packaged in a plastic package. The quad flat no lead package is manufactured through the following steps of: thinning and scribing a wafer; manufacturing a lead frame; loading the chip; performing pressure welding and plastic packaging; performing post-curing; printing; electroplating; separating the leads; separating a product; and testing / braiding. According to the package, the problems of few leads, long welding wire, high welding cost and limited frequency application during single-face packaging of the existing normal quad flat no lead package are solved.

Owner:TIANSHUI HUATIAN TECH +1

Quad flat non-leaded package structure

InactiveUS20090206459A1Improve reliabilityAvoid damageSemiconductor/solid-state device detailsSolid-state devicesQuad Flat No-leads packageElectrical and Electronics engineering

A quad flat non-leaded package structure including a die pad, a plurality of leads, a chip, and a molding compound is provided. The die pad has a top surface and an opposite bottom surface, and the leads are disposed around the die pad. A concave portion is disposed at the end of each leads. The chip is disposed on the top surface of the die pad and is electrically connected to the leads. The molding compound encapsulates the chip, a portion of the leads and the die pad, and fills the gaps between the leads.

Owner:CHIPMOS TECH INC

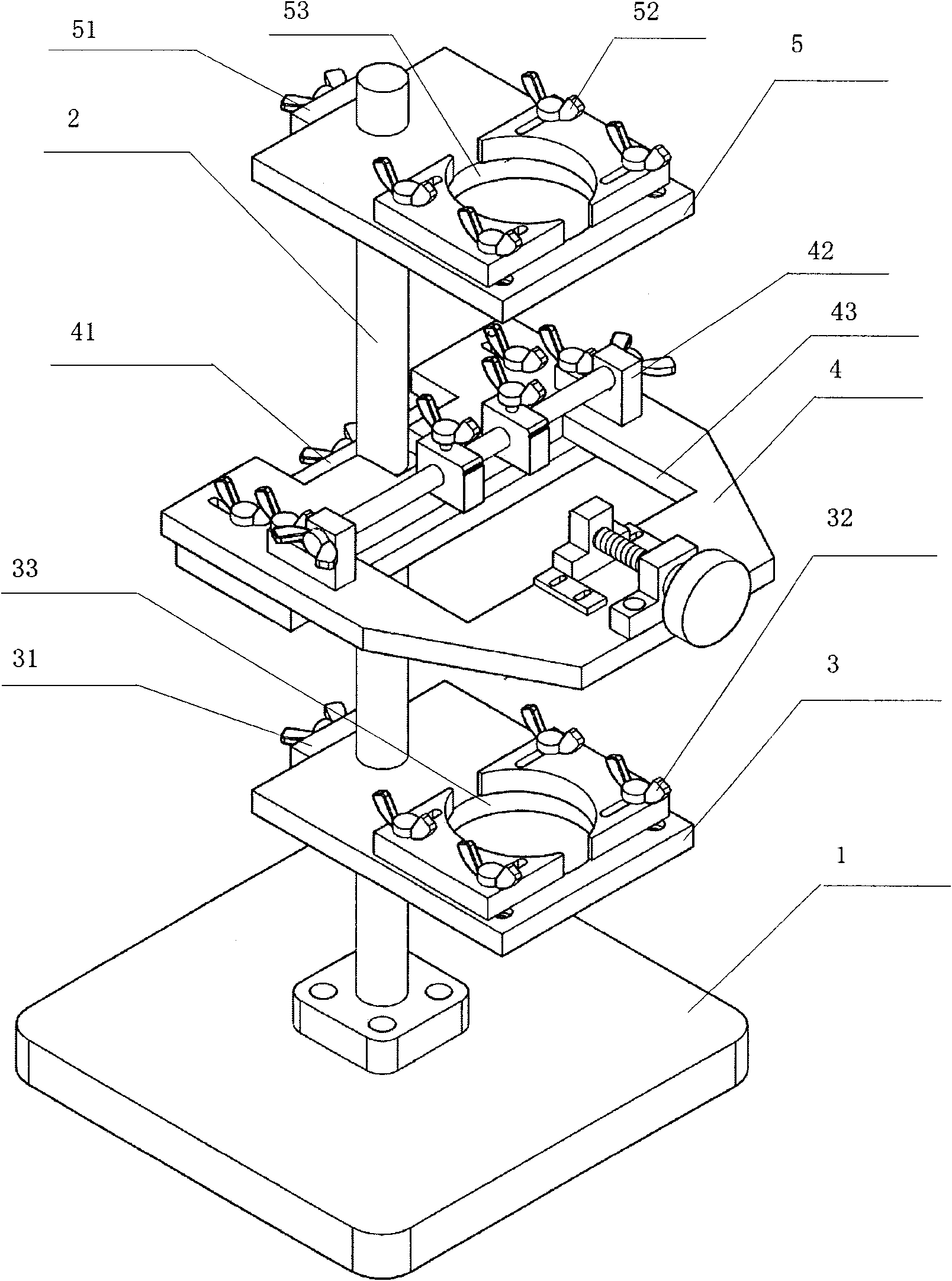

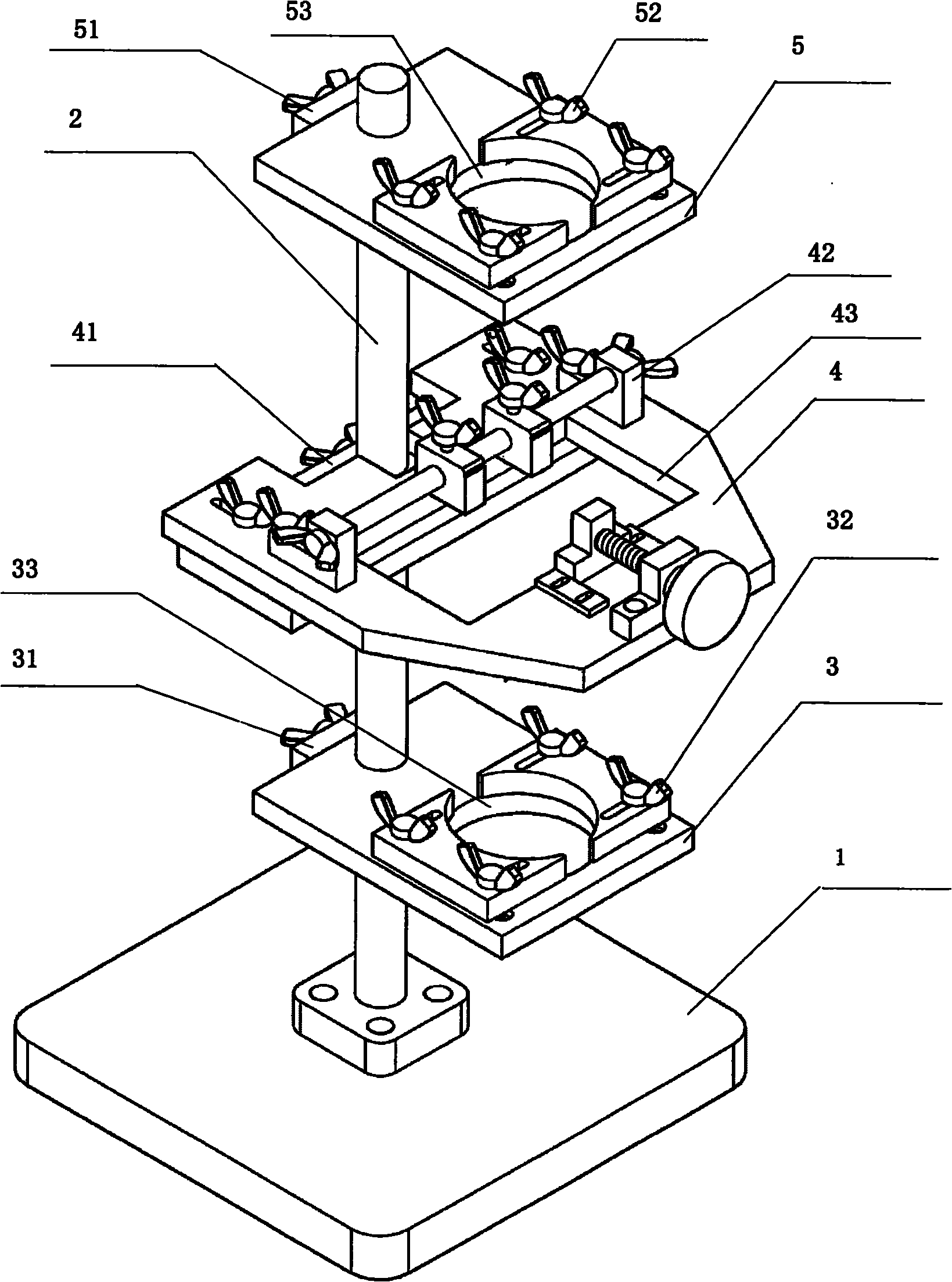

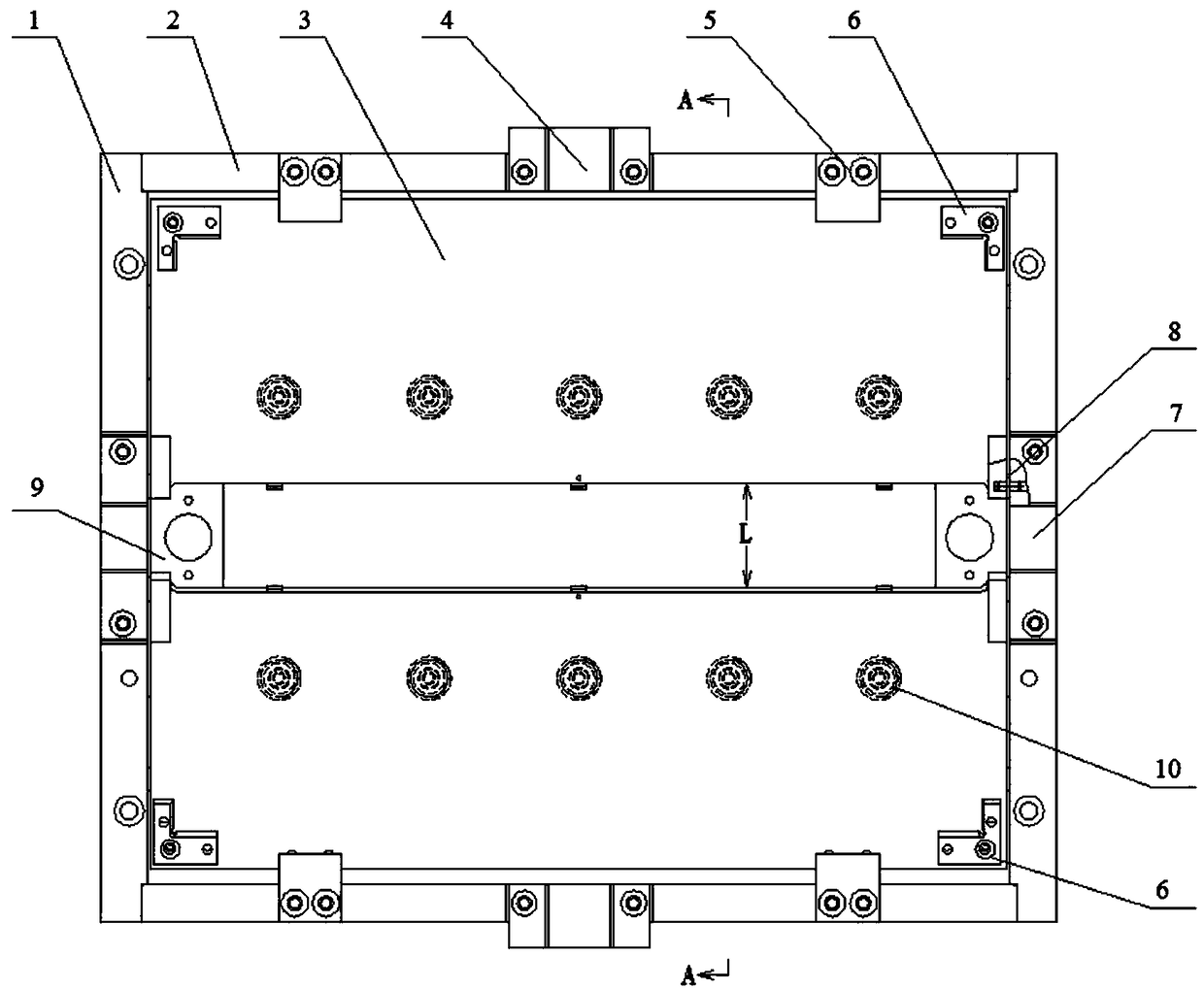

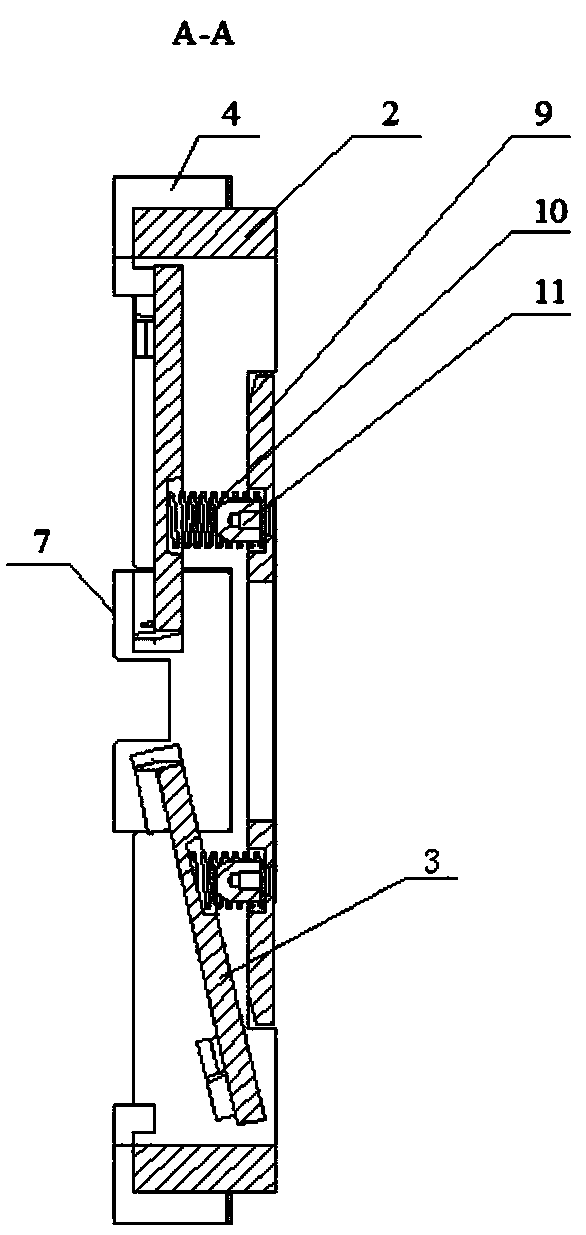

Method for maintaining AQFN (Advanced Quad Flat No-Lead Package) mobile phone motherboard and maintenance table

InactiveCN102335790AImprove maintenance efficiencyLow heating temperaturePrinted circuit assemblingMetal working apparatusProduction lineEngineering

The invention discloses a method for maintaining an AQFN (Advanced Quad Flat No-Lead Package) mobile phone motherboard and a maintenance table. The method comprises the following steps of: 1, fixing the motherboard to be maintained, an upper air gun and a lower air gun on respective fixing tables which are adjusted in place respectively; 2, setting proper temperature and air speed of the upper air gun and the lower air gun respectively; 3, simultaneously starting the upper air gun and the lower air gun for heating and unsoldering; 4, cleaning a bonding pad; 5, smoothly coating a solder wire of the bonding pad; 6, performing chip balling; and 7, simultaneously starting the upper air gun and the lower air gun for heating and reflow soldering. The maintenance table comprises a pedestal 1, a stand 2, a lower air gun fixing table 3, a motherboard fixing table 4 and an upper air gun fixing table 5, wherein the stand 2 is fixed at a middle position of the pedestal 1; the lower air gun fixing table, the motherboard fixing table and the upper air gun fixing table are sleeved on the stand respectively; and each fixing table is provided with an adjusting, locking and fixing structure opposite to the stand. The maintenance method and the maintenance table have the advantages of high maintenance efficiency and low reject ratio; and the maintenance table is low in cost, has small occupied area and is suitable to be arranged on a mobile phone production line.

Owner:HUAQIN TECH CO LTD

Surface mount technology process for advanced quad flat no-lead package process and stencil used therewith

The invention provides a surface mount technology process for an advanced quad flat no-lead package process and a stencil used therewith. The surface mount technology process for an advanced quad flat no-lead package includes providing a printed circuit board. A stencil with first openings is mounted over the printed circuit board. A solder paste is printed passing the first openings to form first solder paste patterns. The stencil is taken off. A component placement process is performed to place the advanced quad flat no-lead package comprising a die pad on the printed circuit board, wherein the first solder paste patterns contact a lower surface of the die pad, and an area ratio of the first openings to the lower surface of the die pad is between 1:2 and 1:10. A reflow process is performed to melt the first solder paste patterns to surround a sidewall of the die pad.

Owner:MEDIATEK SINGAPORE PTE LTD SINGAPORE

Area array quad flat no lead package (AAQFN) package body package in package (PiP) piece with solder balls and production method

ActiveCN103730442AReduce thicknessMeet ultra-thin packaging requirementsSemiconductor/solid-state device detailsSolid-state devicesSolder ballWafer thinning

Provided are an area array quad flat no lead package (AAQFN) package body package in package (PiP) piece with solder balls and a production method. The AAQFN package body PiP piece with the solder balls comprises a bare copper frame with multiple pits, an IC chip with salient points is mounted on the front face of the bare copper frame inversely, lower packing is filled between the salient points of the chip and the pits, a first groove is formed in the bare copper frame, two leads which are not connected with each other are formed on the two sides of the first groove, plastic package is carried out on the IC chips with salient points, connecting layers connected with the corresponding leads are arranged on the lower faces of the leads, the solder balls are arranged on the surfaces of all the connecting layers, two layers of IC chips are attached to a first plastic package body, the two layers of IC chips are connected through bonding wires and are connected with the leads through bonding wires respectively, and secondary plastic package is carried out. Through the working procedures of wafer thinning and dicing, bare copper frame processing, upper chip inverse mounting, passivation layer coating and etching, chemical sedimentation and the like, the AAQFN package body PiP piece with the solder balls is prepared. The PiP piece product is smaller in size, higher in packaging density, more in function and capable of replacing parts of BGA PiP and CSP PiP.

Owner:TIANSHUI HUATIAN TECH

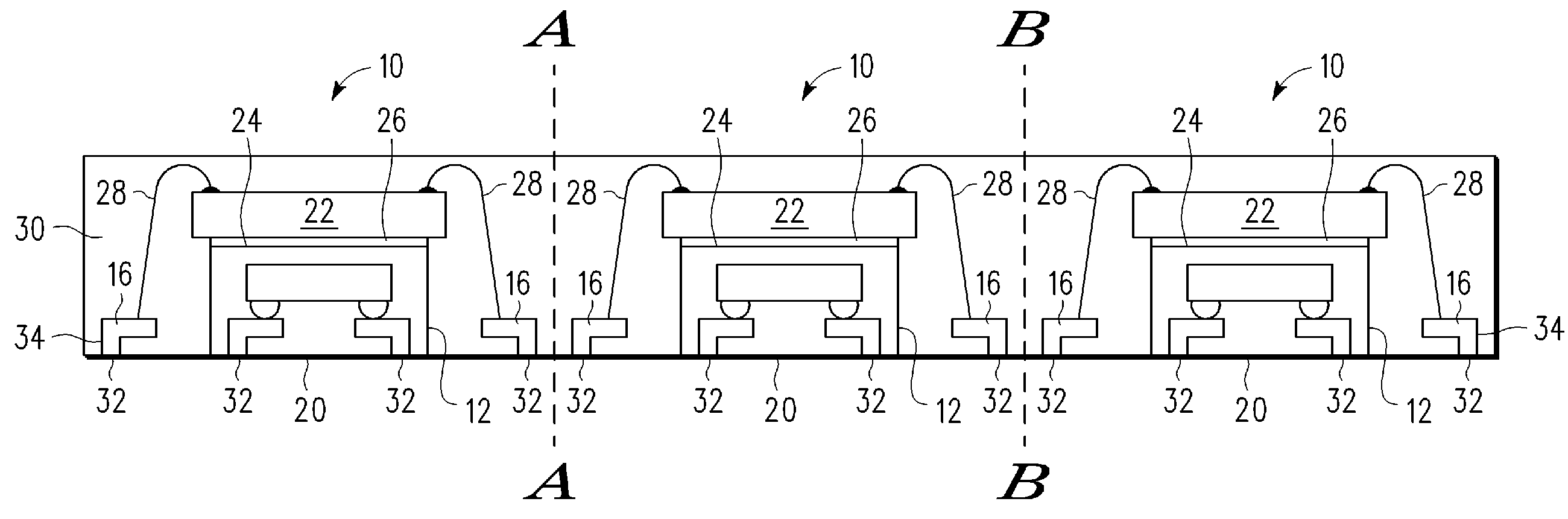

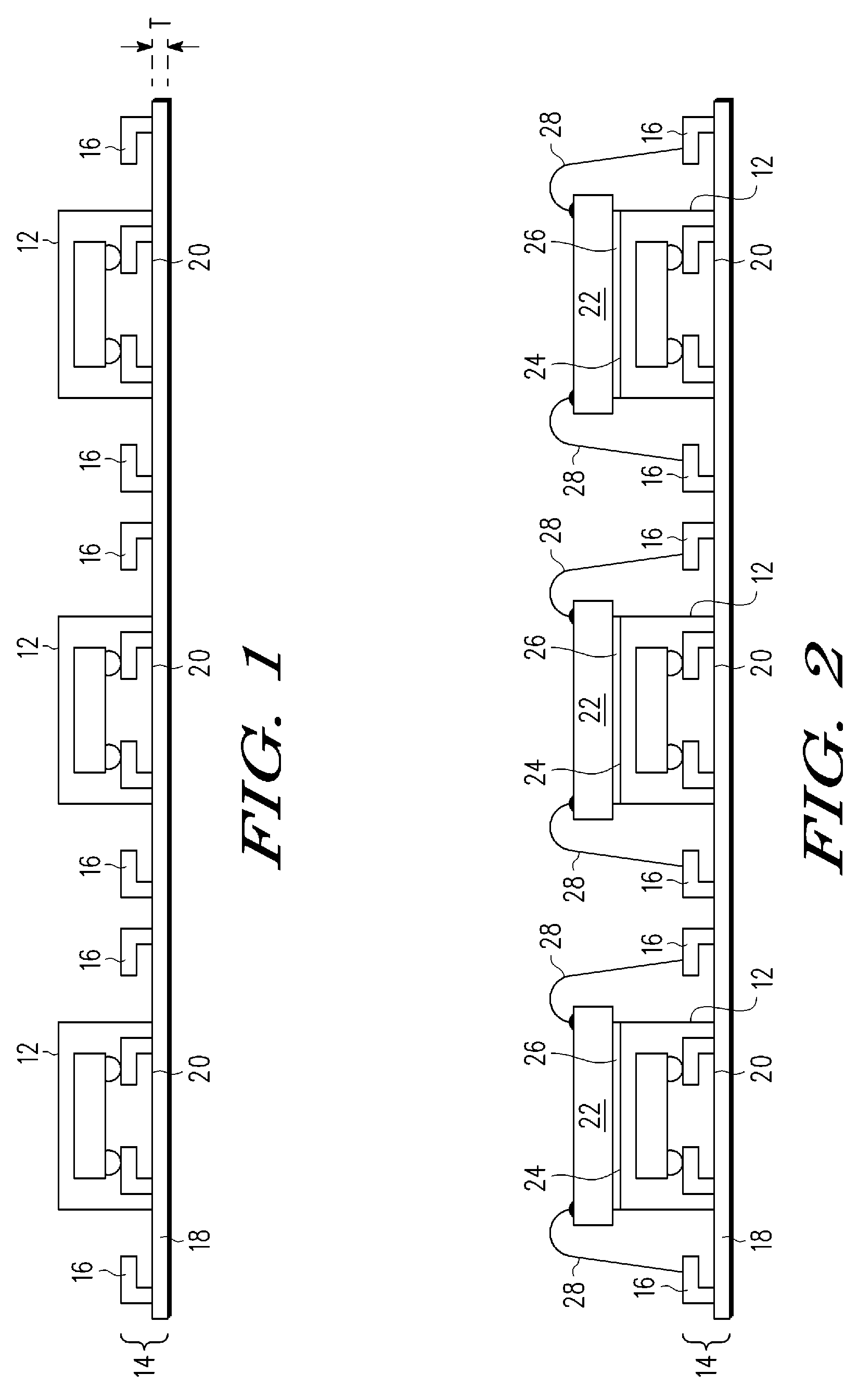

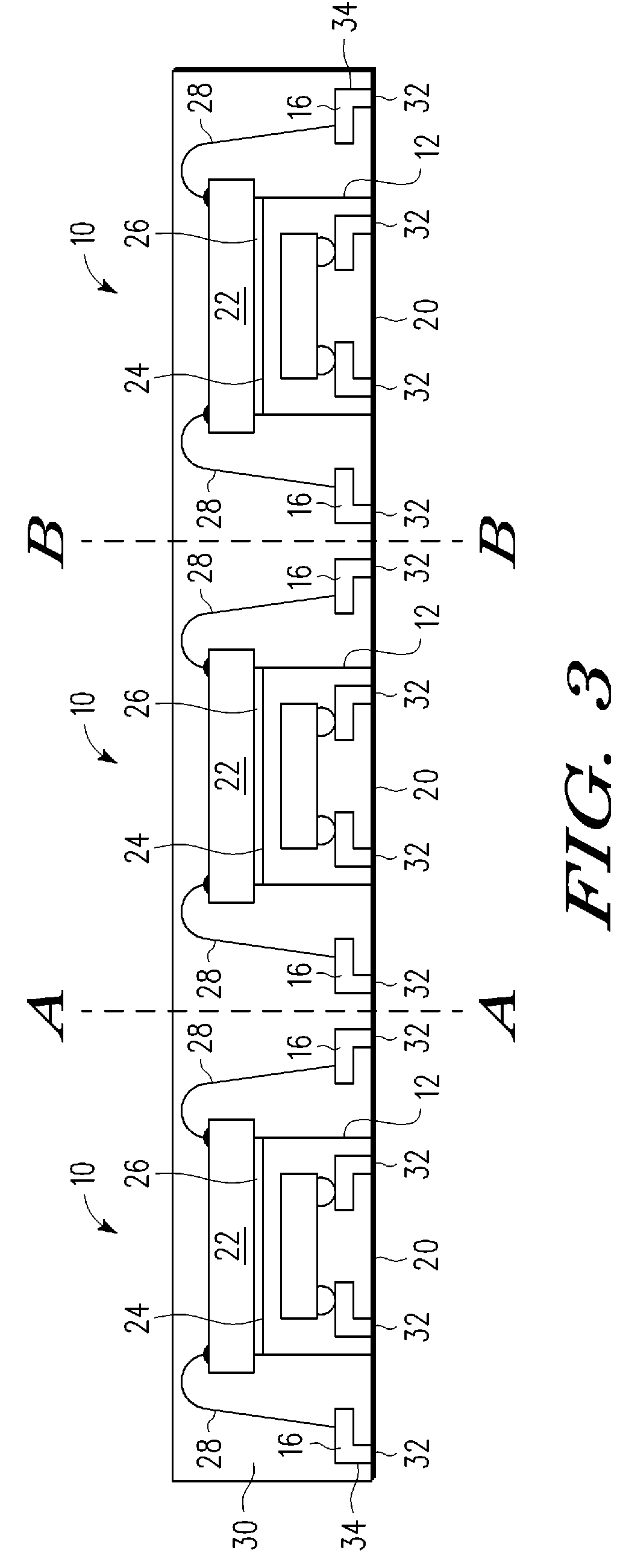

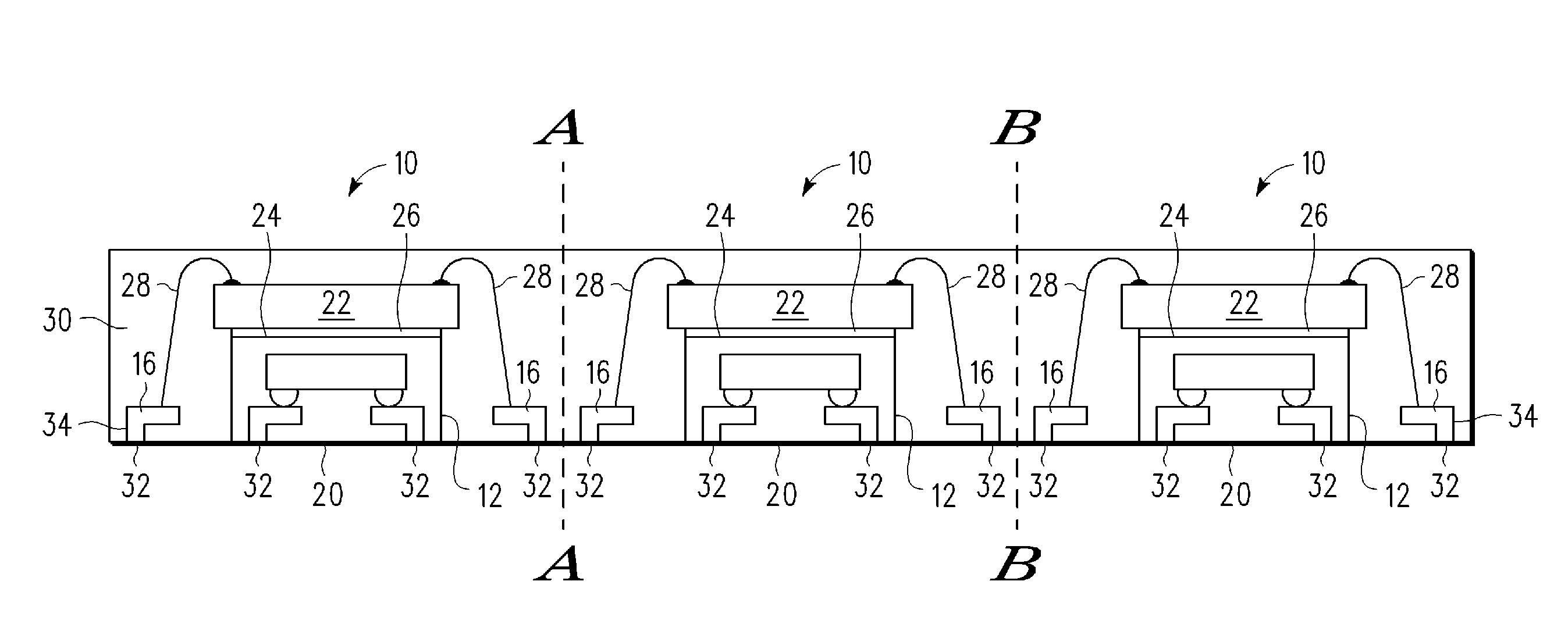

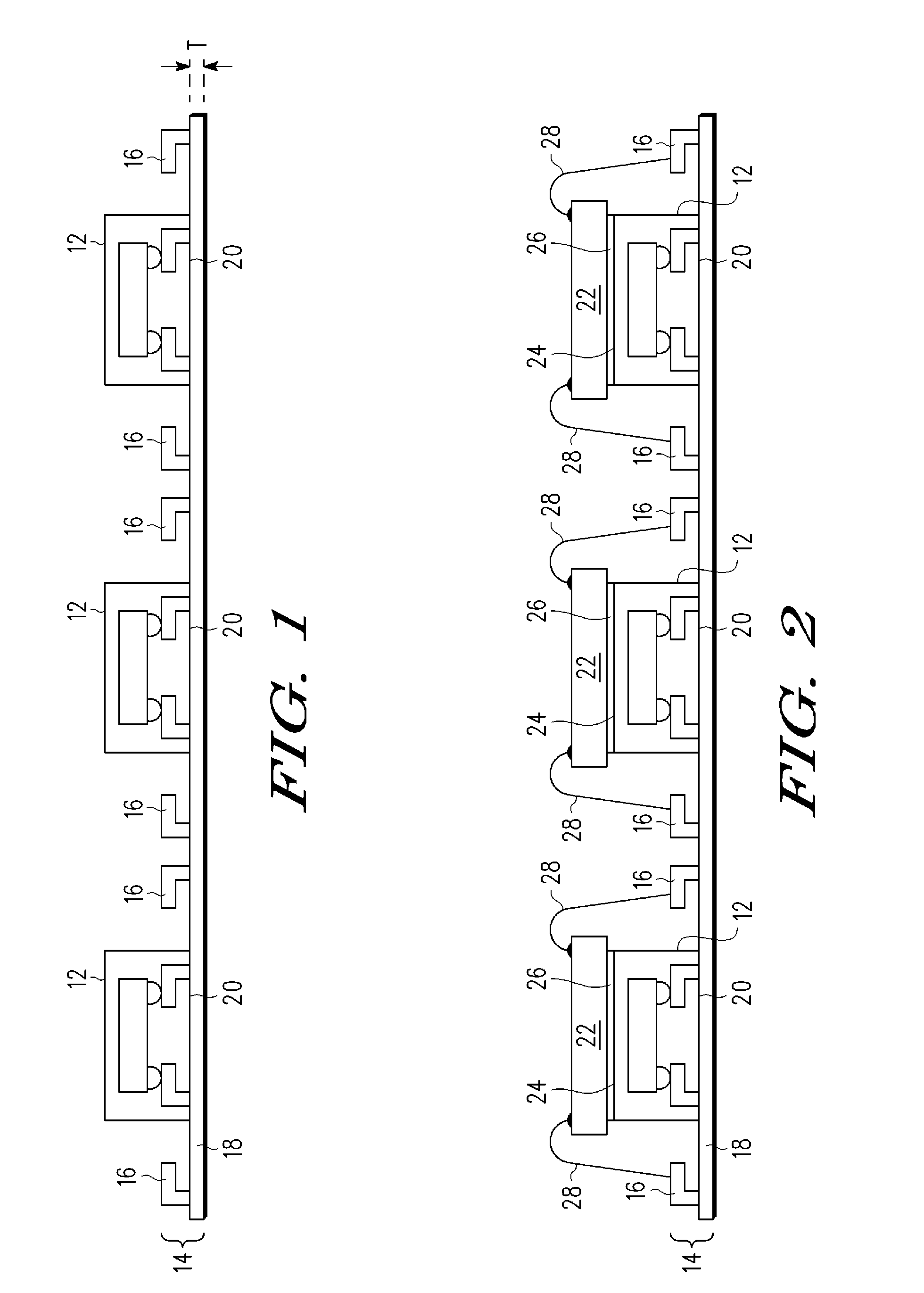

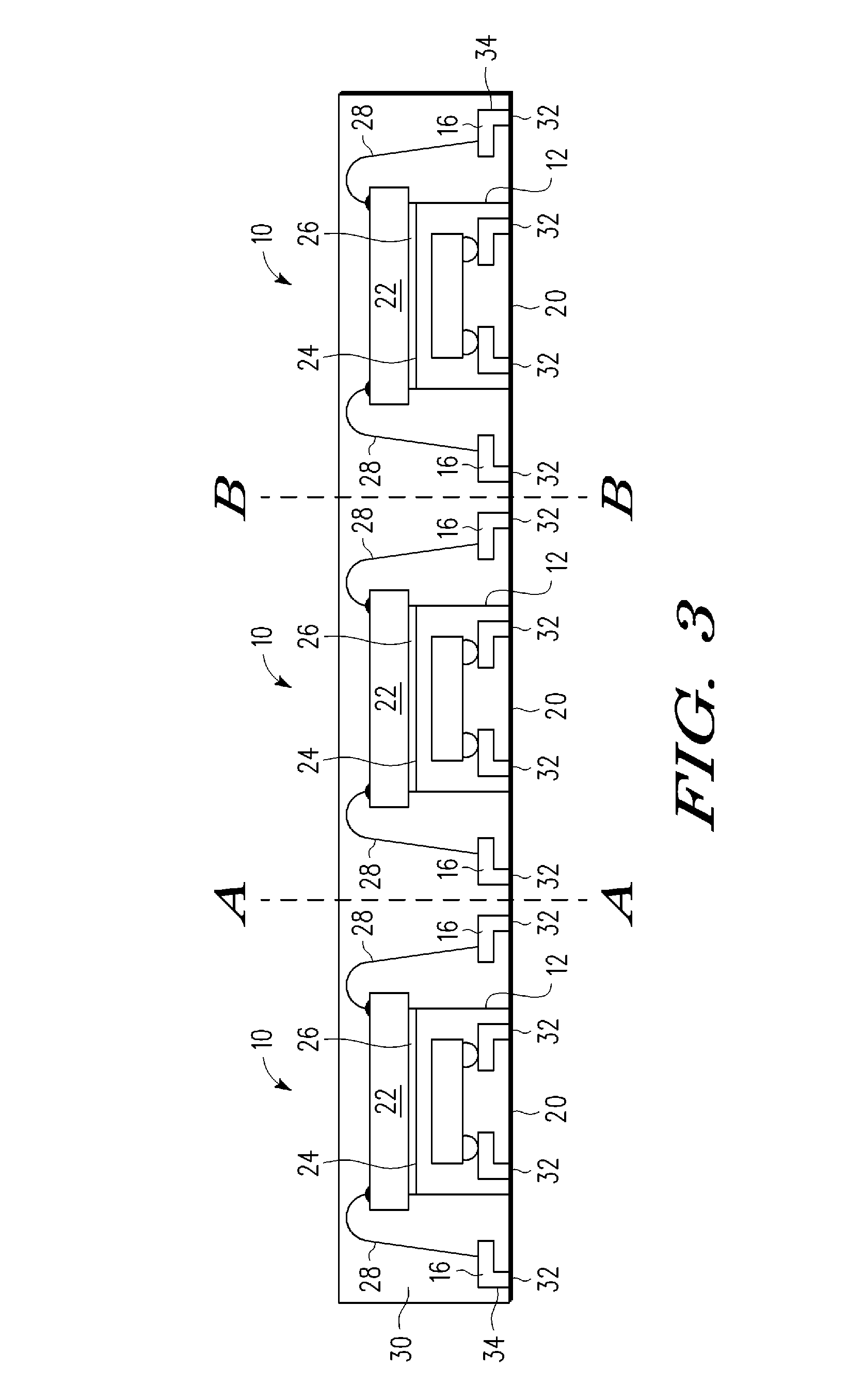

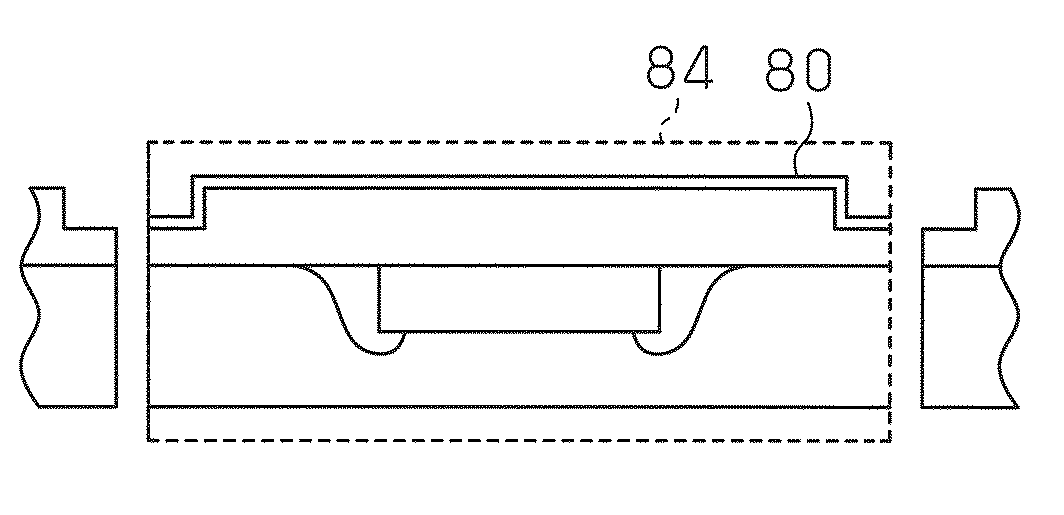

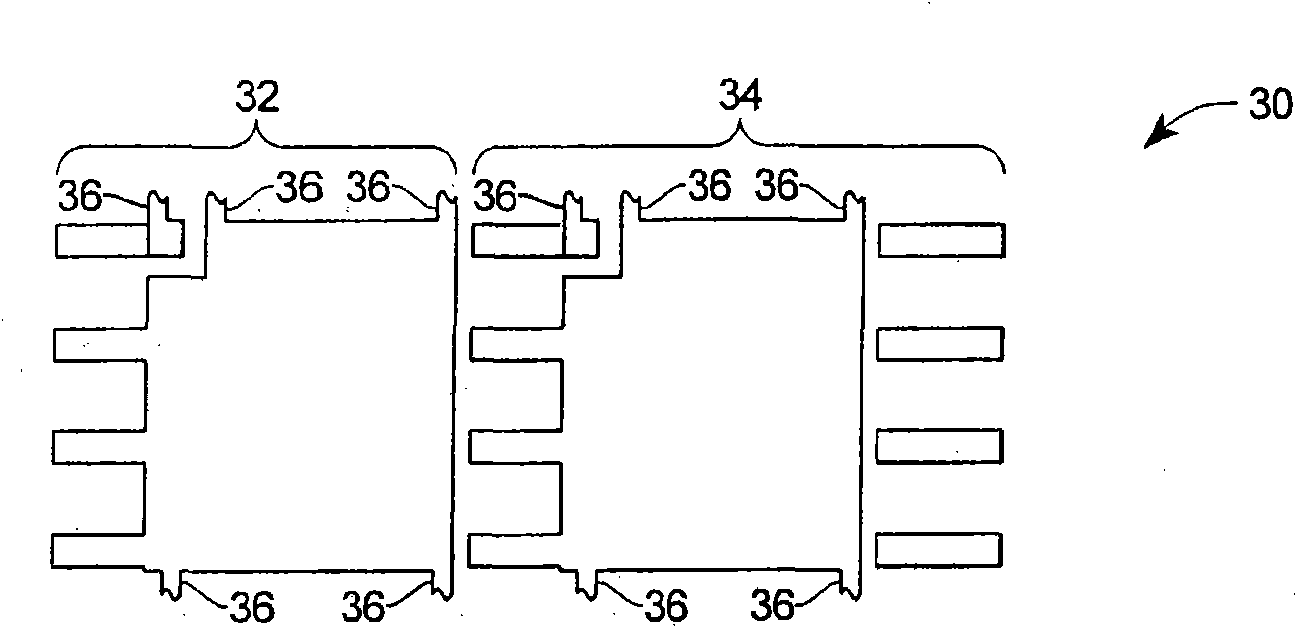

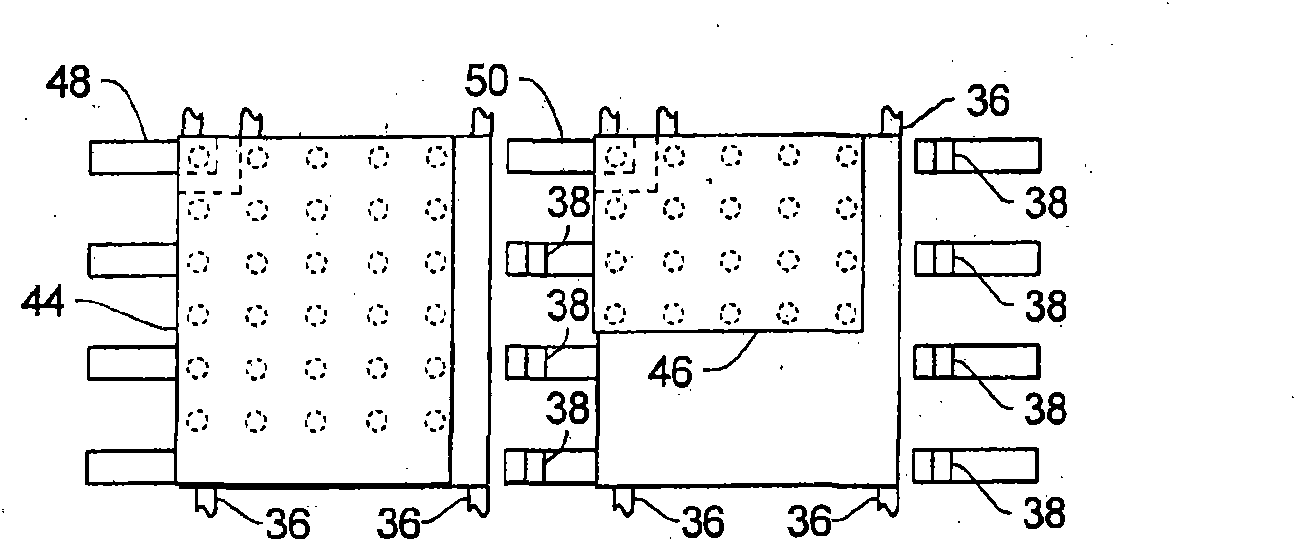

Array quad flat no-lead package and method of forming same

ActiveUS7531383B2Semiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

An array QFN package (10) includes a first semiconductor package (12) and a lead frame (14) having a plurality of leads (16). A first IC die (22) is attached on a first side to the first semiconductor package (12) and is electrically connected to the leads (16) of the lead frame (14). A mold compound (30) encapsulates the first IC die (22), a portion of the first semiconductor package (12) and a portion of the leads (16) such that a plurality of I / O terminals (32) on the semiconductor package (10) is exposed.

Owner:NORTH STAR INNOVATIONS

Production method of resin-based diamond cutting chip for cutting QFN (Quad Flat No-lead Package) substrates

The invention provides a production method of resin-based diamond cutting chip for cutting QFN (Quad Flat No-lead Package) substrates. The resin-based cutting chip is produced by combining superfine resin powder, a superfine inorganic filler, superfine metal powder and Ni-plated diamond according to a certain ratio, wherein the content of the superfine resin powder is 50wt%; the content of the superfine inorganic filler is 30wt%; the content of the superfine metal powder is 20wt%; the content of the diamond is 18.75-58vol%. The production method of the resin-based diamond cutting chip comprises the following steps: firstly proportioning the powder and then uniformly mixing the powder by using a hot-press forming device, then pressing the mixture into a cutting chip blank under certain hot-press forming process conditions, curing the cutting chip blank under certain curing process conditions and finally precisely grinding and machining the cured cutting chip blank to obtain the resin-based diamond cutting chip which meets the required specification and has thickness of 0.10-0.20mm. Through the production method of resin-based diamond cutting chip for cutting QFN substrates, the strength, the rigidity, the heat resistance and the abrasion resistance of the cutting chip can be effectively improved; the service life of the cutting chip can be effectively prolonged; compared with cutting chips produced by conventional components and processes for cutting the QFN substrates with the thickness of 0.7-1.1mm, the service life of the cutting chip is prolonged by 100-120%.

Owner:西安拓为精密工具有限公司

Quad flat non-leaded package structure with electromagnetic interference shielding function and method for fabricating the same

ActiveUS8736030B2Ease of mass productionOvercomes drawback of turbulenceSemiconductor/solid-state device detailsSolid-state devicesElectromagnetic interferenceEngineering

A quad flat non-leaded (QFN) package structure with an electromagnetic interference (EMI) shielding function is proposed, including: a lead frame having a die pad, a plurality of supporting portions connecting to the die pad and a plurality of leads disposed around the periphery of the die pad without connecting to the die pad; a chip mounted on the die pad; bonding wires electrically connecting the chip and the leads; an encapsulant for encapsulating the chip, the bonding wires and the lead frame and exposing the side and bottom surfaces of the leads and the bottom surface of the die pad; and a shielding film disposed on the top and side surfaces of the encapsulant and electrically connecting to the supporting portions for shielding from EMI. A method of fabricating the package structure as described above is further proposed.

Owner:SILICONWARE PRECISION IND CO LTD

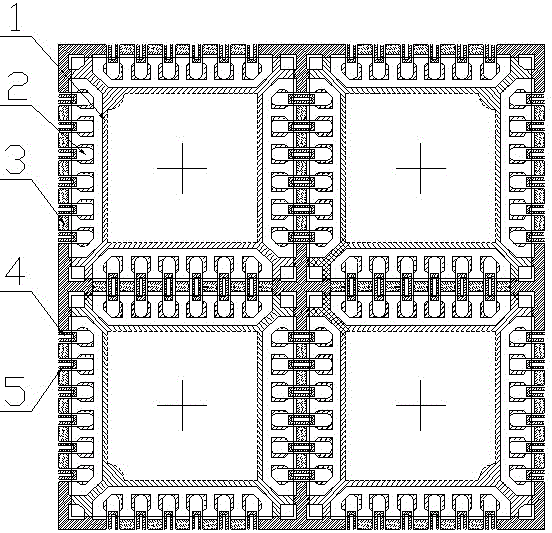

Quad flat no-lead package lead frame structure and package structure

ActiveCN104659010AMetal Thickness ReductionReduce thicknessSemiconductor/solid-state device detailsSolid-state devicesGlutenEngineering

The invention relates to a quad flat no-lead package lead frame structure. The quad flat no-lead package lead frame structure comprises a plurality of bearing units in matrix arrangement and middle glutens (3) arranged between and used for fixing the bearing units, wherein each bearing unit comprises a chip carrier (1) and a pin array (2) arranged at the periphery of the chip carrier; each middle gluten (3) is connected between the pin arrays (2) of two adjacent bearing units of the bearing units; a half-etched groove (4) is formed in the back, close to the corresponding middle gluten (3) , of each of the pin arrays (2). According to the quad flat no-lead package lead frame structure, as the half-etched grooves are formed in the root parts of pins, during applying of solder paste to a PCB, the solder paste can more successfully climb to the side edges of the pins through the siphonic effect, and accordingly, combination of the pins and the PCB is enhanced; as the half-etched grooves are formed in the root parts of the pins, the thickness of metal at the root parts of the pins is reduced, accordingly, tool abrasion is reduced and the quad flat no-lead cutting efficiency is greatly improved.

Owner:JCET GROUP CO LTD

Array quad flat no-lead package and method of forming same

ActiveUS20080099784A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

An array QFN package (10) includes a first semiconductor package (12) and a lead frame (14) having a plurality of leads (16). A first IC die (22) is attached on a first side to the first semiconductor package (12) and is electrically connected to the leads (16) of the lead frame (14). A mold compound (30) encapsulates the first IC die (22), a portion of the first semiconductor package (12) and a portion of the leads (16) such that a plurality of I / O terminals (32) on the semiconductor package (10) is exposed.

Owner:NORTH STAR INNOVATIONS

Method of packaging semiconductor device

InactiveUS20110165729A1Semiconductor/solid-state device detailsSolid-state devicesVisual inspectionSemiconductor

Quad Flat No-Lead packaged devices are manufactured using two singulation operations with two different saw blades of varying widths with the first singulation operation using a wider saw blade than the second singulation operation. Between singulation operations, the exposed portions of the leads are plated with a solderable metal. By performing the second singulation operation within the first cut made by the first singulation, at least half of the exposed metal of the leads remains plated. Thus, better solder joints may be formed, which allows for simpler visual inspection.

Owner:FREESCALE SEMICON INC

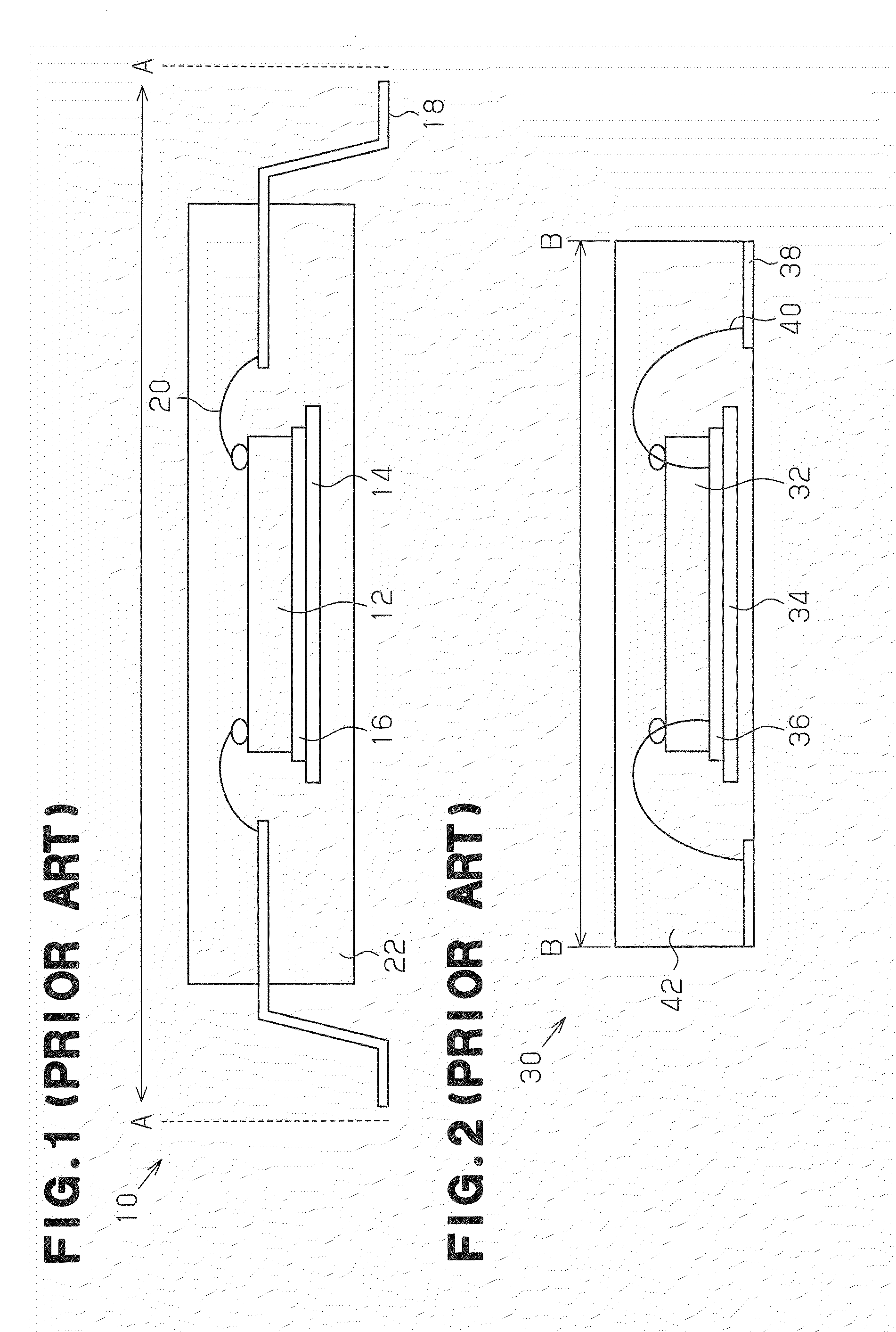

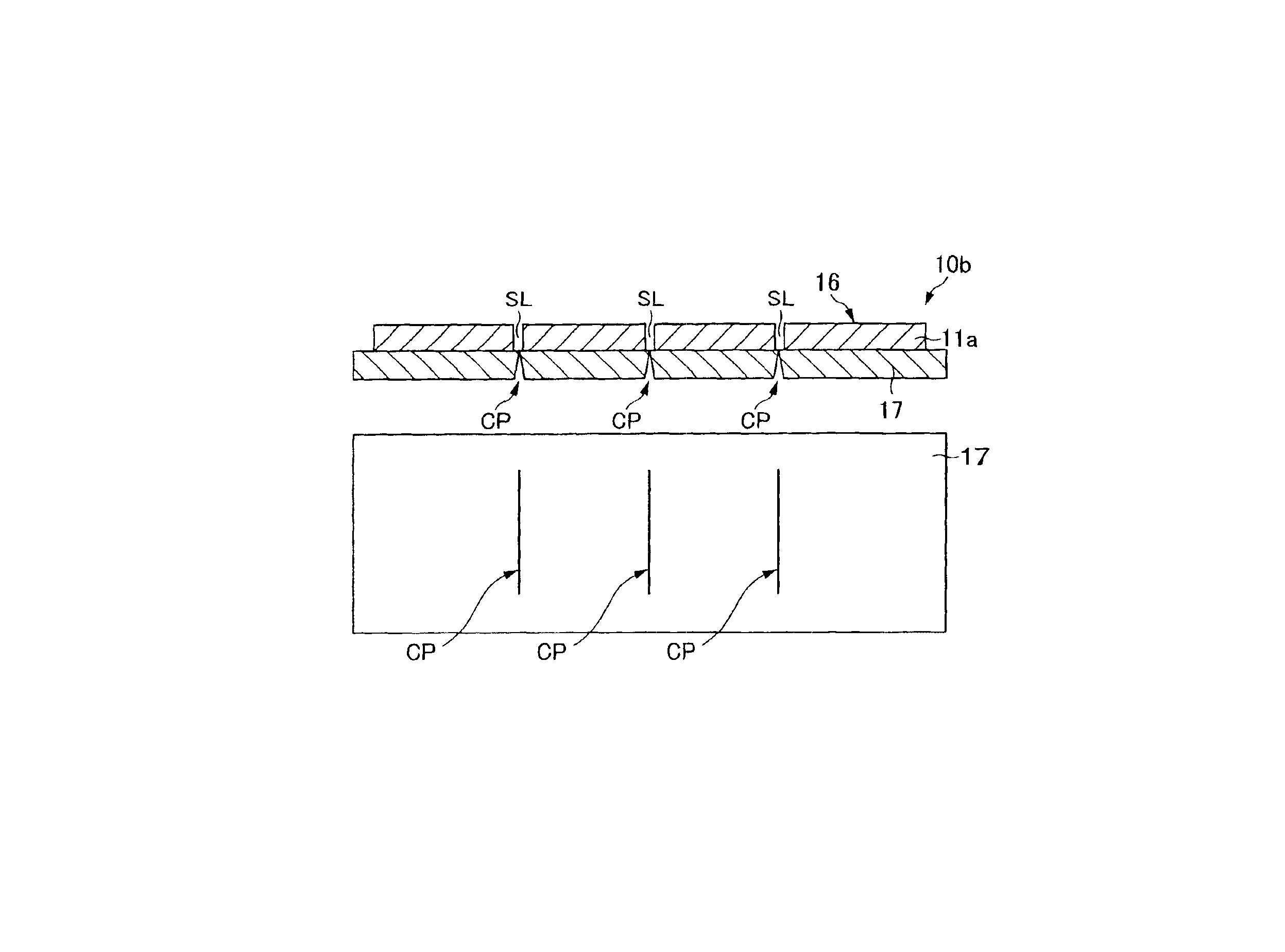

Lead frame, method of manufacturing the same, and method of manufacturing a semiconductor device using the same

InactiveUS6875630B2Reduce warpageReduce loadSemiconductor/solid-state device detailsSolid-state devicesEngineeringLead frame

In a method of manufacturing a lead frame for use in a leadless package such as a quad flat non-leaded package (QFN), a base frame is first formed which includes a region for resin-molding a plurality of semiconductor elements to be mounted on one surface of the base frame, the region being partitioned into land shapes, and in which a die-pad portion and lead portions around the die-pad portion are defined severally for the individual semiconductor elements to be mounted in each of the partitioned regions for resin-molding. Next, an adhesive tape is attached to the other surface of the base frame, and subsequently a cut portion is provided at a portion corresponding to a region between two adjacent partitioned regions for resin-molding, of the adhesive tape.

Owner:SHINKO ELECTRIC IND CO LTD

Dual side cooling integrated power device package and module and methods of manufacture

InactiveCN101681897ASemiconductor/solid-state device detailsSolid-state devicesQuad Flat No-leads packageTransistor

An integrated power device module having a leadframe structure with first and second spaced pads and one or more common source-drain leads located between said first and second pads, first and secondtransistors flip chip attached respectively to said first and second pads, wherein the source of said second transistor is electrically connected to said one or more common source-drain leads, and a first clip attached to the drain of said first transistor and electrically connected to said one or more common source-drain leads. In another embodiment a partially encapsulated power quad flat no-lead package having an exposed top thermal drain clip which is substantially perpendicular to said with a folded stud exposed top thermal drain clip, and an exposed thermal source pad.

Owner:FAIRCHILD SEMICON CORP

Down folding type runner removal device for automated packaging system

PendingCN109015896AThe overall structure is simple and reliableAdapt to development needsMetal working apparatusPunchingEngineering

The invention provides a down folding type runner removal device for an automated packaging system. The down folding type runner removal device comprises a concave die mechanism and a convex die mechanism, wherein the concave die mechanism comprises two first frames, two second frames, two concave dies, two first concave die locking blocks, two second concave die locking blocks, a fixed plate anda plurality of springs; the convex die mechanism comprises a main frame and CULL adsorption mechanism and two convex die folding mechanisms; the main frame and CULL adsorption mechanism comprises fourconvex die locking blocks, two internal storage limiting blocks, a substrate, two CULL linear bearings, two punching plates, a CULL pressing plate and a plurality of suction cups; and each convex diefolding mechanism comprises a pressing plate, a linear guide rail, an intermediate connecting plate and a bent plate. The down folding type runner removal device for the automated packaging system issimple and reliable in structure, can realize the packaging mode that a runner is on an upper die, and achieves runner removal technological processes of high-end package such as Quad Flat No-lead Package (QFN) and Ball Grid Array (BGA) of integrated circuits.

Owner:ANHUI DAHUA SEMICON TECH CO LTD

Quad-flat no-leads package structure and method of manufacturing the same

InactiveUS20150279796A1Simple manufacturing processLow production costSemiconductor/solid-state device detailsSolid-state devicesContact padFront end of line

A method of manufacturing a quad-flat no-leads package (QFN) structure includes: forming a conducting layer on a surface of a thin-film layer; forming a plurality of conduction wirings from the conducting layer by a means of circuit layout; electrically connecting contact pads of a die to front ends of the conduction wirings, respectively; forming a plurality of through-holes in the thin-film layer by a means of drilling, such that terminal ends of the conduction wirings are exposed from the through-holes, respectively; and forming a plurality of metal bumps at the through-holes, respectively, such that signals from the die are sent to a bottom surface of the thin-film layer through the conduction wirings. Hence, the QFN structure and the method of manufacturing the same based on application of wafer-level chip-scale package (WLCSP) and extension of tape QFN to simplify the package manufacturing process, cut production costs, and enhance production yield.

Owner:LINGSEN PRECISION INDS

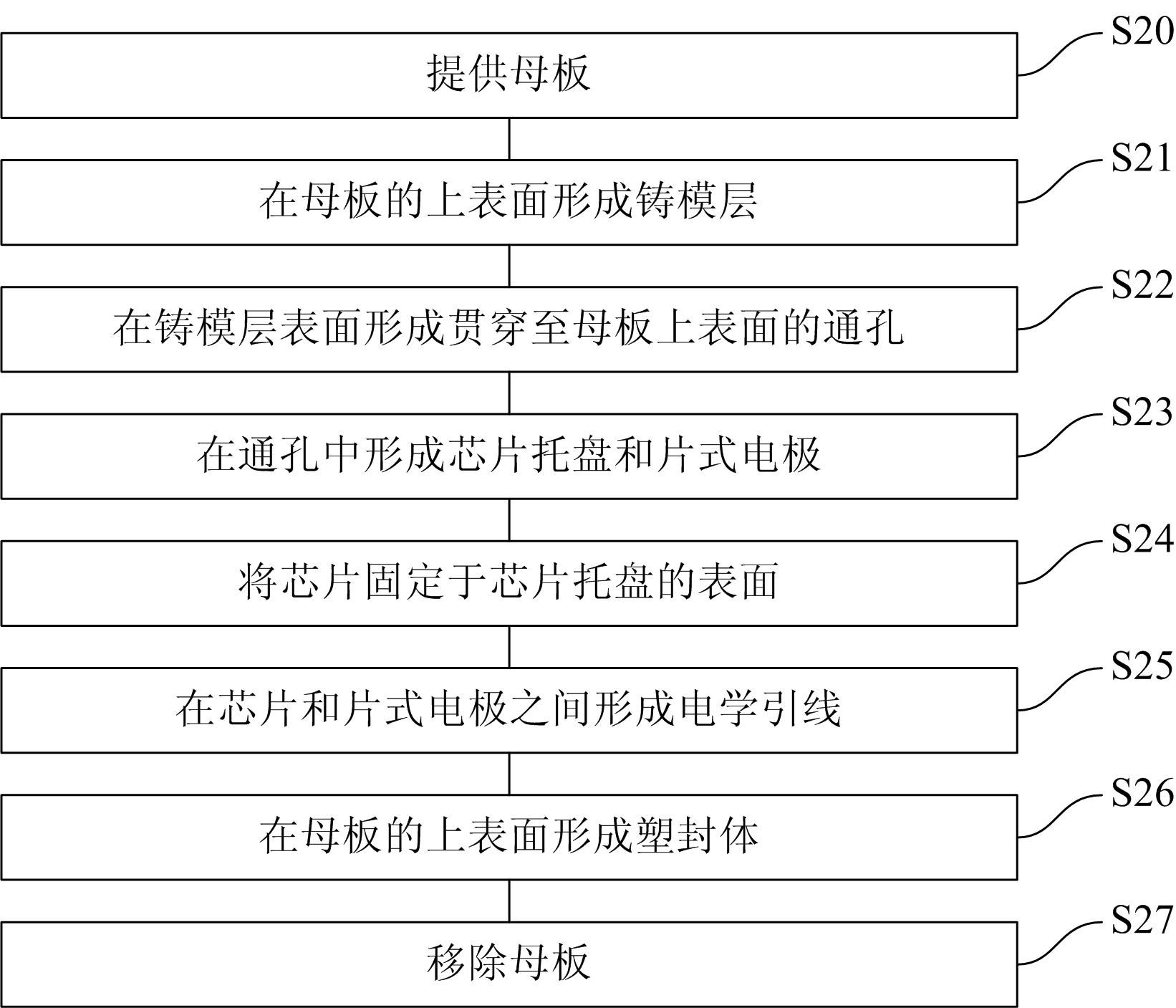

Quad flat no-lead package and manufacturing method thereof

InactiveCN102290358AEasy to fixReduce thermal stressSemiconductor/solid-state device detailsSolid-state devicesSurface layerCasting mold

The invention provides a method for manufacturing a quad flat no-lead package, comprising the following steps: providing a motherboard; forming a mold layer on the upper surface of the motherboard; forming a through hole penetrating to the upper surface of the motherboard on the surface of the mold layer, The opening area of the through hole close to the upper surface of the motherboard is smaller than the opening area of the other side; the chip tray and the chip electrode are formed in the through hole; the chip is fixed on the surface of the chip tray; between the chip and the chip electrode forming electrical leads between them; forming a plastic package on the upper surface of the motherboard; removing the motherboard to expose the chip tray and chip electrodes embedded in the plastic package.

Owner:SHANGHAI KAIHONG ELECTRONICS CO LTD +2

Method for fabricating quad flat non-leaded package structure with electromagnetic interference shielding function

ActiveUS20140227830A1Ease of mass productionOvercomes drawback of turbulenceSemiconductor/solid-state device detailsSolid-state devicesElectromagnetic interferenceEngineering

A quad flat non-leaded (QFN) package structure with an electromagnetic interference (EMI) shielding function is proposed, including: a lead frame having a die pad, a plurality of supporting portions connecting to the die pad and a plurality of leads disposed around the periphery of the die pad without connecting to the die pad; a chip mounted on the die pad; bonding wires electrically connecting the chip and the leads; an encapsulant for encapsulating the chip, the bonding wires and the lead frame and exposing the side and bottom surfaces of the leads and the bottom surface of the die pad; and a shielding film disposed on the top and side surfaces of the encapsulant and electrically connecting to the supporting portions for shielding from EMI. A method of fabricating the package structure as described above is further proposed.

Owner:SILICONWARE PRECISION IND CO LTD

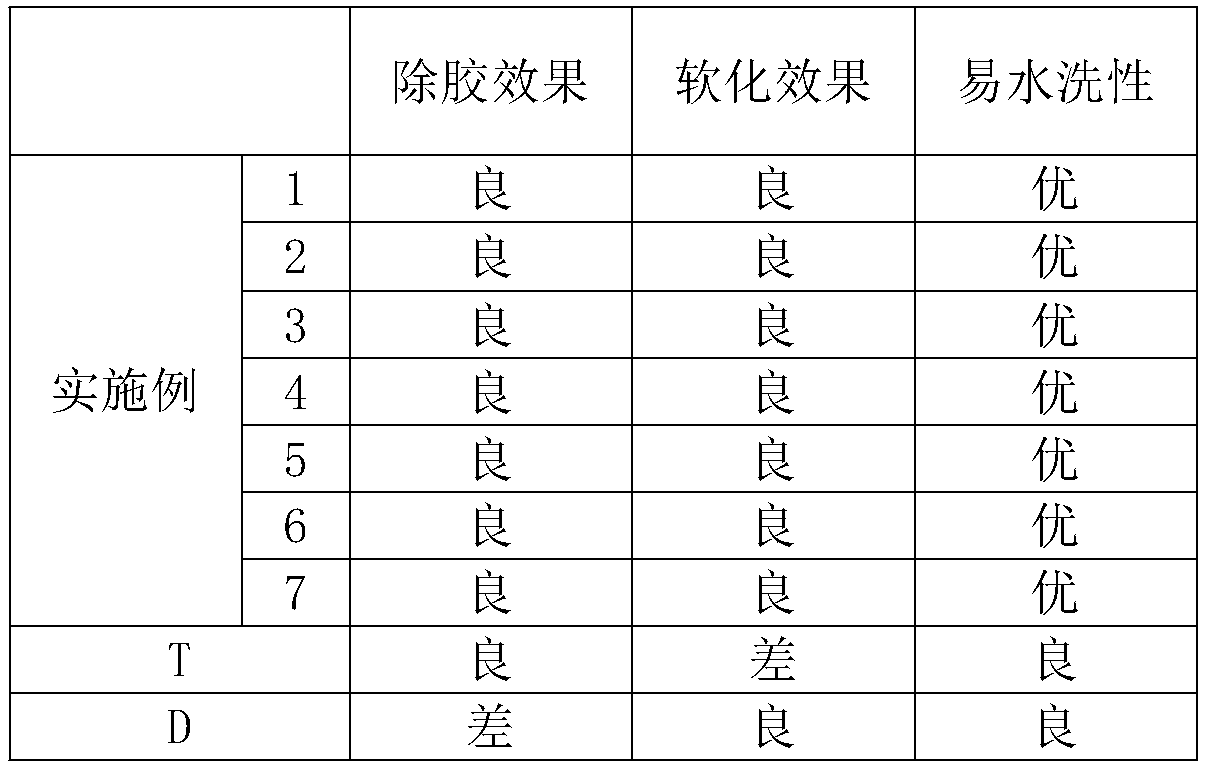

QFN (quad flat no-lead package) adhesive removal and softening integrated soak solution

InactiveCN109370792AEasy to remove glueImprove softening effectInorganic/elemental detergent compounding agentsOrganic detergent compounding agentsPolymer sciencePolypropylene

The invention belongs to the technical field of package, and relates to QFN (quad flat no-lead package) adhesive removal and softening integrated soak solution. The QFN adhesive removal and softeningintegrated soak solution in a formula comprises 0.5-5 wt% of block polyether surfactants, 20-40 wt% of organic alkali, 0.1-5 wt% of inorganic alkali, 30-50 wt% of organic solvents, 20-30 wt% of alcohol ether dispersing agents, 0.01-0.05 wt% of metal corrosion inhibitors and the balance deionized water. The block polyether surfactants comprise one or two types of propylene glycol polyoxyethylene polypropylene oxide block polymers and allyl polyoxyethylene polypropylene oxide methyl ether. The QFN adhesive removal and softening integrated soak solution has the advantages that the QFN adhesive removal and softening integrated soak solution is excellent in adhesive removal and softening ability and easy to clean, integral technologies only take the total time of 25-45 min, processes can be shortened to be 1 / 4 of the original processes, and accordingly the productivity can be greatly improved; the solution soak time is only 1 / 4 of the original solution soak time, and plastic package bodiescan be prevented from being damaged.

Owner:JIANGSU AISEN SEMICON MATERIAL CO LTD

Thin quad flat no-lead package method

ActiveCN101533783AImprove cooling efficiencyThe overall thickness is thinSemiconductor/solid-state device detailsSolid-state devicesLead bondingEngineering

Owner:SHANGHAI KAIHONG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com

![[quad flat no-lead package structure and manufacturing method thereof] [quad flat no-lead package structure and manufacturing method thereof]](https://images-eureka-patsnap-com.libproxy1.nus.edu.sg/patent_img/9b07bc5c-5b04-45bc-8282-35c9e2e1004d/US20050073055A1-20050407-D00000.png)

![[quad flat no-lead package structure and manufacturing method thereof] [quad flat no-lead package structure and manufacturing method thereof]](https://images-eureka-patsnap-com.libproxy1.nus.edu.sg/patent_img/9b07bc5c-5b04-45bc-8282-35c9e2e1004d/US20050073055A1-20050407-D00001.png)

![[quad flat no-lead package structure and manufacturing method thereof] [quad flat no-lead package structure and manufacturing method thereof]](https://images-eureka-patsnap-com.libproxy1.nus.edu.sg/patent_img/9b07bc5c-5b04-45bc-8282-35c9e2e1004d/US20050073055A1-20050407-D00002.png)