Thin quad flat no-lead package method

A flat leadless, packaging method technology, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of device thickness restrictions, increase packaging manufacturing costs, restrictions, etc., and achieve thin device thickness and improved The effect of cooling efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The specific implementation of the thin four-sided flat no-lead packaging method according to the present invention will be described in detail below in conjunction with the accompanying drawings.

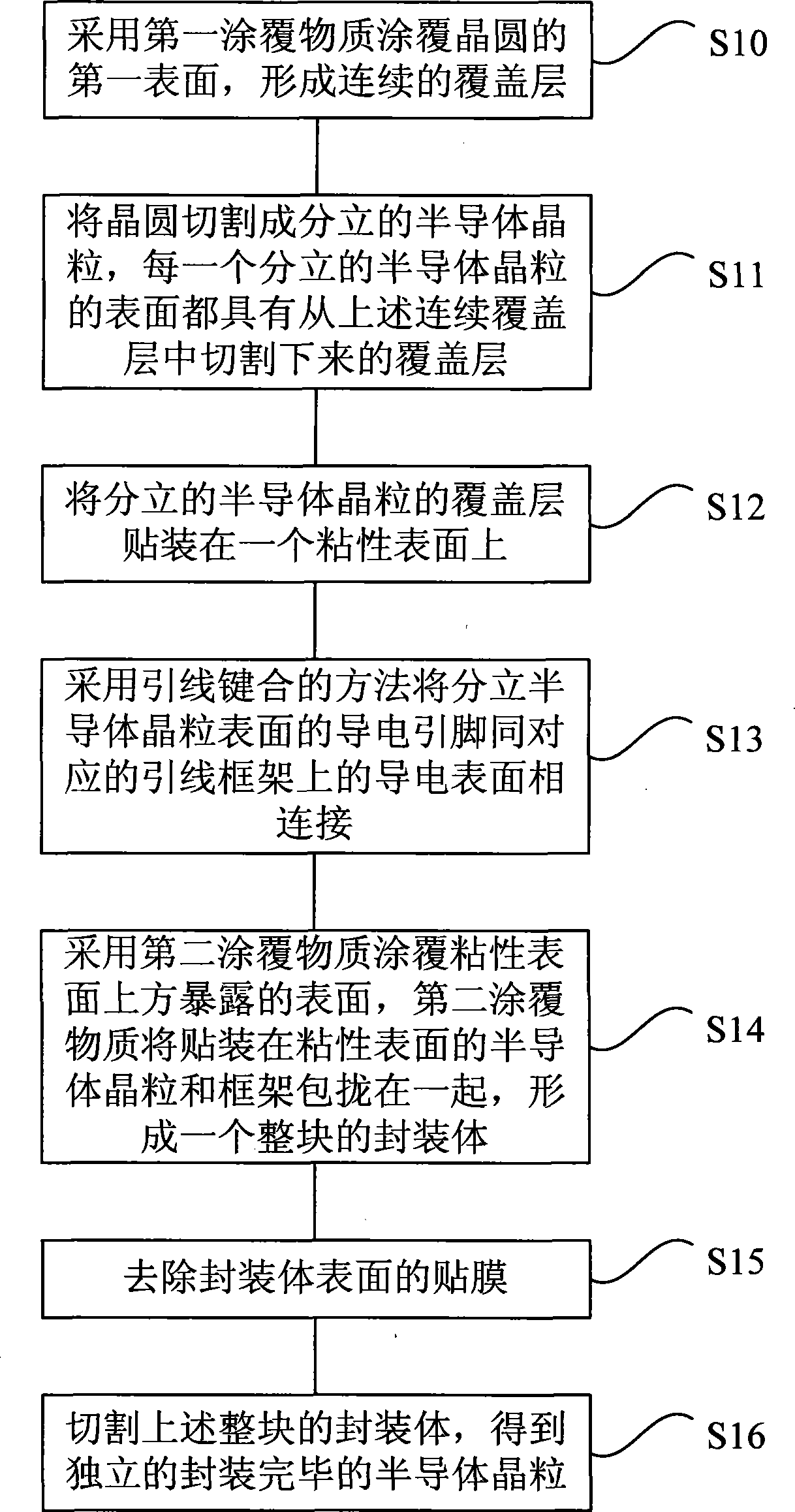

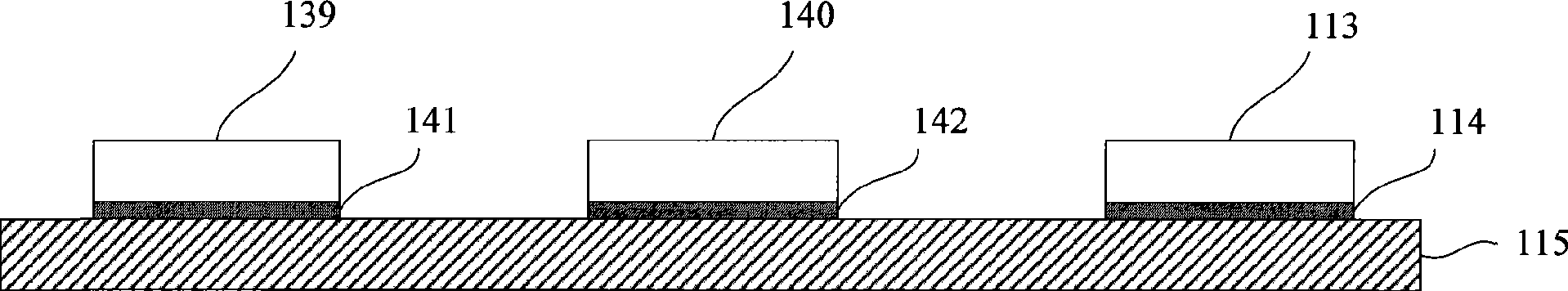

[0028] attached figure 1 Shown is a process flow chart of a specific embodiment of the thin four-sided flat no-lead packaging method described in the present invention. In step S10, the first surface of the wafer is coated with a first coating substance to form a continuous covering layer; in step S11, the wafer is cut into discrete semiconductor crystal grains, and the surface of each discrete semiconductor crystal grain has from The covering layer cut off from the above-mentioned continuous covering layer; step S12, attaching the covering layer of discrete semiconductor crystal grains on an adhesive surface; step S13, adopting the method of wire bonding to separate the conductive contacts on the surface of semiconductor crystal grains Connect with the conductive pins on t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com