Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

45results about How to "Improve electrical connection quality" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

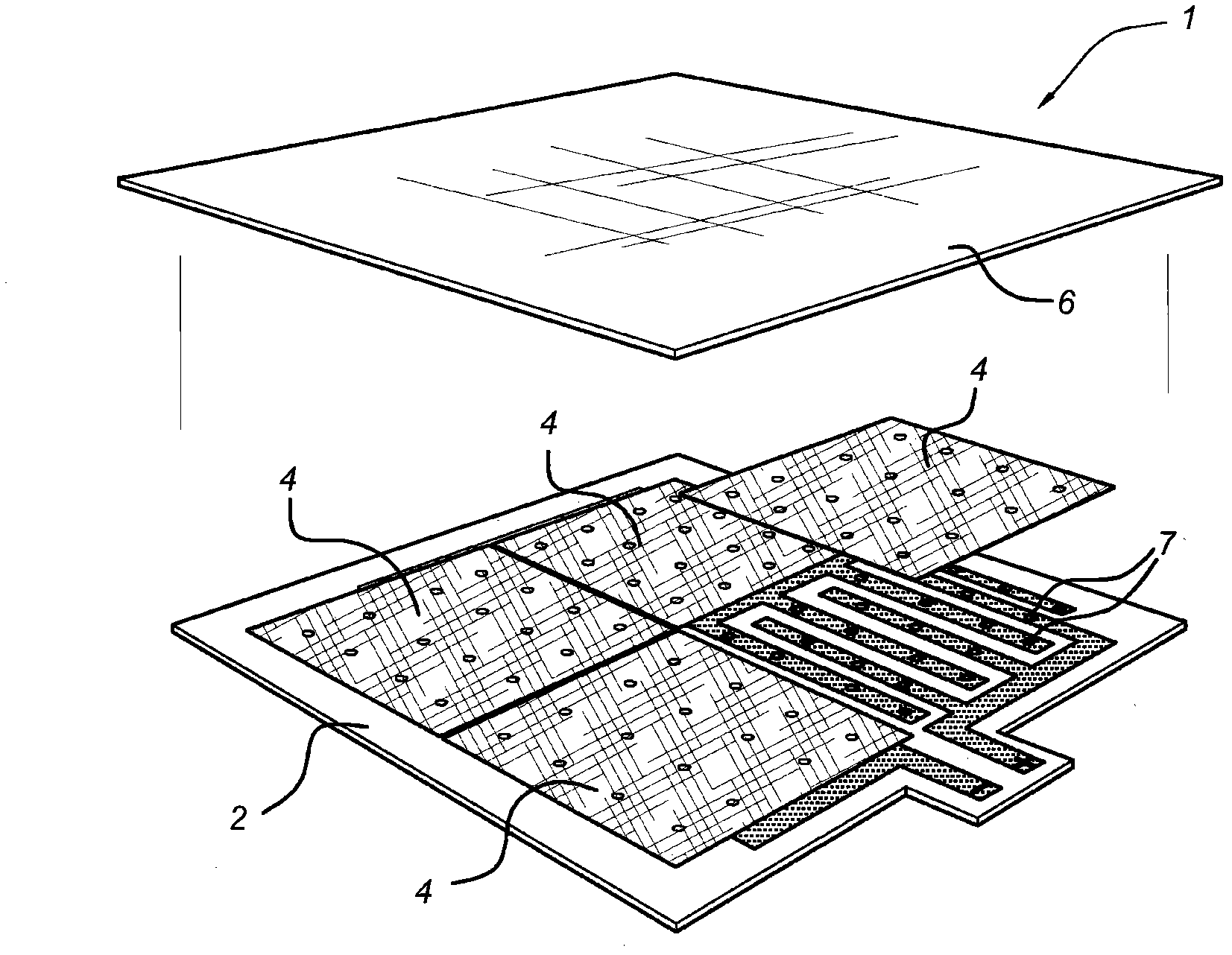

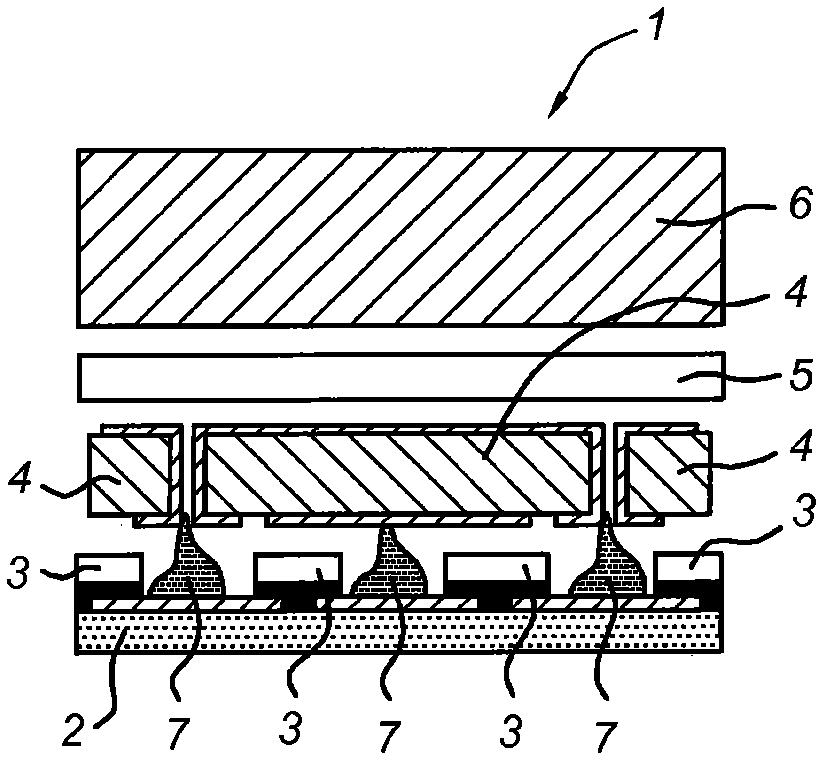

Method of monolithic photo-voltaic module assembly

InactiveCN102217095AImprove electrical connection qualitySoldering apparatusPhotovoltaic energy generationElectricityComputer module

Method for manufacturing a photovoltaic module (1) comprising: a) providing an electrically conductive substrate, the substrate being provided with a predetermined electrical pattern; b) depositing a solder paste (7) onto the electrically conductive substrate at pre-defined interconnection locations; c) placing a first encapsulant layer (3) provided with a pattern of openings onto the electrically conductive substrate, the pattern of openings corresponding with the locations of the solder paste (7); d) placing back-contact solar cells (4) on the first encapsulant layer so as to have a match of the electrical pattern of the back-contact solar cells with the electrical pattern of the electrically conductive substrate; e) placing a second encapsulant layer (5) on the back-contact solar cells (4), and placing a glass layer (6) on the second encapsulant layer (5); ; f) applying heat and pressure to the components (2, 3, 4, 5, 6, 7) to cause the encapsulant materials to flow and form a monolithic photovoltaic module, characterised by local application of at the interconnection locations utilizing a laser to couple its energy locally into the solar cell from the side of the glass layer, so as to cause the solder paste to reflow between each interconnection location and its respective matching connection location on the back-contact solar cell for establishing electrical interconnection between the back-contact solar cells and the electrically conductive substrate.

Owner:琴科尔普公司

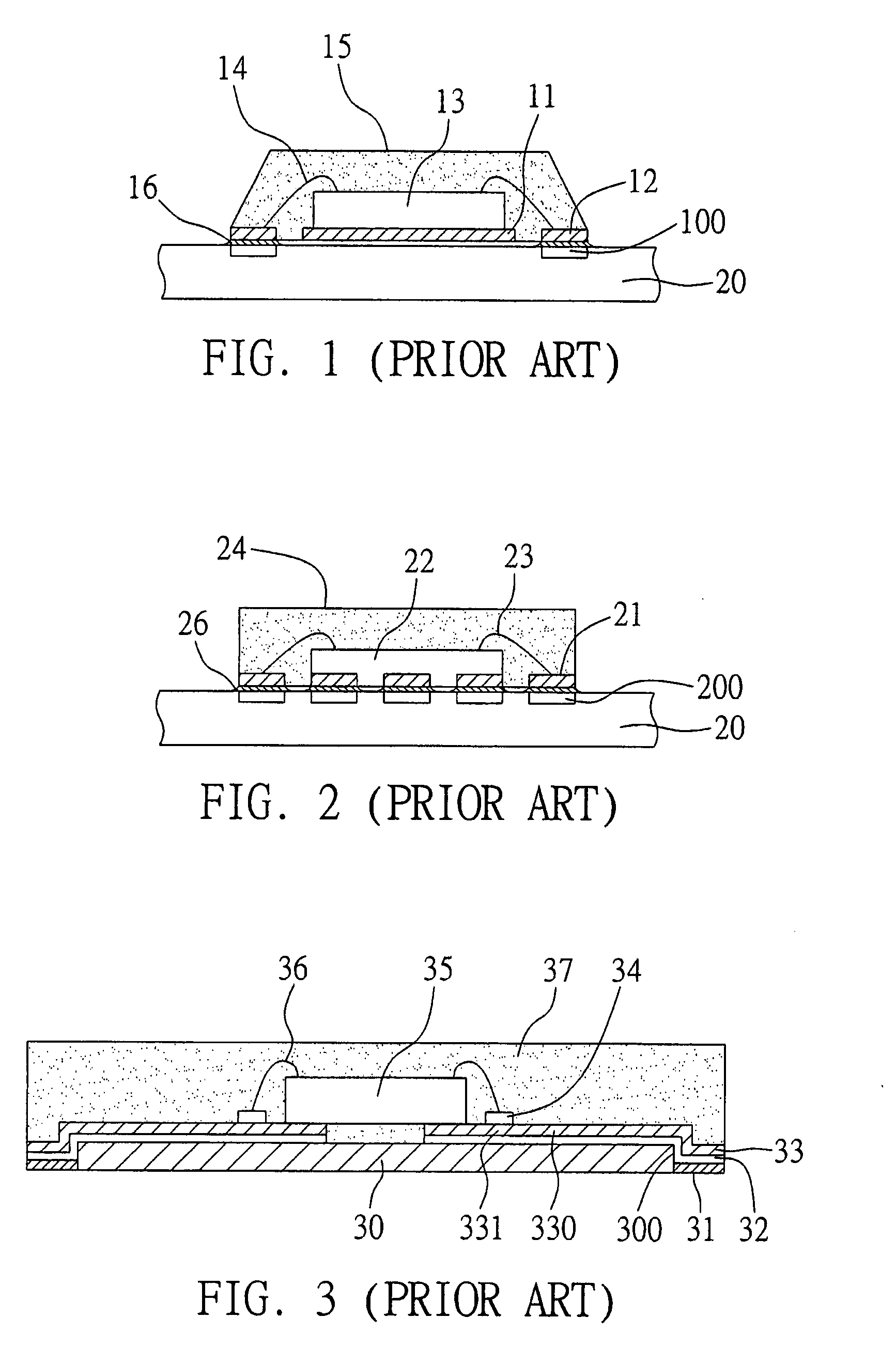

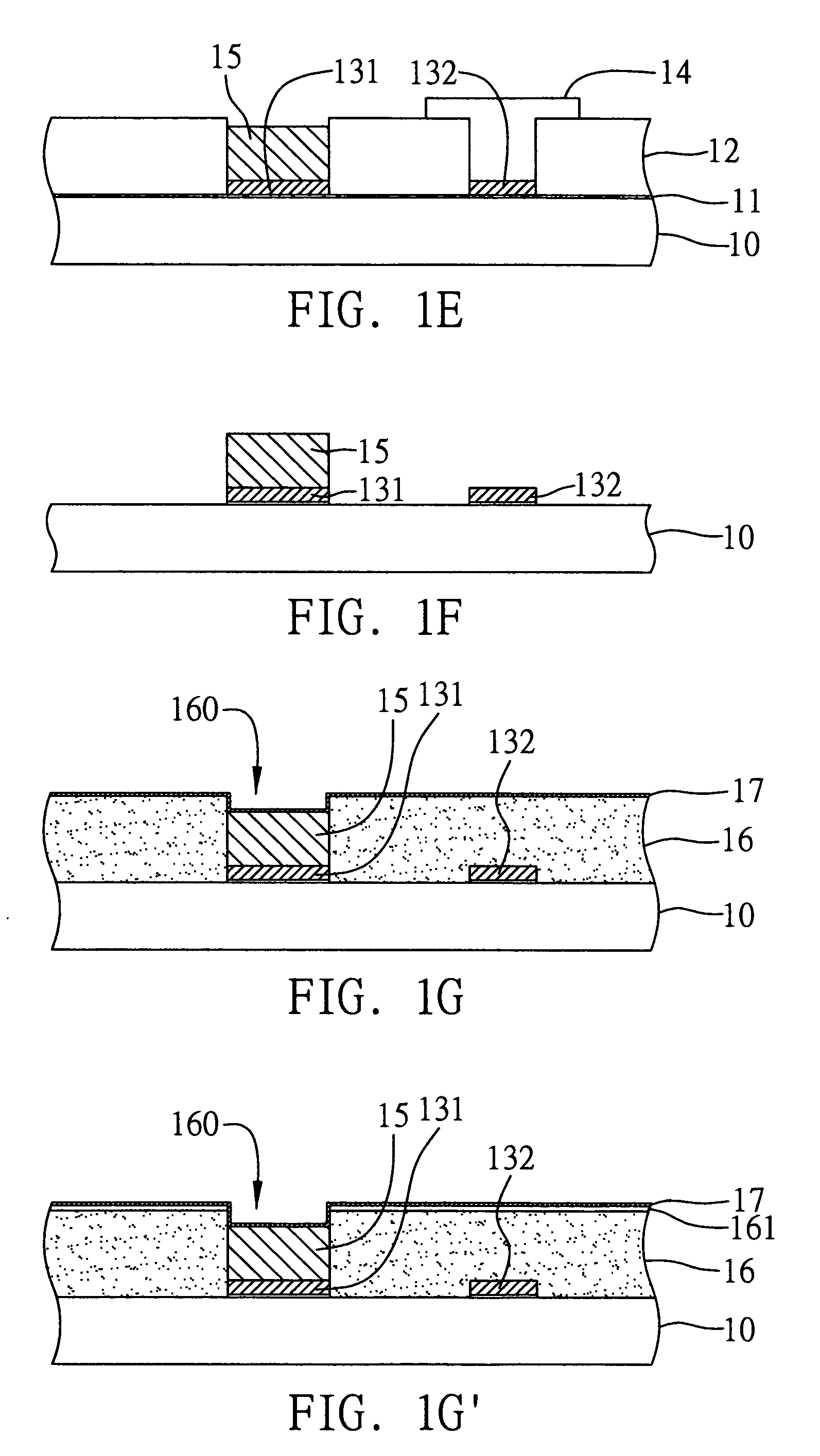

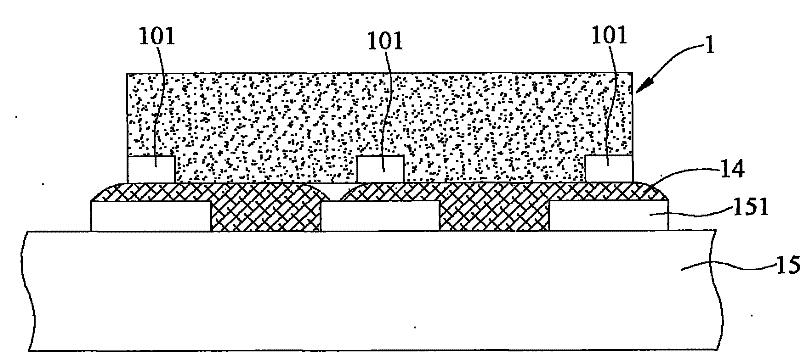

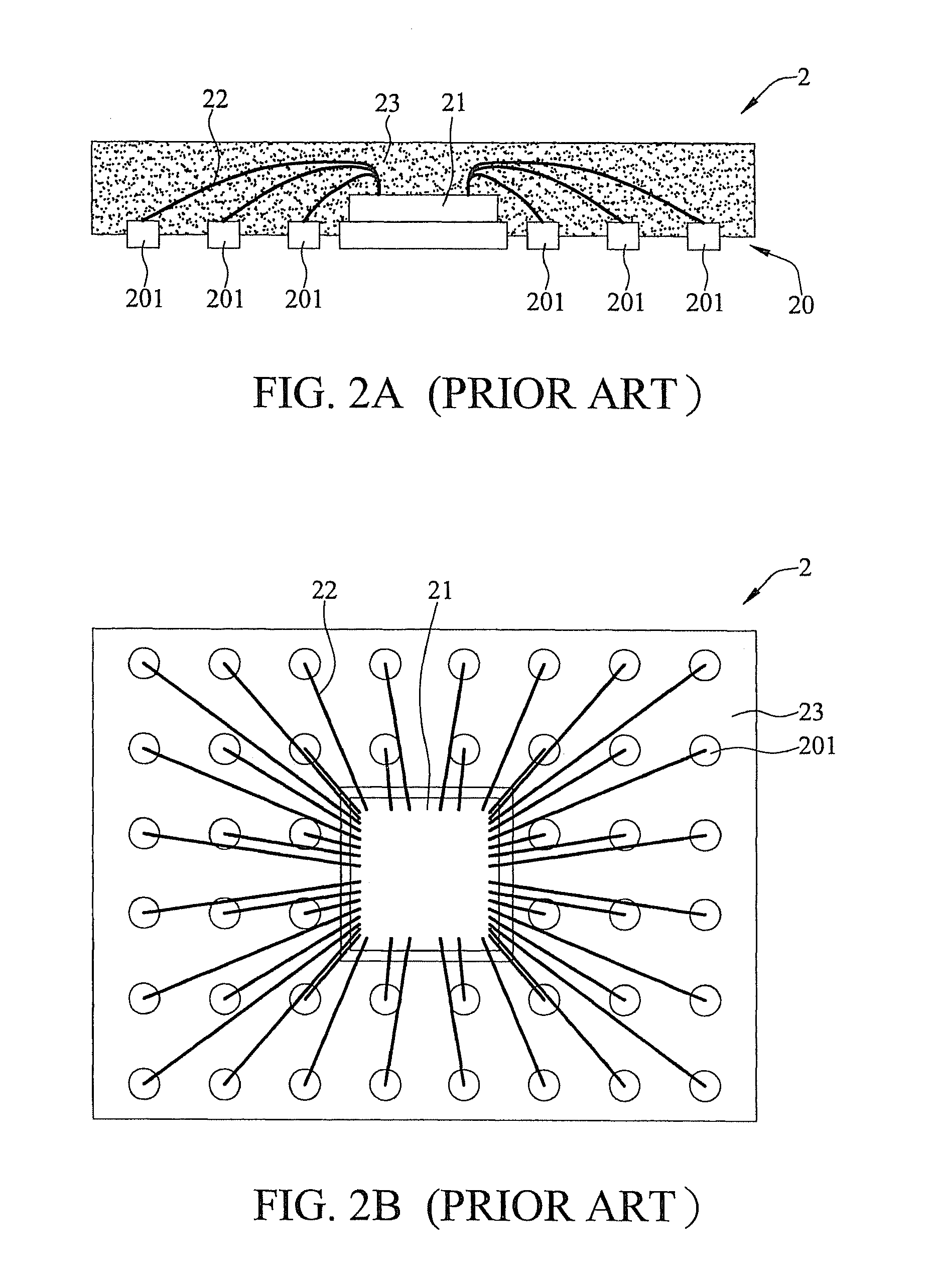

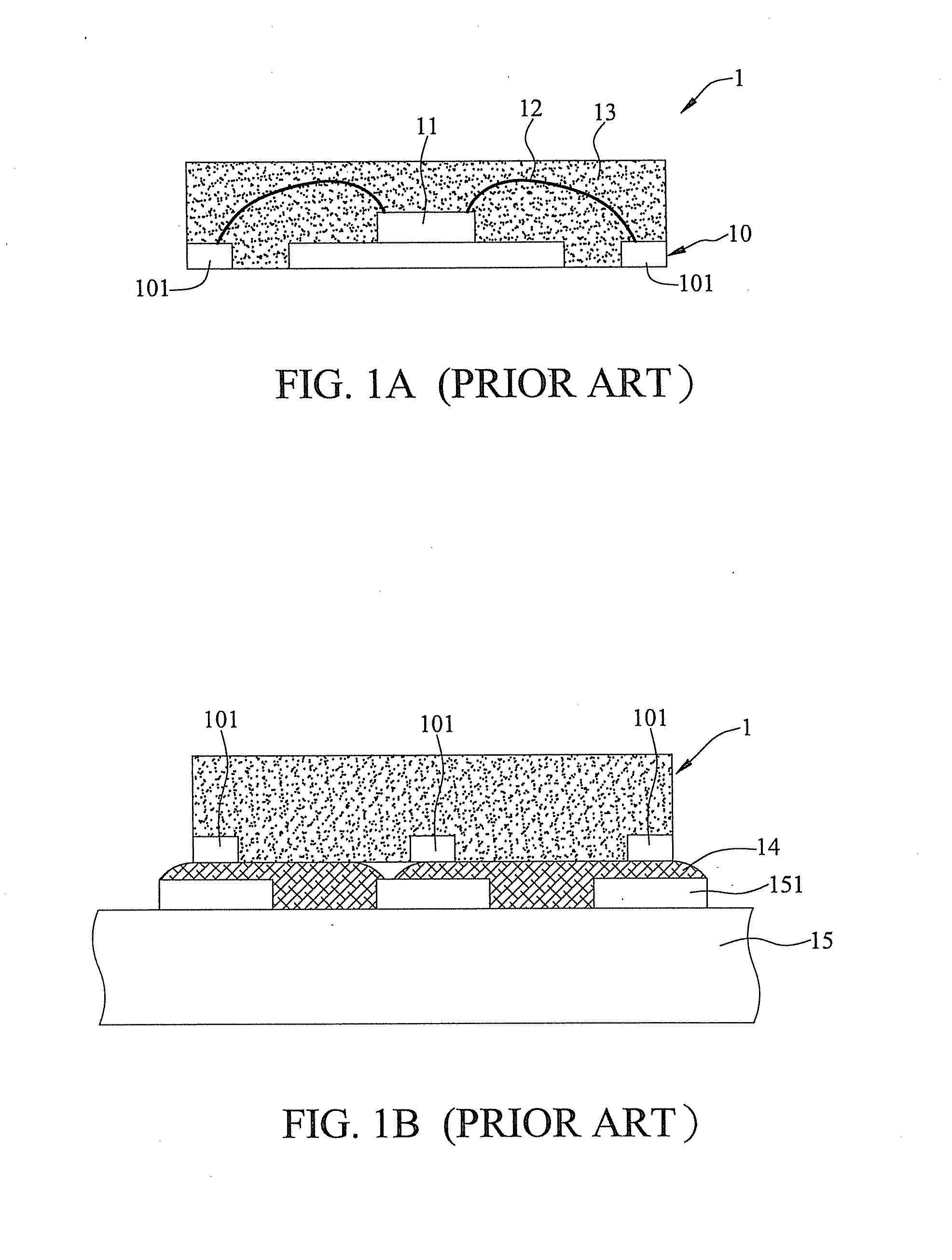

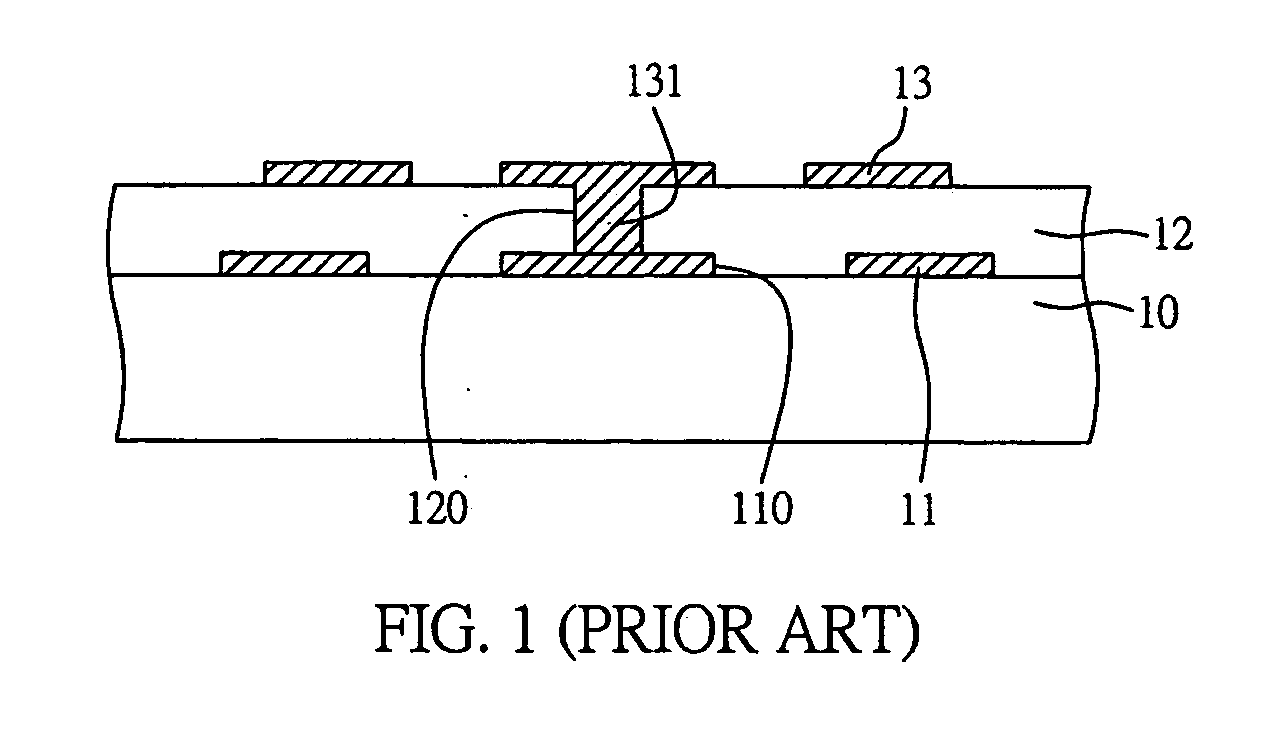

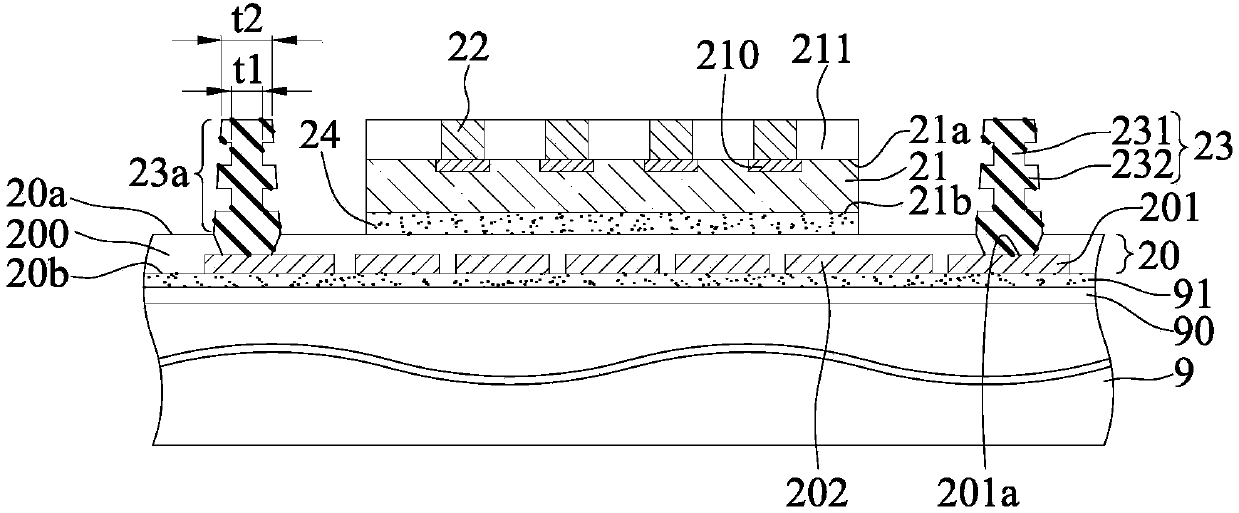

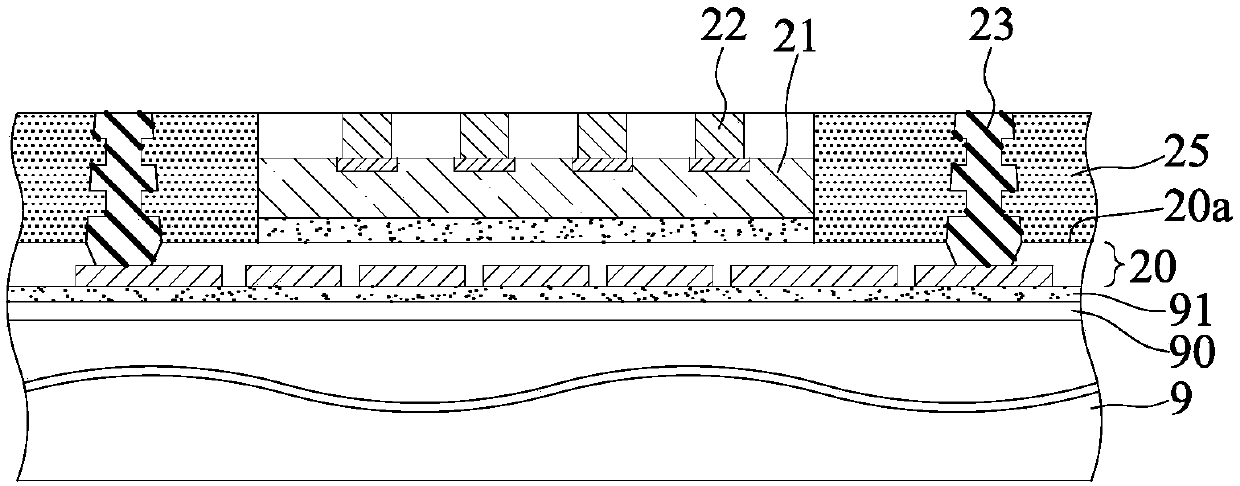

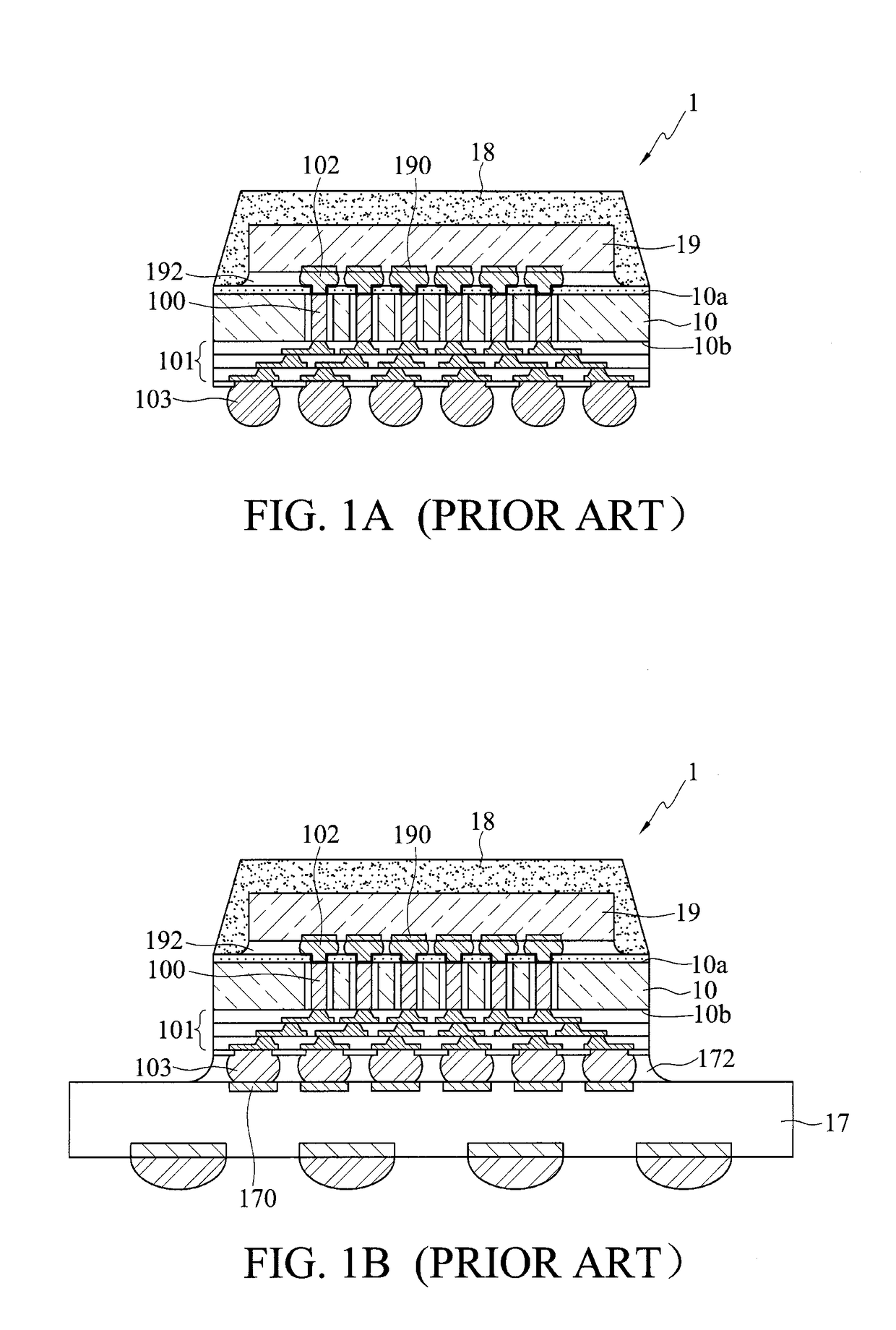

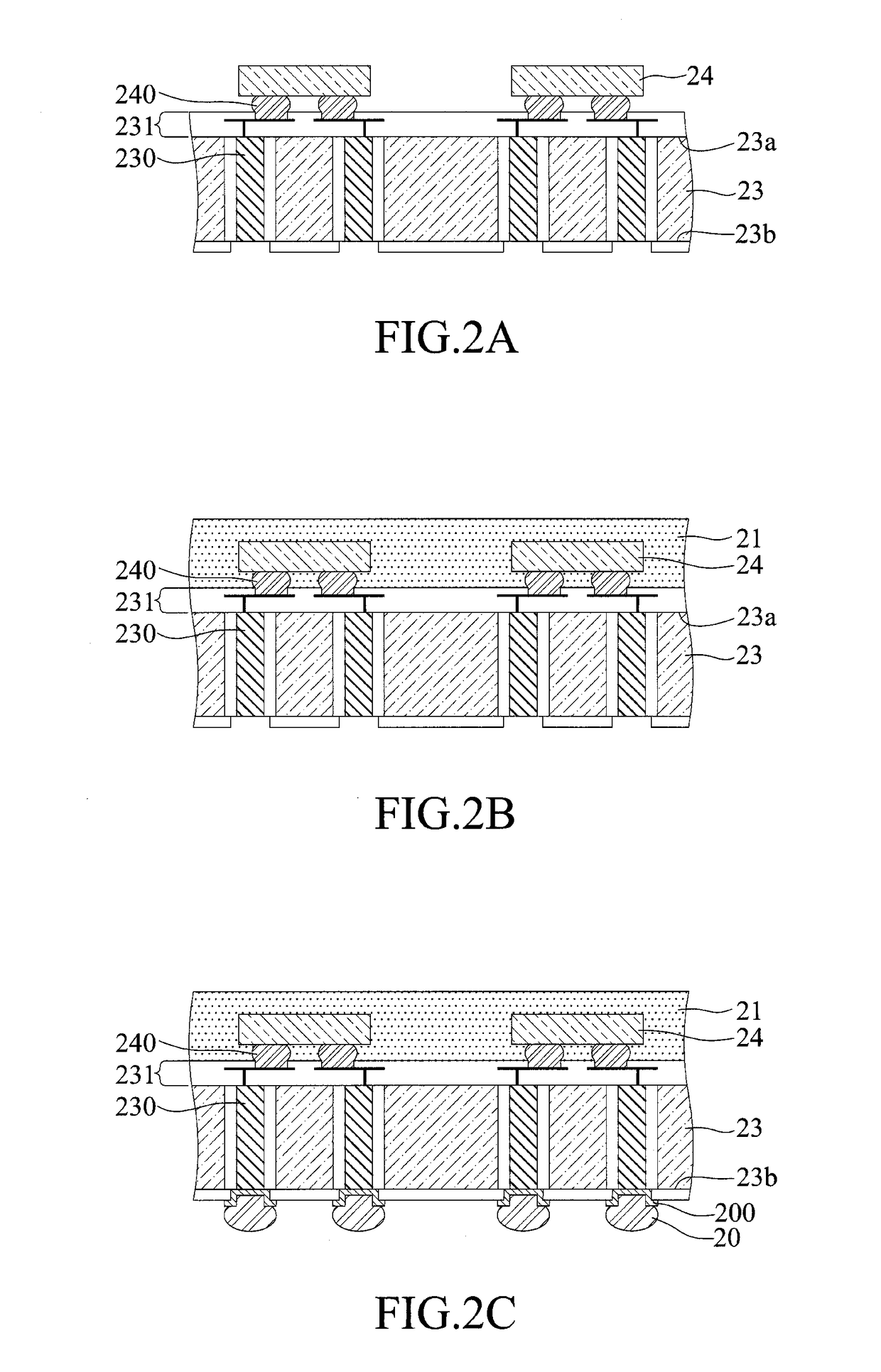

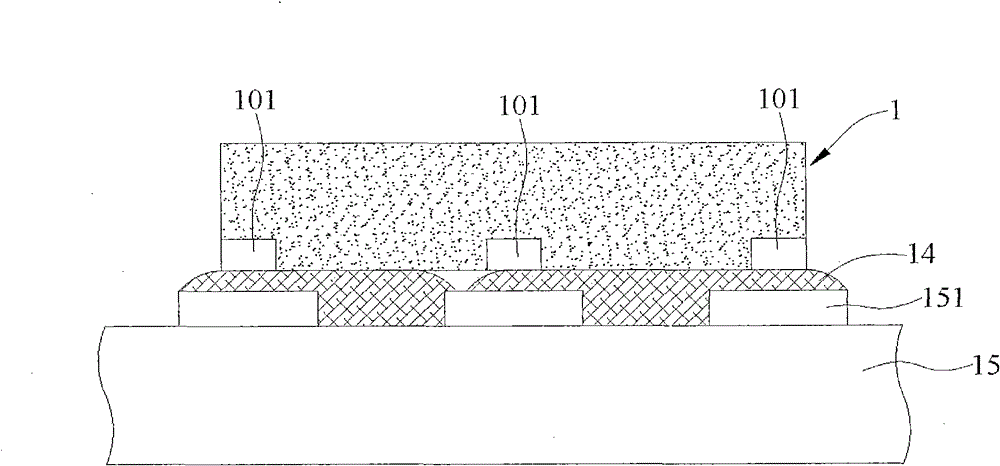

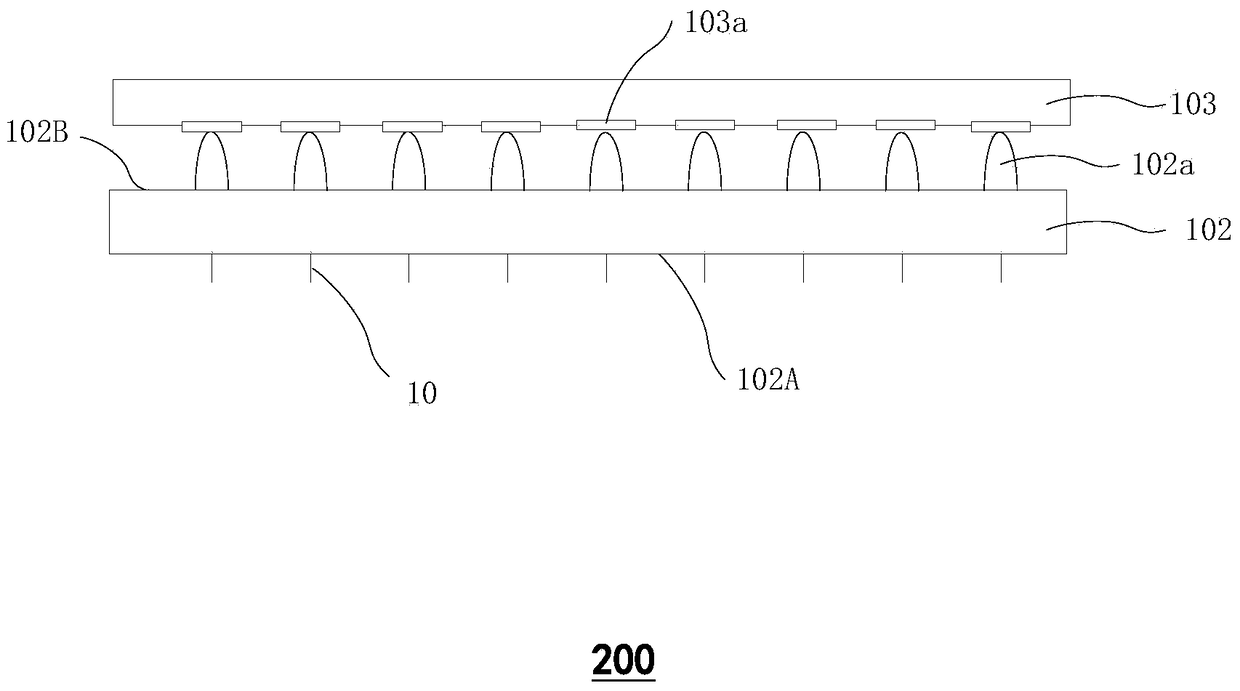

Semiconductor package and fabrication method thereof

ActiveUS20080116580A1Reduce thermal stressImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesInsulation layerSemiconductor package

A semiconductor package and a fabrication method are disclosed. The fabrication method includes applying a sacrificial layer on one surface of a metal carrier, applying an insulation layer on the sacrificial layer, and forming through holes in the sacrificial layer and the insulation layer to expose the metal carrier; forming a conductive metallic layer in each through hole; forming a patterned circuit layer on the insulation layer to be electrically connected to the conductive metallic layer; mounting at least a chip on the insulation layer and electrically connecting the chip to the patterned circuit layer; forming an encapsulant to encapsulate the chip and the patterned circuit layer; and removing the metal carrier and the sacrificial layer to expose the insulation layer and conductive metallic layer to allow the conductive metallic layer to protrude from the insulation layer. In the present invention, the distance between the semiconductor package and the external device is increased, and thermal stress caused by difference between the thermal expansion coefficients is reduced, so as to enhance the reliability of the product.

Owner:SILICONWARE PRECISION IND CO LTD

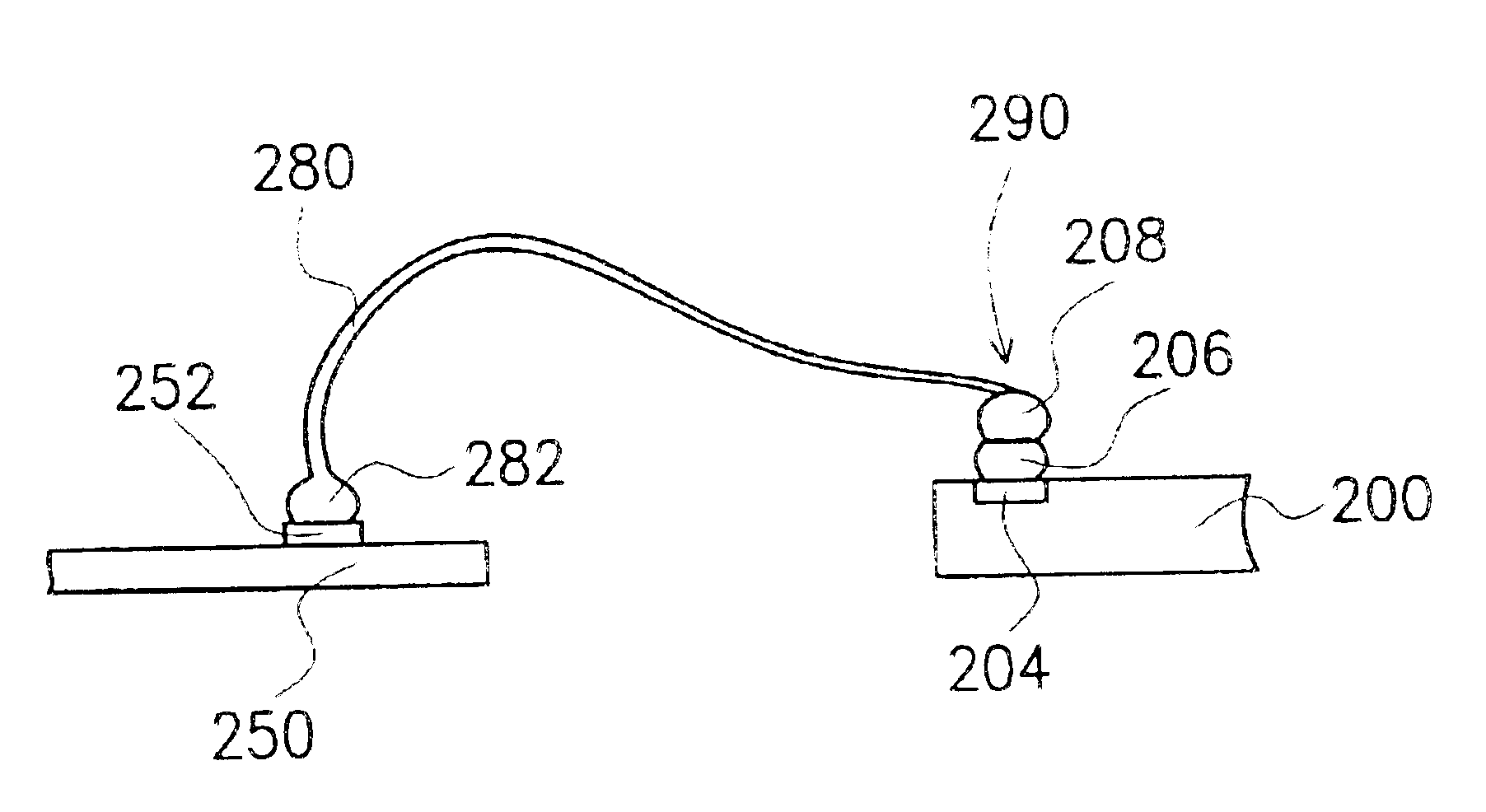

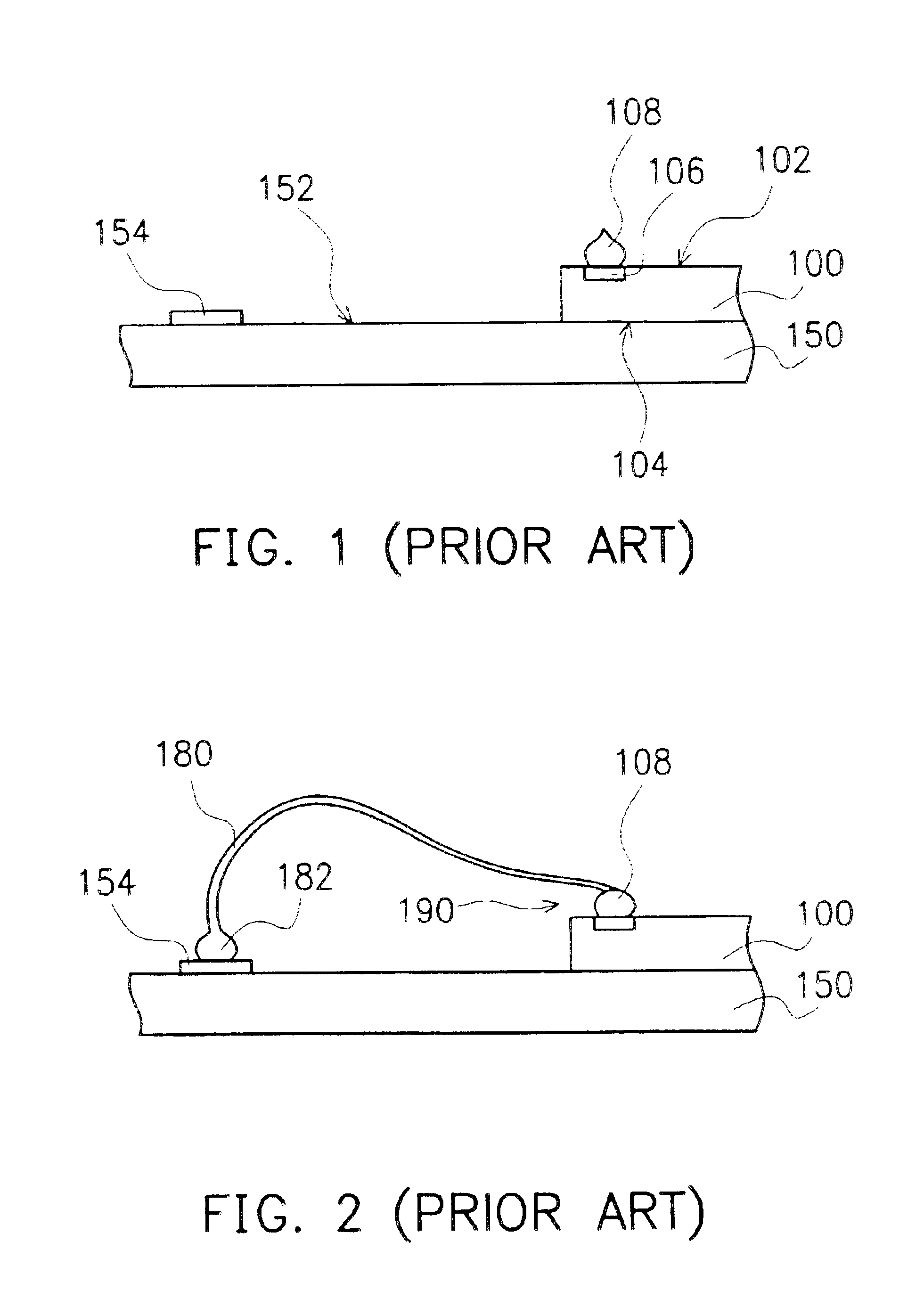

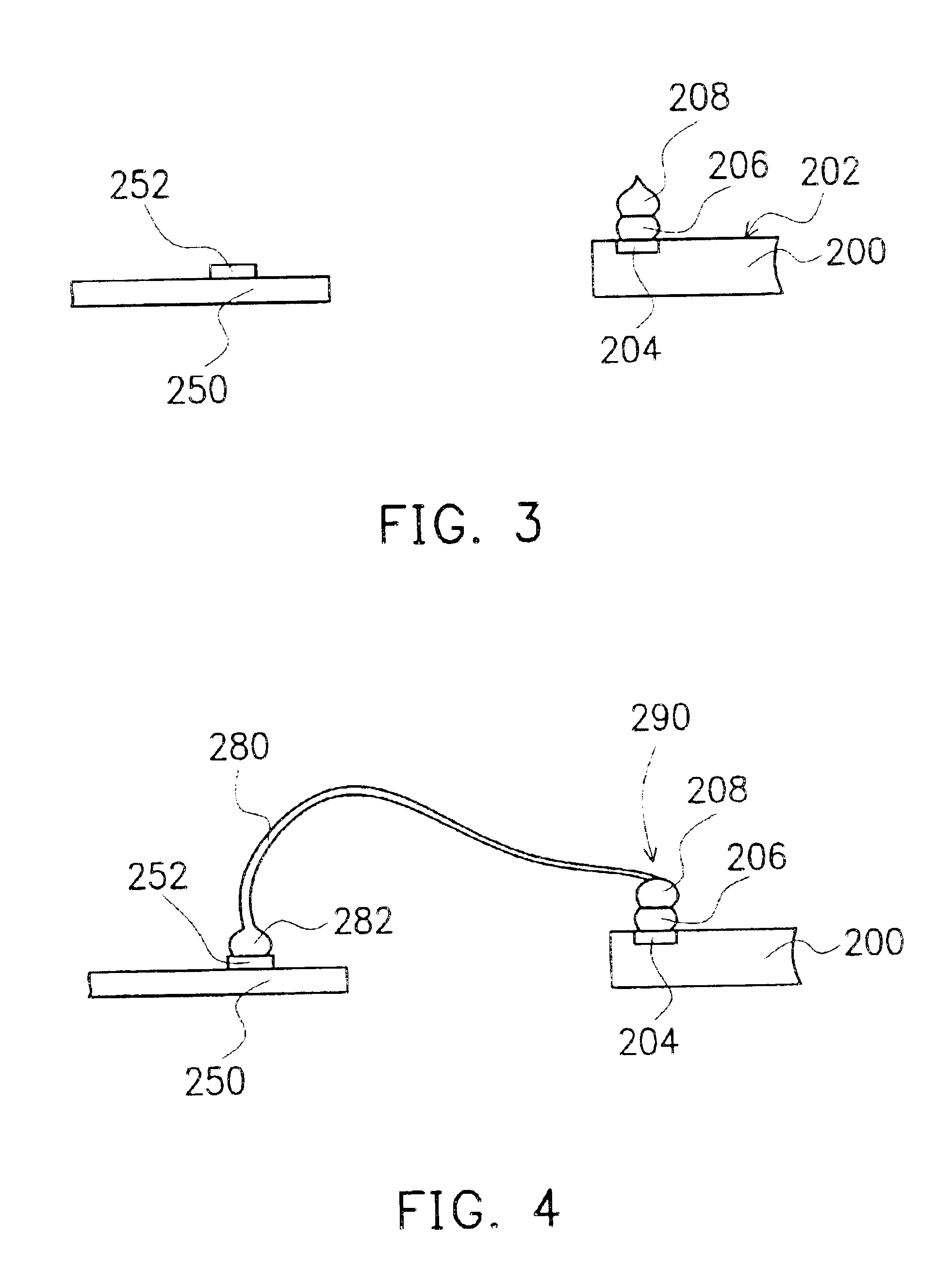

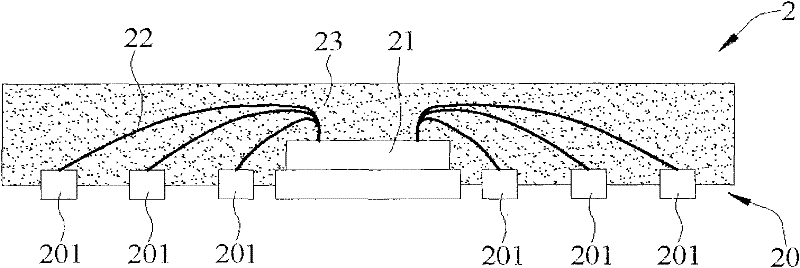

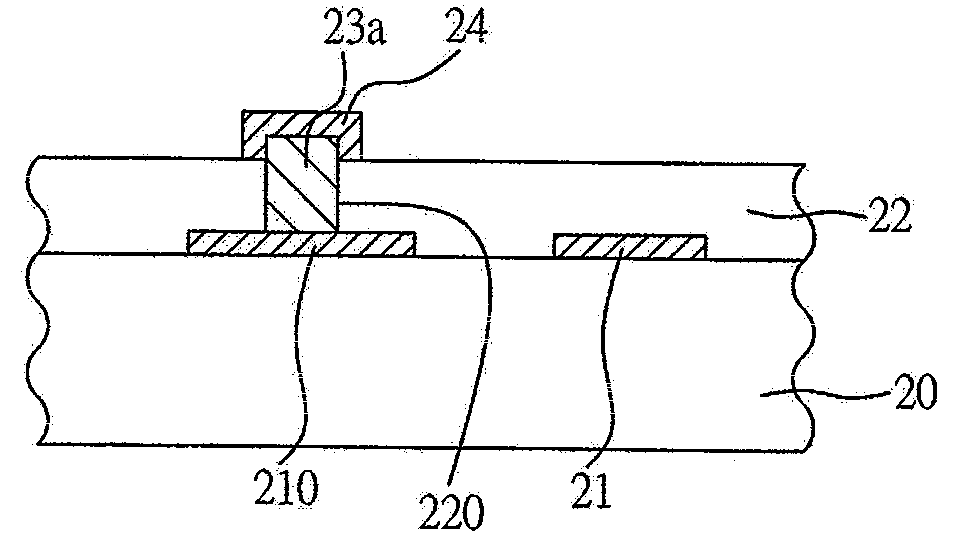

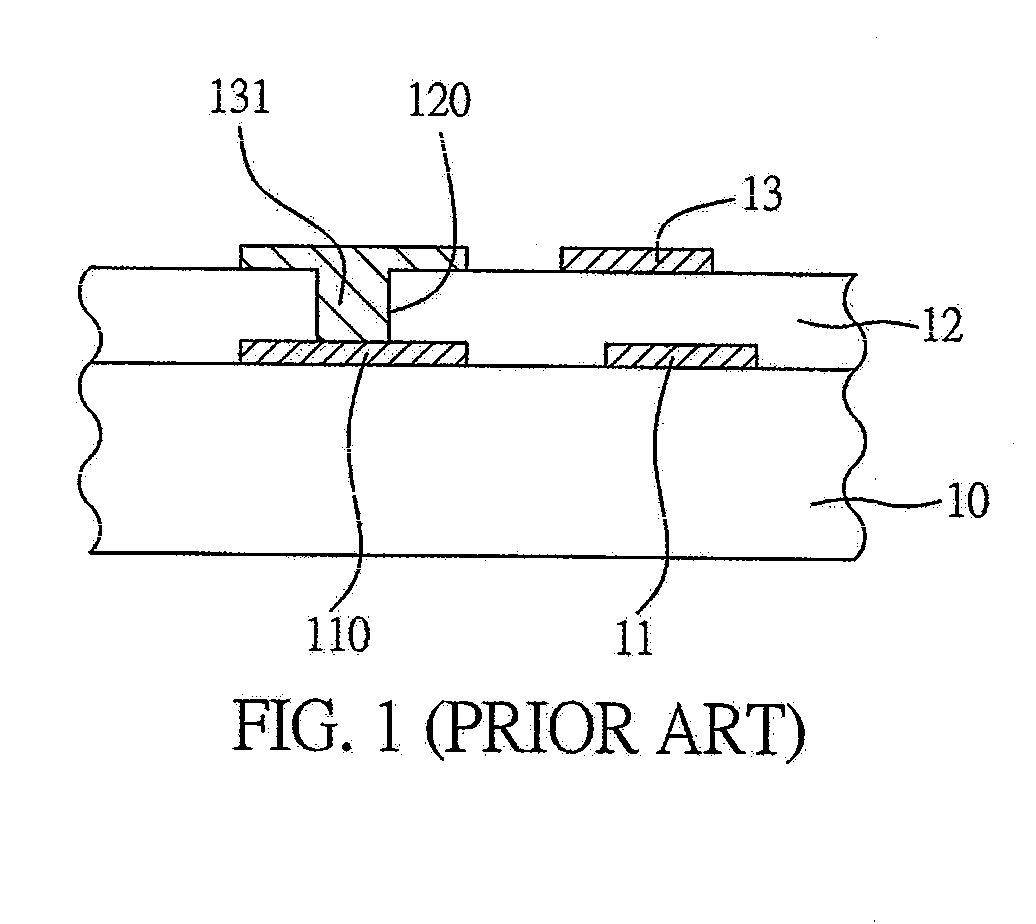

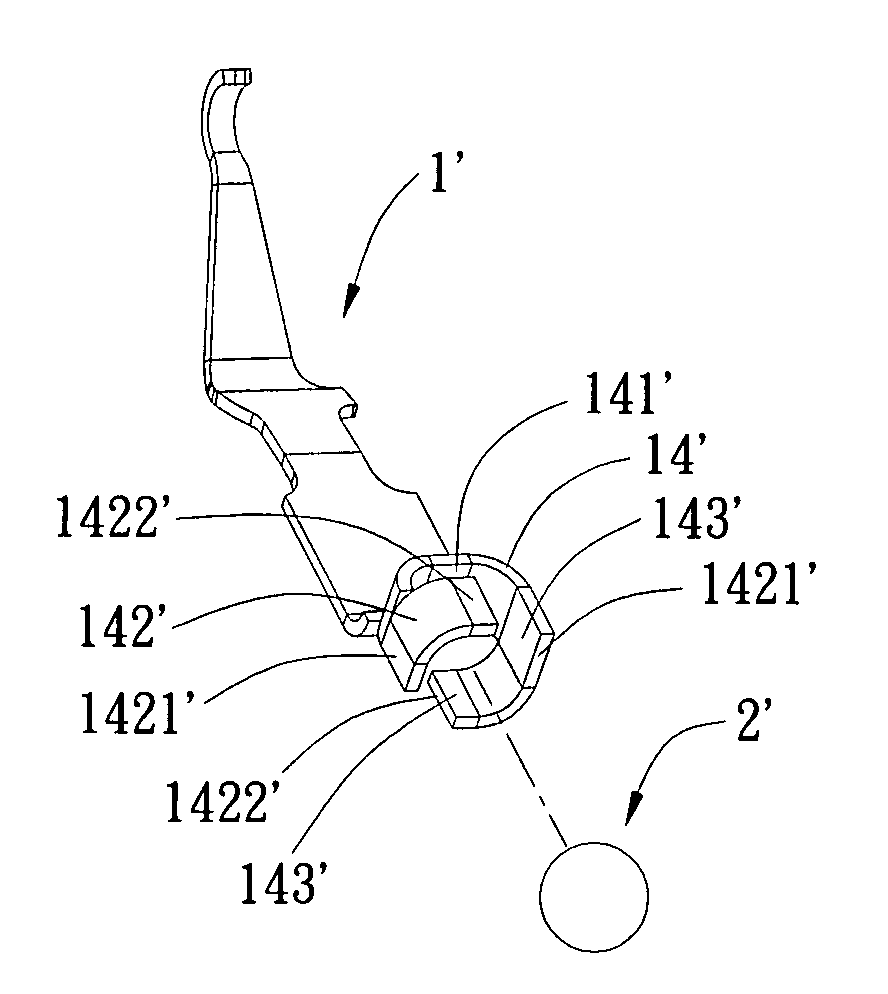

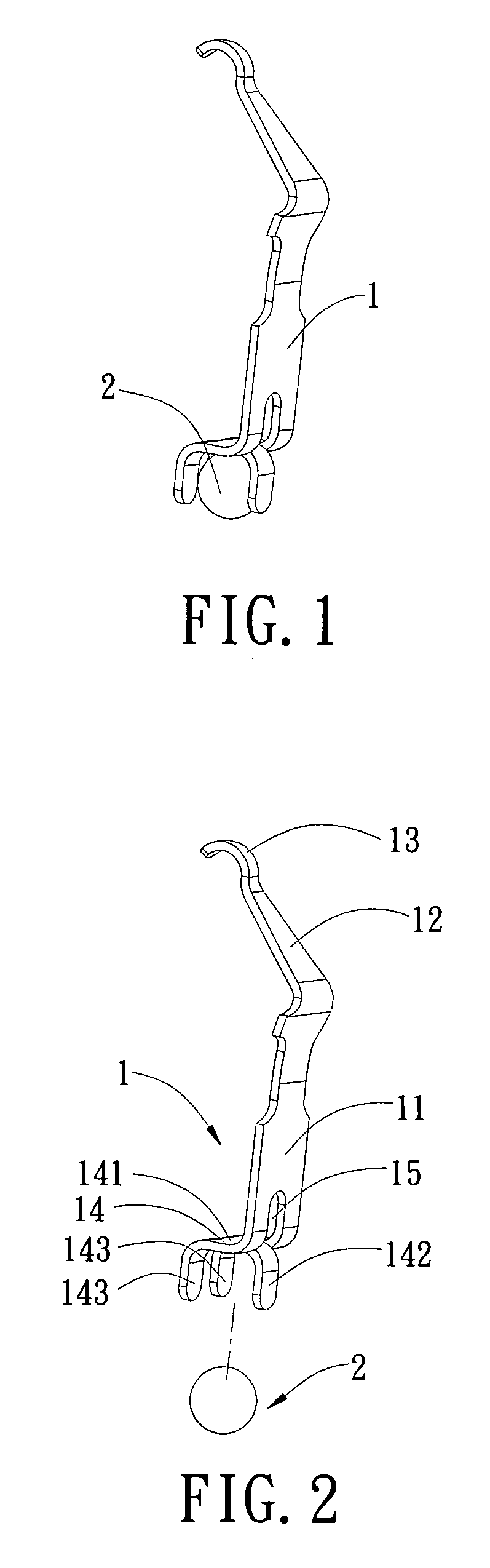

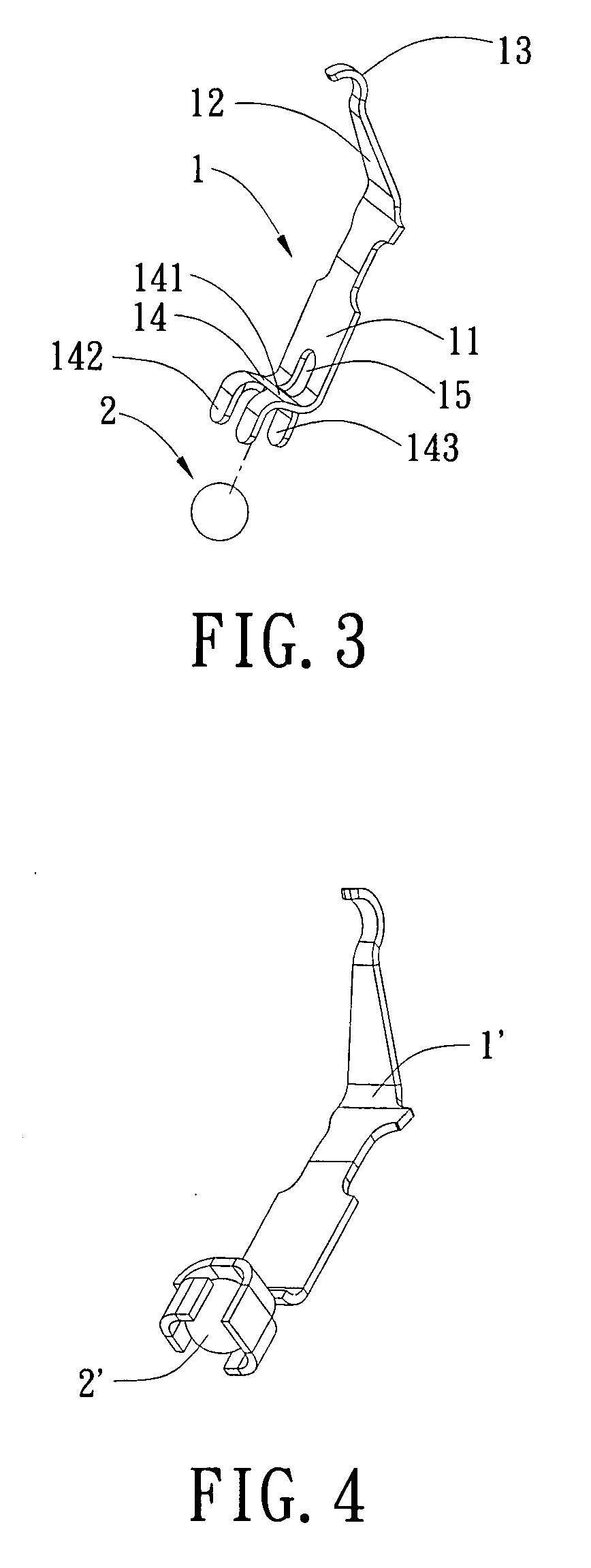

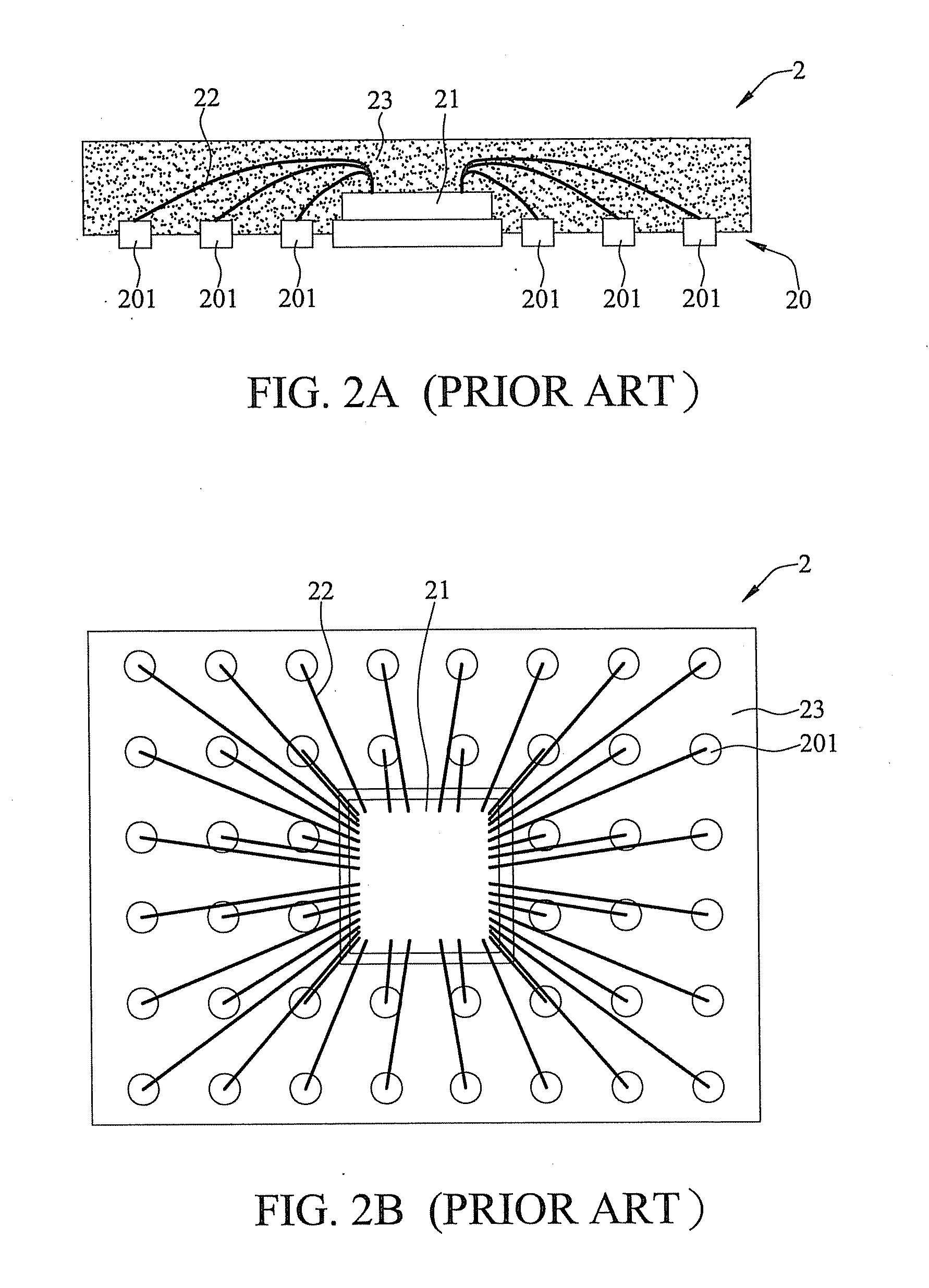

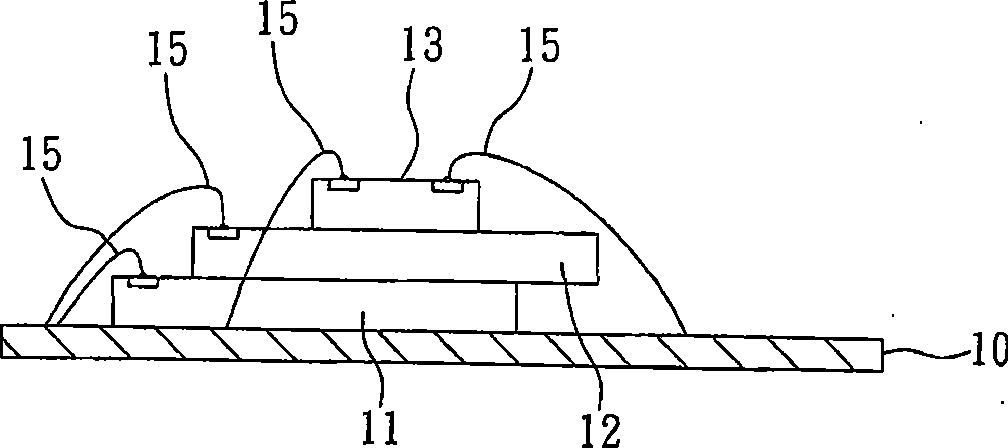

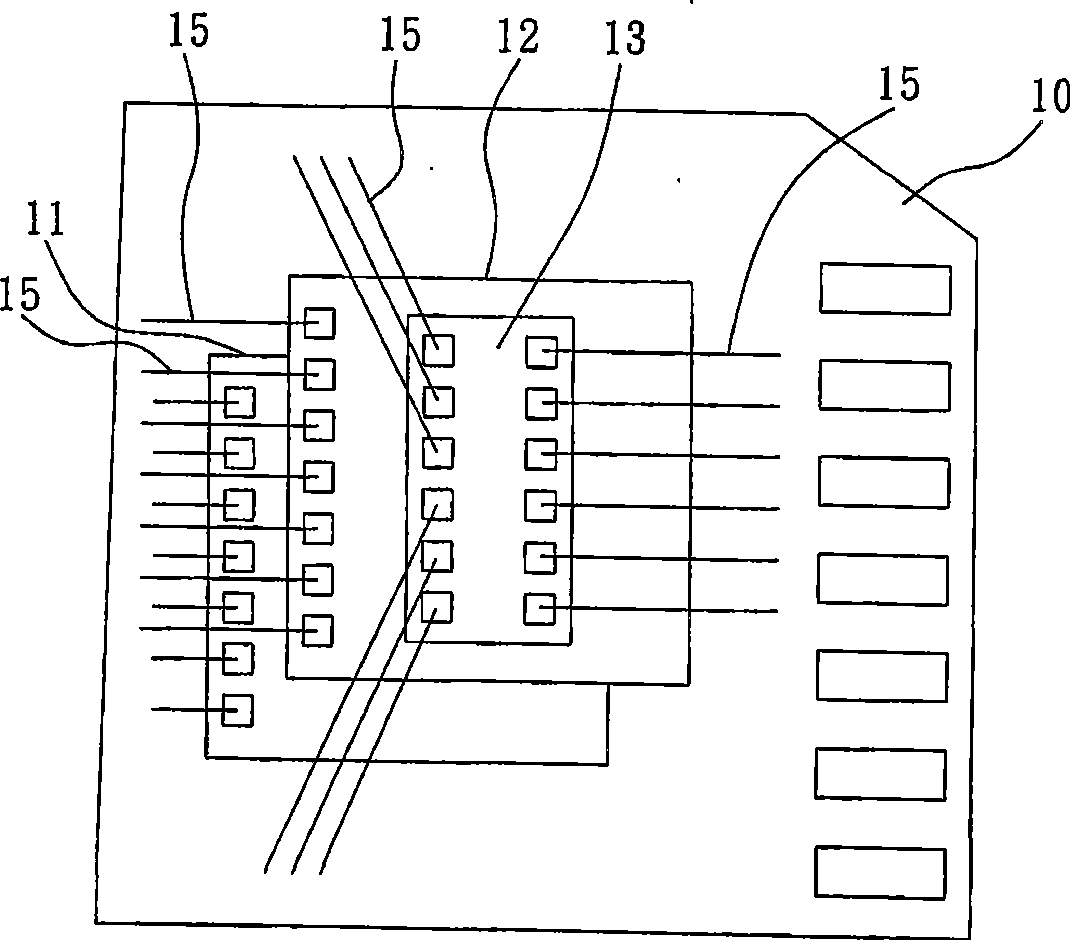

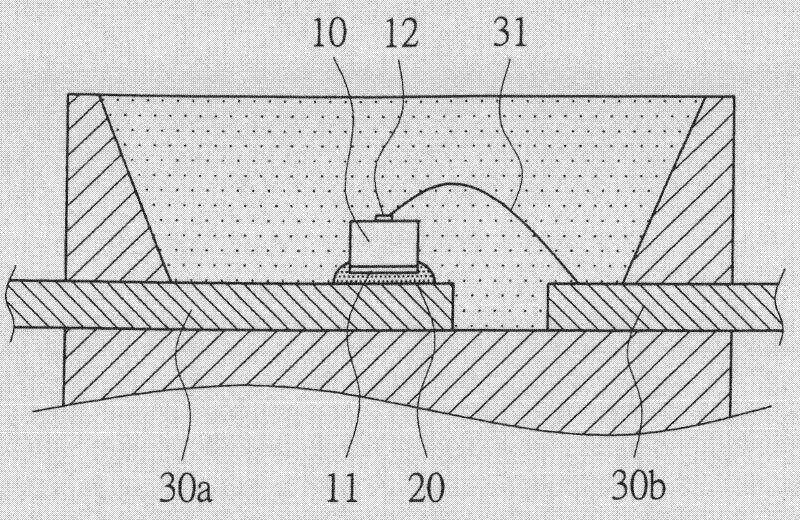

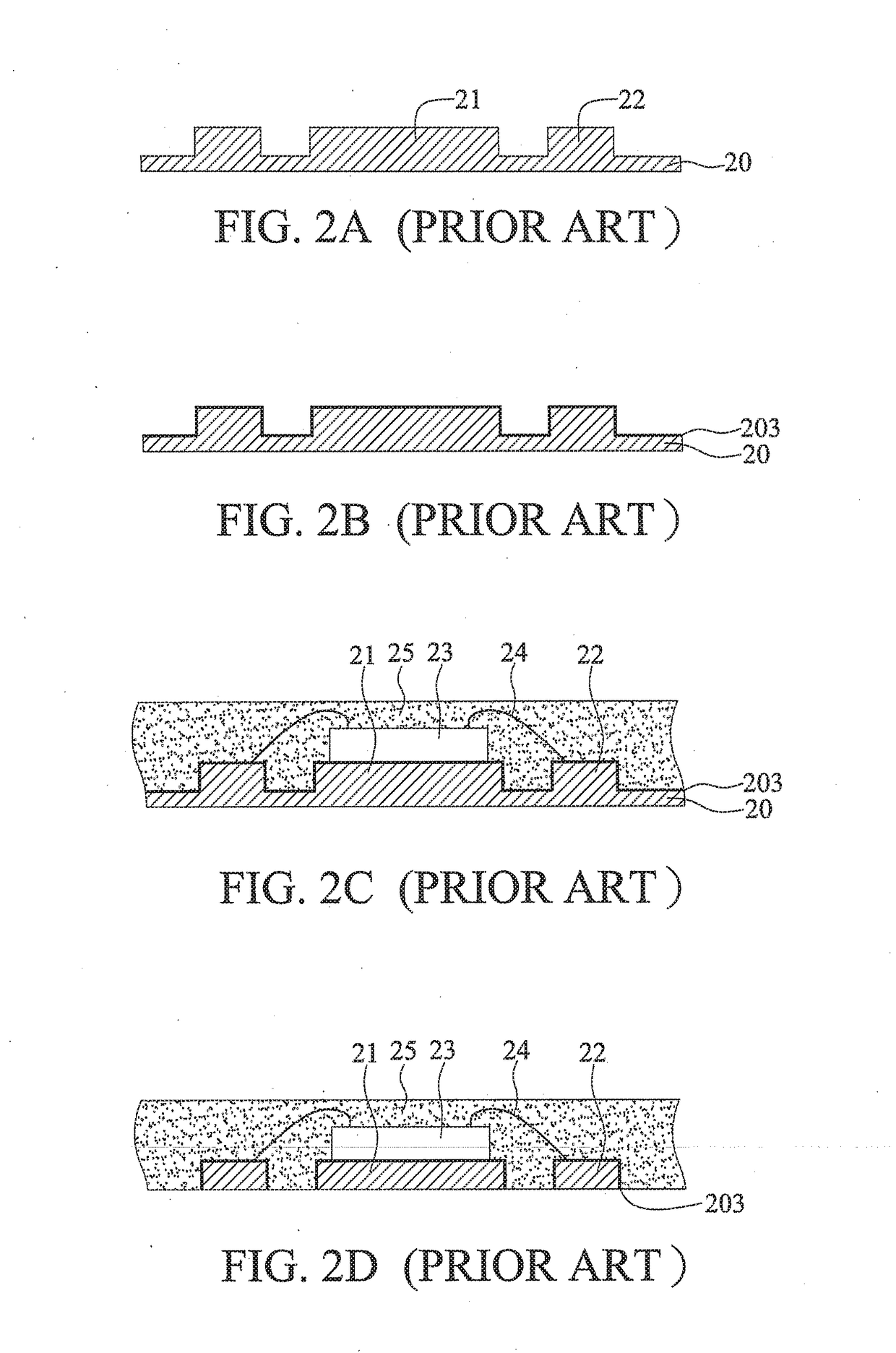

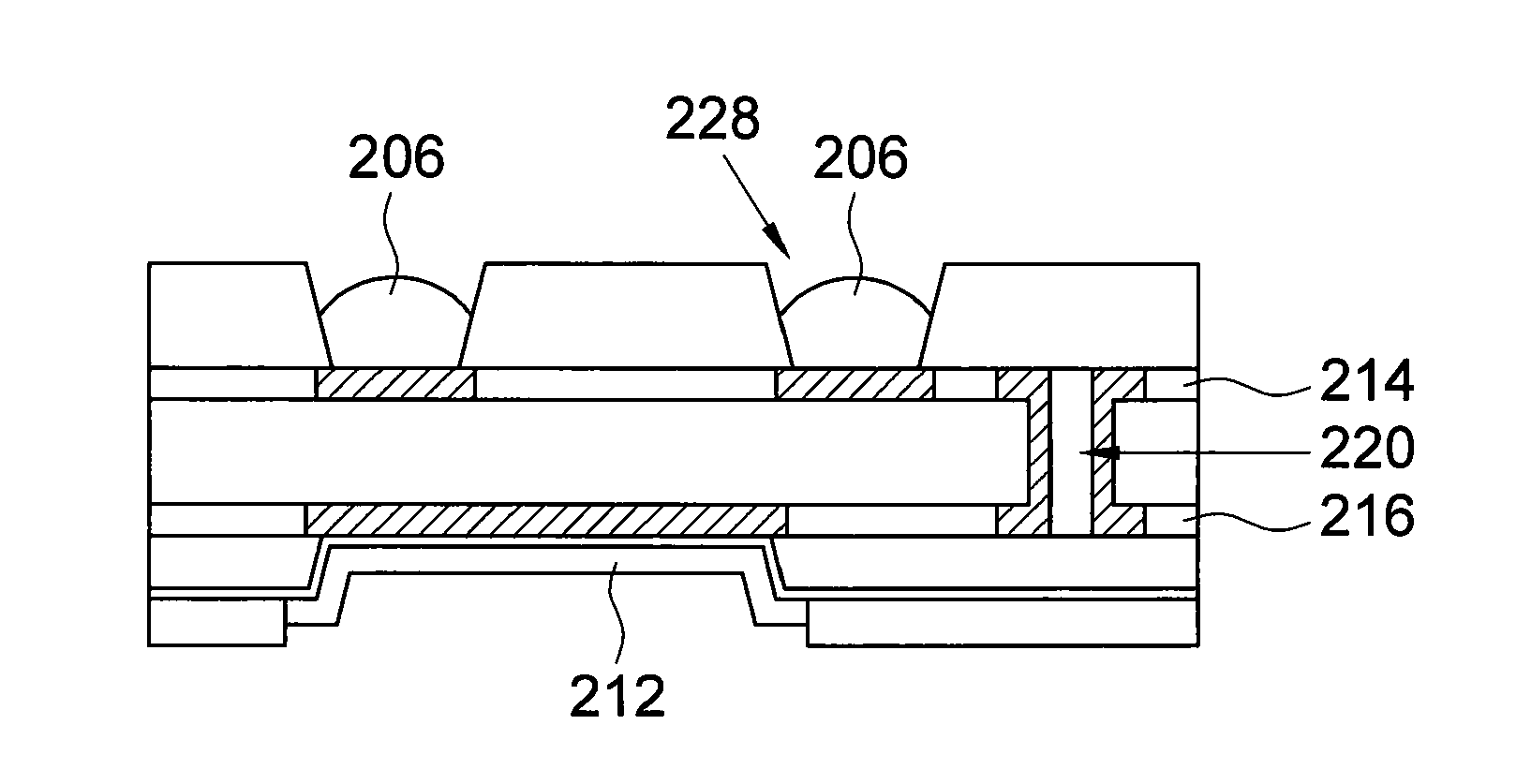

Wire bonding process and wire bond structure

InactiveUS6863208B2Improve reliabilityImprove electrical connection qualityElectrically conductive connectionsSemiconductor/solid-state device detailsContact padLead bonding

In a wire-bonding process, a chip is provided with at least a first contact pad. A chip carrier is further provided with at least a second contact pad. A plurality of stacked conductive bumps are formed on the first contact pad. A conductive wire is formed by a reverse bonding process. The conductive wire electrically connects the second contact pad of the chip carrier to the stacked conductive bumps over the first contact pad of the chip.

Owner:ADVANCED SEMICON ENG INC

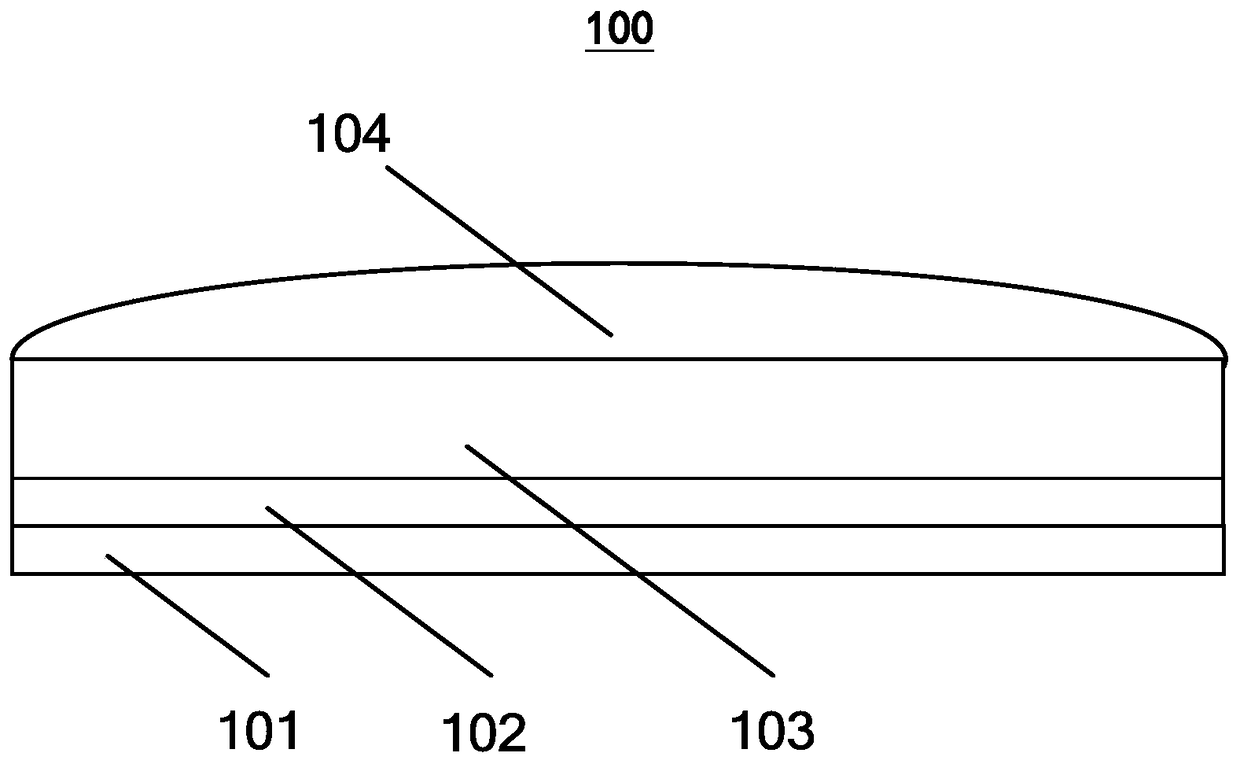

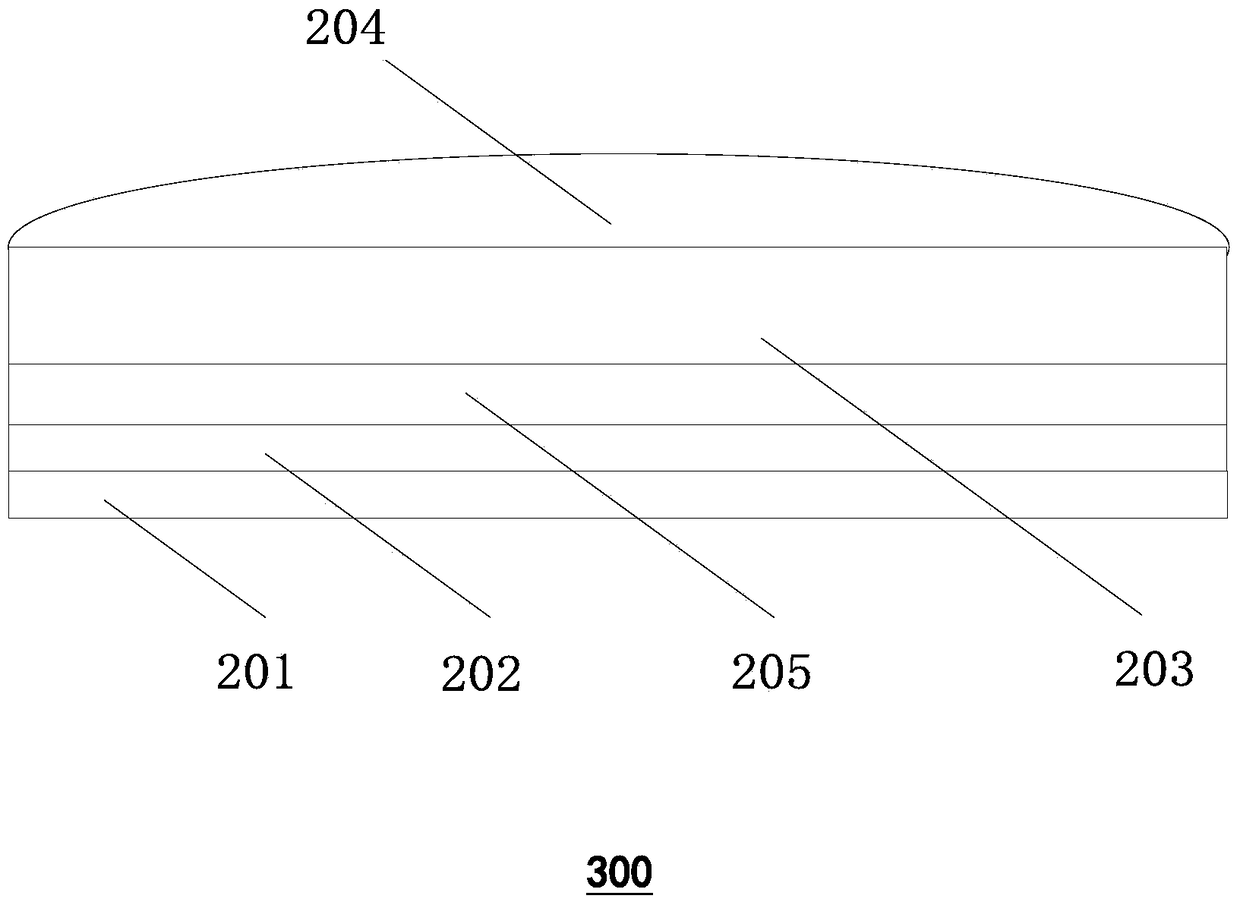

Photovoltaic laminating piece, preparation method thereof and photovoltaic module

InactiveCN105489682AAvoid crackingPrevent spillageFinal product manufacturePhotovoltaic energy generationElectricityElectrical battery

The invention relates to a photovoltaic laminating piece. The photovoltaic laminating piece comprises a transparent cover plate, a first sealing layer, a battery piece layer, a second sealing layer and a back plate which are laminated in sequence, wherein the battery piece layer comprises a plurality of connected battery pieces and a converge belt electrically connected onto the battery pieces; an electrode exposing hole is formed in the back plate, and the electrode exposing hole passes through the back plate and the second sealing layer so that the converge belt is leaked out. According to the photovoltaic laminating piece, the hidden cracking problem of the battery pieces caused by improper outgoing line penetration is avoided; and the manual workload can be greatly reduced. Moreover, the electrical connection quality of the photovoltaic laminating piece and a junction box is improved, the workload of subsequent cleaning stations is reduced, and the cleaning frequency and workload of a laminating machine are reduced. The invention also provides a preparation method of the photovoltaic laminating piece and a photovoltaic module comprising the photovoltaic laminating piece.

Owner:ZHANGJIAGANG GCL INTEGRATION TECH CO LTD

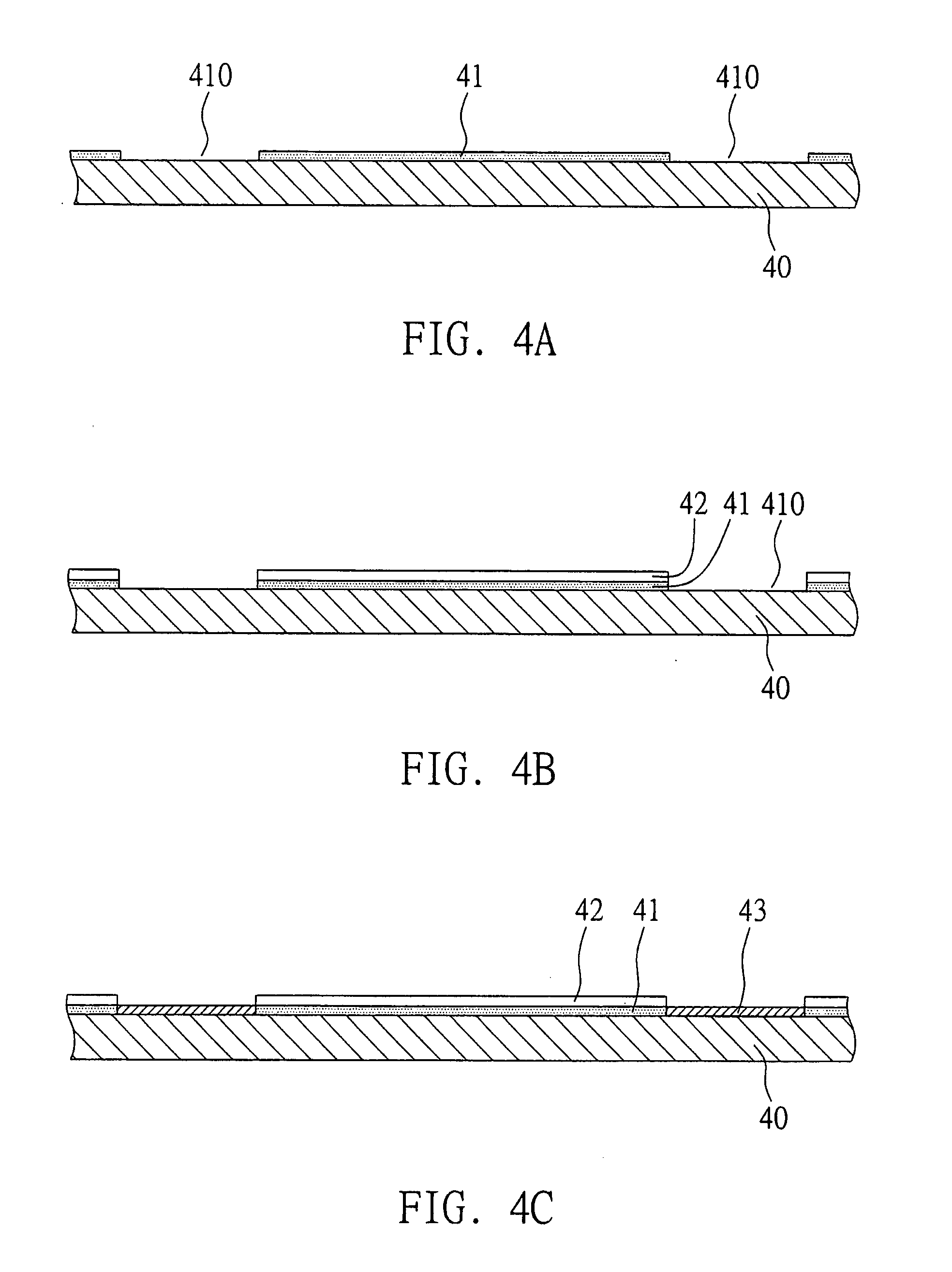

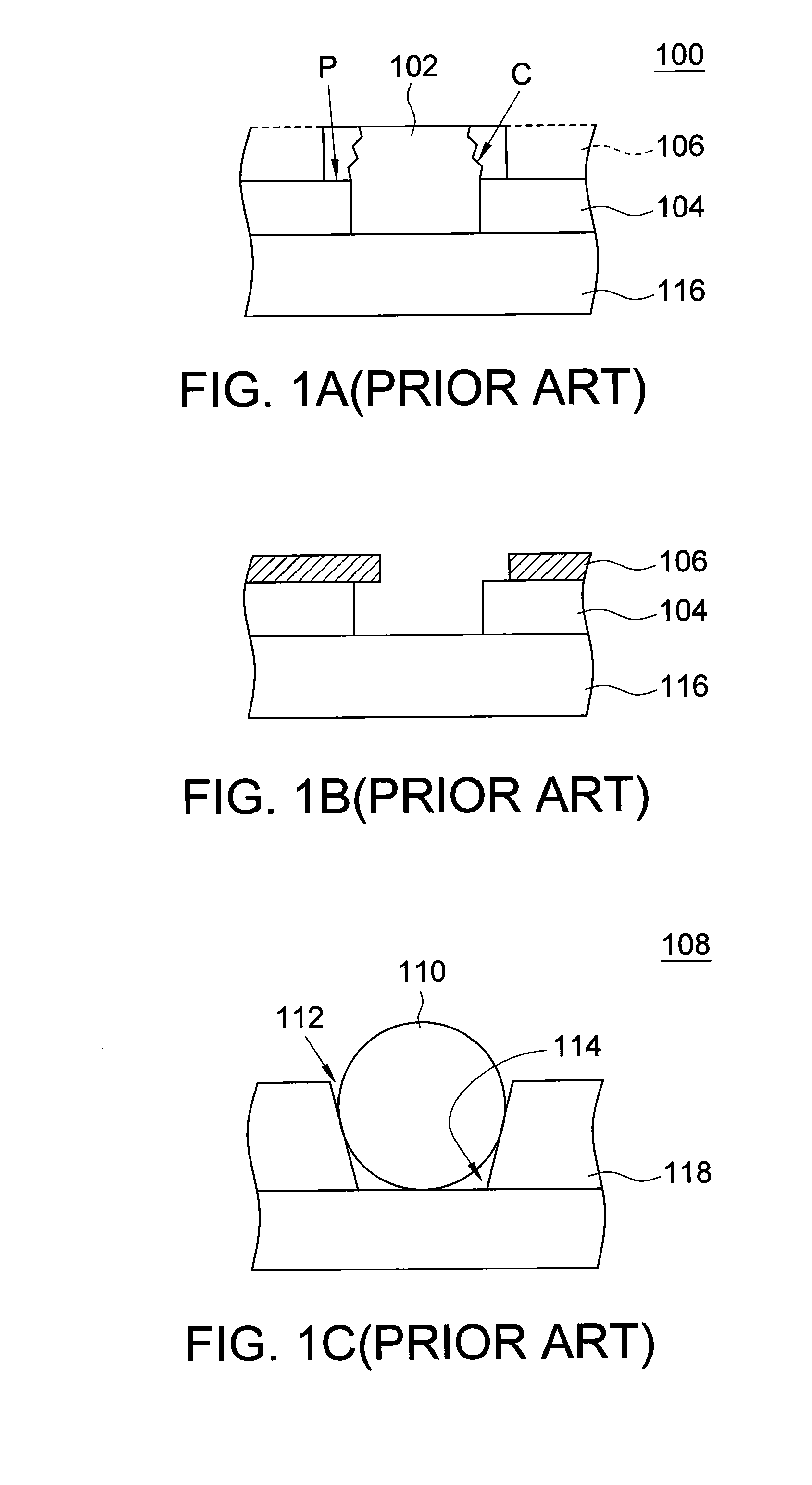

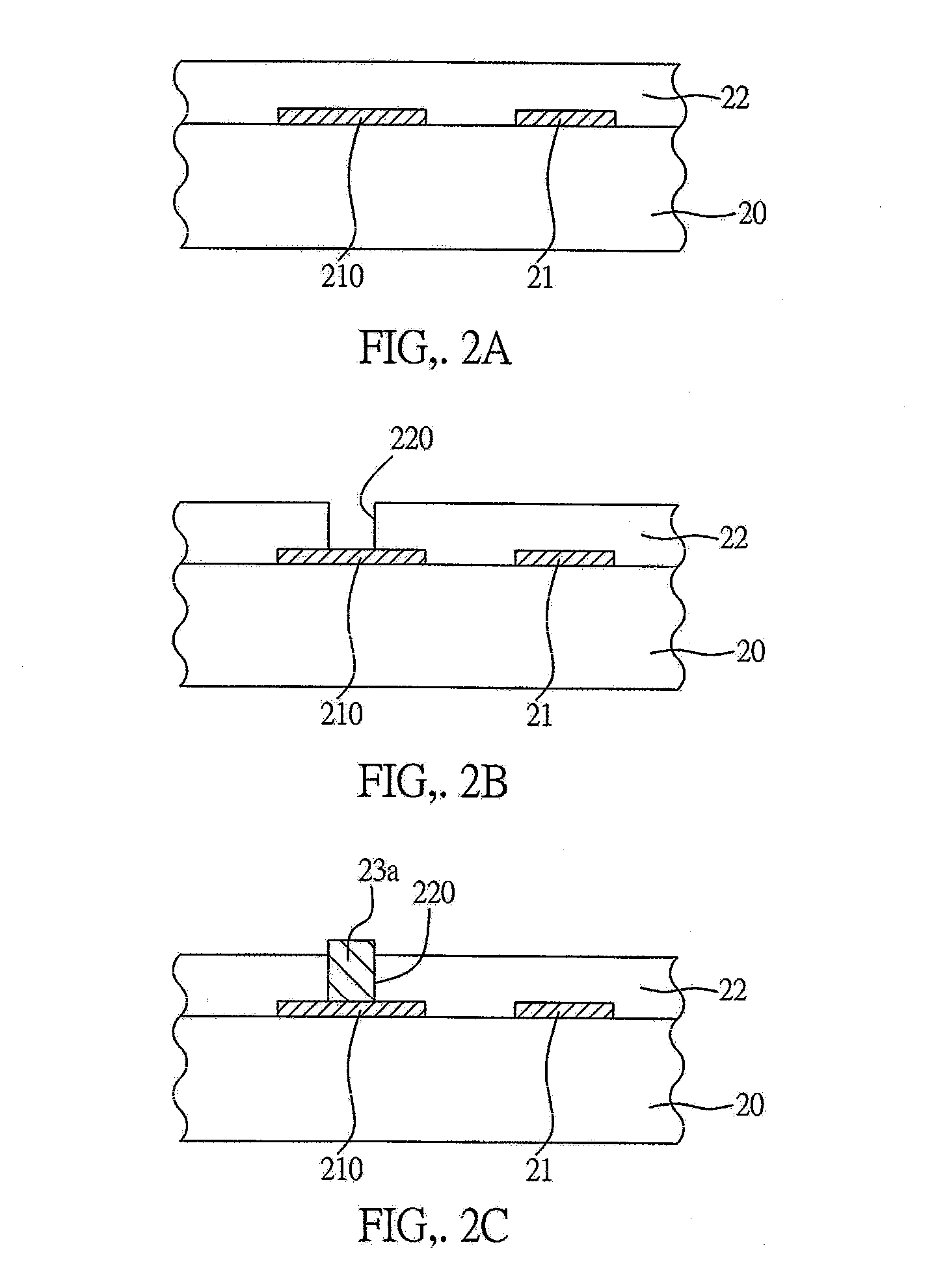

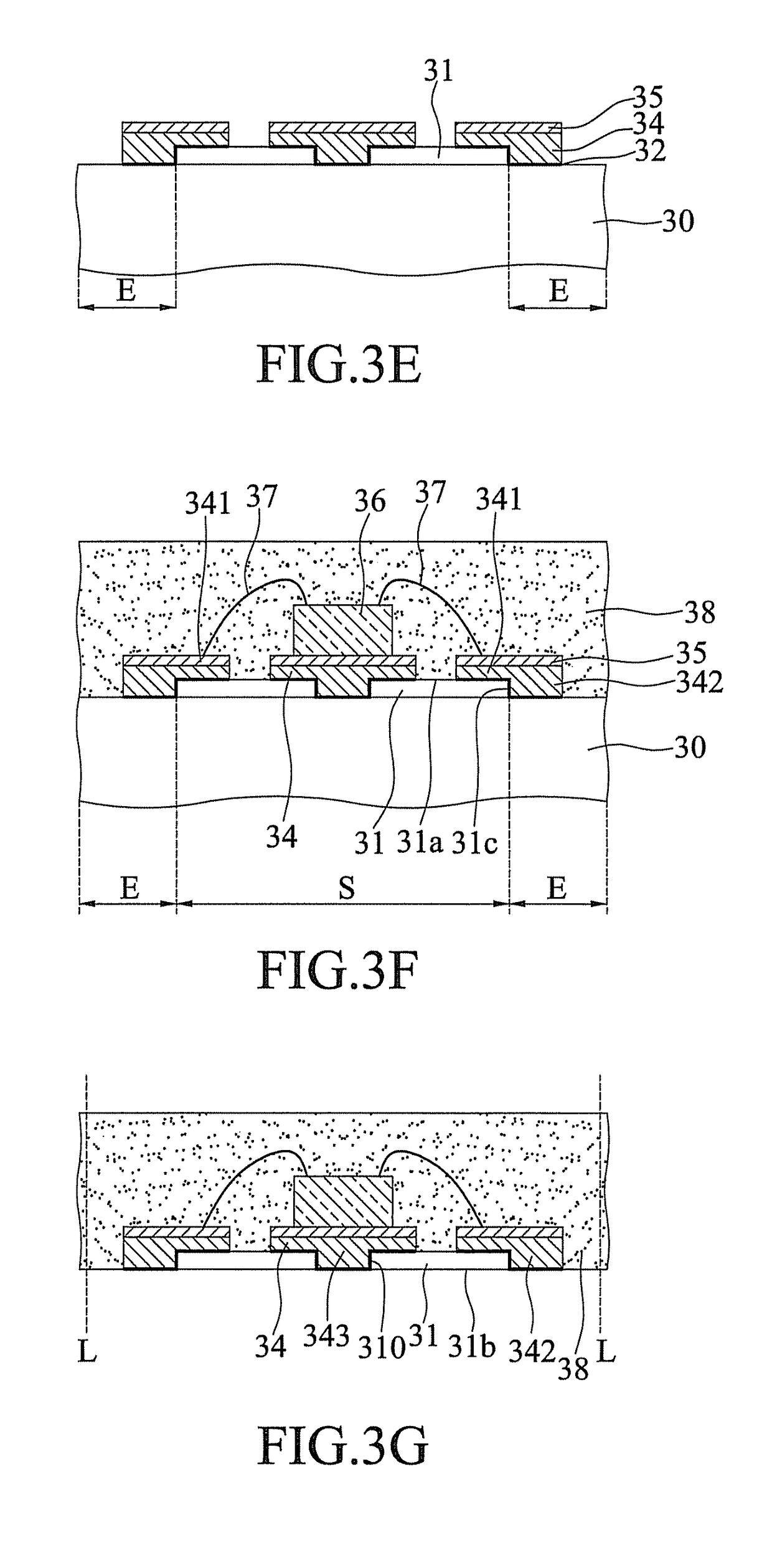

Circuit board having electrically conductive structure formed between circuit layers thereof and method for fabricating the same

InactiveUS7253364B2Improve electrical connection qualitySimplify the manufacturing processStacked resist layersConductive pattern formationResistEngineering

A circuit board and a fabrication method thereof. Providing the insulating layer with a first conductive layer formed thereon; wherein the insulating layer was formed on a core substrate with at least one patterned circuit layer thereon. A first resist layer is applied on a first conductive layer, forming first openings to expose the first conductive layer. A first patterned circuit layer, including conductive pads and traces, is formed in the first openings. A second resist layer is applied to cover the traces, and a conductive post is formed on each conductive pad. The first and second resist layers and the first conductive layer underneath the first resist layer are removed. A dielectric material layer is formed on the insulating layer with first patterned circuit layer, forming second openings to expose the conductive posts. A second conductive layer is formed on the dielectric material layer and in the second openings. A third resist layer is applied on the second conductive layer, forming third openings of the third resist layer to expose the second conductive layer. A second patterned circuit layer is formed in the second and third openings.

Owner:PHOENIX PRECISION TECH CORP

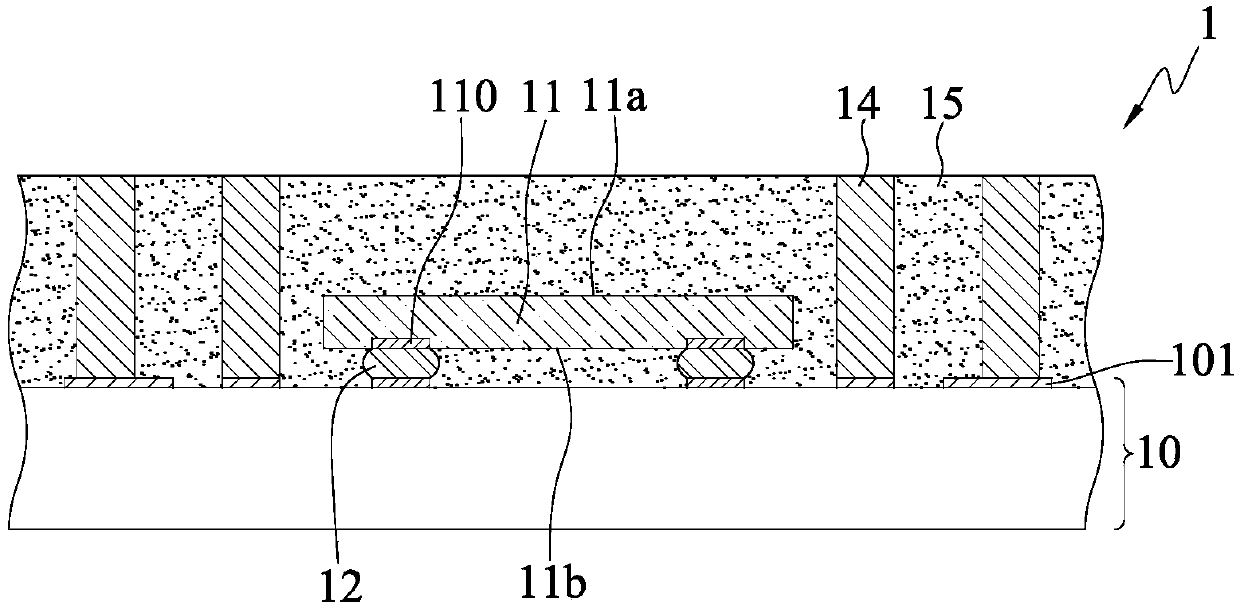

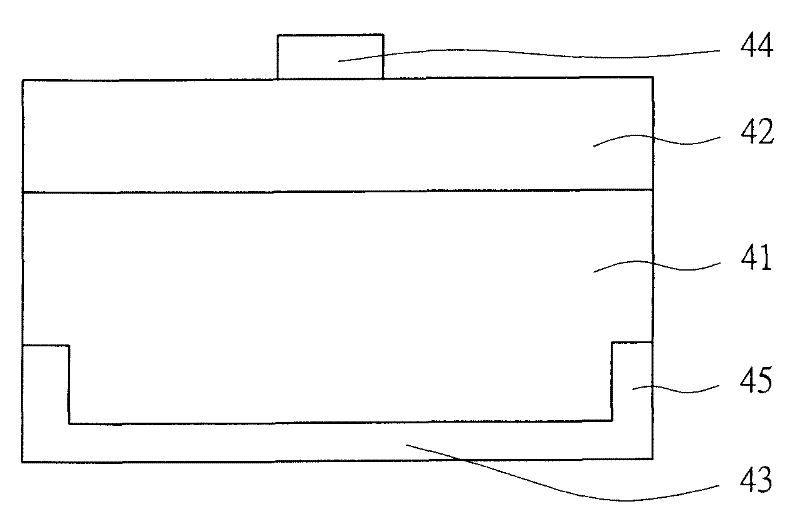

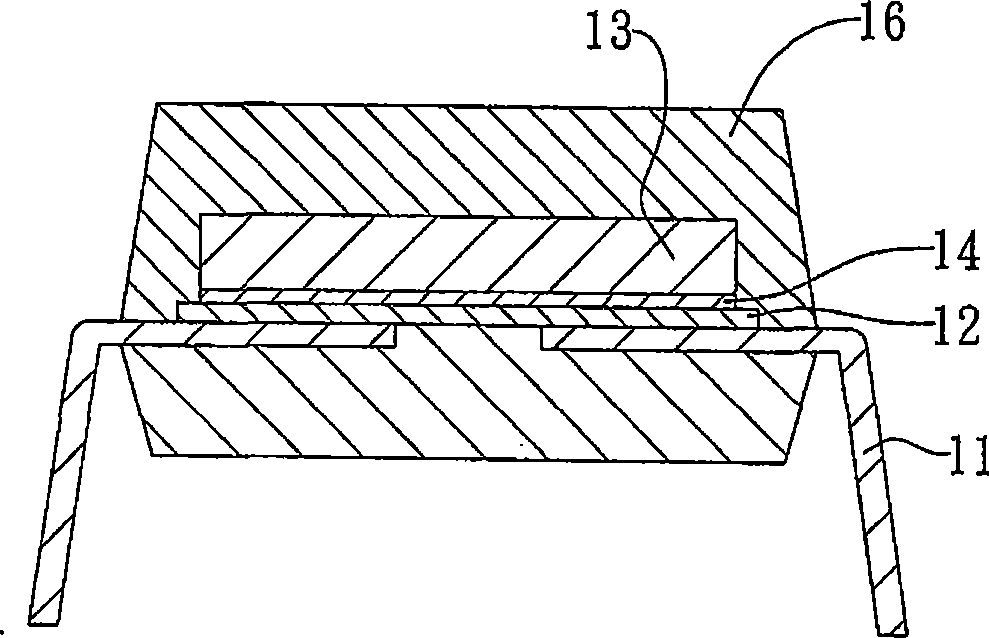

Semiconductor packaging structure and making method thereof

ActiveCN102130088AStrong jointImprove electrical connection qualitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

The invention relates to a semiconductor packaging structure comprising a dielectric layer, a metal layer, a plurality of metal posts, semiconductor chips and packaging colloid, wherein the metal is arranged on the dielectric layer and comprises a chip accommodating gasket and a plurality of path lines, each path line comprises a line body, a welded gasket extending to the periphery of the chip accommodating gasket and an opposite path line terminal; each metal post passes through the dielectric layer, one end of each metal post is connected with the chip accommodating gasket and the respective path line terminal, and the other end of the metal post protrudes out of the dielectric layer; the semiconductor chips are arranged on the chip accommodating gasket and electrically connected with the respective welded packets; and the packaging colloid is used for covering the semiconductor chips, welding wires, the metal layer and the dielectric layer. In the semiconductor packaging structure, a chip accommodating side is provided with the path lines with the welded gaskets, so that the welding wires are not too long and are prevented from cross and tightness, and a phenomenon of solder bridge is difficult to generate when the semiconductor packaging structure is welded to a circuit board because the metal posts protrude out of the bottom surface of the dielectric layer. The inventionalso provides a making method of the semiconductor packaging structure.

Owner:SILICONWARE PRECISION IND CO LTD

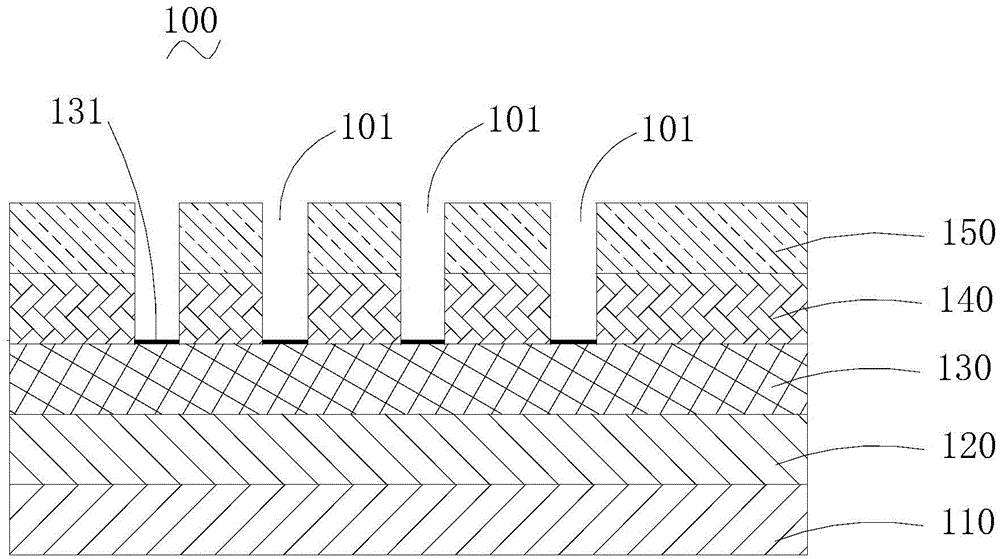

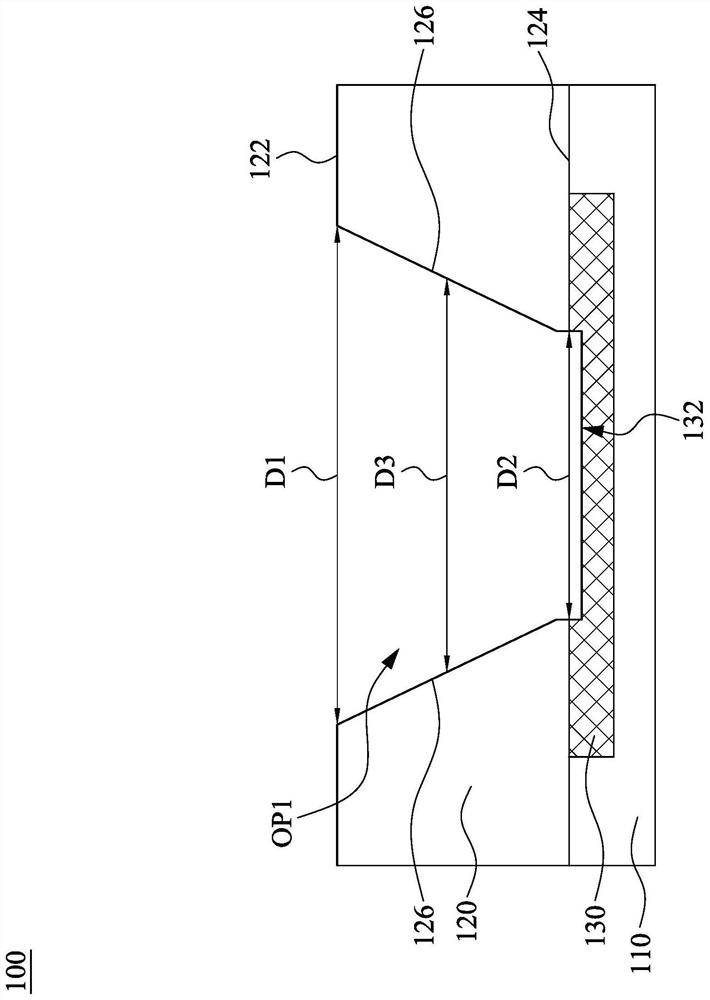

Substrate structure and manufacturing method thereof

ActiveUS20100163287A1Improve electrical connection qualityQuality improvementDecorative surface effectsSemiconductor/solid-state device detailsInsulation layerEngineering

A substrate structure is provided. The substrate structure includes a substrate, a first insulation layer, a conductive part, a second insulation layer, a seed layer and a conductive layer. The substrate has a first circuit pattern layer and a second circuit pattern layer, which are located on two opposite surfaces of the substrate respectively. The first insulation layer formed on the first circuit pattern layer has a first insulation hole, which exposes a first opening in the outer surface of the first insulation layer. The conductive part formed on the first insulation hole for electrically connecting with a chip is enclosed by the edge of the first opening. The second insulation layer formed on the second circuit pattern layer has a second insulation hole in which the seed layer is formed. The conductive layer is formed on the seed layer for electrically connecting with a circuit board.

Owner:ADVANCED SEMICON ENG INC

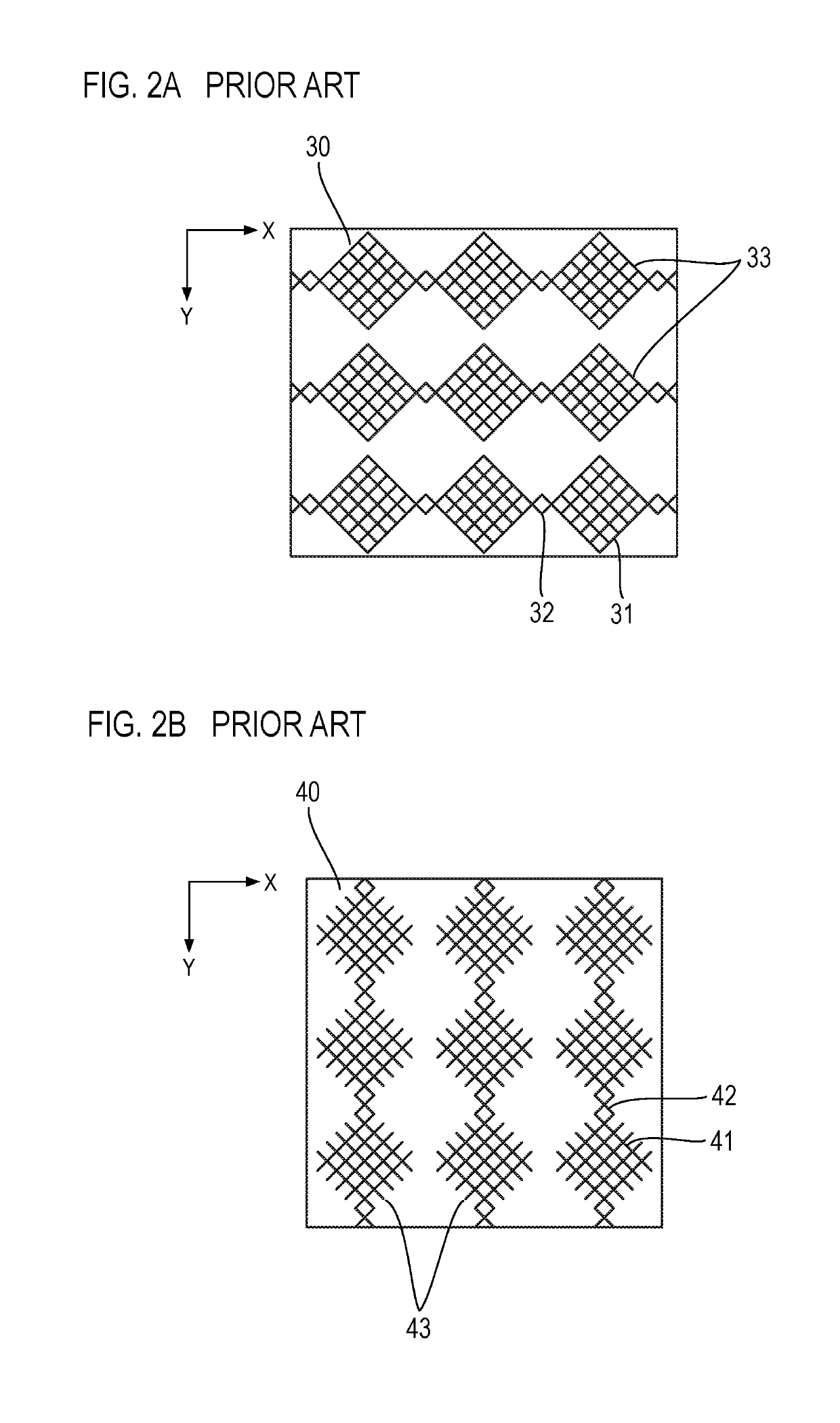

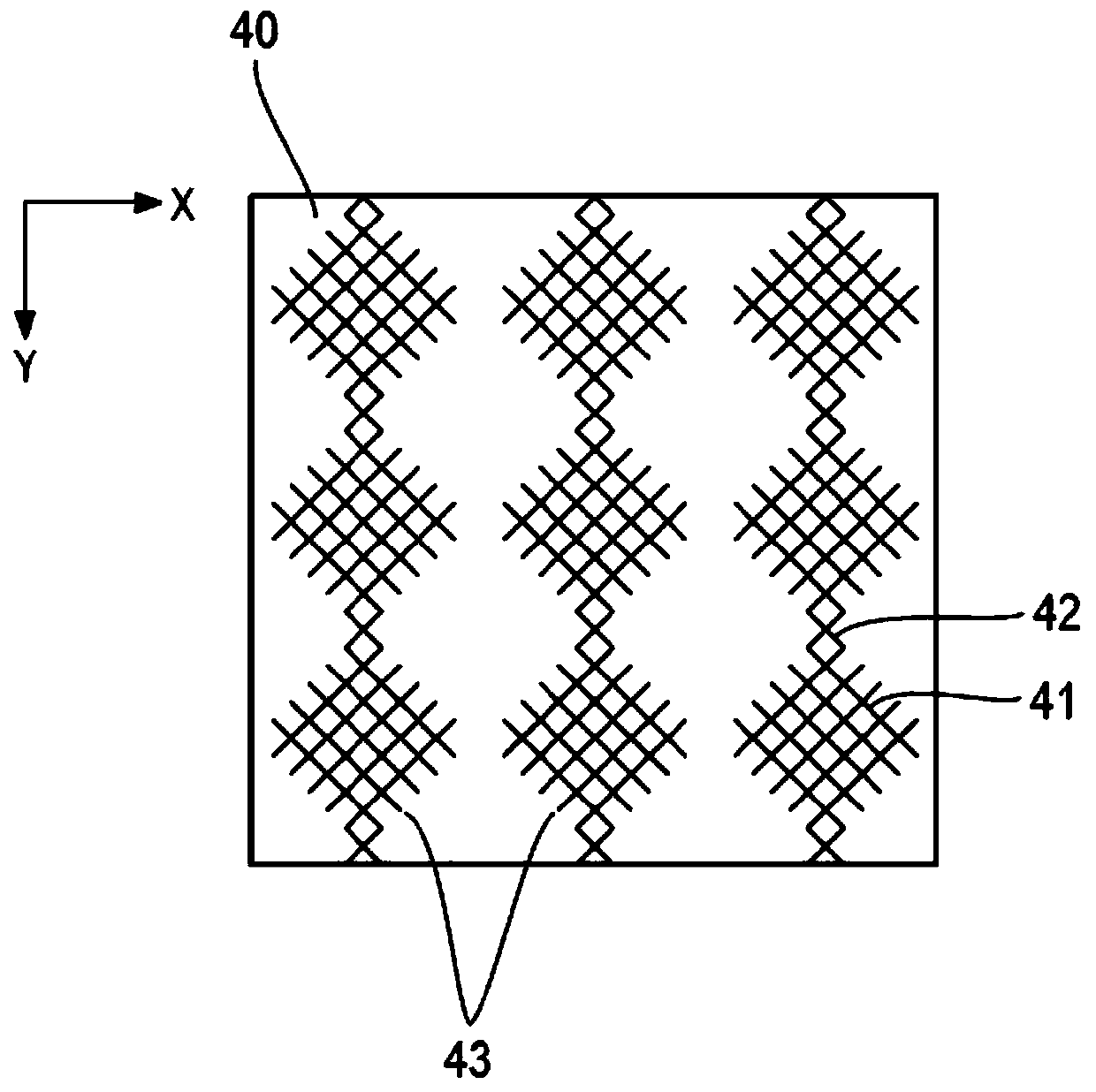

Circuit board device with fine conductive structure

InactiveUS20070158847A1Stress strength of be reinforceElectrically connect quality be improveSemiconductor/solid-state device detailsSolid-state devicesElectrically conductiveDuctility

A circuit board device with a fine conductive structure is proposed. A circuit board having at least a circuit layer is provided and the circuit layer has at least one electrically conductive pad. At least one first dielectric layer is formed on surfaces of the circuit board and the circuit layer and has at least one opening to expose the electrically conductive pad of the circuit layer. At least a first fine conductive structure made of conductive material with high ductility is formed in the opening of the first dielectric layer and is electrically connected to the electrically conductive pad of the circuit layer. The top surface of the first fine conductive structure is higher than, level with or lower than the surface of the first dielectric layer. Moreover, a conductive pad may be further formed on the top surface of the first fine conductive structure. Since the first fine conductive structure is made of conductive material with high ductility, the stress strength of the first fine conductive structure is reinforced and the electrically connecting quality between layers of the circuit board is improved.

Owner:PHOENIX PRECISION TECH CORP

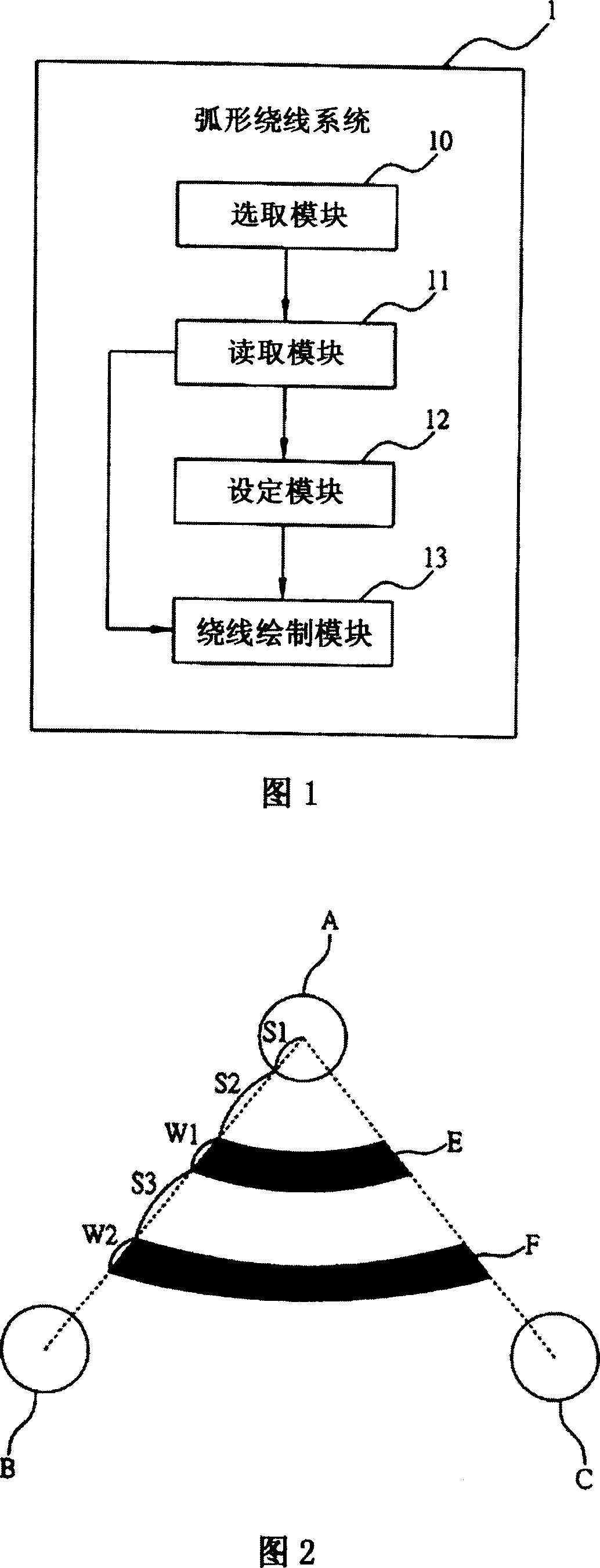

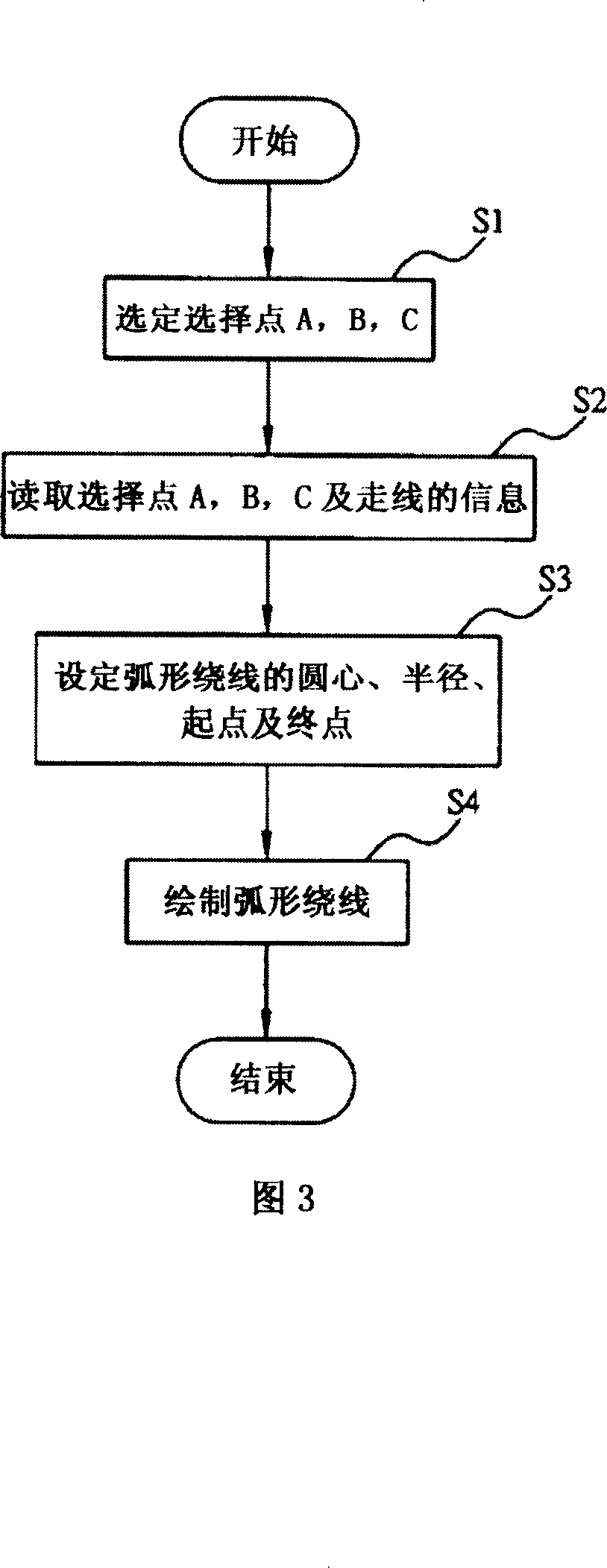

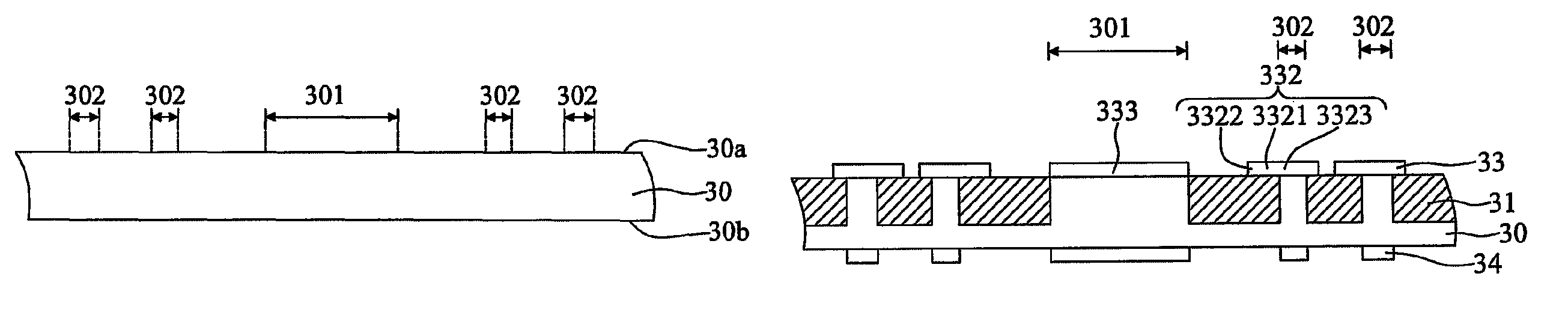

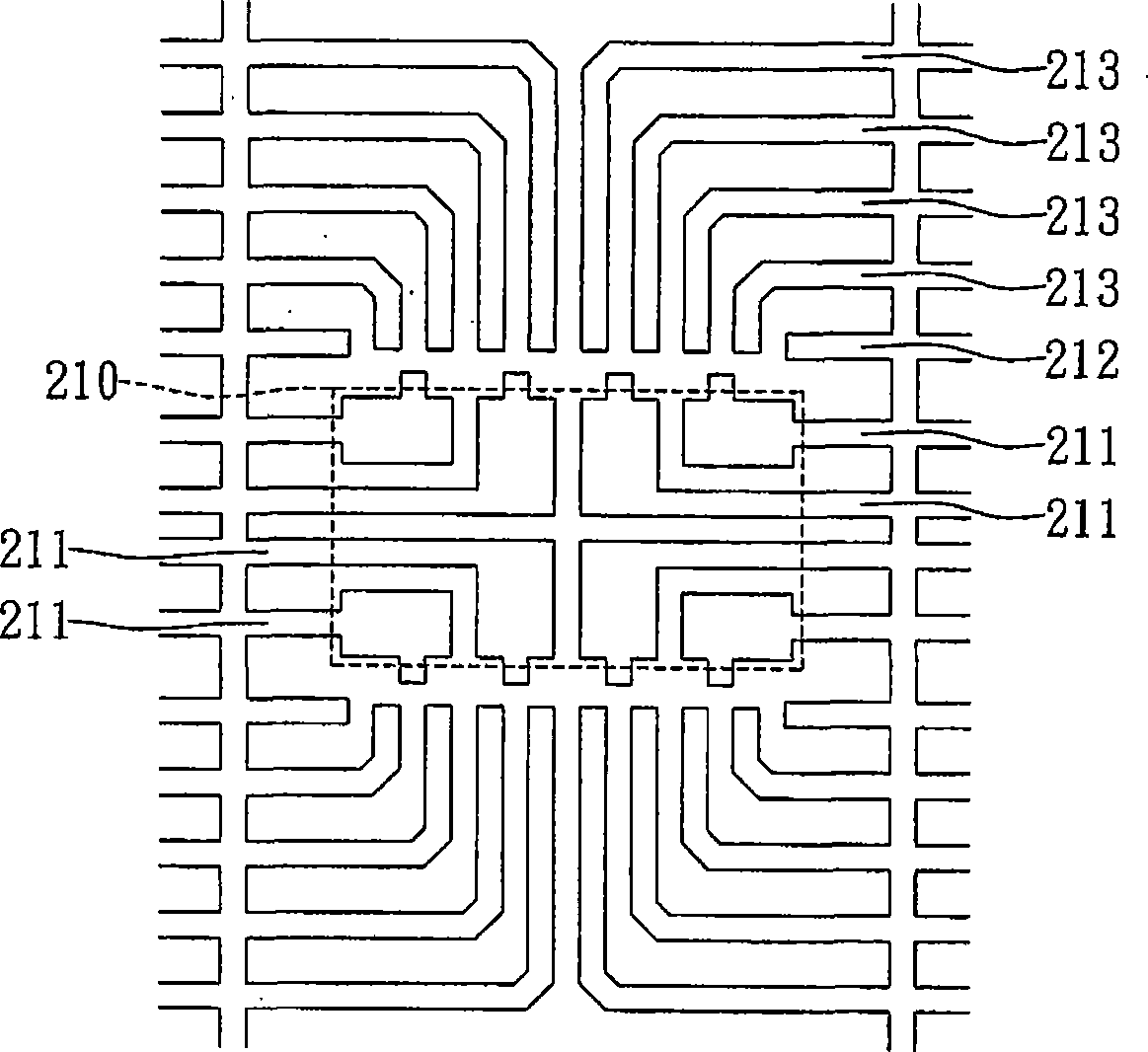

Arc-shape winding system and method

InactiveCN1980532AImprove electrical connection qualityImprove wiring efficiencyConductive pattern formationSpecial data processing applicationsRelevant informationComputer module

This circuit composition aid system composites in the hi density area of circuit board including many components. A selection module selects 3 selection points along both sides of the circuit line. One point is on one side and the other two on the other side. The reading module (RM) fetches the related info and the wire-going info of the selected points. According to the info from RM, the enactment module (EM) enacts the center position and the radius of the arc and enacts the start / end points of the arc-type winding. A winding drawing module draws the arc-type winding pattern according to the center position, the radium, the start point, and the end point from EM and wire-going info from RM. This invention raises the wire composition efficiency and the electric connecting quality of circuit boards.

Owner:INVENTEC CORP

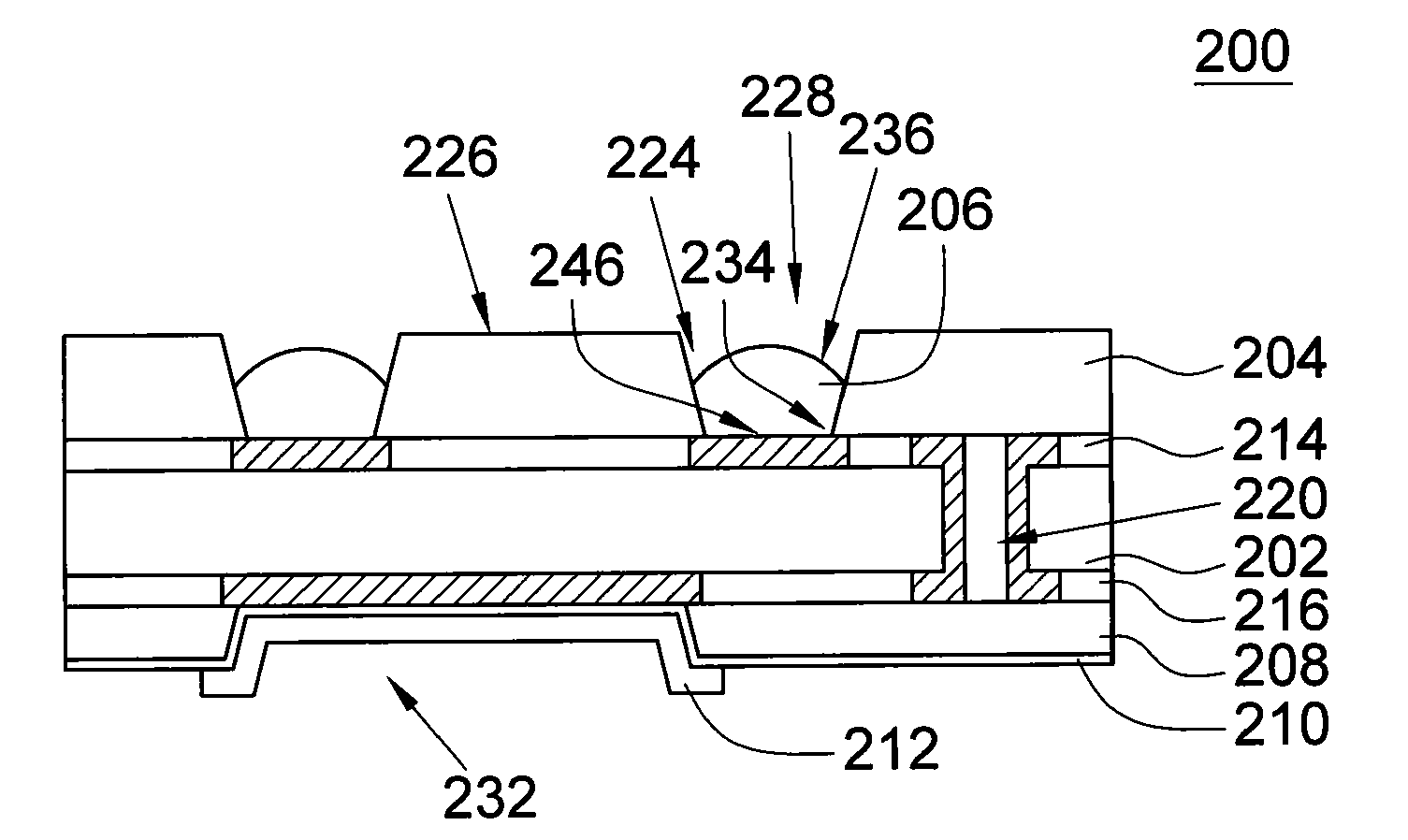

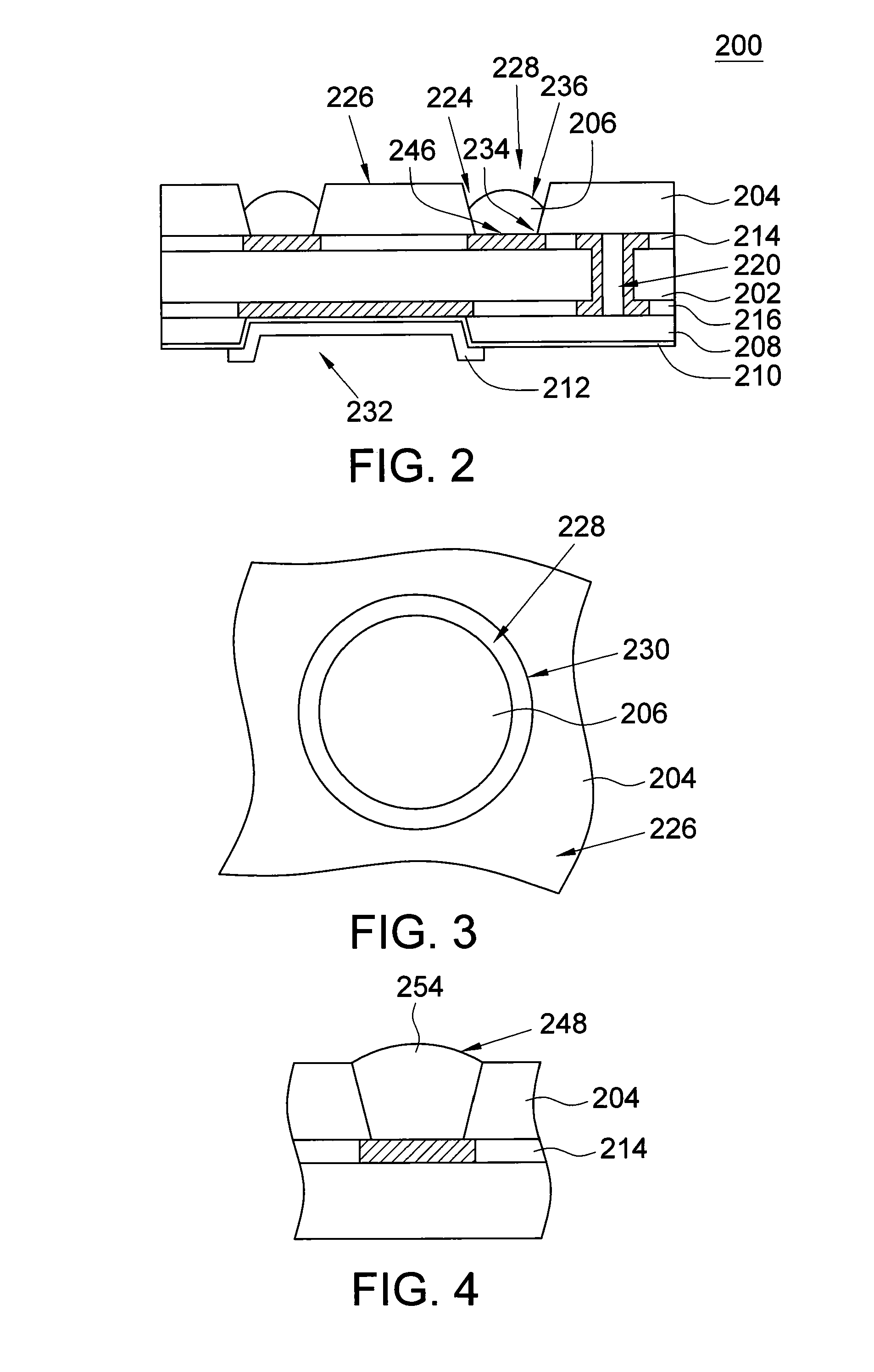

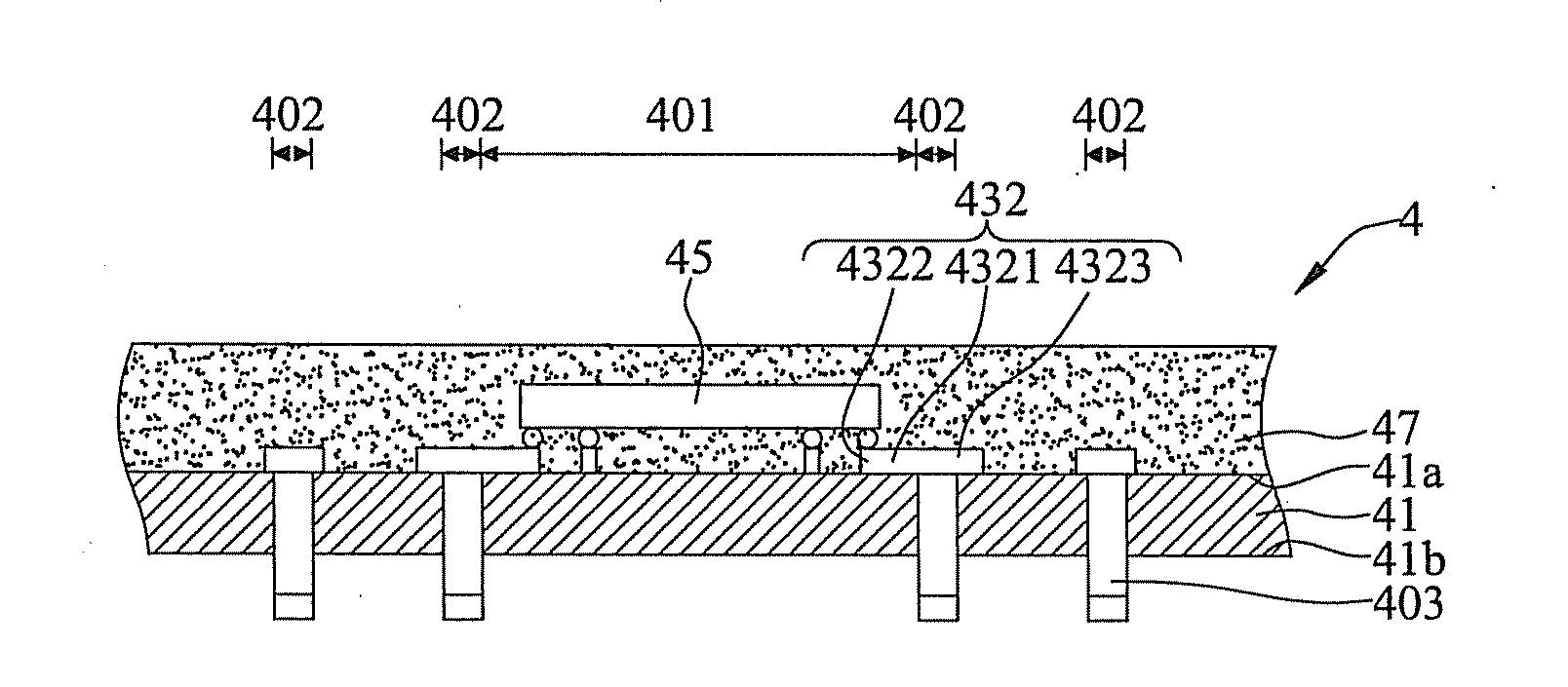

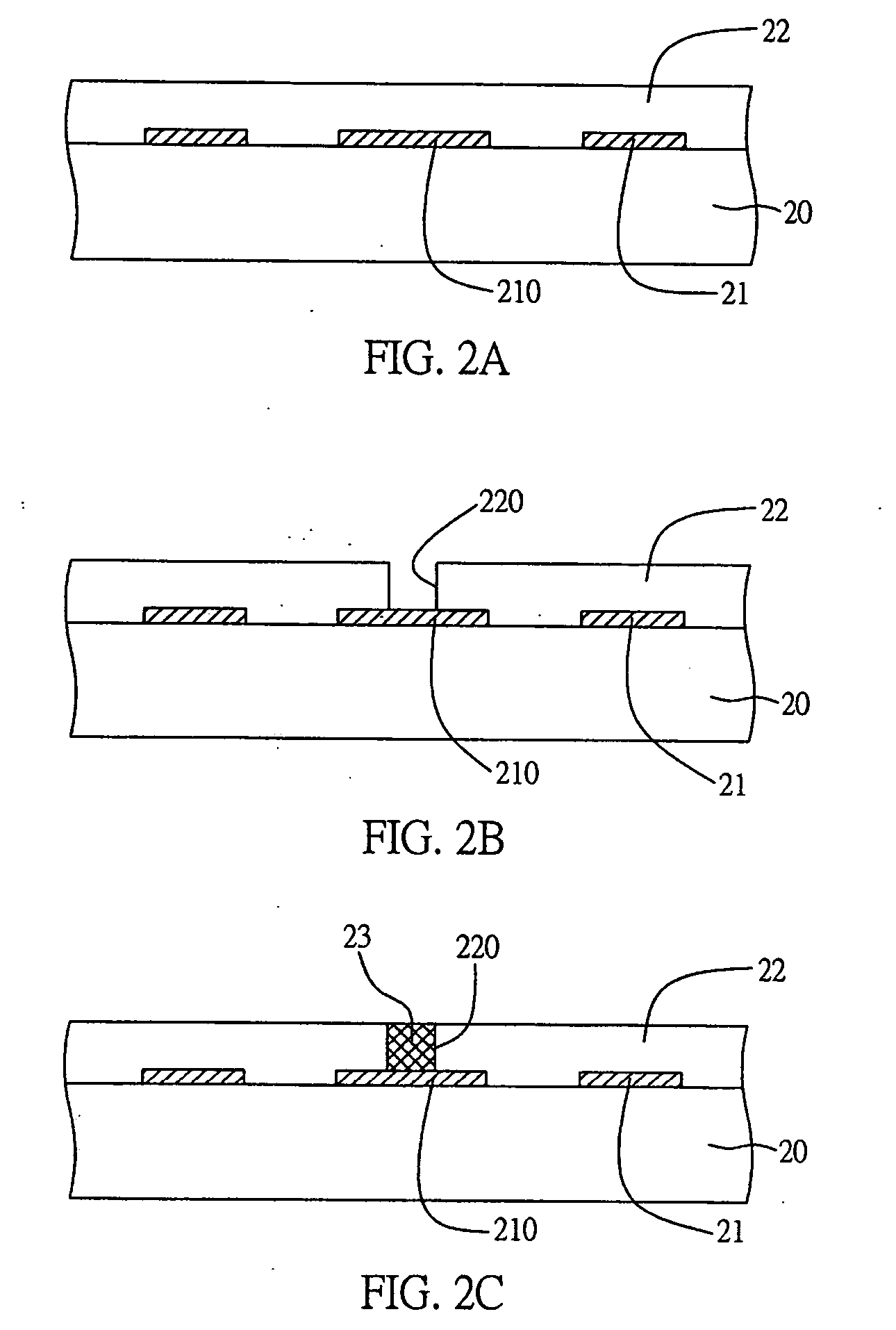

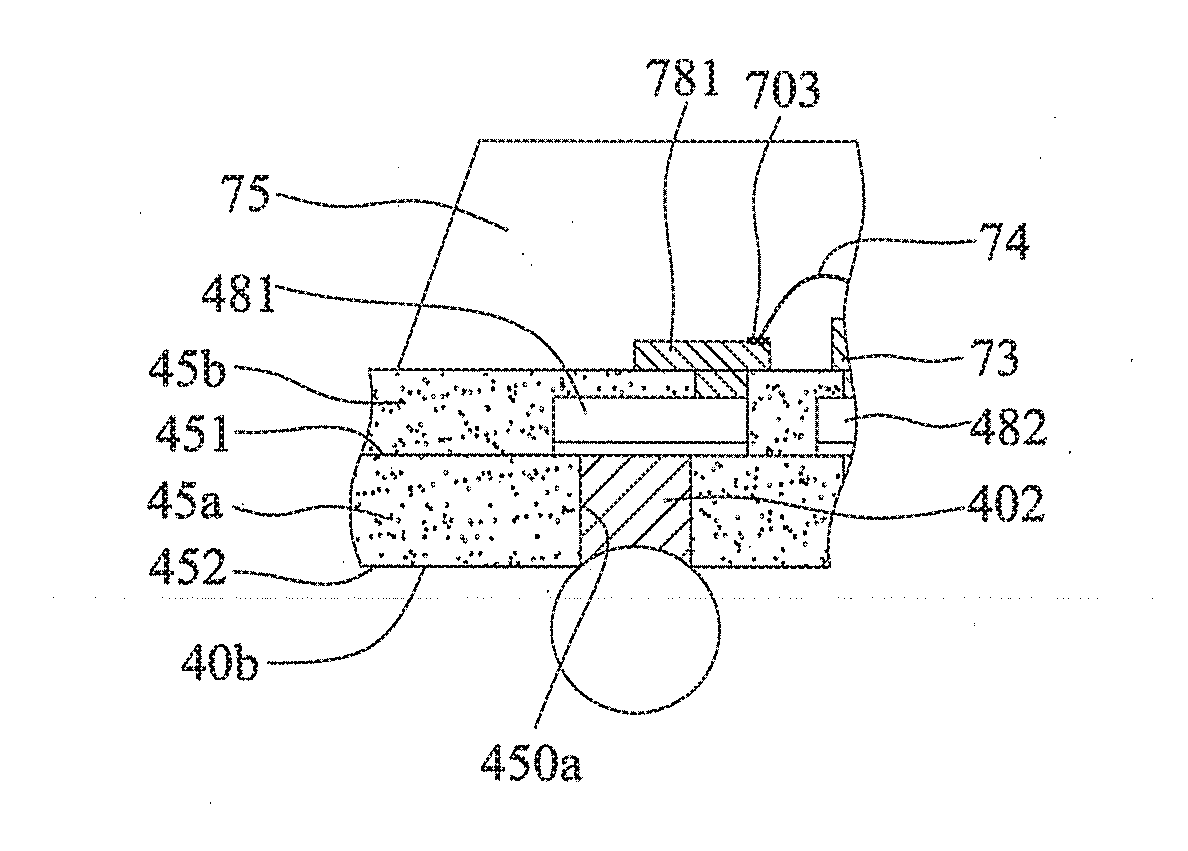

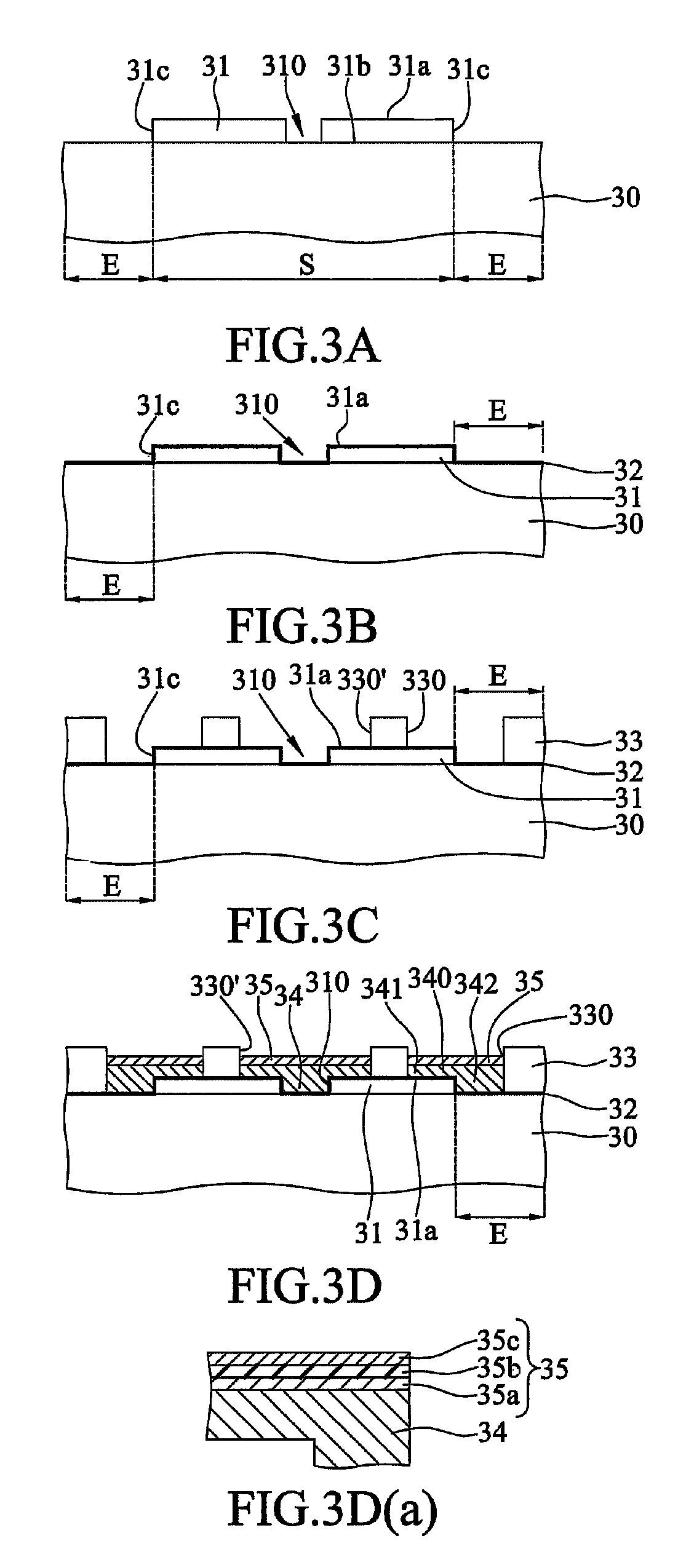

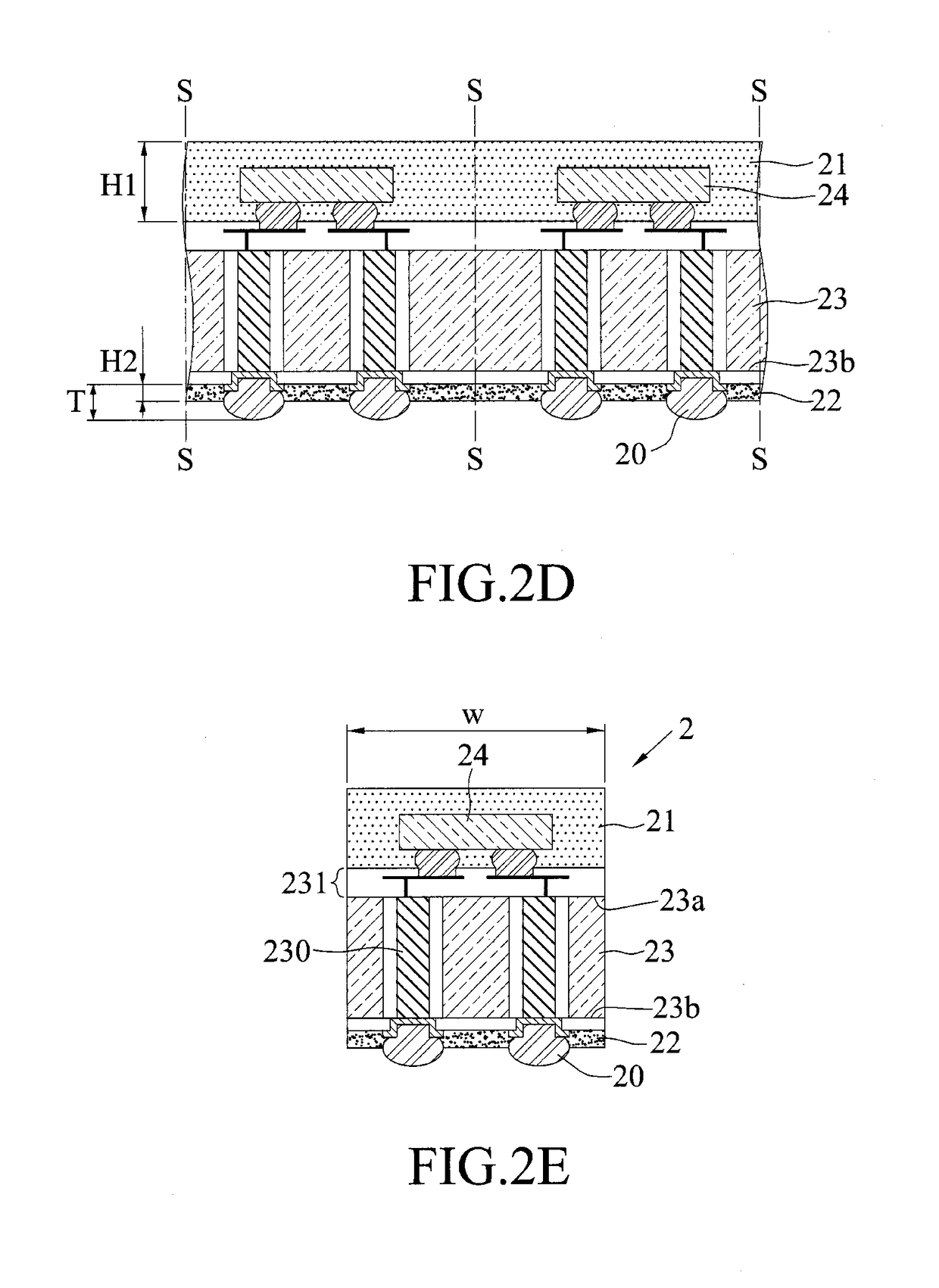

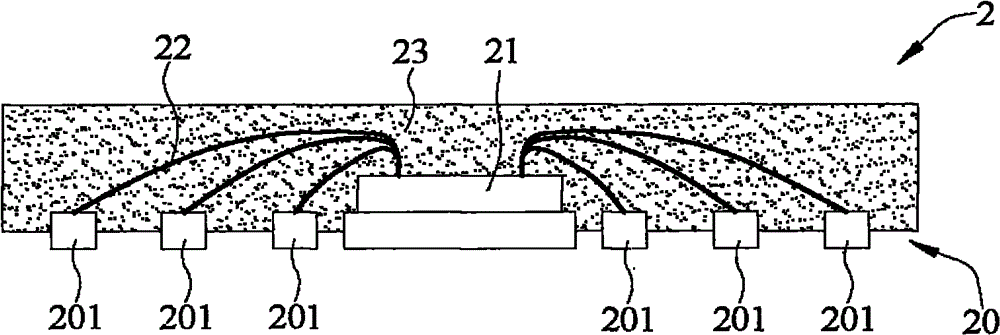

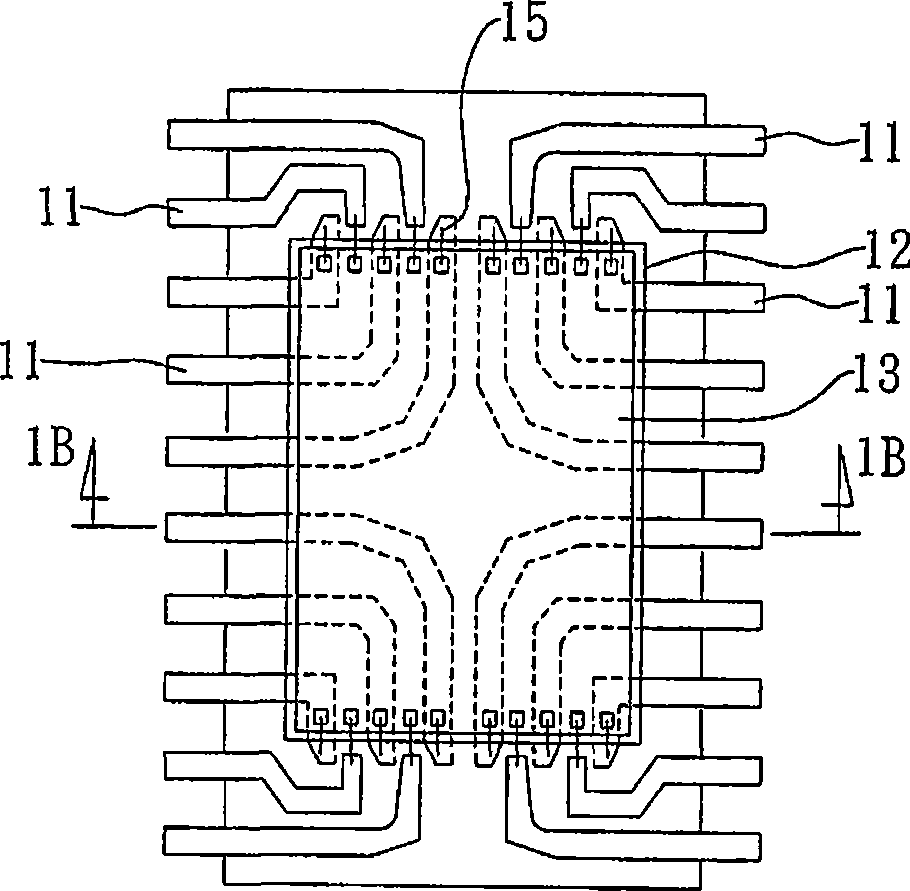

Fabrication method of semiconductor package structure

ActiveUS8304268B2Reduce bondingAvoid tanglesLine/current collector detailsSemiconductor/solid-state device detailsSemiconductor chipSemiconductor package

A fabrication method of a semiconductor package structure includes: patterning a metal plate having first and second surfaces; forming a dielectric layer on the metal plate; forming a metal layer on the first surface and the dielectric layer; forming metal pads on the second surface, the metal layer having a die pad and traces each having a bond pad; mounting a semiconductor chip on the die pad, followed by connecting electrically the semiconductor chip to the bond pads through bonding wires; forming an encapsulant to cover the semiconductor chip and the metal layer; removing portions of the metal plate not covered by the metal pads so as to form metal pillars; and performing a singulation process. The fabrication method is characterized by disposing traces with bond pads close to the die pad to shorten the bonding wires and forming metal pillars protruding from the dielectric layer to avoid solder bridging.

Owner:SILICONWARE PRECISION IND CO LTD

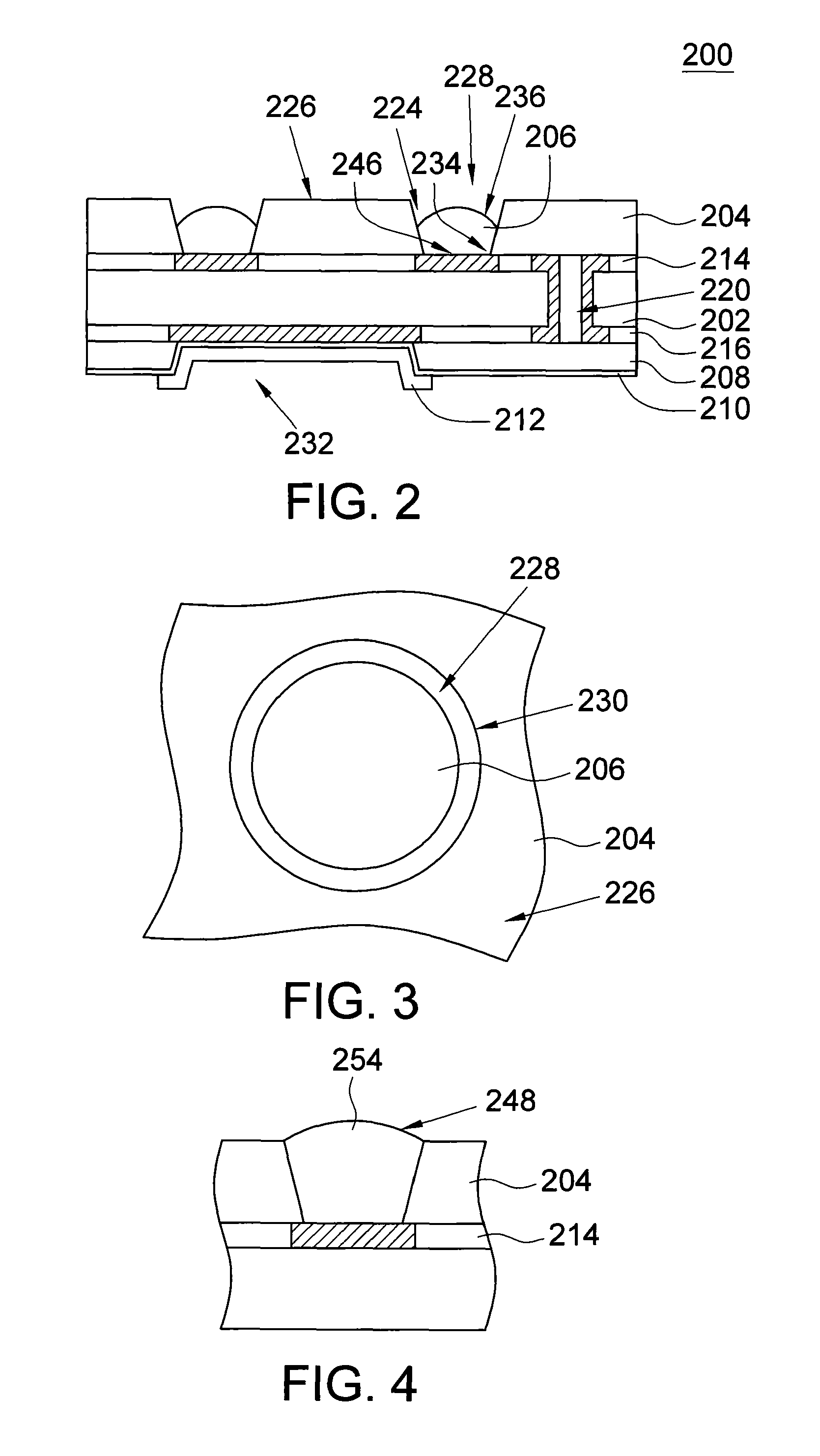

Electrical terminal

InactiveUS20080160820A1Avoid problemsLow impurity contentFinal product manufactureSoldered/welded conductive connectionsElectrical connectionSoldering

An electrical terminal for gripping a solder includes a body, an elastic arm extending from the body, which has a contact at the end of the elastic arm, and a welding portion extending downwardly from the body, wherein the welding portion includes a baffle and at least two gripping pieces, the baffle extends from the underside of the body and abuts against the solder, and the gripping pieces extend bendly from the baffle and grip the solder. The present invention ensures the solder is gripped within the welding portion in order to decrease the amount of impurities interfused in the soldering fluid, and prevents the soldering fluid of the electrical terminals from blending with each other when the solder is welded on the printed circuit board. Therefore the solder is kept clear to improve the quality of the electrical connection and strengthen the welding bond.

Owner:LOTES

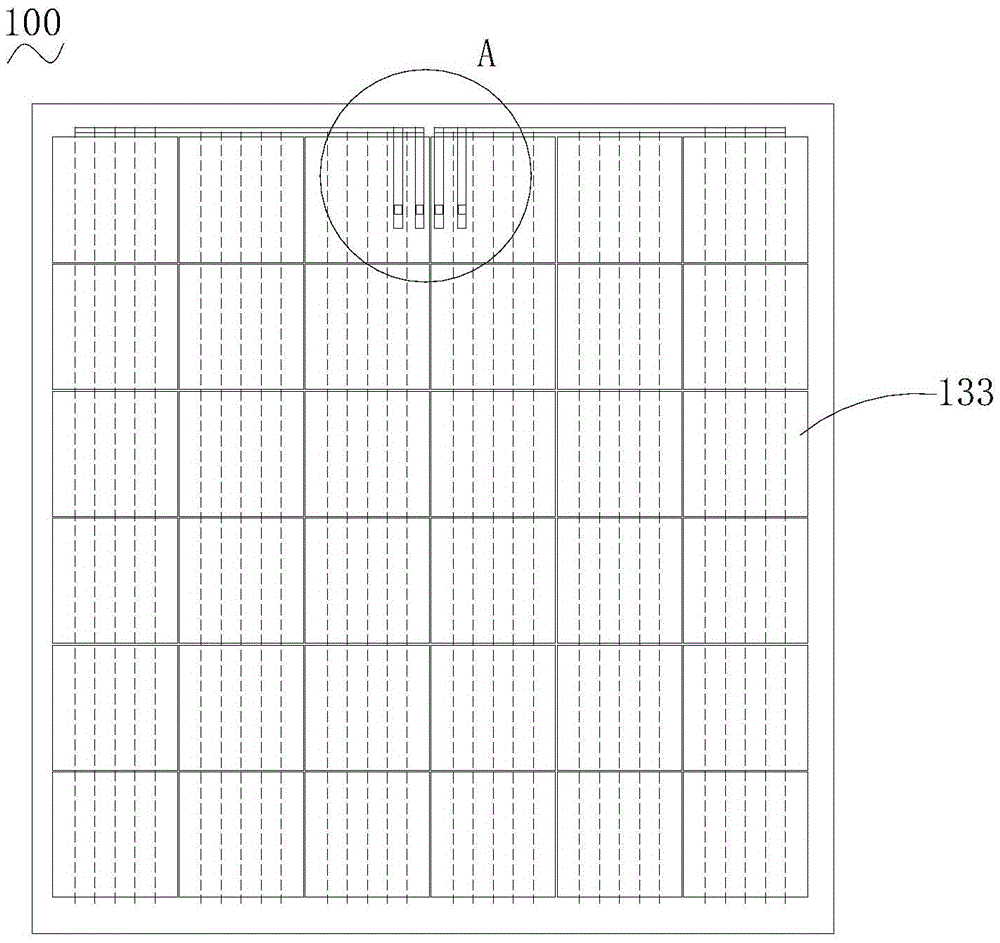

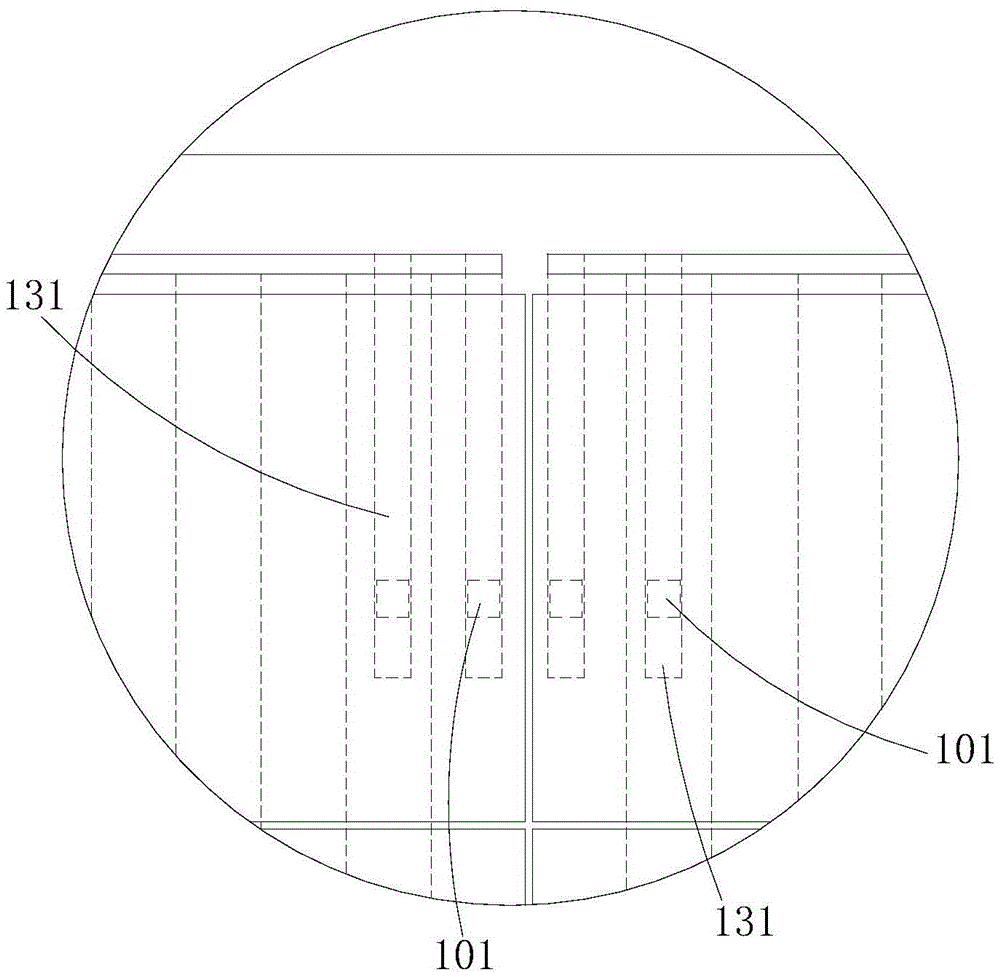

Photomask structure and method for forming through holes in negative photoresistive pattern, as well as application

InactiveCN107908074AIncrease exposureImprove electrical connection qualityOriginals for photomechanical treatmentElectrical connectionComputer science

The application discloses a photomask structure and a method for forming through holes in a negative photoresistive pattern, as well as application. The photoresistive structure comprises shading parts corresponding to the through holes, each shading part is defined with a central shading region and a peripheral shading region distributed around the central shading region, a plurality of vertically hollowed slits are distributed in an array in the peripheral shading regions in at least one radial direction of the shading parts, and the widths of the slits meet: bn is larger than bn+1, where bnand bn+1 are the widths of two adjacent slits and bn is farther away from the central shading region compared with the slit corresponding to bn+1. According to the photomask structure, the method andthe application, the hollowed slits are formed in the array in the shading parts, so that the exposure of the positions of the through holes is increased; gentle slopes are formed on the edges of thethrough holes, so that the quality of electrical connections between pixel electrodes and signal wires of metal layers of thin film transistors is improved, meanwhile, film breakage of protective layers in a back-end process is reduced, and the quality and the yield of a product is improved.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Fabrication method of semiconductor package structure

ActiveUS20110159643A1Reduce decreaseAvoid tanglesLine/current collector detailsSemiconductor/solid-state device detailsSemiconductor chipSemiconductor package

A fabrication method of a semiconductor package structure includes: patterning a metal plate having first and second surfaces; forming a dielectric layer on the metal plate; forming a metal layer on the first surface and the dielectric layer; forming metal pads on the second surface, the metal layer having a die pad and traces each having a bond pad; mounting a semiconductor chip on the die pad, followed by connecting electrically the semiconductor chip to the bond pads through bonding wires; forming an encapsulant to cover the semiconductor chip and the metal layer; removing portions of the metal plate not covered by the metal pads so as to form metal pillars; and performing a singulation process. The fabrication method is characterized by disposing traces with bond pads close to the die pad to shorten the bonding wires and forming metal pillars protruding from the dielectric layer to avoid solder bridging.

Owner:SILICONWARE PRECISION IND CO LTD

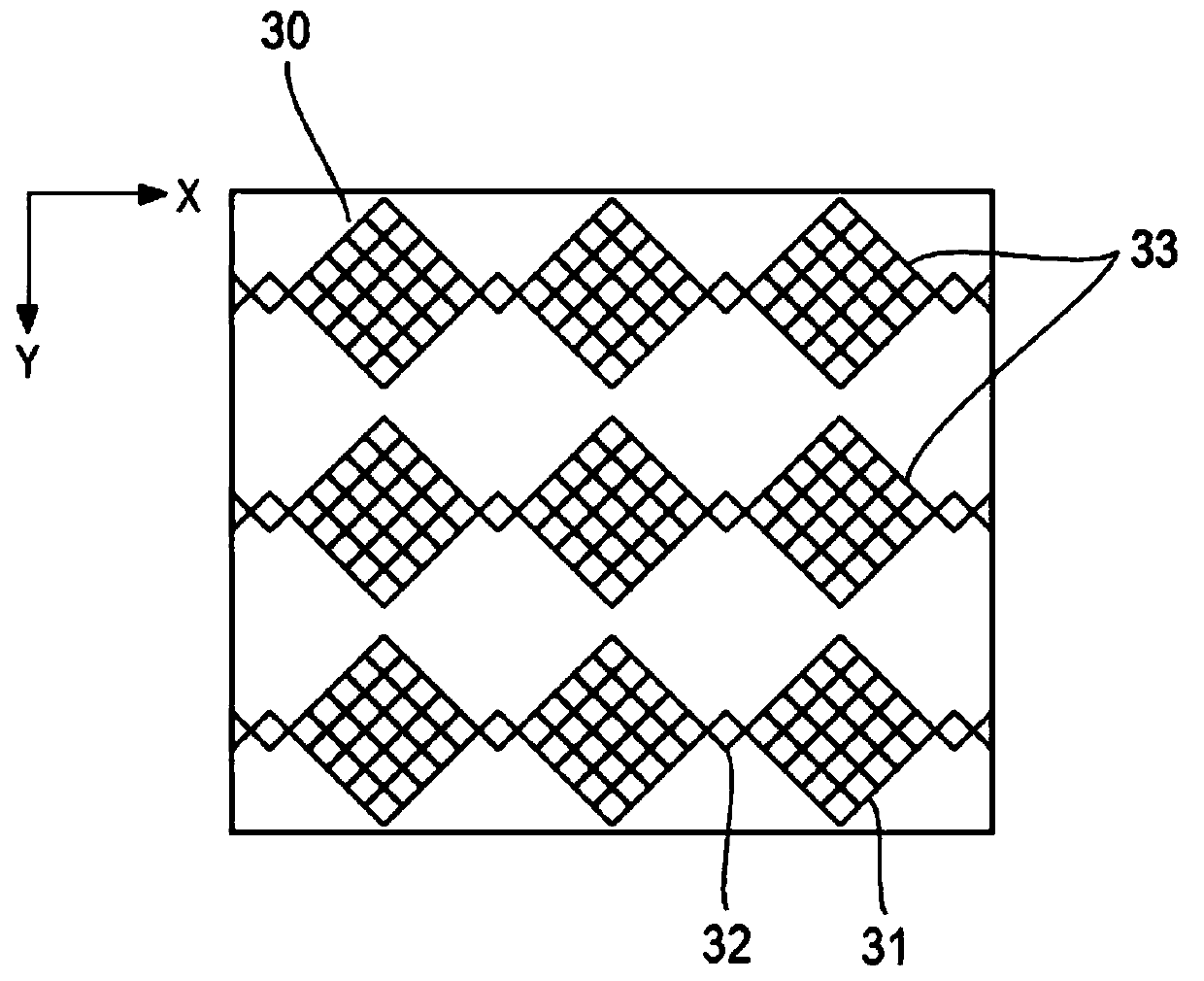

Circuit board assembly with fine electrically connecting structure

InactiveUS20070144774A1Improve electrical connection qualityHigh reliability in electrical connectionPrinted circuit manufactureElectrical connection printed elementsElectrical connectionEngineering

A circuit board assembly with a fine electrically connecting structure is proposed, which includes at least a first circuit layer and at least a dielectric layer formed on surfaces of a circuit board and the first circuit layer. At least one opening is formed penetrating through the dielectric layer for exposing the first circuit layer. Also, at least a fine electrically connecting structure which is electrically connected to the first circuit layer is formed in the opening of the dielectric layer. The fine electrically connecting structure is made of a conductive composite material with a net-like interconnection configuration. At least a second circuit layer which includes at least a circuit and an electrical pad is formed on surfaces of the dielectric layer and the fine electrically connecting structure. By such arrangement, the first circuit layer can be electrically connected to the second circuit layer by the means of the fine electrically connecting structure, so as to achieve electrical connection of fine openings.

Owner:PHOENIX PRECISION TECH CORP

Electronic package and method of manufacturing the same

InactiveCN109817600AStable supportImprove bindingSemiconductor/solid-state device detailsSolid-state devicesBond propertiesEngineering

The invention provides an electronic package and a method of manufacturing the same. The electronic package includes a first line structure, an electronic component coupled to the first line structure, a plurality of conductive pillars coupled to the first line structure, and a cladding layer covering the conductive pillars, wherein the conductive pillar includes a first pillar portion and a second pillar portion; and the width of the first pillar portion is different from the width of the second pillar portion, thereby increasing the bonding property between the conductive pillar and the cladding layer.

Owner:SILICONWARE PRECISION IND CO LTD

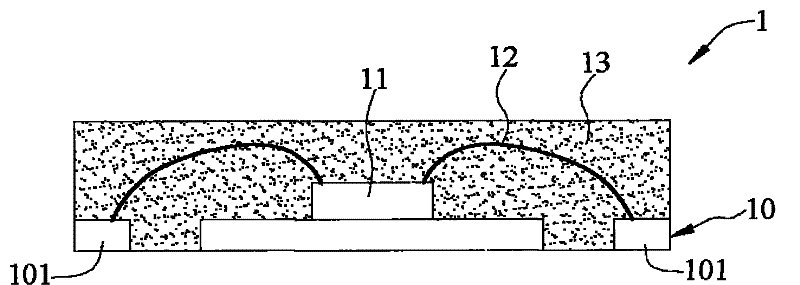

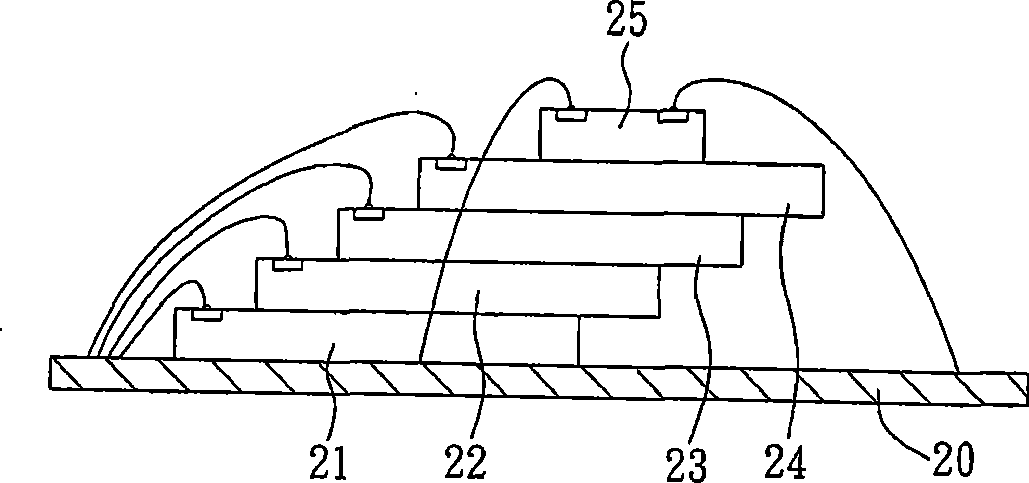

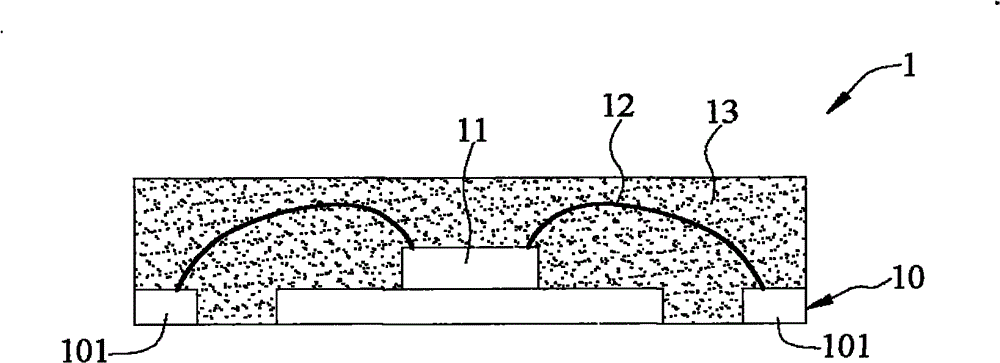

Multi-chip stacking structure and preparation thereof

ActiveCN101452861AIncrease the number of stacked layersAvoiding the problem of increasing structural heightSemiconductor/solid-state device detailsSolid-state devicesState of artChip stacking

The invention discloses a multichip stacking structure and a method for manufacturing the same. The multichip stacking structure comprises a first chip set which is provided with a plurality of first chips and is connected with a chip bearing piece in a stepped mode; the first chip of the topmost layer of the first chip set is connected with a second chip so that the first chip and the second chip are in electric connection with the chip bearing piece through a welding wire; adhesive film over wire technology (Film over Wire, FOW) is utilized to stack a third chip alternated with an insulating adhesive film on the first chip and the second chip so that the insulating adhesive film covers part of the welding wire end of the first chip of the topmost layer of the first chip set and at least one part of the second chip and is in electric connection with the third chip and the chip bearing piece through the welding wire, thereby solving the problem that when the second chip with planar dimension far less than that of the first chip is directly stacked on the first chip in the prior art, the height of the whole structure and the difficulty of wire welding operation are increased.

Owner:SILICONWARE PRECISION IND CO LTD

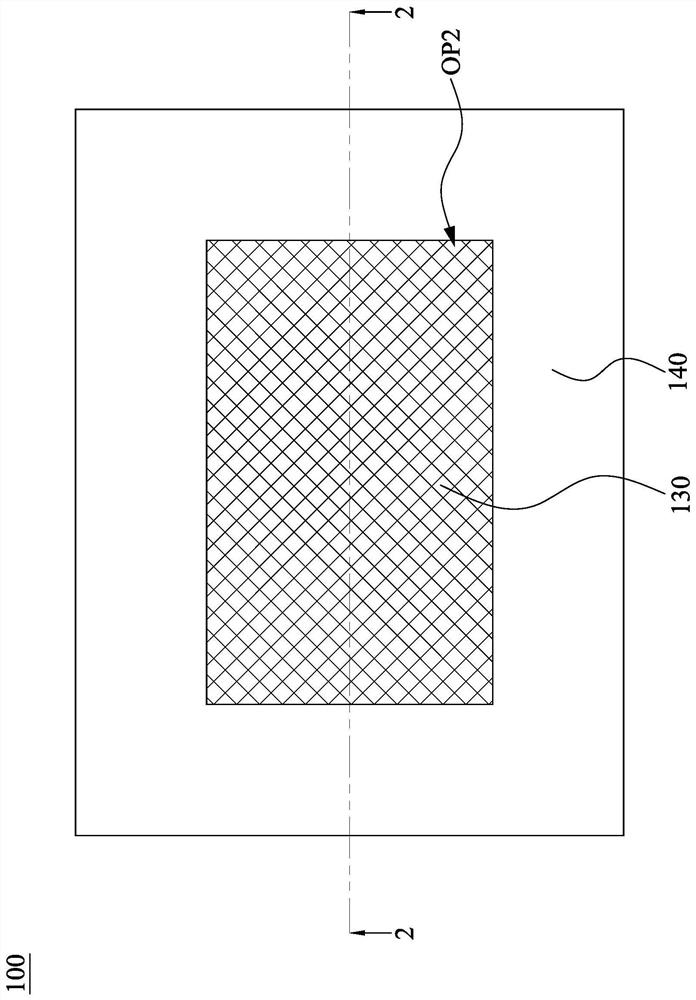

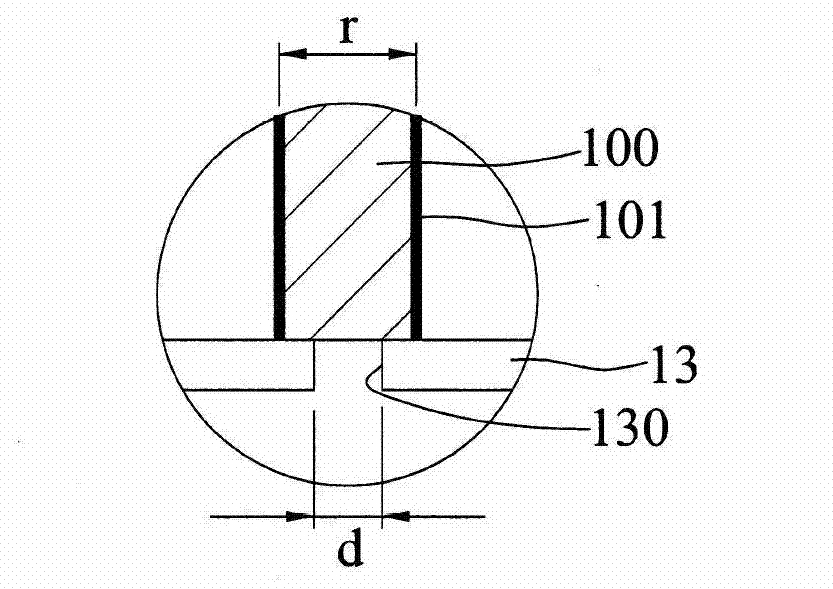

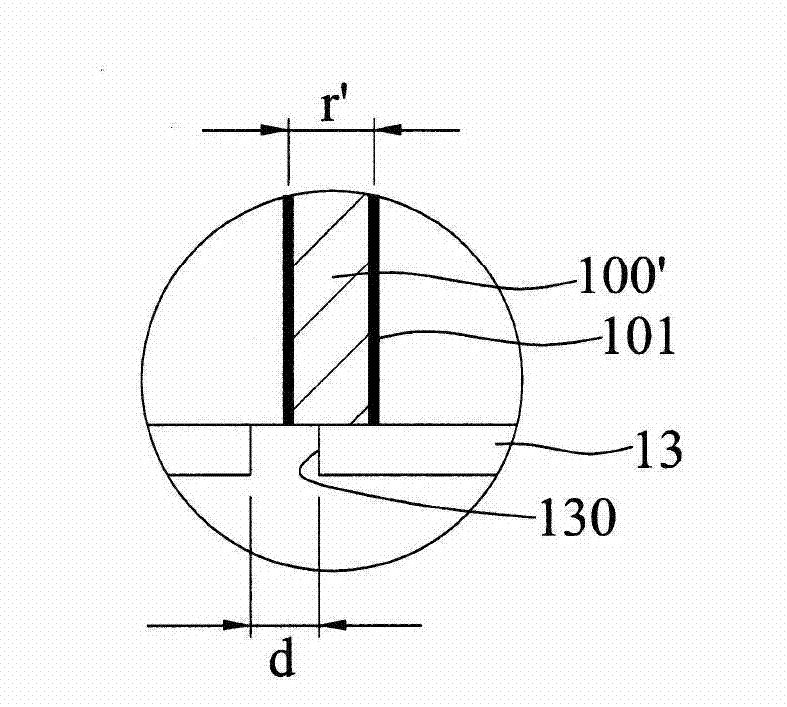

Conductive via structure

PendingUS20220102165A1Improve connection qualityImprove electrical connection qualitySemiconductor/solid-state device detailsSolid-state devicesRedistribution layerDielectric layer

A conductive via structure includes a first dielectric layer, a conductive pad in the first dielectric layer, a second dielectric layer, and a redistribution layer. The second dielectric layer is disposed above the first dielectric layer and has an opening. The conductive pad is in the opening. The opening has a first width at a top surface of the second dielectric layer, a second width at a bottom surface of the second dielectric layer, and a third width between the top surface and the bottom surface of the second dielectric layer. A difference between the first and second width is in a range from about 3 um to about 6 um. The redistribution layer extends from the top surface of the second dielectric layer to the conductive pad. The third width is gradually decreased from the top surface to the bottom surface of the second dielectric layer.

Owner:NAN YA TECH

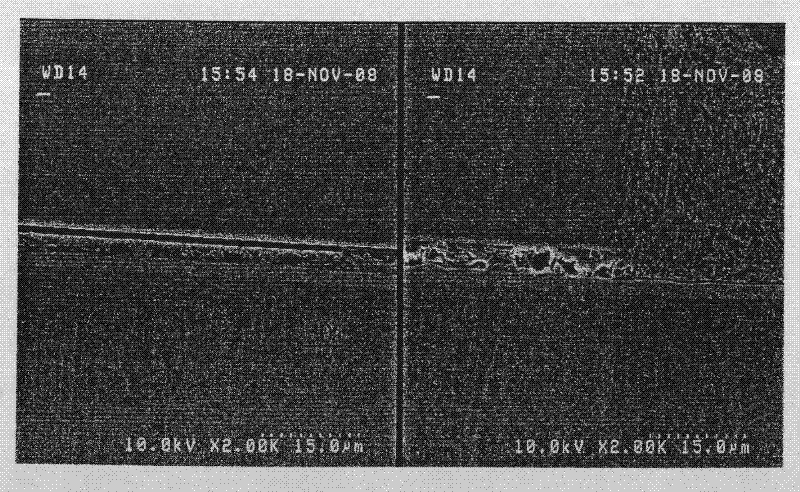

Crystal grain structure of light-emitting diode and method for manufacturing bottom electrode of crystal grain structure

InactiveCN102214761AImprove electrical connection qualitySemiconductor devicesCrystal structureGrain structure

The invention discloses a crystal grain structure of light-emitting diode and a method for manufacturing a bottom electrode of the crystal grain structure. The crystal grain structure of the light-emitting diode comprises a substrate, a light-emitting layer, at least one bottom surface electrode, at least one top surface electrode and at least one side surface electrode, wherein the light-emitting layer is formed on the top surface of the substrate; the bottom surface electrode is formed on the bottom surface of the substrate; the top surface electrode is formed on the top surface of the light-emitting layer; and the side surface electrode is formed on the bottom side surface of the substrate. In the method for manufacturing a bottom electrode, the crystal grain structure of the light-emitting diode comprises a substrate, a light-emitting layer, at least one bottom surface electrode, at least one top surface electrode and at least one side surface electrode, wherein the light-emitting layer is formed on the top surface of the substrate; the bottom surface electrode is formed on the bottom surface of the substrate; the top surface electrode is formed on the top surface of the light-emitting layer; and the side surface electrode is formed on the bottom side surface of the substrate. The method for manufacturing the bottom electrode comprises the following steps of: forming a groove with a certain depth on the bottom surface of a substrate of a light-emitting diode wafer; plating a metal film on a bottom surface and inside the groove with a metal plating technology; and cutting the wafer into crystal grains along the groove. The invention has the advantages of improving the electric connection quality between a die bonding adhesive and crystal grains of a light-emitting diode.

Owner:ARIMA OPTOELECTRONICS

Carrier-free semiconductor package and fabrication method

ActiveUS20170200671A1Reduce manufacturing costReduce usageSemiconductor/solid-state device detailsSolid-state devicesManufacturing cost reductionResist

A method for fabricating a carrier-free semiconductor package includes: half-etching a metal carrier to form a plurality of recess grooves and a plurality of metal studs each serving in position as a solder pad or a die pad; filing each of the recess grooves with a first encapsulant; forming on the metal studs an antioxidant layer such as a silver plating layer or an organic solderable protection layer; and performing die-bonding, wire-bonding and molding processes respectively to form a second encapsulant encapsulating the chip. The recess grooves are filled with the first encapsulant to enhance the adhesion between the first encapsulant and the metal carrier, thereby solving the conventional problem of having a weak and pliable copper plate and avoiding transportation difficulty. The invention eliminates the use of costly metals as an etching resist layer to reduce fabrication cost, and further allows conductive traces to be flexibly disposed on the metal carrier to enhance electrical connection quality.

Owner:SILICONWARE PRECISION IND CO LTD

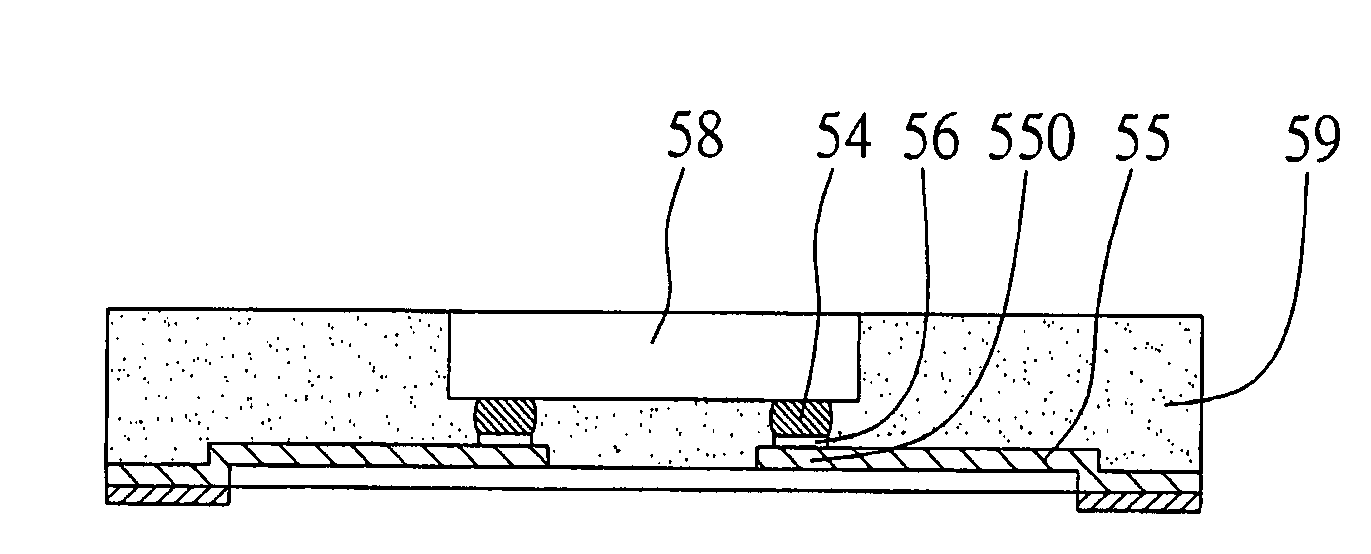

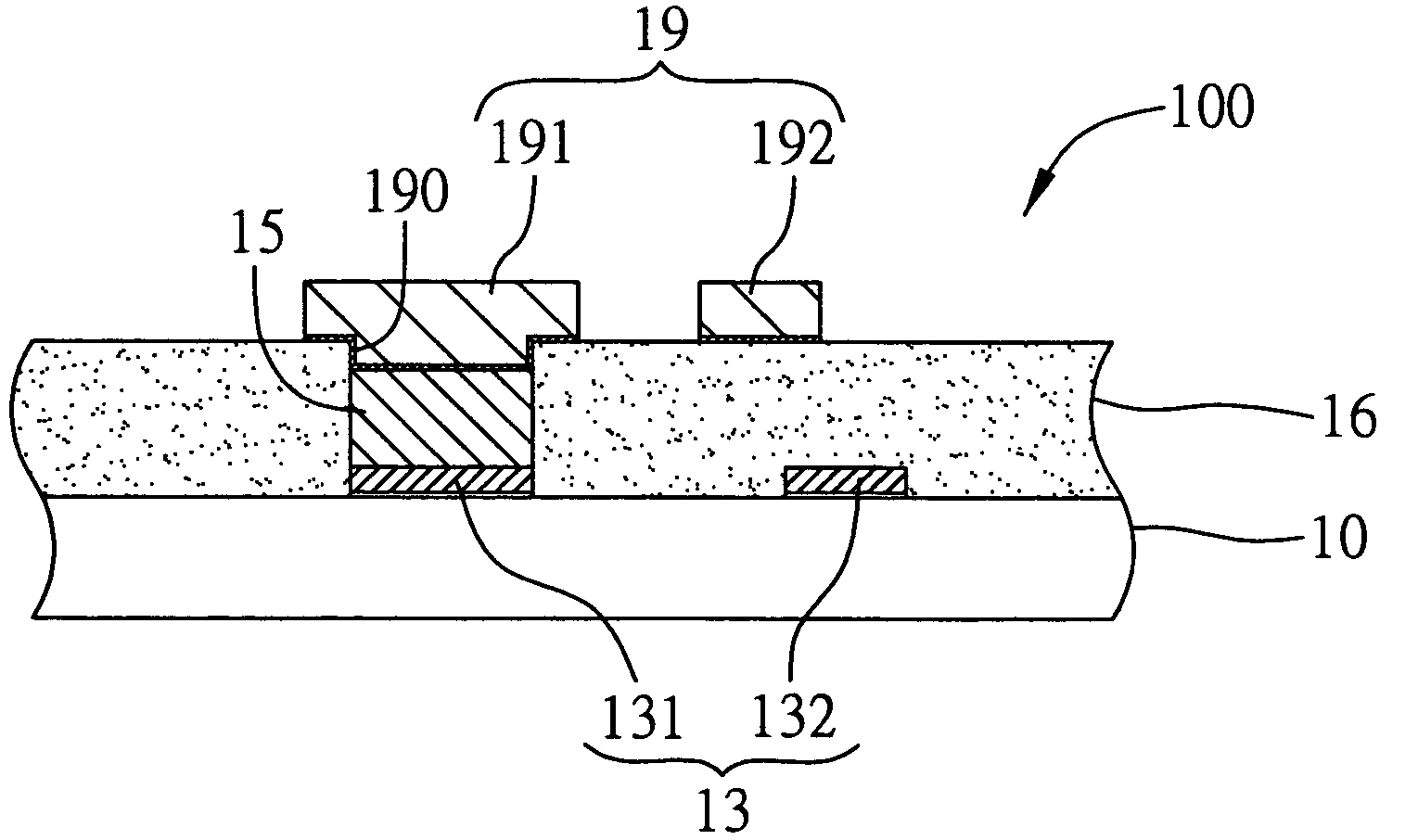

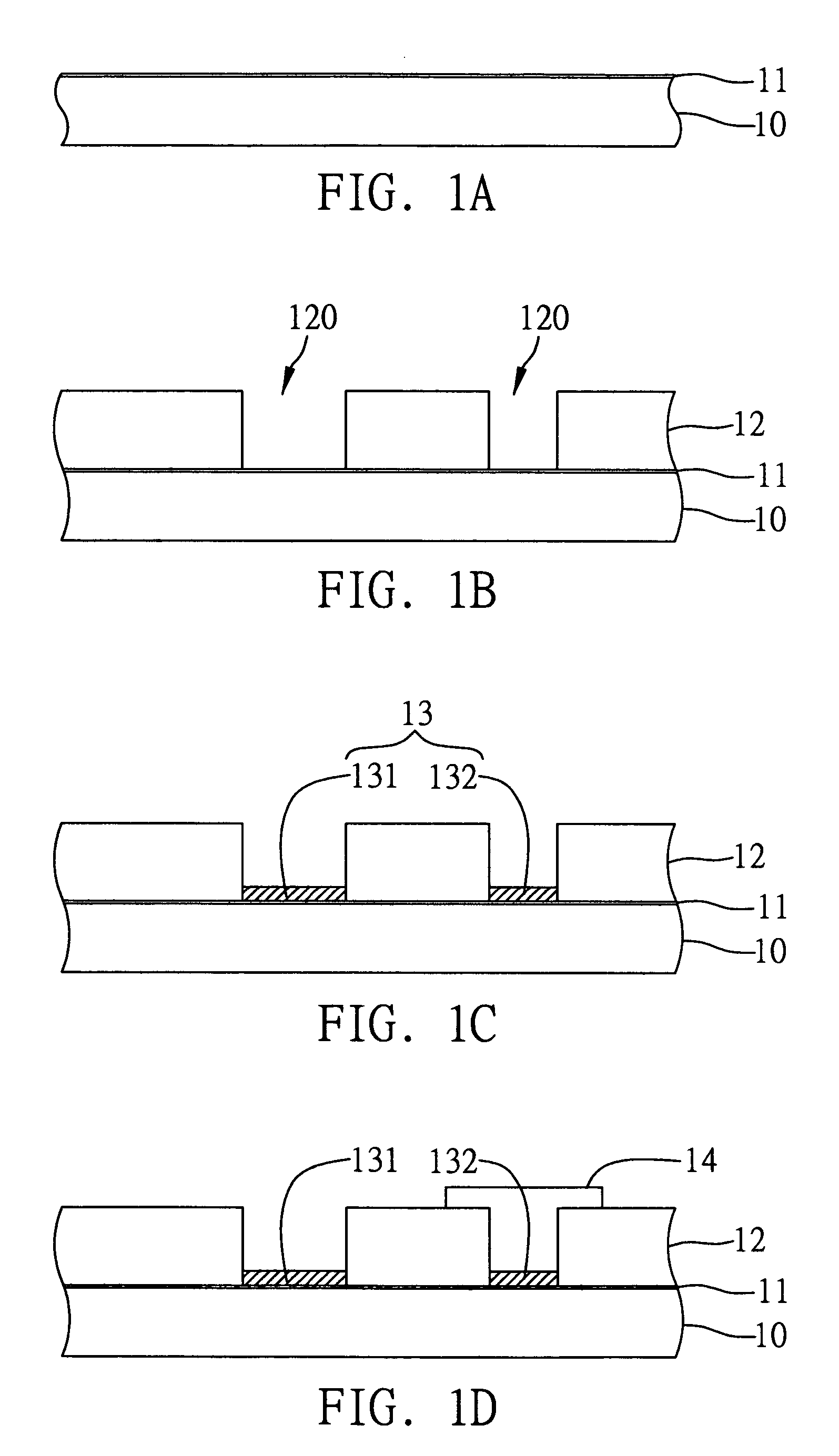

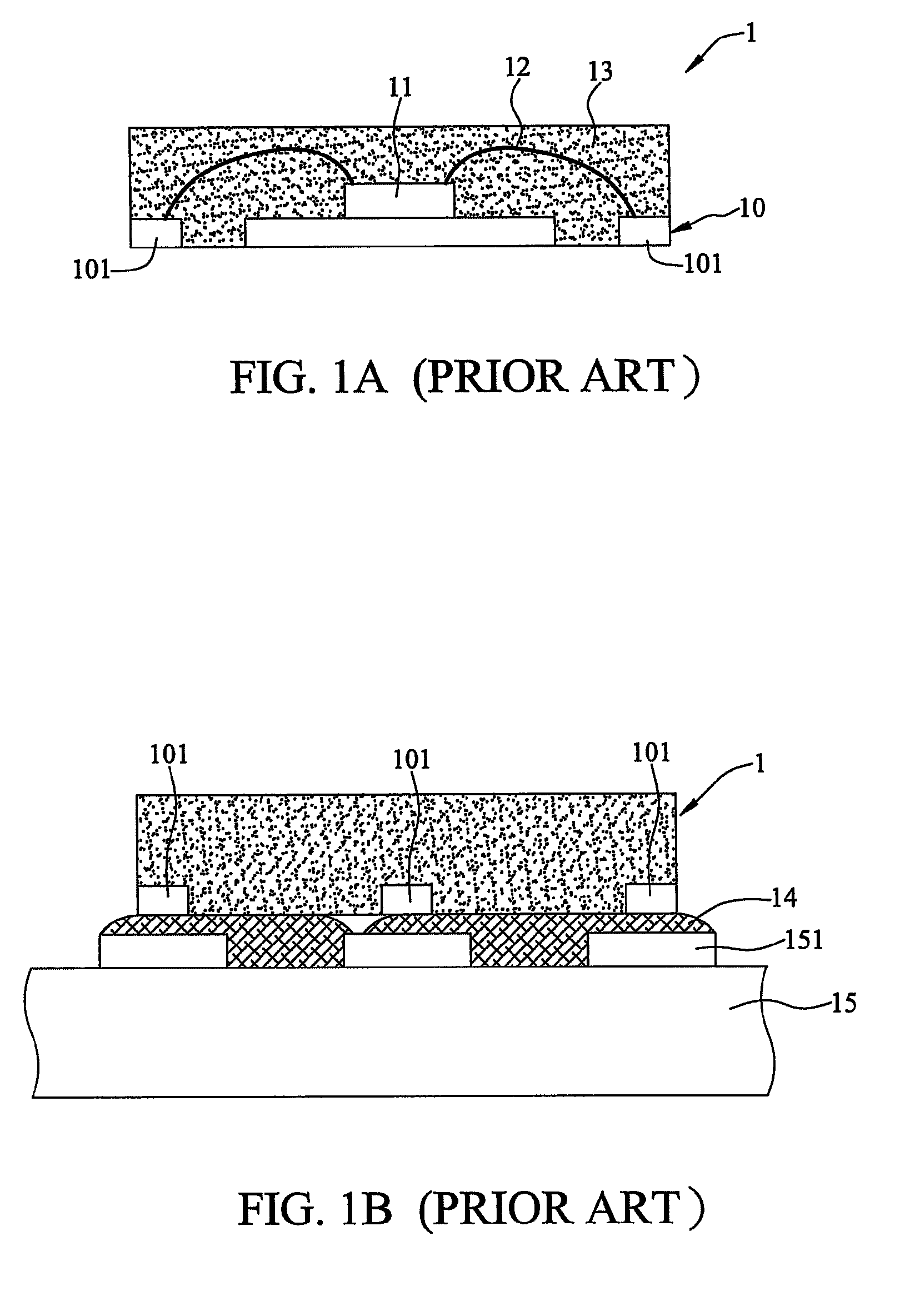

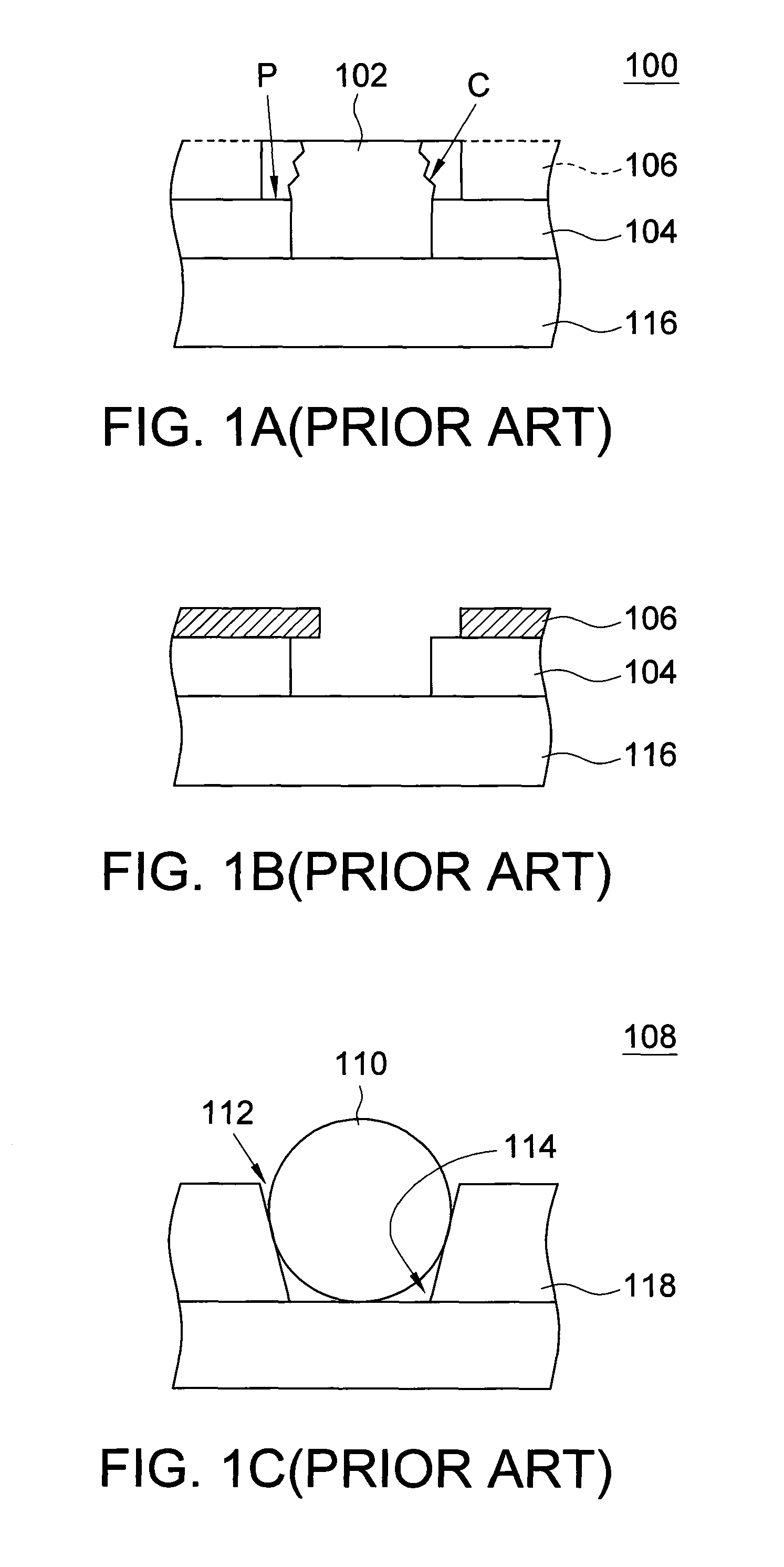

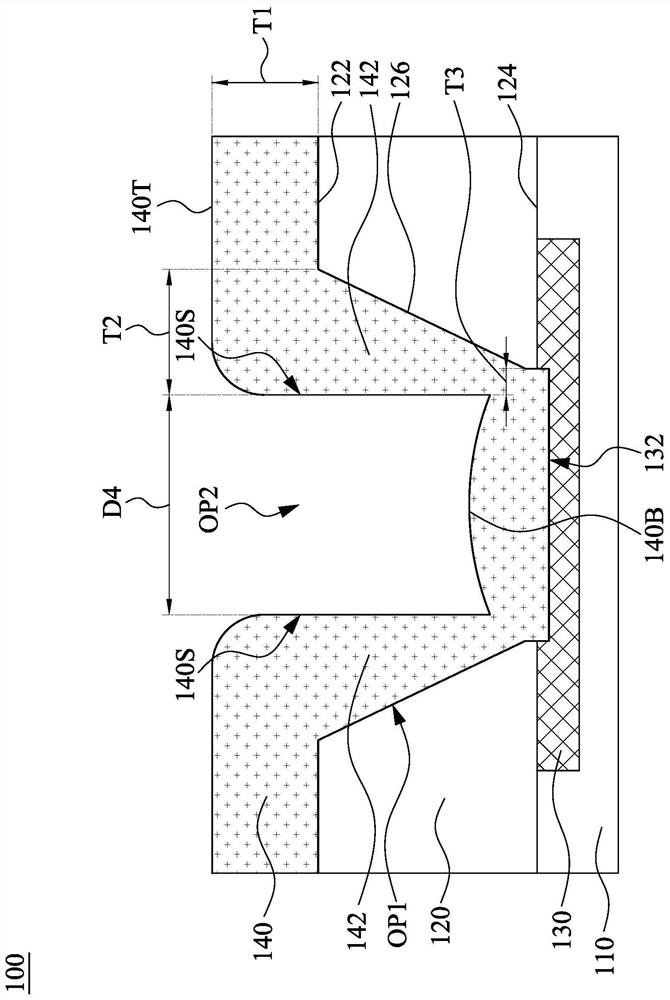

Semiconductor package and fabrication method thereof

ActiveUS8471383B2Improve electrical connection qualityReliable electrical connectionSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionSemiconductor chip

A semiconductor package includes: a dielectric layer having opposing first and second surfaces and side surfaces; a copper wiring layer disposed on the first surface of the dielectric layer and having extension pads; a surface processing layer disposed on the wiring layer; a semiconductor chip disposed on the wiring layer and electrically connected to the surface processing layer; and an encapsulant disposed on the first surface of the dielectric layer for encapsulating the semiconductor chip, the wiring layer and the surface processing layer while exposing the second surface of the dielectric layer. Further, vias are disposed between the side surfaces of the dielectric layer and the encapsulant such that the extension pads are exposed from the vias so as for solder balls to be disposed thereon. Due to improved electrical connection between the copper and solder materials, the electrical connection quality of the package is improved.

Owner:SILICONWARE PRECISION IND CO LTD

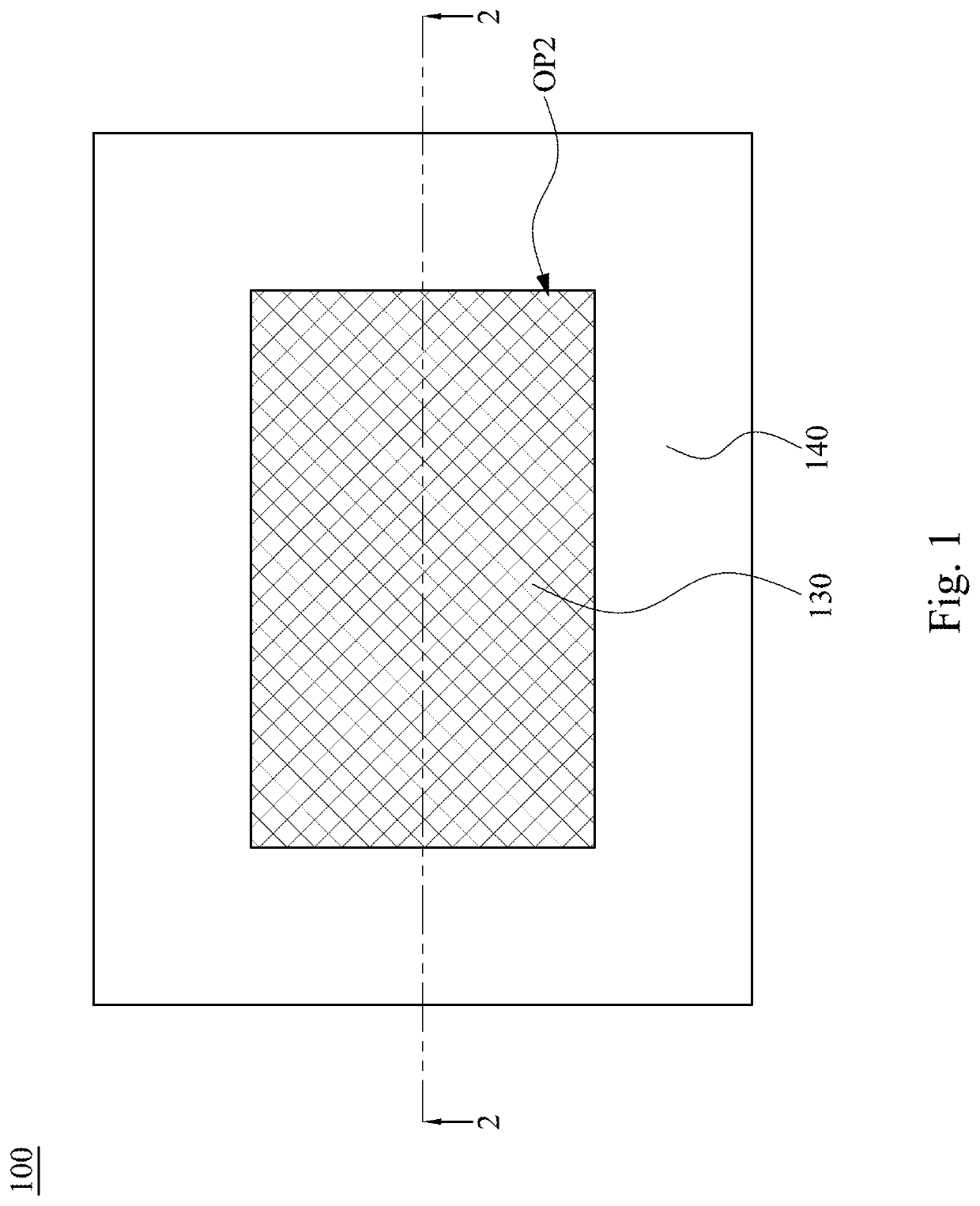

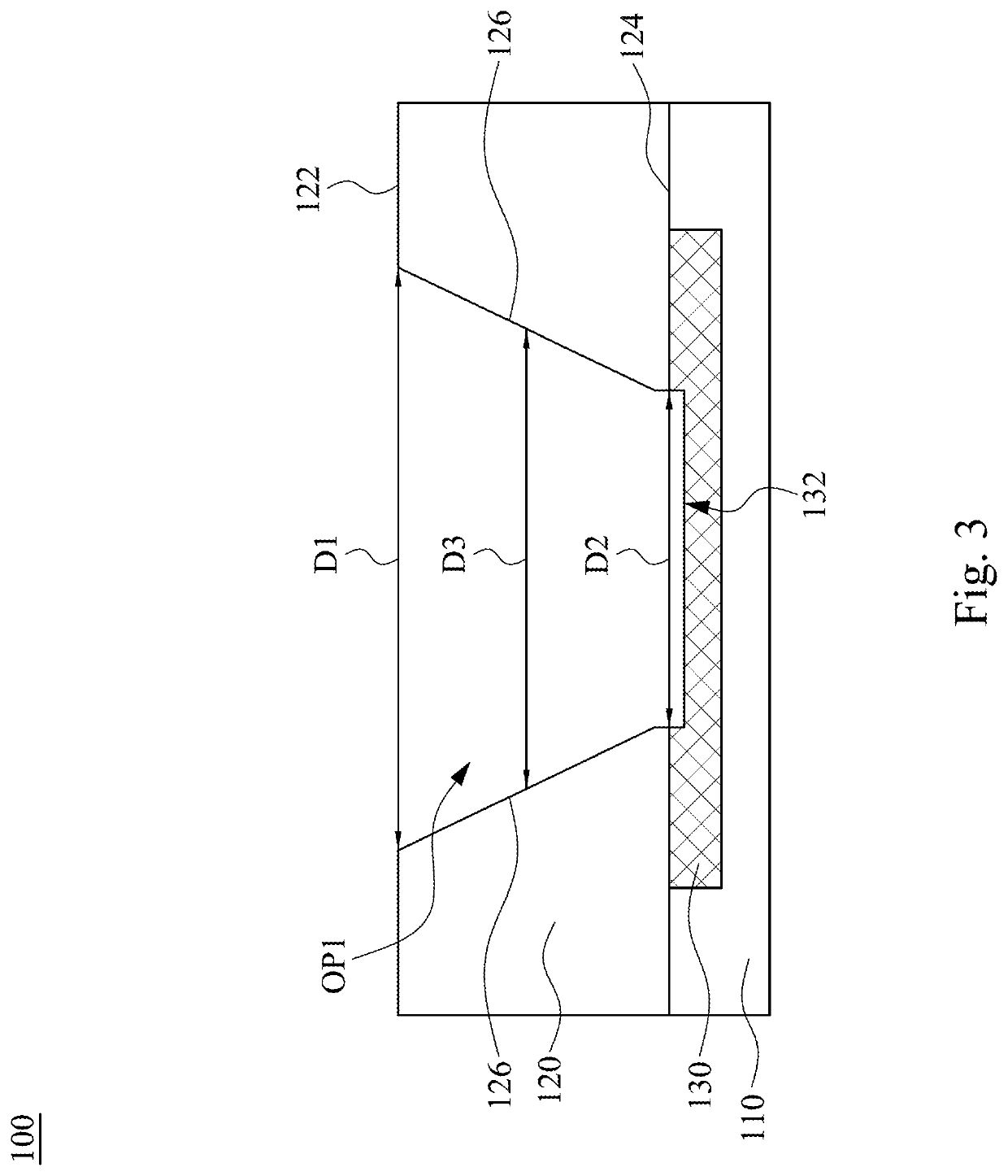

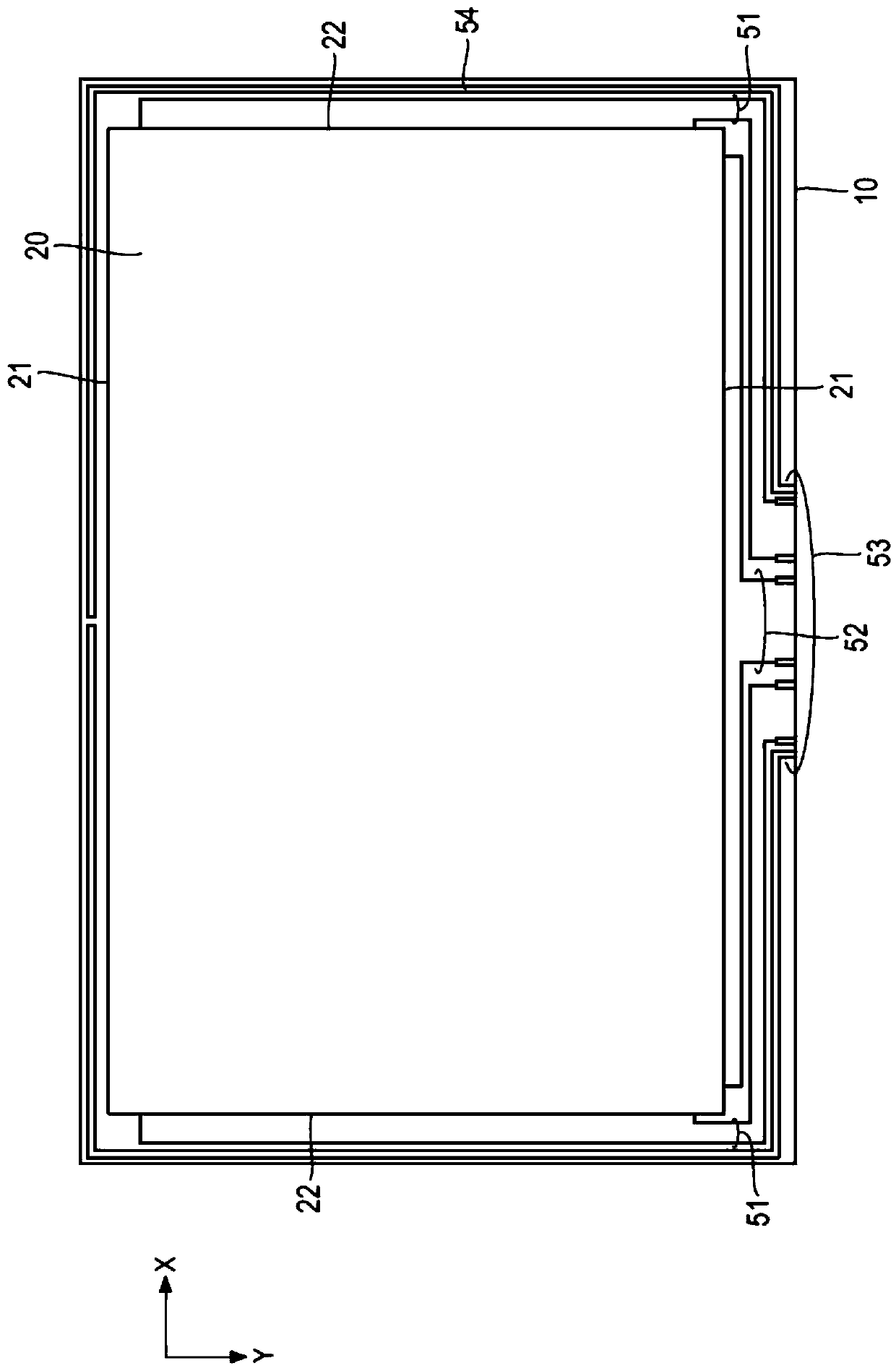

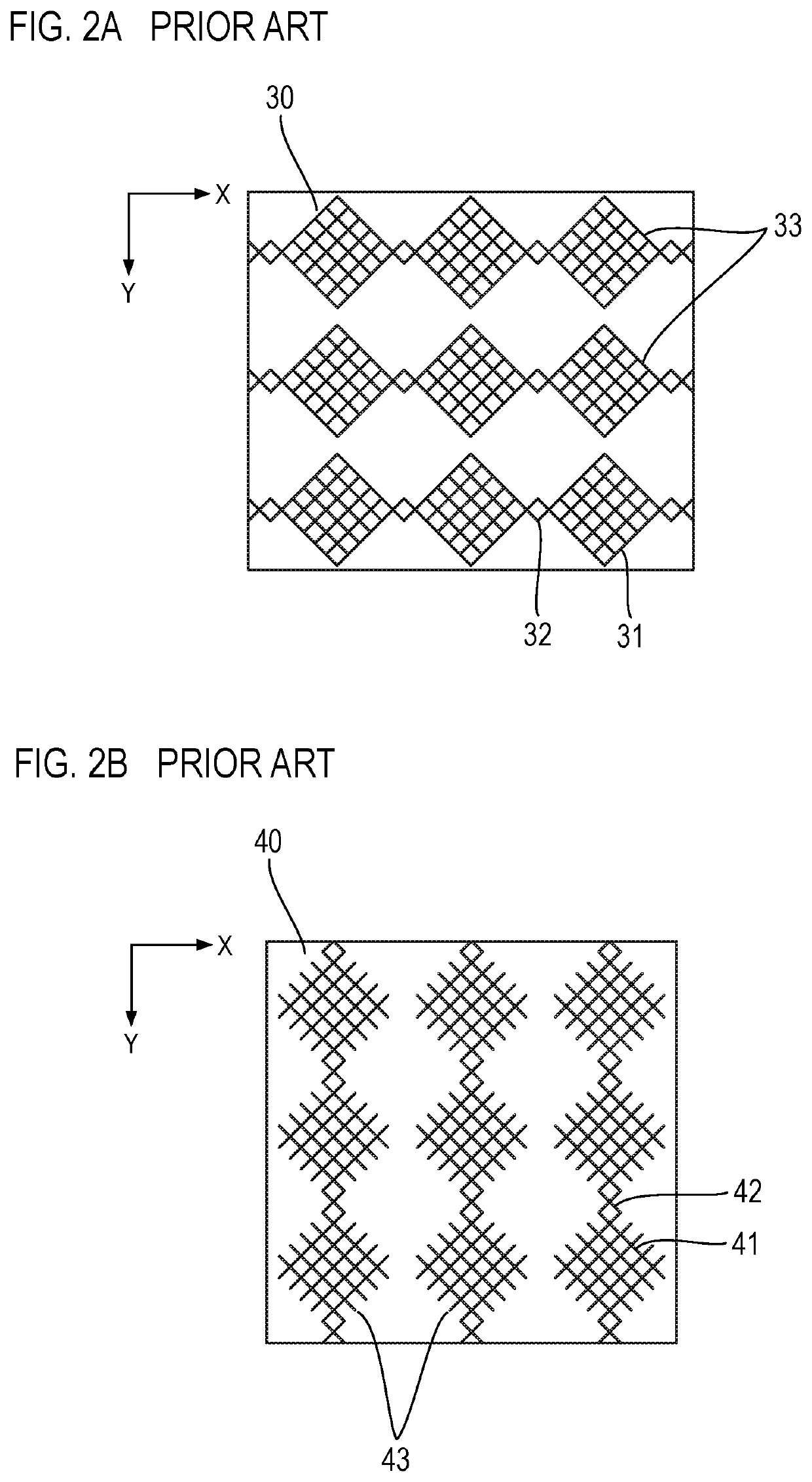

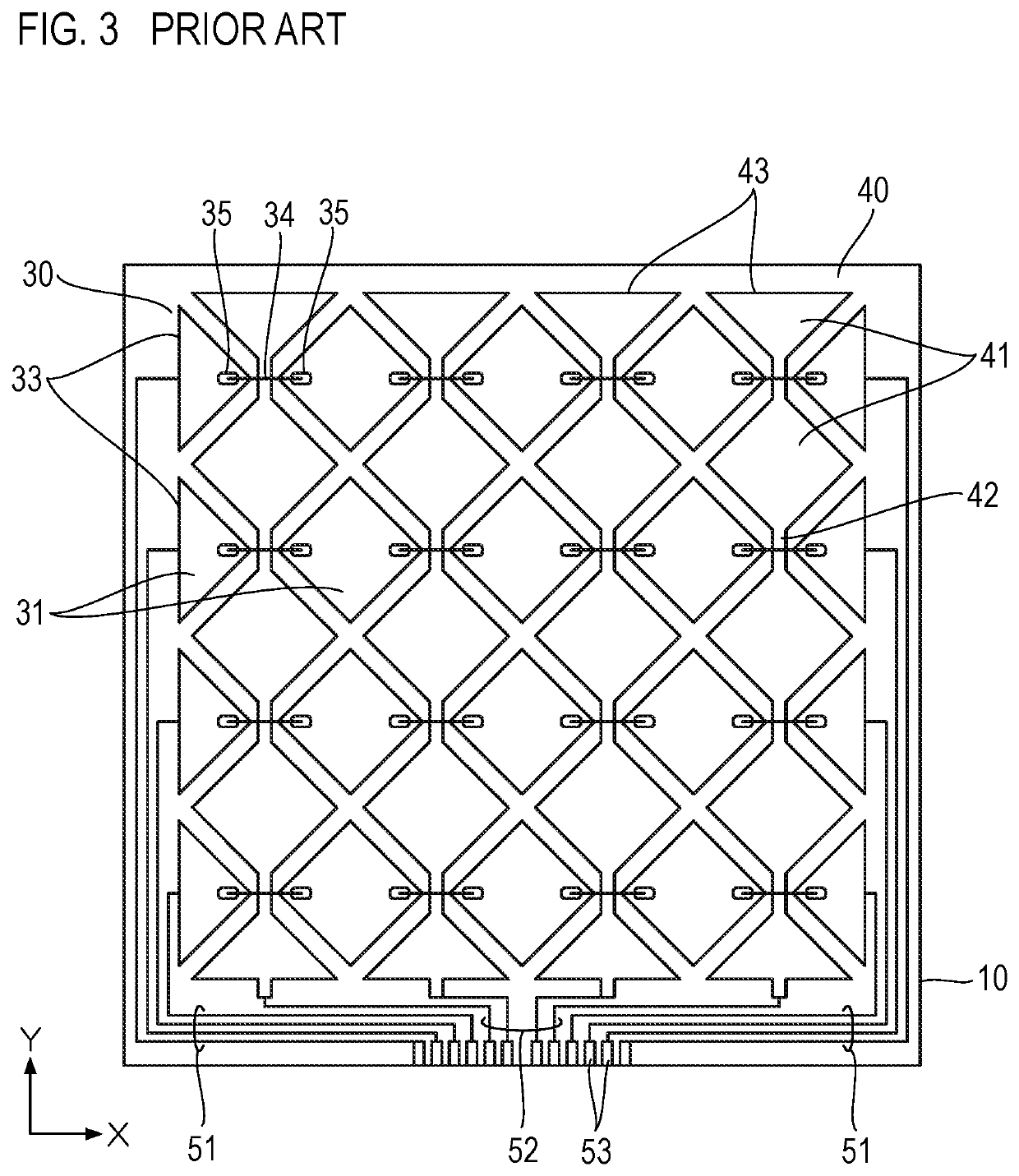

Touch panel and touch panel production method

ActiveUS20190129536A1Improve electrical connection qualityGood and stable electrical connectionPattern printingRotary pressesLayered structureTouch panel

A touch panel comprises, a substrate, a layered structure formed in a sensing region defined on one side of the substrate, the layered structure including at least a first conductor layer made of a first hardened conductive ink, a second conductor layer made of a second hardened conductive ink and an insulating layer disposed therebetween, and an external connection terminal formed outside the sensing region on the one side of the substrate, wherein the external connection terminal comprises a first terminal layer made of the first hardened conductive ink and a second terminal layer made of the second hardened conductive ink, such that the first terminal layer and the second terminal layer are directly overlaid on each other.

Owner:JAPAN AVIATION ELECTRONICS IND LTD

Electronic package and method of fabricating the same

InactiveUS20190057917A1Pressure balanceReduce warpageSemiconductor/solid-state device detailsSolid-state devicesInterposerEngineering

An electronic package and a method of fabricating the same are provided. The method includes disposing an electronic component on a first side of an interposer, forming a first encapsulant on the first side of the interposer to encapsulate the electronic component, forming a plurality of conductive elements on a second side of the interposer, and forming a second encapsulant on the second side of the interposer to encapsulate the conductive elements. During thermal cycling of the electronic package, shrinkage forces of the first encapsulant and the second encapsulant can offset each other so as to mitigate warping of the interposer.

Owner:SILICONWARE PRECISION IND CO LTD

Method of manufacturing a substrate structure

ActiveUS8377506B2Improve electrical connection qualityQuality improvementSemiconductor/solid-state device detailsSolid-state devicesInsulation layerEngineering

A substrate structure is provided. The substrate structure includes a substrate, a first insulation layer, a conductive part, a second insulation layer, a seed layer and a conductive layer. The substrate has a first circuit pattern layer and a second circuit pattern layer, which are located on two opposite surfaces of the substrate respectively. The first insulation layer formed on the first circuit pattern layer has a first insulation hole, which exposes a first opening in the outer surface of the first insulation layer. The conductive part formed on the first insulation hole for electrically connecting with a chip is enclosed by the edge of the first opening. The second insulation layer formed on the second circuit pattern layer has a second insulation hole in which the seed layer is formed. The conductive layer is formed on the seed layer for electrically connecting with a circuit board.

Owner:ADVANCED SEMICON ENG INC

Semiconductor packaging structure and making method thereof

ActiveCN102130088BStrong jointImprove electrical connection qualitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

Owner:SILICONWARE PRECISION IND CO LTD

Touch panel and touch panel production method

ActiveCN109725762AImprove electrical connection qualityEfficient productionPattern printingRotary pressesTouch panelConductive ink

The invention provides a touch panel and a touch panel production method. The touch panel comprises, a substrate, a layered structure formed in a sensing region defined on one side of the substrate, the layered structure including at least a first conductor layer made of a first hardened conductive ink, a second conductor layer made of a second hardened conductive ink and an insulating layer disposed therebetween, and an external connection terminal formed outside the sensing region on the one side of the substrate, wherein the external connection terminal comprises a first terminal layer madeof the first hardened conductive ink and a second terminal layer made of the second hardened conductive ink, such that the first terminal layer and the second terminal layer are directly overlaid oneach other.

Owner:JAPAN AVIATION ELECTRONICS IND LTD

Conductive wire type semiconductor device and conductive wire rack thereof

ActiveCN101488494ACan enhance electrical functionReduce ground bounce issuesSemiconductor/solid-state device detailsSolid-state devicesGround bounceSemiconductor chip

The invention discloses a lead frame type semiconductor device and the lead frame thereof. The lead frame which comprises a plurality of signal pins, a plurality of ground pins and a plurality of power supply pins is provided; a plurality of ground pins (or power supply pins) form a chip connecting zone while the other signal pins and power supply pins (or ground pins) are distributed around the chip connecting zone; therefore, the ground pins or the power supply pins are isolated, thus improving the problem of ground bounce and reinforcing electrical property; meanwhile the size of the ground pins (or power supply pins) in the chip connecting zone is larger than the size of the signal pins and the power supply pins (or ground pins) around the chip connecting area, thus a semiconductor chip on the chip connecting zone can have good heat radiation function.

Owner:SILICONWARE PRECISION IND CO LTD

A signal processing device and smart clothing

ActiveCN105662337BReduce shockImprove reliabilityRespiratory organ evaluationSensorsComputer moduleElectrical connection

The invention relates to the field of smart clothing sport monitoring, and in particular to a signal processing apparatus and a smart clothing. The signal processing apparatus at least includes: a fixing seat, a line board connecting module, a function module, and a top cover. The line board connecting module and the function module are disposed between the fixing seat and the top cover. The fixing seat is used for fixing to the smart clothing and is provided with a first through hole thereon. The line board connecting module is provided with a first end surface relative to the fixing seat and a second end surface relative to the function module. The first end surface is used for connecting a wire which passes the first through hole. The second end surface is provided with a conductive buffering structure thereon which is connected to the wire. The conductive buffering structure is in electrical connection with the function module.

Owner:BODYPLUS TECH BEIJING CO LTD

Conductive via structure

PendingCN112242364AImprove electrical connection qualitySemiconductor/solid-state device detailsSolid-state devicesRedistribution layerDielectric layer

Owner:NAN YA TECH

Package substrate and method of forming the same

InactiveCN103779314AIncreasing the thicknessImprove the layout densitySemiconductor/solid-state device detailsSolid-state devicesEngineeringInterposer

A package substrate and a method for forming the package substrate are disclosed. The package substrate includes an interposer having a plurality of conductive through vias and a first insulating layer formed on the sidewalls of the conductive through vias, a second insulating layer formed on one side of the interposer, and a plurality of conductive vias formed in the second insulating layer and electrically connected to the conductive through vias. By increasing the thickness of the first insulating layer, the face diameter of the conductive through vias can be reduced, and the layout density of the conductive through vias in the interposer can thus be increased.

Owner:IND TECH RES INST +1

Touch panel including a layered structure with first and second mesh terminal layers directly overlaid on each other and touch panel production method

ActiveUS11029791B2Improve electrical connection qualityGood and stable electrical connectionPattern printingRotary pressesTouch panelMaterials science

A touch panel comprises, a substrate, a layered structure formed in a sensing region defined on one side of the substrate, the layered structure including at least a first conductor layer made of a first hardened conductive ink, a second conductor layer made of a second hardened conductive ink and an insulating layer disposed therebetween, and an external connection terminal formed outside the sensing region on the one side of the substrate, wherein the external connection terminal comprises a first terminal layer made of the first hardened conductive ink and a second terminal layer made of the second hardened conductive ink, such that the first terminal layer and the second terminal layer are directly overlaid on each other.

Owner:JAPAN AVIATION ELECTRONICS IND LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com