Multi-chip stacking structure and preparation thereof

A stacked structure, multi-chip technology, applied in the fields of semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems of short circuit, time-consuming process control, and unfavorable thin electronic device production.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 2 example

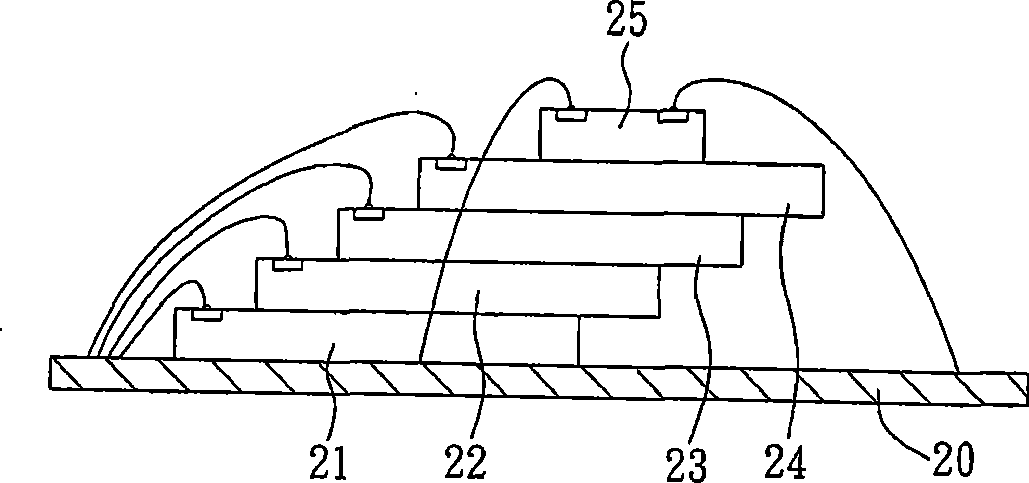

[0067] see again Figure 5 , is a schematic diagram of the second embodiment of the multi-chip stacking structure and its manufacturing method of the present invention. This embodiment is substantially the same as the previous embodiments, the main difference is that the first chip and the second chip on the topmost layer of the first chip set can be electrically connected to the chip carrier by reverse wire bonding.

[0068]As shown in the figure, the outer ends of the bonding wires 46 ′ that are used to connect the first chip 41 and the second chip 42 on the topmost layer of the first chip group 41 ′ and the chip carrier 40 can be firstly sintered and soldered to the first chip set 41 ′. The welding pad 410 of the chip 41 and the welding pad 420 of the second chip 42 form a bump (not shown), and then form a spherical solder joint on the chip carrier 40, and weld it to the bump to form a seam solder joint. In this way, the arc height of the first and second chips 41, 42 elec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com