Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

25286 results about "Protection layer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Protection Layer. The Protection layer is your first line of defense against rain, snow, sleet, wind or any combination of elements that conspire to make you miserable. In this category, gear is either completely waterproof or highly water-resistant, yet breathability is not ignored to help prevent you from getting wet on the inside.

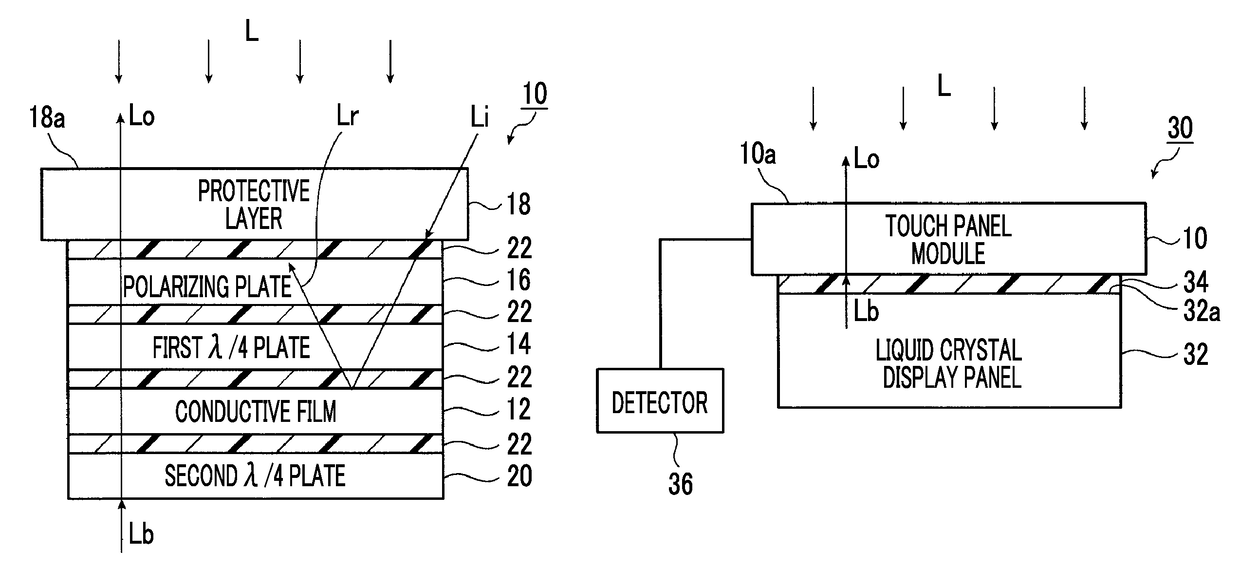

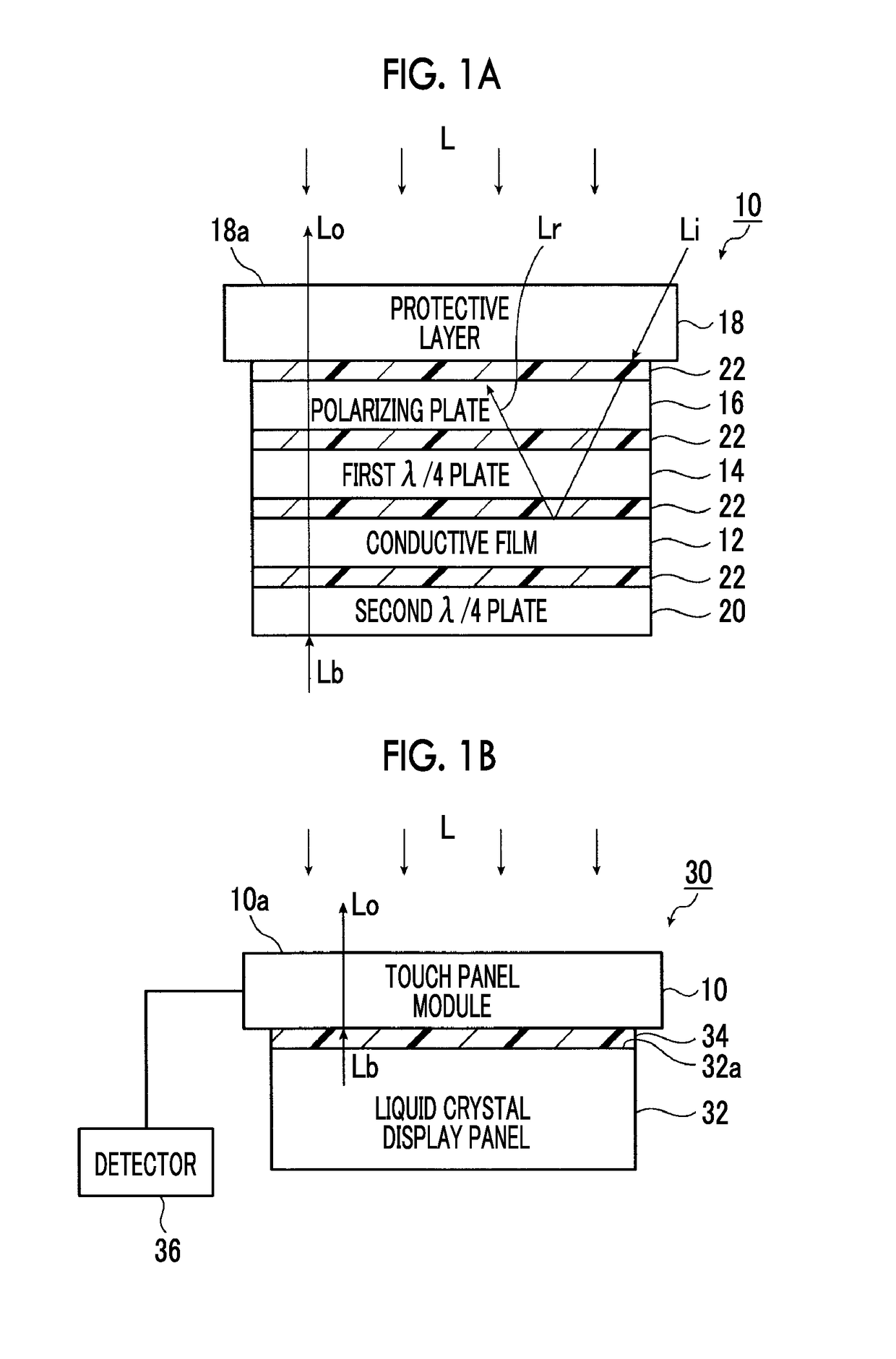

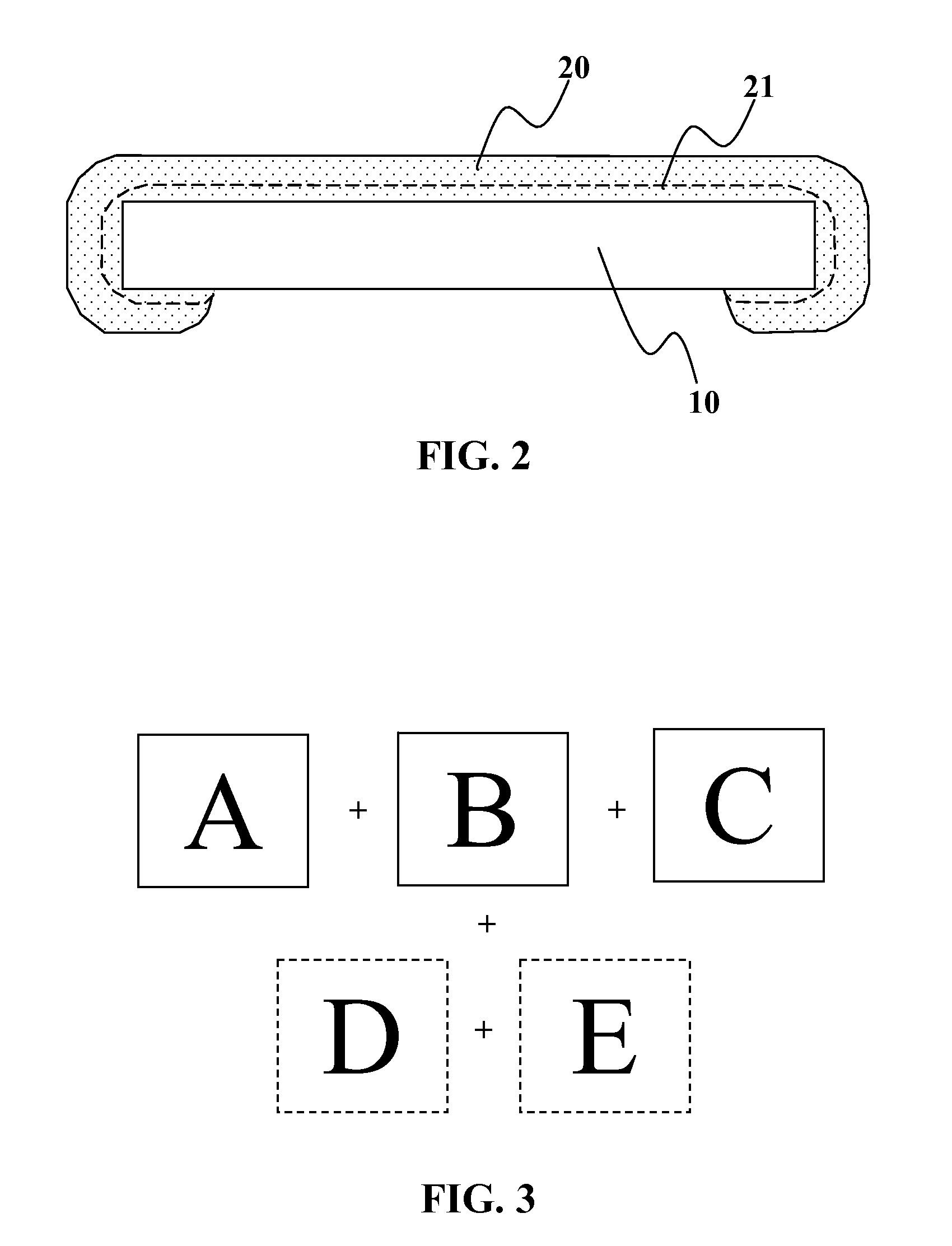

Touch panel module and electronic apparatus

ActiveUS10101861B2Improve visibilityLower resistanceInput/output processes for data processingMetal electrodesProtection layer

A touch panel module in which a conductive film in which a mesh conductive layer composed of a mesh-like metal electrode is formed on a support, a λ / 4 plate, a polarizing plate, and a protective layer are arranged in this order. A λ / 4 plate is further arranged on a side of the conductive film opposite to the protective layer. The touch panel module has a visible light diffuse reflectivity of 2% or less, which is measured from the protective layer.

Owner:FUJIFILM CORP

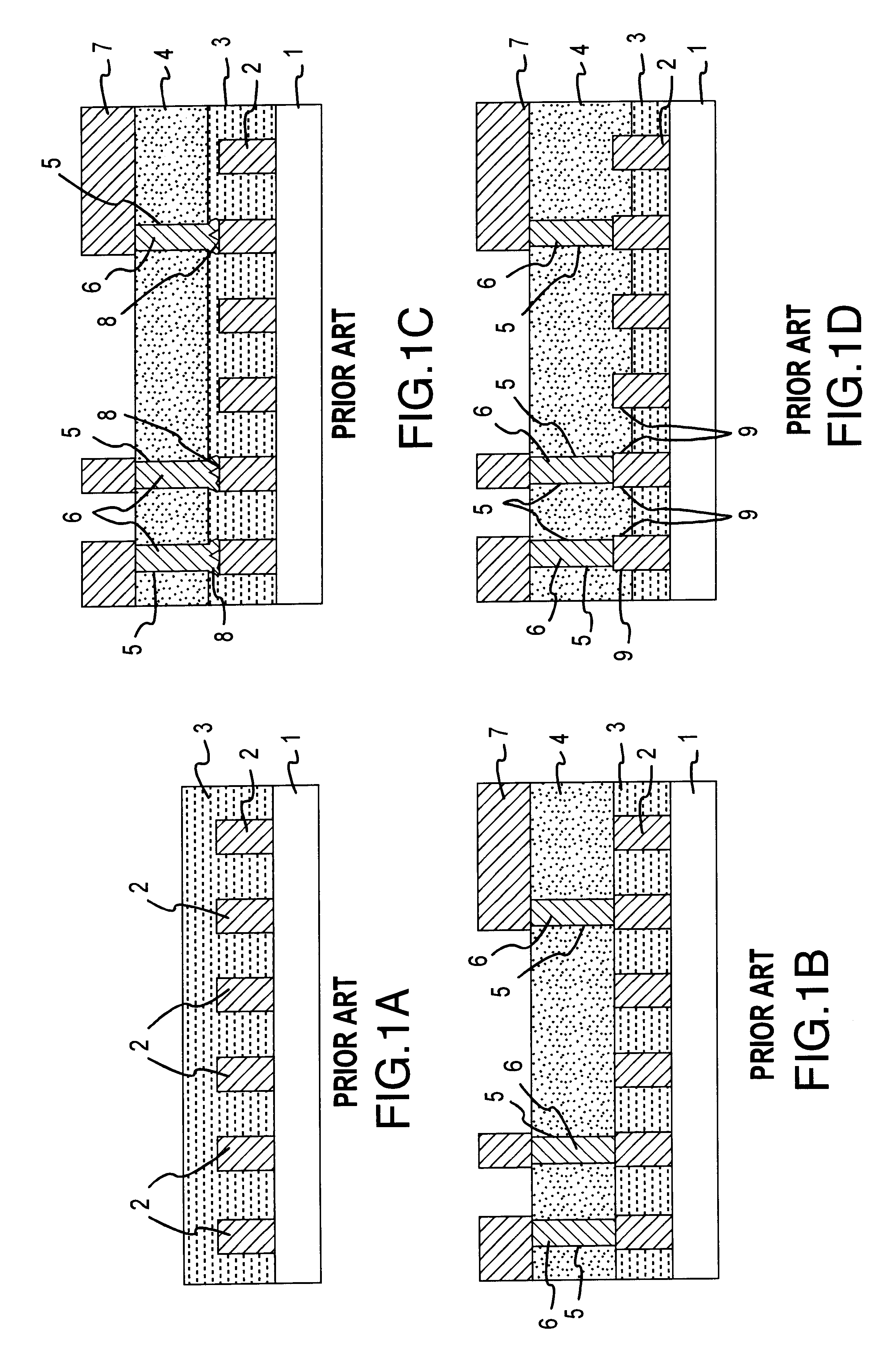

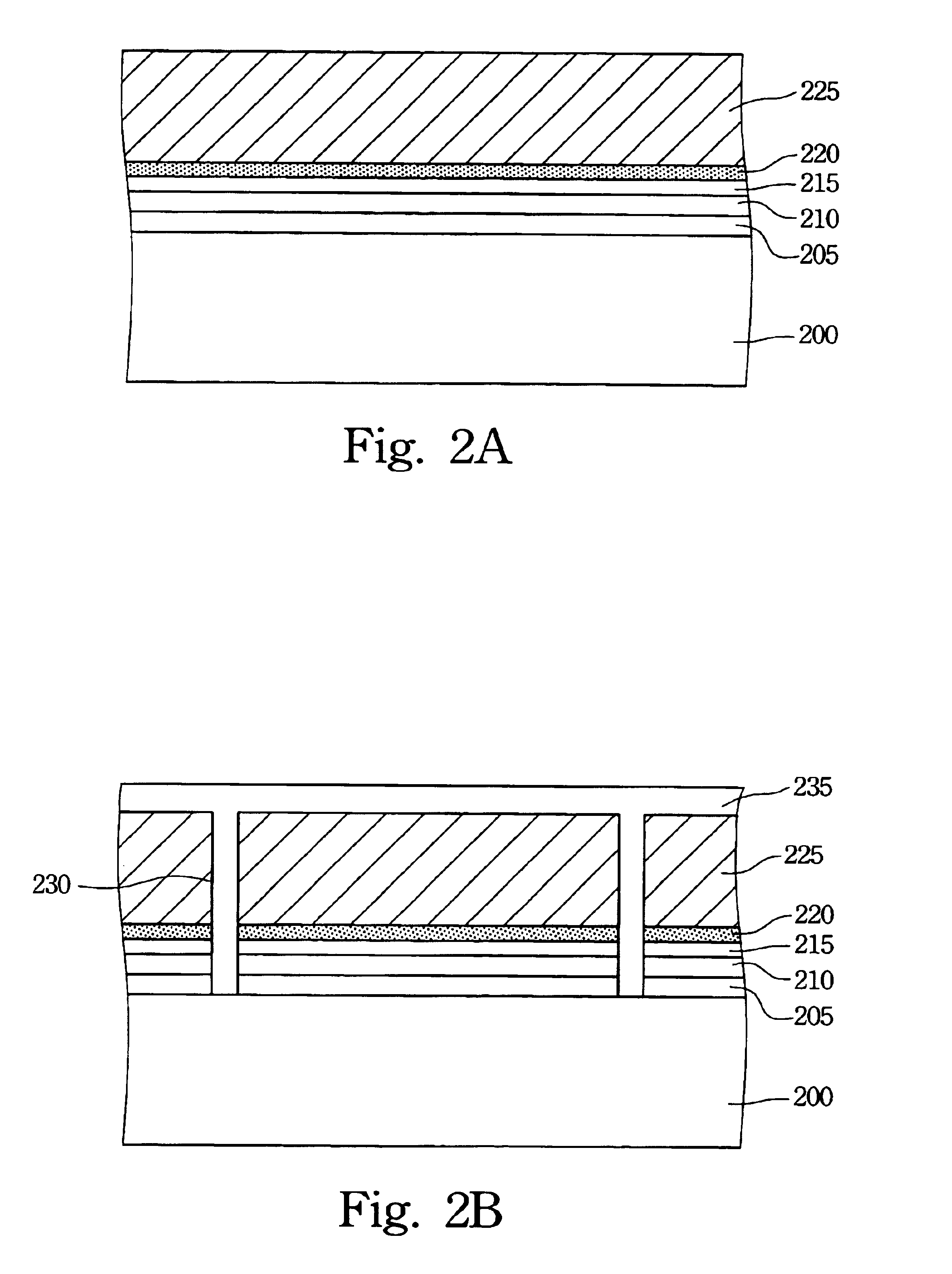

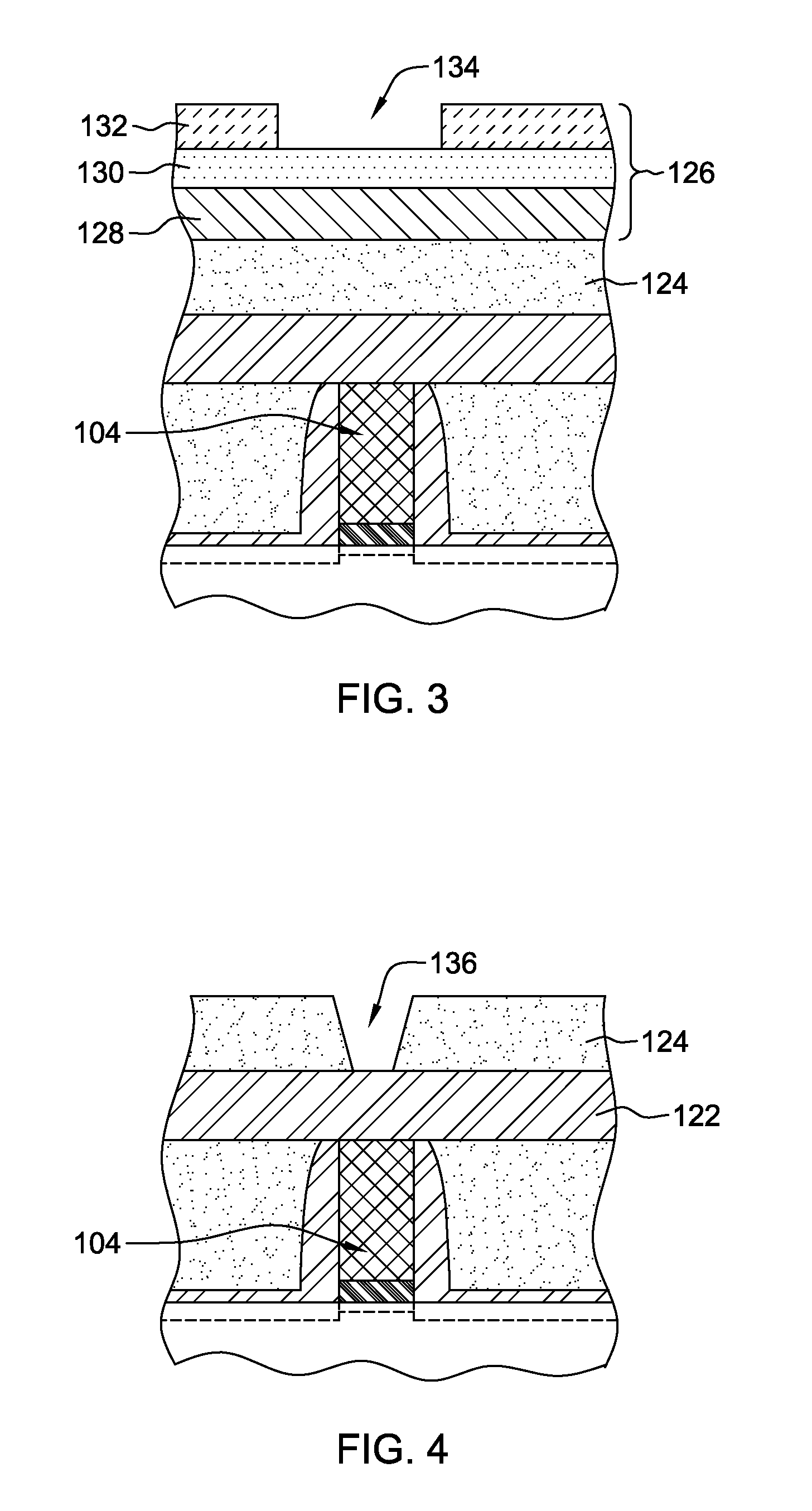

Interconnect with low dielectric constant insulators for semiconductor integrated circuit manufacturing

InactiveUS6187672B1Semiconductor/solid-state device manufacturingResistIntegrated circuit manufacturing

A method is provided for forming an improved interconnect structure on a semiconductor body. A first metal layer is deposited on the semiconductor body. A sacrificial layer having a height is deposited on the first metal layer. The sacrificial layer and the metal layer are patterned to form separate metal lines with the sacrificial layer remaining on said metal lines. A low-k material is then deposited to fill the gaps between metal lines and to cover the sacrificial layer. The low-k material is then removed to a level within the height of the sacrificial layer. The sacrificial layer is then removed. A protective layer is deposited on top of the metal lines and the low-k material. A dielectric layer is deposited over the protective layer. The protective layer protects the low-k material from attack by chemicals utilized by subsequent process steps to etch vias in the dielectric layer, to strip photo-resist, and to clean the vias. The protective layer is then selectively etched away to make contact between a via plug and the metal lines.

Owner:NEWPORT FAB

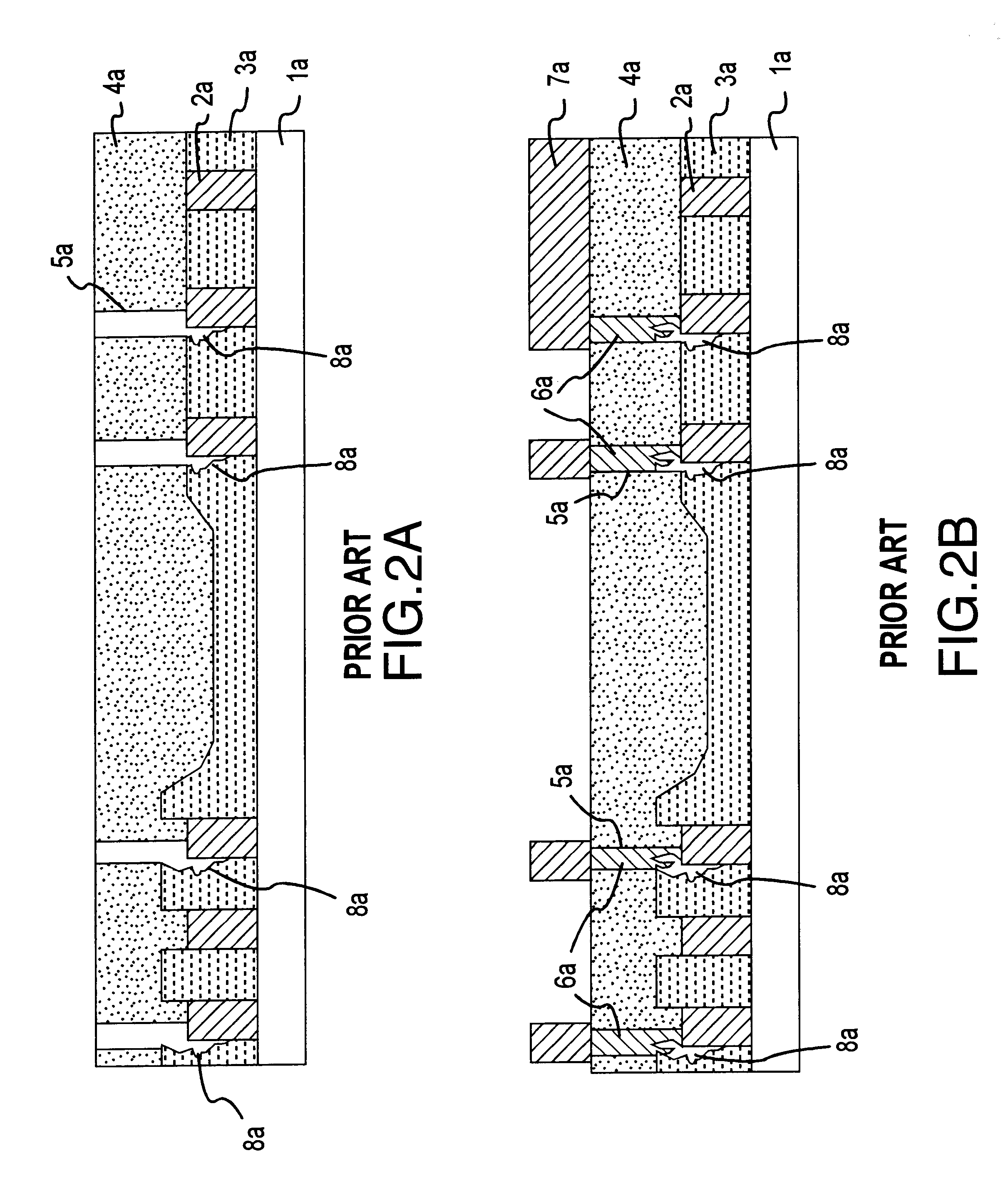

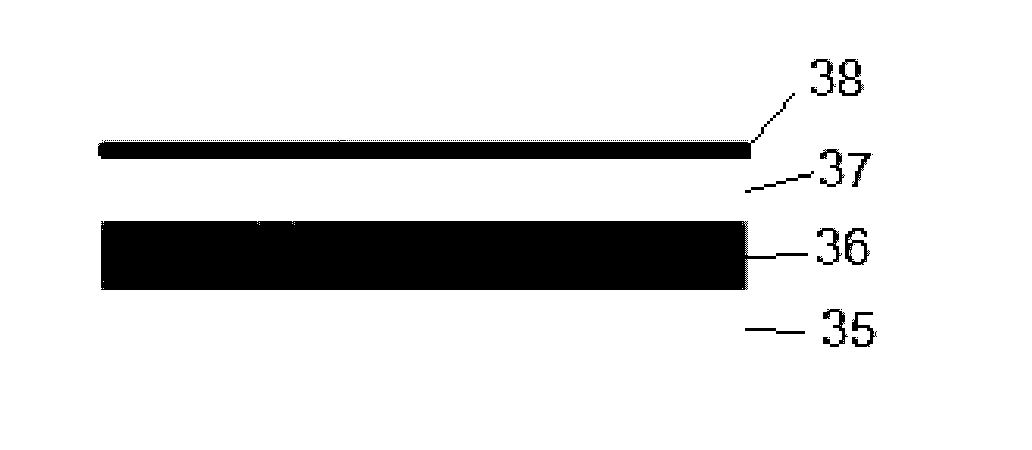

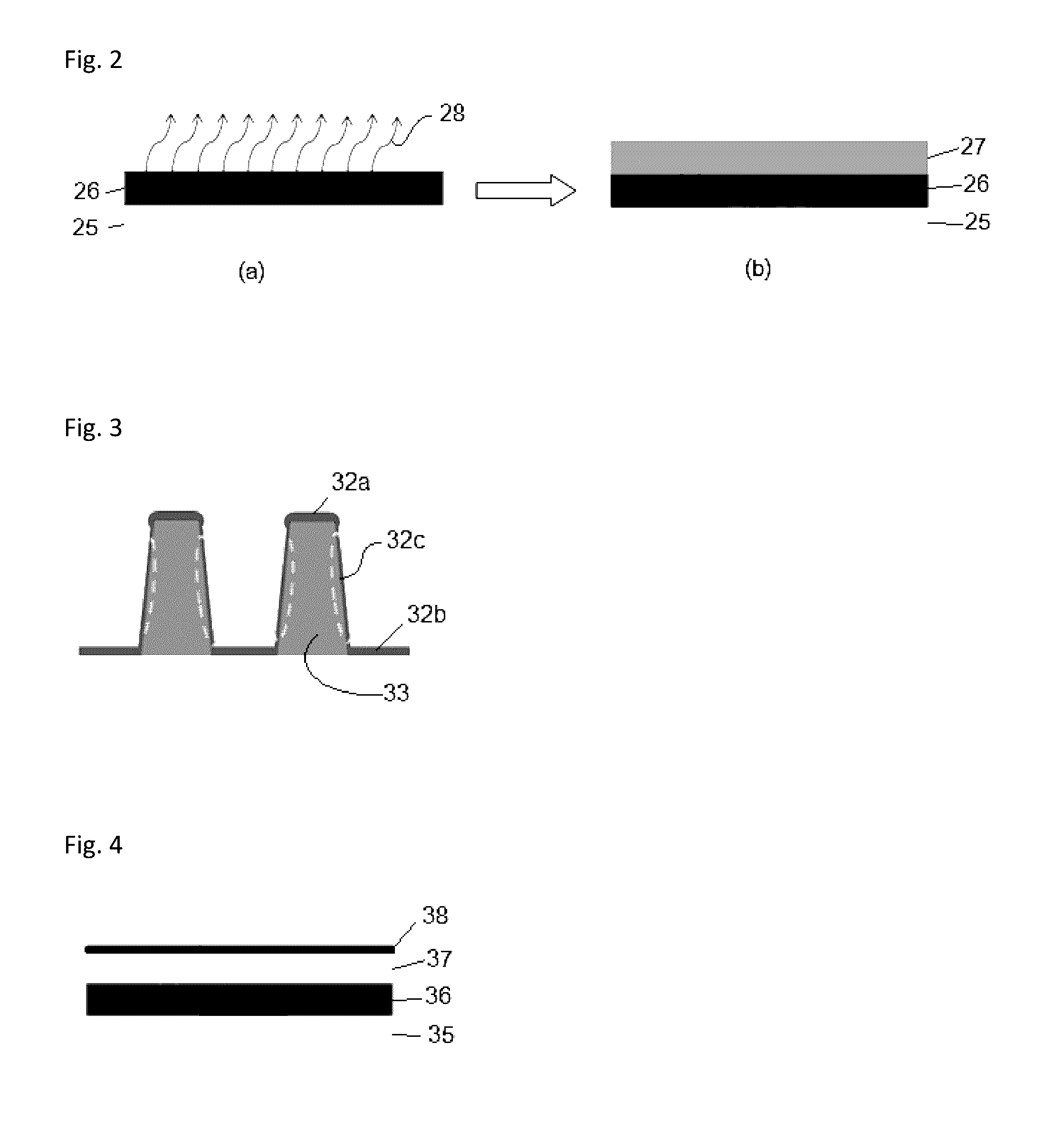

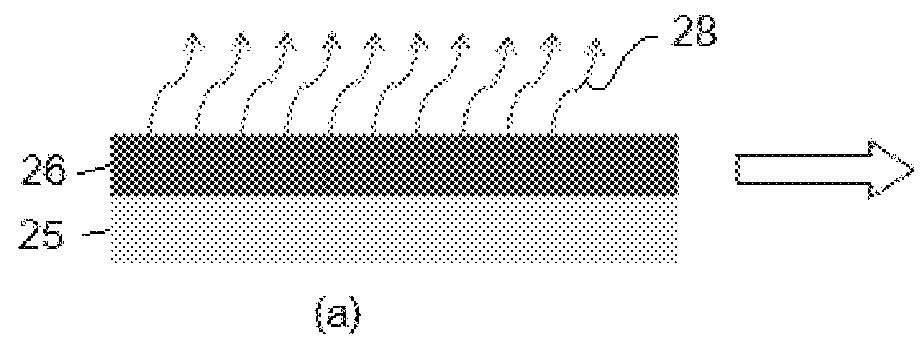

Method for protecting layer by forming hydrocarbon-based extremely thin film

ActiveUS20170018477A1Improve concentrationGood chemical resistanceSemiconductor/solid-state device detailsSolid-state devicesNoble gasProtection layer

A method for protecting a layer includes: providing a substrate having a target layer and forming a protective layer on the target layer, said protective layer contacting and covering the target layer and containing a hydrocarbon-based layer constituting at least an upper part of the protective layer, which hydrocarbon-based layer is formed by plasma-enhanced atomic layer deposition (PEALD) using an alkylaminosilane precursor and a noble gas without a reactant.

Owner:ASM IP HLDG BV

Method for protecting layer by forming hydrocarbon-based extremely thin film

ActiveUS10043661B2Improve concentrationGood chemical resistanceSemiconductor/solid-state device manufacturingChemical vapor deposition coatingNoble gasProtection layer

A method for protecting a layer includes: providing a substrate having a target layer; depositing a protective layer on the target layer, which protective layer contacts and covers the target layer and is constituted by a hydrocarbon-based layer; and depositing an oxide layer on the protective layer so that the protective layer in contact with the oxide layer is oxidized. The hydrocarbon-based layer is formed by plasma-enhanced atomic layer deposition (PEALD) using an alkylaminosilane precursor and a noble gas without a reactant.

Owner:ASM IP HLDG BV

Encapsulating OLED devices

InactiveUS20050248270A1Discharge tube luminescnet screensElectroluminescent light sourcesMoisture penetrationFrit

An encapsulated OLED device includes a substrate having a predetermined glass seal area and defining a sealed region and one or more OLED unit(s) provided over the substrate, each OLED unit having a light-emitting portion including at least one first electrode, at least one second electrode spaced from the first electrode, and an organic EL media layer provided between the first and second electrodes, wherein the light-emitting portion is provided within the sealed region. The device also includes an inorganic protection layer provided over the glass seal area and over at least a portion of the sealed region, a cover provided over the substrate and OLED unit(s), and sintered glass frit seal material provided in the glass seal area and in contact with both the cover and the inorganic protection layer to bond the cover to the inorganic protection layer and provide sealing against moisture penetration into the sealed region.

Owner:EASTMAN KODAK CO

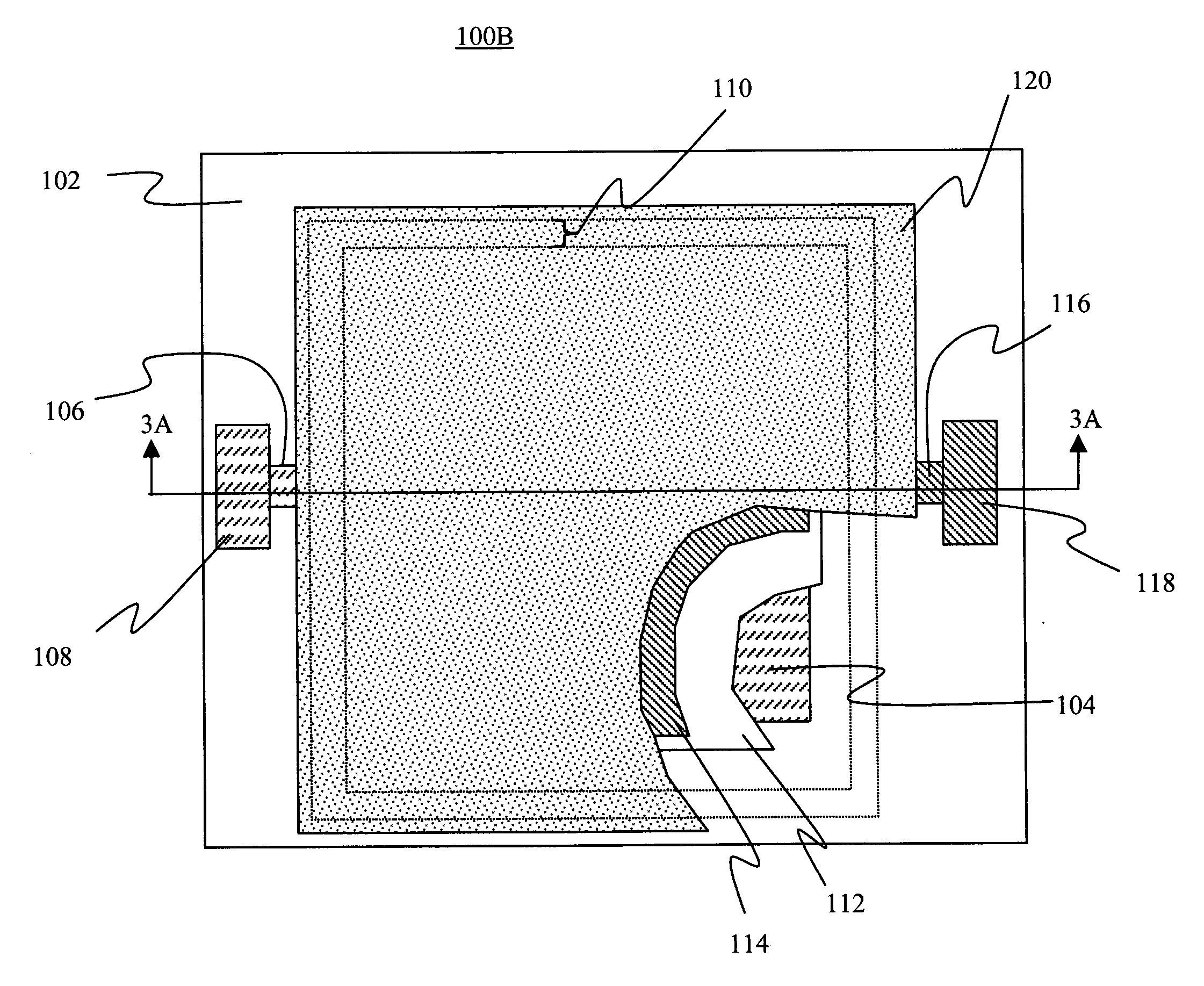

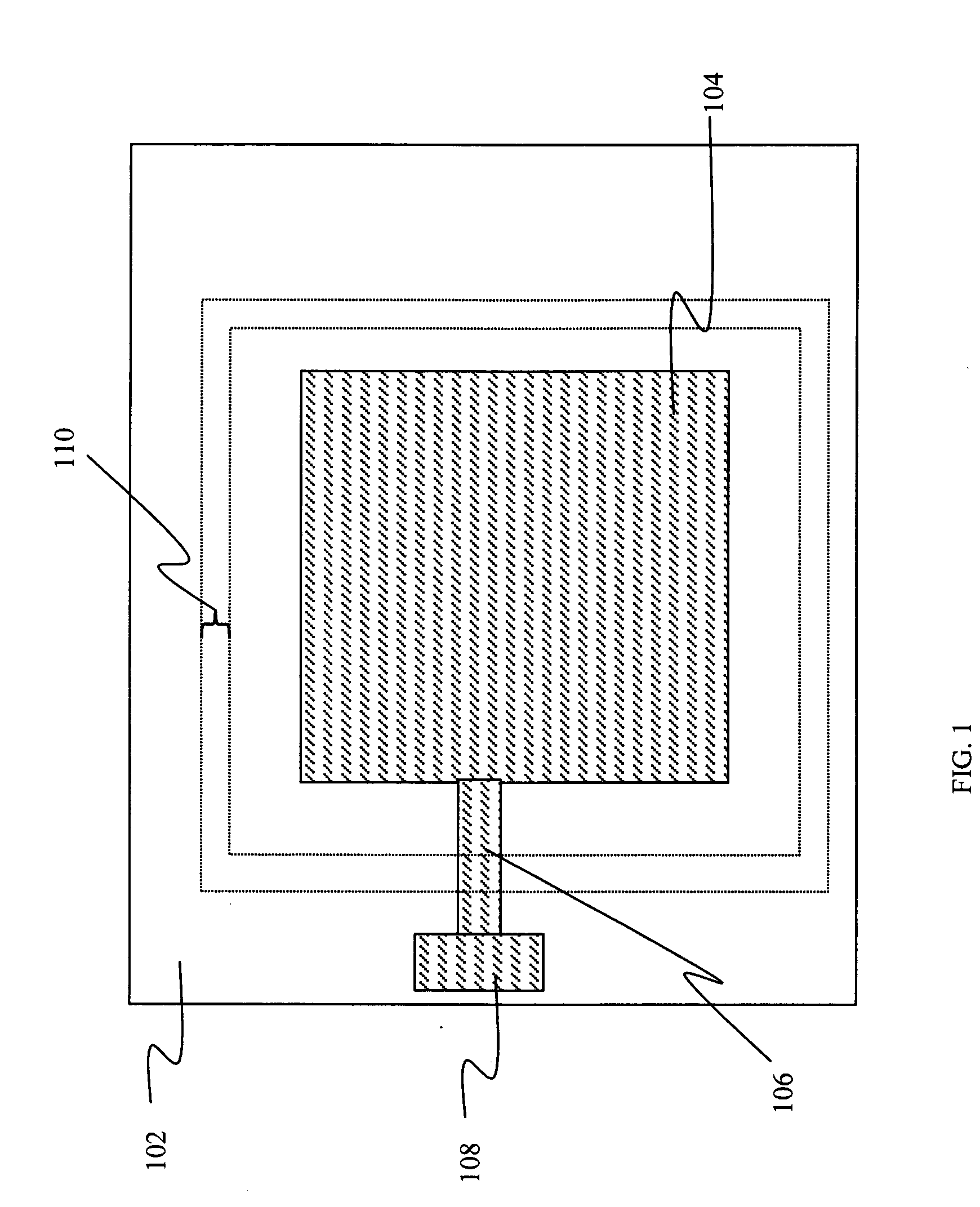

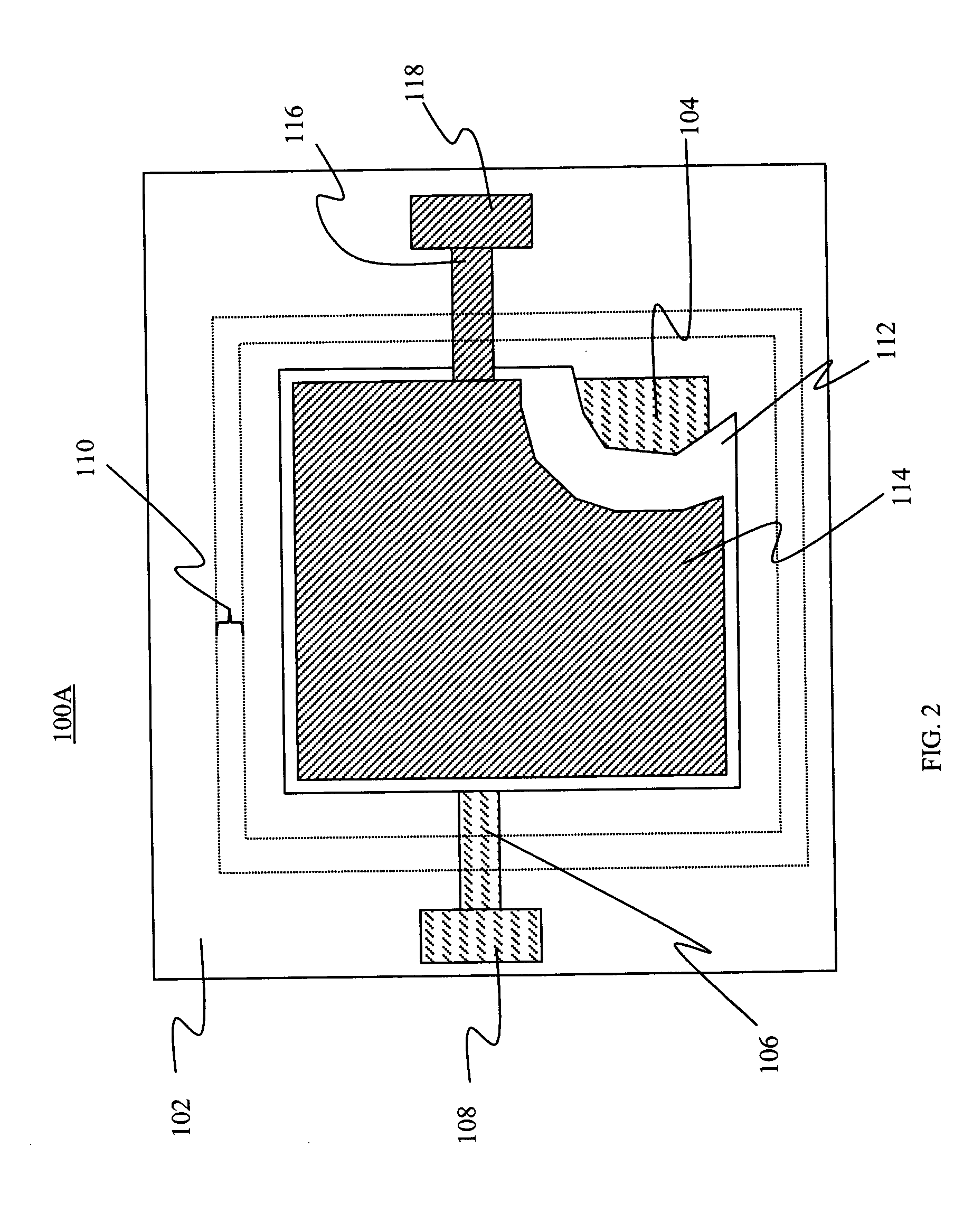

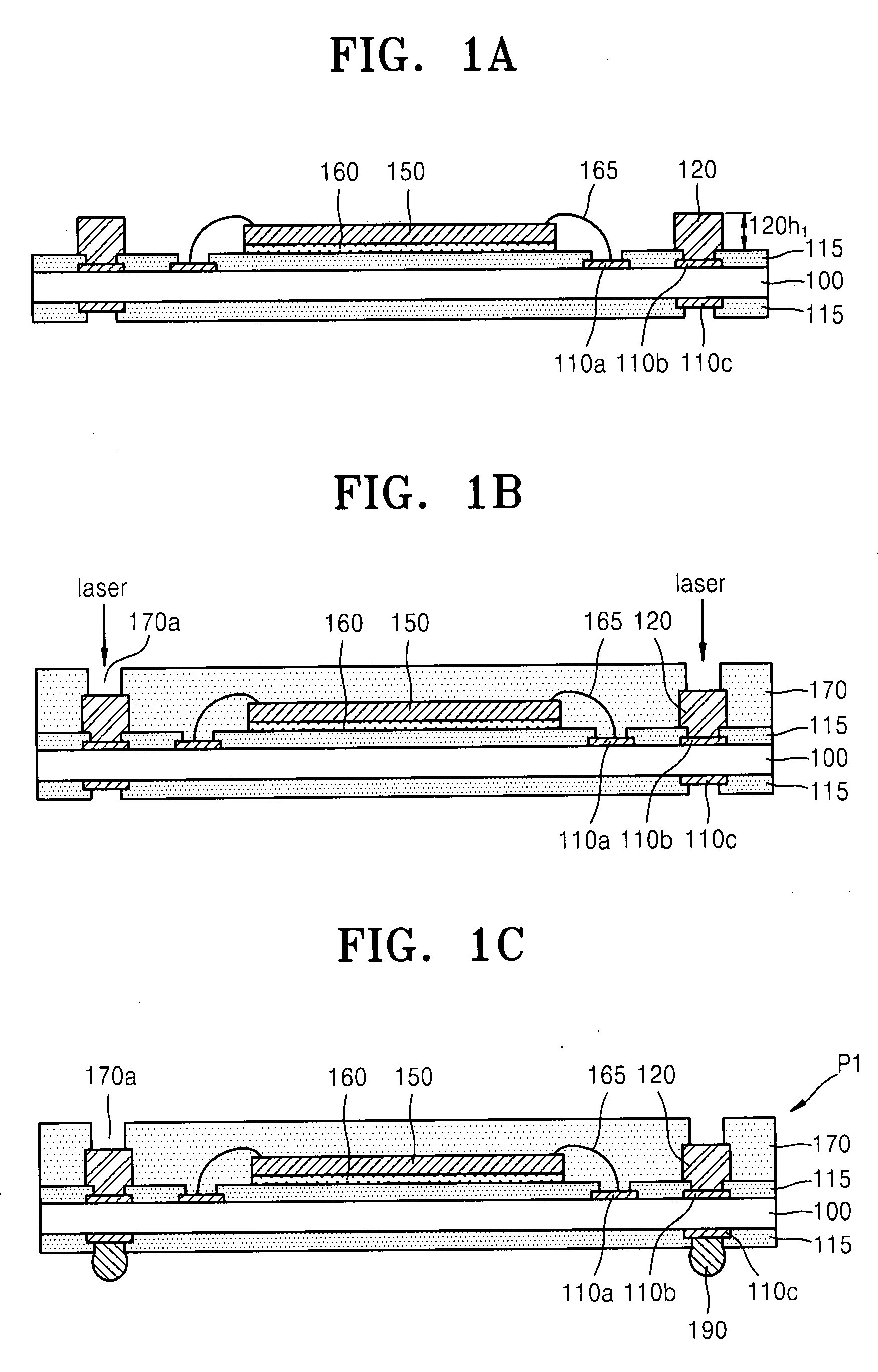

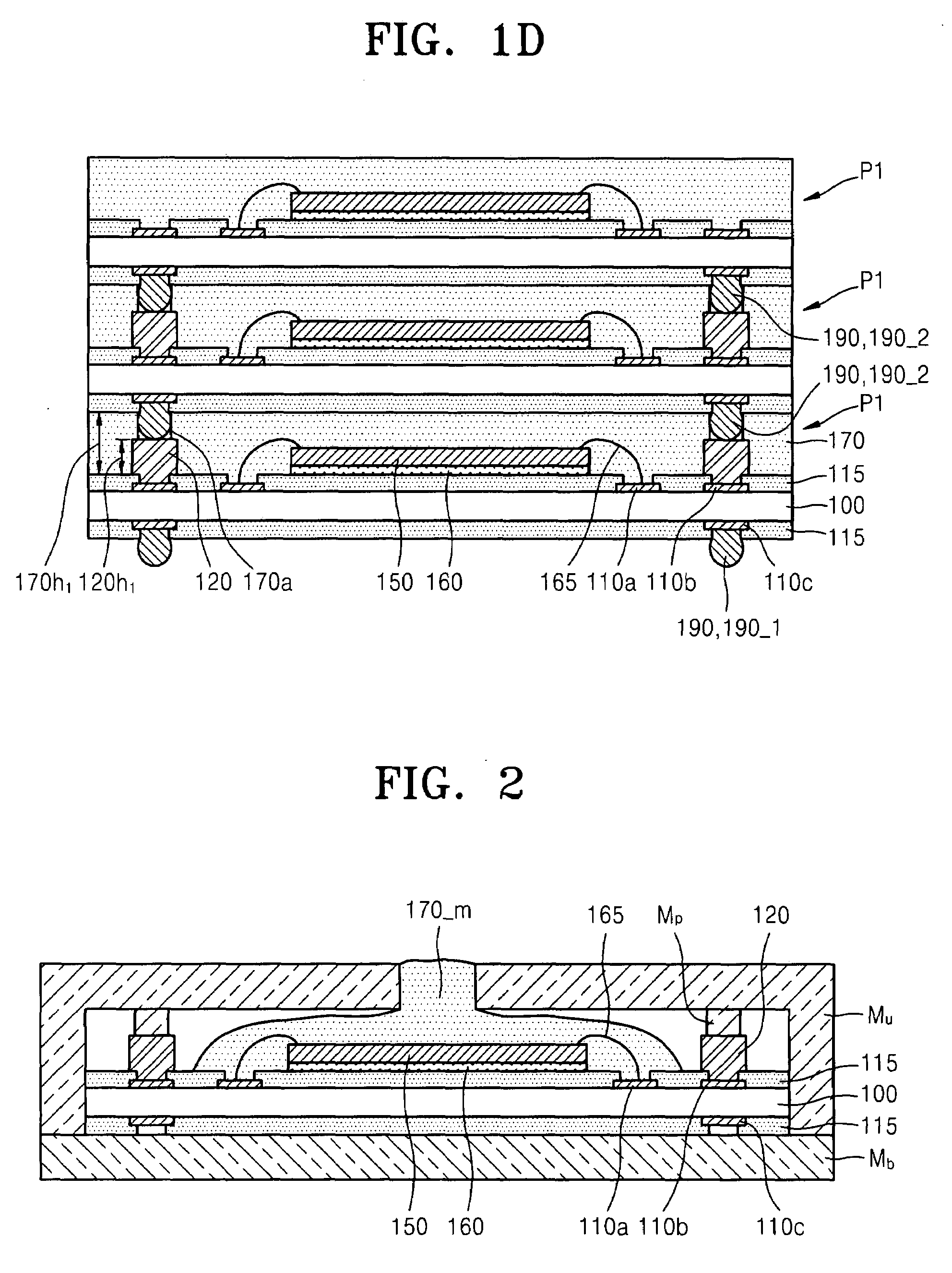

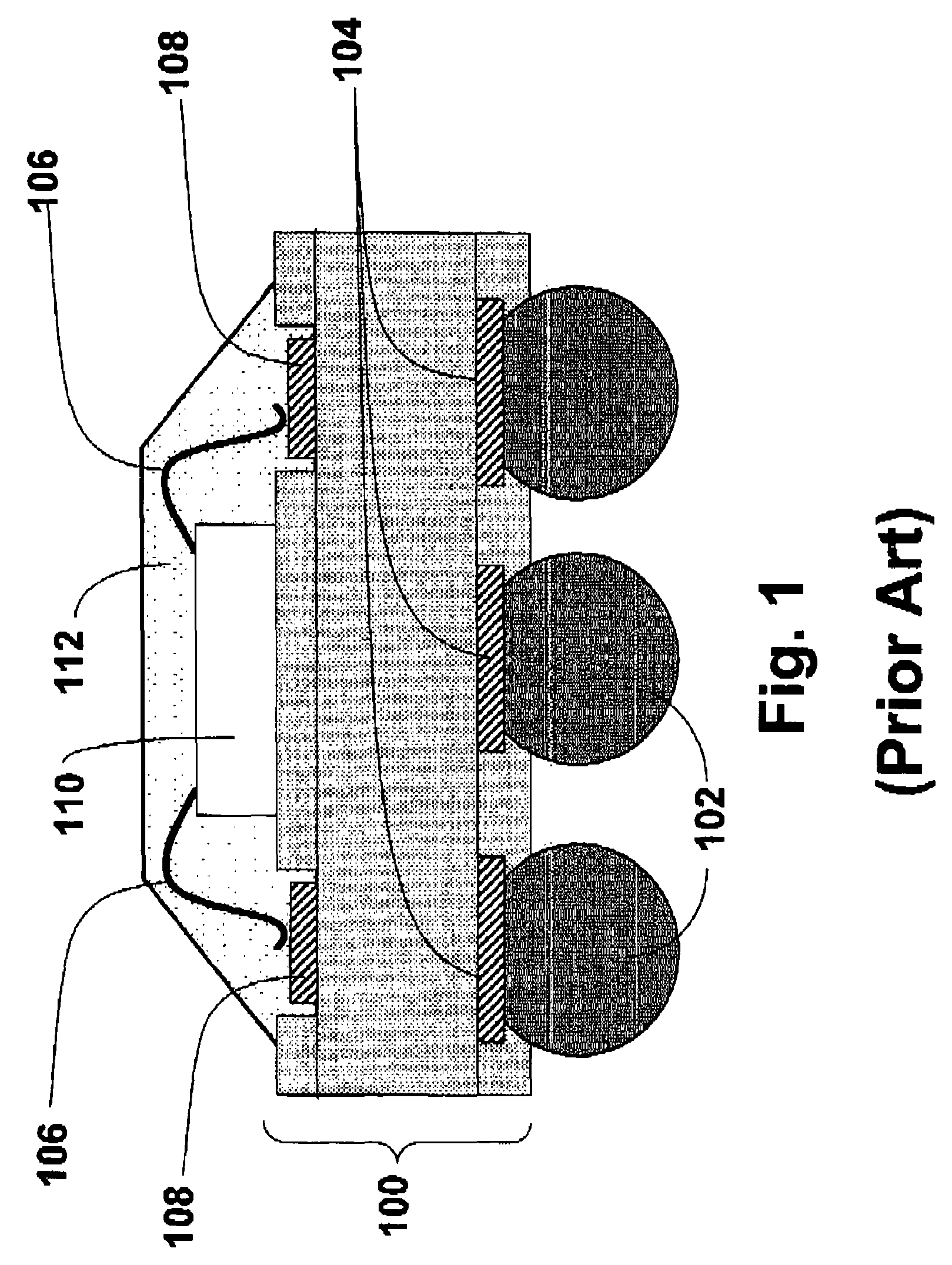

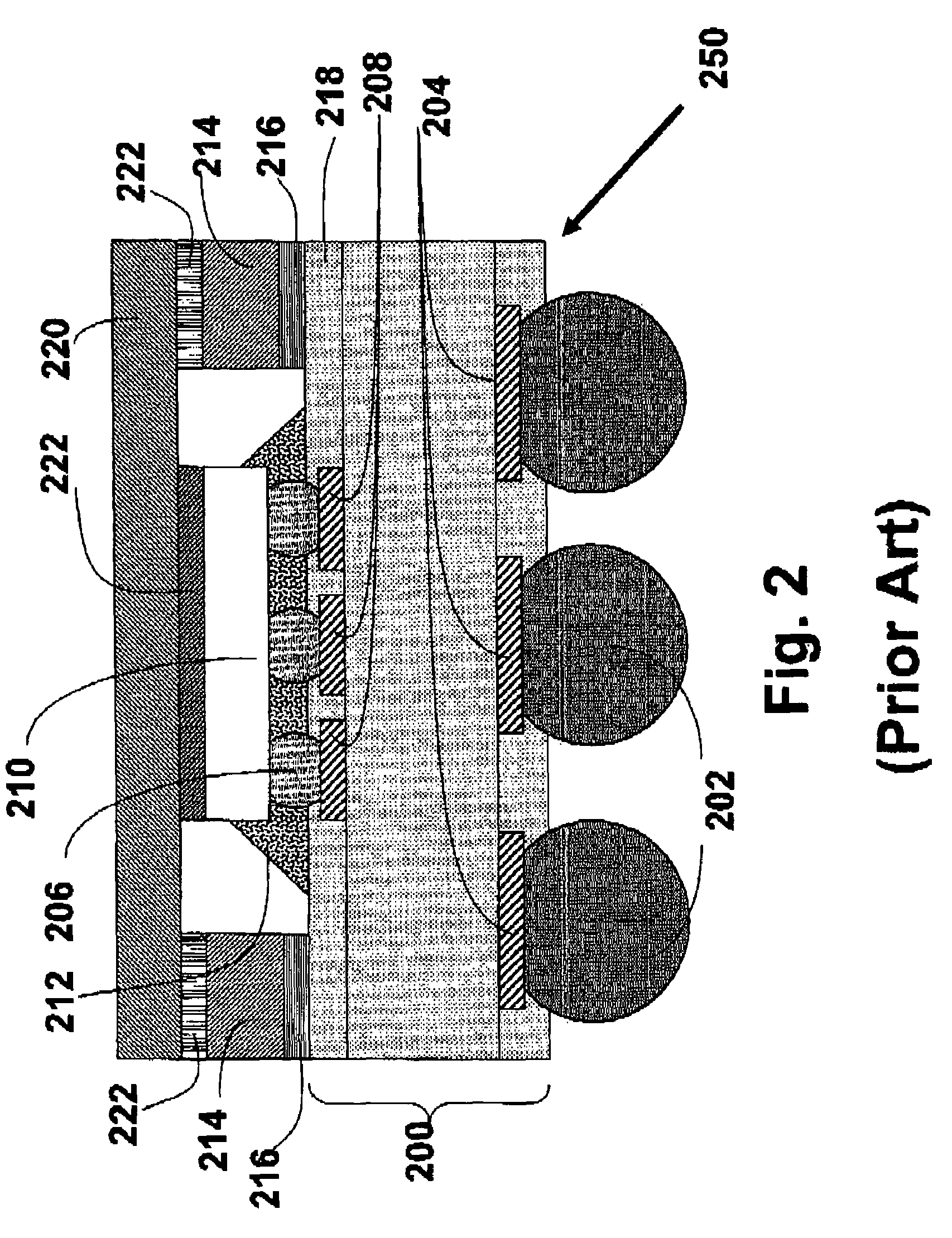

Stack type semiconductor package and method of fabricating the same

InactiveUS20080017968A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A stack type semiconductor package, and a method of fabricating the same are provided. The stack type semiconductor package may include a lower unit package and an upper unit package. The lower unit package may include a substrate, and a semiconductor chip on an upper surface of the substrate. A bump may be on an upper surface of the substrate, and a protecting layer, covering the semiconductor chip, may be formed. The protecting layer may include a via hole partially exposing the bump. The upper unit package may be on the protecting layer, and may include an internal connection solder ball on a lower surface of the upper unit package. The internal connection solder ball may be inserted into the via hole and connected to the bump.

Owner:SAMSUNG ELECTRONICS CO LTD

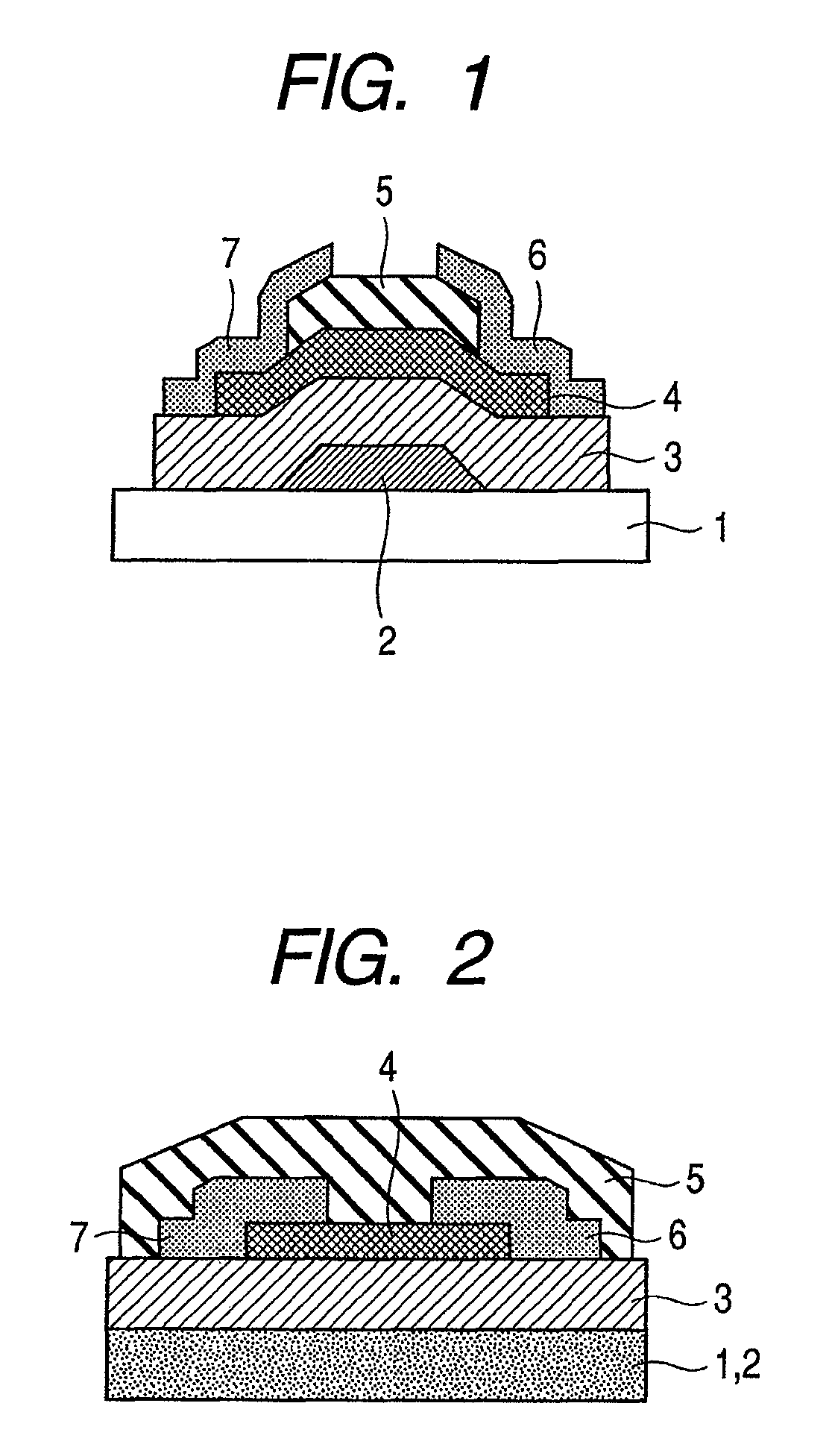

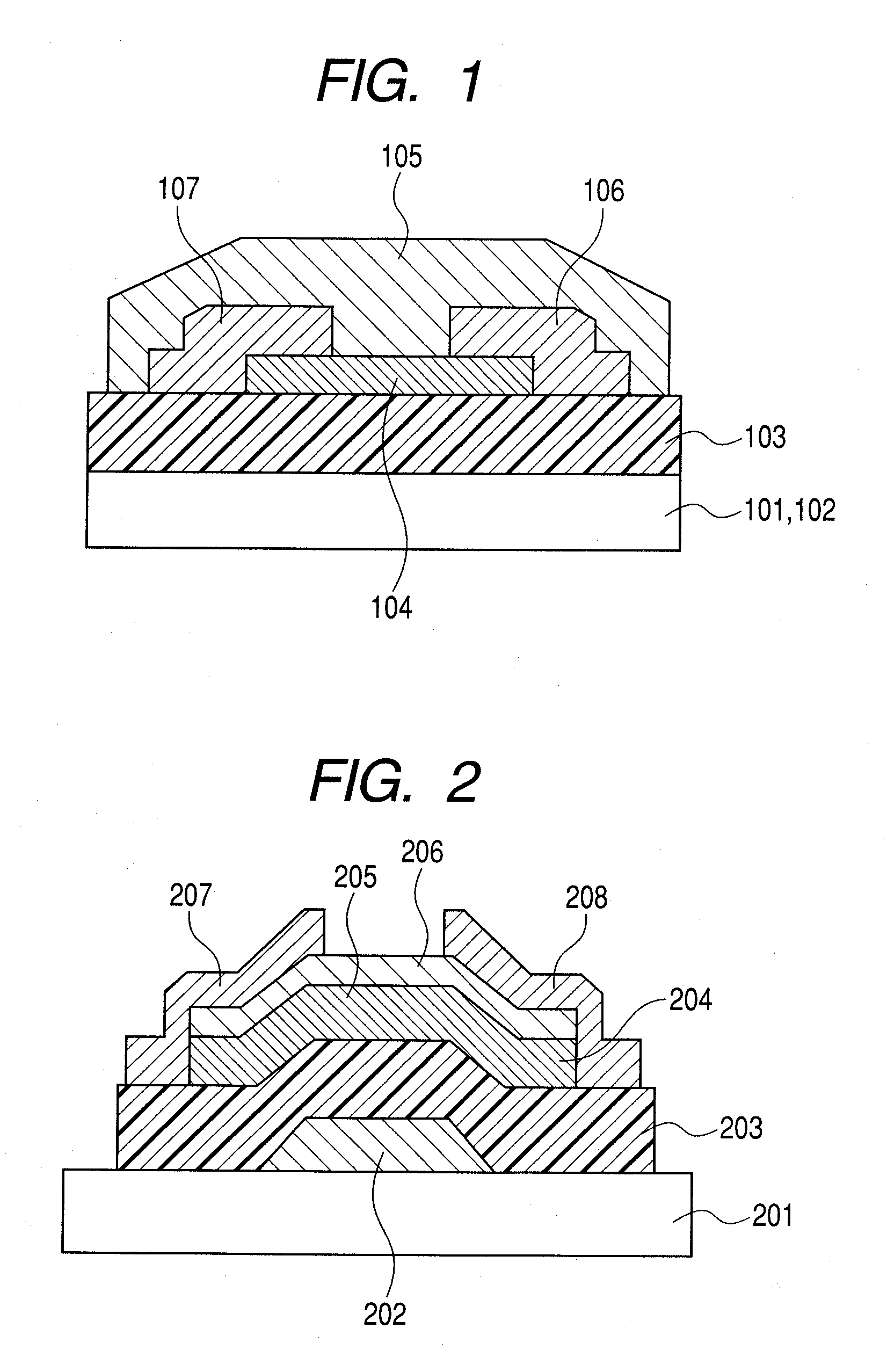

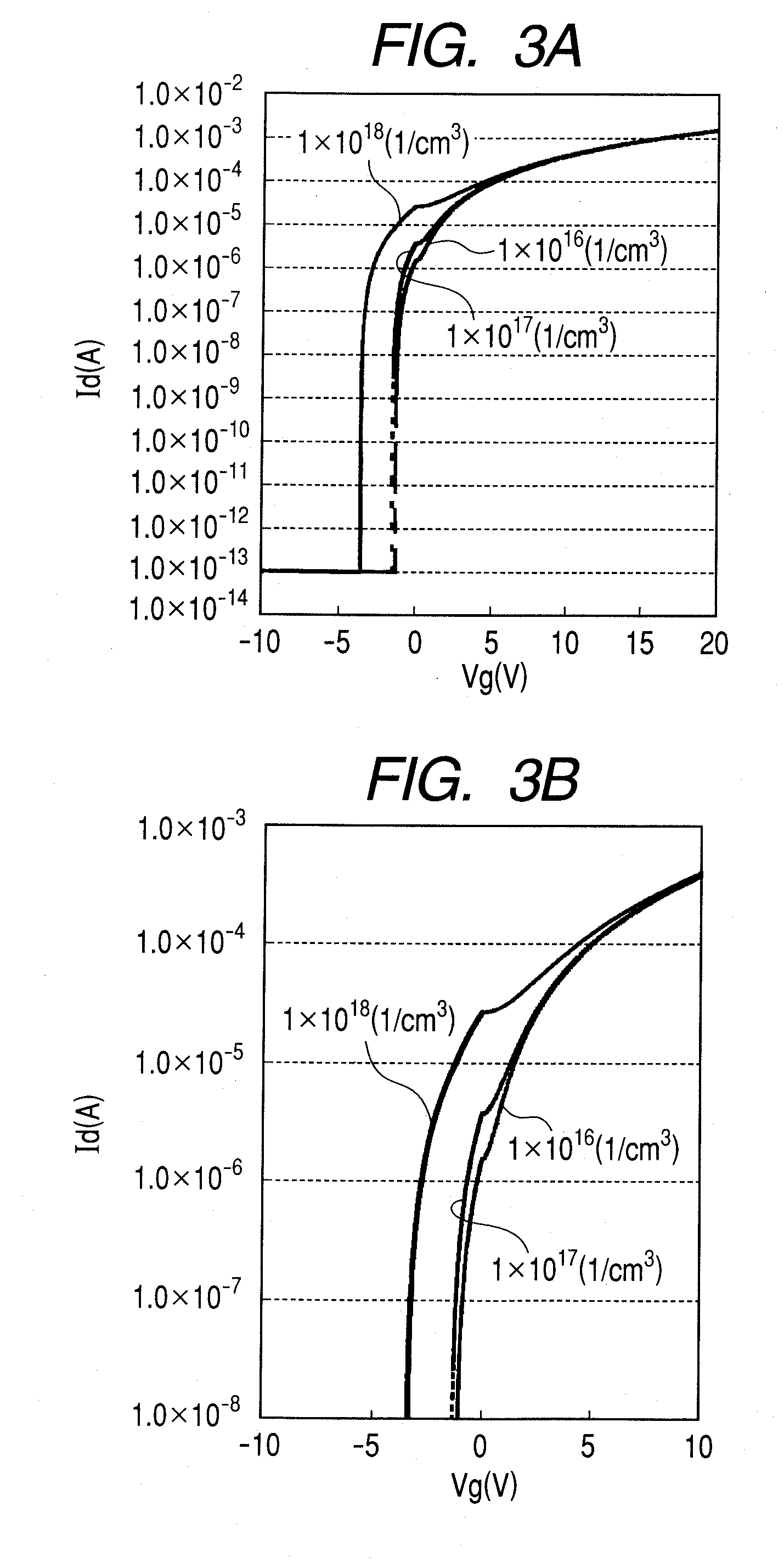

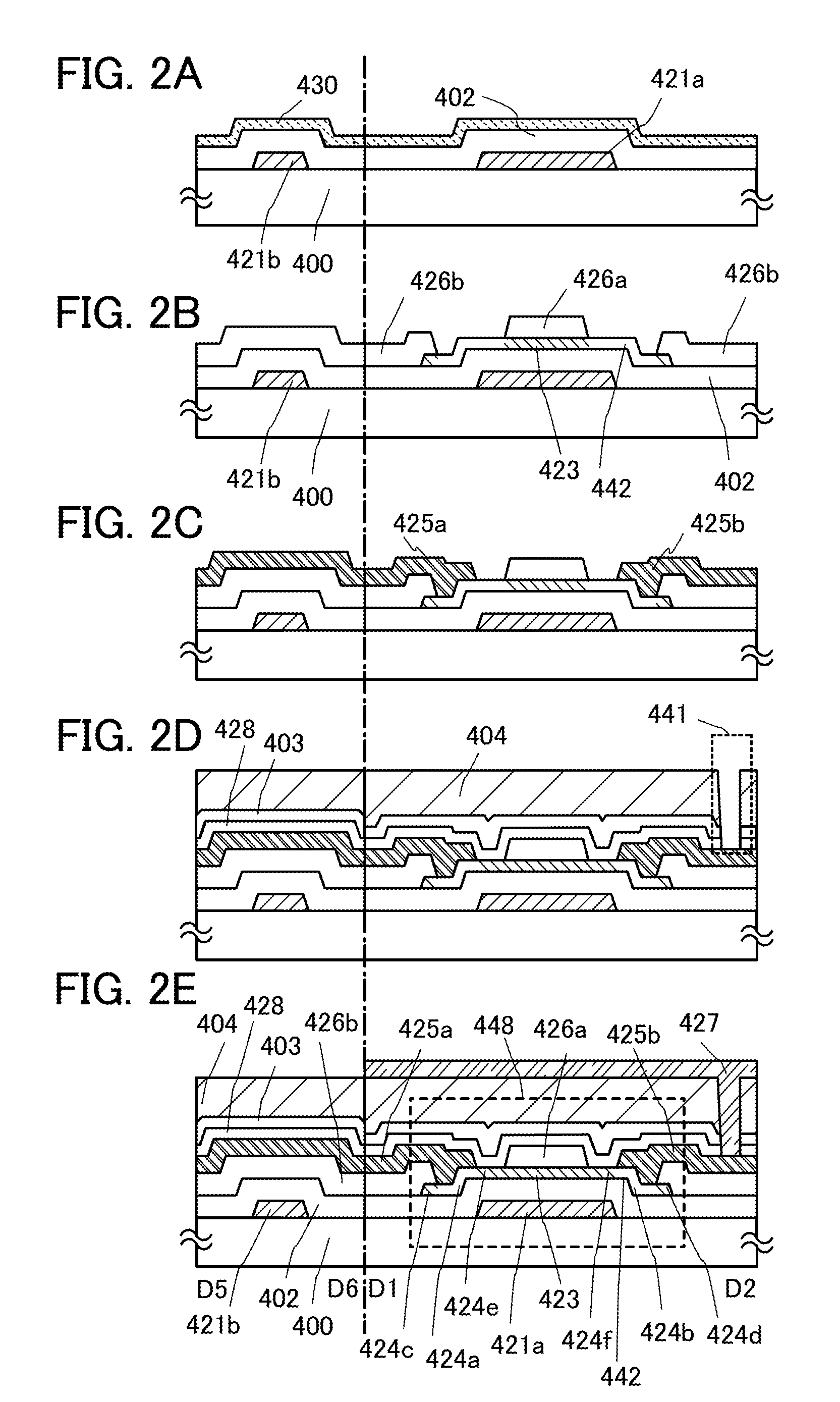

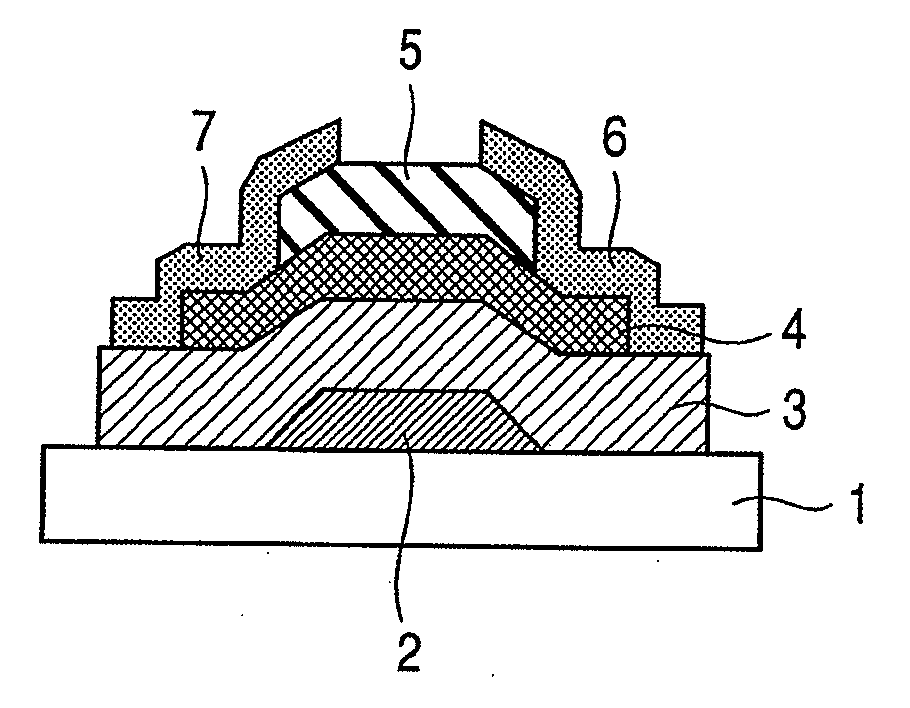

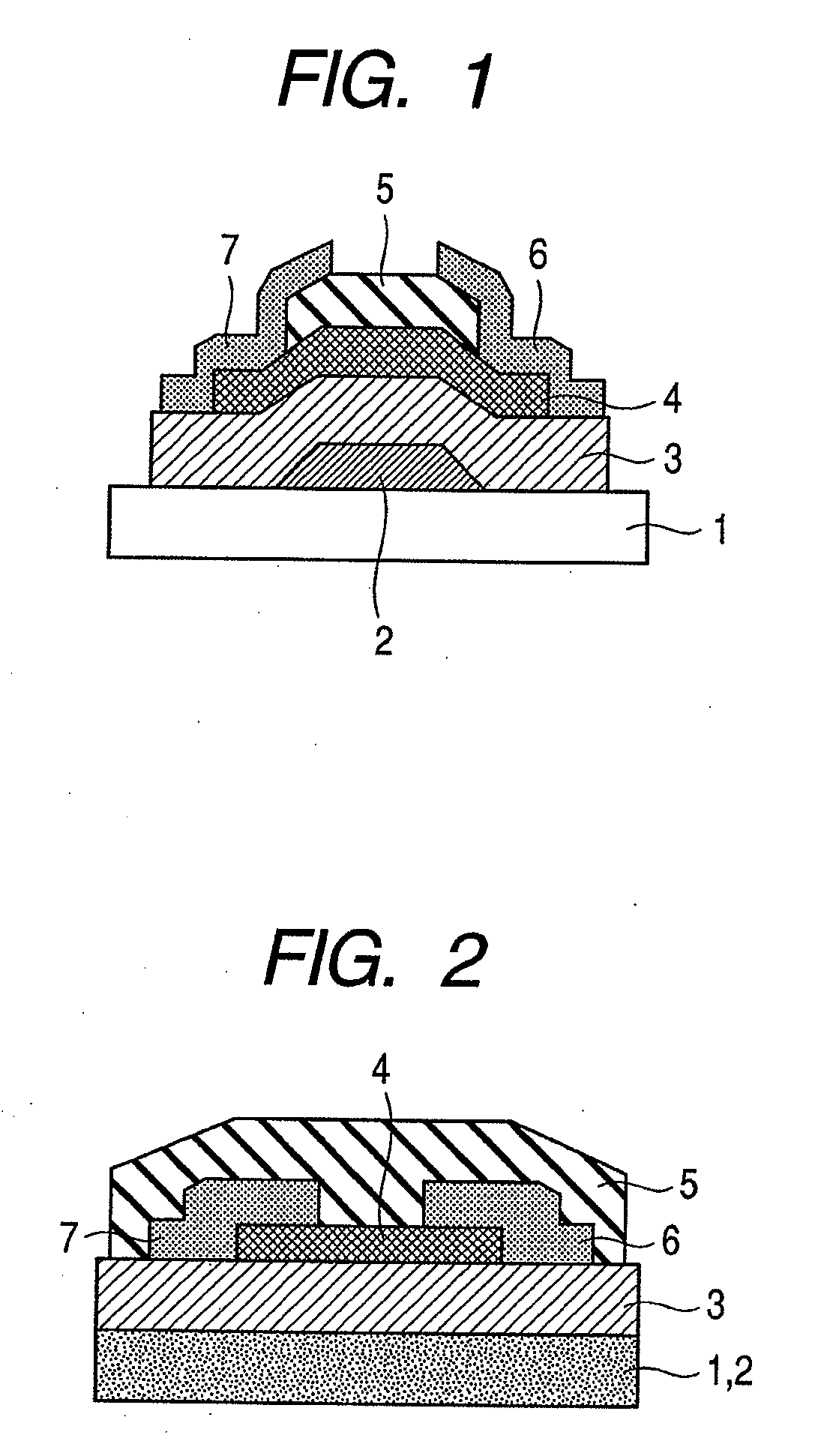

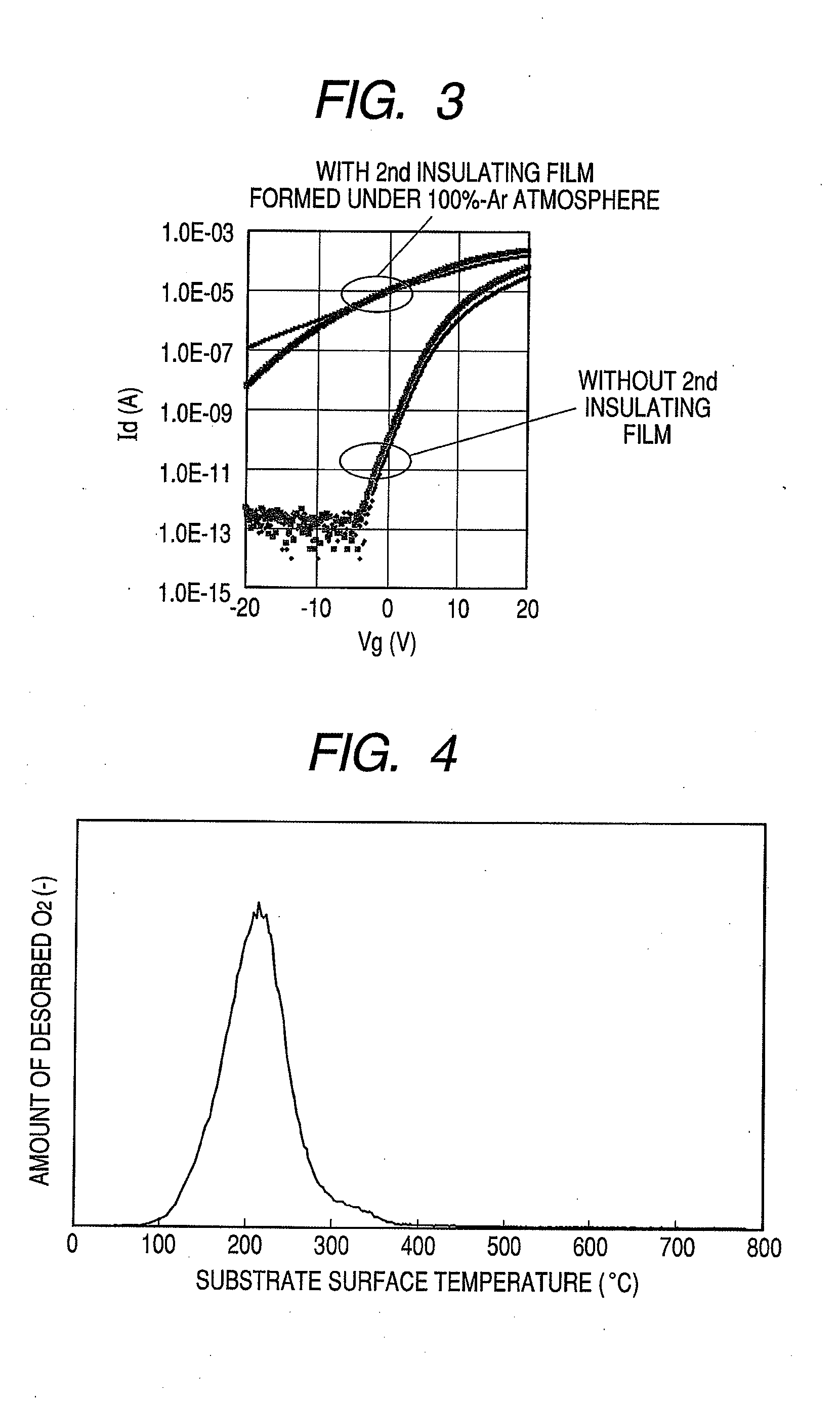

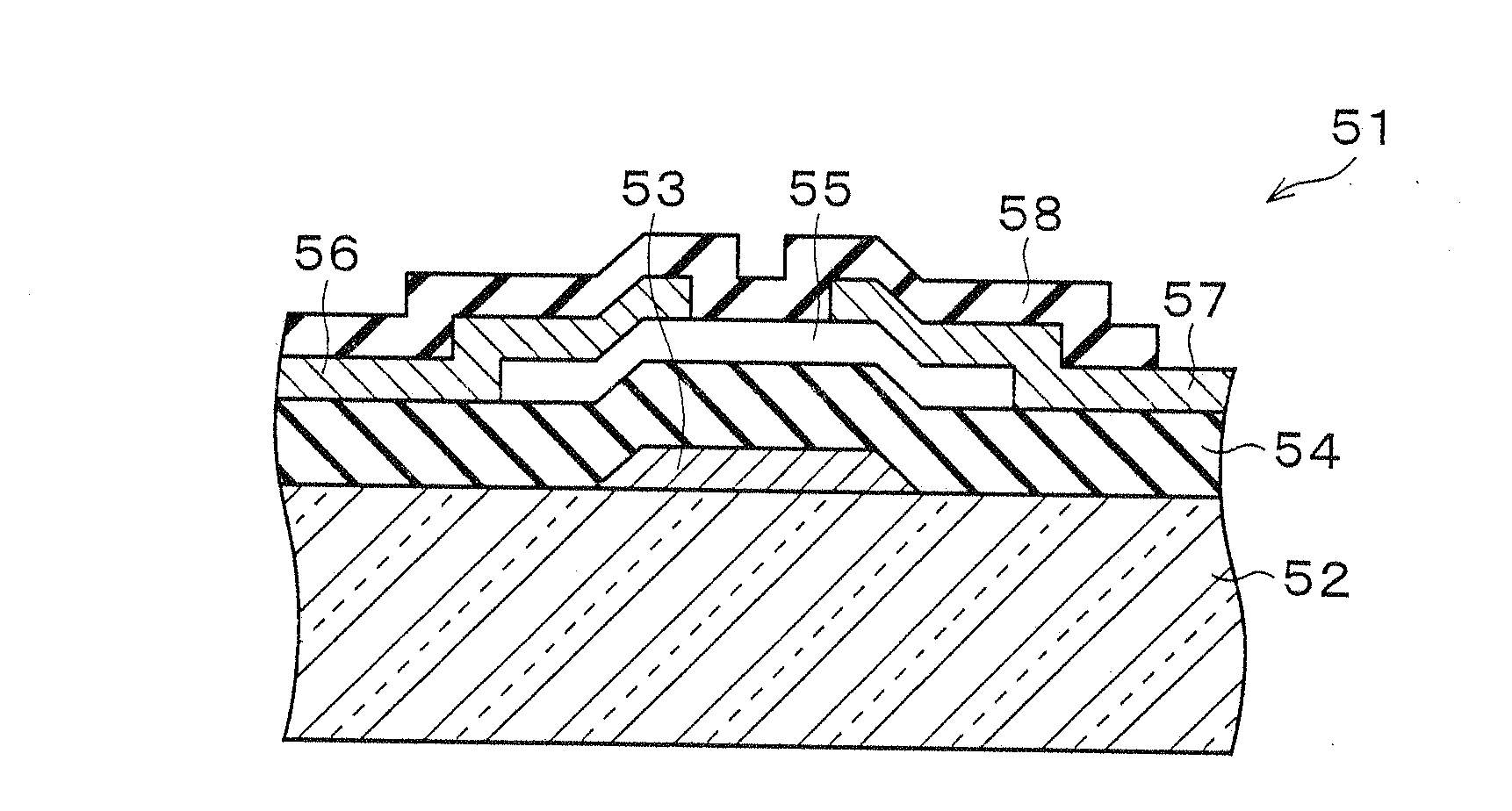

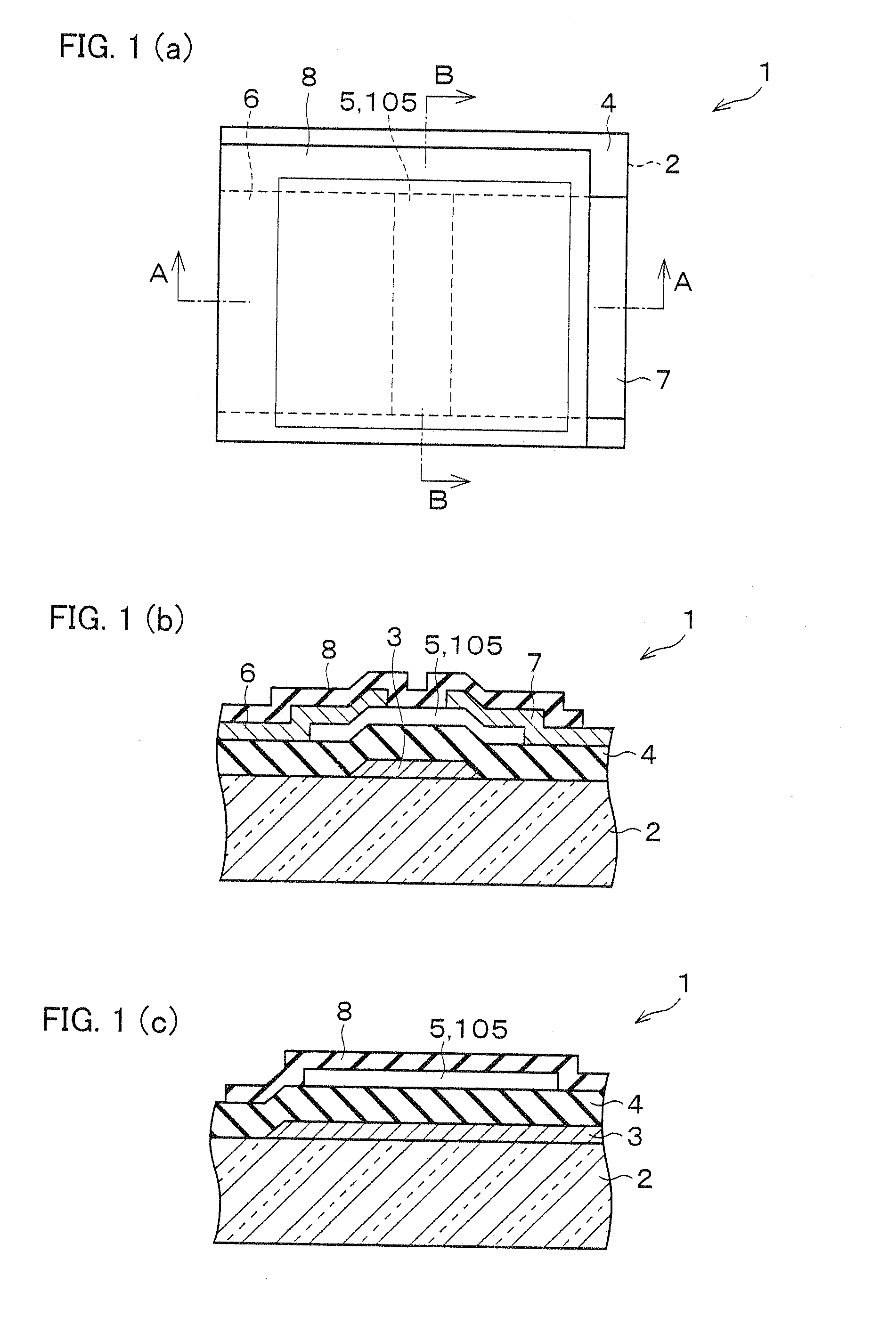

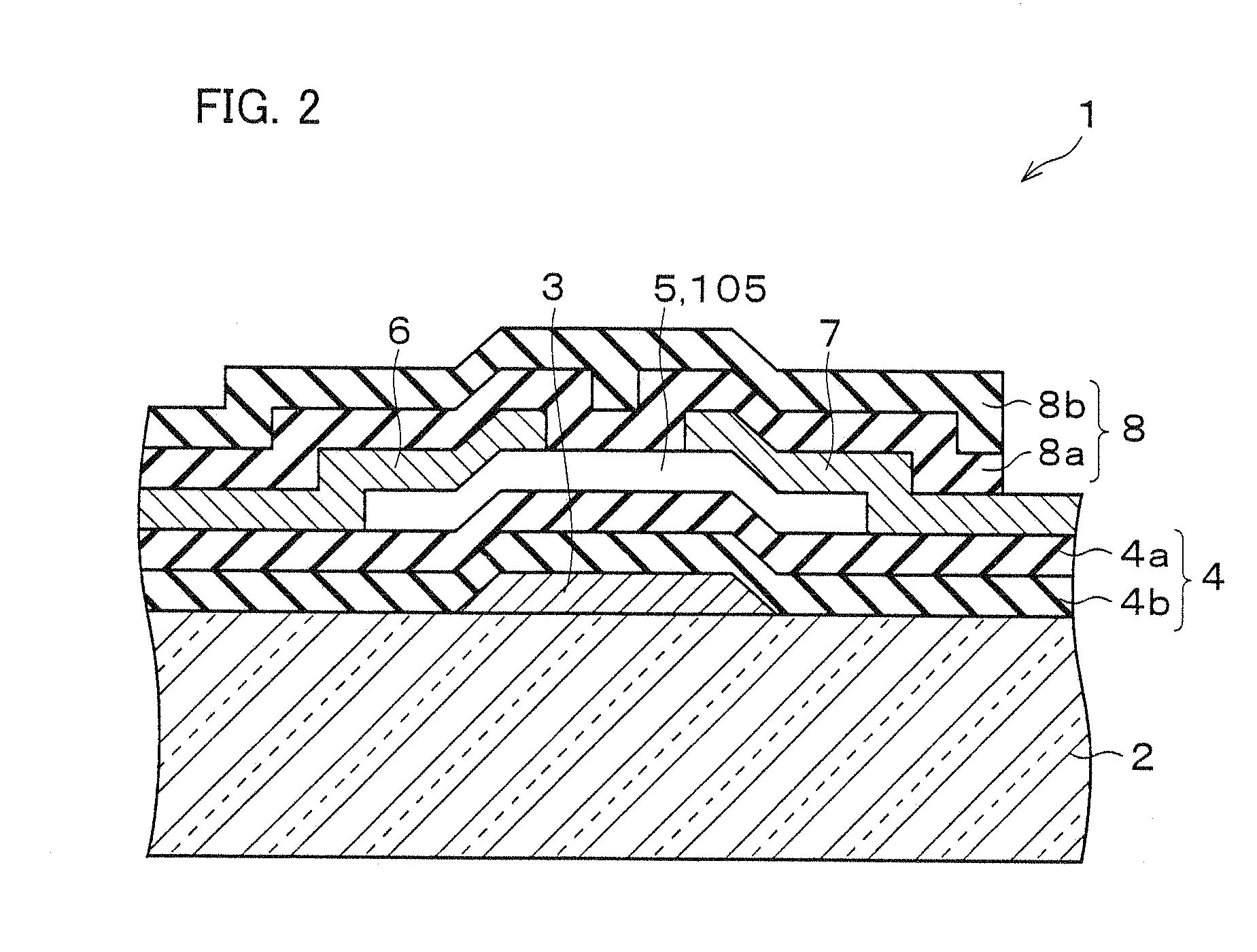

Bottom gate type thin film transistor, method of manufacturing the same, and display apparatus

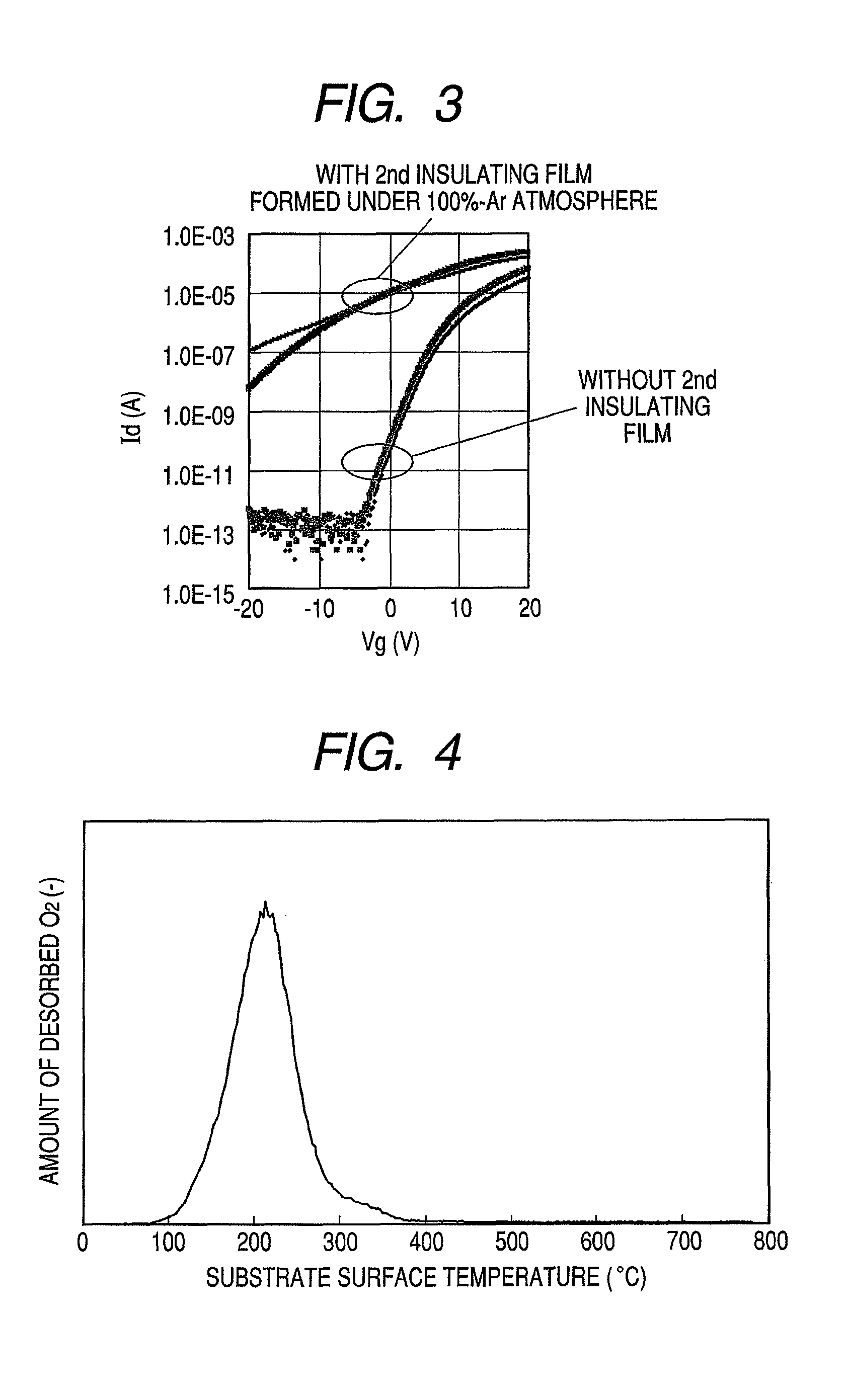

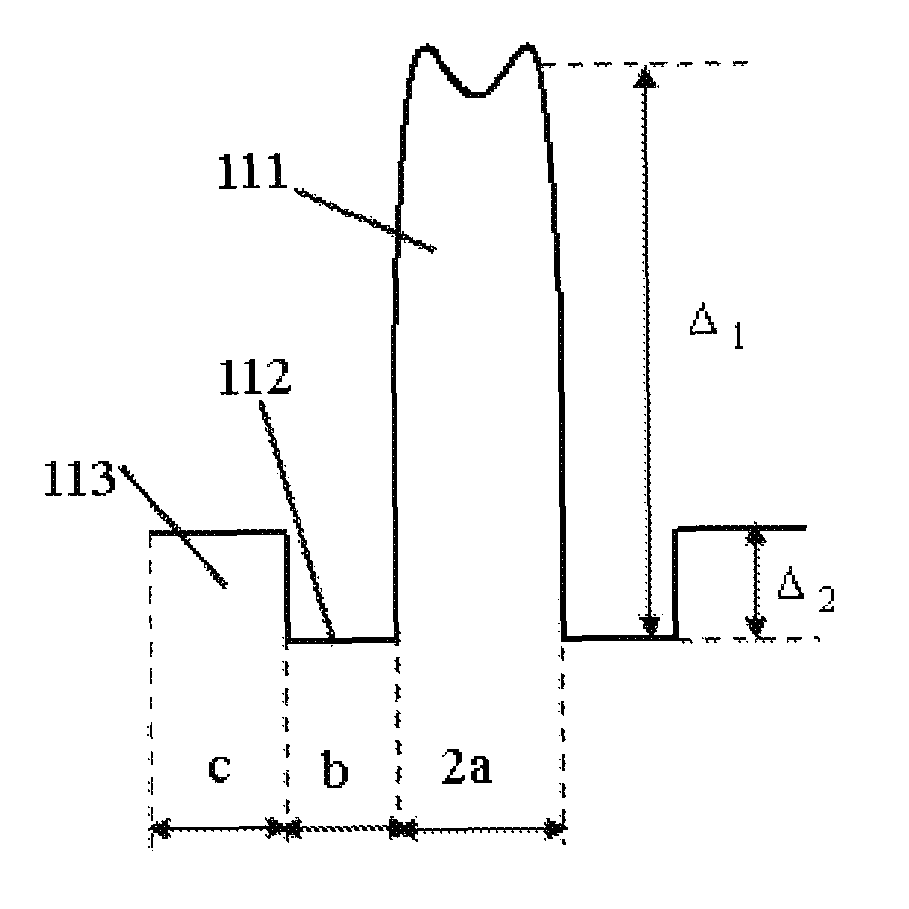

InactiveUS8148721B2Optimise total massImprove batch productivityTransistorElectroluminescent light sourcesDesorptionBottom gate

Provided is a bottom gate type thin film transistor including on a substrate (1) a gate electrode (2), a first insulating film (3) as a gate insulating film, an oxide semiconductor layer (4) as a channel layer, a second insulating film (5) as a protective layer, a source electrode (6), and a drain electrode (7), in which the oxide semiconductor layer (4) includes an oxide including at least one selected from the group consisting of In, Zn, and Sn, and the second insulating film (5) includes an amorphous oxide insulator formed so as to be in contact with the oxide semiconductor layer (4) and contains therein 3.8×1019 molecules / cm3 or more of a desorbed gas observed as oxygen by temperature programmed desorption mass spectrometry.

Owner:CANON KK

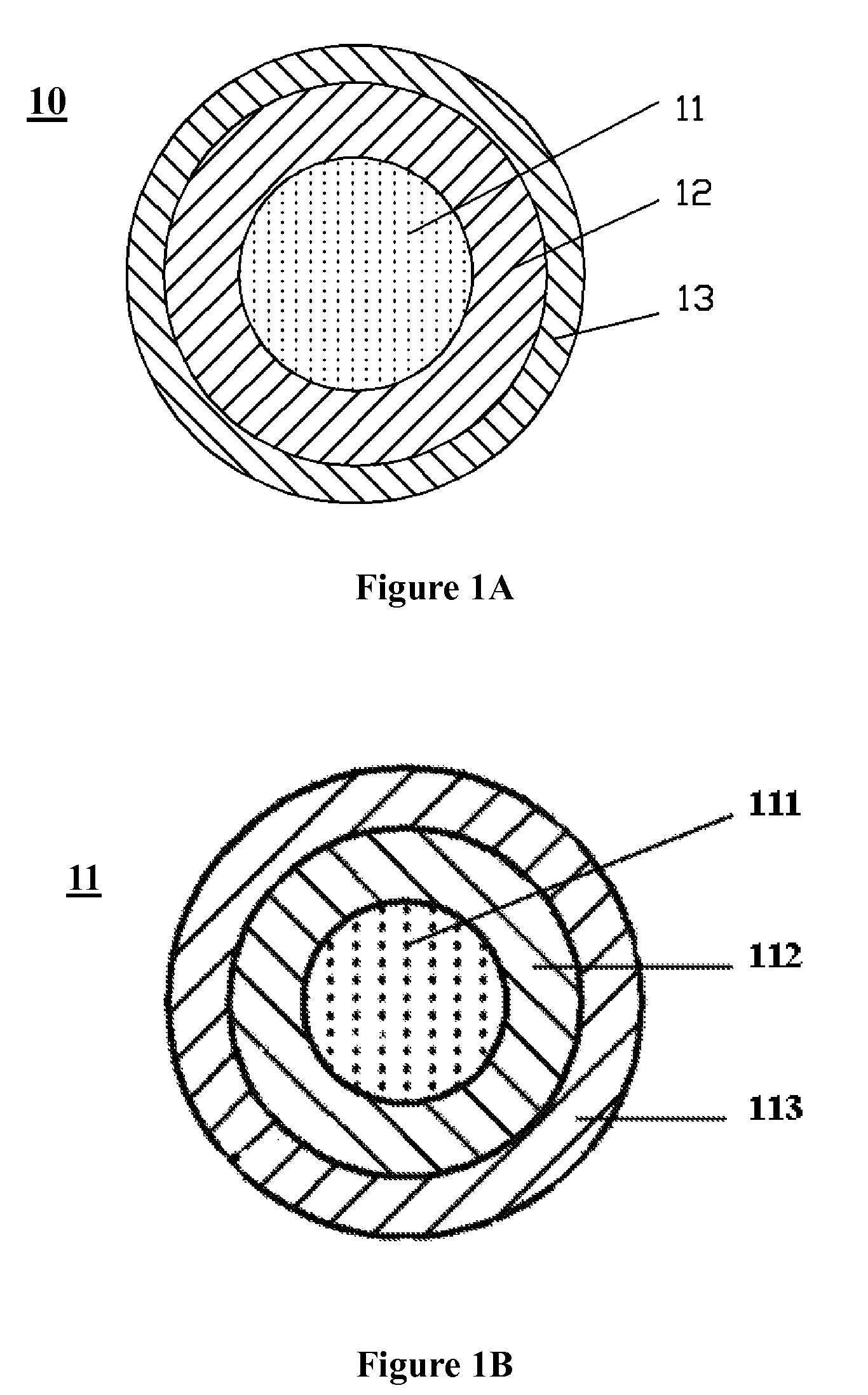

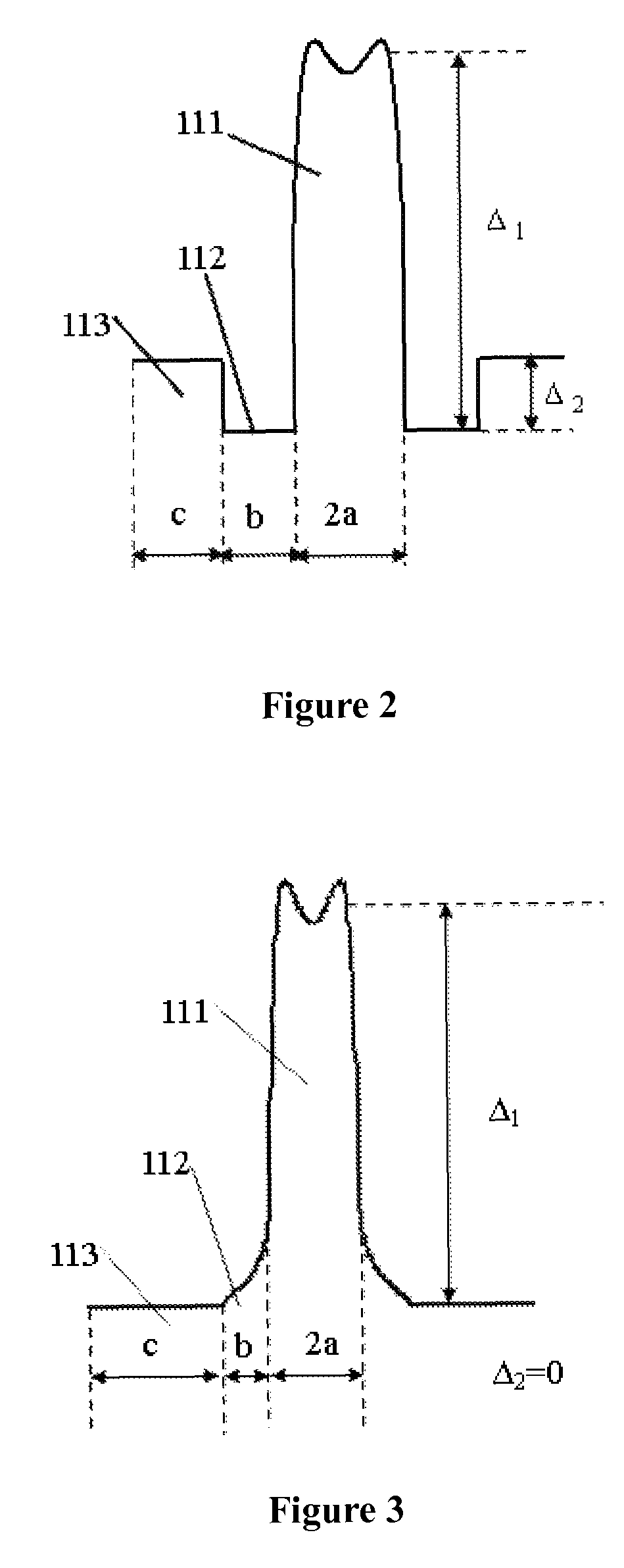

Bend insensitive single mode fiber

ActiveUS8750664B2Manufacturing toleranceReduce manufacturing costGlass optical fibreOptical fibre with multilayer core/claddingGlass fiberAccess network

This invention discloses a bend insensitive single mode fiber, which is composed by a bare glass fiber with a round cross section and two resin protective layers with circular cross sections surrounding the outer of the bare glass fiber. It is characterized in that the bare glass fiber is composed by a core layer with a round cross section and two claddings with circular cross sections. The refractive index of the core layer is higher than the index of the two claddings and the refractive index difference between the core layer and the first cladding is larger than the difference between the first and second claddings. The second cladding is made of pure SiO2. The refractive index profile of the core layer follows a power function, and the refractive index profile of the two claddings follow a ladder-type distribution. The loss of the invented fiber is insensitive to the bending of the fiber, which meets the requirements of ITU.T G.657.A and G.657.B standards, respectively. It is applicable to the Fiber To The Home (FTTH) and other local area network and the access network systems.

Owner:FUTONG GROUP CO LTD

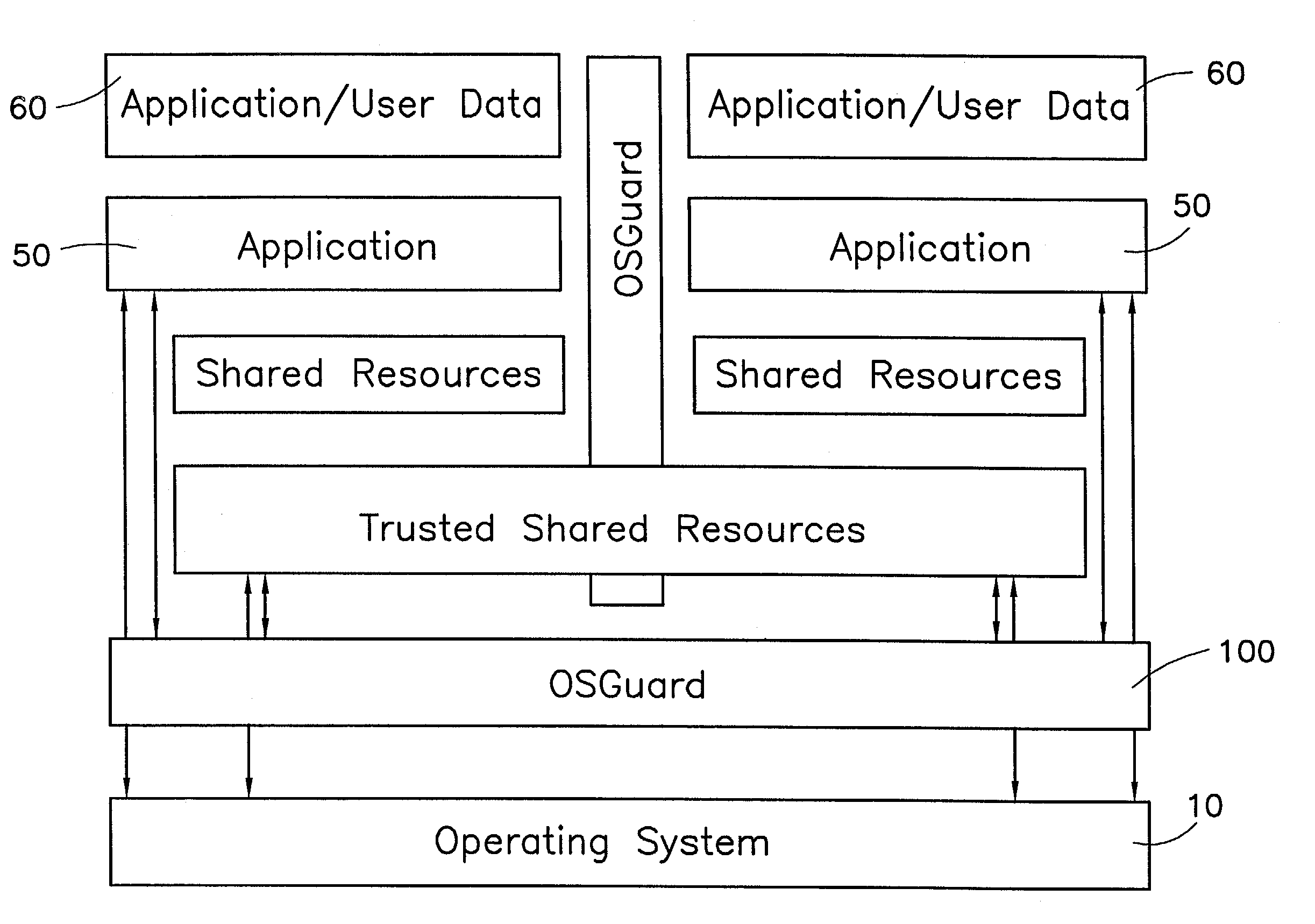

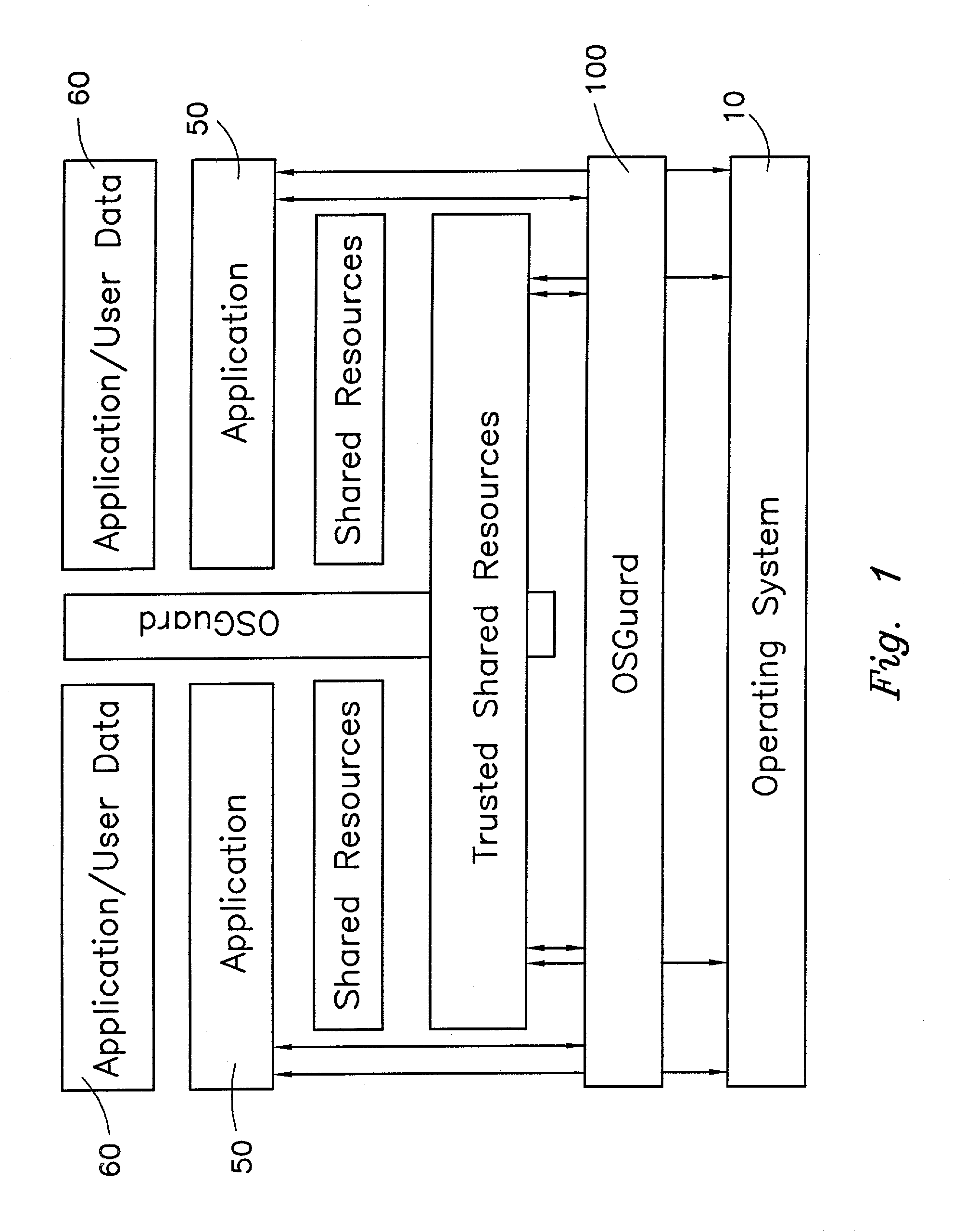

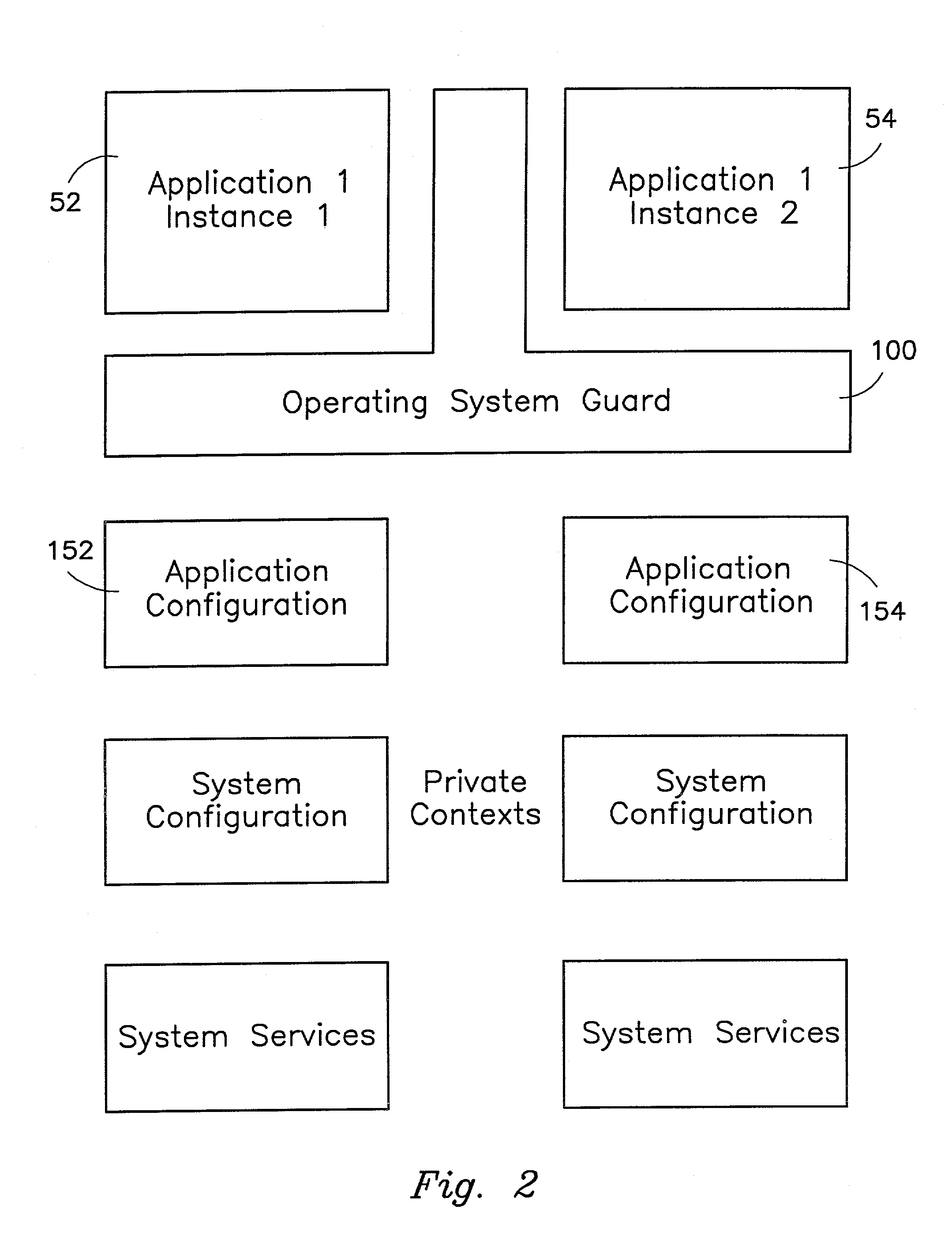

Operating system abstraction and protection layer

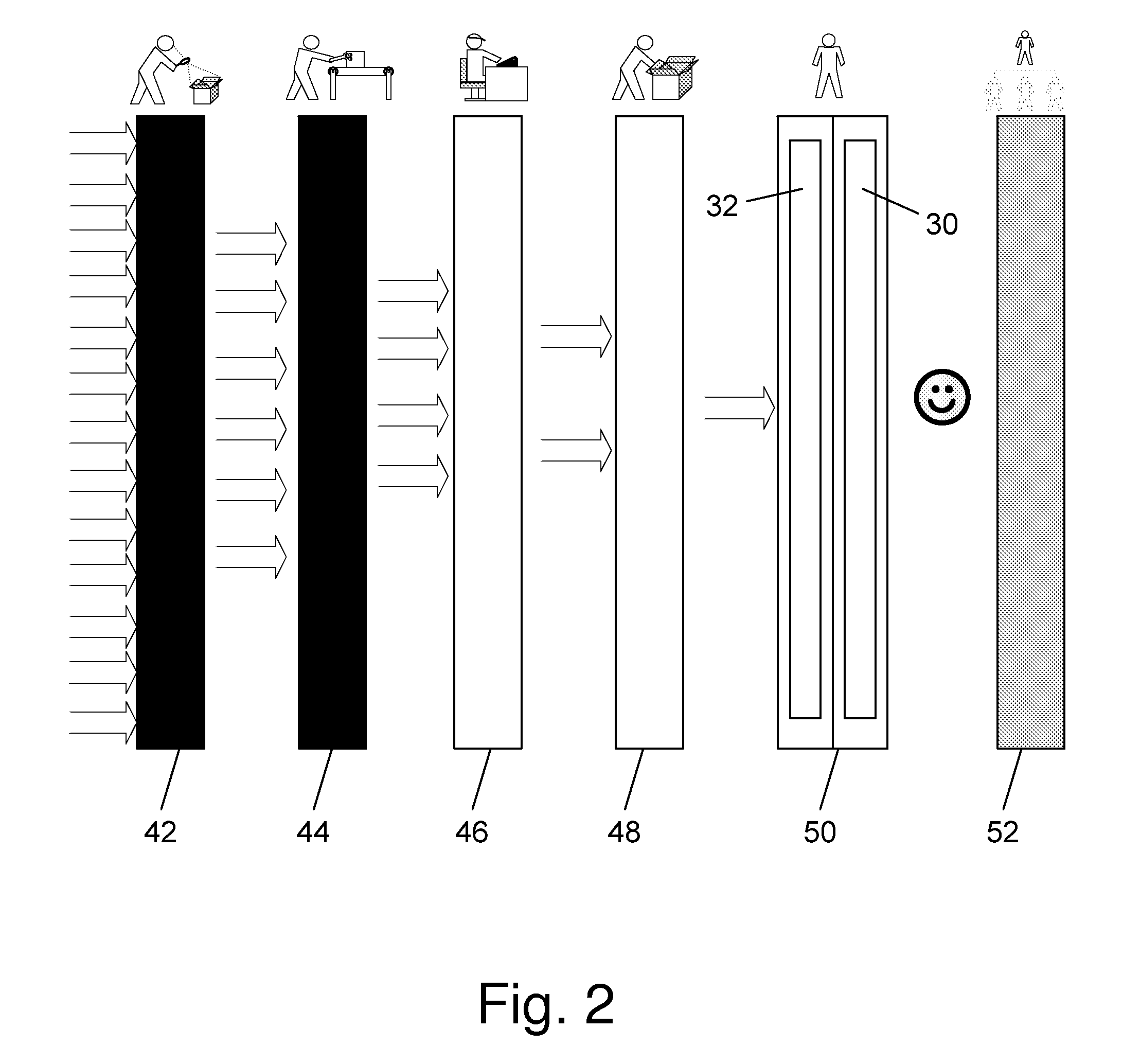

InactiveUS7028305B2Avoid changeInhibition of informationInterprogram communicationDigital computer detailsOperational systemConfiguration item

The present invention provides a system for creating an application software environment without changing an operating system of a client computer, the system comprising an operating system abstraction and protection layer, wherein said abstraction and protection layer is interposed between a running software application and said operating system, whereby a virtual environment in which an application may run is provided and application level interactions are substantially removed. Preferably, any changes directly to the operating system are selectively made within the context of the running application and the abstraction and protection layer dynamically changes the virtual environment according to administrative settings. Additionally, in certain embodiments, the system continually monitors the use of shared system resources and acts as a service to apply and remove changes to system components. The present thus invention defines an “Operating System Guard.” These components cover the protection semantics required by .DLLs and other shared library code as well as system device drivers, fonts, registries and other configuration items, files, and environment variables.

Owner:MICROSOFT TECH LICENSING LLC

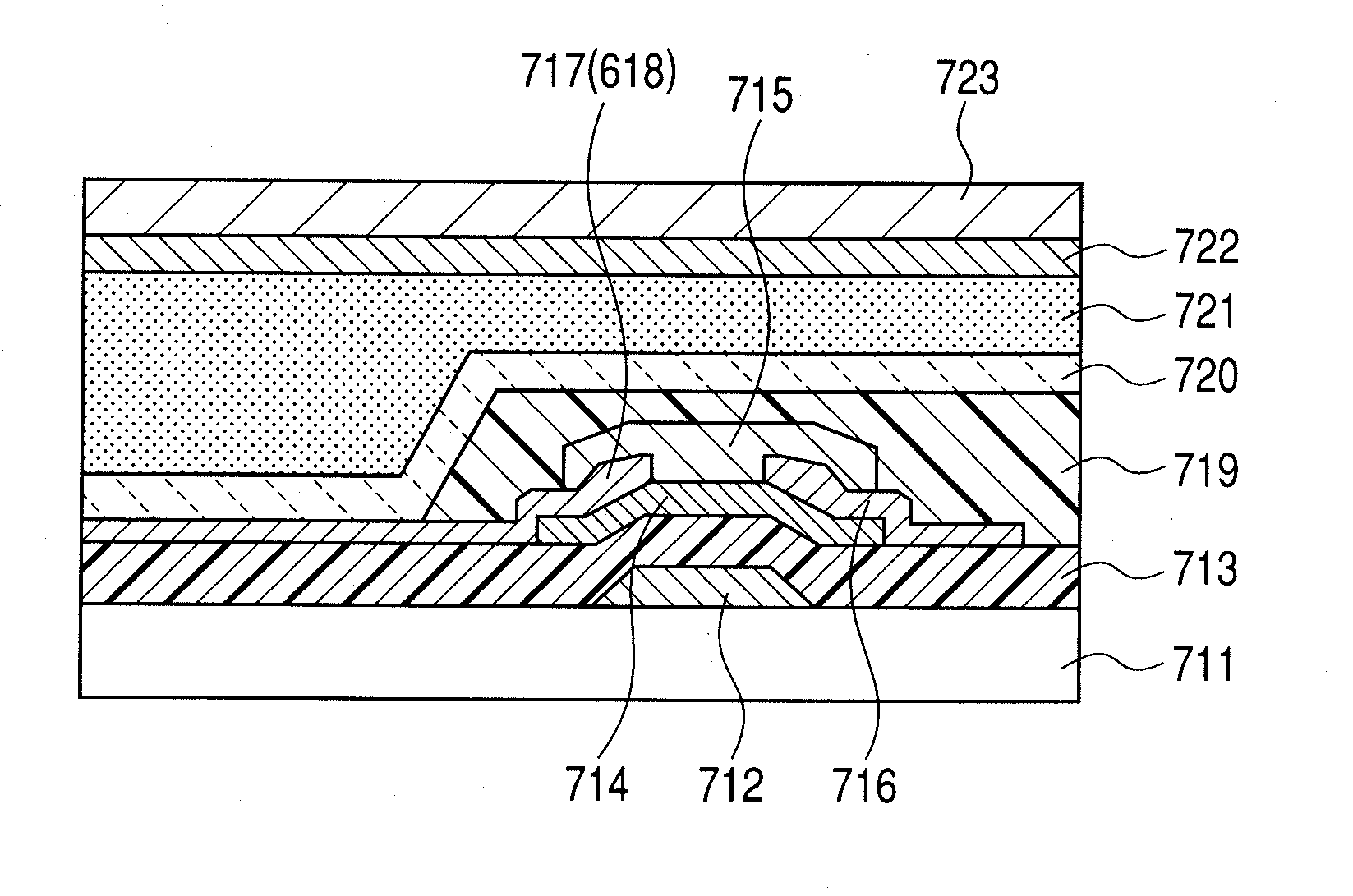

Thin-film transistor and method of manufacturing same

There is provided a thin-film transistor including at least a substrate, a gate electrode, a gate insulating layer, an oxide semiconductor layer, a source electrode, a drain electrode and a protective layer, wherein the oxide semiconductor layer is an amorphous oxide containing at least one of the elements In, Ga and Zn, the gate electrode-side carrier density of the oxide semiconductor layer is higher than the protective layer-side carrier density thereof, and the film thickness of the oxide semiconductor layer is 30 nm±15 nm.

Owner:CANON KK

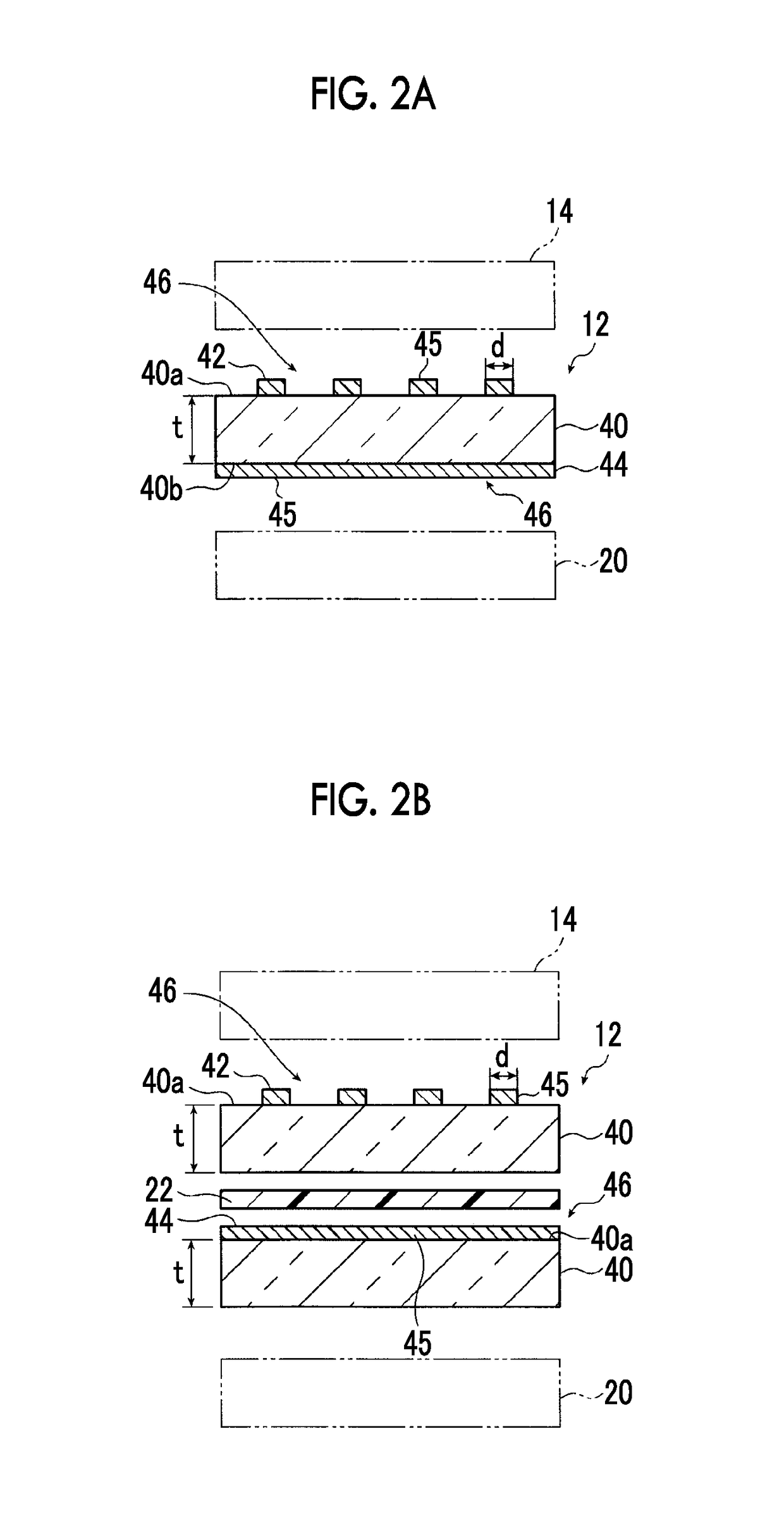

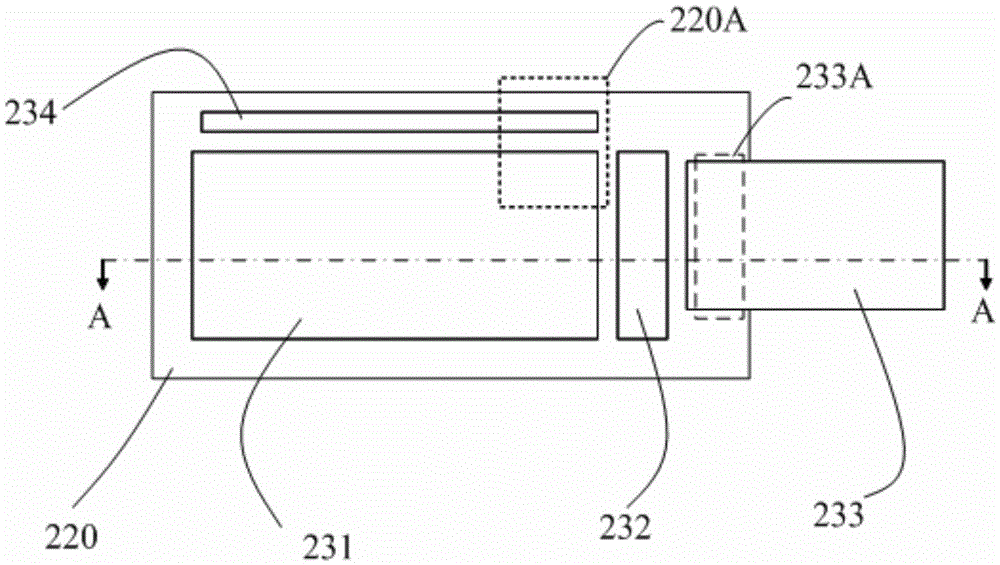

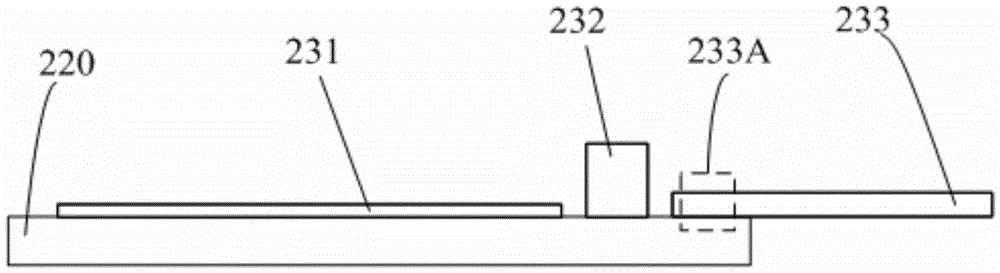

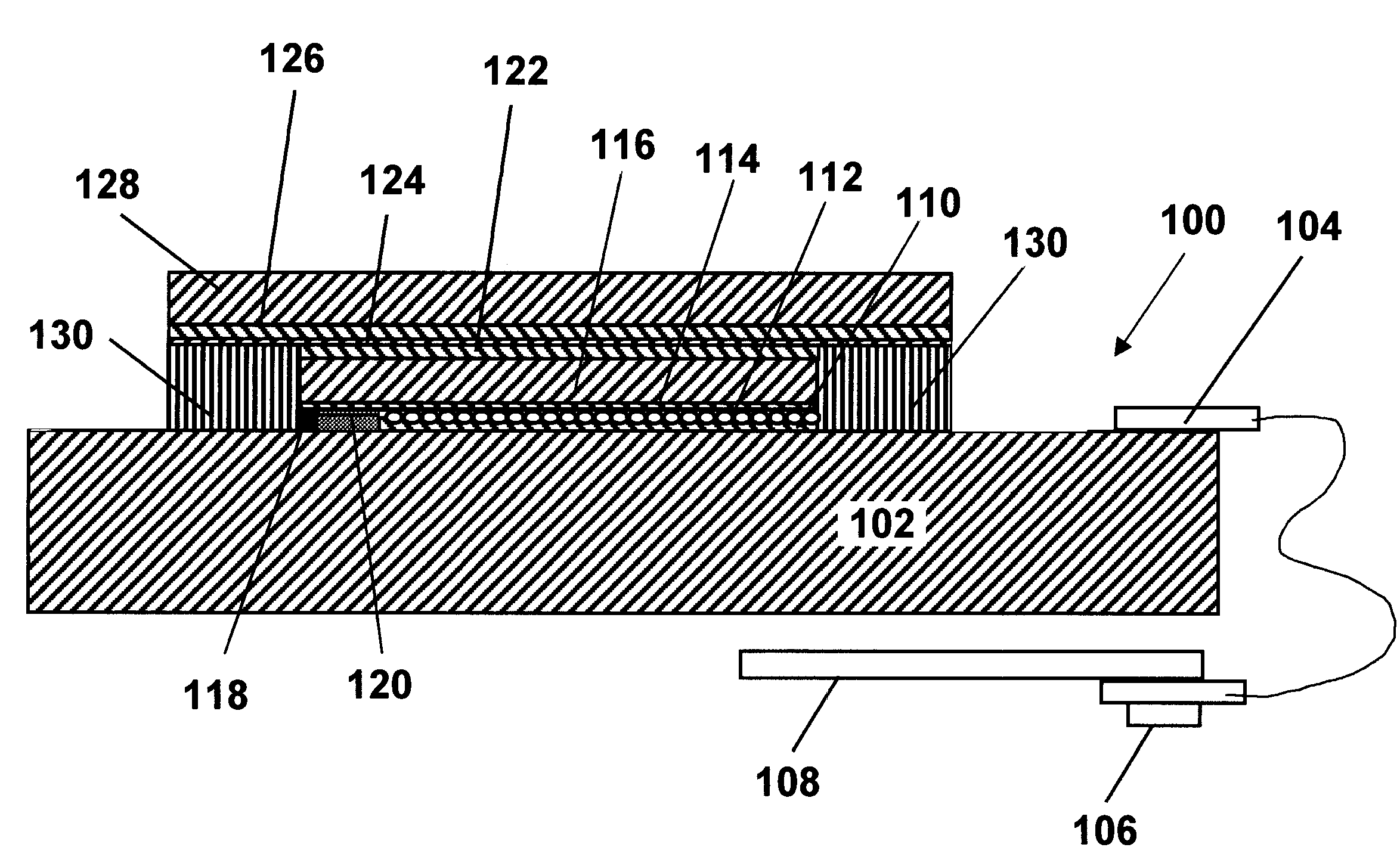

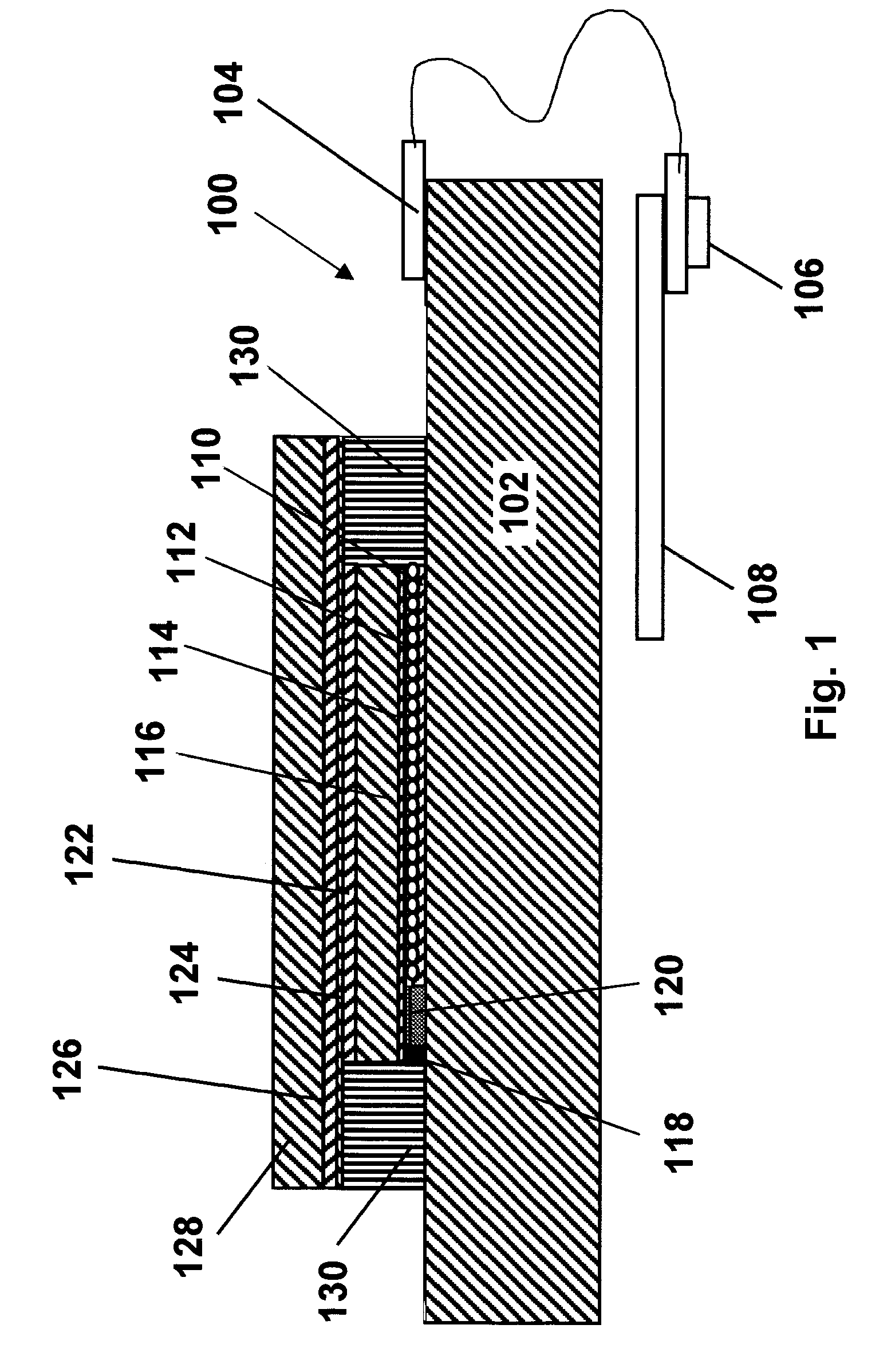

Interferometric modulation pixels and manufacturing method thereof

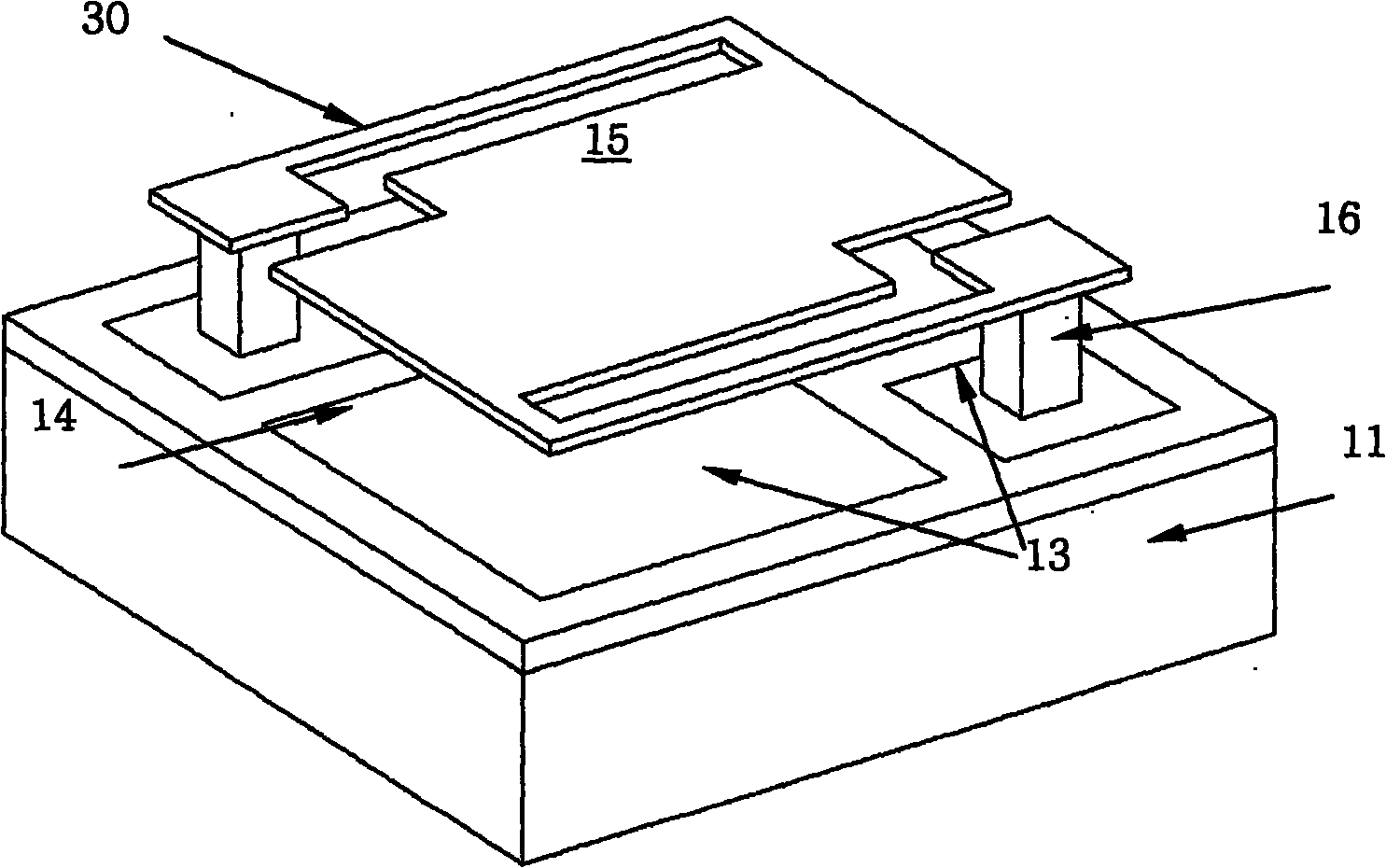

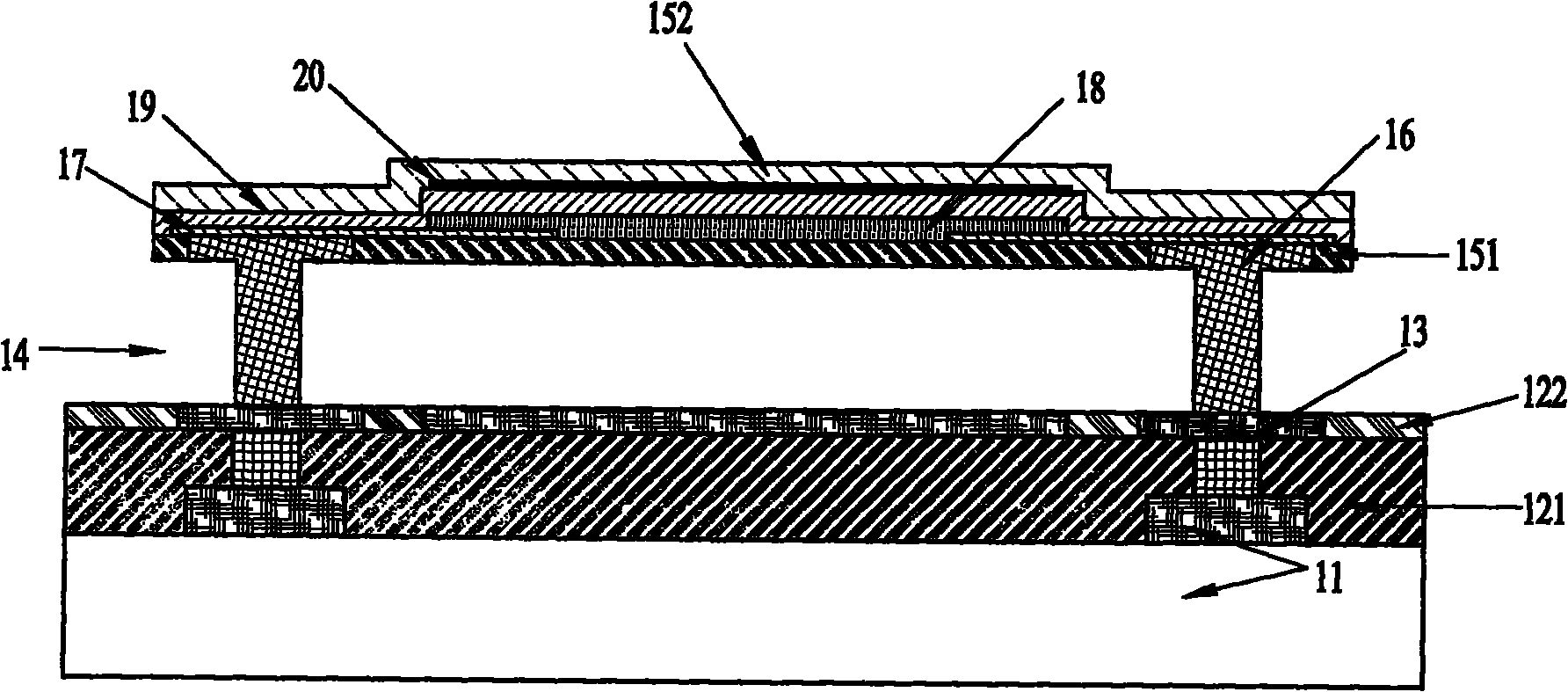

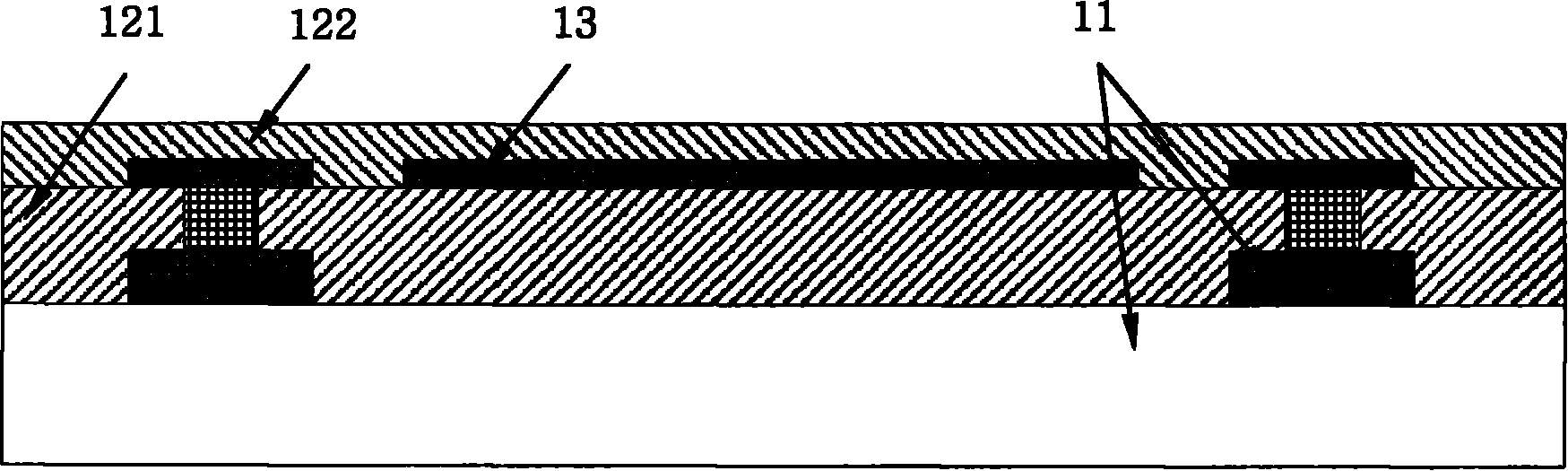

ActiveUS6952303B2Upper surfaceQuality improvementNon-linear opticsOptical elementsLength waveProtection layer

A protection layer covers the cavity-side surface of a bottom electrode of a interferometric modulation pixel. Consequently, the protective layer protects the surface of the bottom electrode while a sacrificial layer between the bottom electrode and the top electrode is being etched. Thus, the distance between the bottom electrode and the top electrode is maintained, thereby ensuring that only the light with desired wavelengths is reflected by the interferometric modulation pixel.

Owner:SNAPTRACK

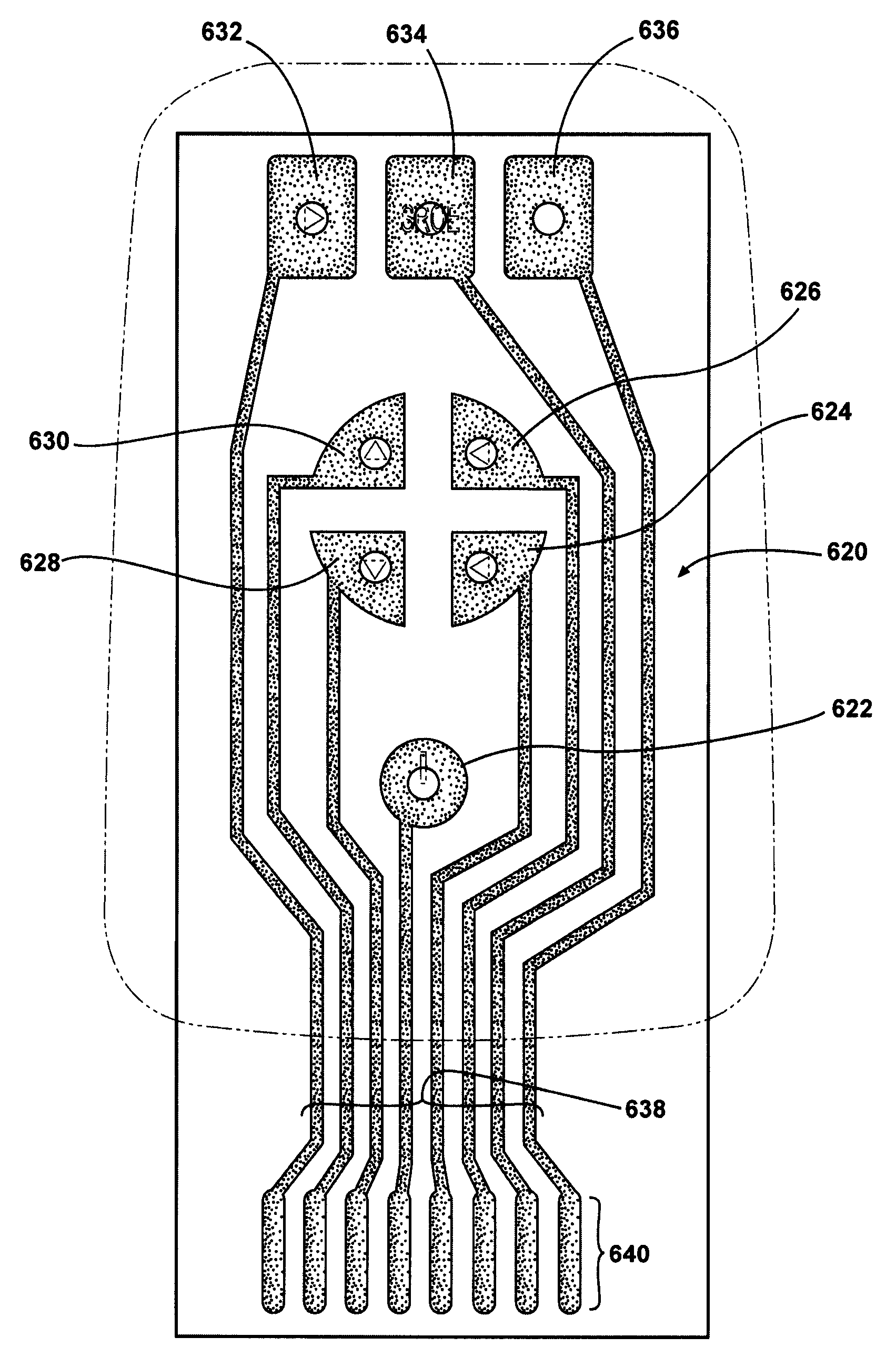

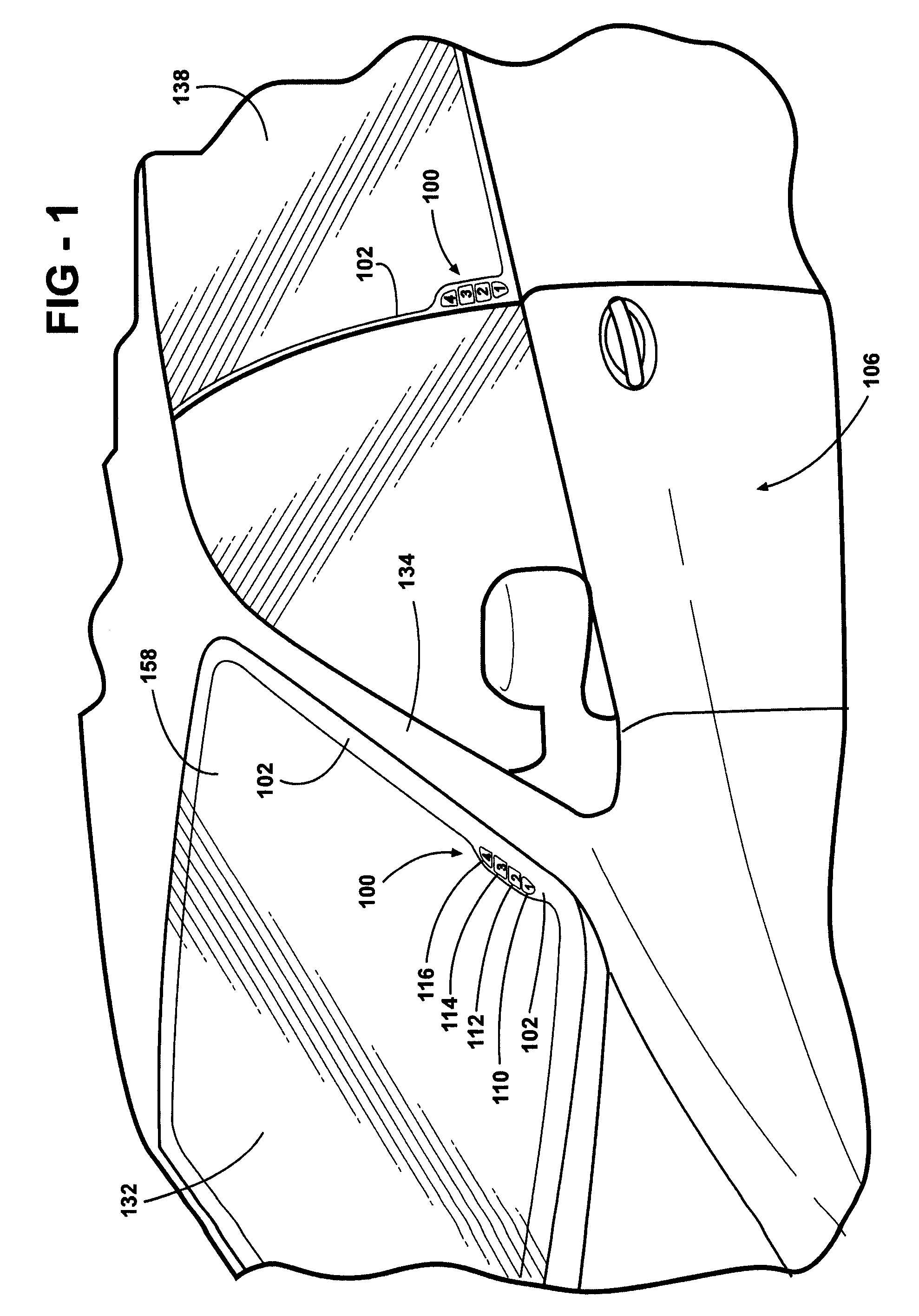

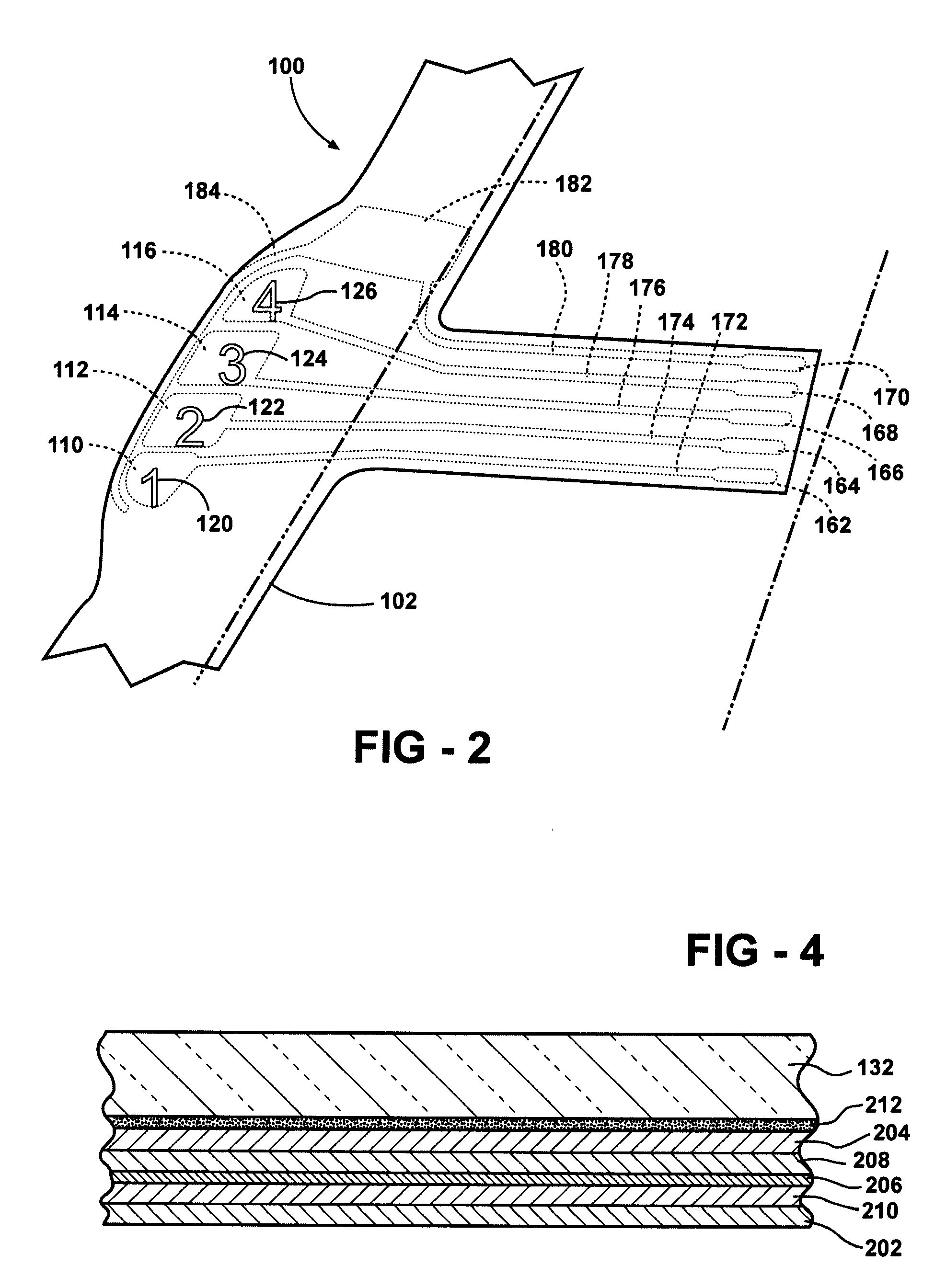

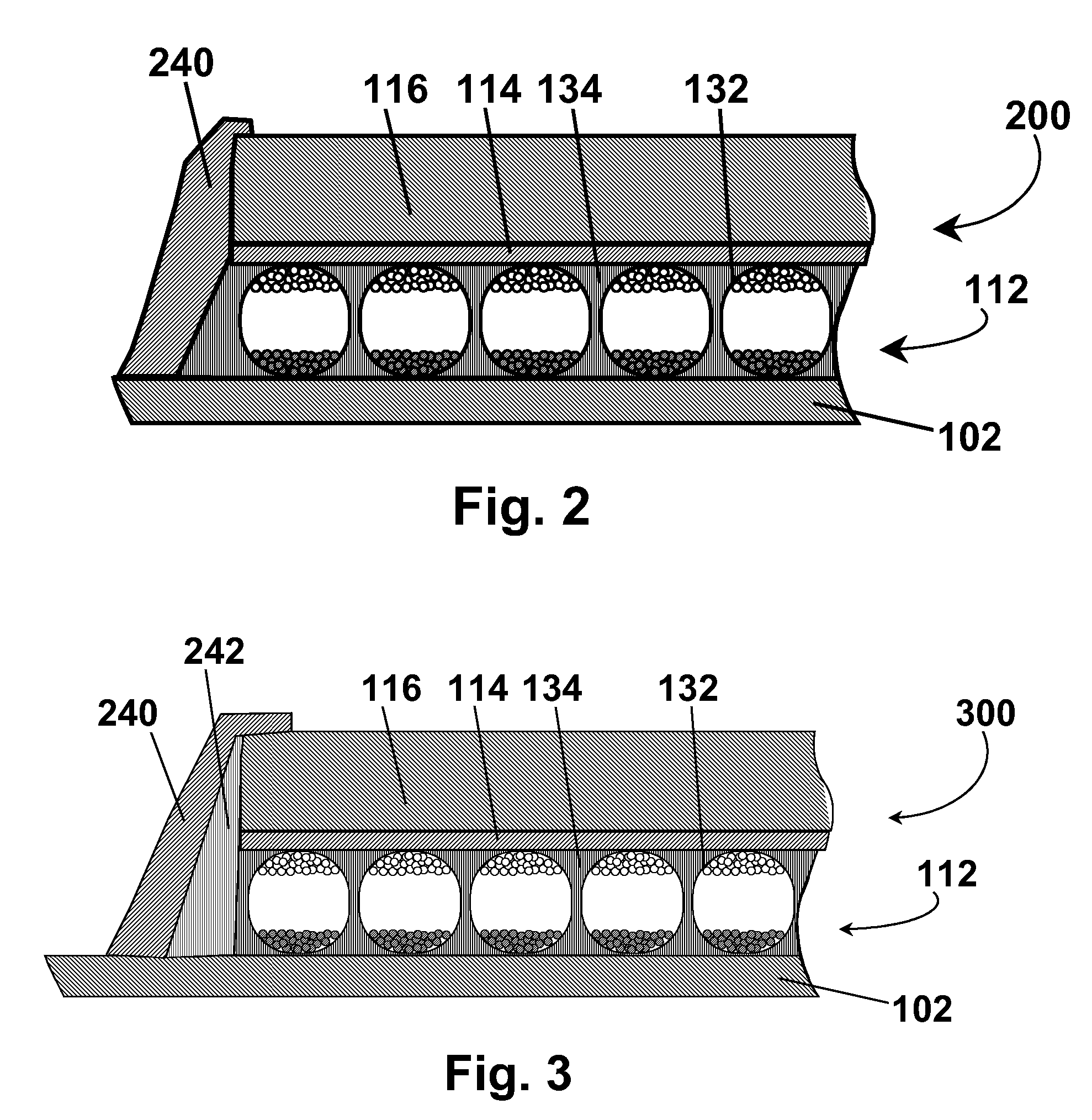

Proximity sensor for a vehicle

InactiveUS20080202912A1Aesthetically pleaseElectronic switchingElectric switchesProximity sensorEngineering

A proximity sensor for controlling a component that may be installed on a window, on an interior or exterior pillar of a vehicle, on a control panel or any suitable location on a vehicle or any other structure. The sensor includes a substrate and a conductive layer disposed on the substrate. The conductive layer is formed from a conductive ink composition with the conductive layer defining at least one circuit for controlling the component when a user is in proximity to the conductive layer. A protective layer is disposed over the conductive layer. At least one of the conductive layer and the protective layer defines a graphic formed through the layer for visual identification to the user.

Owner:T INK INC

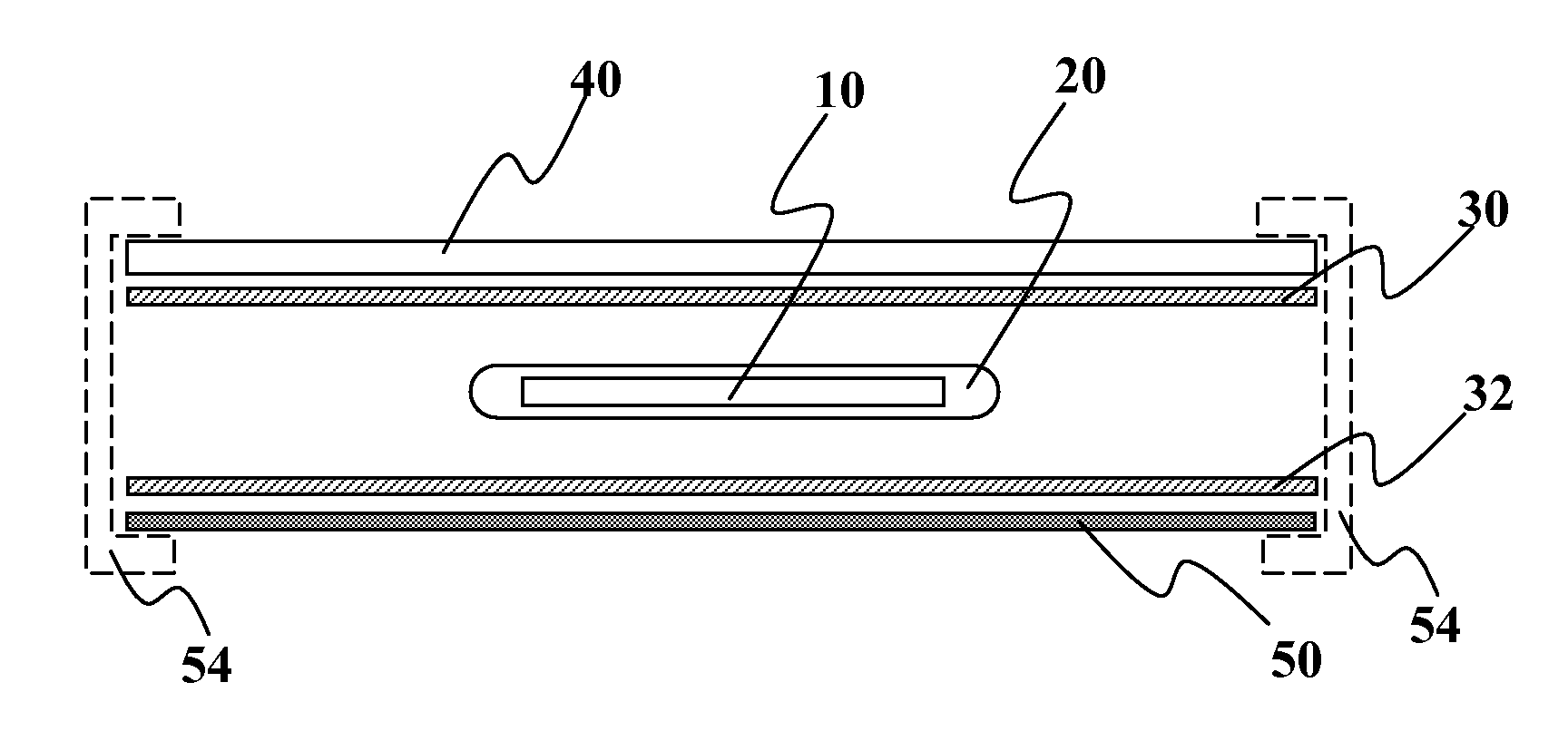

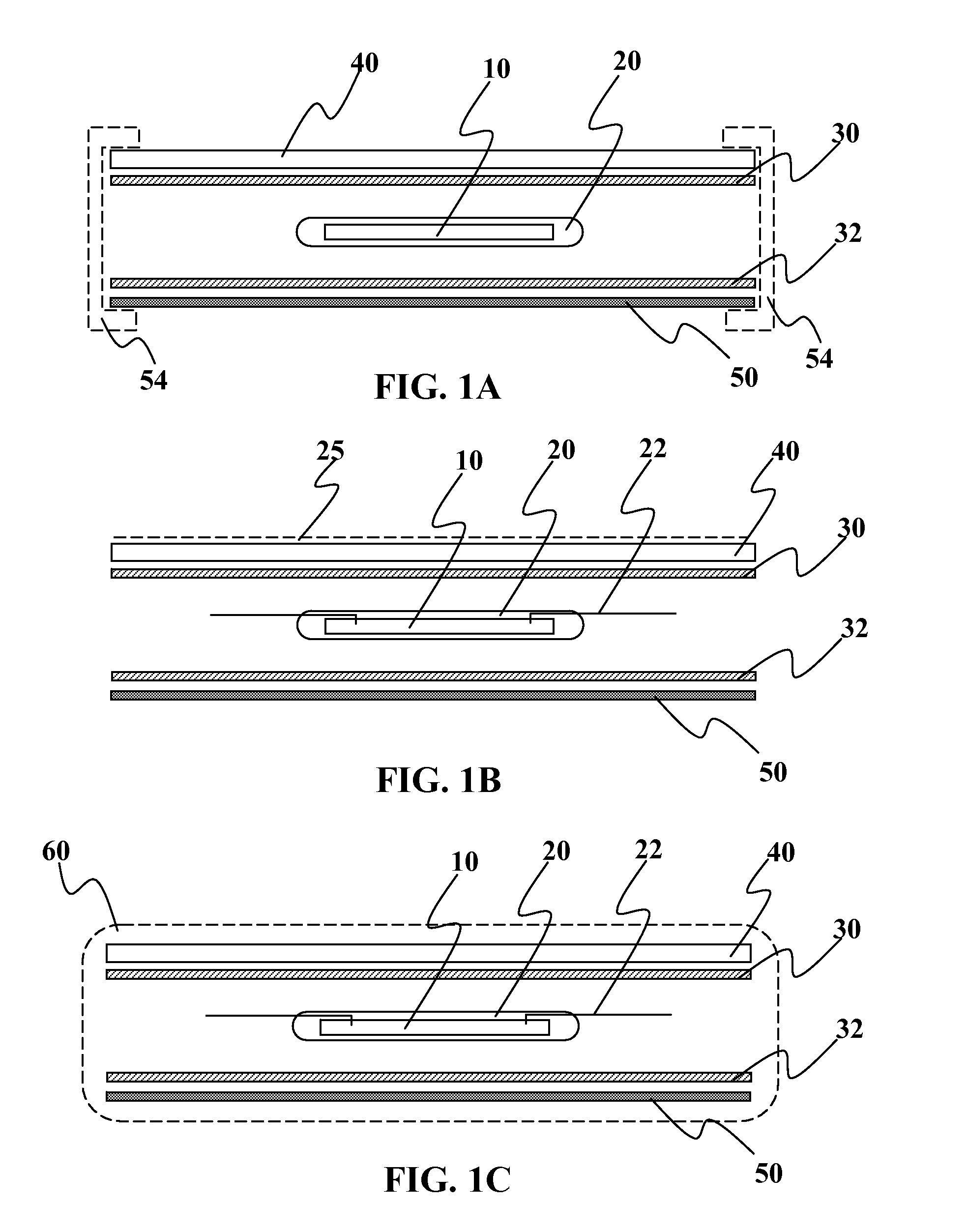

Edge seals for, and processes for assembly of, electro-optic displays

An electro-optic display comprises a backplane; a layer of electro-optic material disposed adjacent the backplane; a protective layer; and a sealing layer of a metal or a ceramic extending between the backplane and the protective layer, and thus sealing the layer of electro-optic material from the outside environment.

Owner:E INK CORPORATION

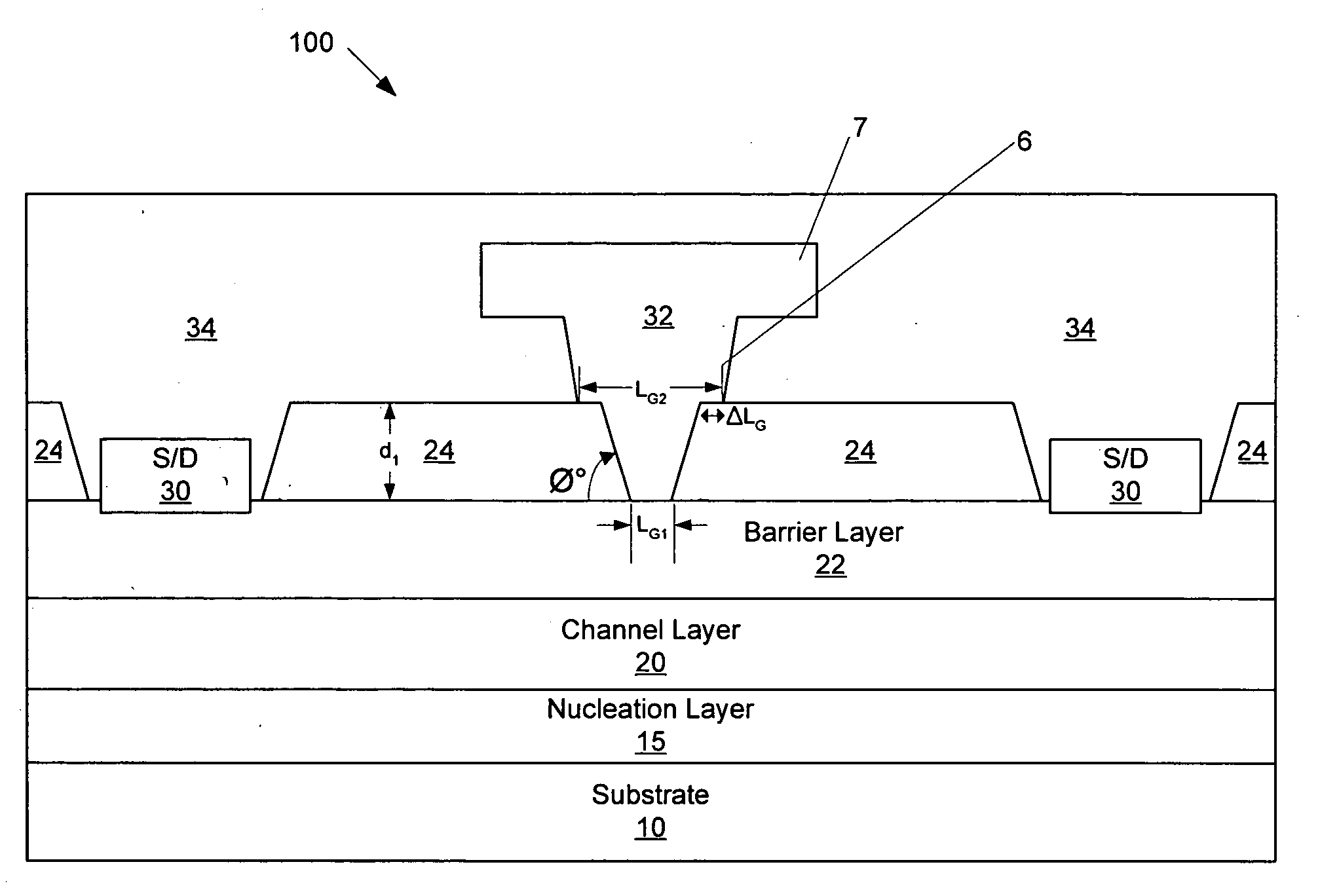

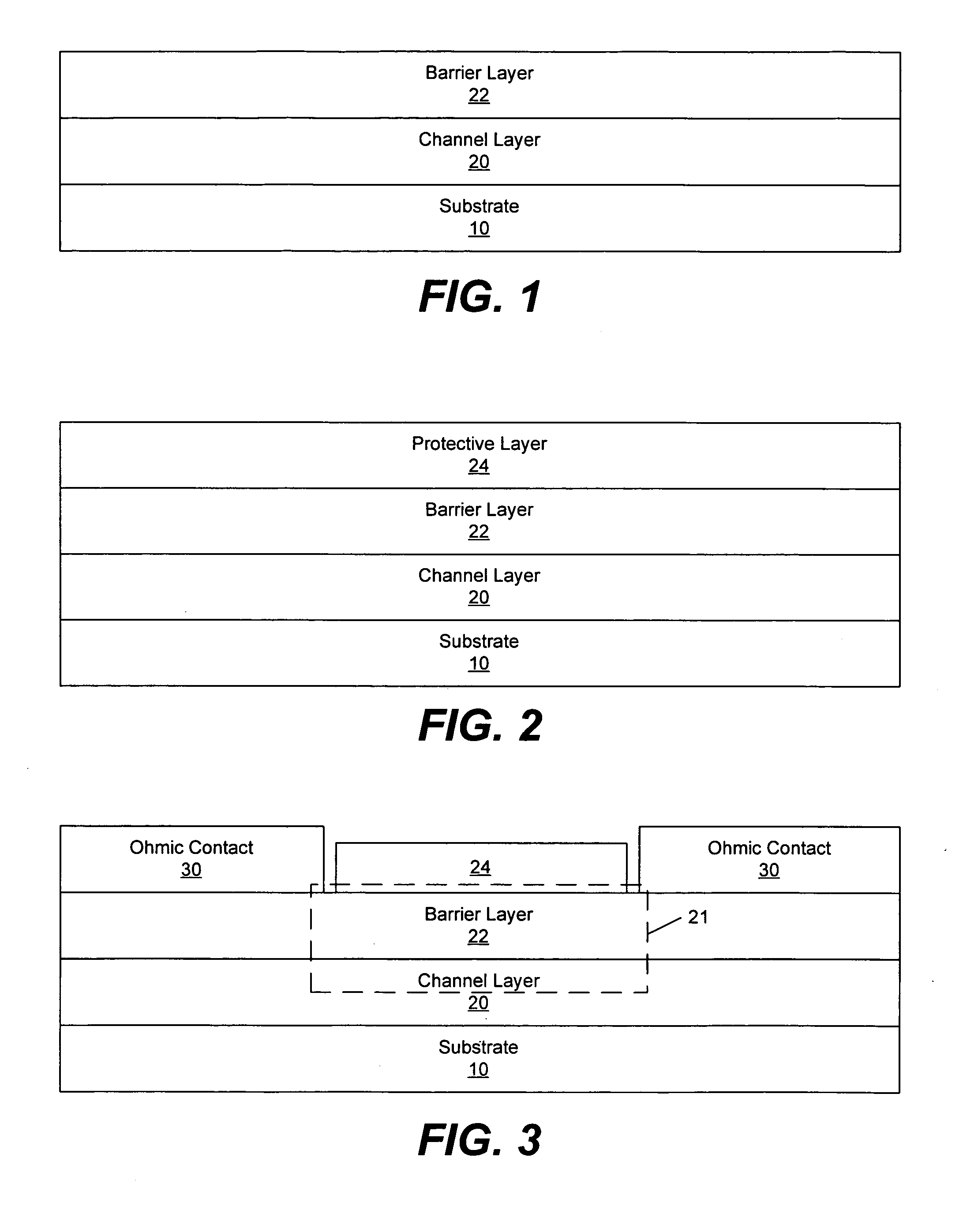

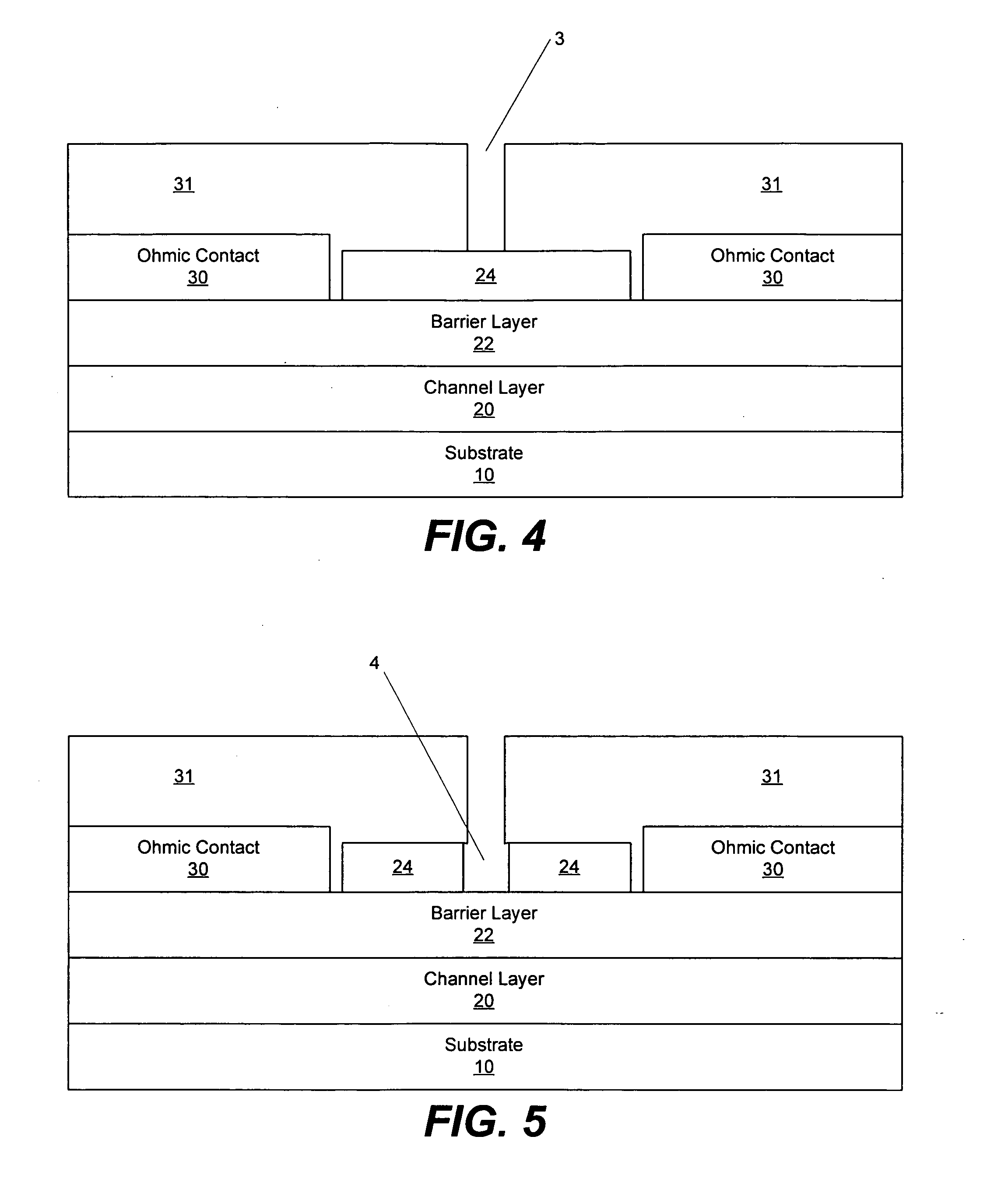

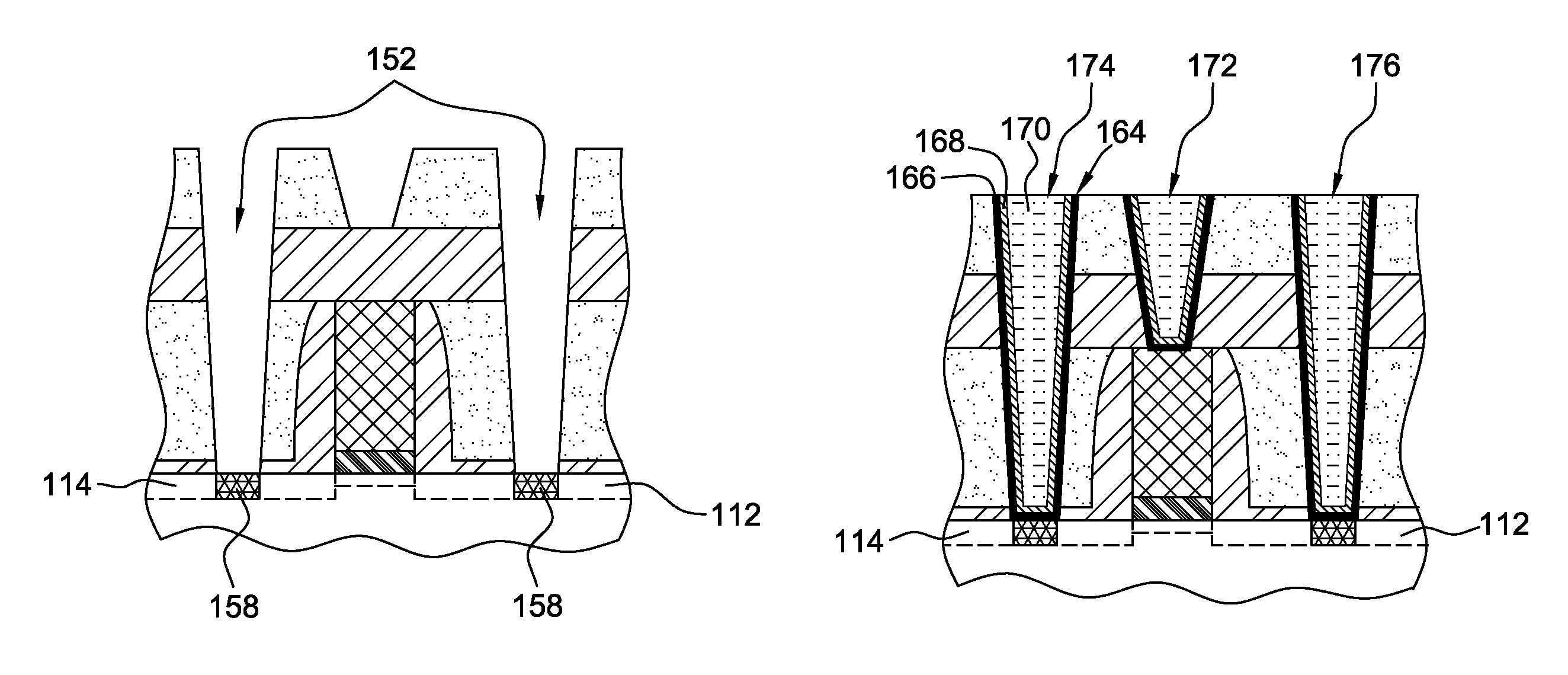

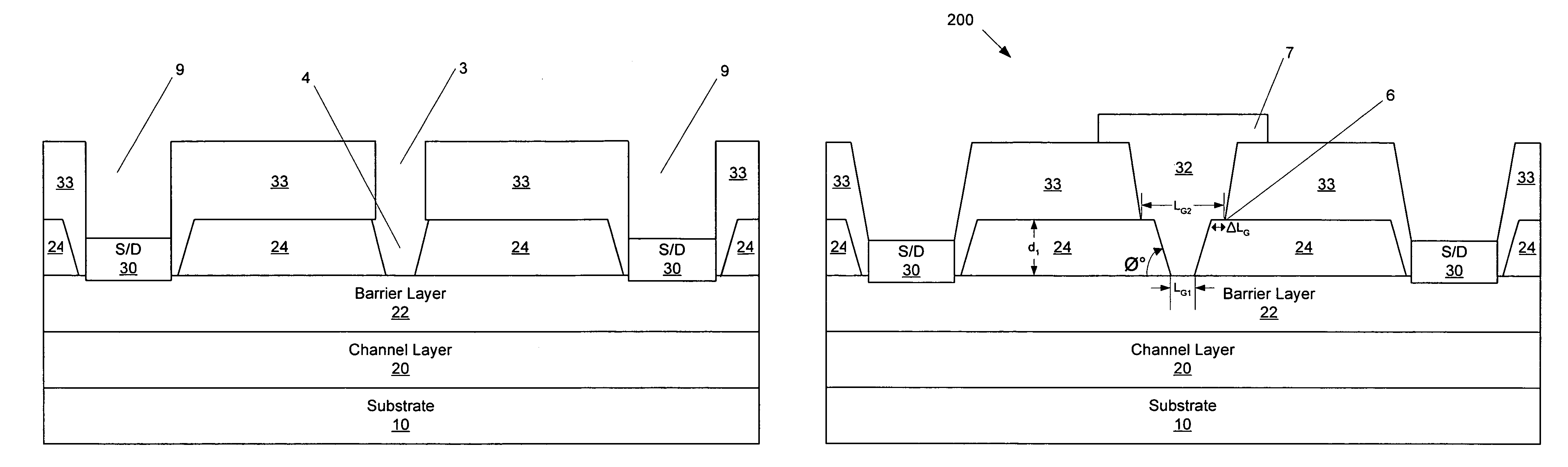

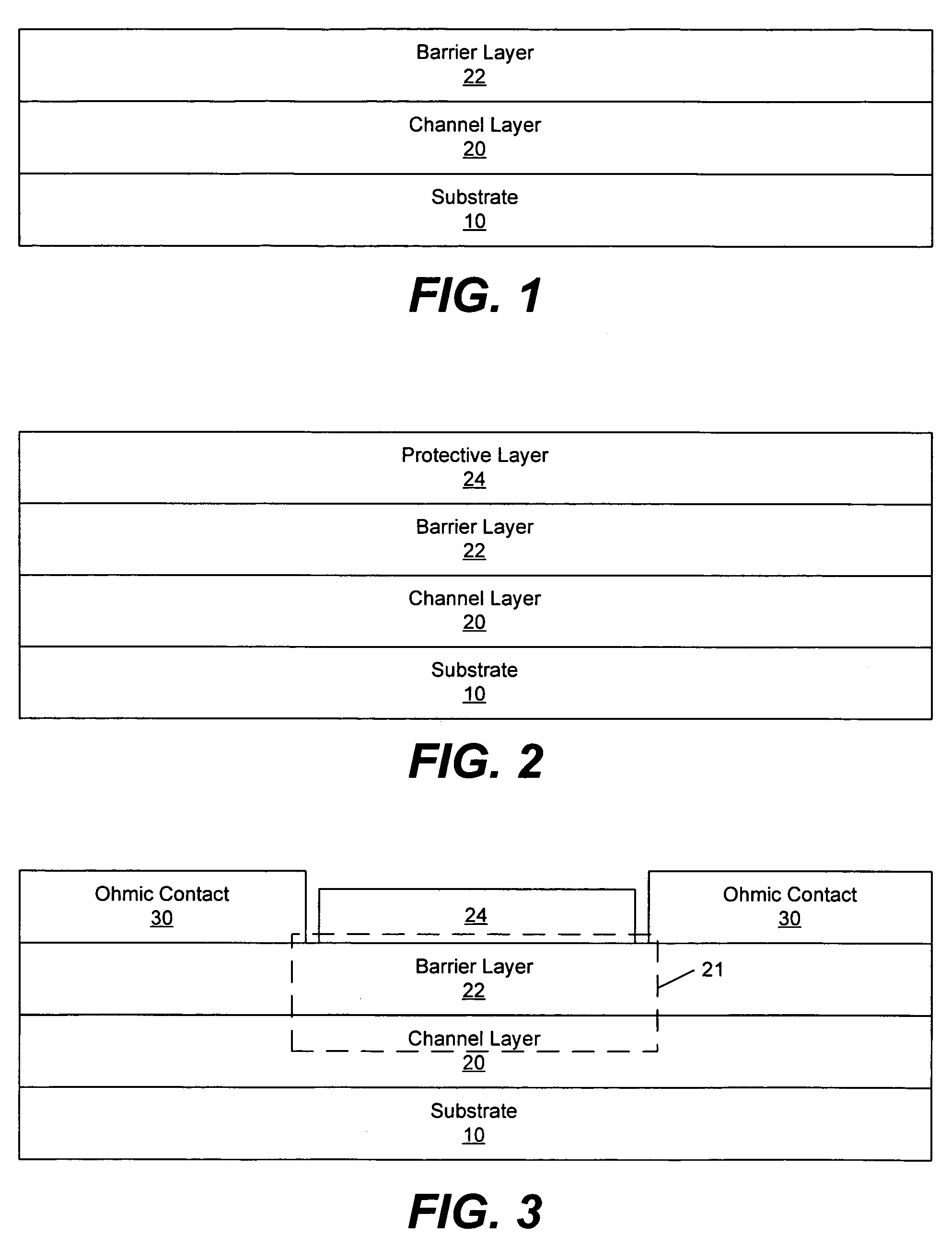

Methods of fabricating transistors including dielectrically-supported gate electrodes and related devices

ActiveUS20070164322A1Increasing the thicknessReduce gate-to-drainTransistorSemiconductor/solid-state device manufacturingEngineeringProtection layer

Transistors are fabricated by forming a protective layer having a first opening extending therethrough on a substrate, forming a dielectric layer on the protective layer having a second opening extending therethrough that is wider than the first opening, and forming a gate electrode in the first and second openings. A first portion of the gate electrode laterally extends on surface portions of the protective layer outside the first opening, and a second portion of the gate electrode is spaced apart from the protective layer and laterally extends beyond the first portion on portions of the dielectric layer outside the second opening. Related devices and fabrication methods are also discussed.

Owner:CREE INC

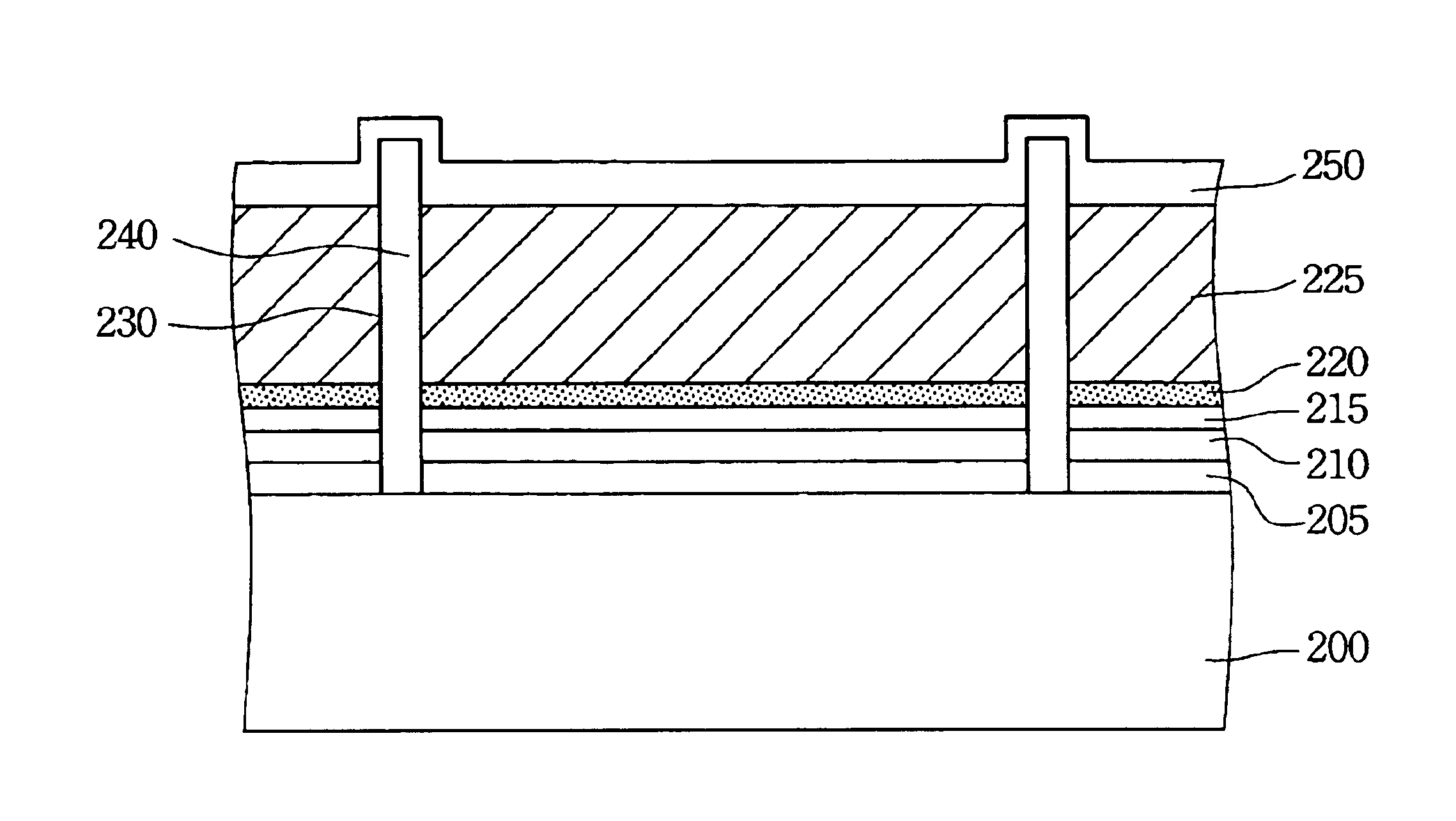

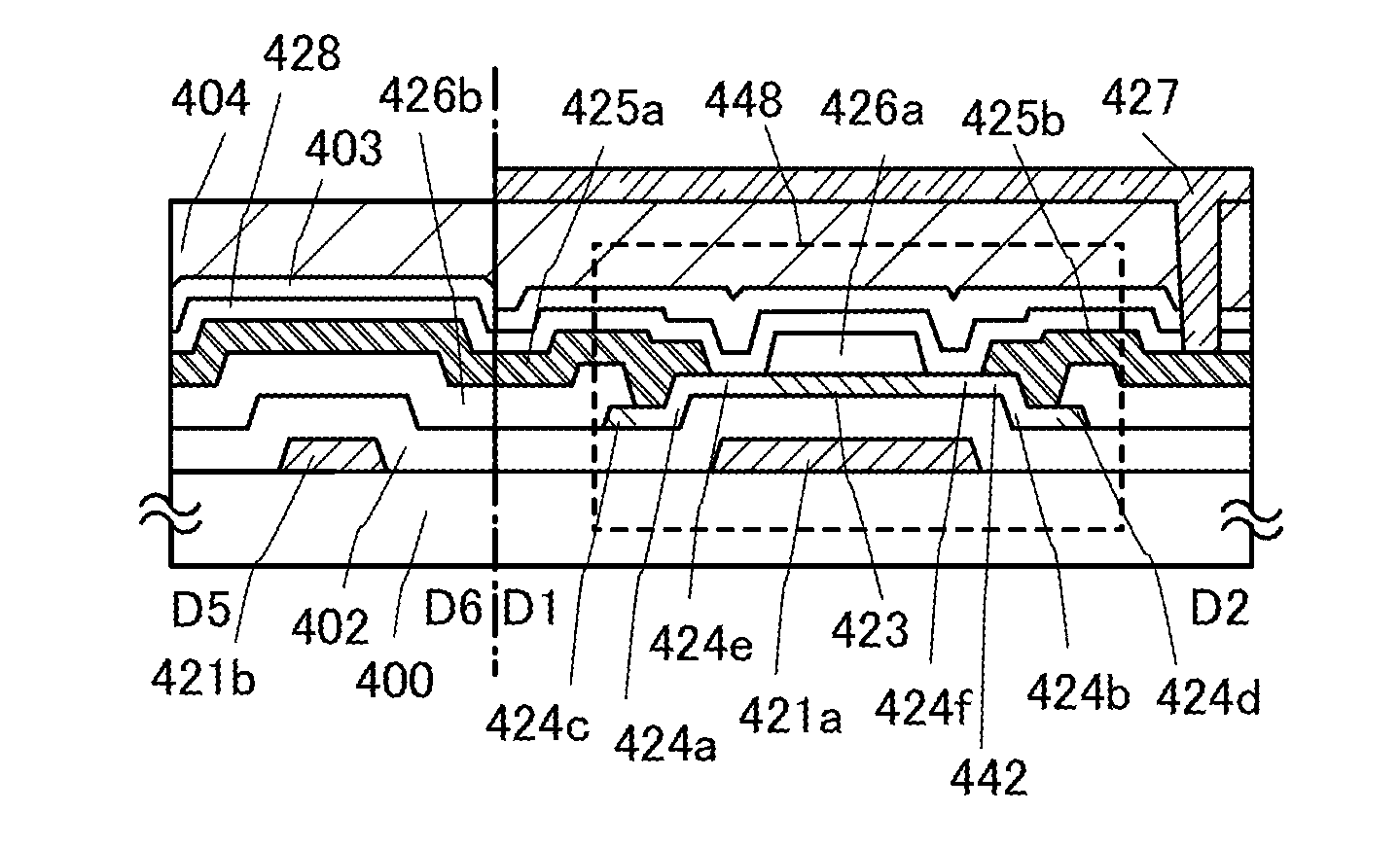

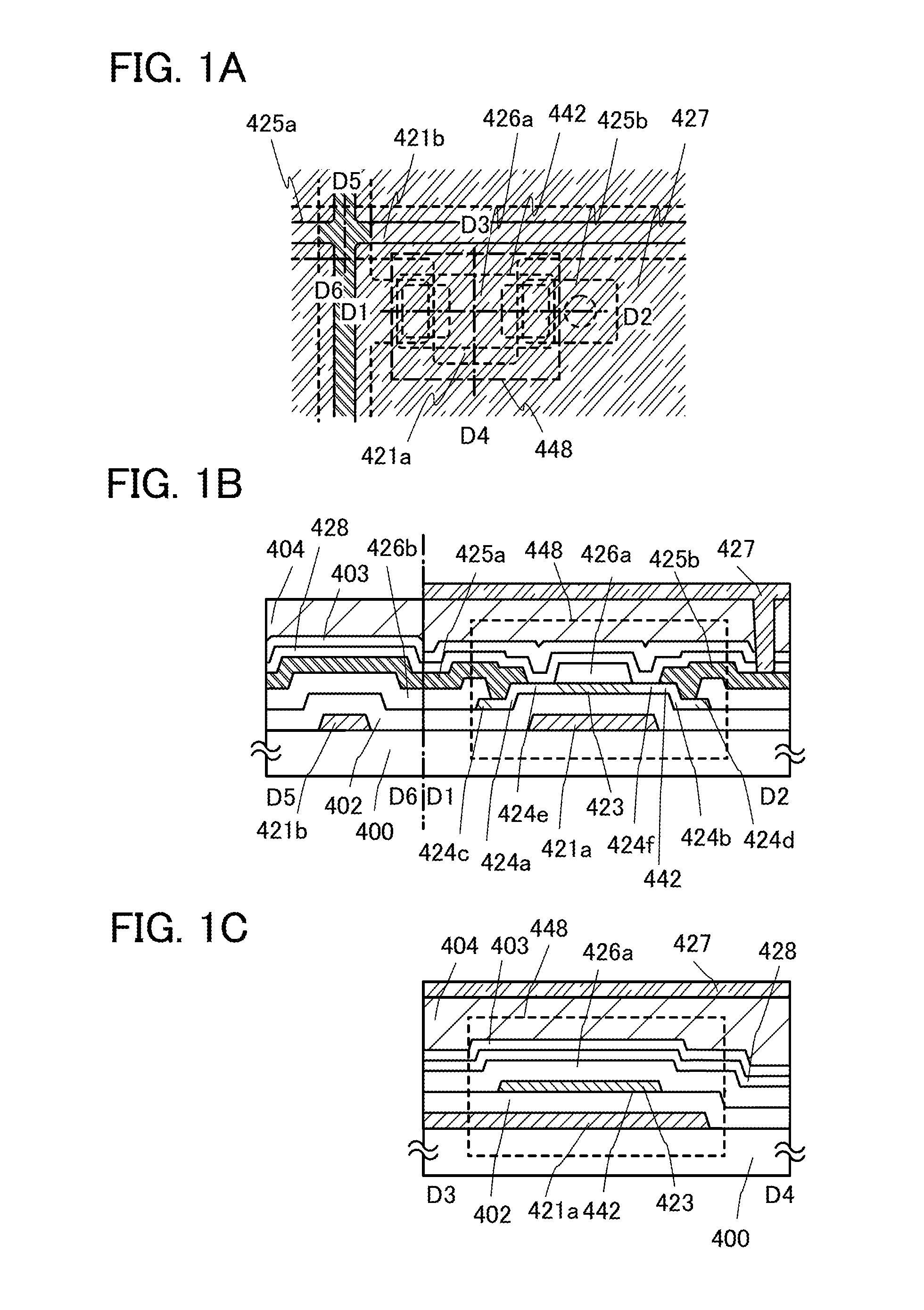

Semiconductor device and manufacturing method thereof

ActiveUS20110031491A1Reduce parasitic capacitanceOff-current can be reducedTransistorStatic indicating devicesBottom gateParasitic capacitance

An object is to provide a semiconductor device having a structure in which parasitic capacitance between wirings can be efficiently reduced. In a bottom gate thin film transistor using an oxide semiconductor layer, an oxide insulating layer used as a channel protection layer is formed above and in contact with part of the oxide semiconductor layer overlapping with a gate electrode layer, and at the same time an oxide insulating layer covering a peripheral portion (including a side surface) of the stacked oxide semiconductor layer is formed. Further, a source electrode layer and a drain electrode layer are formed in a manner such that they do not overlap with the channel protection layer. Thus, a structure in which an insulating layer over the source electrode layer and the drain electrode layer is in contact with the oxide semiconductor layer is provided.

Owner:SEMICON ENERGY LAB CO LTD

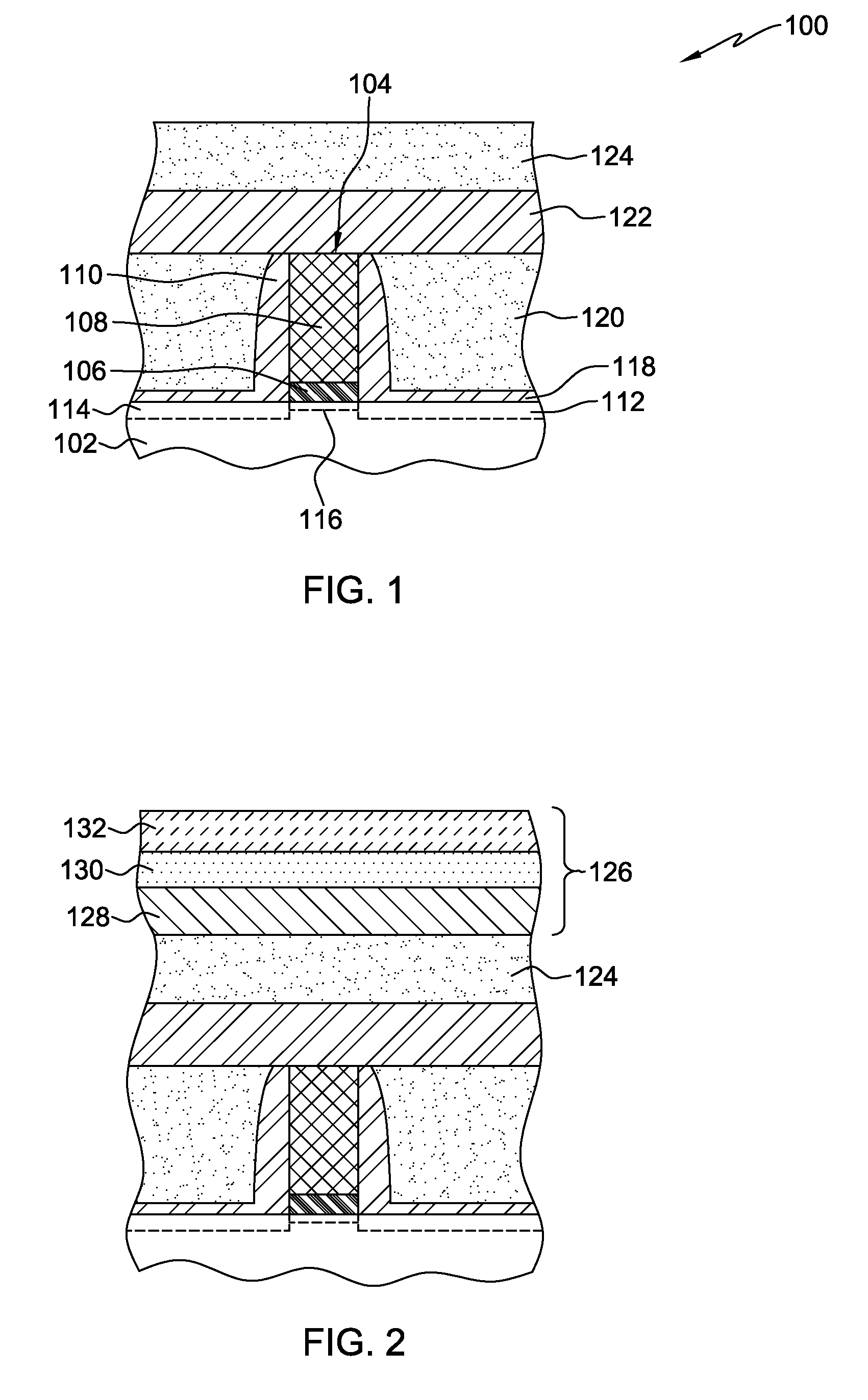

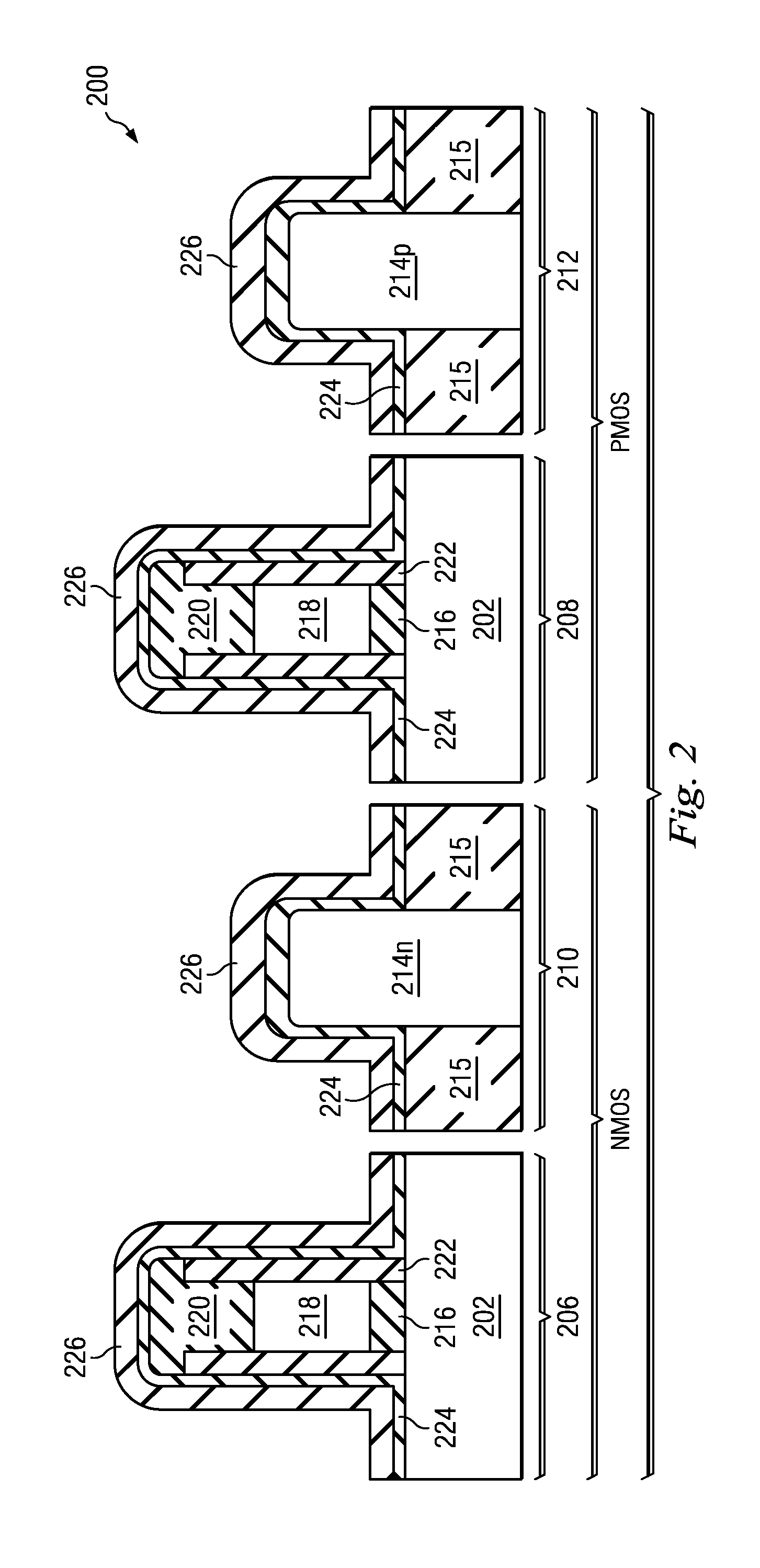

Silicide protection during contact metallization and resulting semiconductor structures

ActiveUS9111907B2Avoid damageOvercomes shortcomingSemiconductor/solid-state device detailsSolid-state devicesSalicideSemiconductor structure

Owner:GLOBALFOUNDRIES U S INC

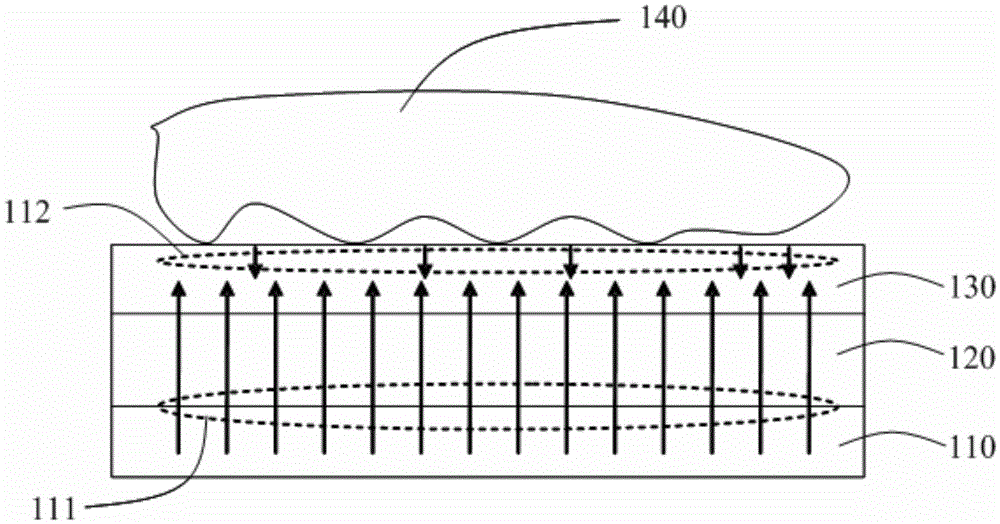

Optical fingerprint sensor module

InactiveCN105550664AReduce mutual interferenceImprove clarityPrint image acquisitionProtection layerTransmitted light

The invention discloses an optical fingerprint sensor module, comprising a protection layer and an optical fingerprint sensor located under the protection layer; the optical fingerprint sensor is equipped with a light transmitting substrate and an instruction layer; the instrument layer is equipped with multiple pixels; every pixel is equipped with a light transmitting region and a light proof region; the light proof region is equipped with a sensing element; the light transmitting region enables the lights to transmit the instrument layer; a backlight source is located under the optical fingerprint sensor; the instrument layer is located between the backlight source and the light transmitting substrate; or the light transmitting substrate is located between the backlight source and the instrument layer; at least one of a light condensing layer and a light straightening layer is arranged between the optical fingerprint sensor and the backlight source; the angle range of the transmitted lights is reduced by the light condensing layer and the light straightening layer. The definition of the fingerprint image formed by the optical fingerprint sensor module is improved.

Owner:SHANGHAI OXI TECH

Individually encapsulated solar cells and solar cell strings having a substantially inorganic protective layer

InactiveUS20070295390A1Avoid moisture damageLow costPhotovoltaic supportsPV power plantsChemical compositionEngineering

Methods and devices are provided for improved environmental protection for photovoltaic devices and assemblies. In one embodiment, the device comprises of an individually encapsulated solar cell, wherein the encapsulated solar cell includes at least one protective layer coupled to at least one surface of the solar cell and the protective layer may be formed from a substantially inorganic material. The protective layer has a chemical composition that prevents moisture from entering the solar cell and wherein light passes through the protective layer to reach an absorber layer in the solar cell.

Owner:NANOSOLAR

Edge seals for, and processes for assembly of, electro-optic displays

Owner:E INK CORPORATION

Bottom gate type thin film transistor, method of manufacturing the same, and display apparatus

InactiveUS20100051936A1Excels in mass productionOptimise total massTransistorElectroluminescent light sourcesDesorptionBottom gate

Provided is a bottom gate type thin film transistor including on a substrate (1) a gate electrode (2), a first insulating film (3) as a gate insulating film, an oxide semiconductor layer (4) as a channel layer, a second insulating film (5) as a protective layer, a source electrode (6), and a drain electrode (7), in which the oxide semiconductor layer (4) includes an oxide including at least one selected from the group consisting of In, Zn, and Sn, and the second insulating film (5) includes an amorphous oxide insulator formed so as to be in contact with the oxide semiconductor layer (4) and contains therein 3.8×1019 molecules / cm3 or more of a desorbed gas observed as oxygen by temperature programmed desorption mass spectrometry.

Owner:CANON KK

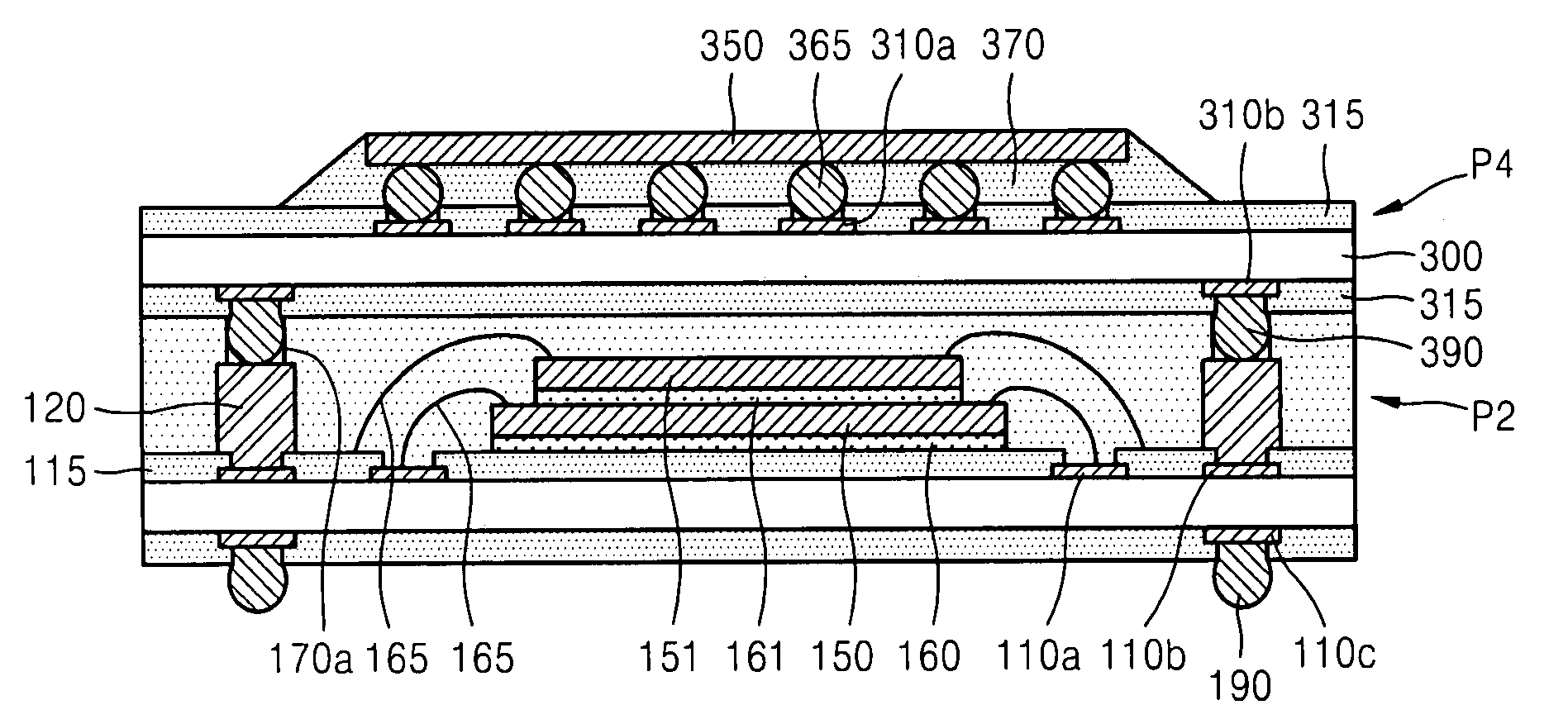

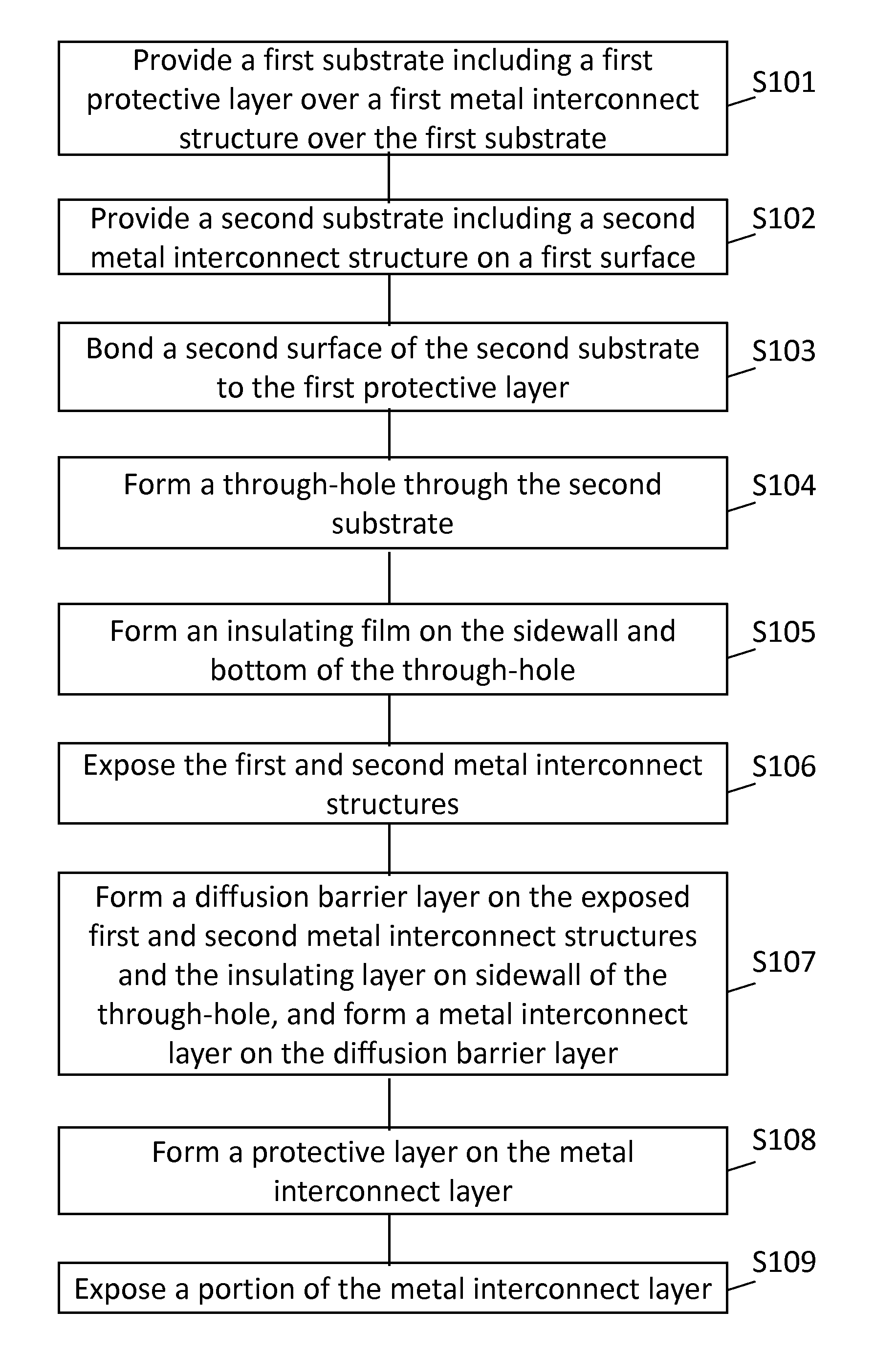

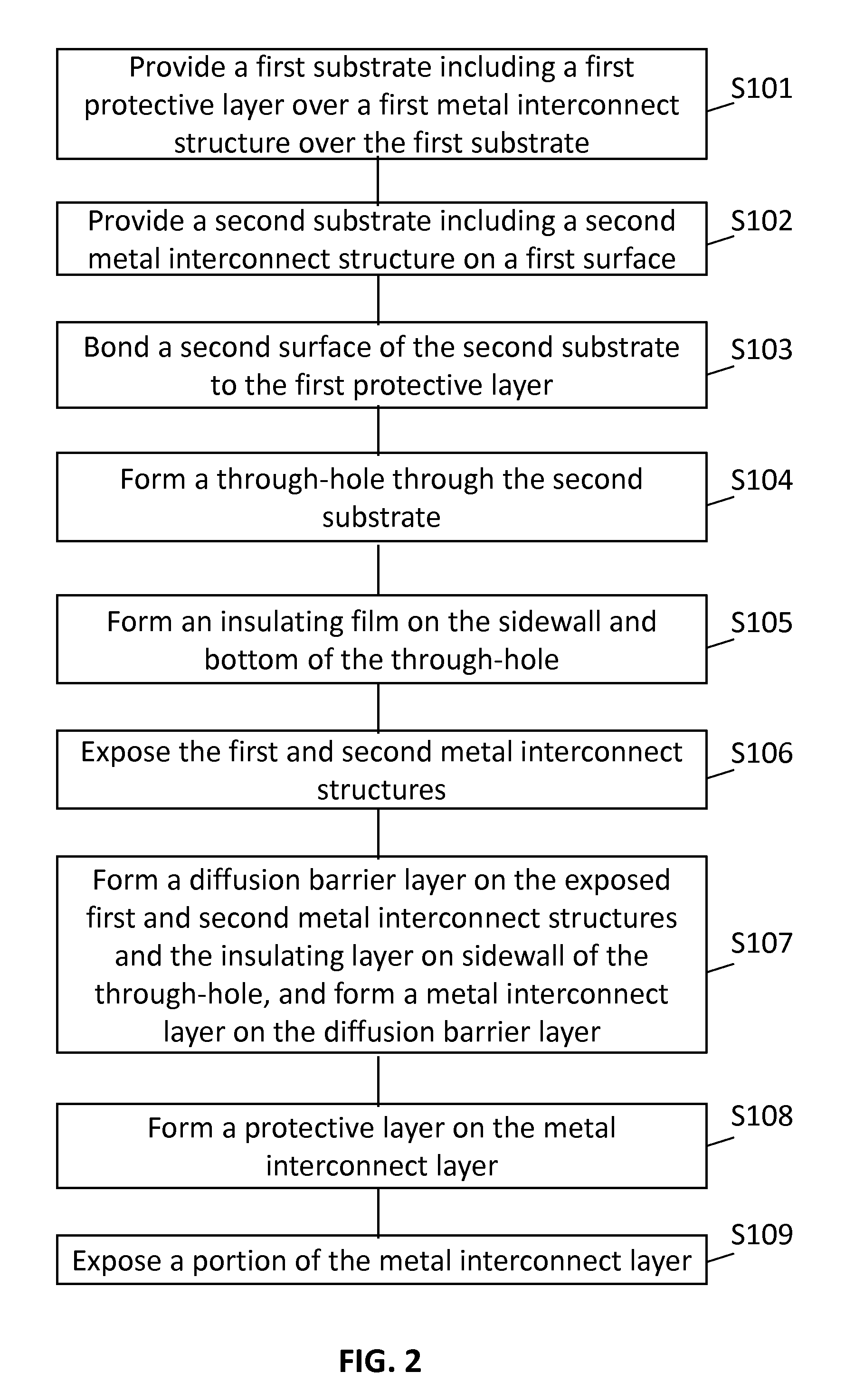

IC device including package structure and method of forming the same

ActiveUS20140015136A1Semiconductor/solid-state device detailsSolid-state devicesMetal interconnectEngineering

Various embodiments provide semiconductor devices including a package structure and methods of forming the semiconductor devices. In one embodiment, the package structure can include a through-hole at least partially filled by one or more layers of material(s) to form a through-hole interconnect between semiconductor devices in the package structure. The through-hole can be filled by an insulating layer, a diffusion barrier layer, a metal interconnect layer, and / or a protective layer having a total thickness from the sidewall of the through-hole of less than or equal to the radius of the through-hole.

Owner:SEMICON MFG INT (SHANGHAI) CORP

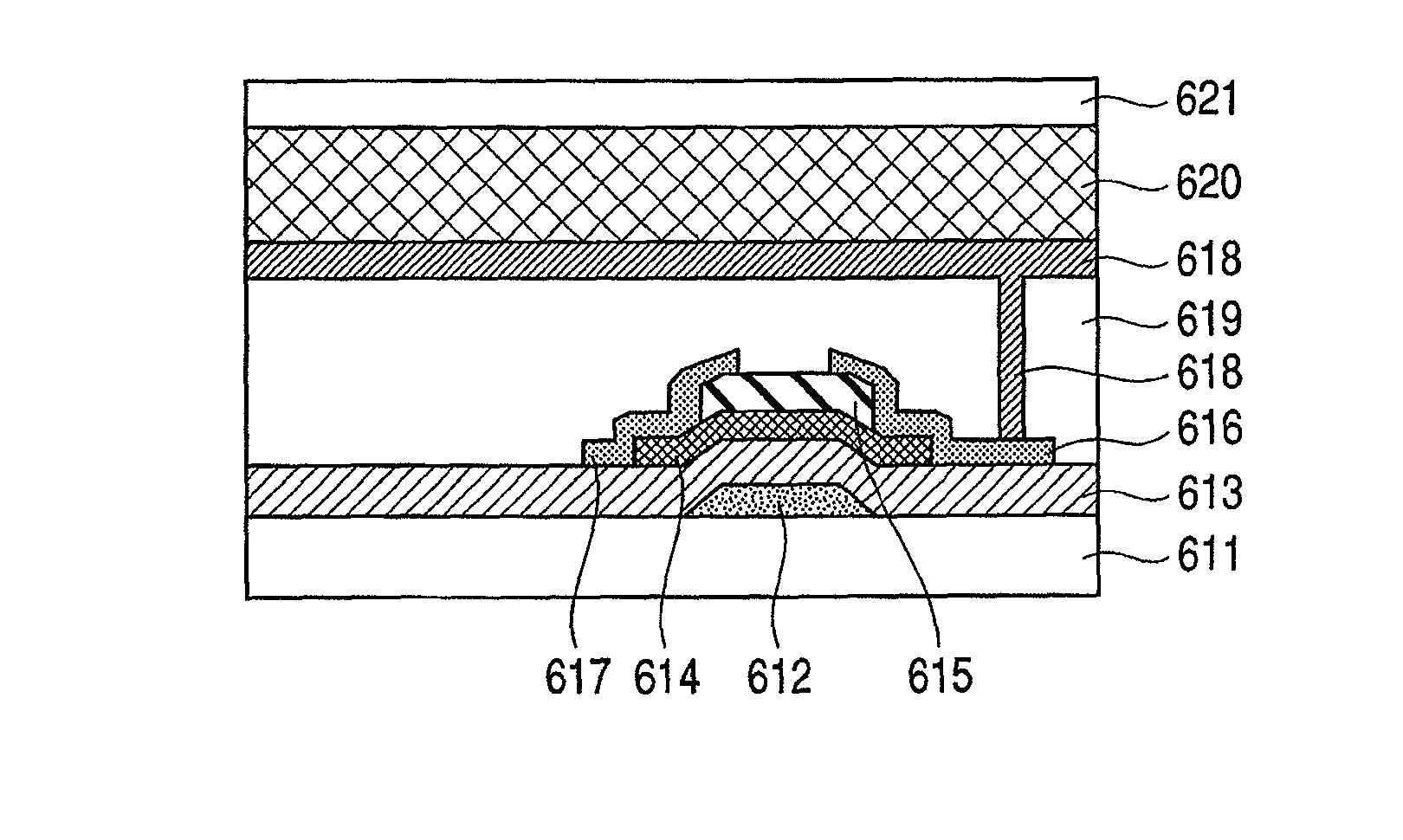

Semiconductor device, manufacturing method thereof, and electronic device

InactiveUS20110175090A1Low costFree electronTransistorSemiconductor/solid-state device manufacturingSemiconductor packageProtection layer

In a thin film transistor, a gate insulating layer is formed on a gate electrode formed on an insulating substrate. Formed on the gate insulating layer is a semiconductor layer. Formed on the semiconductor layer are a source electrode and a drain electrode. A protective layer covers them, so that the semiconductor layer is blocked from an atmosphere. The semiconductor layer (active layer) is made of, e.g., a semiconductor containing polycrystalline ZnO to which, e.g., a group V element is added. This allows practical use of a semiconductor device which has an active layer made of zinc oxide and which includes an protective layer for blocking the active layer from an atmosphere.

Owner:SHARP KK +2

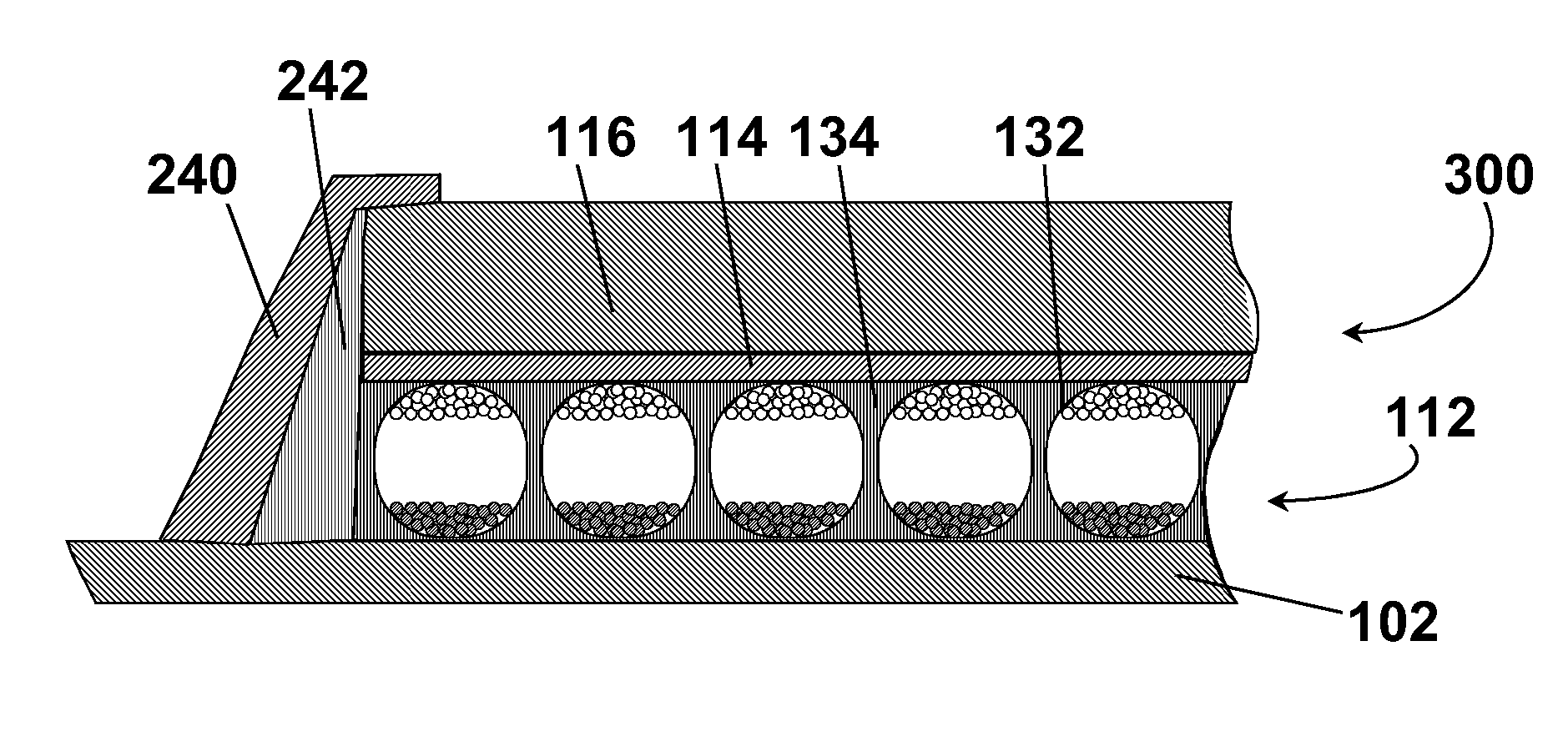

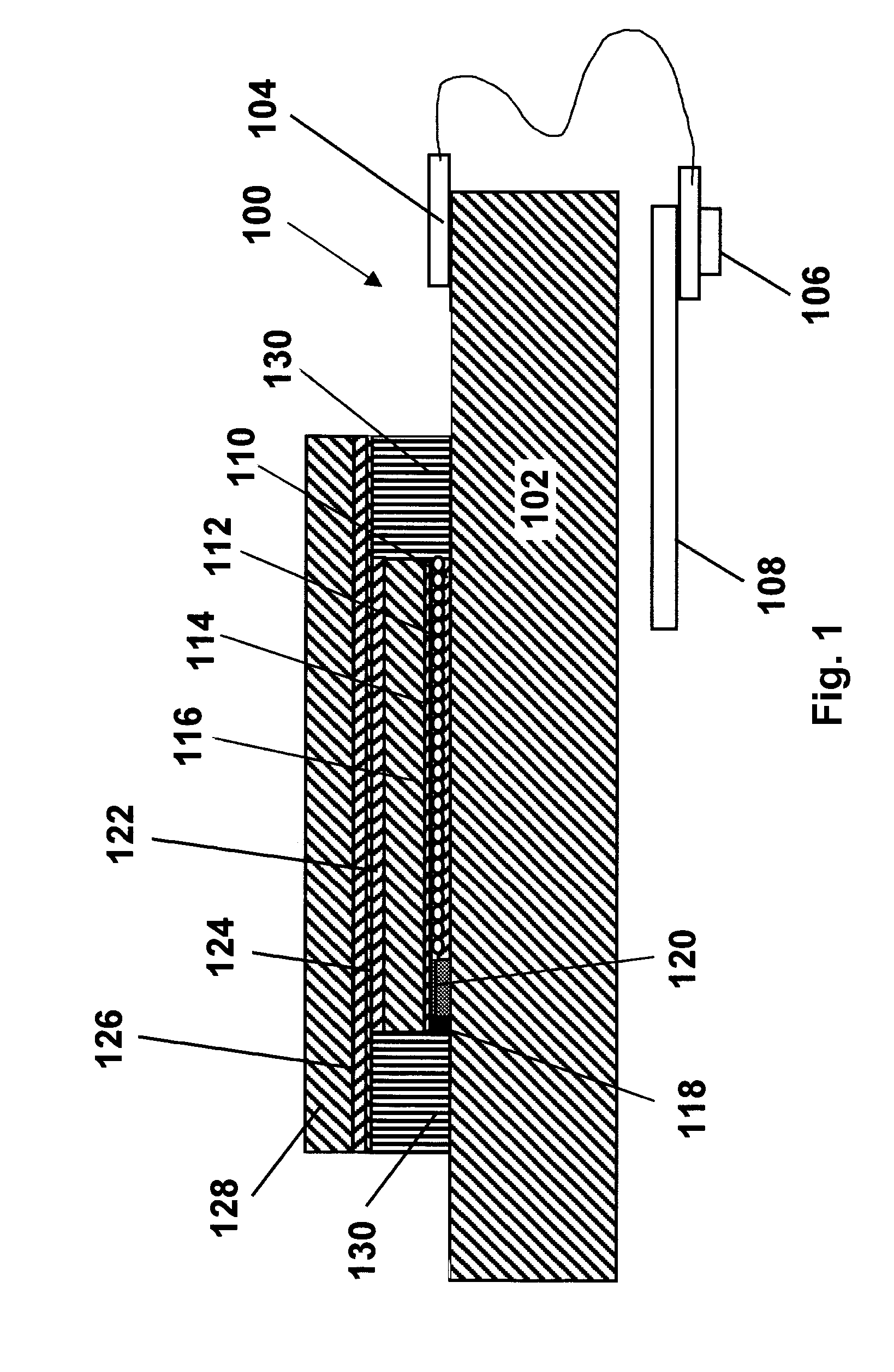

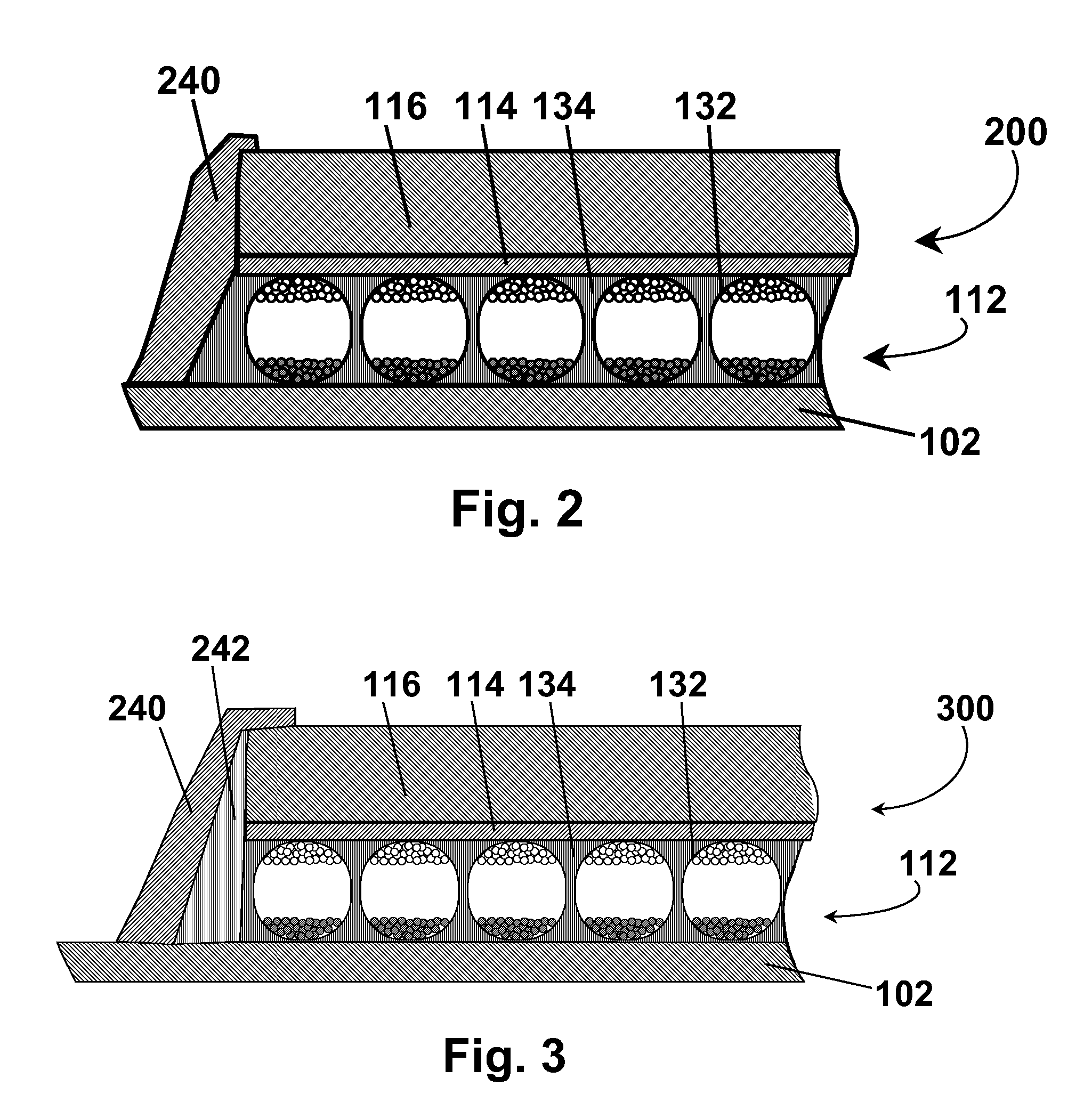

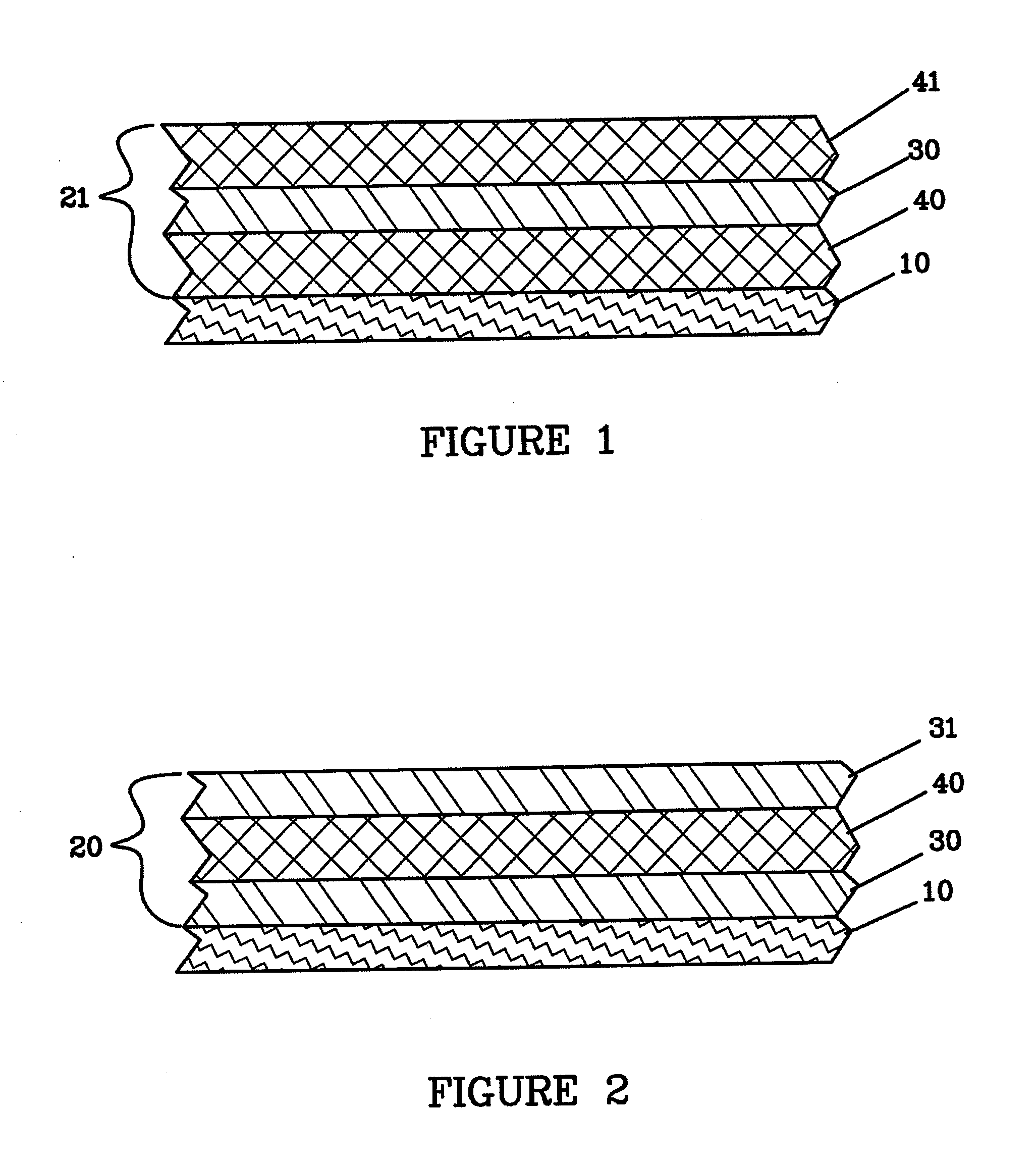

Integrated circuit support structures and their fabrication

ActiveUS7635641B2Suitable for mass productionHigh yieldSemiconductor/solid-state device detailsPrinted circuit aspectsEngineering physicsProtection layer

A method of fabricating an electronic substrate comprising the steps of; (A) selecting a first base layer; (B) depositing a first etchant resistant barrier layer onto the first base layer; (C) building up a first half stack of alternating conductive layers and insulating layers, the conductive layers being interconnected by vias through the insulating layers; (D) applying a second base layer onto the first half stack; (F) applying a protective coating of photoresist to the second base layer; (F) etching away the first base layer; (G) removing the protective coating of photoresist; (H) removing the first etchant resistant barrier layer; (I) building up a second half stack of alternating conductive layers and insulating layers, the conductive layers being interconnected by vias through the insulating layers, wherein the second half stack has a substantially symmetrical lay up to the first half stack; (J) applying an insulating layer onto the second hall stack of alternating conductive layers and insulating layers, (K) removing the second base layer, and (L) terminating the substrate by exposing ends of vias on outer surfaces of the stack and applying terminations thereto.

Owner:ZHUHAI ADVANCED CHIP CARRIERS & ELECTRONICS SUBSTRATE SOLUTIONS TECH

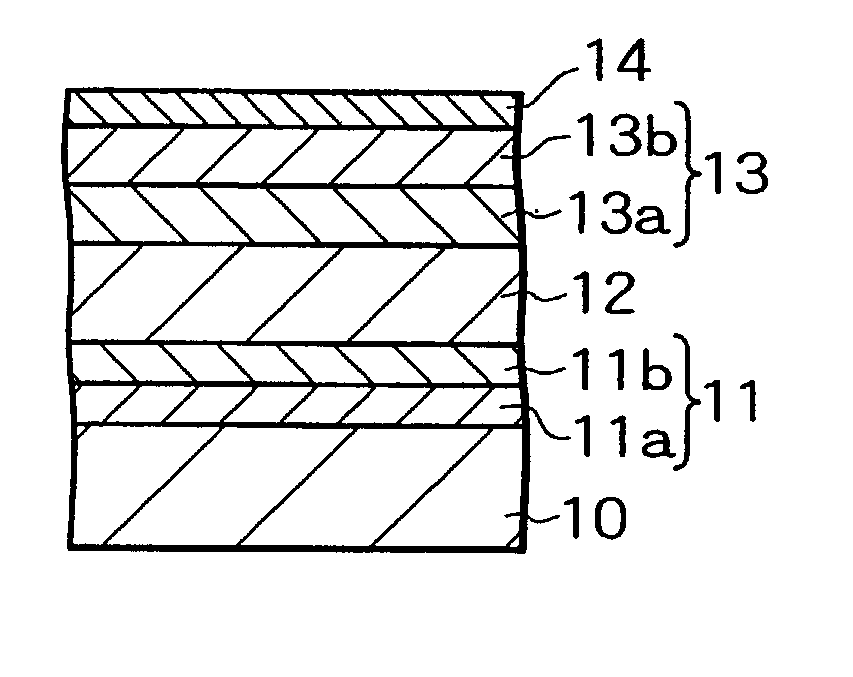

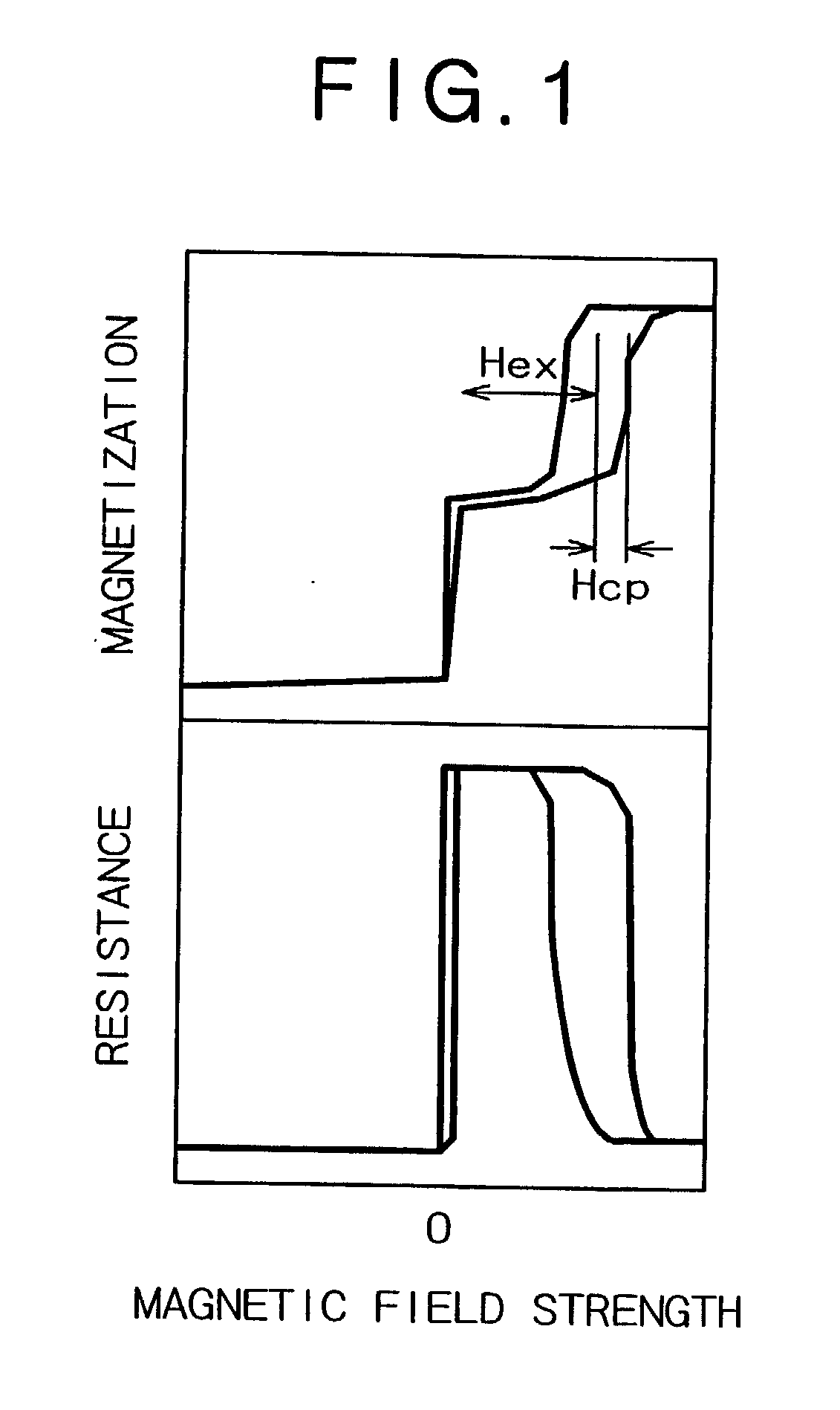

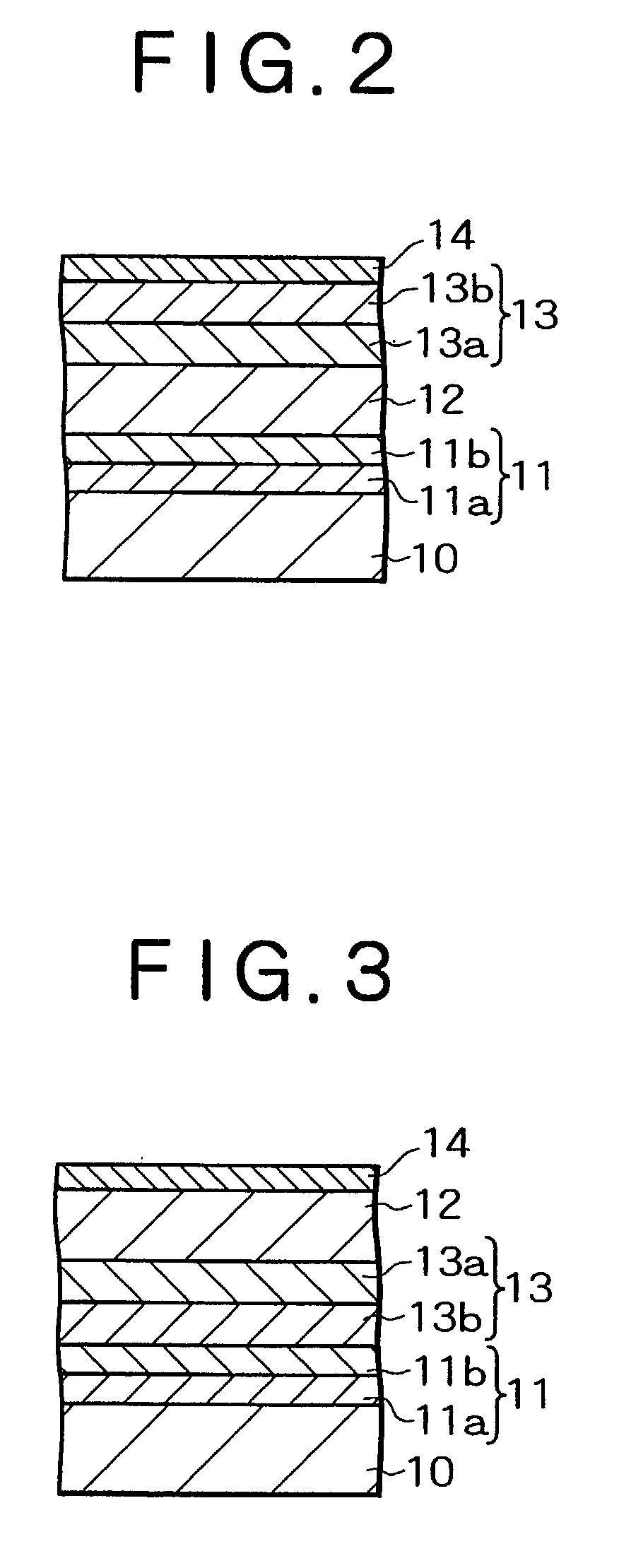

Exchange coupling film, magneto-resistance effect device, magnetic head, and magnetic random access memory

A foundation layer increasing adhesive properties to a substrate, another foundation layer controlling orientation of an antiferromagnetic layer, the antiferromagnetic layer including a disordered alloy of IrMn, a pinning layer, and a cap protection layer are formed in the order on the substrate. The pinning layer includes two layers having an exchange coupling giving layer which exchange-couples to the antiferromagnetic layer and an exchange coupling enhancement layer which enhances the exchange coupling, the exchange coupling giving layer is made of a ferromagnetic material including Co or a Co100-XFeX alloy (O<=X<25) having face-centered cubic structure. The exchange coupling enhancement layer is made of Fe or a Co100-YFeY alloy (25<=Y<=100) having body-centered cubic structure.

Owner:NEC CORP

Methods of fabricating transistors including dielectrically-supported gate electrodes

ActiveUS7709269B2Reduce gate-to-drainTransistorSemiconductor/solid-state device manufacturingProtection layerDielectric layer

Transistors are fabricated by forming a protective layer having a first opening extending therethrough on a substrate, forming a dielectric layer on the protective layer having a second opening extending therethrough that is wider than the first opening, and forming a gate electrode in the first and second openings. A first portion of the gate electrode laterally extends on surface portions of the protective layer outside the first opening, and a second portion of the gate electrode is spaced apart from the protective layer and laterally extends beyond the first portion on portions of the dielectric layer outside the second opening. Related devices and fabrication methods are also discussed.

Owner:CREE INC

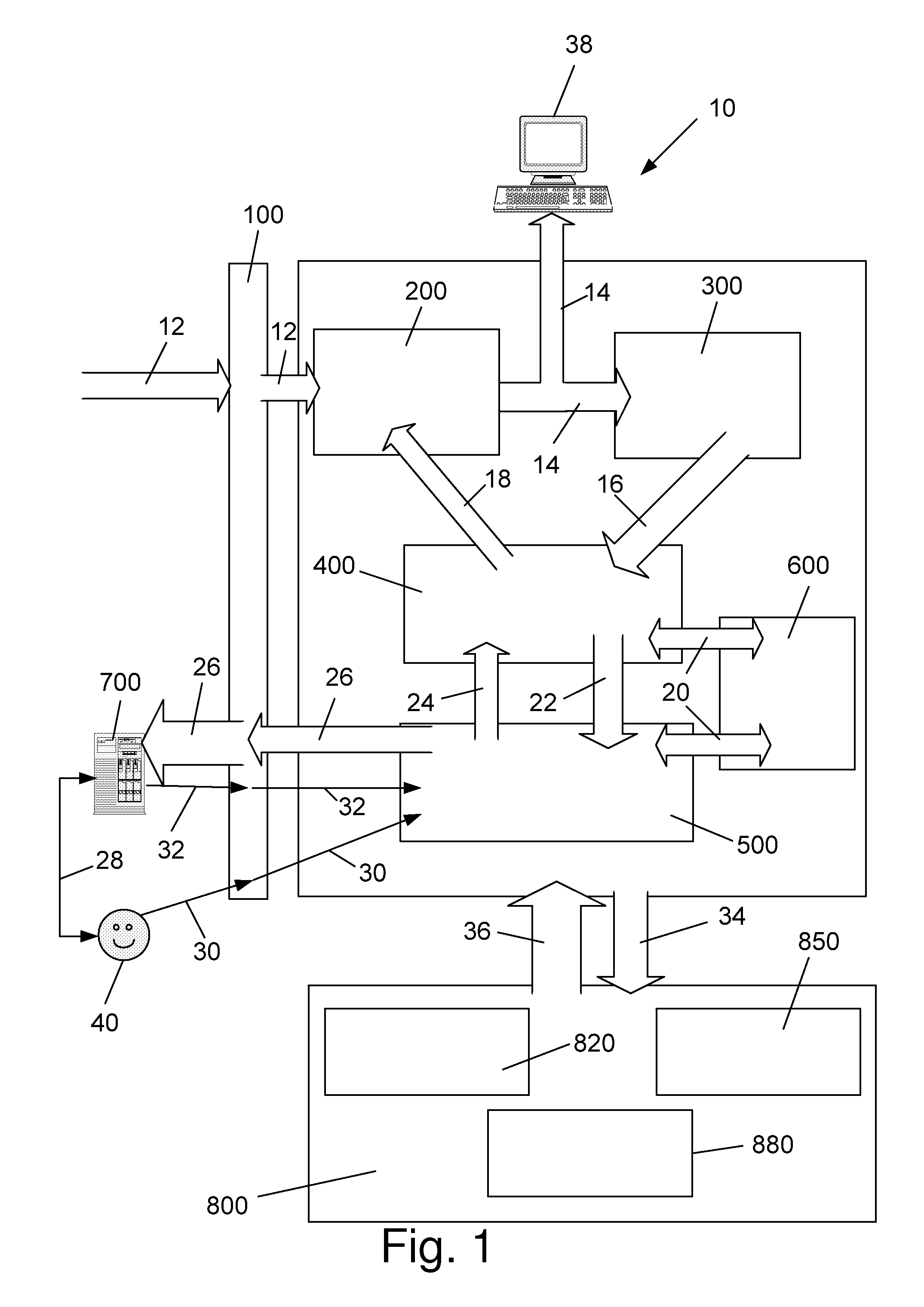

System that provides early detection, alert, and response to electronic threats

InactiveUS20100031358A1Memory loss protectionDigital data processing detailsData streamProtection layer

The invention is a computer system that provides early detection alert and response to electronic threats (eThreats) in large wide area networks, e.g. the network of an Internet Services Provider or a Network Services Provider. The system of the invention accomplishes this by harnessing the processing power of dedicated hardware, software residing in specialized servers, distributed personal computers connected to the network, and the human brain to provide multi-layered early detection, alarm and response. The layers comprise: a Protection Layer, which detects and eliminates from the network data stream eThreats known to the system; a Detection Layer, which detects and creates signatures for new eThreats that are unknown to the system; an Expert Analysis Layer, which comprises a group of human experts who receive information from various components of the system and analyze the information to confirm the identity of new eThreats; and a Collaborative Detection & Protection Layer, which detects potential new eThreats by processing information received from various system agents and users. A Dynamic Sandbox Protection Layer associated with the distributed personal computers connected to the network. can optionally be part of the system of the invention.

Owner:DEUTSCHE TELEKOM AG

Infrared detector with micro-bridge structure and manufacturing method thereof

ActiveCN101927976AFacilitate subsequent processingRealize the CMP processTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesElectromechanicsLithographic artist

The invention relates to an infrared detector with a micro-bridge structure, which belongs to the technical field of micro-electromechanics, and comprises a silicon substrate as a read-out circuit of the infrared detector; a metal reflecting layer deposited on the silicon substrate; a dielectric layer which is deposited in a groove of the metal reflecting layer and has the height being consistentwith that of the metal reflecting layer; a sacrifice layer and a first release protection layer used as protection of release of the sacrifice layer which are deposited on the dielectric layer and the metal reflecting layer and form through holes by lithography and etching; a copper or tungsten pier which is deposited in the through hole of the sacrifice layer; a metal electrode deposited on the copper or tungsten pier and the first release protection layer; and a sensitive material detecting layer which is deposited on the metal electrode and the first release protection layer. A Cu-column micro-bridge structure is manufactured by using the damascene process, and a flat micro-bridge plane is manufactured by introducing the chemical mechanical polishing process (CMP), thereby being conductive to the follow-up process and improving the performances.

Owner:ZHEJIANG DALI TECH +1

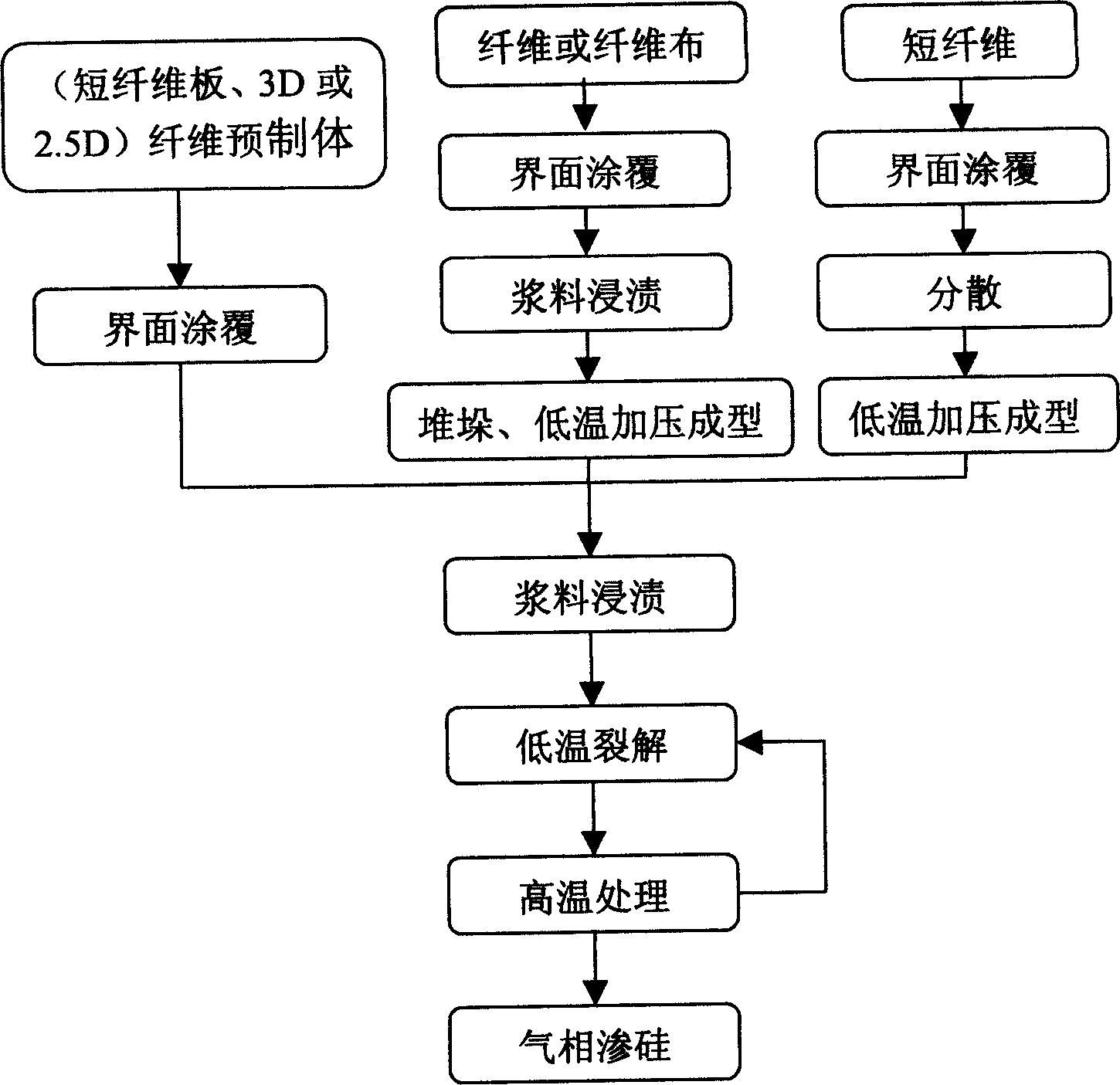

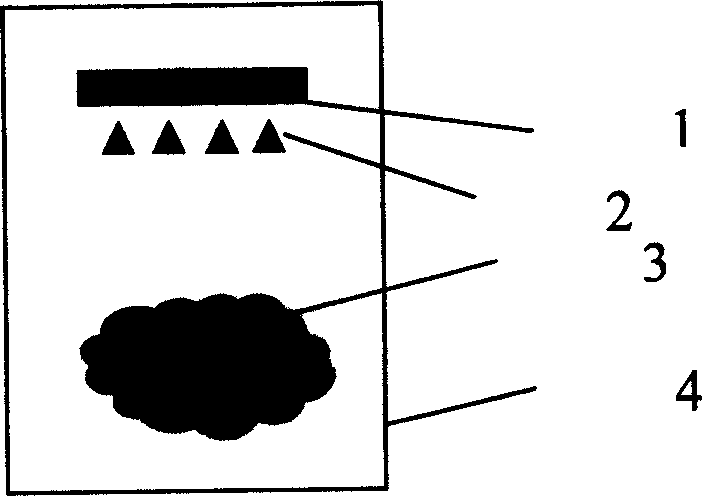

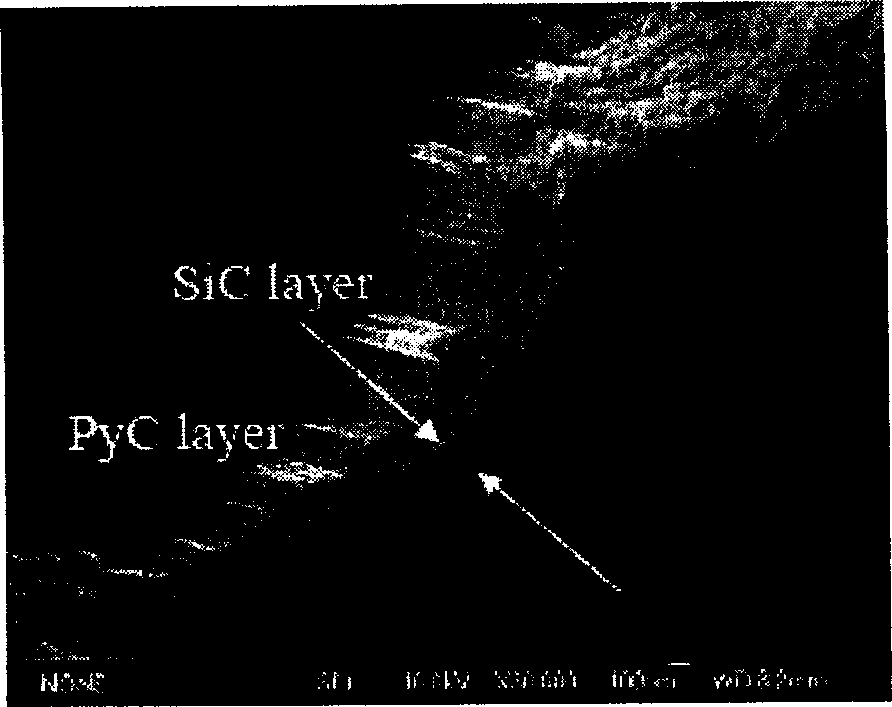

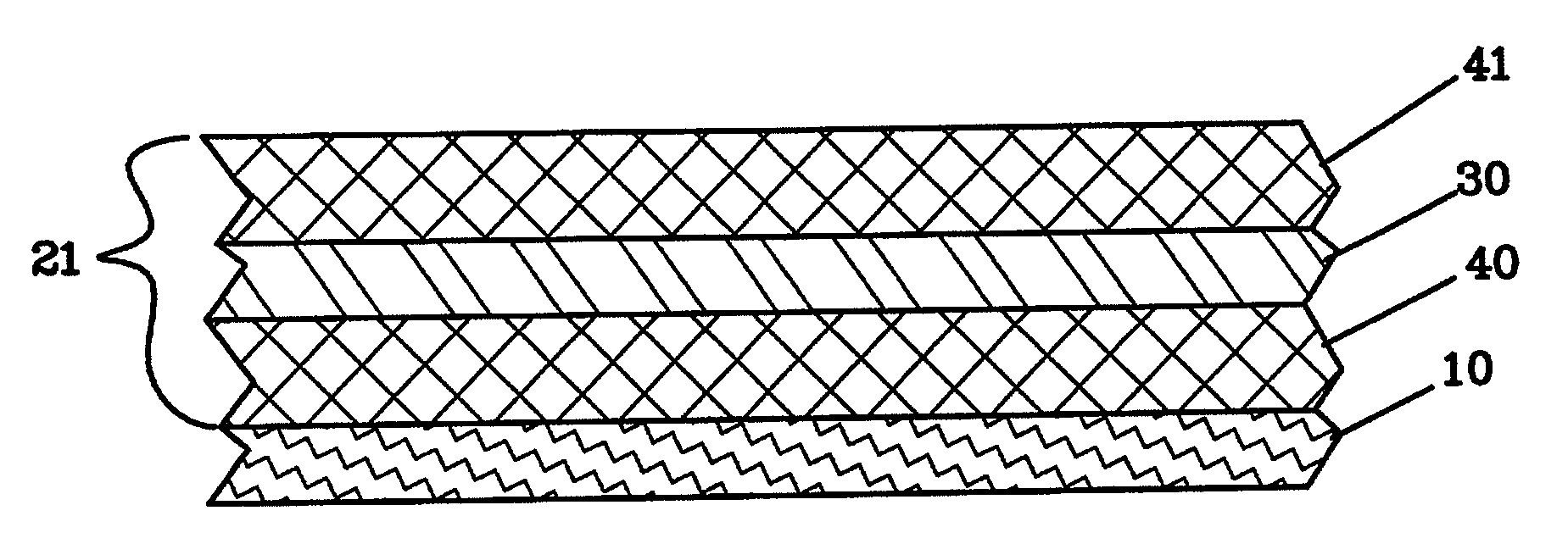

Method for preparing carbon-fiber reinforced silicon carbonate base composite by gas-phase siliconizing technology

This invention relates to preparation method gas phase siliconizing technique preparing high compact fiber reinforcement SiC group composite material. Protection layer interface is formed on fiber surface through gas phase or liquid phase, then they are dipped and cracked through nm SiC slime to make certain density precast body of fiber reinforcement SiC group. Carbon is added into the body through dipping and cracking way to form group body with certain pore, the group body penetrates inner part of the multi-hole body through gas phase silicon after it is high temperature treated, then it reacts with carbon and fills the pore to get compact basal body. The density of the material can reach 2.25-2.30g / cm3, open porosity is 3-6 percent; it is large more higher than traditional method of getting Cf / SiC material.

Owner:SHANGHAI INST OF CERAMIC CHEM & TECH CHINESE ACAD OF SCI

Protection of anodes for electrochemical cells

InactiveUS20100104948A1Light weightAlkaline accumulatorsElectrode manufacturing processesSulfur containingElectrochemical cell

Provided is an anode for use in electrochemical cells, wherein the anode active layer has a first layer comprising lithium metal and a multi-layer structure comprising single ion conducting layers and polymer layers in contact with the first layer comprising lithium metal or in contact with an intermediate protective layer, such as a temporary protective metal layer, on the surface of the lithium-containing first layer. Another aspect of the invention provides an anode active layer formed by the in-situ deposition of lithium vapor and a reactive gas. The anodes of the current invention are particularly useful in electrochemical cells comprising sulfur-containing cathode active materials, such as elemental sulfur.

Owner:SION POWER CORP

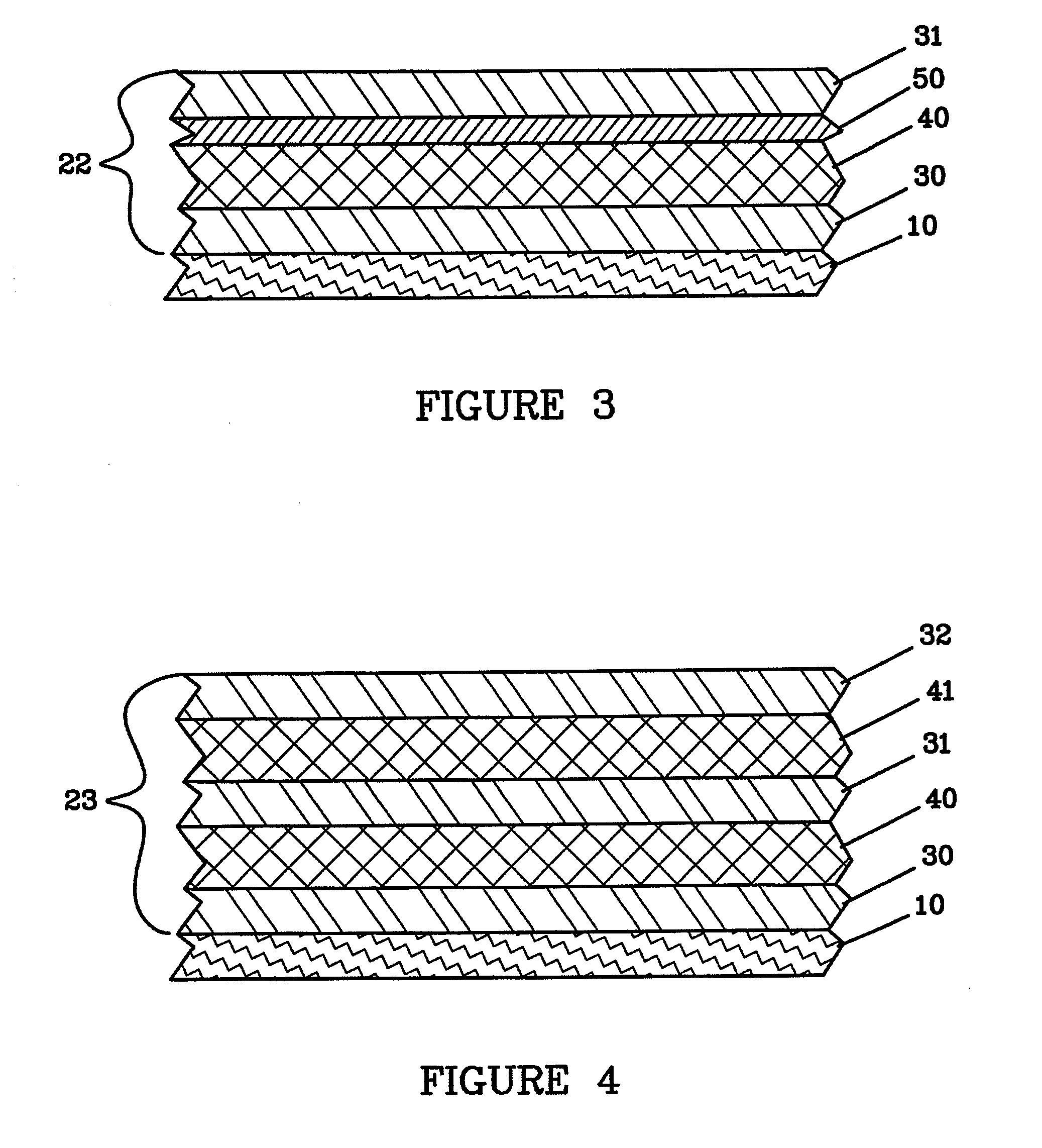

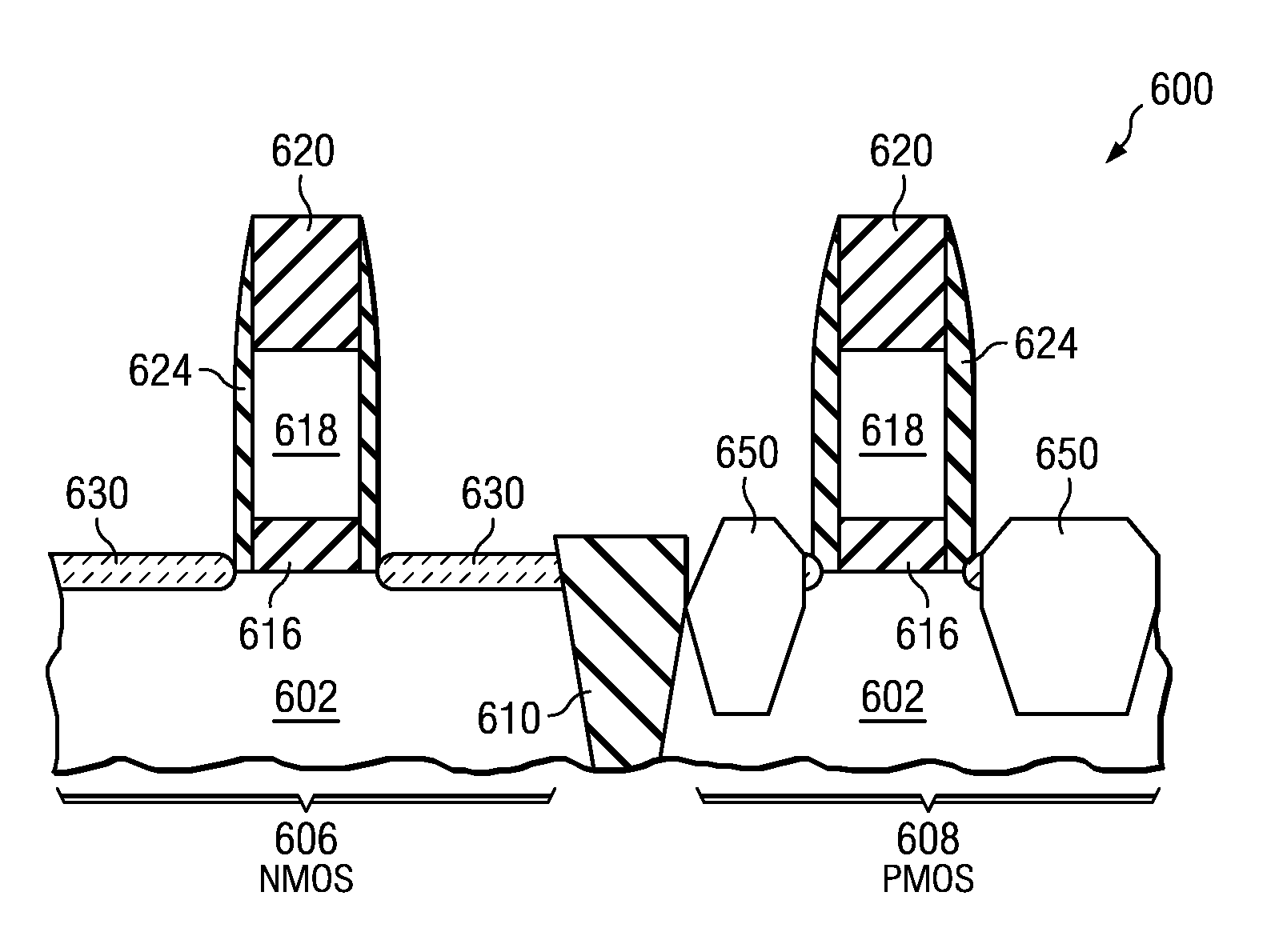

Method of Dual EPI Process For Semiconductor Device

ActiveUS20110201164A1Semiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceSemiconductor materials

The present disclosure provides a method of fabricating a semiconductor device that includes forming first and second gate structures over first and second regions of a substrate, respectively, forming spacers on sidewalls of the first and second gate structures, the spacers being formed of a first material, forming a capping layer over the first and second gate structures, the capping layer being formed of a second material different from the first material, forming a protection layer over the second region to protect the second gate structure, removing the capping layer over the first gate structure; removing the protection layer over the second region, epitaxially (epi) growing a semiconductor material on exposed portions of the substrate in the first region, and removing the capping layer over the second gate structure by an etching process that exhibits an etching selectivity of the second material to the first material.

Owner:TAIWAN SEMICON MFG CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com