Semiconductor device, manufacturing method thereof, and electronic device

a technology of semiconductor devices and manufacturing methods, applied in the direction of semiconductor devices, electrical devices, transistors, etc., can solve the problems of too many free electrons and wholly blocked active layers, and achieve the effect of stabilizing the element property of semiconductor devices, reducing manufacturing costs of semiconductor devices, and facilitating semiconductor device manufacturing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

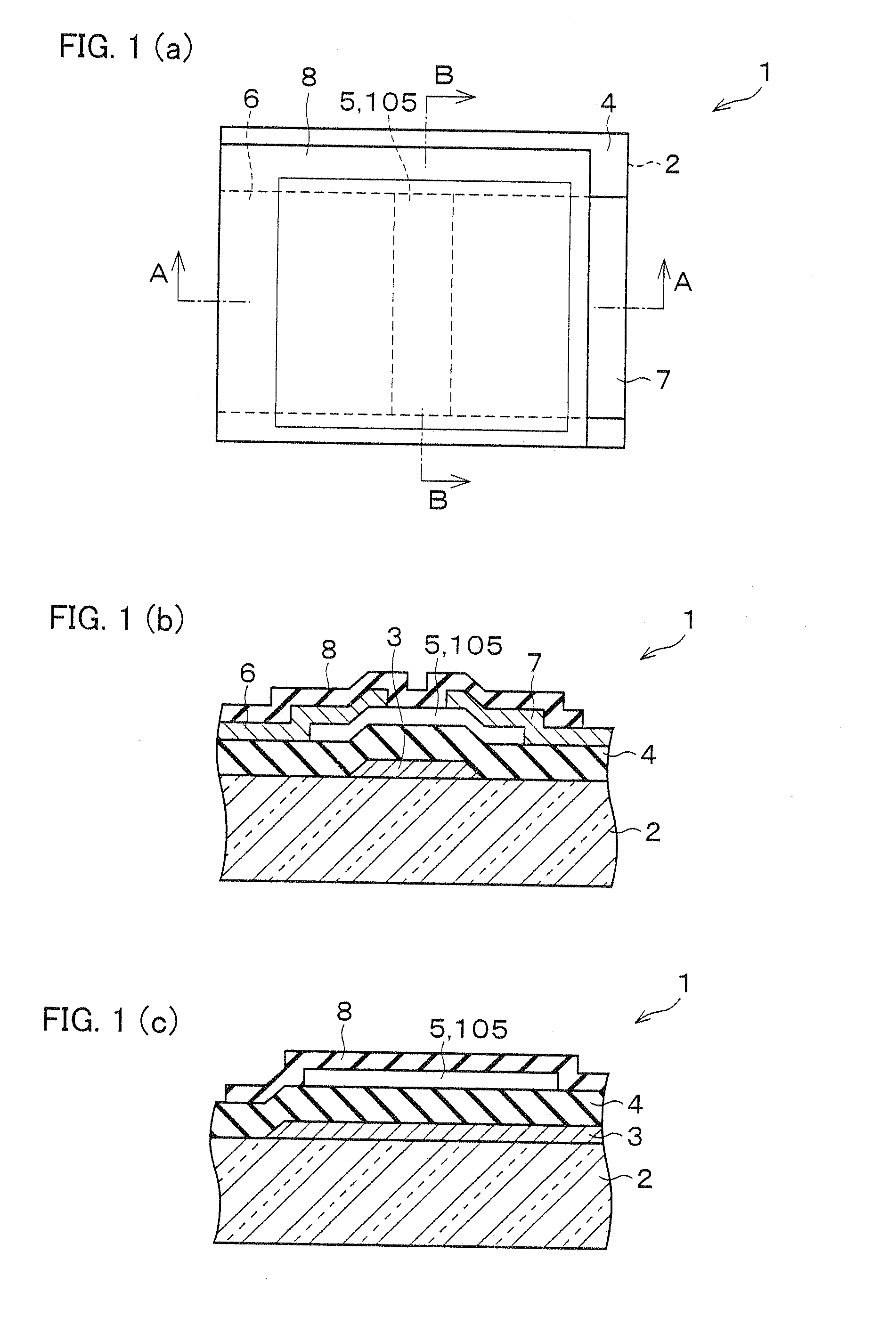

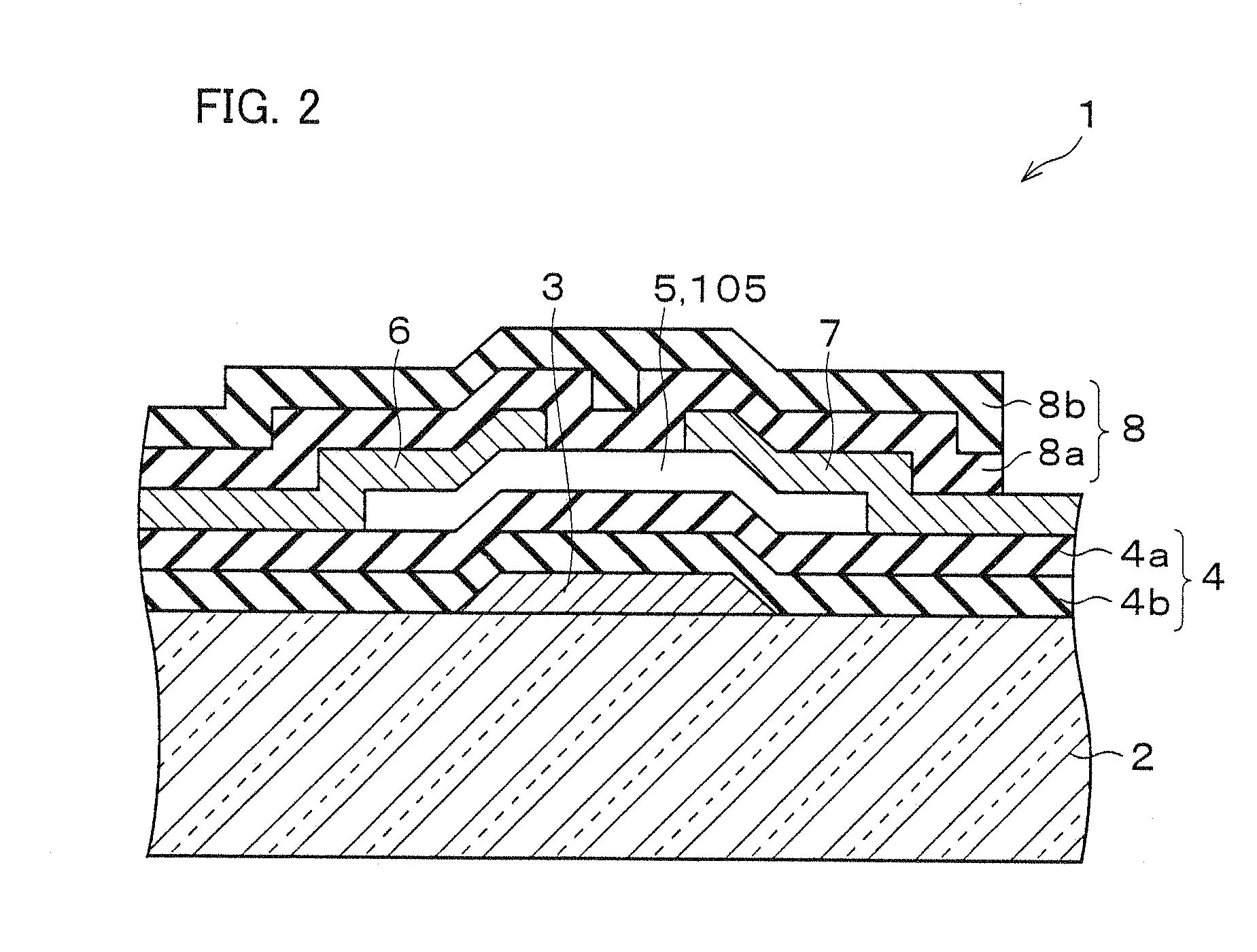

[0088]Embodiment 1 of the present invention will be explained below with reference to FIG. 1 through FIG. 5.

[0089]FIG. 1(a) is a plan view illustrating a thin film transistor 1 according to the present embodiment. FIG. 1(b) is a cross sectional view taken along line A-A of FIG. 1(a). FIG. 1(c) is a cross sectional view taken along line B-B of FIG. 1(a). Note that, although FIG. 1(b) and FIG. 1(c) describes rise and recess each formed in the central portion of the surface of a protective layer 8, FIG. 1(a) does not describe the rise and the recess for the sake of simplicity.

[0090]As shown in FIG. 1(a) through FIG. 1(c), the thin film transistor 1 serving as a semiconductor device has the inverse staggered structure. Specifically, a gate electrode 3 is formed on an insulating substrate 2. On the insulating substrate 2 and the gate electrode 3, a gate insulating layer 4 is provided. Provided on the gate insulating layer 4 is a semiconductor layer 5. Provided on the semiconductor layer ...

embodiment 2

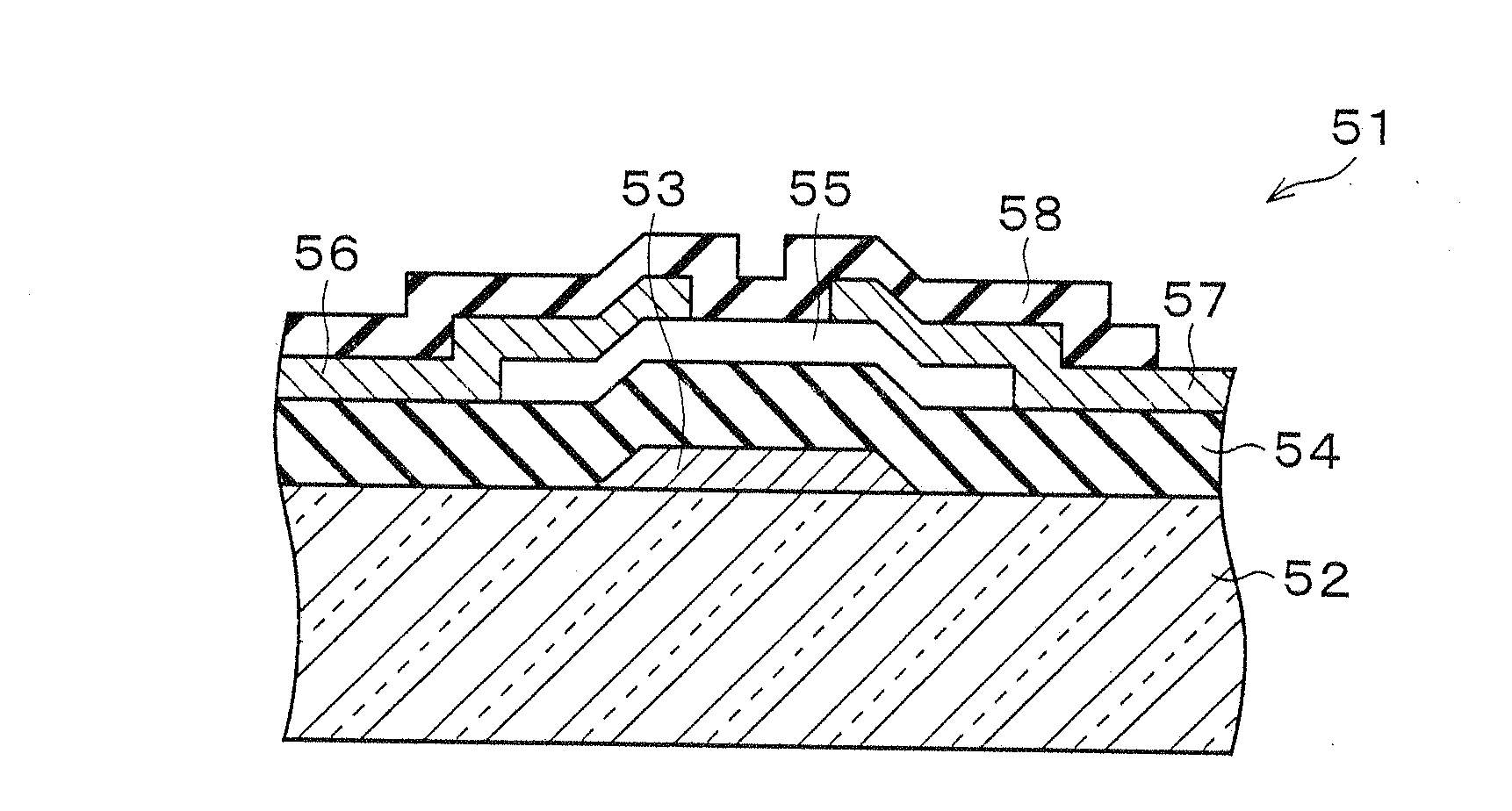

[0110]Embodiment 2 of the present invention will be explained below with reference to FIG. 6 through FIG. 8.

[0111]FIG. 6(a) is a plan view illustrating a thin film transistor 11 according to the present embodiment. FIG. 6(b) is a cross sectional view taken along line C-C of FIG. 6(a). FIG. 6(c) is a cross sectional view taken along line D-D of FIG. 6(a). Note that, although FIG. 6(b) and FIG. 6(c) describes rise and recess each formed in the central portion of the surface of a protective layer 19, FIG. 6(a) does not describe the rise and the recess for the sake of simplicity.

[0112]As shown in FIG. 6(a) through FIG. 6(c), the thin film transistor 11 serving as a semiconductor device has the staggered structure. Specifically, a priming insulating layer 13 is formed on an insulating substrate 12. A source electrode 14 and a drain electrode 15 are formed on the priming insulating layer 13 with a space therebetween. Formed on and above the source electrode 14, the drain electrode 15, and...

embodiment 3

[0135]Embodiment 3 of the present invention will be described below with reference to FIG. 9 through FIG. 11.

[0136]FIG. 9(a) is a plan view illustrating a thin film transistor 21 according to the present embodiment. Further, FIG. 9(b) is a cross sectional view taken along line E-E of FIG. 9(a). FIG. 9(c) is a cross sectional view taken along line F-F of FIG. 9(a).

[0137]As shown in FIG. 9(a) through FIG. 9(c), the thin film transistor 21 serving as a semiconductor device is arranged as follows. That is, a priming insulating layer 23 is formed on an insulating substrate 22. Formed on the priming insulating layer 23 are a source electrode 24 and a drain electrode 25. Further, a semiconductor layer 26 is formed on the priming insulating layer 23, the source electrode 24, and the drain electrode 25. Formed on the semiconductor layer 26 is a first gate insulating layer 27. The semiconductor layer 26 and the first gate insulating layer 27 are covered with a second gate insulating layer 28 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com