Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

131results about How to "Upper surface" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

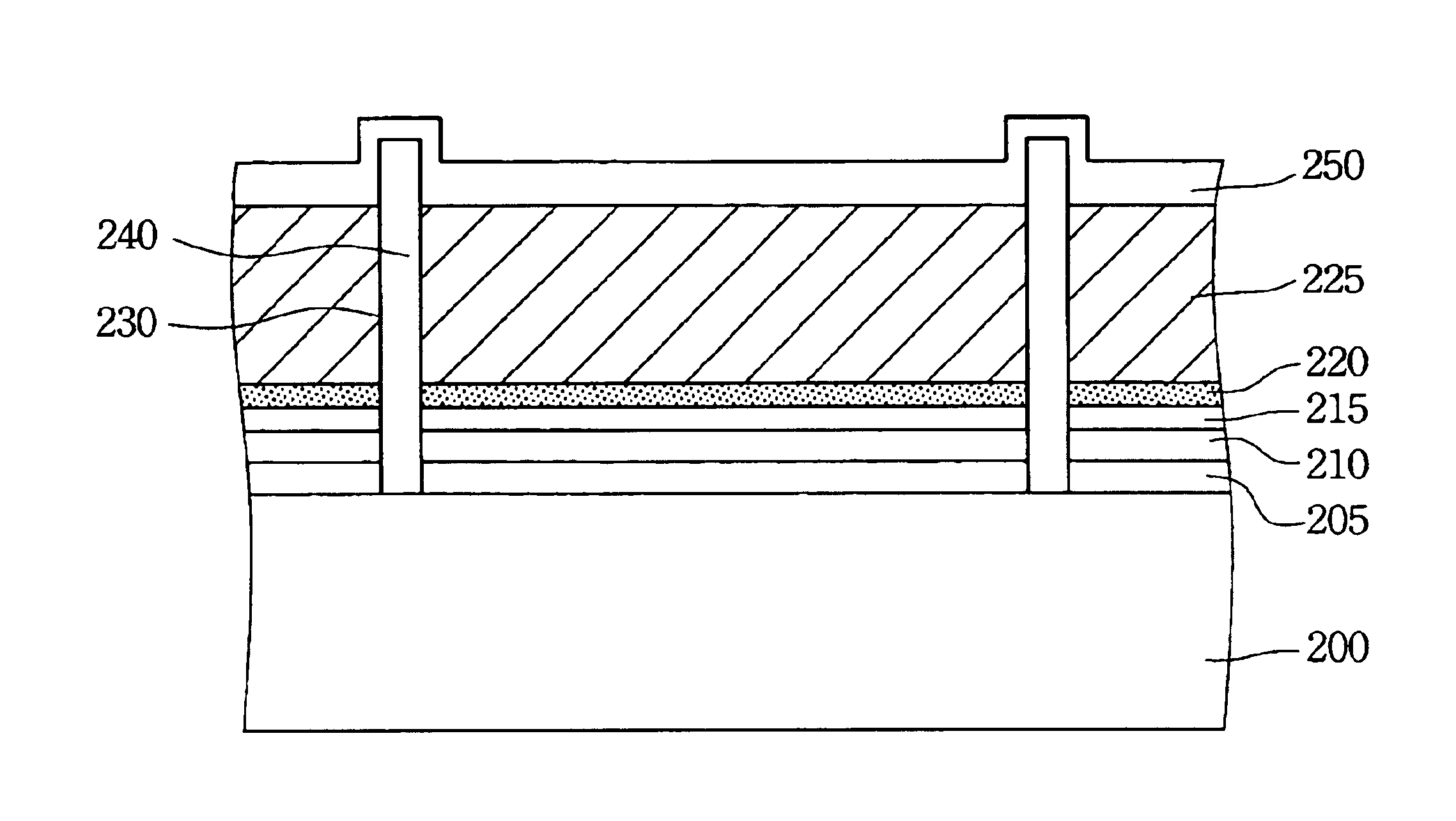

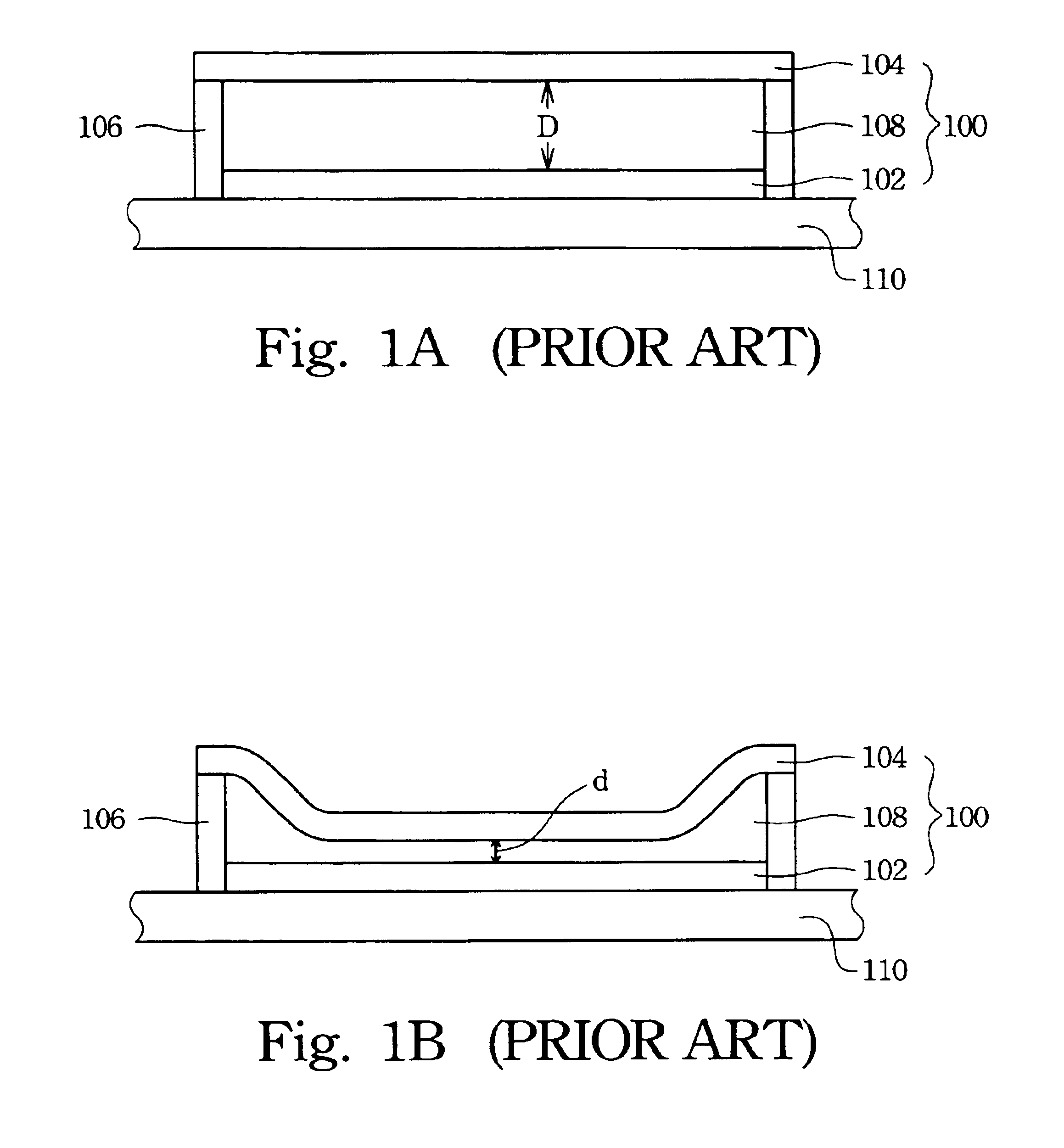

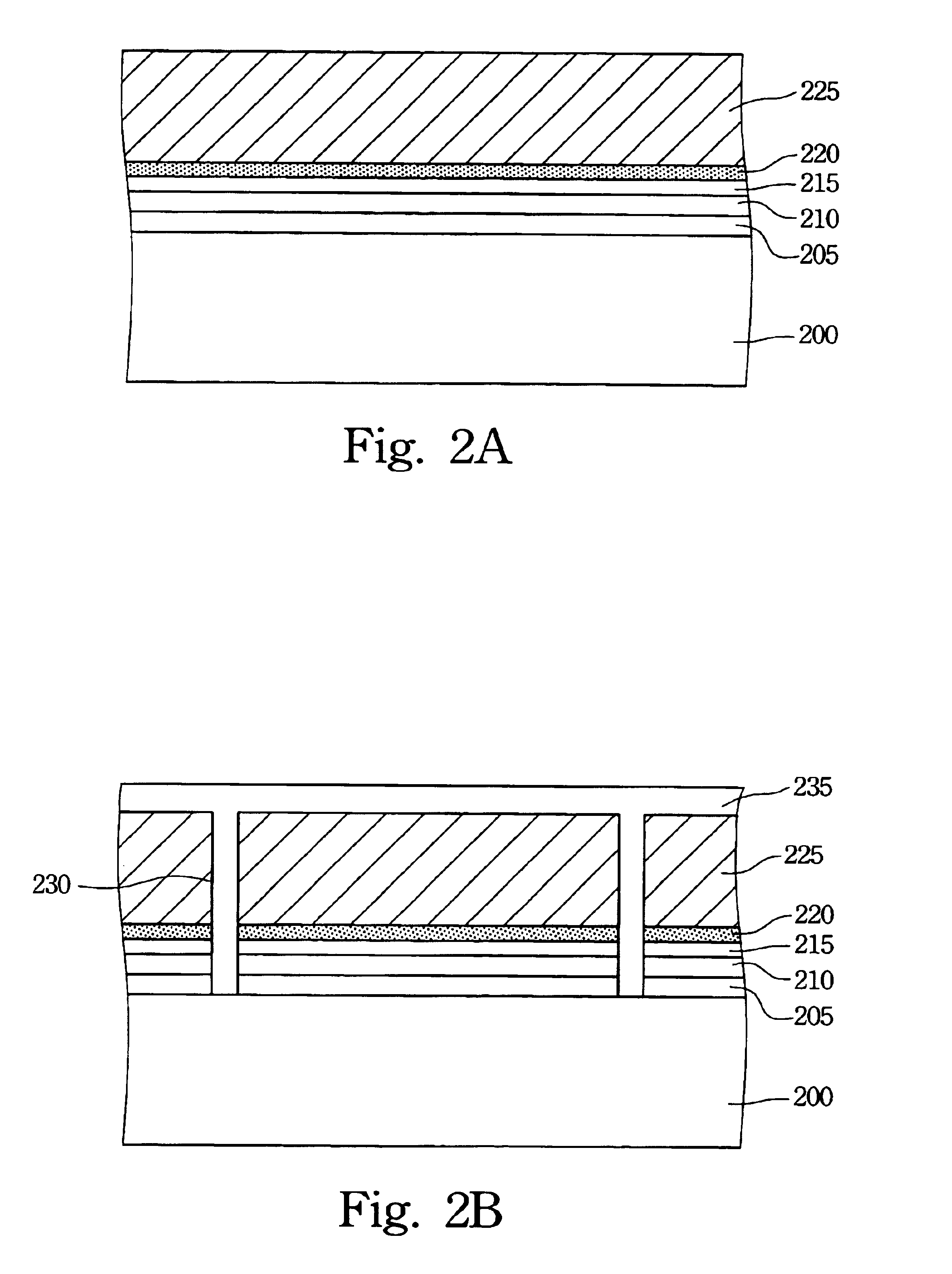

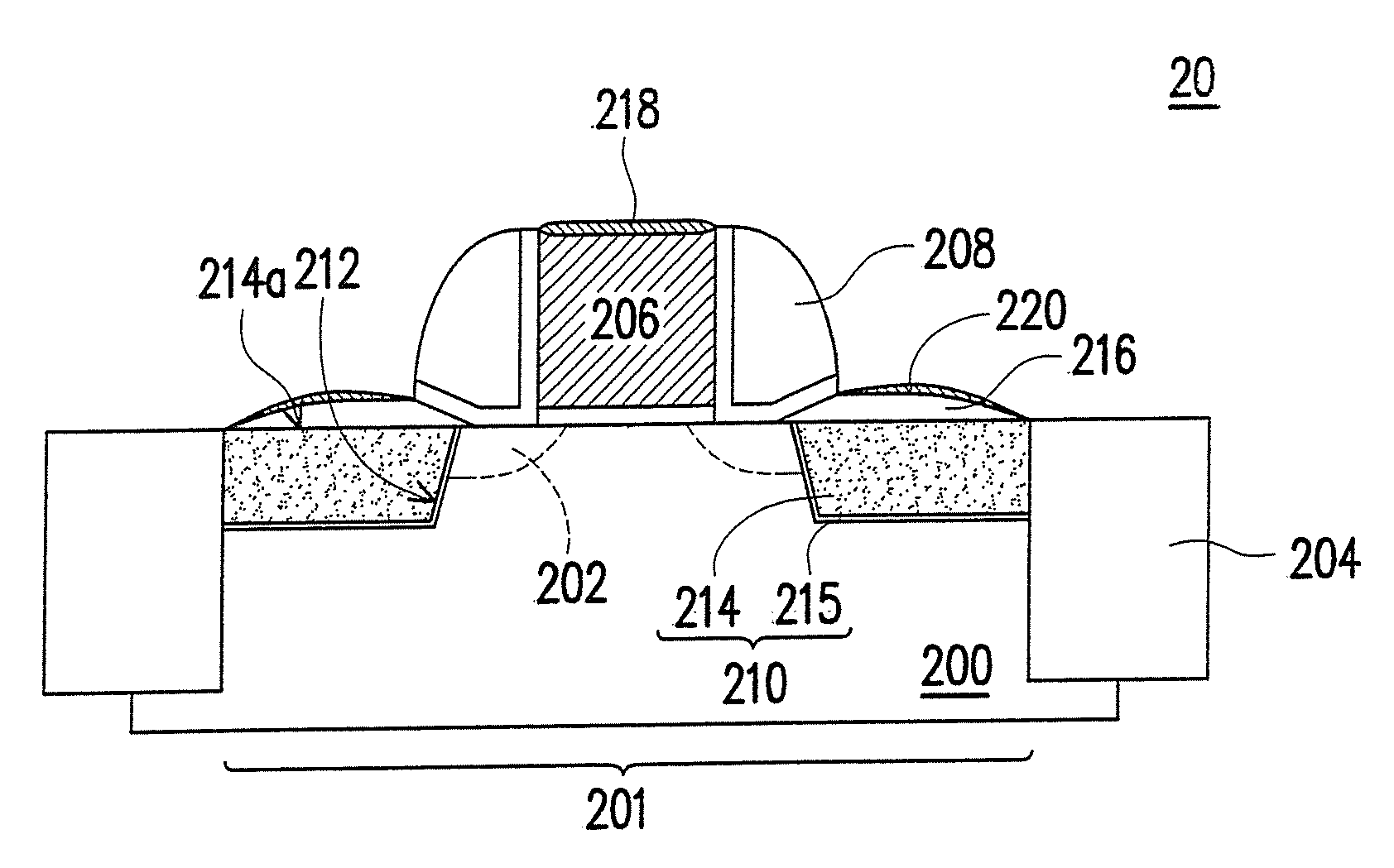

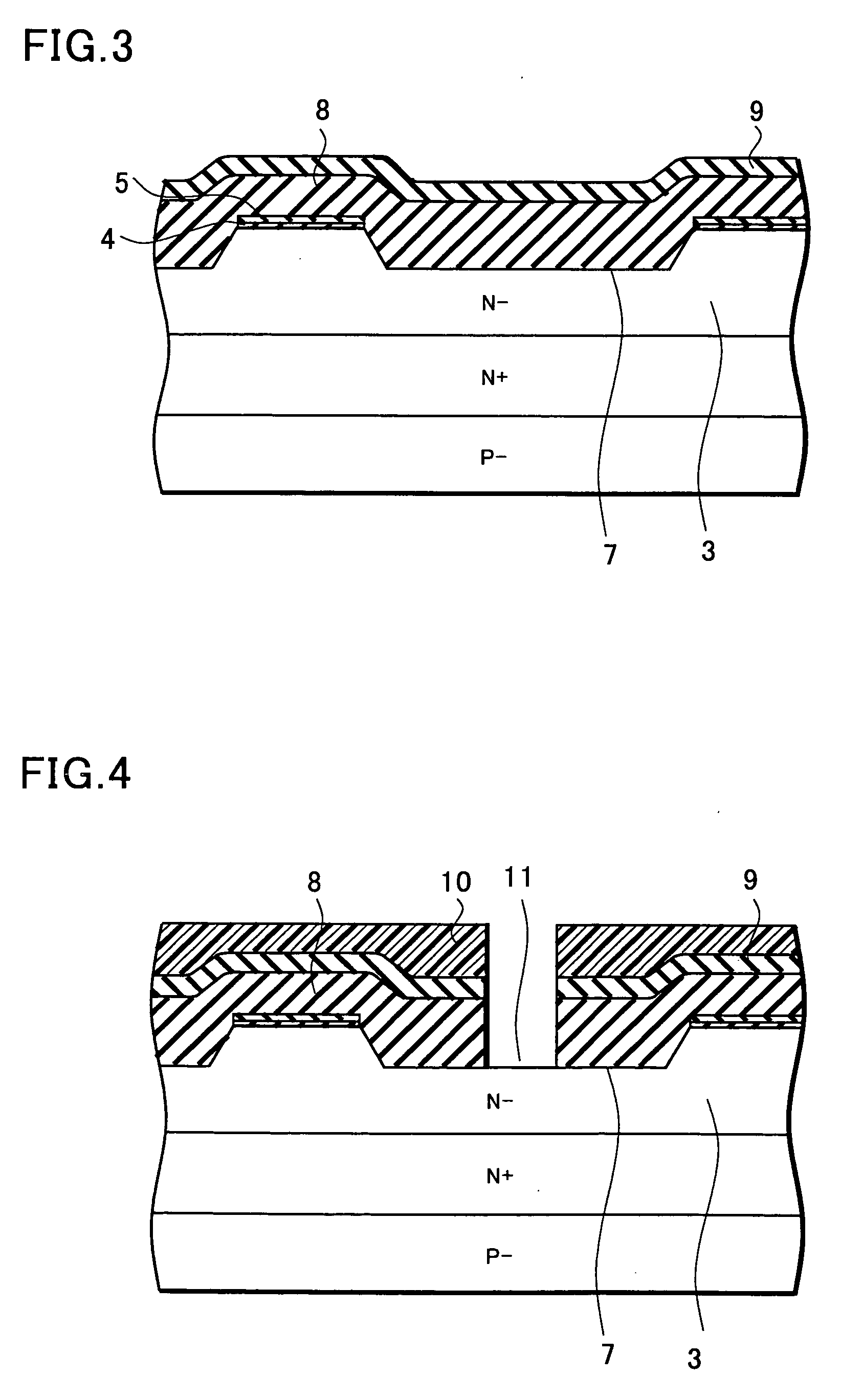

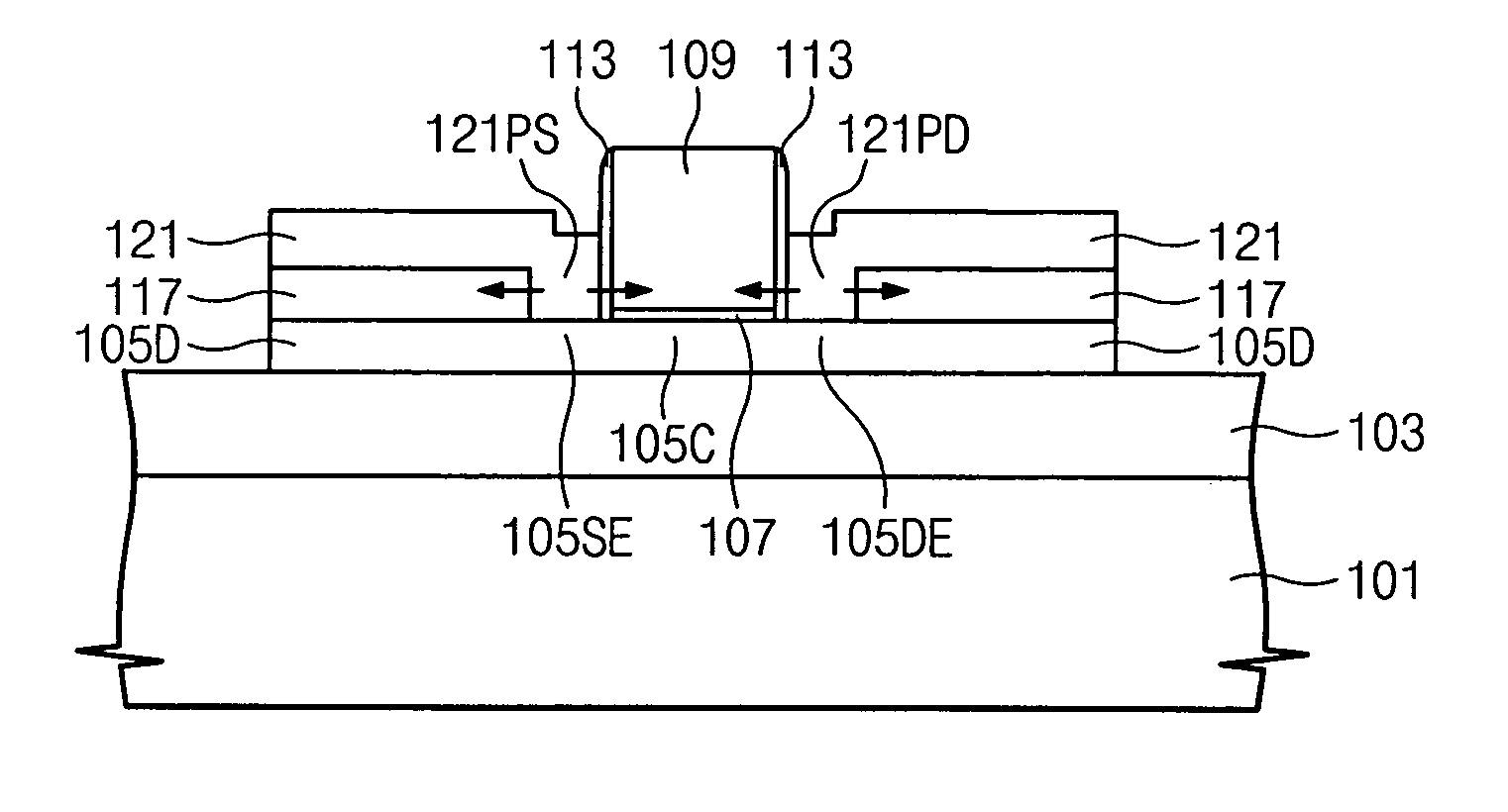

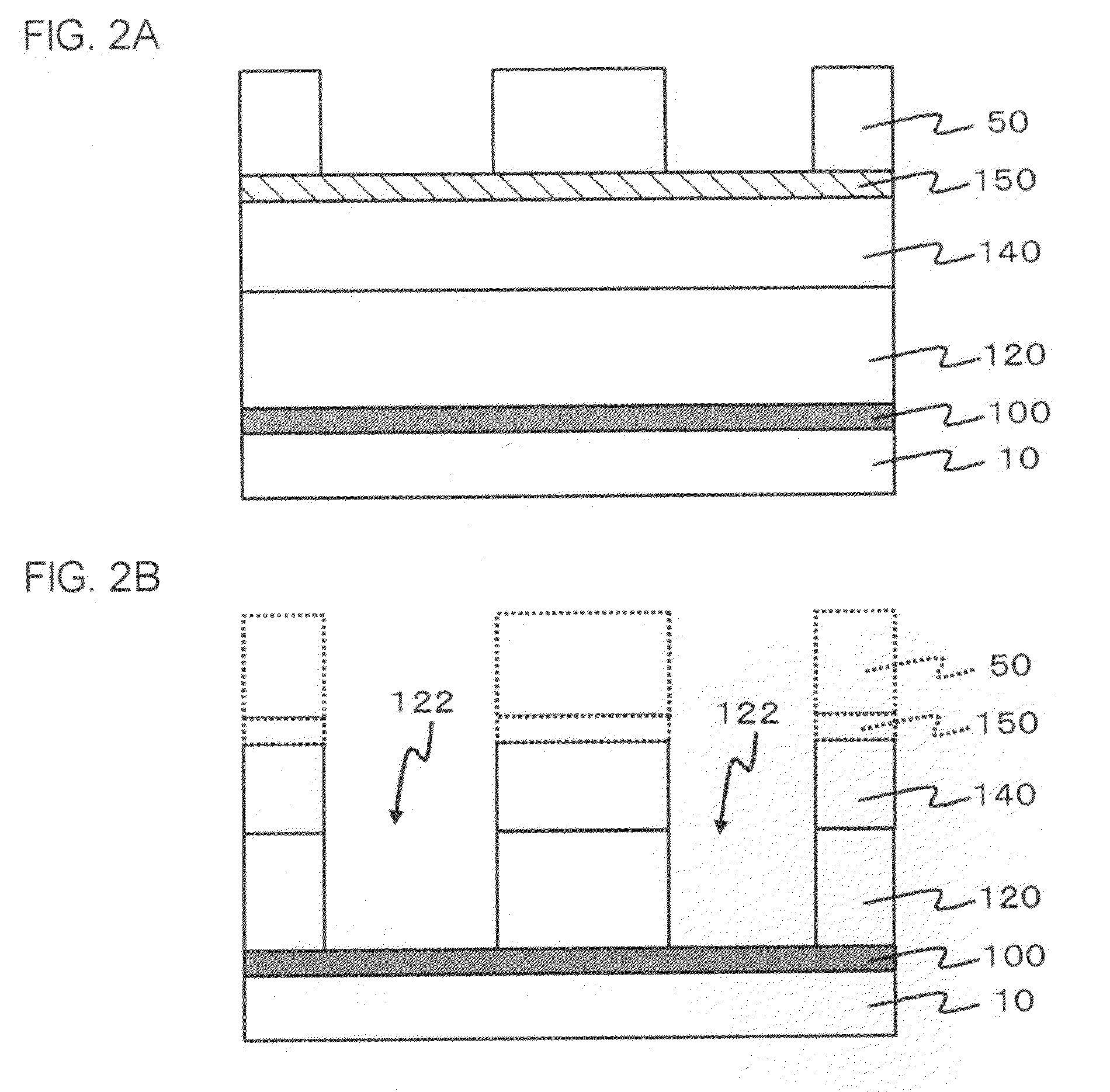

Interferometric modulation pixels and manufacturing method thereof

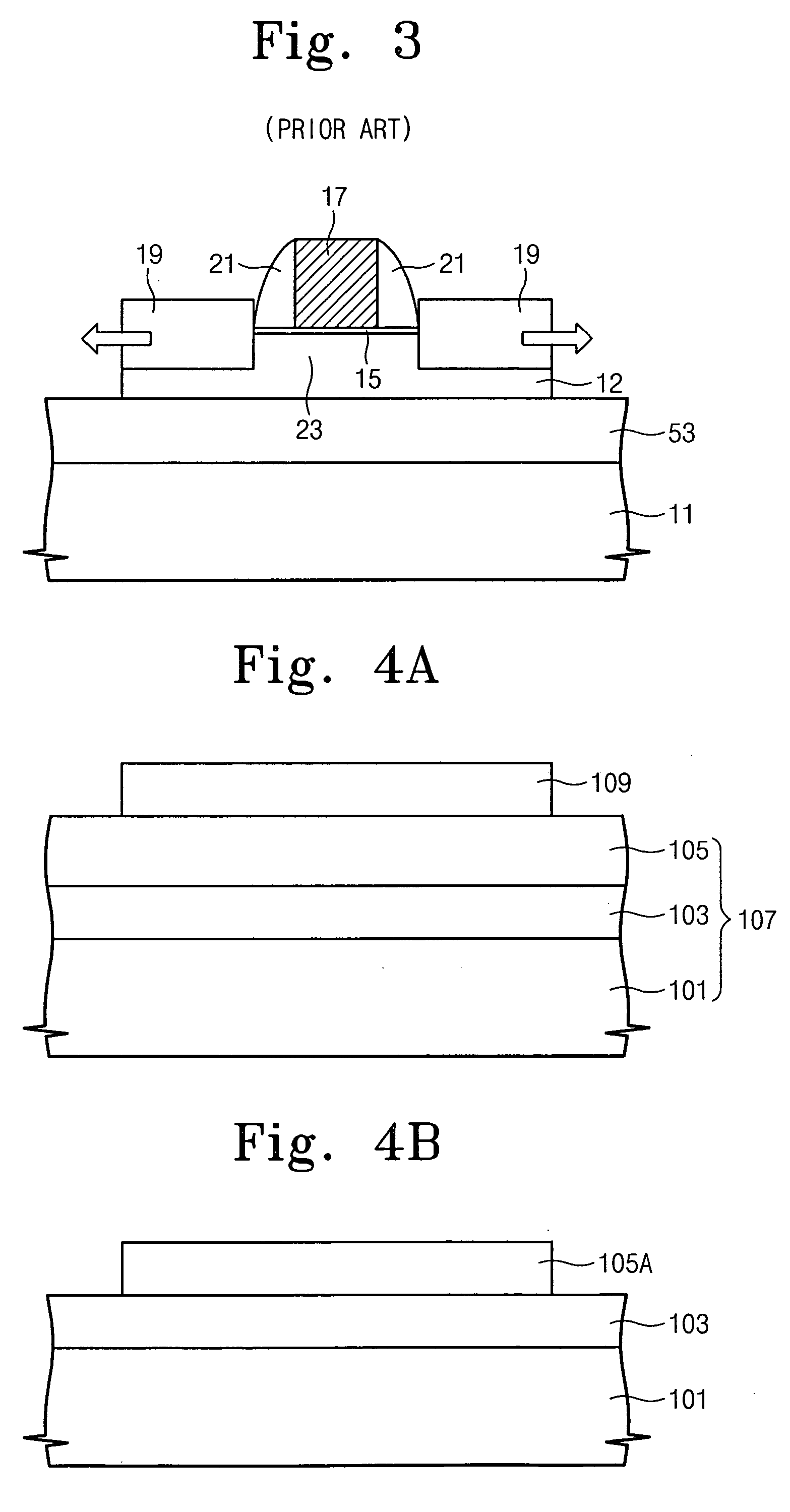

ActiveUS6952303B2Upper surfaceQuality improvementNon-linear opticsOptical elementsLength waveProtection layer

A protection layer covers the cavity-side surface of a bottom electrode of a interferometric modulation pixel. Consequently, the protective layer protects the surface of the bottom electrode while a sacrificial layer between the bottom electrode and the top electrode is being etched. Thus, the distance between the bottom electrode and the top electrode is maintained, thereby ensuring that only the light with desired wavelengths is reflected by the interferometric modulation pixel.

Owner:SNAPTRACK

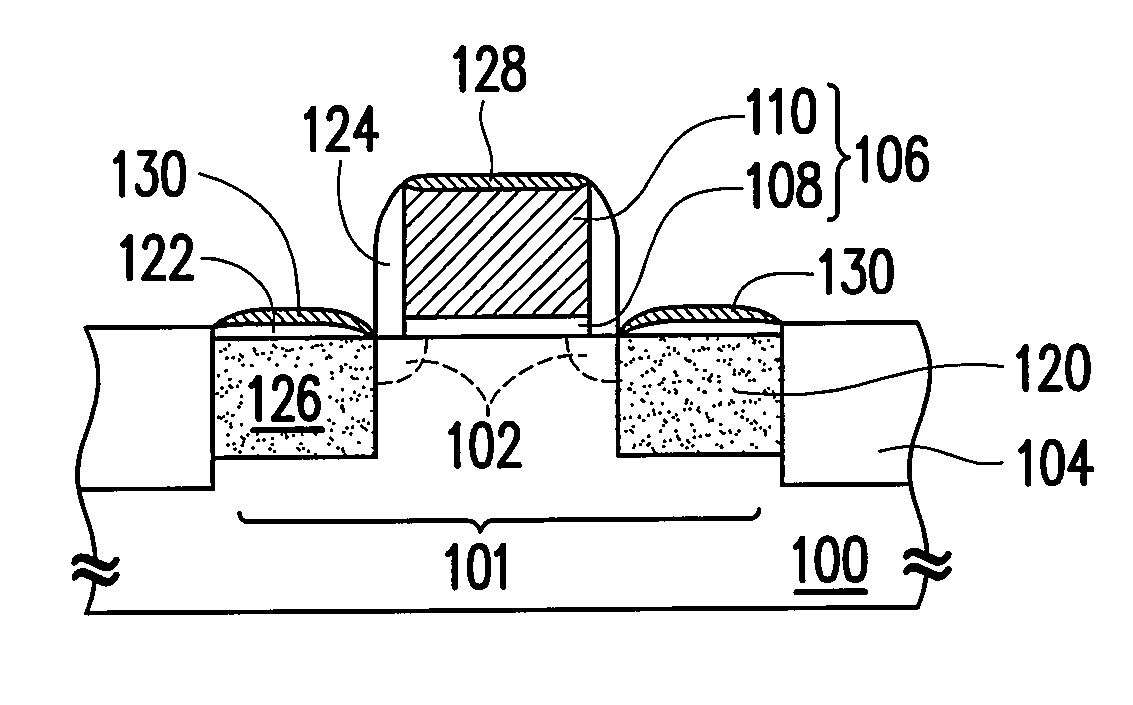

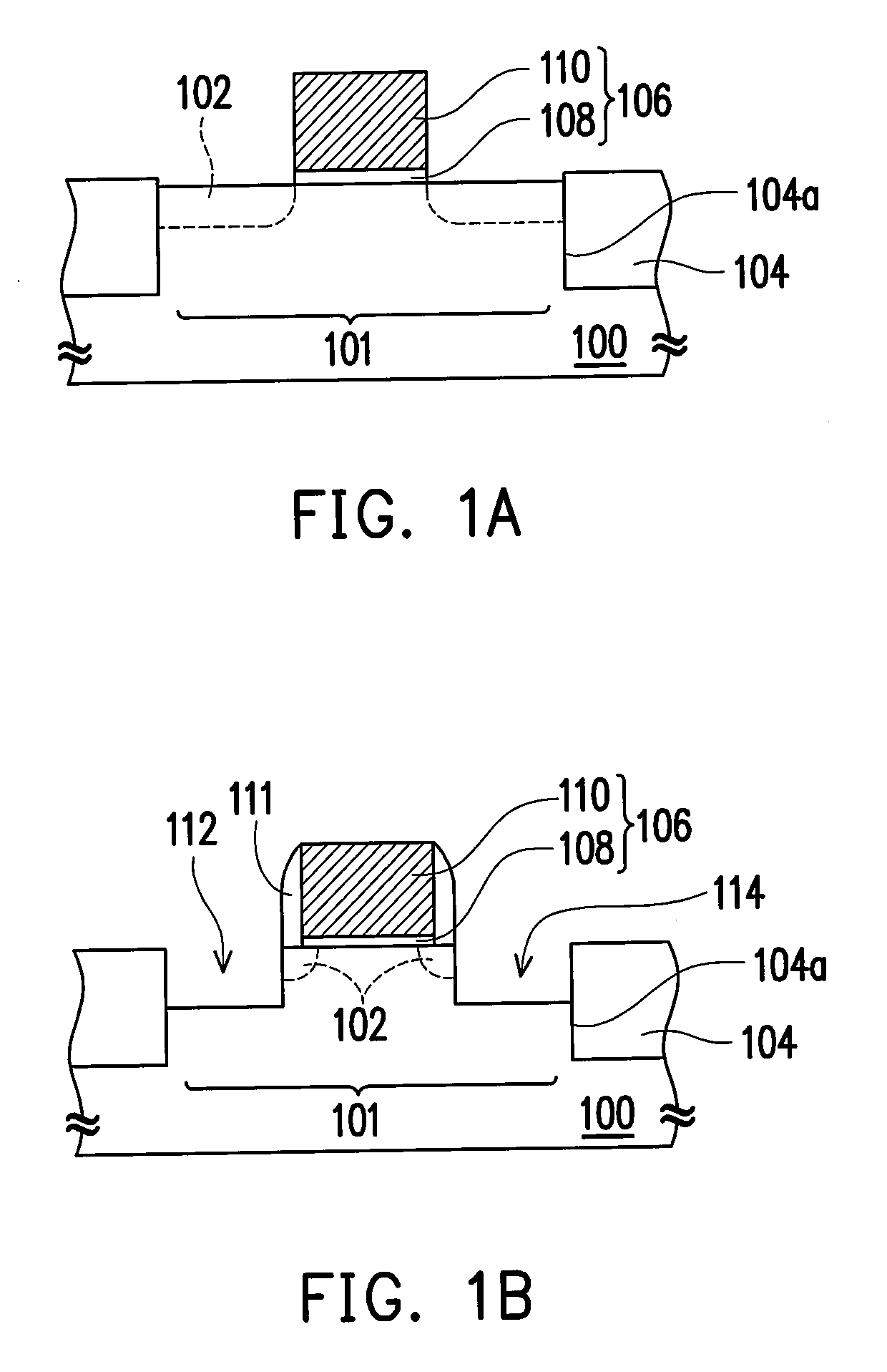

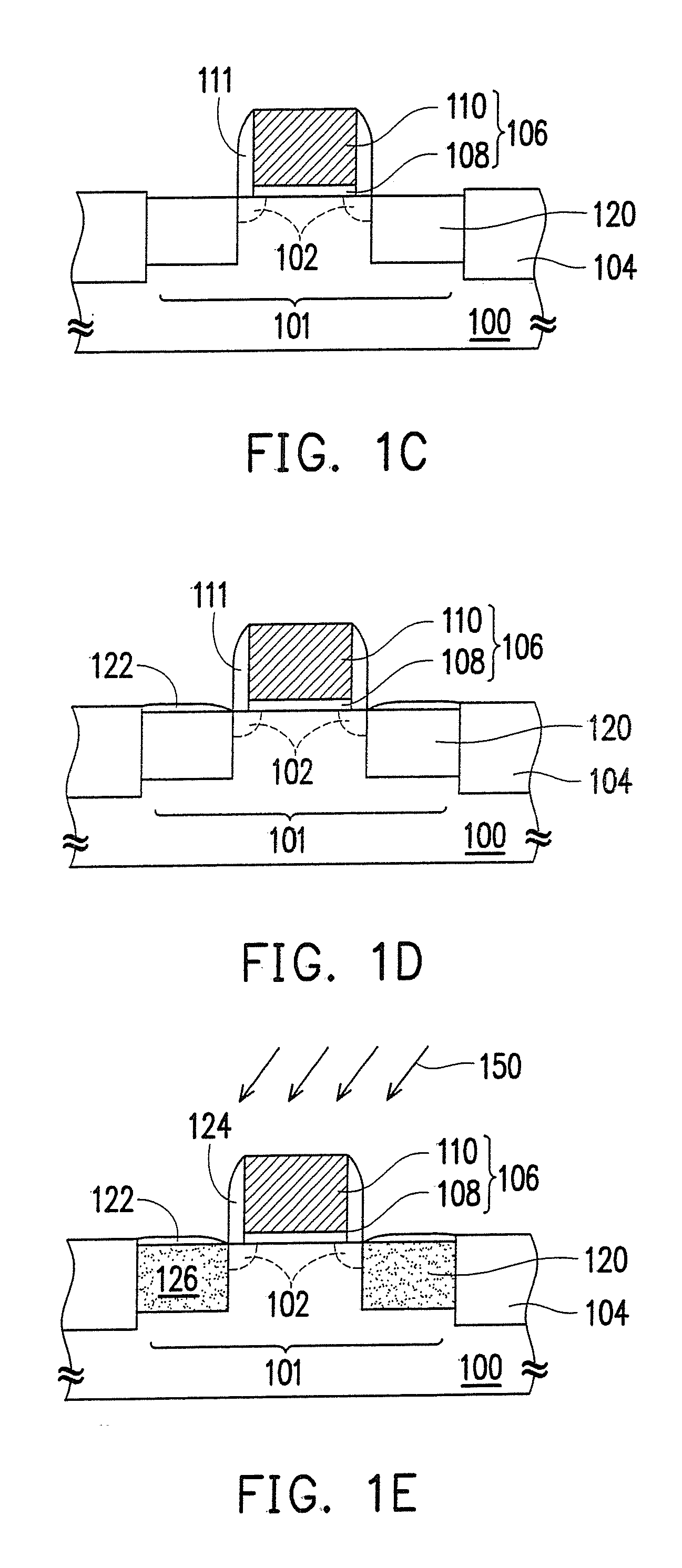

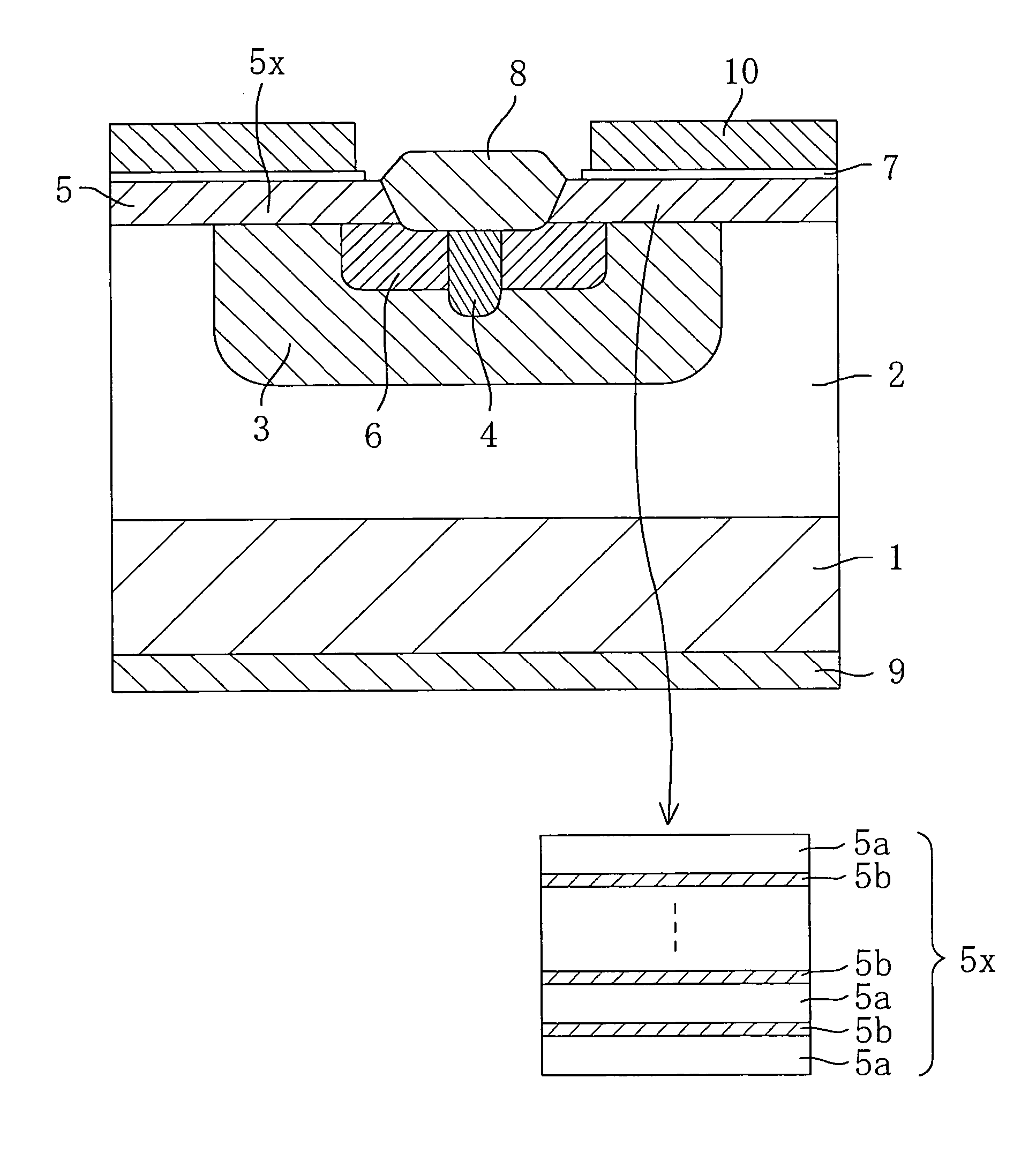

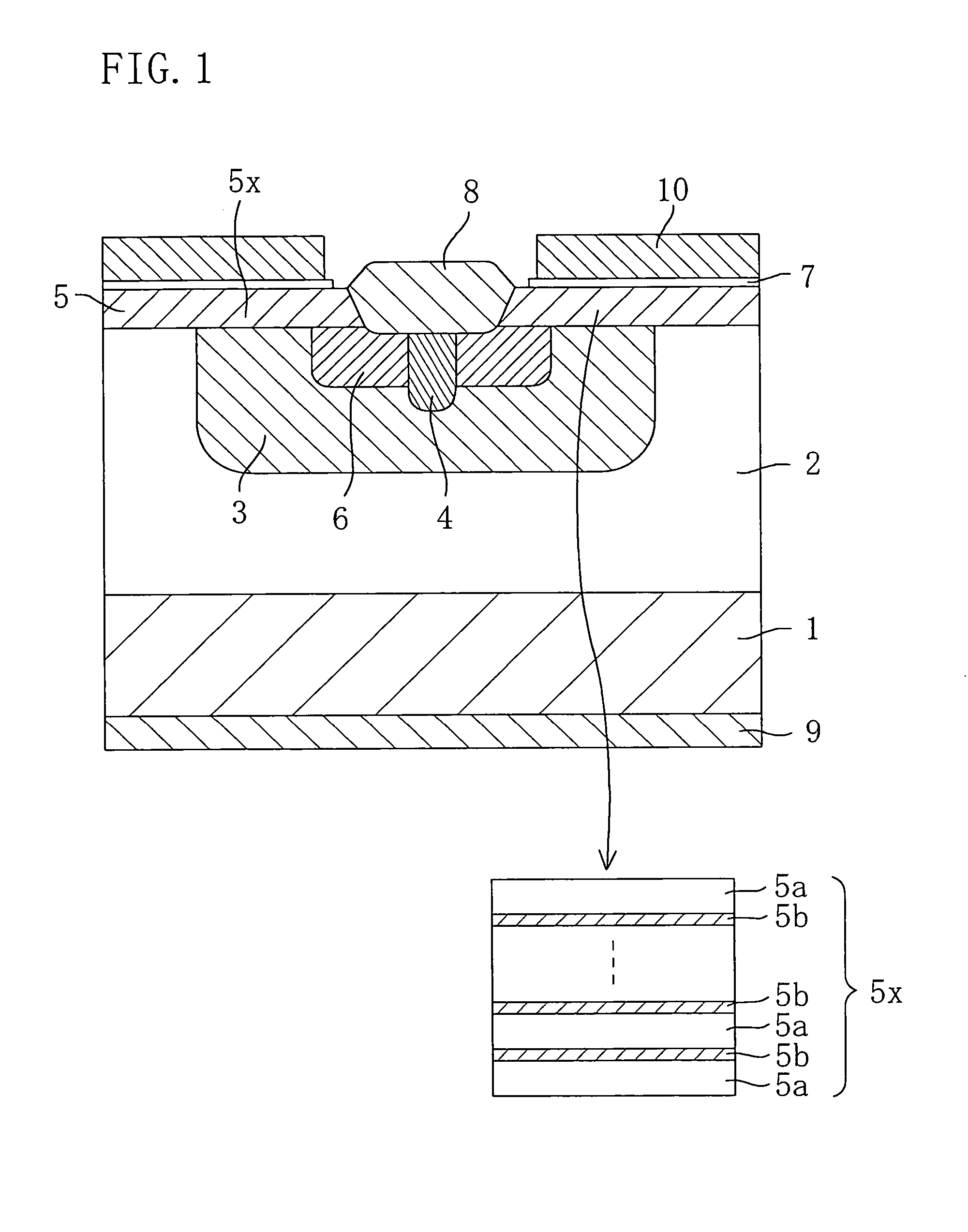

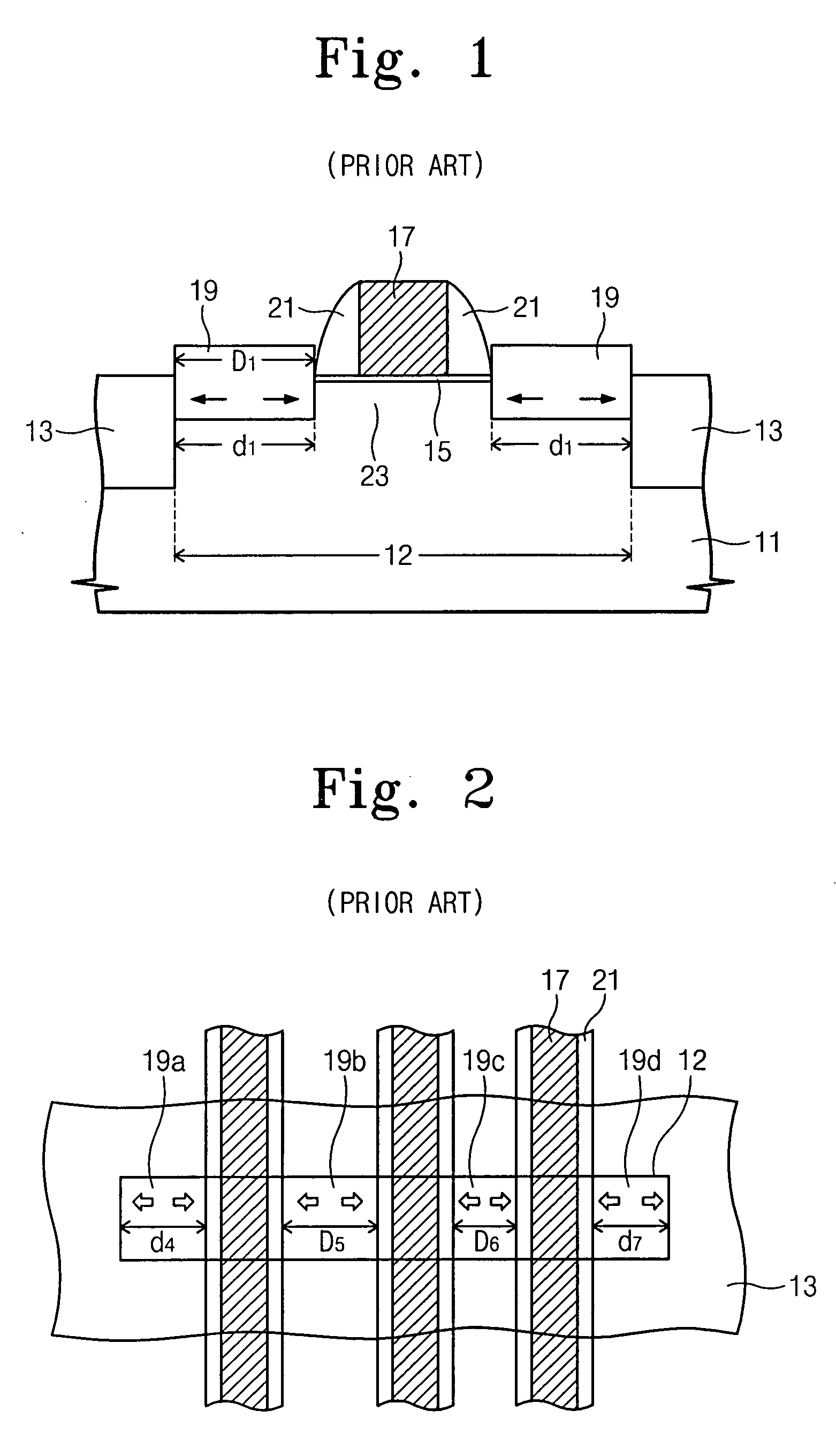

Mos device structure

InactiveUS20090166625A1Restrain boron channeling effectReduce harmTransistorSemiconductor/solid-state device manufacturingComputational physicsSemiconductor

The present invention provides a method for forming a metal-oxide-semiconductor (MOS) device and the structure thereof. The method includes at least the steps of forming a silicon germanium layer by the first selective epitaxy growth process and forming a cap layer on the silicon germanium layer by the second selective epitaxy growth process. Hence, the undesirable effects caused by ion implantation can be mitigated.

Owner:UNITED MICROELECTRONICS CORP

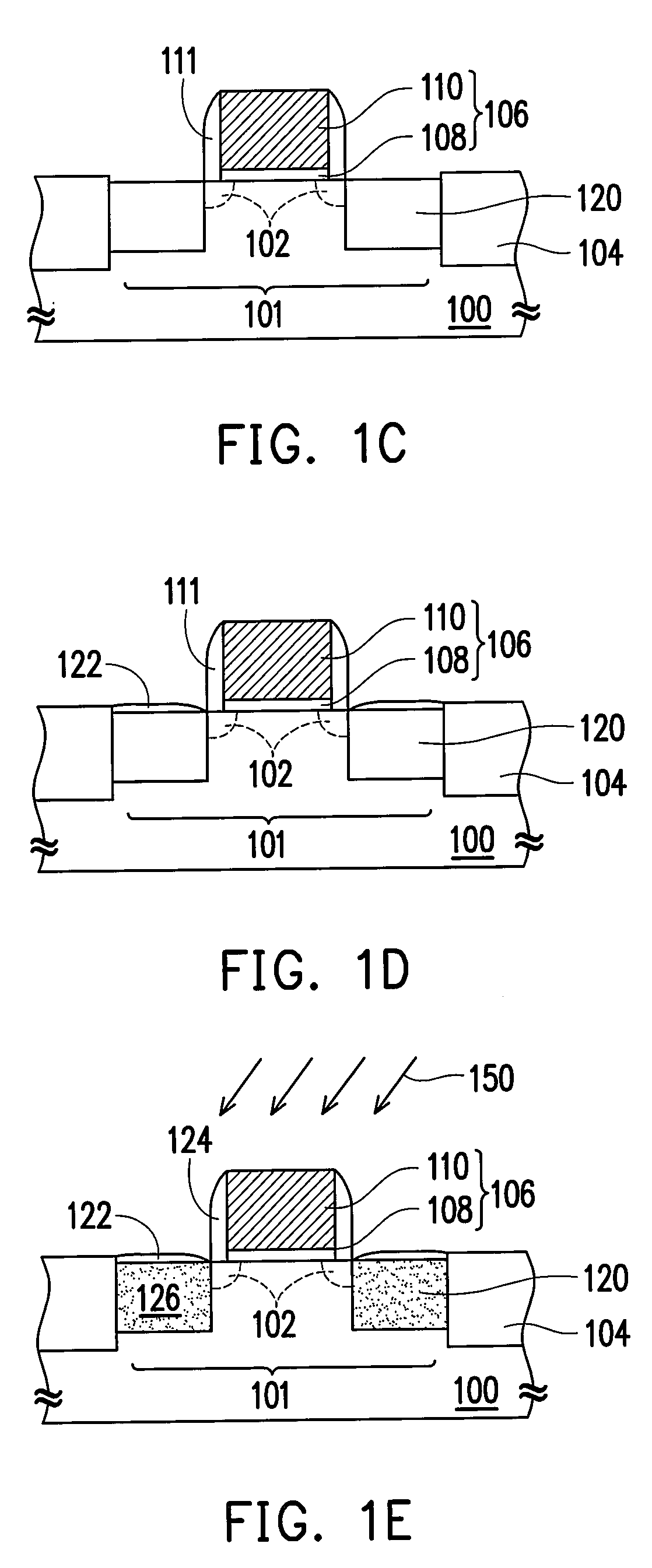

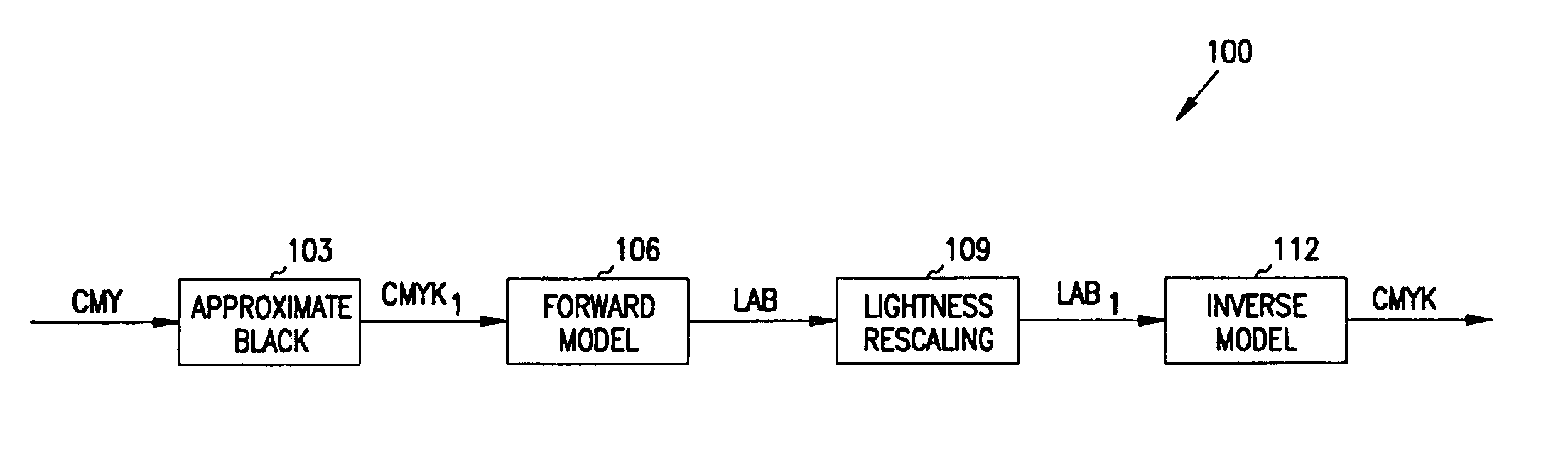

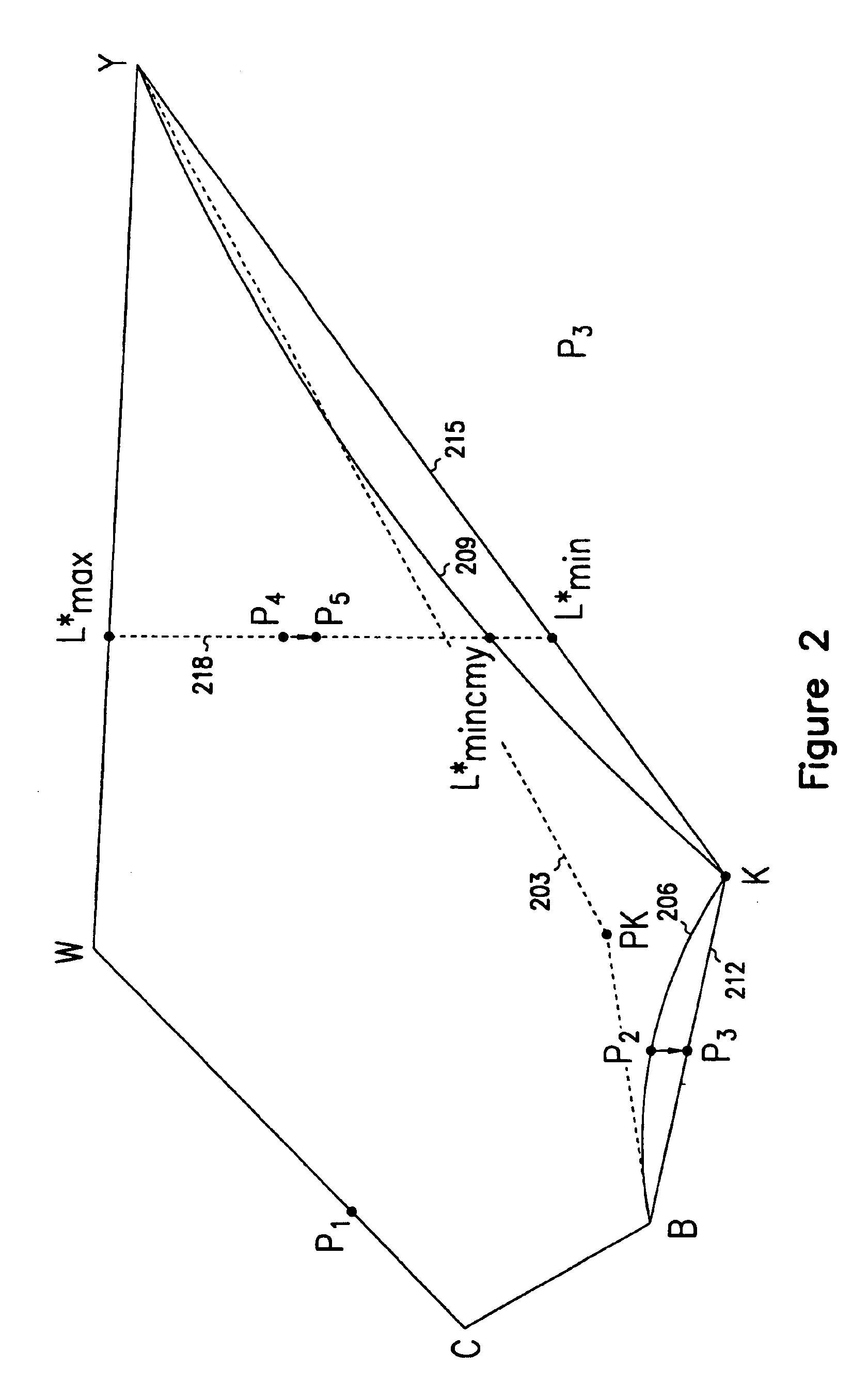

Method and apparatus for expanding a color gamut

InactiveUS6867883B1Upper surfaceLower surfaceDigitally marking record carriersDigital computer detailsGamutGeometric distortion

A color gamut in a first color space is expanded to utilize a larger gamut in a second color space. The gamut in the first color space is first converted by black generation or geometric distortion to a gamut in a second color space. The gamut in the second color space is converted by forward mapping to a gamut in a third color. The gamut in the third color space is expanded by linear rescaling. Finally, the linearly rescaled gamut is mapped to a gamut in the second color space through inverse modeling to form a final color gamut. The final color gamut utilizes the gamut available in the second color space, which is larger than the gamut available in the first color space.

Owner:LEXMARK INT INC

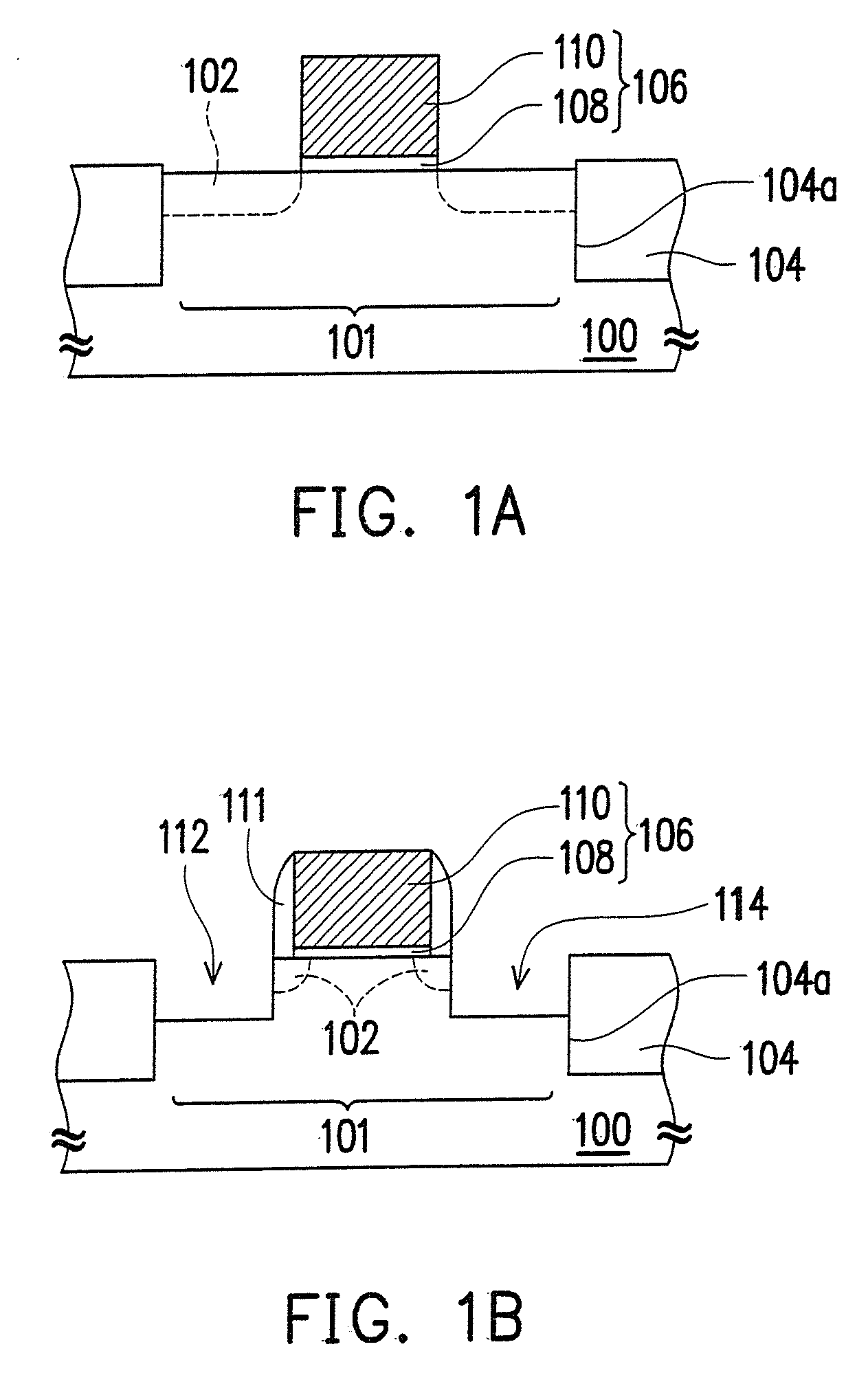

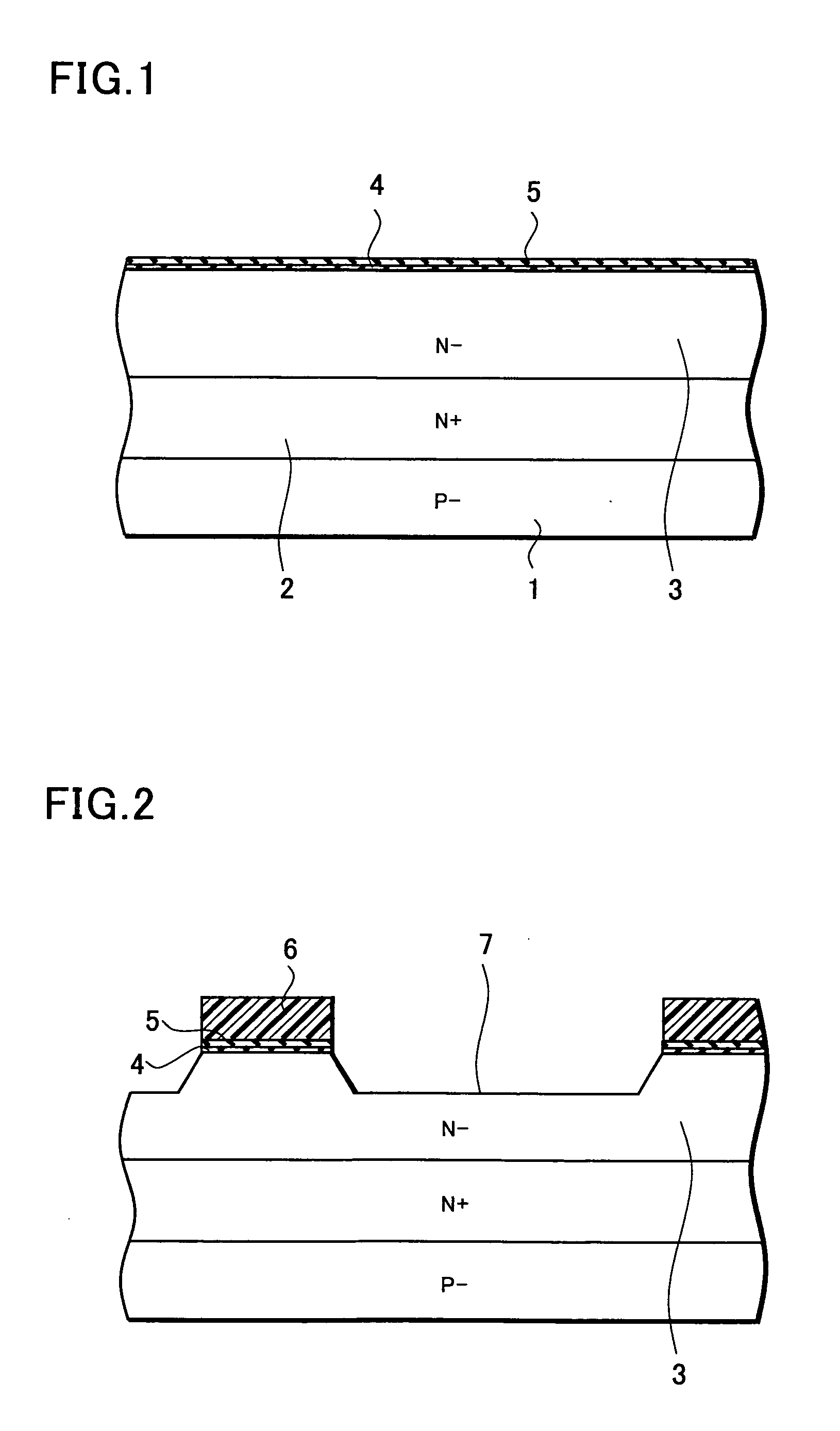

Method of forming mos device

ActiveUS20090239347A1Inhibition effectReduce harmTransistorSemiconductor/solid-state device manufacturingSemiconductorIon implantation

The present invention provides a method for forming a metal-oxide-semiconductor (MOS) device. The method includes at least the steps of forming a silicon germanium layer by the selective epitaxy growth process and forming a cap layer on the silicon germanium layer by the selective growth process. Hence, the undesirable effects caused by ion implantation can be mitigated.

Owner:UNITED MICROELECTRONICS CORP

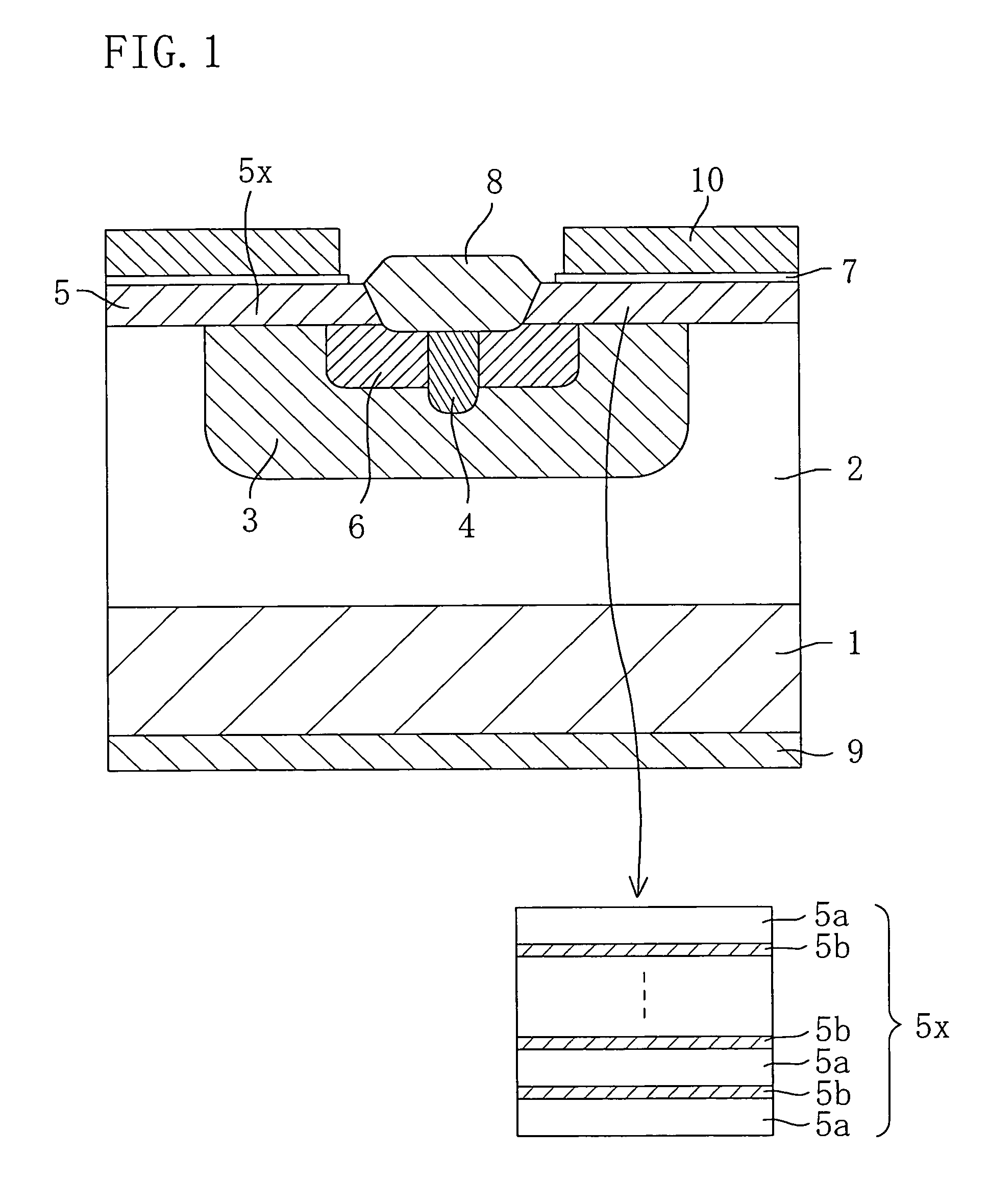

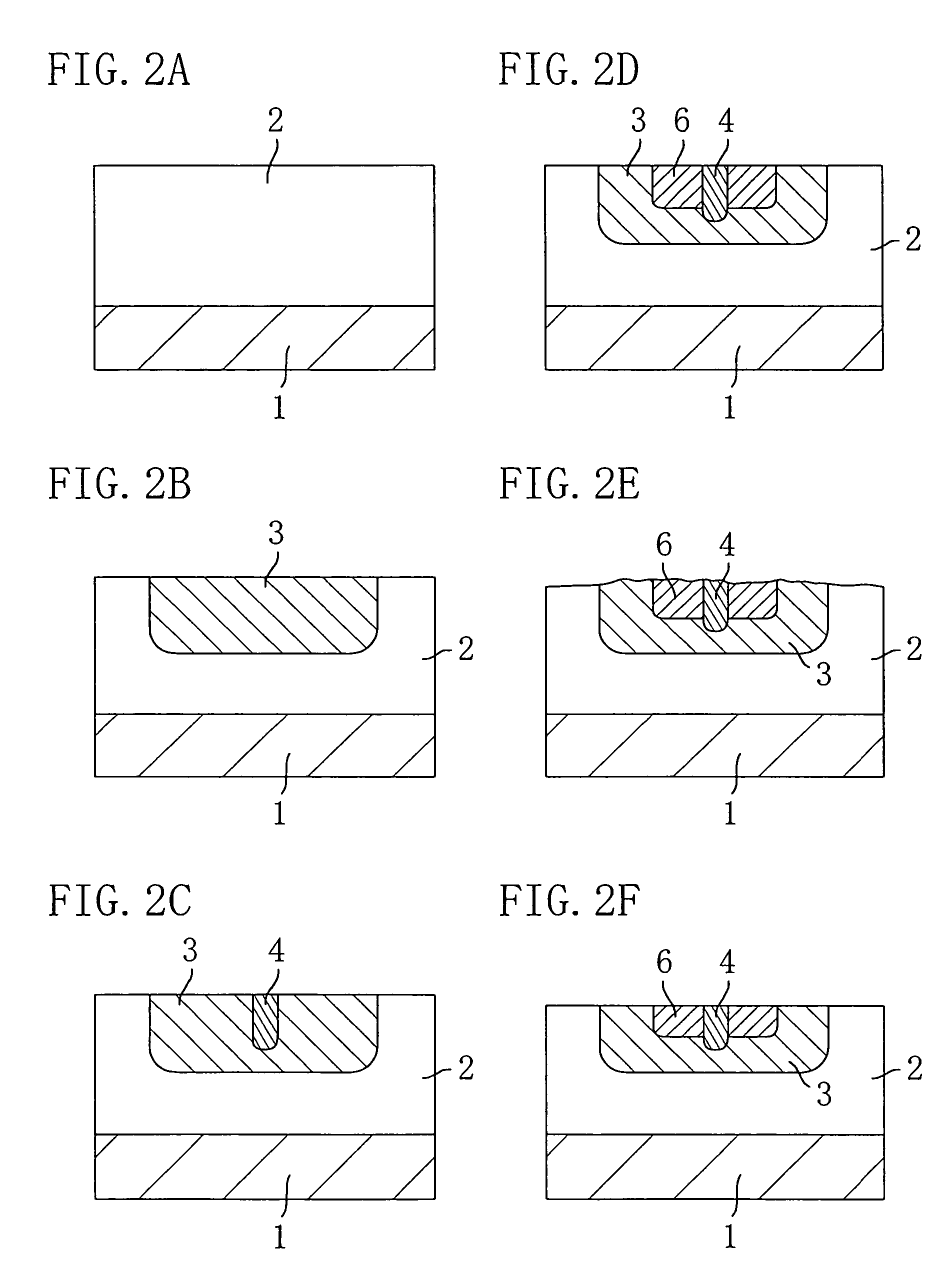

Semiconductor device and method for fabricating the same

ActiveUS20050001217A1Reduced carrier mobilityHigh carrier mobilityTransistorSemiconductor/solid-state device manufacturingHigh resistanceCarbon film

Ion implantation is carried out to form a p-well region and a source region in parts of a high resistance SiC layer on a SiC substrate, and a carbon film is deposited over the substrate. With the carbon film deposited over the substrate, annealing for activating the implanted dopant ions is performed, and then the carbon film is removed. Thus, a smooth surface having hardly any surface roughness caused by the annealing is obtained. Furthermore, if a channel layer is epitaxially grown, the surface roughness of the channel layer is smaller than that of the underlying layer. Since the channel layer having a smooth surface is provided, it is possible to obtain a MISFET with a high current drive capability.

Owner:PANASONIC CORP

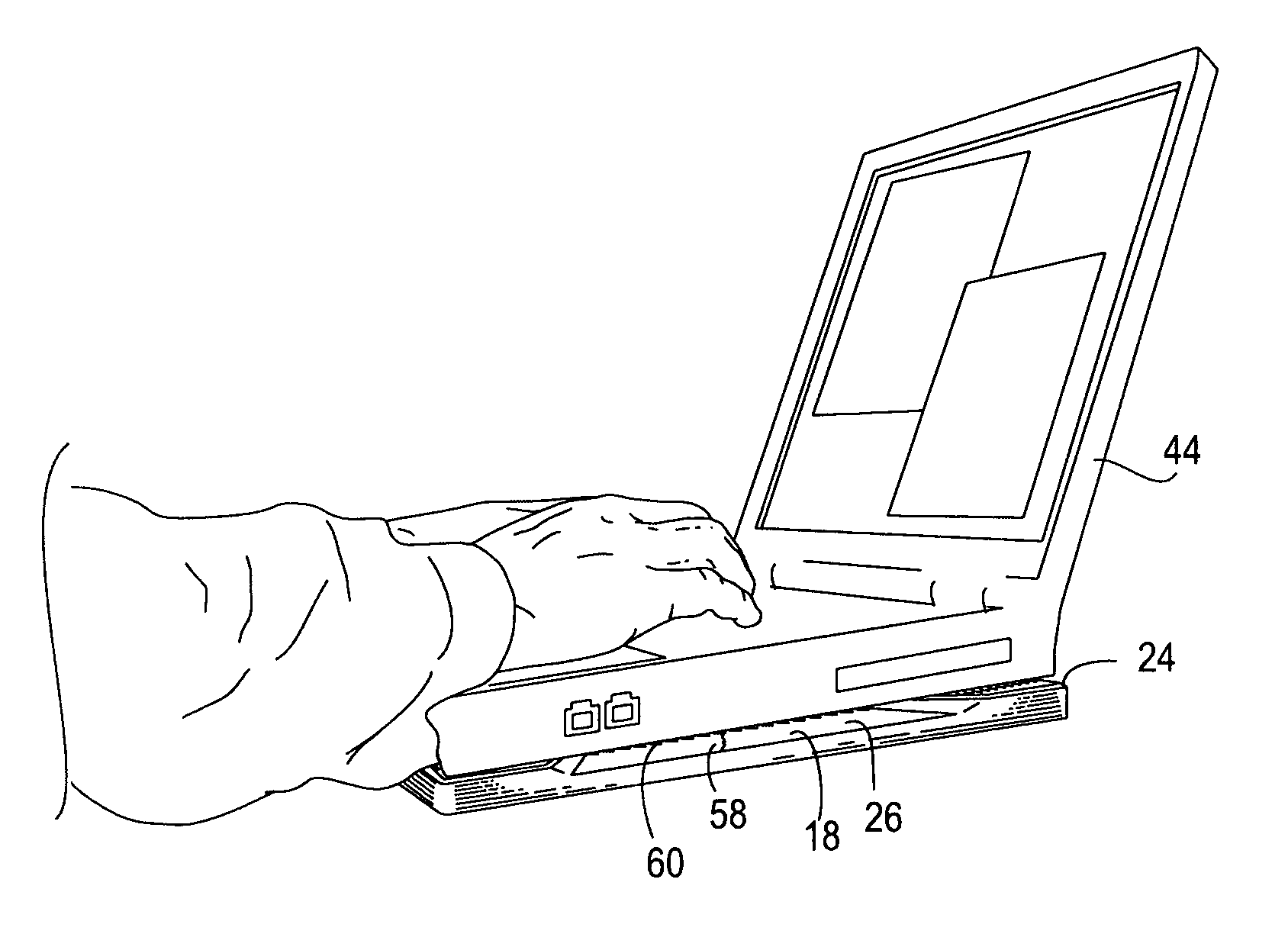

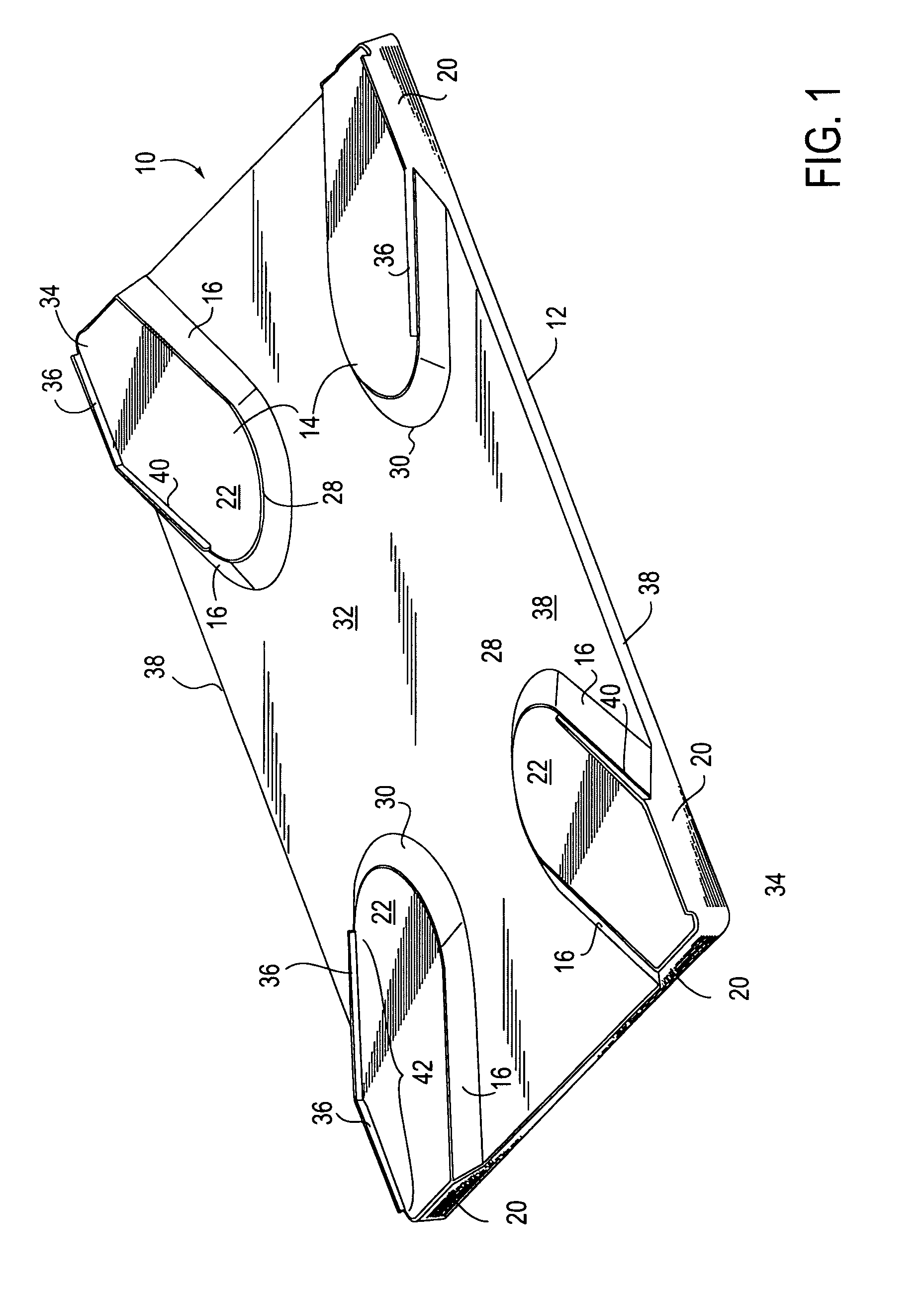

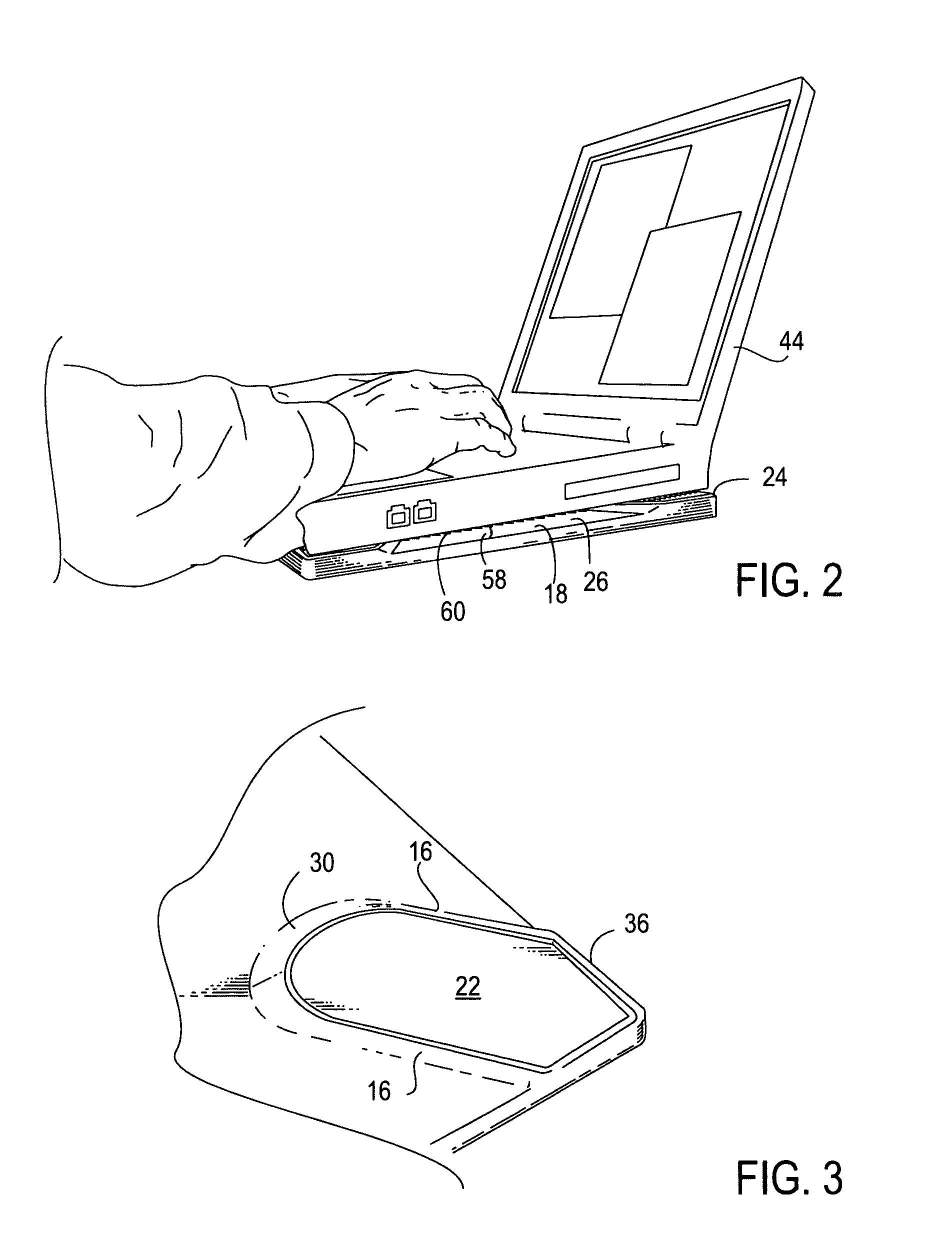

Thermal insulating board for laptop computers

InactiveUS7161799B2Increase rigidity and stiffnessComfortable contact surfaceDigital data processing detailsStands/trestlesEngineeringUpper floor

Owner:LIM MICHAEL Z

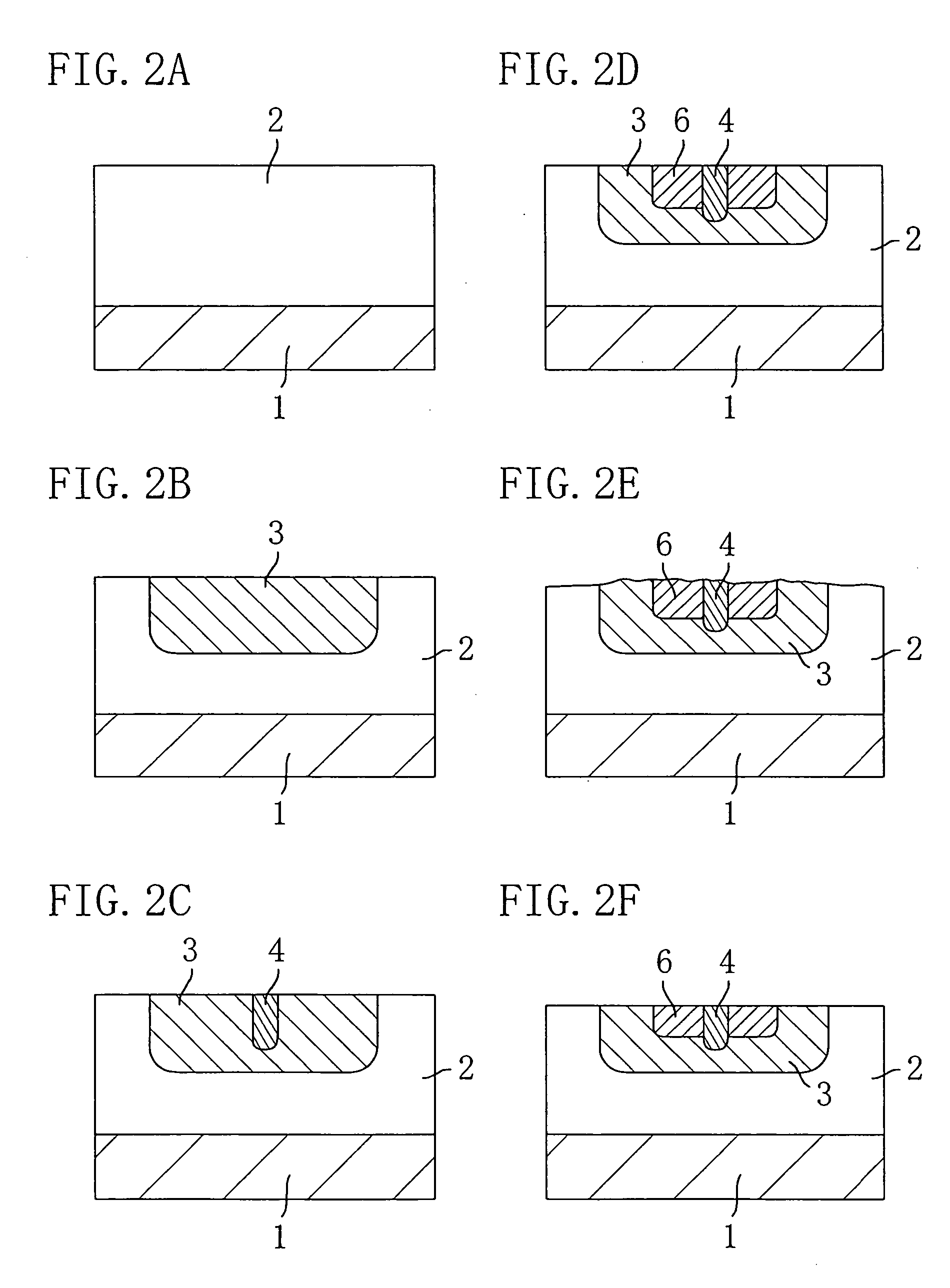

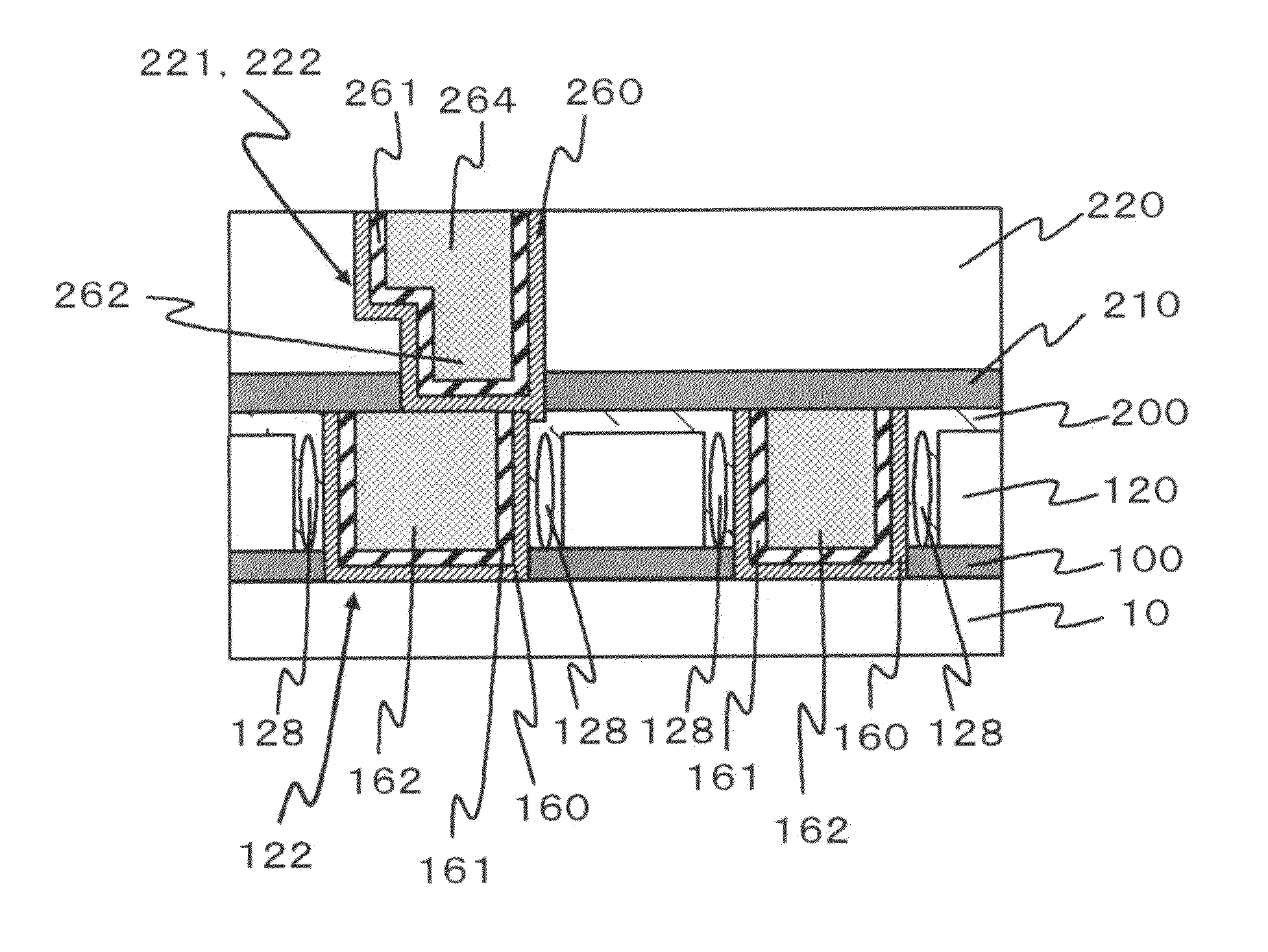

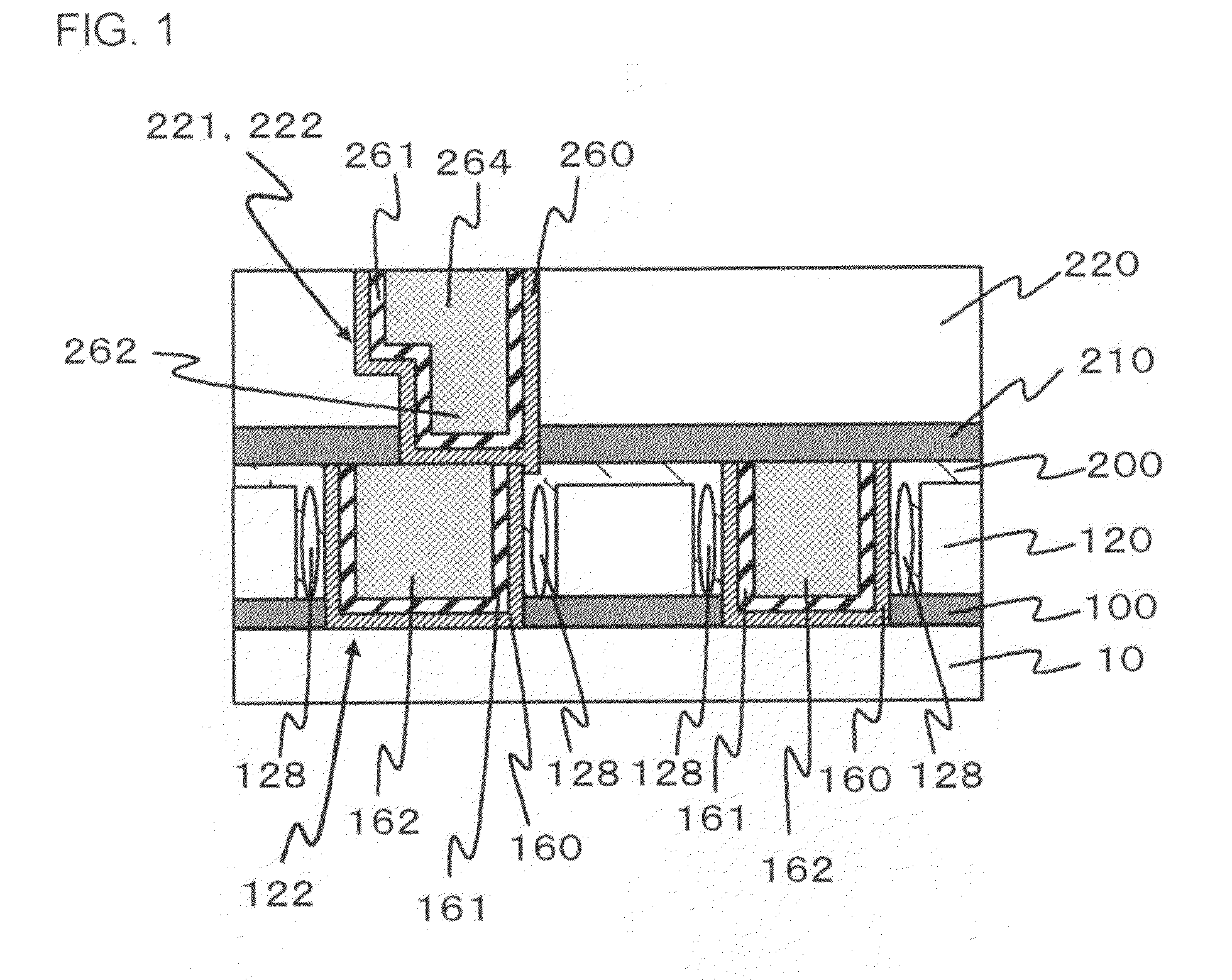

Method for manufacturing semiconductor device

InactiveUS20050287765A1Prevent disconnectionAvoid layeringSemiconductor/solid-state device manufacturingCapacitanceEngineering

In a conventional method for manufacturing a semiconductor device, there are problems that a concave part is formed in a formation region of an isolation region, no flat surface is formed in the isolation region, and a wiring layer is disconnected above the concave part. In a method for manufacturing a semiconductor device of the present invention, when a silicon oxide film used for a STI method is removed, an HTO film covering an inner wall of a trench is partially removed to form a concave part in an isolation region. Thereafter, a TEOS film is deposited on an epitaxial layer including the concave part and is etched back. Accordingly, an insulating spacer is buried in the concave part. Thus, an upper surface of the isolation region becomes a substantially flat surface. Consequently, even if a wiring layer is formed above the concave part in the isolation region, disconnection thereof can be prevented. Moreover, in the isolation region, the substantially flat surface makes it possible to form a passive element such as a capacity element.

Owner:SEMICON COMPONENTS IND LLC

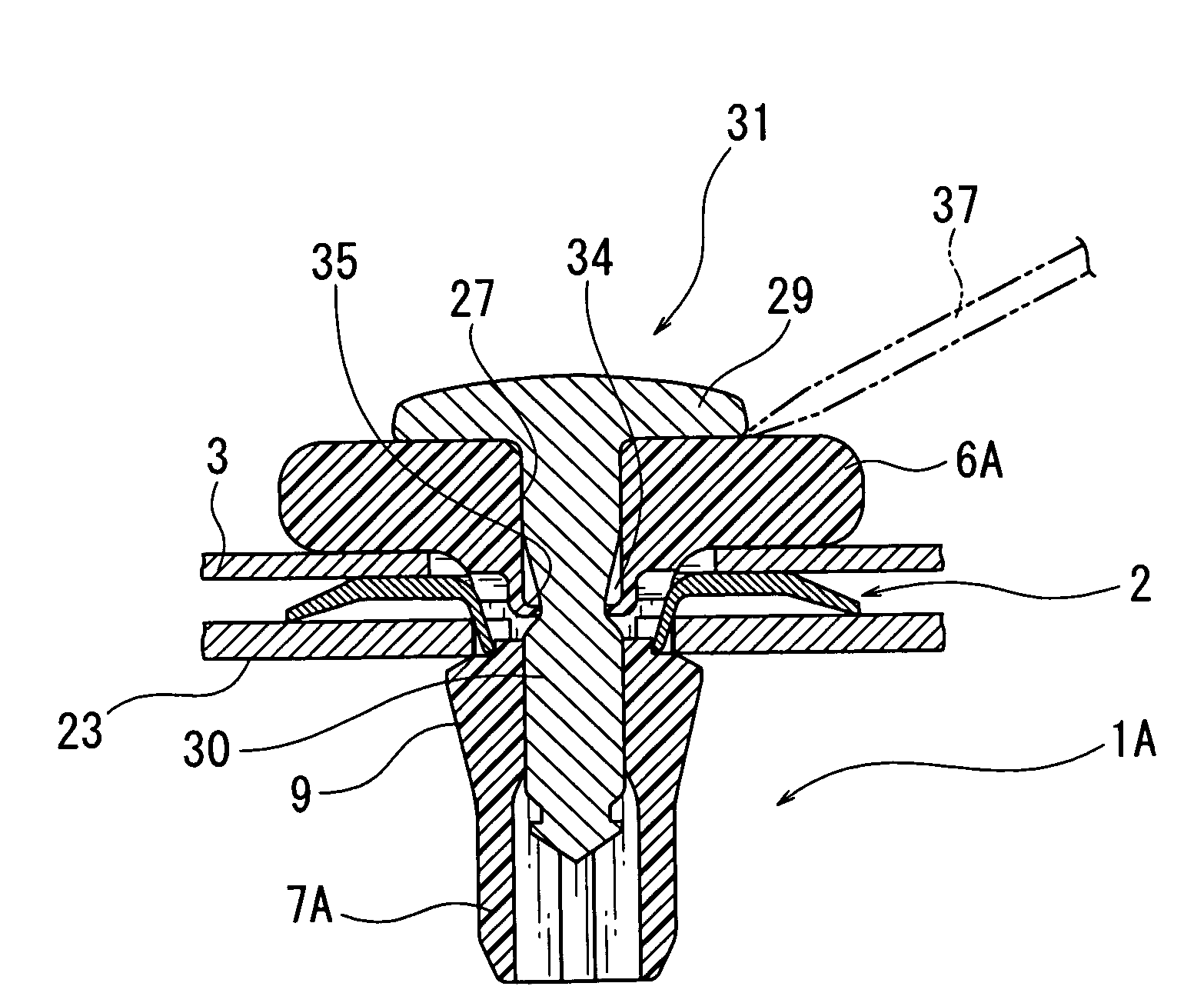

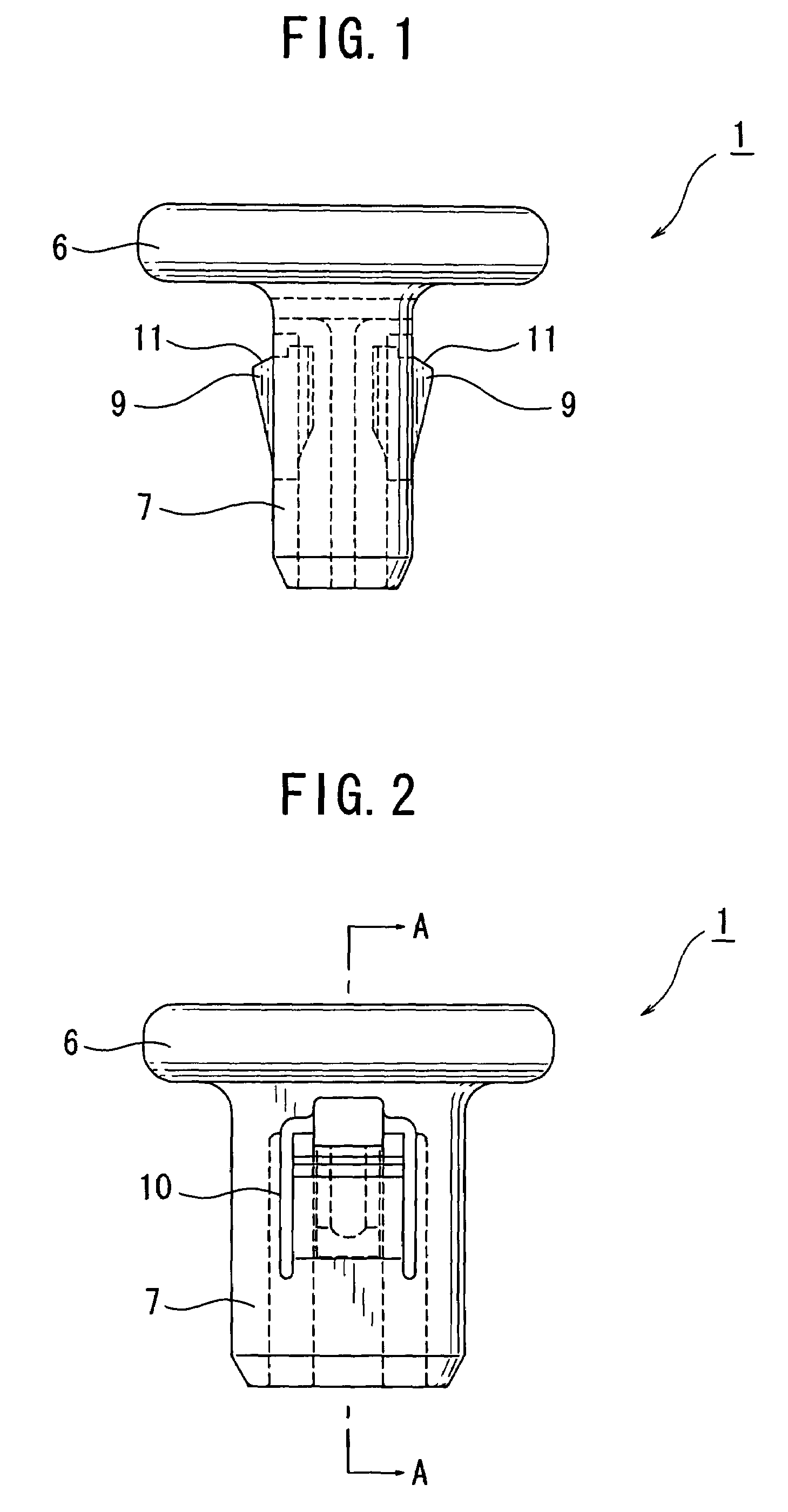

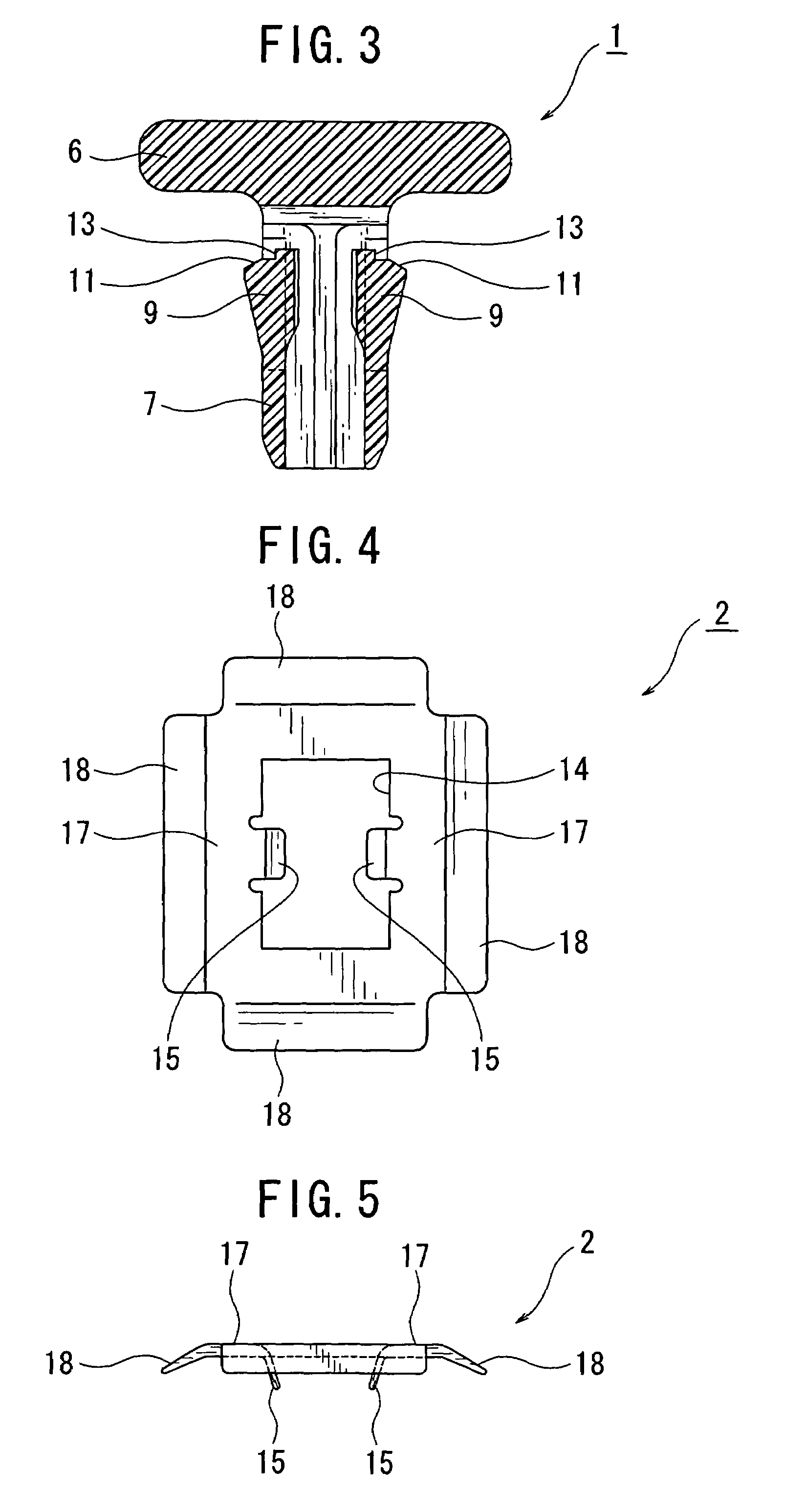

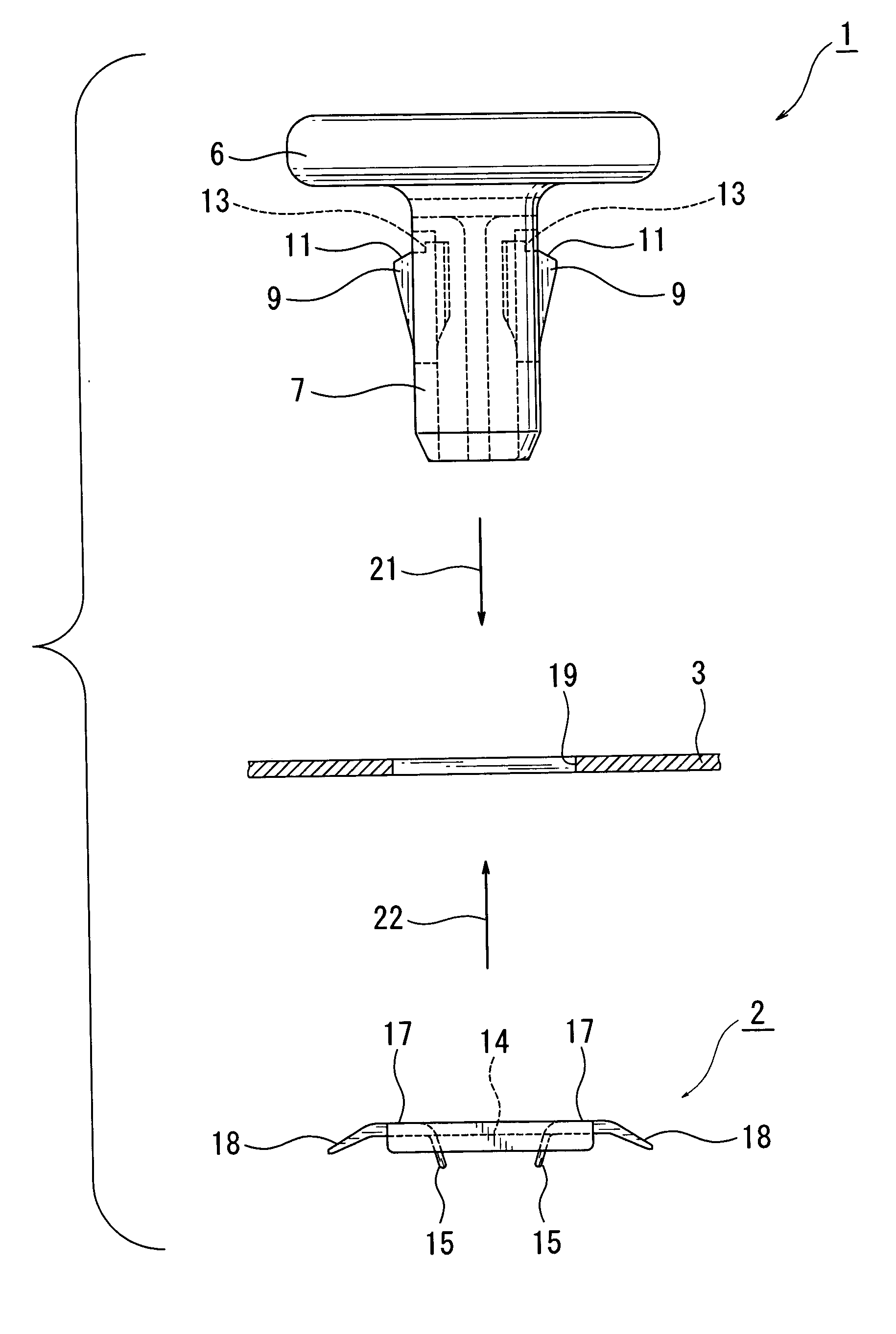

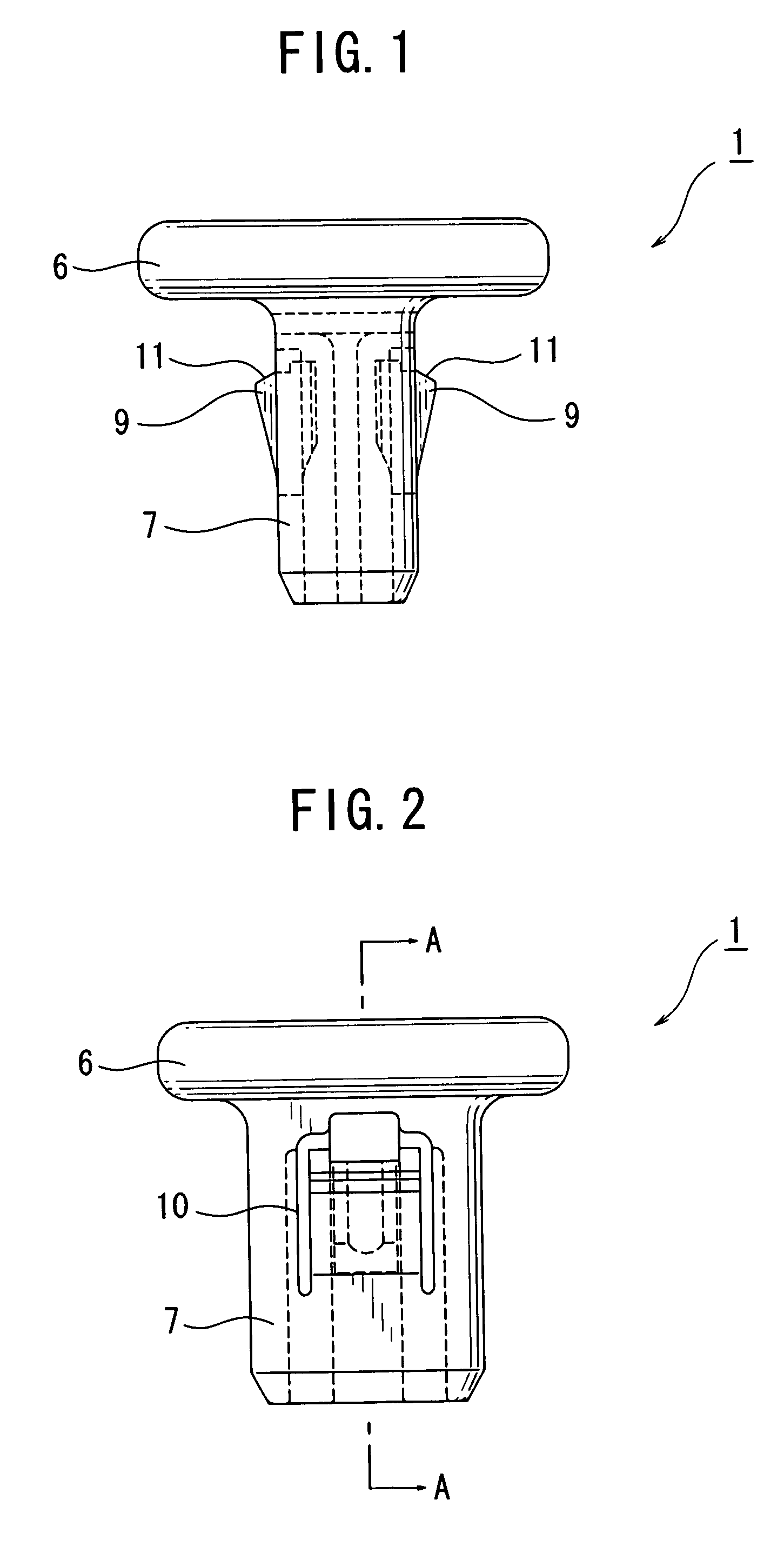

Fastener device

A fastener device for connecting a first component to a second component comprises a clip having a flange and a shank, and a retaining plate cooperable with the clip to embrace the first component between the flange and the retaining plate when the shank is passed through a hole in the first component and a hole in the retaining plate. When the shank is passed through a hole in the second component, first elastic engagement leaves on the shank engage an edge of that hole. Second elastic engagement leaves on the retaining plate engage portions of the first elastic engagement leaves, and the retaining plate is interposed between the components.

Owner:NEWFREY

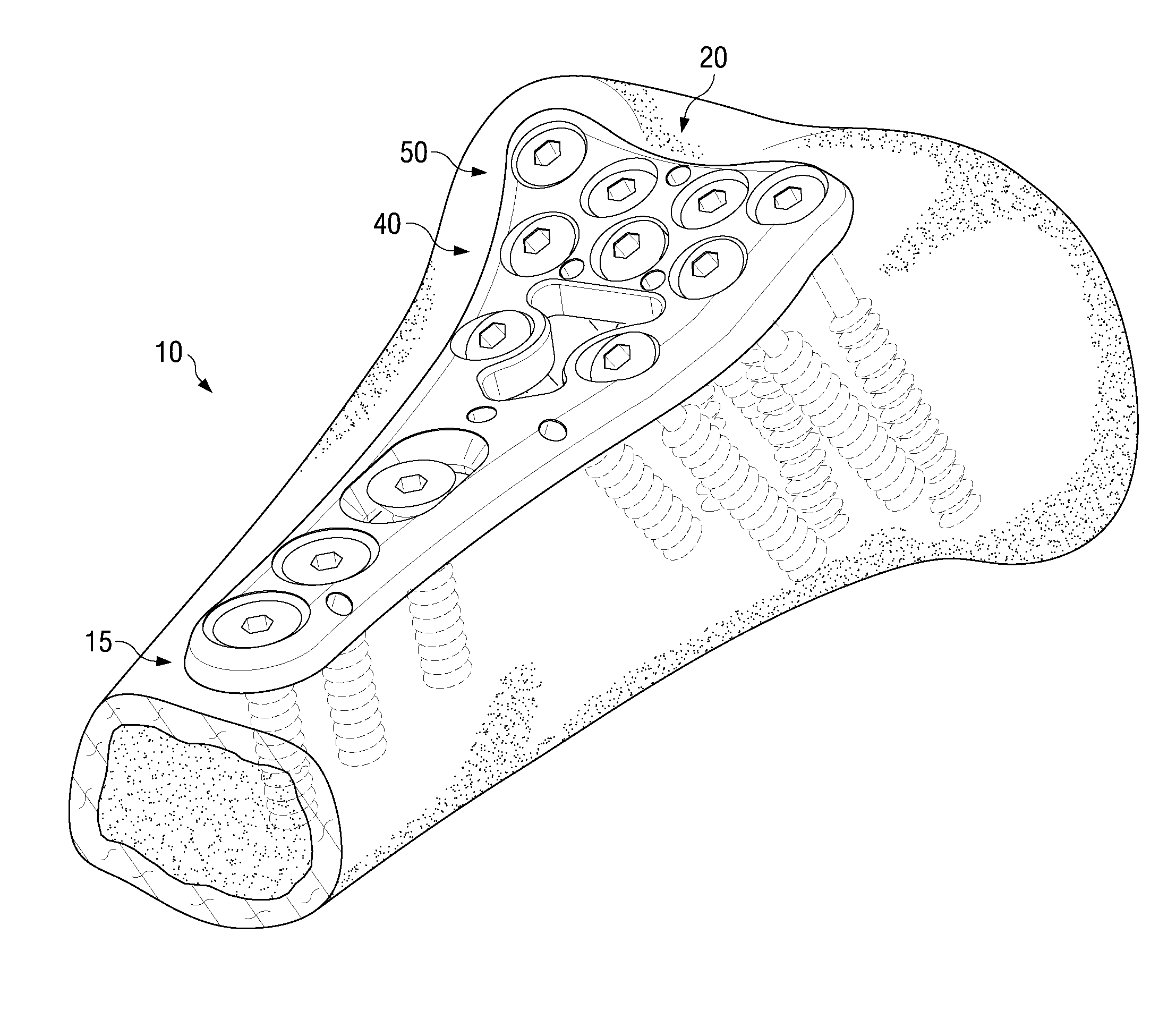

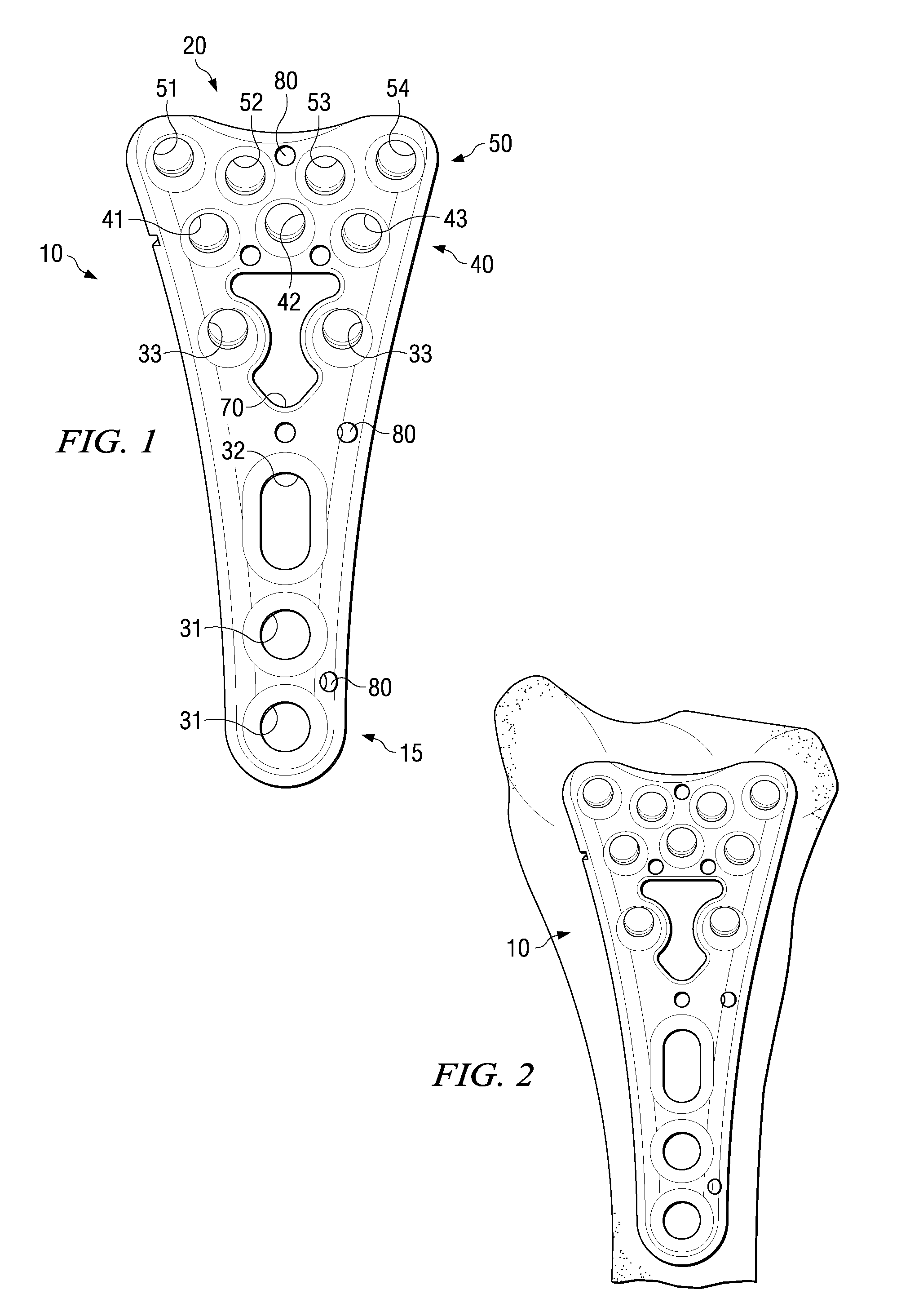

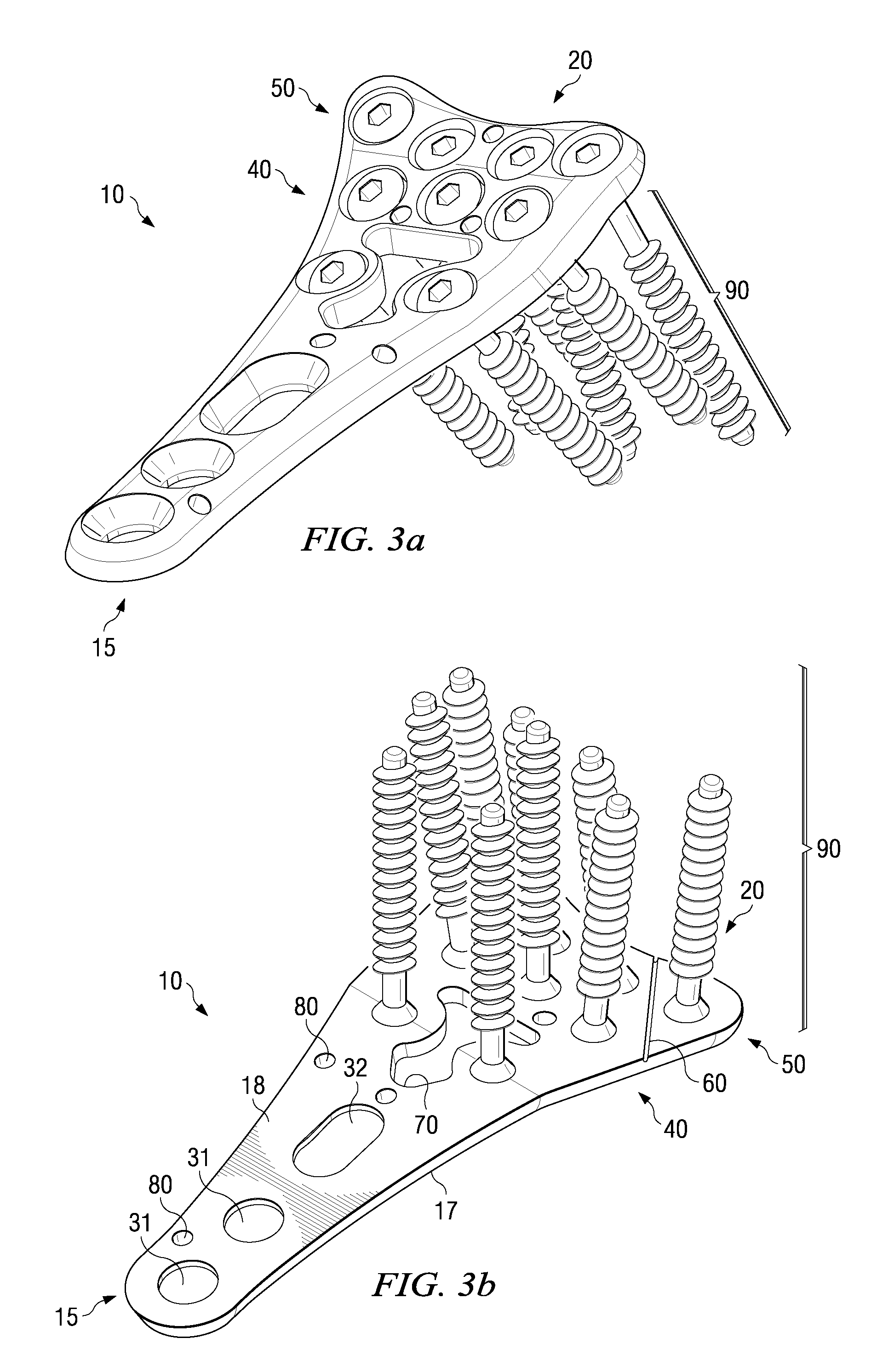

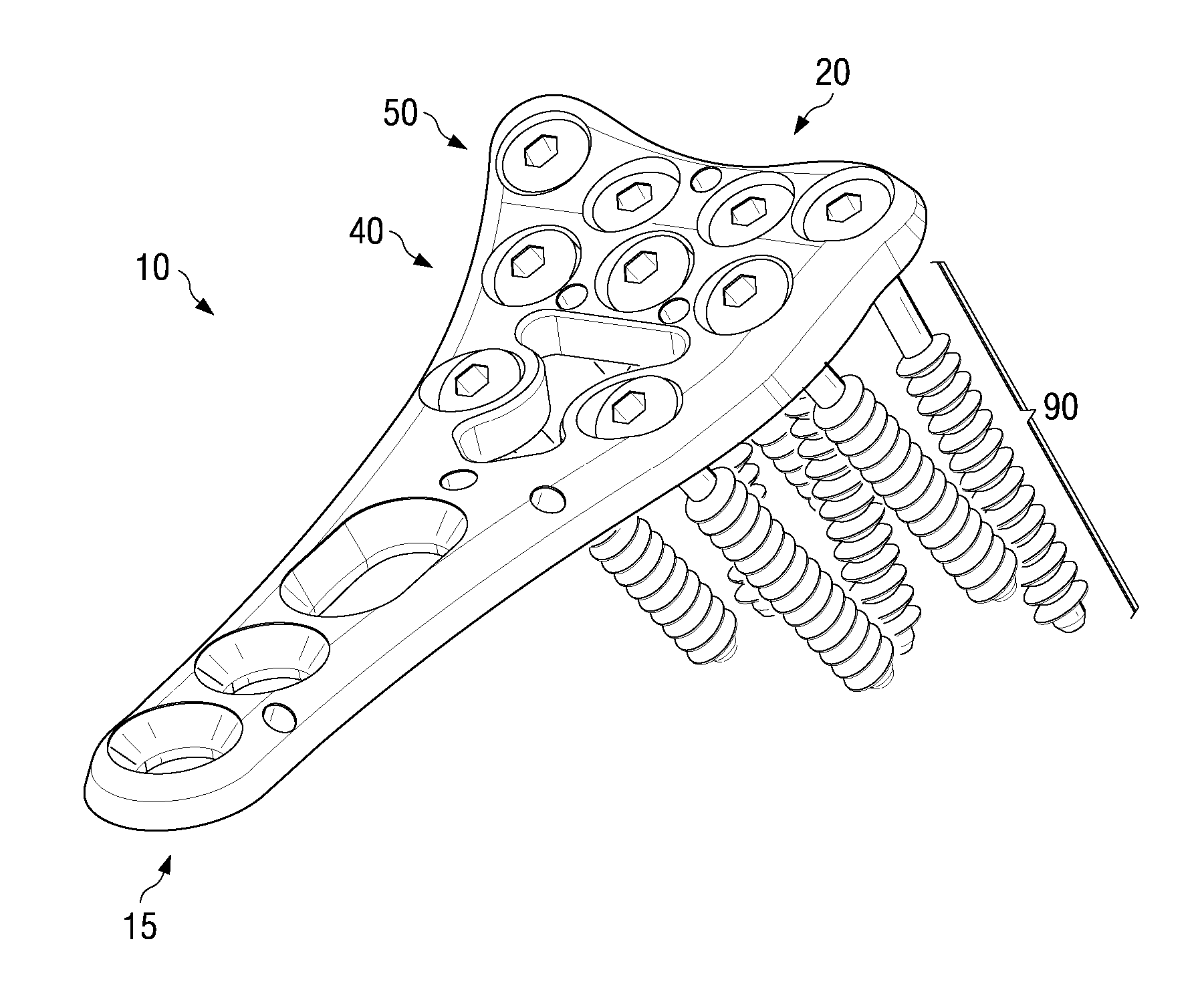

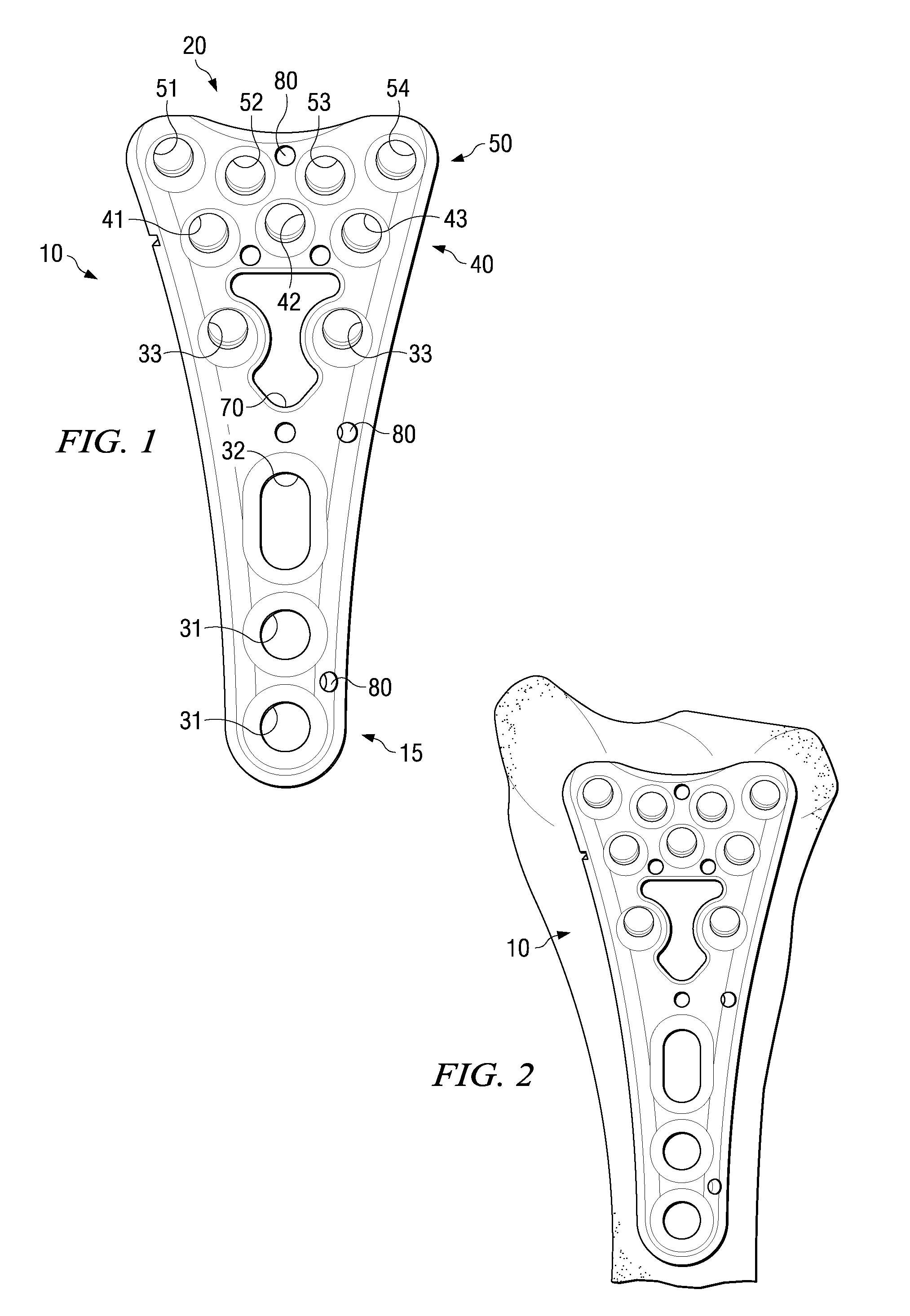

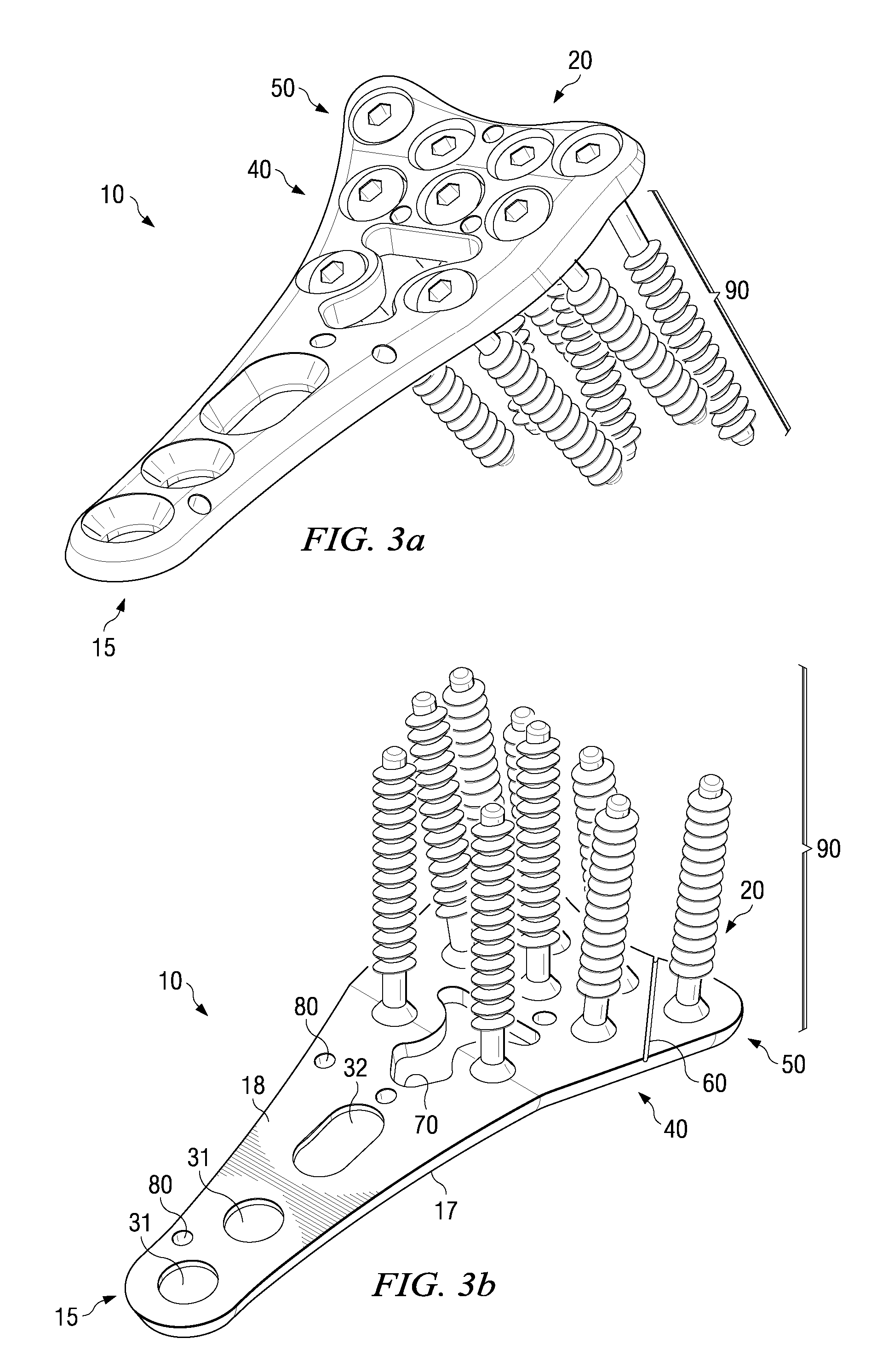

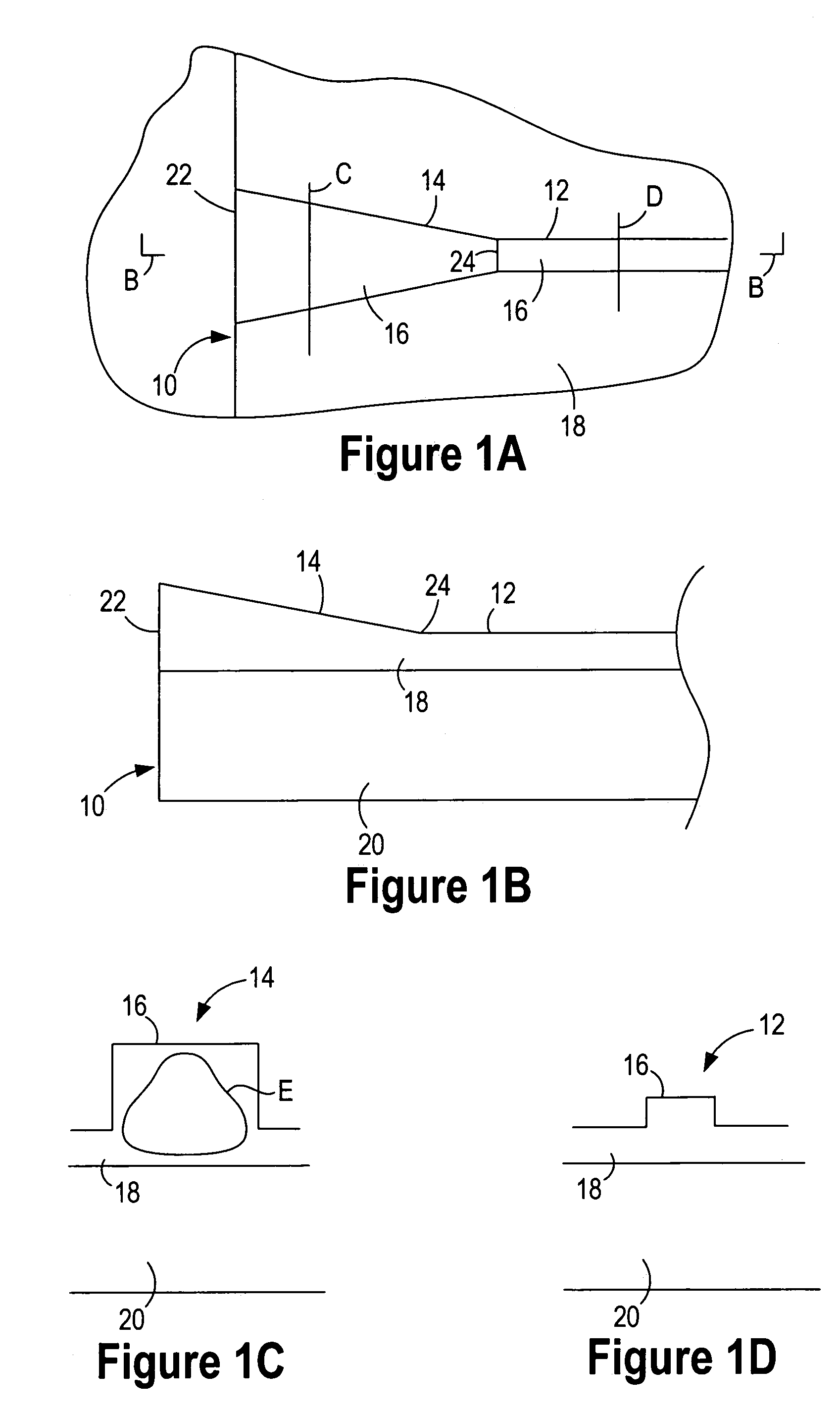

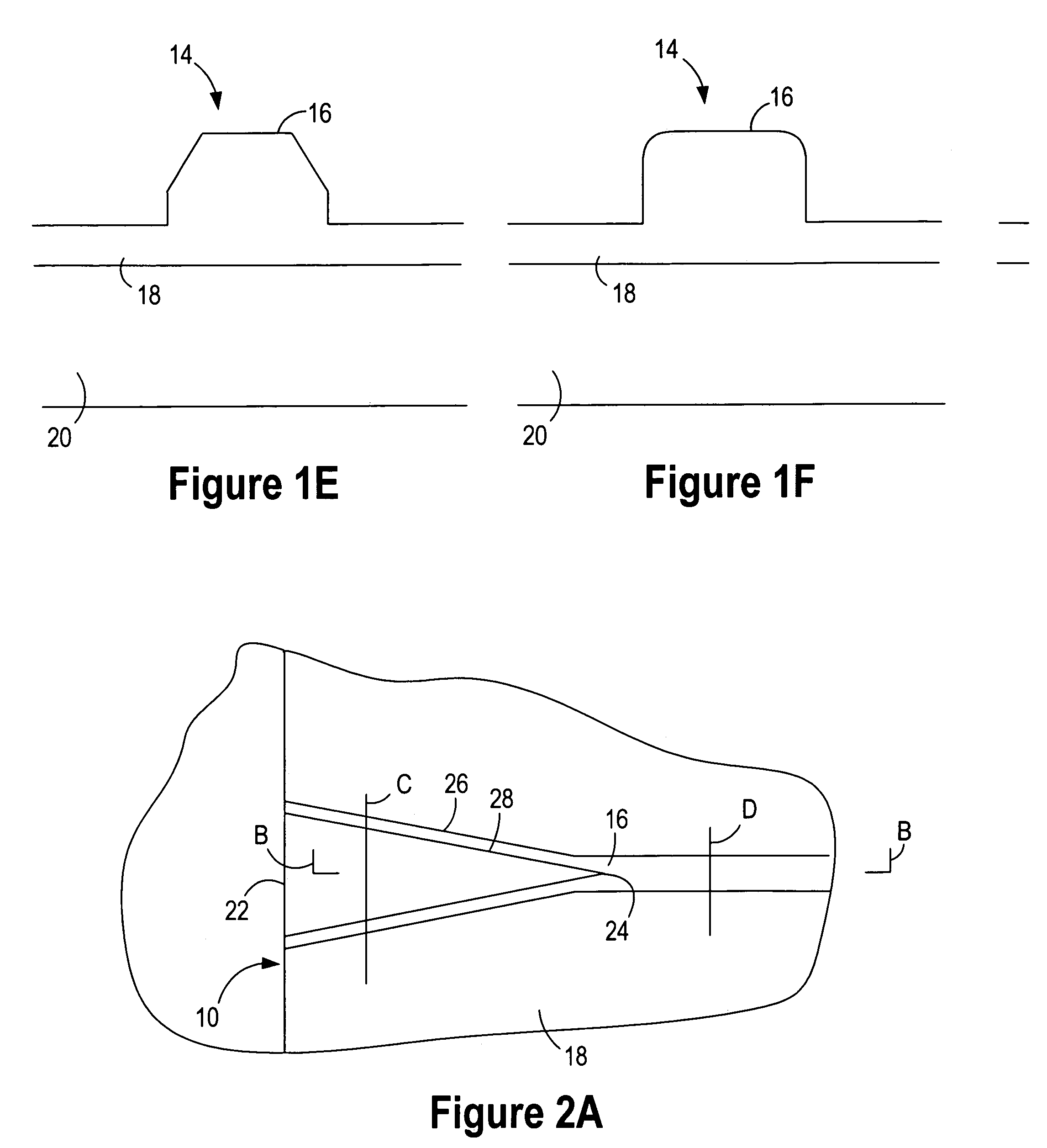

Volar plate fixation device

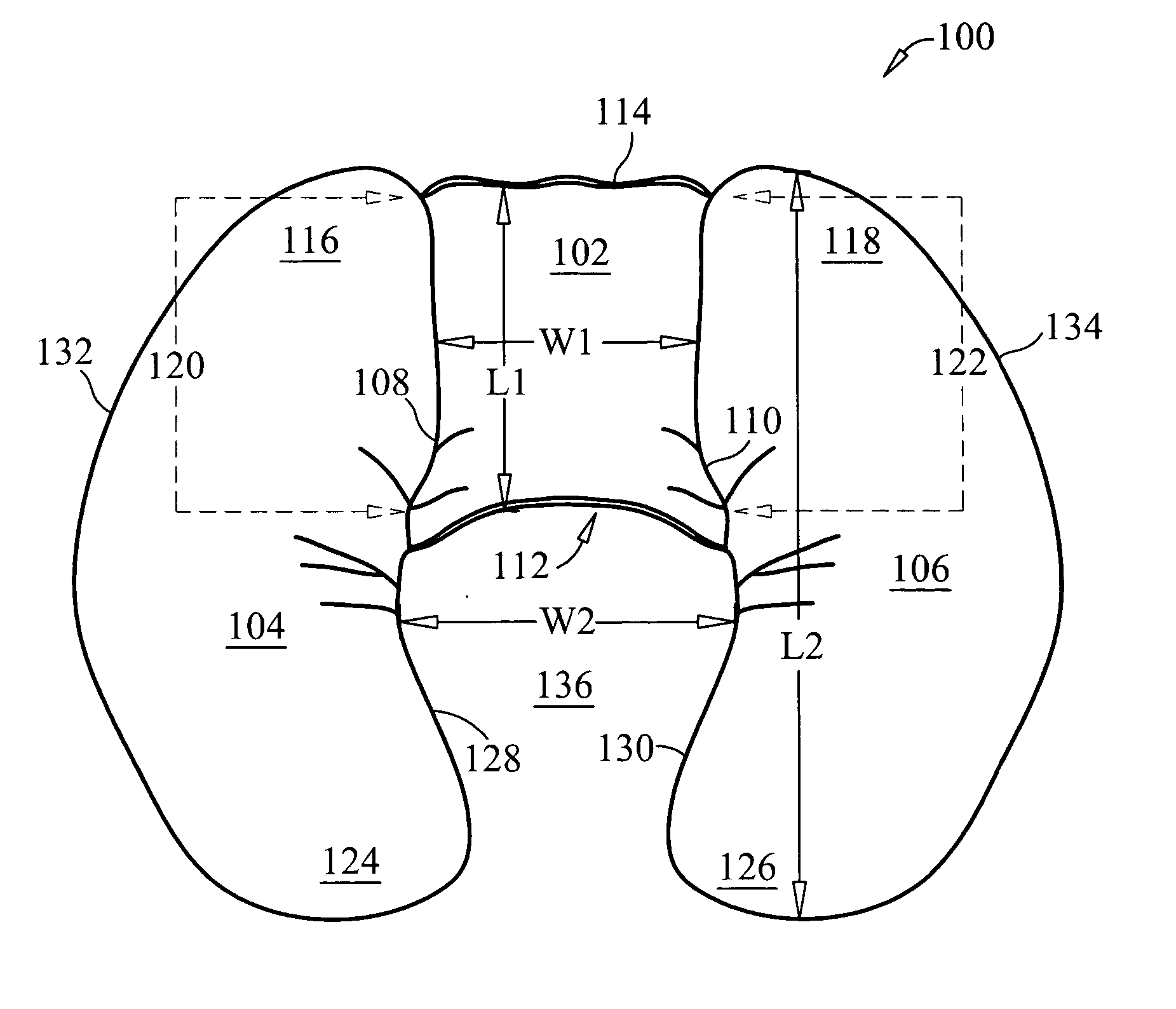

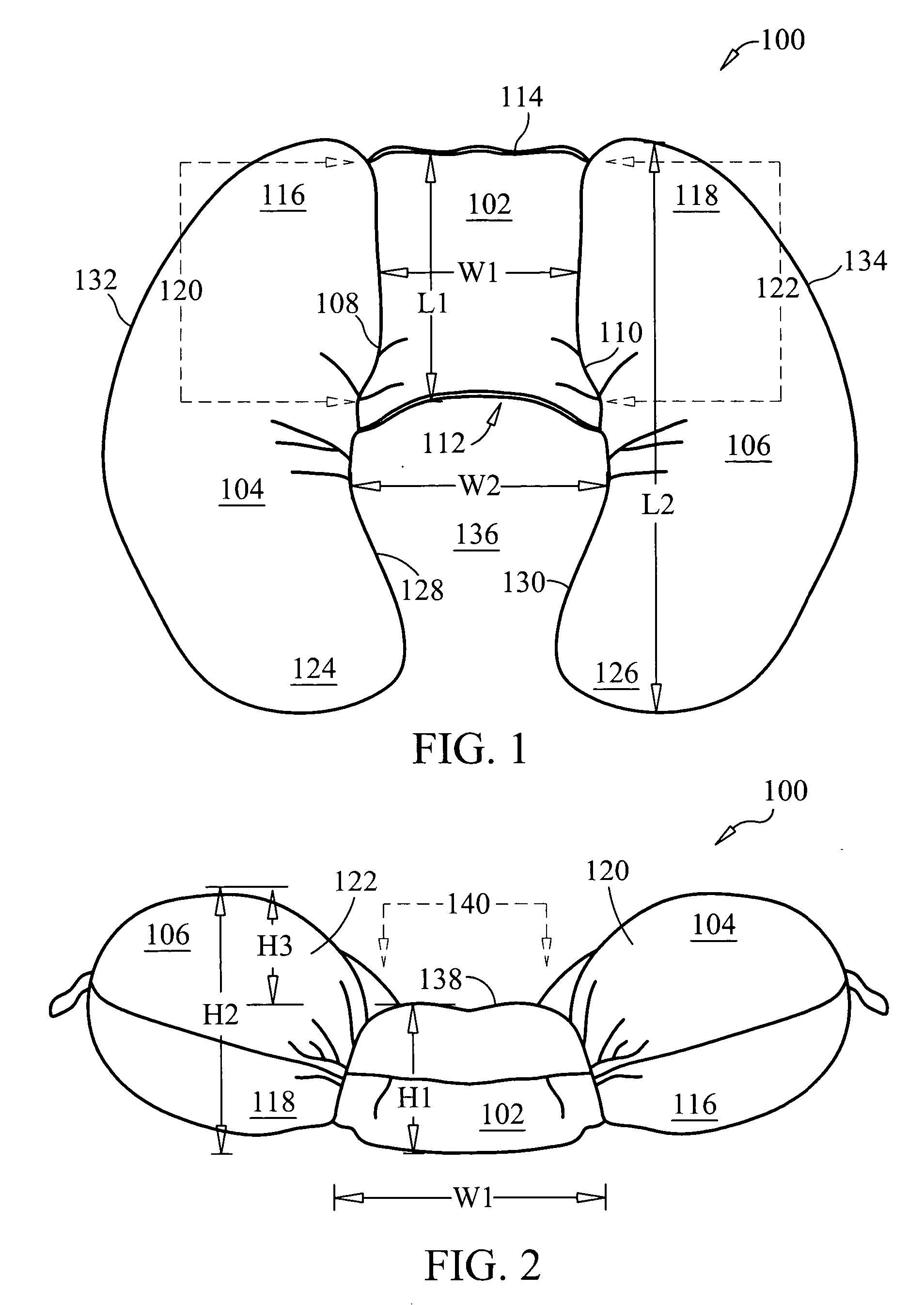

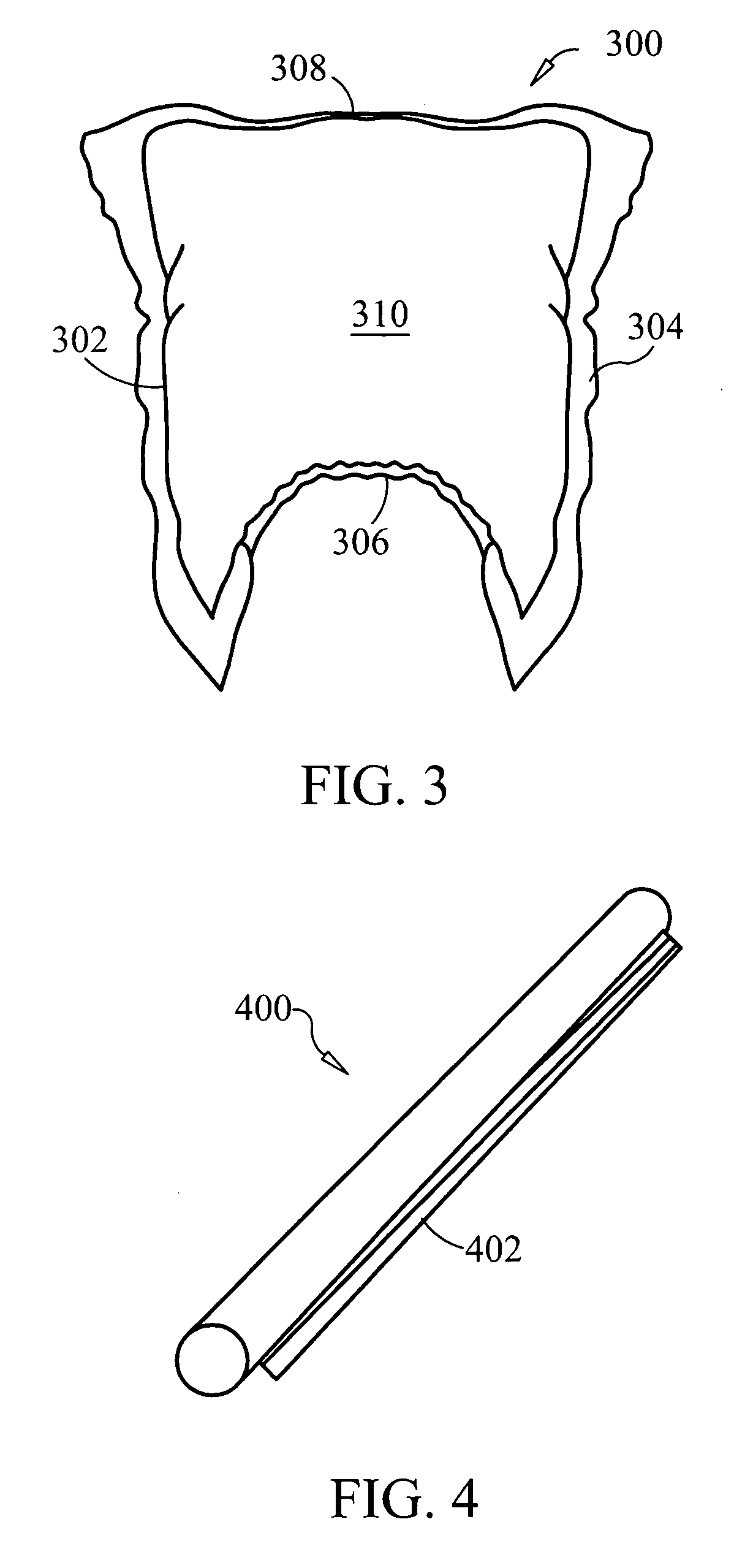

ActiveUS20080140127A1Easy accessEasy to installDiagnosticsBone platesAnatomical featureBiomedical engineering

Disclosed embodiments describe a volar plate generally for use treating distal volar fractures. The volar plate is designed in accordance with anatomical features and is generally Y-shaped, having a wider distal head portion that tapers to a narrower proximal body portion. A plurality of holes in the distal head of the volar plate allow for fixation means to fix the position of bone fragments with respect to the volar plate. The plurality of holes in the distal head basically form two substantially non-linear rows, with the distal row generally curving inward proximally and the proximal row generally curving outward distally such that the fixation means inserted through the holes generally converge. A central cavity may be located in the proximal body of the volar plate to promote bone growth, and mounting screws may border the central cavity on either side to provide secure support. Additionally, K-wire holes may be included which are visually linked to corresponding holes in the distal head.

Owner:ORTHOFIX SRL

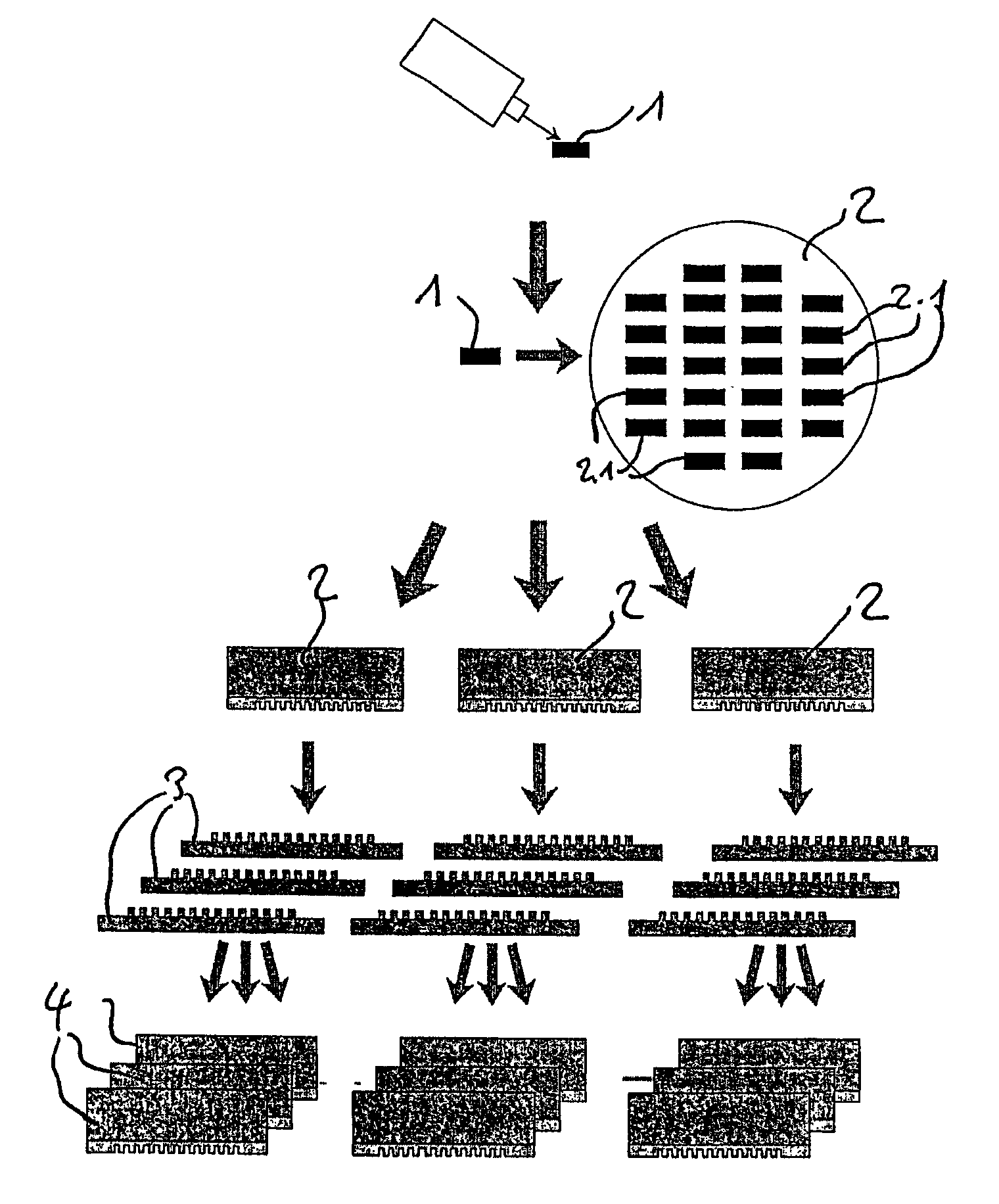

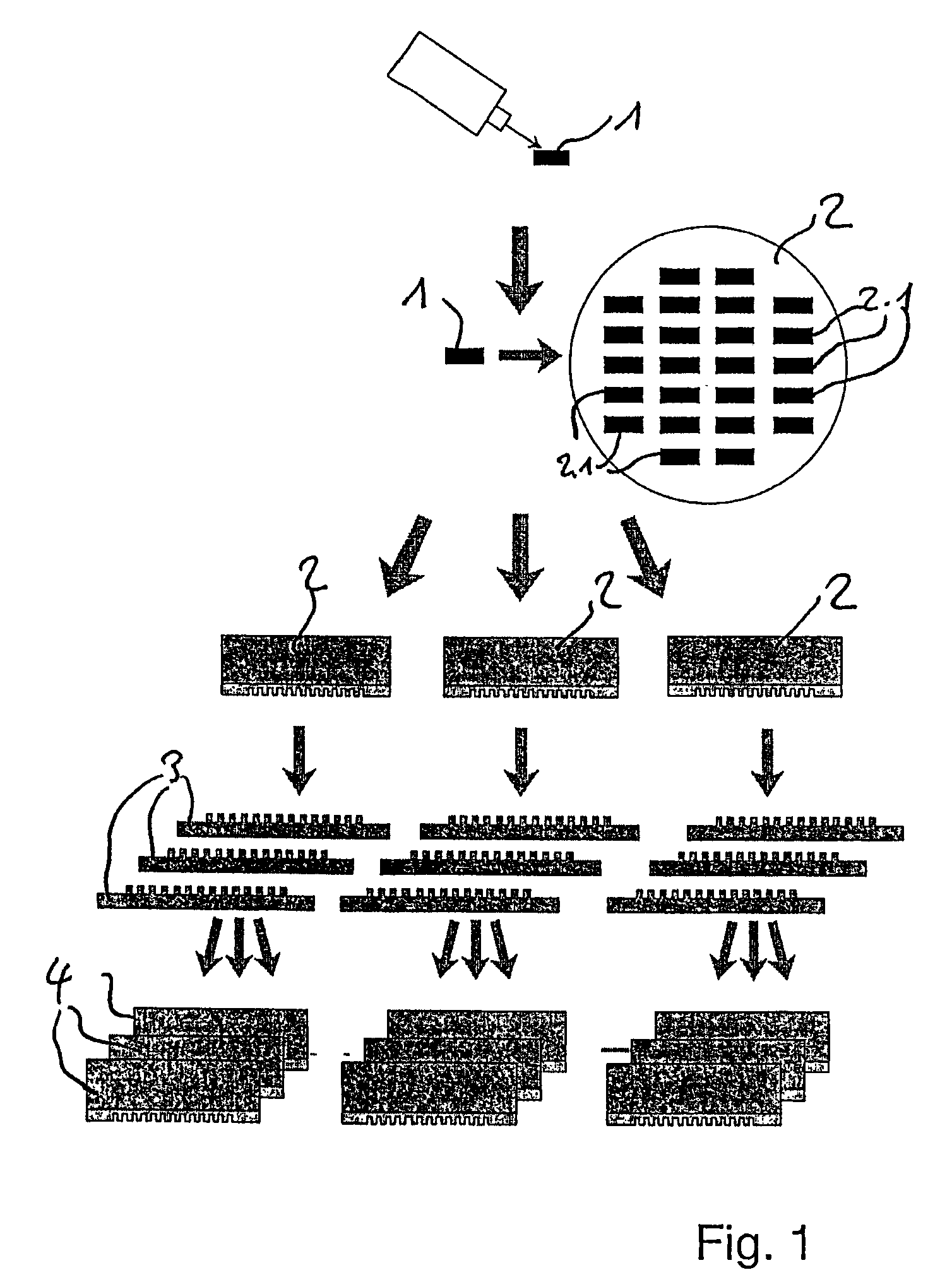

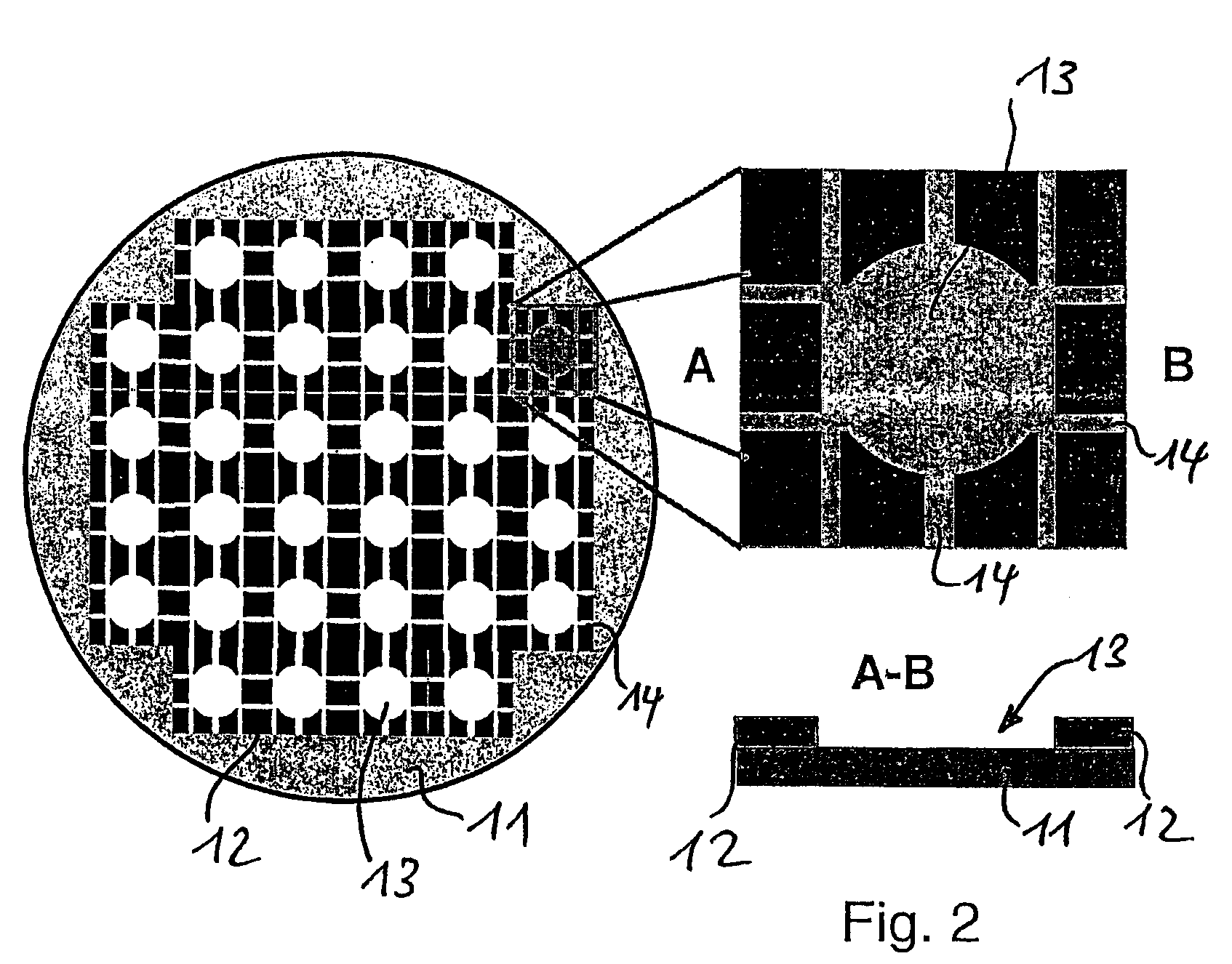

Manufacturing a replication tool, sub-master or replica

ActiveUS20060259546A1Easy to implementLarge scaleNanoinformaticsConfectioneryStructuring elementManufacturing engineering

Owner:AMS SENSORS SINGAPORE PTE LTD

Volar plate fixation device

ActiveUS8398687B2Effective and stableEffective therapyDiagnosticsBone platesProximal pointBone growth

Disclosed embodiments describe a volar plate generally for use treating distal volar fractures. The volar plate is designed in accordance with anatomical features and is generally Y-shaped, having a wider distal head portion that tapers to a narrower proximal body portion. A plurality of holes in the distal head of the volar plate allow for fixation means to fix the position of bone fragments with respect to the volar plate. The plurality of holes in the distal head basically form two substantially non-linear rows, with the distal row generally curving inward proximally and the proximal row generally curving outward distally such that the fixation means inserted through the holes generally converge. A central cavity may be located in the proximal body of the volar plate to promote bone growth, and mounting screws may border the central cavity on either side to provide secure support. Additionally, K-wire holes may be included which are visually linked to corresponding holes in the distal head.

Owner:ORTHOFIX SRL

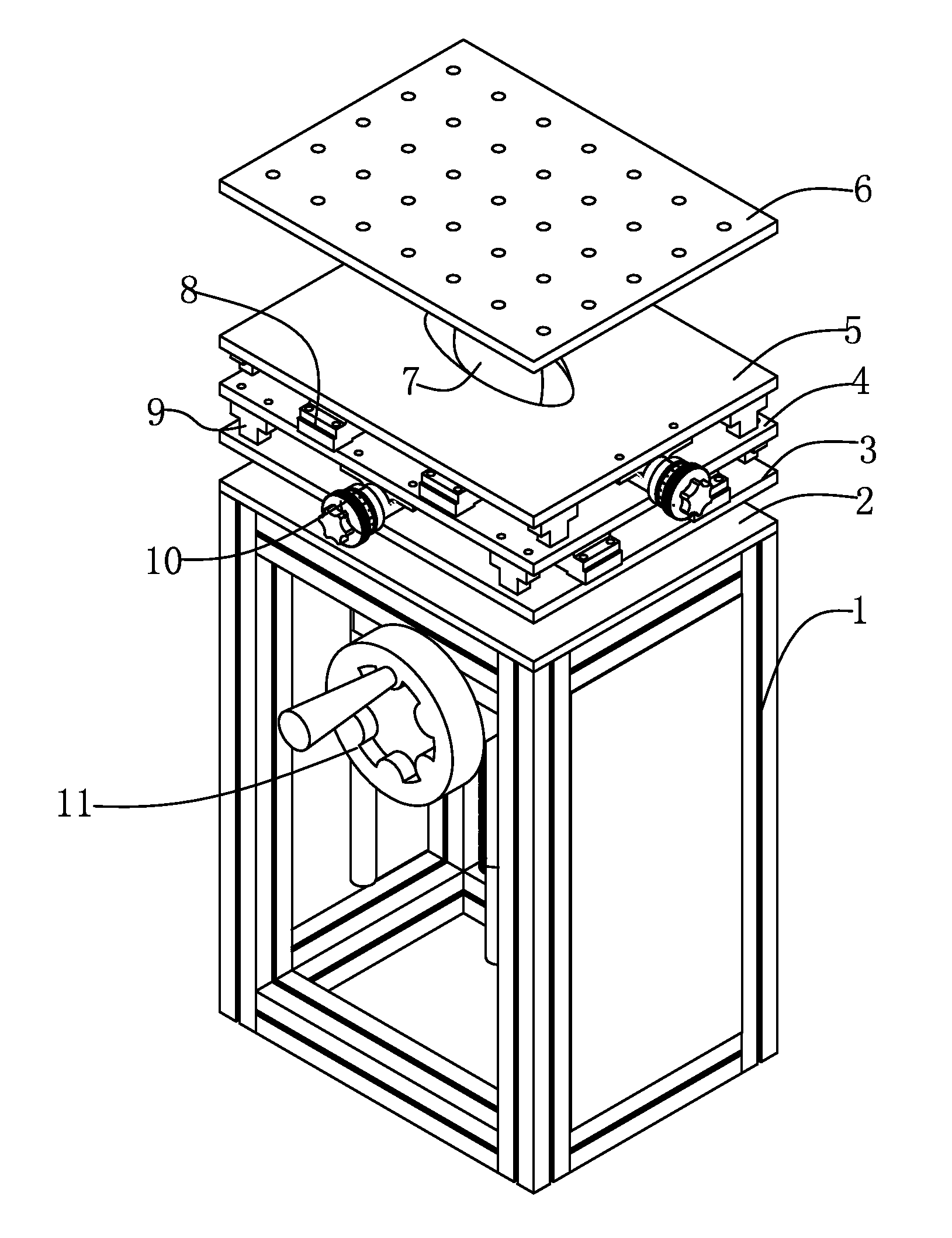

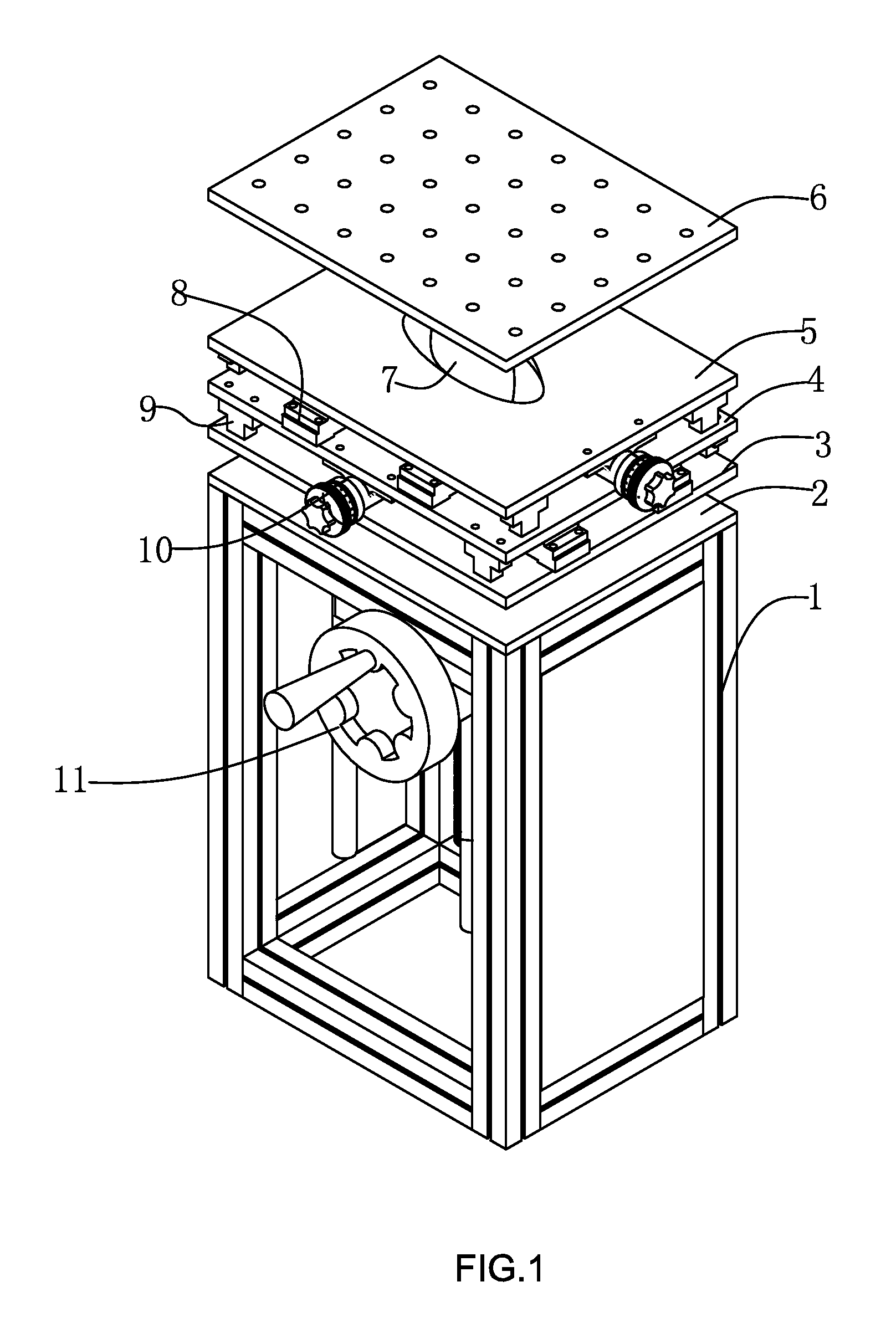

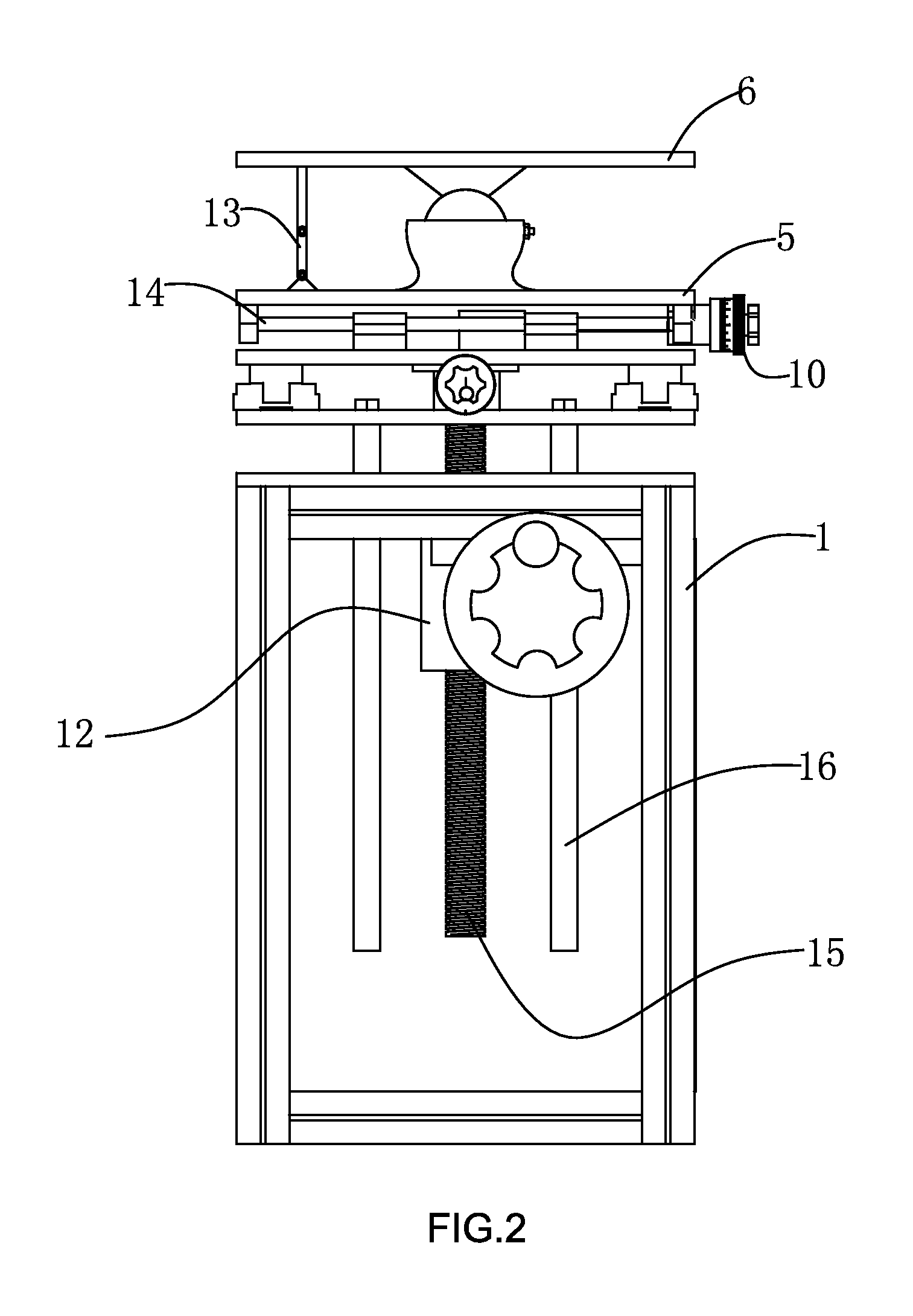

Operating Table with Multiple Degrees of Freedom

ActiveUS20130200561A1Increase spacingImprove distributionWork benchesLarge fixed membersEngineeringMultiple degrees of freedom

Disclosed is an operating table with multiple degrees of freedom which is capable of moving and rotating in various directions. The operating table comprises an elevating mechanism, a moving mechanism on a horizontal plane and a multiple angle rotation mechanism, with the elevating mechanism and the moving mechanism adopting a leadscrew structure, the multiple angle rotation mechanism comprising a universal joint device (7) and a locking mechanism. The moving mechanism can drive the operating table (6) to move on a horizontal plane and ensure the operating table (6) can reach any location within a valid region on a horizontal plane, the moving mechanisms in the X and Y directions can operate separately as well as cooperatively, and the multiple angle rotation mechanism drives the surface of the operating table to tilt. These mechanisms work in combination to accomplish the location change of the operating table.

Owner:ZHEJIANG LINIX MOTOR

Support device for positioning a patient in a prone position

Owner:MOORE JOHN

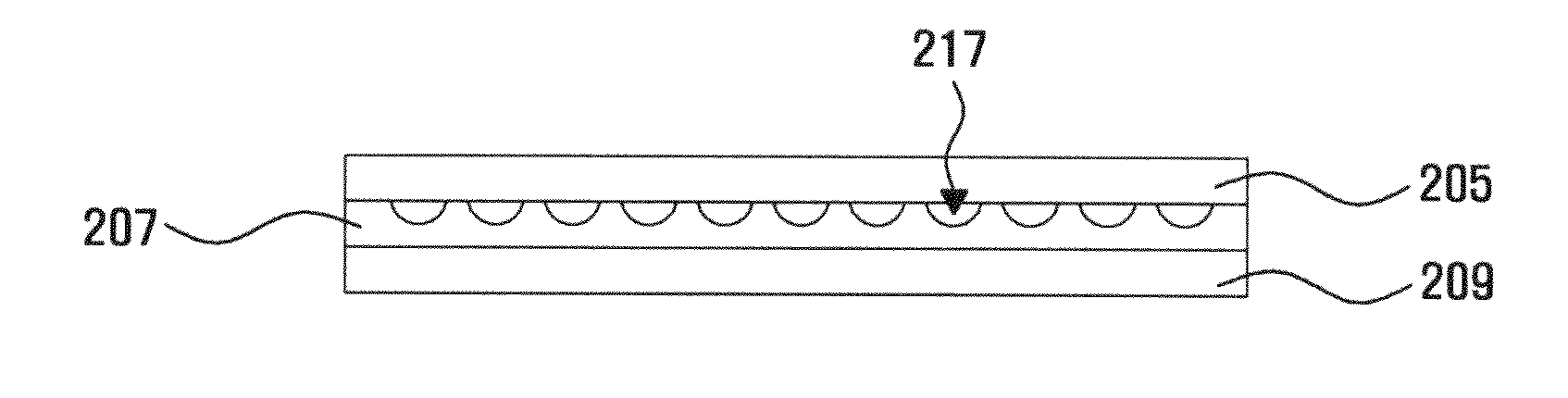

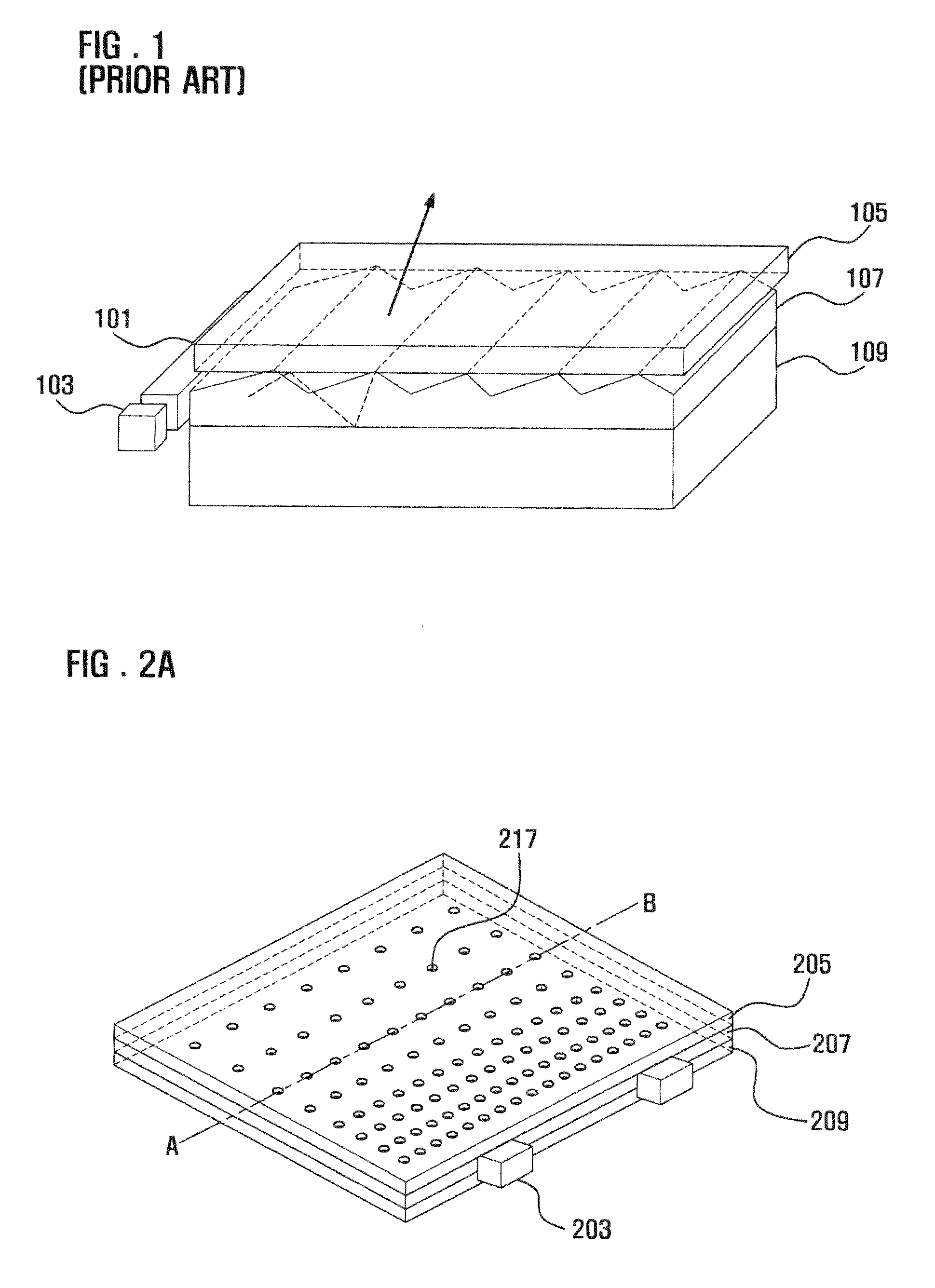

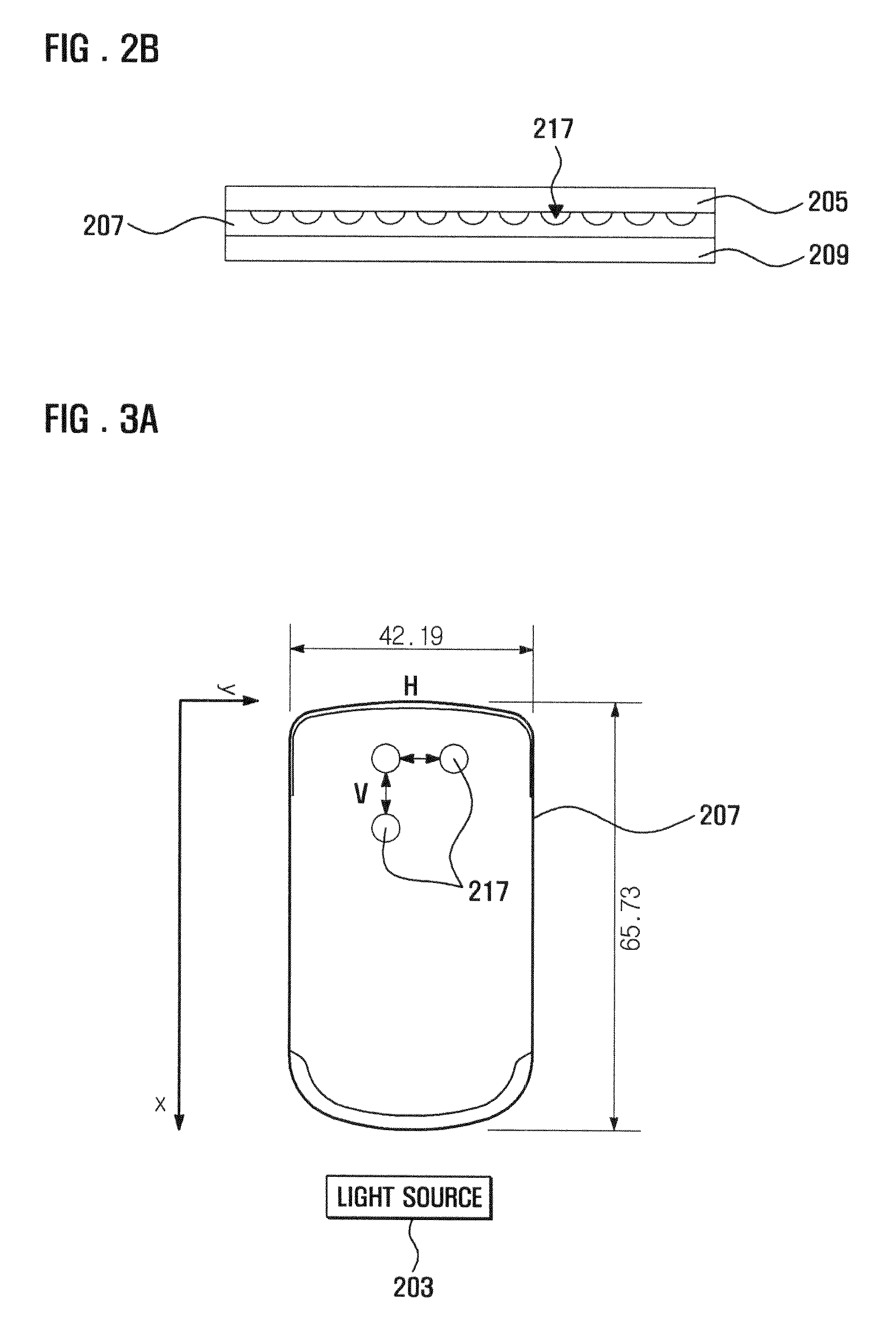

Reflection type display apparatus and method for manufacturing light guide plate

A reflection-type display apparatus that includes cavities dispersed on a light guide plate and is a type of flexible thin film, and a method for manufacturing a light guide plate. The reflection-type display apparatus includes: a reflection-type display; a light source provided on one side of the reflection-type display; a light guide plate bonded to the upper surface of the reflection-type display to scatter light introduced from the light source and having cavities transversely and longitudinally disposed by predetermined intervals on the upper surface thereof; and a film bonded to the upper surface of the light guide plate to protect the upper surface of the light guide plate.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device and method for forming the same

InactiveUS20060081896A1High speedLower surfaceSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialCharge carrier mobility

The present invention disclosed herein is a semiconductor device and a method for forming the same. The semiconductor device includes a first semiconductor pattern defining an active region, second semiconductor patterns placed on the first semiconductor pattern apart from each other, an insulated gate electrode spaced apart from the second semiconductor patterns to be placed therebetween, and stress generating patterns filling intervals between the insulated gate electrode and the second semiconductor patterns. The stress generating patterns apply a stress to a channel region defined by the first semiconductor pattern under the gate electrode, thereby increasing carrier mobility.

Owner:SAMSUNG ELECTRONICS CO LTD

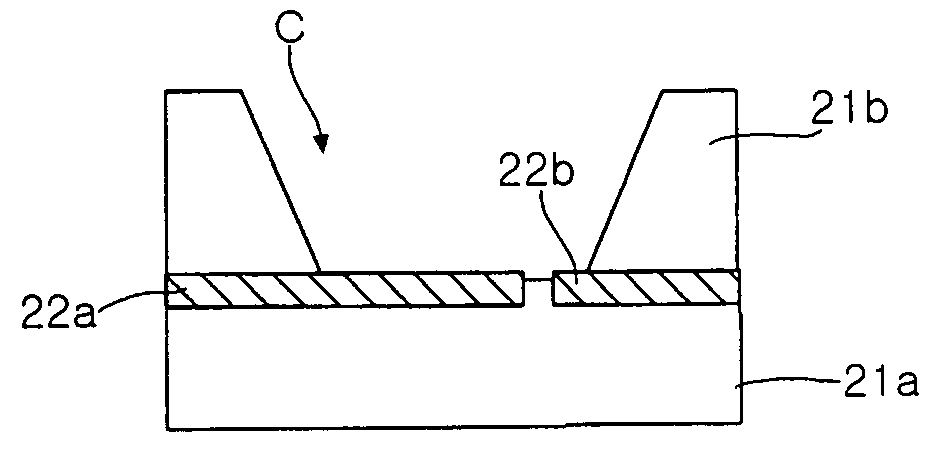

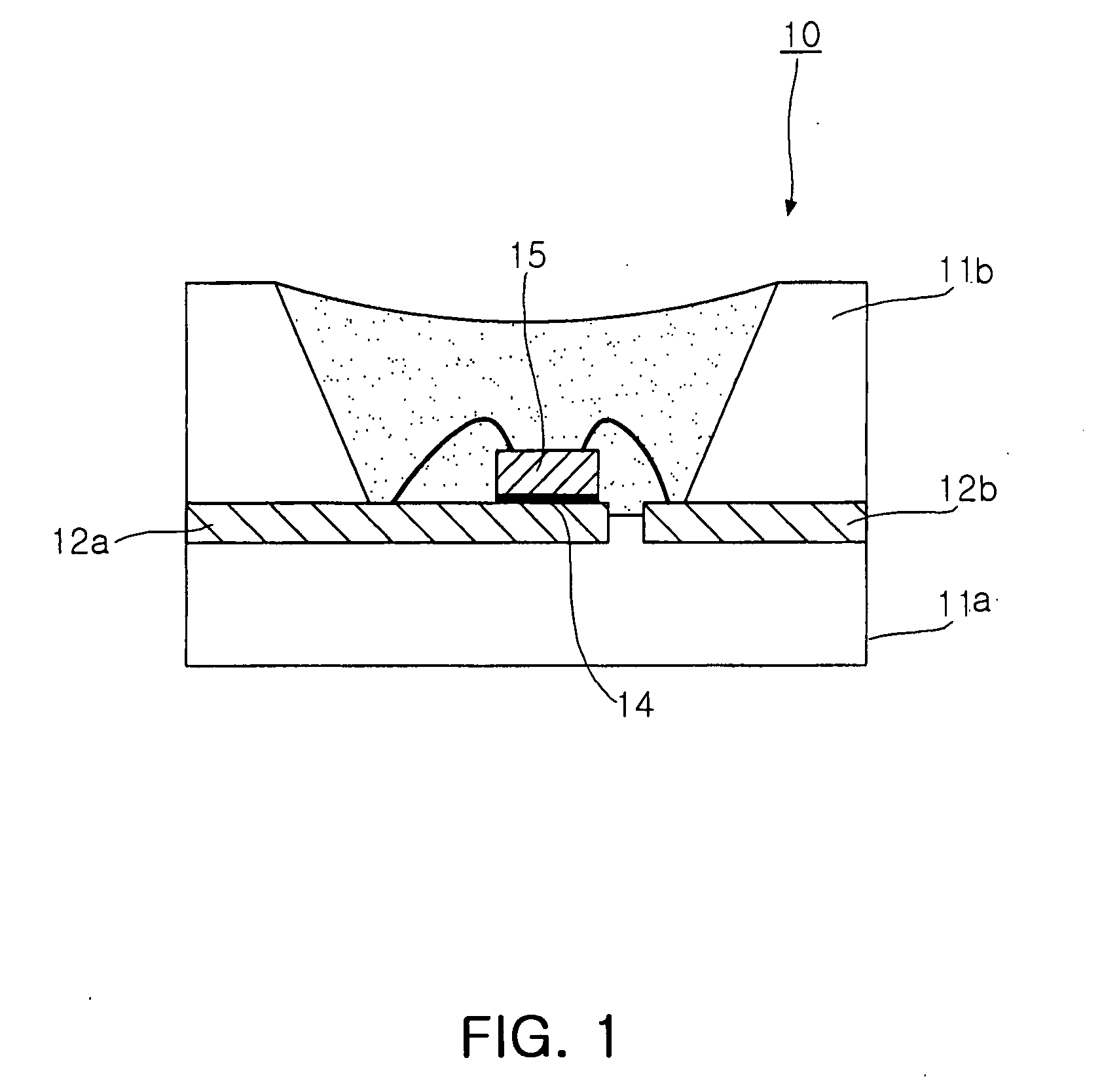

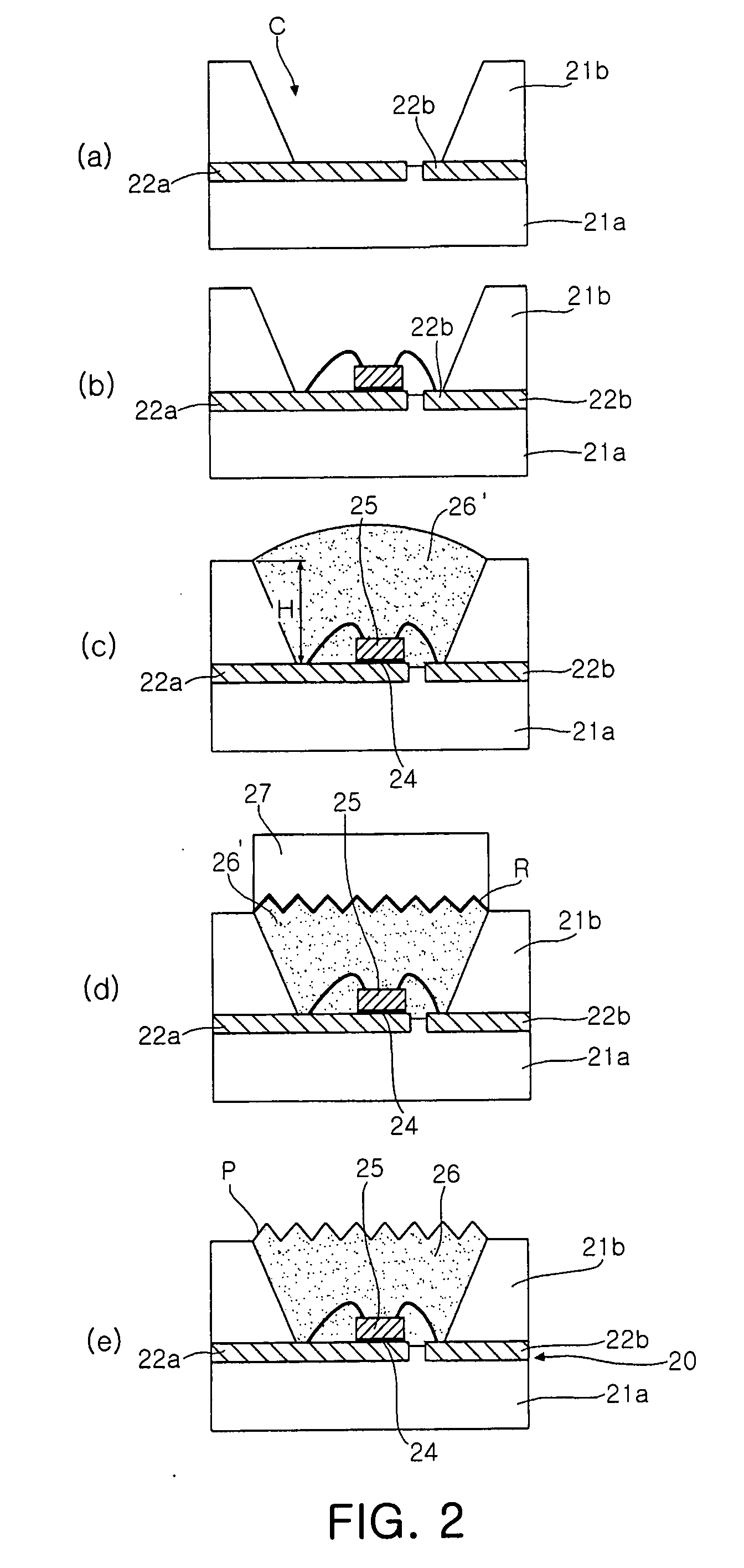

Method of manufacturing light emitting diode package

ActiveUS20070196939A1Easy to disassembleMinimize damageDischarge tube luminescnet screensLamp detailsLiquid stateEngineering

A method of manufacturing a light emitting diode package. A cup-shaped package structure with a recess formed therein and an electrode structure formed on a bottom of the recess is prepared. A light emitting diode chip is mounted on a bottom of the recess with a terminal of the chip electrically connected to the electrode structure. A liquid-state transparent resin is injected in the recess and before the liquid-state transparent resin is completely cured, a stamp with a micro rough pattern engraved thereon is applied on an upper surface of the resin. The liquid-state transparent resin is cured with the stamp applied thereon to form a resin encapsulant and the stamp is removed from the resin encapsulant.

Owner:SAMSUNG ELECTRONICS CO LTD

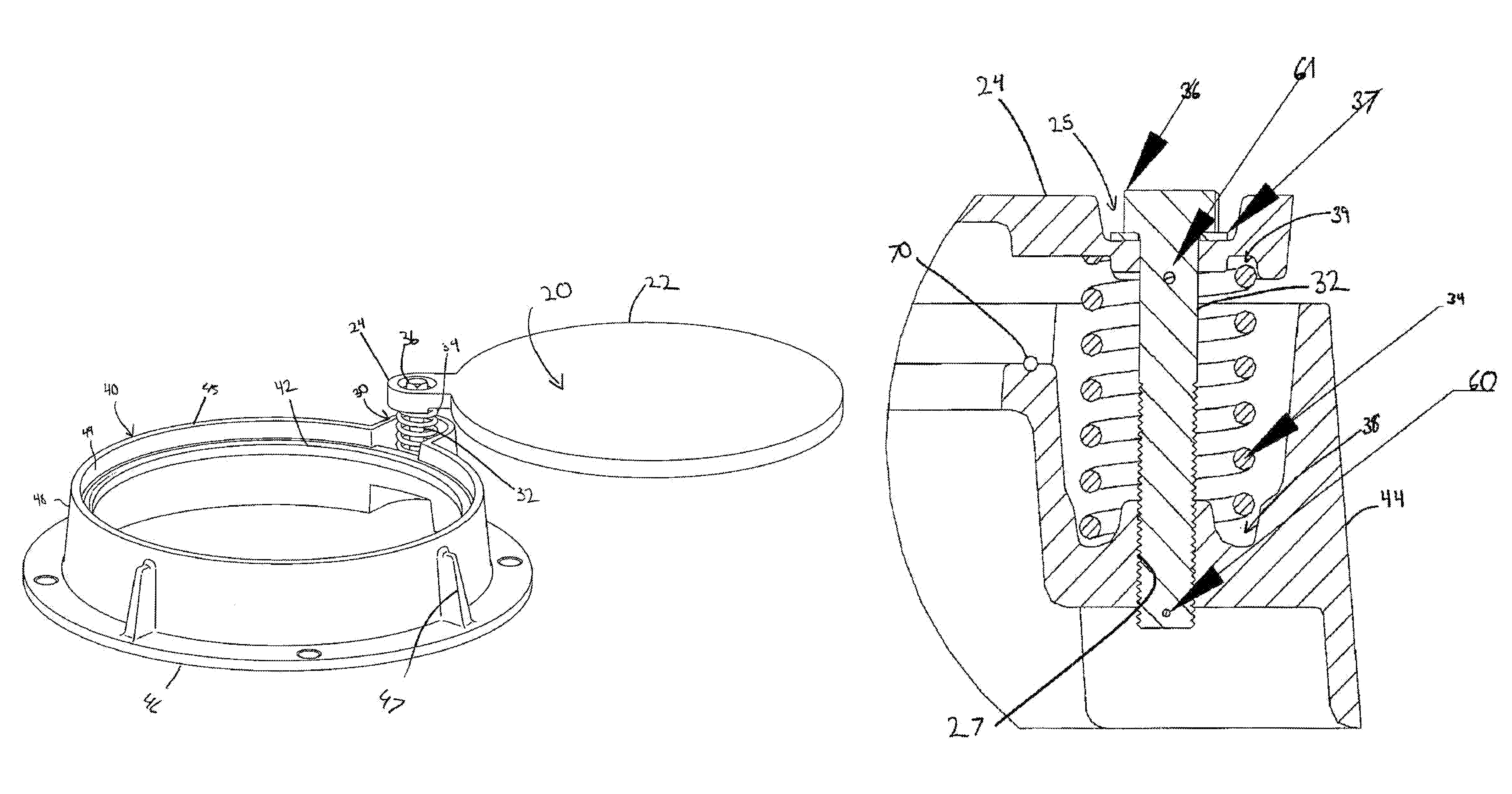

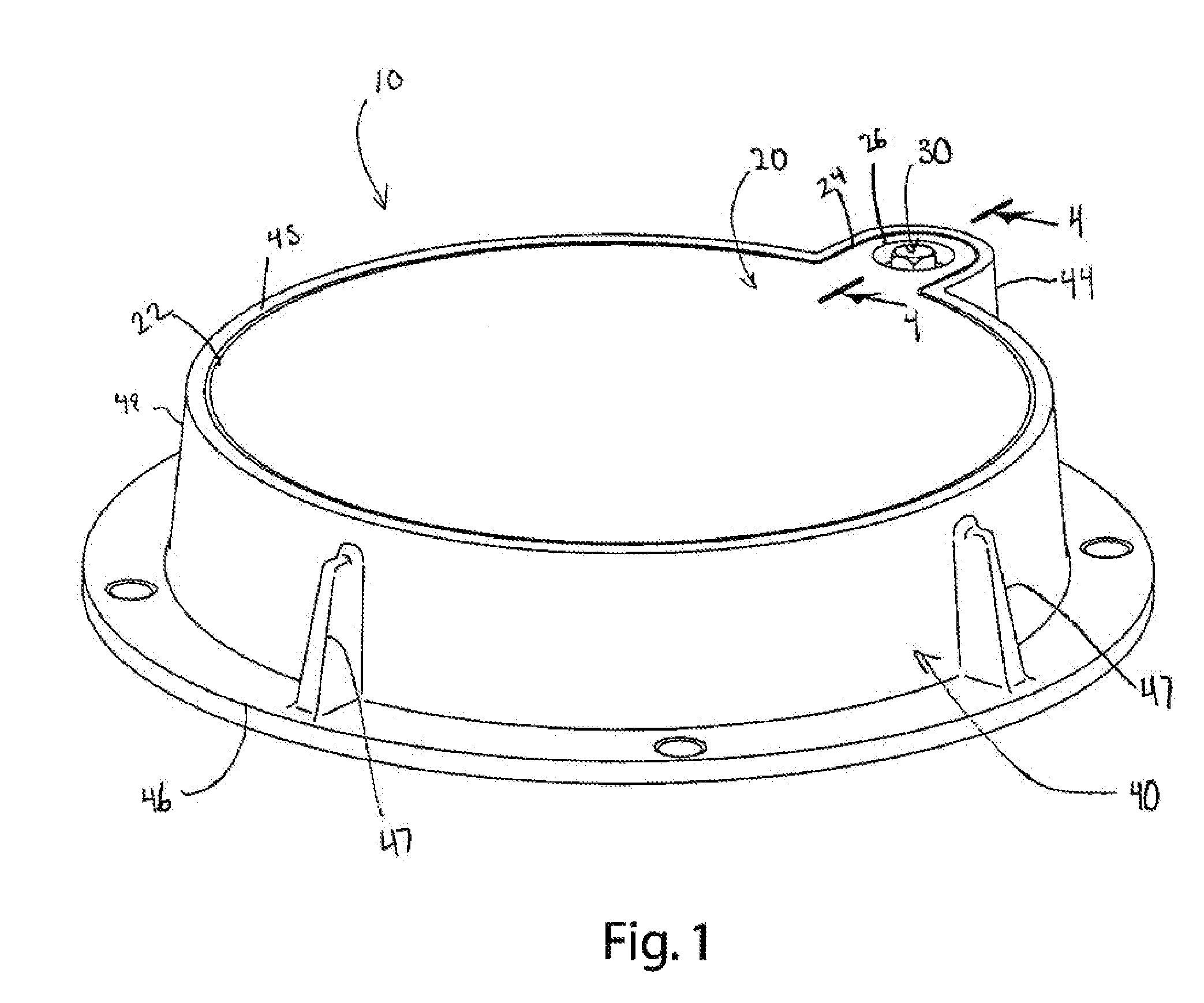

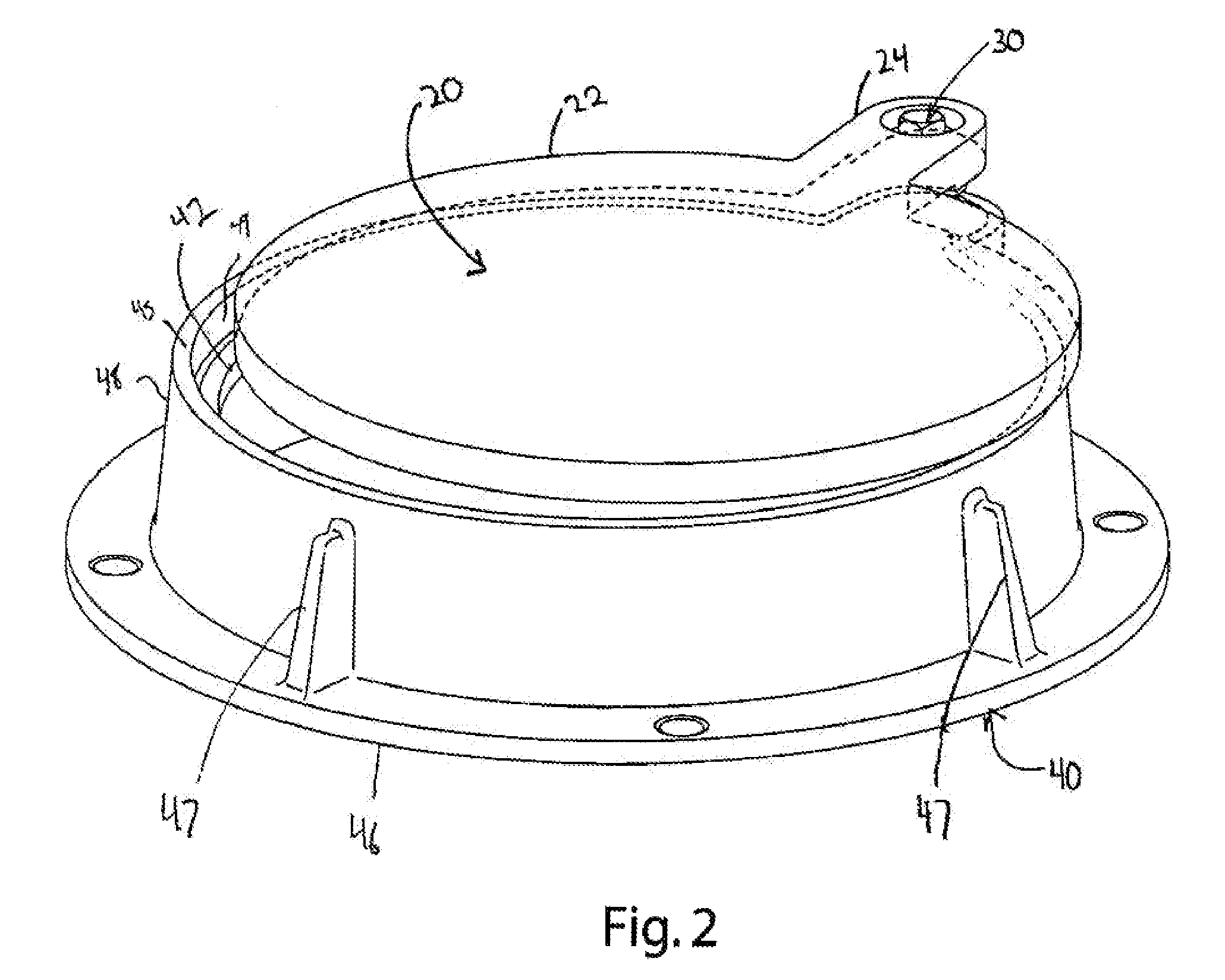

Lift-assisted manhole cover

InactiveUS7341398B2Easily raisedThe process is simple and effectiveArtificial islandsPipesEngineeringMechanical engineering

A lift-assisted manhole cover assembly with a flush surface and external pivot shaft. The cover includes a mounting tab that extends beyond the general periphery of the cover. The mounting tab may be connected to a shaft that is threadedly engaged with the frame. A spring may be mounted between the frame and the mounting tab, for example, in a sleeve, to provide a mechanical assist in lifting the cover. The sleeve may be disposed outside the manhole opening where it does not block access to the manhole opening.

Owner:EAST JORDAN IRON WORKS

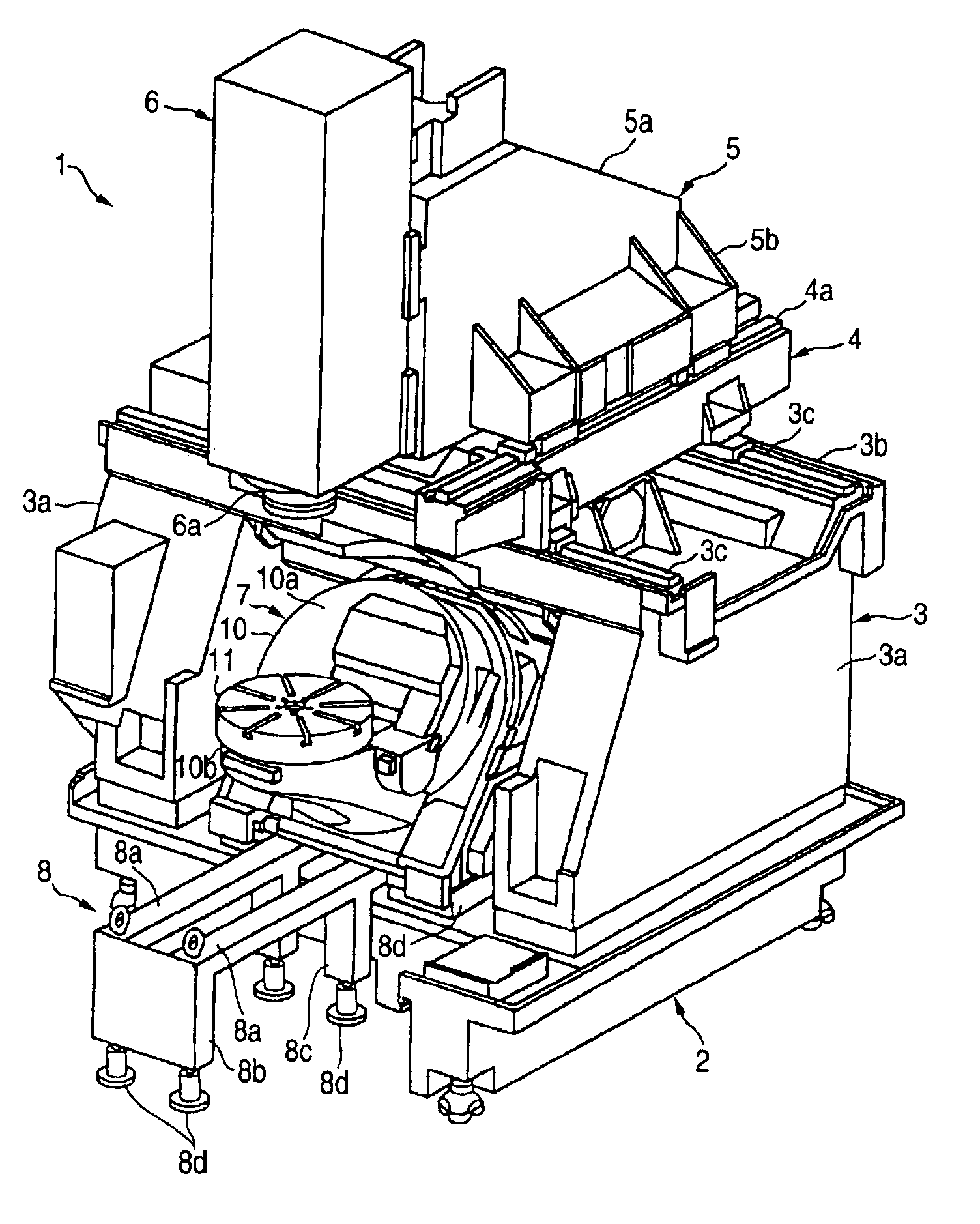

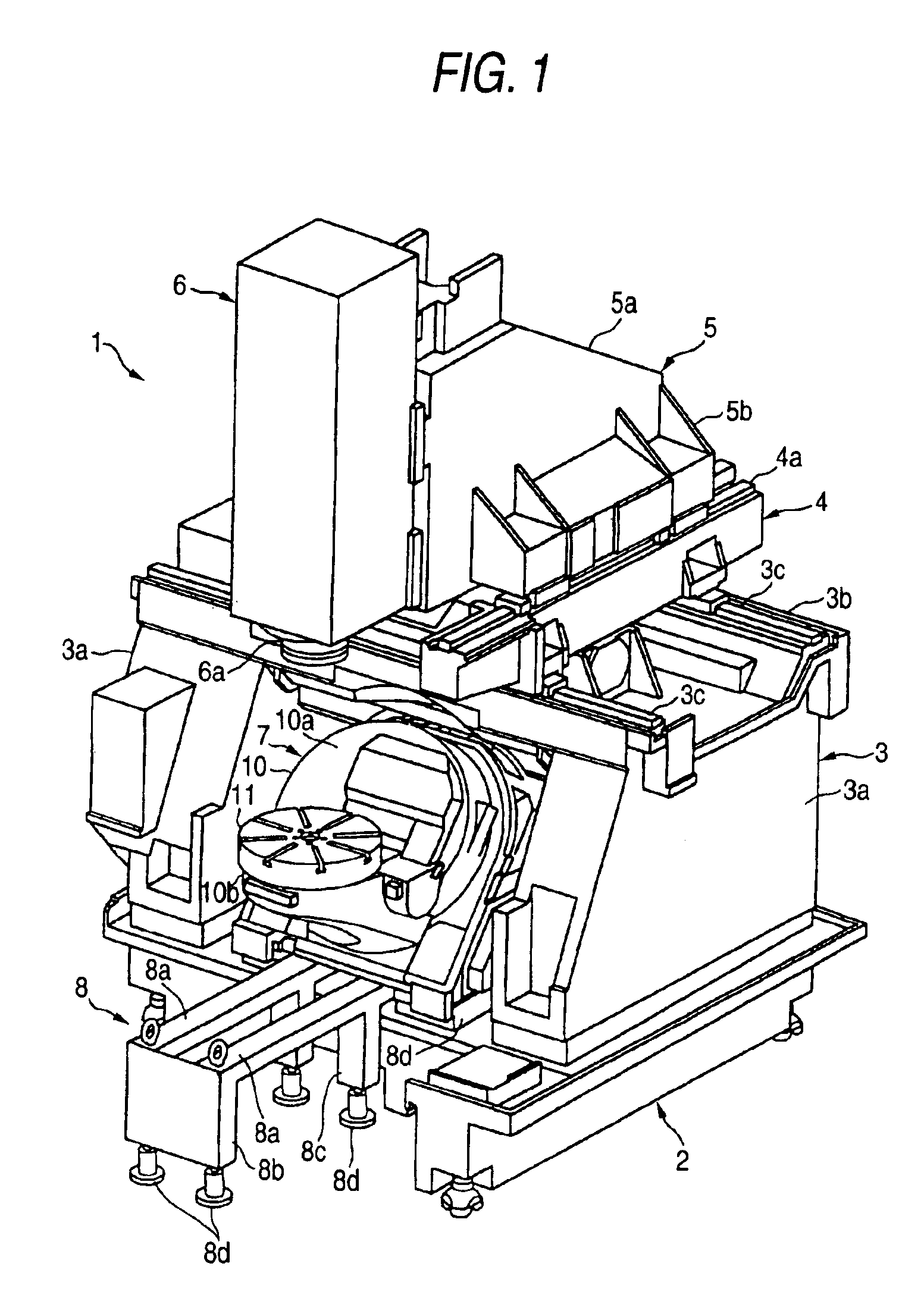

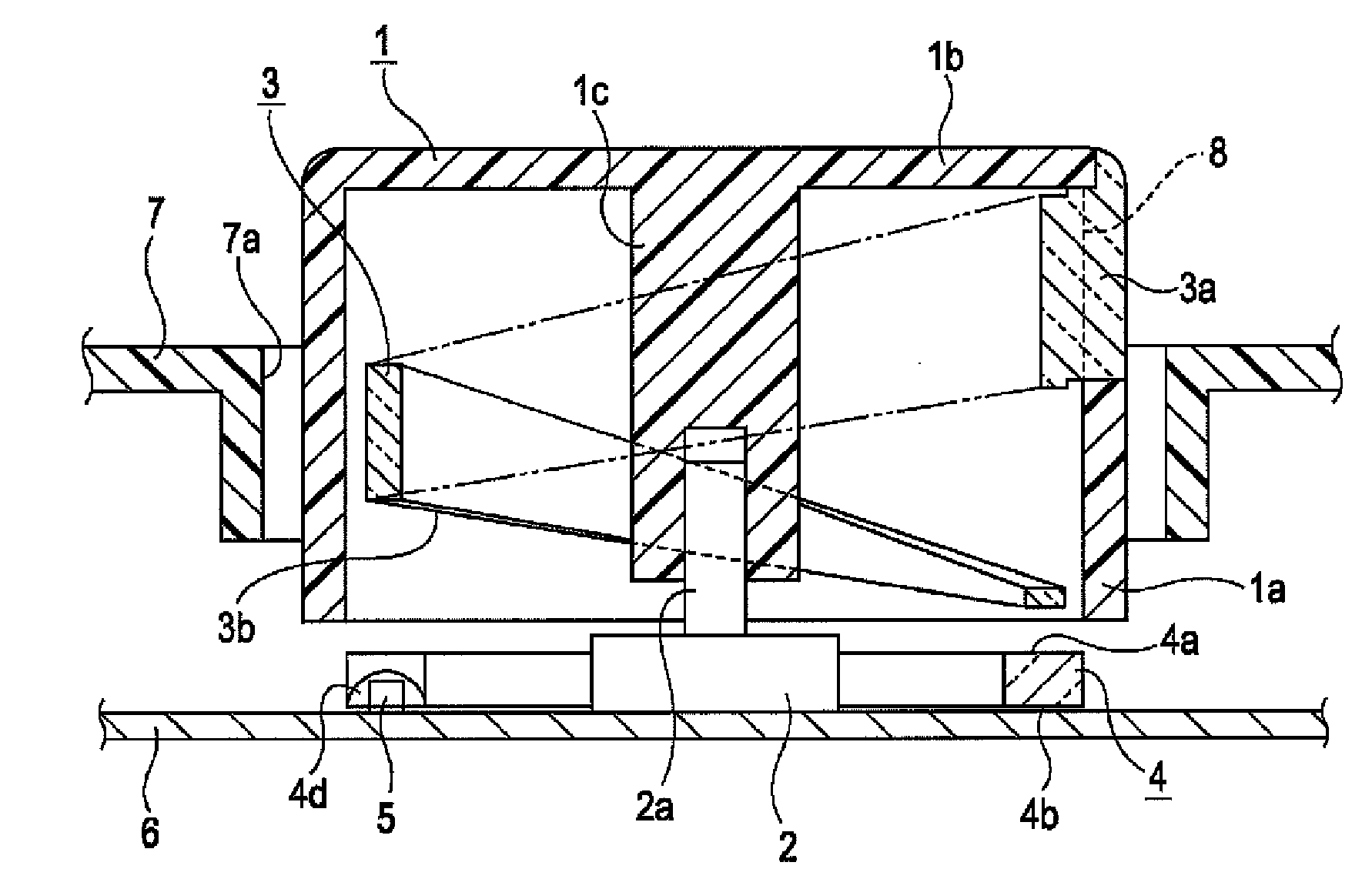

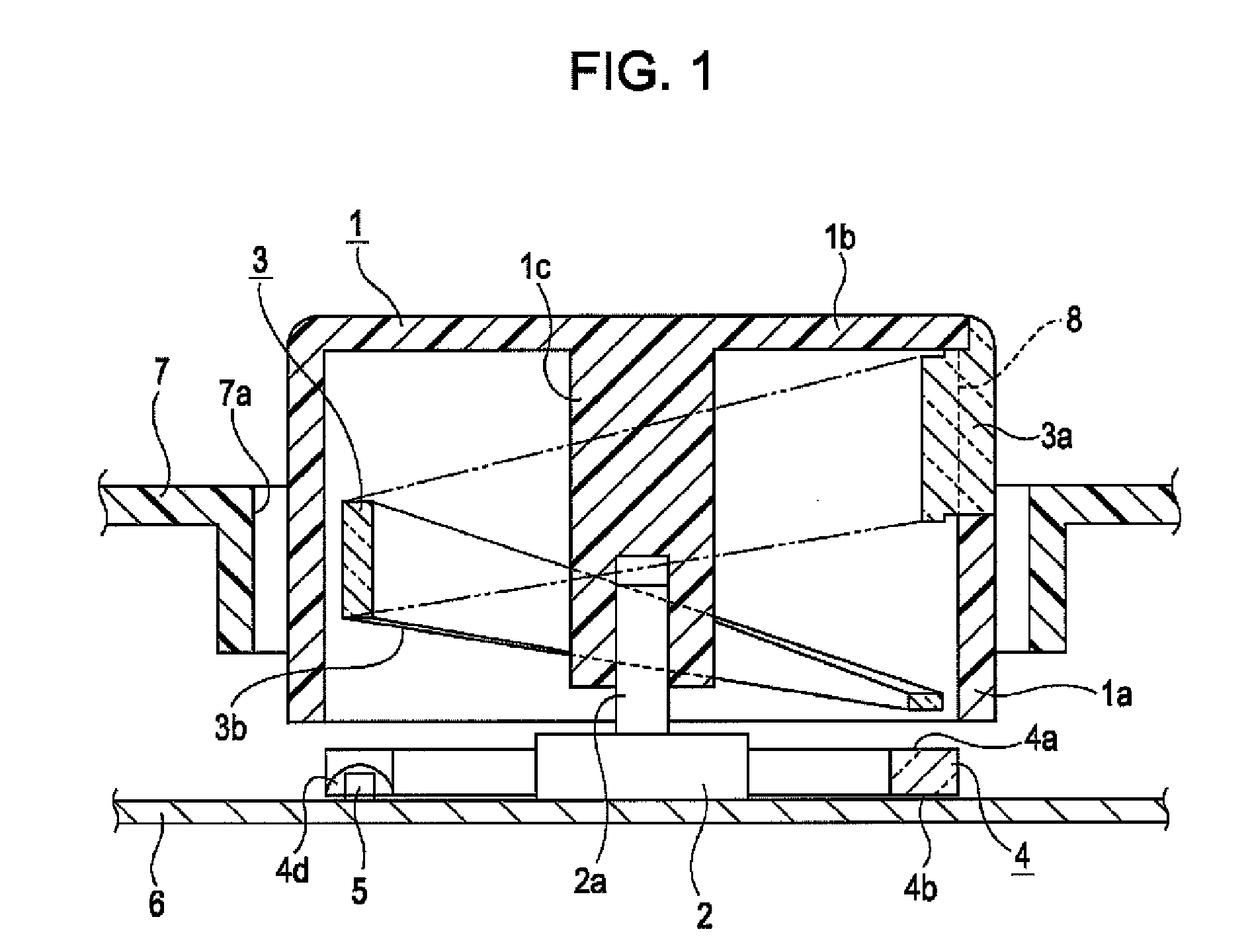

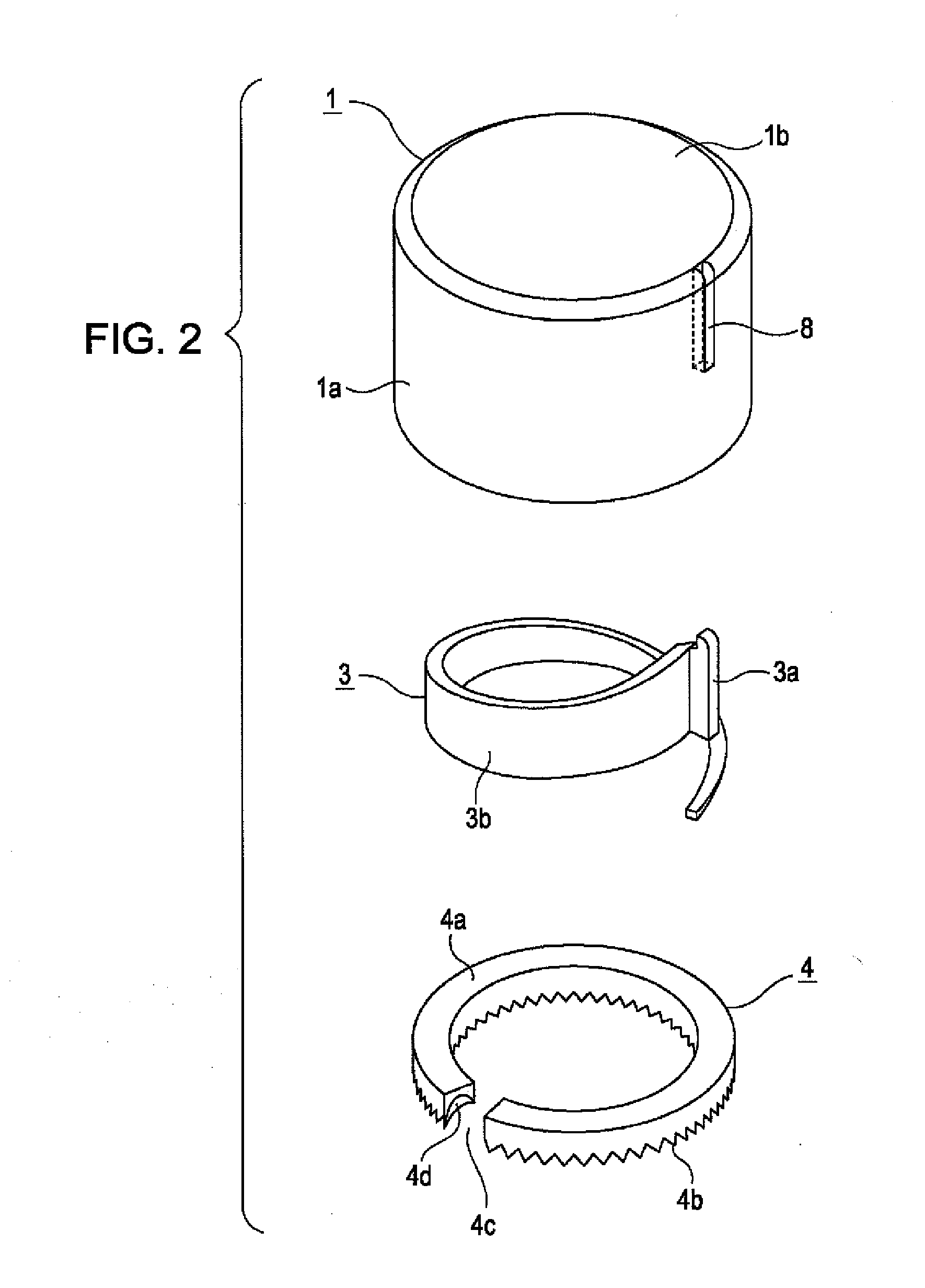

Multi-axial machine tool and table unit mounting jig

InactiveUS6948894B2Drawback can be obviatedAccurate adjustmentDrilling/boring measurement devicesThread cutting machinesEngineeringMachine tool

In the multi-axial machine tool, a table unit is detachably mounted on the upper surface of the interior portion of a portal bed disposed on a leg. The table unit comprises a table base fixed to the upper surface of the leg, a turning table which, when it is viewed at a reference working position, is turnably disposed on an inclined turning surface of the table base formed so as to be inclined in a descending manner toward a front side of the machine tool, and a work table disposed on the table support portion of the turning table so as to be turnable around axes lying in parallel with the axis of a spindle.

Owner:DMG MORI SEIKI CO LTD

Illumination-type rotational control device

InactiveUS20070195513A1Effective lightingLength in directionControlling membersMeasurement apparatus componentsRotary switchLight guide

A rotatable control knob for actuating a rotary switch includes a slit serving as a pointer display element. An illuminating portion of a light guiding unit attached to the control knob is disposed in the slit. A strip light-guiding portion extends spirally from the illuminating portion is secured to the inner surface of the control knob. Thus, light emerging from a planar light-emitting unit disposed under the control knob is incident on the lower surface of the strip light-guiding portion and is guided through the strip light-guiding portion to the illuminating portion. This allows the illuminating portion illuminated with high intensity in the slit so as to function as an indicator.

Owner:ALPS ALPINE CO LTD

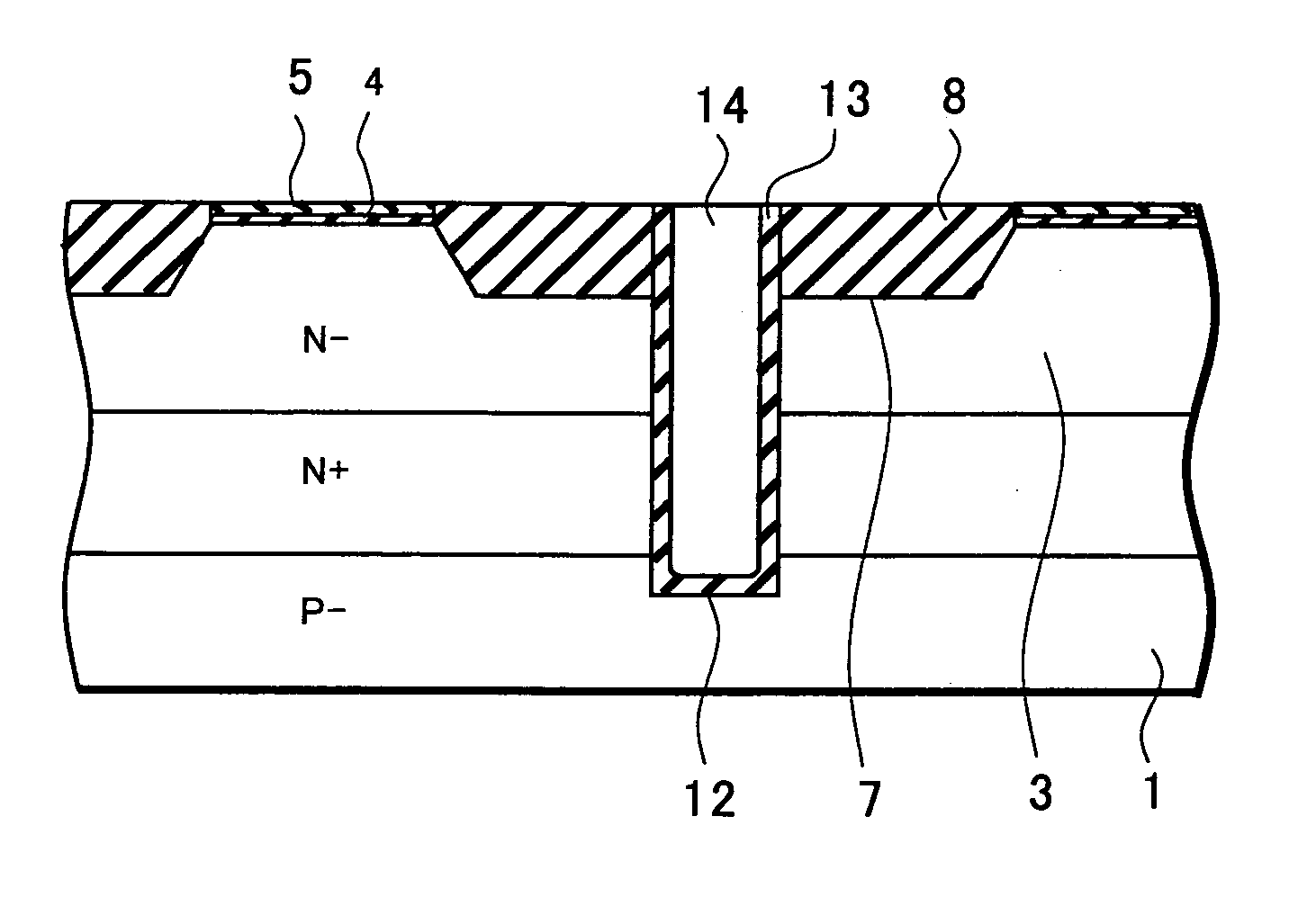

Semiconductor device and method of manufacturing semiconductor device

ActiveUS20100270677A1Avoid connectionUpper surfaceSemiconductor/solid-state device detailsSolid-state devicesSemiconductorSemiconductor device

An interconnect is provided in a first insulating layer and the upper surface of the interconnect is higher than the upper surface of the first insulating layer. An air gap is disposed between the interconnect and the first insulating layer. A second insulating layer is formed at least over the first insulating layer and the air gap. The second insulating layer does not cover the interconnect. An etching stopper film is formed at least over the second insulating layer. The etching stopper film is formed over the second insulating layer and the interconnect. A third insulating layer is formed over the etching stopper film. A via is provided in the third insulating layer so as to be connected to the interconnect.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device and method for fabricating the same

ActiveUS7473929B2Reduced carrier mobilityHigh carrier mobilityTransistorSemiconductor/solid-state device manufacturingCarbon filmHigh resistance

Ion implantation is carried out to form a p-well region and a source region in parts of a high resistance SiC layer on a SiC substrate, and a carbon film is deposited over the substrate. With the carbon film deposited over the substrate, annealing for activating the implanted dopant ions is performed, and then the carbon film is removed. Thus, a smooth surface having hardly any surface roughness caused by the annealing is obtained. Furthermore, if a channel layer is epitaxially grown, the surface roughness of the channel layer is smaller than that of the underlying layer. Since the channel layer having a smooth surface is provided, it is possible to obtain a MISFET with a high current drive capability.

Owner:PANASONIC CORP

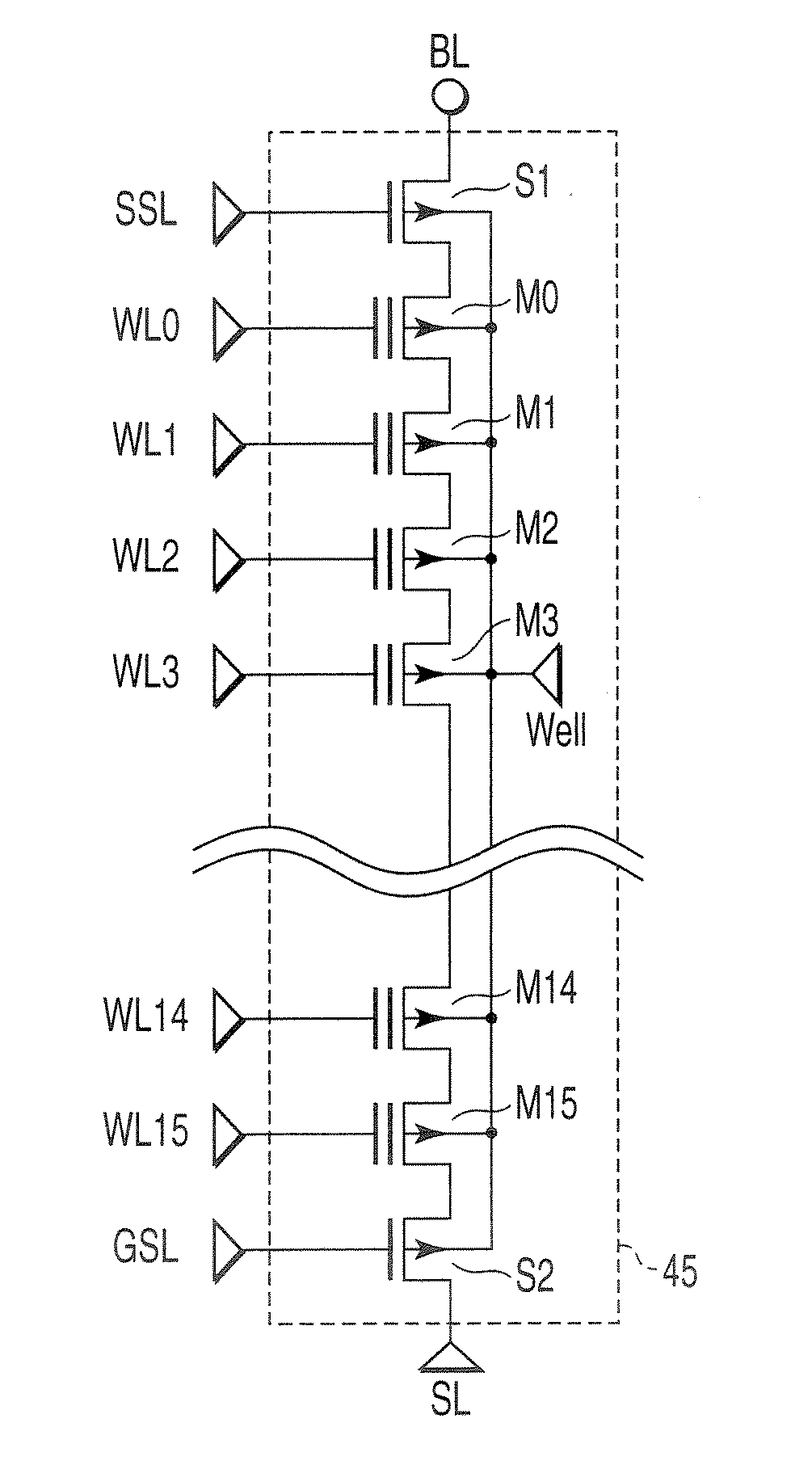

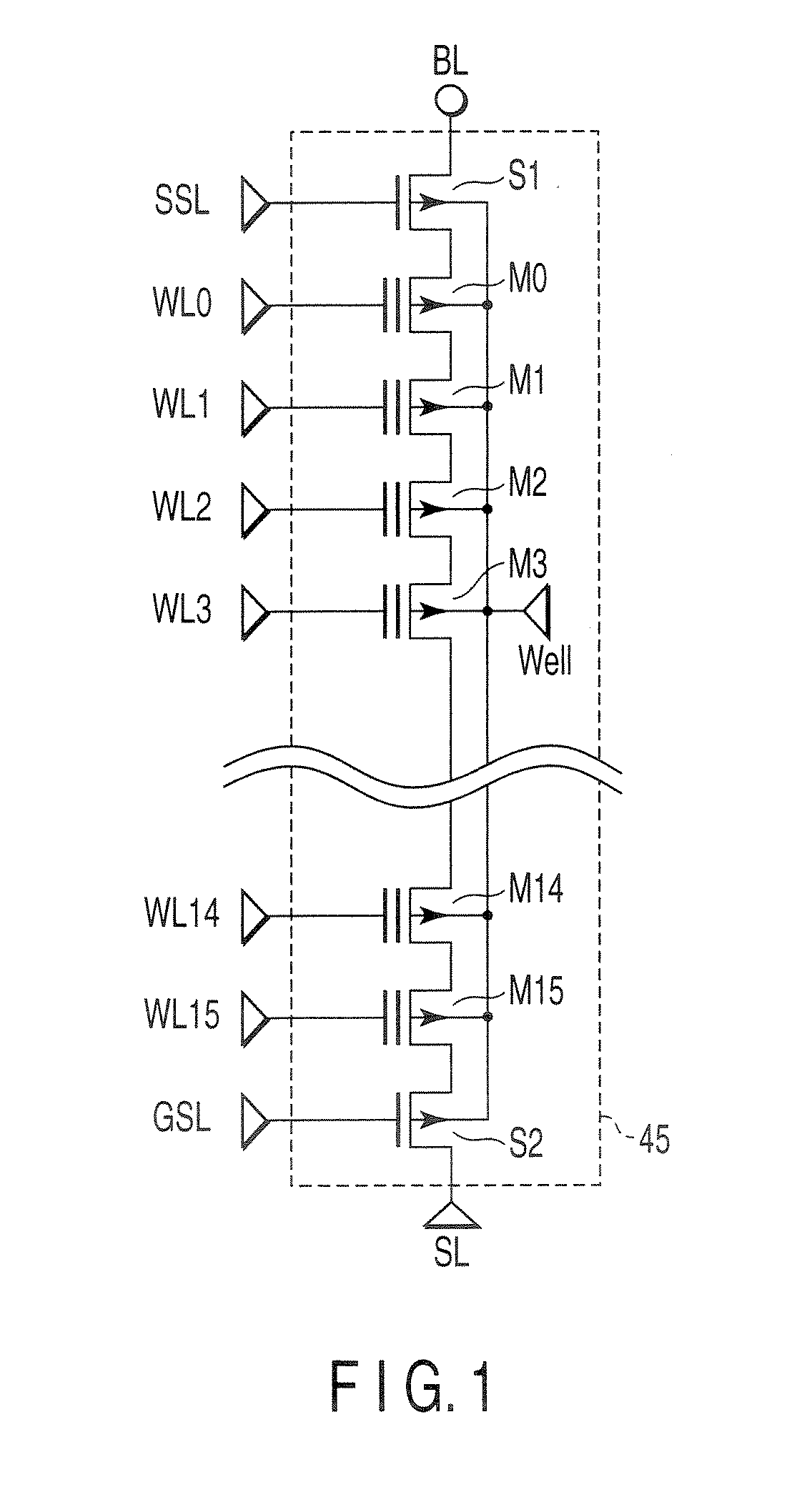

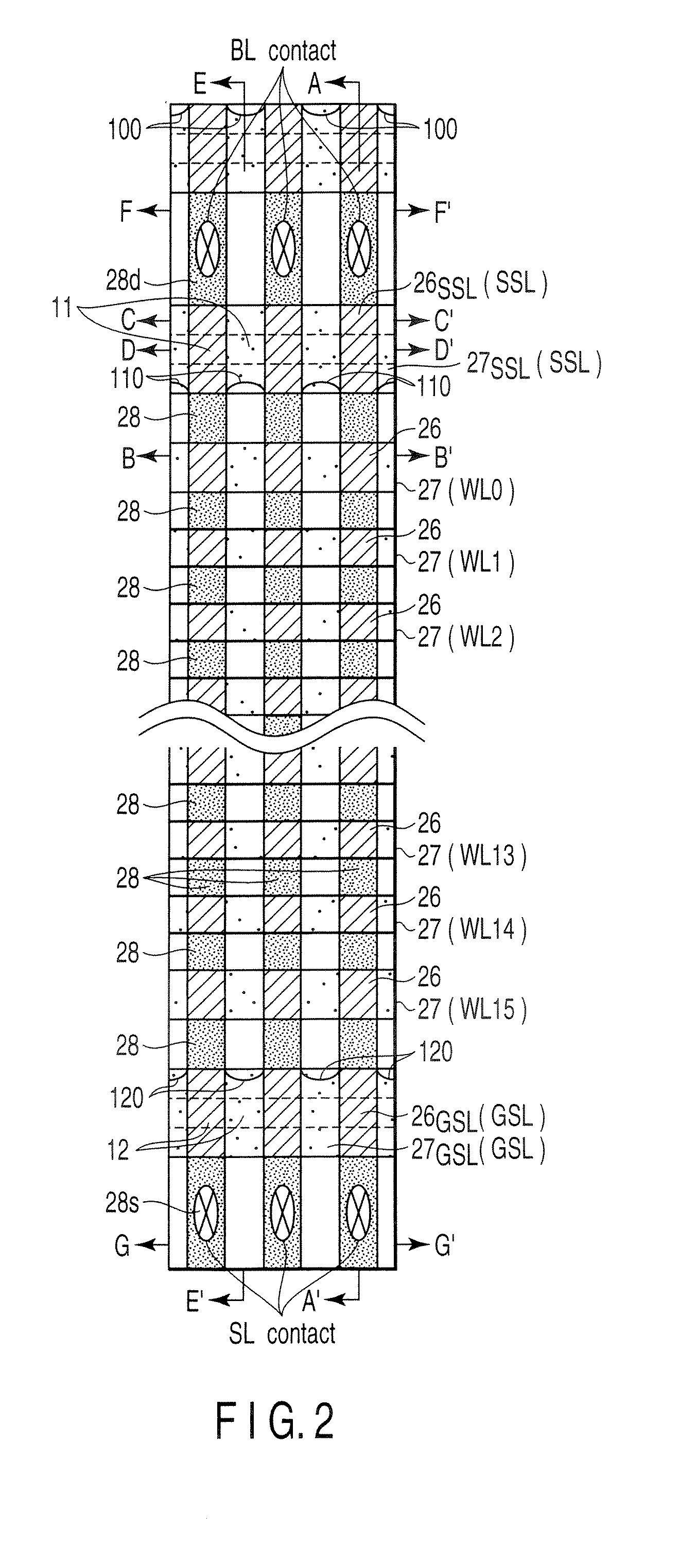

Nonvolatile semiconductor storage device

InactiveUS20070171720A1Upper surfaceSolid-state devicesRead-only memoriesSemiconductor memorySemiconductor

In a nonvolatile semiconductor storage device having a plurality of NAND strings, each NAND string includes a memory cell block obtained by connecting a plurality of nonvolatile memory cells in series, a first selection gate transistor connected to a data transfer line contact, and a second selection gate transistor connected to a source line contact. The upper surface of an isolation insulating film between adjacent data transfer line contacts is higher than the major surface of a semiconductor substrate in a device area between the first selection gate transistor and data transfer line contact. Alternatively, the upper surface of an isolation insulating film between adjacent source line contacts is higher than the major surface of the semiconductor substrate in a device area between the second selection gate transistor and source line contact.

Owner:KK TOSHIBA

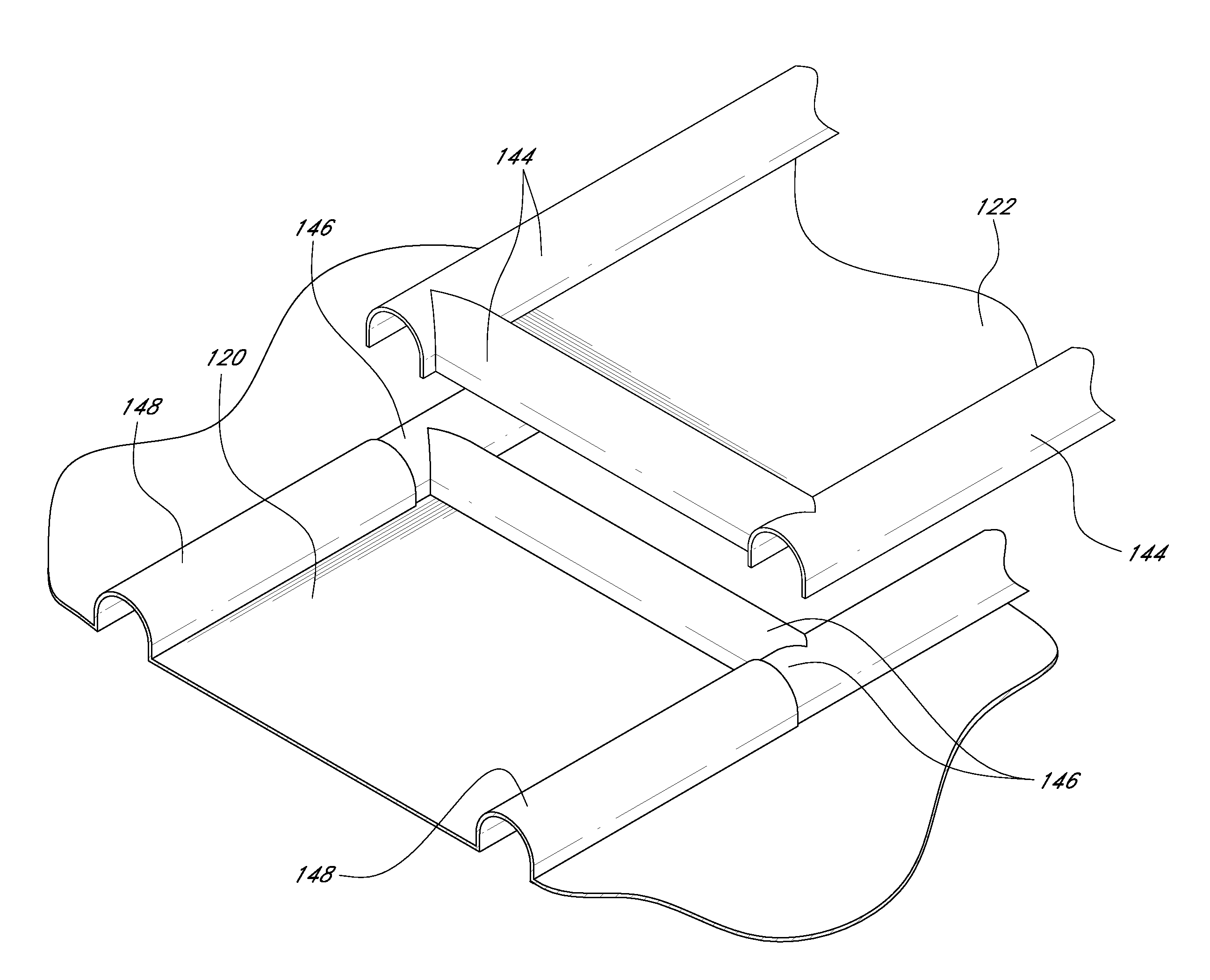

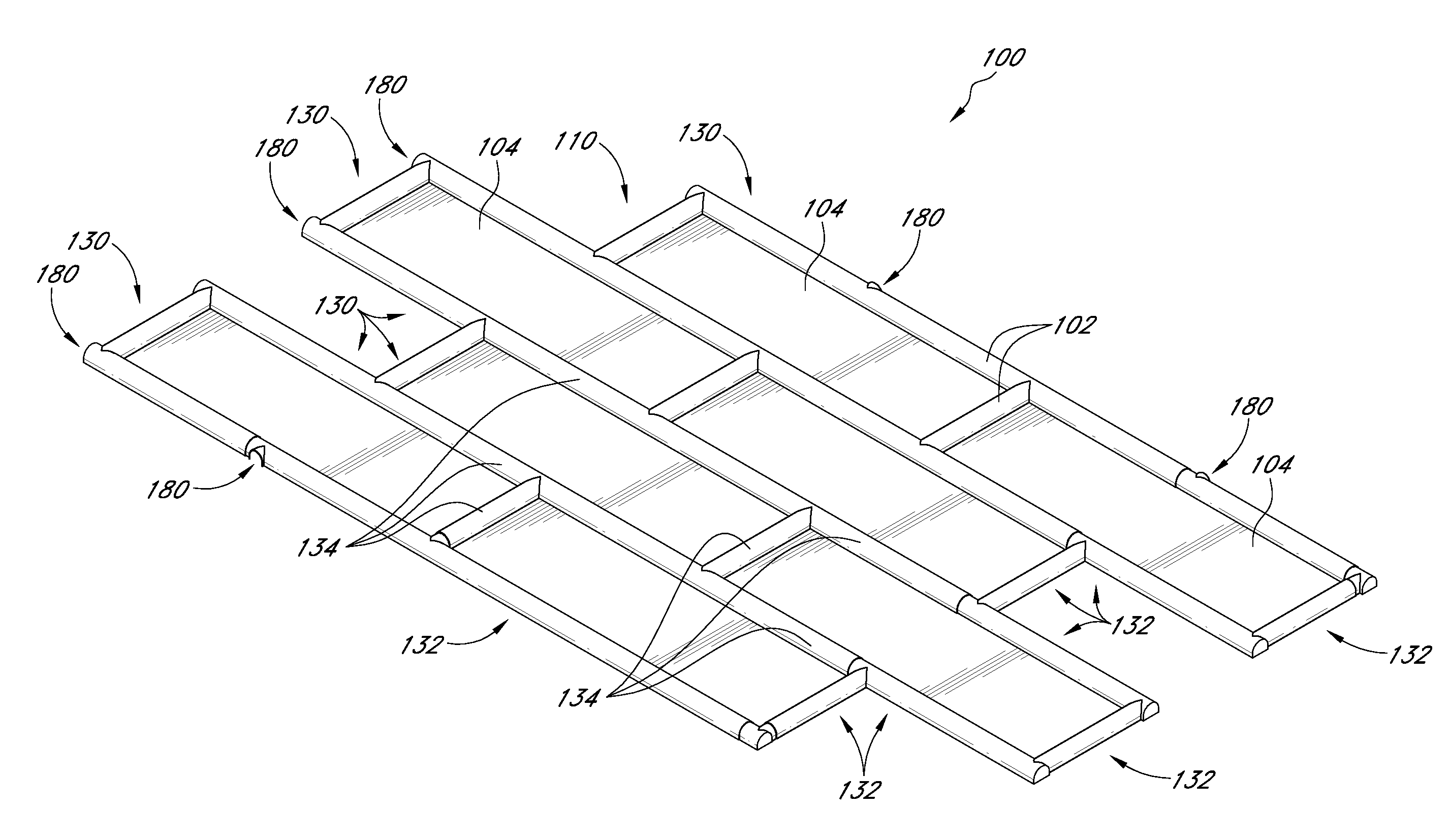

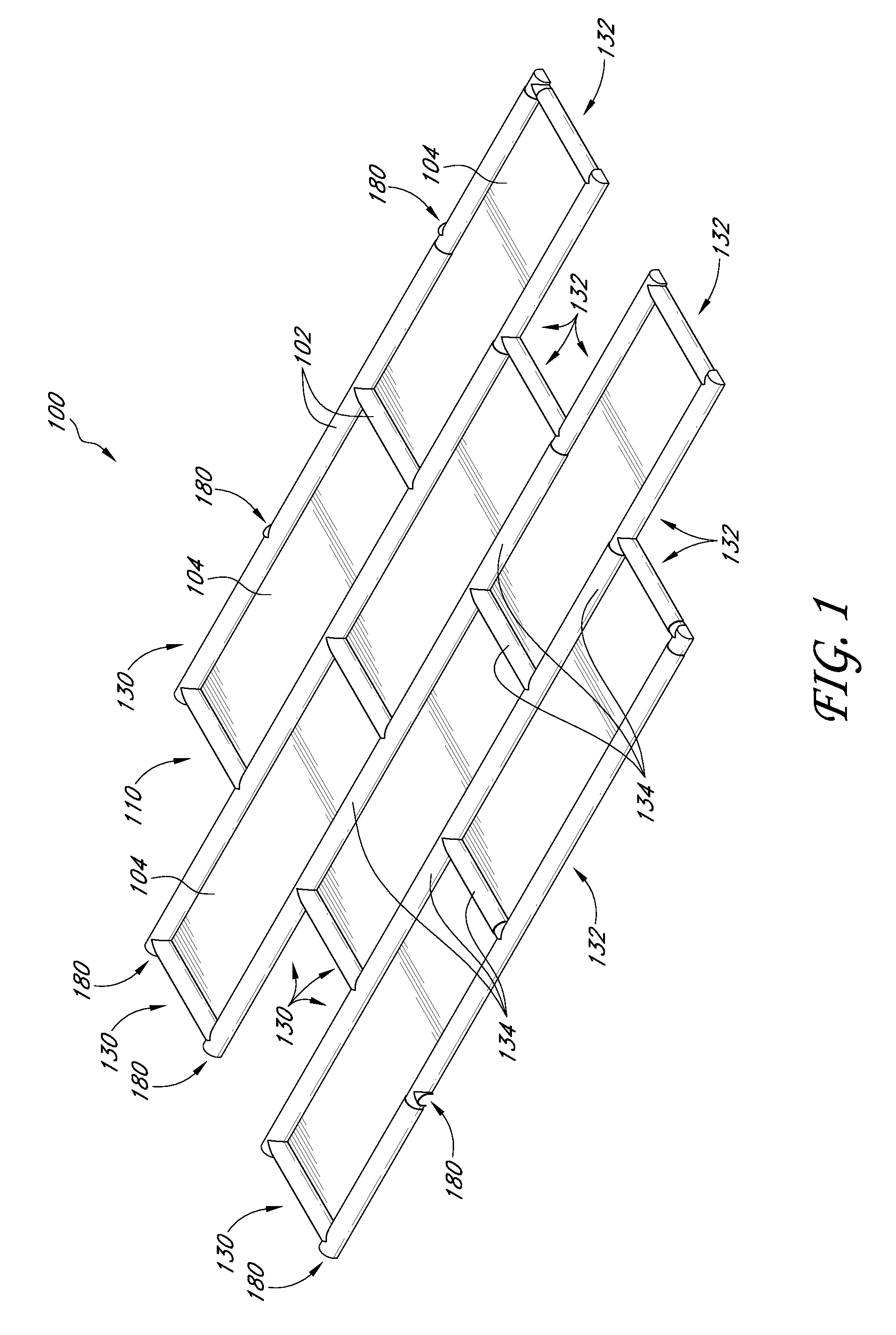

Formliner and method of use

ActiveUS7963499B2Minimizing and eliminating seamEliminate seamsLiquid surface applicatorsCovering/liningsEngineering

Owner:PRIME FORMING & CONSTR SUPPLIES INC DBA FITZGERALD FORMLINERS +1

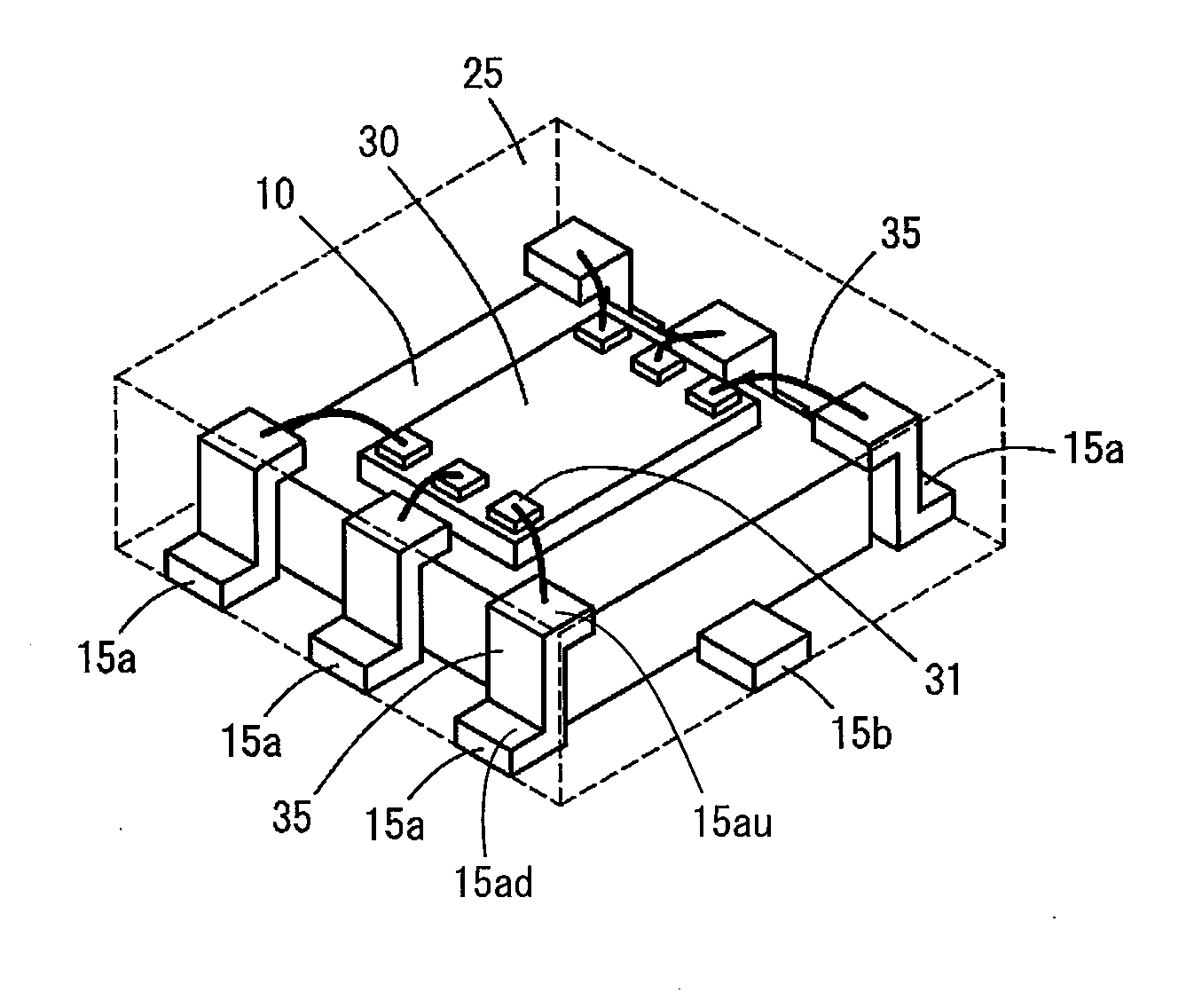

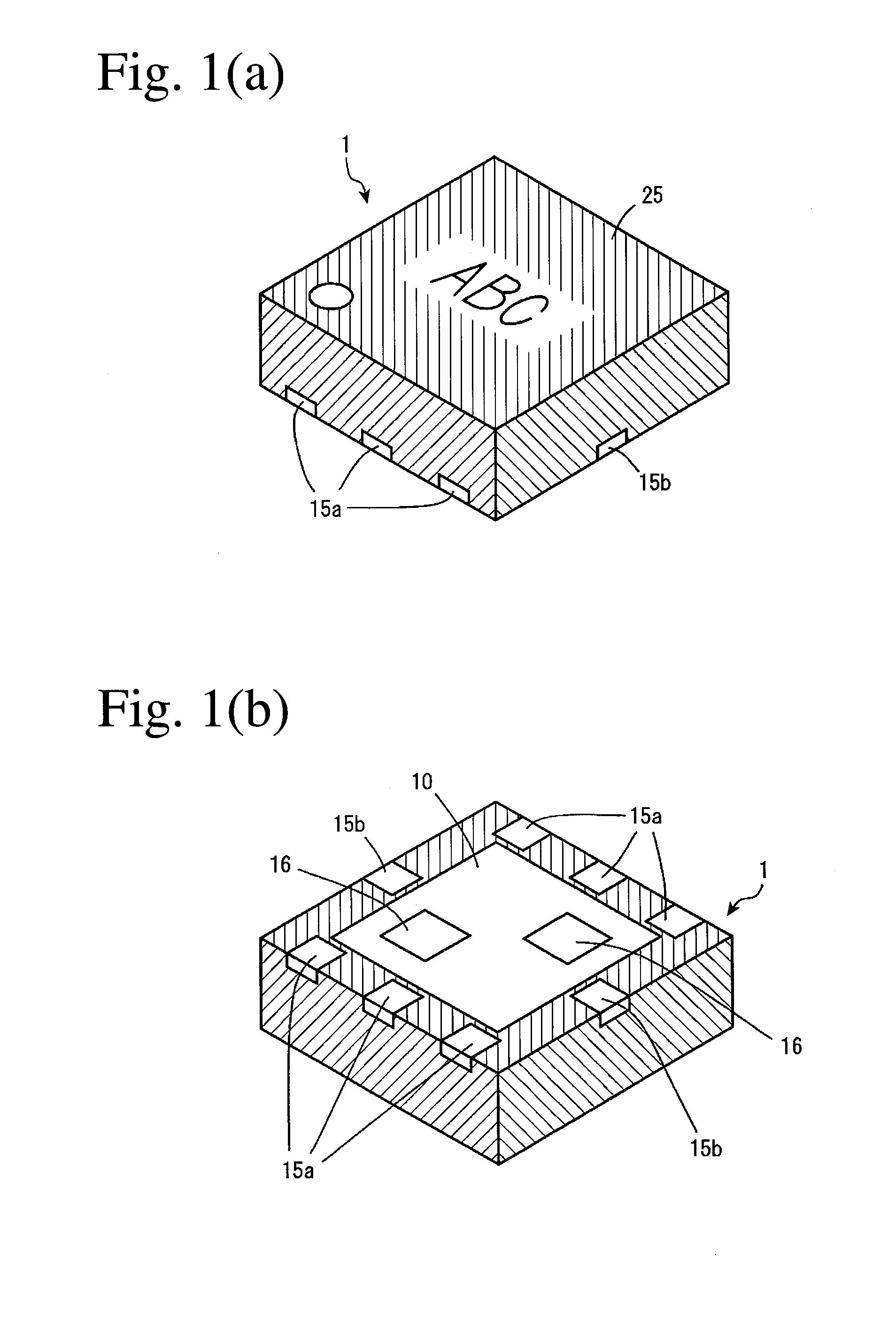

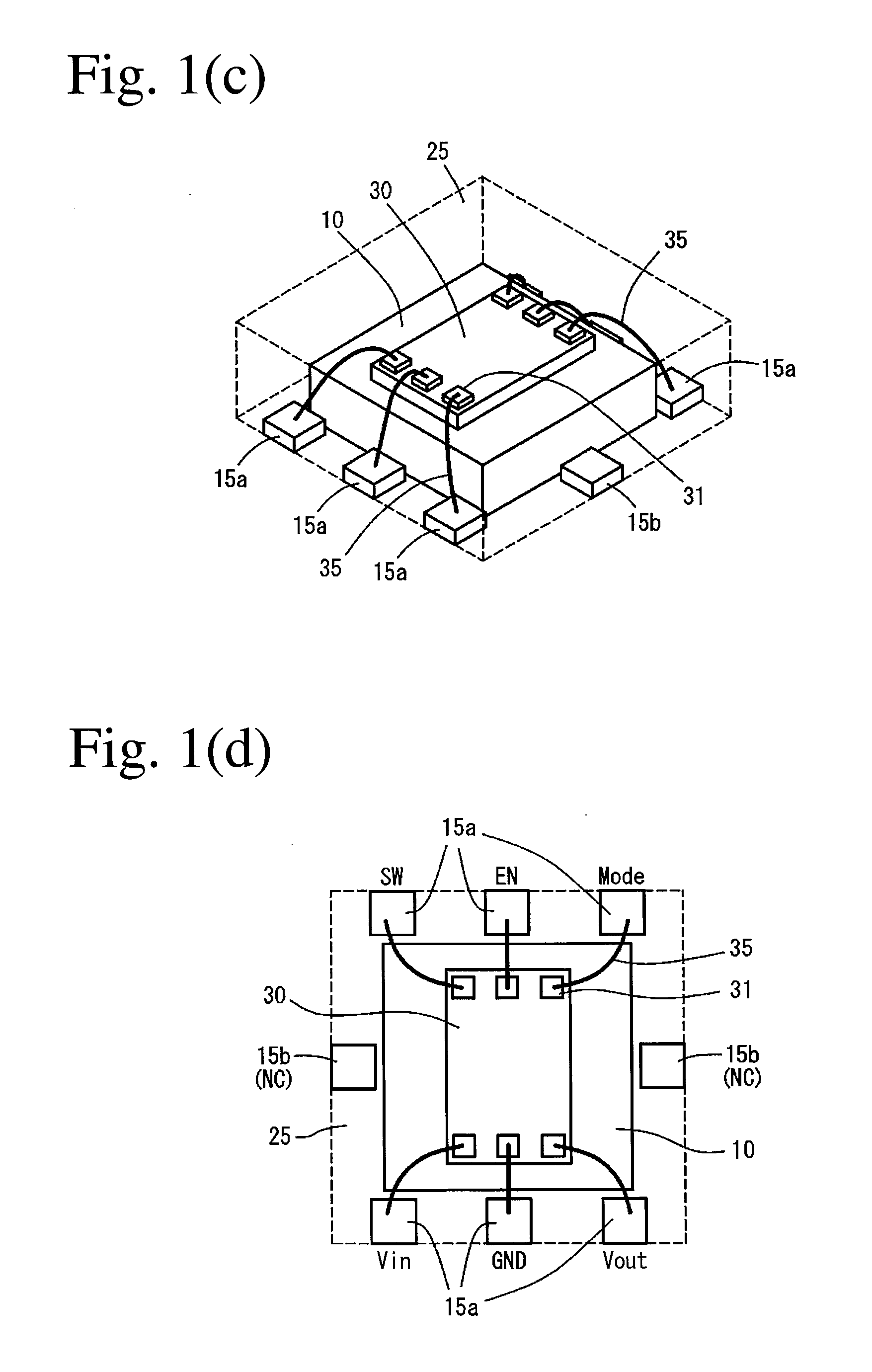

Semiconductor apparatus and power supply circuit

InactiveUS20110284989A1Improve cooling effectGuaranteed uptimeTransformers/inductances casingsSemiconductor/solid-state device detailsInductorSemiconductor

A semiconductor apparatus comprising an integrated semiconductor circuit device having pluralities of electrode pads, pluralities of first external terminals connected to the electrode pads of the integrated semiconductor circuit device, an inductor disposed in a region surrounded by the first external terminals, and a resin portion sealing them, the integrated semiconductor circuit device being arranged on an upper surface of the inductor, and the inductor being exposed from a lower surface of the resin portion together with the first external terminals.

Owner:HITACHI METALS LTD

Fastener device

A fastener device for connecting a first component to a second component comprises a clip having a flange and a shank, and a retaining plate cooperable with the clip to embrace the first component between the flange and the retaining plate when the shank is passed through a hole in the first component and a hole in the retaining plate. When the shank is passed through a hole in the second component, first elastic engagement leaves on the shank engage an edge of that hole. Second elastic engagement leaves on the retaining plate engage portions of the first elastic engagement leaves, and the retaining plate is interposed between the components.

Owner:NEWFREY

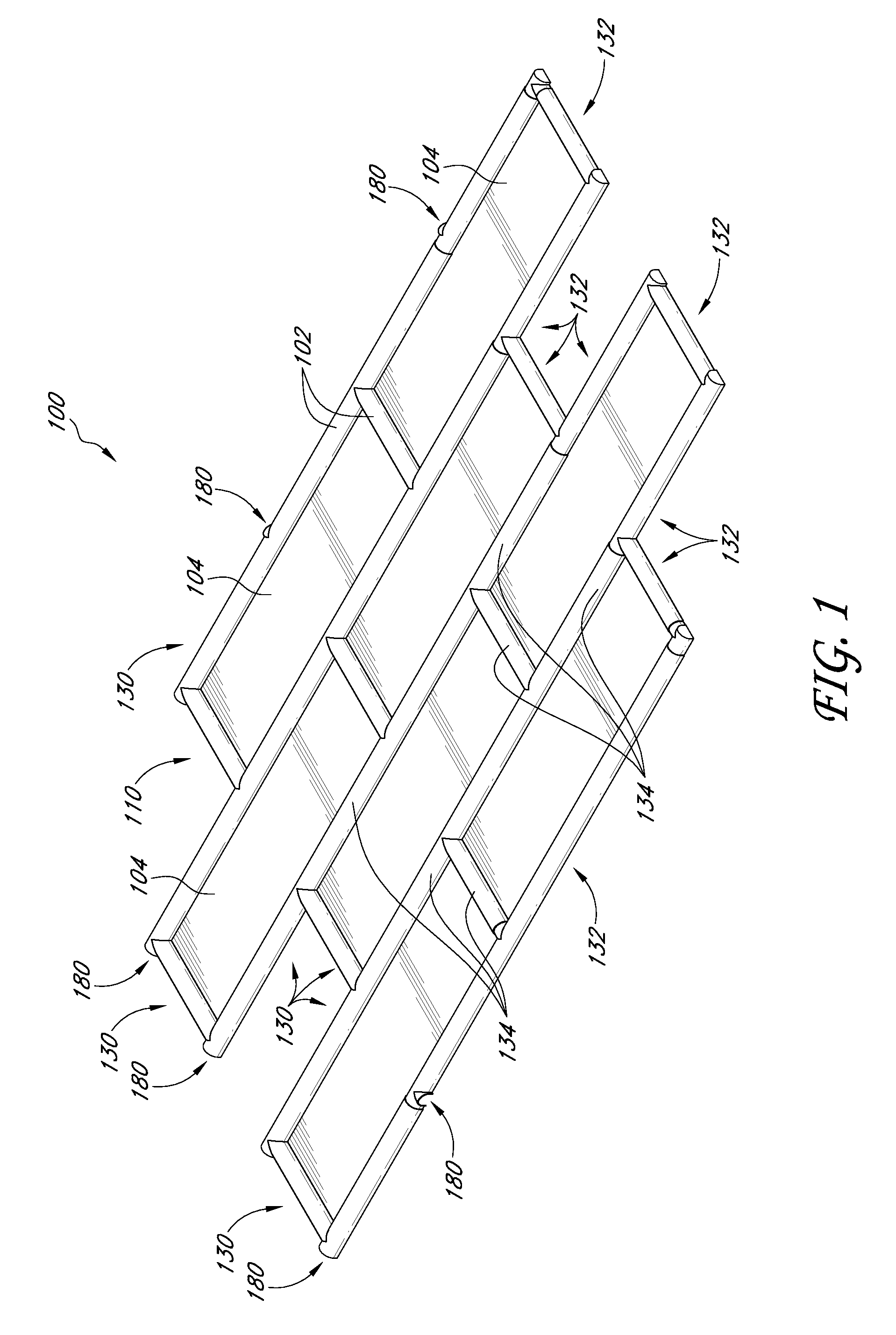

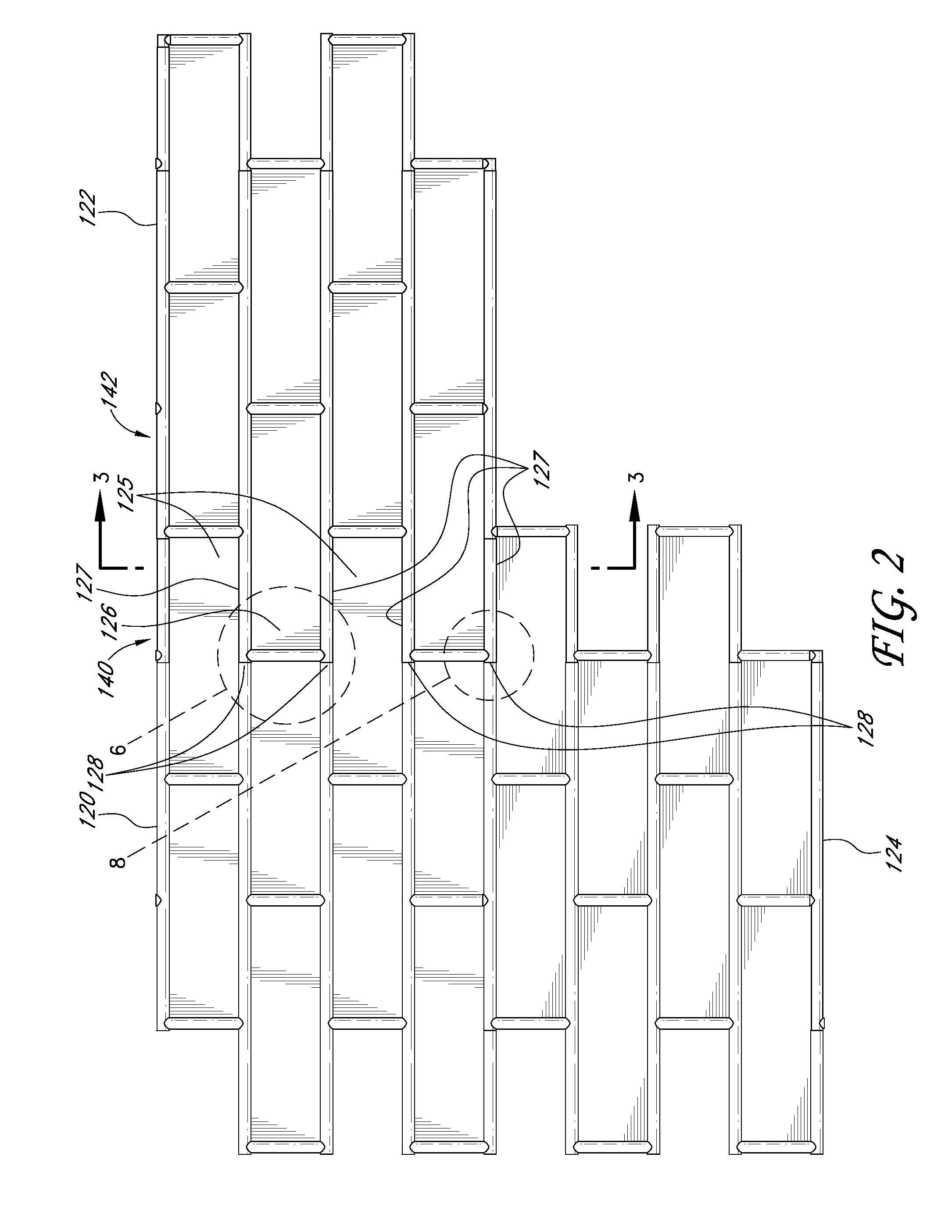

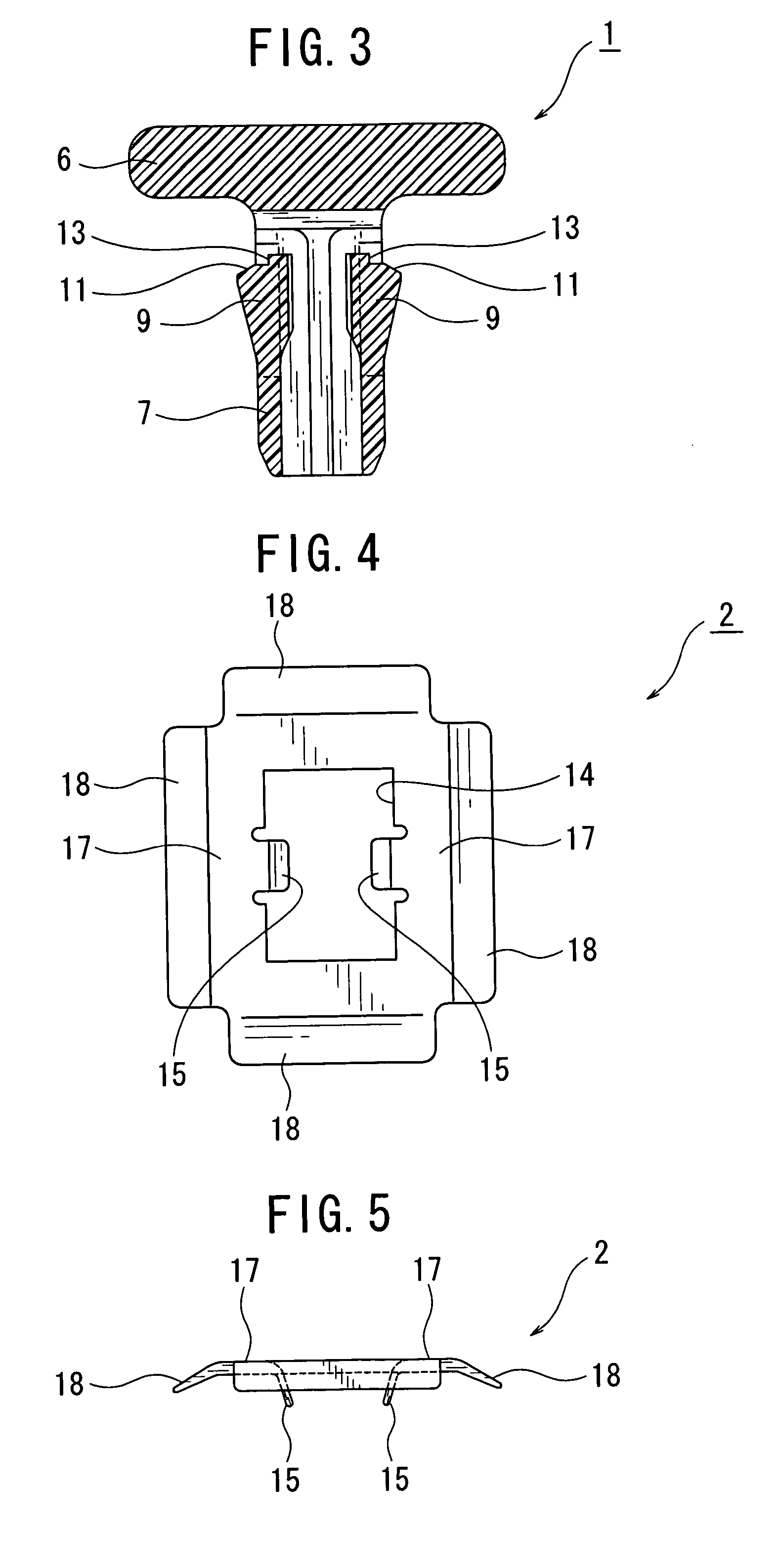

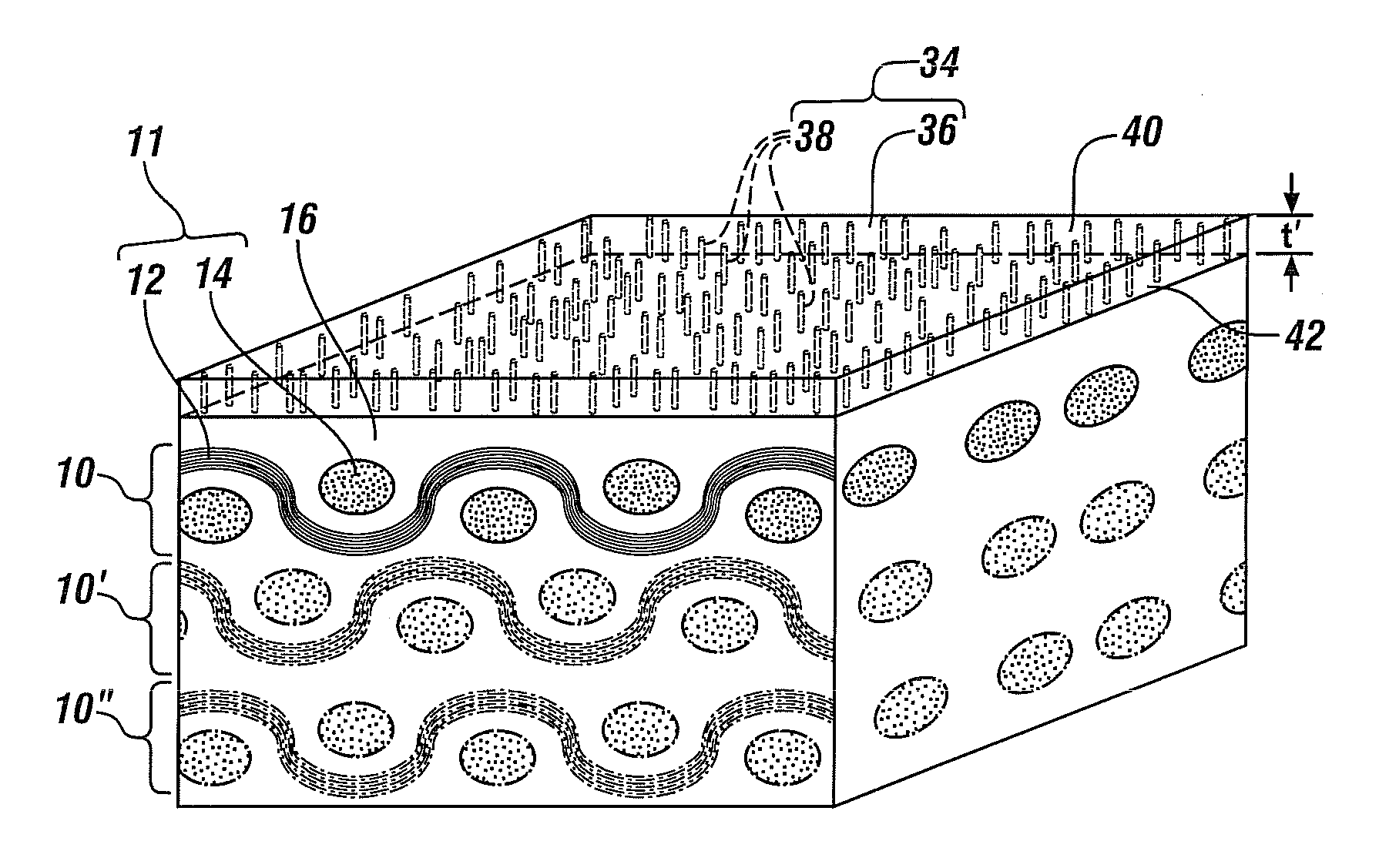

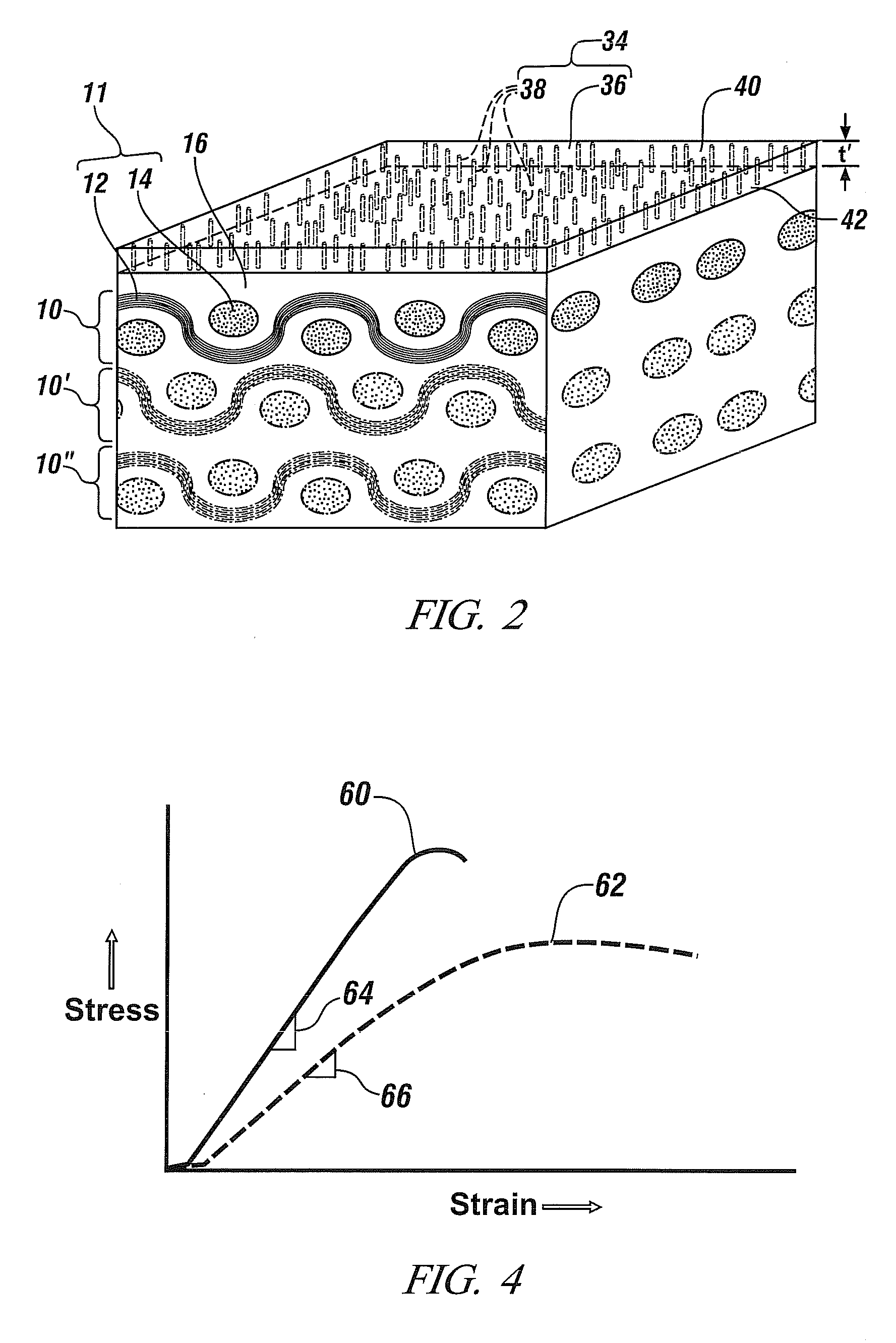

Print through reduction in long fiber reinforced composites by addition of carbon nanotubes

ActiveUS20130029089A1Minimizing print through distortionQuality improvementMaterial nanotechnologySynthetic resin layered productsPolymer scienceCarbon nanotube

Polymer articles are often reinforced by addition of fibers which may be assembled into a structured reinforcement such as a woven mat or sheet and the mat or sheet serves as the reinforcement. Such woven fiber-reinforced polymer composite articles may exhibit undesirable variations in surface height which mimic the geometry of the underlying reinforcements, a phenomenon known as print through. By forming, on the surface of the article, a relatively thin, layer of a compatible polymer incorporating closely-spaced, short, carbon nanotubes more or less uniformly dispersed throughout the layer and oriented normal to the article surface, print through may be reduced or eliminated. Methods for fabricating such an article are detailed.

Owner:GM GLOBAL TECH OPERATIONS LLC

Controlled selectivity etch for use with optical component fabrication

A method of fabricating an optical component includes forming a mask on an optical component precursor. The method also includes etching through at least a portion of the mask so as to etch an underlying medium concurrently with remaining mask and transfer a feature of an upper surface of the mask onto an upper surface of the underlying medium. The etch can be configured such that a ratio of the underlying medium etch rate to the mask etch rate is less than about 1.5:1. In some instances, the underlying medium is silicon and the mask is a photoresist.

Owner:KOTURA

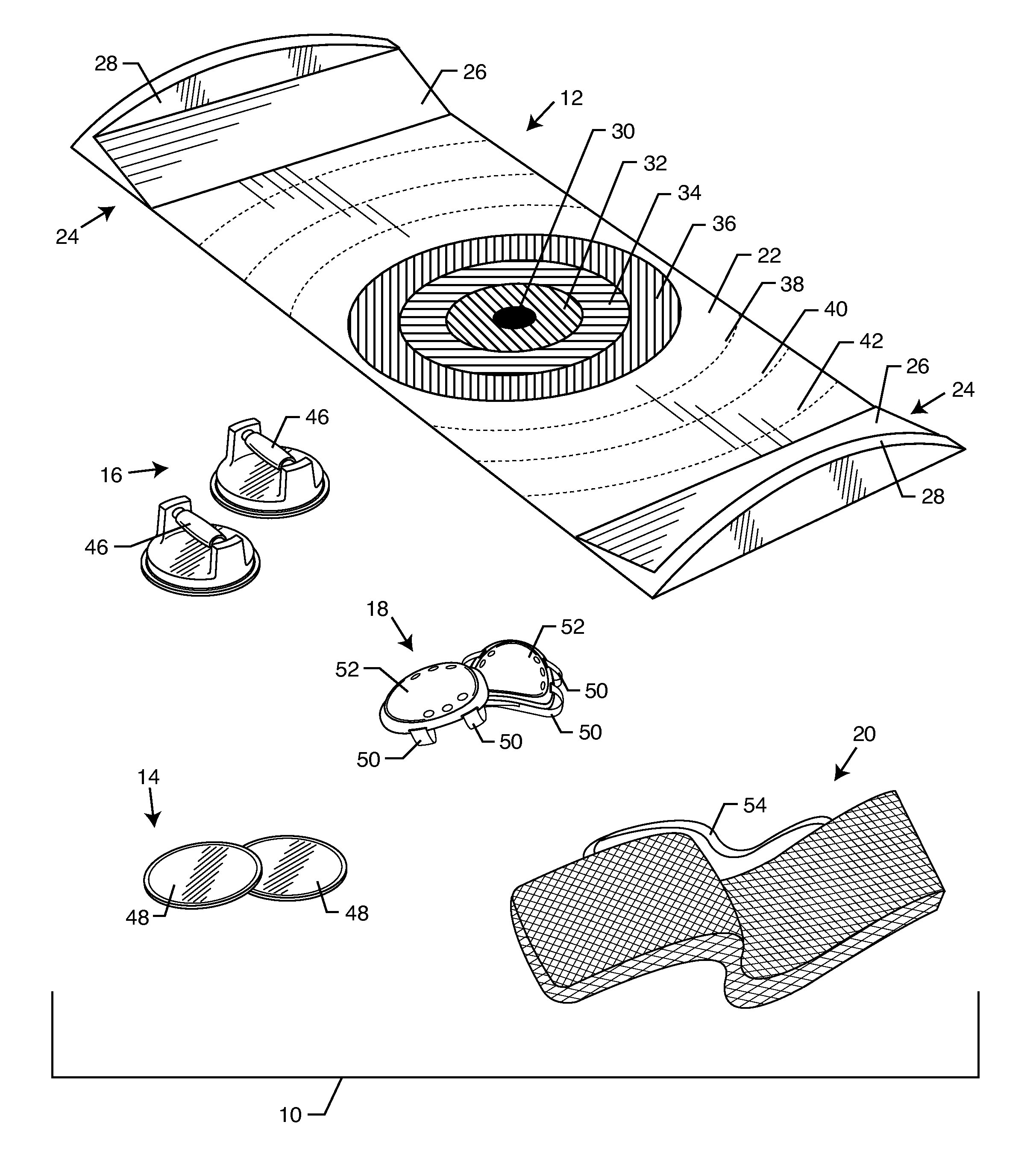

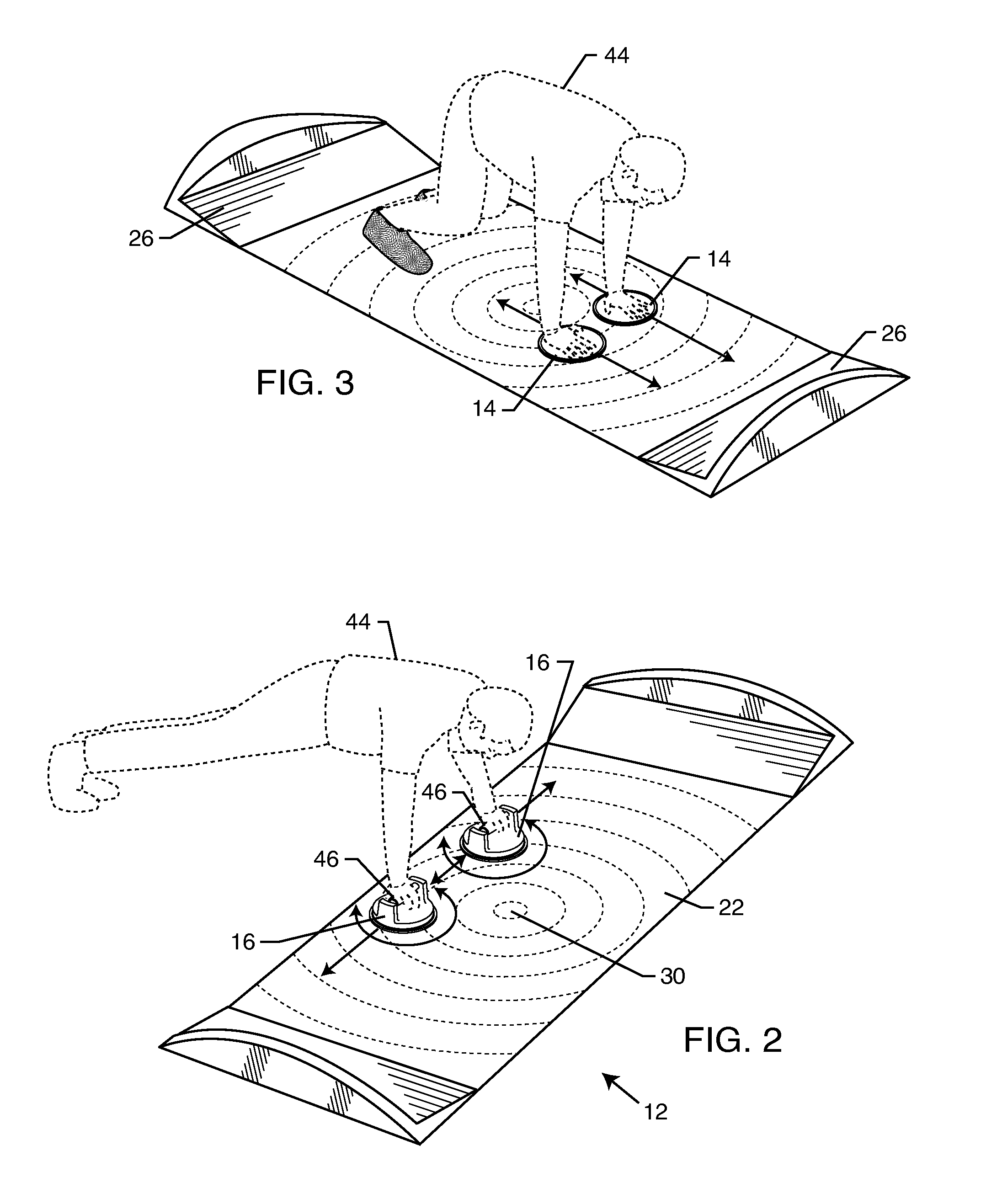

Multi-exercise slide board

InactiveUS20110230312A1Easy to slideFacilitates rotating movementStiltsMuscle exercising devicesPush upsVisual perception

The multi-exercise trainer includes a portable workout board having a low-friction upper surface. The low-friction upper surface includes a set of indicia concentrically spaced from one another to provide visual guidance for performing exercises thereon. The multi-exercise trainer further includes a hand pad slidable and rotatable over the low-friction upper surface. The indicia designate defined distances on the low-friction upper surface so a user may selectively position and slide the hand pad thereon while simultaneously performing push-ups.

Owner:BORG UNLTD

Formliner and method of use

ActiveUS20100071308A1Without costMinimizing and eliminating seamLiquid surface applicatorsCovering/liningsEngineering

Owner:PRIME FORMING & CONSTR SUPPLIES INC DBA FITZGERALD FORMLINERS +1

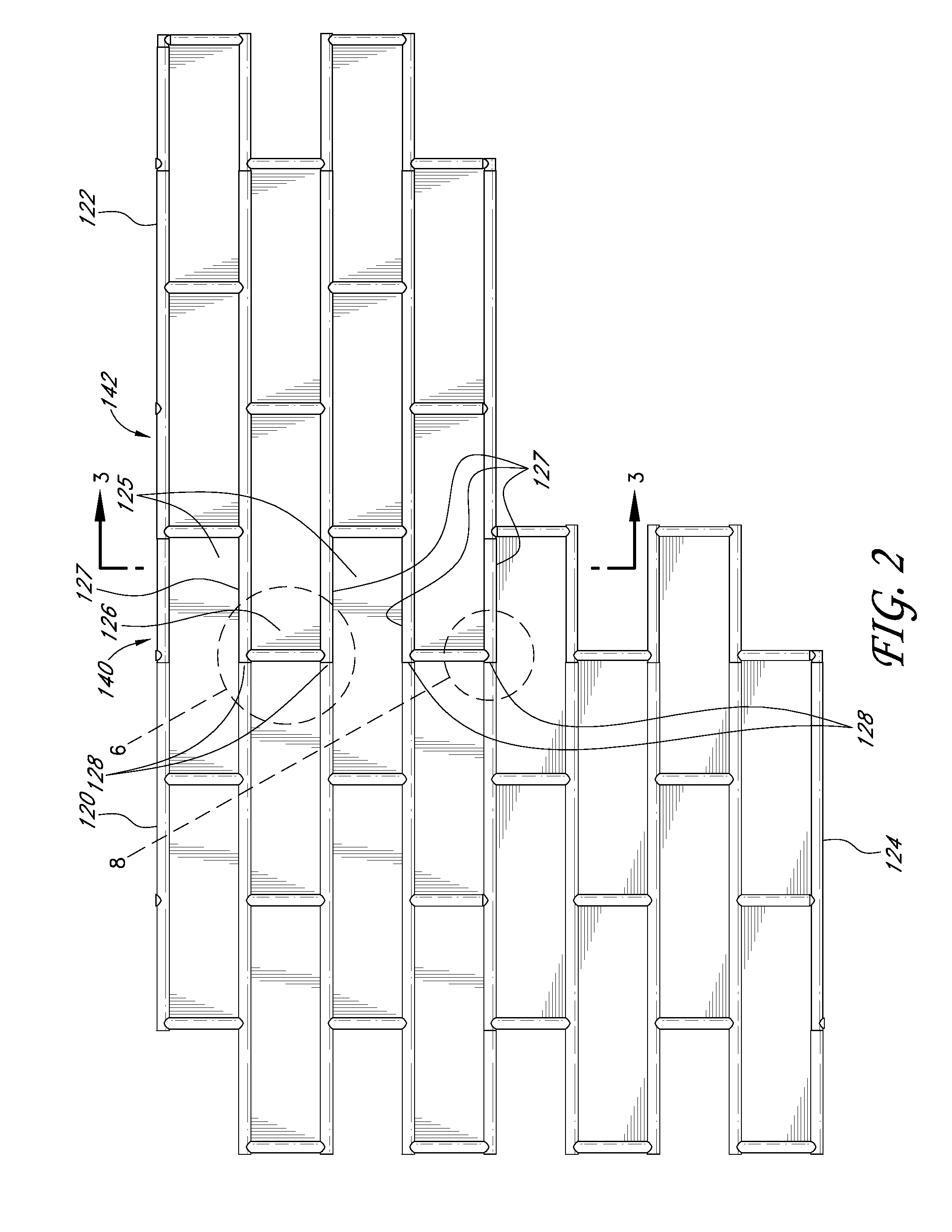

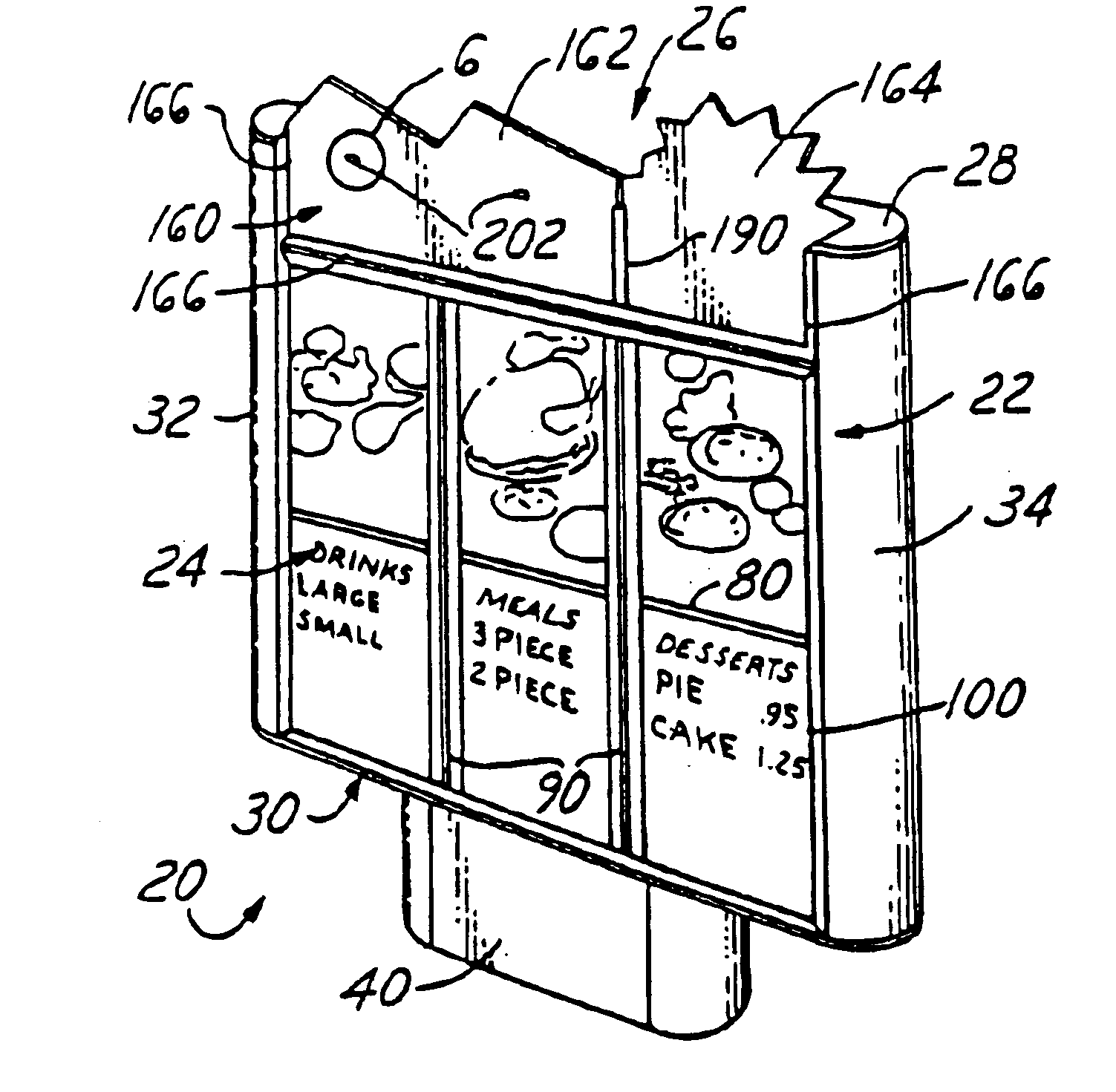

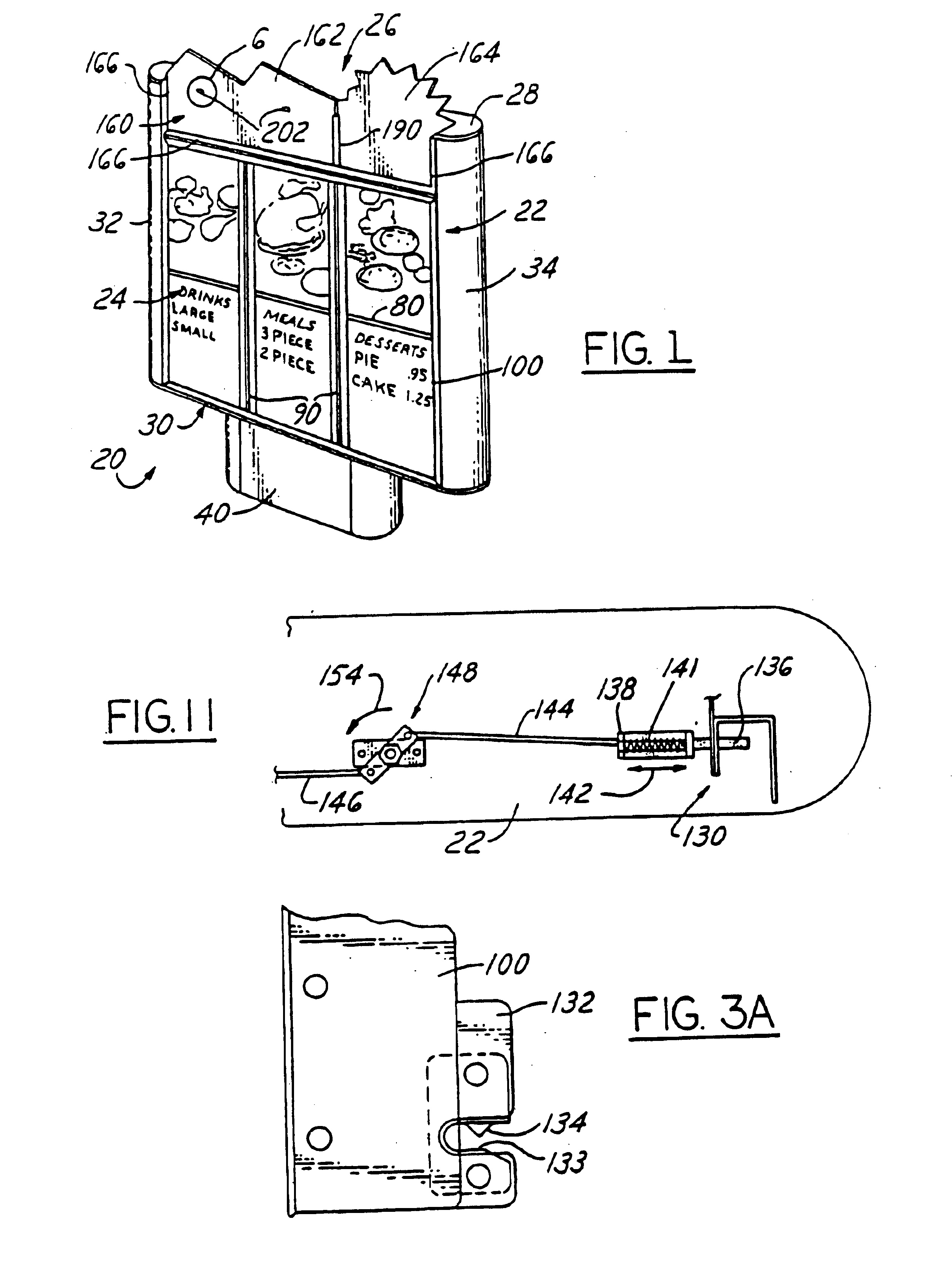

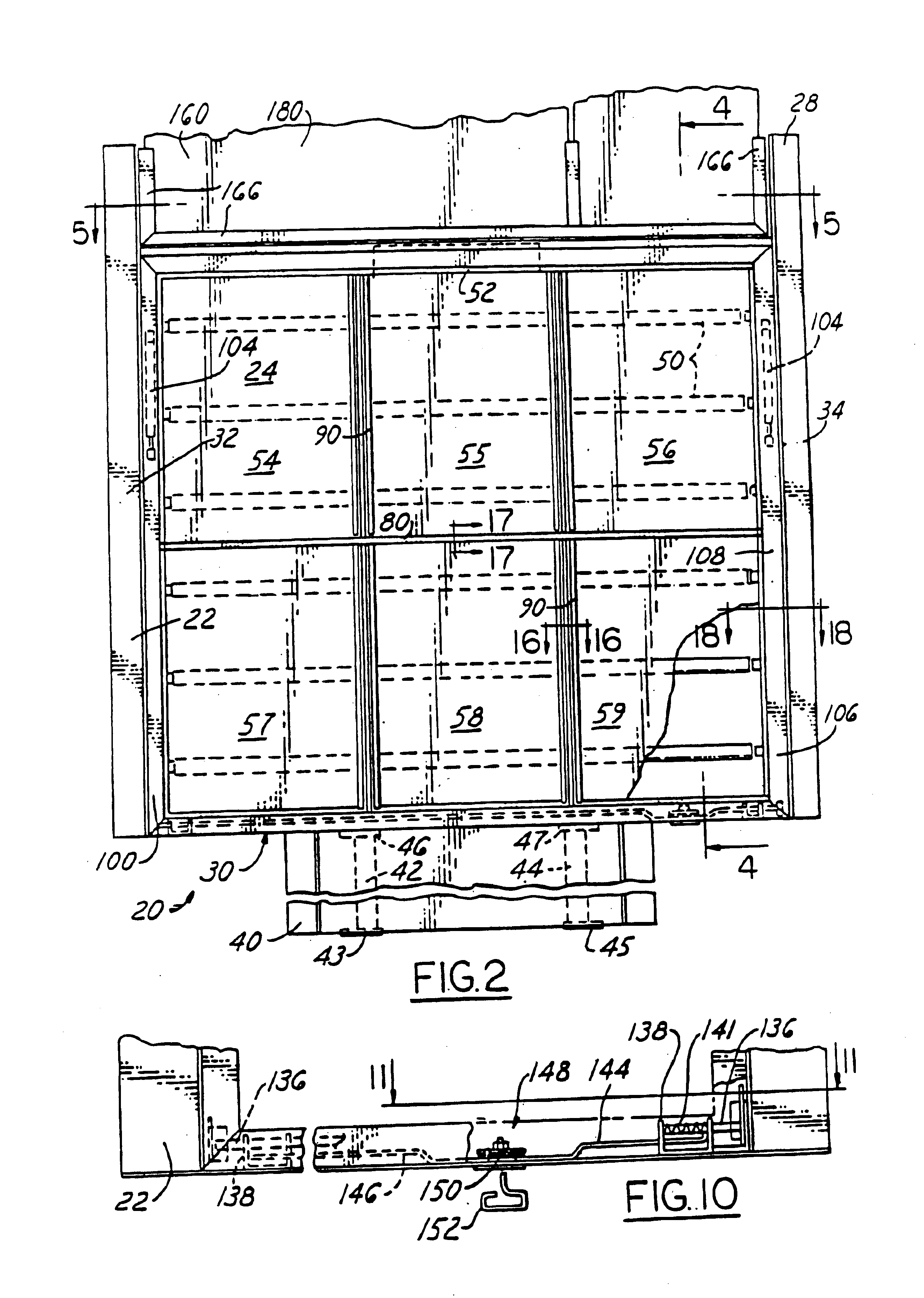

Menu display device

An improved outdoor illuminated display device. The device generally comprises a modular housing, a base member and a plurality of lights positioned in the housing—either horizontally or vertically. A plurality of display modules are positioned on the housing and backlit by the lights. A door member is pivotally connected along its upper edge to the housing covering the modules. A pair of gas-assisted spring members are provided between the door member and the housing. Air gaps or air vents are provided in order to allow air circulation in the housing. A second member above the door member is provided for holding and displaying posters and other advertising and promotional materials. A plurality of clamping members hold the display materials in place. The second member can be illuminated or non-illuminated. Various modular units can be provided to increase the size and display space provided by the device. The display modules include a plurality of horizontal divider members removably secured to retainer members. Menu strips, pricing units and display members can be positioned between channels in the divider members and / or the frame members forming the display modules. The pricing units are adapted to be backlit by lights in the display device.

Owner:MARKETING DISPLAY

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com