Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2753results about How to "Avoid layering" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

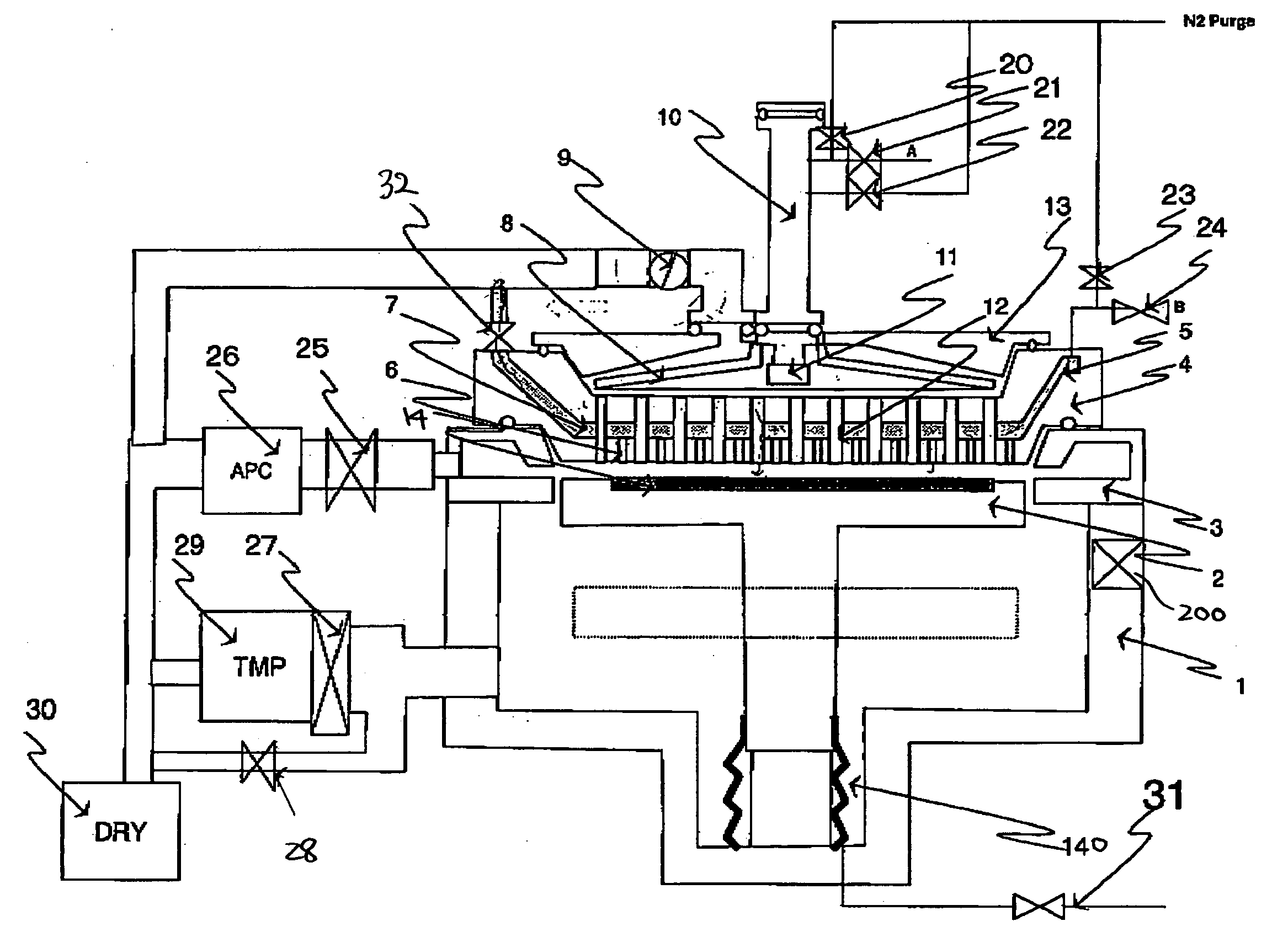

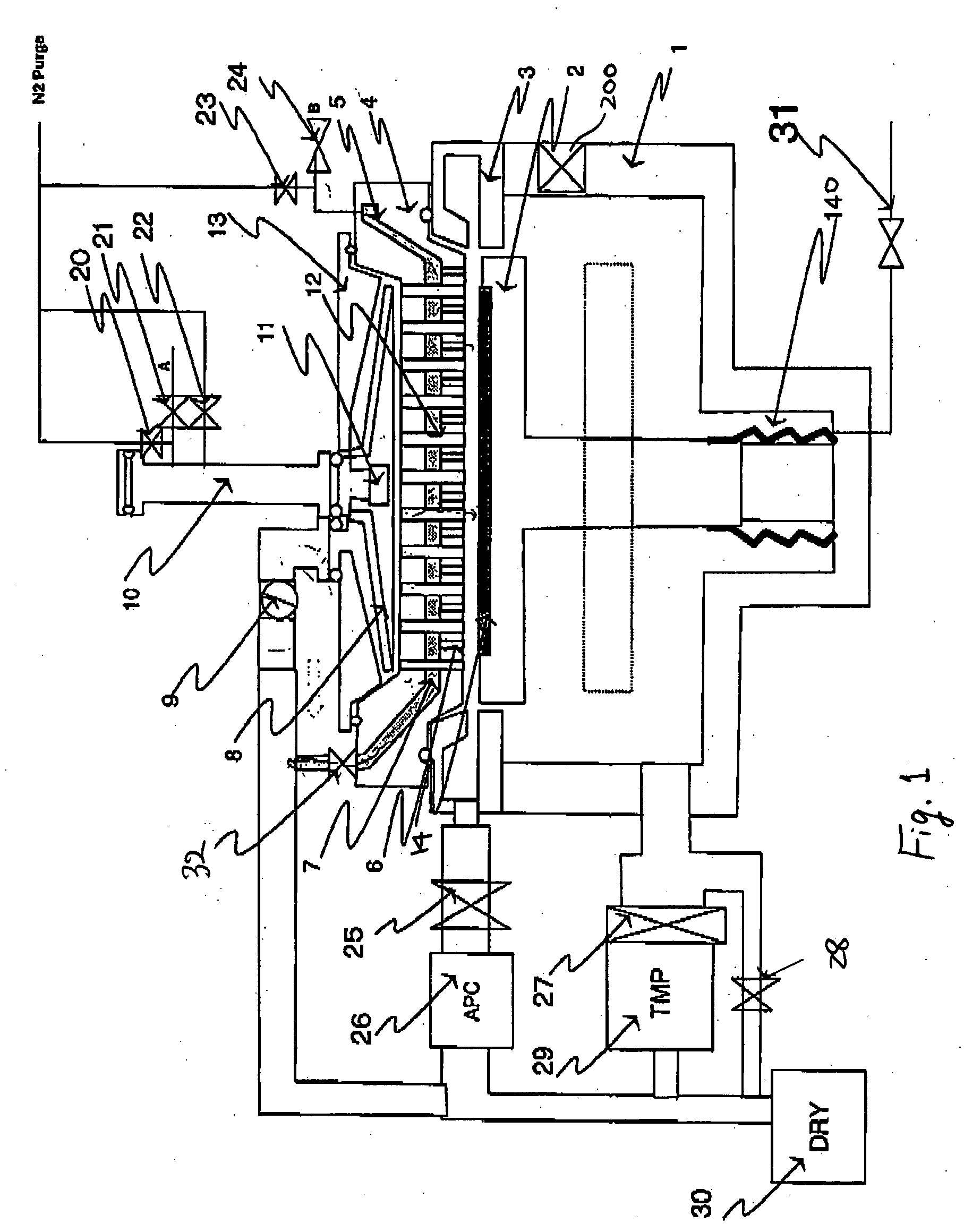

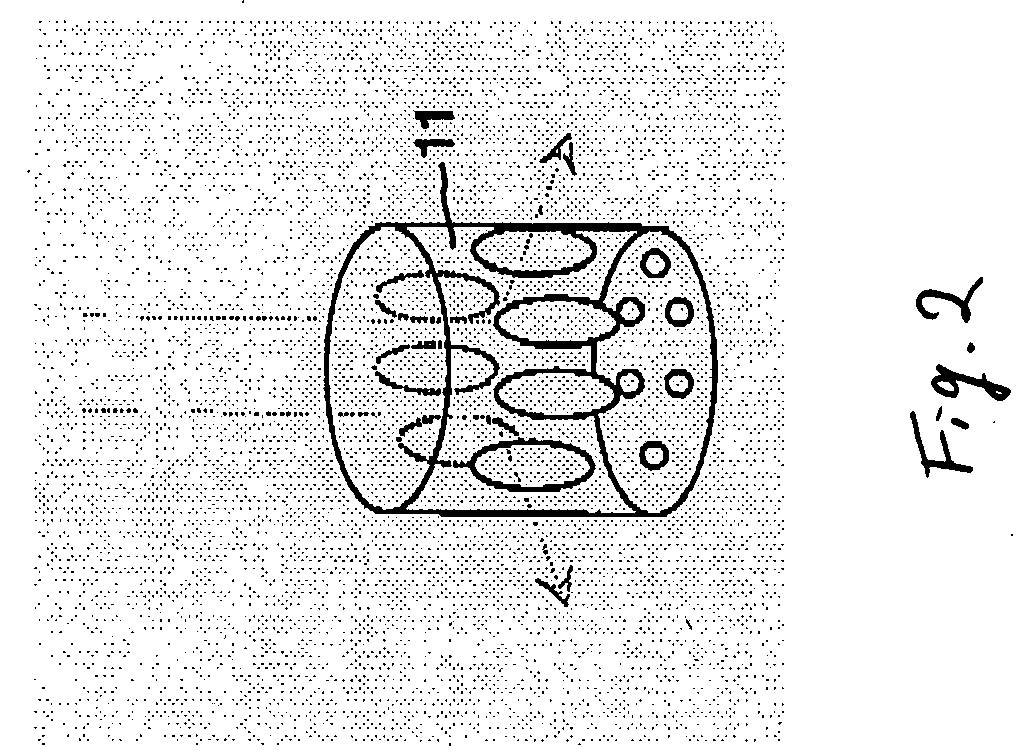

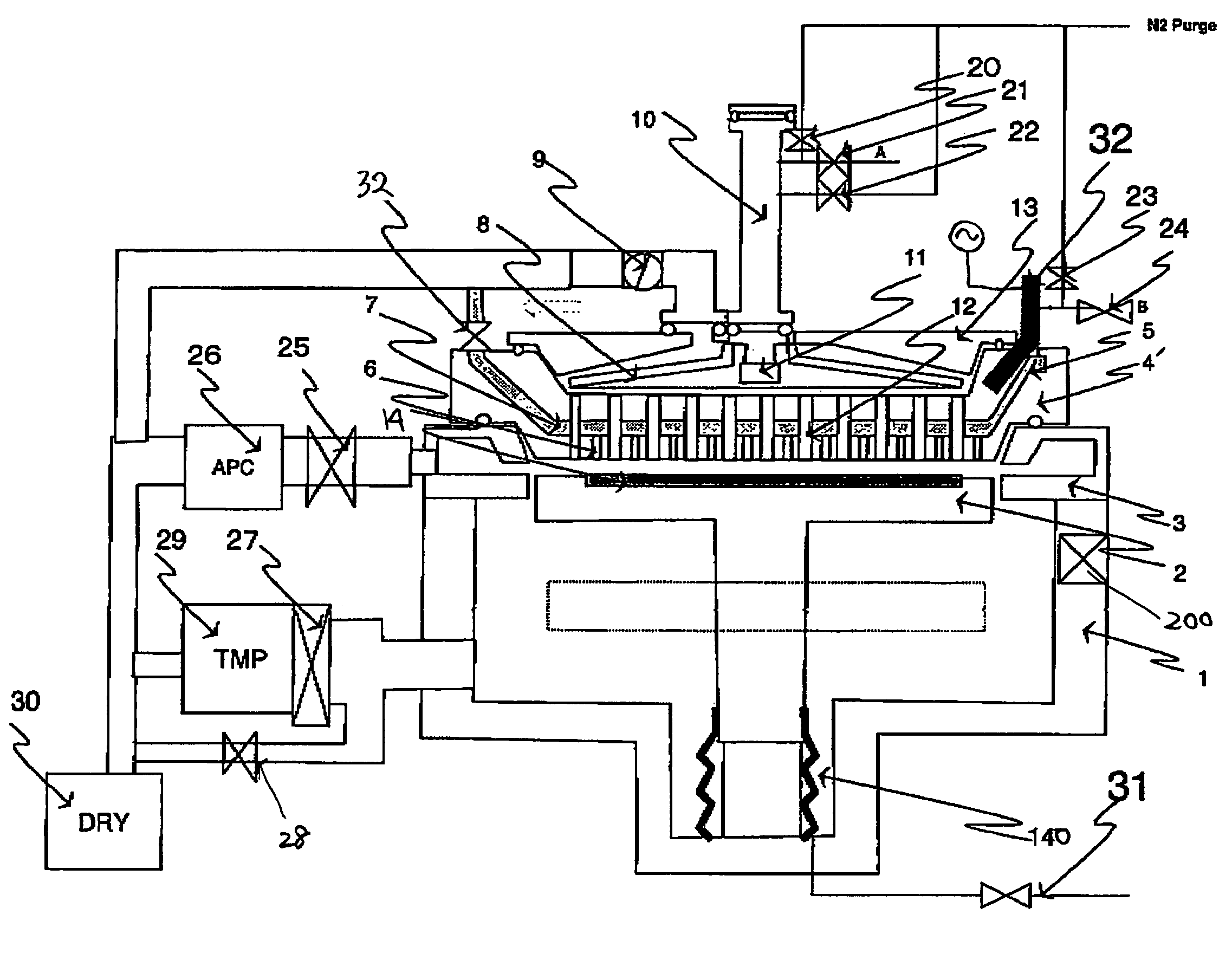

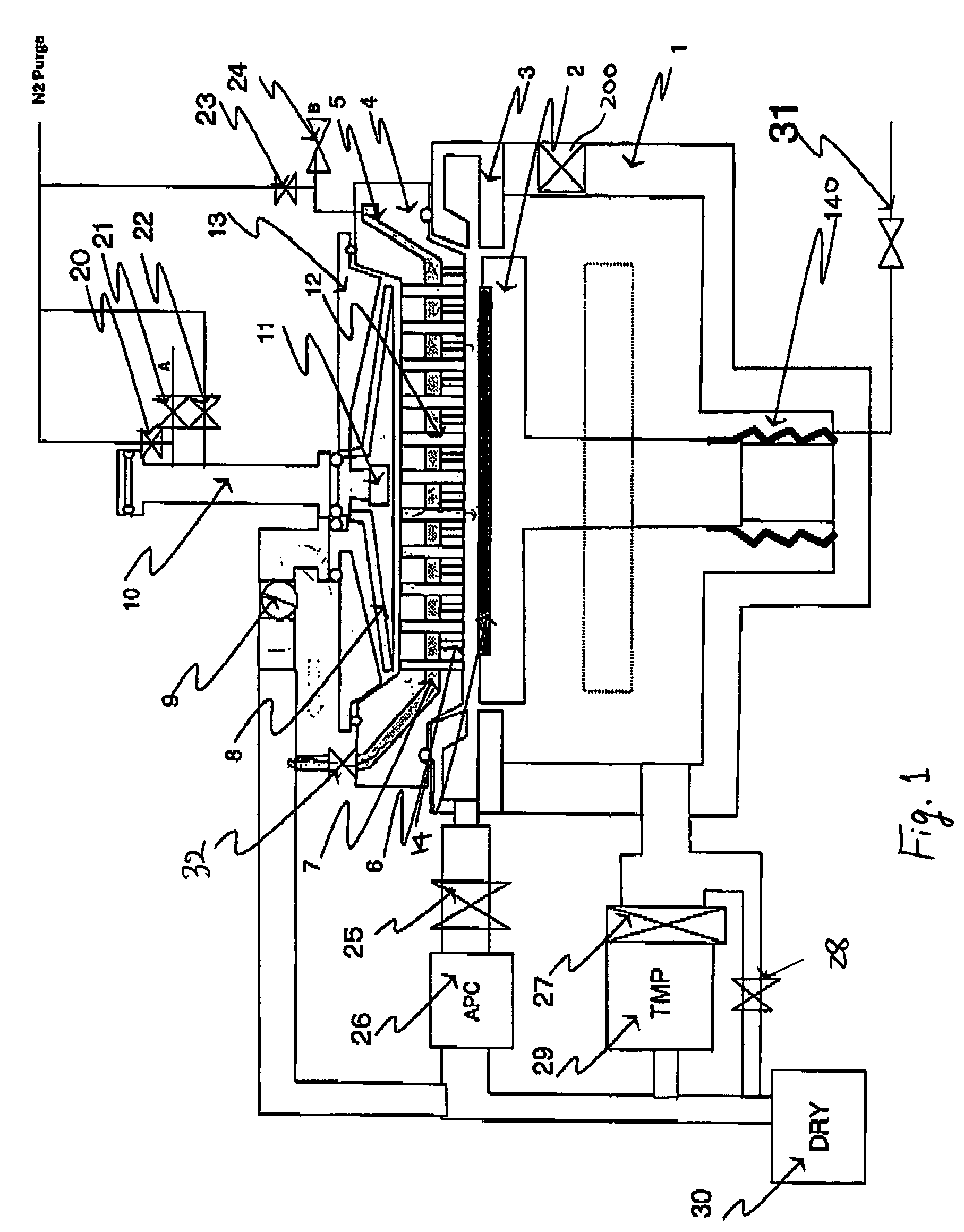

Thin-film deposition apparatus

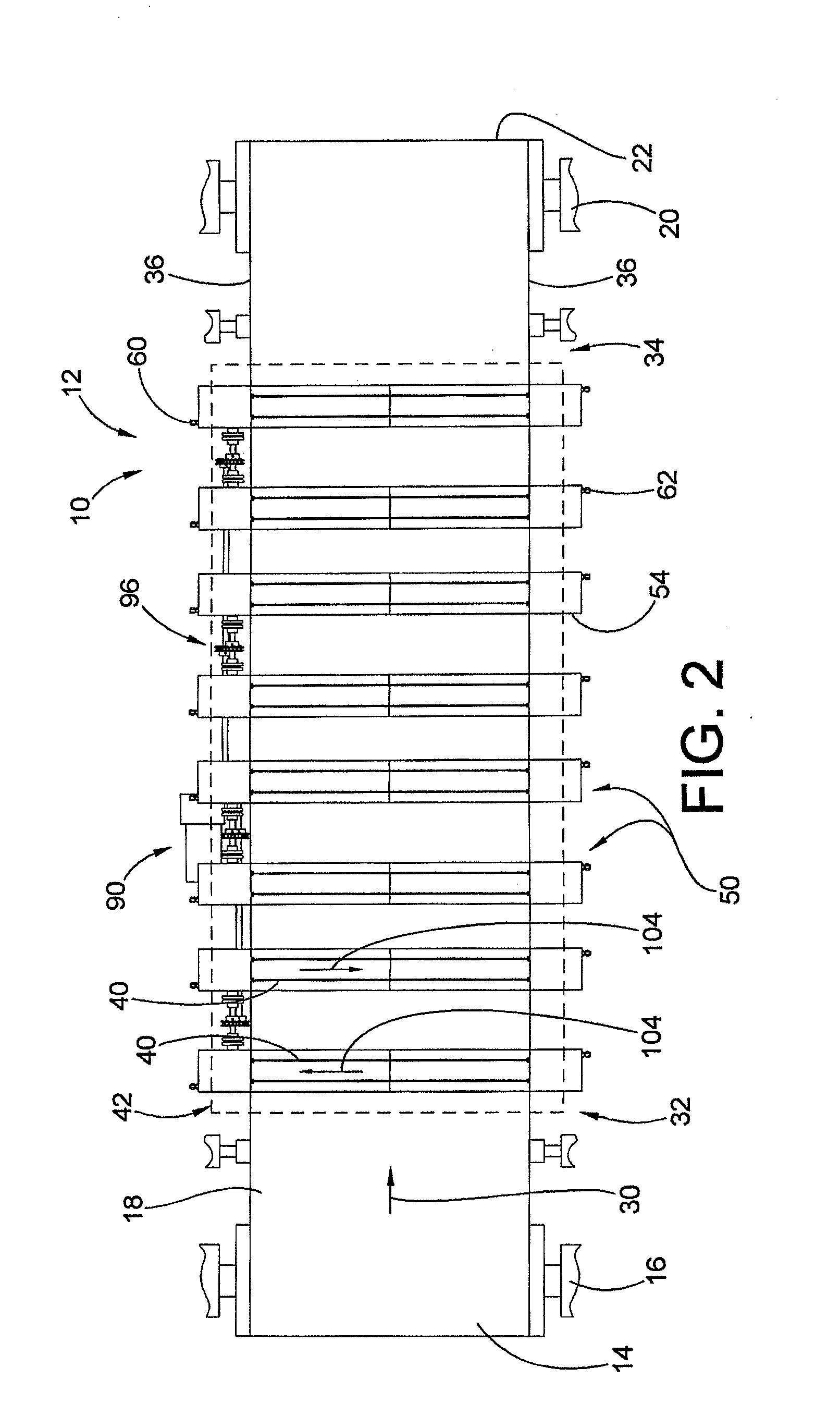

ActiveUS20050229848A1Hinder reactionAvoid reactionSemiconductor/solid-state device manufacturingChemical vapor deposition coatingProduct gasEngineering

A gas-feeding apparatus configured to be connected to an evacuatable reaction chamber includes a gas-distribution head for introducing gases into the chamber through a head surface. The gas-feeding head includes a first section for discharging a gas through the head surface toward a susceptor and a second section for discharging a gas through the head surface toward the susceptor. The first and the second sections are isolated from each other in the gas-distribution head, at least one of which section is coupled to an exhaust system for purging therefrom a gas present in the corresponding section without passing through the head surface.

Owner:ASM JAPAN

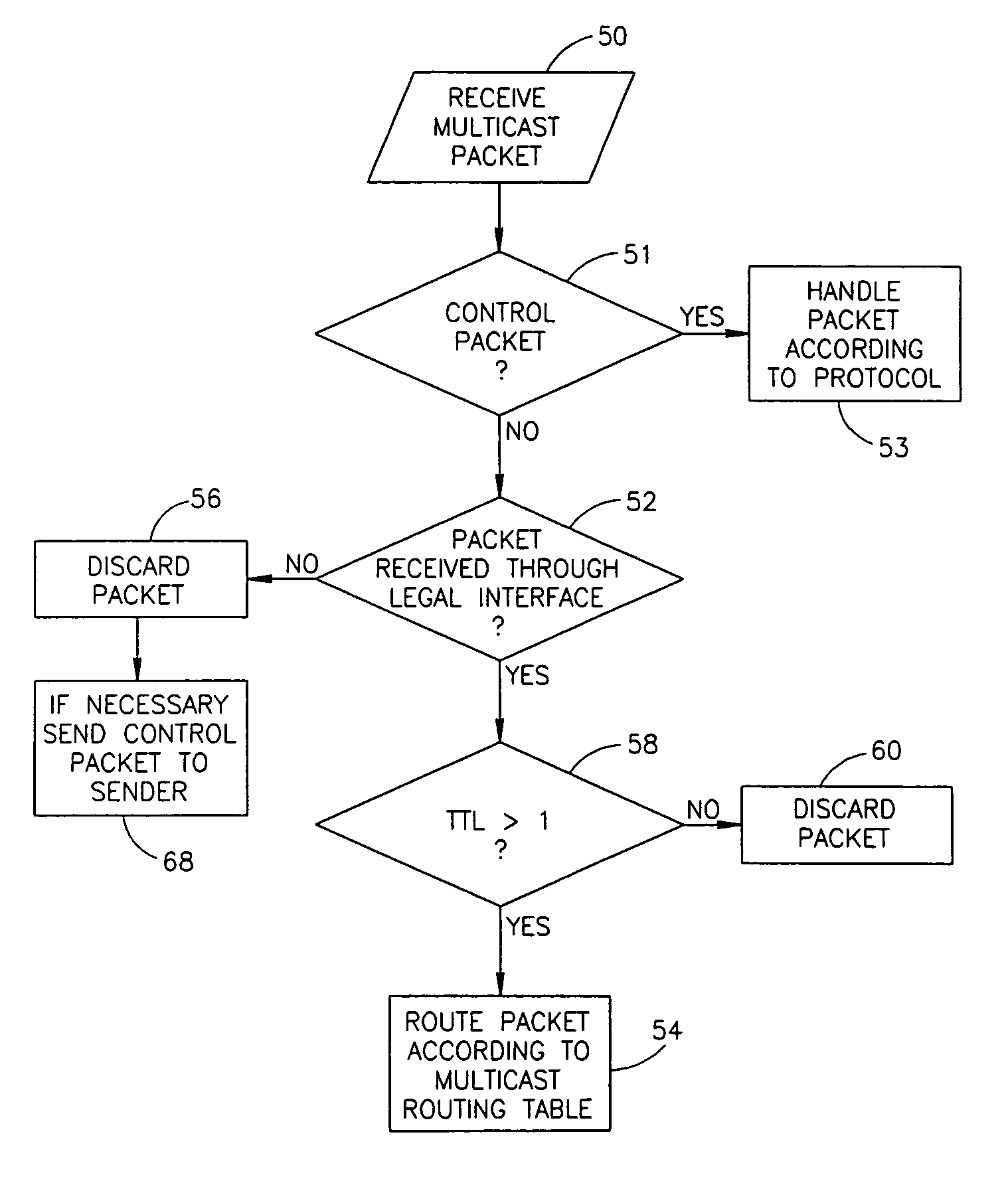

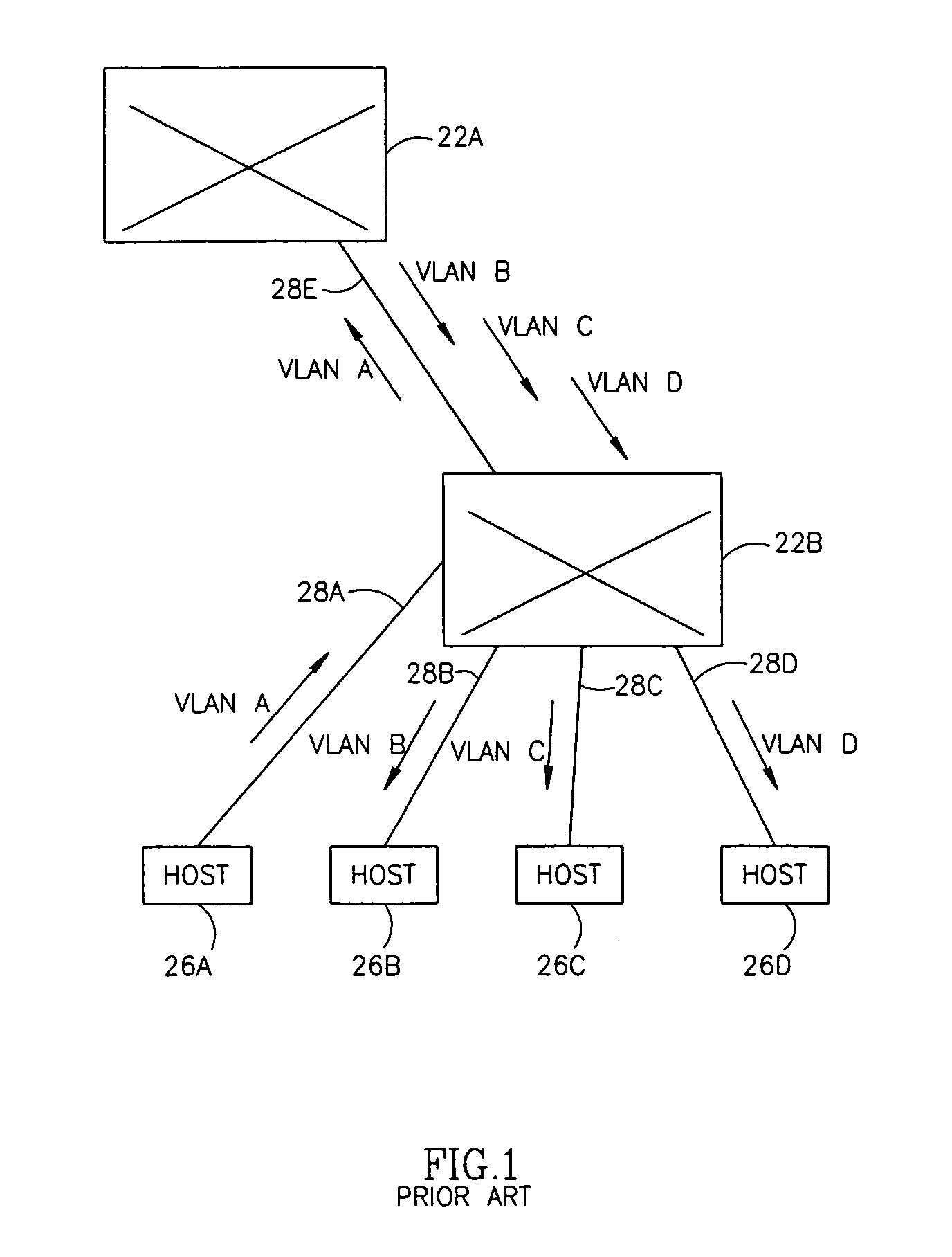

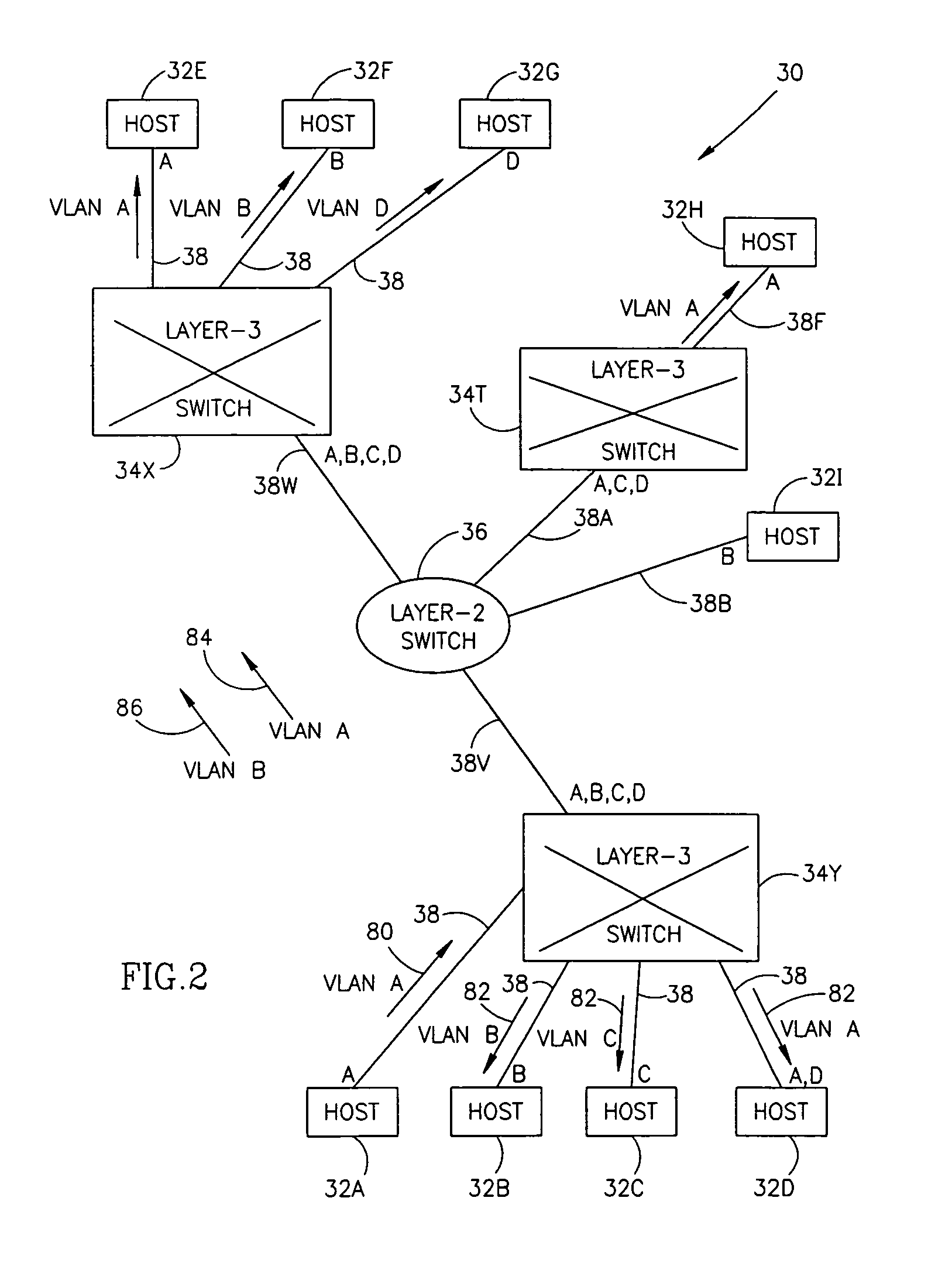

IP multicast in VLAN environment

ActiveUS7924837B1Avoid layeringEasy to implementError preventionTransmission systemsRouting tableVirtual LAN

A method of determining local multicast information of a local area network (LAN), comprising dividing the LAN to a number of segments larger than the number of virtual LANs (VLANs) in the network and creating a layer-3 multicast routing table, which relates to each of the segments separately.

Owner:AVAYA TECH CORP +1

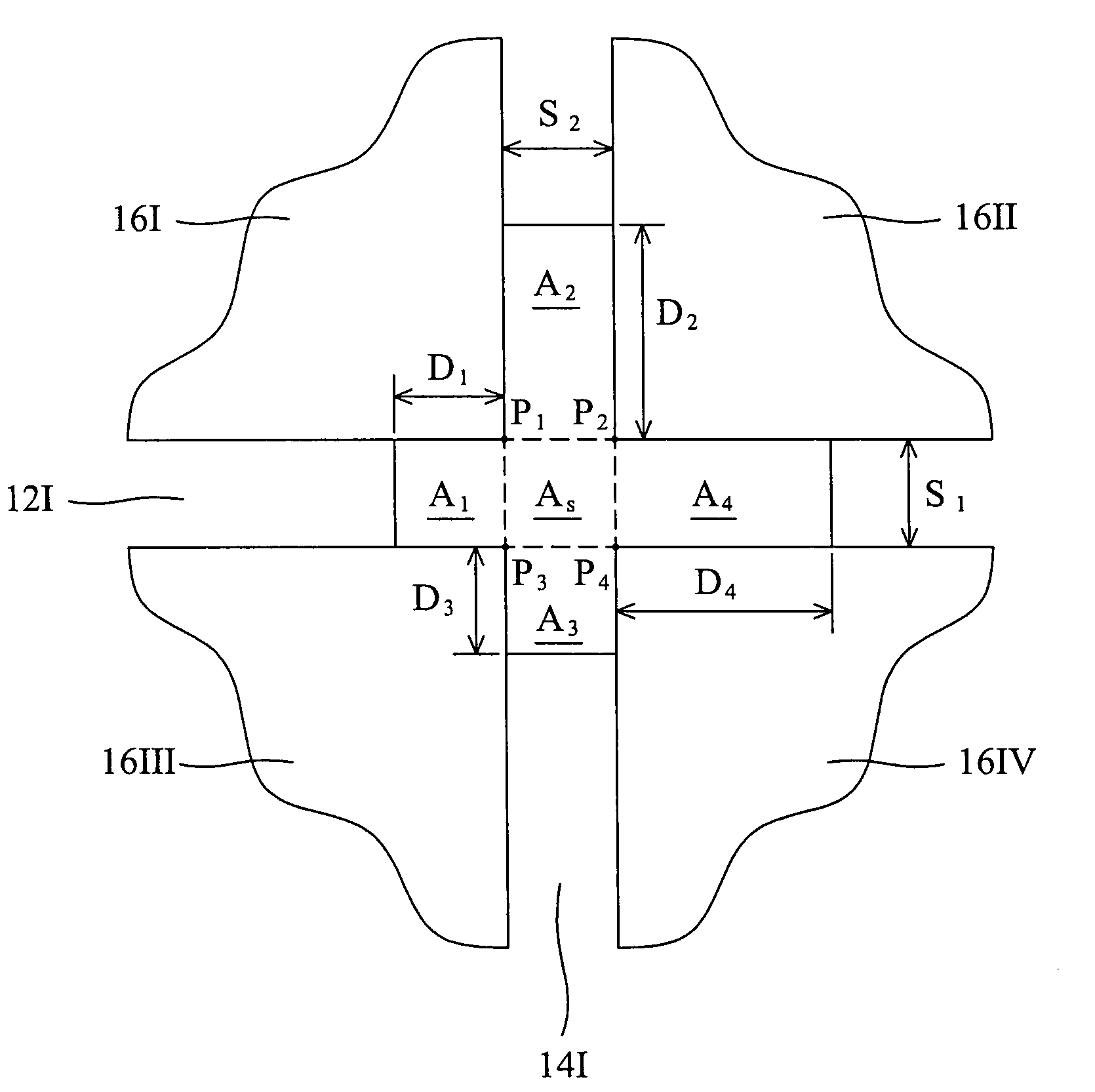

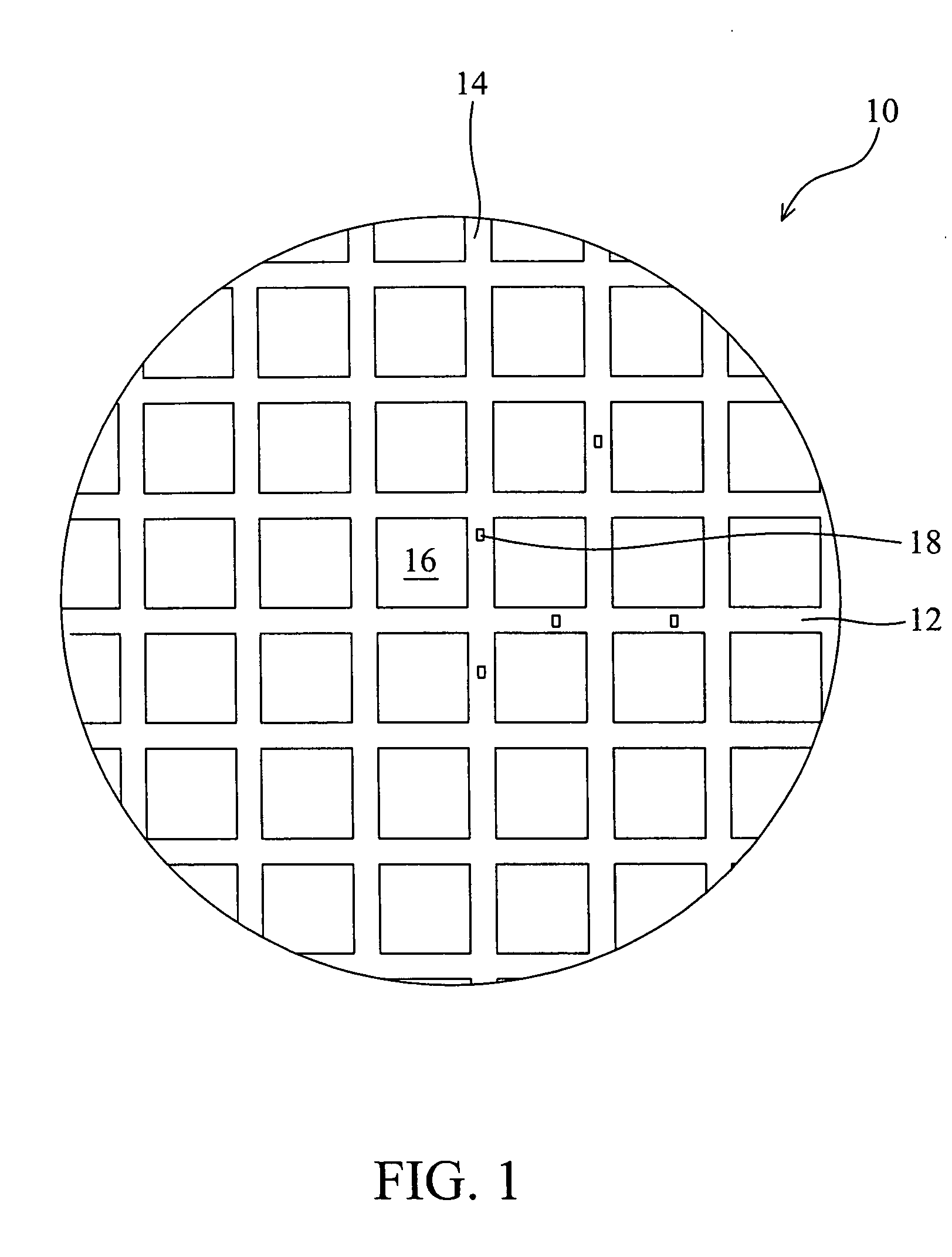

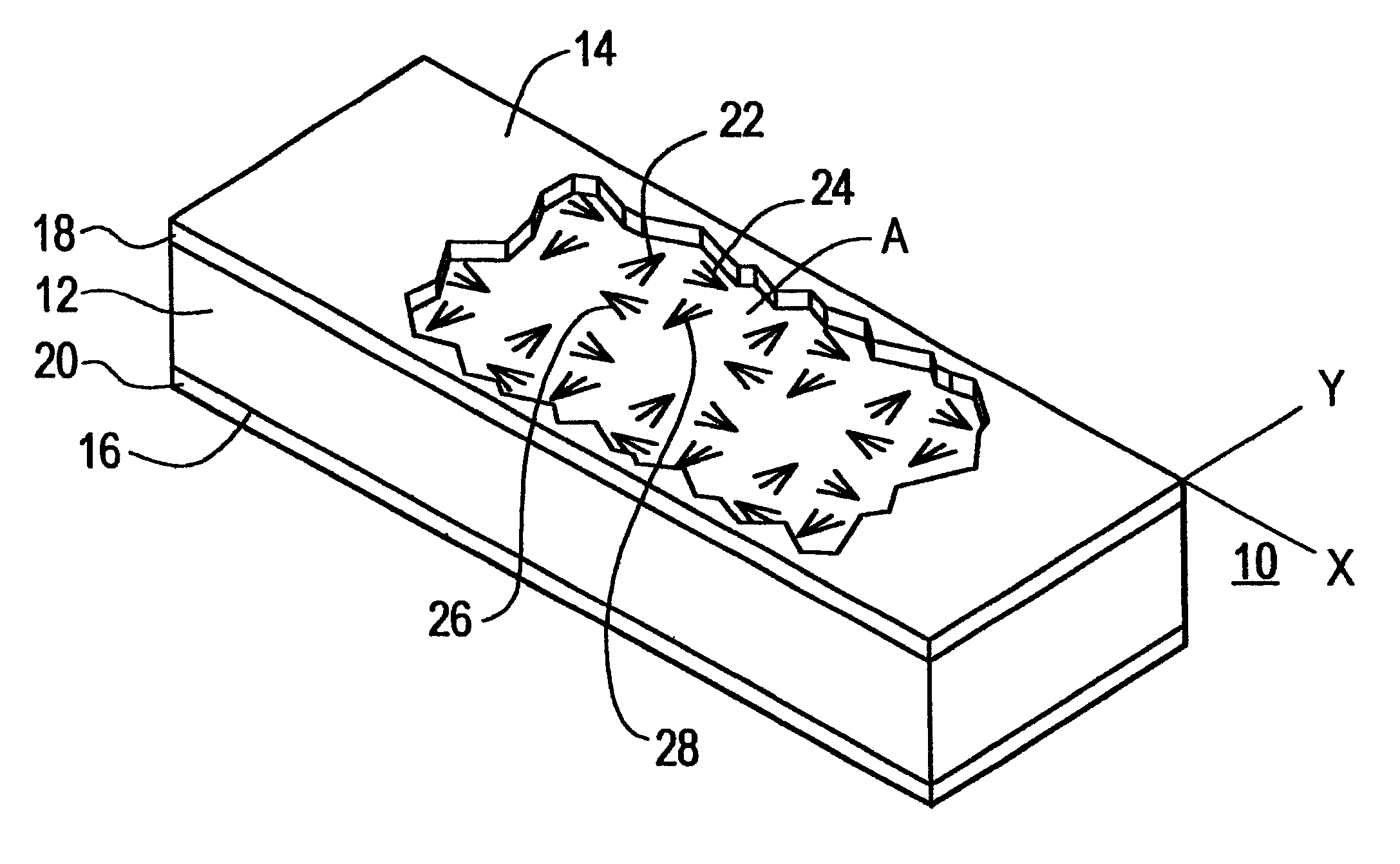

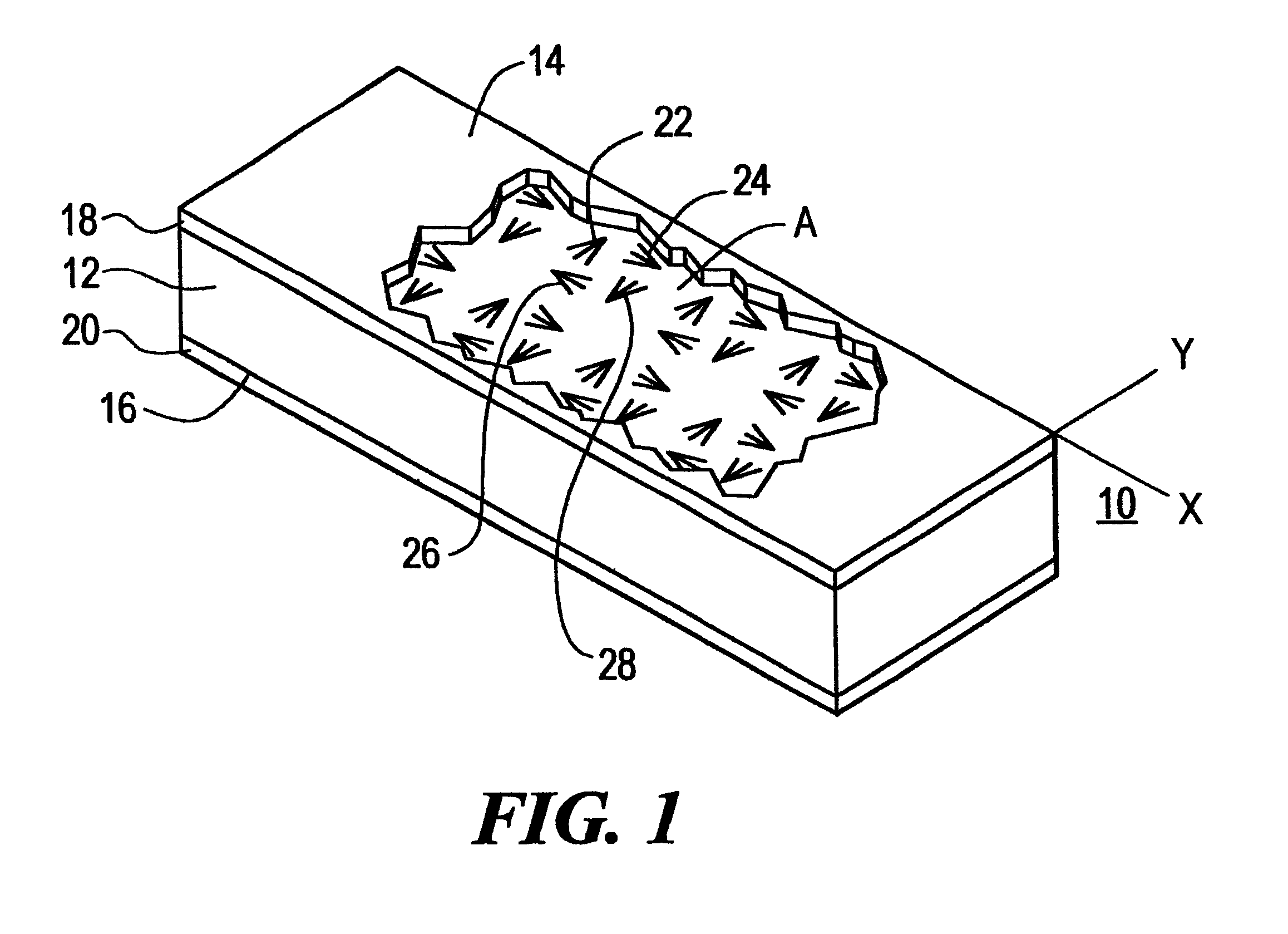

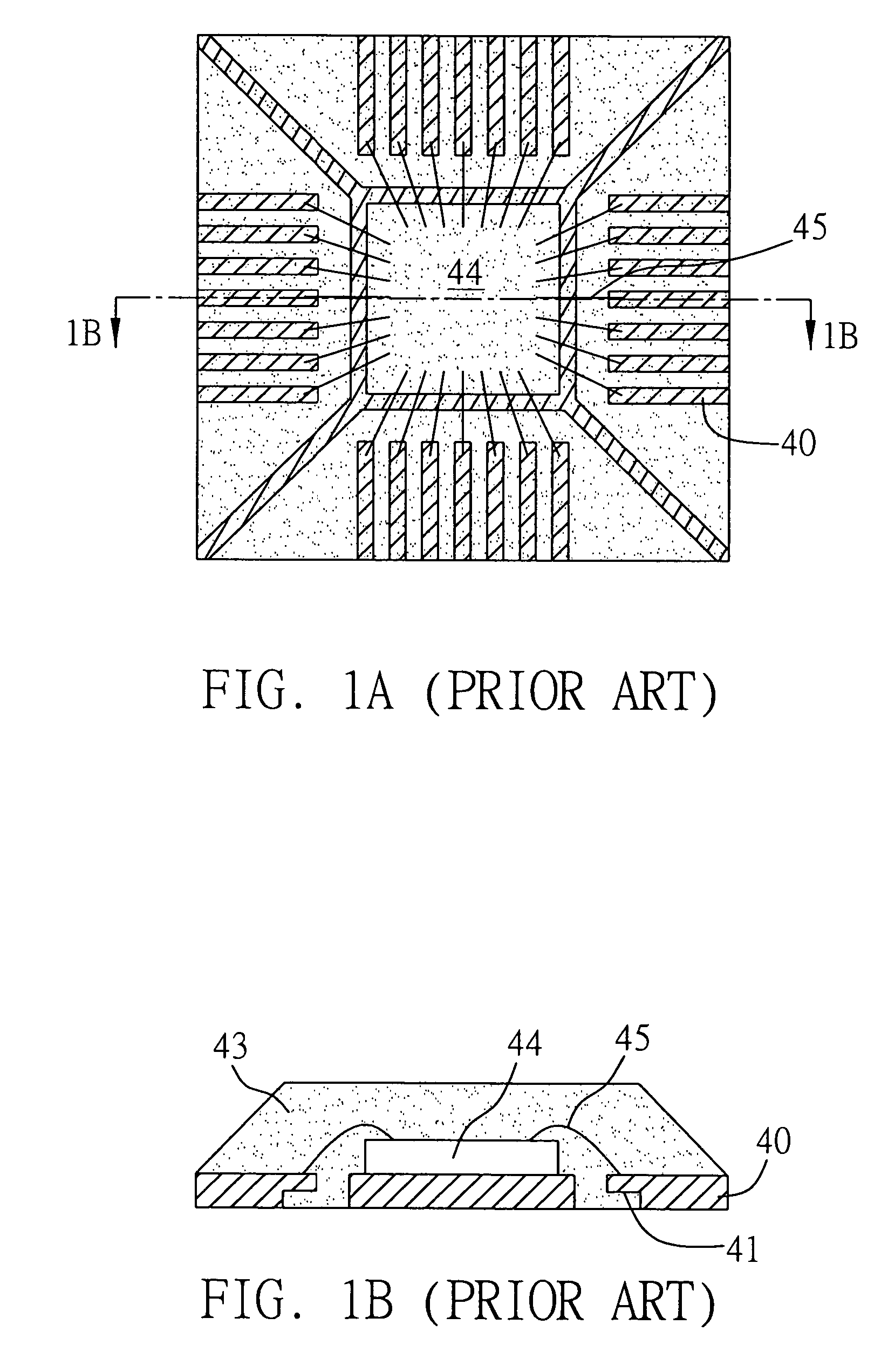

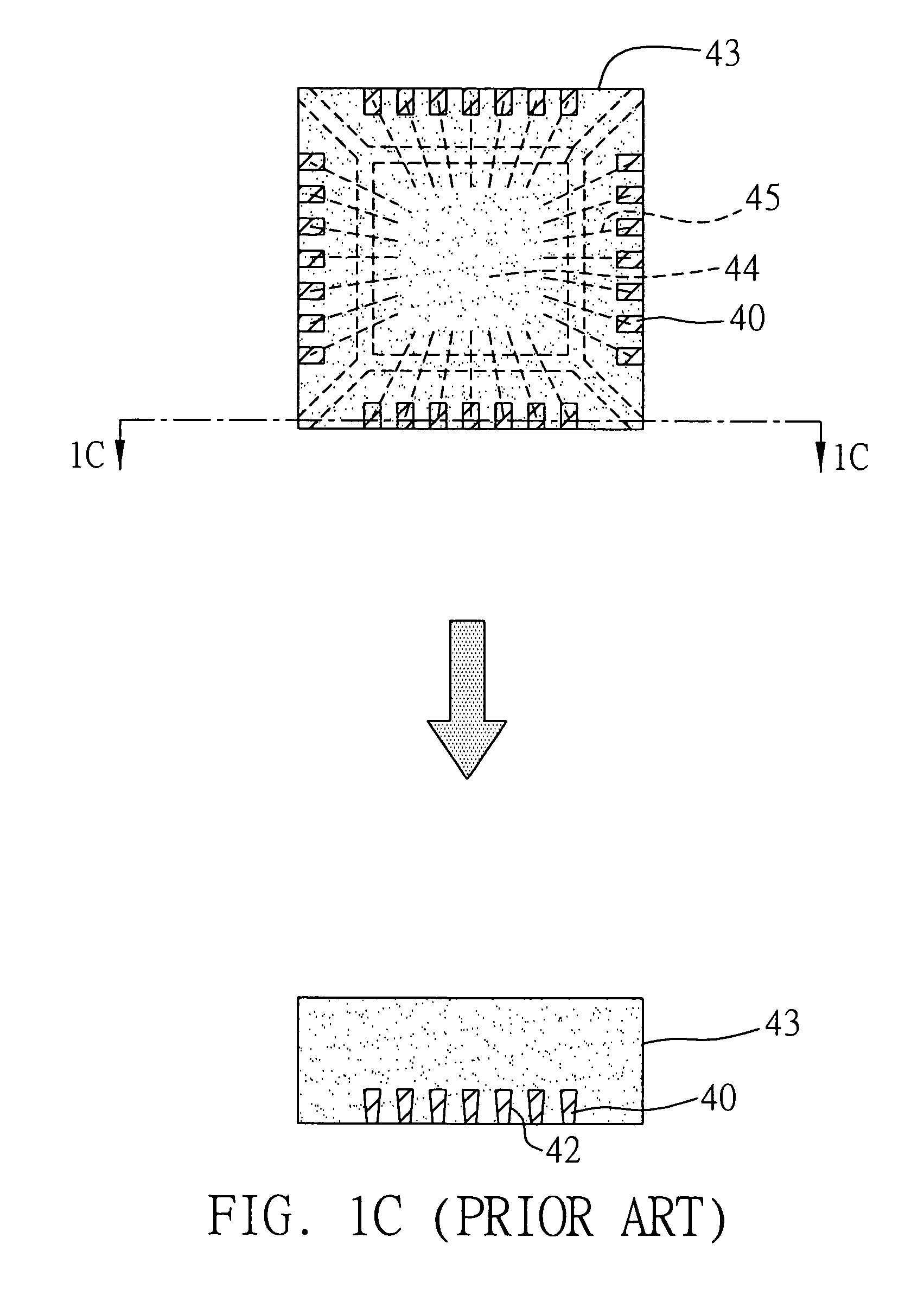

Apparatus and method for manufacturing a semiconductor wafer with reduced delamination and peeling

InactiveUS20060261490A1Avoid layeringAvoid crackingSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSemiconductor structureLow-k dielectric

A multi-layered semiconductor structure with free areas limiting the placement of test keys. First and second scribe lines intersect to define one corner point of a die. The first and second scribe lines are part of the multilayered structure and at least one layer of the multi-layer structure is a low-k dielectric layer. Free area A1 is defined on the first scribe line and is defined by the equation A1=D1×S1, where D1 is the distance from the corner point of the die toward the main area of the die, and S1 is the width of the first scribe line. Free area AS is defined at the intersection of the first scribe line and the second scribe line adjacent the die and is defined by the equation AS=S1×S2, where S2 is the width of the second scribe line.

Owner:TAIWAN SEMICON MFG CO LTD

Sandwich structure and method of making same

InactiveUS6291049B1Eliminating expenseEliminating impracticabilitySynthetic resin layered productsWoven fabricsEngineeringFace sheet

A sandwich structure including a core having opposing top and bottom surfaces, a plurality of discrete pins disposed through the core and extending beyond the top and bottom surfaces of the core, a face sheet on the top core surface, and a face sheet on the bottom core surface. The ends of each pin are bent over and lie between the respective core surfaces and the face sheets to secure the face sheets to the core, improve the strength of the core, and to provide a physical connection between the two face sheets. Also disclosed is a reinforced core for a sandwich structure which does not yet have the face sheets assembled to it. Also disclosed is a method of making such a reinforced core and completed sandwich structures including such a core.

Owner:AZTEX

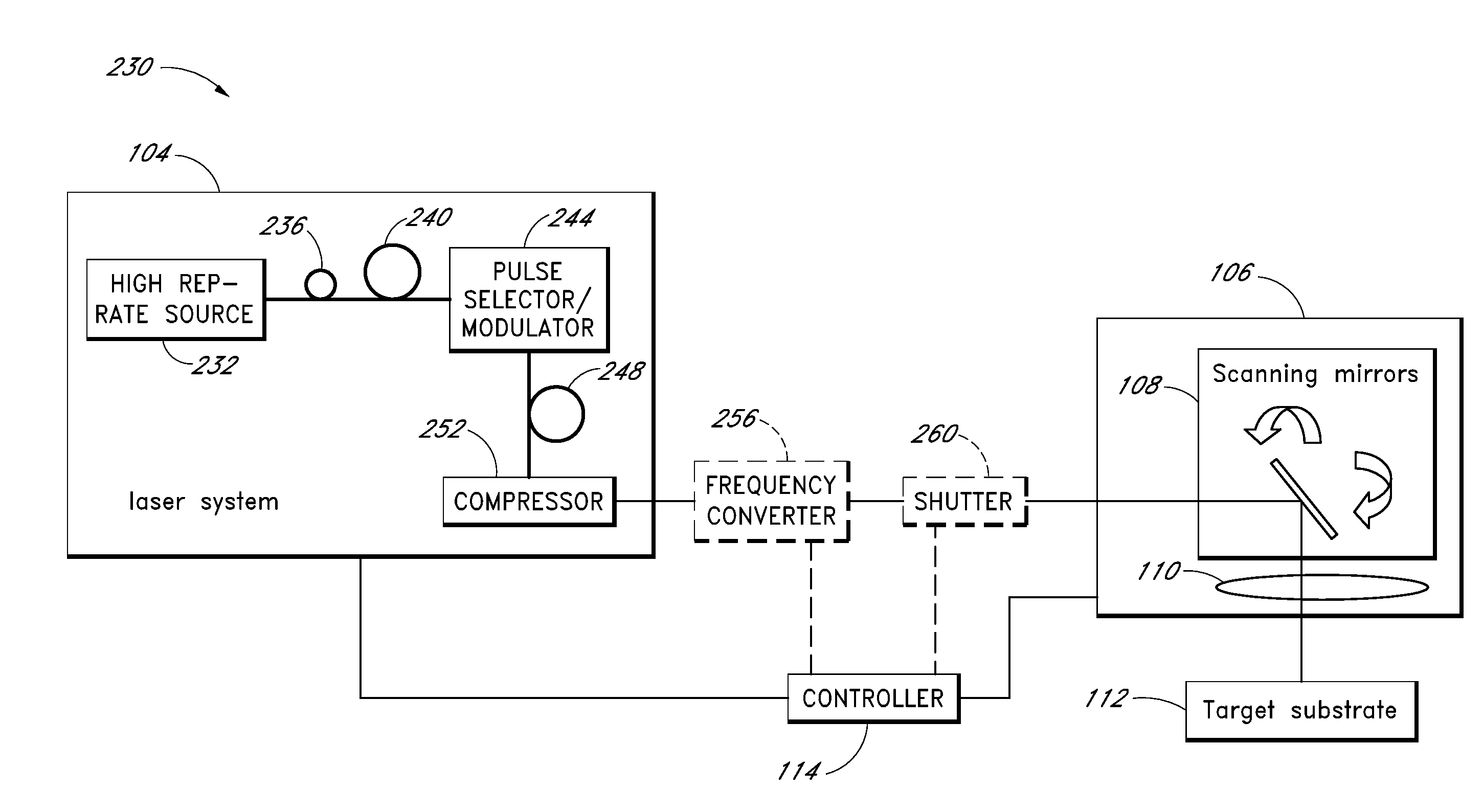

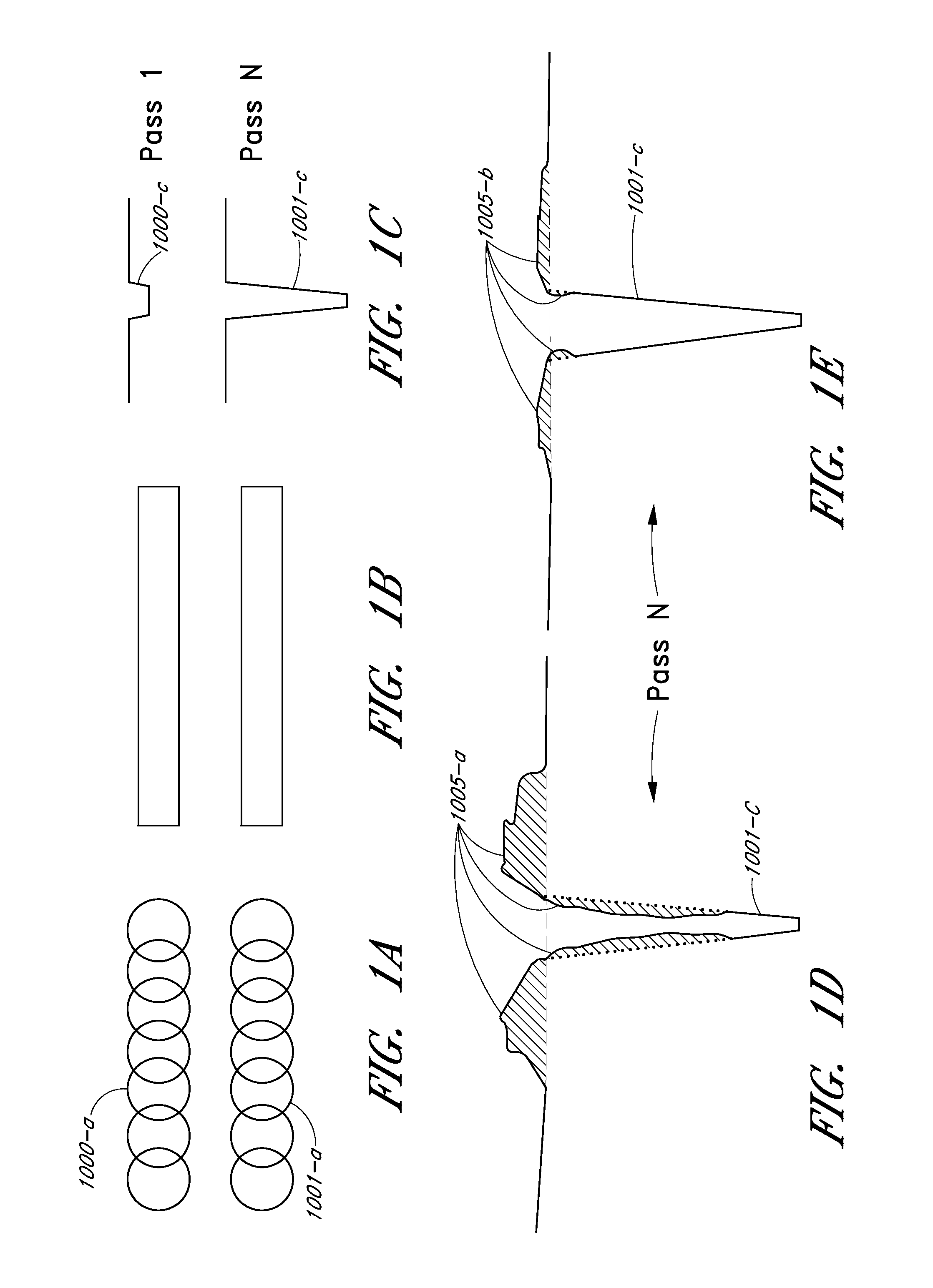

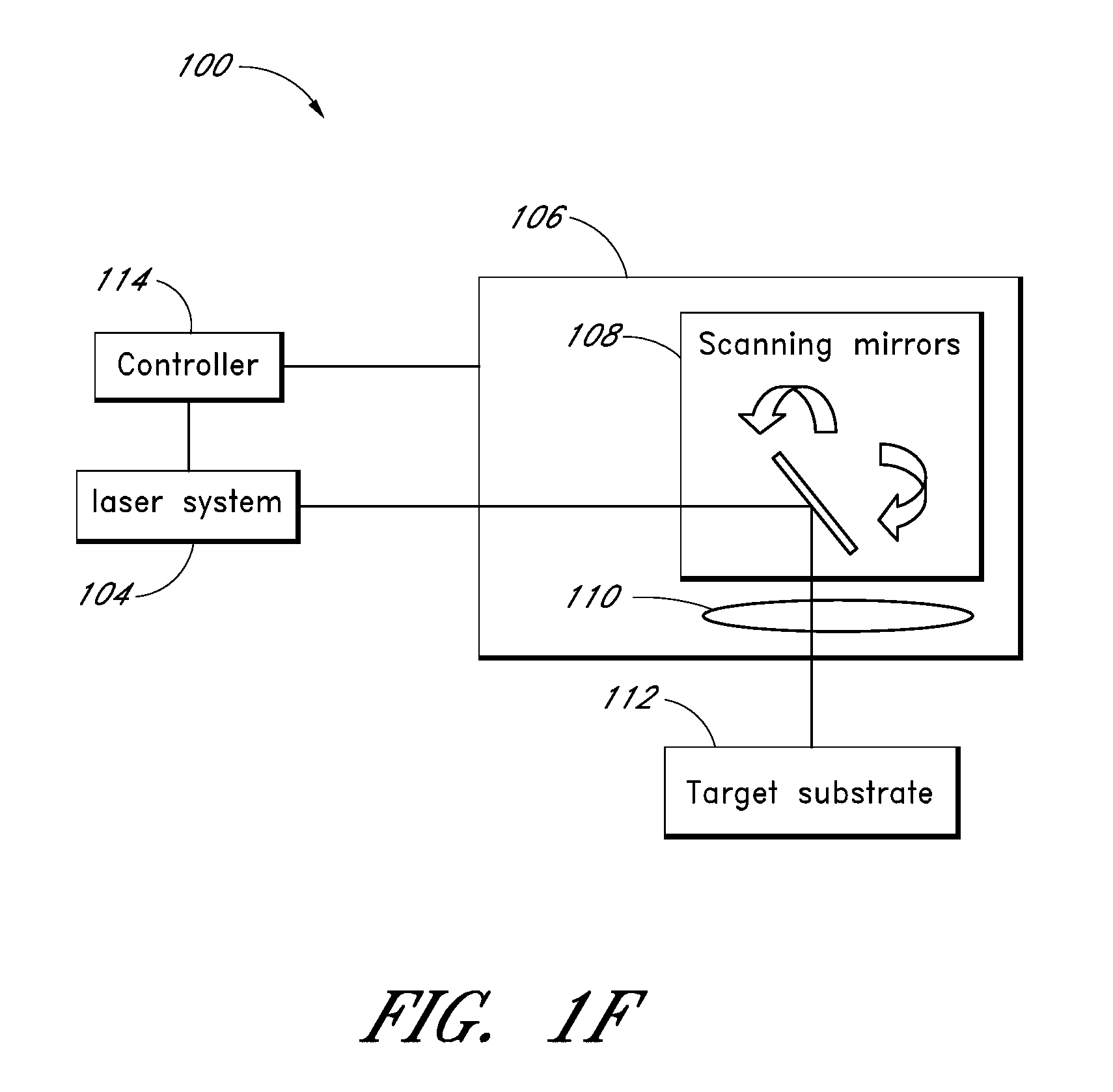

Laser-based material processing methods and systems

ActiveUS20100197116A1Efficient removalAvoid accumulationSemiconductor/solid-state device manufacturingWelding/soldering/cutting articlesDielectricMaterials processing

Various embodiments may be used for laser-based modification of target material of a workpiece while advantageously achieving improvements in processing throughput and / or quality. Embodiments of a method of processing may include focusing and directing laser pulses to a region of the workpiece at a pulse repetition rate sufficiently high so that material is efficiently removed from the region and a quantity of unwanted material within the region, proximate to the region, or both is reduced relative to a quantity obtainable at a lower repetition rate. In at least one embodiment, an ultrashort pulse laser system may include at least one of a fiber amplifier or fiber laser. Various embodiments are suitable for at least one of dicing, cutting, scribing, and forming features on or within a semiconductor substrate. Workpiece materials may also include metals, inorganic or organic dielectrics, or any material to be micromachined with femtosecond and / or picosecond pulses, and in some embodiments with pulse widths up to a few nanoseconds.

Owner:IMRA AMERICA

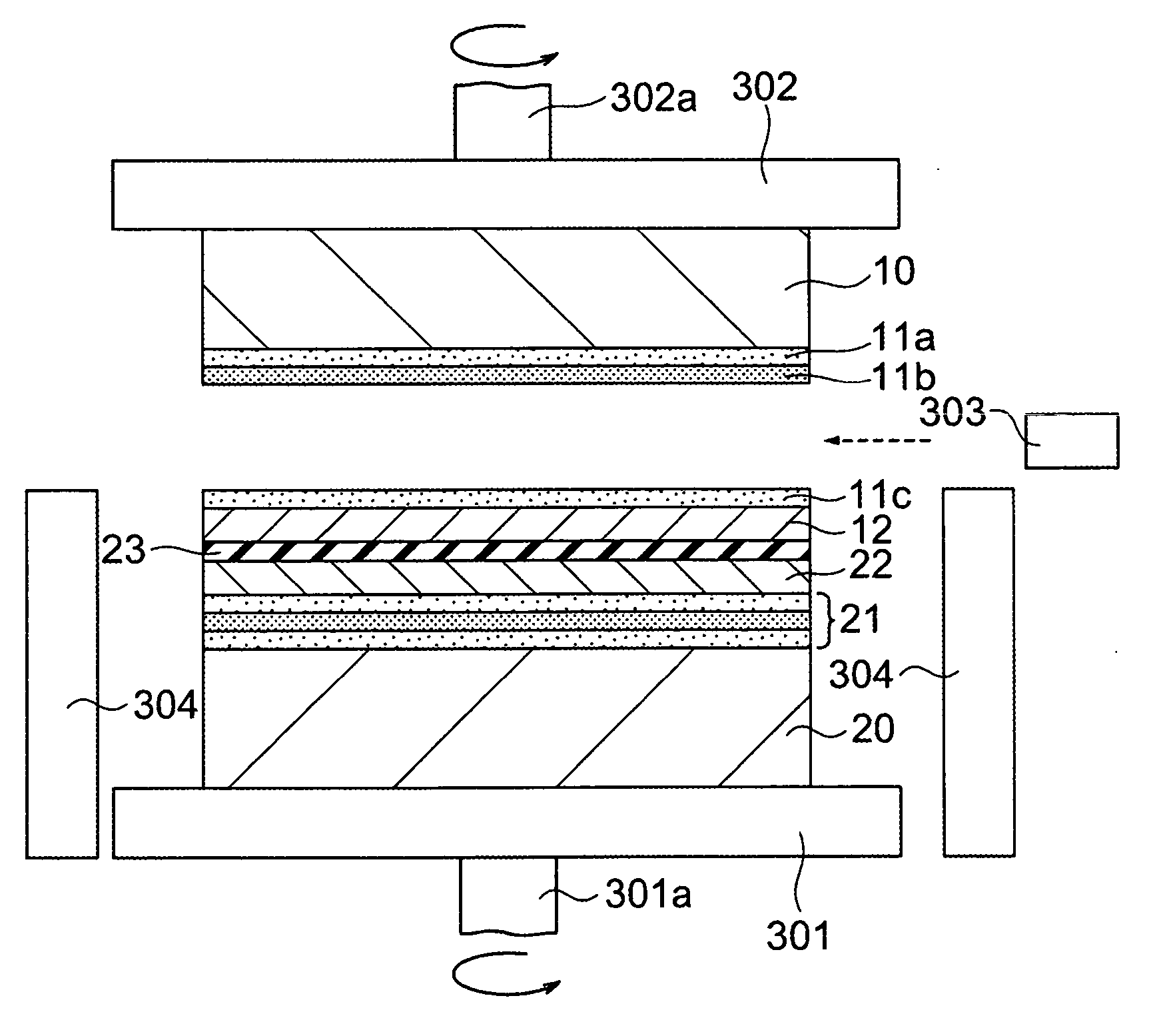

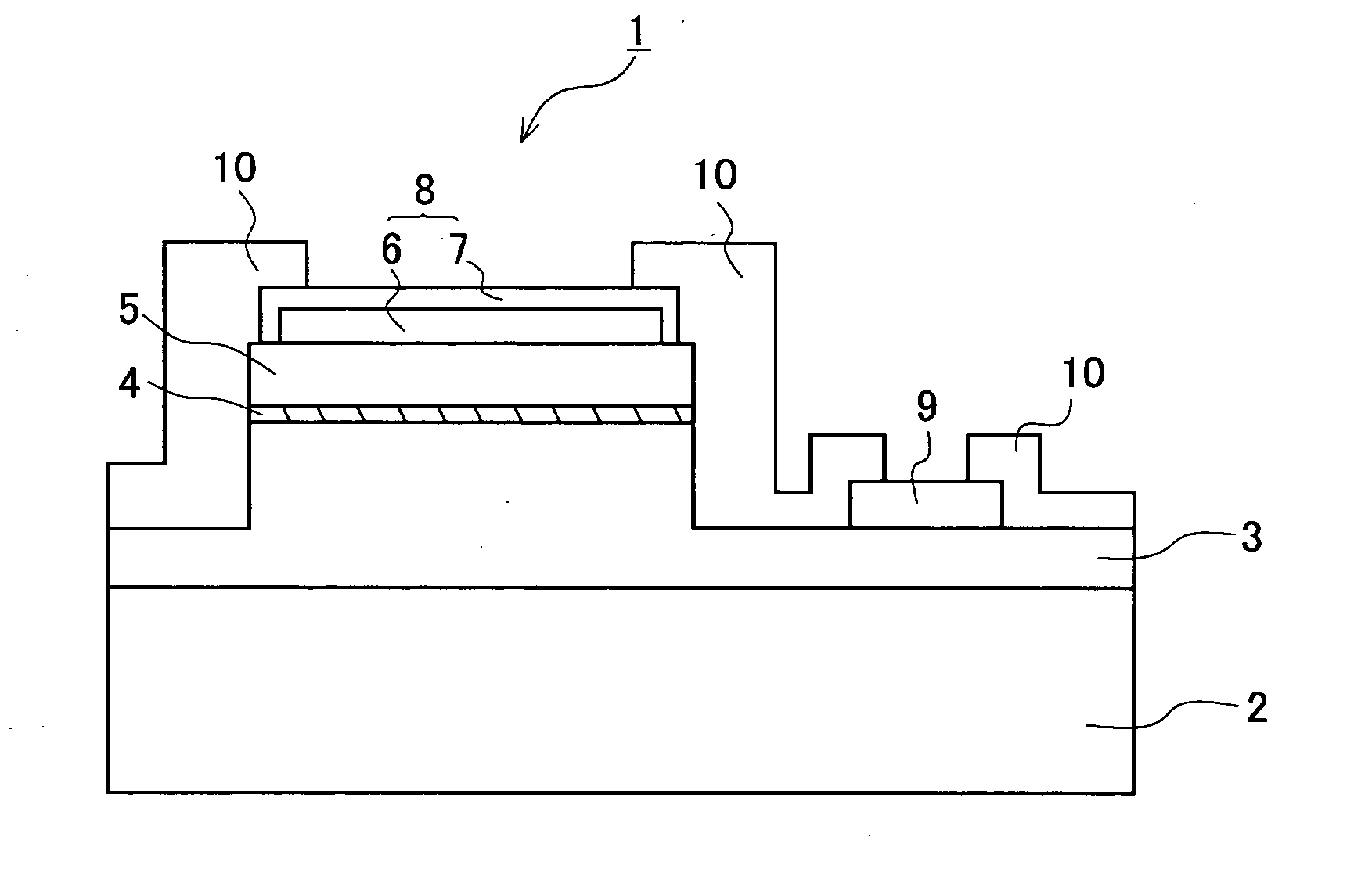

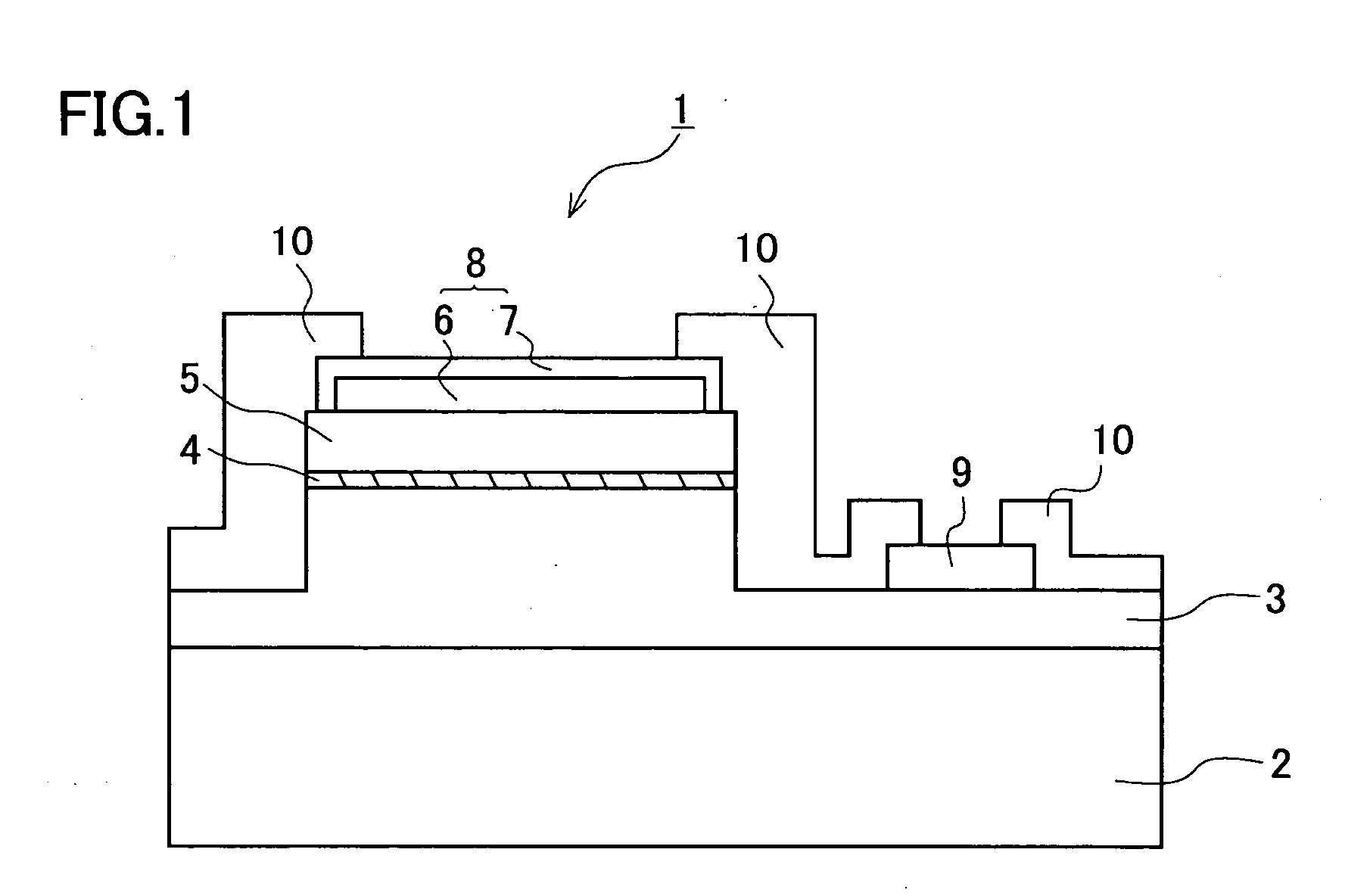

Method and apparatus for producing ultra-thin semiconductor chip and method and apparatus for producing ultra-thin back-illuminated solid-state image pickup device

InactiveUS20050074954A1Easy to separateIncrease productivitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A method for producing an ultra-thin semiconductor chip and an ultra-thin back-illuminated solid-state image pickup device utilizing a semiconductor layer formed on a support substrate via an insulating layer to improve separation performance of a semiconductor layer from a support substrate and thereby improve the productivity and quality. The method uses two porous peeling layers on opposite sides of a substrate to produce an ultra-thin substrate.

Owner:SONY CORP

Electrostatic chuck member

InactiveUS20090080136A1Avoid damageAvoid layeringSemiconductor/solid-state device manufacturingElectrostatic holding devicesSurface roughnessSpray coating

An electrostatic chuck member comprises an electrode layer and an electric insulating layer, wherein a spray coating layer of an oxide of a Group 3A element in the Periodic Table is formed as an outermost layer of the member and a surface of the spray coating layer is rendered into a densified re-melting layer having an average surface roughness (Ra) Of 0.8-3.0 μm.

Owner:TOKYO ELECTRON LTD +1

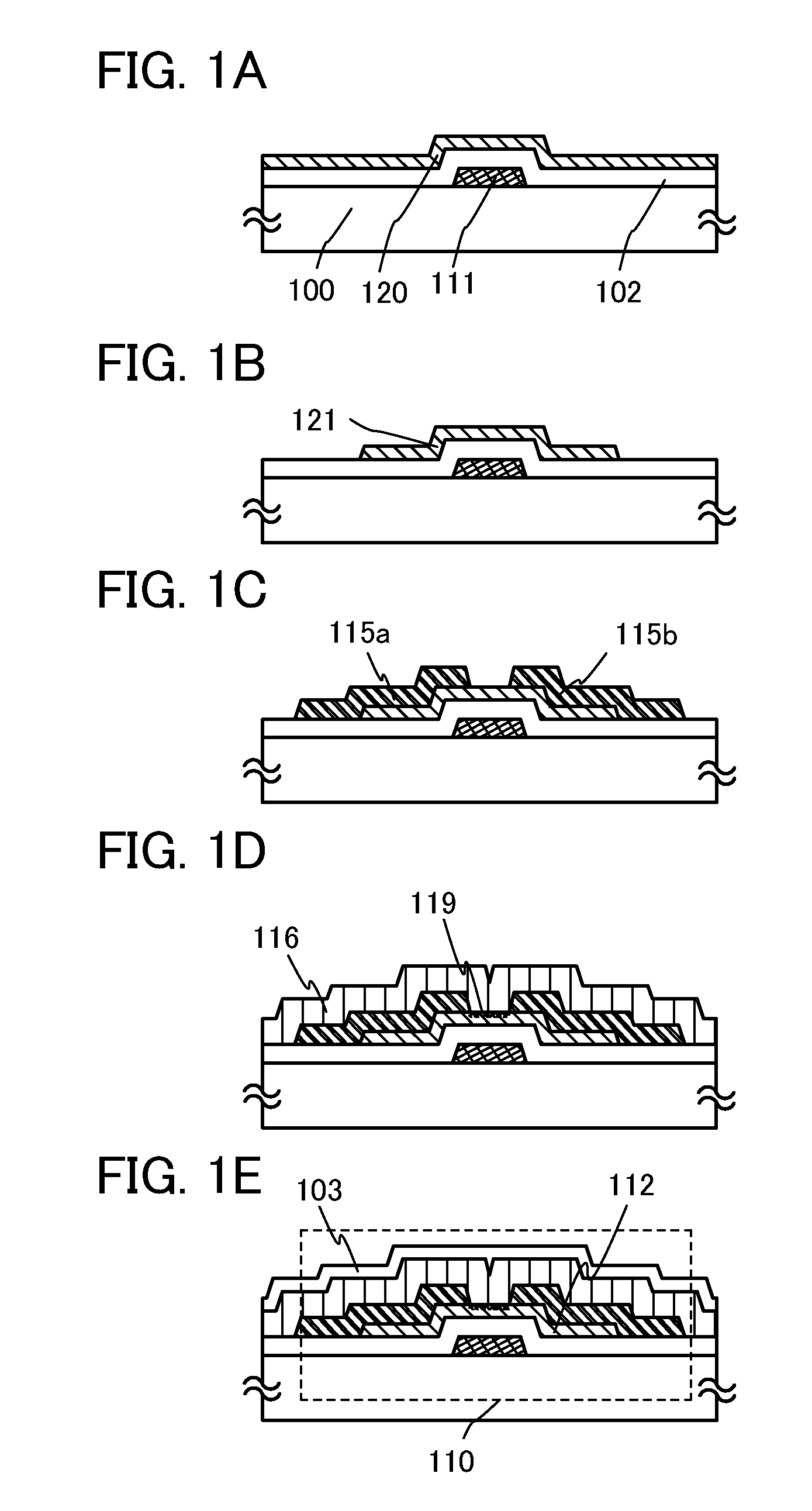

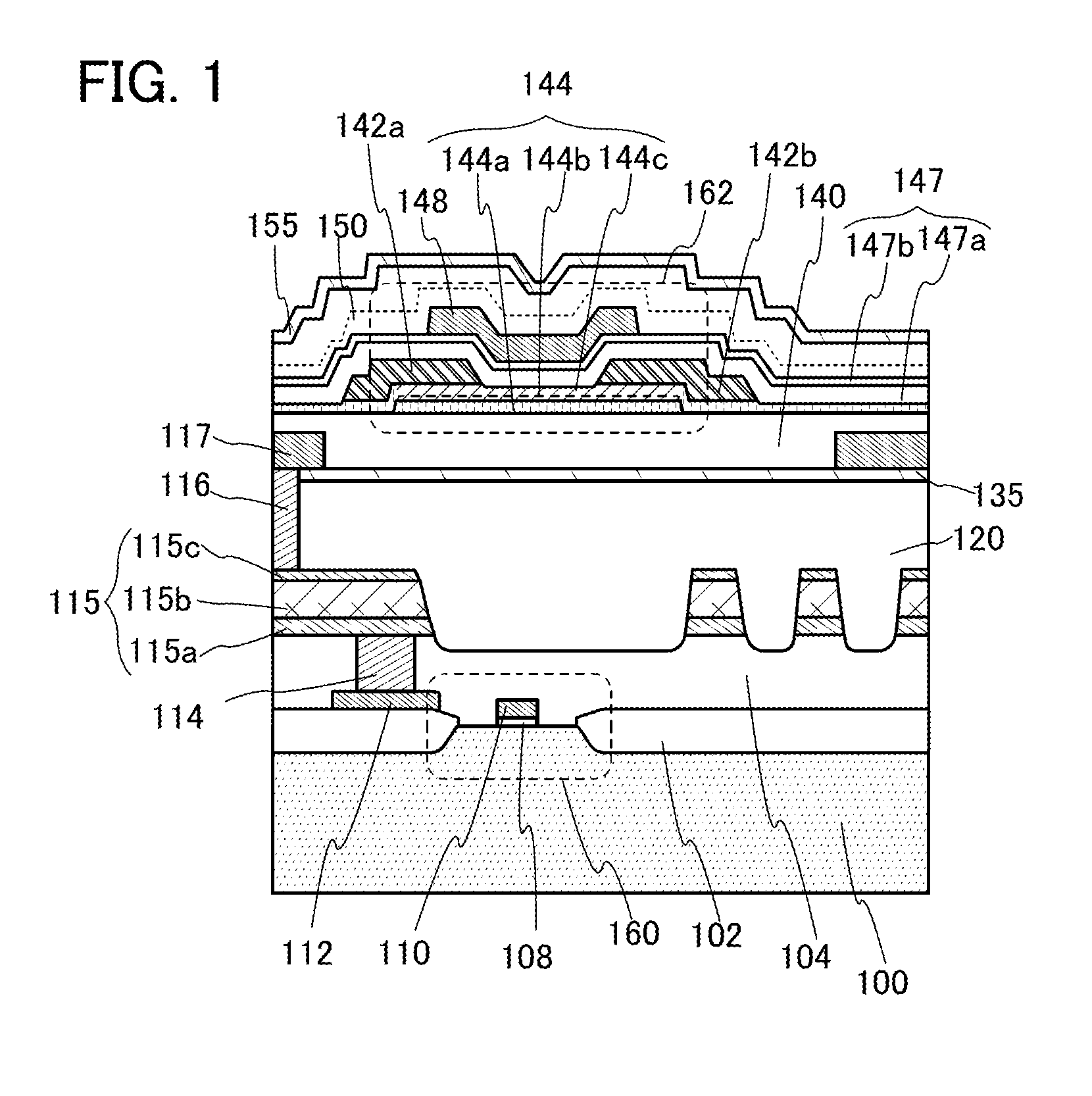

Semiconductor device and method for manufacturing the same

InactiveUS20110101335A1Stable electrical characteristicsReduce impurity concentrationSolid-state devicesSemiconductor/solid-state device manufacturingHydrogen atomDangling bond

An object is to provide a semiconductor device including an oxide semiconductor with stable electric characteristics can be provided. An insulating layer having many defects typified by dangling bonds is formed over an oxide semiconductor layer with an oxygen-excess mixed region or an oxygen-excess oxide insulating layer interposed therebetween, whereby impurities in the oxide semiconductor layer, such as hydrogen or moisture (a hydrogen atom or a compound including a hydrogen atom such as H2O), are moved through the oxygen-excess mixed region or oxygen-excess oxide insulating layer and diffused into the insulating layer. Thus, the impurity concentration of the oxide semiconductor layer is reduced.

Owner:SEMICON ENERGY LAB CO LTD

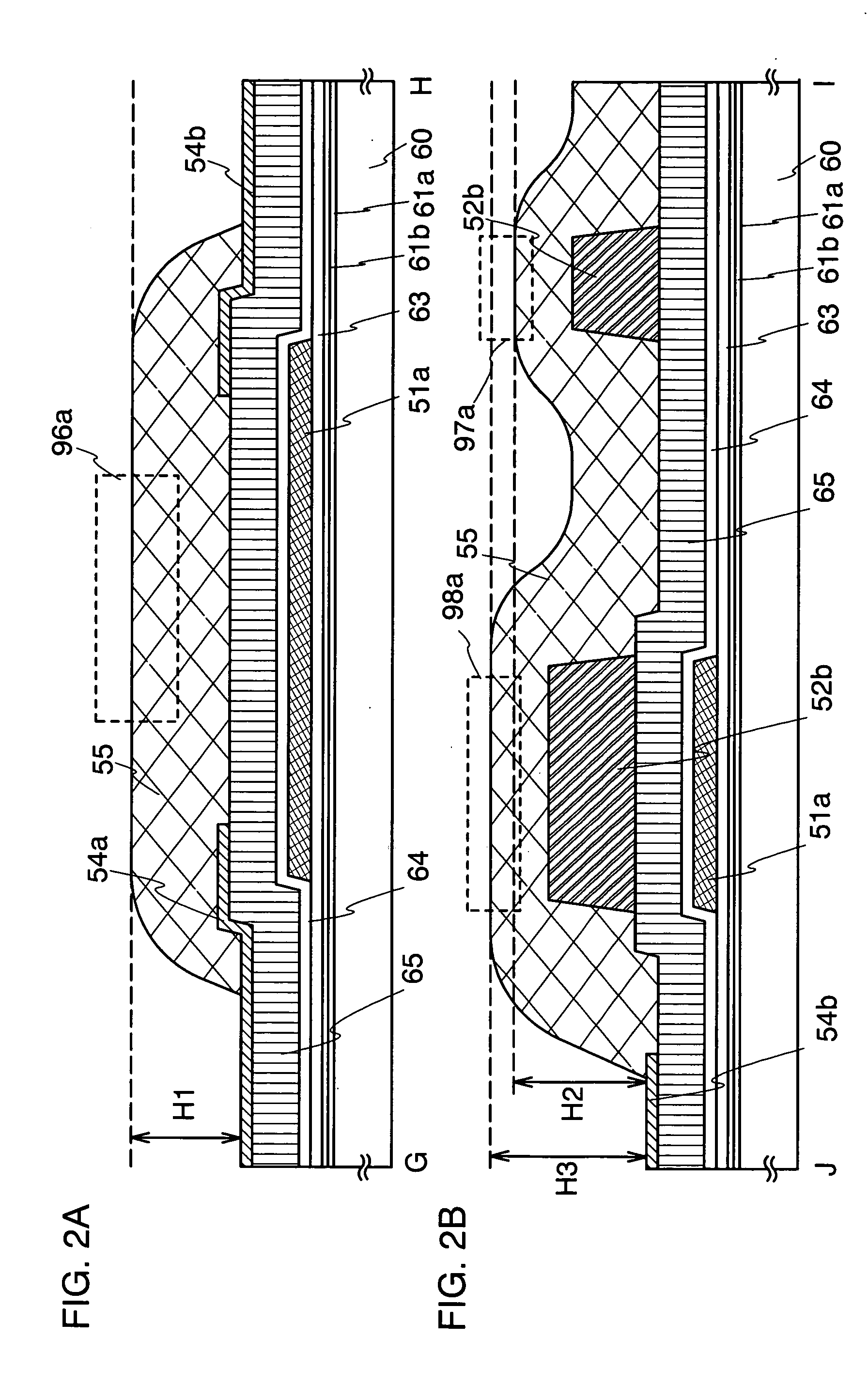

Display device

InactiveUS20060081844A1Avoid damageAvoid deformationElectroluminescent light sourcesSolid-state devicesImaging qualityDisplay device

The invention provides a technique to manufacture a display device with high image quality and reliability at low cost with high yield. According to the invention, a spacer is provided over a pixel electrode layer in a pixel region. Moreover, a surface of an insulating layer which functions as a partition which covers the periphery of the pixel electrode layer is formed at a high position from the surface of the pixel electrode due to stacked layers under the insulating layer. These spacer and insulator which function as a spacer support a mask used for selectively forming a light emitting material over a pixel electrode layer, thereby preventing the mask from contacting the pixel electrode layer due to a twist and deflection of the mask. Accordingly, such a damage as a crack does not occur in the pixel electrode layer which results in having no defect in shape. Therefore, a display device which performs a high resolution display with high reliability can be manufactured.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor element

ActiveUS20070023777A1High luminous intensityExtended service lifeSolid-state devicesSemiconductor devicesAlloyNitride semiconductors

It is an object of the present invention to provide a highly reliable and high-quality semiconductor element by effectively preventing the migration of silver to a nitride semiconductor when an electrode main entirely or mostly of silver having high reflection efficiency is formed in contact with a nitride semiconductor layer. A semiconductor element comprises a nitride semiconductor layer, an electrode connected to said nitride semiconductor layer, and an insulating film covering at least part of said electrode, wherein the electrode comprises: a first metal film including silver or a silver alloy and in contact with the nitride semiconductor layer; and a second metal film completely covering the first metal film, and the insulating film comprises a nitride film.

Owner:NICHIA CORP

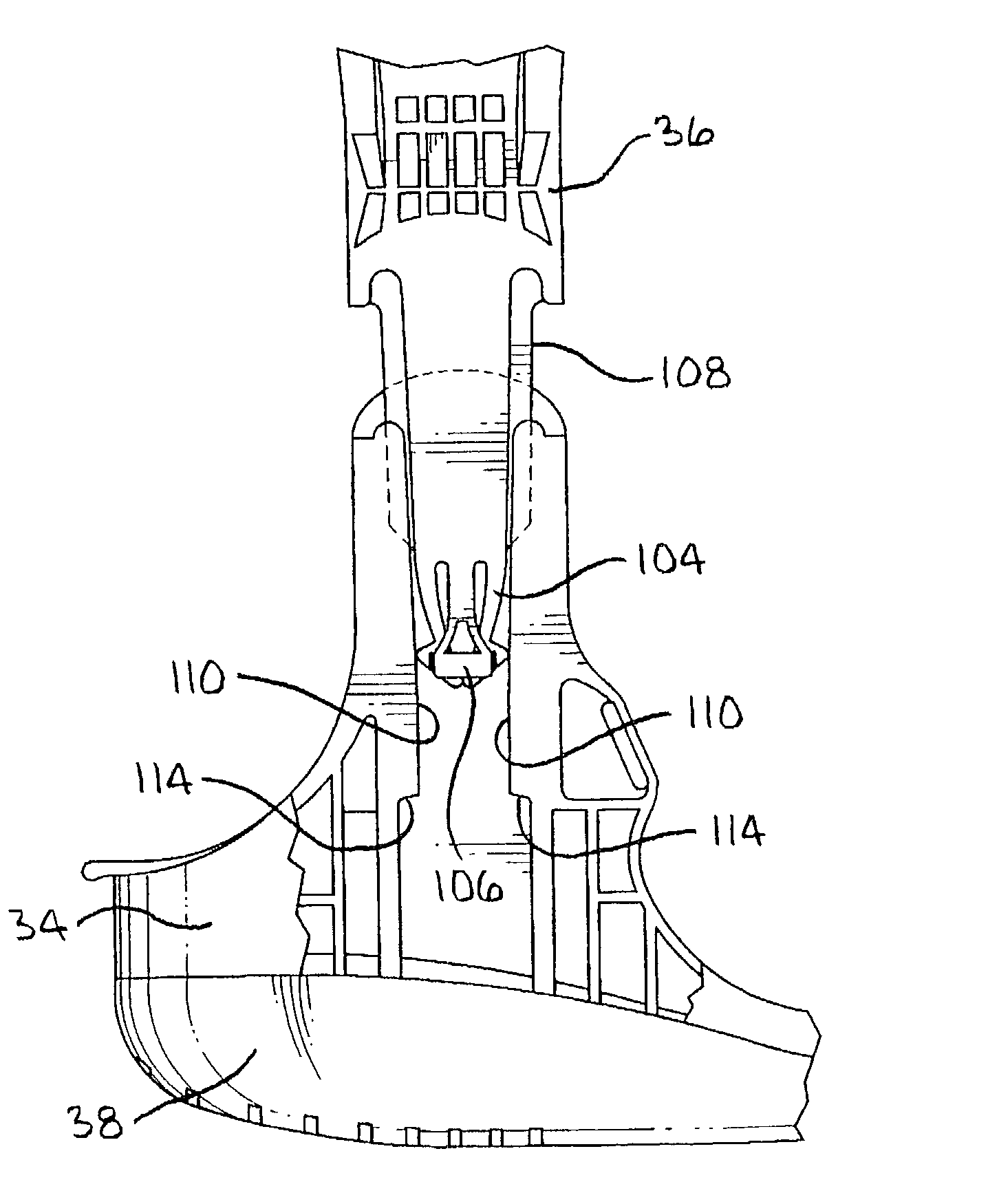

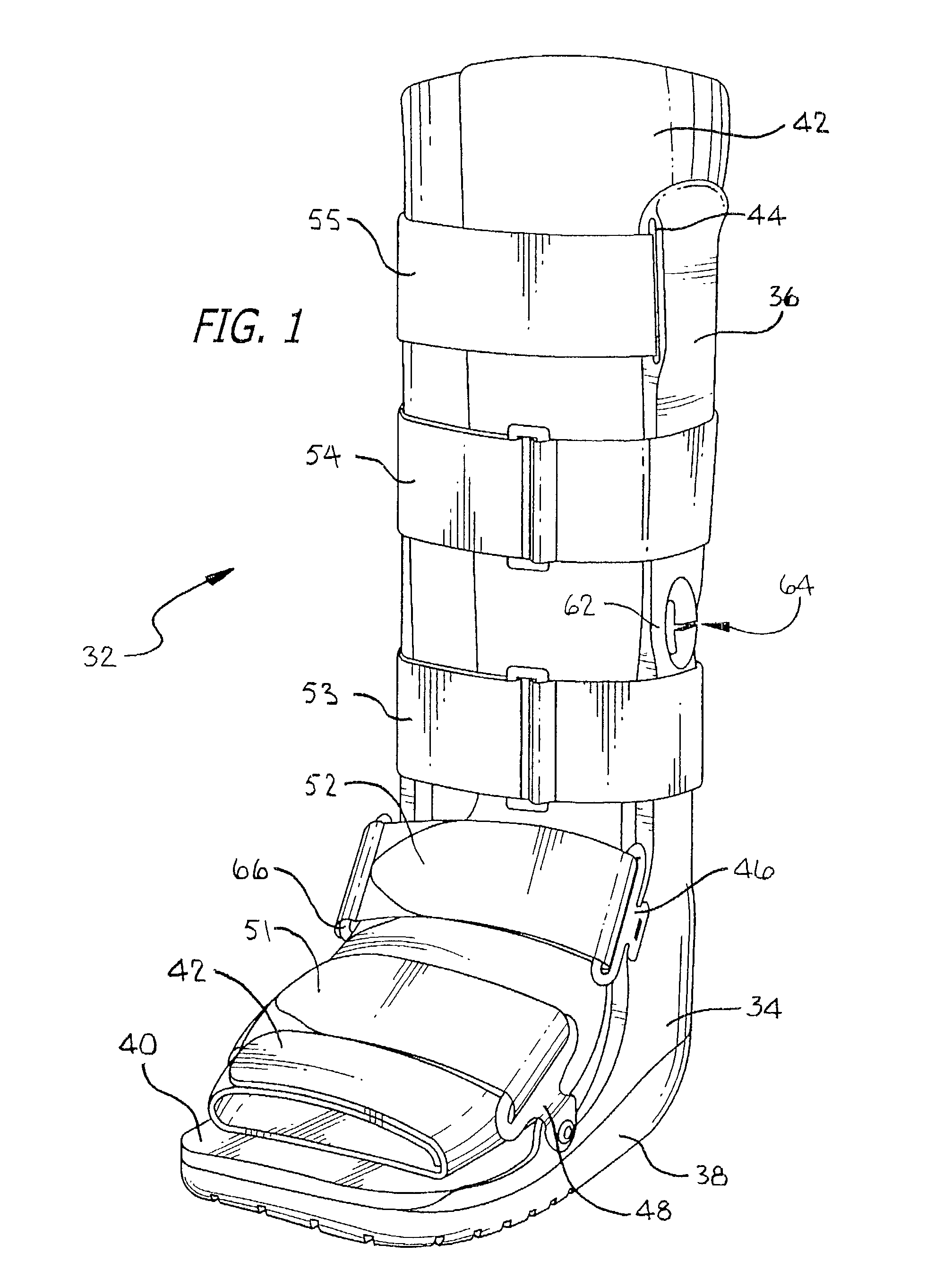

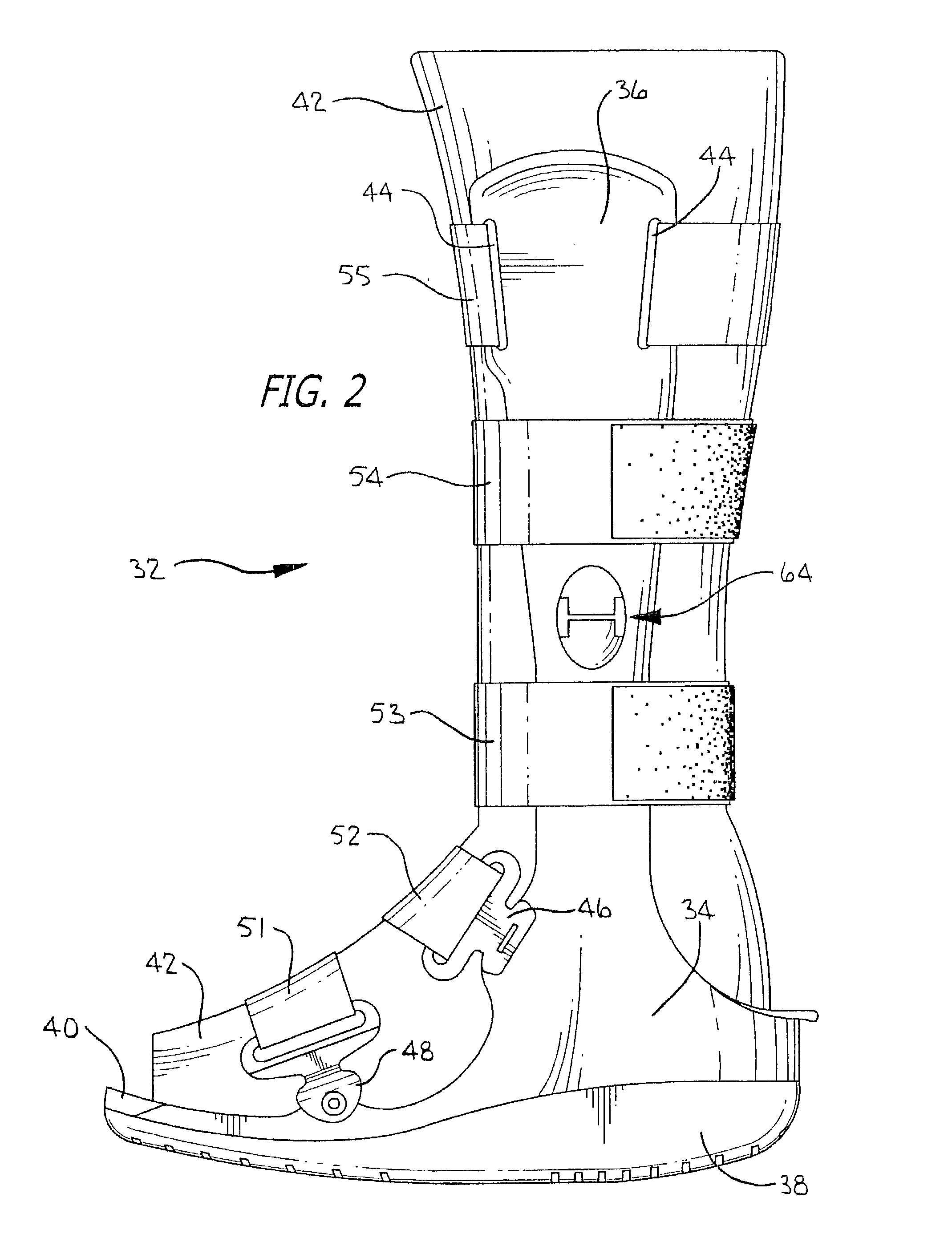

Versatile orthopaedic leg mounted walkers

ActiveUS7303538B2Cost reductionIncreased surface contact and grip actionWalking aidsNon-surgical orthopedic devicesPlastic surgeryMechanical engineering

A versatile orthopedic walker includes a high strength engineered plastic base with spaced upper and lower surfaces and upwardly extending slotted strut supports. The base may be laterally and vertically cored, and an outer sole is provided which extends upward over the core openings, with the upper edges of the outsole being ridged to fit into a peripheral groove in the base to provide a smooth exterior surface. Struts of different lengths are provided, and all of the struts have identical arrangements for interlocking with the base. All of the struts may be provided with a three pronged construction to triply lock the struts into the base. The struts may have areas of reduced cross-section providing pivot points or areas of flexibility to accommodate different size patients, and limiting stops may be provided to assure adequate orthopedic support. Fully integrally molded pivoting D-rings may hold walker straps in place.

Owner:OSSUR HF

Electroluminescent device

ActiveUS20060049745A1Avoid layeringAvoid light decayDischarge tube luminescnet screensElectroluminescent light sourcesDark spotLight scattering

The electroluminescent device successively comprises a cathode, an electroluminescent layer, a transparent electrode layer, an evanescent light-scattering layer comprising a matrix composed of a low-refractive material containing light-scattering particles, and a transparent sheet / plate. Such an electroluminescent device is decreased in total reflection not only at a boundary surface between a transparent substrate and an outside air layer but also at a boundary surface of the transparent electrode layer on its light extraction side, and therefore, is considerably improved in light extraction efficiency. In addition, in the electroluminescent device provided with a barrier layer, the transparent electrode layer and the electroluminescent layer can be well protected so that deterioration of electroluminescent pigments and occurrence of dark spots can be effectively prevented, resulting in enhanced life of the device.

Owner:MITSUBISHI CHEM CORP

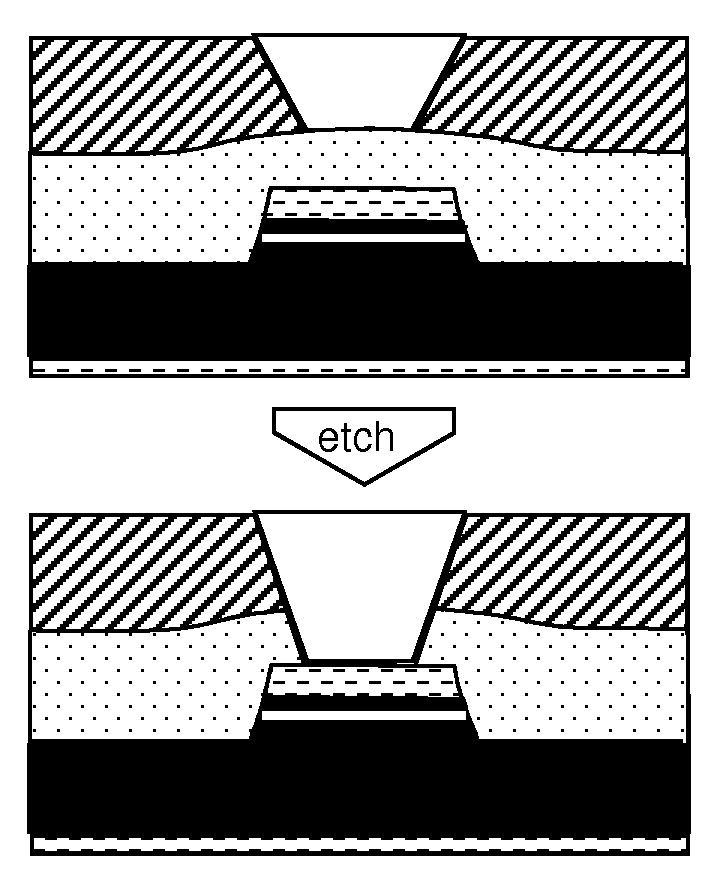

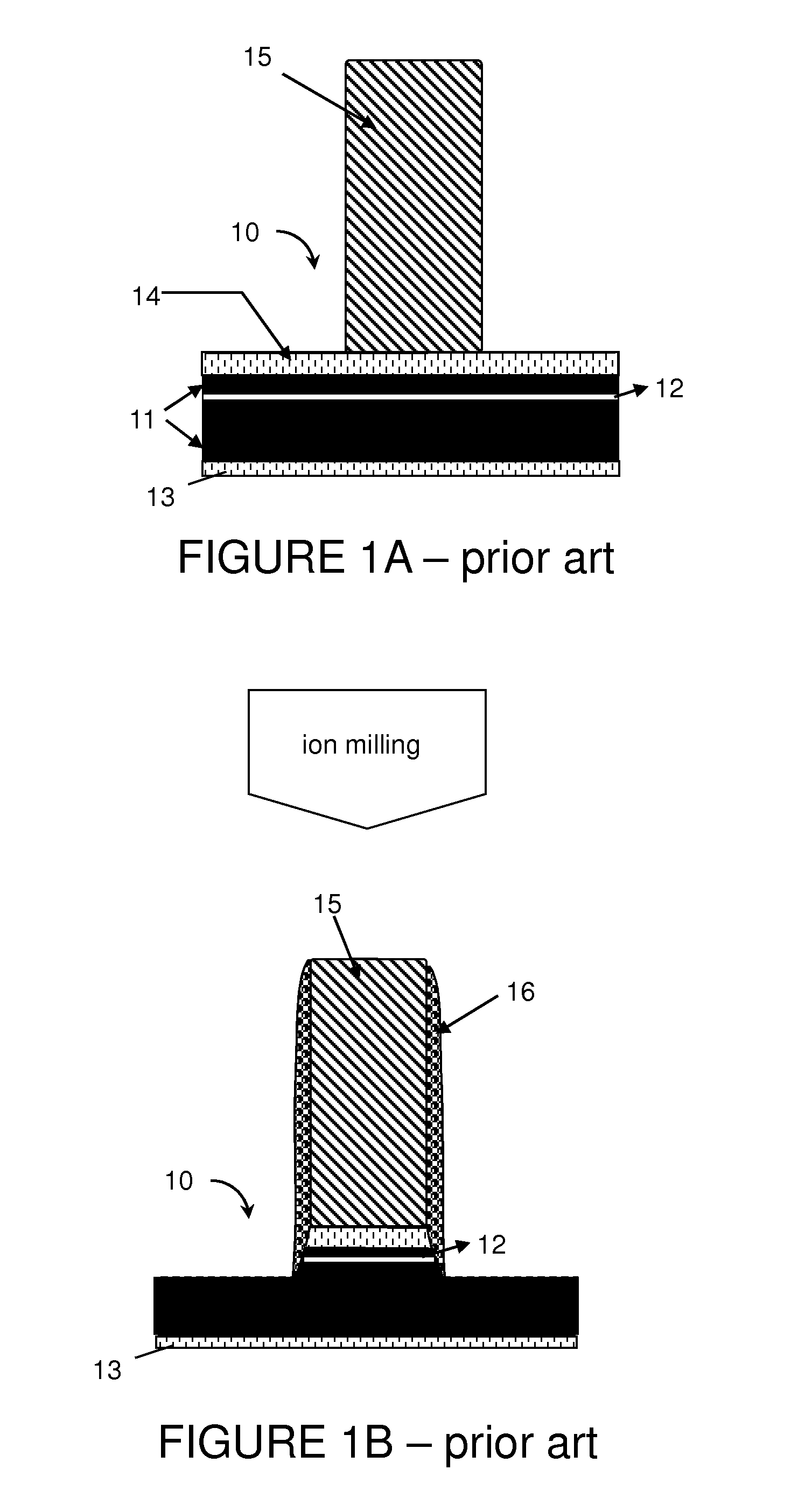

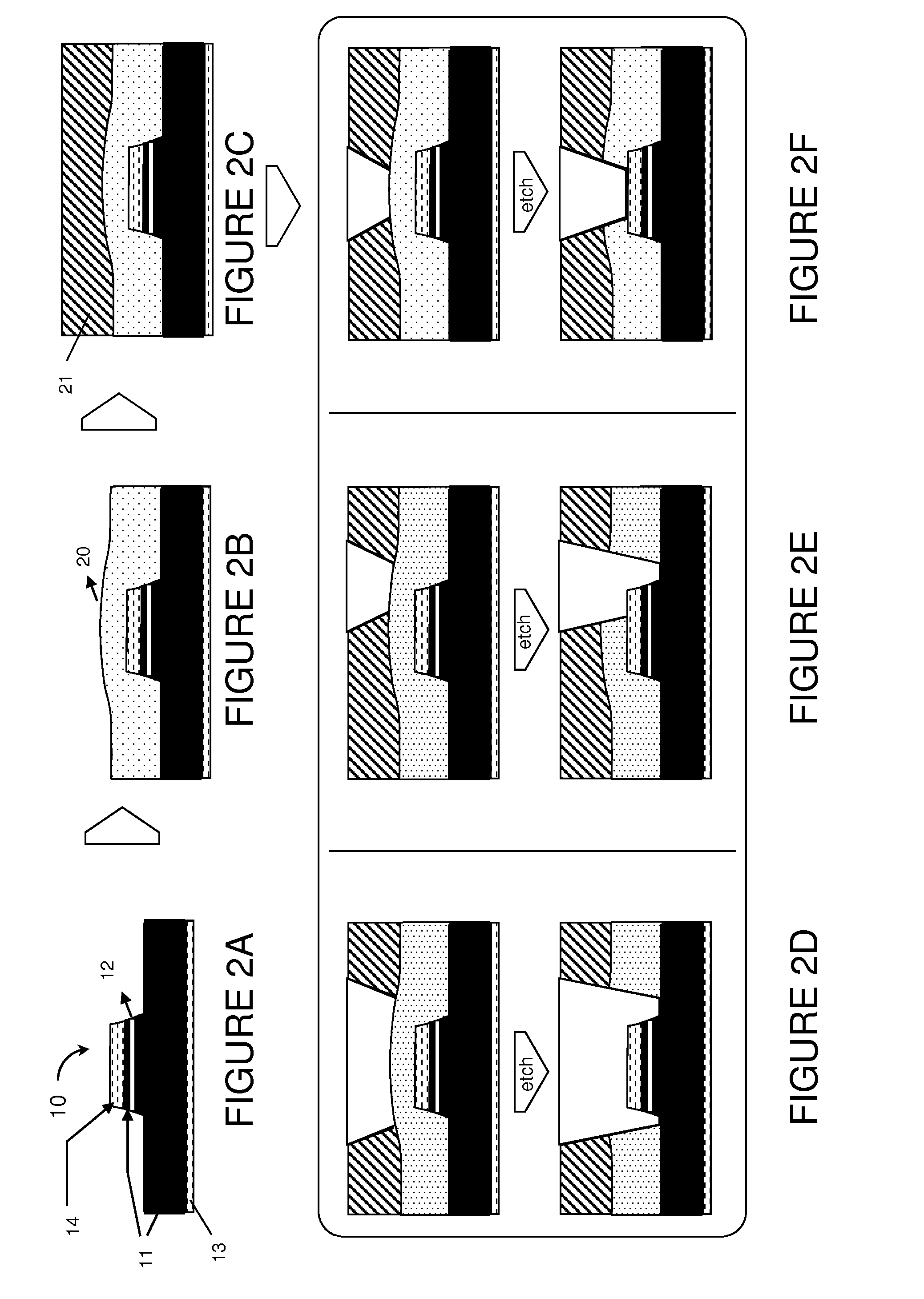

Patterning of and contacting magnetic layers

InactiveUS20120052258A1Reduce impactEasy to controlDecorative surface effectsLayered productsMagnetic layerElectrical and Electronics engineering

A method according to embodiments of the present invention comprises providing a magnetic stack comprising a magnetic layer sub-stack comprising magnetic layers and a bottom conductive electrode and a top conductive electrode electrically connecting the magnetic layer sub-stack at opposite sides thereof; providing a sacrificial pillar on top of the magnetic stack, the sacrificial pillar having an undercut with respect to an overlying second sacrificial material and a sloped foot with increasing cross-sectional dimension towards the magnetic stack, using the sacrificial pillar for patterning the magnetic stack, depositing an insulating layer around the sacrificial pillar, selectively removing the sacrificial pillar, thus creating a contact hole towards the patterned magnetic stack, and filling the contact hole with electrically conductive material.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW) +1

Lighting device

ActiveUS20070058357A1Avoid layeringPlanar light sourcesPoint-like light sourceEffect lightLength wave

A lighting device having: a light-emitting diode lamp having a light-emitting diode device sealed by a glass sealing part; and a fluorescent layer disposed on the side of an illuminated object of the light-emitting diode lamp. The fluorescent layer is operable to radiate a wavelength-converted light by being excited by light emitted from the light-emitting diode device.

Owner:TOYODA GOSEI CO LTD

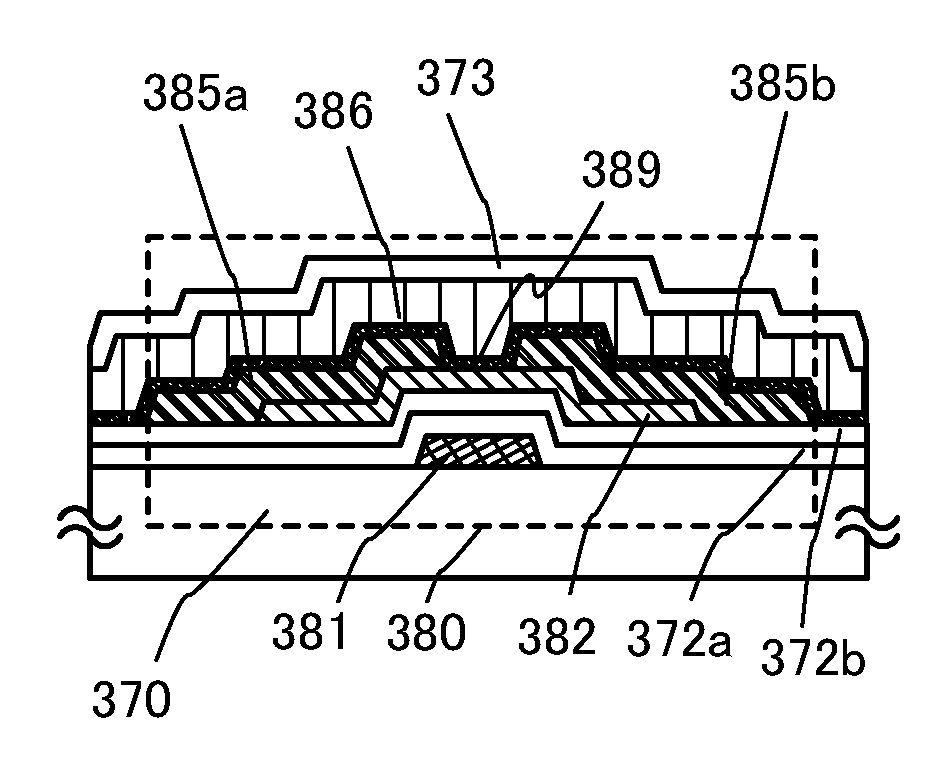

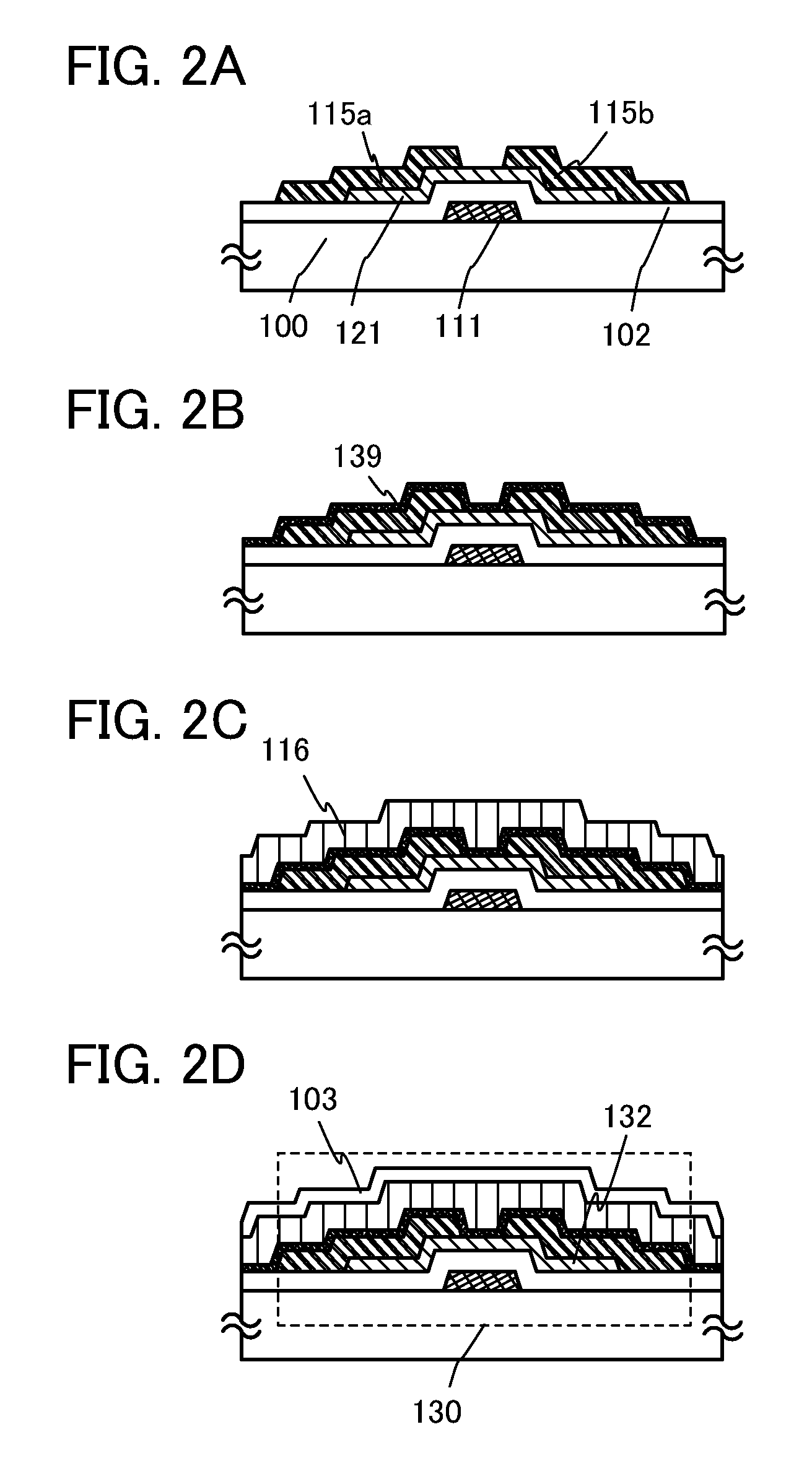

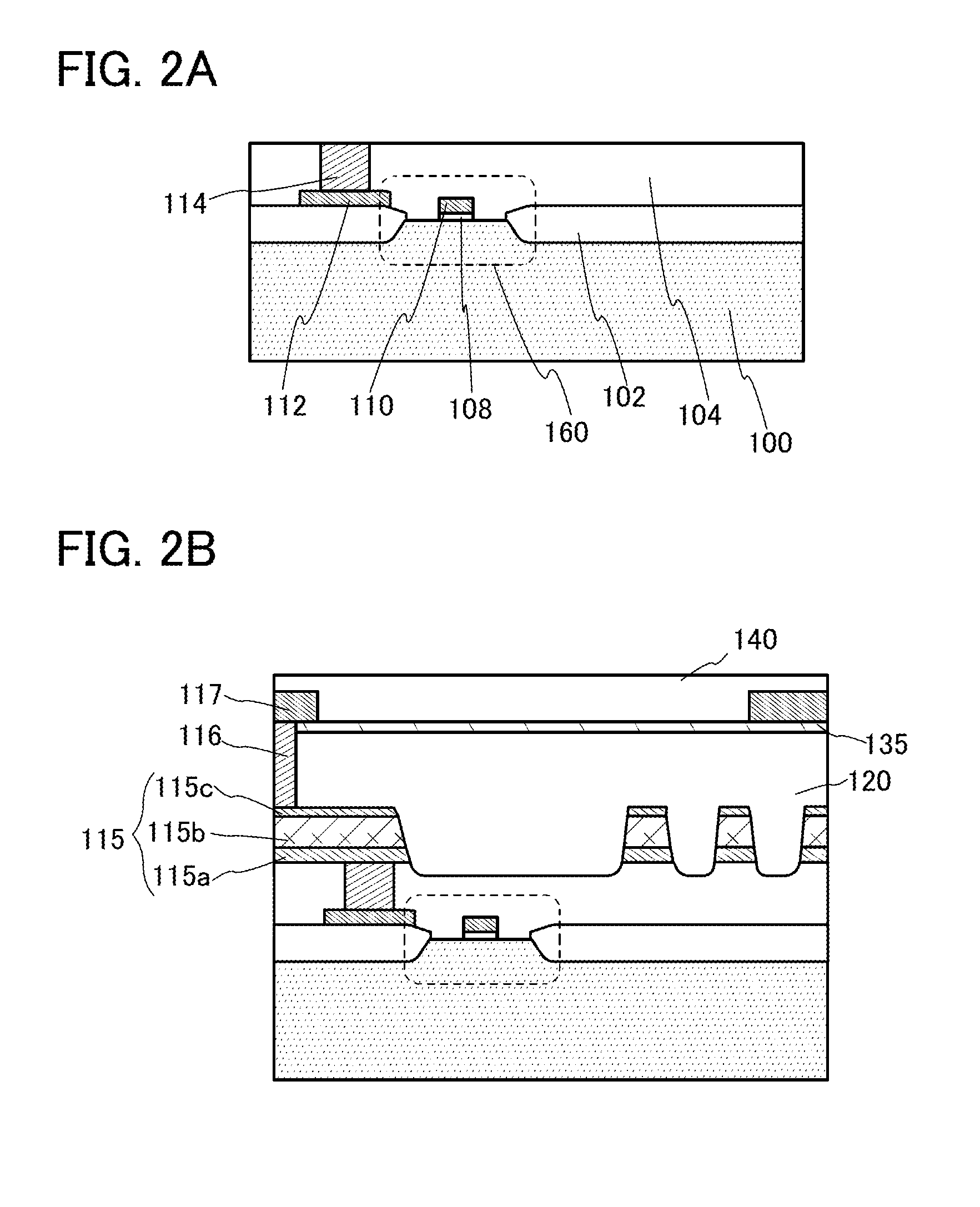

Semiconductor device and method for fabricating the same

ActiveUS20140042433A1Stable electrical characteristicsImprove reliabilityTransistorIndiumCrystal structure

To provide a highly reliable semiconductor device exhibiting stable electrical characteristics. To fabricate a highly reliable semiconductor device. Included are an oxide semiconductor stack in which a first oxide semiconductor layer, a second oxide semiconductor layer, and a third oxide semiconductor layer are stacked, a source and a drain electrode layers contacting the oxide semiconductor stack, a gate electrode layer overlapping with the oxide semiconductor layer with a gate insulating layer provided therebetween, and a first and a second oxide insulating layers between which the oxide semiconductor stack is sandwiched. The first to the third oxide semiconductor layers each contain indium, gallium, and zinc. The proportion of indium in the second oxide semiconductor layer is higher than that in each of the first and the third oxide semiconductor layers. The first oxide semiconductor layer is amorphous. The second and the third oxide semiconductor layers each have a crystalline structure.

Owner:SEMICON ENERGY LAB CO LTD

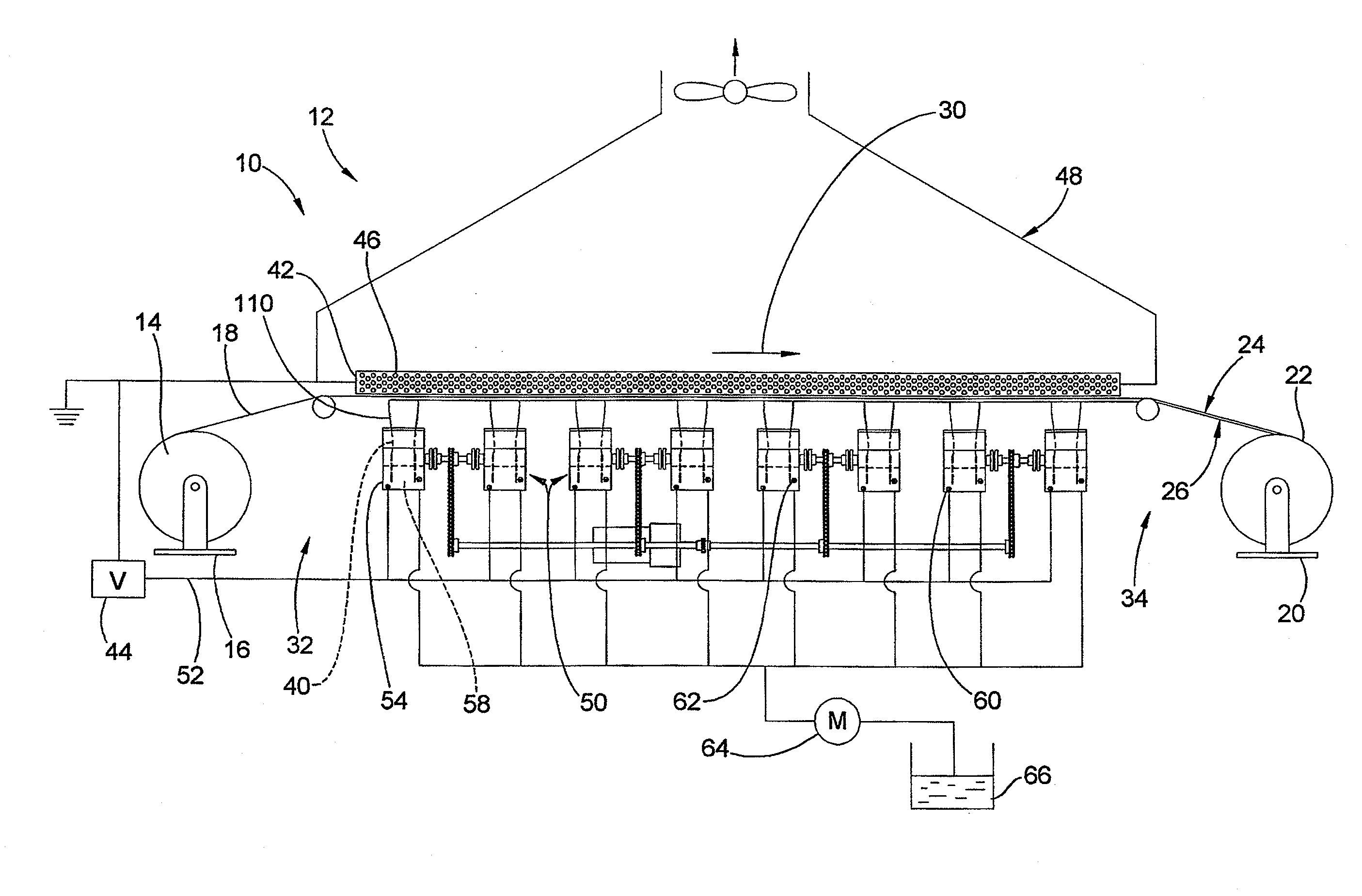

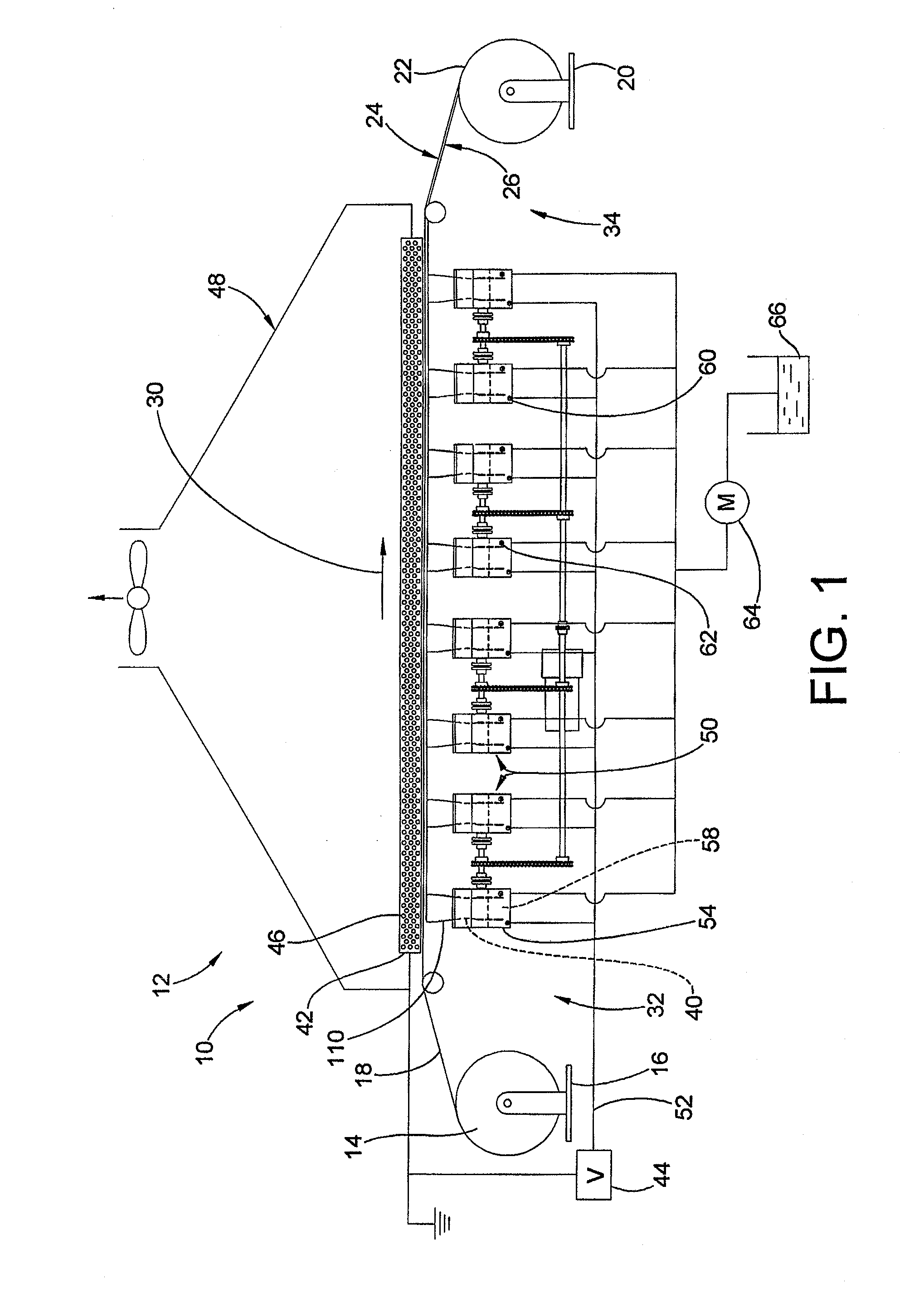

Filtration Medias, Fine Fibers Under 100 Nanometers, and Methods

InactiveUS20090199717A1Avoid layeringMaterial nanotechnologyIsotope separationAcetic acidElectrospinning

An electrospinning fine fiber production methodology for generating a significant amount of fibers with diameters of less than 100 nanometers is provided. Also, a filter media composite comprising a substrate layer and an electrospun fine fiber layer having a increased efficiency relative to pressure drop and / or a controlled pore size distribution is provided. According to some embodiments nylon is electrospun from a solvent combination of formic and acetic acids.

Owner:ELMARCO SRO

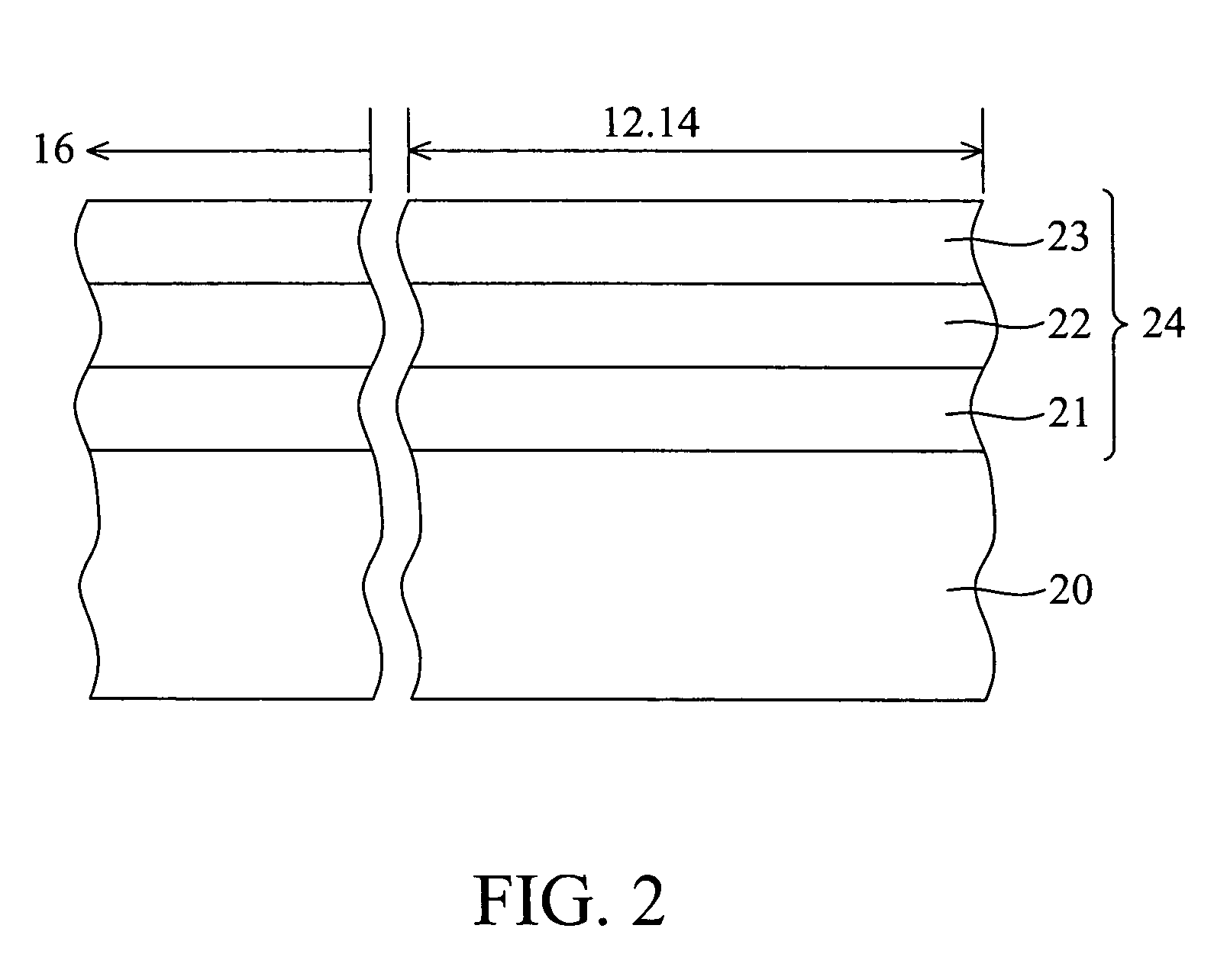

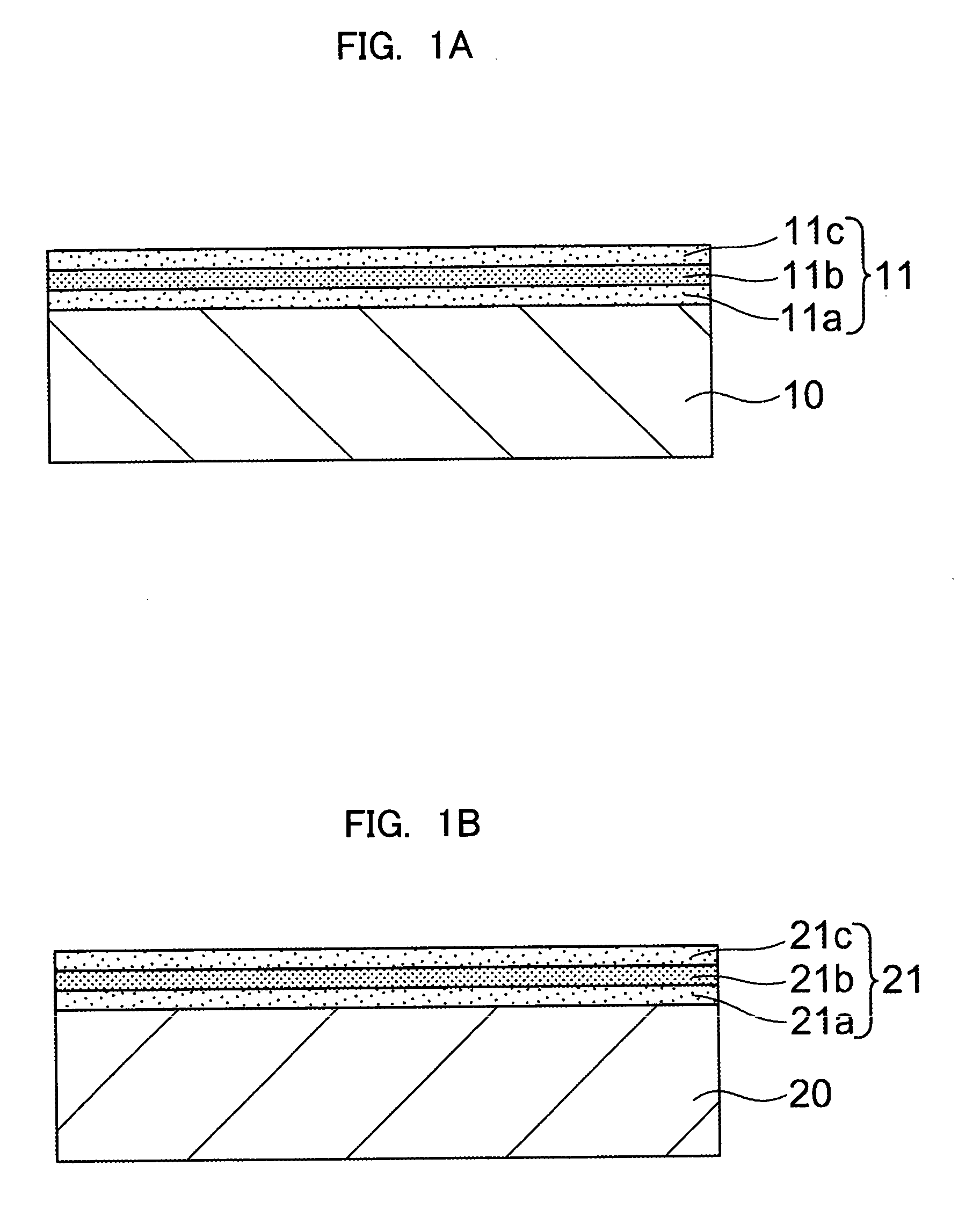

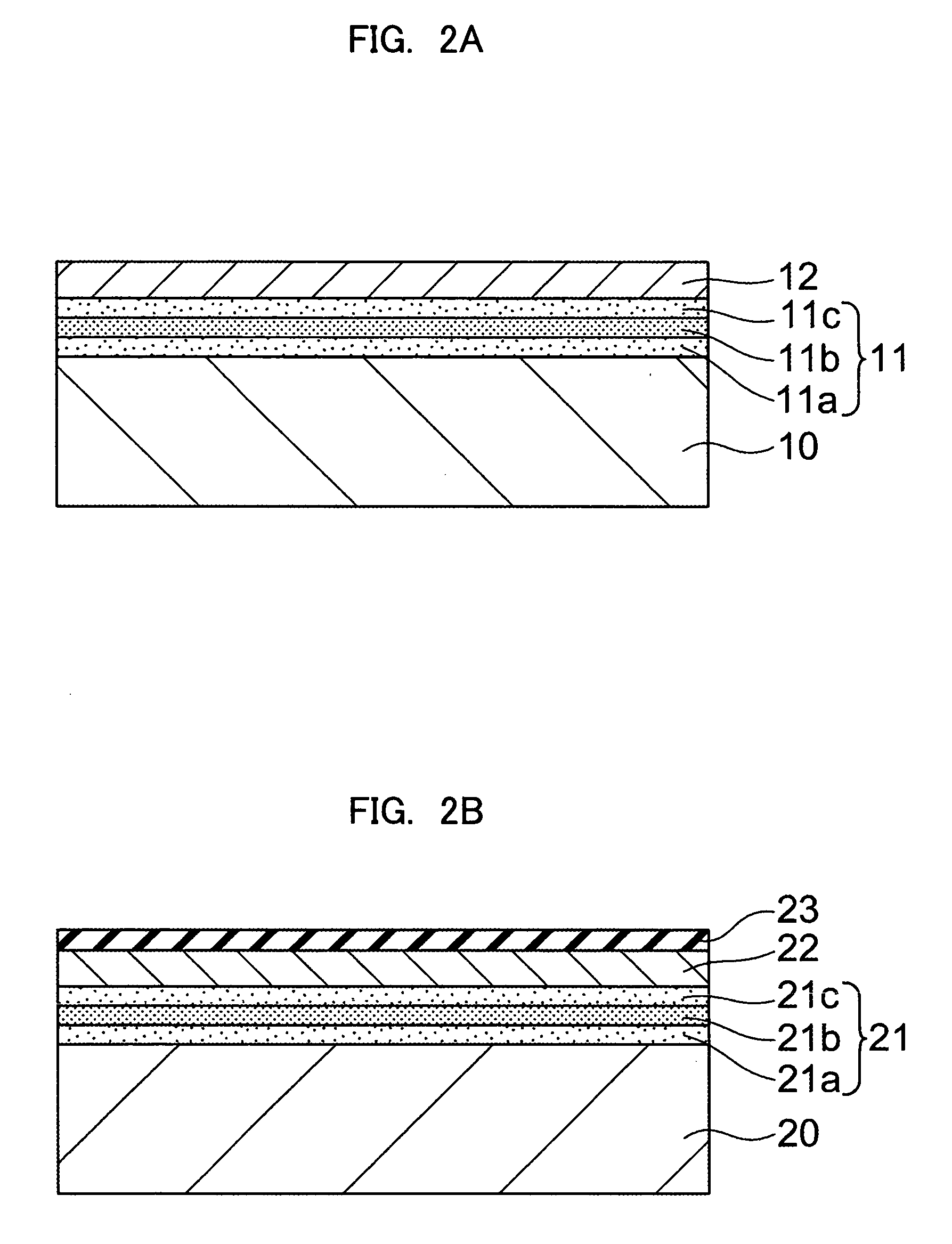

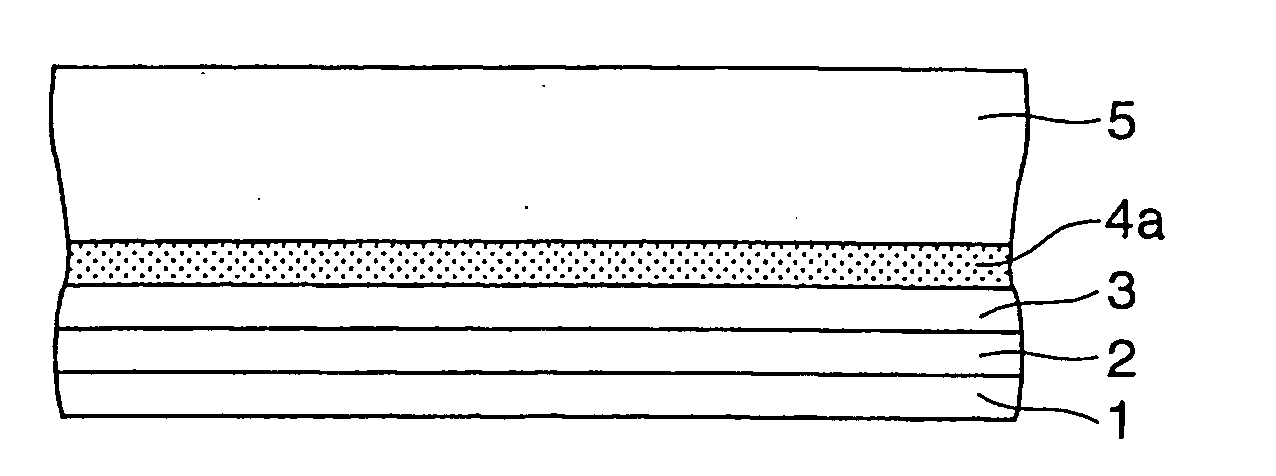

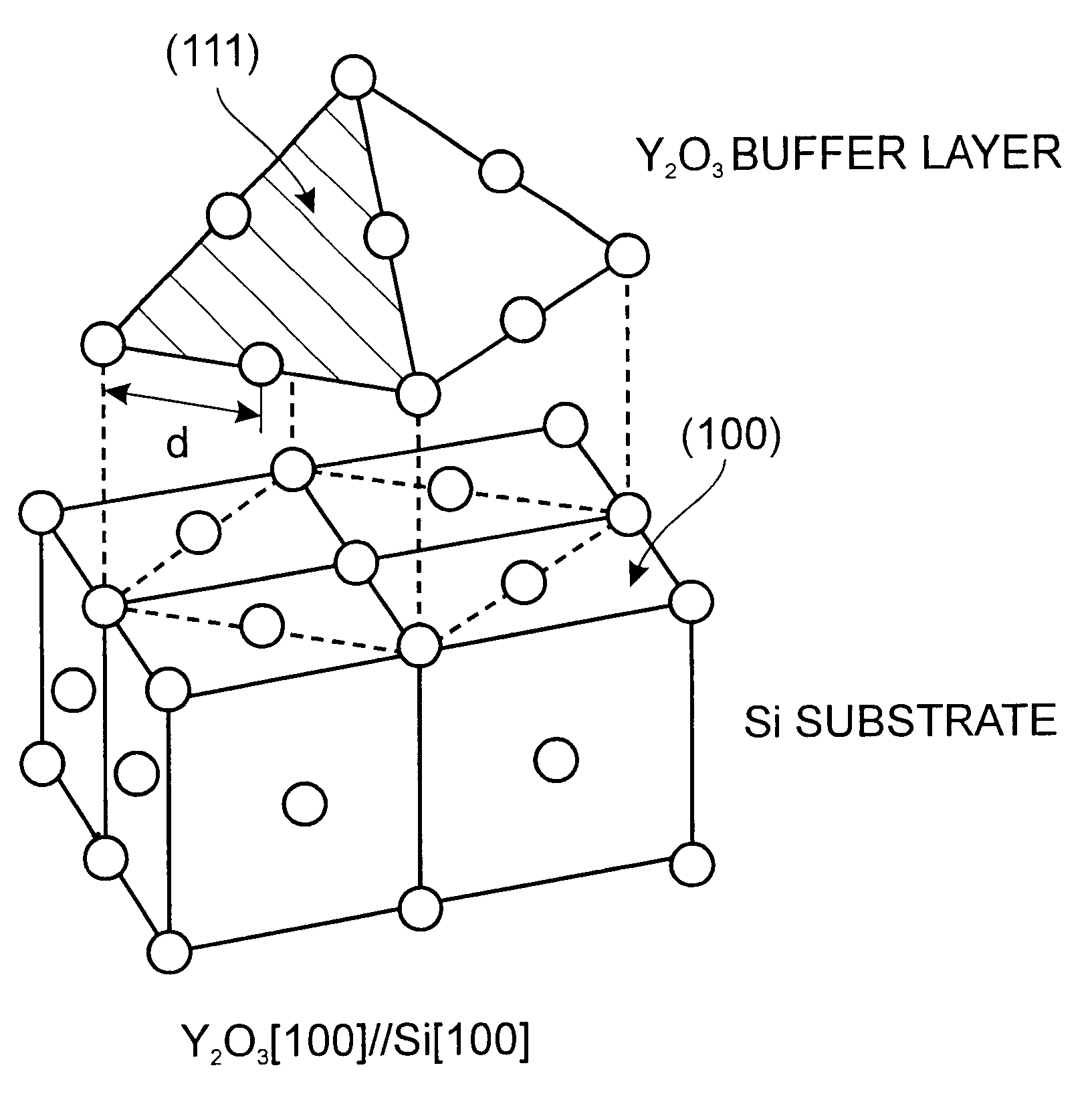

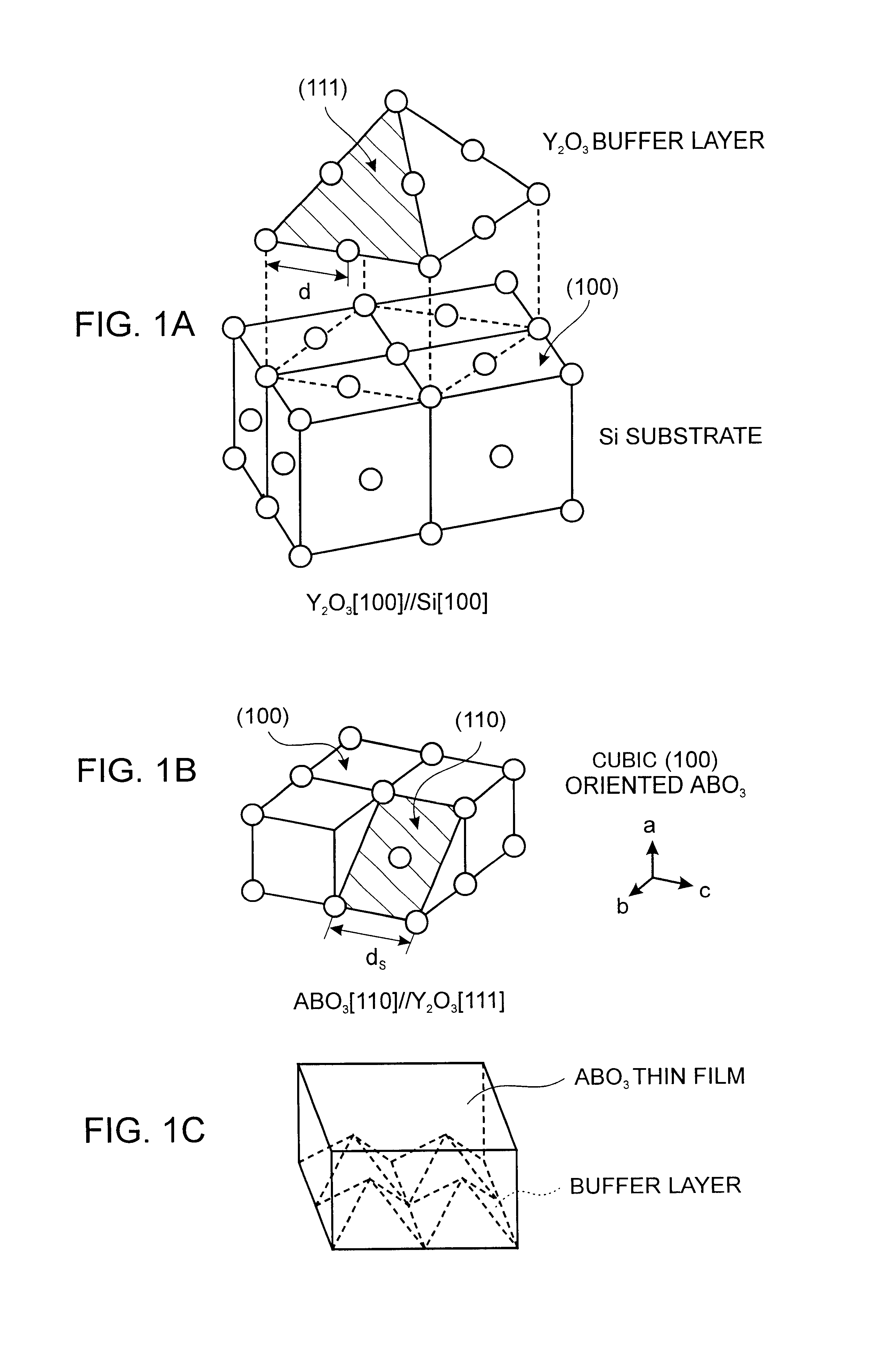

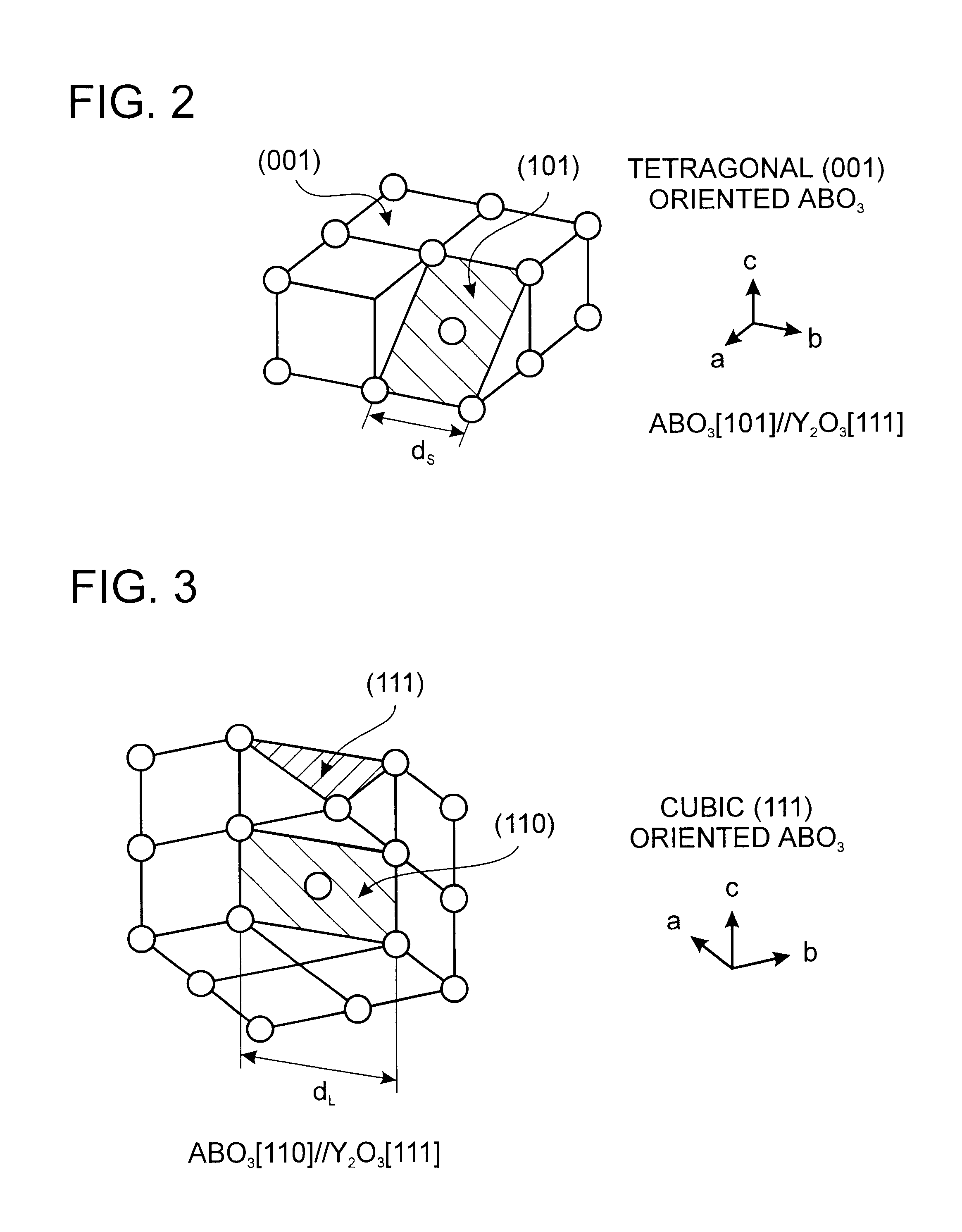

Multilayer thin film

InactiveUS6258459B1High crystallinityIncrease the buffer functionSemiconductor/solid-state device detailsSolid-state devicesCrystallinityMaterials science

The first object of the invention is to provide means that enables a perovskite oxide thin film having (100) orientation, (001) orientation or (111) orientation to be easily obtained, and the second object of the invention is to provide a multilayer thin film comprising a unidirectionally oriented metal thin film of good crystallinity. The multilayer thin film according to the first embodiment of the invention comprises a buffer layer and a perovskite oxide thin film present thereon. The interface between the buffer layer and the perovskite oxide thin film is made up of a {111} facet plane. Substantially parallel to the facet plane there is present a {110} face of a cubic, rhombohedral, tetragonal or orthorhombic crystal of the perovskite oxide thin film, a {101} face of the tetragonal or orthorhombic crystal or a {011} face of the orthorhombic crystal. The multilayer thin film according to the second embodiment of the invention comprises a metal thin film that is a cubic (100) unidirectionally oriented epitaxial film, and a buffer layer where a {111} facet plane is present on the interface of the buffer layer in contact with the metal thin film.

Owner:SNAPTRACK

Thin-film deposition apparatus

ActiveUS7273526B2Avoid reactionPurge very quicklySemiconductor/solid-state device manufacturingChemical vapor deposition coatingSusceptorEngineering

Owner:ASM JAPAN

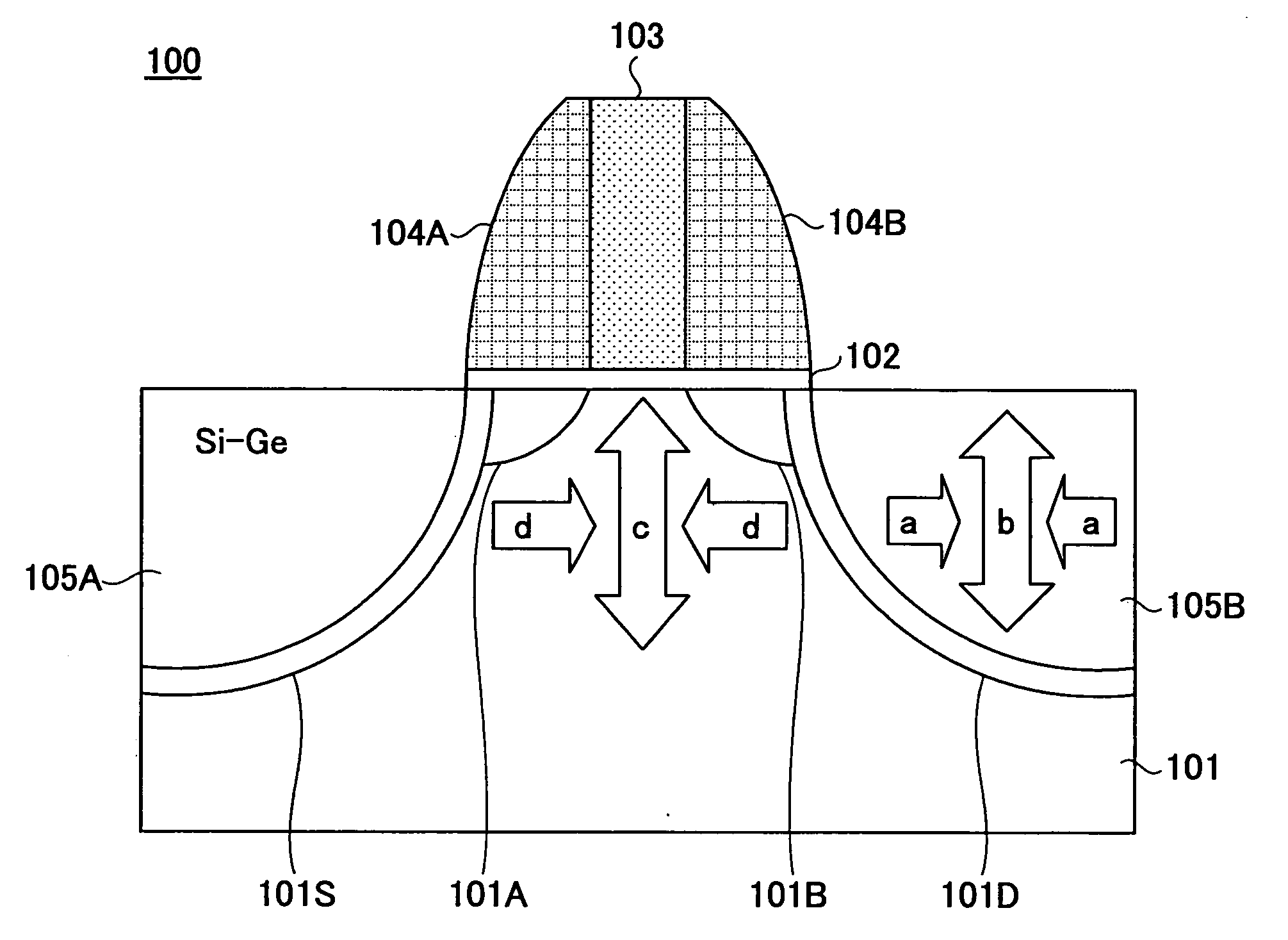

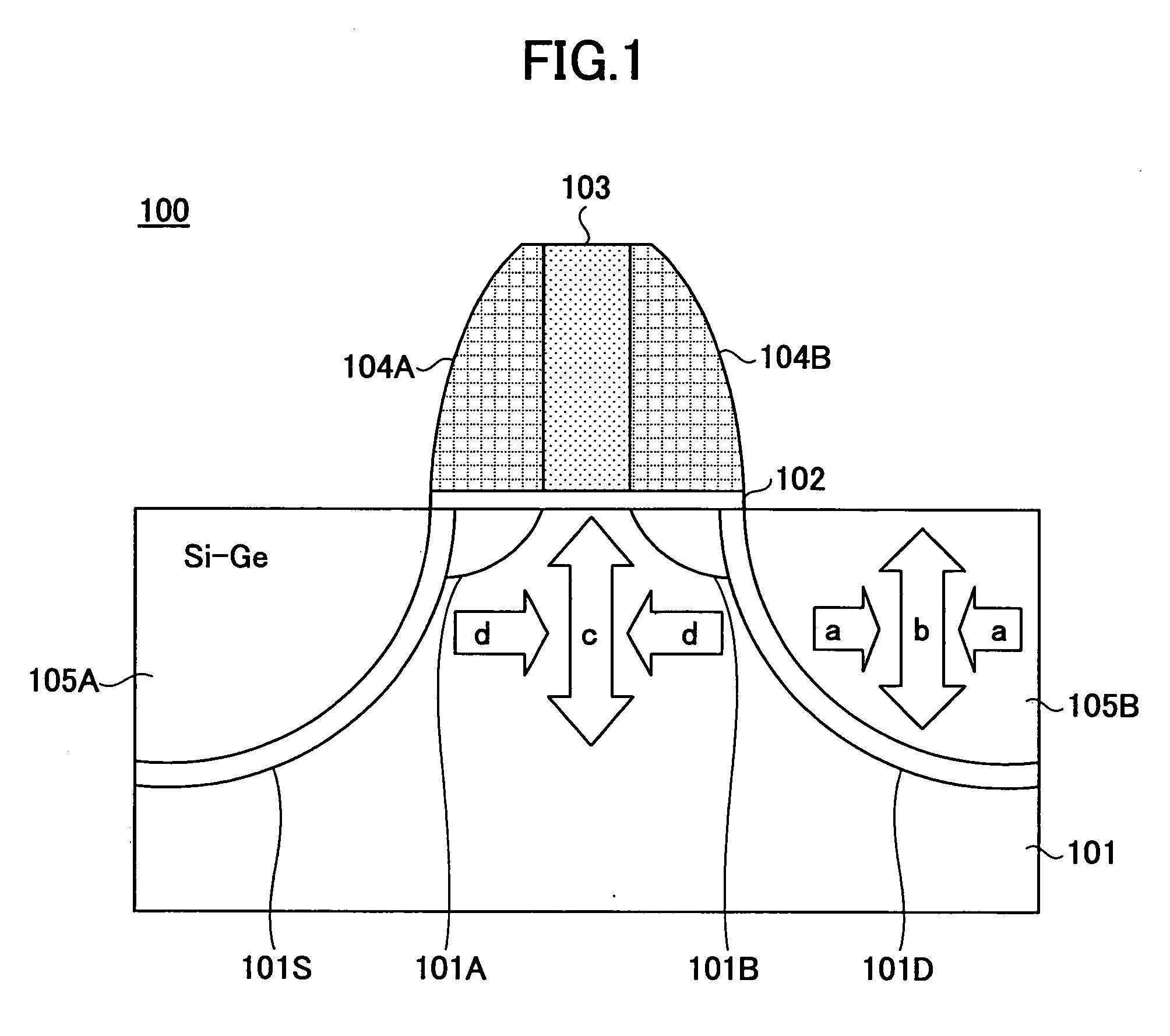

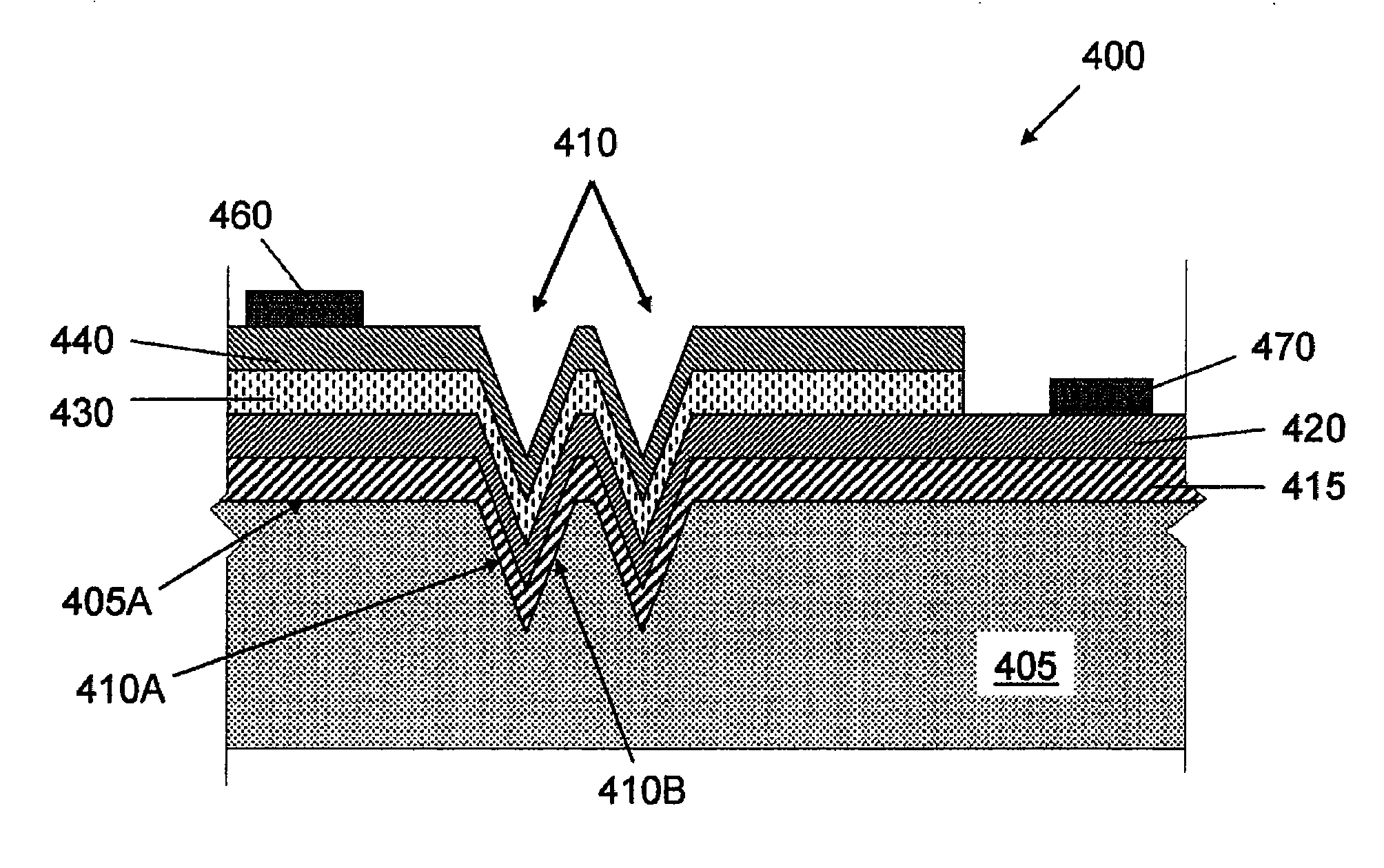

Semiconductor device and production method thereof

ActiveUS20060289856A1Suppression of short channel effectsHigh carrier mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesShort-channel effectEngineering

A method of fabricating a semiconductor device is disclosed that is able to suppress a short channel effect and improve carrier mobility. In the method, trenches are formed in a silicon substrate corresponding to a source region and a drain region. When epitaxially growing p-type semiconductor mixed crystal layers to fill up the trenches, the surfaces of the trenches are demarcated by facets, and extended portions of the semiconductor mixed crystal layers are formed between bottom surfaces of second side wall insulating films and a surface of the silicon substrate, and extended portion are in contact with a source extension region and a drain extension region.

Owner:FUJITSU SEMICON LTD

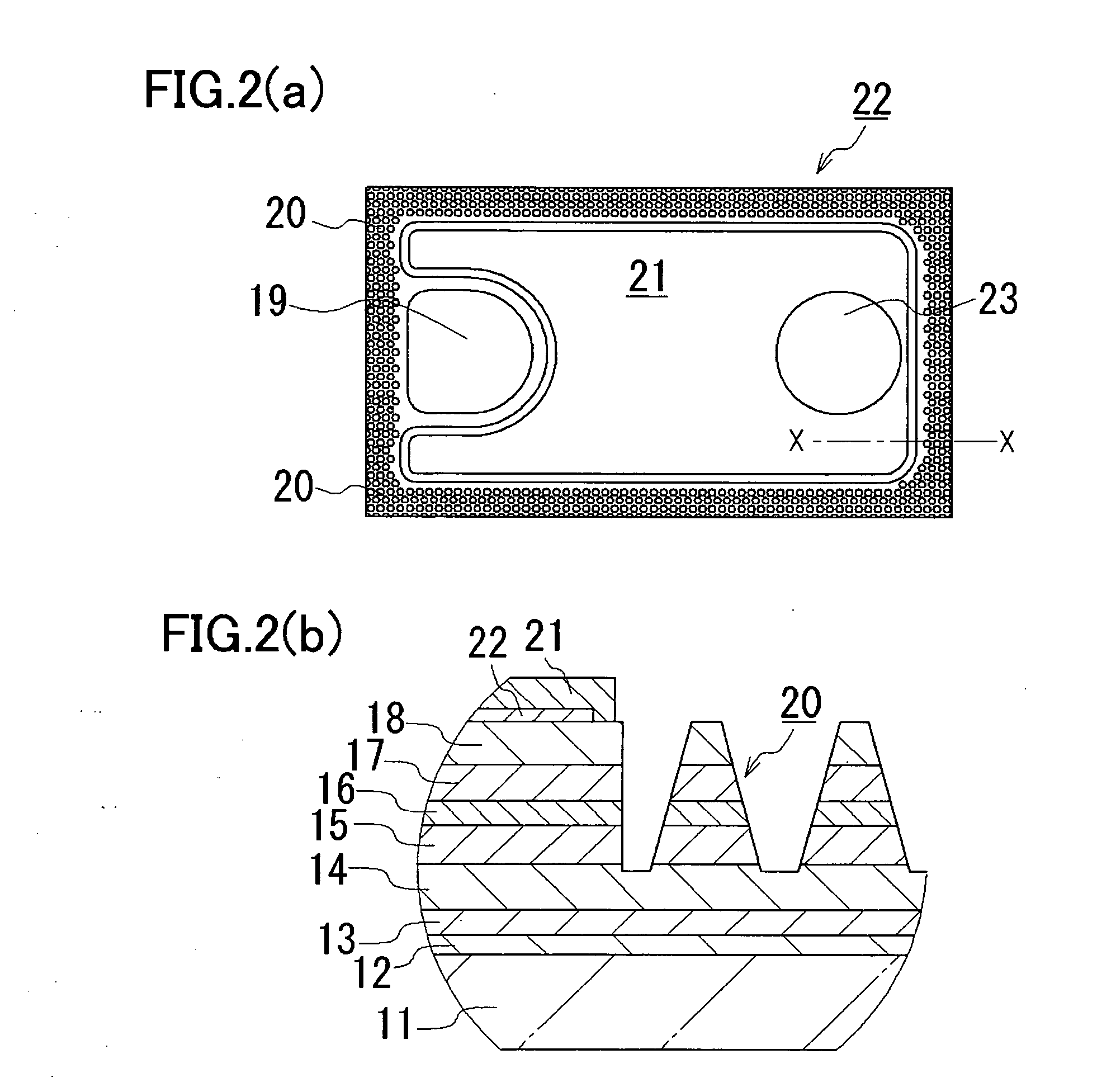

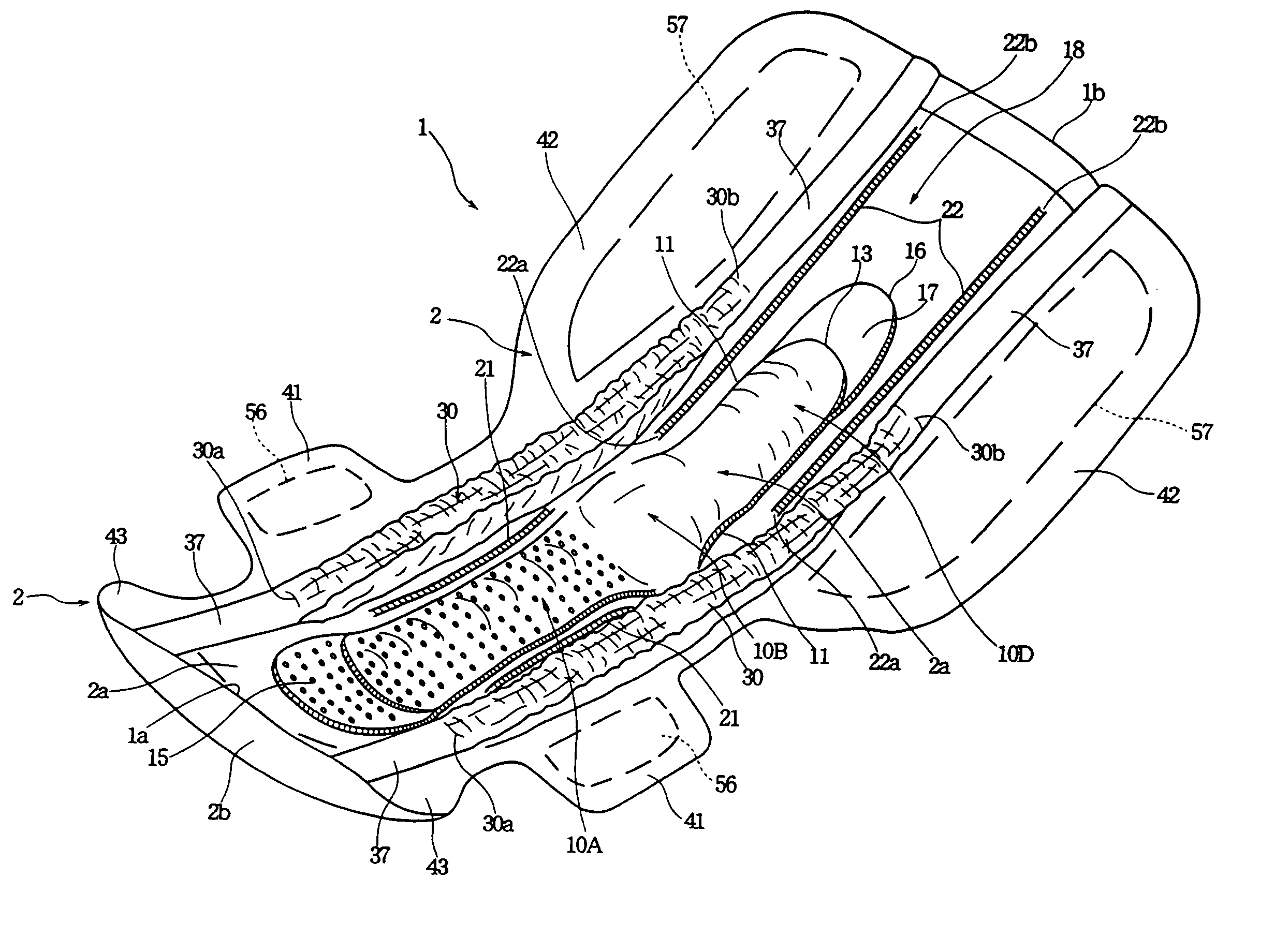

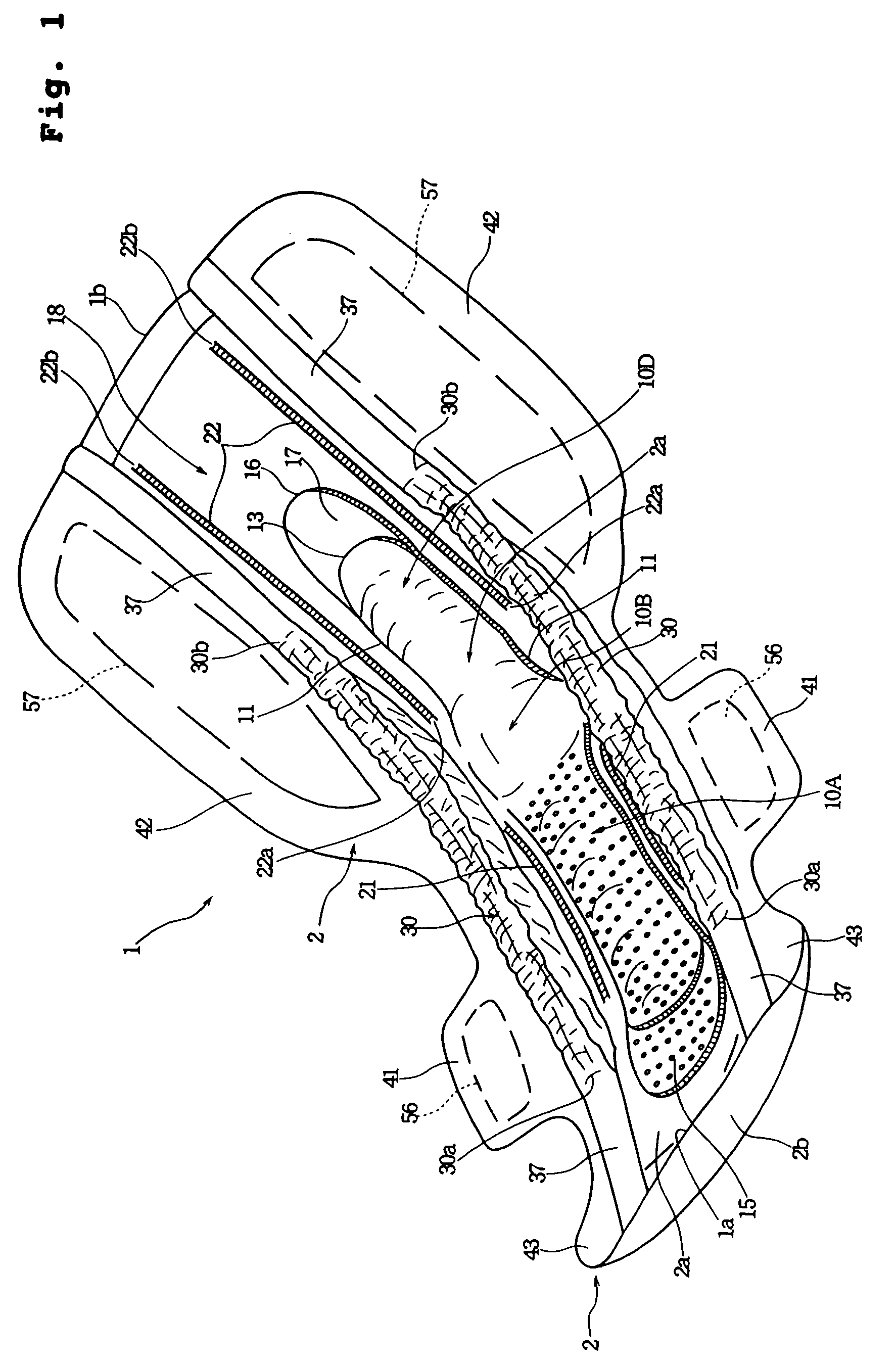

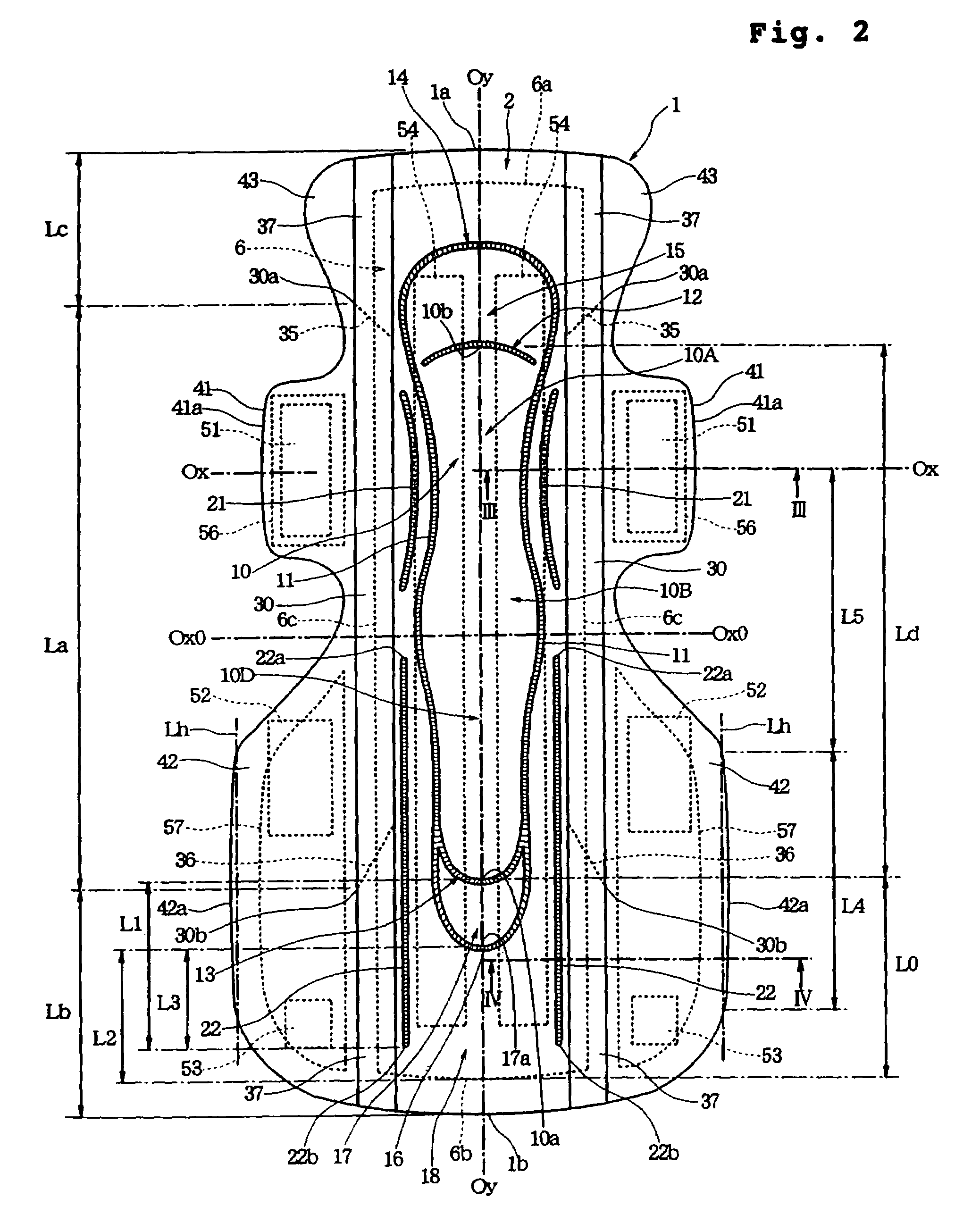

Sanitary napkin with compressed grooves

A sanitary napkin in which diffusing liquid hardly reaches a rear end edge is adapted to make a liquid absorbent layer less deformable in a rear region so that it can easily be kept in close contact with the wearer's buttocks. The sanitary napkin has an elongated main absorbent region surrounded by compressed grooves that are formed in a skin-side surface. Since a rear end of the main absorbent region is far away from a rear end edge of the napkin to provide a relatively large rear region, worries about rearward leakage may be relieved. Furthermore, since auxiliary longitudinal grooves are provided in the rear region, a liquid absorbent layer may hardly be twisted.

Owner:UNI CHARM CORP

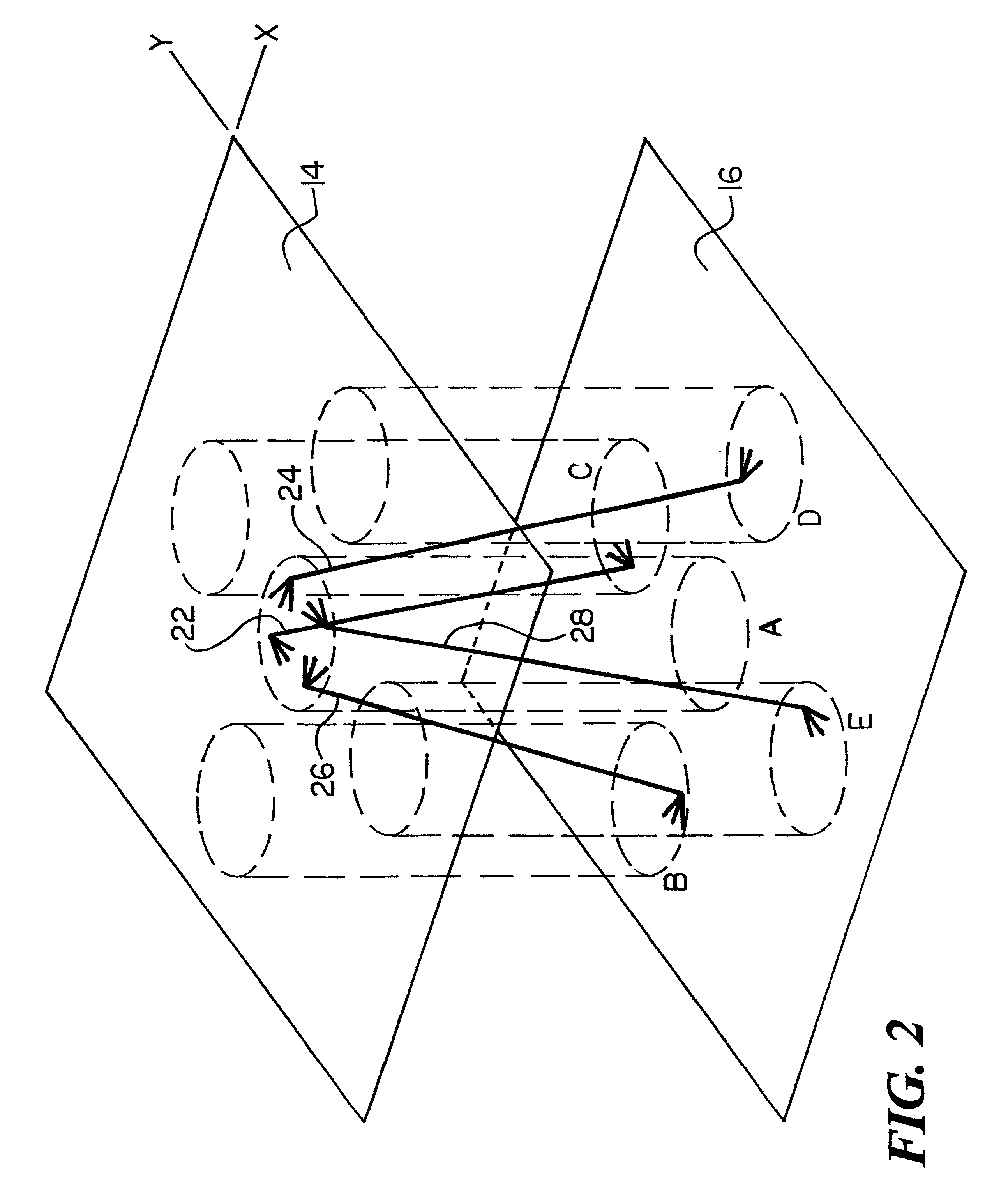

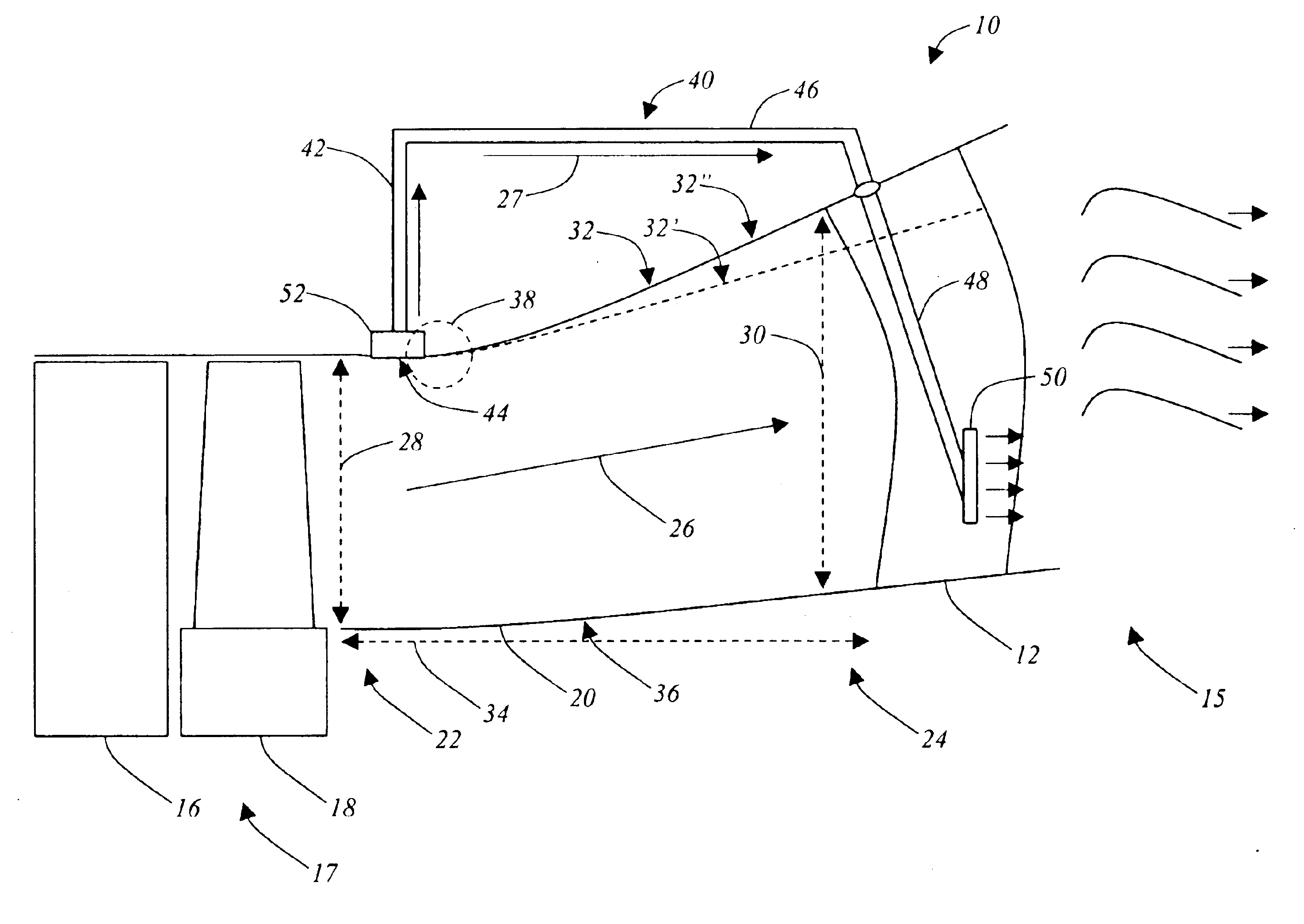

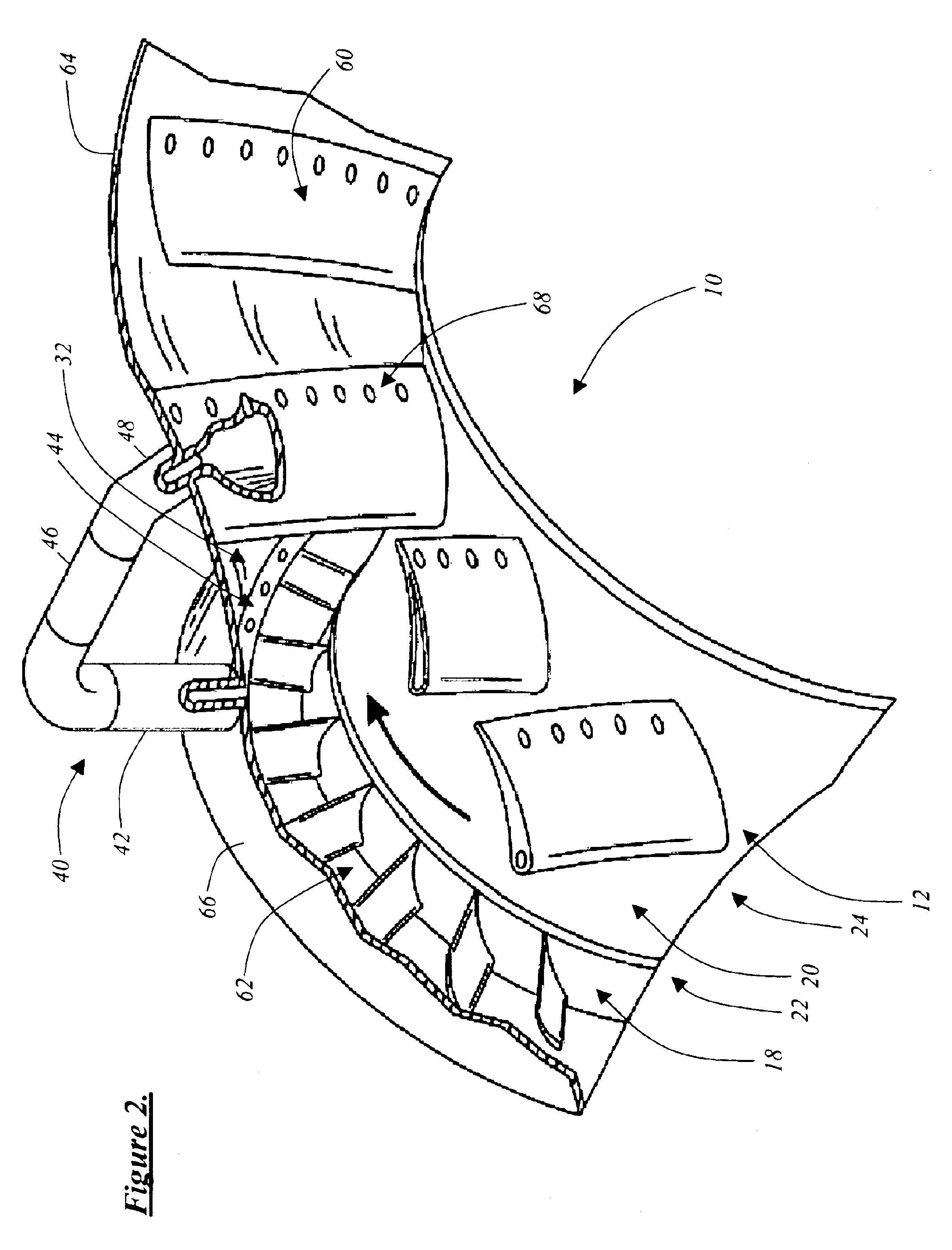

Self-aspirating high-area-ratio inter-turbine duct assembly for use in a gas turbine engine

InactiveUS6851264B2Improve performanceEnhanced aerodynamic benefitWind motor controlCombination enginesPressure differenceHigh pressure

In various embodiments, the present invention provides a means for improving gas turbine engine performance by applying fluid flow control to the inter-turbine duct joining a high-pressure turbine spool and an associated low-pressure turbine spool, allowing the low-pressure turbine spool to have a relatively larger diameter than the high-pressure turbine spool. One or more unobstructed fluid flow paths between one or more boundary layer suction ports disposed within the upstream end of the outer-body surface of the inter-turbine duct and the suction side of the associated low-pressure turbine nozzle are provided. Advantageously, the natural static pressure difference between these points results in a self-aspirating assembly. The fluid flow control provided by the respective suction and blowing forces generated allows for a relatively larger diameter low-pressure turbine spool and / or relatively fewer low-pressure turbine nozzles to be used than is possible with conventional systems, assemblies, and methods. Thus, a gas turbine engine weight savings and optimized performance may be achieved.

Owner:GENERAL ELECTRIC CO

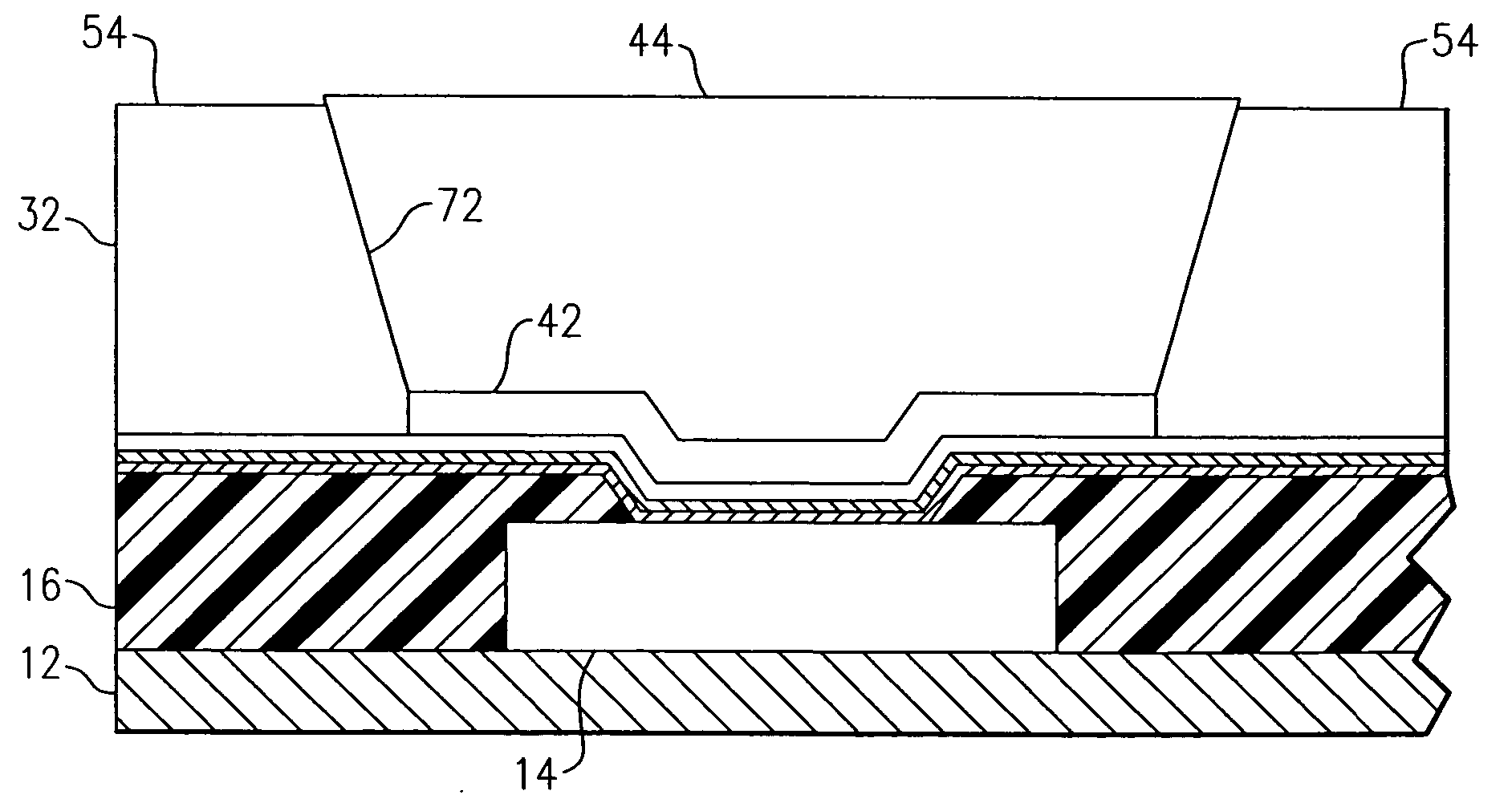

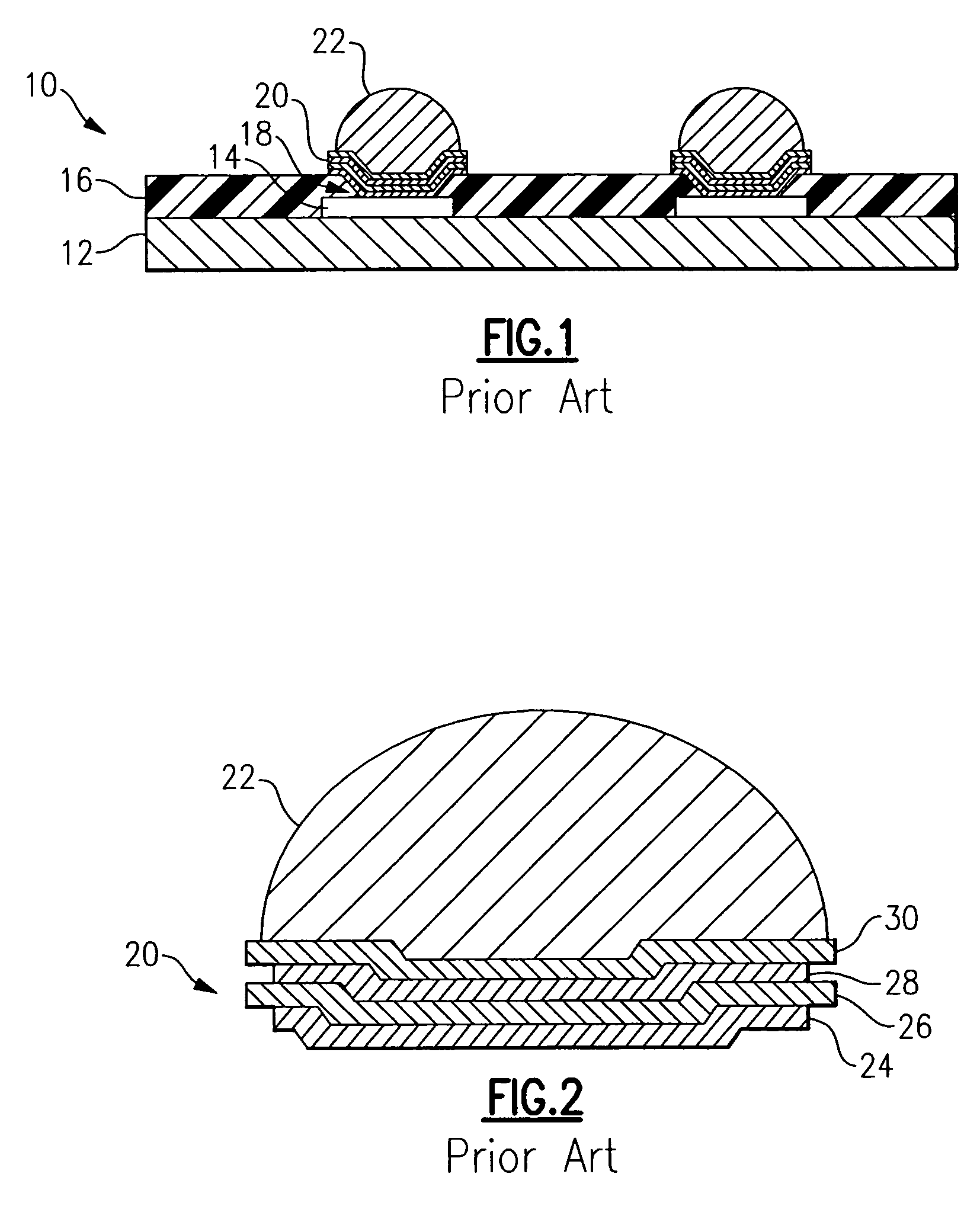

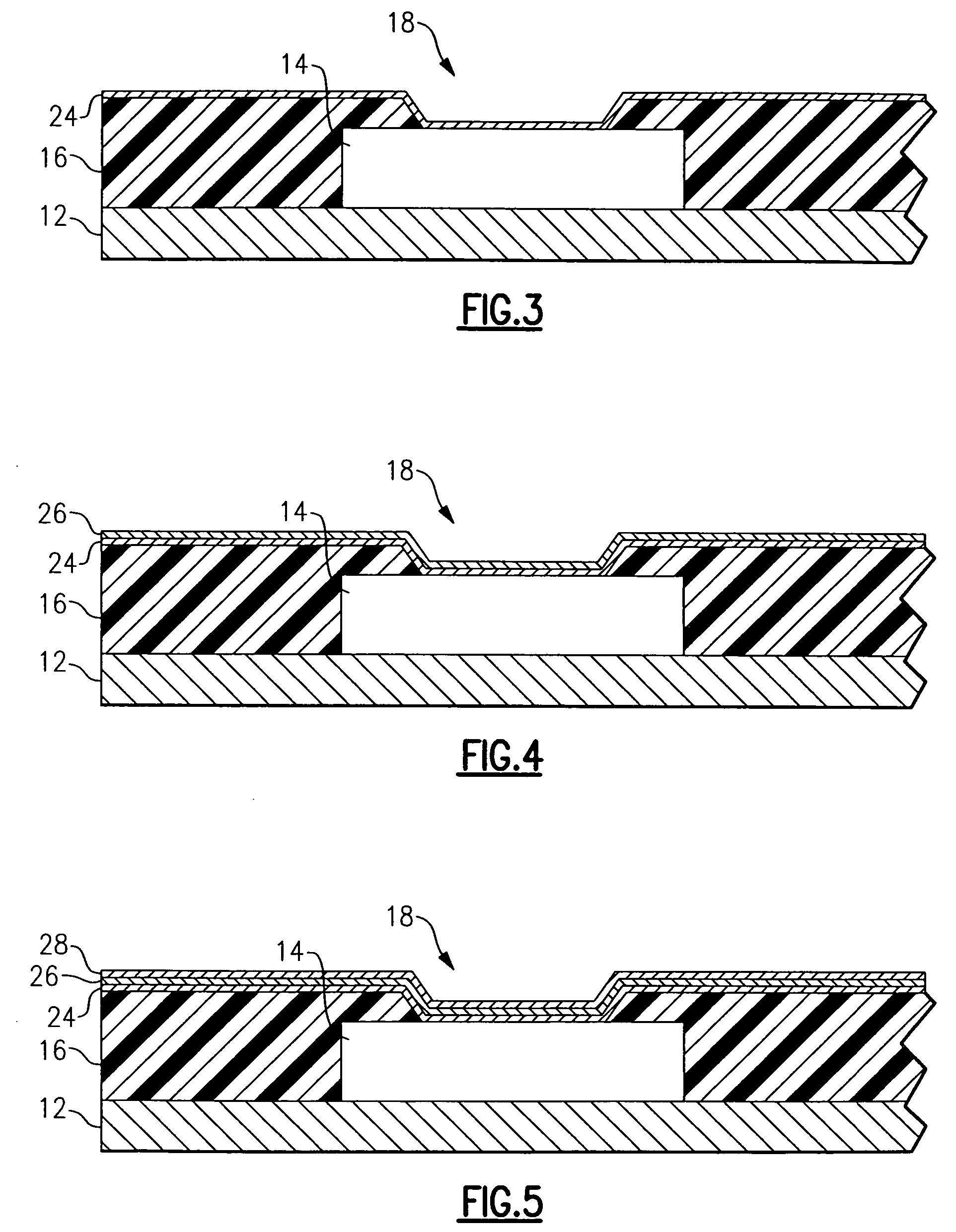

Resist sidewall spacer for C4 BLM undercut control

InactiveUS20060076677A1Avoid undercutAvoid layeringSemiconductor/solid-state device detailsSolid-state devicesResistEngineering

A method and system for preventing undercutting of the solder bump in a C4 package by forming a barrier of resist that effectively widens the footprint of the solder bump. The BLM is then etched to the perimeter edge of the barrier rather than the solder bump, thereby precluding any undercutting of the solder bump by the BLM. The barrier may formed by using a half-tone mask that fully exposes the immediately surrounding regions to define a sidewall enclosing the C4 cavity. The barrier may also be formed by applying a second resist prior to, or after, plating the solder and then patterning to inhibit etching directly adjacent to the C4 cavity. The barrier may additionally be formed by overfilling solder into the C4 cavity so that it spreads laterally over the sidewall portion of the resist layer. The resist is then etched anisotropically to leave the barrier. In another embodiment, a taper is introduced into the profile of the C4 cavity by reflowing the resist by an annealing step. The resist is then etched anisotropically to leave the barrier surrounding the C4 solder.

Owner:IBM CORP

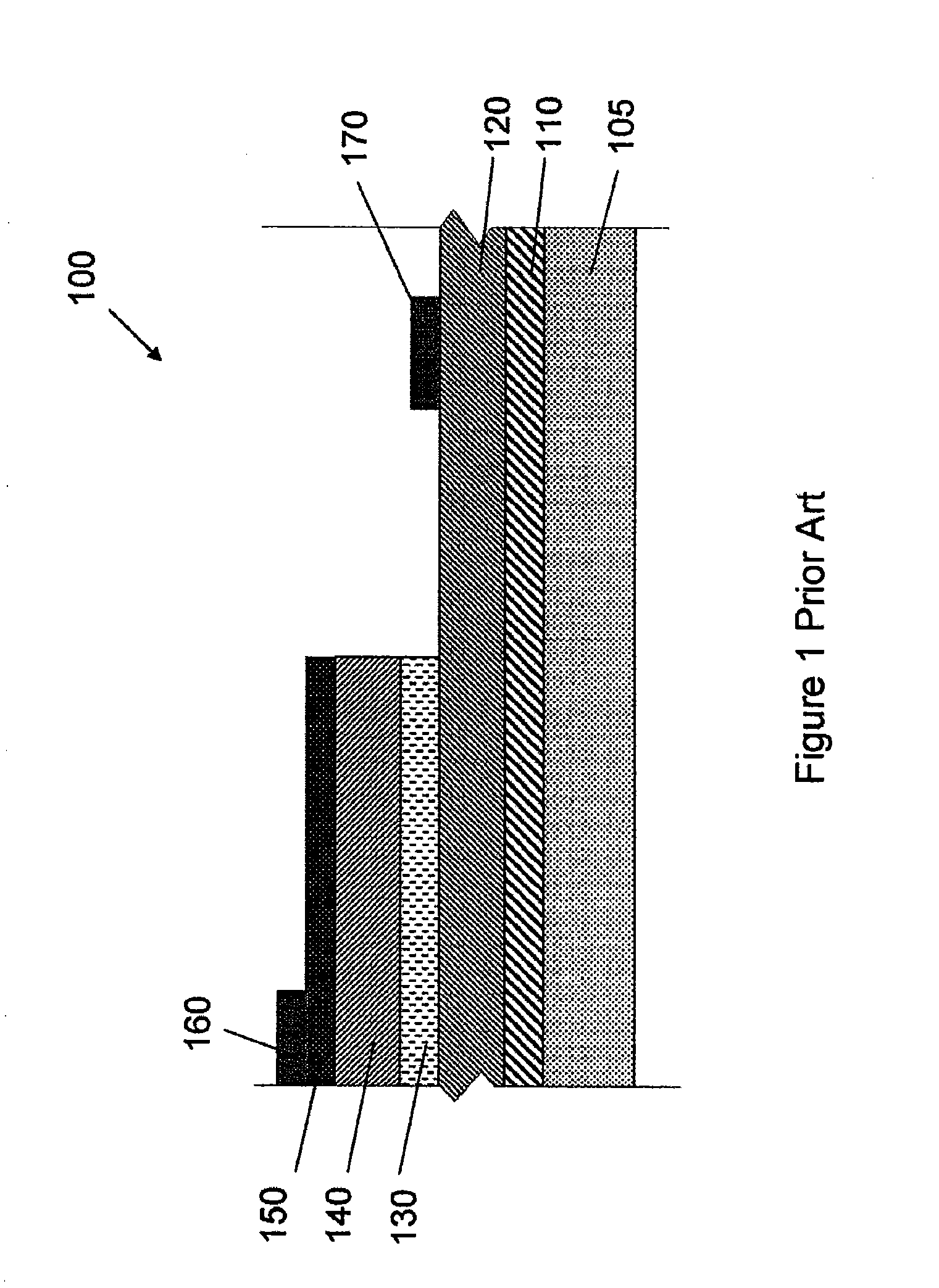

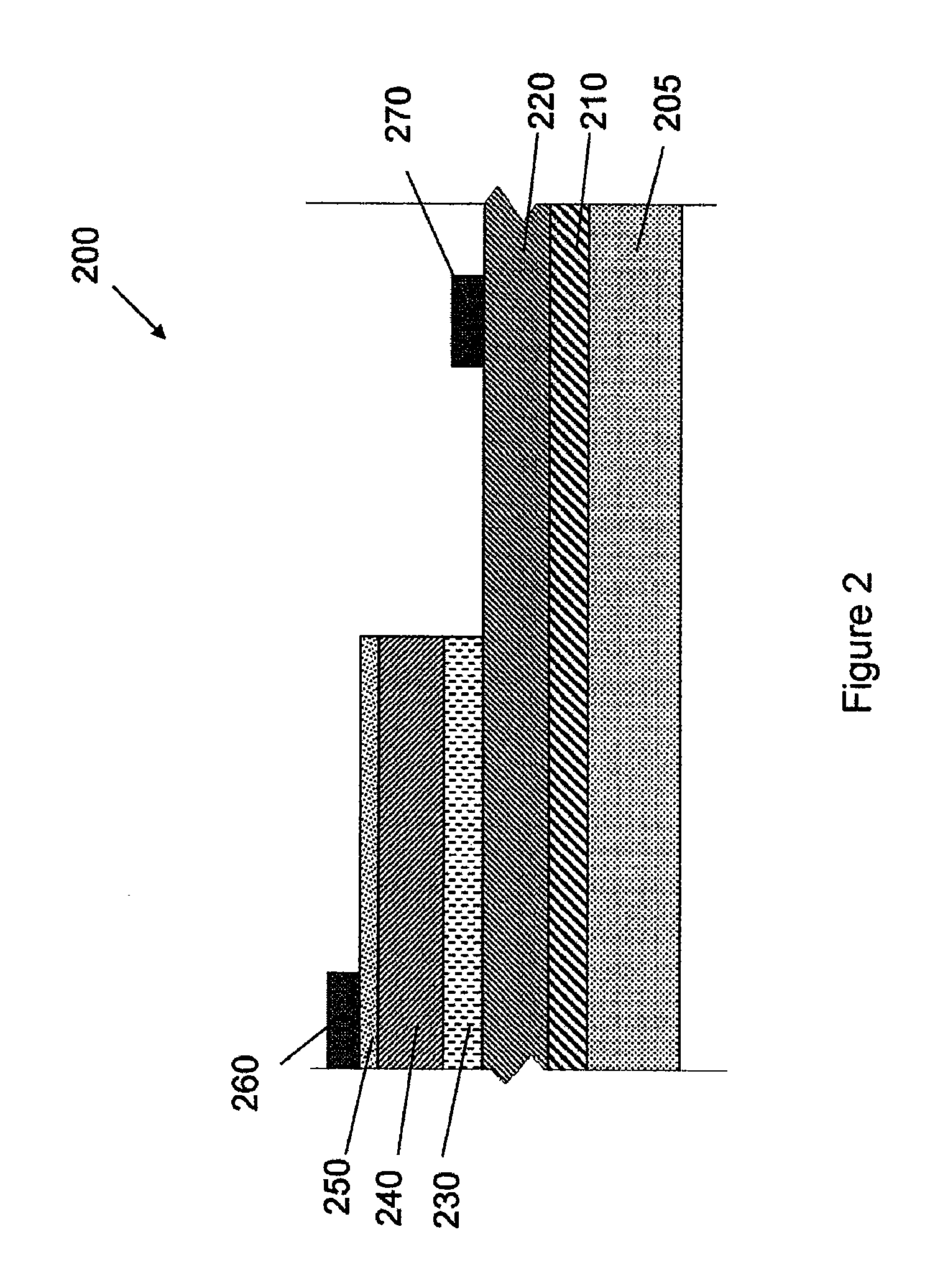

Method for fabricating CMOS image sensor protecting low temperature oxide delamination

ActiveUS20050090035A1Avoid layeringTelevision system detailsSemiconductor/solid-state device detailsCMOSSemiconductor

A method for fabricating a complementary metal oxide semiconductor image sensor is capable of protecting a low temperature oxide from delaminating a passivation layer. The method includes the steps of: forming a passivation layer on a pad metal; exposing a predetermined part of the pad metal by patterning the passivation layer using a first pad mask; forming an oxide layer on the exposed pad metal and the passivation layer formed around the pad open region; forming a color filter, a planarization layer and a microlens, sequentially; forming a low temperature oxide layer on the above structure to protect the microlens; and opening the pad metal by selectively etching the low temperature oxide layer and the oxide layer formed around the pad open region by a second pad mask.

Owner:INTELLECTUAL VENTURES II

Silicon based solid state lighting

InactiveUS20110108800A1Prevent associated layer crackingImprove luminous efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesPower flowNitride

A semiconductor device includes a substrate comprising a first surface having a first orientation and a second surface having a second orientation and a plurality of III-V nitride layers on the substrate, wherein the plurality of III-V nitride layers are configured to emit light when an electric current is produced in one or more of the plurality of III-V nitride layers.

Owner:SIPHOTON

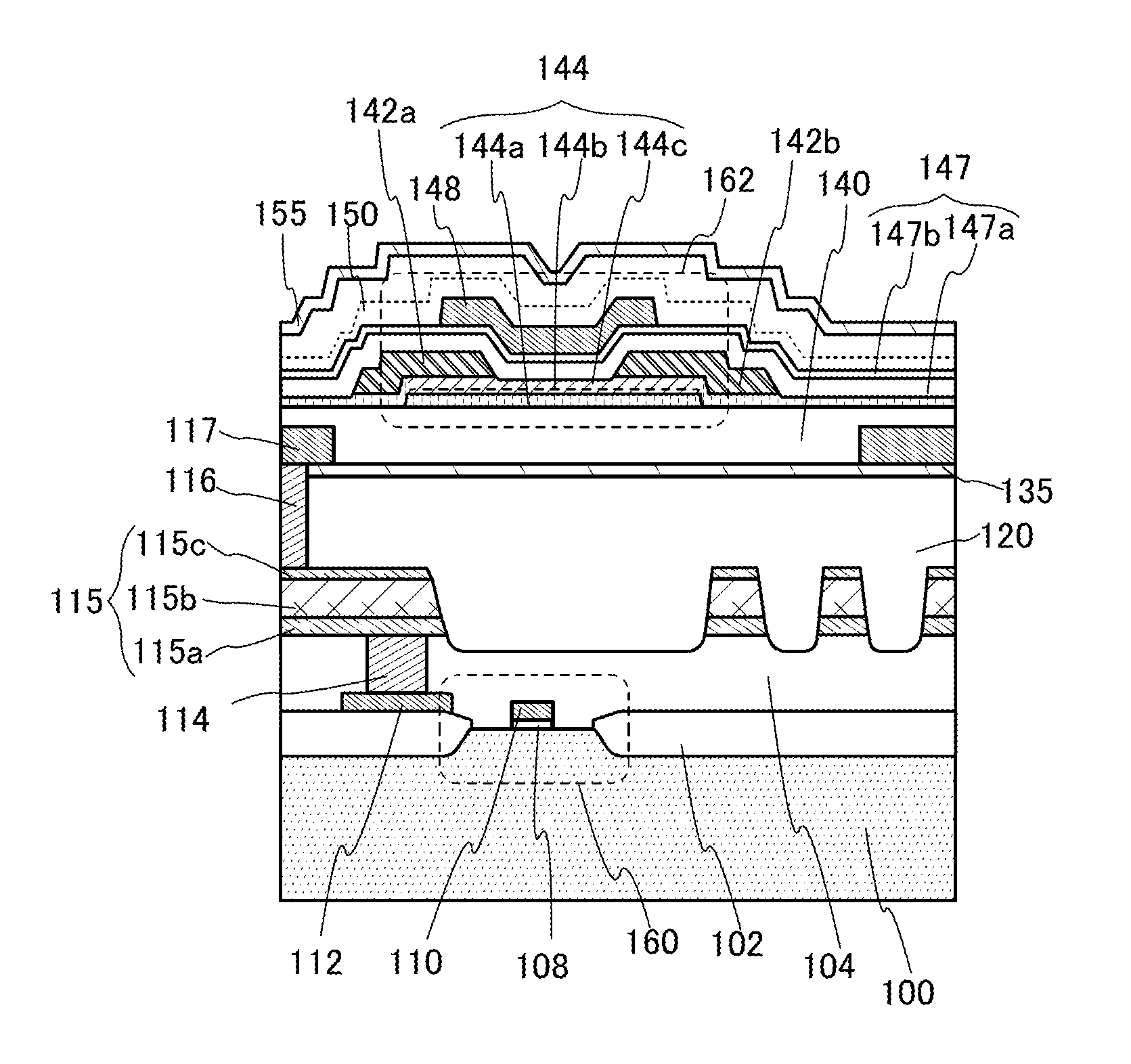

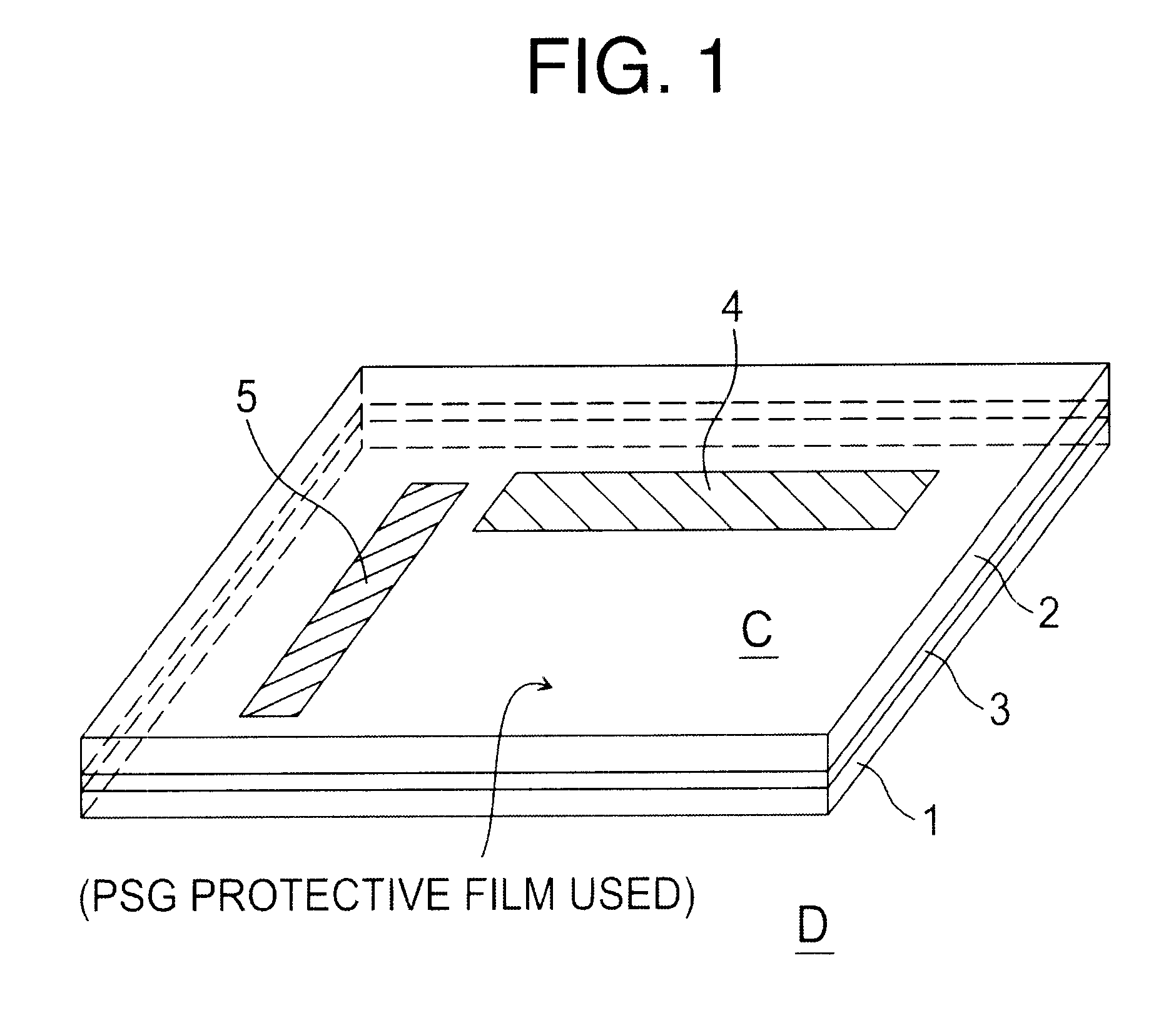

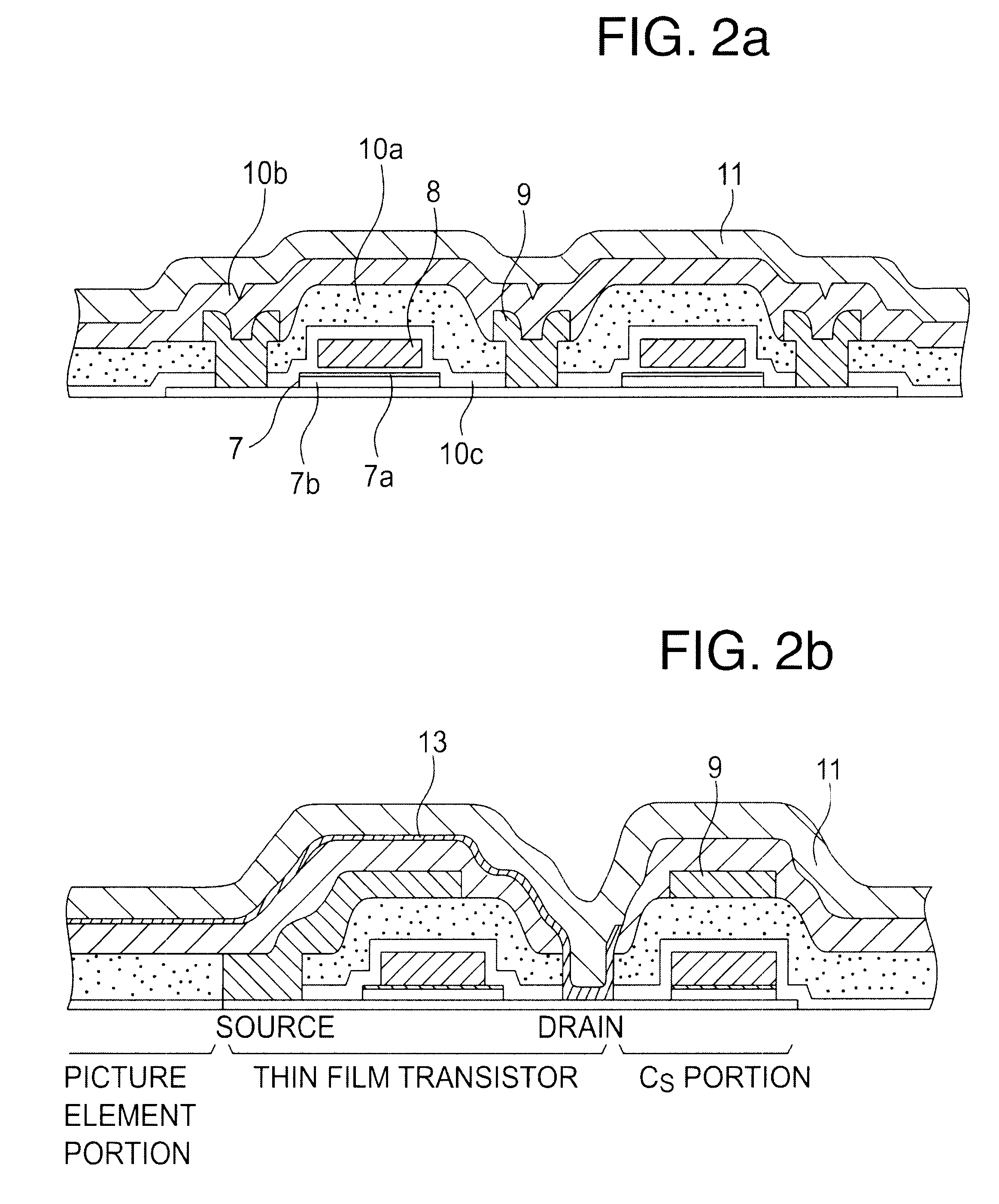

Liquid crystal display device

InactiveUS6556257B2Stable characteristicsThin is prevented degradationSolid-state devicesNon-linear opticsLiquid-crystal displayEngineering

A liquid crystal display device of the monolithic type which comprises a first substrate, a plurality of display elements arranged in a matrix on the first substrate to define a display area of the liquid crystal display device, each of the display elements comprising a picture element or pixel electrode and a switching or pixel transistor associated with the picture element or pixel electrode, a driving circuit formed on the first substrate and connected to the display area. The driving circuit includes a horizontal driver and a vertical driver. The device further includes a second substrate substantially entirely opposed to the first substrate, and a liquid crystal layer disposed between the first and second substrates. A passivation layer is provided to cover the display area or pixel transistors and driving circuit.

Owner:SONY CORP

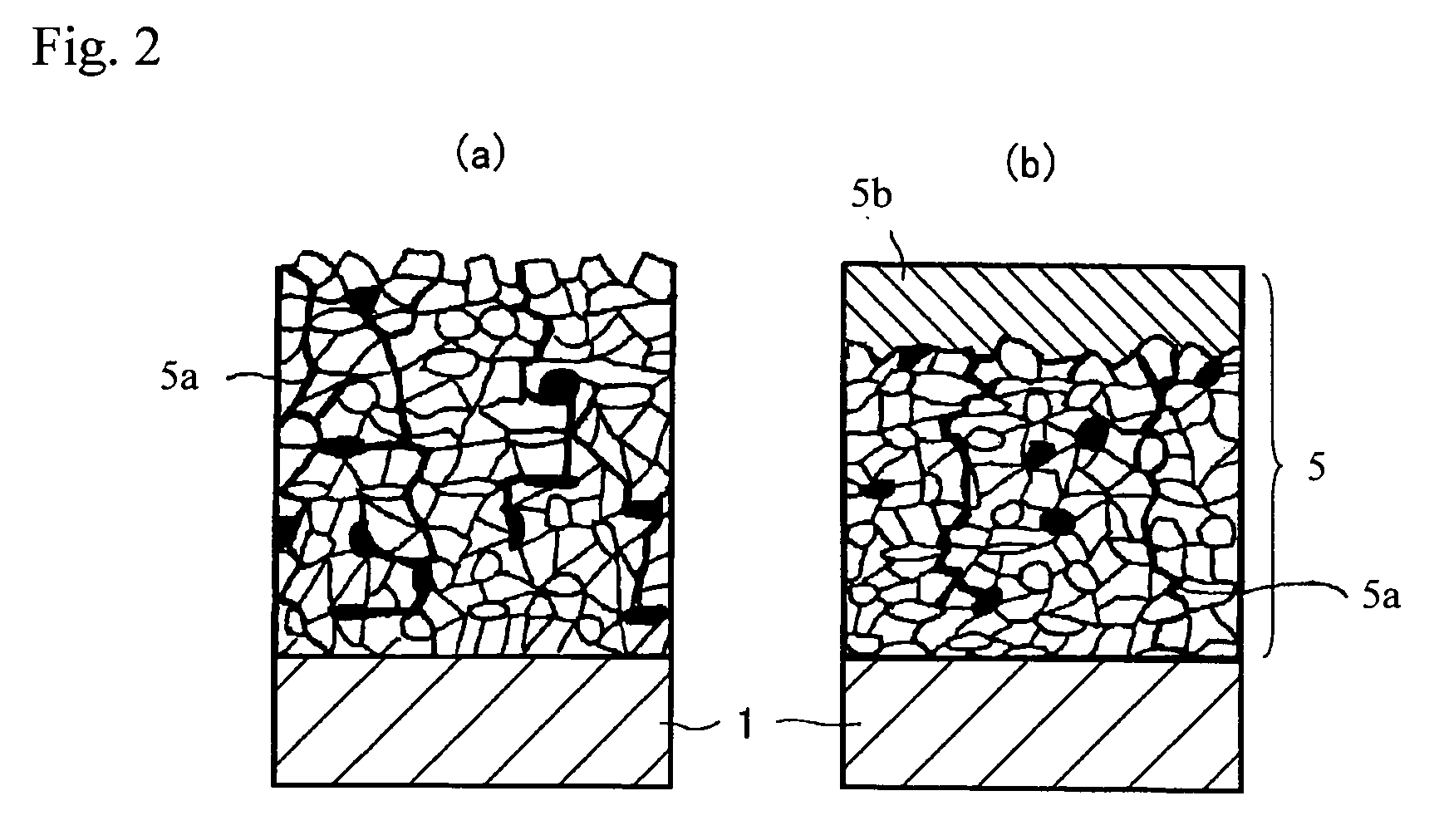

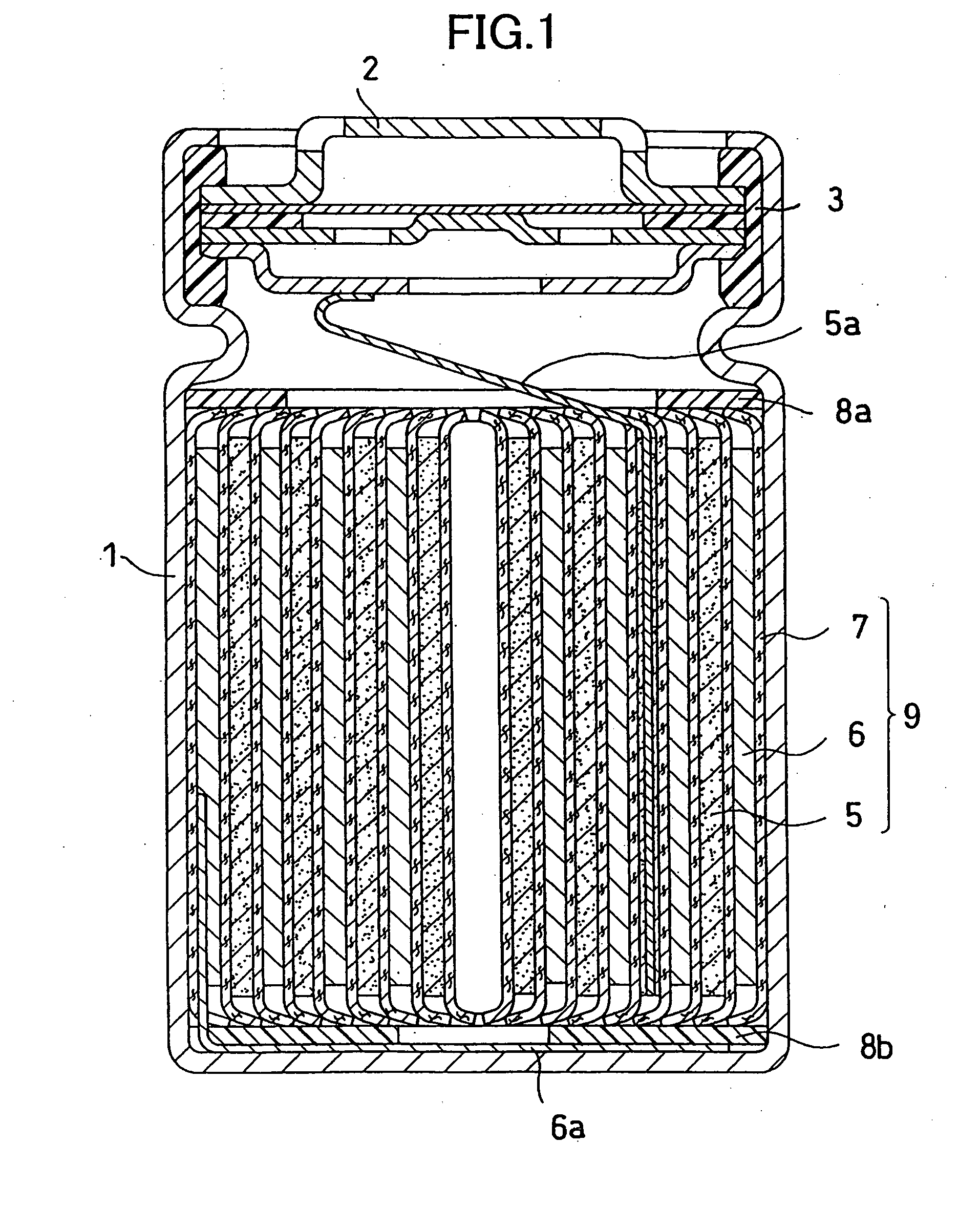

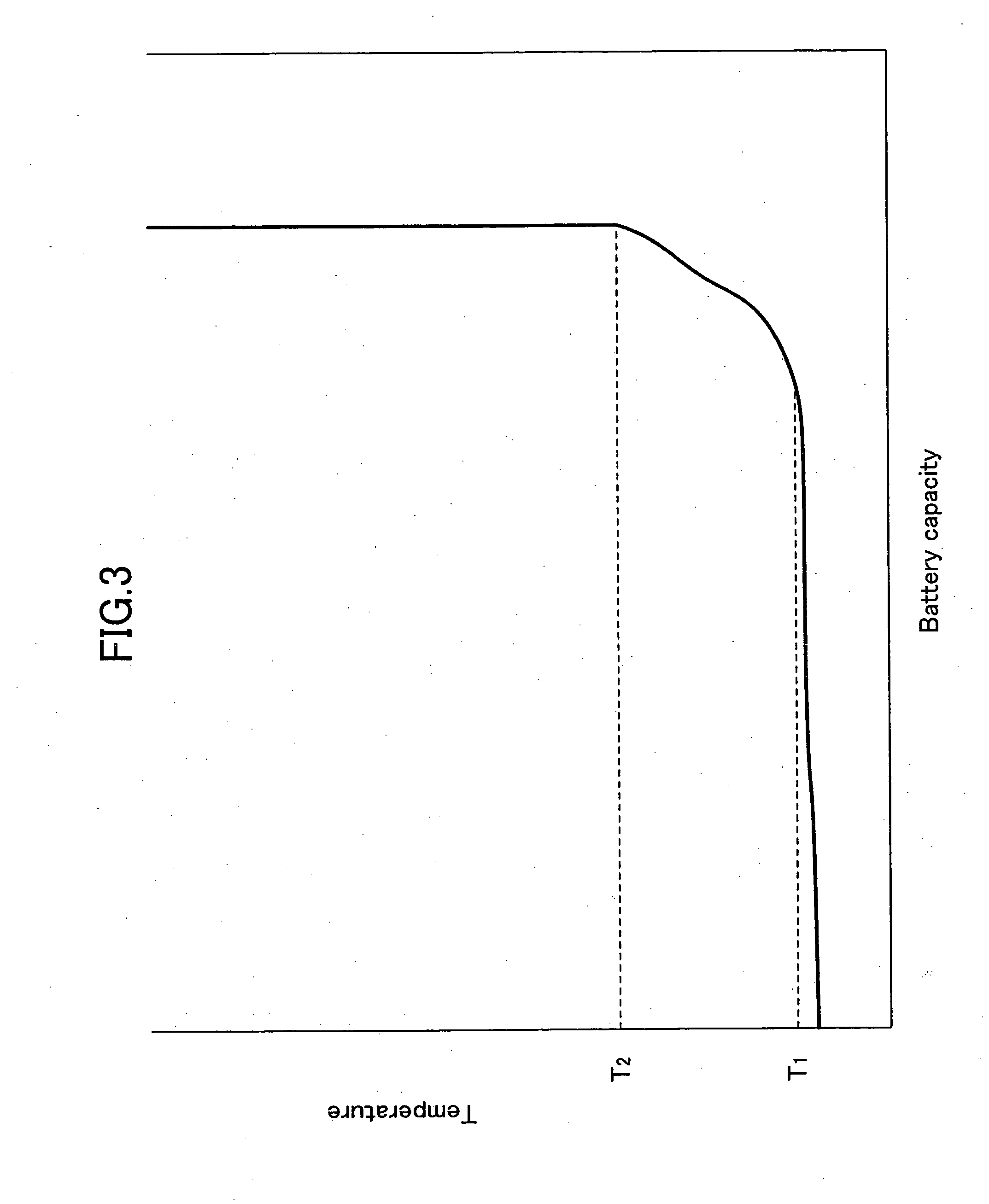

Nonaqueous electrolyte secondary battery and method for manufacturing the same

InactiveUS20080241684A1Avoid smooth surfaceReduce temperature rise rateElectrode manufacturing processesCell seperators/membranes/diaphragms/spacersLithiumEngineering

A lithium ion secondary battery includes a positive electrode, a negative electrode, a porous insulating layer and a nonaqueous electrolyte. The porous insulating layer is provided between the positive electrode material mixture layer and the negative electrode material mixture layer and contains a material which does not have a shutdown function. The positive electrode is provided with a PTC layer extending substantially parallel to the positive electrode collector and the negative electrode is provided with a PTC layer extending substantially parallel to the negative electrode collector. Each of the PTC layers contains a material having a positive temperature coefficient of resistance.

Owner:PANASONIC CORP

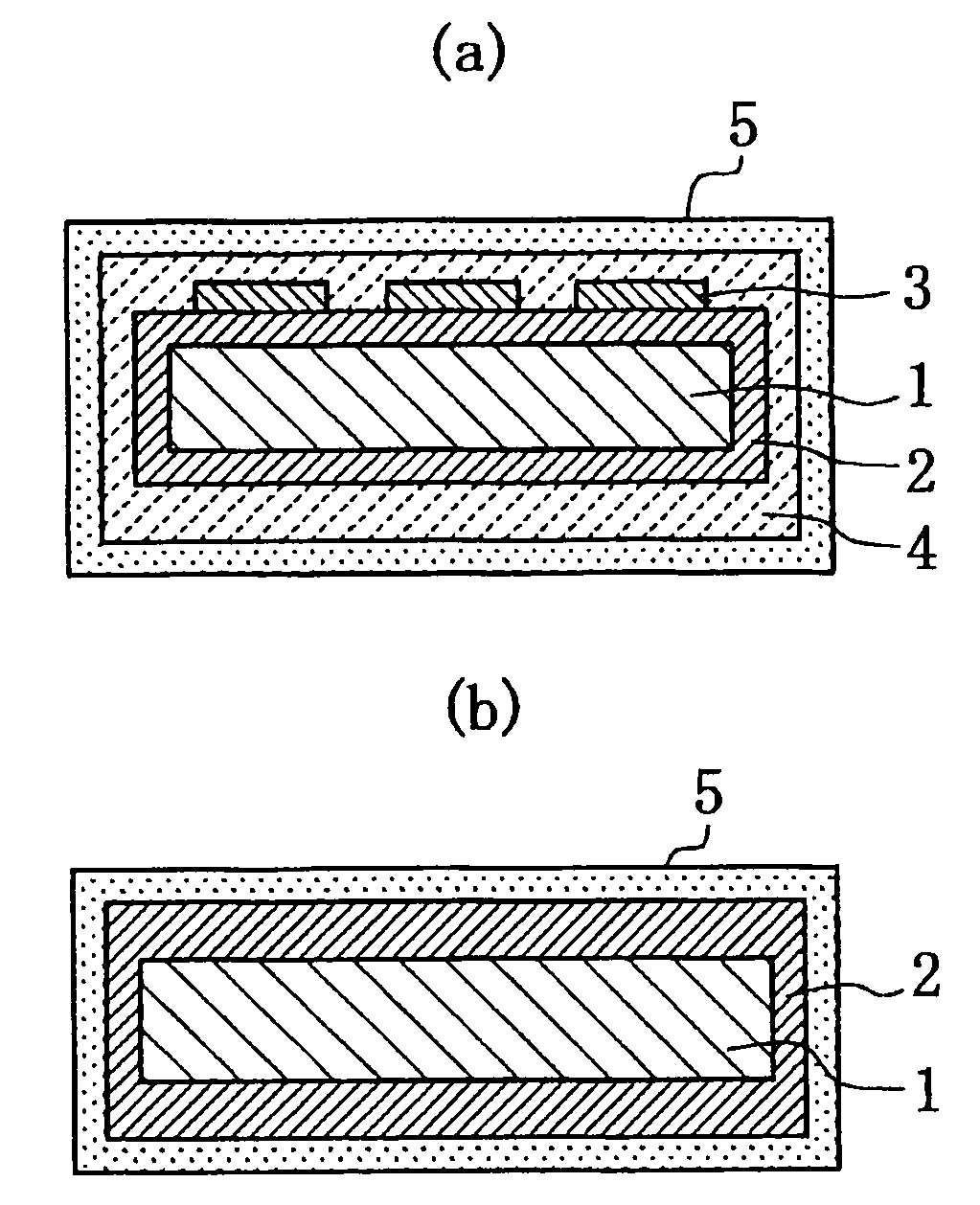

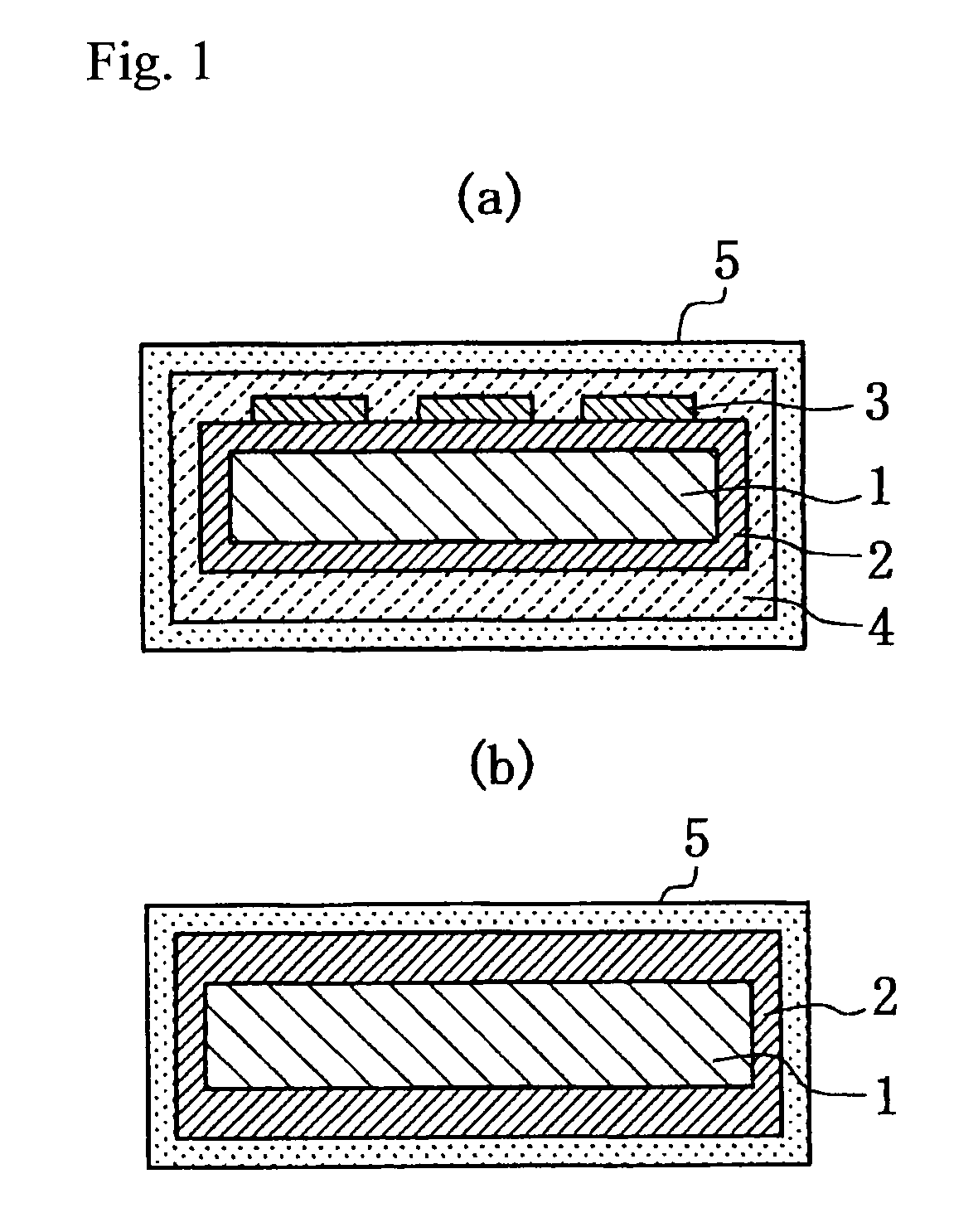

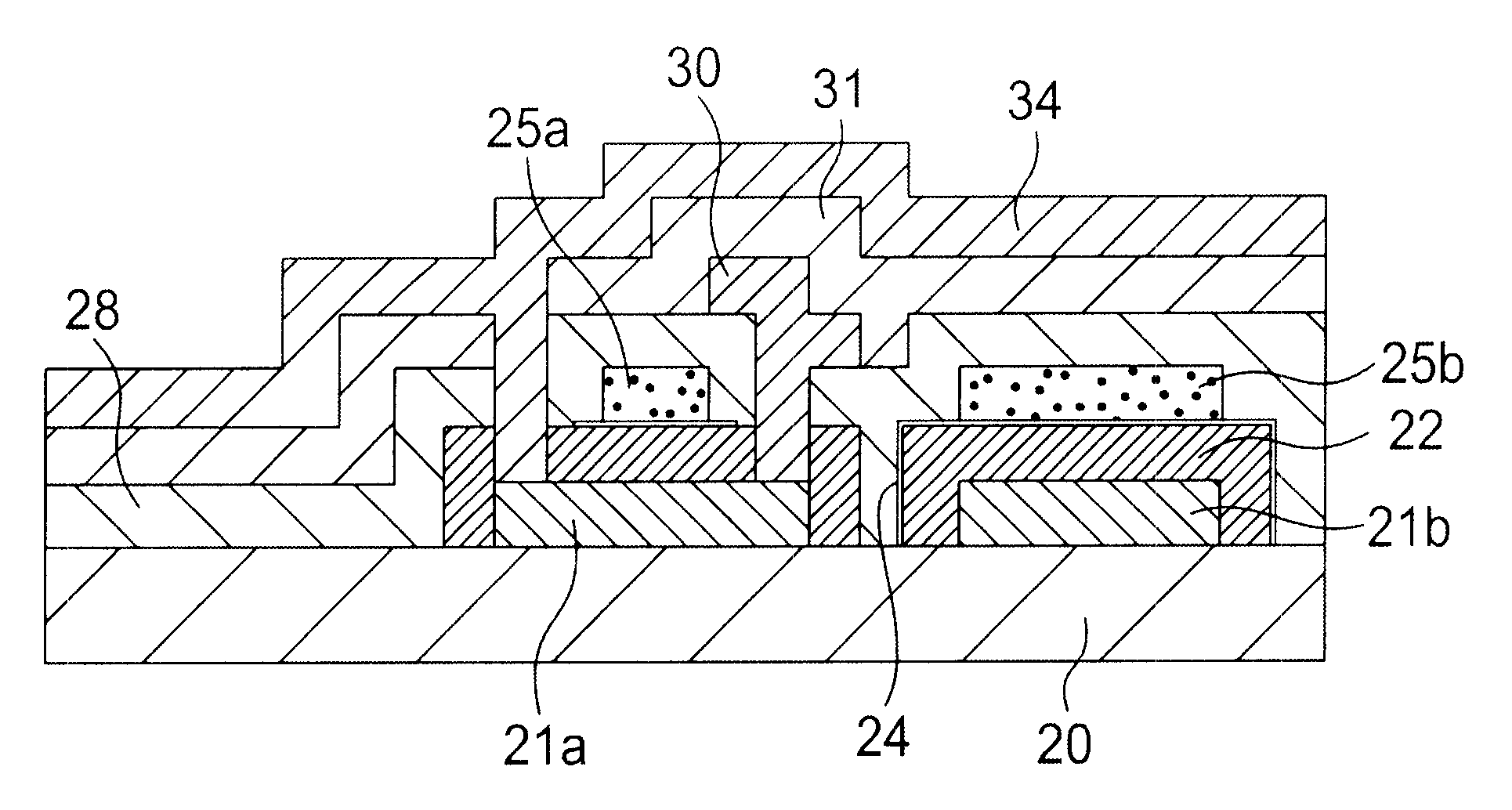

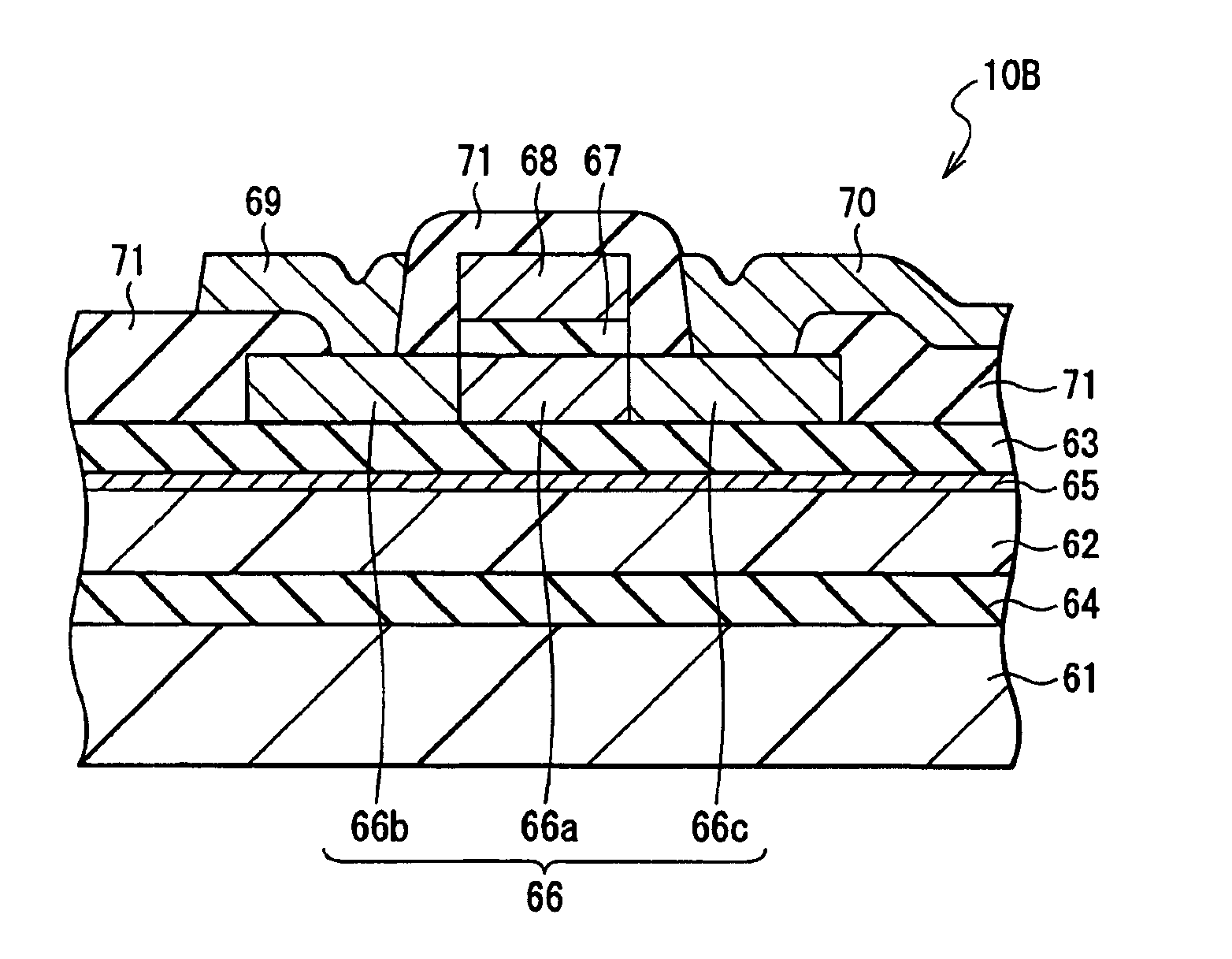

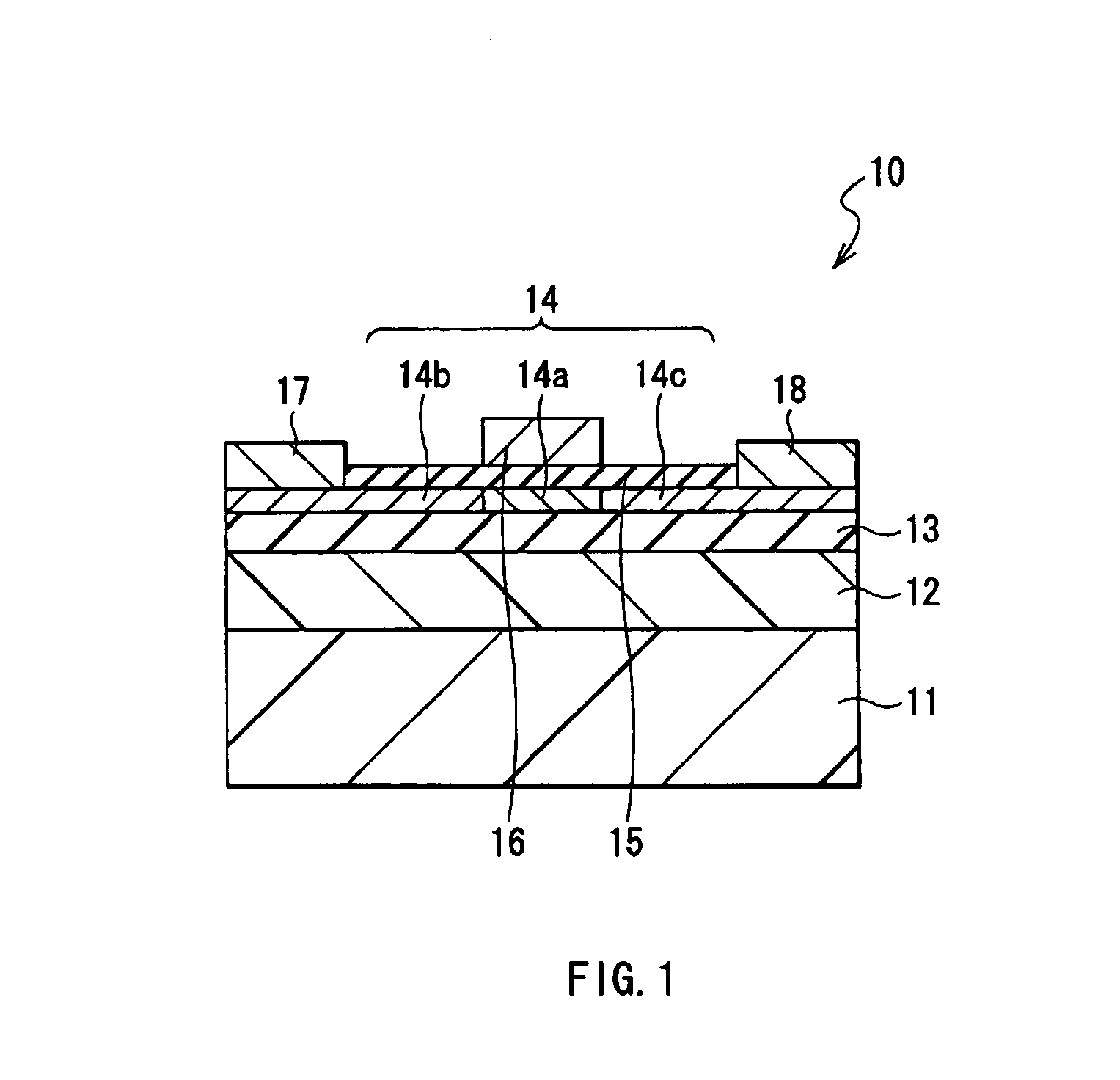

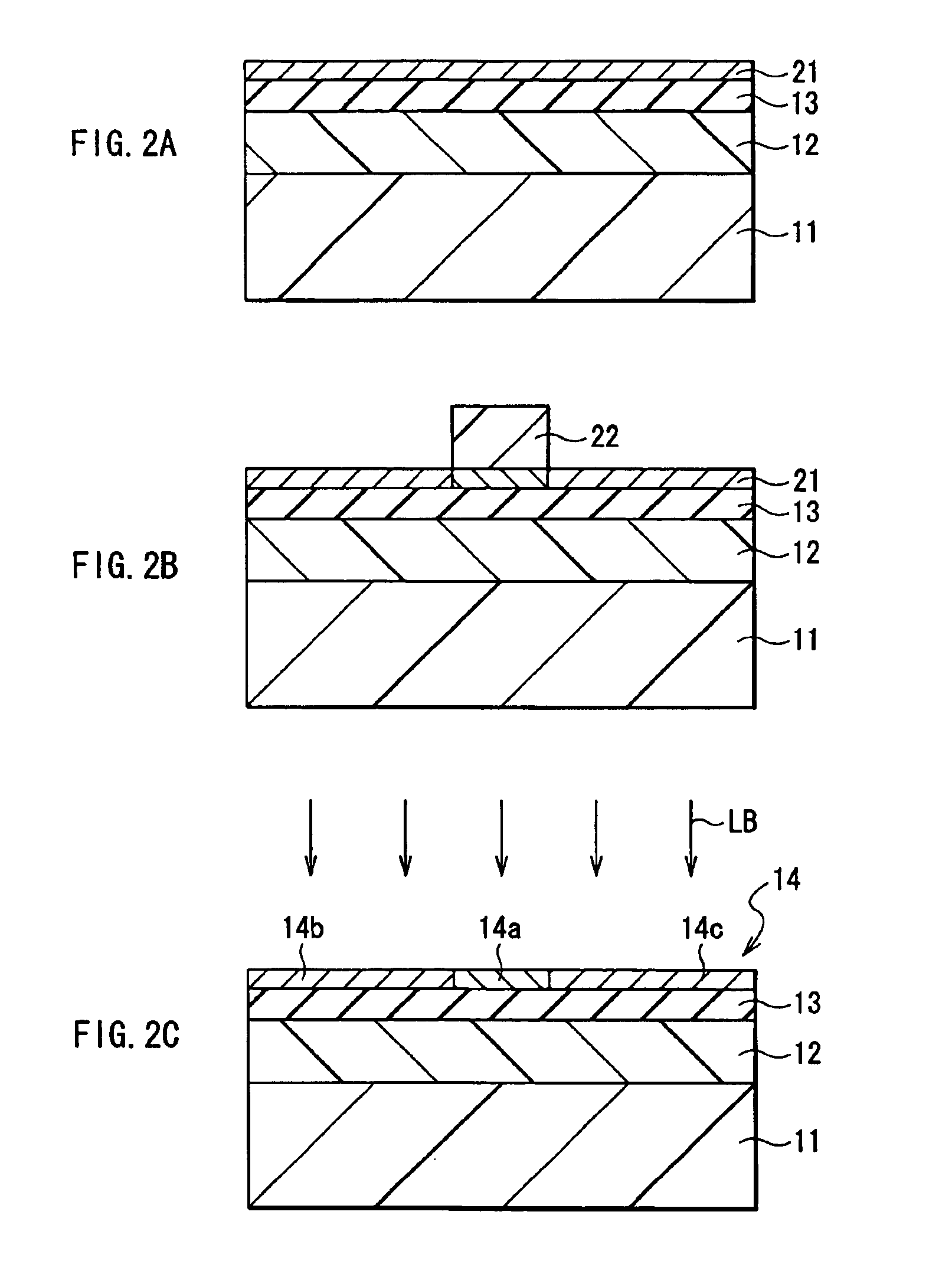

Functional device and method of manufacturing the same

InactiveUS6953754B2Avoid layeringOccurrence can be preventedTransistorLayered productsEpoxyAcrylic resin

The invention provides a functional device having no cracks and capable of delivering good functional characteristics and a method of manufacturing the same. A functional layer (14) is formed by crystallizing an amorphous silicon layer as a precursor layer by laser beam irradiation. A laser beam irradiation conducts heat up to a substrate (11) to cause it to try to expand; a stress to be produced by the difference in thermal expansion coefficient between the substrate (11) and the functional layer (14) is shut off by an organic polymer layer (12) lower in thermal expansion coefficient than the substrate (11), thereby causing no cracks nor separations in the functional layer (14). The organic polymer layer (12) is preferably made of an acrylic resin, an epoxy resin, or a polymer material containing these that is deformed by an optical or thermal process to undergo a three-dimensional condensation polymerization, for higher compactness and hardness. Inserting a metal layer and an inorganic heat resistant layer between the substrate (11) and the functional layer (14) will permit a more powerful laser irradiation.

Owner:SONY CORP

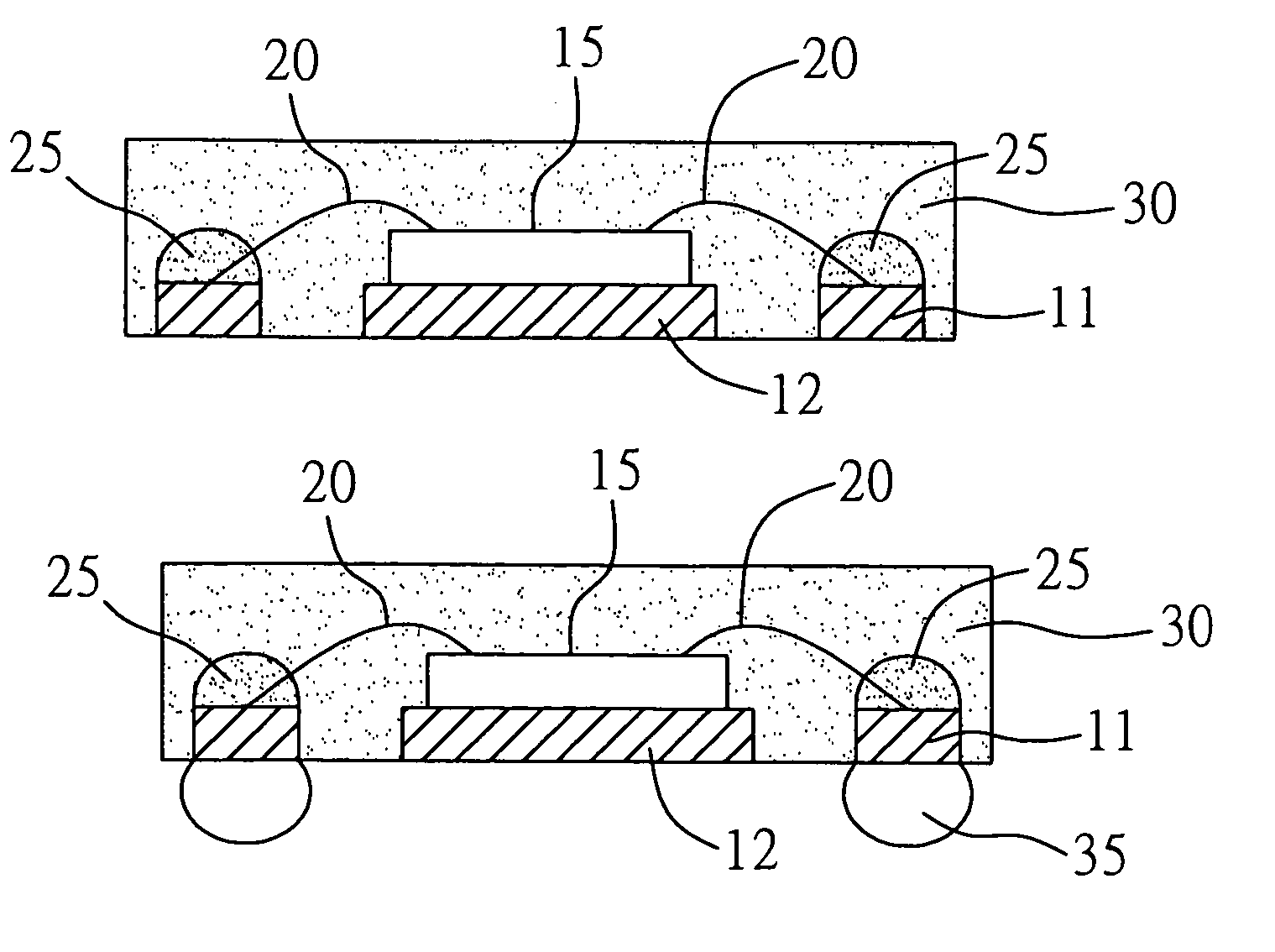

Carrier-free semiconductor package and fabrication method thereof

InactiveUS7314820B2Improve bond strengthAvoid delaminationSemiconductor/solid-state device detailsSolid-state devicesSealantCoating

A carrier-free semiconductor package and a fabrication method thereof are provided. The fabrication method includes the steps of: providing a carrier having a plurality of electrical contacts formed thereon; mounting at least one chip on the carrier; electrically connecting the chip to the electrical contacts via a plurality of bonding wires; forming a coating layer on each of the electrical contacts to encapsulate a bonded end of each of the bonding wires on the electrical contacts; performing a molding process to form an encapsulant for encapsulating the chip, the bonding wires and the electrical contacts; and removing the carrier, such that bottom surfaces of the electrical contacts are exposed from the encapsulant. This obtains a semiconductor package not having a carrier, and the coating layers can enhance adhesion between the electrical contacts and the encapsulant.

Owner:SILICONWARE PRECISION IND CO LTD

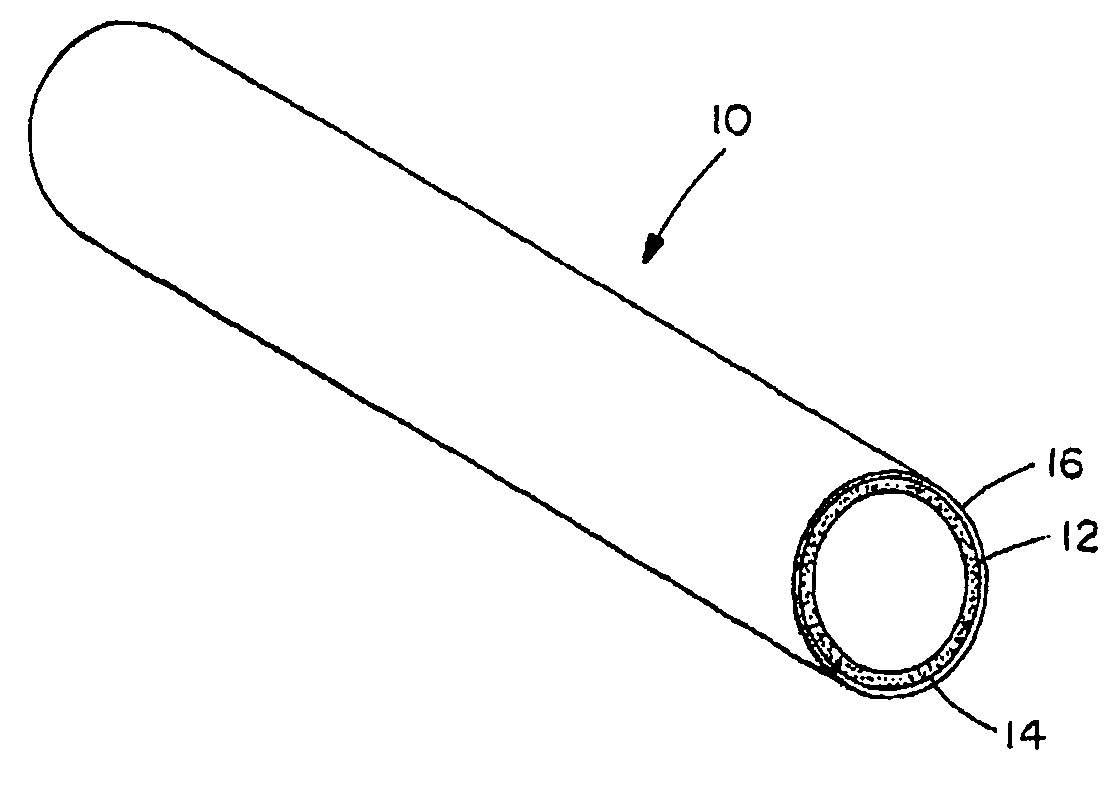

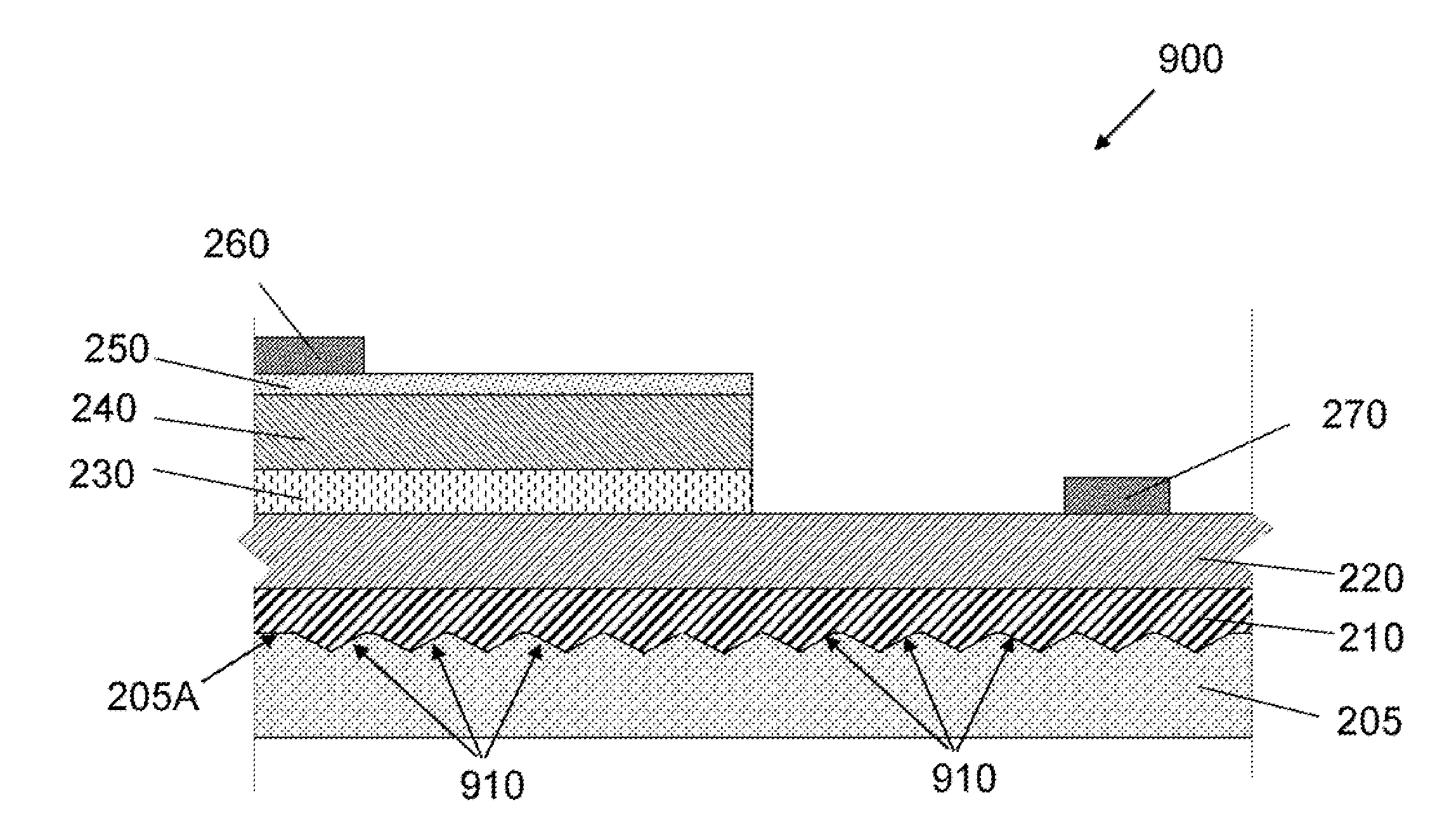

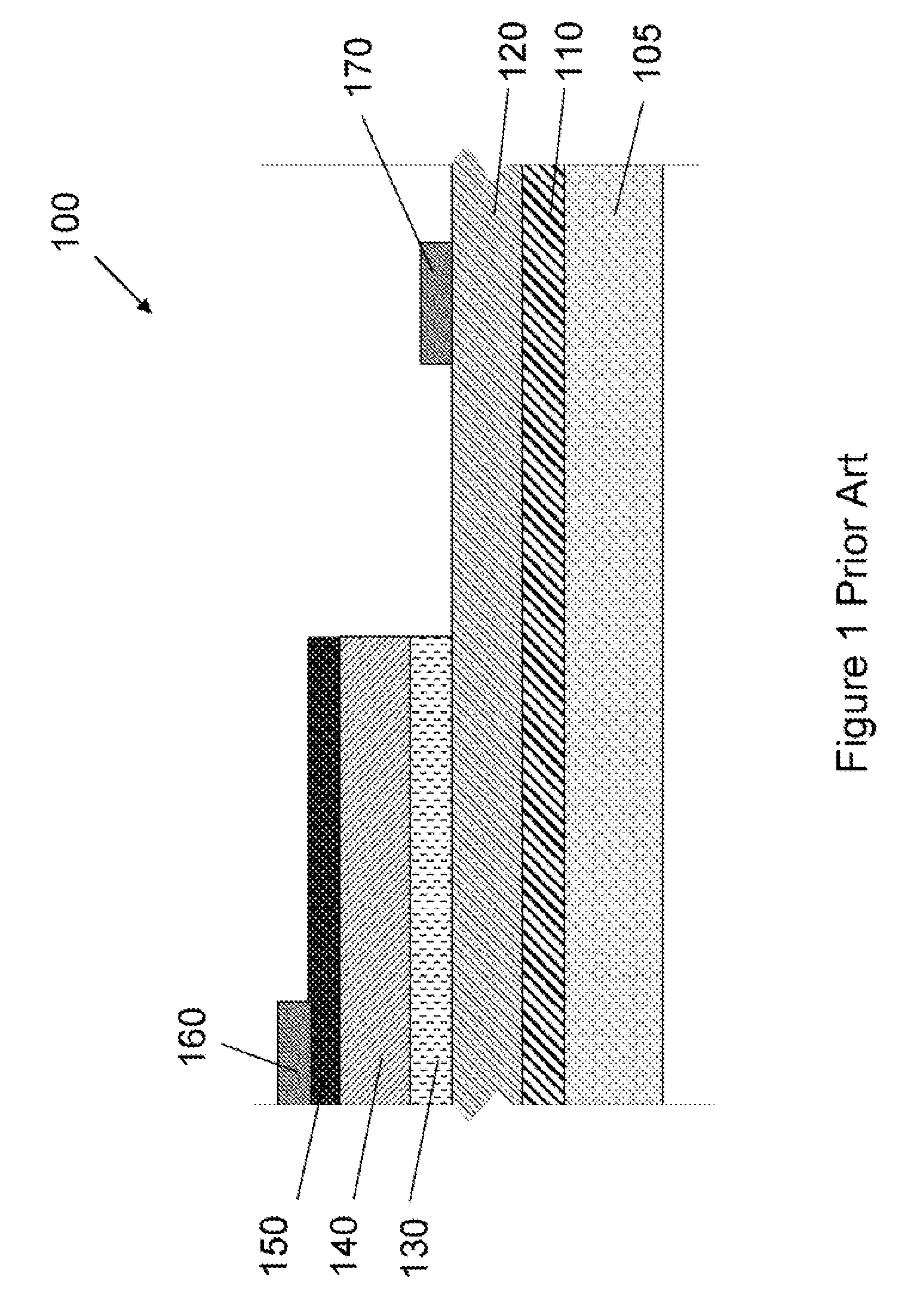

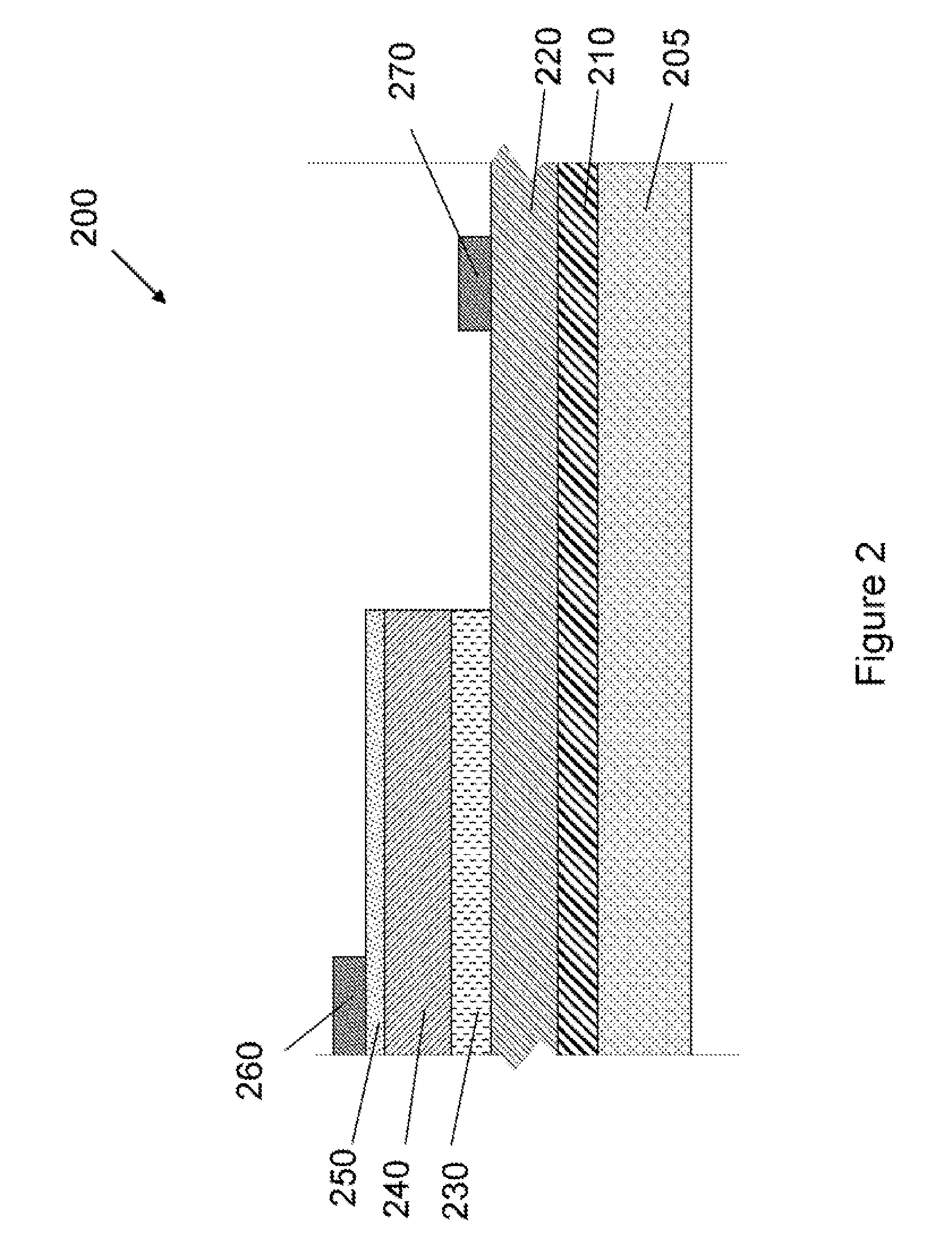

Composite gas separation modules having intermediate porous metal layers

InactiveUS7175694B2Reduce fluxControl performanceMembranesSemi-permeable membranesHydrogenProduct gas

The present invention relates to a composite gas separation module and to methods for fabricating a composite gas separation module. The present invention also relates to methods for selectively separating hydrogen gas from a hydrogen gas-containing gaseous stream. In one embodiment, the composite gas separation module includes a porous metal substrate; an intermediate porous metal layer, wherein the intermediate porous metal layer overlies the porous metal substrate; and a dense hydrogen-selective membrane, wherein the dense hydrogen-selective membrane overlies the intermediate porous metal layer. The intermediate porous metal layer can include palladium and a Group IB metal. For example, the intermediate porous metal layer can contain alternating layers of palladium and a Group IB metal.

Owner:WORCESTER POLYTECHNIC INSTITUTE

Silicon based solid state lighting

InactiveUS20080308835A1Prevent associated layer crackingImprove luminous efficiencyLaser detailsSemiconductor/solid-state device manufacturingNitrideSemiconductor

A semiconductor device includes a substrate comprising a first surface having a first orientation and a second surface having a second orientation and a plurality of III-V nitride layers on the substrate, wherein the plurality of III-V nitride layers are configured to emit light when an electric current is produced in one or more of the plurality of III-V nitride layers.

Owner:SIPHOTON

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com