Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

265results about How to "Reduce impurity concentration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor integrated circuit device

InactiveUS20080157157A1High operation speedLow power consumptionTransistorSolid-state devicesPhysicsSulfur dioxide

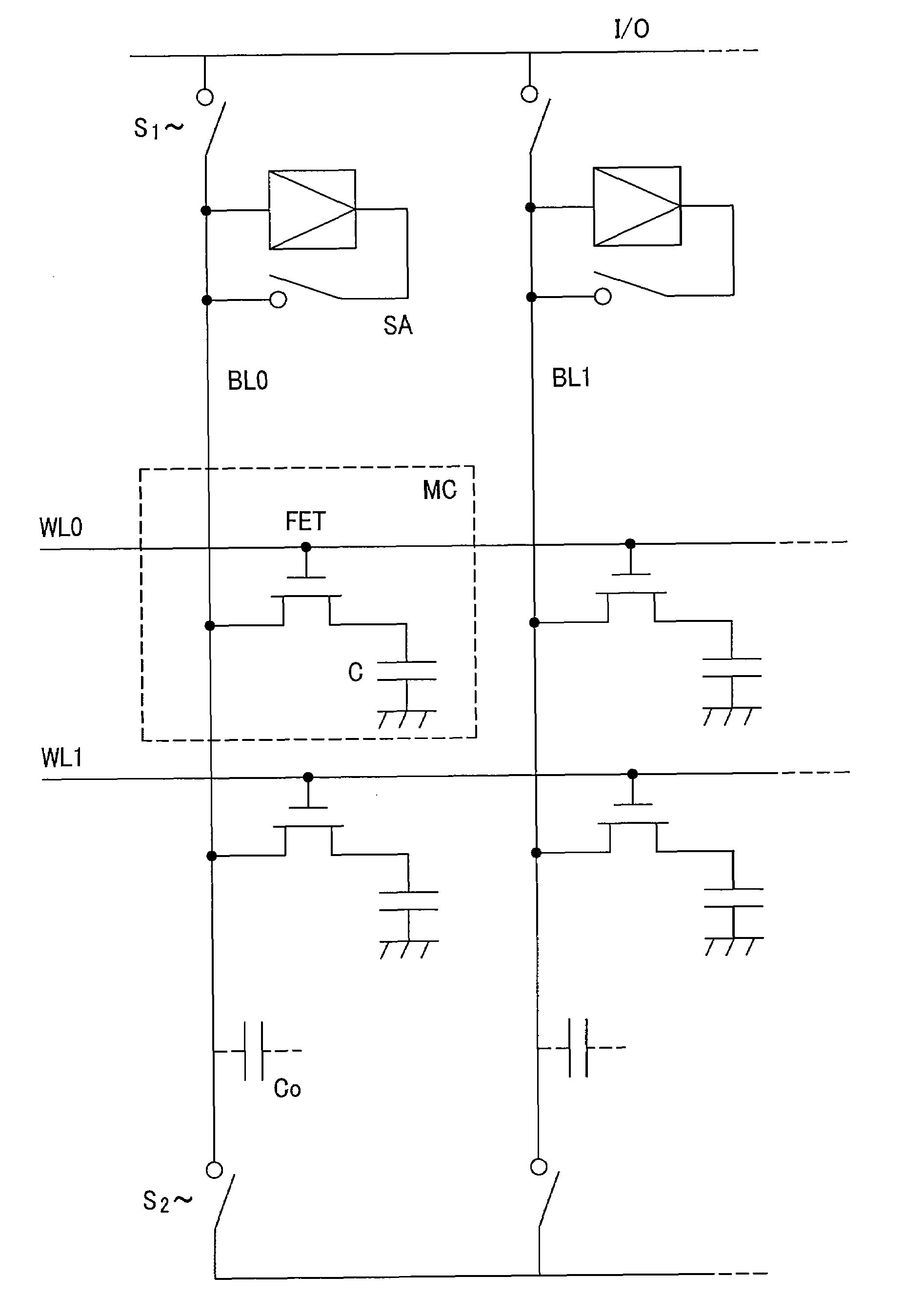

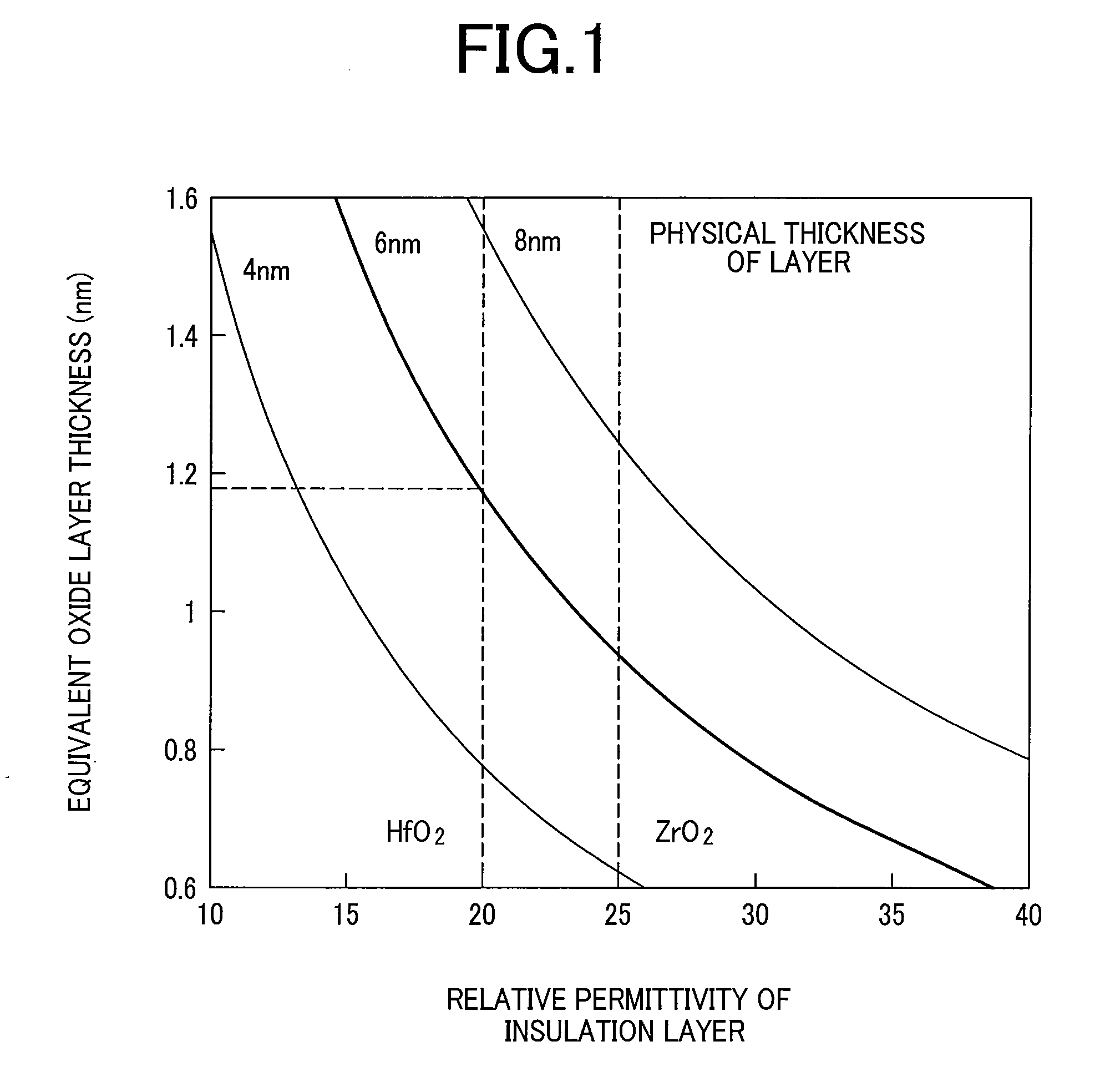

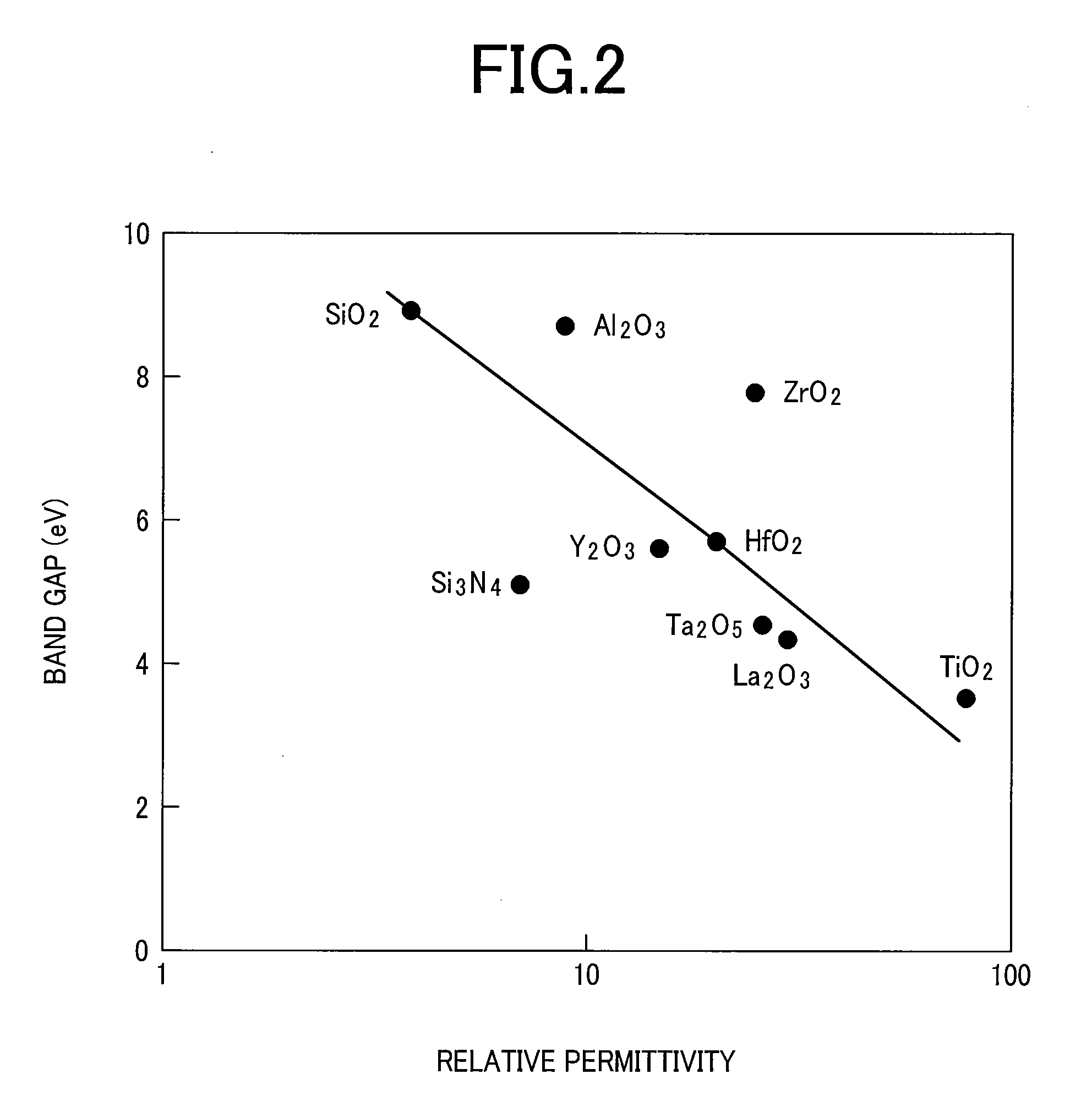

A DRAM capacitor uses ruthenium or ruthenium oxide as an upper electrode and hafnium dioxide or zirconium oxide as an insulation layer. The DRAM capacitor is intended to suppress diffusion of ruthenium, etc. into hafnium dioxide. Tantalum pentoxide or niobium oxide having a higher permittivity than that of the insulation layer is inserted as a cap insulation layer to the boundary between the upper electrode of ruthenium or ruthenium oxide and the insulation layer of hafnium dioxide or zirconium oxide to thereby suppress diffusion of ruthenium, etc. into hafnium dioxide, etc.

Owner:HITACHI LTD

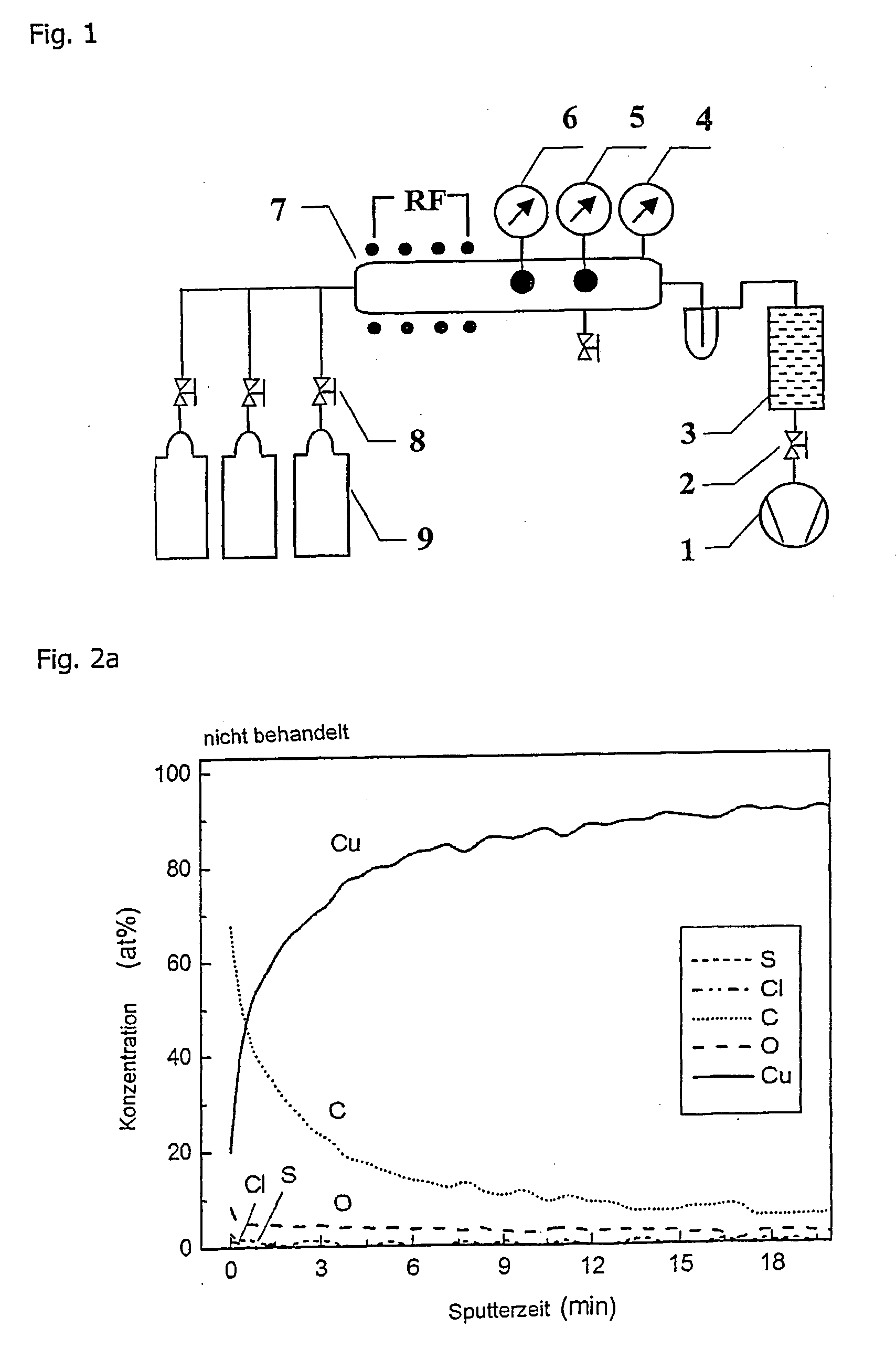

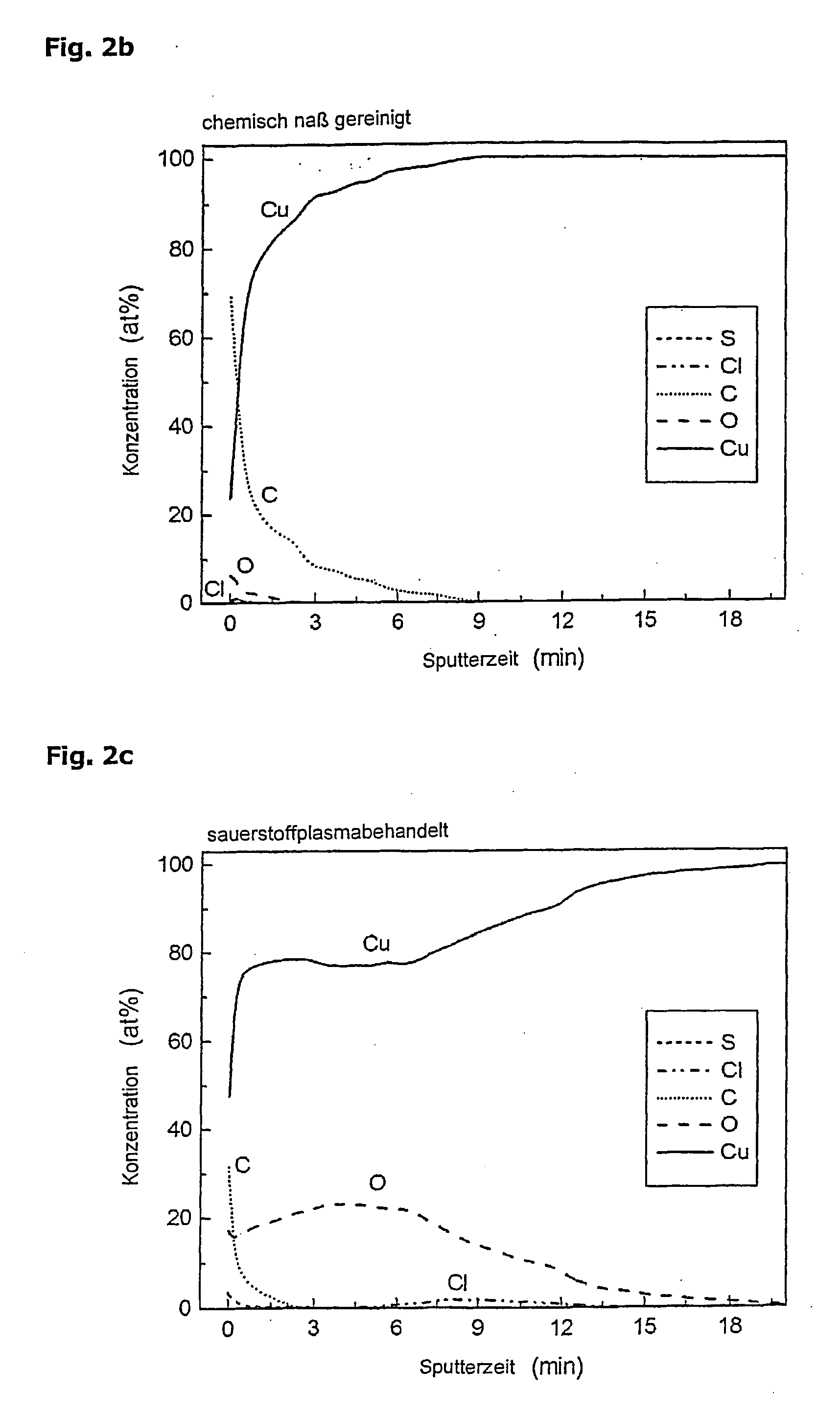

Plasma treatment for purifying copper or nickel

InactiveUS20060054184A1Reduce connection resistanceReduce impuritySoldering apparatusElectrostatic cleaningAlloyOxygen

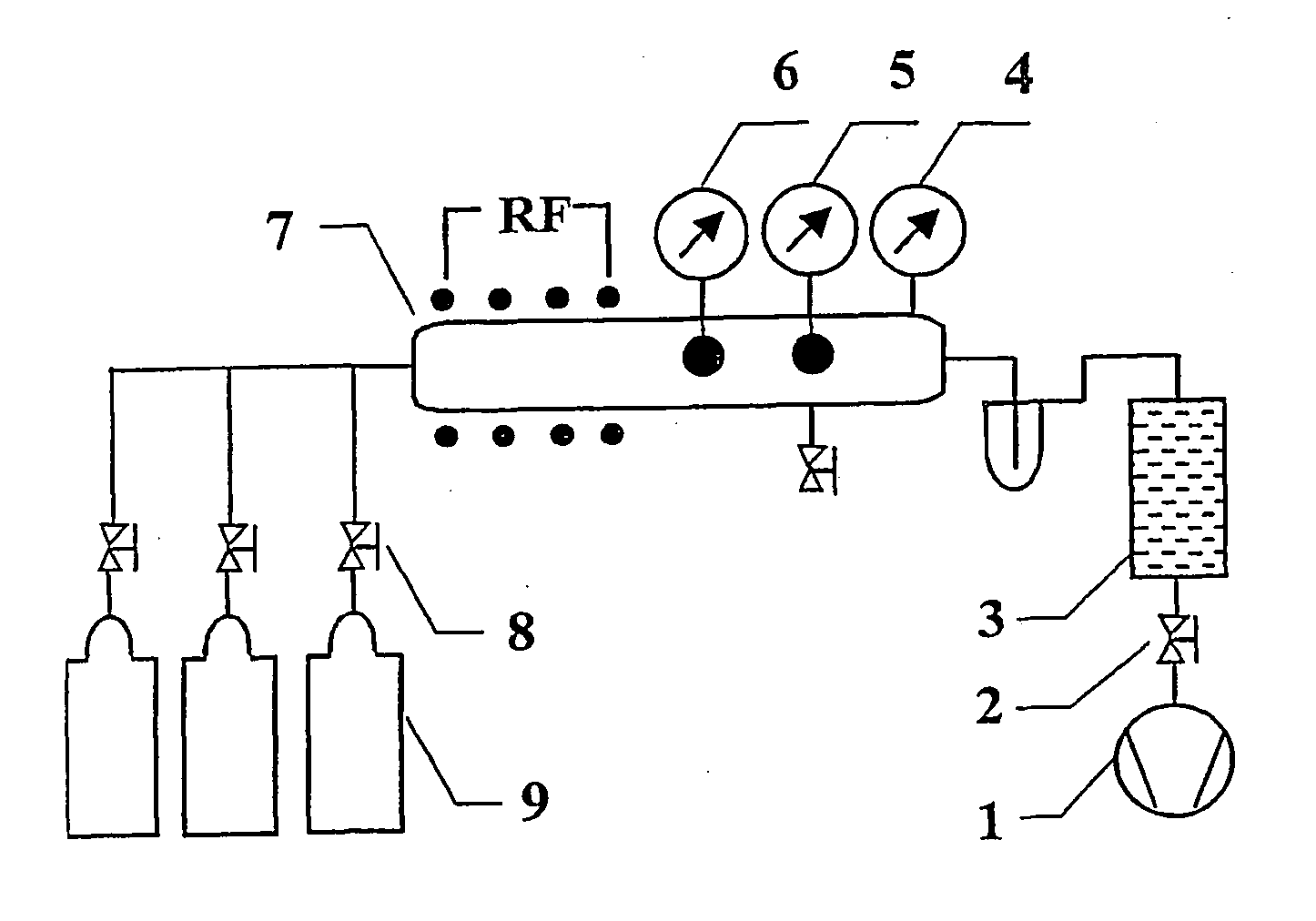

A method for treating electronic components made of copper, nickel or alloys thereof or with materials such as brass or plated therewith and includes the steps of arranging the components in a treatment chamber, generating a vacuum in the treatment chamber, introducing oxygen into the treatment chamber, providing a pressure ranging between 10−1 and 50 mbar in the treatment chamber and exciting a plasma in the chamber, allowing the oxygen radicals to act on the components, generating a vacuum in the treatment chamber, introducing hydrogen into the treatment chamber, providing a pressure ranging between 10−1 and 50 mbar in the treatment chamber and exciting a plasma in the chamber and allowing the hydrogen radicals to act on the components.

Owner:KOLEKTOR GRP D O O

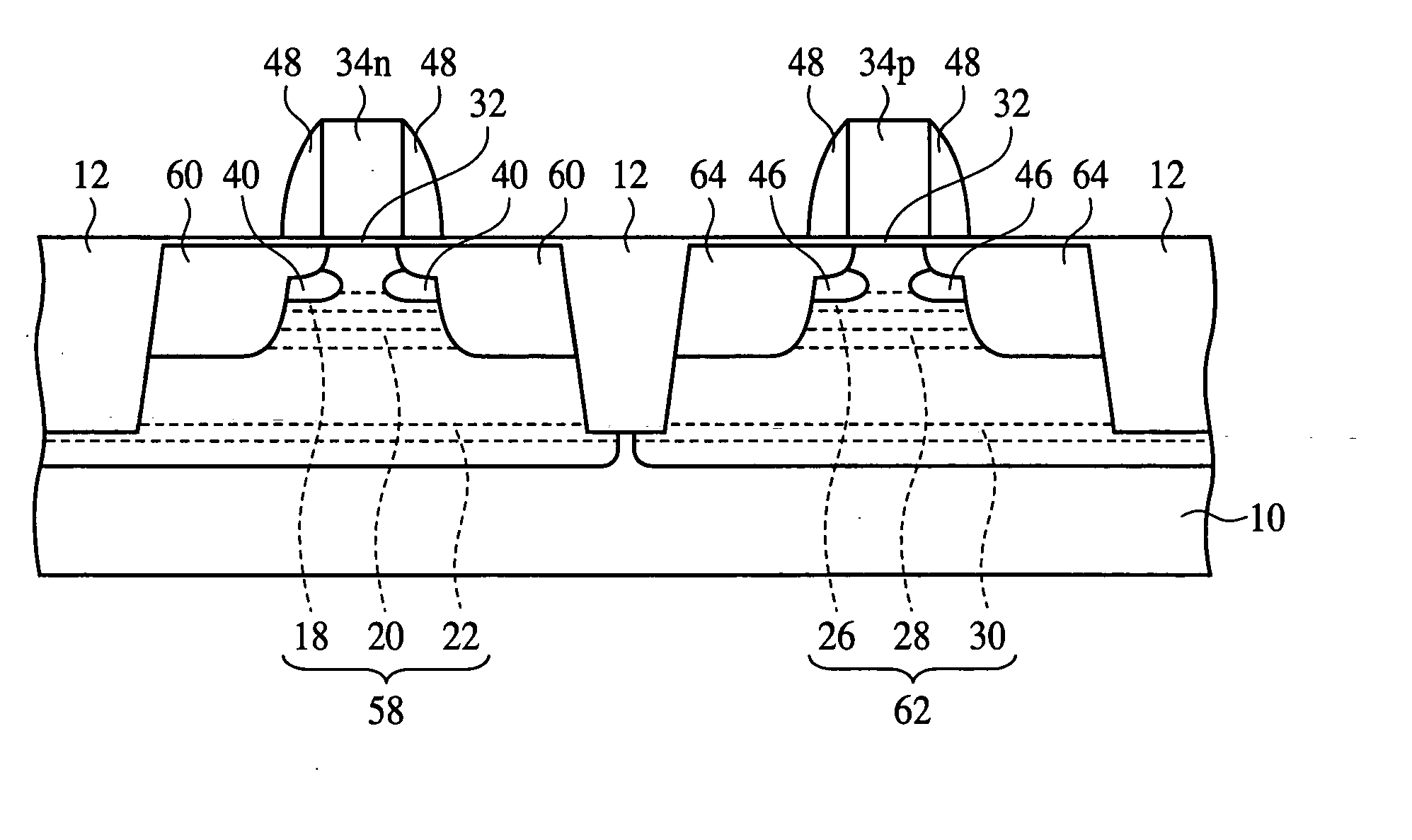

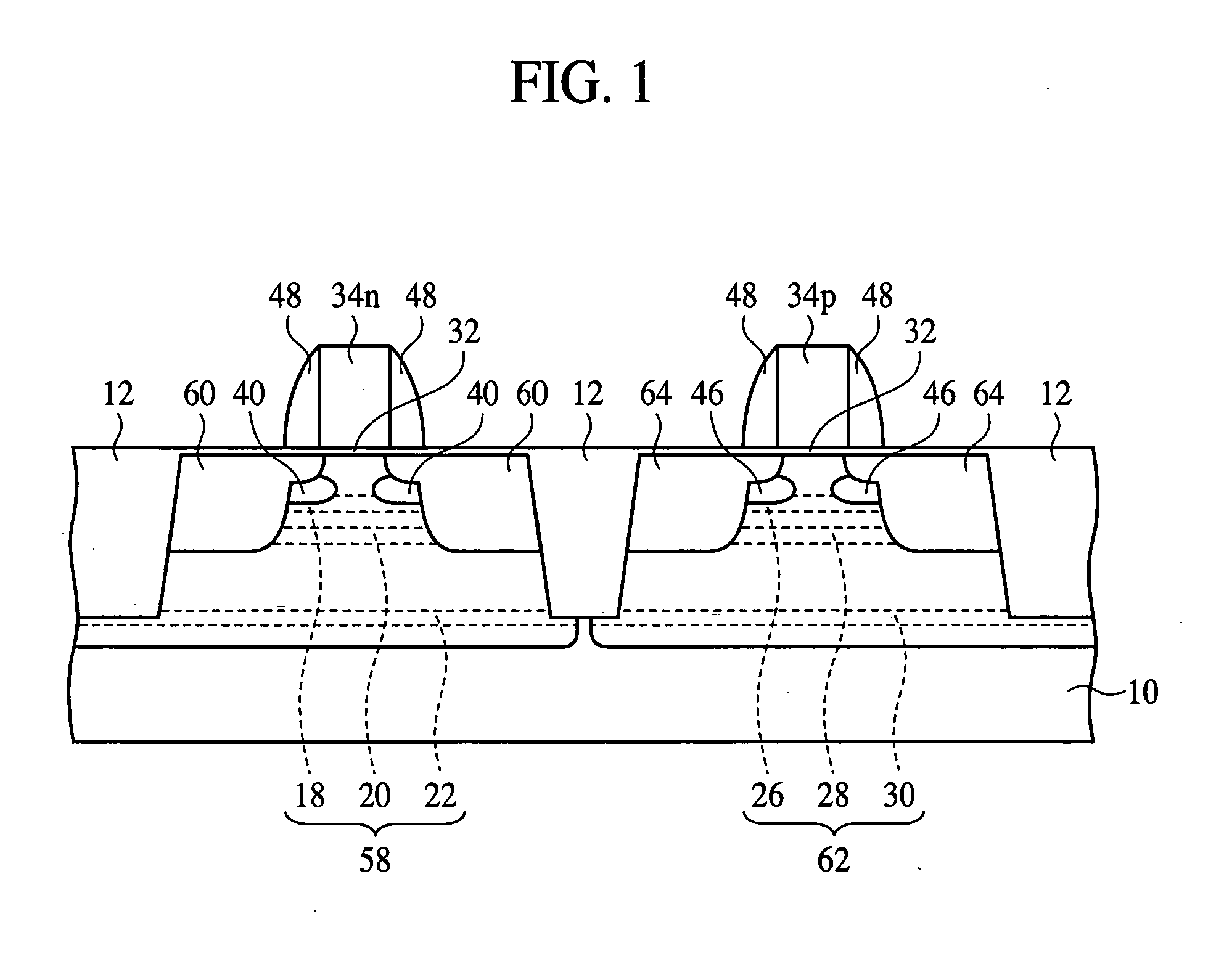

Semiconductor device and method for fabricating the same

InactiveUS20060071278A1High carrier mobilityReduce impurity concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorImpurity

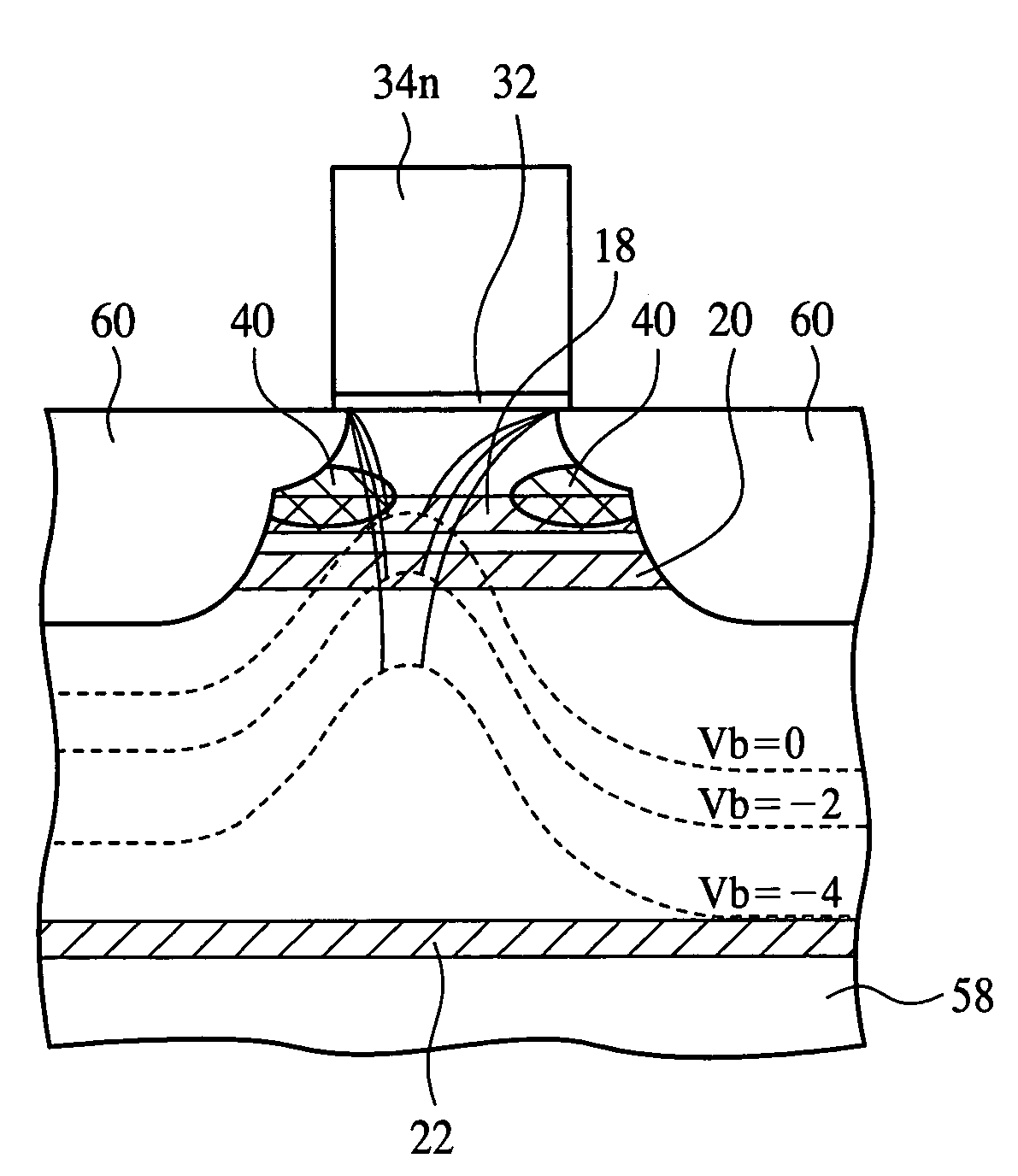

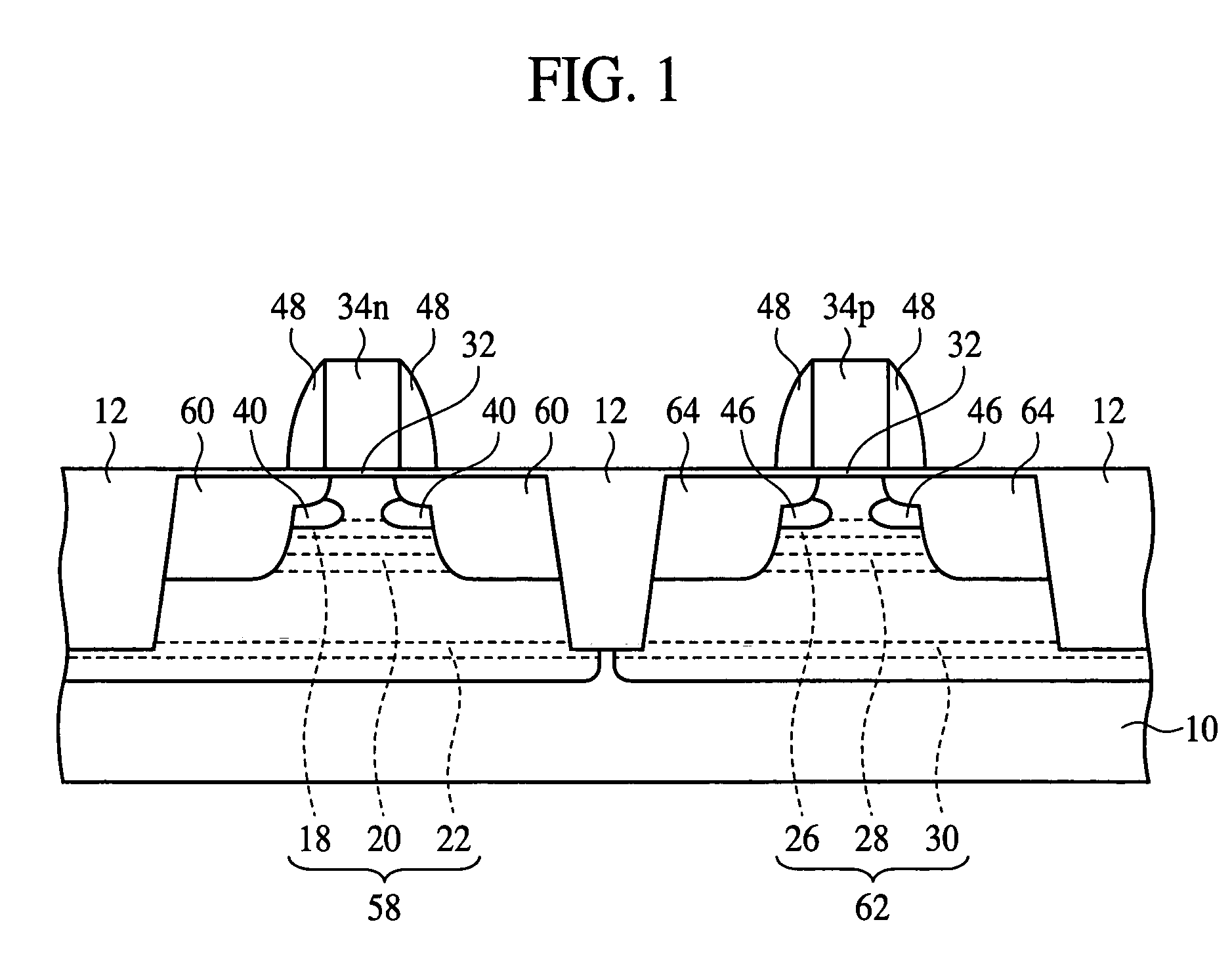

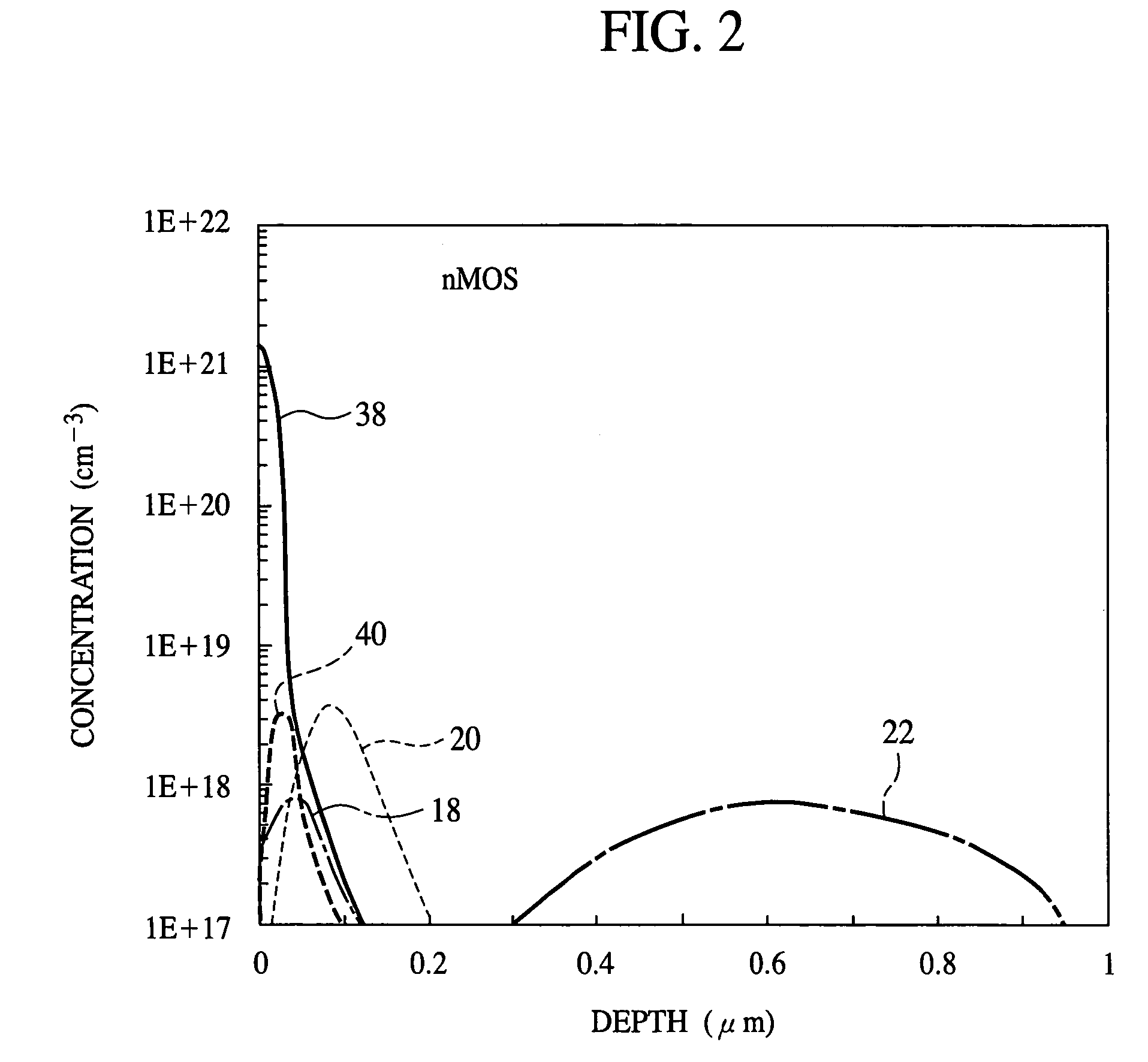

The semiconductor device comprises a well 58 formed in a semiconductor substrate 10 and having a channel region; a gate electrode 34n formed over the channel region with an insulating film 32 interposed therebetween; source / drain regions 60 formed in the well 58 on both sides of the gate electrode 34n, sandwiching the channel region; and a pocket region 40 formed between the source / drain region and the channel region. The well 58 has a first peak of an impurity concentration at a depth deeper than the pocket region 40 and shallower than the bottom of the source / drain regions 60, and a second peak of the impurity concentration at a depth near the bottom of the source / drain regions 60.

Owner:SOCIONEXT INC

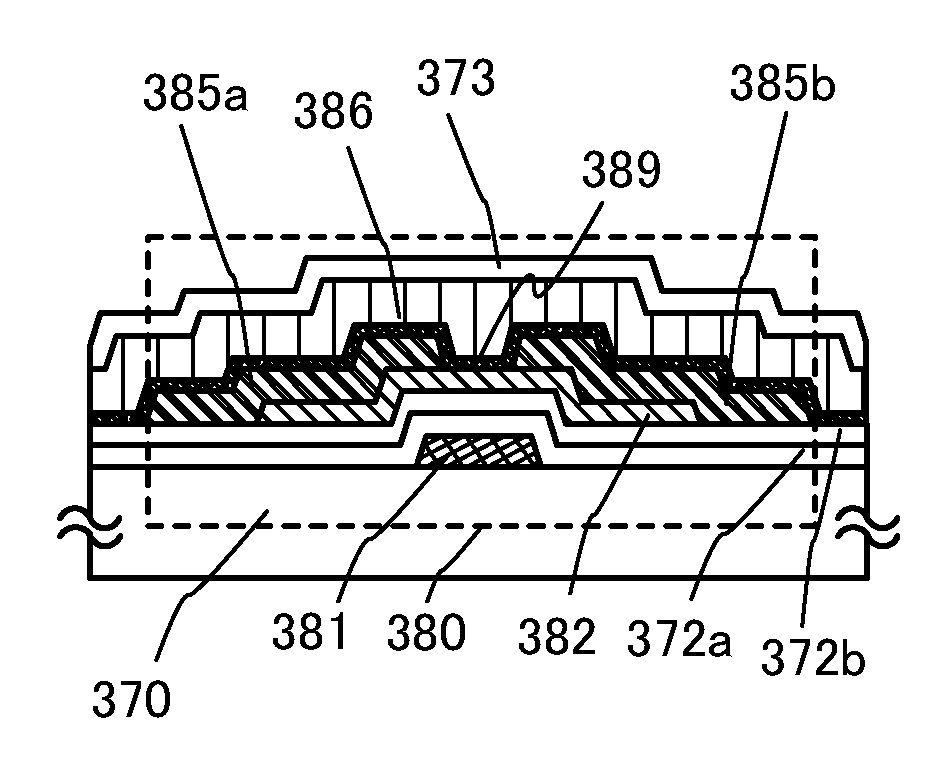

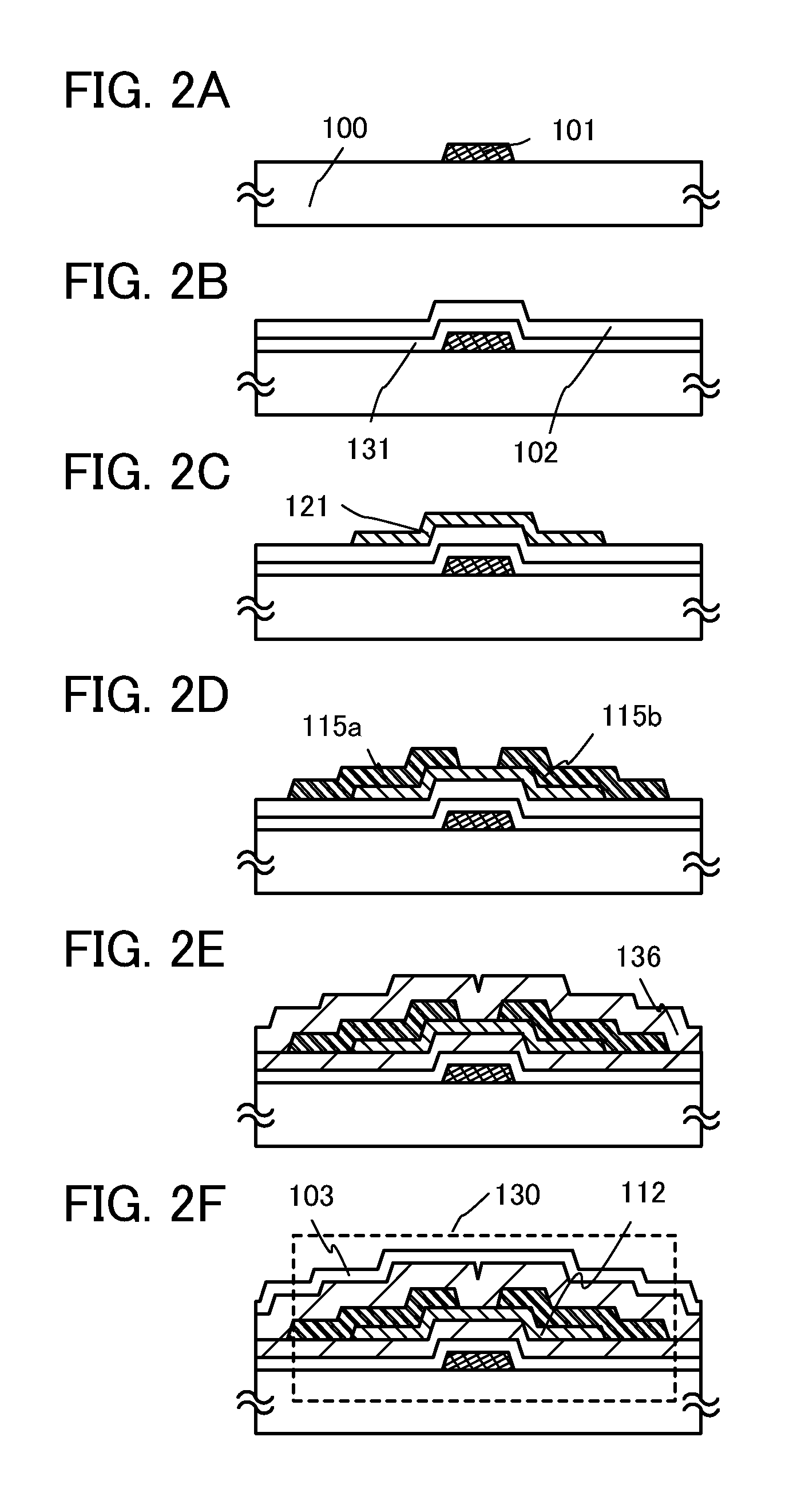

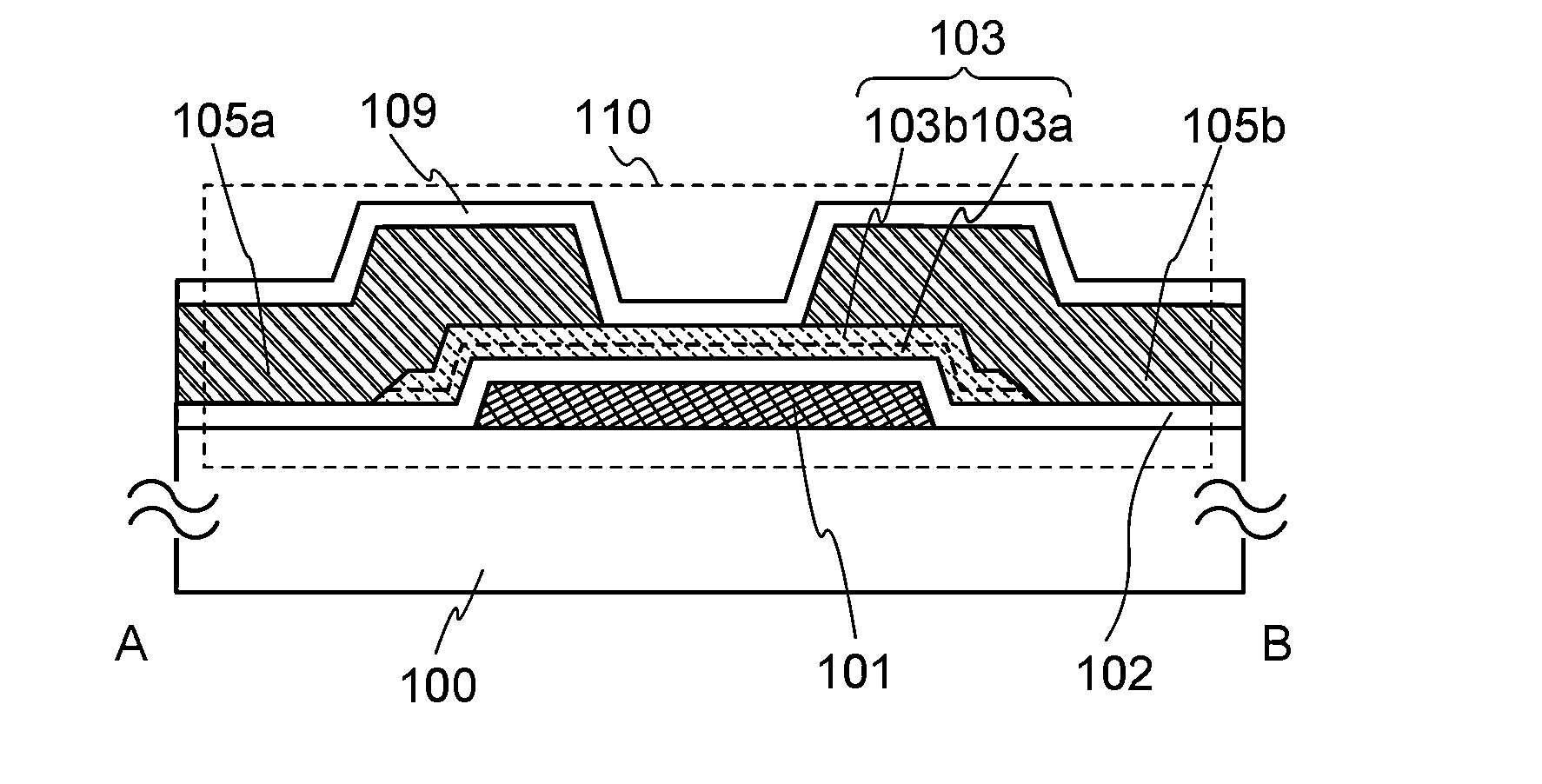

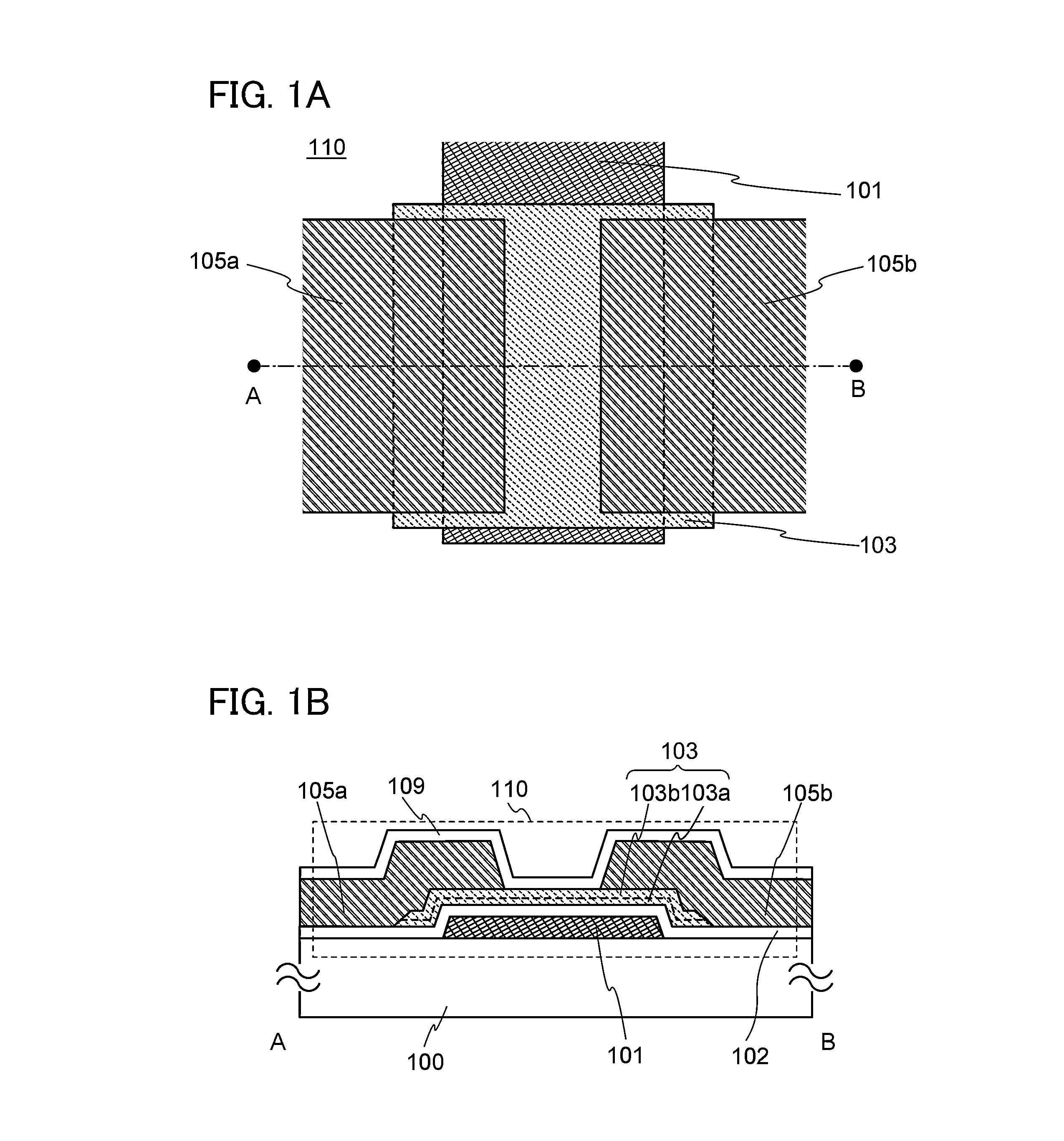

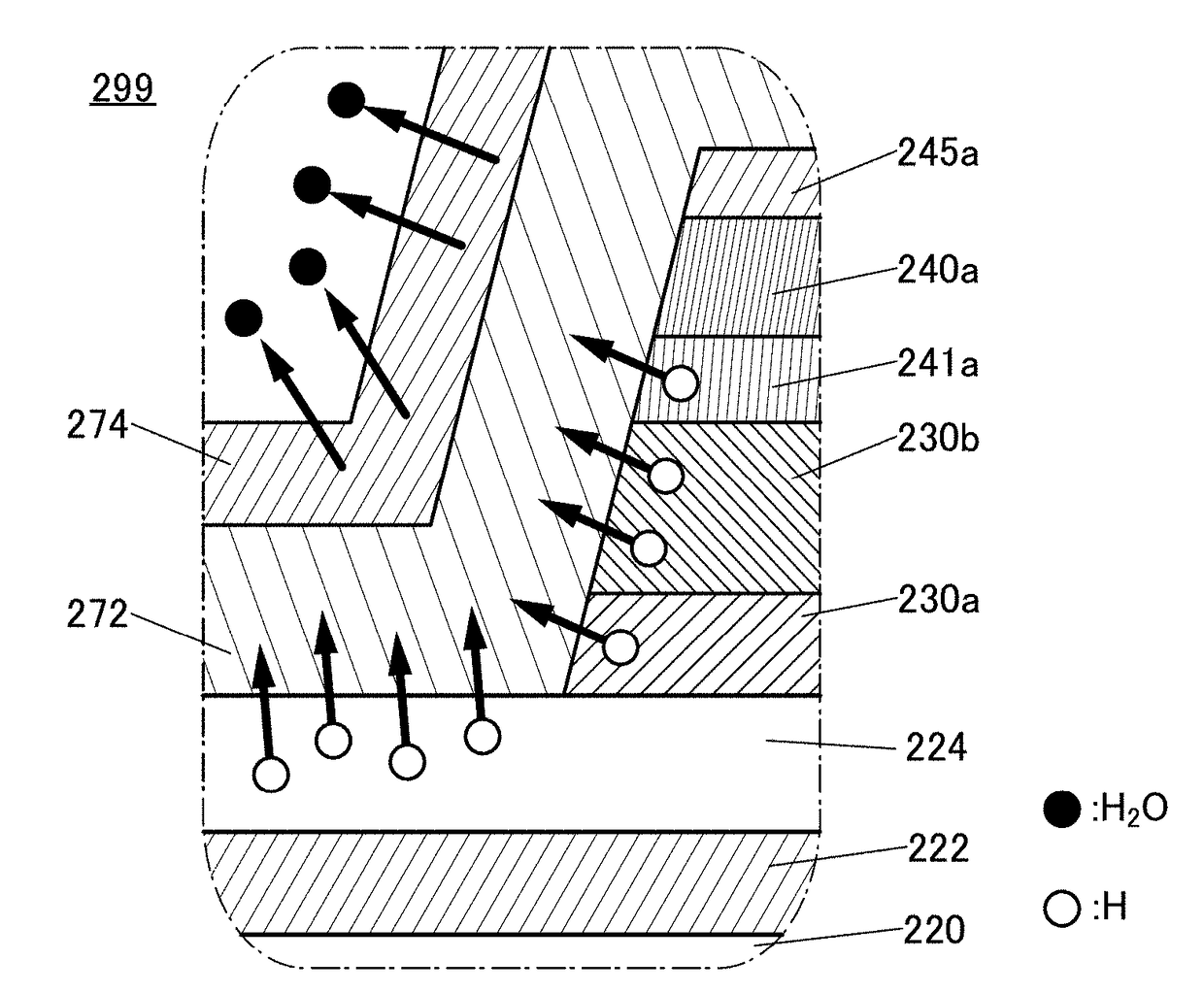

Semiconductor device and method for manufacturing the same

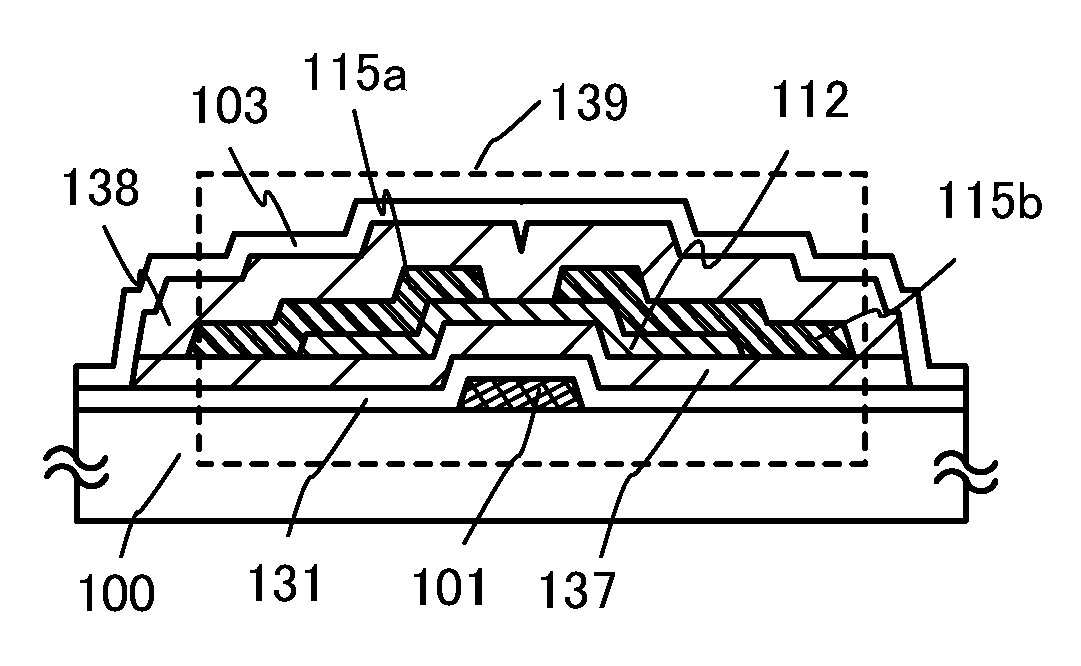

InactiveUS20110101335A1Stable electrical characteristicsReduce impurity concentrationSolid-state devicesSemiconductor/solid-state device manufacturingHydrogen atomDangling bond

An object is to provide a semiconductor device including an oxide semiconductor with stable electric characteristics can be provided. An insulating layer having many defects typified by dangling bonds is formed over an oxide semiconductor layer with an oxygen-excess mixed region or an oxygen-excess oxide insulating layer interposed therebetween, whereby impurities in the oxide semiconductor layer, such as hydrogen or moisture (a hydrogen atom or a compound including a hydrogen atom such as H2O), are moved through the oxygen-excess mixed region or oxygen-excess oxide insulating layer and diffused into the insulating layer. Thus, the impurity concentration of the oxide semiconductor layer is reduced.

Owner:SEMICON ENERGY LAB CO LTD

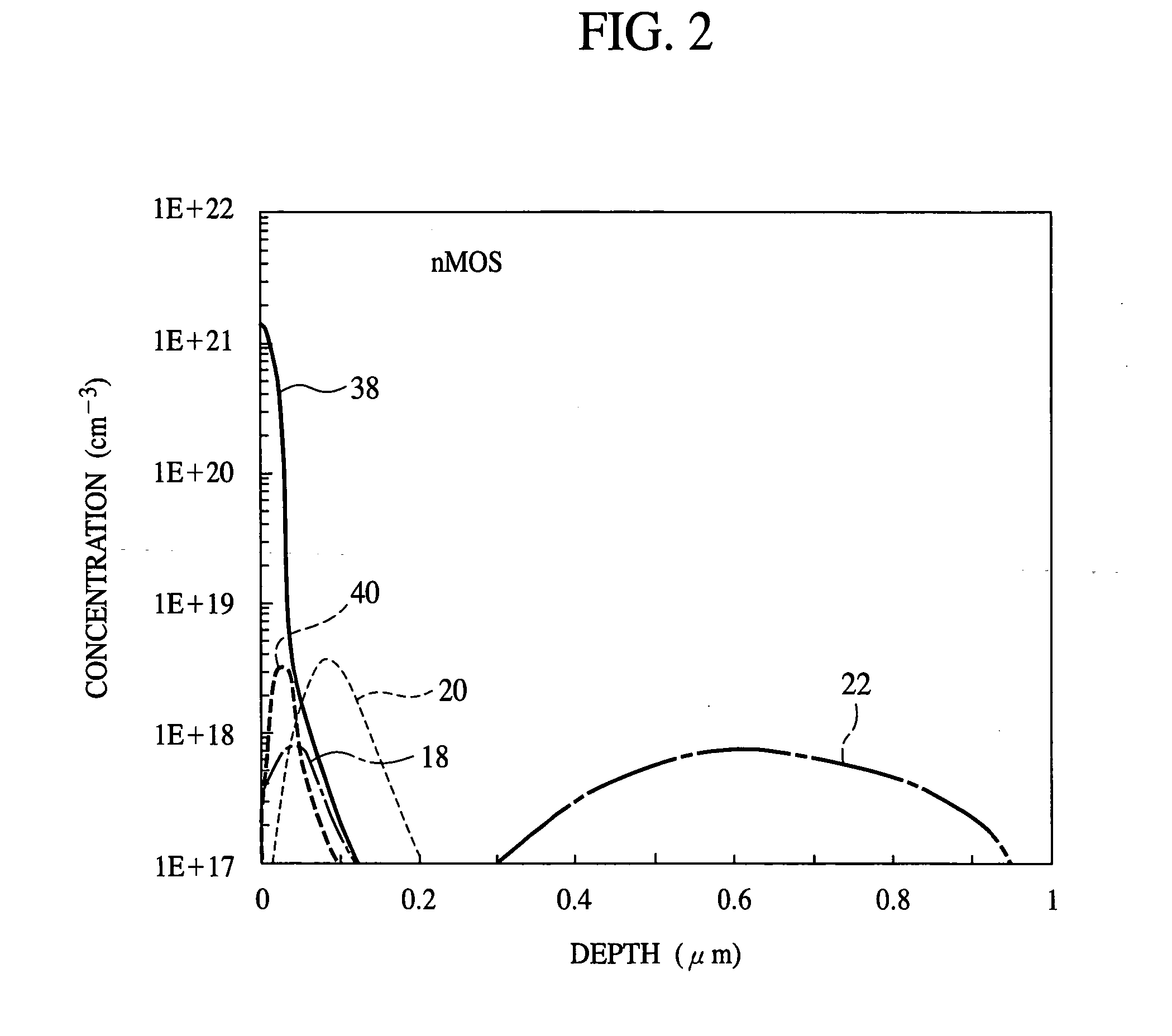

Semiconductor device having well with peak impurity concentrations and method for fabricating the same

InactiveUS7592241B2Improve performanceCarrier scattering by the dopant ions is decreasedSemiconductor/solid-state device manufacturingSemiconductor devicesPeak valueSemiconductor

The semiconductor device comprises a well 58 formed in a semiconductor substrate 10 and having a channel region; a gate electrode 34n formed over the channel region with an insulating film 32 interposed therebetween; source / drain regions 60 formed in the well 58 on both sides of the gate electrode 34n, sandwiching the channel region; and a pocket region 40 formed between the source / drain region and the channel region. The well 58 has a first peak of an impurity concentration at a depth deeper than the pocket region 40 and shallower than the bottom of the source / drain regions 60, and a second peak of the impurity concentration at a depth near the bottom of the source / drain regions 60.

Owner:SOCIONEXT INC

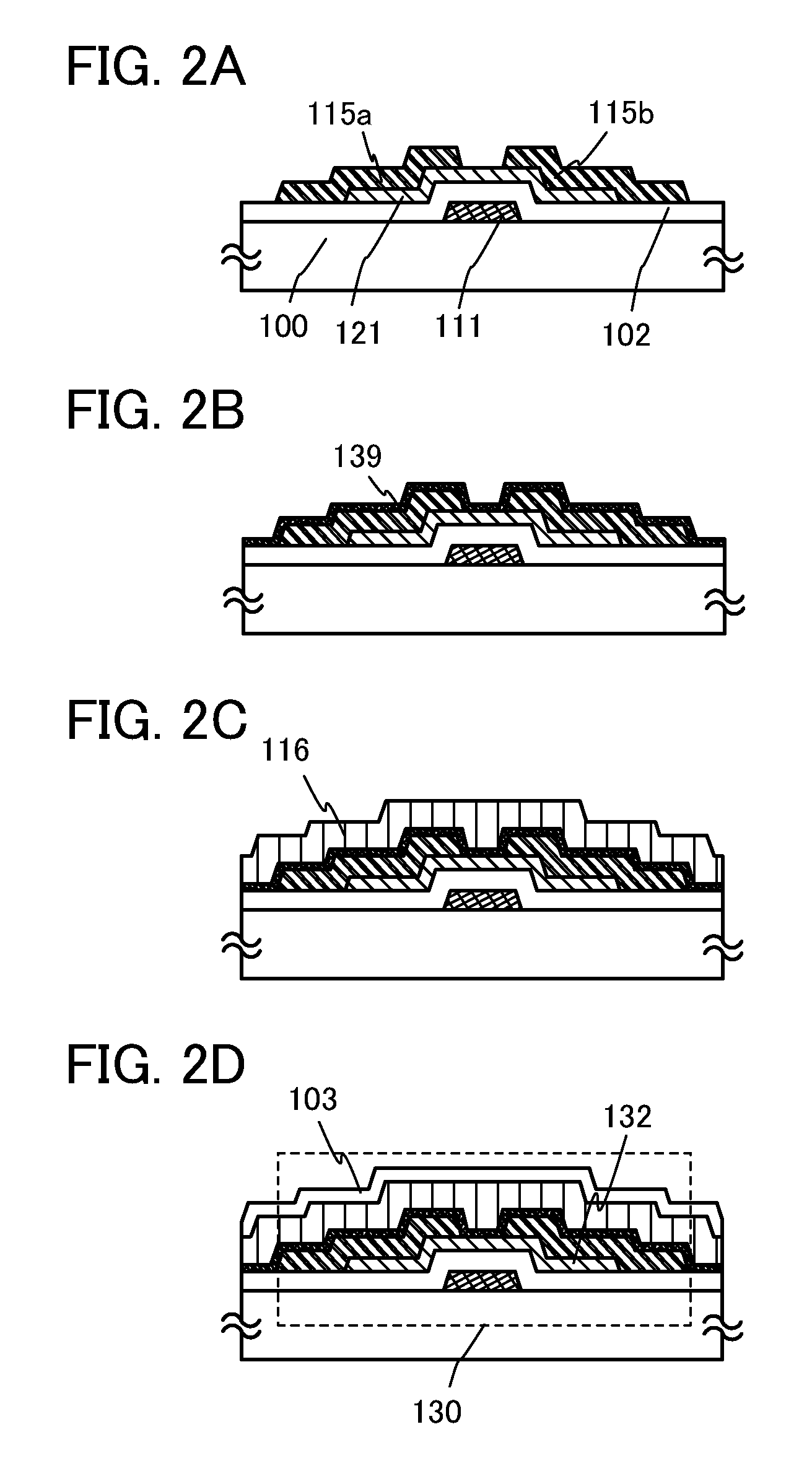

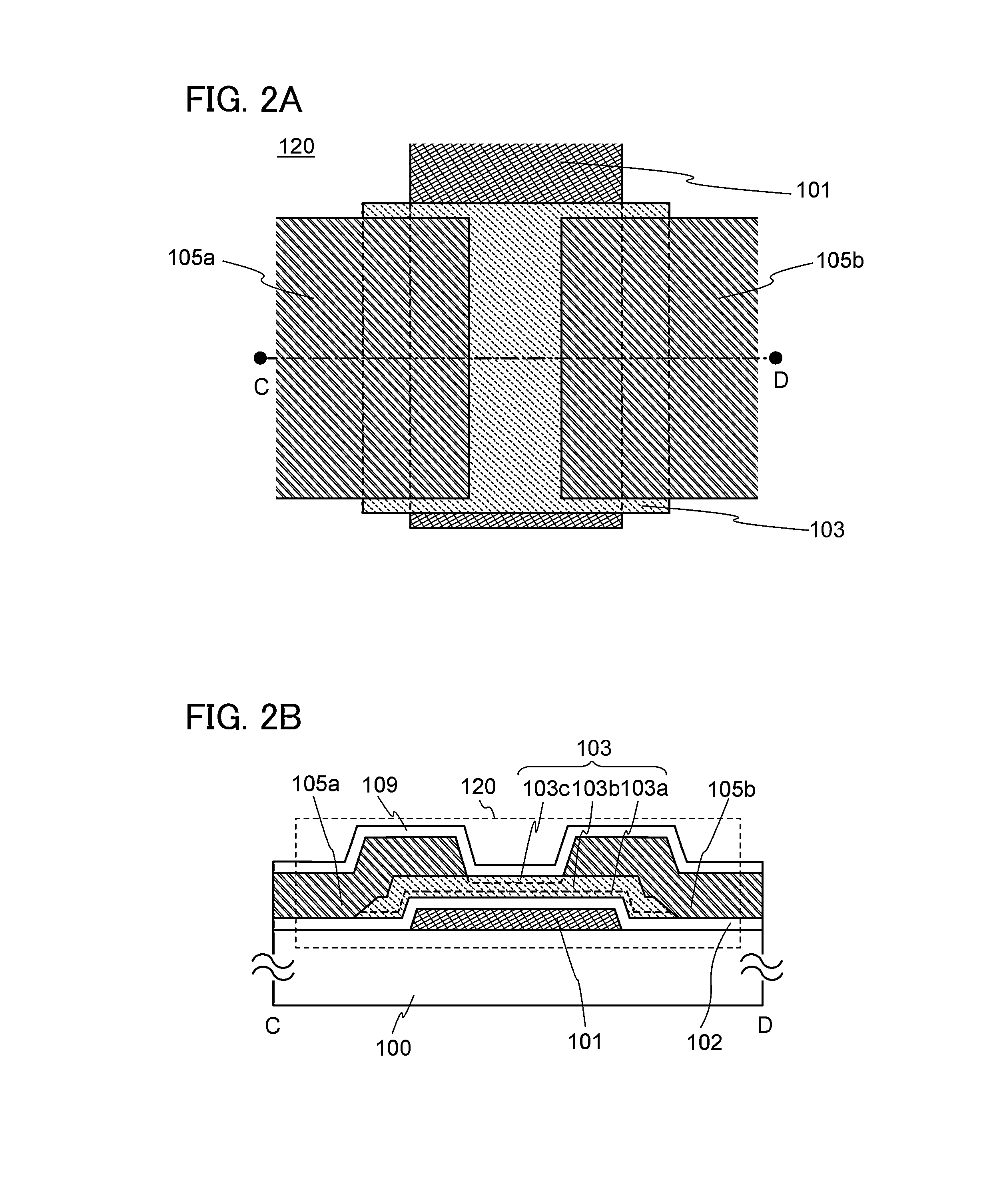

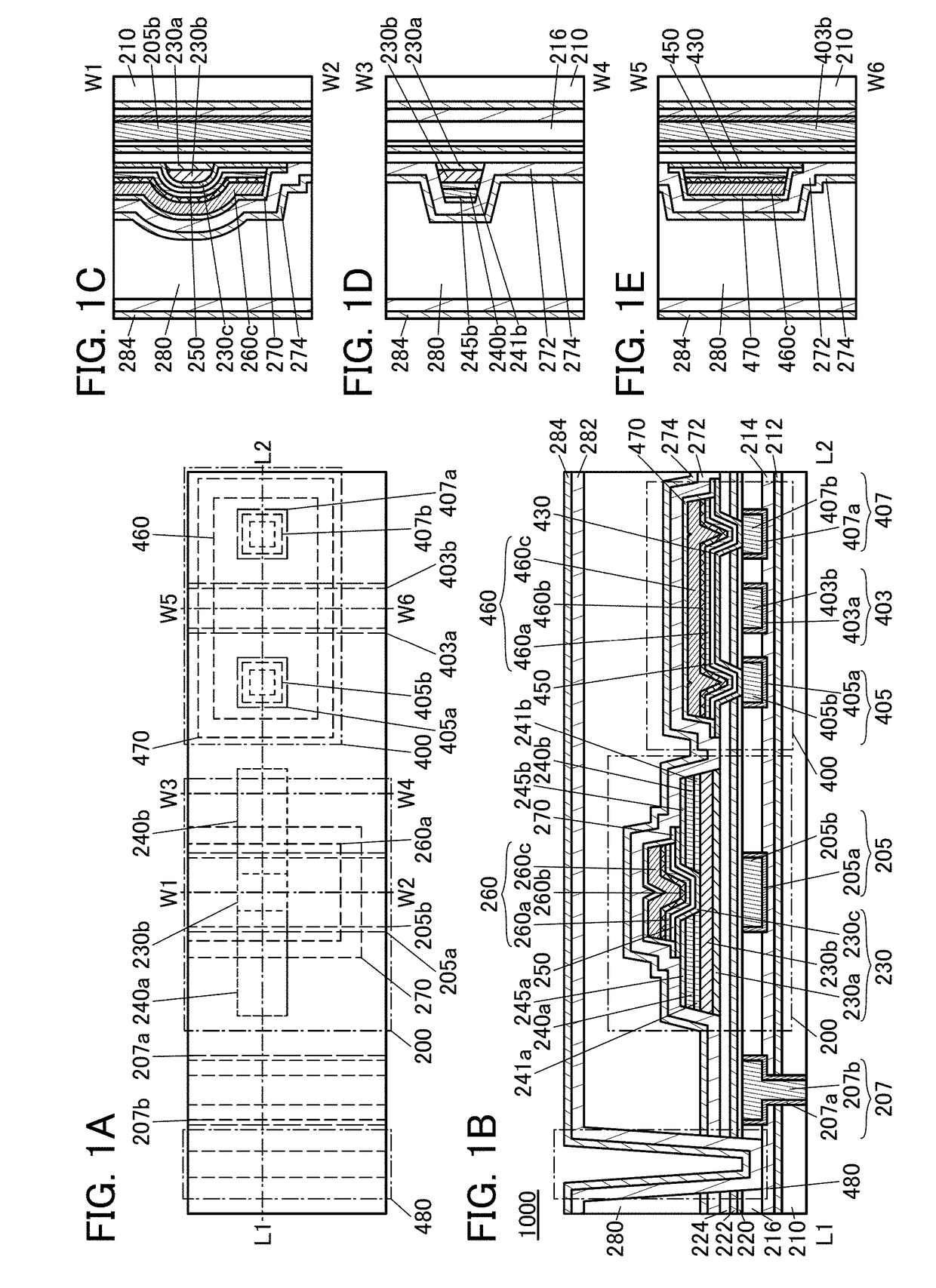

Semiconductor device and method for manufacturing the same

ActiveUS20110089416A1Reduce concentration of impurityHigh binding energySemiconductor/solid-state device detailsSolid-state devicesOxide semiconductorPlasma treatment

An object is to provide a semiconductor device with stable electric characteristics in which an oxide semiconductor is used. An impurity such as hydrogen or moisture (e.g., a hydrogen atom or a compound containing a hydrogen atom such as H2O) is eliminated from an oxide semiconductor layer with use of a halogen element typified by fluorine or chlorine, so that the impurity concentration in the oxide semiconductor layer is reduced. A gate insulating layer and / or an insulating layer provided in contact with the oxide semiconductor layer can be formed to contain a halogen element. In addition, a halogen element may be attached to the oxide semiconductor layer through plasma treatment under an atmosphere of a gas containing a halogen element.

Owner:SEMICON ENERGY LAB CO LTD

Method of manufacturing a semiconductor device

InactiveUS7402467B1Avoid erosionRemove pollutantsSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

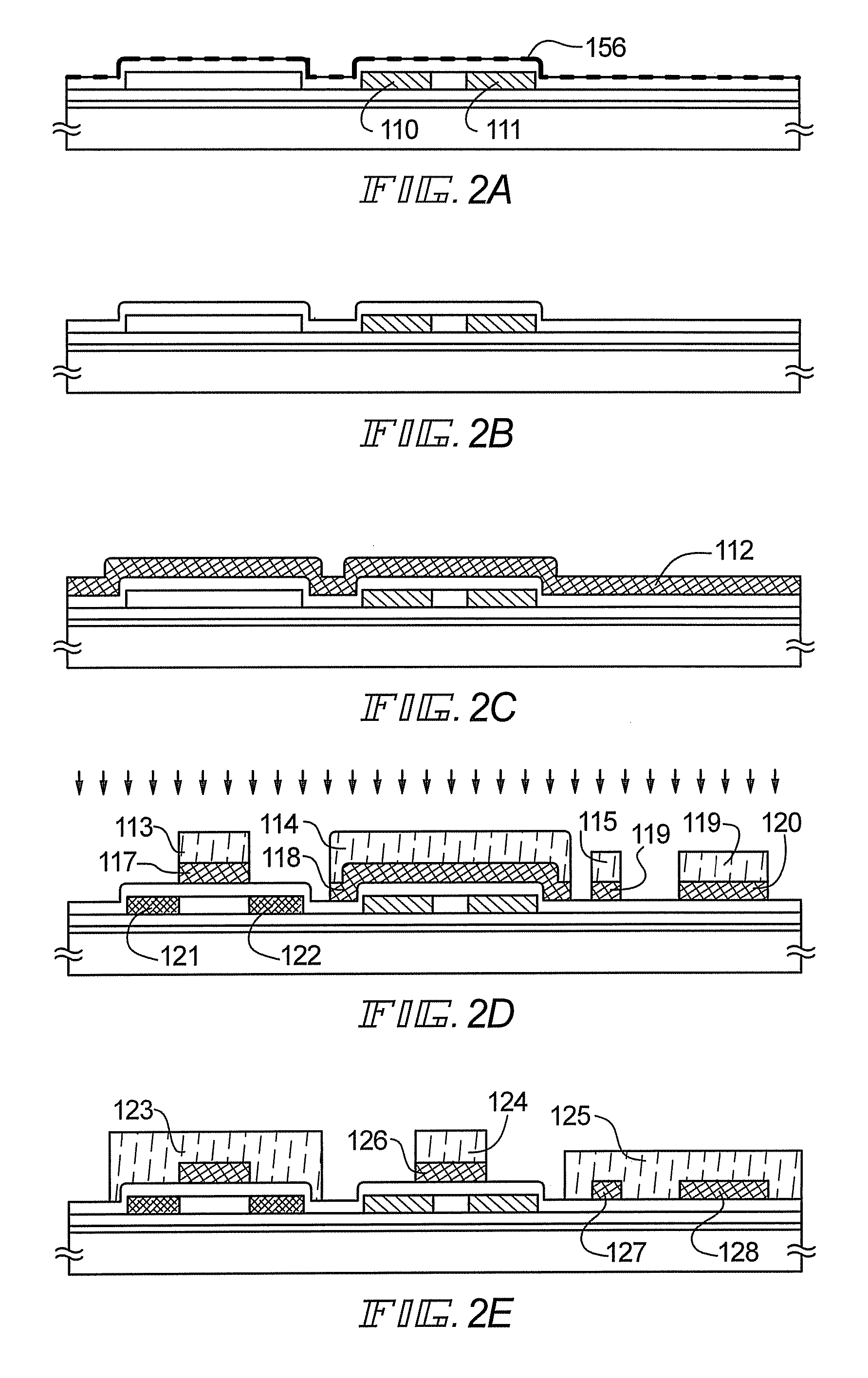

A reduction in contaminating impurities in a TFT, and a TFT which is reliable, is obtained in a semiconductor device which uses the TFT. By removing contaminating impurities residing in a film interface of the TFT using a solution containing fluorine, a reliable TFT can be obtained.

Owner:SEMICON ENERGY LAB CO LTD

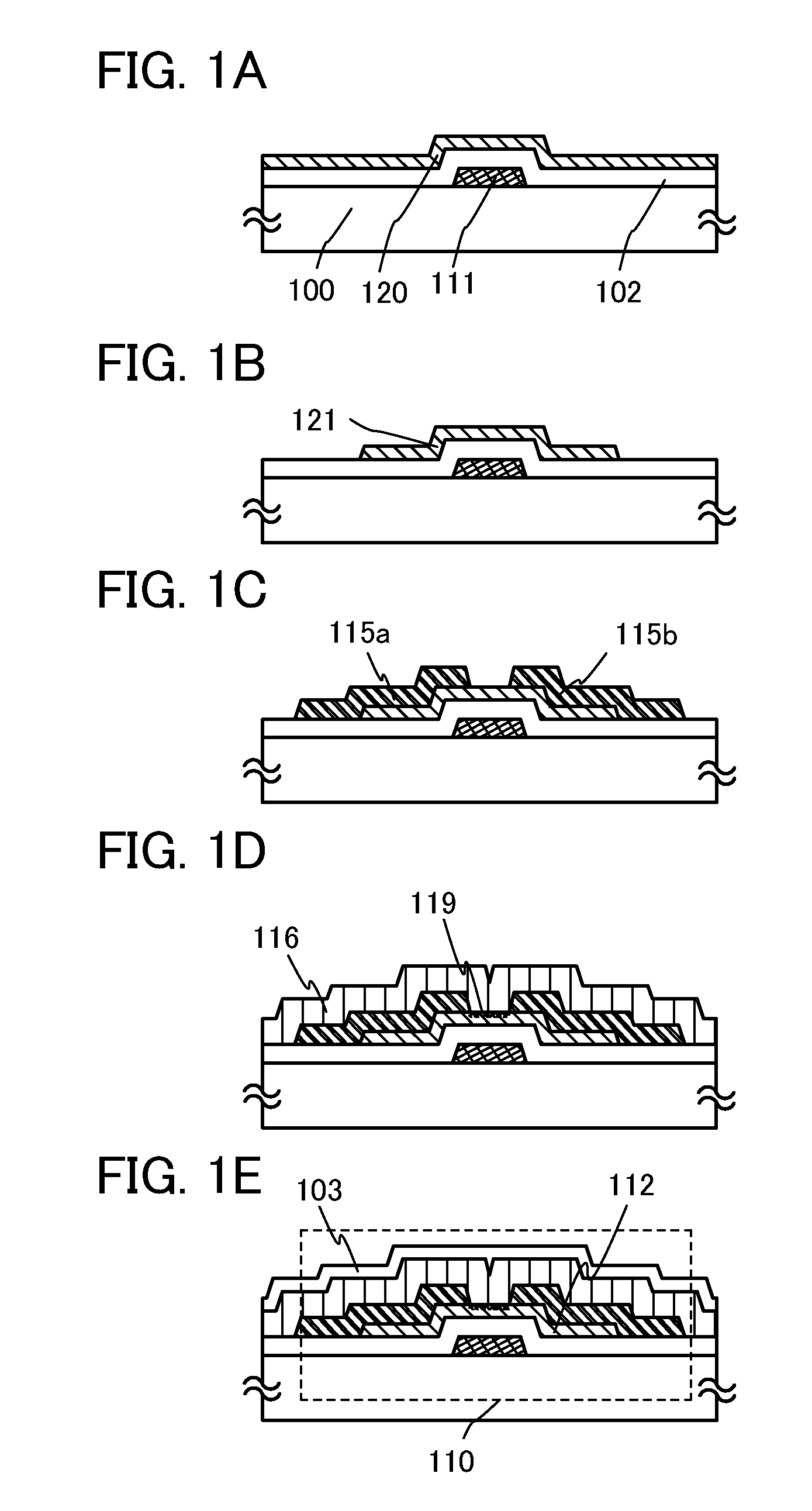

Semiconductor element and method for manufacturing the same

ActiveUS20110068336A1Improve reliabilityIncrease computing speedSolid-state devicesSemiconductor/solid-state device manufacturingHydrogen atomCharge carrier

An object is to provide a thin film transistor and a method for manufacturing the thin film transistor including an oxide semiconductor with a controlled threshold voltage, high operation speed, a relatively easy manufacturing process, and sufficient reliability. An impurity having influence on carrier concentration in the oxide semiconductor layer, such as a hydrogen atom or a compound containing a hydrogen atom such as H2O, may be eliminated. An oxide insulating layer containing a large number of defects such as dangling bonds may be formed in contact with the oxide semiconductor layer, such that the impurity diffuses into the oxide insulating layer and the impurity concentration in the oxide semiconductor layer is reduced. The oxide semiconductor layer or the oxide insulating layer in contact with the oxide semiconductor layer may be formed in a deposition chamber which is evacuated with use of a cryopump whereby the impurity concentration is reduced.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and method of manufacturing the same

ActiveUS20050045892A1Reduce impurity concentrationImprove pressure resistanceSemiconductor/solid-state device manufacturingDiodeHeterojunctionDevice material

An aspect of the present invention provides a semiconductor device that includes a first semiconductor region of a first conductivity type and a second semiconductor region of a second conductivity type, having a different band gap from the first semiconductor region and forming a heterojunction with the first semiconductor region.

Owner:NISSAN MOTOR CO LTD

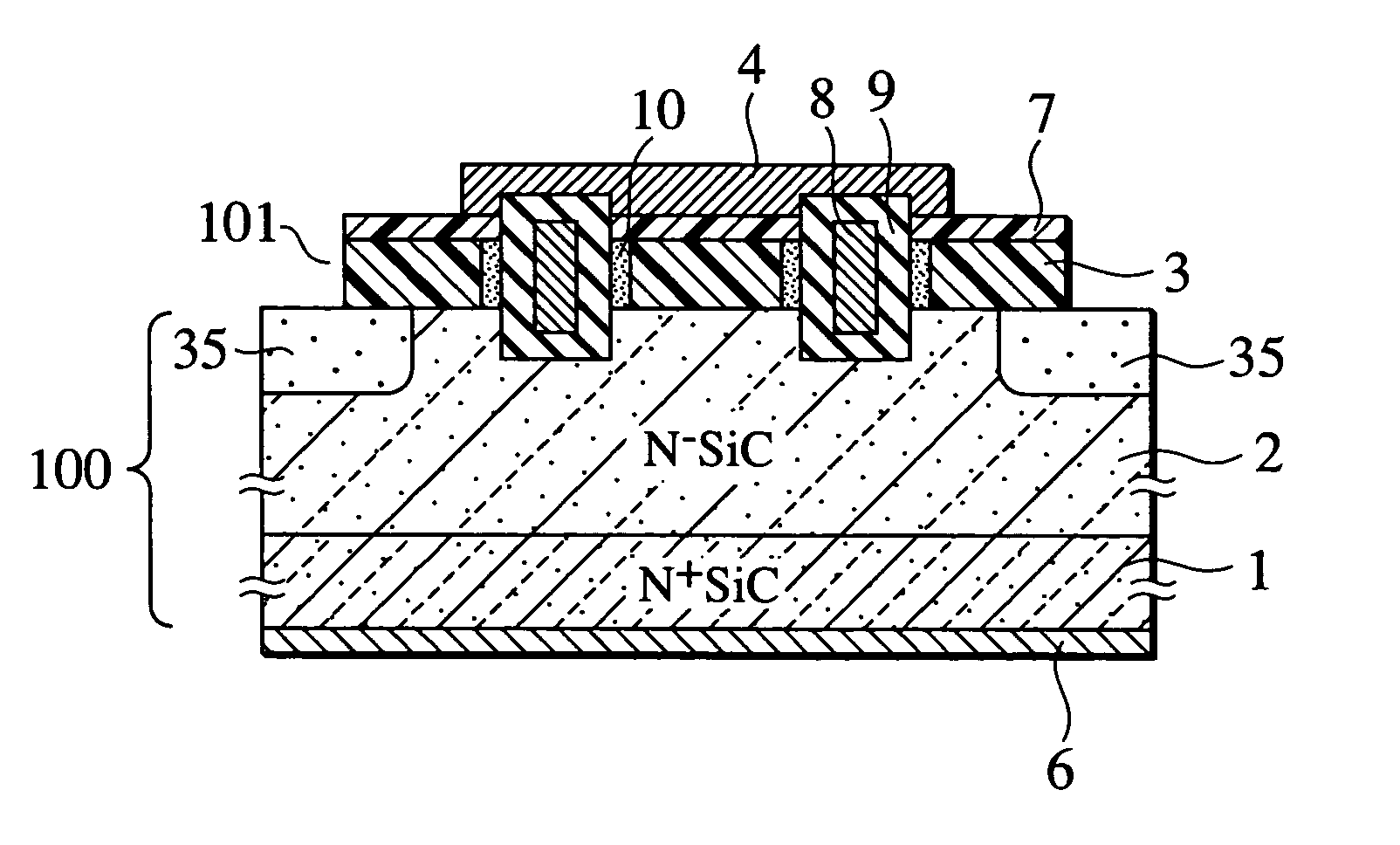

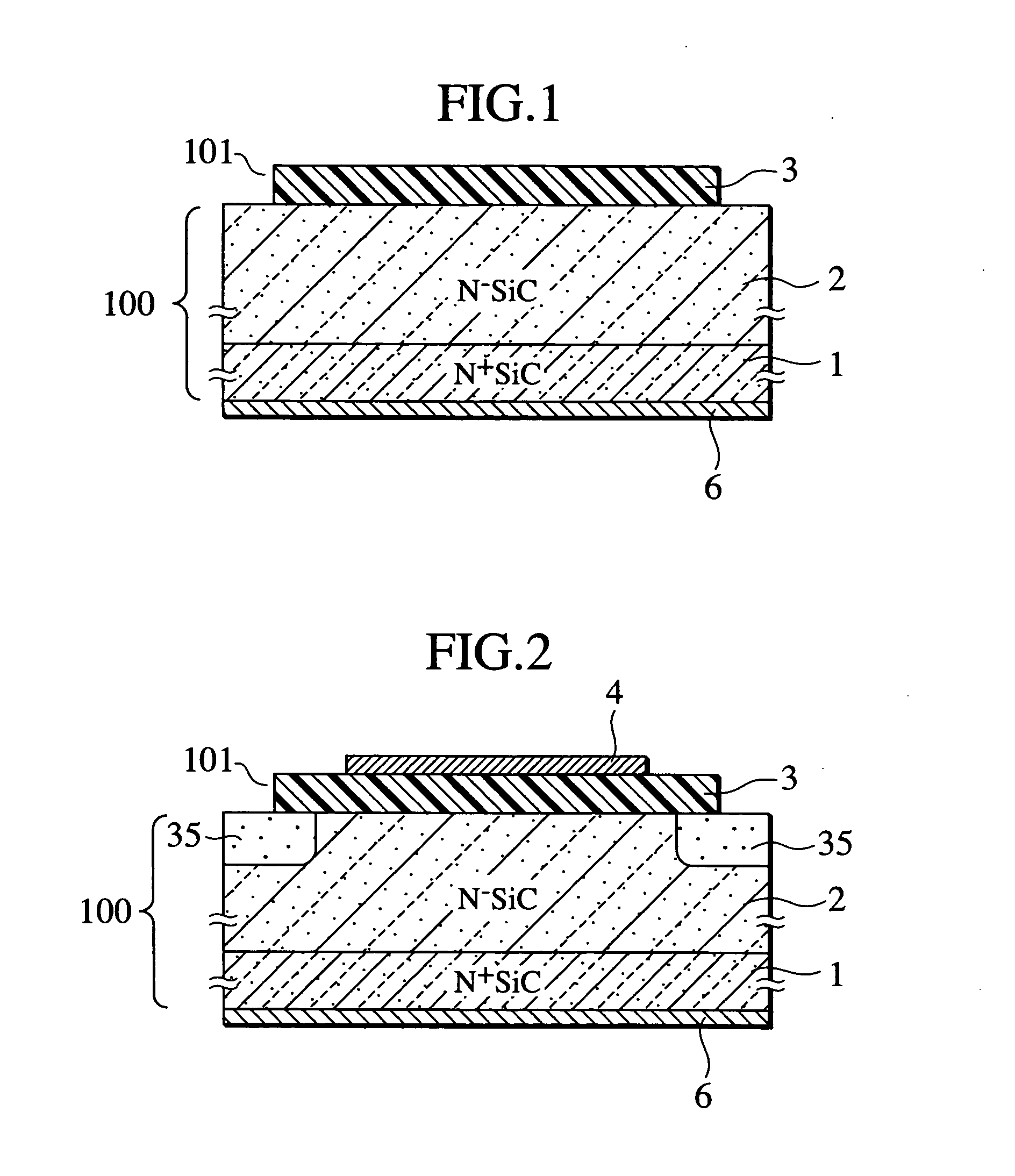

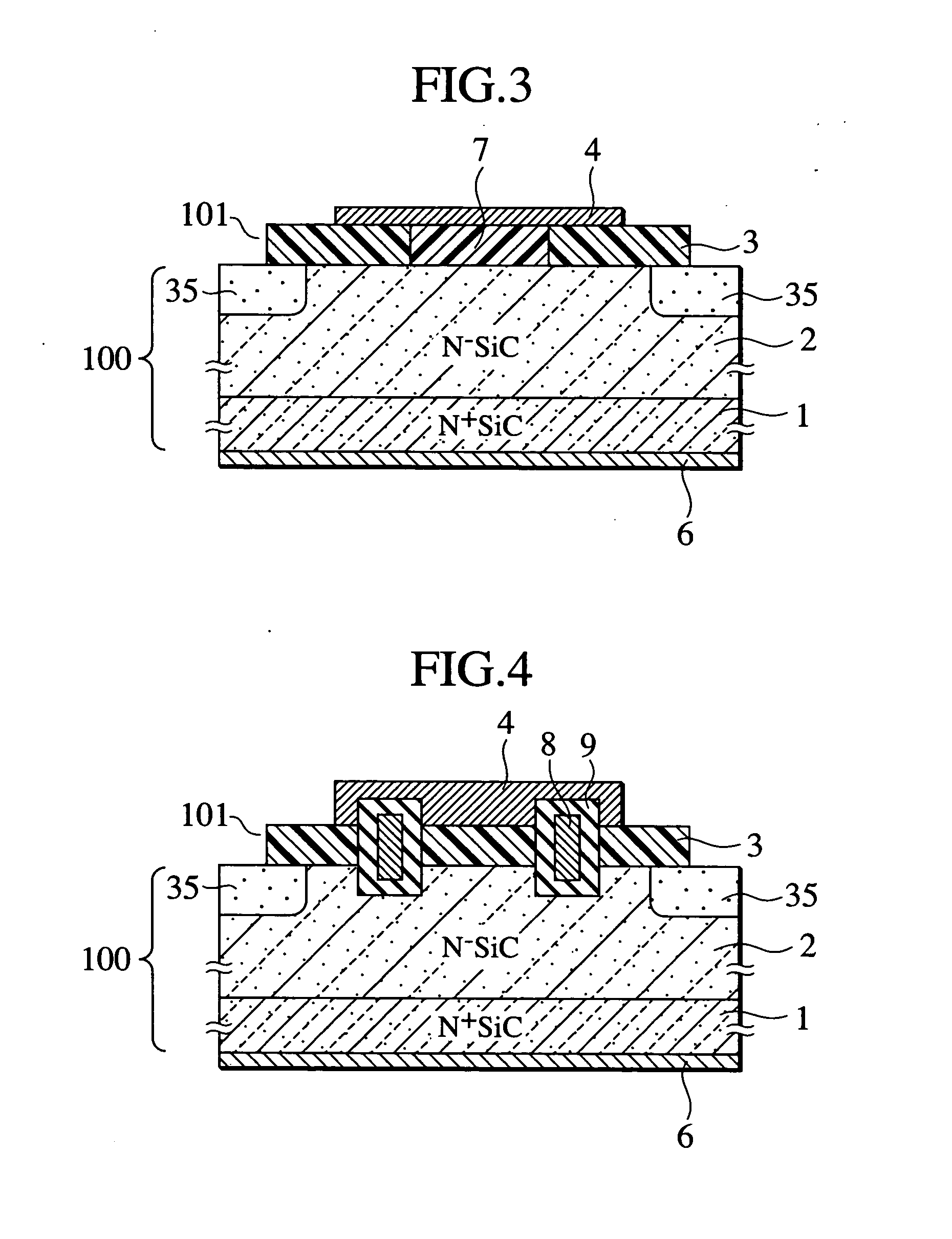

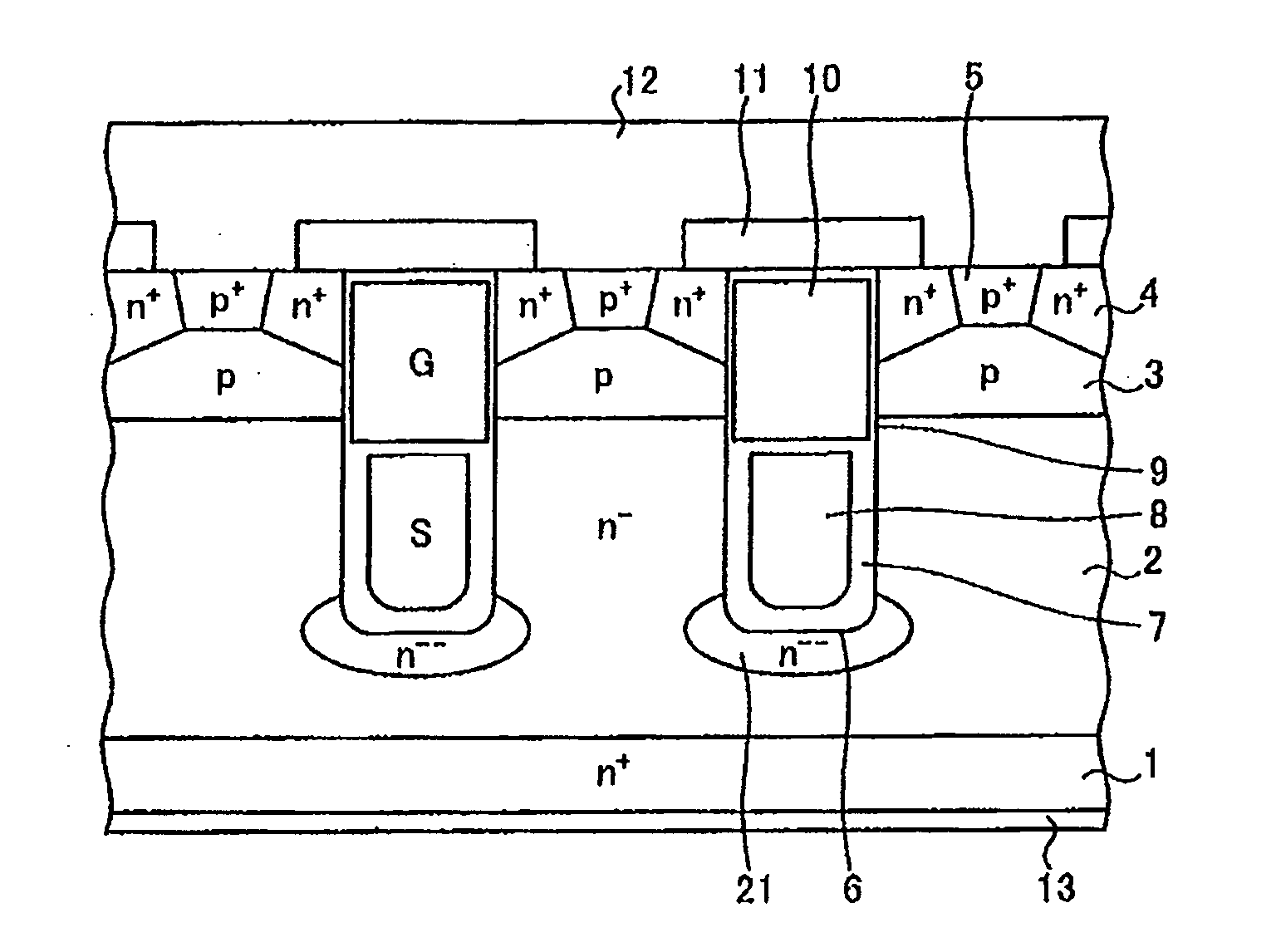

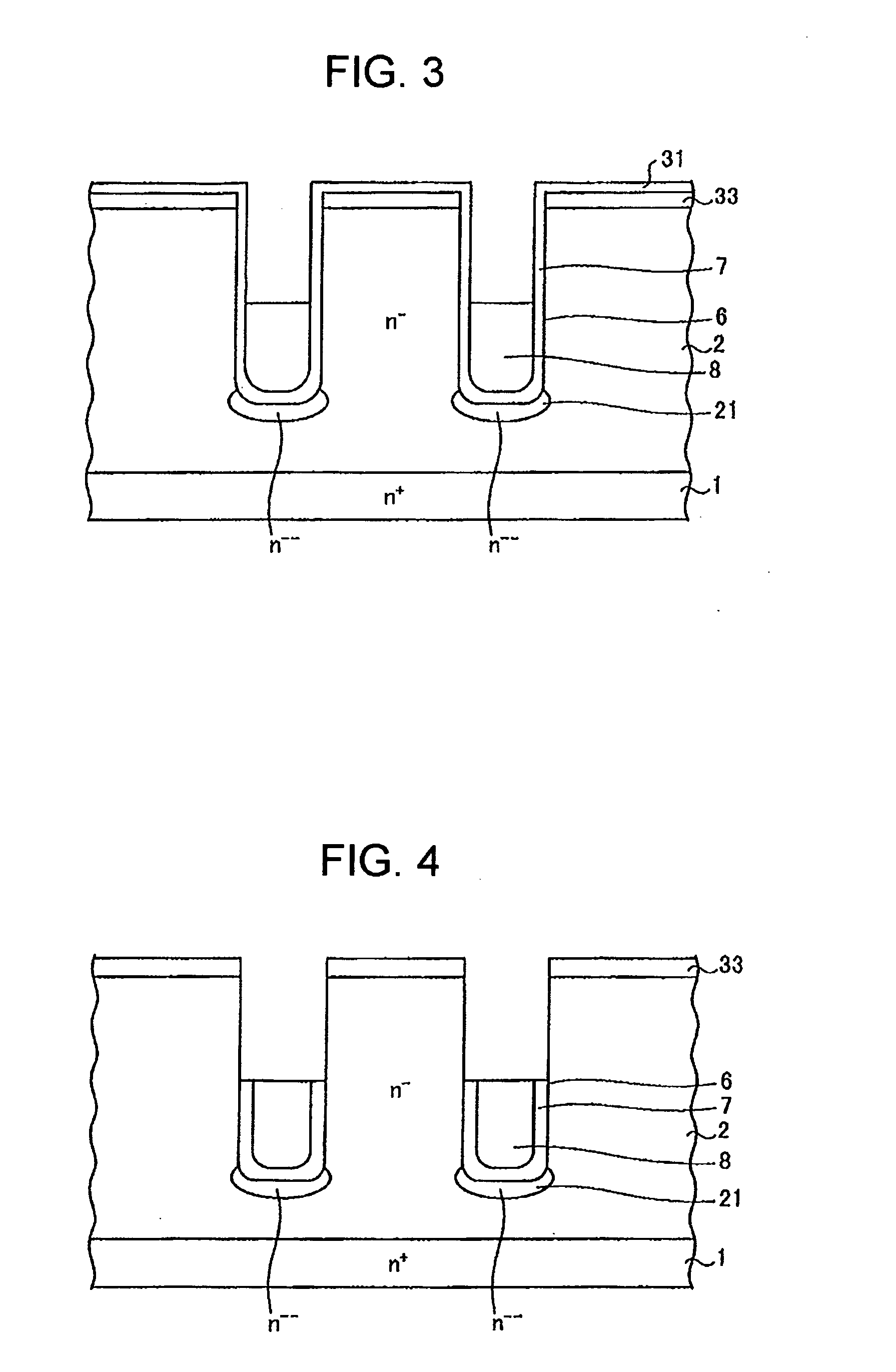

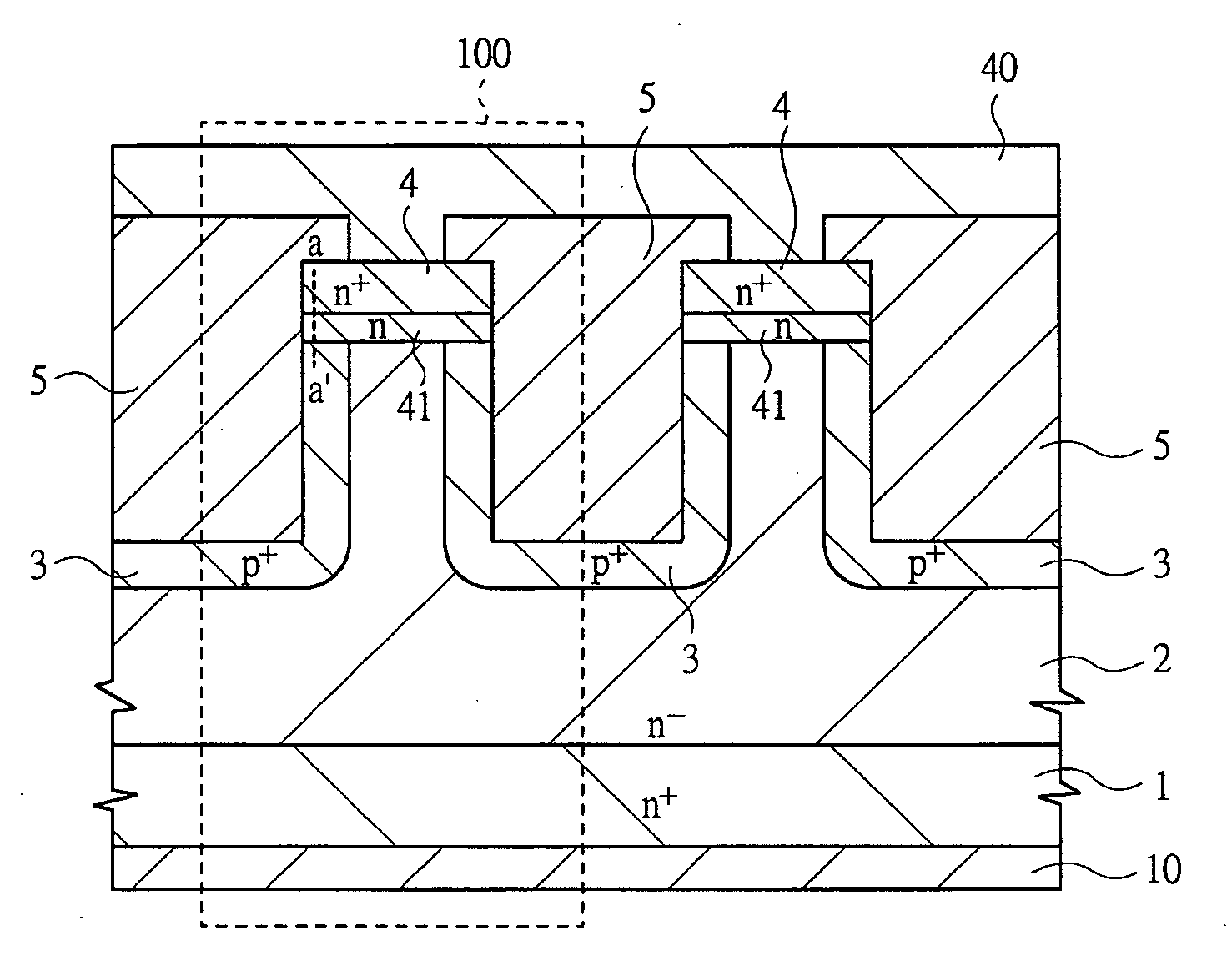

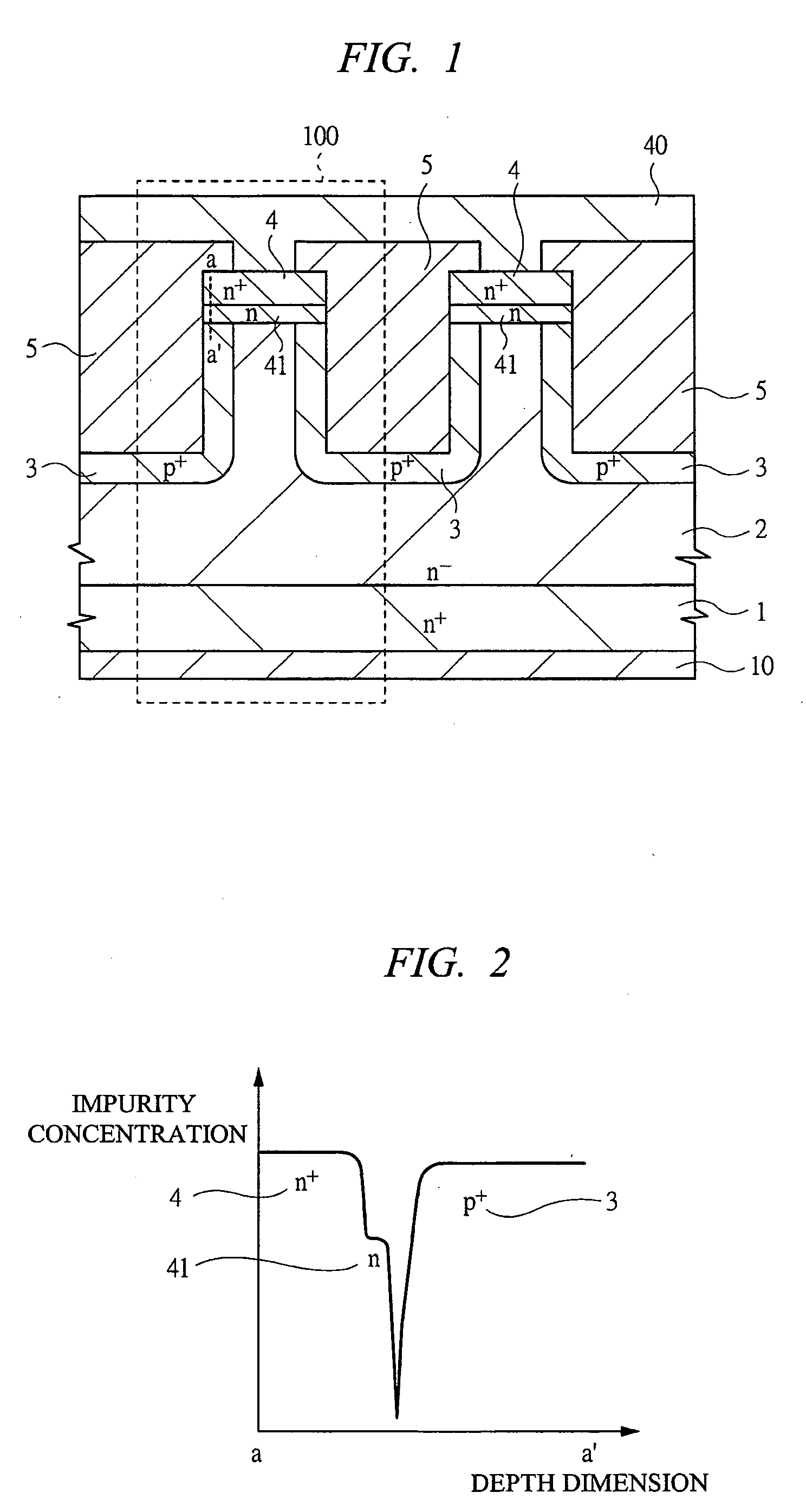

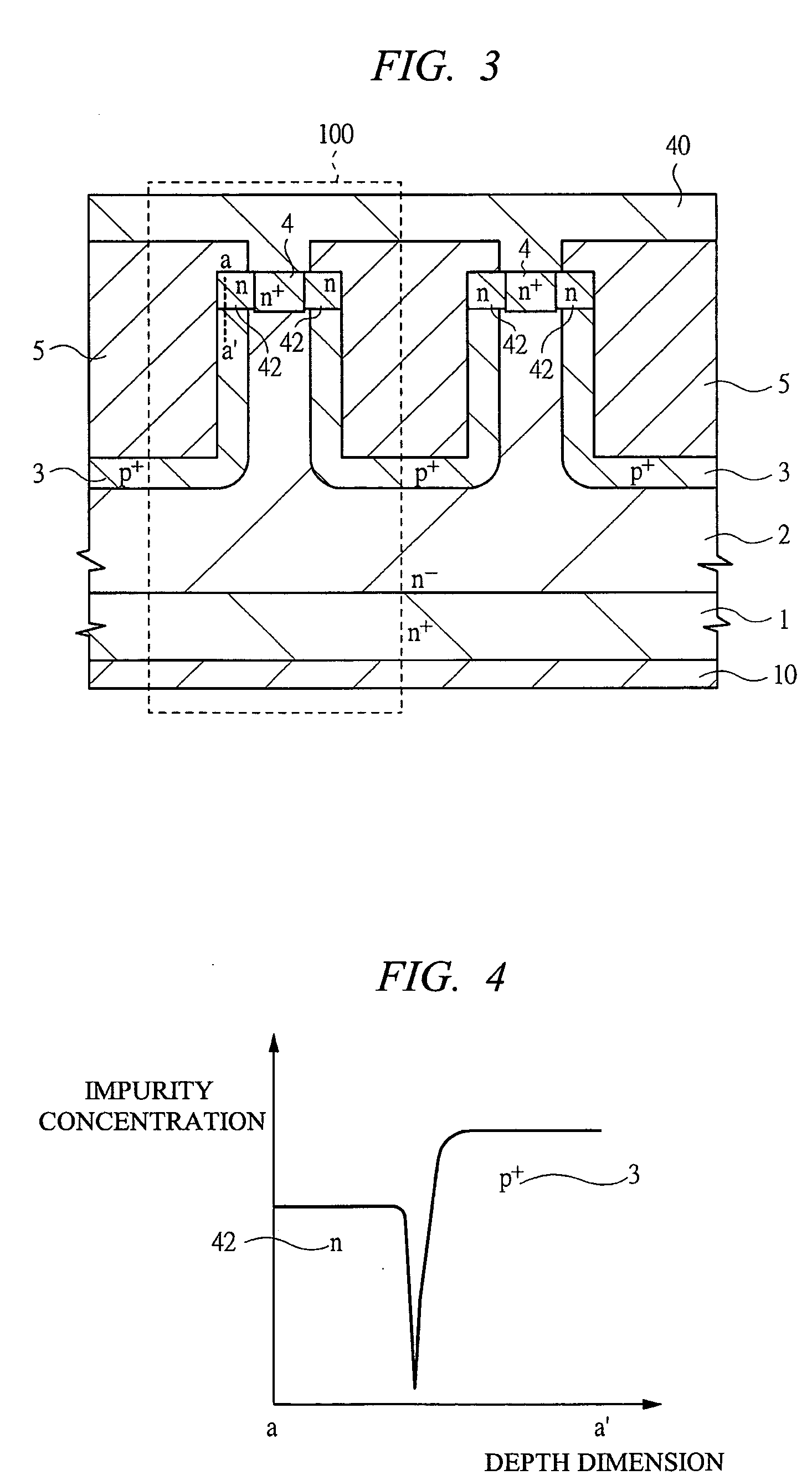

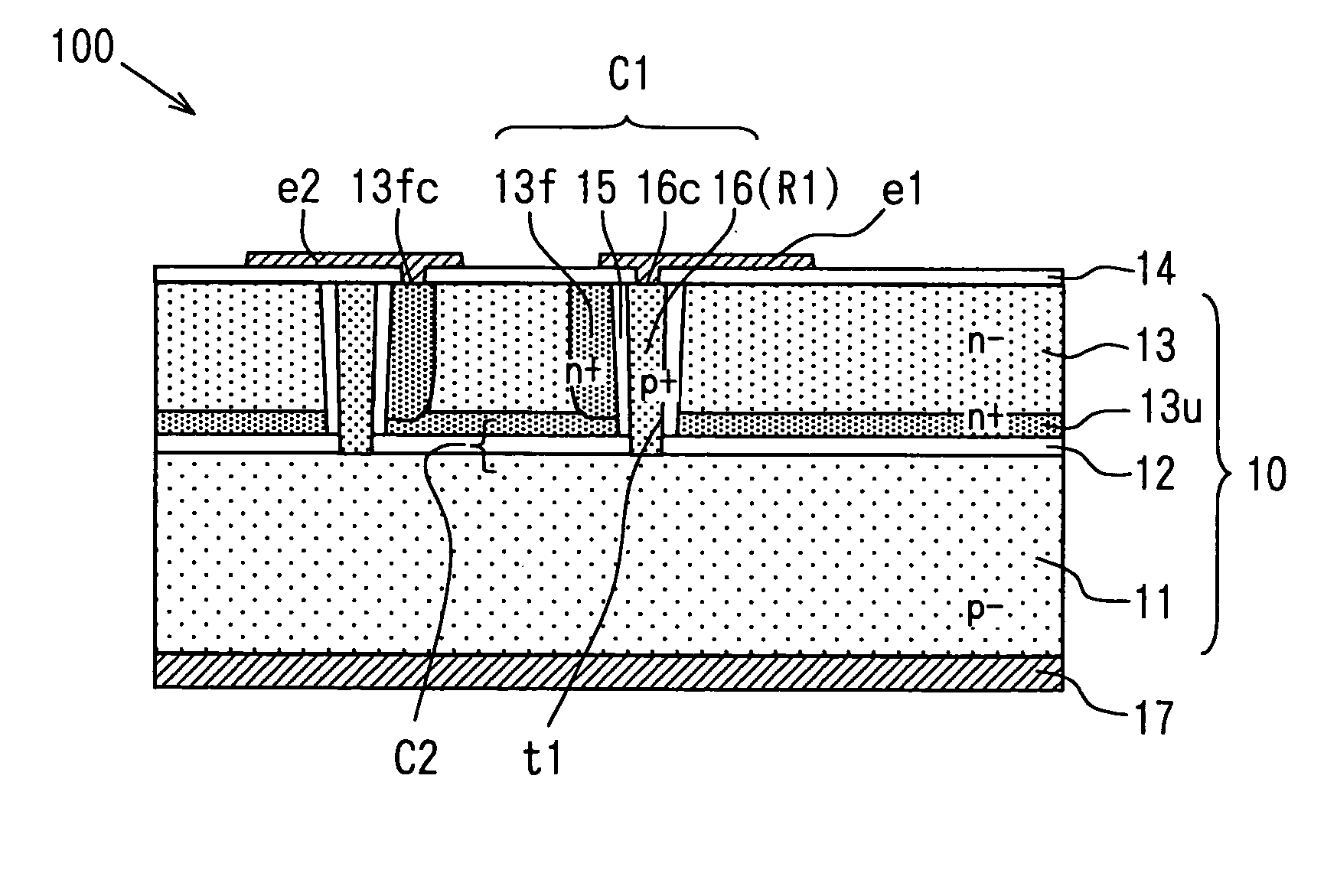

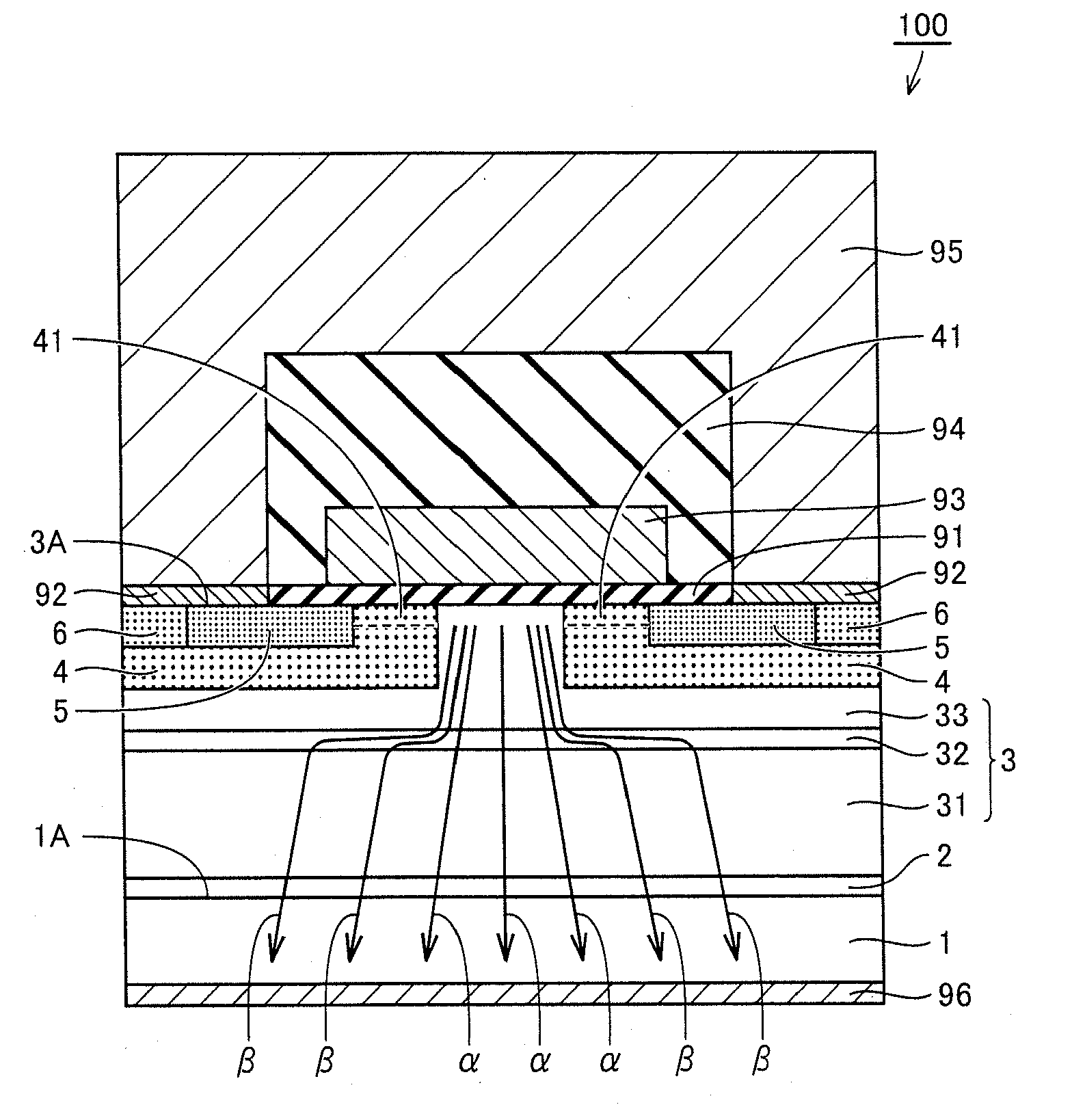

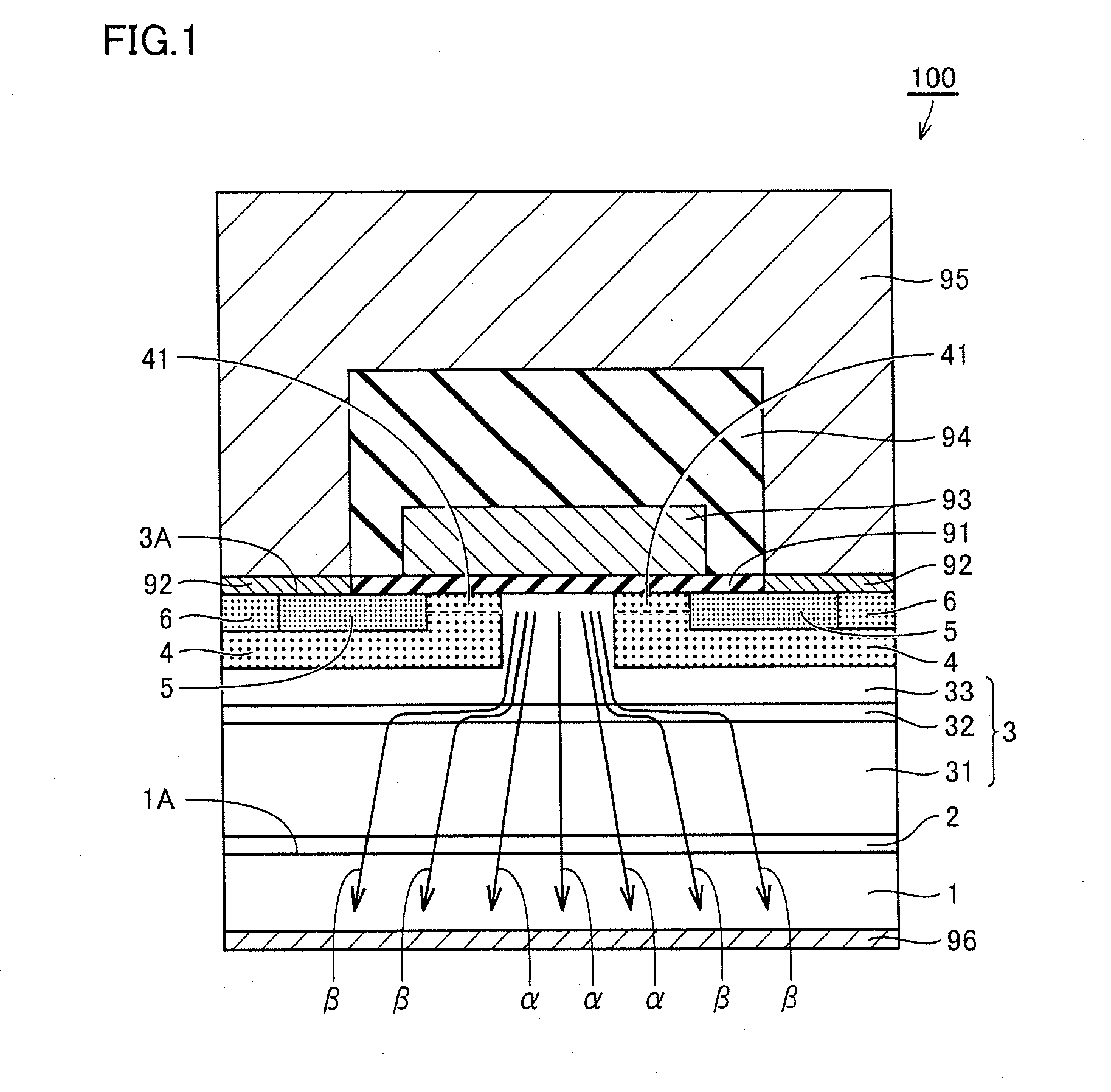

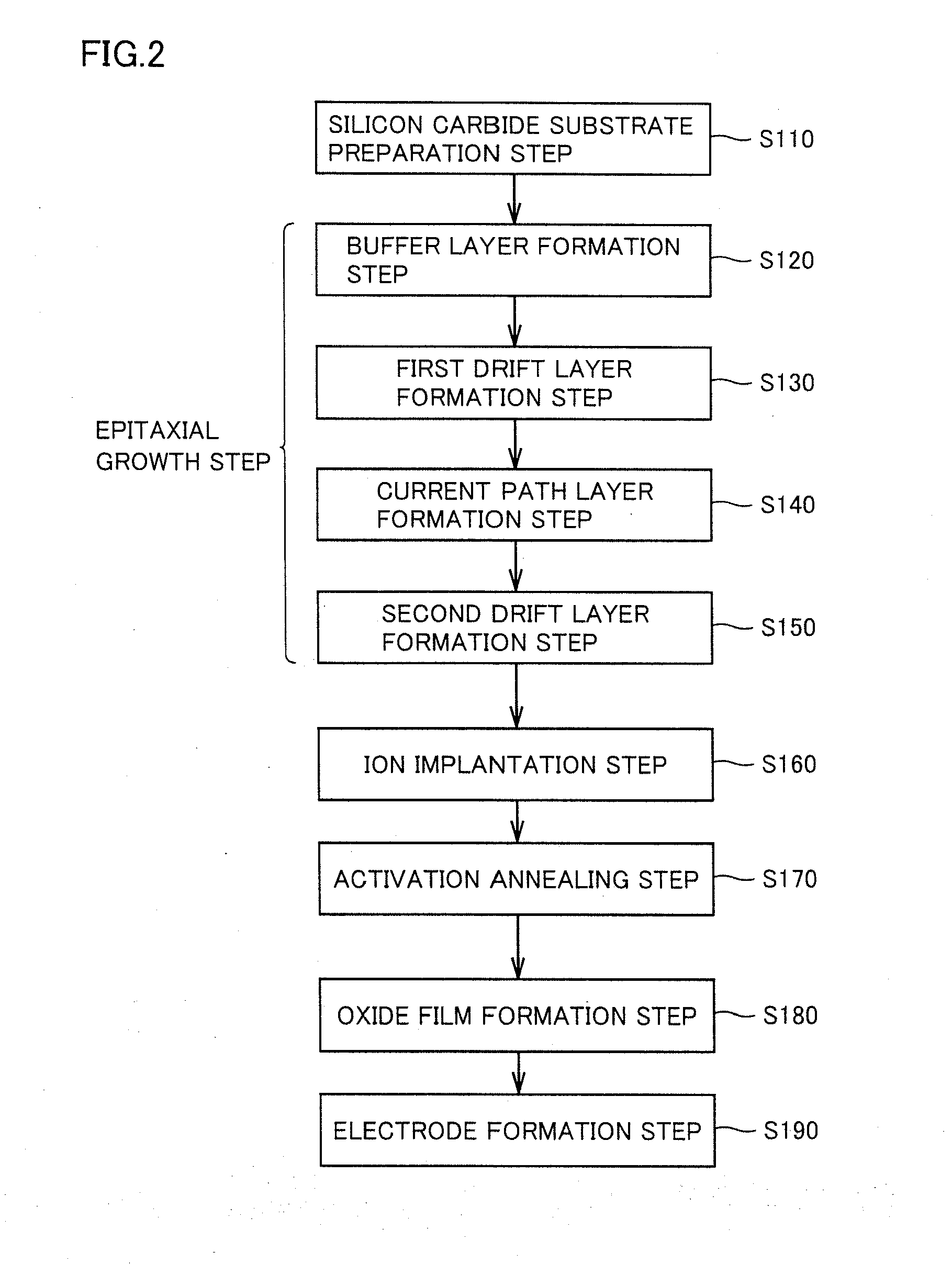

Semiconductor device and the method of manufacturing the same

ActiveUS20110303925A1Lower on-state resistanceLow impurity concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesManufacturing cost reductionPower semiconductor device

A semiconductor device according to the invention includes p-type well region 3 and n+ source region 4, both formed selectively in the surface portion of n− drift region 2; trench 6 in contact with n+ source region 4 and extending through p-type well region 3 into n− drift region 2; field plate 8 formed in trench 6 with first insulator film 7 interposed between the trench 6 inner surface and field plate 8; gate electrode 10 formed in trench 6 with second insulator film 9 interposed between the trench 6 side wall and gate electrode 10, gate electrode 10 being formed above field plate 8; first insulator film 7 being thicker than second insulator film 9; and n−− lightly doped region 21 in n− drift region 2, n−− lightly doped region 21 crossing under the bottom surface of trench 6 from the corner portion thereof, n−− lightly doped region 21 covering the bottom surface of trench 6.The semiconductor device according to the invention and the method of manufacturing the semiconductor device according to the invention facilitate lowering the ON-state voltage, preventing the breakdown voltage from lowering, lowering the gate capacitance, and reducing the manufacturing costs.

Owner:FUJI ELECTRIC CO LTD

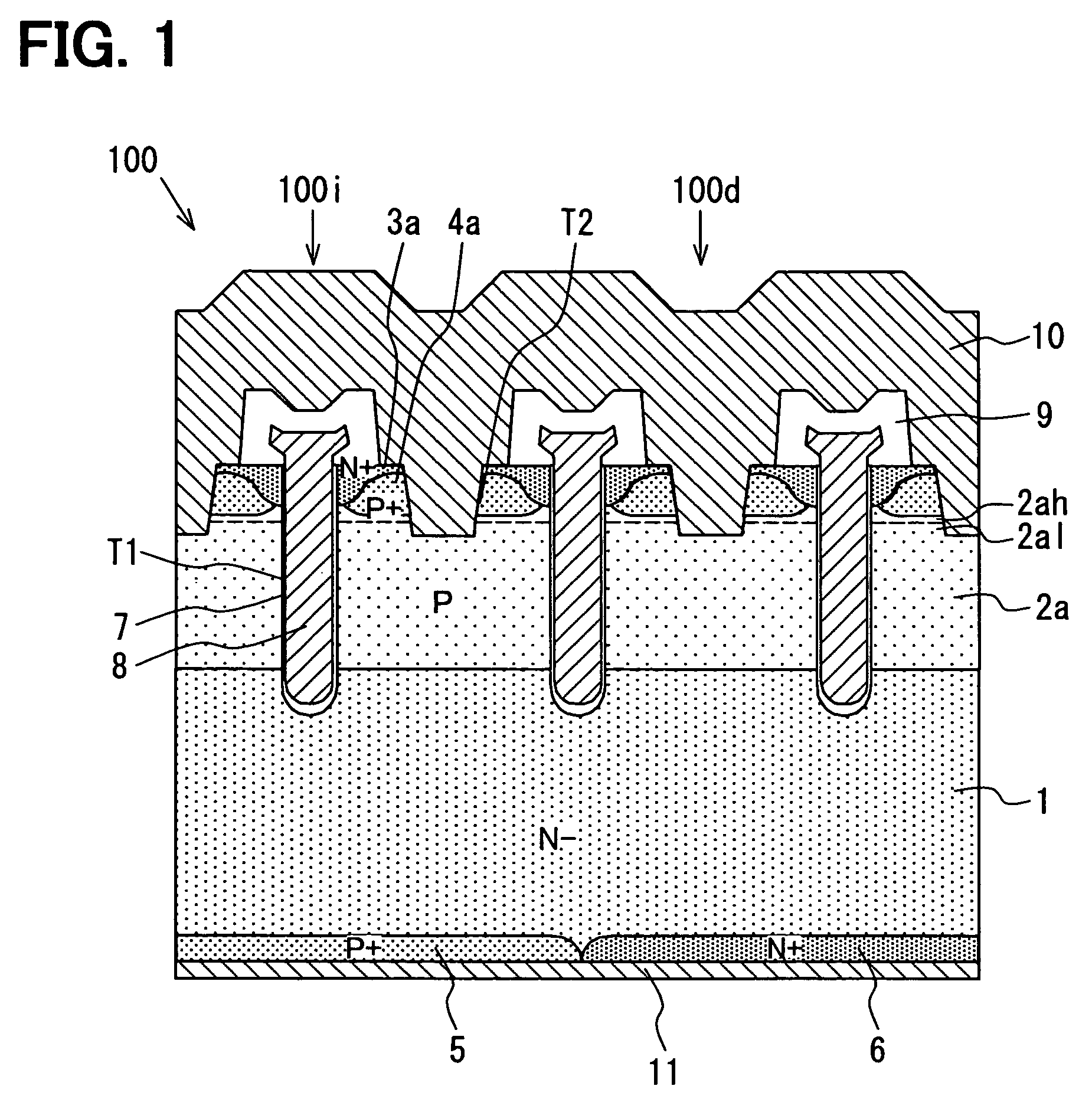

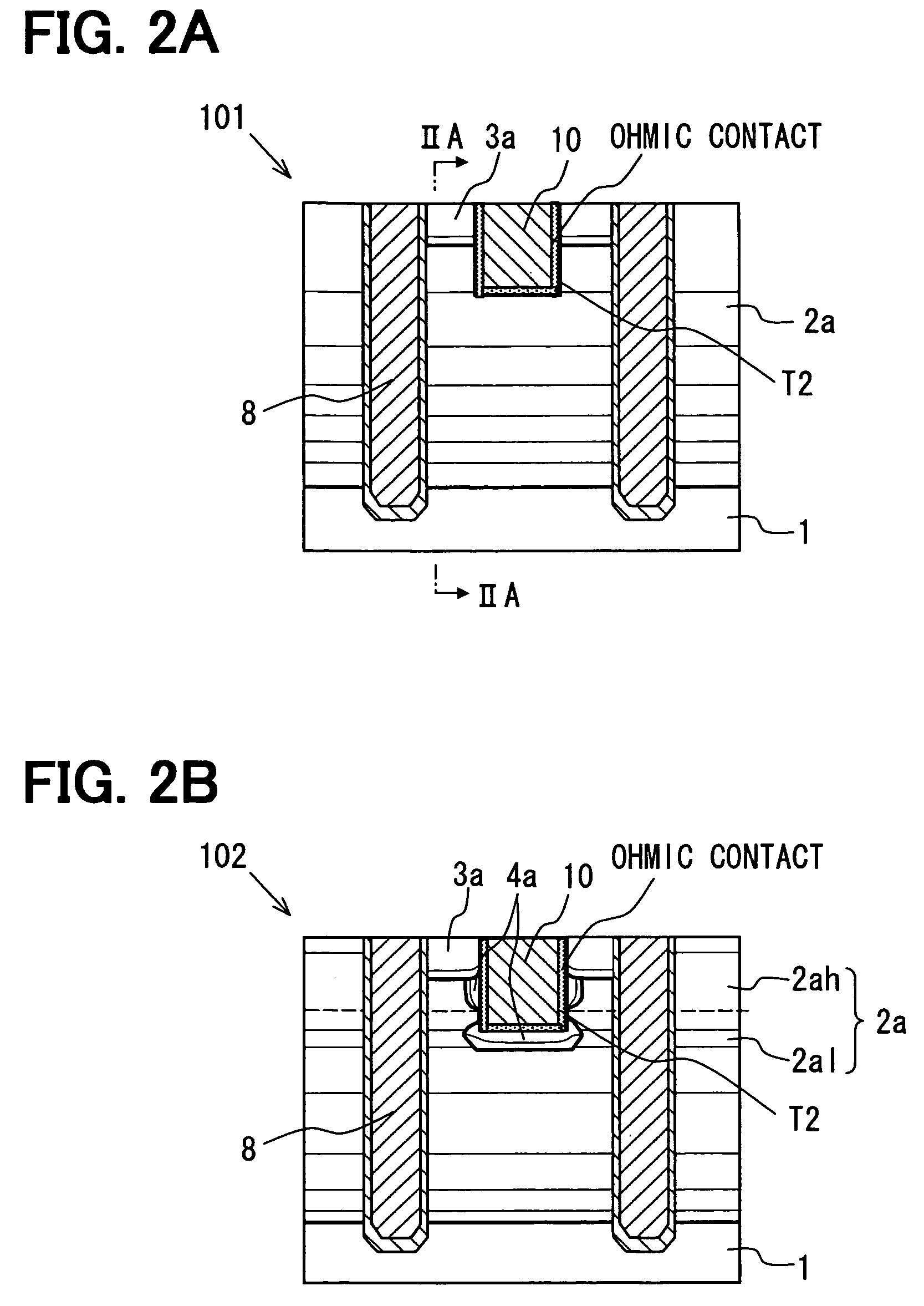

Semiconductor device having IGBT and diode

ActiveUS20070170549A1Sufficient performanceSufficient surge withstand voltageTransistorDiodeSemiconductorSemiconductor device

A semiconductor device includes: a substrate having a first side and a second side; an IGBT; and a diode. The substrate includes a first layer, a second layer on the first layer, a first side N region on the second layer, second side N and P regions on the second side of the first layer, a first electrode in a first trench for a gate electrode, a second electrode on the first side N region and in a second trench for an emitter electrode and an anode electrode, and a third electrode on the second side N and P regions for a collector electrode and a cathode. The first trench penetrates the first side N region and the second layer, and reaches the first layer. The second trench penetrates the first side N region, and reaches the second layer.

Owner:DENSO CORP

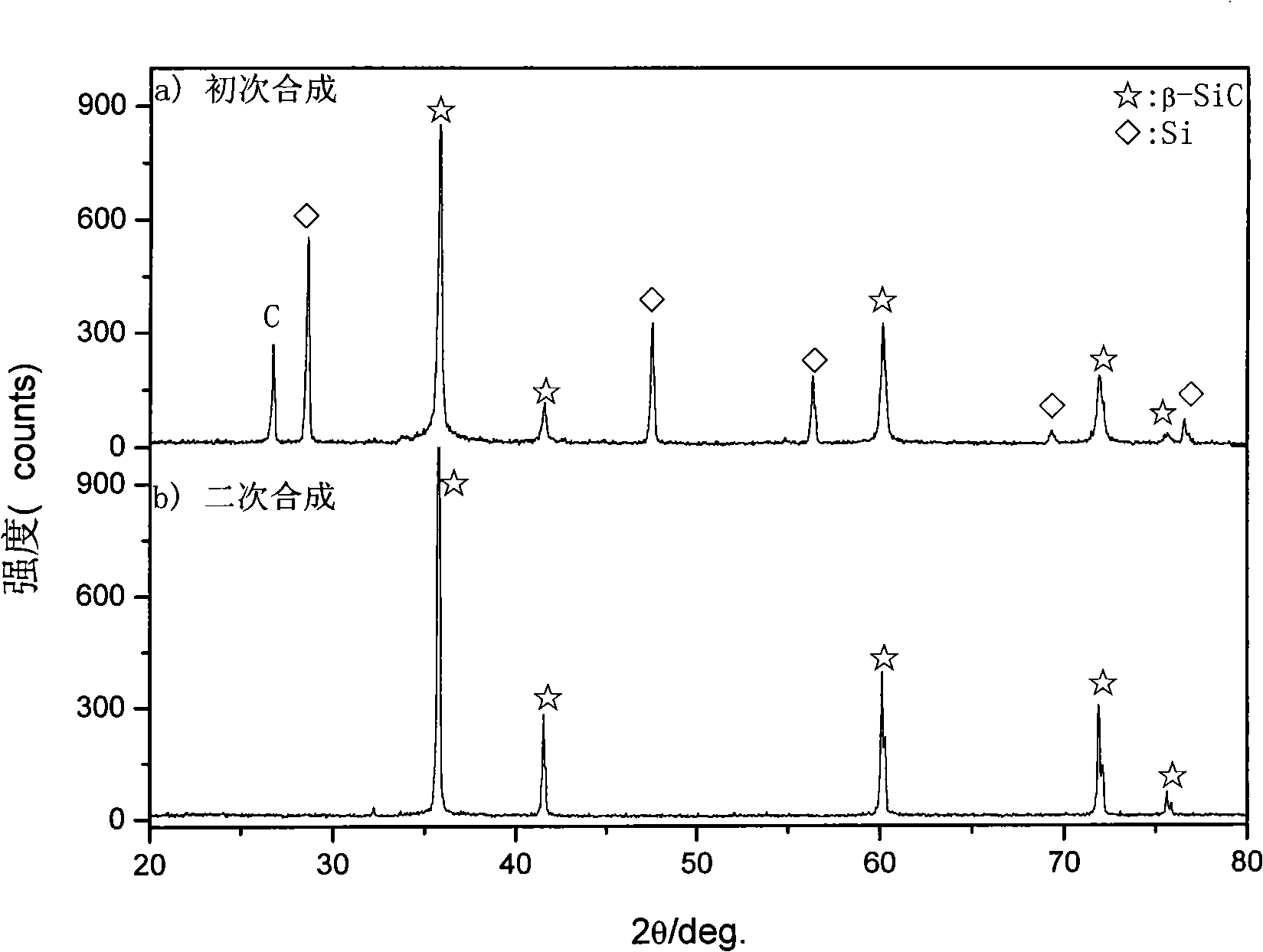

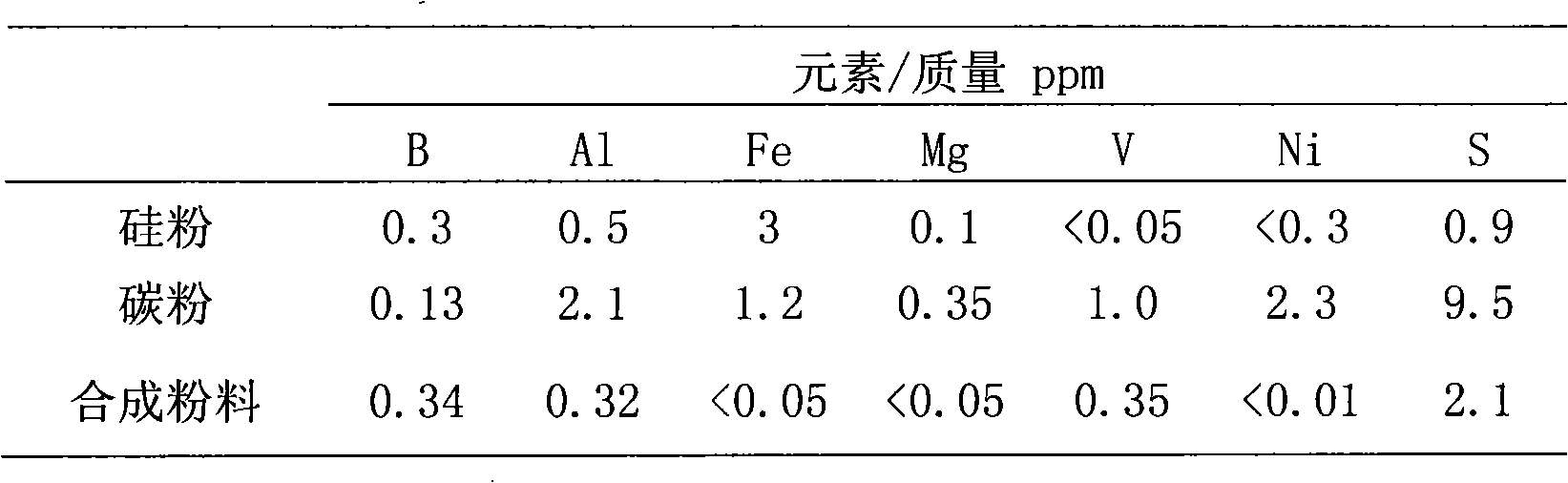

Artificial synthetic method of high-pure SiC power for semiconductor single-crystal growth

The invention provides a method for artificially synthesizing high-purity carborundum powder used for growing semiconductor single crystal. The method comprises the following steps of: (1) taking Si powder and C powder according to a mol ratio of 1 to 1; (2) putting the Si powder and the C powder into a crucible after the Si powder and the C powder are mixed uniformly, putting the crucible in a medium frequency induction heating furnace, vacuumizing a growth chamber of the heating furnace, and increasing the temperature to 1000 DEG C; charging high-purity argon gas, helium gas or mixture of argon gas and hydrogen into the growth chamber, heating the mixed gas up to a synthetic temperature of 1000 DEG C, and reducing the synthetic temperature to room temperature after maintaining for certain reaction time; (3) uniformly mixing powder of a product acquired in the primary synthesis, heating the product up to a secondary synthetic temperature of between 1600 and 2000 DEG C, synthesizing for 2 to 10 hours, and reducing the synthesized product to the room temperature to acquire high-purity SiC powder lot applicable to the semiconductor SiC single crystal growth. The method adopts a secondary synthetic method, not only can ensure that Si and C simple substance which are remained during the primary synthesis can completely react, but also can effectively remove most impurity elements carried in the Si powder and the C powder.

Owner:SICC CO LTD

Switching semiconductor devices and fabrication process

InactiveUS20070096145A1Avoid misuseImprove breakdown voltageSemiconductor devicesManufacturing technologyDevice material

A switching semiconductor device is provided, in which a negative gate voltage can be applied to the semiconductor device in an OFF state so as to increase a breakdown voltage of the gate junction without impairing a normally-off function of the semiconductor device and the ON-resistance. The switching semiconductor device is fabricated by using a semiconductor substrate with a band gap of 2.0 eV or more. In a JFET structure where a p+ type gate region and an n type source region are in contact so that a negative gate voltage can be applied, the p+ type gate region and an n+ type source region with a high impurity concentration are disposed with interposing an n type source region with an impurity concentration lower than that of the p+ type gate region and higher than that of a drift region of the JFET therebetween.

Owner:RENESAS ELECTRONICS CORP

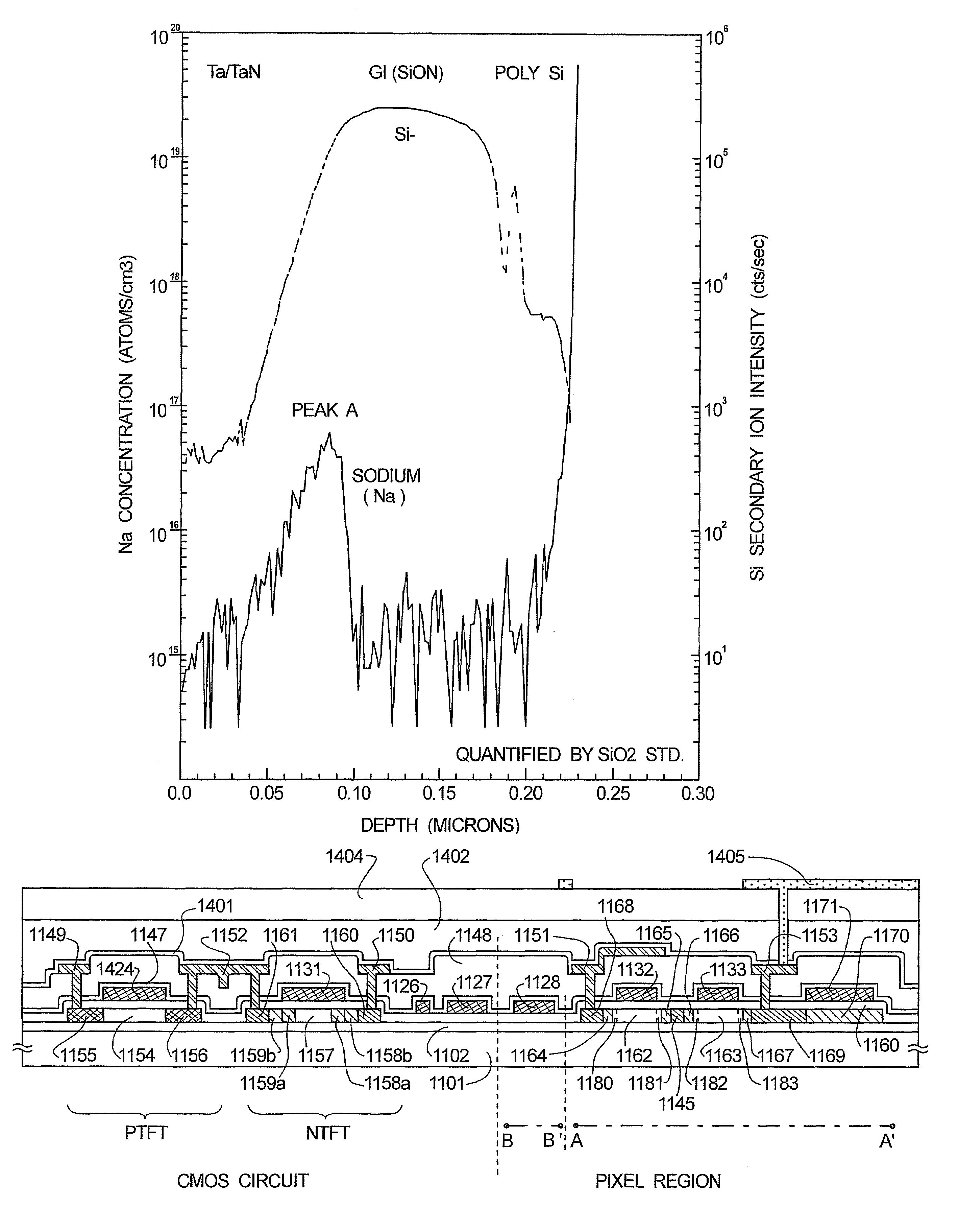

Thin film transistor and method for manufacturing the same

InactiveUS8119468B2High purityImprove featuresTransistorSolid-state devicesAmorphous siliconCrystalline particle

Disclosed is a thin film transistor which includes, over a substrate having an insulating surface, a gate insulating layer covering a gate electrode; a semiconductor layer which functions as a channel formation region; and a semiconductor layer including an impurity element imparting one conductivity type. The semiconductor layer exists in a state that a plurality of crystalline particles is dispersed in an amorphous silicon and that the crystalline particles have an inverted conical or inverted pyramidal shape. The crystalline particles grow approximately radially in a direction in which the semiconductor layer is deposited. Vertexes of the inverted conical or inverted pyramidal crystal particles are located apart from an interface between the gate insulating layer and the semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

ActiveUS20130082262A1Stable electrical characteristicsHigh crystallinityTransistorSolid-state devicesSiliconSemiconductor

A semiconductor device includes a gate electrode, a gate insulating film which includes oxidized material containing silicon and covers the gate electrode, an oxide semiconductor film provided to be in contact with the gate insulating film and overlap with at least the gate electrode, and a source electrode and a drain electrode electrically connected to the oxide semiconductor film. In the oxide semiconductor film, a first region which is provided to be in contact with the gate insulating film and have a thickness less than or equal to 5 nm has a silicon concentration lower than or equal to 1.0 at. %, and a region in the oxide semiconductor film other than the first region has lower silicon concentration than the first region. At least the first region includes a crystal portion.

Owner:SEMICON ENERGY LAB CO LTD

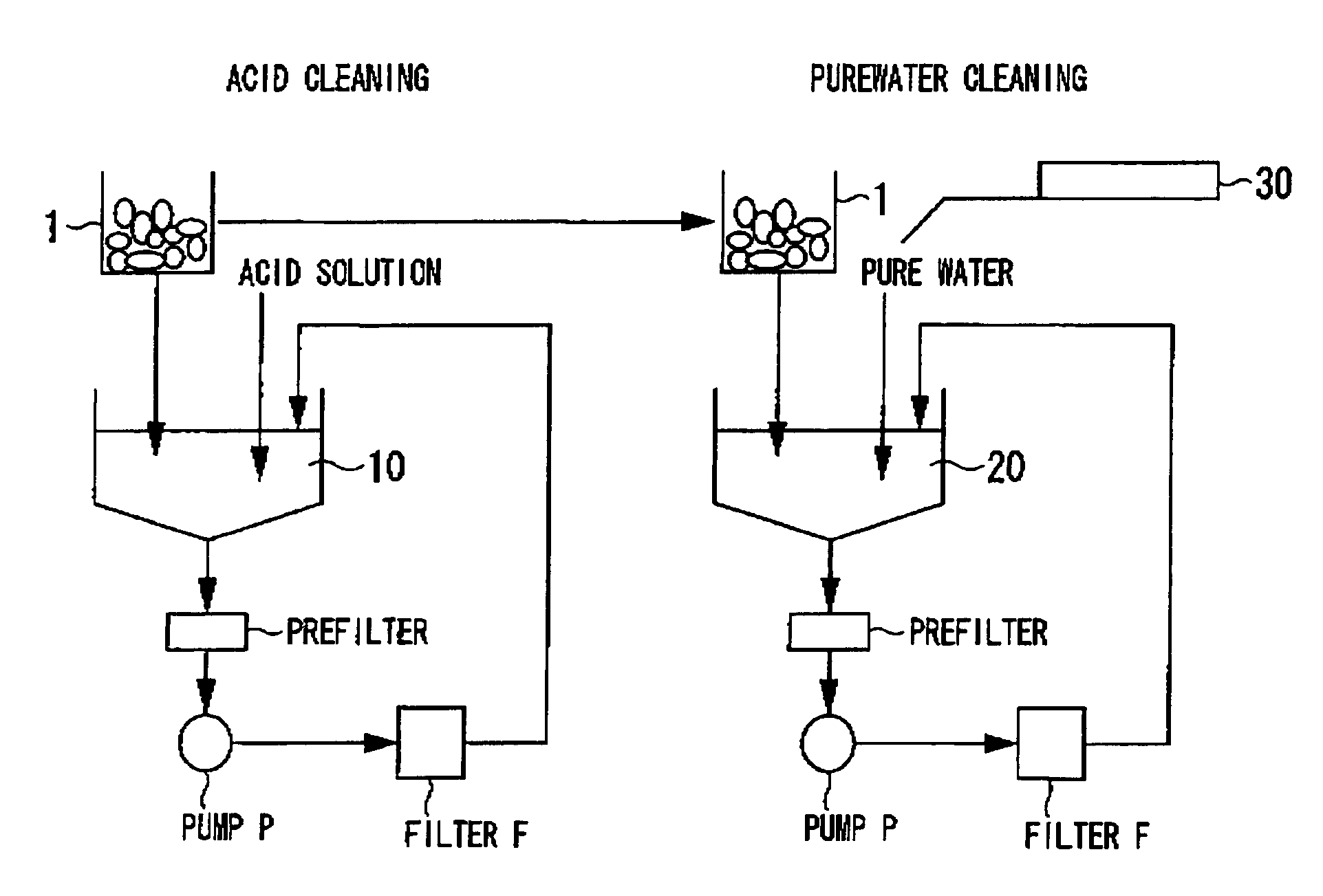

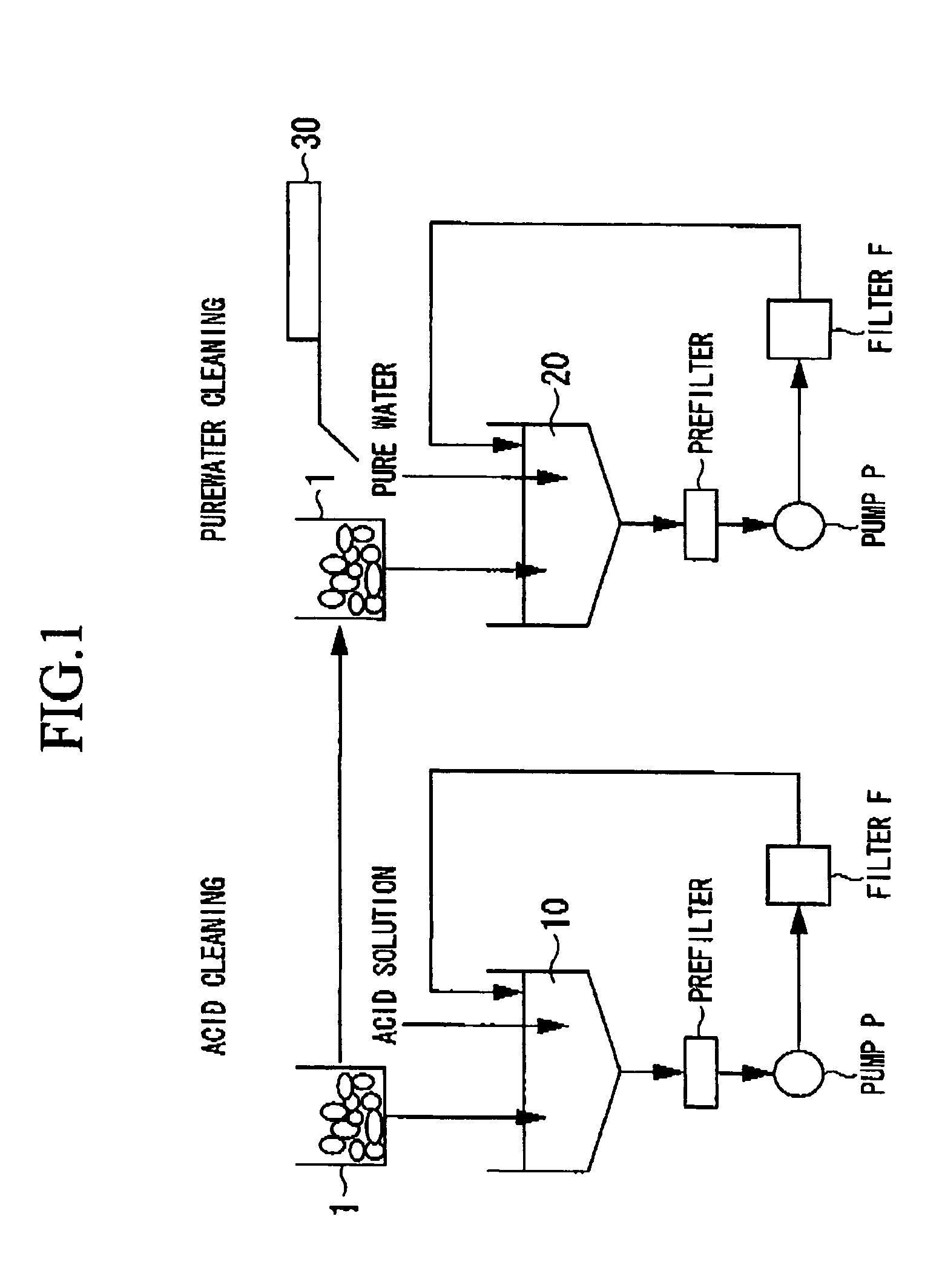

Silicon cleaning method for semiconductor materials and polycrystalline silicon chunk

ActiveUS20060042539A1Reduce impurity concentrationGood removal effectPolycrystalline material growthBy pulling from meltSemiconductor materialsReverse osmosis

A cleaning method cleans silicon for semiconductor materials using pure water treated by a reverse osmosis treatment and by ion exchange treatment and reduces the aluminum and iron remaining on the silicon surface.

Owner:MITSUBISHI POLYCRYSTALLINE SILICON AMERICA MIPSA +1

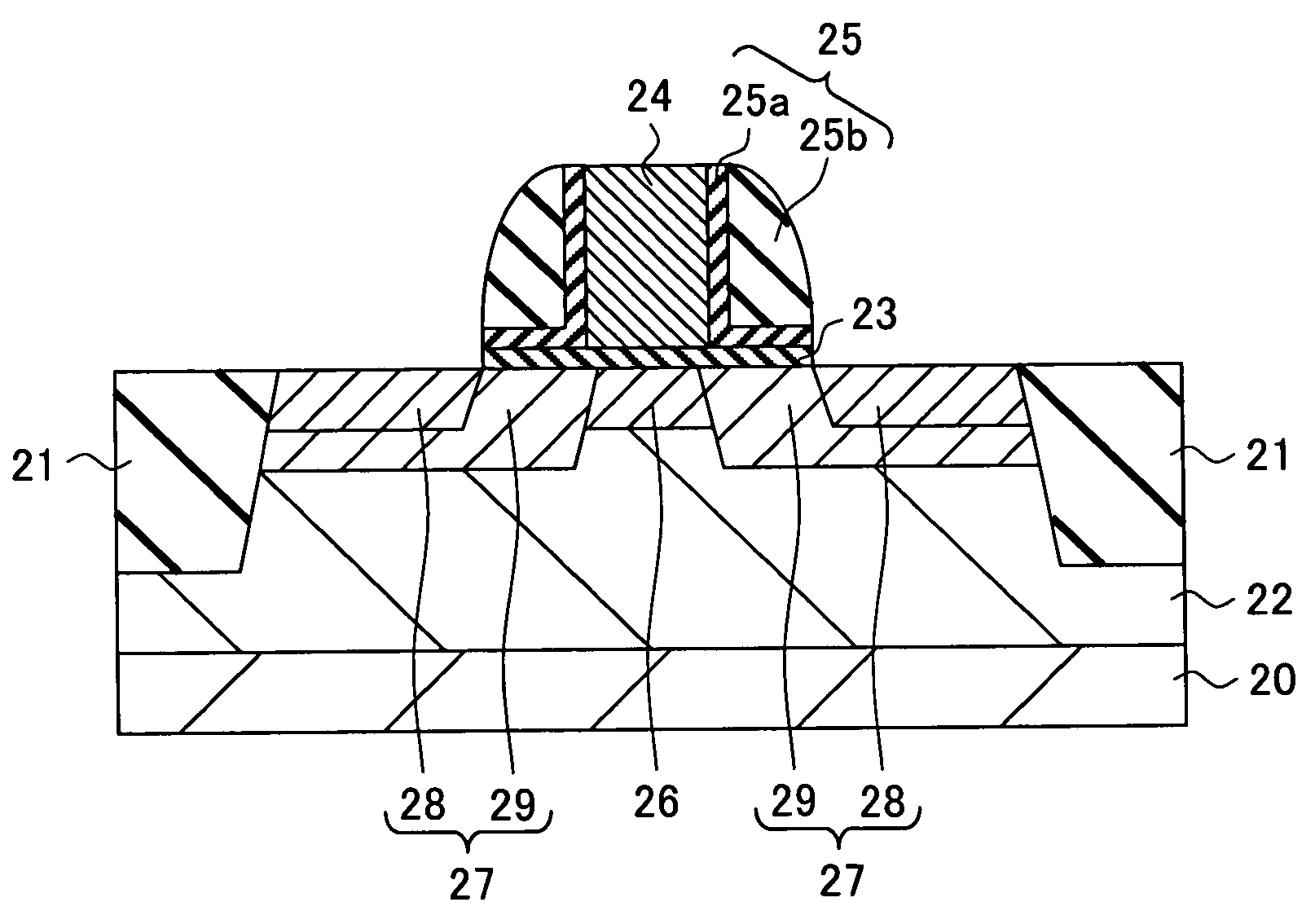

Semiconductor device and method of producing same

InactiveUS20060275990A1Reduce noiseImprove linearityTransistorTelevision system detailsDevice materialSemiconductor

A semiconductor device suitable for a source-follower circuit, provided with a gate electrode formed on a semiconductor substrate via a gate insulation film, a first conductivity type layer formed in the semiconductor substrate under a conductive portion of the gate electrode and containing a first conductivity type impurity, first source / drain regions of the first conductivity type impurity formed in the semiconductor substrate and extended from edge portions of the gate electrode, and second source / drain regions having a first conductivity type impurity concentration lower than that in the first source / drain regions and formed adjoining the gate insulation film and the first source / drain regions in the semiconductor substrate so as to overlap portions of the conductive portion of the gate electrode.

Owner:SONY SEMICON SOLUTIONS CORP

Semiconductor device

ActiveUS20150236012A1Increase currentHigh concentrationTransistorSolid-state devicesRefluxPower semiconductor device

In a semiconductor device having a built-in Schottky barrier diode as a reflux diode, a maximum unipolar current is increased in a reflux state and a leakage current is reduced in an OFF state. A Schottky electrode is provided in at least a part of a surface between adjacent well regions of a second conductivity type disposed on a surface layer side of a drift layer of a first conductivity type, and an impurity concentration of a first conductivity type in a first region provided in a lower part of the Schottky electrode and provided between the adjacent well regions is set to be higher than a first impurity concentration of a first conductivity type in the drift layer and to be lower than a second impurity concentration of a second conductivity type in the well region.

Owner:MITSUBISHI ELECTRIC CORP

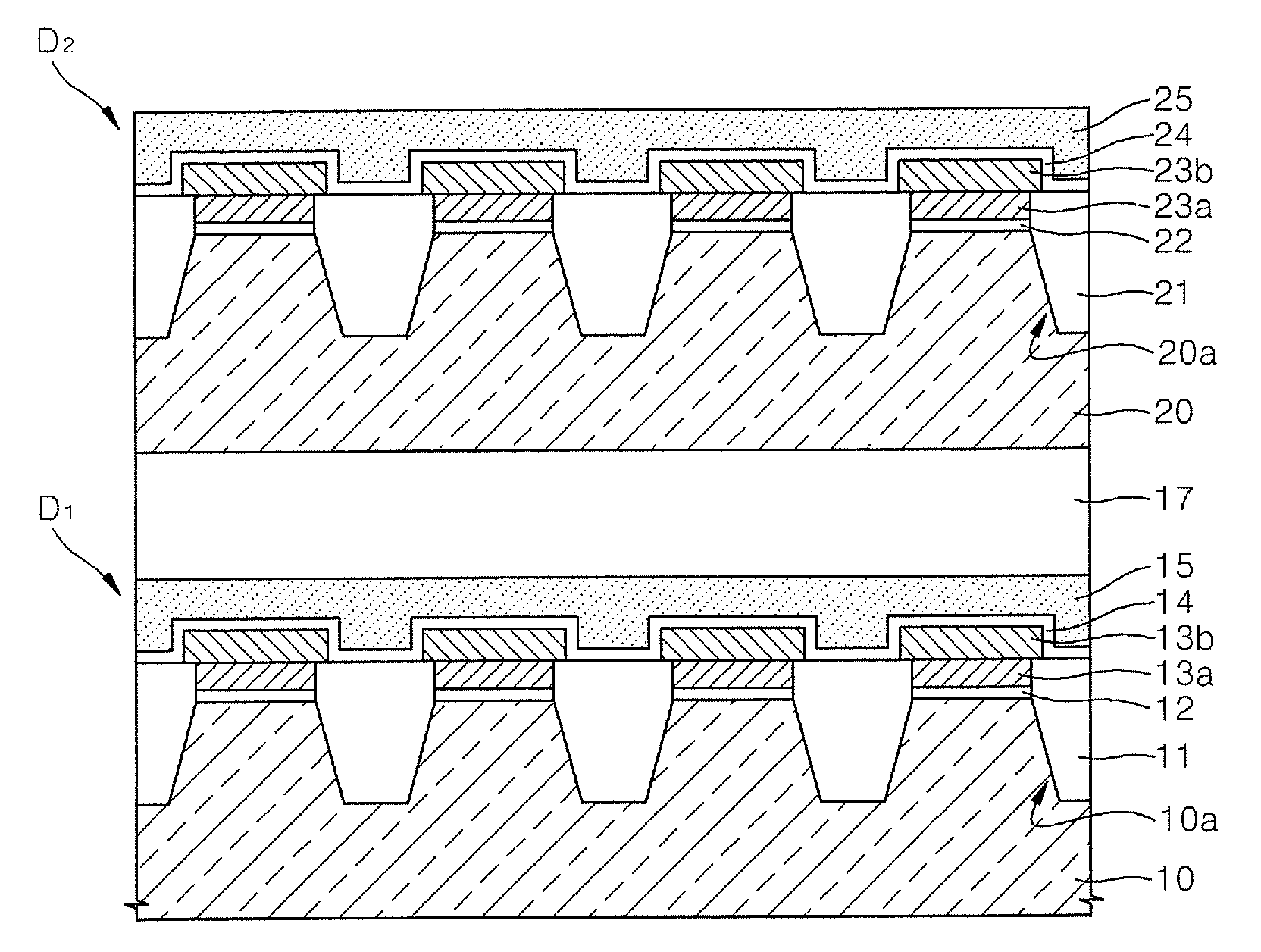

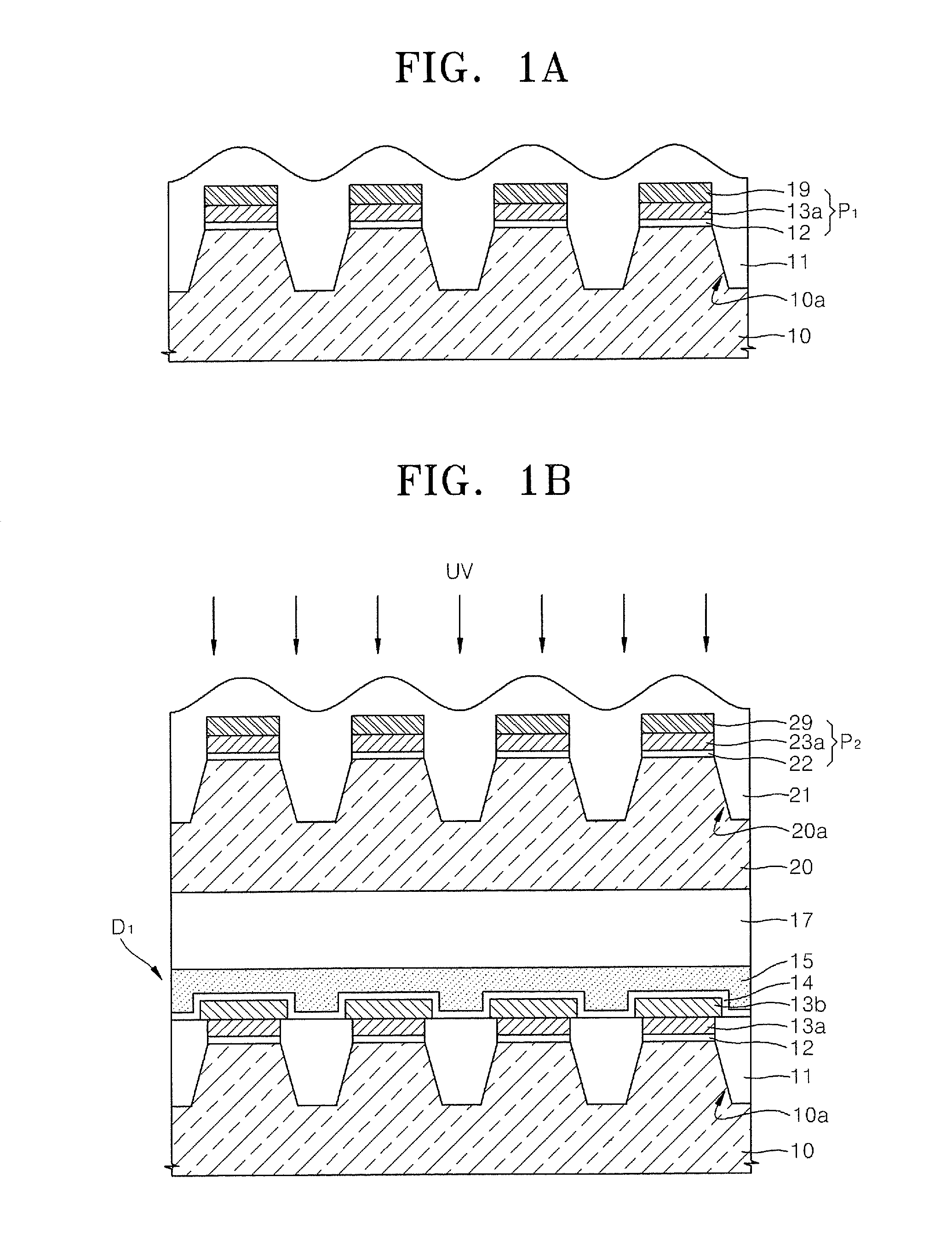

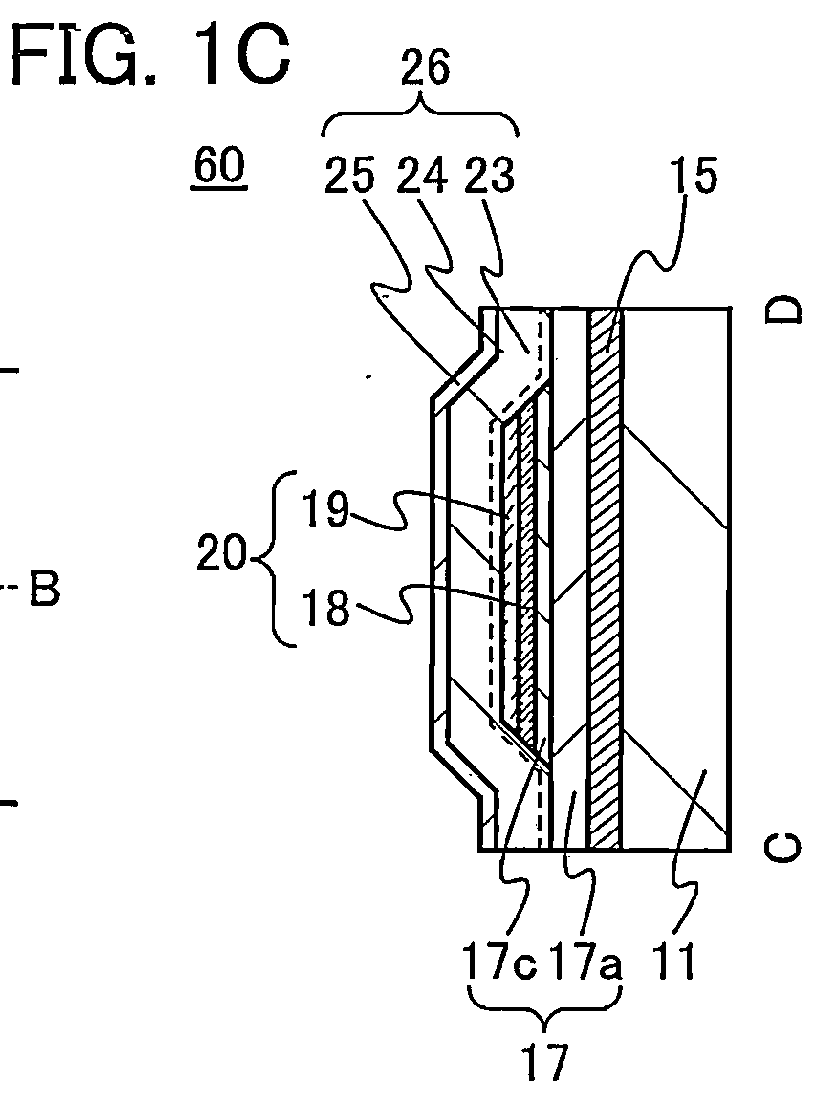

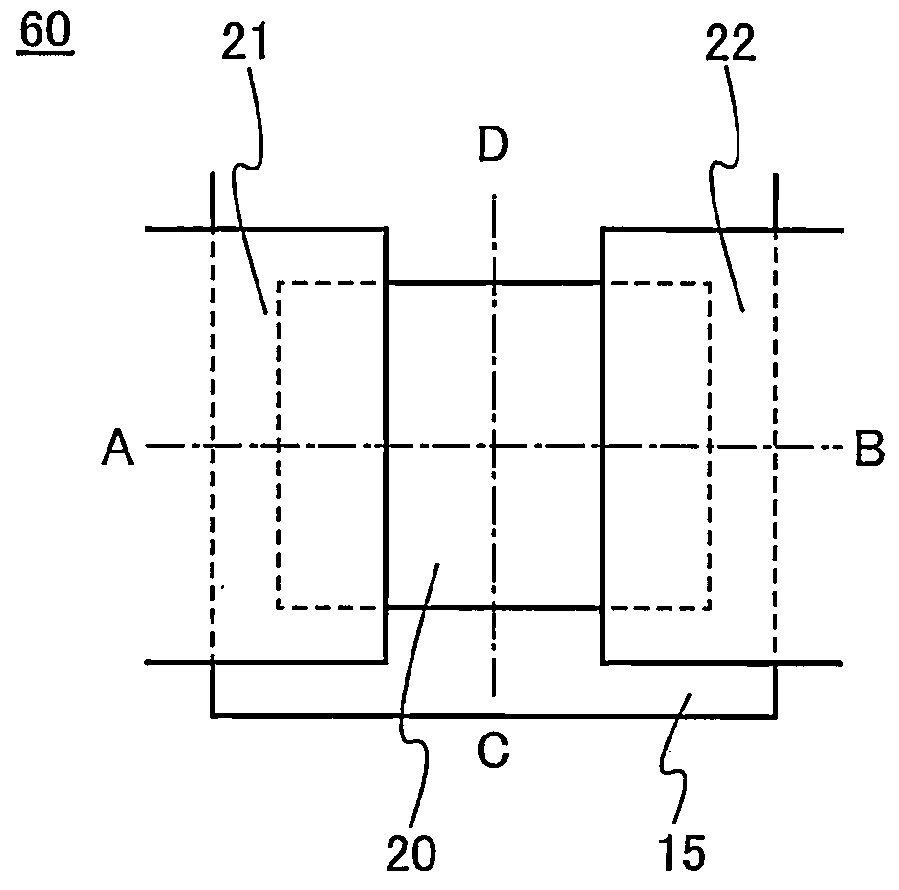

Methods of reducing impurity concentration in isolating films in semiconductor devices

ActiveUS20080206954A1Reduce impurity concentrationHot-air central heatingSolid-state devicesDevice materialUltraviolet lights

A method of fabricating a semiconductor device includes forming a lower device on a lower semiconductor substrate, and forming an interlayer insulating film on the lower device. An upper semiconductor substrate is formed on the interlayer insulating film such that the interlayer insulating film is between the lower and upper semiconductor substrates. Upper trenches are formed within the upper semiconductor substrate. An upper device isolating film is formed within the upper trenches. The upper device isolating film is irradiated with ultraviolet light having a wavelength configured to break chemical bonds of impurities in the upper device isolating film to reduce an impurity concentration thereof.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device

ActiveUS20140306221A1Increase stabilityReduce concentration of impurityTransistorSolid-state devicesOxide semiconductorOxide

The stability of a step of processing a wiring formed using copper, aluminum, gold, silver, molybdenum, or the like is increased. Moreover, the concentration of impurities in a semiconductor film is reduced. Moreover, the electrical characteristics of a semiconductor device are improved. In a transistor including an oxide semiconductor film, an oxide film in contact with the oxide semiconductor film, and a pair of conductive films being in contact with the oxide film and including copper, aluminum, gold, silver, molybdenum, or the like, the oxide film has a plurality of crystal parts and has c-axis alignment in the crystal parts, and the c-axes are aligned in a direction parallel to a normal vector of a top surface of the oxide semiconductor film or the oxide film.

Owner:SEMICON ENERGY LAB CO LTD

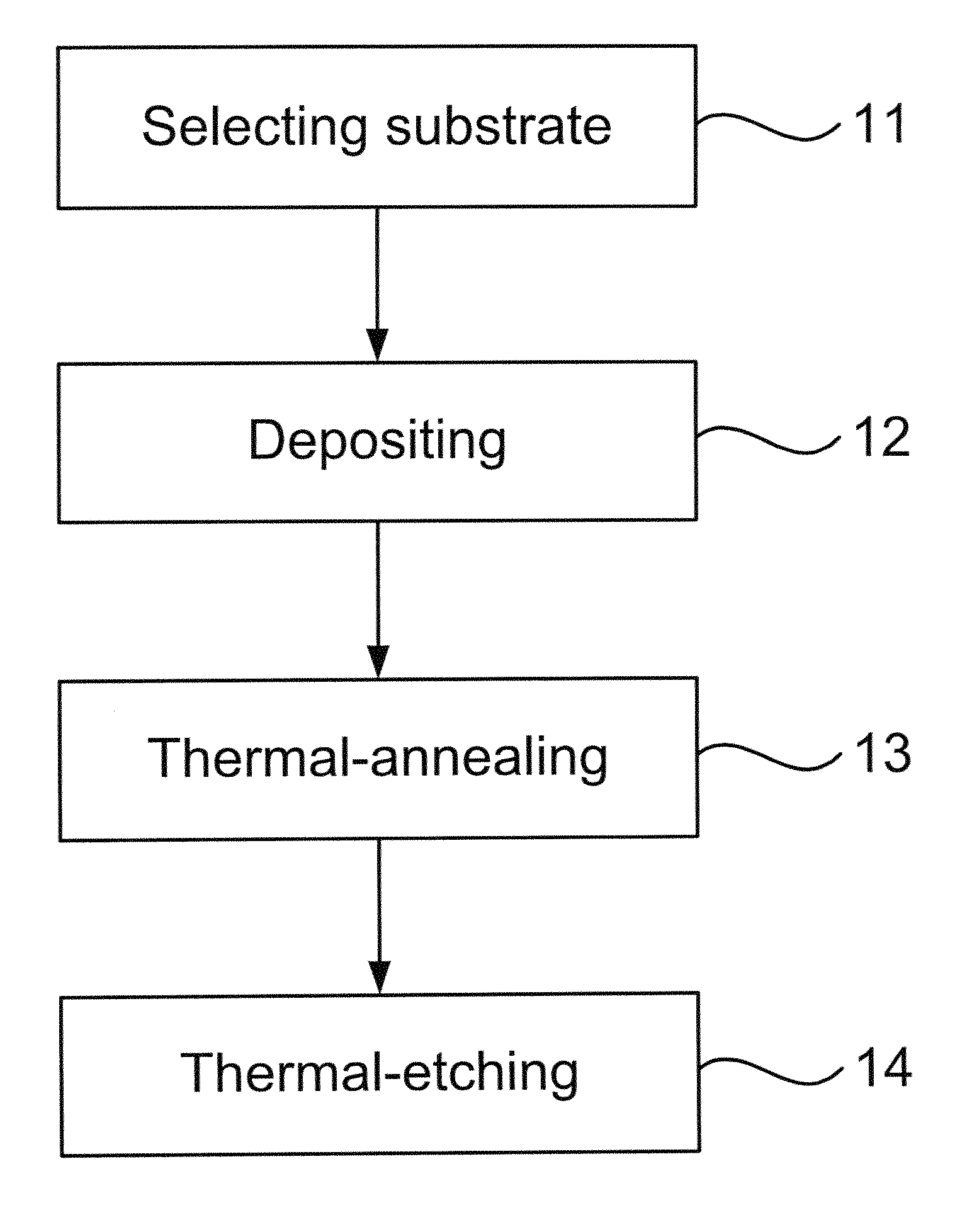

Method of Fabricating Upgraded Metallurgical Grade Silicon by External Gettering Procedure

InactiveUS20100279492A1Reduce impurity concentrationSemiconductor/solid-state device manufacturingSource materialSolar cell

Upgraded metallurgical grade silicon (UMG-Si) is fabricated by a ‘green’ (environmental protected) external gettering procedure. Impurities concentration of the fabricated UMG-Si is reduced for 100 times than its source material. The UMG-Si obtained has a purity ratio reaching 4N to 6N. Thus, substrates made of the UMG-Si can be used in solar cells and related photoelectrical applications.

Owner:INST NUCLEAR ENERGY RES ROCAEC

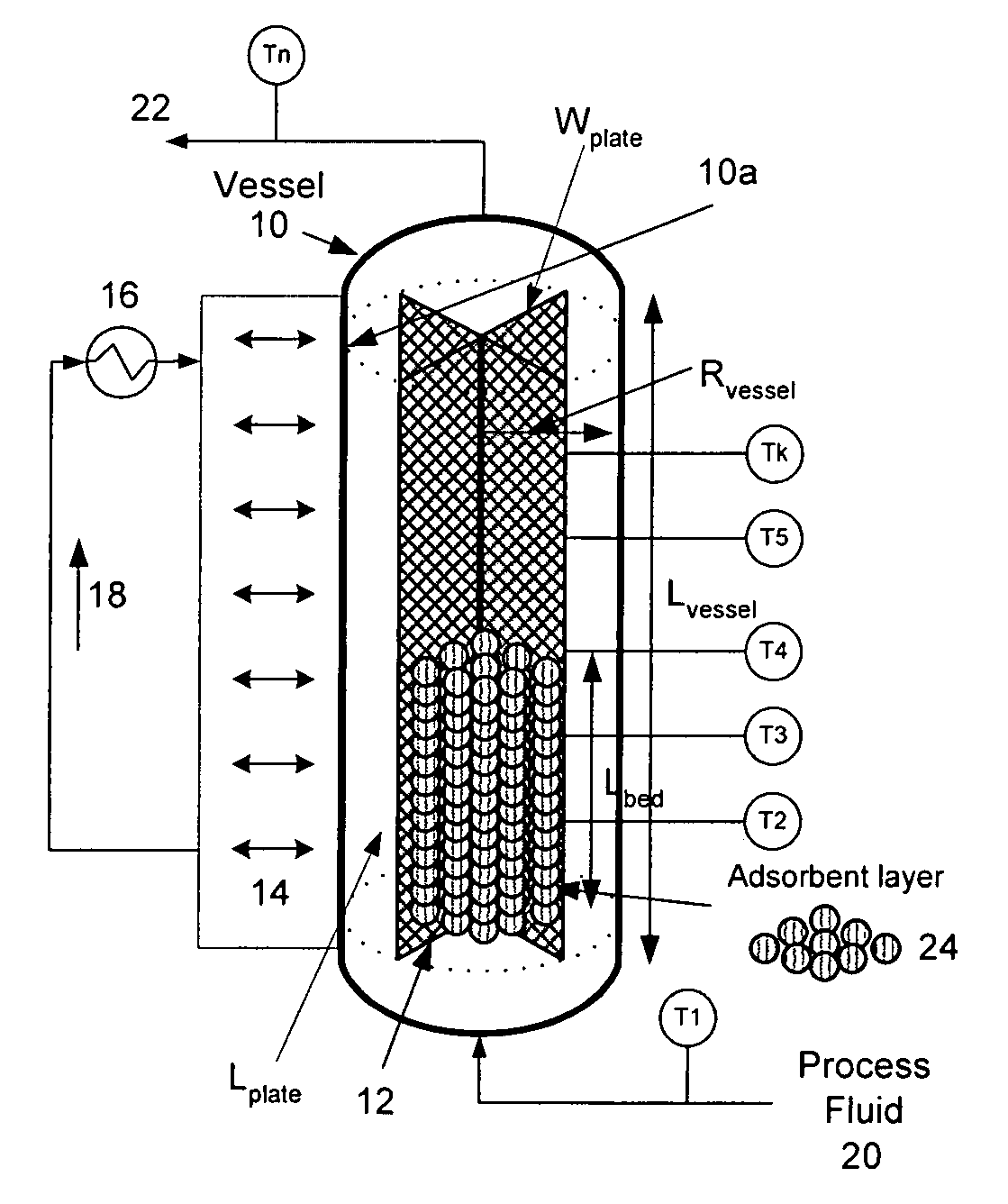

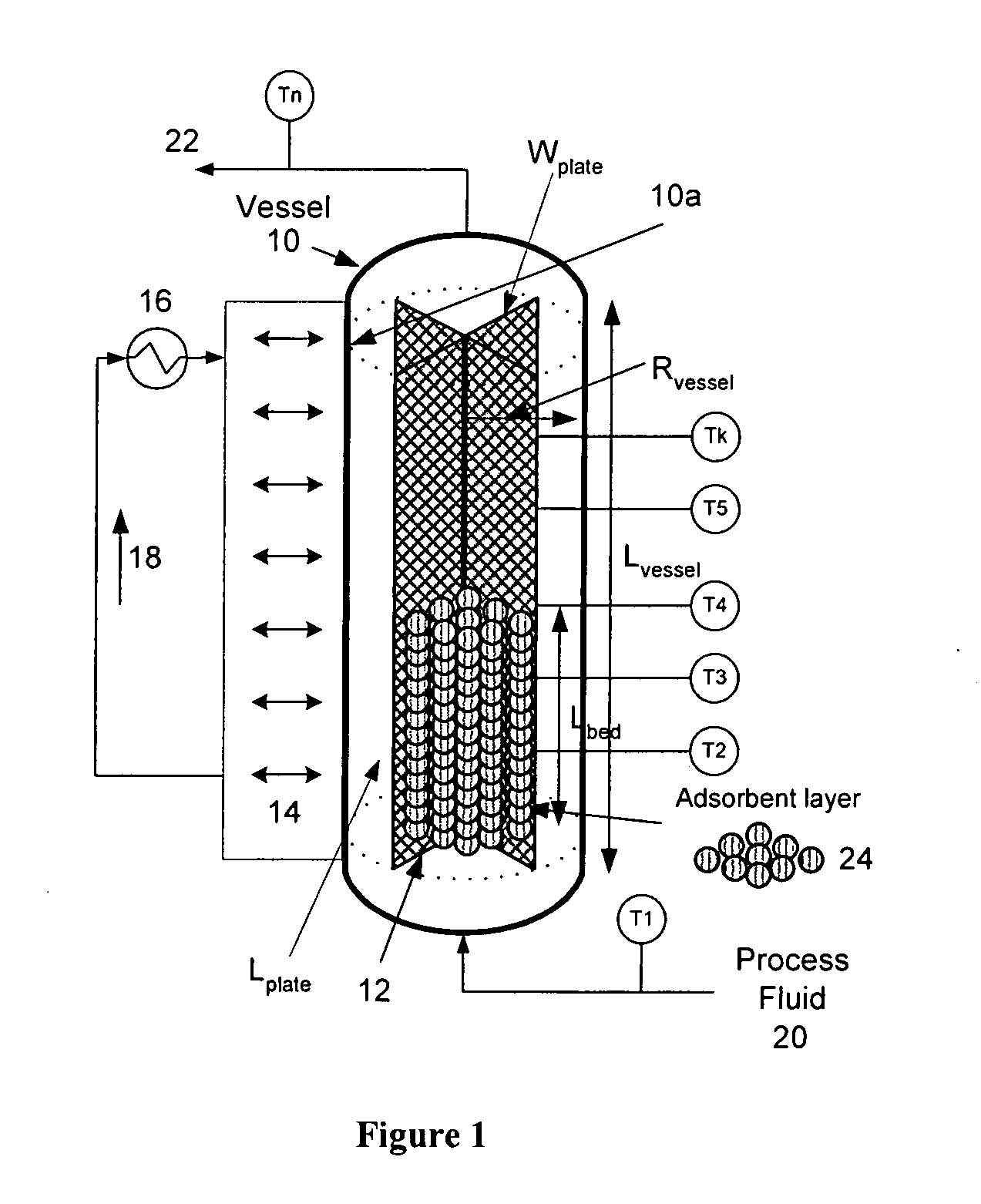

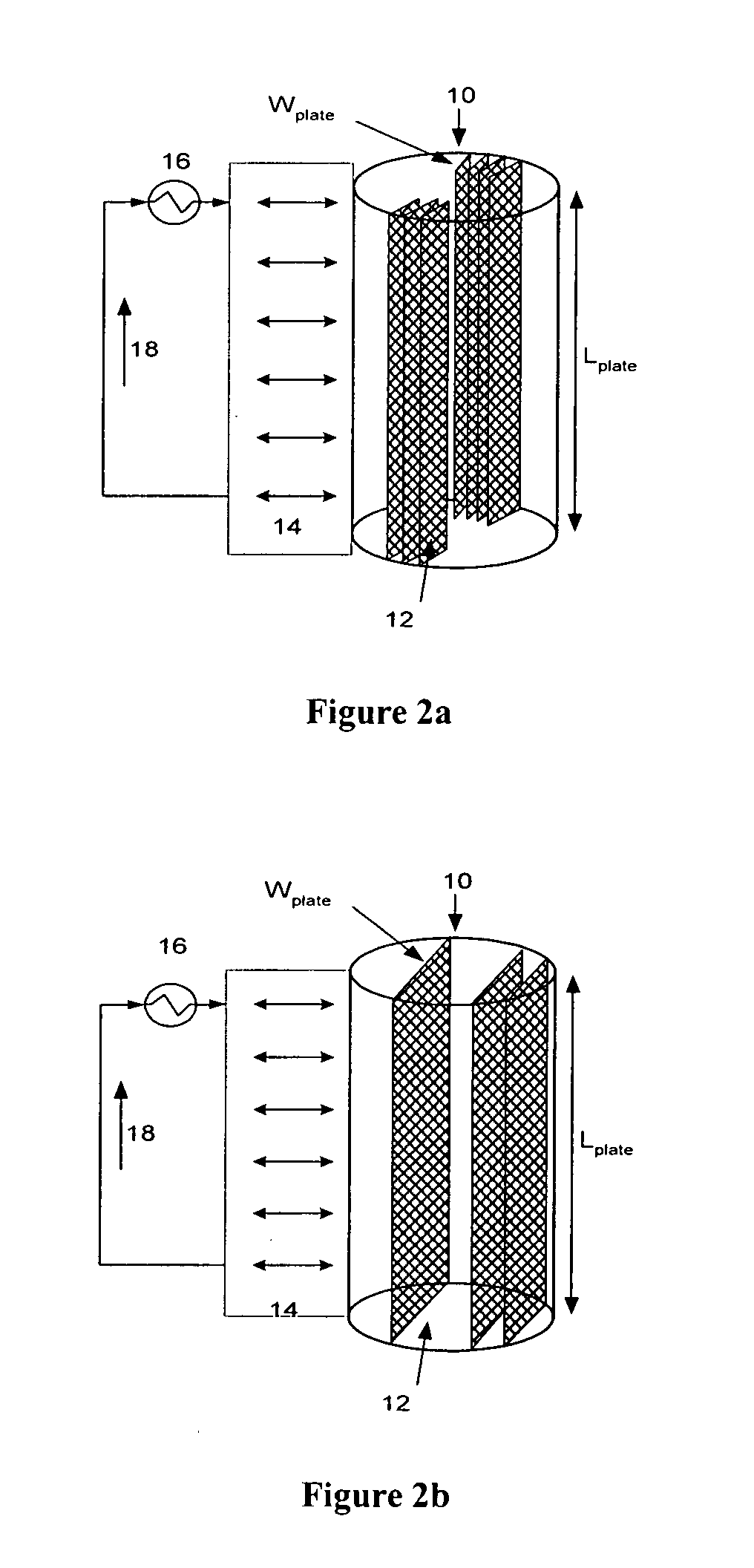

Methods and systems for purifying gases

InactiveUS20080237131A1Improve heat transfer performanceReduce impurity concentrationIon-exchange process apparatusGas treatmentPurification methodsSorbent

The present invention relates to methods and systems for purifying gases, such as for example semiconductor process gases. The invention more particularly relates to fluid purification methods and systems having improved heat transfer capabilities and controls such that the purified fluid produced from the process contains reduced impurity levels and / or exhibits more uniform concentrations within the final product. In another aspect of the invention, the activation time for adsorbent beds used in such processes and systems can be reduced.

Owner:PRAXAIR TECH INC

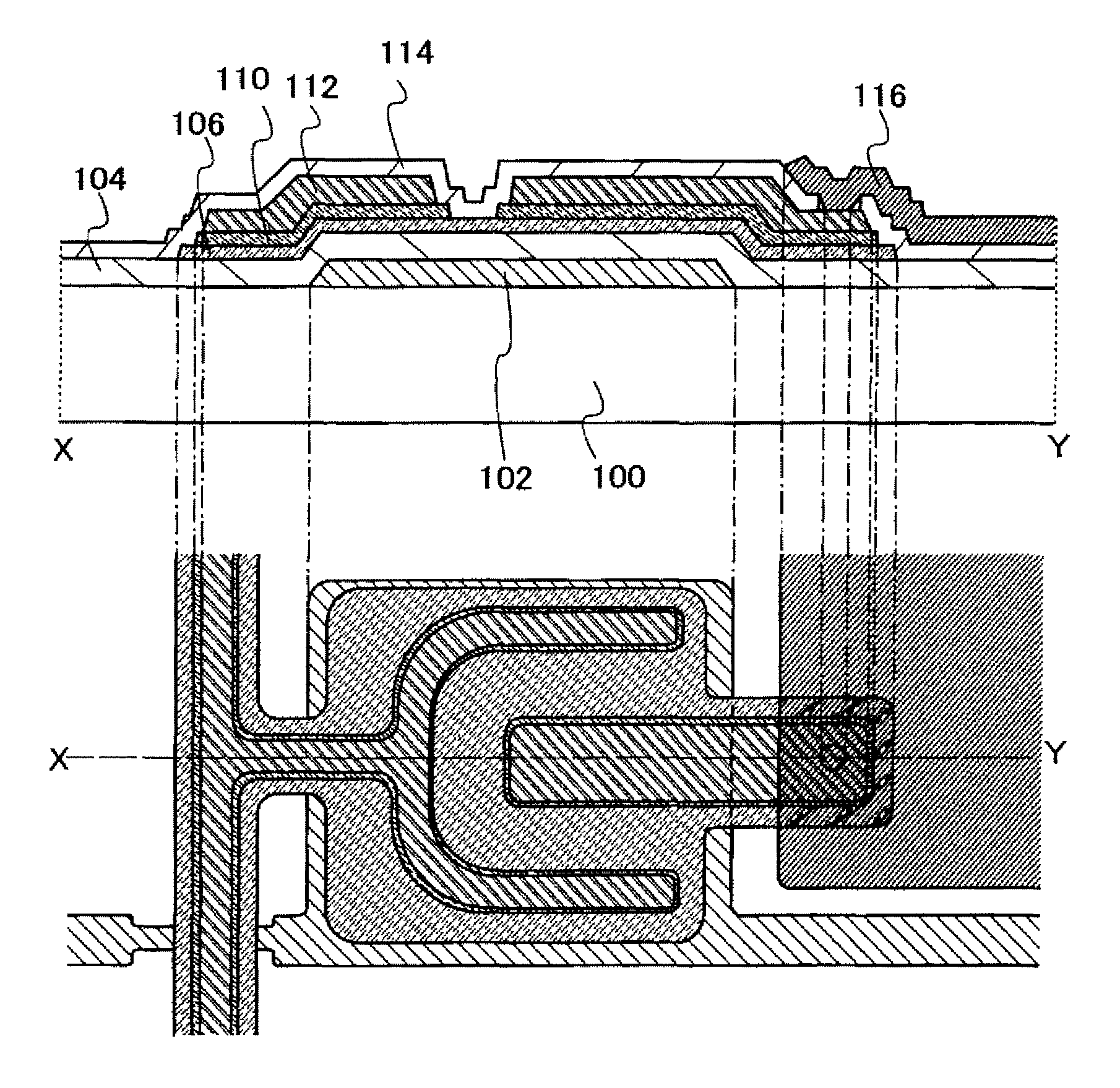

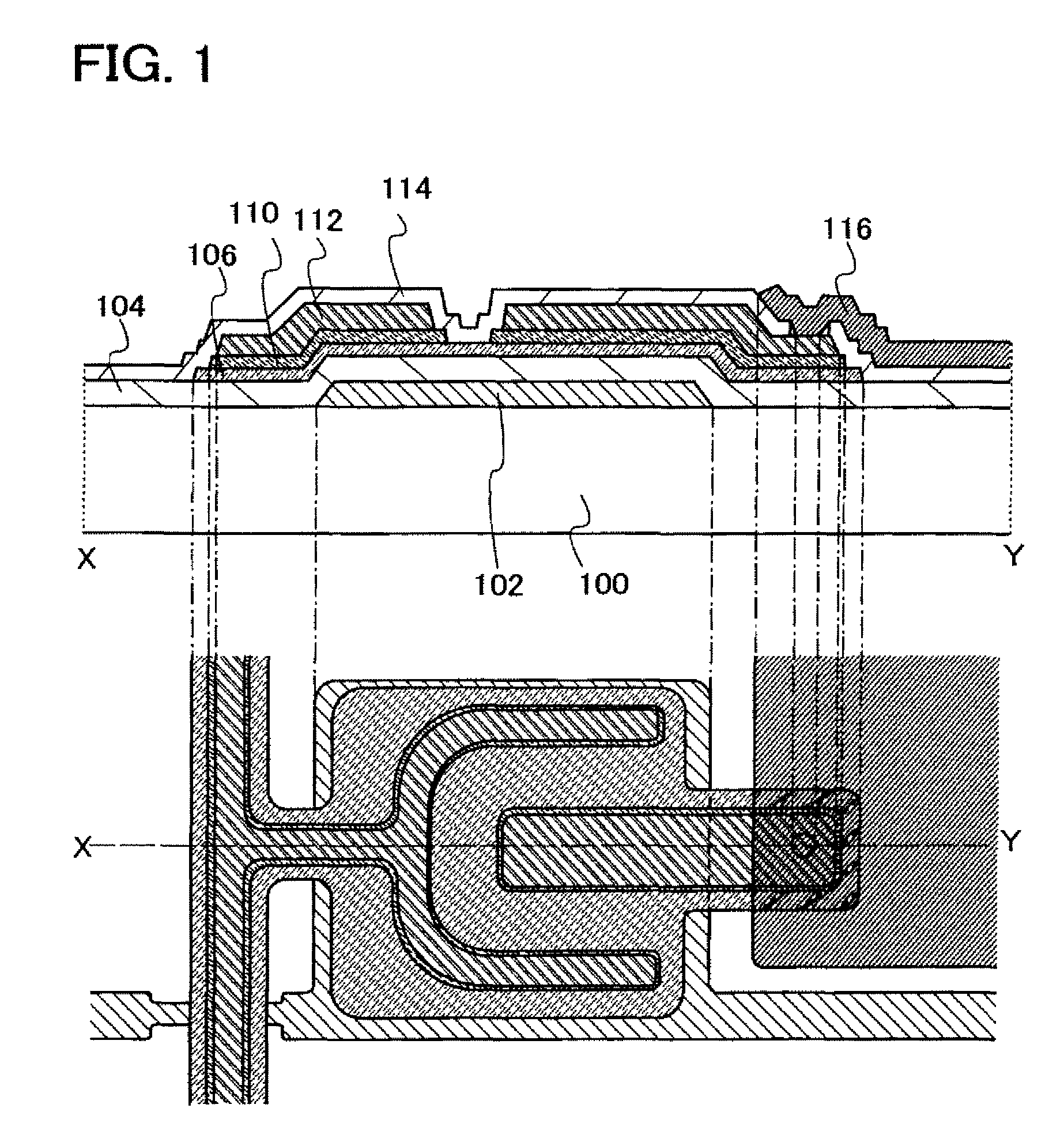

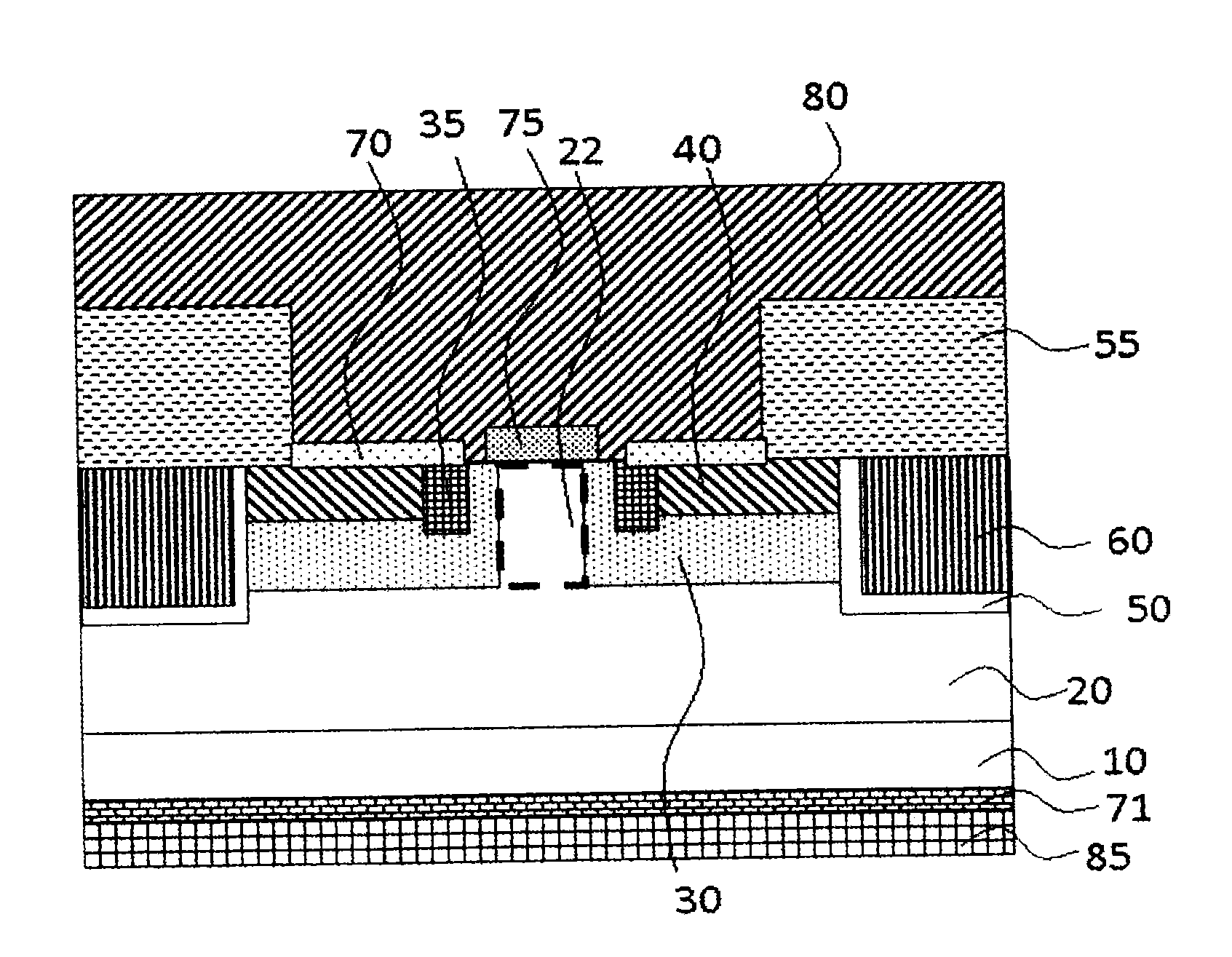

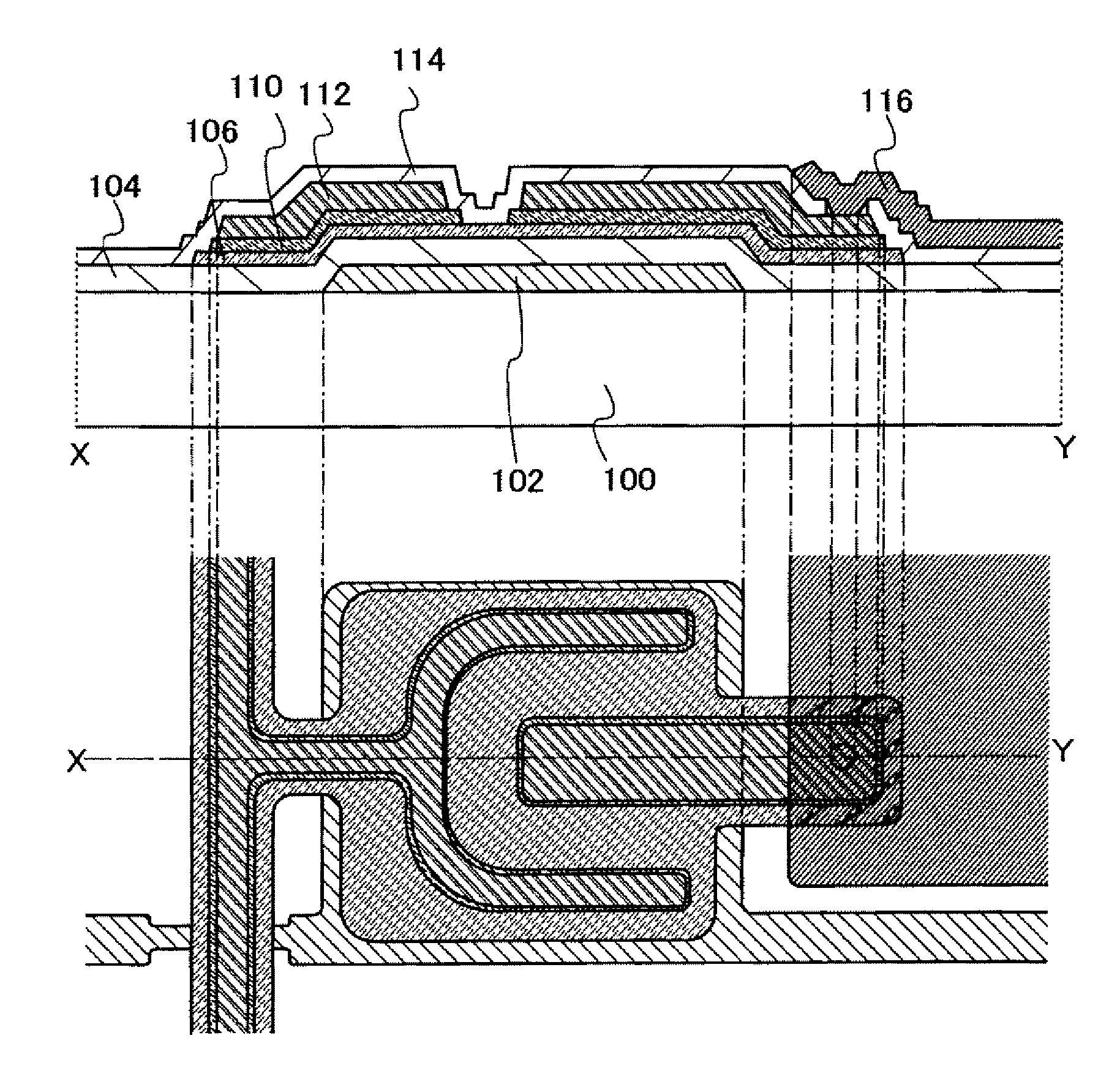

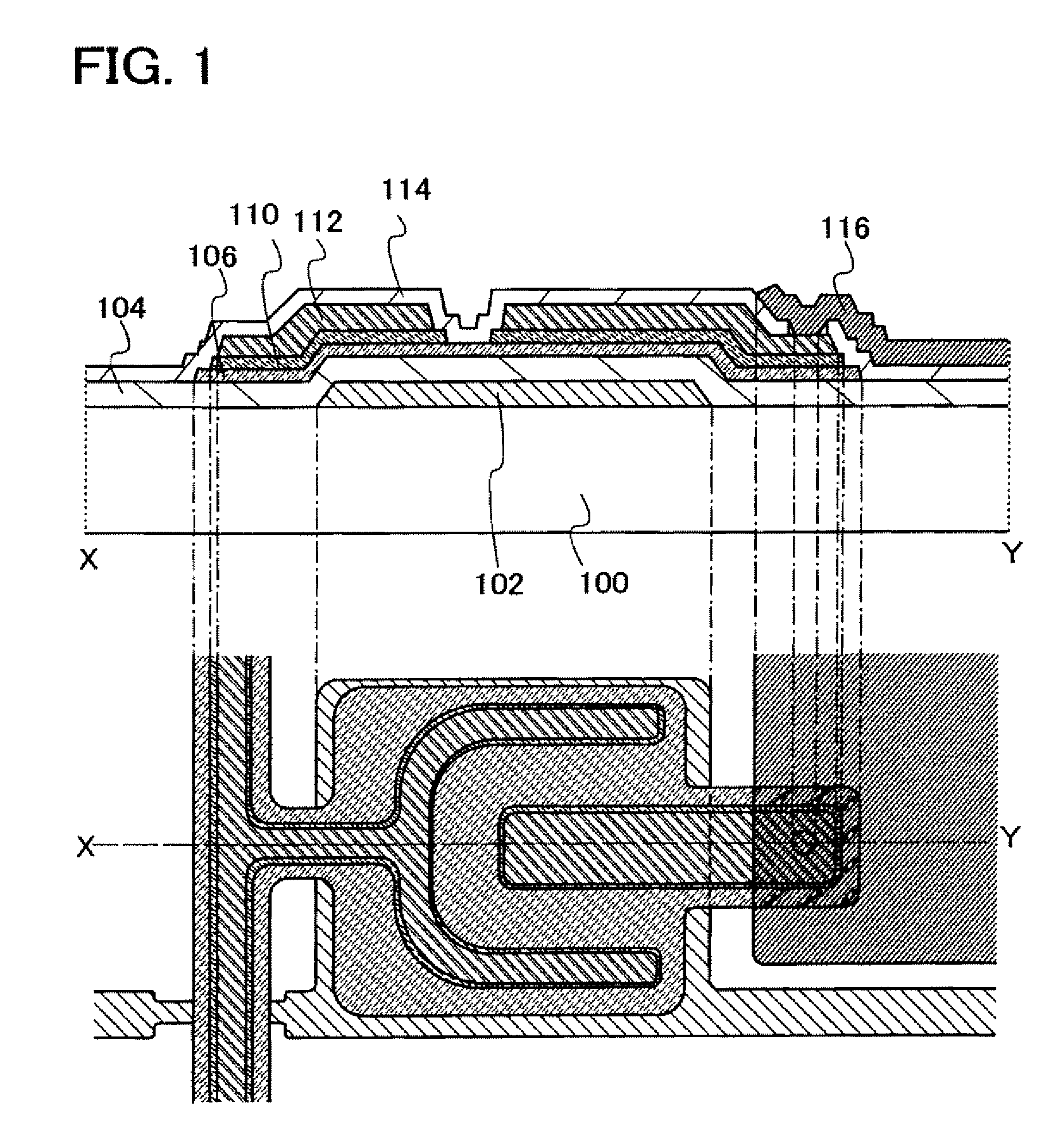

Semiconductor device having SOI construction

ActiveUS20050110116A1Noise reduction effectReduce noiseThyristorSemiconductor/solid-state device detailsInsulation layerElectrical conductor

A semiconductor device includes: a semiconductor substrate including a first semiconductor layer, an insulation layer and a second semiconductor layer, which are laminated in this order; a trench penetrating both of the second semiconductor layer and the insulation layer and reaching the first semiconductor layer; and a third semiconductor layer. The trench has a ring shape on a principal surface of the substrate so that a part of the second semiconductor layer and a part of the insulation layer are surrounded with the trench. The third semiconductor layer is disposed in the trench through a first insulation film disposed on a sidewall of the trench so that the third semiconductor layer contacts the first semiconductor layer at a bottom of the trench.

Owner:DENSO CORP

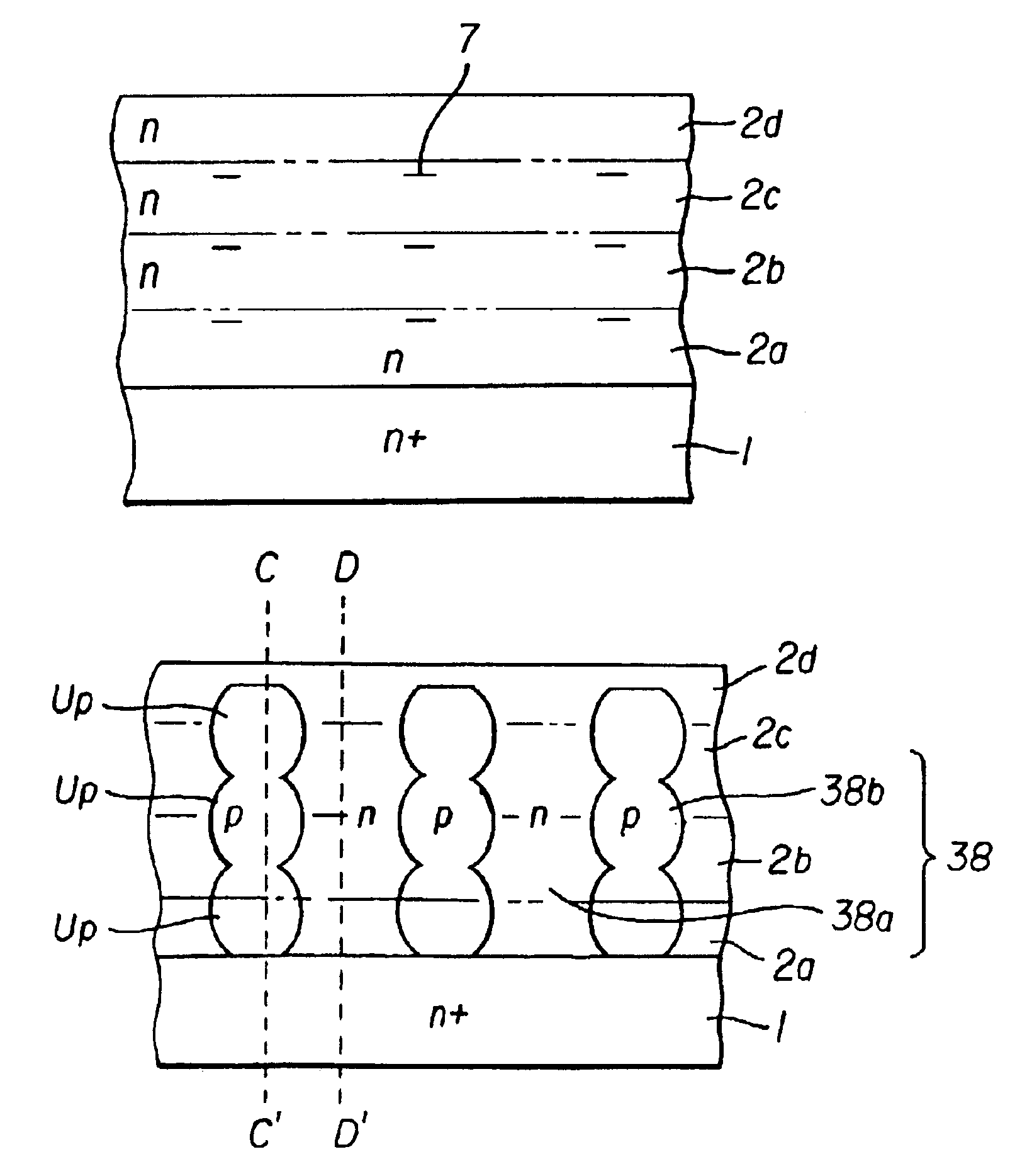

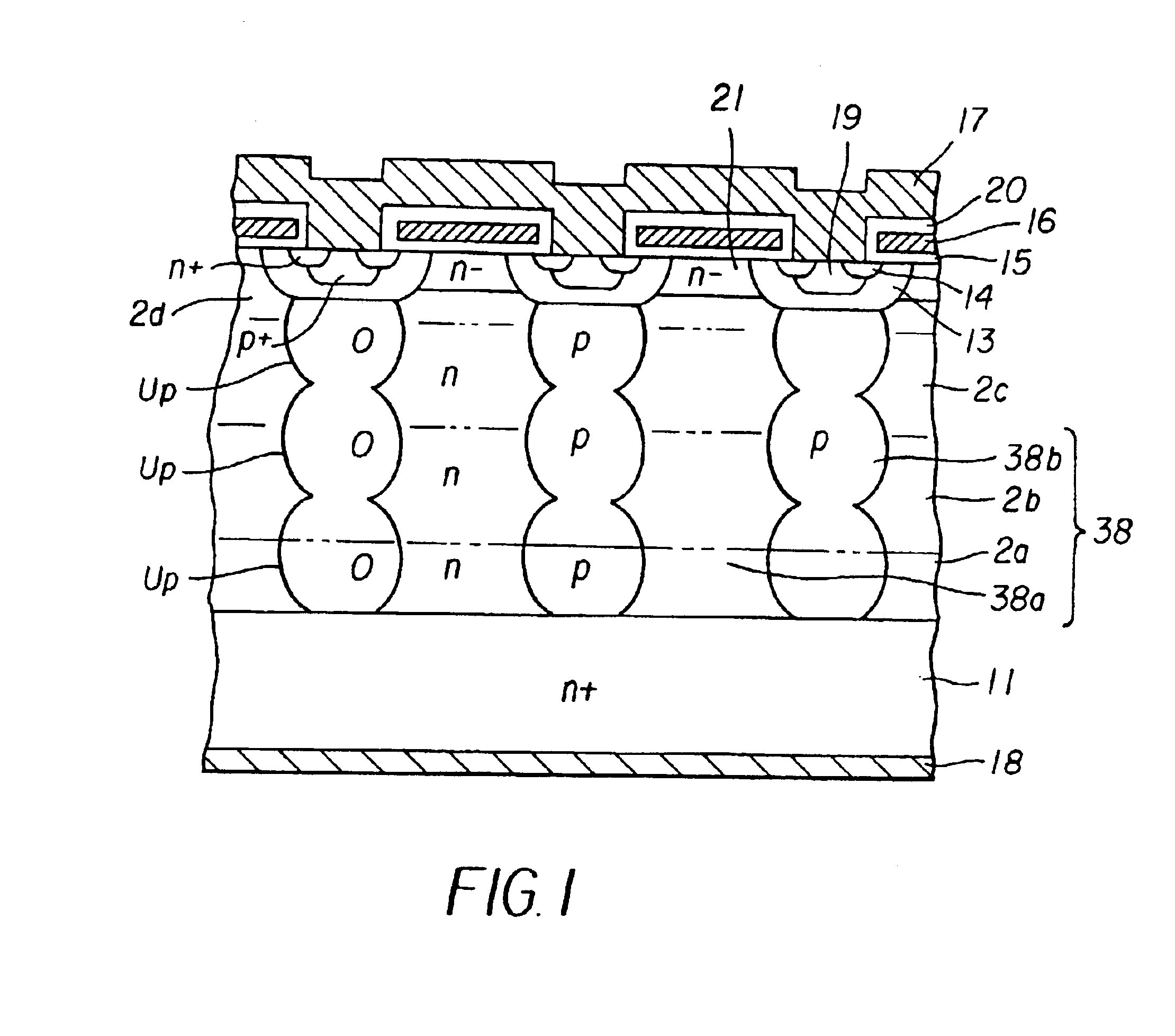

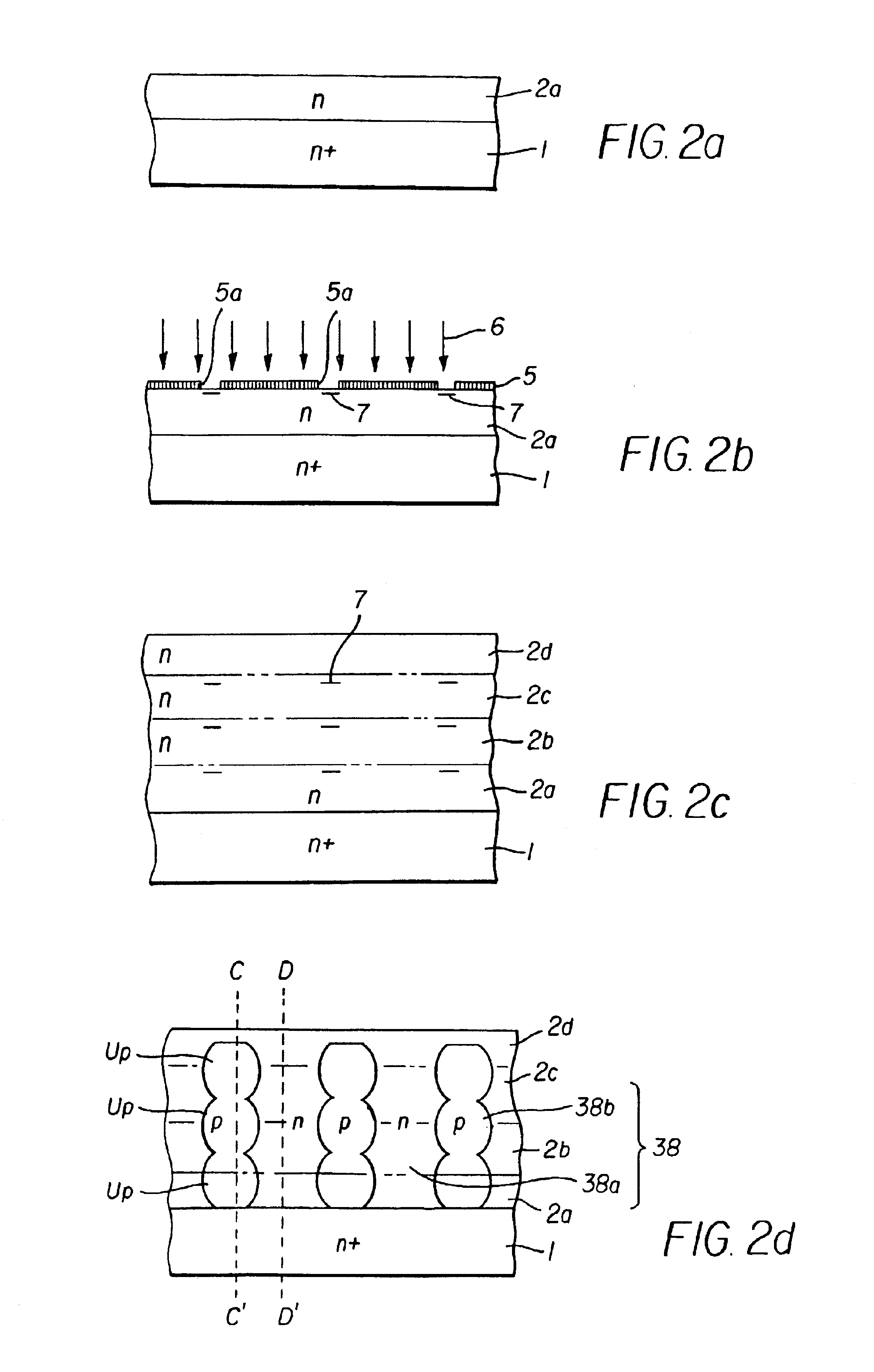

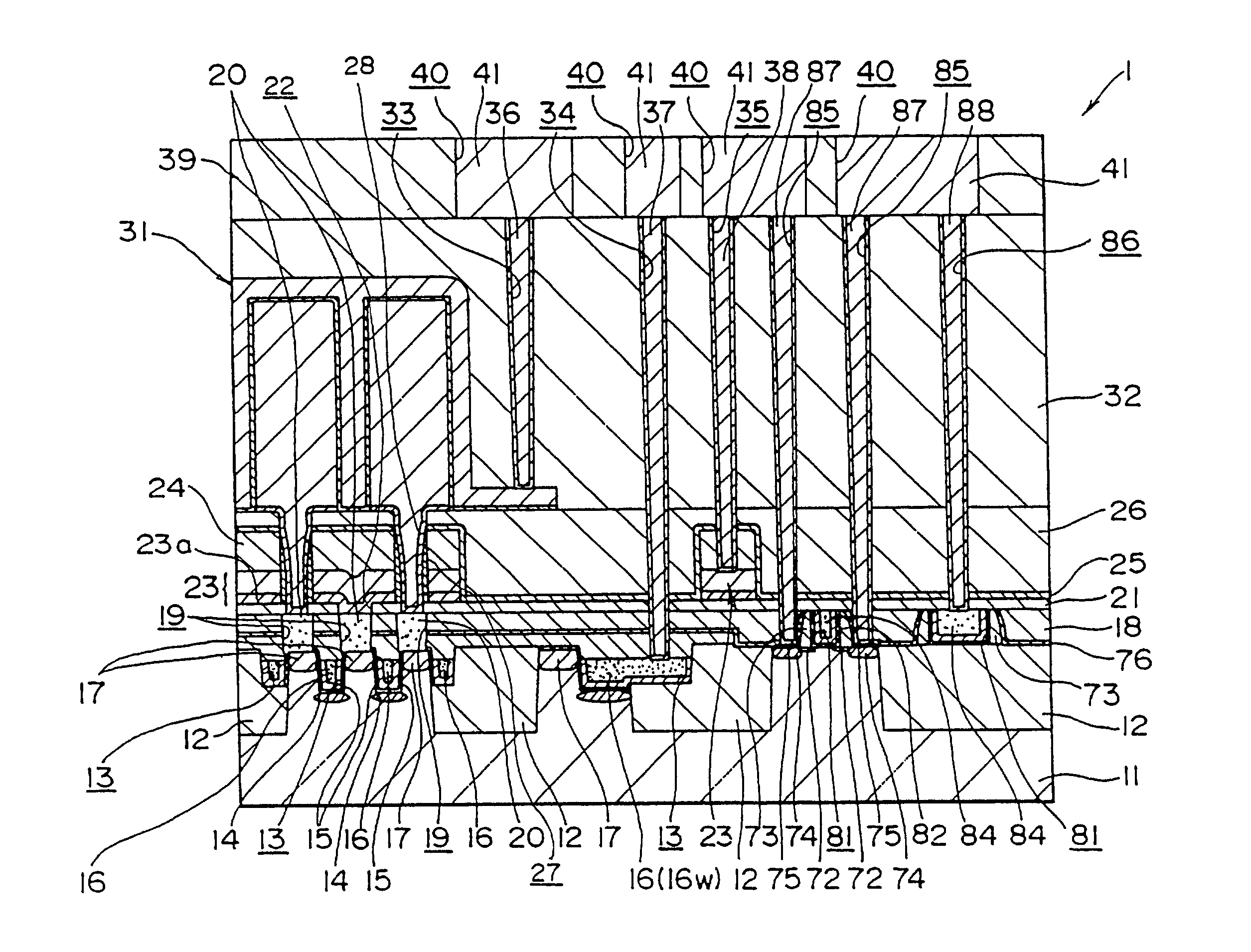

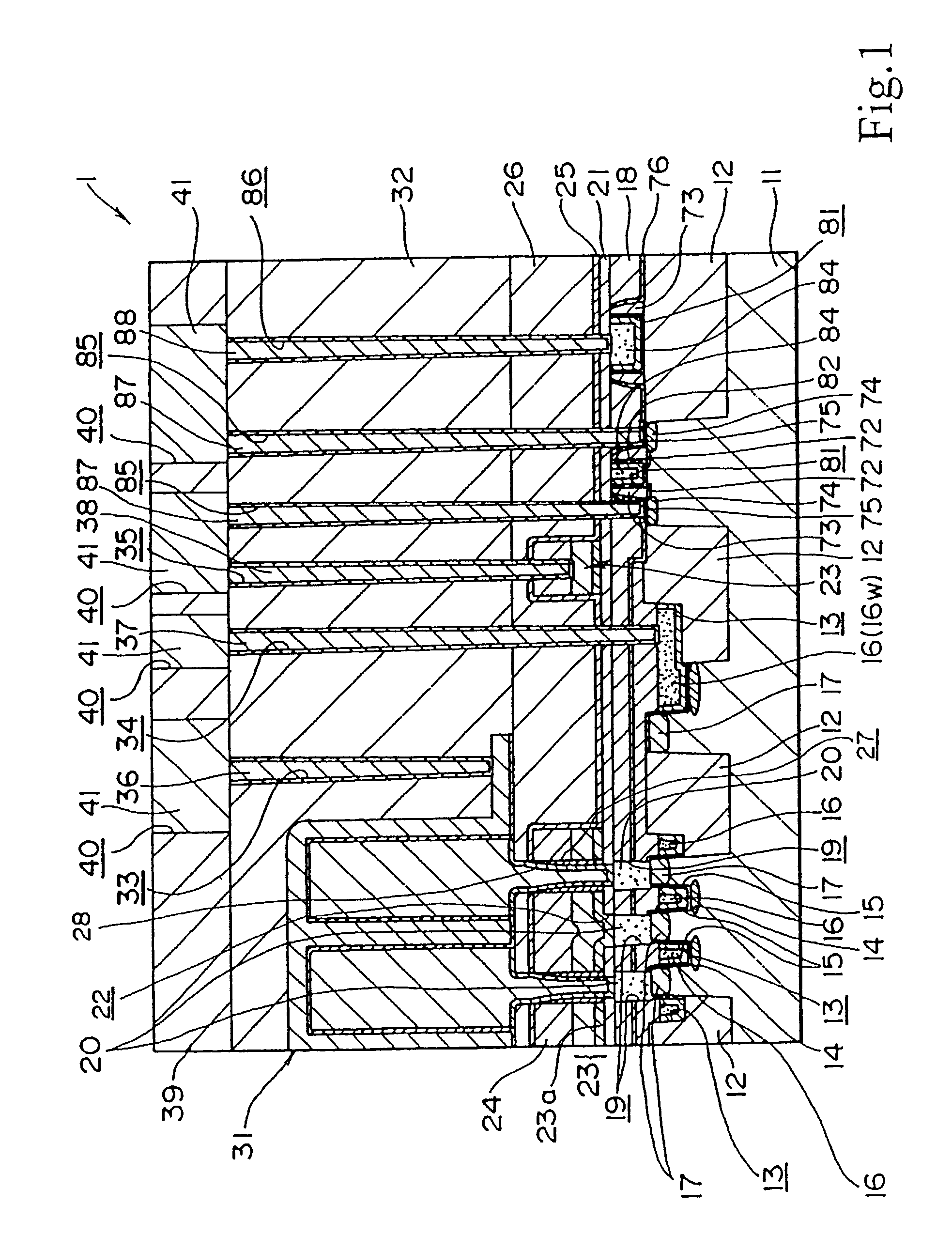

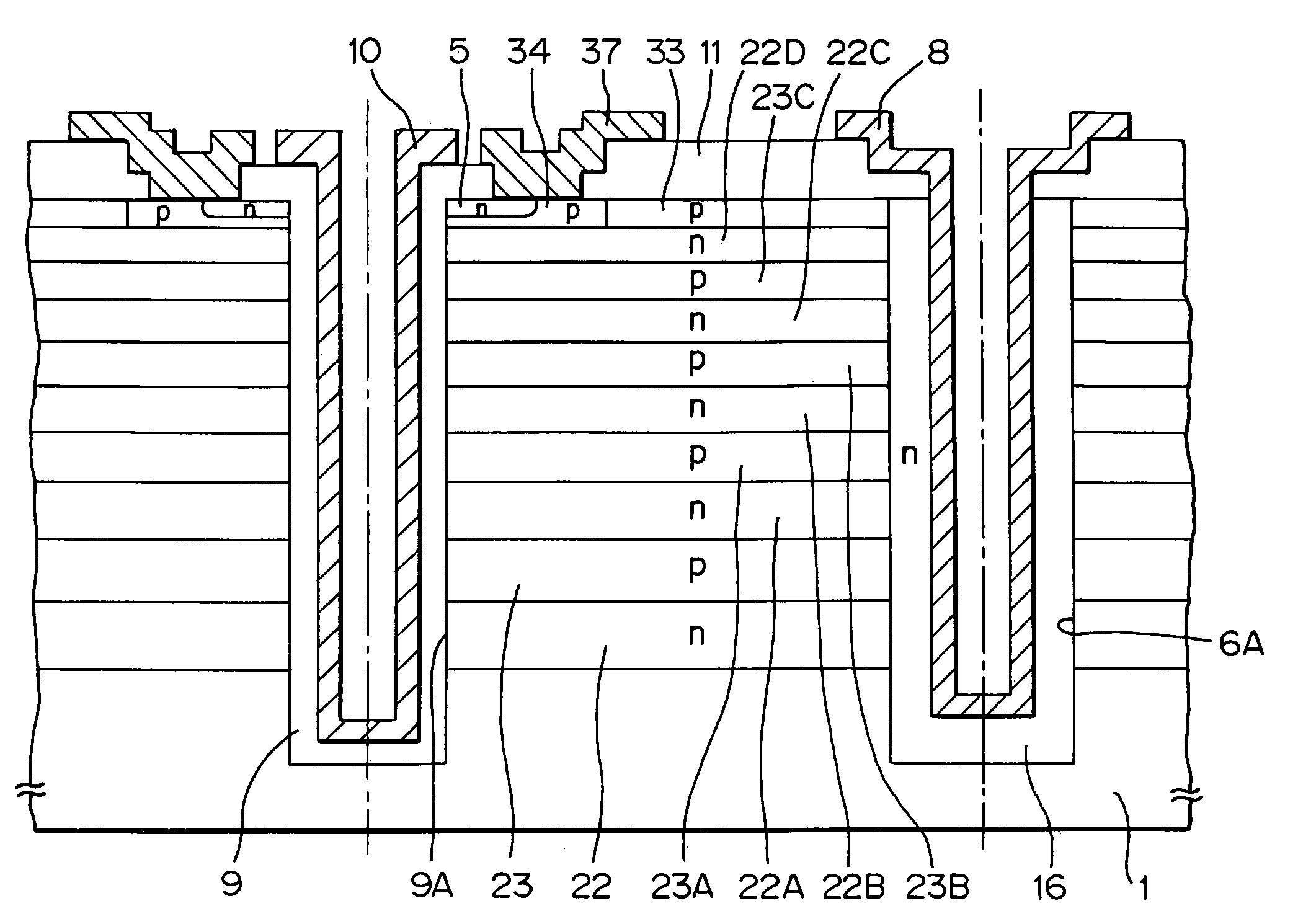

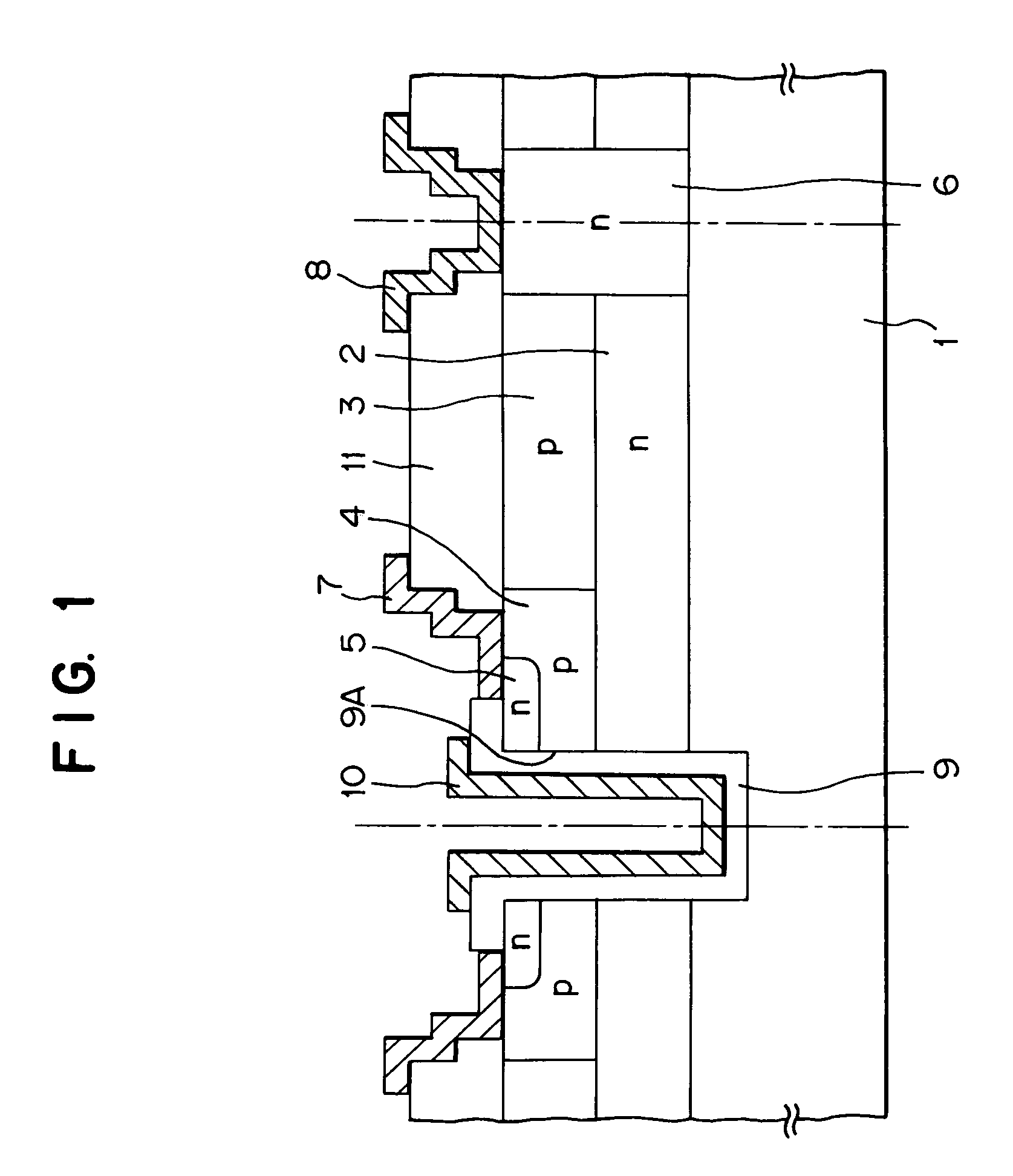

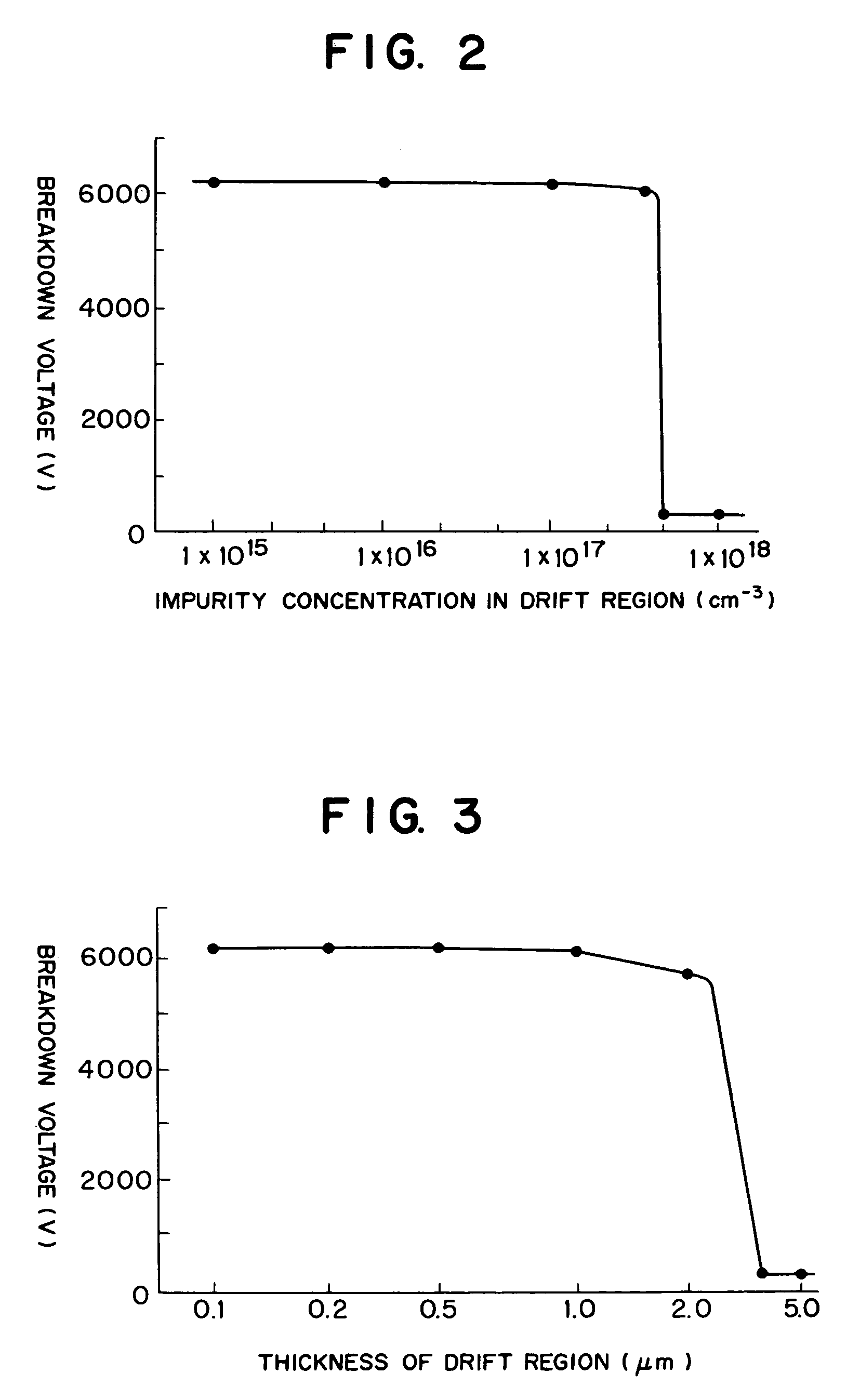

Method of manufacturing a semiconductor device with a vertical drain drift layer of the alternating-conductivity-type

InactiveUS6900109B2High densityImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETImpurity ions

A semiconductor device includes an improved drain drift layer structure of alternating conductivity types, that is easy to manufacture, and that facilitates realizing a high current capacity and a high breakdown voltage and to provide a method of manufacturing the semiconductor device. The vertical MOSFET according to the invention includes an alternating-conductivity-type drain drift layer on an n+-type drain layer as a substrate. The alternating-conductivity-type drain drift layer is formed of n-type drift current path regions and p-type partition regions alternately arranged laterally with each other. The n-type drift current path regions and p-type partition regions extend in perpendicular to n+-type drain layer. Each p-type partition region is formed by vertically connecting p-type buried diffusion unit regions Up. The n-type drift current path regions are residual regions, left after connecting p-type buried diffusion unit regions Up, with the conductivity type thereof unchanged. The alternating-conductivity-type drain drift layer is formed by repeating the step of epitaxial layer growth and the step of implanting p-type impurity ions and by diffusing the impurity ions at once from the impurity sources located on multiple levels.

Owner:FUJI ELECTRIC CO LTD

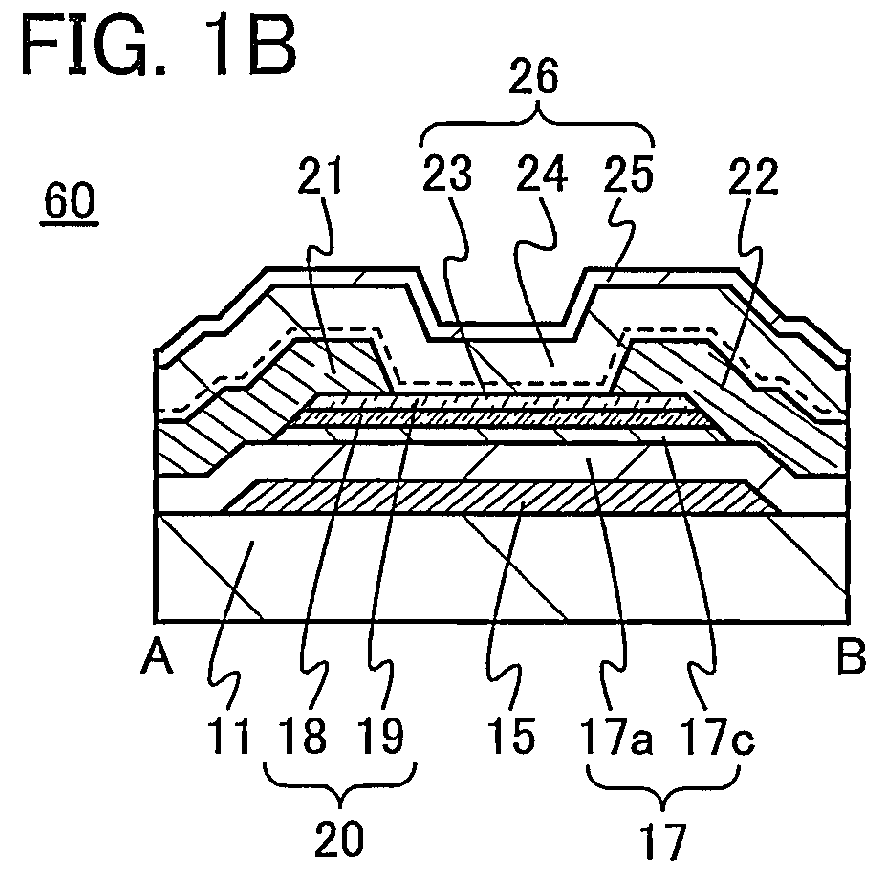

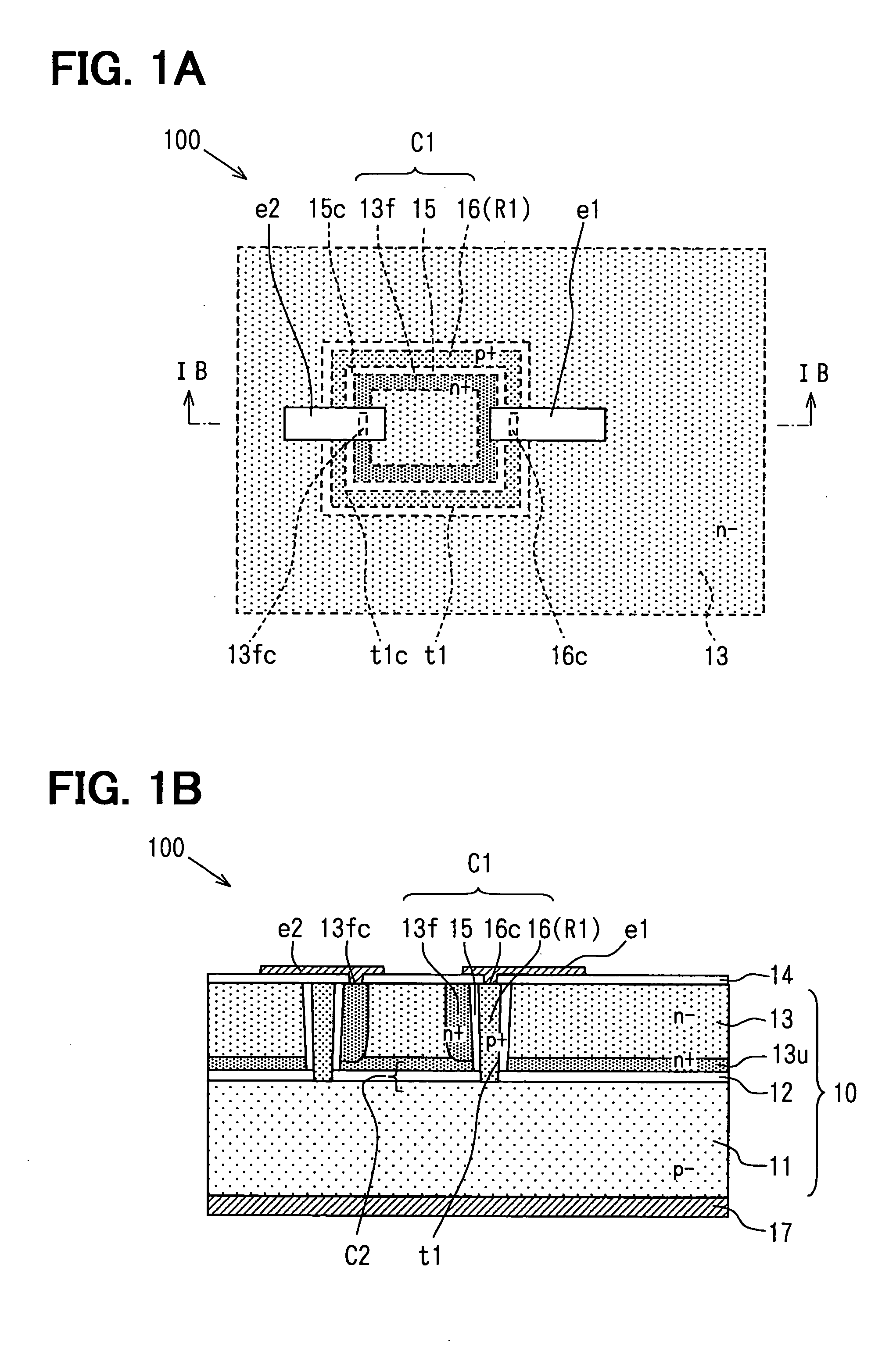

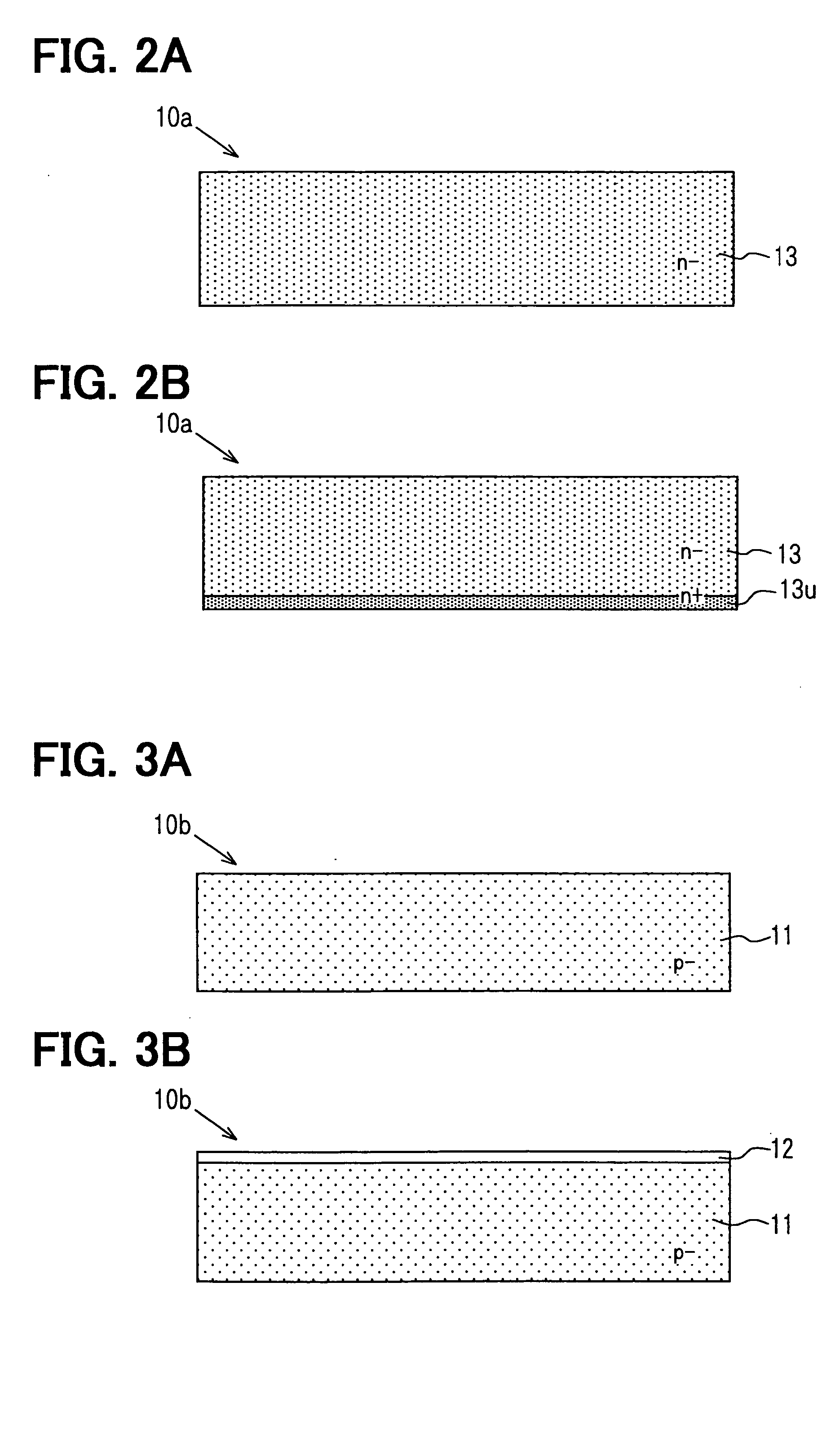

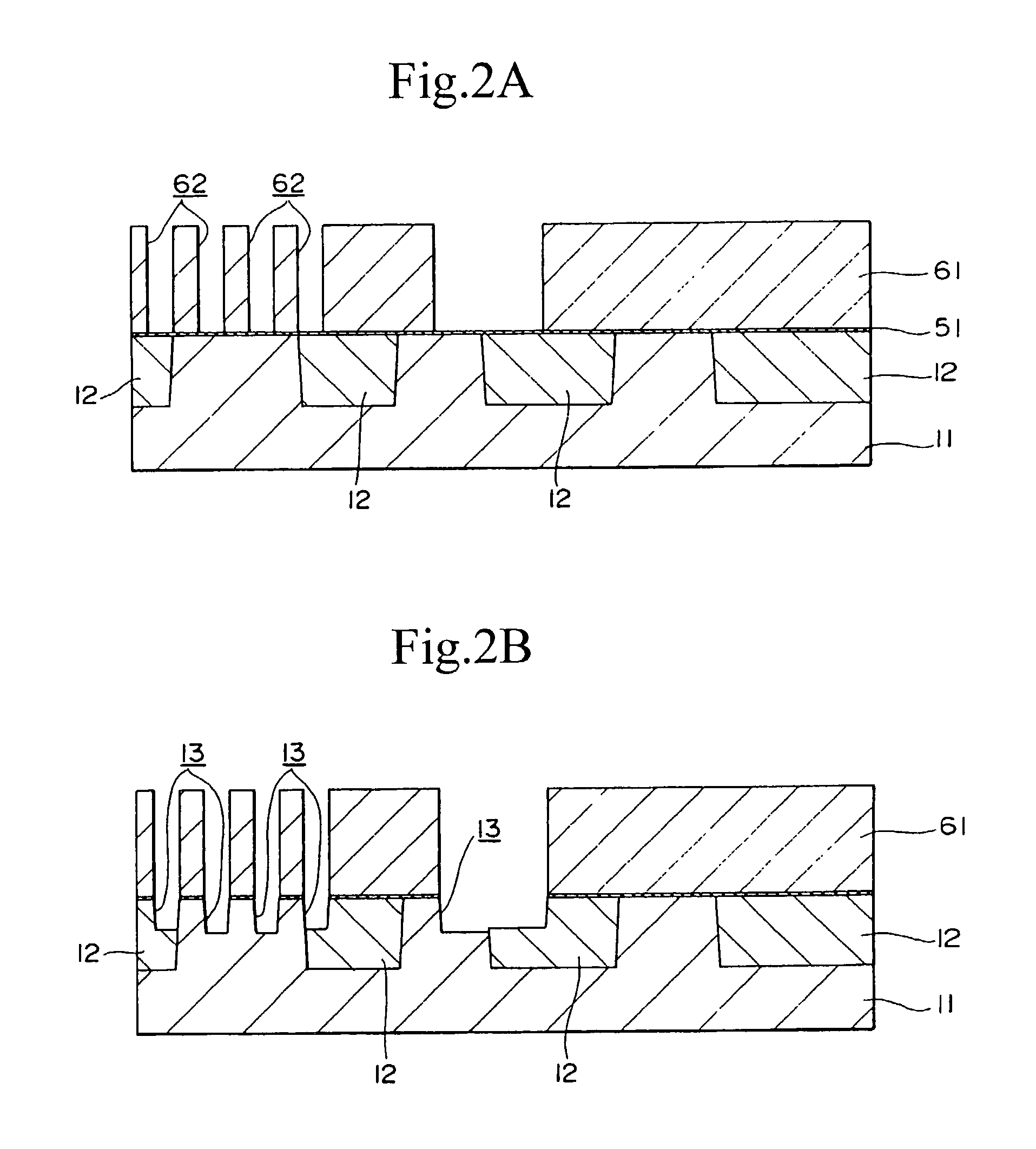

Semiconductor device and it's manufacturing method

InactiveUS7087956B2Effective channel length can be sufficientlyReduce contact resistanceTransistorSolid-state devicesDiffusion layerImpurity

In a semiconductor device having a memory element and a logic element formed on the same semiconductor substrate, a transistor of the memory element comprises a gate electrode (16) embedded within a trench (13) formed in a semiconductor substrate (11) through a gate insulating film (15) and a diffusion layer (17) formed on the side of the semiconductor substrate (11) at a sidewall of the trench (13), and a take-out electrode (20) connected to the diffusion layer (17) is provided so that the take-out electrode overlaps the gate electrode (16) through a first interlayer insulating film (insulating film) (18) on the gate electrode (16). A word line (16) is provided in the trench (13) and an impurity concentration of the diffusion layer (17) is decreased as a depth thereof is increased.

Owner:SONY CORP

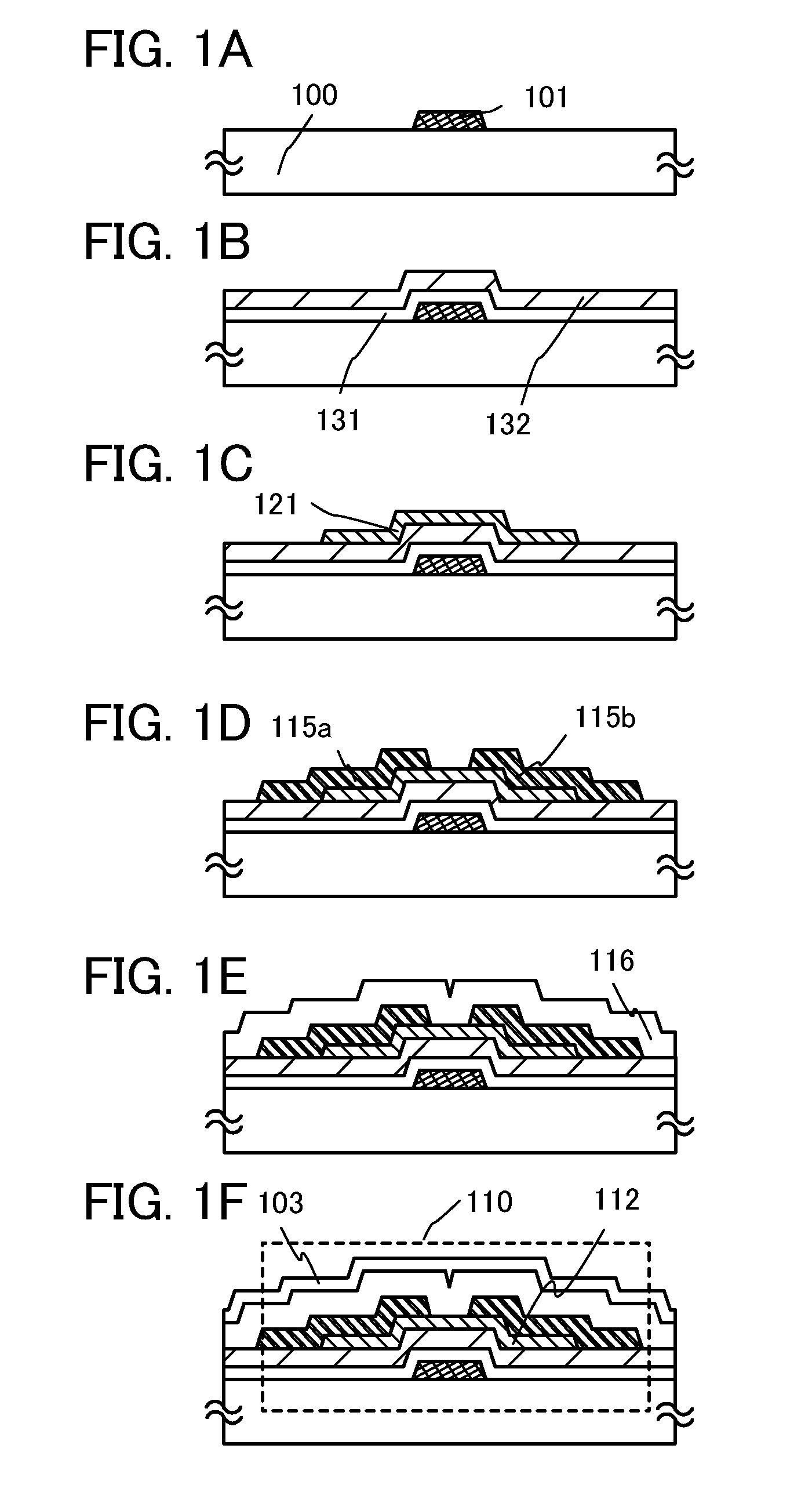

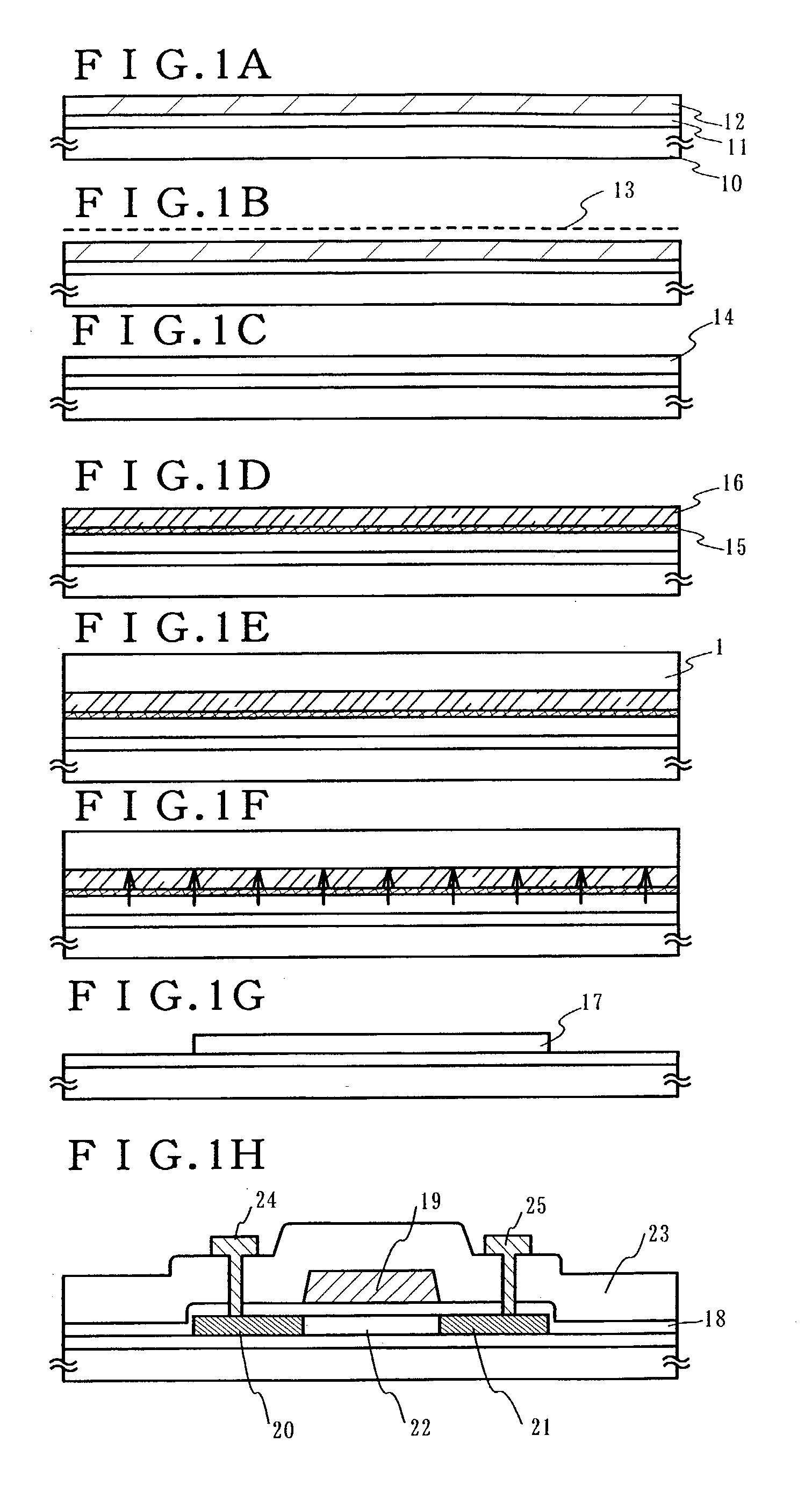

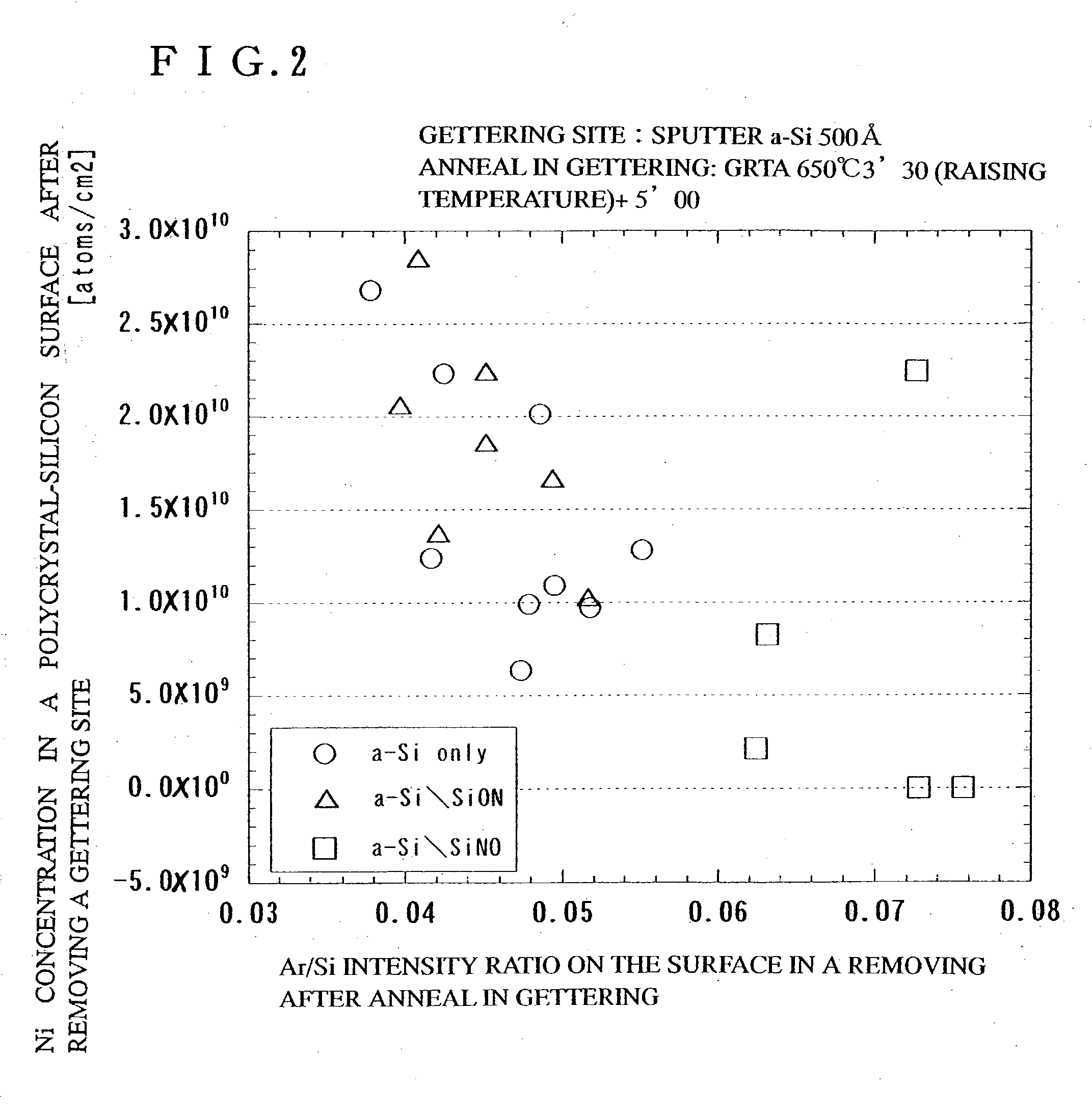

Semiconductor device and a method for fabricating the device

InactiveUS20030232468A1Reduce impurity concentrationTransistorSolid-state devicesElectrical conductorSemiconductor

A technique, where a semiconductor film having a crystal structure is obtained using a metal element that helps crystallization of the semiconductor film, then that metal element remained in the film is effectively removed, as a result variation among elements is reduced, is provided. In a process for forming a gettering site, a semiconductor film containing a rare-gas element is formed, then an anti-diffusion film for preventing diffusion of the rare-gas element is formed, thereby the metal element in another semiconductor film is effectively removed, particularly in a gettering that is a heating treatment at a high temperature of 600° C. or more.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and method for manufacturing the same

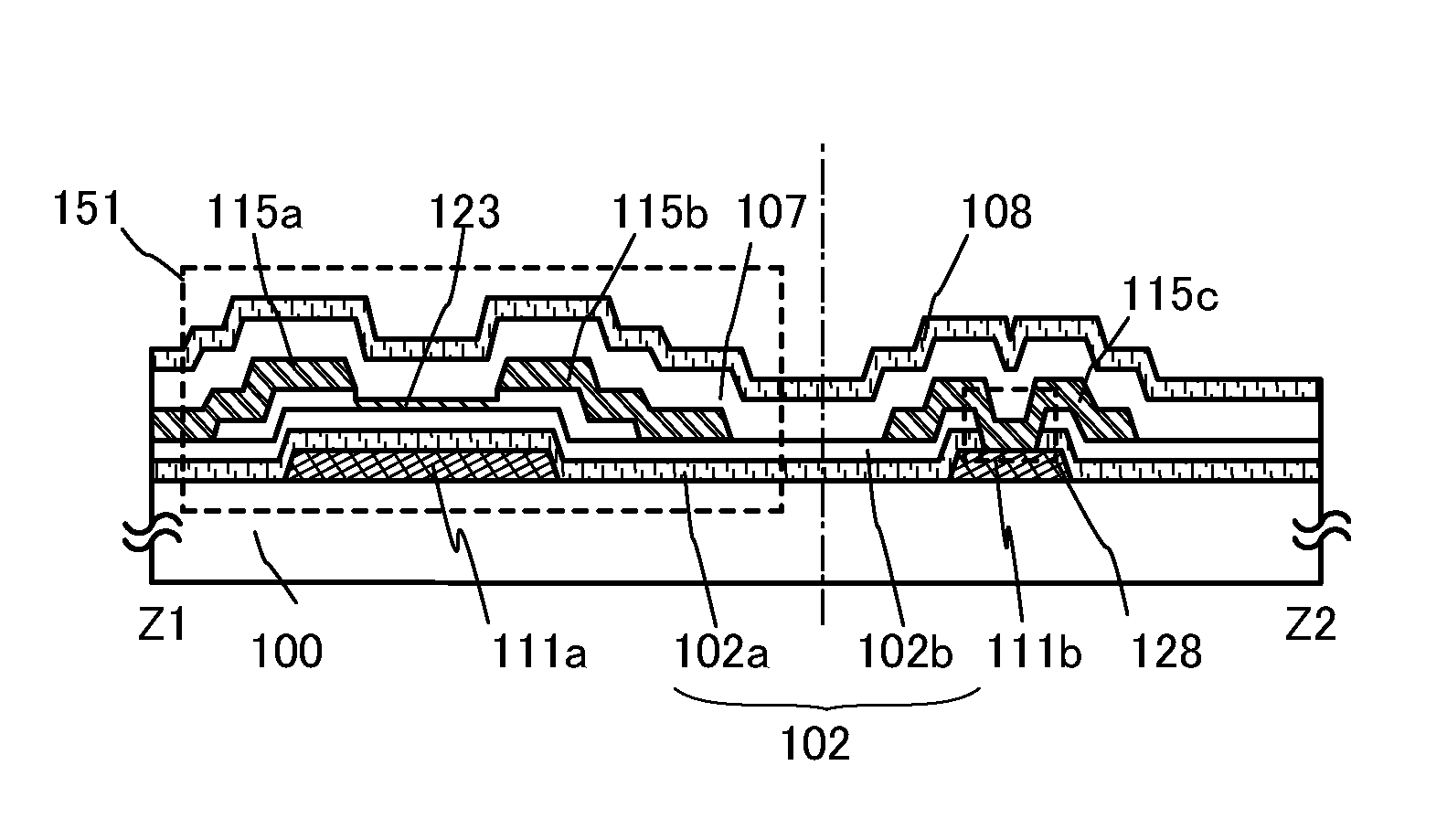

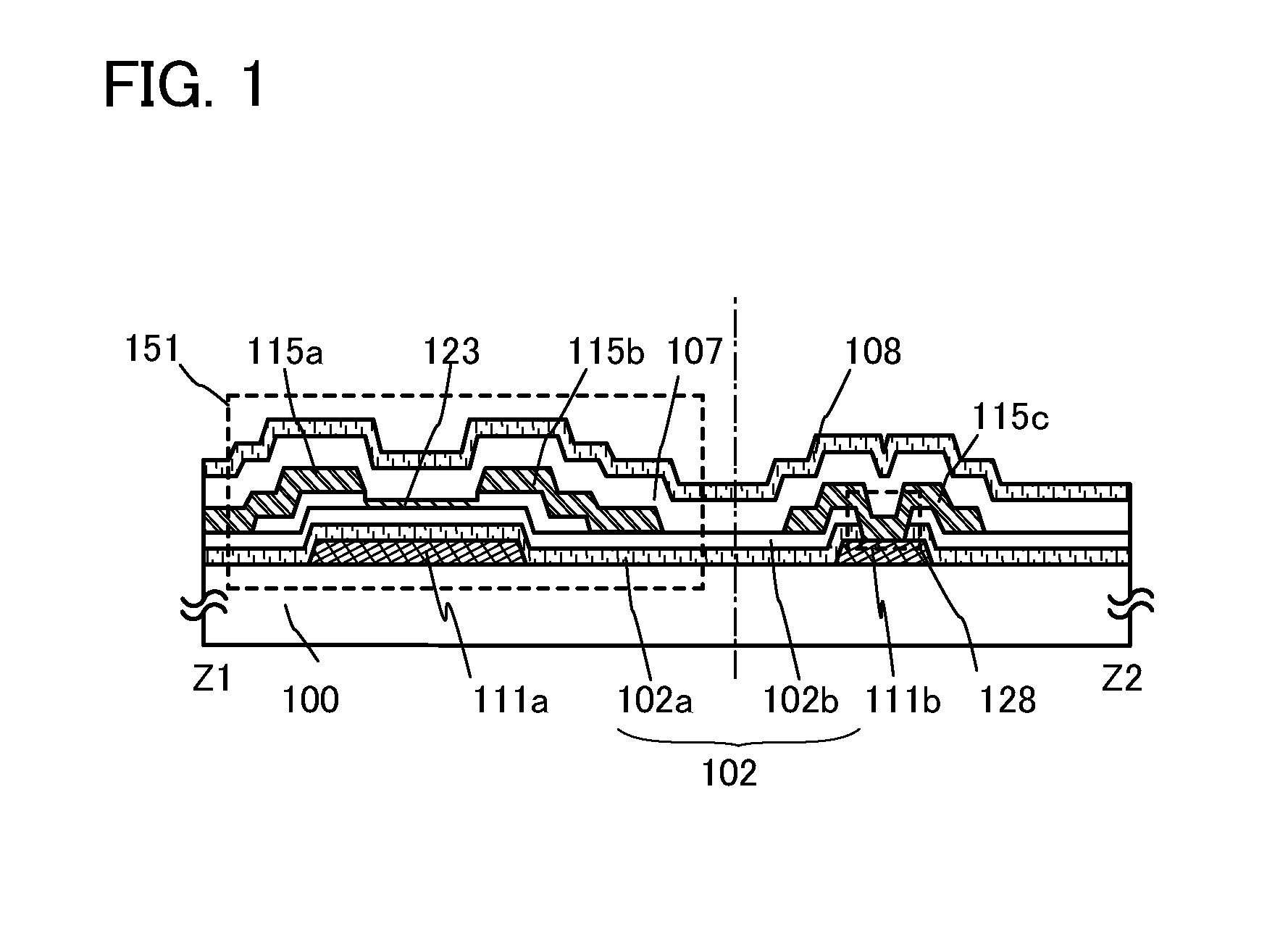

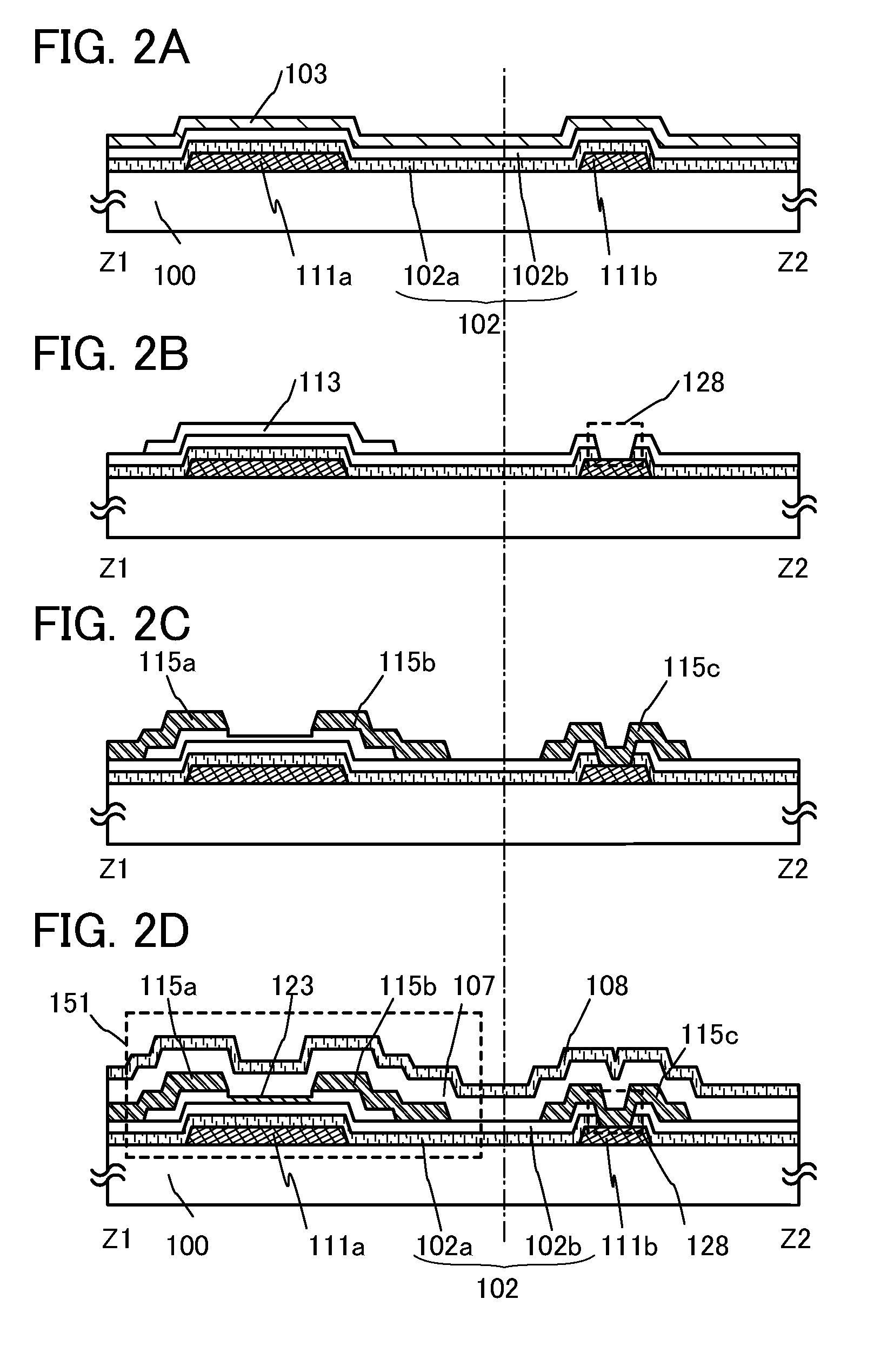

InactiveUS20170309752A1Improve reliabilityReduce impurity concentrationTransistorSolid-state devicesHydrogenOxygen vacancy

A highly reliable semiconductor device is provided. The semiconductor device includes a first barrier insulating film; a first gate electrode thereover; a first gate insulating film thereover; an oxide semiconductor film thereover; source and drain electrodes over the oxide semiconductor film; a second gate insulating film over the oxide semiconductor film; a second gate electrode over the second gate insulating film; a second barrier insulating film that covers the oxide semiconductor film, the source and the drain electrodes, and the second gate electrode, and is in contact with side surfaces of the oxide semiconductor film and the source and drain electrodes; and a third barrier insulating film thereover. The first to third barrier insulating films are less likely to transmit hydrogen, water, and oxygen than the first and second gate insulating films. The third barrier insulating film is thinner than the second barrier insulating film. The source and drain electrodes each includes a conductive oxide film in contact with the oxide semiconductor film. The conductive oxide film has more oxygen vacancies than the oxide semiconductor film.

Owner:SEMICON ENERGY LAB CO LTD

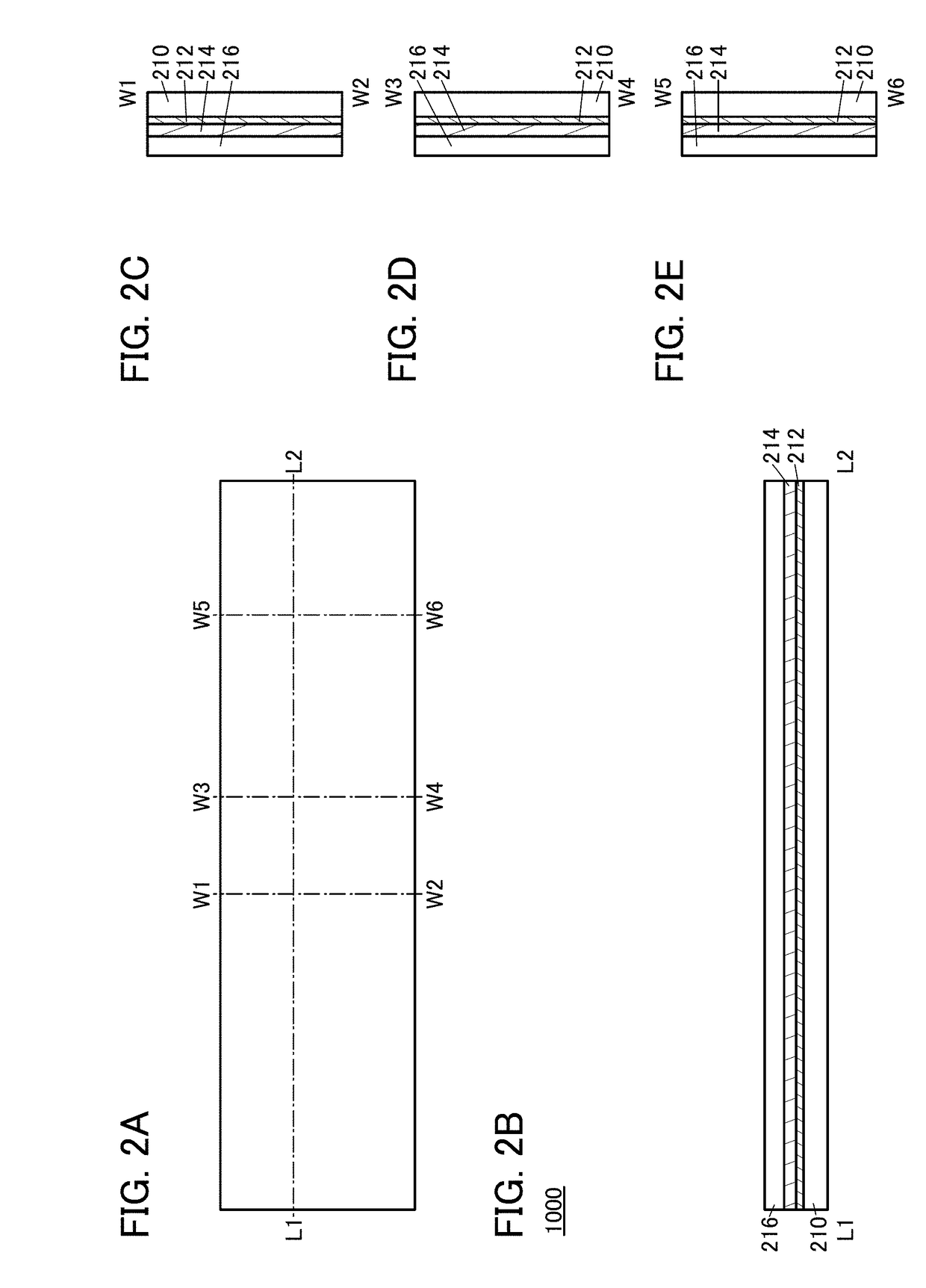

Semiconductor device

InactiveUS20120292742A1Lower on-resistanceEase concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceMOSFET

A MOSFET includes a silicon carbide substrate, a buffer layer made of silicon carbide formed on the silicon carbide substrate, a drift layer made of silicon carbide of an n conductivity type formed on the buffer layer, a p type body region of a p conductivity type formed in the drift layer to include a main surface of the drift layer opposite to the buffer layer, a source contact electrode formed on the p type body region, and a drain electrode formed on a main surface of the silicon carbide substrate opposite to the buffer layer. A current path region having an impurity concentration higher than that of another region in the drift layer is formed in a region in the drift layer sandwiched between the buffer layer and the body region.

Owner:SUMITOMO ELECTRIC IND LTD

High-voltage power semiconductor device with body regions of alternating conductivity and decreasing thickness

InactiveUS7470960B1Improve pressure resistanceLower on-resistanceTransistorThyristorPower semiconductor deviceElectrical resistance and conductance

A semiconductor device which eases an electric field at a drift portion without a reduction in impurity concentrations, and has a high withstand voltage and a low on-resistance, wherein, when a rated voltage is applied between a body region and a drain region formed on an insulating semiconductor substrate, the thicknesses of two, p-type and n-type, drift regions sandwiched between the body and drain regions are selected so as to completely deplete the drift regions.

Owner:THE KANSAI ELECTRIC POWER CO

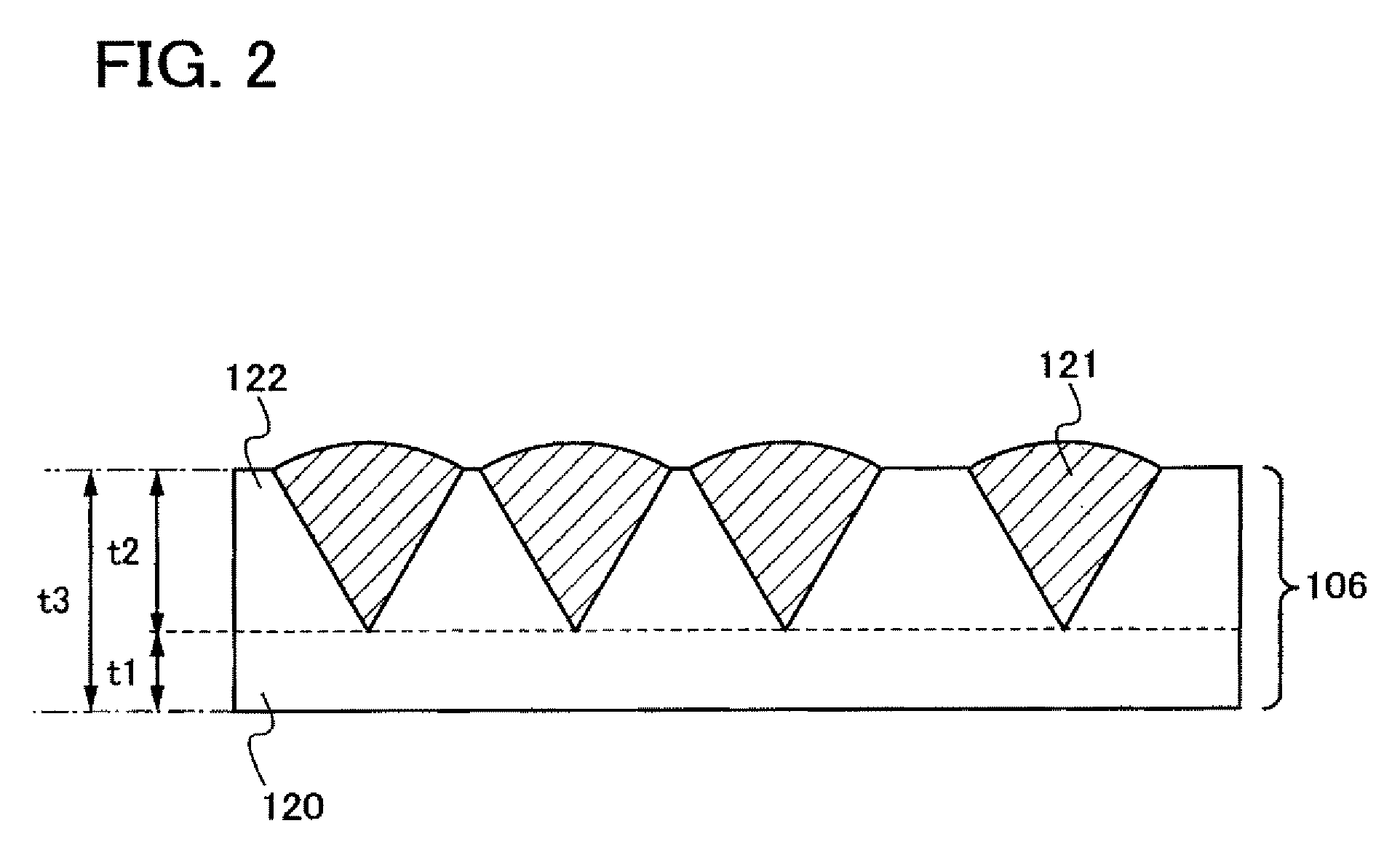

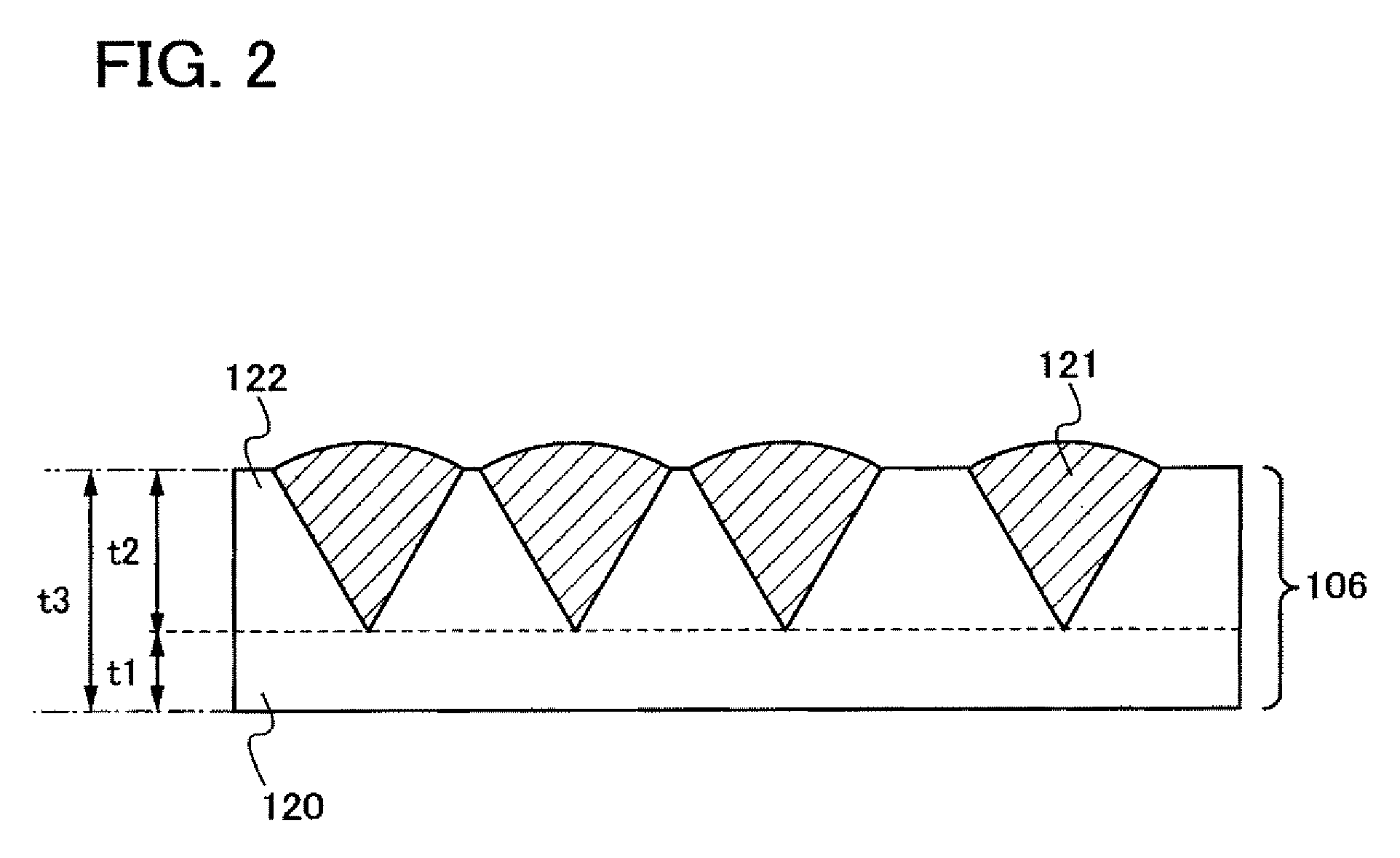

Thin film transistor and method for manufacturing the same

InactiveUS20090261328A1Increase currentHigh purityTransistorSolid-state devicesAmorphous siliconCrystalline particle

Disclosed is a thin film transistor which includes, over a substrate having an insulating surface, a gate insulating layer covering a gate electrode; a semiconductor layer which functions as a channel formation region; and a semiconductor layer including an impurity element imparting one conductivity type. The semiconductor layer exists in a state that a plurality of crystalline particles is dispersed in an amorphous silicon and that the crystalline particles have an inverted conical or inverted pyramidal shape. The crystalline particles grow approximately radially in a direction in which the semiconductor layer is deposited. Vertexes of the inverted conical or inverted pyramidal crystal particles are located apart from an interface between the gate insulating layer and the semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com