Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

524 results about "Dangling bond" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In chemistry, a dangling bond is an unsatisfied valence on an immobilized atom. An atom with a dangling bond is also referred to as an immobilized free radical or an immobilized radical, a reference to its structural and chemical similarity to a free radical.

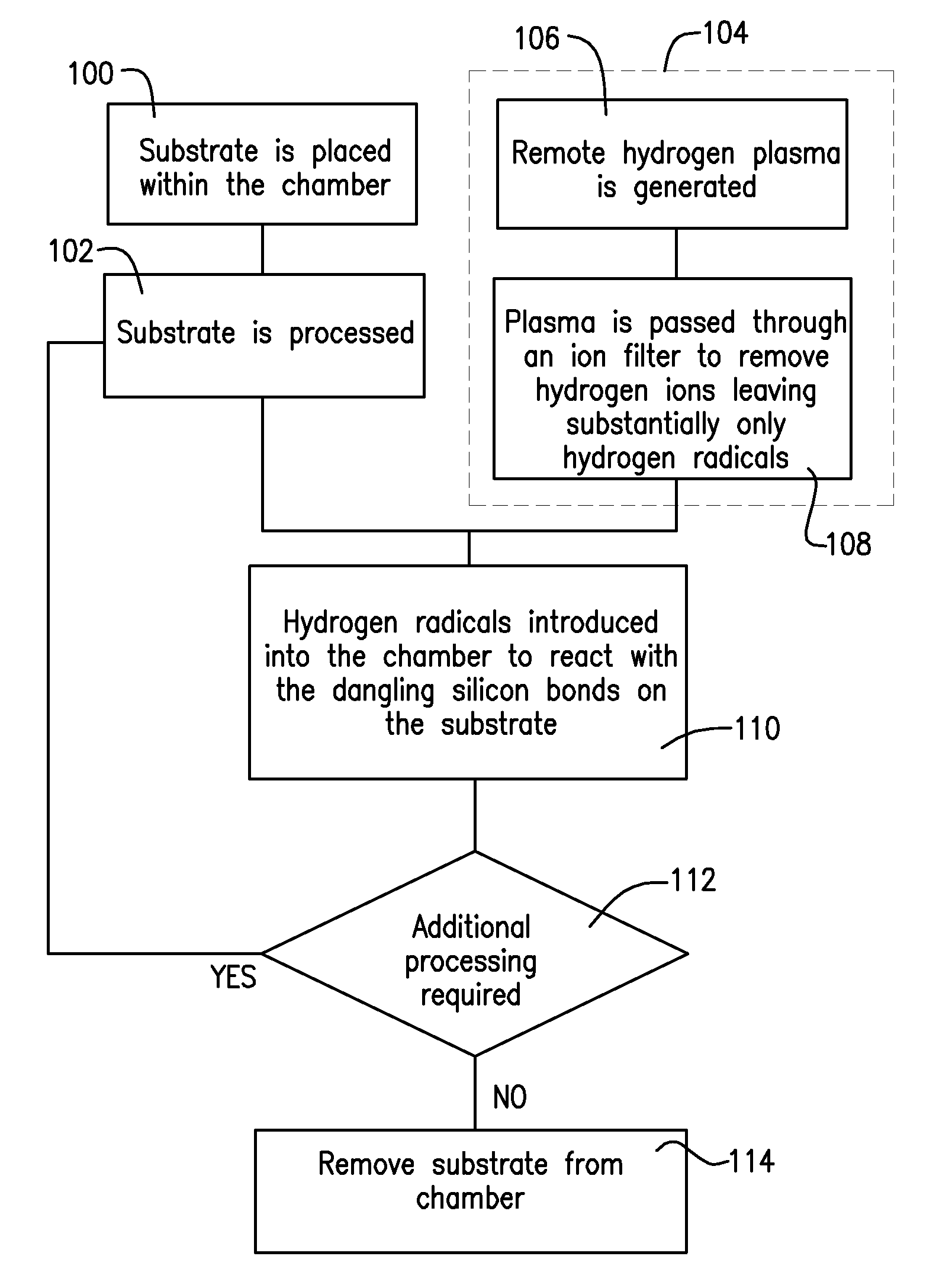

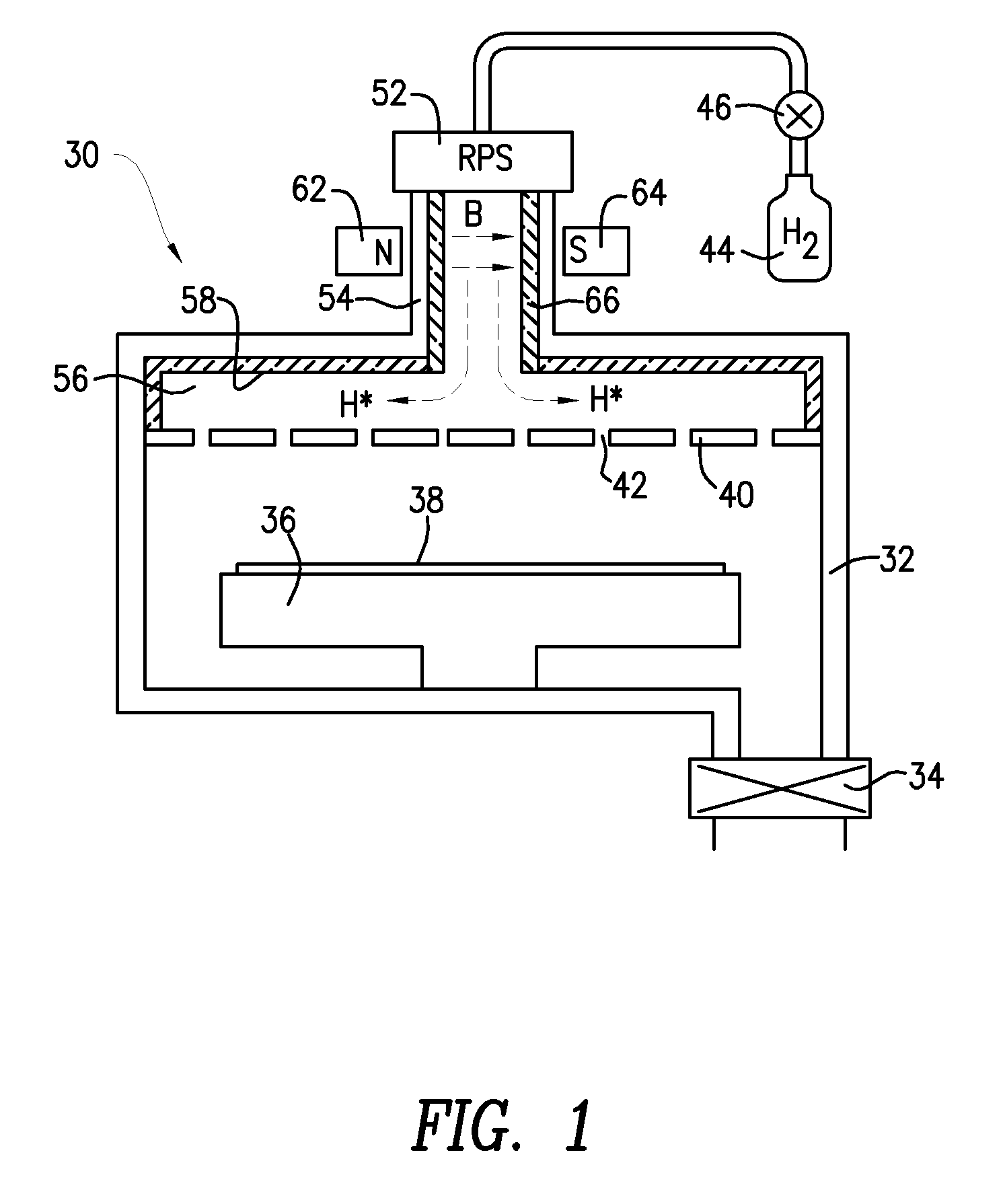

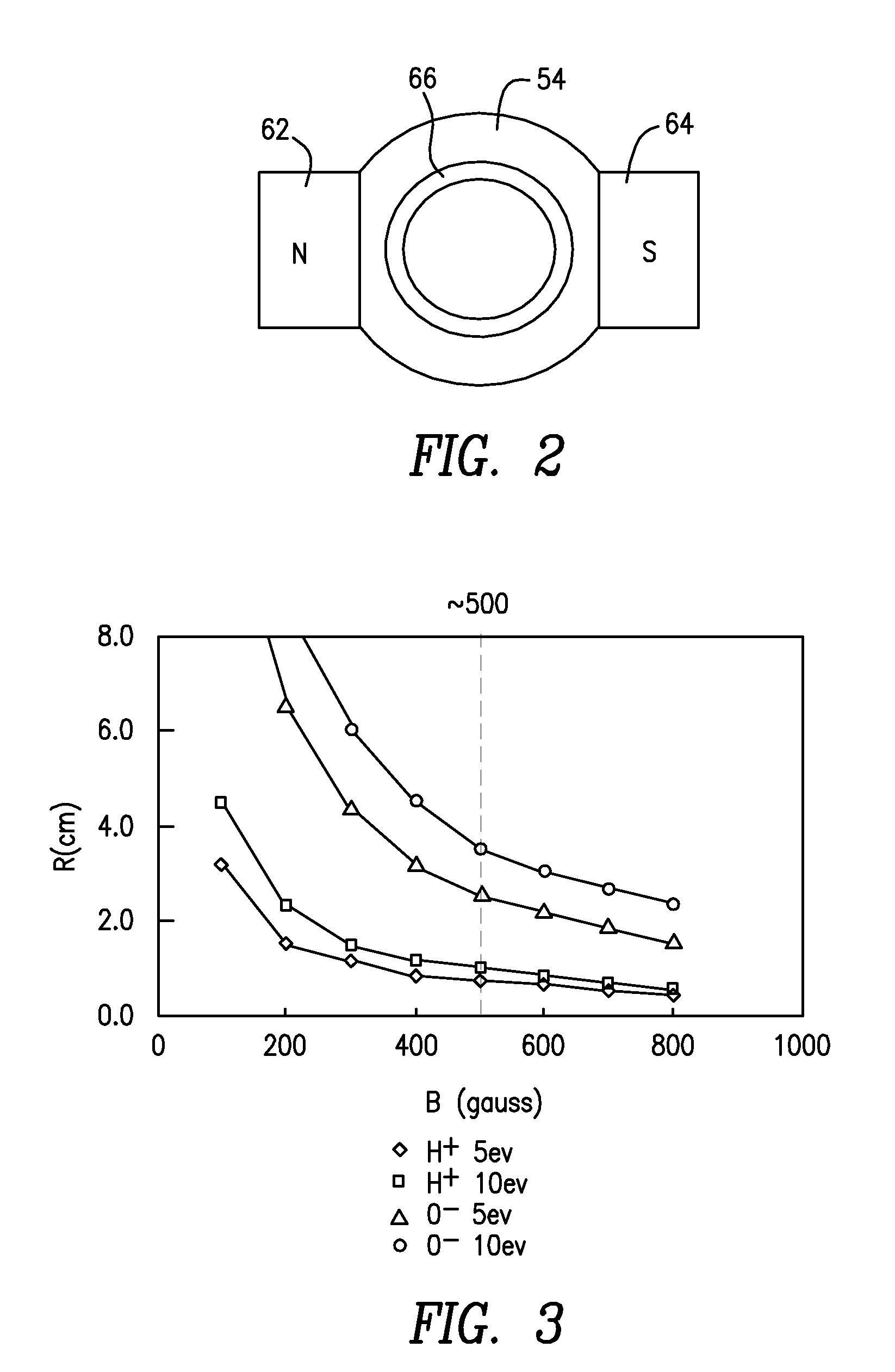

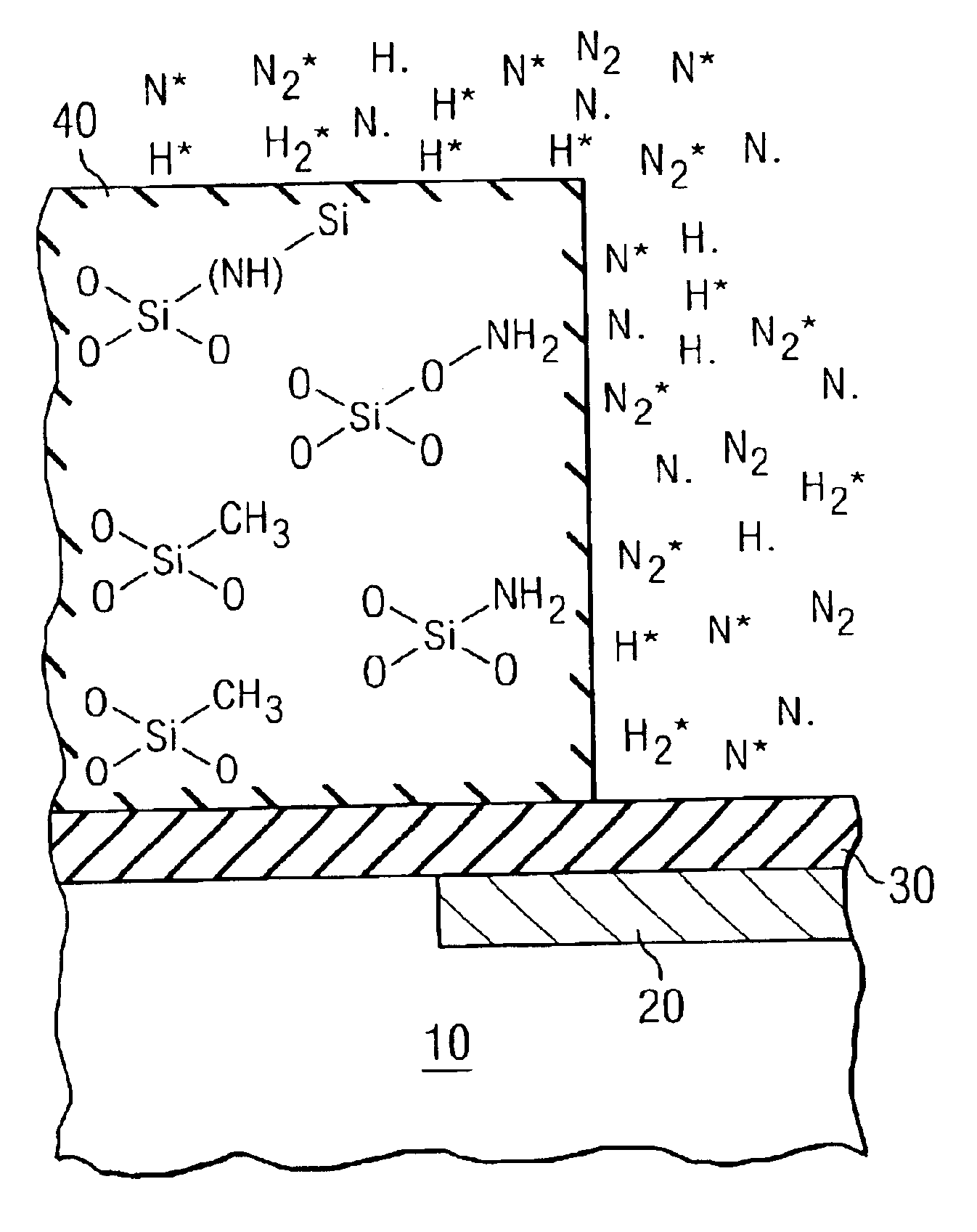

Remote Hydrogen Plasma With Ion Filter for Terminating Silicon Dangling Bonds

InactiveUS20110008950A1Avoid damageElectric discharge tubesFinal product manufactureDangling bondSemiconductor

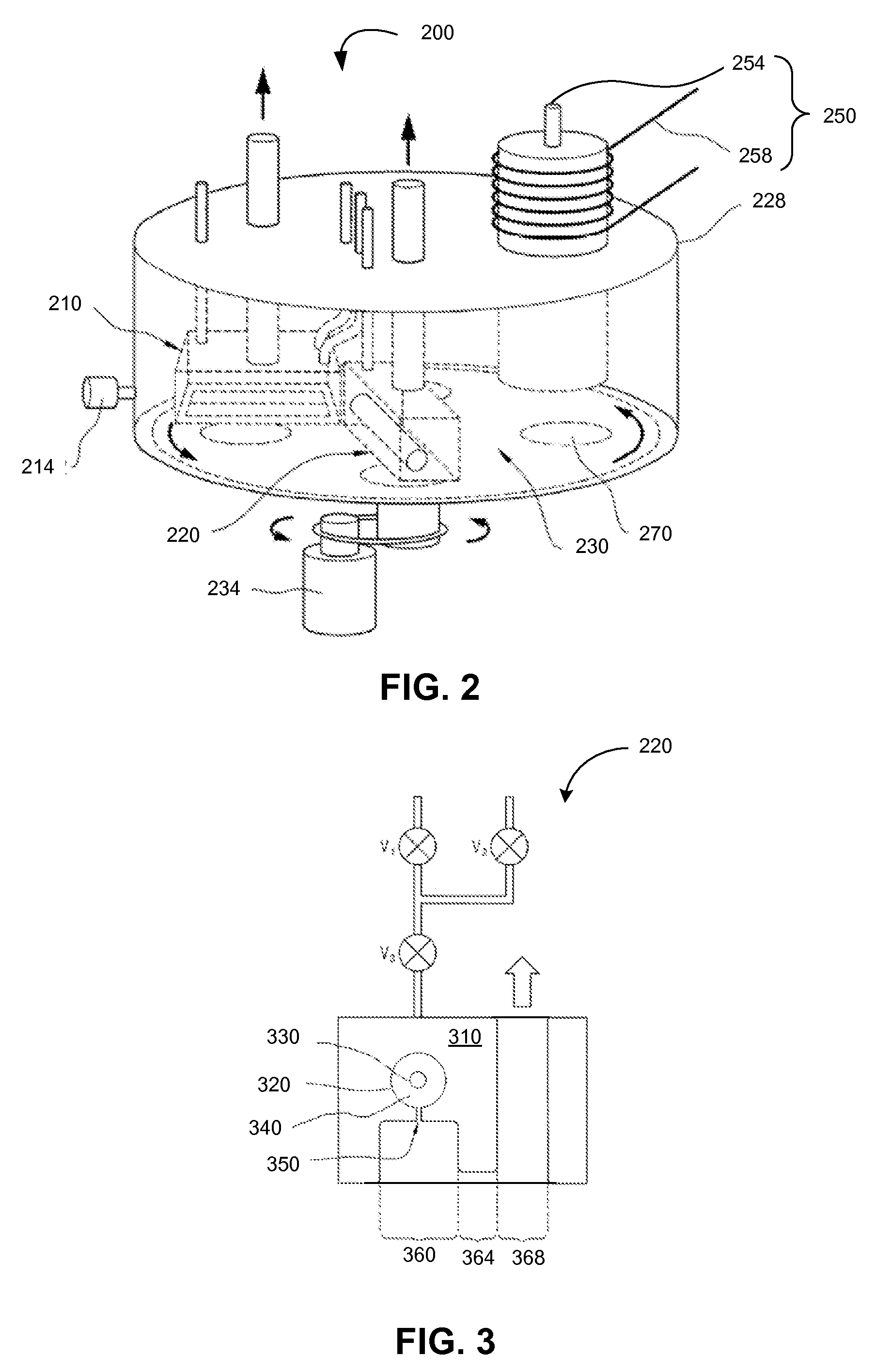

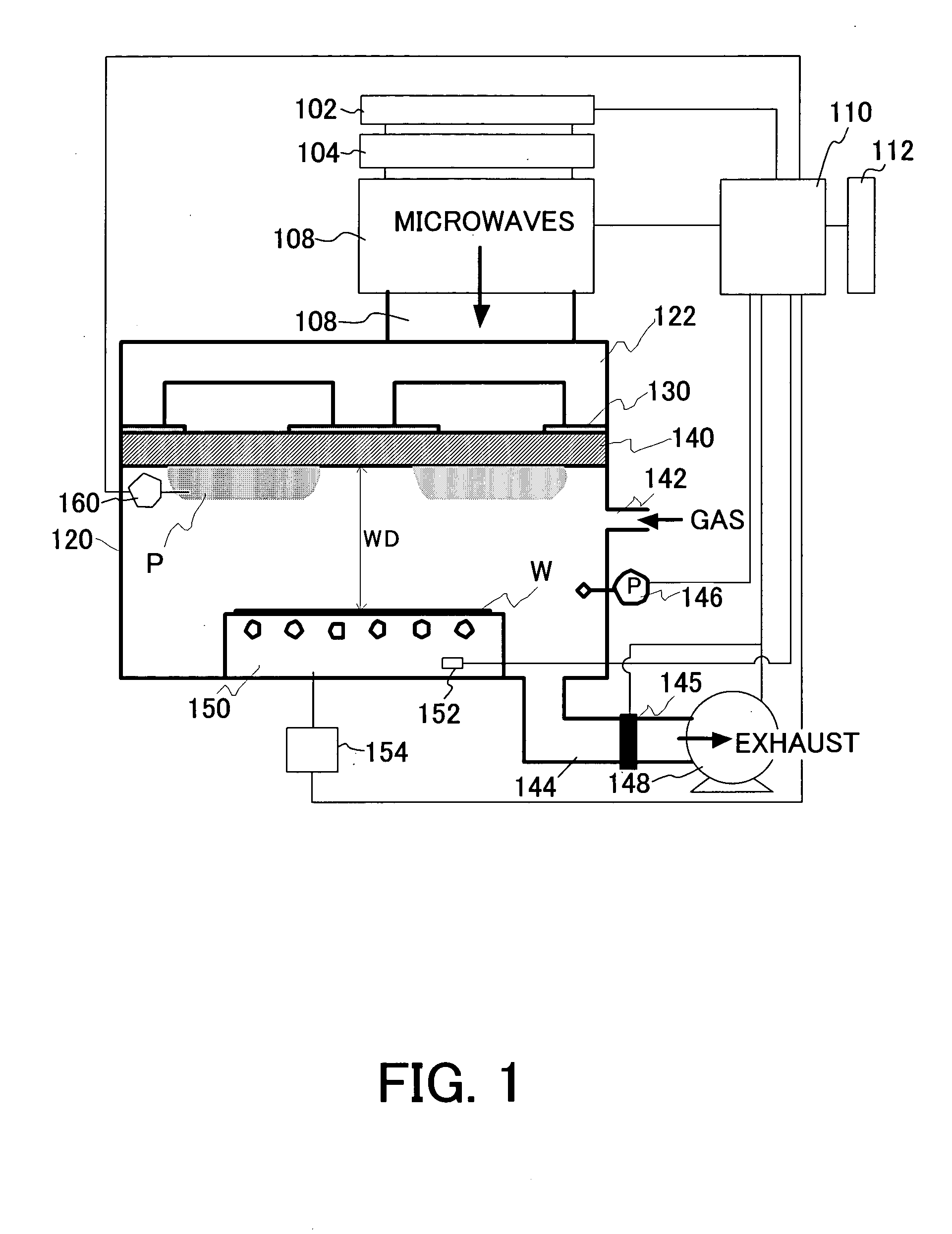

Apparatus and methods for repairing silicon dangling bonds resulting from semiconductor processing are disclosed. The silicon dangling bonds can be repaired by introducing hydrogen radicals with substantially no hydrogen ions into the processing chamber to react with the silicon dangling bonds, eliminating them.

Owner:APPLIED MATERIALS INC

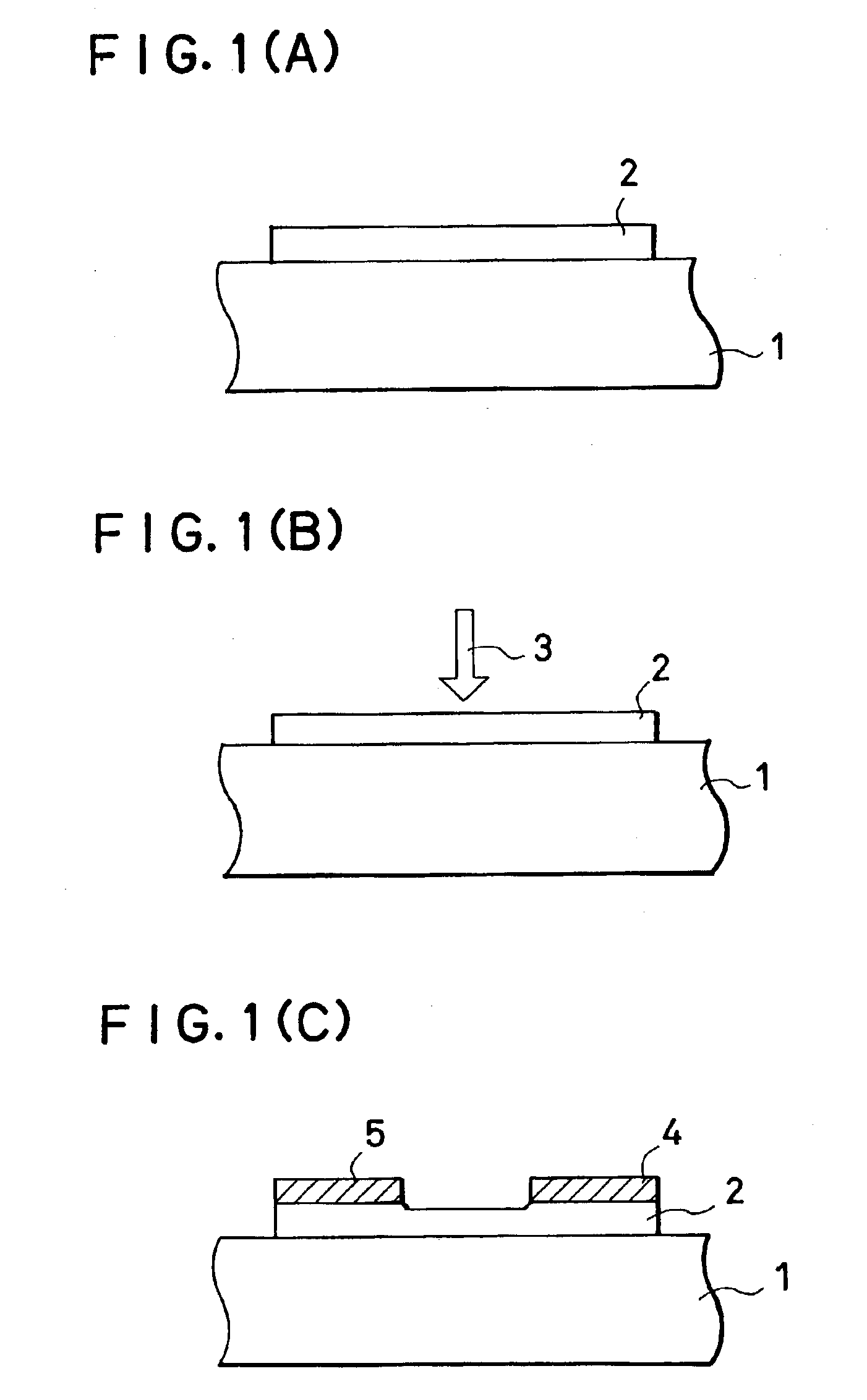

Method of forming an oxide film

InactiveUS6960812B2Improve performanceReduce the temperatureSolid-state devicesVacuum evaporation coatingAlkali ionsSputtering

A method of forming an oxide film and a method of manufacturing an electronic device utilizing the oxide film is disclosed. A silicon oxide film is formed on a substrate by sputtering. Therefore, the film formation is carried out at a low temperature. The sputtering atmosphere comprises an oxidizing gas and an inert gas such as argon. In order to prevent fixed electric charges from being generated in the film and to obtain an oxide film of good properties, the proportion of argon is adjusted to 20% or less. Alternatively, a gas including halogen elements such as fluorine is added to the above sputtering atmosphere at a proportion less than 20%. Hereupon, alkali ions and dangling bonds of silicon in the oxide film are neutralized by the halogen elements, whereby a fine oxide film is obtained.

Owner:SEMICON ENERGY LAB CO LTD

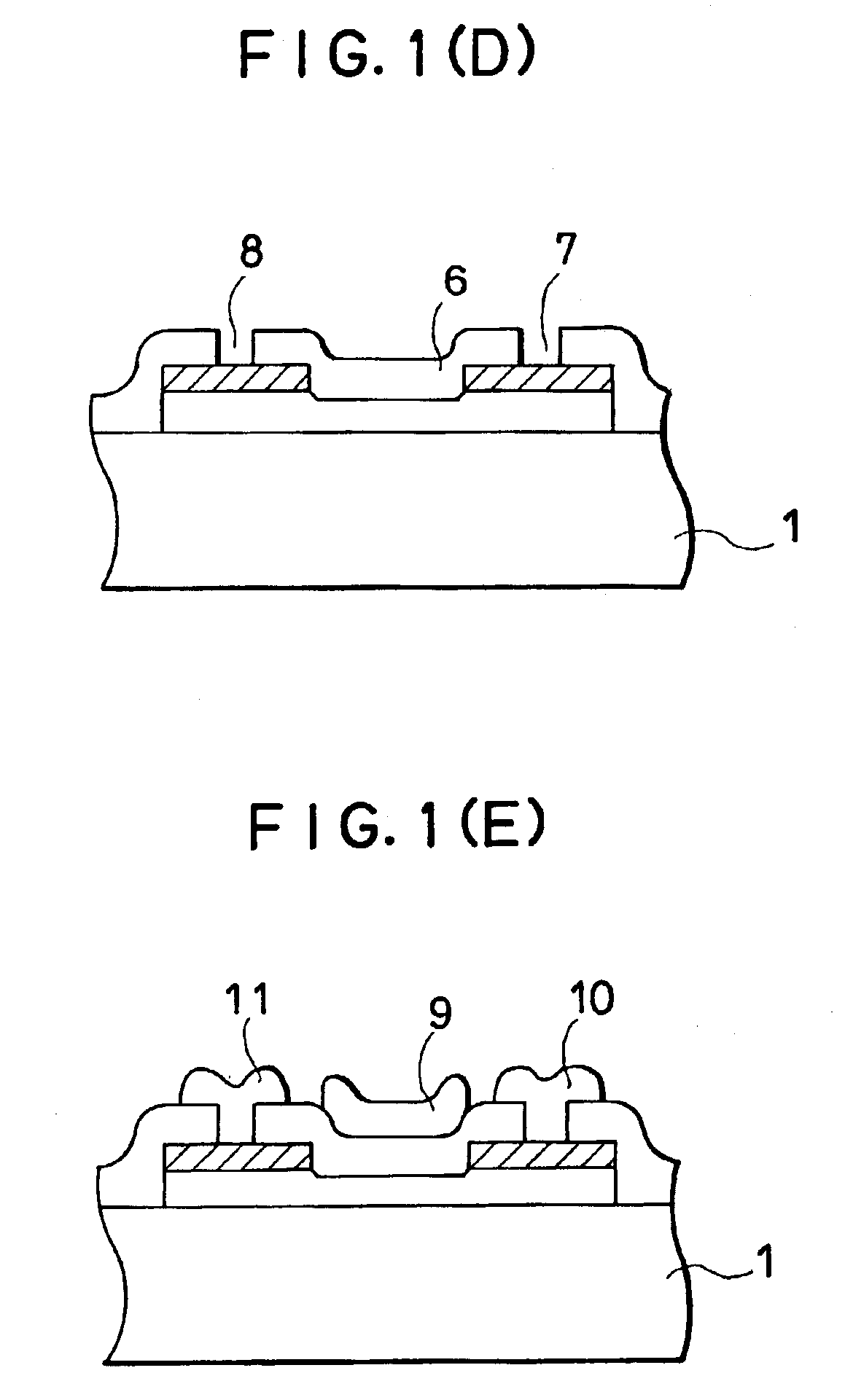

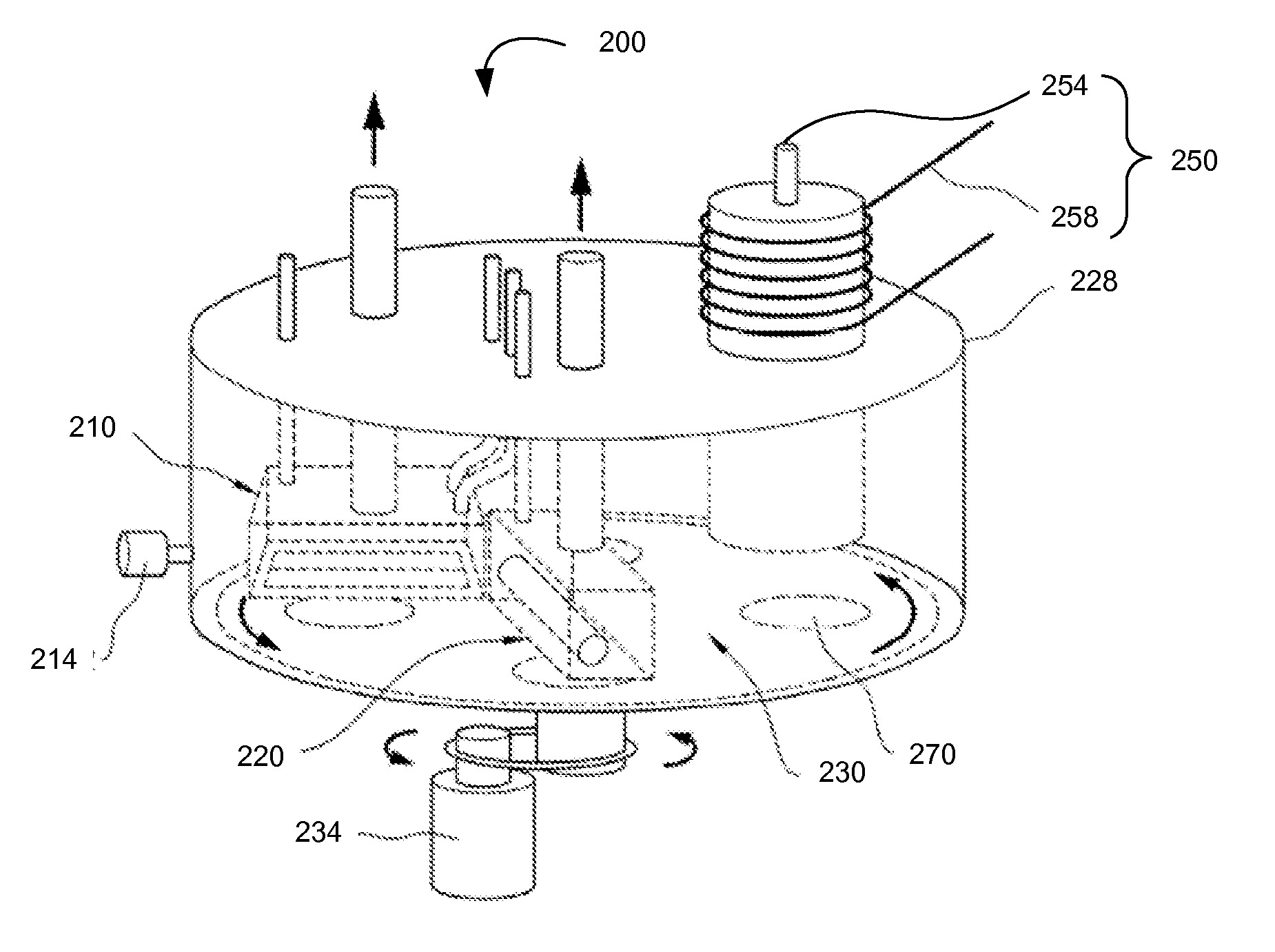

Treating Surface of Substrate Using Inert Gas Plasma in Atomic Layer Deposition

InactiveUS20120021252A1Increase deposition rateElectric discharge tubesSemiconductor/solid-state device manufacturingDangling bondGas plasma

Depositing one or more layers of material on a substrate using atomic layer deposition (ALD) followed by surface treating the substrate with radicals of inert gas before subjecting the substrate to further deposition of layers. The radicals of the inert gas appear to change the surface state of the deposited layer to a state more amenable to absorb subsequent source precursor molecules. The radicals of the inert gas disconnect bonding of molecules on the surface of the substrate, and render the molecules on the surface to have dangling bonds. The dangling bonds facilitate absorption of subsequently injected source precursor molecules into the surface. Exposure to the radicals of the inert gas thereby increases the deposition rate and improves the properties of the deposited layer.

Owner:VEECO ALD

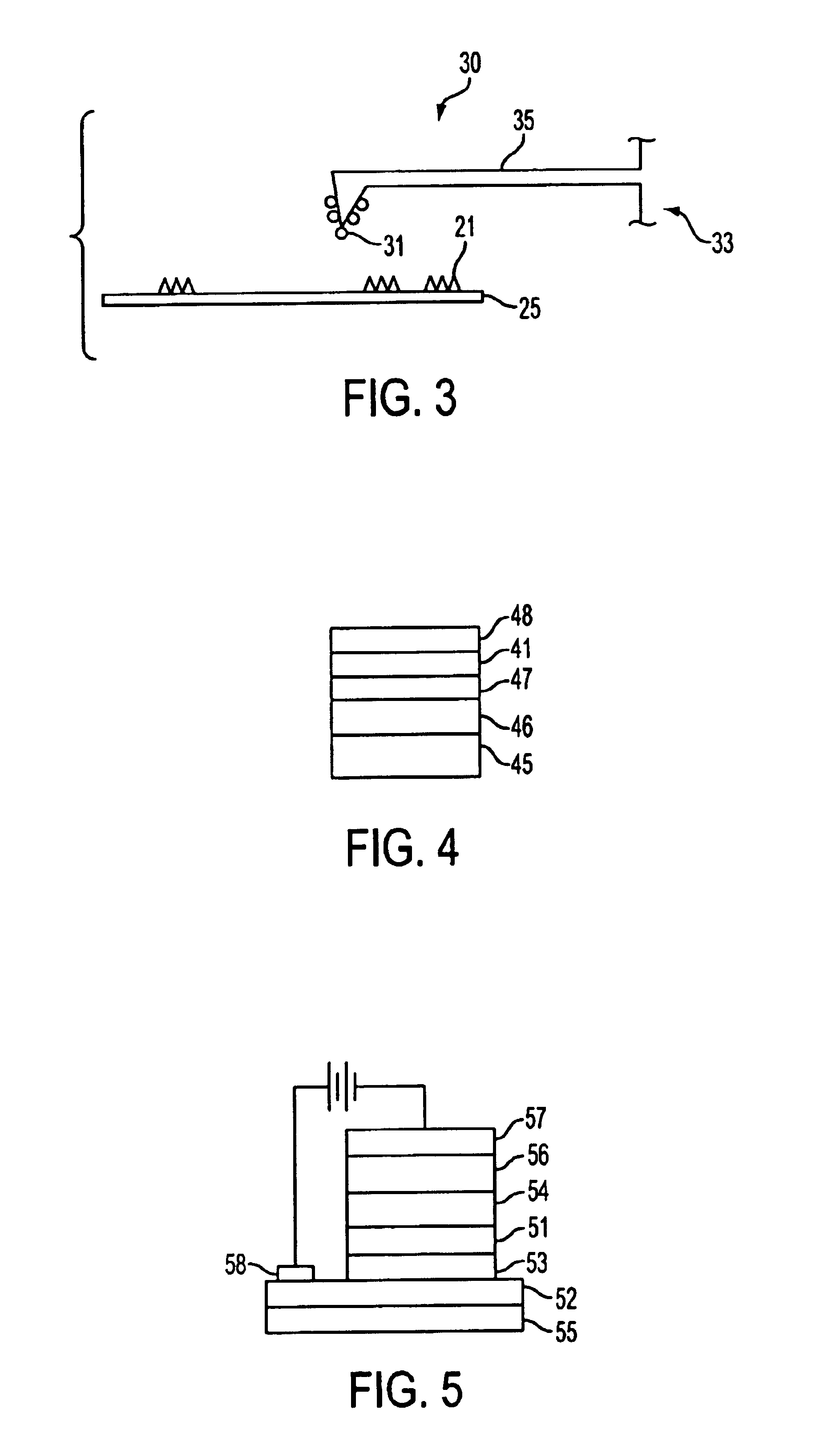

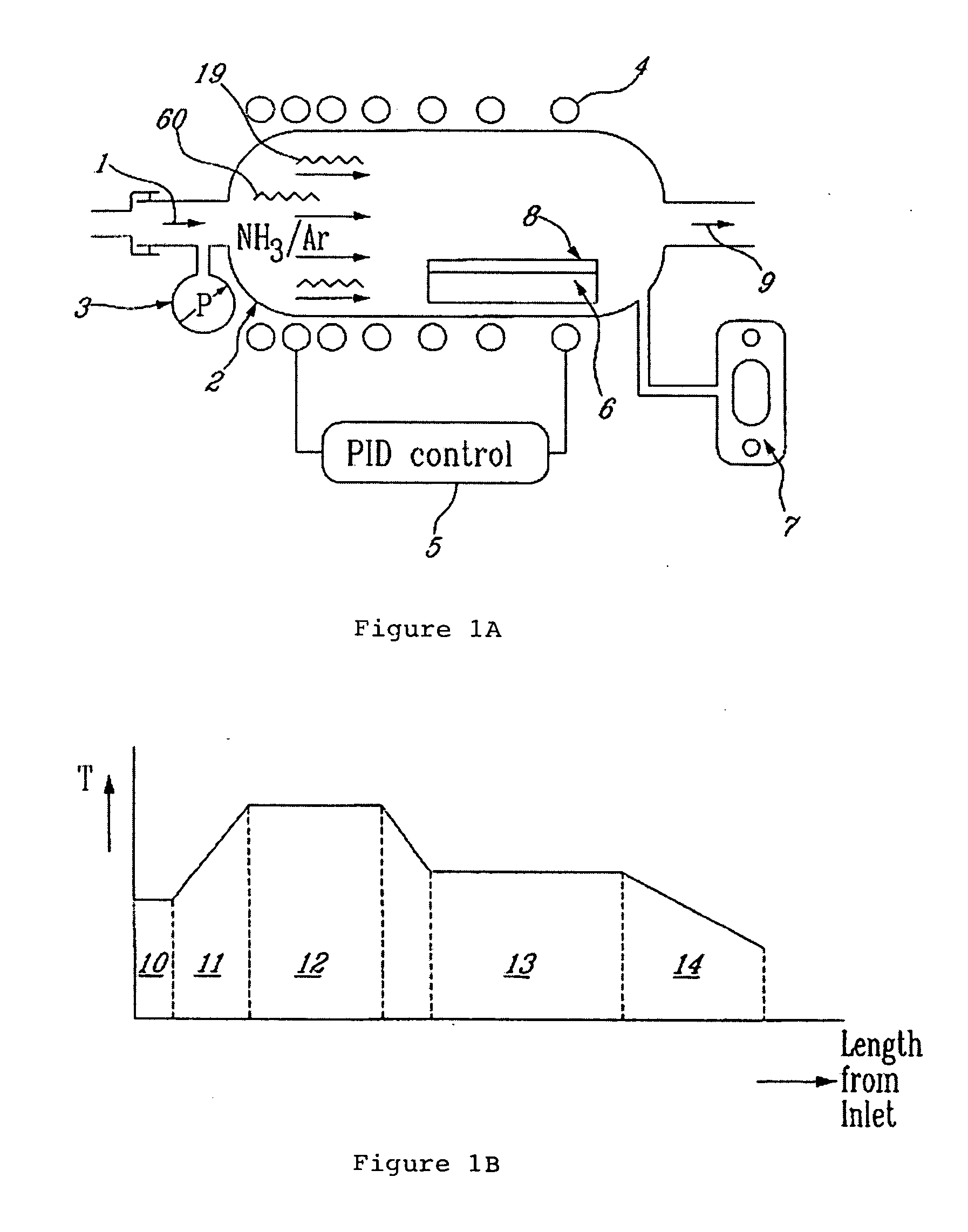

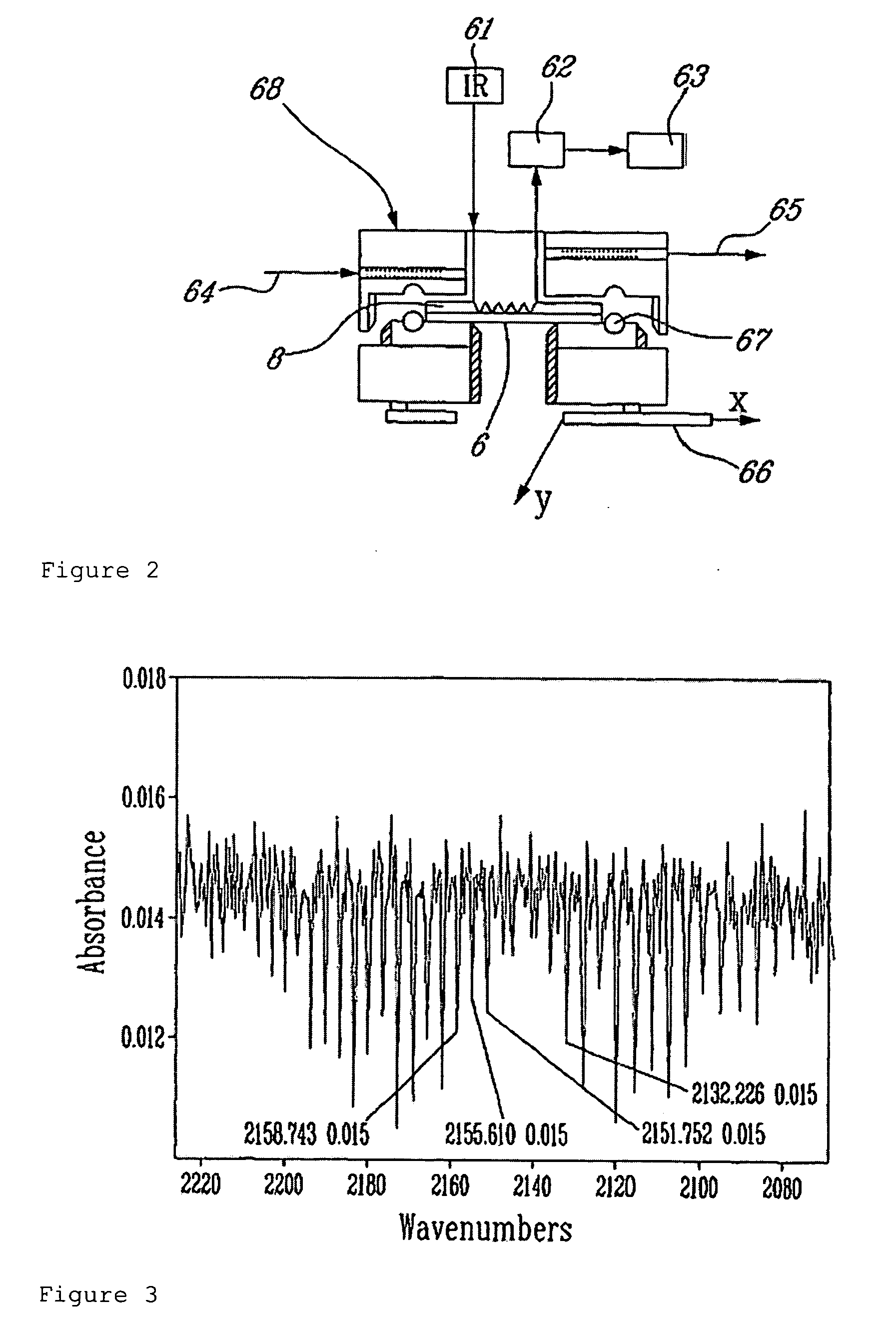

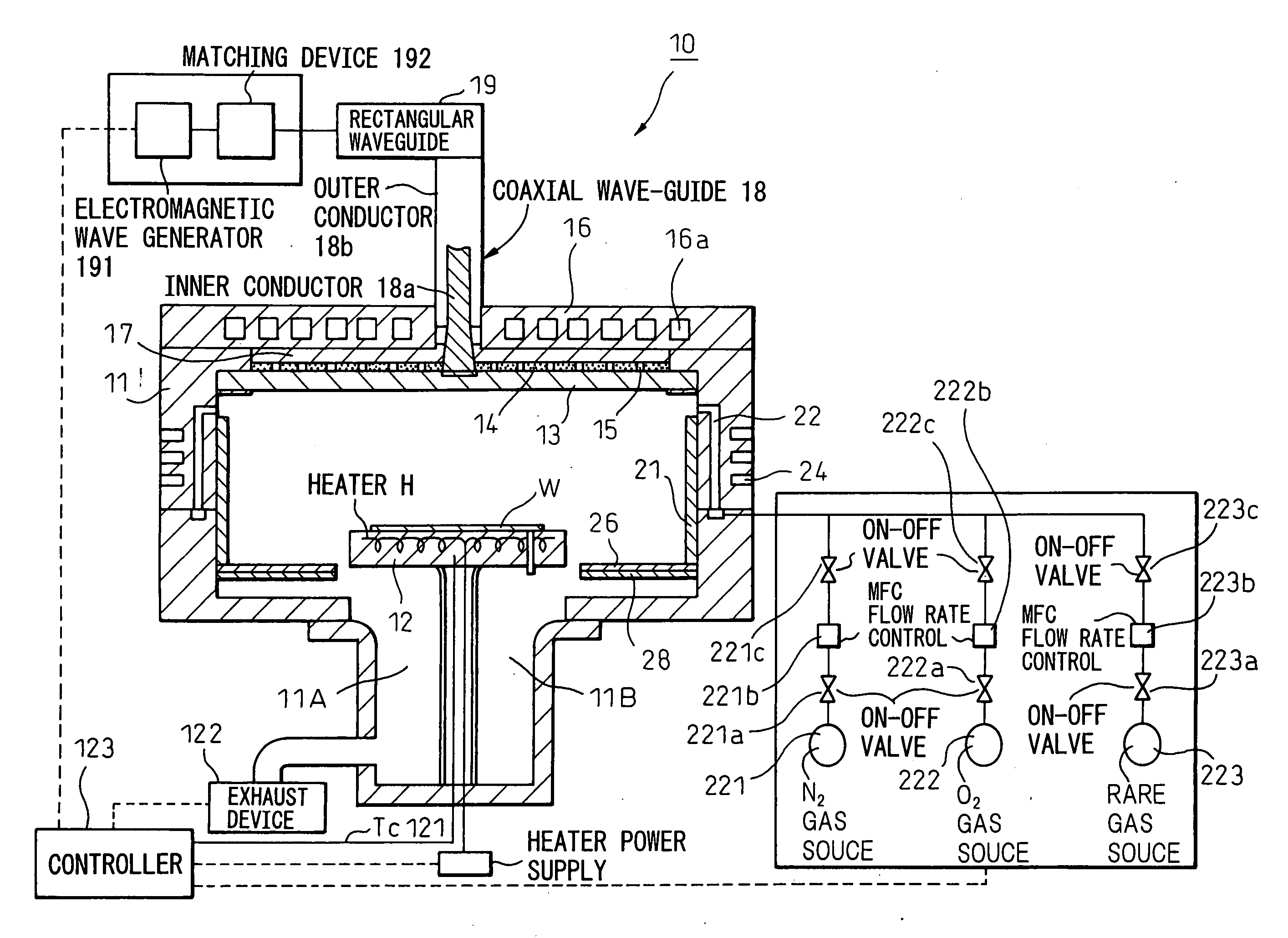

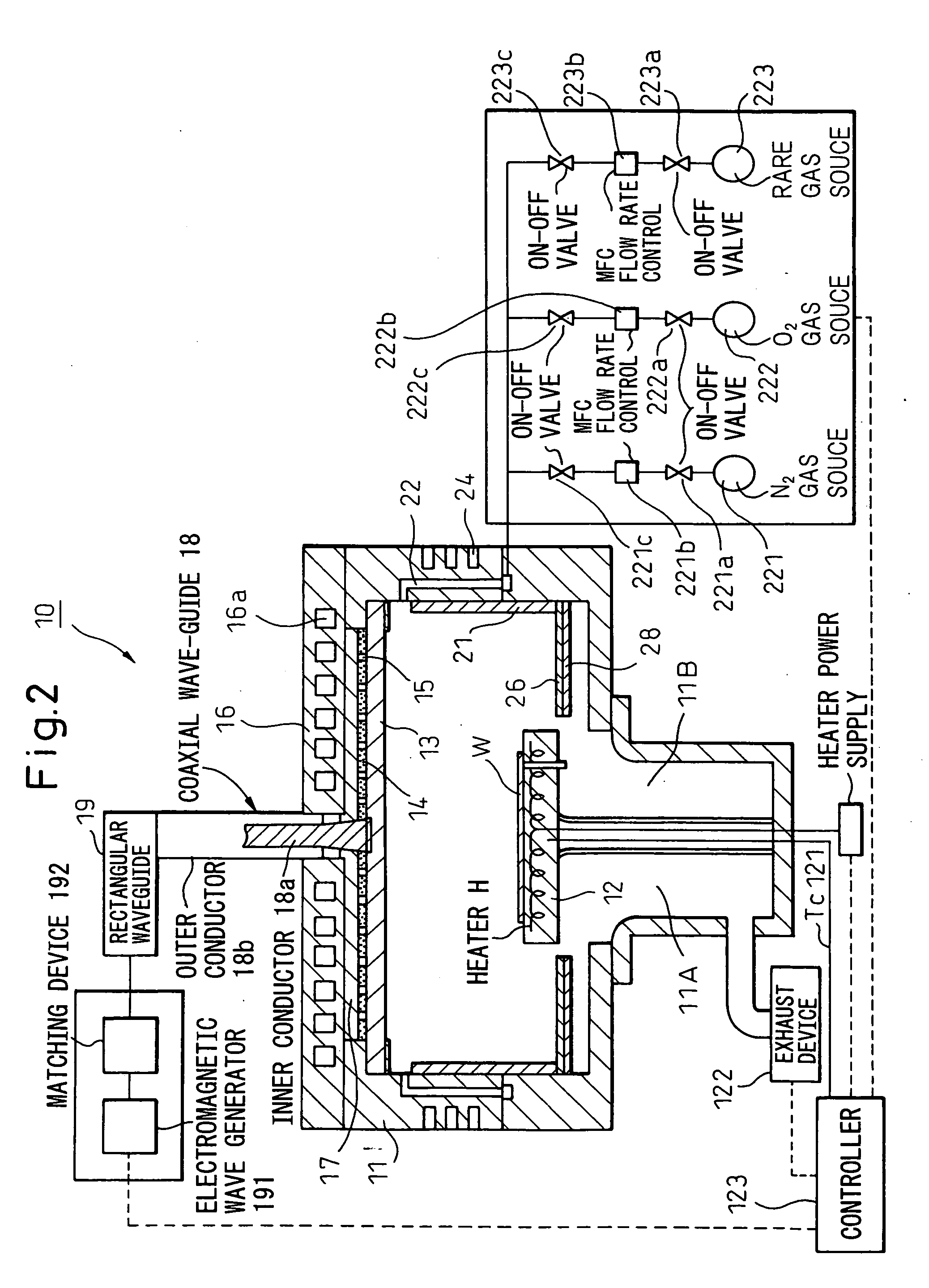

Processing apparatus and method

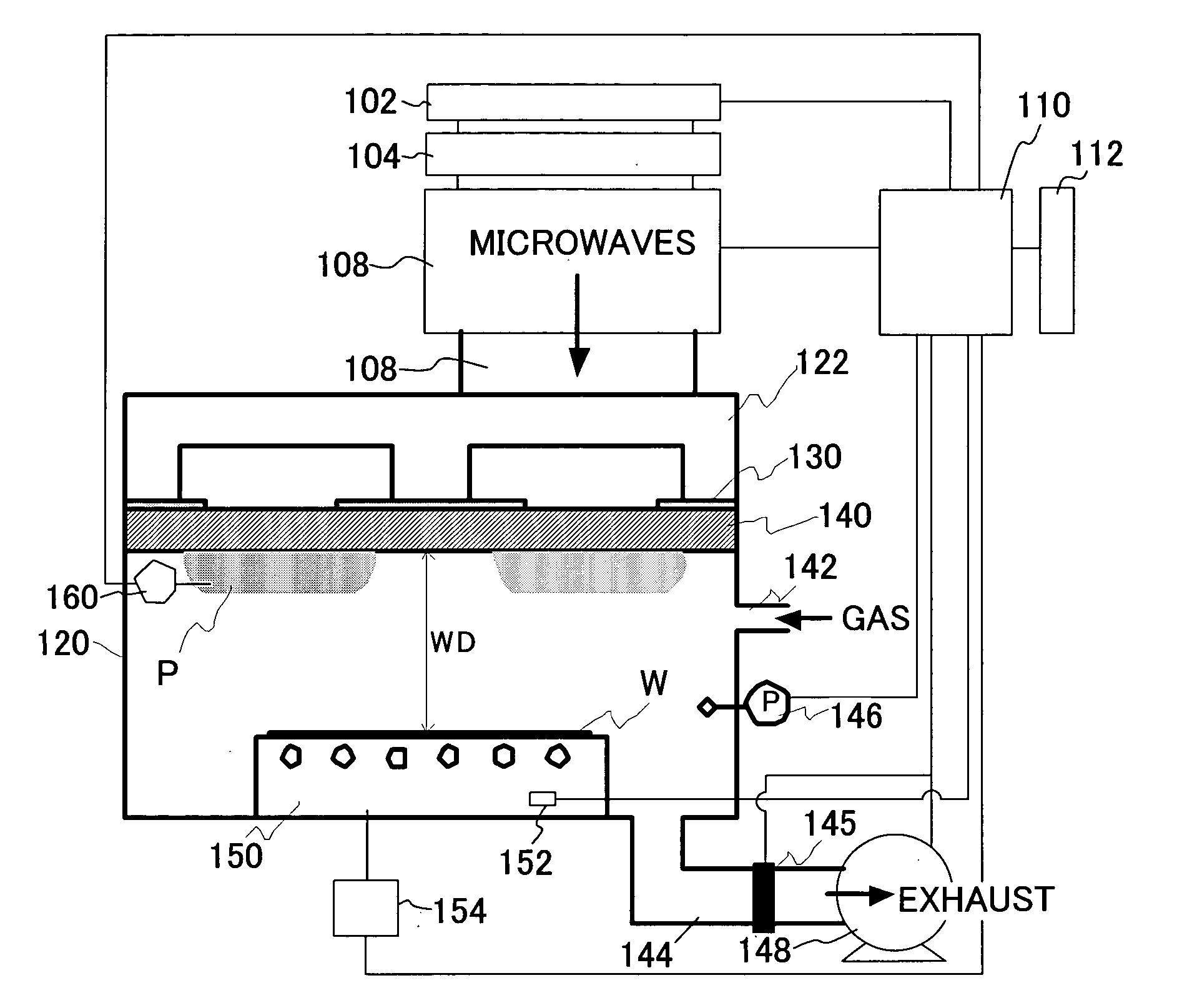

InactiveUS20050090078A1Minimized plasma damageEfficient terminationTransistorElectric discharge tubesDielectricTemperature control

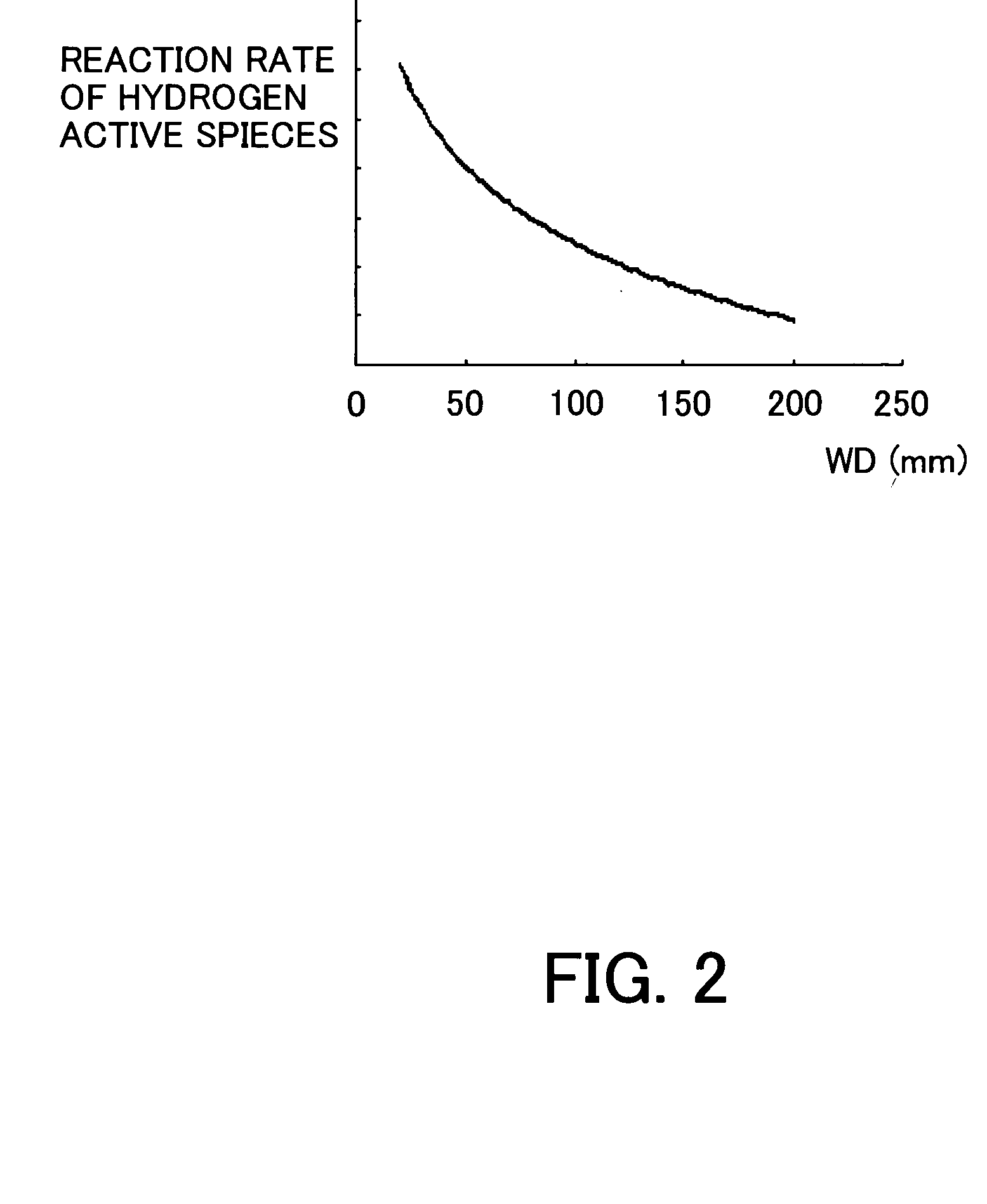

A processing method that uses process gas plasma that contains at least hydrogen to terminate dangling bonds in an object that at least partially contains a silicon system material includes the steps of placing the object on a susceptor in a process chamber that includes a dielectric window and the susceptor, and controlling a temperature of the susceptor to a predetermined temperature, controlling a pressure in the process chamber to a predetermined pressure, introducing the process gas into the process chamber, and introducing, via the dielectric window, microwaves for a plasma treatment to the object into the process chamber so that plasma of the process gas has plasma density of 1011 cm−3 or greater, wherein a distance between the dielectric window and the object is maintained between 20 mm and 200 mm.

Owner:CANON KK

Semiconductor device and method for manufacturing the same

InactiveUS20110101335A1Stable electrical characteristicsReduce impurity concentrationSolid-state devicesSemiconductor/solid-state device manufacturingHydrogen atomDangling bond

An object is to provide a semiconductor device including an oxide semiconductor with stable electric characteristics can be provided. An insulating layer having many defects typified by dangling bonds is formed over an oxide semiconductor layer with an oxygen-excess mixed region or an oxygen-excess oxide insulating layer interposed therebetween, whereby impurities in the oxide semiconductor layer, such as hydrogen or moisture (a hydrogen atom or a compound including a hydrogen atom such as H2O), are moved through the oxygen-excess mixed region or oxygen-excess oxide insulating layer and diffused into the insulating layer. Thus, the impurity concentration of the oxide semiconductor layer is reduced.

Owner:SEMICON ENERGY LAB CO LTD

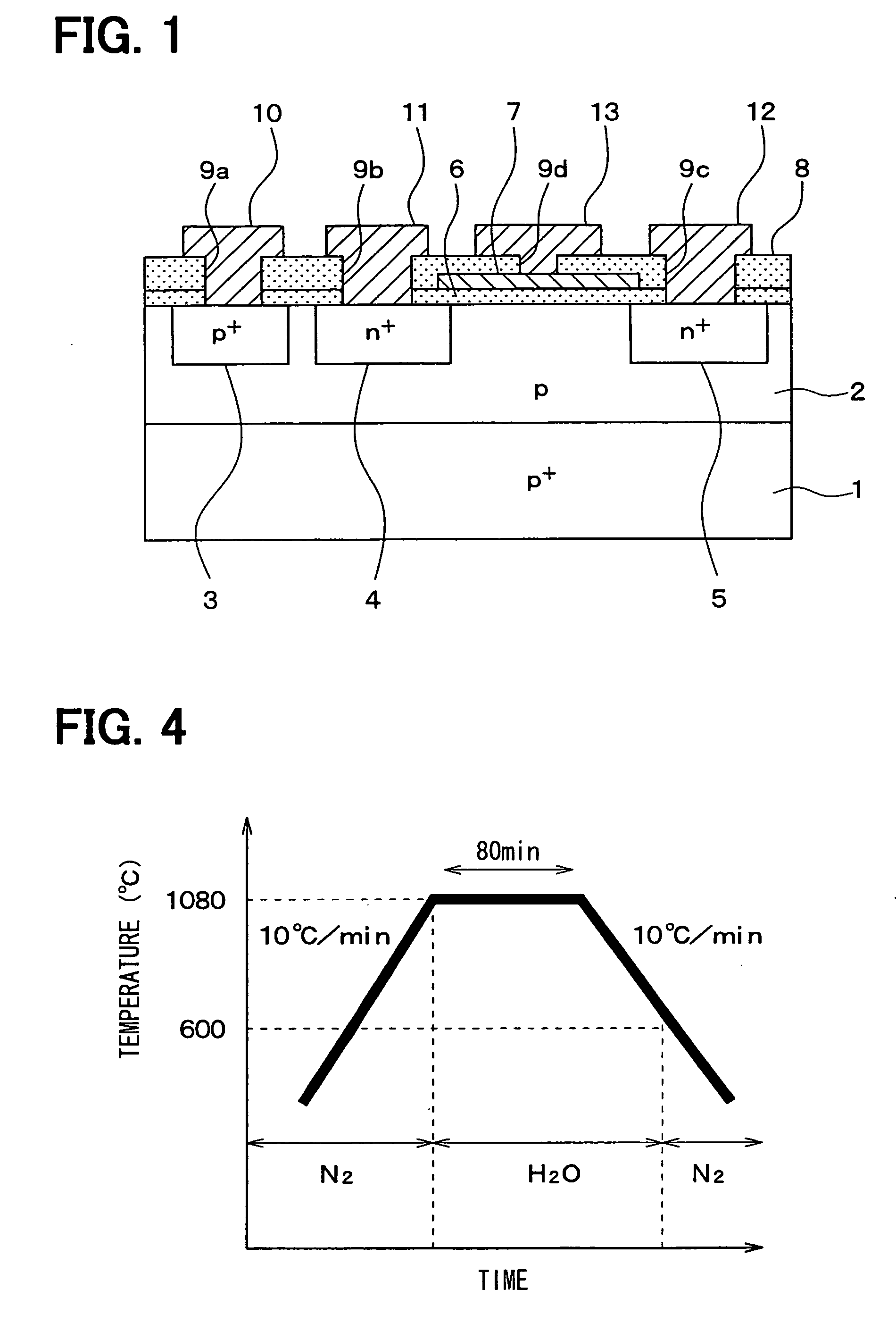

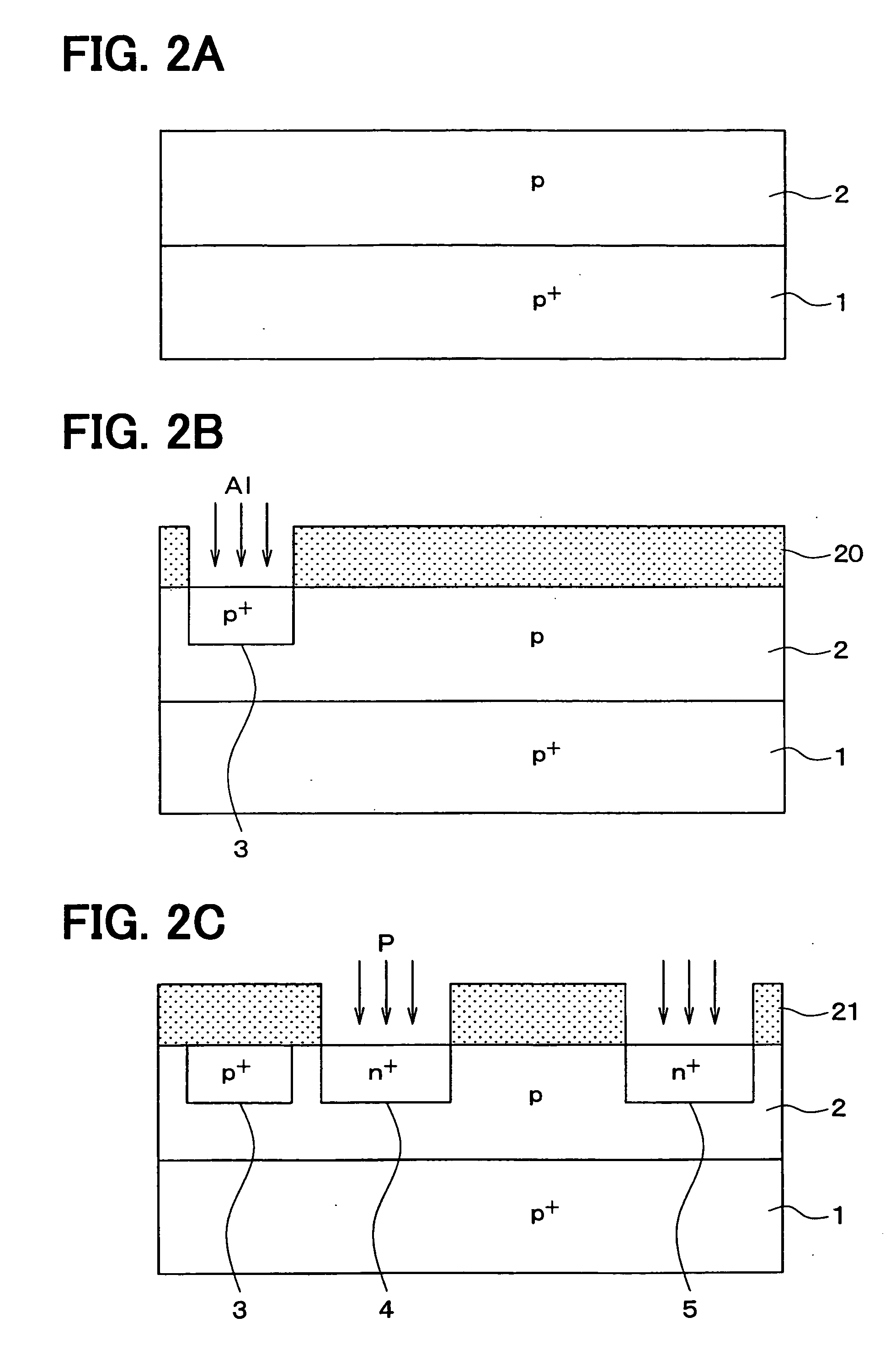

Silicon carbide semiconductor device having high channel mobility and method for manufacturing the same

ActiveUS20070045631A1Improve channel mobilityImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesHydrogen concentrationHydrogen atom

A silicon carbide semiconductor device having a MOS structure includes: a substrate; a channel area in the substrate; a first impurity area; a second impurity area; a gate insulating film on the channel area; and a gate on the gate insulating film. The channel area provides an electric current path. The channel area and the gate insulating film have an interface therebetween. The interface includes a dangling bond, which is terminated by a hydrogen atom or a hydroxyl. The interface has a hydrogen concentration equal to or larger than 2.6×1020 cm−3.

Owner:DENSO CORP

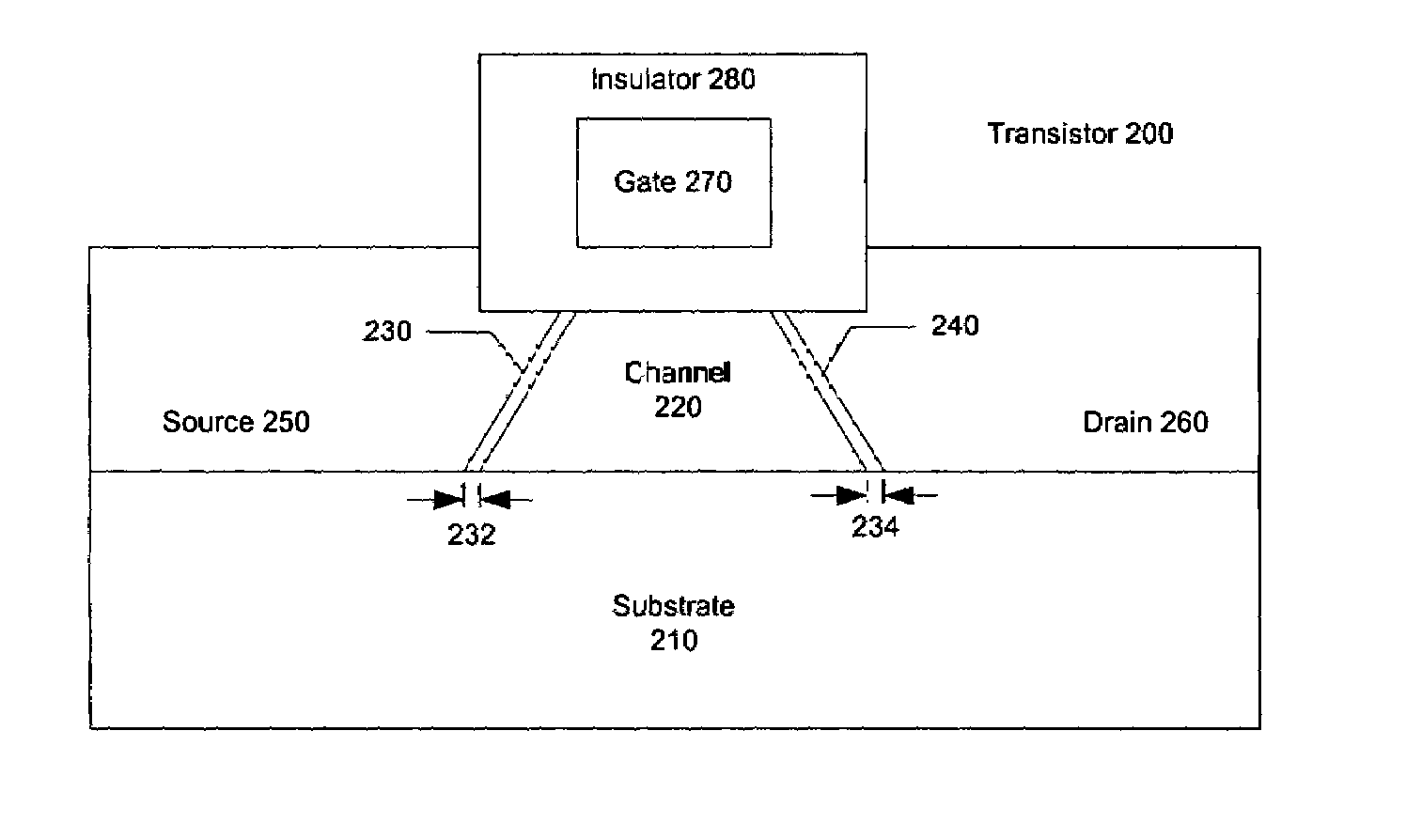

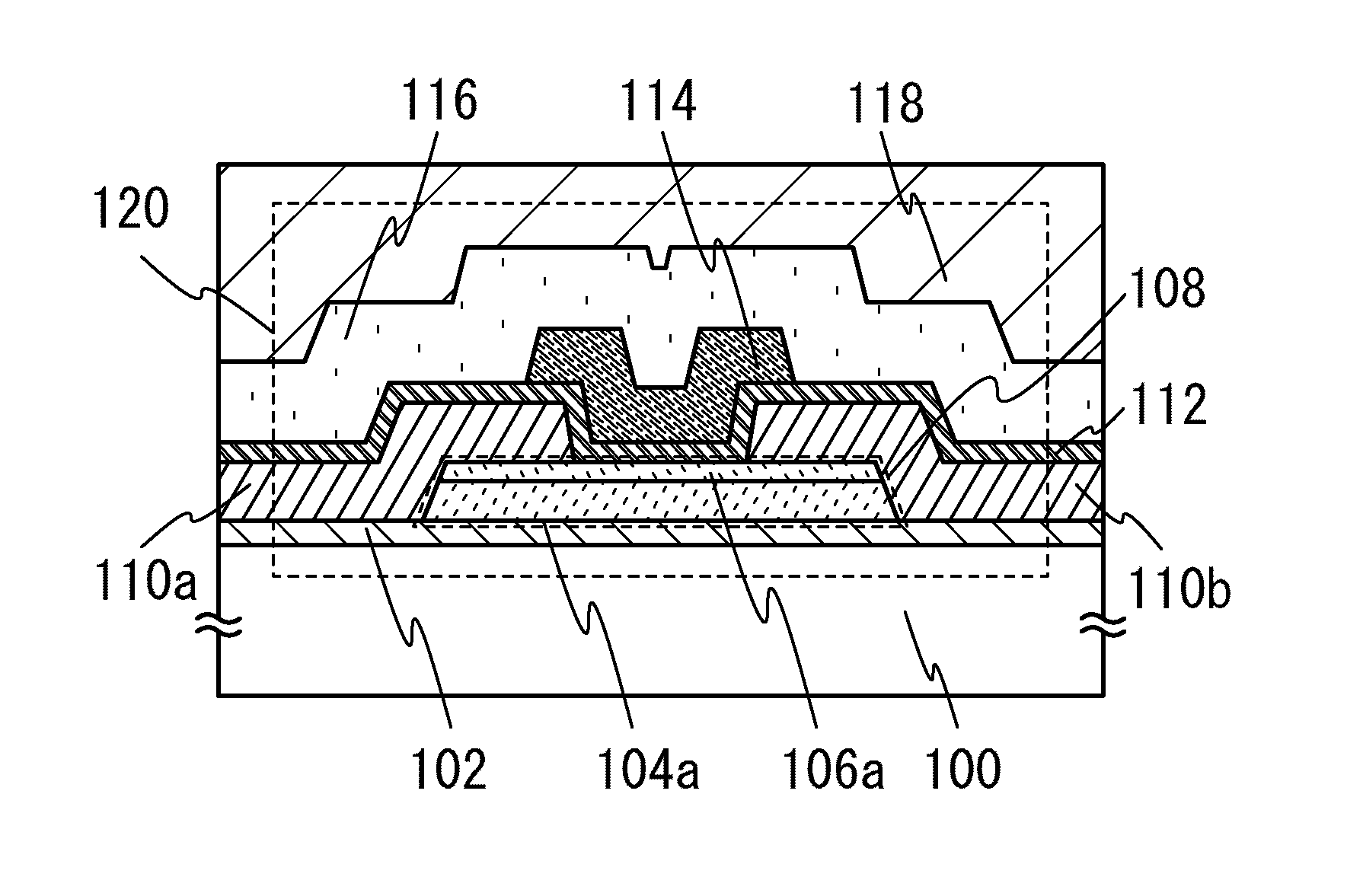

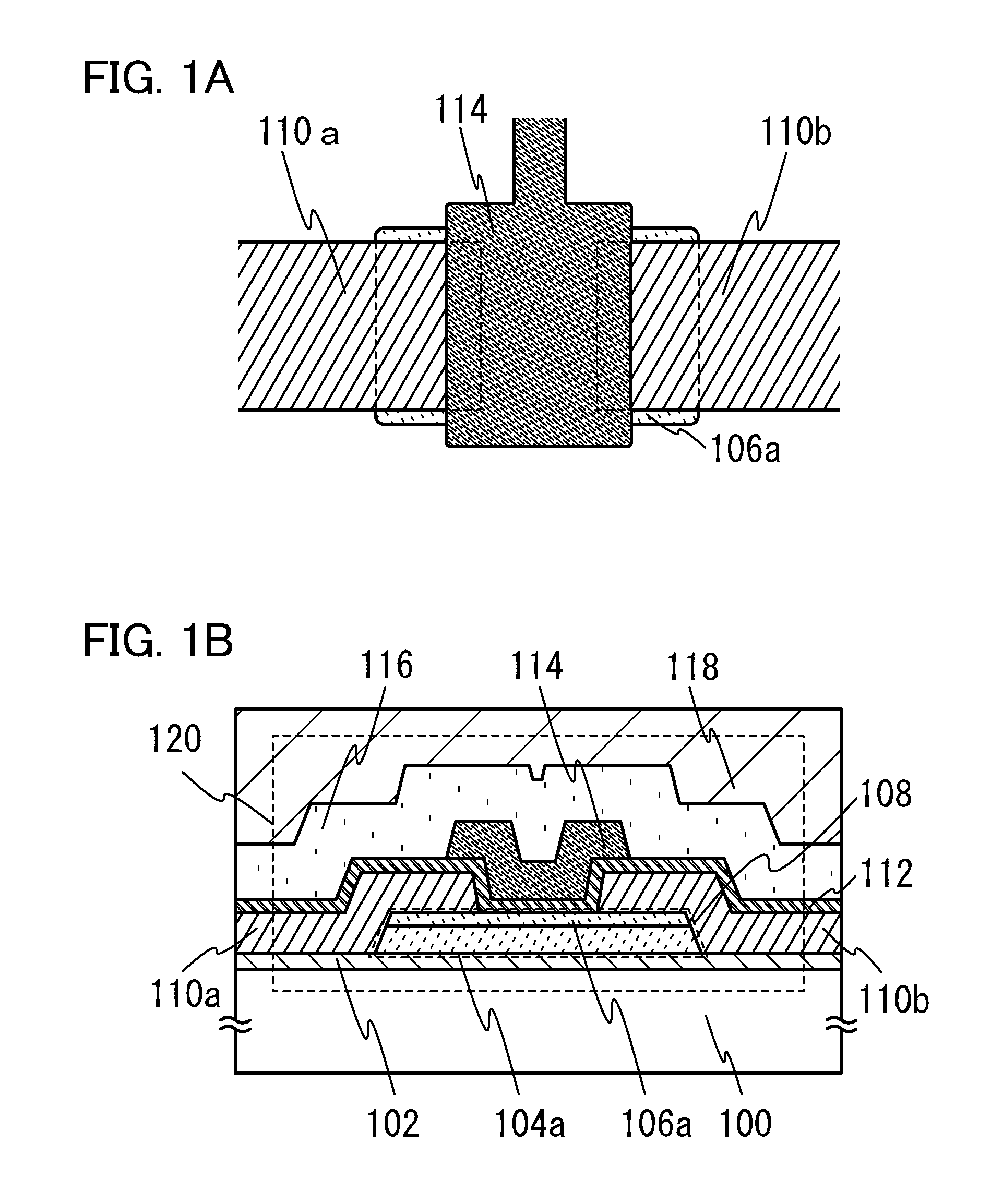

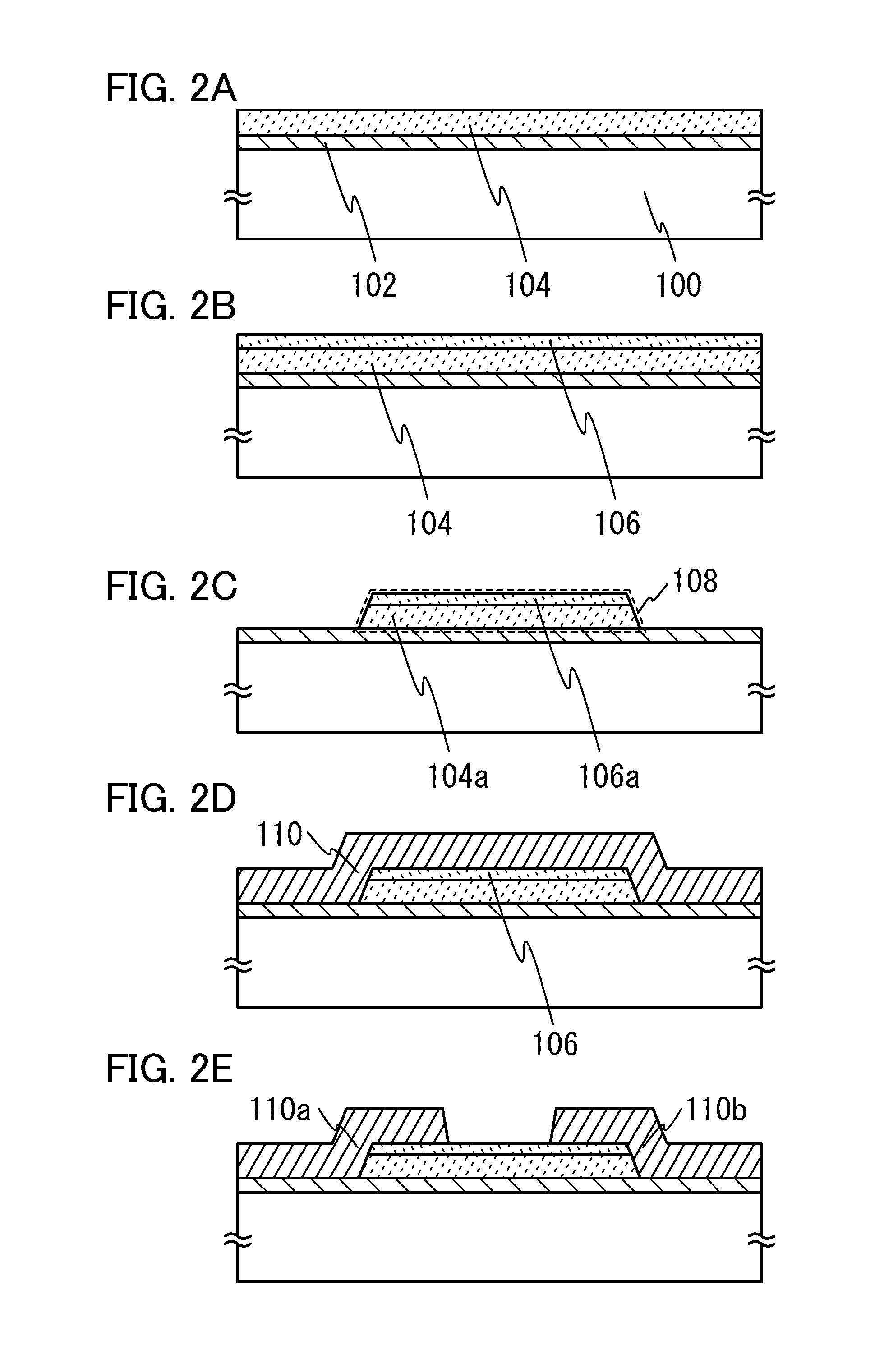

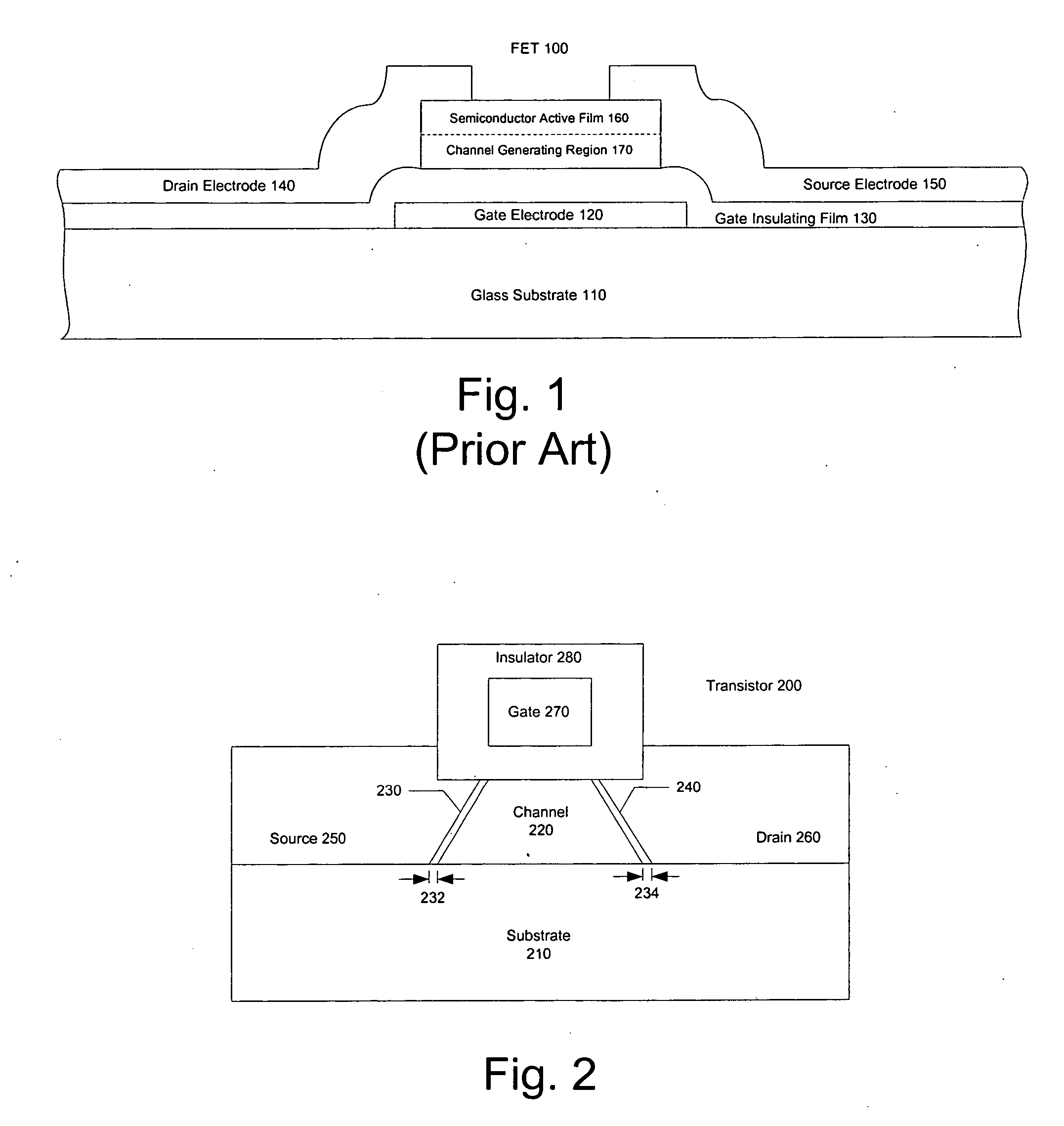

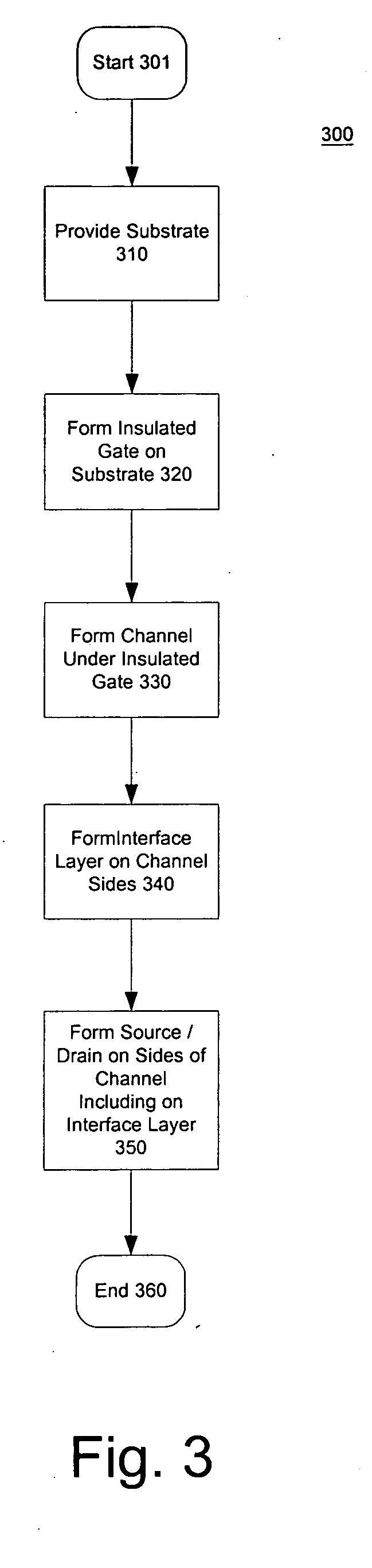

Insulated gate field effect transistor having passivated Schottky barriers to the channel

InactiveUS7112478B2Reduce the impactReduce impactTransistorSemiconductor/solid-state device detailsEngineeringField-effect transistor

A transistor includes a semiconductor channel disposed nearby a gate and in an electrical path between a source and a drain, wherein the channel and at least one of the source or the drain are separated by an interface layer so as to form a channel-interface layer-source / drain junction in which a Fermi level of the semiconductor channel is depinned in a region near the junction and the junction has a specific contact resistance of less than approximately 1000 Ω-μm2. The interface layer may include a passivating material such as a nitride, a fluoride, an oxide, an oxynitride, a hydride and / or an arsenide of the semiconductor of the channel. In some cases, the interface layer consists essentially of a monolayer configured to depin the Fermi level of the semiconductor of the channel, or an amount of passivation material sufficient to terminate all or a sufficient number of dangling bonds of the semiconductor channel to achieve chemical stability of the surface. Also, the interface layer may include a separation layer of a material different than the passivating material. Where used, the separation layer has a thickness sufficient to reduce effects of metal-induced gap states in the semiconductor channel.

Owner:ACORN SEMI LLC

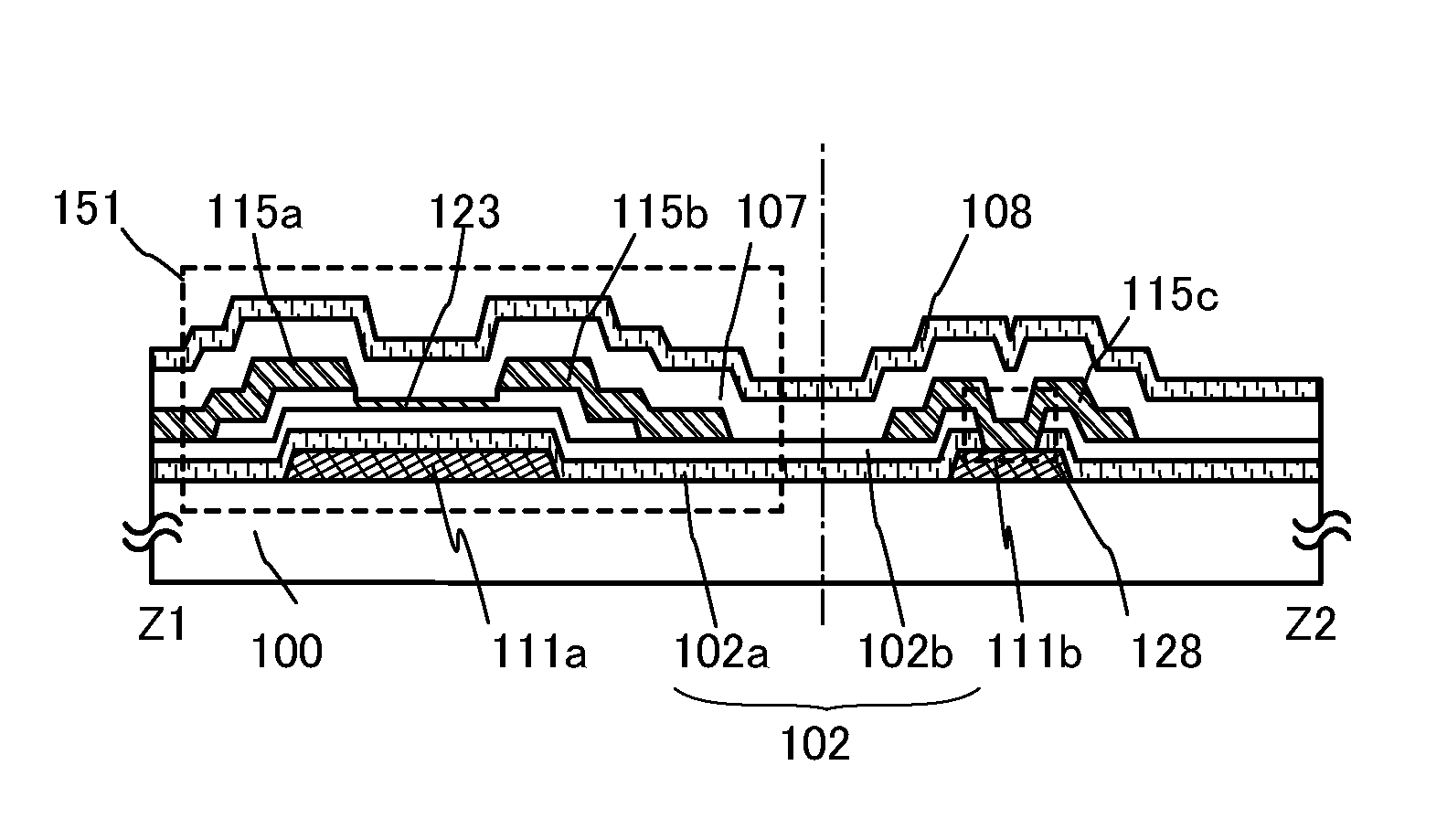

Oxide semiconductor element and semiconductor device

A semiconductor element having high mobility, which includes an oxide semiconductor layer having crystallinity, is provided. The oxide semiconductor layer includes a stacked-layer structure of a first oxide semiconductor film and a second oxide semiconductor film having a wider band gap than the first oxide semiconductor film, which is in contact with the first oxide semiconductor film. Thus, a channel region is formed in part of the first oxide semiconductor film (that is, in an oxide semiconductor film having a smaller band gap) which is in the vicinity of an interface with the second oxide semiconductor film. Further, dangling bonds in the first oxide semiconductor film and the second oxide semiconductor film are bonded to each other at the interface therebetween. Accordingly, a decrease in mobility resulting from an electron trap or the like due to dangling bonds can be reduced in the channel region.

Owner:SEMICON ENERGY LAB CO LTD

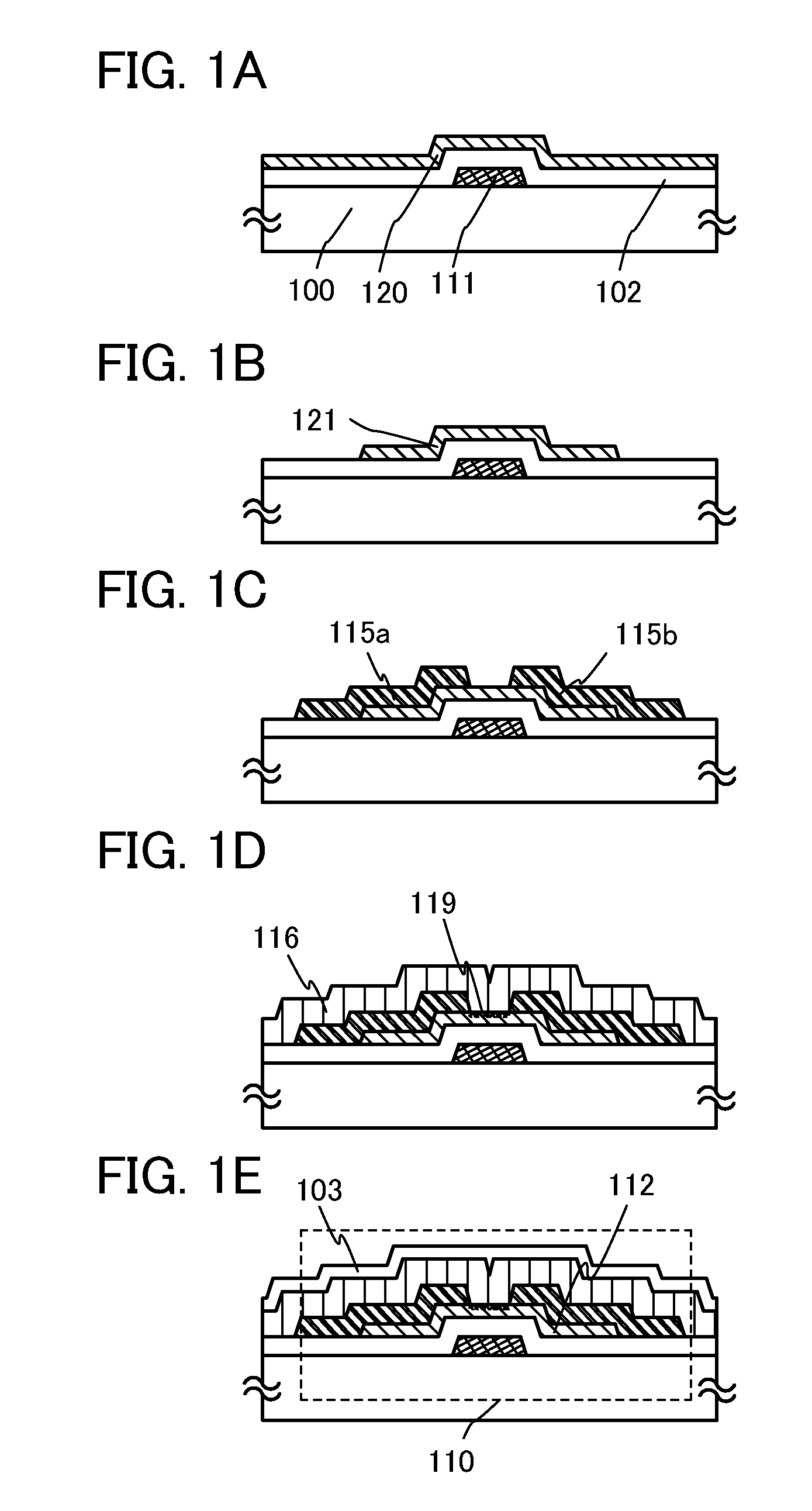

Semiconductor device and manufacturing method thereof

ActiveUS20110079778A1Easily brokenEasy to spreadElectroluminescent light sourcesSolid-state devicesHydrogen atomSilicon oxide

An object is to provide a semiconductor device with stable electric characteristics in which an oxide semiconductor is used. The impurity concentration in the oxide semiconductor layer is reduced in the following manner: a silicon oxide layer including many defects typified by dangling bonds is formed in contact with the oxide semiconductor layer, and an impurity such as hydrogen or moisture (a hydrogen atom or a compound including a hydrogen atom such as H2O) included in the oxide semiconductor layer is diffused into the silicon oxide layer. Further, a mixed region is provided between the oxide semiconductor layer and the silicon oxide layer. The mixed region includes oxygen, silicon, and at least one kind of metal element that is included in the oxide semiconductor.

Owner:SEMICON ENERGY LAB CO LTD

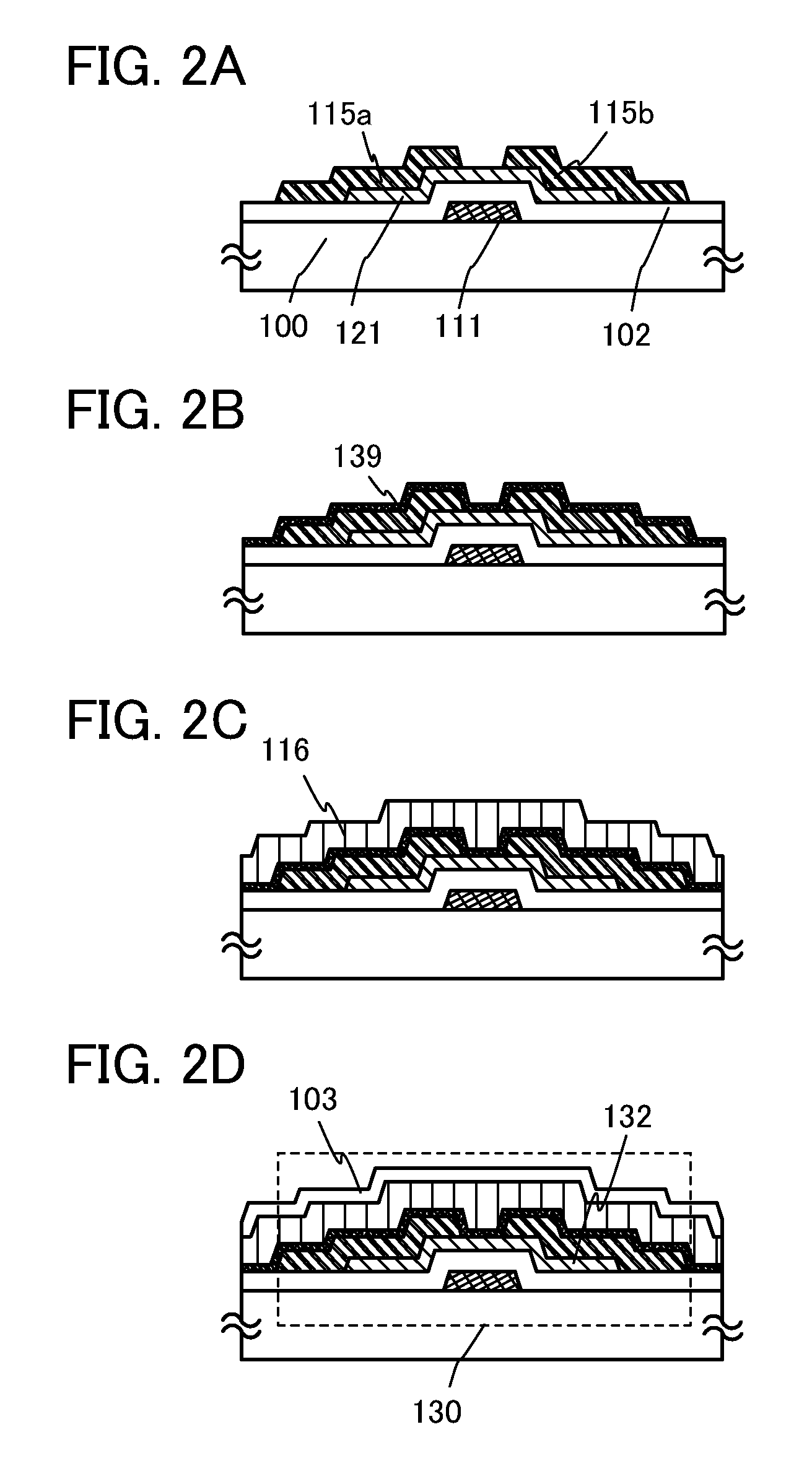

Semiconductor element and method for manufacturing the same

ActiveUS20110068336A1Improve reliabilityIncrease computing speedSolid-state devicesSemiconductor/solid-state device manufacturingHydrogen atomCharge carrier

An object is to provide a thin film transistor and a method for manufacturing the thin film transistor including an oxide semiconductor with a controlled threshold voltage, high operation speed, a relatively easy manufacturing process, and sufficient reliability. An impurity having influence on carrier concentration in the oxide semiconductor layer, such as a hydrogen atom or a compound containing a hydrogen atom such as H2O, may be eliminated. An oxide insulating layer containing a large number of defects such as dangling bonds may be formed in contact with the oxide semiconductor layer, such that the impurity diffuses into the oxide insulating layer and the impurity concentration in the oxide semiconductor layer is reduced. The oxide semiconductor layer or the oxide insulating layer in contact with the oxide semiconductor layer may be formed in a deposition chamber which is evacuated with use of a cryopump whereby the impurity concentration is reduced.

Owner:SEMICON ENERGY LAB CO LTD

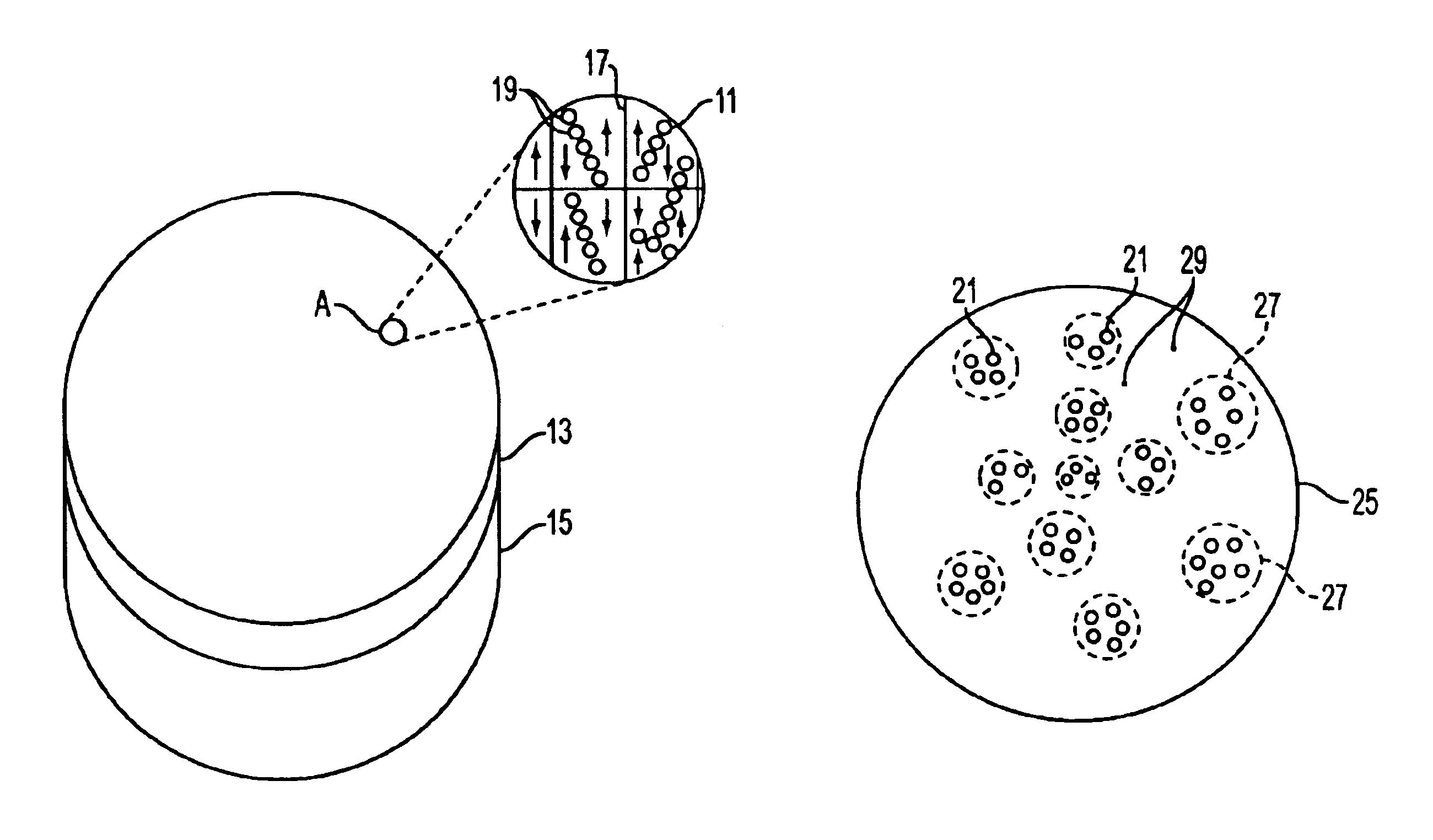

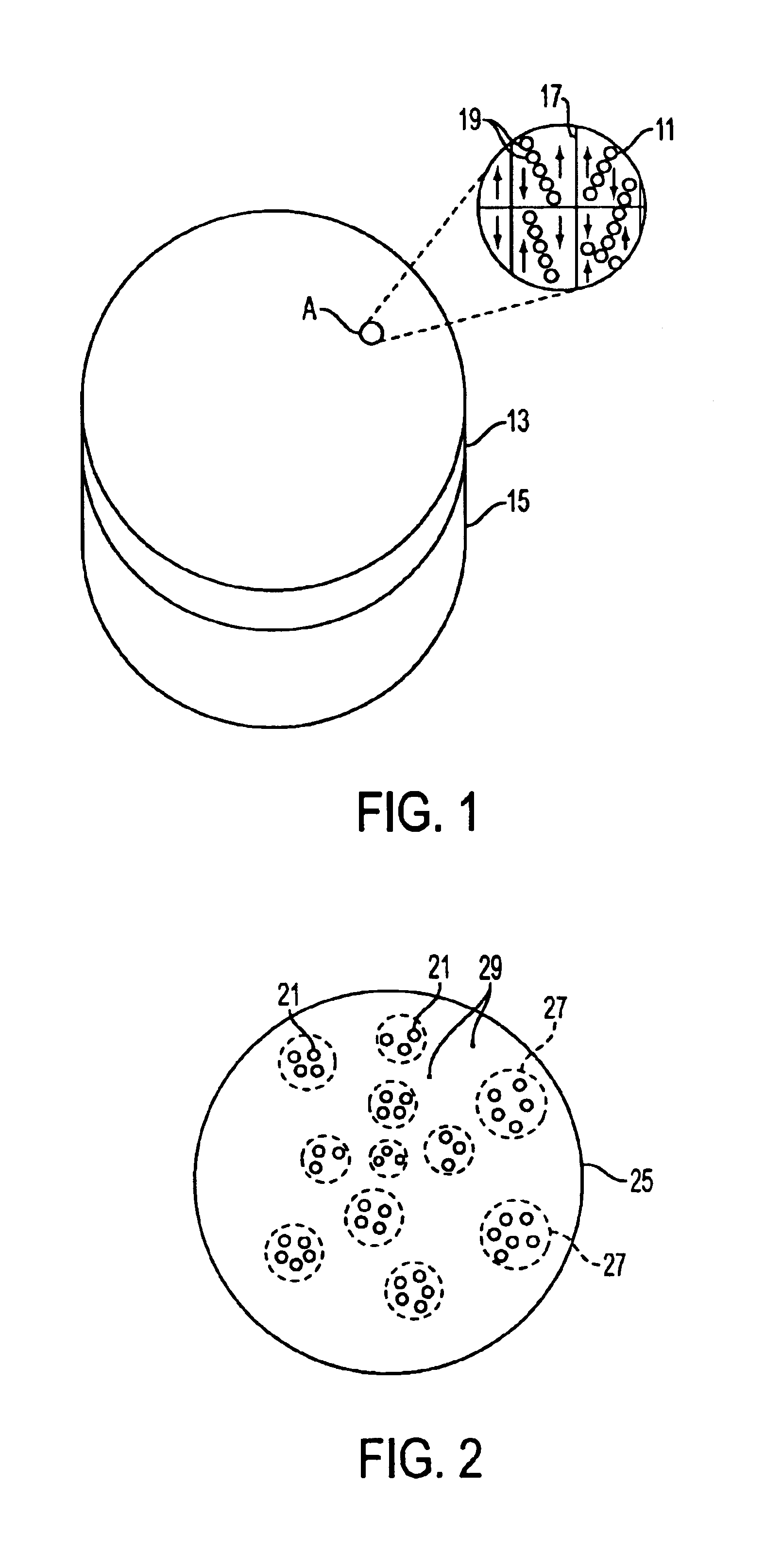

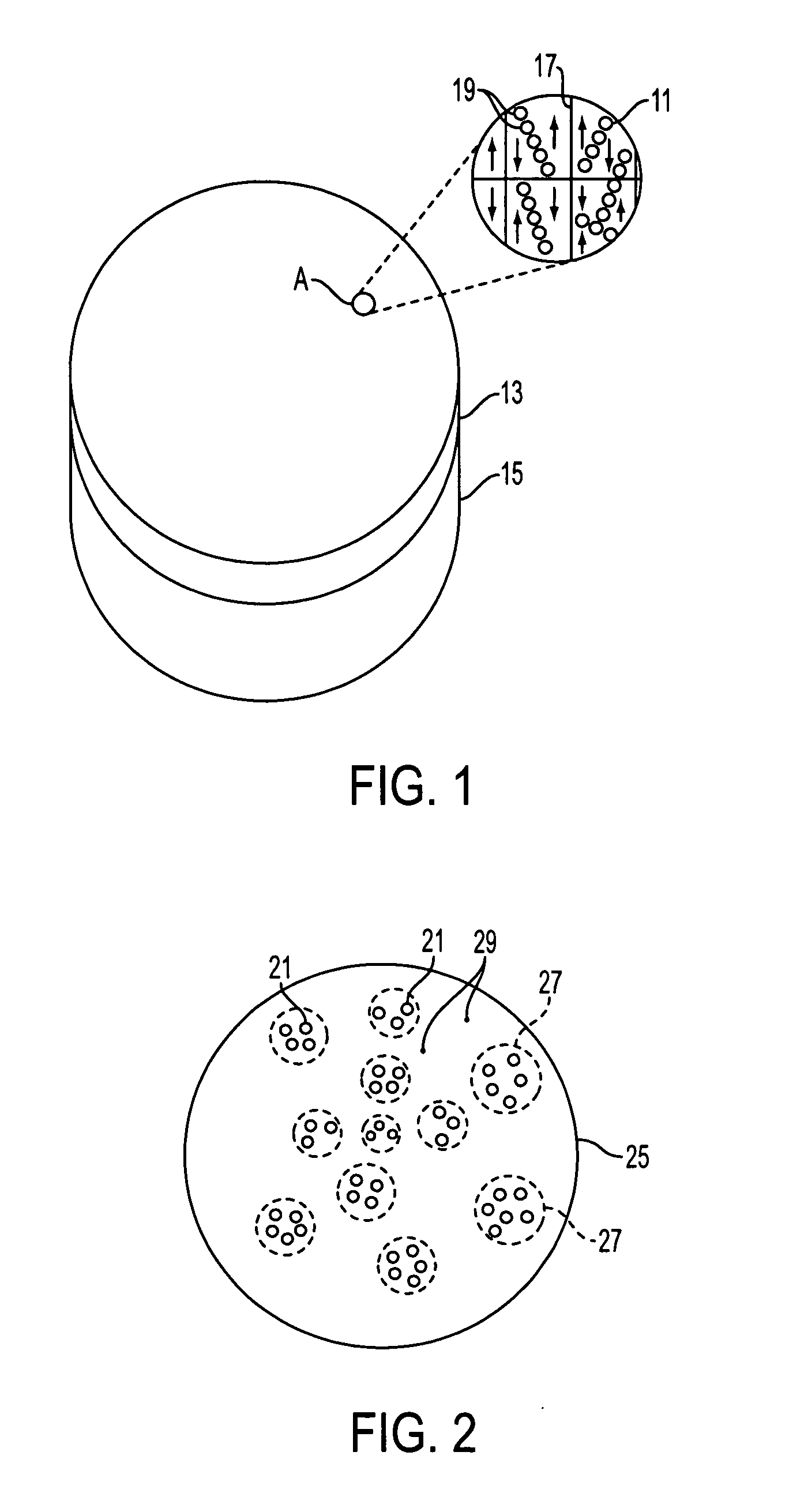

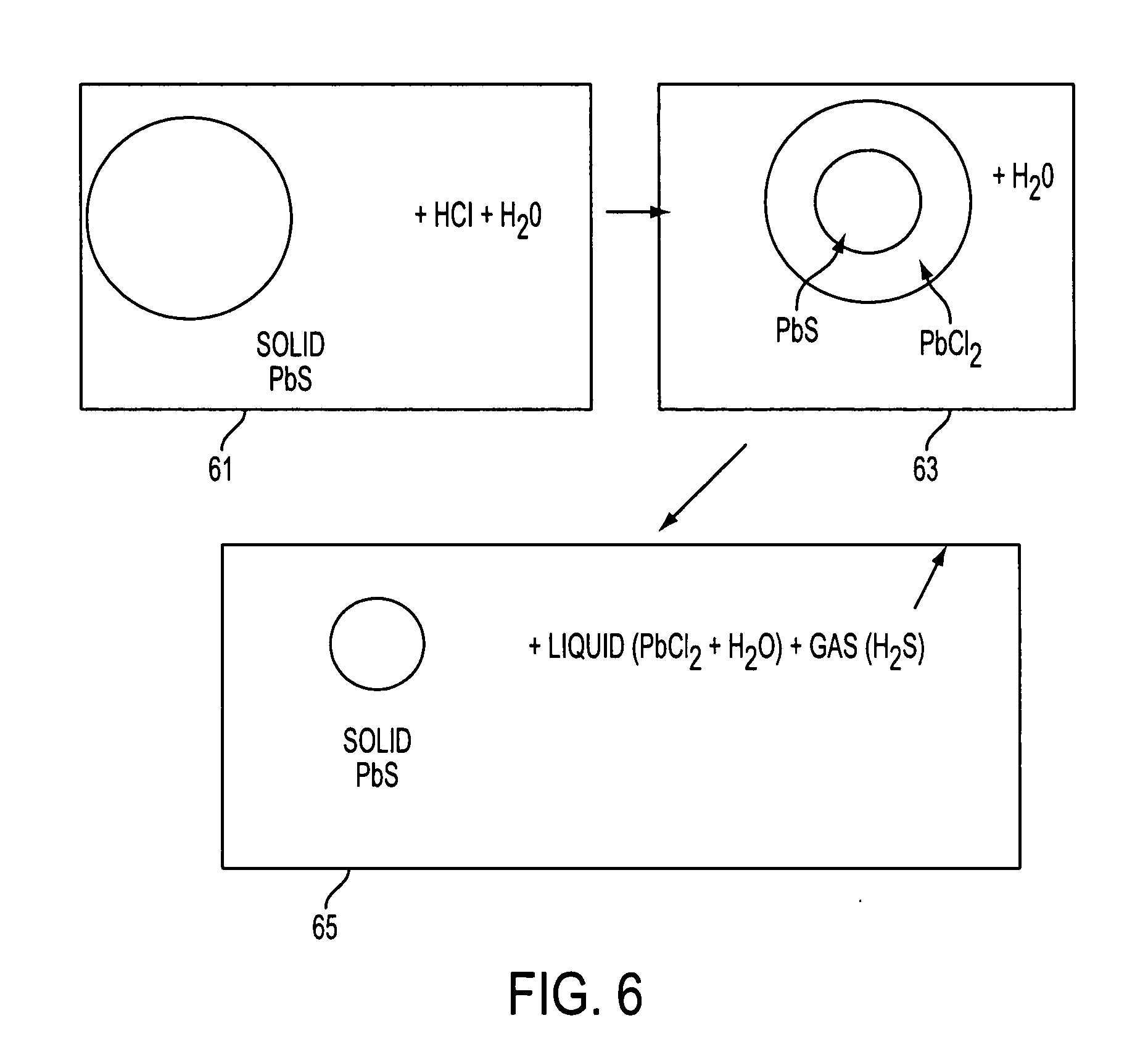

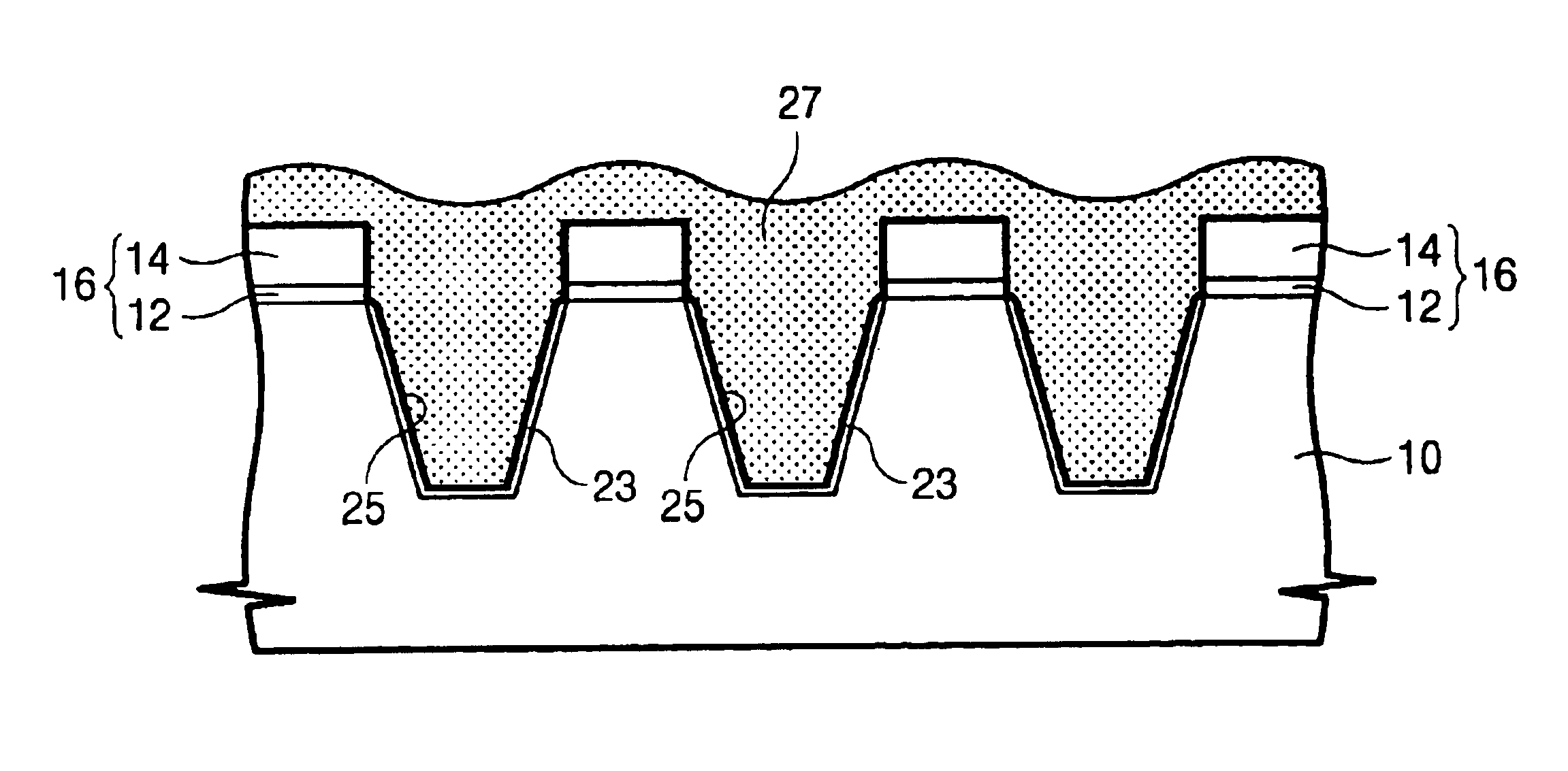

Passivated nanoparticles, method of fabrication thereof, and devices incorporating nanoparticles

A plurality of semiconductor nanoparticles having an elementally passivated surface are provided. These nanoparticles are capable of being suspended in water without substantial agglomeration and substantial precipitation on container surfaces for at least 30 days. The method of making the semiconductor nanoparticles includes reacting at least a first reactant and a second reactant in a solution to form the semiconductor nanoparticles in the solution. A first reactant provides a passivating element which binds to dangling bonds on a surface of the nanoparticles to passivate the surface of the nanoparticles. The nanoparticle size can be tuned by etching the nanoparticles located in the solution to a desired size.

Owner:RENESSELAER POLYTECHNIC INST

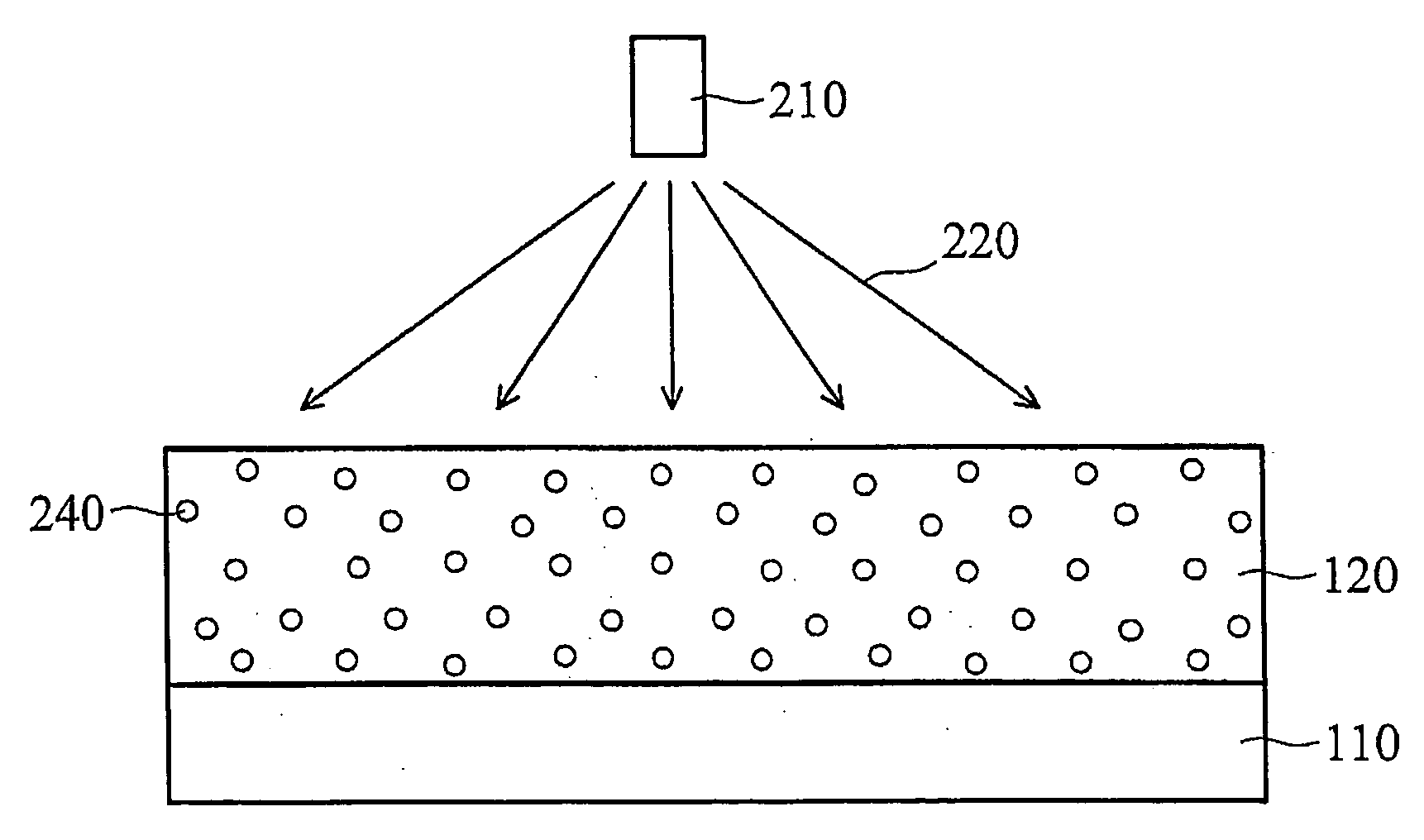

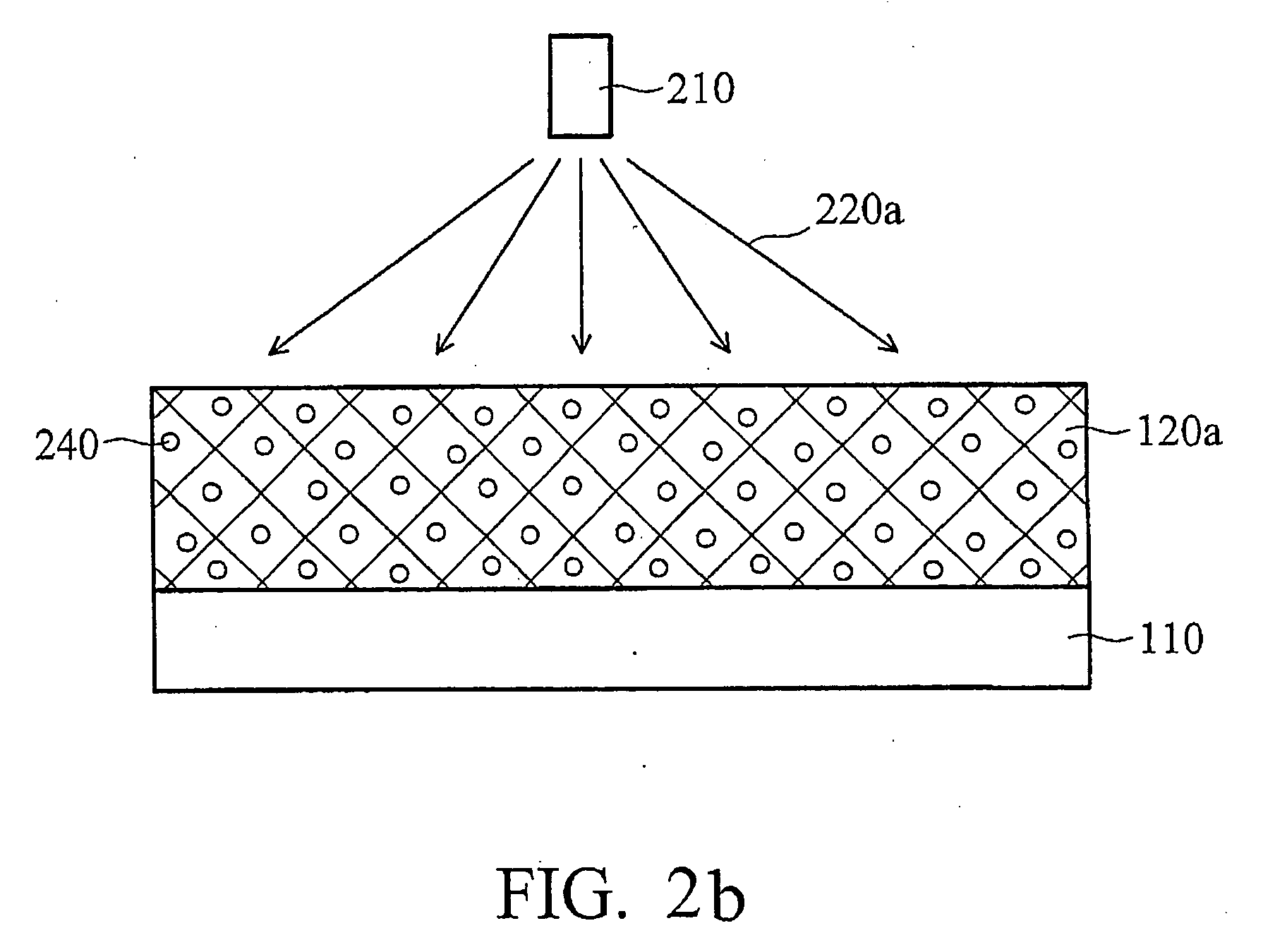

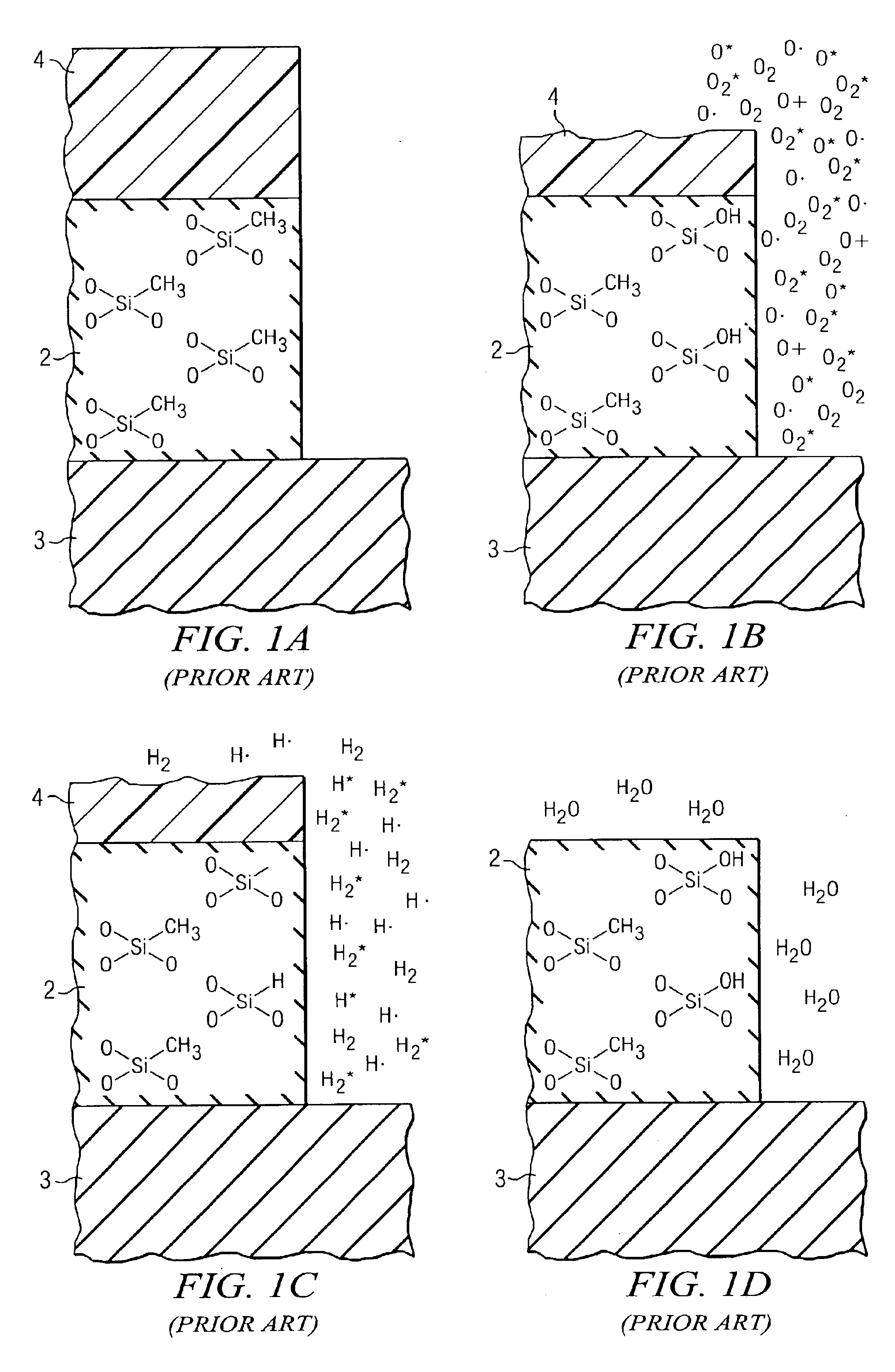

UV curing of low-k porous dielectrics

InactiveUS20070161230A1Solid-state devicesSemiconductor/solid-state device manufacturingCross-linkDevice material

A method of manufacturing a semiconductor device having a low-k dielectric layer is provided. An embodiment comprises forming a dielectric layer on a substrate, wherein the layer comprises a pore generating material dispersed in an uncured matrix. A second step comprises forming pores in the uncured matrix by irradiating the layer with radiation having a first wavelength. After pore forming, a third step comprises cross-linking the dielectric by irradiating it at a second wavelength, the second being less than the first. In an embodiment, the irradiating wavelengths comprise ultra-violet radiation. Embodiments may further include repairing processing damage wherein the damage includes dangling bonds or silanol formation. The repairing includes annealing in a carbon-containing ambient such as C2H4, C3H6, or hexamethyldisilazane (HMDS).

Owner:TAIWAN SEMICON MFG CO LTD

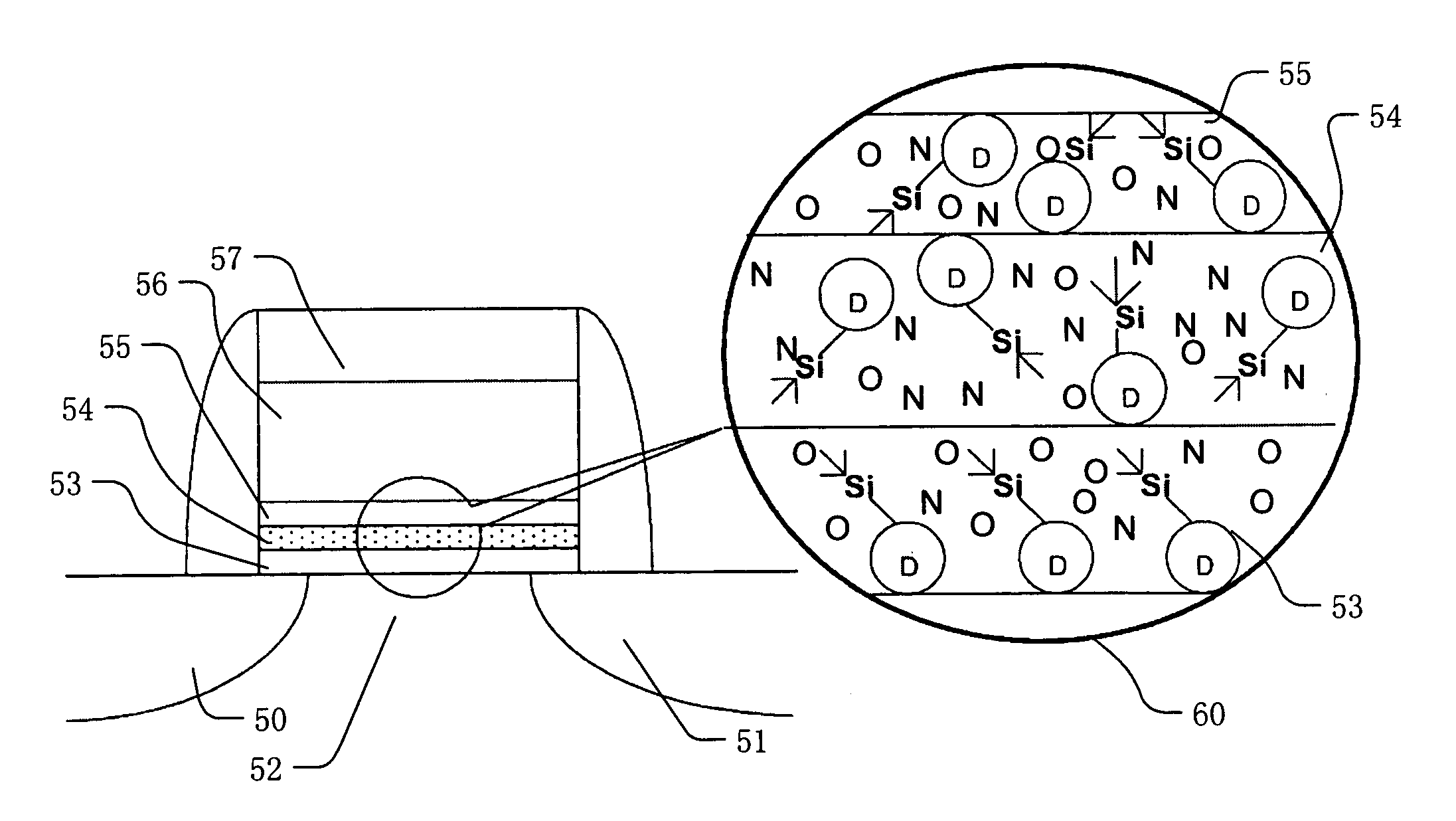

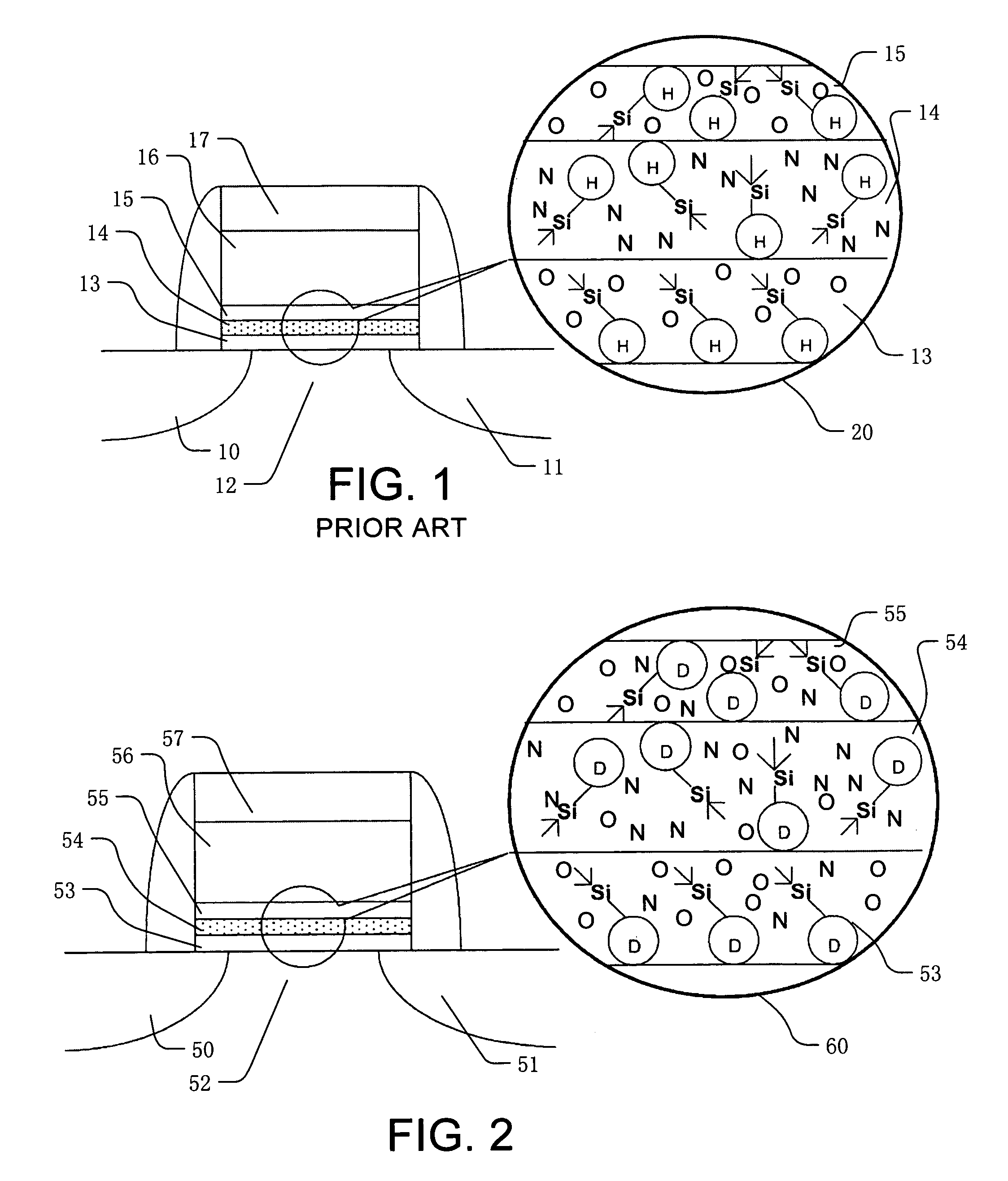

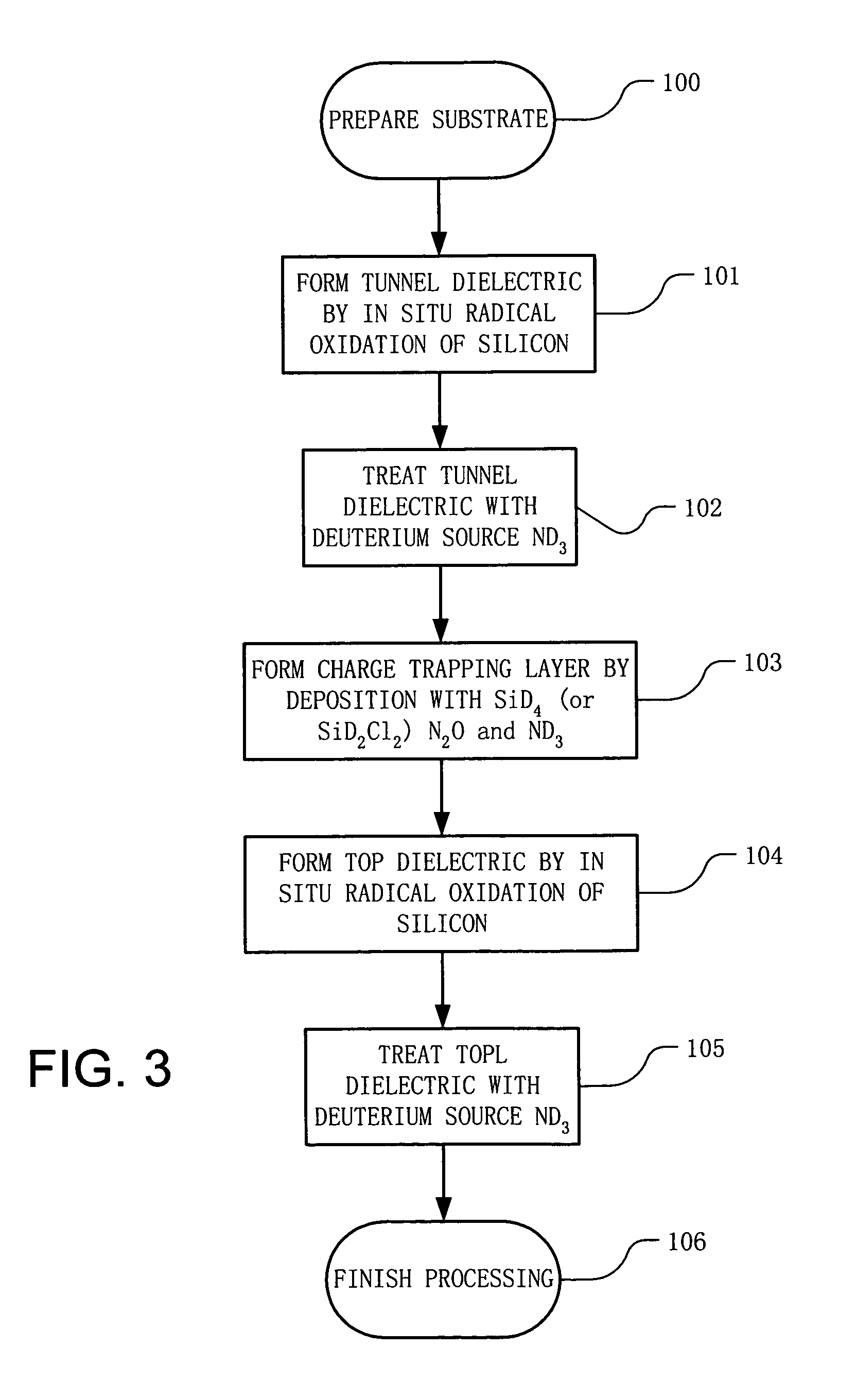

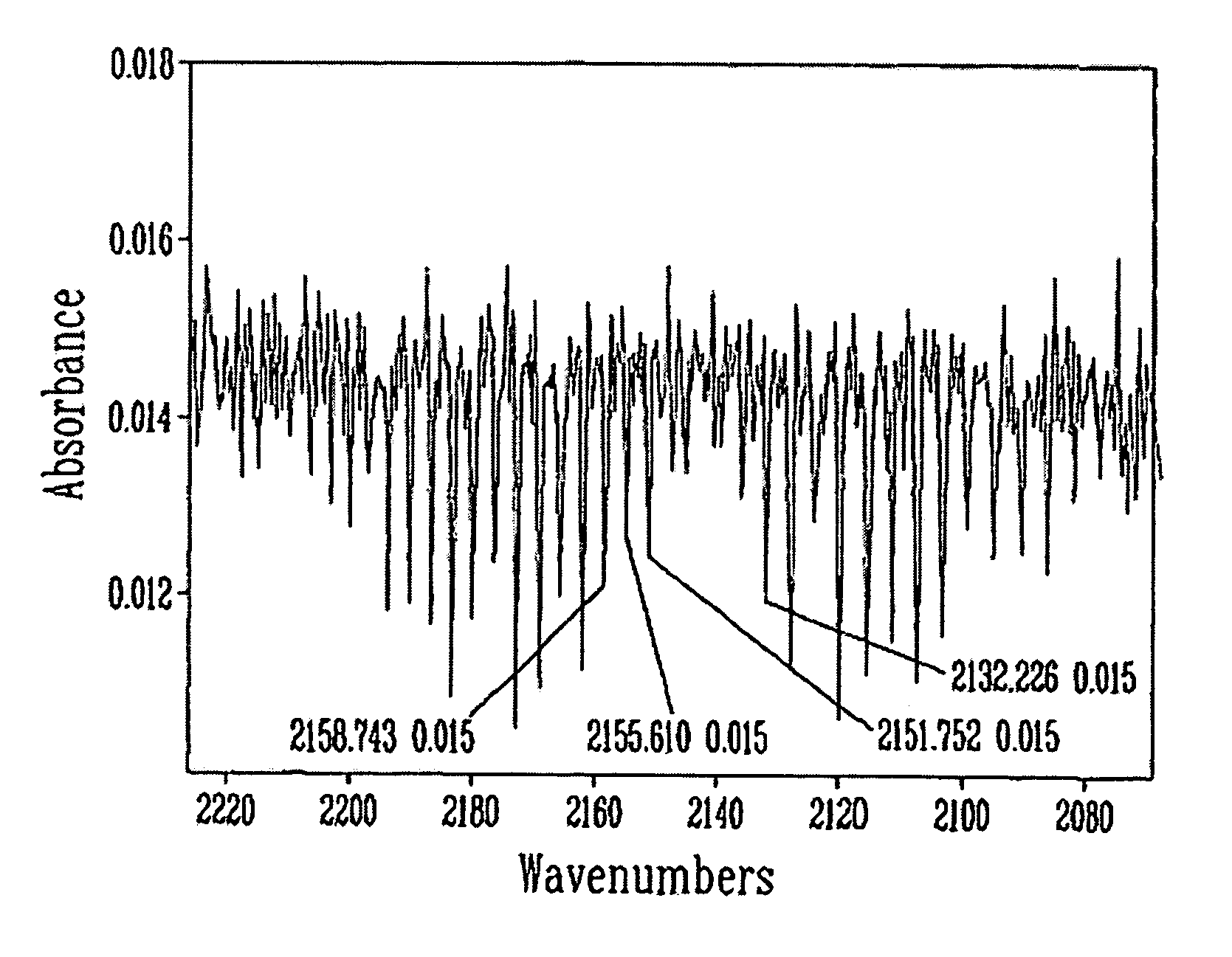

Memory device and method of manufacturing including deuterated oxynitride charge trapping structure

ActiveUS7060594B2Improved data retention characteristicReduce in quantitySemiconductor/solid-state device manufacturingSemiconductor devicesTrappingIsotope

A method for manufacturing a charge storage stack including a bottom dielectric layer, a charge trapping structure on the bottom dielectric layer, and a top dielectric layer, each comprising silicon oxynitride, are formed using reactant gases that comprise hydrogen, where the hydrogen comprises at least 90 percent deuterium isotope. The bottom dielectric layer, charge trapping structure, and top dielectric layer each have respective relative concentrations of oxygen and nitrogen. The relative concentration of nitrogen in the charge trapping structure is high enough for the material to act as a charge trapping structure with an energy gap that is lower than the energy gaps in the bottom dielectric layer and the top dielectric layer. The presence of oxygen in the charge trapping structure reduces the number of available dangling bonding sites, and thereby reduces the number of hydrogen inclusions in the structure.

Owner:MACRONIX INT CO LTD +1

Ceramic thin film on various substrates, and process for producing same

InactiveUS20050139966A1Semiconductor/solid-state device detailsSolid-state devicesHydrogen concentrationAmorphous silicon

A thin film of an amorphous silicon-based material on a substrate. The thin film has the property of any one of a carrier concentration of 1013 to 1018 cm−3 in a depletion zone next to the substrate, an electron mobility of 5 to 30 cm2V−1s−1, a dangling bond concentration of 1012 to 1019 cm−3, no solvent-related defects, or a residual hydrogen concentration of 0 to 25 atomic %. The thin film may be used to fabricate many devices such as solar cells, light-emitting diodes, transistors, photothyristors, and integrated monolithic devices on a single chip.

Owner:BISHOP'S UNIVERSITY +1

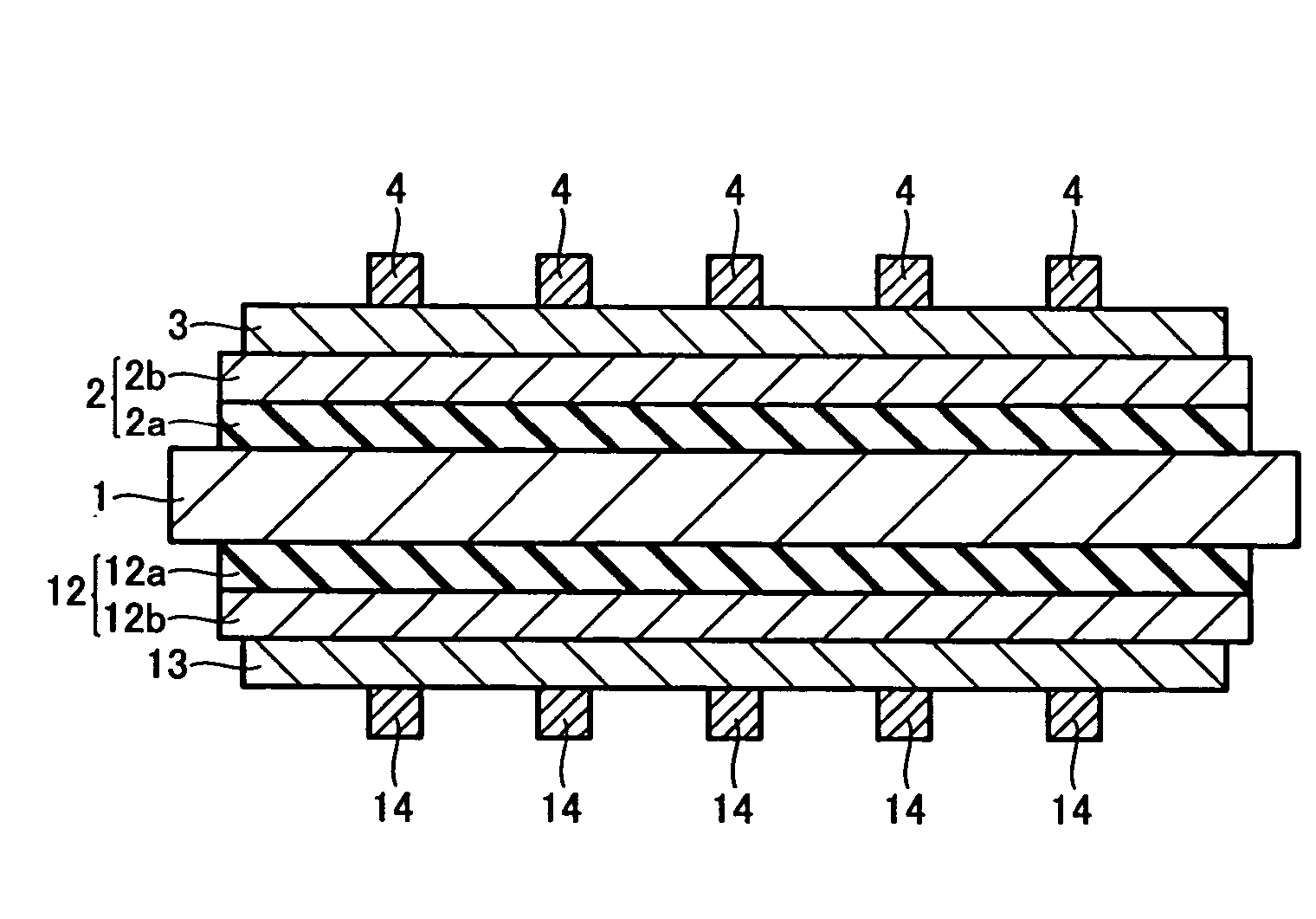

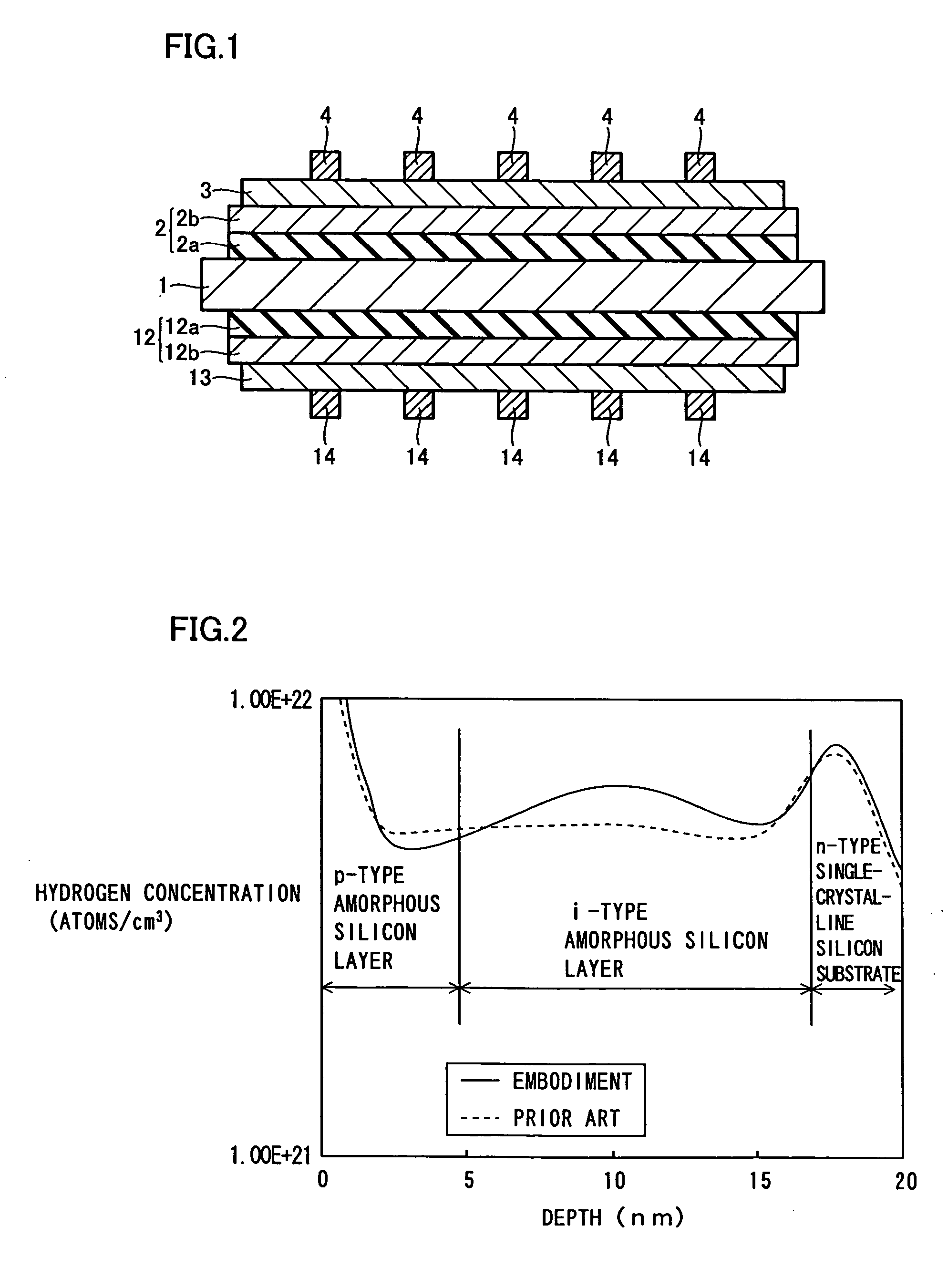

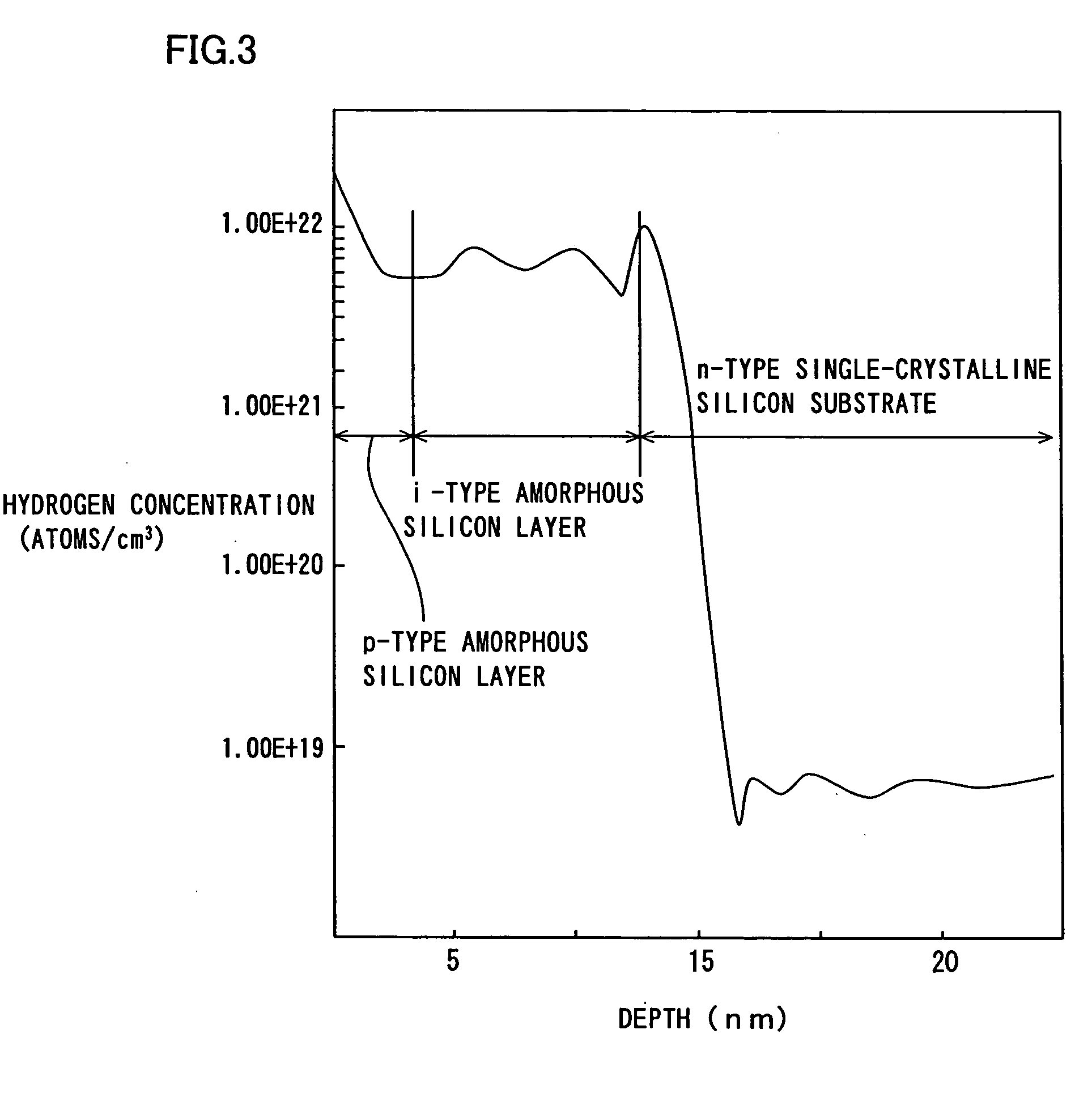

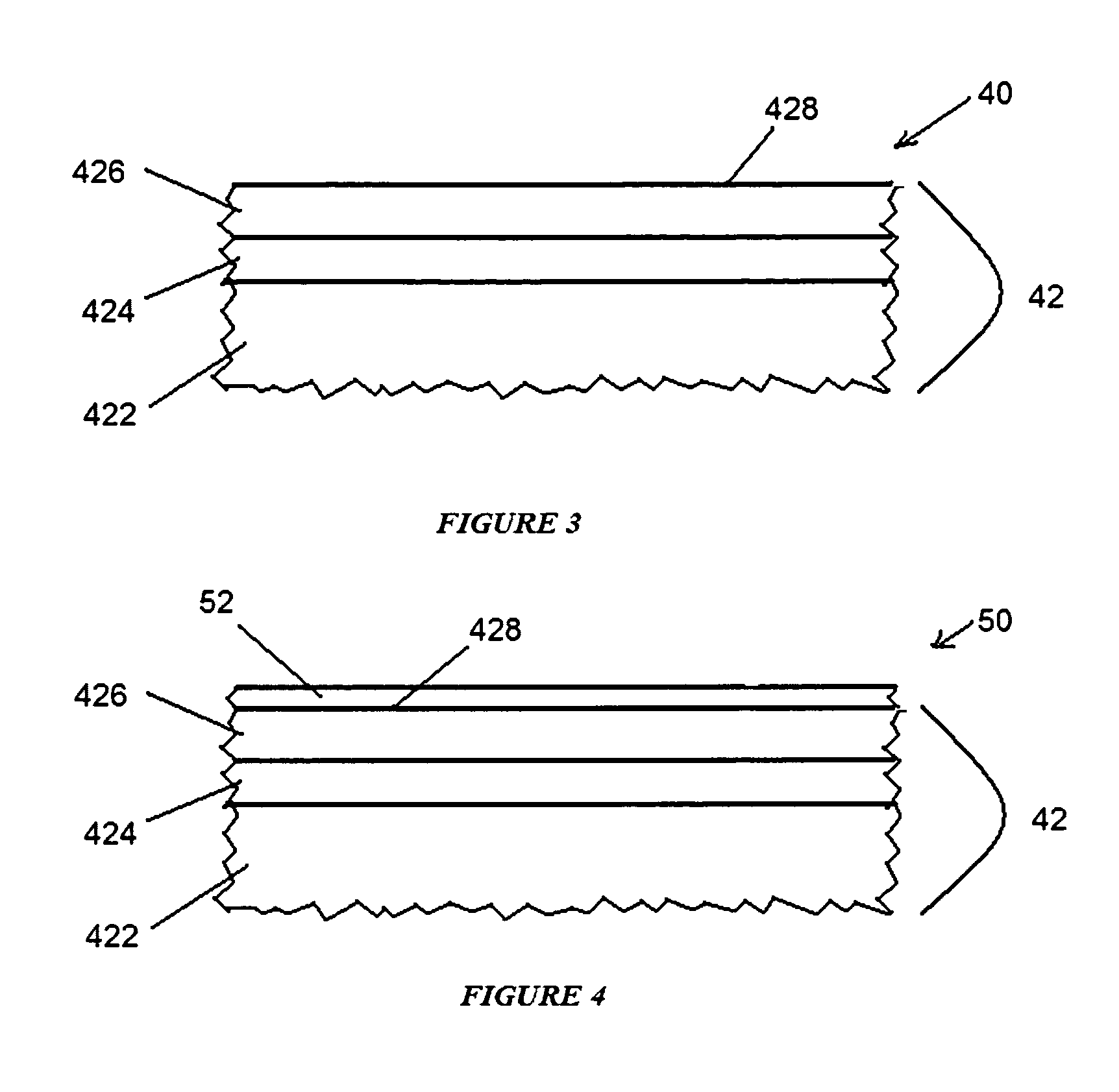

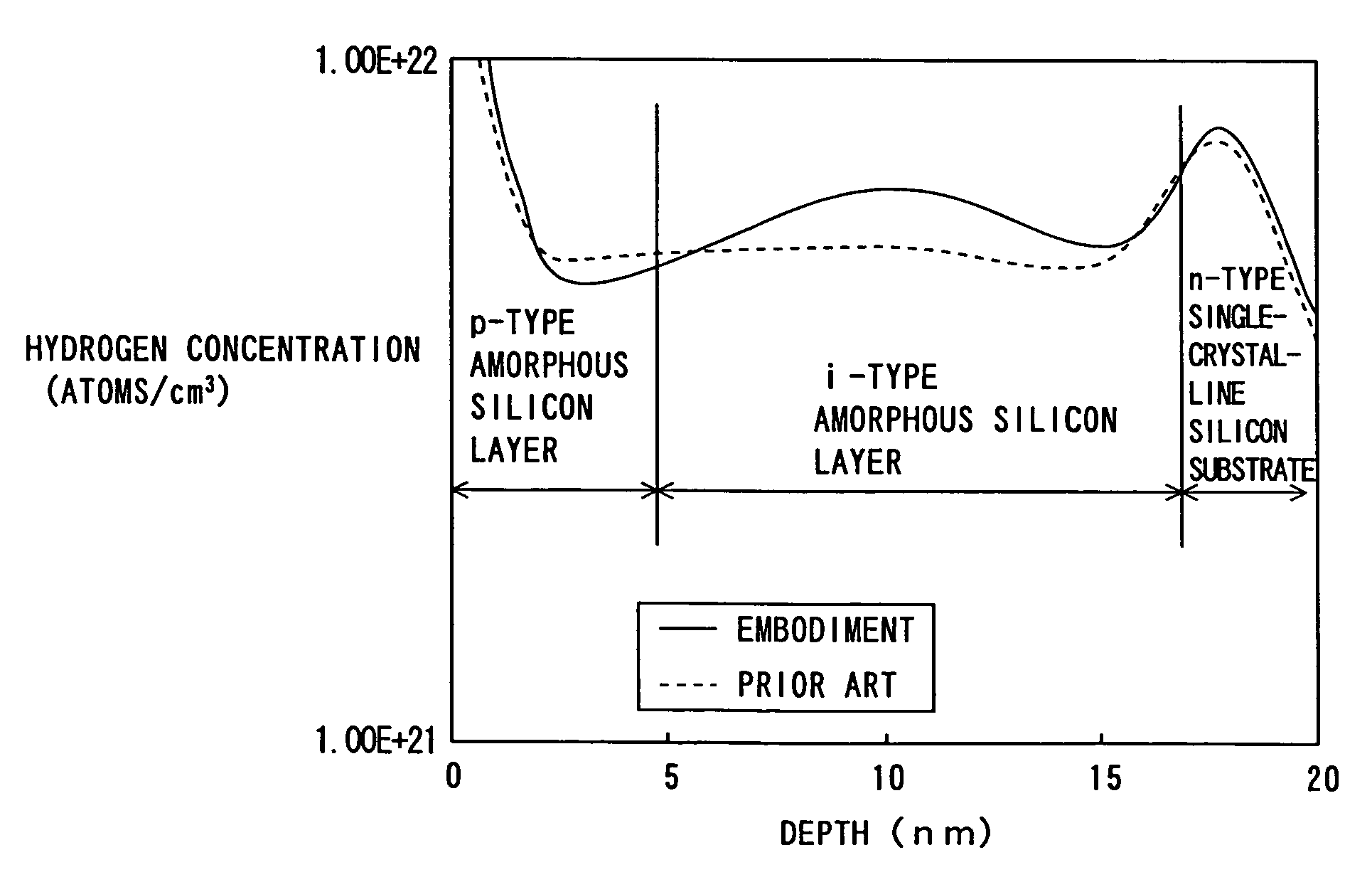

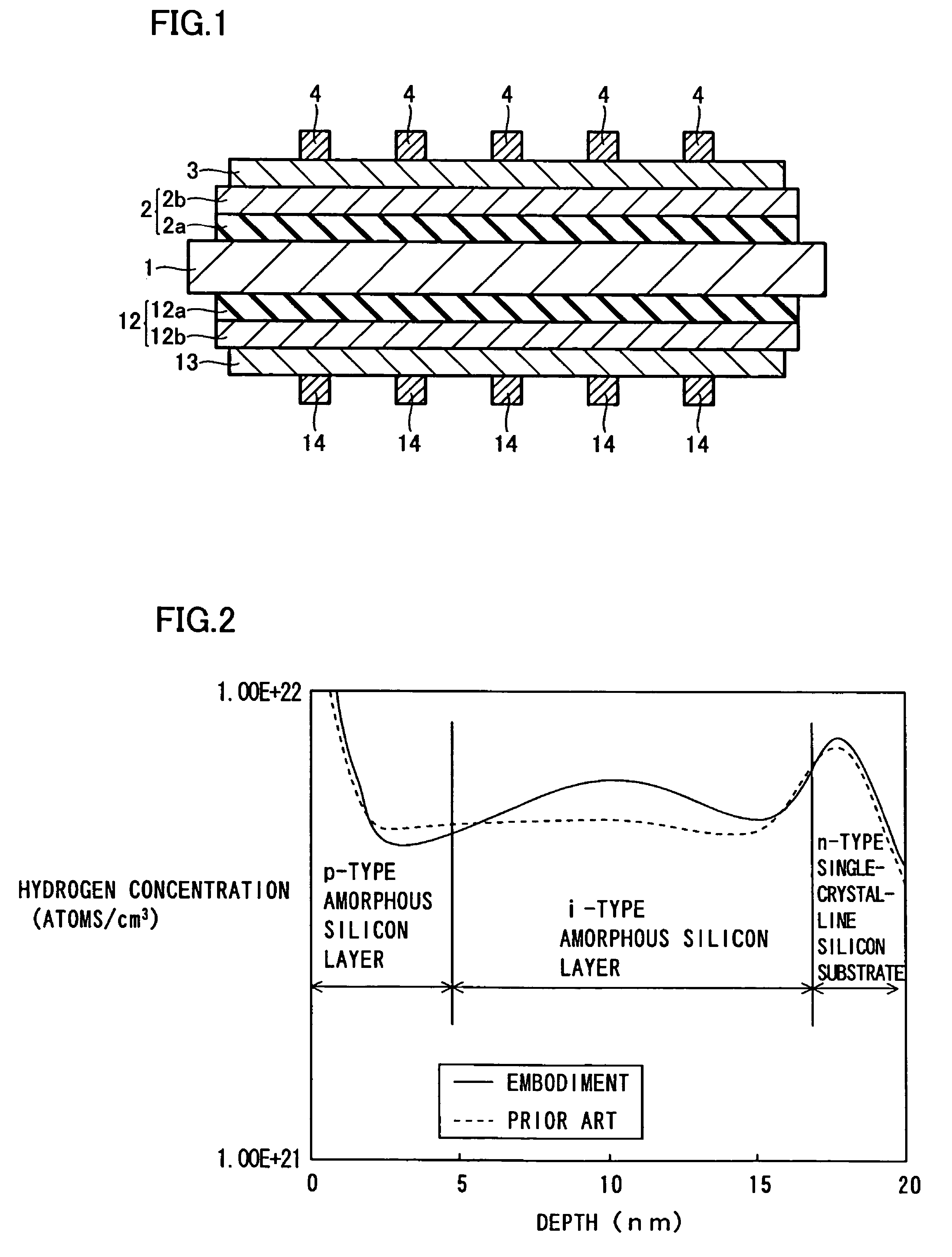

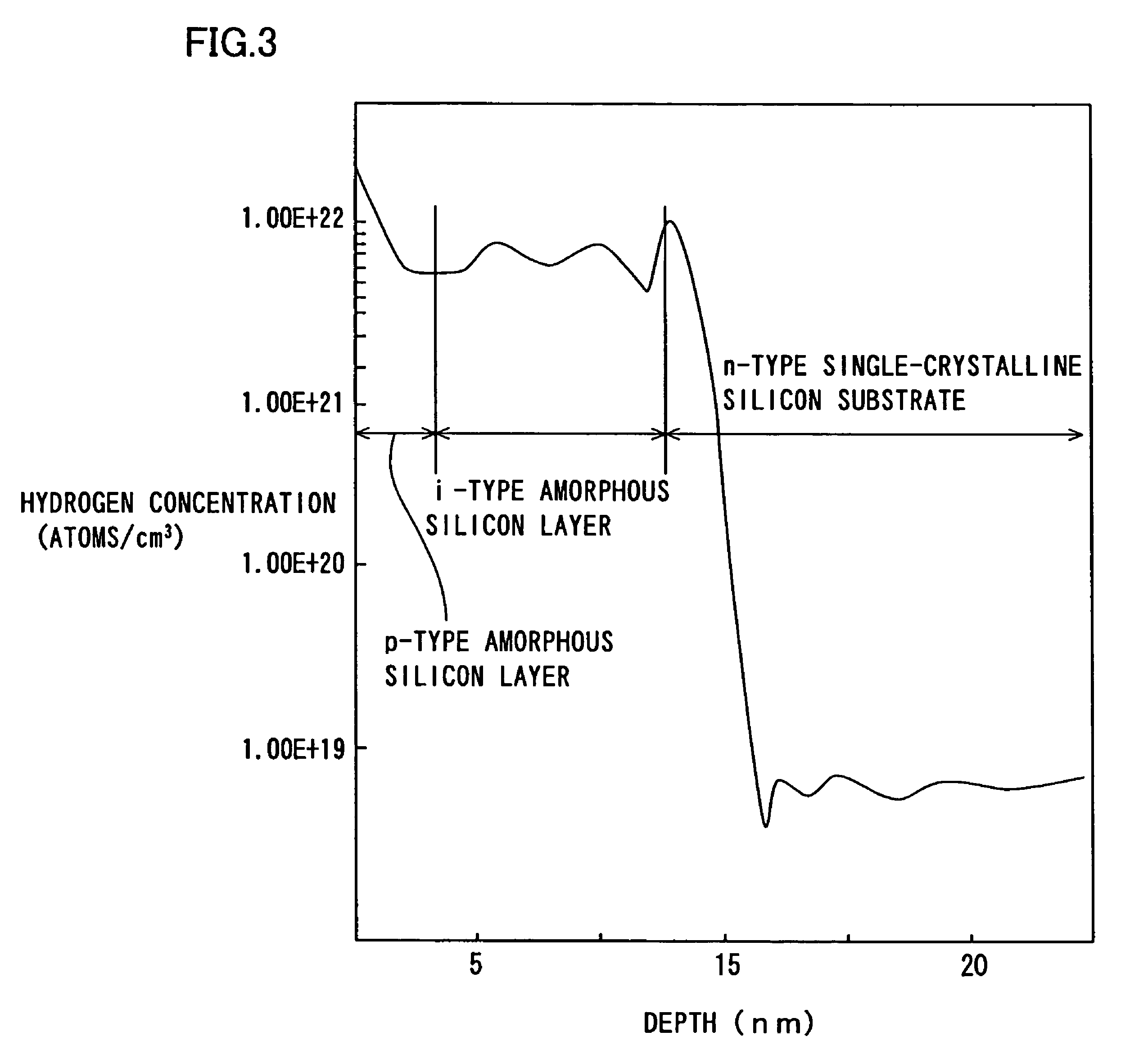

Photovoltaic device

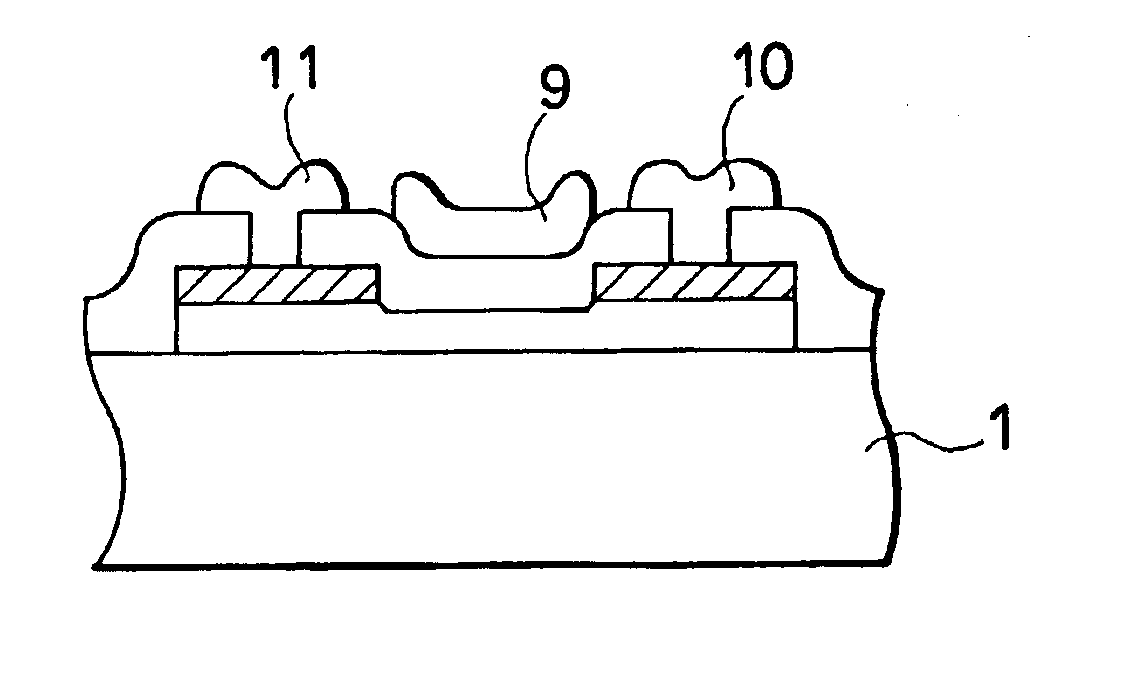

ActiveUS20040182433A1Reduce in quantityIncrease the number ofPV power plantsFinal product manufactureHydrogen concentrationHydrogen atom

A photovoltaic device capable of improving output characteristics is provided. This photovoltaic device comprises a crystalline semiconductor member, a substantially intrinsic first amorphous semiconductor layer formed on the front surface of the crystalline semiconductor member and a first conductivity type second amorphous semiconductor layer formed on the front surface of the first amorphous semiconductor layer, and has a hydrogen concentration peak in the first amorphous semiconductor layer. Thus, the quantity of hydrogen atoms in the first amorphous semiconductor layer is so increased that the hydrogen atoms increased in quantity can be bonded to dangling bonds of silicon atoms forming defects in the first amorphous semiconductor layer for inactivating the dangling bonds.

Owner:SANYO ELECTRIC CO LTD

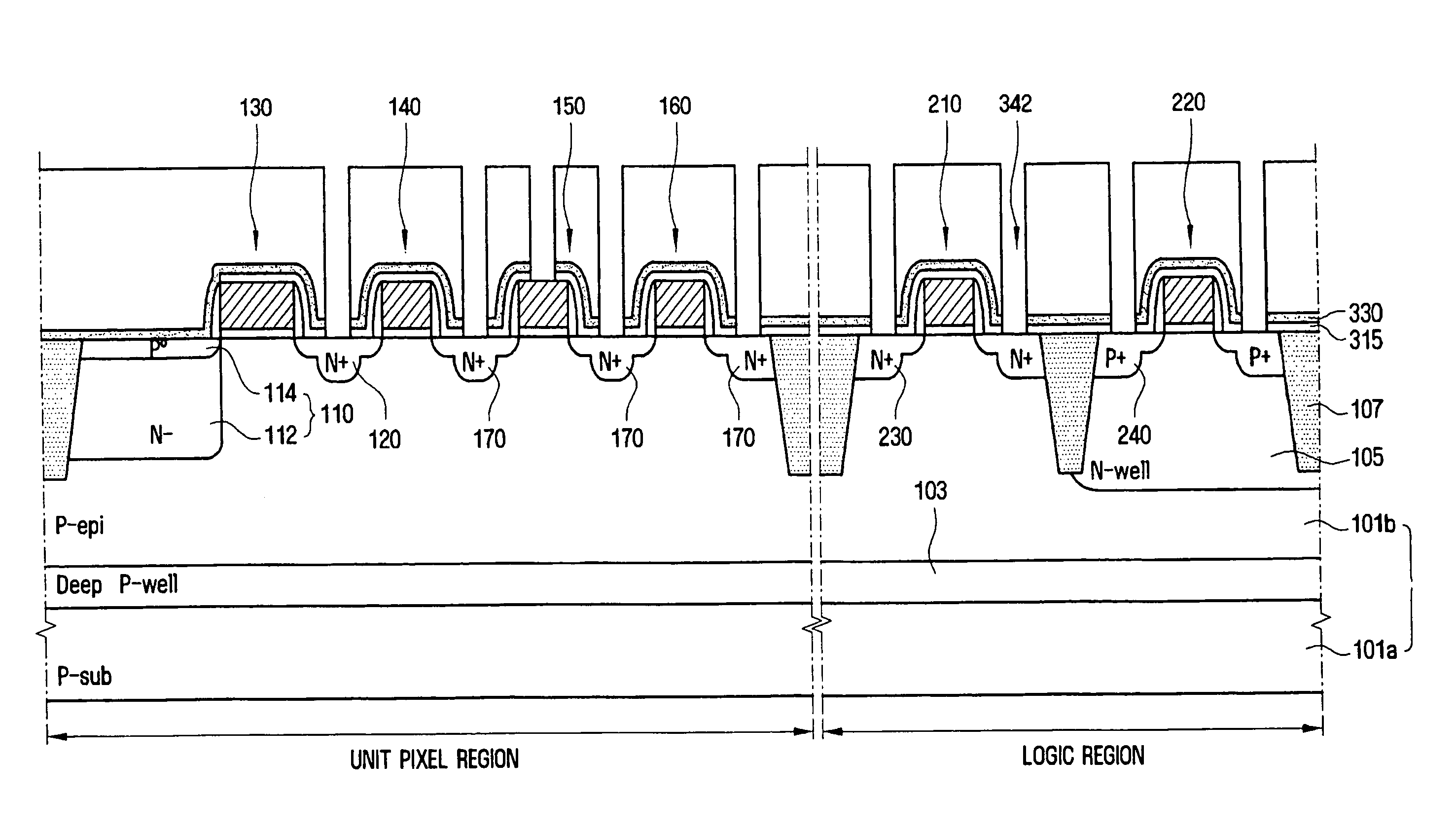

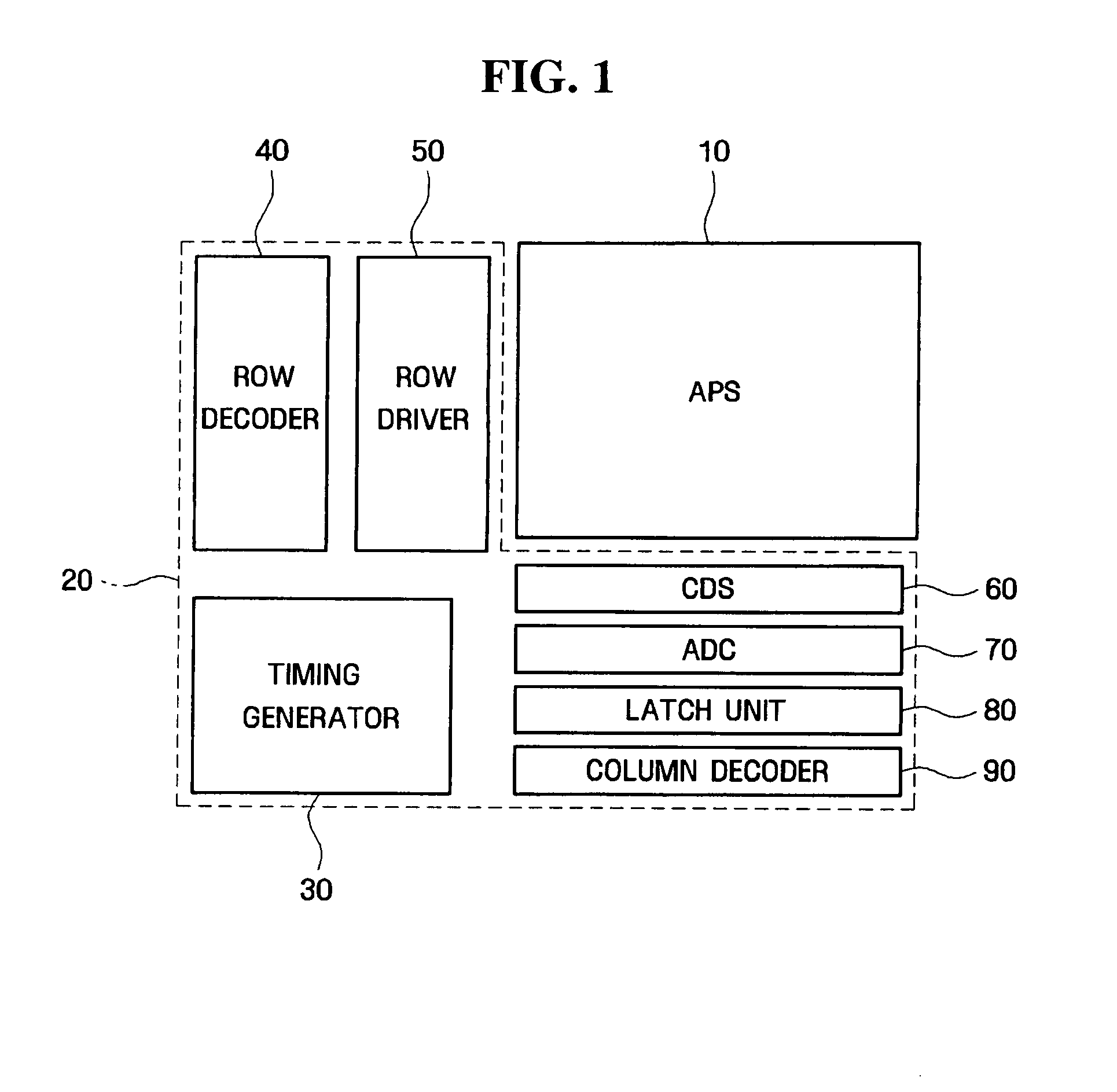

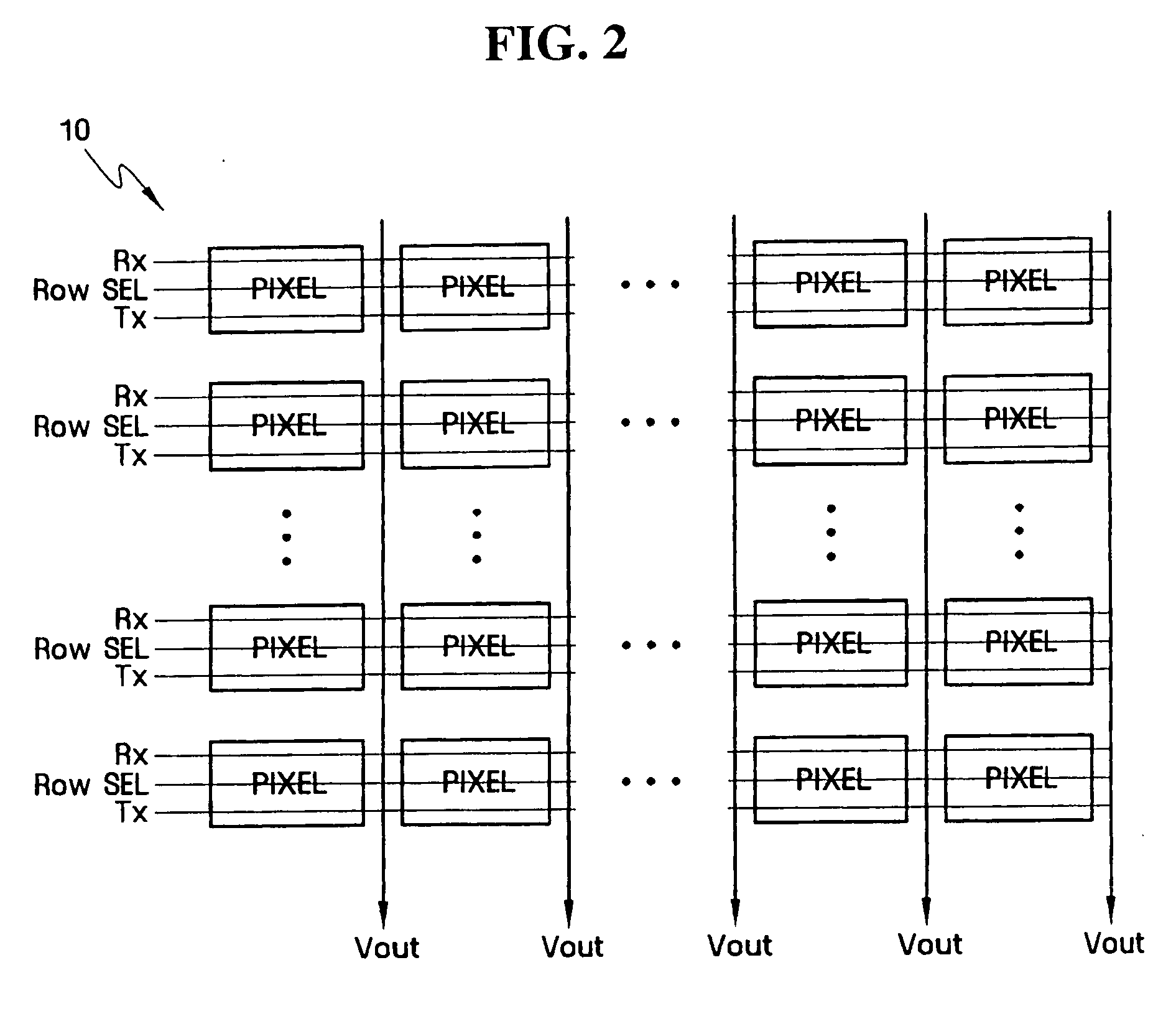

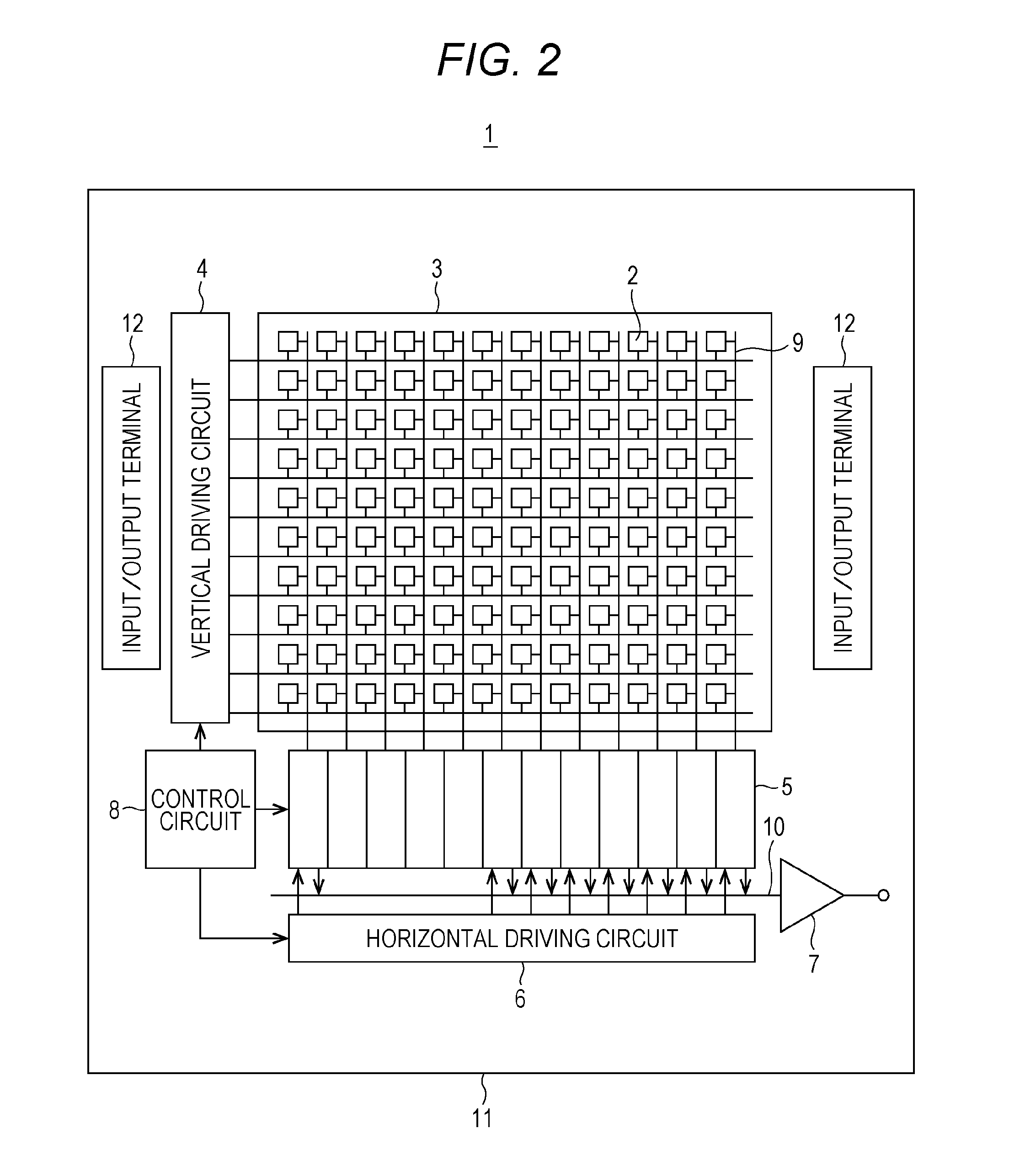

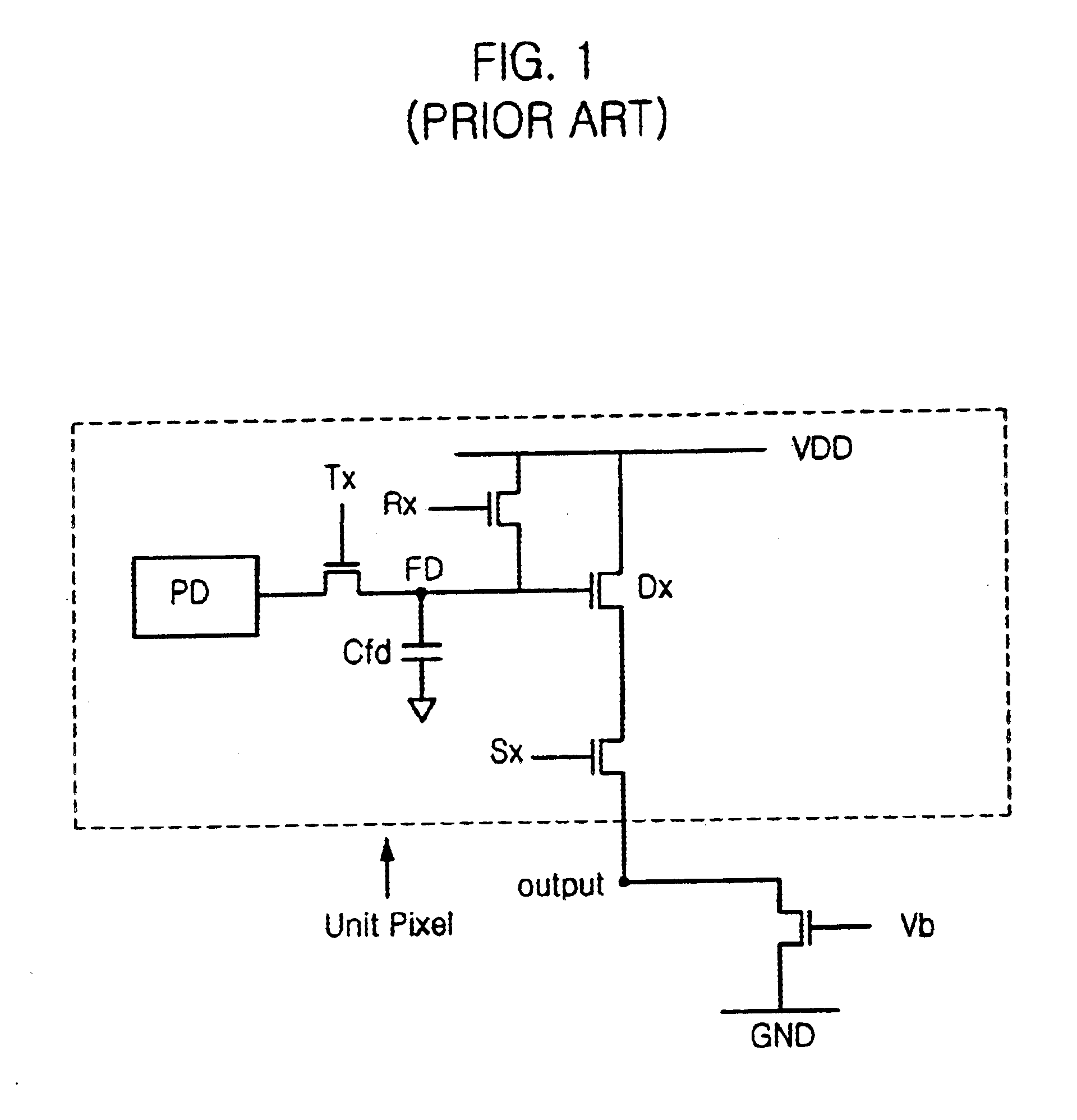

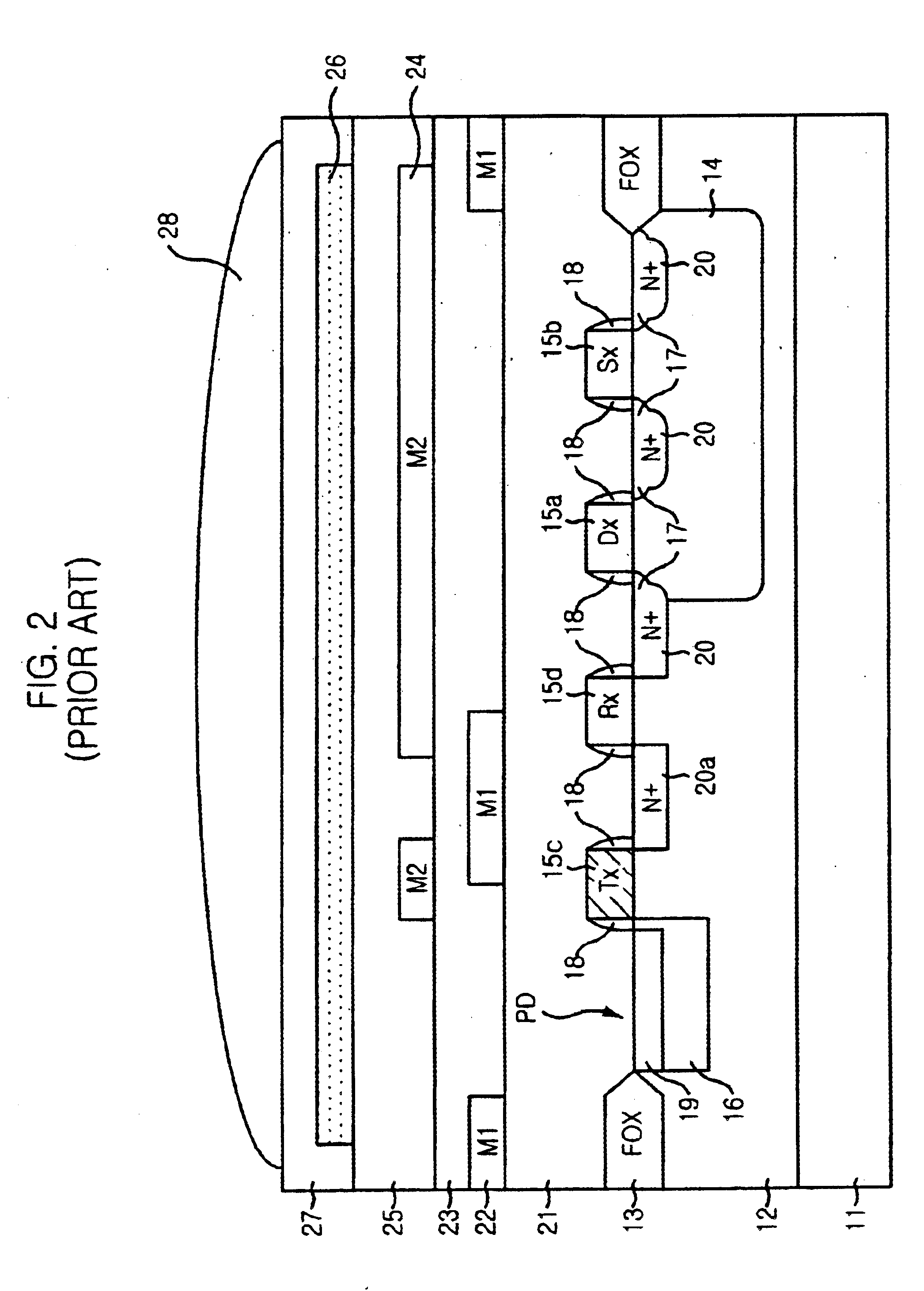

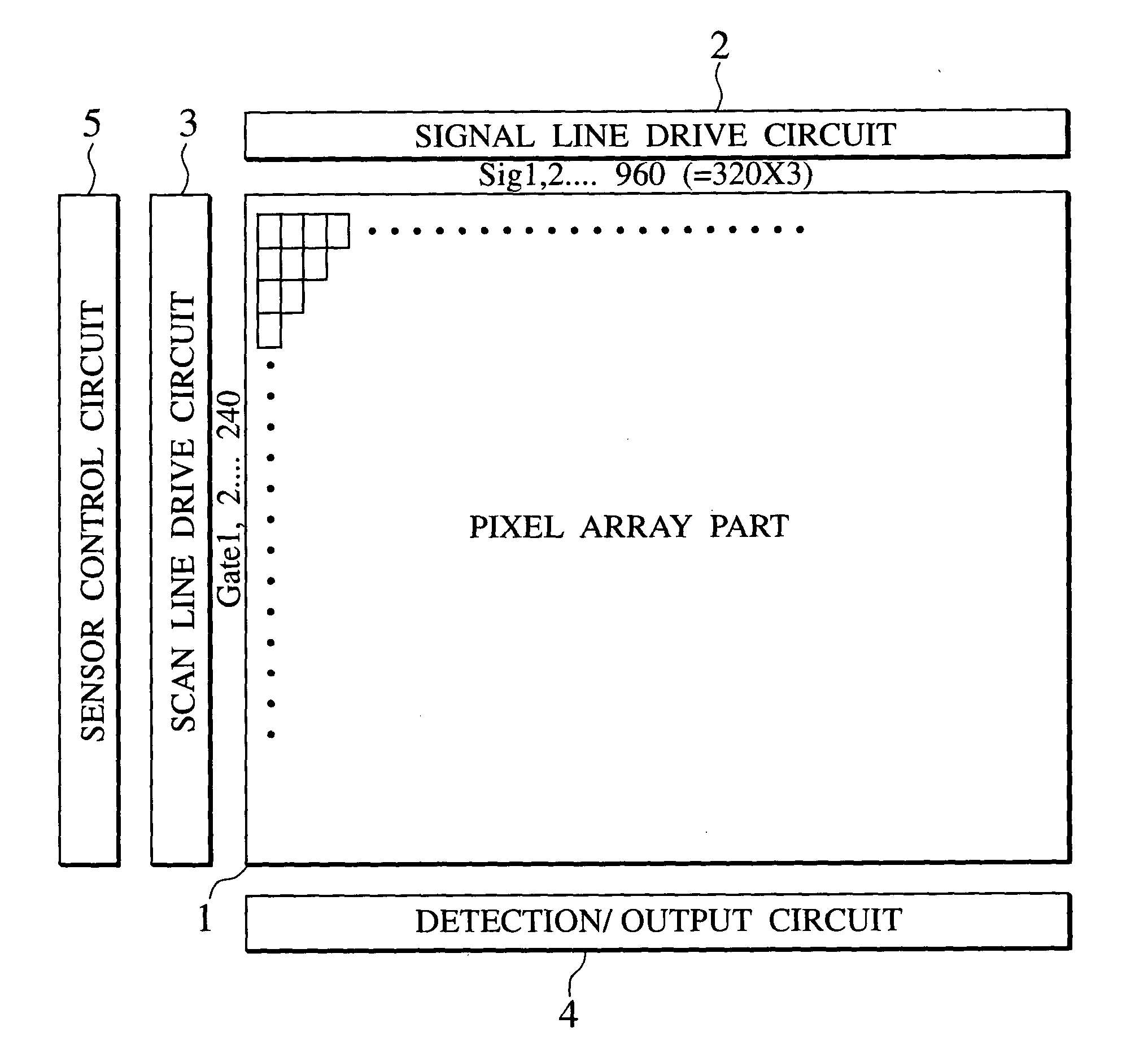

Image sensor having reduced dark current

InactiveUS20090057735A1Improve business performanceMinimizing dark currentSolid-state devicesSemiconductor/solid-state device manufacturingDangling bondField-effect transistor

An image sensor includes a light receiving device, a field effect transistor, a stress layer pattern, and a surface passivation material. The light receiving device is formed in a first region of a substrate. The field effect transistor is formed in a second region of the substrate. The stress layer pattern is formed over the field effect transistor for creating stress therein to improve transistor performance. The surface passivation material is formed on the first region of the substrate for passivating dangling bonds at the surface of the light receiving device.

Owner:SAMSUNG ELECTRONICS CO LTD

Passivated nanoparticles, method of fabrication thereof, and devices incorporating nanoparticles

InactiveUS20050201963A1Material nanotechnologyPigmenting treatmentDangling bondSemiconductor Nanoparticles

A plurality of semiconductor nanoparticles having an elementally passivated surface are provided. These nanoparticles are capable of being suspended in water without substantial agglomeration and substantial precipitation on container surfaces for at least 30 days. The method of making the semiconductor nanoparticles includes reacting at least a first reactant and a second reactant in a solution to form the semiconductor nanoparticles in the solution. A first reactant provides a passivating element which binds to dangling bonds on a surface of the nanoparticles to passivate the surface of the nanoparticles. The nanoparticle size can be tuned by etching the nanoparticles located in the solution to a desired size.

Owner:RENESSELAER POLYTECHNIC INST

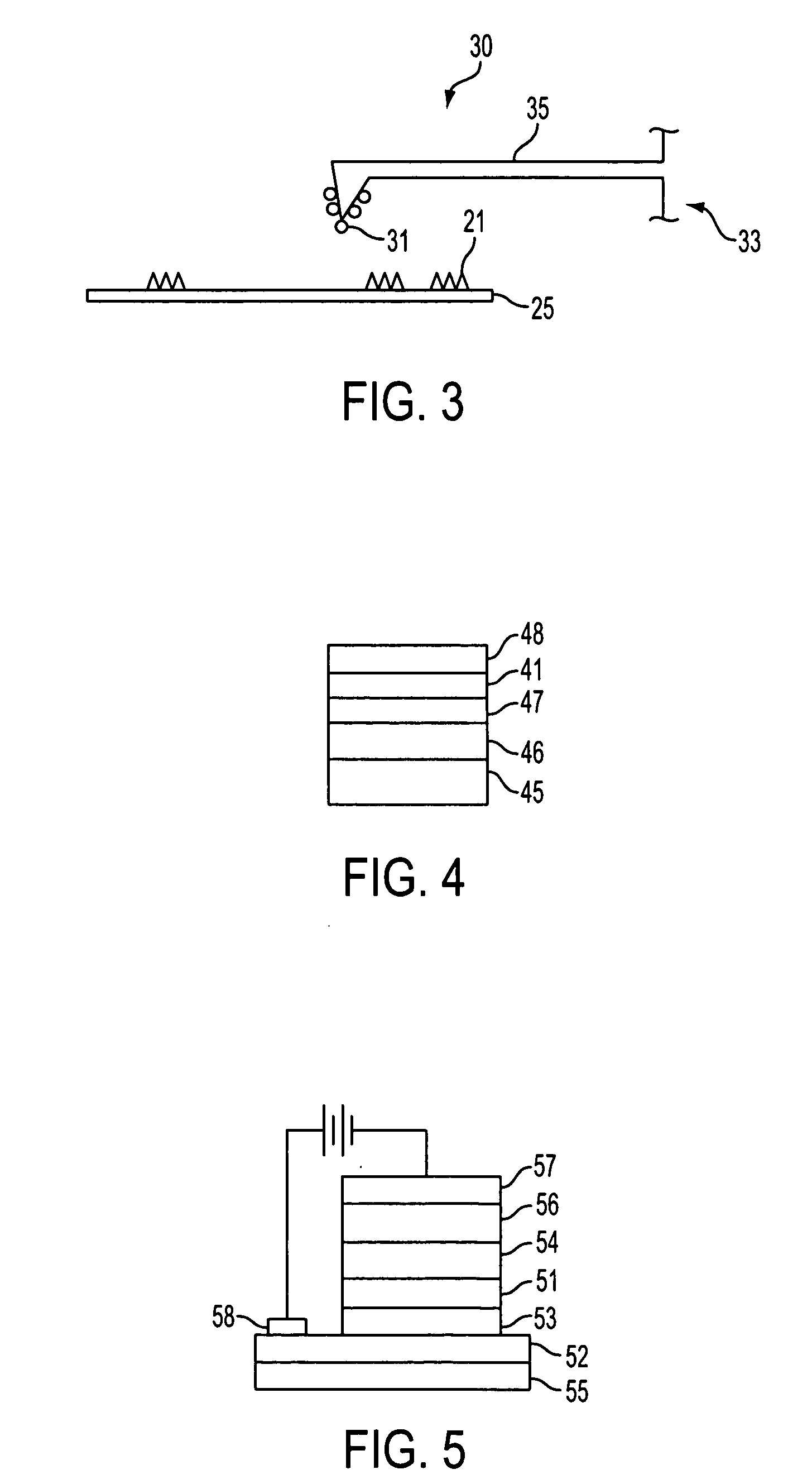

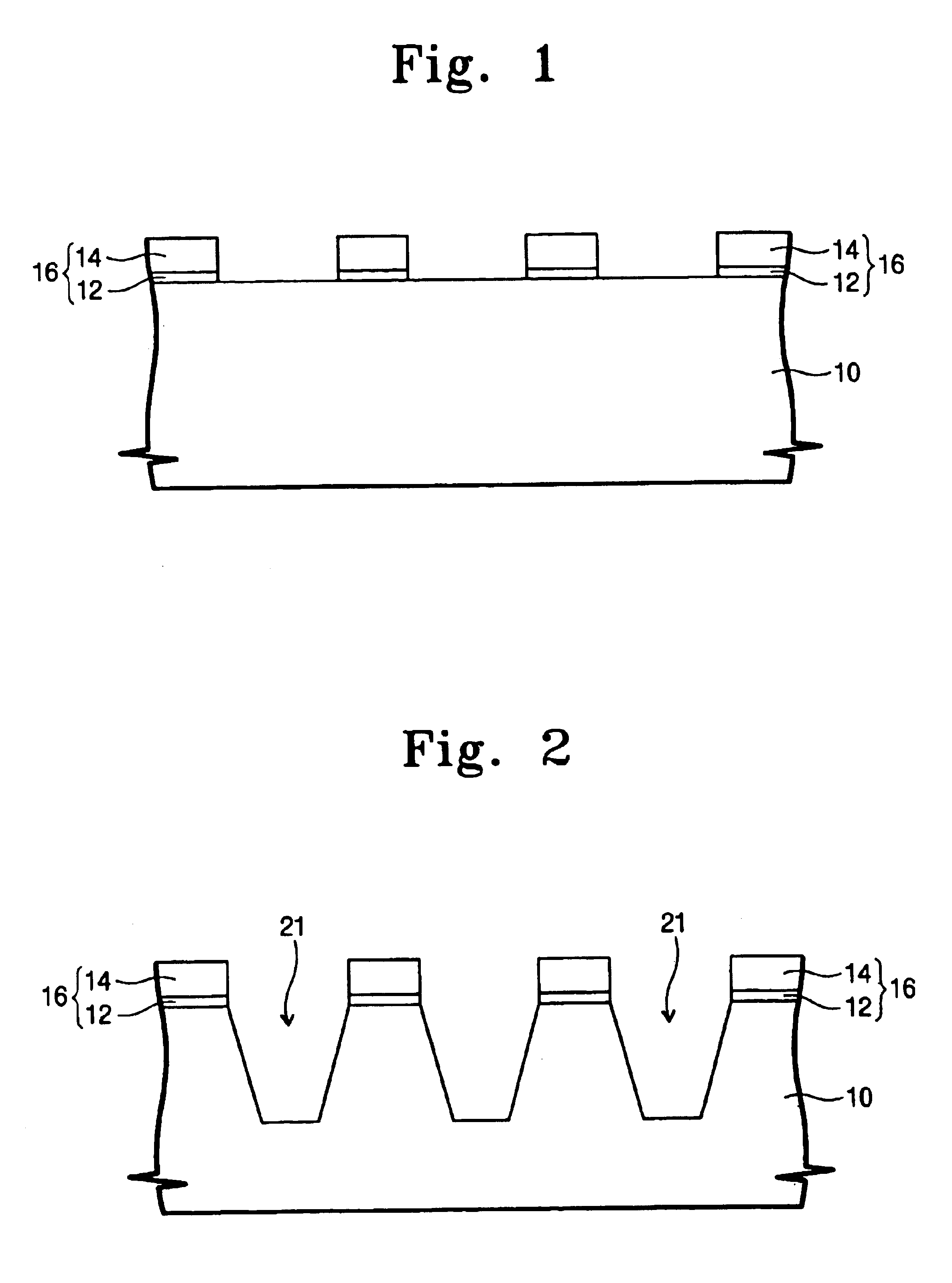

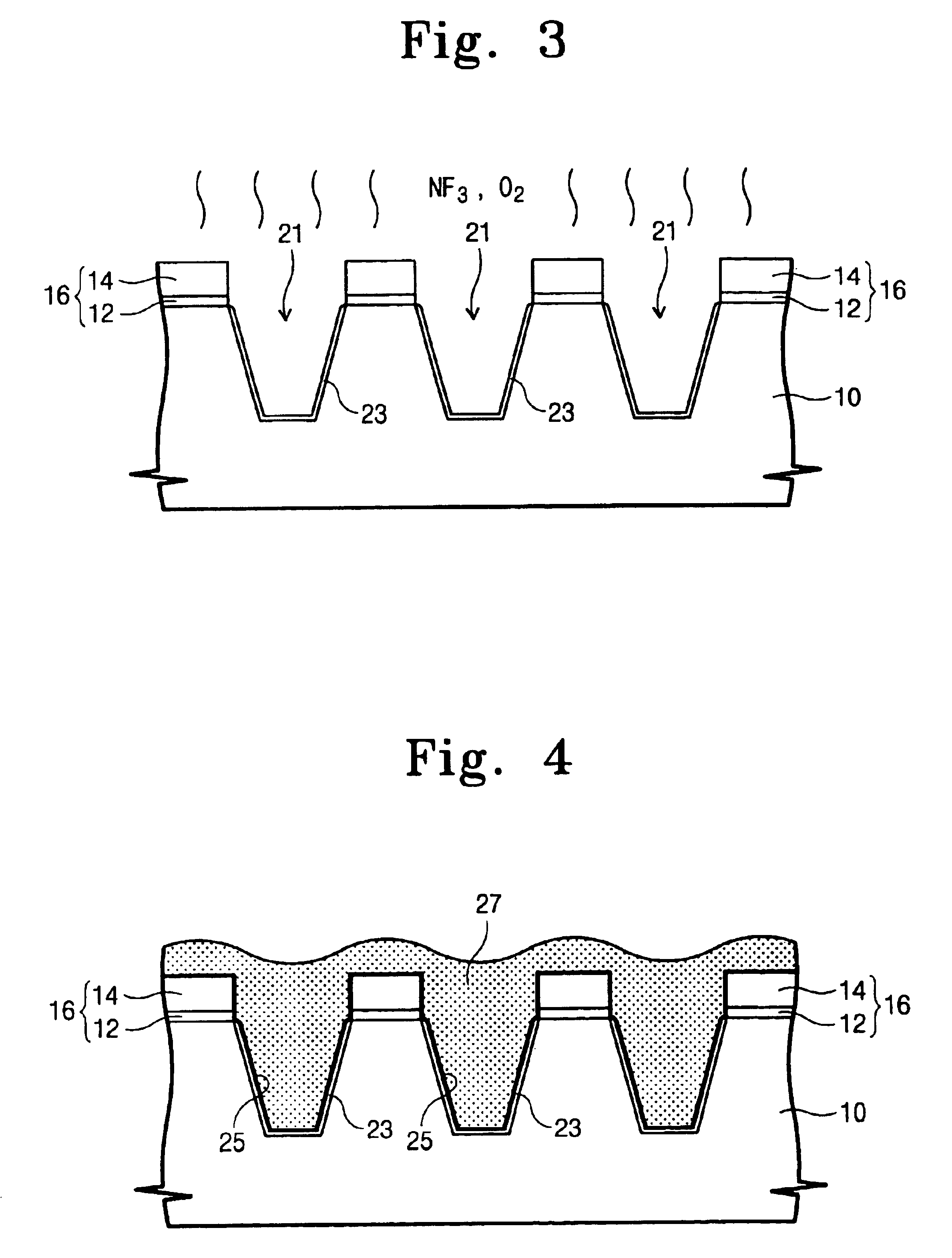

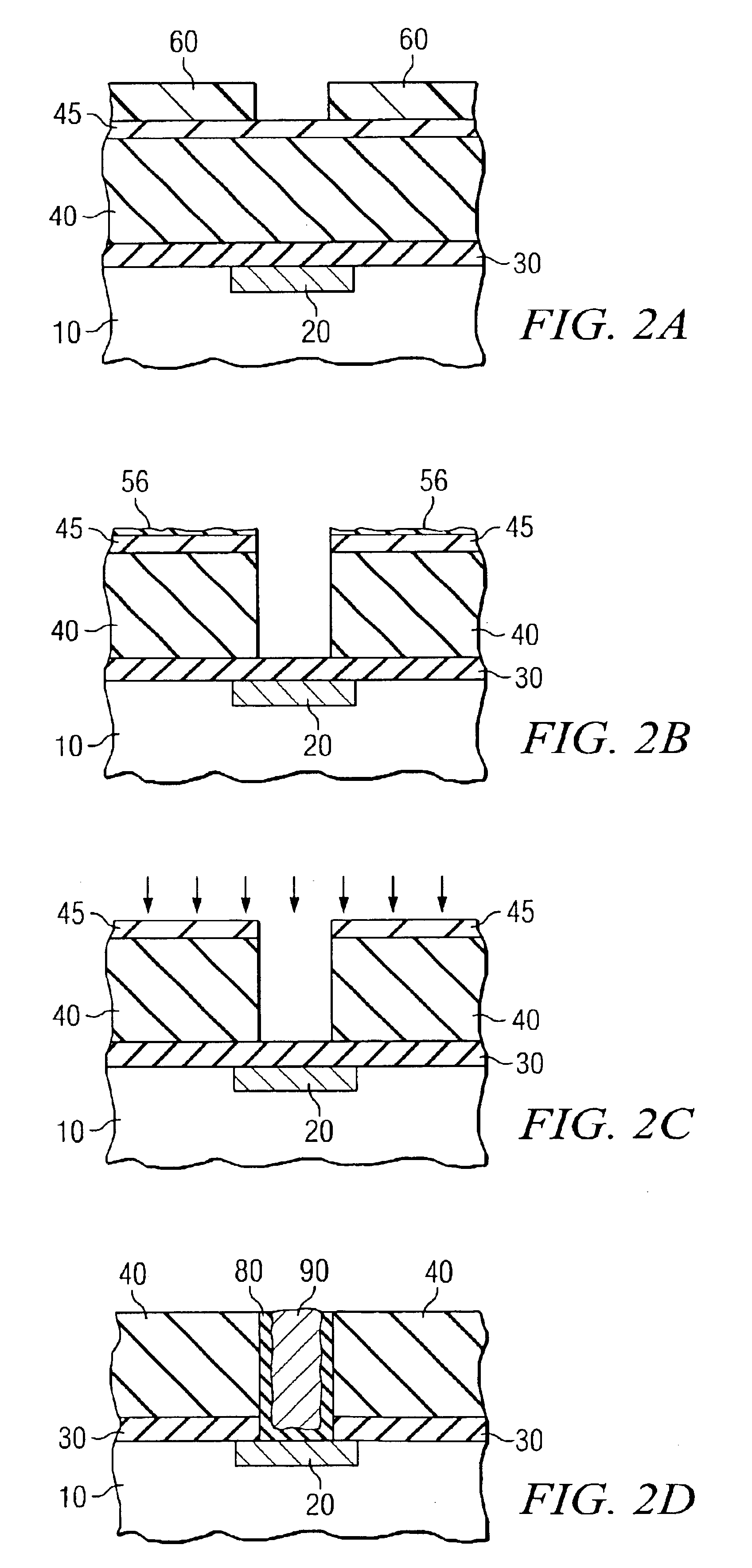

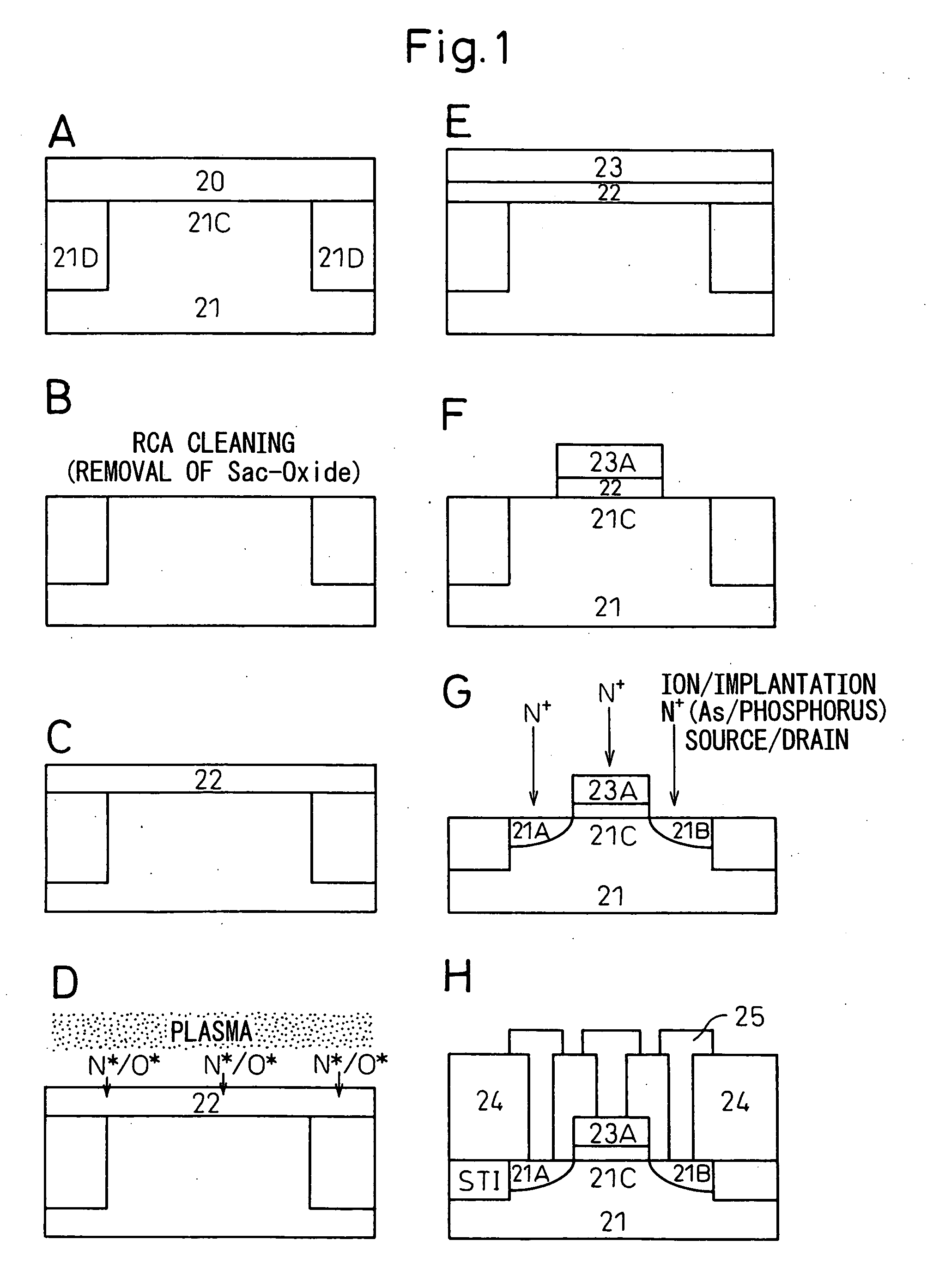

Method and device for forming an STI type isolation in a semiconductor device

InactiveUS6849520B2Improve device characteristicsReduce charge leakageSemiconductor/solid-state device manufacturingDevice materialIsolation layer

A trench isolation in a semiconductor device, and a method for fabricating the same, includes: forming a trench having inner sidewalls for device isolation in a silicon substrate; forming an oxide layer on a surface of the silicon substrate that forms the inner sidewalls of the trench; supplying healing elements to the silicon substrate to remove dangling bonds; and filling the trench with a device isolation layer, thereby forming the trench isolation without dangling bonds causing electrical charge traps.

Owner:SAMSUNG ELECTRONICS CO LTD

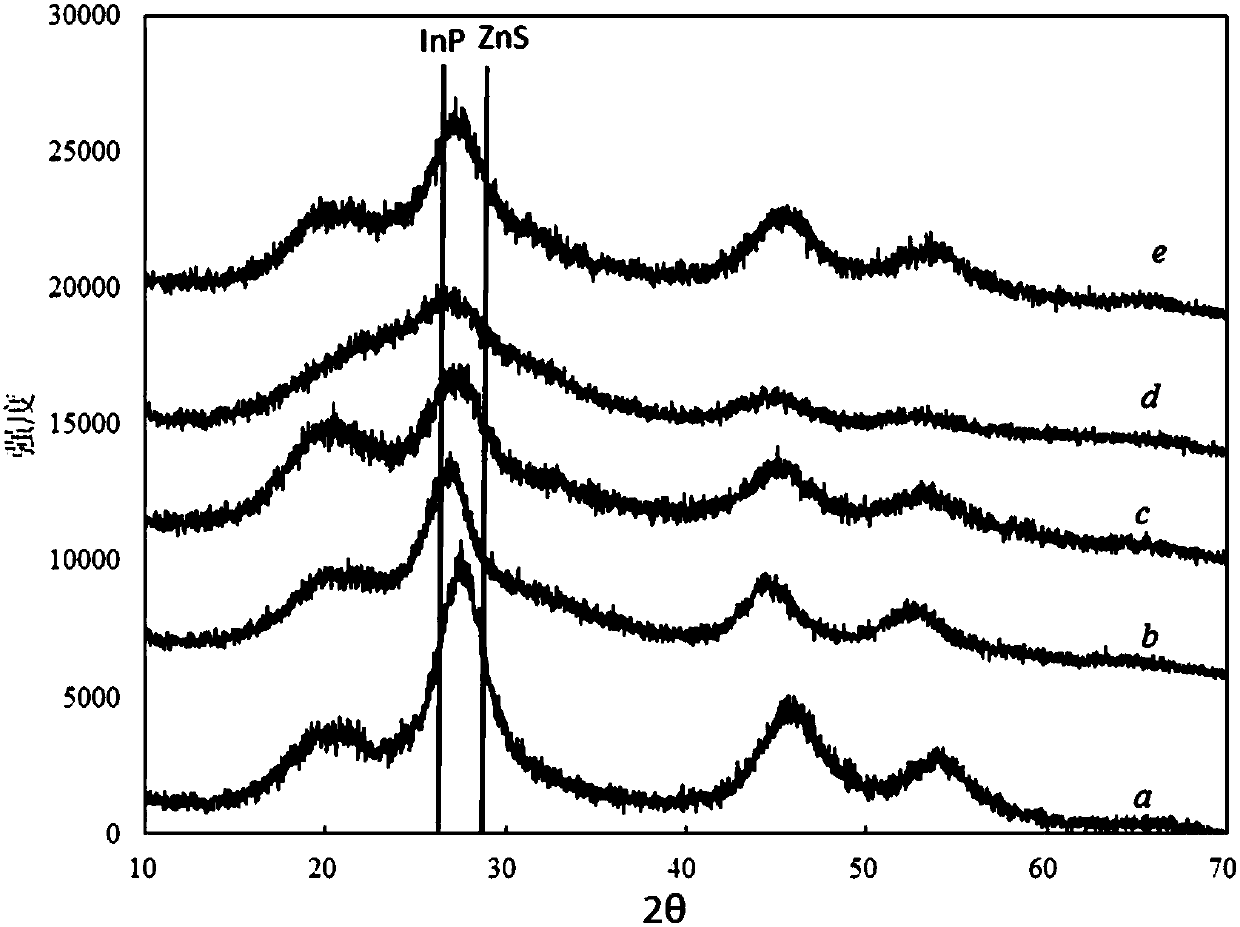

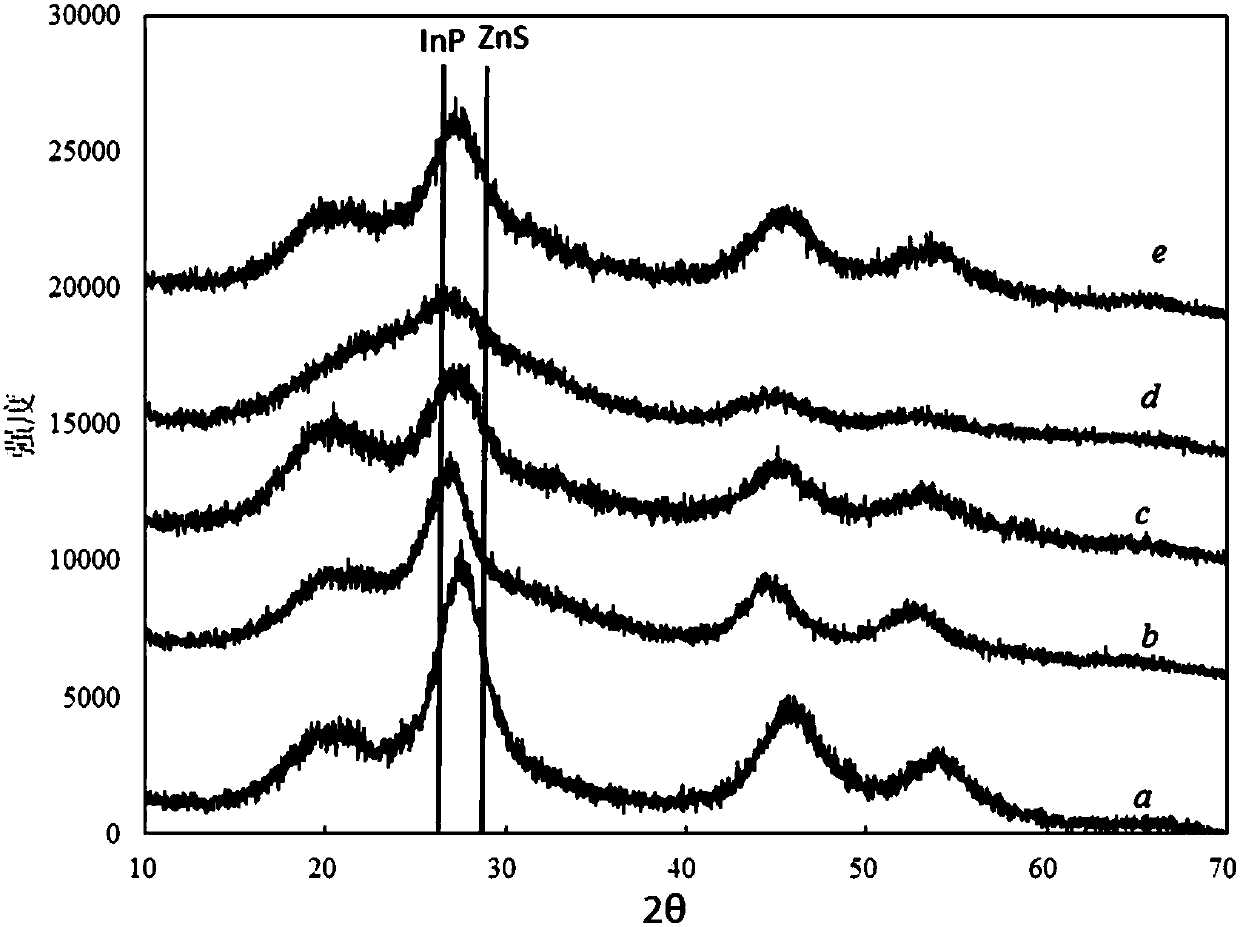

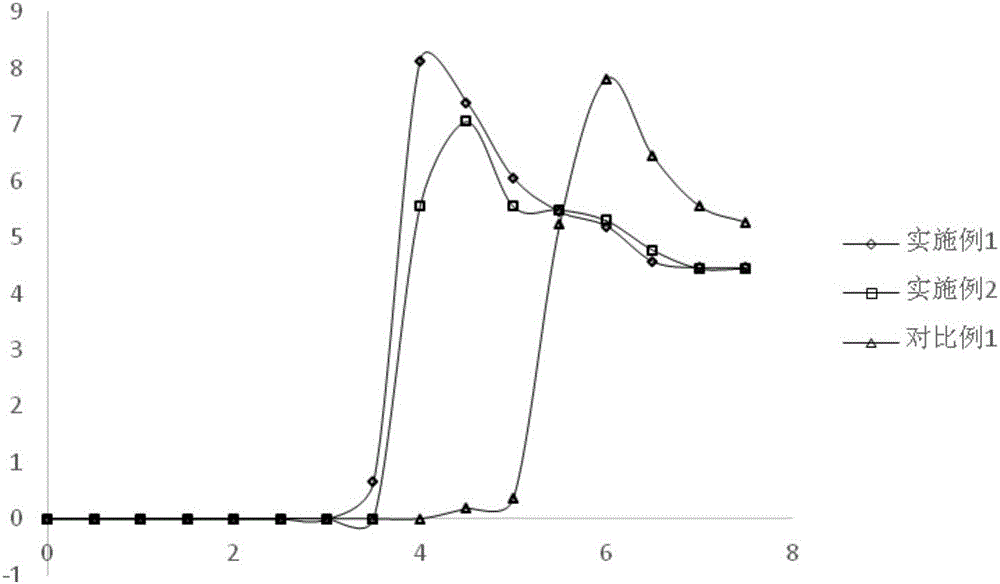

InP quantum dot and preparation method therefor

ActiveCN106701059AReduce lossHigh fluorescence quantum yieldMaterial nanotechnologyNanoopticsQuantum yieldQuantum efficiency

The invention provides an InP quantum dot and a preparation method therefor. The InP quantum dot comprises an InP core modified with a metal salt and a shell wrapping the core, wherein the shell is ZnSe / ZnS or ZnSexS(1-x), x is greater than 0 and is not greater than 1, the half-peak breadth of the InP quantum dot is less than or equal to 50nm, and the quantum efficiency is more than or equal to 70%. Due to the modification of the metal salt, dangling bonds on the surface of InP are eliminated, the loss of energy in form of non-optical properties can be reduced, and the fluorescent quantum yield of quantum dots with metal salt modified InP is increased; in addition, the difference of lattice constants of InP and ZnSe is relatively small, so that the shell with S and Se can relatively easily coat the surface of the InP core, and then, the InP quantum dot provided by the invention has relatively high quantum efficiency and stability; and meanwhile, the half-peak breadth of the InP quantum dot is less than or equal to 50nm, so that the particle size of the quantum dots is relatively uniform.

Owner:NANJING TECH CORP LTD

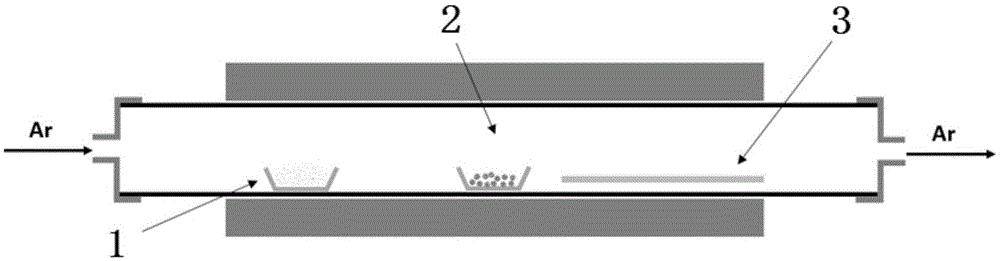

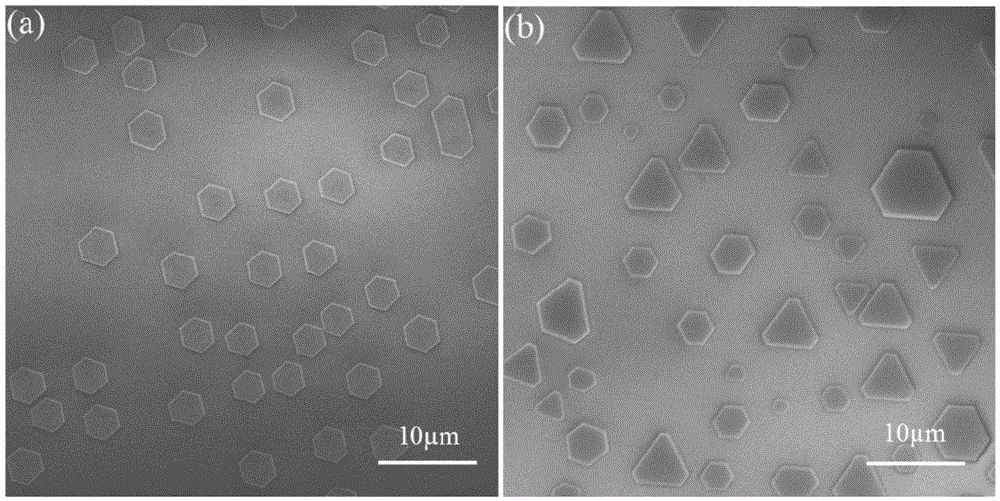

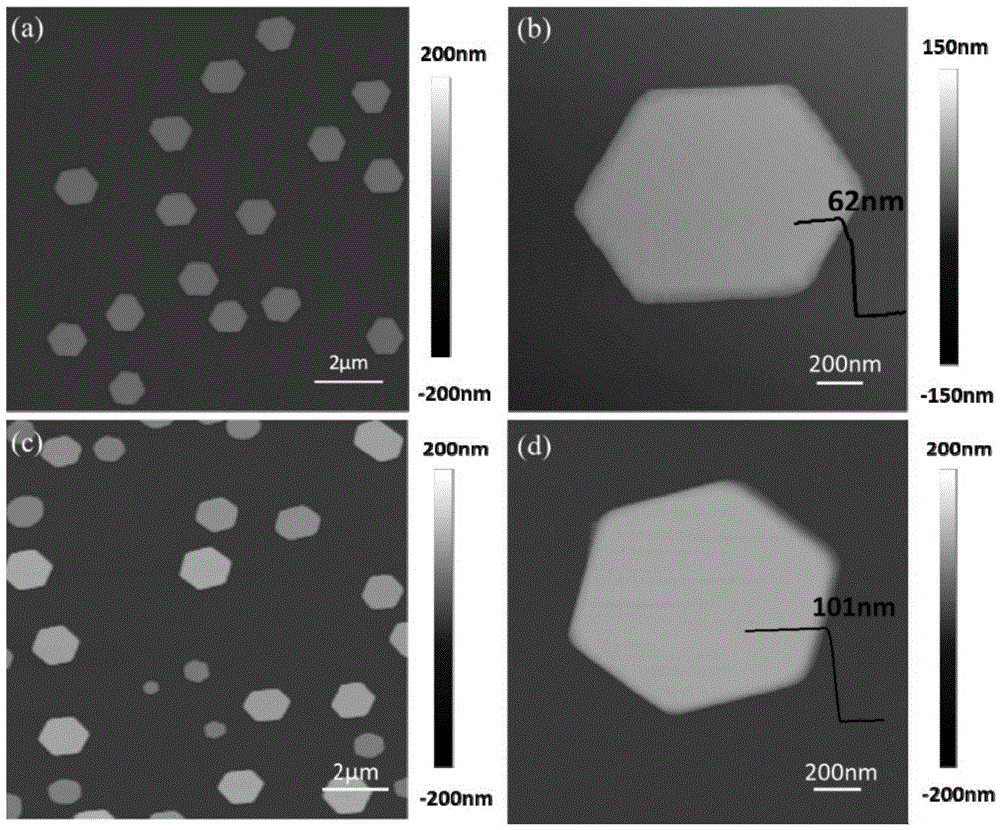

Preparation method of cadmium selenide or cadmium sulfide two-dimensional monocrystal nanosheet

ActiveCN105463580AIncrease the areaHigh crystallinityPolycrystalline material growthFrom chemically reactive gasesSource materialSingle crystal

The invention discloses a preparation method of a cadmium selenide or cadmium sulfide two-dimensional monocrystal nanosheet. The method comprises the steps that the CdSe or CdS two-dimensional monocrystal nanosheet is prepared through a van der Waals epitaxial growth technology, the method is characterized in that a mica sheet which is smooth in surface and free of chemical dangling bond is adopted to serve as a substrate, CdCl2 powder or Se powder or S powder serves as a source material, argon serves as carrier gas, CdCl2 stream is reacted with Se or S steam to form CdSe or CdS steam at high temperature, and the steam is deposited on the mica sheet for nucleation and epitaxially grows into the CdSe or CdS two-dimensional monocrystal nanosheet. The preparation method of the cadmium selenide or cadmium sulfide two-dimensional monocrystal nanosheet is easy to operate, low in cost and strong in controllability, the obtained CdSe or CdS has the advantages of being good in size uniformity, high in degree of crystallinity and the like, and important research value and wide application prospect in the fields of solar cells, field effect transistors, photoelectric detectors, photocatalyses and the like are achieved.

Owner:TECHNICAL INST OF PHYSICS & CHEMISTRY - CHINESE ACAD OF SCI

Chemical treatment of low-k dielectric films

InactiveUS6838300B2Semiconductor/solid-state device detailsSolid-state devicesChemical treatmentNitrogen

Owner:TEXAS INSTR INC

Method of modifying insulating film

ActiveUS20060199398A1Increased modificationShorten treatment timeTransistorSemiconductor/solid-state device manufacturingDangling bondMaterials science

An insulting film is modified by subjecting the insulting film to a modification treatment comprising a combination of a plasma treatment and a thermal annealing treatment. There is provided a method of enhancing the characteristic of an insulating film by improving deterioration in the characteristic of the insulating film due to carbon, a suboxide, a dangling bond or the like contained in the insulating film.

Owner:TOKYO ELECTRON LTD

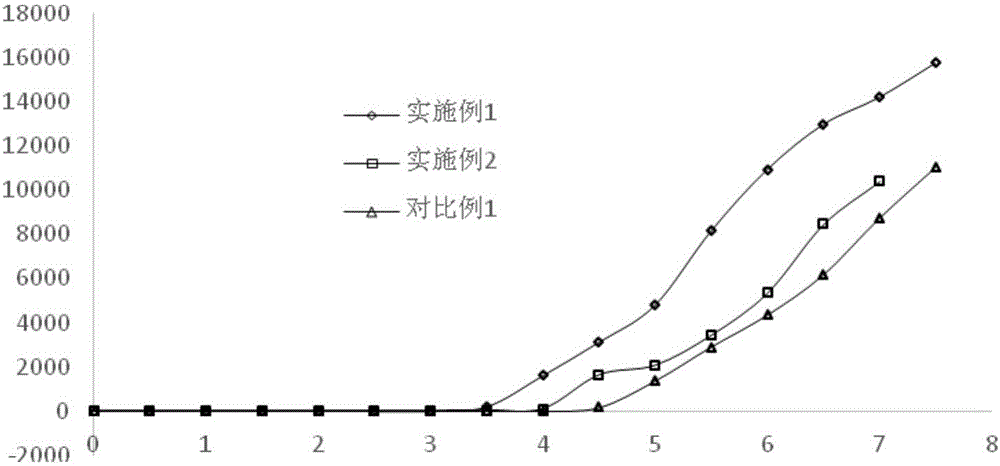

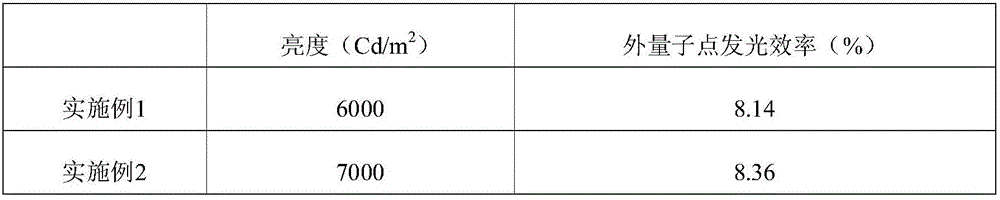

Zinc oxide nanocrystal, preparation method thereof, zinc oxide nanocrystal ink and electro-luminescence device

ActiveCN106634948AReduced electron mobilityIncrease distanceSolid-state devicesSemiconductor/solid-state device manufacturingSulfurQuantum dot

The invention provides a zinc oxide nanocrystal, a preparation method thereof, a zinc oxide nanocrystal ink and an electro-luminescence device. The zinc oxide nanocrystal comprises surface ligands, which are S-P-R1, R2, R3, wherein R1, R2 and R3 are separately independently selected from any of alkyls of C1-10. The surface ligands of the zinc oxide nanocrystal together with the zinc oxide nanocrystal can form a layer of coating ZnS, which can not only weaken defect luminescence mainly led to by dangling bonds of Zn on the surface of the zinc oxide nanocrystal, but also conveniently adjust the surface ligands of the zinc oxide nanocrystal by adjusting the variety of sulfur precursors to further adjust the electronic mobility of ZnO. The electrical property of zinc oxide nanocrystal film formed by the zinc oxide nanocrystal is improved, and further the problem of defect luminescence of quantum dot light emitting diodes can be solved.

Owner:NANJING TECH CORP LTD

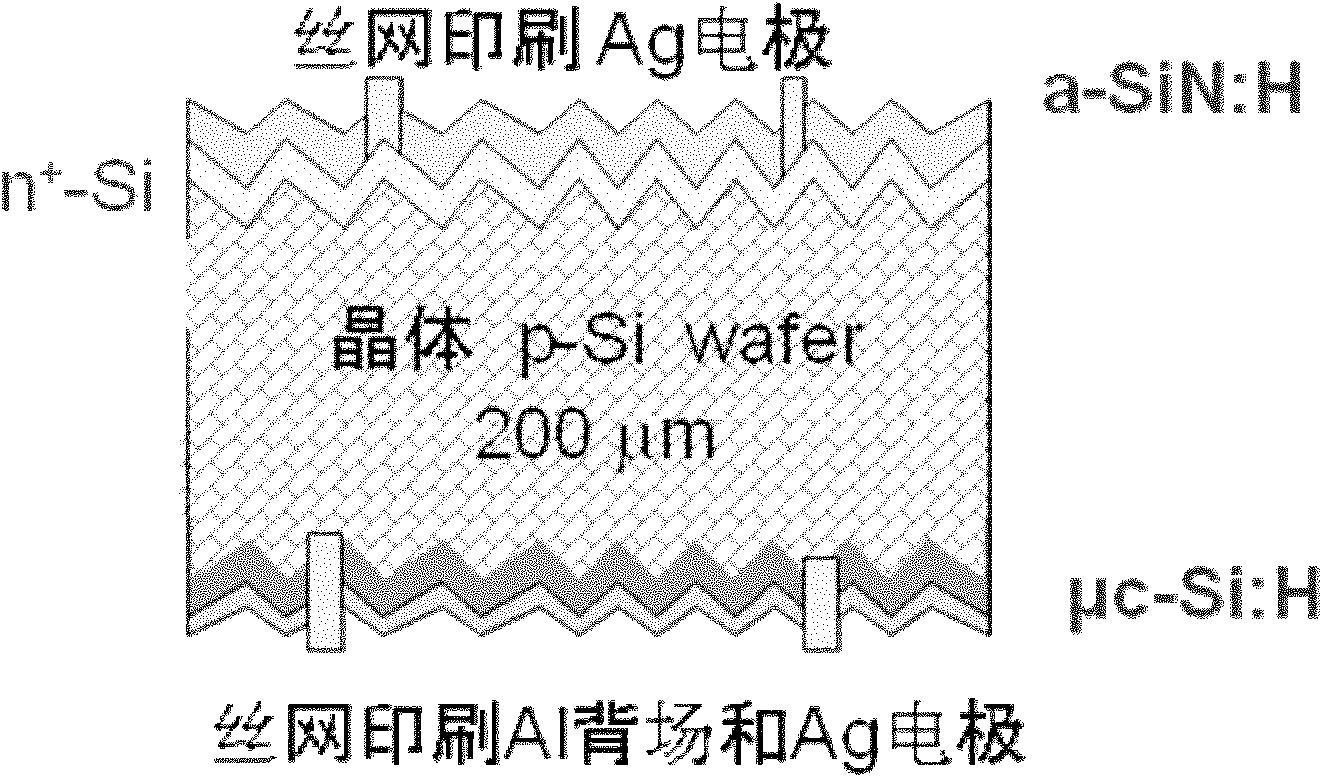

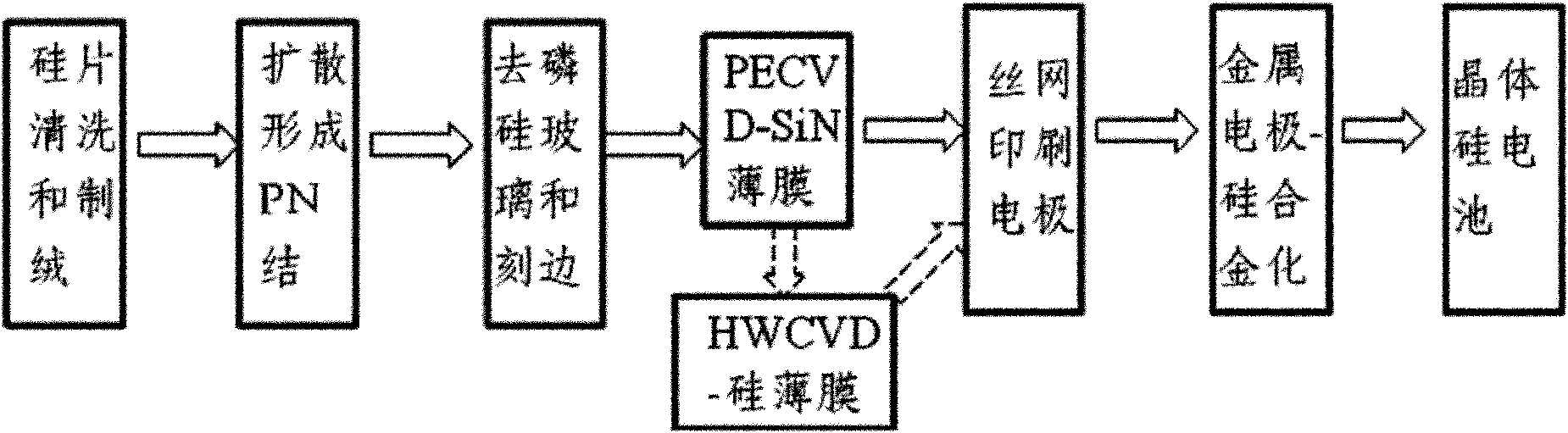

Preparation method of double-sided passivated crystalline silicon solar cell

InactiveCN101937944APrevent escapeAdjustable bandgapSemiconductor devicesP type siliconMicrocrystalline silicon

The invention discloses a preparation method of a double-sided passivated crystalline silicon solar cell, belonging to the technical field of photovoltaic power generation. The preparation method comprises the following steps of: firstly, respectively carrying out surface precleaning and surface texturing on P-shaped single crystal silicon and a polycrystalline silicon wafer by adopting an alkaline solution and an acid solution; secondly, diffusing by using phosphorus oxychloride as a diffusion source to form a PN junction; thirdly, removing a phosphosilicate glass on the surface of the silicon wafer by adopting a chemical wet method, and etching the edge of the silicon wafer by adopting a plasma; fourthly, preparing a silicon nitride film on the surface of an emitting region of a P-type silicon wafer by adopting a plasma enhanced chemical vapor deposition method; fifthly, preparing a mixed phase film material of hydrogenated microcrystalline silicon and amorphous silicon by adopting a hot filament chemical vapor deposition method, depositing a film at one side of the P-type silicon wafer, and passivating the defects and a dangling bond on the surface of the P-type silicon wafer; and sixthly, sintering a screen printing back electrode and a screen printing positive electrode to form the solar cell. The invention lowers the probability of compounding photo-generated minority carriers on the back surface, enhances the long-wave light quantum efficiency and creates the conditions of transportation and collection of the photo-generated carriers.

Owner:SHANGHAI JIAO TONG UNIV

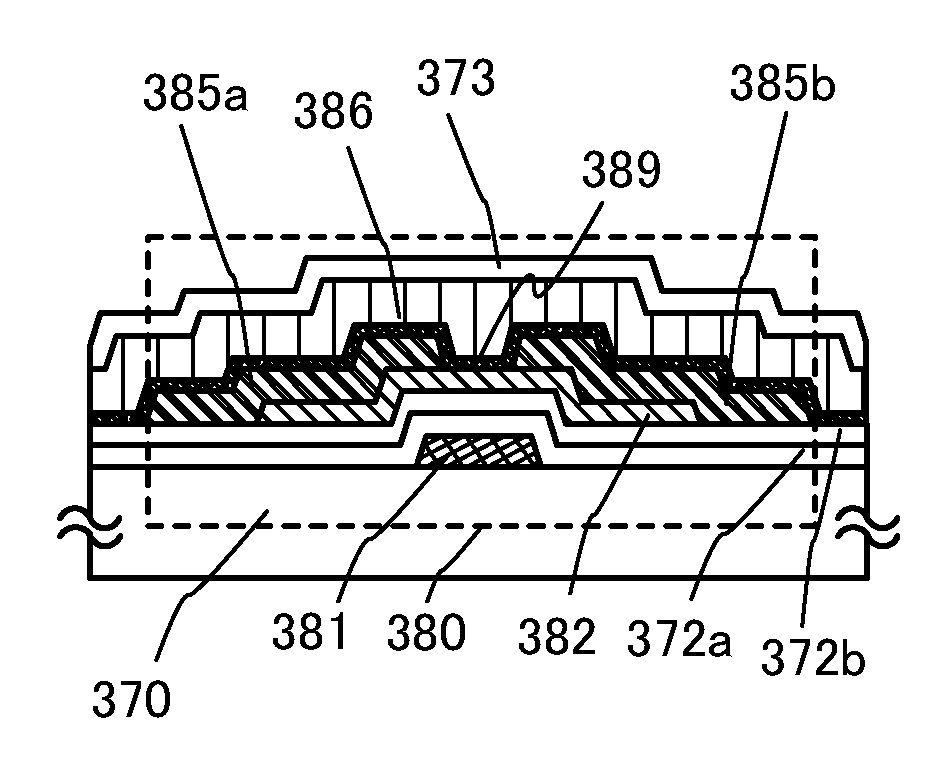

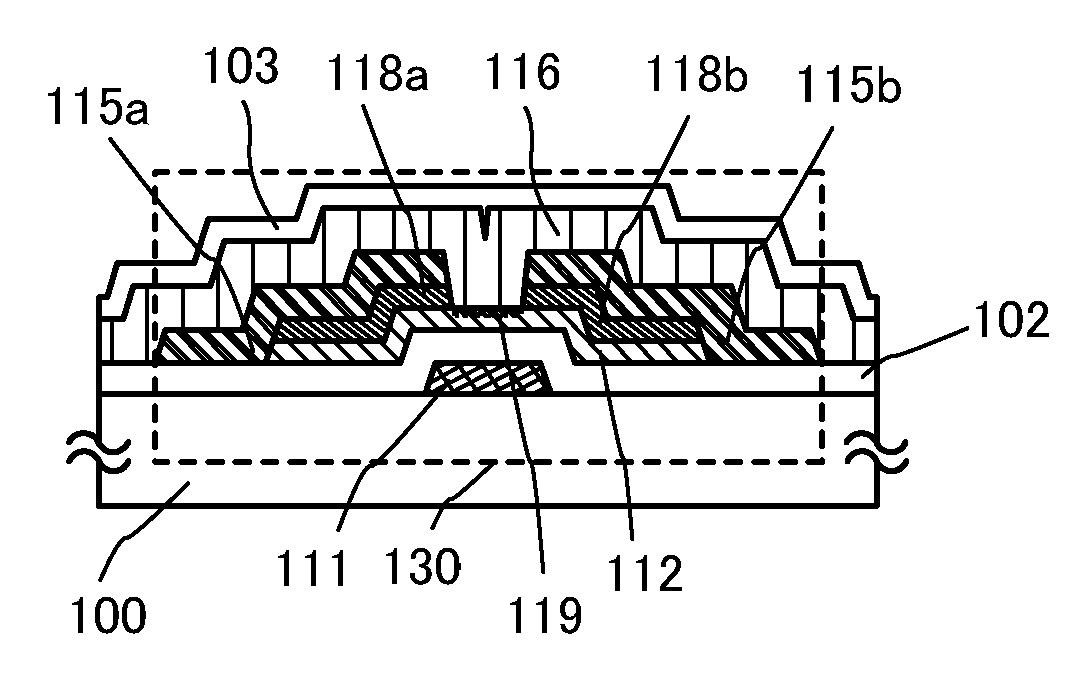

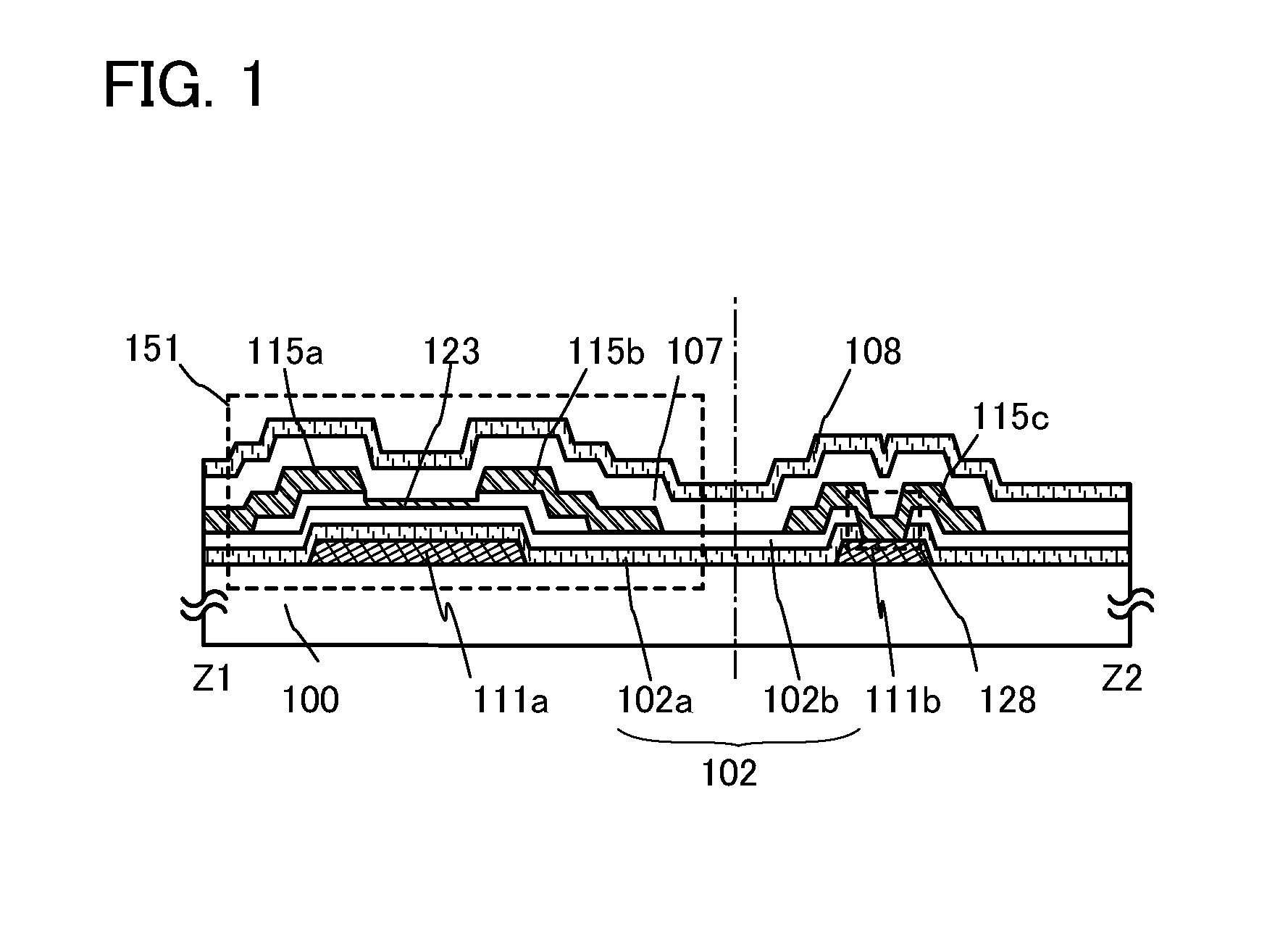

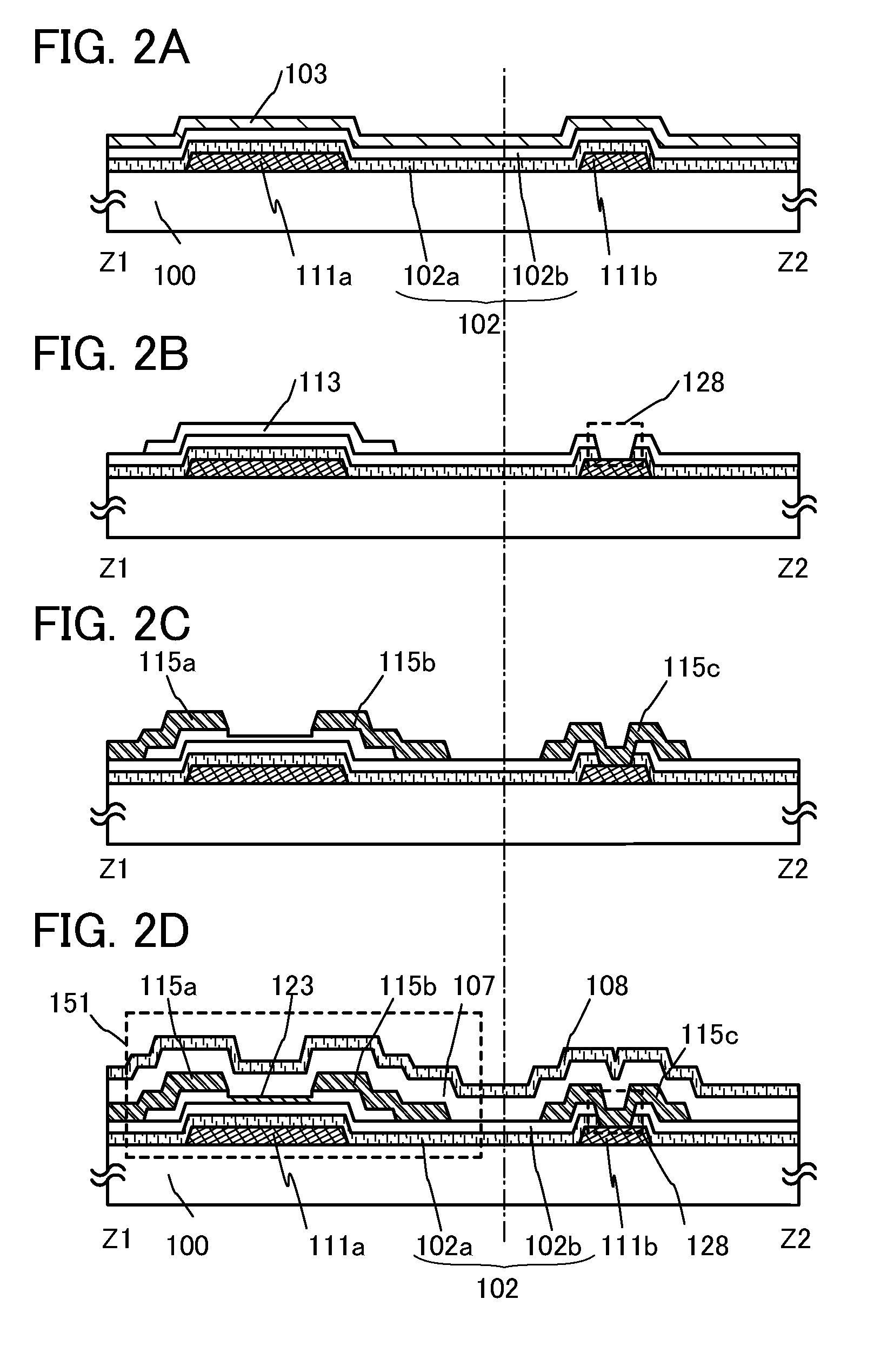

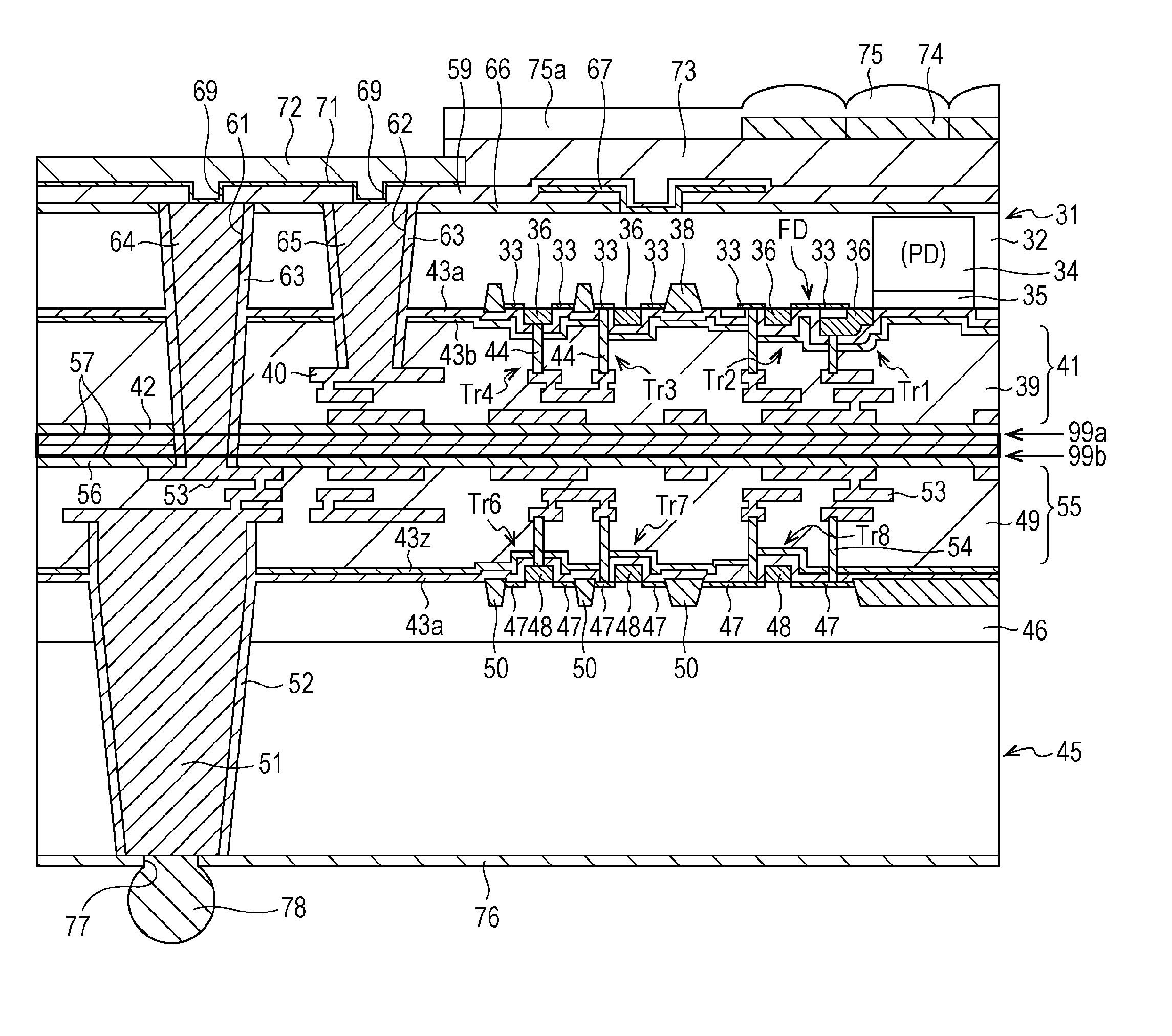

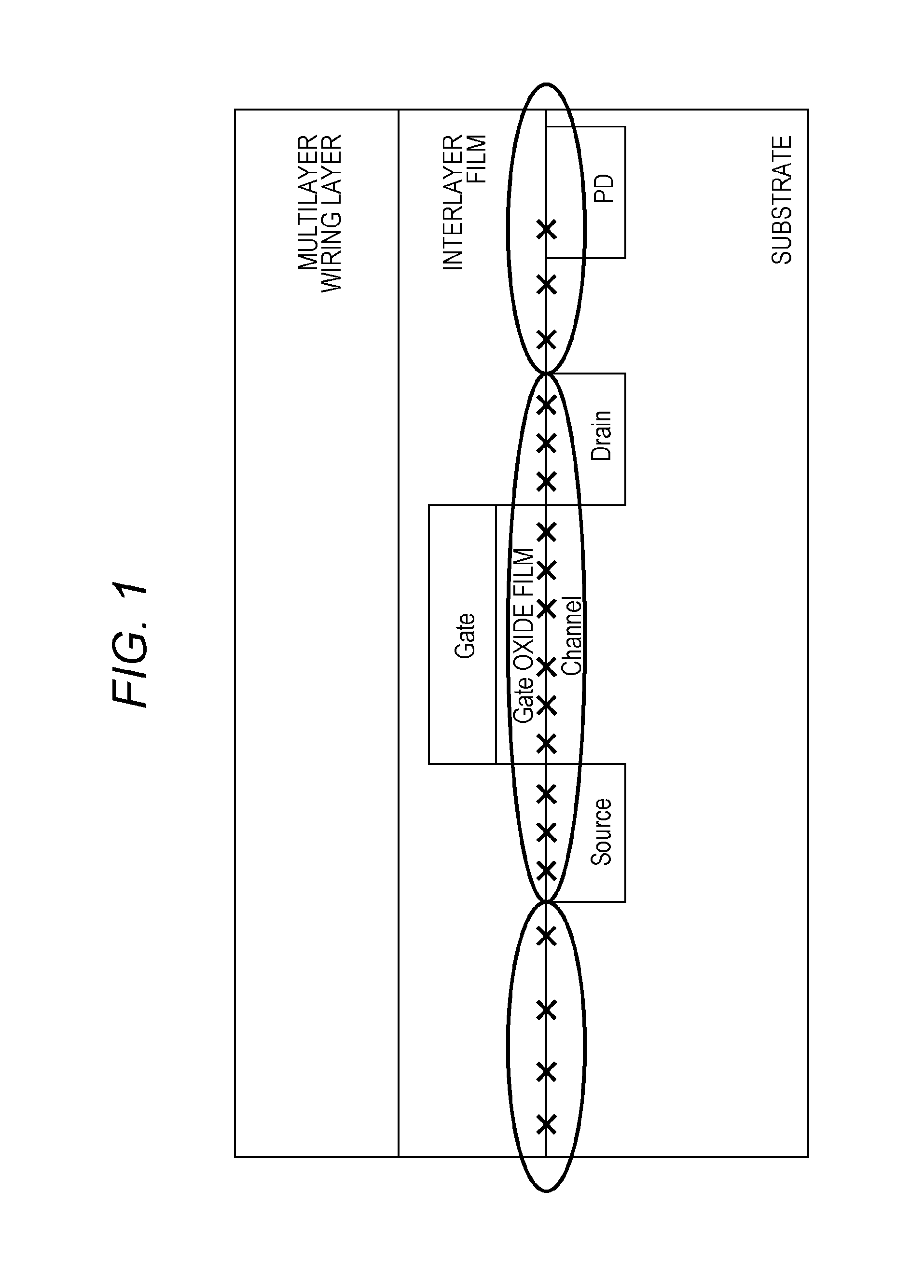

Semiconductor device and electronic appliance

ActiveUS20150221694A1Easy maintenanceSignal output characteristic is improvedSolid-state devicesRadiation controlled devicesDevice formDangling bond

The present technique relates to a semiconductor device and an electronic appliance in which the reliability of the fine transistor can be maintained while the signal output characteristic is improved in a device formed by stacking semiconductor substrates.The semiconductor device includes a first semiconductor substrate, a second semiconductor substrate providing a function different from a function provided by the first semiconductor substrate, and a diffusion prevention film that prevents diffusion of a dangling bond terminating atom used for reducing the interface state of the first semiconductor substrate and the second semiconductor substrate, wherein at least two semiconductor substrates are stacked and the semiconductor substrates are electrically connected to each other, and the first semiconductor substrate and the second semiconductor substrate are stacked with the diffusion prevention film inserted between an interface of the first semiconductor substrate and an interface of the second semiconductor substrate.

Owner:SONY CORP

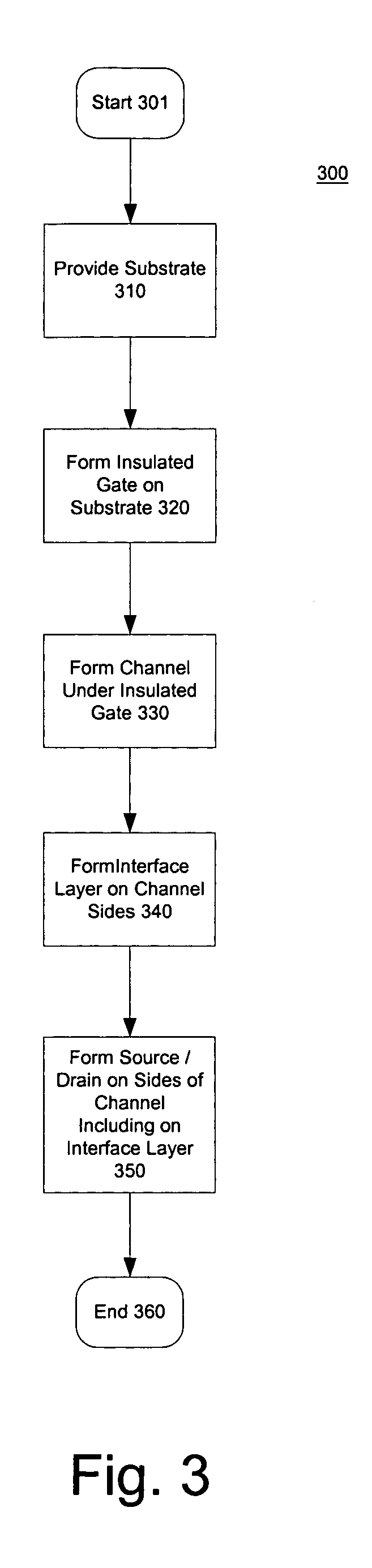

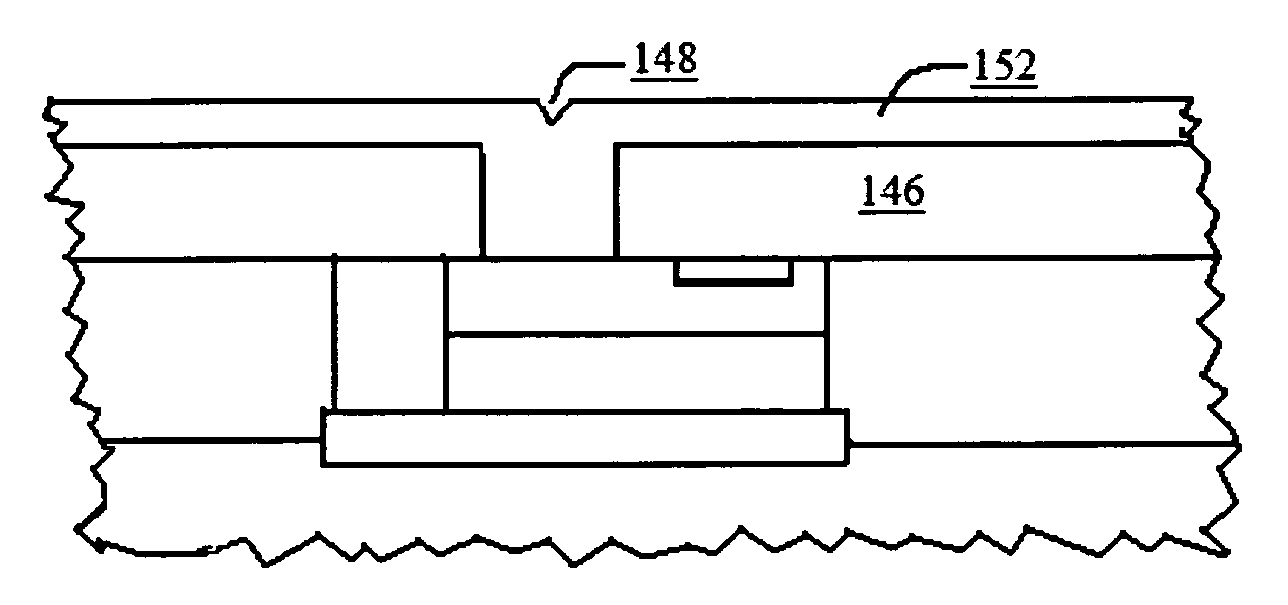

Insulated gate field effect transistor having passivated schottky barriers to the channel

InactiveUS20070026591A1Reduce impactTransistorSemiconductor/solid-state device detailsEngineeringField-effect transistor

A transistor includes a semiconductor channel disposed nearby a gate and in an electrical path between a source and a drain, wherein the channel and at least one of the source or the drain are separated by an interface layer so as to form a channel-interface layer-source / drain junction in which a Fermi level of the semiconductor channel is depinned in a region near the junction and the junction has a specific contact resistance of less than approximately 1000 Ω-μm2. The interface layer may include a passivating material such as a nitride, a fluoride, an oxide, an oxynitride, a hydride and / or an arsenide of the semiconductor of the channel. In some cases, the interface layer consists essentially of a monolayer configured to depin the Fermi level of the semiconductor of the channel, or an amount of passivation material sufficient to terminate all or a sufficient number of dangling bonds of the semiconductor channel to achieve chemical stability of the surface. Also, the interface layer may include a separation layer of a material different than the passivating material. Where used, the separation layer has a thickness sufficient to reduce effects of metal-induced gap states in the semiconductor channel.

Owner:ACORN SEMI LLC

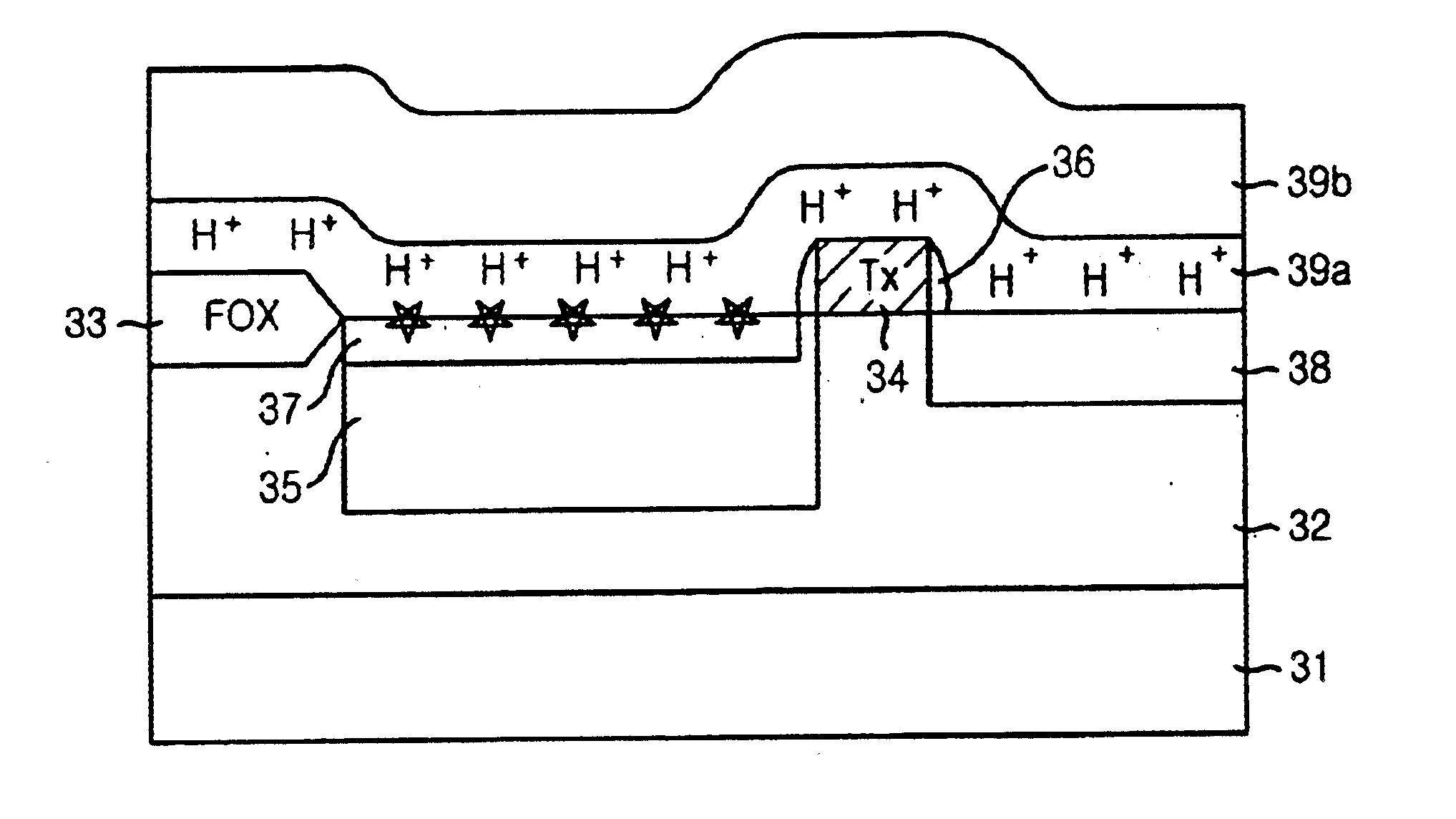

Method of manufacturing image sensor for reducing dark current

InactiveUS6835590B2Preventing Image Quality DeteriorationSolid-state devicesSemiconductor/solid-state device manufacturingDangling bondEngineering

The disclosed method provides a method capable of removing dangling bonds generated on a surface of photodiode. The method includes steps of: forming a photodiode in a semiconductor substrate; forming a transfer transistor, a reset transistor, a drive transistor and a select transistor on the semiconductor substrate; forming a first interlayer insulating layer on the semiconductor substrate, wherein the first interlayer insulating layer contains hydrogen ions; forming a second interlayer insulating layer on the first interlayer insulating layer; and flattening the second interlayer insulating layer by flowing and simultaneously diffusing the hydrogen ions into a surface of the photodiode.

Owner:INTELLECTUAL VENTURES II

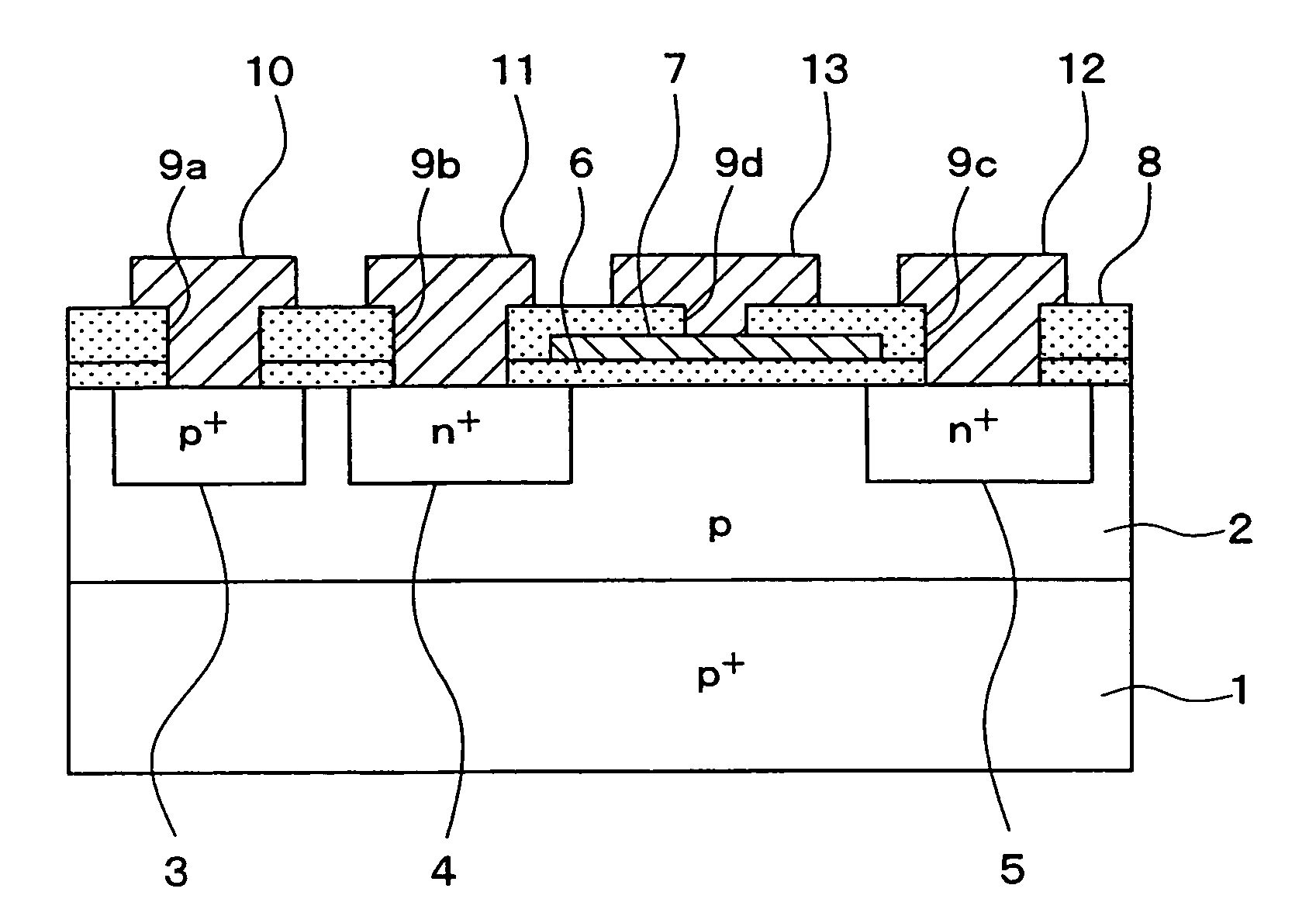

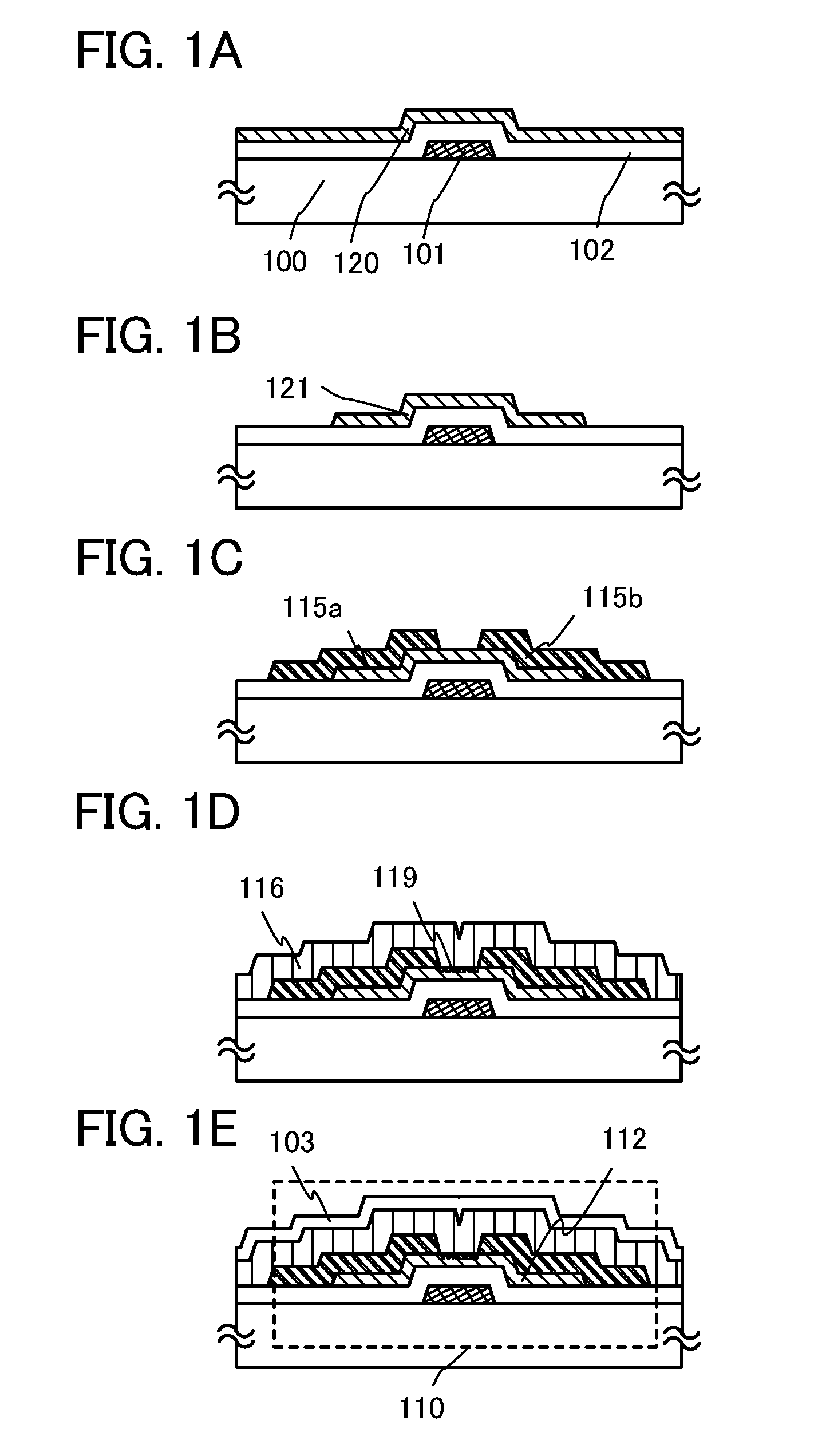

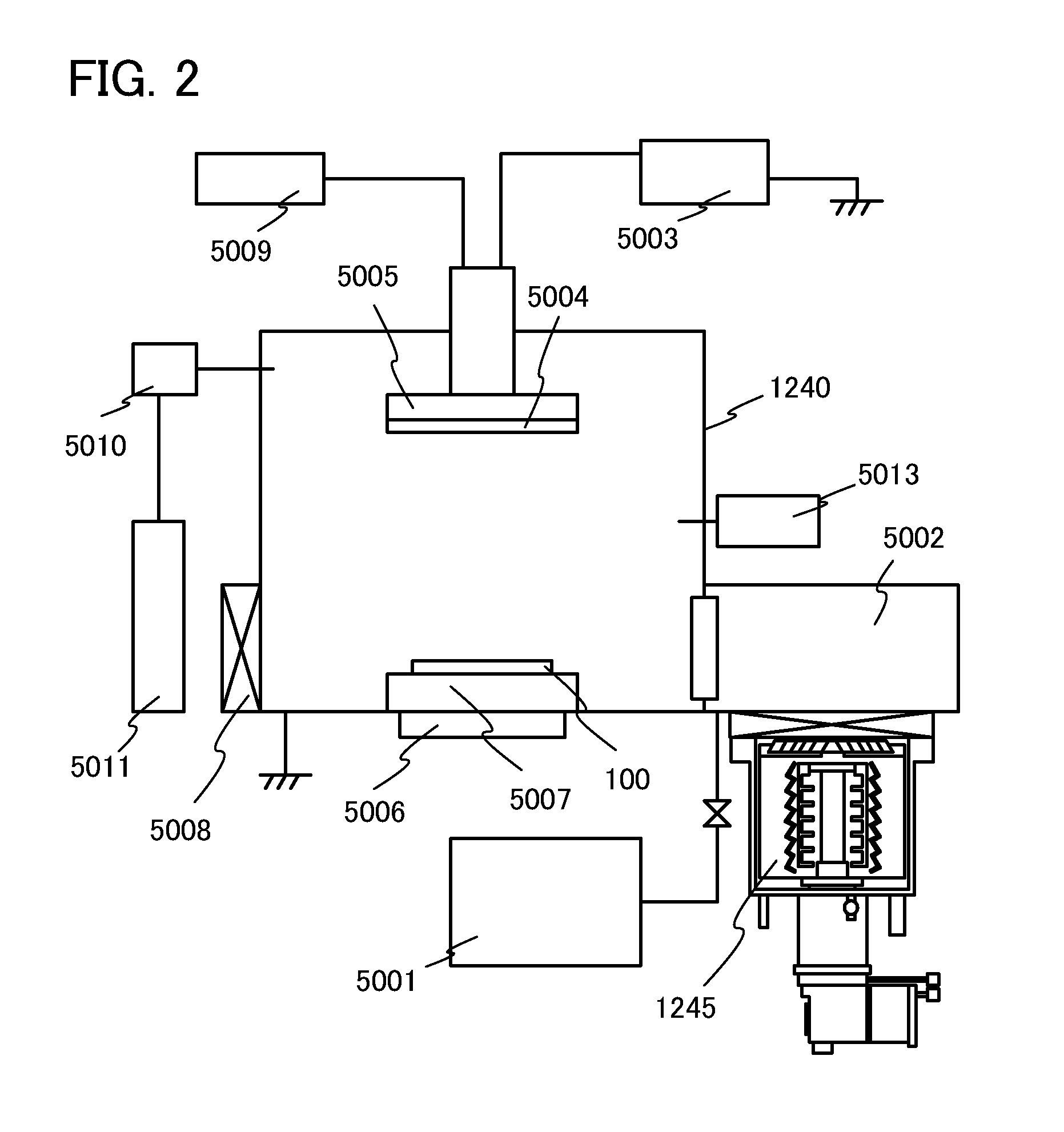

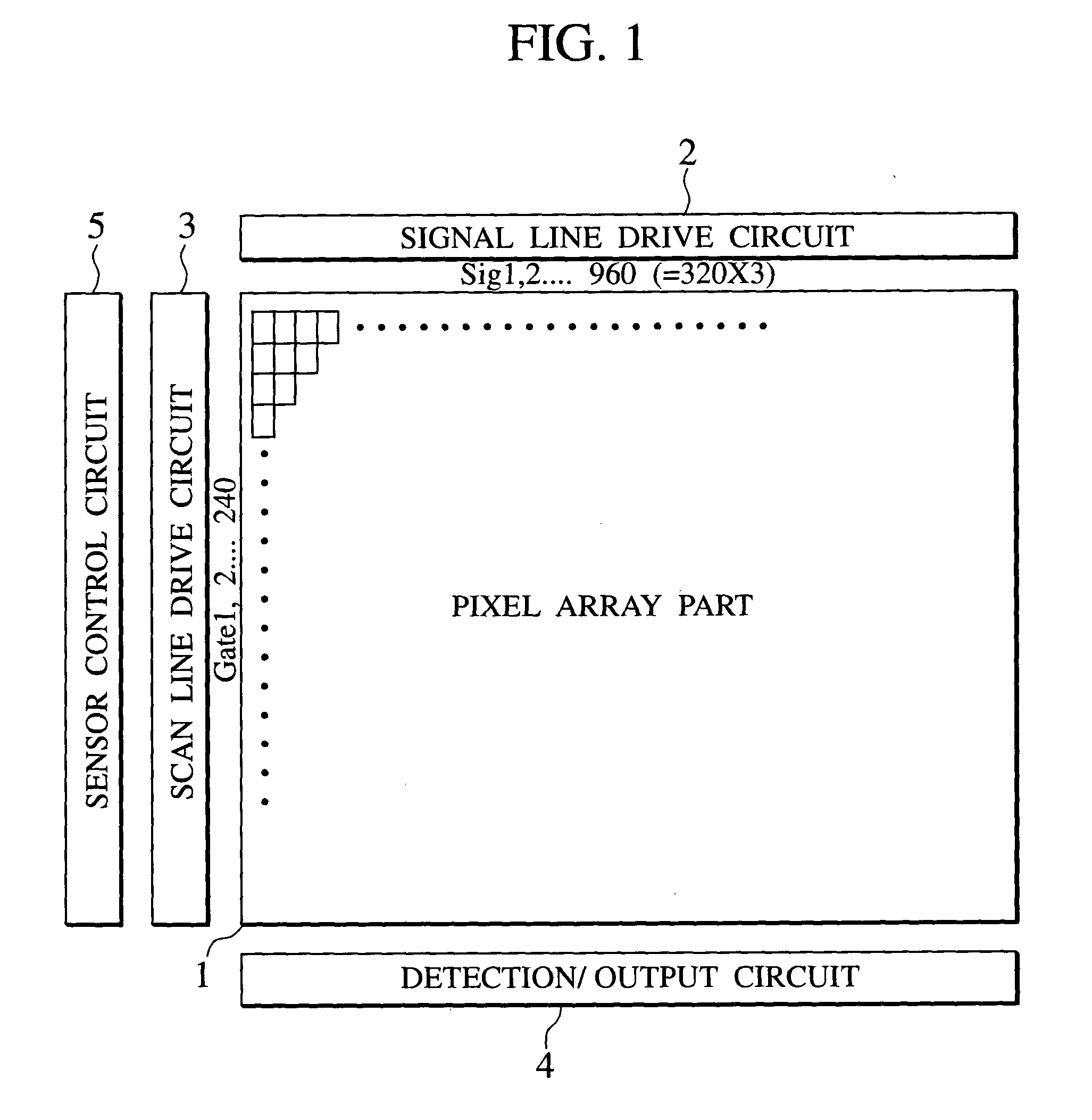

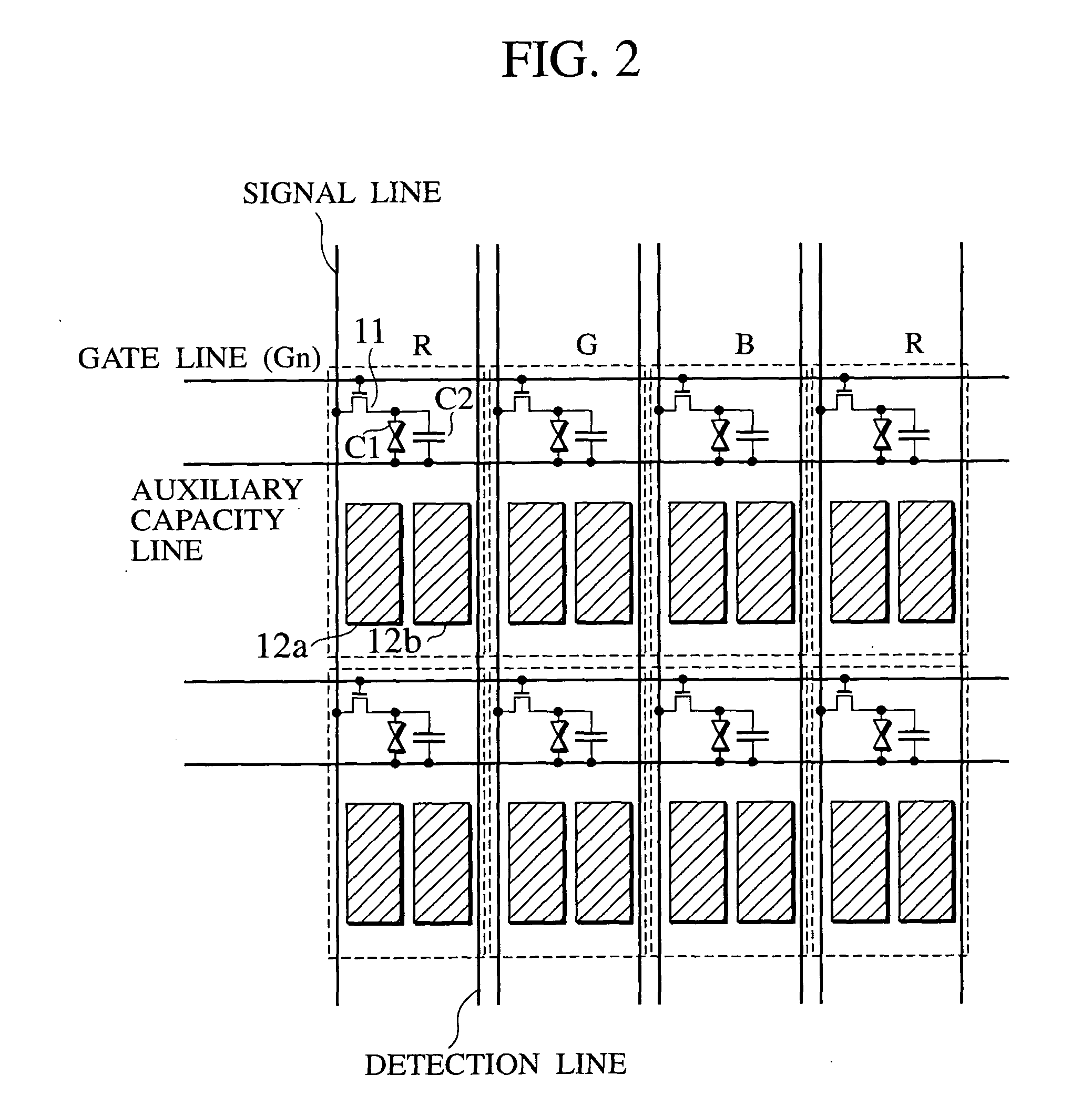

Suppression of leakage current in image acquisition

ActiveUS20040043676A1Current can be suppressedHigh sensitivityTransistorElectrically conductive connectionsDisplay deviceDangling bond

In a manufacturing process of a display device, hydrogenation in an I layer of photodiodes D1 and D2 is progressed less than that in a channel portion of a pixel TFT, and a defect density due to dangling bonds not terminated in the I layer of the photodiodes D1 and D2 is made higher than a defect density in the channel portion of the pixel TFT. Thus, while suppressing a leakage current of the pixel TFT, the sensitivity of the photodiodes D1 and D2 to light is improved. Moreover, a gate electrode is provided above an i region of a pin-type optical sensor diode with an insulating film interposed therebetween. Thus, a gate voltage can control a threshold of a bias voltage when a current starts to flow into the optical sensor diode and a leakage current is prevented from flowing into the optical sensor diode.

Owner:JAPAN DISPLAY CENT INC

Electrical passivation of silicon-containing surfaces using organic layers

InactiveUS7491642B2Improve electrical performanceImprove electronic efficiencySemiconductor/solid-state device detailsSolid-state devicesSemiconductor materialsElectrical devices

Electrical structures and devices may be formed and include an organic passivating layer that is chemically bonded to a silicon-containing semiconductor material to improve the electrical properties of electrical devices. In different embodiments, the organic passivating layer may remain within finished devices to reduce dangling bonds, improve carrier lifetimes, decrease surface recombination velocities, increase electronic efficiencies, or the like. In other embodiments, the organic passivating layer may be used as a protective sacrificial layer and reduce contact resistance or reduce resistance of doped regions. The organic passivation layer may be formed without the need for high-temperature processing.

Owner:CALIFORNIA INST OF TECH

Photovoltaic device

ActiveUS7863518B2Improve output characteristicsFinal product manufacturePV power plantsHydrogen concentrationHydrogen atom

A photovoltaic device capable of improving output characteristics is provided. This photovoltaic device comprises a crystalline semiconductor member, a substantially intrinsic first amorphous semiconductor layer formed on the front surface of the crystalline semiconductor member and a first conductivity type second amorphous semiconductor layer formed on the front surface of the first amorphous semiconductor layer, and has a hydrogen concentration peak in the first amorphous semiconductor layer. Thus, the quantity of hydrogen atoms in the first amorphous semiconductor layer is so increased that the hydrogen atoms increased in quantity can be bonded to dangling bonds of silicon atoms forming defects in the first amorphous semiconductor layer for inactivating the dangling bonds.

Owner:SANYO ELECTRIC CO LTD

Popular searches

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com