Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

6604 results about "Trapping" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Animal trapping, or simply trapping, is the use of a device to remotely catch an animal. Animals may be trapped for a variety of purposes, including food, the fur trade, hunting, pest control, and wildlife management.

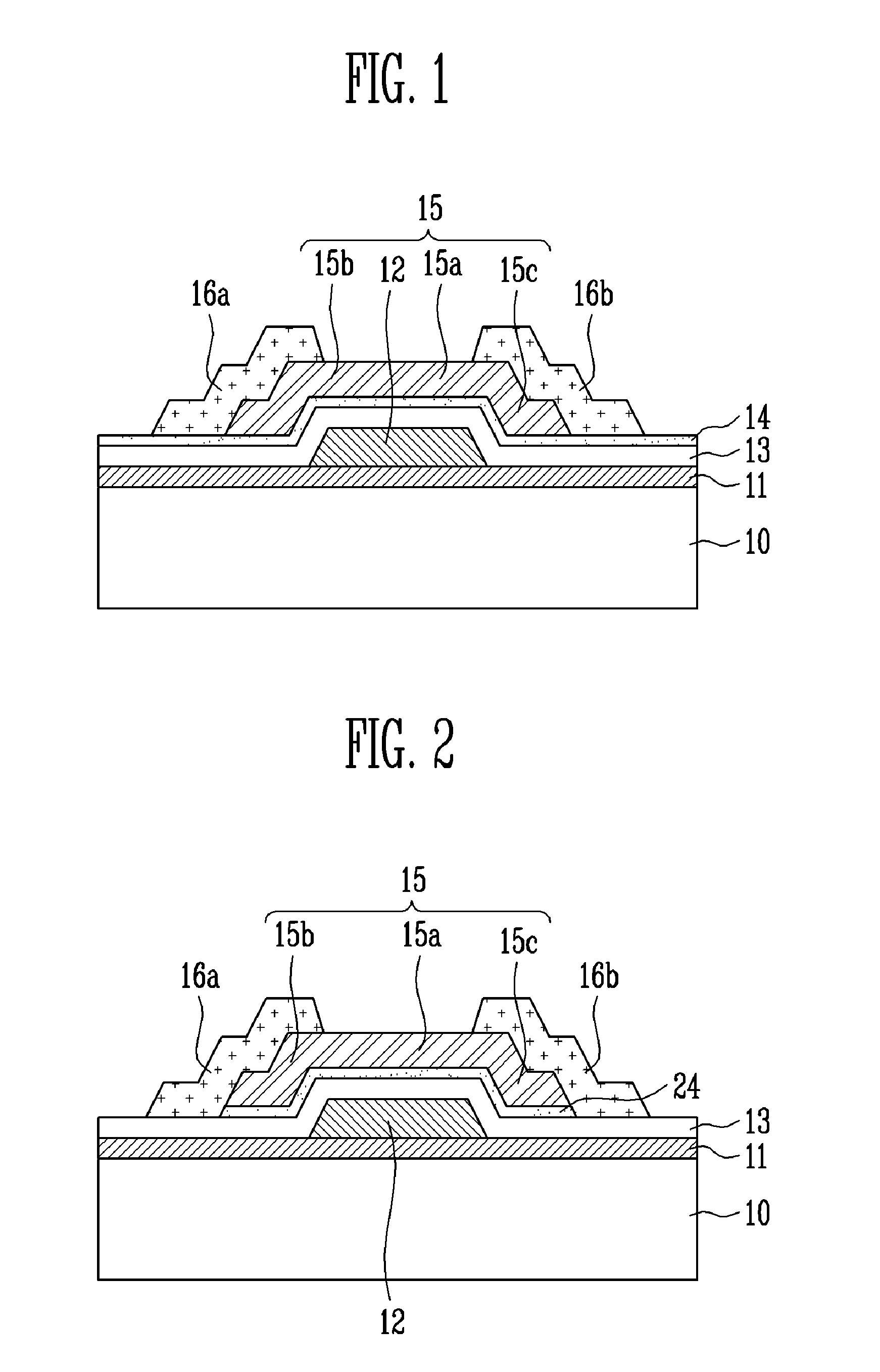

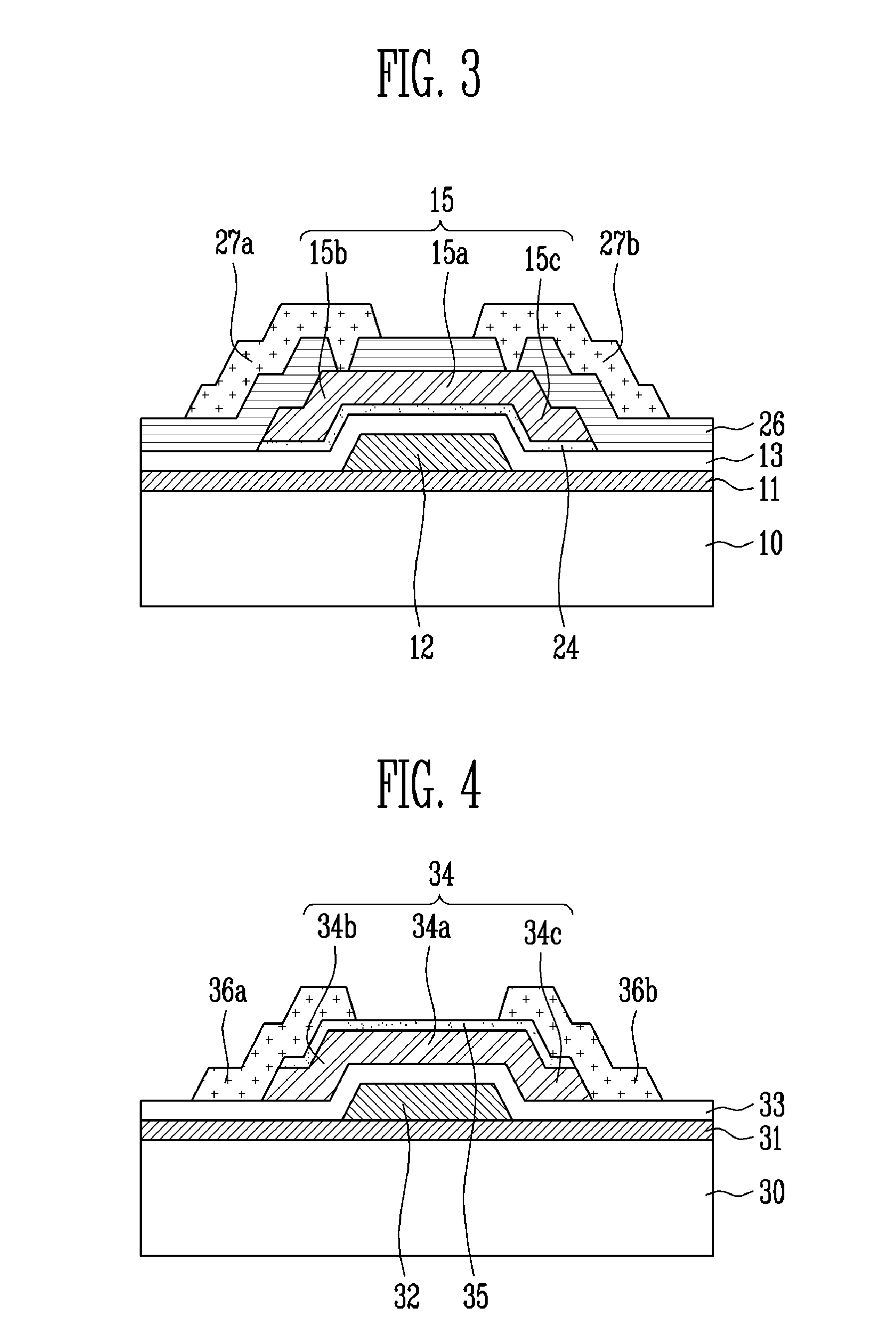

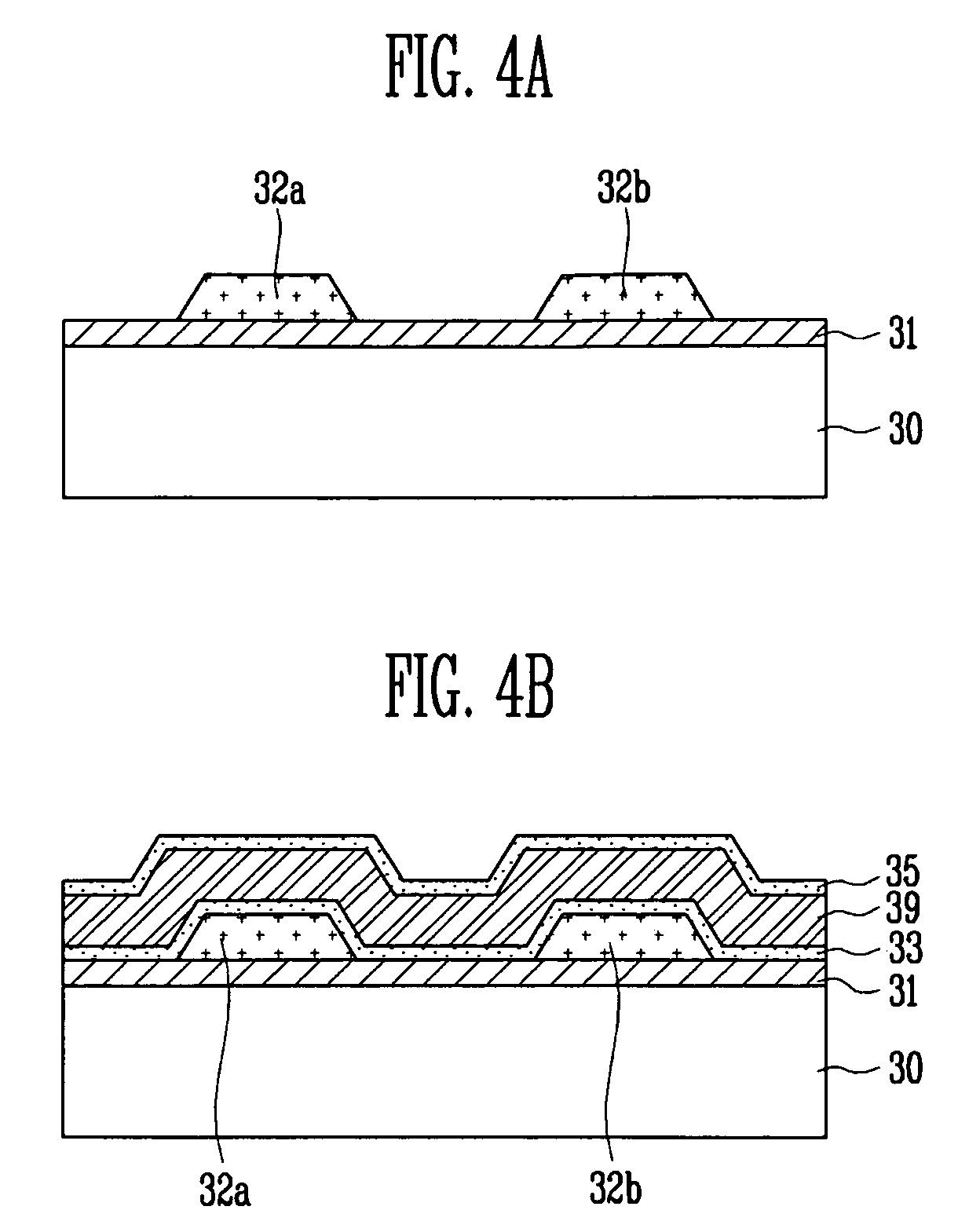

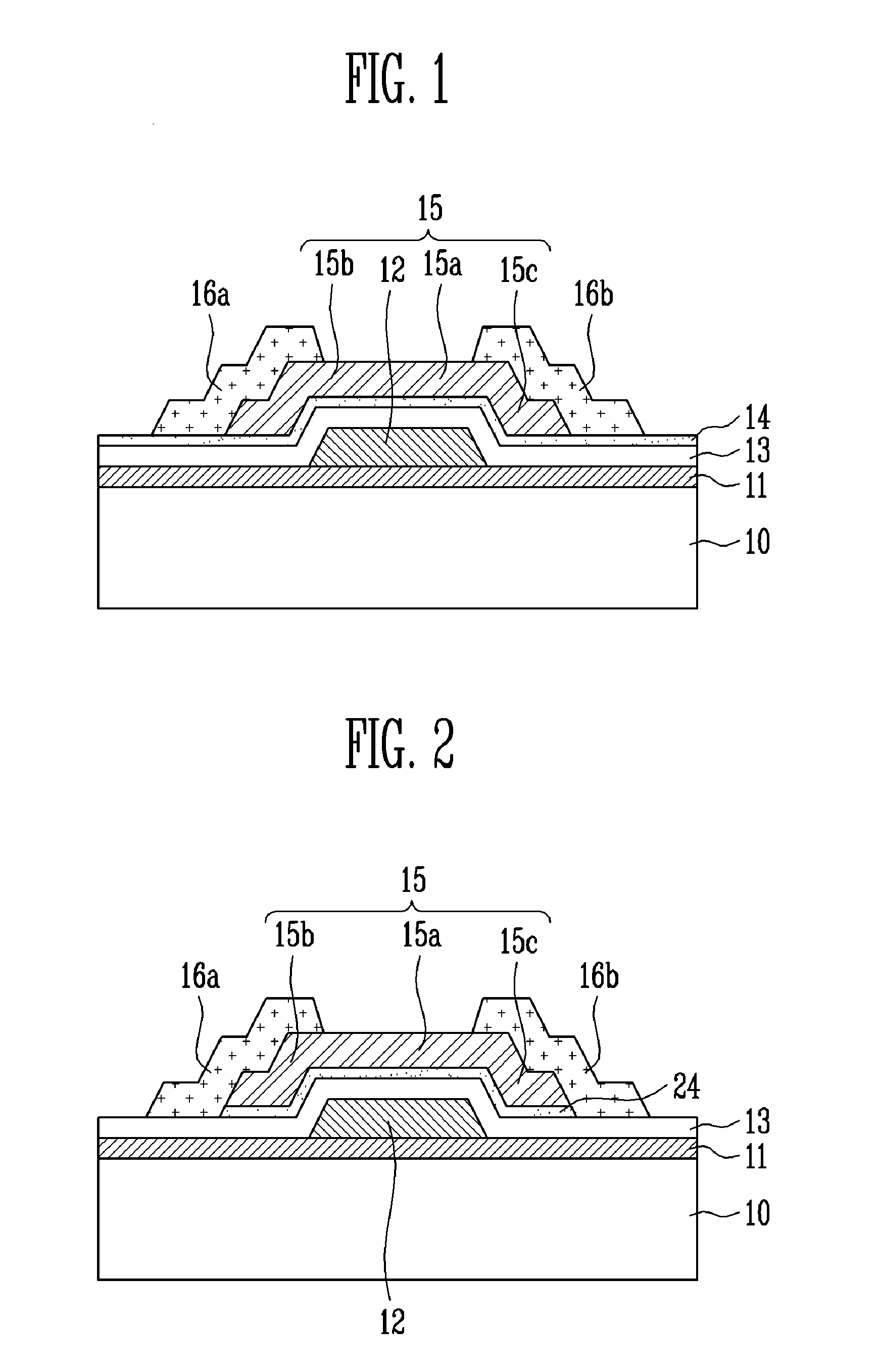

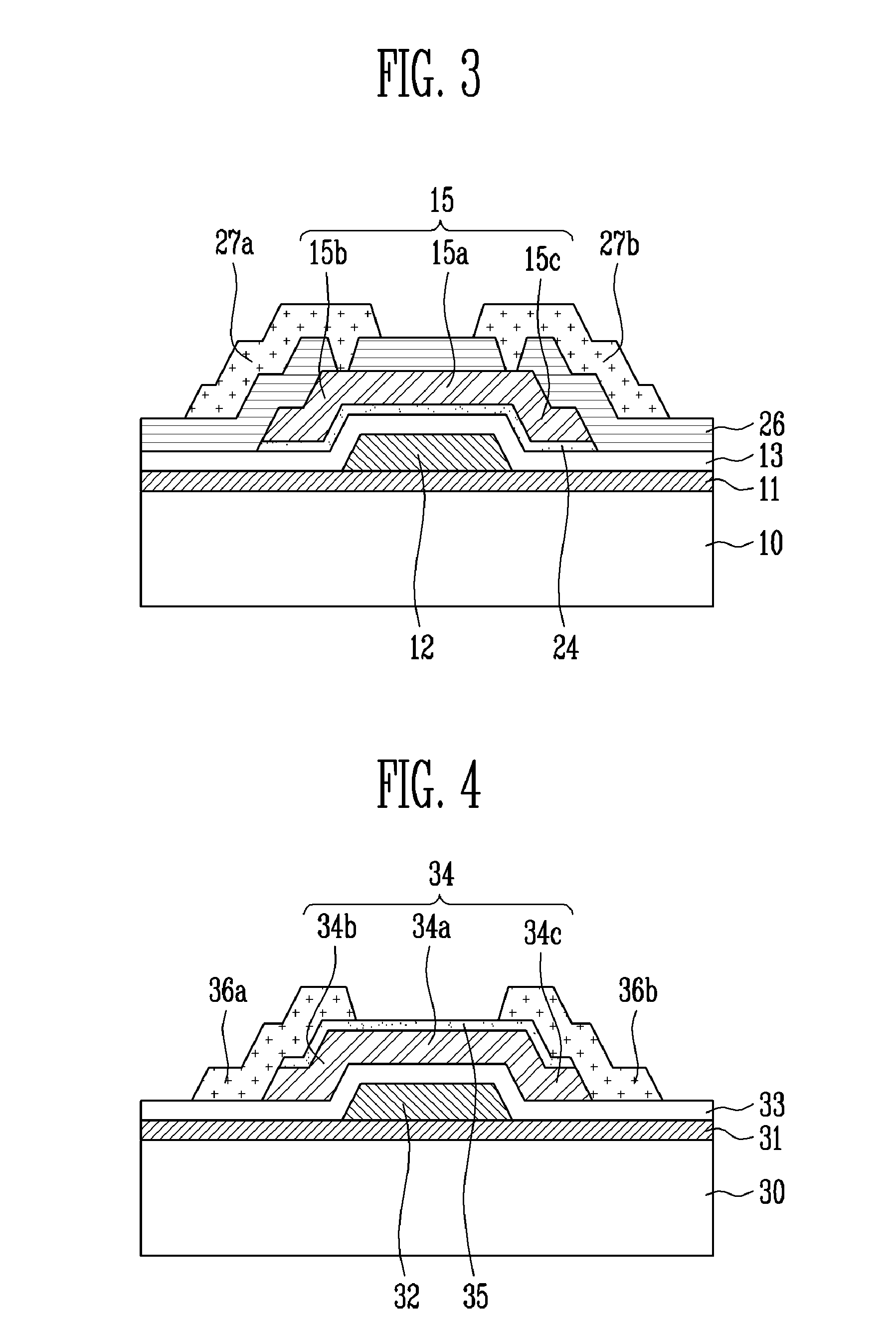

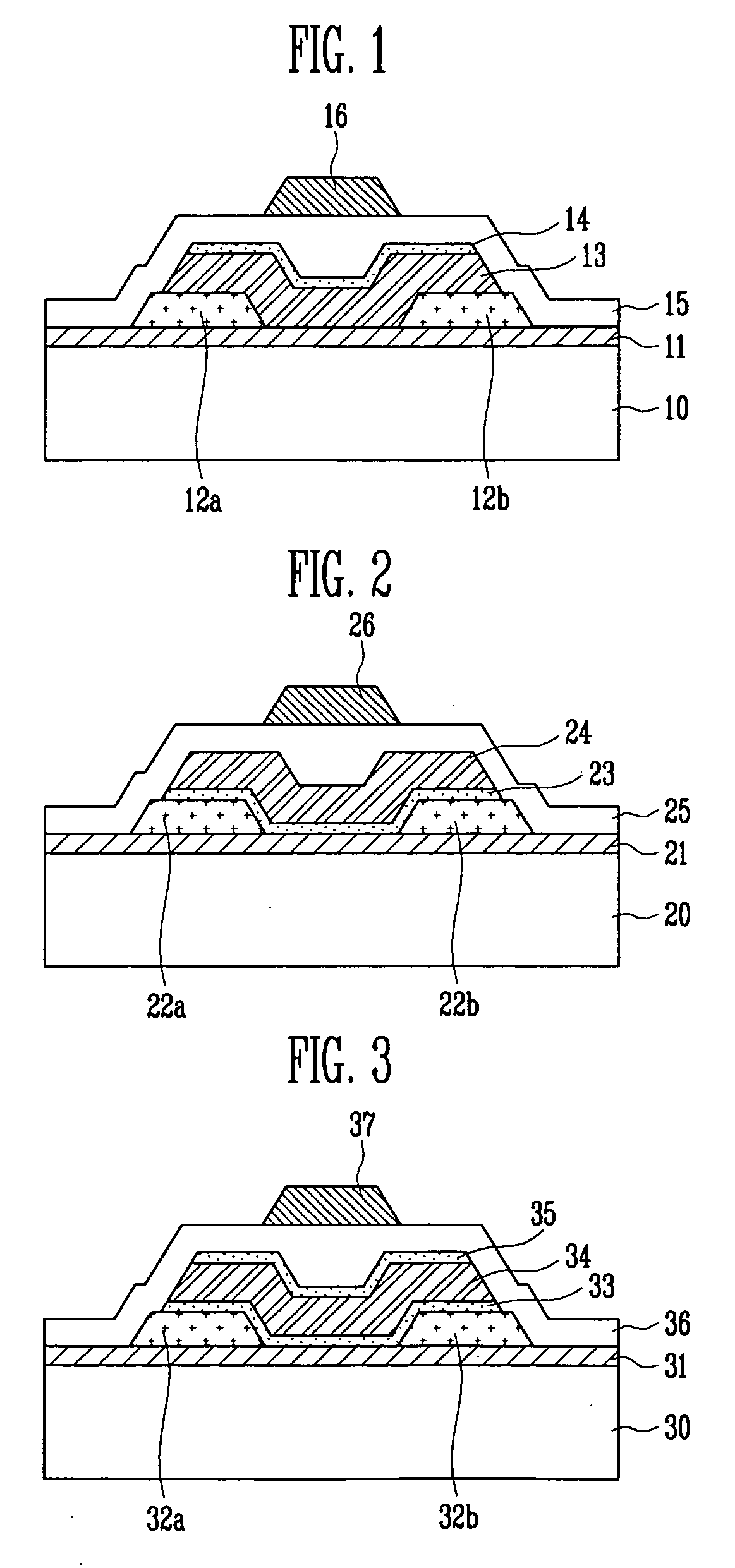

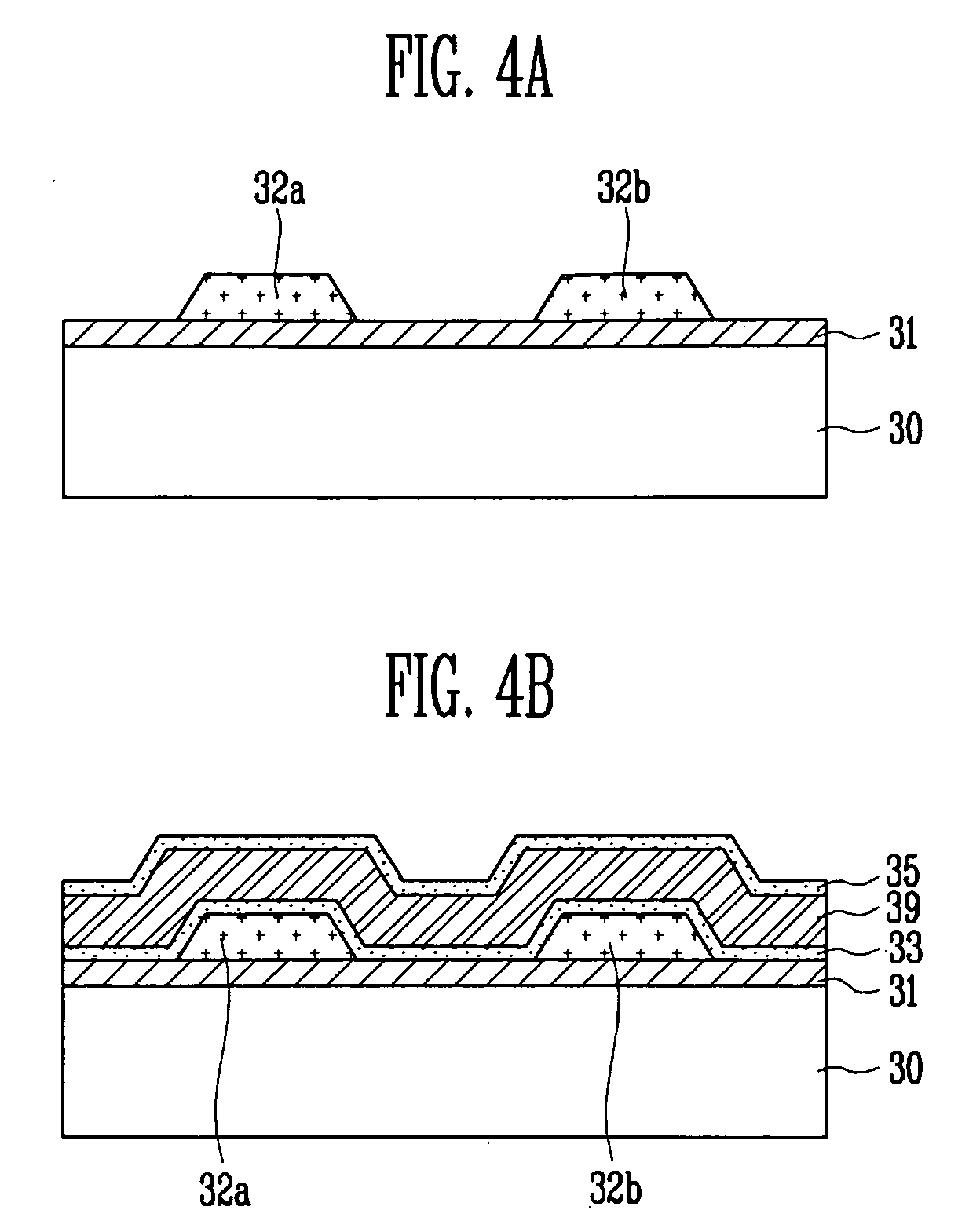

Thin film transistor, method of manufacturing the same and flat panel display device having the same

ActiveUS8148779B2Improve featuresAvoid chargingSolid-state devicesSemiconductor/solid-state device manufacturingTrappingEngineering

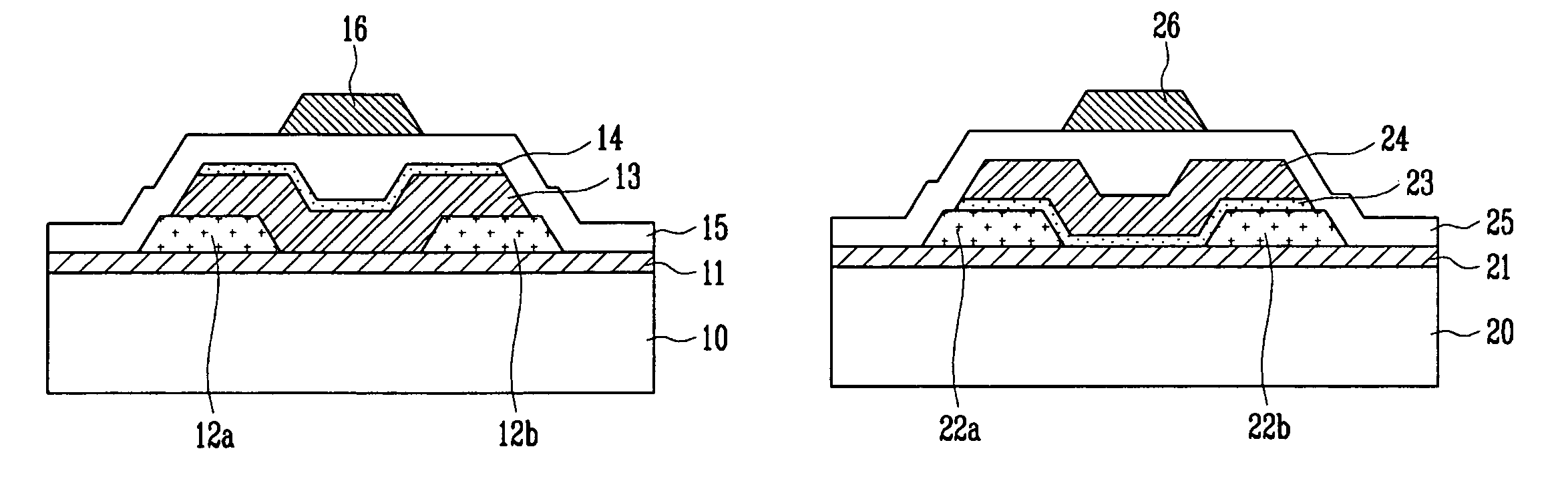

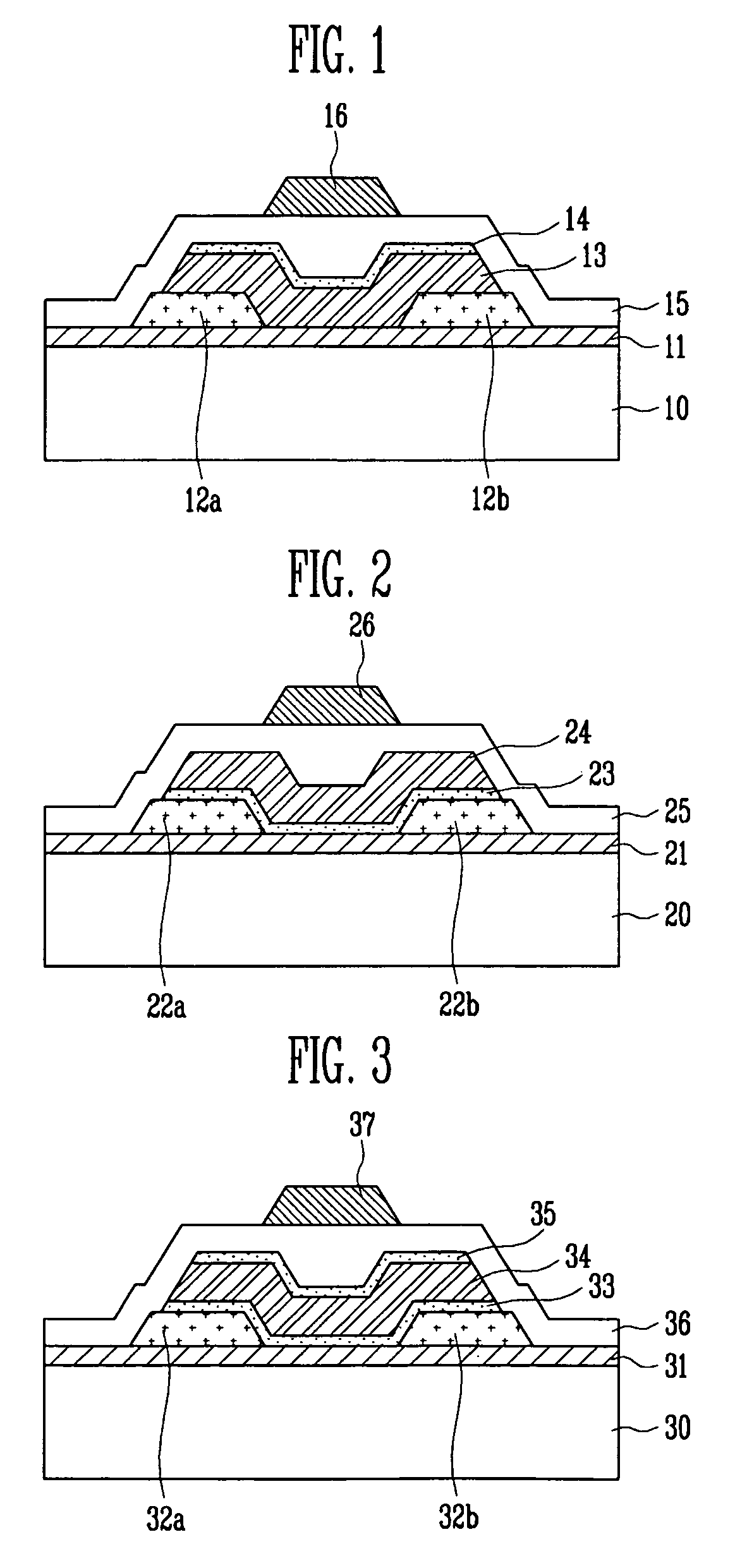

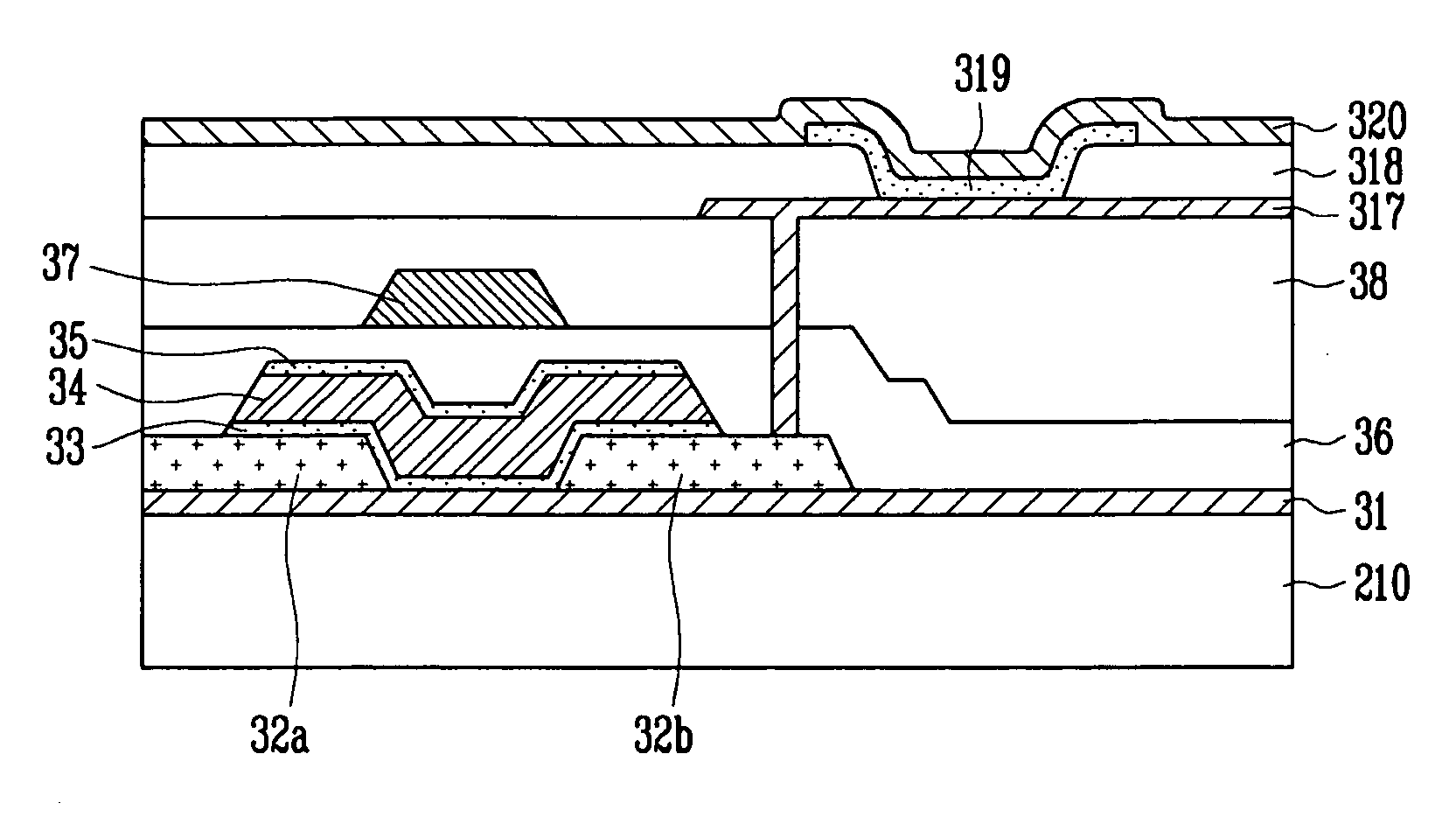

A thin film transistor (TFT) using an oxide semiconductor as an active layer, a method of manufacturing the TFT, and a flat panel display device having the TFT include a gate electrode formed on a substrate; an active layer made of an oxide semiconductor and insulated from the gate electrode by a gate insulating layer; source and drain electrodes coupled to the active layer; and an interfacial stability layer formed on one or both surfaces of the active layer. In the TFT, the interfacial stability layer is formed of an oxide having a band gap of 3.0 to 8.0 eV. Since the interfacial stability layer has the same characteristic as a gate insulating layer and a passivation layer, chemically high interface stability is maintained. Since the interfacial stability layer has a band gap equal to or greater than that of the active layer, charge trapping is physically prevented.

Owner:SAMSUNG DISPLAY CO LTD

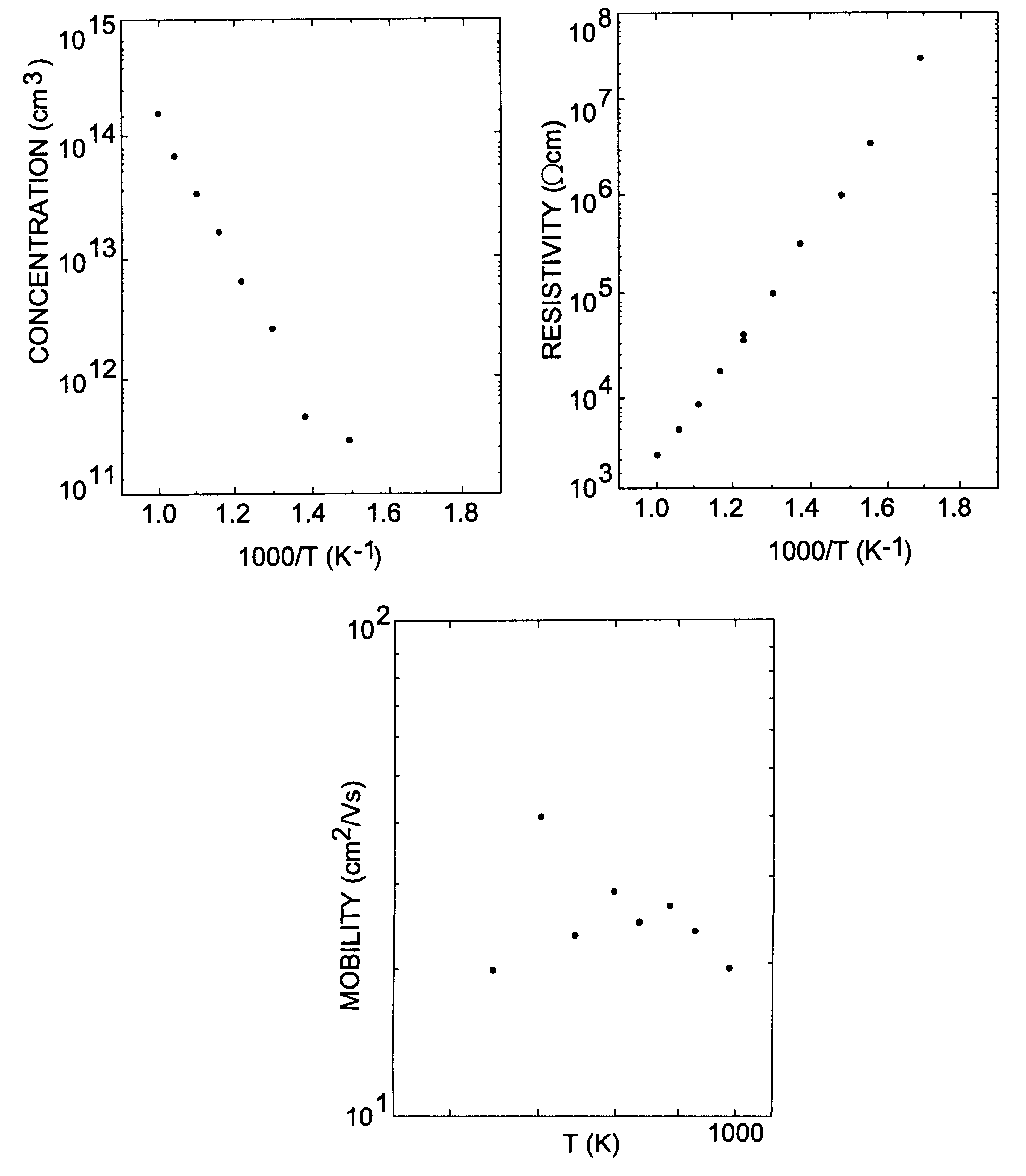

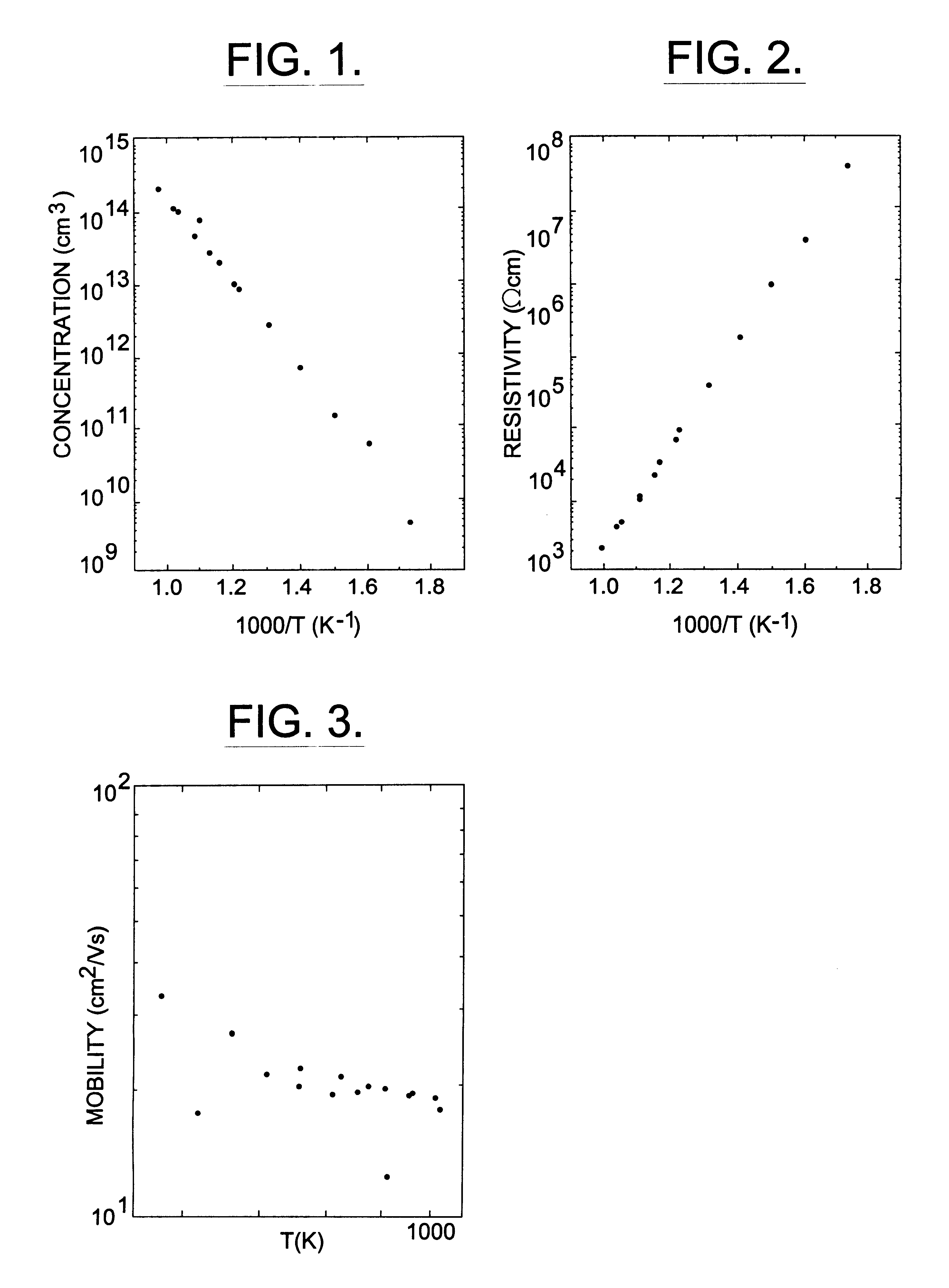

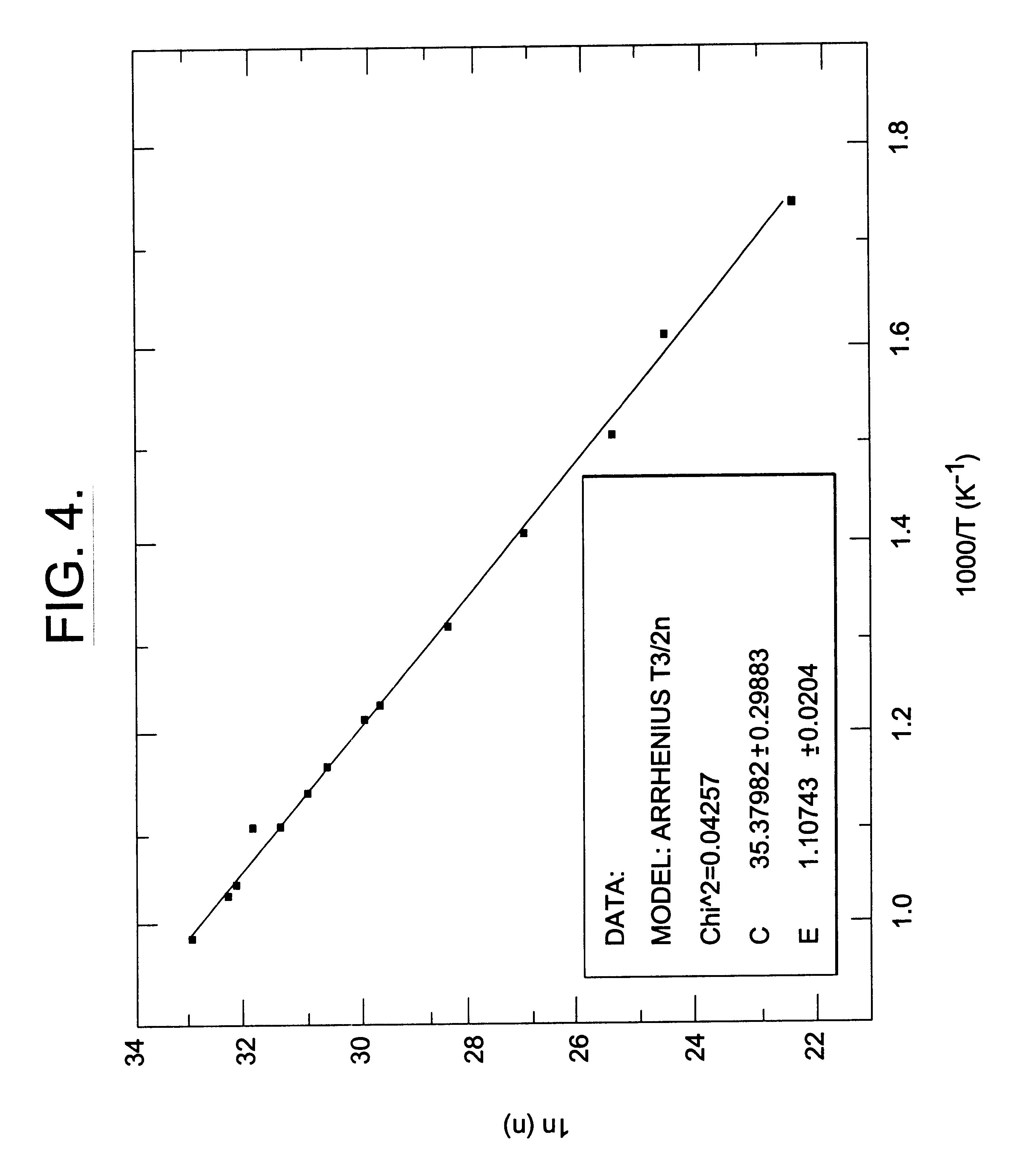

Semi-insulating silicon carbide without vanadium domination

InactiveUS6218680B1Reduce the amount requiredIncrease the number ofPolycrystalline material growthAfter-treatment detailsDevice formTrapping

Owner:CREE INC

Thin film transistor, method of manufacturing the same and flat panel display device having the same

ActiveUS7994500B2Improve featuresAvoid chargingSemiconductor/solid-state device detailsSolid-state devicesTrappingOxide thin-film transistor

A thin film transistor (TFT) using an oxide semiconductor as an active layer, a method of manufacturing the TFT, and a flat panel display device having the TFT include source and drain electrodes formed on a substrate; an active layer formed of an oxide semiconductor disposed on the source and drain electrodes; a gate electrode; and an interfacial stability layer formed on at least one of top and bottom surfaces of the active layer. In the TFT, the interfacial stability layer is formed of an oxide having a band gap of 3.0 to 8.0 eV. Since the interfacial stability layer has the same characteristics as a gate insulating layer and a passivation layer, chemically high interface stability is maintained. Since the interfacial stability layer has a band gap equal to or greater than that of the active layer, charge trapping is physically prevented.

Owner:SAMSUNG DISPLAY CO LTD

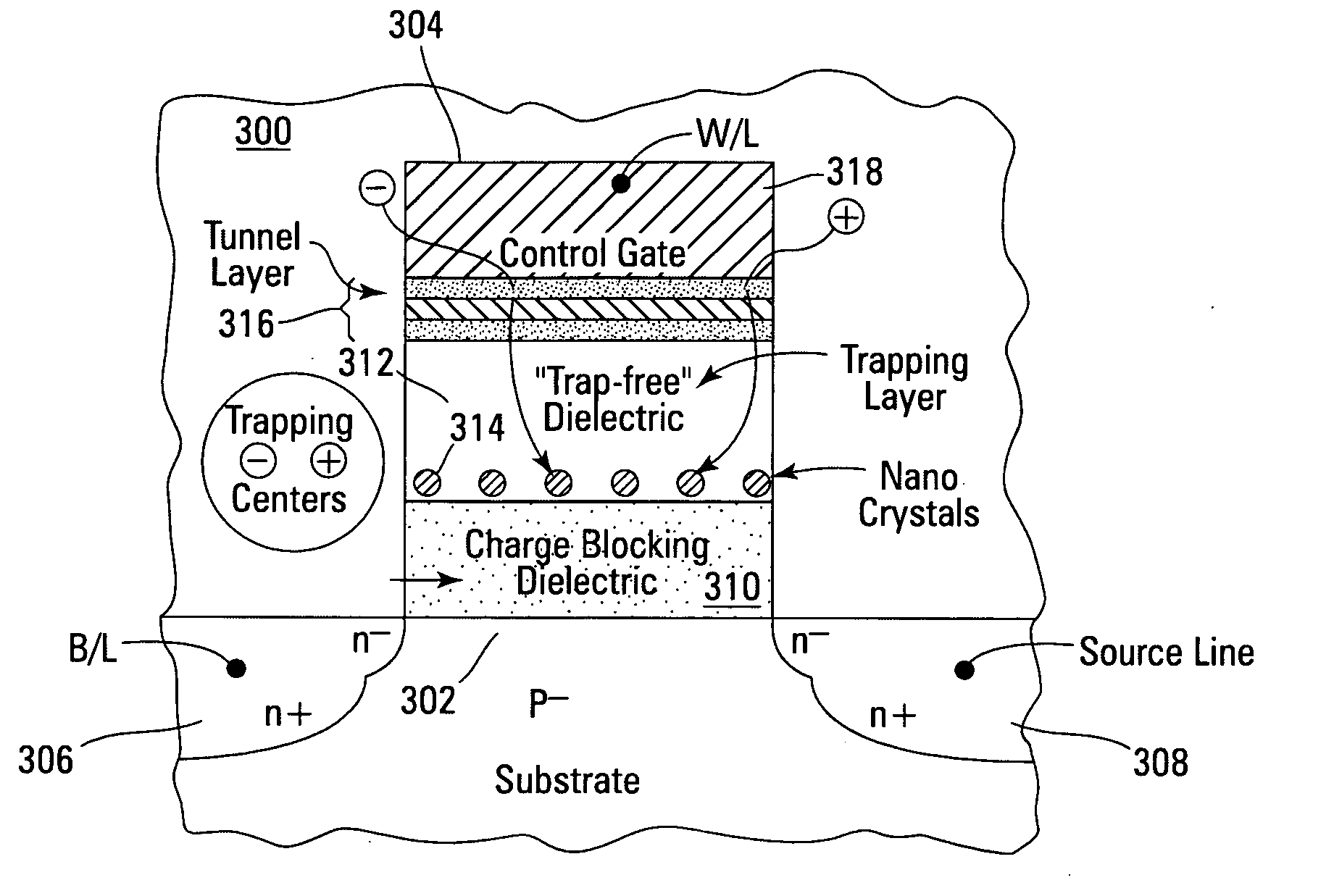

Flash memory cell and methods for programming and erasing

ActiveUS20060291282A1Facilitate device scaling effortsMitigates and avoids interface damageRead-only memoriesSemiconductor/solid-state device manufacturingElectricityElectrical battery

Owner:MONTEREY RES LLC

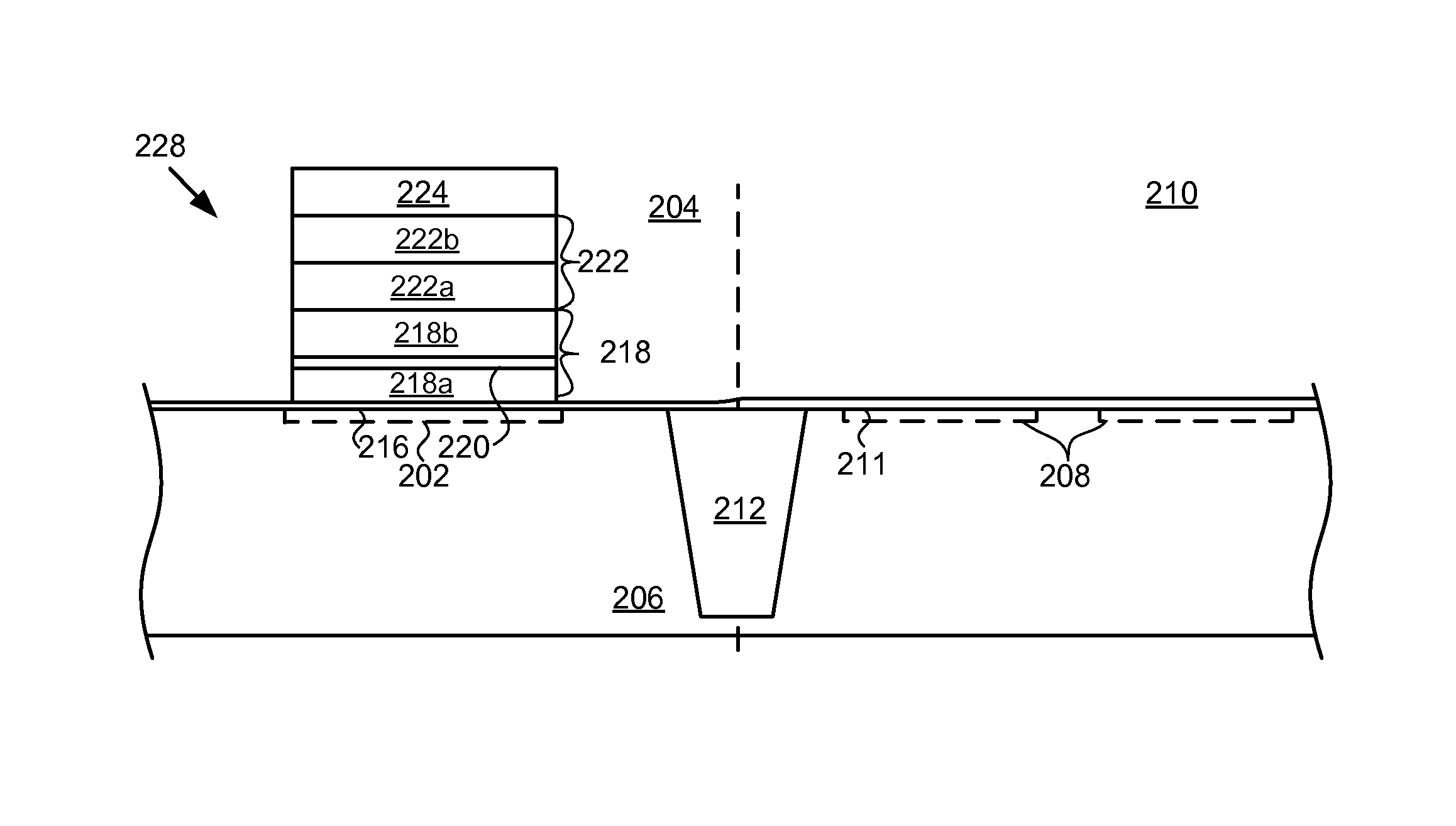

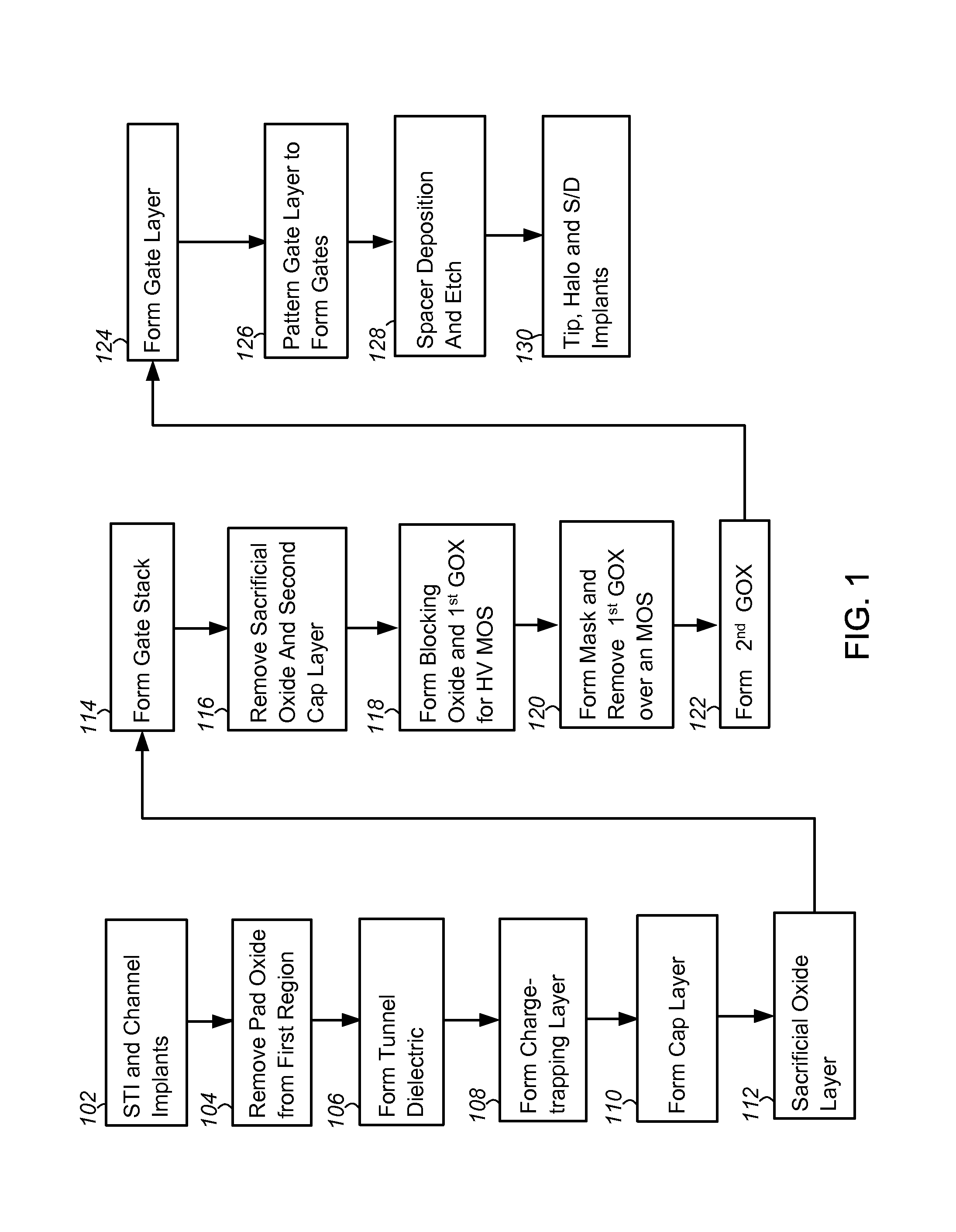

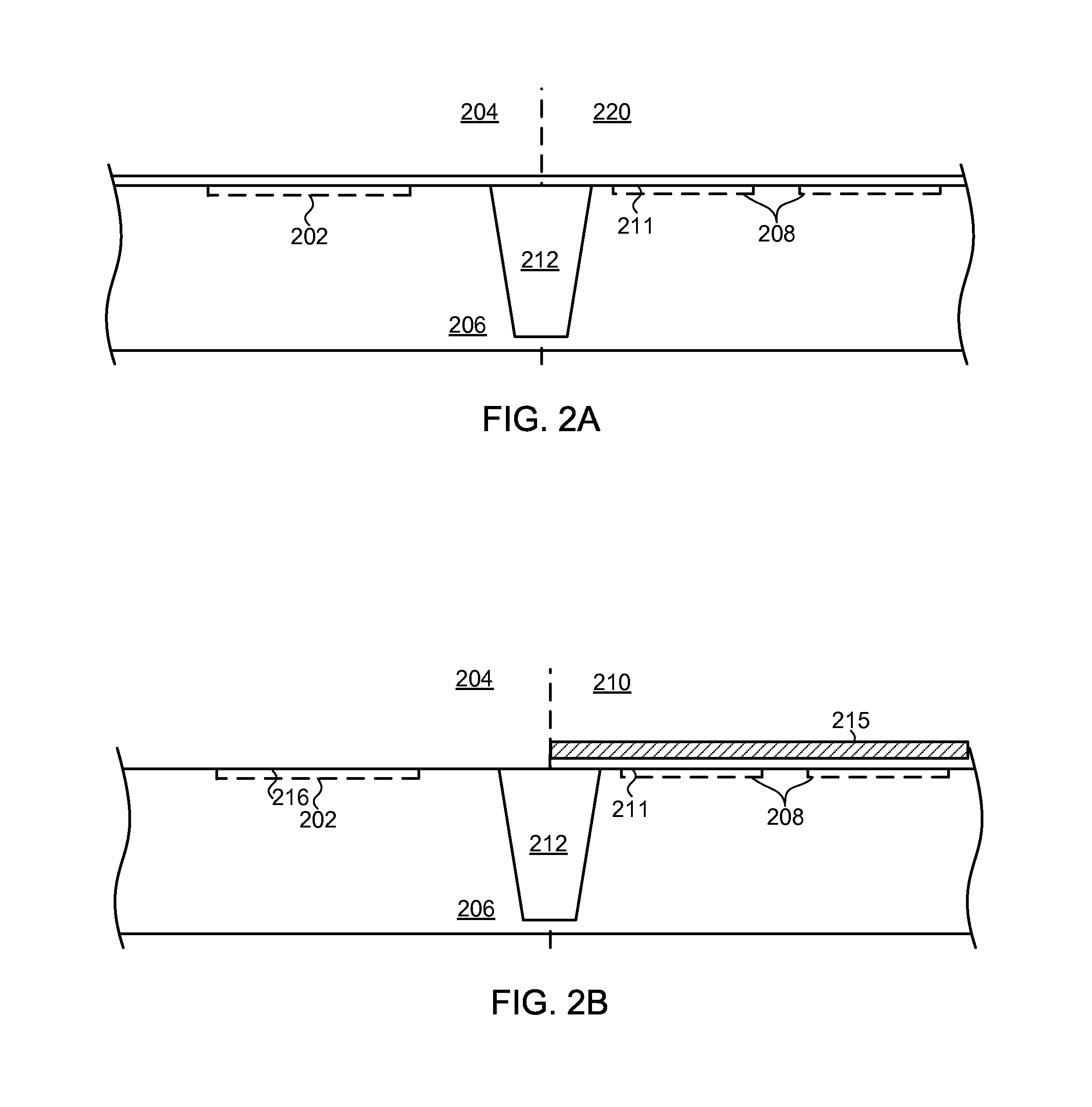

Method of fabricating a charge-trapping gate stack using a CMOS process flow

ActiveUS8993457B1Semiconductor/solid-state device manufacturingSemiconductor devicesDielectricTrapping

A method of fabricating a memory device is described. Generally, the method includes: forming on a surface of a substrate a dielectric stack including a tunneling dielectric and a charge-trapping layer overlying the tunneling dielectric; depositing a first cap layer comprising an oxide over the dielectric stack; forming a second cap layer comprising a nitride over the first cap layer; patterning the first and second cap layers and the dielectric stack to form a gate stack of a memory device; removing the second cap layer; and performing an oxidation process to form a blocking oxide over the charge-trapping layer, wherein the oxidation process consumes the first cap layer. Other embodiments are also described.

Owner:LONGITUDE FLASH MEMORY SOLUTIONS LTD

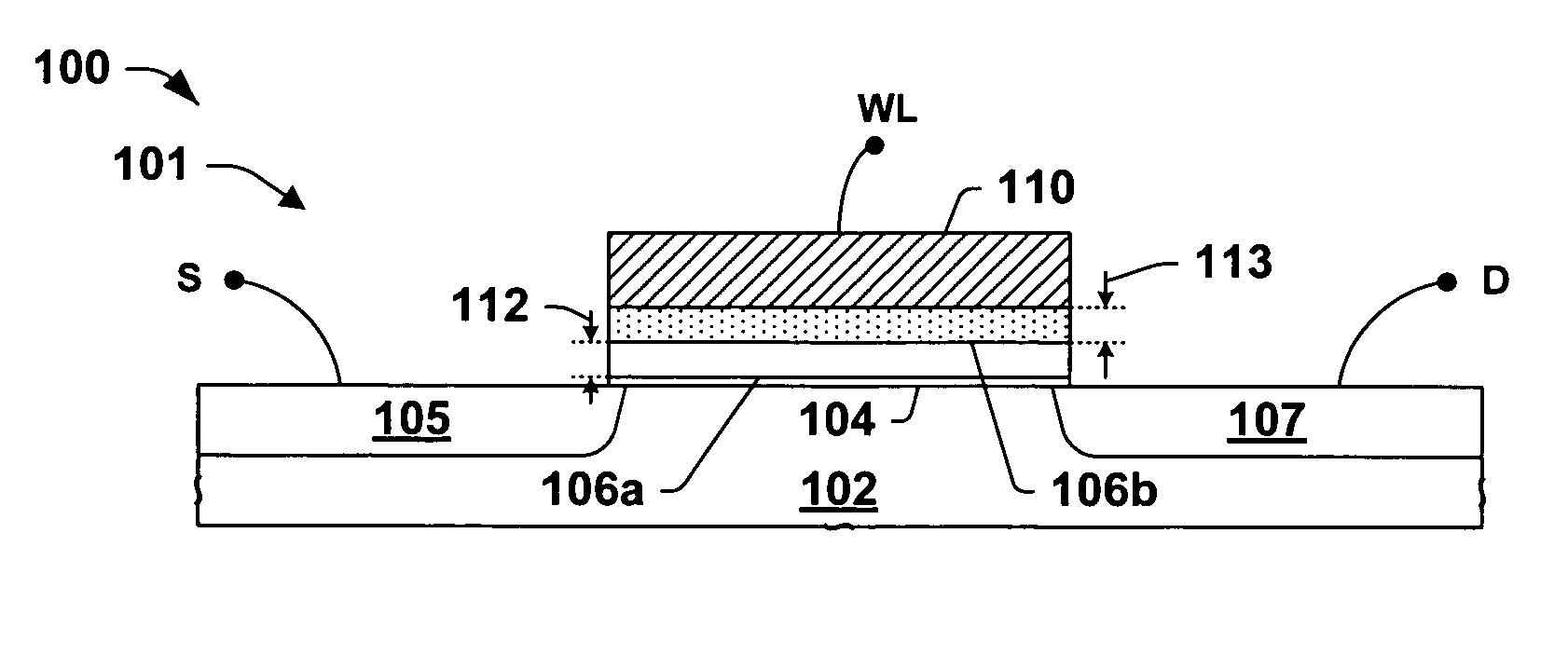

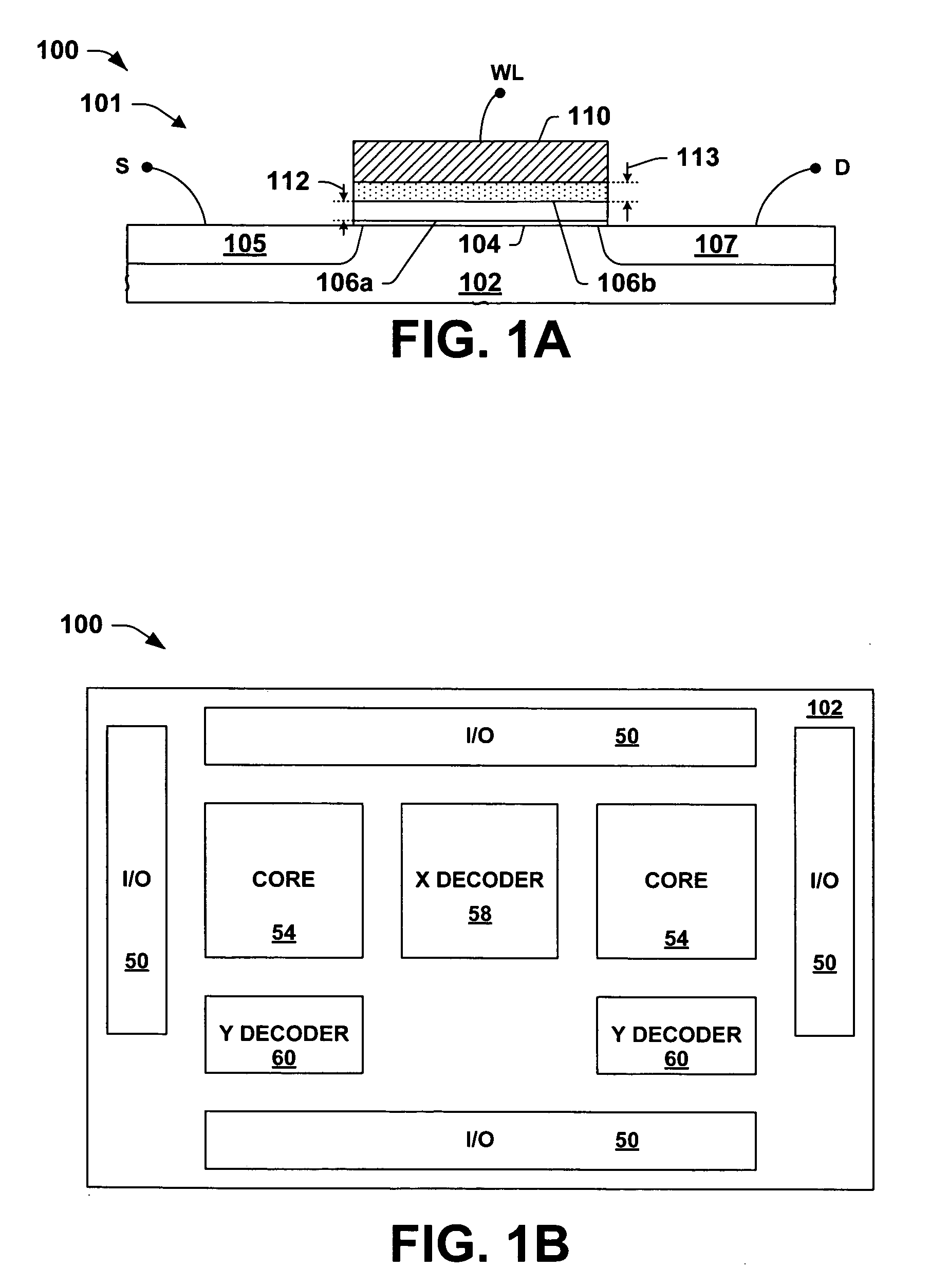

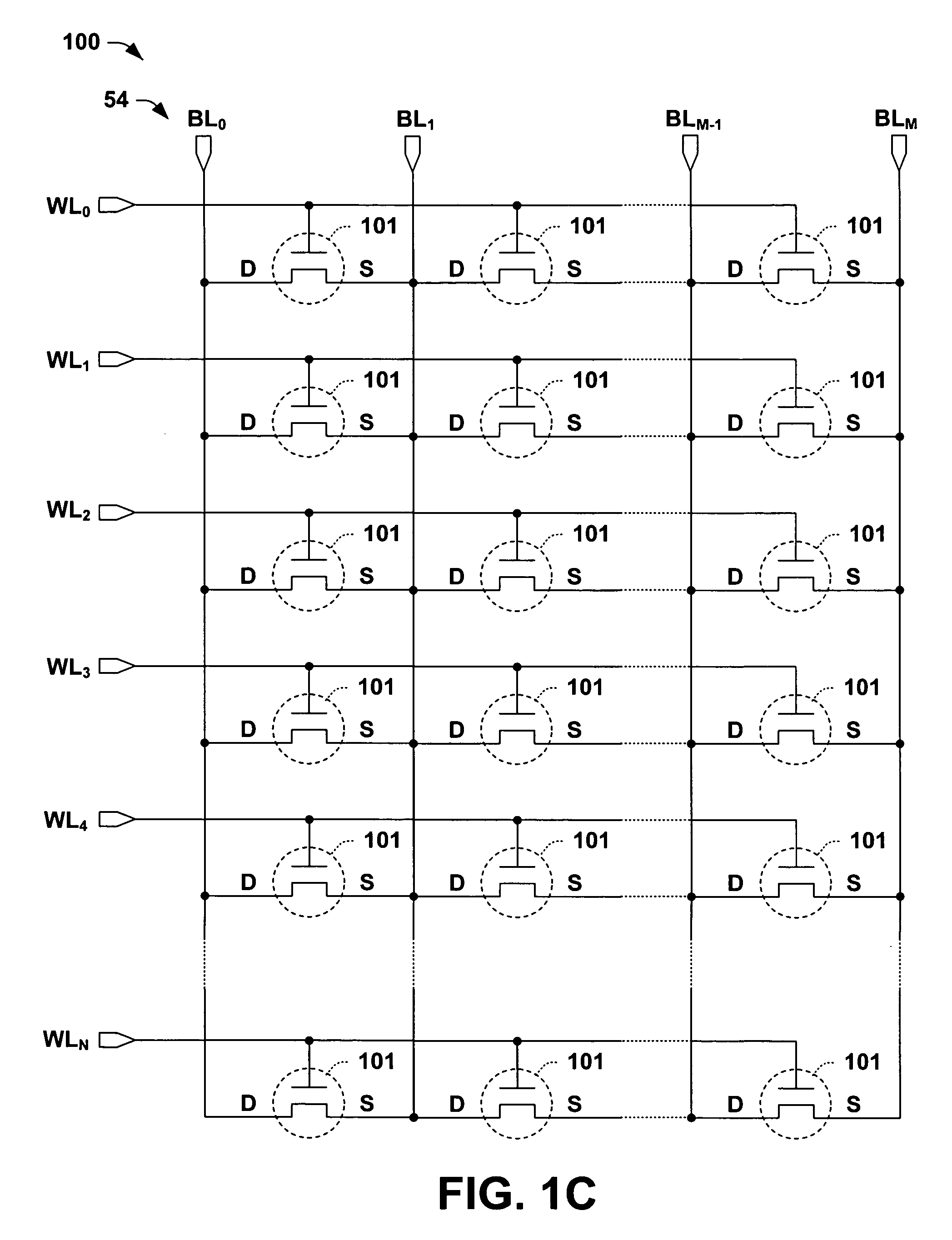

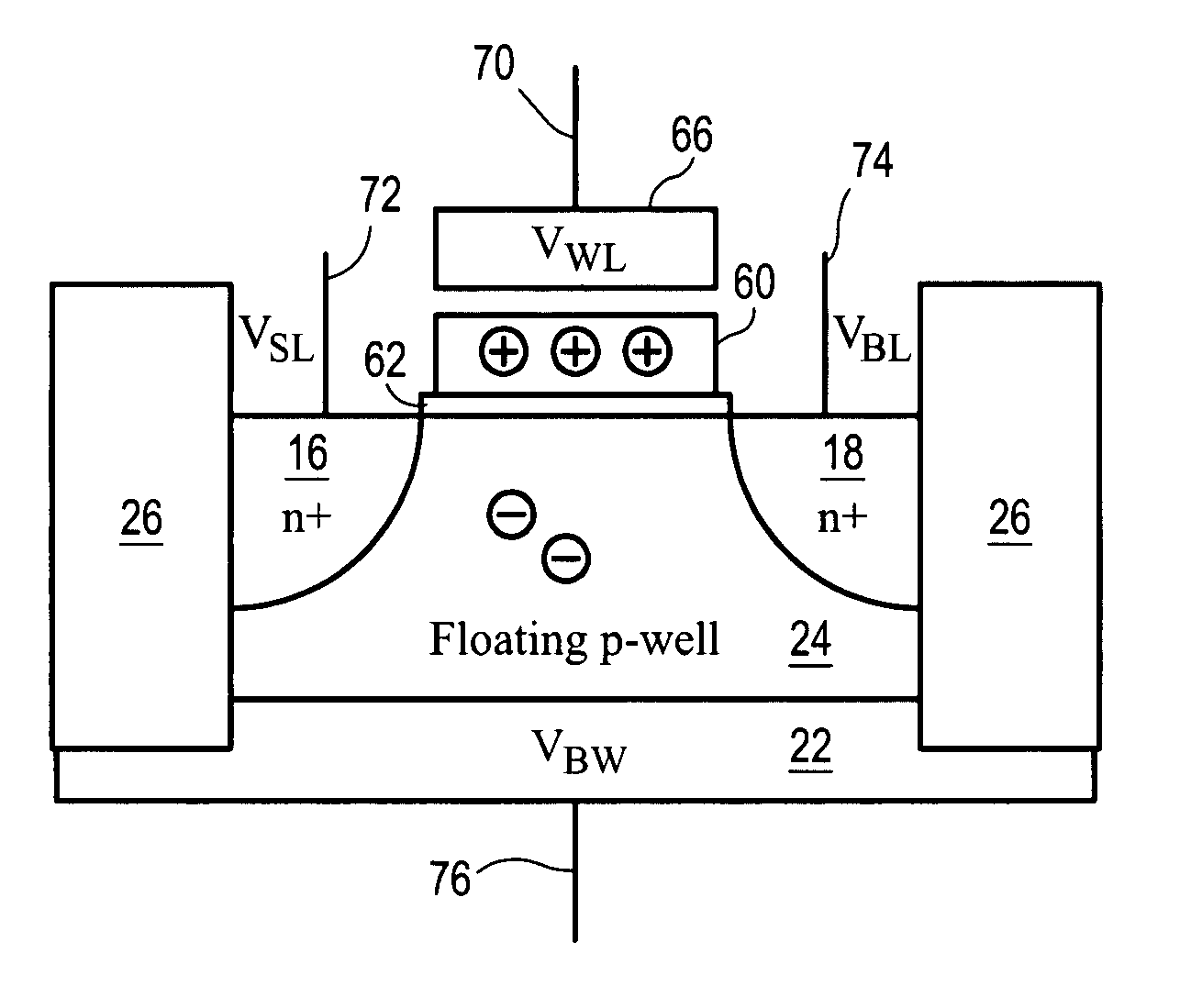

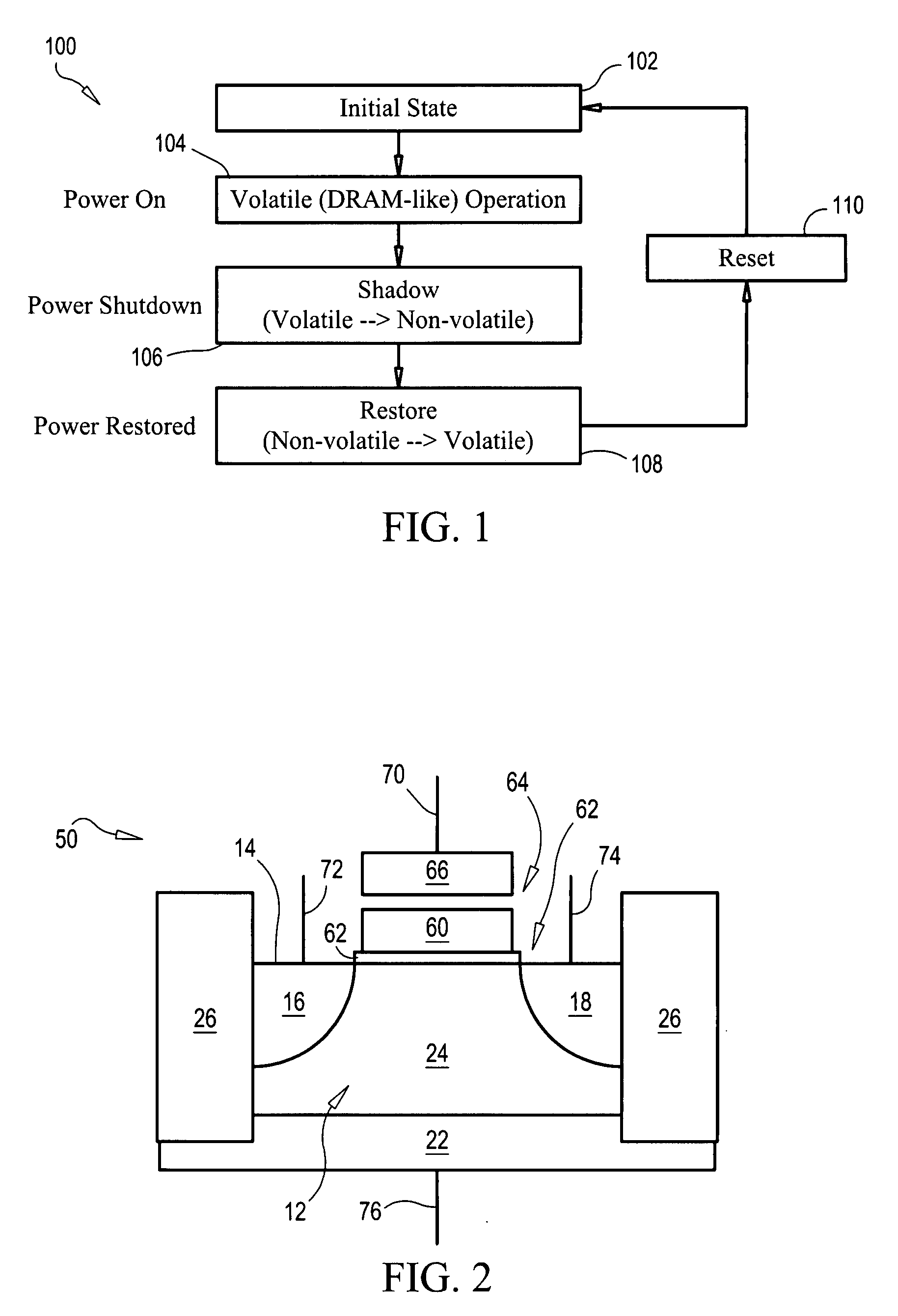

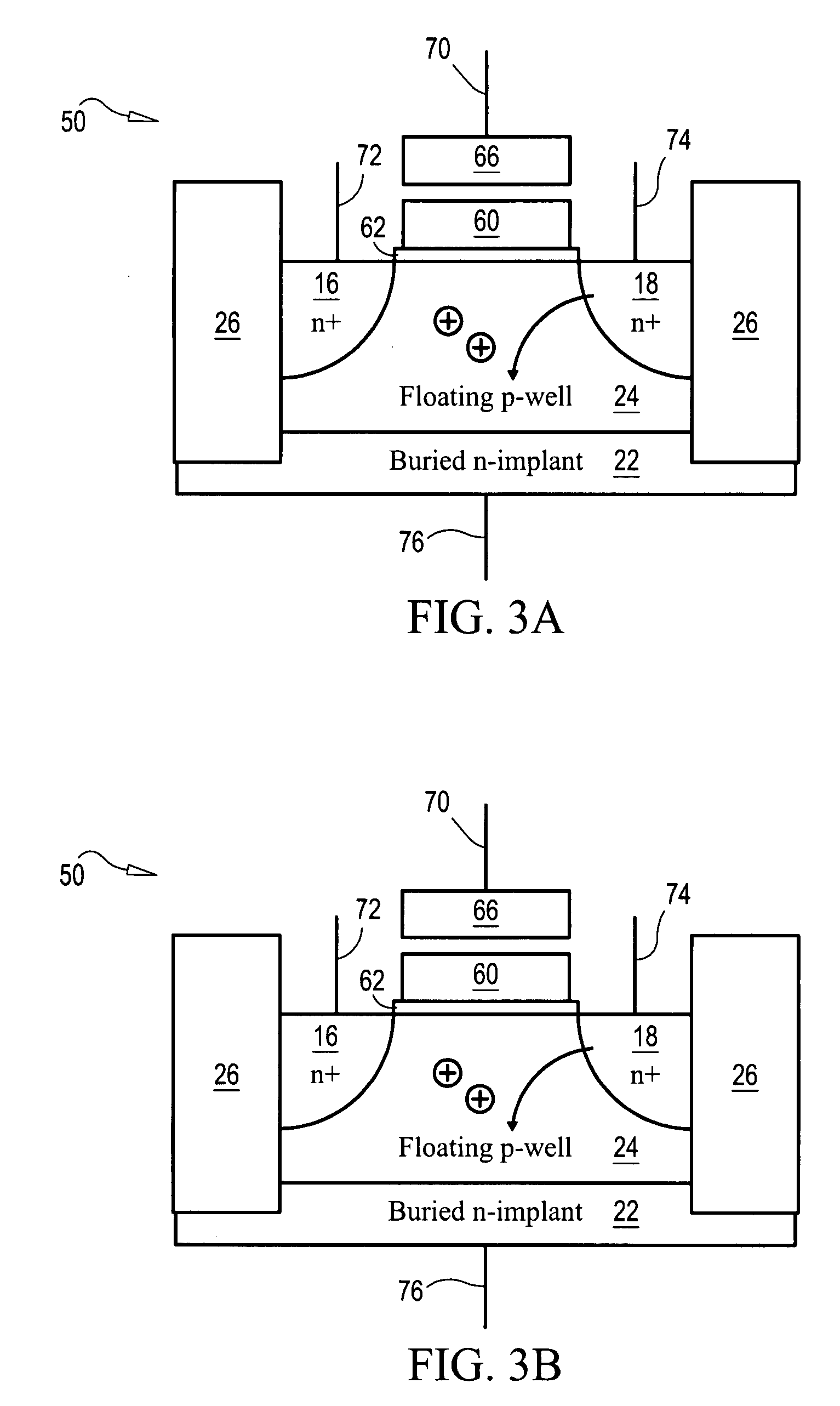

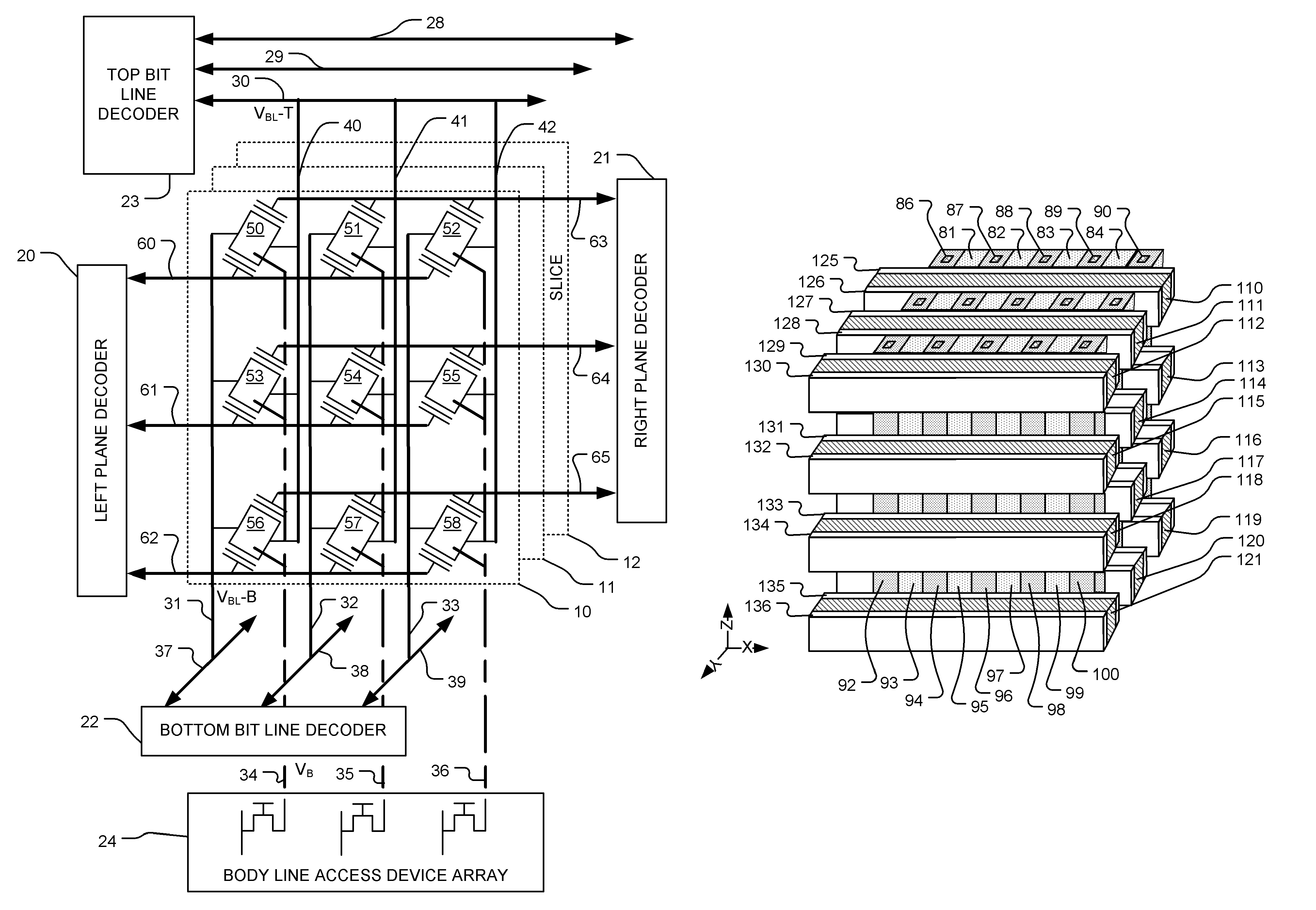

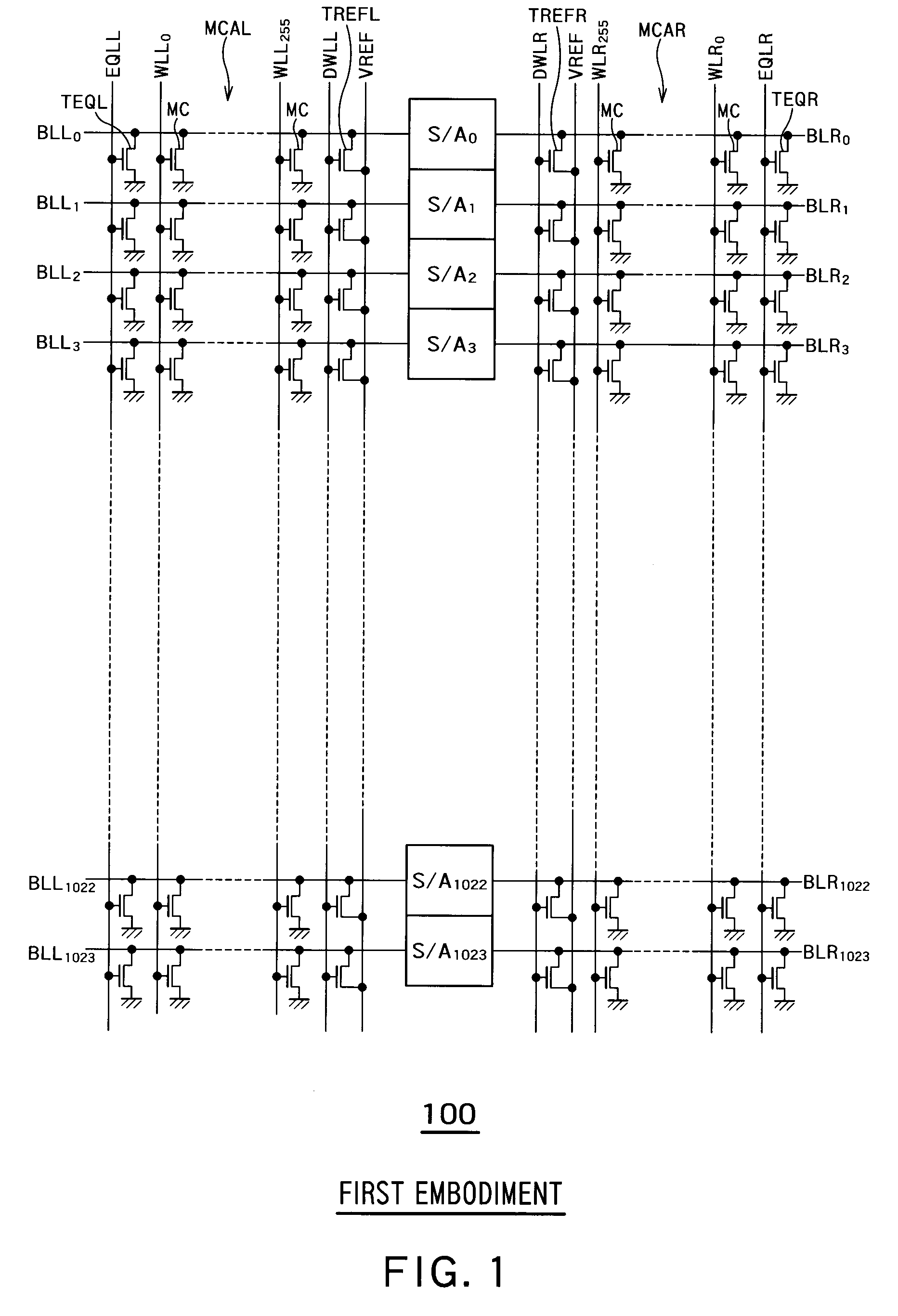

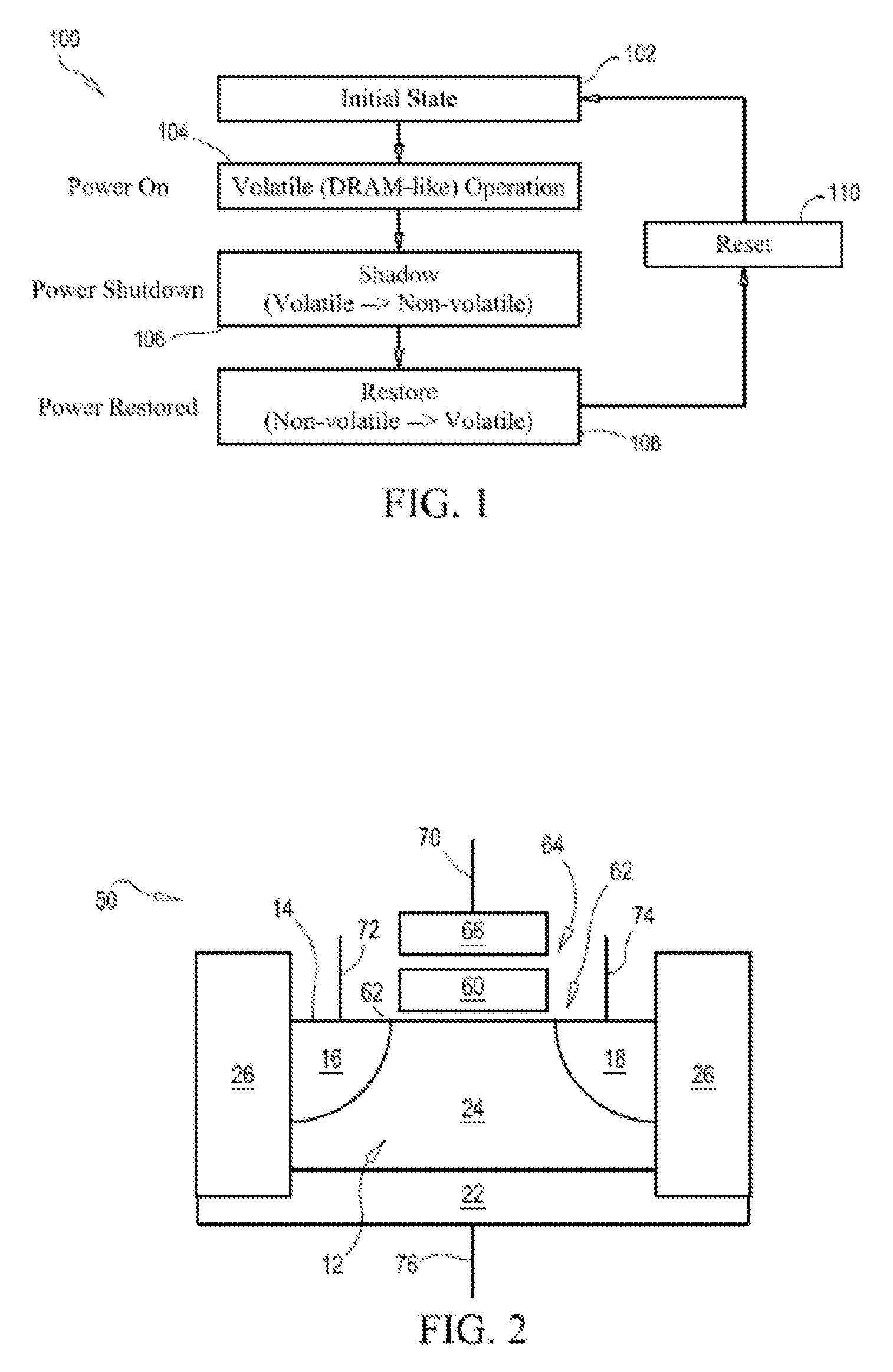

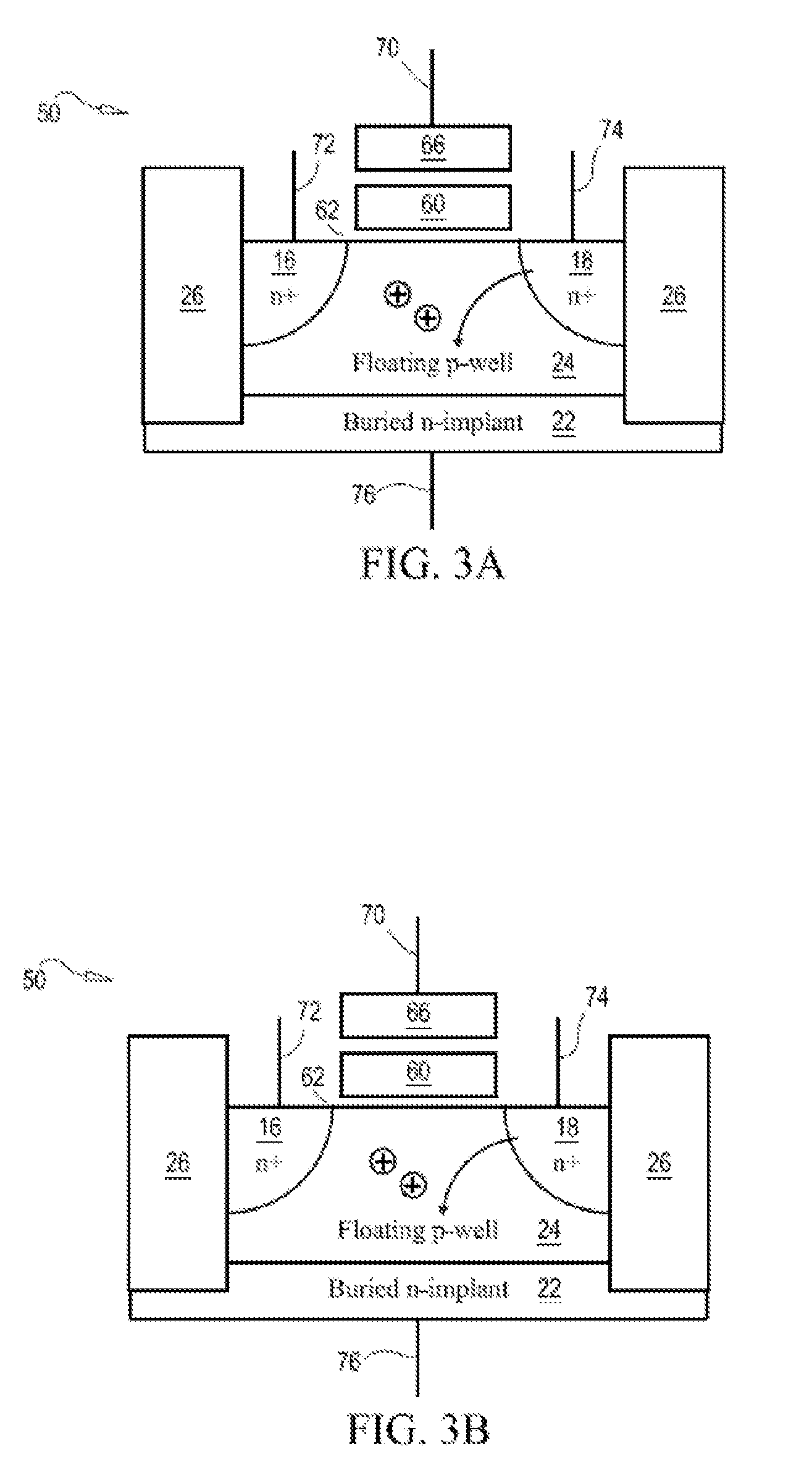

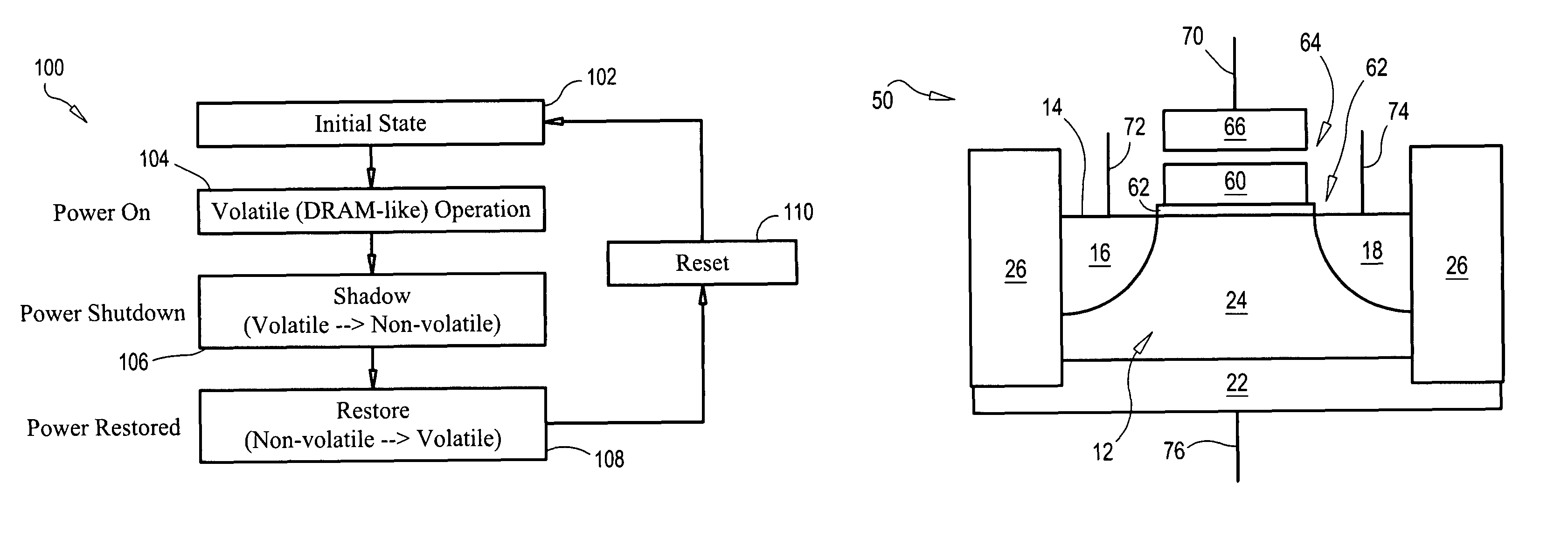

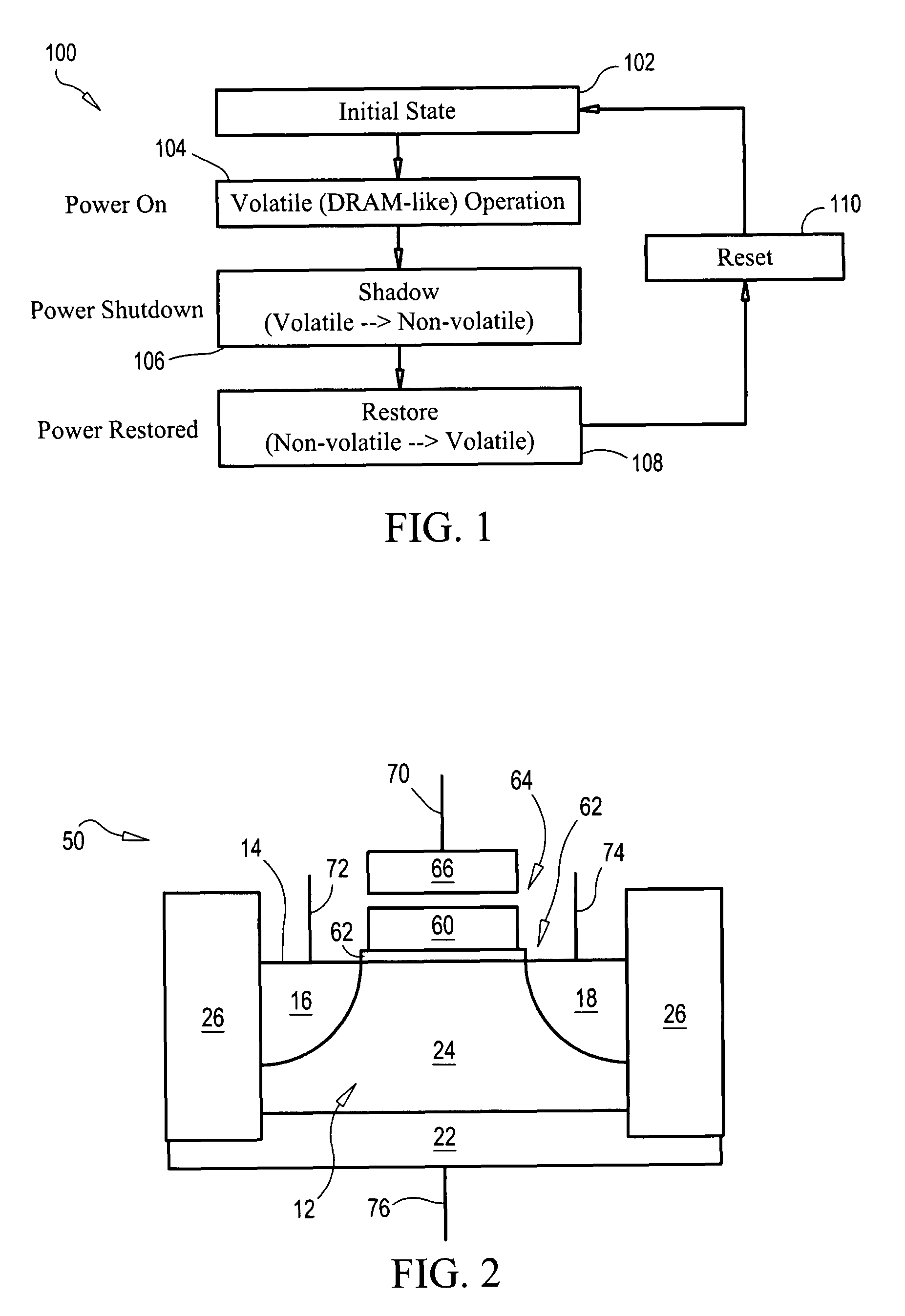

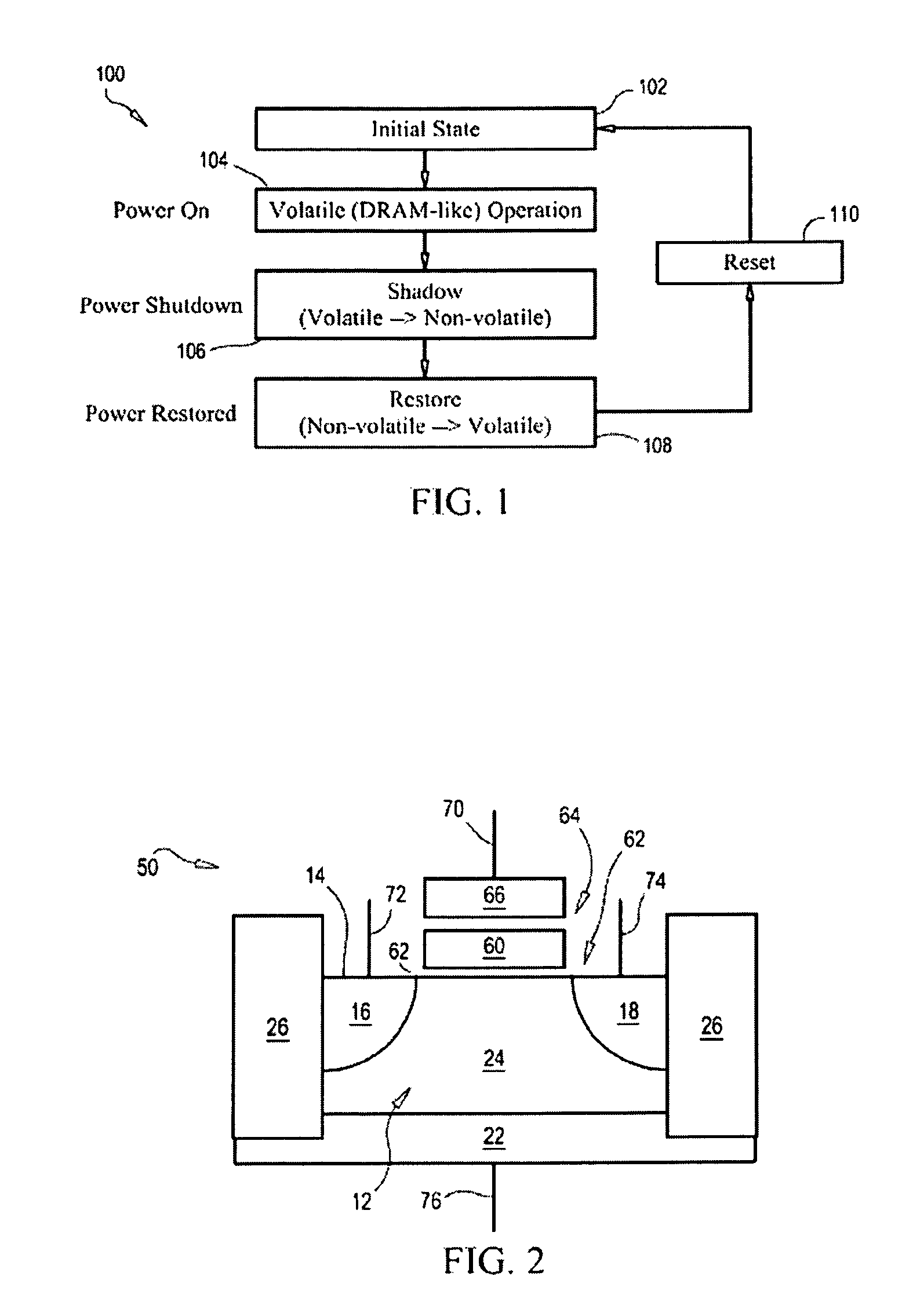

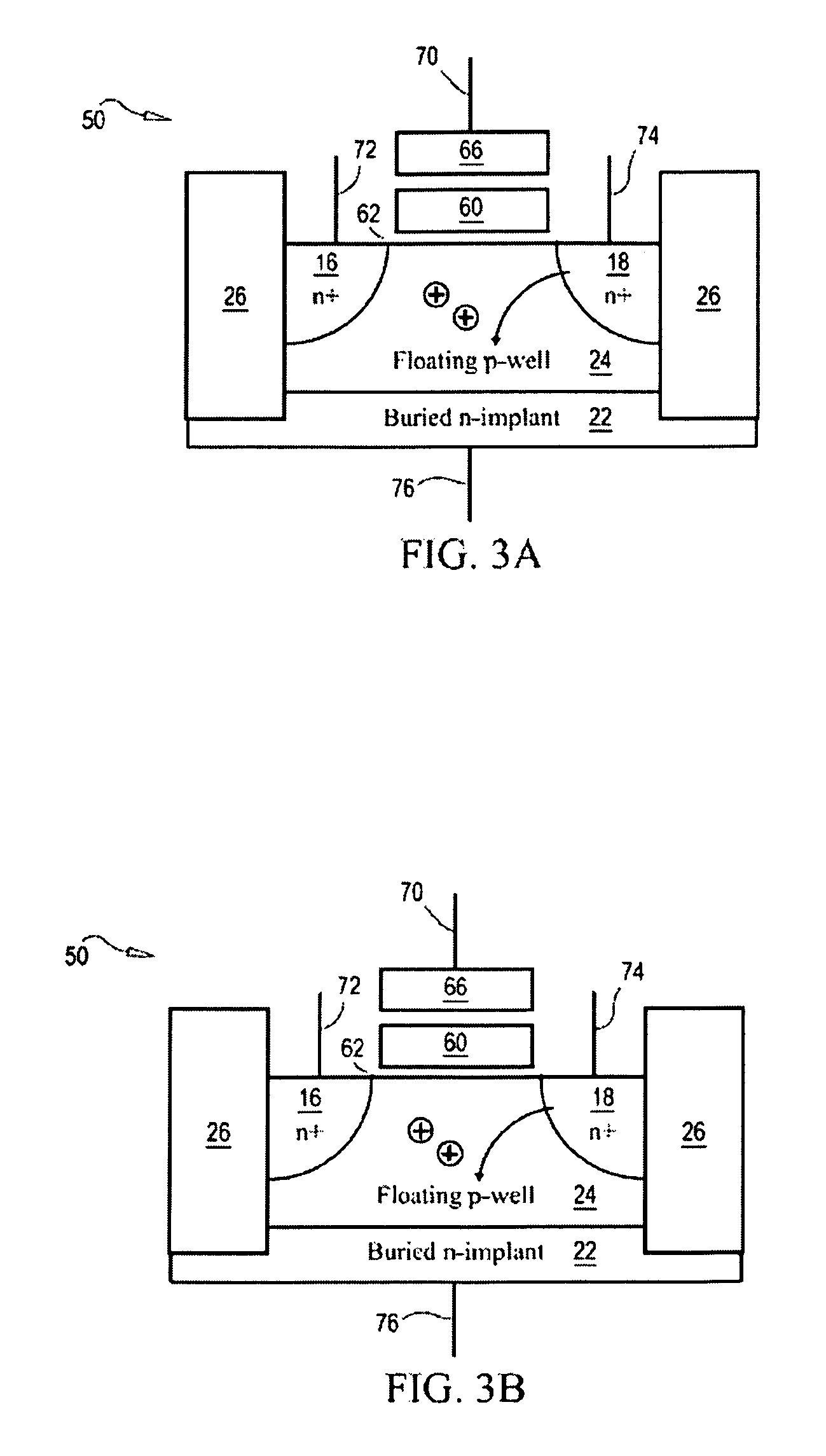

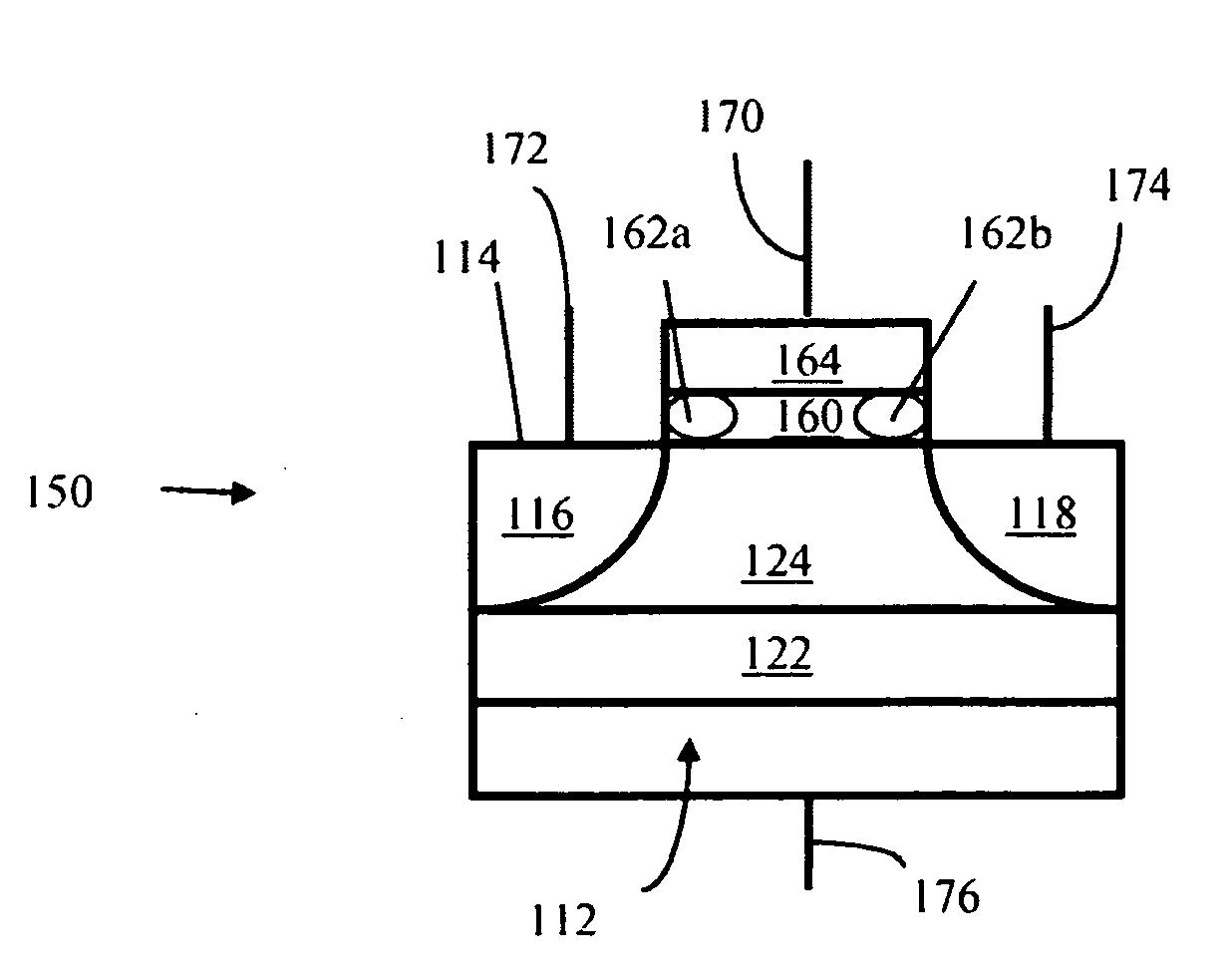

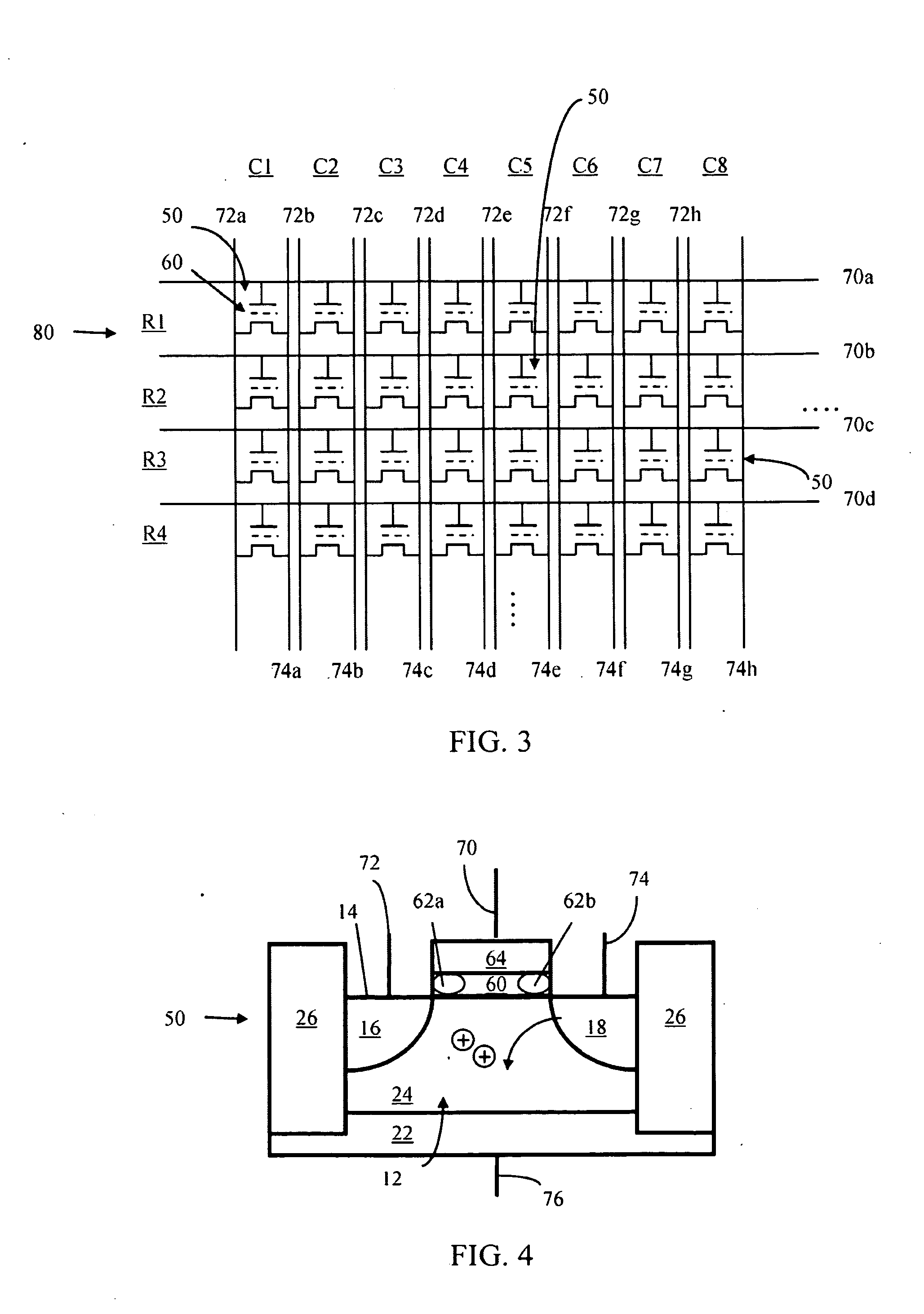

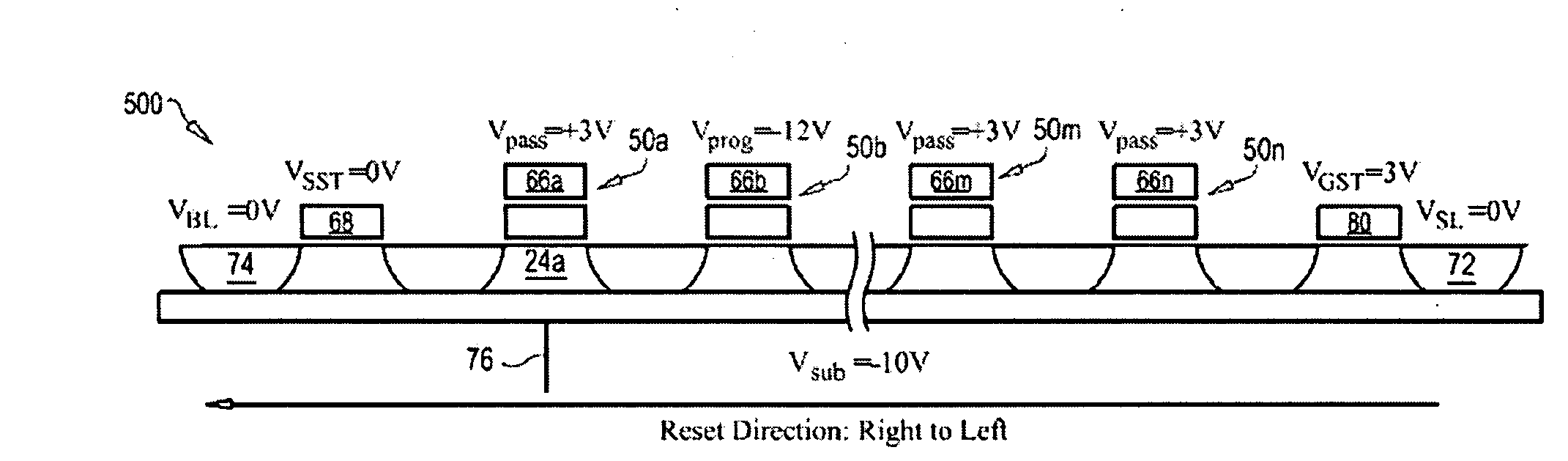

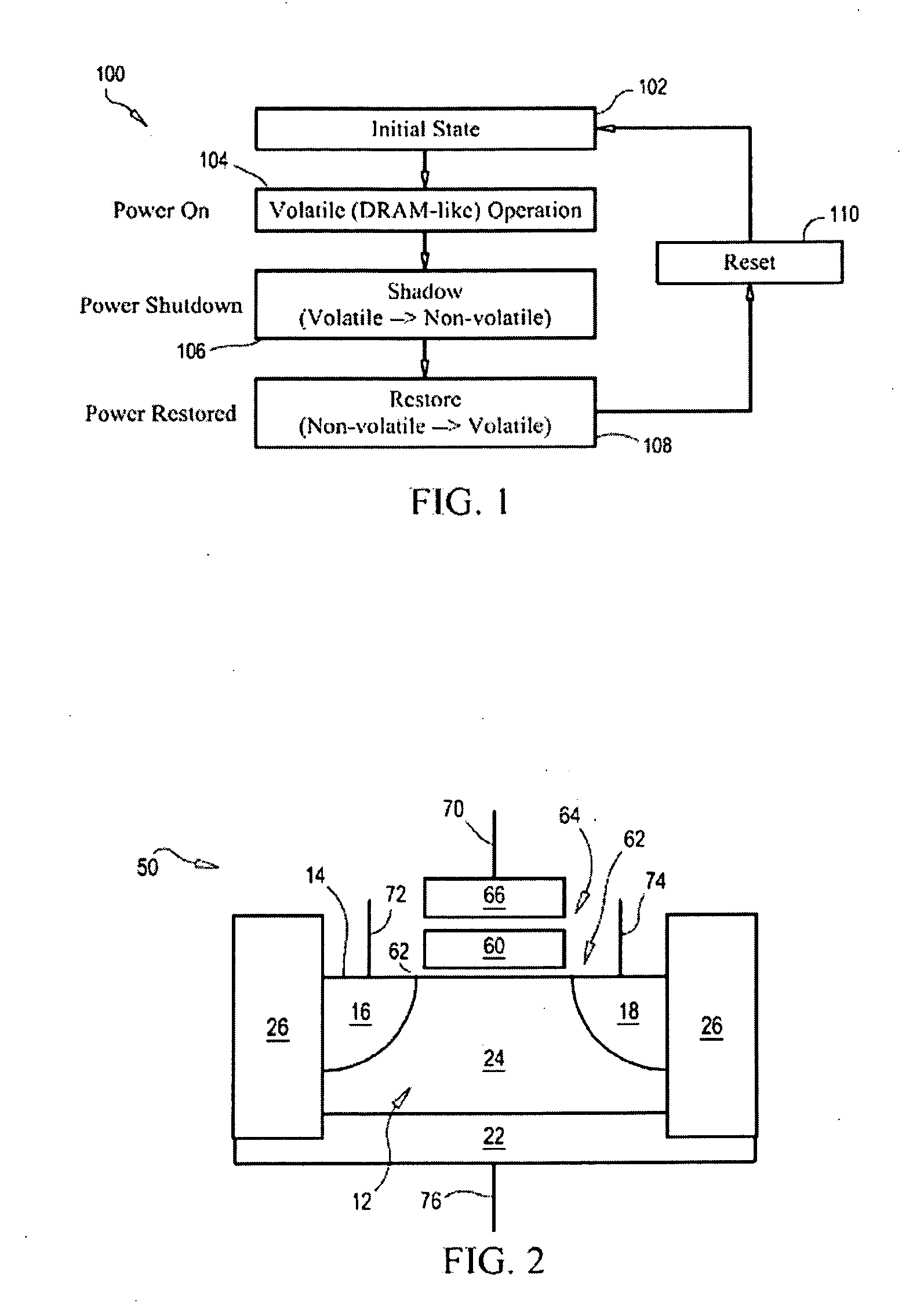

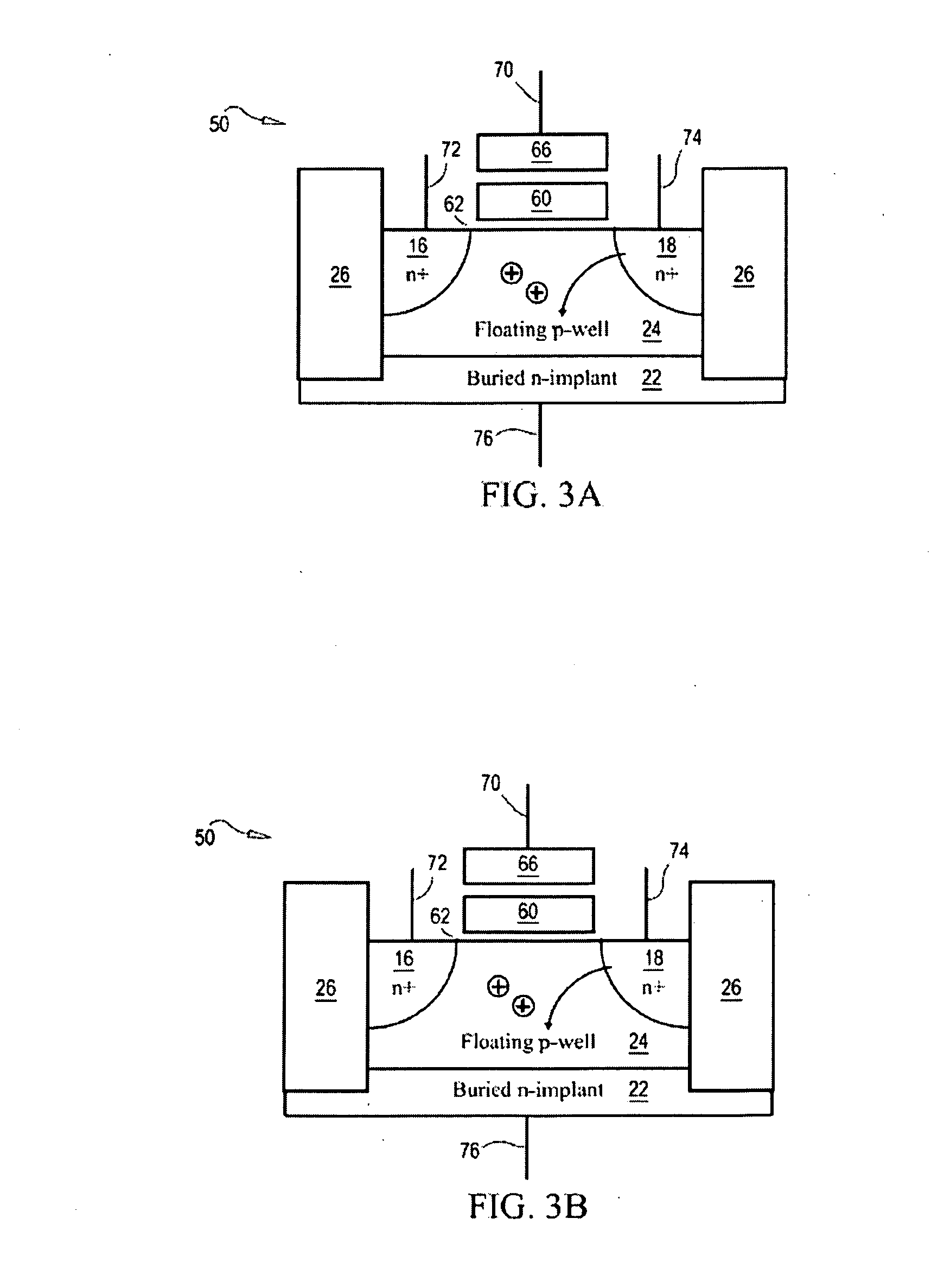

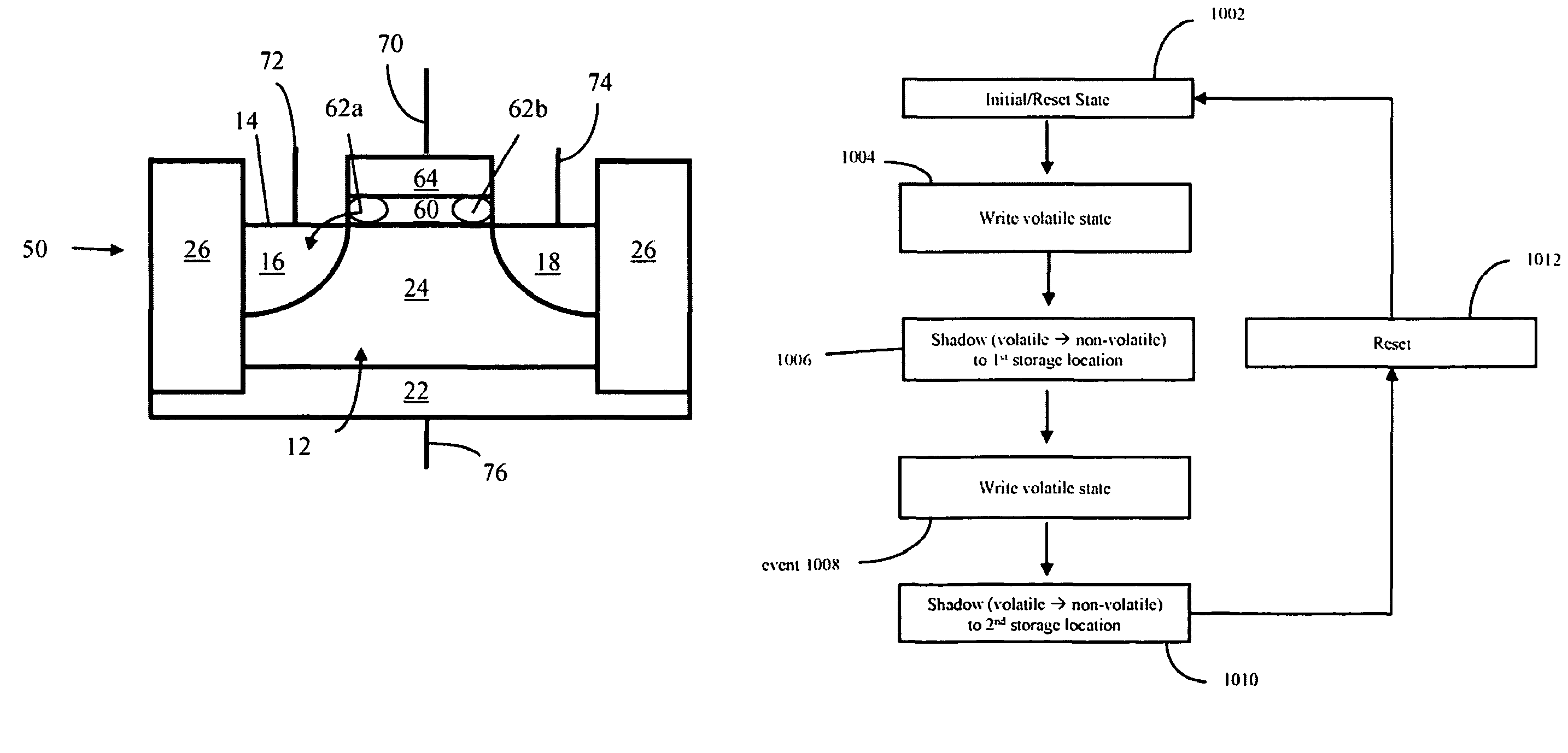

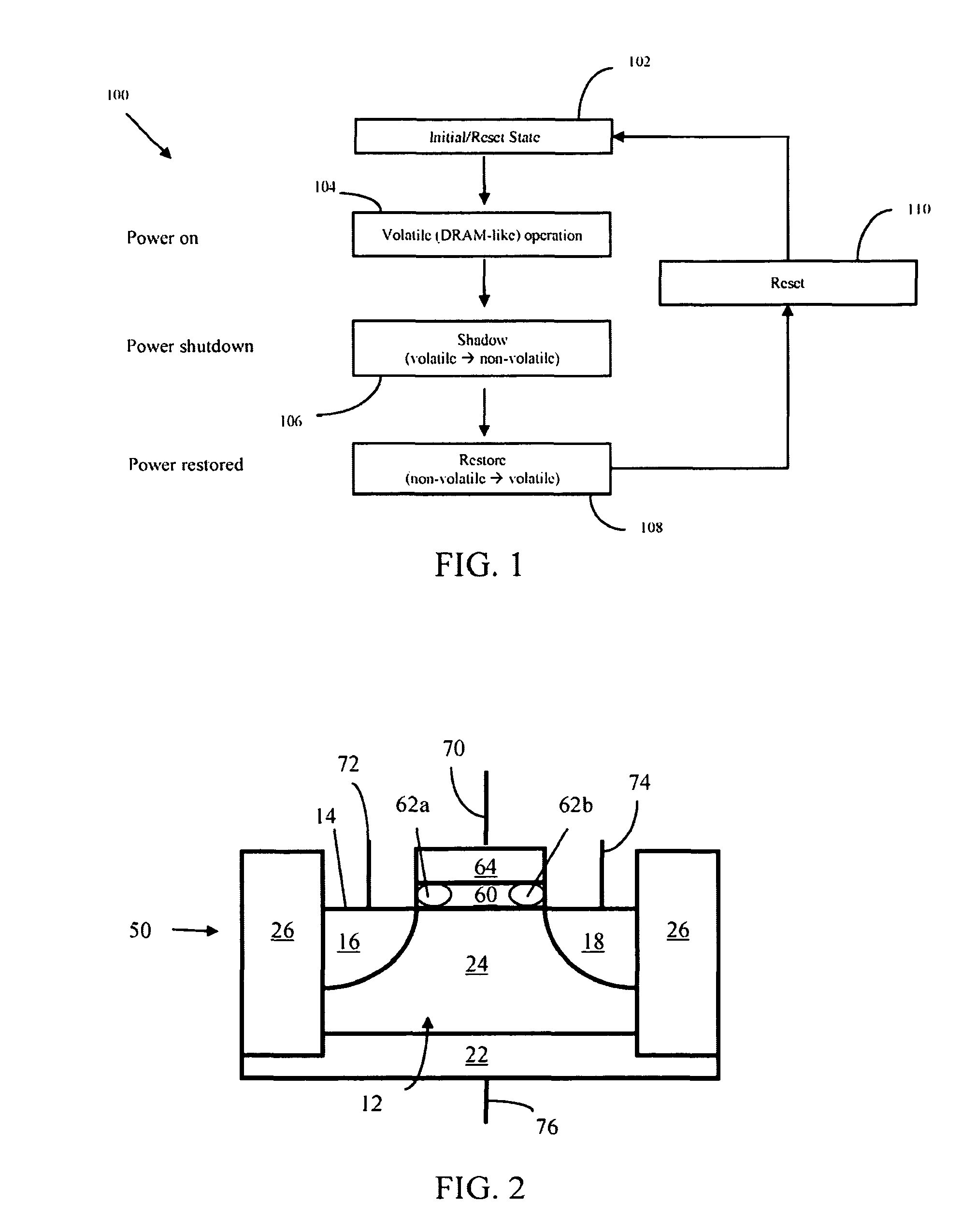

Semiconductor memory having both volatile and non-volatile functionality and method of operating

Semiconductor memory having both volatile and non-volatile modes and methods of operation. A semiconductor memory cell includes a substrate having a first conductivity type; a first region embedded in the substrate at a first location of the substrate and having a second conductivity type; a second region embedded in the substrate at a second location the substrate and have the second conductivity type, such that at least a portion of the substrate having the first conductivity type is located between the first and second locations and functions as a floating body to store data in volatile memory; a floating gate or trapping layer positioned in between the first and second locations and above a surface of the substrate and insulated from the surface by an insulating layer; the floating gate or trapping layer being configured to receive transfer of data stored by the volatile memory and store the data as nonvolatile memory in the floating gate or trapping layer upon interruption of power to the memory cell; and a control gate positioned above the floating gate or trapping layer and a second insulating layer between the floating gate or trapping layer and the control gate.

Owner:ZENO SEMICON

Deposition of charge trapping layers

ActiveUS20180122959A1Solid-state devicesSemiconductor/solid-state device manufacturingTrappingAluminum oxynitride

A semiconductor device and method for manufacturing the semiconductor device are disclosed. Specifically, the semiconductor device may include a charge trapping layer with improved retention and speed for VNAND applications. The charge trapping layer may comprise an aluminum nitride (AlN) or aluminum oxynitride (AlON) layer.

Owner:ASM IP HLDG BV

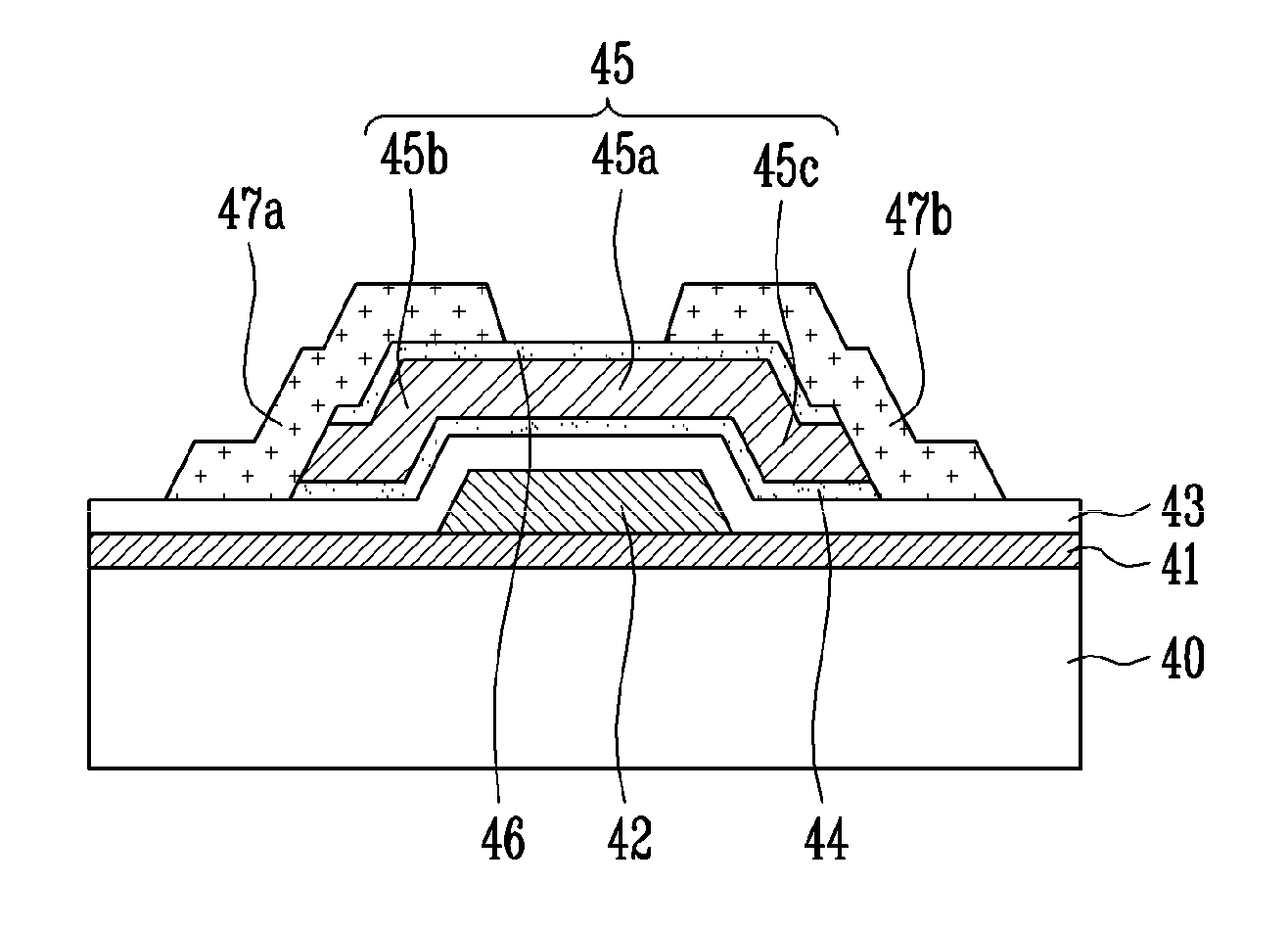

Thin film transistor, method of manufacturing the same and flat panel display device having the same

ActiveUS20090321731A1Improve featuresAvoid chargingSemiconductor/solid-state device manufacturingNon-linear opticsTrappingEngineering

A thin film transistor (TFT) using an oxide semiconductor as an active layer, a method of manufacturing the TFT, and a flat panel display device having the TFT include a gate electrode formed on a substrate; an active layer made of an oxide semiconductor and insulated from the gate electrode by a gate insulating layer; source and drain electrodes coupled to the active layer; and an interfacial stability layer formed on one or both surfaces of the active layer. In the TFT, the interfacial stability layer is formed of an oxide having a band gap of 3.0 to 8.0 eV. Since the interfacial stability layer has the same characteristic as a gate insulating layer and a passivation layer, chemically high interface stability is maintained. Since the interfacial stability layer has a band gap equal to or greater than that of the active layer, charge trapping is physically prevented.

Owner:SAMSUNG DISPLAY CO LTD

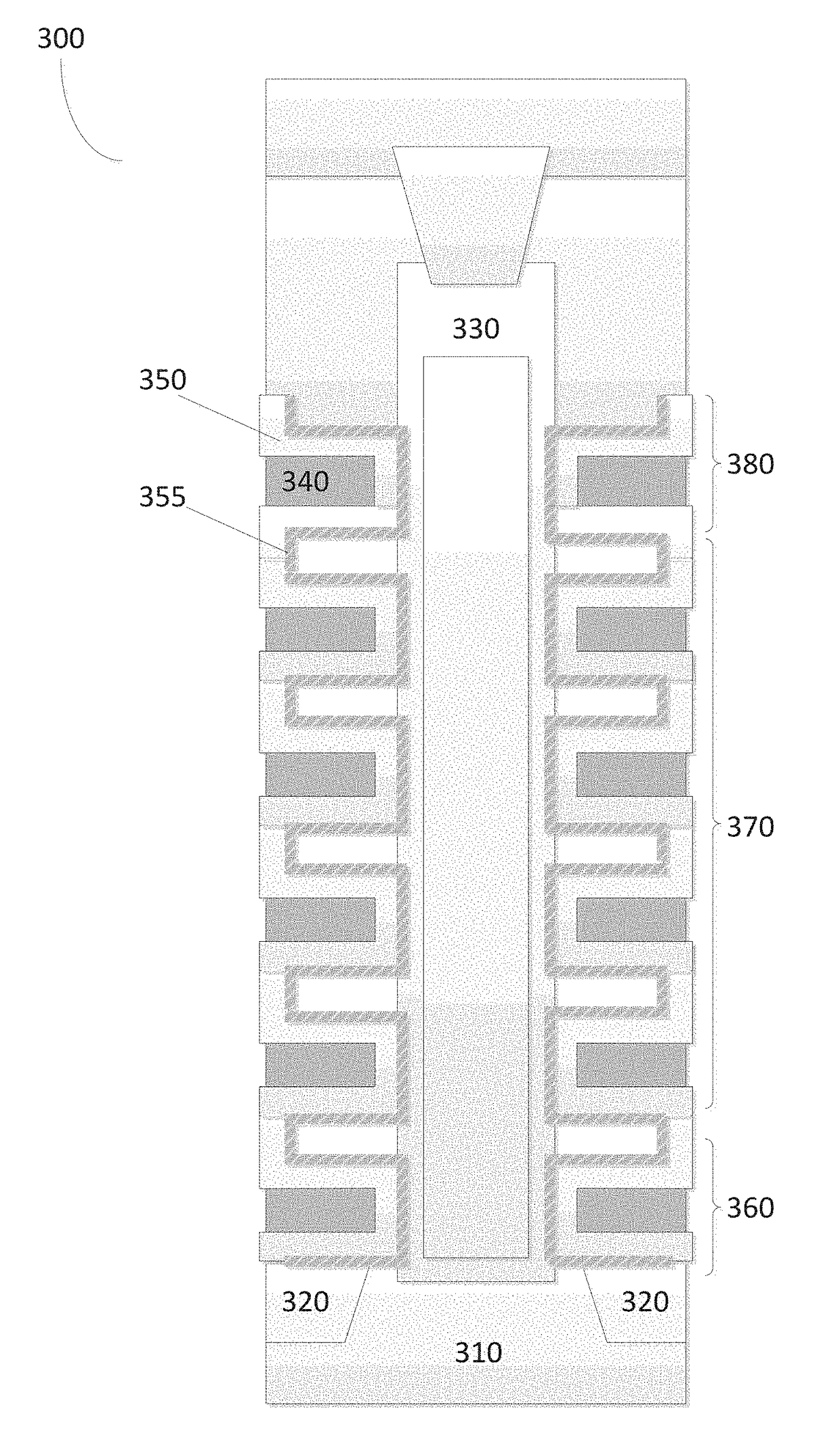

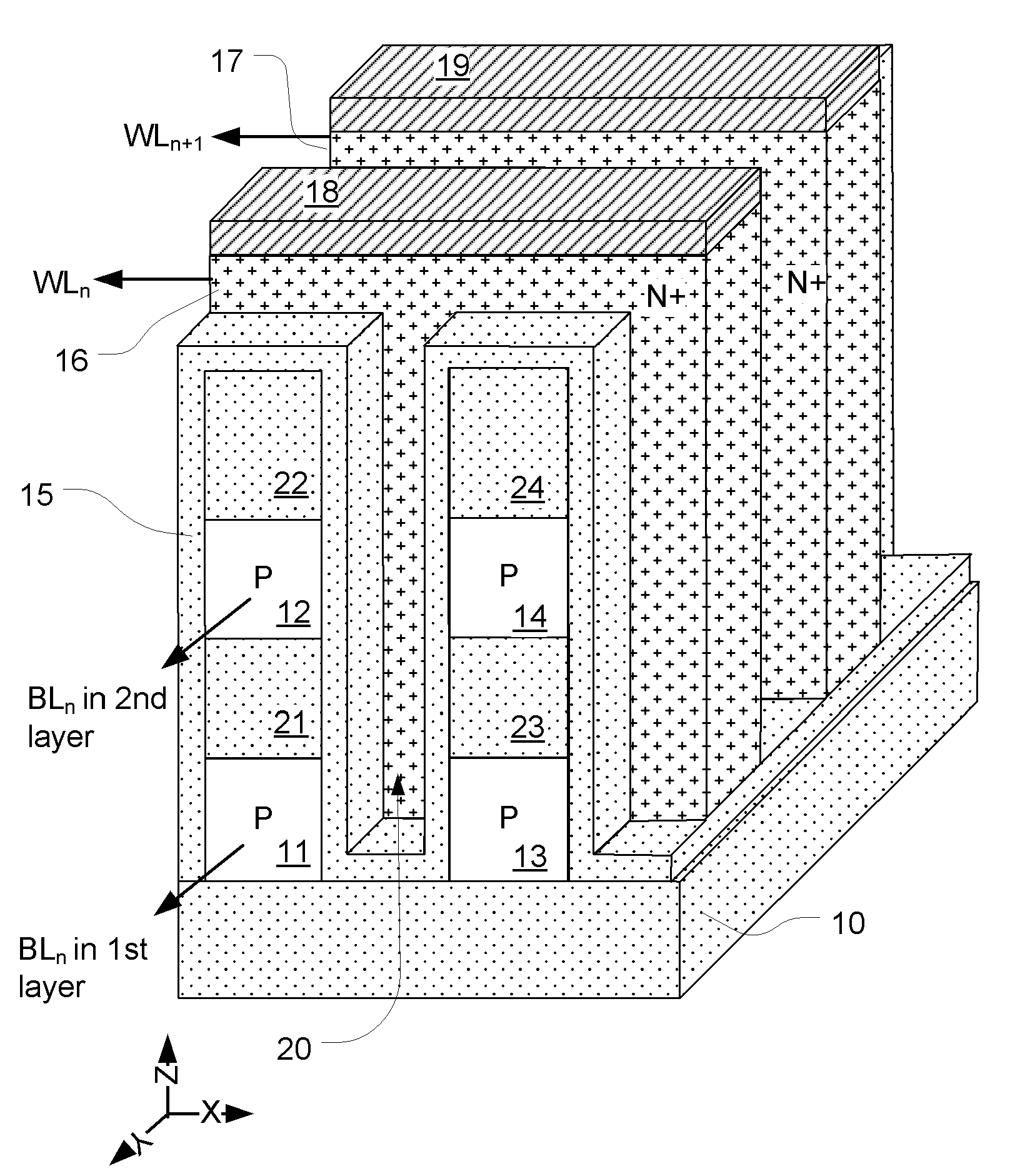

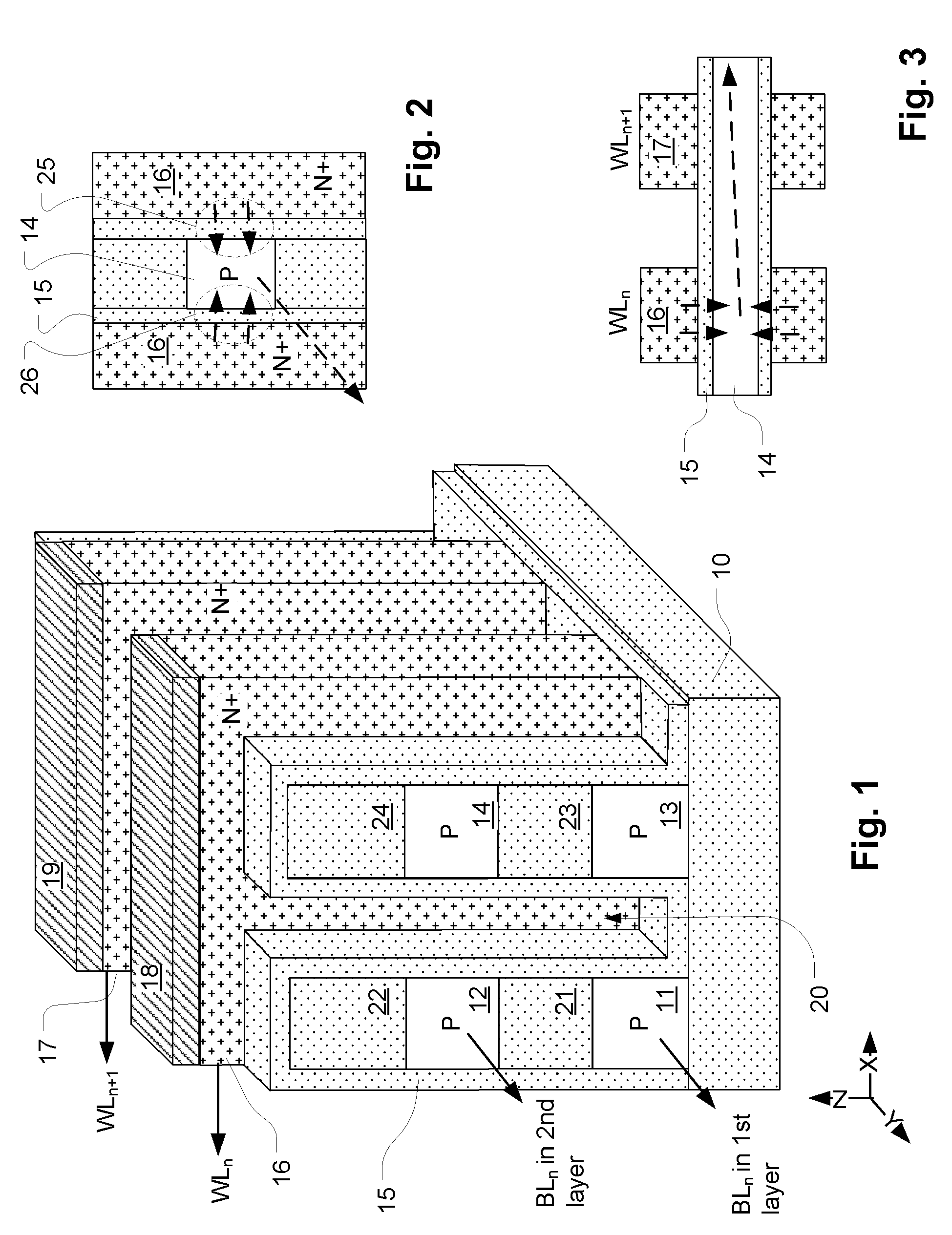

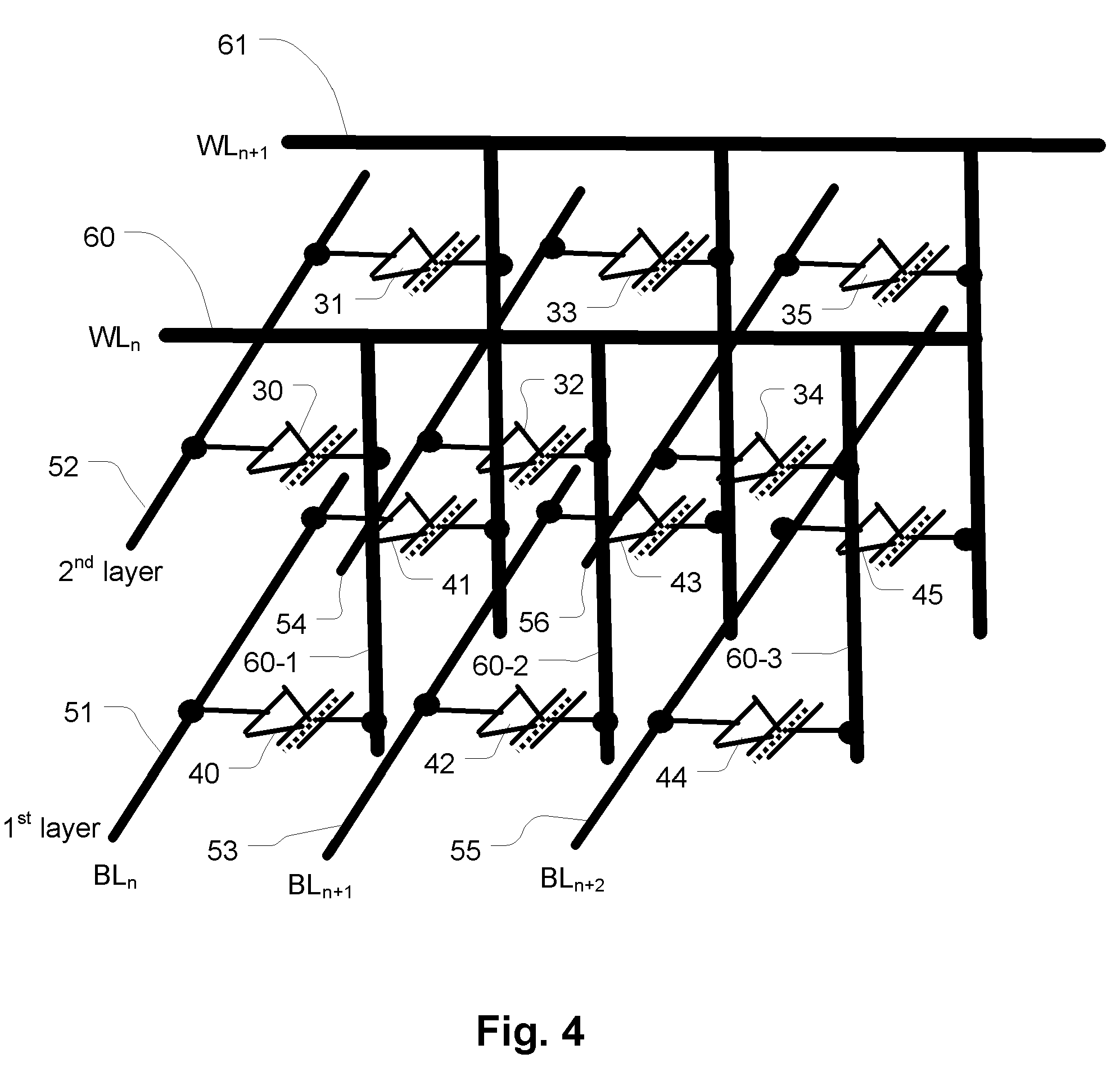

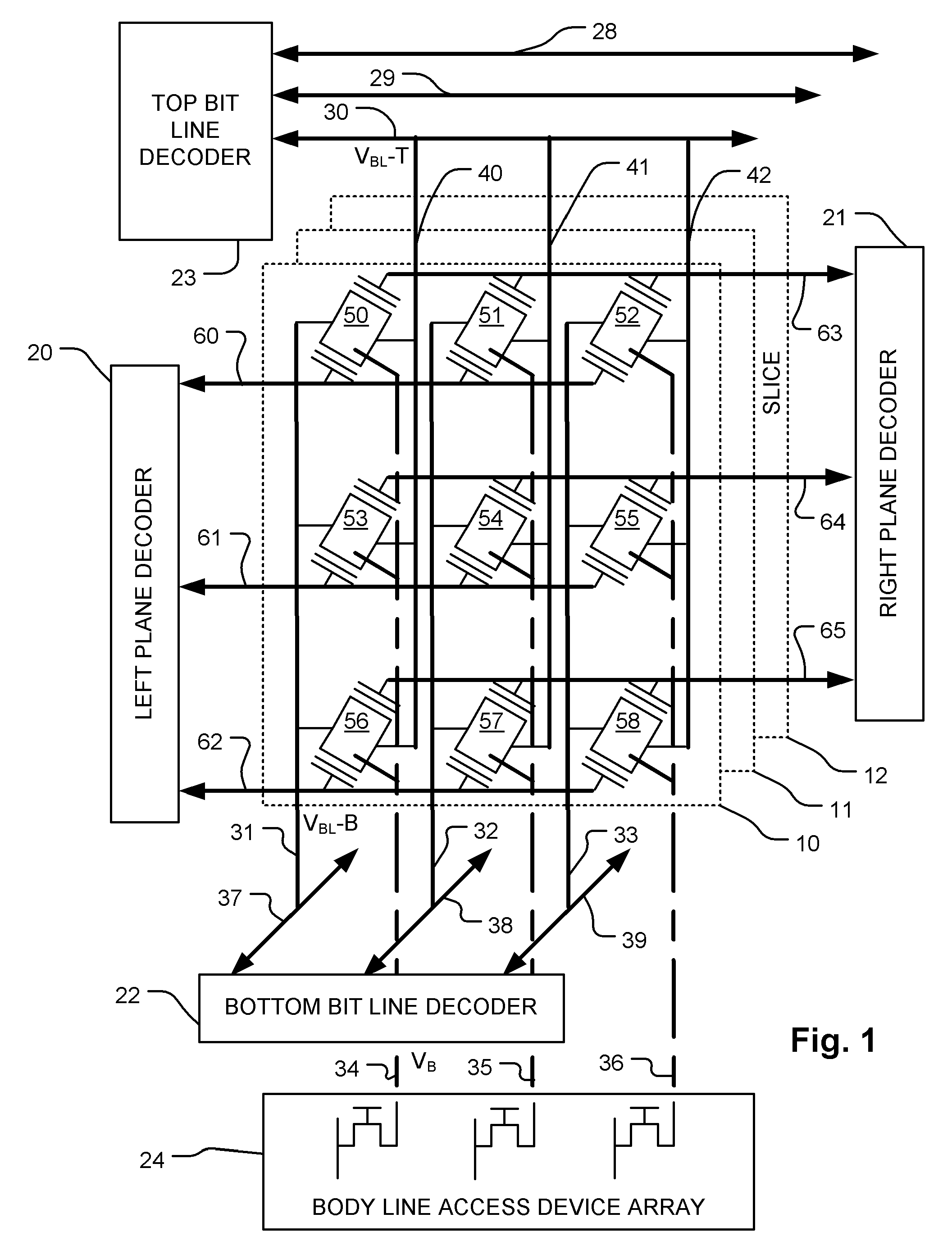

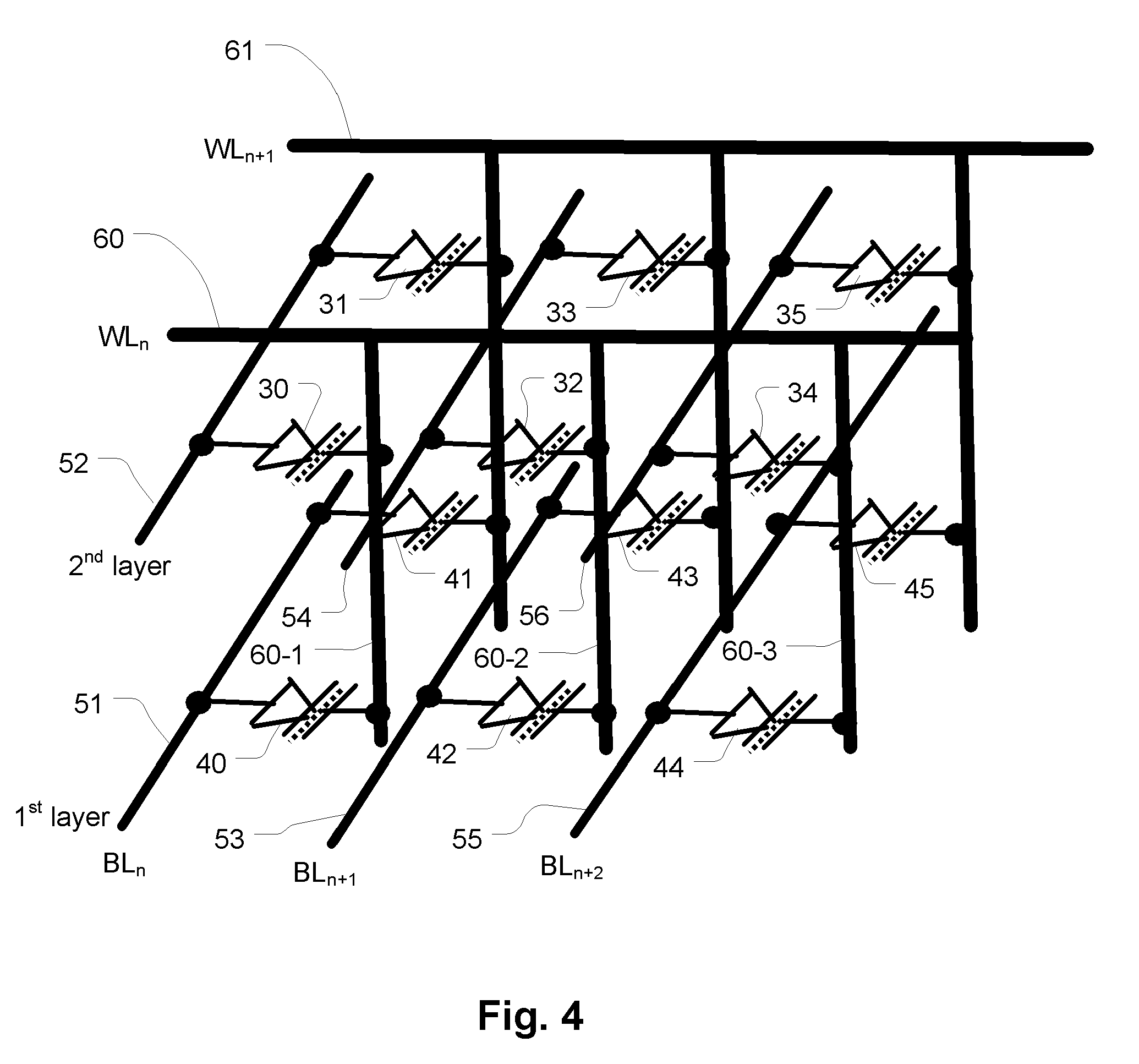

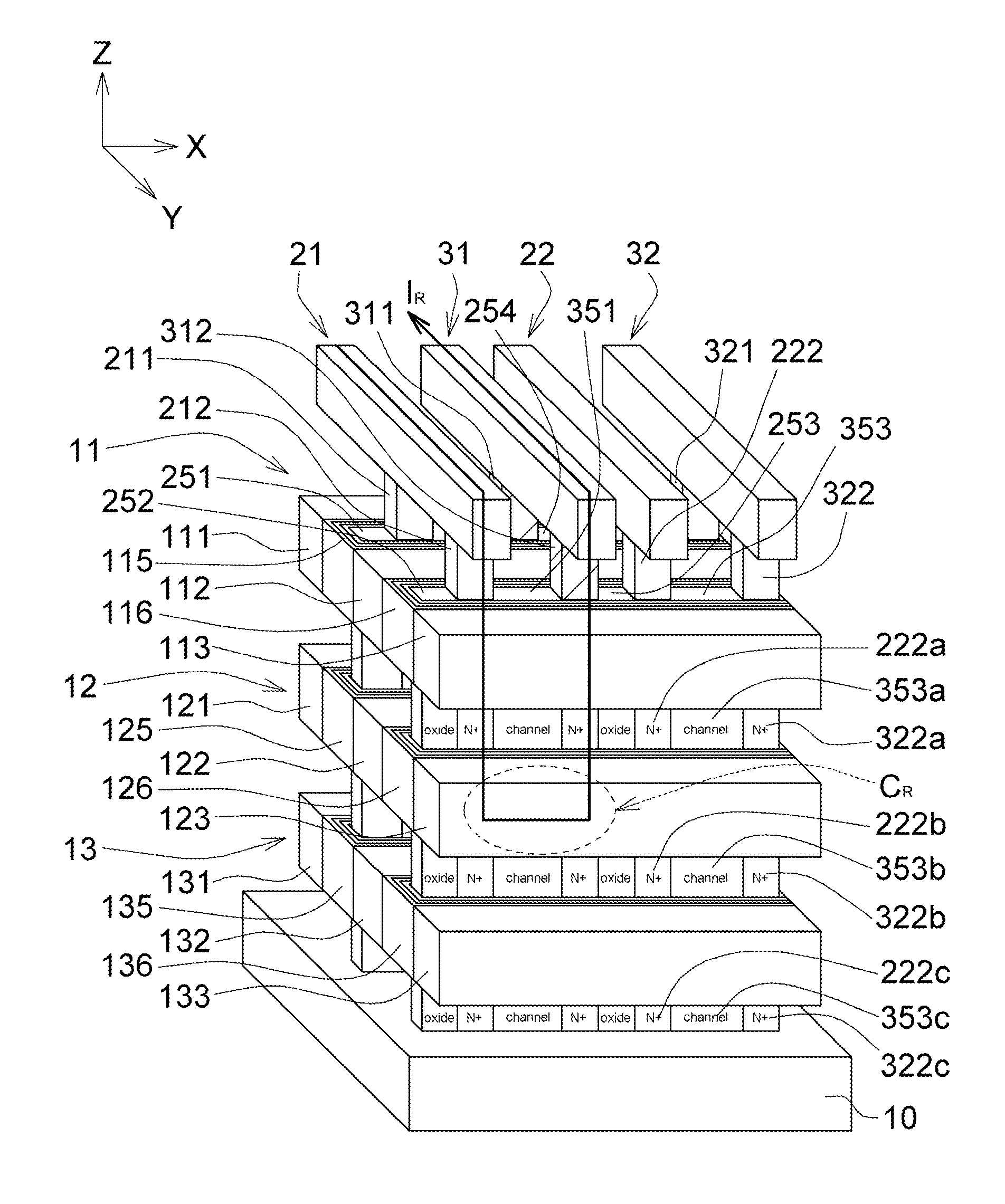

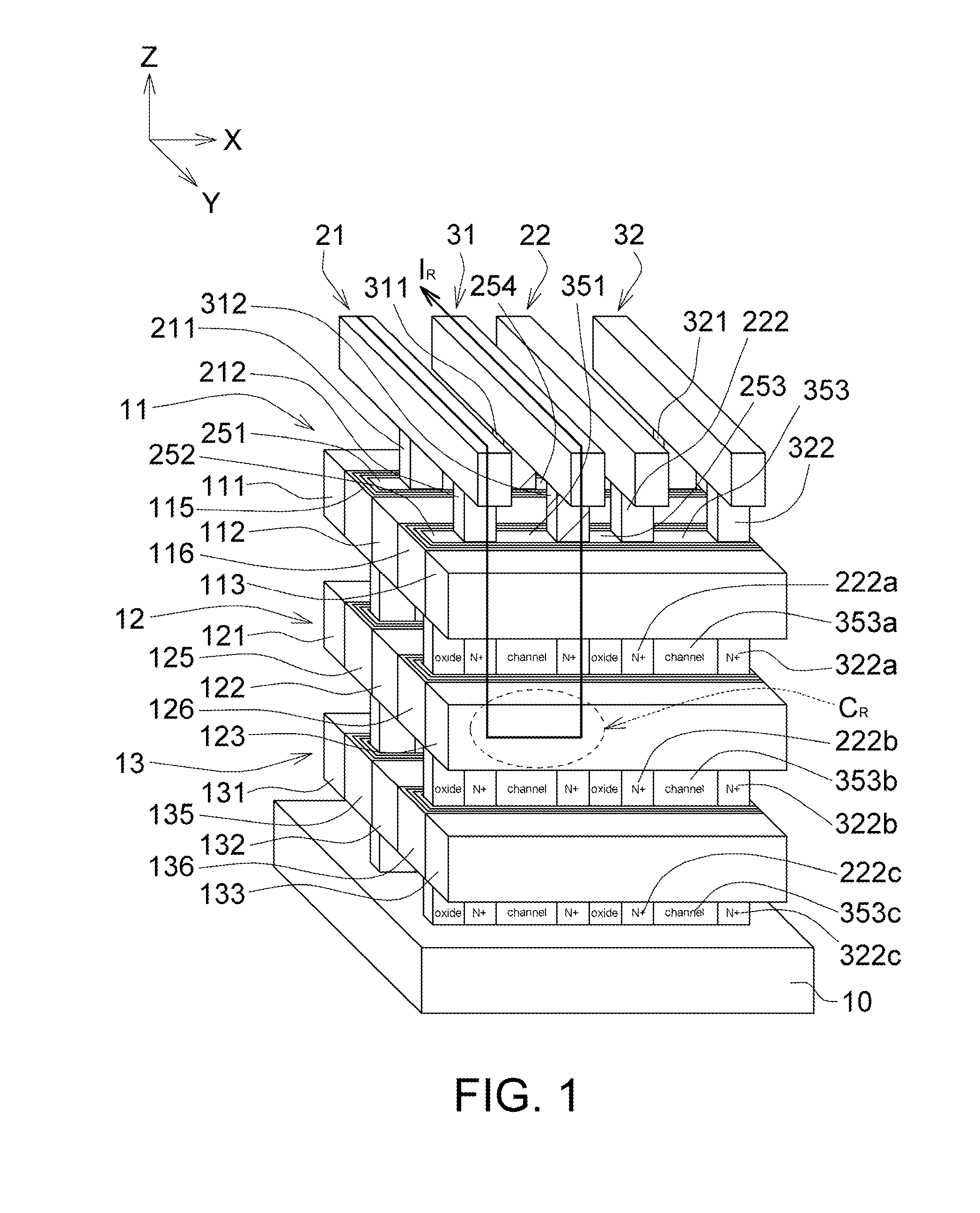

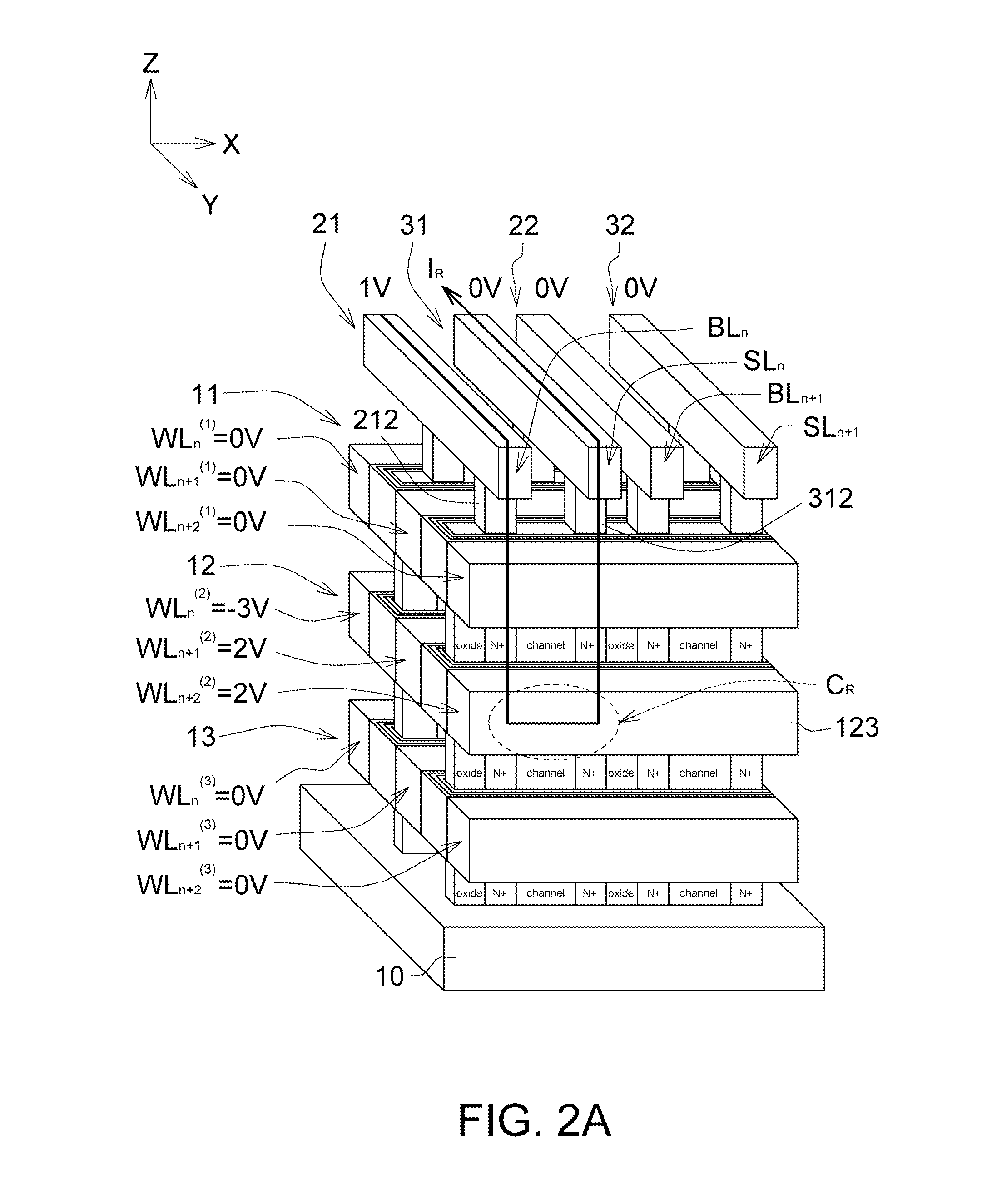

Integrated circuit self aligned 3D memory array and manufacturing method

A 3D memory device includes a plurality of ridge-shaped stacks, in the form of multiple strips of conductive material separated by insulating material, arranged as bit lines which can be coupled through decoding circuits to sense amplifiers. The strips of conductive material have side surfaces on the sides of the ridge-shaped stacks. A plurality of conductive lines arranged as word lines which can be coupled to row decoders, extends orthogonally over the plurality of ridge-shaped stacks. The conductive lines conform to the surface of the stacks. Memory elements lie in a multi-layer array of interface regions at cross-points between side surfaces of the conductive strips on the stacks and the conductive lines. The memory elements are programmable, like the anti-fuses or charge trapping structures. The 3D memory is made using only two critical masks for multiple layers.

Owner:MACRONIX INT CO LTD

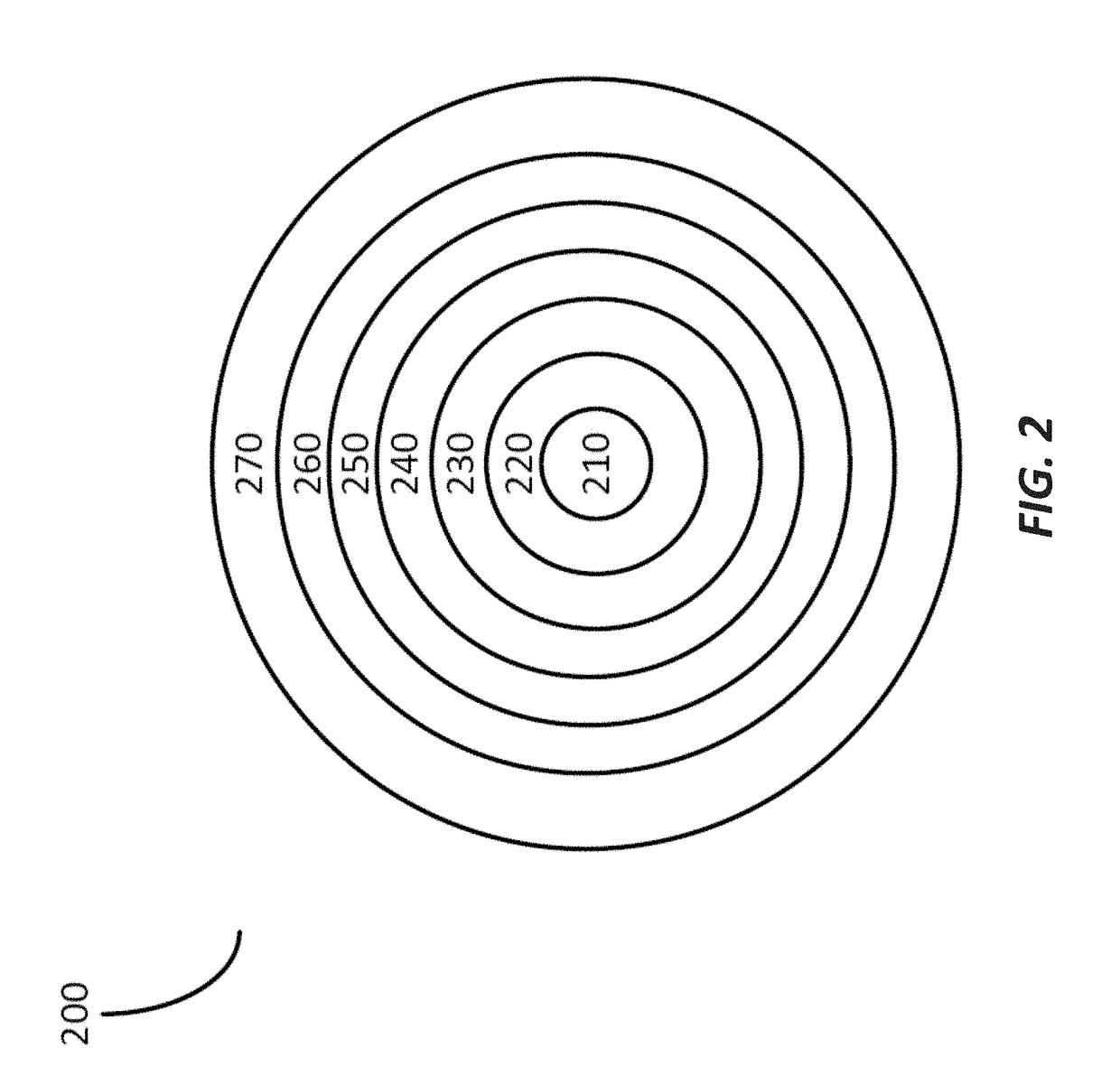

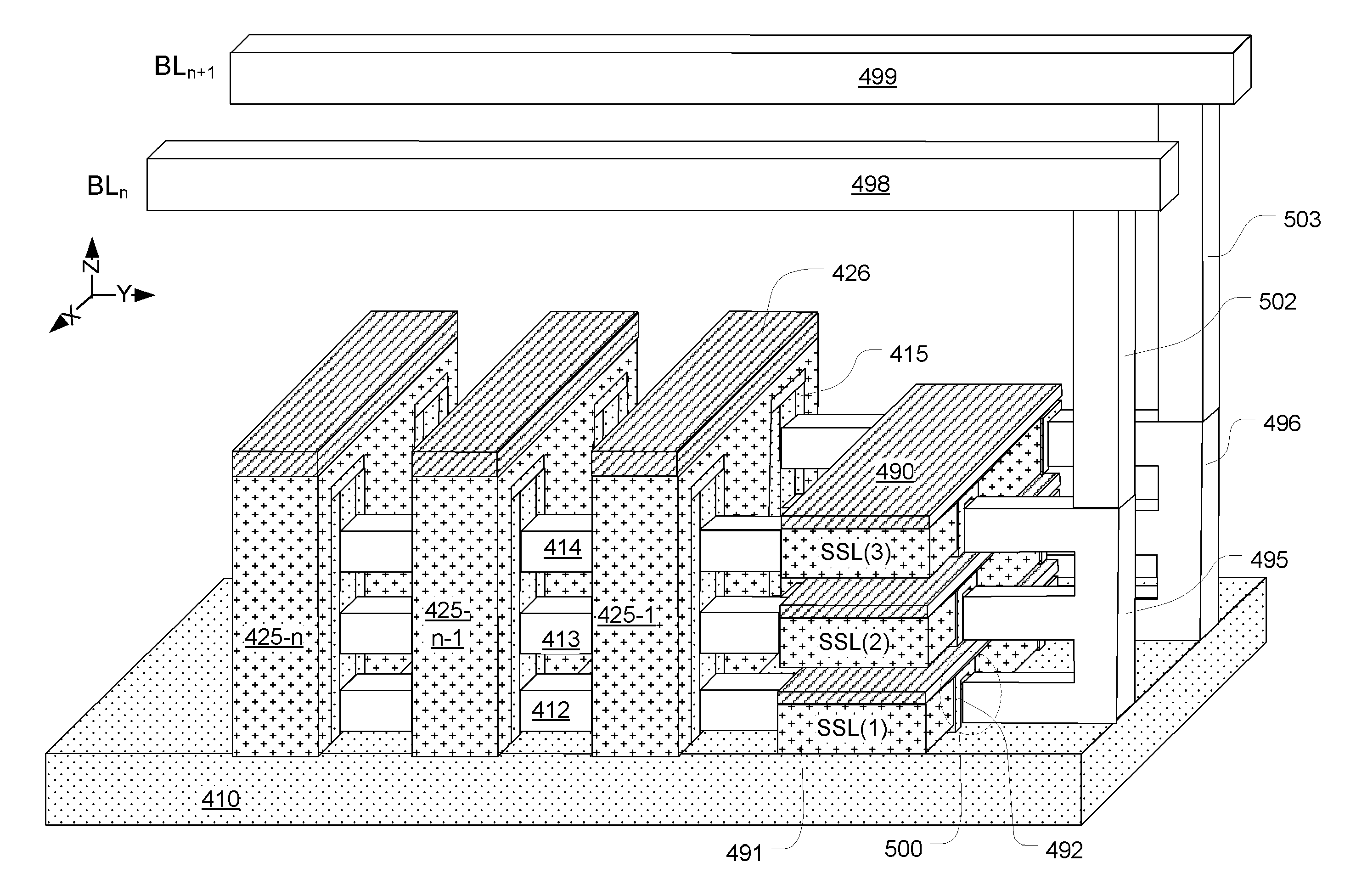

3D memory array arranged for FN tunneling program and erase

A 3D memory device includes an array of semiconductor body pillars and bit line pillars, dielectric charge trapping structures, and a plurality of levels of word line structures arranged orthogonally to the array of semiconductor body pillars and bit line pillars. The semiconductor body pillars have corresponding bit line pillars on opposing first and second sides, providing source and drain terminals. The semiconductor body pillars have first and second channel surfaces on opposing third and fourth sides. Dielectric charge trapping structures overlie the first and second channel surfaces, providing data storage sites on two sides of each semiconductor body pillar in each level of the 3D array. The device can be operated as a 3D AND-decoded flash memory.

Owner:MACRONIX INT CO LTD

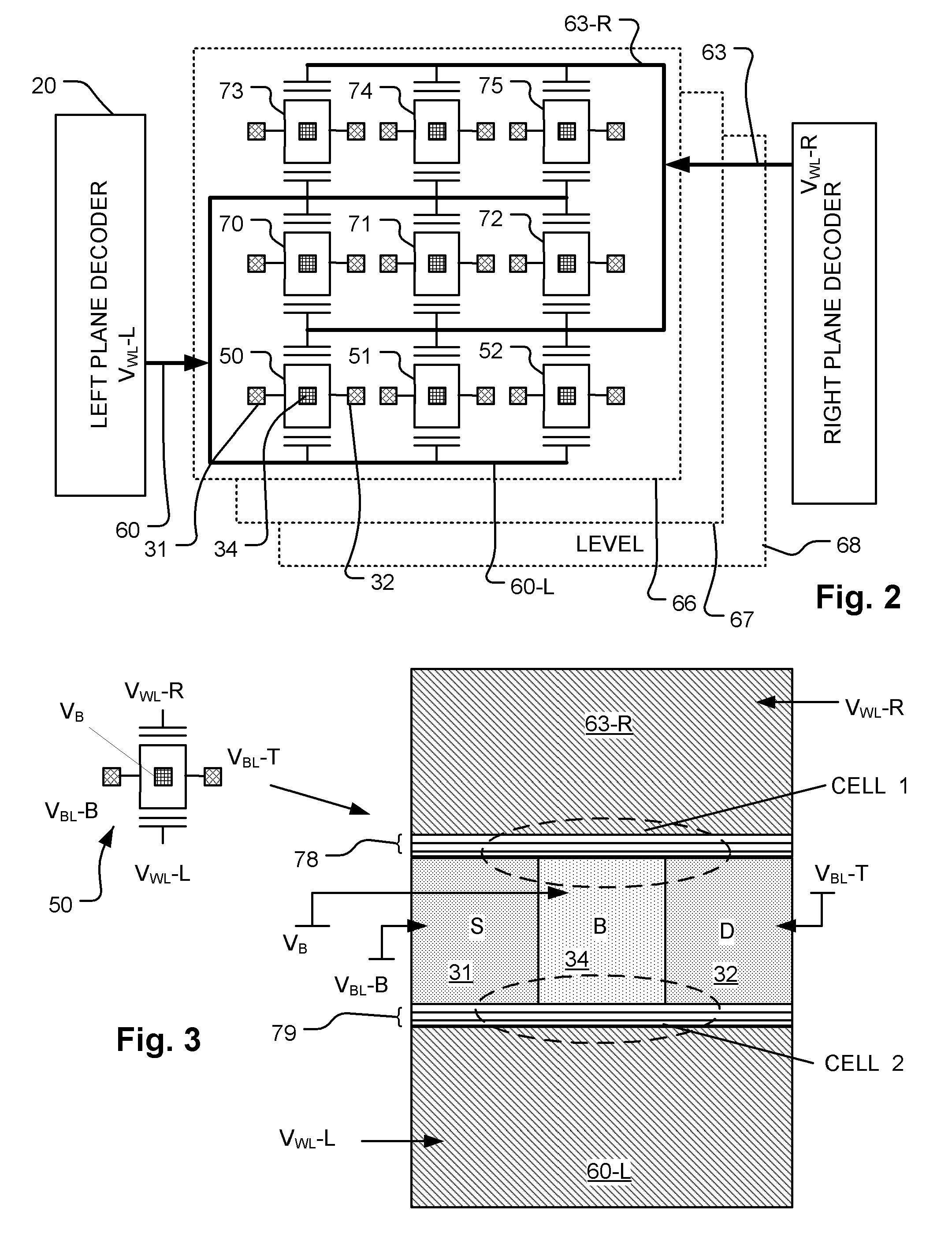

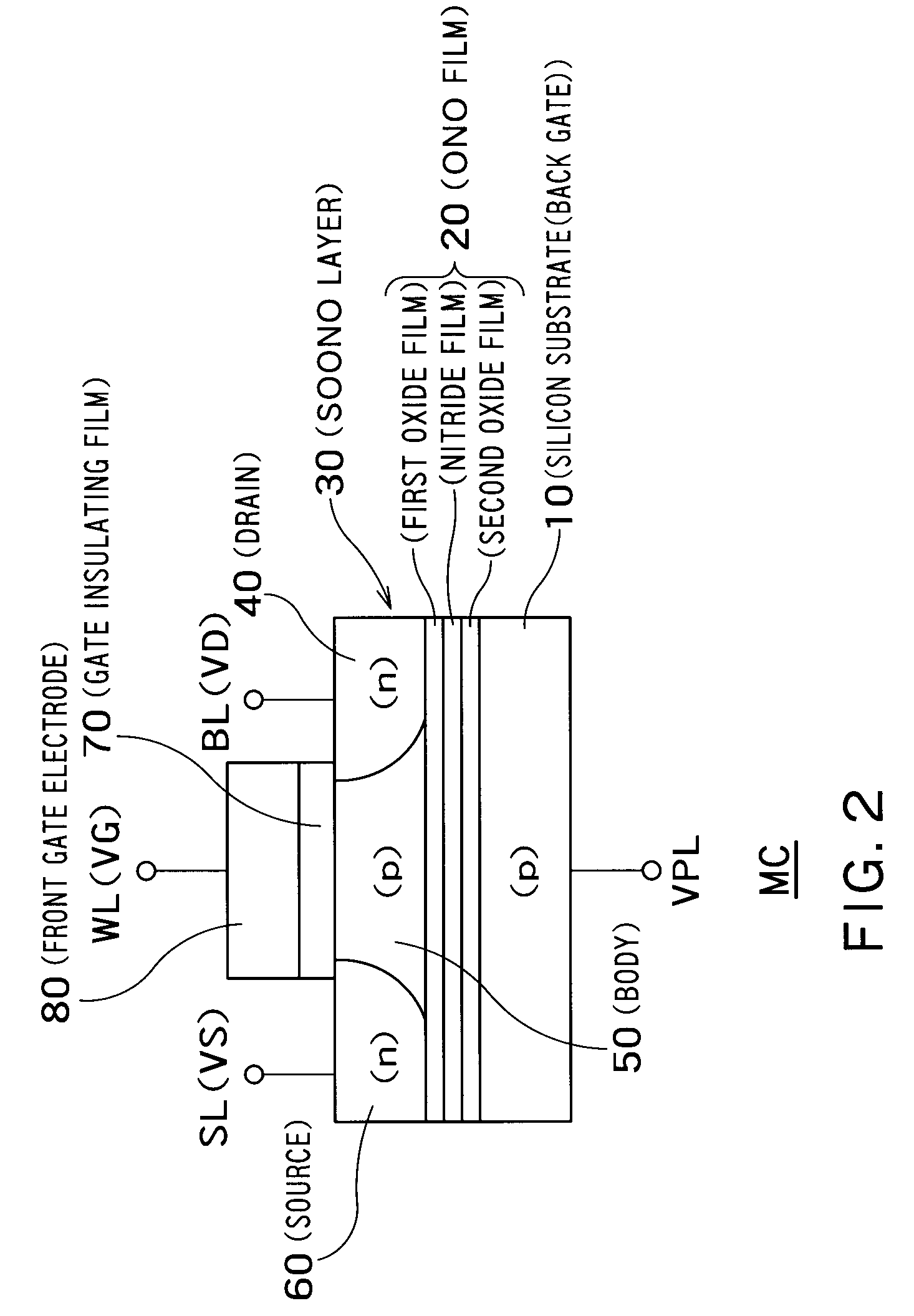

Semiconductor memory device

This disclosure concerns a memory comprising a charge trapping film; a gate insulating film; a back gate on the charge trapping film; a front gate on the gate insulating film; and a body region provided between a drain and a source, wherein the memory includes a first storage state for storing data depending on the number of majority carriers in the body region and a second storage state for storing data depending on the amount of charges in the charge trapping film, and the memory is shifted from the first storage state to the second storage state by converting the number of majority carriers in the body region into the amount of charges in the charge trapping film or from the second storage state to the first storage state by converting the amount of charges in the charge trapping film into the number of majority carriers in the body region.

Owner:TOSHIBA MEMORY CORP

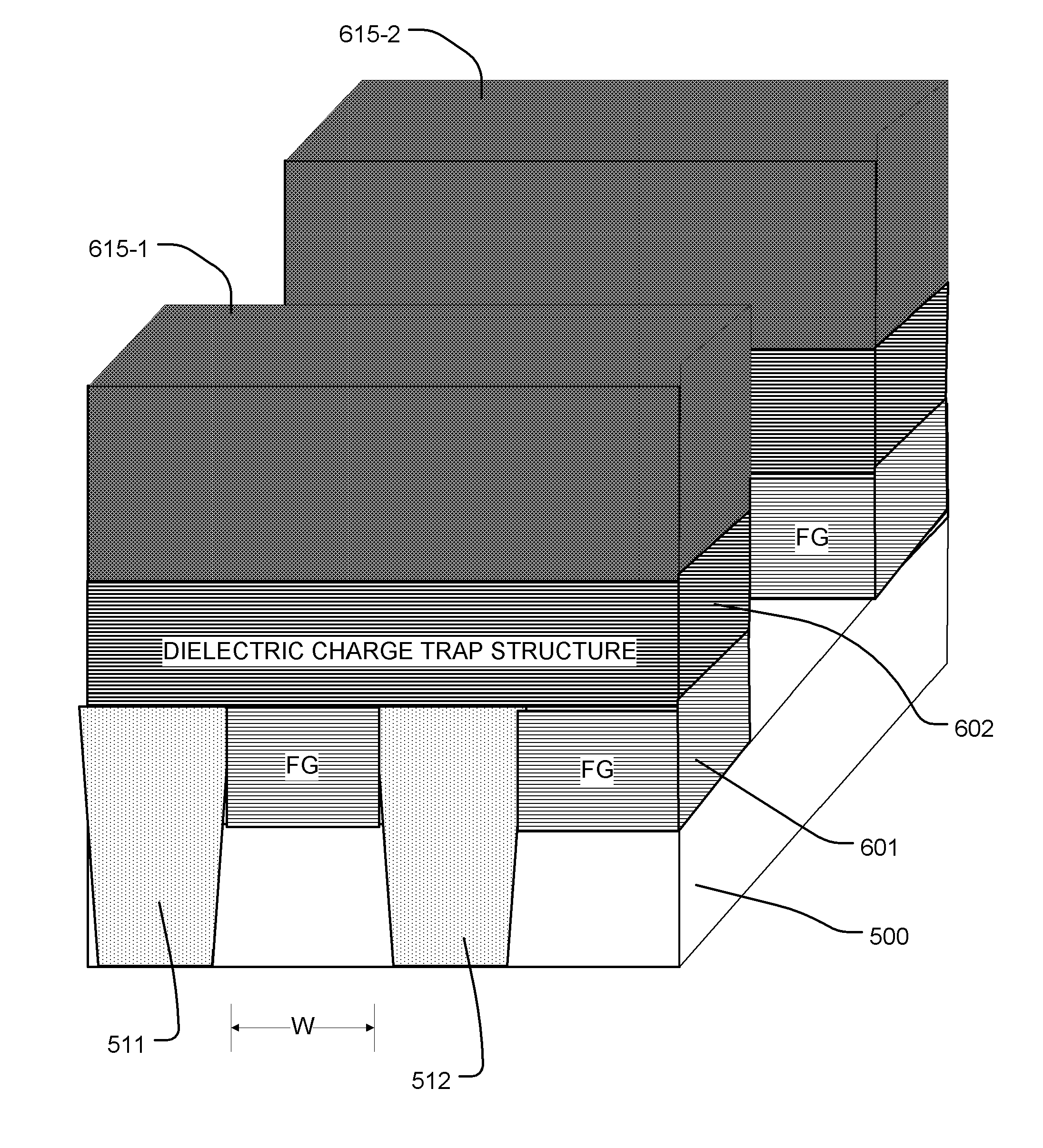

Floating gate memory device with interpoly charge trapping structure

ActiveUS20090262583A1Constant threshold voltageReduce distractionsTransistorSolid-state devicesElectrical conductorTrapping

A charge trapping floating gate is described with asymmetric tunneling barriers. The memory cell includes a source region and a drain region separated by a channel region. A first tunneling barrier structure is disposed above the channel region. A floating gate is disposed above the first tunneling barrier structure covering the channel region. A second tunneling barrier is disposed above the floating gate. A dielectric charge trapping structure disposed above the second tunneling barrier and a blocking dielectric structure is disposed above the charge trapping structure. A top conductive layer disposed above the top dielectric structure acts as a gate. The second tunneling barrier is a more efficient conductor of tunneling current, under bias conditions applied for programming and erasing the memory cell, than the first tunneling barrier structure.

Owner:MACRONIX INT CO LTD

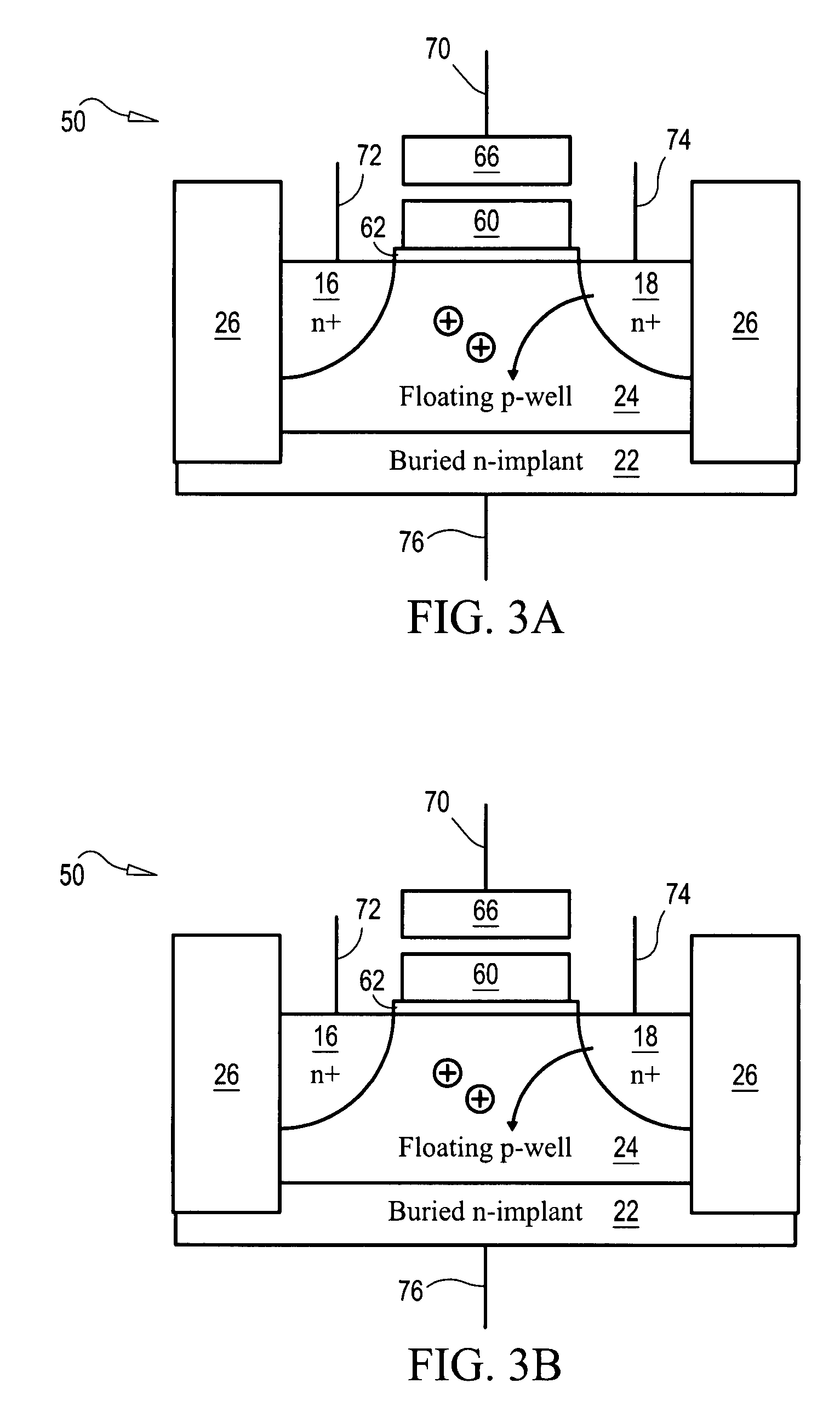

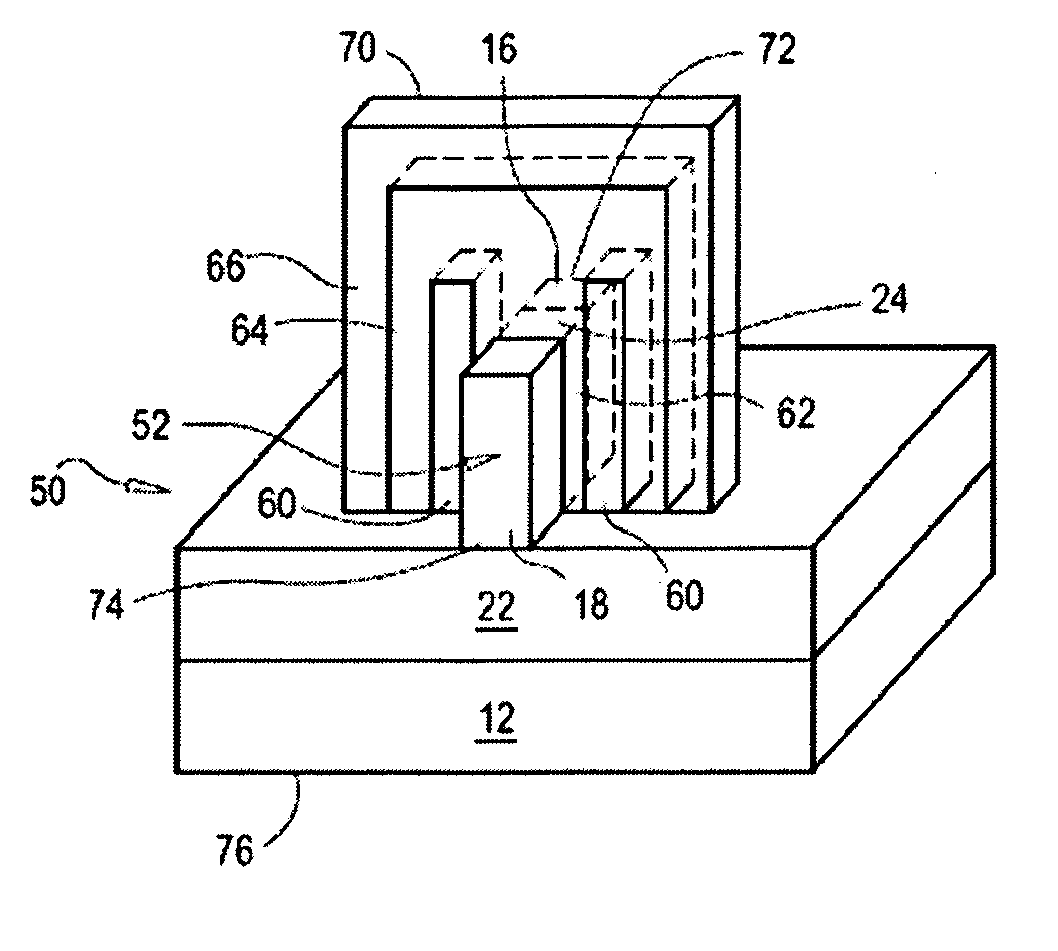

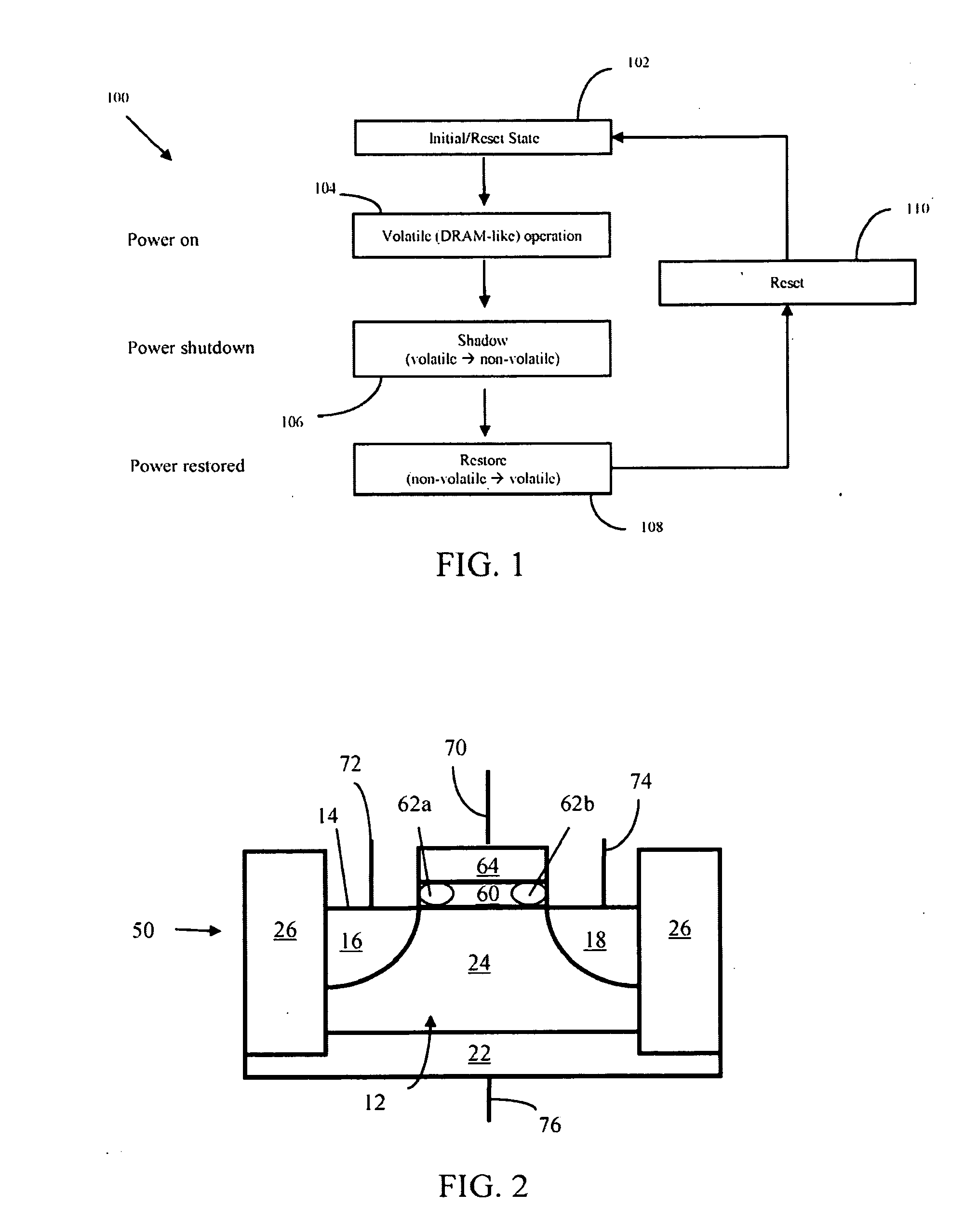

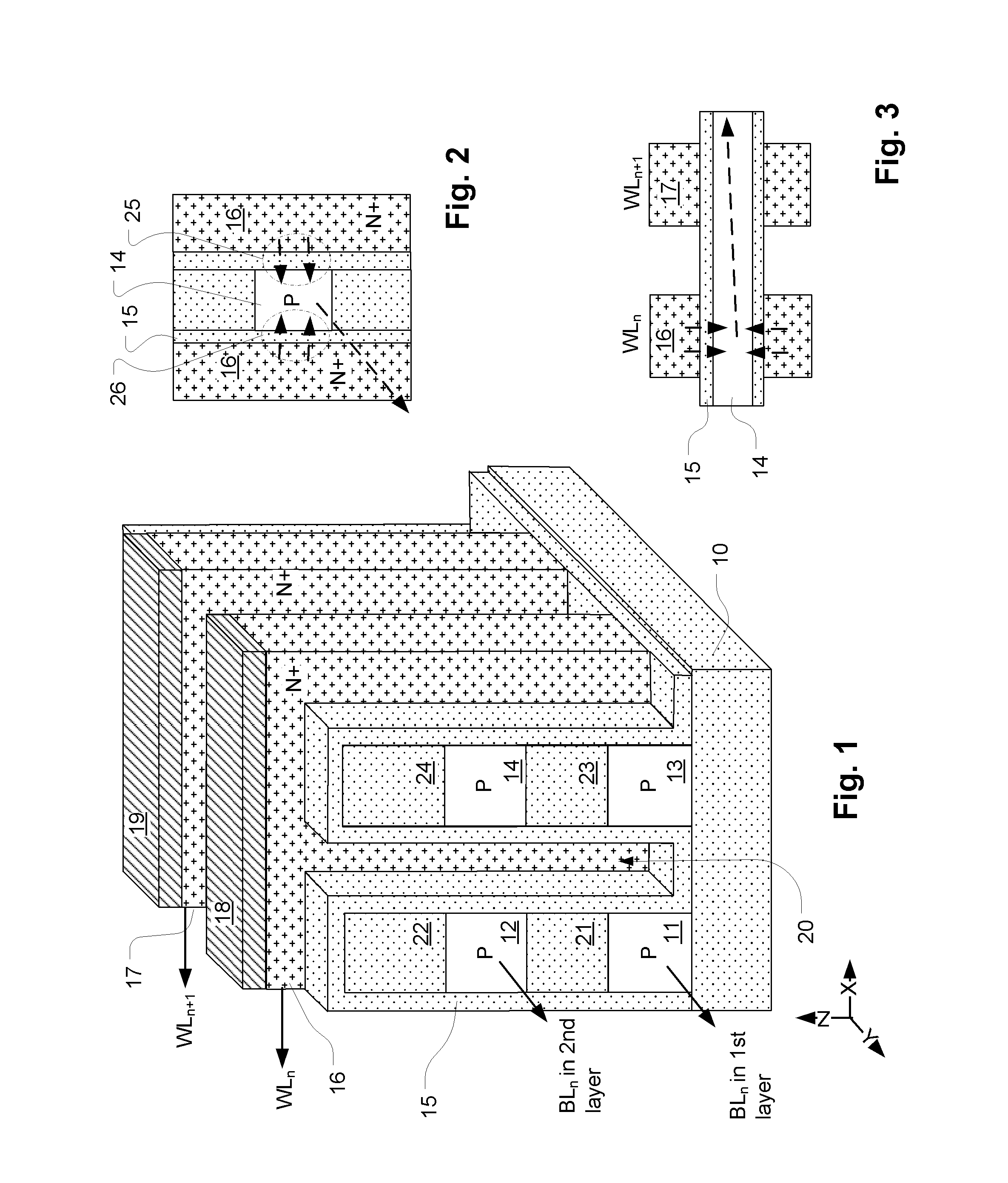

Semiconductor memory having both volatile and non-volatile functionality and method of operating

Semiconductor memory having both volatile and non-volatile modes and methods of operation. A semiconductor memory cell includes a fin structure extending from a substrate, the fin structure including a floating substrate region having a first conductivity type configured to store data as volatile memory; first and second regions interfacing with the floating substrate region, each of the first and second regions having a second conductivity type; first and second floating gates or trapping layers positioned adjacent opposite sides of the floating substrate region; a first insulating layer positioned between the floating substrate region and the floating gates or trapping layers, the floating gates or trapping layers being configured to receive transfer of data stored by the volatile memory and store the data as nonvolatile memory in the floating gates or trapping layers upon interruption of power to the memory cell; a control gate wrapped around the floating gates or trapping layers and the floating substrate region; and a second insulating layer positioned between the floating gates or trapping layers and the control gate; the substrate including an isolation layer that isolates the floating substrate region from a portion of the substrate below the isolation layer.

Owner:ZENO SEMICON

Semiconductor memory having both volatile and non-volatile functionality and method of operating

Semiconductor memory having both volatile and non-volatile modes and methods of operation. A semiconductor memory cell includes a substrate having a first conductivity type; a first region embedded in the substrate at a first location of the substrate and having a second conductivity type; a second region embedded in the substrate at a second location the substrate and have the second conductivity type, such that at least a portion of the substrate having the first conductivity type is located between the first and second locations and functions as a floating body to store data in volatile memory; a floating gate or trapping layer positioned in between the first and second locations and above a surface of the substrate and insulated from the surface by an insulating layer; the floating gate or trapping layer being configured to receive transfer of data stored by the volatile memory and store the data as nonvolatile memory in the floating gate or trapping layer upon interruption of power to the memory cell; and a control gate positioned above the floating gate or trapping layer and a second insulating layer between the floating gate or trapping layer and the control gate.

Owner:ZENO SEMICON

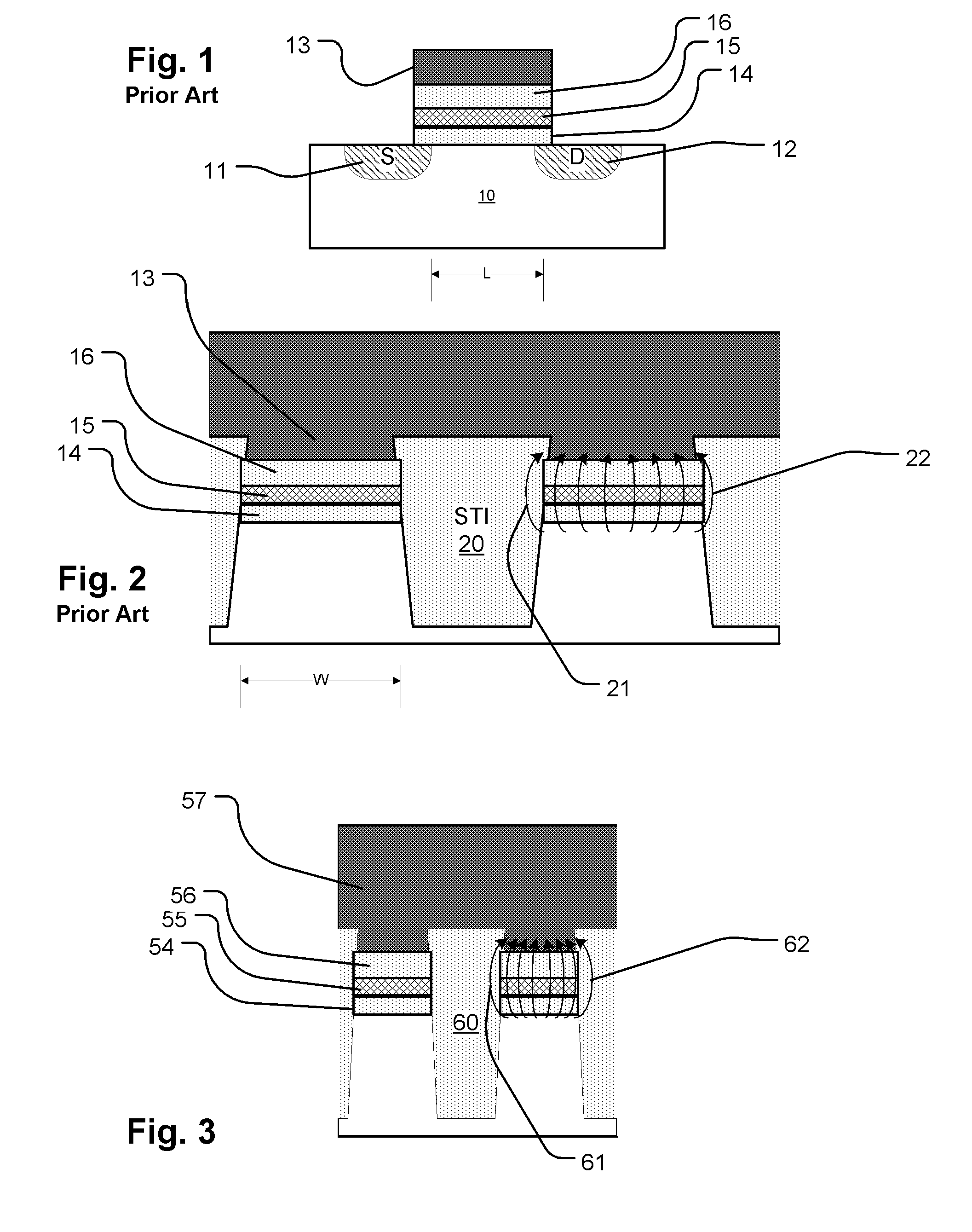

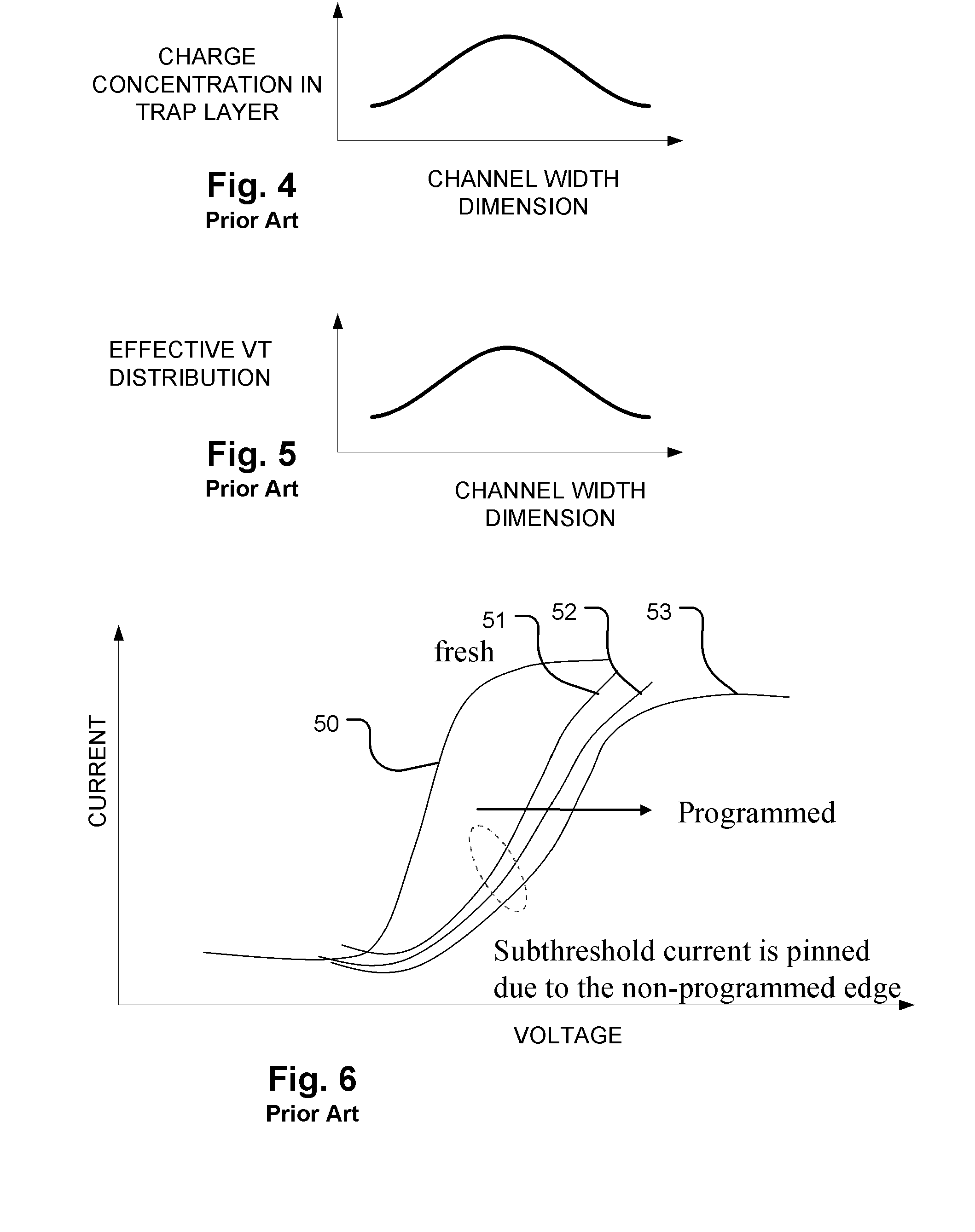

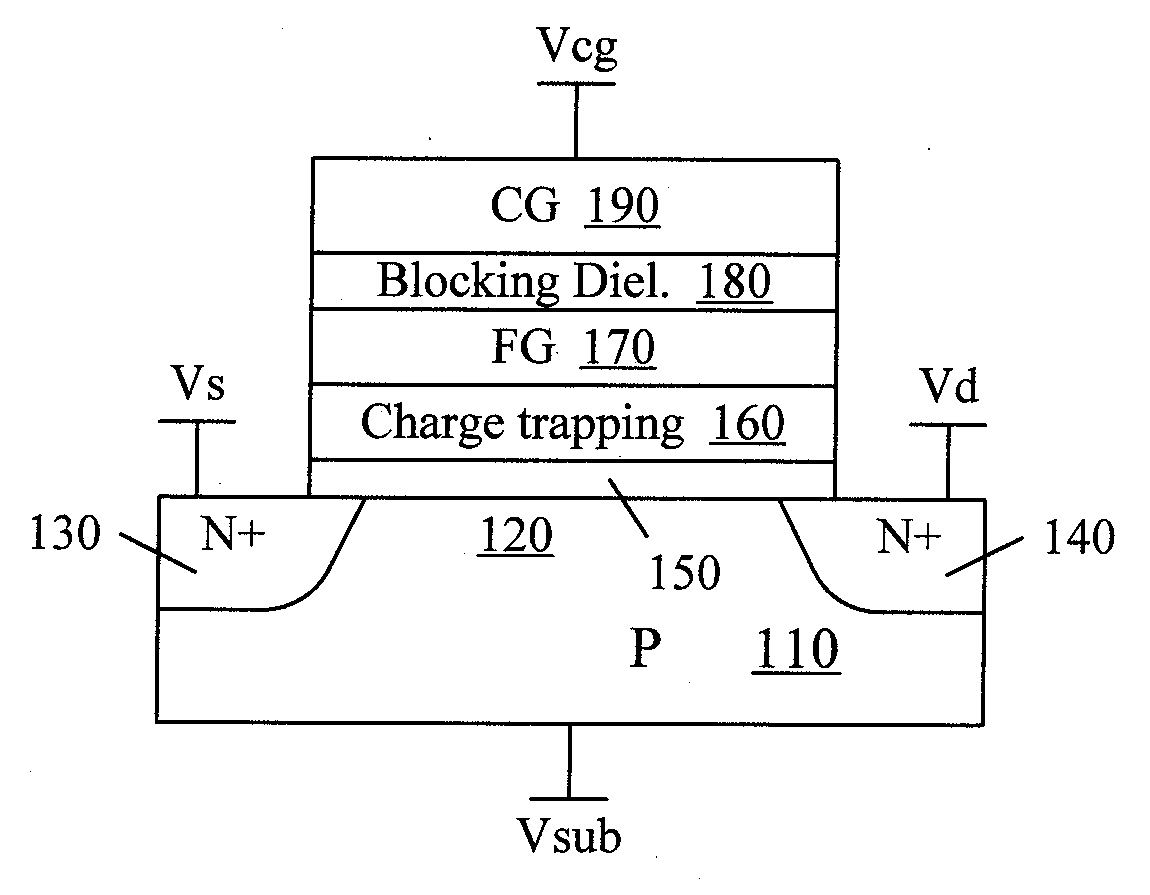

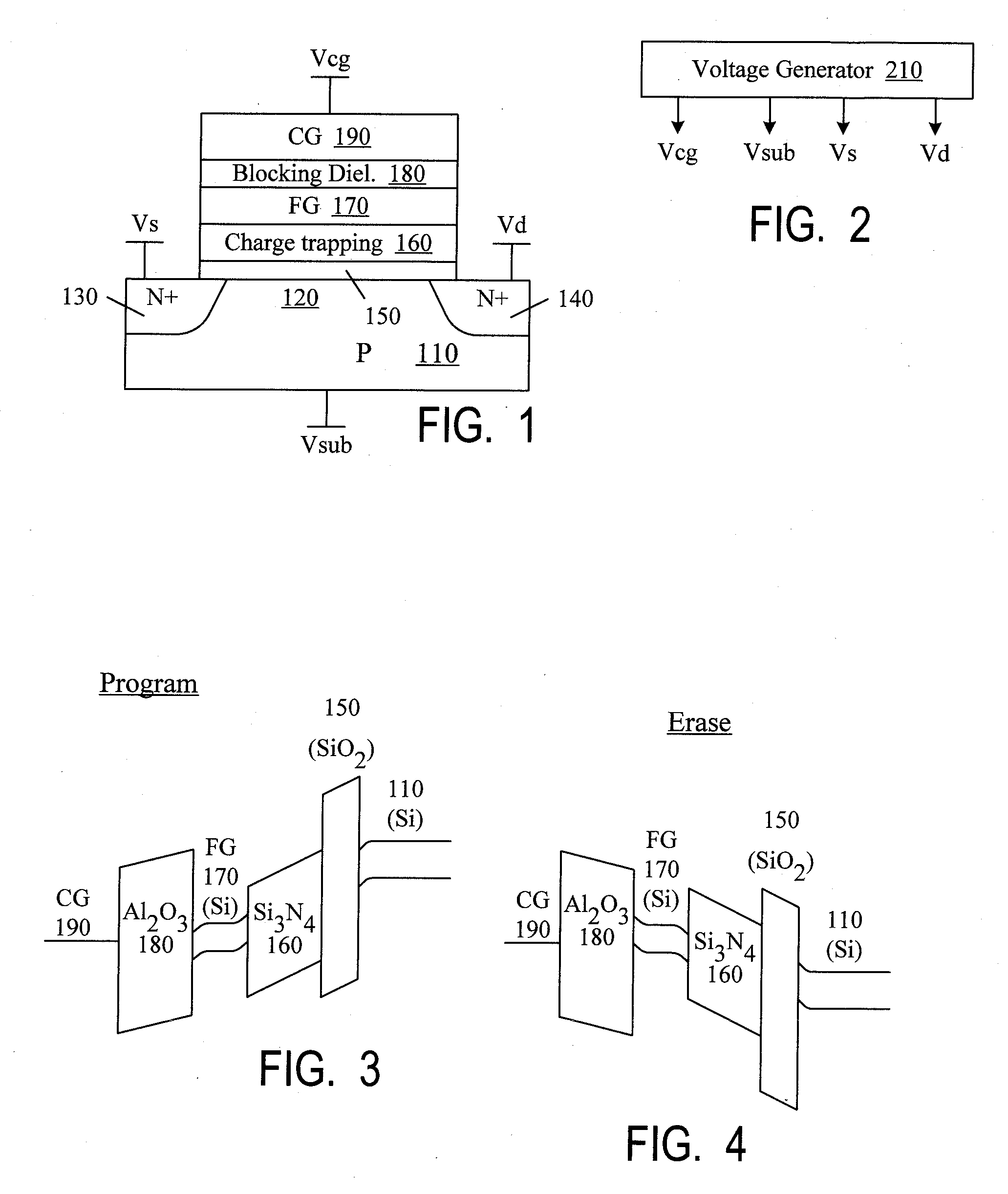

Nonvolatile memories which combine a dielectric, charge-trapping layer with a floating gate

InactiveUS20090096009A1Increased charge storage capacityGate thickness can be reducedTransistorSemiconductor/solid-state device manufacturingTrappingNon-volatile memory

A nonvolatile memory cell stores at least 50% of the charge in a dielectric, charge-trapping layer (160) and at least 20% of the charge in a floating gate (170). The floating gate is at most 20 nm thick.

Owner:PROMOS TECH PTE LTD

Semiconductor memory having both volatile and non-volatile functionality and method of operating

Semiconductor memory having both volatile and non-volatile modes and methods of operation. A semiconductor memory cell includes a fin structure extending from a substrate, the fin structure including a floating substrate region having a first conductivity type configured to store data as volatile memory; first and second regions interfacing with the floating substrate region, each of the first and second regions having a second conductivity type; first and second floating gates or trapping layers positioned adjacent opposite sides of the floating substrate region; a first insulating layer positioned between the floating substrate region and the floating gates or trapping layers, the floating gates or trapping layers being configured to receive transfer of data stored by the volatile memory and store the data as nonvolatile memory in the floating gates or trapping layers upon interruption of power to the memory cell; a control gate wrapped around the floating gates or trapping layers and the floating substrate region; and a second insulating layer positioned between the floating gates or trapping layers and the control gate; the substrate including an isolation layer that isolates the floating substrate region from a portion of the substrate below the isolation layer.

Owner:ZENO SEMICON

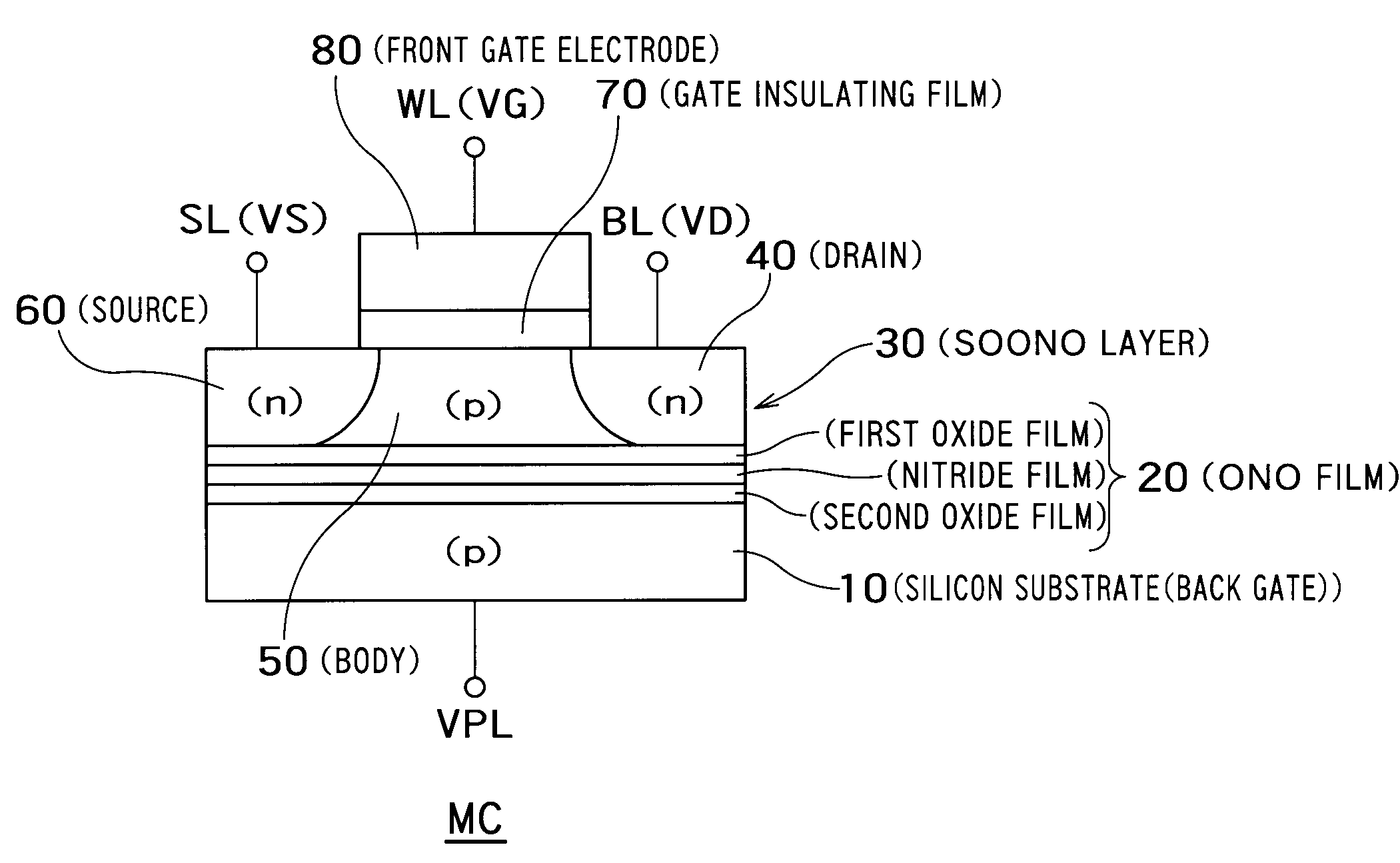

Semiconductor memory having volatile and multi-bit, non-volatile functionality and methods of operating

A semiconductor memory cell, semiconductor memory devices comprising a plurality of the semiconductor memory cells, and methods of using the semiconductor memory cell and devices are described. A semiconductor memory cell includes a substrate having a first conductivity type; a first region embedded in the substrate at a first location of the substrate and having a second conductivity type; a second region embedded in the substrate at a second location of the substrate and have the second conductivity type, such that at least a portion of the substrate having the first conductivity type is located between the first and second locations and functions as a floating body to store data in volatile memory; a trapping layer positioned in between the first and second locations and above a surface of the substrate; the trapping layer comprising first and second storage locations being configured to store data as nonvolatile memory independently of one another; and a control gate positioned above the trapping layer.

Owner:ZENO SEMICON

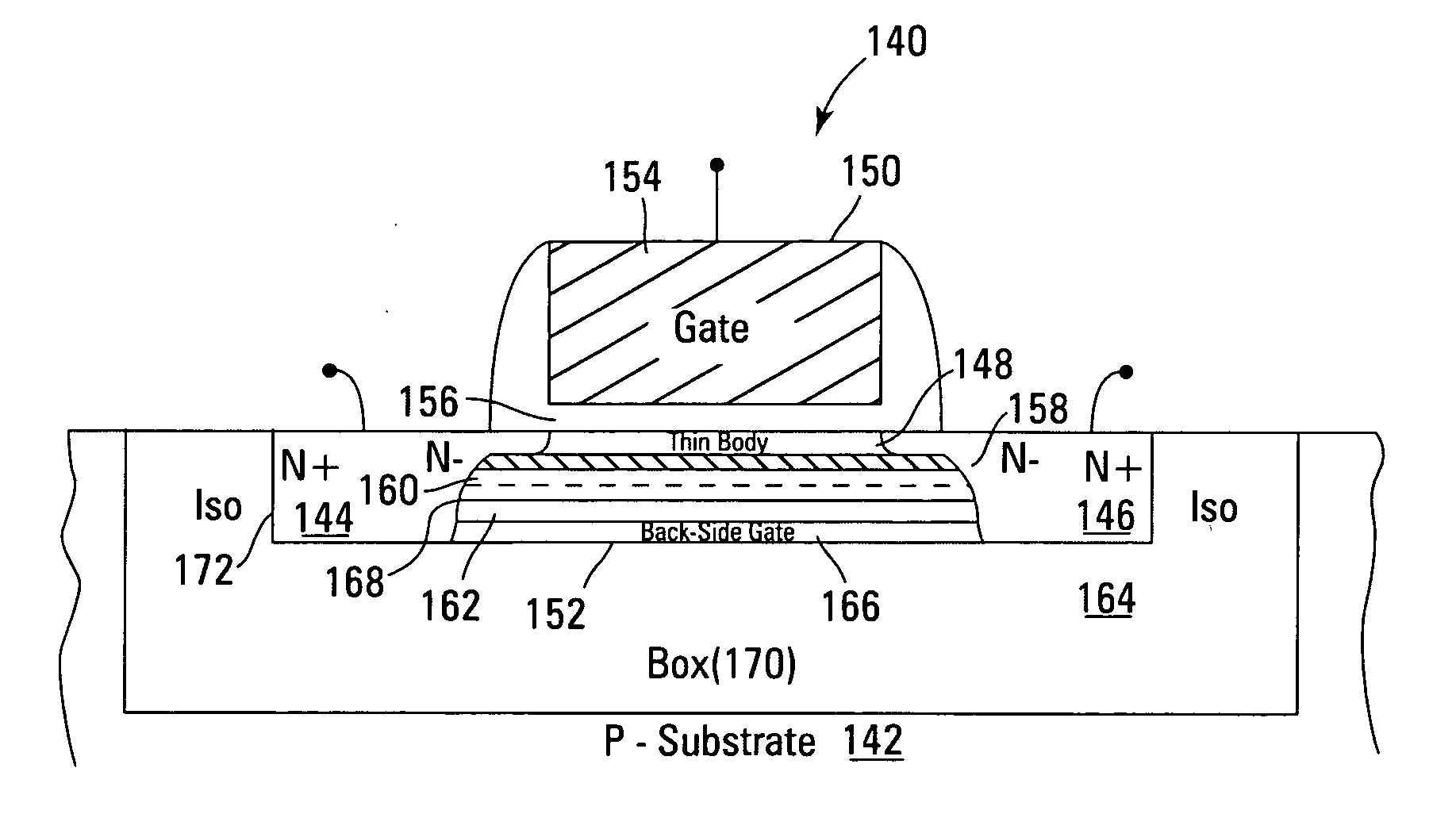

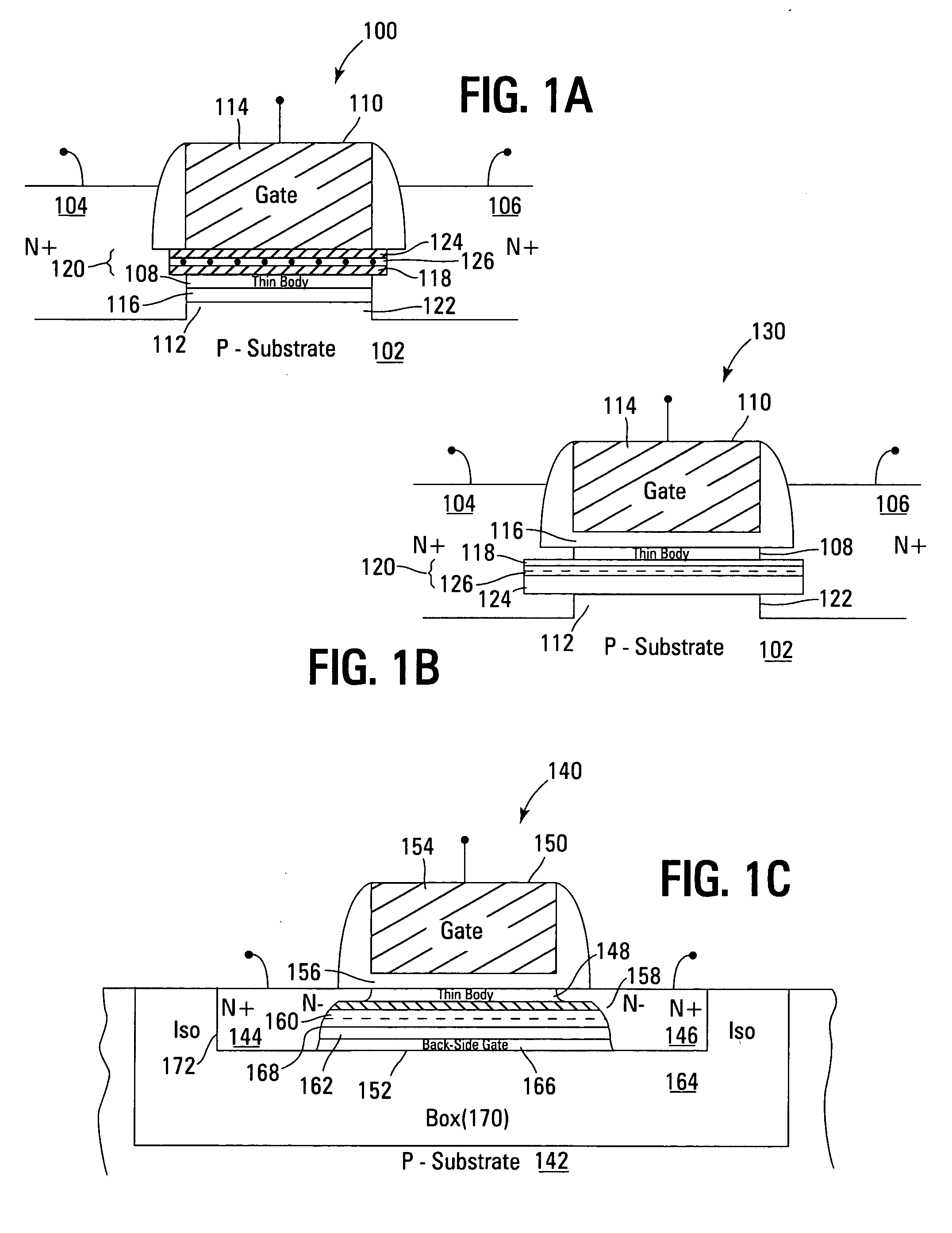

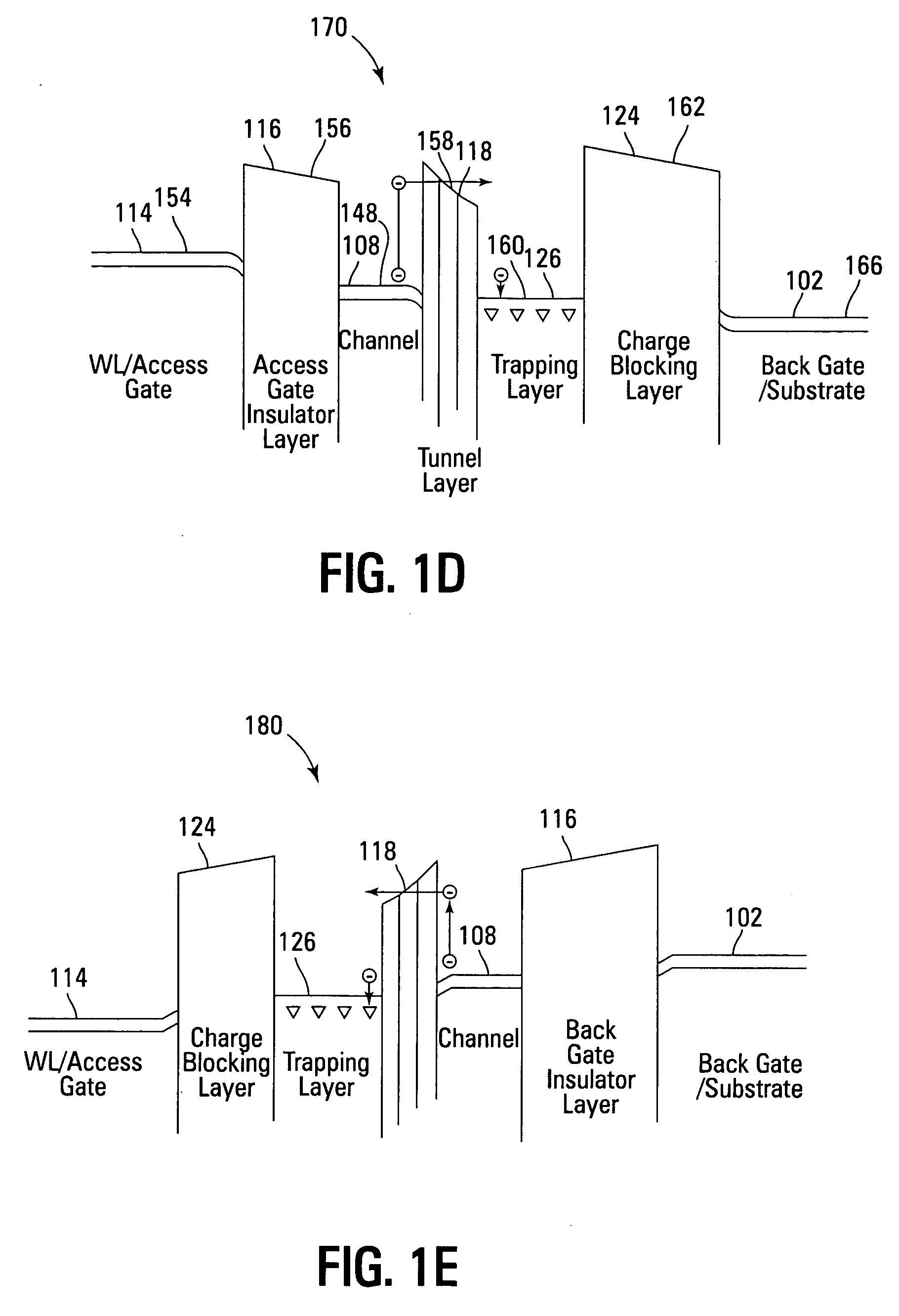

High density NAND non-volatile memory device

ActiveUS20070012988A1Efficient eraseReduce harmSolid-state devicesRead-only memoriesCharge retentionLow voltage

Non-volatile memory devices and arrays are described that utilize dual gate (or back-side gate) non-volatile memory cells with band engineered gate-stacks that are placed above or below the channel region in front-side or back-side charge trapping gate-stack configurations in NAND memory array architectures. The band-gap engineered gate-stacks with asymmetric or direct tunnel barriers of the floating node memory cells of embodiments of the present invention allow for low voltage tunneling programming and efficient erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention. The memory cell architecture also allows for improved high density memory devices or arrays with the utilization of reduced feature word lines and vertical select gates.

Owner:MICRON TECH INC

Semiconductor memory having both volatile and non-volatile functionality and method of operating

Semiconductor memory having both volatile and non-volatile modes and methods of operation. A semiconductor memory cell includes a fin structure extending from a substrate, the fin structure including a floating substrate region having a first conductivity type configured to store data as volatile memory; first and second regions interfacing with the floating substrate region, each of the first and second regions having a second conductivity type; first and second floating gates or trapping layers positioned adjacent opposite sides of the floating substrate region; a first insulating layer positioned between the floating substrate region and the floating gates or trapping layers, the floating gates or trapping layers being configured to receive transfer of data stored by the volatile memory and store the data as nonvolatile memory in the floating gates or trapping layers upon interruption of power to the memory cell; a control gate wrapped around the floating gates or trapping layers and the floating substrate region; and a second insulating layer positioned between the floating gates or trapping layers and the control gate; the substrate including an isolation layer that isolates the floating substrate region from a portion of the substrate below the isolation layer.

Owner:ZENO SEMICON

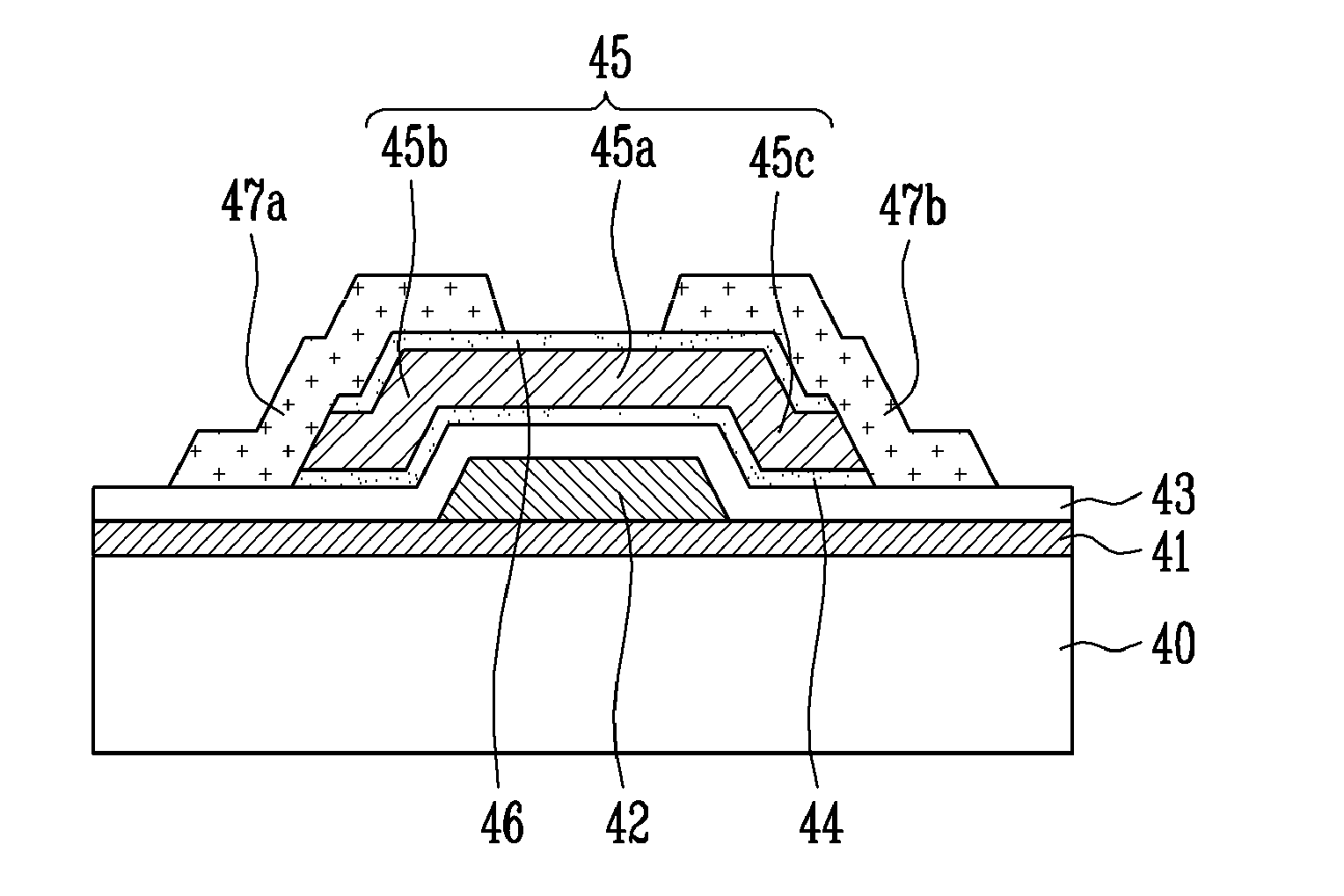

Thin film transistor, method of manufacturing the same and flat panel display device having the same

ActiveUS20090321732A1Improve featuresAvoid chargingSemiconductor/solid-state device manufacturingNon-linear opticsTrappingEngineering

A thin film transistor (TFT) using an oxide semiconductor as an active layer, a method of manufacturing the TFT, and a flat panel display device having the TFT include source and drain electrodes formed on a substrate; an active layer formed of an oxide semiconductor disposed on the source and drain electrodes; a gate electrode; and an interfacial stability layer formed on at least one of top and bottom surfaces of the active layer. In the TFT, the interfacial stability layer is formed of an oxide having a band gap of 3.0 to 8.0 eV. Since the interfacial stability layer has the same characteristics as a gate insulating layer and a passivation layer, chemically high interface stability is maintained. Since the interfacial stability layer has a band gap equal to or greater than that of the active layer, charge trapping is physically prevented.

Owner:SAMSUNG DISPLAY CO LTD

Semiconductor memory having volatile and multi-bit, non-volatile functionality and methods of operating

A semiconductor memory cell, semiconductor memory devices comprising a plurality of the semiconductor memory cells, and methods of using the semiconductor memory cell and devices are described. A semiconductor memory cell includes a substrate having a first conductivity type; a first region embedded in the substrate at a first location of the substrate and having a second conductivity type; a second region embedded in the substrate at a second location of the substrate and have the second conductivity type, such that at least a portion of the substrate having the first conductivity type is located between the first and second locations and functions as a floating body to store data in volatile memory; a trapping layer positioned in between the first and second locations and above a surface of the substrate; the trapping layer comprising first and second storage locations being configured to store data as nonvolatile memory independently of one another; and a control gate positioned above the trapping layer.

Owner:ZENO SEMICON

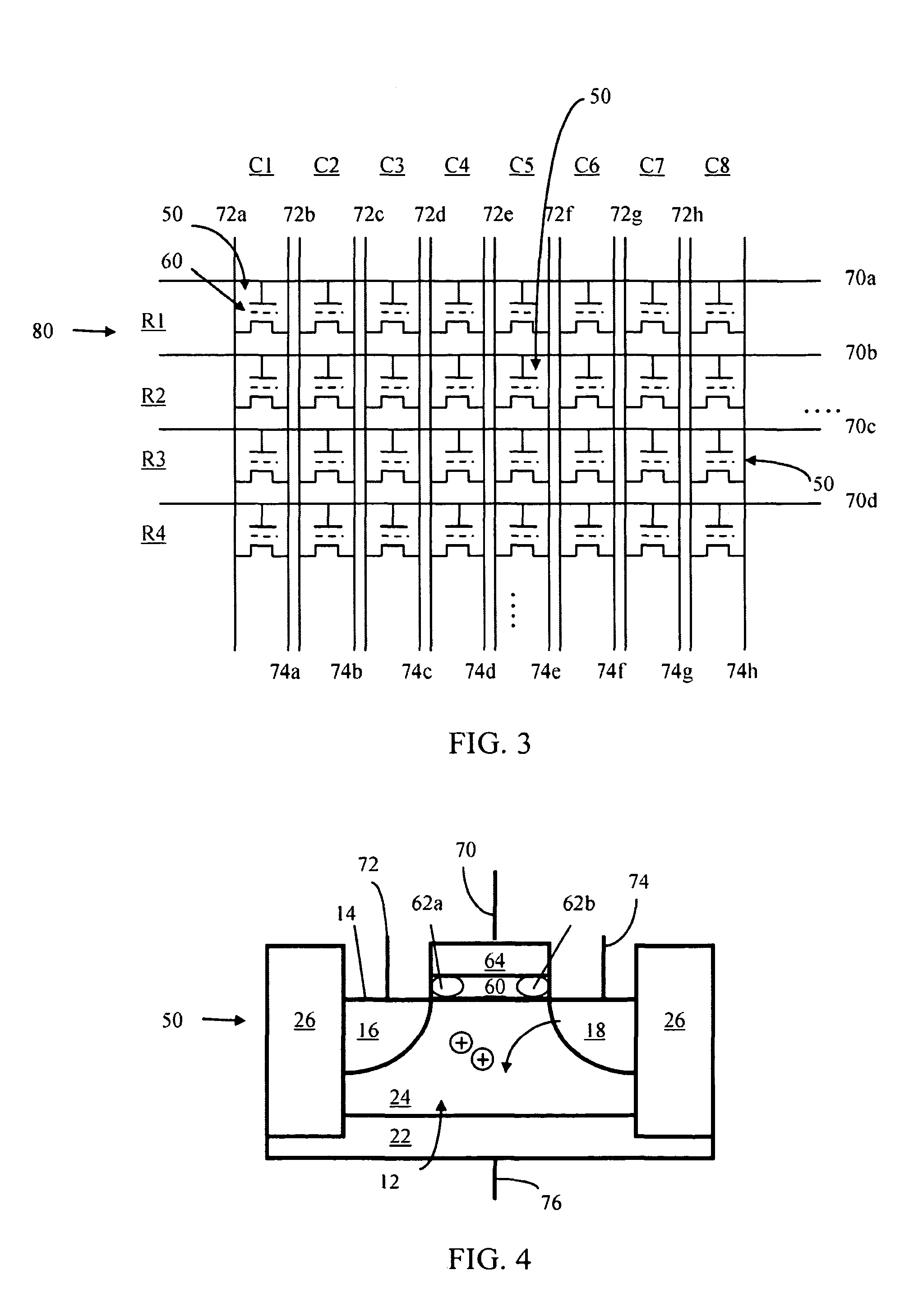

Integrated circuit self aligned 3D memory array and manufacturing method

ActiveUS20100226195A1Semiconductor/solid-state device detailsSolid-state devicesBit lineAudio power amplifier

A 3D memory device includes a plurality of ridge-shaped stacks, in the form of multiple strips of conductive material separated by insulating material, arranged as bit lines which can be coupled through decoding circuits to sense amplifiers. The strips of conductive material have side surfaces on the sides of the ridge-shaped stacks. A plurality of conductive lines arranged as word lines which can be coupled to row decoders, extends orthogonally over the plurality of ridge-shaped stacks. The conductive lines conform to the surface of the stacks. Memory elements lie in a multi-layer array of interface regions at cross-points between side surfaces of the conductive strips on the stacks and the conductive lines. The memory elements are programmable, like the anti-fuses or charge trapping structures. The 3D memory is made using only two critical masks for multiple layers.

Owner:MACRONIX INT CO LTD

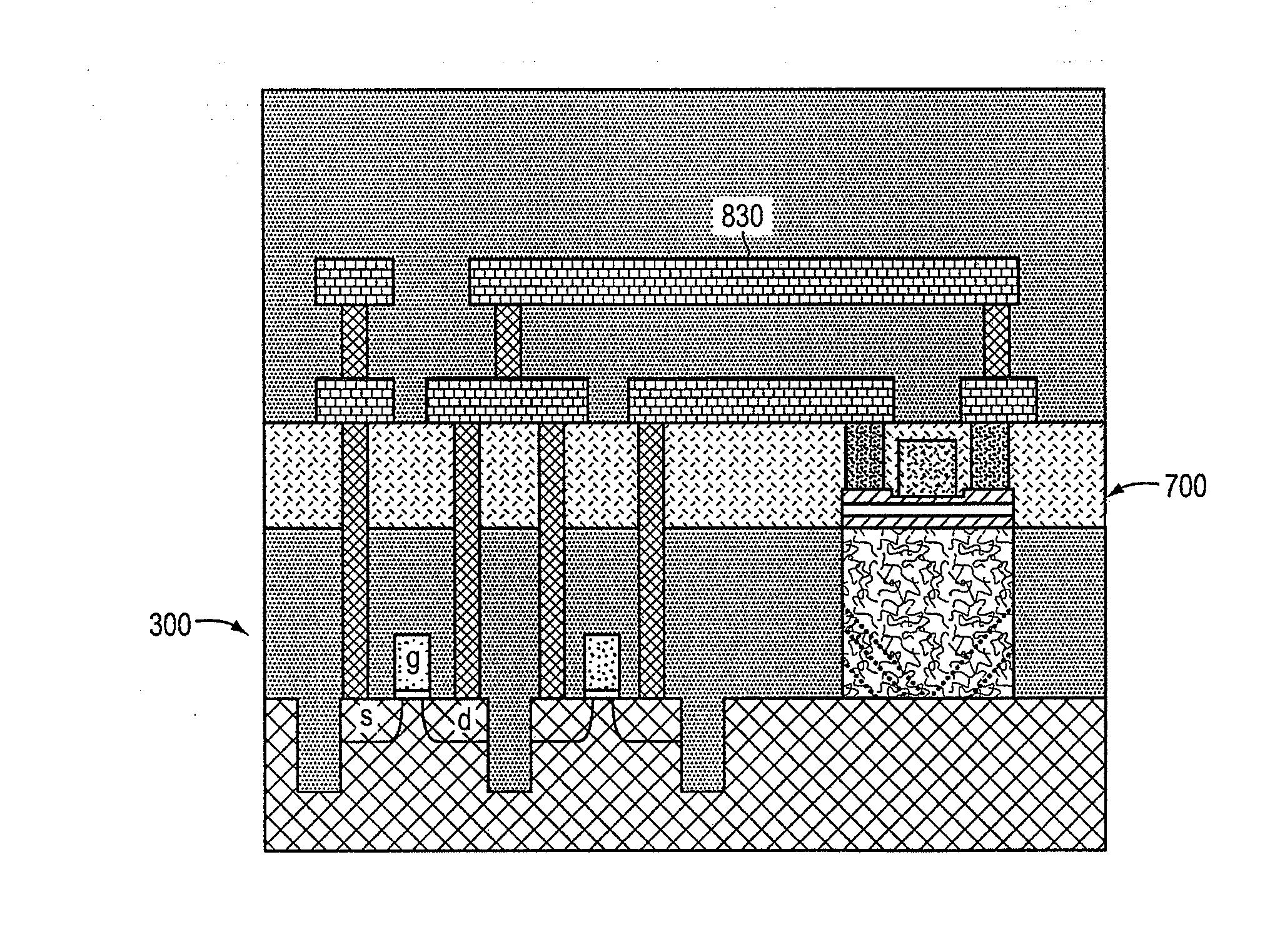

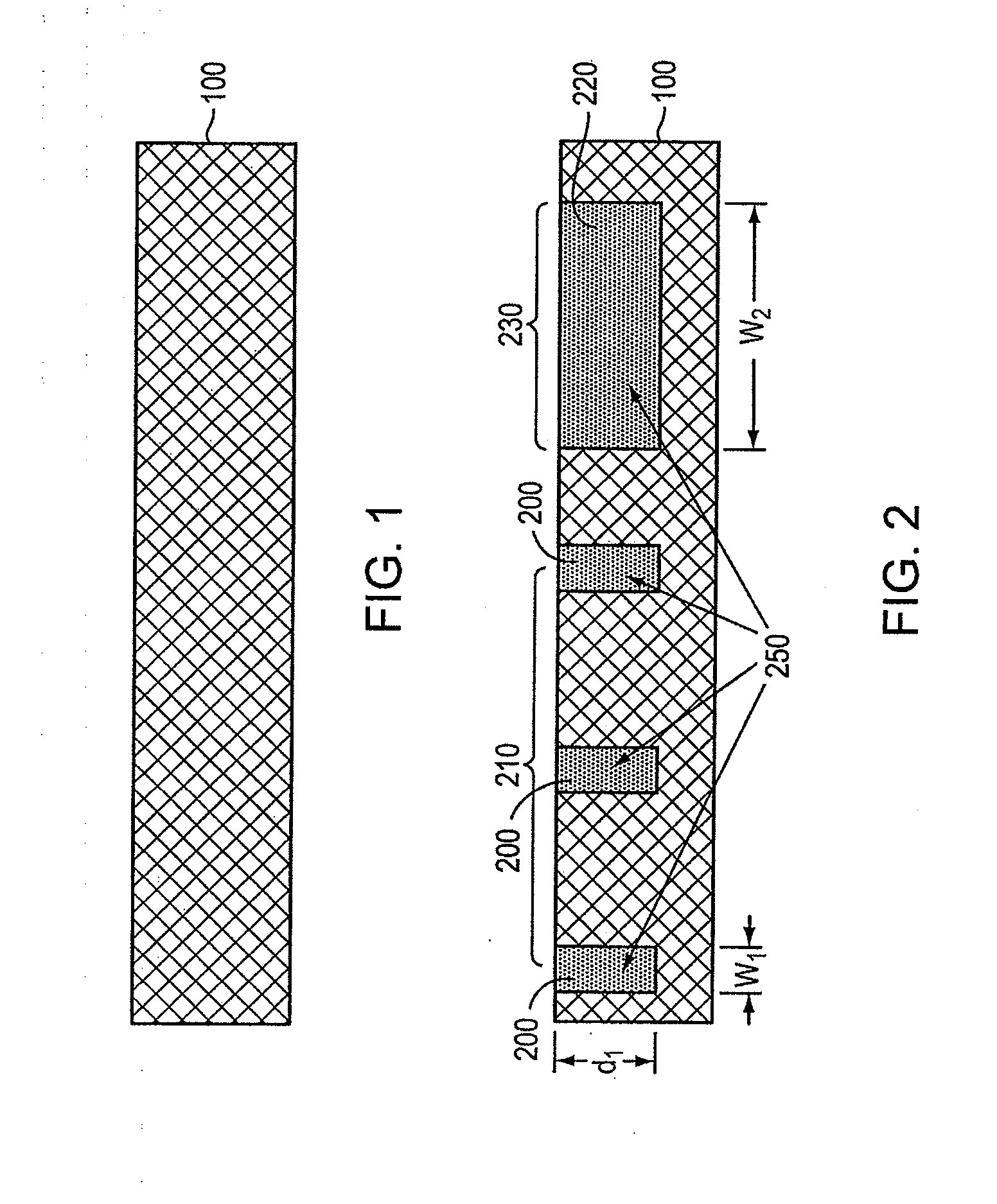

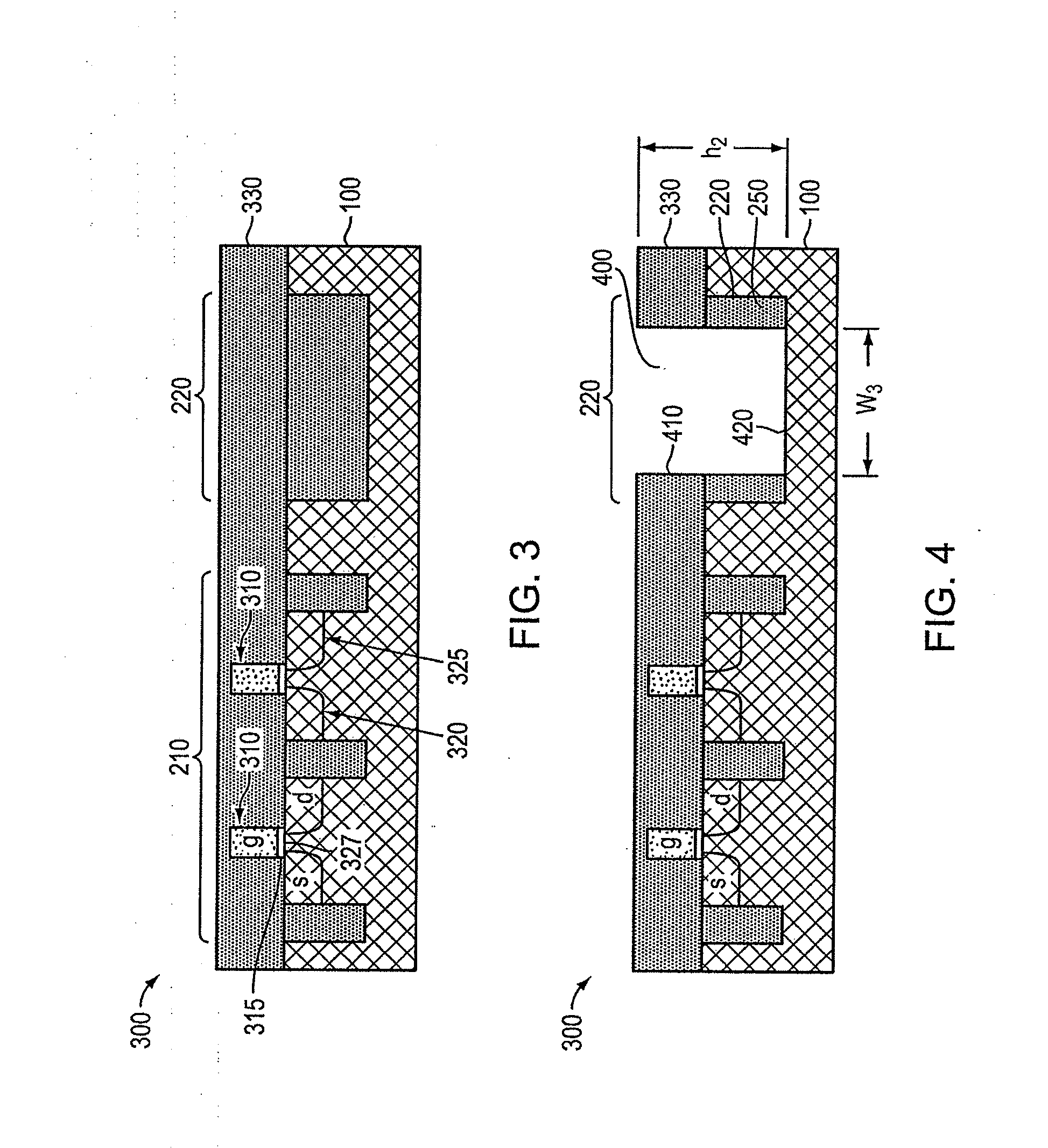

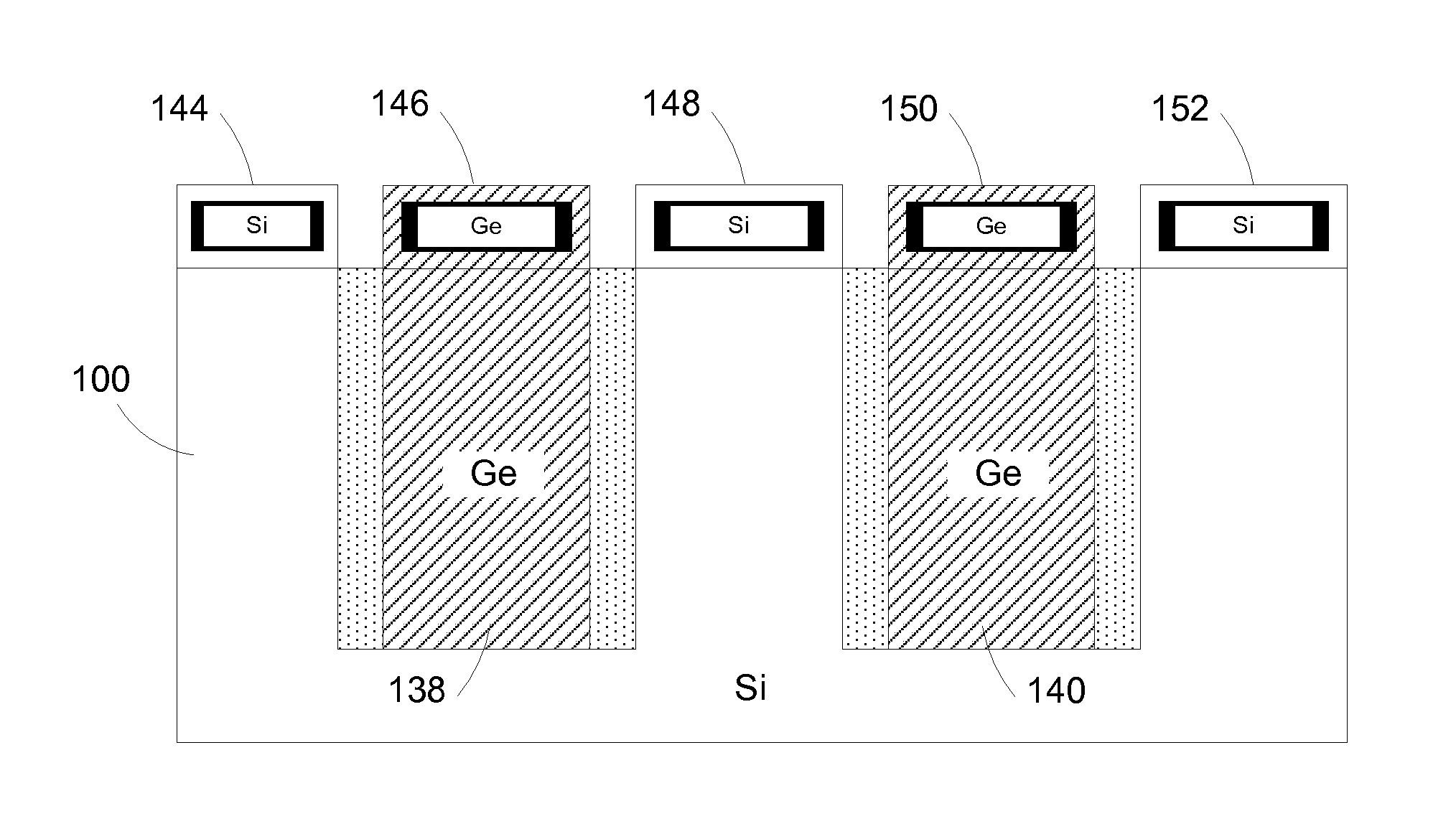

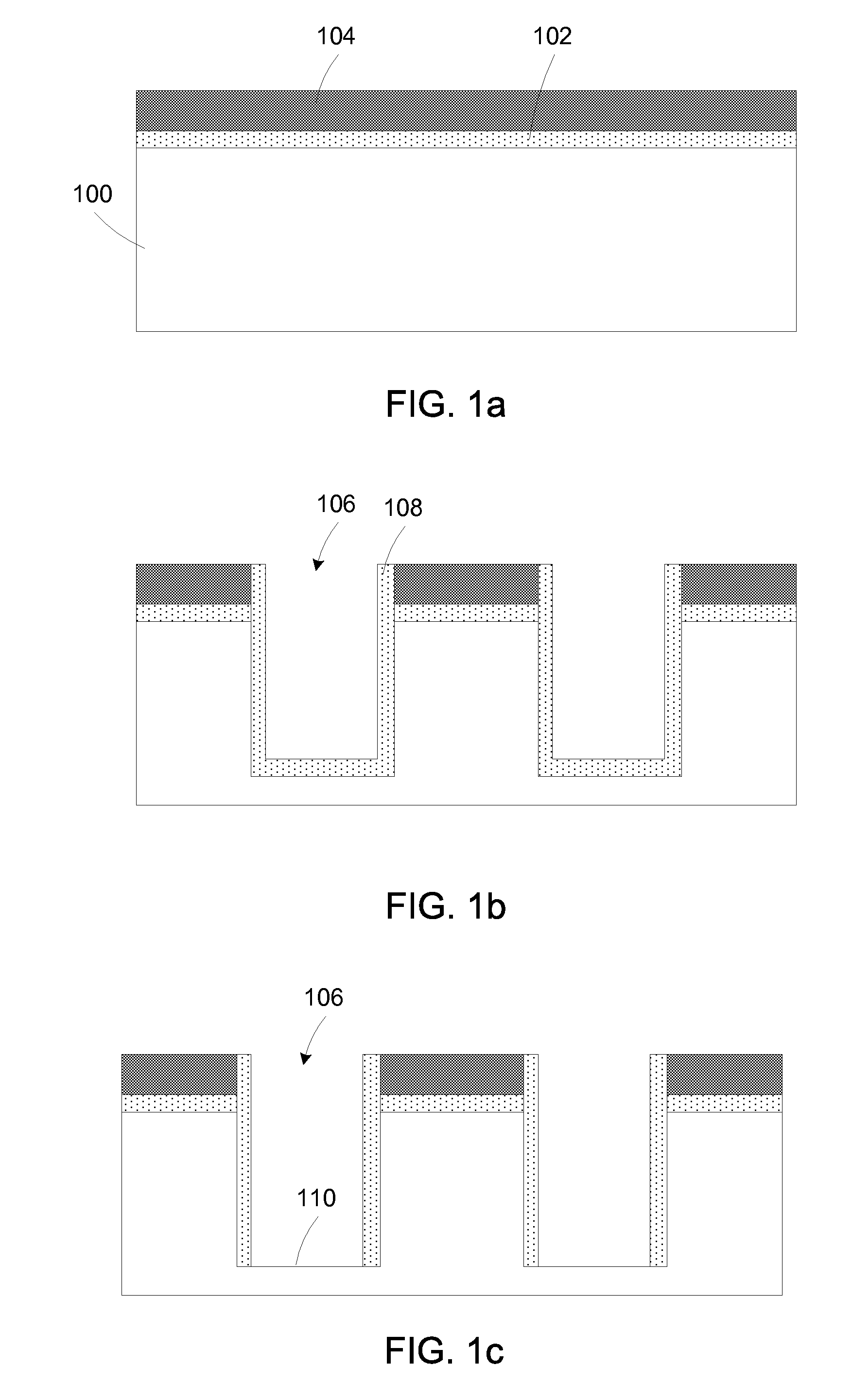

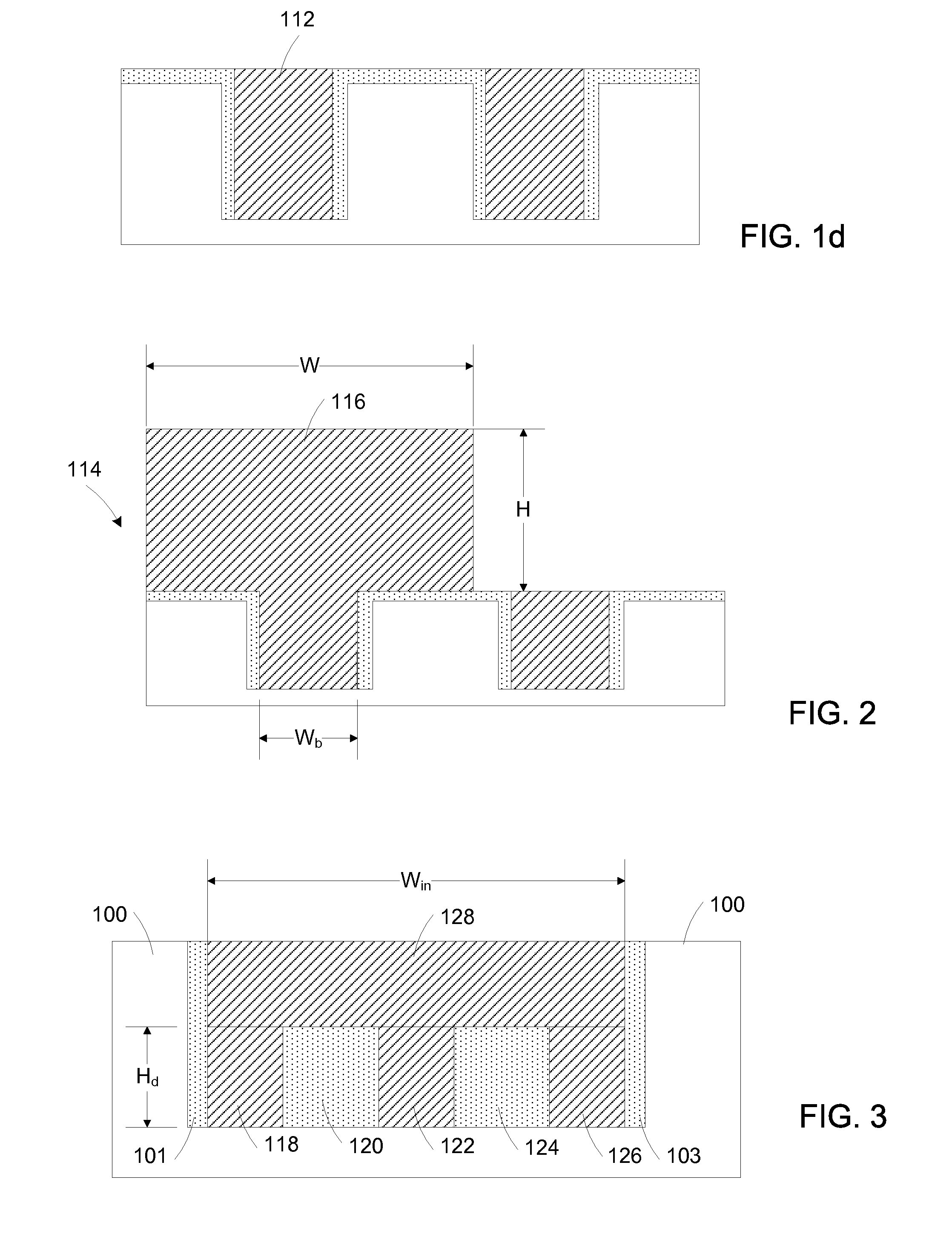

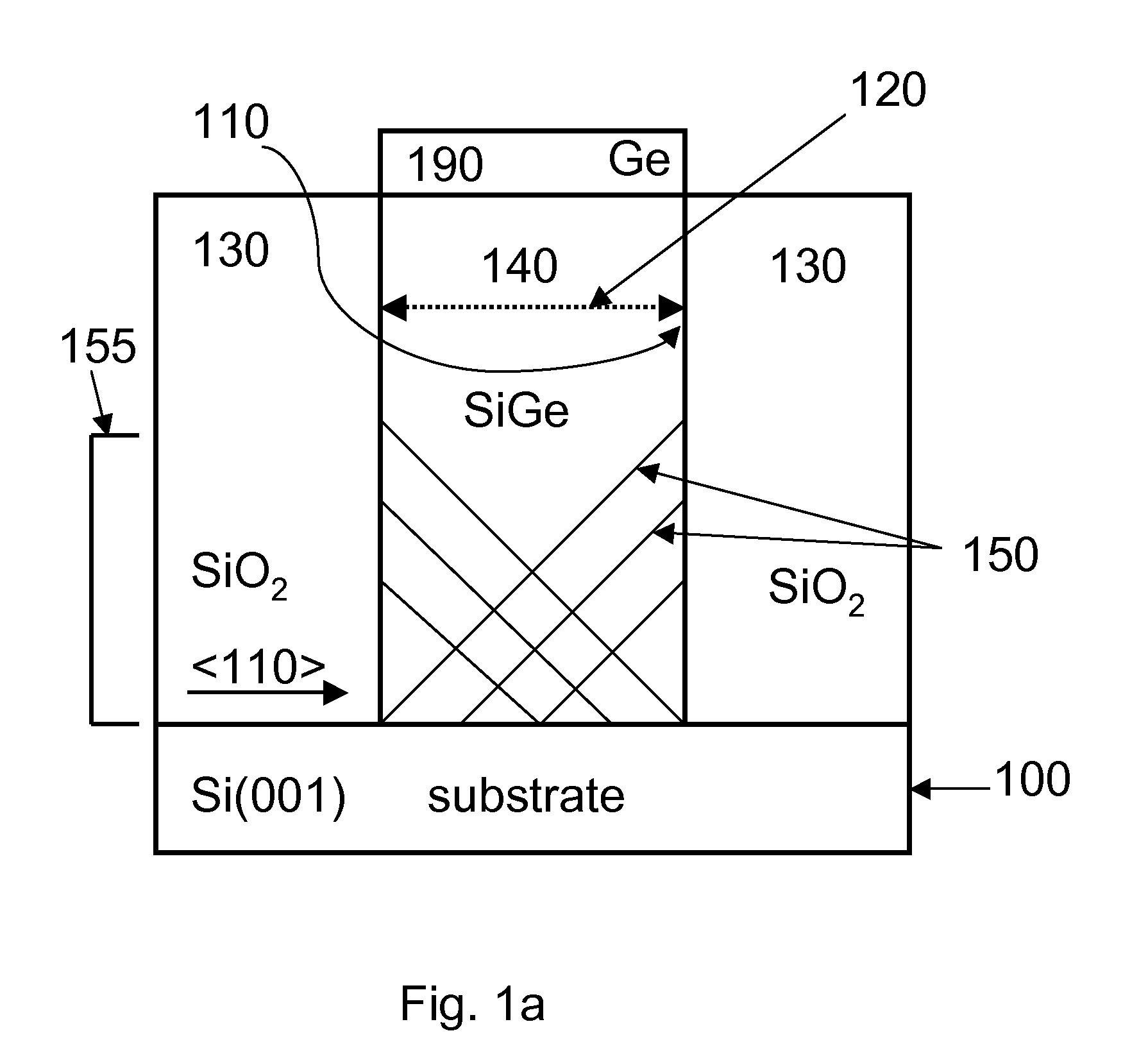

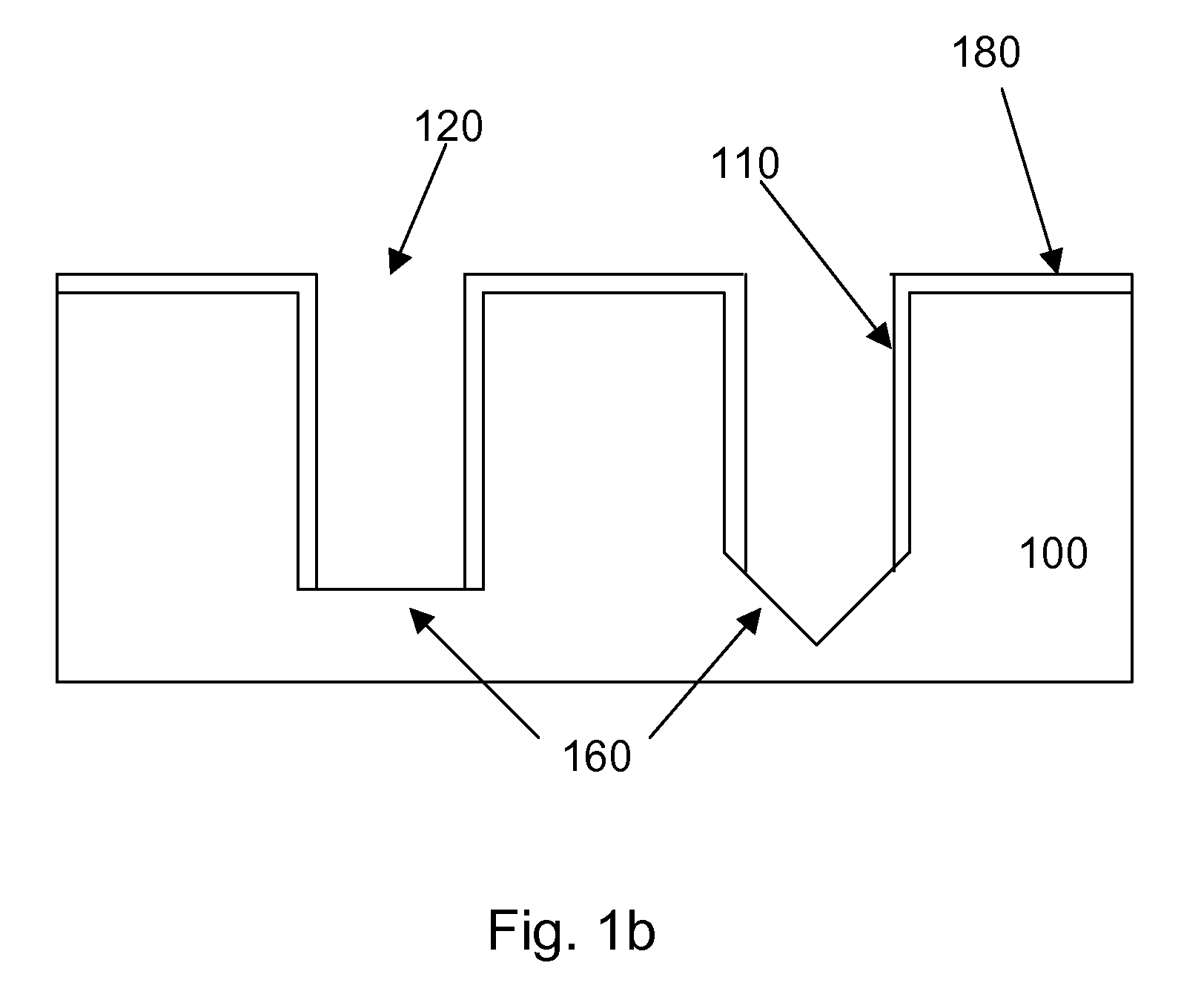

Aspect ratio trapping for mixed signal applications

InactiveUS20080070355A1Suitable for integrationReduce complicationsSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsTrapping

Structures and methods for their formation include a substrate comprising a first semiconductor material, with a second semiconductor material disposed thereover, the first semiconductor material being lattice mismatched to the second semiconductor material. Defects are reduced by using an aspect ratio trapping approach.

Owner:AMBERWAVE SYST

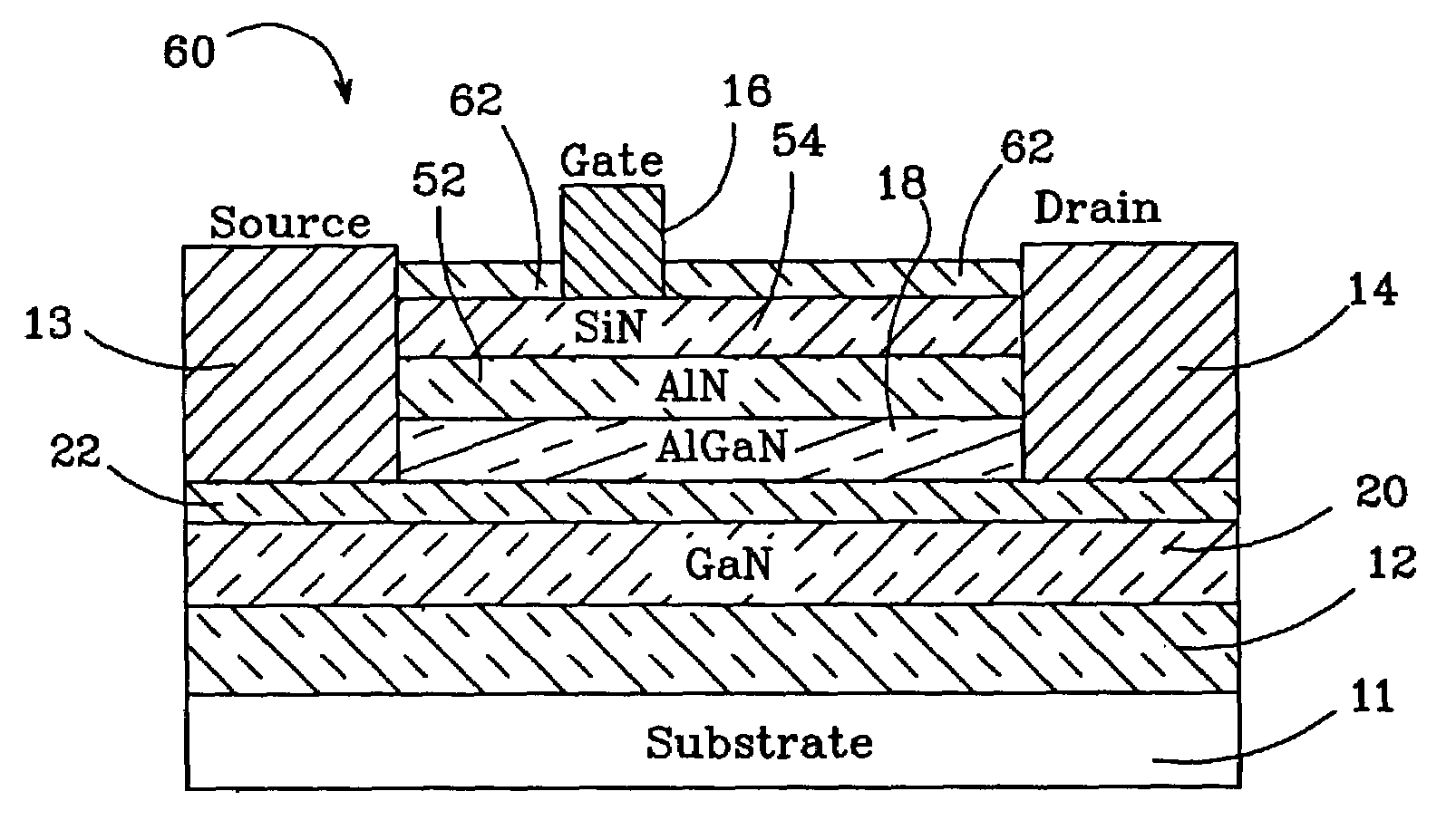

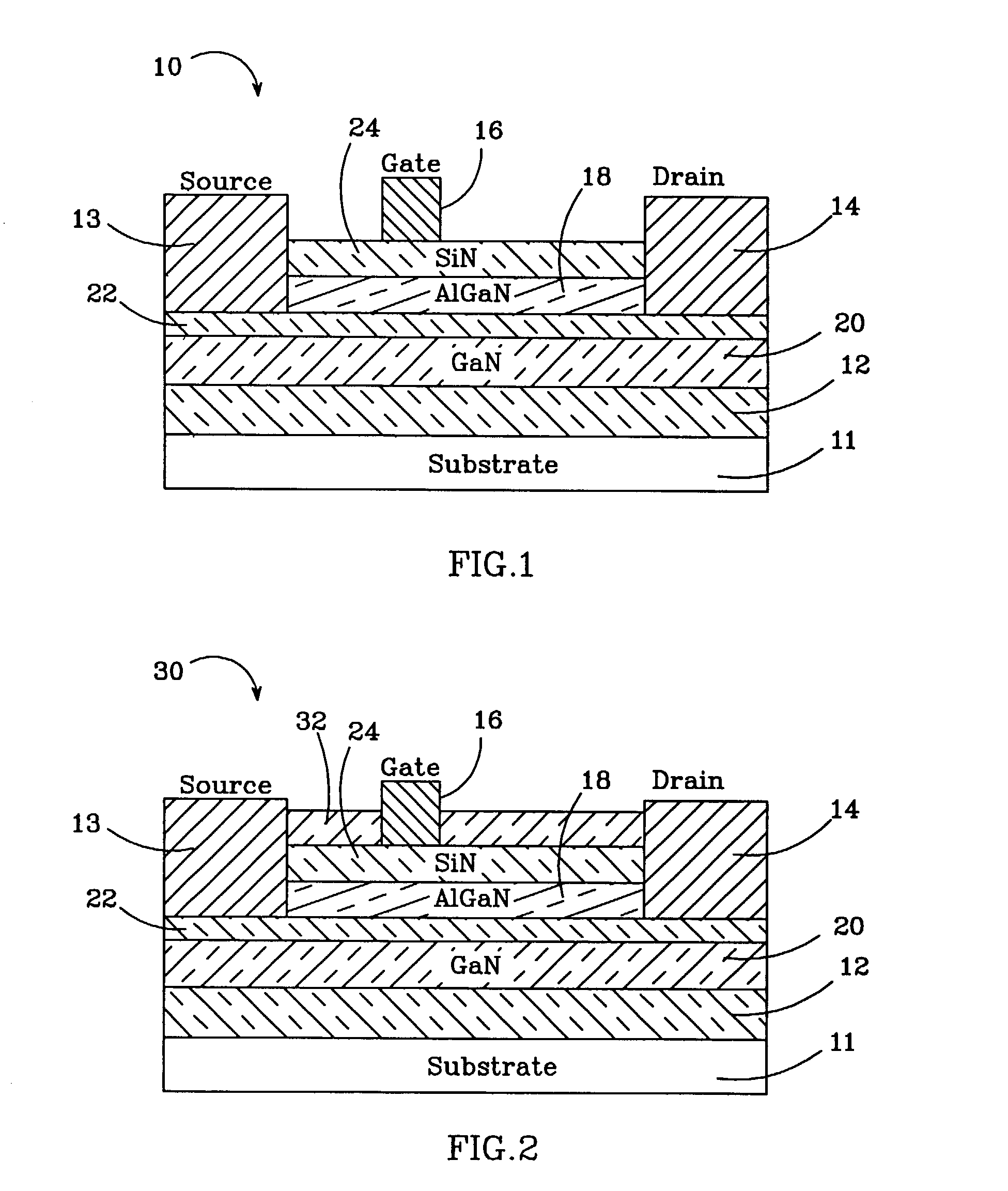

Insulating gate AlGaN/GaN HEMT

InactiveUS7230284B2Reduce trappingReduce gate leakageSemiconductor/solid-state device detailsSolid-state devicesGate leakage currentDriving current

AlGaN / GaN HEMTs are disclosed having a thin AlGaN layer to reduce trapping and also having additional layers to reduce gate leakage and increase the maximum drive current. One HEMT according to the present invention comprises a high resistivity semiconductor layer with a barrier semiconductor layer on it. The barrier layer has a wider bandgap than the high resistivity layer and a 2DEG forms between the layers. Source and drain contacts contact the barrier layer, with part of the surface of the barrier layer uncovered by the contacts. An insulating layer is included on the uncovered surface of the barrier layer and a gate contact is included on the insulating layer. The insulating layer forms a barrier to gate leakage current and also helps to increase the HEMT's maximum current drive. The invention also includes methods for fabricating HEMTs according to the present invention. In one method, the HEMT and its insulating layer are fabricated using metal-organic chemical vapor deposition (MOCVD). In another method the insulating layer is sputtered onto the top surface of the HEMT in a sputtering chamber.

Owner:CREE INC

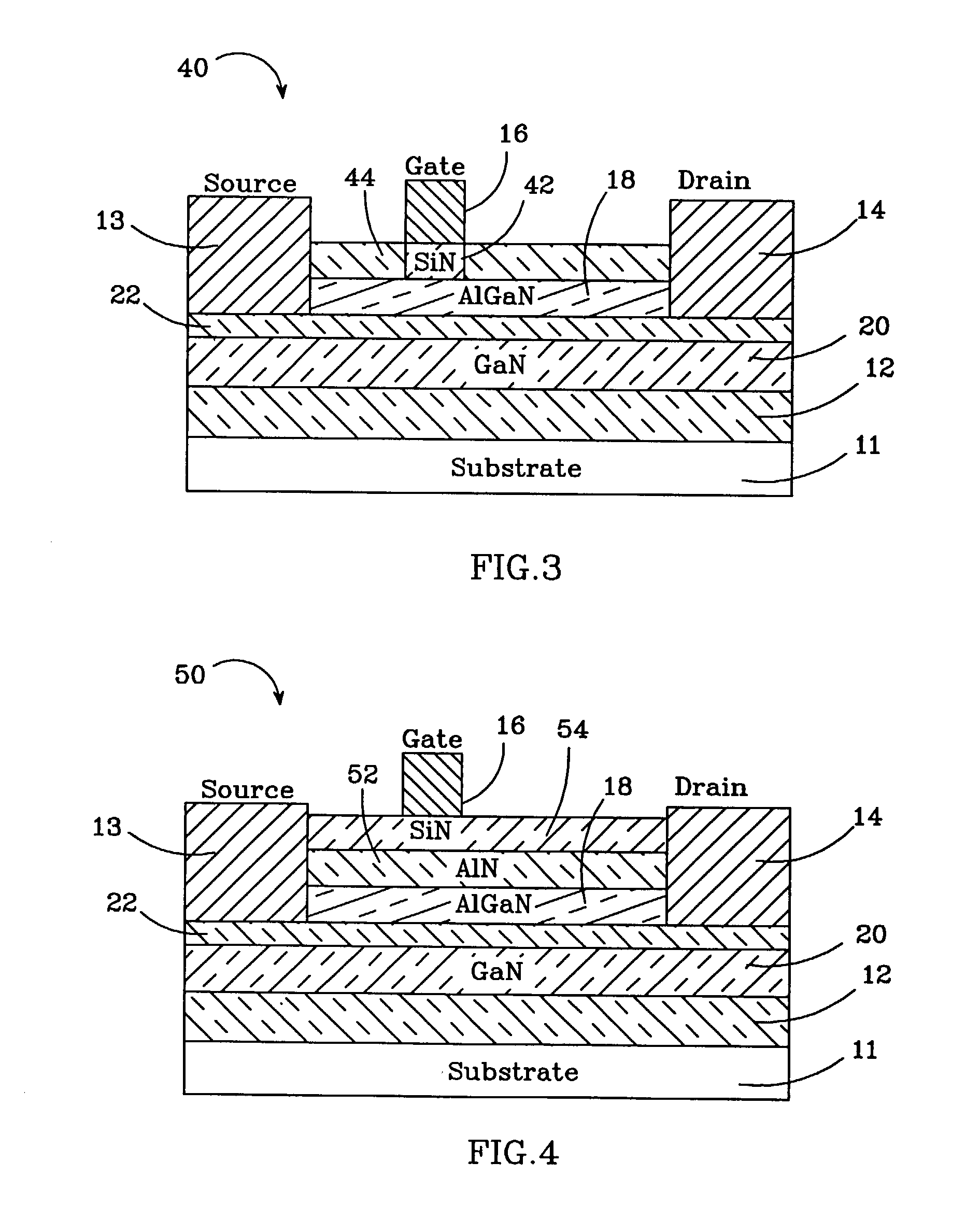

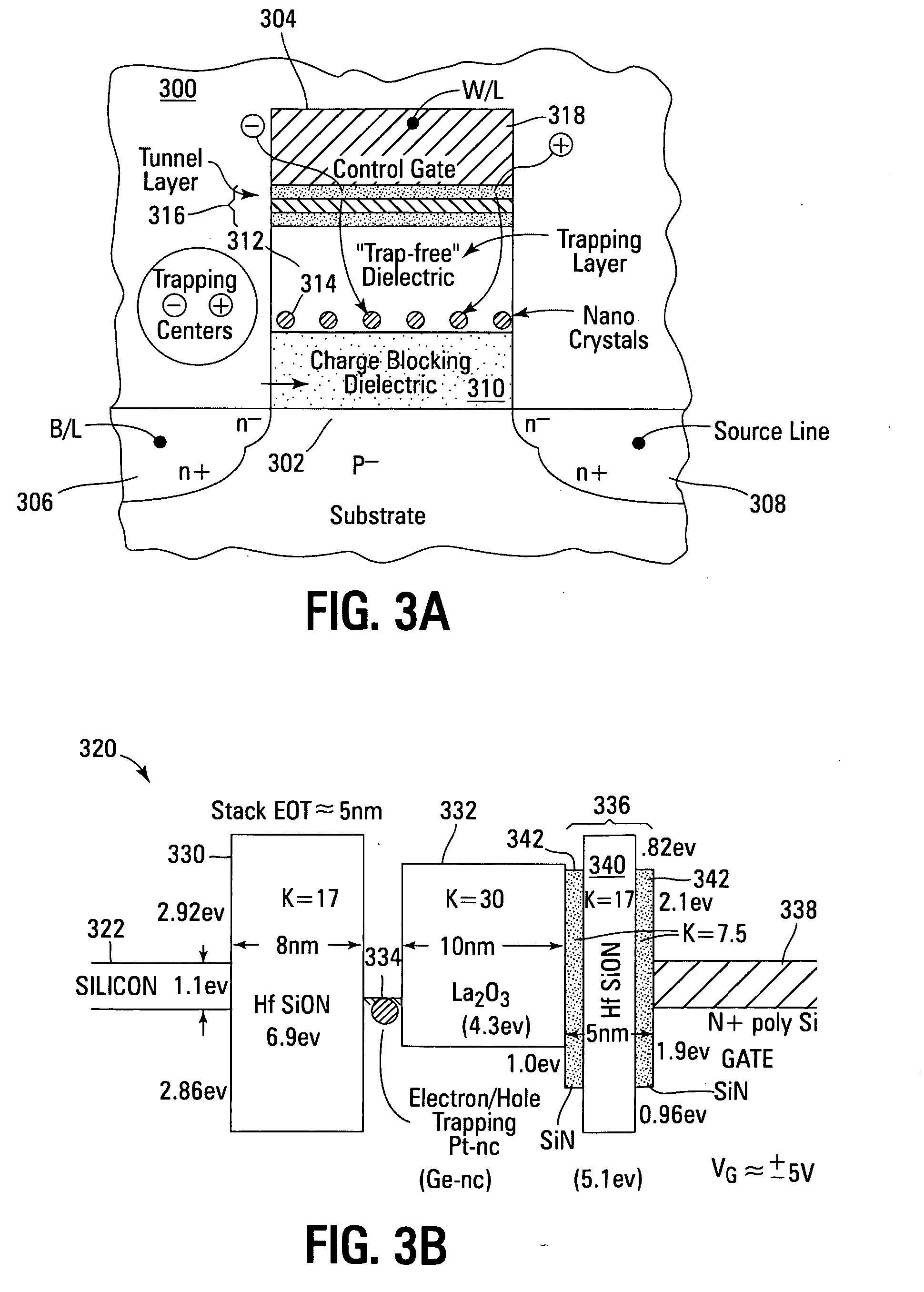

Band engineered nano-crystal non-volatile memory device utilizing enhanced gate injection

ActiveUS20070045718A1Increased device feature scalingEfficient erasureTransistorNanoinformaticsCharge retentionNon symmetric

Non-volatile memory devices and arrays are described that utilize reverse mode non-volatile memory cells that have band engineered gate-stacks and nano-crystal charge trapping in EEPROM and block erasable memory devices, such as Flash memory devices. Embodiments of the present invention allow a reverse mode gate-insulator stack memory cell that utilizes the control gate for programming and erasure through a band engineered crested tunnel barrier. Charge retention is enhanced by utilization of high work function nano-crystals in a non-conductive trapping layer and a high K dielectric charge blocking layer. The band-gap engineered gate-stack with symmetric or asymmetric crested barrier tunnel layers of the non-volatile memory cells of embodiments of the present invention allow for low voltage tunneling programming and erase with electrons and holes, while maintaining high charge blocking barriers and deep carrier trapping sites for good charge retention.

Owner:MICRON TECH INC

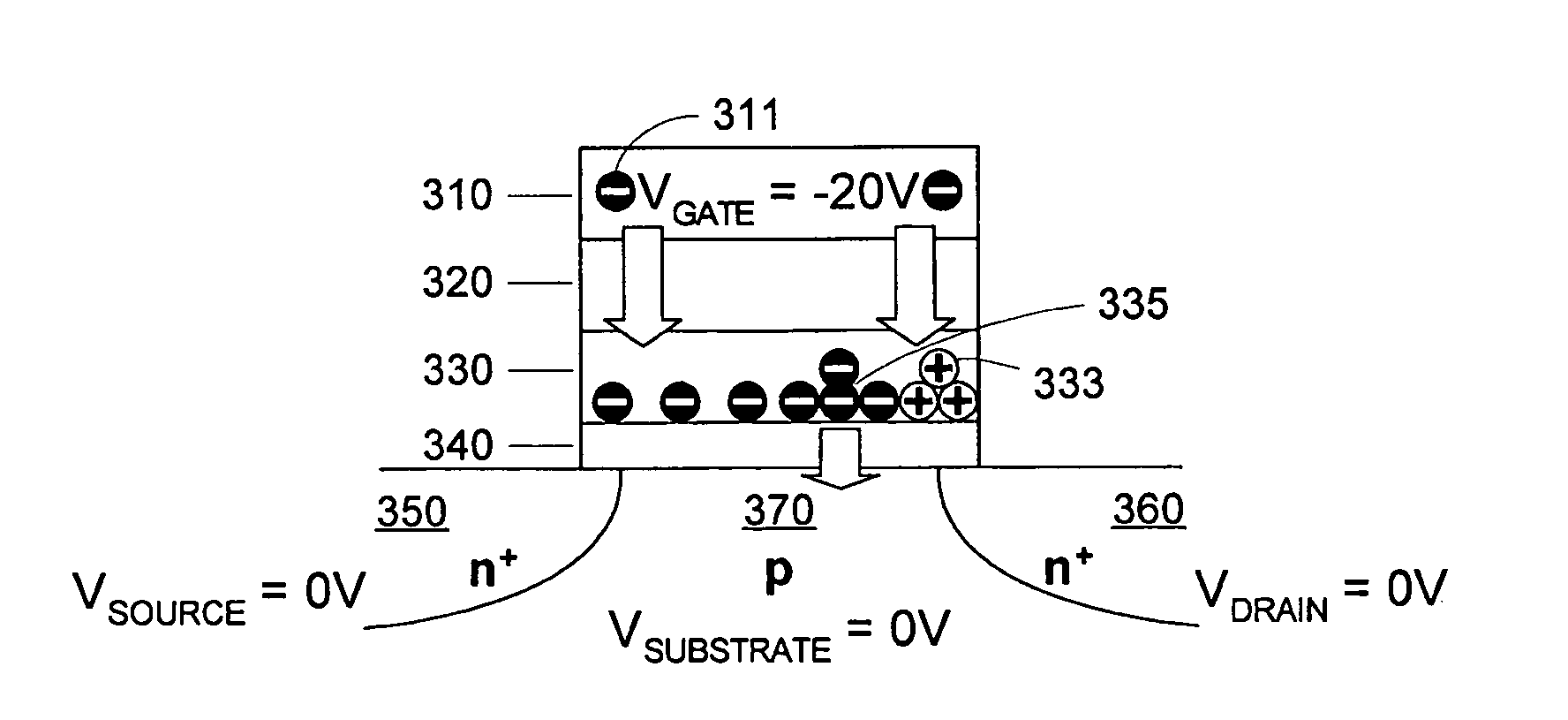

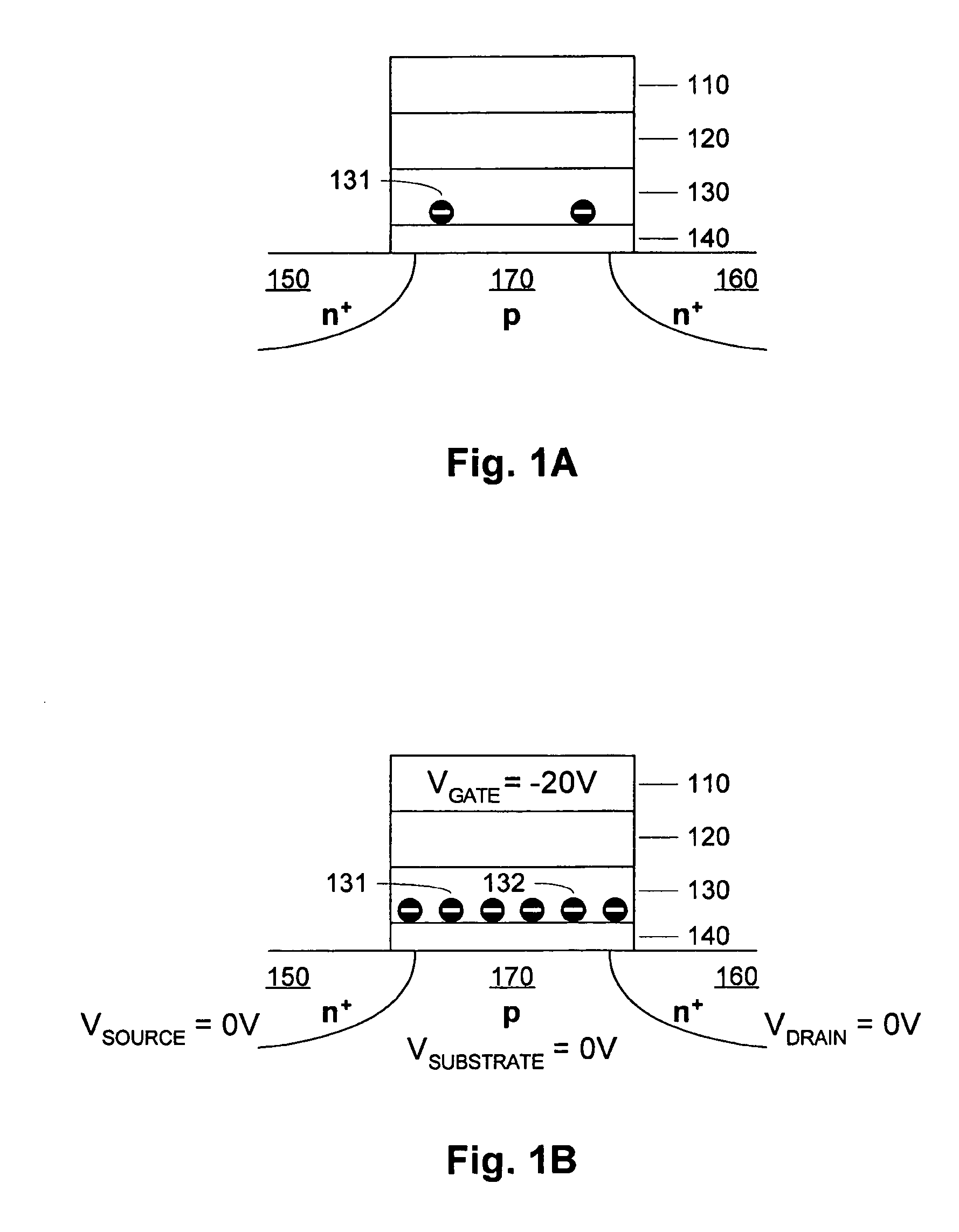

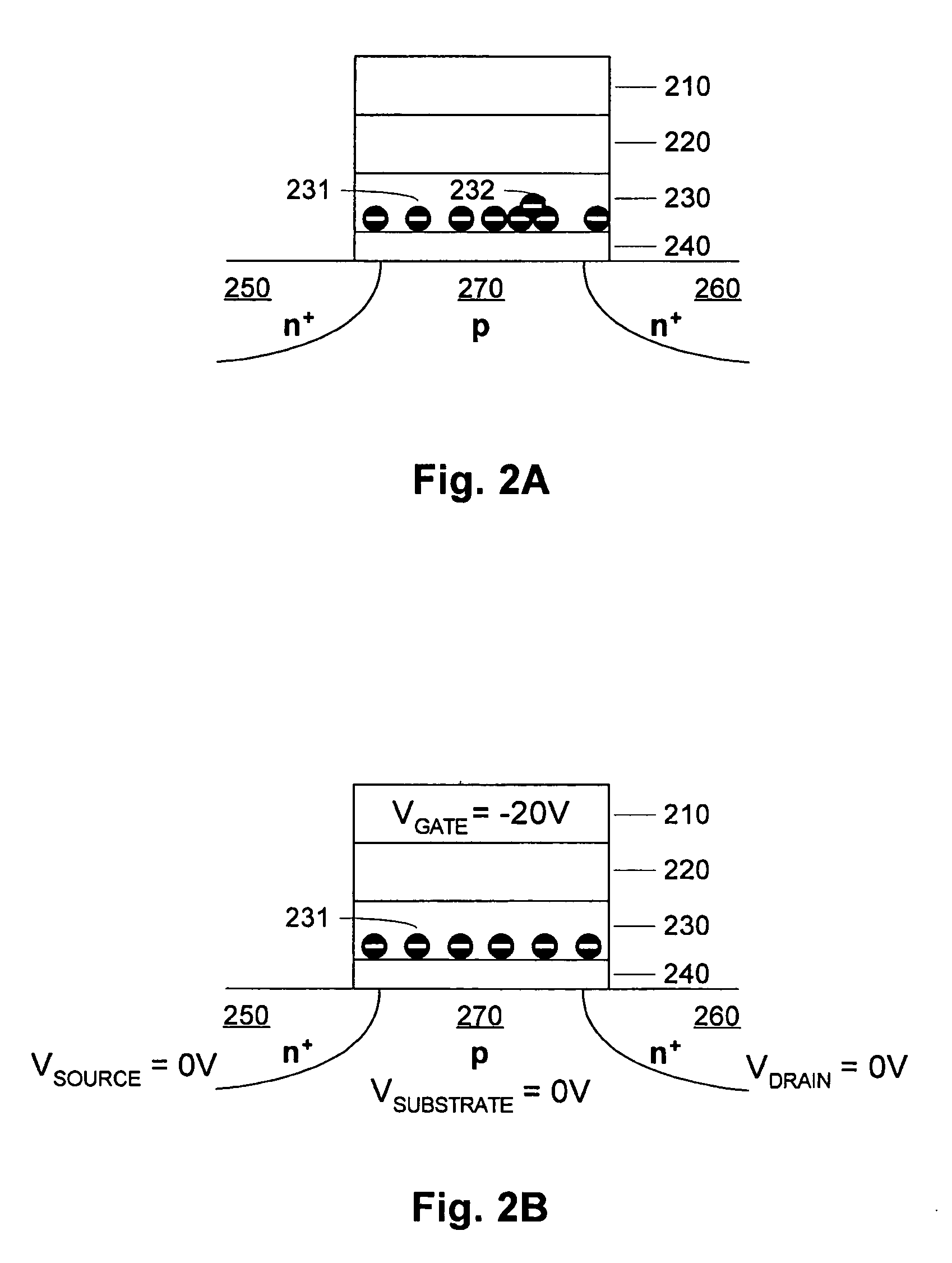

Operation scheme with charge balancing erase for charge trapping non-volatile memory

A method of operating a memory cell comprises applying a first procedure (typically erase) to establish a low threshold state including a first bias arrangement causing reduction in negative charge in the charge trapping structure, and a second bias arrangement tending to the induce balanced charge tunneling between the gate and the charge trapping structure and between the charge trapping structure in the channel. A second procedure (typically program) is used to establish a high threshold state in the memory cell, including a third bias arrangement that causes an increase in negative charge in the charge trapping structure.

Owner:MACRONIX INT CO LTD

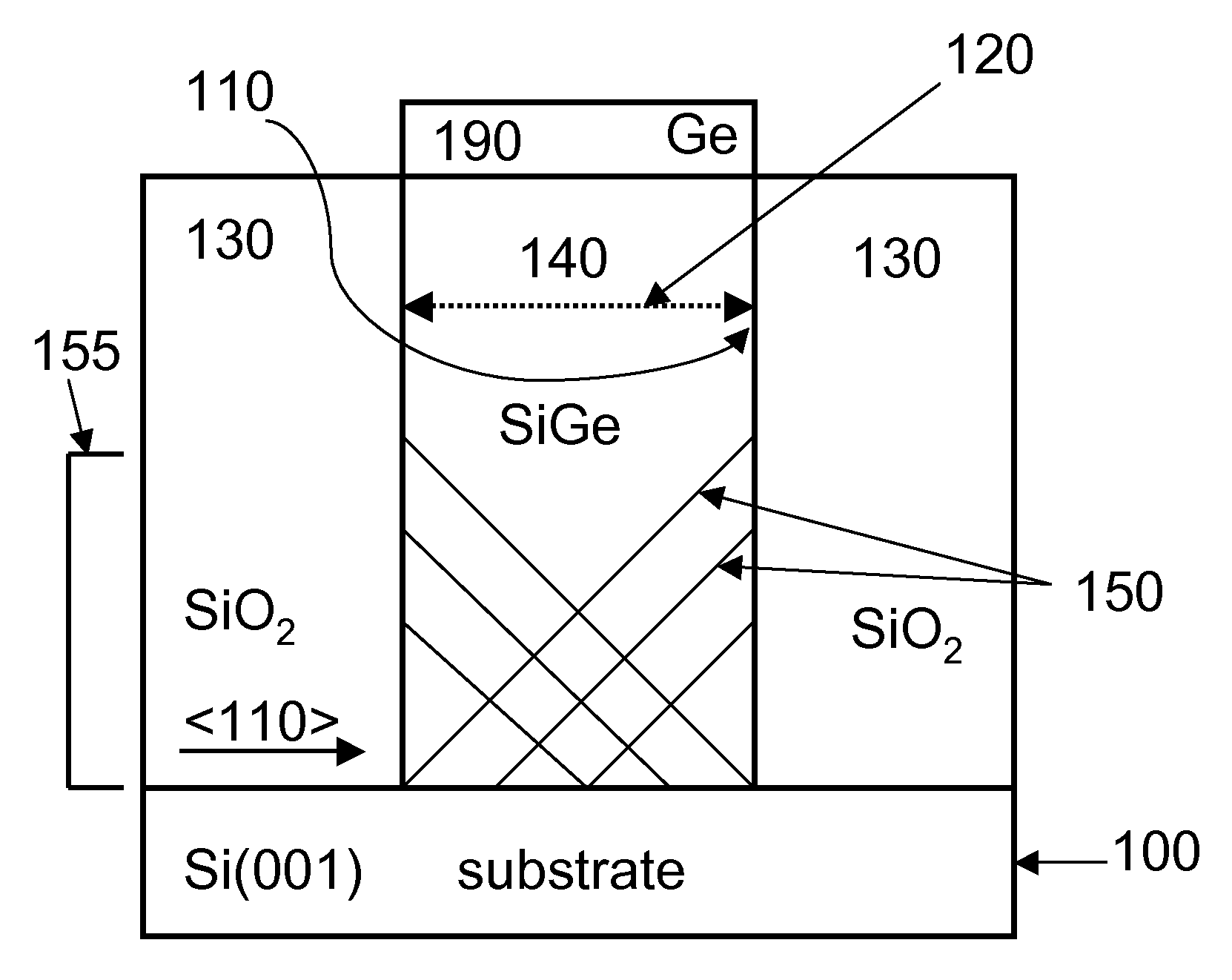

Semiconductor sensor structures with reduced dislocation defect densities and related methods for the same

Non-silicon based semiconductor devices are integrated into silicon fabrication processes by using aspect-ratio-trapping materials. Non-silicon light-sensing devices in a least a portion of a crystalline material can output electrons generated by light absorption therein. Exemplary light-sensing devices can have relatively large micron dimensions. As an exemplary application, complementary-metal-oxide-semiconductor photodetectors are formed on a silicon substrate by incorporating an aspect-ratio-trapping technique.

Owner:TAIWAN SEMICON MFG CO LTD

Fabrication and structures of crystalline material

InactiveUS20100072515A1Reduce surface roughnessReduce the presence of impuritiesSemiconductor/solid-state device manufacturingSemiconductor devicesTrappingCrystalline materials

A surface of the first semiconductor crystalline material has a reduced roughness. A semiconductor device includes a low defect, strained second semiconductor crystalline material over the surface of the first crystalline material. A surface of the strained second semiconductor crystalline material has a reduced roughness. One example includes obtaining a surface with reduced roughness by creating process parameters that reduce impurities at an interfacial boundary between the first and second semiconductor crystalline materials. In one embodiment, the first semiconductor crystalline material can be confined by an opening in an insulator having an aspect ratio sufficient to trap defects using Aspect Ratio Trapping techniques.

Owner:TAIWAN SEMICON MFG CO LTD

Three-dimensional stacked and-type flash memory structure and methods of manufacturing and operating the same hydride

A 3D stacked AND-type flash memory structure comprises several horizontal planes of memory cells arranged in a three-dimensional array, and each horizontal plane comprising several word lines and several of charge trapping multilayers arranged alternately, and the adjacent word lines spaced apart from each other with each charge trapping multilayer interposed between; a plurality of sets of bit lines and source lines arranged alternately and disposed vertically to the horizontal planes; and a plurality of sets of channels and sets of insulation pillars arranged alternatively, and disposed perpendicularly to the horizontal planes, wherein one set of channels is sandwiched between the adjacent sets of bit lines and source lines.

Owner:MACRONIX INT CO LTD

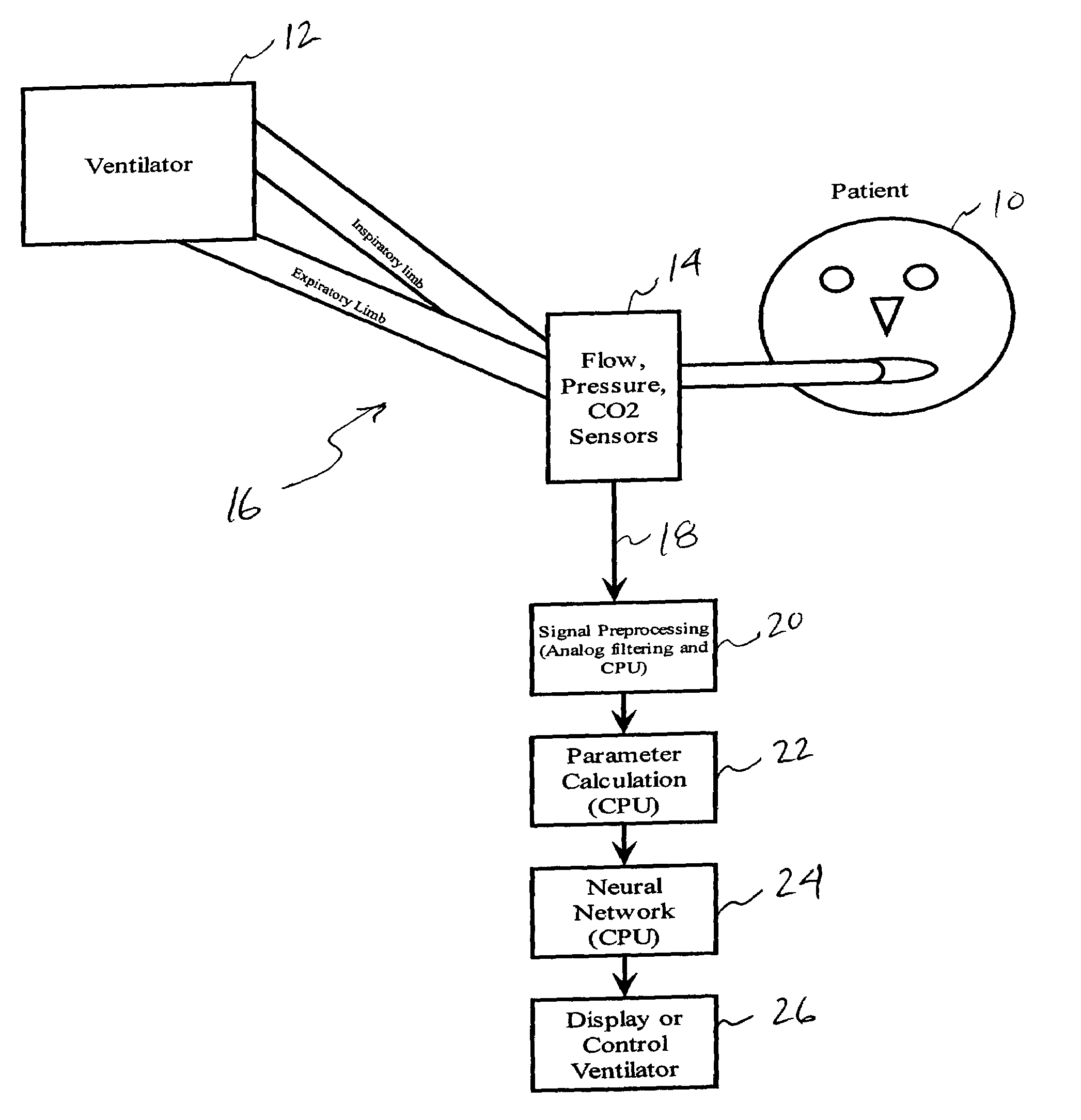

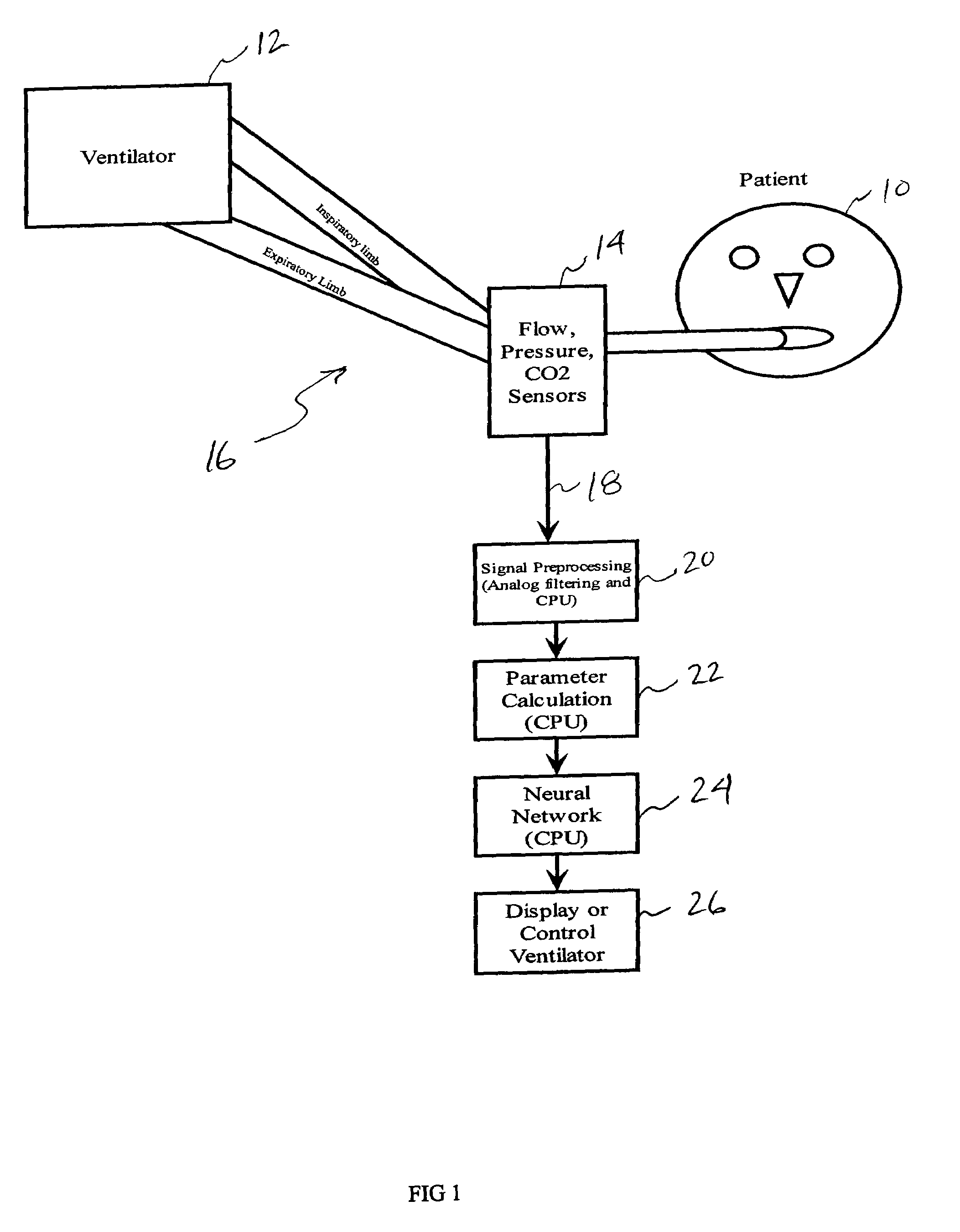

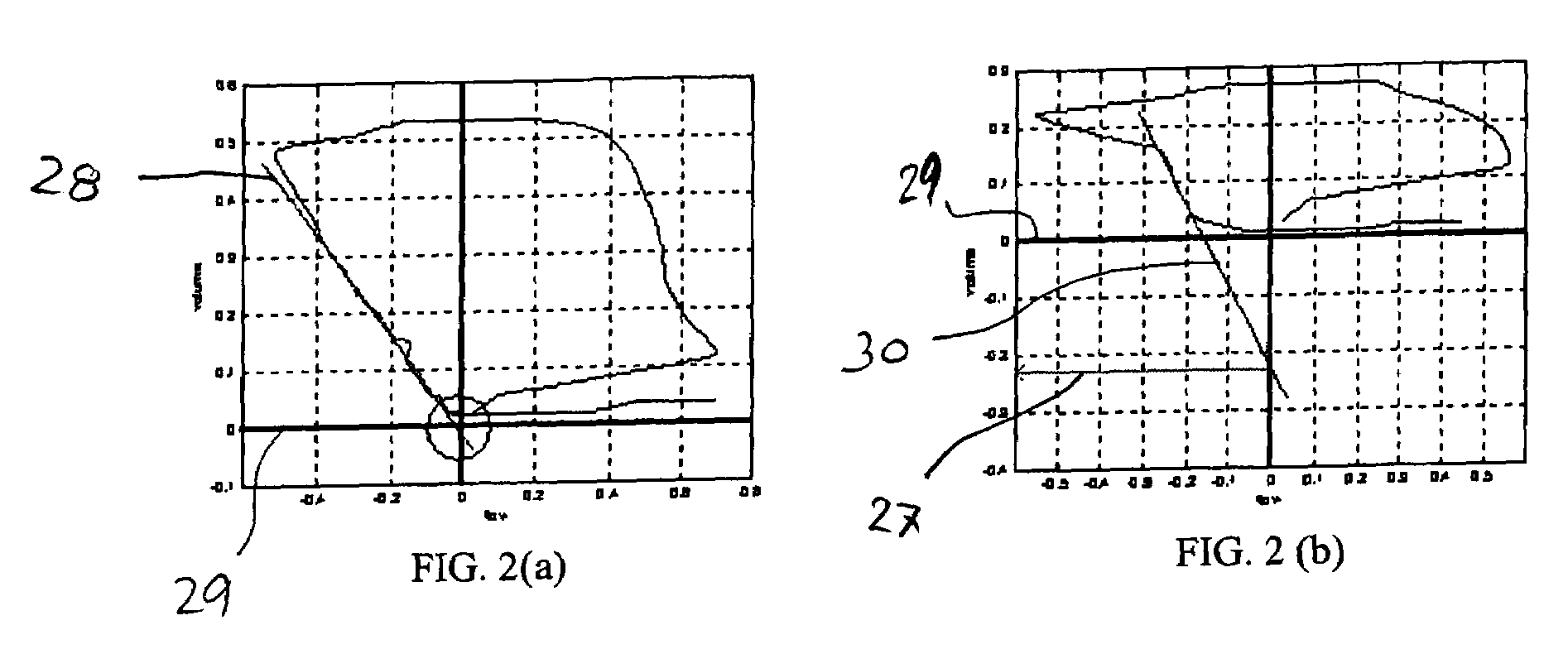

Method and apparatus for non-invasive prediction of intrinsic positive end-expiratory pressure (PEEPi) in patients receiving ventilator support

ActiveUS7562657B2Accurate detection and quantificationBetter informed of patient statusRespiratorsOperating means/releasing devices for valvesAir volumeTrapping

The present invention describes a method and apparatus for non-invasive prediction of the “intrinsic positive end-expiratory pressure” (PEEPi) which is secondary to a trapping of gas, over and above that which is normal in the lungs; the presence of PEEPi imposes an additional workload upon the spontaneously breathing patient. Several indicators or markers are presented to detect and quantify PEEPi non-invasively The markers may include an expiratory air flow versus expiratory air volume trajectory, an expiratory carbon dioxide flow versus expiratory air volume trajectory, an expiratory carbon dioxide volume to expiratory air volume ratio, an expiratory air flow at onset of inhalation, a model of an expiratory waveform, a peak to mid-exhalation airflow ratio, duration of reduced exhaled airflow, and a Capnograph waveform shape.

Owner:CONVERGENT ENG

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com