Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

9028 results about "Contact hole" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

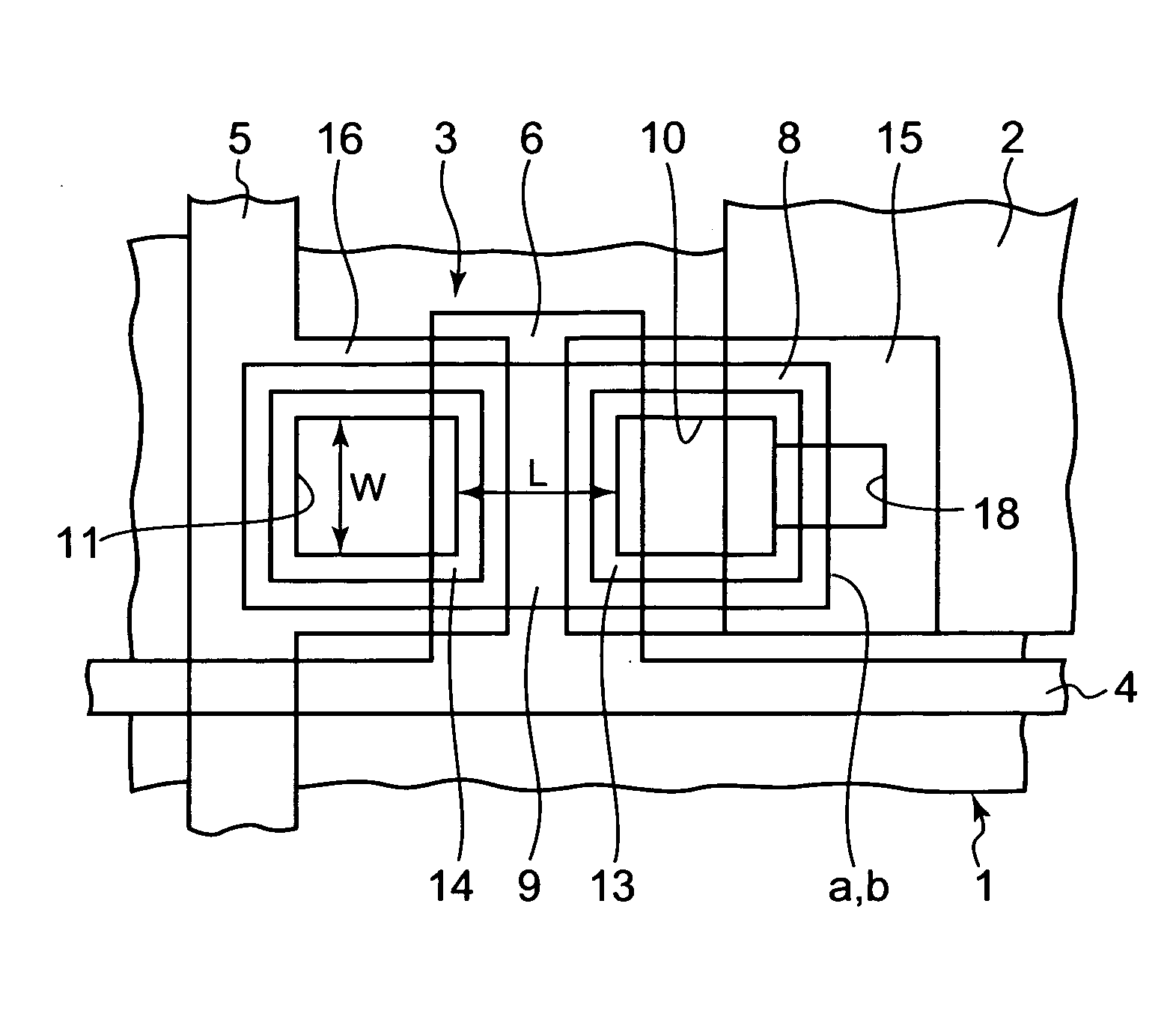

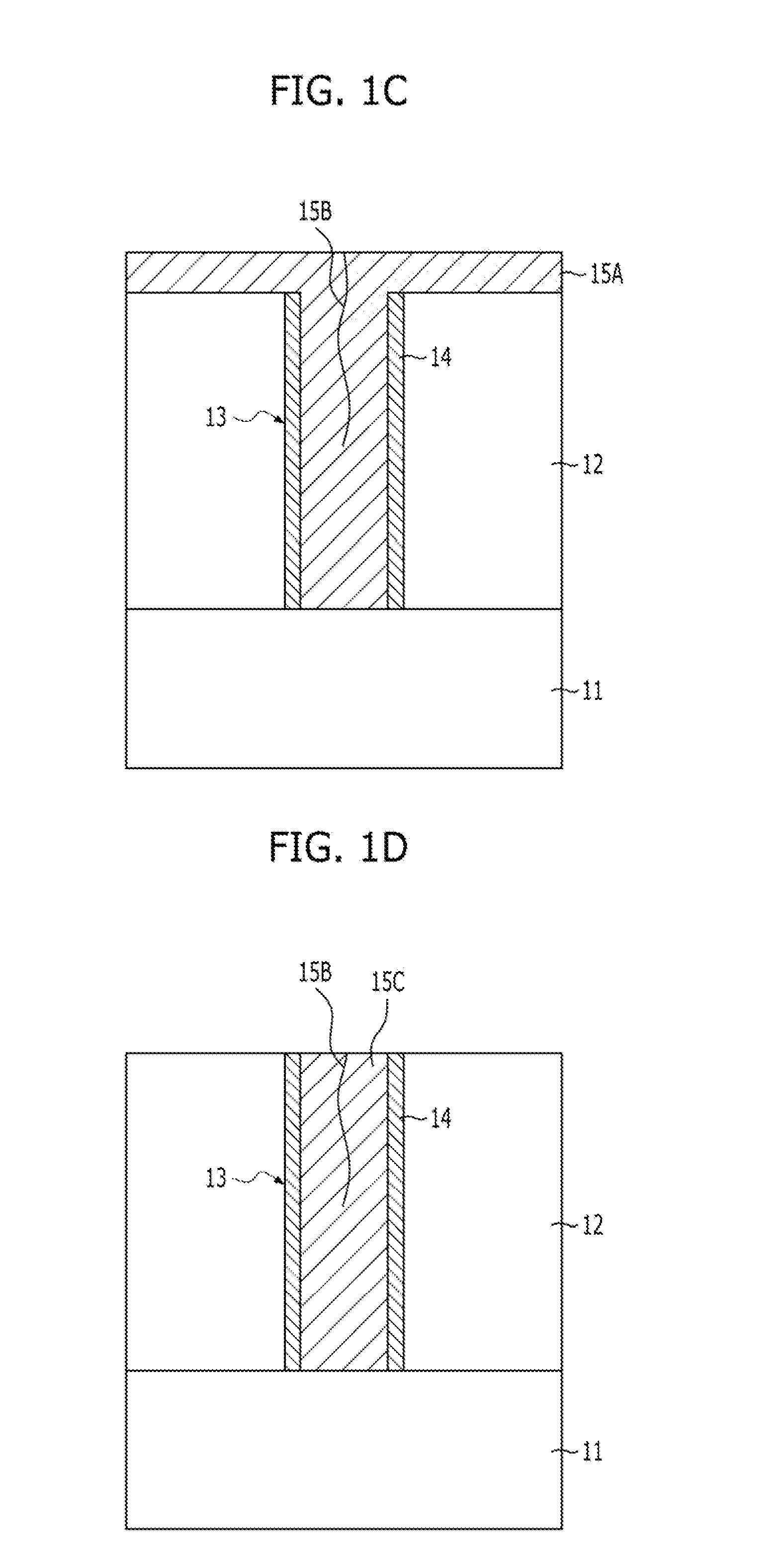

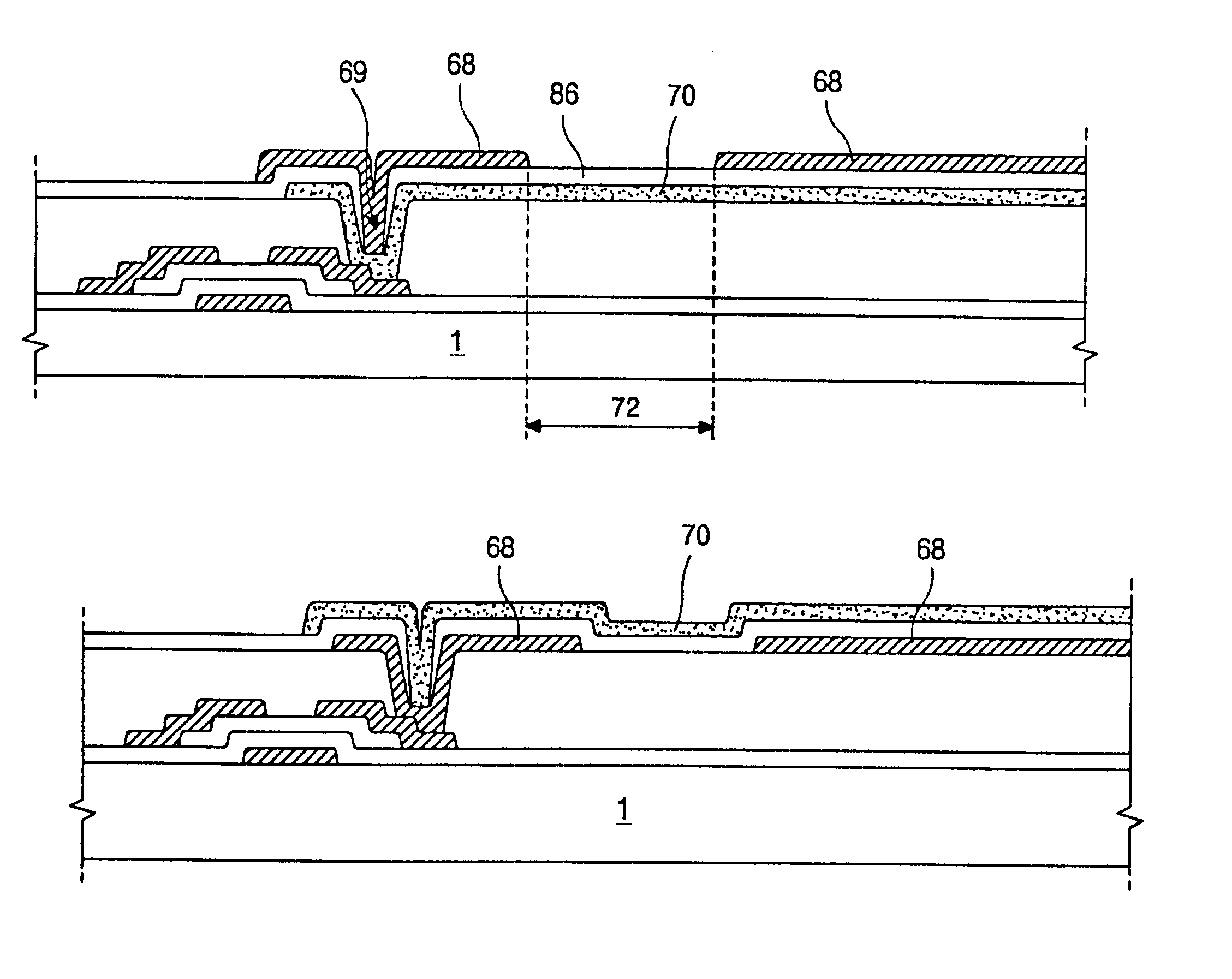

Thin film transistor having an etching protection film and manufacturing method thereof

InactiveUS7385224B2Improve machining accuracySolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorSemiconductor thin films

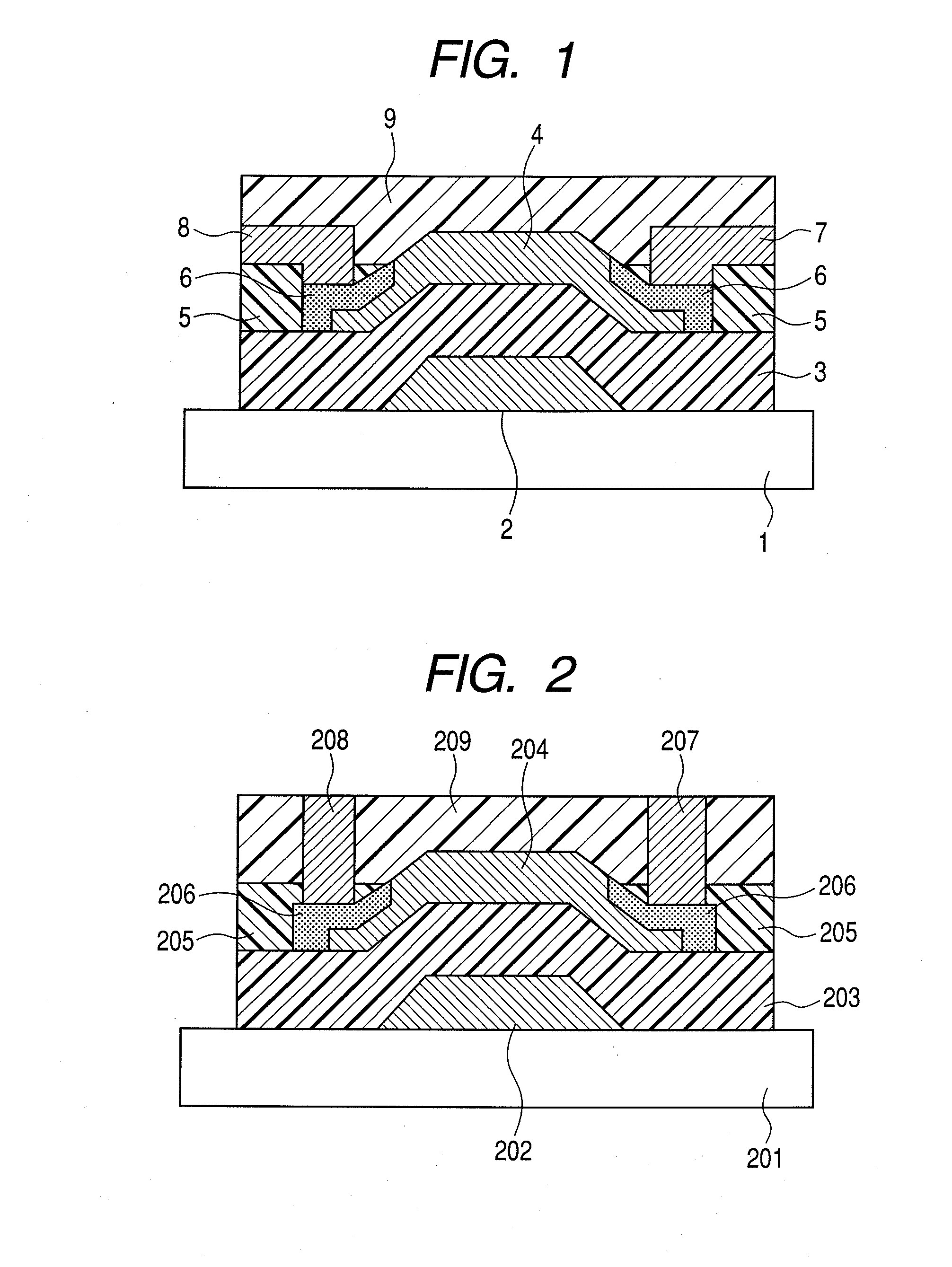

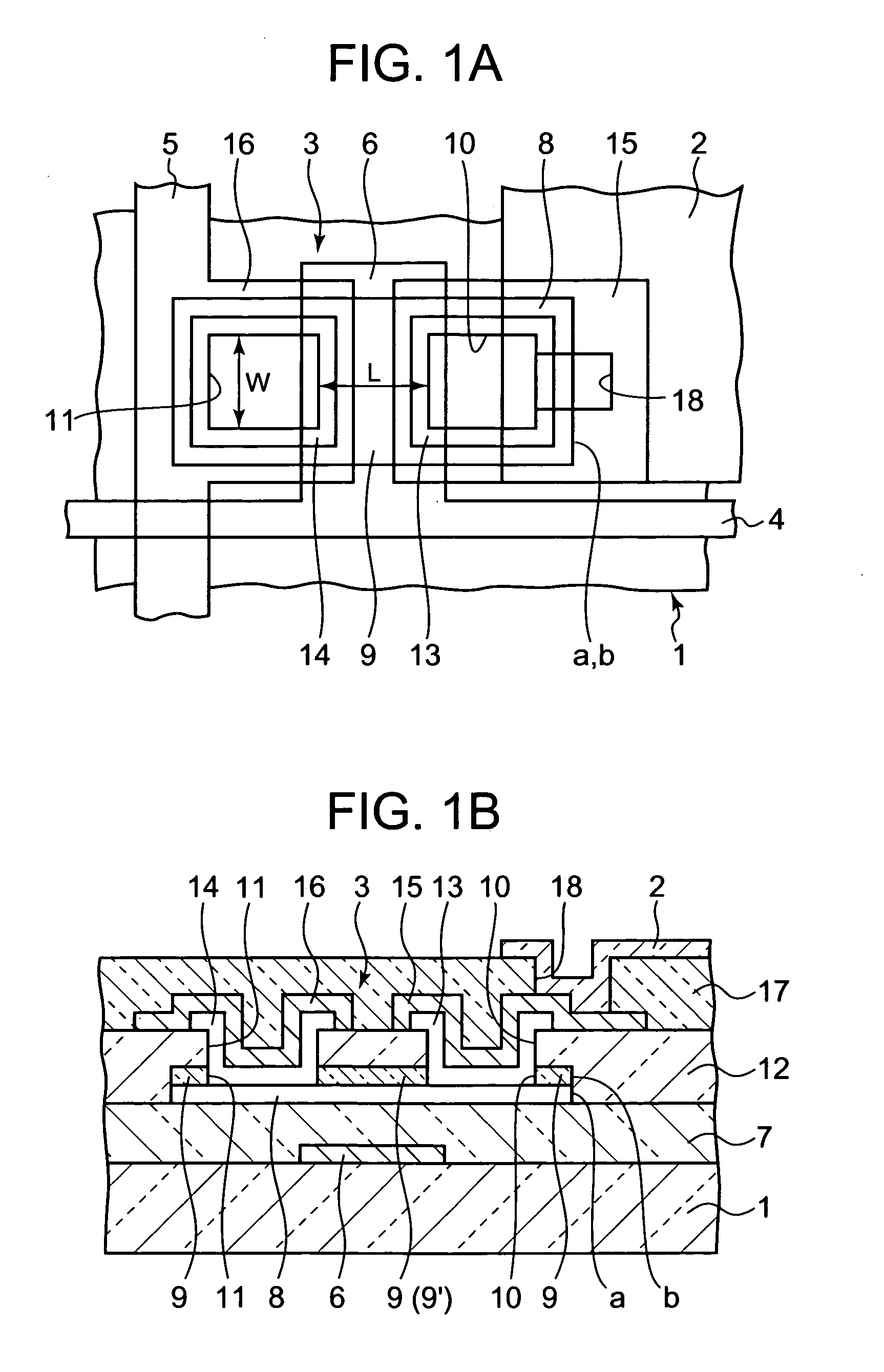

A thin film transistor of the present invention includes a semiconductor thin film (8); a gate insulating film (7) formed on one surface of the semiconductor thin film (8); a gate electrode (6) formed to be opposite to the semiconductor thin film (8) through the gate insulating film (7); a source electrode (15) and a drain electrode (16) electrically connected to the semiconductor thin film (8); a source region; a drain region; and a channel region. The thin film transistor further includes an insulating film (9) formed on a peripheral portion corresponding to at least the source region and the drain region of the semiconductor thin film (8), and having a contact hole (10, 11) through which at least a part of each of the source region and the drain region is exposed wherein the source electrode (15) and the drain electrode (16) are connected to the semiconductor thin film (8) through the contact hole (10, 11).

Owner:CASIO COMPUTER CO LTD

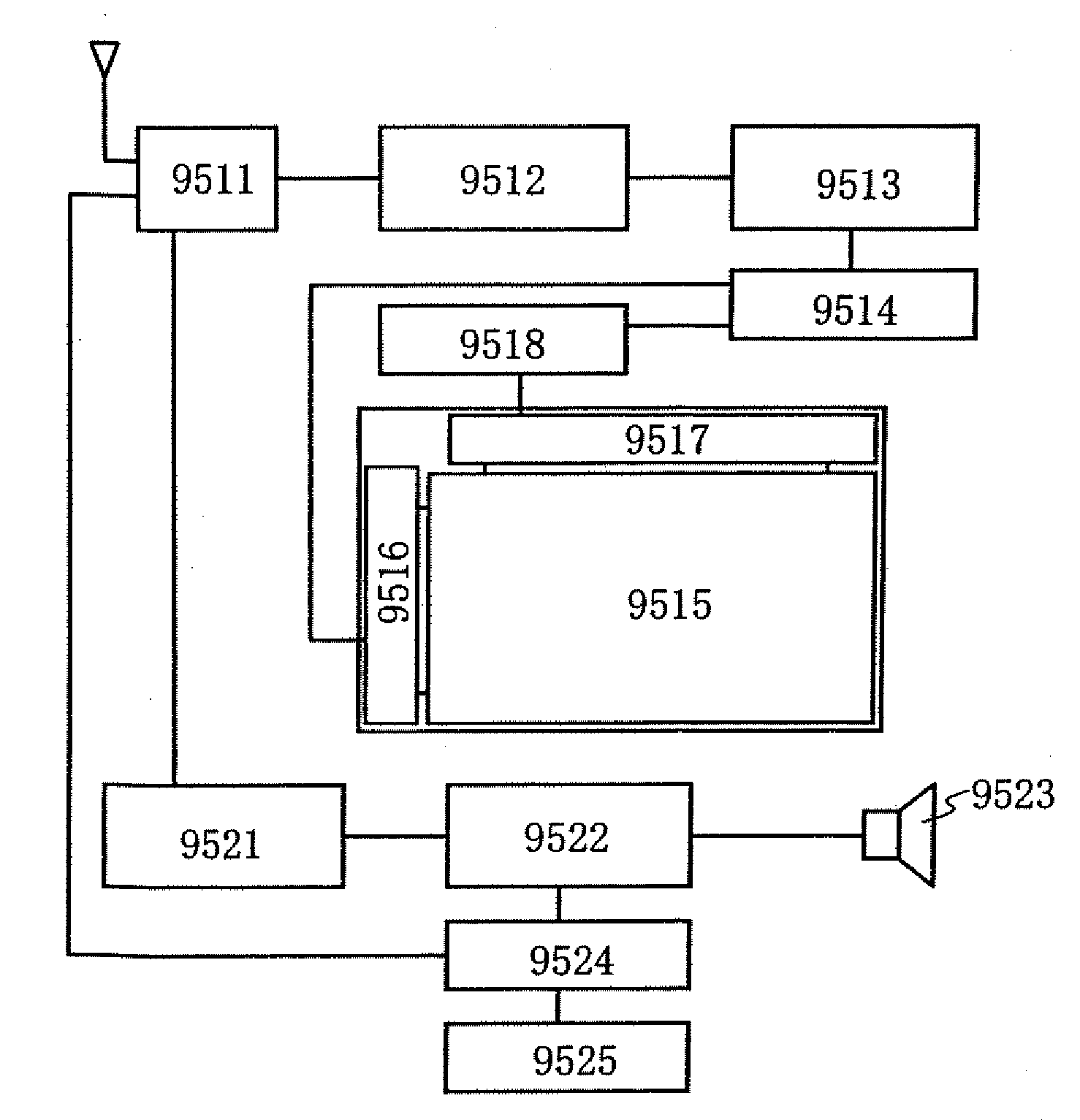

Semiconductor device and method for manufacturing the same, and electric device

InactiveUS20090073325A1Simple stepsHighly integratedTransistorTelevision system detailsElectrical resistance and conductanceLongest Diameter

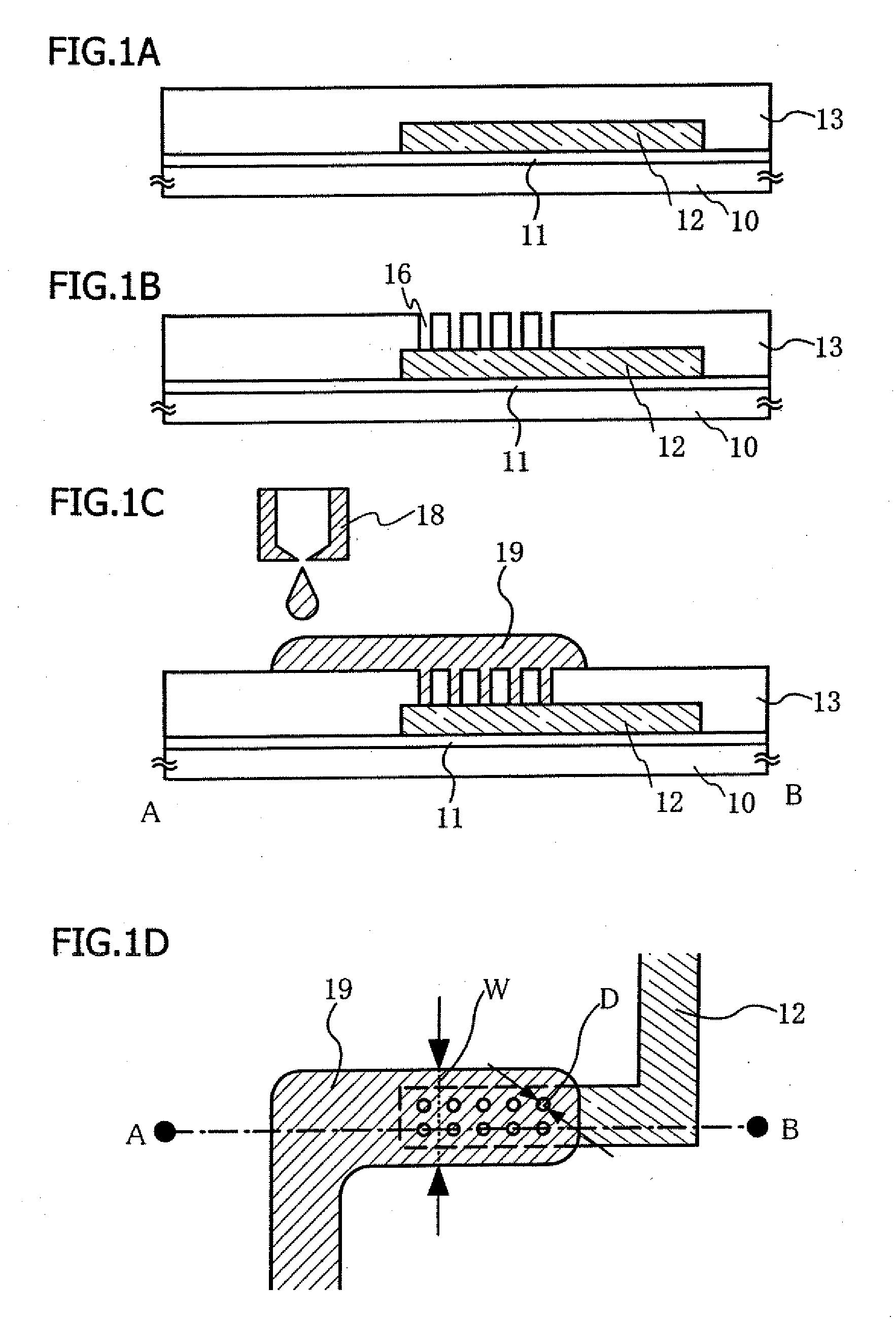

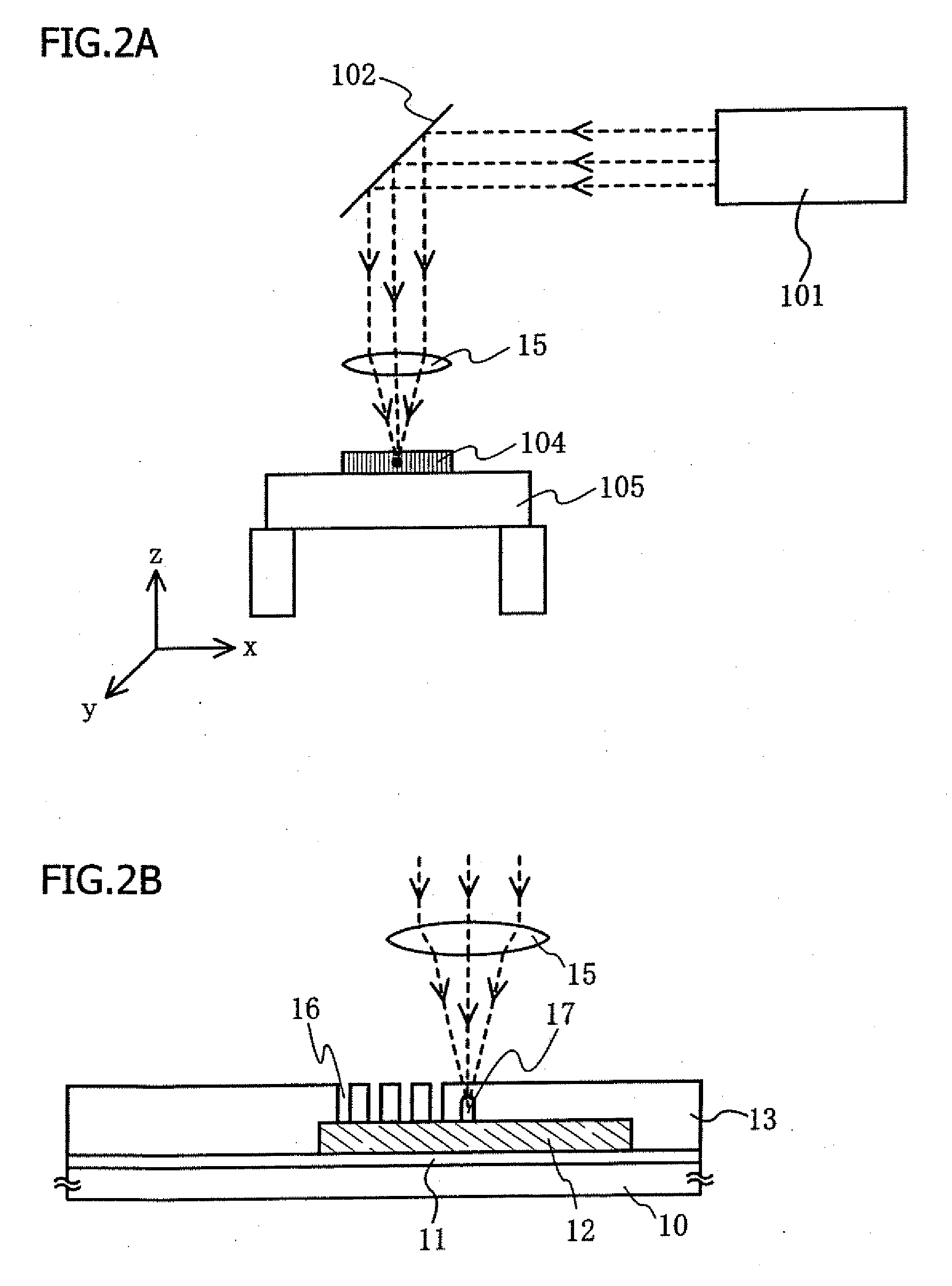

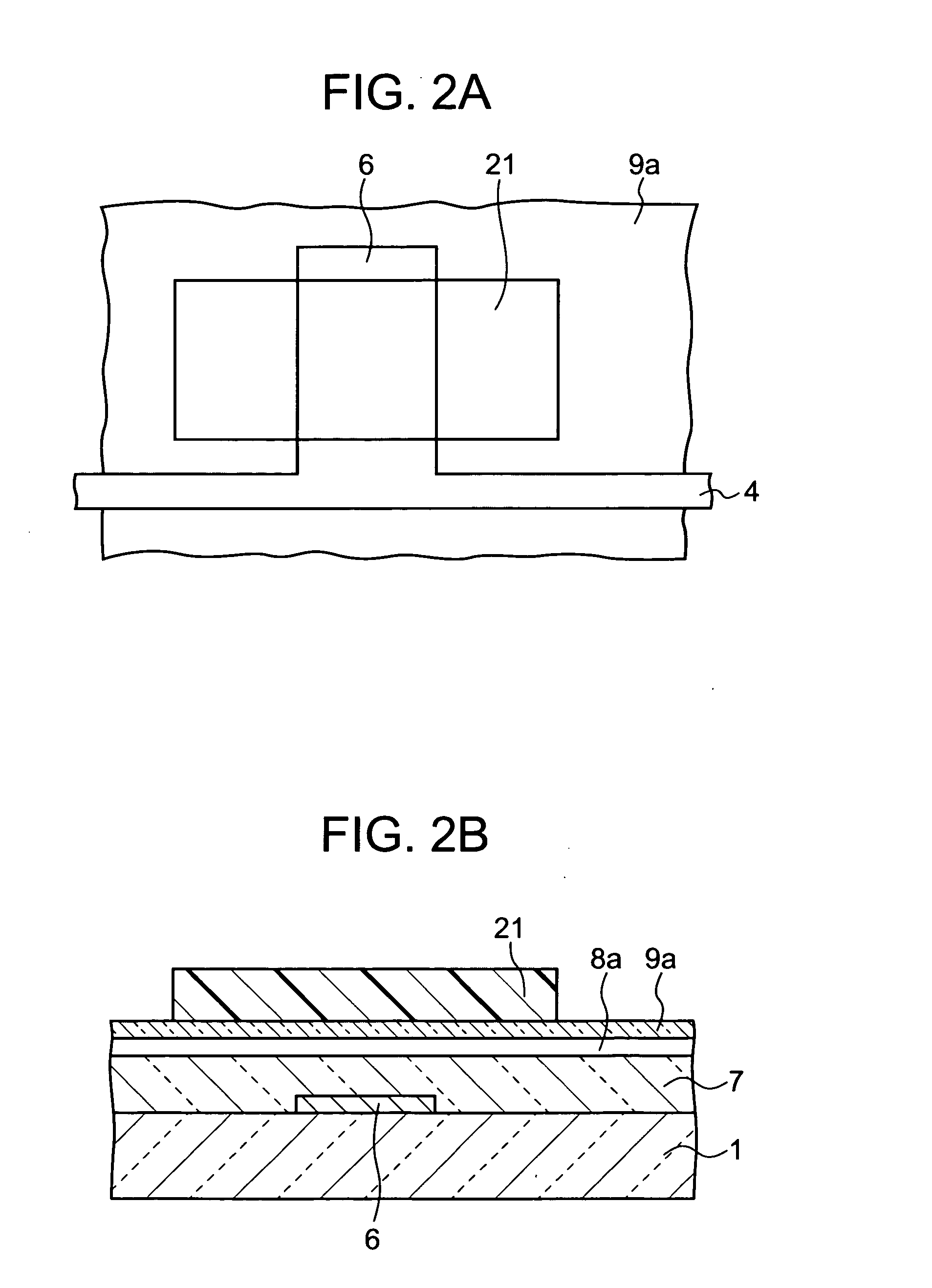

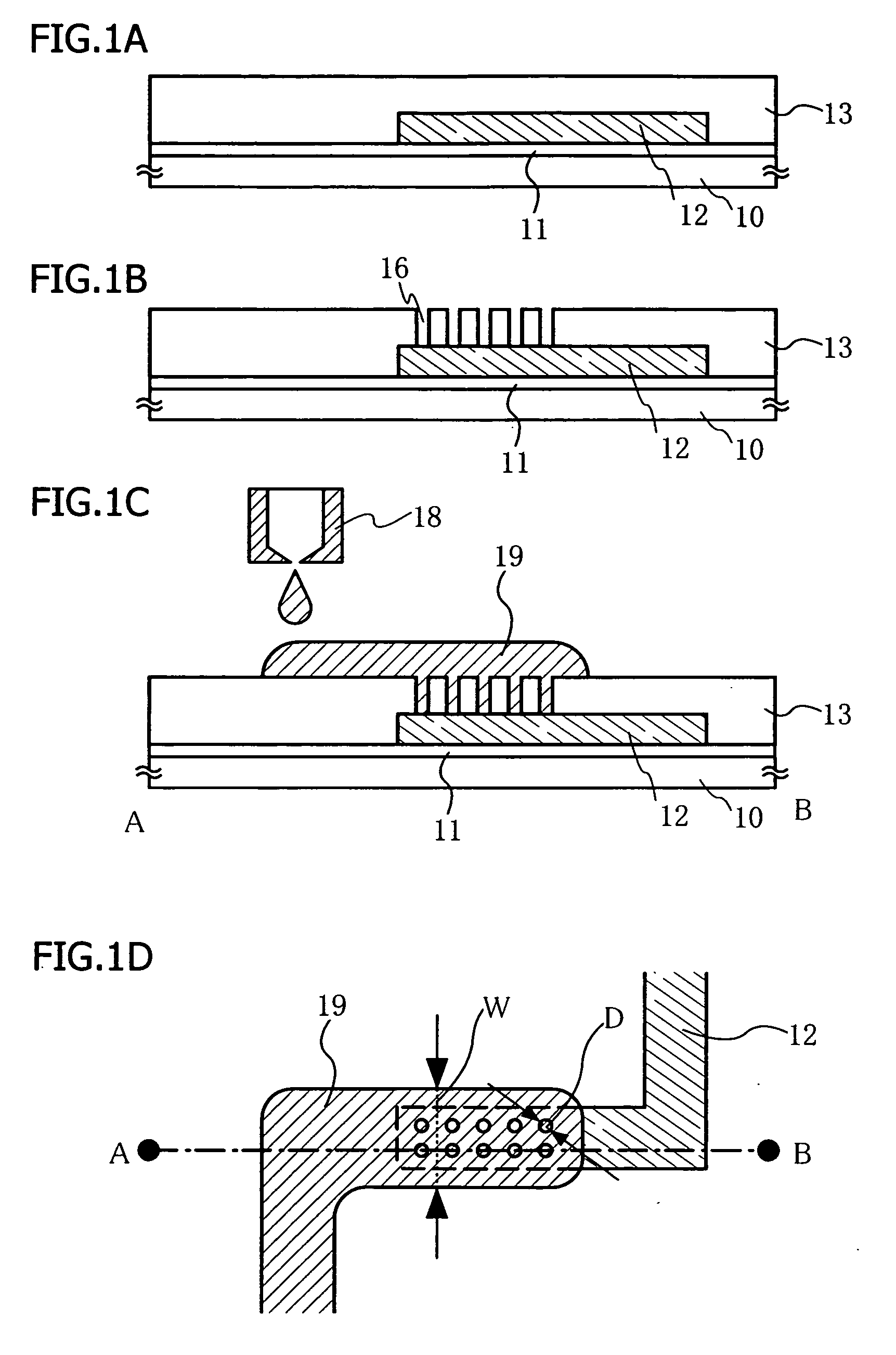

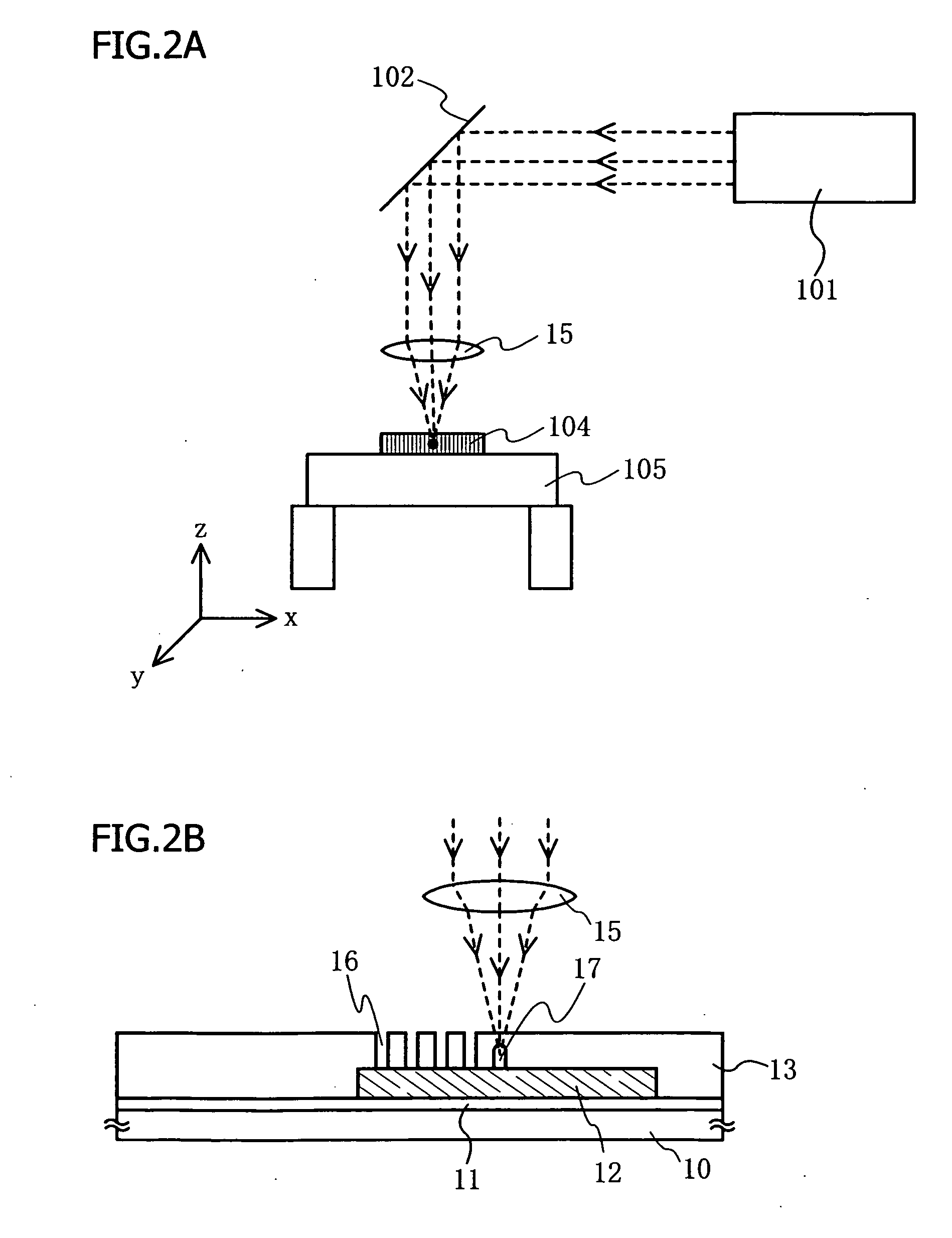

It is an object of the present invention to simplify steps needed to process a wiring in forming a multilayer wiring. In addition, when a droplet discharging technique or a nanoimprint technique is used to form a wiring in a contact hole having a comparatively long diameter, the wiring in accordance with the shape of the contact hole is formed, and the wiring portion of the contact hole is likely to have a depression compared with other portions. A penetrating opening is formed by irradiating a light-transmitting insulating film with laser light having high intensity and a pulse high in repetition frequency. A plurality of openings having a minute contact area is provided instead of forming one penetrating opening having a large contact area to have an even thickness of a wiring by reducing a partial depression and also to ensure contact resistance.

Owner:SEMICON ENERGY LAB CO LTD

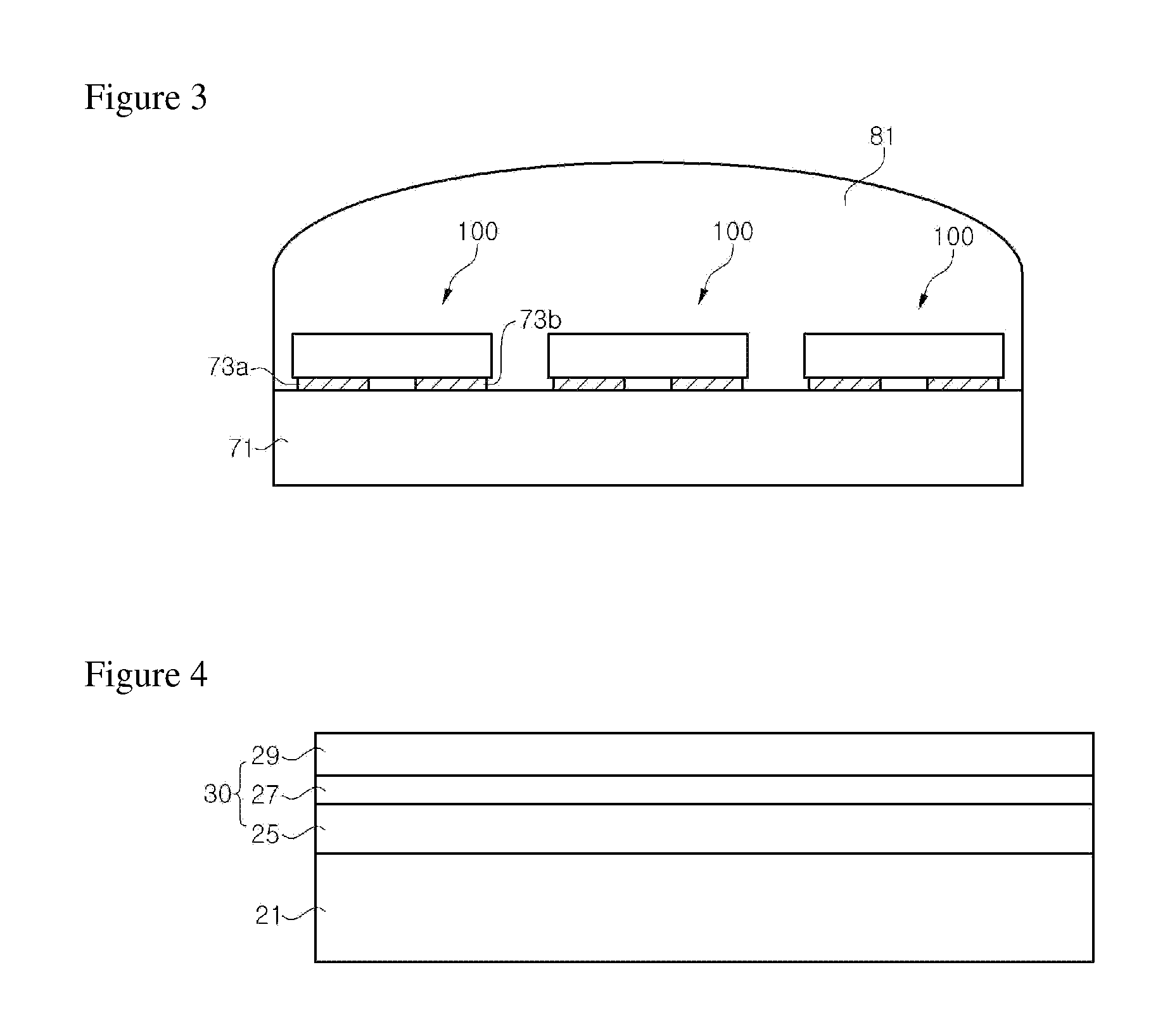

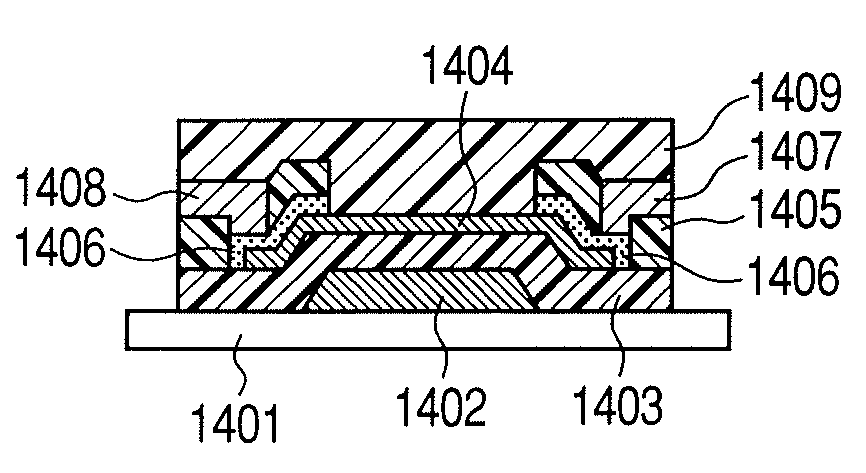

Wafer-level light emitting diode package and method of fabricating the same

ActiveUS20120074441A1Improve efficiencyImprove cooling effectSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

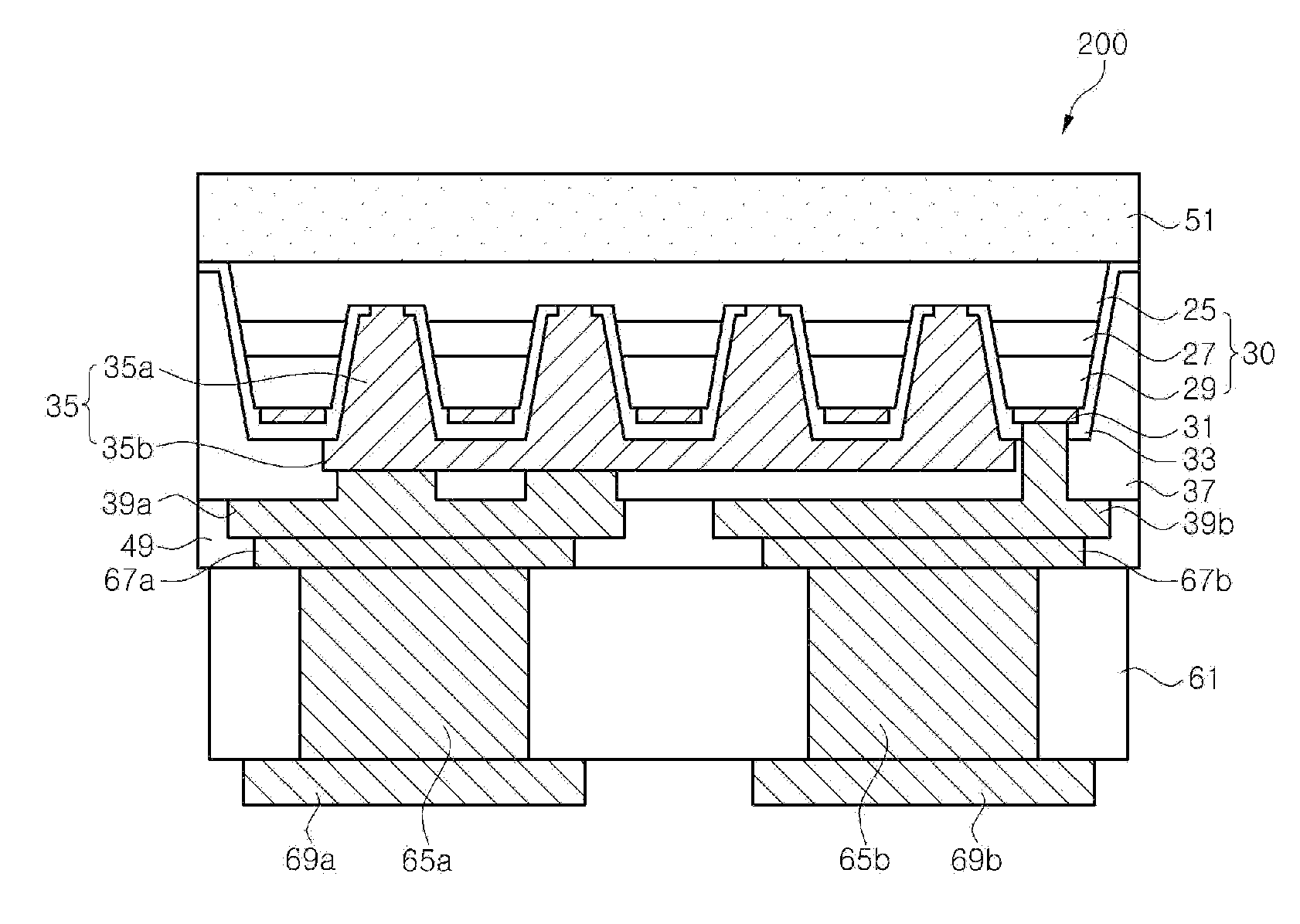

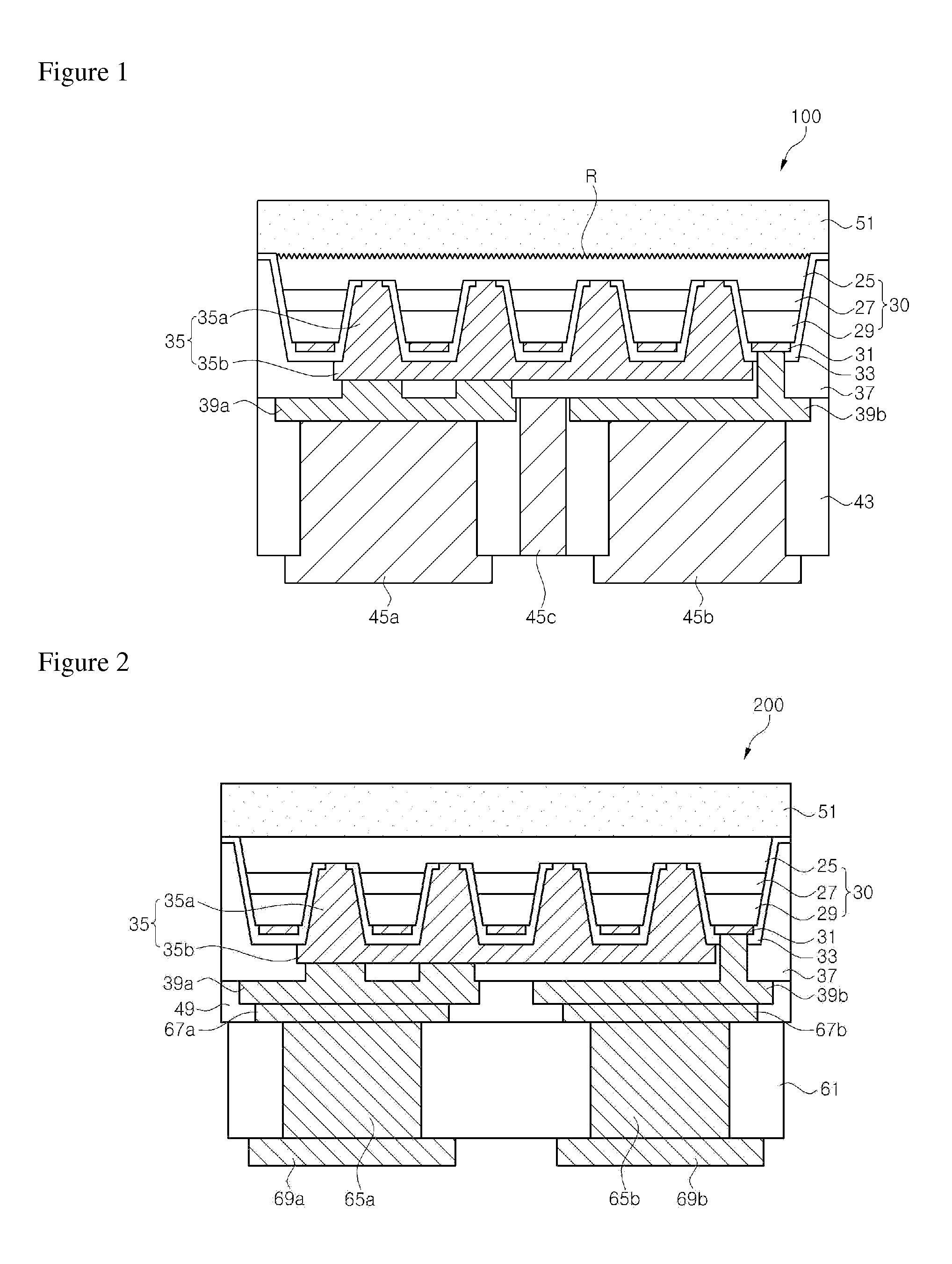

Exemplary embodiments of the present invention provide a wafer-level light emitting diode (LED) package and a method of fabricating the same. The LED package includes a semiconductor stack including a first conductive type semiconductor layer, an active layer, and a second conductive type semiconductor layer; a plurality of contact holes arranged in the second conductive type semiconductor layer and the active layer, the contact holes exposing the first conductive type semiconductor layer; a first bump arranged on a first side of the semiconductor stack, the first bump being electrically connected to the first conductive type semiconductor layer via the plurality of contact holes; a second bump arranged on the first side of the semiconductor stack, the second bump being electrically connected to the second conductive type semiconductor layer; and a protective insulation layer covering a sidewall of the semiconductor stack.

Owner:SEOUL SEMICONDUCTOR

Method of manufacturing a contact interconnection layer containing a metal and nitrogen by atomic layer deposition for deep sub-micron semiconductor technology

ActiveUS7235482B2Good step coverageSafe handlingSemiconductor/solid-state device detailsSolid-state devicesAtomic layer depositionContamination

An atomic layer deposition method is used to deposit a TiN or TiSiN film having a thickness of about 50 nm or less on a substrat. A titanium precursor which is tetrakis(dimethylamido)titanium (TDMAT), tetrakis(diethylamido)titanium (TDEAT), or Ti{OCH(CH3)2}4 avoids halide contamination from a titanium halide precursor and is safer to handle than a titanium nitrate. After a monolayer of the titanium precursor is deposited on a substrate, a nitrogen containing reactant is introduced to form a TiN monolayer which is followed by a second purge. For TiSiN, a silicon source gas is fed into the process chamber after the TiN monolayer formation. The process is repeated several times to produce a composite layer comprised of a plurality of monolayers that fills a contact hole. The ALD method is cost effective and affords an interconnect with lower impurity levels and better step coverage than conventional PECVD or CVD processes.

Owner:TAIWAN SEMICON MFG CO LTD

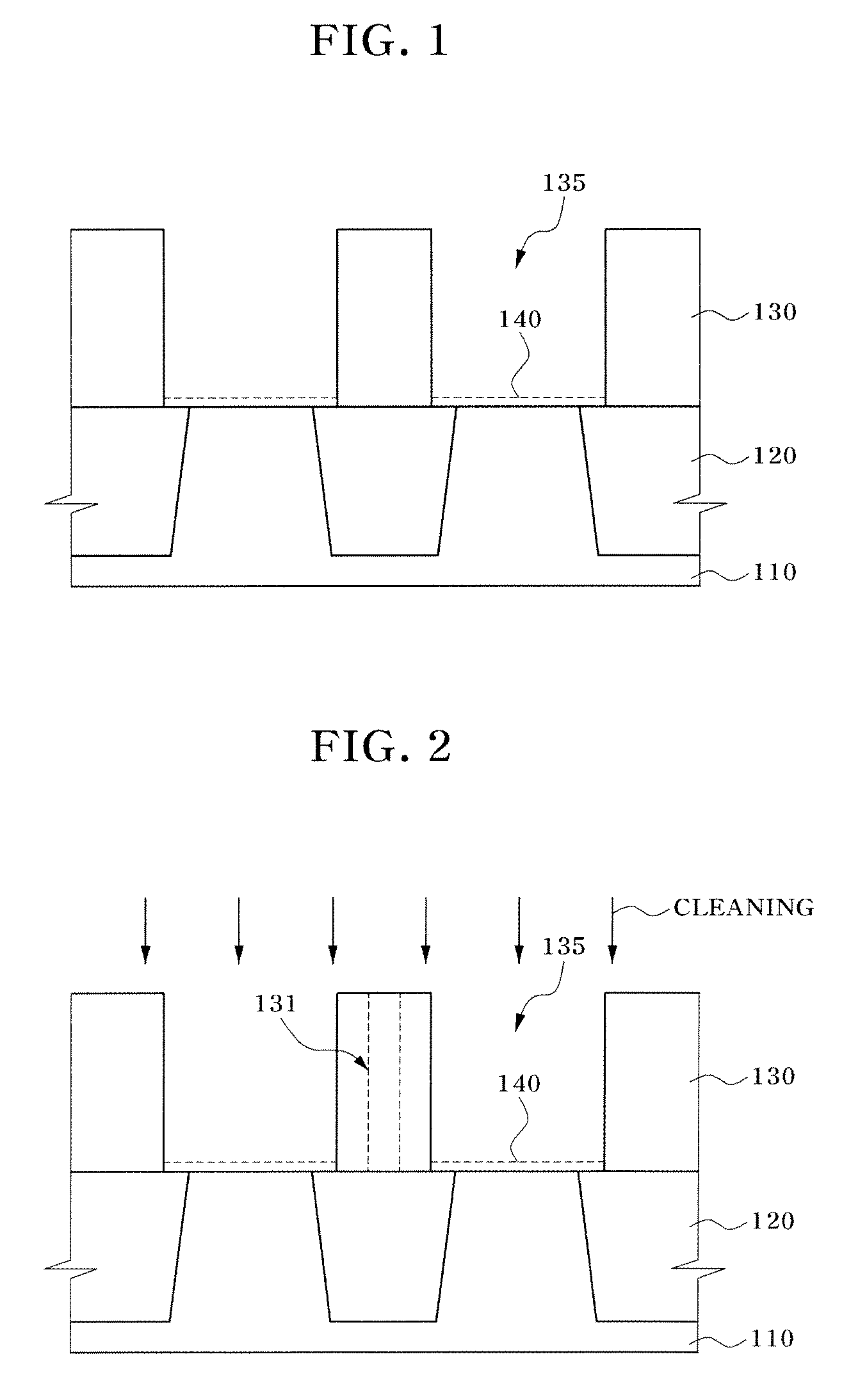

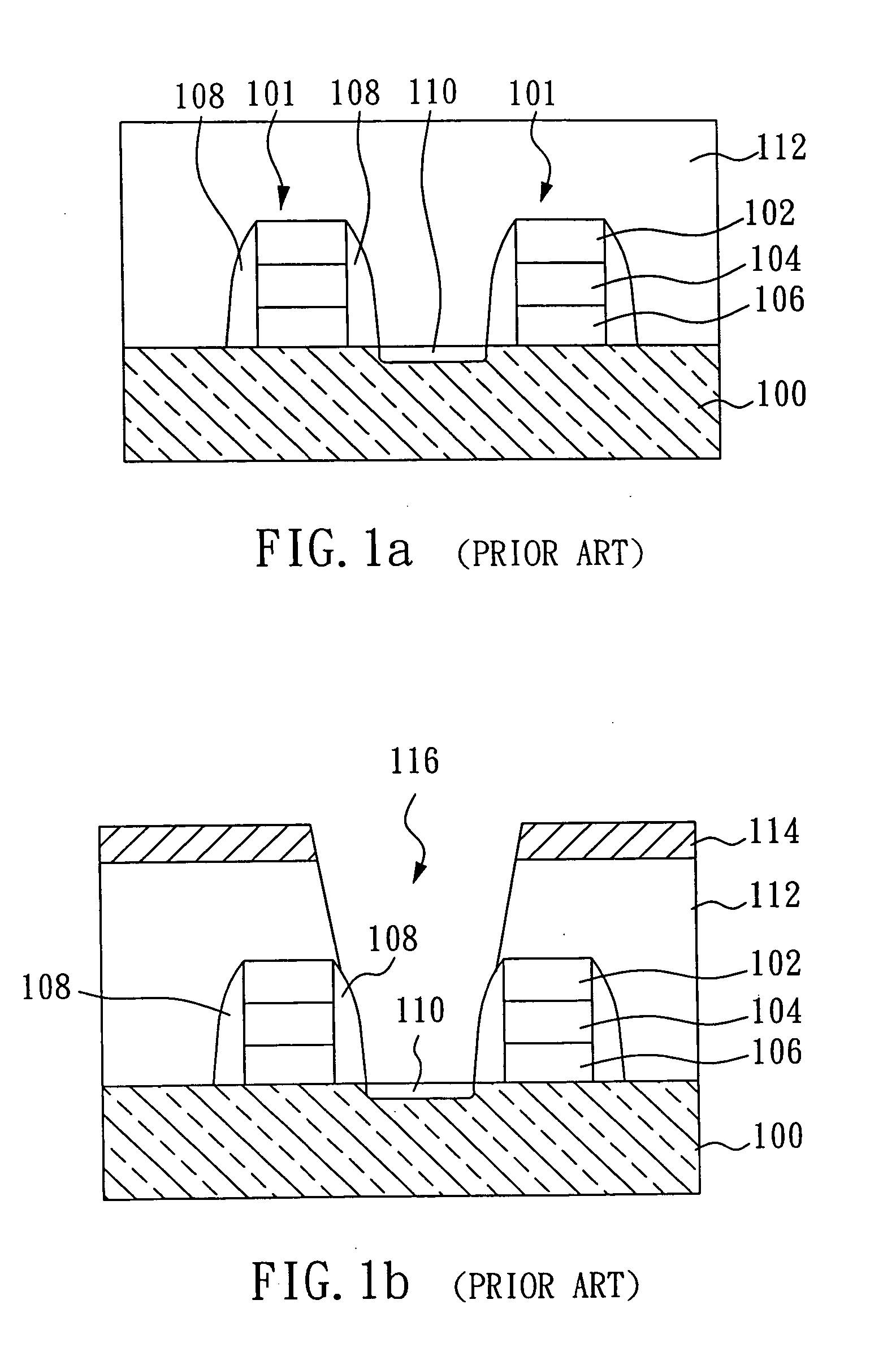

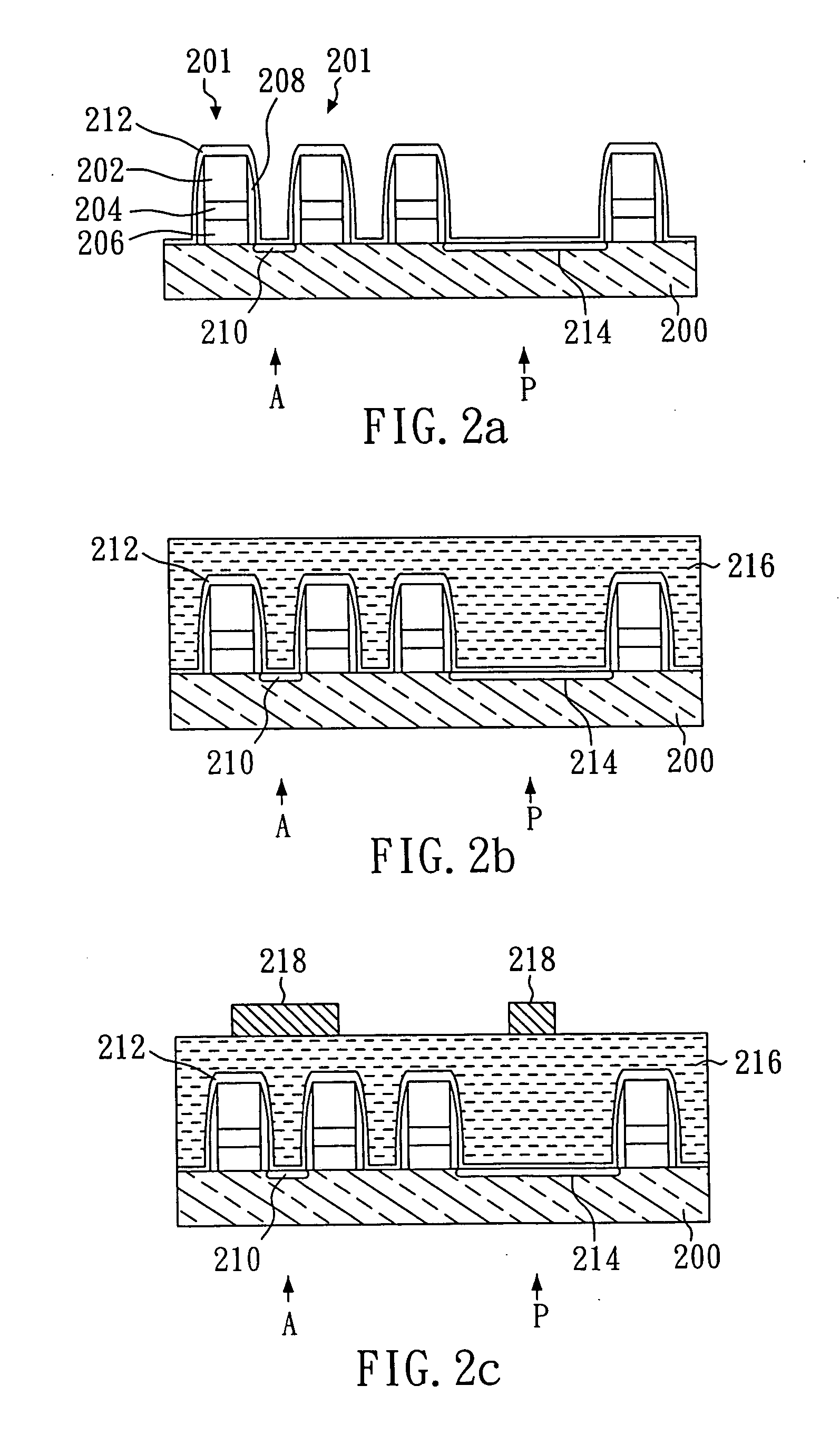

Method for forming fine pattern in semiconductor device

ActiveUS20110124196A1The process steps are simpleDecorative surface effectsPhotomechanical apparatusEngineeringSemiconductor

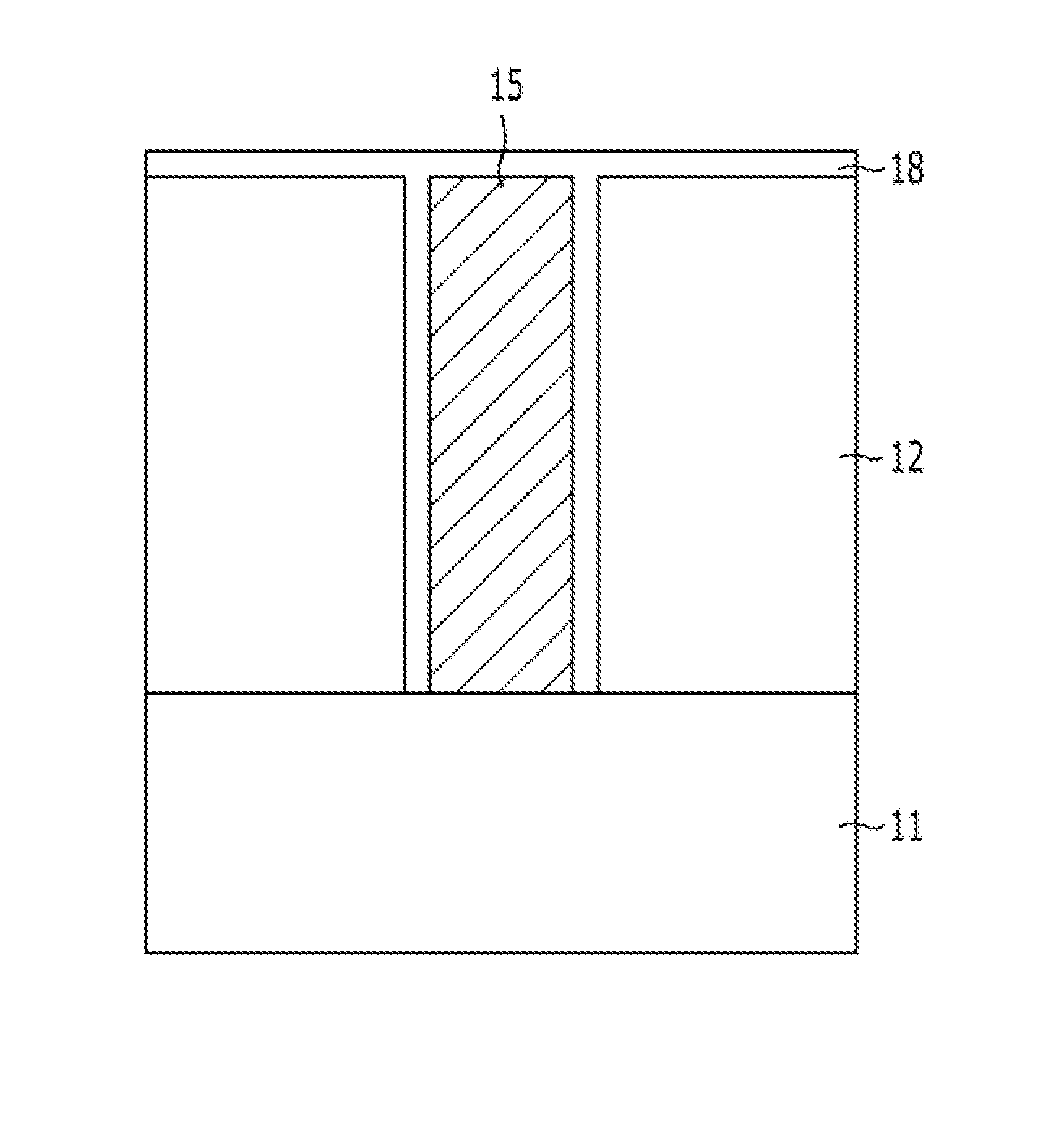

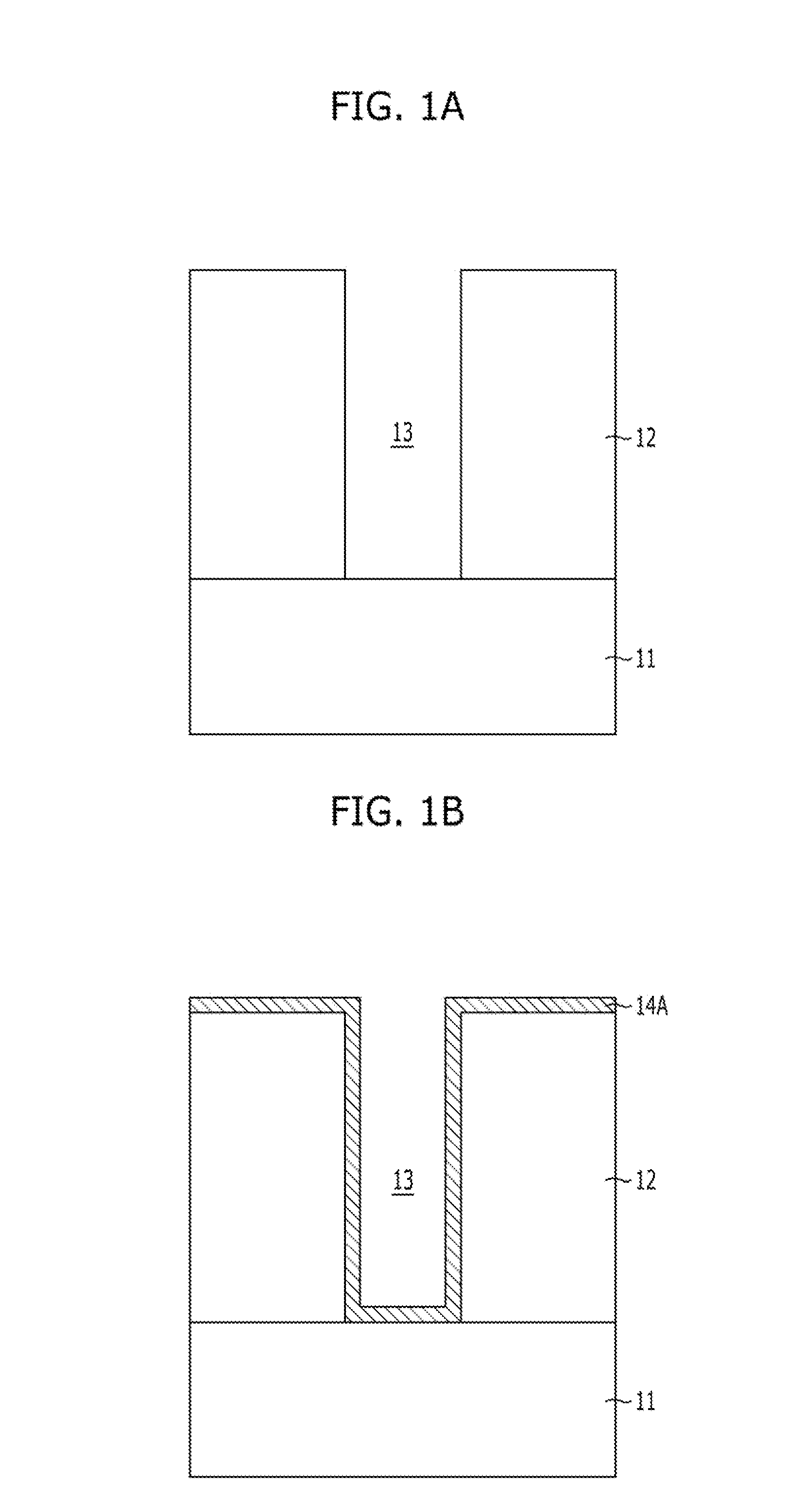

A method for forming a contact hole of a semiconductor device according to the present invention forms a contact hole which is defined as a new contact hole region (a second contact hole region), between spacers as well as a contact hole defined within the spacer (a first contact hole region) by a spacer patterning technology (SPT). The present invention with this method can help to form a fine contact hole as a double patterning is used, even with one mask.

Owner:SK HYNIX INC

Transparent thin film transistor (TFT) and its method of manufacture

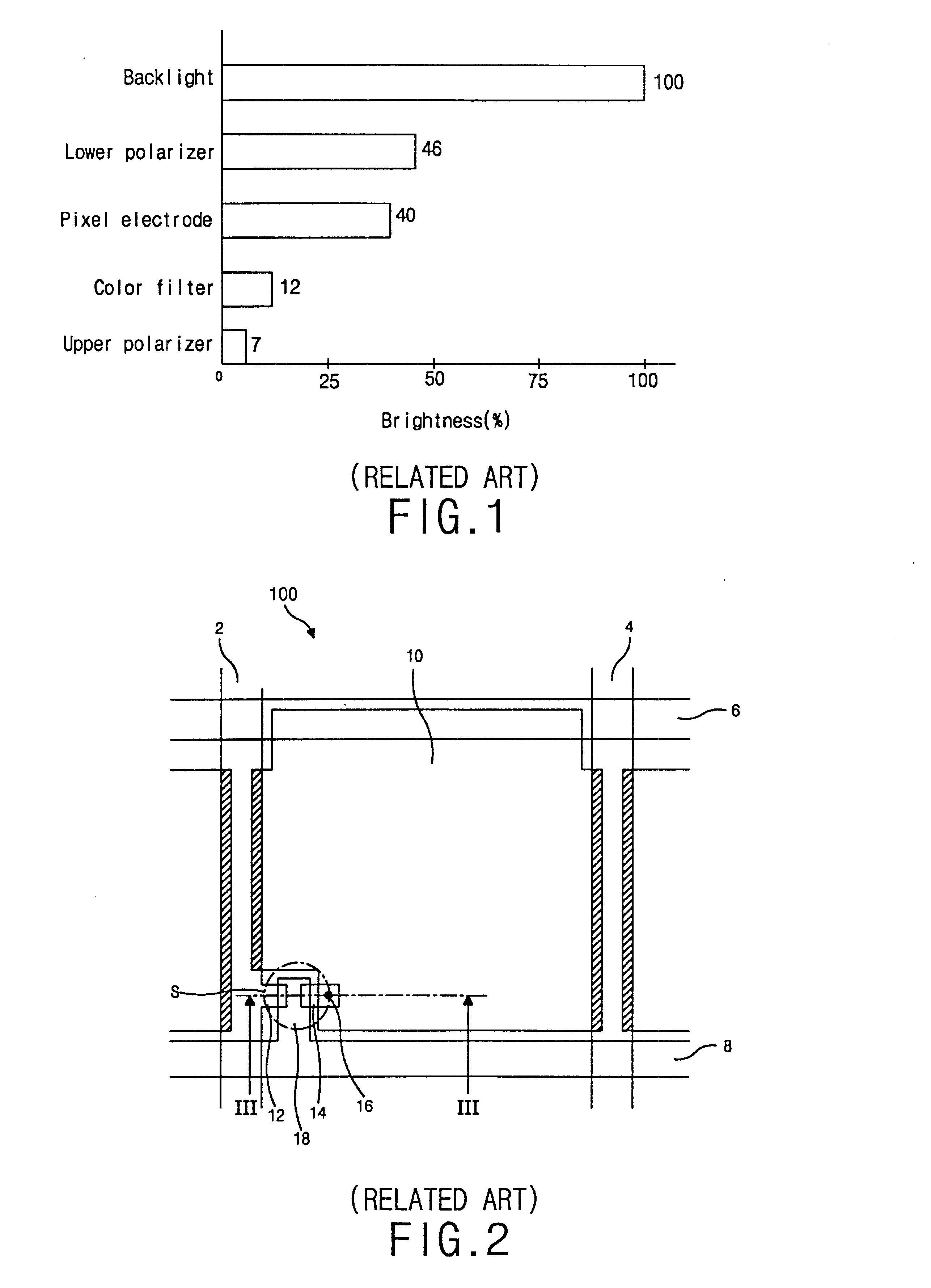

InactiveUS20070057261A1Increase the aperture ratioIncrease display resolutionNon-linear opticsSemiconductor devicesCarbideNitride

A transparent thin film transistor (TFT) and its method of manufacture includes: a substrate, a transparent semiconductor layer formed by coating the substrate with an oxide, a nitride, or a carbide to pattern the material, a gate insulating layer formed on the transparent semiconductor layer, a gate electrode formed on the gate insulating layer to correspond to the transparent semiconductor layer, an interlayer insulating layer formed on the gate electrode, and source and drain electrodes electrically connected to the transparent semiconductor layer through contact holes formed in the interlayer insulating layer and the gate insulating layer.

Owner:SAMSUNG MOBILE DISPLAY CO LTD

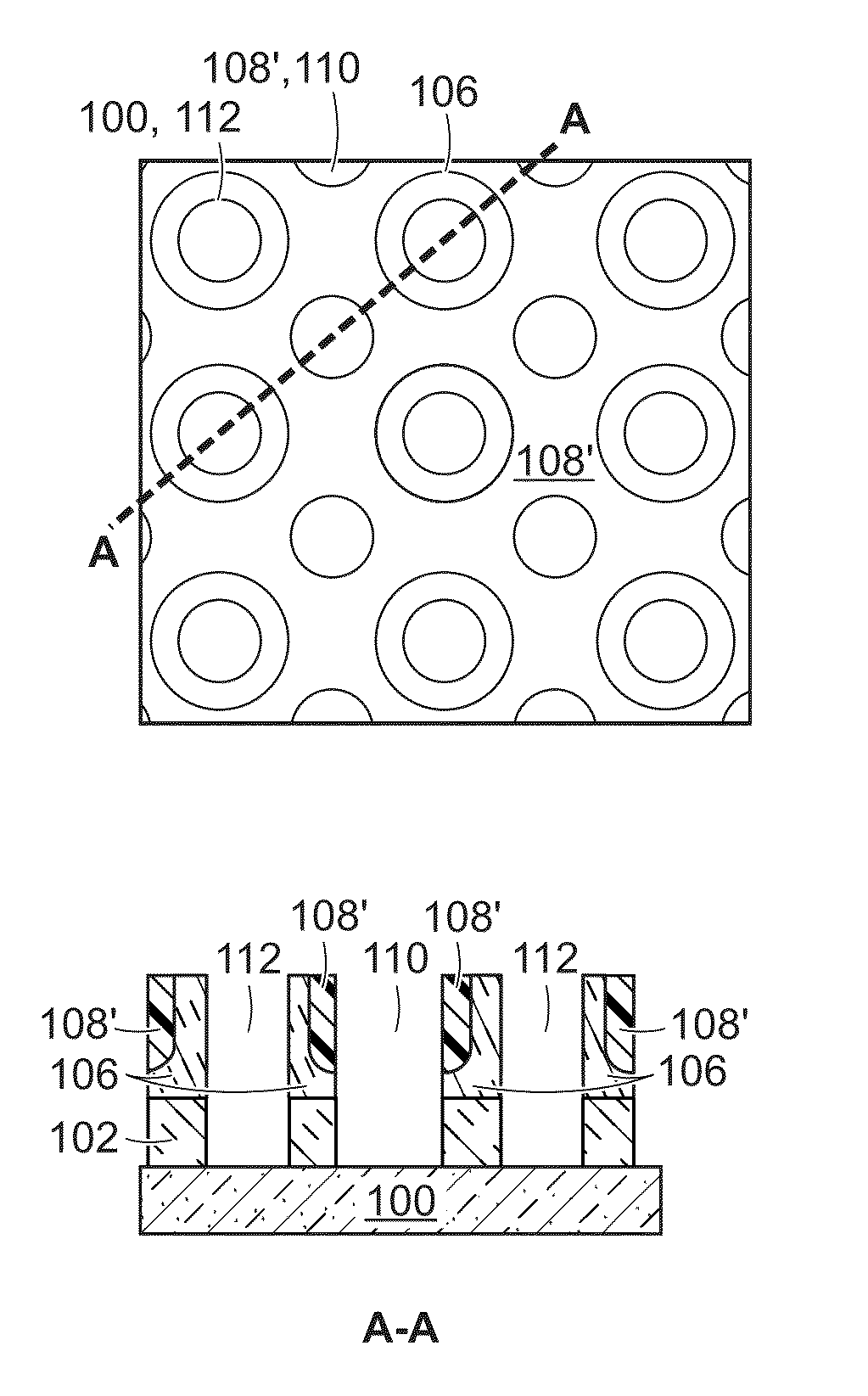

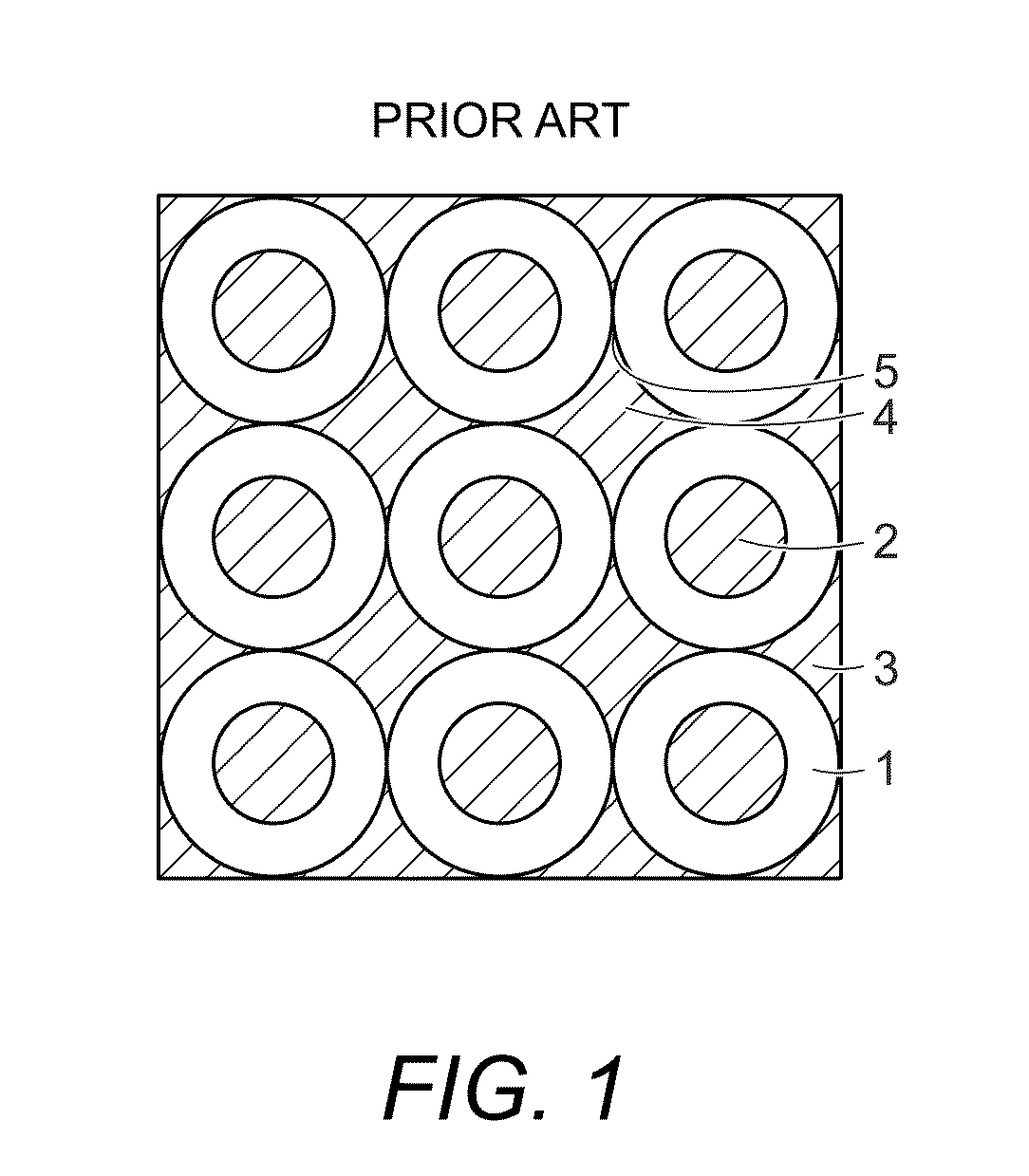

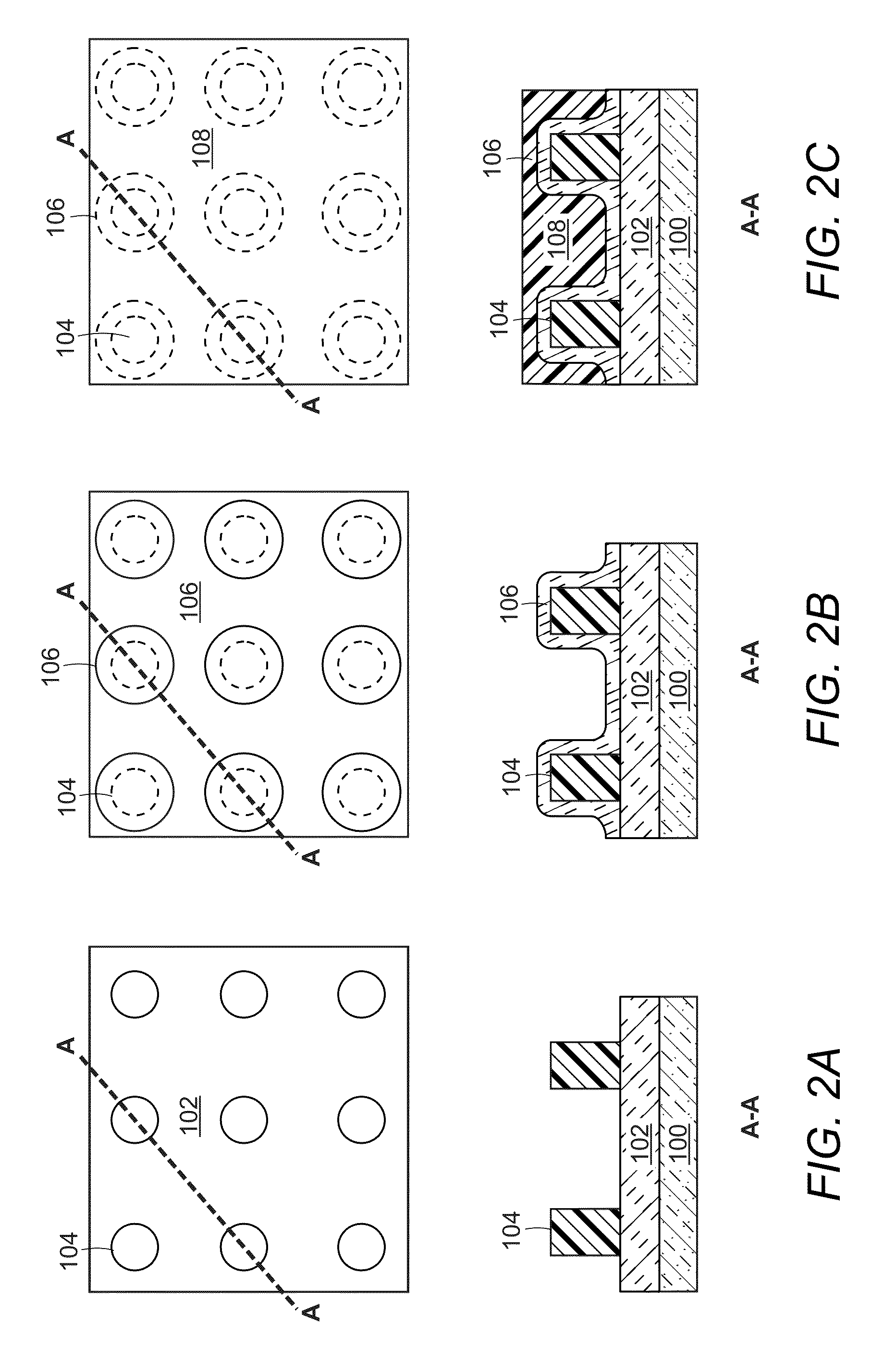

Contact hole formation methods

Methods of forming contact holes comprising: (a) providing a substrate comprising a plurality of post patterns over a layer to be patterned; (b) forming a hardmask layer over the post patterns and the layer to be patterned; (c) coating a pattern treatment composition over the hardmask layer, wherein the pattern treatment composition comprises a polymer comprising a reactive surface attachment group and a solvent; and optionally baking the substrate; wherein the polymer becomes bonded to the hardmask layer to form a polymer layer over the hardmask layer; and (d) treating the substrate with a rinsing agent comprising a solvent to remove residual, unbound said polymer, thereby forming a first hole disposed between a plurality of surrounding post patterns. The method is free of exposing the polymer to activating radiation from coating the pattern treatment composition to treating the substrate with the solvent. Also provided are pattern treatment compositions and electronic devices formed by the methods. The inventions find particular applicability in the manufacture of semiconductor devices for providing high resolution contact hole patterns.

Owner:DOW GLOBAL TECH LLC +1

Method of Fabricating Landing Plug in Semiconductor Device

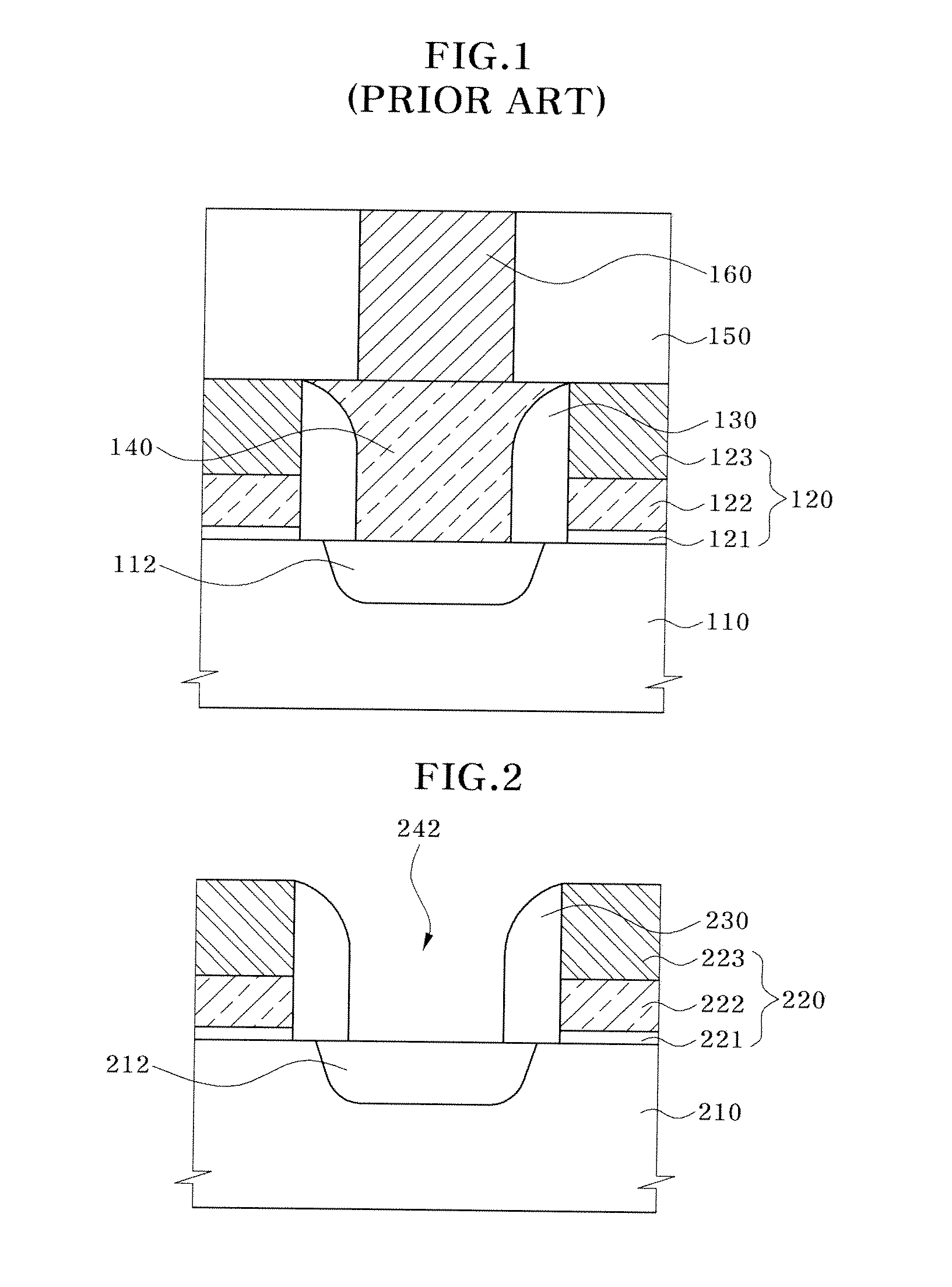

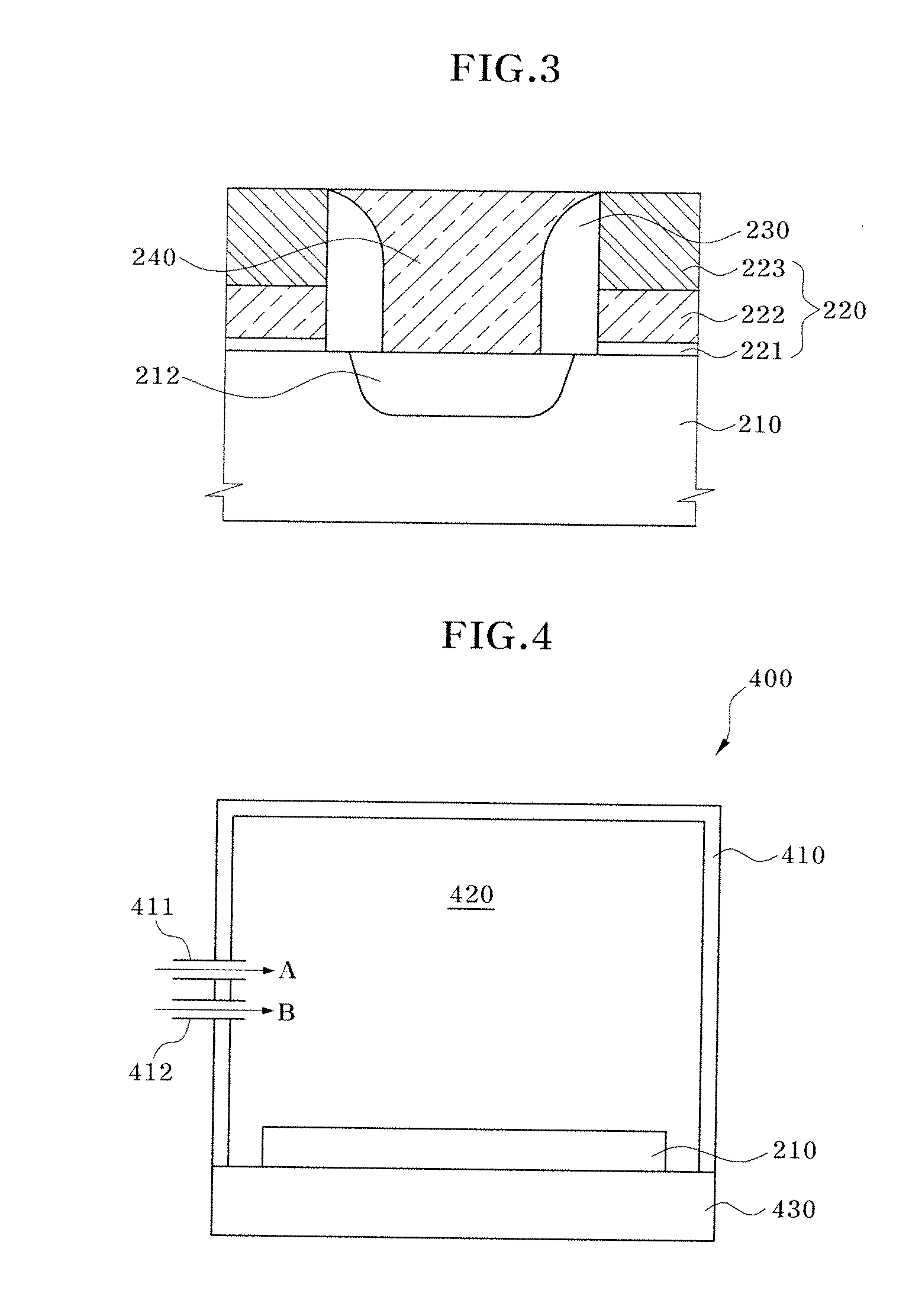

InactiveUS20100330801A1Improve resistance performanceSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

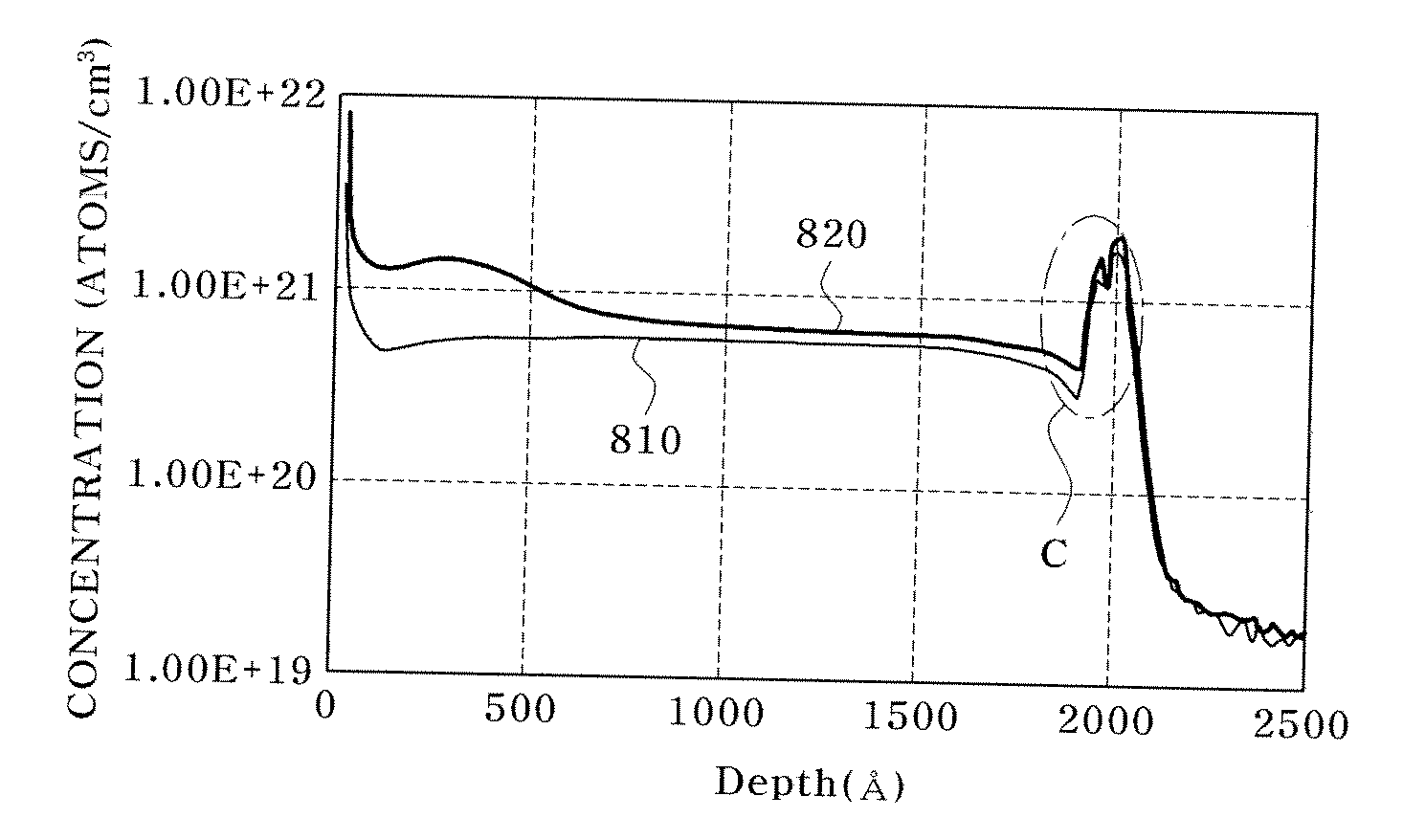

A method of fabricating a landing plug in a semiconductor memory device, which in one embodiment includes forming a landing plug contact hole on a semiconductor substrate having an impurity region to expose the impurity region; forming a landing plug by filling the landing plug contact hole with a polysilicon layer, wherein the landing plug is divided into a first region, a second region, a third region, and a fourth region from a lower portion of the landing plug, and the first region is doped with a first doping concentration that is relatively lowest, the second region is doped with a second doping concentration that is higher than the first doping concentration, the third region is doped with a third doping concentration that is higher than the second doping concentration and the fourth region is not doped; and annealing the resulting product formed with the landing plug.

Owner:SK HYNIX INC

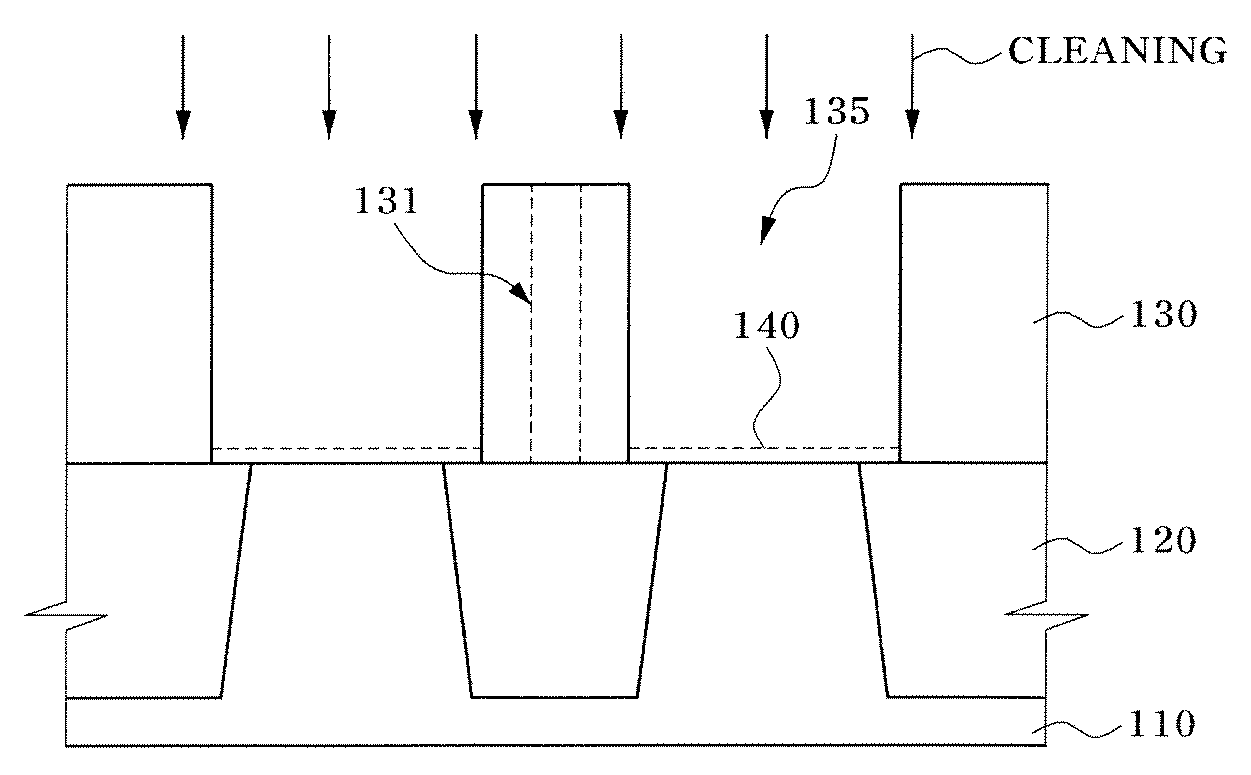

Method for Fabricating A Semiconductor Device Comprising Surface Cleaning

InactiveUS20080044990A1Efficient removalPreventing corrosion lossSemiconductor/solid-state device manufacturingAlcoholSurface cleaning

A method for fabricating a semiconductor device including surface cleaning includes forming a gate stack on a semiconductor substrate, cleaning contaminants present on the surface of the semiconductor substrate exposed through a contact hole using an etchant including a fluorine (F)-containing species dispersed in an alcohol, and filling a contact hole with a conductive layer to form a connection contact. The etchant preferably has a low selectivity of 1 or less.

Owner:SK HYNIX INC

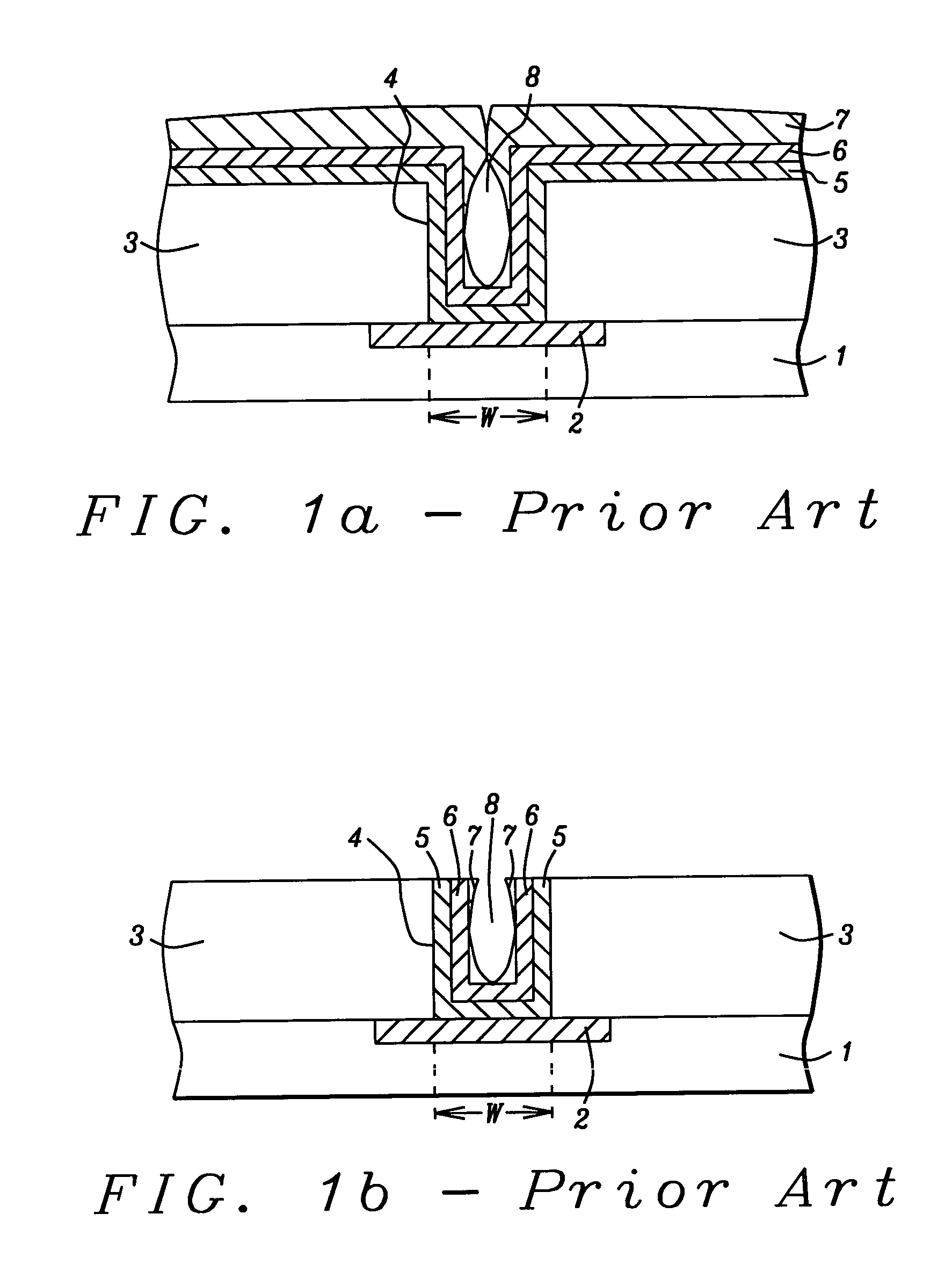

Phase changeable memory cells and methods of forming the same

InactiveUS20060118913A1Solid-state devicesSemiconductor/solid-state device manufacturingPhase-change memoryPhase-change material

A phase changeable memory cell is provided. The phase changeable memory cell includes a lower interlayer dielectric layer formed on a semiconductor substrate and a lower conductive plug passing through the lower interlayer dielectric layer. The lower conductive plug is in contact with a phase change material pattern disposed on the lower interlayer dielectric layer. The phase change material pattern and the lower interlayer dielectric layer are covered with an upper interlayer dielectric layer. The phase change material pattern is in direct contact with a conductive layer pattern, which is disposed in a plate line contact hole passing through the upper interlayer dielectric layer. Methods of fabricating the phase changeable memory cell is also provided.

Owner:SAMSUNG ELECTRONICS CO LTD

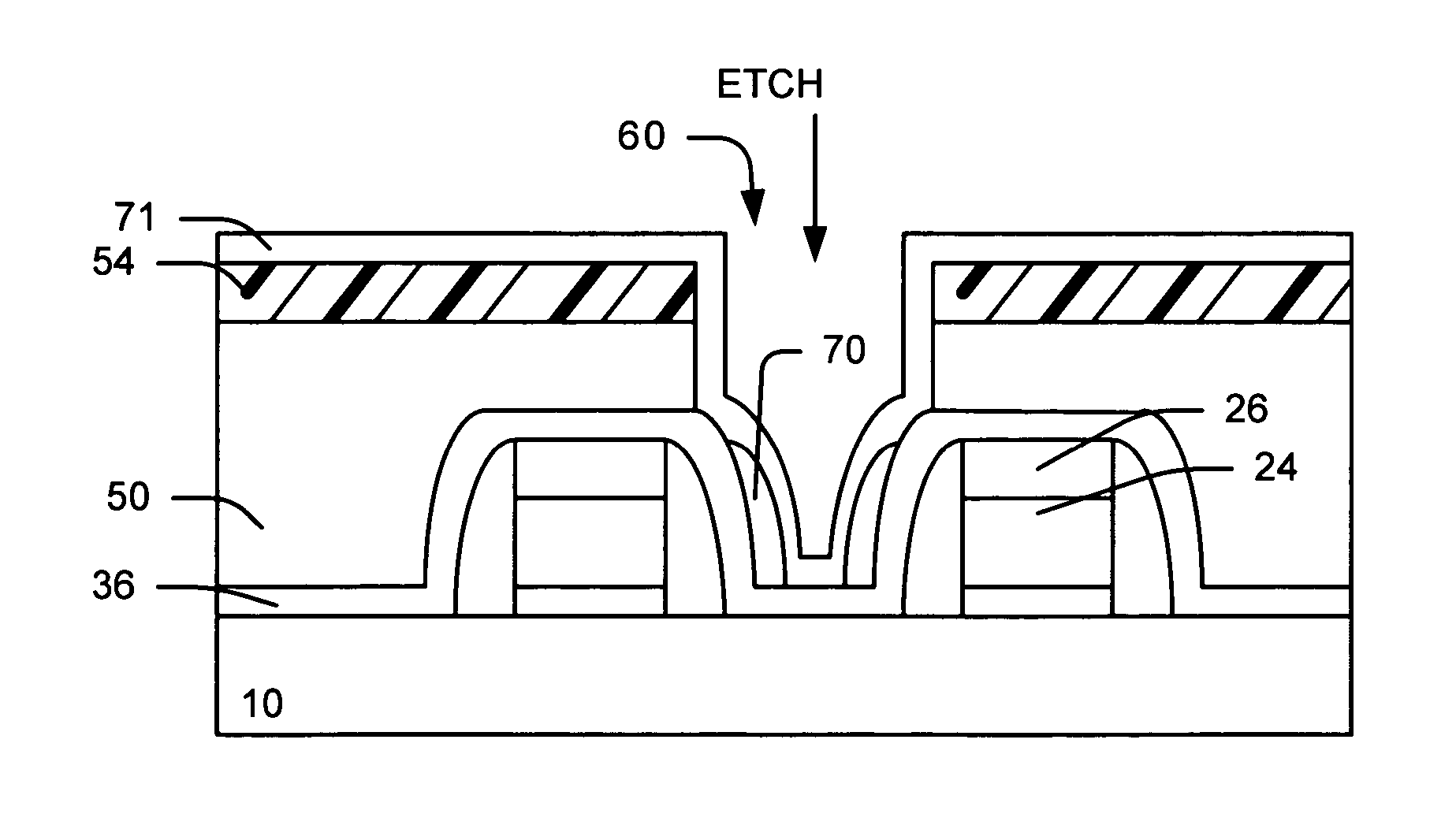

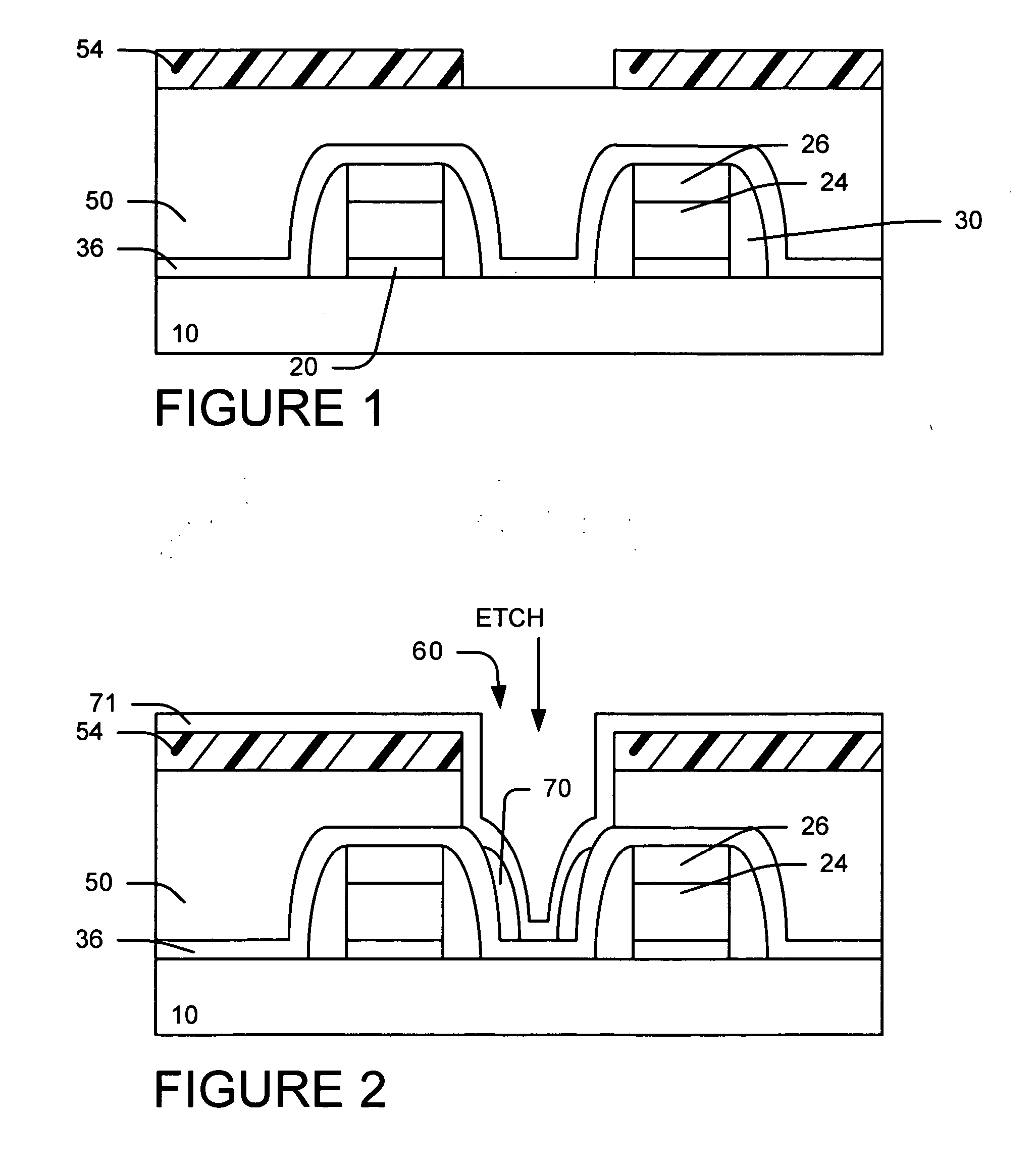

Method to form a contact hole

InactiveUS20050181588A1Reduce duplicationSemiconductor/solid-state device manufacturingCompound (substance)Fluorocarbon

A example method of forming of a contact hole by removing residue and oxide spacer beside a nitride spacer after a CF containing etch. We provide a gate structure with nitride spacers on the sidewalls of the gate. We provide a dielectric layer (oxide) over the substrate and gate structure. We form a contact photoresist pattern over the oxide dielectric layer. We etch the oxide dielectric layer using fluorocarbons (CxFy) to form contact openings and residual spacer. The photoresist is striped. Preferably, a NF3 and N2 and H2 plasma treatment is performed to deposit a byproducts layer over the residual spacer. The byproducts layer and residual spacer are removed preferably using one of the following processes: (1) heat (2) DI rinse or (3) IR or UV radiation.

Owner:TAIWAN SEMICON MFG CO LTD

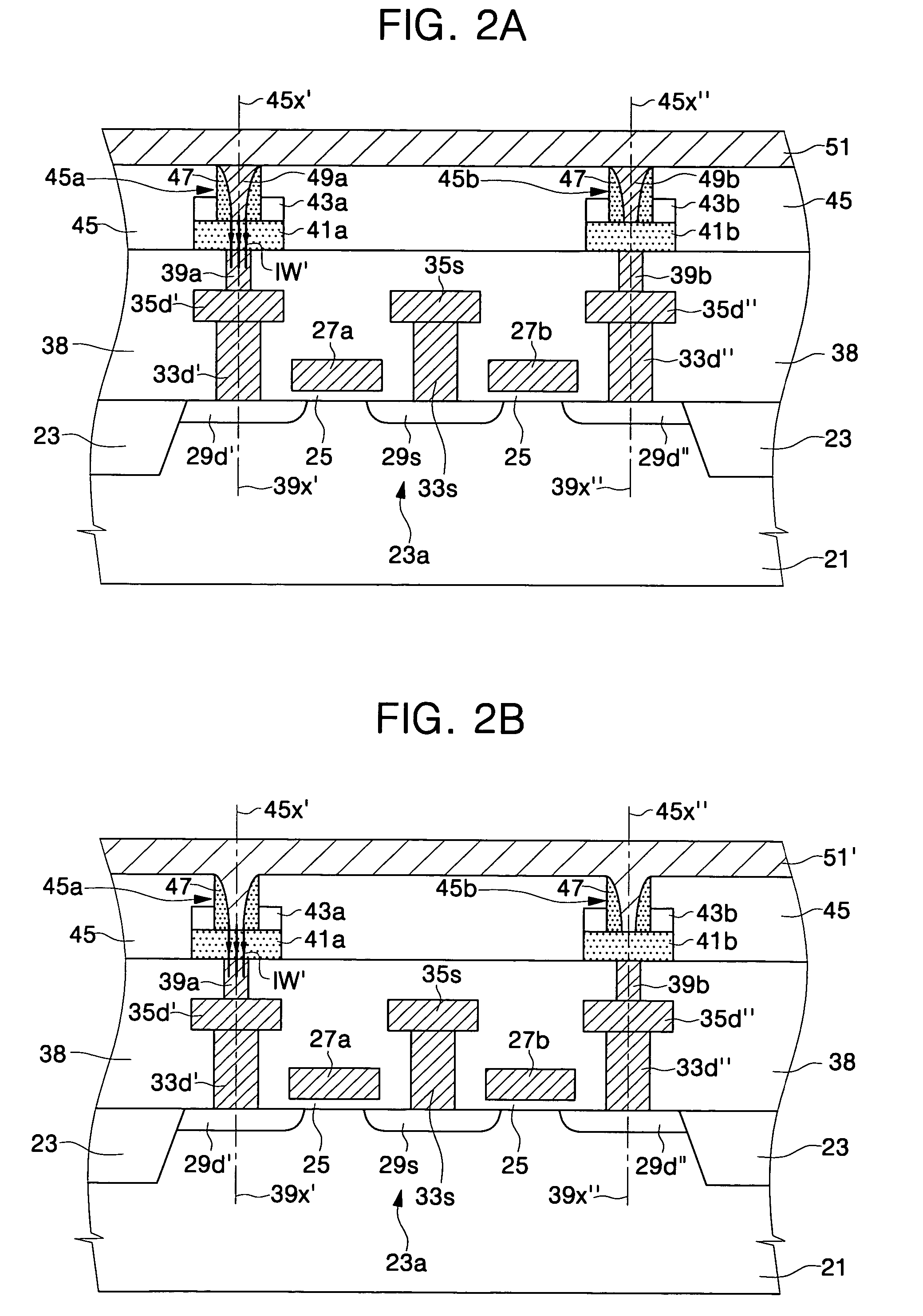

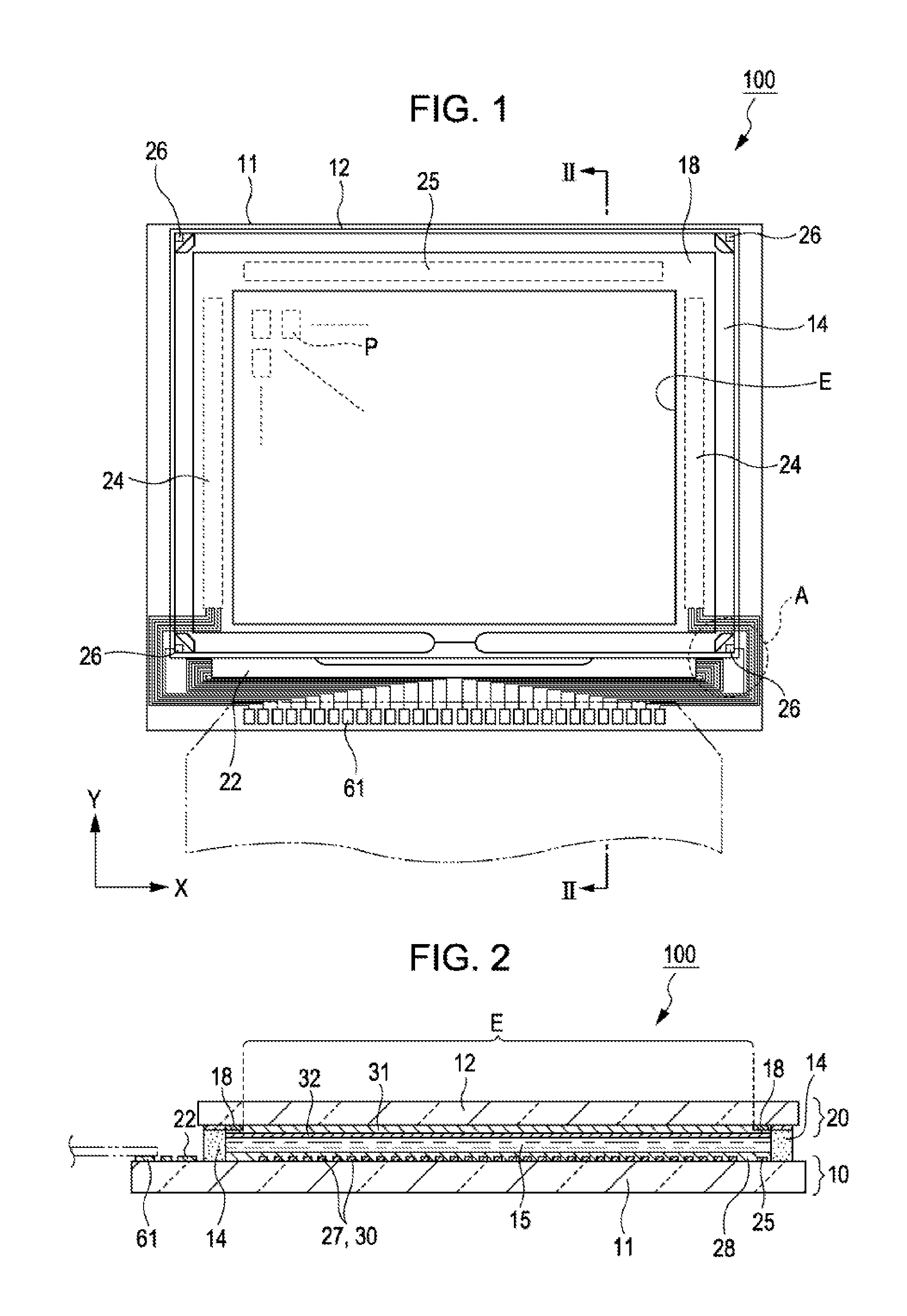

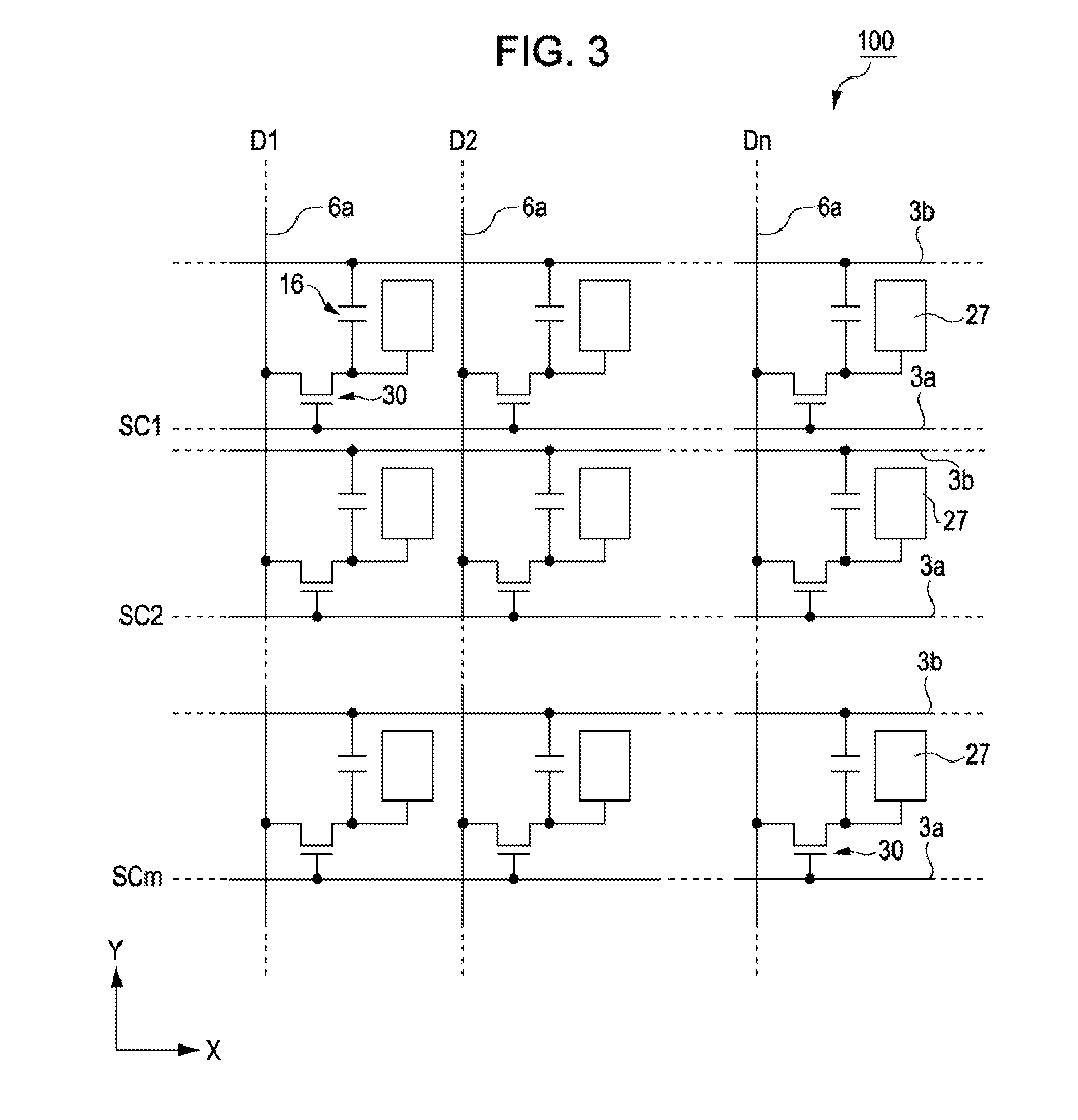

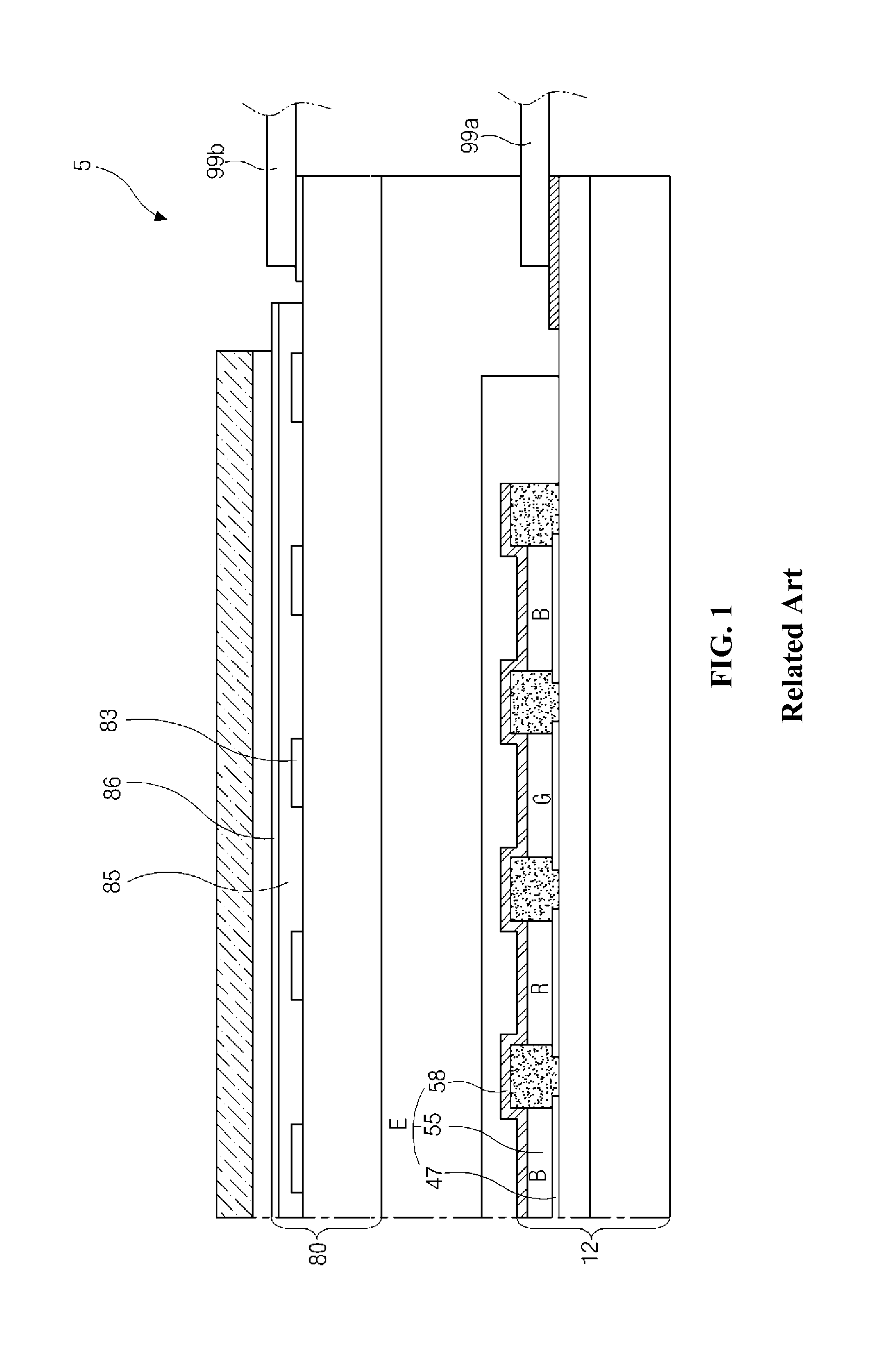

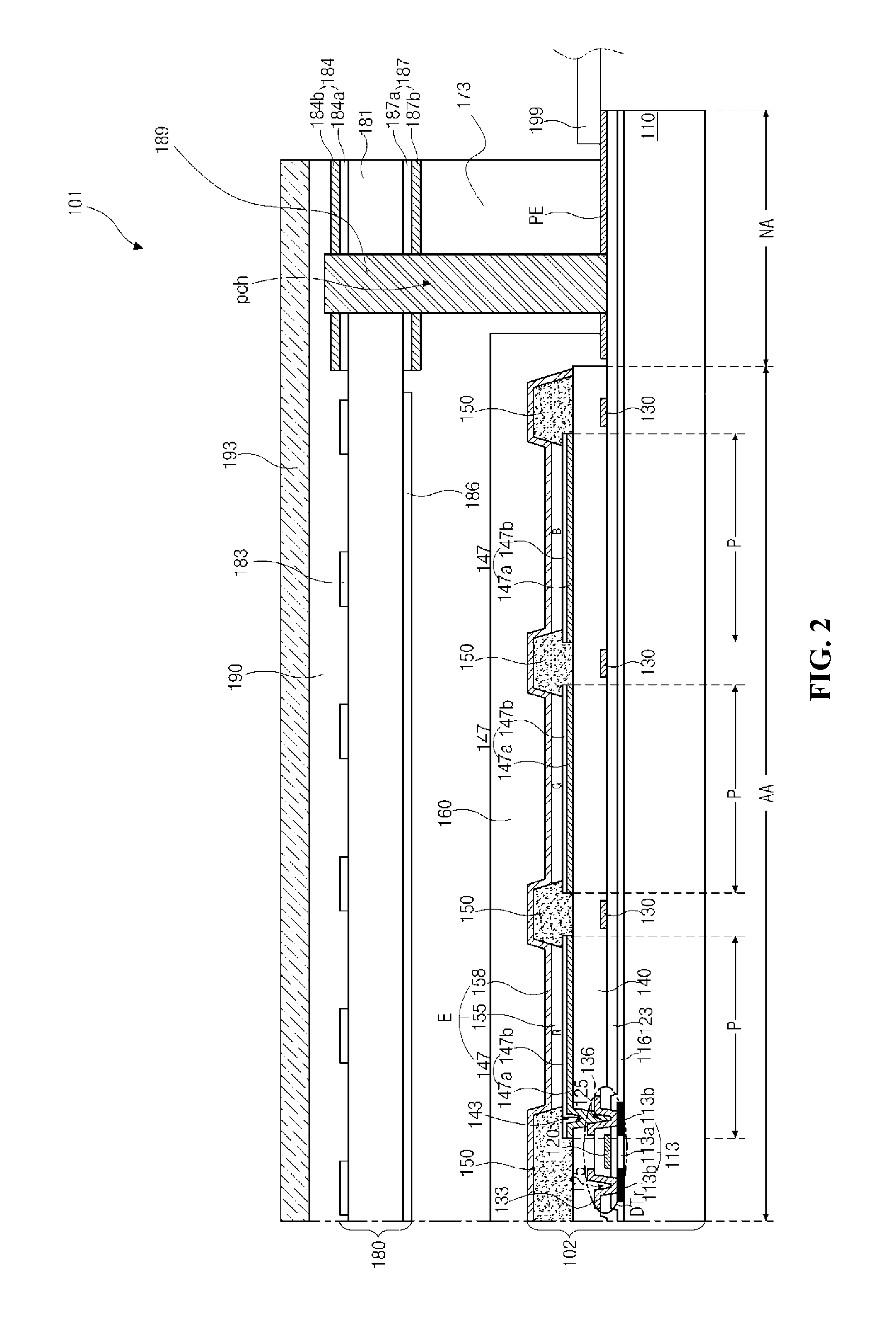

Electro-optical device and electronic apparatus

ActiveUS8803867B2Improve reliabilityCathode-ray tube indicatorsNon-linear opticsElectricityElectrical conductor

A liquid crystal device includes a scanning line driving circuit, a data line driving circuit, a first VDD power supply wiring line that supplies power to the data line driving circuit, a second VDD power supply wiring line that supplies power to the scanning line driving circuit, and a common wiring line that electrically connects the first VDD power supply wiring line and the second VDD power supply wiring line to each other in an integrated manner. The common wiring line includes electrical conductors, a wiring line, and contact holes.

Owner:SEIKO EPSON CORP

Resistive random access memory and method for manufacturing the same

ActiveUS20100112810A1Improve the immunityReduce power consumptionSemiconductor/solid-state device manufacturingSemiconductor devicesStatic random-access memoryRandom access memory

A resistive random access memory including, an insulating layer, a hard mask layer, a bottom electrode, a memory cell and a top electrode is provided. The insulating layer is disposed on the bottom electrode. The insulating layer has a contact hole having a first width. The hard mask layer has an opening. A portion of the memory cell is exposed from the opening and has a second width smaller than the first width. The top electrode is disposed on the insulating layer and is coupled with the memory cell.

Owner:MACRONIX INT CO LTD

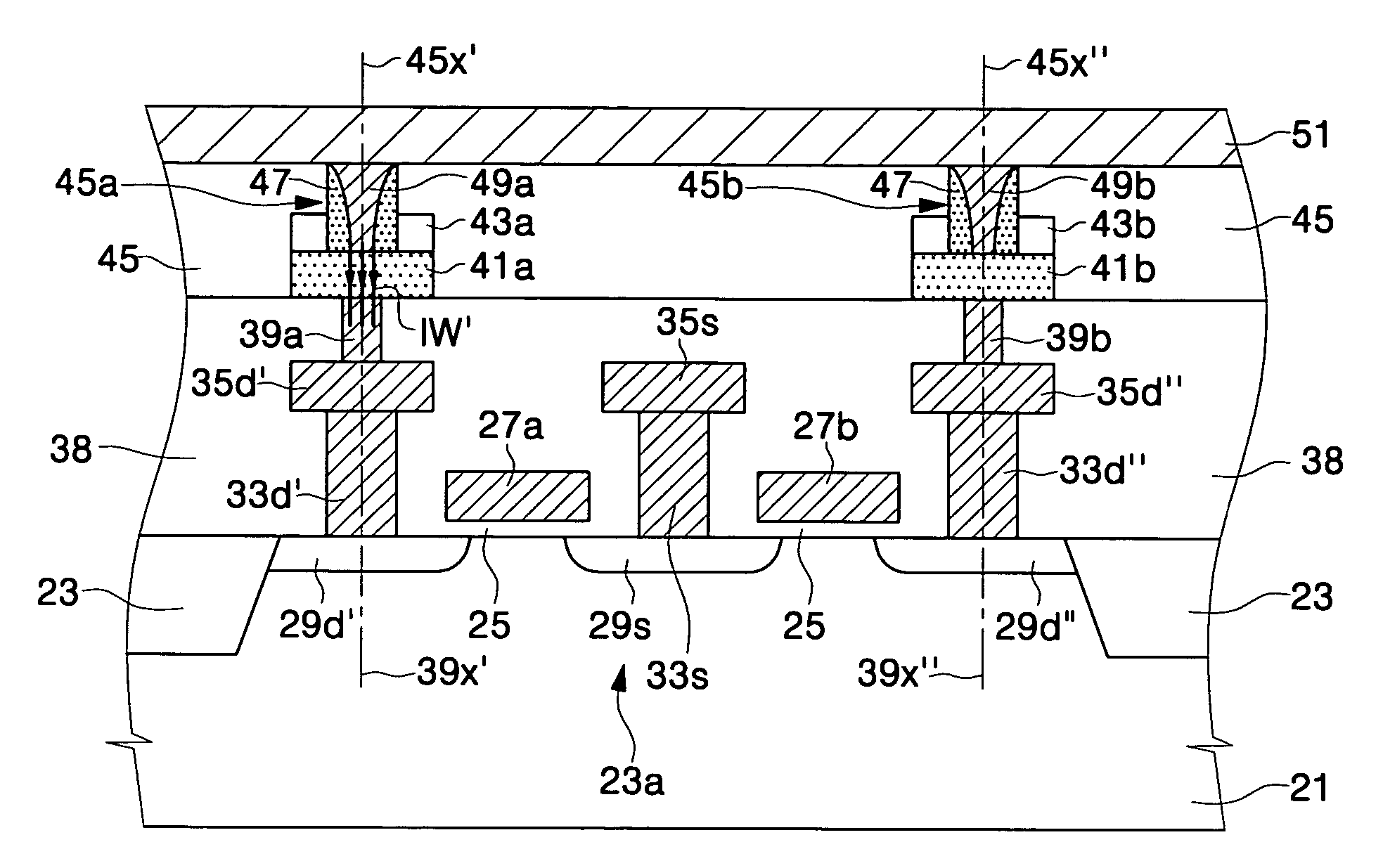

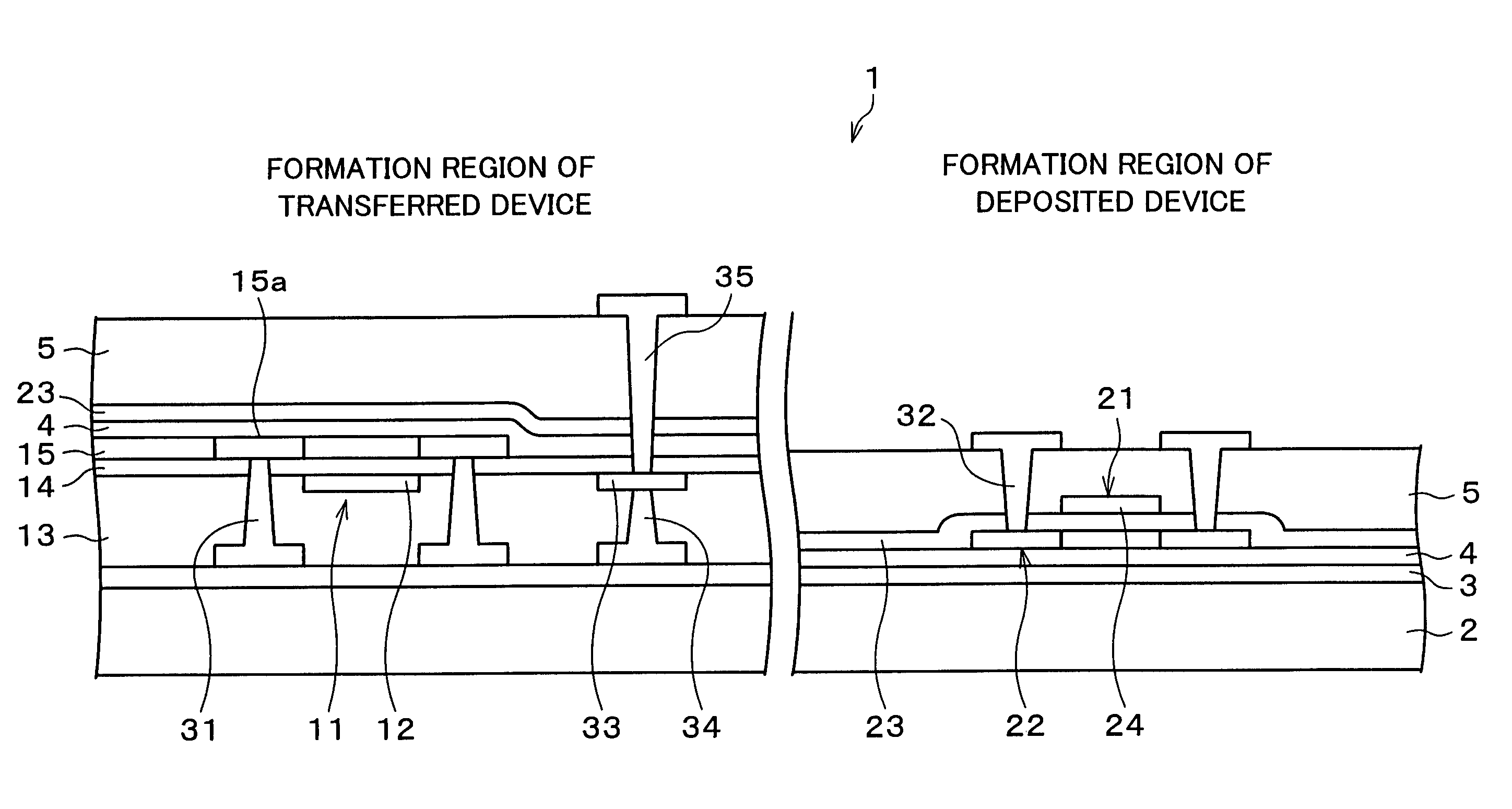

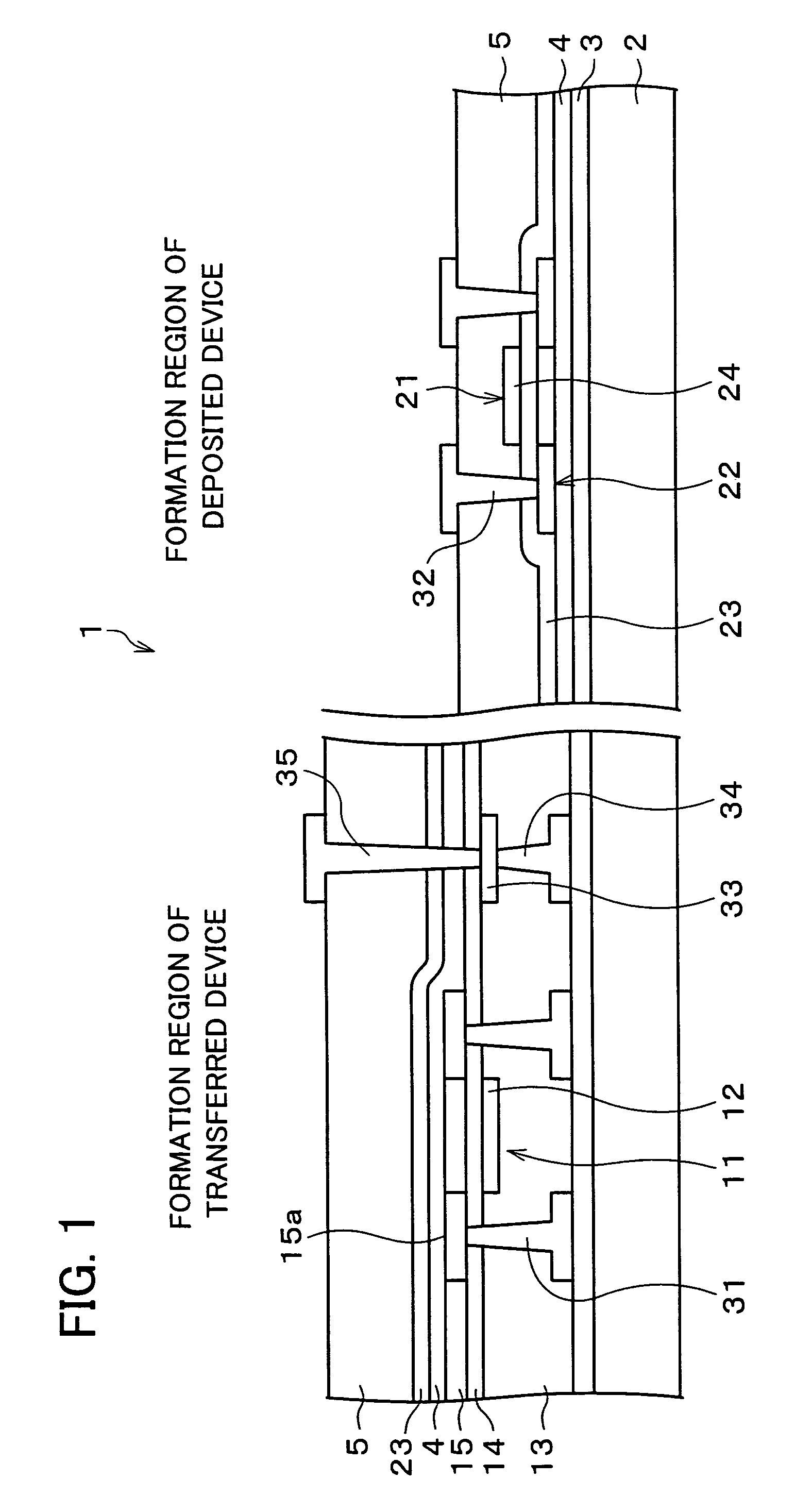

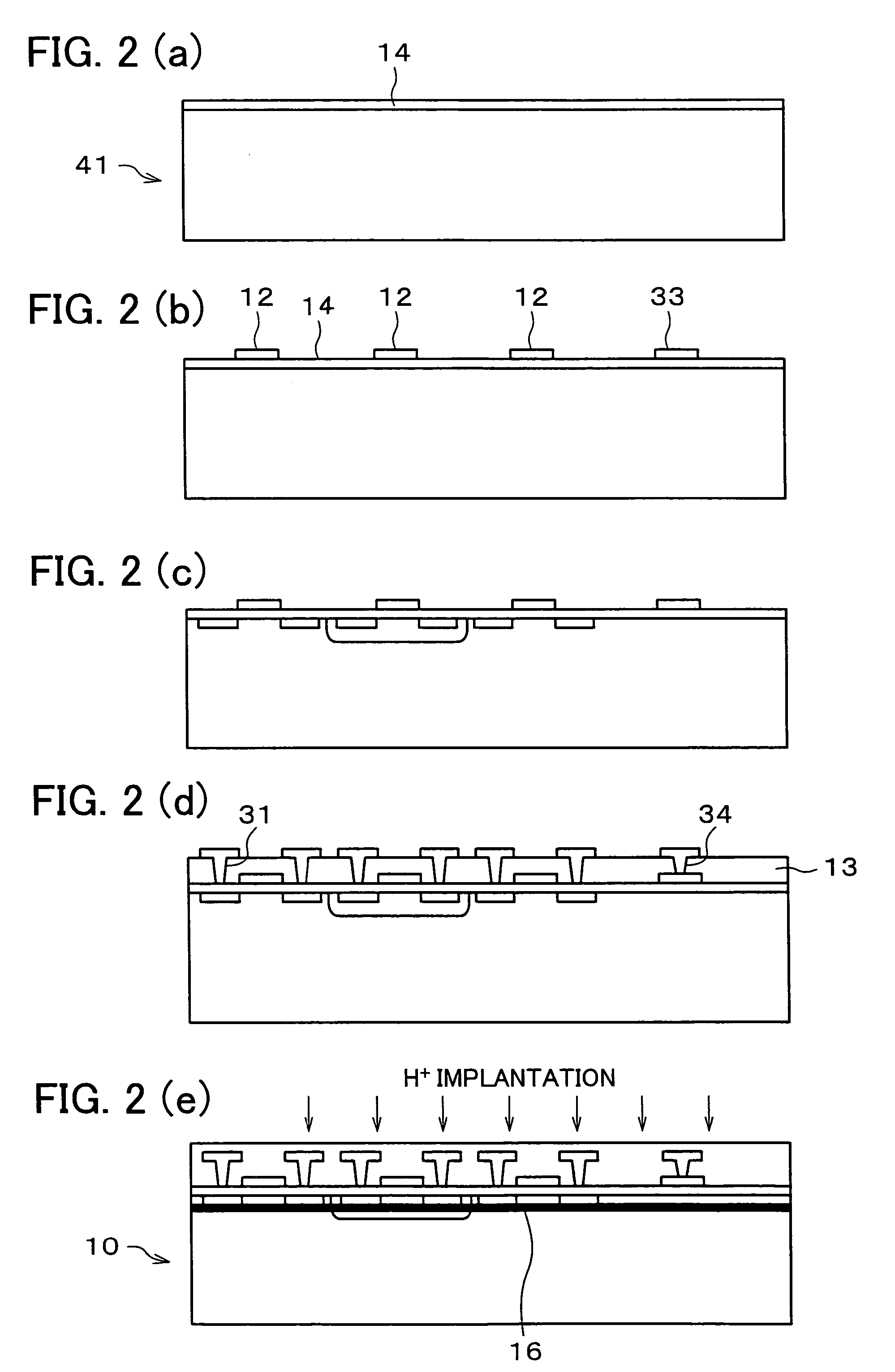

Thin film semiconductor device and fabrication method therefor

InactiveUS7488980B2Restraining aspect ratioSmall sizeTransistorSemiconductor/solid-state device detailsInsulation layerEngineering

A relaying pad is formed in a predetermined portion in an insulation layer of the single-crystal thin film device, in a region where the single-crystal thin film device is formed. The relaying pad is for providing connection wiring through the insulator substrate. With this configuration it is possible to prevent an increase in an aspect ratio of a contact hole formed in an insulation layer in a region in which a transferred device is formed, the semiconductor device including a substrate on which the transferred device and a deposited device coexist.

Owner:SHARP KK

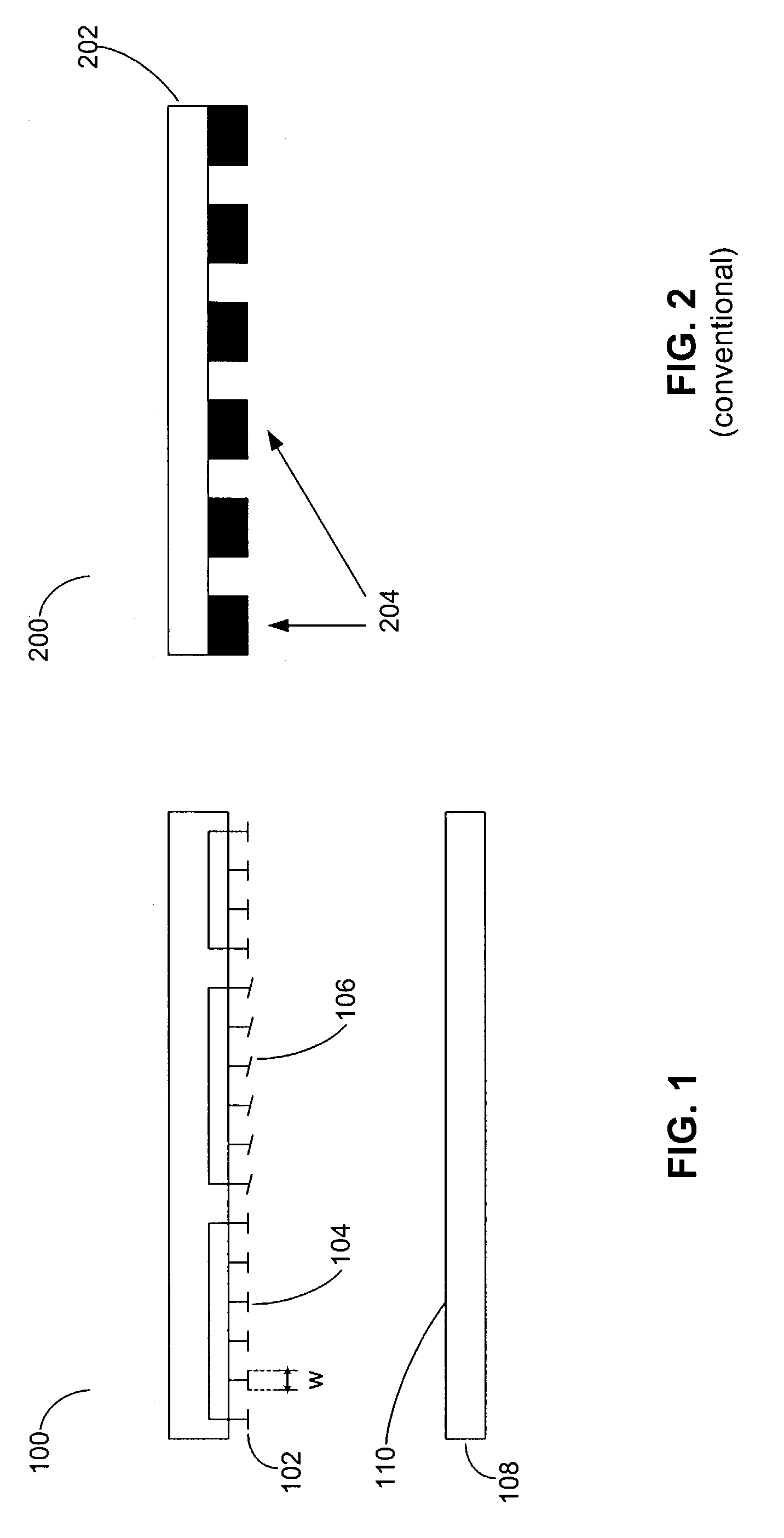

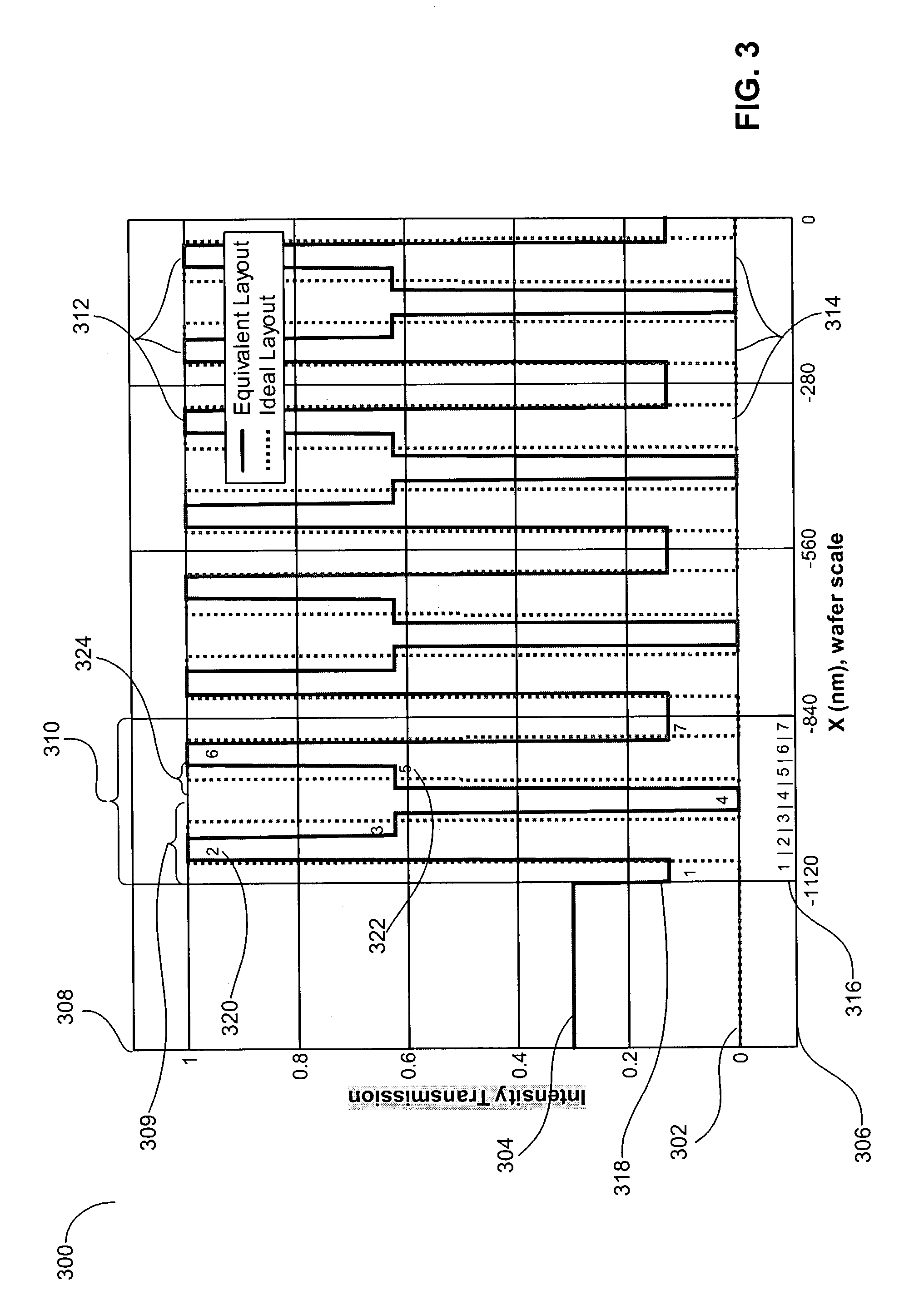

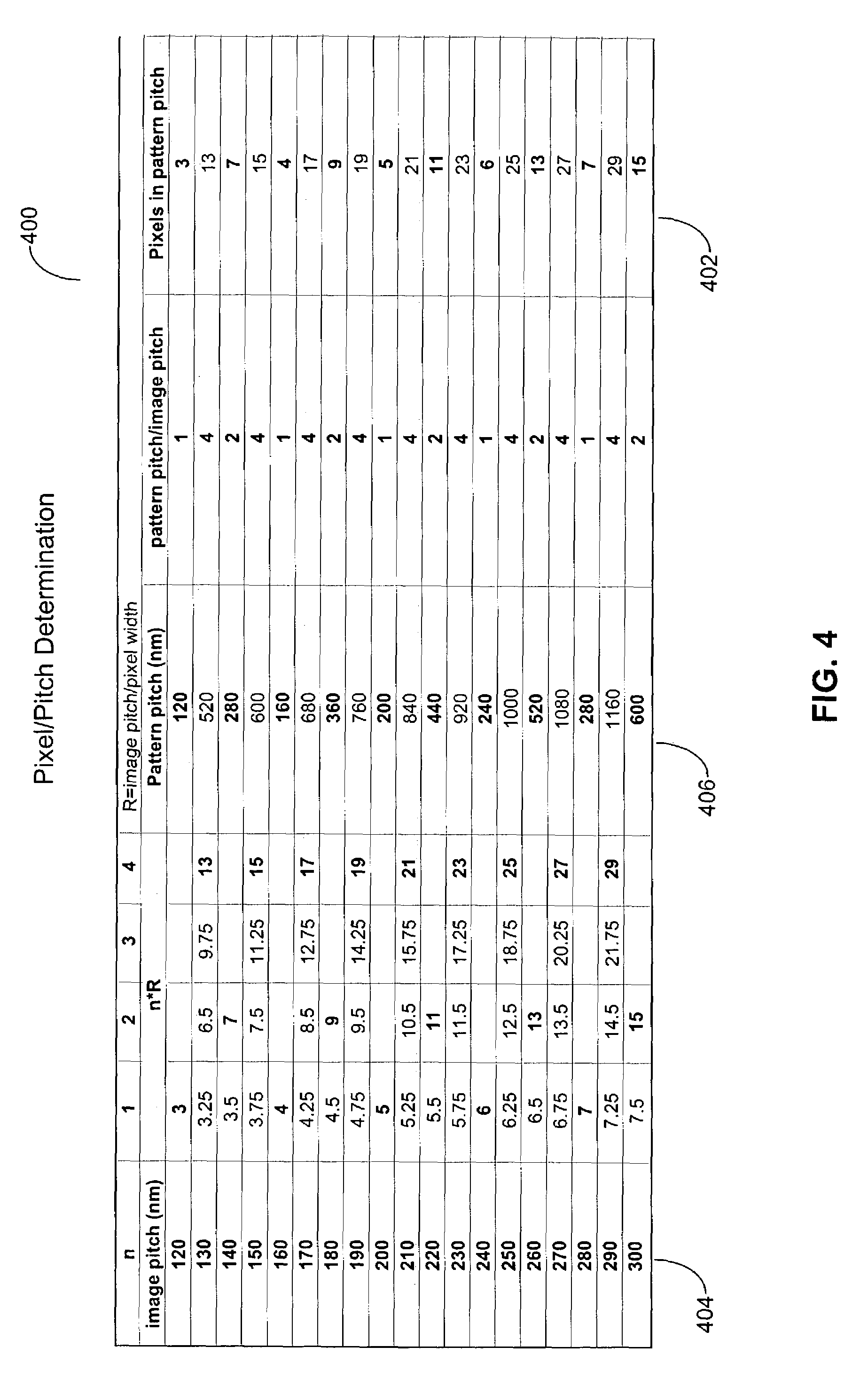

Method for the generation of variable pitch nested lines and/or contact holes using fixed size pixels for direct-write lithographic systems

ActiveUS7063920B2Semiconductor/solid-state device manufacturingPhotomechanical exposure apparatusEngineeringMicromirror array

Provided is a method and system for developing a lithographic mask layout. The lithographic mask layout is adapted for configuring an array of micro-mirrors in a maskless lithography system. The method includes generating an ideal mask layout representative of image characteristics associated with a desired image. Next, an equivalent mask is produced in accordance with an average intensity of the ideal mask layout.

Owner:ASML HLDG NV

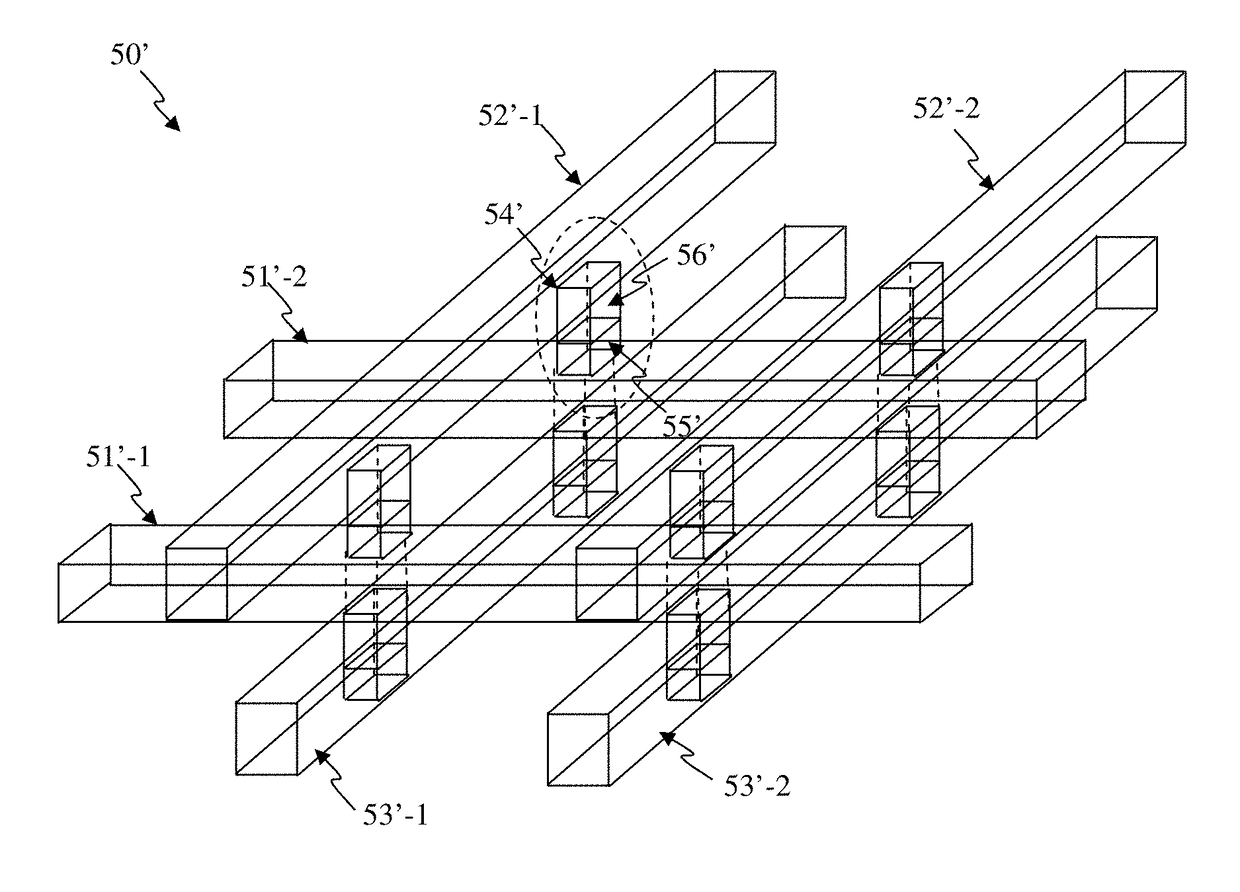

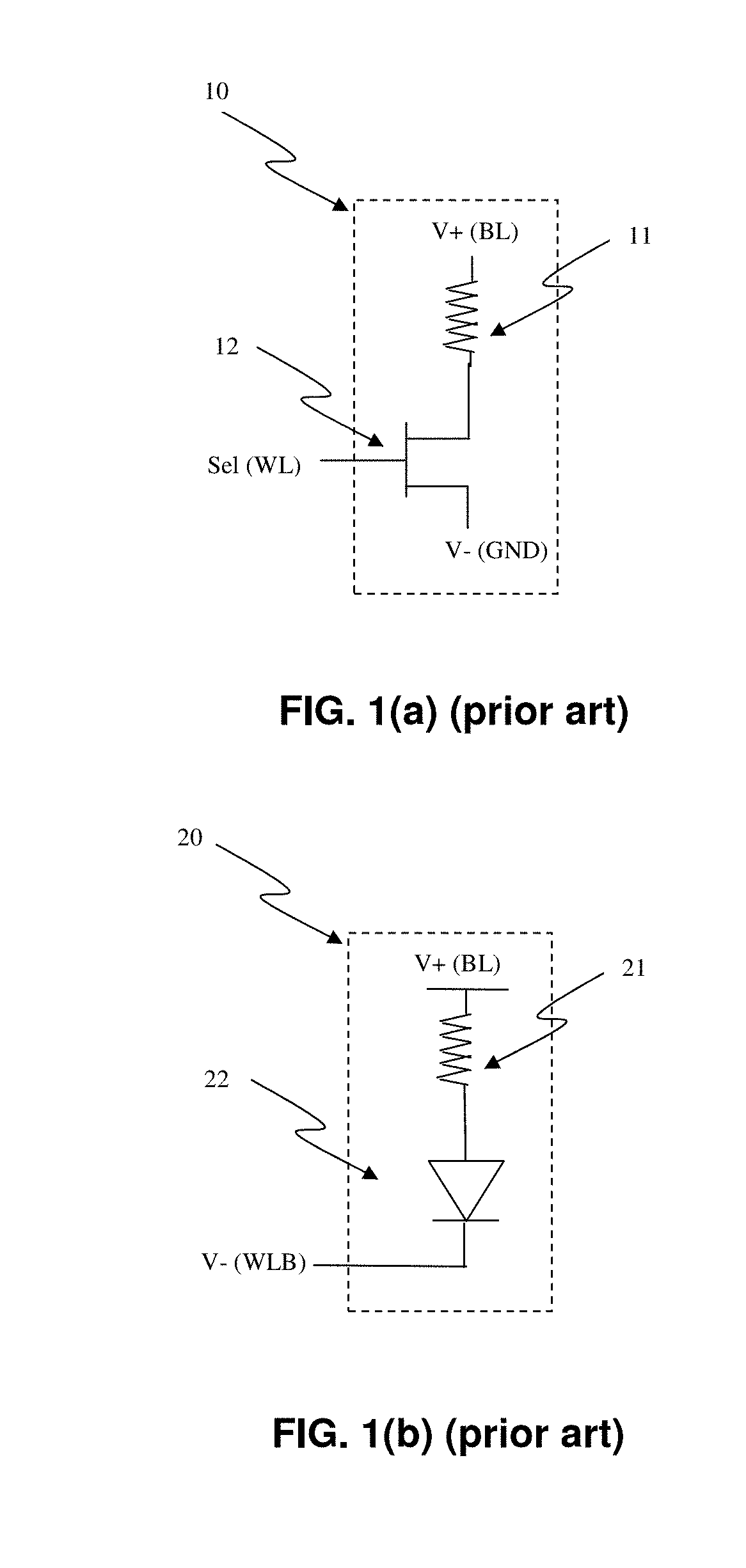

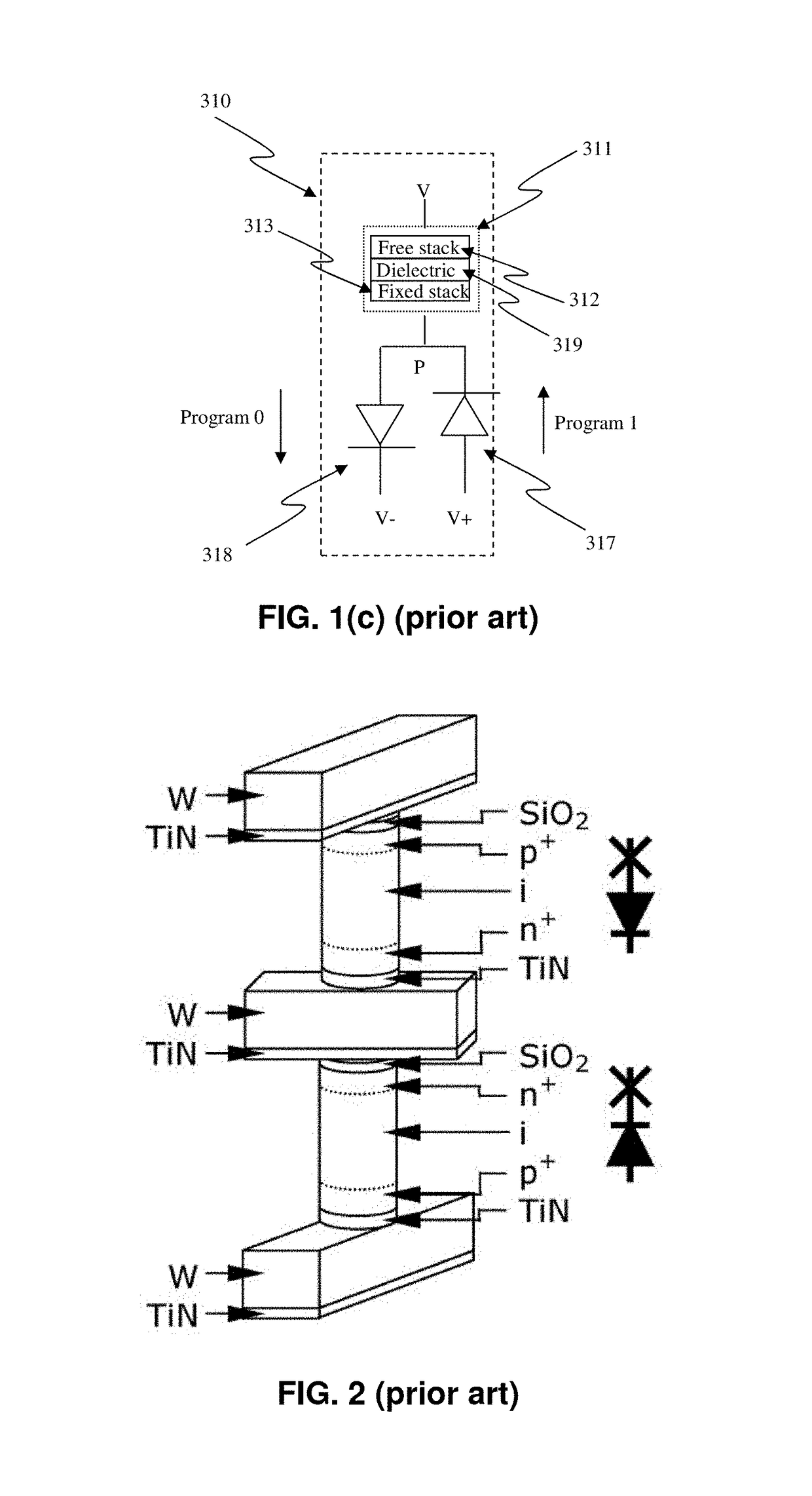

Programmable resistive device and memory using diode as selector

Building programmable resistive devices in contact holes at the crossover of a plurality of conductor lines in more than two vertical layers is disclosed. There are plurality of first conductor lines and another plurality of second conductor lines that can be substantially perpendicular to each other, though in two different vertical layers. A diode and / or a programmable resistive element can be fabricated in the contact hole between the first and second conductor lines. The programmable resistive element can be coupled to another programmable resistive device or shared between two programmable devices whose diodes conducting currents in opposite directions and / or coupled to a common conductor line. The programmable resistive memory can be configured to be programmable by applying voltages to conduct current flowing through the programmable resistive element to change its resistance for a different logic state.

Owner:ATTOPSEMI TECH CO LTD

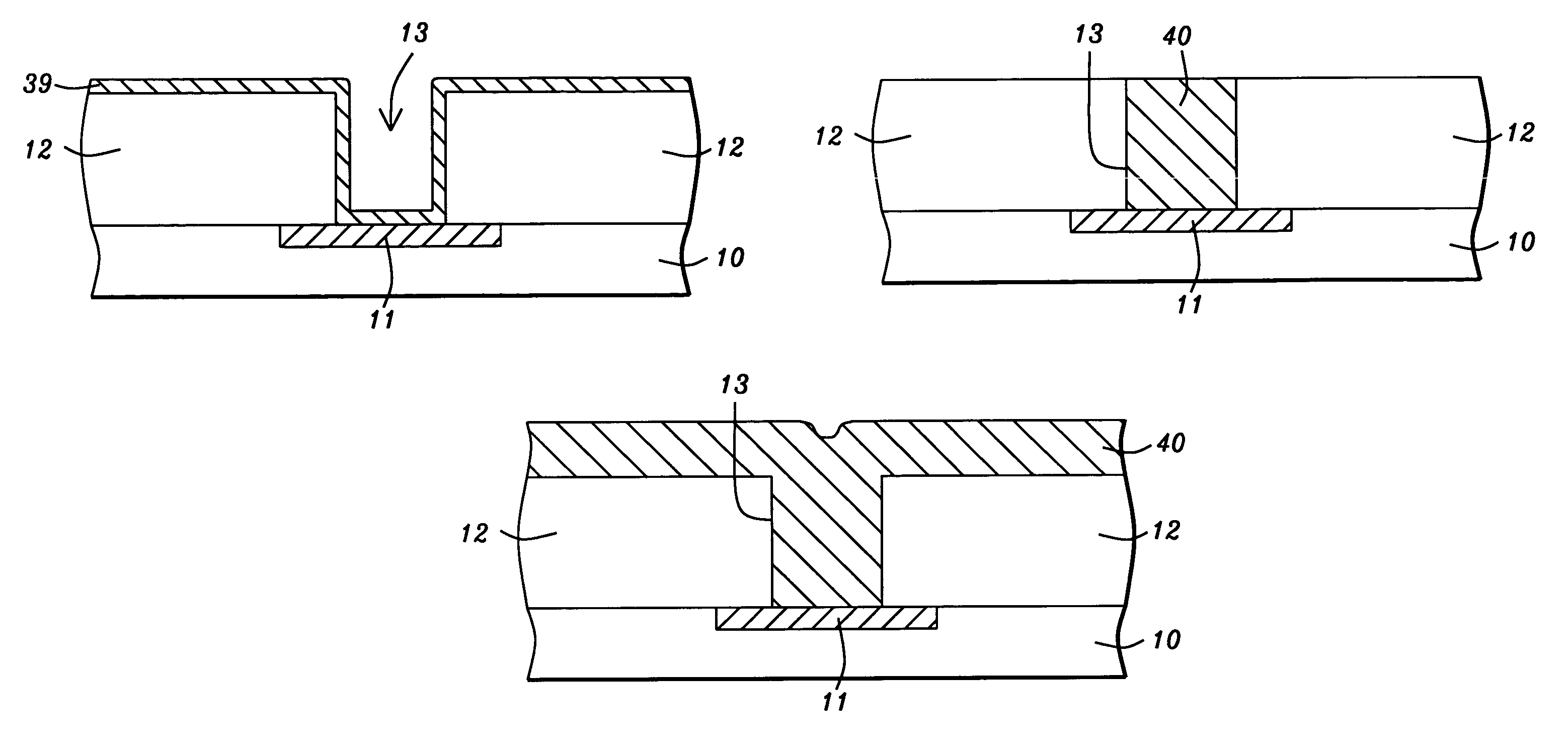

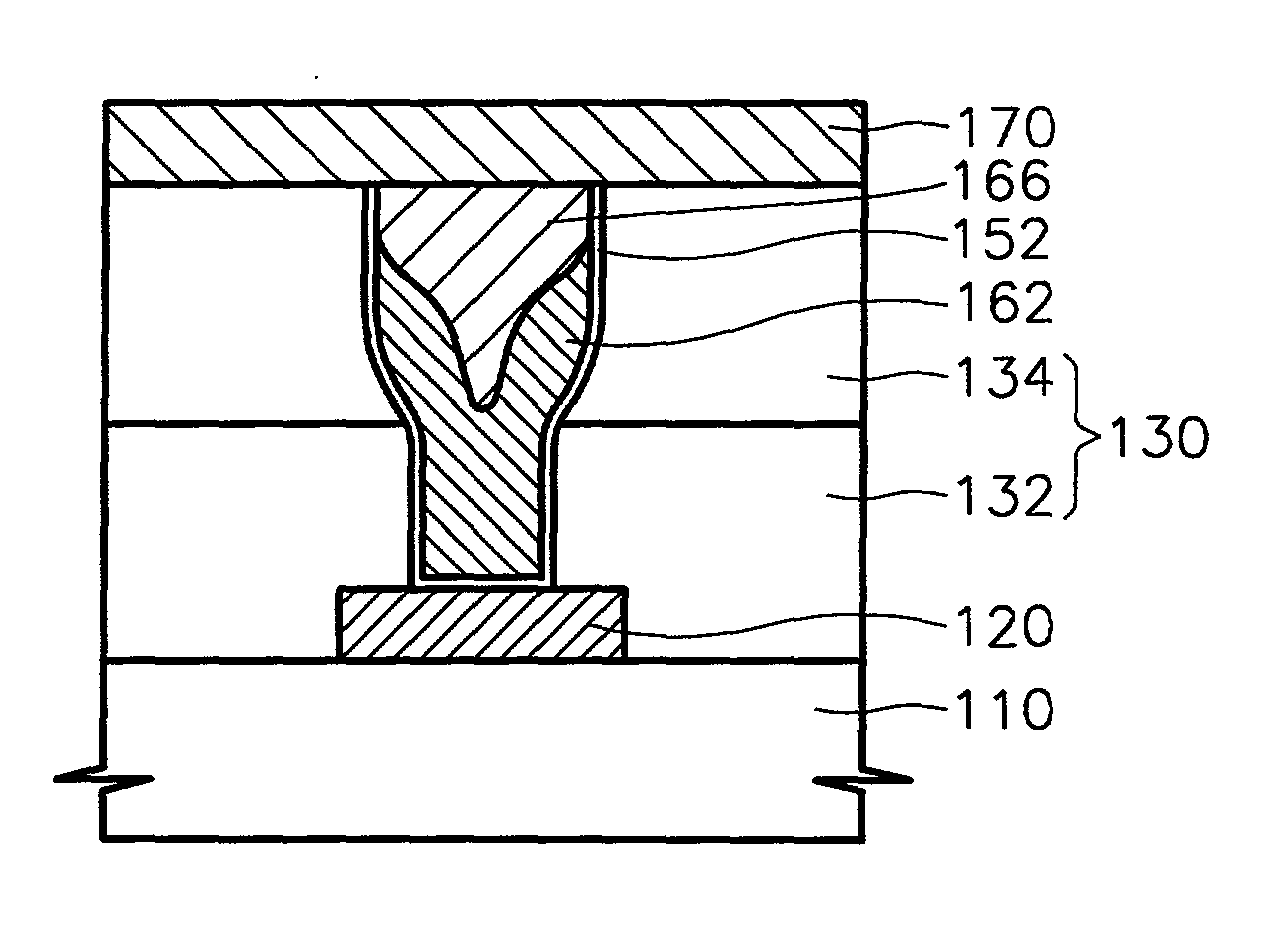

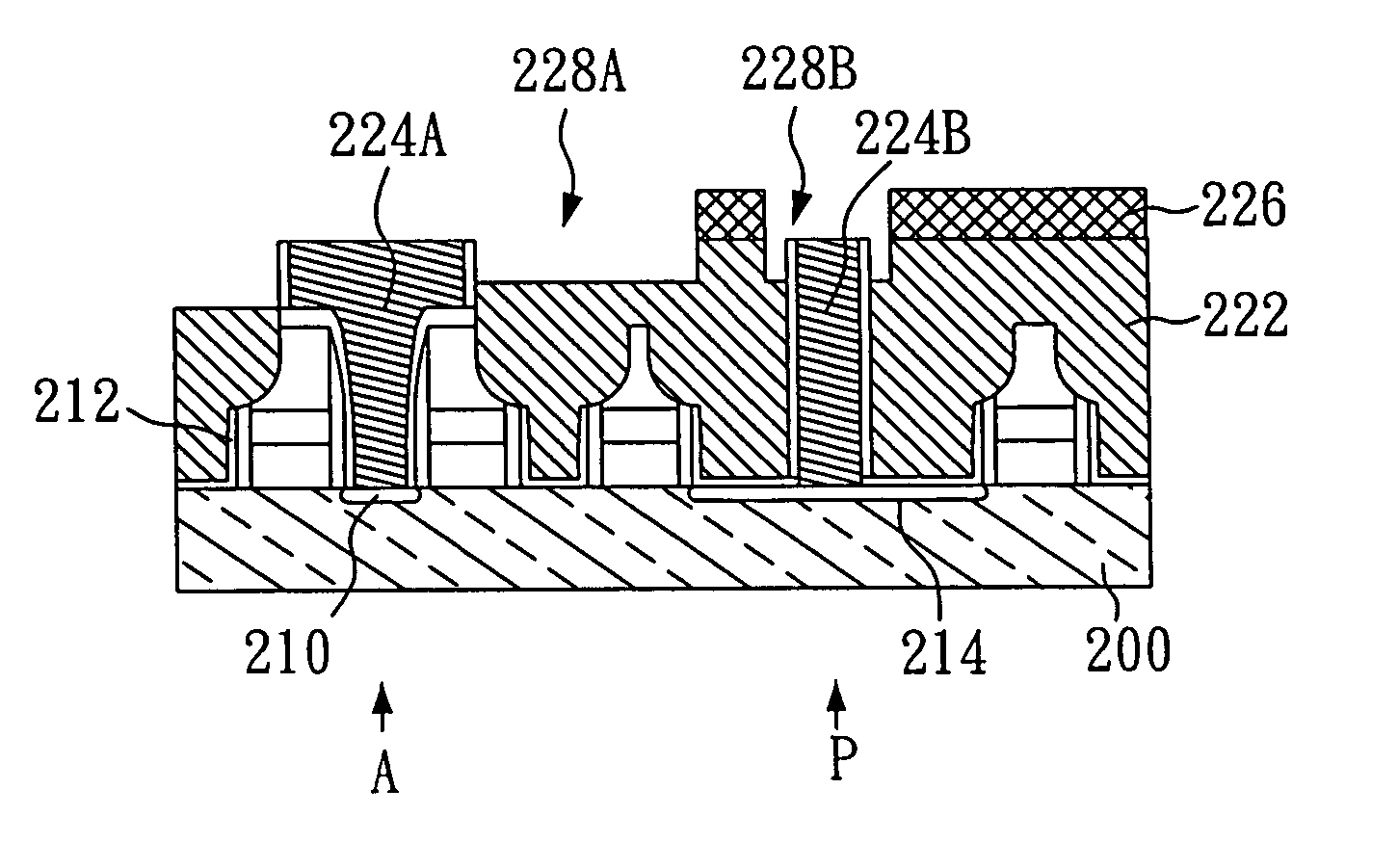

Metal contact structure in semiconductor device and method for forming the same

InactiveUS20020070457A1Semiconductor/solid-state device detailsSolid-state devicesContact holeSemiconductor

A metal contact structure of a semiconductor device and a method for forming the same are provided. The diameter of the upper portion of a contact hole that exposes a region of a lower conductive layer is formed to be larger than the diameter of the lower portion of the contact hole. The metal contact structure is formed without a void or a key hole. This is accomplished by forming at least two metal layers to fill the contact hole by performing a first deposition, an etch back, and a second deposition. The metal layer which fills the contact hole is etched back using a barrier metal layer formed on the entire surface of the contact hole as an etching stop layer. Thus, a void or key hole is not generated by making the upper portion of the contact hole to be wider than the lower portion of the contact hole and by depositing the metal which fills the contact hole through the processes of firstly depositing the metal, etching back the metal, and secondly depositing the metal.

Owner:SAMSUNG ELECTRONICS CO LTD

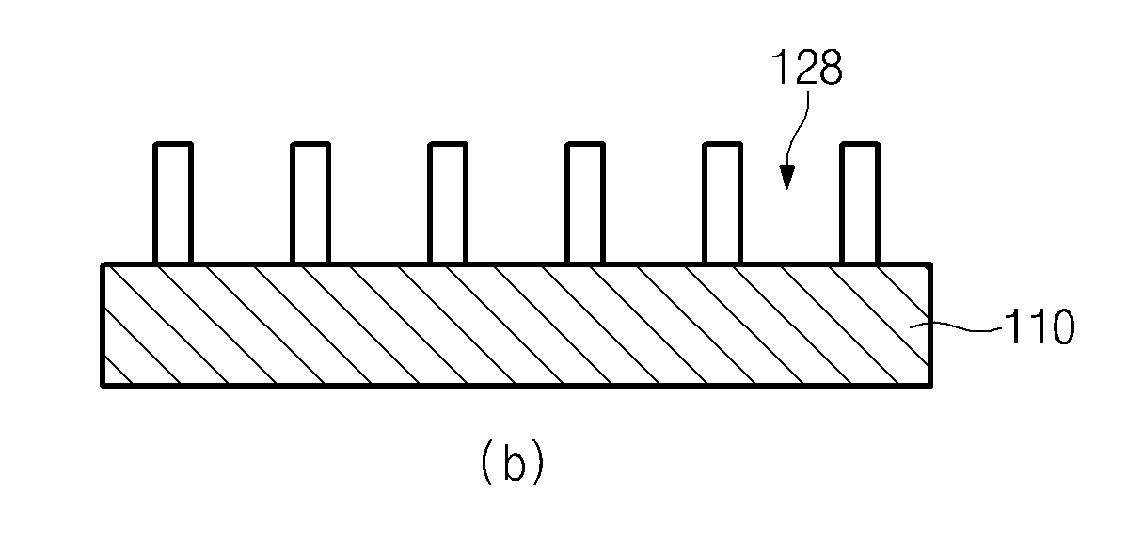

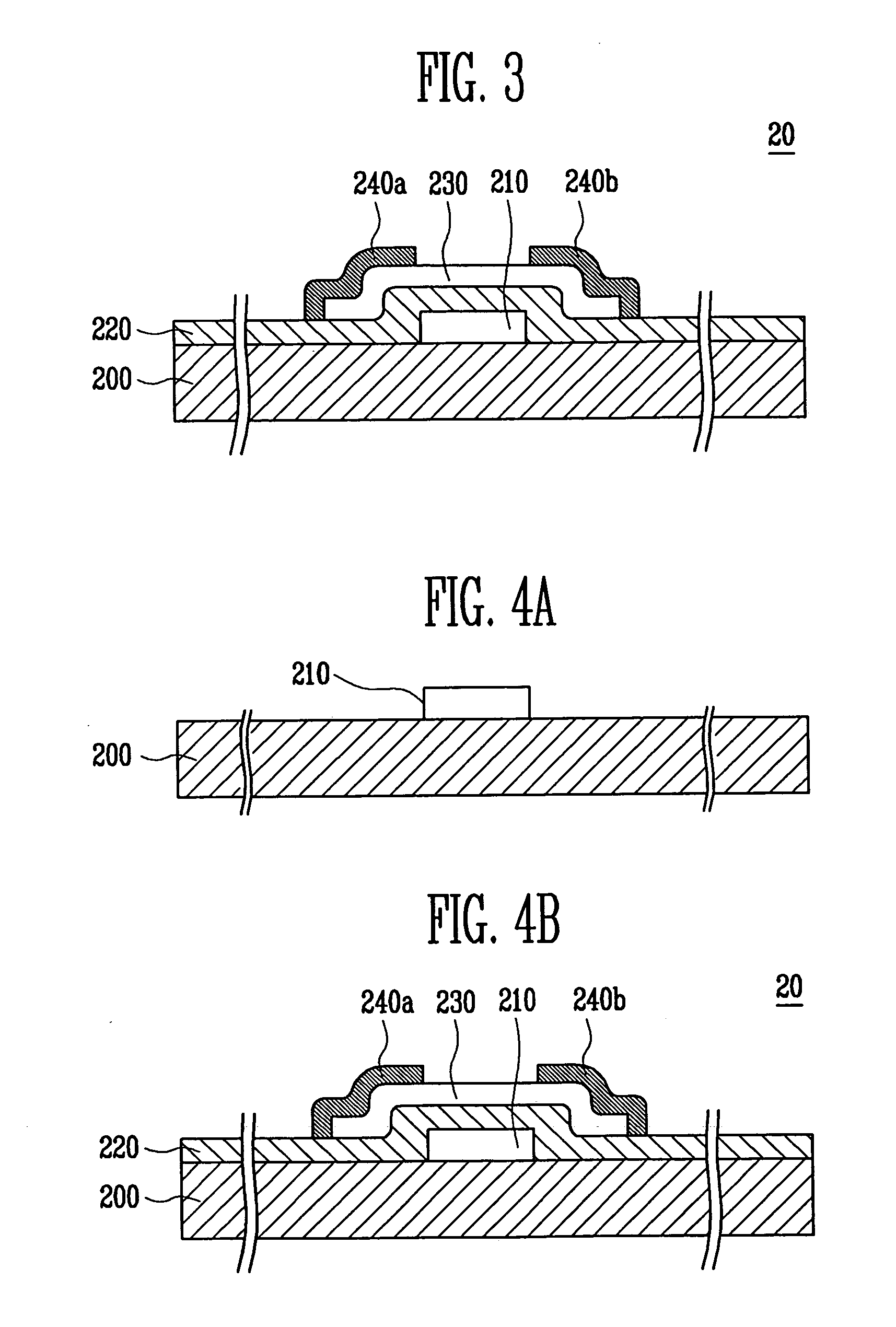

Manufacturing method of thin film transistor using oxide semiconductor

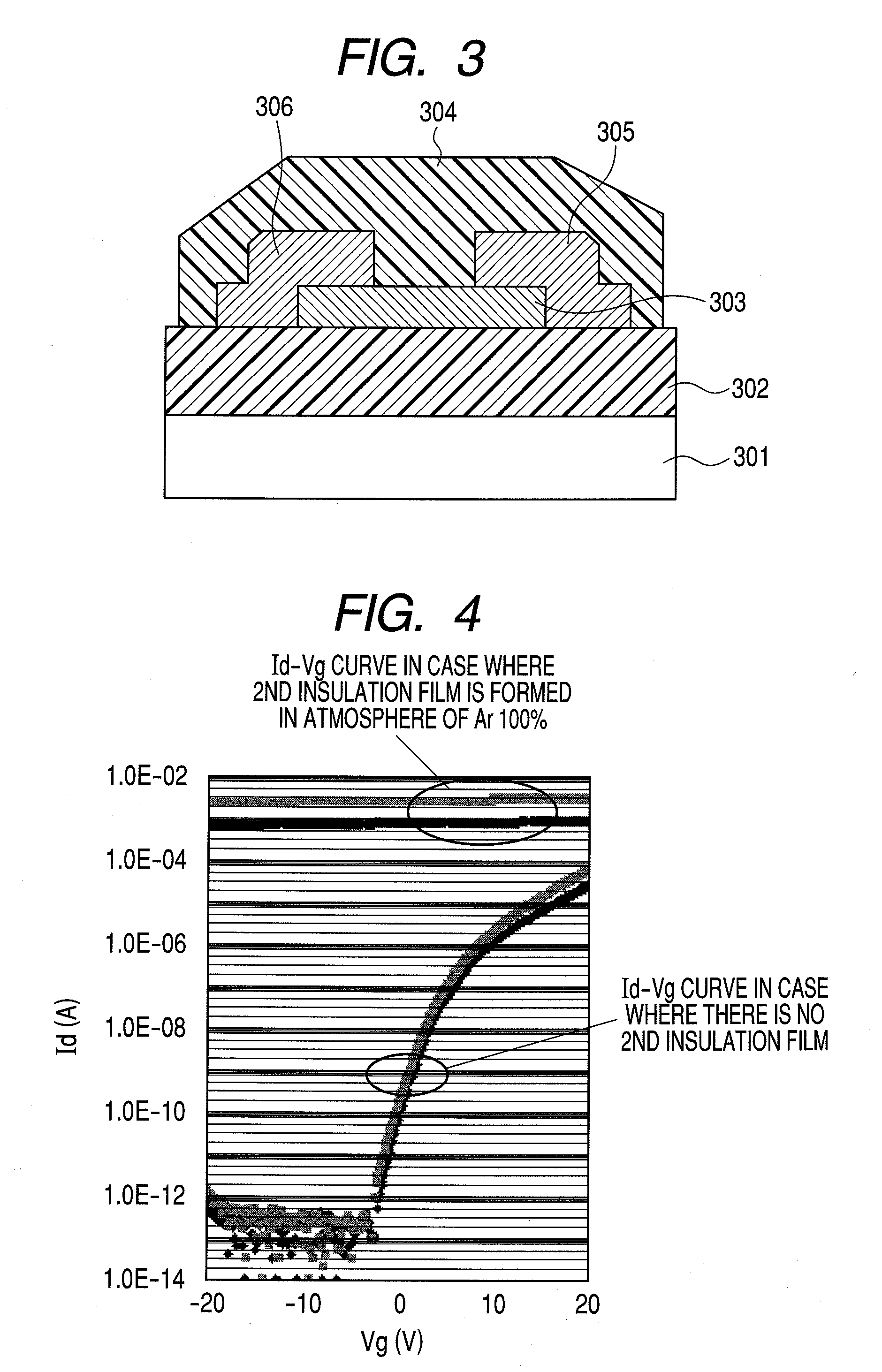

InactiveUS8193045B2Improve transistor characteristicsReduced contact areaSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A manufacturing method of a thin film transistor having at least a gate electrode, a gate insulation film, an oxide semiconductor layer, a first insulation film, a source electrode, a drain electrode, and a second insulation film on a substrate, including: forming the gate electrode on the substrate; forming the gate insulation film on the gate electrode; forming a semiconductor layer including amorphous oxide on the gate insulation film; patterning the gate insulation film; patterning the oxide semiconductor layer; reducing the oxide semiconductor layer in resistance by forming the first insulation film on the oxide semiconductor layer in the atmosphere not including an oxidized gas; patterning the first insulation film and forming a contact hole between the source electrode and the drain electrode and the oxide semiconductor layer; forming a source electrode layer and a drain electrode layer in the oxide semiconductor layer through the contact hole; forming the source electrode and the drain electrode through the contact hole and allowing the first insulation film to be exposed; patterning the exposed first insulation film and allowing a channel region of the oxide semiconductor layer to be exposed; and increasing the channel region in resistance by forming the second insulation film on the surface including the channel region of the oxide semiconductor layer in the atmosphere including an oxidized gas.

Owner:CANON KK

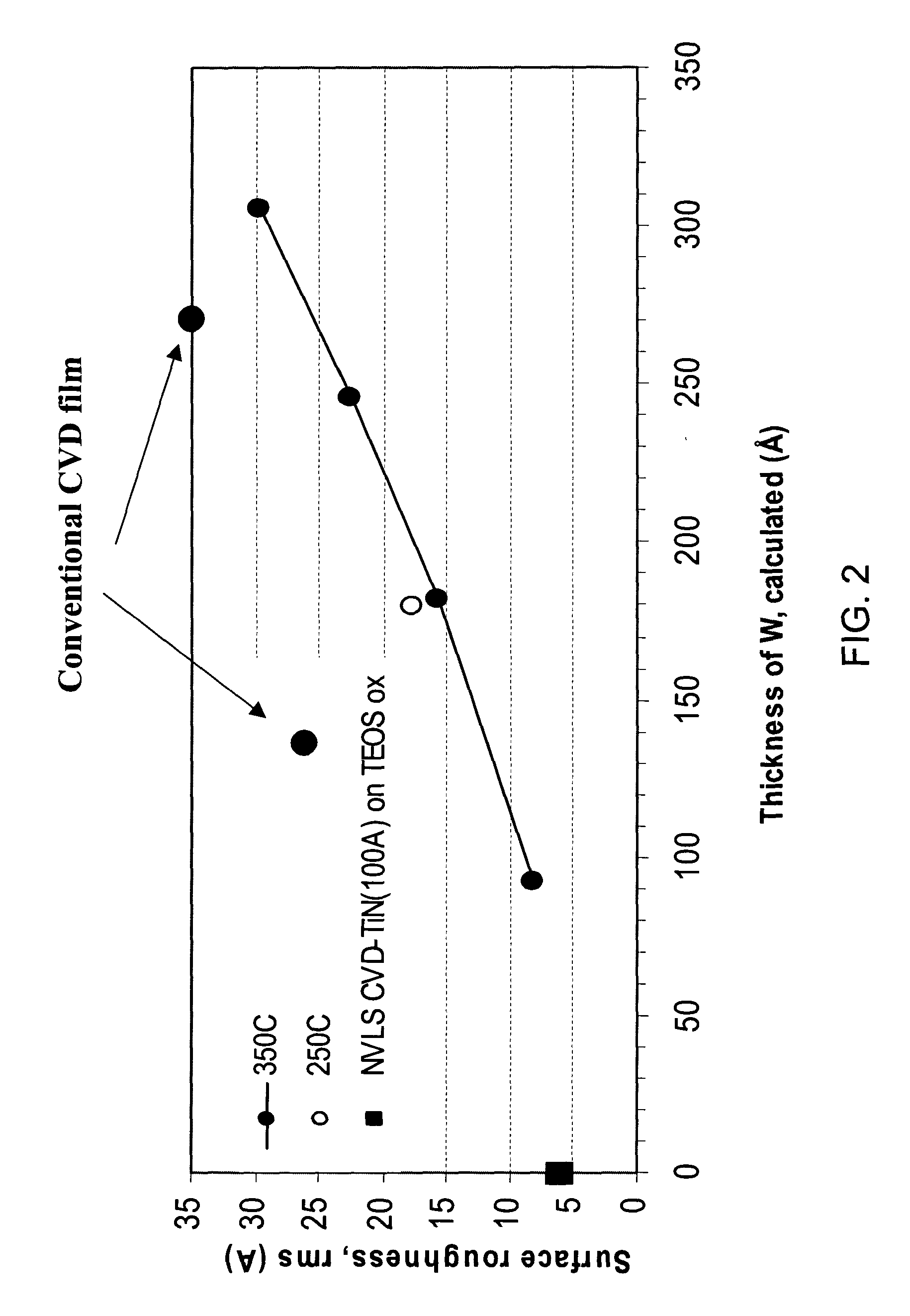

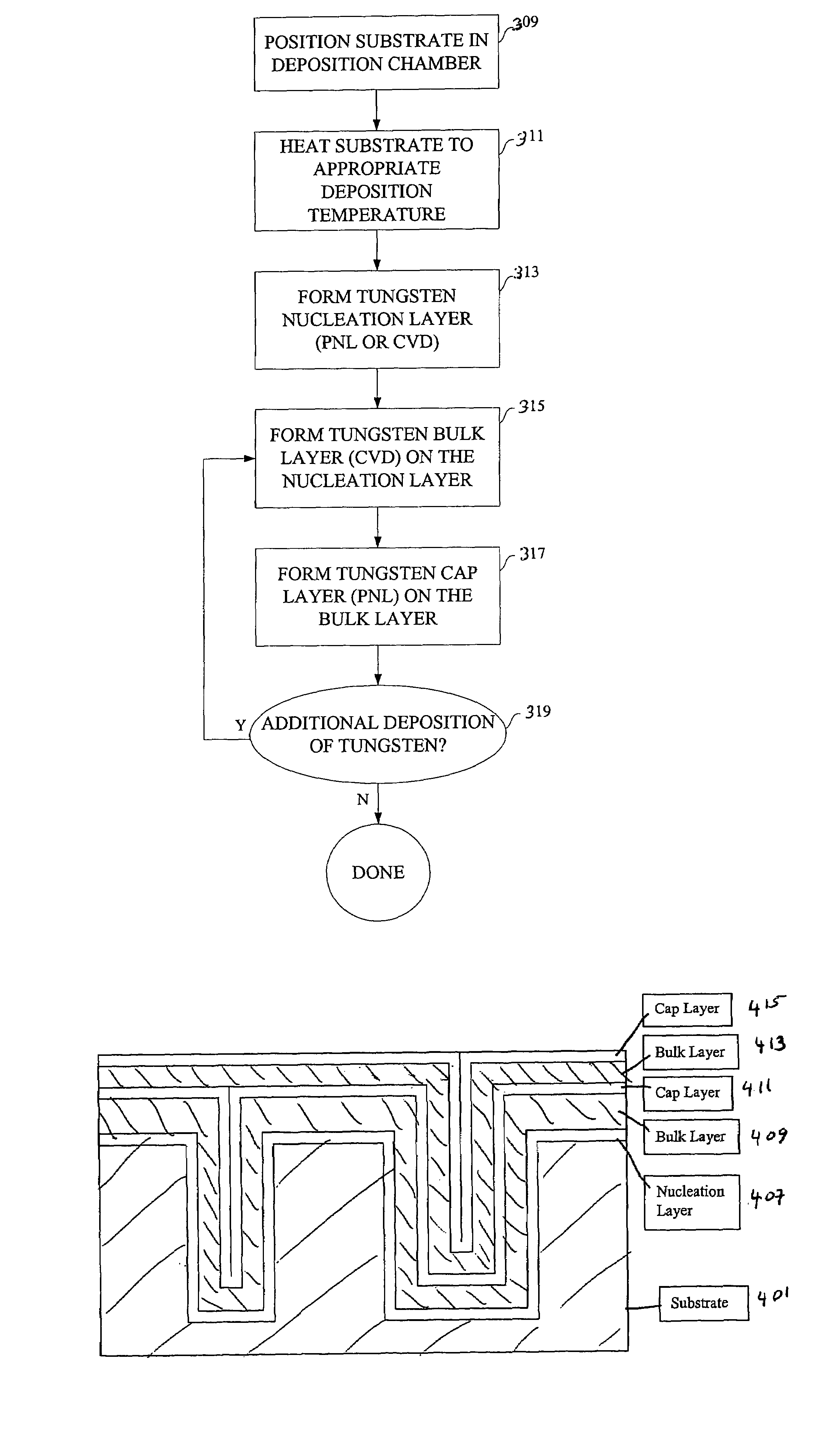

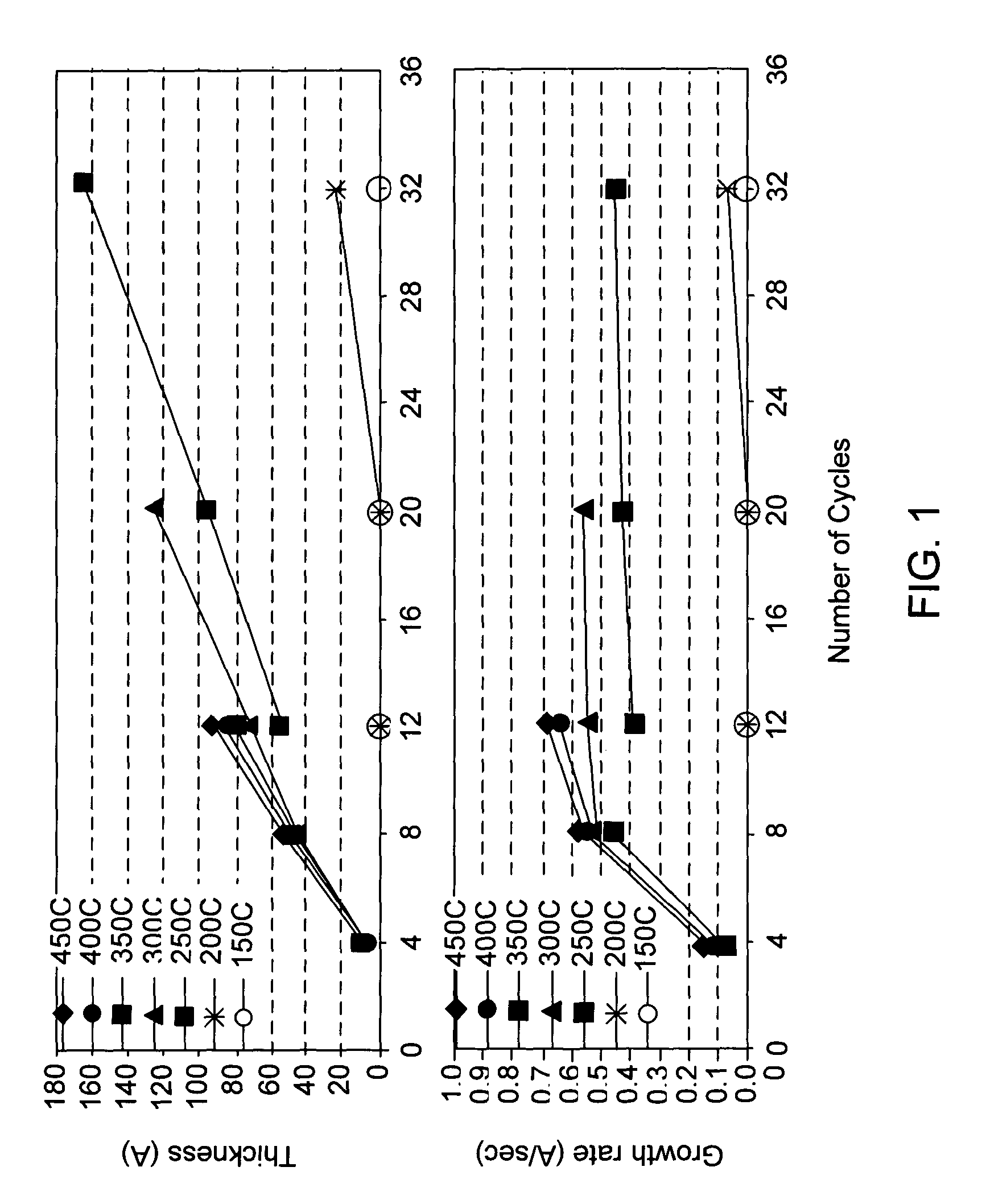

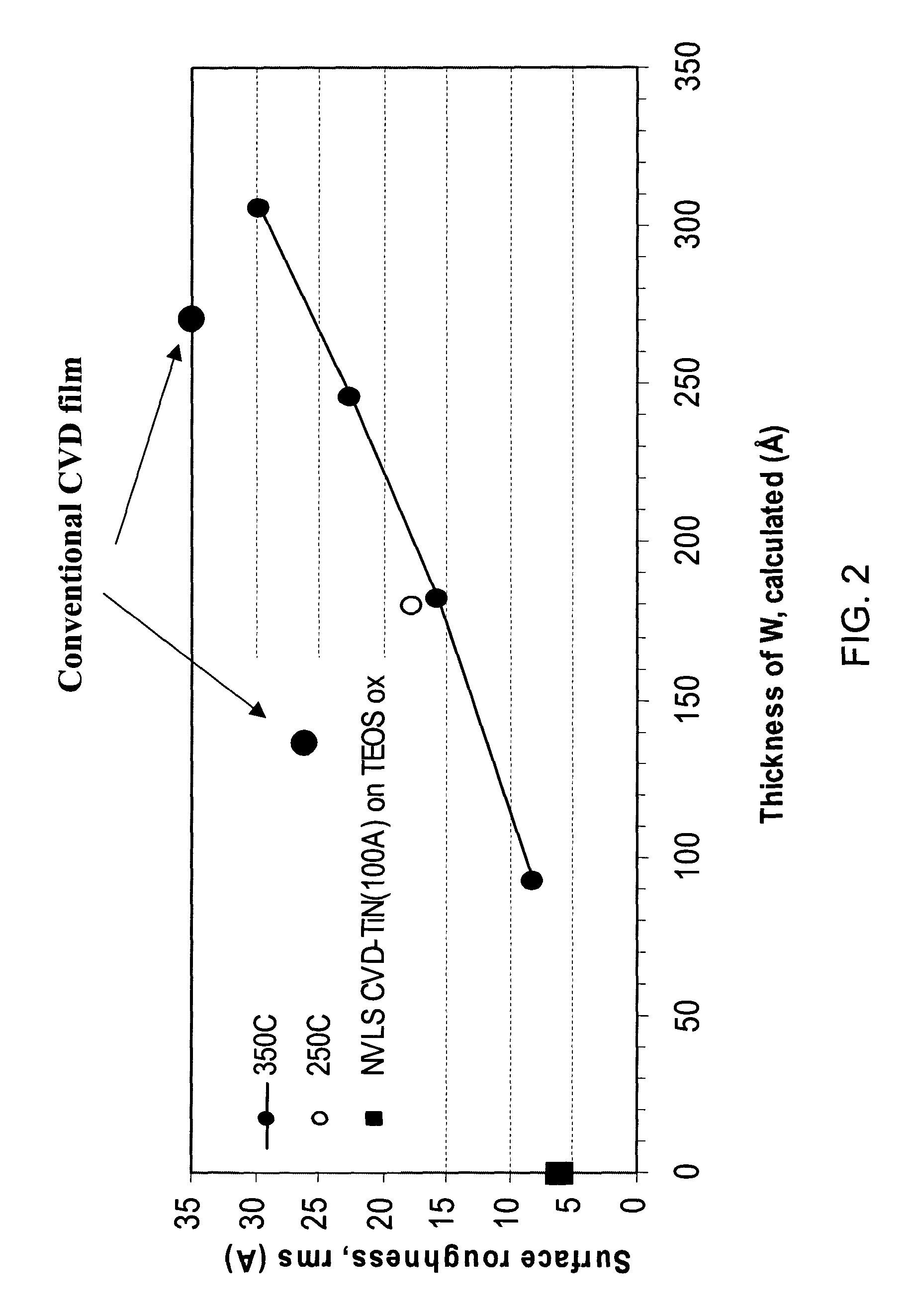

Method for reducing tungsten film roughness and improving step coverage

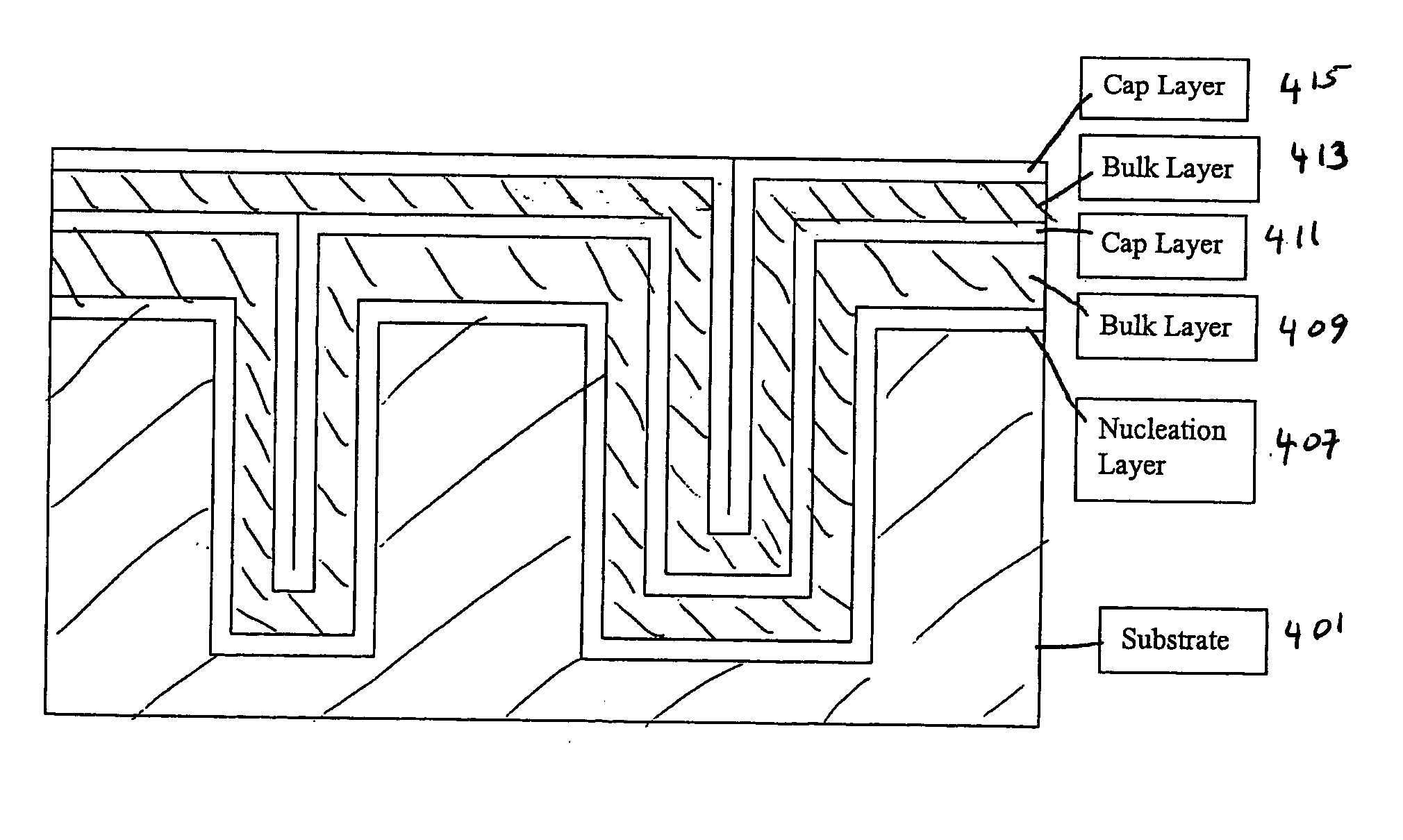

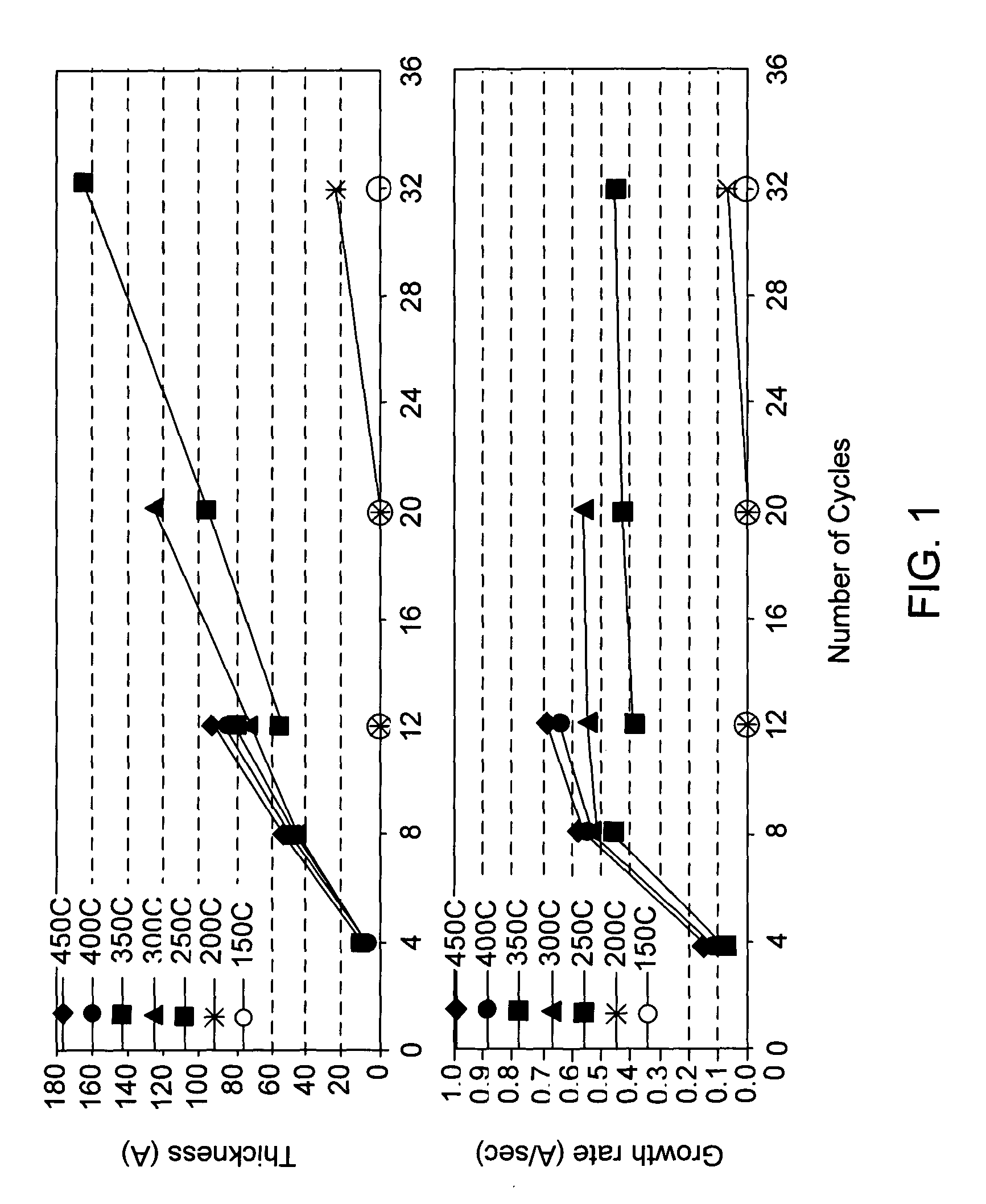

InactiveUS20050031786A1Increase probabilityLow resistivitySemiconductor/solid-state device manufacturingRefuse receptaclesNucleationSemiconductor

A tungsten nucleation film is formed on a surface of a semiconductor substrate by alternatively providing to that surface, reducing gases and tungsten-containing gases. Each cycle of the method provides for one or more monolayers of the tungsten film. The film is conformal and has improved step coverage, even for a high aspect ratio contact hole.

Owner:NOVELLUS SYSTEMS

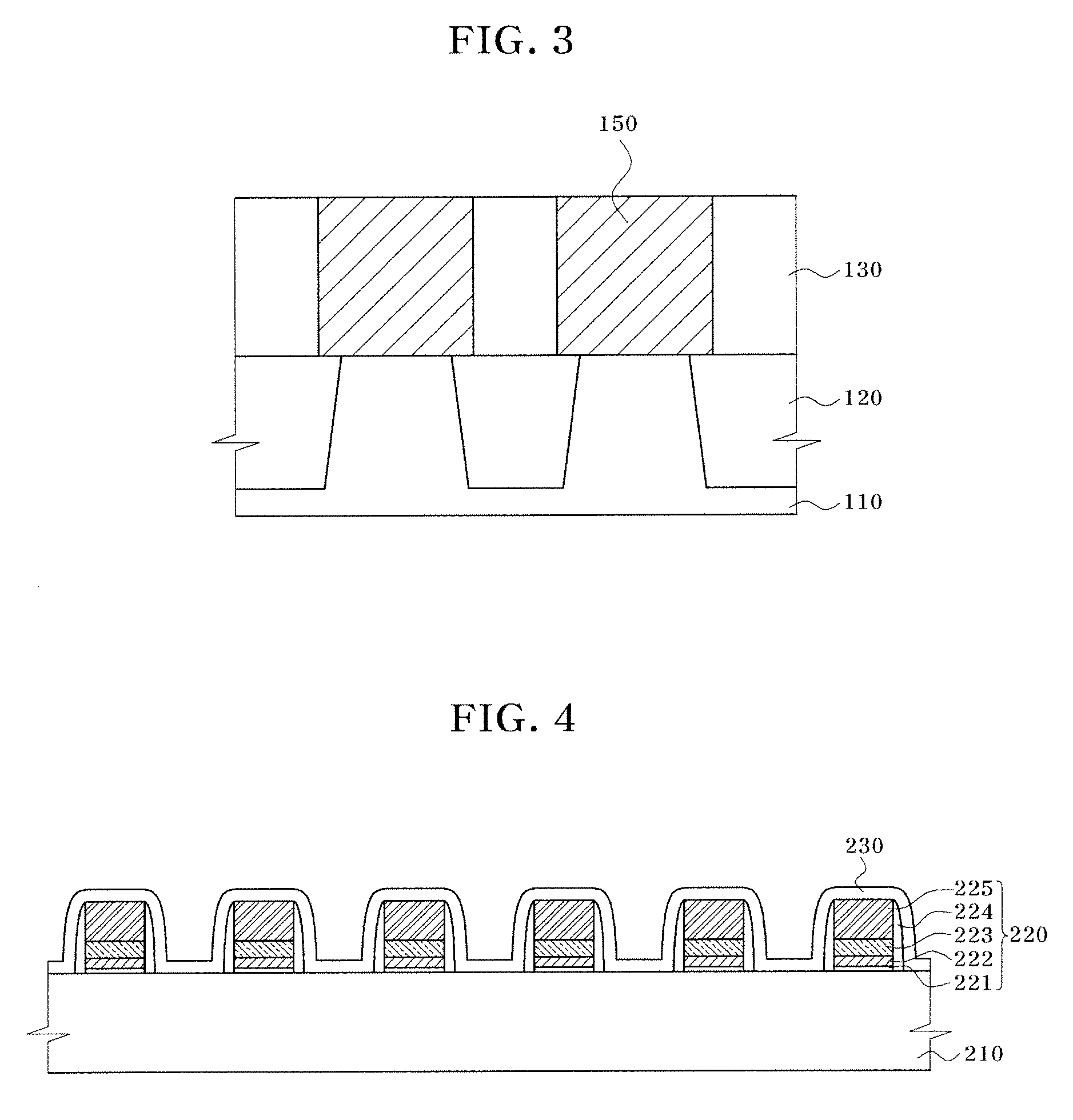

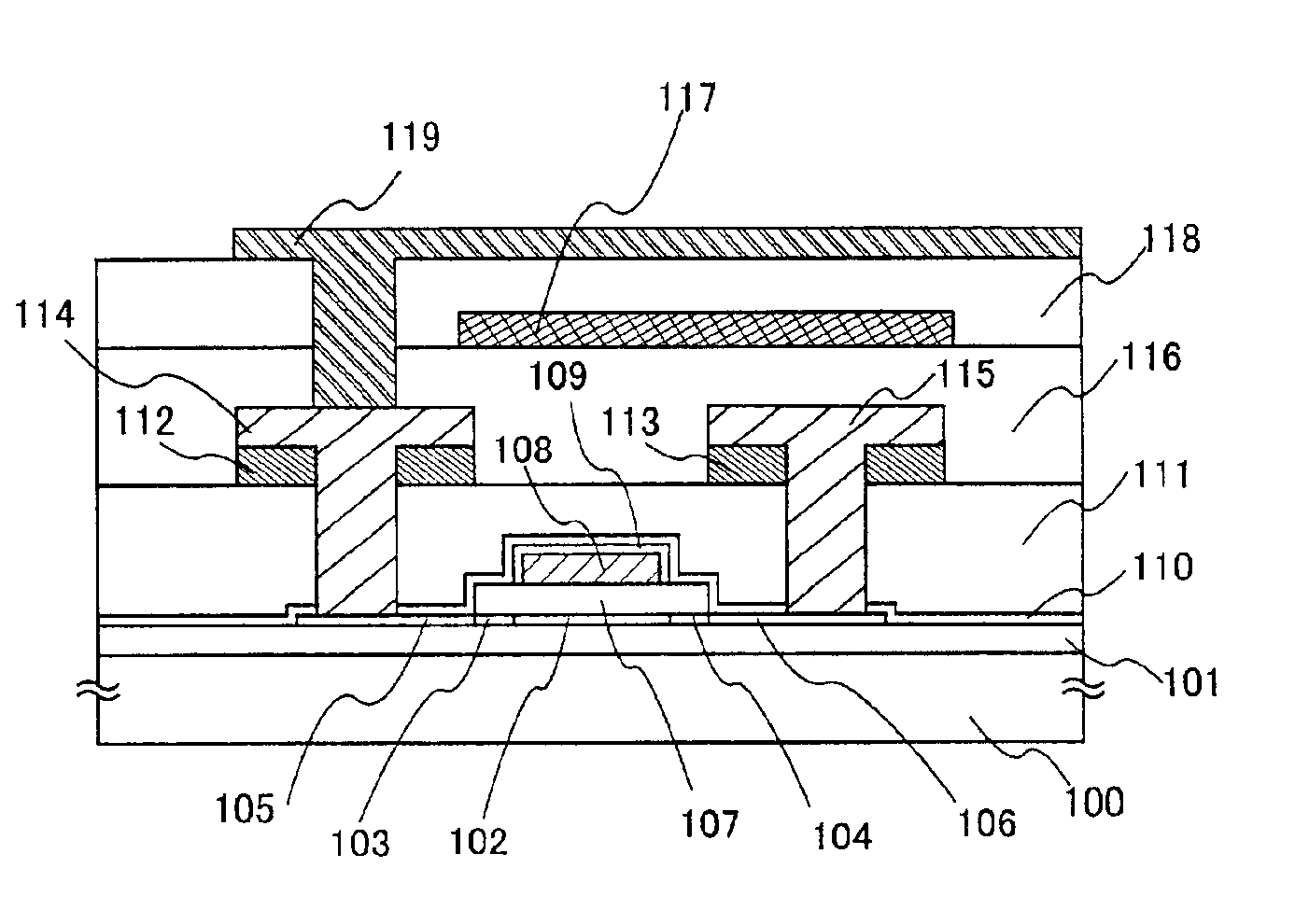

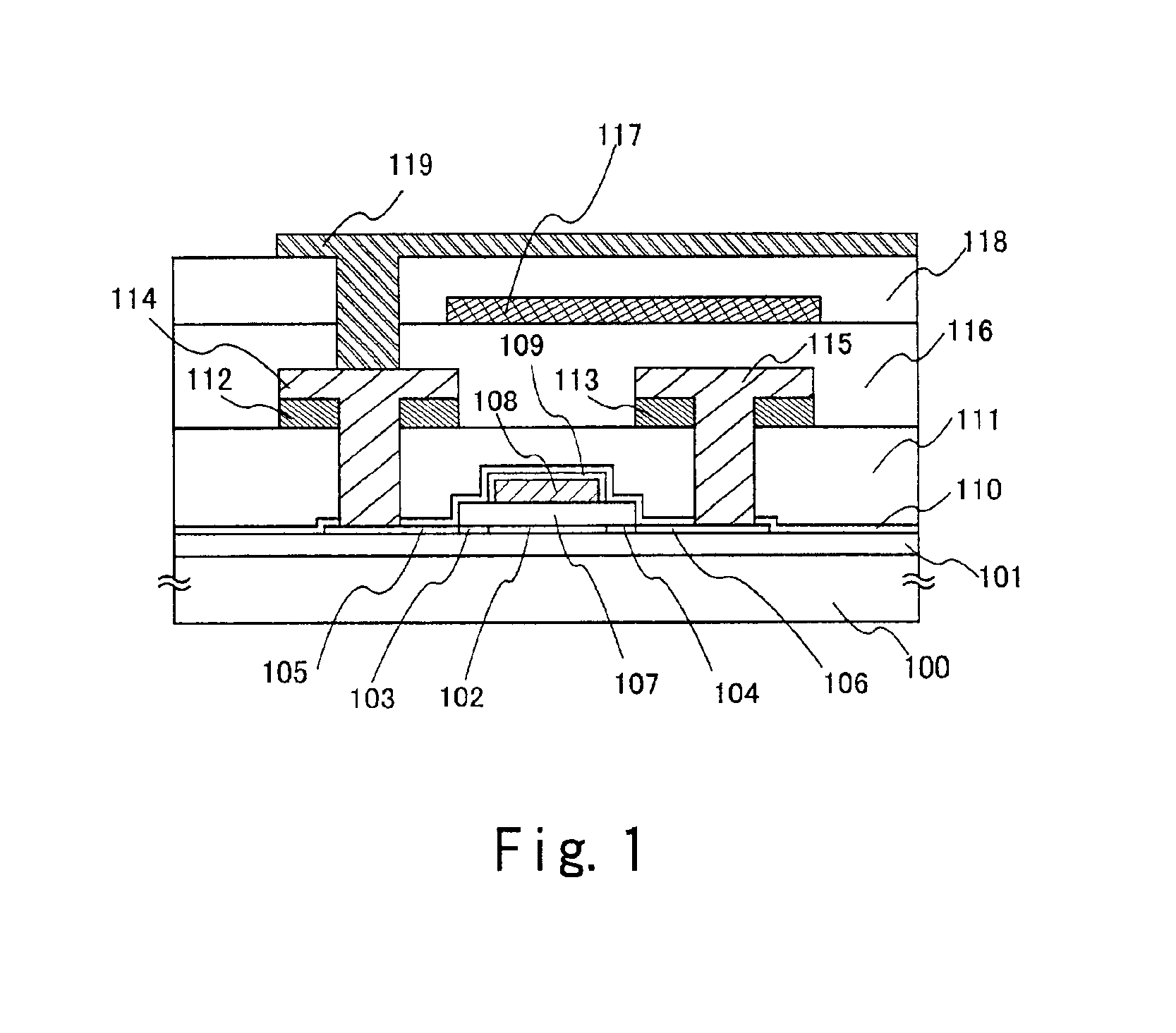

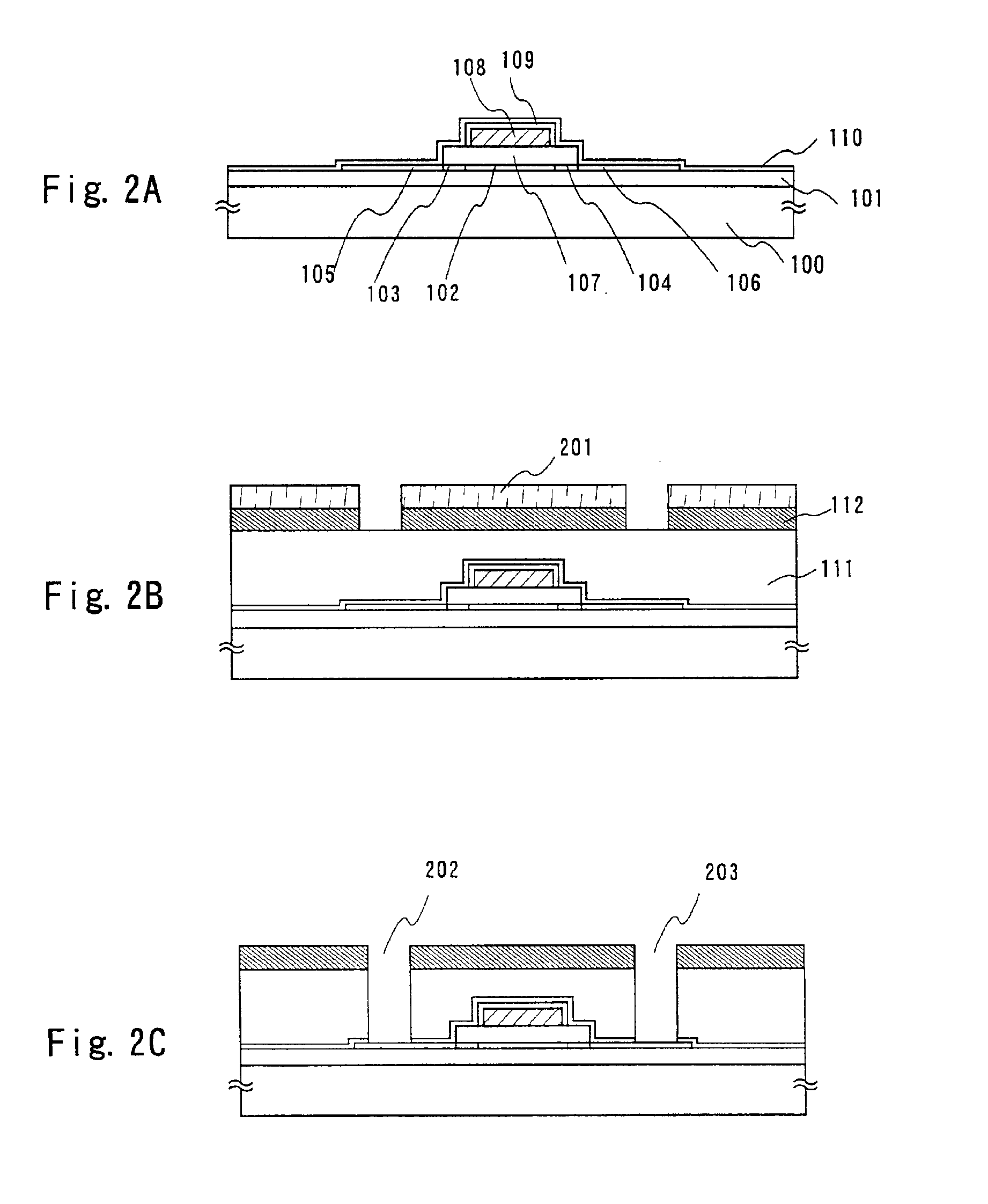

Semiconductor device having multi-layer wiring

InactiveUS6861670B1Lower resistanceIncrease contactTransistorSemiconductor/solid-state device detailsInter layerDevice material

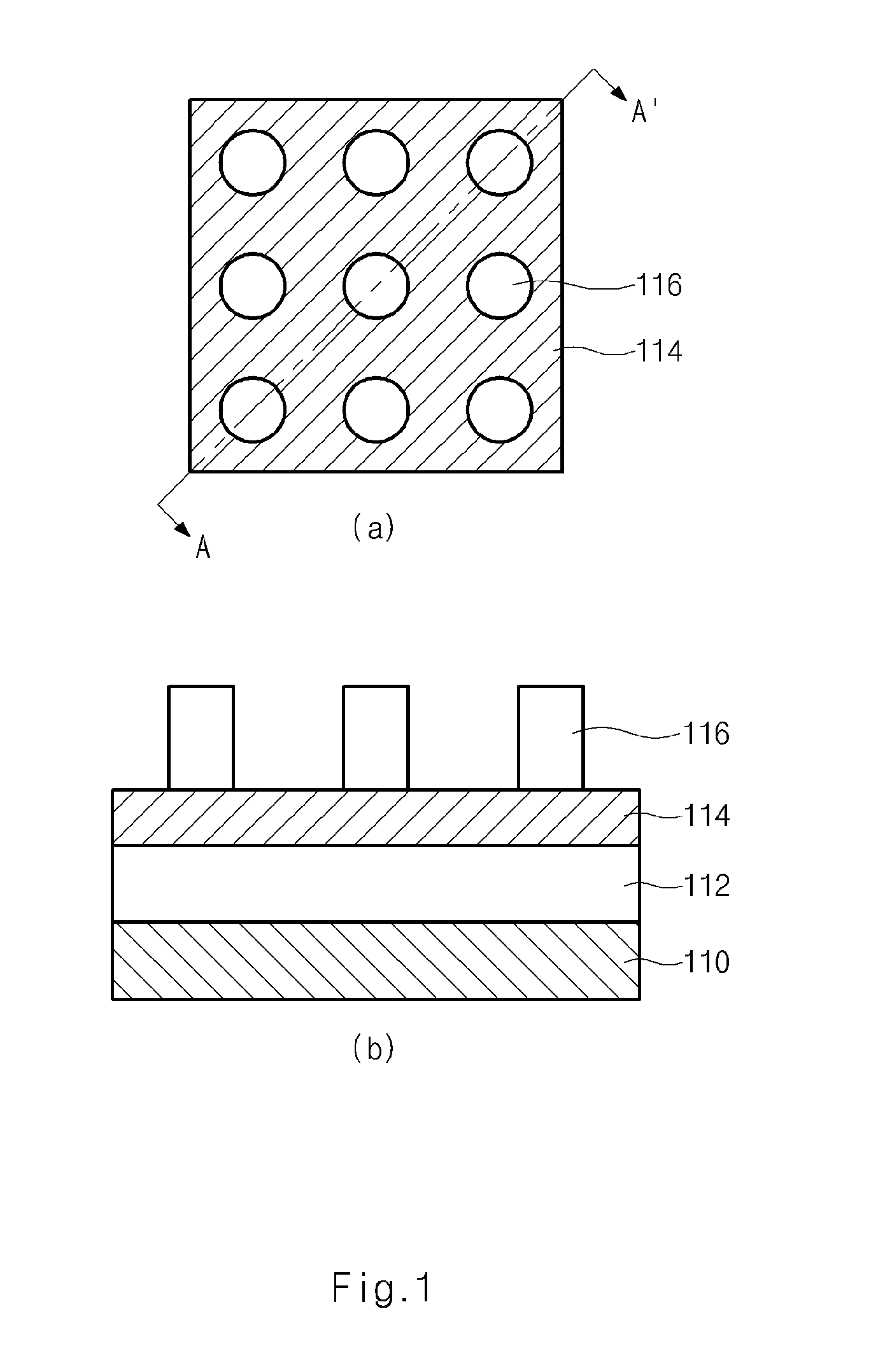

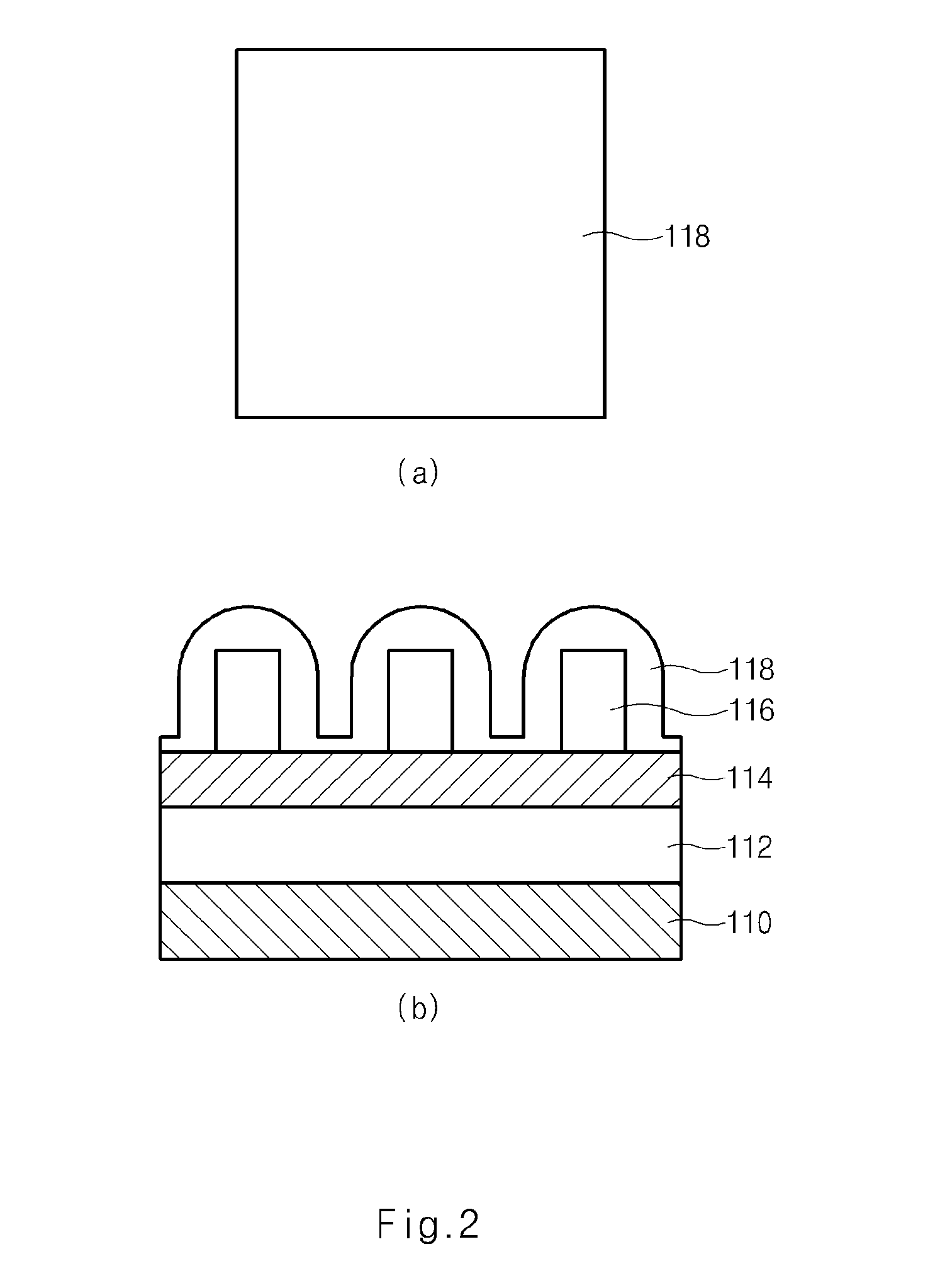

The object is to pattern extremely fine integrated circuits by forming fine contact holes. The dry etching method is employed to form contact holes to pattern a wiring (114), using a mask made of metallic film (112) and an organic material as an inter-layer insulating film (111) for covering switching elements and each of the wirings.

Owner:SEMICON ENERGY LAB CO LTD

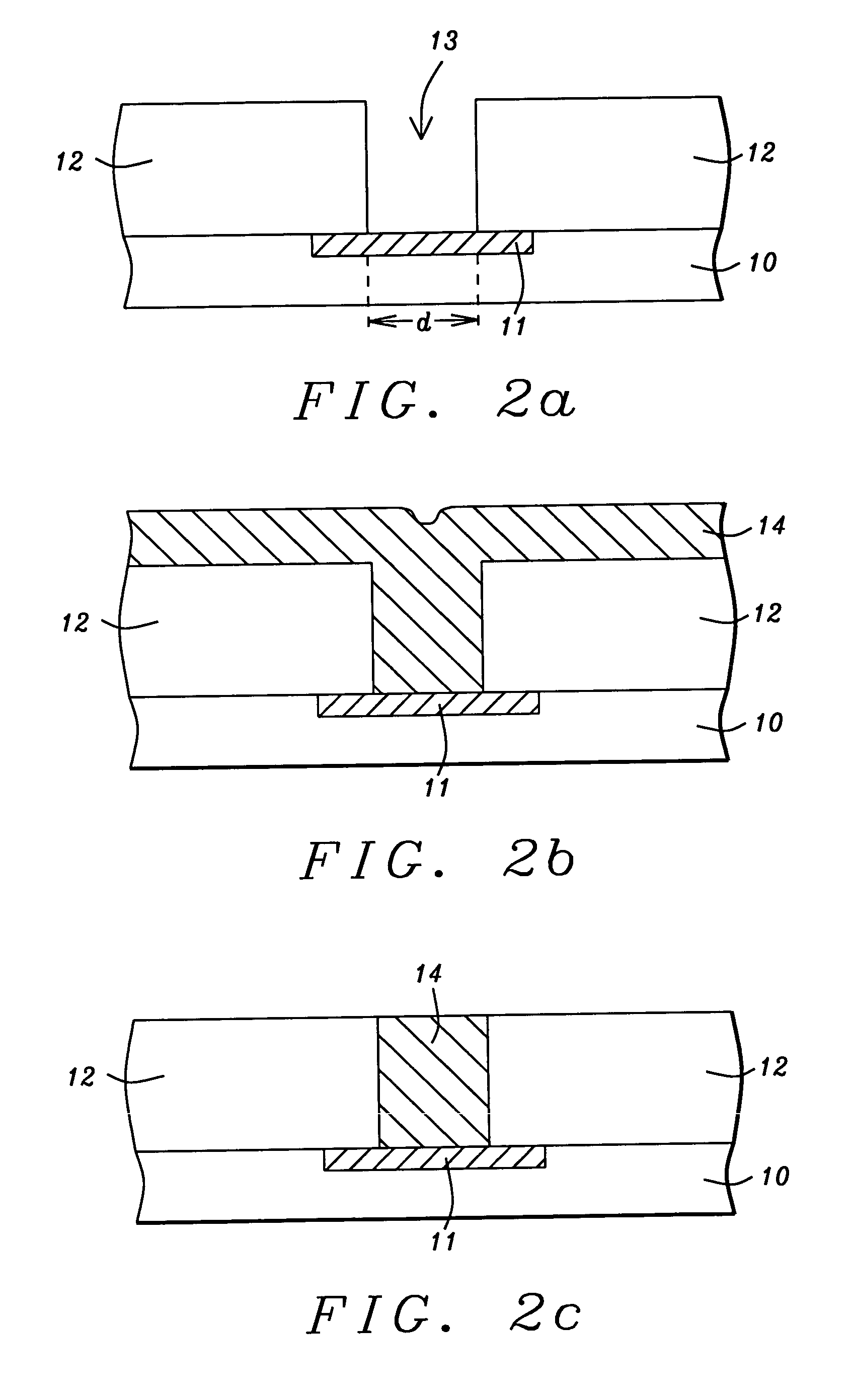

Method for forming self-aligned contact in semiconductor device

ActiveUS20050239282A1Prevent short-circuitingRule out the possibilitySemiconductor/solid-state device manufacturingDevice materialEngineering

A method for forming a self-aligned contact on a semiconductor substrate provided with a plurality of field-effect transistors. The method comprises the steps of forming a first insulating layer comprising a nitride along a profile of a gate structure and a junction region, forming a temporary layer comprising a doped oxide on the first insulating layer, removing a portion of the temporary layer by performing a selective etch of the oxide with a mask while leaving a plug portion of the temporary layer over the junction region, forming a second insulating layer comprising an undoped oxide in a region where the portion of the temporary layer is removed, removing the plug portion by performing a selective etch of the undoped oxide to form a contact hole, removing a portion of the first insulating layer at a bottom of the contact hole, and forming a conductive contact in the contact hole.

Owner:NAN YA TECH

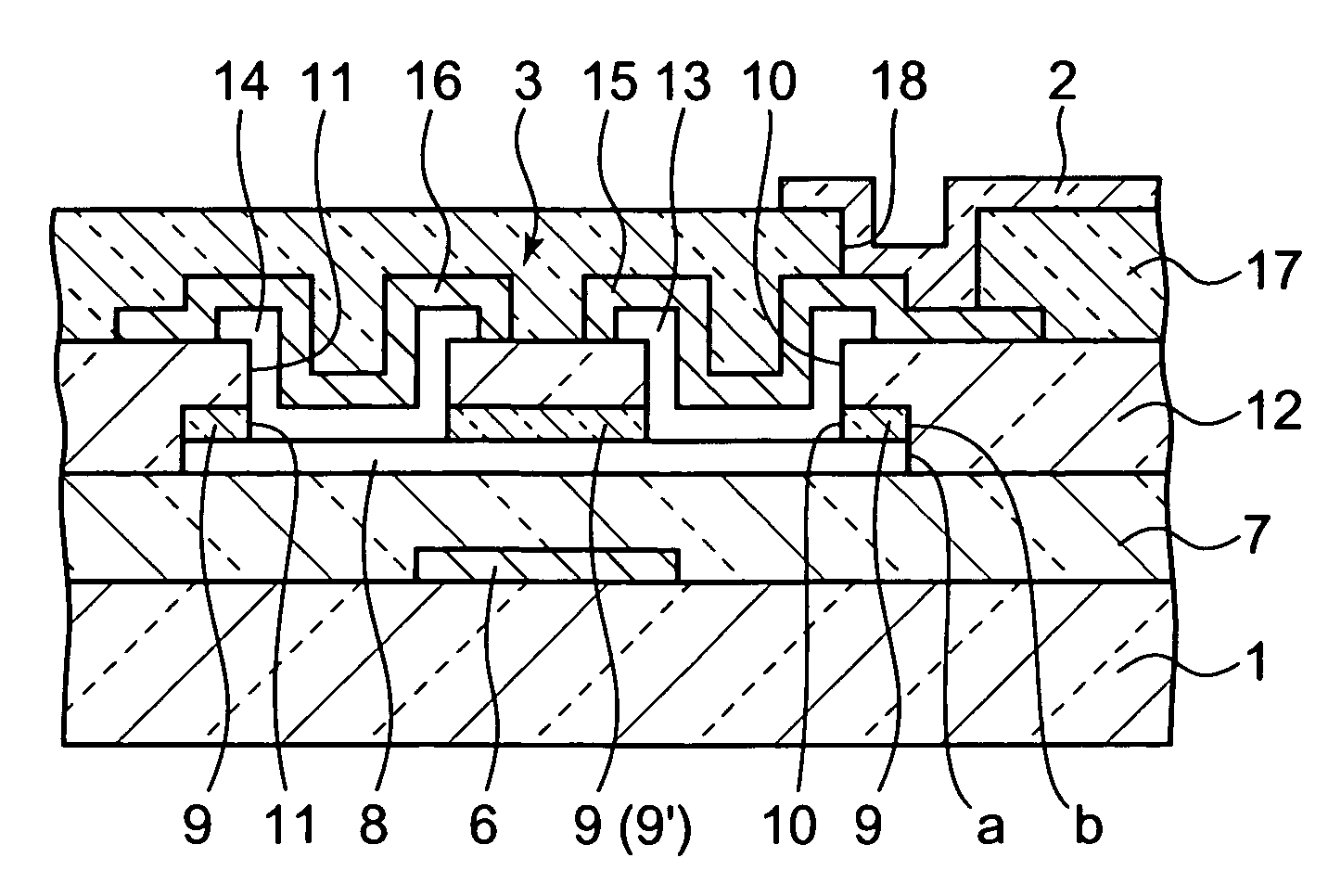

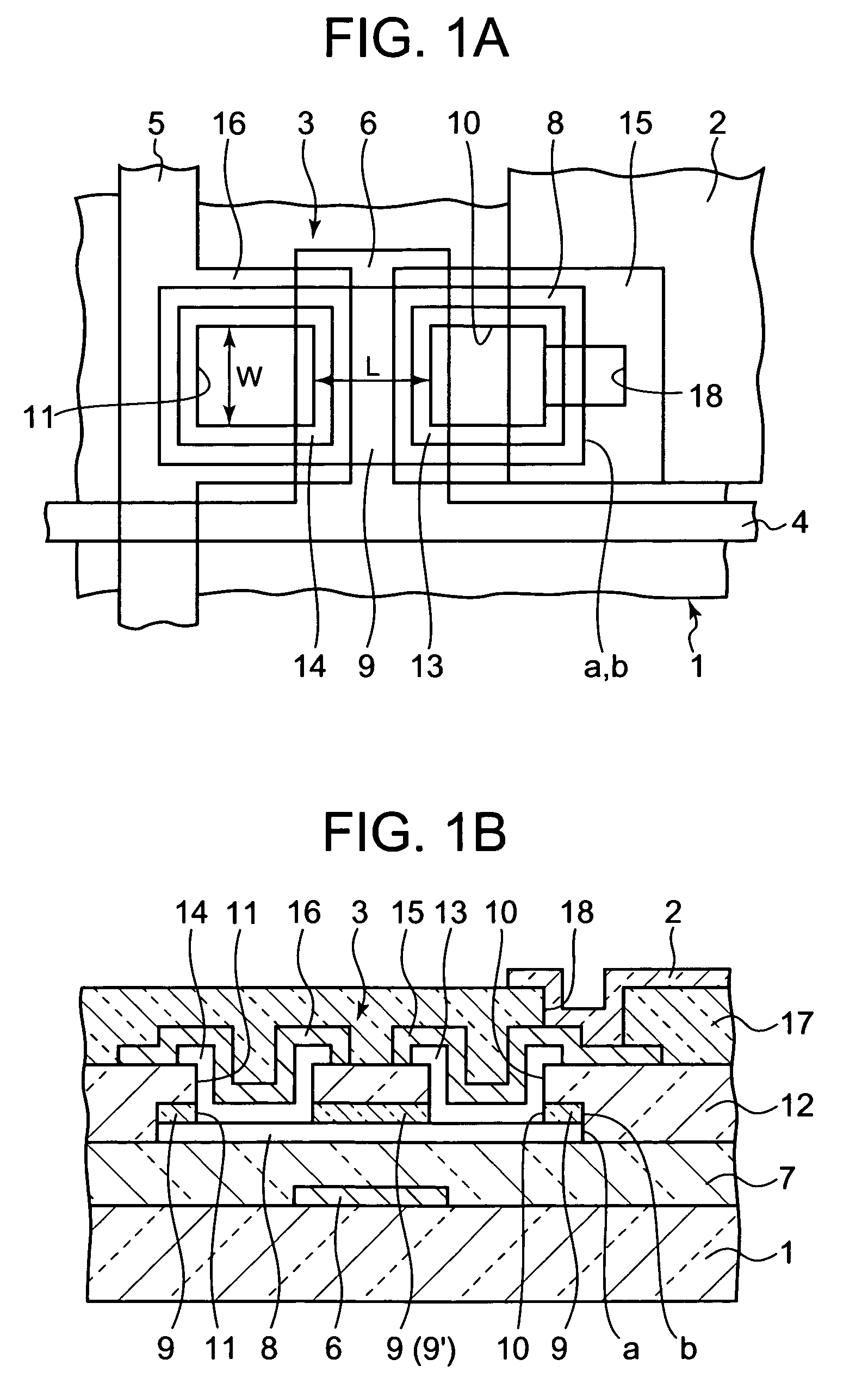

Thin film transistor having an etching protection film and manufacturing method thereof

InactiveUS20060043447A1Improve machining accuracySolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorSemiconductor thin films

A thin film transistor of the present invention includes a semiconductor thin film (8); a gate insulating film (7) formed on one surface of the semiconductor thin film (8); a gate electrode (6) formed to be opposite to the semiconductor thin film (8) through the gate insulating film (7); a source electrode (15) and a drain electrode (16) electrically connected to the semiconductor thin film (8); a source region; a drain region; and a channel region. The thin film transistor further includes an insulating film (9) formed on a peripheral portion corresponding to at least the source region and the drain region of the semiconductor thin film (8), and having a contact hole (10, 11) through which at least a part of each of the source region and the drain region is exposed wherein the source electrode (15) and the drain electrode (16) are connected to the semiconductor thin film (8) through the contact hole (10, 11).

Owner:CASIO COMPUTER CO LTD

Method for forming void-free polysilicon and method for fabricating semiconductor device using the same

ActiveUS20140179092A1Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductorHeat treated

A method for fabricating a semiconductor device includes forming a buried gate electrode in a semiconductor substrate. An insulating layer is formed over the buried gate electrode and is etched to form a contact hole exposing the semiconductor substrate. A sacrificial spacer is formed on sidewalls of the insulating layer defining the contact hole. A polysilicon layer pattern is formed in the contact hole. The sacrificial spacer is removed to form an air gap around the polysilicon layer pattern. A thermal process is performed to remove a seam existing in the polysilicon layer pattern.

Owner:SK HYNIX INC

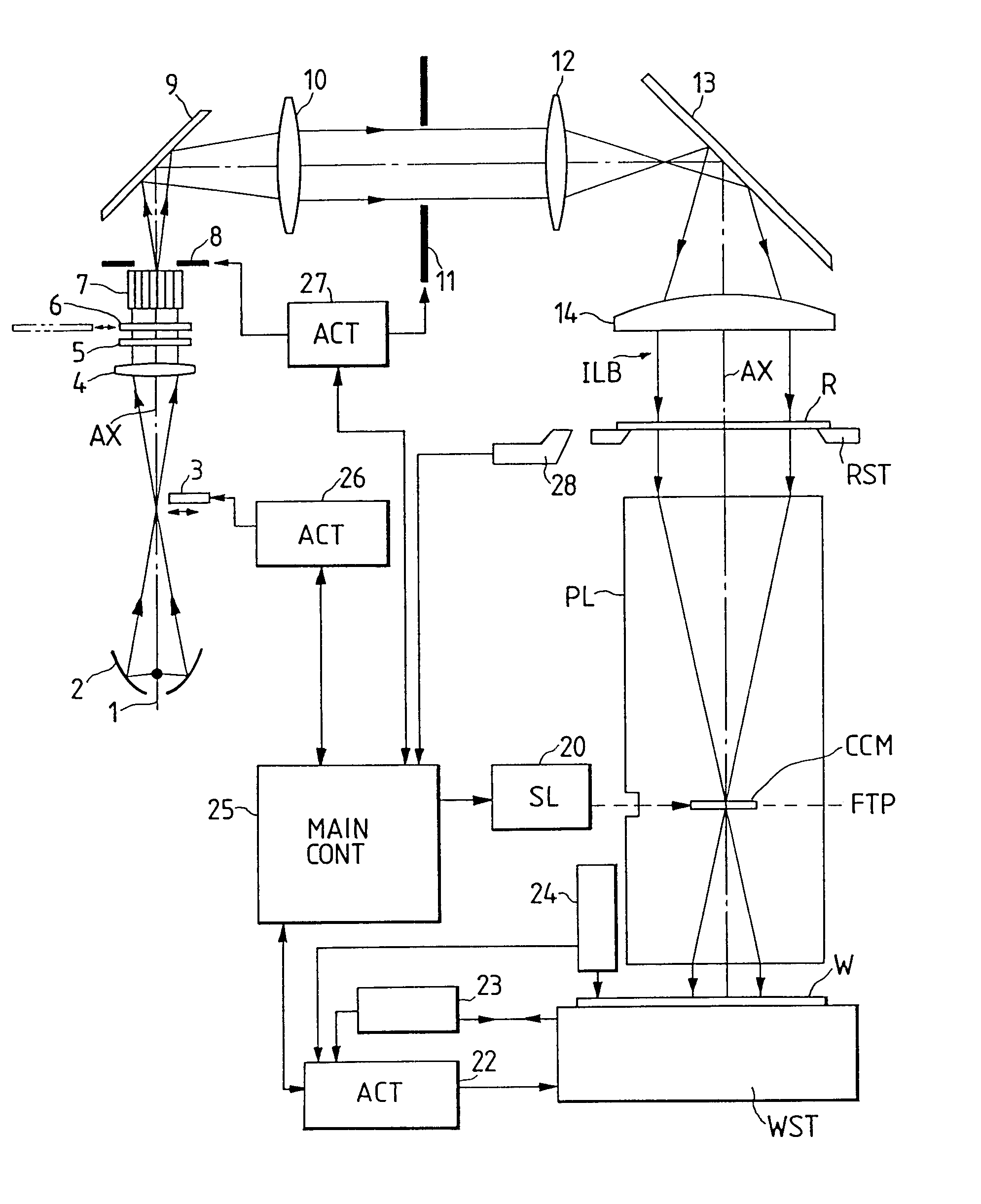

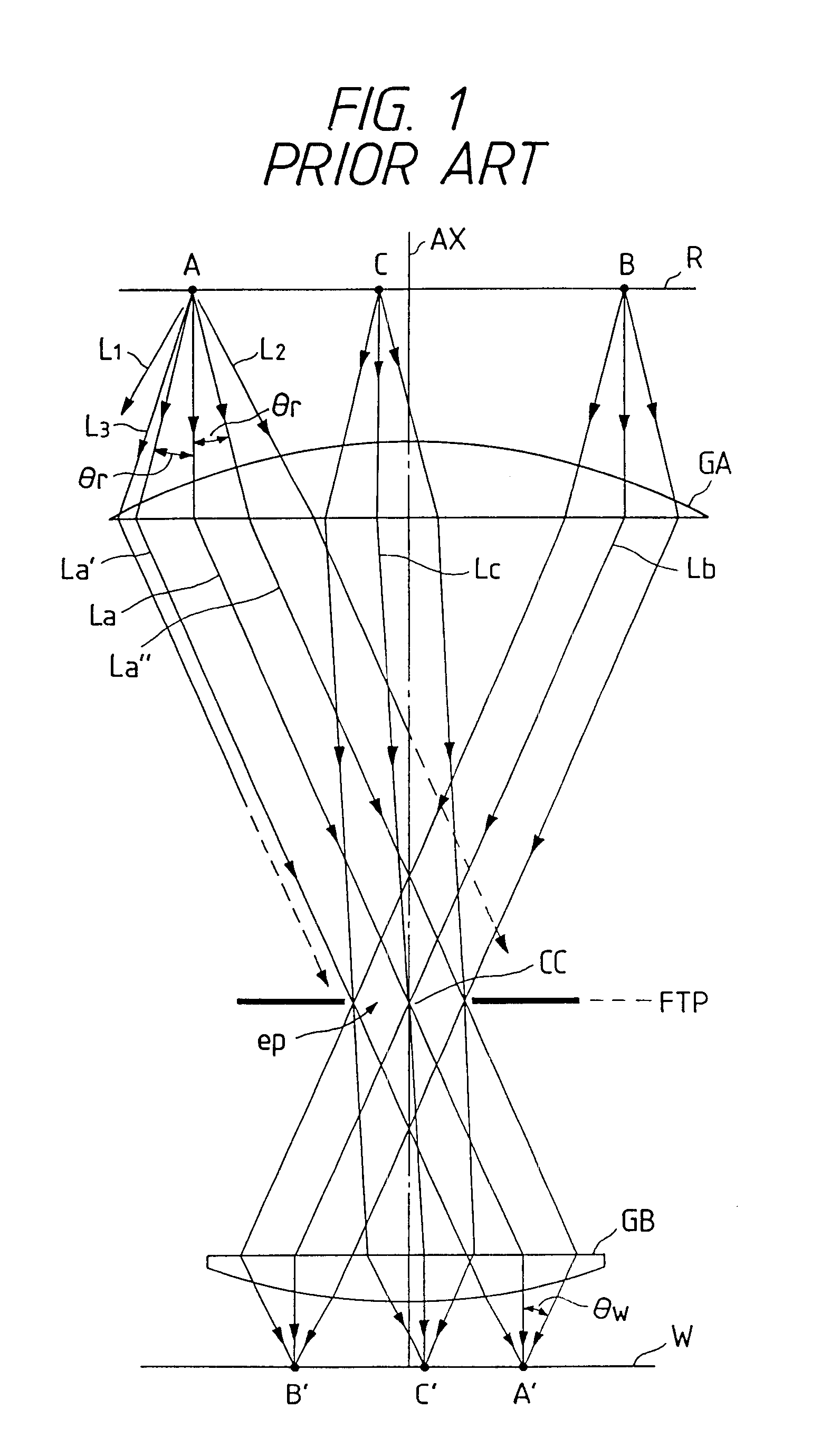

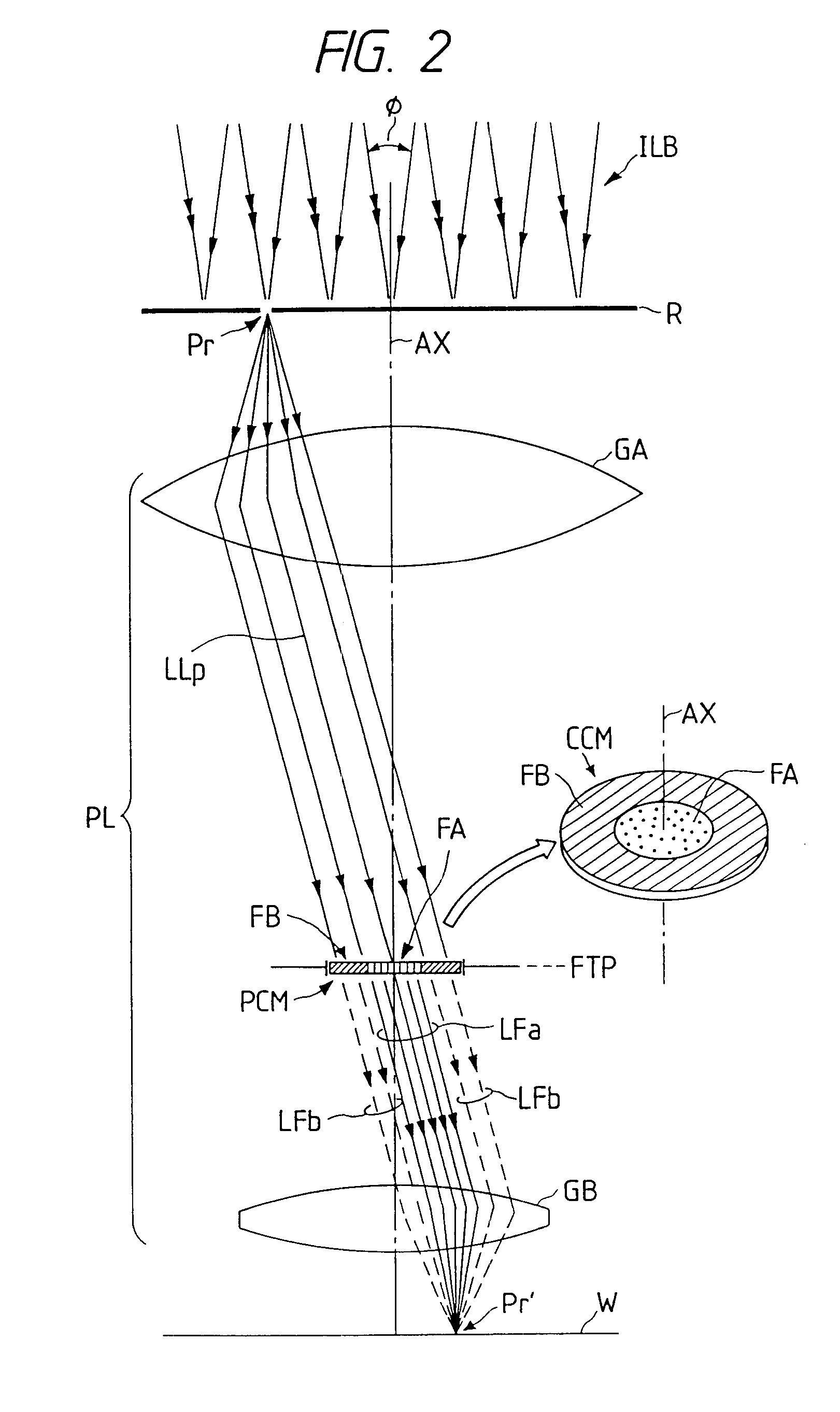

Projection exposure method and apparatus

InactiveUS6404482B1Photomechanical exposure apparatusMicrolithography exposure apparatusOptical axisFourier transform on finite groups

In projection exposure of isolated pattern such as a contact hole, in order to increase the depth of focus a coherence reducing member is disposed on a Fourier transform plane in an image-forming optical path between a mask and a sensitized base, so that coherence is reduced between image-forming beams respectively passing through a plurality of different, concentric regions around the optical axis of the projection optical system on the Fourier transform plane. The coherence reducing member may be a polarization state control member for making a difference in polarization state, a member for making a difference in optical path length, or space filters with different shapes.

Owner:NIKON CORP

Method for reducing tungsten film roughness and improving step coverage

InactiveUS7141494B2Increase probabilityLow resistivitySemiconductor/solid-state device manufacturingRefuse receptaclesNucleationTungsten film

A tungsten nucleation film is formed on a surface of a semiconductor substrate by alternatively providing to that surface, reducing gases and tungsten-containing gases. Each cycle of the method provides for one or more monolayers of the tungsten film. The film is conformal and has improved step coverage, even for a high aspect ratio contact hole.

Owner:NOVELLUS SYSTEMS

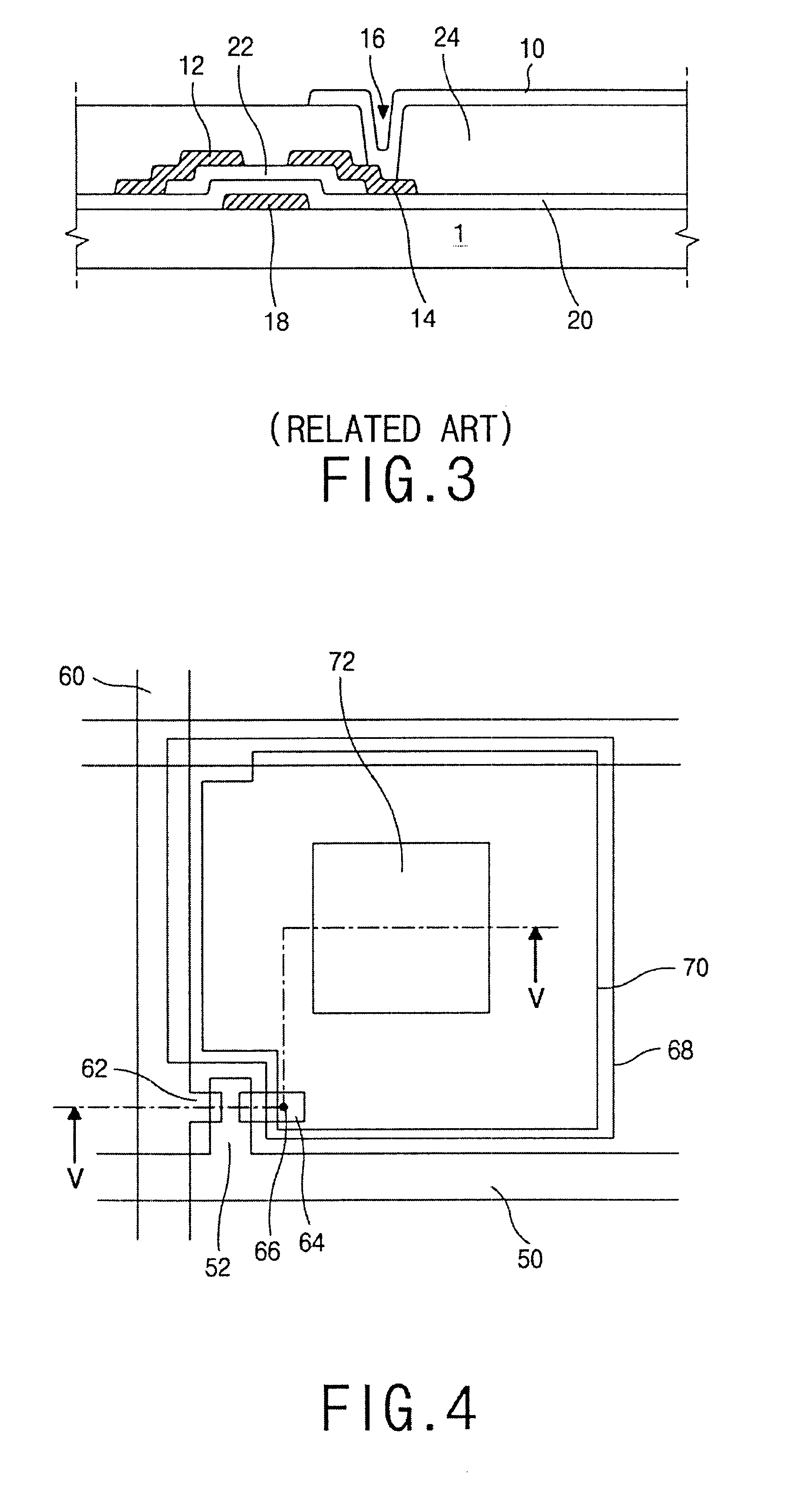

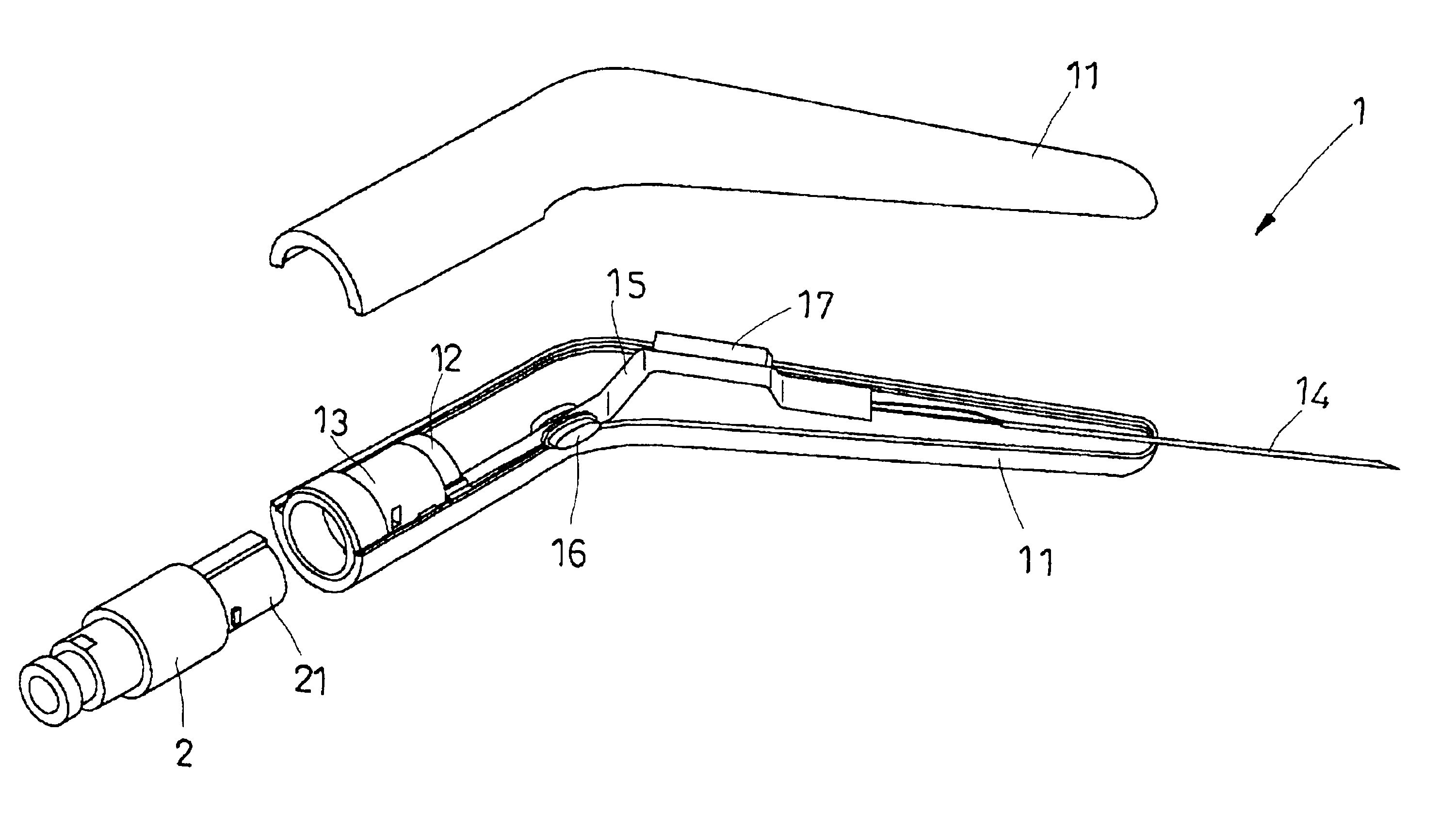

Transflective liquid crystal display device and method of manufacturing the same

The present invention discloses A transflective liquid crystal display device including a first substrate having a color filter; a second substrate having: a)a gate electrode formed on the second substrate; b) a first insulating layer formed on the exposed surface of the second substrate while covering the gate electrode; c) a semiconductor layer formed on the first insulating layer and over the gate electrode; d)a source electrode overlapping one end portion of the semiconductor layer; e) a drain electrode overlapping the other end portion of the semiconductor layer and spaced apart from the source electrode; f) a second insulating layer formed on the exposed surface of the first insulating layer while covering the source and drain electrode, having a first contact hole formed on a portion of the drain electrode; g) a pixel electrode formed on the second insulating layer and electrically connected with the drain electrode through the first contact hole; h) a third insulating layer on the pixel electrode and having a second contact hole over the first contact hole; and i) a reflective electrode formed on the third insulating layer and having a light transmitting hole and electrically connected with the pixel electrode through the second contact hole, the light transmitting hole transmitting light and covered by the pixel electrode; a liquid crystal display layer interposed between the first and second substrates; and a back light device for supplying light and located under the second substrate.

Owner:LG DISPLAY CO LTD

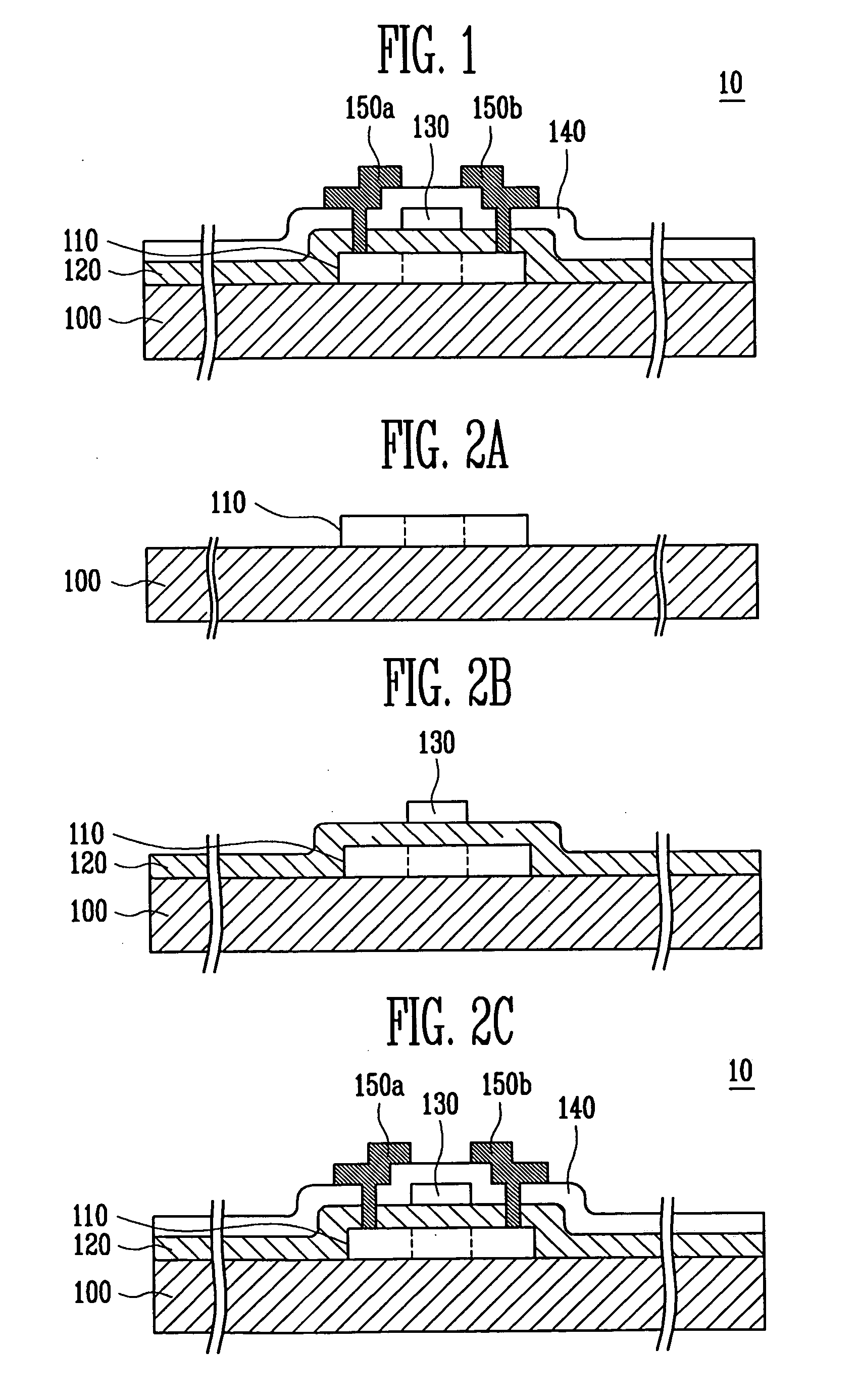

Method for manufacturing thin film transistor array panel for liquid crystal display

Simplified method of manufacturing liquid crystal displays. A gate wire including a gate line, a gate pad and a gate electrode is formed on the substrate by using the first mask. A gate insulating layer, a semiconductor layer, a ohmic contact layer and a metal layer are sequentially deposited to make a quadruple layers, and patterned by a dry etch of using the second mask. At this time, the quadruple layers is patterned to have a matrix of net shape layout and covering the gate wire. An opening exposing the substrate is formed in the display area and a contact hole exposing the gate pad is formed in the peripheral area. Next, ITO is deposited and a photoresist layer coated on the ITO. Then, the ITO layer is patterned by using the third mask and a dry etch, and the data conductor layer and the ohmic contact layer not covered by the ITO layer is dry etched. After depositing a passivation layer, a opening is formed by using the fourth mask and the exposed semiconductor layer through the opening is etched to separate the semiconductor layer under the adjacent data line.

Owner:SAMSUNG ELECTRONICS CO LTD

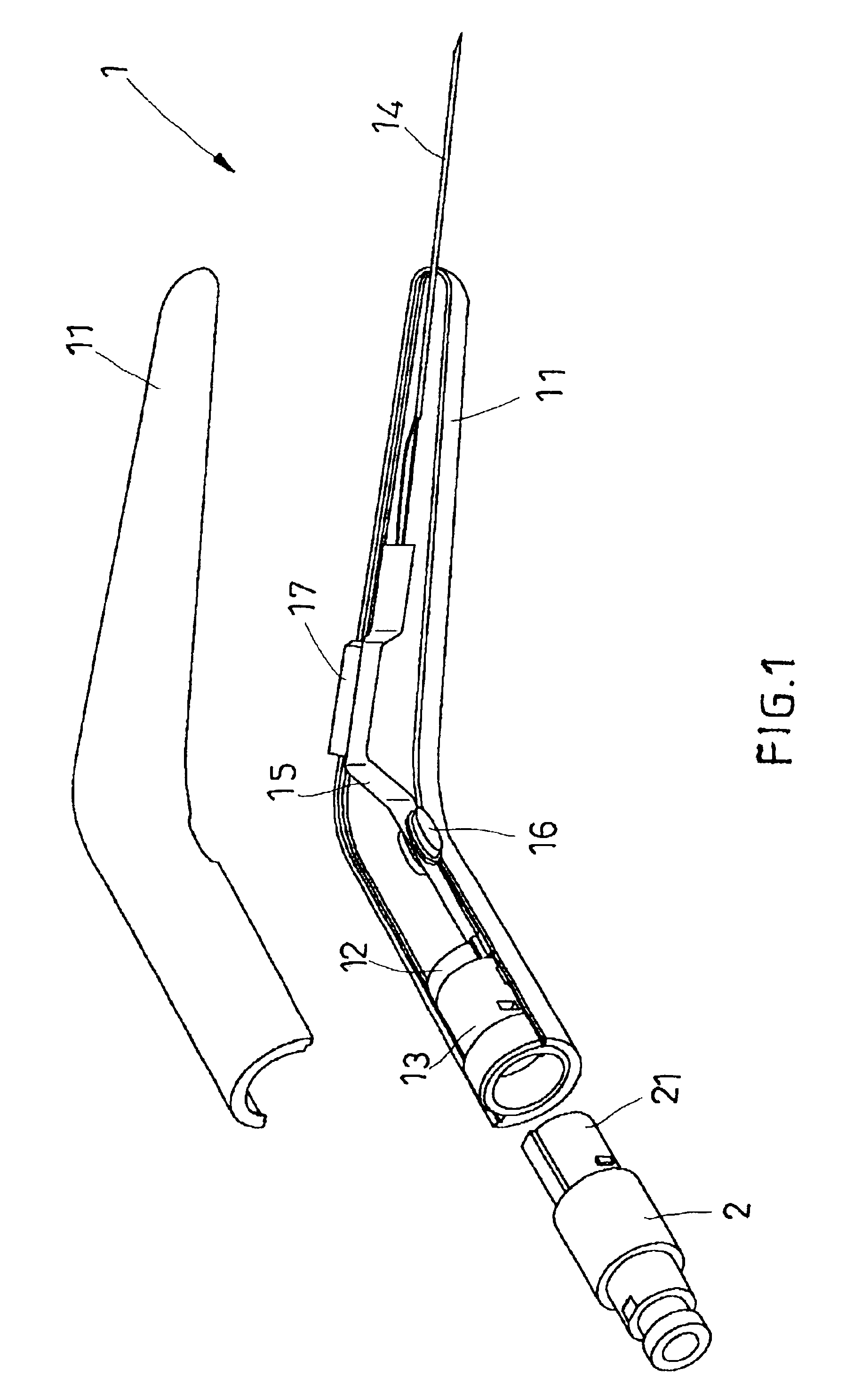

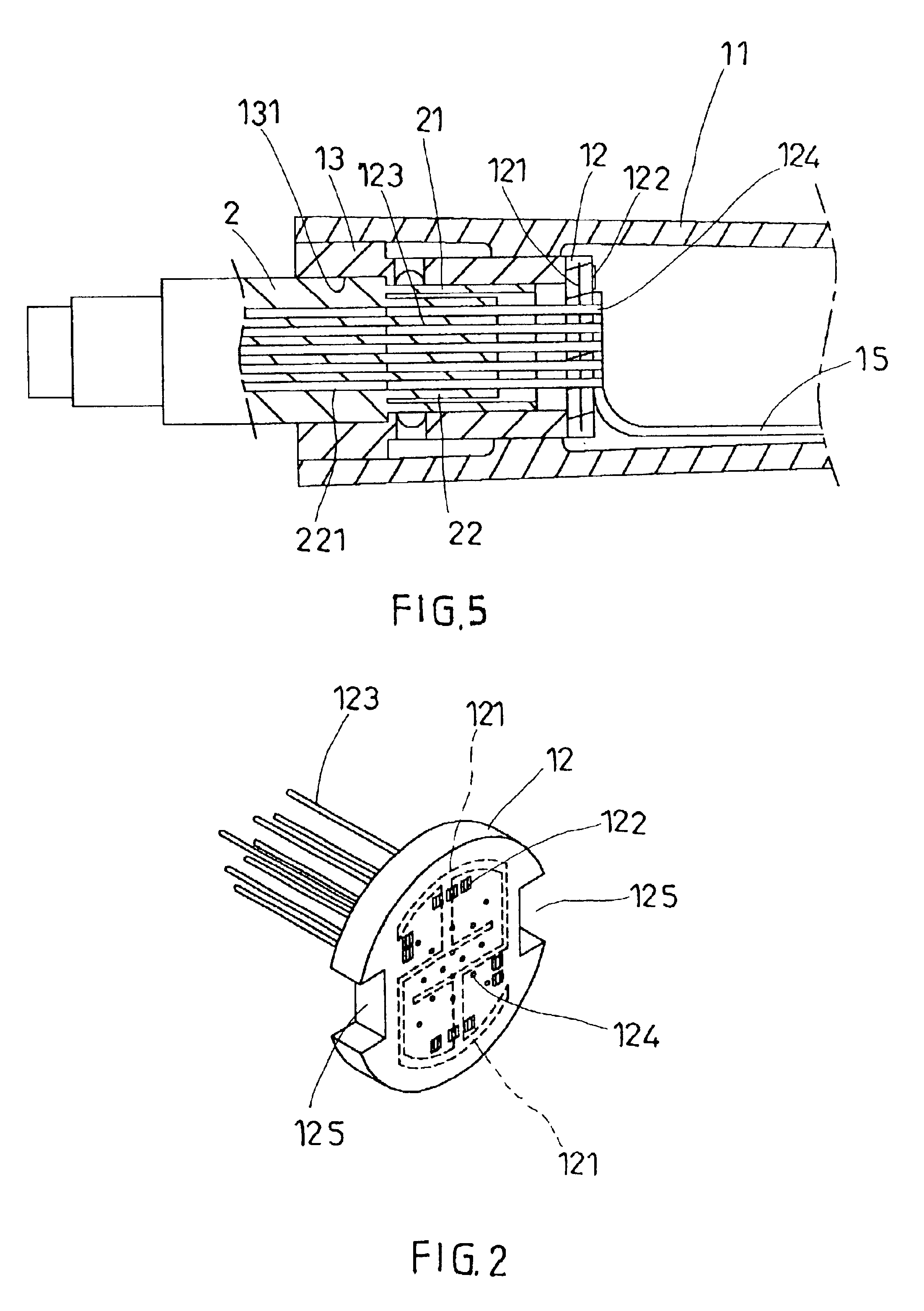

Disposable surgical devices

InactiveUS6849074B2Consume less timeConsume less laborSurgical instruments for heatingElectricityFlexible circuits

A disposable surgical device is constructed to include a shell, a smart block mounted in one end of the shell, the smart block electronic having components mounted to a circuit embedded therein, front contact pins for insertion into respective contact holes in the connector of an industry standard connector interface, and rear wire terminal points, a medical treatment terminal installed in the other side of the shell and adapted for performing surgery and treatments, and a flex circuit termination electrically connected between the smart block and the medical treatment terminal, the flex circuit termination having embedded conductor lines respectively connected to the medical treatment terminal and wire terminal points at the ends of the conductor lines respectively soldered to the wire terminal points of the smart block.

Owner:ATL TECH LLC

Organic light emitting diode display device with touch screen and method of fabricating the same

ActiveUS20150185942A1Low costReduce the numberStatic indicating devicesSolid-state devicesDisplay deviceLight-emitting diode

An OLED display device with a touch screen includes first and second substrates; organic light emitting diodes in the display area over the first substrate; first pads and second pads in the non-display area over the first substrate; first and second touch electrodes in the display area over the second substrate; touch pads in the non-display area over the second substrate and corresponding to and overlapping the second pads, respectively; and a first adhesive layer between the first and second substrates and exposing the first and second pads, wherein pad contact holes pass through the second substrate, the touch pads, and the first adhesive layer and expose the second pads, respectively, and wherein a conduction means is disposed in each of the pad contact holes and electrically connects each of the touch pads with a corresponding second pad.

Owner:LG DISPLAY CO LTD

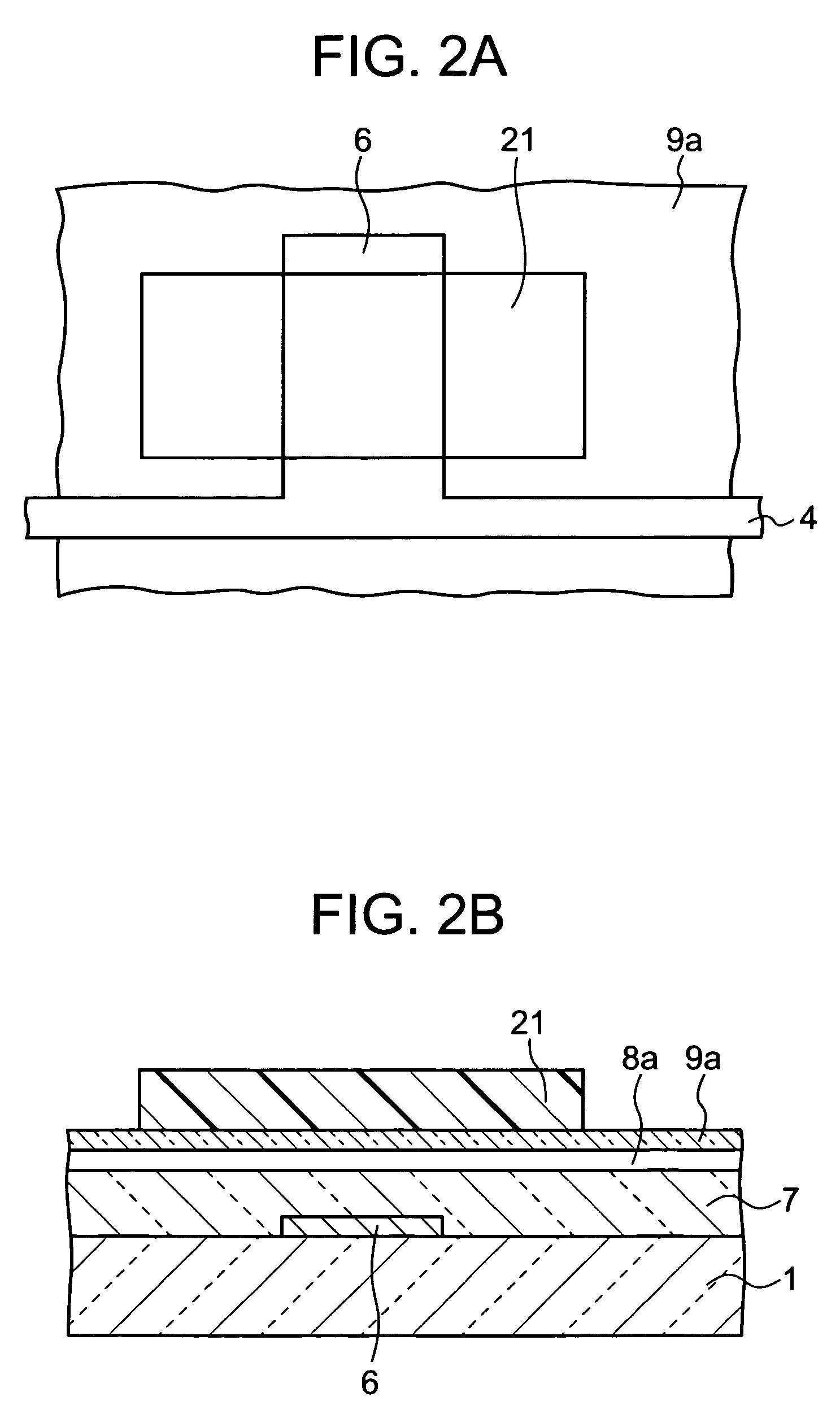

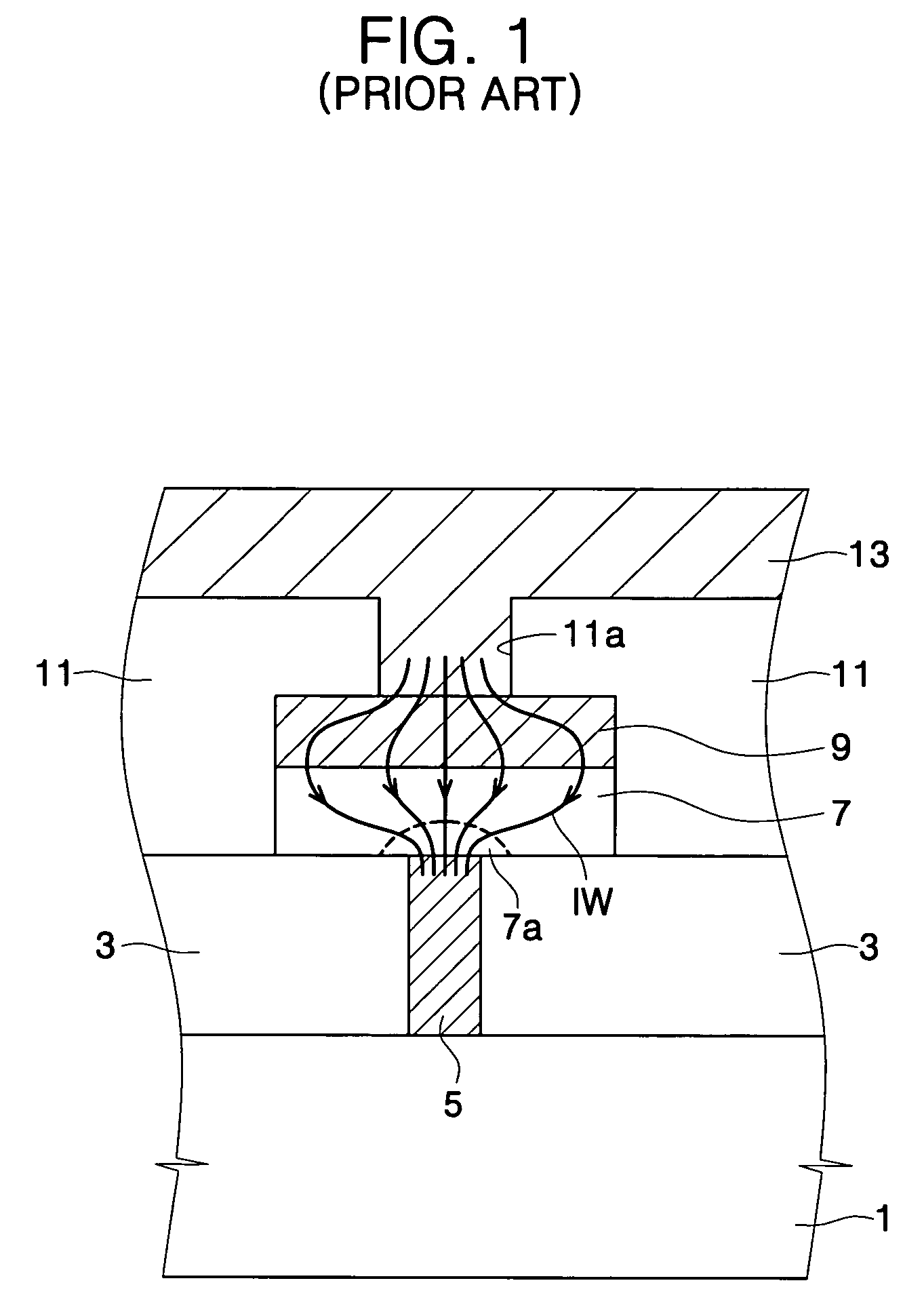

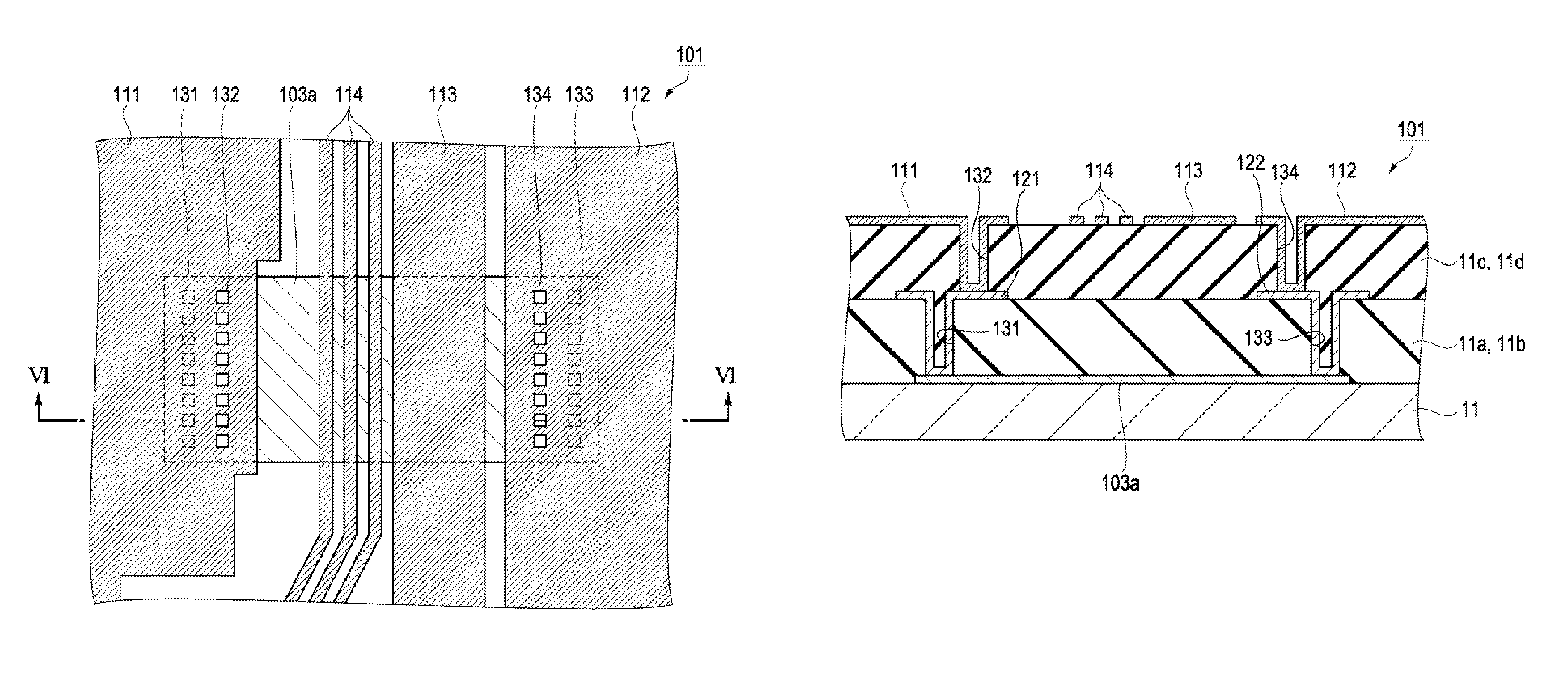

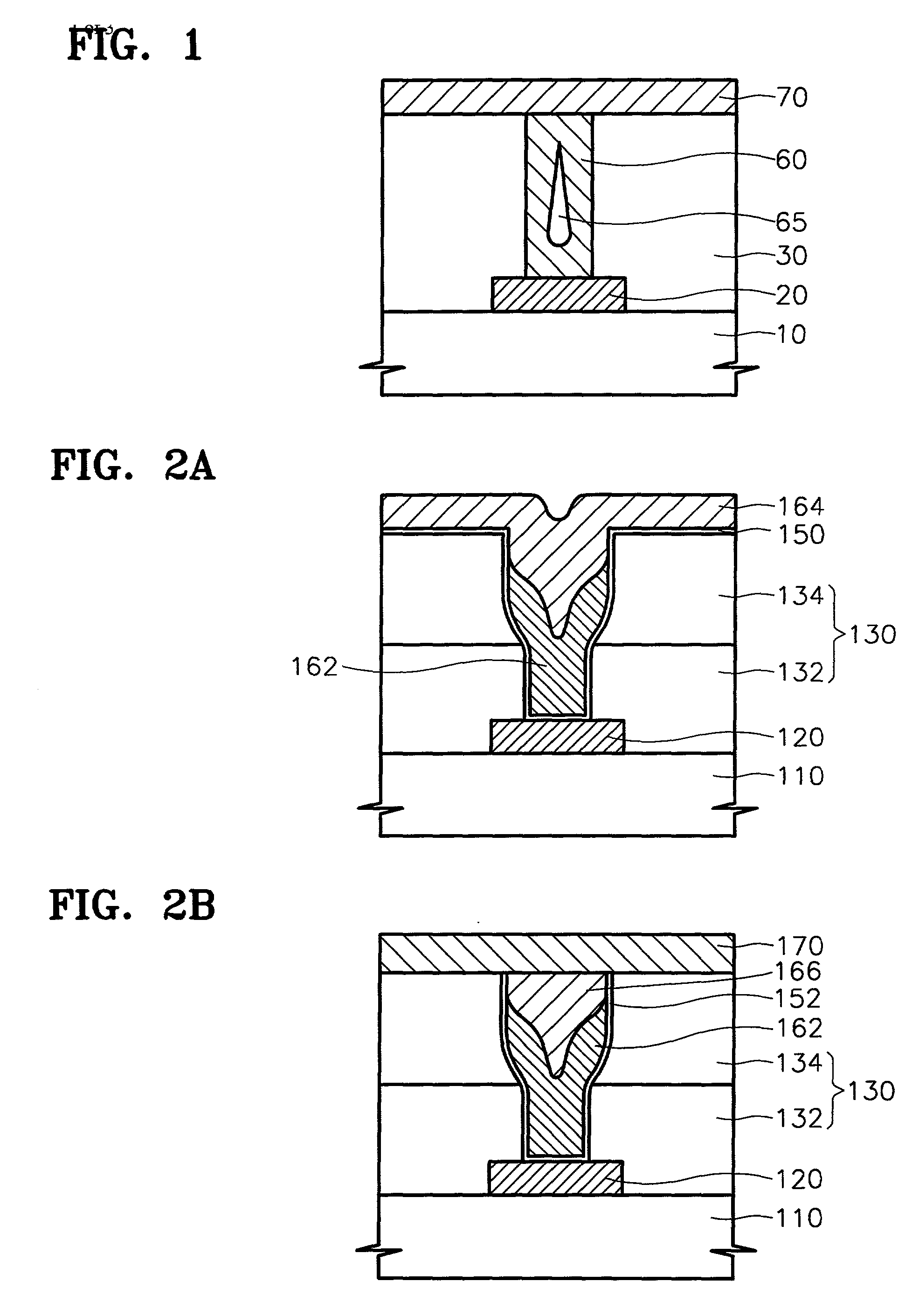

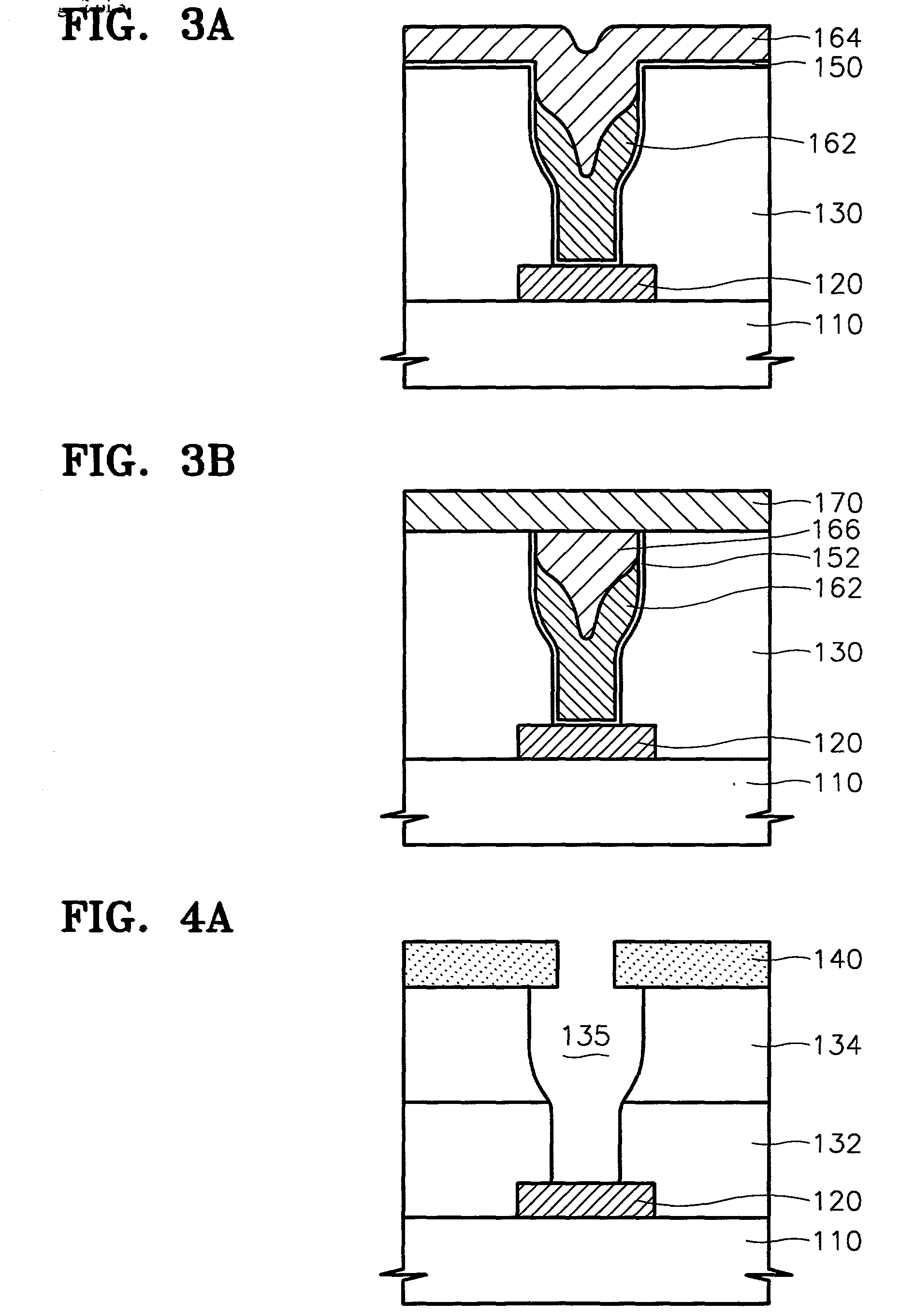

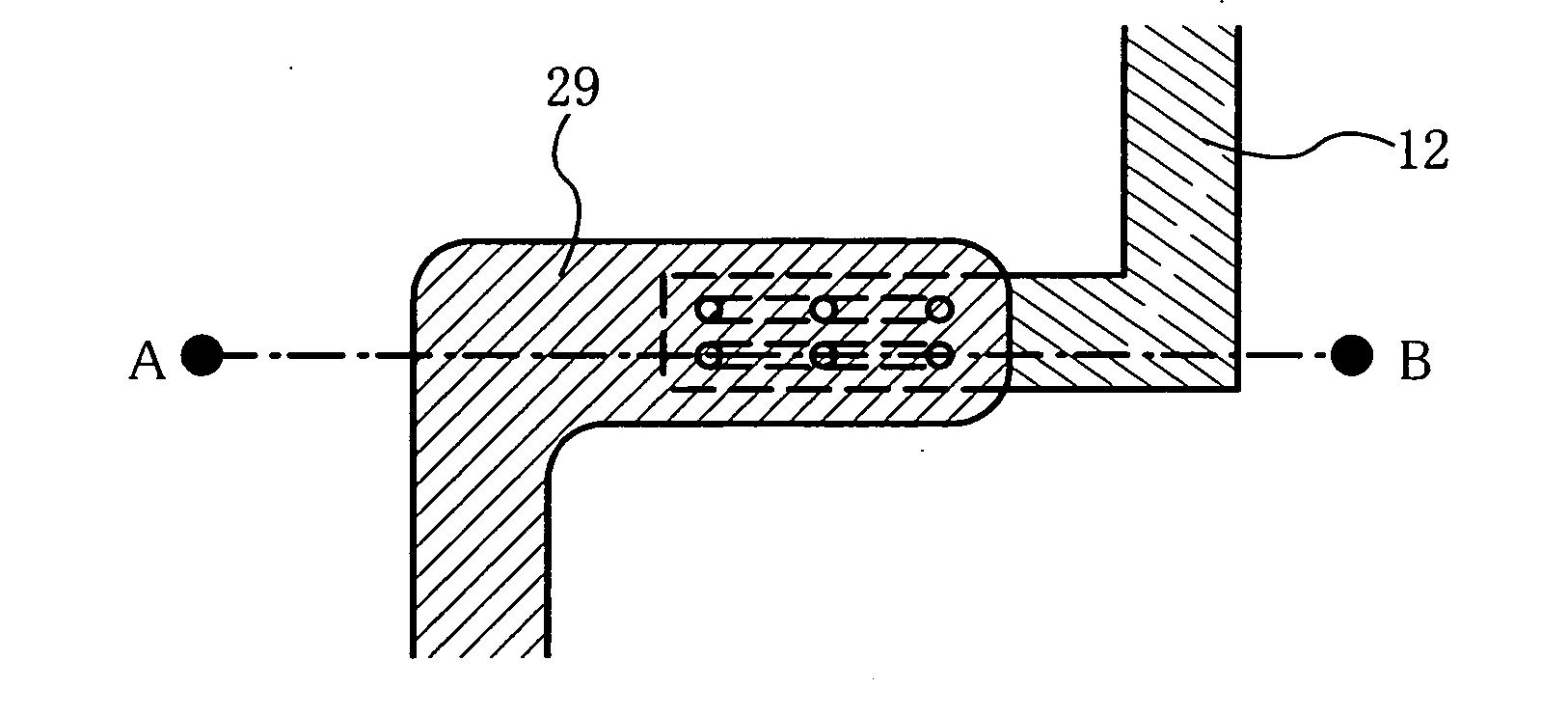

Semiconductor device and method for manufacturing the same, and electric device

InactiveUS20060163743A1Simple stepsHighly integratedSemiconductor/solid-state device detailsElectroluminescent light sourcesElectrical resistance and conductanceLongest Diameter

It is an object of the present invention to simplify steps needed to process a wiring in forming a multilayer wiring. In addition, when a droplet discharging technique or a nanoimprint technique is used to form a wiring in a contact hole having a comparatively long diameter, the wiring in accordance with the shape of the contact hole is formed, and the wiring portion of the contact hole is likely to have a depression compared with other portions. A penetrating opening is formed by irradiating a light-transmitting insulating film with laser light having high intensity and a pulse high in repetition frequency. A plurality of openings having a minute contact area is provided instead of forming one penetrating opening having a large contact area to have an even thickness of a wiring by reducing a partial depression and also to ensure contact resistance.

Owner:SEMICON ENERGY LAB CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com