Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

53results about How to "Reduced carrier mobility" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

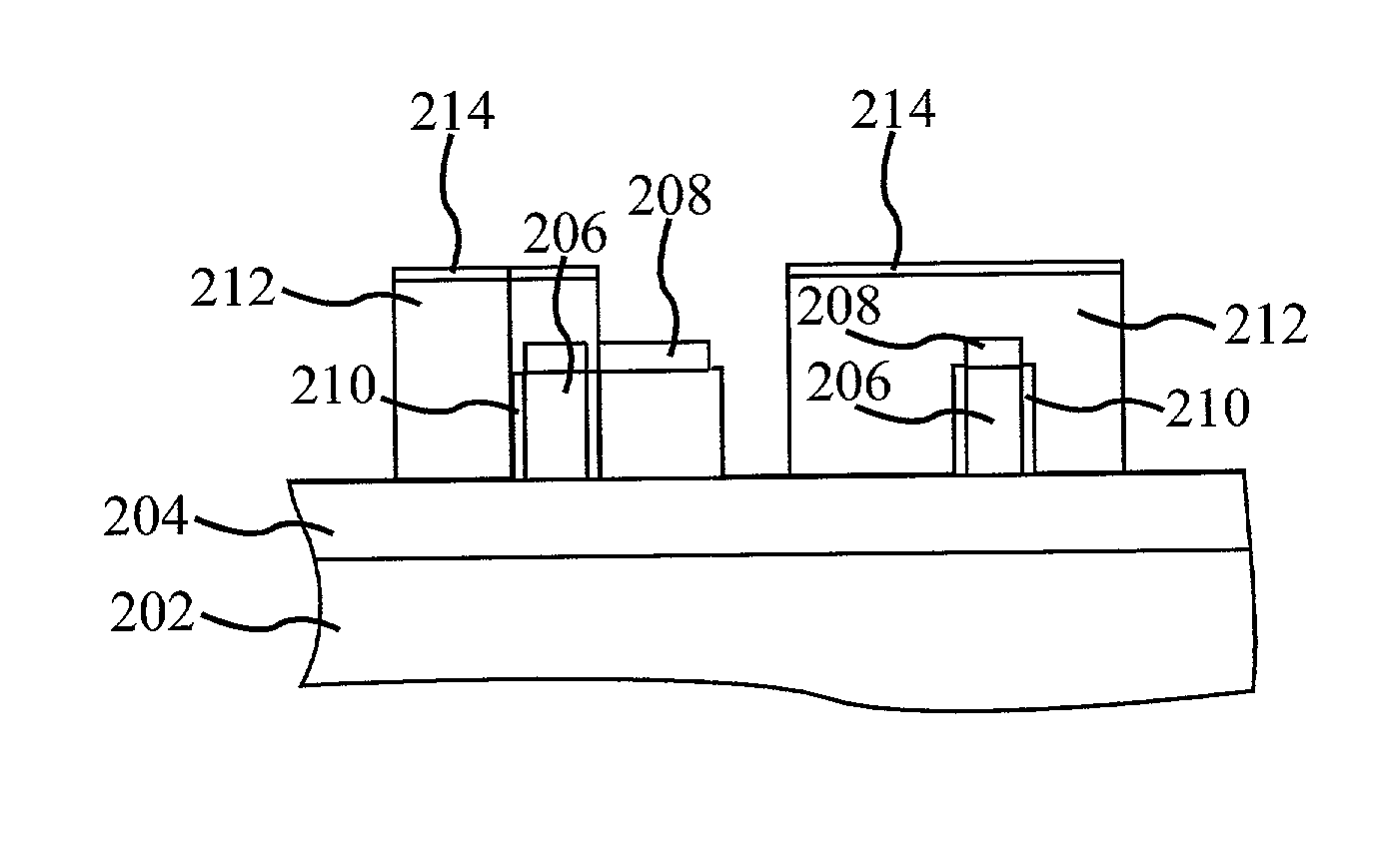

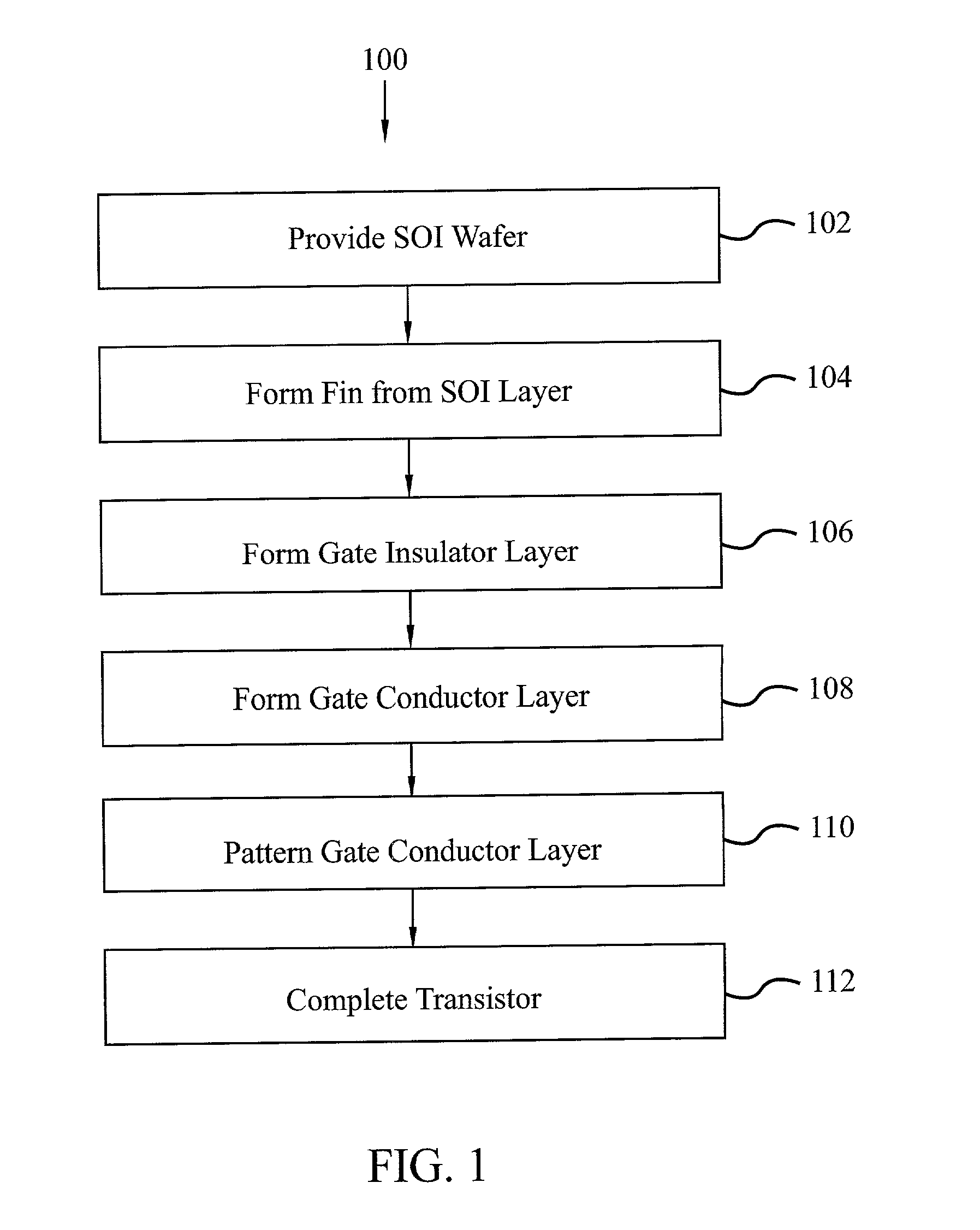

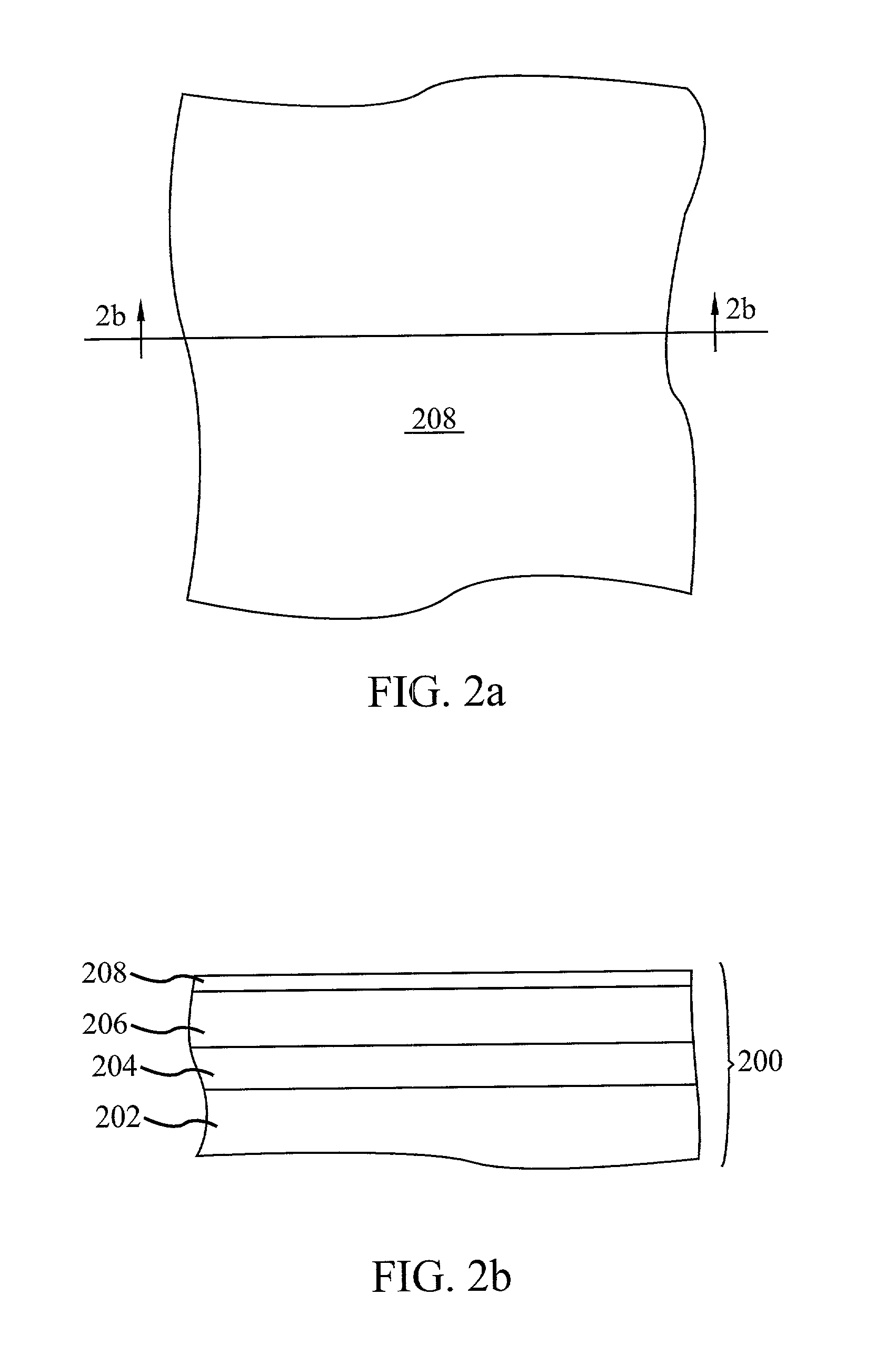

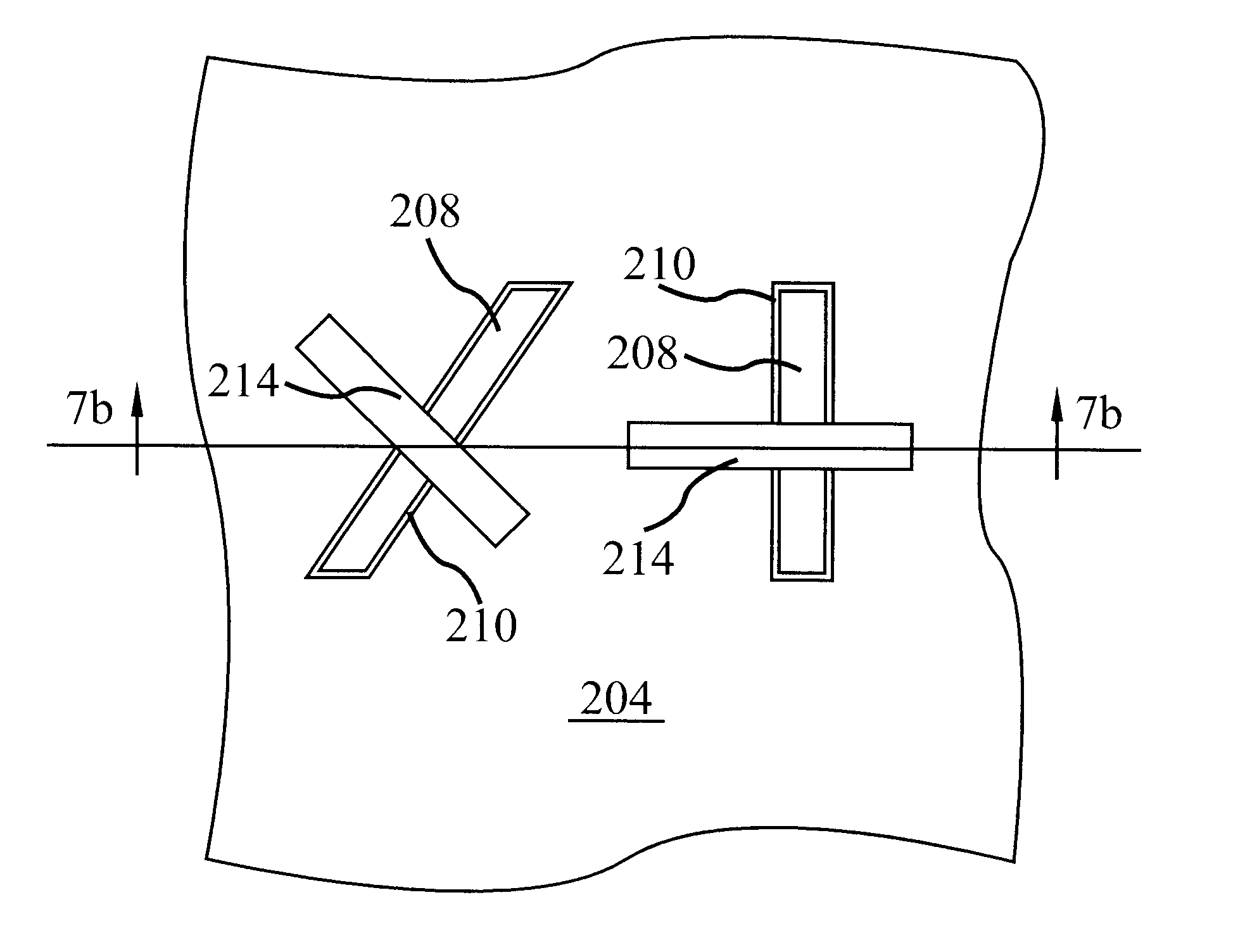

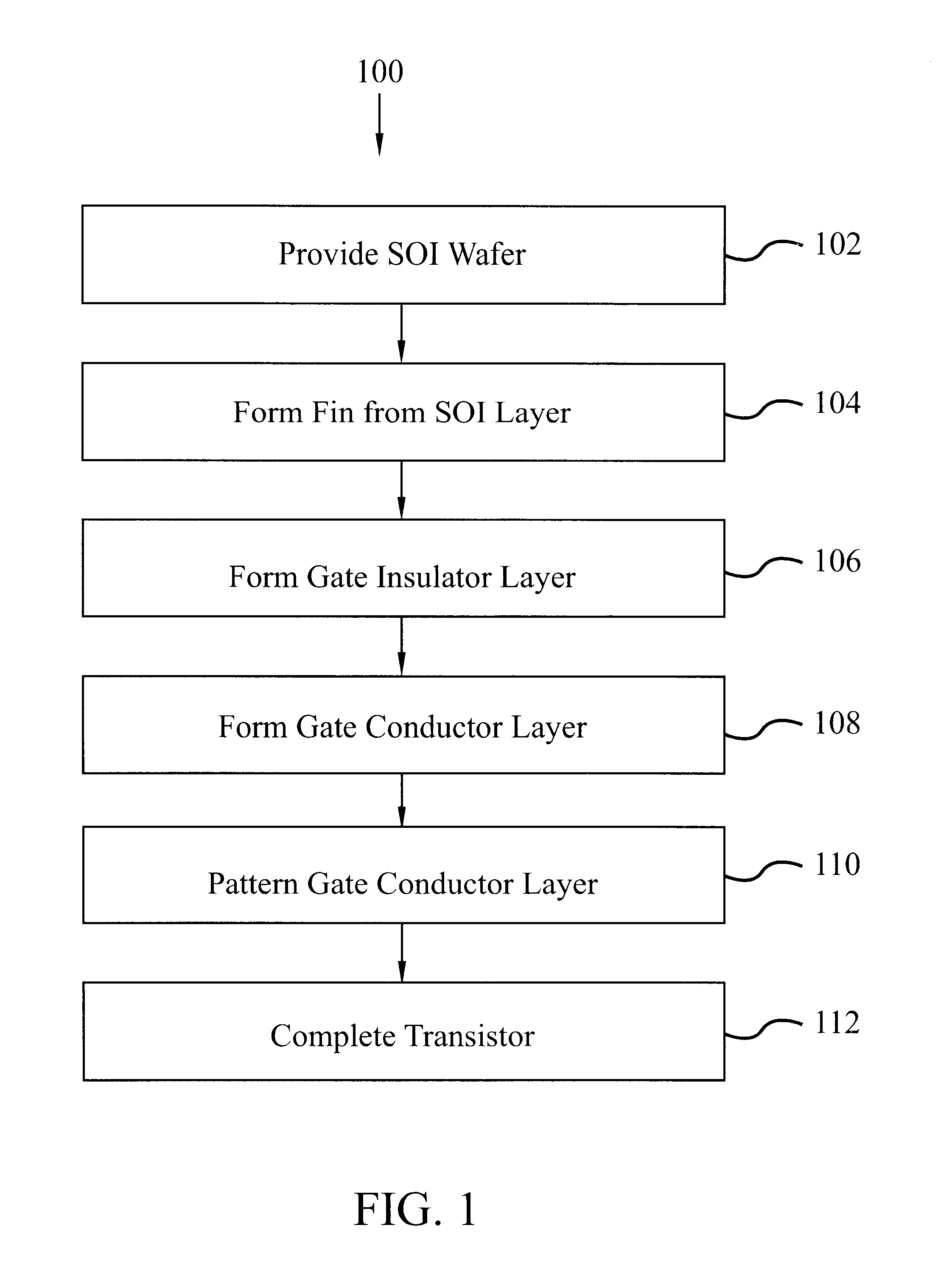

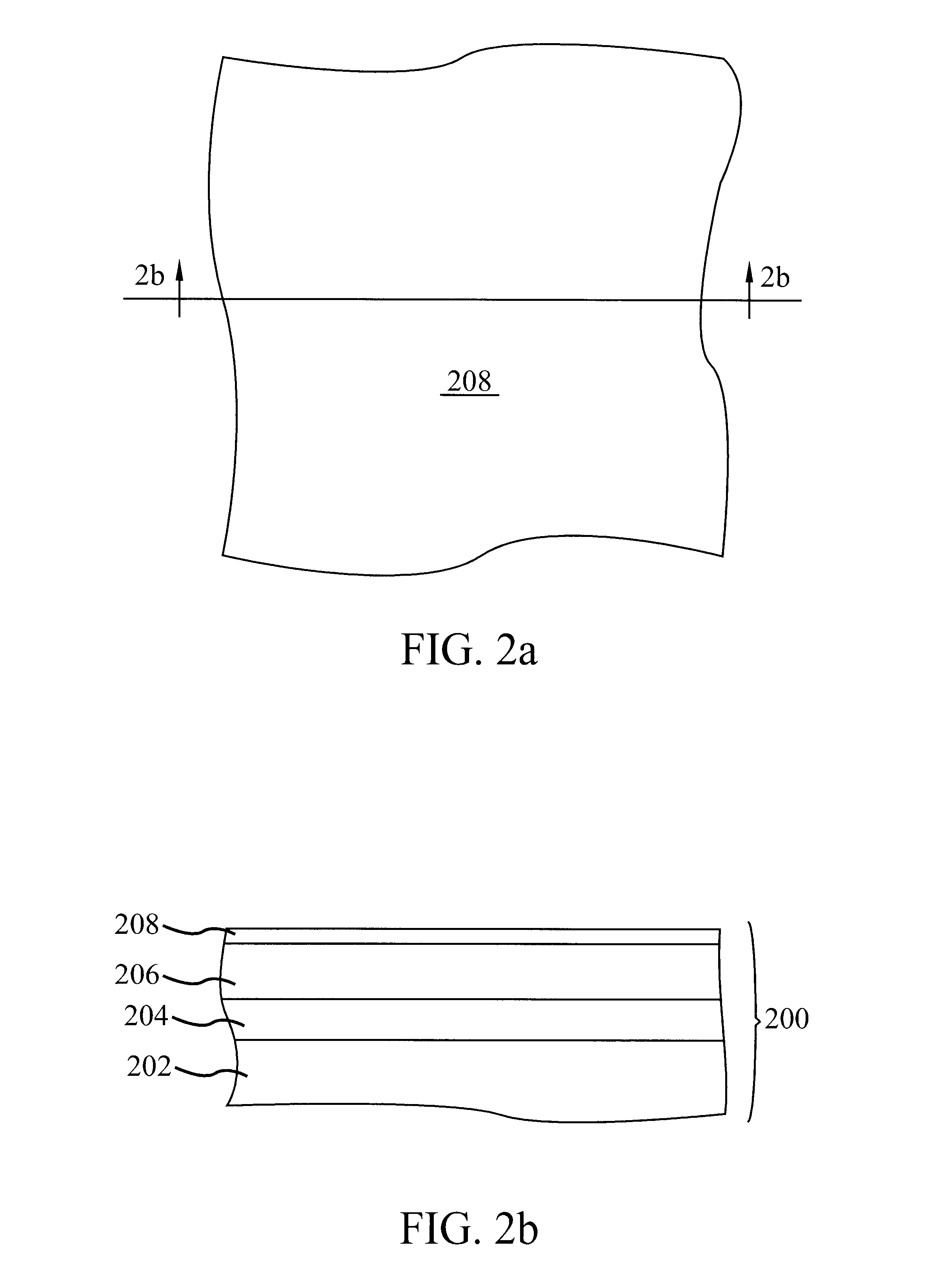

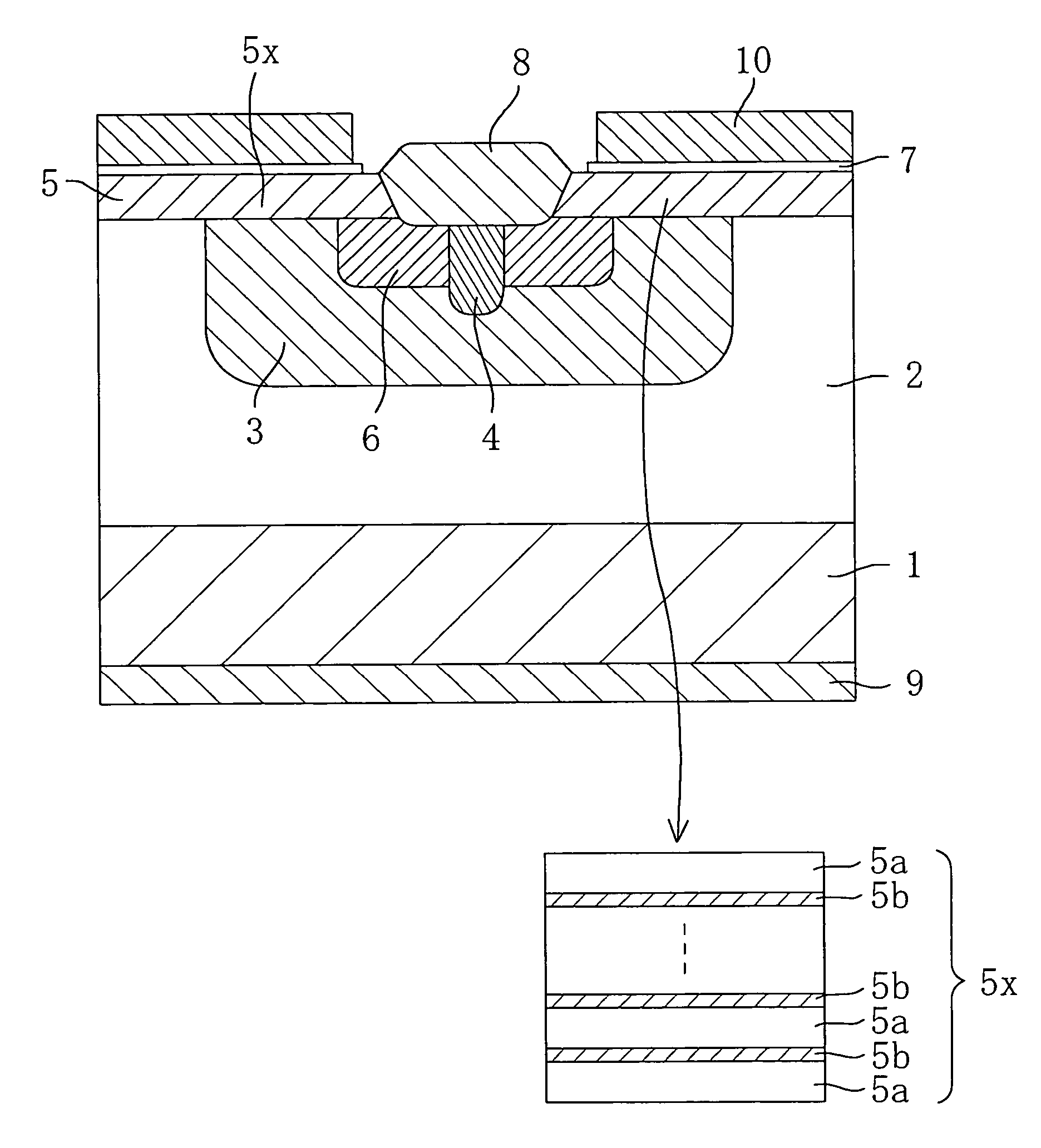

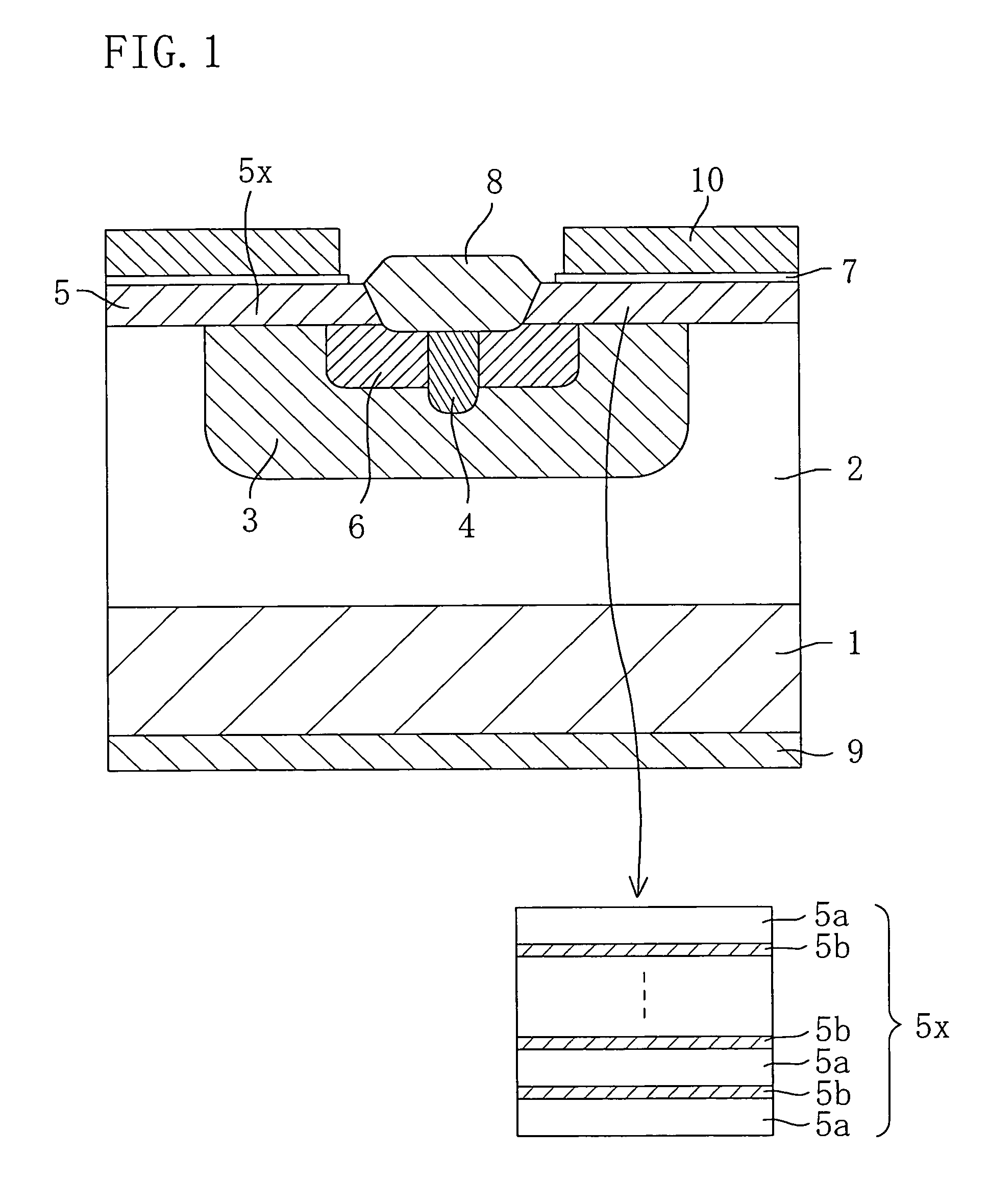

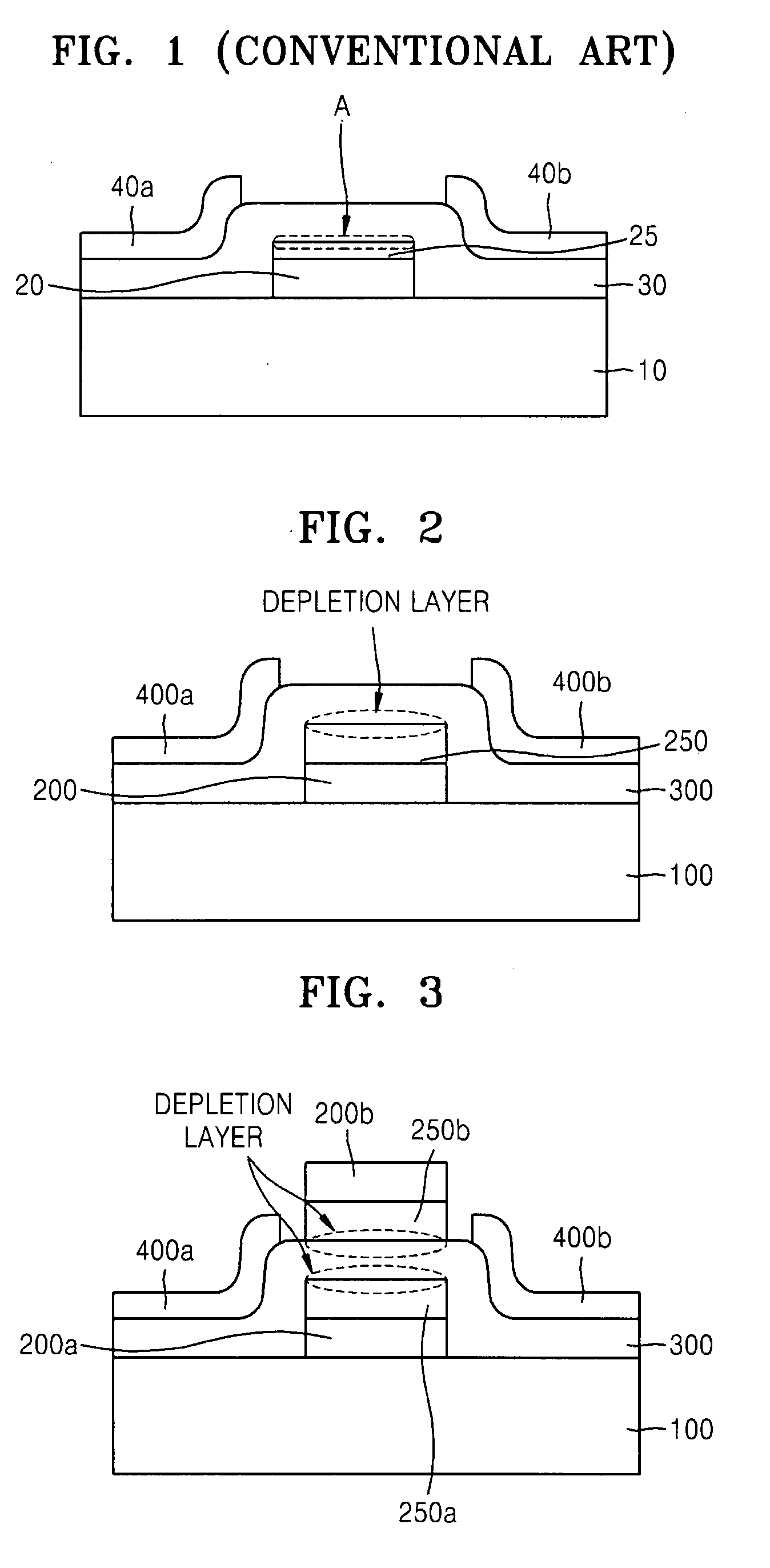

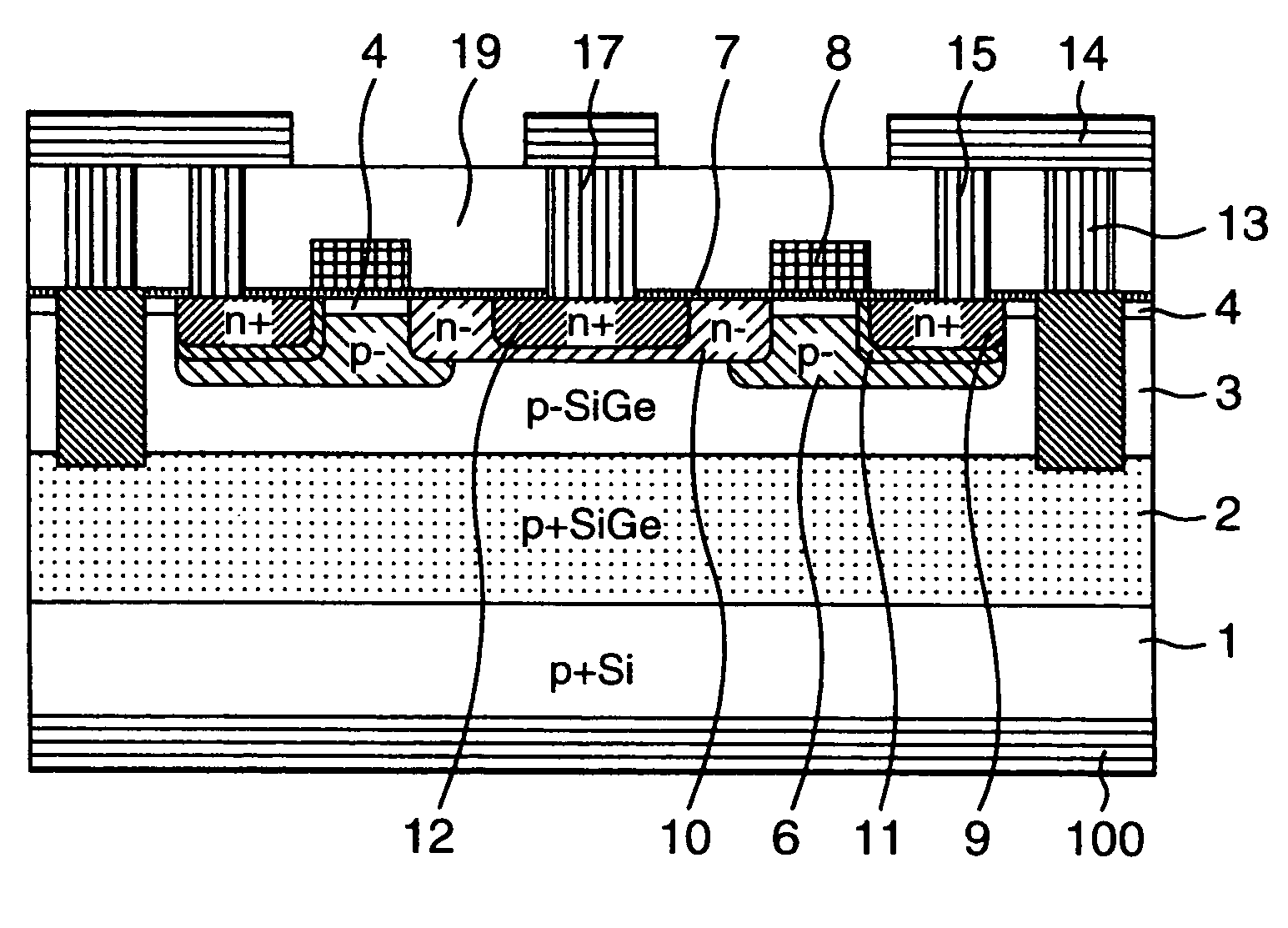

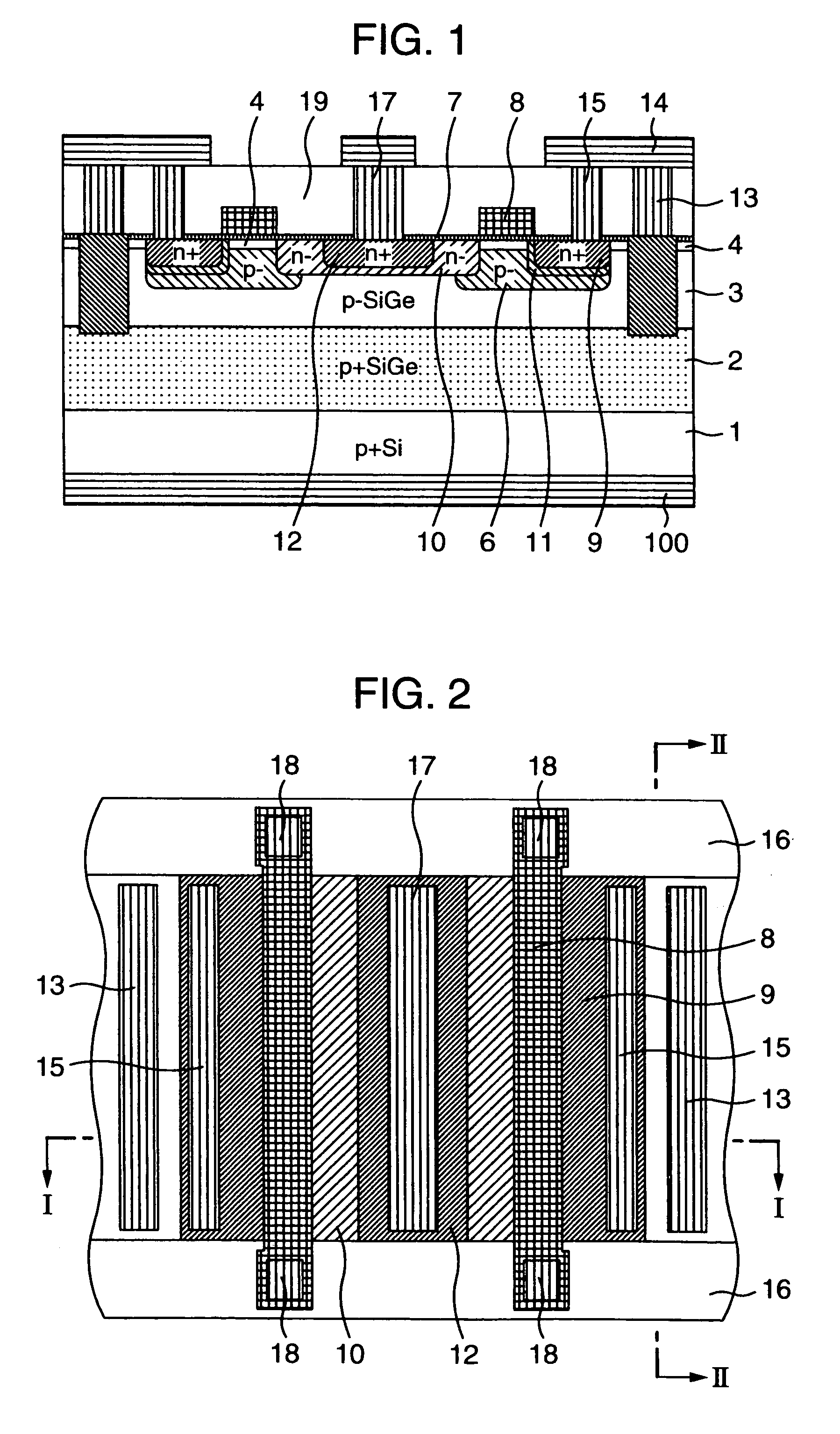

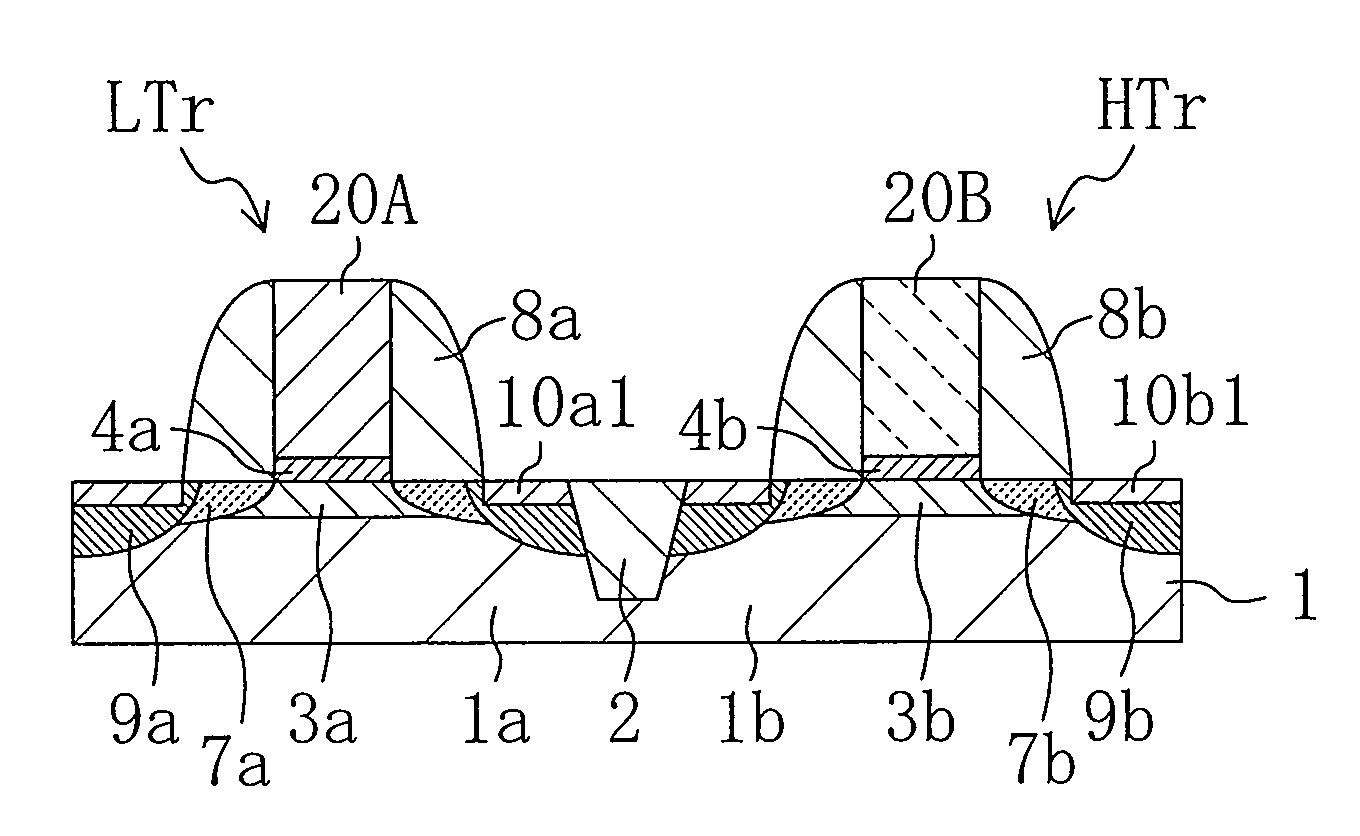

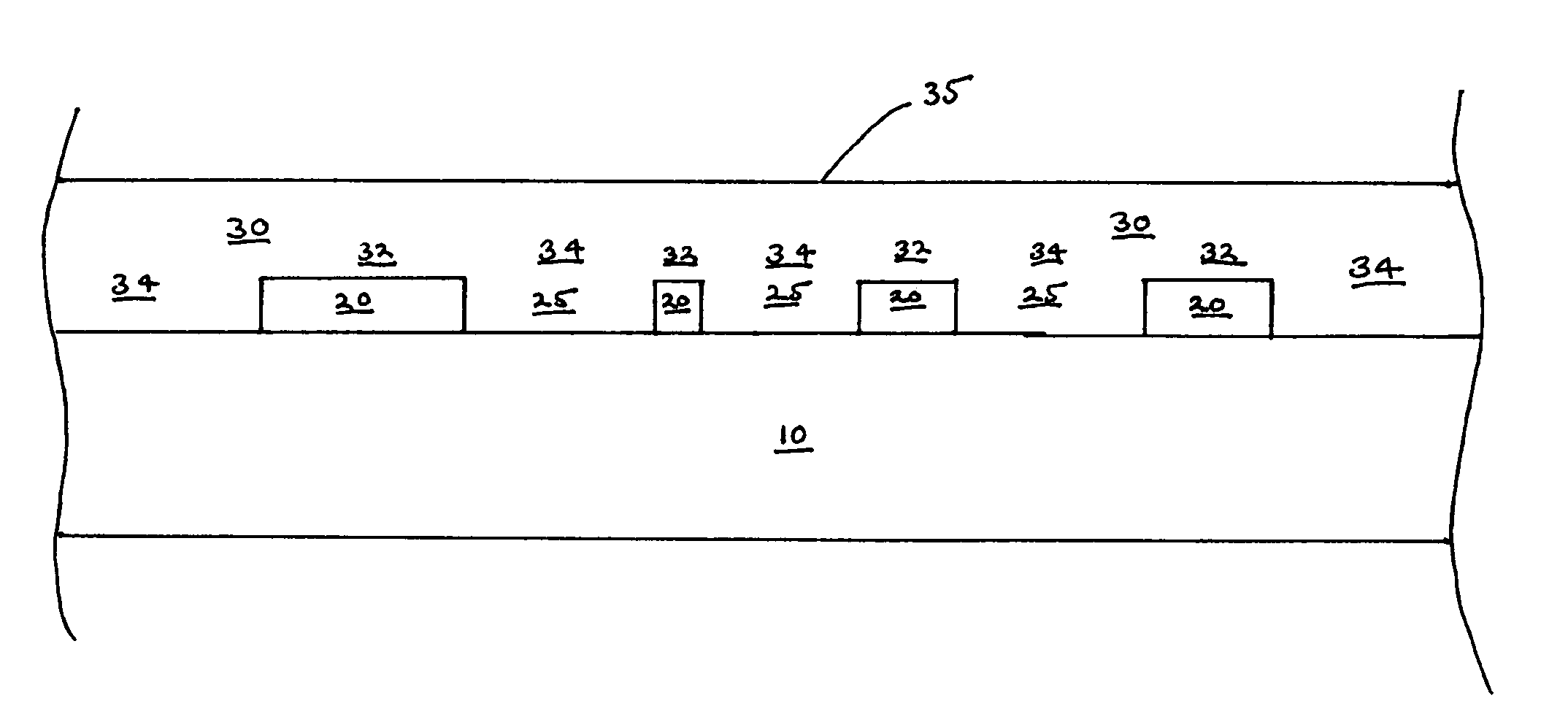

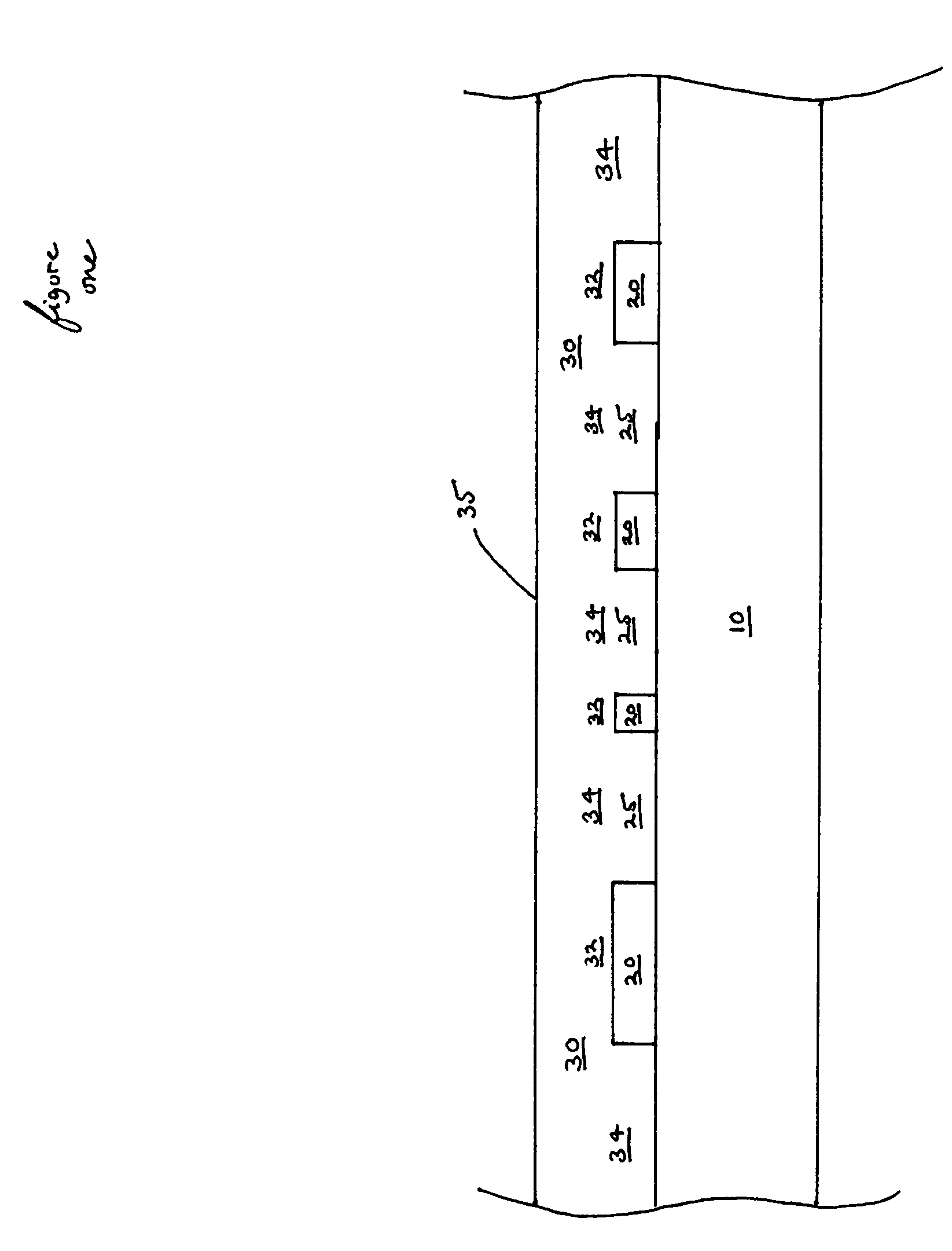

Multiple-plane finFET CMOS

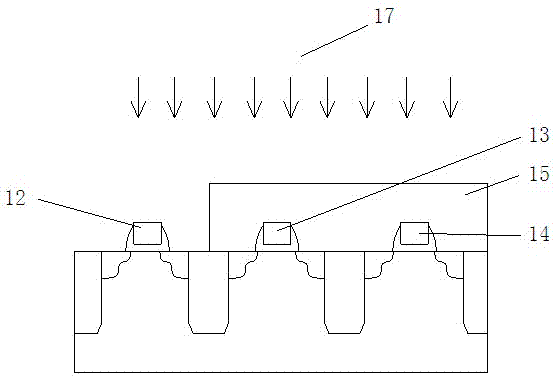

InactiveUS20030102497A1Improve mobilityReduced carrier mobilityTransistorSolid-state devicesCMOSCrystal plane

The present invention provides FinFETs on the same substrate utilizing various crystal planes for FET current channels in order to optimize mobility and / or to reduce mobility. An embodiment of the present invention provides a substrate having a surface oriented on a first crystal plane that enables subsequent crystal planes for channels to be utilized. A first transistor is also provided having a first fin body. The first fin body has a sidewall forming a first channel, the sidewall oriented on a second crystal plane to provide a first carrier mobility. A second transistor is also provided having a second fin body. The second fin body has a sidewall forming a second channel, the sidewall oriented on a third crystal plane to provide a second carrier mobility that is different from the first carrier mobility.

Owner:GLOBALFOUNDRIES US INC

Multiple-plane FinFET CMOS

InactiveUS6657259B2Improve mobilityReduced carrier mobilityTransistorSolid-state devicesCMOSCurrent channel

The present invention provides FinFETs on the same substrate utilizing various crystal planes for FET current channels in order to optimize mobility and / or to reduce mobility. An embodiment of the present invention provides a substrate having a surface oriented on a first crystal plane that enables subsequent crystal planes for channels to be utilized. A first transistor is also provided having a first fin body. The first fin body has a sidewall forming a first channel, the sidewall oriented on a second crystal plane to provide a first carrier mobility. A second transistor is also provided having a second fin body. The second fin body has a sidewall forming a second channel, the sidewall oriented on a third crystal plane to provide a second carrier mobility that is different from the first carrier mobility.

Owner:GLOBALFOUNDRIES U S INC

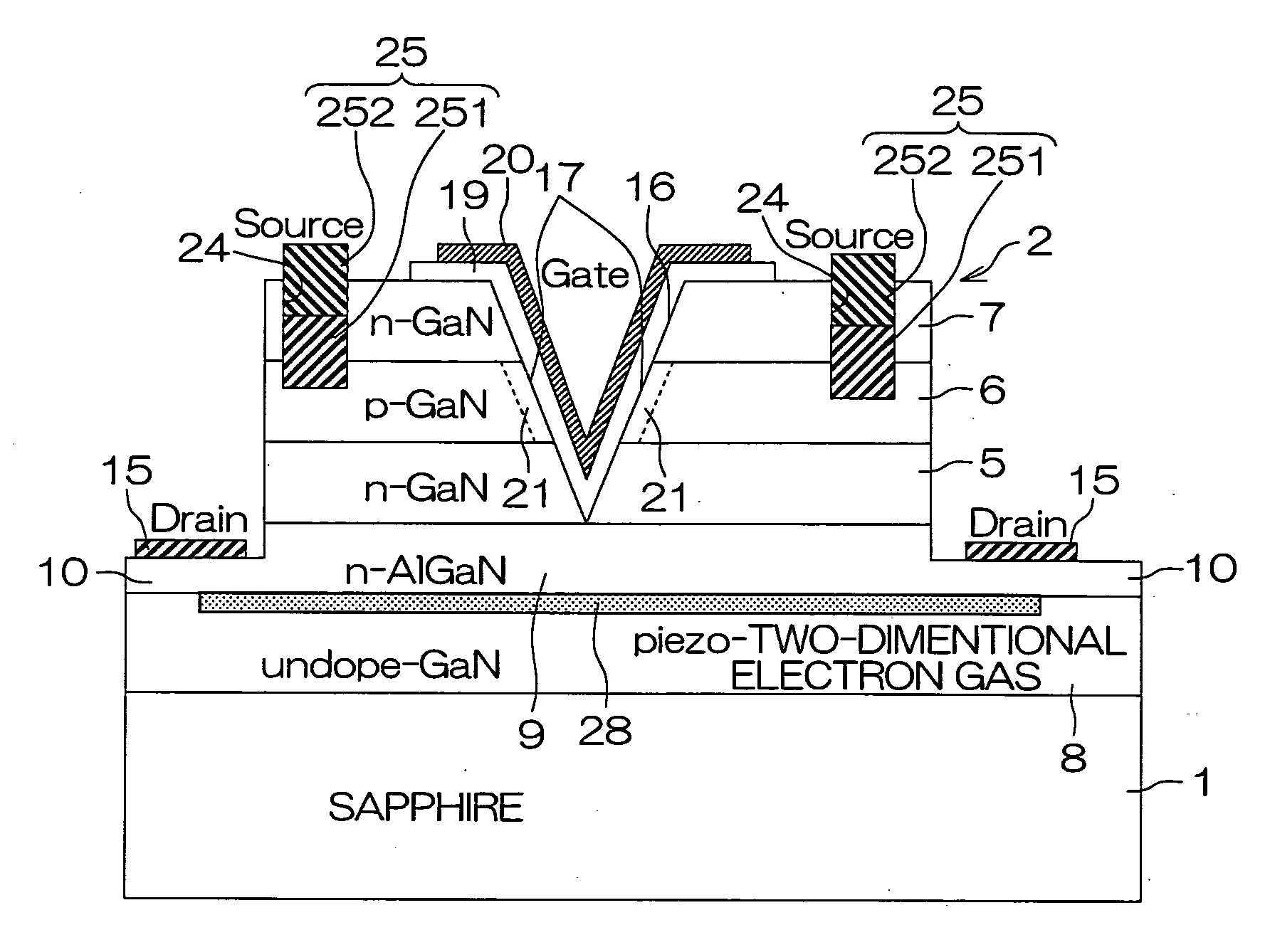

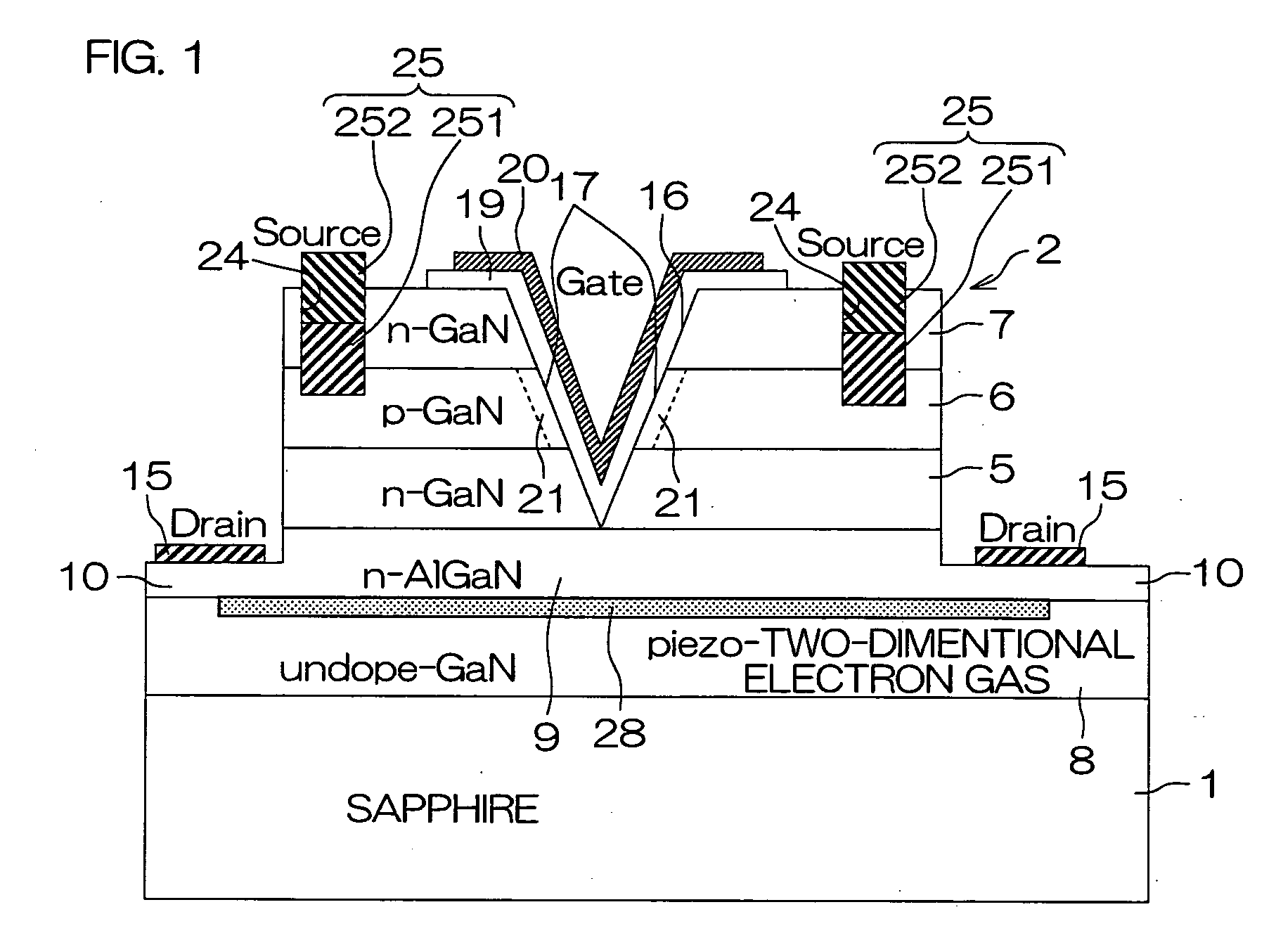

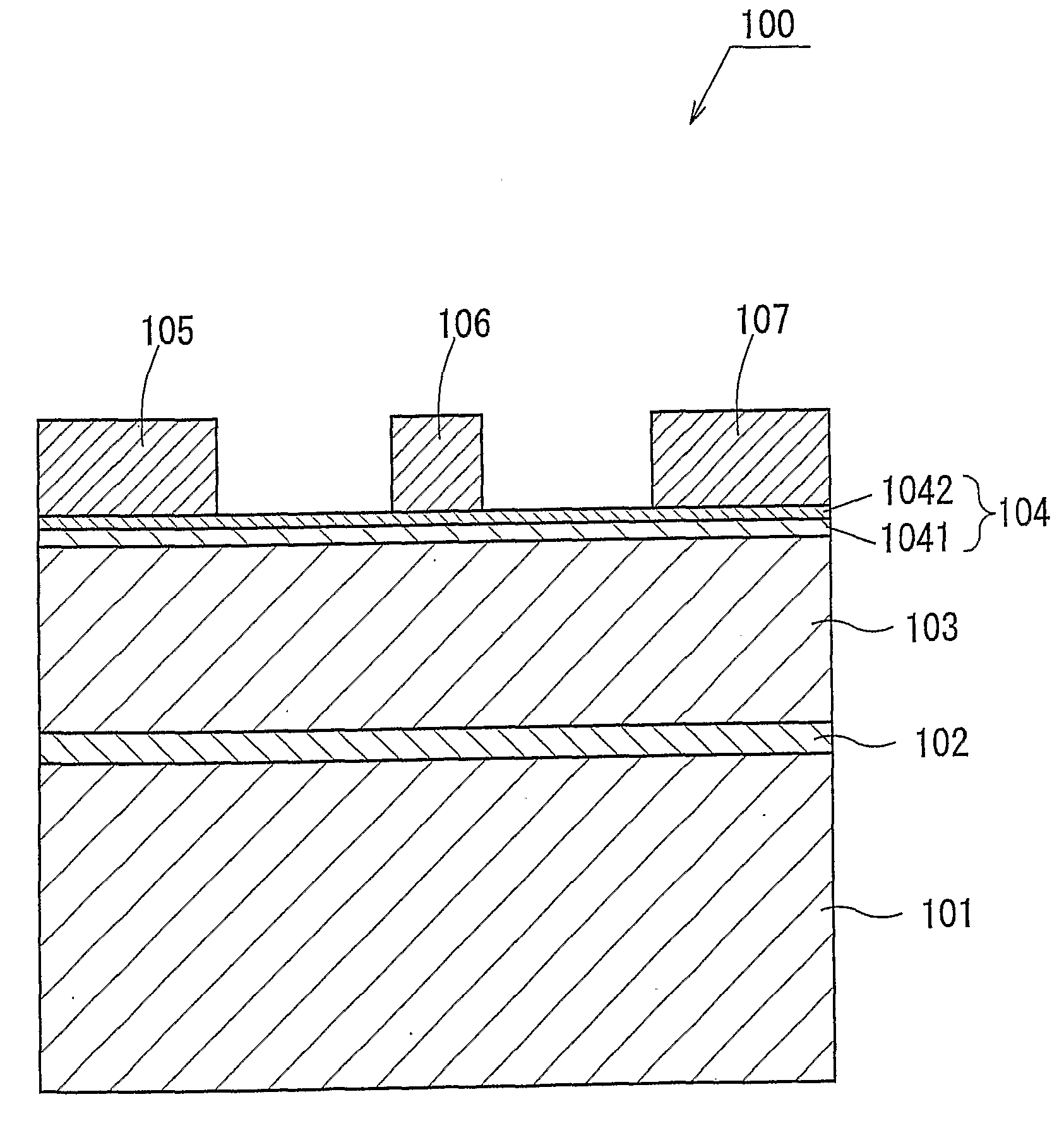

Semiconductor device and method for manufacturing the same

ActiveUS20100006894A1EffectiveHigh currentSemiconductor devicesConductive materialsMaterials science

The semiconductor device includes a P-type group III-V nitride semiconductor layer, an N-type group III-V nitride semiconductor layer, and an electrode in contact with both of the P-type group III-V nitride semiconductor layer and the N-type group III-V nitride semiconductor layer. The electrode includes a first electrode portion made of a first conductive material, and a second electrode portion, made of a second conductive material different from the first conductive material, bonded to the first electrode portion. The first electrode portion is in contact with the P-type group III-V nitride semiconductor layer, and the second electrode portion is in contact with the N-type group III-V nitride semiconductor layer.

Owner:ROHM CO LTD

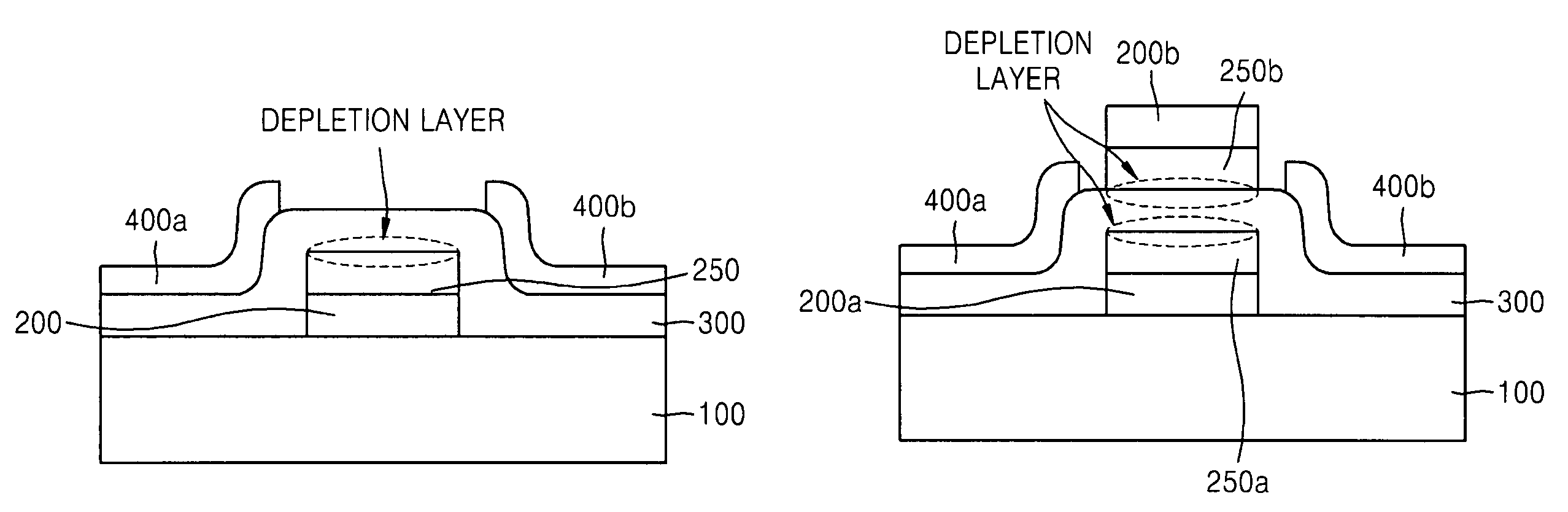

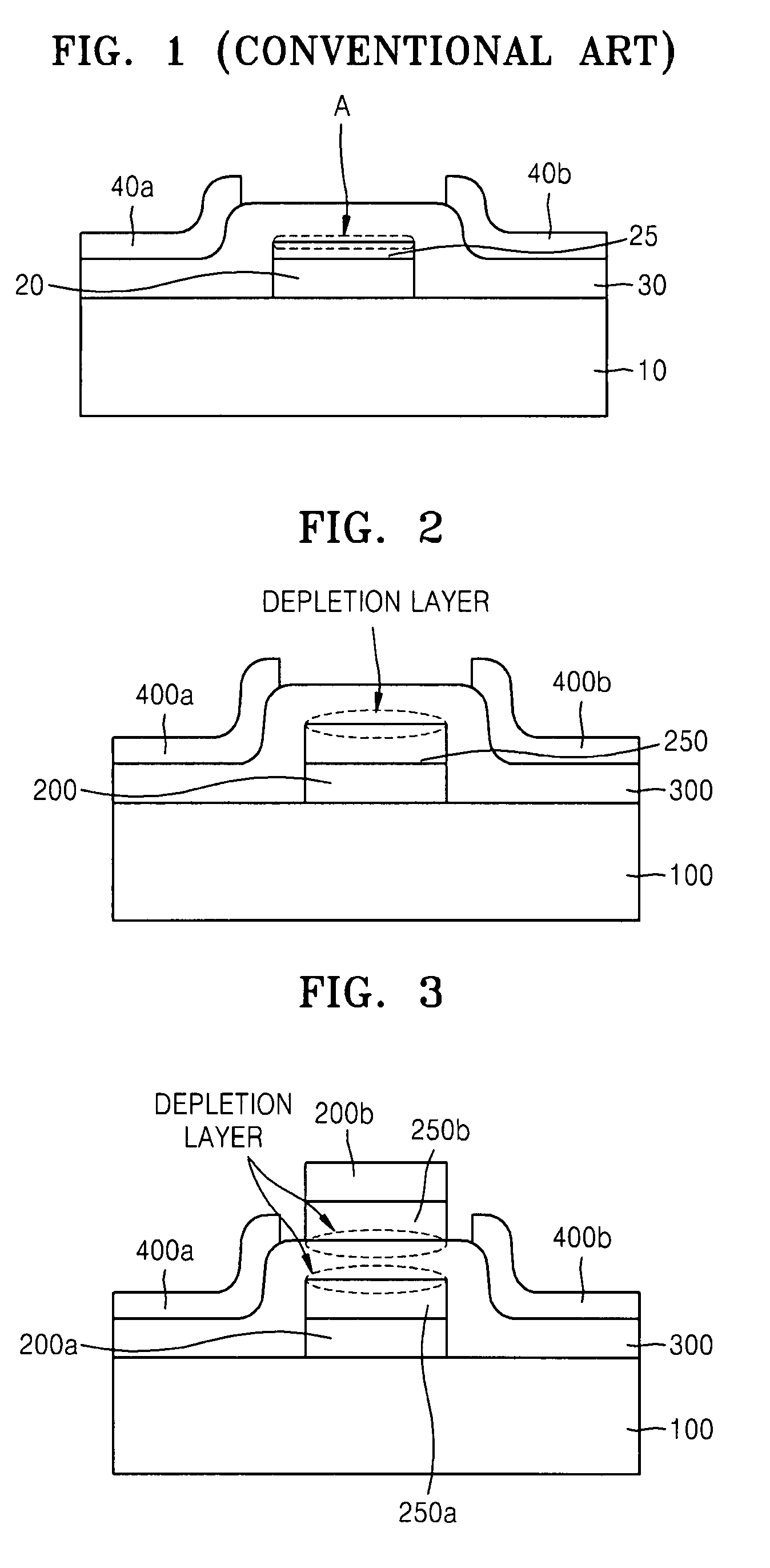

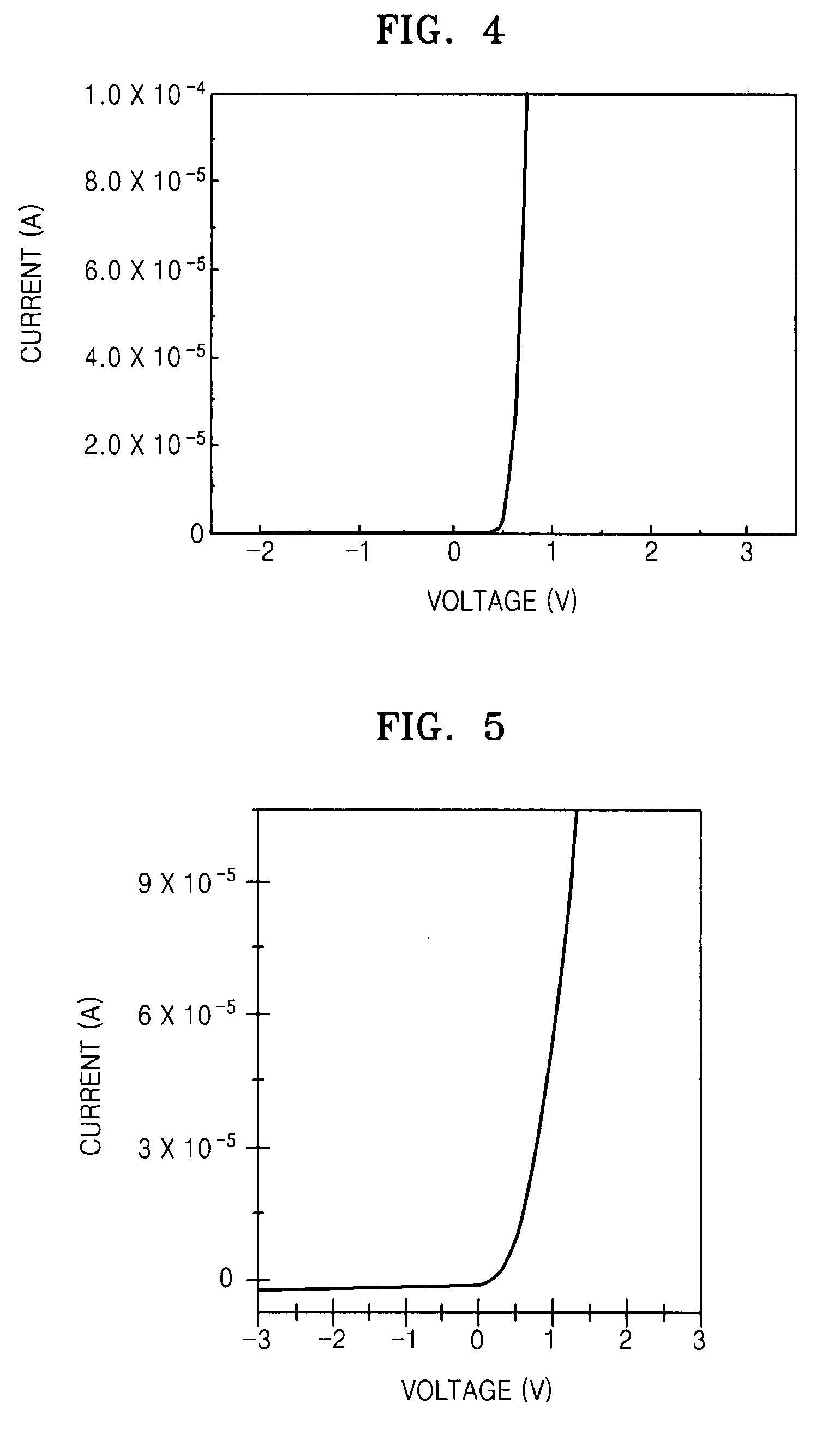

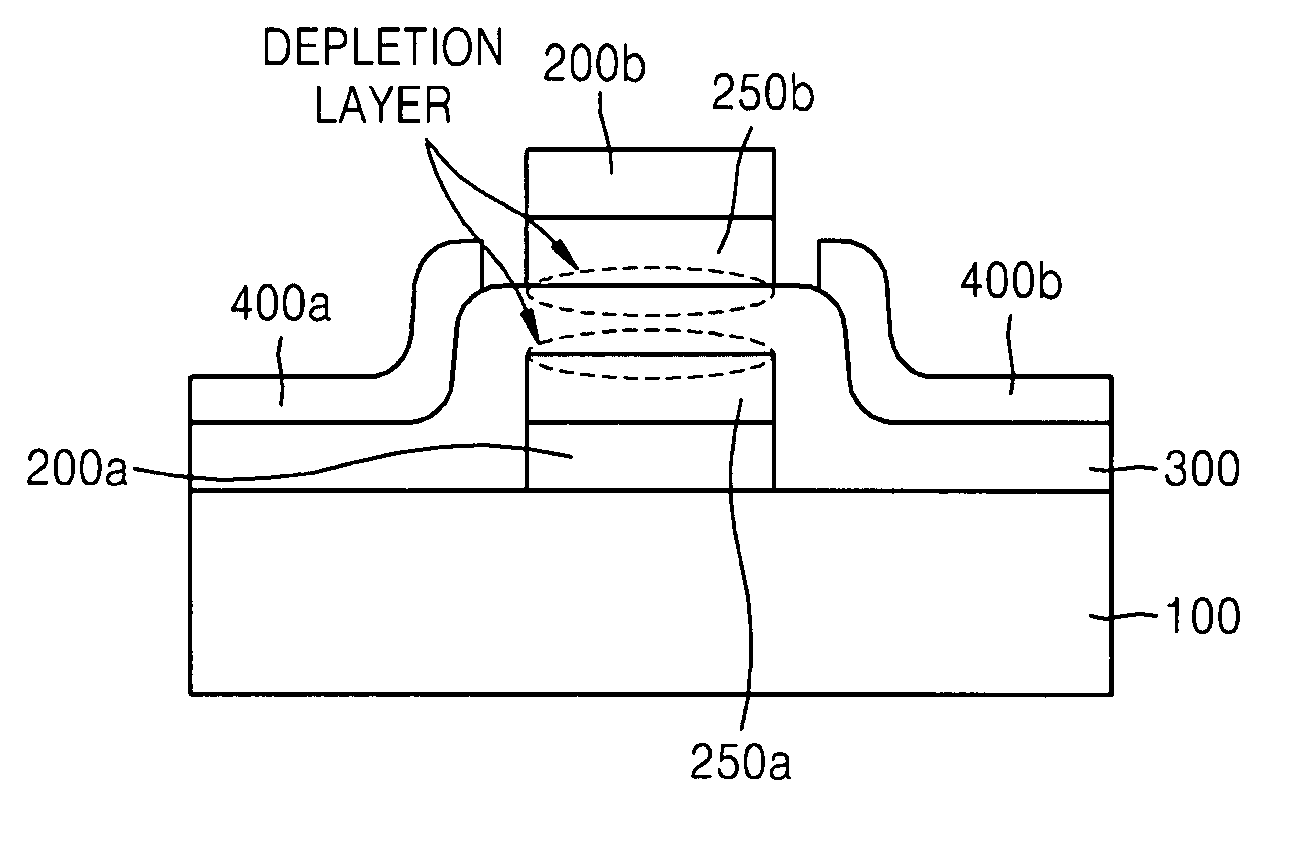

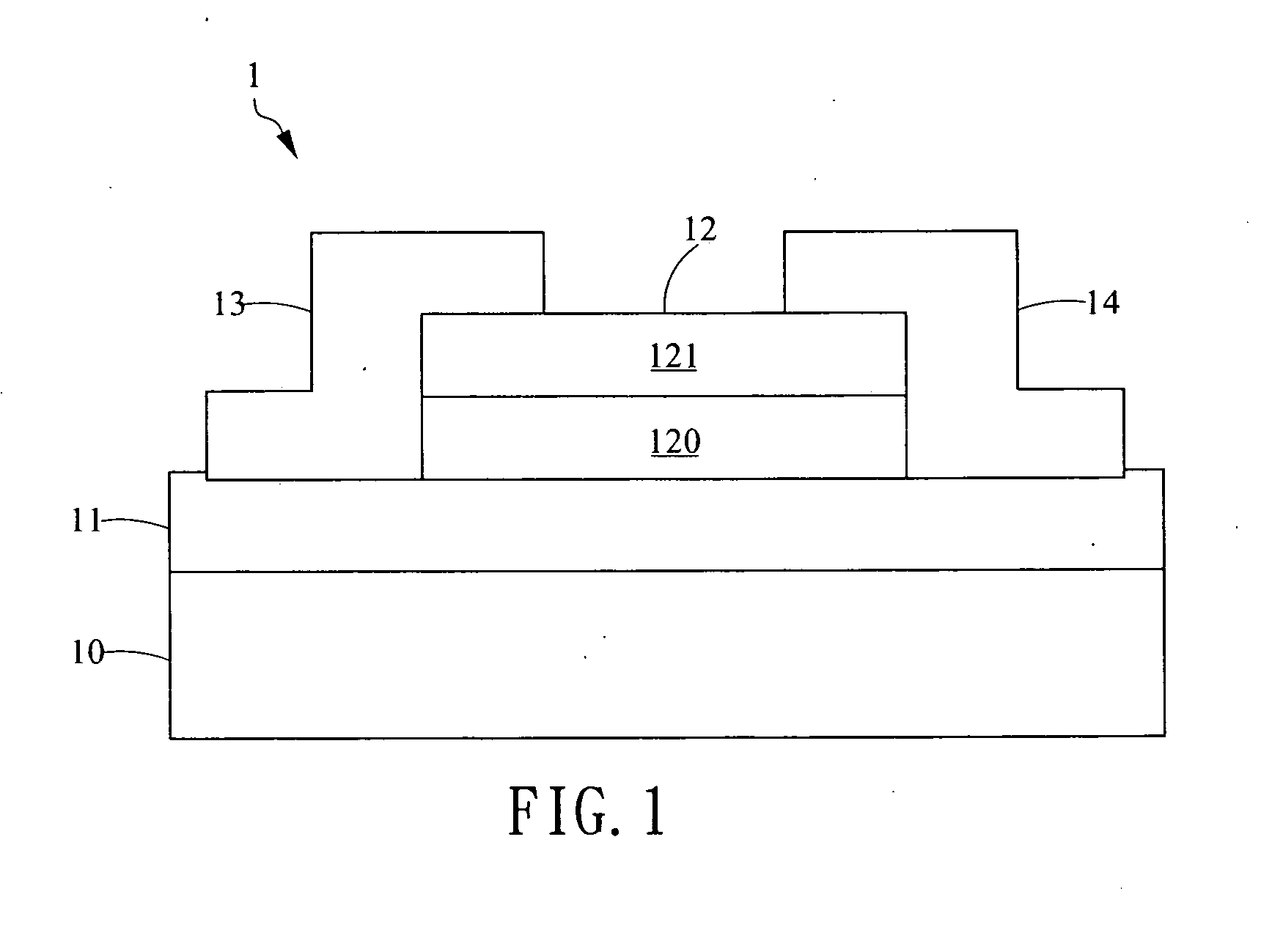

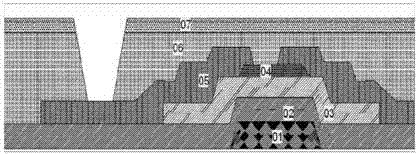

Junction field effect thin film transistor

ActiveUS7491987B2Reduced carrier mobilityTransistorSemiconductor/solid-state device manufacturingSemiconductorTransistor

Example embodiments are directed to a junction field effect thin film transistor (JFETFT) including a first electrode formed on a substrate, a first conductive first gate semiconductor pattern formed on the first gate electrode, a second conductive semiconductor channel layer formed on the substrate and the first conductive first gate semiconductor pattern, and source and drain electrodes formed on the second conductive semiconductor pattern and located at both sides of the first conductive gate semiconductor pattern. The JFETFT may further include a first conductive second gate semiconductor pattern formed on a portion of the second conductive semiconductor channel layer between the source electrode and the drain electrode, and a second gate electrode formed on the first conductive second gate semiconductor pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

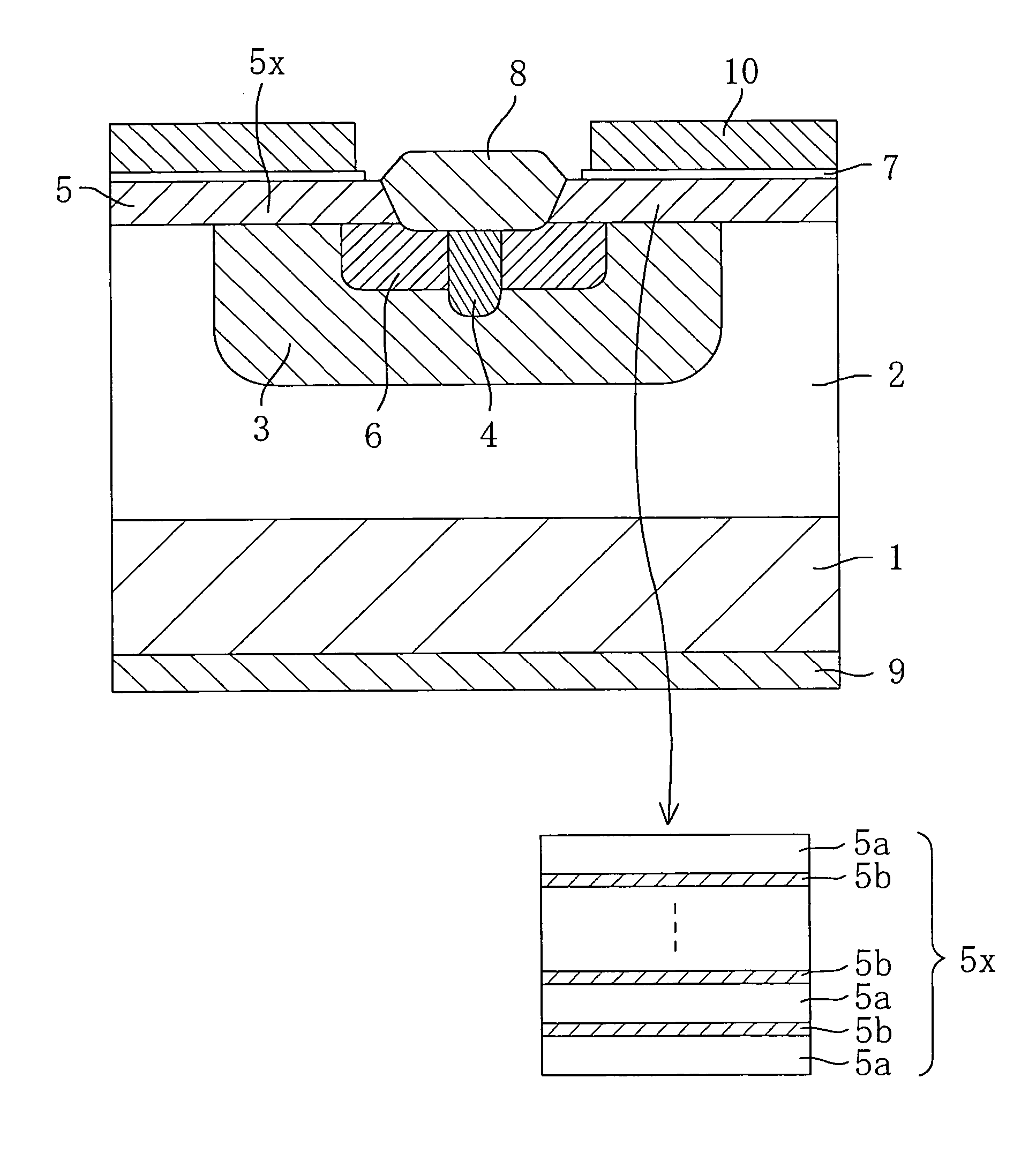

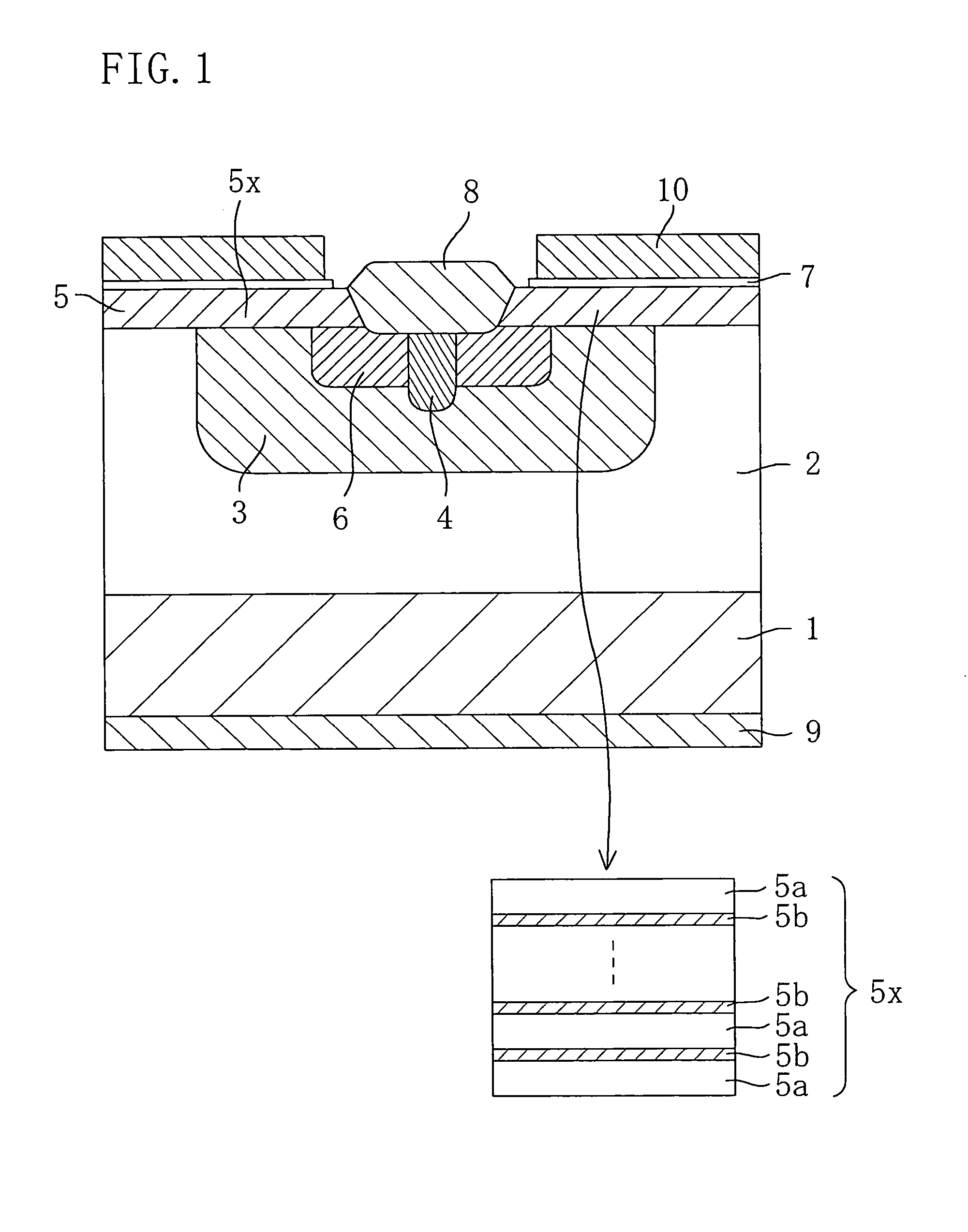

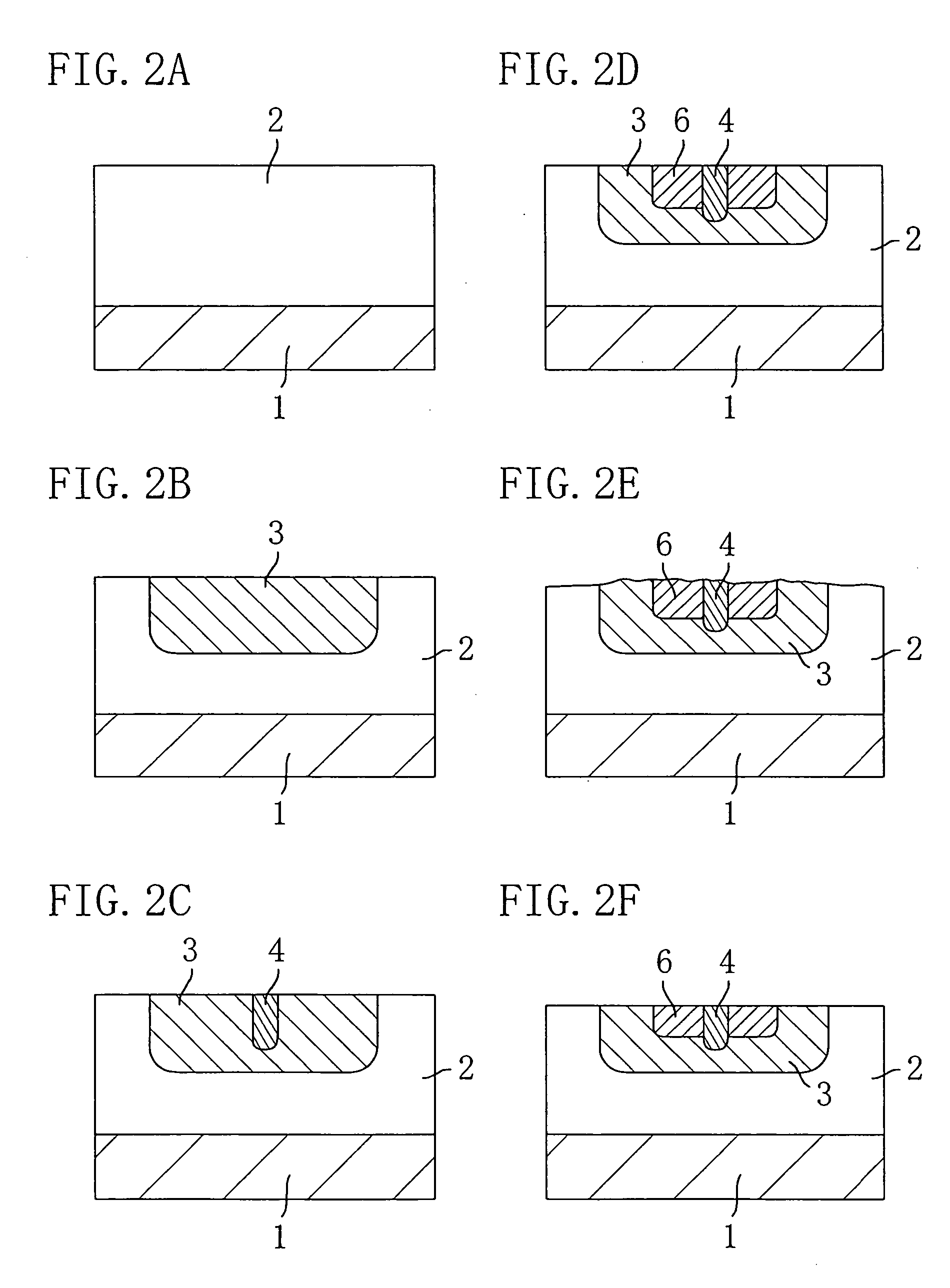

Semiconductor device and method for fabricating the same

ActiveUS20050001217A1Reduced carrier mobilityHigh carrier mobilityTransistorSemiconductor/solid-state device manufacturingHigh resistanceCarbon film

Ion implantation is carried out to form a p-well region and a source region in parts of a high resistance SiC layer on a SiC substrate, and a carbon film is deposited over the substrate. With the carbon film deposited over the substrate, annealing for activating the implanted dopant ions is performed, and then the carbon film is removed. Thus, a smooth surface having hardly any surface roughness caused by the annealing is obtained. Furthermore, if a channel layer is epitaxially grown, the surface roughness of the channel layer is smaller than that of the underlying layer. Since the channel layer having a smooth surface is provided, it is possible to obtain a MISFET with a high current drive capability.

Owner:PANASONIC CORP

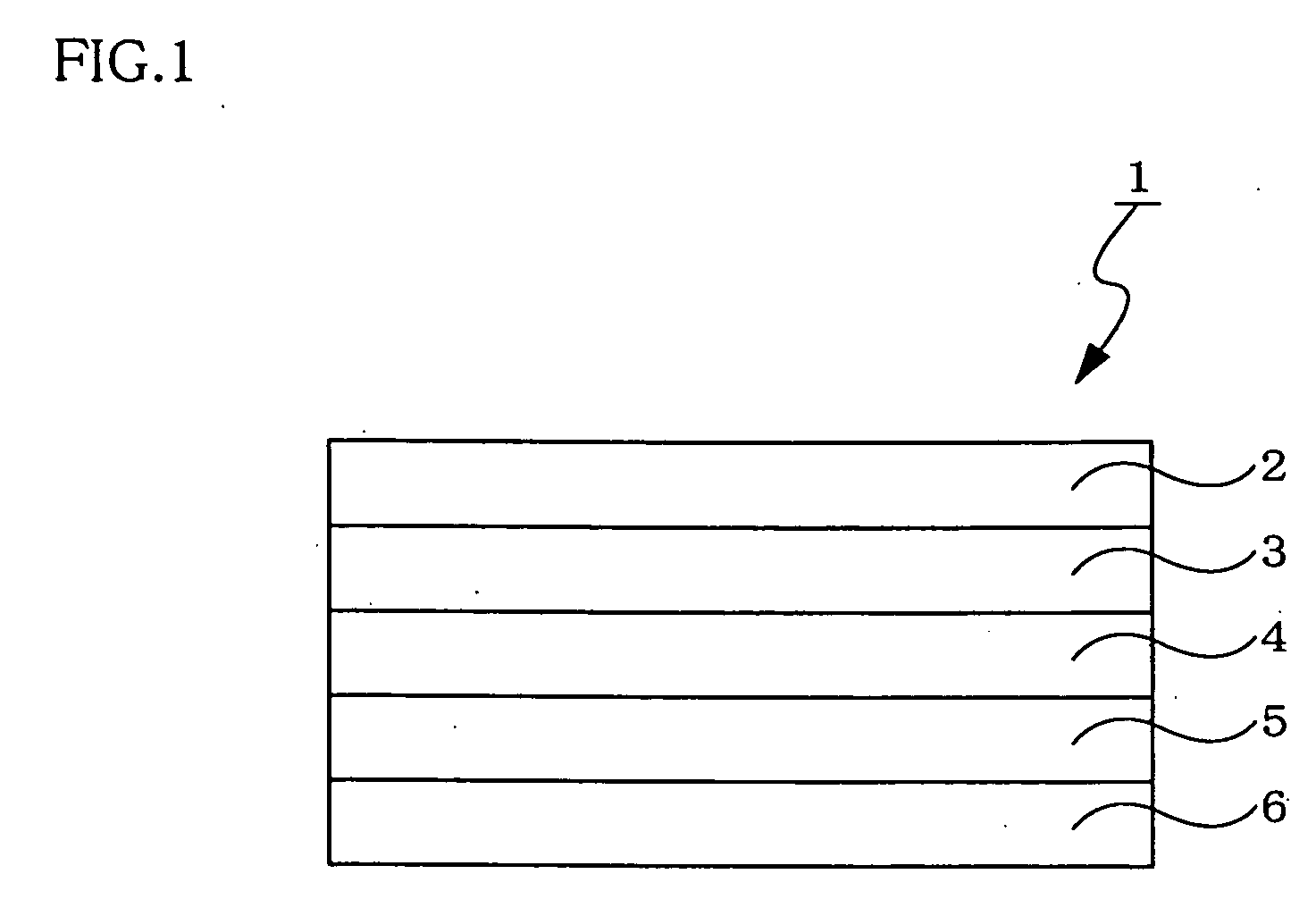

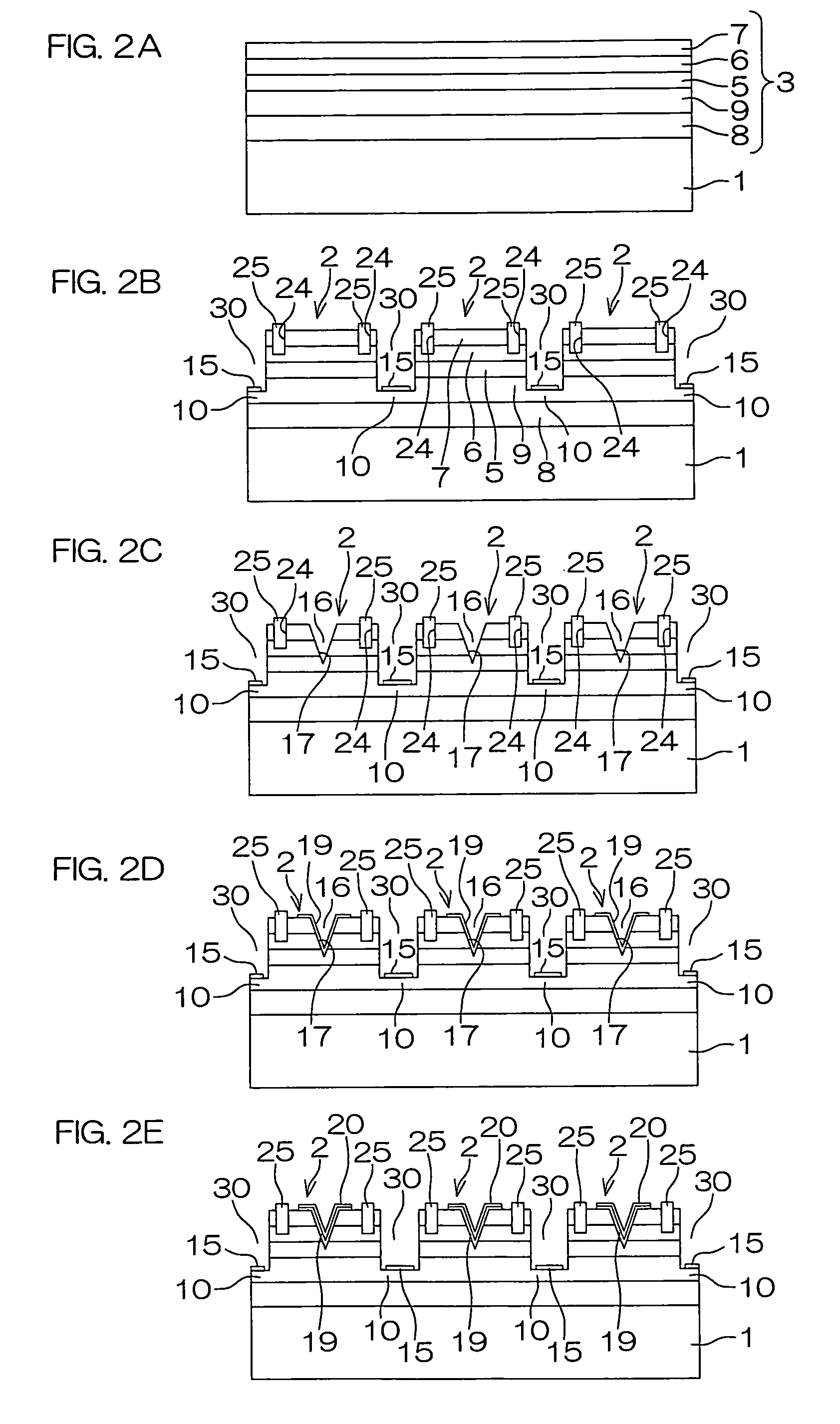

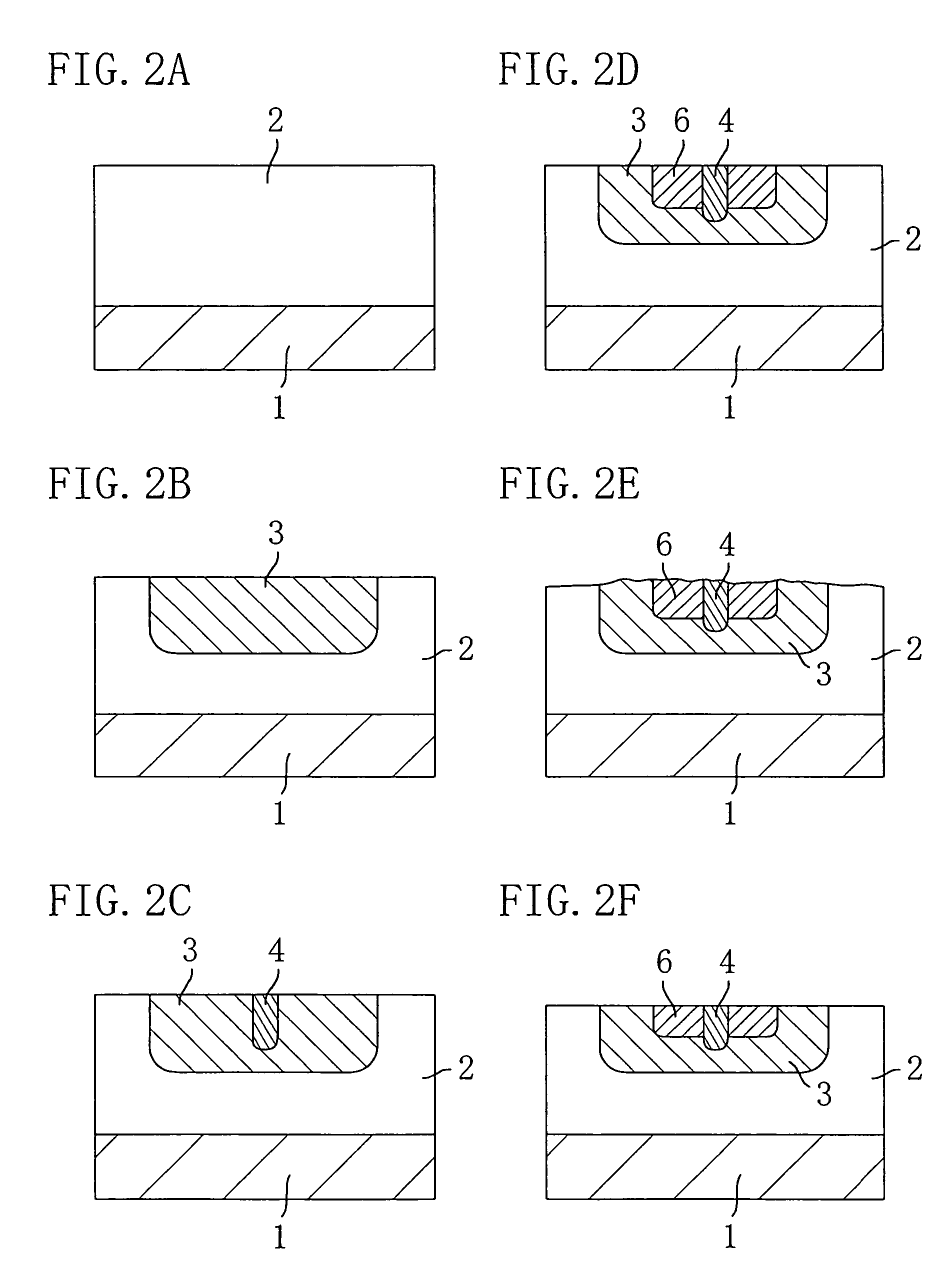

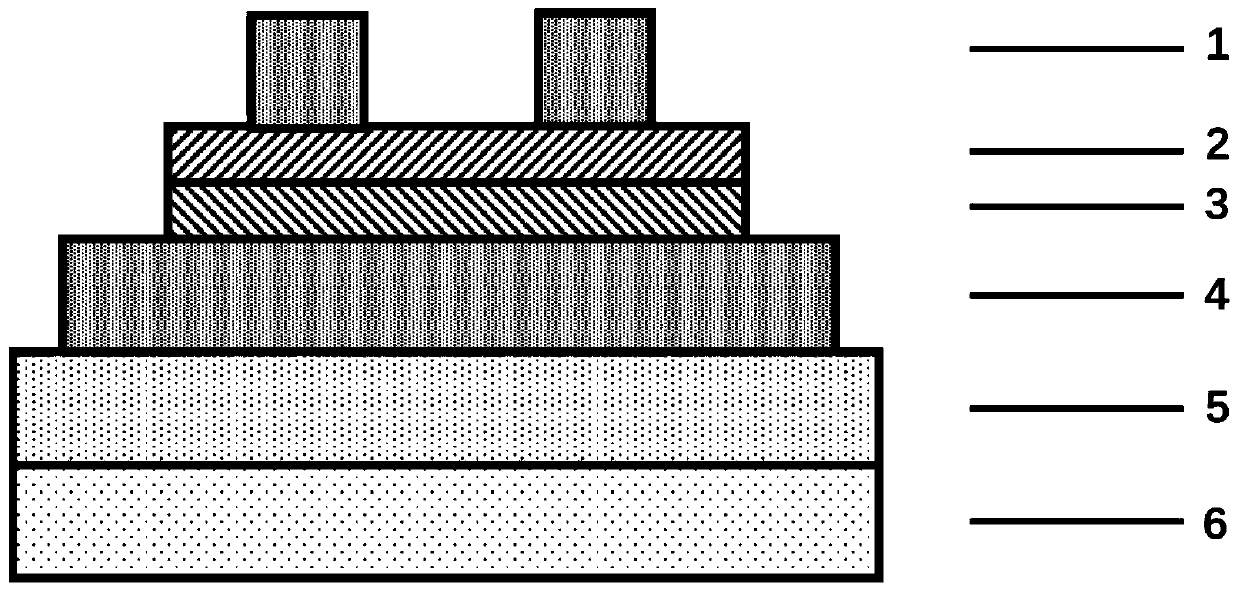

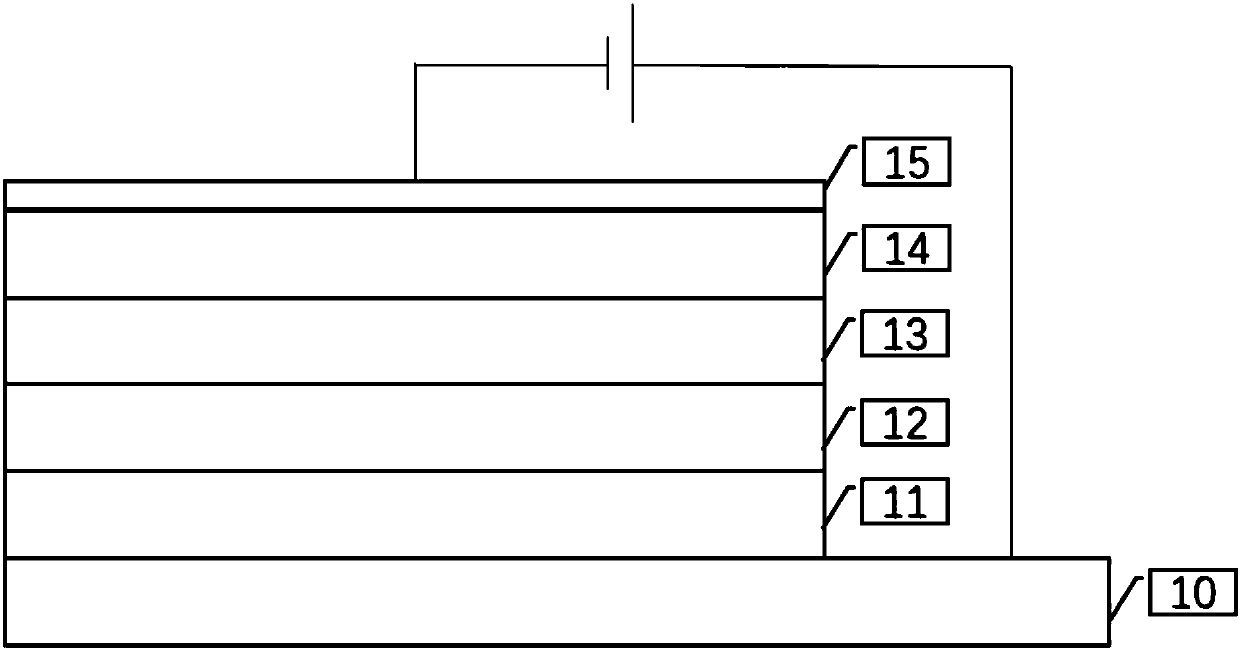

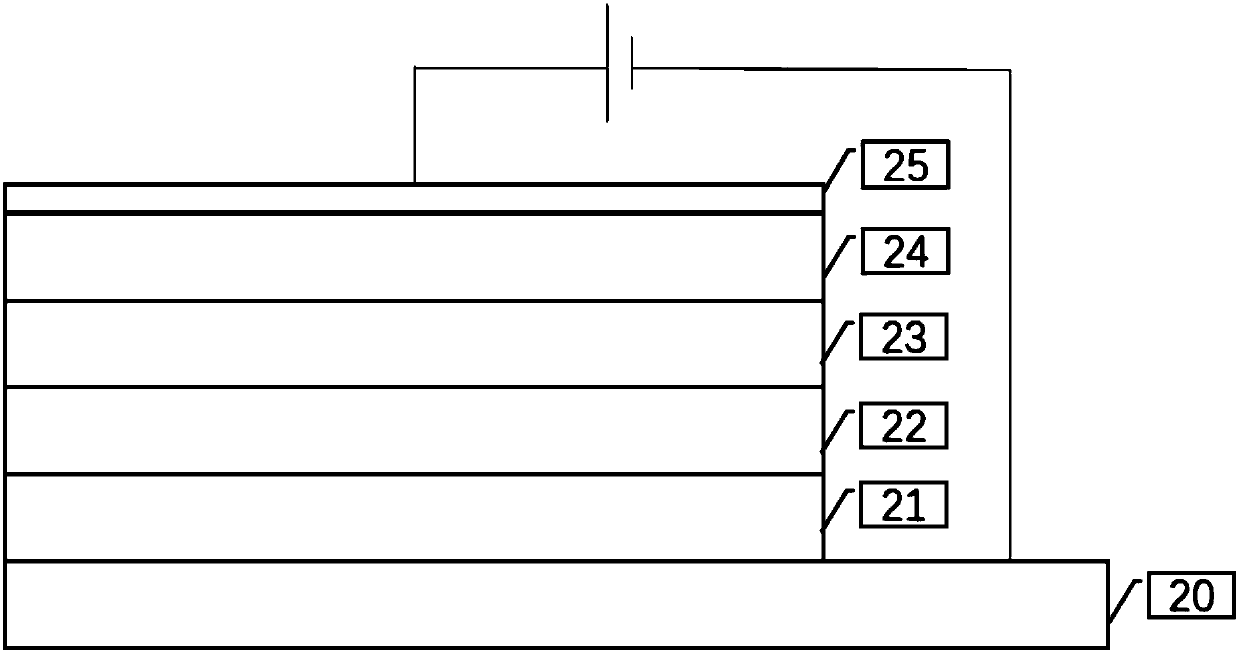

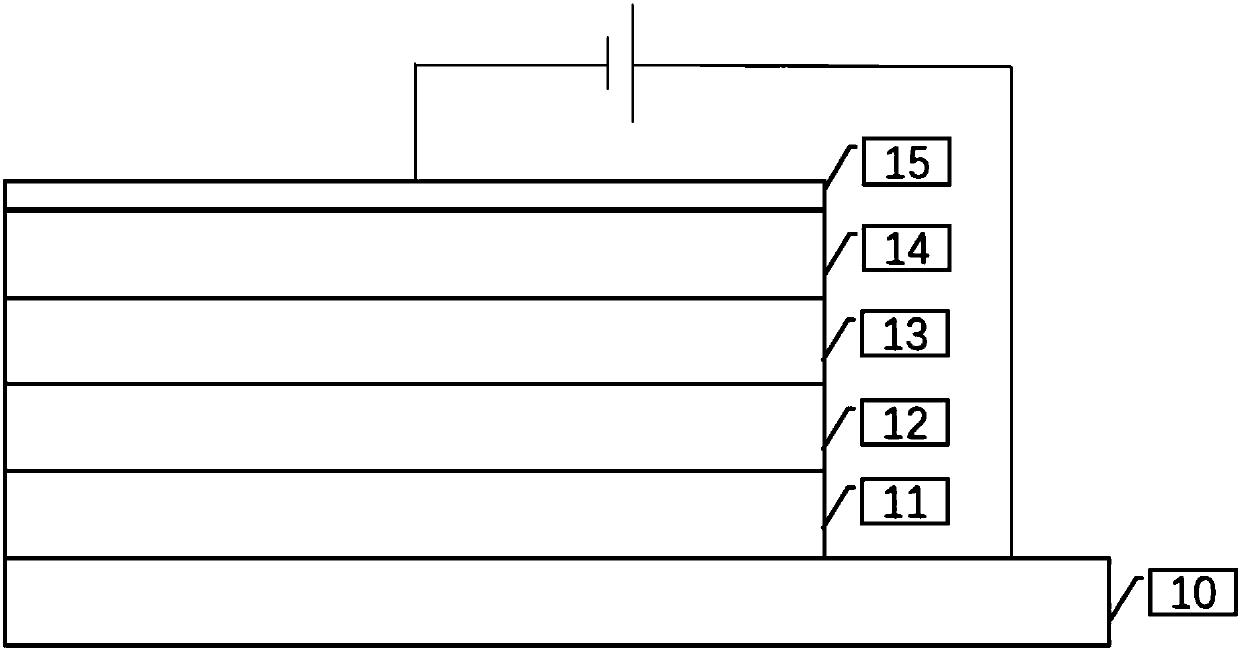

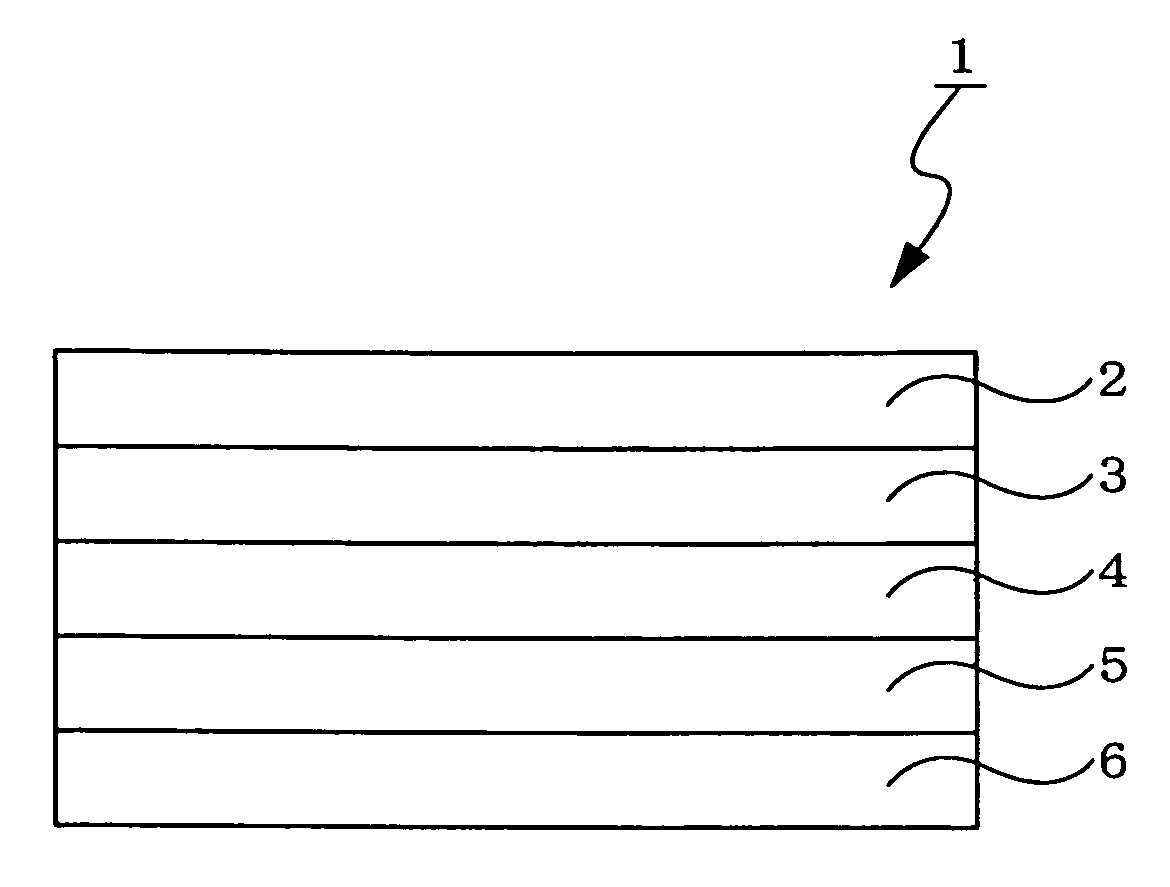

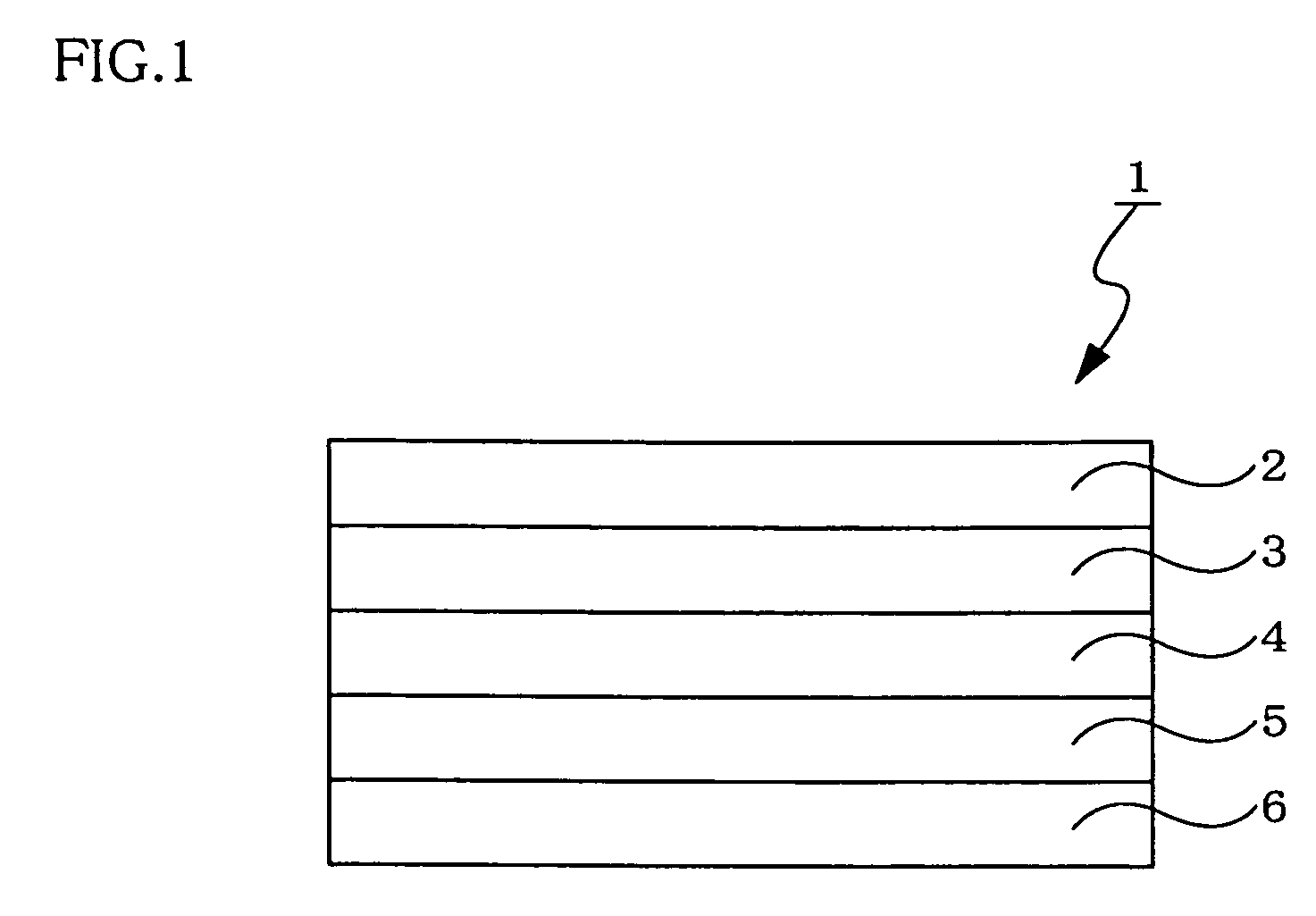

Organic electroluminescence device

ActiveUS20070054151A1Improve efficiencyLong life-timeDischarge tube luminescnet screensLamp detailsHydrogen atomCompound (substance)

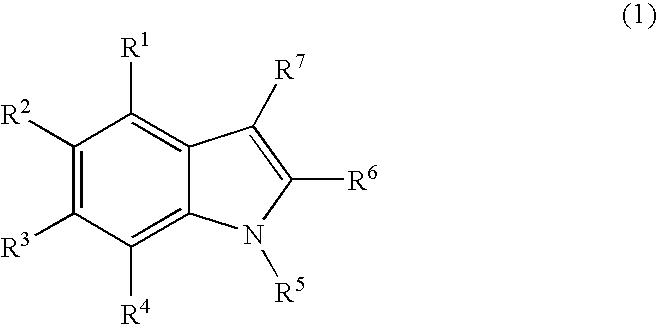

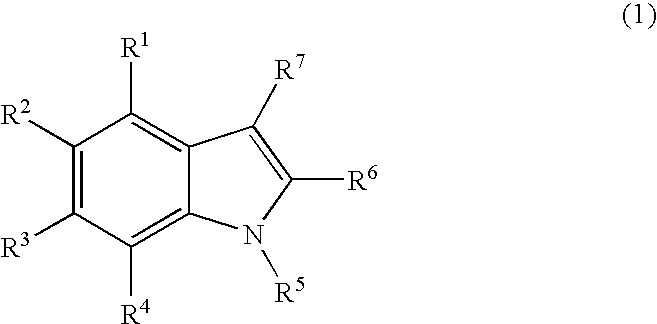

An organic electroluminescent device (1) including an anode (2), a cathode (6), and at least a first layer (3), a second layer (4), and a third layer (5) provided between the anode (2) and the cathode (6) in that order from the anode side. At least one of the first to third layers (3), (4), and (5) includes a phosphorescent compound. At least one of the first to third layers (3), (4), and (5) is an emitting layer. At least three compounds respectively forming the first layer (3), the second layer (4), and the third layer (5) other than the phosphorescent compound are compounds of the following formula (1). wherein R1 to R7 each represent a hydrogen atom or a substituent, provided that adjacent substituents may form a ring.

Owner:IDEMITSU KOSAN CO LTD

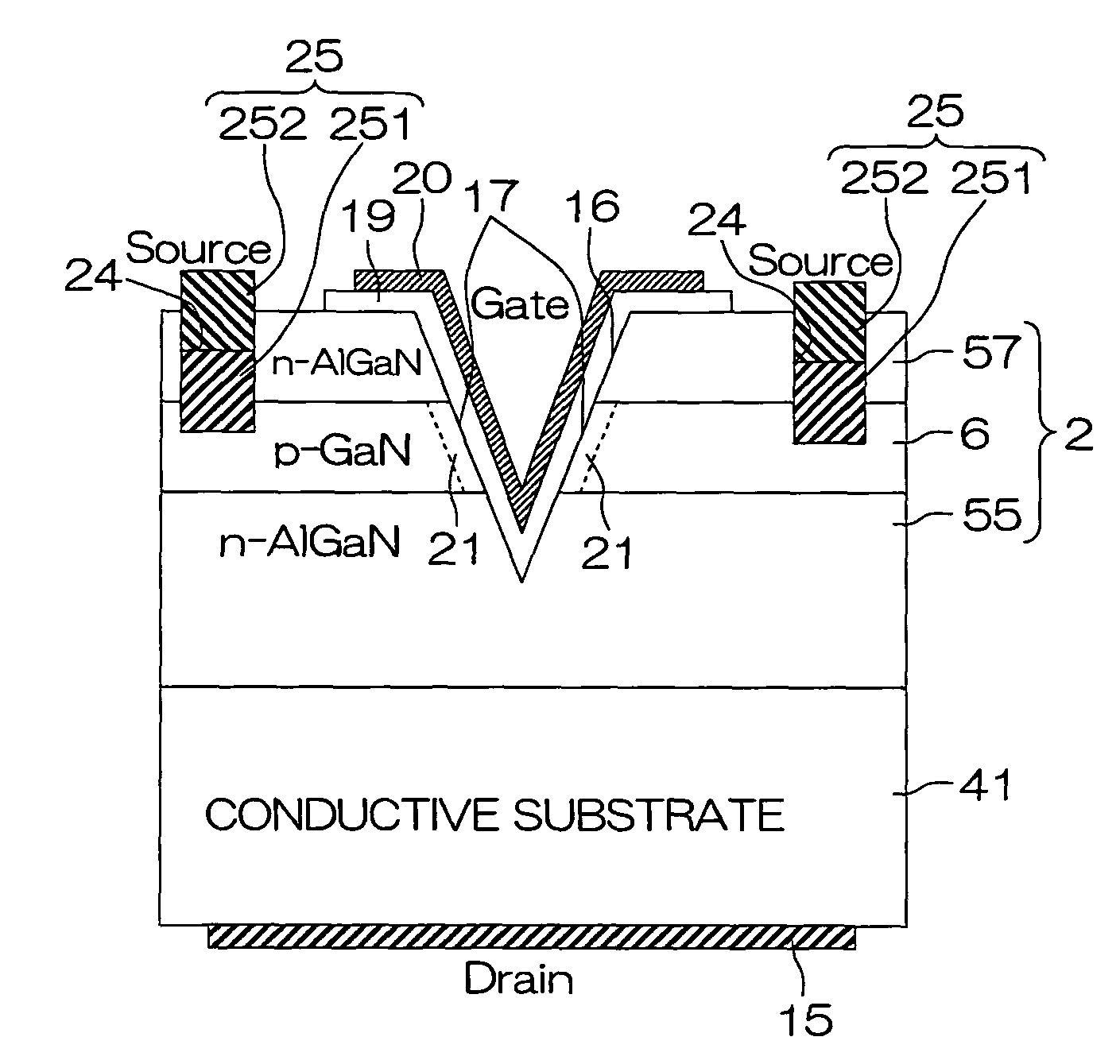

Semiconductor device employing group III-V nitride semiconductors and method for manufacturing the same

ActiveUS8044434B2Reduced carrier mobilityLower Reliability RequirementsSemiconductor devicesPower semiconductor deviceConductive materials

The semiconductor device includes a P-type group III-V nitride semiconductor layer, an N-type group III-V nitride semiconductor layer, and an electrode in contact with both of the P-type group III-V nitride semiconductor layer and the N-type group III-V nitride semiconductor layer. The electrode includes a first electrode portion made of a first conductive material, and a second electrode portion, made of a second conductive material different from the first conductive material, bonded to the first electrode portion. The first electrode portion is in contact with the P-type group III-V nitride semiconductor layer, and the second electrode portion is in contact with the N-type group III-V nitride semiconductor layer.

Owner:ROHM CO LTD

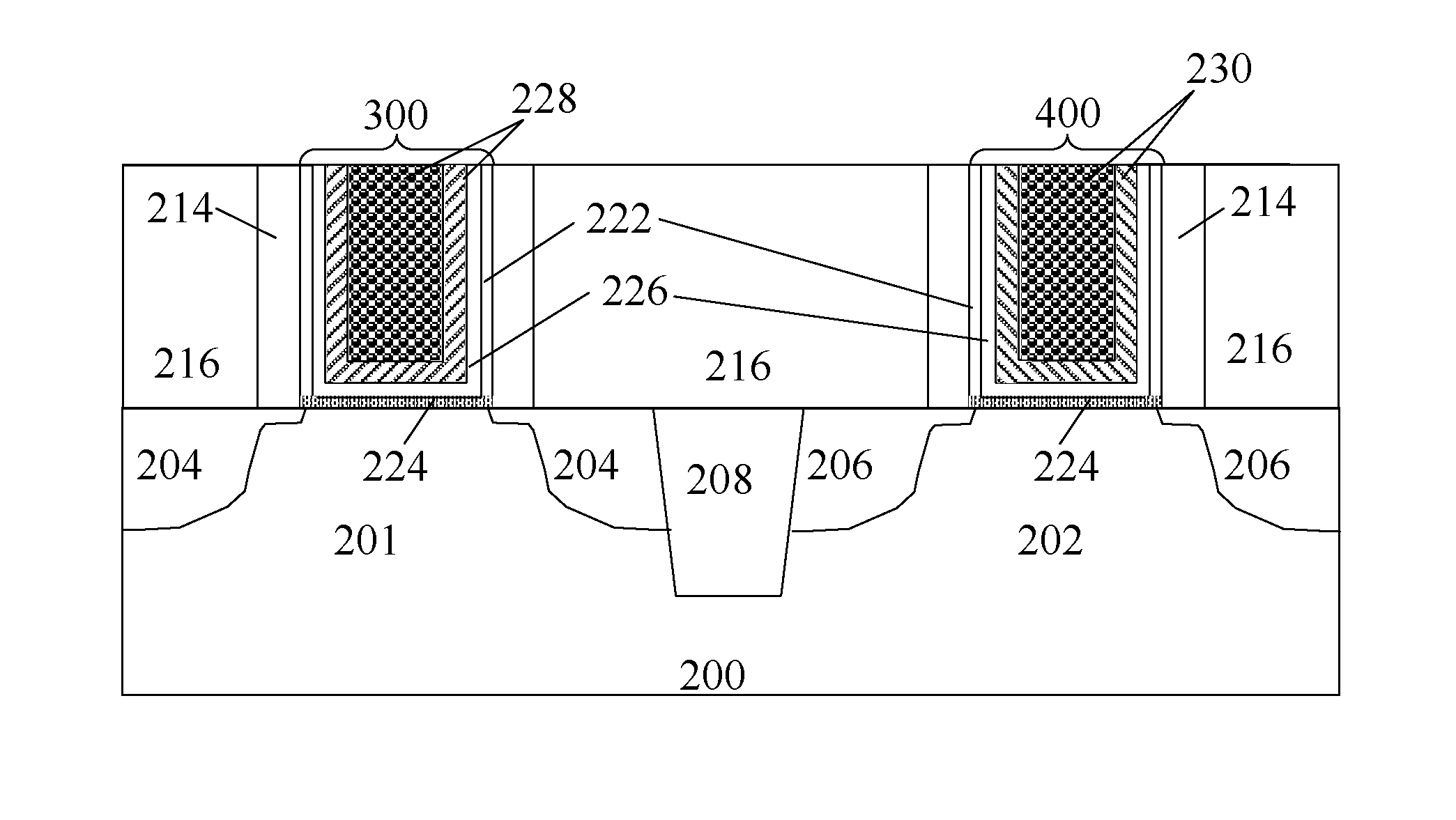

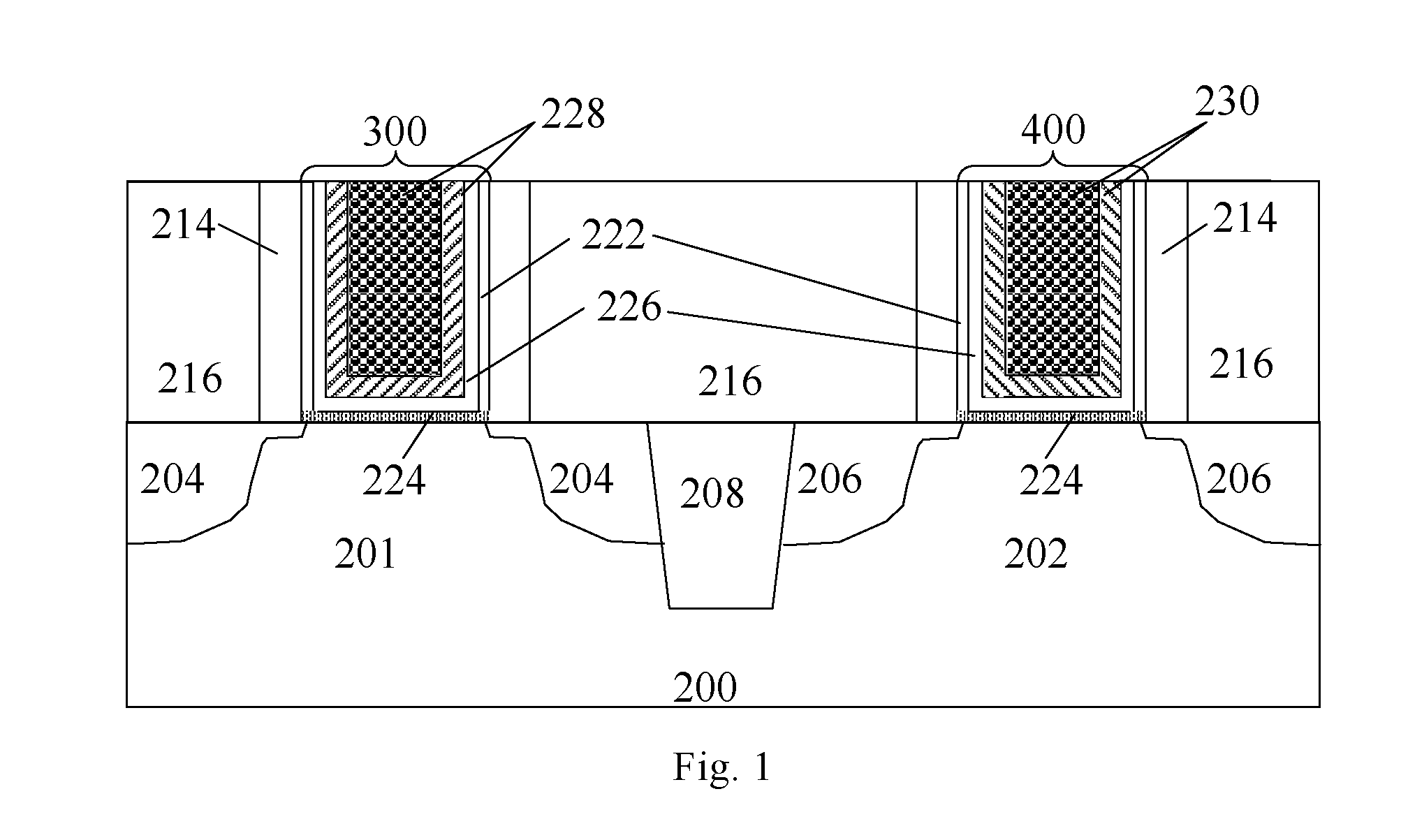

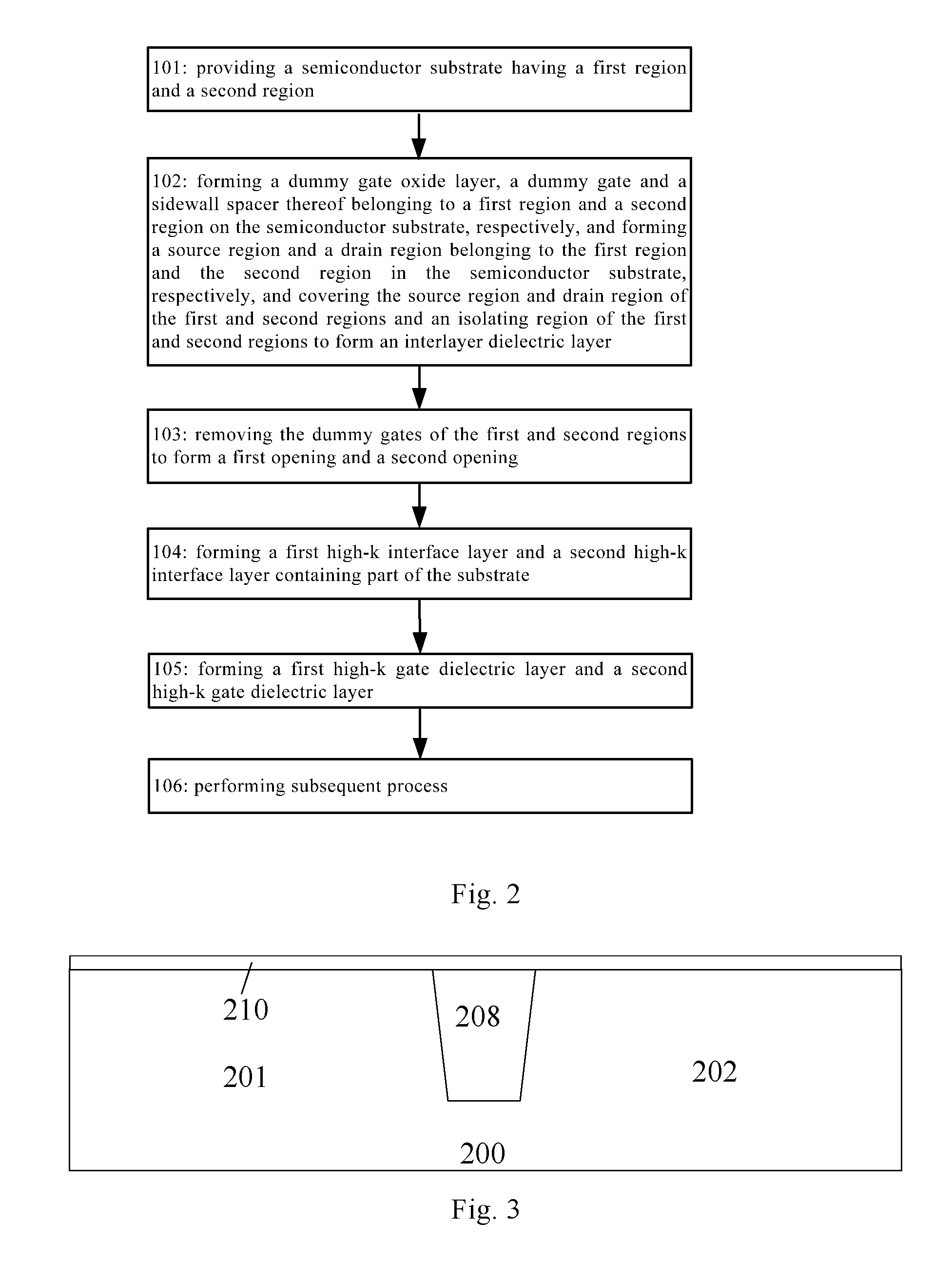

Semiconductor device and method of manufacturing the same

ActiveUS20110254093A1Reduce EOTAvoid degradationTransistorSolid-state devicesDielectricGate dielectric

A semiconductor device and a method of manufacturing the same are provided. A multi-component high-k interface layer containing elements of the substrate is formed from a ultra-thin high-k dielectric material in a single-layer structure of atoms by rapid annealing in the manufacturing of a CMOS transistor by the replacement gate process, and a high-k gate dielectric layer with a higher dielectric constant and a metal gate layer are formed thereon. The EOT of the device is effectively decreased, and the diffusion of atoms in the high-k gate dielectric layer from an upper level thereof is effectively prevented by the optimized high-k interface layer at high-temperature treatment. Thus, the present invention may also avoid the growth of the interface layers and the degradation of carrier mobility. Furthermore, the present invention may further alleviate the problem of high interface state and interface roughness caused by direct contact of the high-k gate dielectric layer with high dielectric constant and the substrate, and thus the overall performance of the device is effectively enhanced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

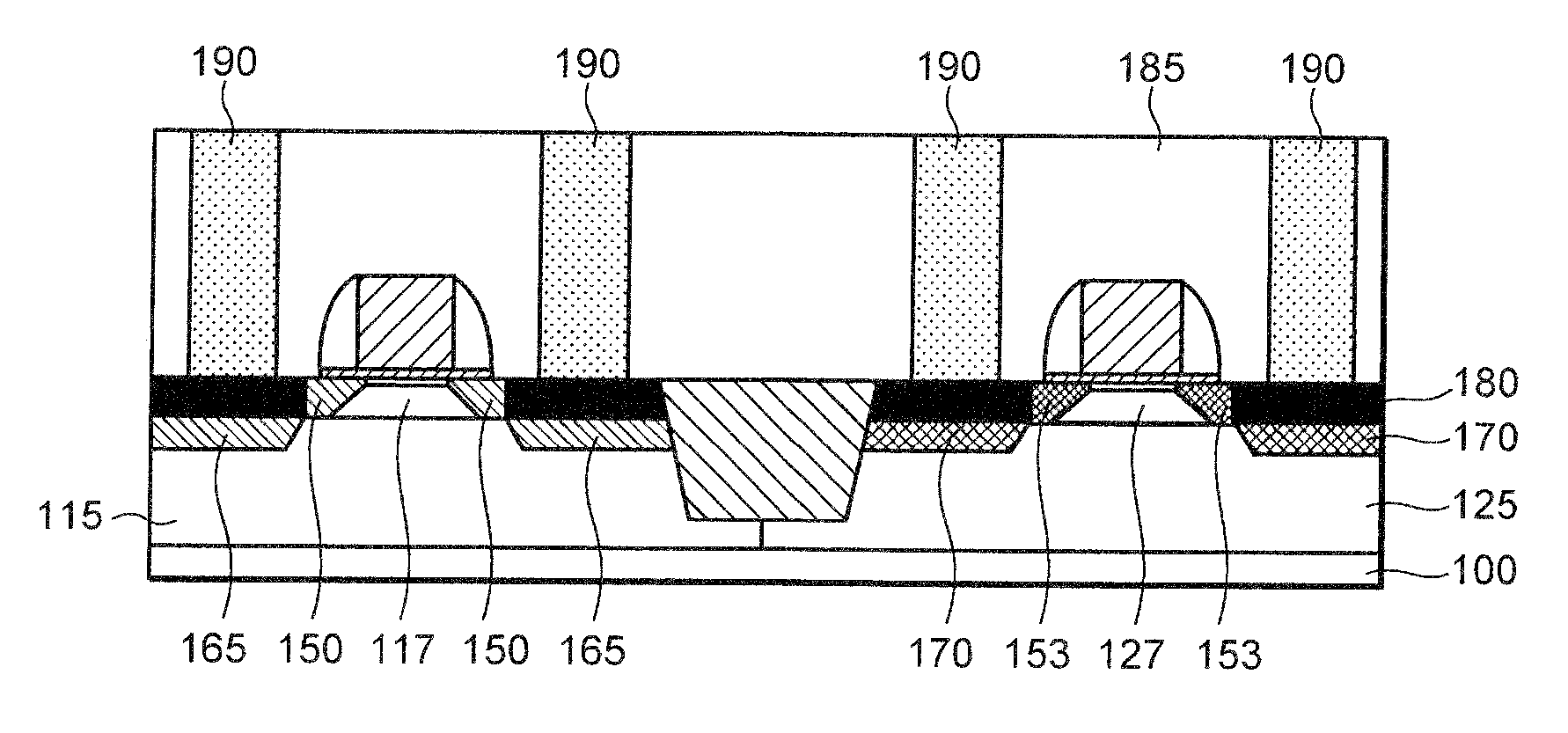

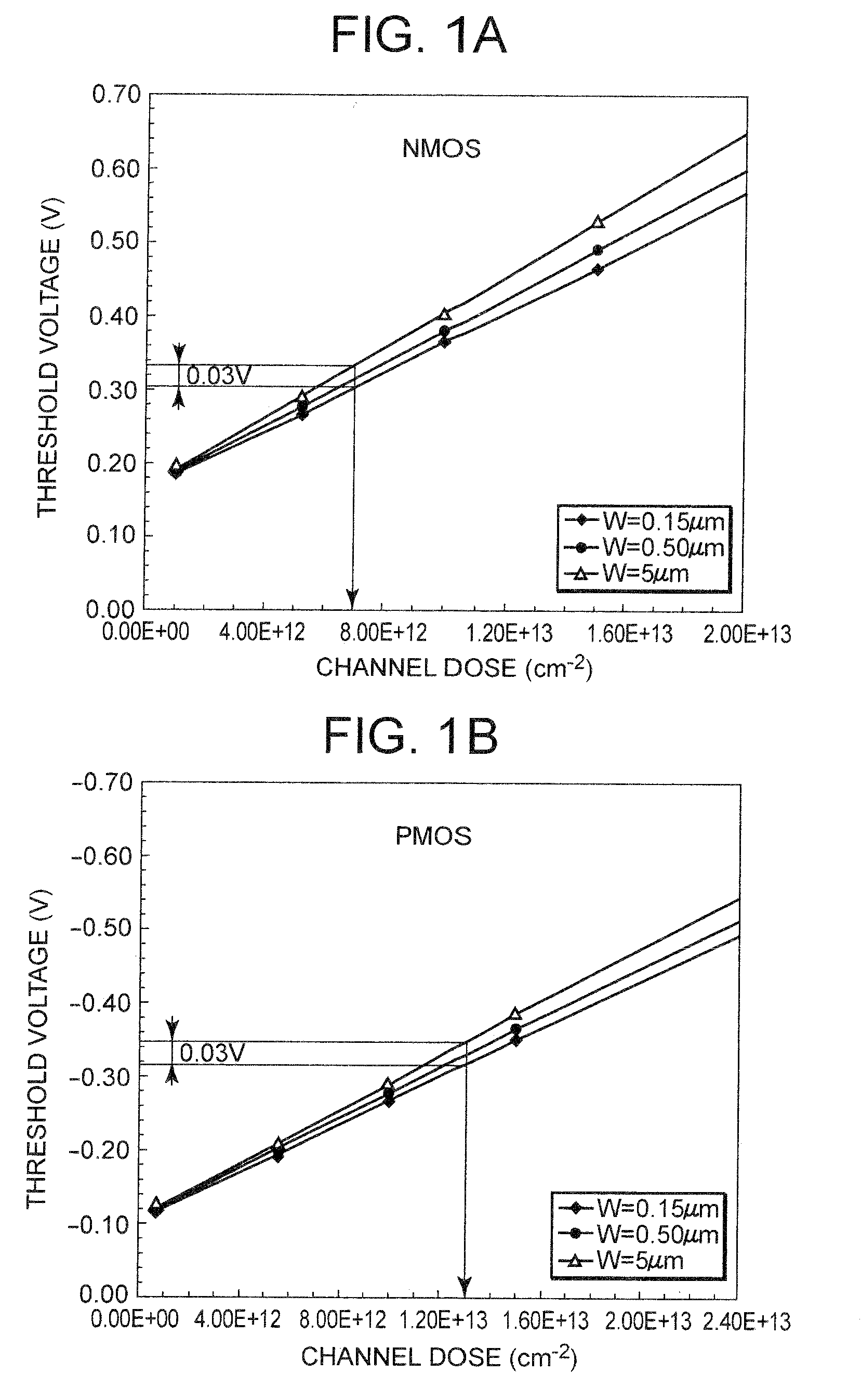

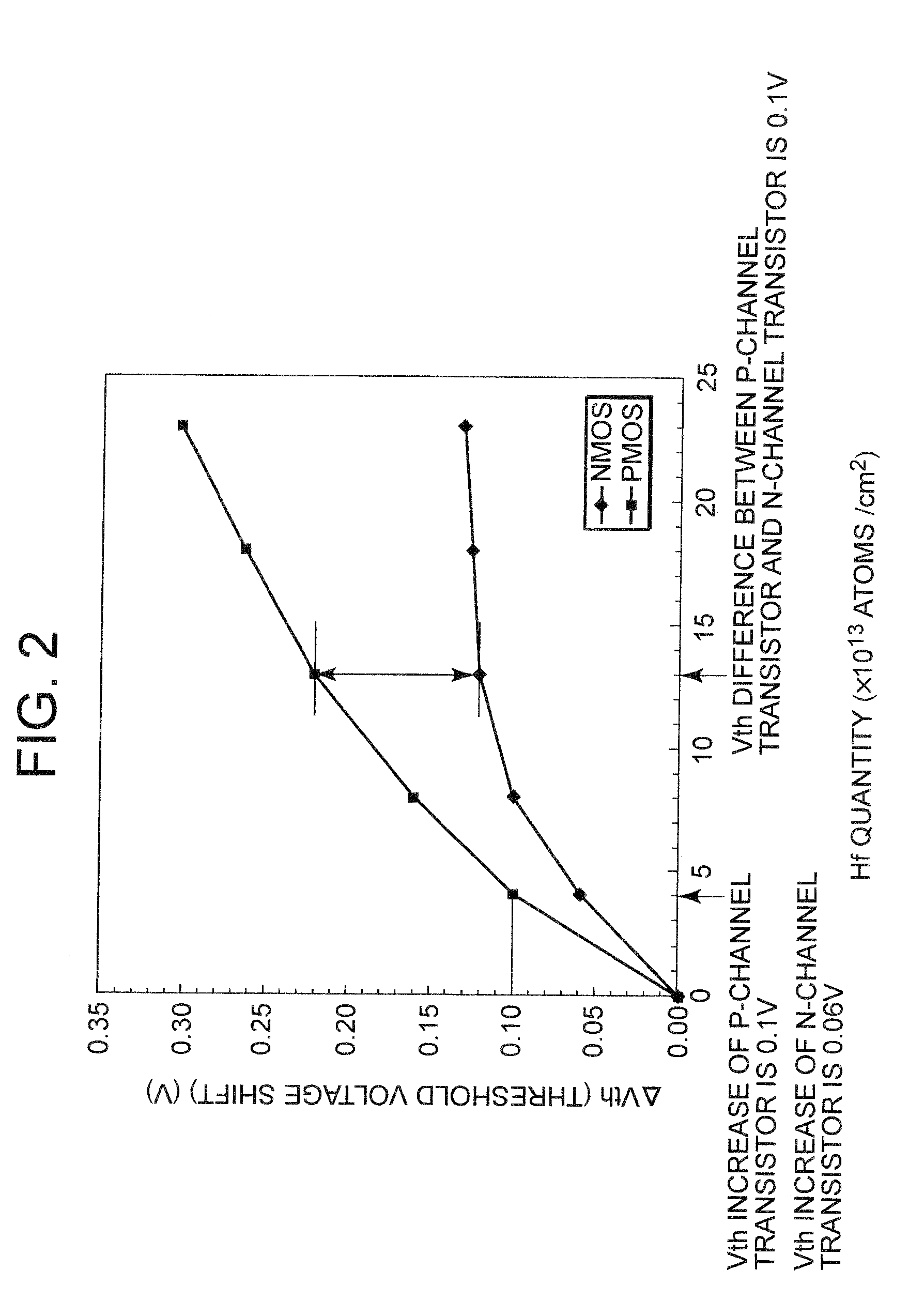

Semiconductor device and method of manufacturing the same

InactiveUS20080093699A1Reduce the differenceIncrease of junction leak can be preventedSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialWork function

The semiconductor device includes a plurality of transistors at least having different channel widths from each other. Threshold voltages of those transistors are set to be substantially equal to each other, by using both of substantially the same channel dose for each of those transistors, and work function control using a predetermined metal to be deposited on a gate insulating of those transistors and / or a gate electrode material of each of those transistors (that is, work function control based on a gate structure (gate insulating film and / or gate electrode) with respect to a channel region of each of those transistors).

Owner:NEC ELECTRONICS CORP

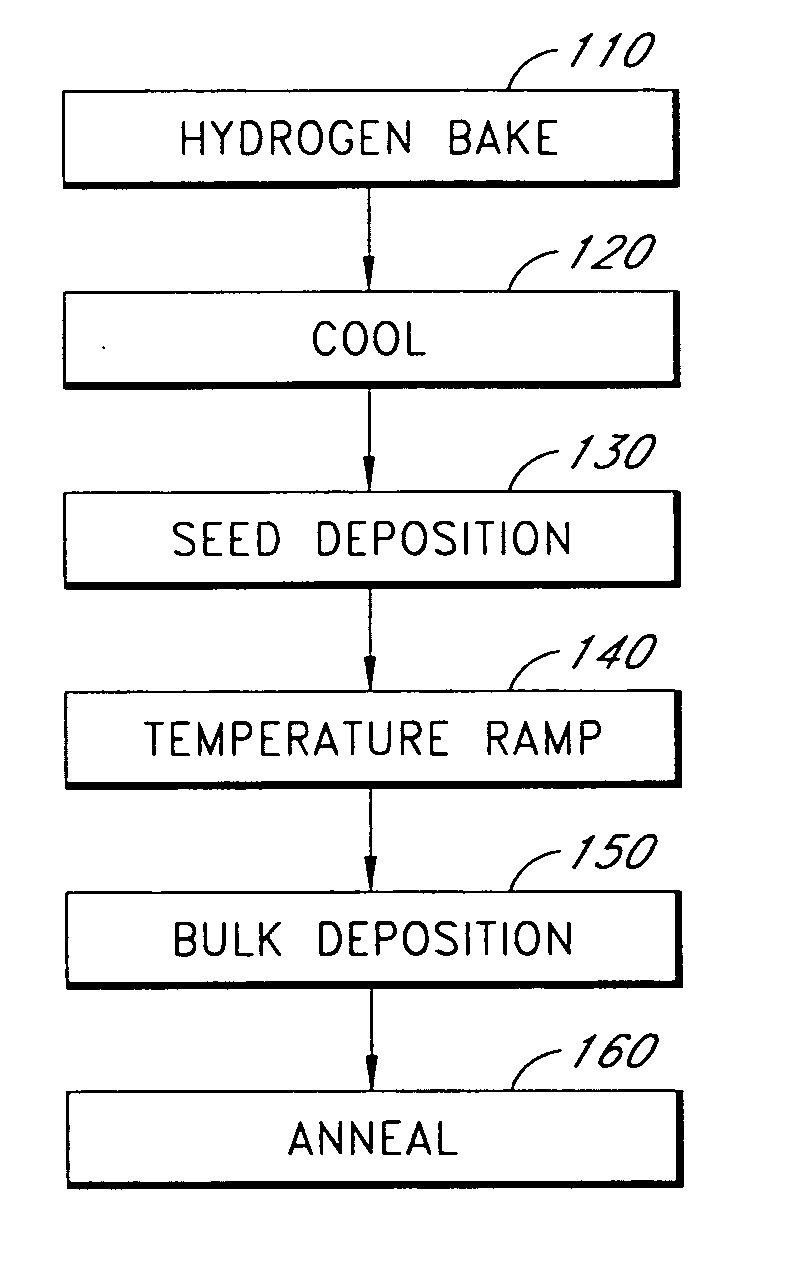

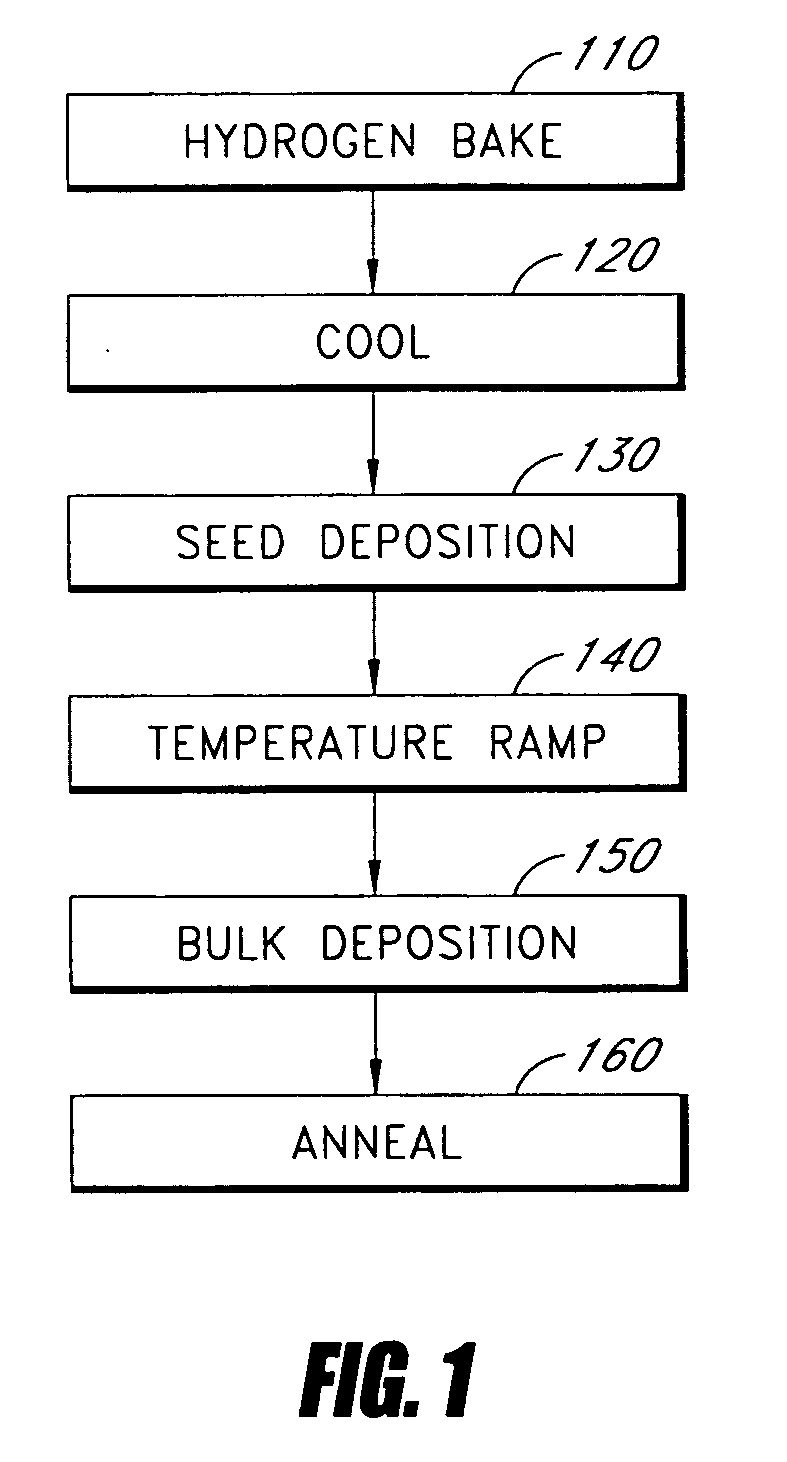

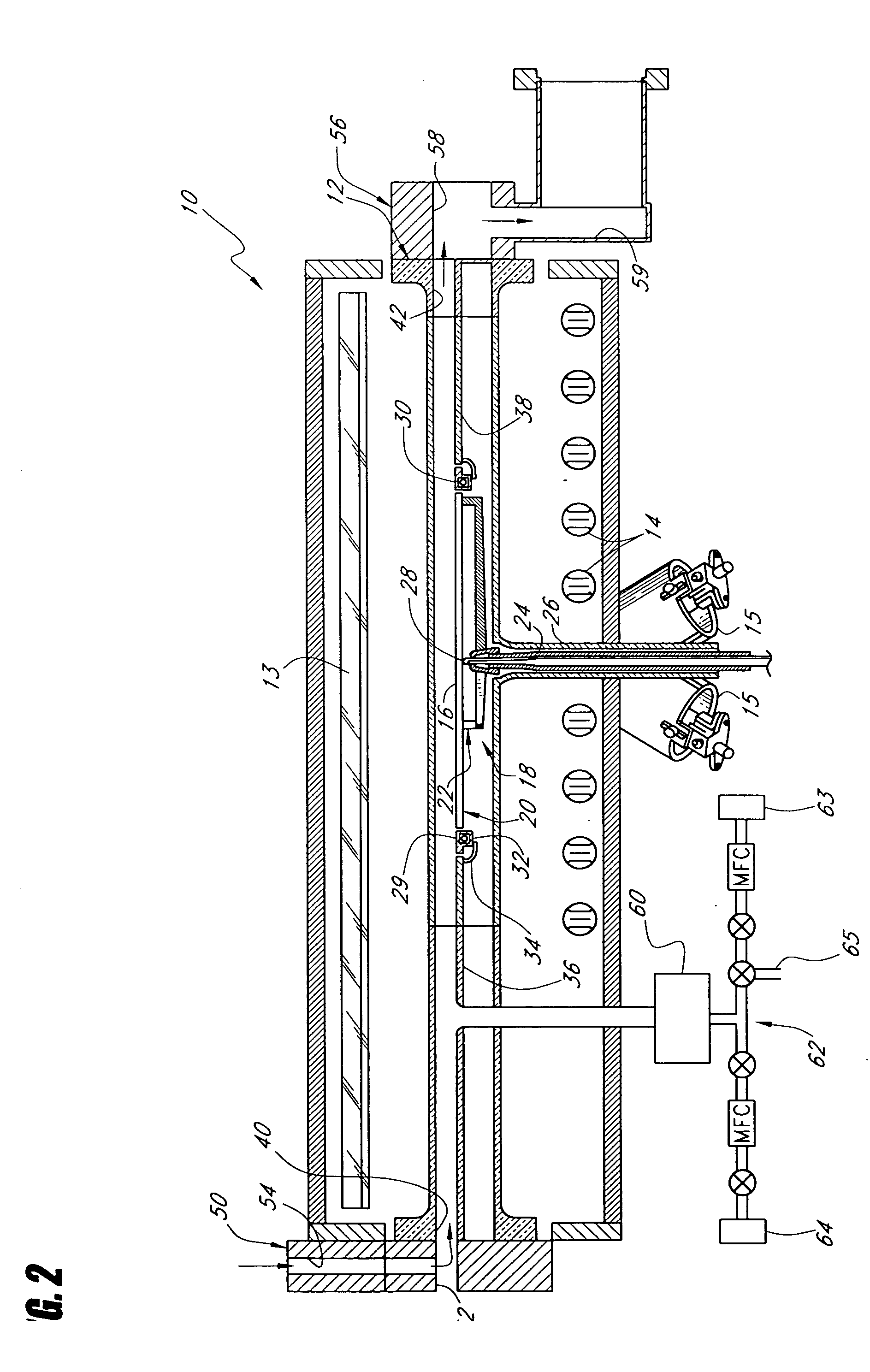

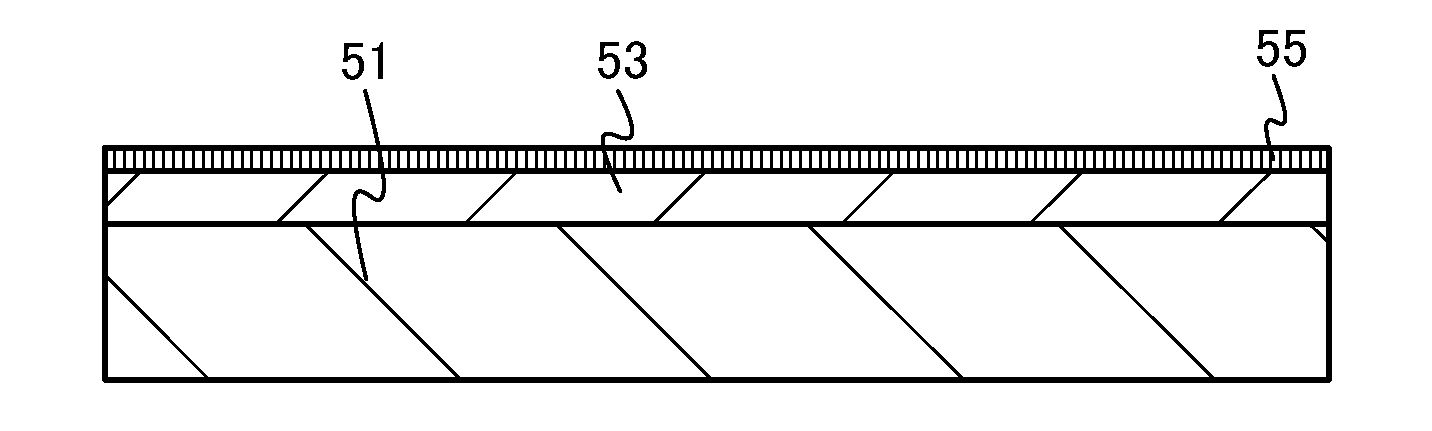

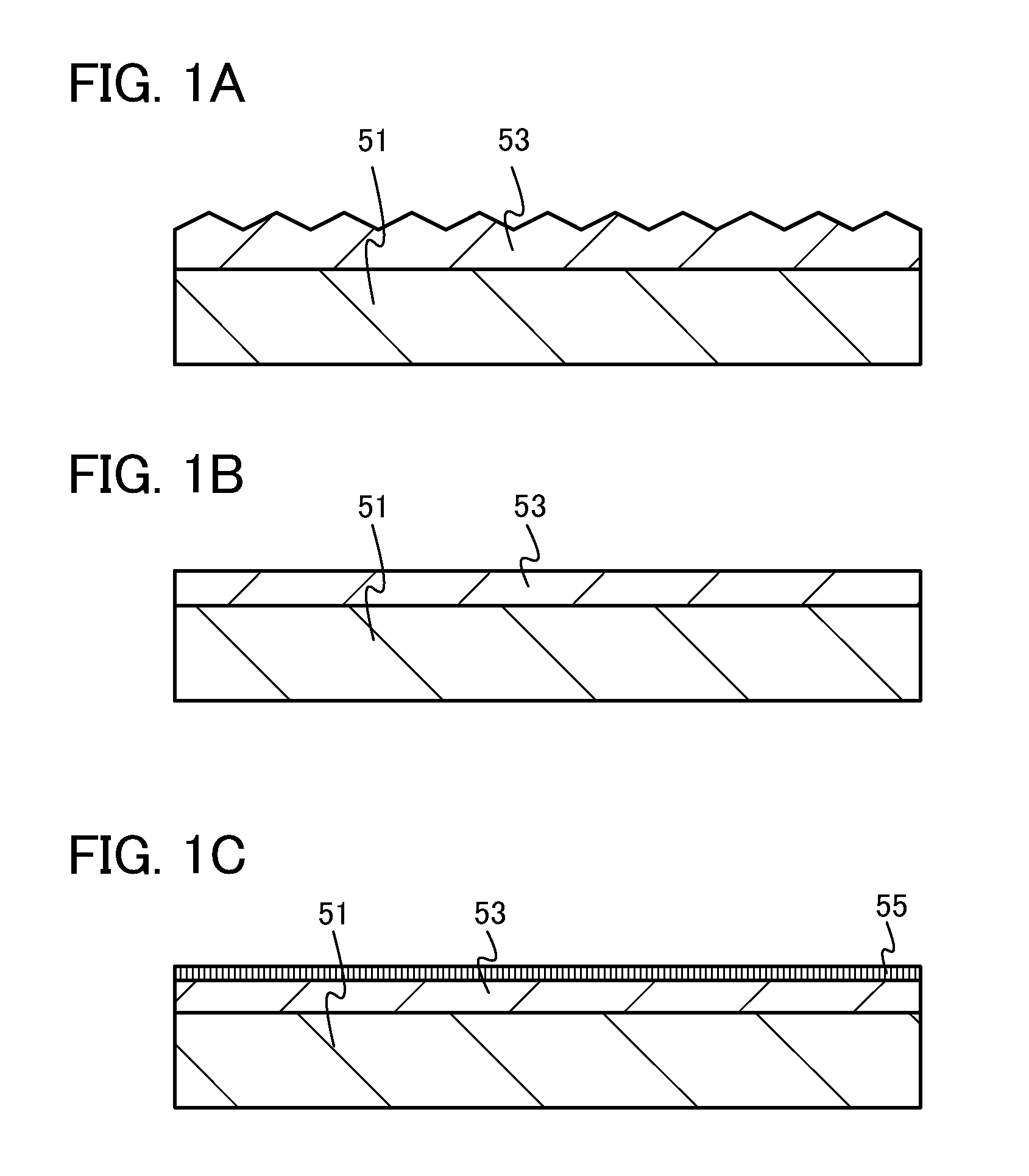

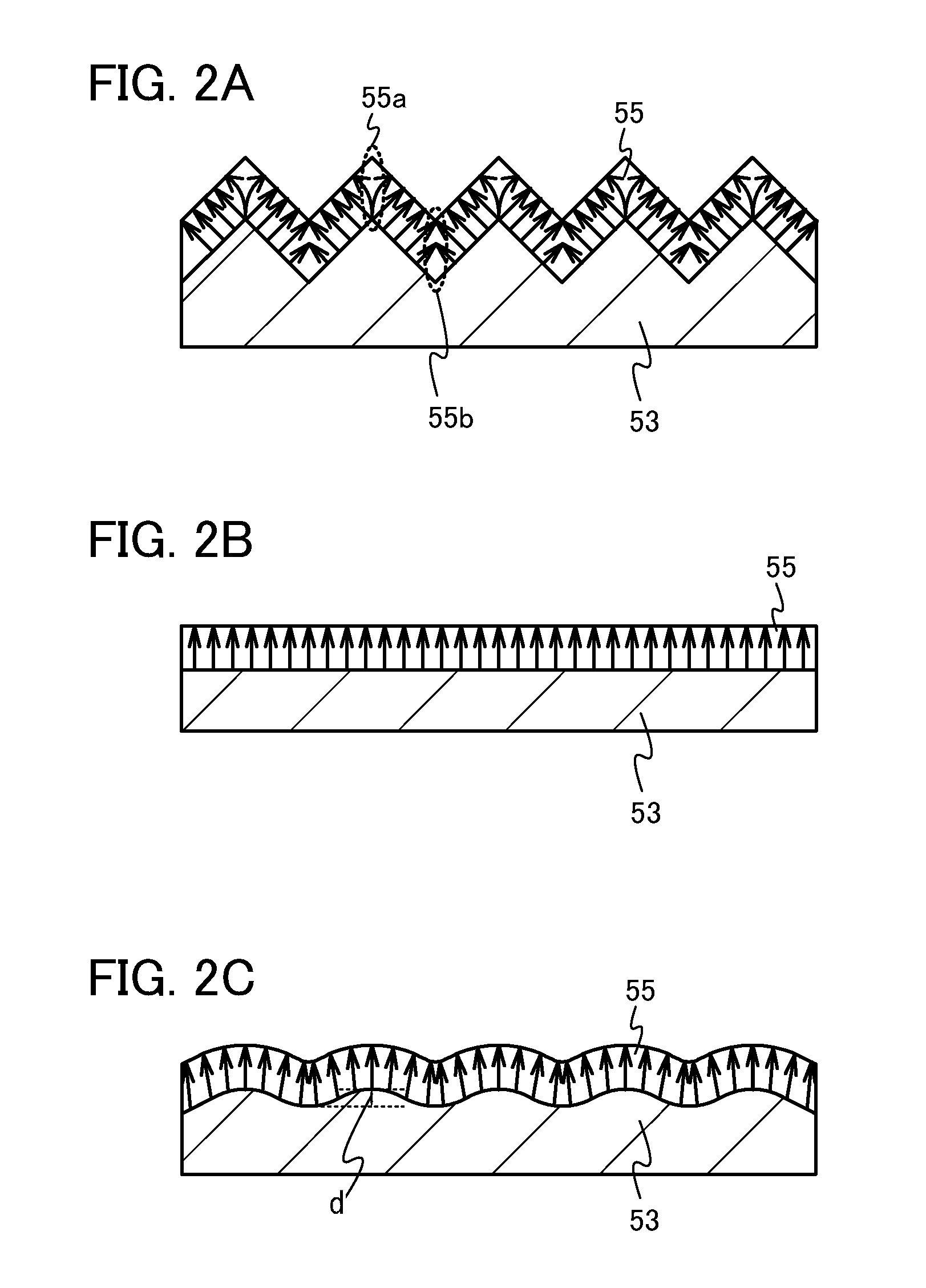

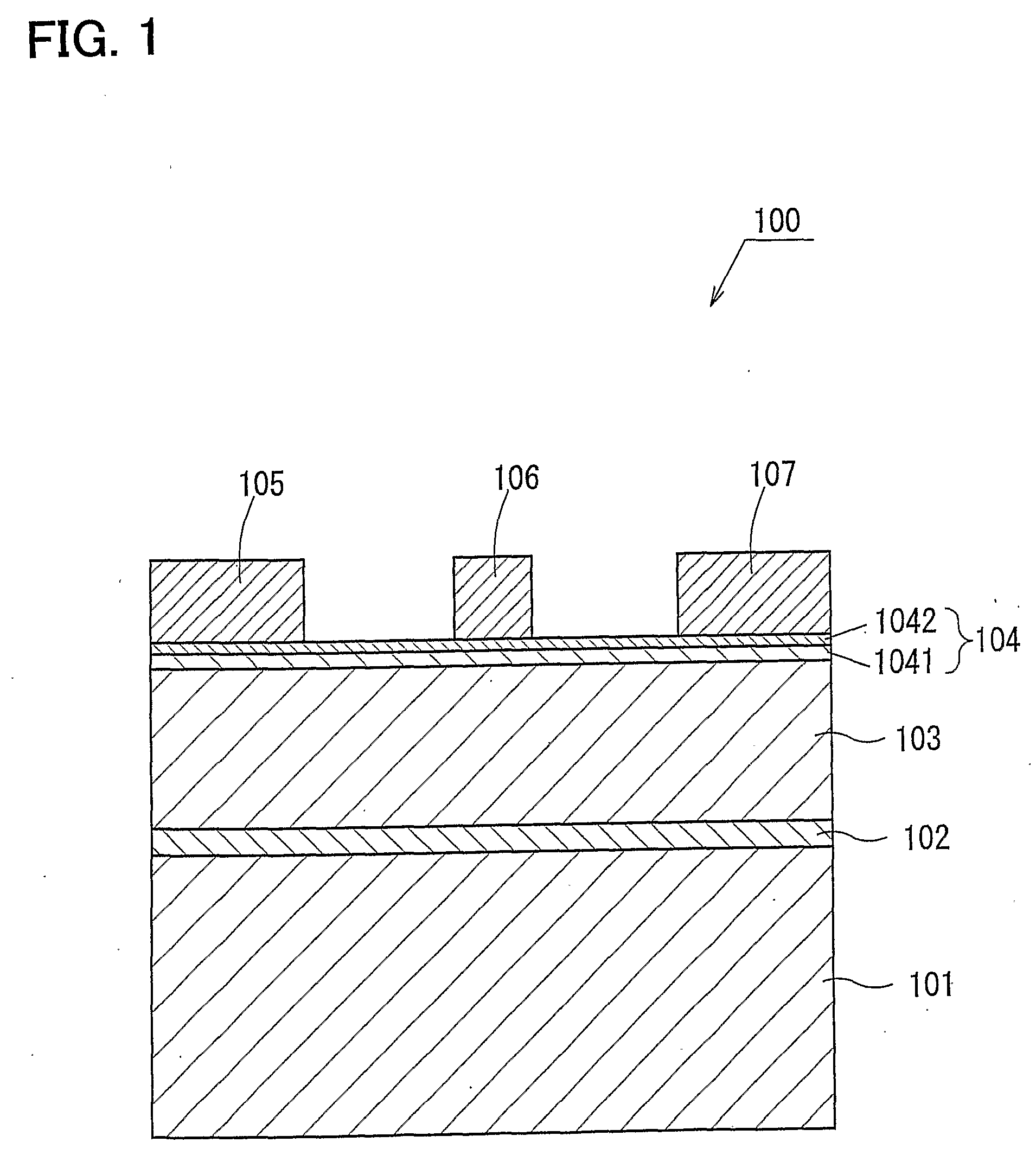

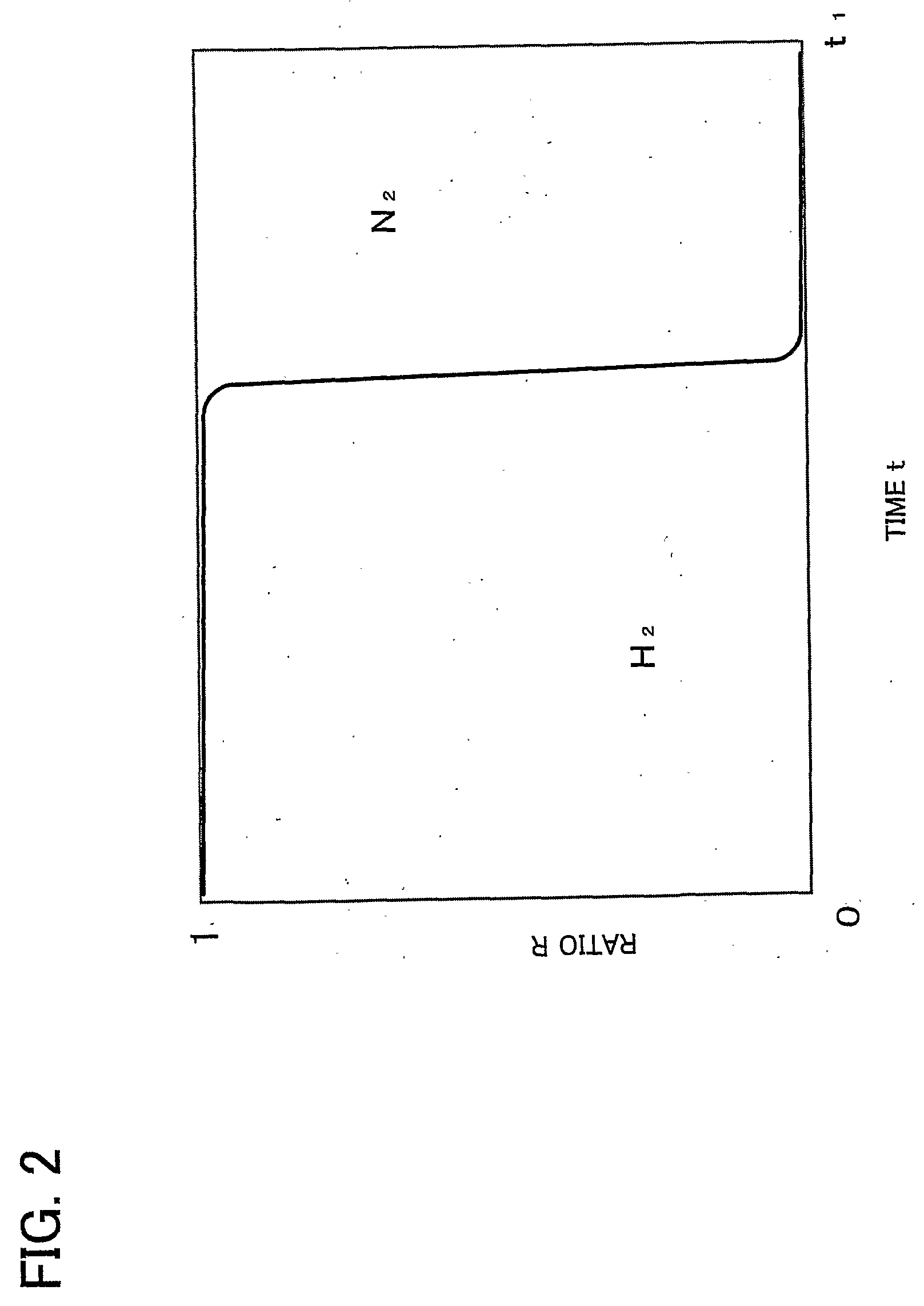

Germanium deposition

ActiveUS20050191826A1MinimizesExcessive surface roughnessPolycrystalline material growthSemiconductor/solid-state device manufacturingReaction chamberMonolayer

A method comprises, in a reaction chamber, depositing a seed layer of germanium over a silicon-containing surface at a first temperature. The seed layer has a thickness between about one monolayer and about 1000 Å. The method further comprises, after depositing the seed layer, increasing the temperature of the reaction chamber while continuing to deposit germanium. The method further comprises holding the reaction chamber in a second temperature range while continuing to deposit germanium. The second temperature range is greater than the first temperature.

Owner:ASM IP HLDG BV

Semiconductor device and method for fabricating the same

ActiveUS7473929B2Reduced carrier mobilityHigh carrier mobilityTransistorSemiconductor/solid-state device manufacturingCarbon filmHigh resistance

Ion implantation is carried out to form a p-well region and a source region in parts of a high resistance SiC layer on a SiC substrate, and a carbon film is deposited over the substrate. With the carbon film deposited over the substrate, annealing for activating the implanted dopant ions is performed, and then the carbon film is removed. Thus, a smooth surface having hardly any surface roughness caused by the annealing is obtained. Furthermore, if a channel layer is epitaxially grown, the surface roughness of the channel layer is smaller than that of the underlying layer. Since the channel layer having a smooth surface is provided, it is possible to obtain a MISFET with a high current drive capability.

Owner:PANASONIC CORP

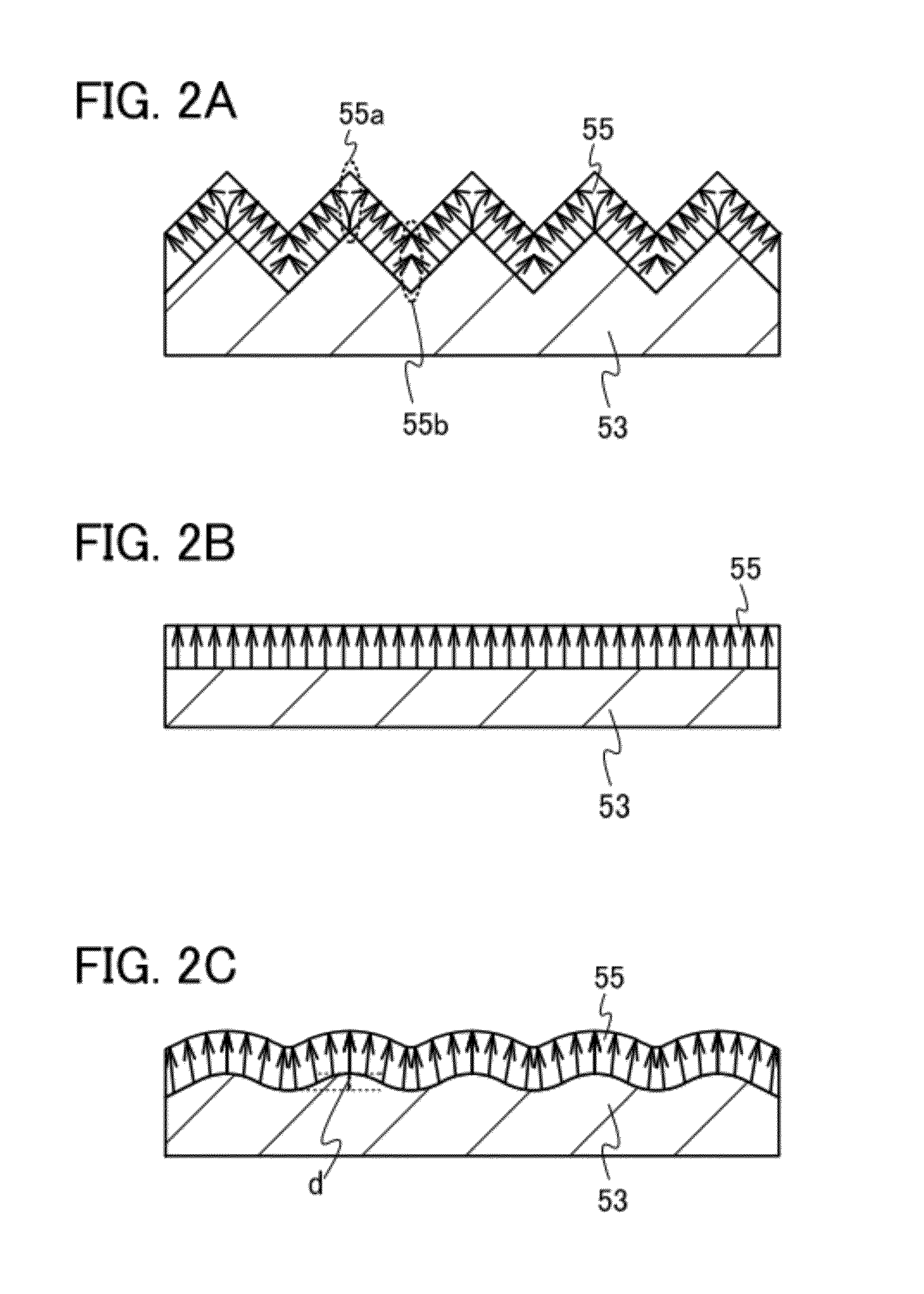

Semiconductor device and method of manufacturing semiconductor device

ActiveUS8987728B2Conductivity easilyDensity is easyTransistorSolid-state devicesCrystalline oxidePower semiconductor device

An object is to provide a highly reliable semiconductor device having stable electric characteristics by using an oxide semiconductor film having stable electric characteristics. Another object is to provide a semiconductor device having higher mobility by using an oxide semiconductor film having high crystallinity. A crystalline oxide semiconductor film is formed over and in contact with an insulating film whose surface roughness is reduced, whereby the oxide semiconductor film can have stable electric characteristics. Accordingly, the highly reliable semiconductor device having stable electric characteristics can be provided. Further, the semiconductor device having higher mobility can be provided.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and method of manufacturing semiconductor device

ActiveUS20120241734A1Reduce defect densityStable electrical characteristicsTransistorSolid-state devicesCrystalline oxidePower semiconductor device

An object is to provide a highly reliable semiconductor device having stable electric characteristics by using an oxide semiconductor film having stable electric characteristics. Another object is to provide a semiconductor device having higher mobility by using an oxide semiconductor film having high crystallinity. A crystalline oxide semiconductor film is formed over and in contact with an insulating film whose surface roughness is reduced, whereby the oxide semiconductor film can have stable electric characteristics. Accordingly, the highly reliable semiconductor device having stable electric characteristics can be provided. Further, the semiconductor device having higher mobility can be provided.

Owner:SEMICON ENERGY LAB CO LTD

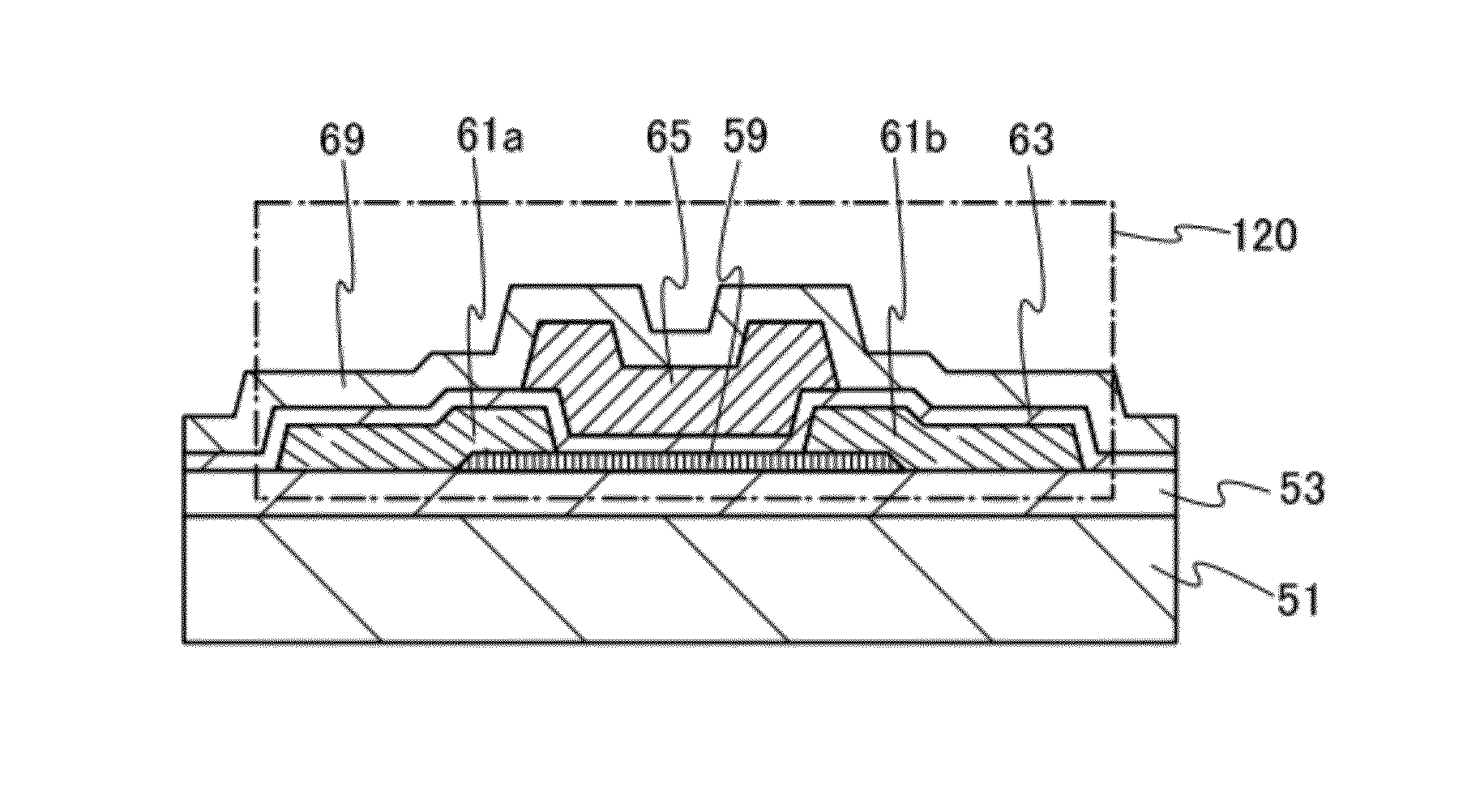

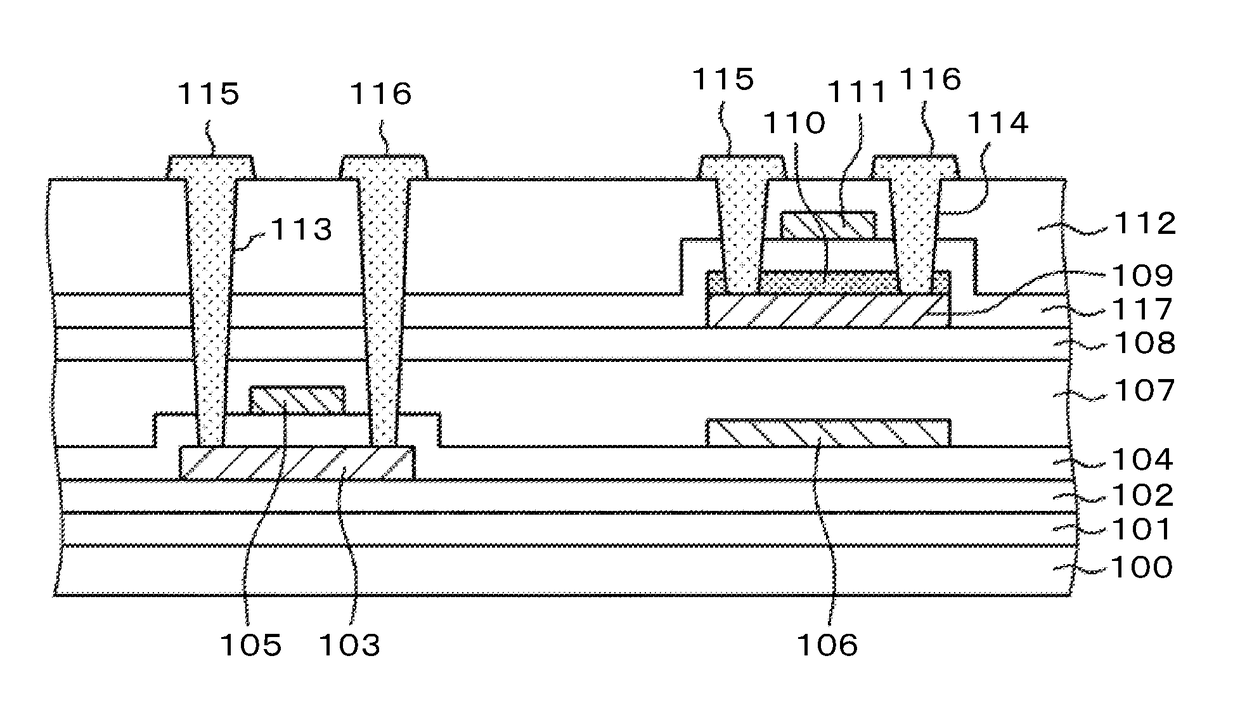

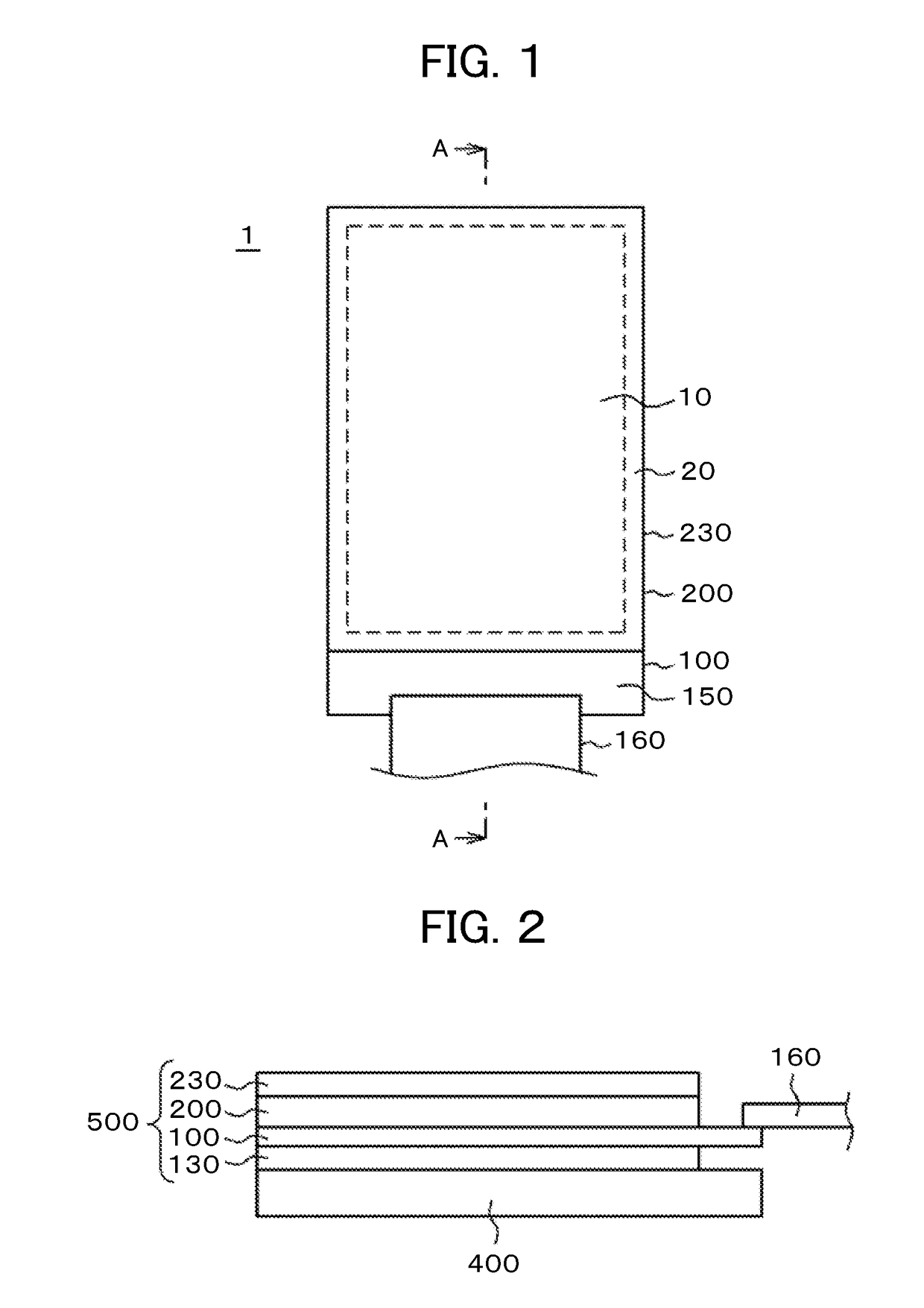

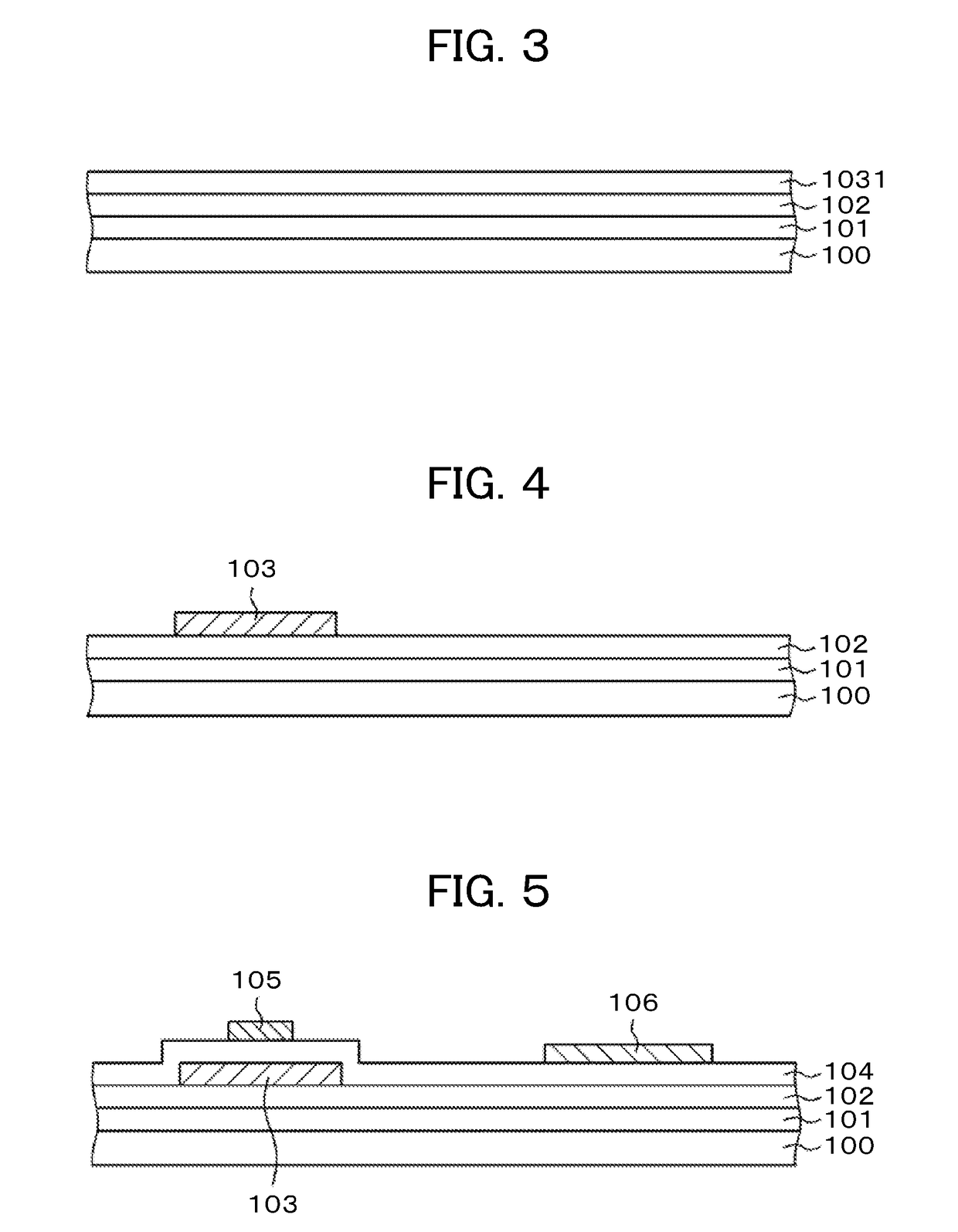

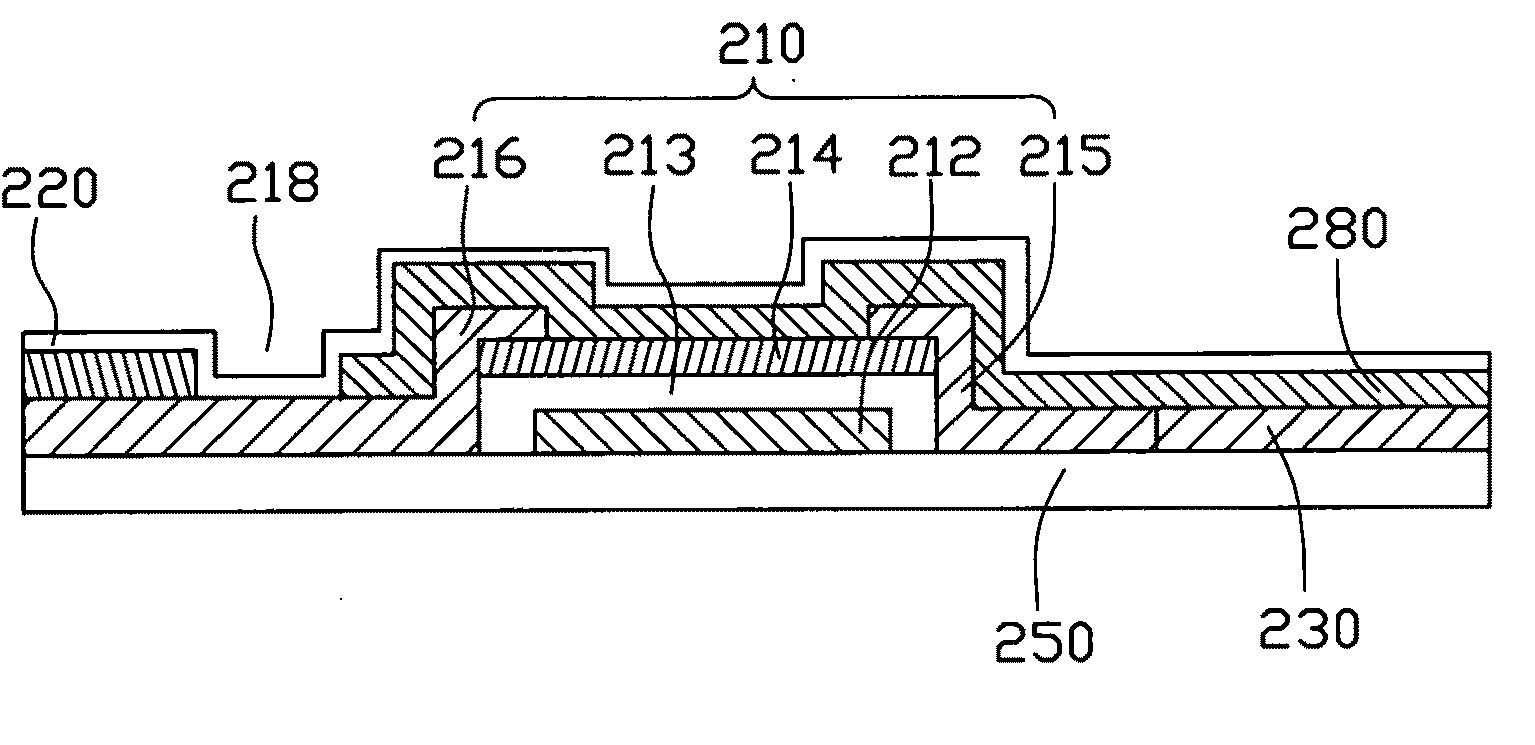

Display device

ActiveUS20170338249A1Reduce leakage currentLeakage currentTransistorStatic indicating devicesDisplay deviceSemiconductor

The object of the present invention is to make it possible to form an LIPS TFT and an oxide semiconductor TFT on the same substrate. A display device includes a substrate having a display region in which pixels are formed. The pixel includes a first TFT using an oxide semiconductor 109. An oxide film 110 as an insulating material is formed on the oxide semiconductor 109. A gate electrode 111 is formed on the oxide film 110. A first electrode 115 is connected to a drain of the first TFT via a first through hole formed in the oxide film 110. A second electrode 116 is connected to a source of the first TFT via a second through hole formed in the oxide film 110.

Owner:JAPAN DISPLAY INC

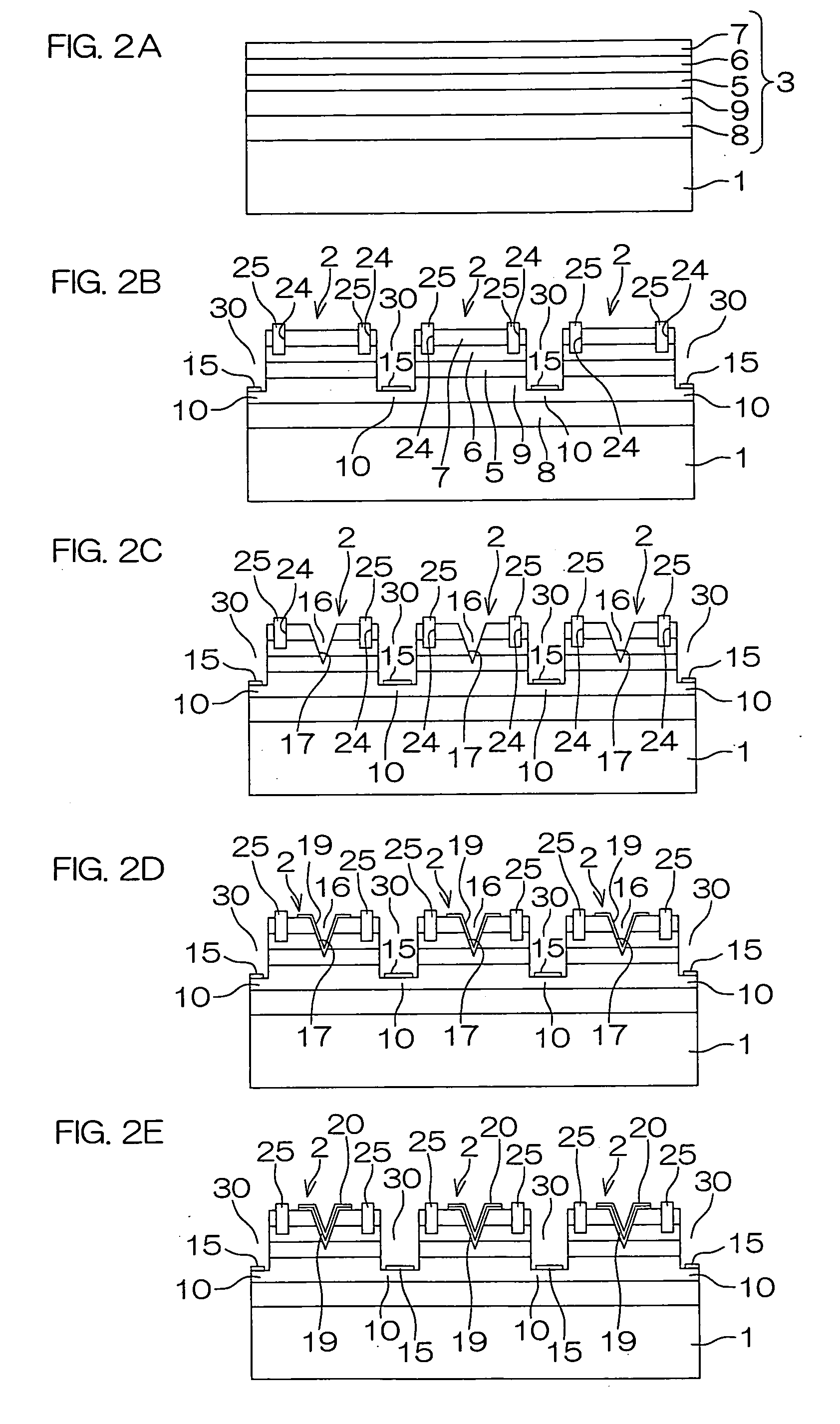

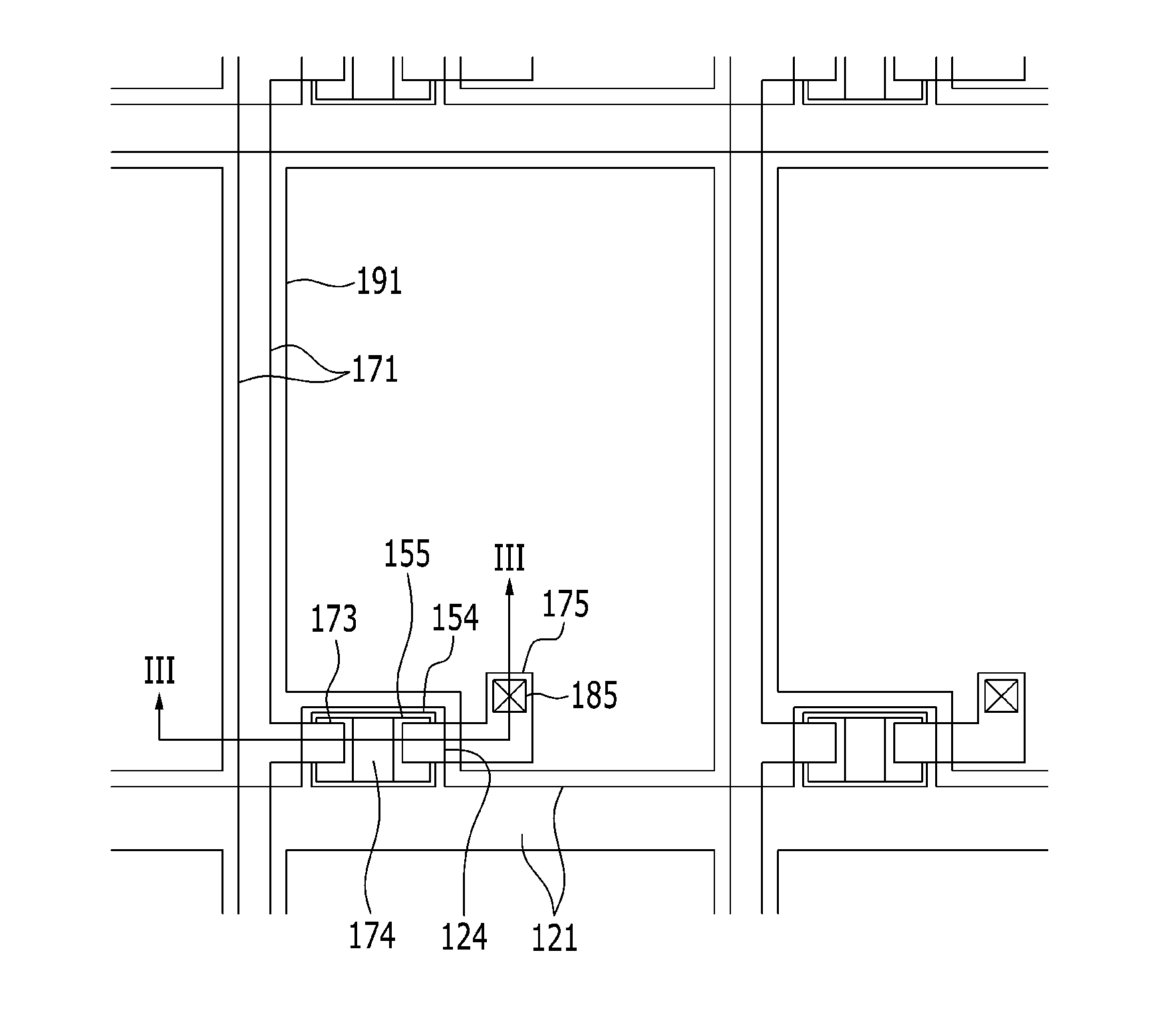

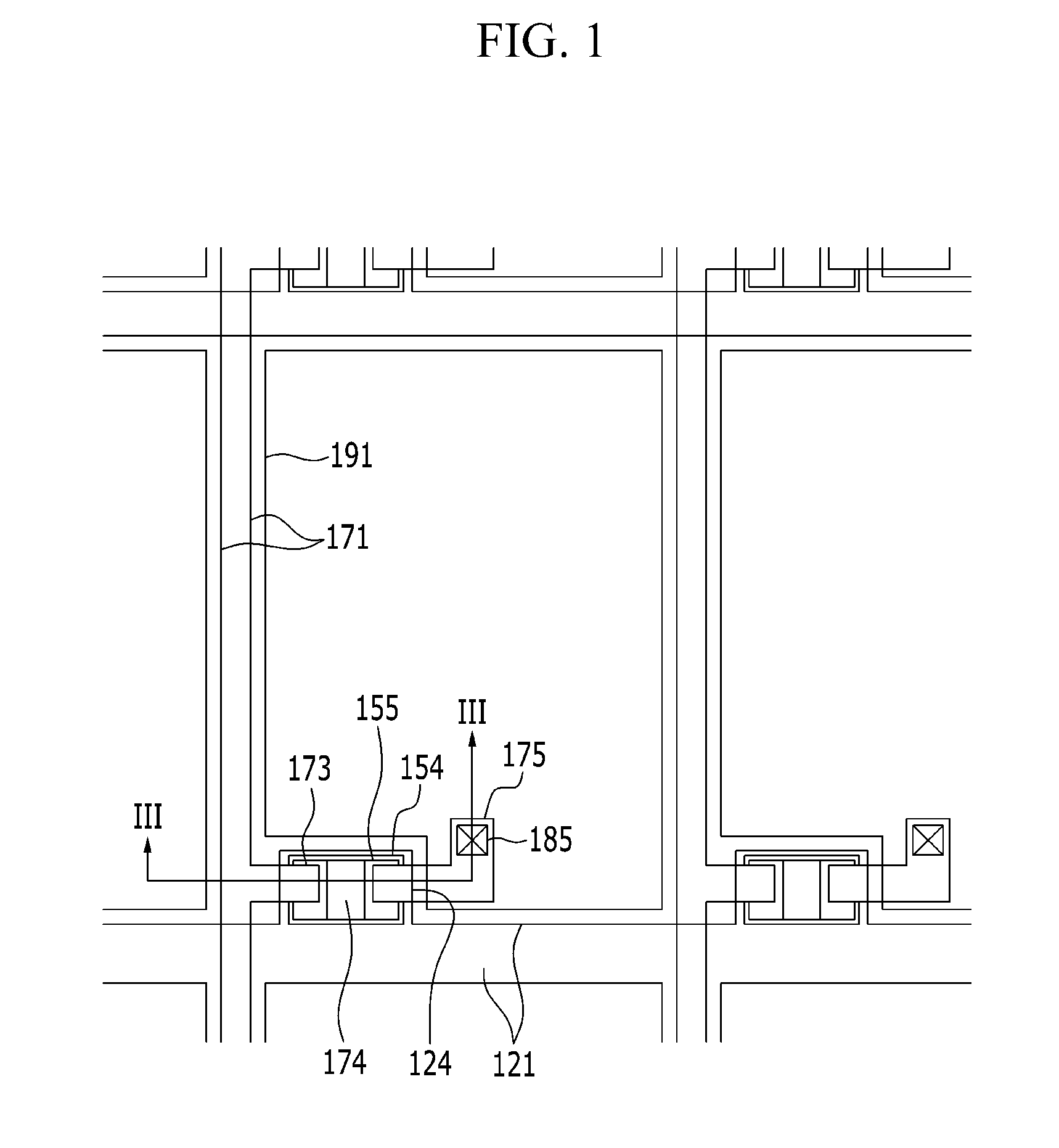

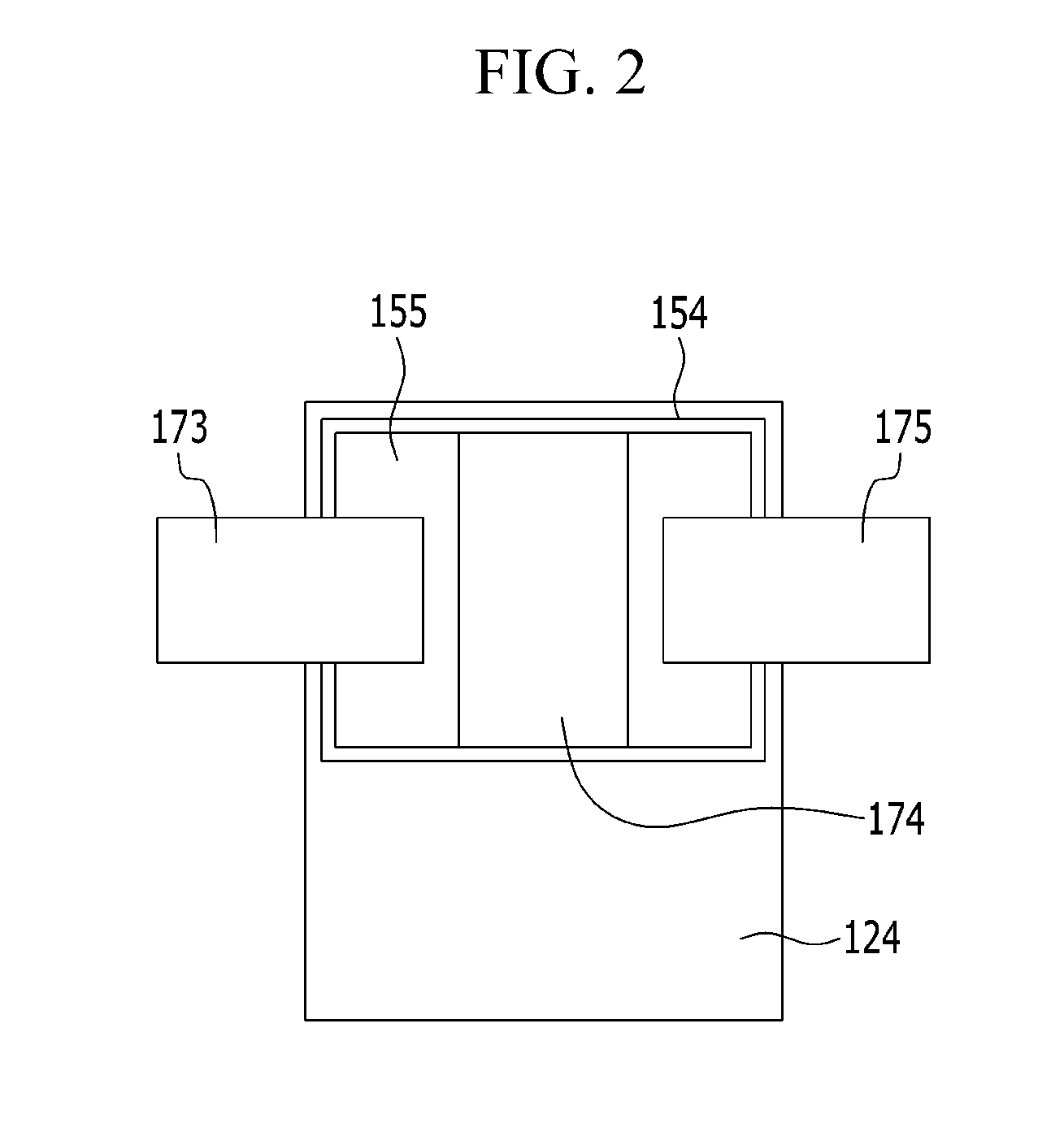

Thin film transistor array panel and manufacturing method thereof

InactiveUS20150270408A1Simple manufacturing processUnified controlTransistorSolid-state devicesEngineeringSemiconductor

A thin film transistor array panel includes: a substrate; a first gate electrode on the substrate; a gate insulating layer on the gate electrode; a semiconductor on the gate insulating layer; an etch stopper on a channel of the semiconductor; a source electrode and a drain electrode on the semiconductor and facing each other with respect to the first gate electrode; and a second gate electrode on the channel of the semiconductor and in a same layer as the source electrode and the drain electrode. The second gate electrode is electrically separated from the source electrode and the drain electrode.

Owner:SAMSUNG DISPLAY CO LTD

Junction field effect thin film transistor

ActiveUS20080001184A1Reduced carrier mobilityTransistorSemiconductor/solid-state device manufacturingOptoelectronicsSemiconductor

Example embodiments are directed to a junction field effect thin film transistor (JFETFT) including a first electrode formed on a substrate, a first conductive first gate semiconductor pattern formed on the first gate electrode, a second conductive semiconductor channel layer formed on the substrate and the first conductive first gate semiconductor pattern, and source and drain electrodes formed on the second conductive semiconductor pattern and located at both sides of the first conductive gate semiconductor pattern. The JFETFT may further include a first conductive second gate semiconductor pattern formed on a portion of the second conductive semiconductor channel layer between the source electrode and the drain electrode, and a second gate electrode formed on the first conductive second gate semiconductor pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

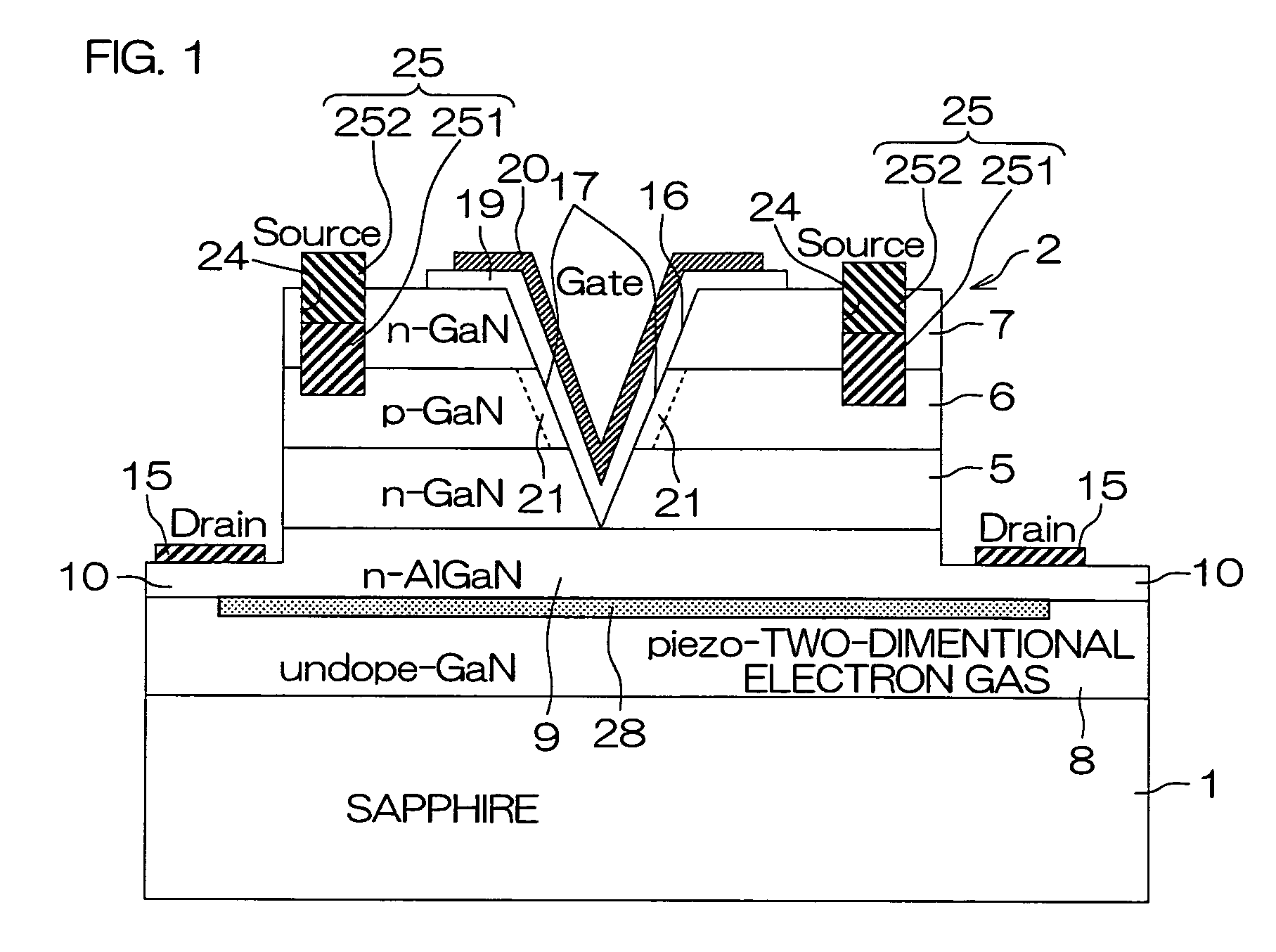

Field-Effect Transistor, Semiconductor Device, a Method for Manufacturing Them, and a Method of Semiconductor Crystal Growth

InactiveUS20070278532A1High crystallinityQuick changeSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialCompound (substance)

A field-effect transistor which comprises a buffer layer and a barrier layer each of which is made of a Group III nitride compound semiconductor and has a channel at the interface inside of the buffer layer to the barrier layer, wherein the barrier layer has multiple-layer structure comprising an abruct interface providing layer which composes the lowest semiconductor layer in said barrier layer and whose composition varies rapidly at the interface of said buffer layer, and an electrode connection plane providing layer which constructs the uppermost semiconductor layer and whose upper surface is formed flat.

Owner:TOYODA GOSEI CO LTD

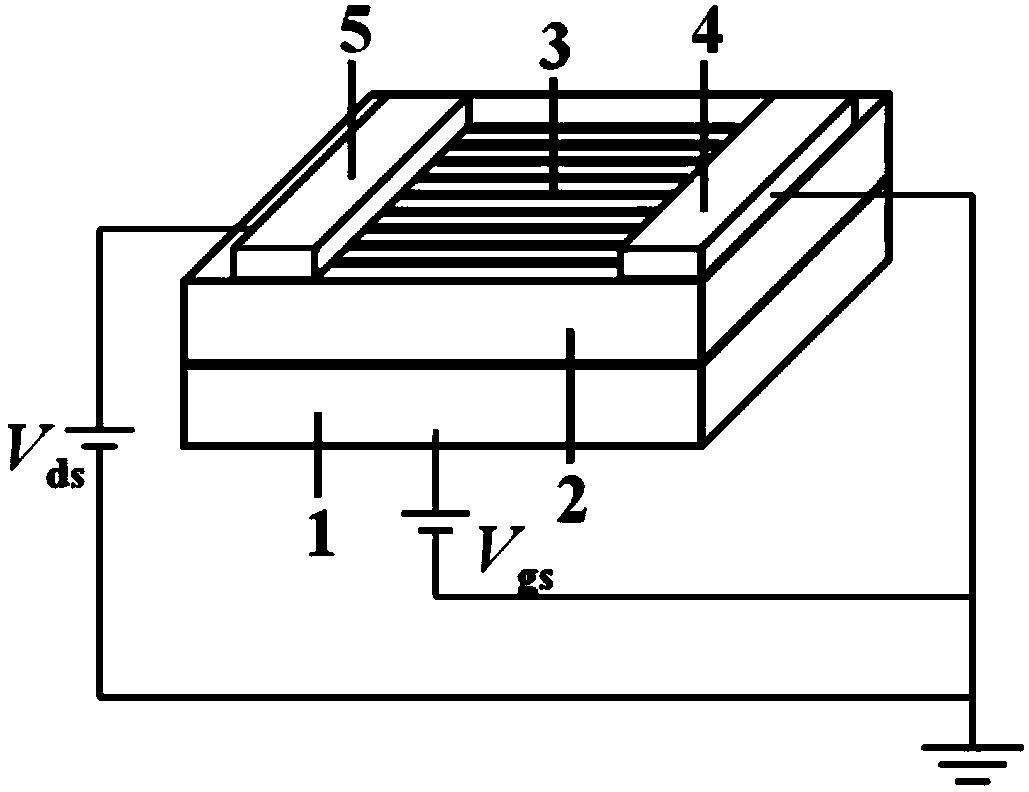

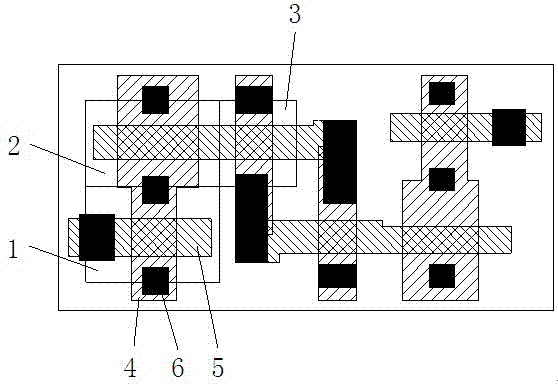

Ferro-electric field effect transistor based on structured carbon nano tube striped array and manufacturing method thereof

InactiveCN104009091AIncrease the on-state currentHigh switching ratioNanoinformaticsSemiconductor/solid-state device manufacturingOrganic field-effect transistorCharge carrier mobility

The invention discloses a ferro-electric field effect transistor based on a structured carbon nano tube striped array and a manufacturing method of the ferro-electric field effect transistor. According to the unit structure of the transistor, a bottom electrode layer (1) is arranged on the bottom layer, a ferro-electric film insulated gate layer (2) and a structured carbon nano tube striped array channel layer (3) are sequentially arranged on the middle layer, and a top layer is arranged on the structured carbon nano tube striped array channel layer (3) and comprises a transistor source electrode (4) and a transistor drain electrode (5); carbon nano tubes are single-walled carbon nano tubes, or double-walled carbon nano tubes or multi-walled carbon nano tubes. According to the ferro-electric field effect transistor, the on-state current and the switch ratio are large, carrier mobility is high, the starting voltage is small, the storage window is wide, and meanwhile the ferro-electric field effect transistor has the advantages of being simple in structure and a buffering layer is not needed, interface contact between a ferro-electric layer and a semiconductor layer is good, and large-area soft devices are easy to obtain. The manufacturing method is simple in technology, convenient to operate and low in cost and dispense with expensive equipment, and large-area and large-scale industrial production is easy to realize.

Owner:XIANGTAN UNIV

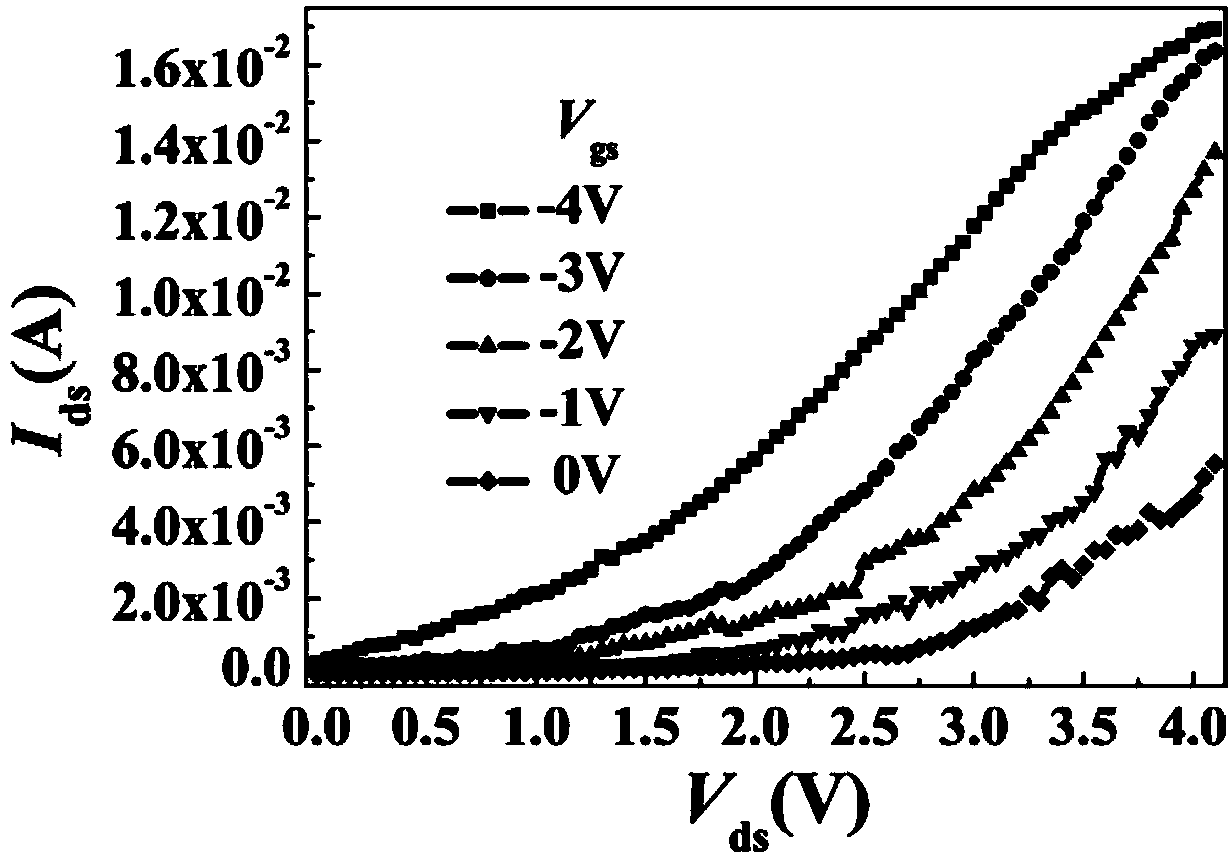

Field-effect type semiconductor device for power amplifier

InactiveUS7045412B2Low efficiencyReduce thicknessTransistorSemiconductor/solid-state device manufacturingAudio power amplifierImpurity

In a semiconductor multi-layer structure in which a first SiGe layer having a first conductivity-type and high impurity concentration, a second SiGe layer having the first conductivity-type and a low impurity concentration and a Si layer having a low impurity concentration are formed one on another in this order on a Si substrate of the first conductivity-type, a channel is formed in a part of the Si layer and a source electrode passes through the second SiGe layer of low impurity concentration to electrically contact the first SiGe layer of high impurity concentration or the substrate.

Owner:TESSERA ADVANCED TECH

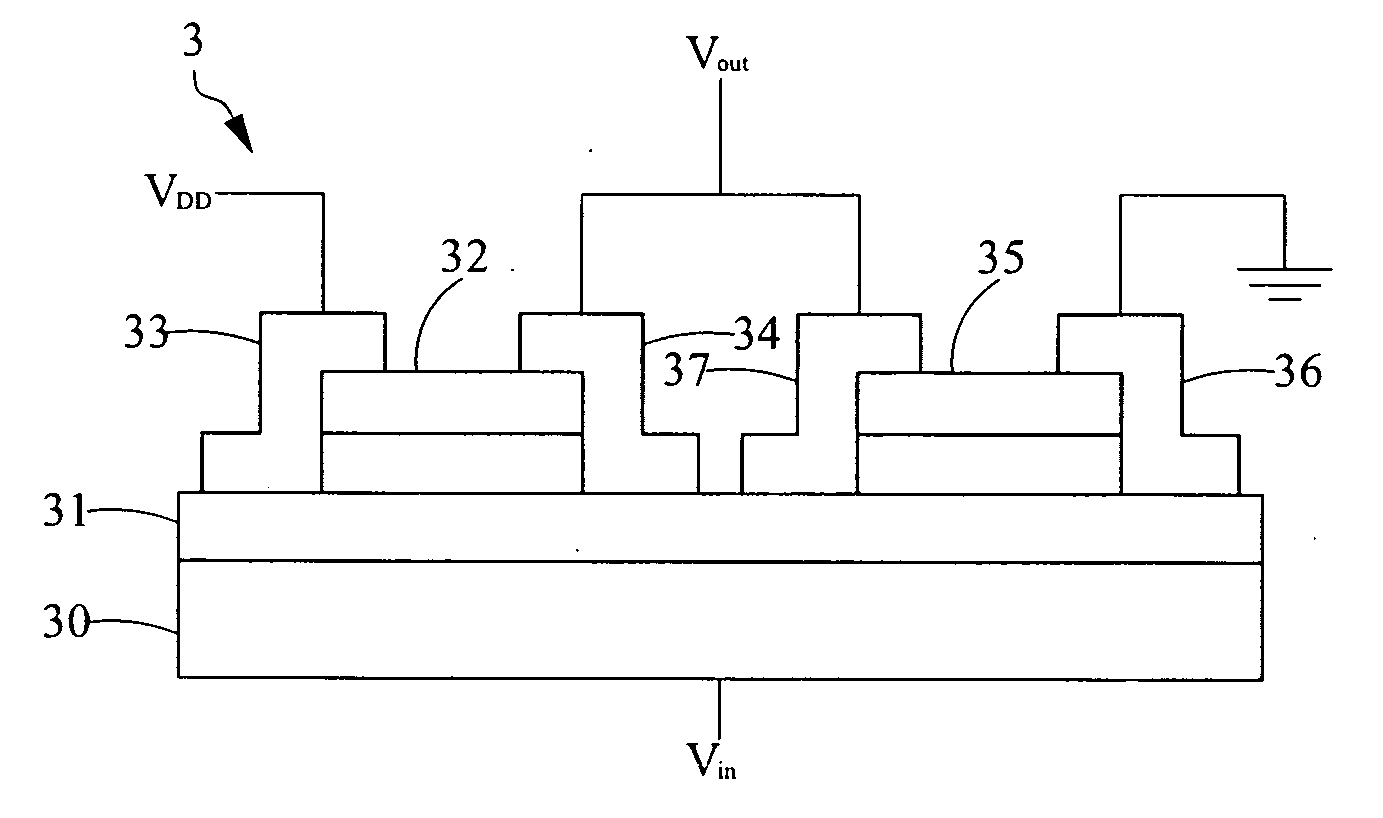

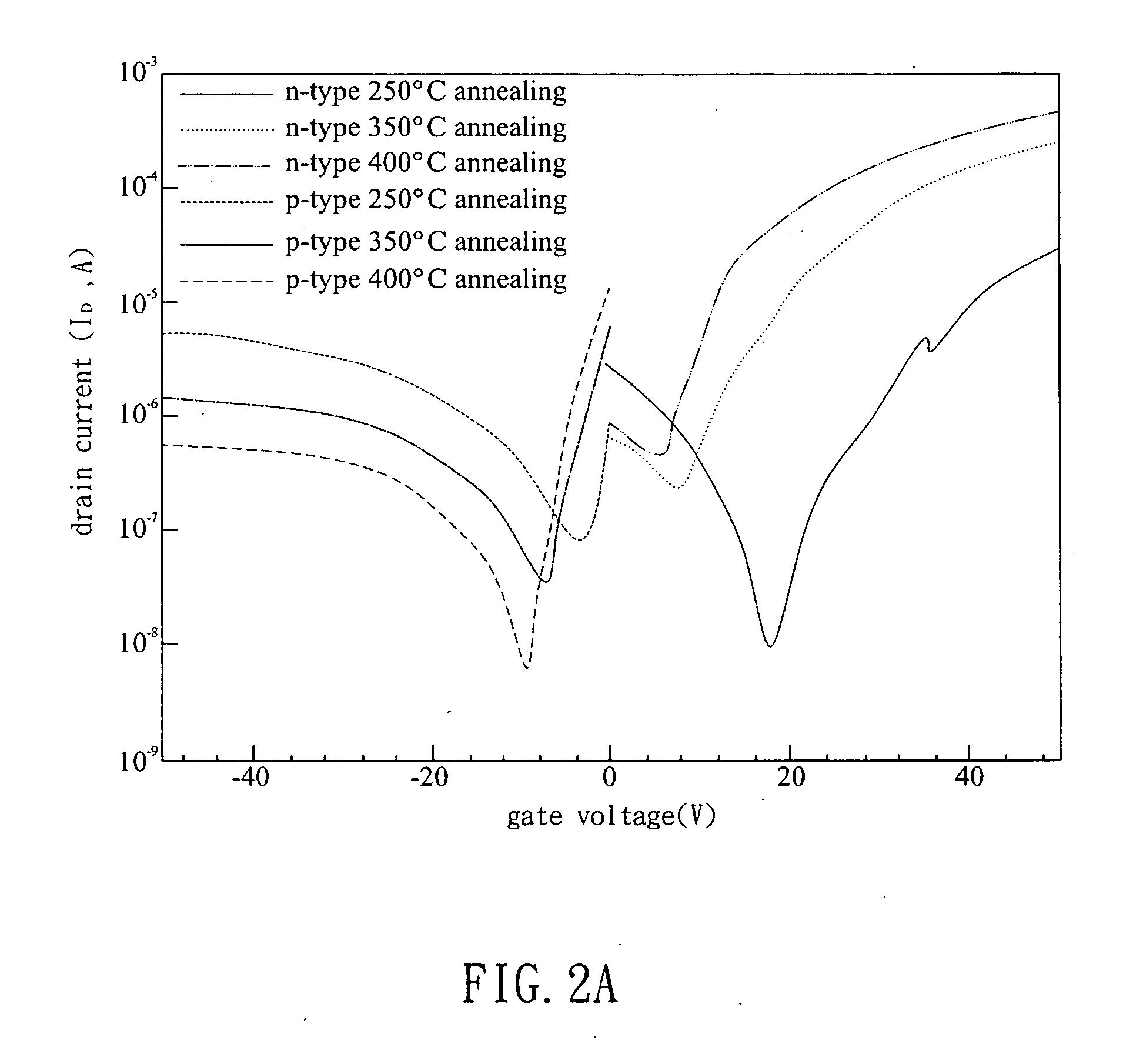

High-Gain Complementary Inverter with Ambipolar Thin Film Transistors and Fabrication Thereof

ActiveUS20120298982A1Reduced carrier mobilityLarge operating voltageSolid-state devicesSemiconductor devicesEngineeringSilicon dioxide

The present invention relates to a high gain complementary inverter with ambipolar thin film transistors and fabrication thereof, comprising: a gate layer, a silica layer, a first active layer, a first source, a first drain, a second active layer, a second source and a second drain for fabrication cost and complexity reduction.

Owner:NAT CHIAO TUNG UNIV

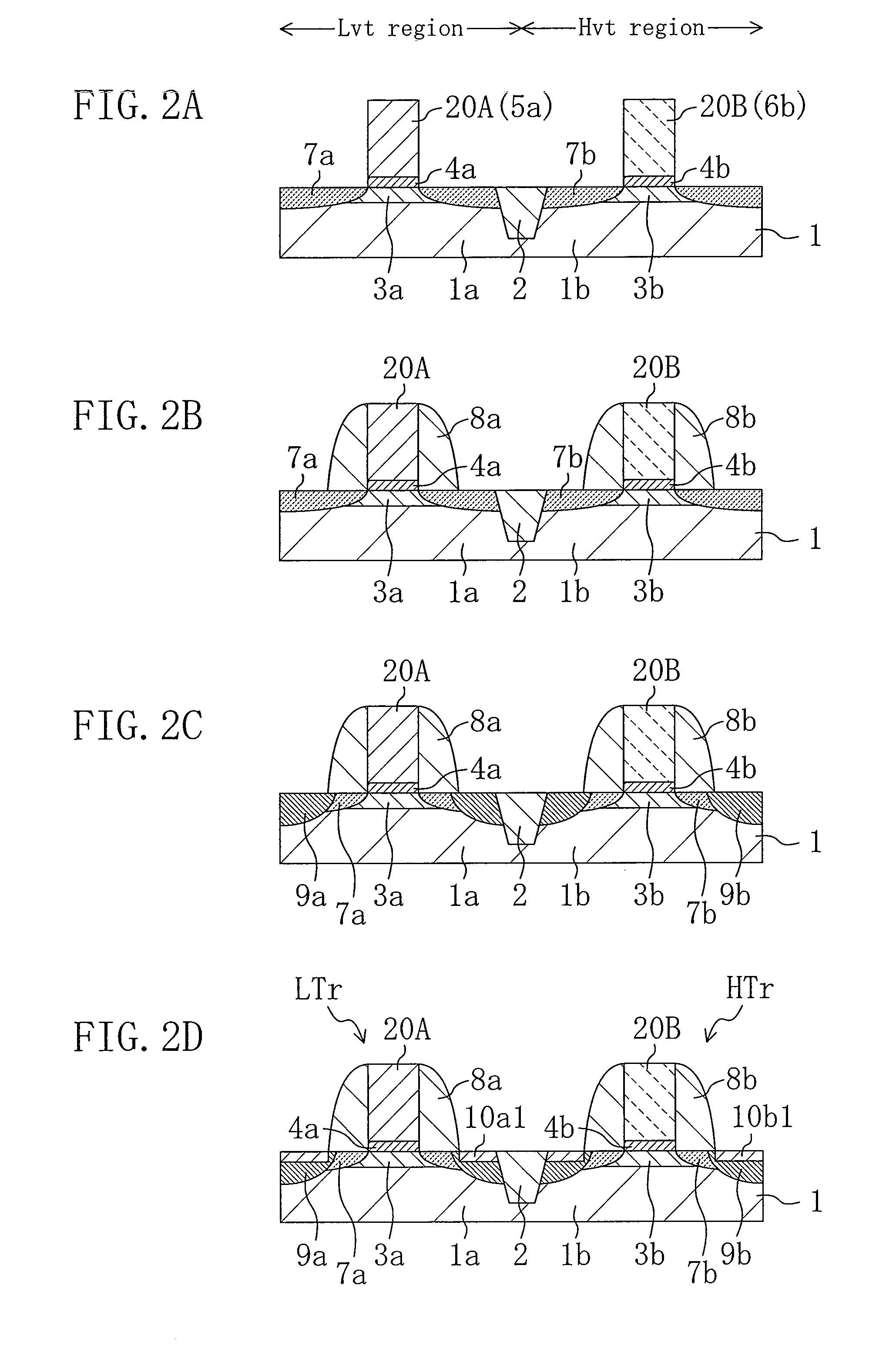

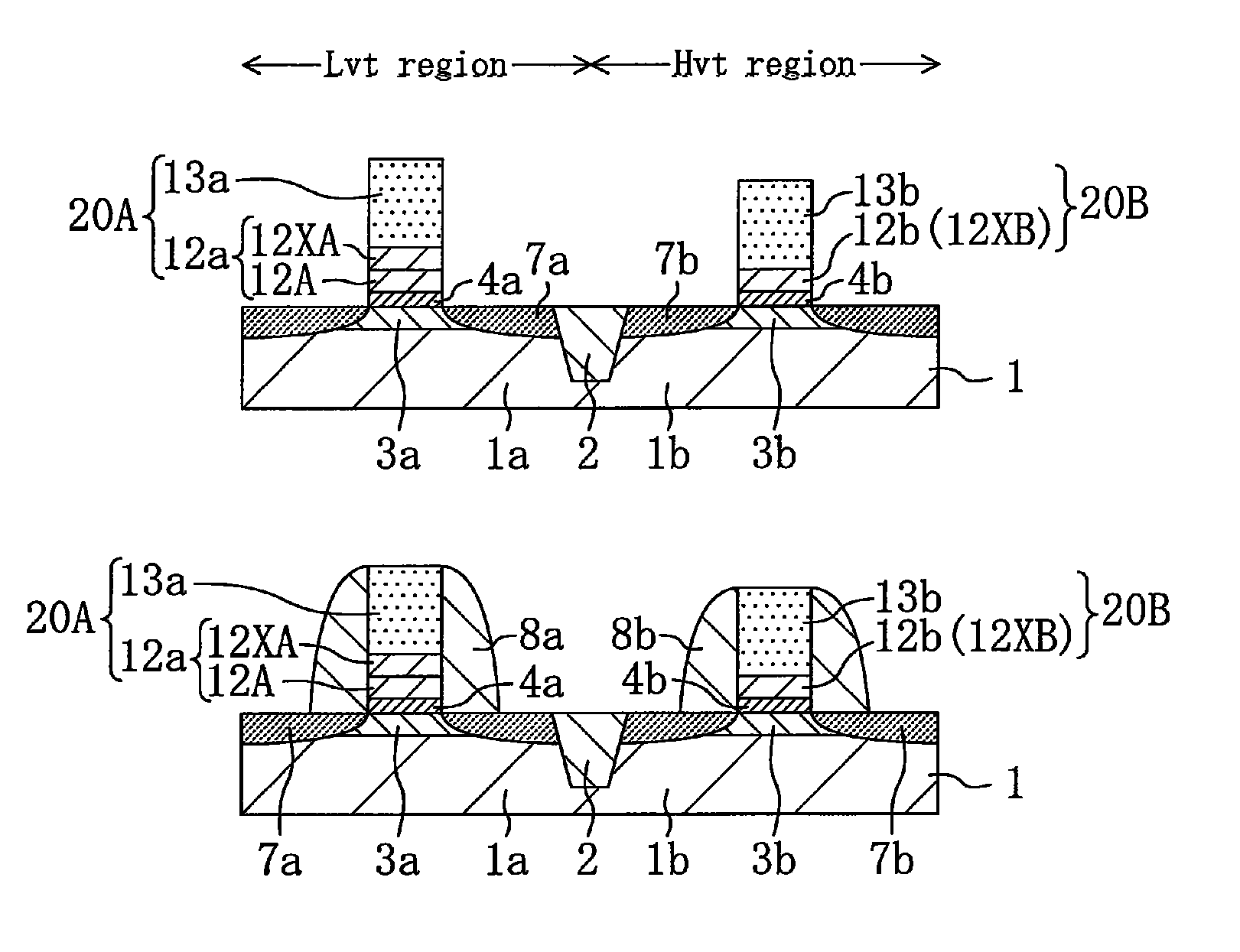

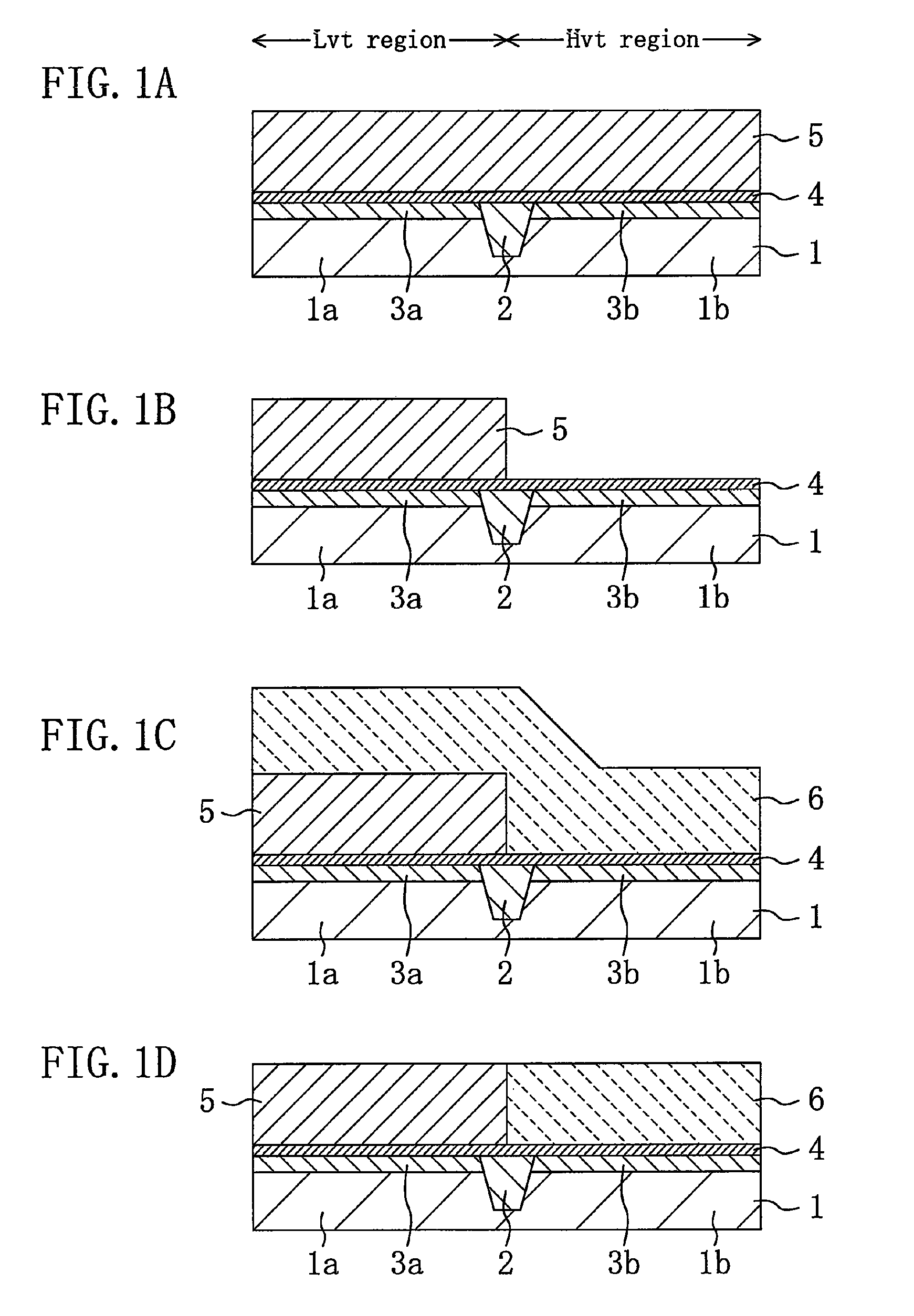

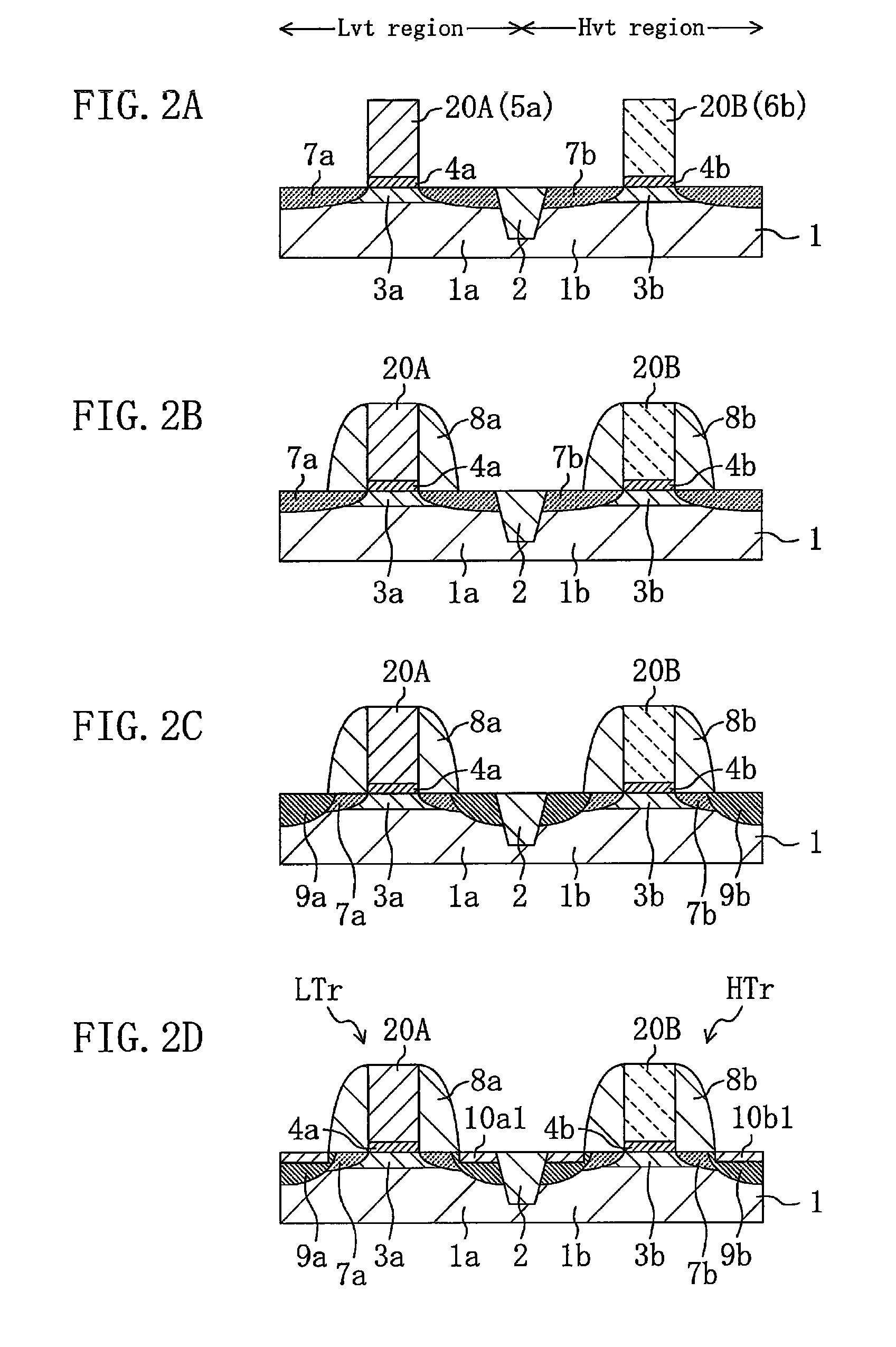

Semiconductor device and its fabrication method

ActiveUS20090189225A1High precisionHigh performanceTransistorSolid-state devicesEngineeringSemiconductor

A semiconductor device includes a first MIS transistor, and a second MIS transistor having a threshold voltage higher than that of the first MIS transistor. The first MIS transistor includes a first gate insulating film made of a high-k insulating film formed on a first channel region, and a first gate electrode having a first conductive portion provided on and contacting the first gate insulating film and a second conductive portion. The second MIS transistor includes a second gate insulating film made of the high-k insulating film formed on a second channel region, and a second gate electrode having a third conductive portion provided on and contacting the second gate insulating film and a fourth conductive portion. The third conductive portion has a film thickness smaller than that of the first conductive portion, and is made of the same composition material as that of the first conductive portion.

Owner:PANNOVA SEMIC

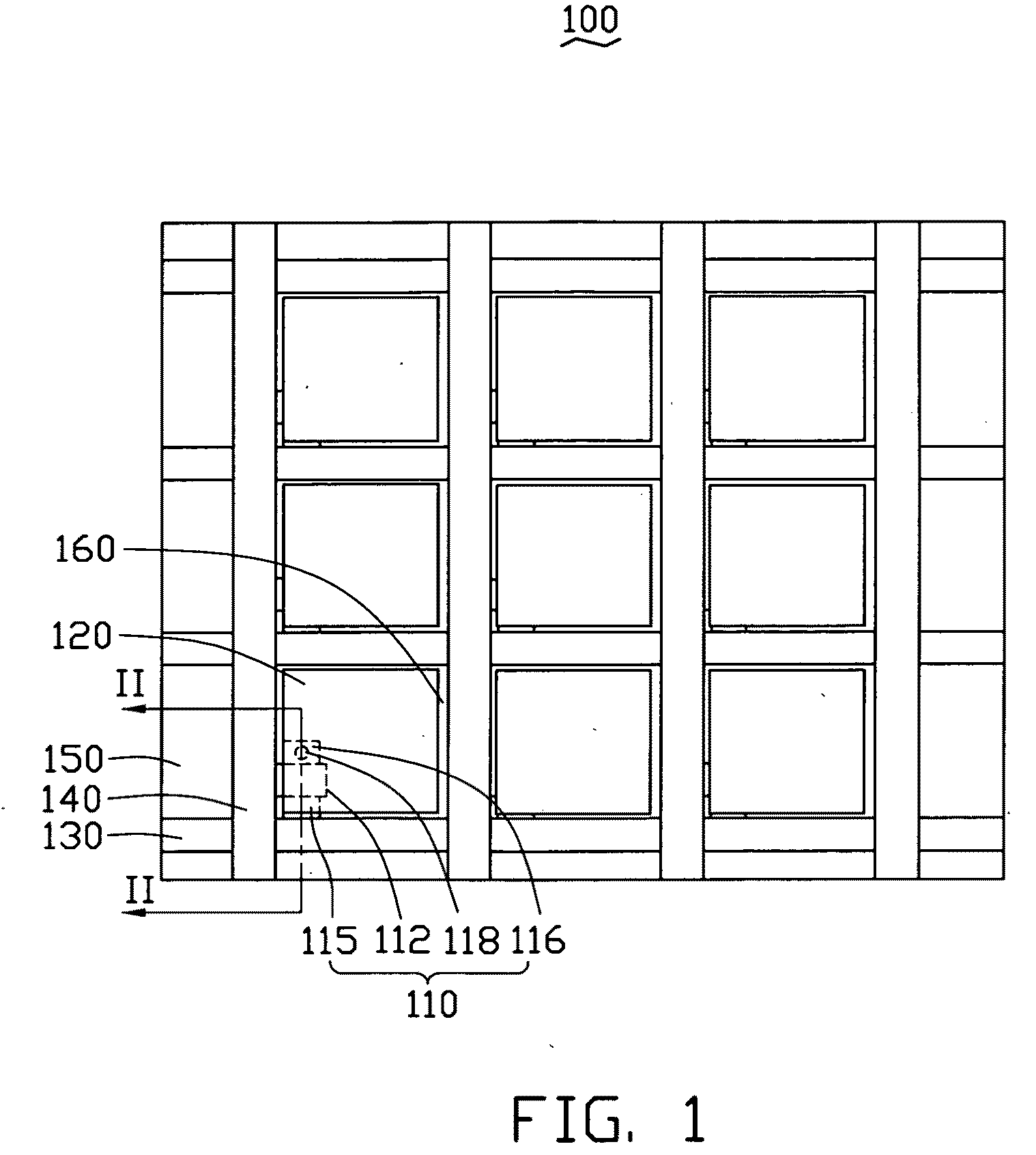

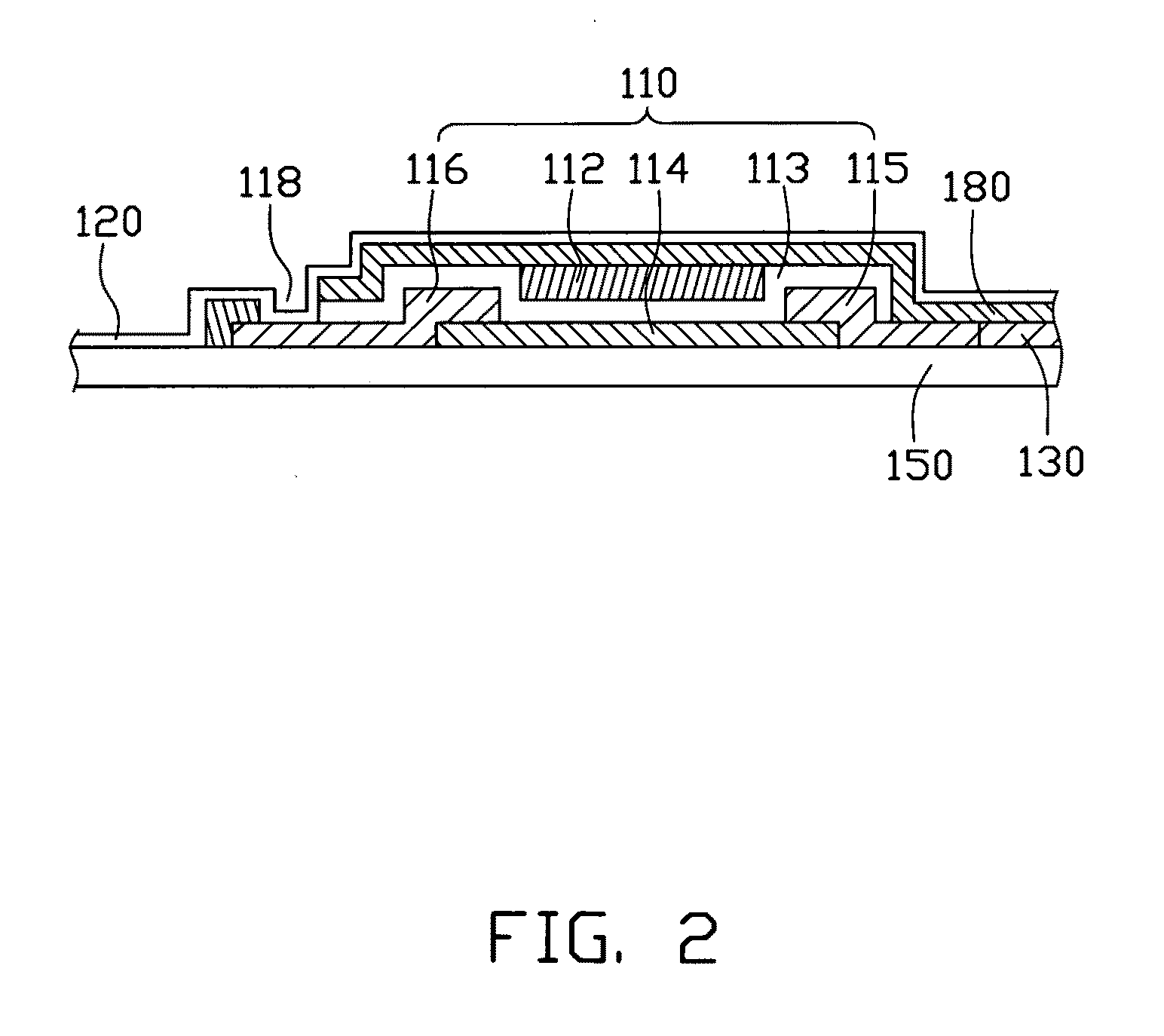

Thin film transistor panel

InactiveUS20090302324A1Reduced carrier mobilityLow mobilityTransistorMaterial nanotechnologyCarbon nanotubeEngineering

A thin film transistor panel includes an insulating substrate. The insulating substrate includes a number of parallel source lines, a number of parallel gate lines crossed with the source lines, and a number of girds defined by the source lines and the gate lines. Each of the girds includes a pixel electrode and a thin film transistor. The thin film transistor includes a source electrode, a drain electrode, a semiconducting layer, and a gate electrode. The source electrode is connected with one of the source lines defining the grid. The drain electrode is spaced from the source electrode and connected with the pixel electrode. The semiconducting layer is connected with the source electrode and the drain electrode. The semiconducting layer includes a semiconducting carbon nanotube layer. The gate electrode is connected with one of the gate lines defining the grid.

Owner:TSINGHUA UNIV +1

Semiconductor device including MISFETs having different threshold voltages

ActiveUS8129794B2Reduced carrier mobilityReduce the driving forceTransistorSolid-state devicesPower semiconductor deviceEngineering

A semiconductor device includes a first MIS transistor, and a second MIS transistor having a threshold voltage higher than that of the first MIS transistor. The first MIS transistor includes a first gate insulating film made of a high-k insulating film formed on a first channel region, and a first gate electrode having a first conductive portion provided on and contacting the first gate insulating film and a second conductive portion. The second MIS transistor includes a second gate insulating film made of the high-k insulating film formed on a second channel region, and a second gate electrode having a third conductive portion provided on and contacting the second gate insulating film and a fourth conductive portion. The third conductive portion has a film thickness smaller than that of the first conductive portion, and is made of the same composition material as that of the first conductive portion.

Owner:PANNOVA SEMIC

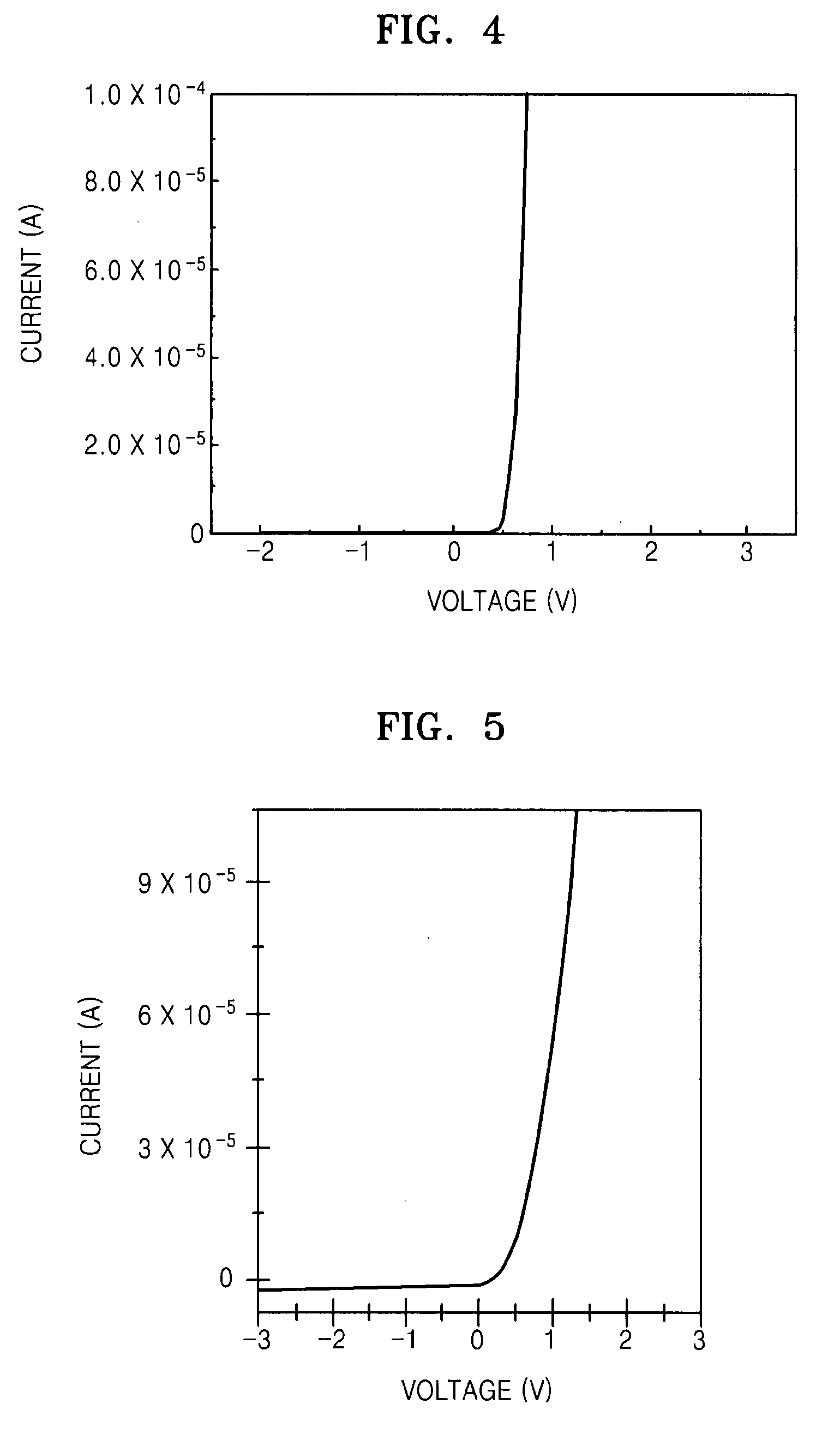

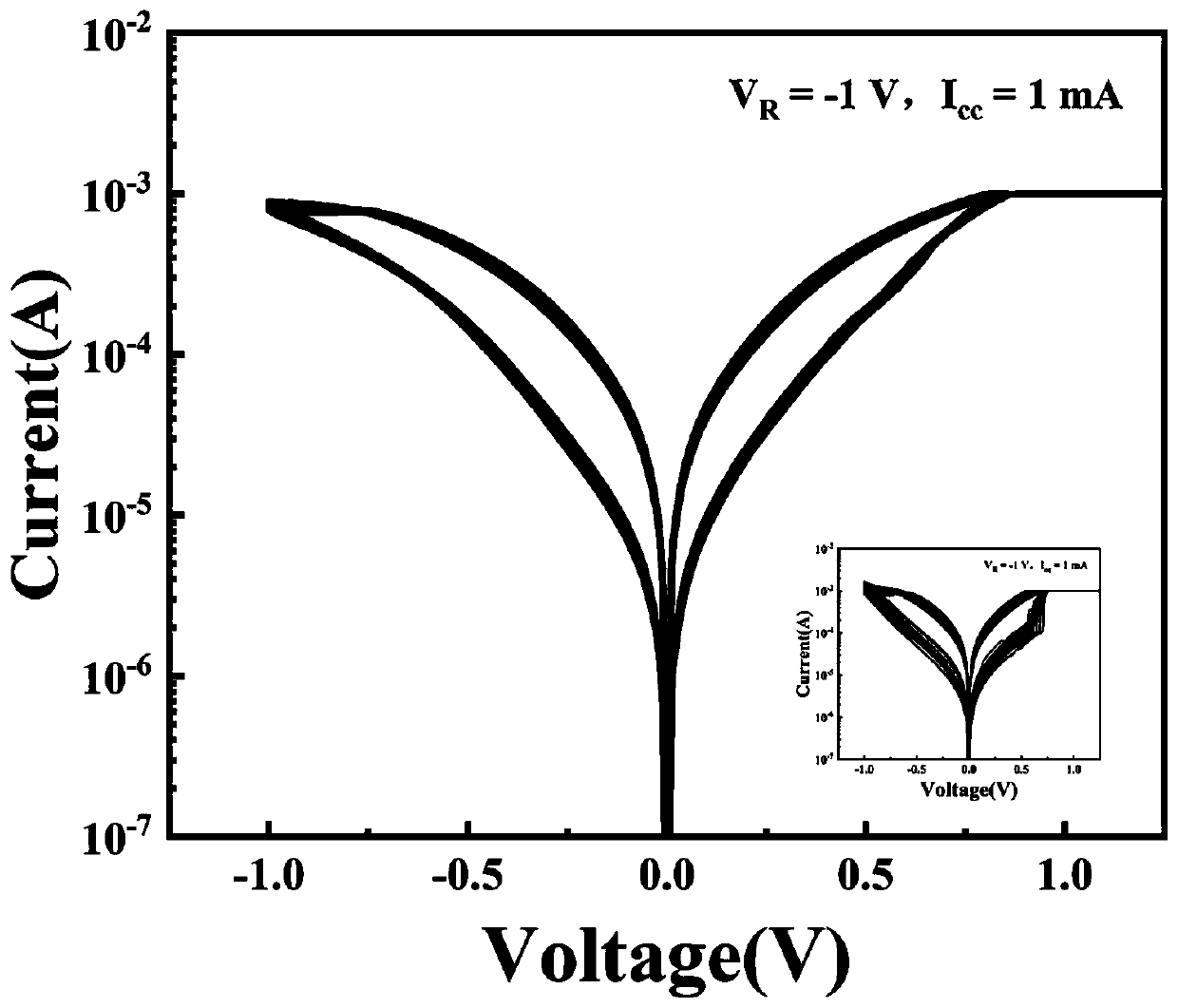

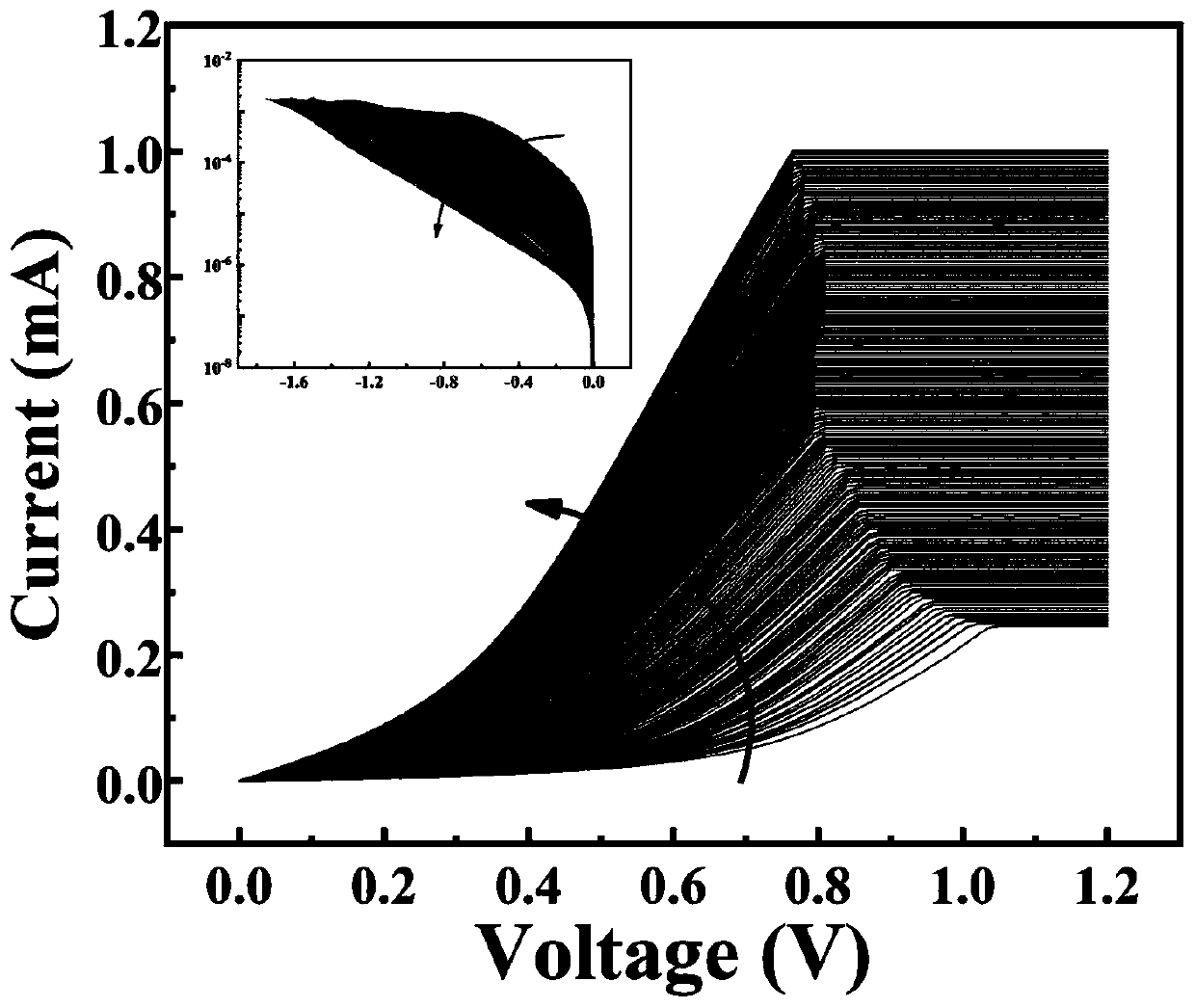

Analog HfOx/HfOy homojunction memristor and regulation and control method thereof

ActiveCN110911559AHigh oxygen vacancy mobilityLower resistanceSemiconductor/solid-state device testing/measurementDigital storageElectronic synapseCondensed matter physics

The invention belongs to the technical field of microelectronic devices. The invention discloses an analog HfOx / HfOy homojunction memristor and a regulation and control method thereof. The homojunction memristor comprises a lower electrode layer, a functional layer and an upper electrode layer which are sequentially stacked from bottom to top, and the functional layer is an HfOx / HfOy homojunctionfunctional layer formed by stacking an HfOx layer and an HfOy layer from bottom to top; for the HfOx / HfOy homojunction functional layer, 1.6<x<1.8, 1.9<y<2, and the thickness of the HfOx layer is larger than that of the HfOy layer. According to the invention, the key device structure, especially the functional layer composition and the like, is improved; the hafnium oxide lamination with high / lowoxygen vacancies grown in a stacked manner is used as the resistive function layer, and compared with the prior art, the technical problems of small resistance gradual change window, low operation speed and poor consistency of an analog memristor and an electronic synaptic bionic device based on the analog memristor can be effectively solved.

Owner:HUAZHONG UNIV OF SCI & TECH

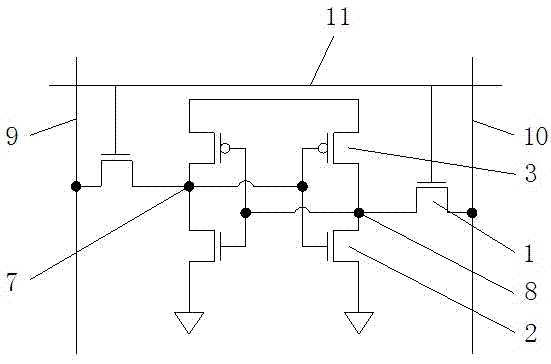

Method for improving write redundancy of high SRAM (static random access memory)

ActiveCN102738084AIncrease the tensile stressIncrease the equivalent resistanceSemiconductor/solid-state device manufacturingOxide semiconductorMetal

The invention discloses a method for improving write redundancy of a high SRAM (static random access memory). An NMOS (n-channel metal oxide semiconductor), a PMOS (p-channel metal oxide semiconductor) and an upper pulling pipe with cover layers are involved. The method comprises the following steps of: firstly simultaneously removing the cover layers of the NMOS device and the upper pulling pipe; and carrying out carbon injection on the PMOS and the upper pulling pipe with the cover layers so that a source drain end of the NMOS and a source drain end of the upper pull pipe form a crystal lattice structure and the tensile stress in a channel direction is improved. Through the method for improving the write redundancy of the high SRAM, disclosed by the invention, a carbon injection process is utilized to the source drain end of the upper pull pipe so that the tensile stress of the upper pull pipe in the channel direction is improved, the carrier mobility of the upper pull pipe is effectively reduced, the equivalent resistance of the upper pull pipe is increased, and simultaneously the write redundancy of an RAM (random-access memory) is improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Organic light emitting display device and preparation method thereof

ActiveCN104752470AStable in natureEasy to useSolid-state devicesSemiconductor/solid-state device manufacturingUltravioletDisplay device

The invention discloses an organic light emitting display device and a preparation method thereof. The organic light emitting display device comprises a substrate, and a thin film transistor and an organic light emitting diode arranged on the substrate, and a first amorphous silicon layer is directly arranged on a metal oxide semiconductor layer in the thin film transistor. The organic light emitting display device is capable of preventing source / drain electrode layer patterning damaging the metal oxide semiconductor layer and effectively preventing the ultraviolet emitting to the metal oxide semiconductor, and the structure of the organic light emitting display device is effectively simplified. The preparation method for the organic light emitting display device is capable of simultaneously realizing the purposes of etching blocking layer and ultraviolet blocking through arranging the amorphous silicon layer on the metal oxide semiconductor layer, the preparation technique is effectively simplified, and the product yield and economical benefit are improved.

Owner:KUNSHAN GO VISIONOX OPTO ELECTRONICS CO LTD

Carrier transport material and preparation method thereof, and QLED device

ActiveCN109980099AReduce defectsSimple processSolid-state devicesSemiconductor/solid-state device manufacturingElectron holeCharge carrier mobility

The present invention belongs to the technical field of quantum dots, especially relates to a carrier transport material and a preparation method thereof, and a QLED device. The carrier transport material comprises metal-oxide semiconductor nanocrystallines modified with an alkoxy silane coupling reagent, the structural general formula is H2NRSi(OM)3, wherein M is the metal-oxide semiconductor nanocrystalline, and R is a non-alkoxy carbon chain in the alkoxy silane coupling reagent. The carrier transport material can perform passivation of the surface of the metal-oxide semiconductor nanocrystalline for isolating from water and oxygen to reduce the negative influences of the surface defects on the hole and electron electron recombination in the quantum dots, increase the distances betweenthe metal-oxide semiconductor nanocrystallines, weaken the carrier mobility of the metal-oxide semiconductor nanocrystallines, have a carrier balance effect on the device and finally improve the luminous efficiency of the device.

Owner:TCL CORPORATION

Method to planarize and reduce defect density of silicon germanium

ActiveUS7427556B2Reduced carrier mobilityImprove flatnessPolycrystalline material growthSemiconductor/solid-state device manufacturingGas phaseVolumetric Mass Density

A method for blanket depositing a SiGe film comprises intermixing a silicon source, a germanium source and an etchant to form a gaseous precursor mixture. The method further comprises flowing the gaseous precursor mixture over a substrate under chemical vapor deposition conditions to deposit a blanket layer of epitaxial SiGe onto the substrate, whether patterned or un-patterned.

Owner:ASM IP HLDG BV

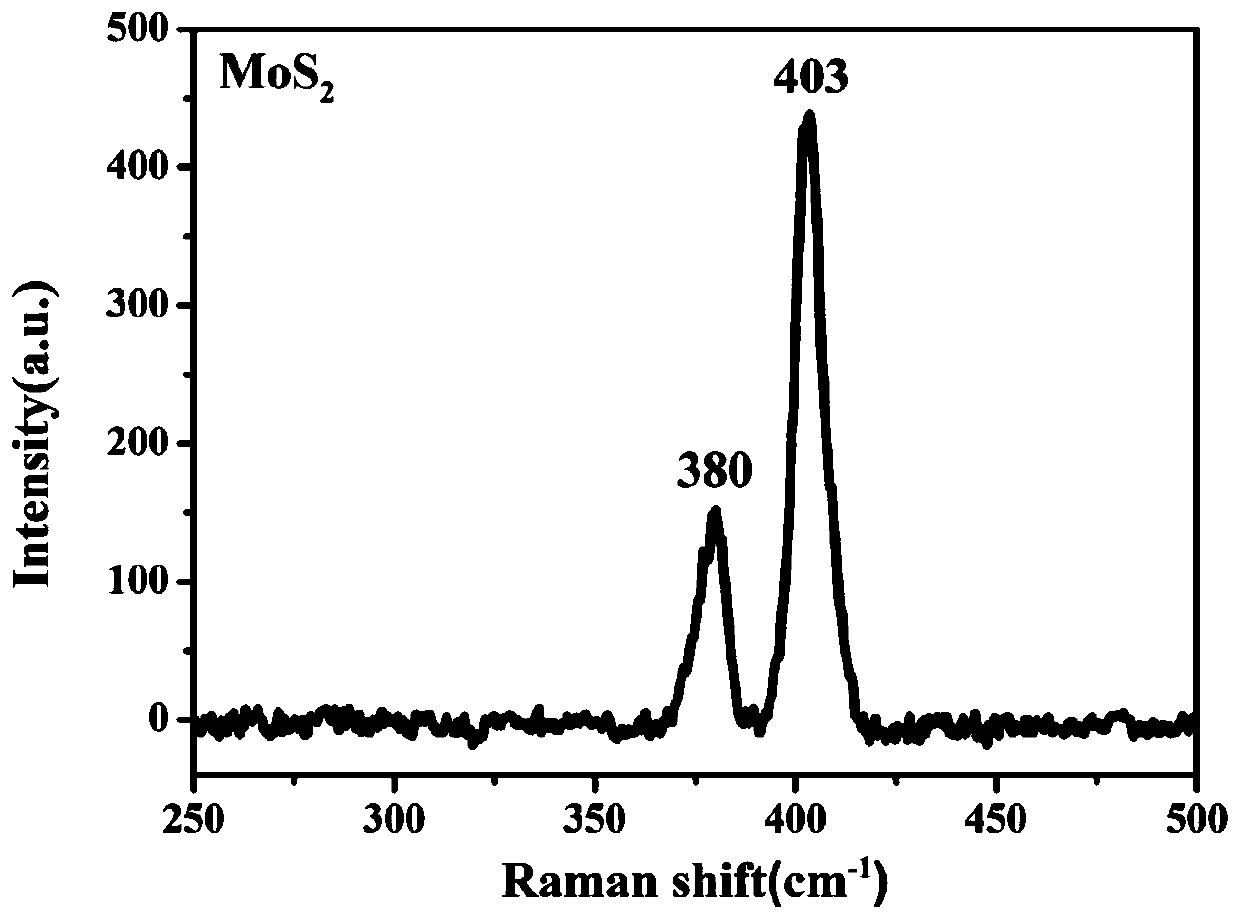

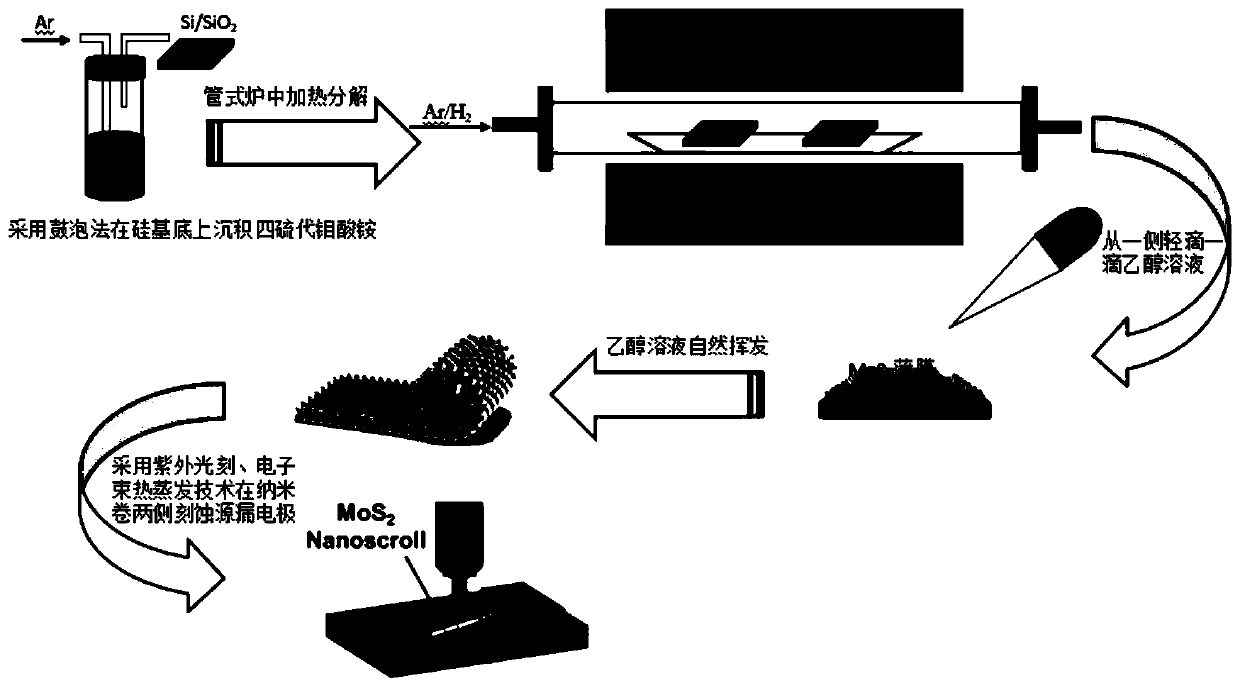

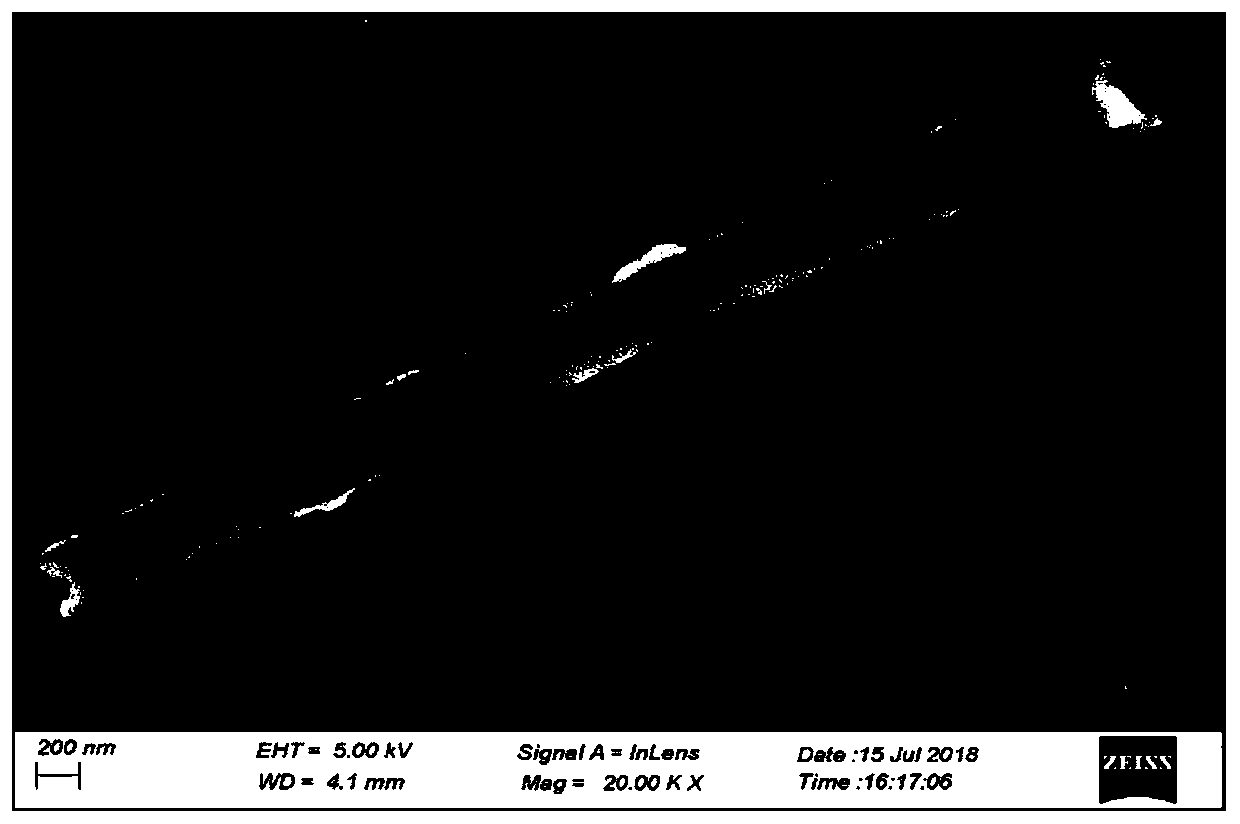

Photoelectric detector with two-dimensional transition metal sulfide film nanoscroll

InactiveCN110021674AImprove light responsivenessPromote absorptionMaterial nanotechnologyFinal product manufactureSurface tension gradientMetallic sulfide

The present invention discloses a photoelectric detector with a two-dimensional transition metal sulfide film nanoscroll, which is made by the following steps: firstly depositing ammonium tetrathiomolybdate on a silicon / silica substrate by a bubbling method, then growing monolayer disulphide on the surface of the substrate by a thermal decomposition method, afterwards putting a drop of ethanol solution gently on one side of the disulphide film, resulting in spontaneous curling of the disulphide film to form the nanoscroll helix structure since volatilization of the ethanol solution produces atemperature gradient and a surface tension gradient at interface contact, finally depositing gold electrodes on both sides of the nanoscroll by a thermal evaporator and connecting the gold electrodesat both sides by the nanoscroll to obtain the photoelectric detector based on the two-dimensional transition metal sulfide film nanoscroll (TMDC-NSs) helix structure. The photoelectric detector of thepresent invention has short photoresponse time, fast recovery time, good stability, low cost and controllability, large-scale production and great application value.

Owner:SHANDONG NORMAL UNIV

Organic electroluminescence device

ActiveUS8039121B2Improve efficiencyLong lastingDischarge tube luminescnet screensLamp detailsOrganic electroluminescenceOrganic chemistry

An organic electroluminescent device (1) including an anode (2), a cathode (6), and at least a first layer (3), a second layer (4), and a third layer (5) provided between the anode (2) and the cathode (6) in that order from the anode side. At least one of the first to third layers (3), (4), and (5) includes a phosphorescent compound. At least one of the first to third layers (3), (4), and (5) is an emitting layer. At least three compounds respectively forming the first layer (3), the second layer (4), and the third layer (5) other than the phosphorescent compound are compounds of the following formula (1).wherein R1 to R7 each represent a hydrogen atom or a substituent, provided that adjacent substituents may form a ring.

Owner:IDEMITSU KOSAN CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com