Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

36results about How to "Reduce EOT" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

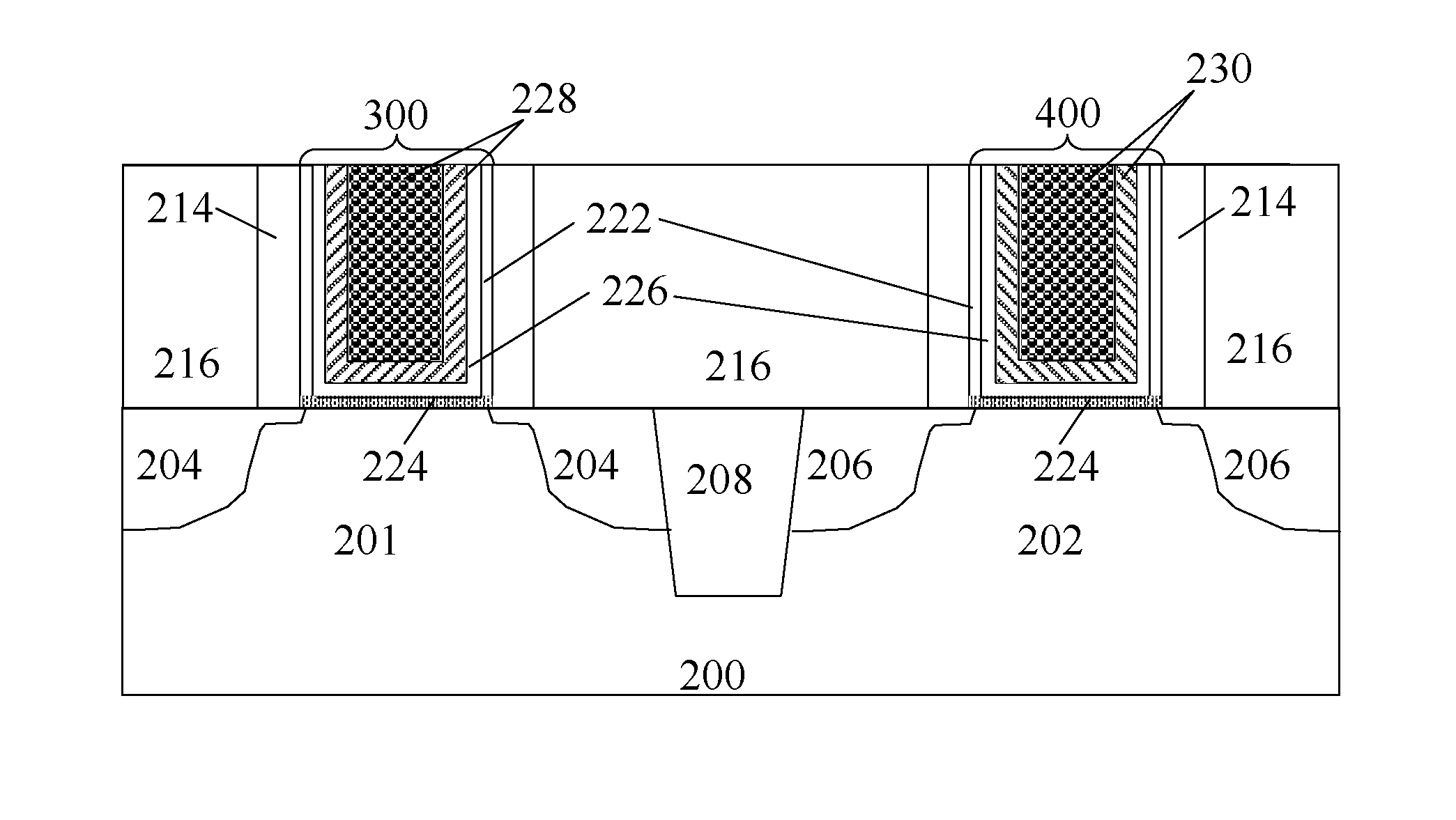

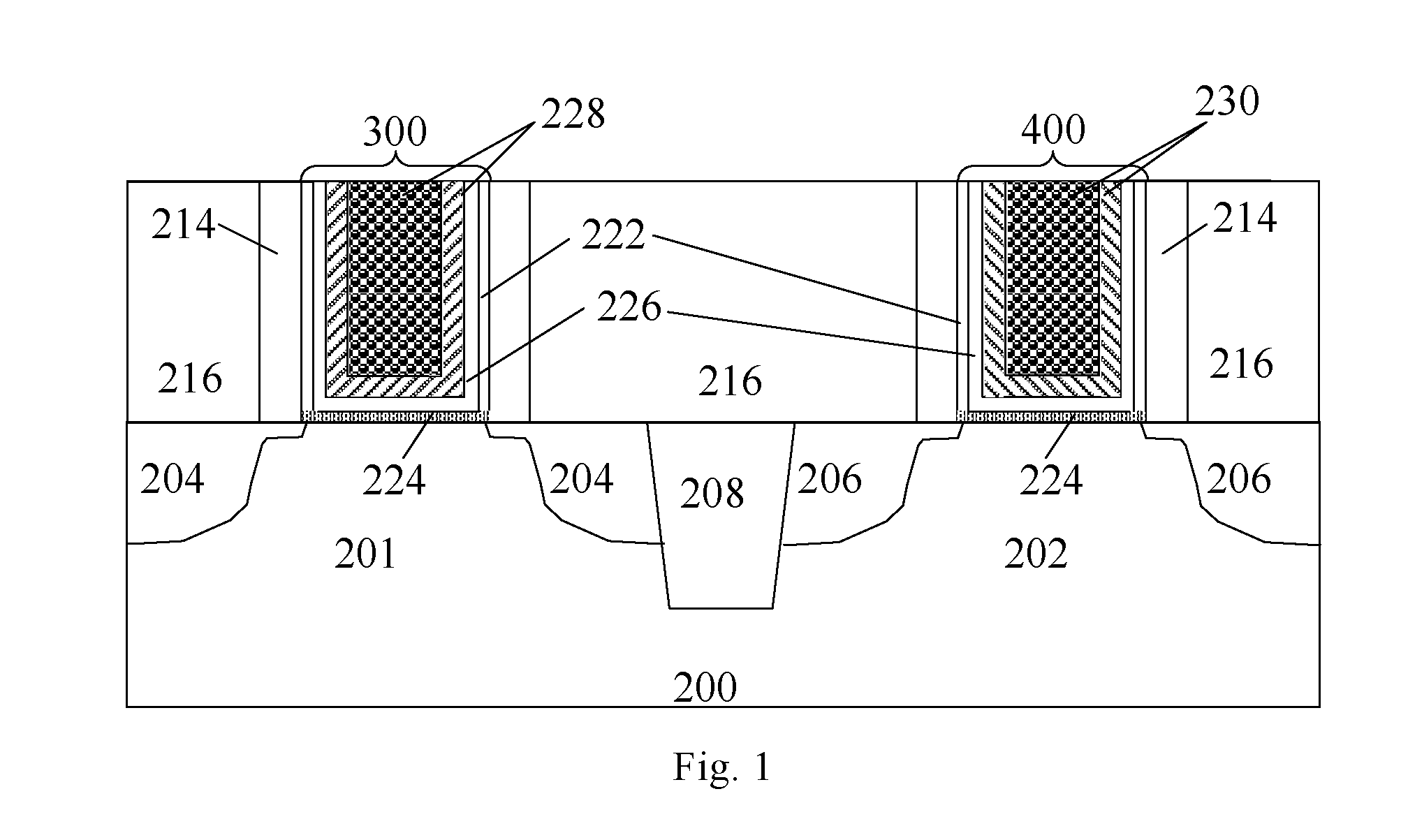

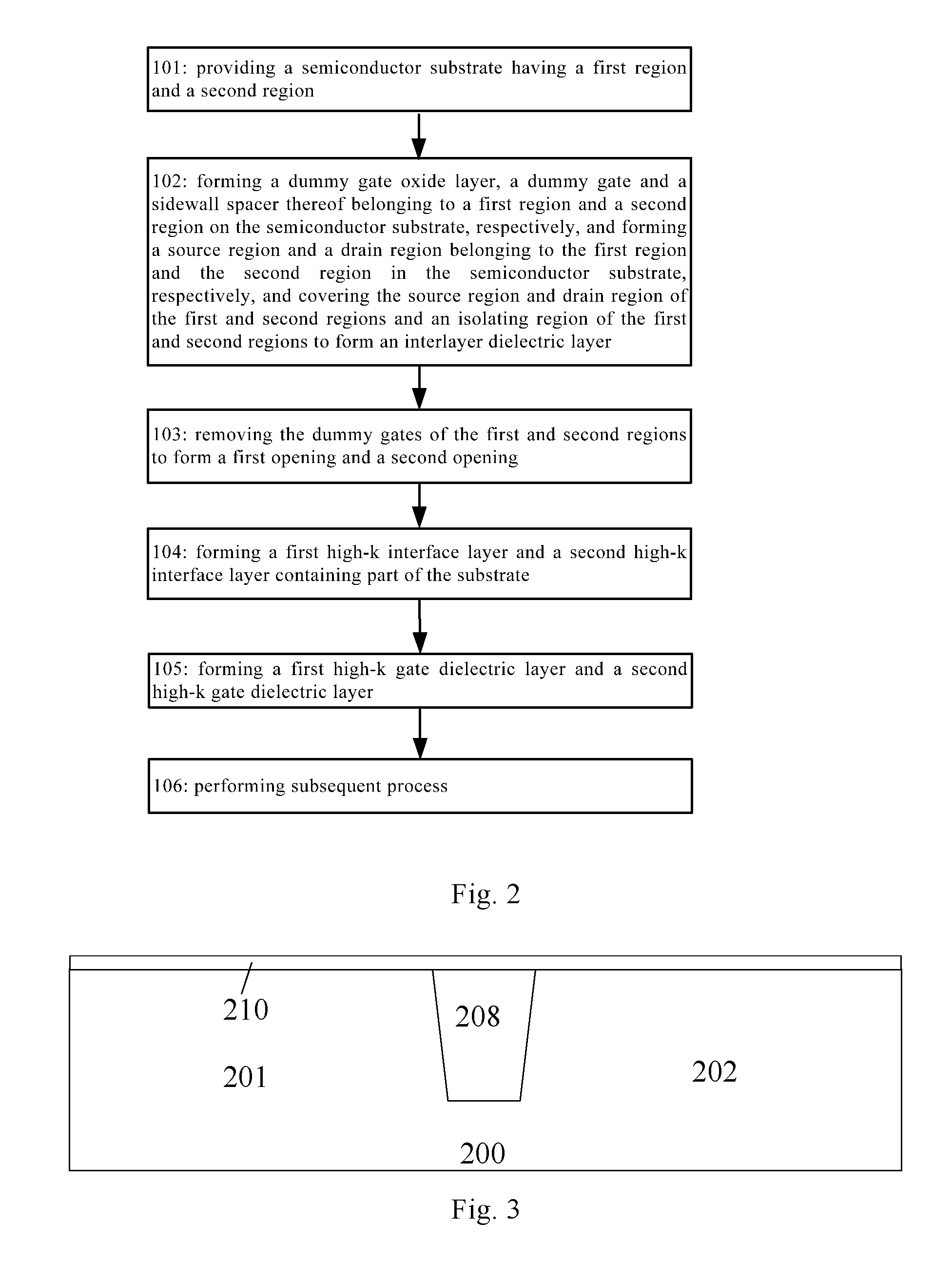

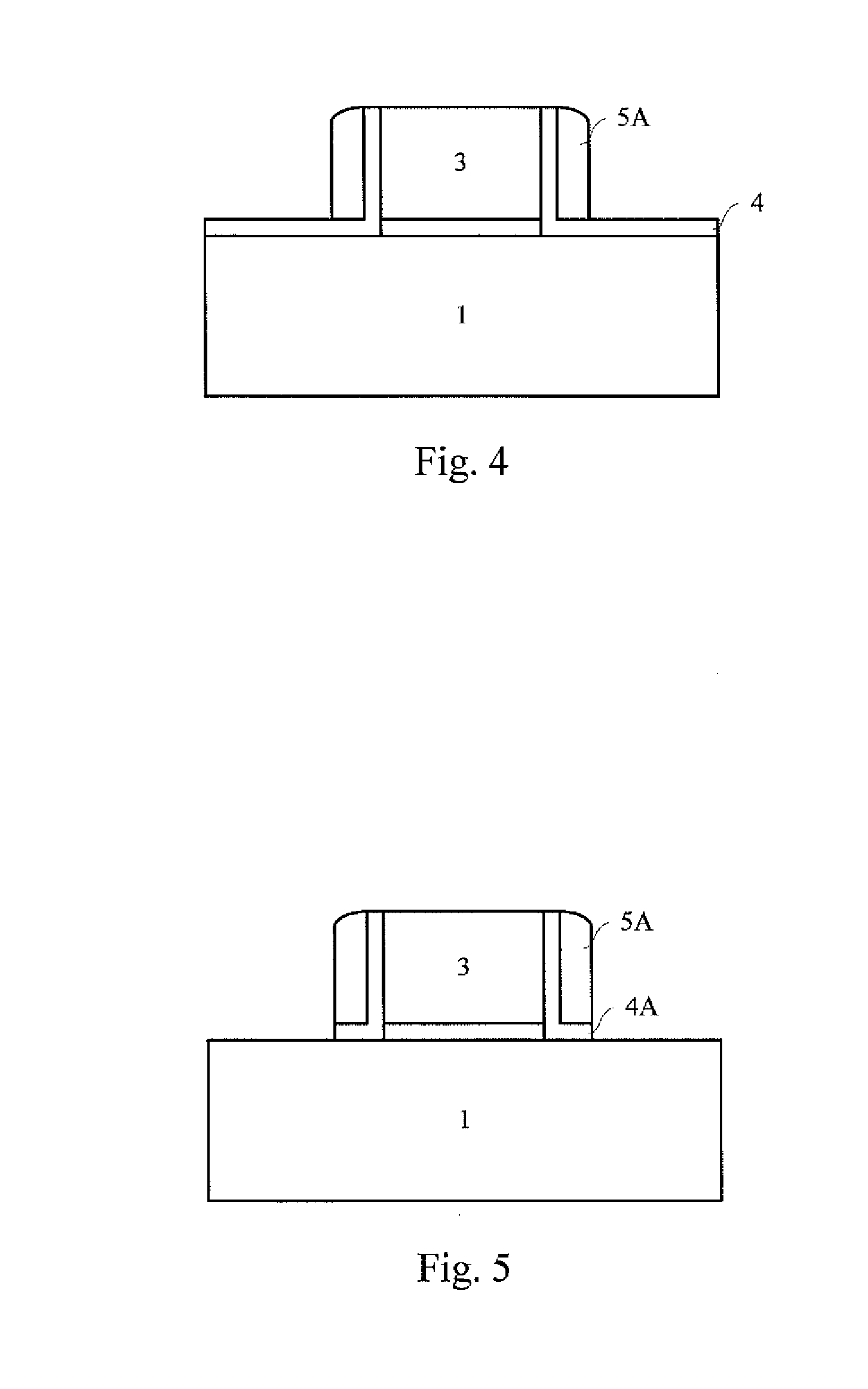

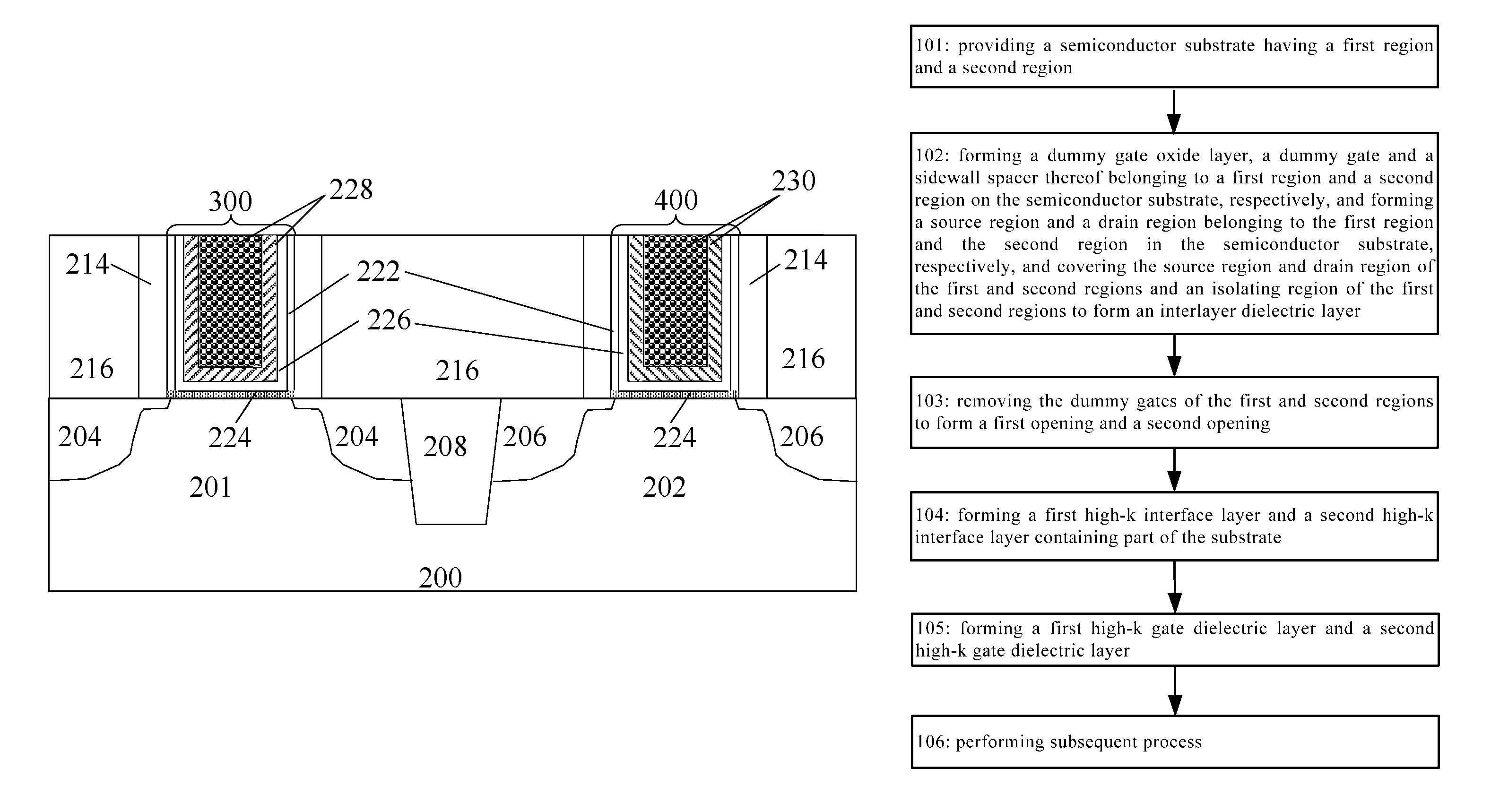

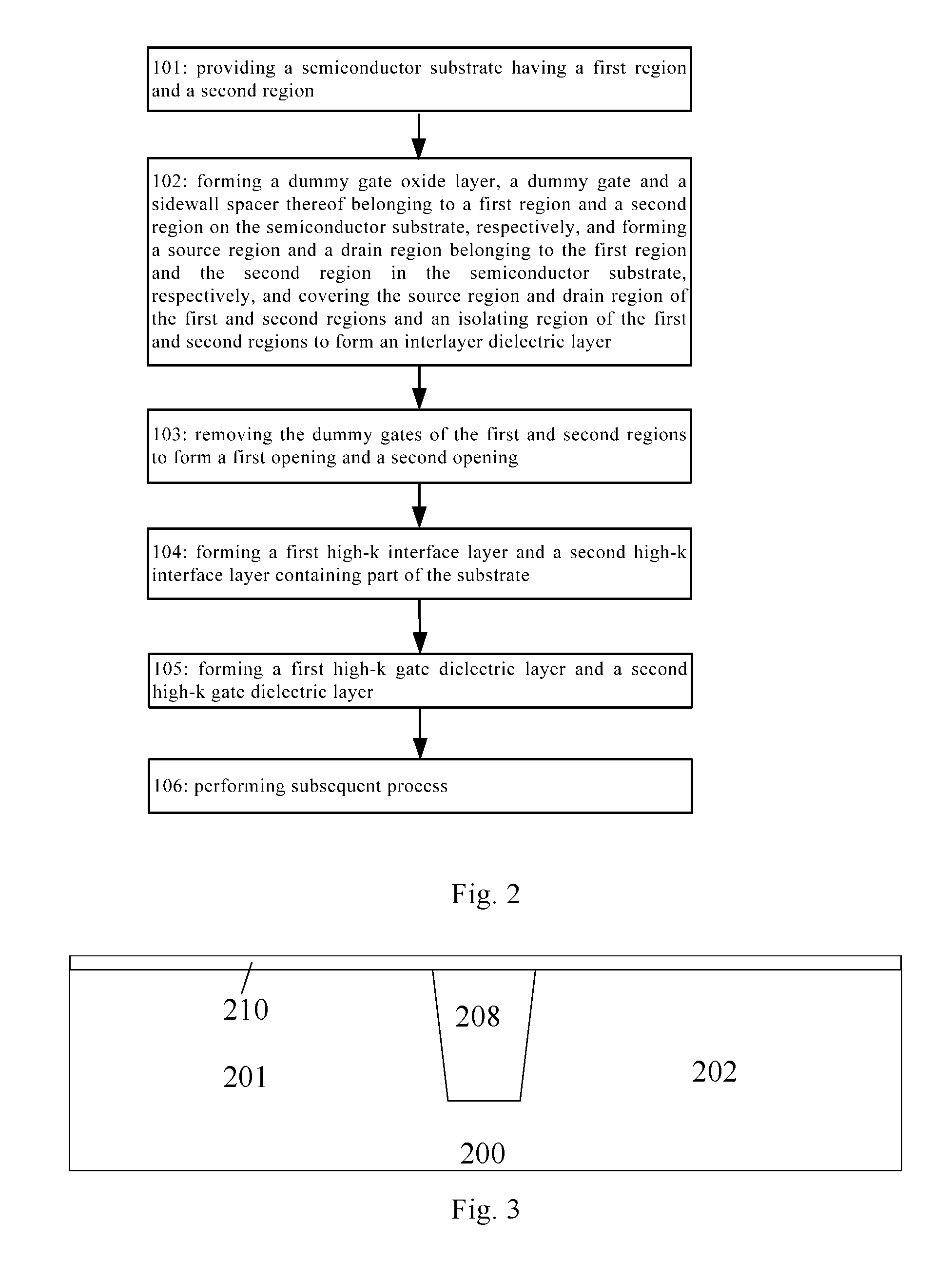

Semiconductor device and method of manufacturing the same

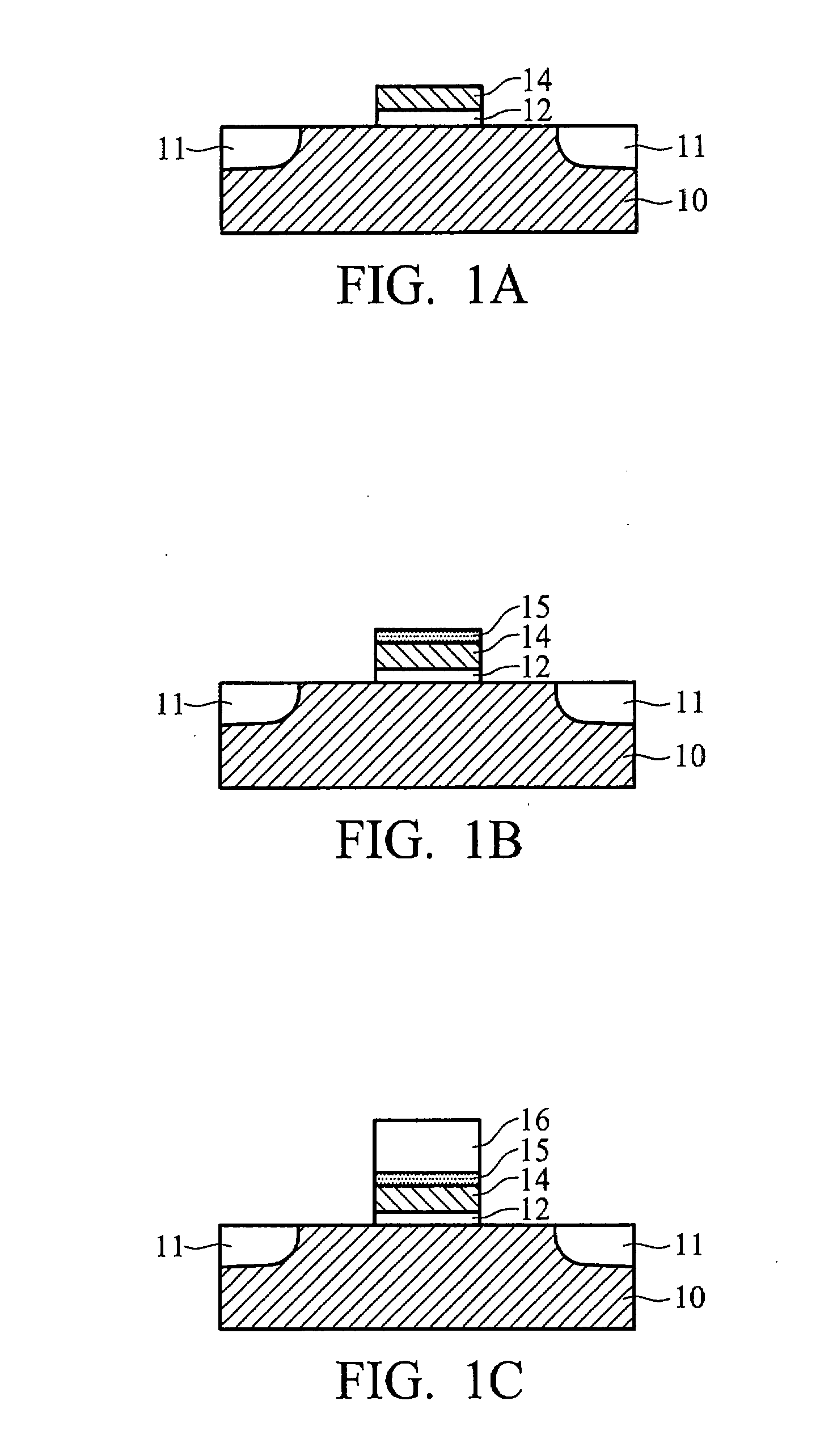

ActiveUS20110254093A1Reduce EOTAvoid degradationTransistorSolid-state devicesDielectricGate dielectric

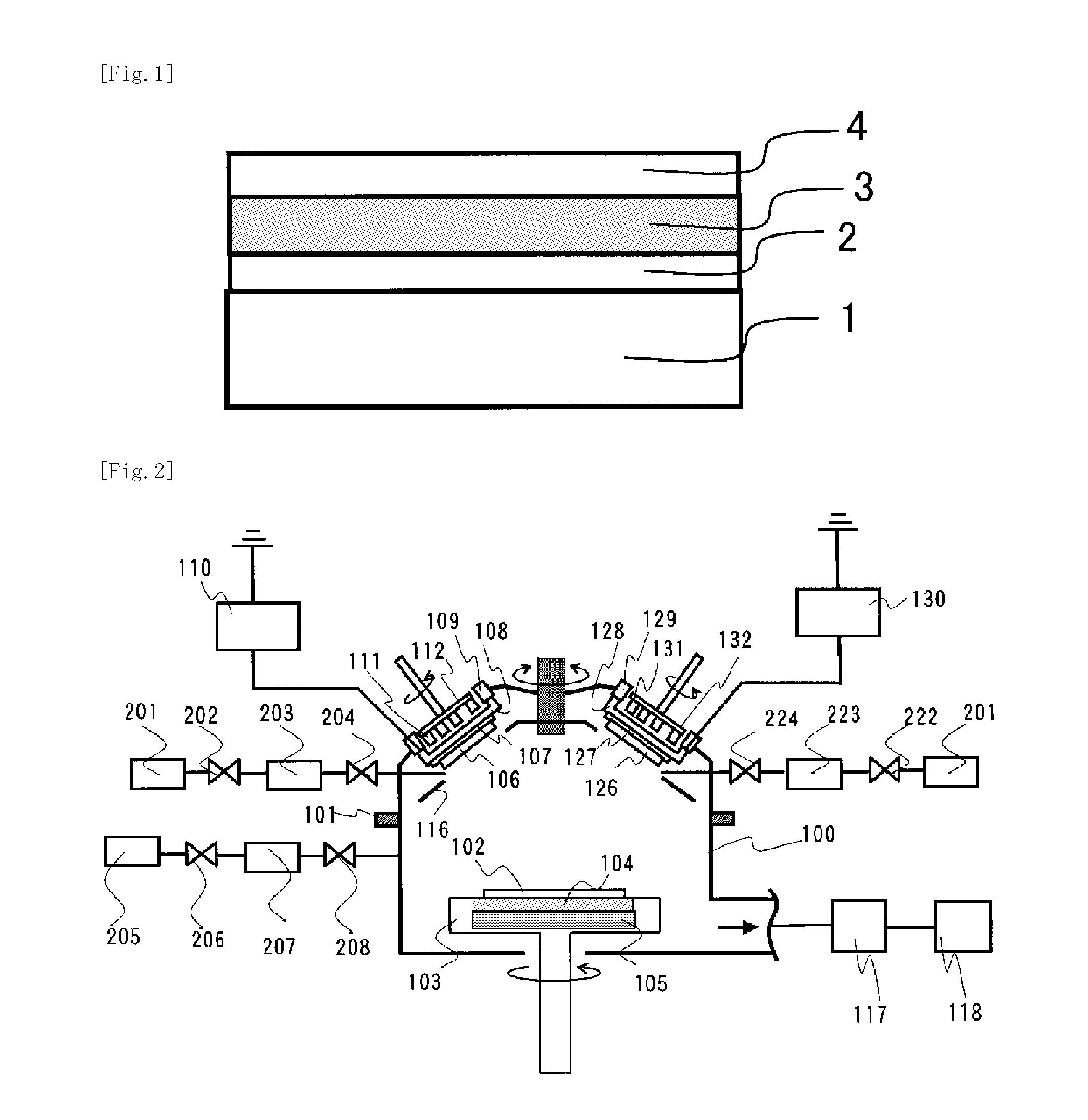

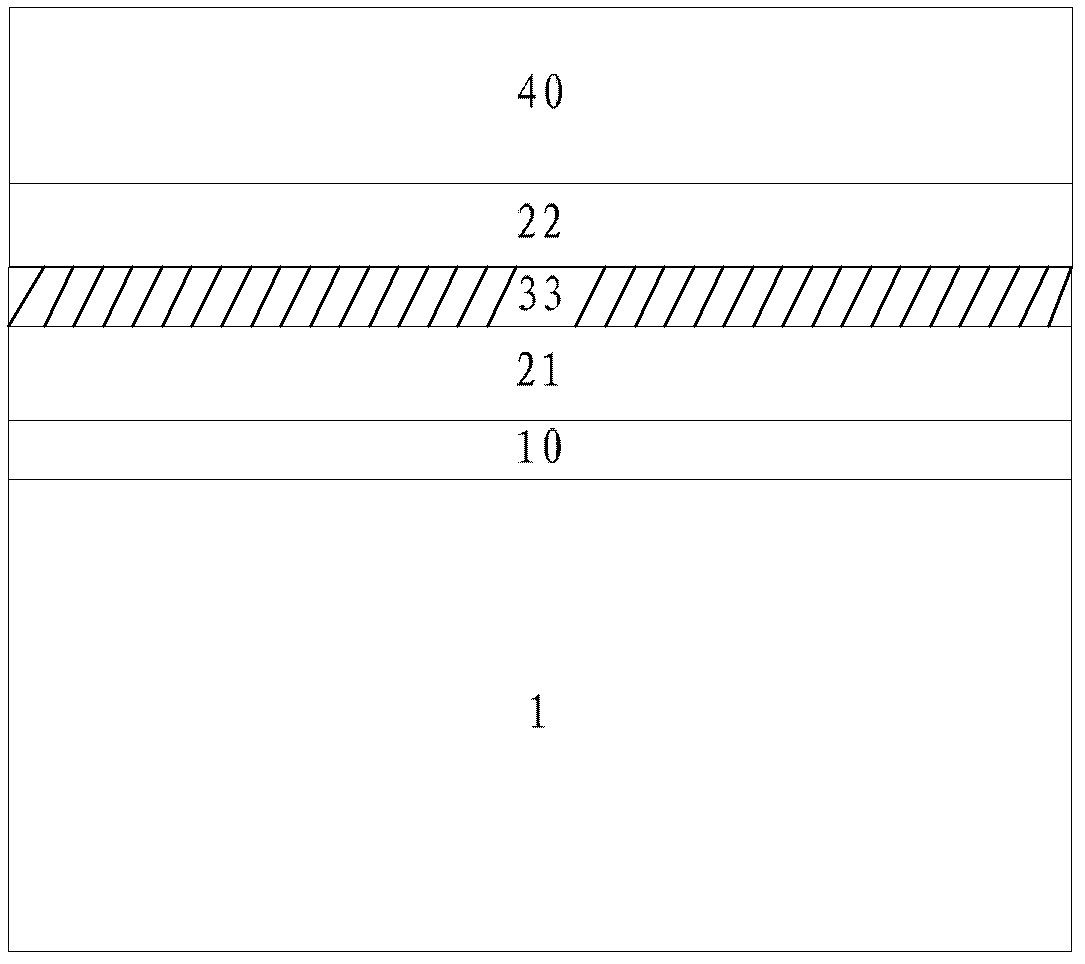

A semiconductor device and a method of manufacturing the same are provided. A multi-component high-k interface layer containing elements of the substrate is formed from a ultra-thin high-k dielectric material in a single-layer structure of atoms by rapid annealing in the manufacturing of a CMOS transistor by the replacement gate process, and a high-k gate dielectric layer with a higher dielectric constant and a metal gate layer are formed thereon. The EOT of the device is effectively decreased, and the diffusion of atoms in the high-k gate dielectric layer from an upper level thereof is effectively prevented by the optimized high-k interface layer at high-temperature treatment. Thus, the present invention may also avoid the growth of the interface layers and the degradation of carrier mobility. Furthermore, the present invention may further alleviate the problem of high interface state and interface roughness caused by direct contact of the high-k gate dielectric layer with high dielectric constant and the substrate, and thus the overall performance of the device is effectively enhanced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

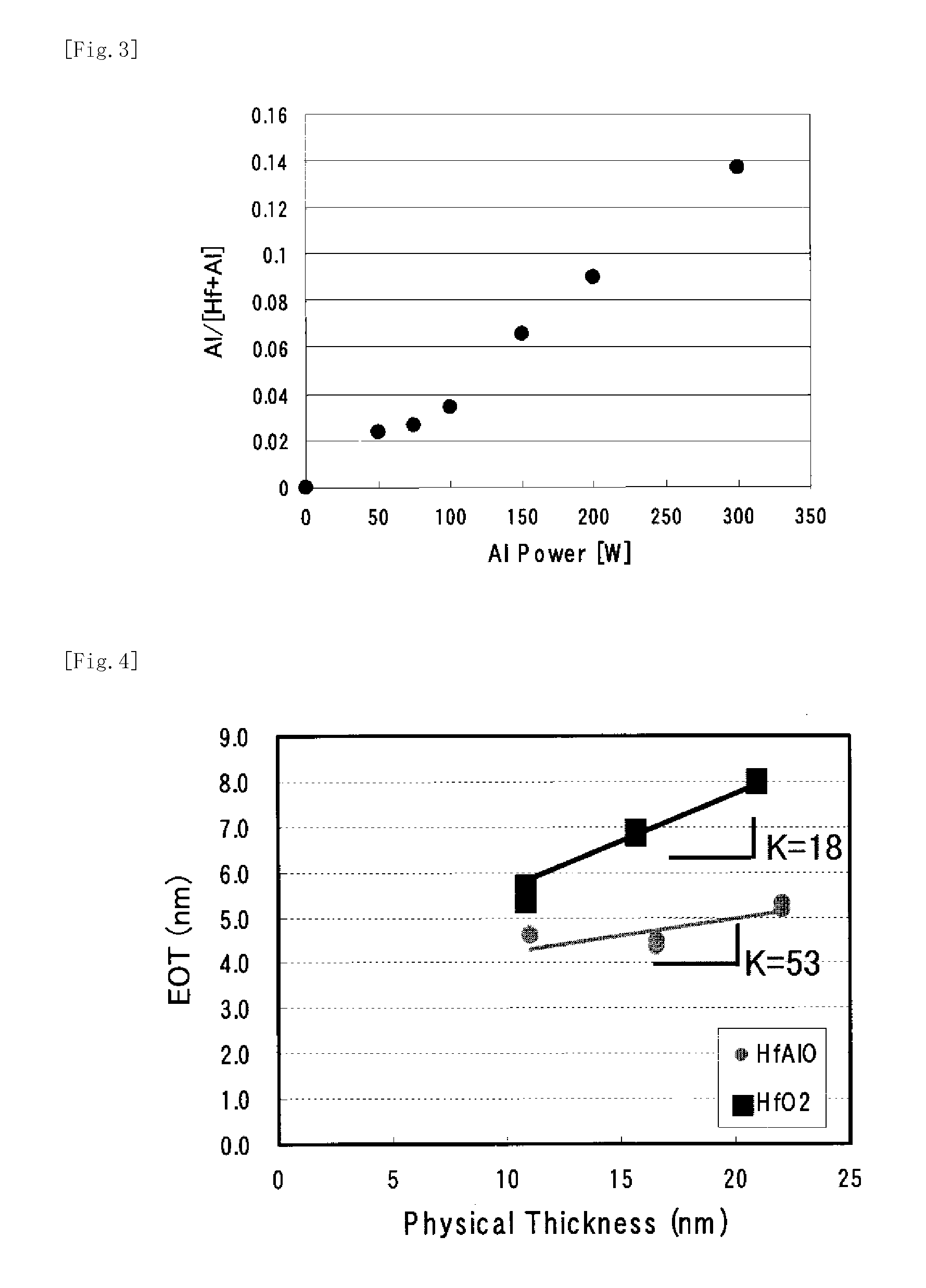

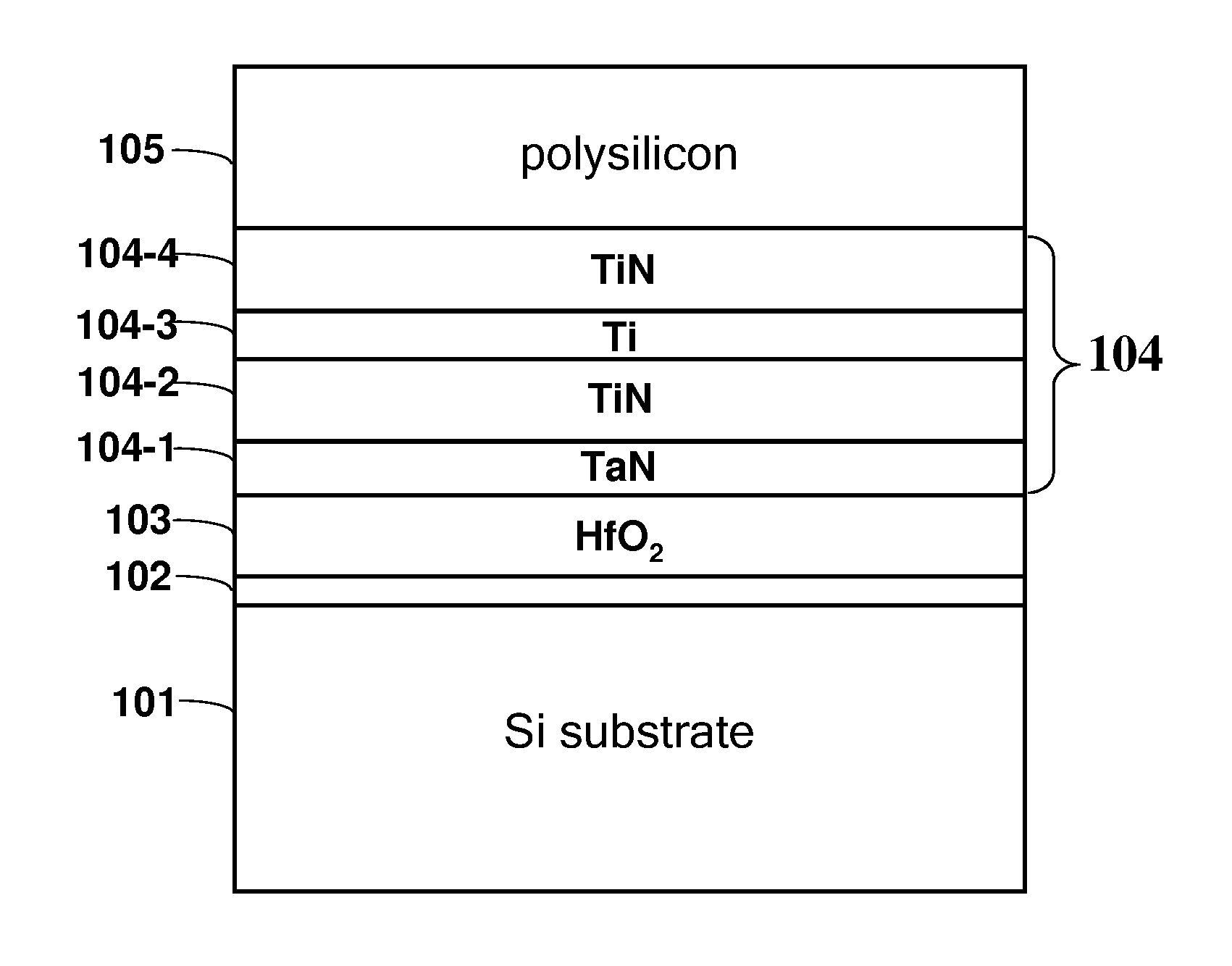

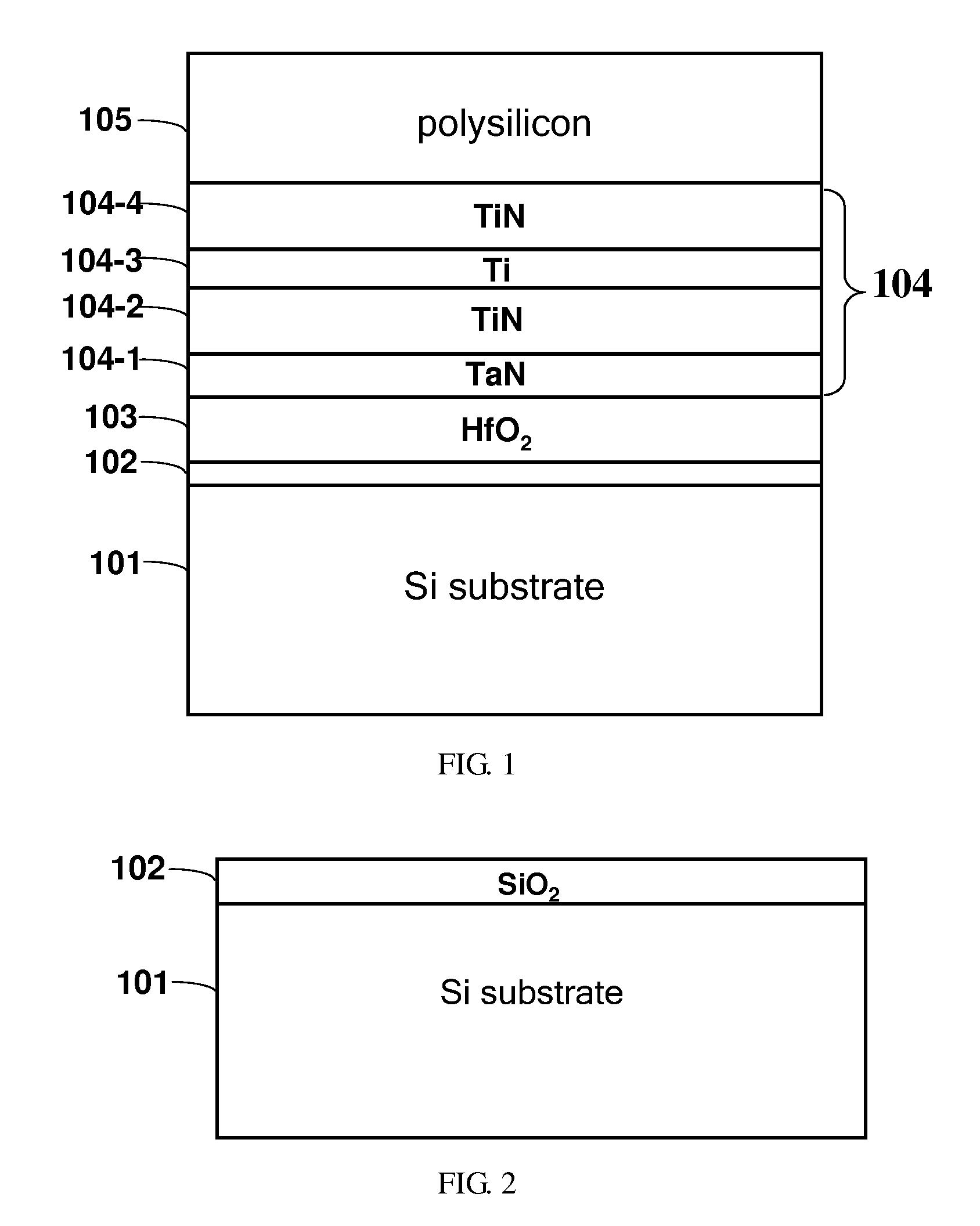

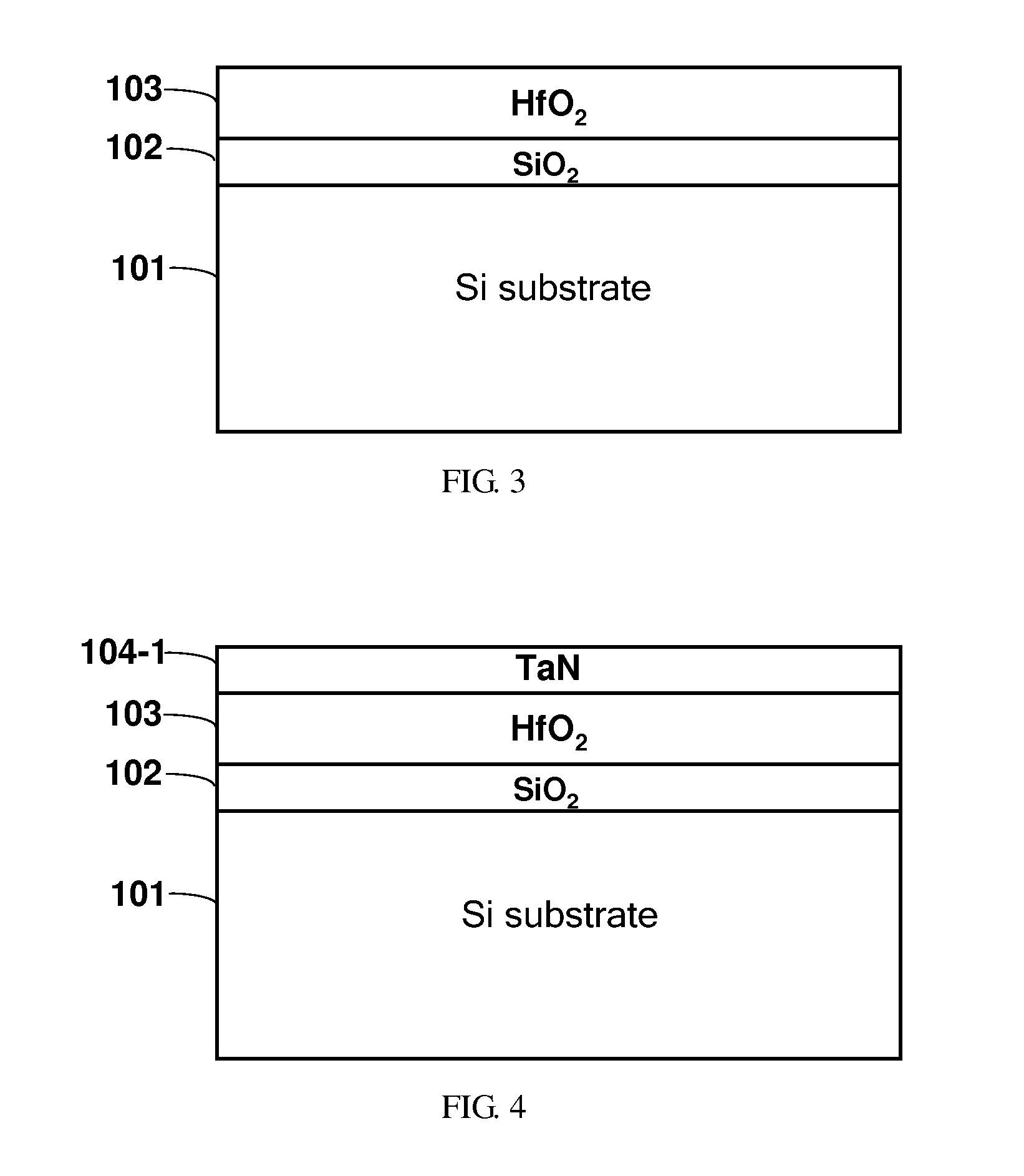

Methods for manufacturing dielectric films

ActiveUS20120021612A1High dielectric constantReduce EOTTransistorVacuum evaporation coatingDielectric thin filmsMetal

A method for manufacturing a dielectric film having a high dielectric constant is provided.The method is a method for forming, on a substrate, a dielectric film including a metal oxide containing O and elements A and B, wherein the element A comprises Hf or a mixture of Hf and Zr and the element B comprises Al or Si, which includes the steps of: forming a metal oxide having an amorphous structure which has a molar ratio between element A and element B, B / (A+B) of 0.02≦(B / (A+B))≦0.095 and a molar ratio between element A and O, O / A of 1.0<(O / A)<2.0; and annealing the metal oxide having the amorphous structure at 700° C. or more to form a metal oxide containing a crystal phase with a cubic crystal content of 80% or more.

Owner:CANON ANELVA CORP

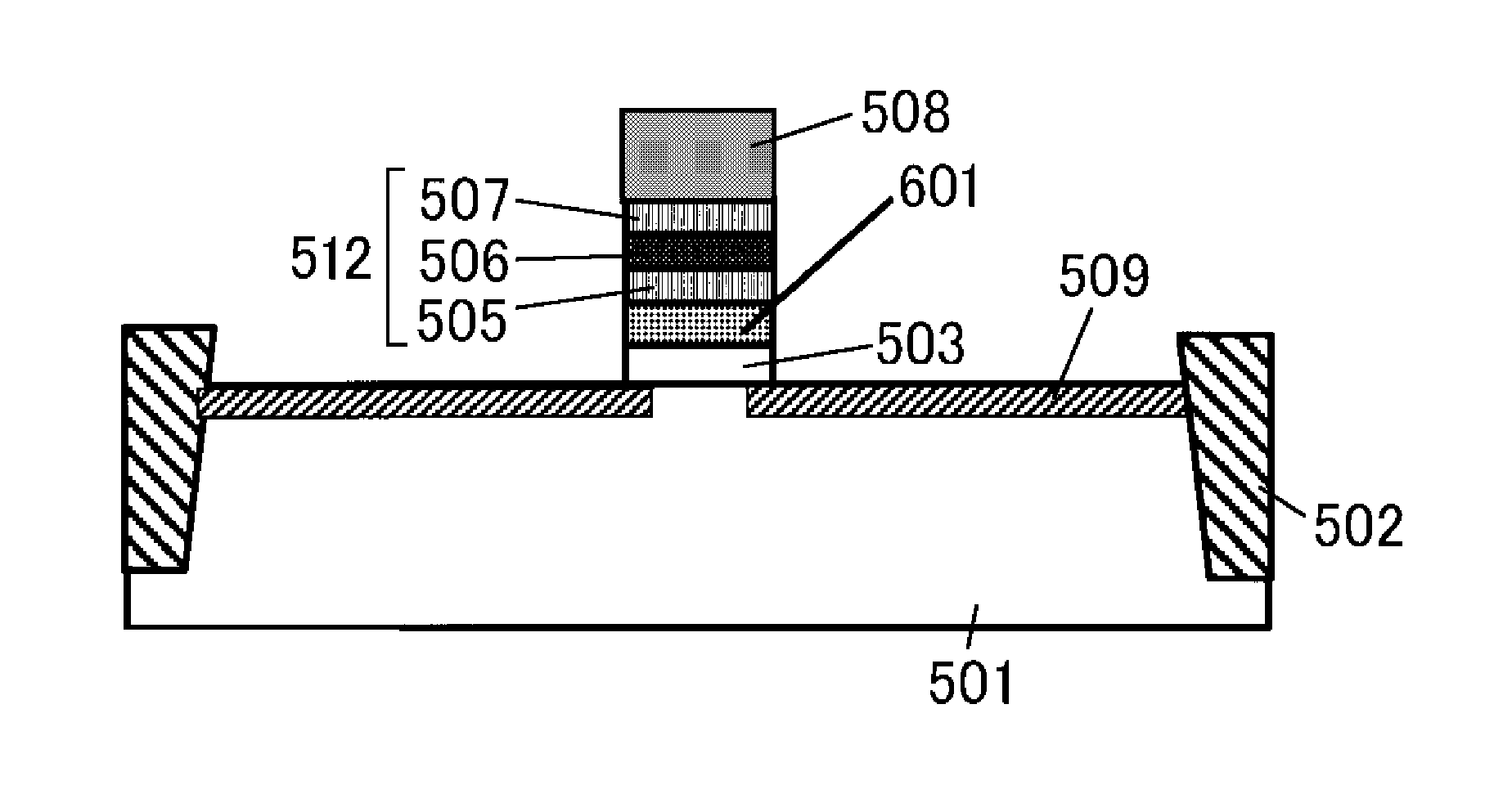

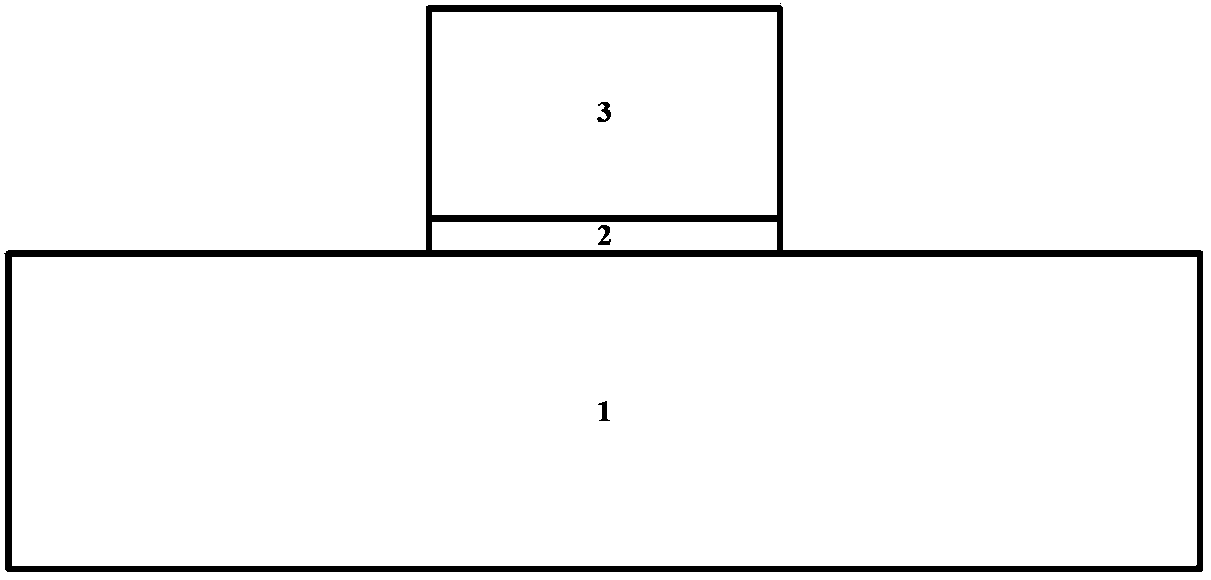

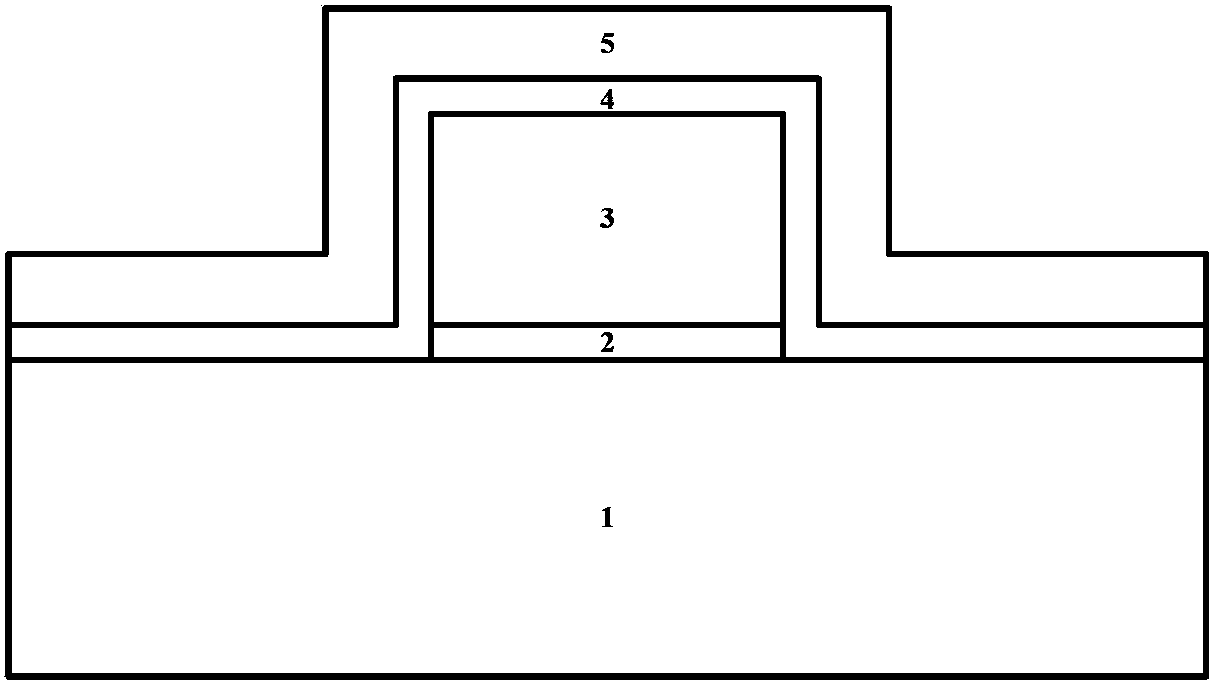

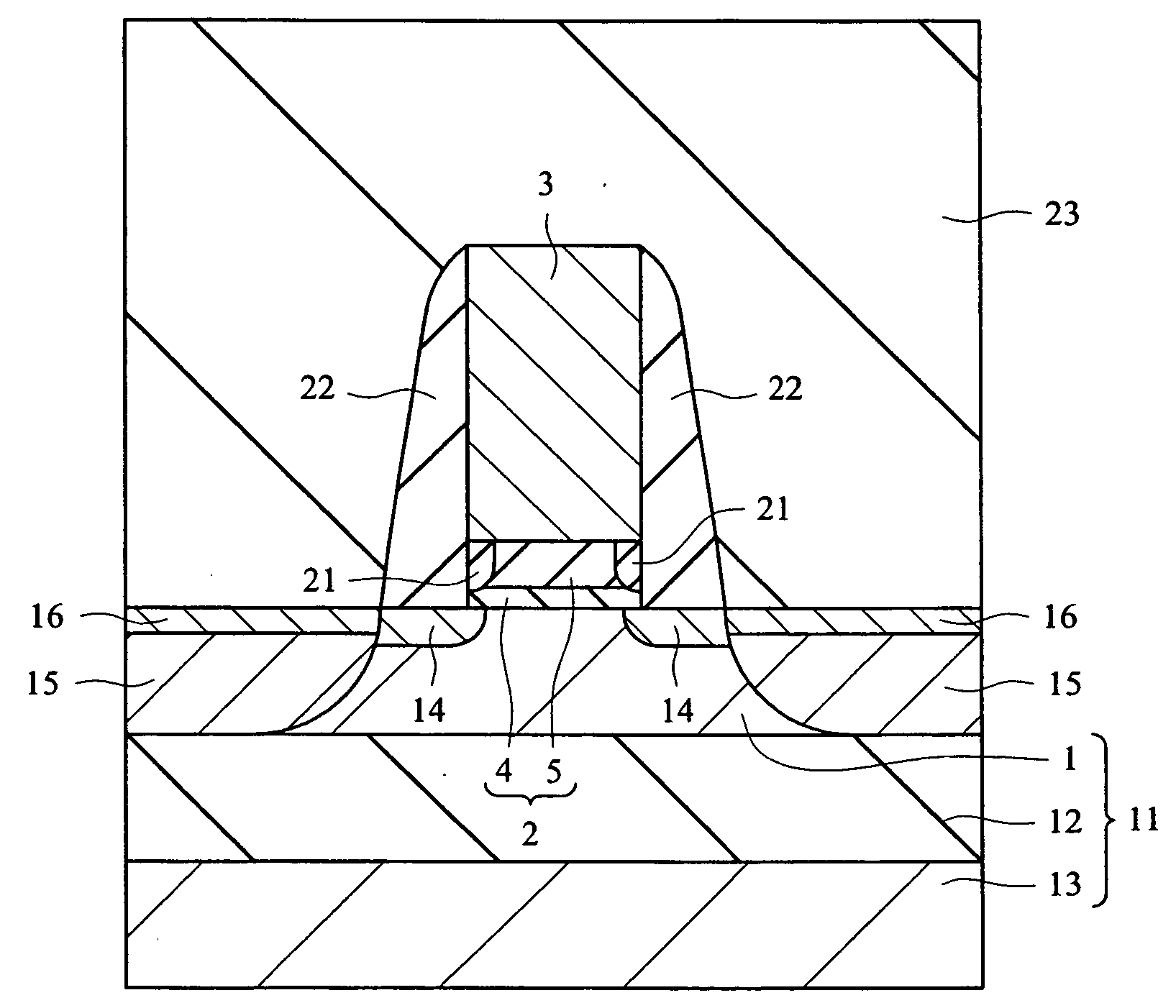

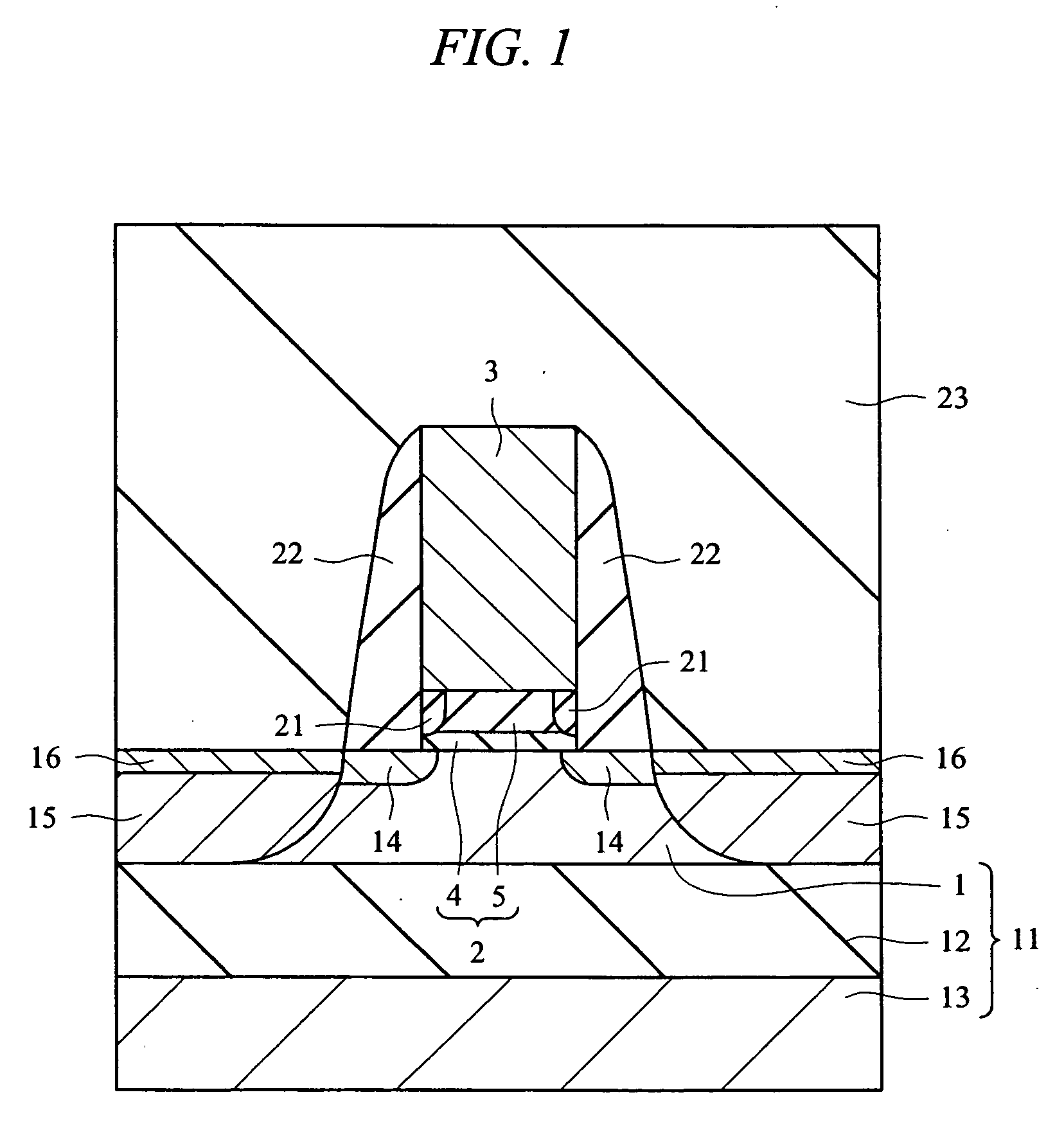

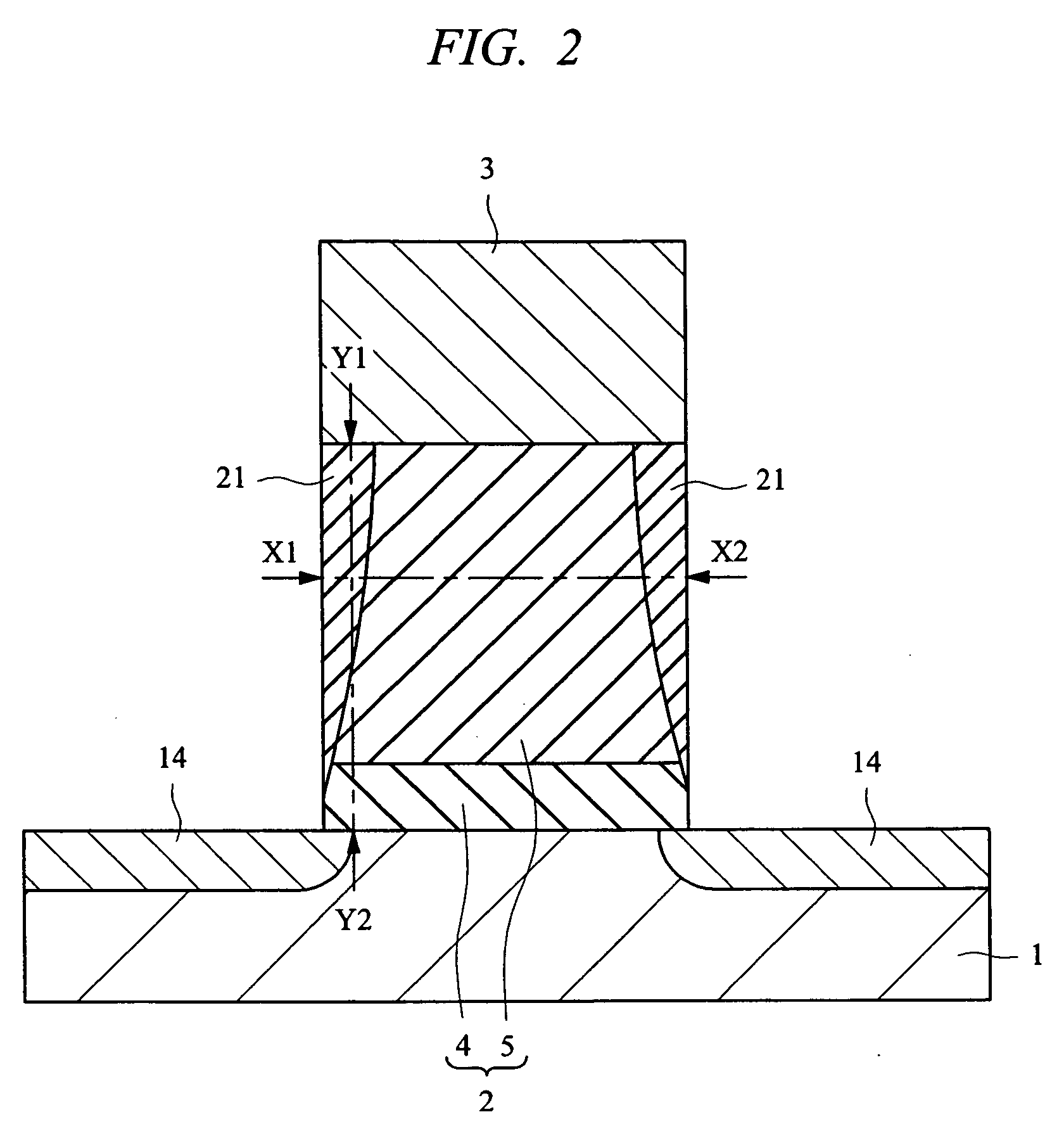

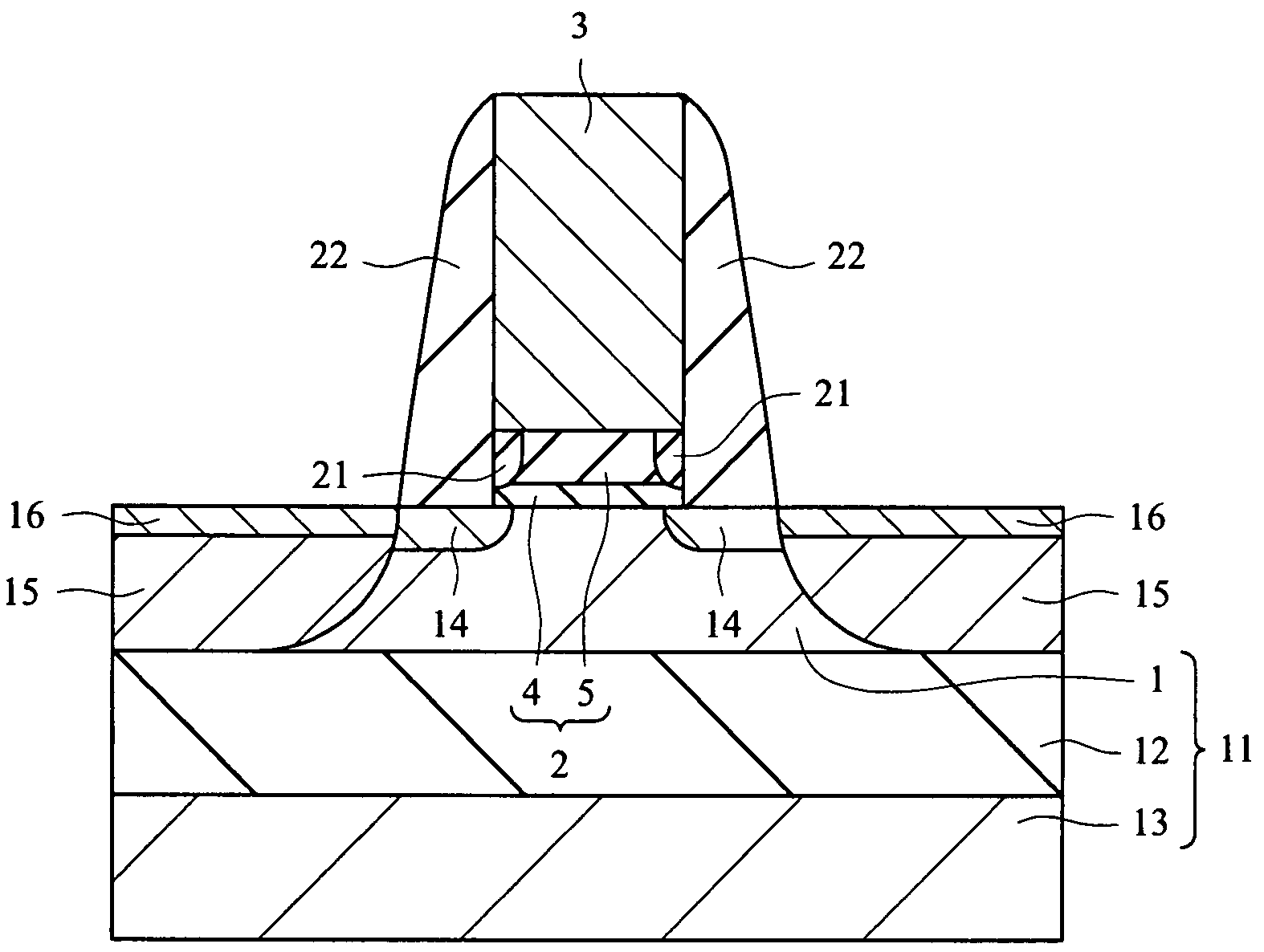

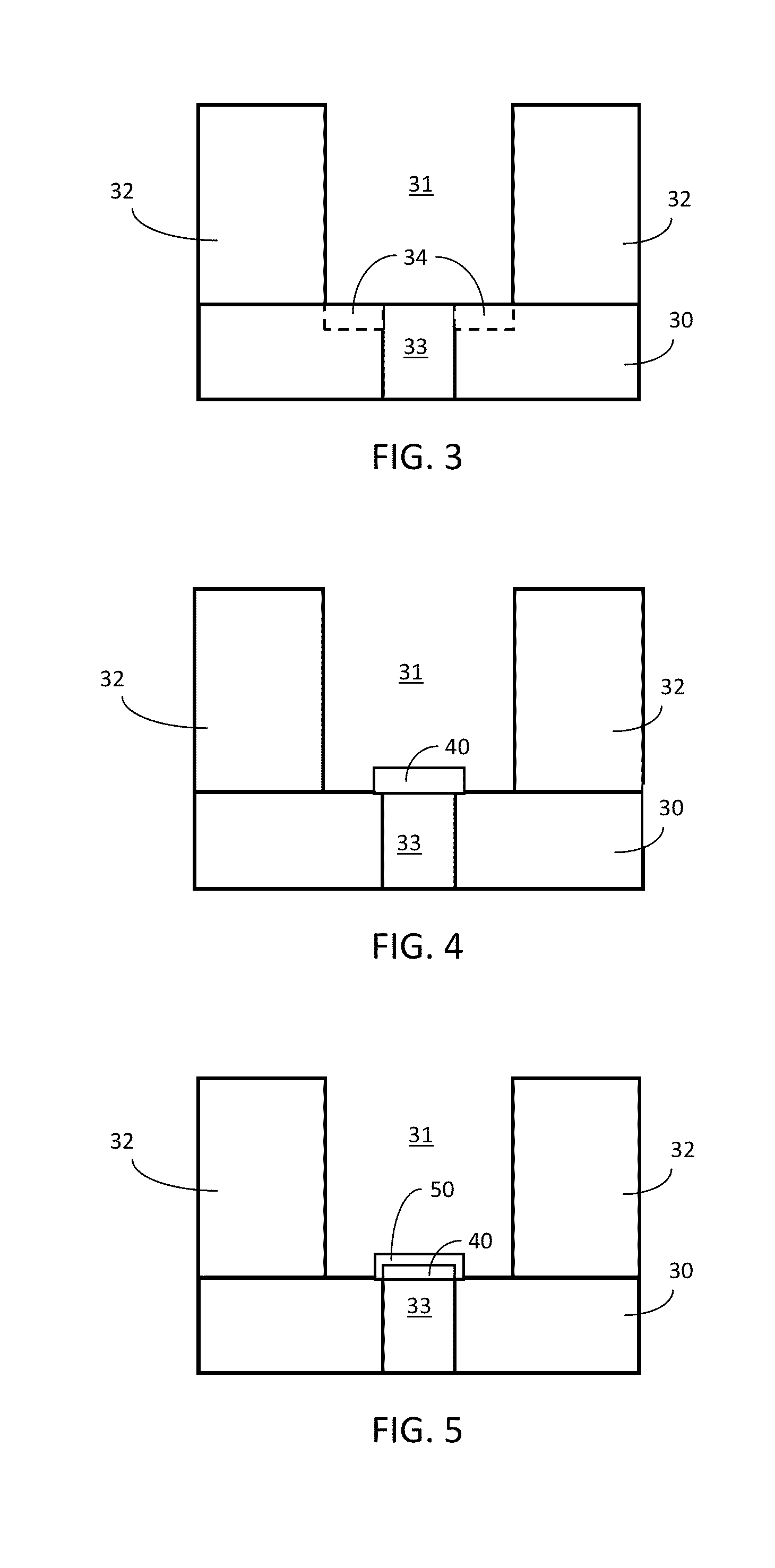

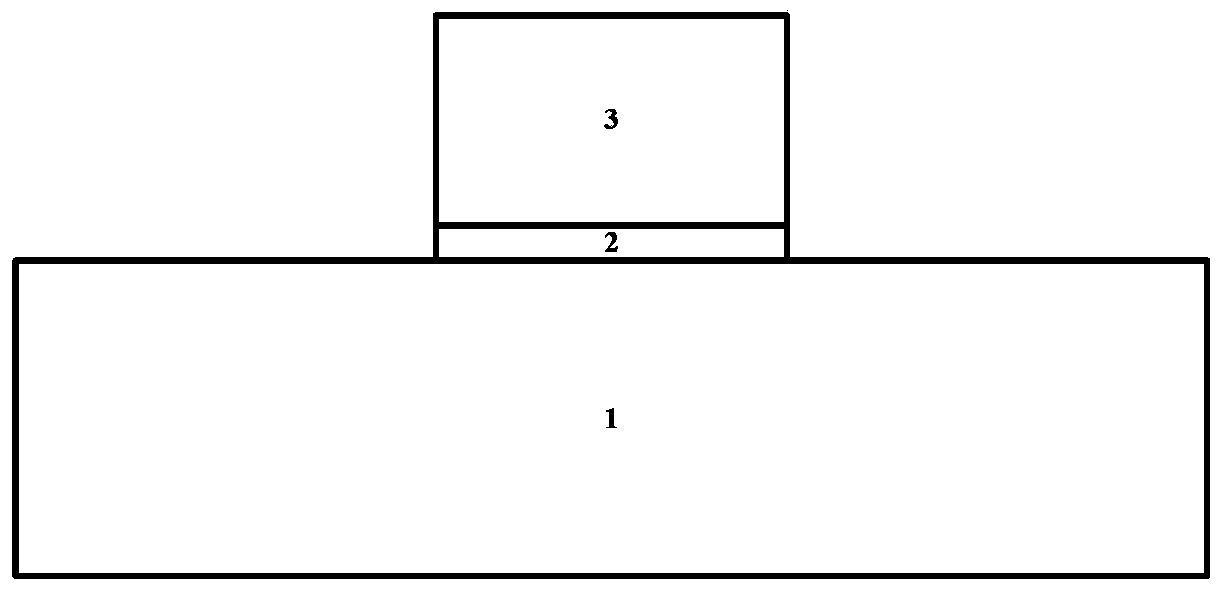

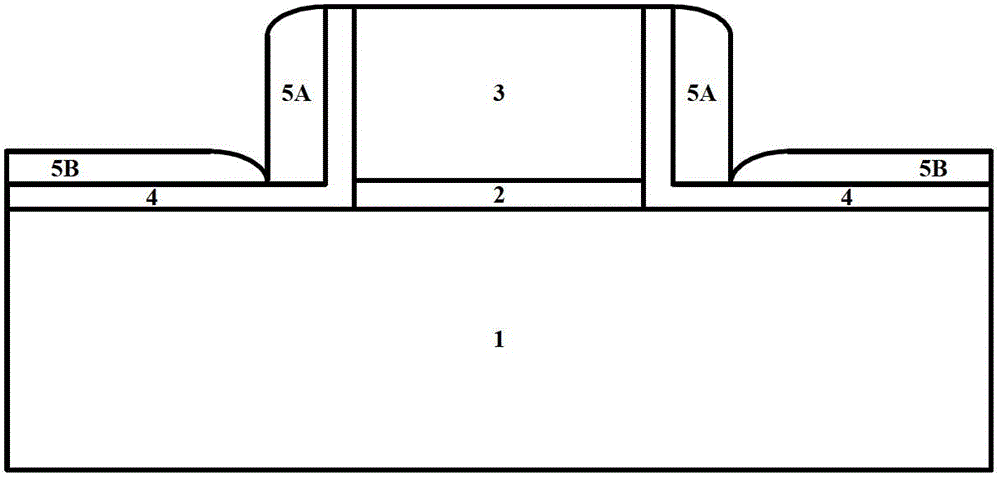

Semiconductor device structure and method for manufacturing the same

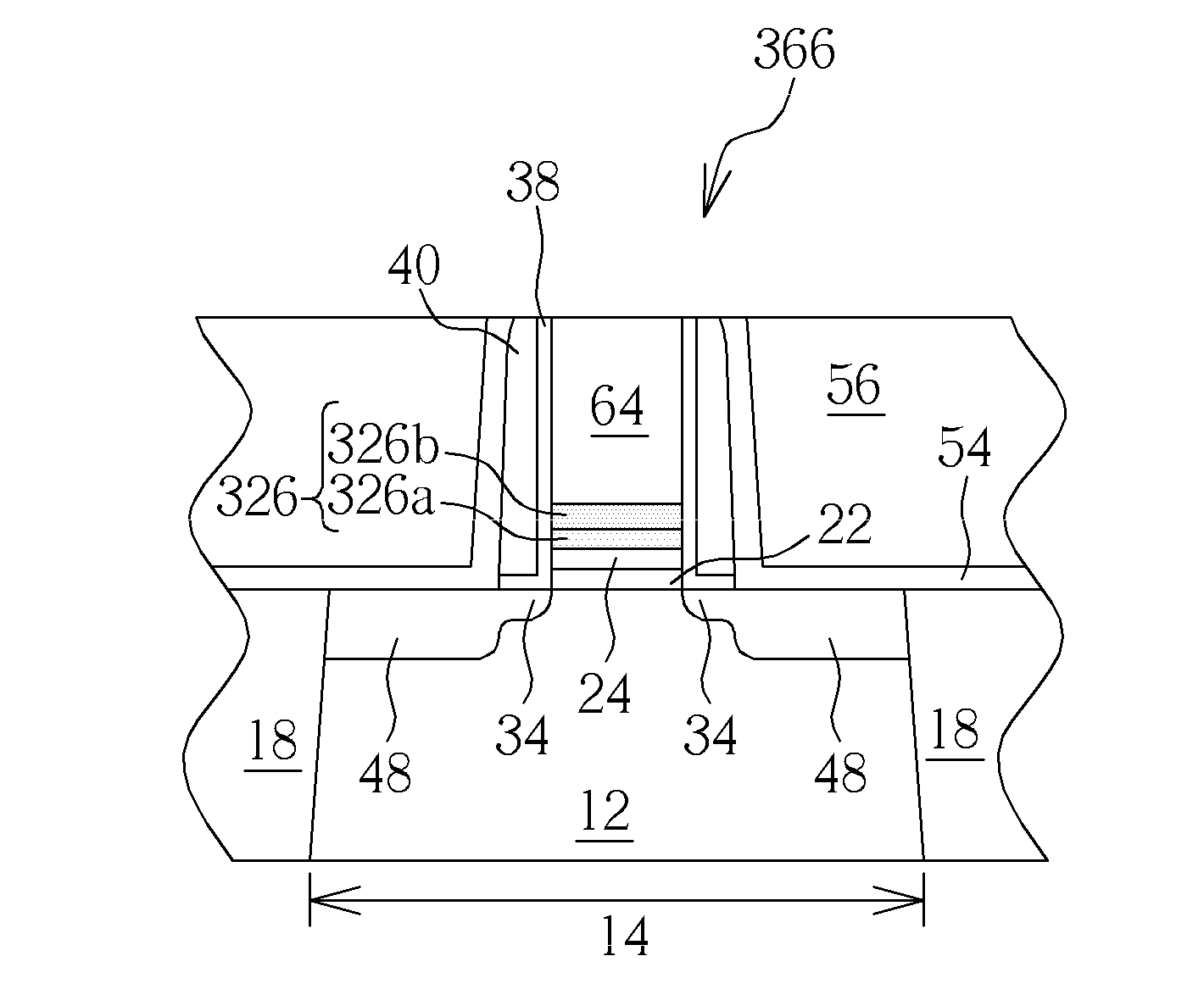

InactiveUS20110254063A1Easy to integrateReduce layeringSemiconductor/solid-state device manufacturingNanotechnologyGate dielectricInterface layer

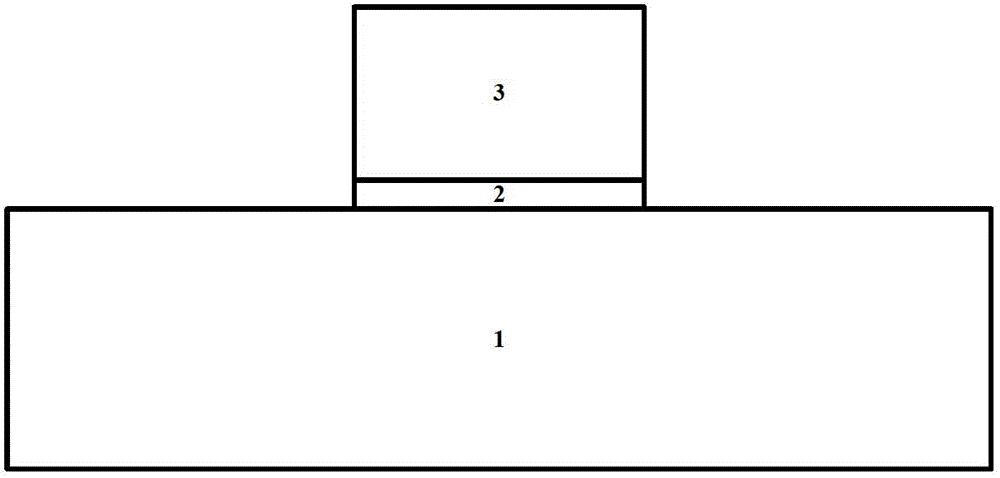

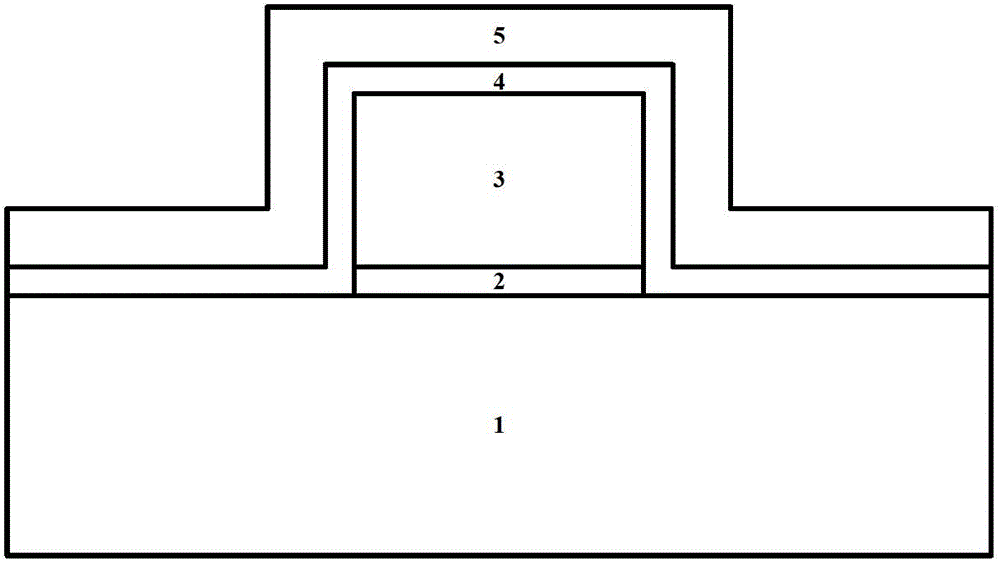

The present invention provides a MOS device, which comprises: a substrate; an interface layer thin film formed on the substrate; a high k gate dielectric layer formed on the interface layer thin film; and a metal gate formed on the high k gate dielectric layer. The metal gate comprises, upwardly in order, a metal gate work function layer, an oxygen absorption element barrier layer, a metal gate oxygen absorbing layer, a metal gate barrier layer and a polysilicon layer. A metal gate oxygen absorbing layer is introduced into the metal gate for the purpose of preventing the outside oxygen from coming into the interface layer and absorbing the oxygen in the interface layer during a annealing process, such that the interface layer is reduced to be thinner and the EOT of MOS devices are effectively reduced; meanwhile, by adding an oxygen absorption element barrier layer, the “oxygen absorption element” is prevented from diffusing into the high k gate dielectric layer and giving rise to unfavorable impact thereon; in this way, the high k / metal gate system can be more easily integrated, and the performance of the device can be further improved accordingly.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

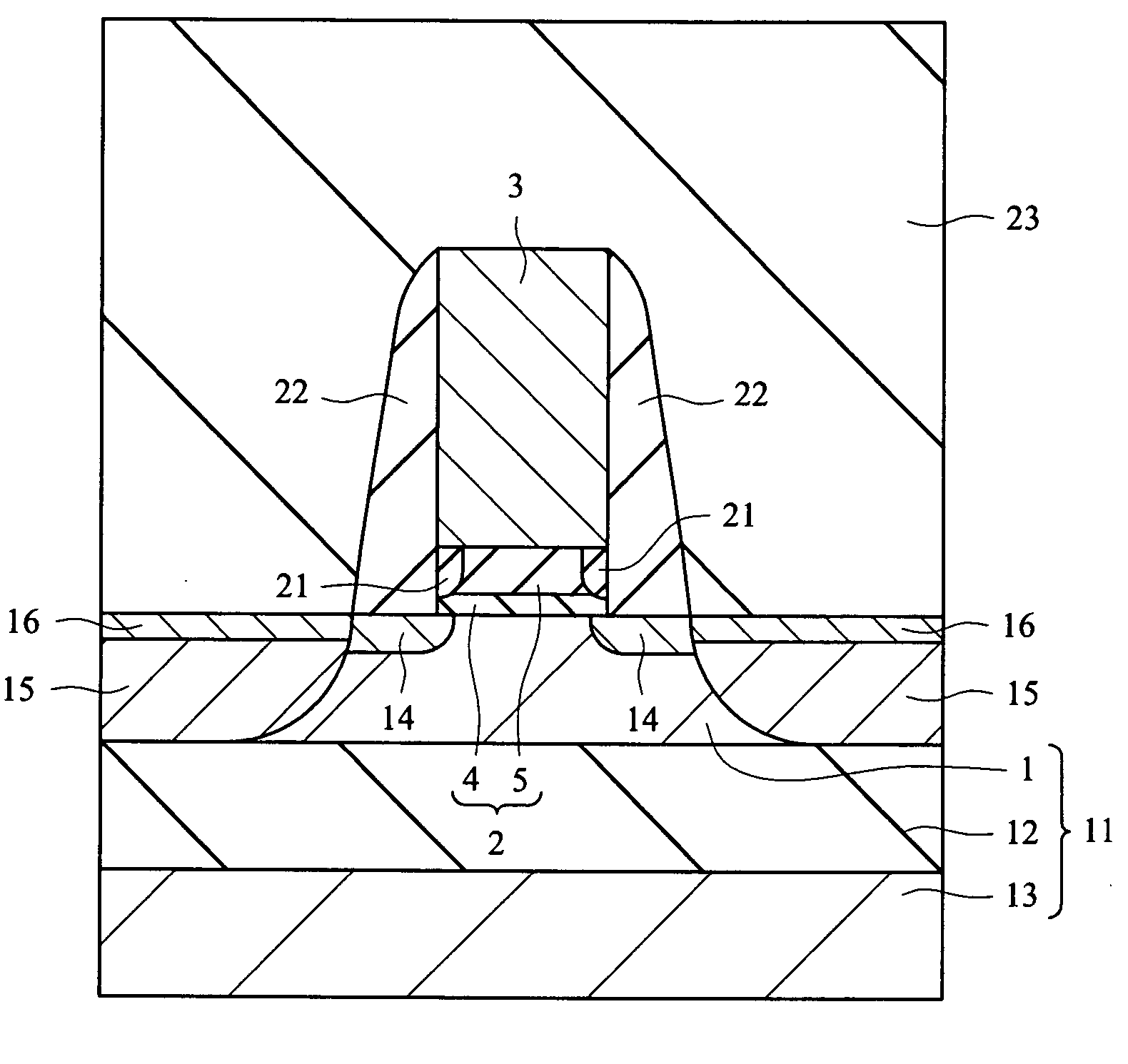

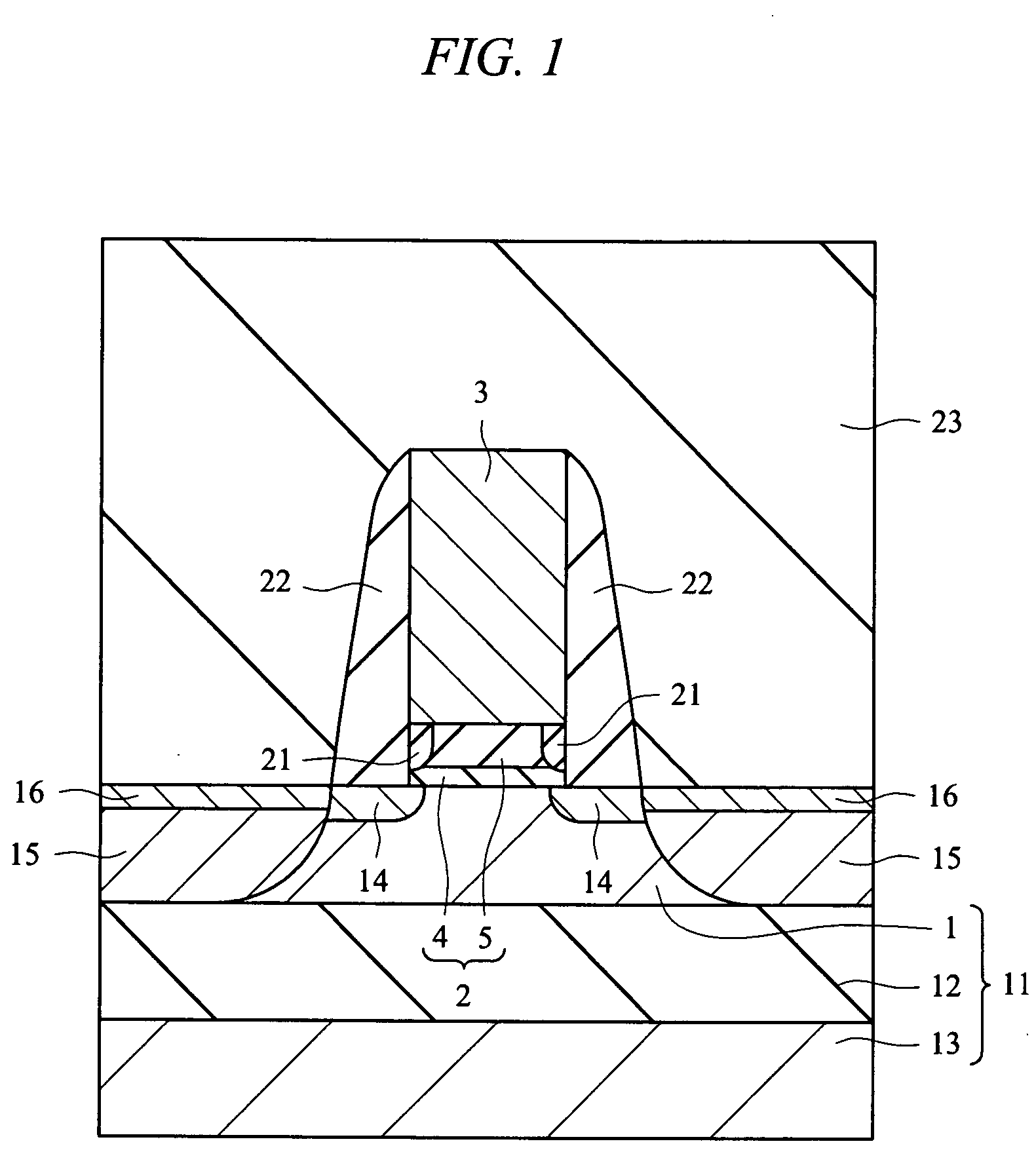

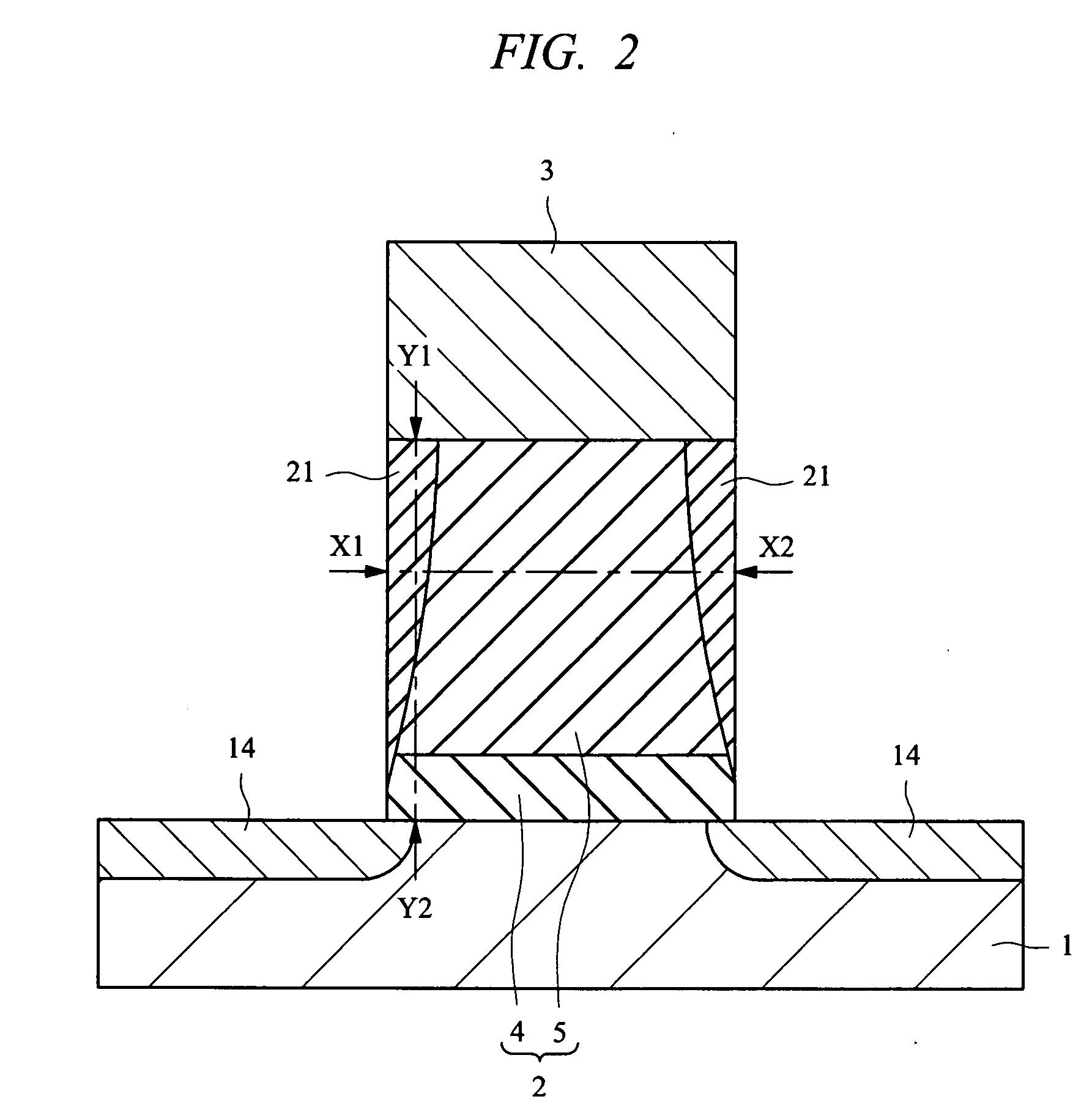

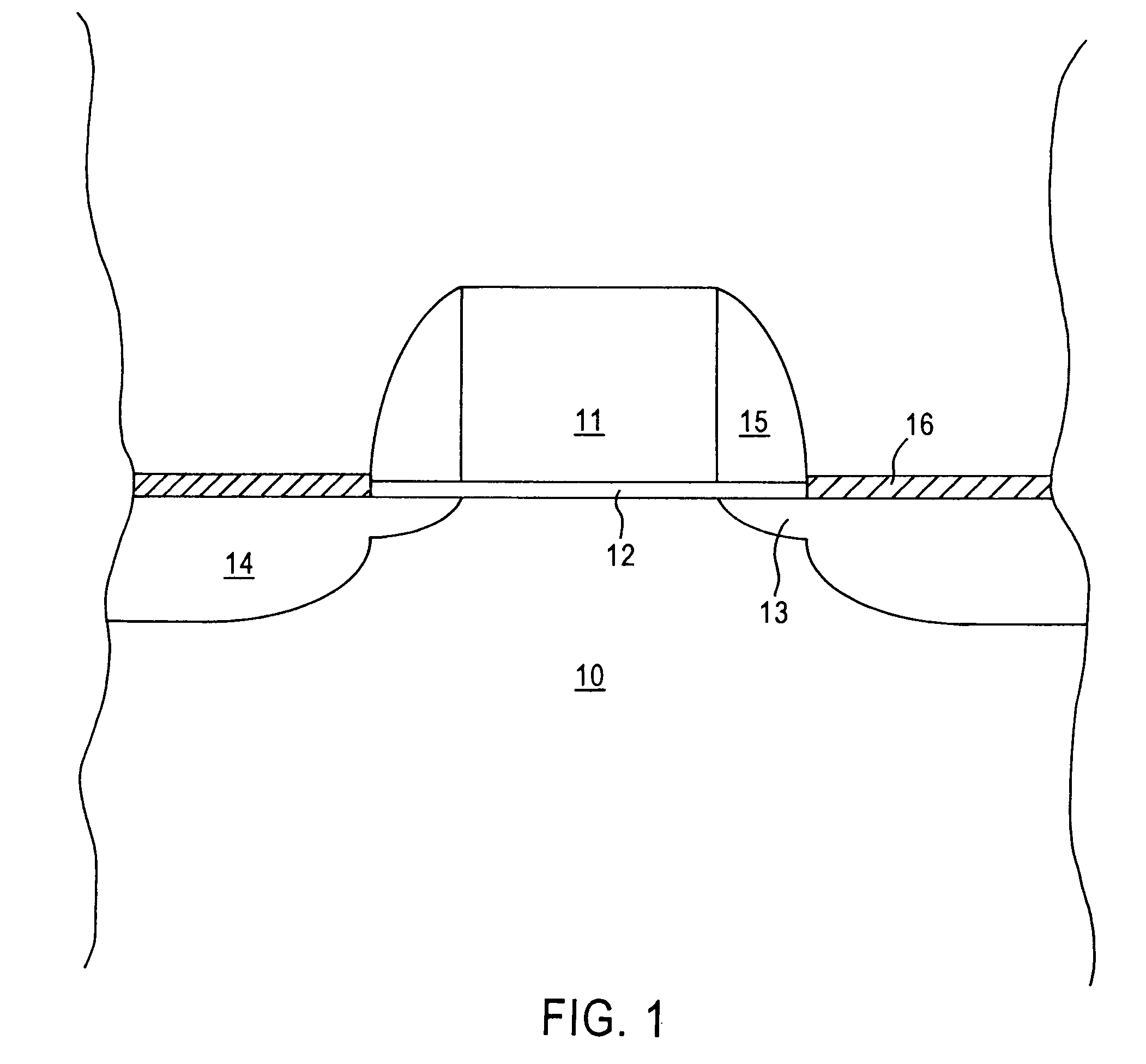

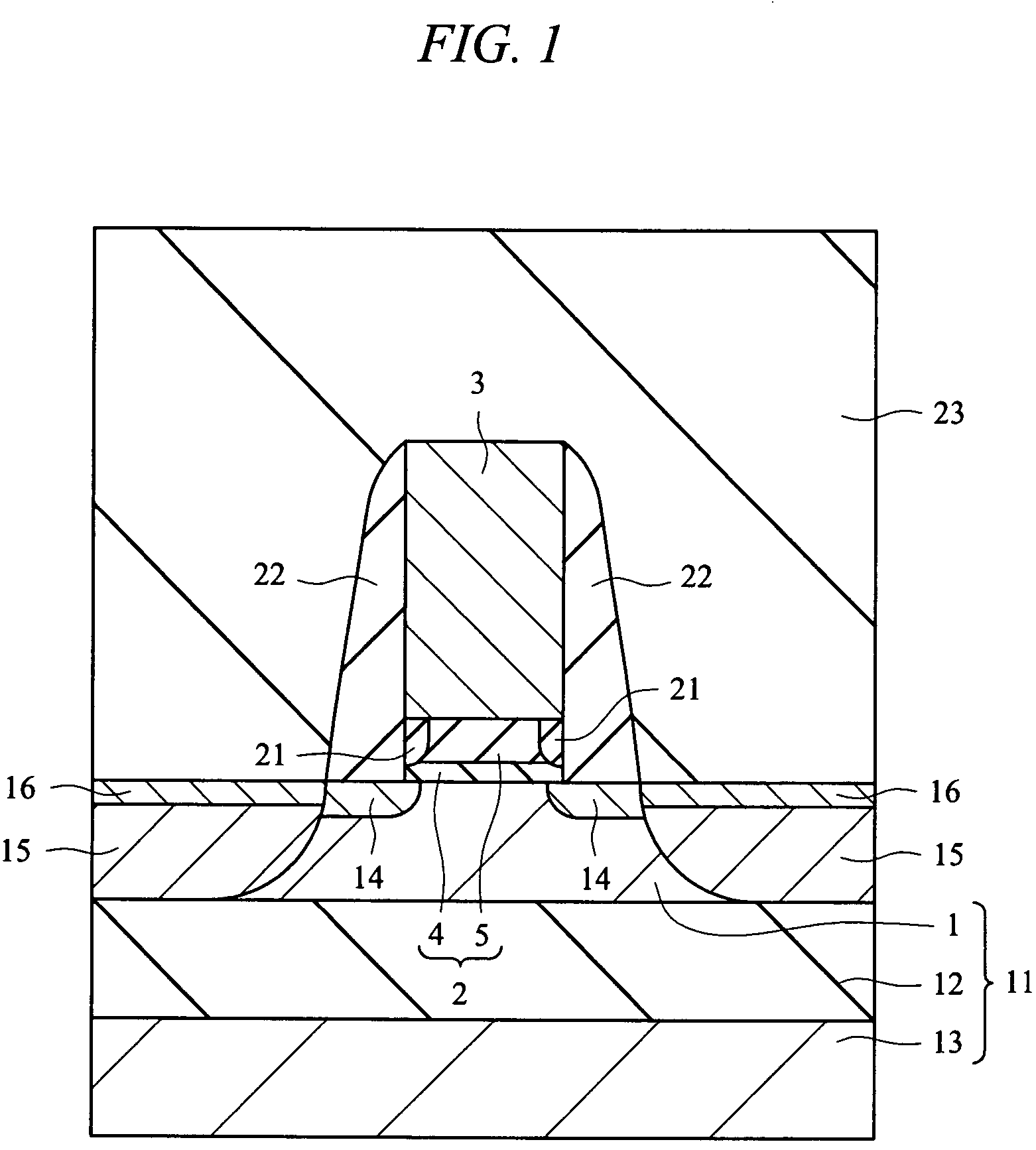

Semiconductor device and manufacturing method thereof

ActiveUS20080083956A1Low mobilityIncreasing EOTSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricDevice material

In a MIS transistor of which gate length is 10 nm or less, a gate insulator comprising a silicon oxide film formed on a silicon substrate and a high-k film formed on the silicon oxide film has a nitrided region including more nitrogen at the lateral side than at the central side in the gate-length direction, and including more nitrogen at the upper side than at the lower side in the film thickness direction. The reliability and characteristics of a MIS transistor using a gate insulator including a high-k (high dielectric constant) film is enhanced.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device and manufacturing method thereof

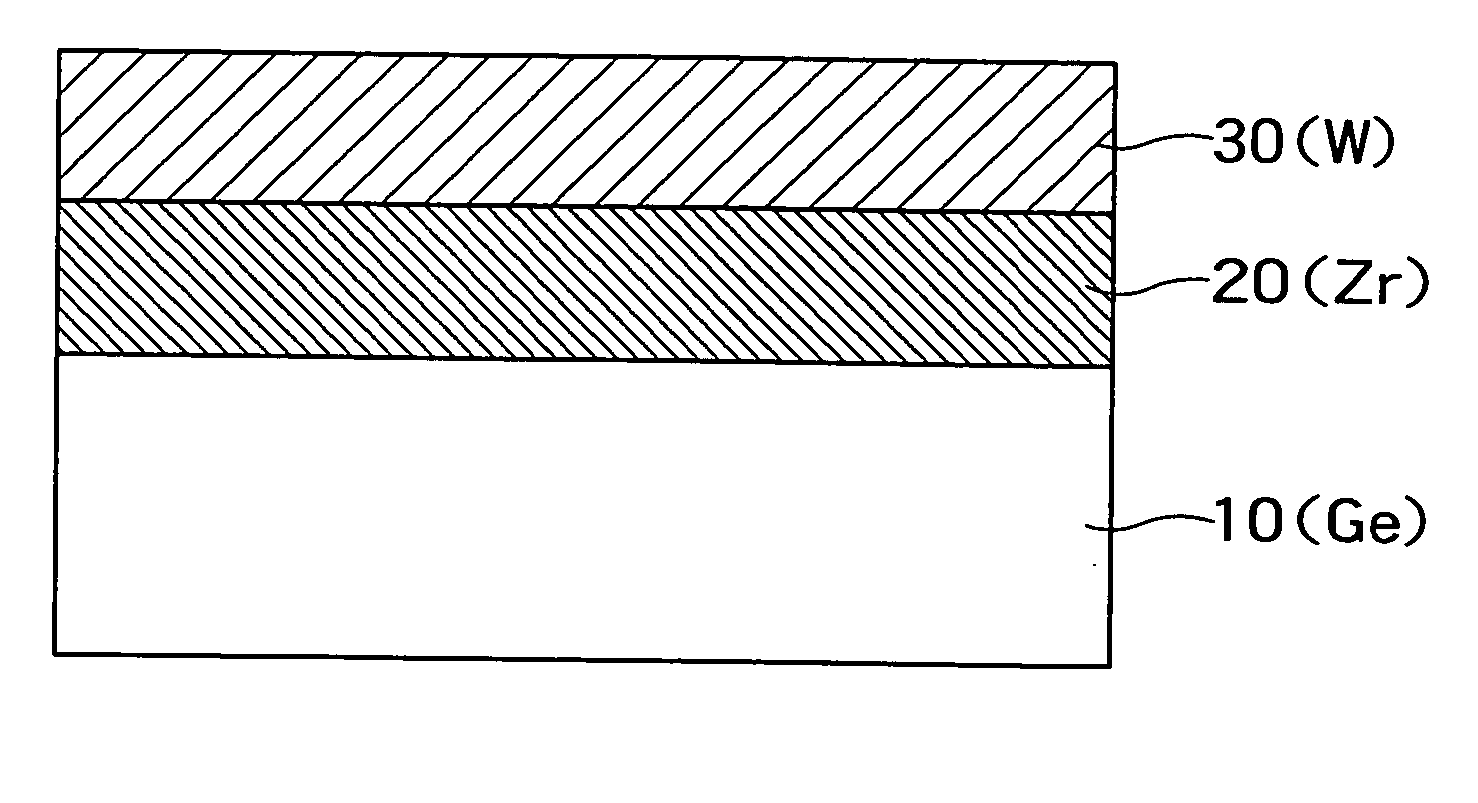

ActiveUS20060170017A1Reduce leakage currentReduce EOTSemiconductor/solid-state device manufacturingSemiconductor devicesGibbs free energySemiconductor materials

A method of manufacturing a semiconductor device includes forming a semiconductor layer containing a semiconductor material having a first oxide-generating Gibbs free energy required to become an oxide; forming a first material for a gate insulator on the semiconductor layer, said first material containing an element having a second oxide-generating Gibbs free energy required to become an oxide and becoming insulative when the element is oxidized or nitrided; and annealing the first material in an atmosphere containing hydrogen atoms, or heavy hydrogen atoms, and oxygen atoms in a temperature range where the first oxide-generating Gibbs free energy is equal to or higher than the second oxide-generating Gibbs free energy.

Owner:KIOXIA CORP

Doping approach of titanium dioxide for dram capacitors

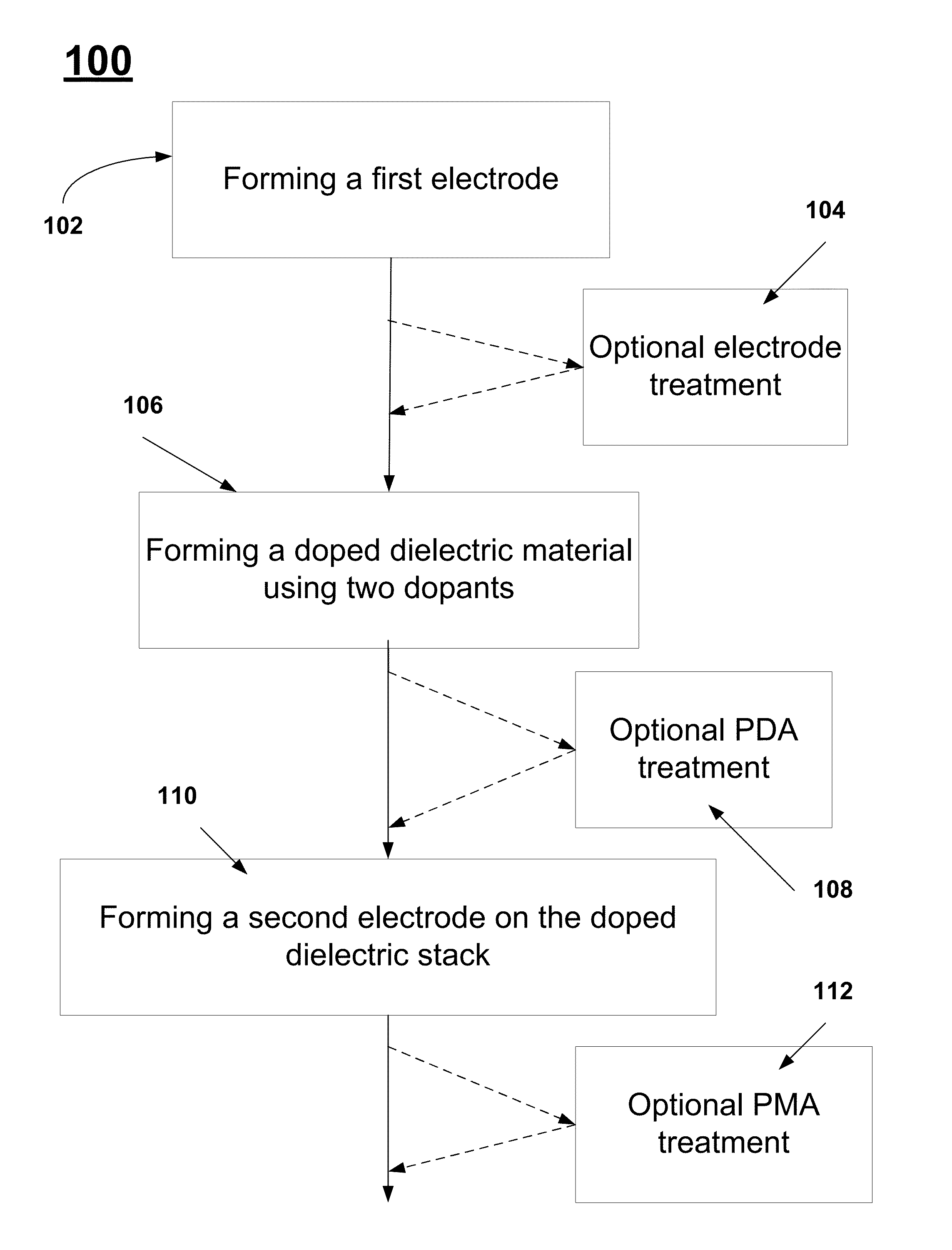

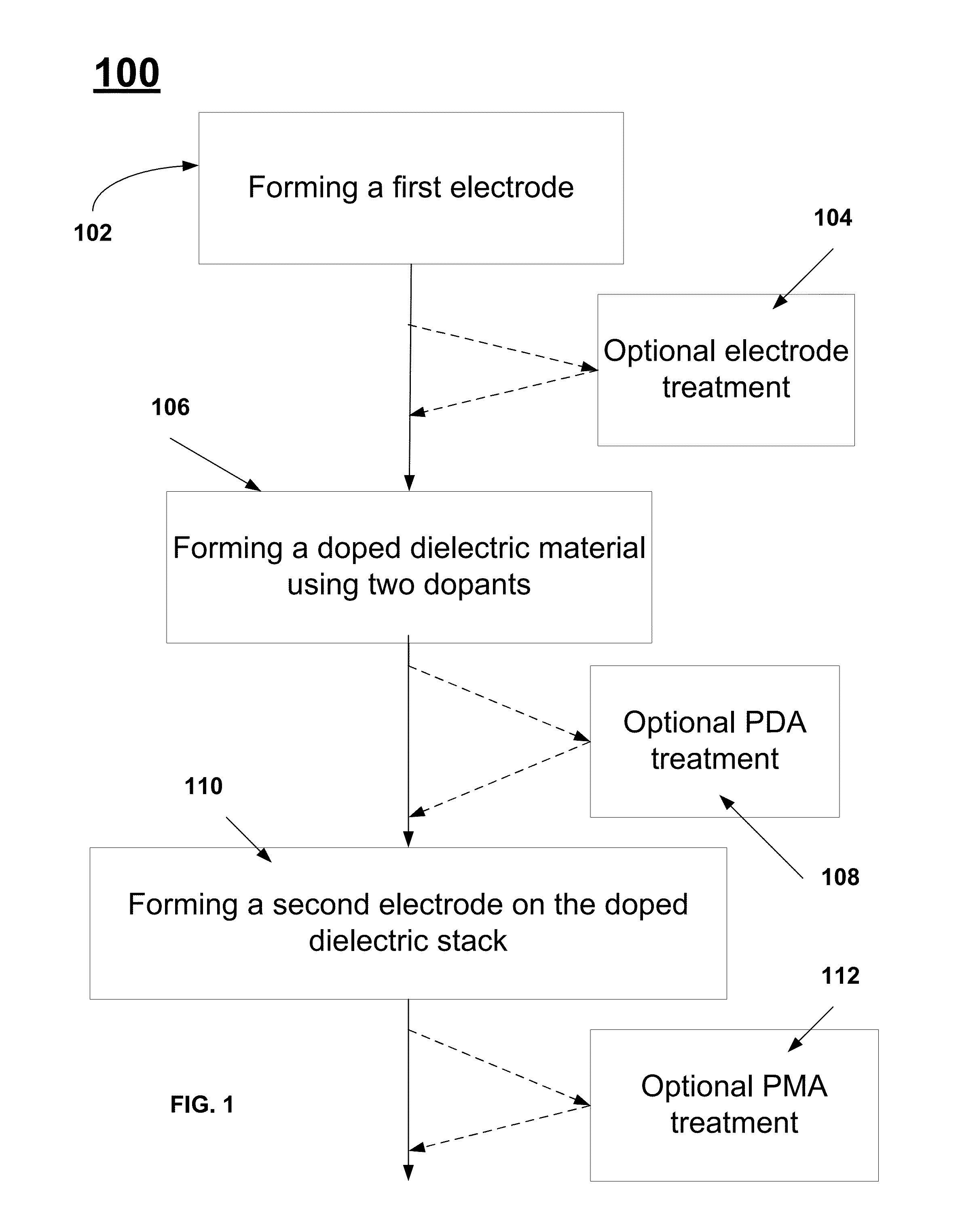

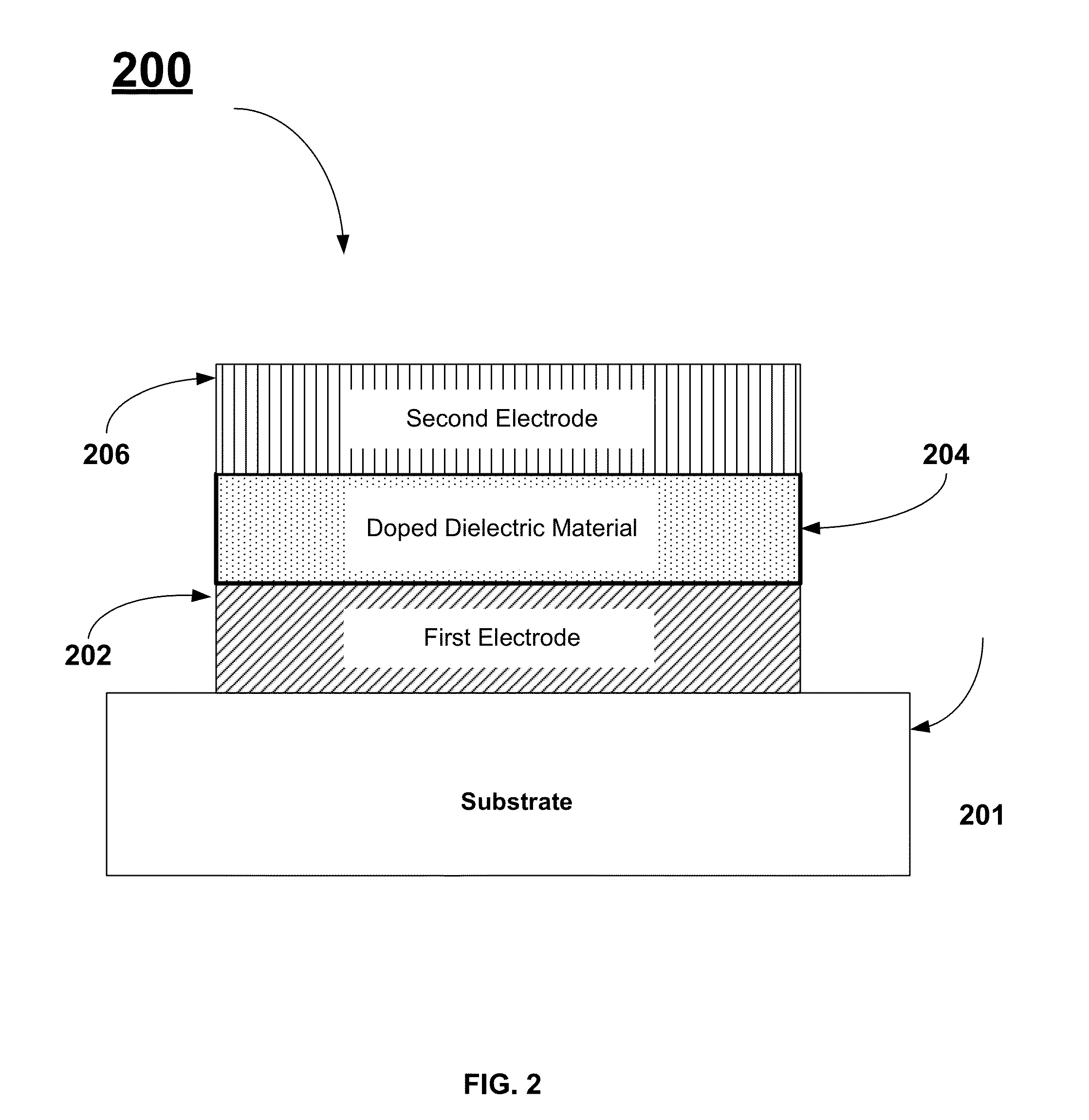

InactiveUS20130052790A1Reduce leakage currentIncreased polarizationSemiconductor/solid-state device manufacturingCapacitorsSolubilityDopant

A method for fabricating a DRAM capacitor stack is described wherein the dielectric material is a doped material formed from a first dopant in concert with a second dopant wherein the second dopant has a different physical size from the first dopant and the presence of the second dopant influences the solubility of the first dopant in the dielectric material. The dielectric material maintains a high k-value while minimizing the leakage current and the EOT value

Owner:INTERMOLECULAR +1

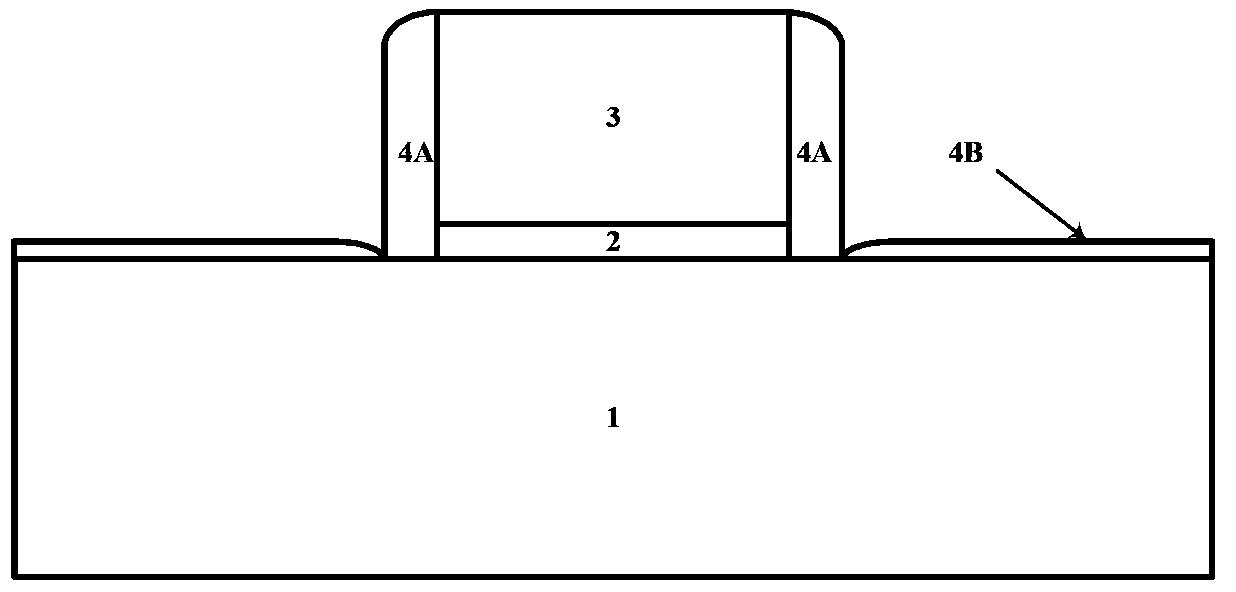

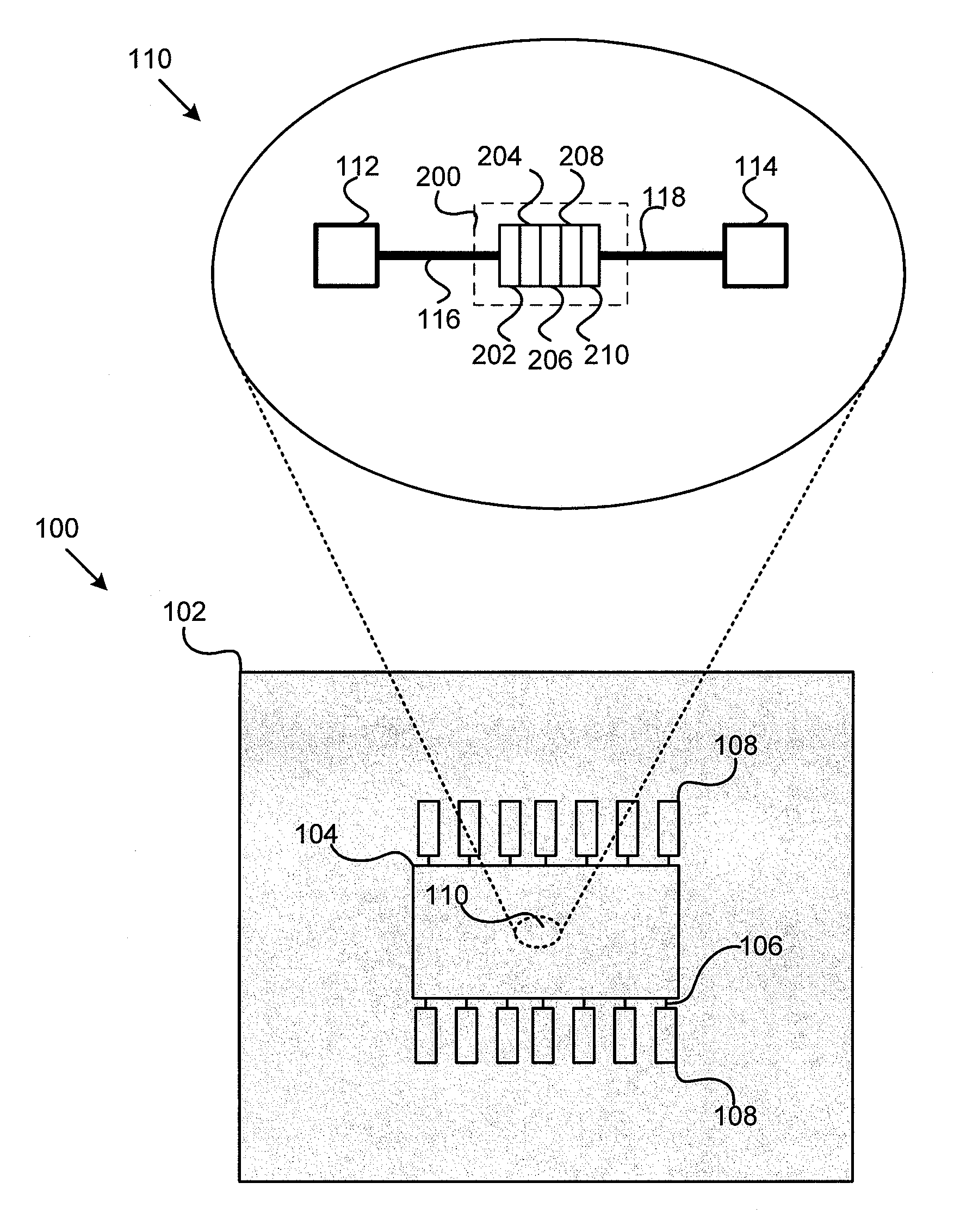

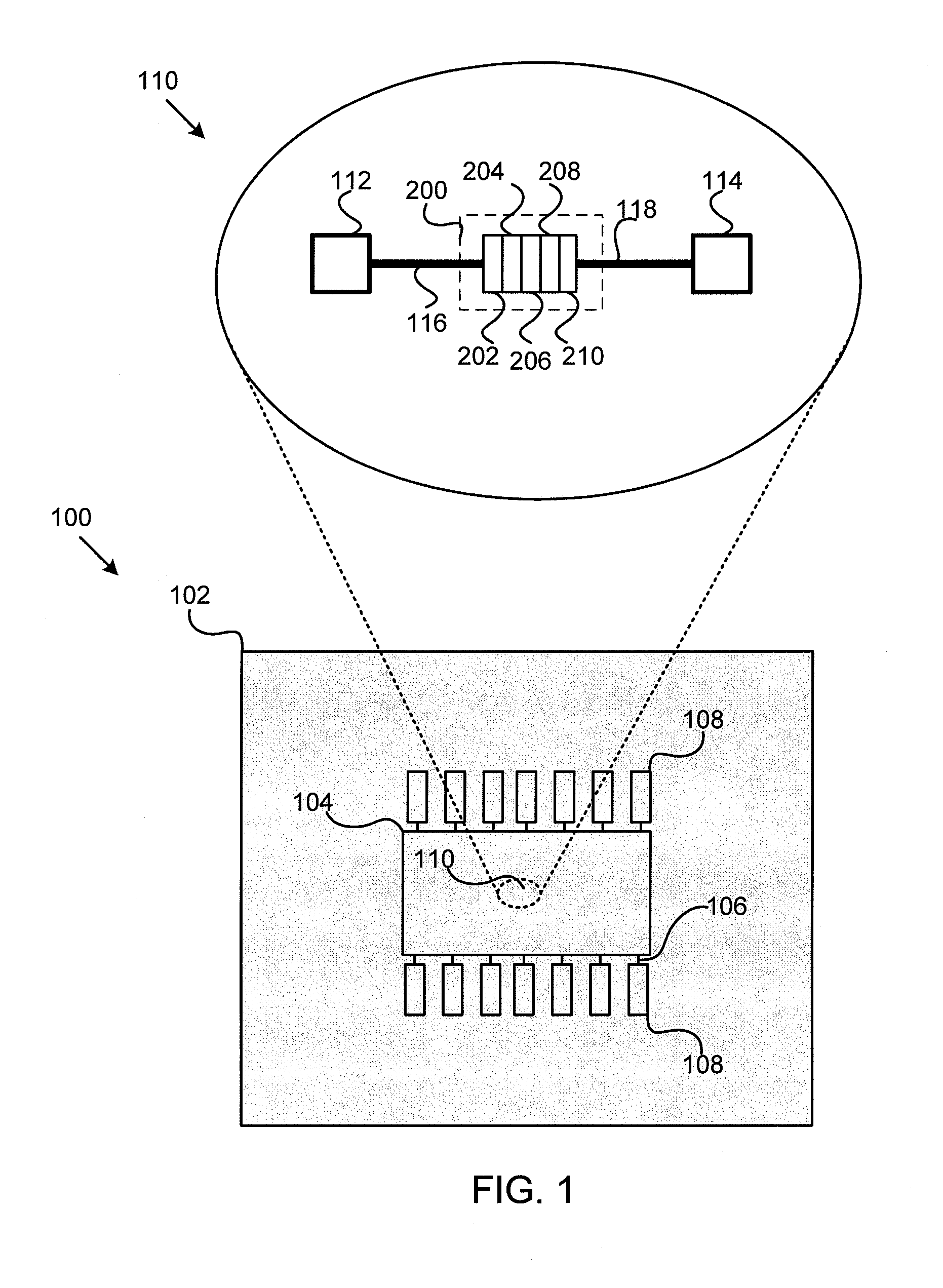

Replacement metal gate transistors with reduced gate oxide leakage

ActiveUS8053849B2Reduce EOTReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesCarbon layerEngineering

Thin effective gate oxide thickness with reduced leakage for replacement metal gate transistors is achieved by forming a protective layer between the gate oxide layer and metal gate electrode, thereby reducing stress. Embodiments include forming a protective layer of amorphous carbon containing metal carbides decreasing in concentration from the metal gate electrode toward the gate oxide layer across the protective layer. Embodiments of methodology include removing the removable gate, depositing a layer of amorphous carbon on the gate oxide layer, forming the metal gate electrode and then heating at an elevated temperature to diffuse metal from the metal gate electrode into the amorphous carbon layer, thereby forming the metal carbides. Embodiments also include metal gate transistors with a gate oxide layer having a high dielectric constant and silicon concentrated at the interfaces with the metal gate electrode and substrate.

Owner:ADVANCED MICRO DEVICES INC

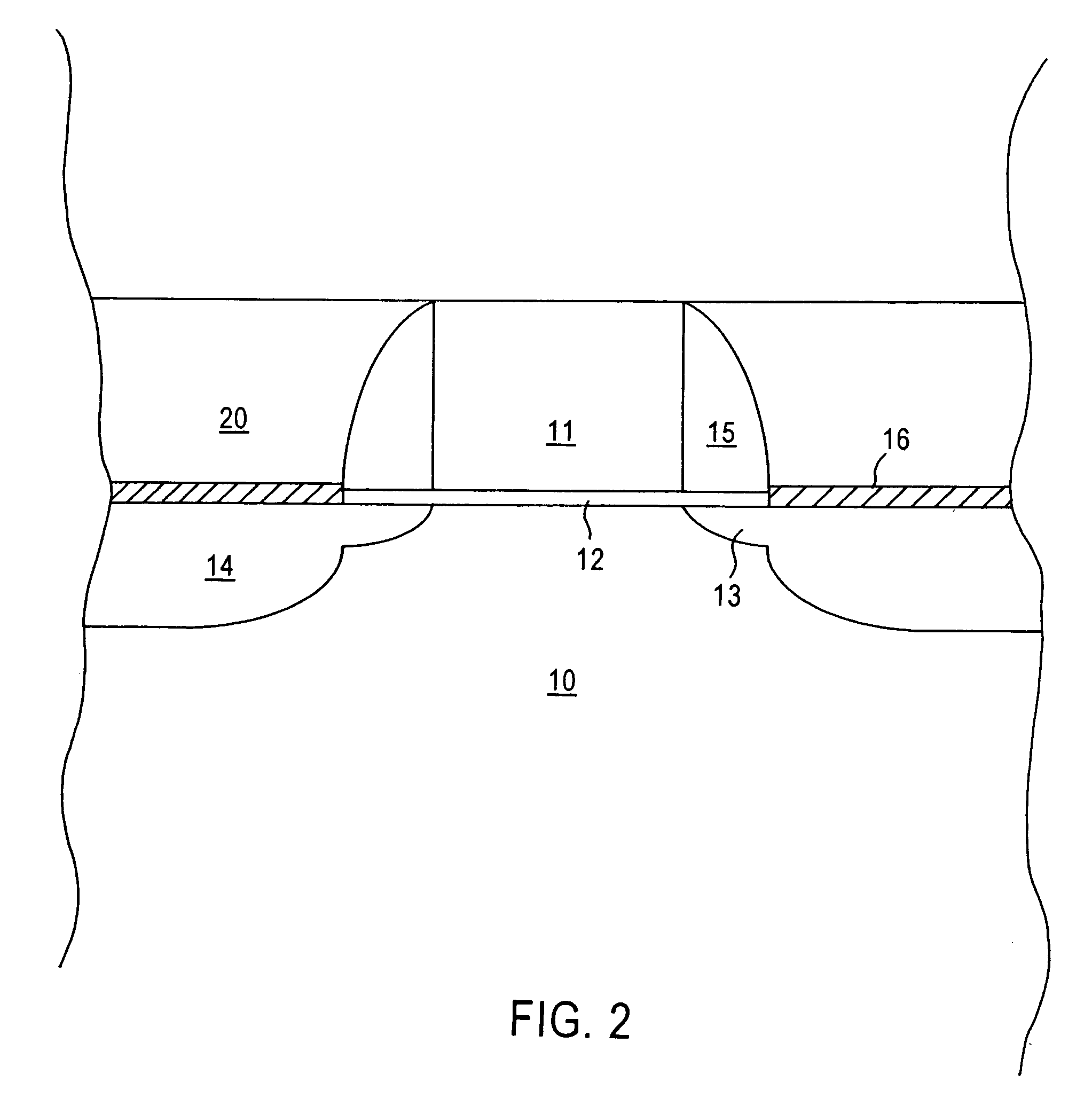

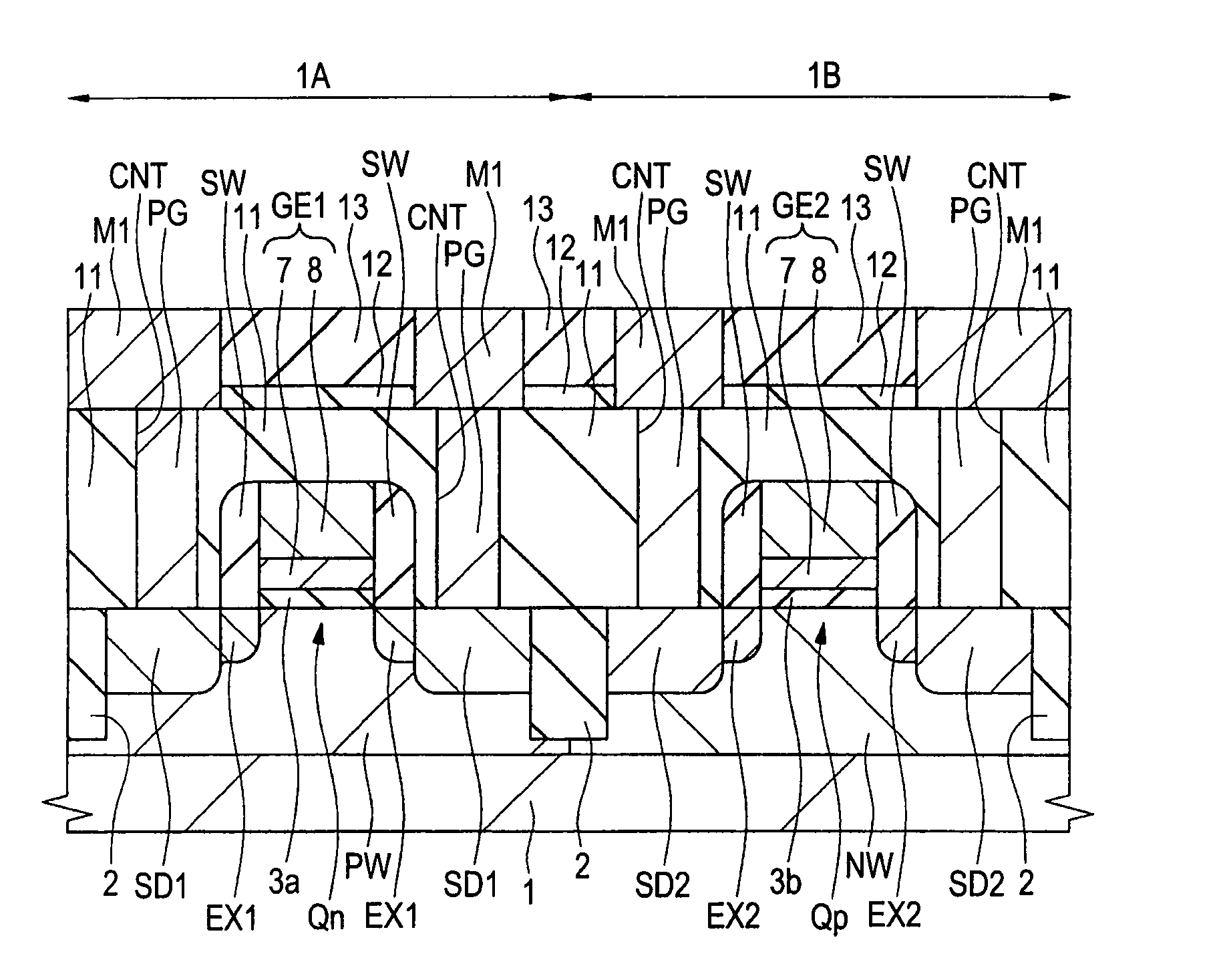

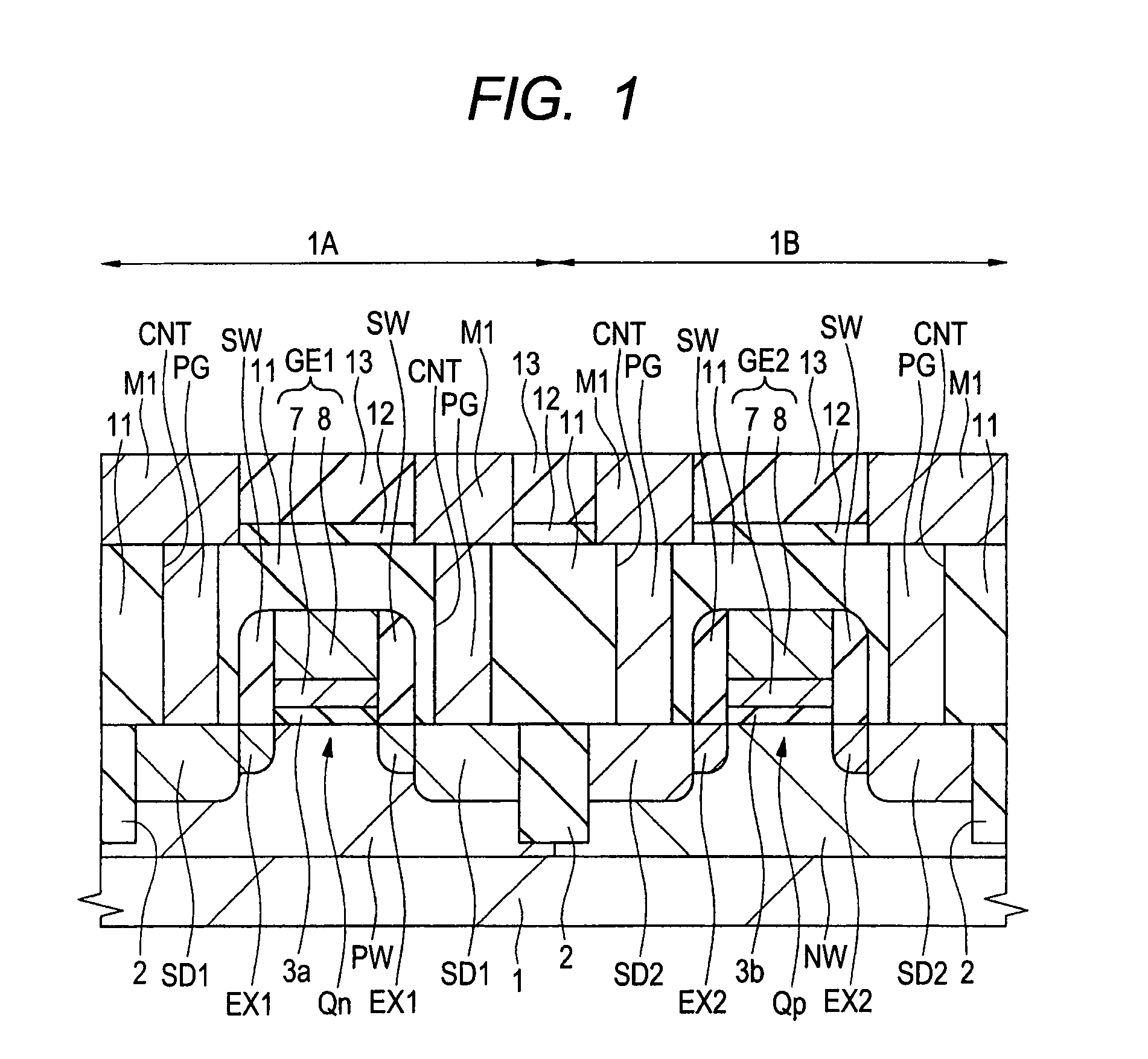

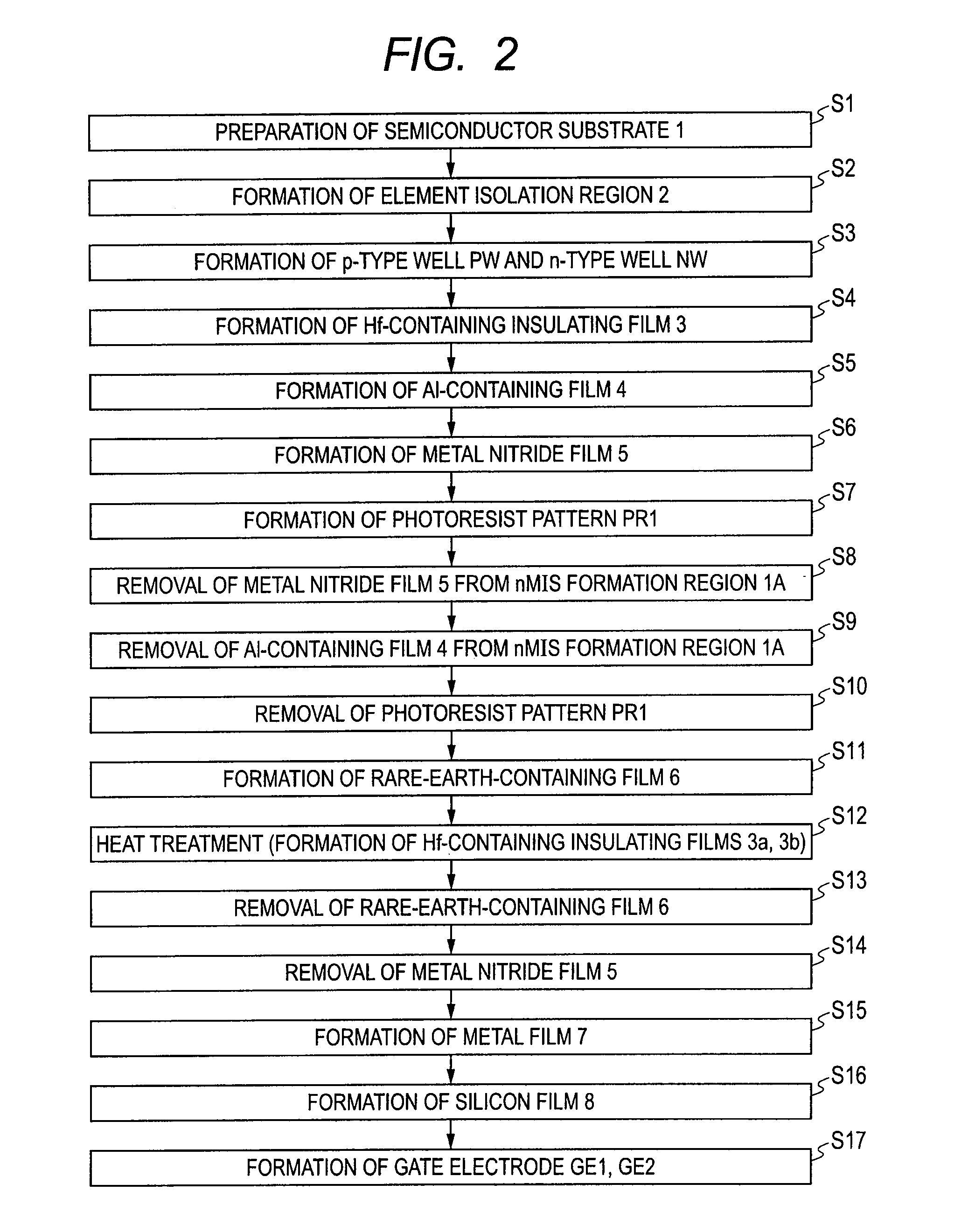

Semiconductor device and manufacturing method thereof

InactiveUS20100320542A1Valid choiceReduce the valueTransistorSemiconductor/solid-state device manufacturingRare-earth elementP channel

To improve the performance of a CMISFET having a high-k gate insulating film and a metal gate electrode. An n-channel MISFET has, over the surface of a p-type well of a semiconductor substrate, a gate electrode formed via a first Hf-containing insulating film serving as a gate insulating film, while a p-channel MISFET has, over the surface of an n-type well, another gate electrode formed via a second Hf-containing insulating film serving as a gate insulating film. These gate electrodes have a stack structure of a metal film and a silicon film thereover. The first Hf-containing insulating film is an insulating material film comprised of Hf, a rare earth element, Si, O, and N or comprised of Hf, a rare earth element, Si, and O, while the second Hf-containing insulating film is an insulating material film comprised of Hf, Al, O, and N or comprised of Hf, Al, and O.

Owner:RENESAS ELECTRONICS CORP

Metal gate structure for MOS device and production method thereof

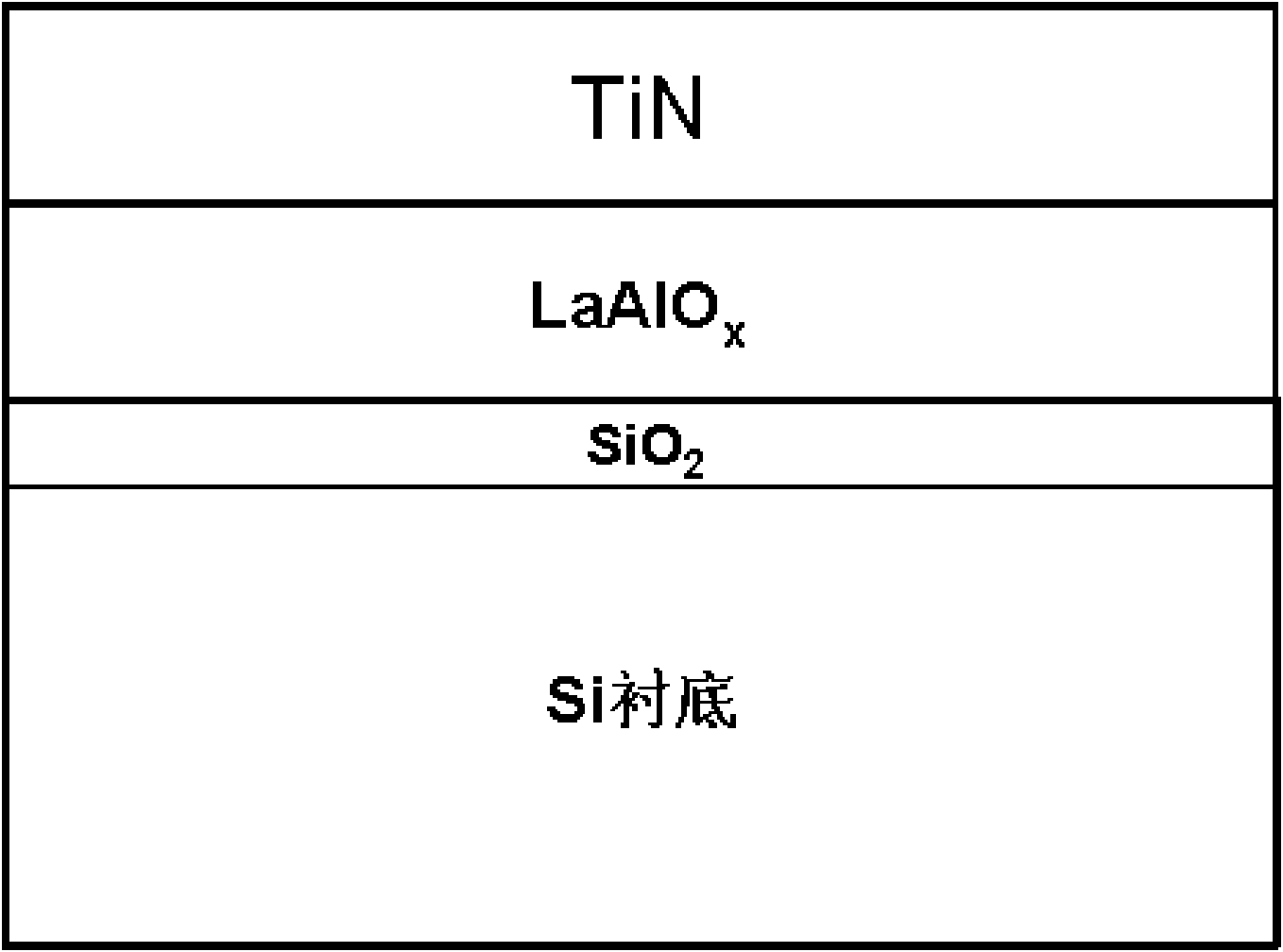

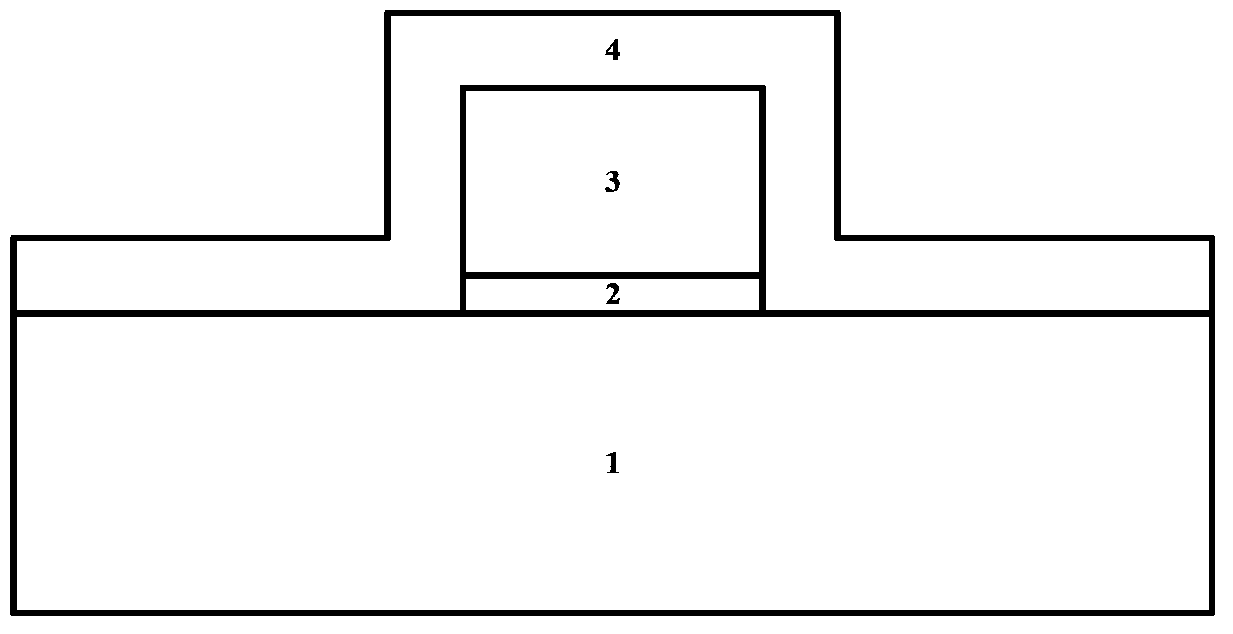

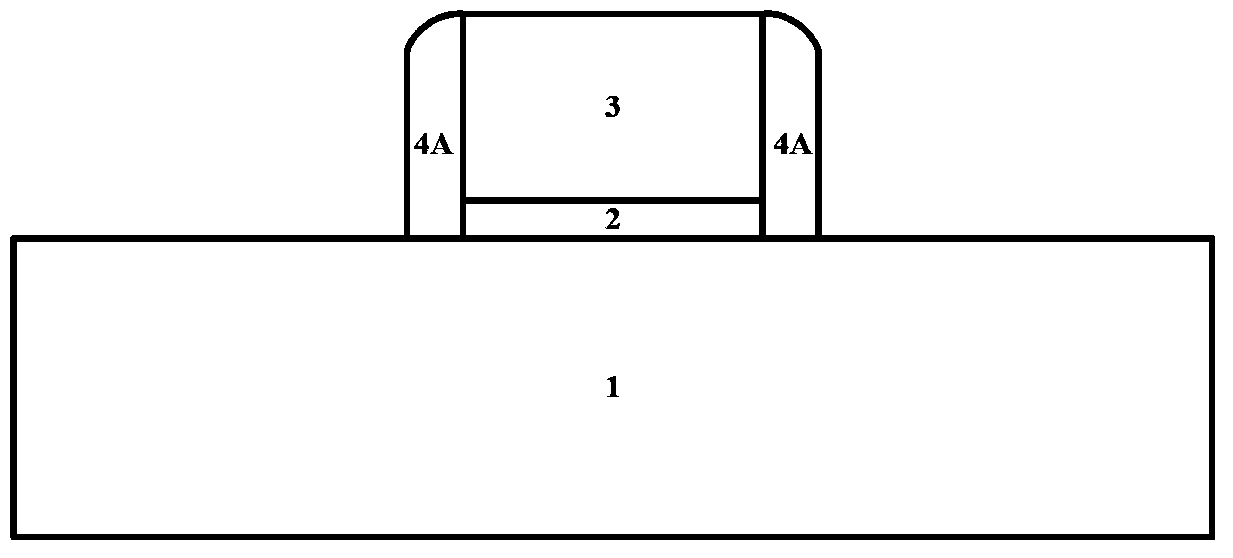

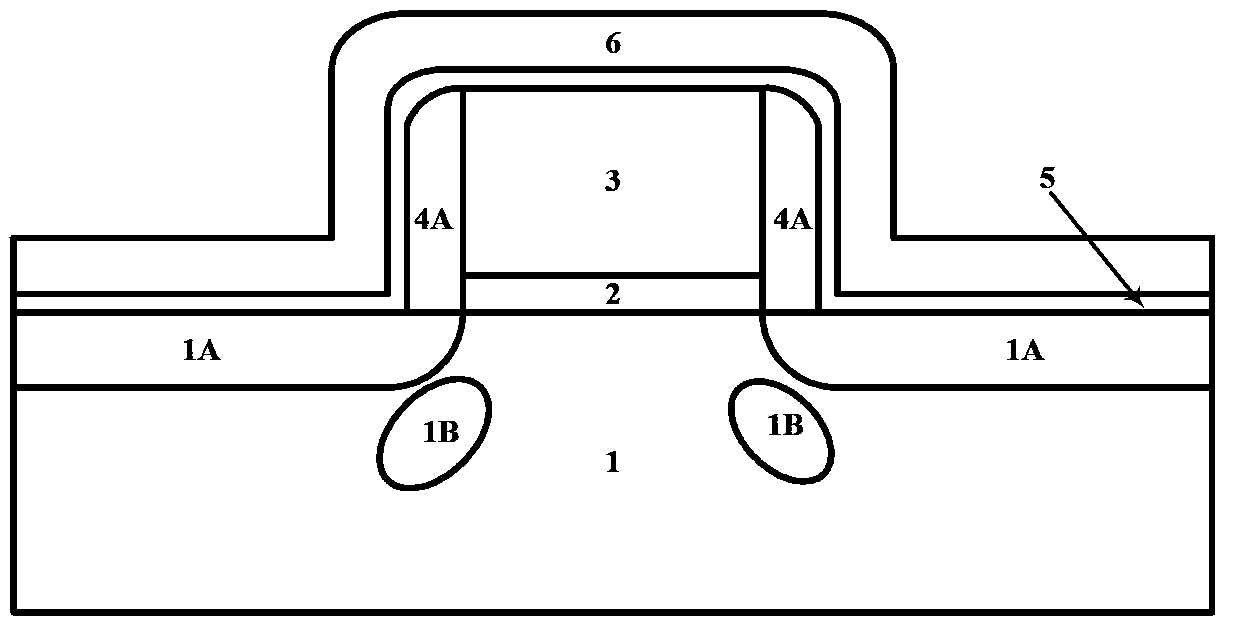

InactiveCN101599436AReduce defectsReduce EOTSemiconductor/solid-state device manufacturingSemiconductor devicesHigh dielectric permittivityOxide

The invention discloses a metal gate structure for an MOS device and a production method thereof, which belong to the technical field of MOS devices in microelectronic technology. The method comprises the steps of: forming an interface layer on a substrate; forming a high dielectric constant gate dielectric layer on the interface layer; forming a metal gate material layer on the high dielectric constant gate dielectric layer; and performing post-metallization annealing treatment on the interface layer, the high dielectric constant gate dielectric layer and the metal gate material layer to form the metal gate structure. The method can form the high-quality and low-defect metal gate structure by performing post-metallization annealing treatment on the metal gate structure, and prevent oxygen from being diffused to an SiO2 / Si interface and substrate silicon to react to form SiO2 during the annealing, thereby ensuring that an equivalent oxide layer of the whole metal gate structure keeps smaller thickness to meet the performance requirement of the MOS device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

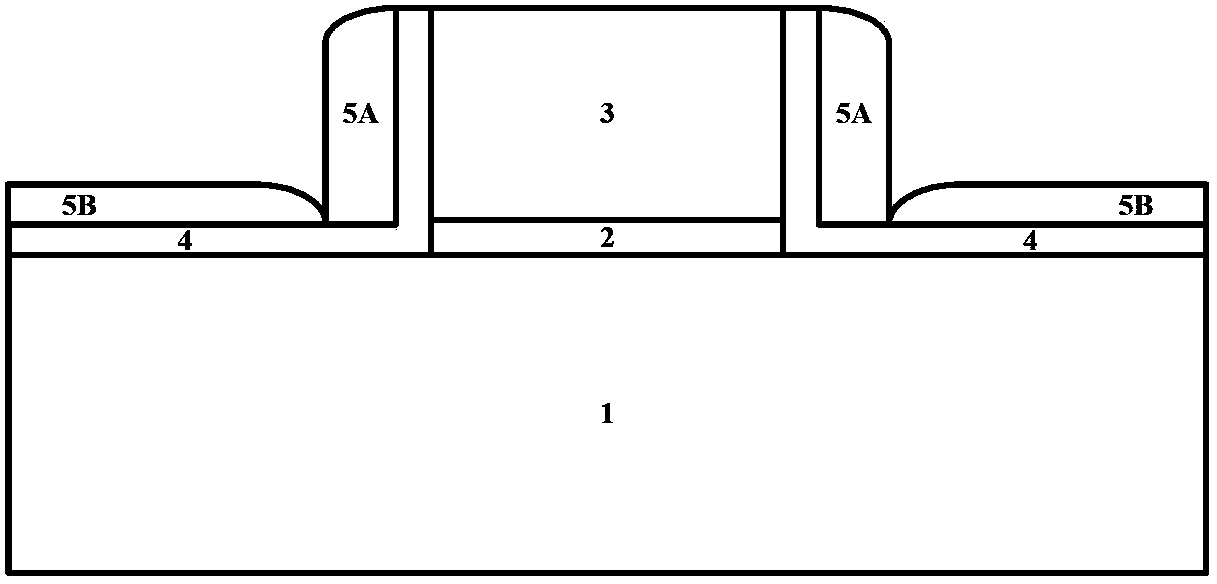

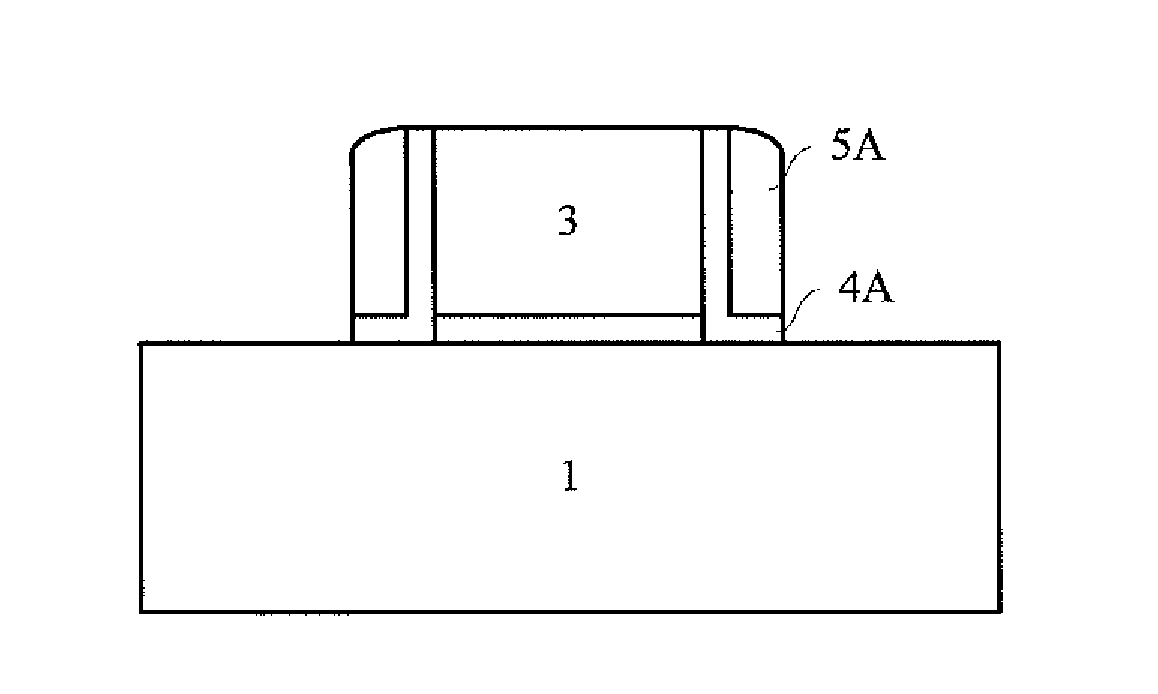

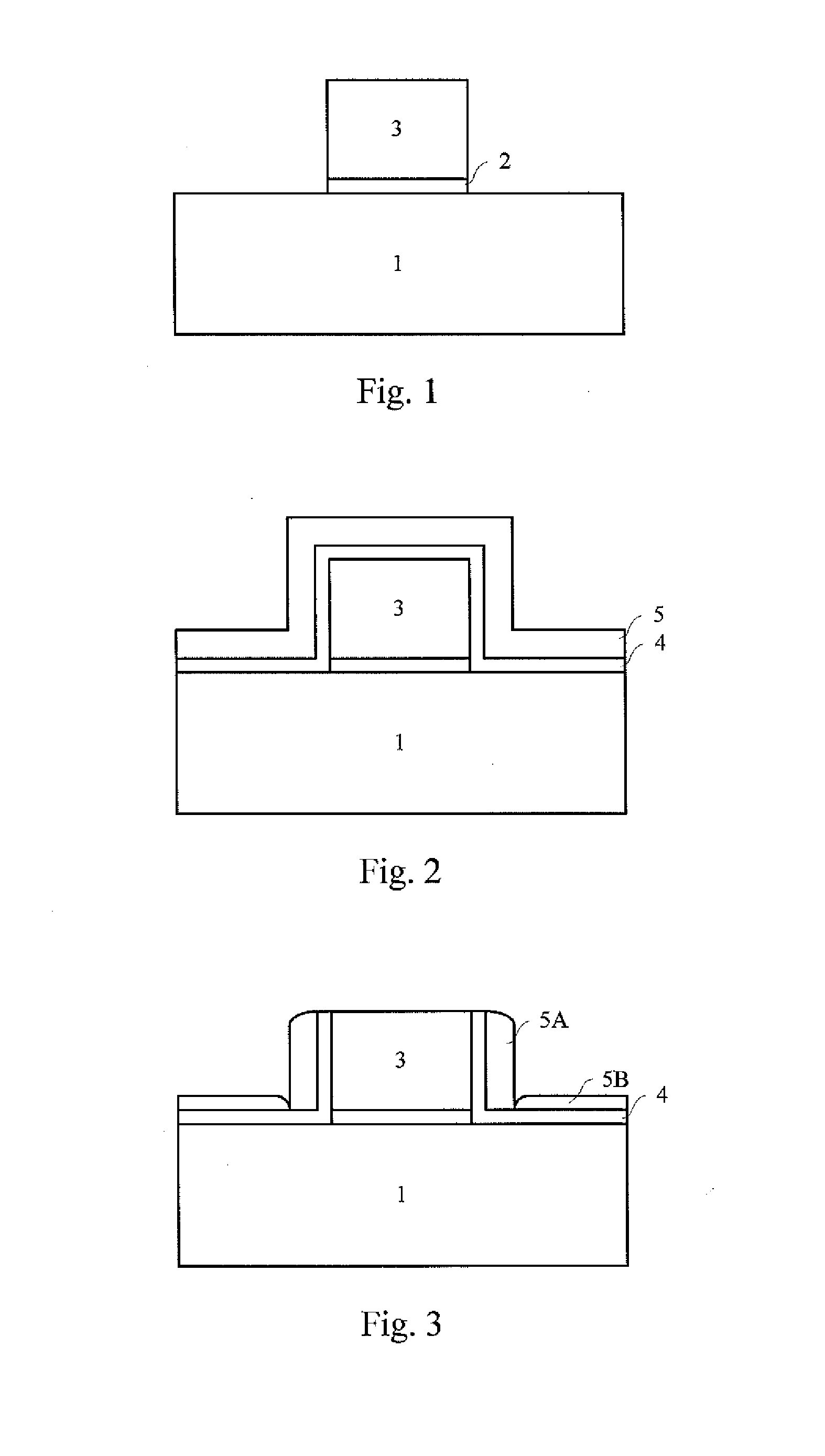

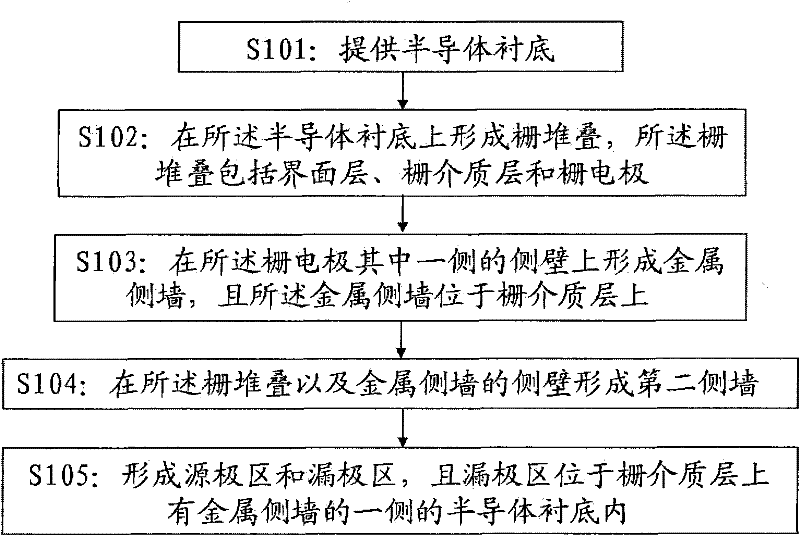

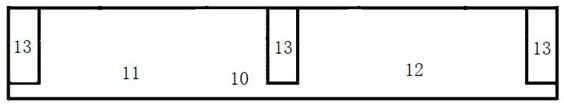

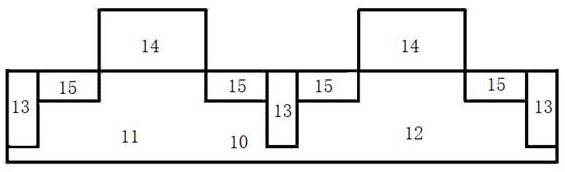

Manufacturing method of semiconductor device

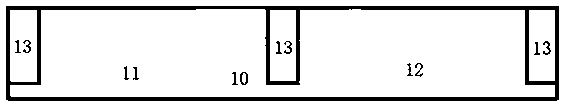

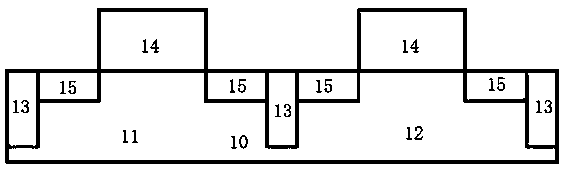

InactiveCN103632943AAvoid damageNON reductionSemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentEtching

Disclosed in the invention is a manufacturing method of a semiconductor device. The manufacturing method comprises the following steps: forming a grid stacking structure at a substrate; depositing a first dielectric material layer at the substrate and the grid stacking structure; etching the first dielectric material layer to form a first side wall; executing LDD and Halo doping injection; successively depositing a second dielectric material layer and a third dielectric material layer at the substrate and the first side wall; and successively etching the third dielectric material layer and the second dielectric material layer so as to form a third side wall and a second side wall respectively. According to the side wall etching method, the NON three-layer composite side wall is used and two-step etching is carries out, thereby reducing the damage on the substrate as well as the process complexity. Besides, the threshold voltage can be optimized; the EoT can be effectively reduced; and the grid-control capability and the drive current can also be improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Method for manufacturing semiconductor device

ActiveCN103531454AAvoid damageReduce process complexitySemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentPower semiconductor device

Provided in the present invention is a method for manufacturing a semiconductor device. The method comprises: forming a stacked gate structure on a substrate; depositing in succession a first dielectric material layer and a second dielectric material layer on the substrate and the stacked gate structure; and etching in succession the second dielectric material layer and the first dielectric material layer by using an etching gas containing helium so as to form a second side wall and a first side wall respectively. According to the method for manufacturing the semiconductor device, a composite side wall with double layers and a two-step etching by use of the etching gas containing the helium are adopted so that while the damage to the substrate is reduced, the process complexity is also reduced, and besides, the threshold voltage can be optimized, the EoT can be effectively reduced, and the gate-control capability and the drive current can be increased.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

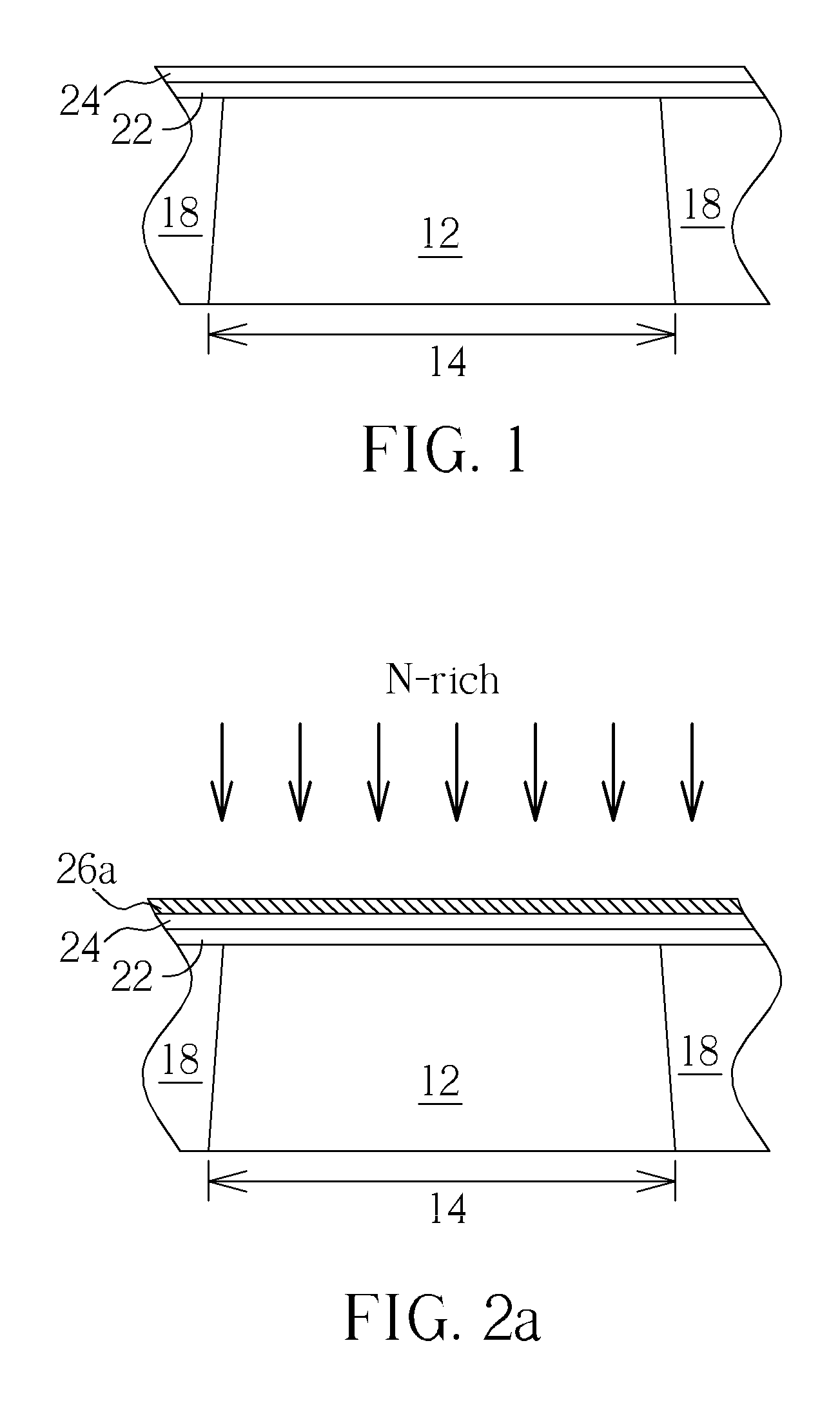

Method of manufacturing semiconductor device

ActiveUS20140011303A1Reduce harmRaise the threshold voltageSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingDevice materialGate stack

A method of manufacturing a semiconductor device is disclosed. The method may comprise: forming a gate stack on a substrate; depositing a first dielectric layer and a second dielectric layer sequentially on the substrate and the gate stack; and etching the second dielectric layer and the first dielectric layer sequentially with an etching gas containing helium to form a second spacer and a first spacer, respectively. According to the method disclosed herein, a dual-layer complex spacer configuration is achieved, and two etching operations where the etching gas comprises the helium gas are performed. As a result, it is possible to reduce damages to the substrate and also to reduce the process complexity. Further, it is possible to optimize a threshold voltage, effectively reduce an EOT, and enhance a gate control capability and a driving current.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

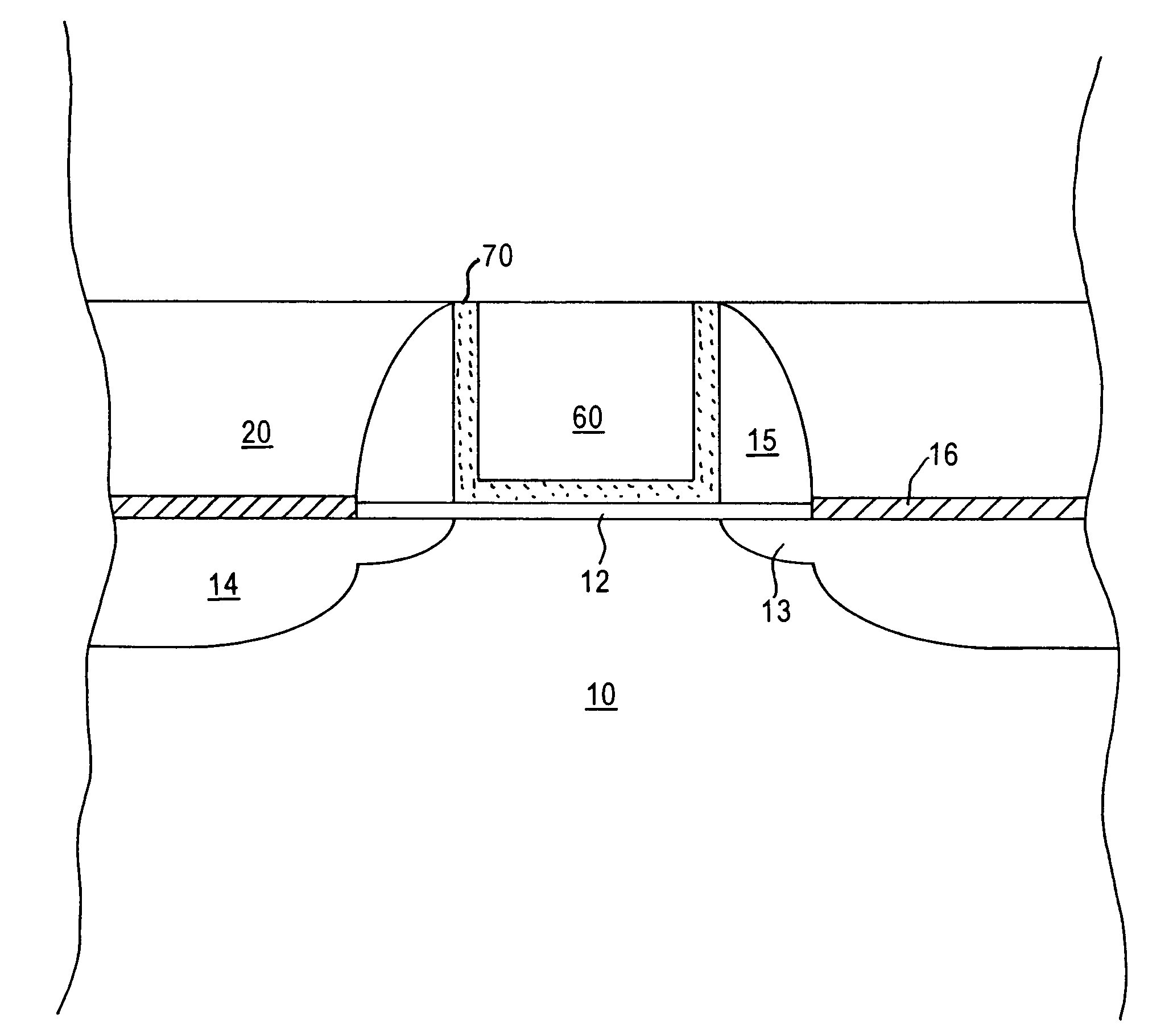

Semiconductor device and method of manufacturing the same

ActiveUS8222099B2Reduce EOTInhibited DiffusionTransistorSolid-state devicesDielectricGate dielectric

A semiconductor device and a method of manufacturing the same are provided. A multi-component high-k interface layer containing elements of the substrate is formed from a ultra-thin high-k dielectric material in a single-layer structure of atoms by rapid annealing in the manufacturing of a CMOS transistor by the replacement gate process, and a high-k gate dielectric layer with a higher dielectric constant and a metal gate layer are formed thereon. The EOT of the device is effectively decreased, and the diffusion of atoms in the high-k gate dielectric layer from an upper level thereof is effectively prevented by the optimized high-k interface layer at high-temperature treatment. Thus, the present invention may also avoid the growth of the interface layers and the degradation of carrier mobility. Furthermore, the present invention may further alleviate the problem of high interface state and interface roughness caused by direct contact of the high-k gate dielectric layer with high dielectric constant and the substrate, and thus the overall performance of the device is effectively enhanced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

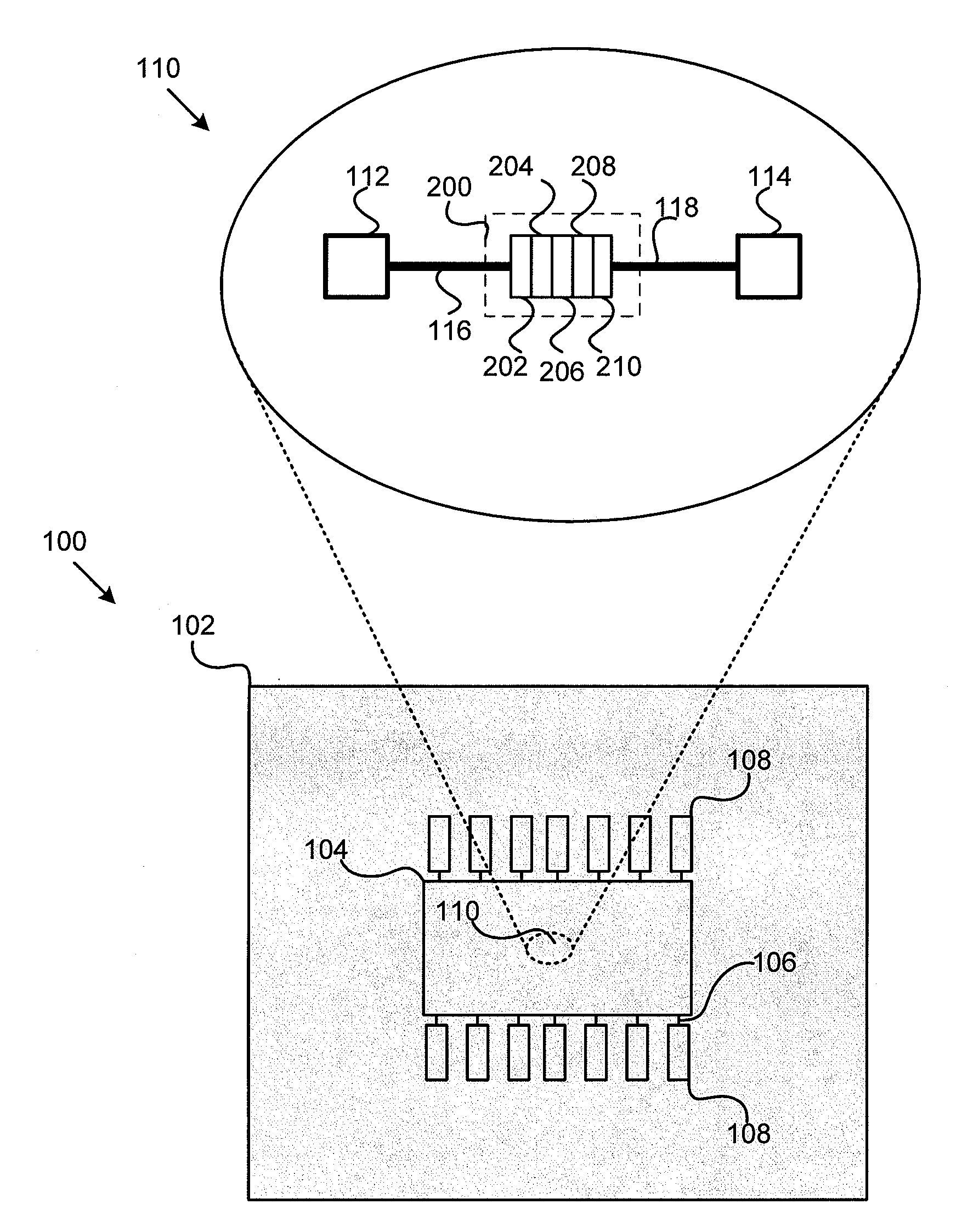

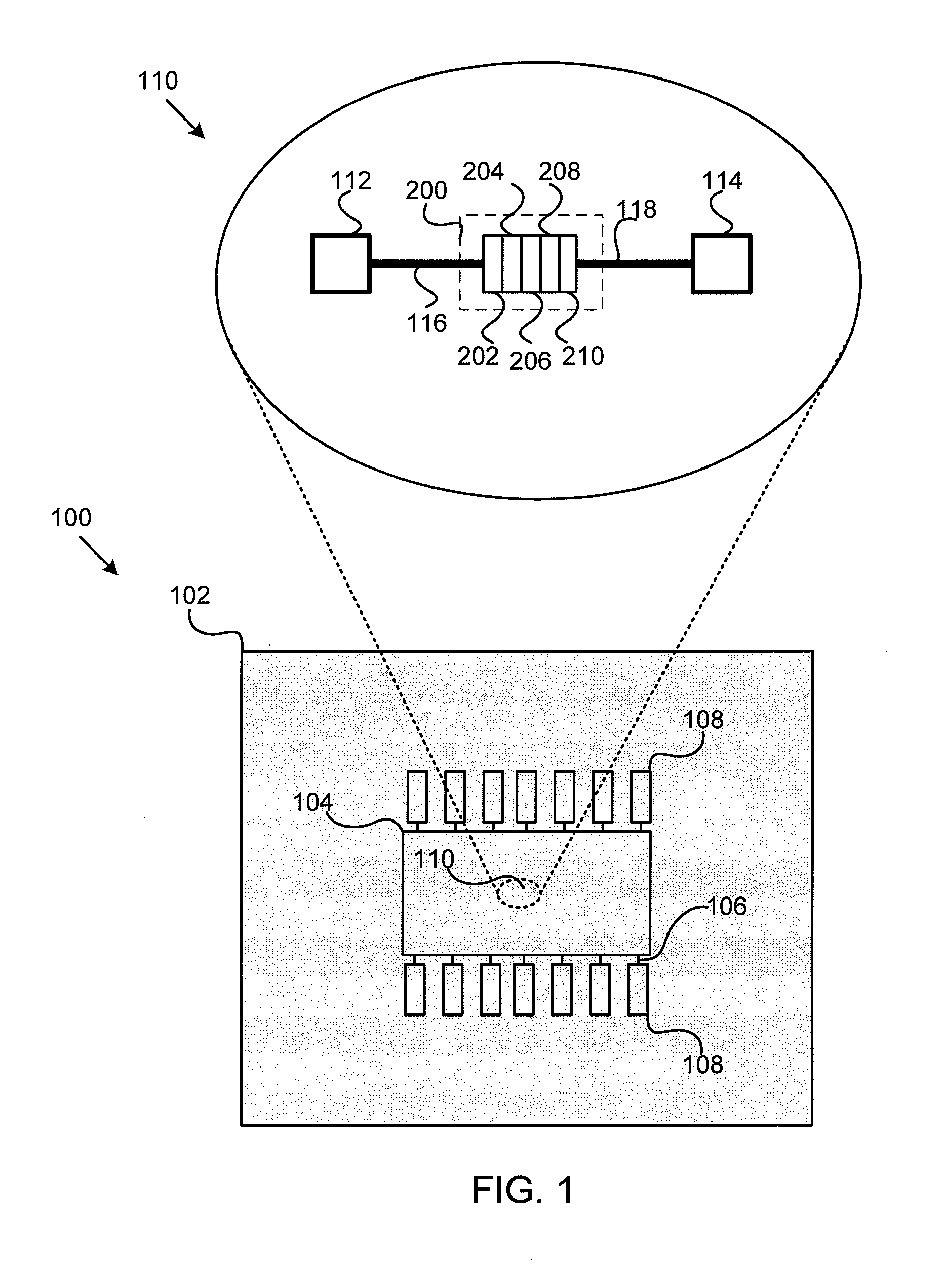

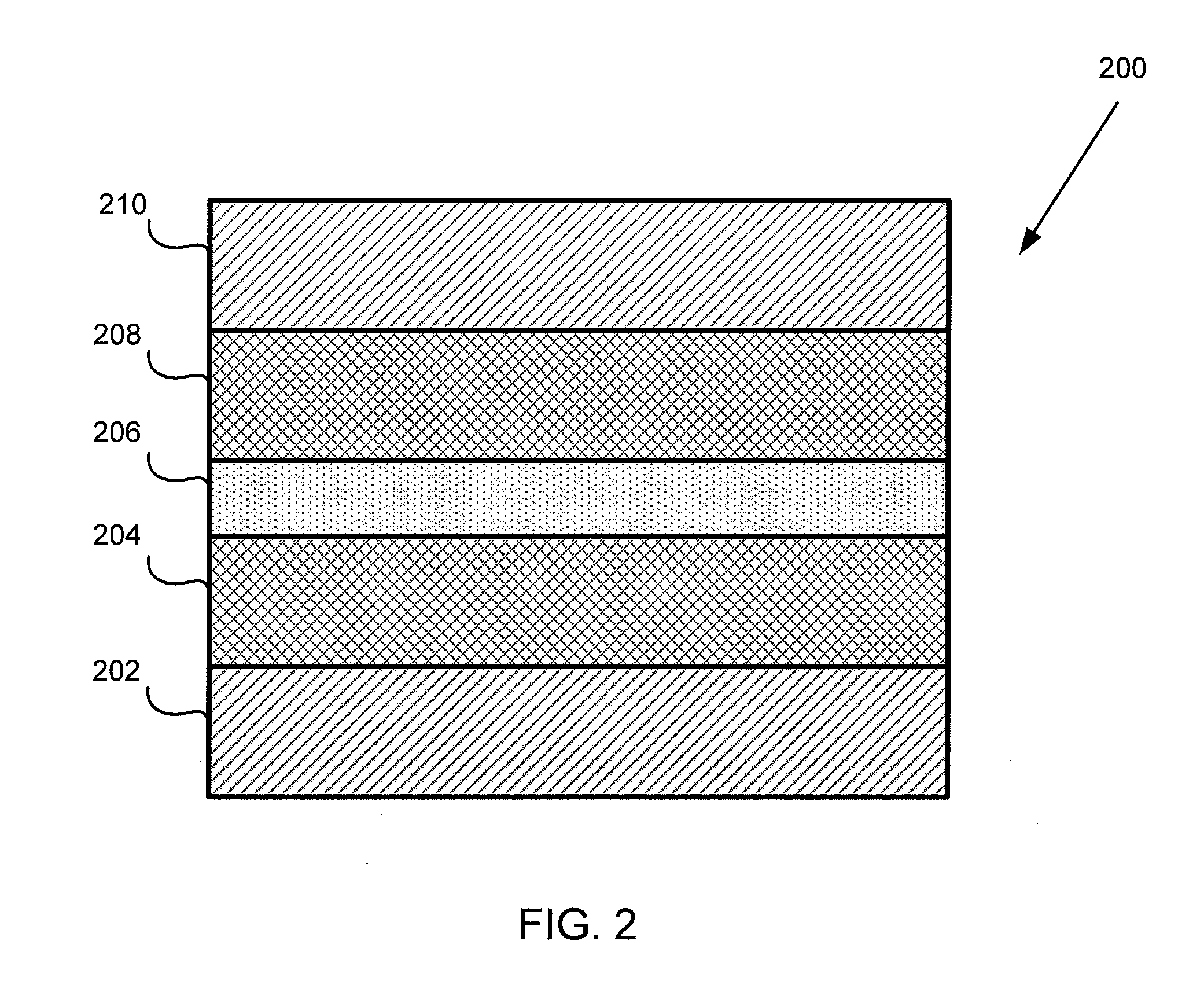

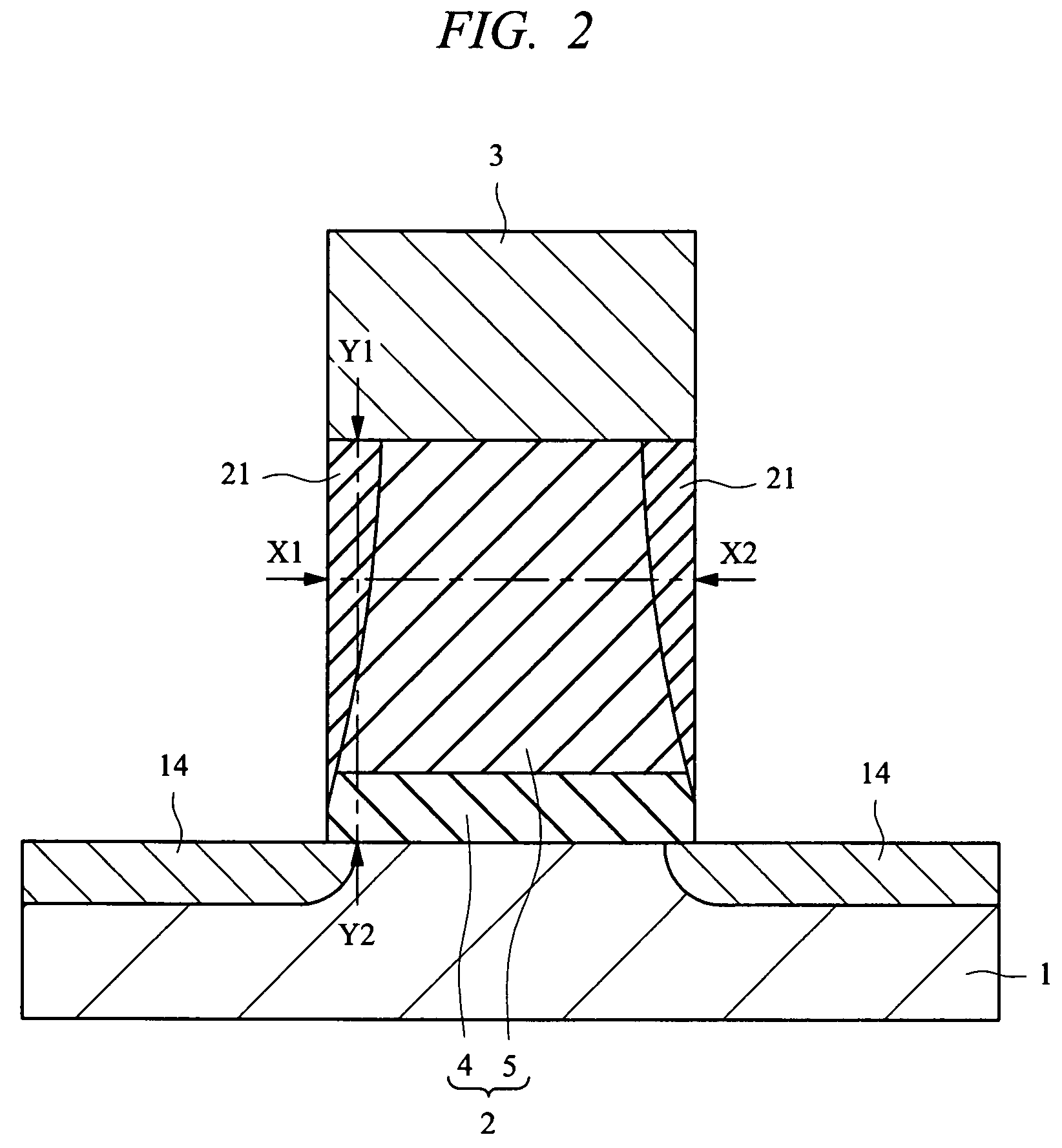

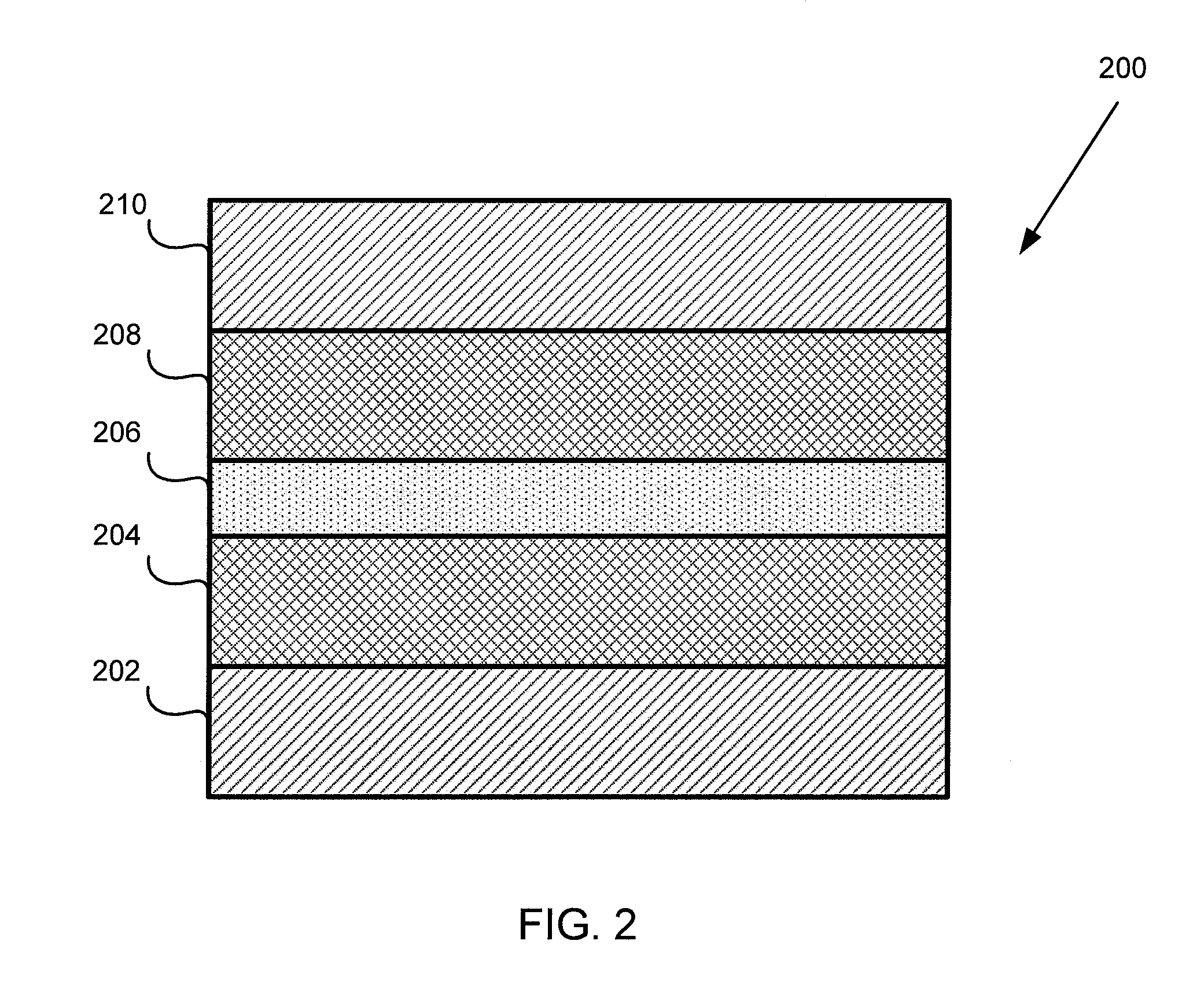

Capacitors, Systems, and Methods

InactiveUS20110298090A1Decreasing effective oxide thicknessReduce leakage currentSemiconductor/solid-state device manufacturingCapacitorsCapacitorElectrical and Electronics engineering

Capacitors, systems, and methods are disclosed. In one embodiment, the capacitor includes a first electrode. The capacitor may also include a first insulator layer having a positive VCC adjacent to the first electrode. The capacitor may further include a second insulator layer having a negative VCC adjacent to the first insulator layer. The capacitor may also include a third insulator layer having a positive VCC adjacent to the second insulator layer. The capacitor may also include a second electrode adjacent to the third insulator layer.

Owner:SEMATECH

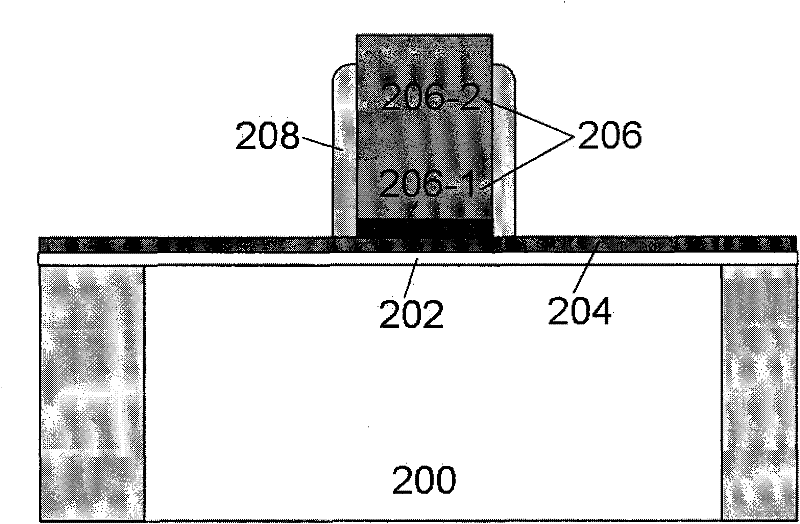

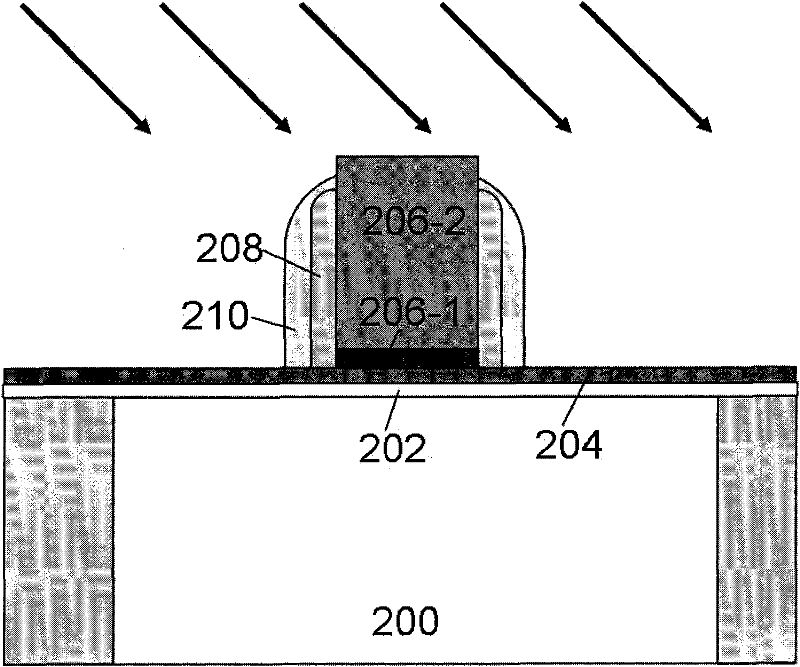

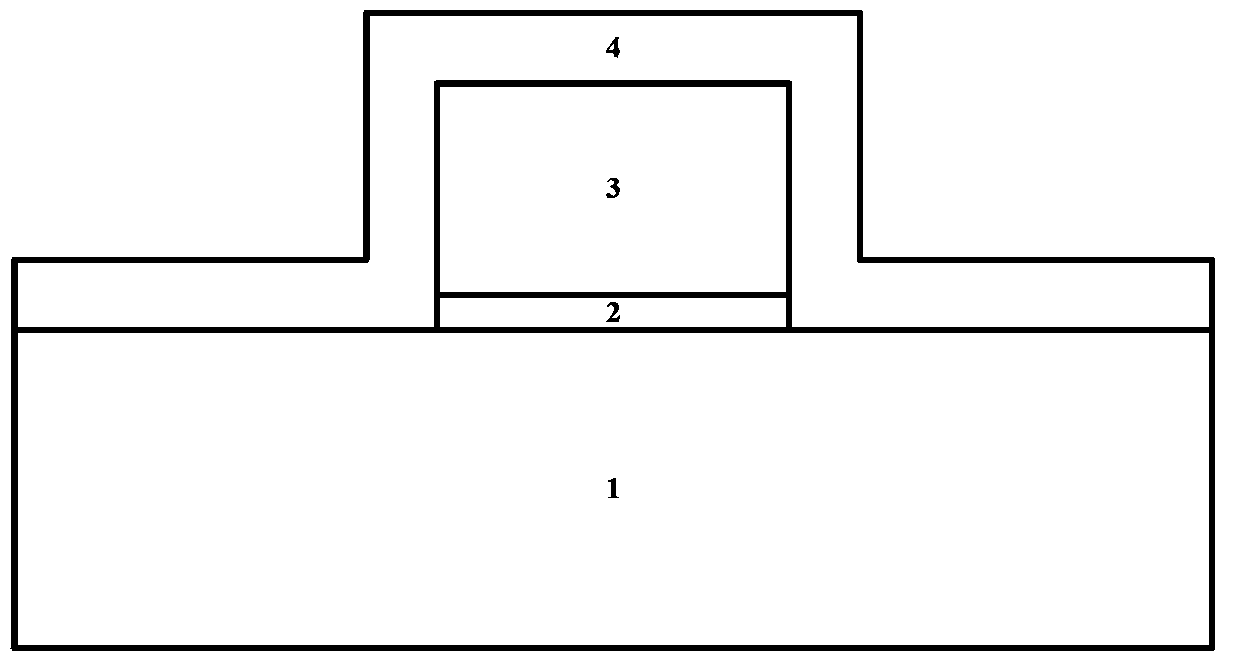

Semiconductor device and manufacturing method thereof

ActiveCN102194870AImprove controlWill not degenerateSemiconductor/solid-state device manufacturingSemiconductor devicesEquivalent oxide thicknessCharge carrier mobility

The invention relates to a semiconductor device and a manufacturing method thereof. The device is provided with a metal lateral wall on the side wall of a grid electrode at one side of a drain electrode region; the metal lateral wall is made of metal, such as Ta, and the like and has an oxygen uptake effect, thereby effectively reducing EOT (Equivalent Oxide Thickness) at one side of the drain electrode region and further effectively promoting the controllability of short channel control. In addition, because the EOT at one side of a source electrode region is larger, carrier drift mobility of the device cannot be deteriorated. Besides, the non-symmetrical device can have a better driving property.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Method for fabricating semiconductor device

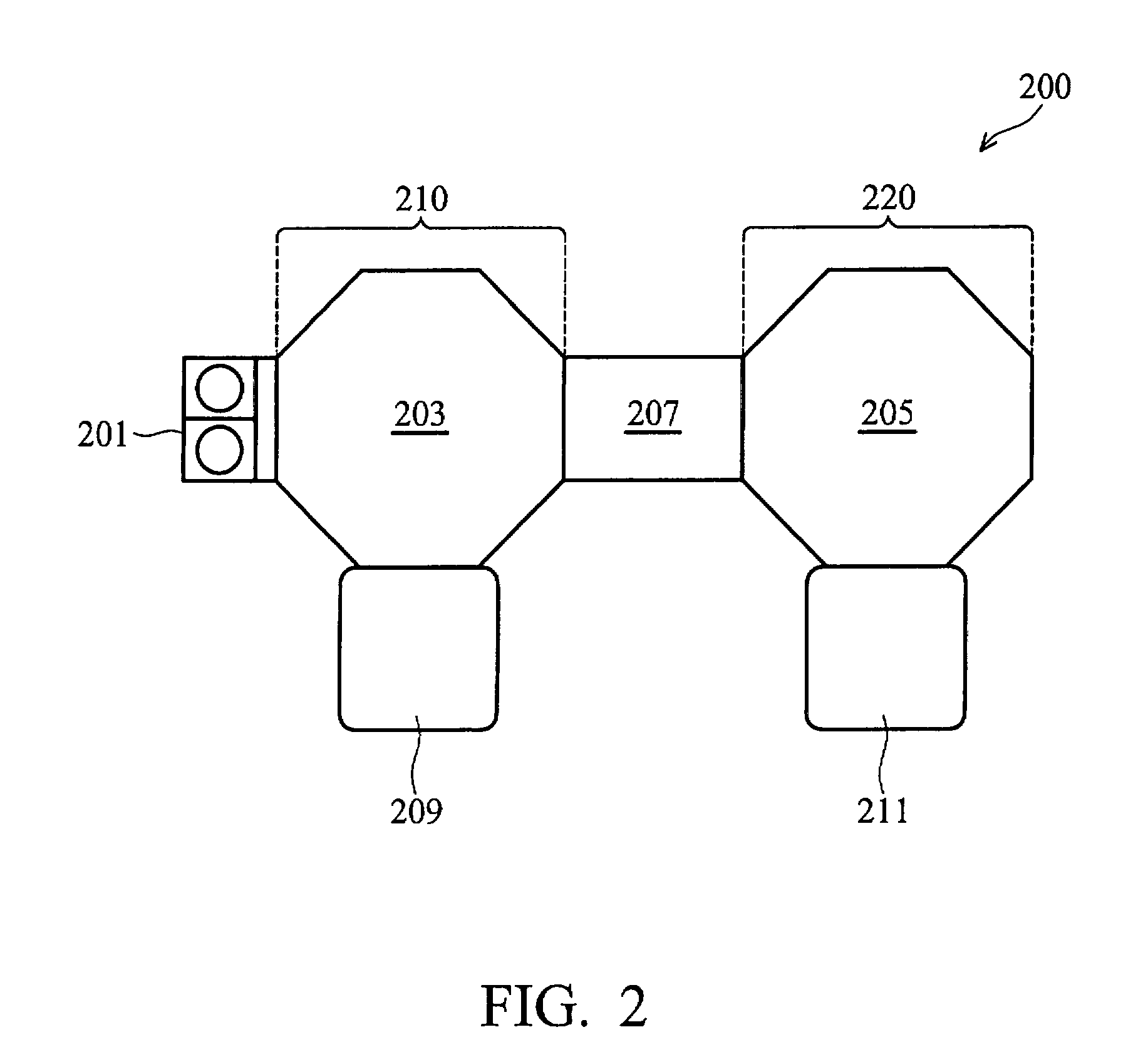

InactiveUS20080242108A1Reduce EOTImprove device performanceSemiconductor/solid-state device manufacturingChemical vapor deposition coatingEngineeringPressure difference

A method for fabricating a semiconductor device is disclosed. The method includes providing a first chamber and a second chamber. The first chamber and the second chamber are connected by a pressure differential unit, for depositing a metallic film over a substrate in the first chamber, transferring the substrate to the second chamber via the pressure differential unit without exposing the substrate to the ambient environment, and depositing a silicon-containing film on the metallic film in the second chamber.

Owner:TAIWAN SEMICON MFG CO LTD

Metal gate structure

ActiveUS8860150B2Reduce EOTEffective work functionTransistorSemiconductor/solid-state device manufacturingMetalMaterials science

The metal gate structure of the present invention can include a TiN complex, and the N / Ti proportion of the TiN complex is decreased from bottom to top. In one embodiment, the TiN complex can include a single TiN layer, which has an N / Ti proportion gradually decreasing from bottom to top. In another embodiment, the TiN complex can include a plurality of TiN layers stacking together. In such a case, the lowest TiN layer has a higher N / Ti proportion than the adjusted TiN layer.

Owner:UNITED MICROELECTRONICS CORP

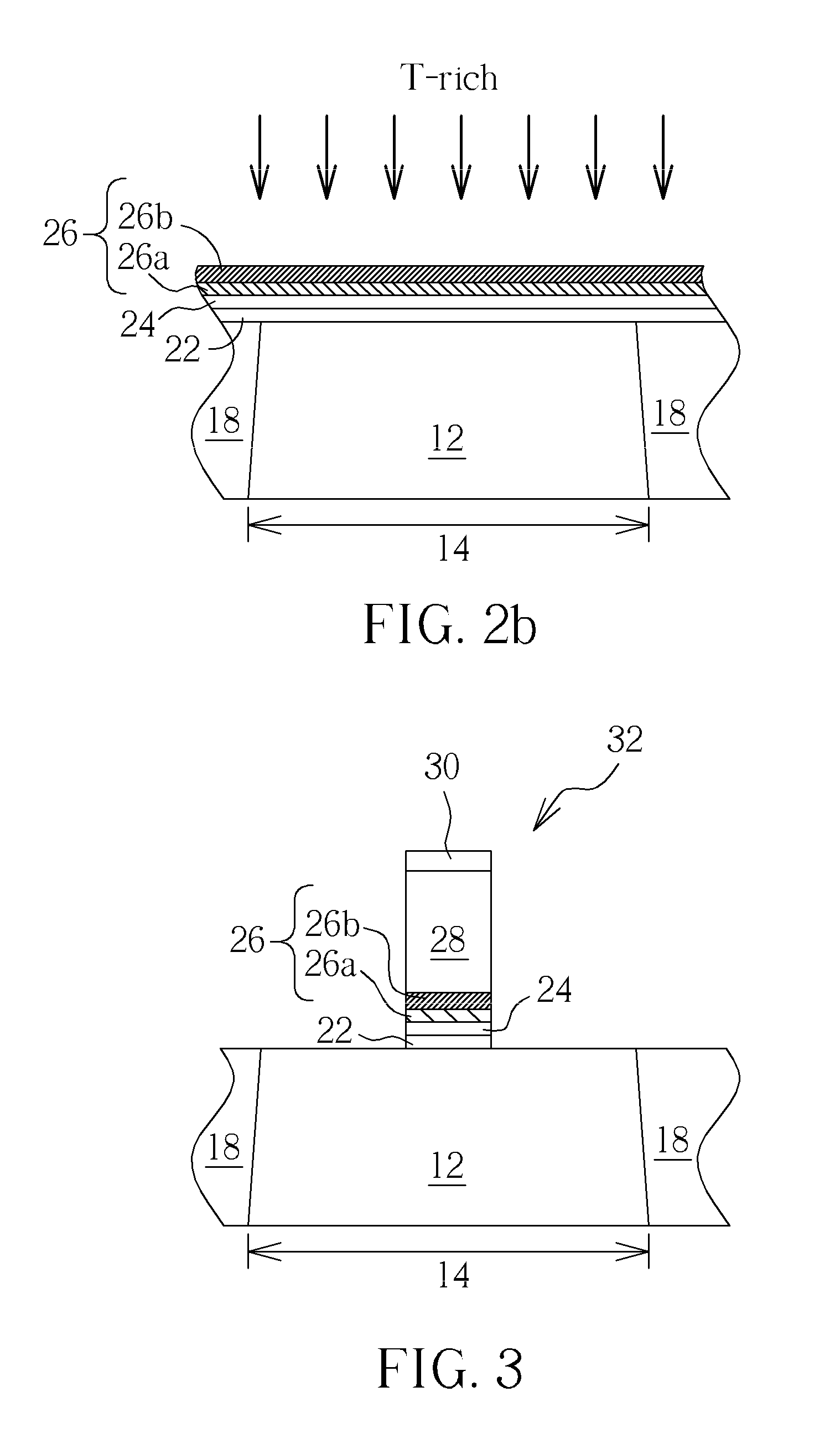

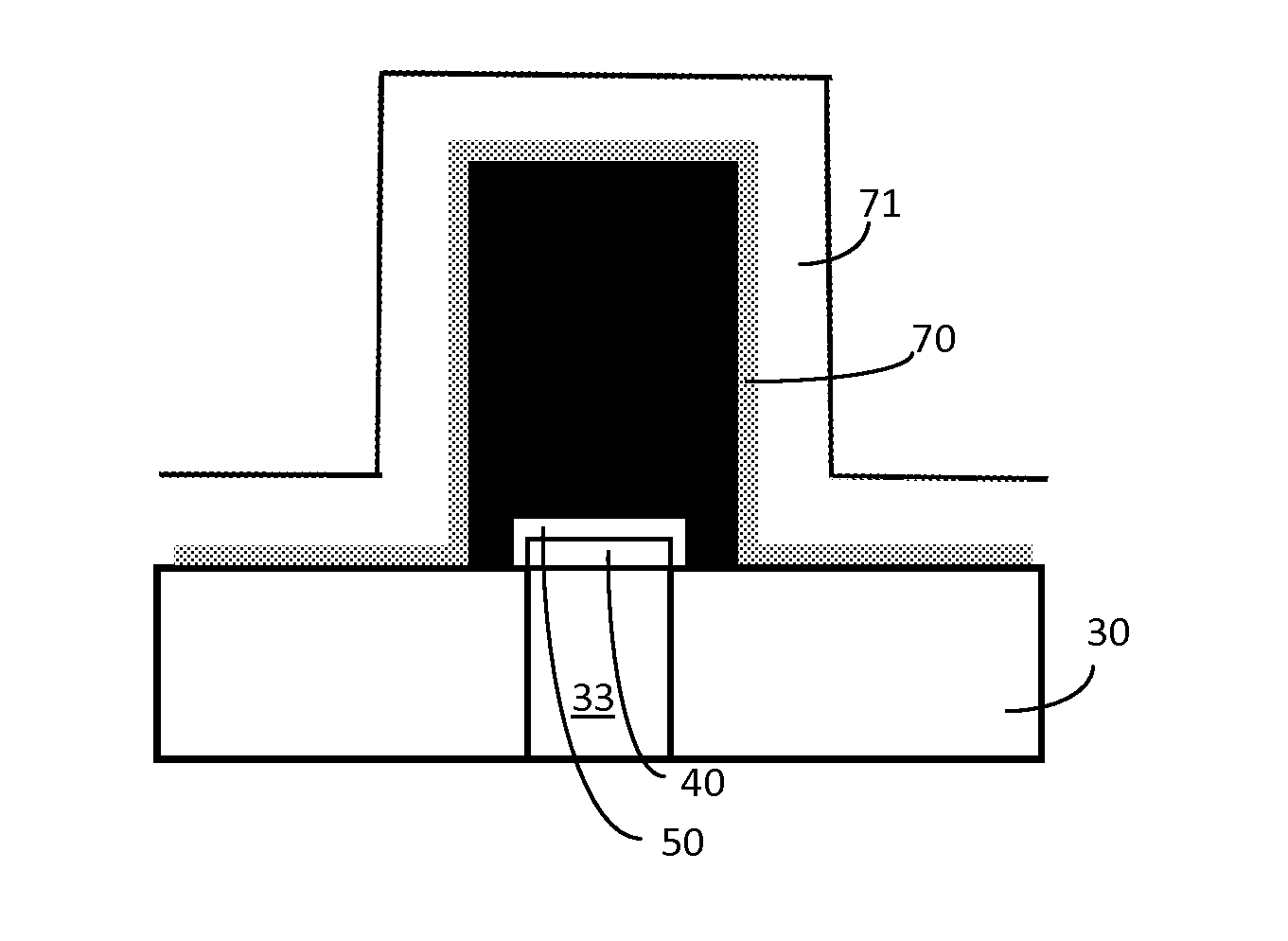

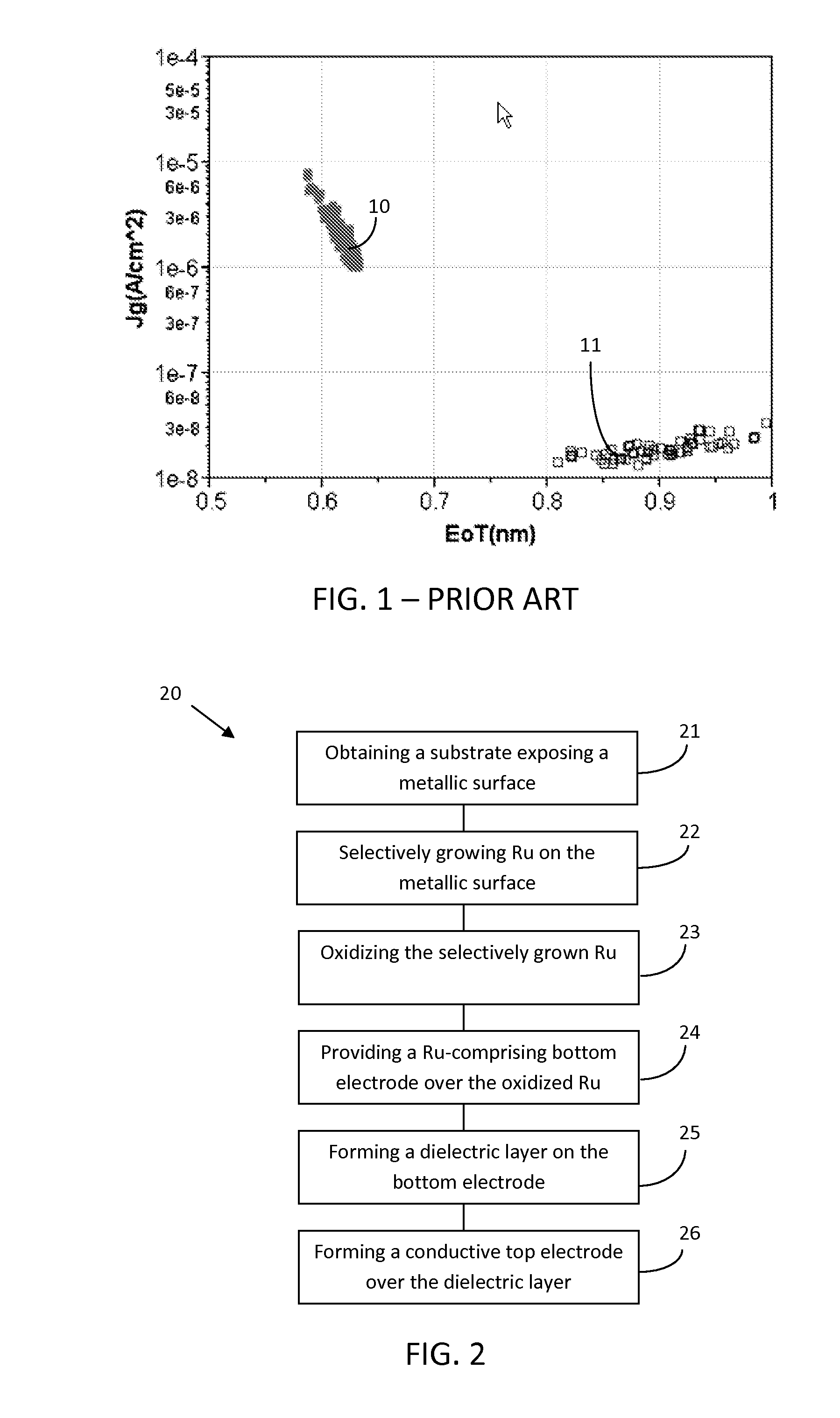

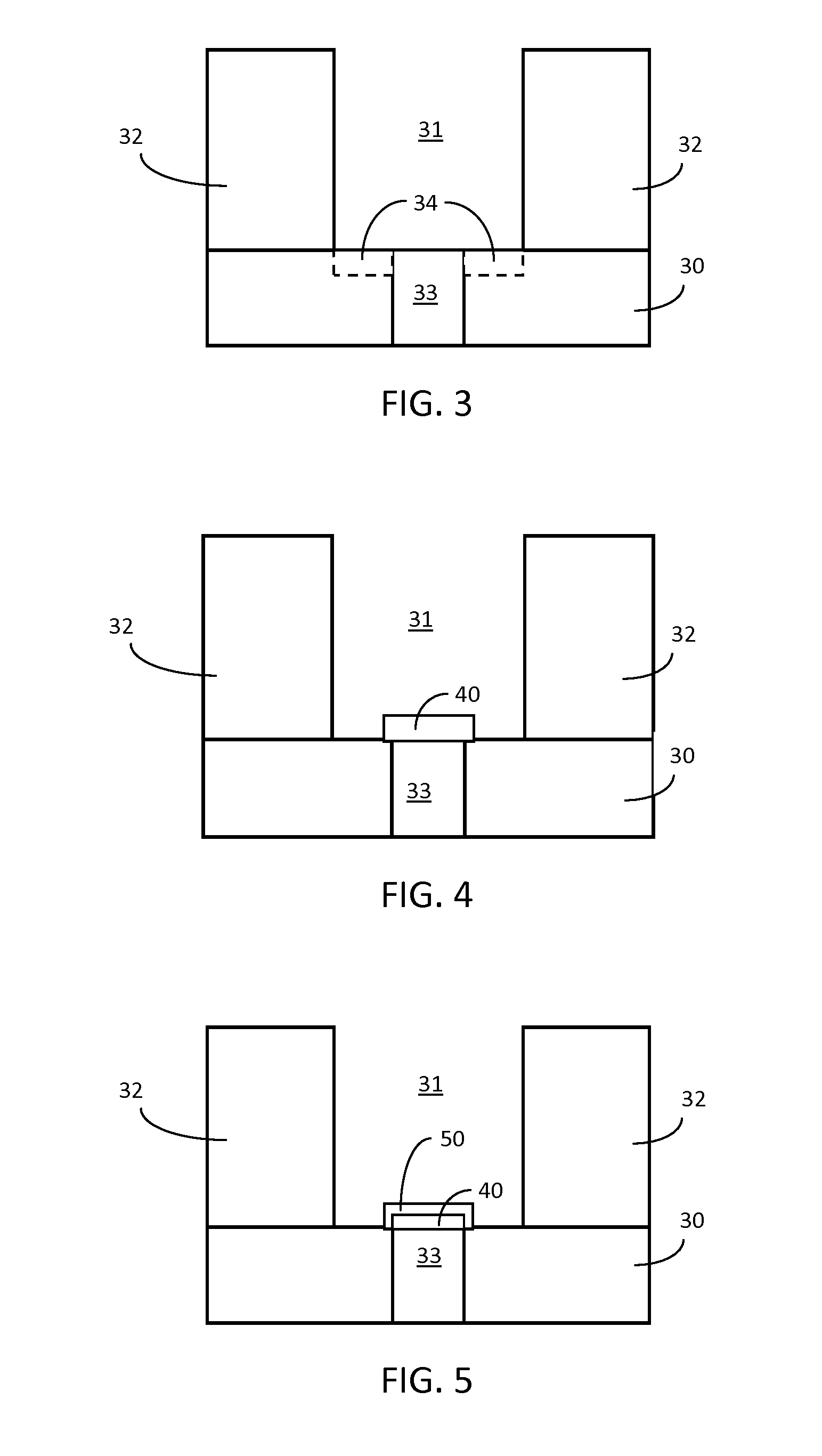

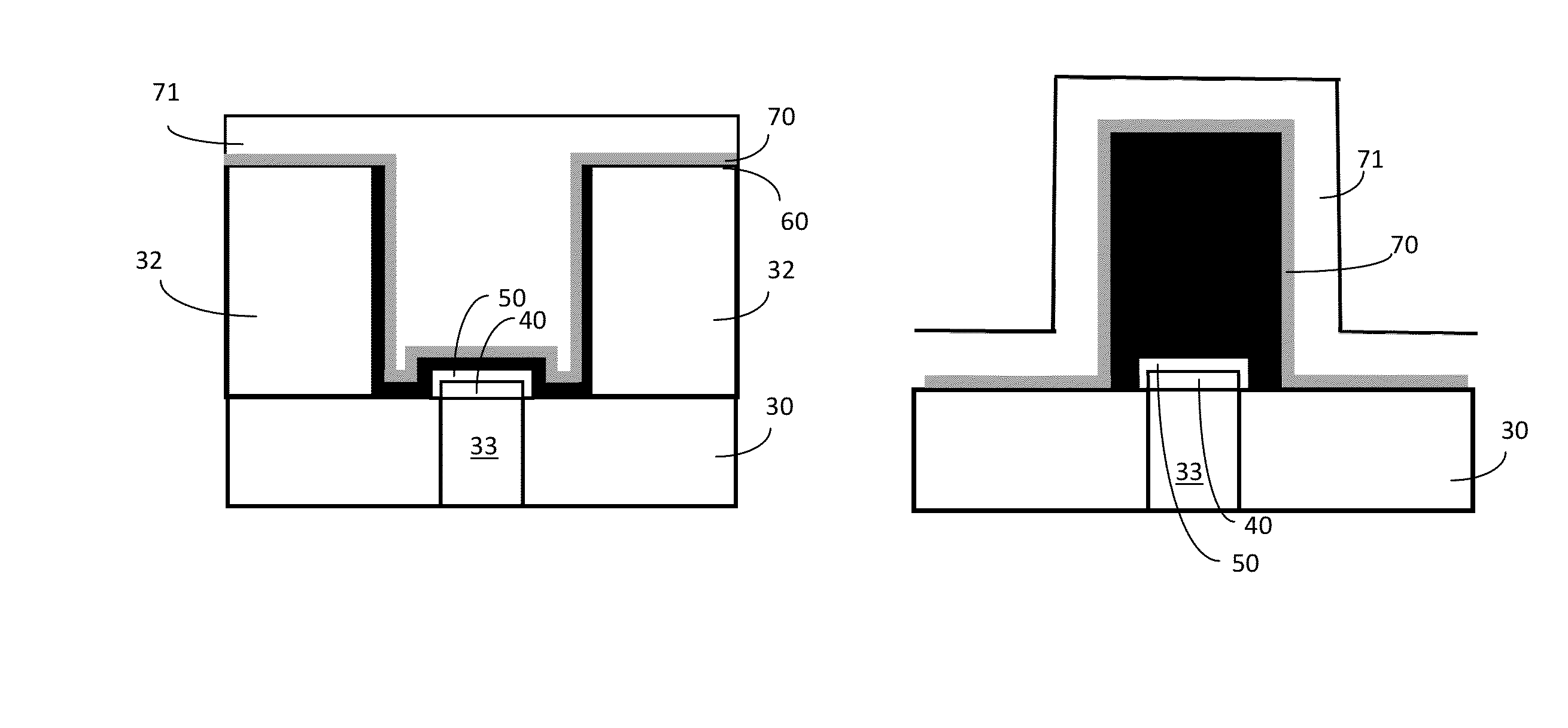

Oxygen Diffusion Barrier Comprising Ru

ActiveUS20130102121A1Reduce EOTReduce leakage currentSemiconductor/solid-state device manufacturingCapacitorsEngineeringDielectric layer

A method for forming a MIM capacitor structure includes the steps of obtaining a base structure provided with a recess, the recess exposing a conductive bottom electrode plug; selectively growing Ru on the bottom electrode plug, based on a difference in incubation time of Ru growth on the bottom electrode plug compared to the base structure material; oxidizing the selectively grown Ru; depositing a Ru-comprising bottom electrode over the oxidized Ru; forming a dielectric layer on the Ru-comprising bottom electrode; and—forming a conductive top electrode over the dielectric layer.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

Semiconductor device and manufacturing method thereof

ActiveUS20090173998A1Reduce leakage currentImprove mobilitySolid-state devicesSemiconductor/solid-state device manufacturingDielectricNitrogen

In a MIS transistor of which gate length is 10 nm or less, a gate insulator comprising a silicon oxide film formed on a silicon substrate and a high-k film formed on the silicon oxide film has a nitrided region including more nitrogen at the lateral side than at the central side in the gate-length direction, and including more nitrogen at the upper side than at the lower side in the film thickness direction. The reliability and characteristics of a MIS transistor using a gate insulator including a high-k (high dielectric constant) film is enhanced.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device and manufacturing method thereof

ActiveUS7507632B2Reduce leakage currentImprove mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesDielectricGate insulator

In a MIS transistor of which gate length is 10 nm or less, a gate insulator comprising a silicon oxide film formed on a silicon substrate and a high-k film formed on the silicon oxide film has a nitrided region including more nitrogen at the lateral side than at the central side in the gate-length direction, and including more nitrogen at the upper side than at the lower side in the film thickness direction. The reliability and characteristics of a MIS transistor using a gate insulator including a high-k (high dielectric constant) film is enhanced.

Owner:RENESAS ELECTRONICS CORP

Oxygen diffusion barrier comprising Ru

ActiveUS8518793B2Reduce EOTReduce leakage currentSemiconductor/solid-state device manufacturingCapacitorsEngineeringDielectric layer

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

Manufacturing method for semiconductor device

ActiveCN103531459AAvoid damageReduce process complexitySemiconductor/solid-state device manufacturingSemiconductor devicesEtchingSilicon oxide

Provided is a manufacturing method for a semiconductor device. The method comprises: forming a stacked gate structure on a substrate; depositing a dielectric material layer on the substrate and the stacked gate structure; performing main etching to etch the dielectric material layer to form a side wall, and leaving residues of the dielectric material layer on the substrate; and performing over-etching to remove the residues of the dielectric material layer. According to the provided manufacturing method for the semiconductor device, instead of using a silicon oxide etching barrier layer, a two-step etching by using an etching gas containing helium is performed so that while the damage to the substrate is reduced, the process complexity is also reduced, and besides, the threshold voltage can be optimized, the EoT can be effectively reduced, and the gate-control capability and the drive current can be increased.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Capacitors, systems, and methods

InactiveUS8432020B2Reduce thicknessReduce leakage currentSemiconductor/solid-state device manufacturingCapacitorsEngineeringCapacitor

Capacitors, systems, and methods are disclosed. In one embodiment, the capacitor includes a first electrode. The capacitor may also include a first insulator layer having a positive VCC adjacent to the first electrode. The capacitor may further include a second insulator layer having a negative VCC adjacent to the first insulator layer. The capacitor may also include a third insulator layer having a positive VCC adjacent to the second insulator layer. The capacitor may also include a second electrode adjacent to the third insulator layer.

Owner:SEMATECH

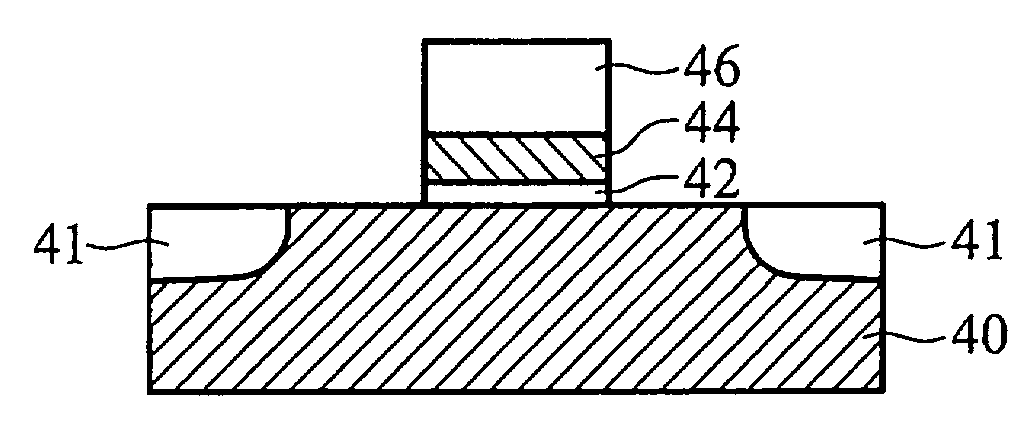

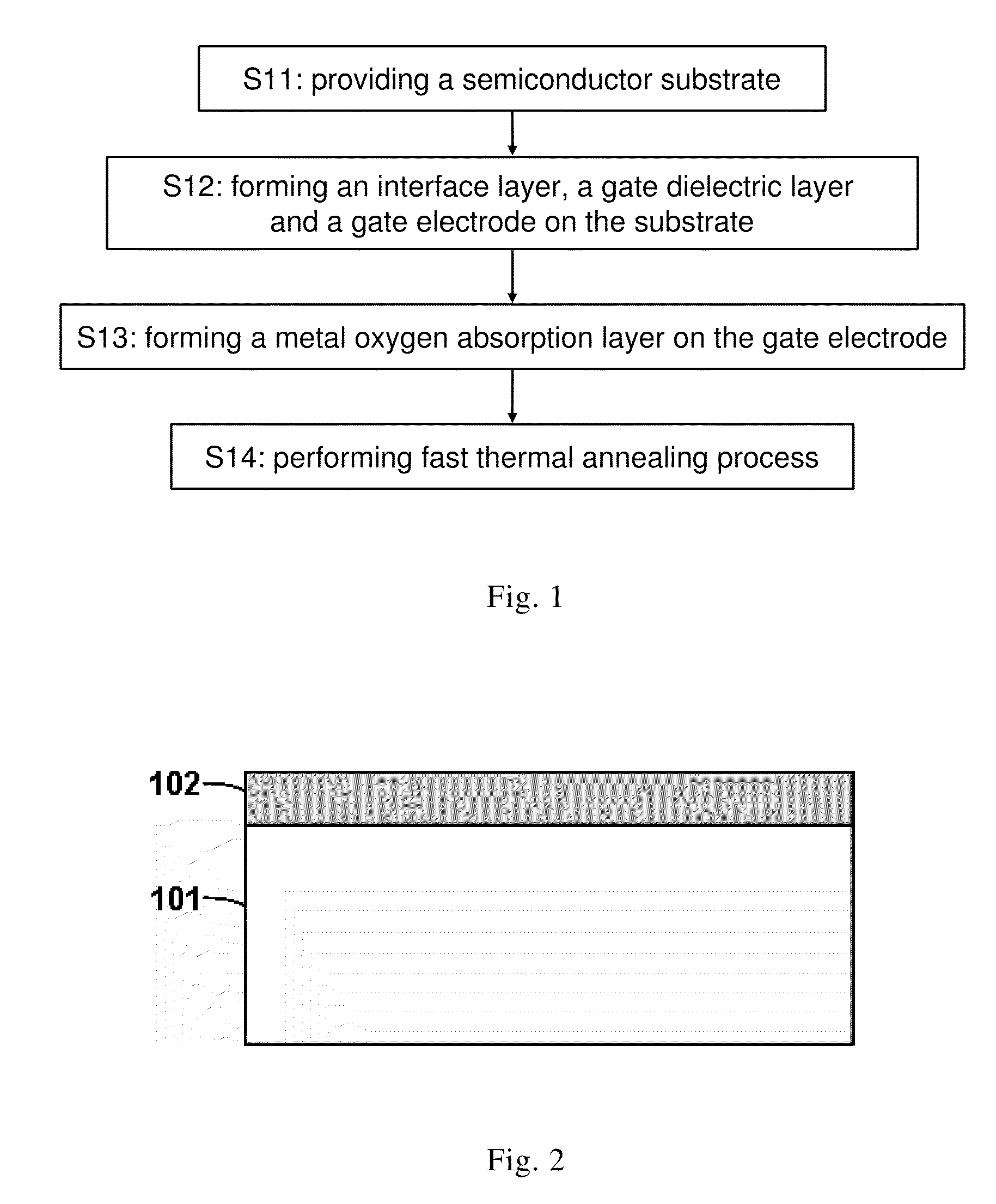

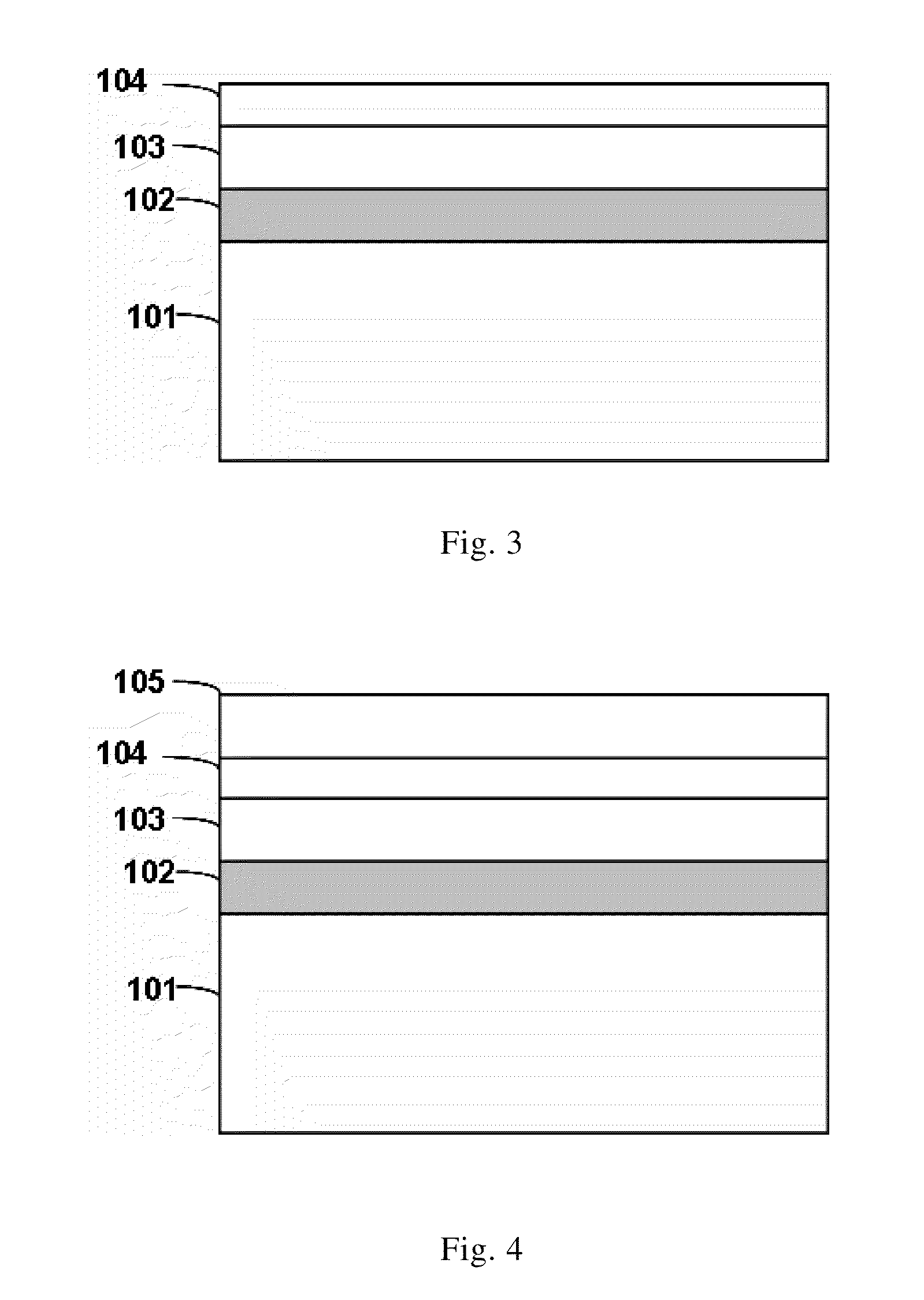

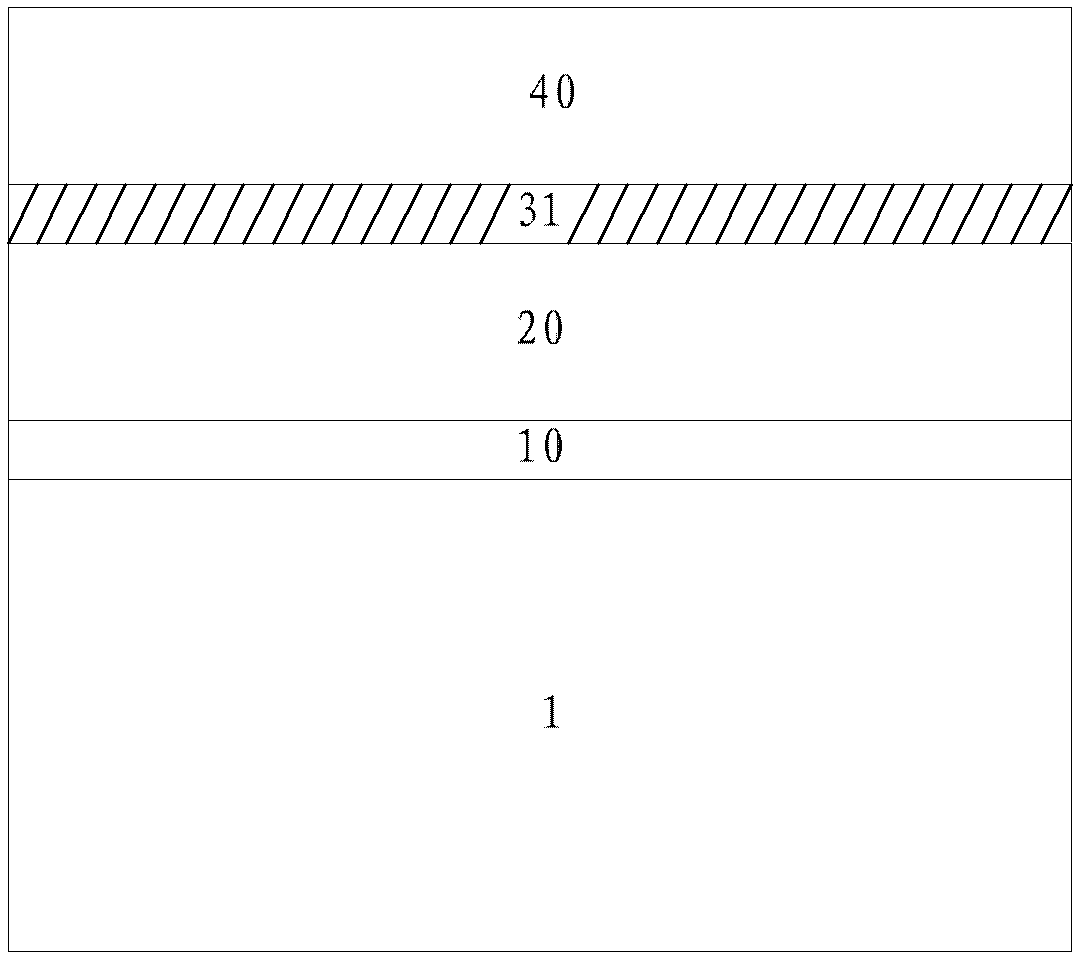

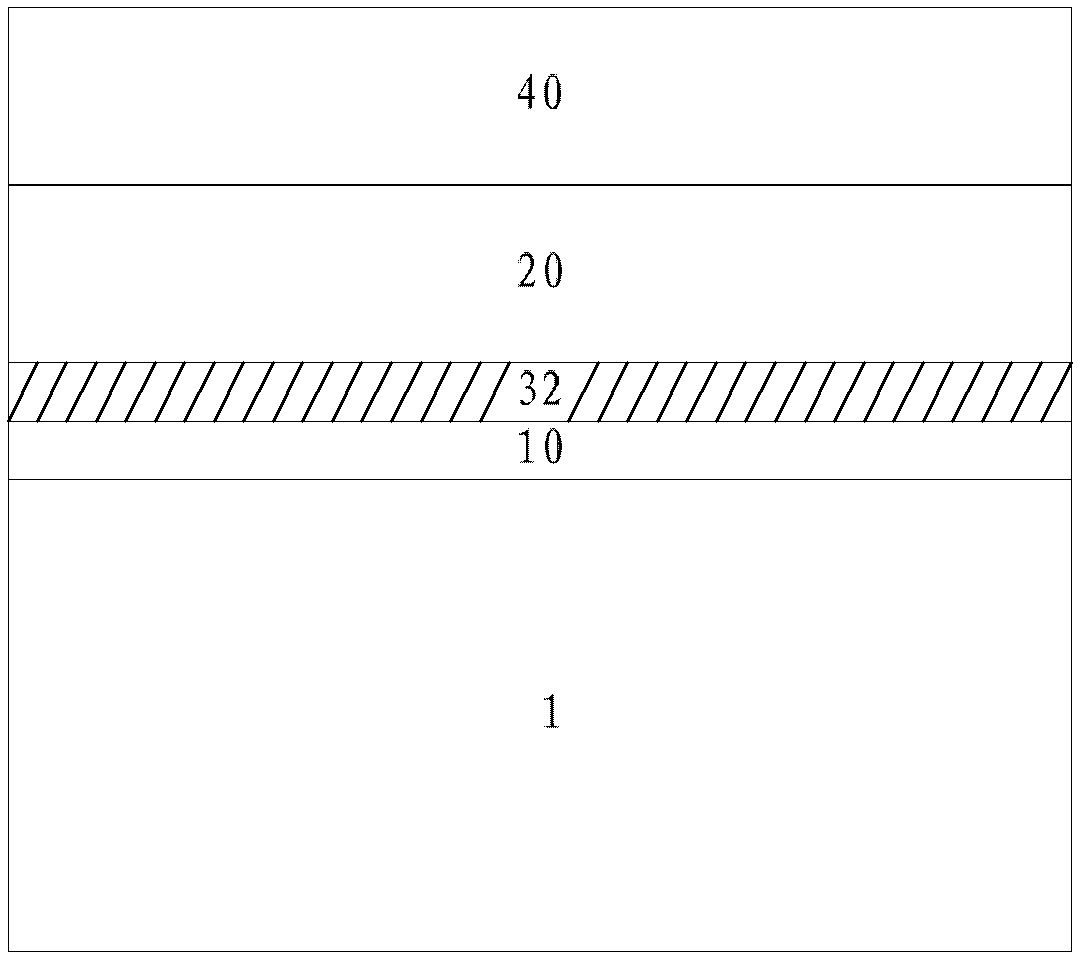

Method of manufacturing a semiconductor device

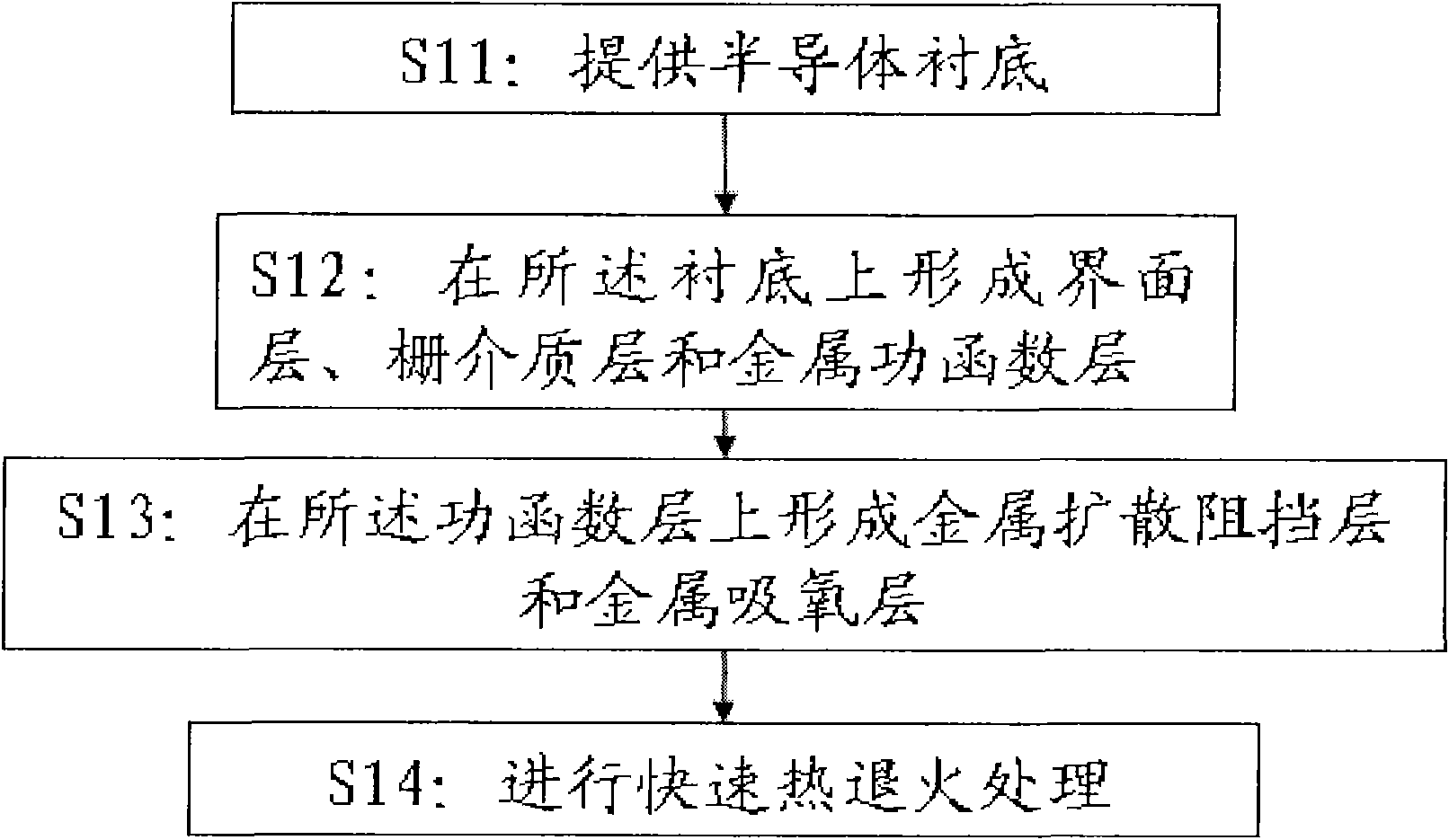

ActiveUS8633098B2Reduce EOTAvoid thickeningSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricInterface layer

The present invention relates to the field of semiconductor manufacturing. The present invention provides a method of manufacturing a semiconductor device, which comprises: providing a semiconductor substrate; forming an interface layer, a gate dielectric layer and a gate electrode on the substrate; forming a metal oxygen absorption layer on the gate electrode; performing a thermal annealing process on the semiconductor device so that the metal oxygen absorption layer absorbs oxygen in the interface layer and the thickness of the interface layer is reduced. By means of the present invention, the thickness of the interface layer can be reduced on one hand, and on the other hand the metal in the metal oxygen absorption layer is made to diffuse into the gate electrode and / or the gate dielectric layer through the annealing process, which further achieves the effects of adjusting the effective work function and controlling the threshold voltage.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Semiconductor structure and manufacturing method thereof

InactiveCN102201436AReduce thicknessImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureInterface layer

The invention provides a semiconductor structure and a manufacturing method thereof. The semiconductor structure comprises an interface layer positioned on a substrate, a gate medium layer positioned on the interface layer, a metal gate electrode layer positioned on the gate medium layer, and at least one oxygen absorbing layer, wherein the combining capacity of metal atoms and oxygen in the oxygen absorbing layer is higher than the combining capacity of the atoms and oxygen in a laminating material under the oxygen absorbing layer. In the invention, the oxygen in the interface layer is absorbed by adding at least one oxygen absorbing layer, so that the aims of reducing the equivalent oxide layer thickness (EOT) and improving the performance of the device are fulfilled.

Owner:TSINGHUA UNIV

Manufacturing method for dual work-function metal gates

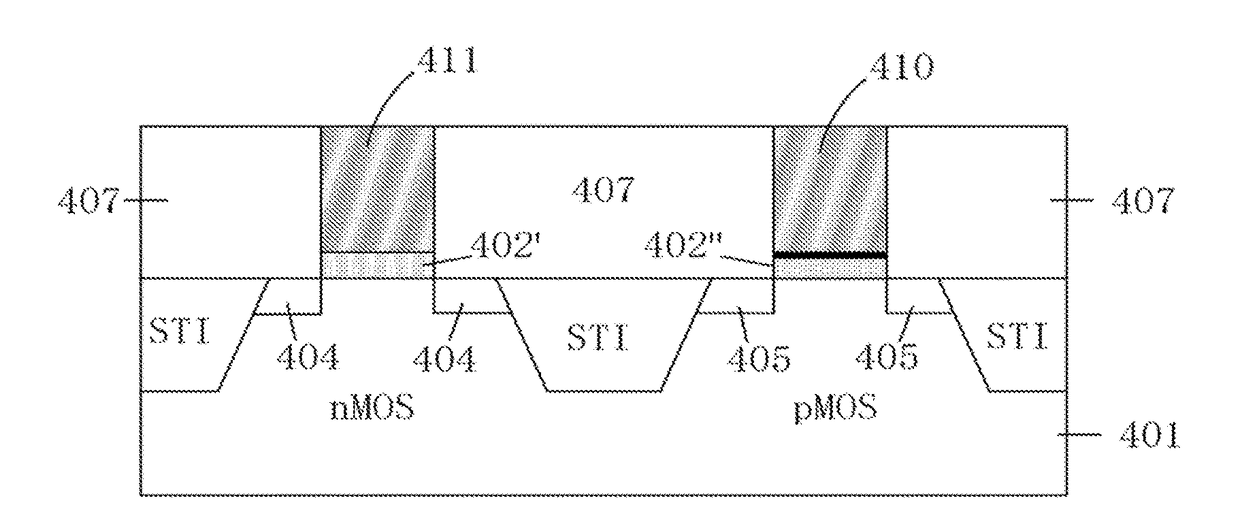

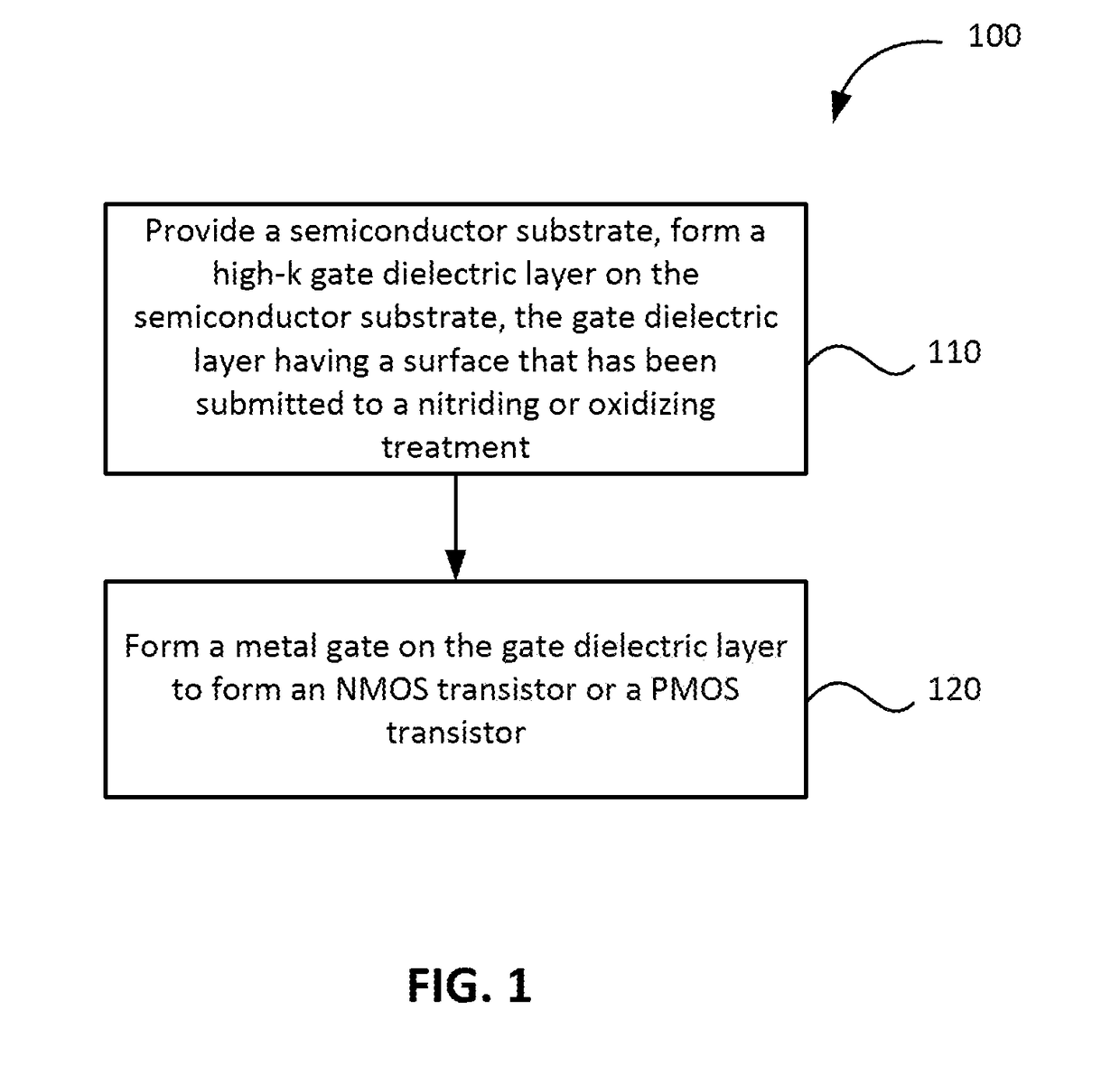

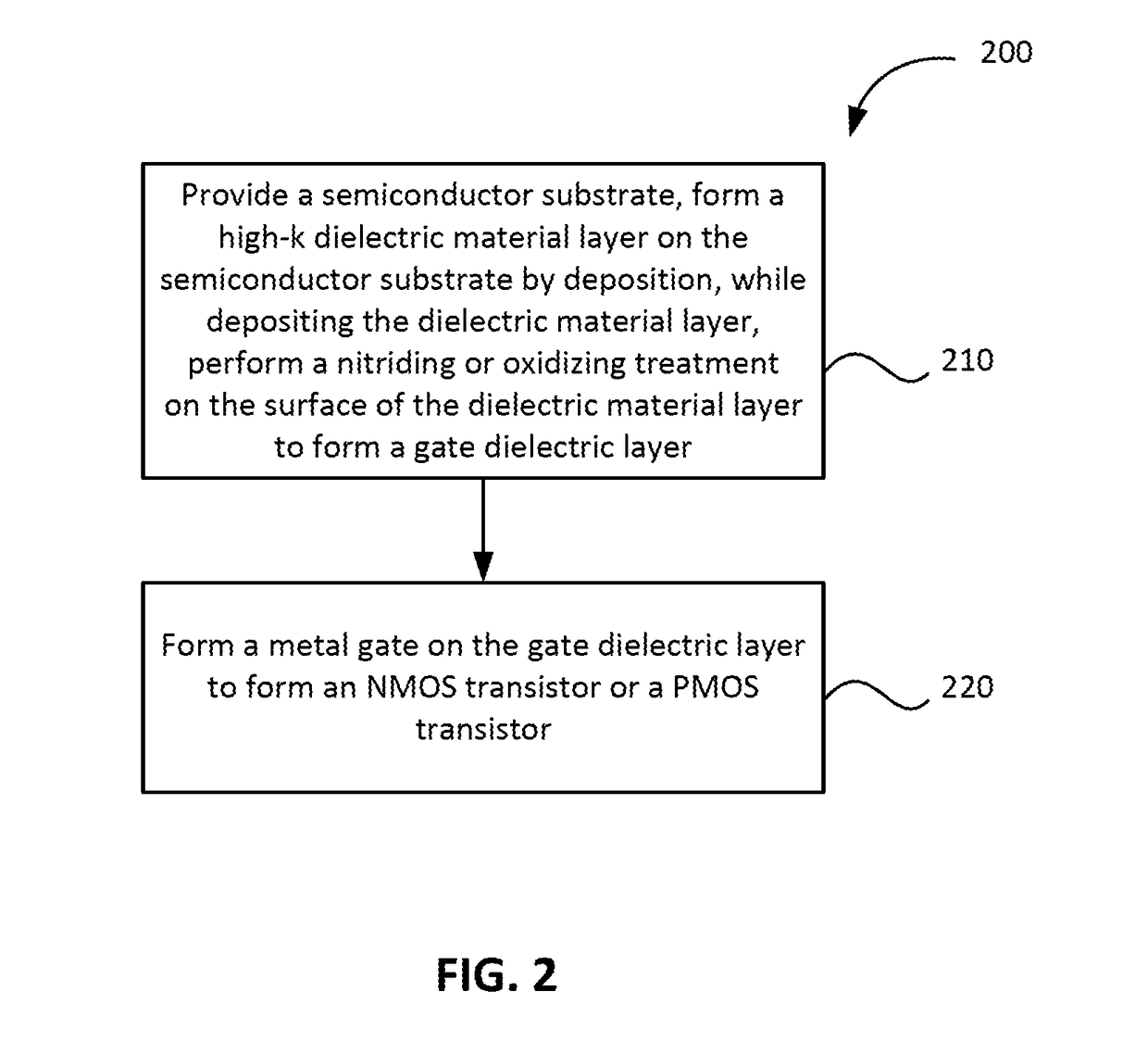

ActiveUS20180211886A1Reduce effective work functionIncrease their effective work functionTransistorSemiconductor/solid-state device manufacturingGate dielectricWork function

A method for manufacturing a semiconductor device includes providing a semiconductor substrate, forming a high dielectric constant (high-k) gate dielectric layer on the semiconductor substrate, the high-k gate dielectric layer including a nitrided surface that has been subjected to a nitriding treatment or an oxidized surface that has been subjected to an oxidizing treatment, forming a metal gate on the nitrided surface of the high-k gate dielectric layer to form an NMOS transistor, or forming a metal gate on the oxidized surface of the high-k gate dielectric layer to form a PMOS transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Method for manufacturing semiconductor device

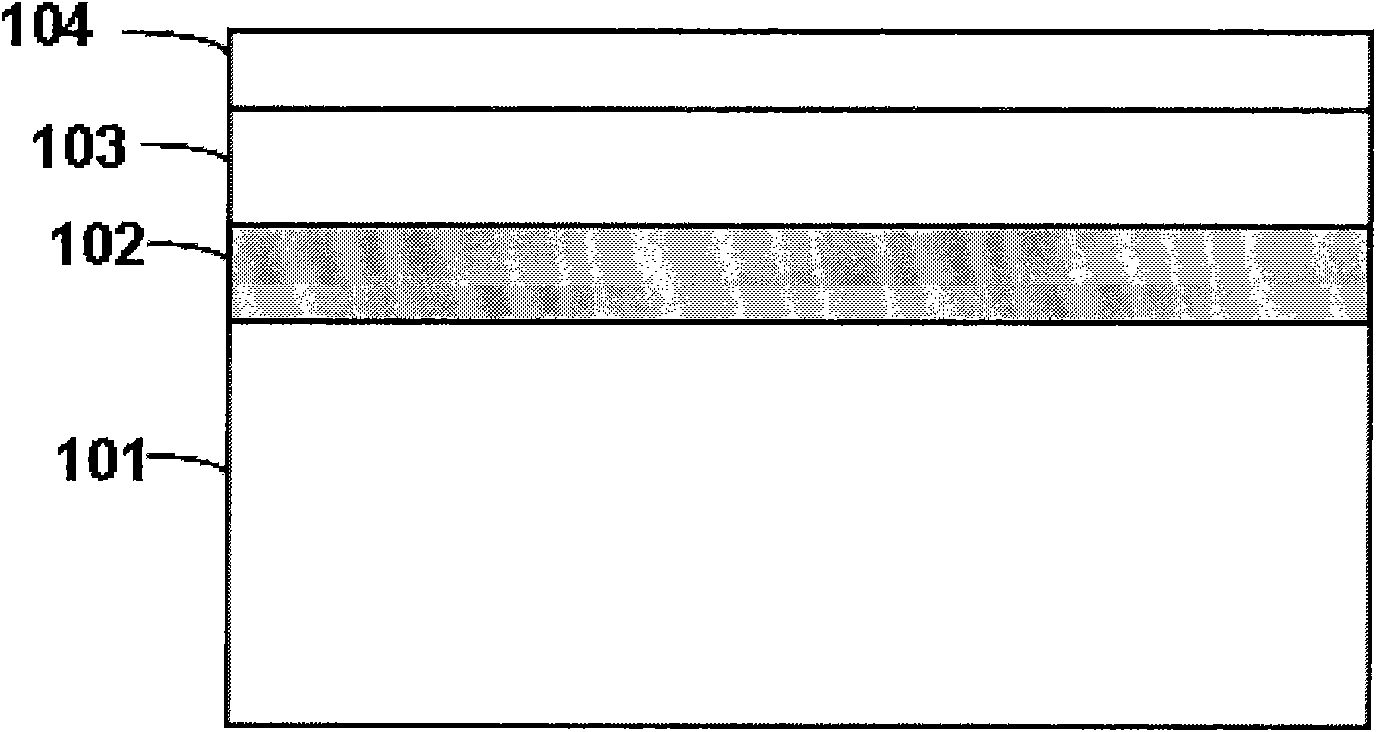

ActiveCN102299061BAvoid enteringIncreasing the thicknessSemiconductor devicesEquivalent oxide thicknessGate dielectric

The invention relates to the field of semiconductor manufacturing and provides a method for manufacturing a semiconductor device. The method comprises the following steps: providing a semiconductor substrate; forming an interface layer, a gate dielectric layer and a metal work function layer on the substrate; forming a diffusion barrier layer on the metal work function layer; forming a metal oxygen absorbing layer on the diffusion barrier layer; and carrying out thermal annealing treatment on the device so as to ensure the metal oxygen absorbing layer to absorb the oxygen in the interface layer to reduce the thickness of the interface layer and ensure the diffusion barrier layer to prevent the oxygen absorbing metals in the metal oxygen absorbing layer from being diffused into the metal work function layer. By adopting the method, the oxygen absorbing metals can be prevented from being diffused into the work function layer and / or gate dielectric layer while the thickness of the interface layer is reduced, thus reducing the equivalent oxide thickness under the premise of not affecting the threshold voltage of the device.

Owner:SOI MICRO CO LTD

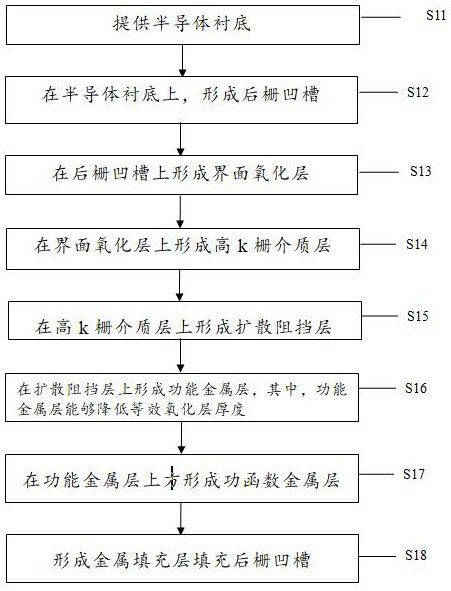

Preparation method of semiconductor device and prepared semiconductor device

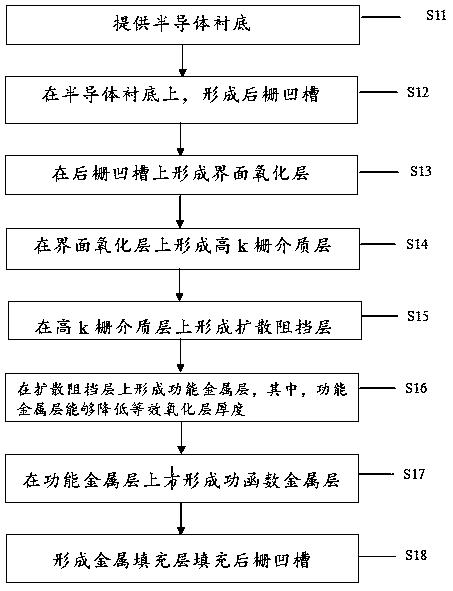

ActiveCN110349915AReduce EOTImprove performanceTransistorSolid-state devicesEquivalent oxide thicknessGate dielectric

The invention provides a preparation method of a semiconductor device and the prepared semiconductor device. The method comprises the steps: providing a semiconductor substrate; forming a rear gate groove on the semiconductor substrate; forming an interface oxide layer on the rear gate groove; forming a high-k gate dielectric layer on the interface oxide layer; forming a diffusion barrier layer onthe high-k gate dielectric layer; forming a functional metal layer on the diffusion barrier layer, wherein the functional metal layer can reduce the equivalent oxide layer thickness; forming a work function metal layer on the functional metal layer; and forming a metal filling layer to fill in the rear gate groove. According to the method for reducing the EOT, the metal layer having the functionof reducing the equivalent oxide thickness (EOT) is used in the gate stack so as to reduce the EOT of the gate stack structure and provide a solution for improving the performance of the small-size device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Semiconductor device manufacturing method

ActiveCN103531454BAvoid damageReduce process complexitySemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentPower flow

The invention discloses a semiconductor device manufacturing method, comprising: forming a gate stack structure on a substrate; sequentially depositing a first dielectric material layer and a second dielectric material layer on the substrate and the gate stack structure; using helium-containing The etching gas sequentially etches the second dielectric material layer and the first dielectric material layer to form the second sidewall and the first sidewall respectively. According to the semiconductor device manufacturing method of the present invention, the double-layer composite sidewall and the etching gas containing helium are used for two-step etching, which reduces the damage to the substrate and also reduces the complexity of the process. In addition, the valve can be optimized. Value voltage, effectively reduce EoT, improve gate control capability and drive current.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

A kind of semiconductor device preparation method and prepared semiconductor device

ActiveCN110349915BReduce EOTImprove performanceTransistorSolid-state devicesEquivalent oxide thicknessGate dielectric

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com