Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

841 results about "Process complexity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

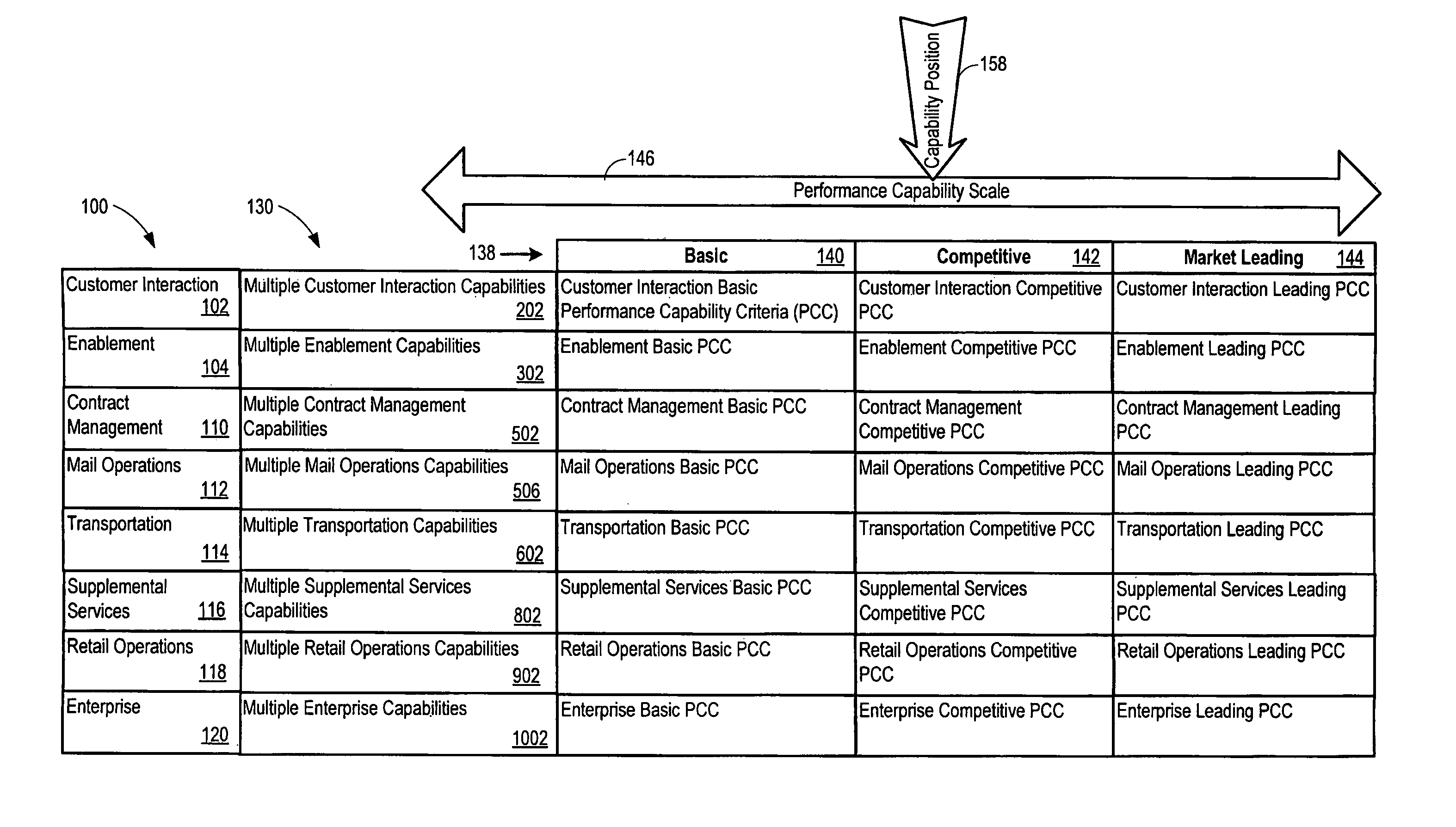

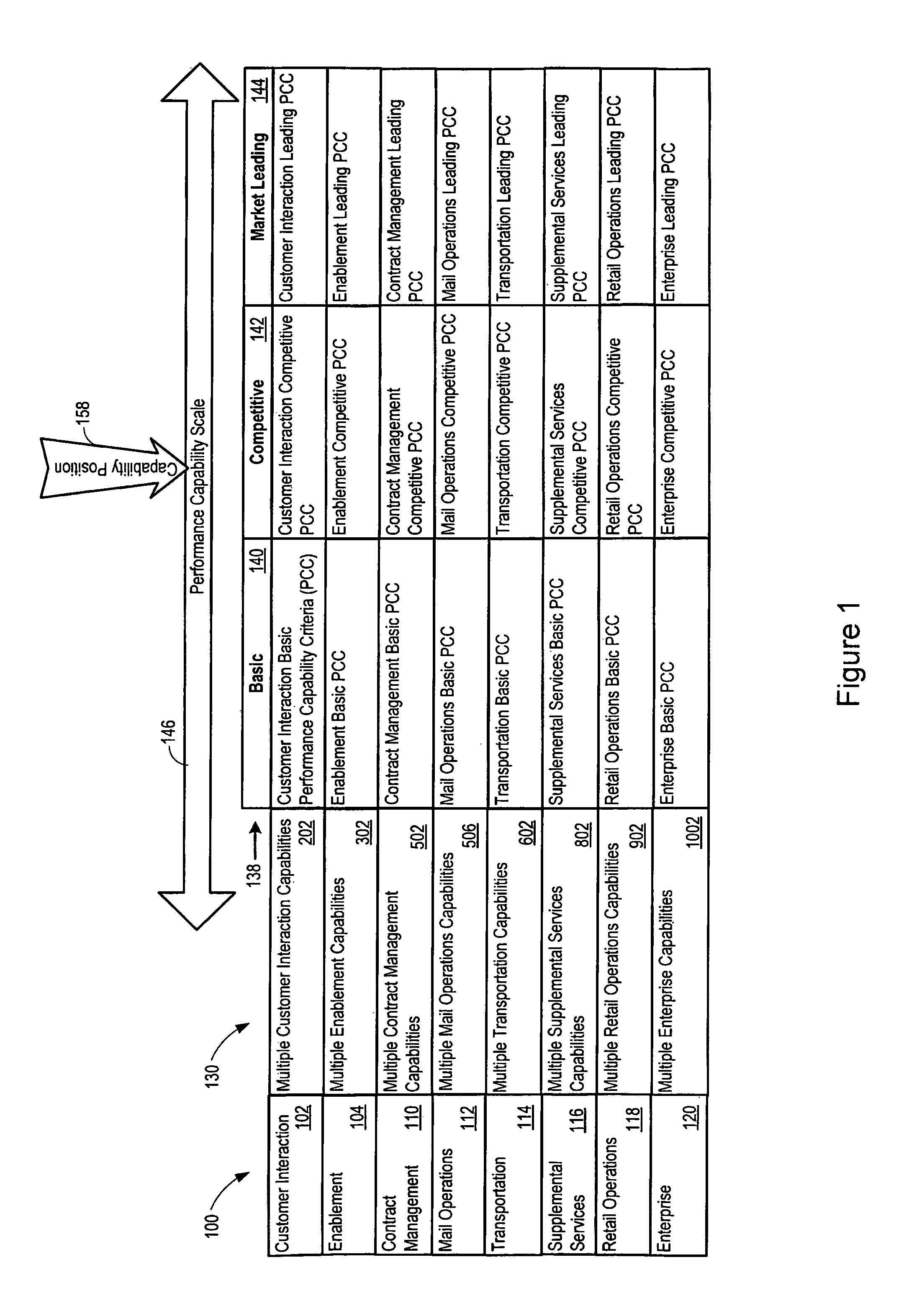

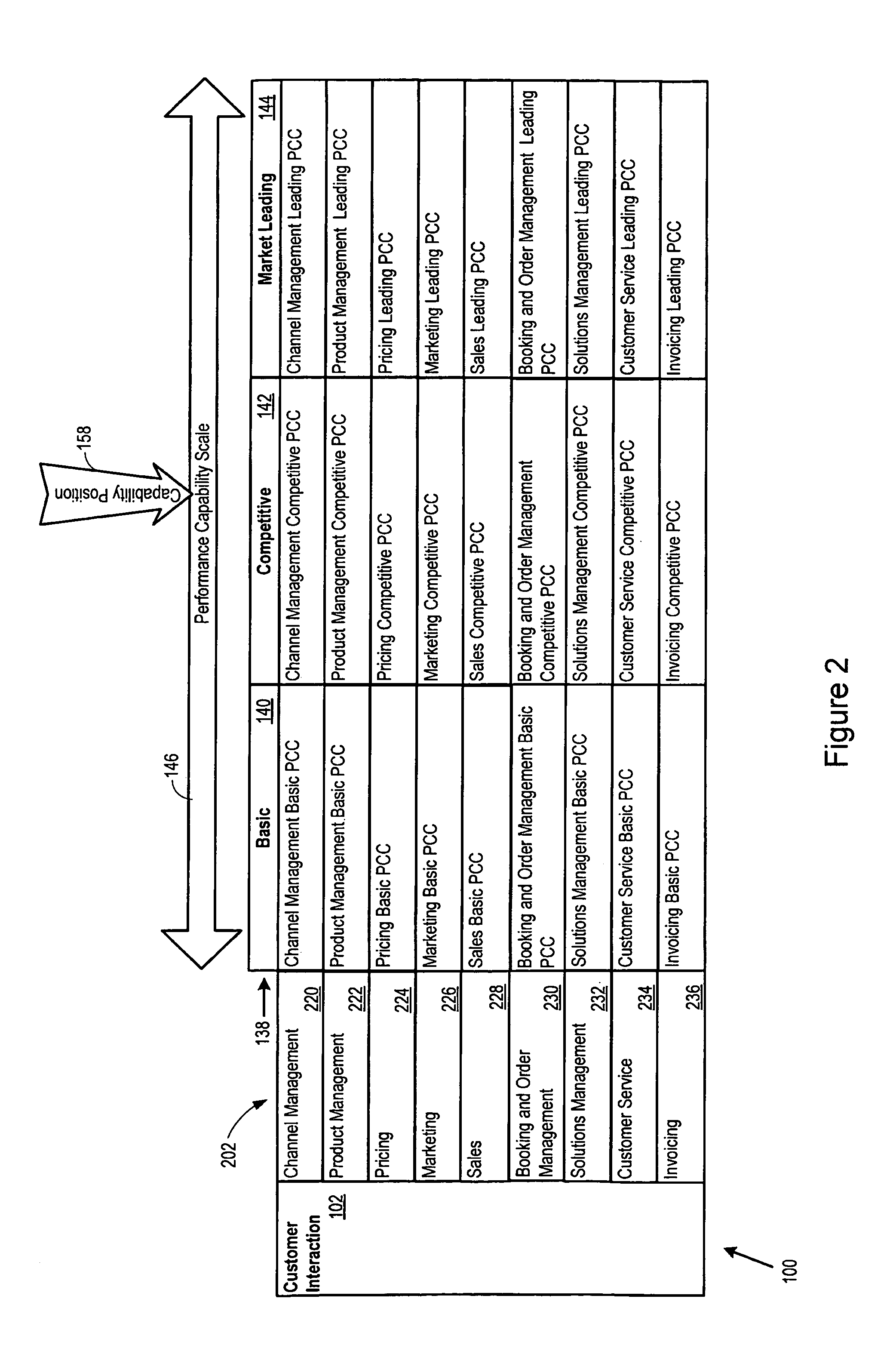

Consumer goods and services high performance capability assessment

ActiveUS8214238B1Easy to findImprove performanceMarket predictionsResourcesProcess complexitySystems engineering

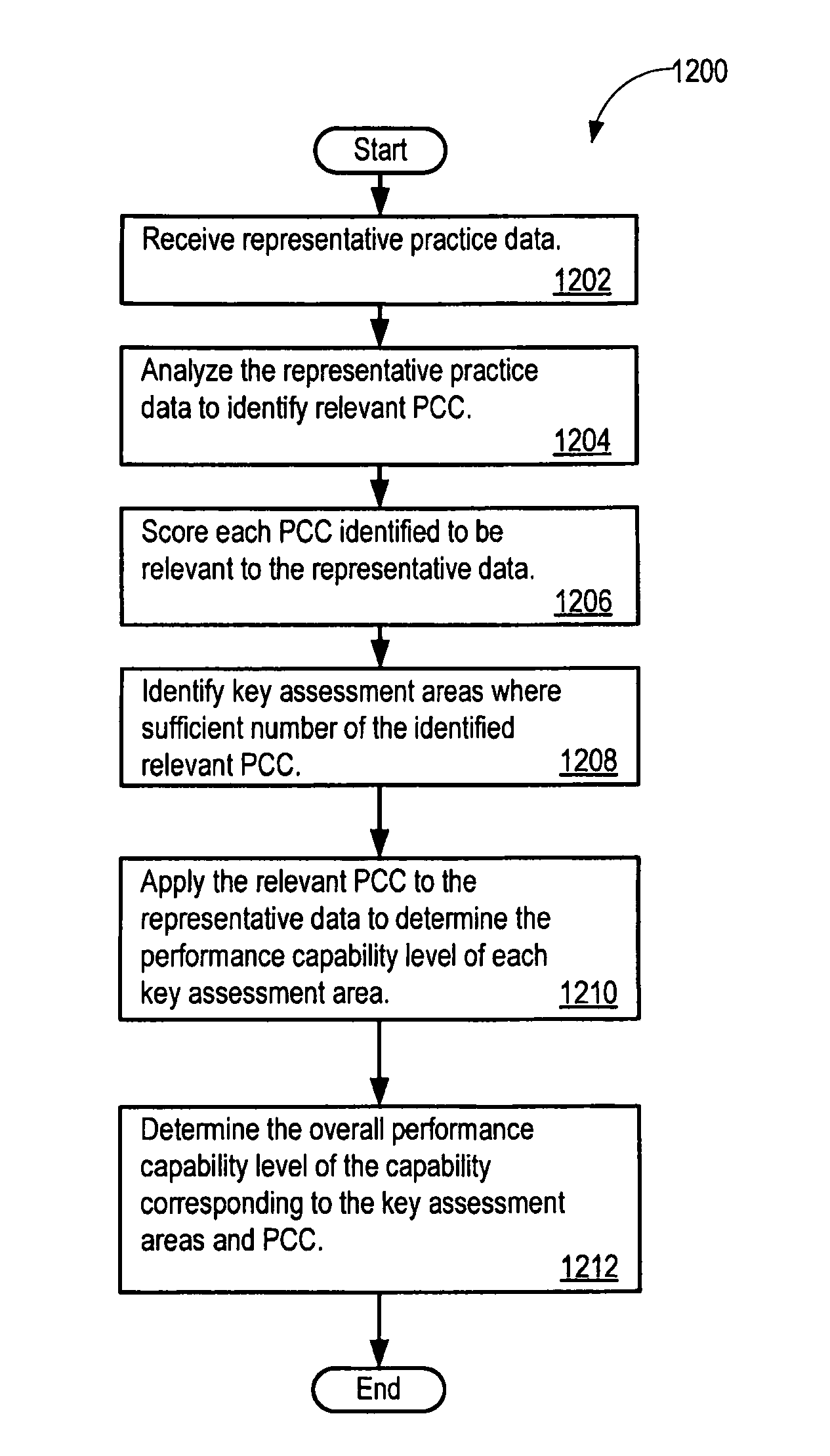

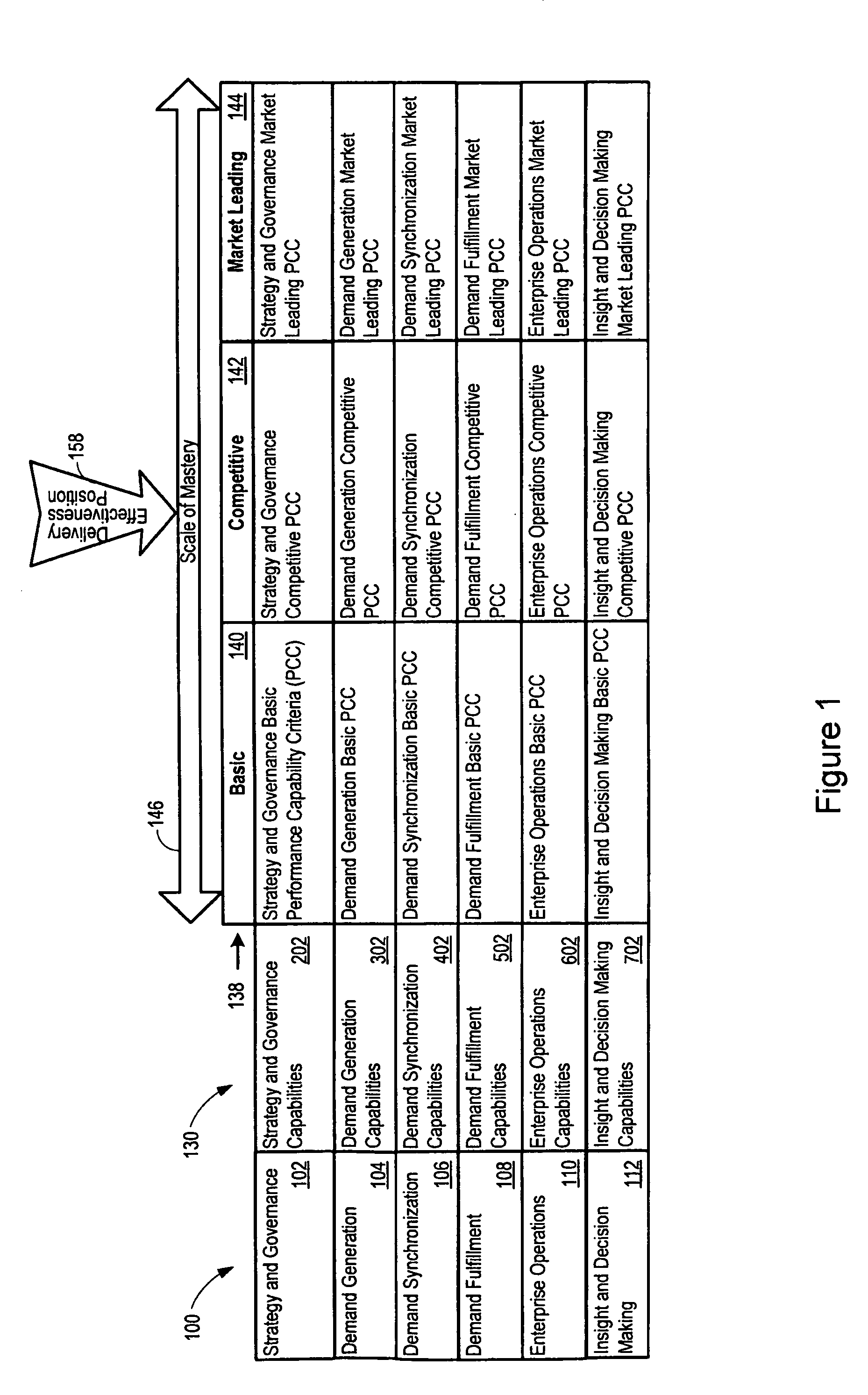

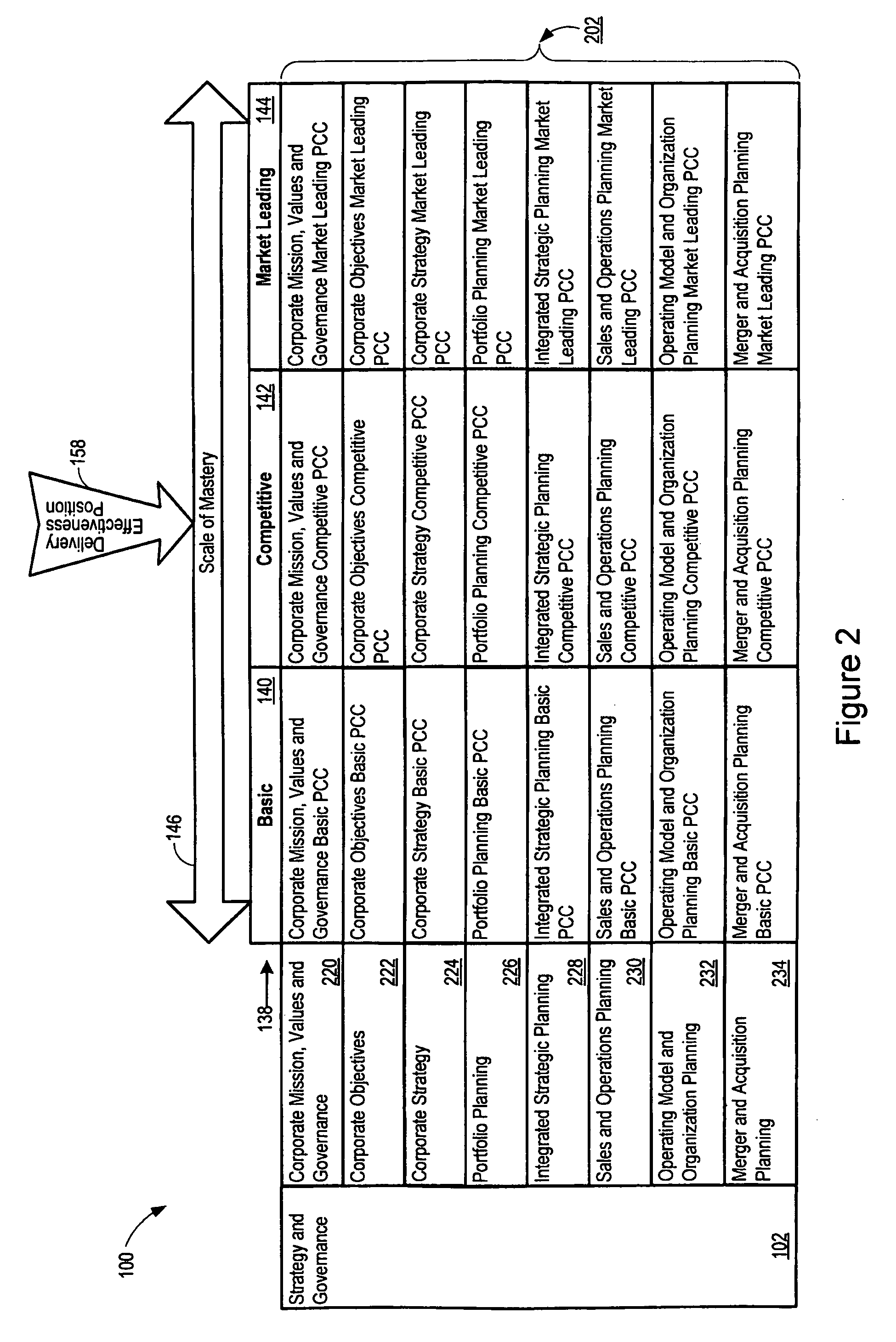

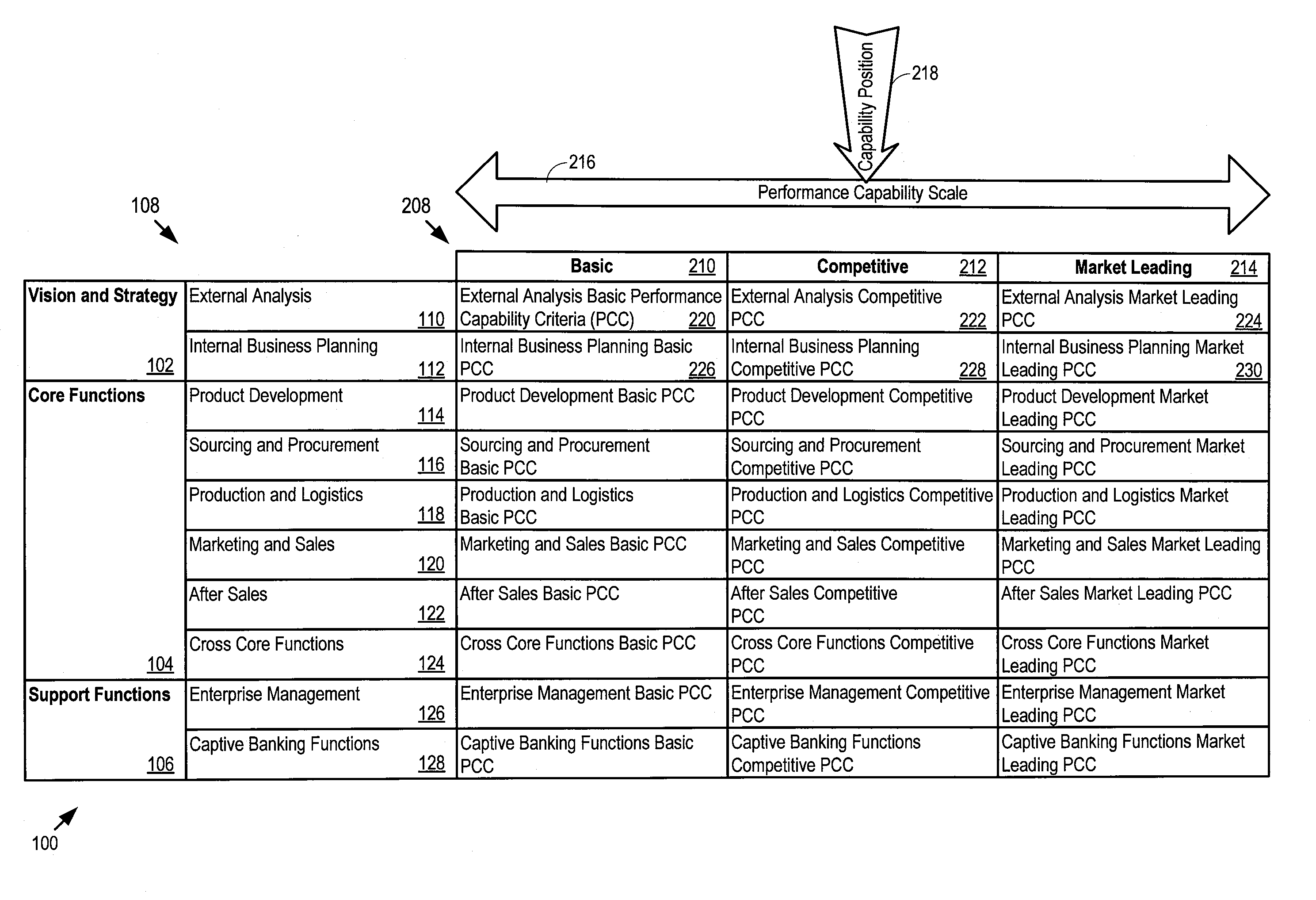

A high performance capability assessment model helps a consumer goods and services business meet the challenges of the global marketplace. As a result, the consumer goods and services business can achieve the clarity, consistency, and well-defined execution of core processes that reduce inefficiencies and waste that result from unnecessary process complexity and exceptions. In addition, the high performance capability assessment model helps the consumer goods and services business to identify specific areas in which improvements may be made and understand how to make the improvements, and establishes levels of capability along the way to reaching an ultimate capability goal.

Owner:ACCENTURE GLOBAL SERVICES LTD

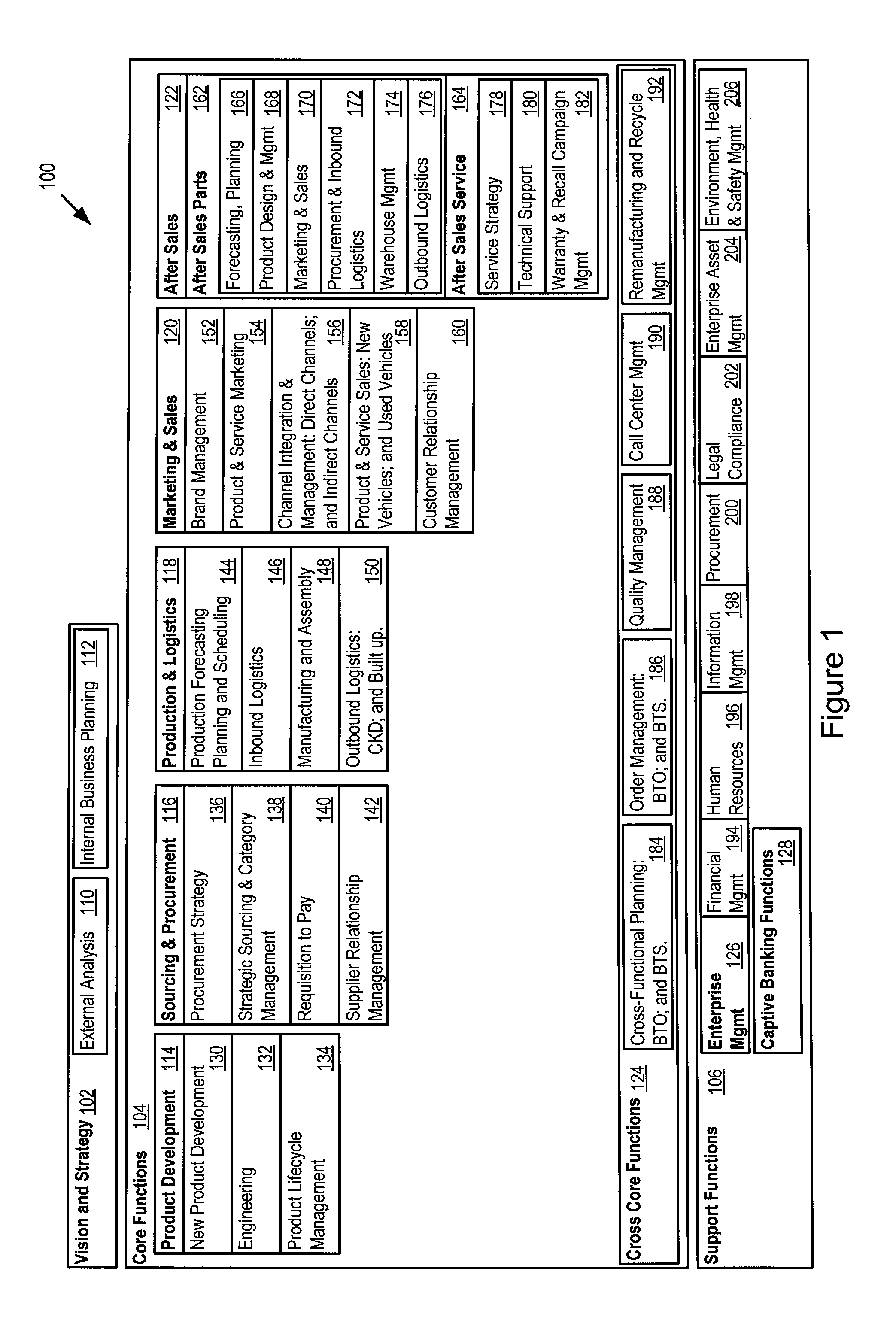

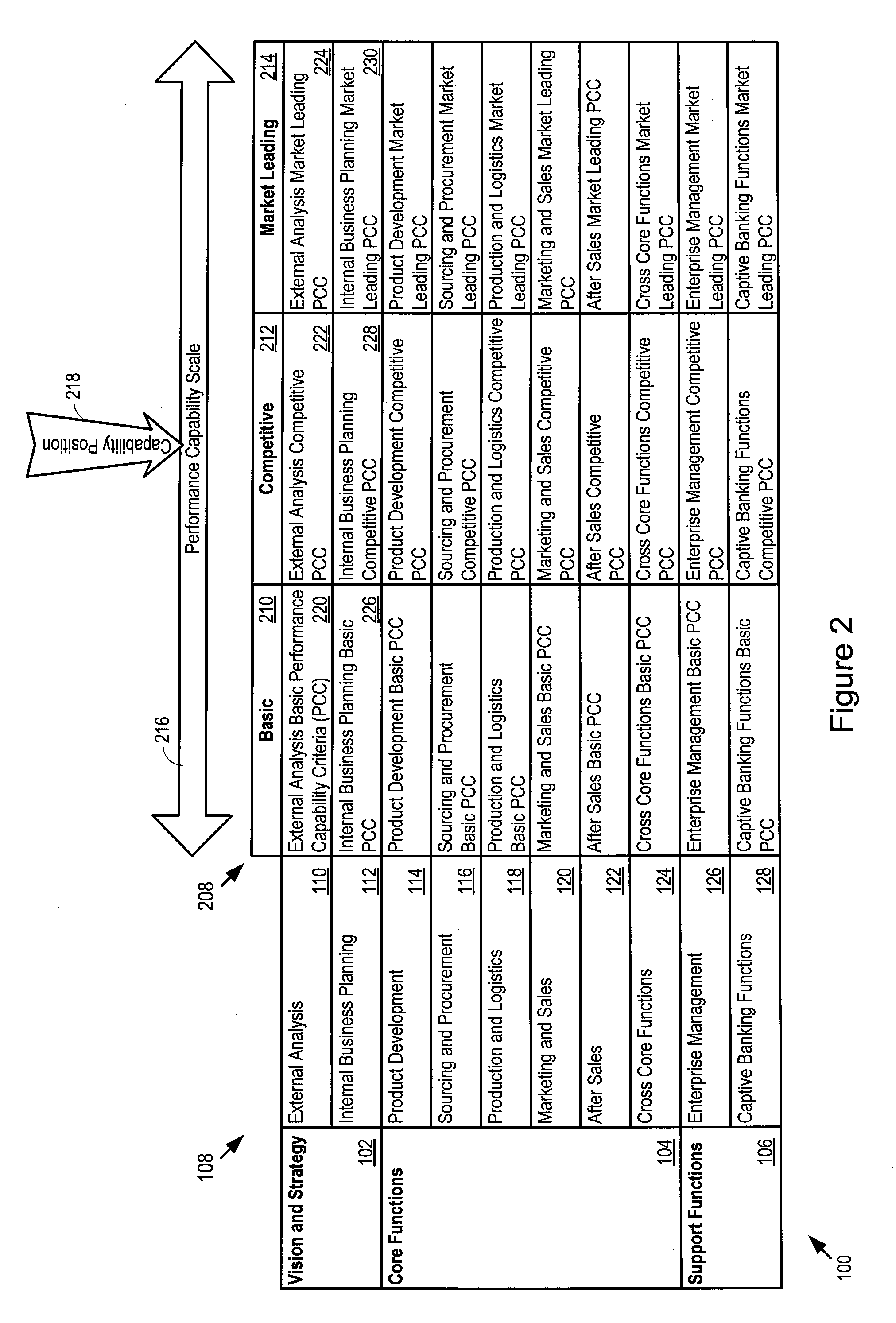

Automotive industry high performance capability assessment

A high performance capability assessment model helps an automotive industry business meet the challenges of the global marketplace. As a result, the automotive industry business can achieve the clarity, consistency, and well-defined execution of core processes that reduce inefficiencies and waste that result from unnecessary process complexity and exceptions. In addition, the high performance capability assessment model helps the automotive industry business to identify specific areas in which improvements may be made and understand how to make the improvements, and establishes levels of capability along the way to reaching an ultimate capability goal.

Owner:ACCENTURE GLOBAL SERVICES GMBH

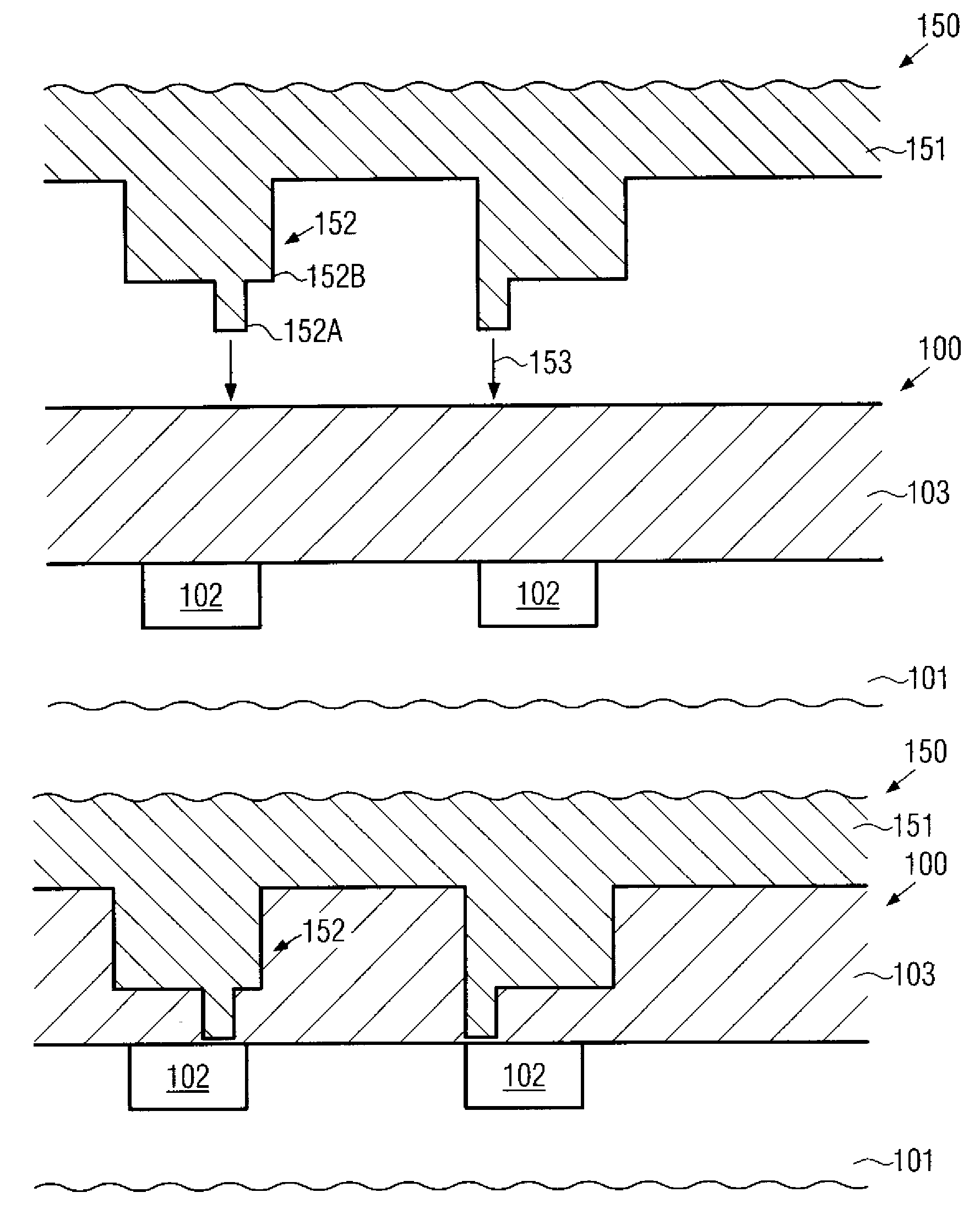

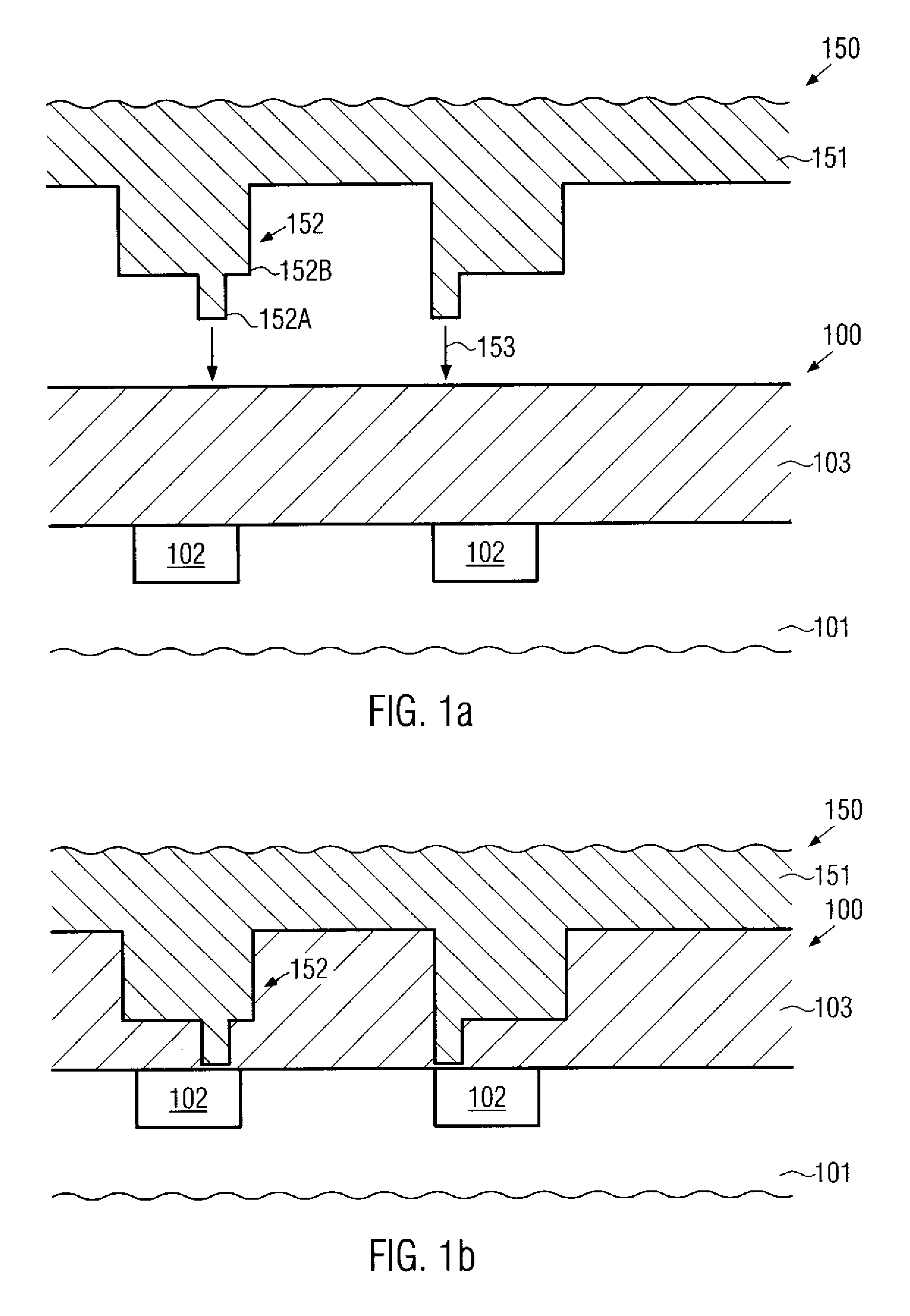

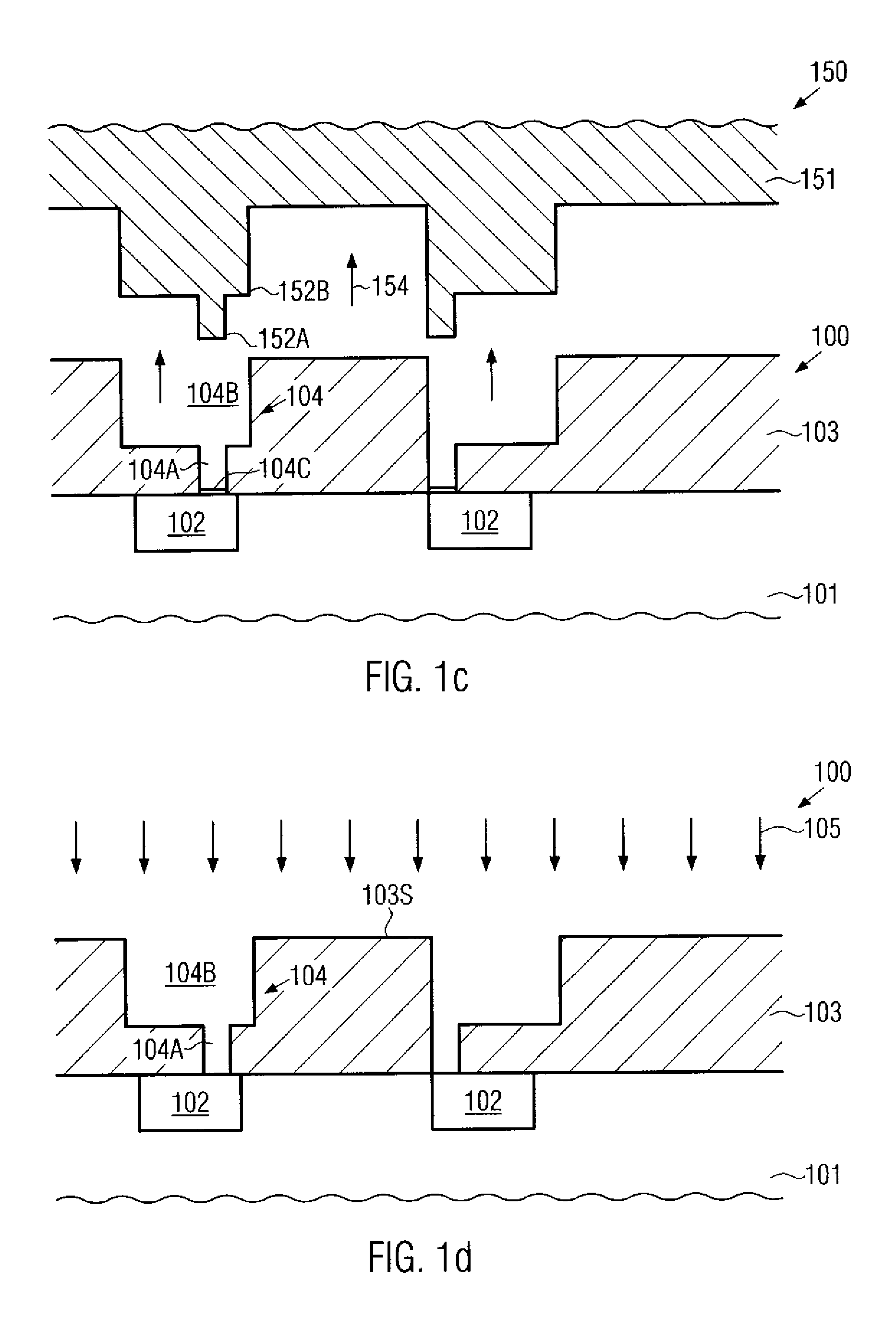

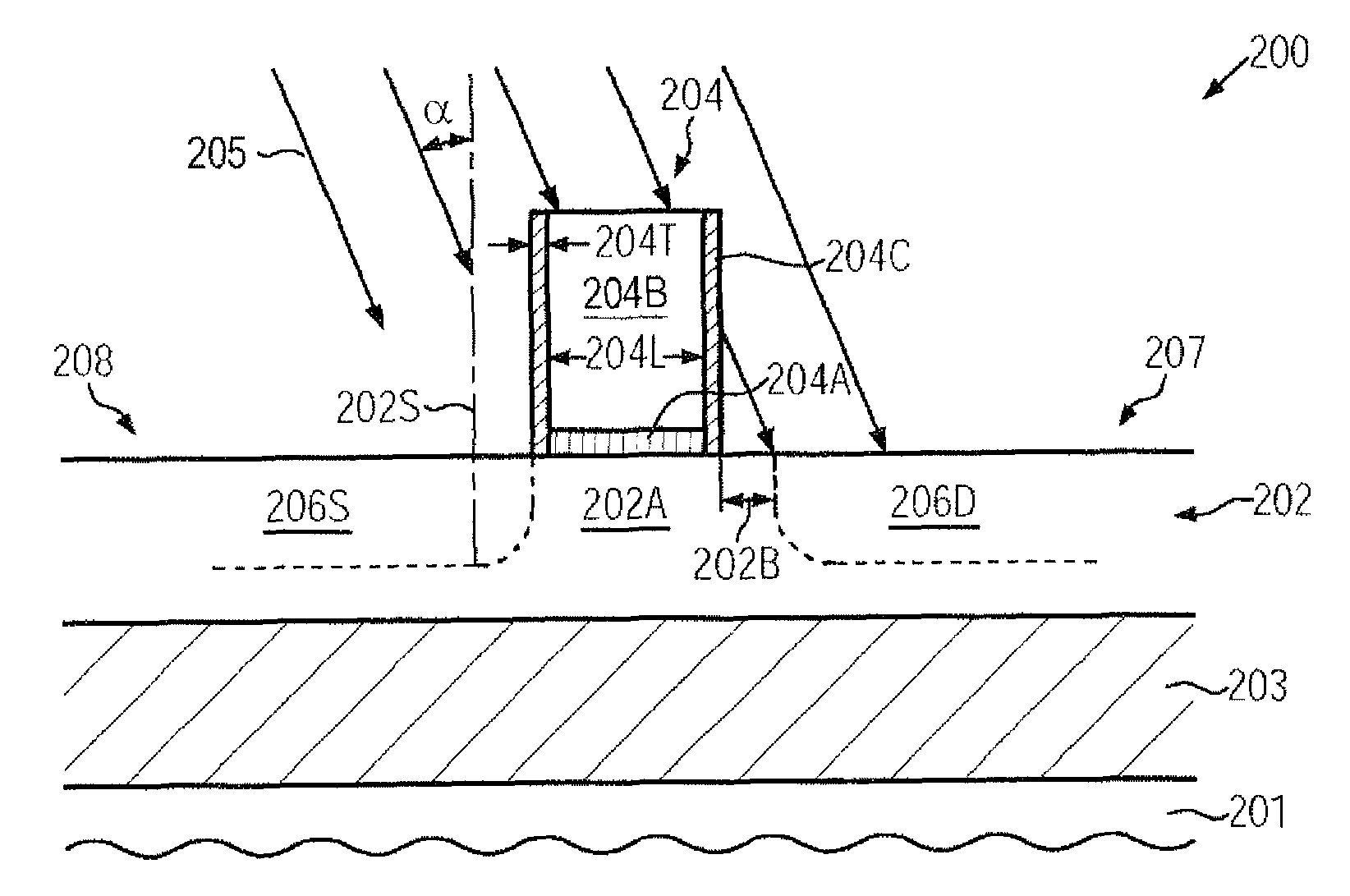

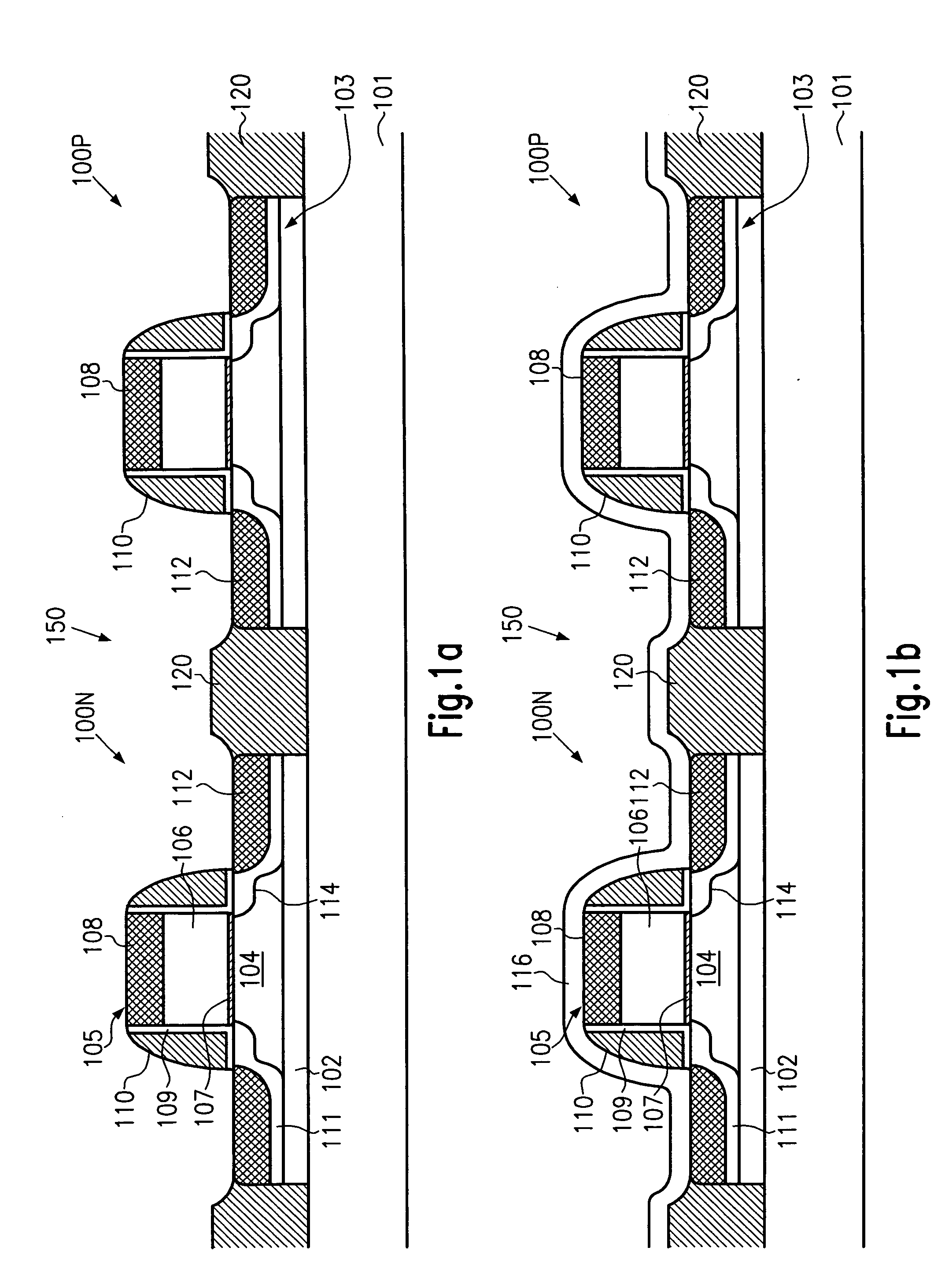

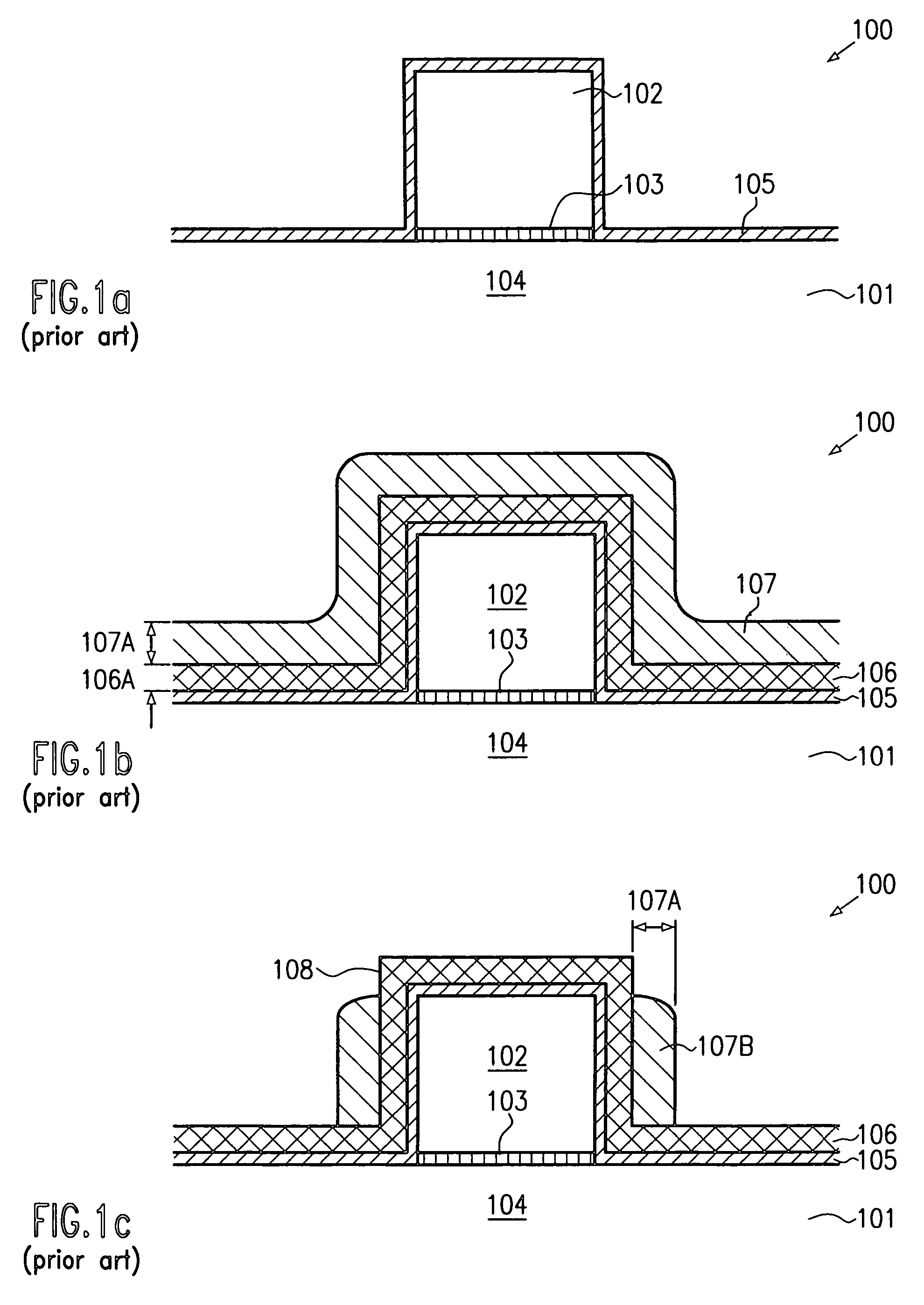

NANO imprint technique with increased flexibility with respect to alignment and feature shaping

ActiveUS20080003818A1Increase flexibilityReduce in quantityNanoinformaticsSolid-state devicesLithographic artistEngineering

By forming metallization structures on the basis of an imprint technique, in which via openings and trenches may be commonly formed, a significant reduction of process complexity may be achieved due to the omission of at least one further alignment process as required in conventional process techniques. Furthermore, the flexibility and efficiency of imprint lithography may be increased by providing appropriately designed imprint molds in order to provide via openings and trenches exhibiting an increased fill capability, thereby also improving the performance of the finally obtained metallization structures with respect to reliability, resistance against electromigration and the like.

Owner:ADVANCED MICRO DEVICES INC

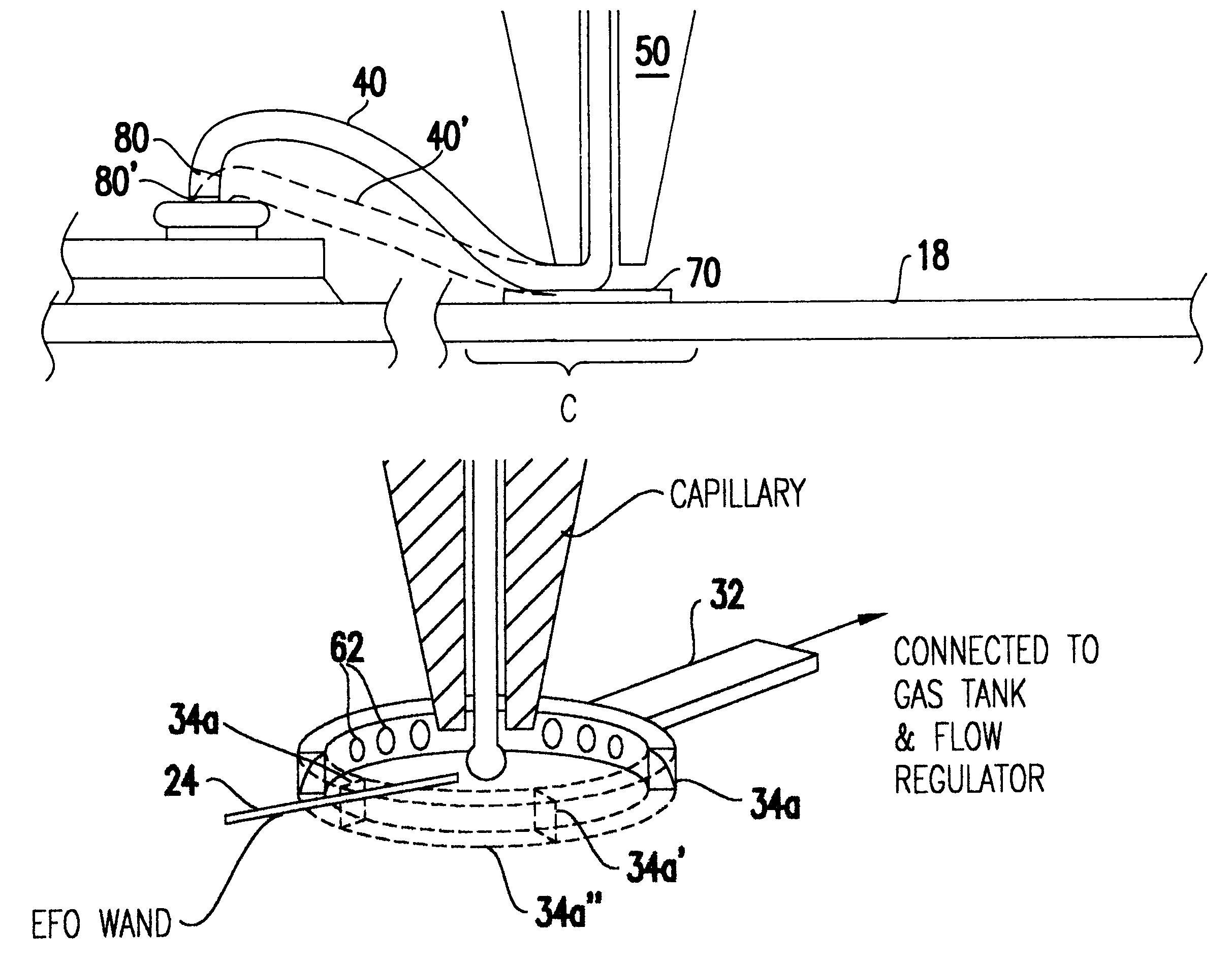

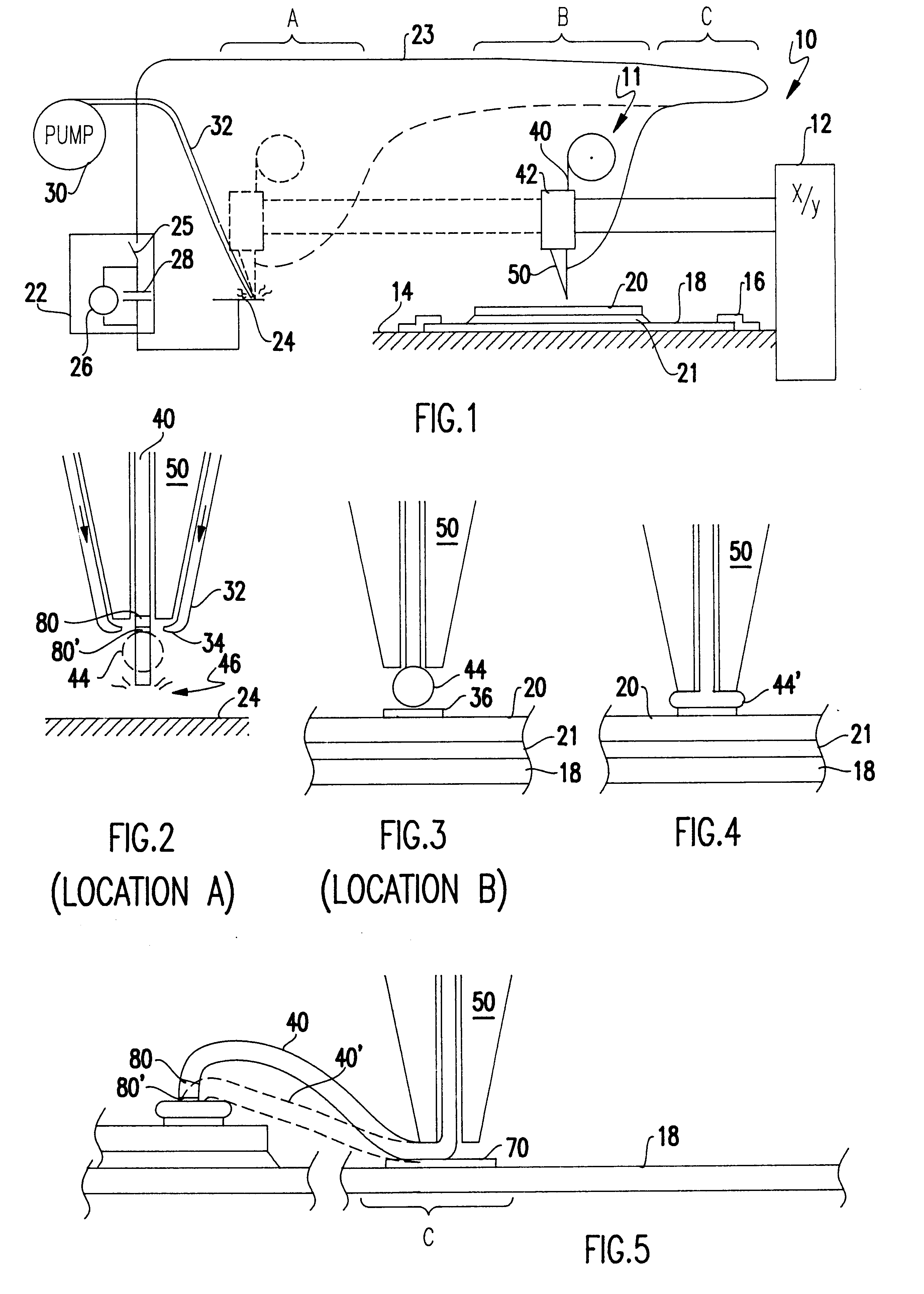

Control of size and heat affected zone for fine pitch wire bonding

InactiveUS6180891B1Electrically conductive connectionsSemiconductor/solid-state device detailsHeat-affected zoneLead bonding

The amount of melting of the bonding wire is closely regulated, and reduction of size and improvement of uniformity of the free air ball is obtained for ball bonding at pitches of less than ninety mils even when bonding wire of reduced diameter is employed. Quenching of the bonding wire adjacent to the free air ball also limits the temperature rise in the bonding wire and the extent of a heat affected zone having less tensile strength and stiffness to less than one micron and with reduced grain enlargement. The present invention provides such a bond for electronic packaging of increased reliability, potential functionality, increased manufacturing yield and reduced process complexity.

Owner:IBM CORP

Postal, freight, and logistics industry high performance capability assessment

A high performance capability assessment model helps a postal industry business meet the challenges of the global marketplace. As a result, the postal industry business can achieve the clarity, consistency, and well-defined execution of core processes that reduce inefficiencies and waste that result from unnecessary process complexity and exceptions. In addition, the high performance capability assessment model helps the postal industry business to identify specific areas in which improvements may be made and understand how to make the improvements, and establishes levels of capability along the way to reaching an ultimate capability goal.

Owner:ACCENTURE GLOBAL SERVICES LTD

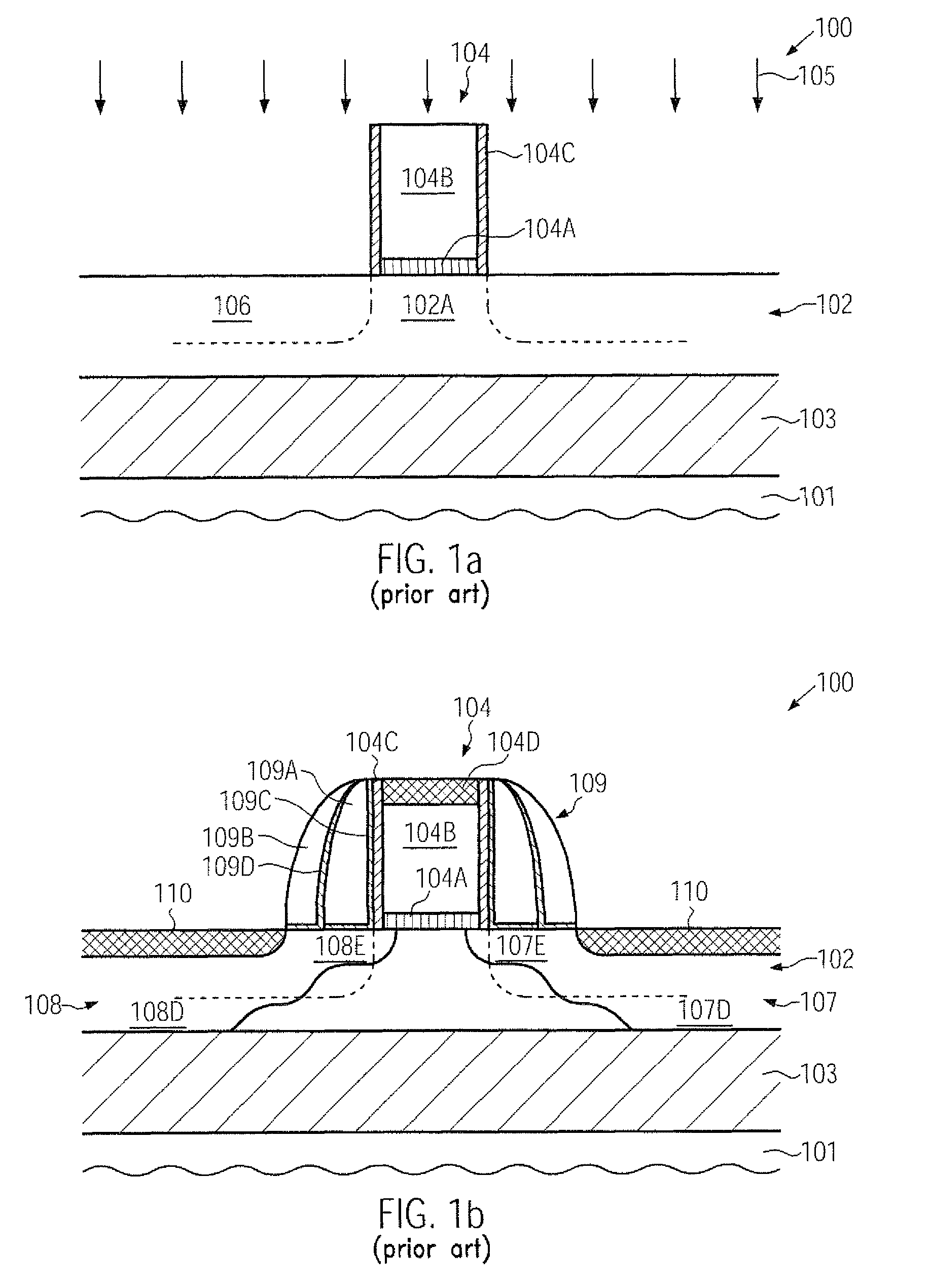

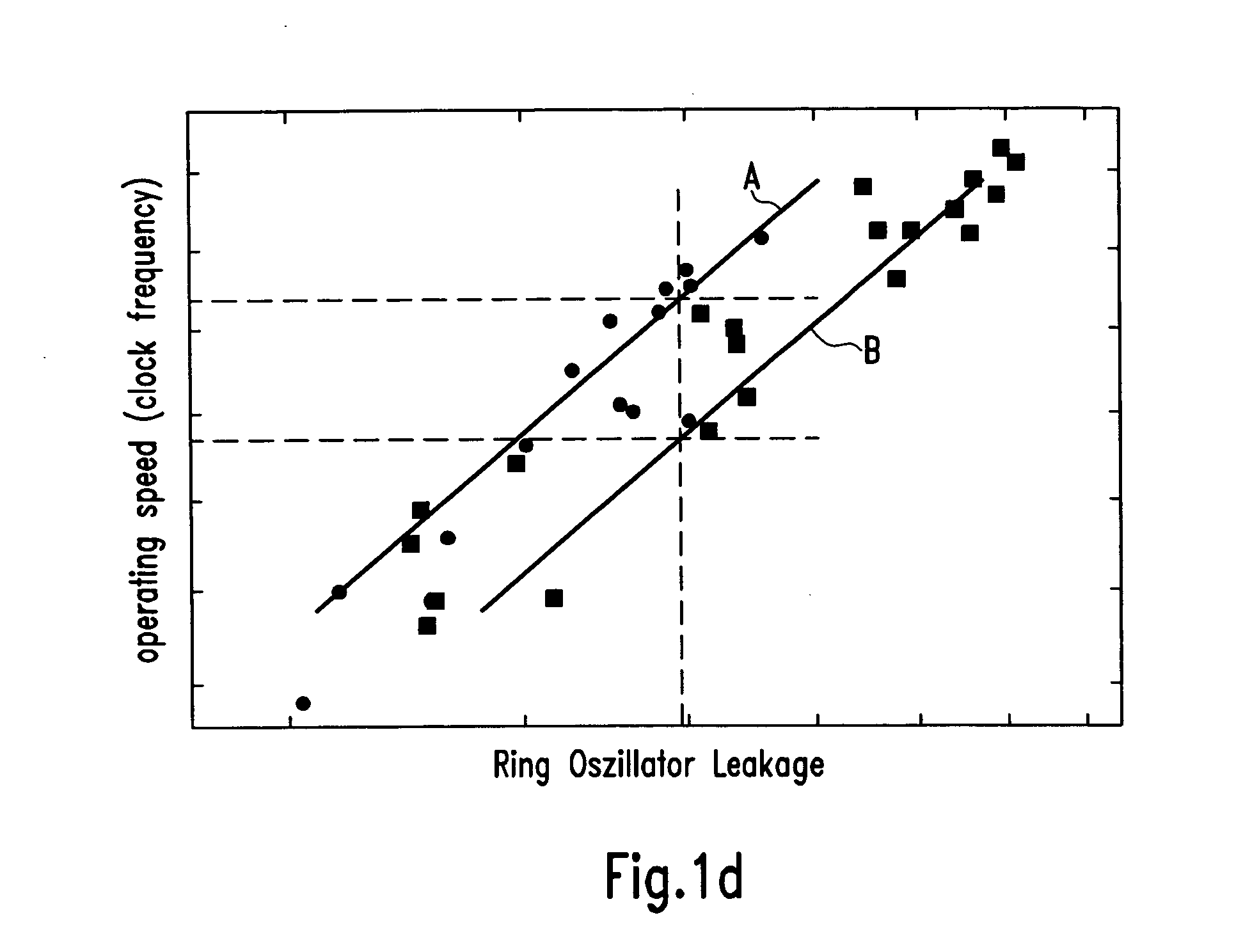

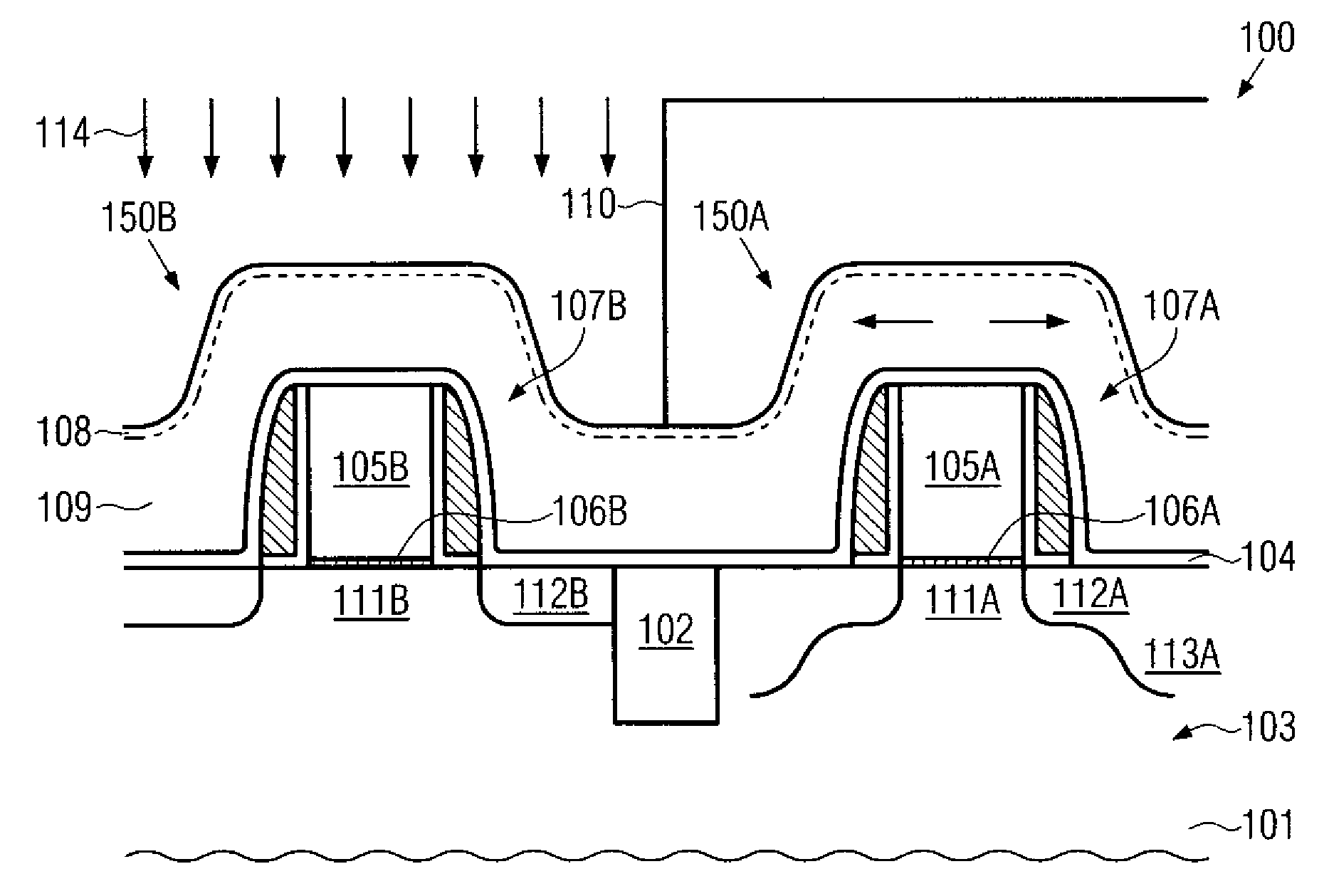

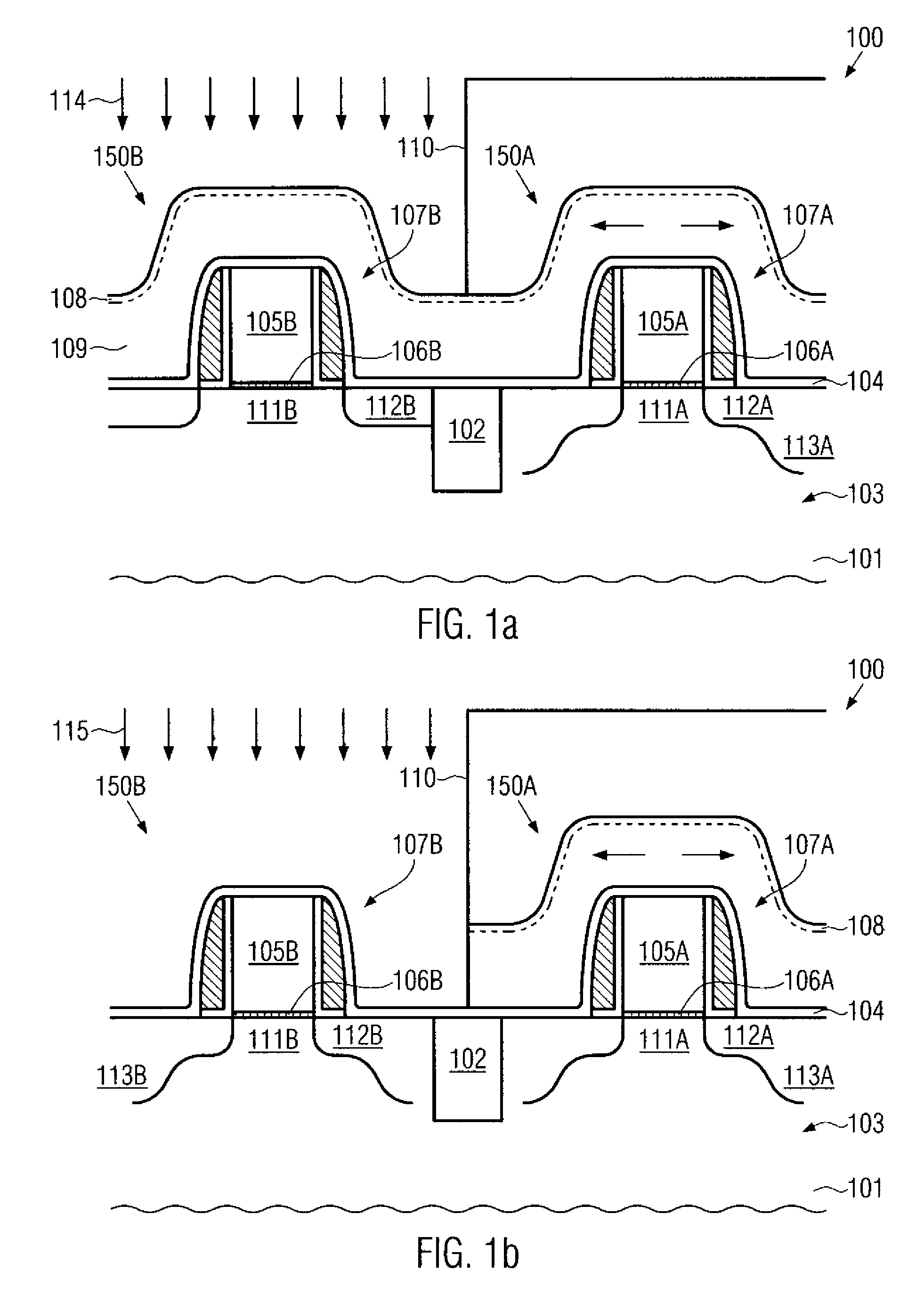

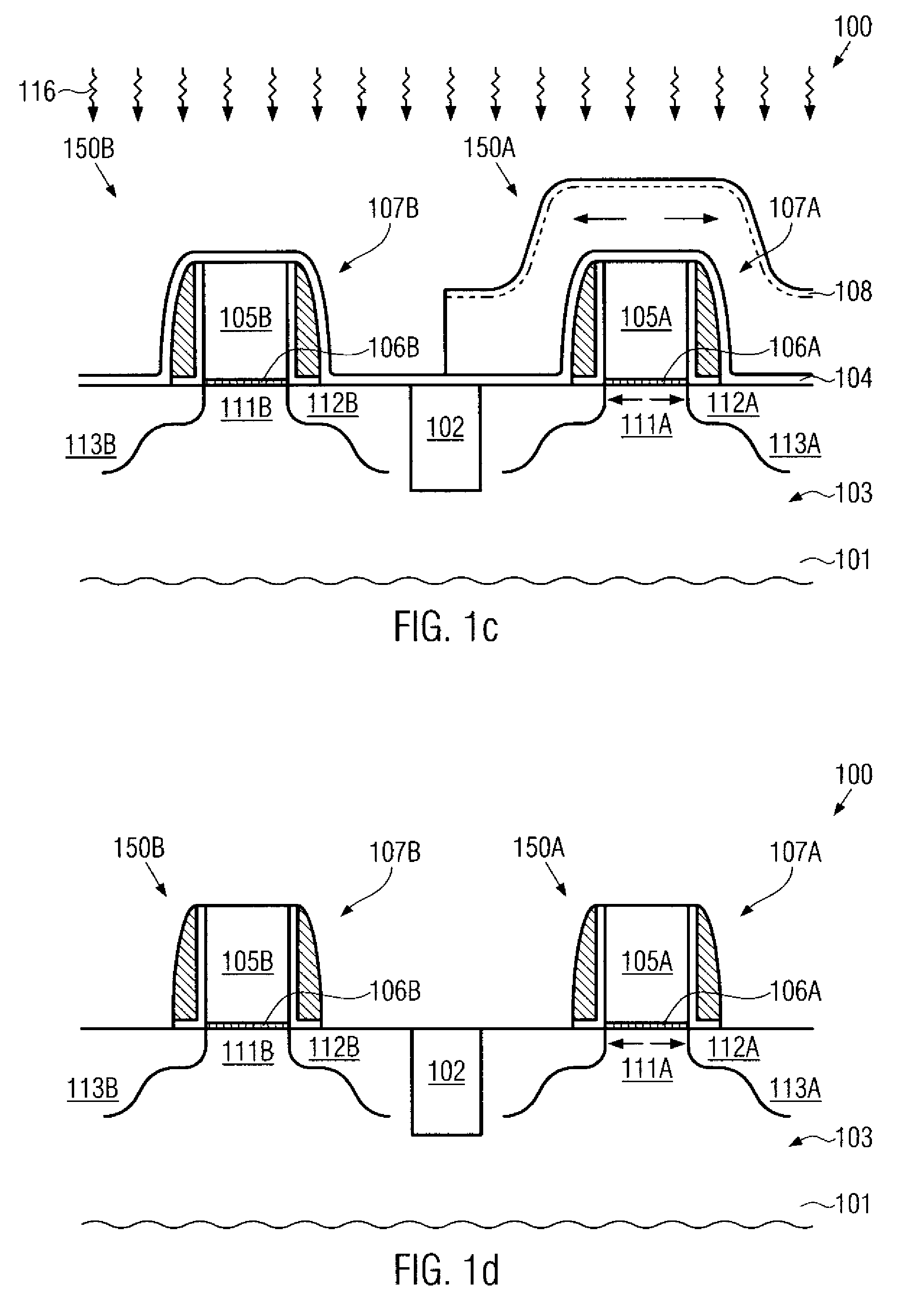

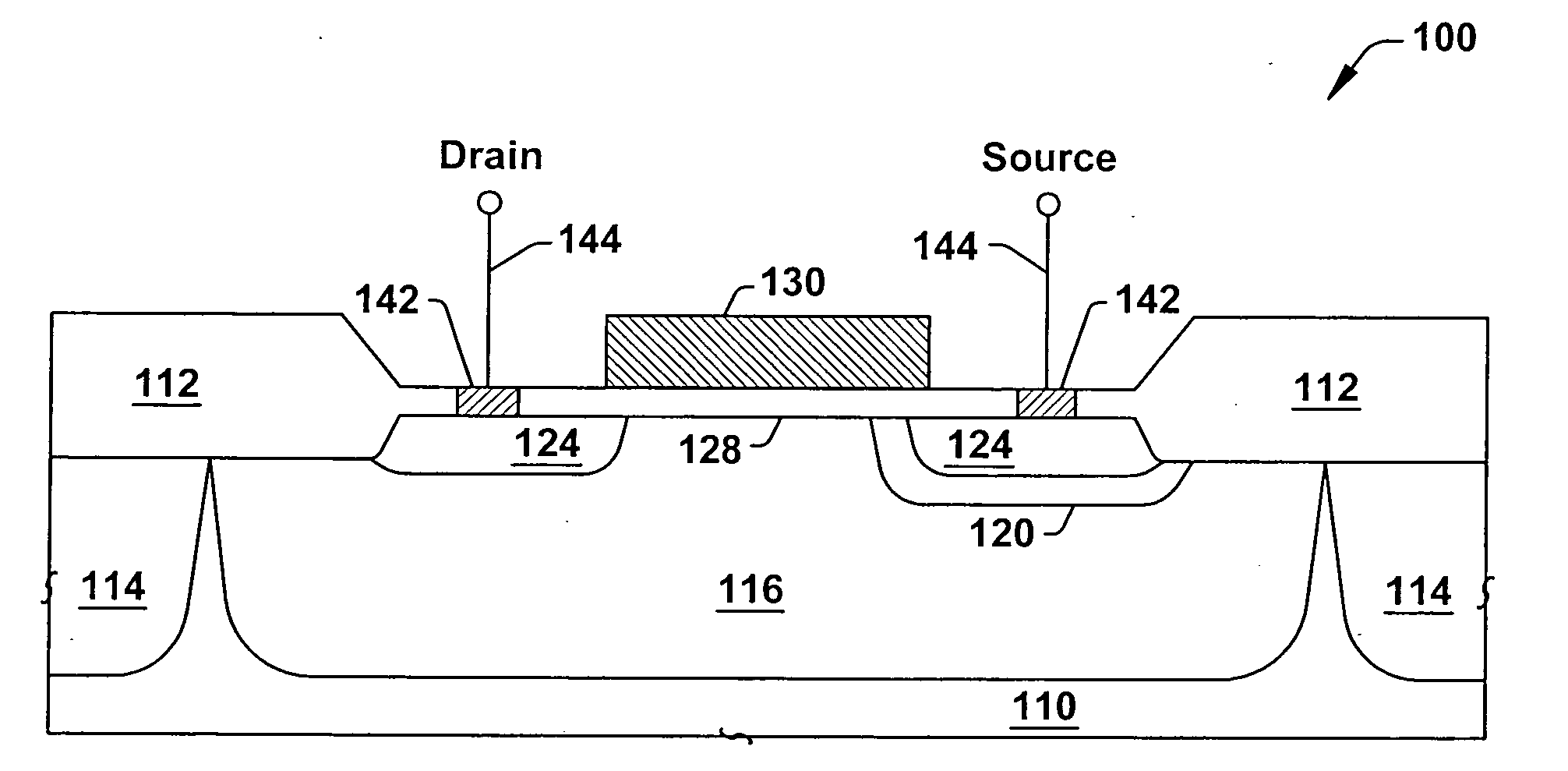

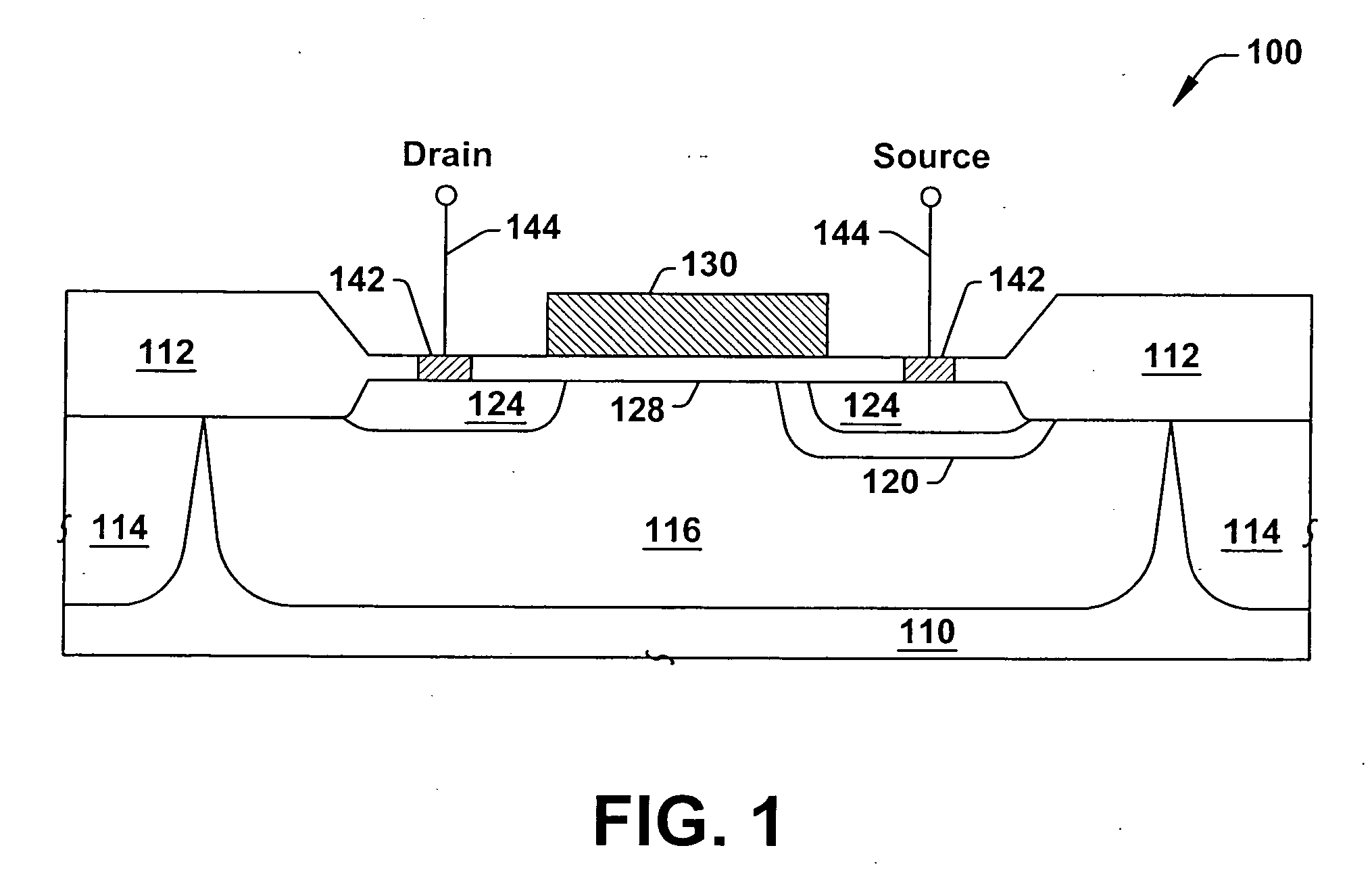

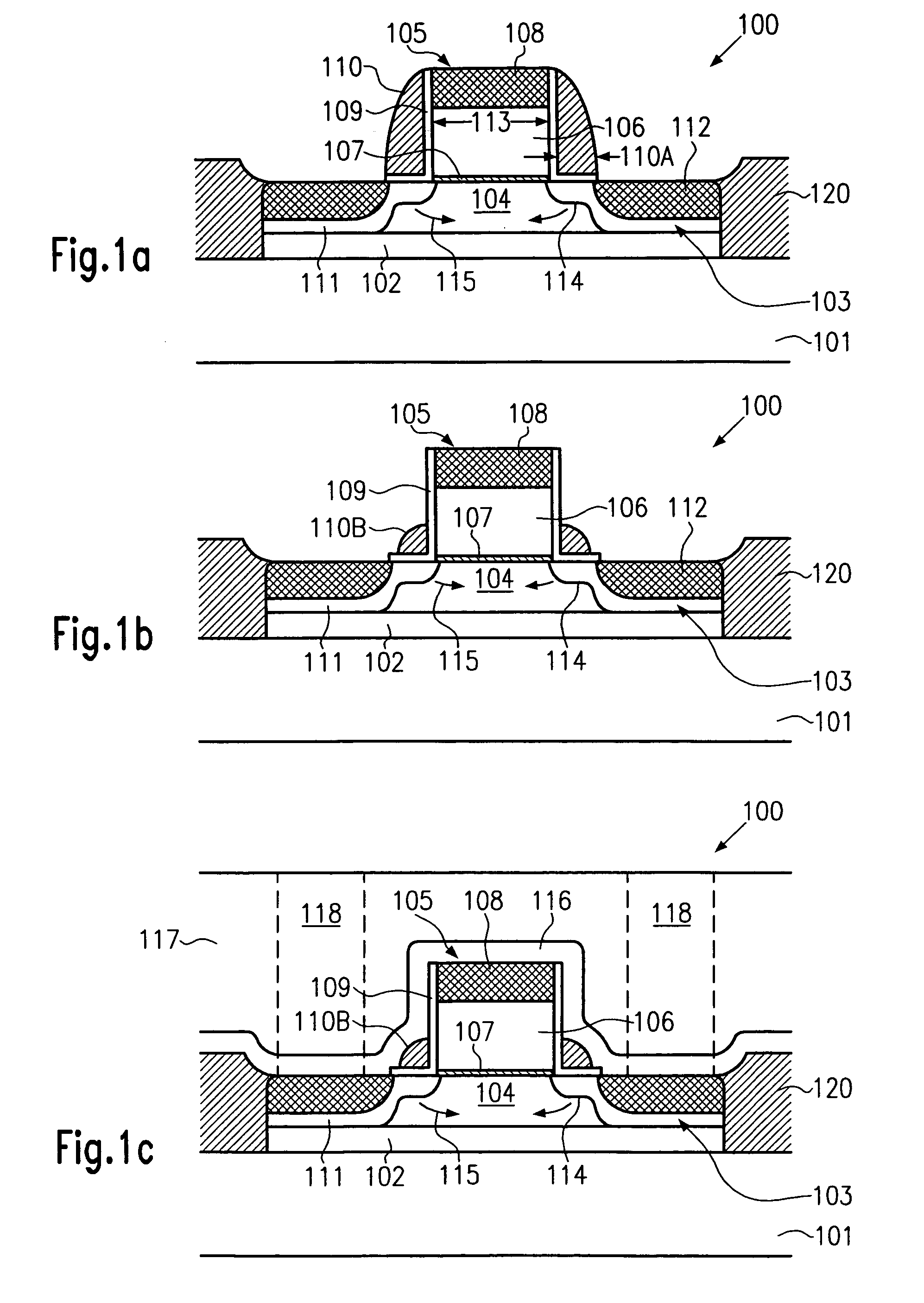

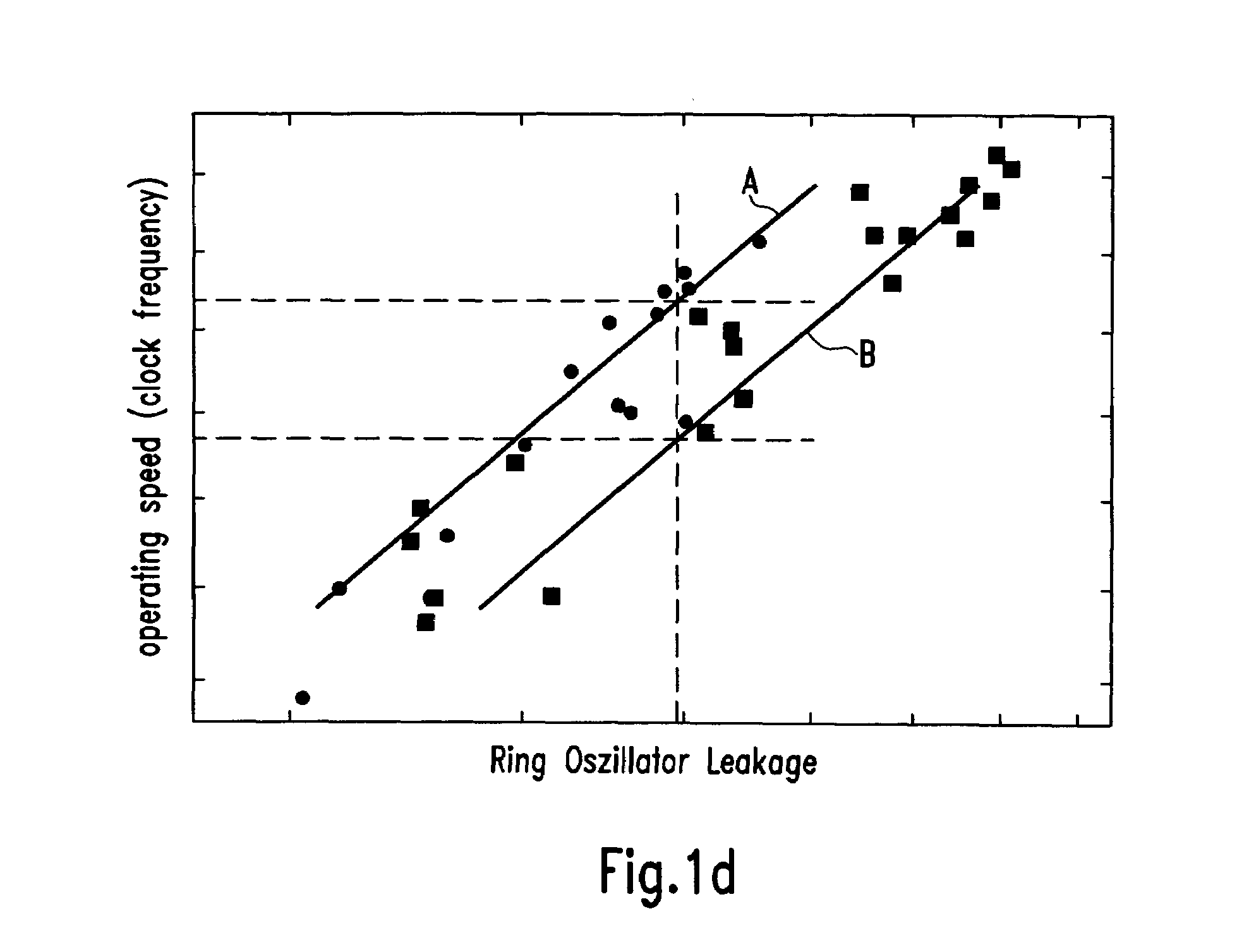

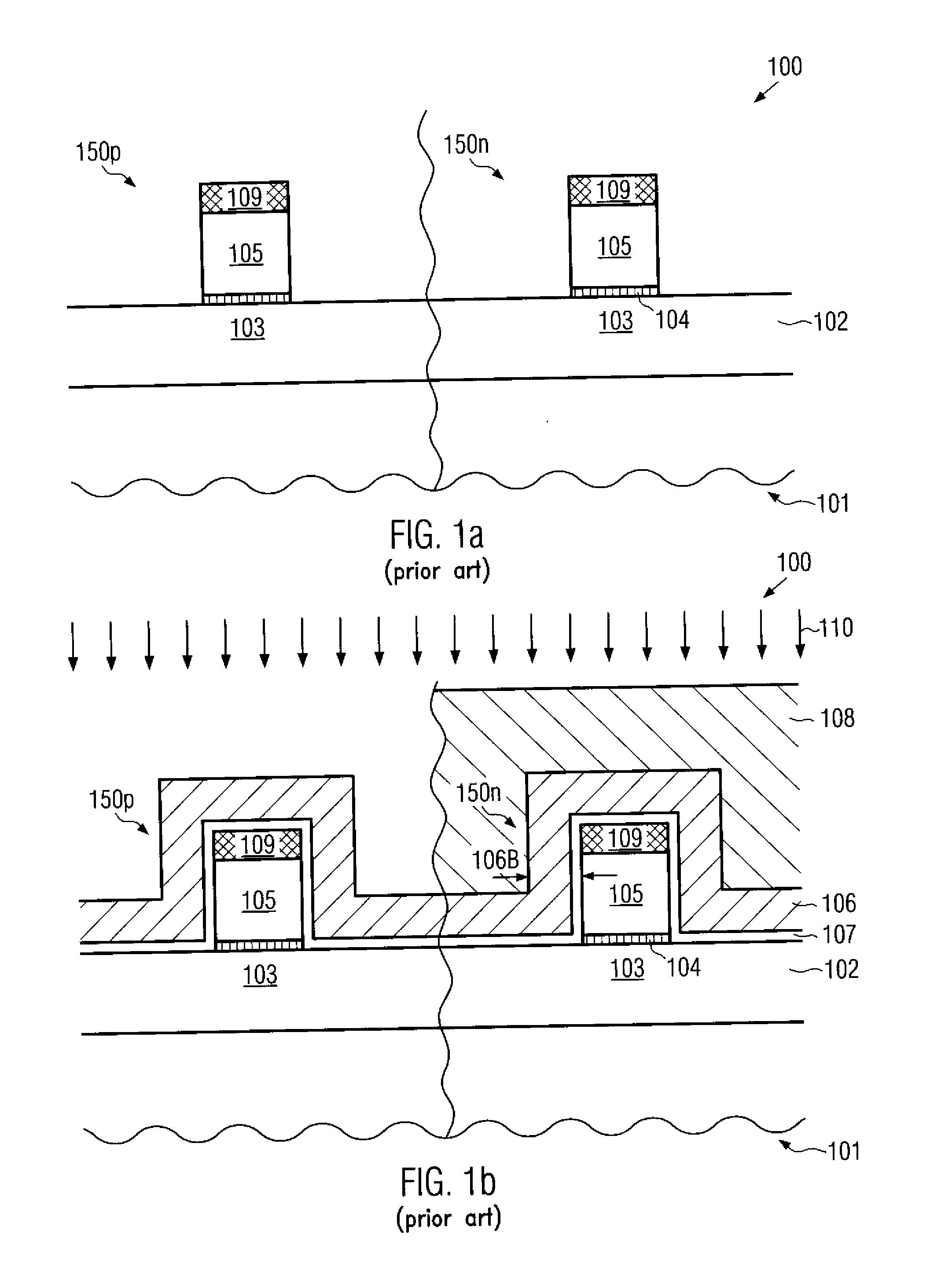

Drive current increase in transistors by asymmetric amorphization implantation

ActiveUS7855118B2Increased complexityImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesDriving currentNon symmetric

By providing a substantially non-damaged semiconductor region between a pre-amorphization region and the gate electrode structure, an increase of series resistance at the drain side during the re-crystallization may be reduced, thereby contributing to overall transistor performance, in particular in the linear operating mode. Thus, symmetric and asymmetric transistor architectures may be achieved with enhanced performance without unduly adding to overall process complexity.

Owner:ADVANCED MICRO DEVICES INC

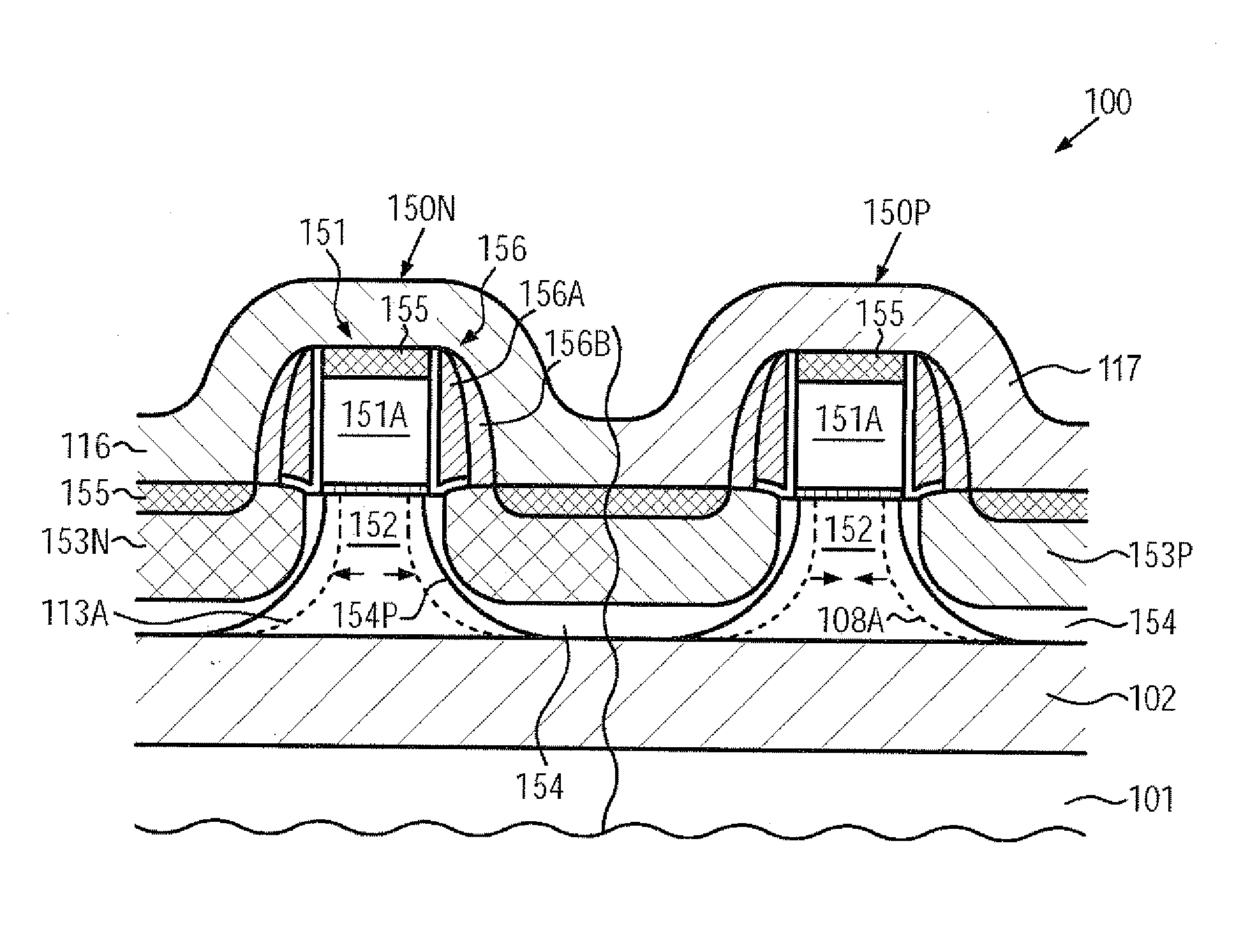

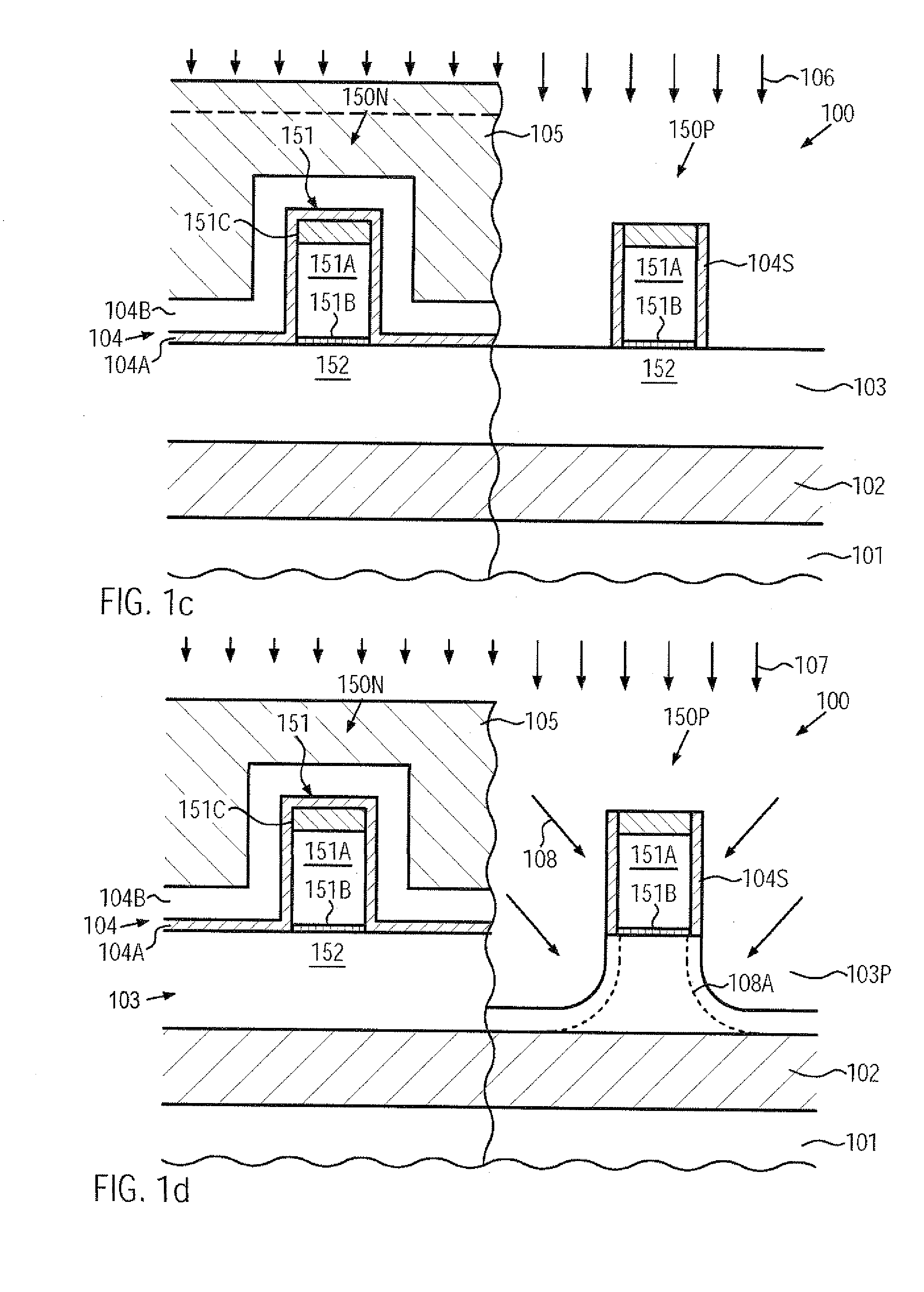

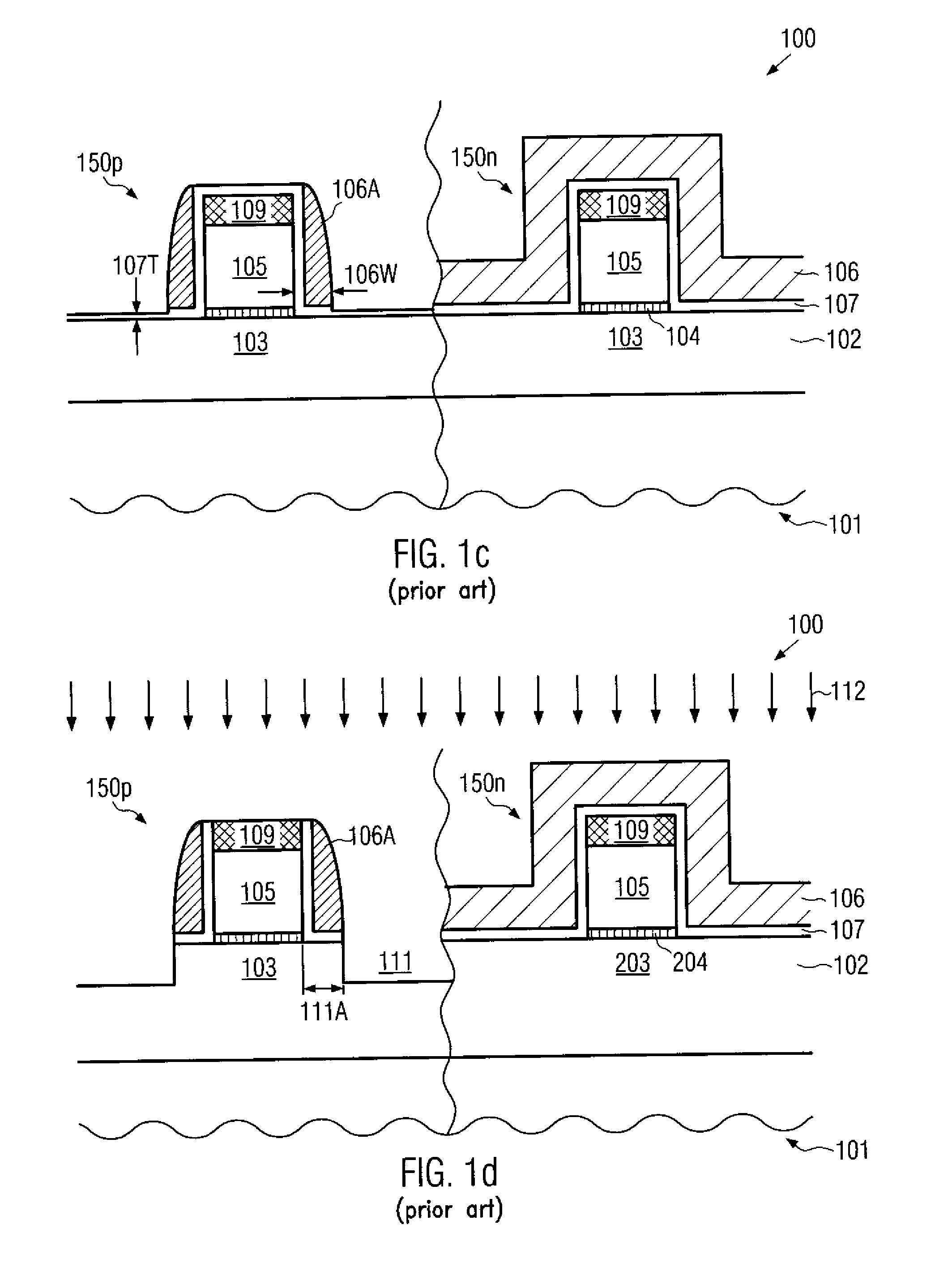

Performance enhancement in pmos and nmos transistors on the basis of silicon/carbon material

InactiveUS20100025771A1Improve production efficiencyImprove featuresTransistorSolid-state devicesTensile strainPerformance enhancement

A silicon / germanium material and a silicon / carbon material may be provided in transistors of different conductivity type on the basis of an appropriate manufacturing regime without unduly contributing to overall process complexity. Furthermore, appropriate implantation species may be provided through exposed surface areas of the cavities prior to forming the corresponding strained semiconductor alloy, thereby additionally contributing to enhanced overall transistor performance. In other embodiments a silicon / carbon material may be formed in a P-channel transistor and an N-channel transistor, while the corresponding tensile strain component may be overcompensated for by means of a stress memorization technique in the P-channel transistor. Thus, the advantageous effects of the carbon species, such as enhancing overall dopant profile of P-channel transistors, may be combined with an efficient strain component while enhanced overall process uniformity may also be accomplished.

Owner:ADVANCED MICRO DEVICES INC

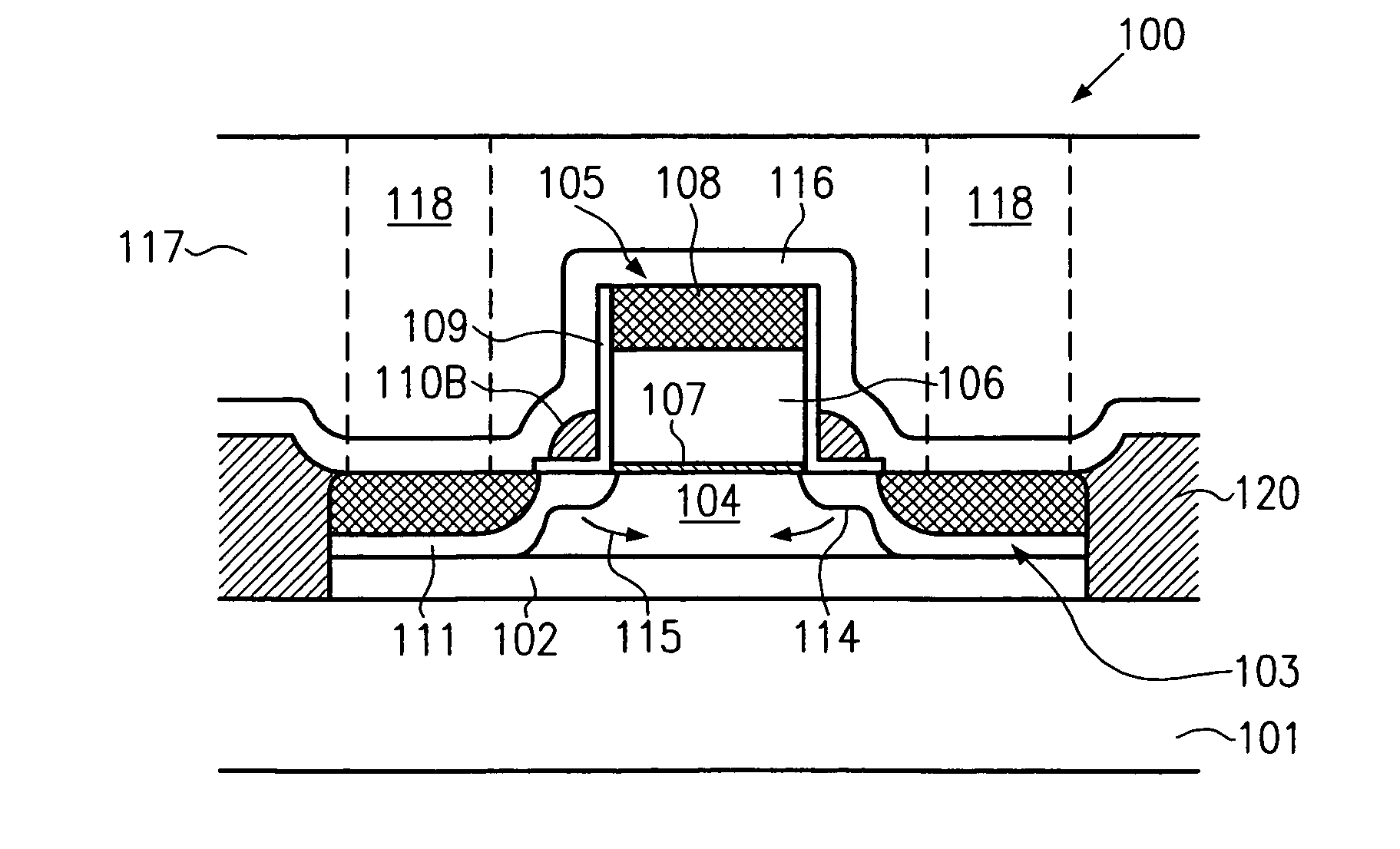

Techique for controlling mechanical stress in a channel region by spacer removal

ActiveUS20050266639A1Increase flexibilitySignificant stressSemiconductor/solid-state device manufacturingSemiconductor devicesCouplingEngineering

During the formation of a transistor element, sidewalls spacers are removed or at least partially etched back after ion implantation and silicidation, thereby rendering the mechanical coupling of a contact etch stop layer to the underlying drain and source regions more effective. Hence, the mechanical stress may be substantially induced by the contact etch step layer rather than by a combination of the spacer elements and the etch stop layer, thereby significantly facilitating the stress engineering in the channel region. By additionally performing a plasma treatment, different amounts of stress may be created in different transistor devices without unduly contributing to process complexity.

Owner:GLOBALFOUNDRIES US INC

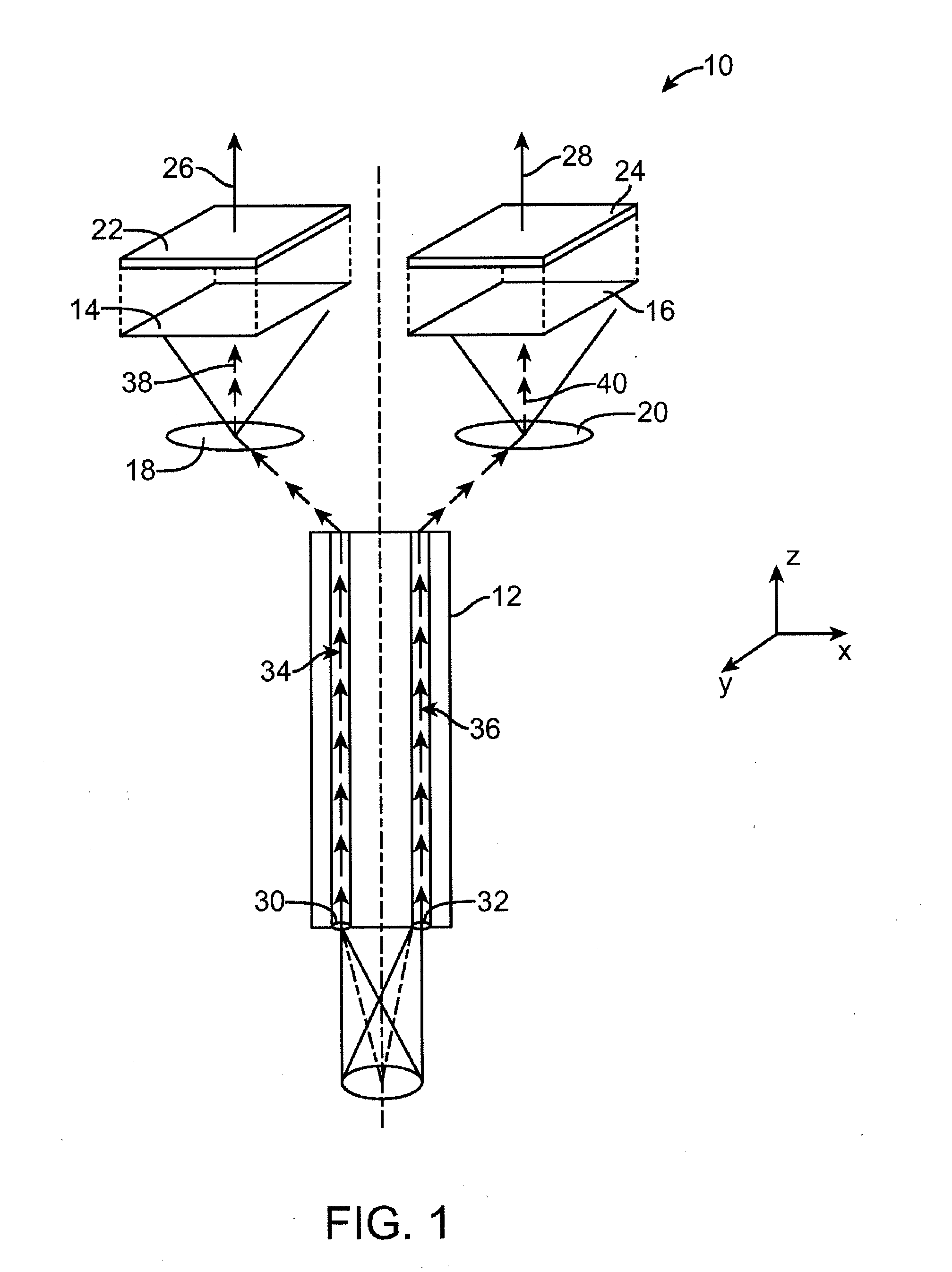

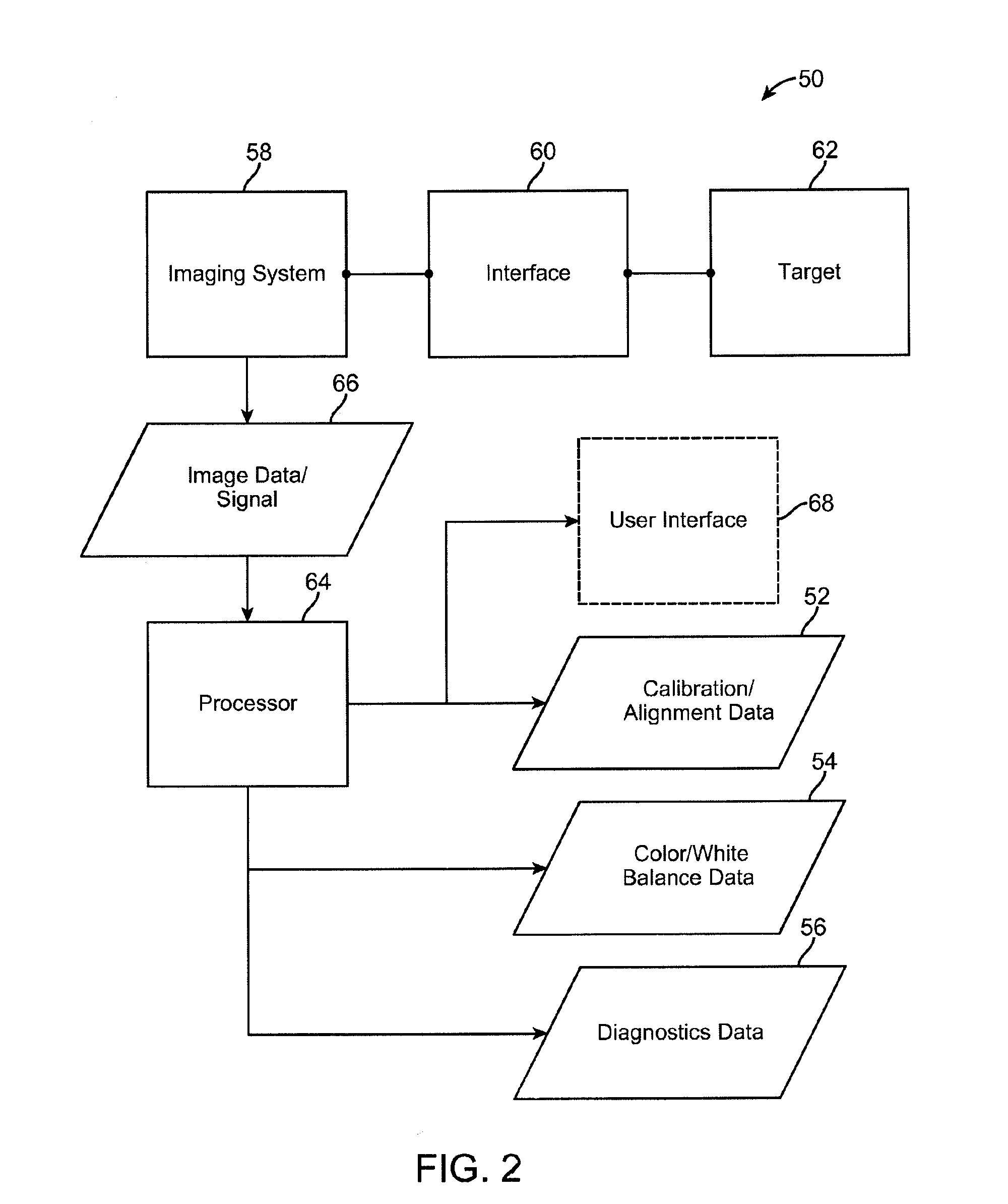

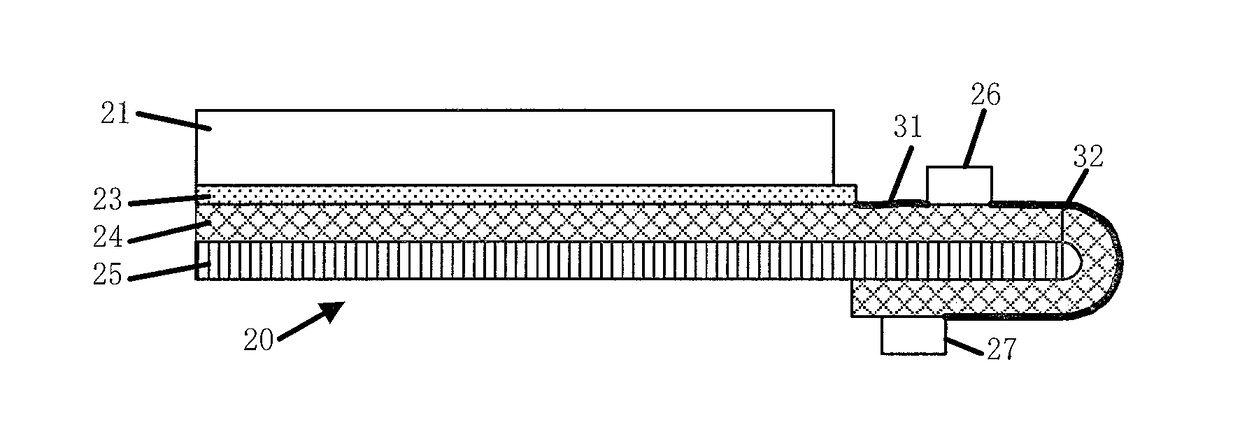

Three-dimensional target devices, assemblies and methods for calibrating an endoscopic camera

The present disclosure relates to calibration target devices, assemblies and methods for use with imaging systems, such as a stereoscopic endoscope. A calibration assembly includes: a target surface extends in three dimensions with calibration markers and a body with an interface that engages an endoscope so the markers are within the field of view. A first calibration marker extends along a first plane of the target surface and a second marker extends along a second plane of the target surface. The planes are different and asymmetric relative to the field of view as seen through the endoscope. Three-dimensional targets, in particular, enable endoscopic calibration using a single image (or pair of images for a stereoscopic endoscope) to reduce the calibration process complexity, calibration time and chance of error as well as allow the efficient calibration of cameras at different focus positions.

Owner:INTUITIVE SURGICAL OPERATIONS INC

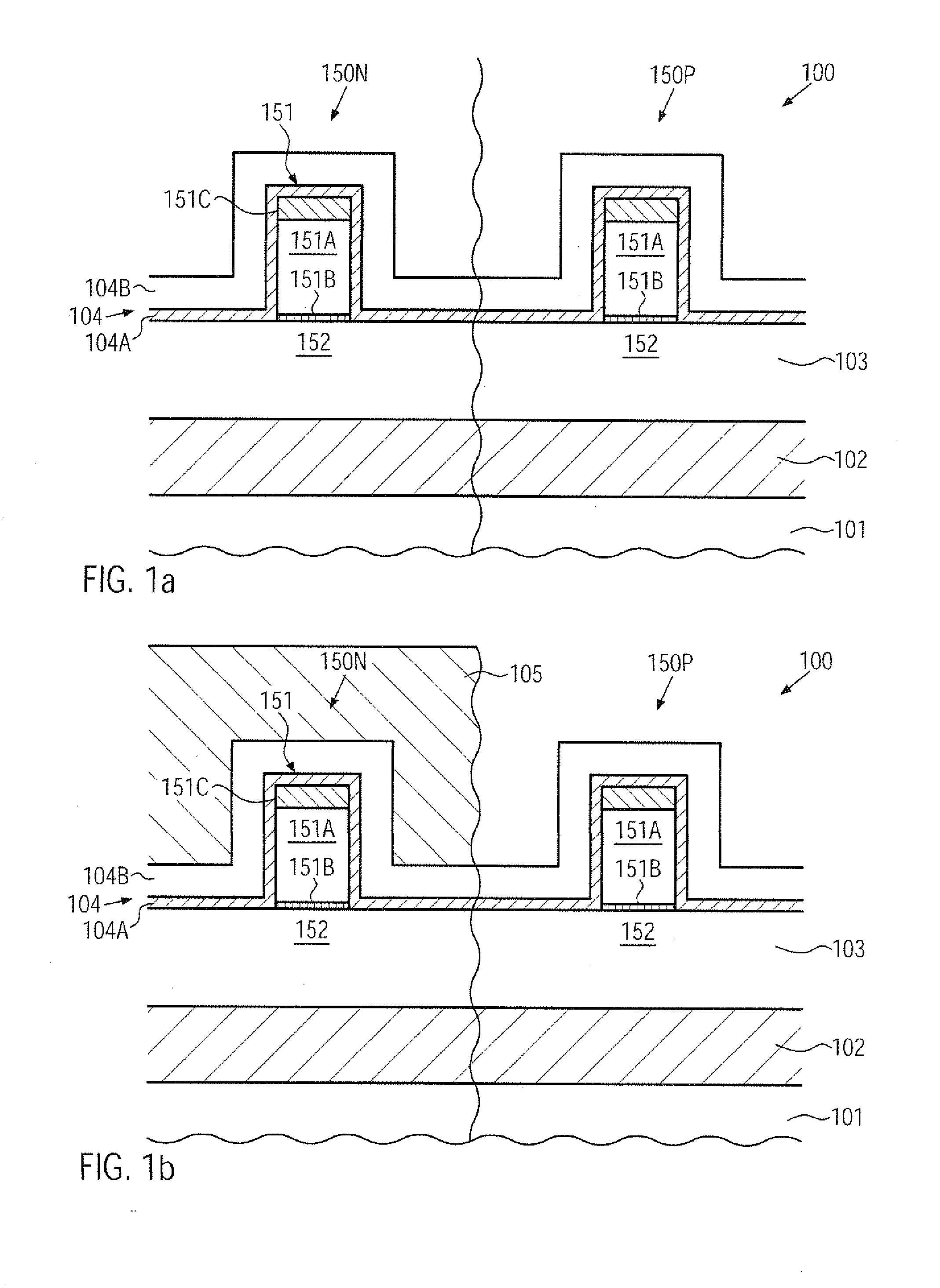

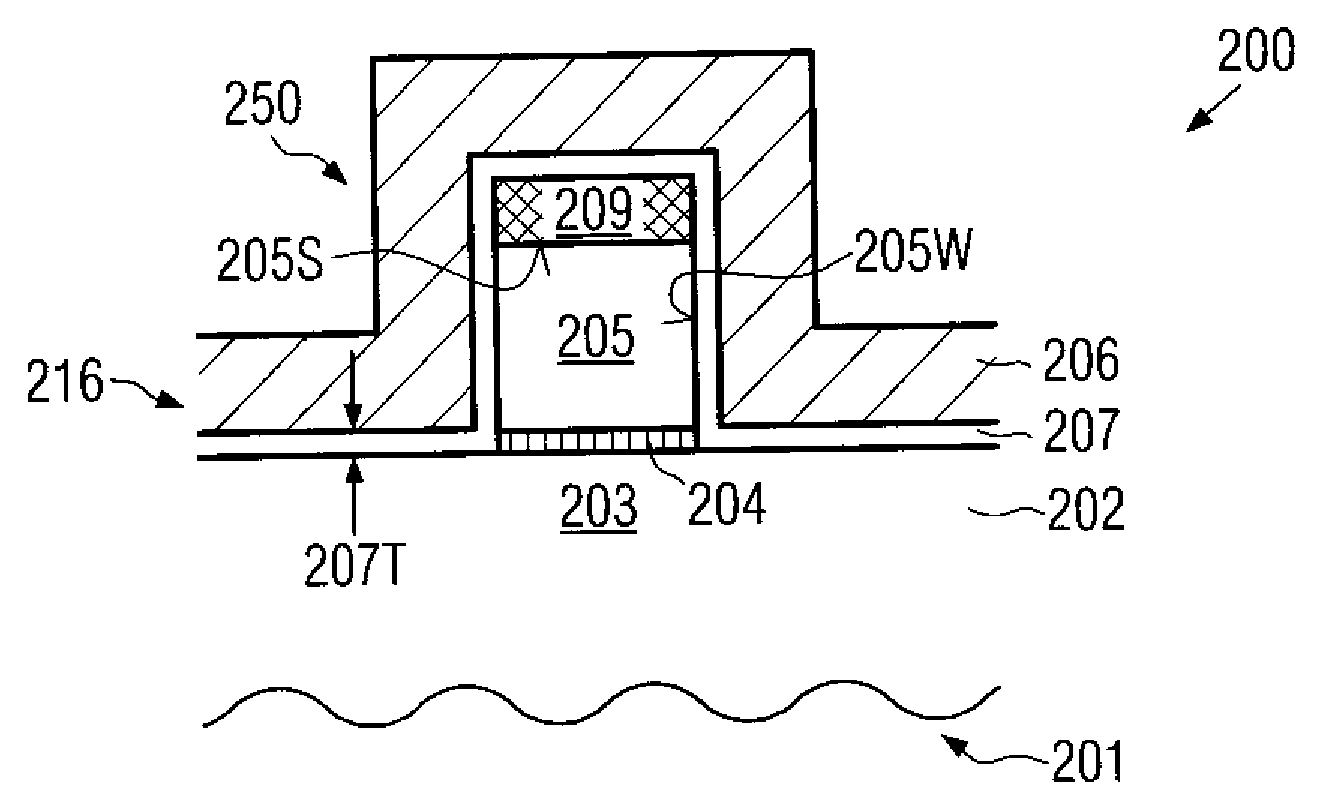

Technique for creating different mechanical stress in different channel regions by forming an etch stop layer having differently modified intrinsic stress

ActiveUS20050263825A1Reliable and precise controlEffective controlTransistorSemiconductor/solid-state device detailsCompound (substance)Engineering

By providing a contact etch stop layer, the stress in channel regions of different transistor types may be effectively controlled, wherein tensile and compressive stress portions of the contact etch stop layer may be obtained by well-established processes, such as wet chemical etch, plasma etch, ion implantation, plasma treatment and the like. Hence, a significant improvement in transistor performance may be obtained while not significantly contributing to process complexity.

Owner:ADVANCED MICRO DEVICES INC

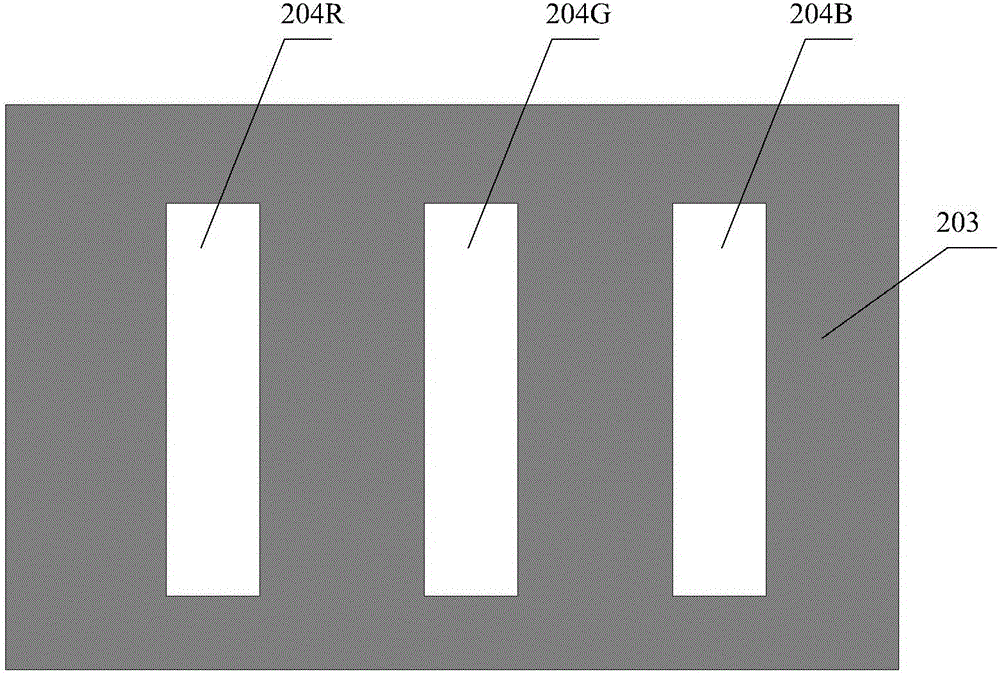

Array substrate, touch display panel and touch display device

ActiveCN105468202ALower resistanceSimple processInput/output processes for data processingData linesProcess complexity

The invention discloses an array substrate, a touch display panel and a touch display device. According to one embodiment, the array substrate comprises a substrate body, a plurality of metal layers, a touch control electrode layer and a plurality of touch control signal lines, wherein the substrate body has a display area and a non-display area, the metal layers are perpendicular to the substrate body and include the first metal layers and the second metal layers, the first metal layers are used for forming scanning lines of the array substrate, and the second metal layers are used for forming data lines of the array substrate; a plurality of pixel units are arranged in the display area and distributed into an array, the line direction of the pixel units is the extending direction of the scanning lines, and the row direction of the pixel units is the extending direction of the data lines; the touch control electrode layer comprises a plurality of touch control electrodes, the touch control signal lines are electrically connected with one touch control electrode and used for transmitting touch control signals to the touch control electrode, and the touch control signal lines and at least one metal layer are located on the same layer. In this way, the complexity of the manufacturing process of the array substrate can be reduced.

Owner:SHANGHAI AVIC OPTOELECTRONICS +1

Brain-computer interface system based on atom magnetometer, and use method thereof

ActiveCN107562188AHigh sensitivityImprove portabilityInput/output for user-computer interactionDiagnostic recording/measuringSystem integrationSupporting system

The invention discloses a brain-computer interface system based on an atom magnetometer, and a use method thereof. The invention combines the work characteristics of the atom magnetometer to design abrain magnetic cap and a magnetic shielding device with practicality; a scheme of separating an atom magnetometer probe from a light source is adopted to improve a system integration level; system probability is intensified; a brain magnetic signal processing process capable of greatly improving operation speed and reducing processing process complexity; and for scenes which may be applied by thesystem, a feasible commutation and peripheral support system is given. By use of the brain-computer interface system provided by the invention, the control of a local and remote application system isfinished conveniently through the brain magnetic signal, and the system owns practicality and good expansion performance.

Owner:BEIJING QUANMAG HEALTHCARE CO LTD

Method for forming a strained transistor by stress memorization based on a stressed implantation mask

ActiveUS20080026572A1Low production costEasy to useTransistorSemiconductor/solid-state device manufacturingLithographic artistProcess complexity

By using an implantation mask having a high intrinsic stress, SMT sequences may be provided in which additional lithography steps may be avoided. Consequently, a strain source may be provided without significantly contributing to the overall process complexity.

Owner:GLOBALFOUNDRIES US INC

Display panel with fingerprint identification function, preparation method and display device

ActiveCN106024836ARealization of fingerprint recognition functionReduce process complexitySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceProcess complexity

The invention provides a display panel with a fingerprint identification function, a preparation method and a display device for achieving an OLED display with the fingerprint identification function, reducing the process complexity and saving the cost. The display panel with the fingerprint identification function provided by the invention comprises an array substrate, an anode layer, a pixel definition region, a plurality of organic light-emitting units, an isolating column, a reuse electrode layer, a second electrode layer and a cover plate, wherein the anode layer is located on the array substrate; the plurality of organic light-emitting units are surrounded by the pixel definition region; the pixel definition region and the organic light-emitting units are located on the anode layer; the isolating column is located on the pixel definition region; the reuse electrode layer is located on the isolating column and the organic light-emitting units; the reuse electrode layer comprises a cathode layer and a first electrode layer; the reuse electrode layer covering the isolating column is taken as a first electrode layer; the reuse electrode layer surrounded by the first electrode layer is taken as the cathode layer; the first electrode layer and the cathode layer are arranged on the same layer and are not connected with each other; the second electrode layer is located on the reuse electrode layer; and the cover plate is located on the second electrode layer.

Owner:BOE TECH GRP CO LTD

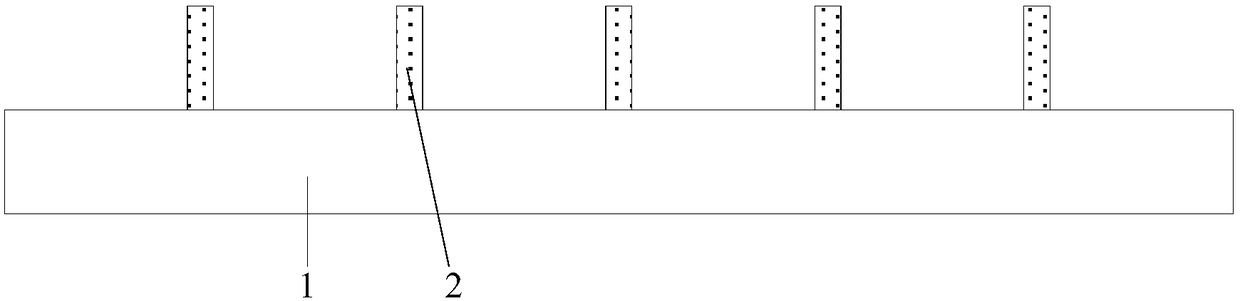

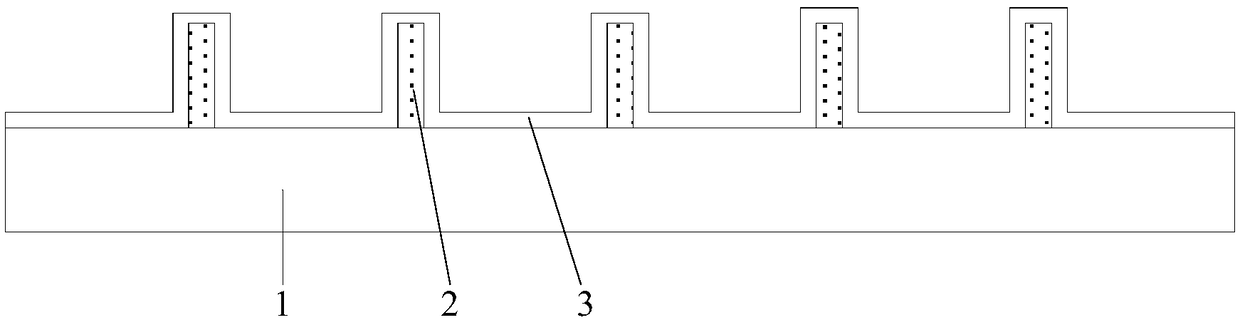

Flexible display substrate, manufacturing method thereof and flexible display device

The disclosure provides a flexible display substrate, a manufacturing method thereof and a flexible display device, aiming to reduce the technical difficulty and process complexity of preparing a stretchable display and reduce the cost. The manufacturing method includes the following steps: manufacturing multiple protrusions on a substrate; manufacturing a base film on one side of each of the multiple protrusions facing away from the substrate; manufacturing a display structure on the surface of the base film facing away from the substrate; peeling off the base film and the display structure from the substrate, and maintaining the multiple protrusions on the substrate after peeling off; and attaching the surface of the base film facing away from the display structure to an elastic base material, and stretching the elastic base material to ensure that the base film is broken at multiple recessed locations. The manufacturing method is applied to the manufacturing of stretchable display devices, and can promote the mass production of the stretchable display devices.

Owner:BOE TECH GRP CO LTD

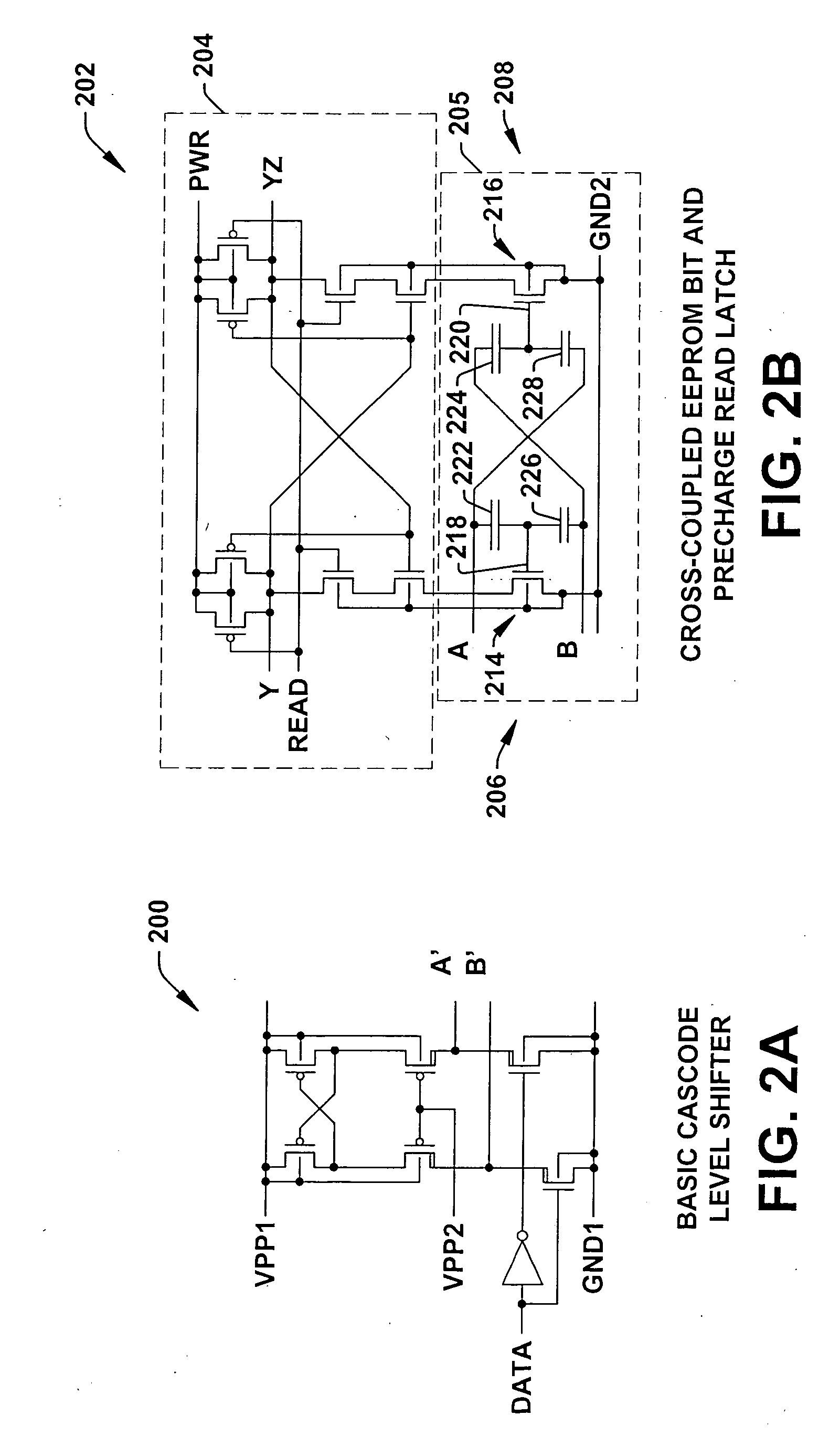

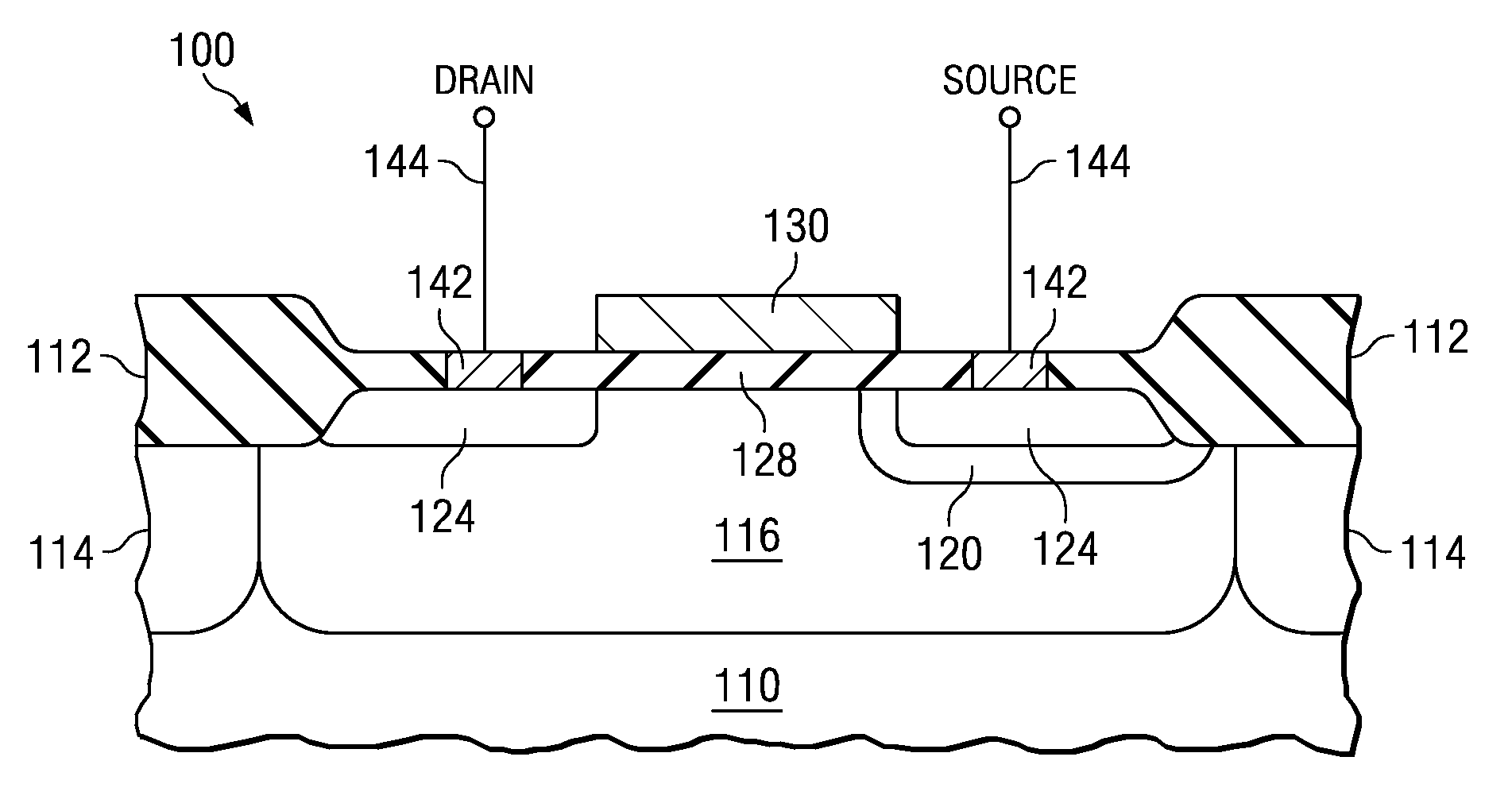

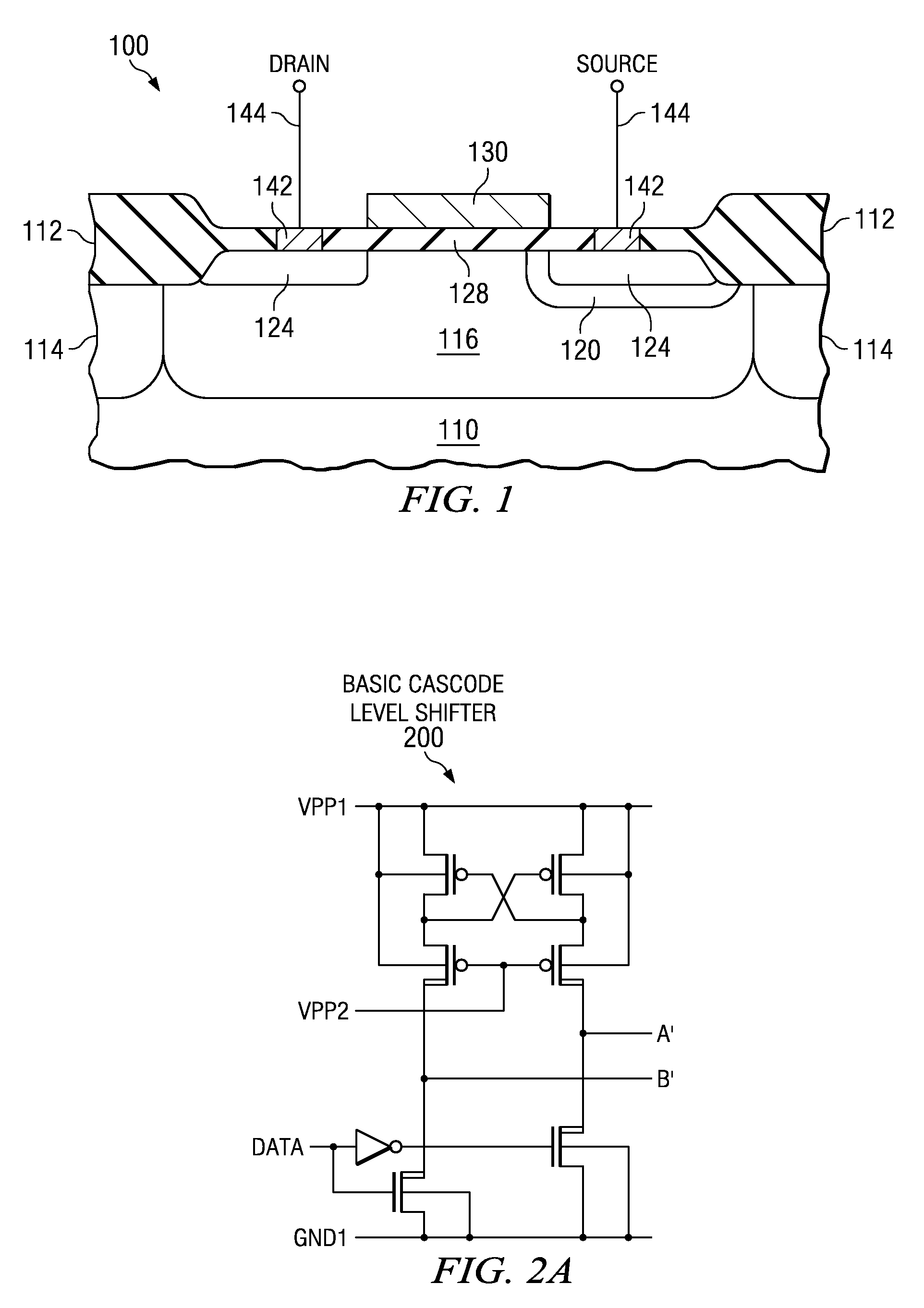

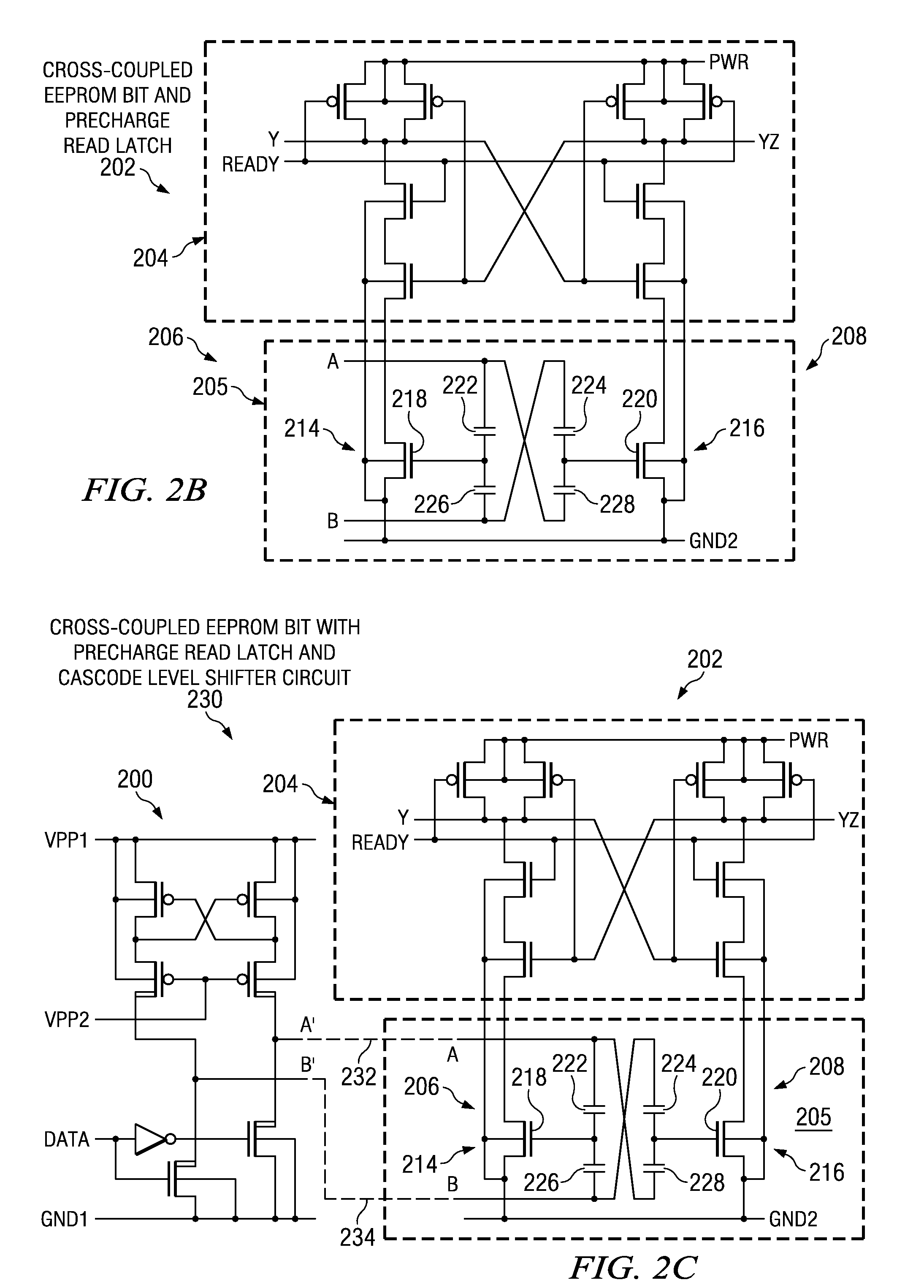

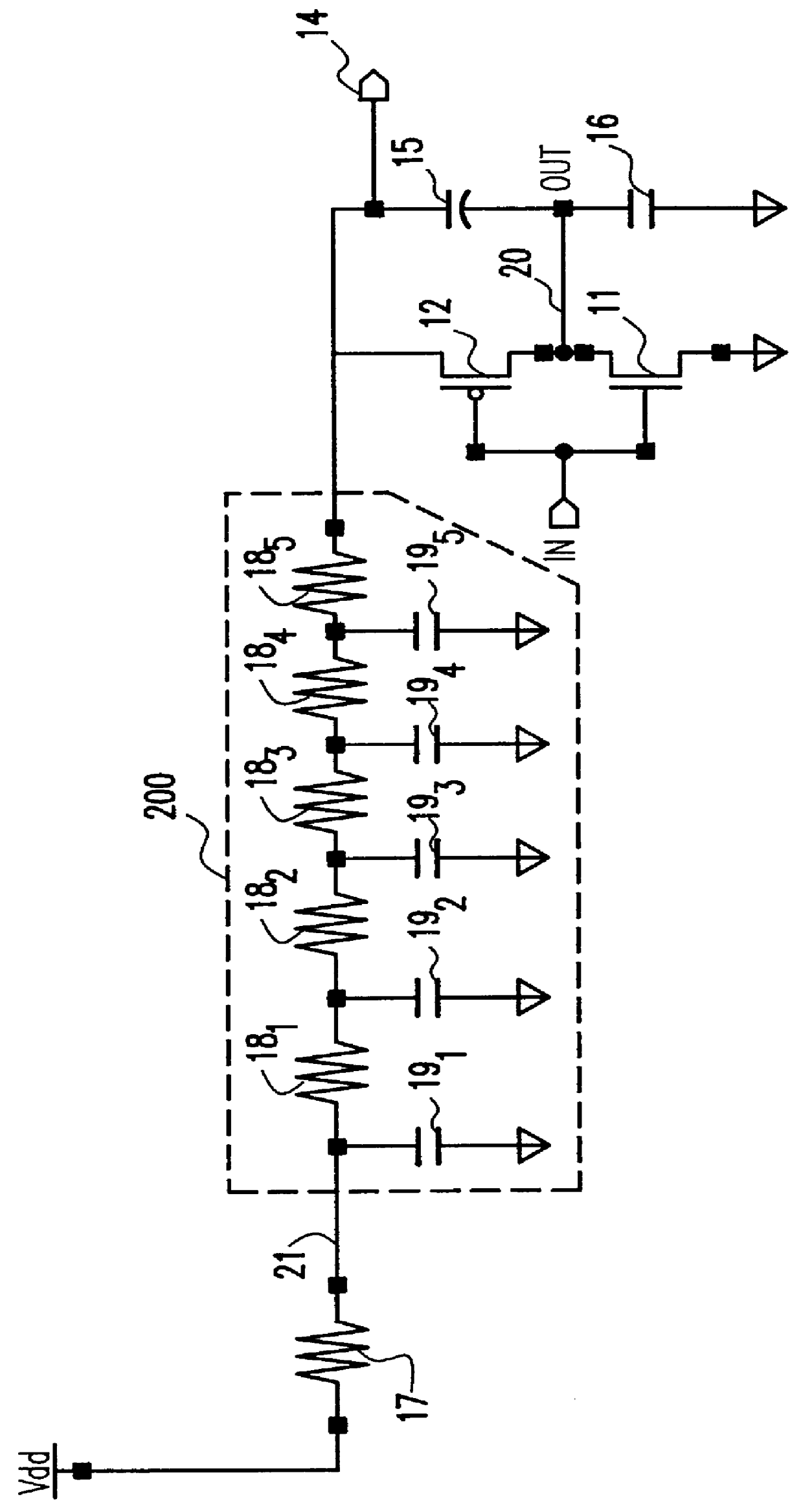

Embedded EEPROM array techniques for higher density

ActiveUS20070064494A1Simple structureWafer Area ReductionSolid-state devicesRead-only memoriesHigh densityHigh voltage transistors

An array structure of single-level poly NMOS EEPROM memory cells and method of operating the array is discussed implemented in a higher density embedded EEPROM layout that eliminates the use of high voltage transistors from the array core region. If they are utilized, the high voltage transistors are moved to row and column drivers in the periphery region to increase array density with little or no added process complexity to allow economic implementation of larger embedded SLP EEPROM arrays. During program or erase operations of the array, the method provides a programming voltage for the selected memory cells of the array, and a half-write (e.g., mid-level) voltage to the remaining unselected memory cells to avoid disturbing the unselected memory cells of the array.

Owner:TEXAS INSTR INC

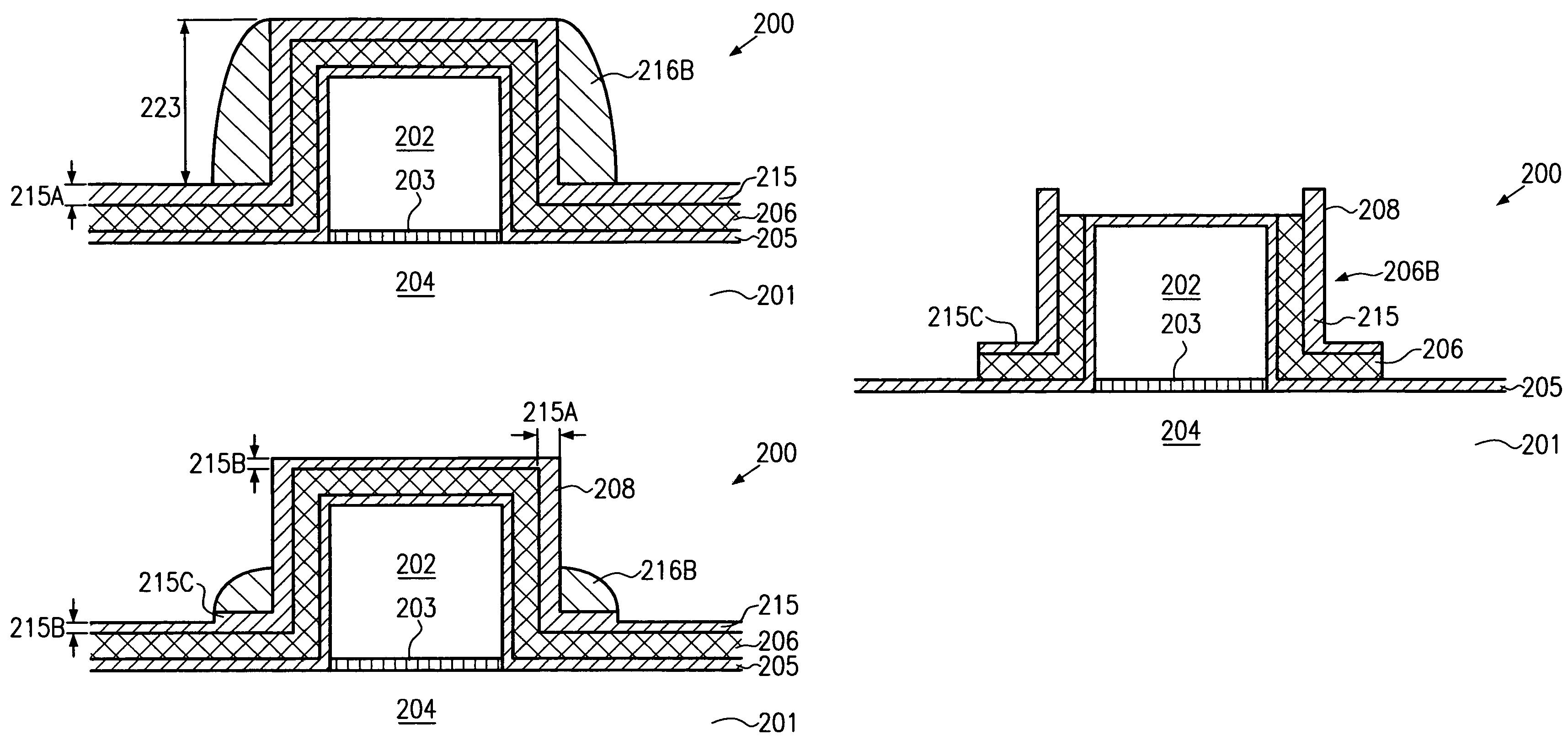

Method of forming a conformal spacer adjacent to a gate electrode structure

ActiveUS7064071B2Semiconductor/solid-state device manufacturingSemiconductor devicesEngineeringProcess complexity

In a process for forming L-shaped sidewall spacers for a conducive line element, such as a gate electrode structure, the sacrificial spacers are formed of a material having a similar etch behavior as the material of the finally obtained L-shaped spacer, thereby improving tool utilization and reducing process complexity compared to conventional processes. In one particular embodiment, a spacer layer stack is provided having a first etch stop layer, a first spacer layer, a second etch stop layer, and a second spacer layer, wherein the first and second spacer layers are comprised of silicon nitride.

Owner:ADVANCED MICRO DEVICES INC

Revenue asset high performance capability assessment

ActiveUS8204779B1Easy to findMaximize operating budgetMarket predictionsTechnology managementCLARITYProcess complexity

A high performance capability assessment model helps a revenue industry agency meet the challenges of the global marketplace. As a result, the revenue industry can achieve the clarity, consistency, and well-defined execution of core processes that reduce inefficiencies and waste that result from unnecessary process complexity and exceptions. In addition, the high performance capability assessment model helps the revenue industry agency to identify specific areas in which improvements may be made and understand how to make the improvements, and establishes levels of capability along the way to reaching an ultimate capability goal.

Owner:ACCENTURE GLOBAL SERVICES GMBH

Nano-composite phase-changing material and preparation method

InactiveCN101429423AGood compatibilityWill not affect the mechanical propertiesHeat-exchange elementsPhase changeProcess complexity

The invention provides a nano composite phase change material and a method for preparing the same, and belongs to the field of material application. The nano composite phase change material comprises the following components in weight portion: 10 to 15 portions of phase change material, 5 to 60 portions of layer-shaped silicate powder, and 20 to 70 portions of deionized water; the phase change point of the phase change material is between 20 and 80 DEG C; the phase change material is heated up to be completely melted; the layer-shaped silicate powder is dispersed in water by a high shear mixed emulsion machine to prepare layer-shaped silicate gel state aqueous dispersion; and the melted phase change material is added to the layer-shaped silicate gel state aqueous dispersion and stirred at high speed by the high shear mixed emulsion machine to obtain the nano composite phase change material with oil-in-water structure. The nano composite phase change material can be directly added to building base materials such as concrete, gypsum, thereby greatly reducing process complexity and preparation cost; moreover, the composite phase change material also has the advantages of simple preparation, large heat storage, and better application prospect.

Owner:GUANGZHOU SUPER CHEM COATING CO LTDGUANGZHOU SUPER CHEM COATING CO LTD

Colorful transparent polished-glazed brick and production method thereof

The invention discloses a colorful transparent polished-glazed brick and a production method thereof. The production method for the colorful transparent polished-glazed brick comprises the following steps: enameling a dried ceramic blank, spreading one or more glazes in different colors and with different burning temperature and different refractive indexes on the brick blank, and performing calcining and profiling soft polishing treatment to obtain the brick. According to the colorful transparent polished-glazed brick and the production method thereof, the layering effects and transition of the surface of the colorful transparent polished-glazed brick are closer to those of a natural stone, and the grade of the product is improved to a certain extent; original color effects can be achieved without adding a coloring material, so that process complexity is reduced, the labor intensity of a worker is reduced, and the production efficiency is favorably improved, and the colorful transparent polished-glazed brick and the production method thereof are suitable for popularization and application.

Owner:GUANGDONG JIA MEI CERAMIC

Embedded EEPROM array techniques for higher density

ActiveUS7471570B2Eliminate useIncrease array densityRead-only memoriesDigital storageHigh densityArray data structure

An array structure of single-level poly NMOS EEPROM memory cells and method of operating the array is discussed implemented in a higher density embedded EEPROM layout that eliminates the use of high voltage transistors from the array core region. If they are utilized, the high voltage transistors are moved to row and column drivers in the periphery region to increase array density with little or no added process complexity to allow economic implementation of larger embedded SLP EEPROM arrays. During program or erase operations of the array, the method provides a programming voltage for the selected memory cells of the array, and a half-write (e.g., mid-level) voltage to the remaining unselected memory cells to avoid disturbing the unselected memory cells of the array.

Owner:TEXAS INSTR INC

Trench capacitor structures

An optimized trench capacitor structure which is useful as a decoupling capacitor or a storage capacitor can be manufactured without added process complexity. As an on-chip decoupling trench capacitor structure, the structure reduces the series resistance to outer and inner plates and results in an acceptable RC delay, while maintaining a high capacitance per unit area. As a storage capacitor with a buried shield, the trench capacitor structure exhibits high immunity to alpha particle and cosmic radiation induced failures. The trench capacitor structure which includes a buried n-well in a silicon substrate. A trench is formed in the substrate and extends through the buried n-well. A dielectric film is formed on an inner surface of the trench, and an inner plate formed as a polysilicon fill within the trench is connected to a surface n+ film formed during definition of peripheral source / drain contacts of the integrated circuit. An outer plate of the capacitor in the form of an out diffusion from the trench provides a low resistance electrical contact with the substrate. A number of these capacitors can be combined in a very efficient X-Y array of decoupling capacitors.

Owner:IBM CORP

Hybrid Field Effect Transistor and Bipolar Junction Transistor Structures and Methods for Fabricating Such Structures

Semiconductor device structures that integrate field effect transistors and bipolar junction transistors on a single substrate, such as a semiconductor-on-insulator substrate, and methods for fabricating such hybrid semiconductor device structures. The field effect and bipolar junction transistors are fabricated using adjacent electrically-isolated semiconductor bodies. During fabrication of the device structures, certain fabrication stages strategically rely on block masks for process isolation. Other fabrication stages are shared during the fabrication process for seamless integration that reduces process complexity.

Owner:IBM CORP

Technique for controlling mechanical stress in a channel region by spacer removal

ActiveUS7314793B2Significant stressLittle elasticitySemiconductor/solid-state device manufacturingSemiconductor devicesCouplingEngineering

During the formation of a transistor element, sidewalls spacers are removed or at least partially etched back after ion implantation and silicidation, thereby rendering the mechanical coupling of a contact etch stop layer to the underlying drain and source regions more effective. Hence, the mechanical stress may be substantially induced by the contact etch step layer rather than by a combination of the spacer elements and the etch stop layer, thereby significantly facilitating the stress engineering in the channel region. By additionally performing a plasma treatment, different amounts of stress may be created in different transistor devices without unduly contributing to process complexity.

Owner:GLOBALFOUNDRIES US INC

Method for fabricating a flip chip substrate structure

ActiveUS20080075836A1Highly integratedSimple processSemiconductor/solid-state device detailsPrinted circuit aspectsResistSolder mask

The present invention relates to a method to fabricate a flip chip substrate structure, which comprises: providing a carrier; forming a patterned resist layer on the surface of the carrier; forming sequentially a first metal layer, an etching-stop layer, and a second metal layer; removing the resist layer, forming a patterned first solder mask, and then forming at least one first circuit build up structure thereon; forming additionally a patterned second solder mask on the circuit build up structure; respectively removing the carrier, the first metal layer, and the etching-stop layer; and forming solder bumps on both sides of the circuit build up structure. The method increases integration and achieves the purpose of miniaturization. The method solves the problem of circuit layer multiplicity and process complexity.

Owner:UNIMICRON TECH CORP

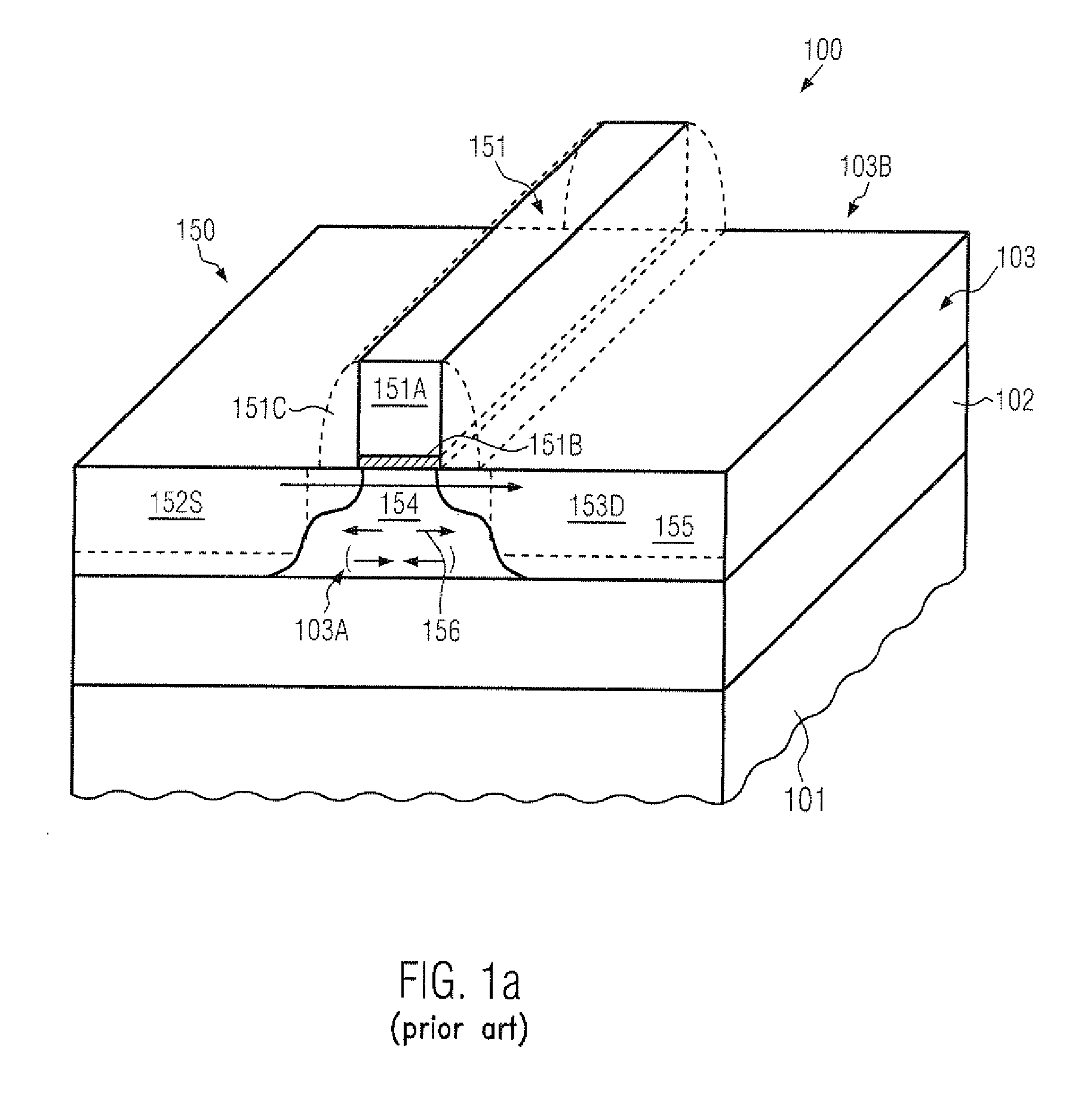

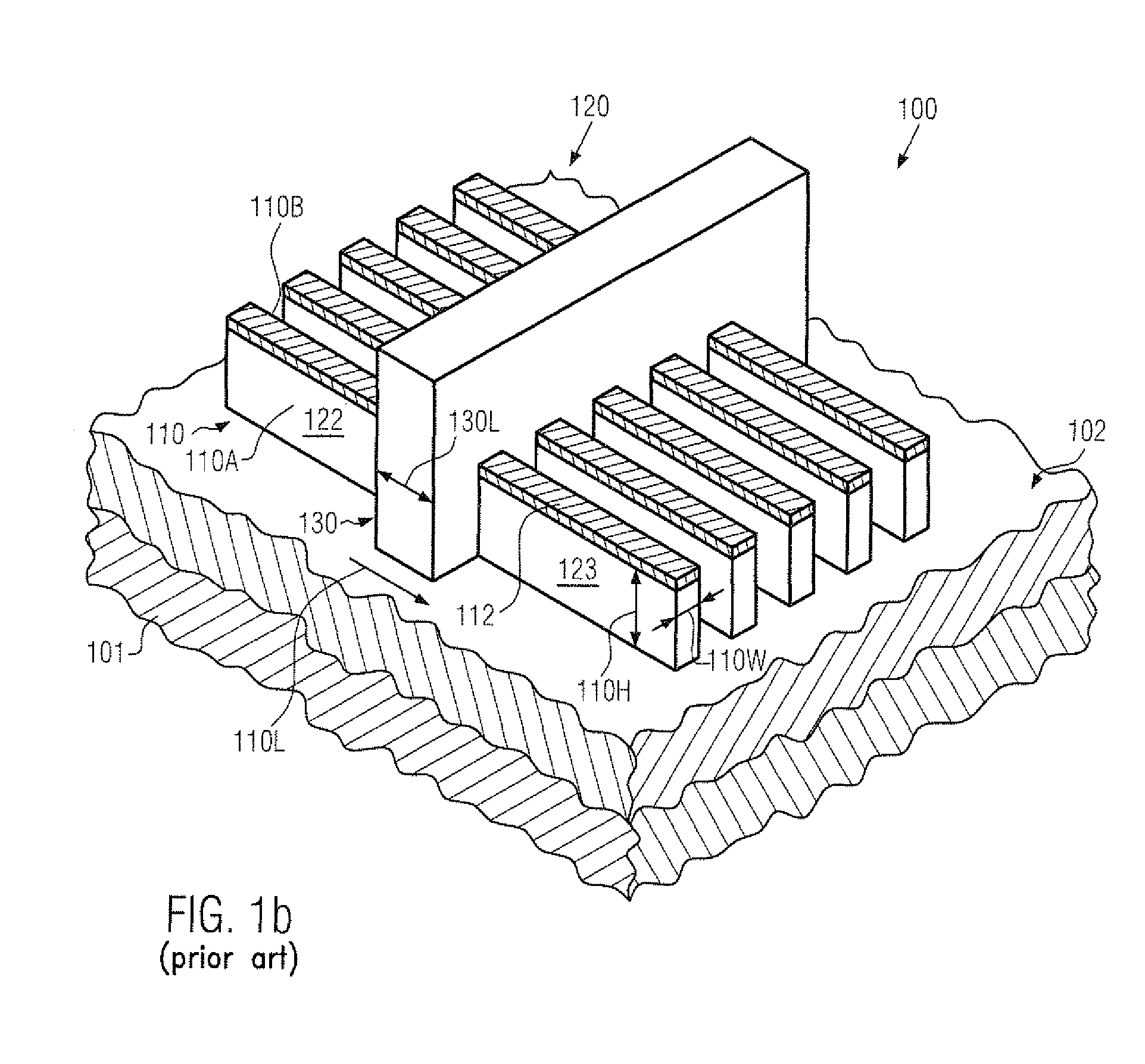

Strain engineering in three-dimensional transistors based on globally strained semiconductor base layers

ActiveUS20110101456A1Modification of charge carrier mobilityIncrease flexibilitySolid-state devicesSemiconductor/solid-state device manufacturingPerformance enhancementSemiconductor materials

Non-planar transistors, such as FINFETs, may be formed on the basis of a globally strained semiconductor material, thereby preserving a high uniaxial strain component in the resulting semiconductor fins. In this manner, a significant performance enhancement may be achieved without adding process complexity when implementing FINFET transistors.

Owner:GLOBALFOUNDRIES US INC

Flexible display panel and method of manufacturing the same, and flexible display apparatus

ActiveUS20170215288A1Printed circuit assemblingFinal product manufactureSystem integrationElectrical connection

The present disclosure provides a flexible display panel and a method of manufacturing the same, and a flexible display apparatus. The flexible display panel includes a flexible substrate, a display device, a driver chip and a connector, the connector is configured to electrically connect the flexible display panel to a system circuit board, the display device, the driver chip and the connector are all provided on the flexible substrate. In the flexible display panel, the flexible substrate is used in place of a conventional COF or FPC, such that physical and electrical connections between the flexible display panel and the system circuit board are achieved directly through the flexible substrate, thereby eliminating steps of manufacturing and bonding the FPC, improving system integration, while reducing process complexity of manufacturing the flexible display panel.

Owner:BOE TECH GRP CO LTD

Health and life sciences medicaid high performance capability assessment

ActiveUS8355926B1Easy to findMaximize operating budgetOffice automationHospital data managementCLARITYProcess complexity

A high-performance capability assessment model helps a Medicaid program meet the challenges of the health market. As a result, the Medicaid program can achieve the clarity, consistency, and well-defined execution of core processes that reduce inefficiencies and waste that result from unnecessary process complexity and exceptions. In addition, the high-performance capability assessment model helps the Medicaid program to identify specific areas in which improvements may be made, to understand how to make said improvements, and to establish levels of capability along the way to reaching an ultimate capability goal.

Owner:ACCENTURE GLOBAL SERVICES LTD

Image compression/decompression method and image coder/decoder and decoding circuit

ActiveCN101060629ASimplify Design GoalsQuality improvementTelevision systemsDigital video signal modificationImage compressionProcess complexity

The disclosed multi-code image compress method selects and labels the optimal result according to error value. It also provides the relative image coding / decoding device and circuits. This invention improves image compressing quality, simplifies logic deign, and reduces process complexity.

Owner:HUAWEI TECH CO LTD

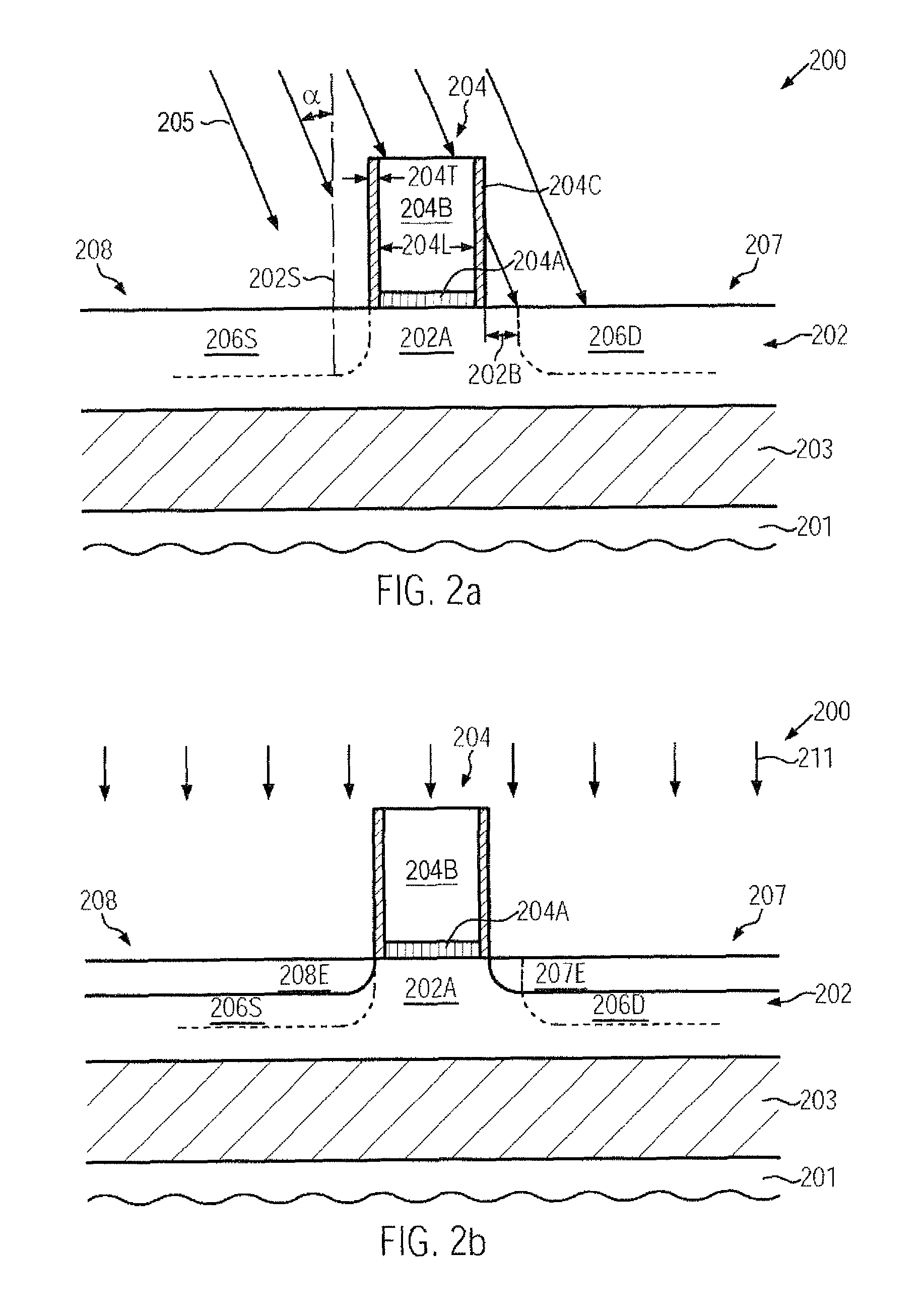

Method for forming embedded strained drain/source regions based on a combined spacer and cavity etch process

ActiveUS20070232006A1Increased processing flexibilityLess complexSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringAnisotropic etching

By patterning a spacer layer stack and etching a cavity in an in situ etch process, the process complexity, as well as the uniformity, during the formation of embedded strained semiconductor layers may be significantly enhanced. In an initial phase, the spacer layer stack may be patterned on the basis of an anisotropic etch step with a high degree of uniformity, since a selectivity between individual stack layers may not be necessary. Thereafter, a cleaning process may be performed followed by a cavity etch process, wherein a reduced over-etch time during the spacer patterning process significantly contributes to the uniformity of the finally obtained cavities, while the in situ nature of the process also provides a reduced overall process time.

Owner:INNOVATIVE FOUNDRY TECH LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com