Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

58results about How to "Increase array density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

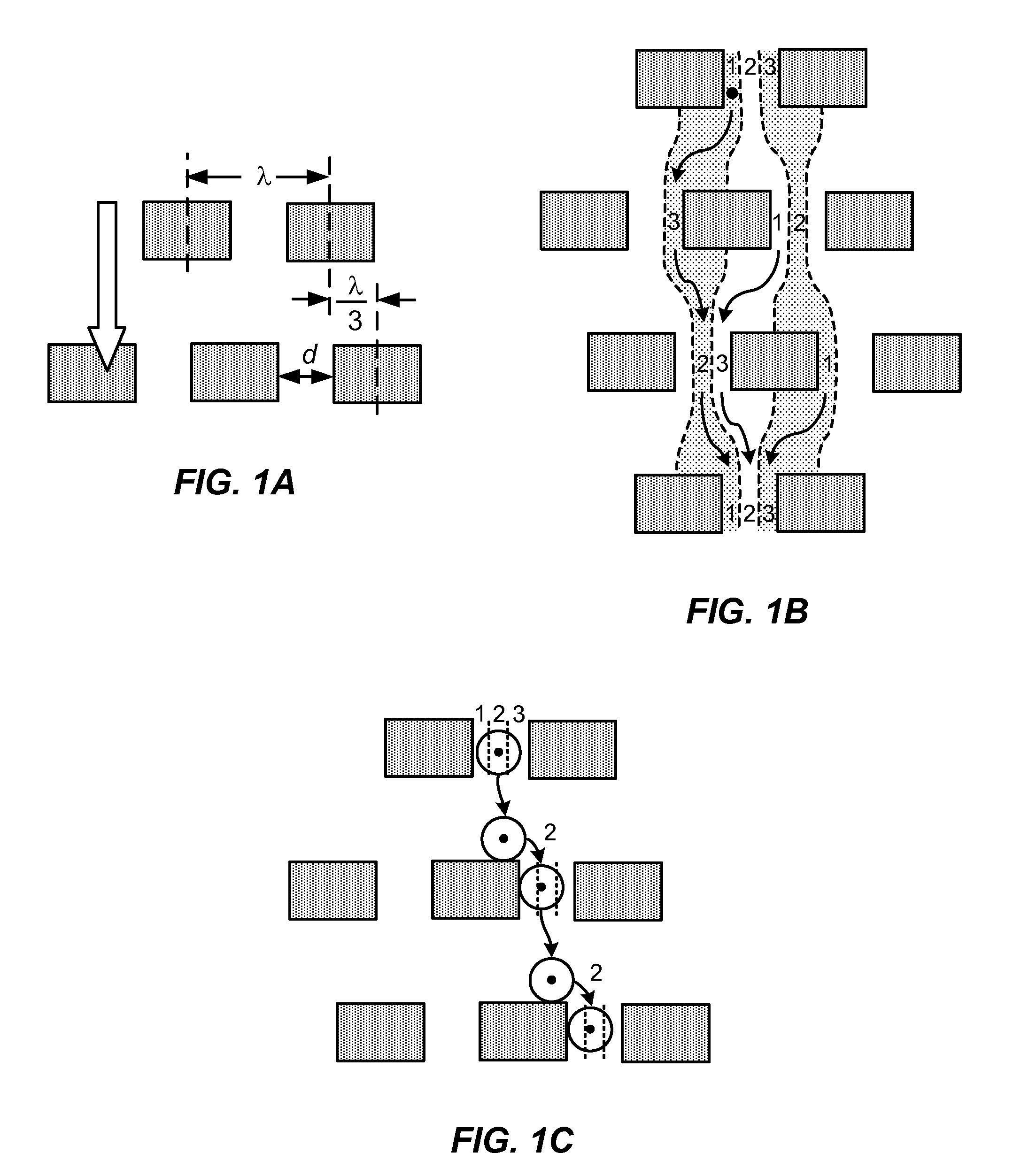

Devices and methods for enrichment and alteration of circulating tumor cells and other particles

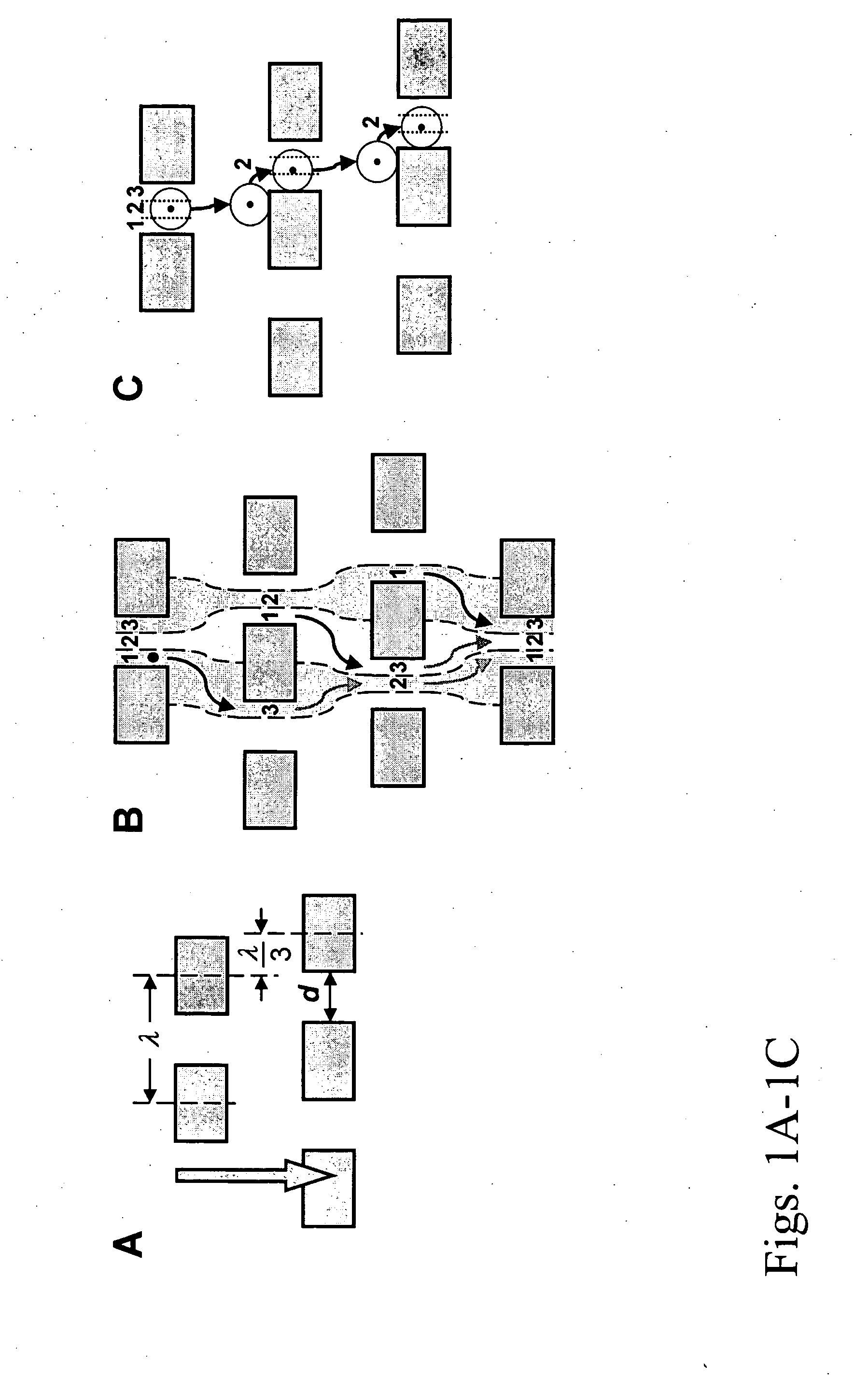

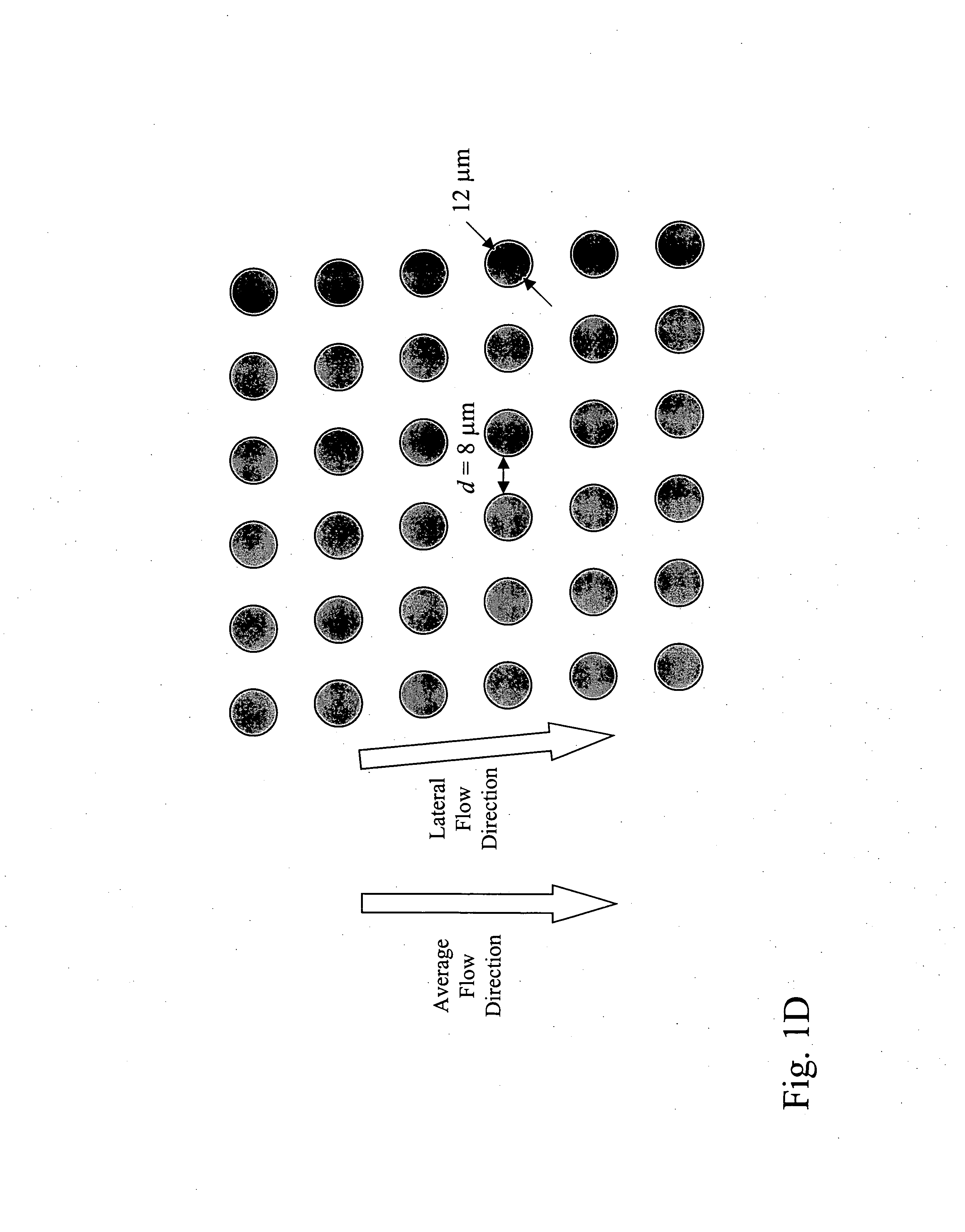

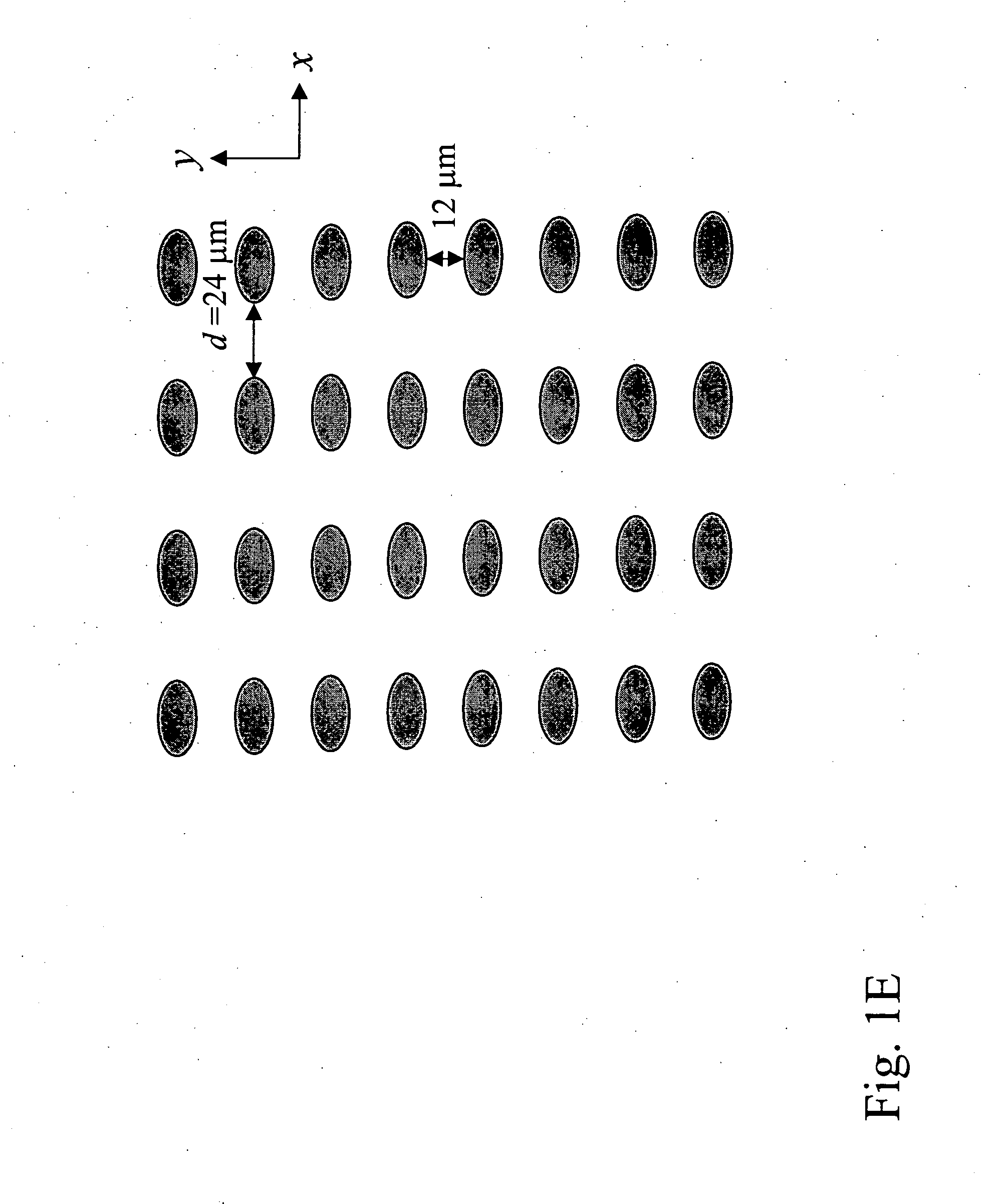

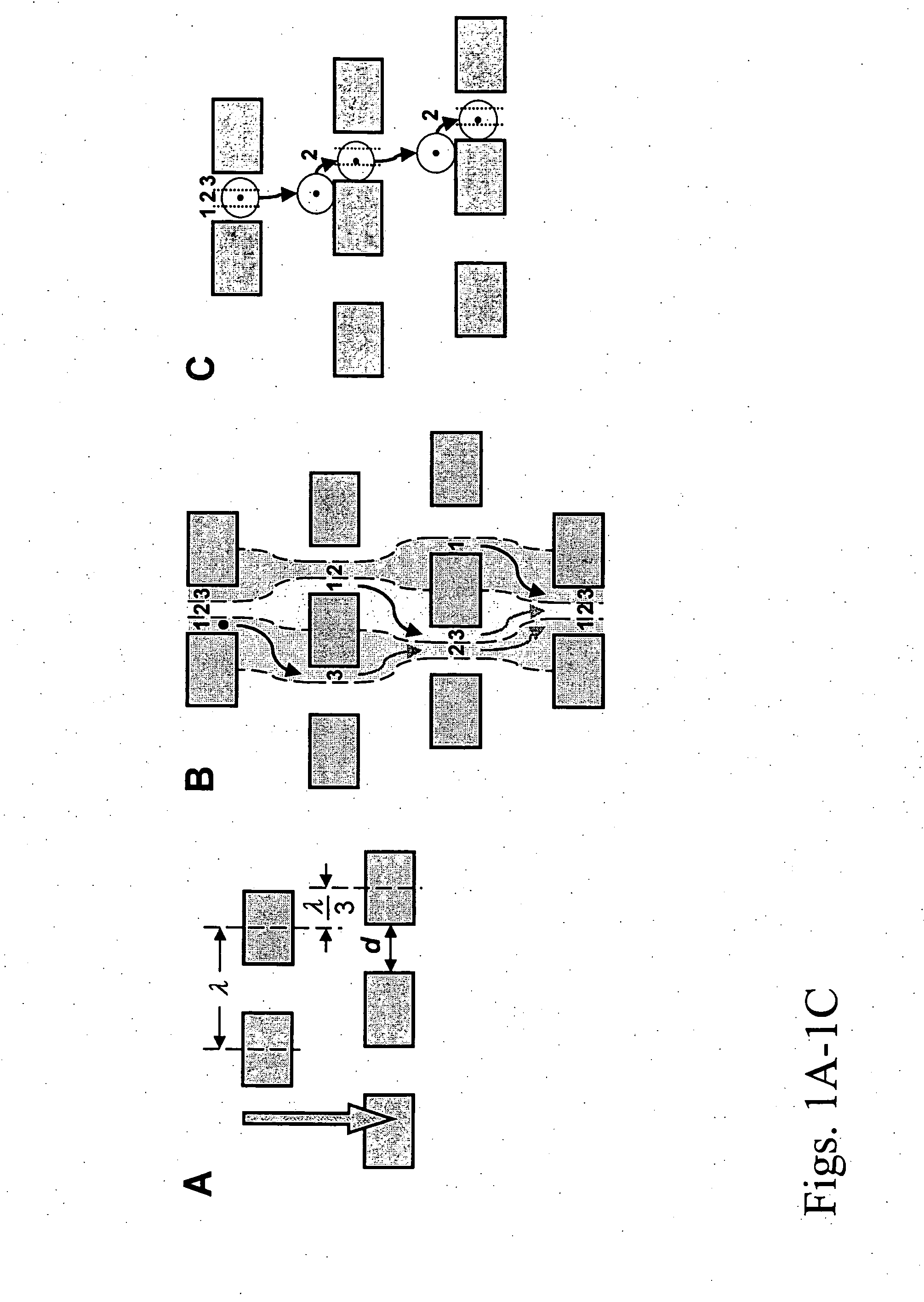

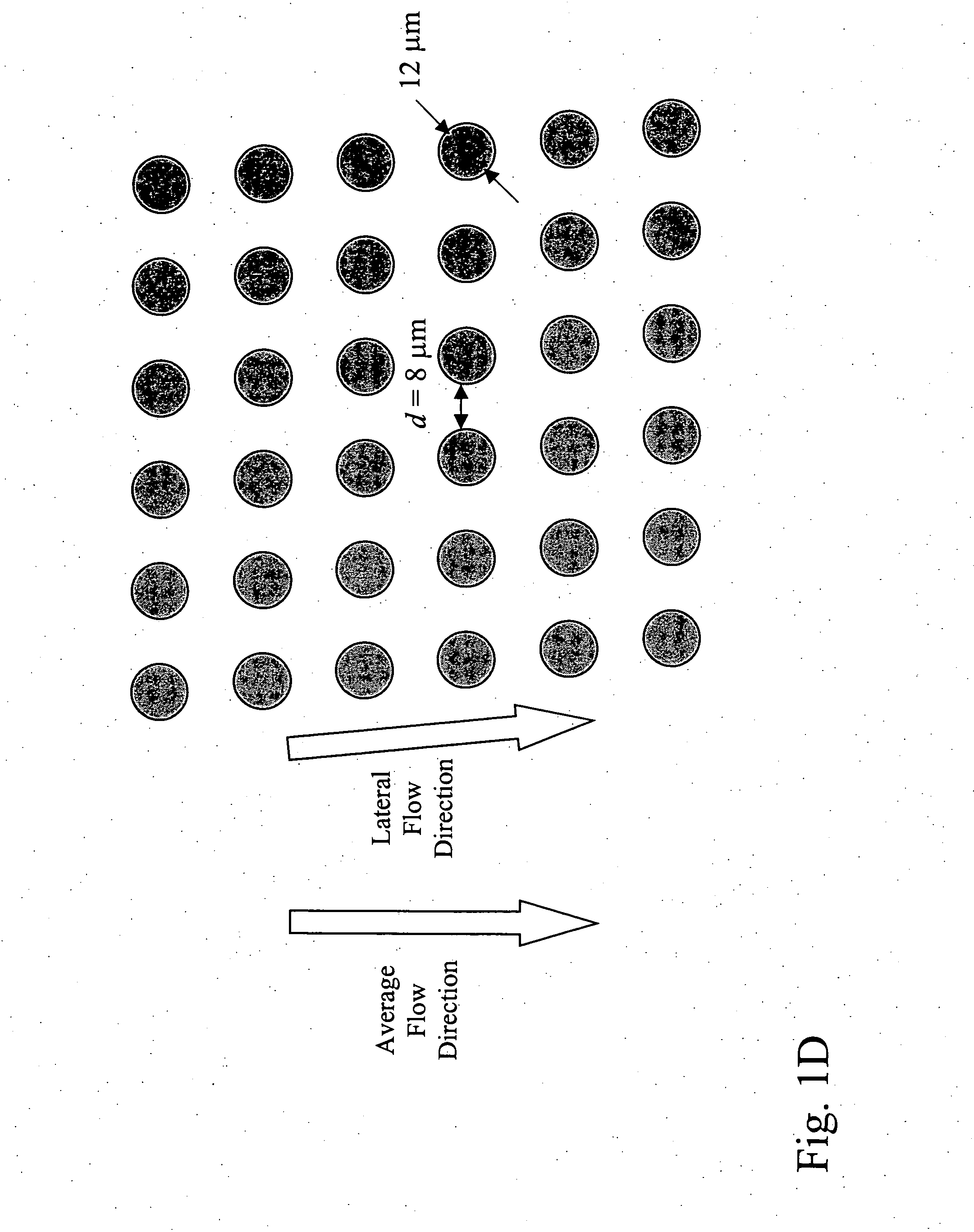

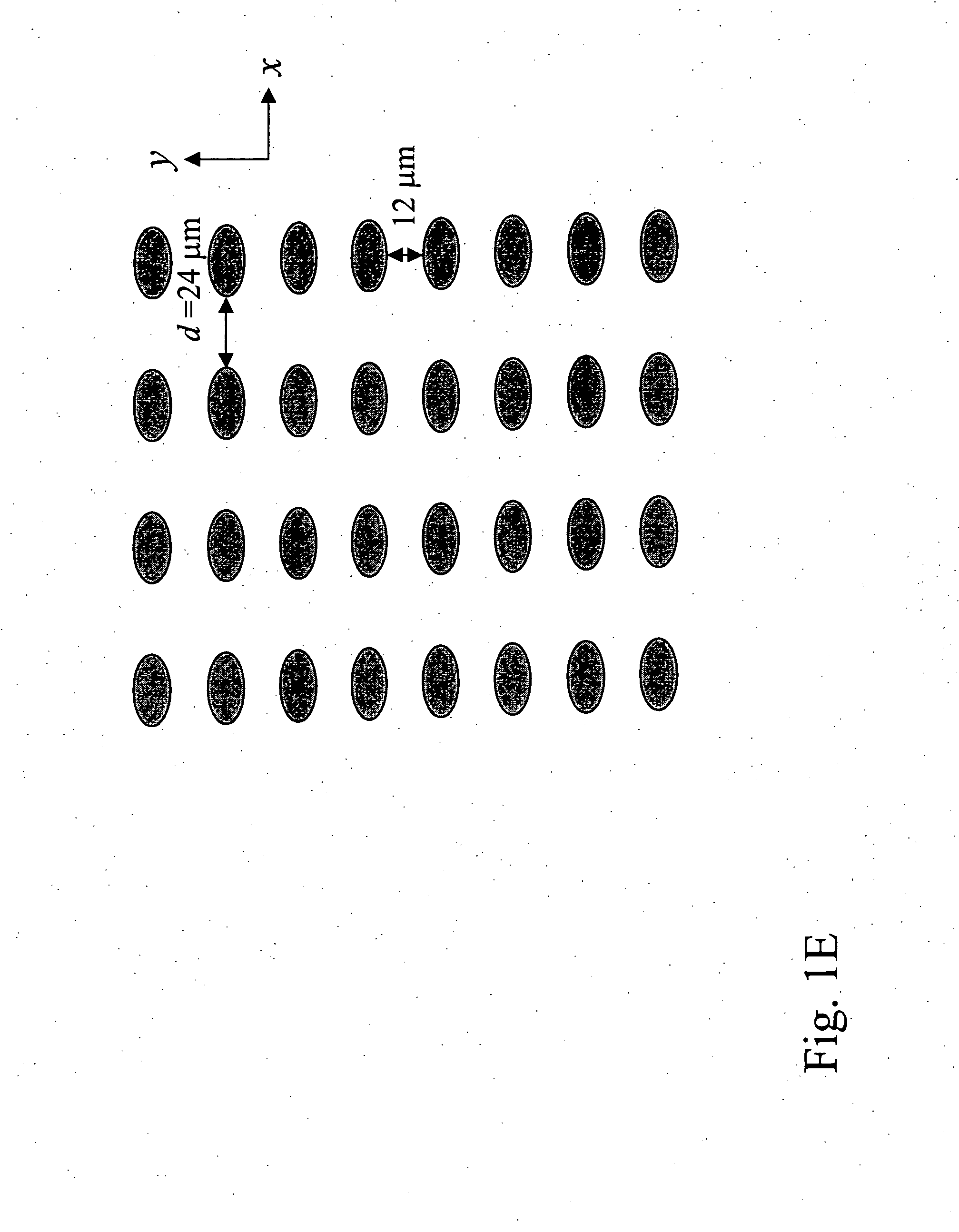

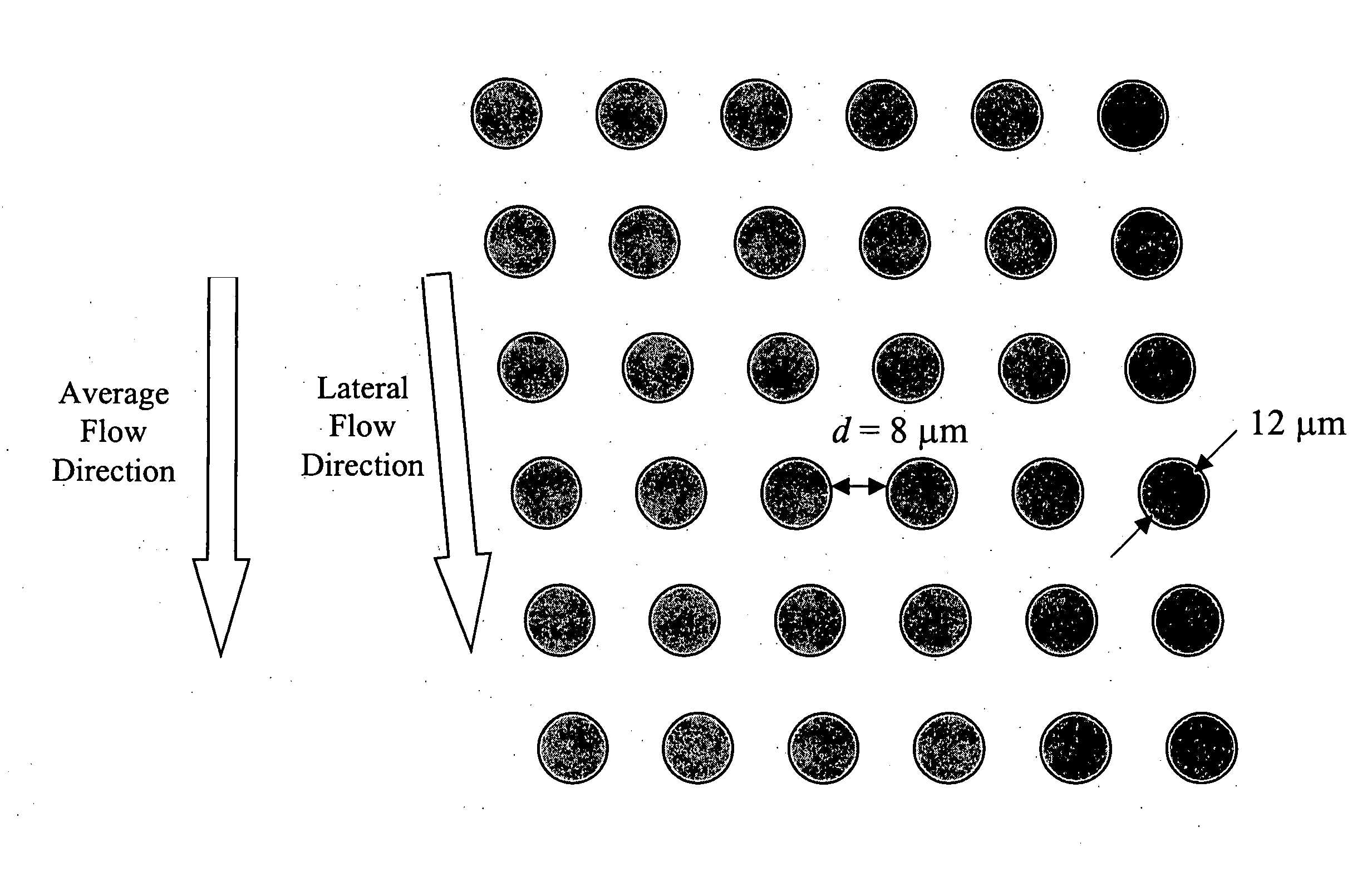

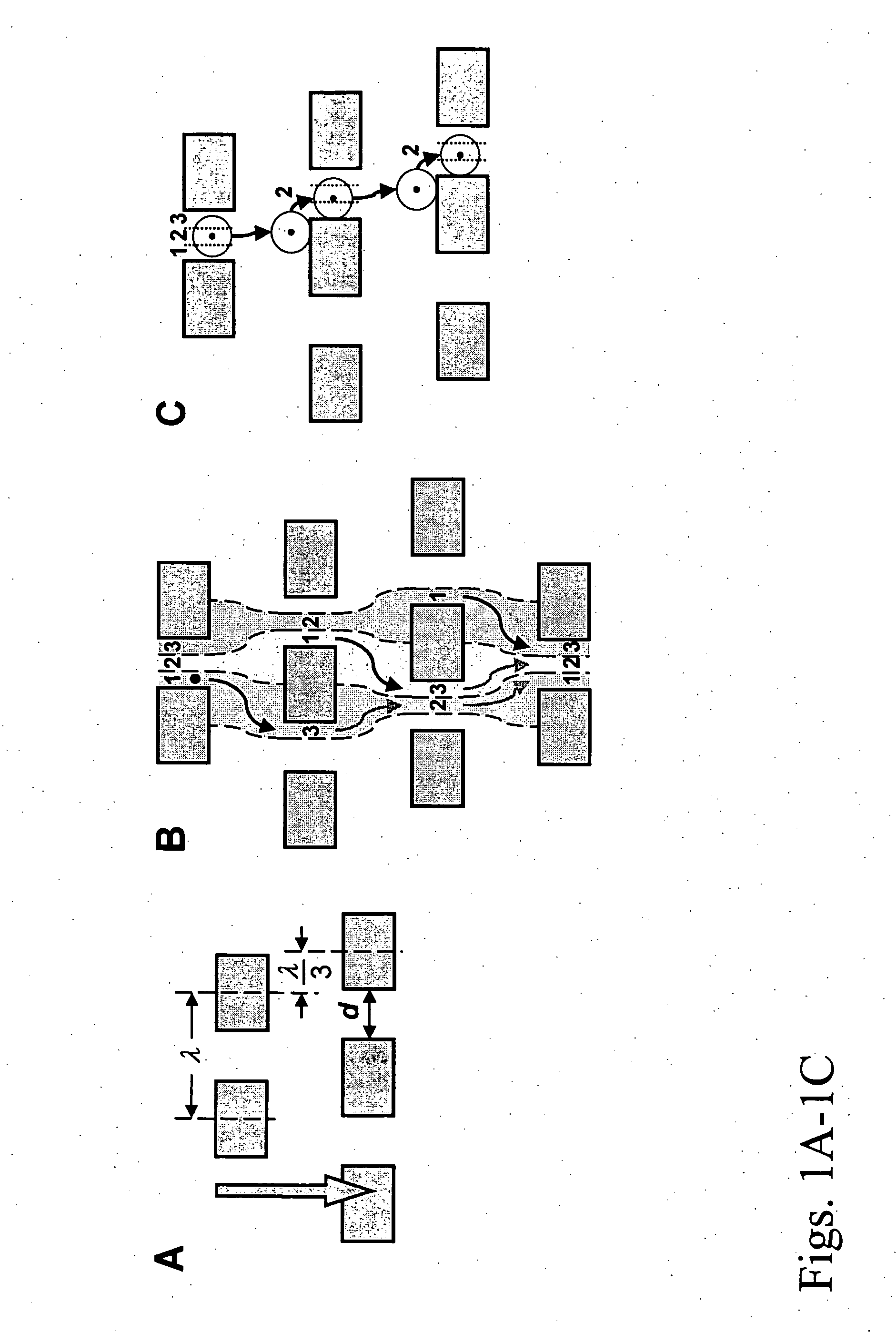

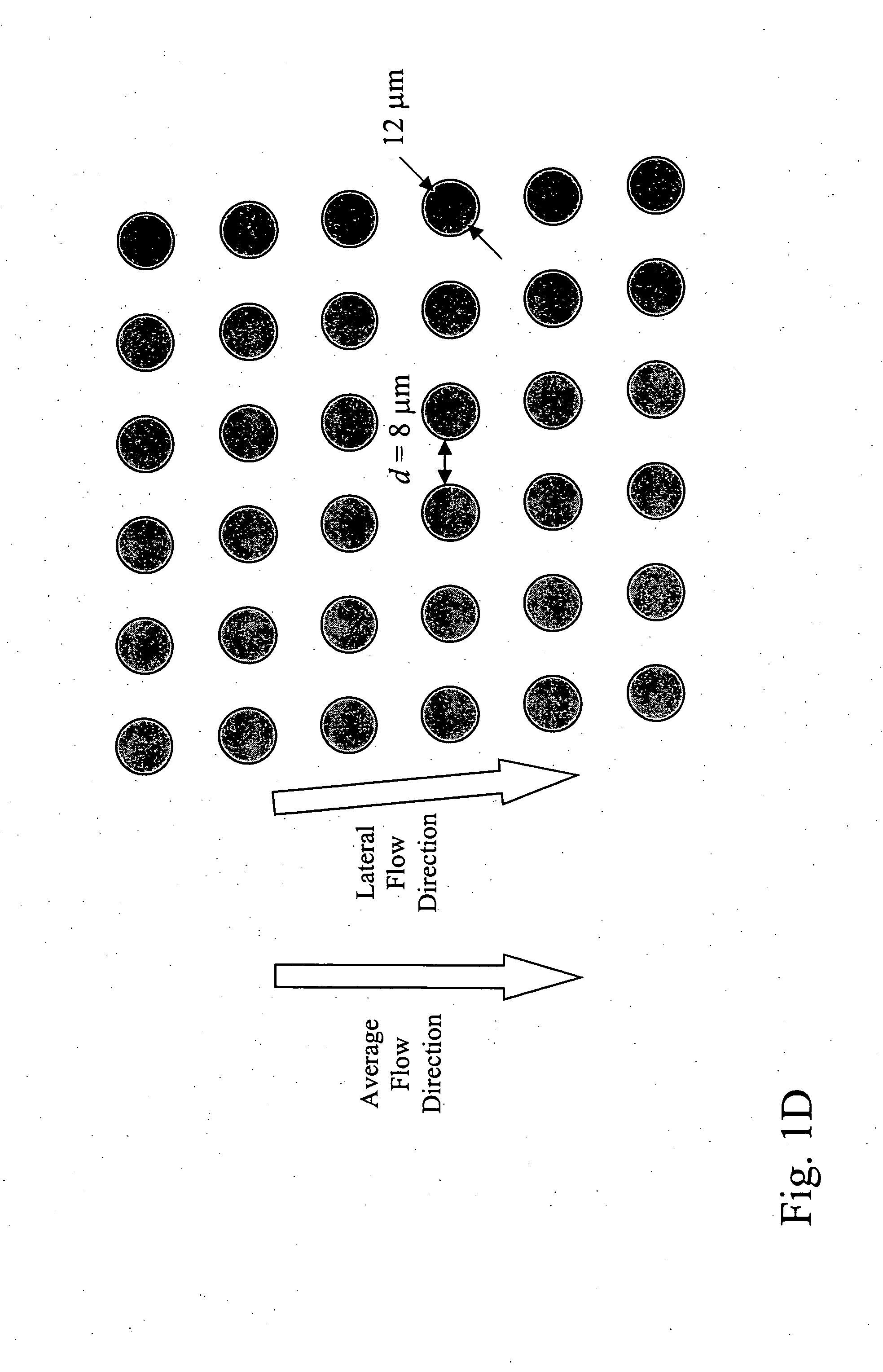

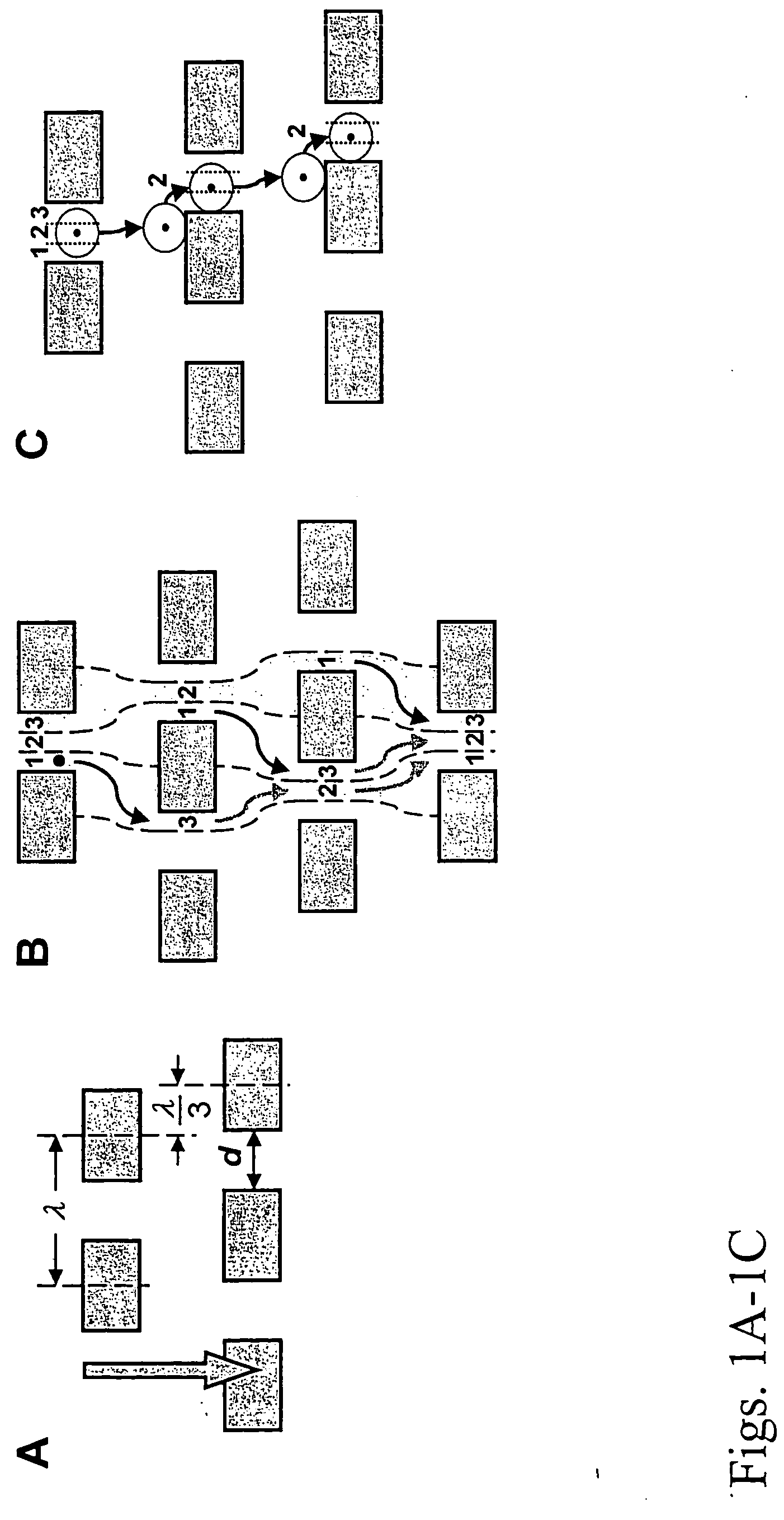

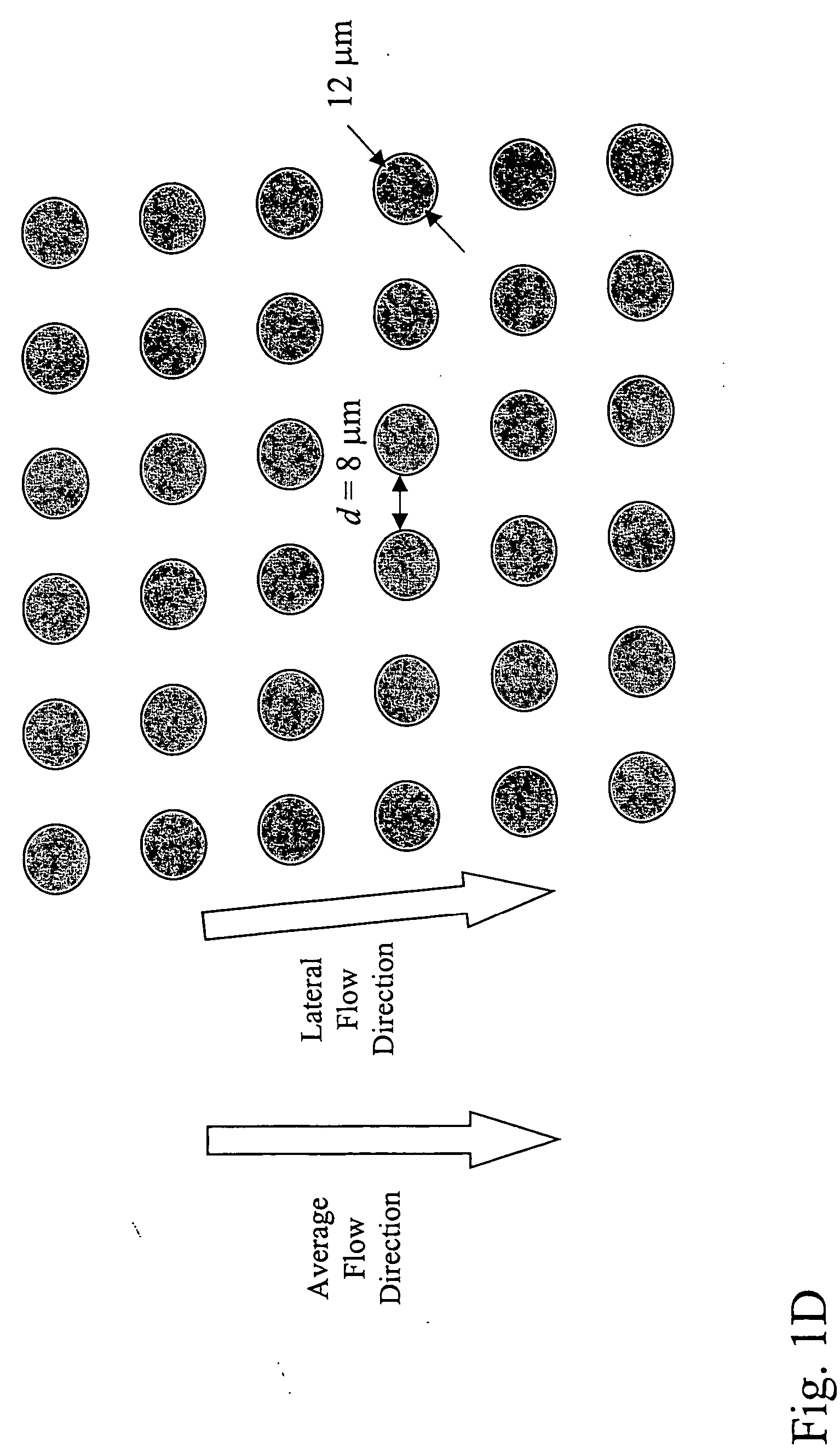

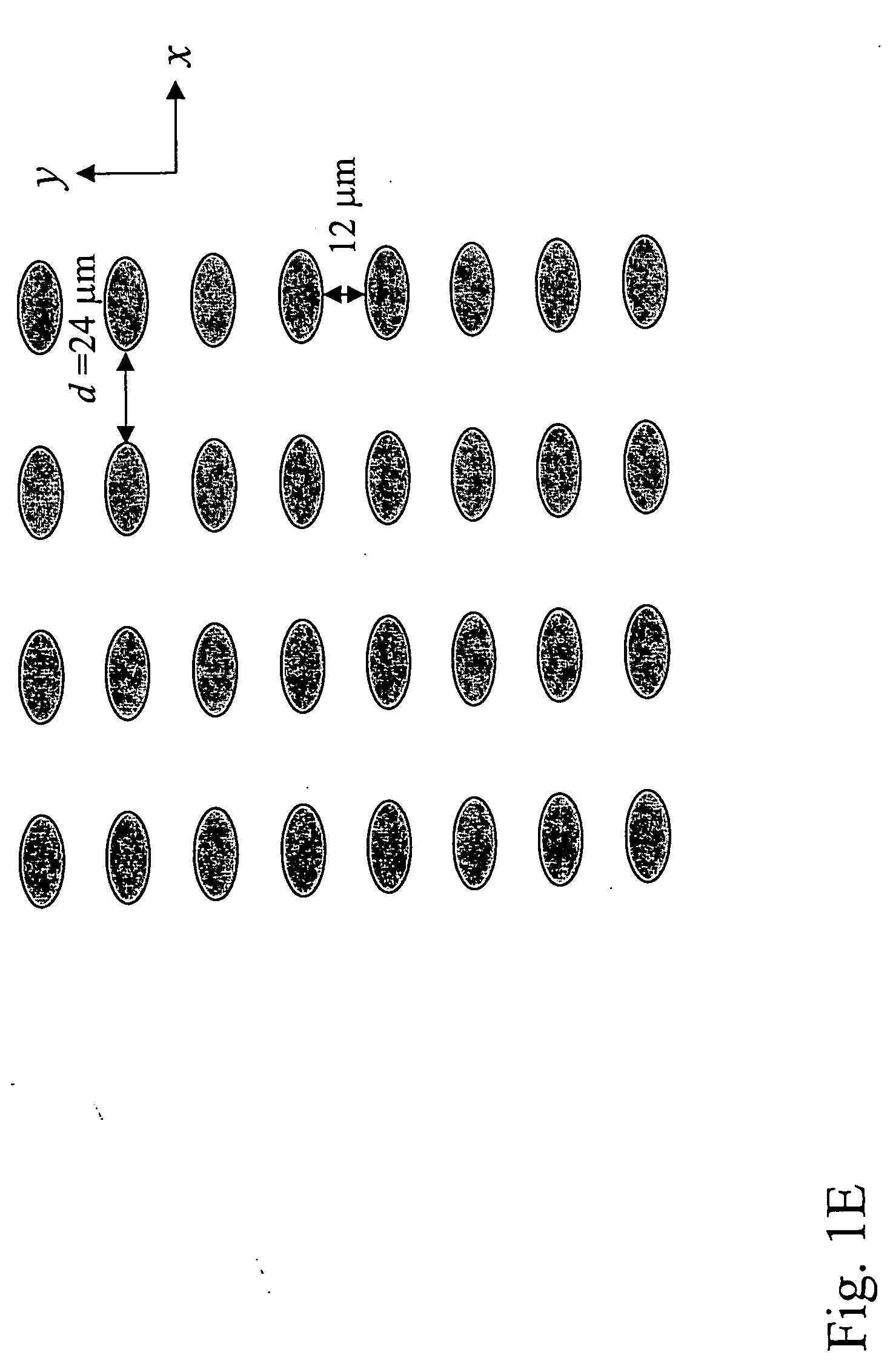

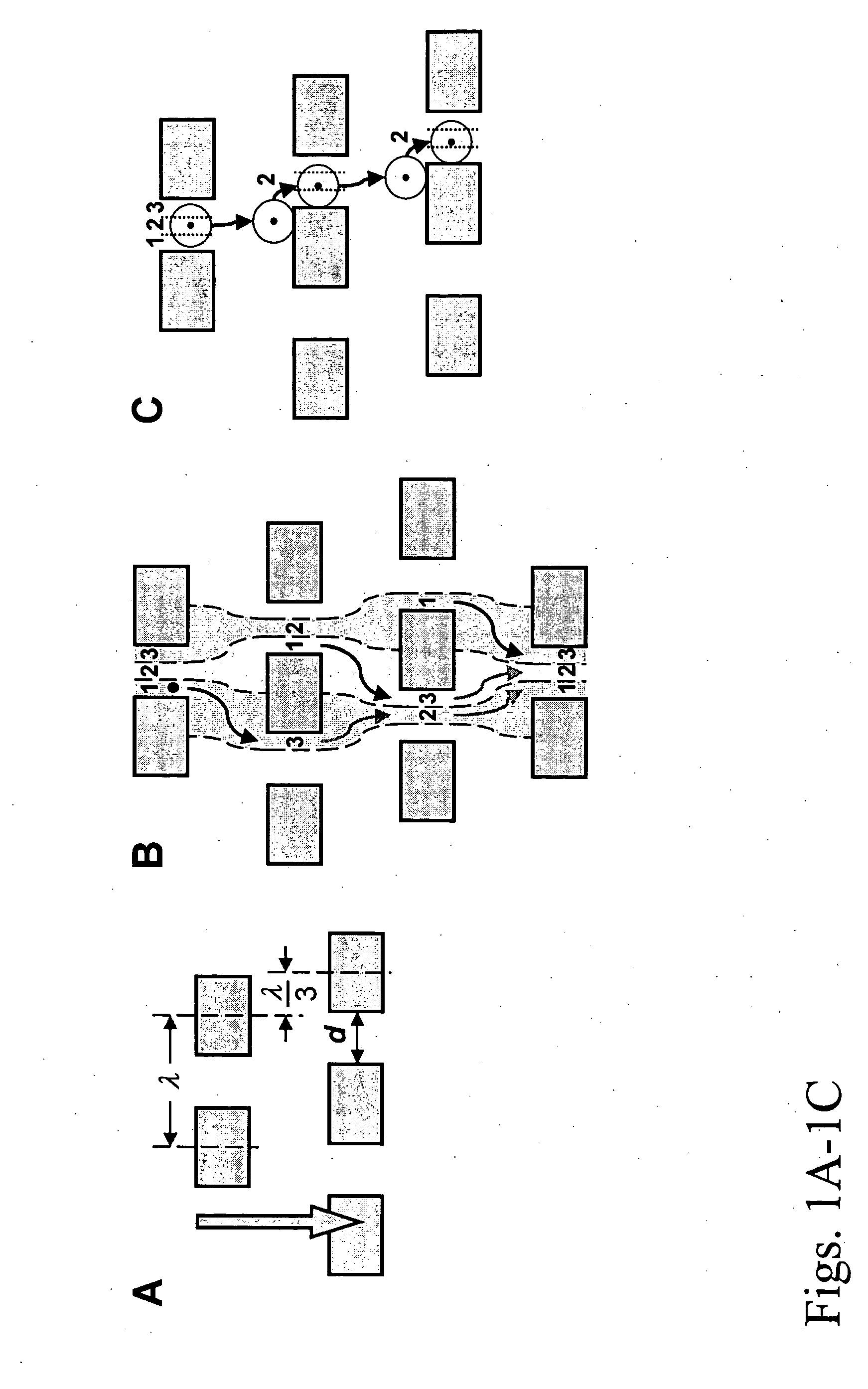

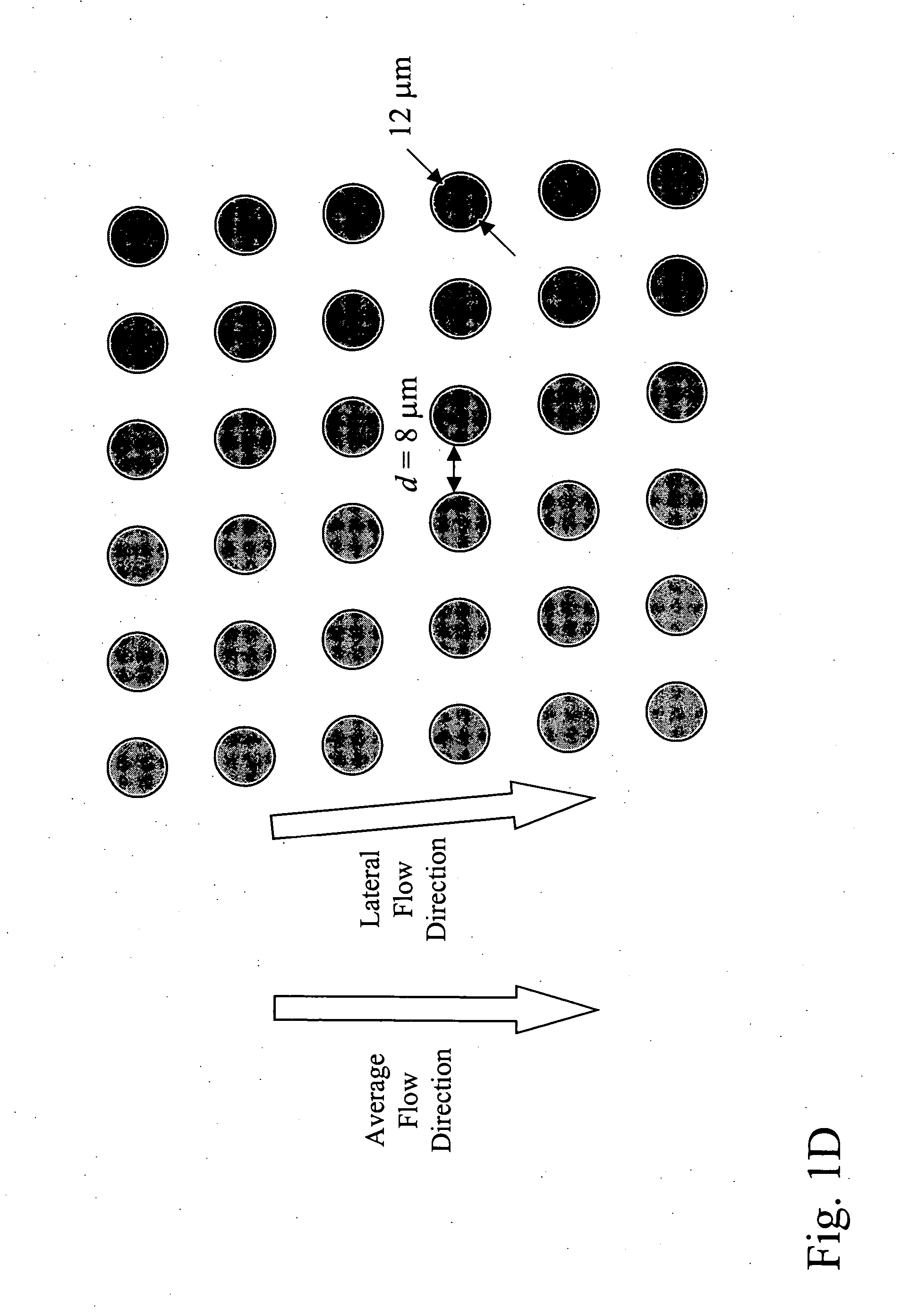

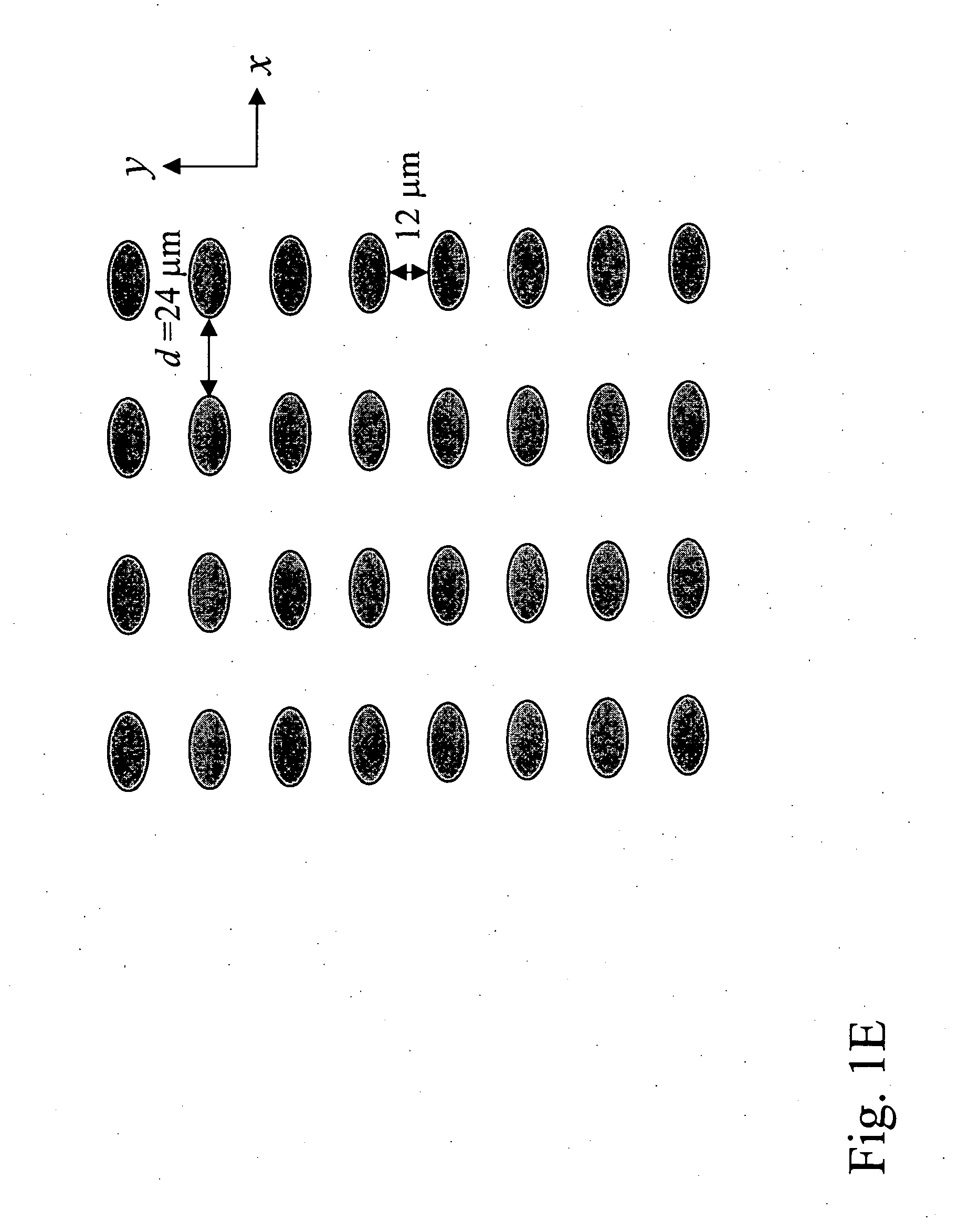

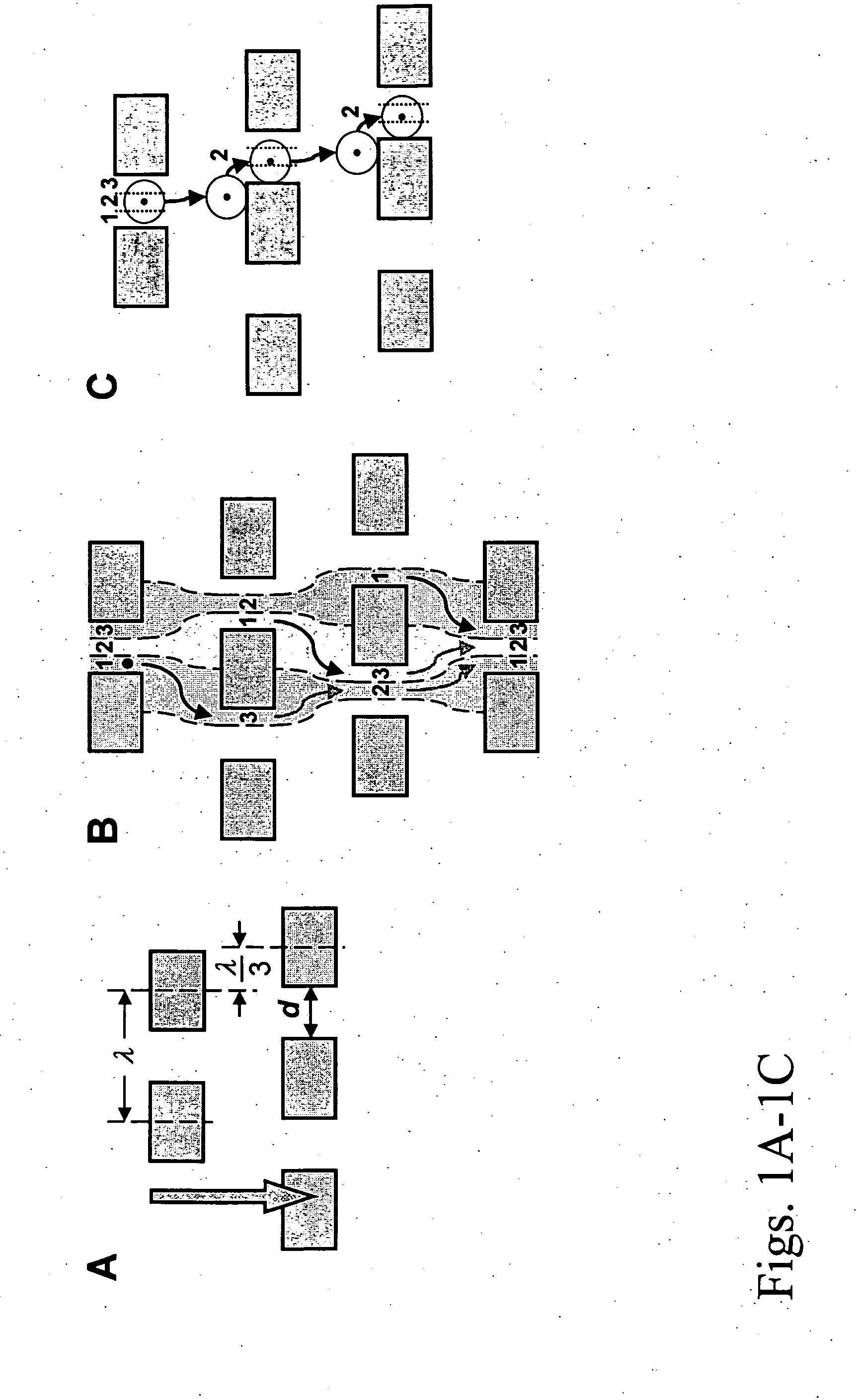

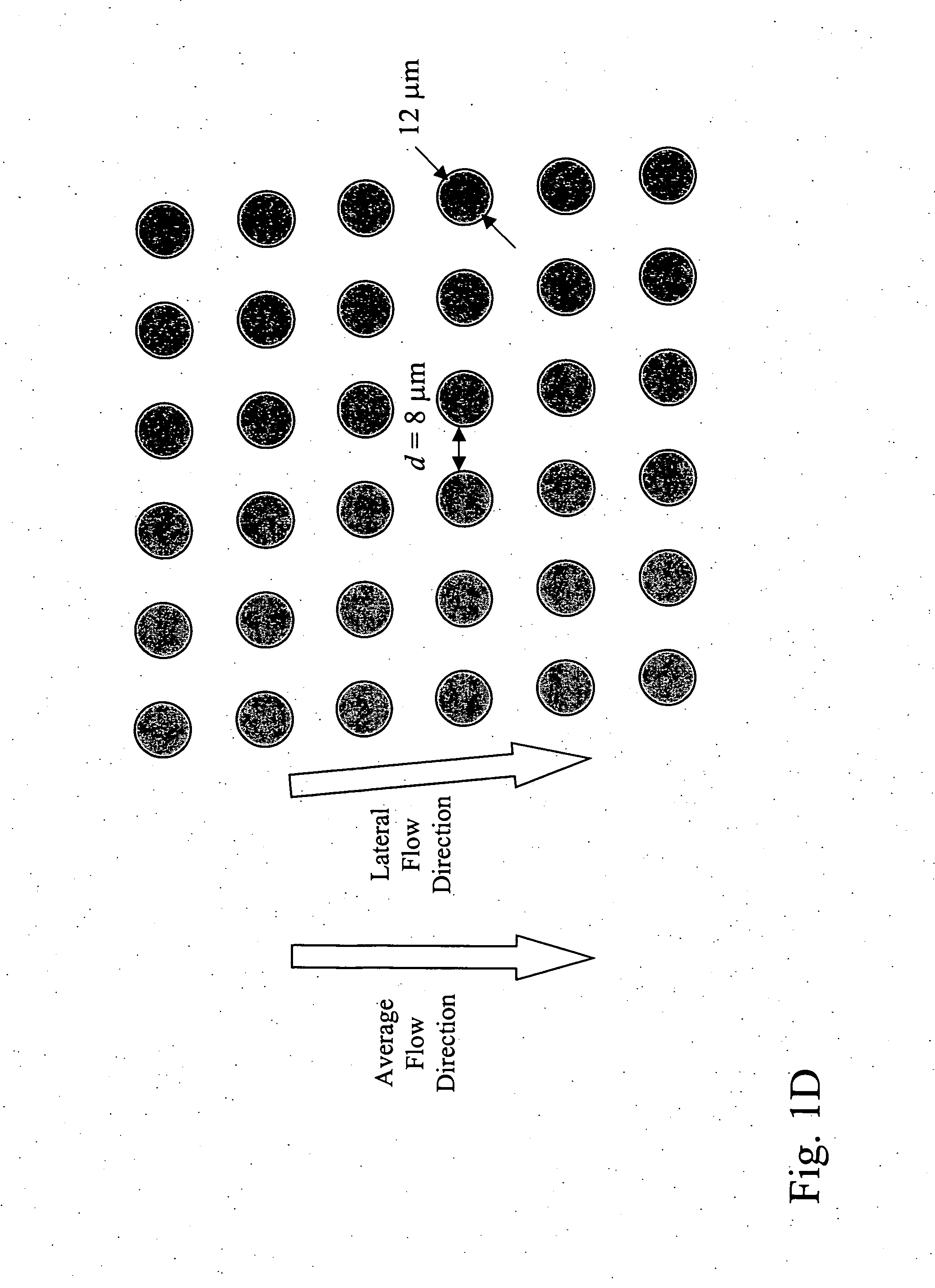

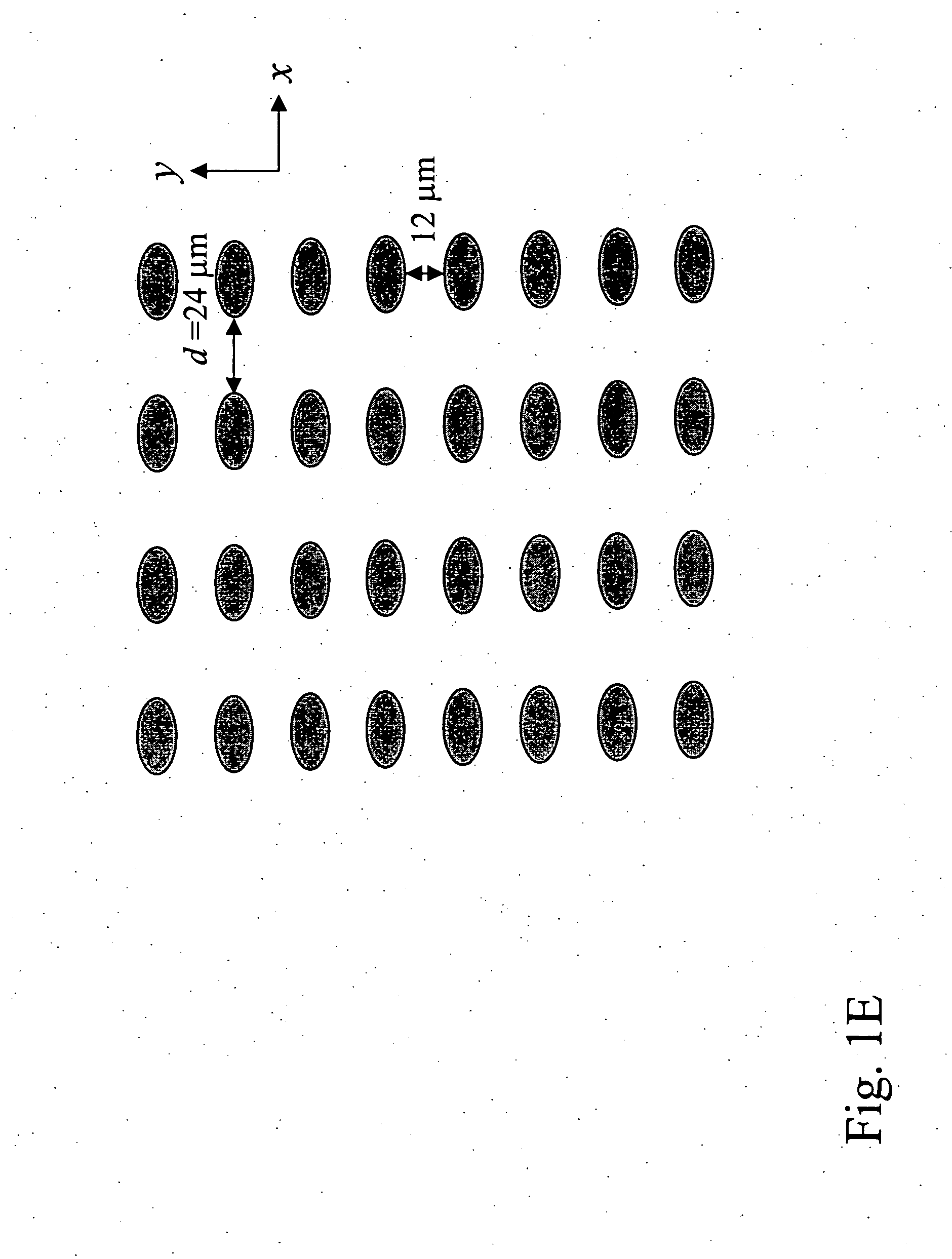

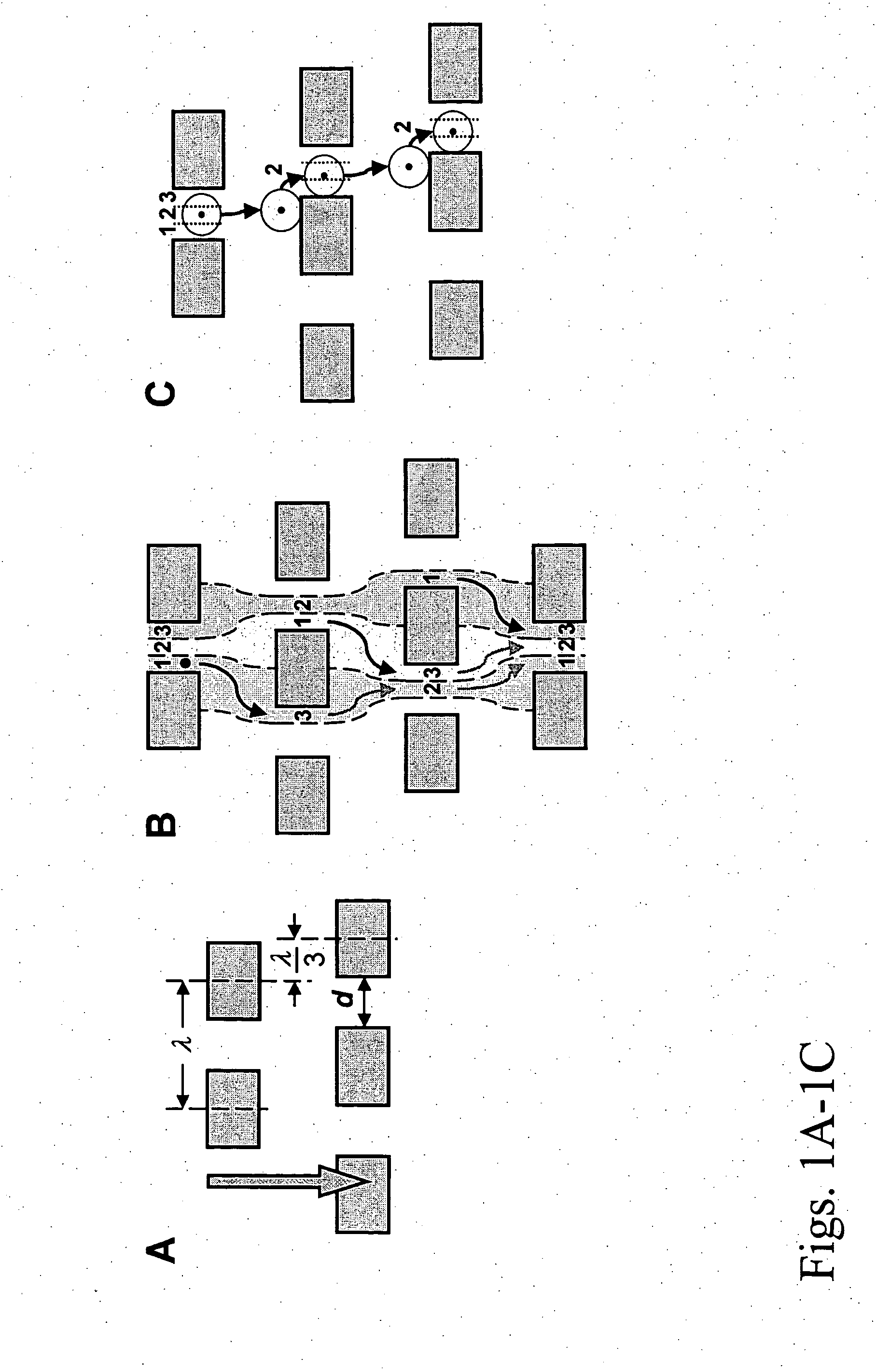

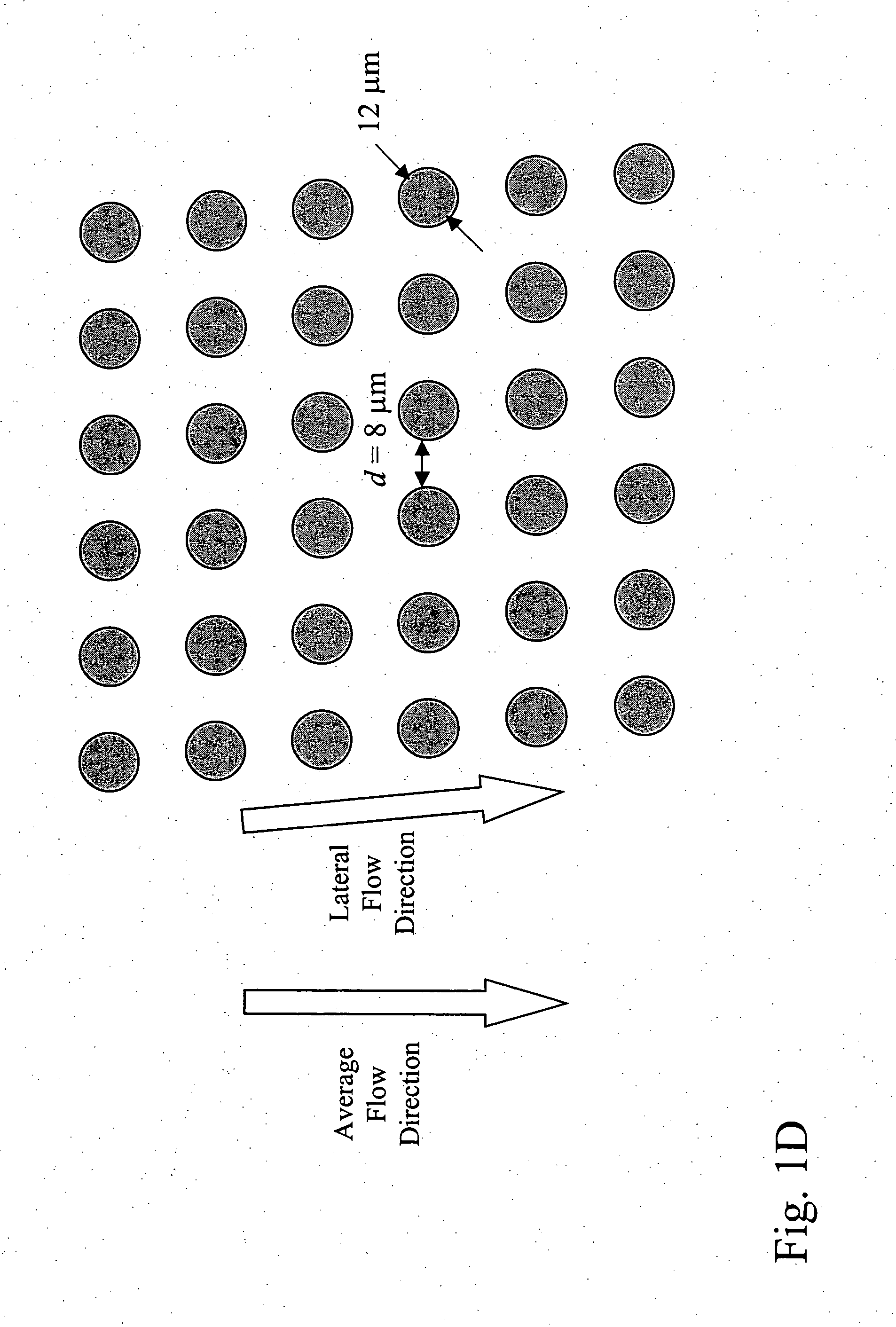

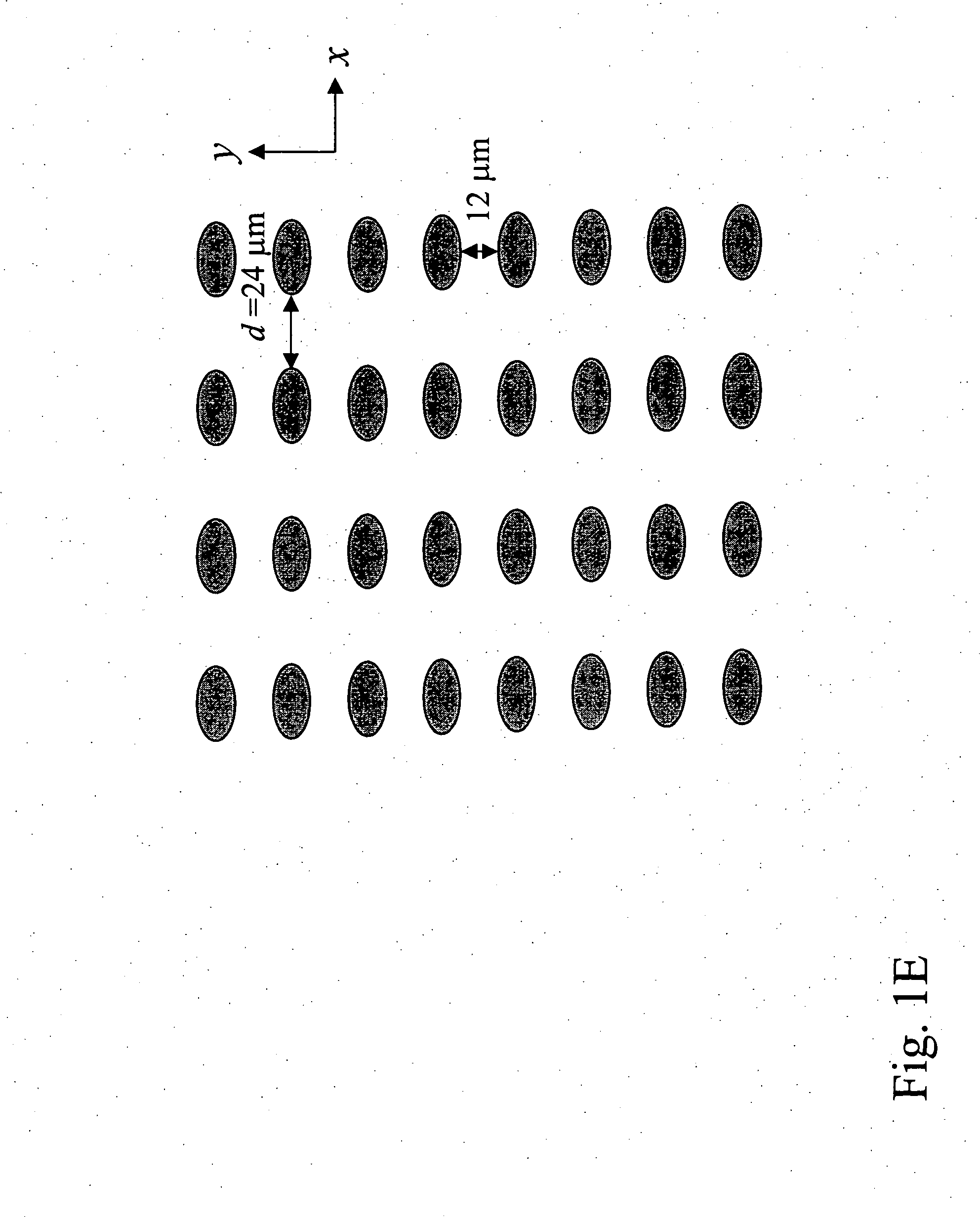

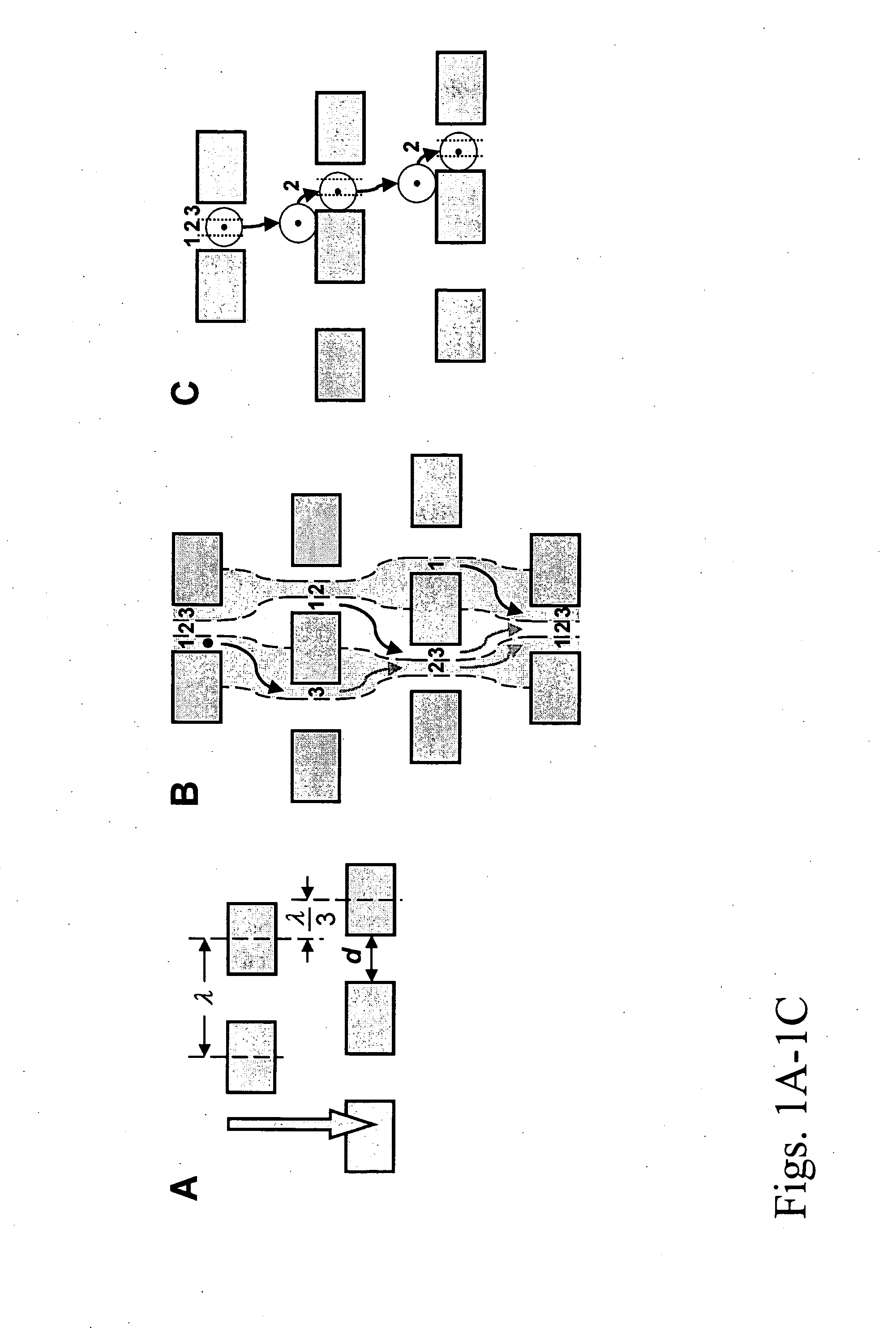

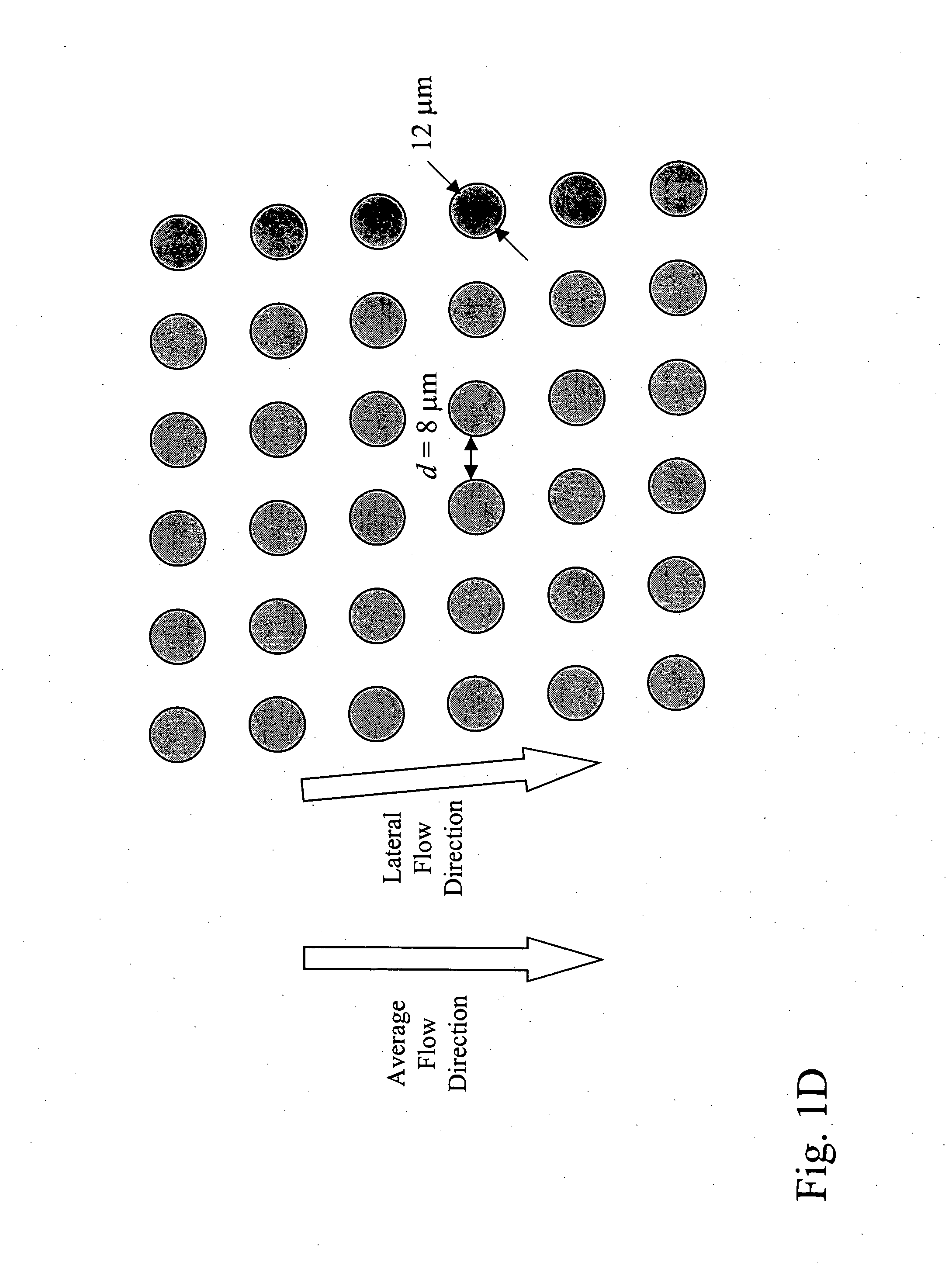

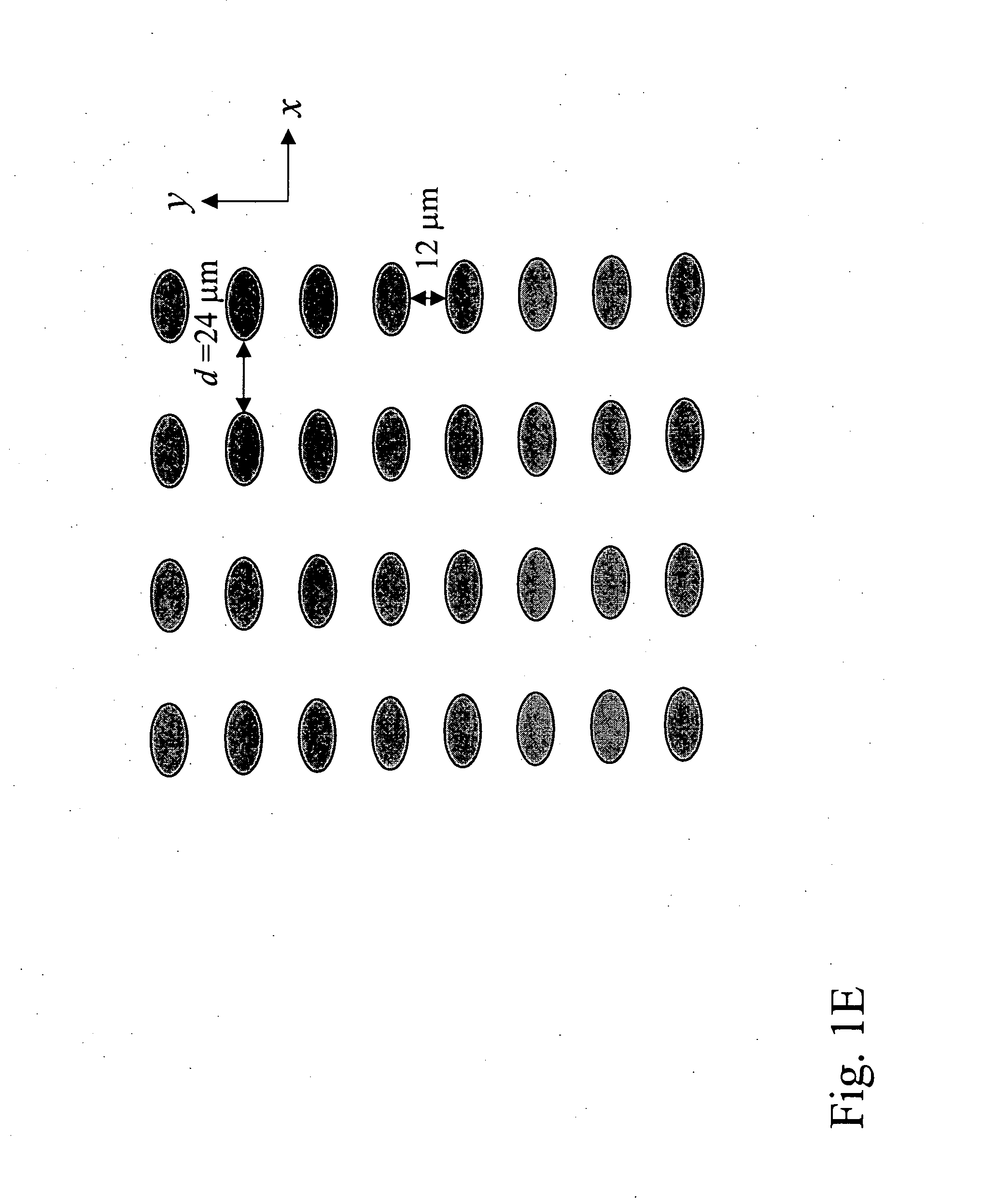

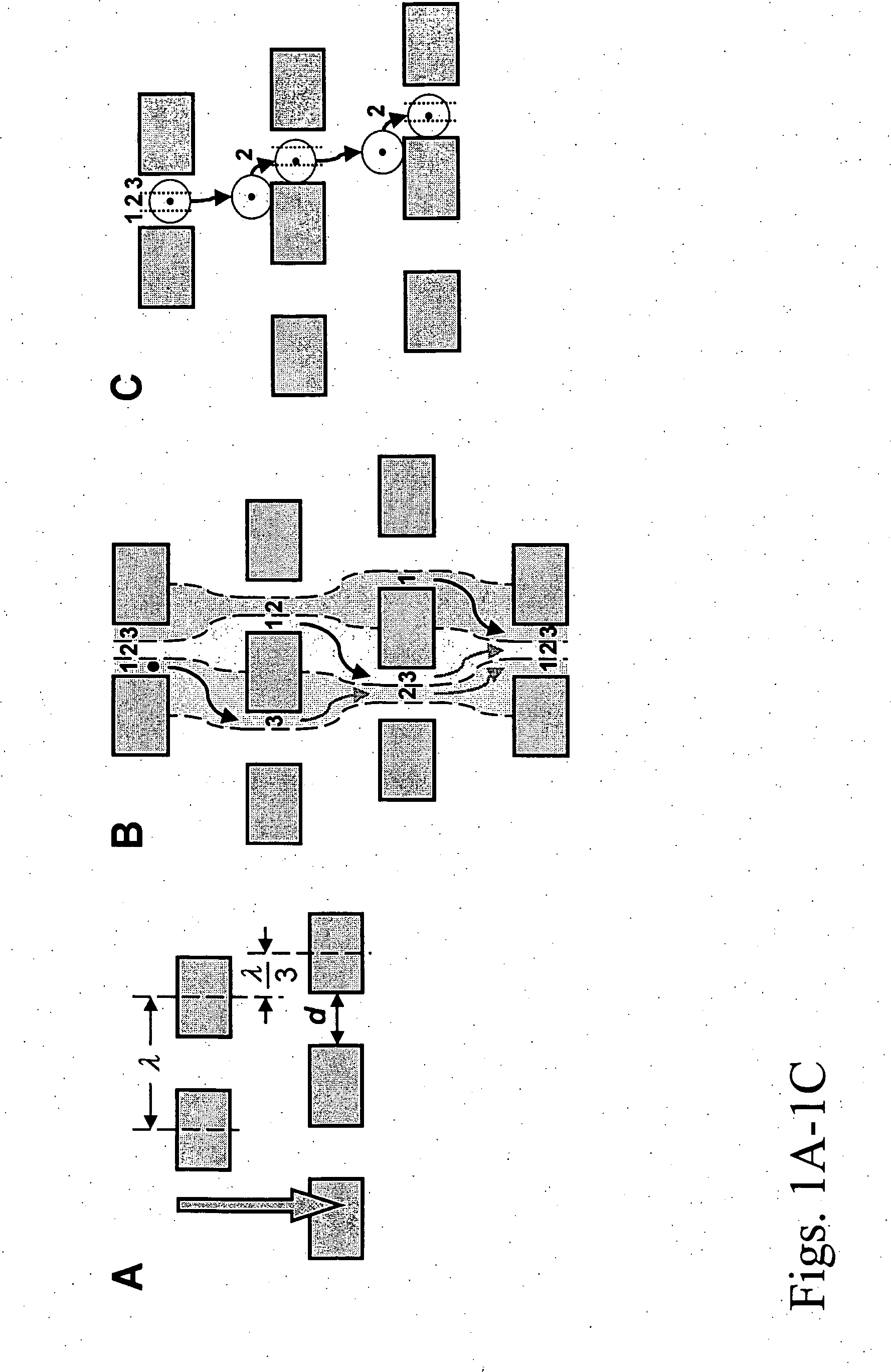

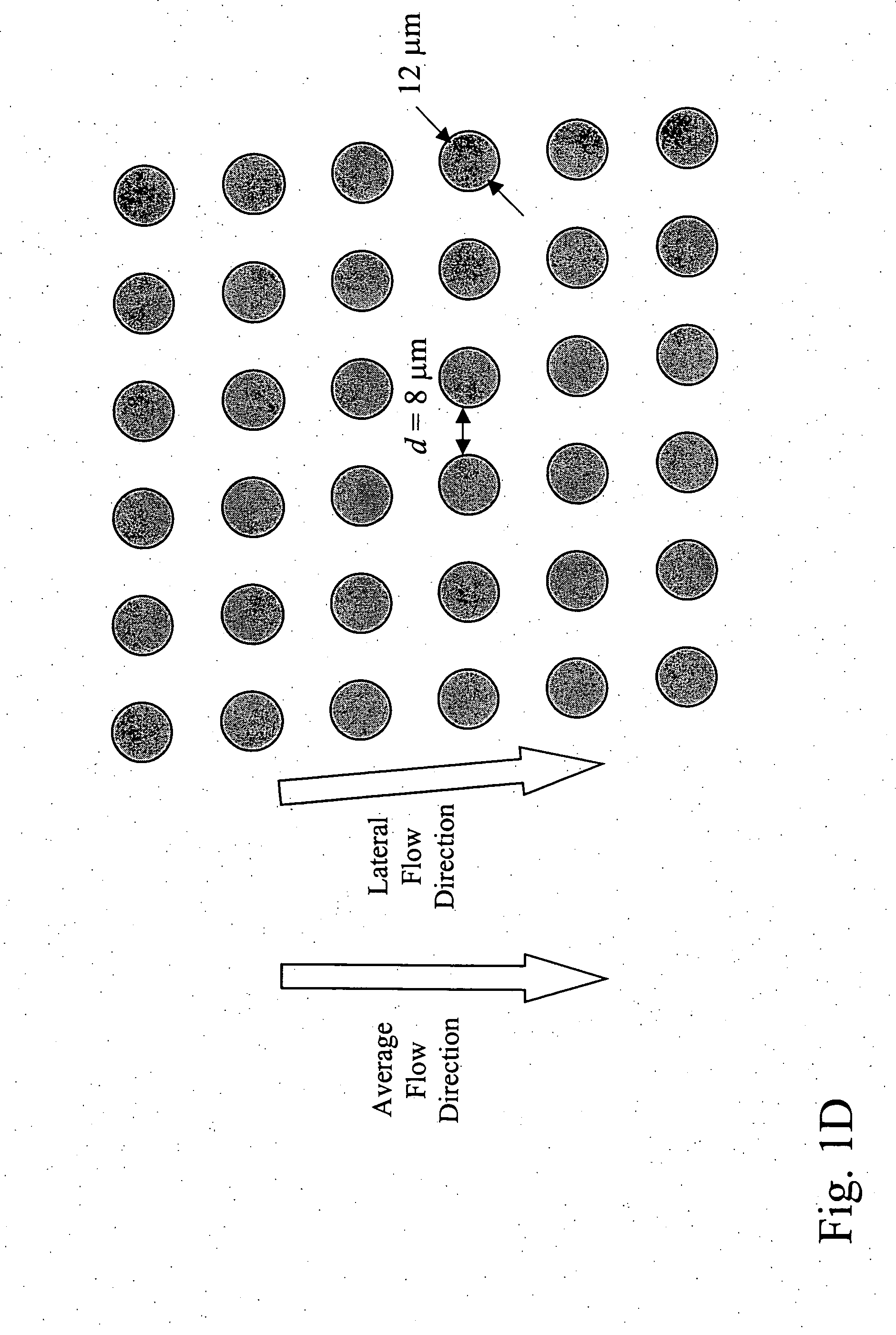

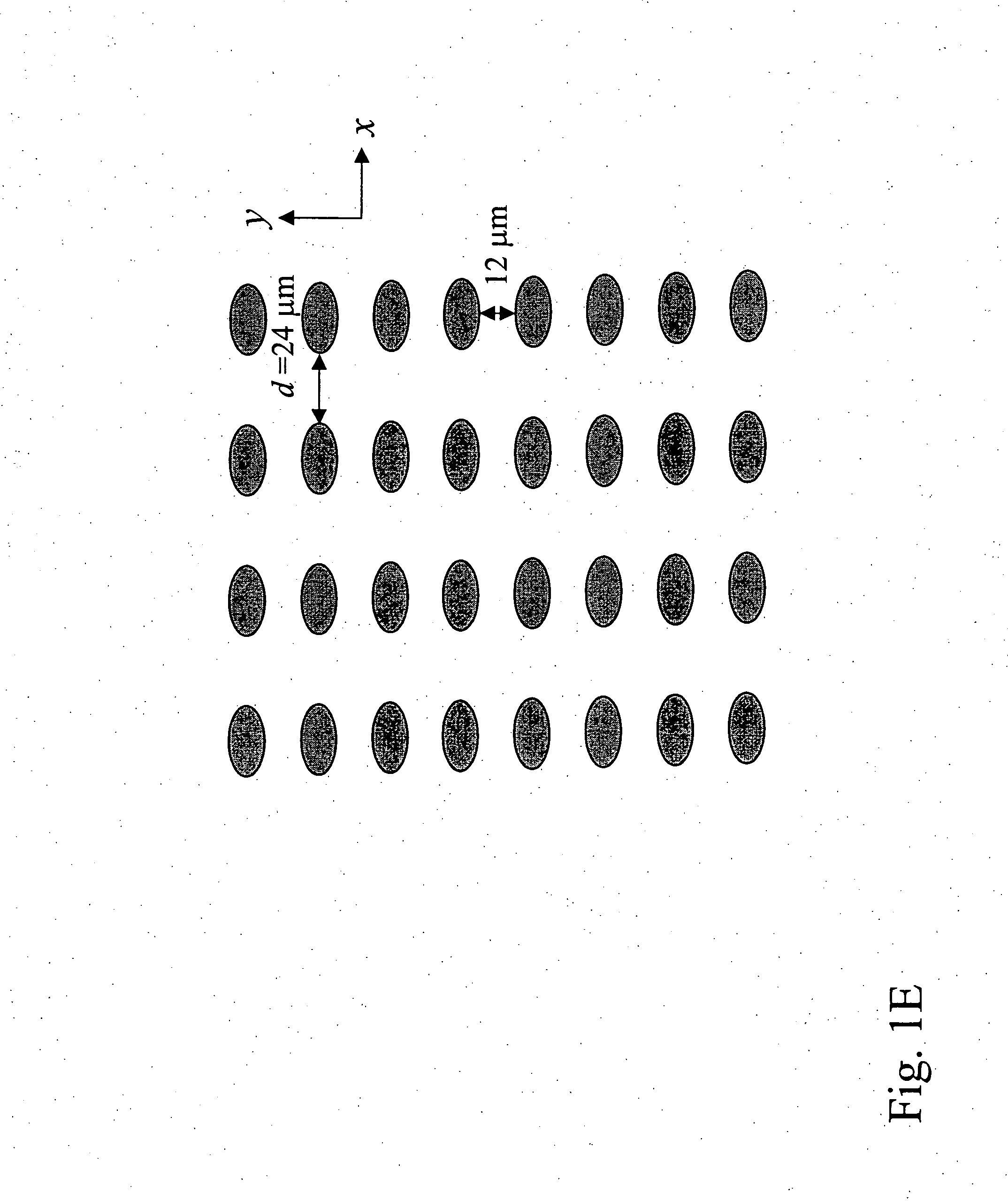

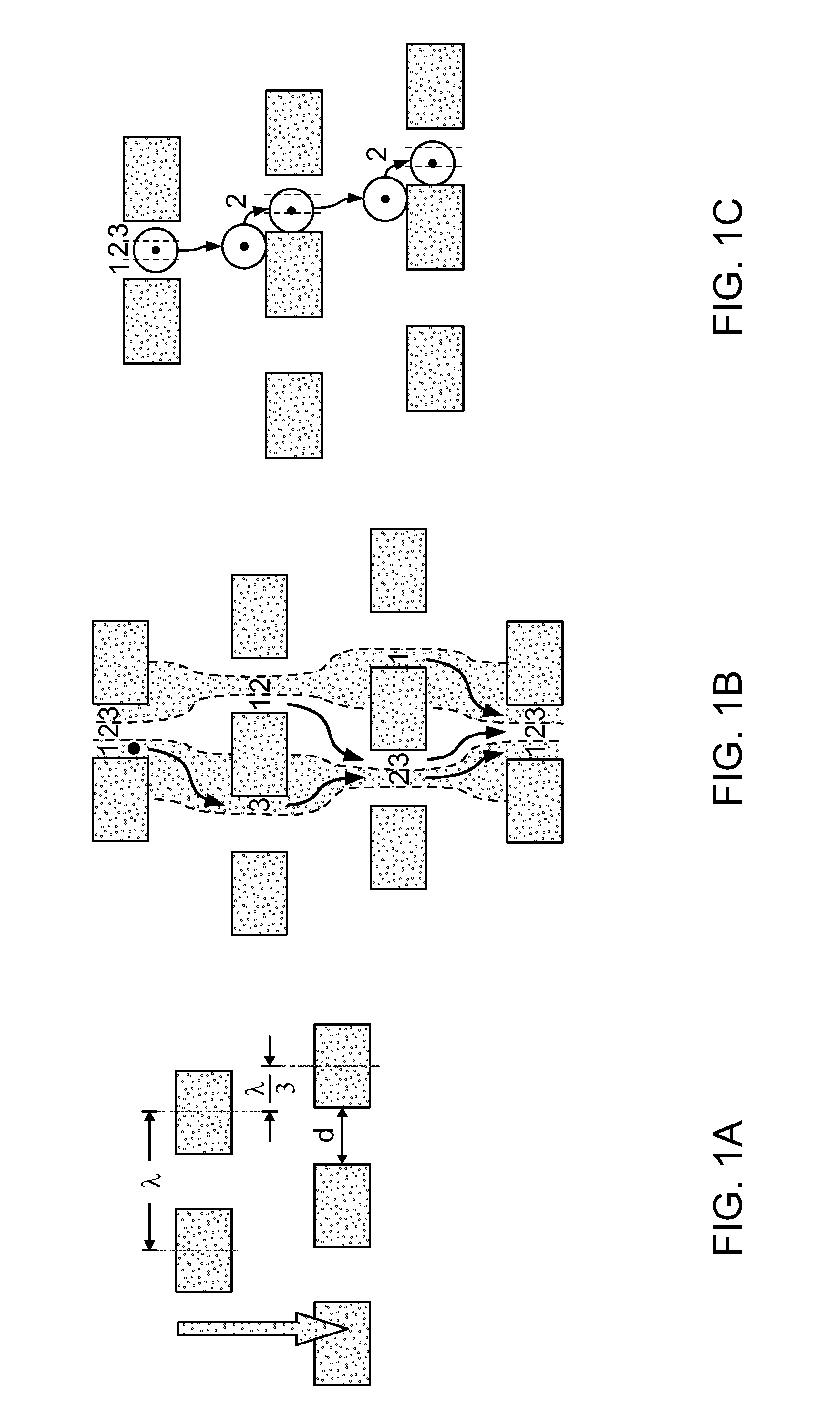

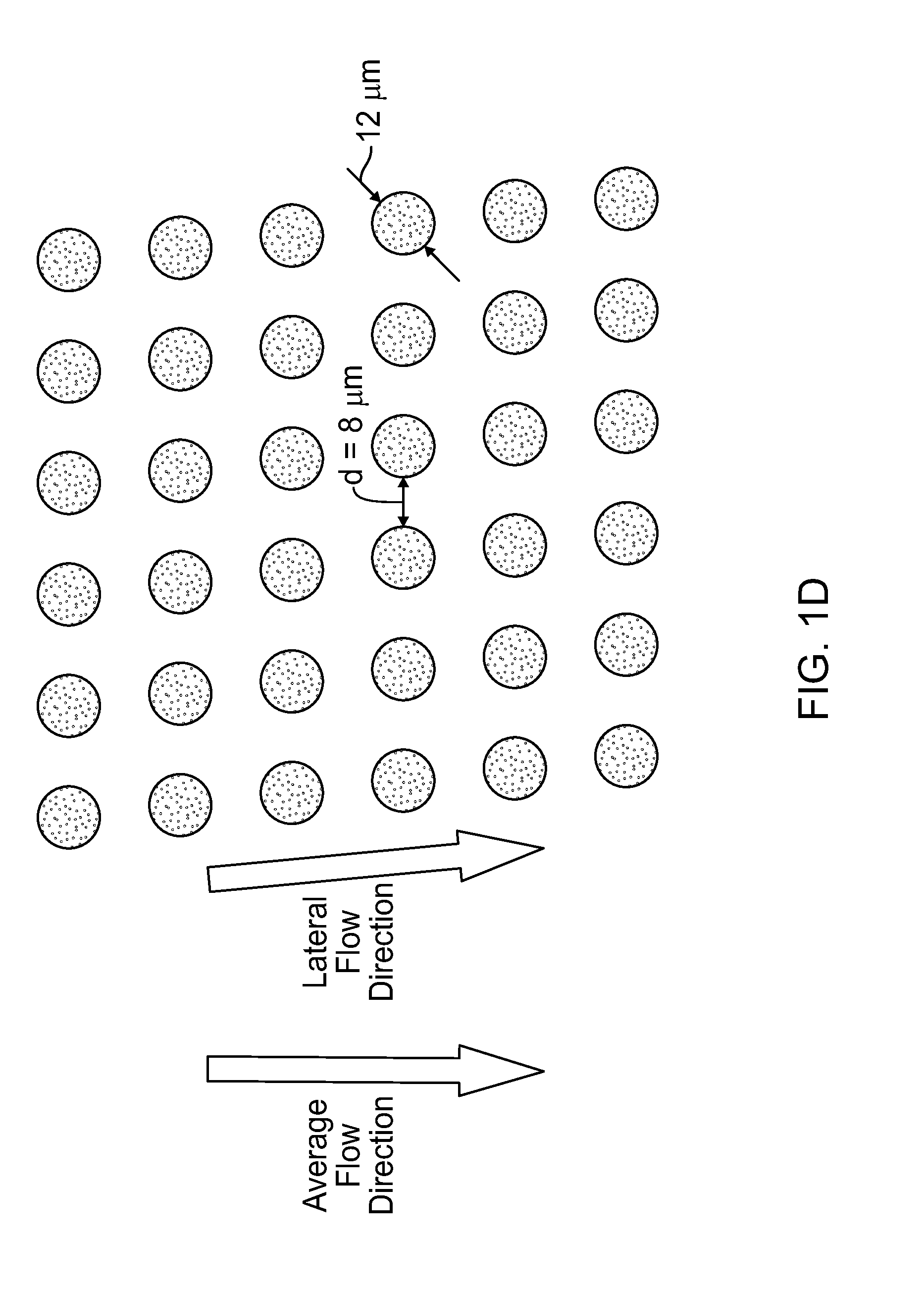

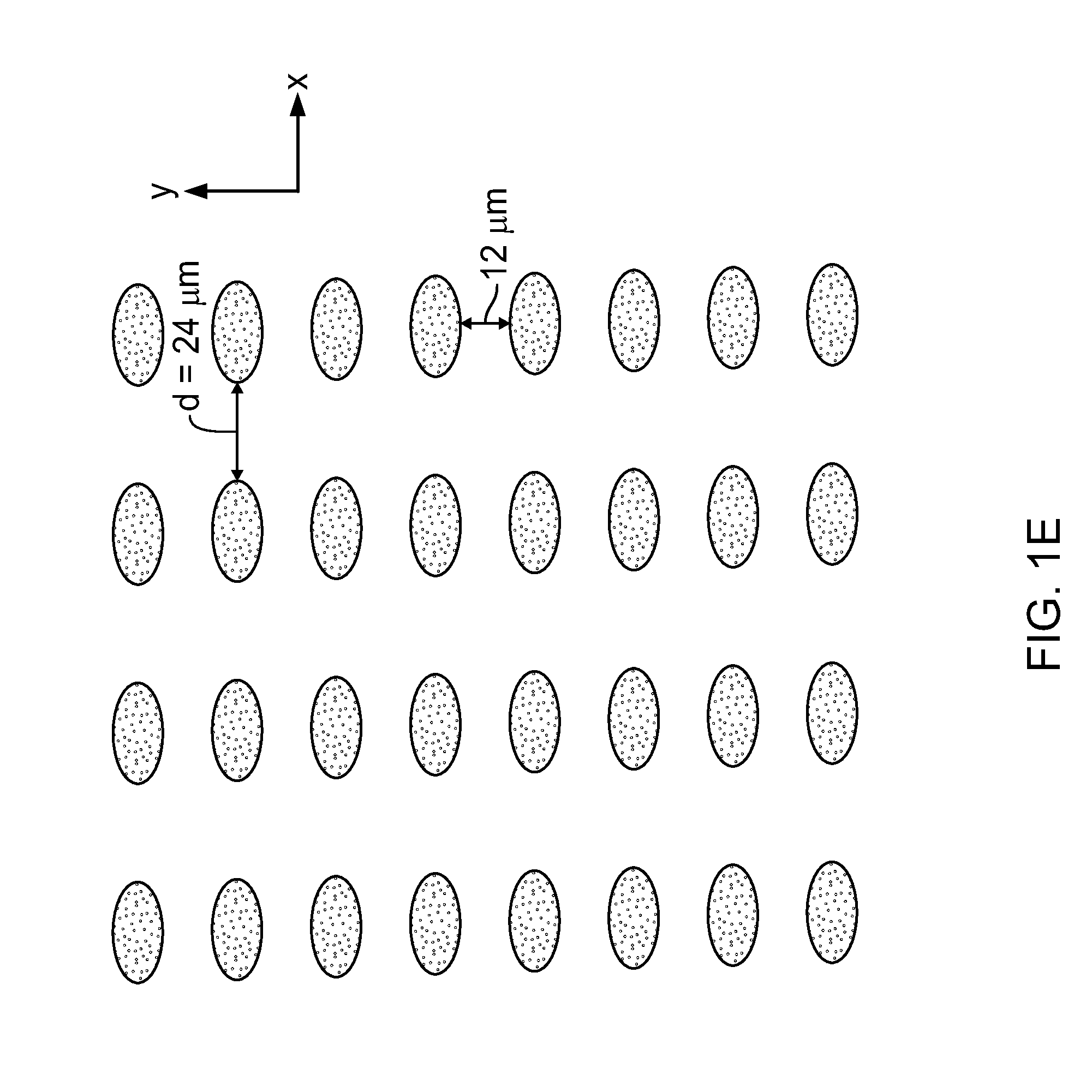

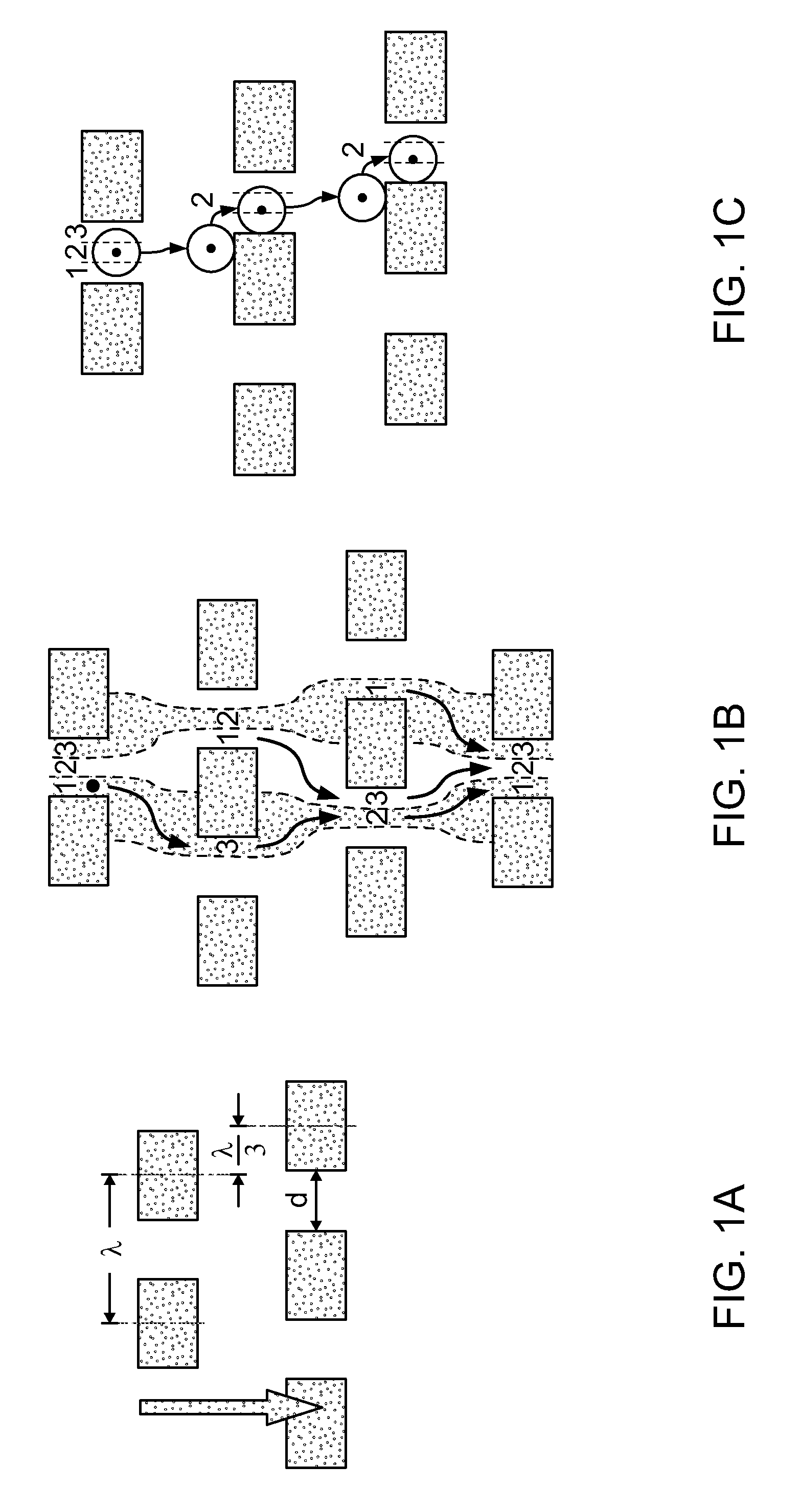

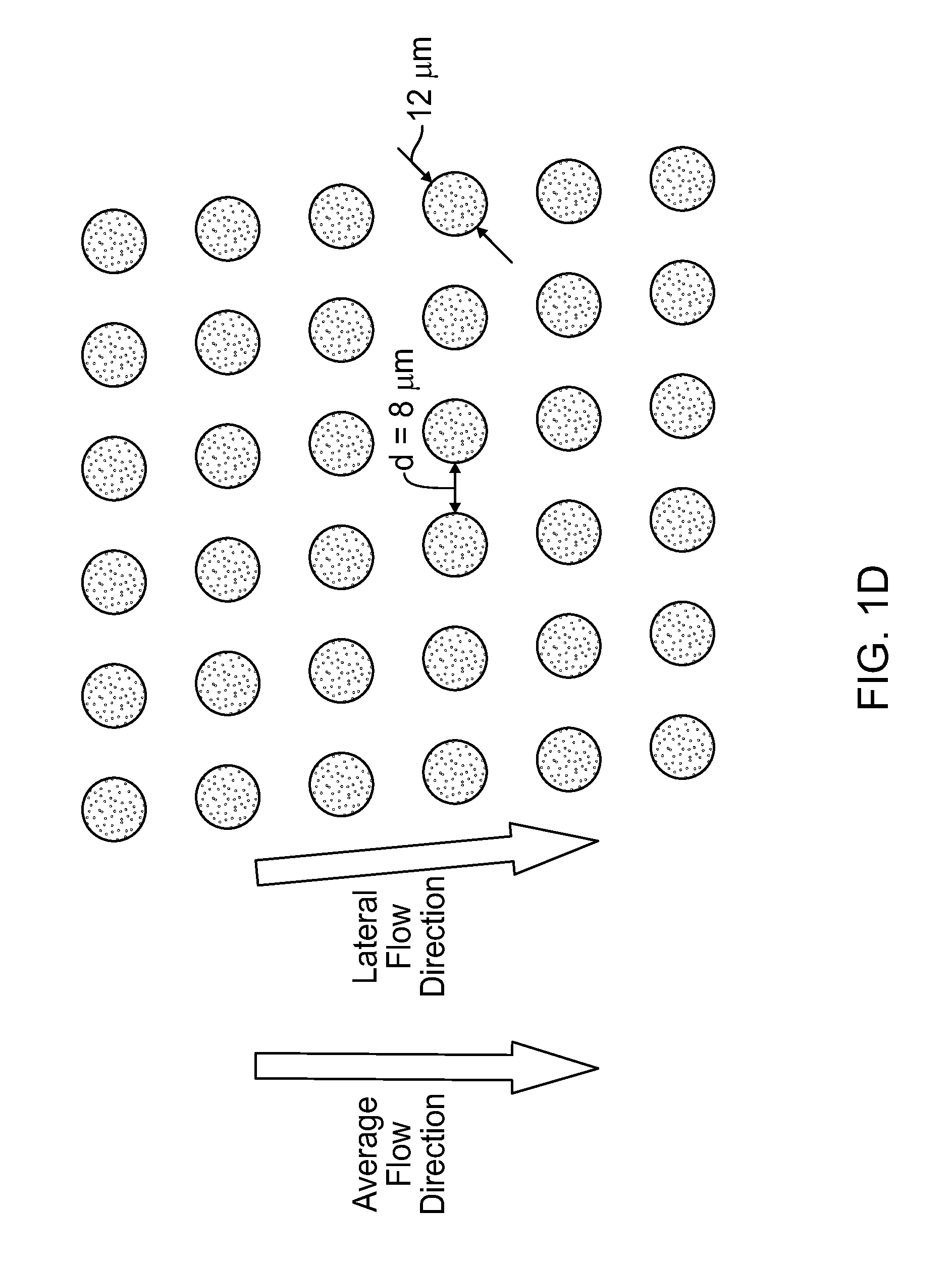

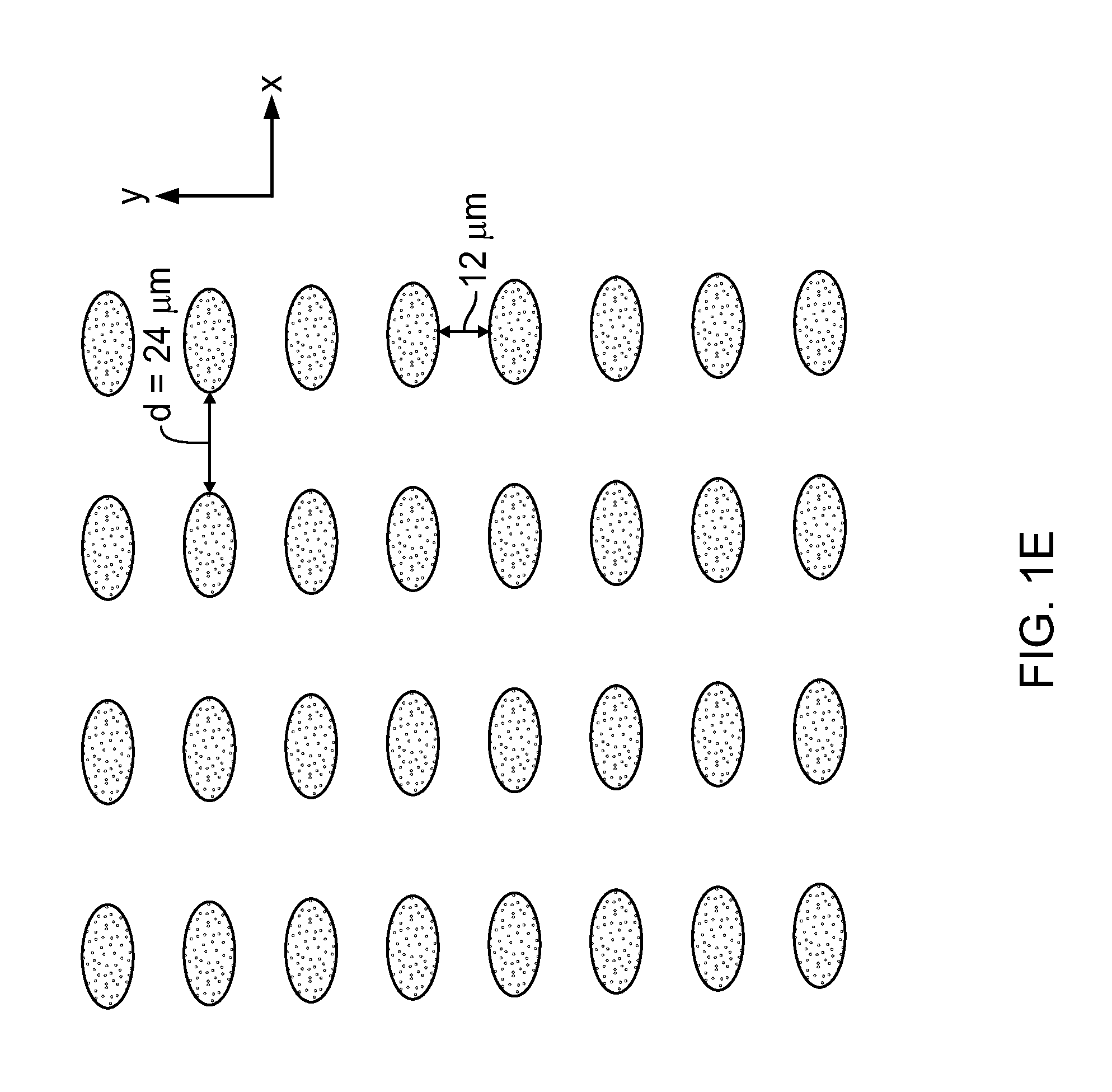

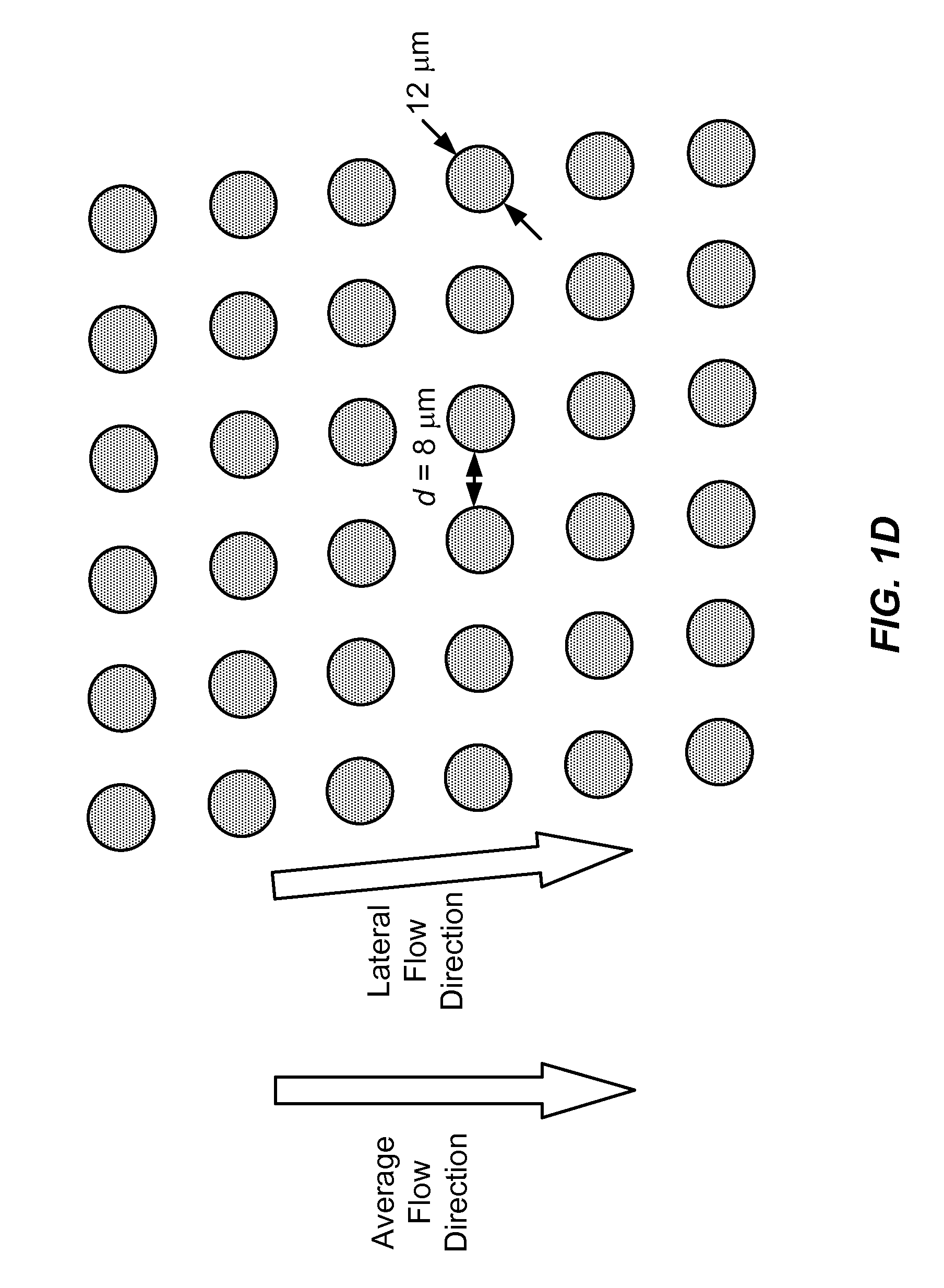

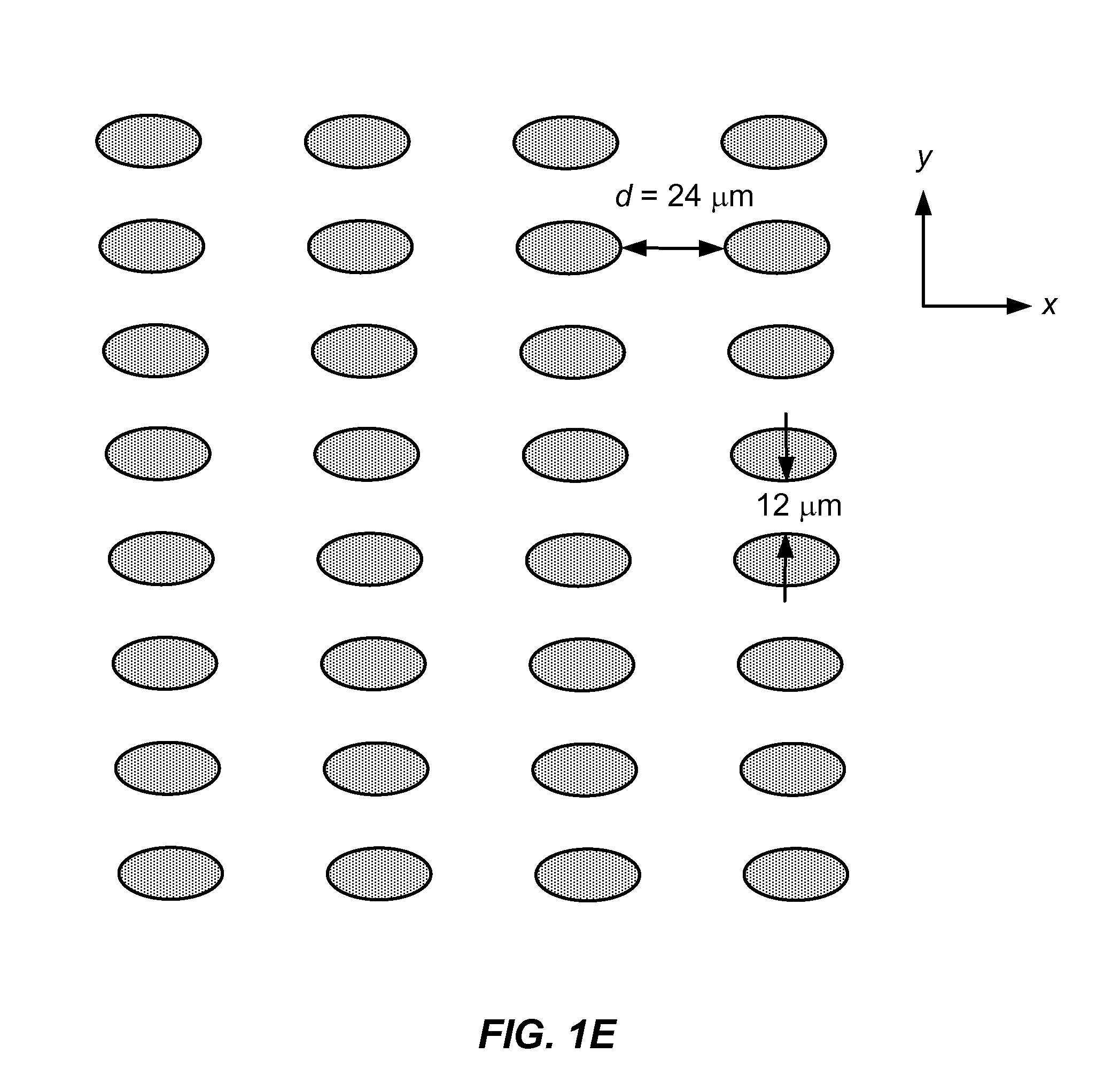

InactiveUS20070026415A1Increase array densitySmall particle sizeBioreactor/fermenter combinationsBiological substance pretreatmentsCirculating cancer cellTumor cells

The invention features devices and methods for detecting, enriching, and analyzing circulating tumor cells and other particles. The invention further features methods of diagnosing a condition, e.g., cancer, in a subject by analyzing a cellular sample from the subject.

Owner:THE GENERAL HOSPITAL CORP +2

Devices and methods for enrichment and alteration of circulating tumor cells and other particles

InactiveUS20070026413A1Increase array densitySmall particle sizeBioreactor/fermenter combinationsBiological substance pretreatmentsCirculating cancer cellTumor cells

The invention features devices and methods for detecting, enriching, and analyzing circulating tumor cells and other particles. The invention further features methods of diagnosing a condition, e.g., cancer, in a subject by analyzing a cellular sample from the subject.

Owner:THE GENERAL HOSPITAL CORP +2

Devices and methods for enrichment and alteration of circulating tumor cells and other particles

ActiveUS20070026469A1Increase array densitySmall particle sizeBioreactor/fermenter combinationsBiological substance pretreatmentsCirculating cancer cellTumor cells

The invention features devices and methods for detecting, enriching, and analyzing circulating tumor cells and other particles. The invention further features methods of diagnosing a condition, e.g., cancer, in a subject by analyzing a cellular sample from the subject.

Owner:GPB SCI

Devices and methods for enrichment and alteration of circulating tumor cells and other particles

InactiveUS20070099207A1Increase in sizeIncrease array densityMicrobiological testing/measurementNanoinformaticsCirculating cancer cellTumor cells

The invention features devices and methods for detecting, enriching, and analyzing circulating tumor cells and other particles. The invention further features methods of diagnosing a condition, e.g., cancer, in a subject by analyzing a cellular sample from the subject.

Owner:THE GENERAL HOSPITAL CORP +2

Devices and methods for enrichment and alteration of circulating tumor cells and other particles

InactiveUS20070026417A1Decrease size of particleDecrease in volumeMicrobiological testing/measurementNanoinformaticsCirculating cancer cellCirculating tumor cell

The invention features devices and methods for detecting, enriching, and analyzing circulating tumor cells and other particles. The invention further features methods of diagnosing a condition, e.g., cancer, in a subject by analyzing a cellular sample from the subject.

Owner:CELLECTIVE DX CORP +2

Devices and methods for enrichment and alteration of circulating tumor cells and other particles

InactiveUS20070026419A1Small particle sizeLower the volumeBioreactor/fermenter combinationsBiological substance pretreatmentsCirculating cancer cellTumor cells

The invention features devices and methods for detecting, enriching, and analyzing circulating tumor cells and other particles. The invention further features methods of diagnosing a condition, e.g., cancer, in a subject by analyzing a cellular sample from the subject.

Owner:CELLECTIVE DX CORP

Devices and methods for enrichment and alteration of circulating tumor cells and other particles

InactiveUS20070026416A1Small particle sizeLower the volumeBioreactor/fermenter combinationsBiological substance pretreatmentsCirculating cancer cellTumor cells

The invention features devices and methods for detecting, enriching, and analyzing circulating tumor cells and other particles. The invention further features methods of diagnosing a condition, e.g., cancer, in a subject by analyzing a cellular sample from the subject.

Owner:CELLECTIVE DX CORP

Devices and methods for enrichment and alteration of circulating tumor cells and other particles

InactiveUS20070026414A1Small particle sizeLower the volumeBioreactor/fermenter combinationsBiological substance pretreatmentsCirculating cancer cellTumor cells

The invention features devices and methods for detecting, enriching, and analyzing circulating tumor cells and other particles. The invention further features methods of diagnosing a condition, e.g., cancer, in a subject by analyzing a cellular sample from the subject.

Owner:THE GENERAL HOSPITAL CORP +2

Devices and methods for enrichment and alteration of circulating tumor cells and other particles

InactiveUS20070026418A1Small particle sizeLower the volumeBioreactor/fermenter combinationsBiological substance pretreatmentsCirculating cancer cellTumor cells

The invention features devices and methods for detecting, enriching, and analyzing circulating tumor cells and other particles. The invention further features methods of diagnosing a condition, e.g., cancer, in a subject by analyzing a cellular sample from the subject.

Owner:CELLECTIVE DX CORP +4

Device and method for detecting a substance of a liquid

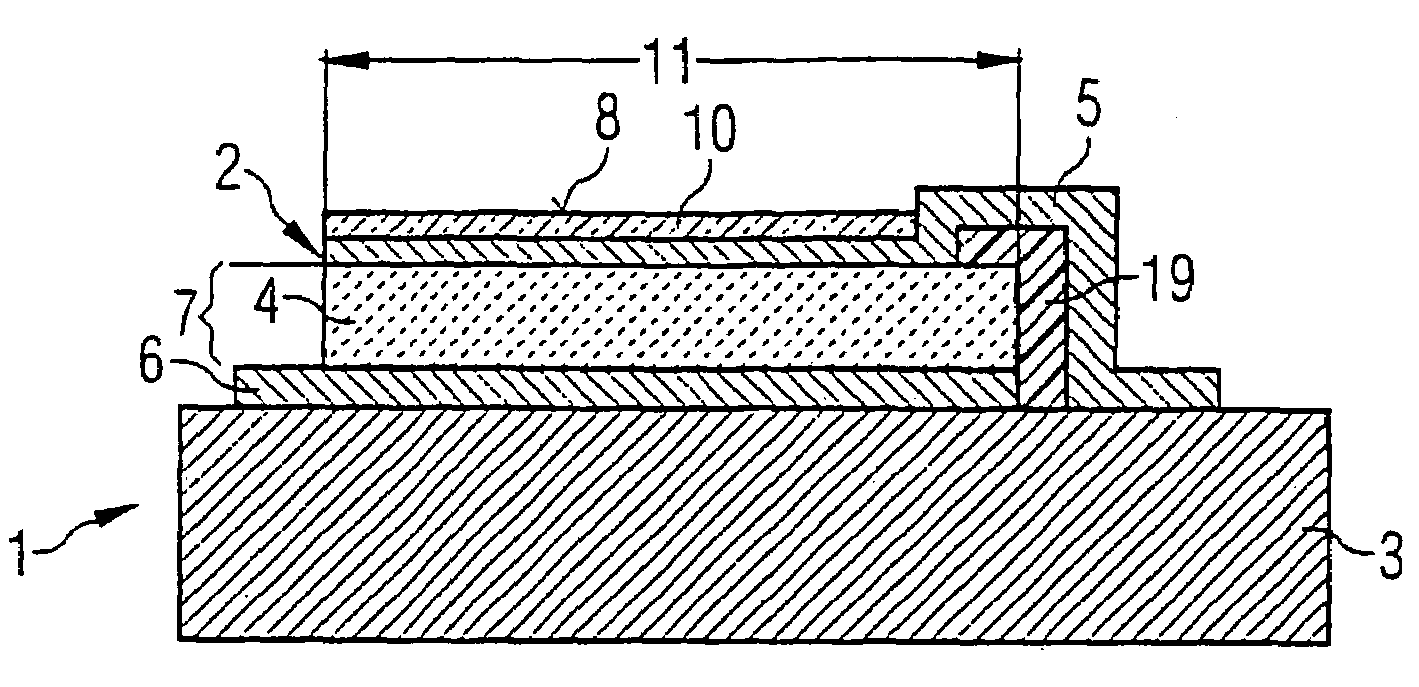

ActiveUS7468608B2Eliminates high-frequency lossEliminates interfering inductanceAnalysing fluids using sonic/ultrasonic/infrasonic wavesShaking/oscillating/vibrating mixersResonancePiezo electric

A device for detecting at least one substance of a fluid includes at least one piezo-acoustic resonator with at least one piezo layer, an electrode arranged on the piezo-electric layer, at least one other electrode arranged on the piezo-electric layer and a surface section used for sorption of the substance of the fluid. The piezo-electric layer, the electrodes and the surface section are disposed in such a way that electric control of the electrodes leads to an oscillation of the resonator at a resonance frequency which depends upon the amount of the substance which is sorbed on the surface section. The thickness of the pioelectric layer is in the region of 0.5 to 20 μm and the resonance frequency of the oscillation ranges from 500 MHz to 2 GHz. The device is a mass sensor with a piezo-acoustic high-frequency thin film resonator.

Owner:BIOMENSIO LTD

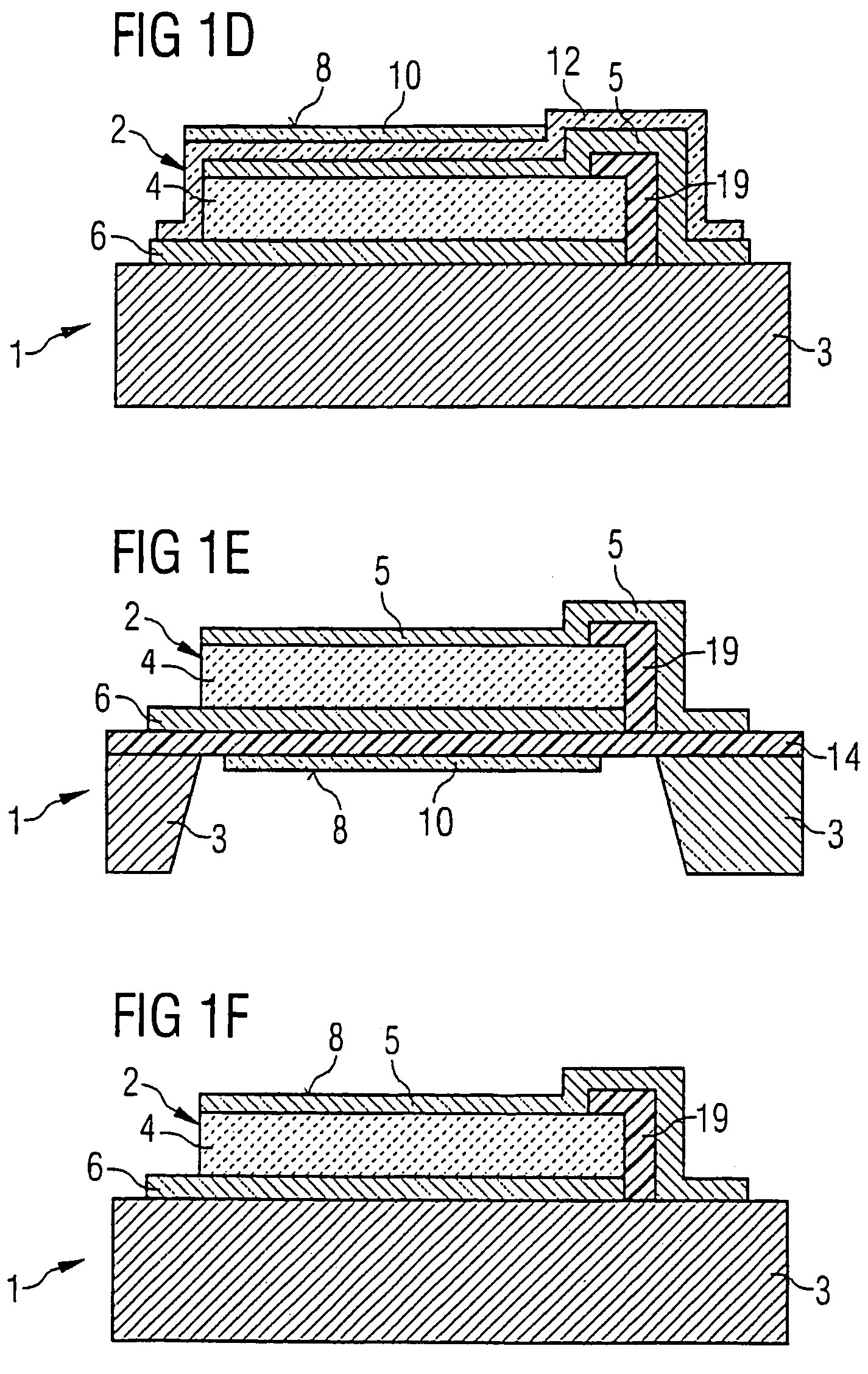

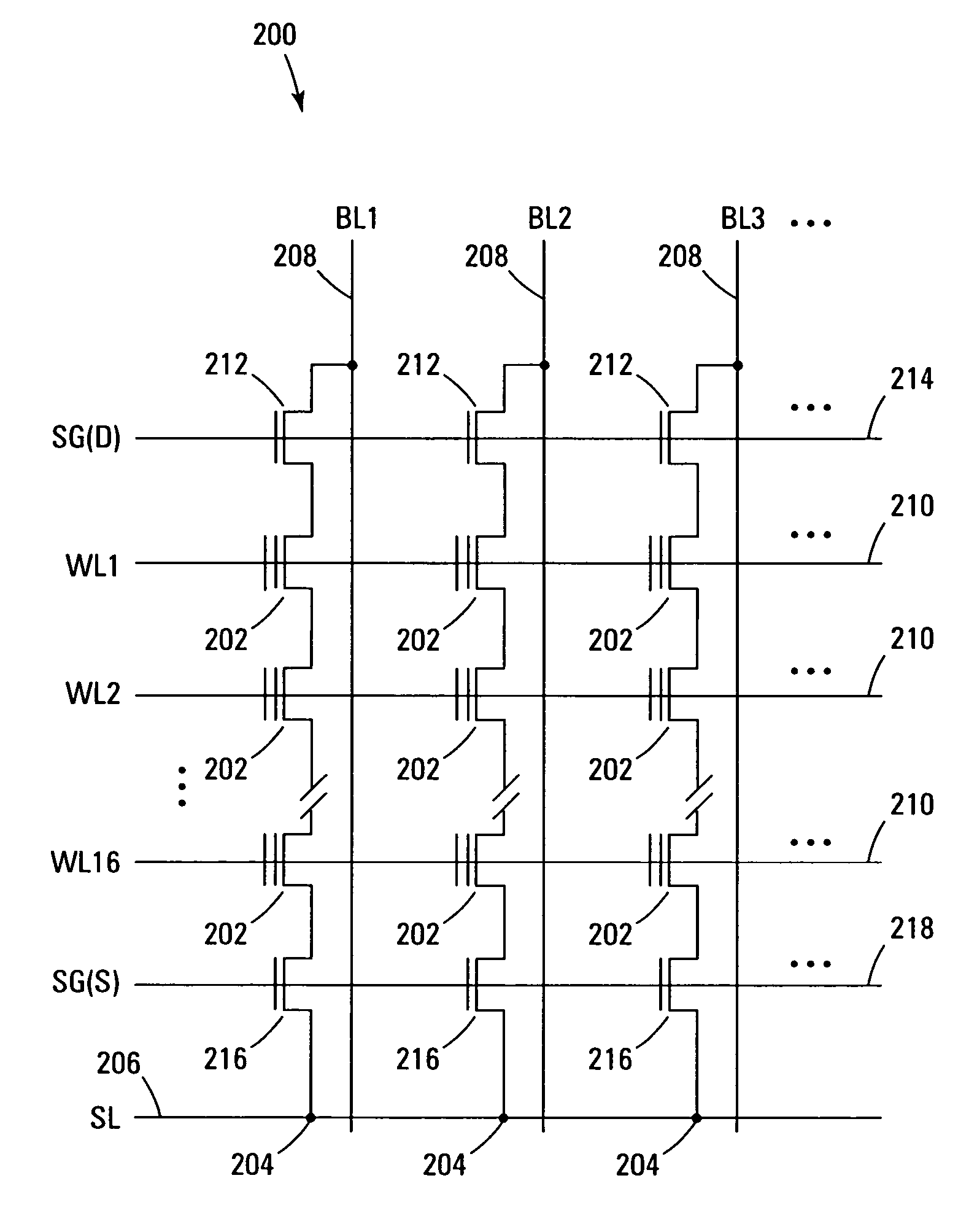

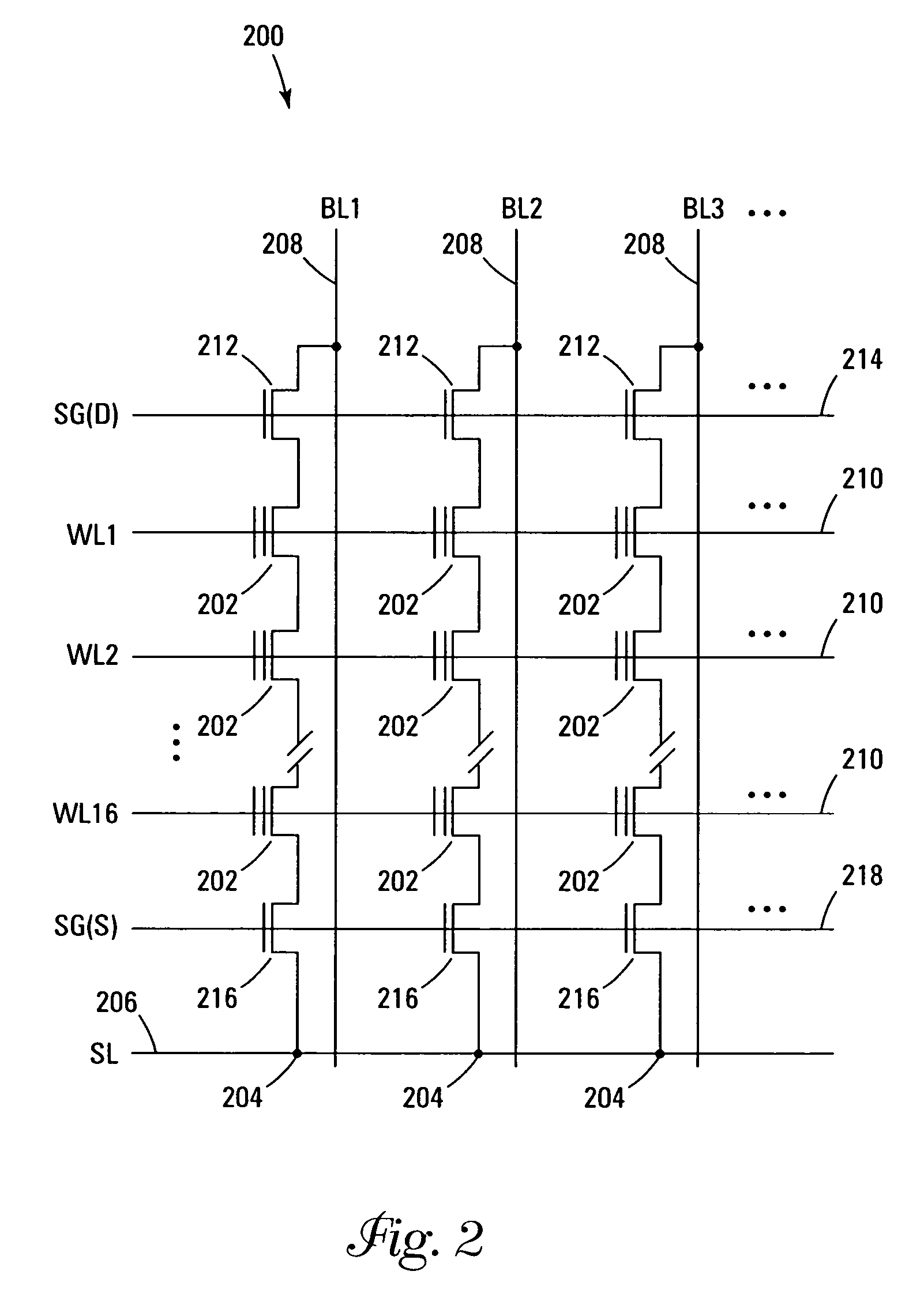

NAND string wordline delay reduction

ActiveUS7064981B2Extension of timeEnhancing Capacitive CouplingRead-only memoriesDigital storageCapacitanceLow voltage

An improved NAND Flash memory and word line selection method has been described, that takes advantage of the asymmetric nature of the word line to word line capacitive coupling to reduce word line selection delay by driving the adjacent word lines to a higher initial voltage and then reducing it to the final target voltage. As the capacitive coupling in between the NAND word lines is a larger effect when the voltages are being lowered, this has the effect of damping out the voltage initially induced in the lower voltage word line by the rising voltages on the adjacent word lines, reducing the overall selection time.

Owner:MICRON TECH INC

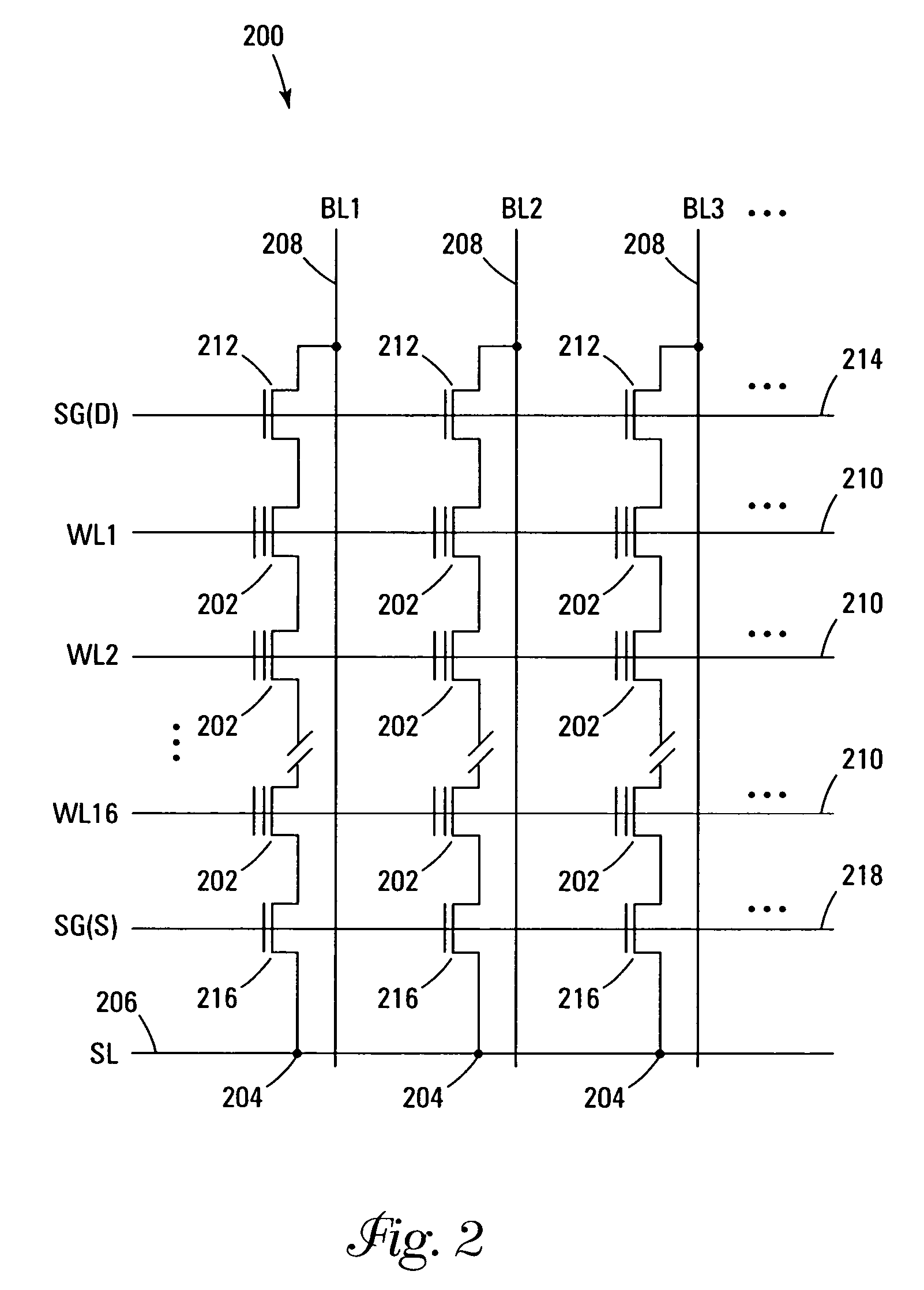

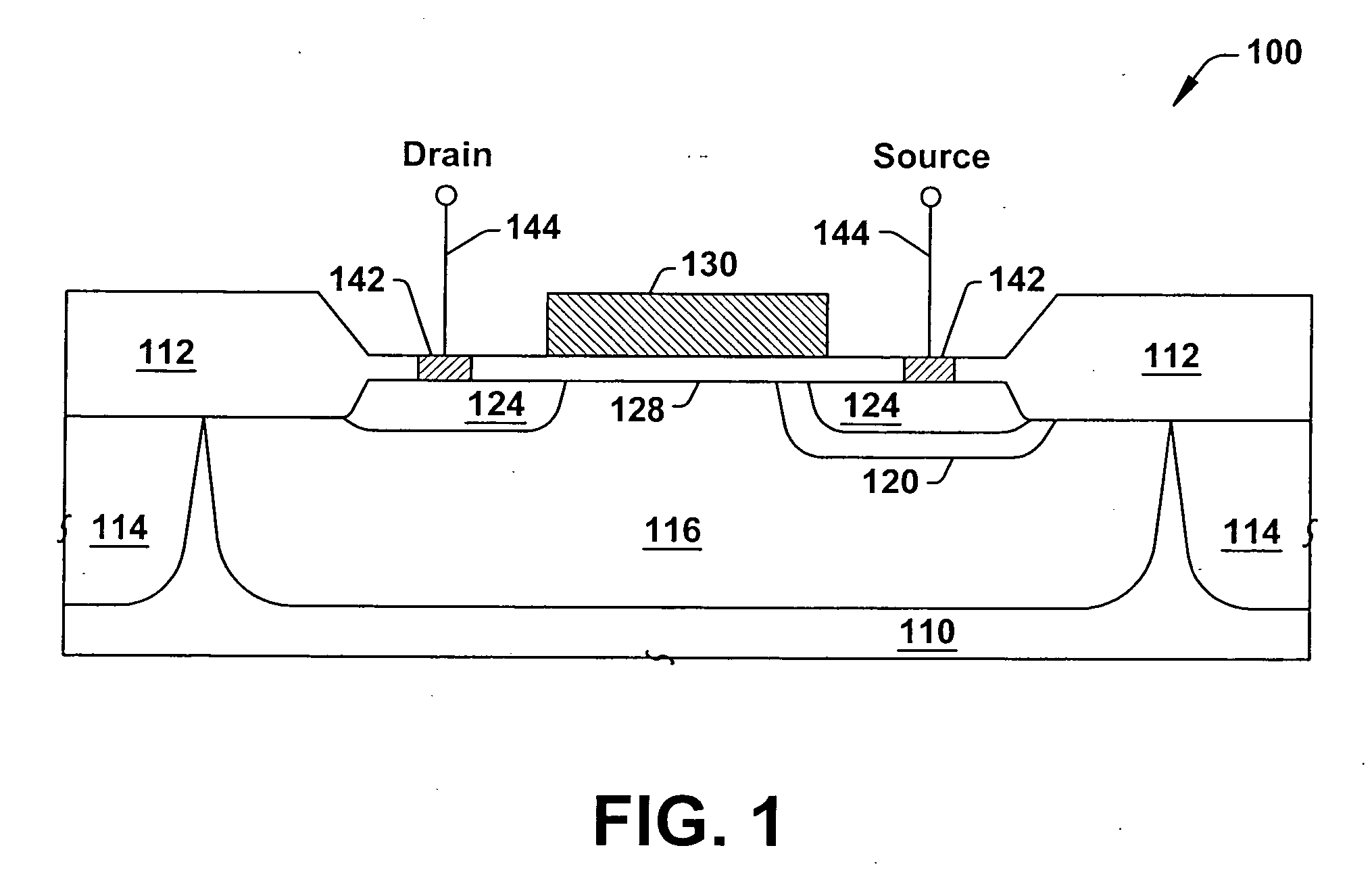

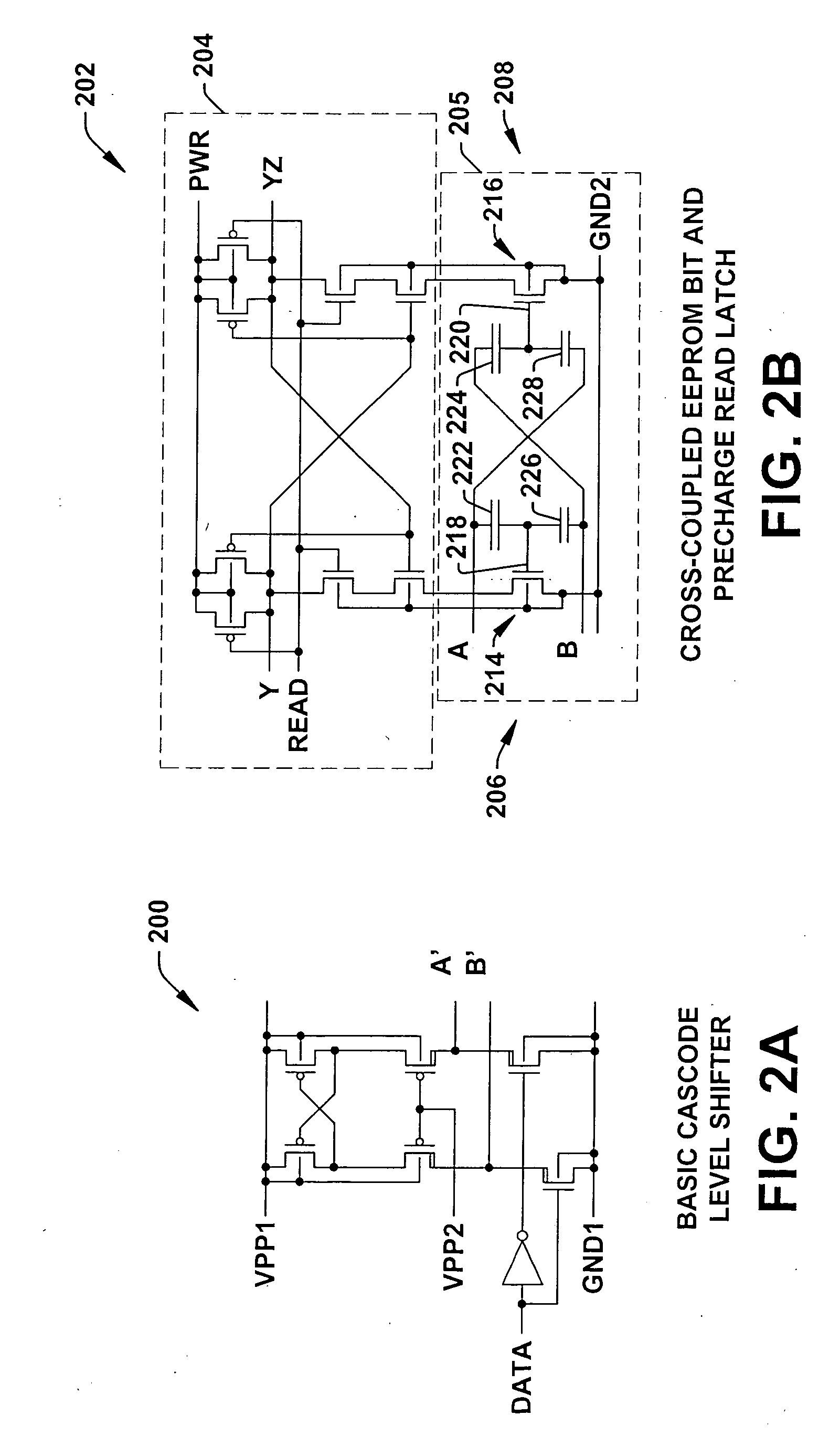

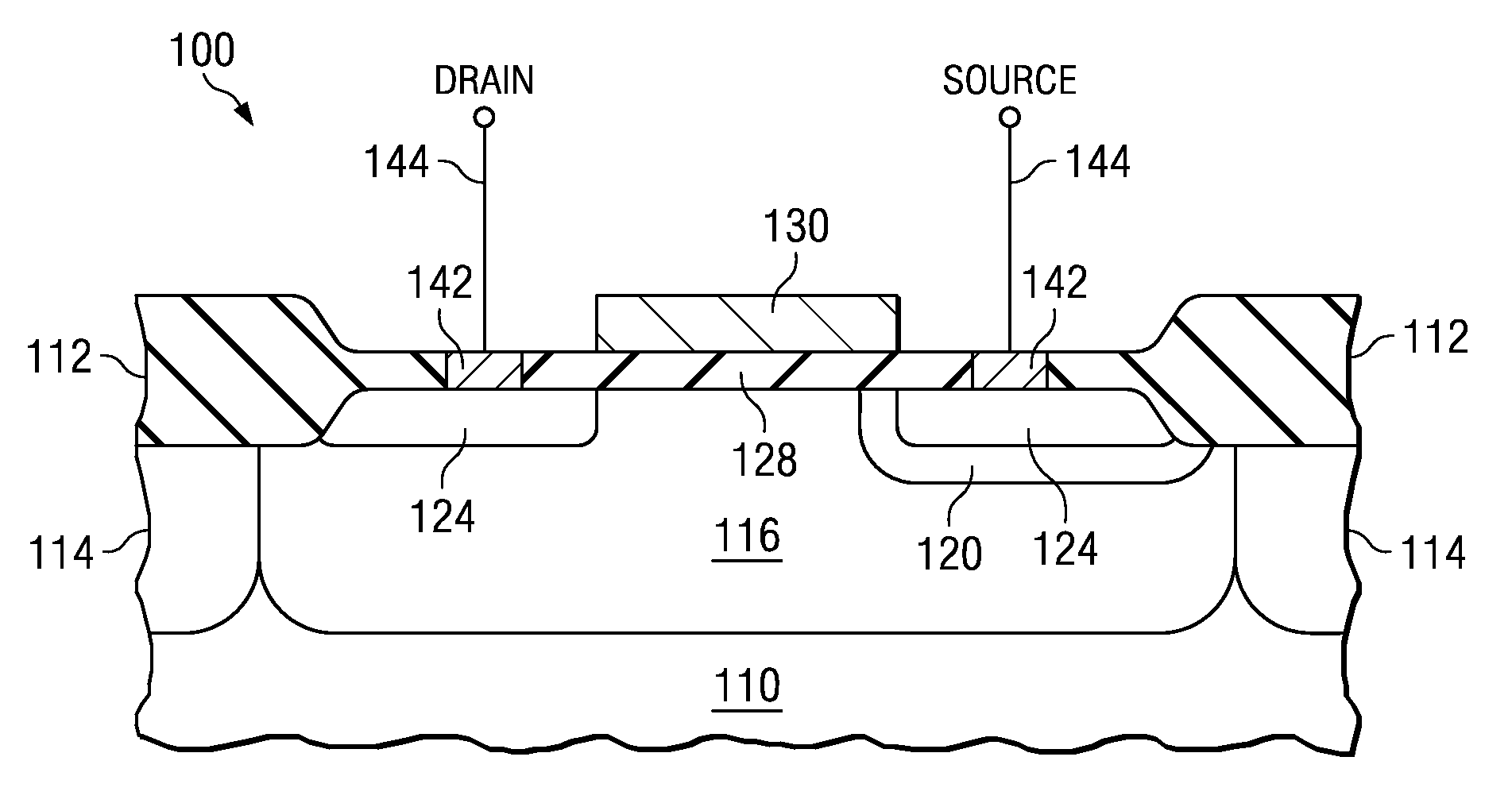

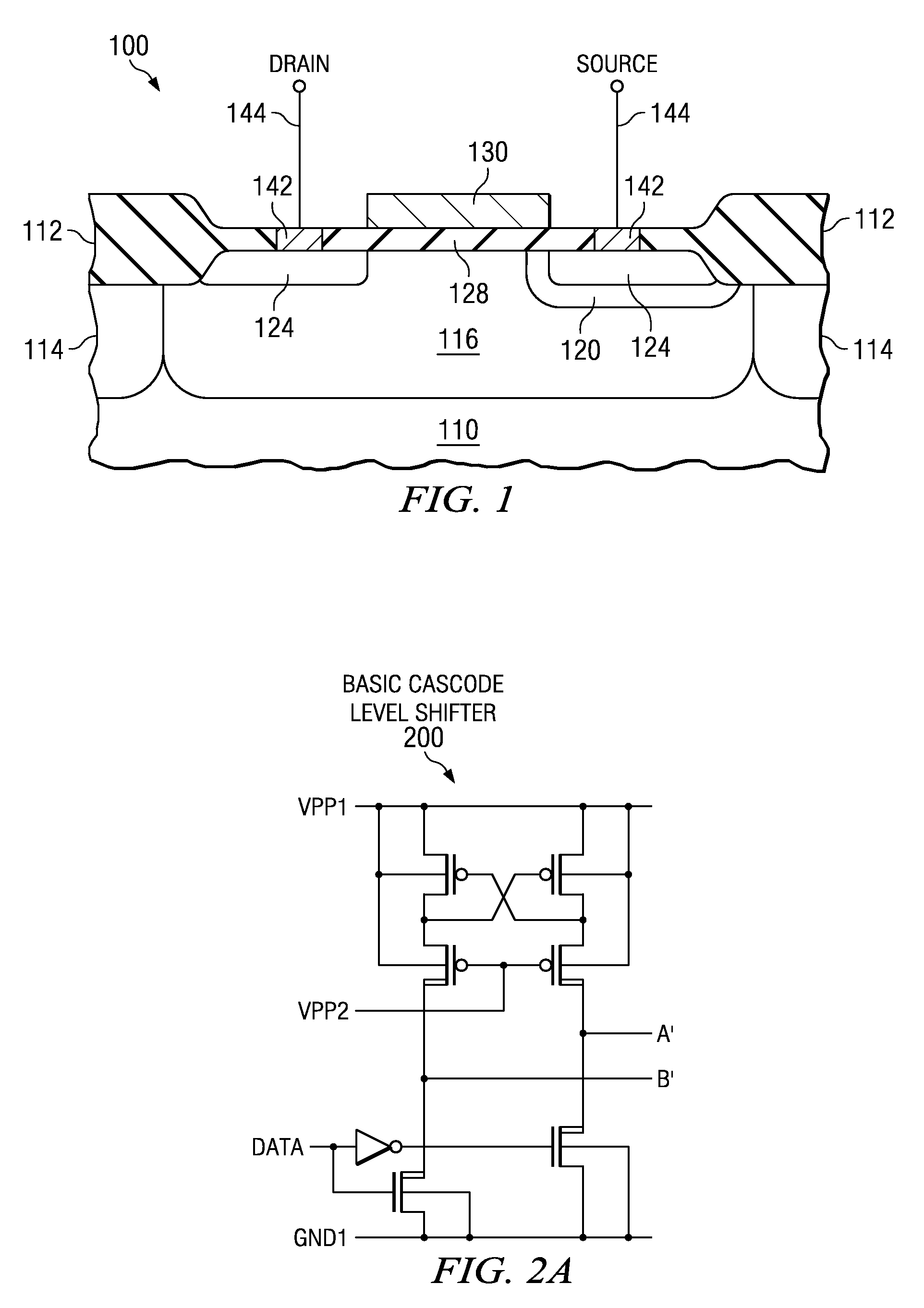

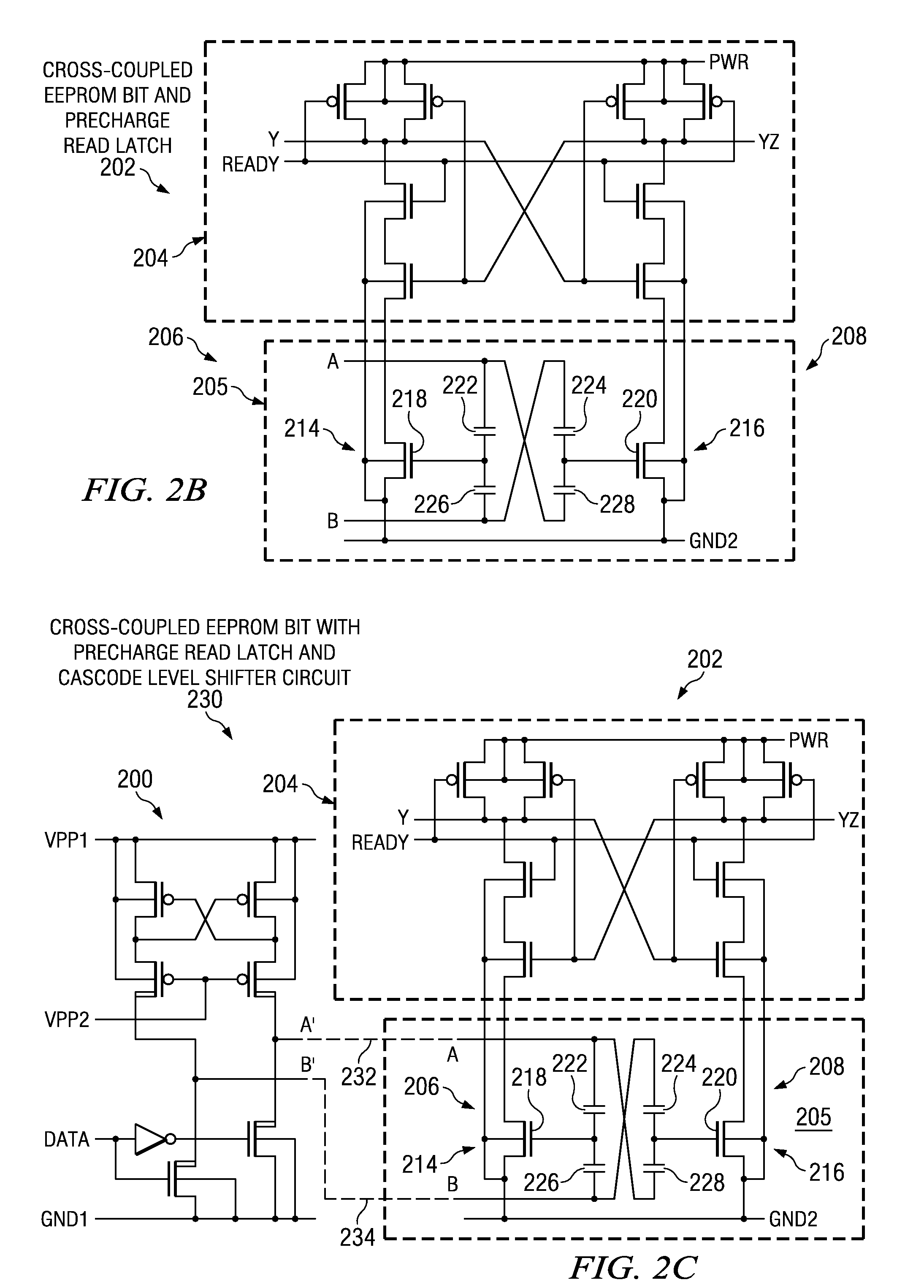

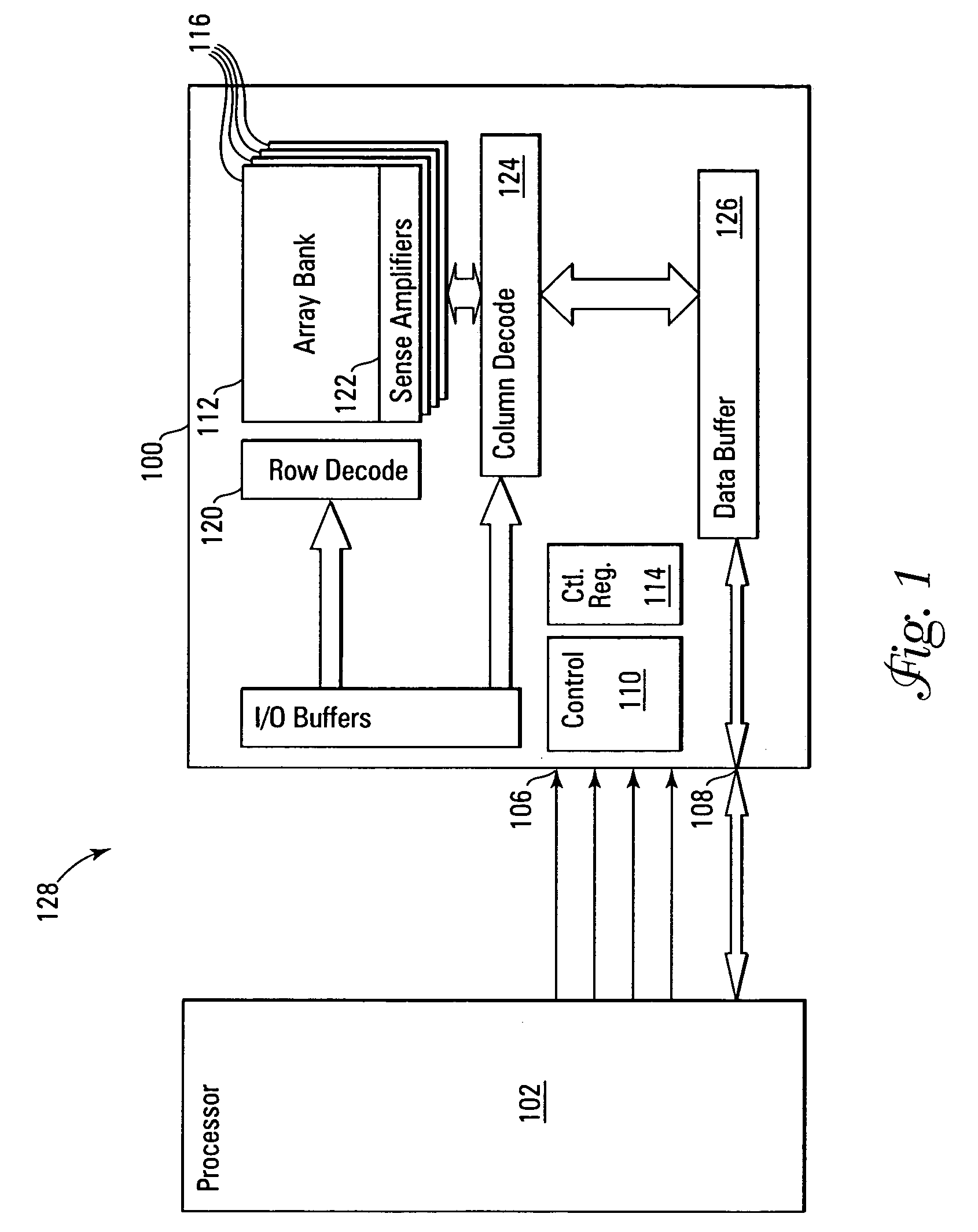

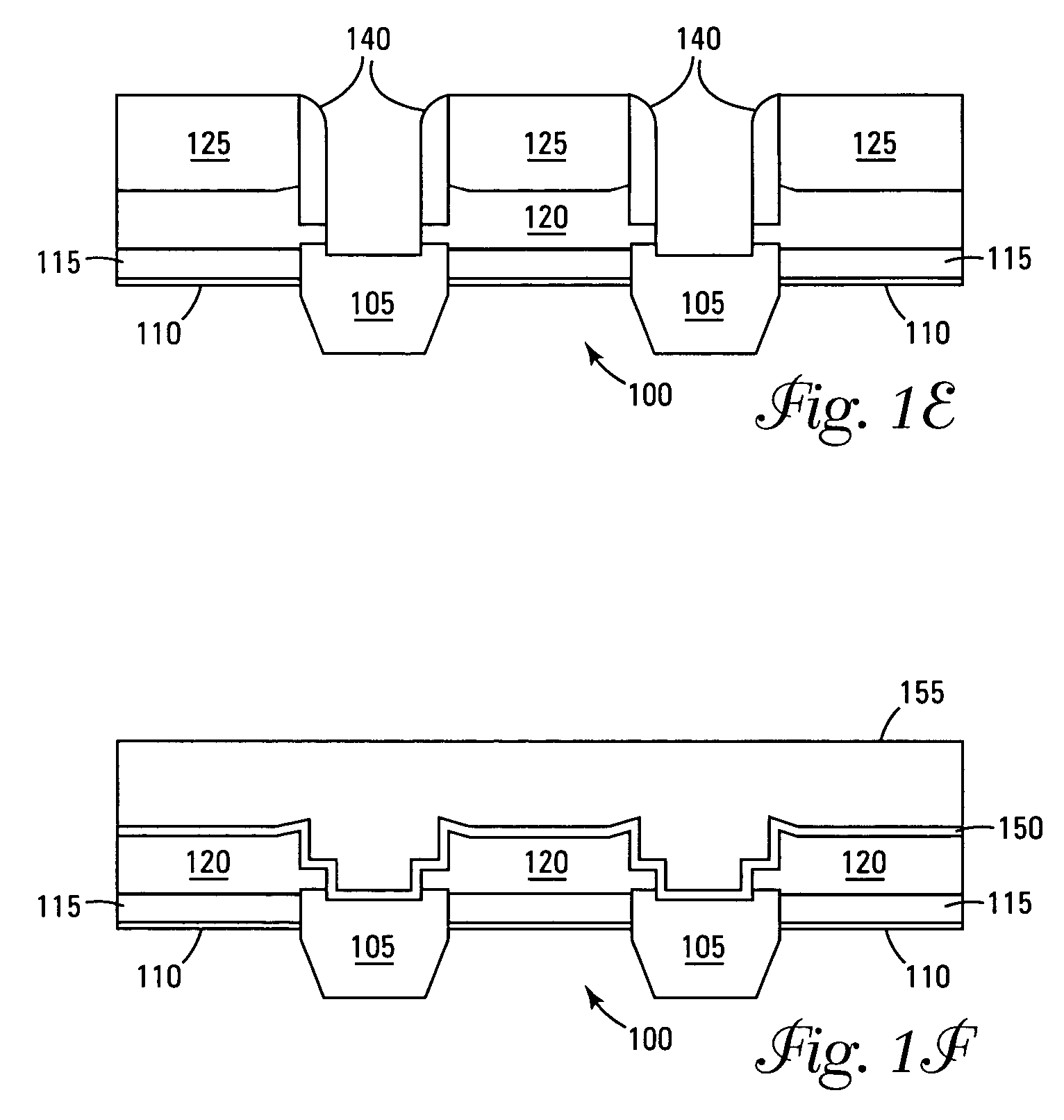

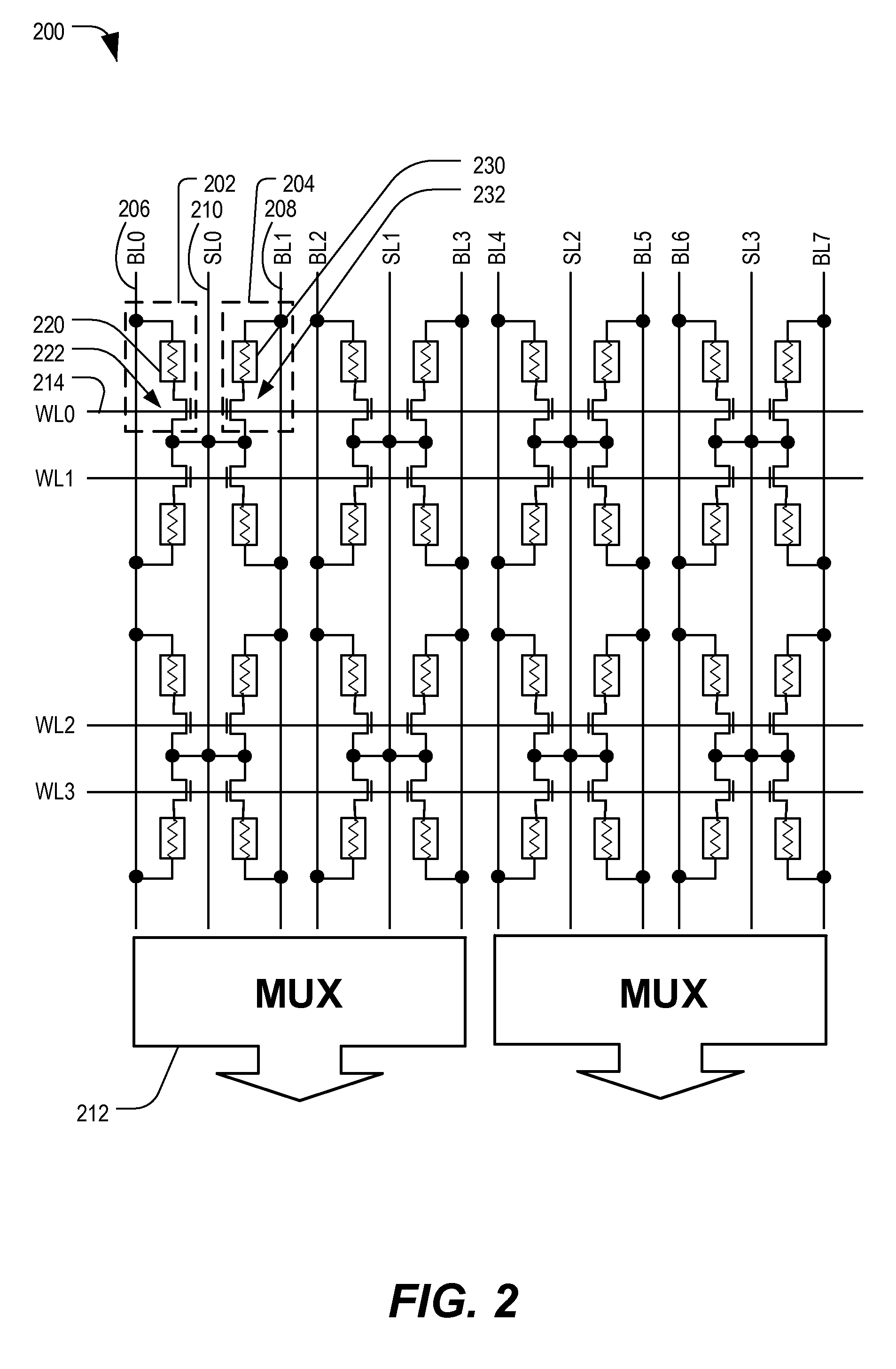

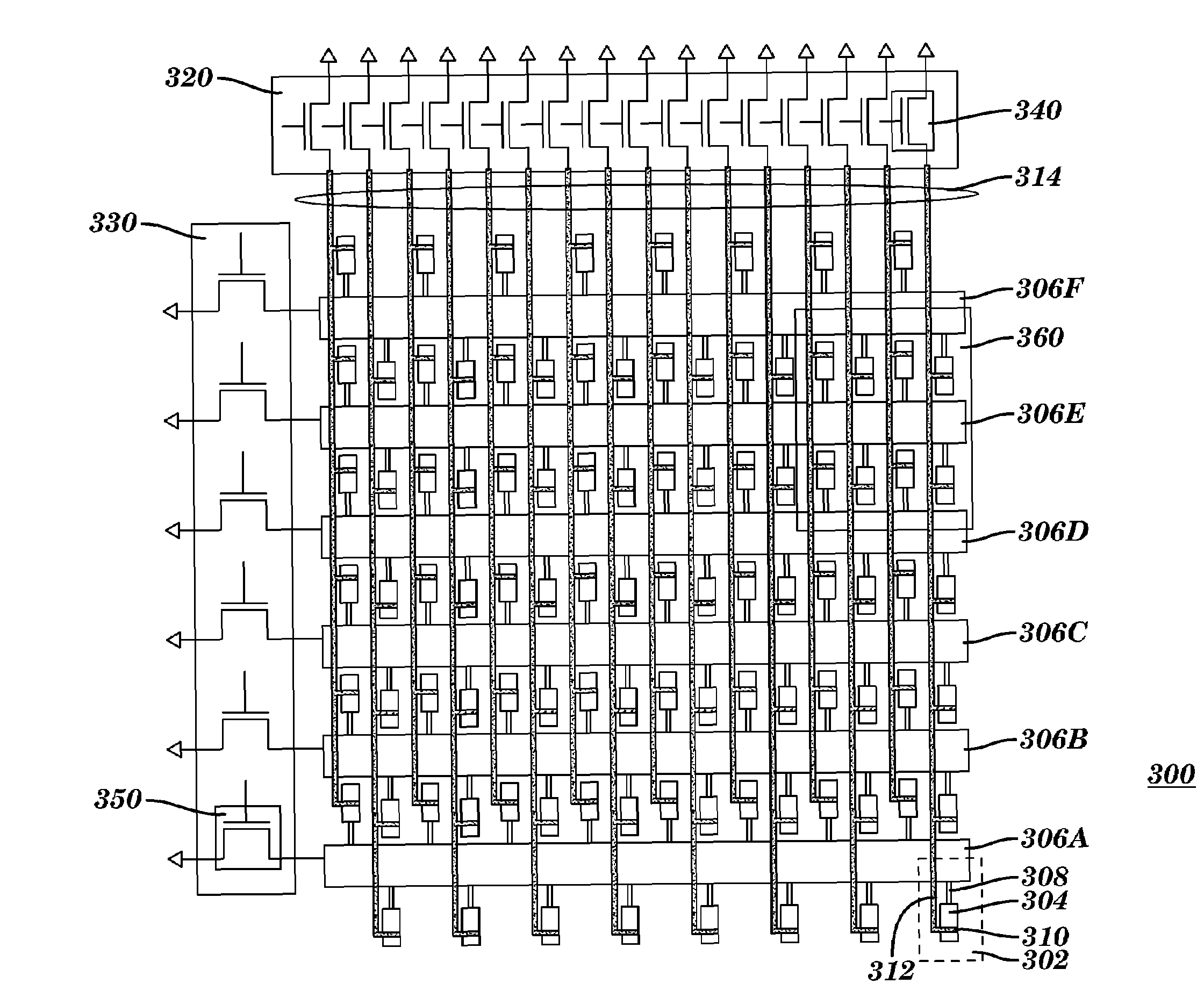

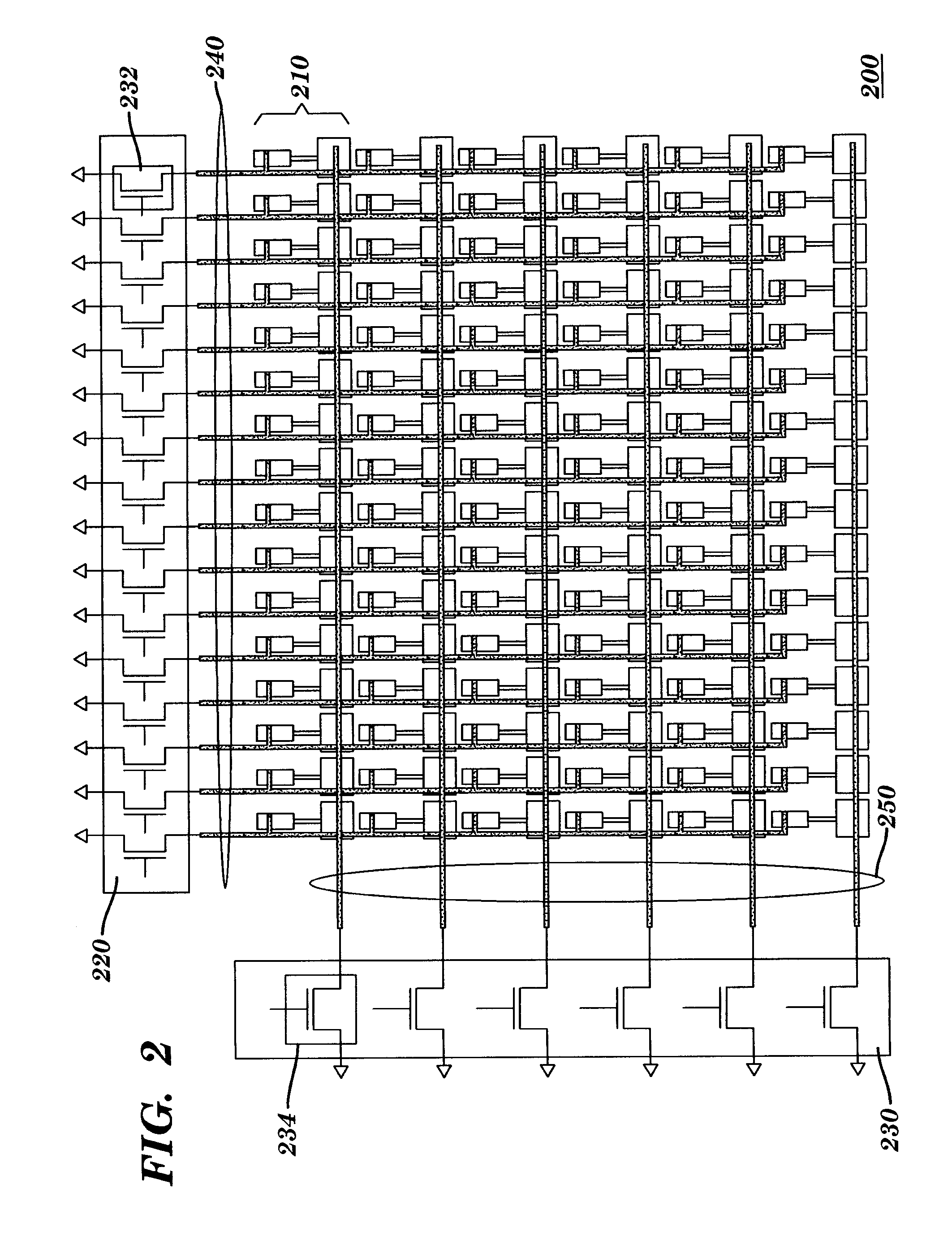

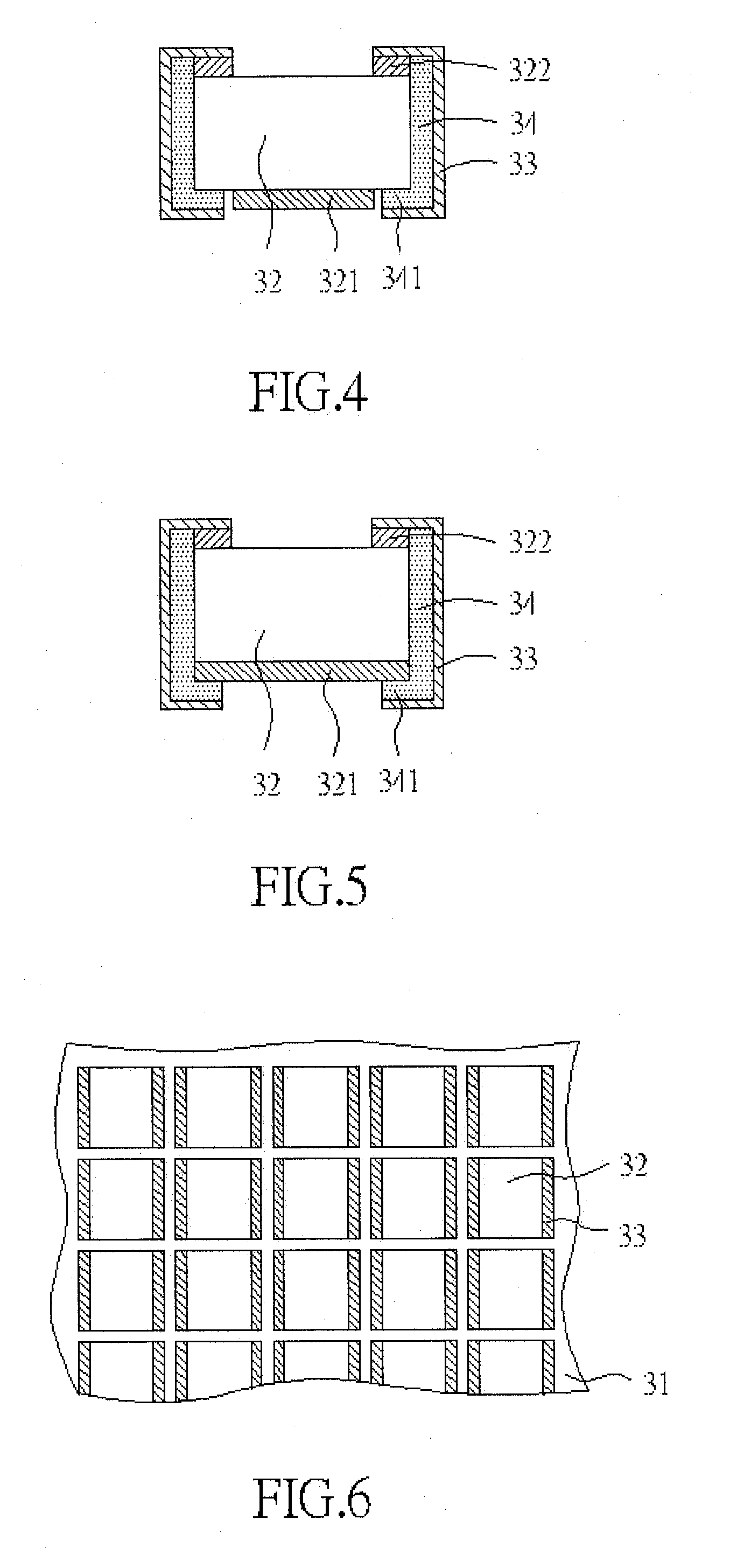

Embedded EEPROM array techniques for higher density

ActiveUS20070064494A1Simple structureWafer Area ReductionSolid-state devicesRead-only memoriesHigh densityHigh voltage transistors

An array structure of single-level poly NMOS EEPROM memory cells and method of operating the array is discussed implemented in a higher density embedded EEPROM layout that eliminates the use of high voltage transistors from the array core region. If they are utilized, the high voltage transistors are moved to row and column drivers in the periphery region to increase array density with little or no added process complexity to allow economic implementation of larger embedded SLP EEPROM arrays. During program or erase operations of the array, the method provides a programming voltage for the selected memory cells of the array, and a half-write (e.g., mid-level) voltage to the remaining unselected memory cells to avoid disturbing the unselected memory cells of the array.

Owner:TEXAS INSTR INC

Embedded EEPROM array techniques for higher density

ActiveUS7471570B2Eliminate useIncrease array densityRead-only memoriesDigital storageHigh densityArray data structure

An array structure of single-level poly NMOS EEPROM memory cells and method of operating the array is discussed implemented in a higher density embedded EEPROM layout that eliminates the use of high voltage transistors from the array core region. If they are utilized, the high voltage transistors are moved to row and column drivers in the periphery region to increase array density with little or no added process complexity to allow economic implementation of larger embedded SLP EEPROM arrays. During program or erase operations of the array, the method provides a programming voltage for the selected memory cells of the array, and a half-write (e.g., mid-level) voltage to the remaining unselected memory cells to avoid disturbing the unselected memory cells of the array.

Owner:TEXAS INSTR INC

Nand string wordline delay reduction

ActiveUS20060028870A1Extension of timeEnhancing Capacitive CouplingRead-only memoriesDigital storageCapacitanceLow voltage

An improved NAND Flash memory and word line selection method has been described, that takes advantage of the asymmetric nature of the word line to word line capacitive coupling to reduce word line selection delay by driving the adjacent word lines to a higher initial voltage and then reducing it to the final target voltage. As the capacitive coupling in between the NAND word lines is a larger effect when the voltages are being lowered, this has the effect of damping out the voltage initially induced in the lower voltage word line by the rising voltages on the adjacent word lines, reducing the overall selection time.

Owner:MICRON TECH INC

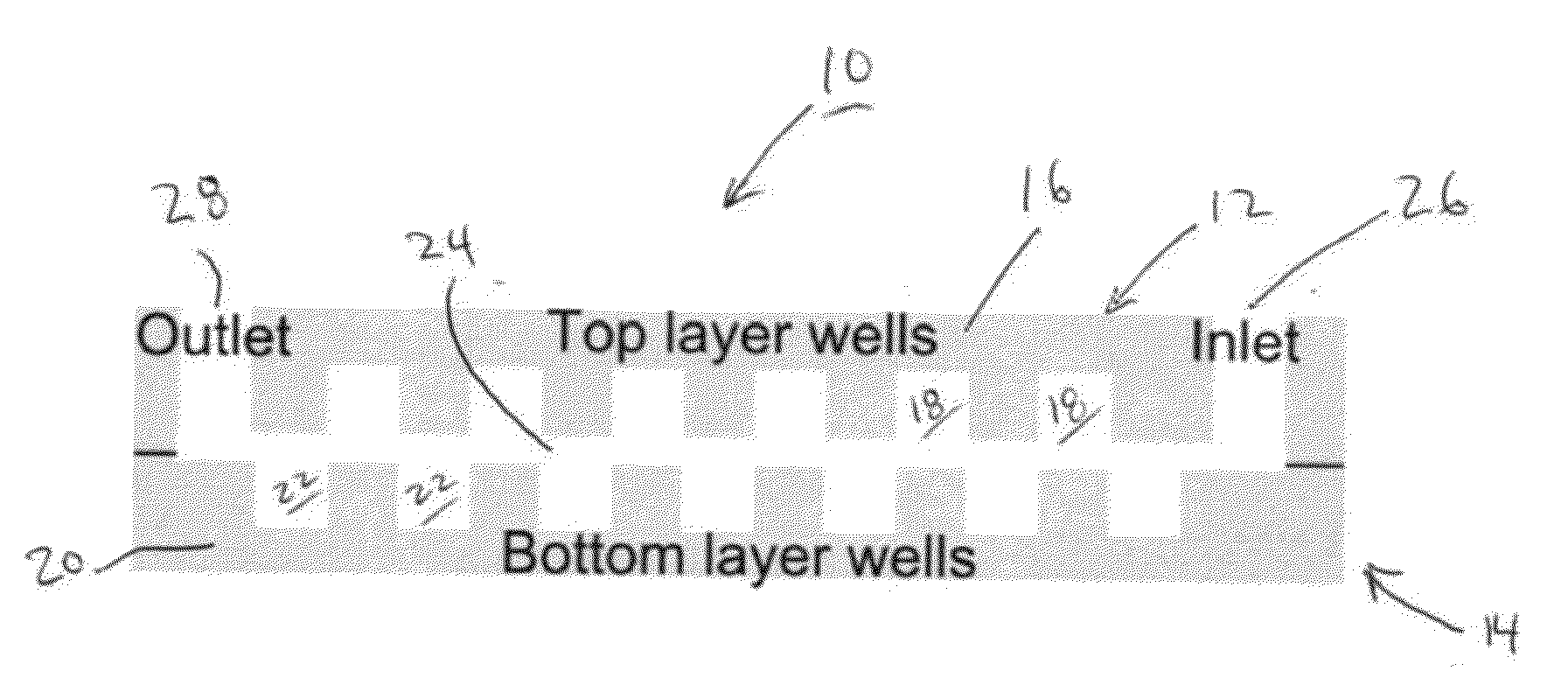

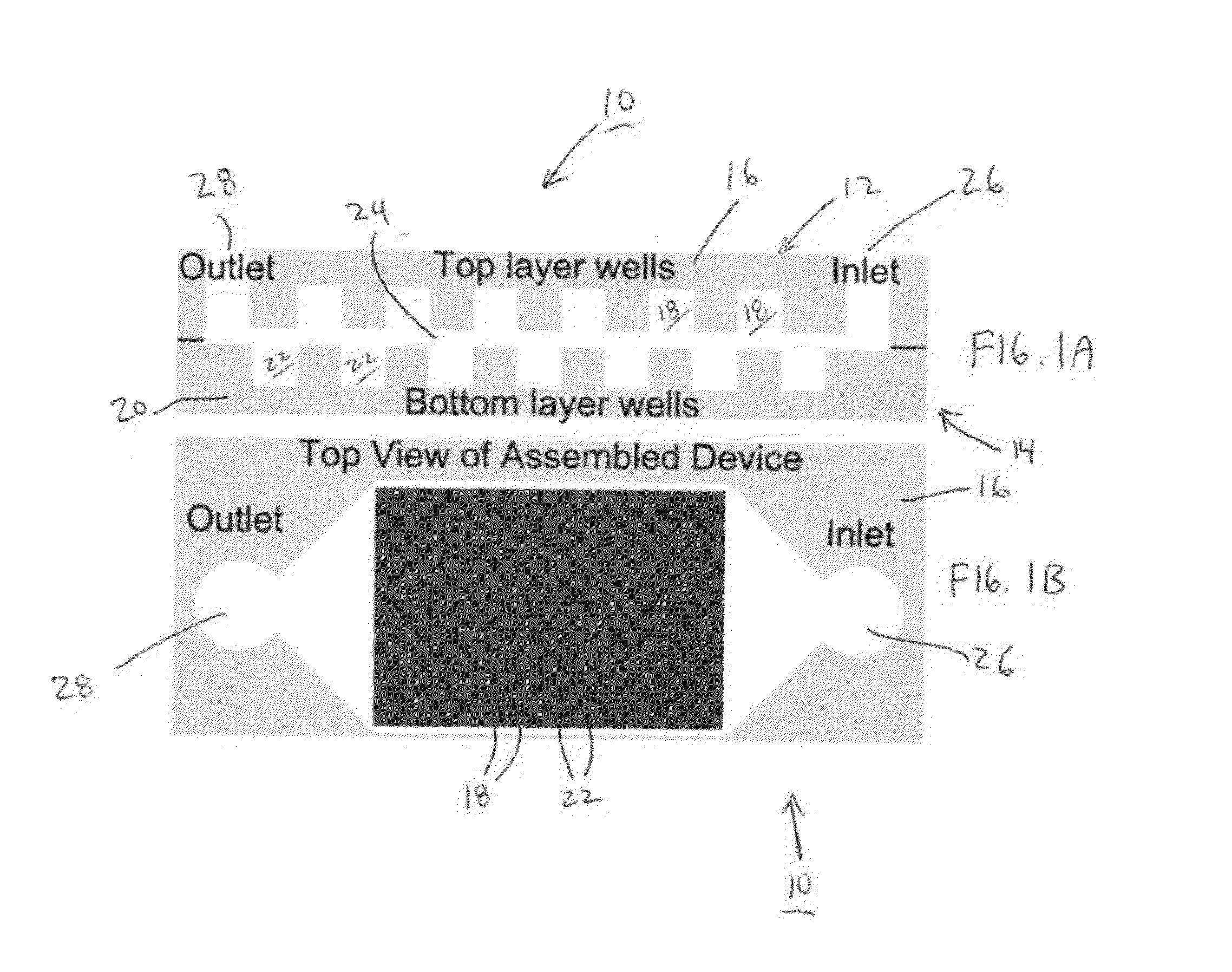

Multilayer high density microwells

ActiveUS20130052649A1Increase densityIncreased array densityBioreactor/fermenter combinationsBiological substance pretreatmentsEngineeringHigh density

Owner:RGT UNIV OF CALIFORNIA

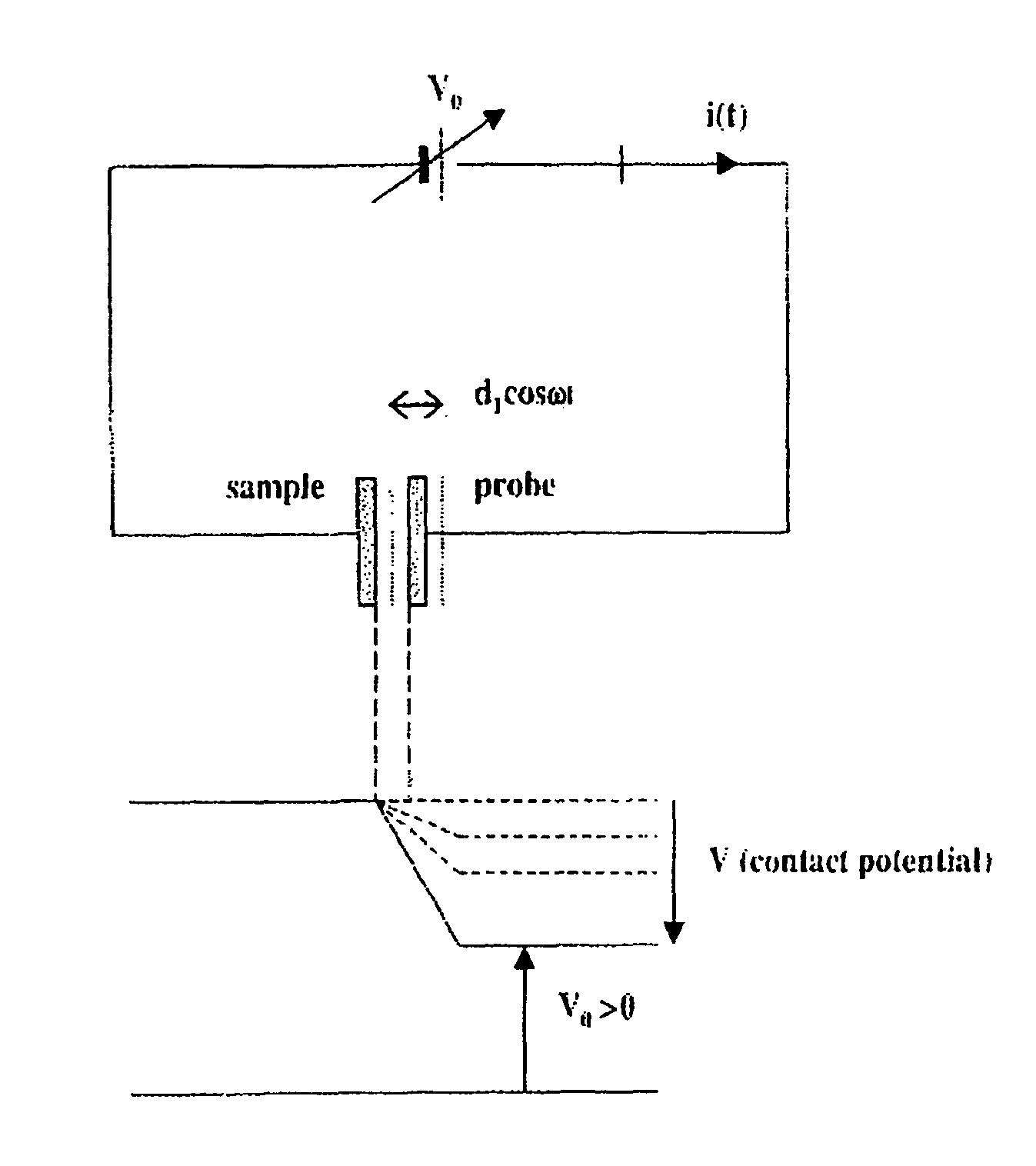

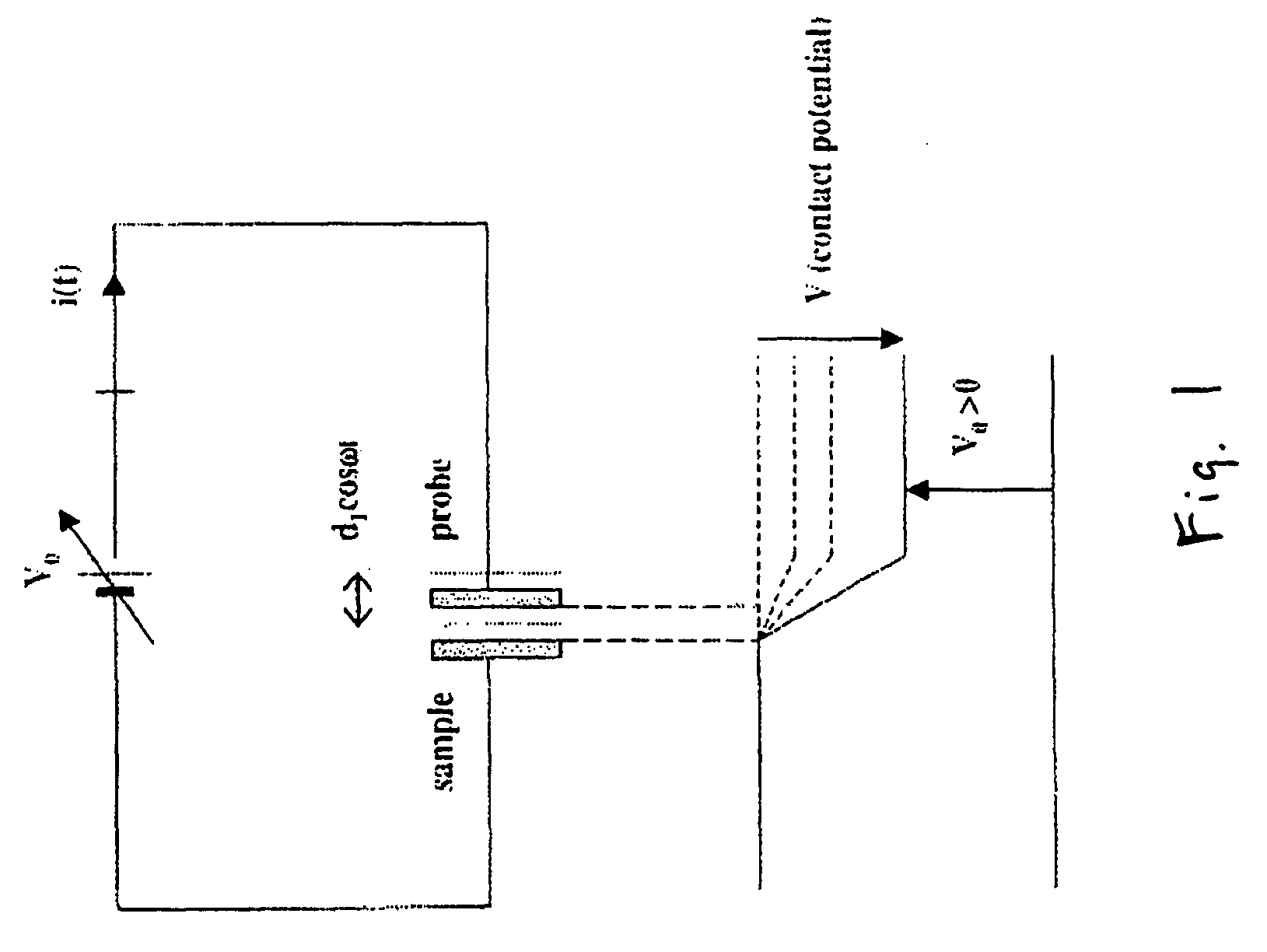

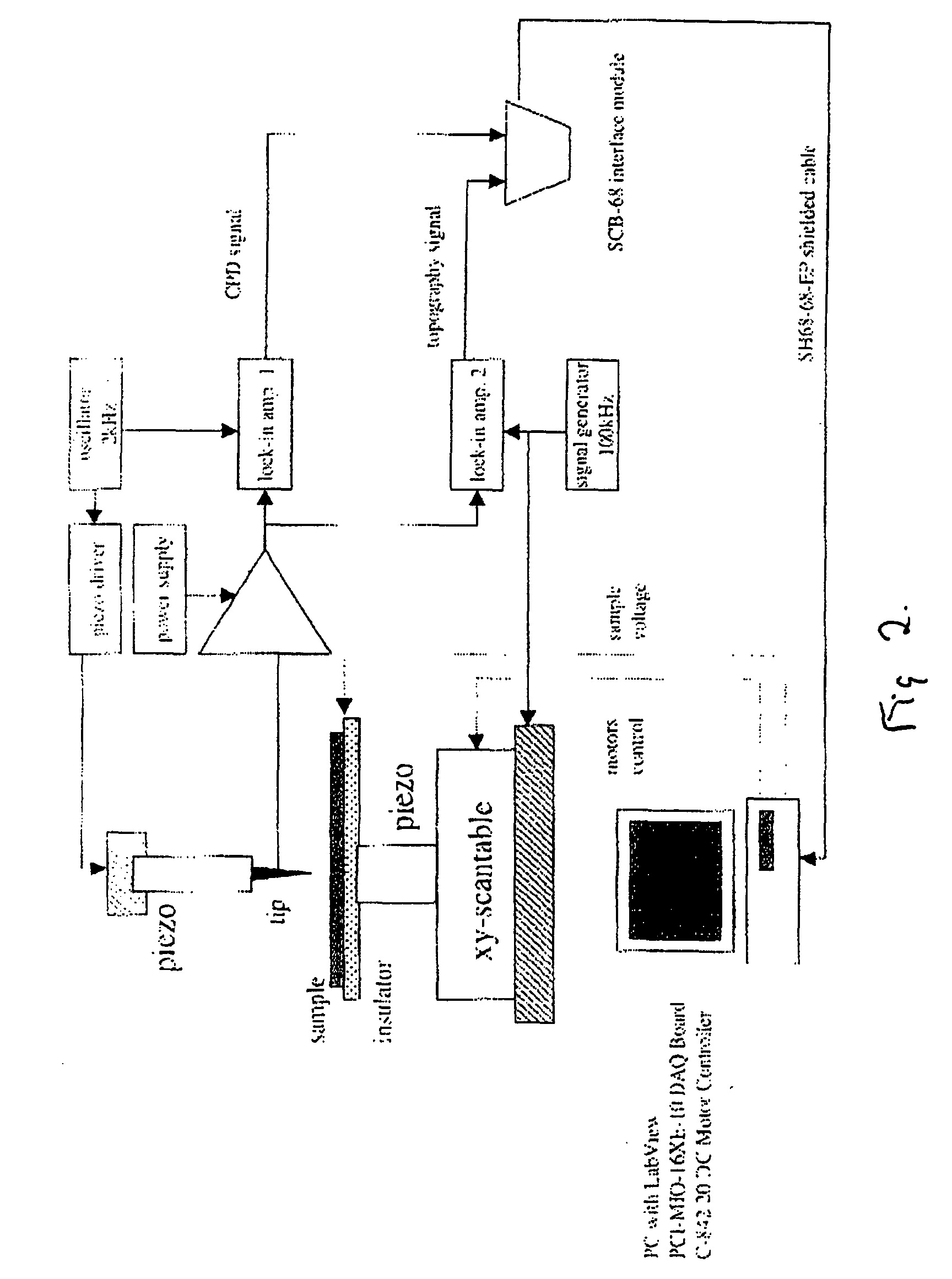

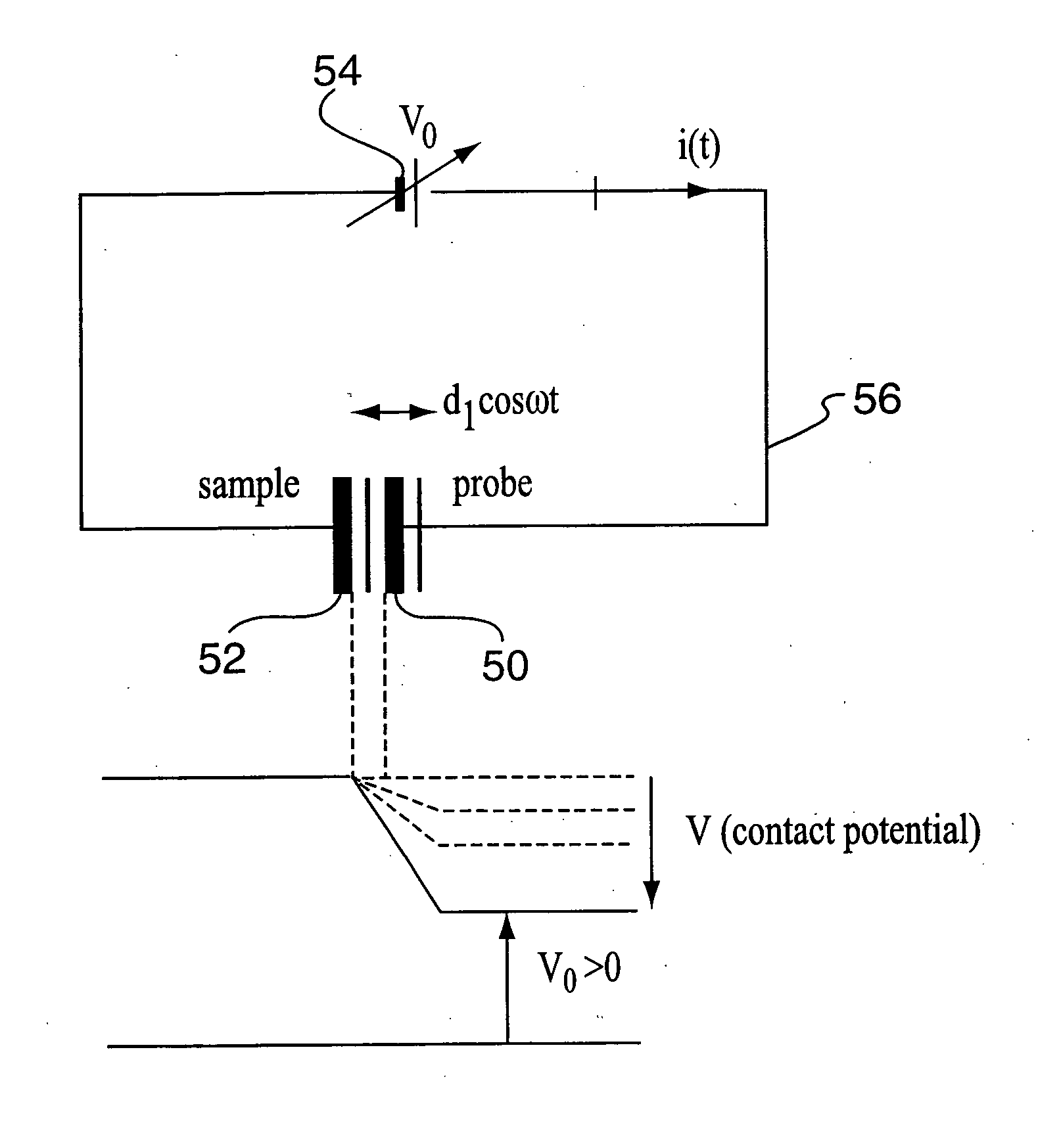

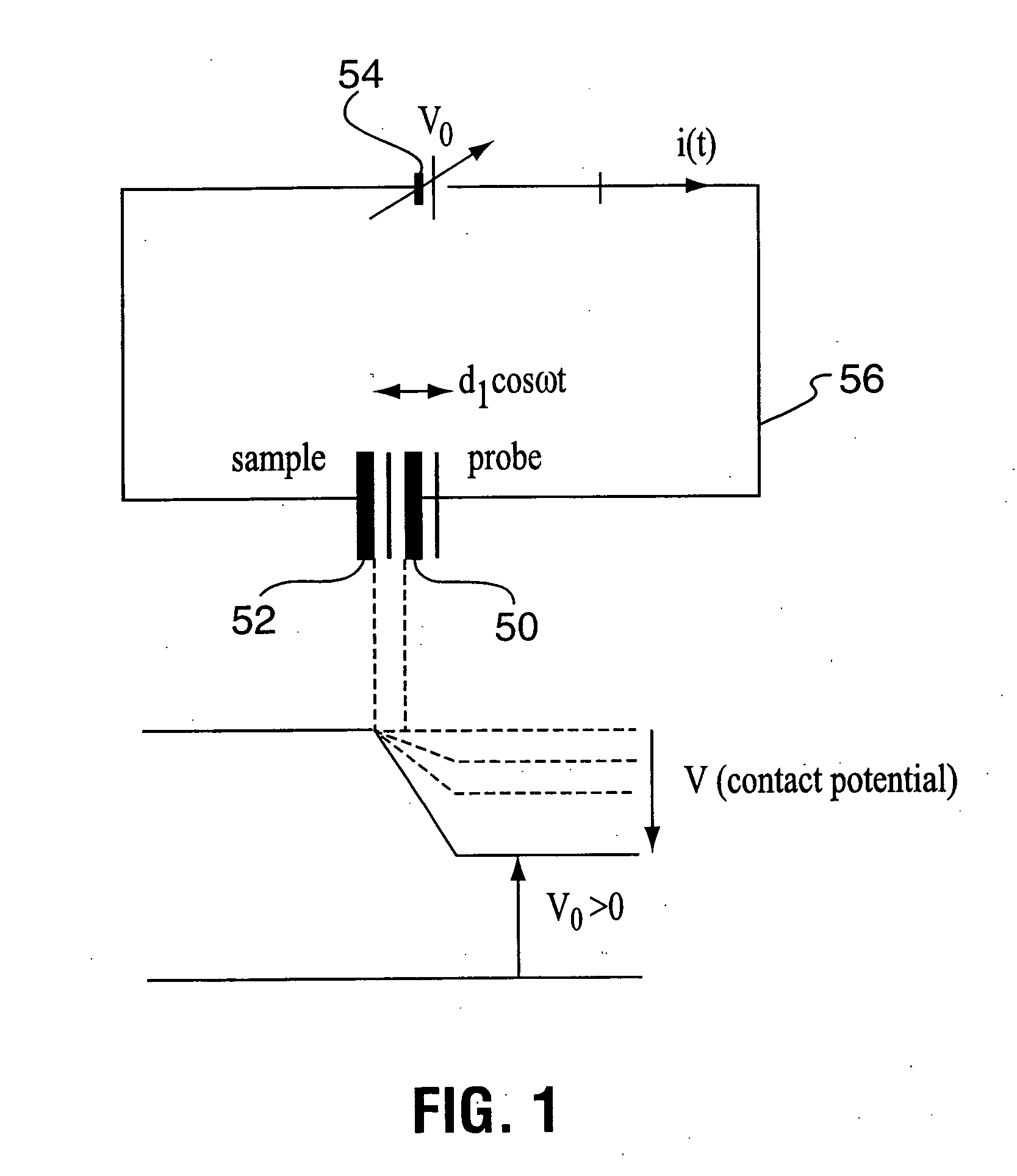

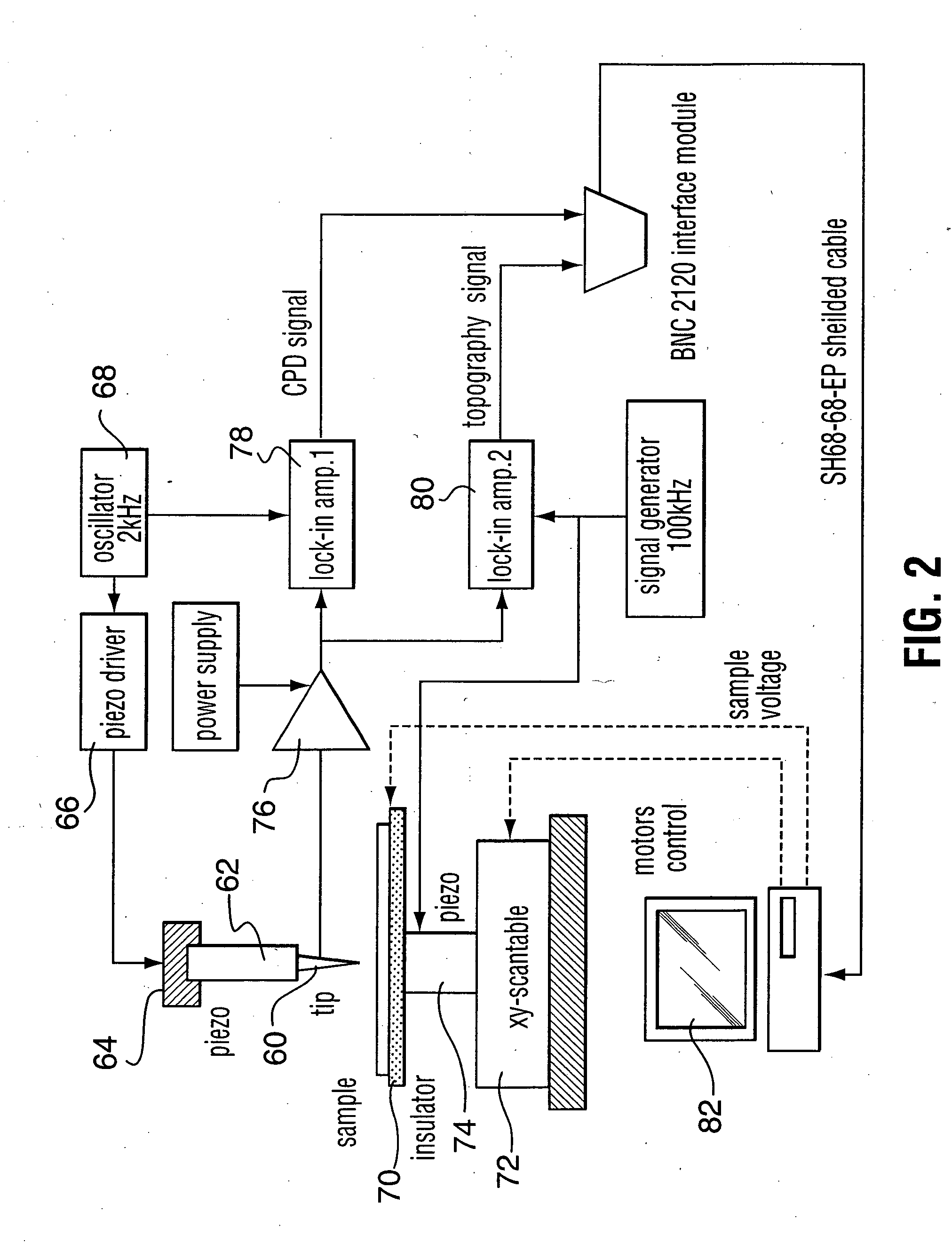

Scanning kelvinmicroprobe system and process for biomolecule microassay

InactiveUS20040029131A1Improve spatial resolutionHigh resolutionBioreactor/fermenter combinationsBiological substance pretreatmentsPotential differenceAntibody antigen

There is provided a system and process for detecting biomolecular interaction on a substrate having a biomolecule immobilized on a surface of the substrate. The system and process incorporate a scanning Kelvin microprobe (SKM) capable of analyzing surface topography as well as a contact potential difference image signal. Also provided is the use of SKM in measuring and analyzing biochemical molecular interactions between a probe bound to the surface of the substrate, and a target suspected to be present in a liquid sample. One of the probe and target combination is a biomolecule such as a nucleic acid, a polypeptide, or a small molecule, and an antibody antigen combination may be used.

Owner:SENSORCHEM INT

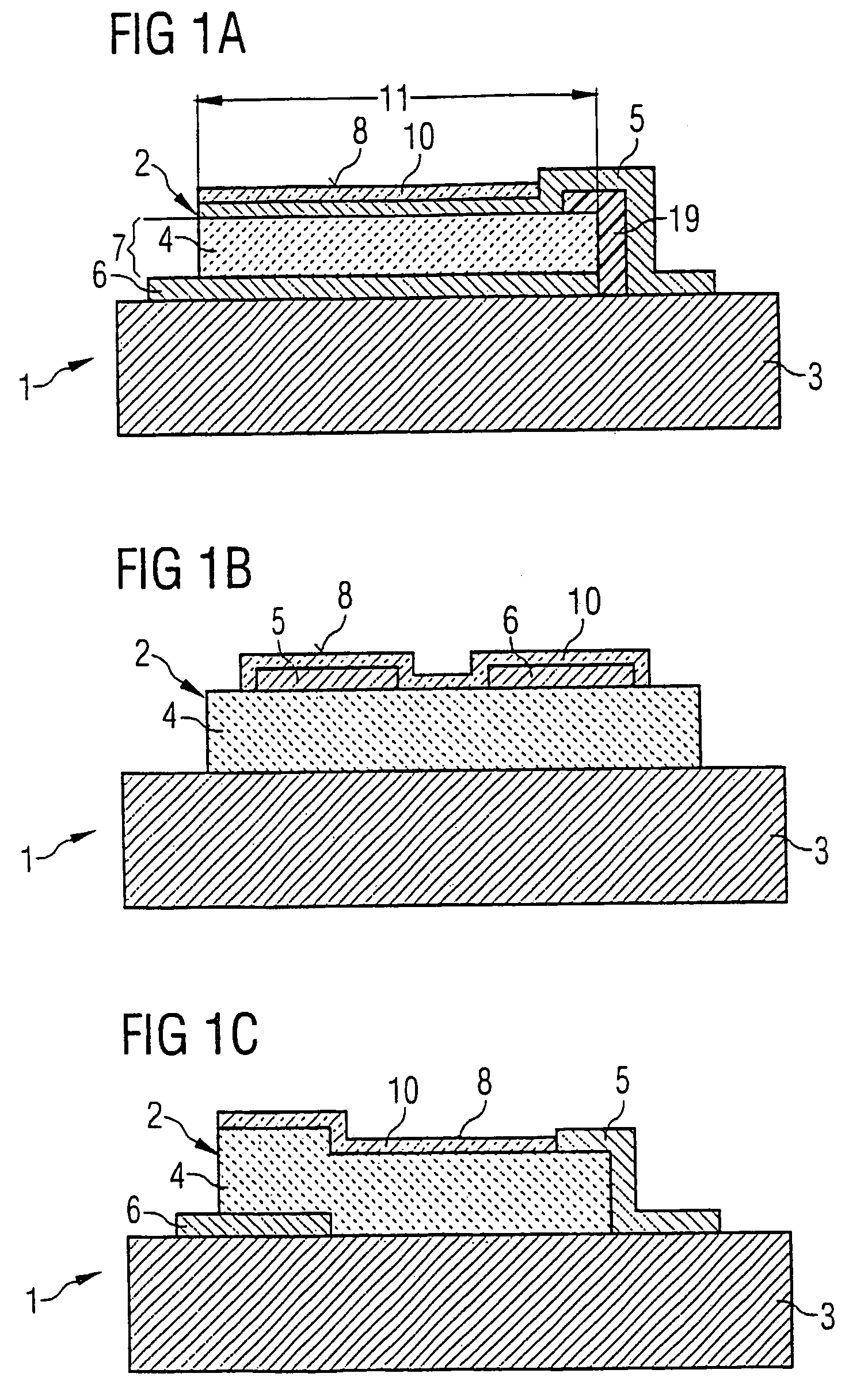

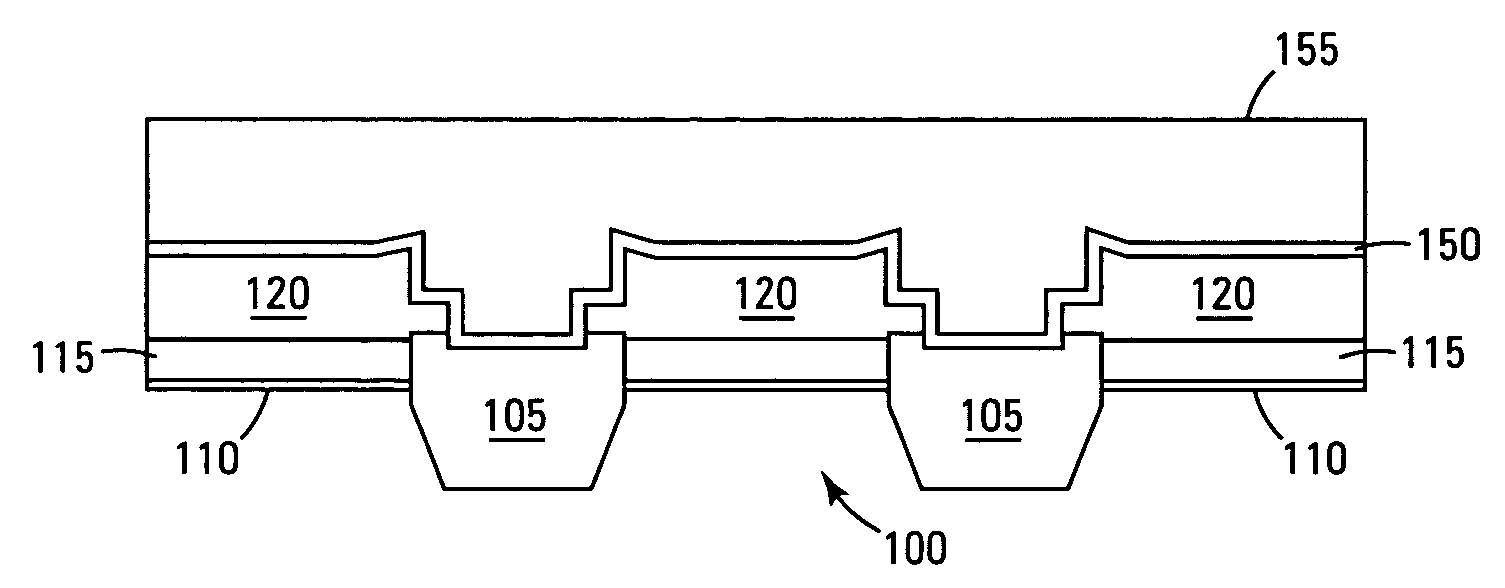

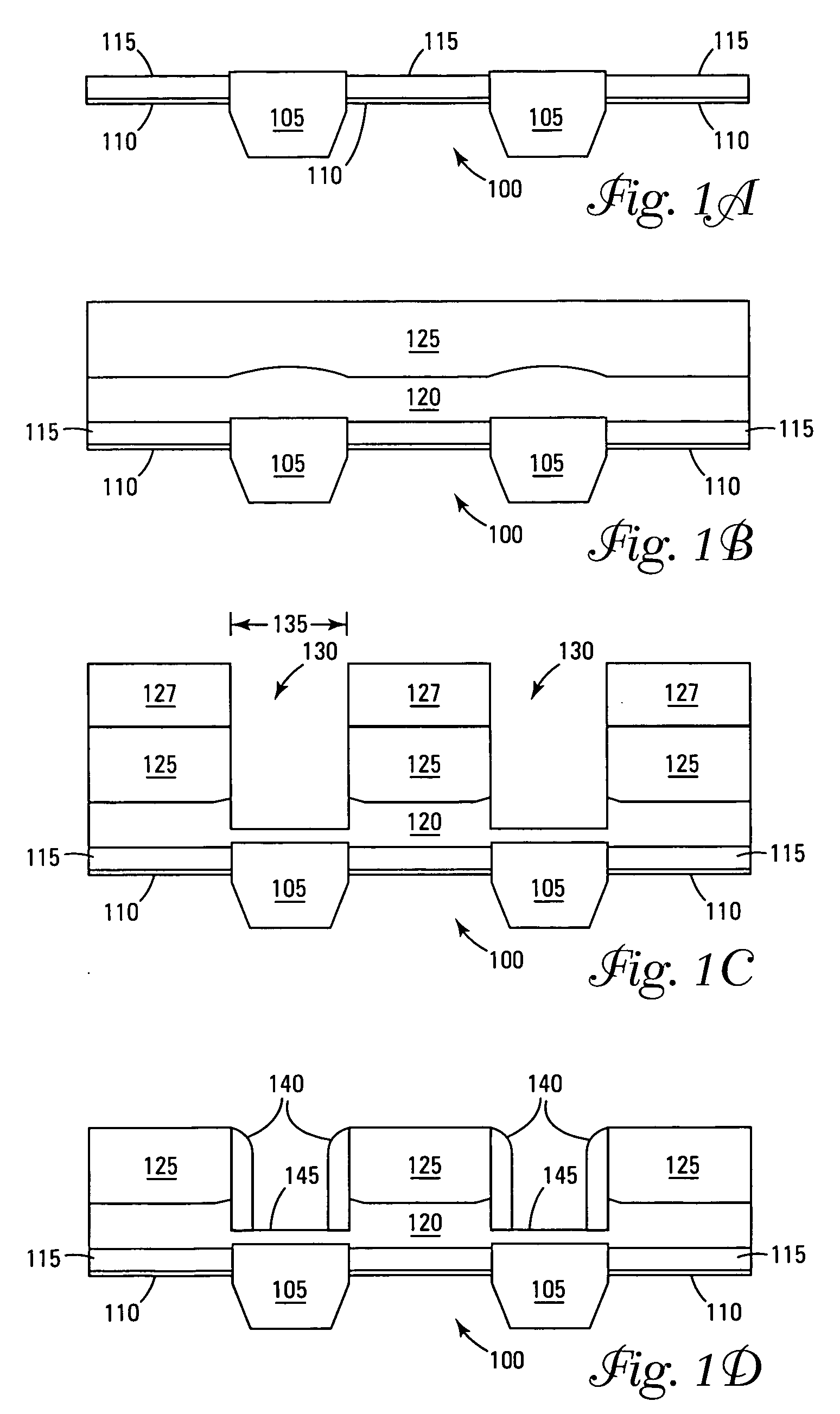

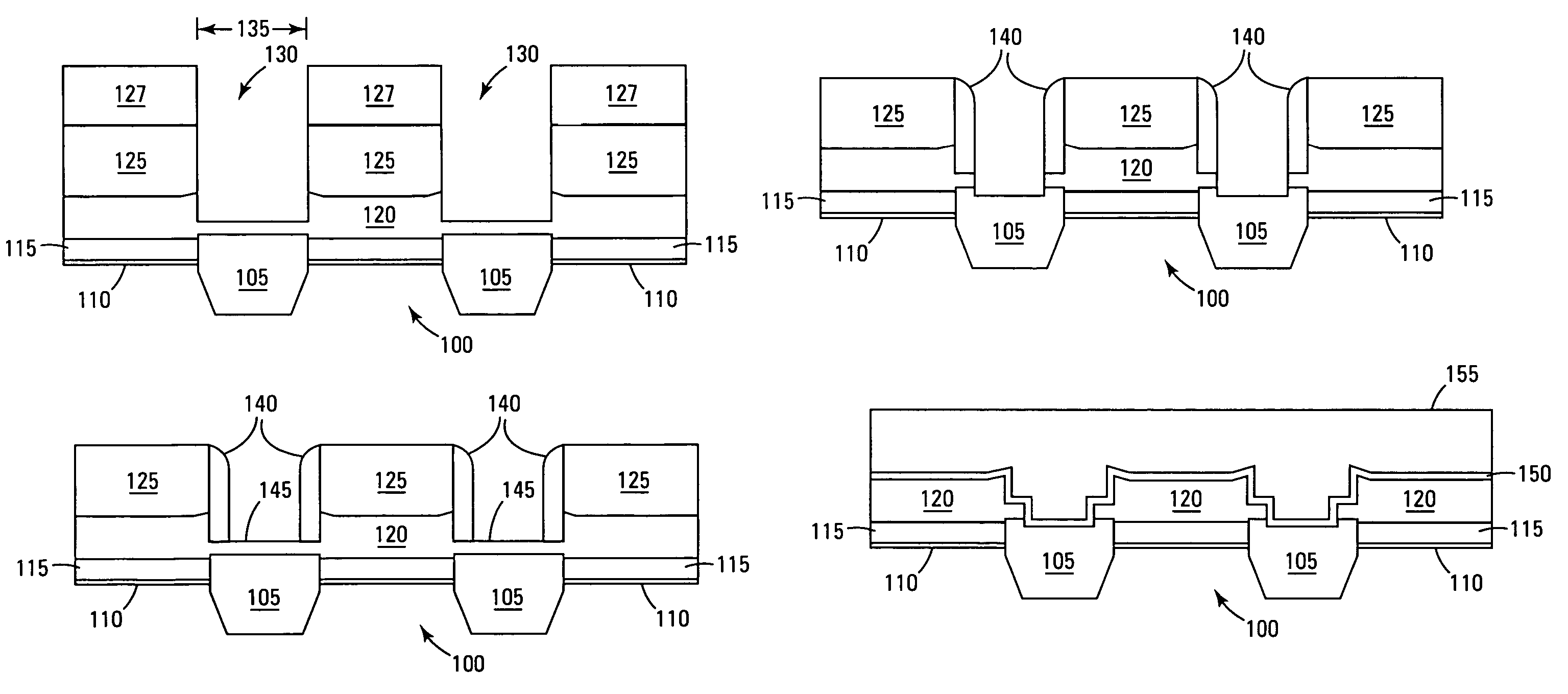

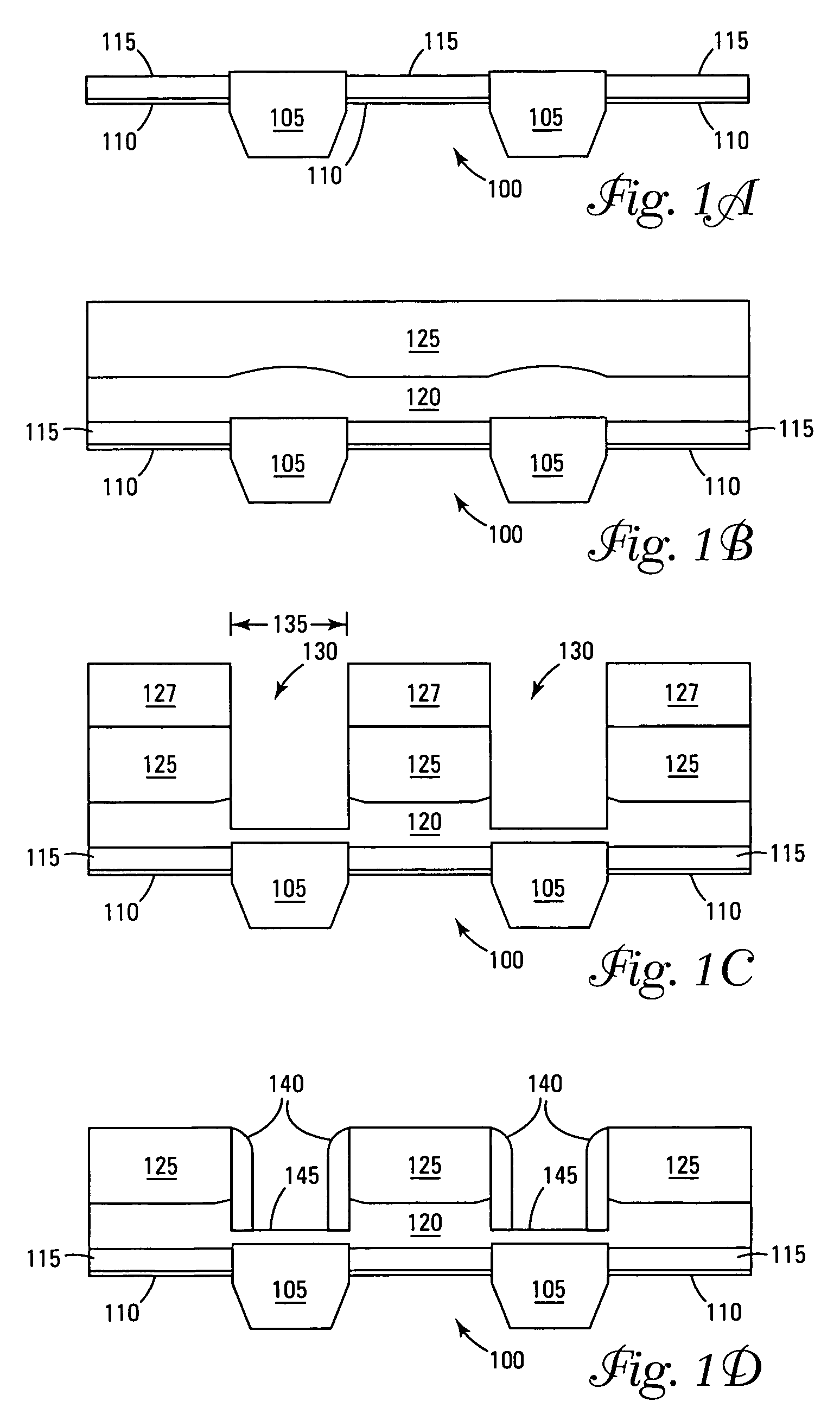

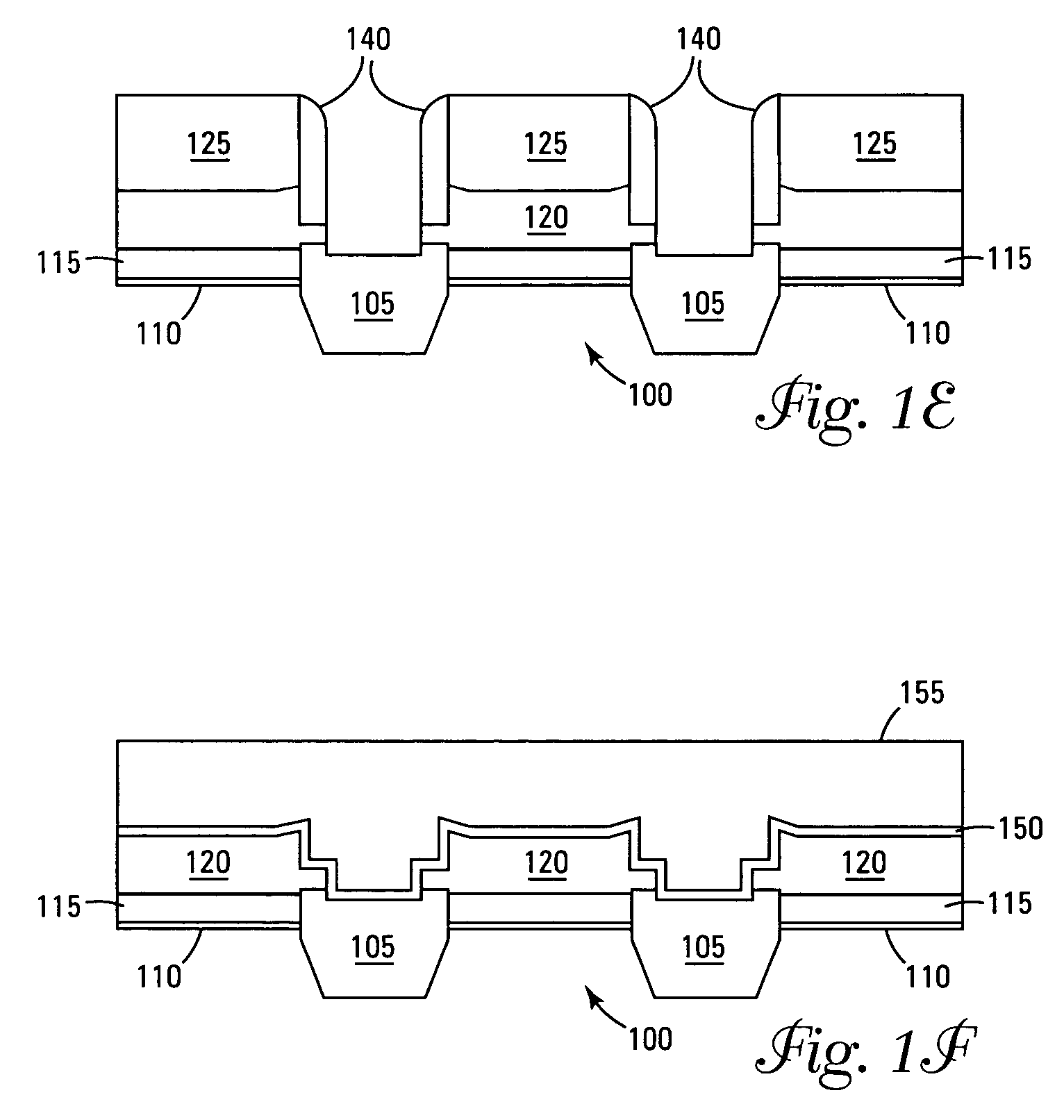

Gate coupling in floating-gate memory cells

ActiveUS20060043458A1Reduce spaceIncreased array densityTransistorSolid-state devicesParasitic capacitanceEngineering

Methods and apparatus utilizing a stepped floating gate structure to facilitate reduced spacing between adjacent cells without significantly impacting parasitic capacitance. The stepped structure results in a reduced surface area of a first floating gate in close proximity to an adjacent floating gate with substantially no reduction in coupling area, thus facilitating a reduction in parasitic capacitance leading to improved gate coupling characteristics. Also, because of the reduced surface area exposed to adjacent floating gates, the floating gates may be formed with reduced spacing, thus further leading to improved gate coupling characteristics.

Owner:MICRON TECH INC

Devices and methods for enrichment and alteration of circulating tumor cells and other particles

InactiveUS20110306043A1Increase in sizeIncrease array densityMicrobiological testing/measurementNanoinformaticsCirculating cancer cellTumor cells

The invention features devices and methods for detecting, enriching, and analyzing circulating tumor cells and other particles. The invention further features methods of diagnosing a condition, e.g., cancer, in a subject by analyzing a cellular sample from the subject.

Owner:THE GENERAL HOSPITAL CORP +1

Devices and Methods for Enrichment and Alteration of Circulating Tumor Cells and Other Particles

InactiveUS20120015835A1Increase array densitySmall particle sizePeptide librariesNanoinformaticsCirculating cancer cellTumor cells

The invention features devices and methods for detecting, enriching, and analyzing circulating tumor cells and other particles. The invention further features methods of diagnosing a condition, e.g., cancer, in a subject by analyzing a cellular sample from the subject.

Owner:THE GENERAL HOSPITAL CORP +1

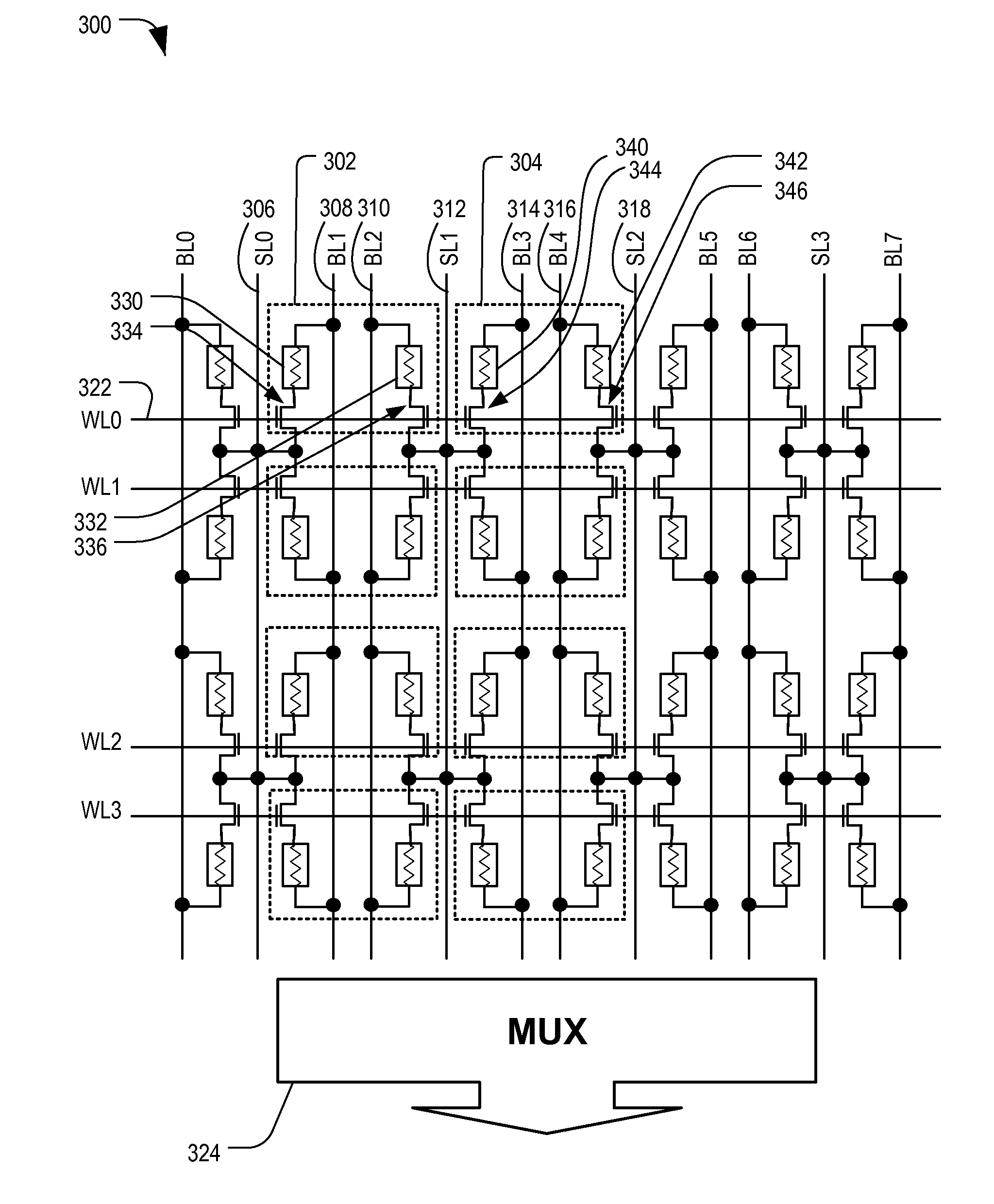

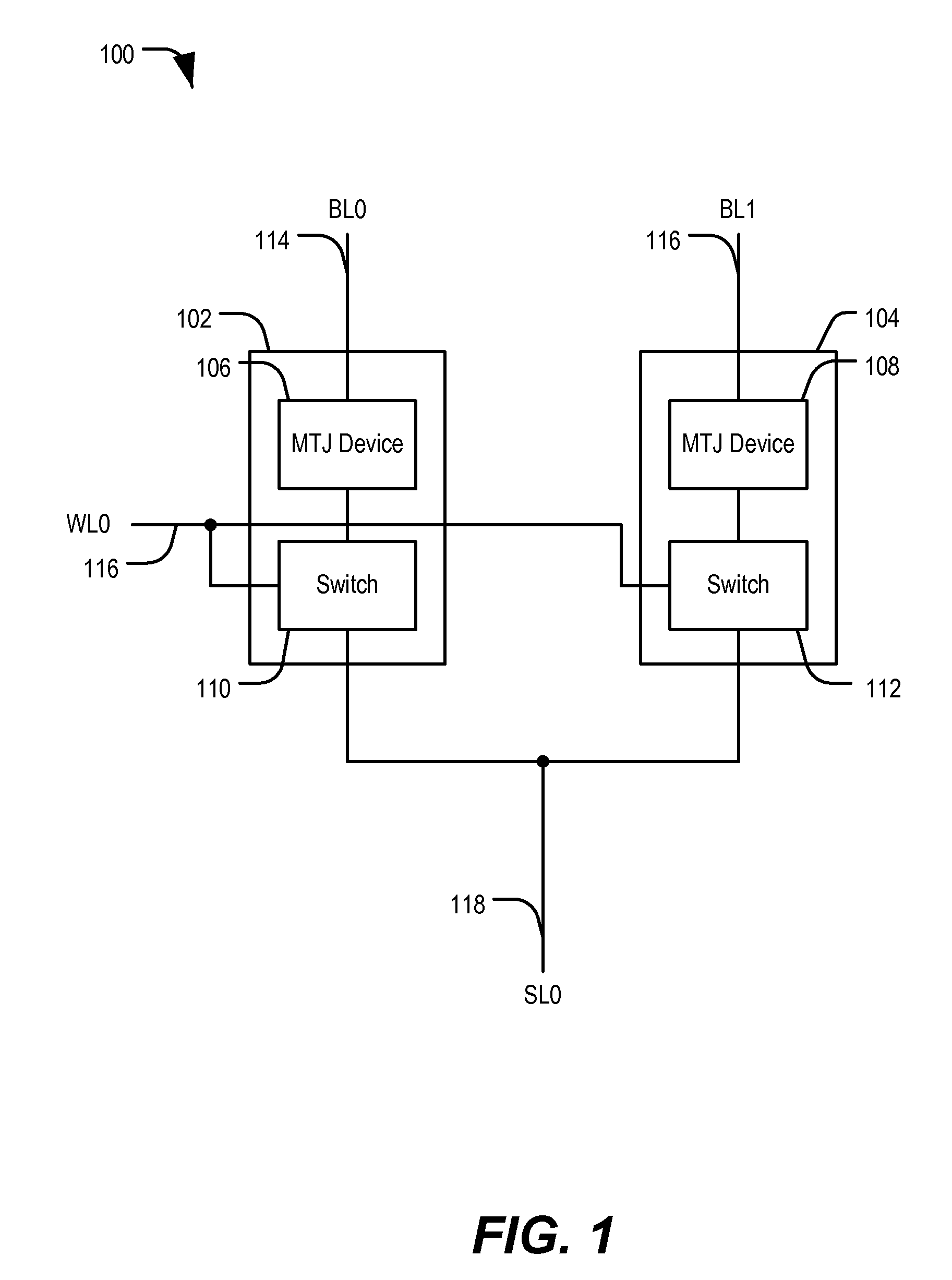

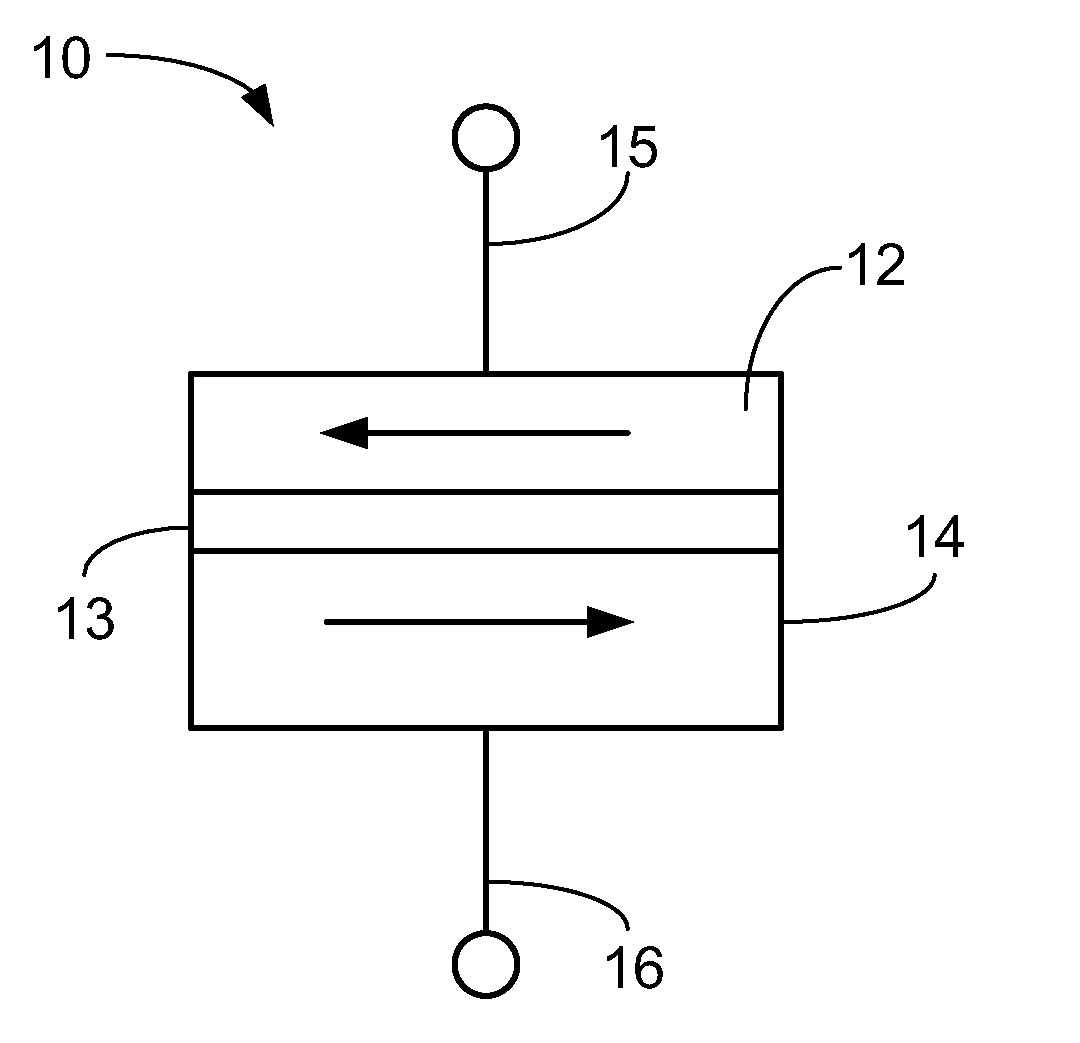

MRAM device with shared source line

In a particular embodiment, a memory device includes a first memory cell and a second memory cell. The memory device also includes a first bit line associated with the first memory cell and a second bit line associated with the second memory cell. The memory device also includes a source line coupled to the first memory cell and coupled to the second memory cell.

Owner:QUALCOMM INC

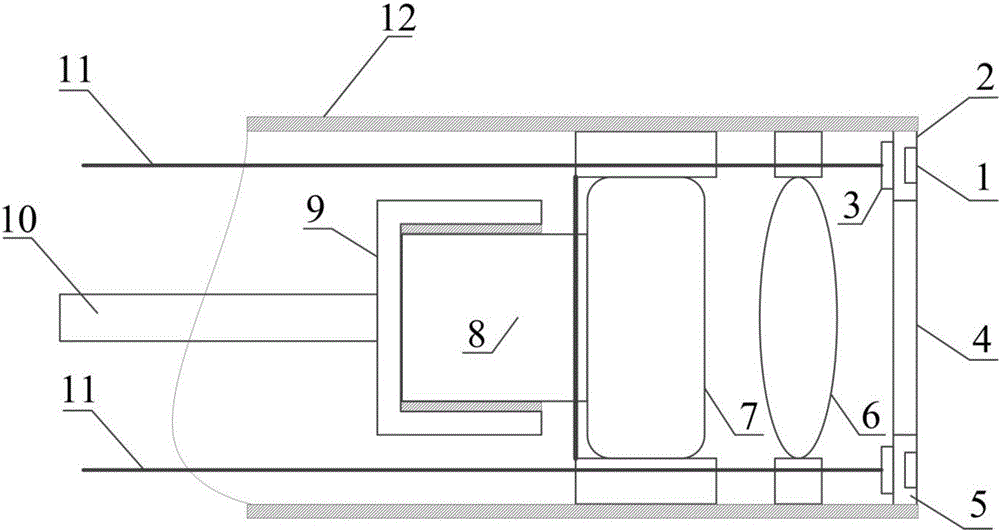

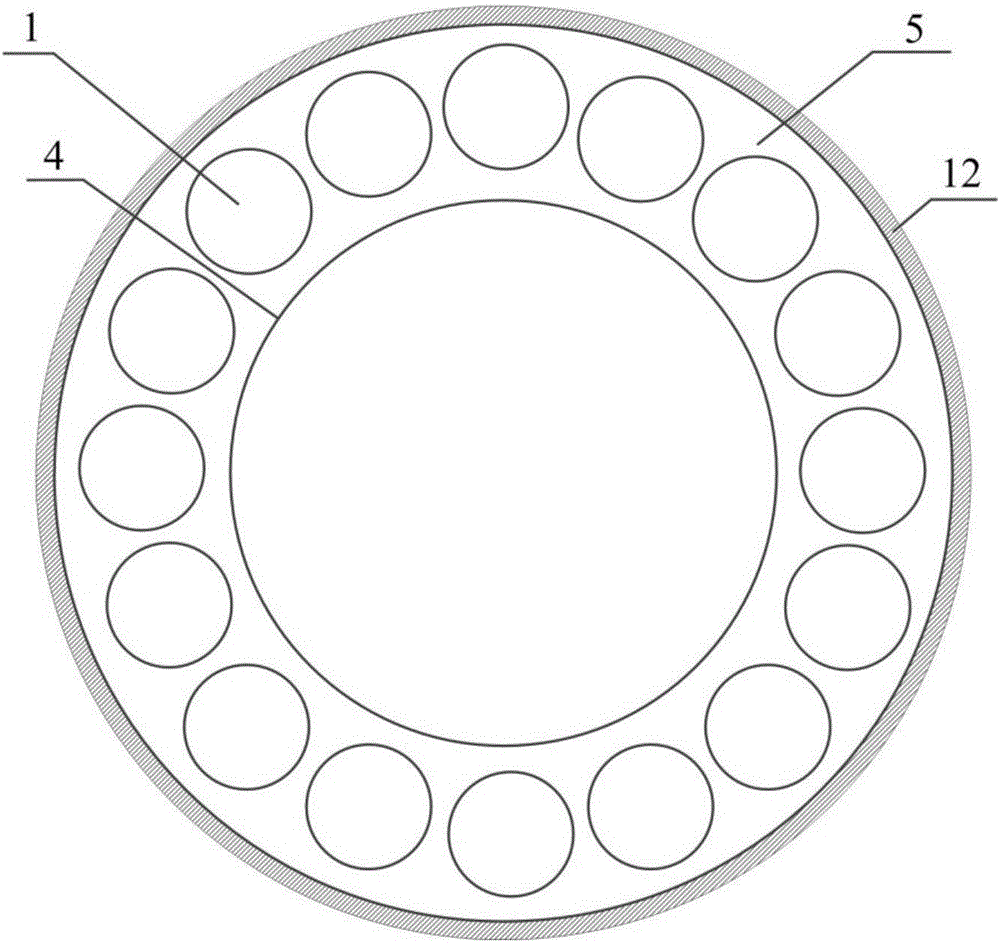

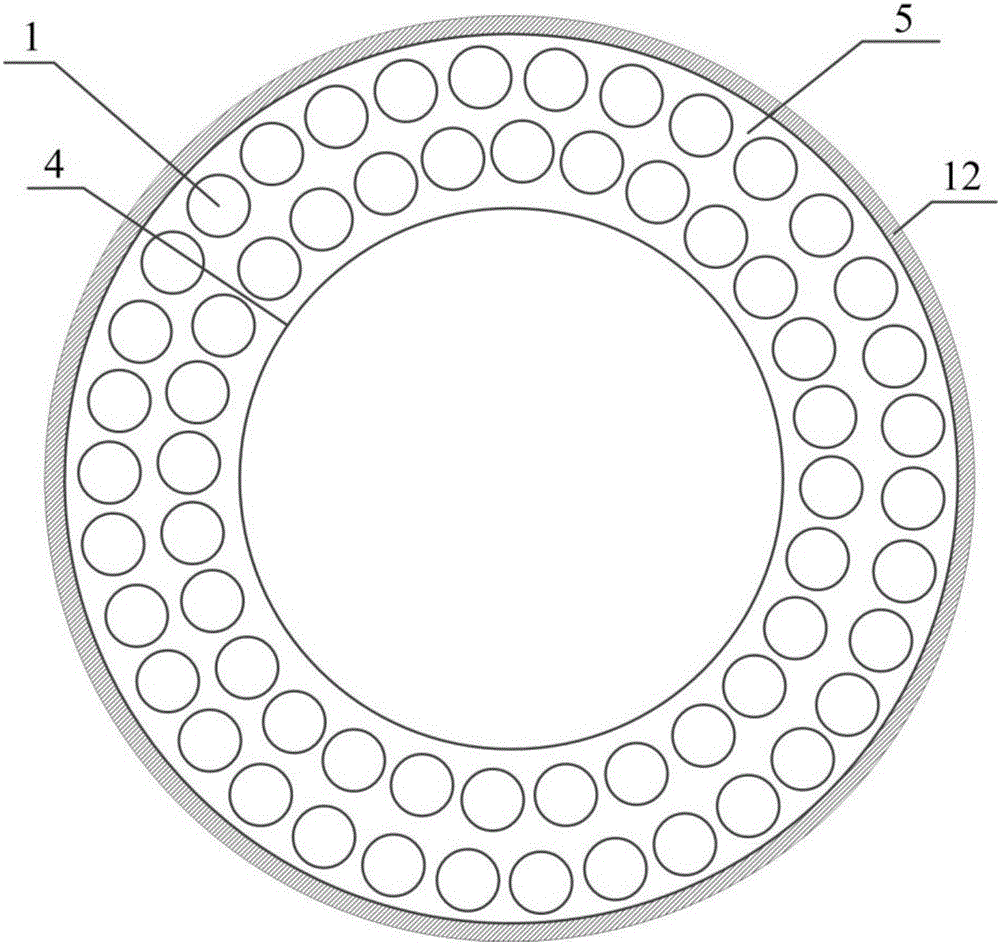

Optoacoustic/ultrasonic dual mode endoscope based on miniature piezoelectric ultrasonic transducer arrays

The invention discloses an optoacoustic / ultrasonic dual mode endoscope based on piezoelectric micromachined ultrasonic transducer arrays. The optoacoustic / ultrasonic dual mode endoscope includes a piezoelectric micromachined ultrasonic transducer (PMUT) array probe (2), a PMUT array element (1), an integrated circuit (3), a plane lens (4), a condenser lens (6), an optical fiber coupling collimator (7), a single-mode fiber (8), an optical fiber FC / APC connector (9), an optical fiber (10), a signal line (11) and an housing (12). The optoacoustic / ultrasonic dual mode endoscope is characterized in that, the piezoelectric micromachined ultrasonic transducers are adopted, the transducers and the integrated circuit are good in compatibility during manufacturing process, and the transducers are easy to form an array; transducer arrays are adopted, the endoscope does not need to rotate, the imaging speed is raised, real time imaging is achieved; and the multiple transducer arrays can effectively raise the signal to noise ratio of a signal, deep imaging through focusing and scanning is achieved. The optoacousitc / ultrasonic dual mode endoscope can be widely applied to fields of medical endoscopes and industrial flaw detection, and particularly has great application value in in-vivo scar tissue identification, assessment of damage of ablation of tissue, atherosclerotic degree assessment and the like.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

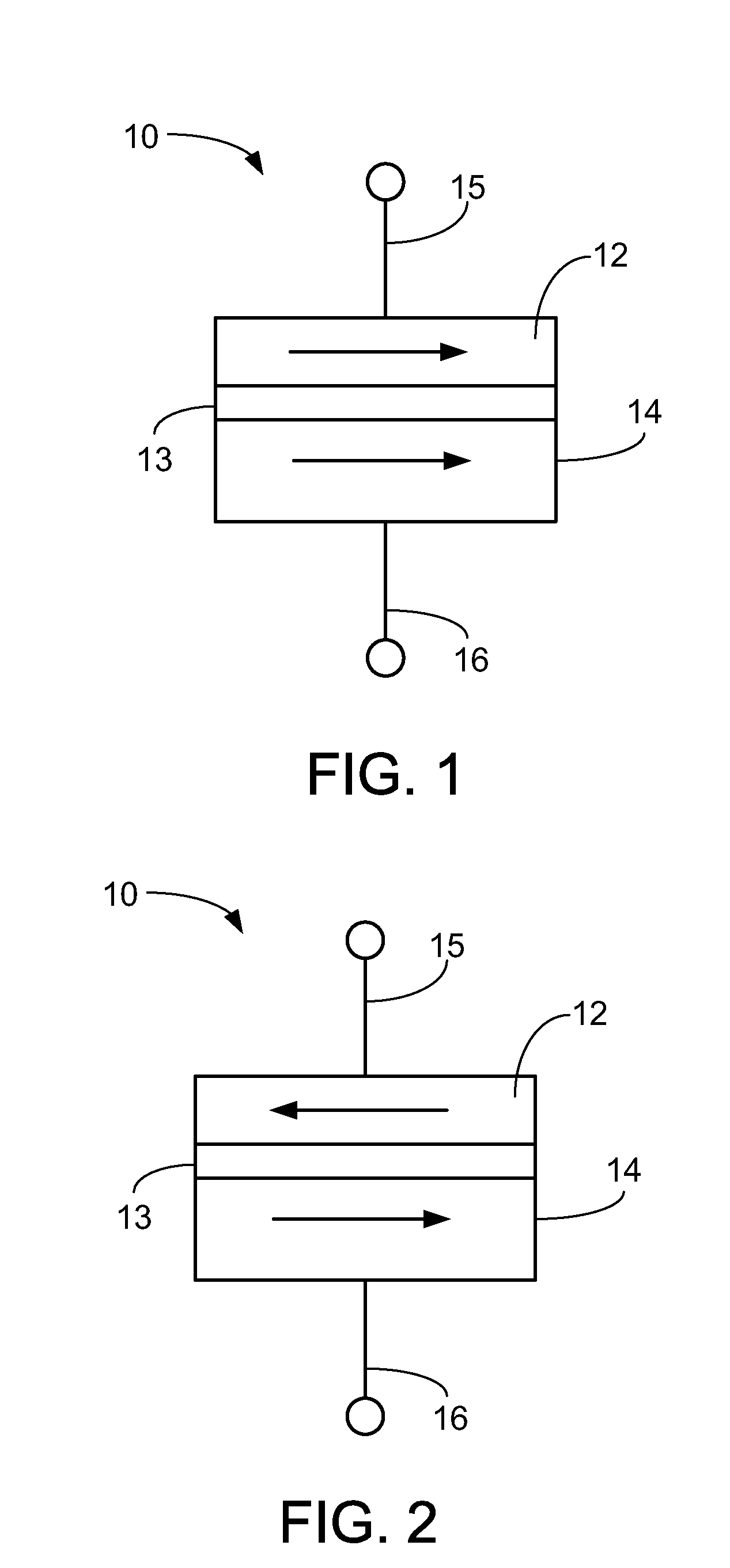

Static source plane in stram

ActiveUS20100080053A1Reduced dimensionIncrease array densityDigital storageSource planeHigh resistance

The present disclosure relates to a memory array including a plurality of magnetic tunnel junction cells arranged in an array. Each magnetic tunnel junction cell is electrically coupled between a bit line and a source line. The magnetic tunnel junction cell is configured to switch between a high resistance state and a low resistance state by passing a write current passing though the magnetic tunnel junction cell. A transistor is electrically between the magnetic tunnel junction cell and the source line. A word line is electrically coupled to a gate of the transistor. The source line is a common source line for the plurality of magnetic tunnel junctions.

Owner:EVERSPIN TECHNOLOGIES

Dynamic random access memory device with the combined open/folded bit-line pair arrangement

InactiveUSRE36993E1High integration densityHighly integratedTransistorSolid-state devicesSense amplifierBit plane

A dynamic random access memory device includes a semiconductor substrate, a plurality of parallel word lines on the substrate, and a plurality of pairs of bit lines transverse to the word lines on the substrate. An array of one-transistor memory cells are selectively arranged at the cross points as defined between the word lines and the bit lines. The array is subdivided into a plurality of subarray sections. A sense amplifier section is connected to the bit lines. The sense amplifier section includes first and second sense amplifier circuits. Adjacent bit-line pairs of the bit lines include a first bit-line pair and a second bit-line pair, one of which has a folded bit-line arrangement being included in a certain subarray section to be connected to the first sense amplifier circuit, and the other of which has an open bit-line arrangement that extends into the subarray section and another subarray section adjacent thereto, and is connected to the second sense amplifier circuit.

Owner:KK TOSHIBA

Devices and methods for enrichment and alteration of circulating tumor cells and other particles

InactiveUS20110294186A1Increase array densitySmall particle sizeBioreactor/fermenter combinationsBiological substance pretreatmentsCirculating cancer cellOncology

Owner:ON Q ITY

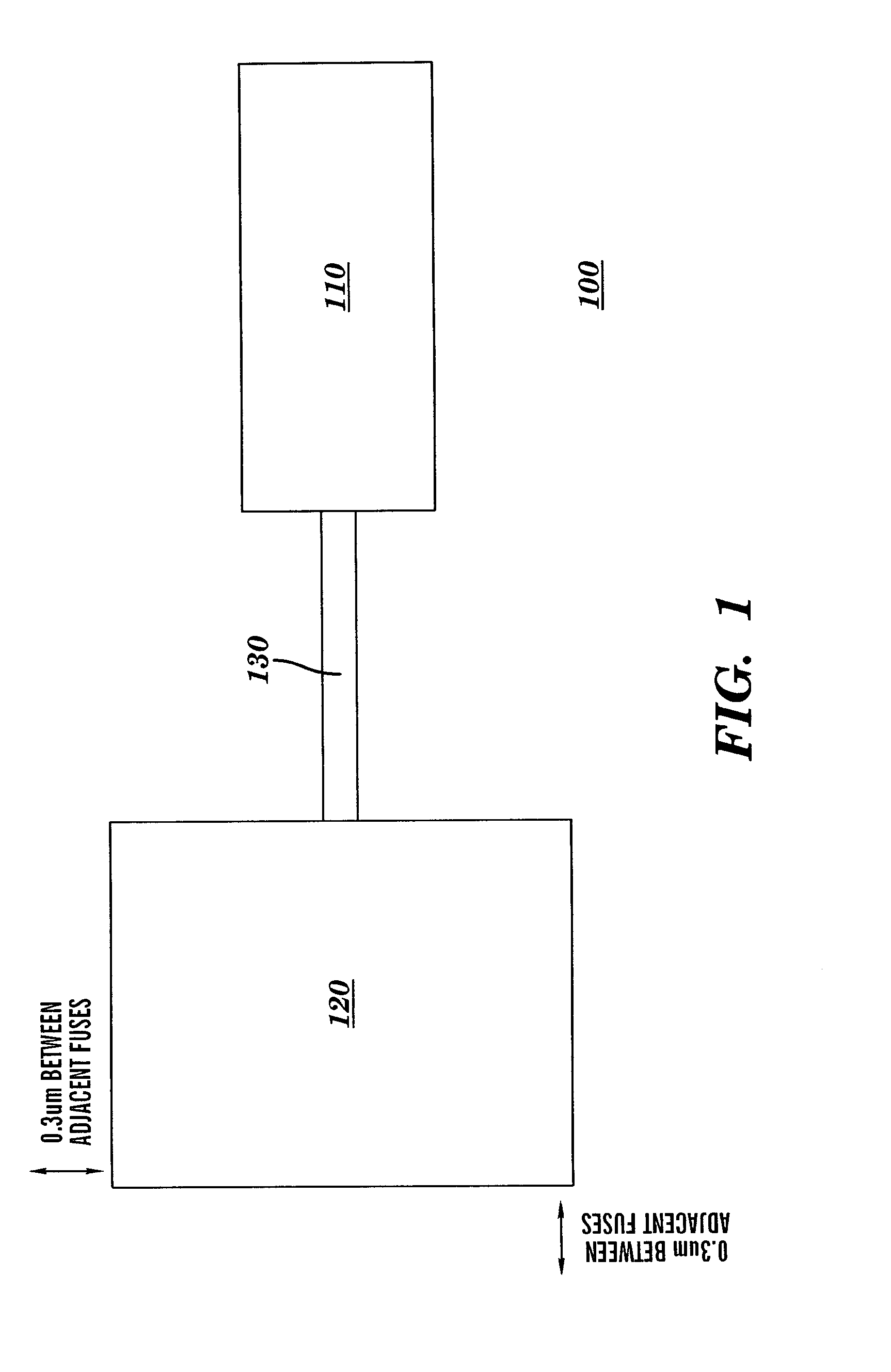

Dense semiconductor fuse array

ActiveUS7227207B2Increase array densityEliminate needSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionEngineering

The present invention provides a dense semiconductor fuse array having common cathodes. The dense semiconductor fuse array of the present invention occupies less area than conventional semiconductor fuse arrays, can comprise integrated diodic components, and can require only one metal wiring layer for making electrical connections to the fuse array.

Owner:GLOBALFOUNDRIES US INC

Gate coupling in floating-gate memory cells

ActiveUS7115458B2Reduce spacingImpacting parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingParasitic capacitance

Methods and apparatus utilizing a stepped floating gate structure to facilitate reduced spacing between adjacent cells without significantly impacting parasitic capacitance. The stepped structure results in a reduced surface area of a first floating gate in close proximity to an adjacent floating gate with substantially no reduction in coupling area, thus facilitating a reduction in parasitic capacitance leading to improved gate coupling characteristics. Also, because of the reduced surface area exposed to adjacent floating gates, the floating gates may be formed with reduced spacing, thus further leading to improved gate coupling characteristics.

Owner:MICRON TECH INC

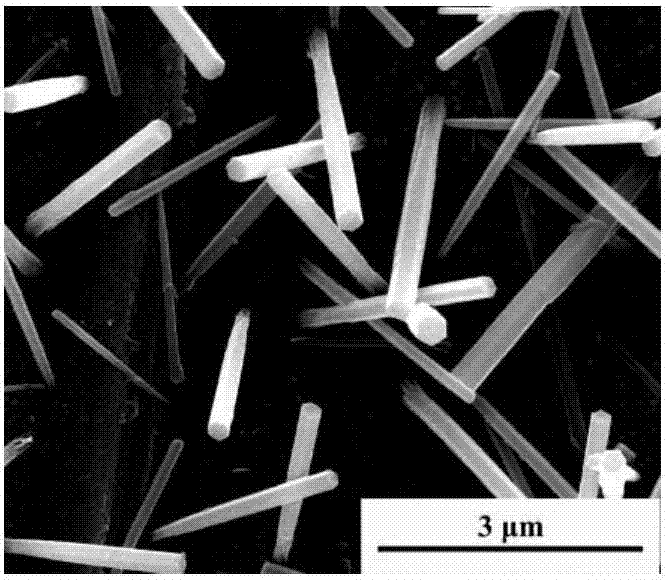

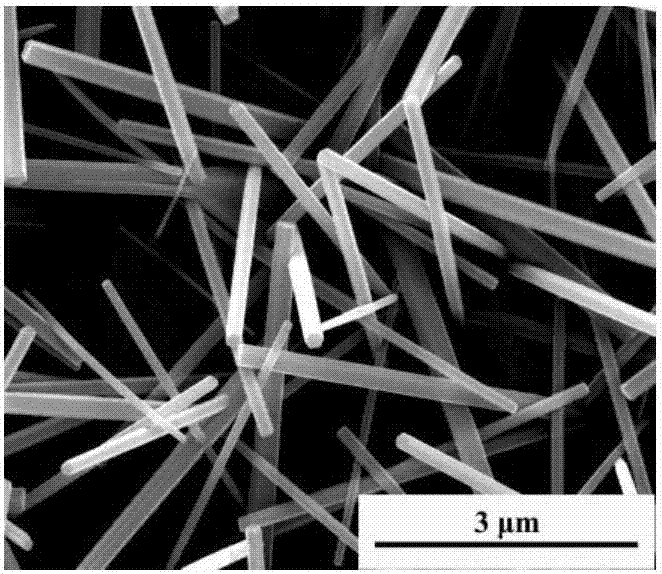

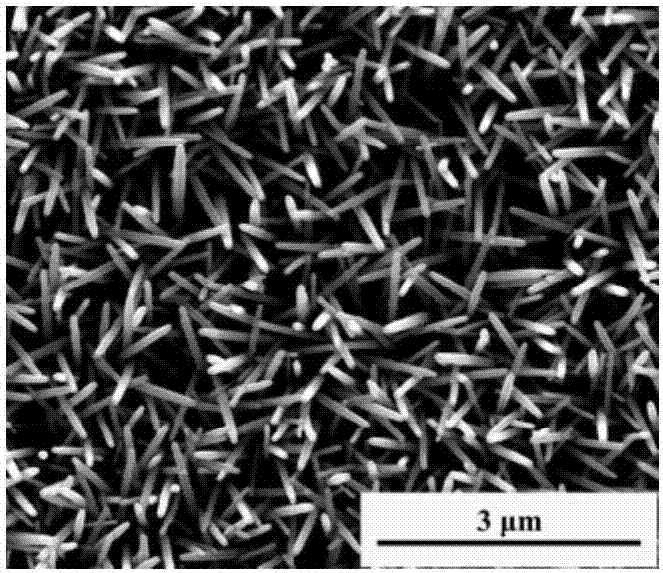

Method for constructing micro-nano structure with antibacterial function on surface of metal substrate

InactiveCN107488838AAchieve killBroad spectrum antibacterialNanotechnologyLiquid/solution decomposition chemical coatingMicro nanoEscherichia coli

The invention discloses a method for constructing a micro-nano structure with an antibacterial function on the surface of a metal substrate. The method comprises the following steps: carrying out technologies of metal surface cleaning, annealing heat treatment, lifting and drawing to prepare a ZnO seed crystal layer and hydrothermal growth of a nano array for surface treatment, and finally obtaining a metal plate target product with a ZnO nano array. The ZnO array prepared by the method has a large number of nanoscale tip array structures, the array density can reach 1*10 <7>-1*10 <9> pieces / cm <2>, and the tip diameter of nanorods forming the array ranges from 30 nm to 150 nm. The surface of the array can rapidly sterilize bacteria by making contact with bacterial strains, the surface bacteria can be killed within 1 minute, the sterilizing rate for the escherichia coli (ATCC 25922) and the staphylococcus aureus (ATCC 6538) can reach more than 99.99%, and the surface of the array has a rapid broad-spectrum bactericidal performance.

Owner:SOUTHWEST JIAOTONG UNIV

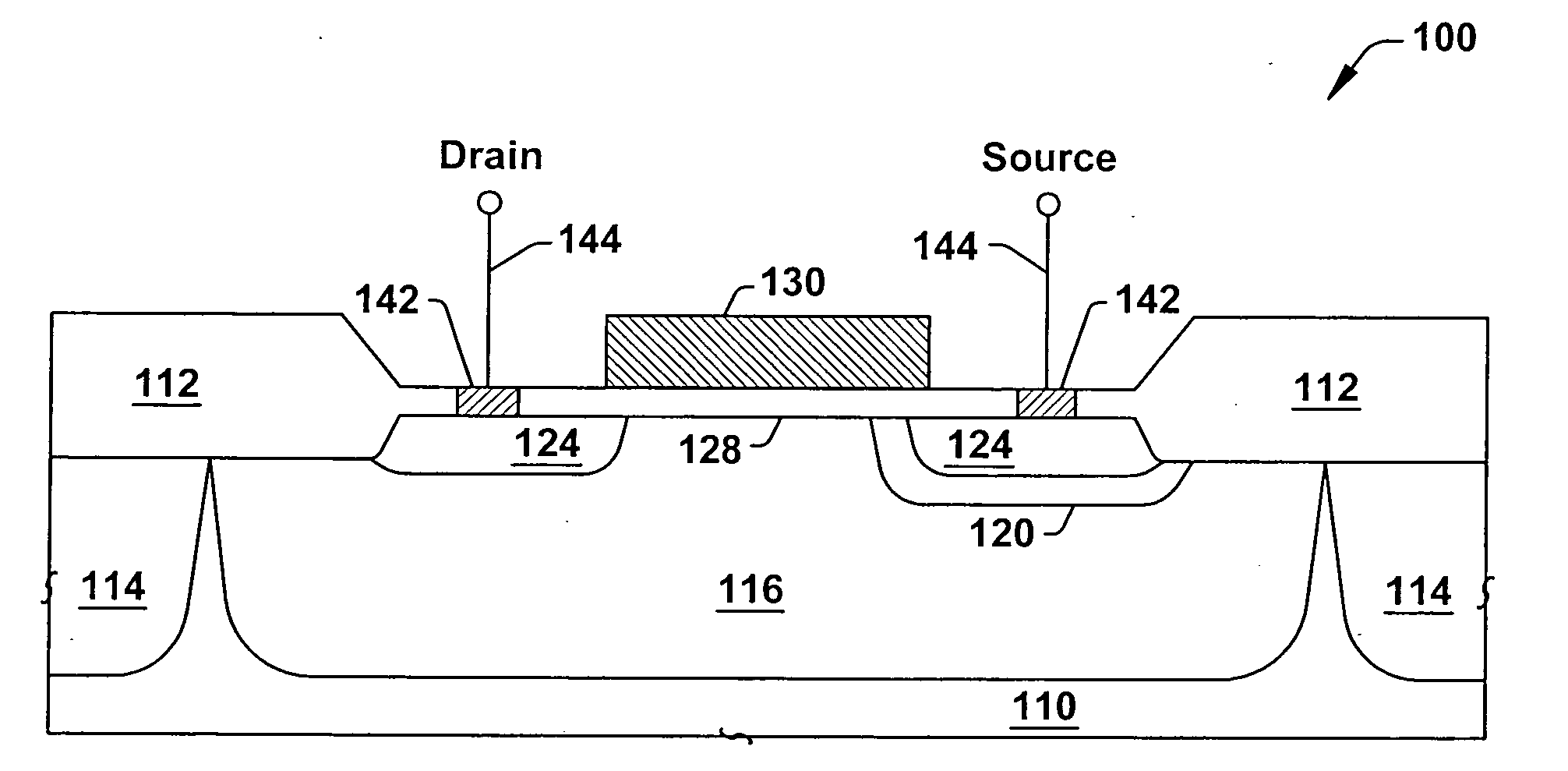

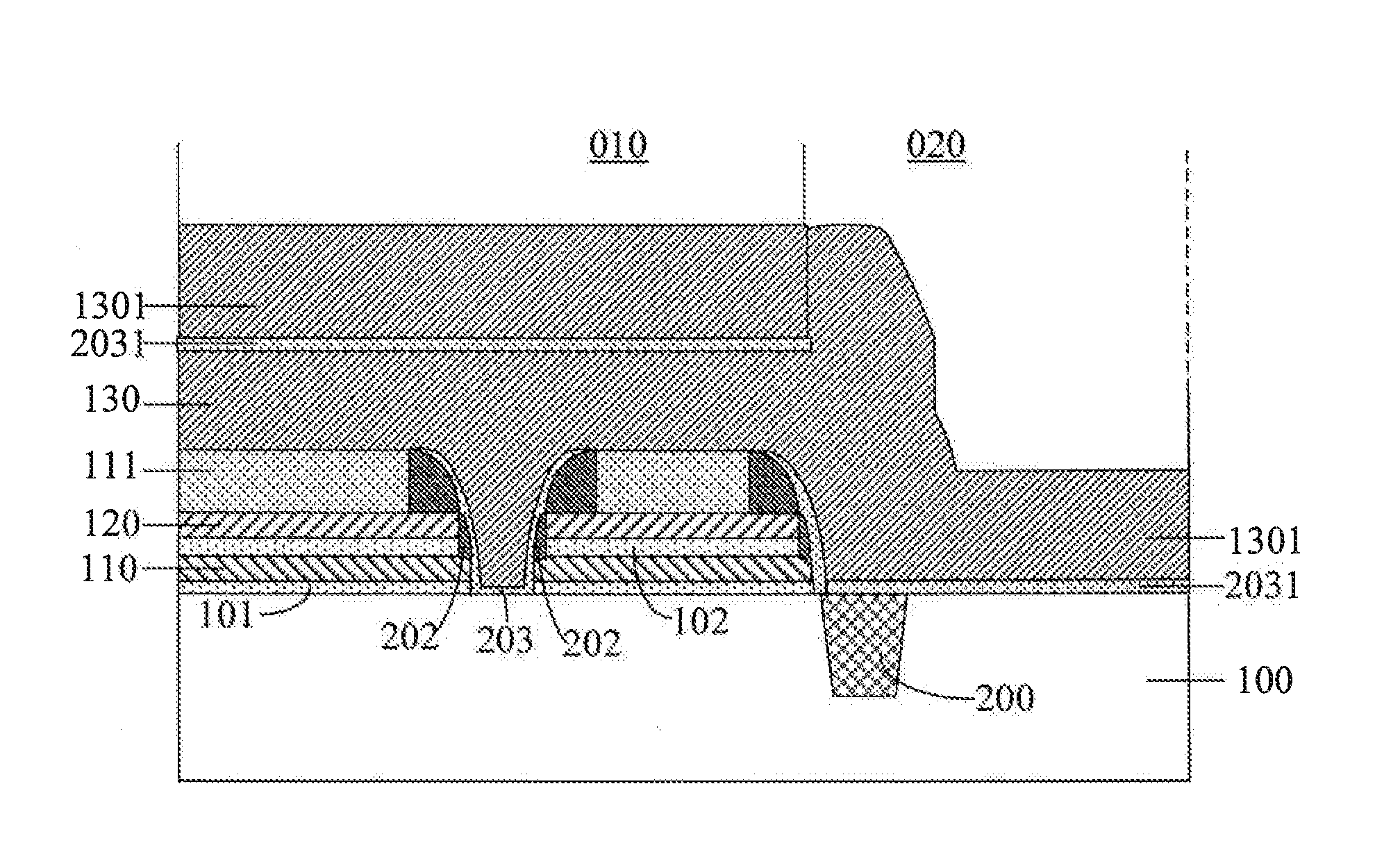

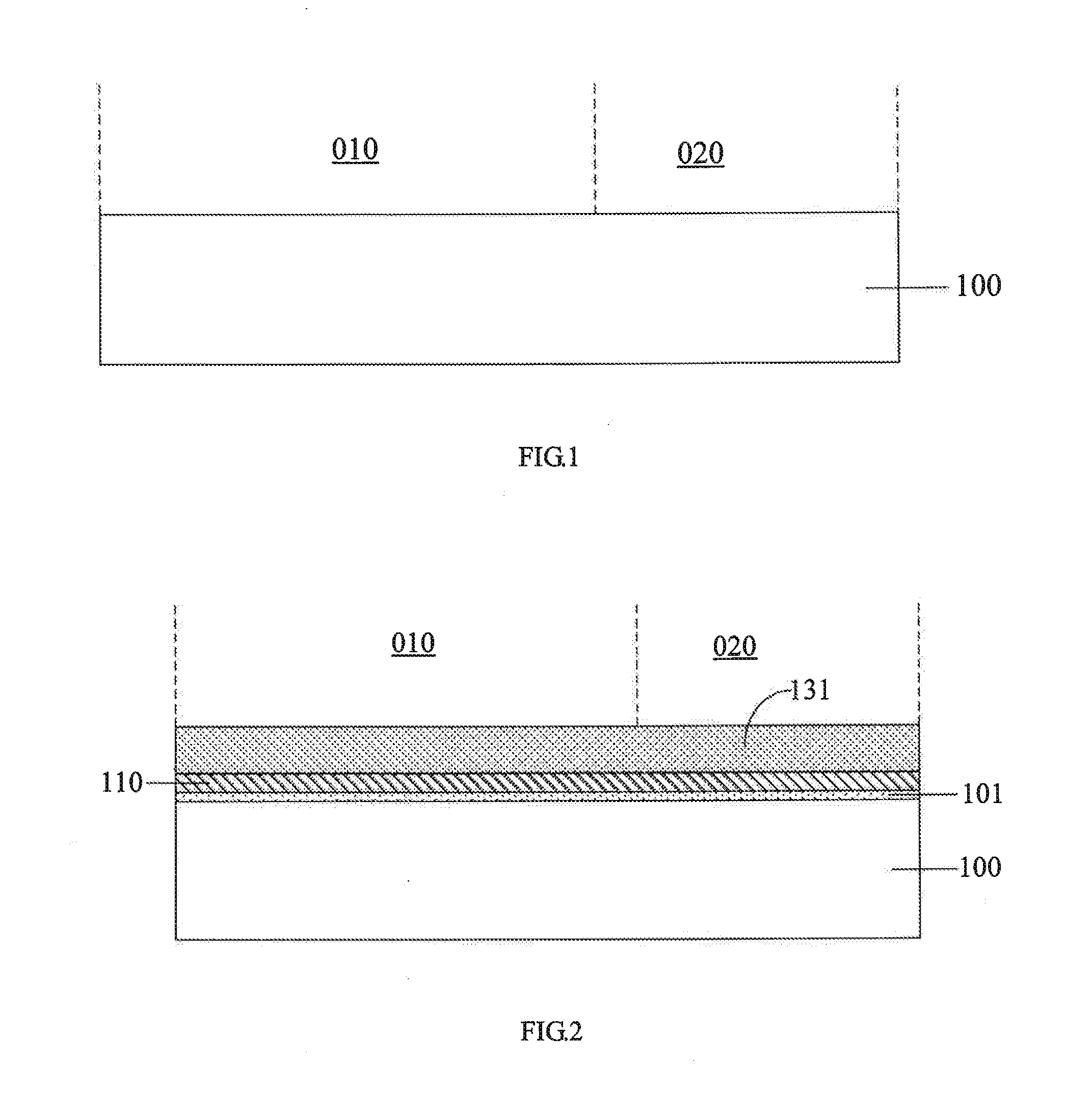

Method of manufacturing semiconductor device

ActiveUS20130330894A1Eliminate the issue of “over-erasure”Increase array densitySemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialGate oxide

A semiconductor device fabrication method particularly suitable for the fabrication of a 90 nm embedded flash memory is disclosed. The method includes: forming a dielectric layer having a first thickness over a first device region and forming a dielectric layer having a second thickness different from the first thickness over a second device region, the dielectric layer having a first thickness serving as a tunnel oxide layer of a split-gate structure, the dielectric layer having a second thickness serving as a gate oxide layer of a MOS transistor. The method enables the fabrication of a MOS transistor including a gate oxide layer with a desired thickness.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

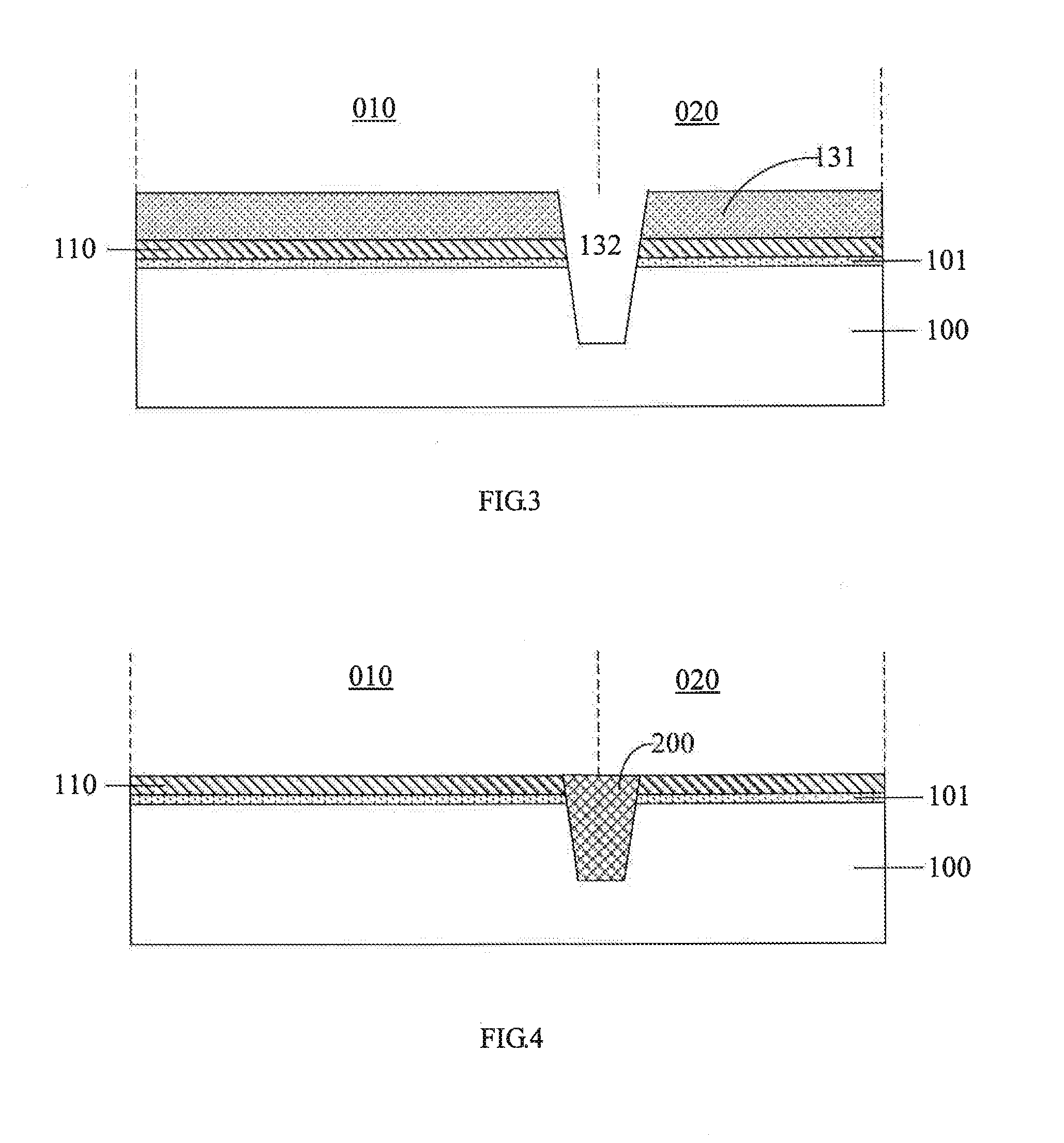

Solar cell package type with surface mount technology structure

InactiveUS20100163105A1Increase array densityReduce manufacturing costSemiconductor/solid-state device manufacturingPhotovoltaic energy generationElectricityEngineering

A solar cell package type with surface mount technology structure, comprising: a solar cell having a first electric terminal at the bottom thereof and a second electric terminal at the top thereof; at least a connection electric terminal capped at both sides of the solar cell in such a way that the top of the connection electric terminal is connected to the second electric terminal; and at least an insulation layer capped at both sides and partially placed at the bottom of the solar cell in such a way that it is interposed between the electric terminal and the solar cell for avoiding the short current and the water penetration. In this way, this package in accordance with the invention tends to increase the array density of the solar cells on the substrate and to minimize the manufacturing cost.

Owner:CHUANG YUNG HUI +1

Scanning kelvin microprobe system and process for biomolecule microassay

InactiveUS20060089825A1Improve spatial resolutionHigh resolutionBioreactor/fermenter combinationsBiological substance pretreatmentsPotential differenceAntibody antigen

There is provided a system and process for detecting biomolecular interaction on a substrate having a biomolecule immobilized on a surface of the substrate. The system and process incorporate a scanning Kelvin microprobe (SKM) capable of analyzing surface topography as well as a contact potential difference image signal. Also provided is the use of SKM in measuring and analyzing biochemical molecular interactions between a probe bound to the surface of the substrate, and a target suspected to be present in a liquid sample. One of the probe and target combination is a biomolecule such as a nucleic acid, a polypeptide, or a small molecule, and an antibody antigen combination may be used.

Owner:THOMPSON MICHAEL +2

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com