Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

46results about How to "Enhancing Capacitive Coupling" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

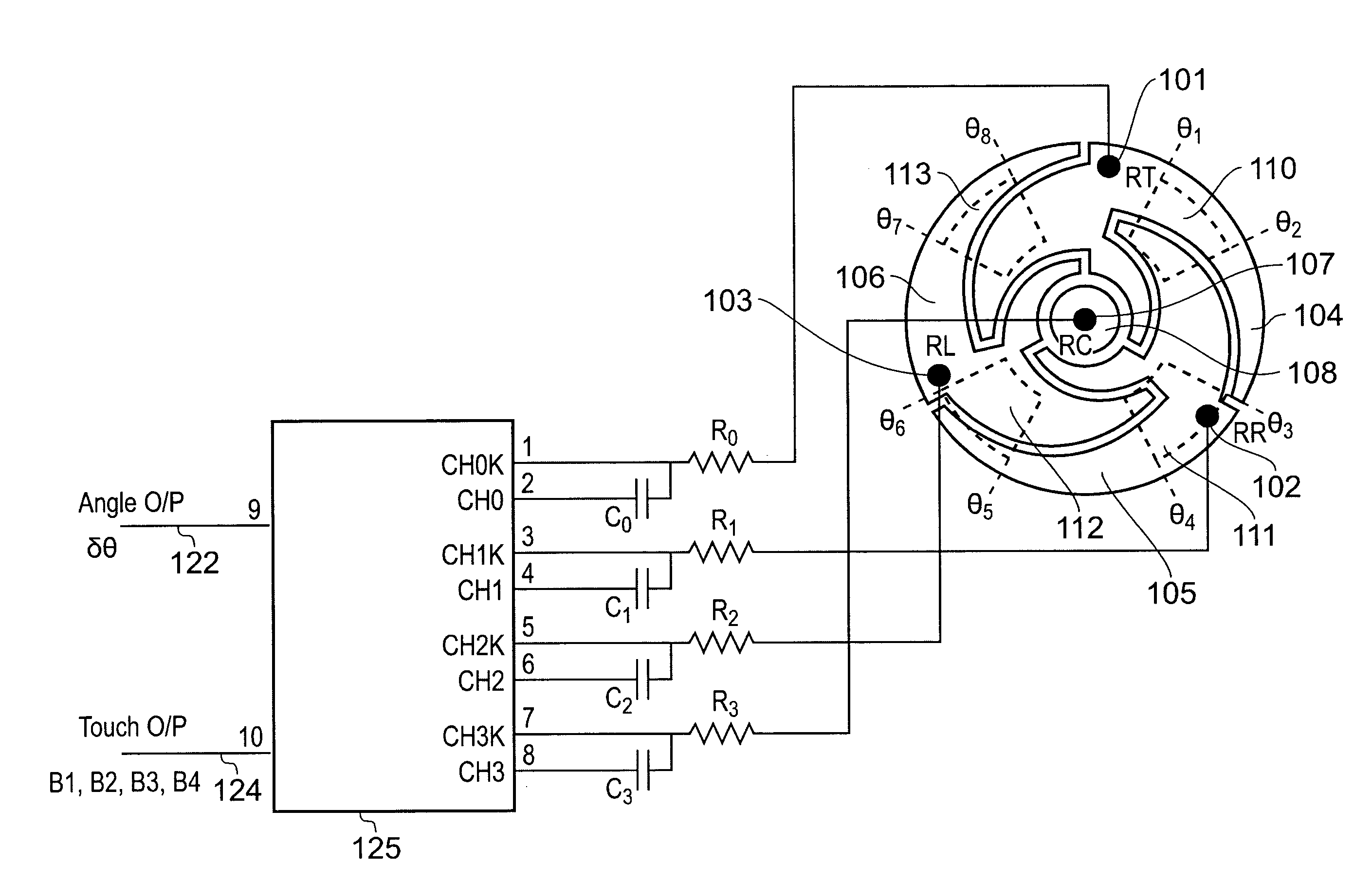

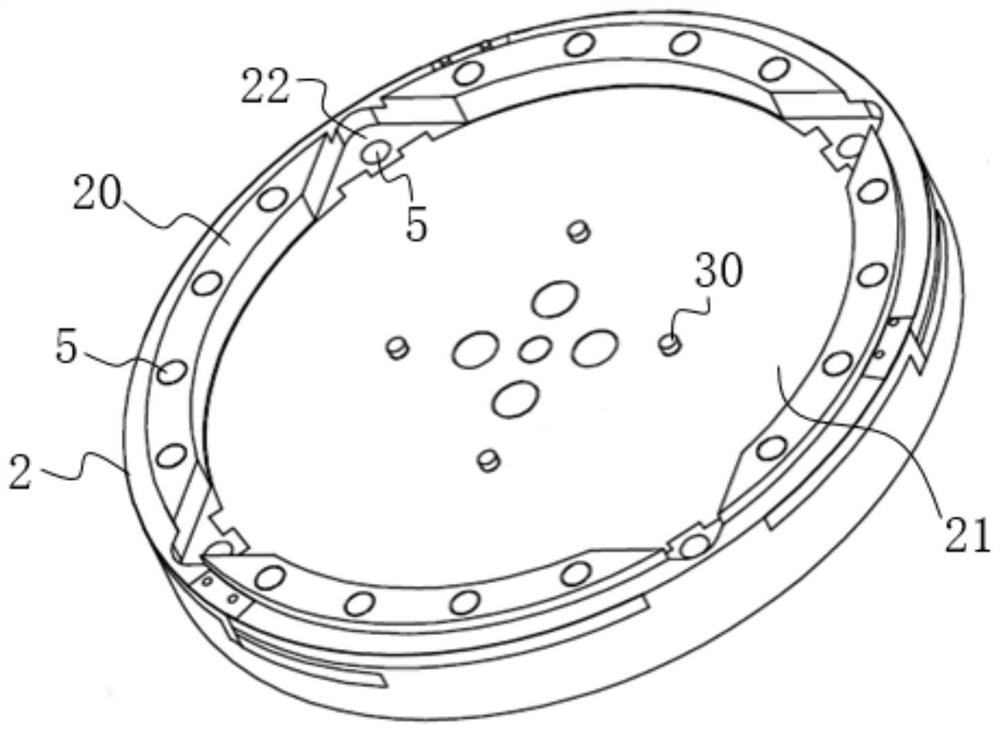

Capacitive Position Sensor

InactiveUS20070291016A1Improve reliabilityReduce power consumptionConverting sensor outputInput/output processes for data processingMicrocontrollerCapacitance

A capacitive position sensor comprising a preferably annular sensing path, the sensing path having one or more virtual buttons designated along its length. The sensing path has a plurality of terminals connected to it to subdivide it into a plurality of sections, each terminal providing a sensing channel for a signal indicative of capacitance. The sensing channels provide the signals to a processor, preferably a microcontroller, that is operable to distinguish between a user making a touch to actuate one of the virtual buttons, and a touch to perform a scrolling function. To be determined as a scroll, it is required that there is a succession of detects which span over at least a threshold distance, for example an angular or linear distance. To be determined as a touch, it is required that there is a succession of detects that all lie within one of the pre-assigned virtual button positions.

Owner:ATMEL CORP

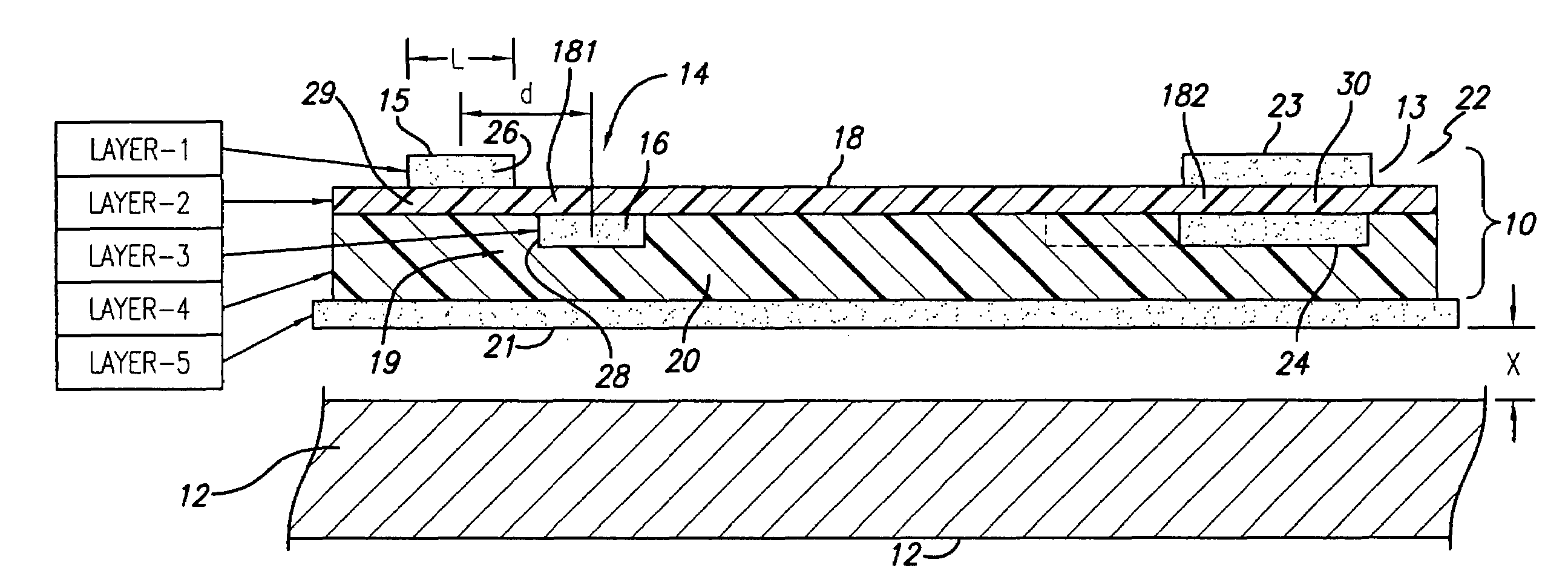

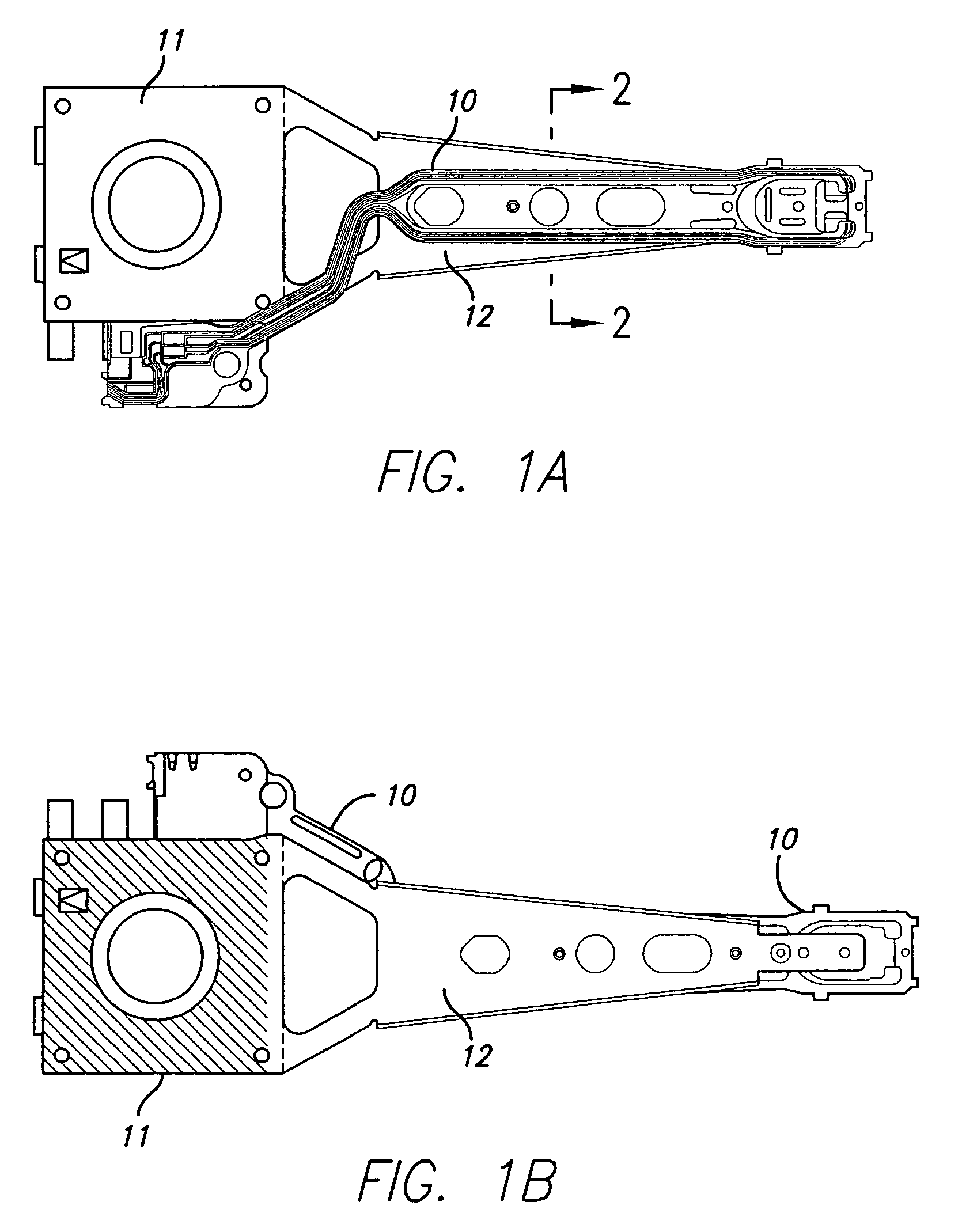

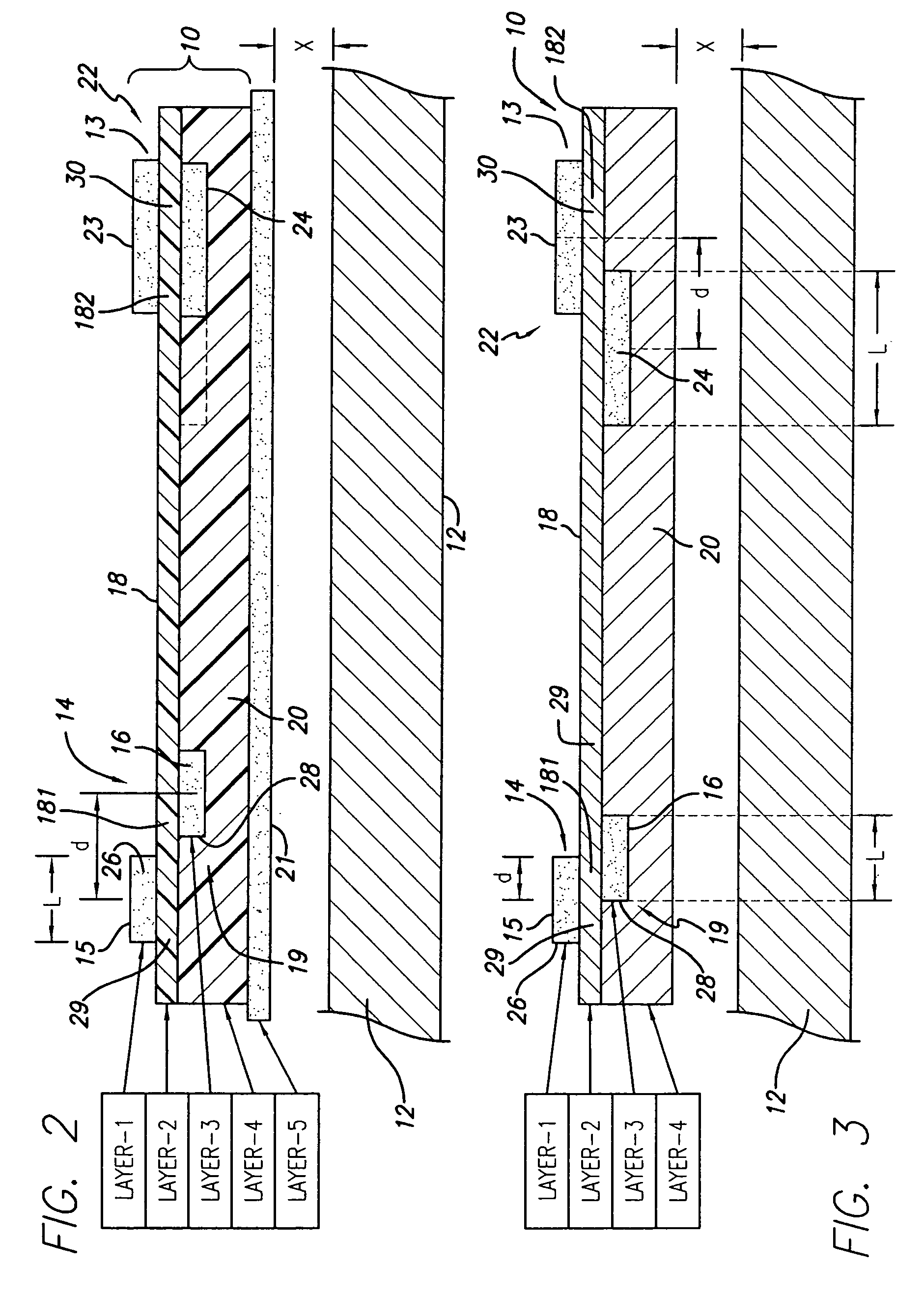

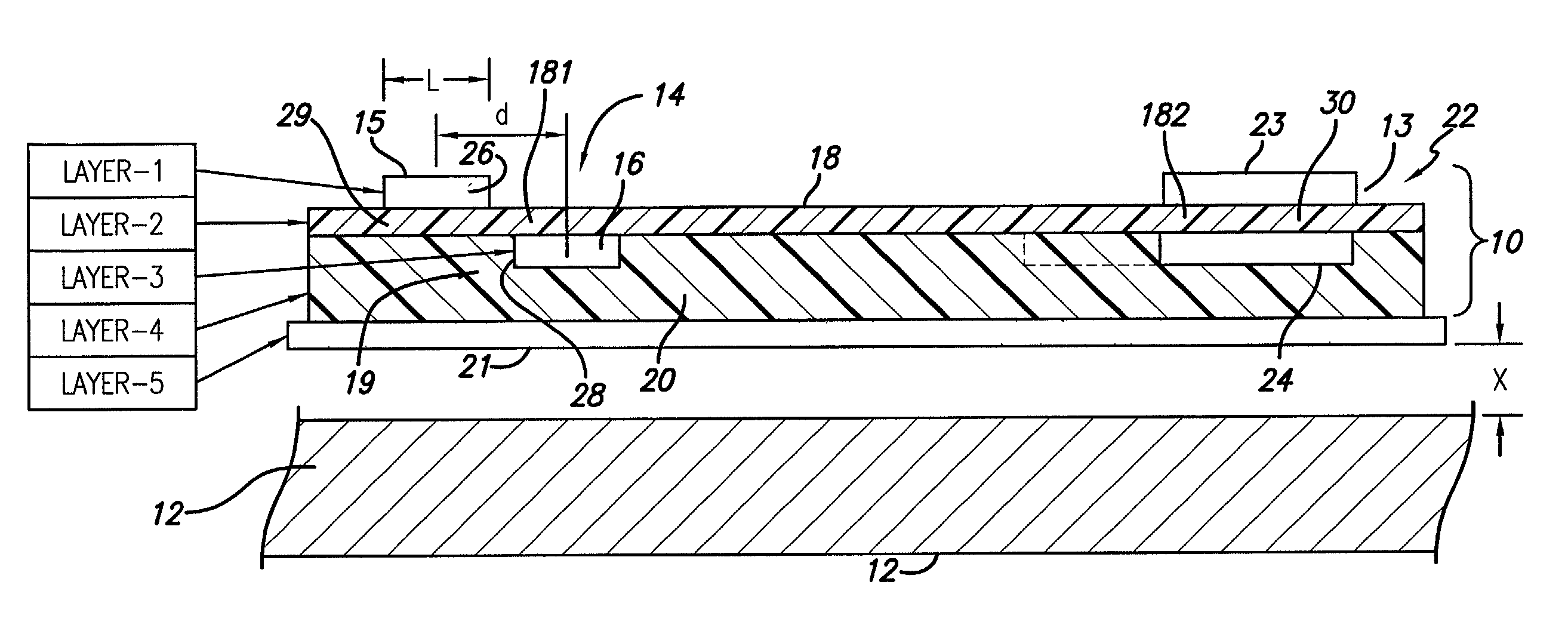

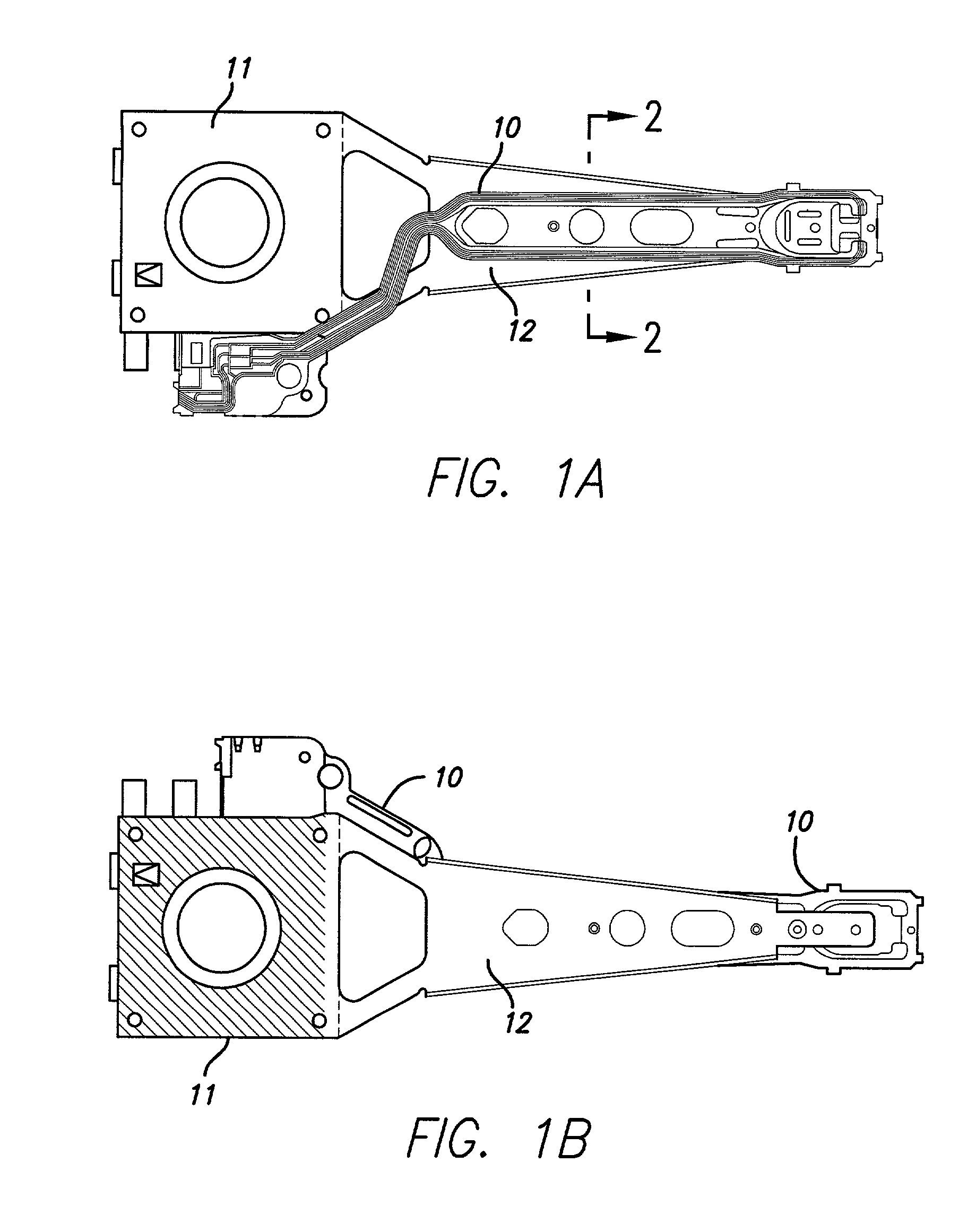

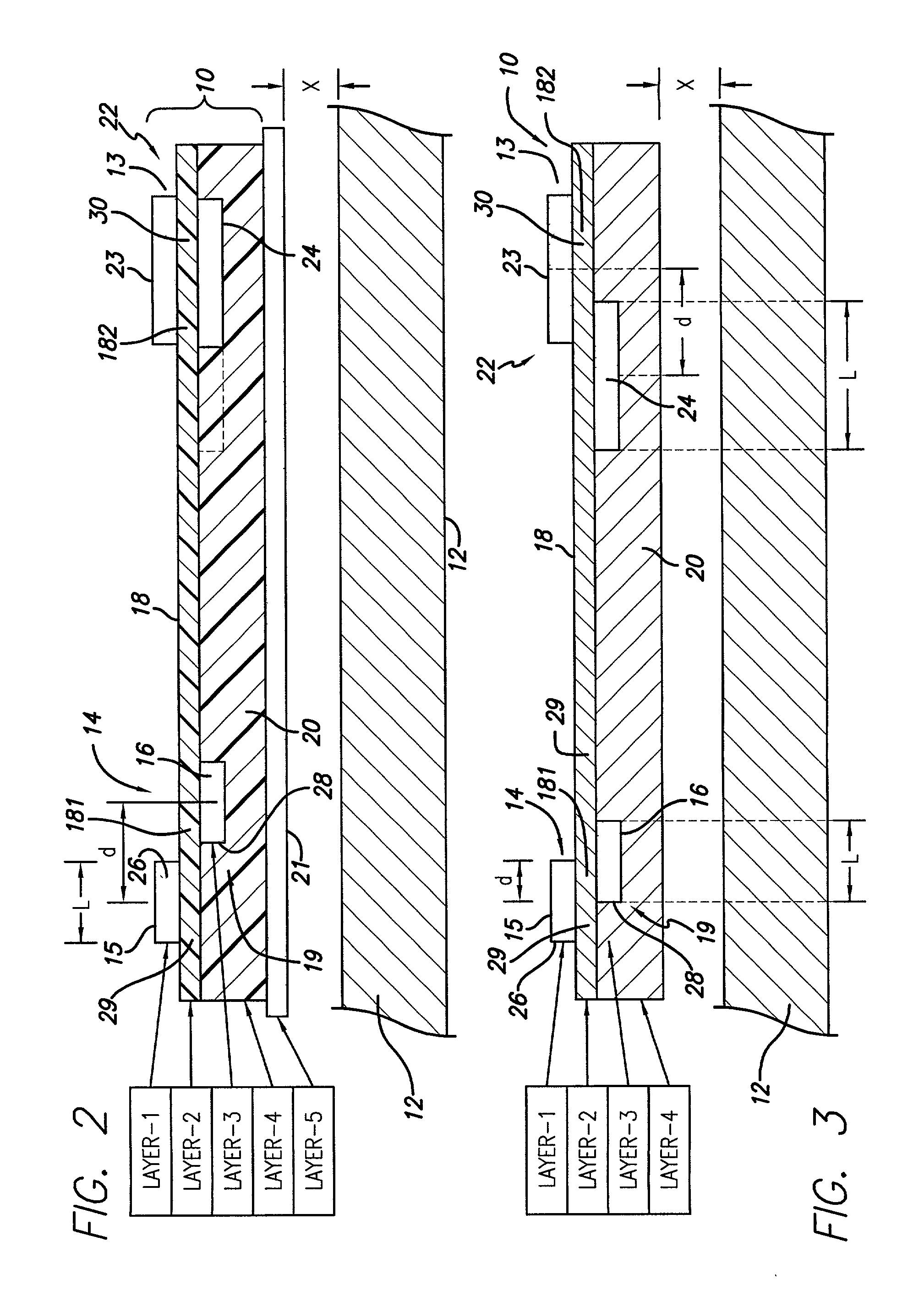

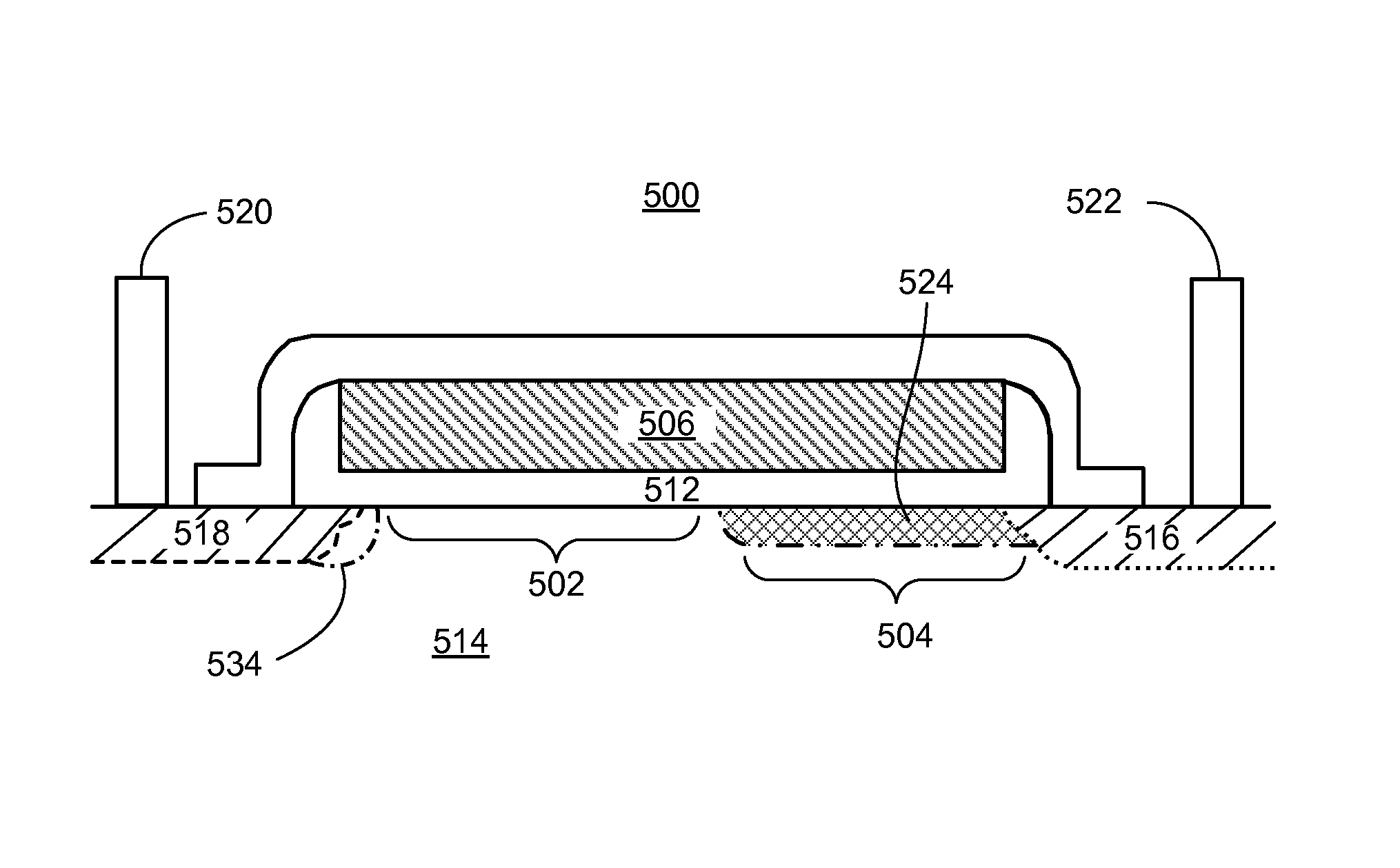

Additive-process suspension interconnect with controlled noise

InactiveUS7079357B1Increase electrical couplingLess sensitiveRecord information storageStructure of arm assemblyAdditive processElectrical interconnect

A disk drive electrical interconnect assembly and additive method therefor. The interconnect assembly has a supporting or fifth layer of metal, a fourth layer of a polyimide precursor or a polyimide with a first face directed away from the fifth layer, a third layer directly attached to the first face and defining a first subset of one or more conductive trace pair members, a second layer on the third and fourth layers of a polyimide precursor or a polyimide with a second face directed away from the third layer, and a first layer directly attached to the second layer and defining a second subset of one or more conductive trace pair members in spaced, paired and laterally offset relation respectively with one or more of the first subset pair members.

Owner:MAGNECOMP

Suspension interconnect with controlled noise

InactiveUS6975488B1Improved disk drive suspensionIncrease electrical couplingCross-talk/noise/interference reductionPrinted circuit aspectsEngineeringMetal

A disk drive suspension and method has a metal load beam and an electrical interconnect assembly. The interconnect assembly has an insulative layer, a read pair of forward and return path conductive traces, a write pair of forward and return path conductive traces that are supported by the insulative layer, preferably in offset relation across the insulative layer, and a metal layer for grounding and mounted on the insulative plastic layer in fixed spaced relation to the conductive traces to be between the interconnect assembly and the load beam. The metal layer shields the conductive traces from variations in impedance occasioned by varying distances between said electrical interconnect and said load beam.

Owner:MAGNECOMP

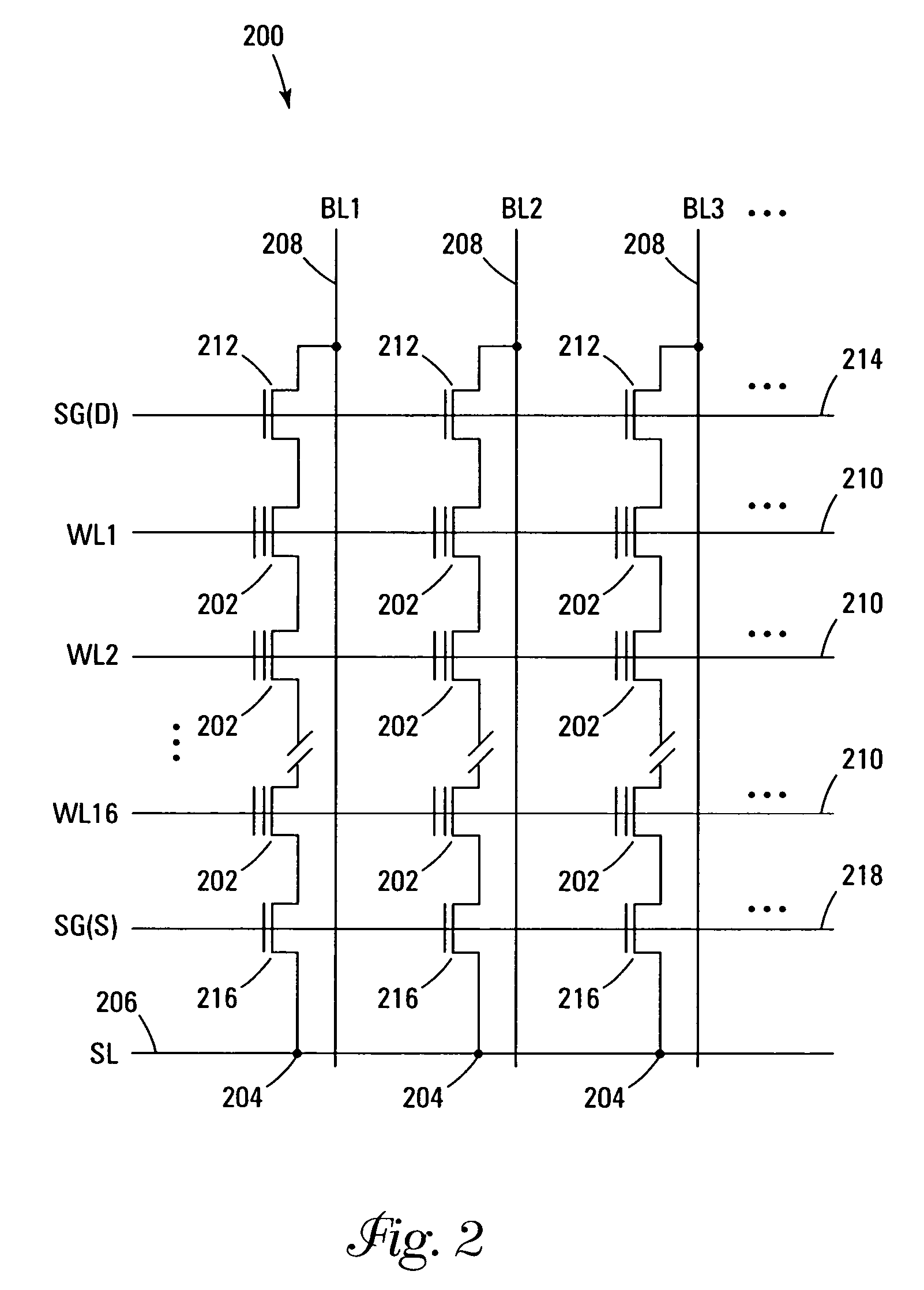

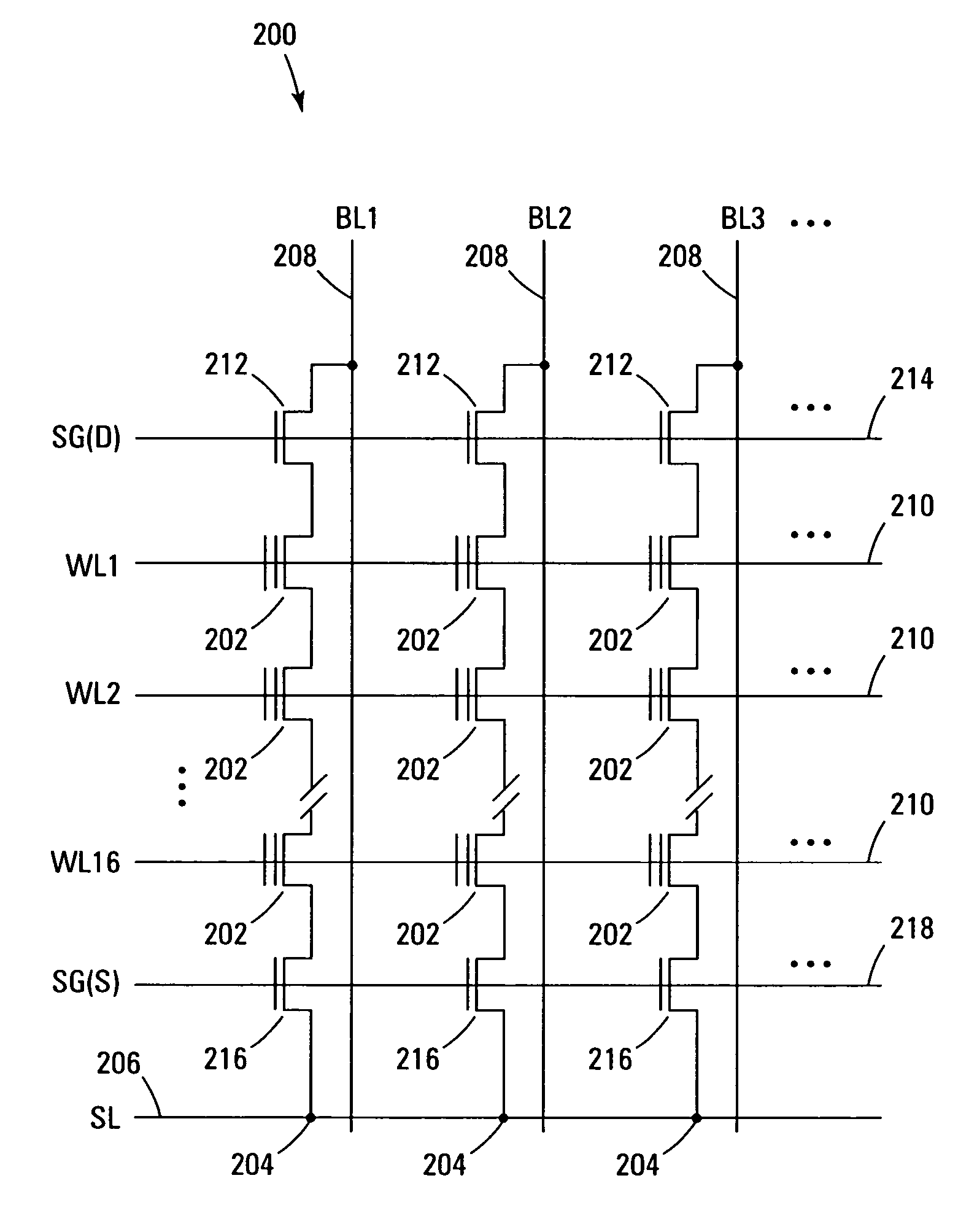

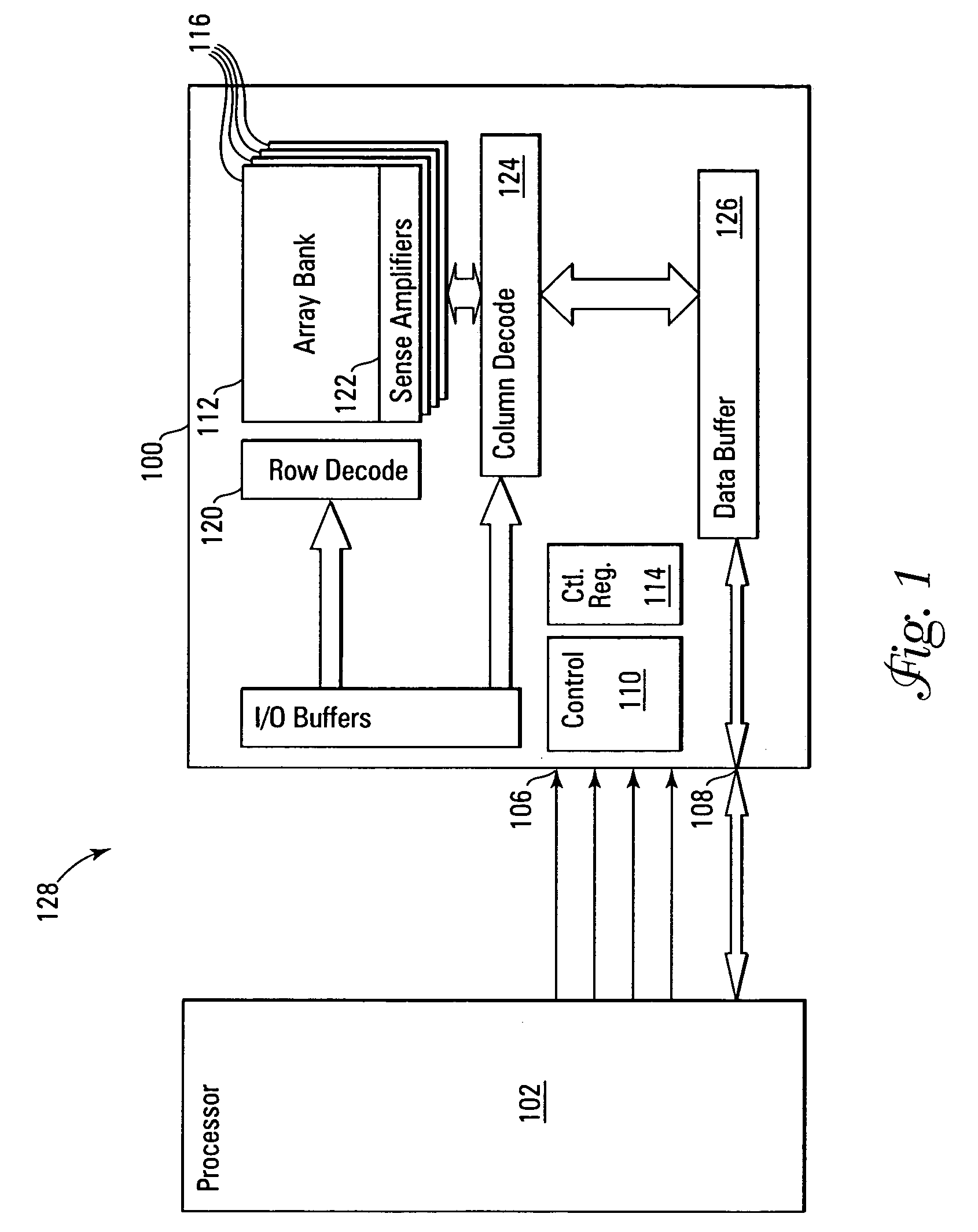

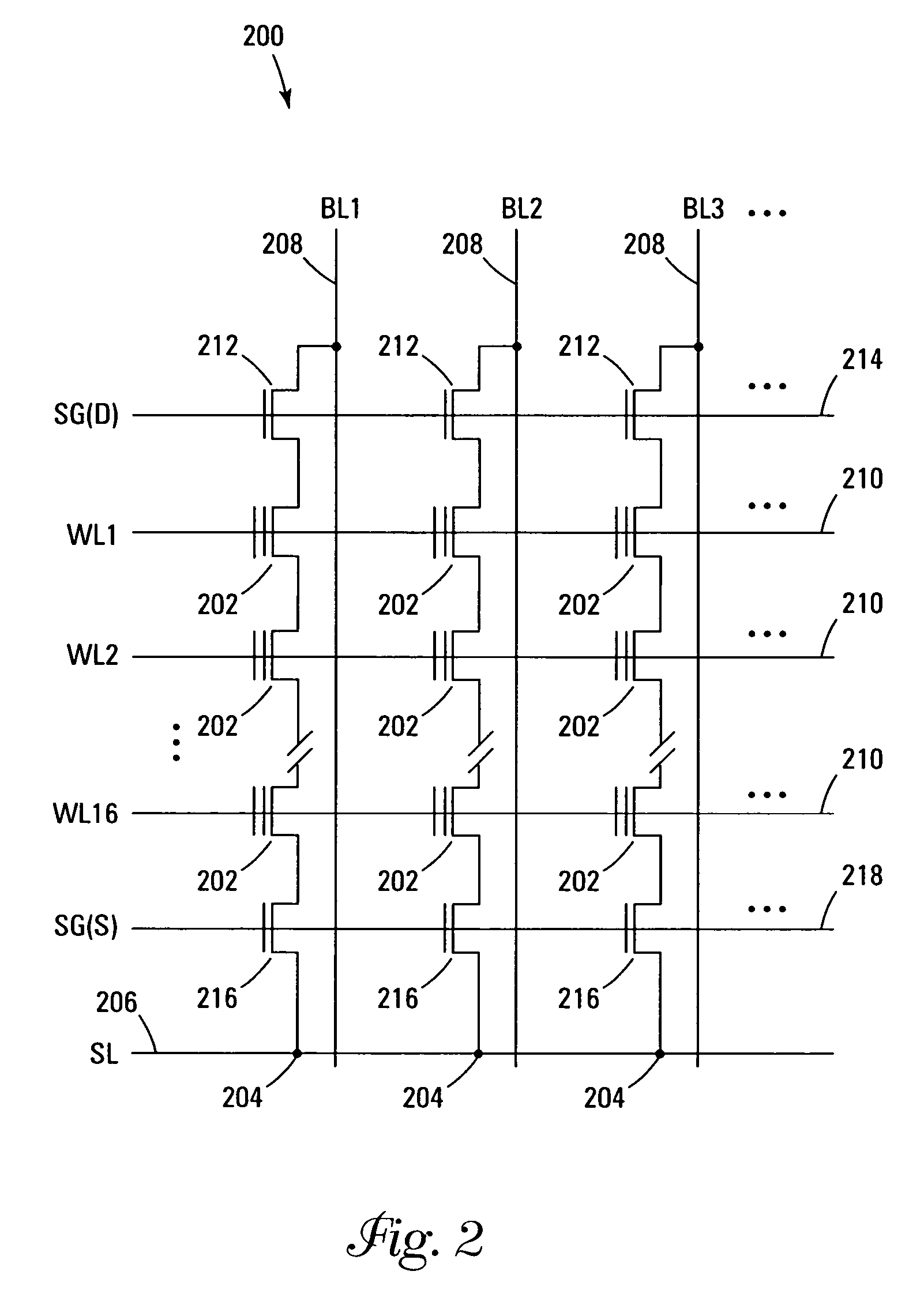

NAND string wordline delay reduction

ActiveUS7064981B2Extension of timeEnhancing Capacitive CouplingRead-only memoriesDigital storageCapacitanceLow voltage

An improved NAND Flash memory and word line selection method has been described, that takes advantage of the asymmetric nature of the word line to word line capacitive coupling to reduce word line selection delay by driving the adjacent word lines to a higher initial voltage and then reducing it to the final target voltage. As the capacitive coupling in between the NAND word lines is a larger effect when the voltages are being lowered, this has the effect of damping out the voltage initially induced in the lower voltage word line by the rising voltages on the adjacent word lines, reducing the overall selection time.

Owner:MICRON TECH INC

Phased array antenna with edge elements and associated methods

InactiveUS6876336B2Easy to useEnhancing Capacitive CouplingSimultaneous aerial operationsRadiating elements structural formsCapacitanceCapacitive coupling

A phased array antenna includes a substrate having a first surface, and a second surface adjacent thereto and defining an edge therebetween. A plurality of dipole antenna elements are on the first surface, and at least a portion of at least one dipole antenna element is on the second surface. Each dipole antenna element includes a medial feed portion and a pair of legs extending outwardly therefrom. Adjacent legs of adjacent dipole antenna elements on the first and second surfaces include respective spaced apart end portions having predetermined shapes and relative positioning for providing increased capacitive coupling between the adjacent dipole antenna elements.

Owner:HARRIS CORP

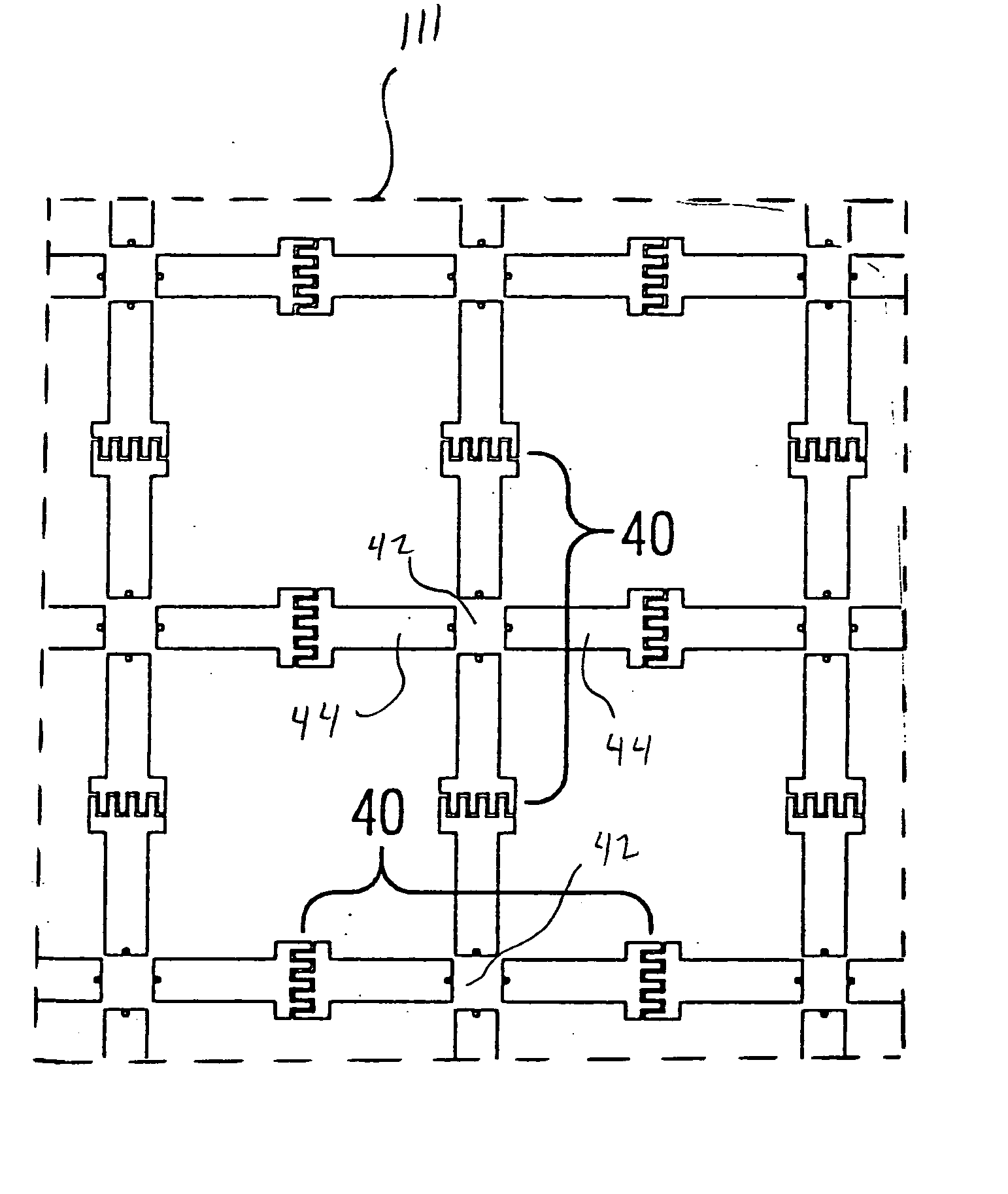

Phased array antenna including transverse circuit boards and associated methods

InactiveUS20070152882A1Reduce signal lossEasy to assembleSimultaneous aerial operationsRadiating elements structural formsEngineeringPhase array antenna

A phased array antenna may include a substrate and a plurality of phased array antenna elements carried by the substrate. A plurality of intermediate circuit boards may be arranged in spaced apart relation and each may extend transversely from the substrate. Each intermediate circuit board may have a forward end connected to a plurality of respective phased array antenna elements. A rear circuit board may be connected to the plurality of intermediate circuit boards at rearward ends thereof opposite the substrate.

Owner:HARRIS CORP

Nand string wordline delay reduction

ActiveUS20060028870A1Extension of timeEnhancing Capacitive CouplingRead-only memoriesDigital storageCapacitanceLow voltage

An improved NAND Flash memory and word line selection method has been described, that takes advantage of the asymmetric nature of the word line to word line capacitive coupling to reduce word line selection delay by driving the adjacent word lines to a higher initial voltage and then reducing it to the final target voltage. As the capacitive coupling in between the NAND word lines is a larger effect when the voltages are being lowered, this has the effect of damping out the voltage initially induced in the lower voltage word line by the rising voltages on the adjacent word lines, reducing the overall selection time.

Owner:MICRON TECH INC

Capacitive proximity device and electronic device comprising the capacitive proximity device

ActiveUS20110084709A1Improve reliabilityEnhancing Capacitive CouplingCapacitance measurementsMaterial analysis by electric/magnetic meansCapacitive couplingElectric field

The invention relates to a capacitive proximity device (30, 40, 50, 60) for sensing a presence and / or absence of an object (32) in the proximity of an electronic device (34). The capacitive proximity device (30, 40, 50, 60) comprises: an emission electrode (TA) capacitively coupled to a receiver electrode ( ), an oscillator (17) for generating an emission-signal (ES) being an alternating electric field ( ) between the emission electrode (TA) and the receiving electrode ( ), and a sensing circuit (70, 72, 74, 76, 78) connected to the receiving electrode ( ). The sensing circuit receives a measured-signal (MS) from the receiver electrode ( ), and comprising a first synchronous detection circuit ( ) together with a low-pass filter (14) for generating an output-signal (OS) being proportional to a distance between the object and the electronic device. The sensing circuit further comprising noise-suppression means for reducing noise from the measured-signal (MS) before entering the first synchronous detection circuit. The inventors have found that additional noise-suppression techniques are required when applying the known capacitive sensors in a electronic device.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

Single-poly 2-transistor based fuse element

InactiveUS20050167728A1Enhancing Capacitive CouplingReduction in fuse programming voltageTransistorSemiconductor/solid-state device detailsCapacitanceCapacitive coupling

An electrically programmable transistor fuse having a double-gate arrangement disposed in a single layer of polysilicon in which a first gate is disposed overlapping a portion of a source region and a second gate is insulated from the first gate and disposed overlapping a portion of a drain region. The first gate includes a terminal for receiving an externally applied control signal and the second gate is capacitively couple to the drain region in which a coupling device is included for increasing the capacitive coupling of the second gate and the drain region for enabling reduction in fuse programming voltage.

Owner:INFINEON TECH AG

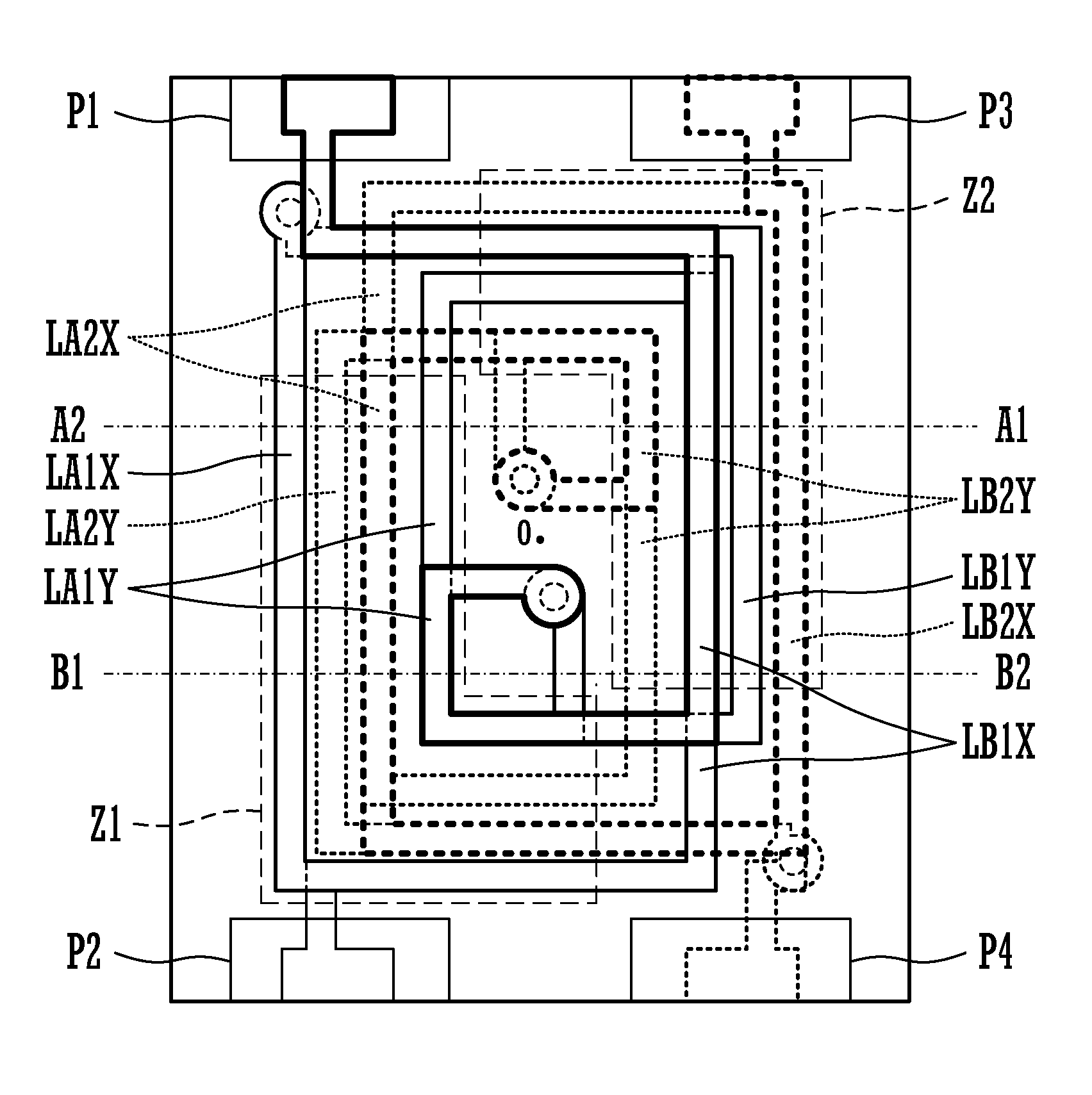

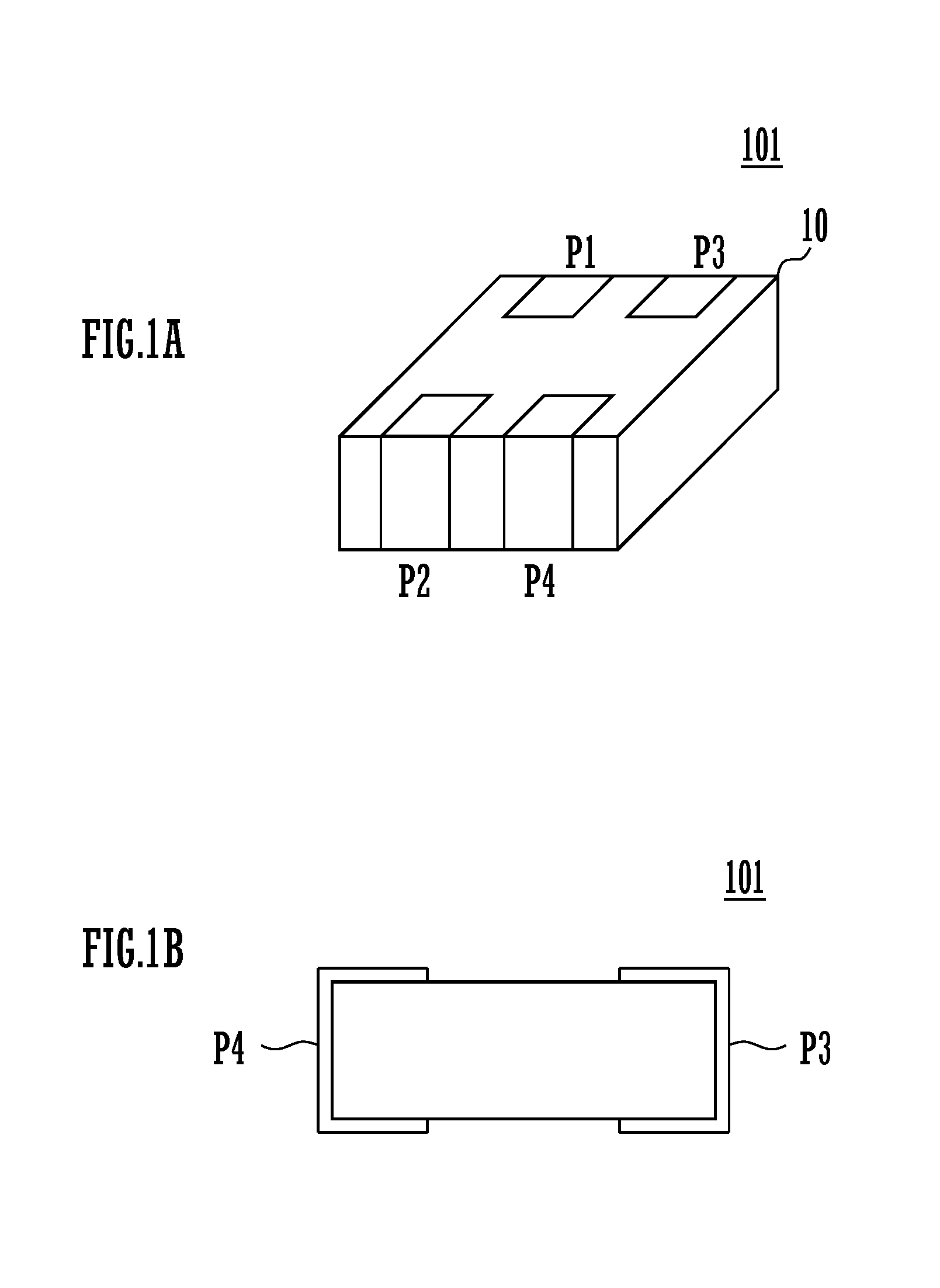

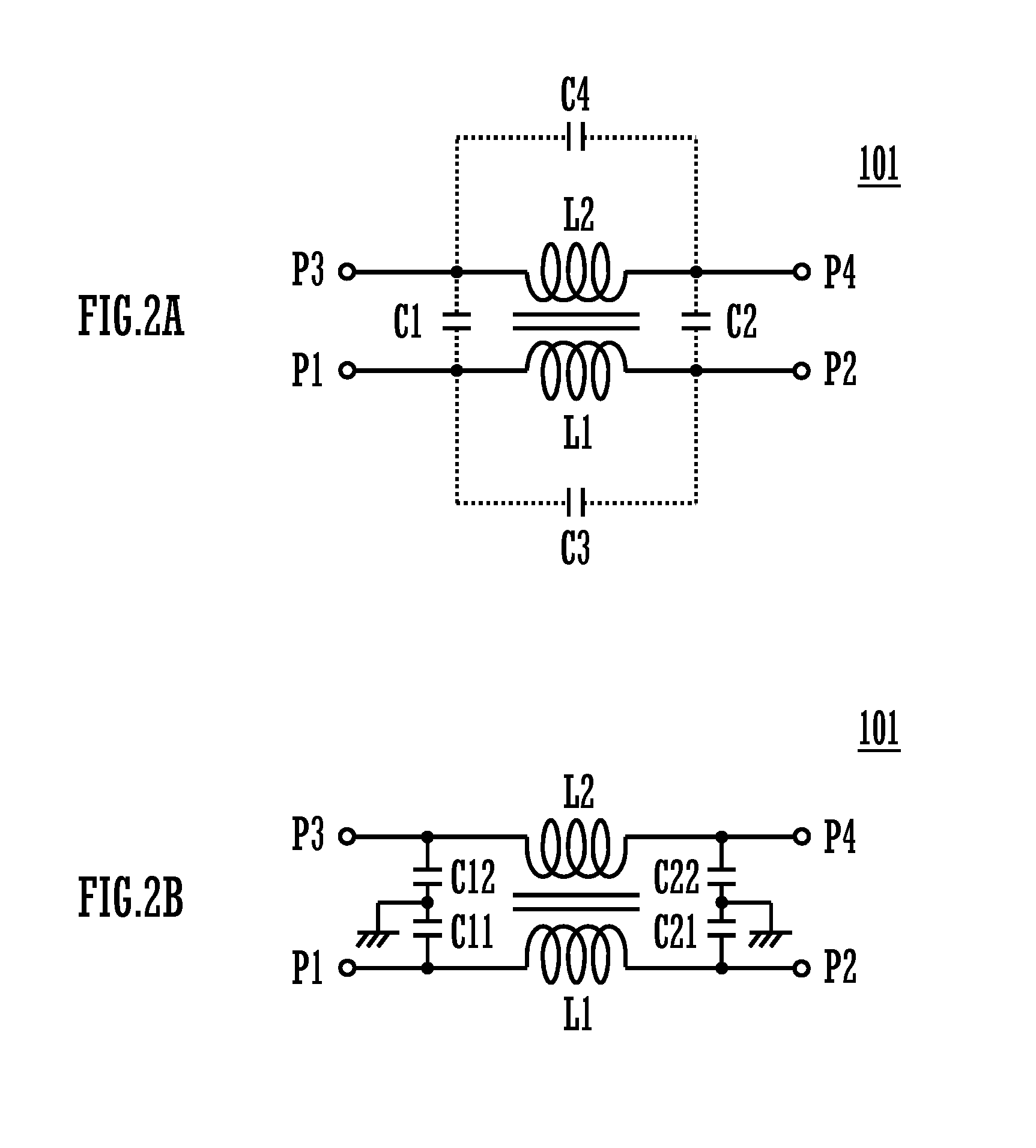

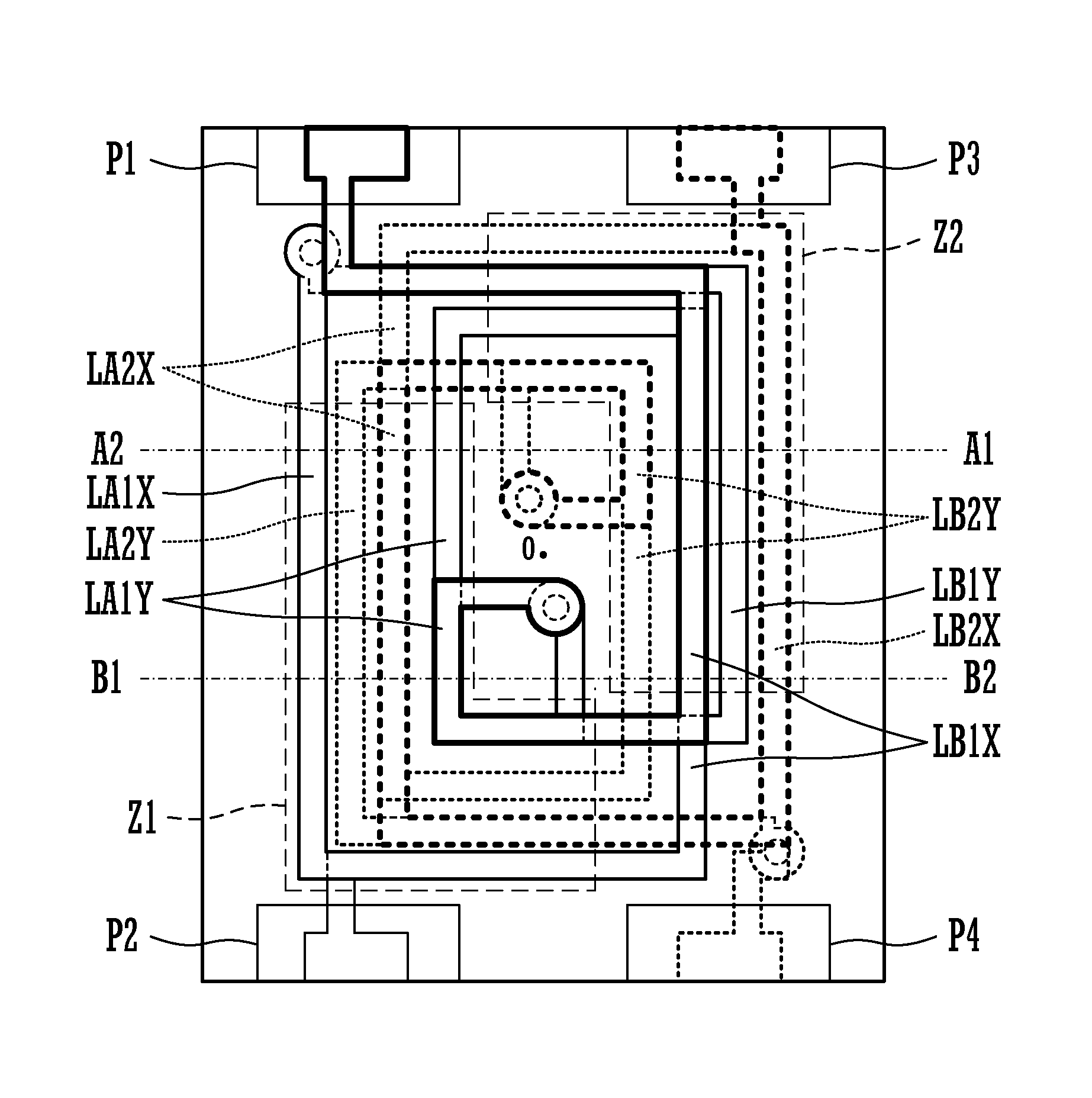

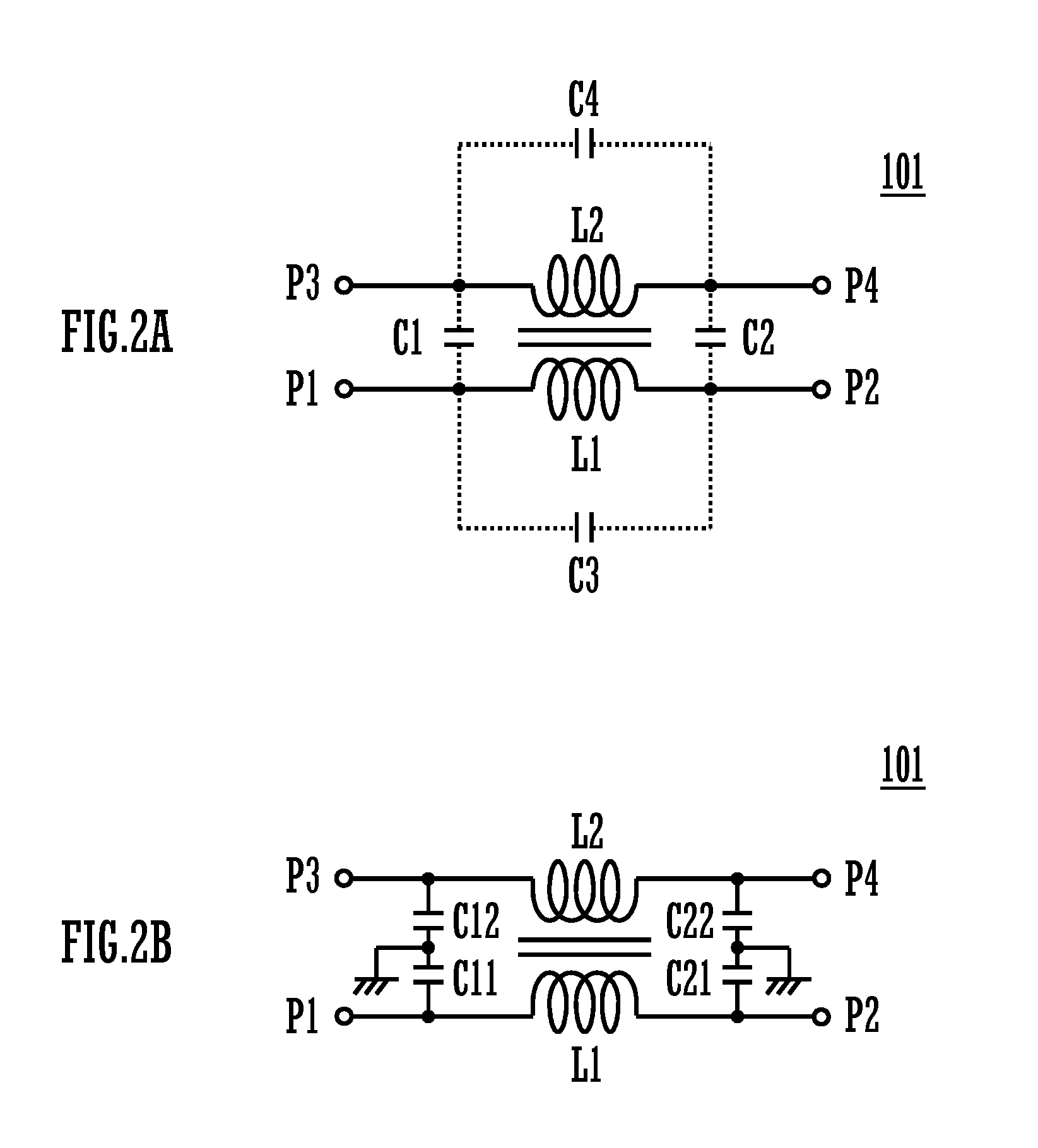

Common mode choke coil

ActiveUS20140368307A1High degree of coupleImprove abilitiesTransformers/inductances coils/windings/connectionsUnwanted magnetic/electric effect reduction/preventionEngineeringElectrical conductor

In a common mode choke coil, electrodes of input / output terminals are located on a bottom surface of a bottom layer. First linear conductors and second linear conductors are located on base material layers. A primary coil includes the first linear conductors and via hole conductors. A secondary coil includes the second linear conductors and via hole conductors. In a plan view as seen from a direction of winding axes of the primary coil and the secondary coil, as for a plurality of first linear conductors and second linear conductors which are adjacent in a plan direction, there are provided a first region in which the second linear conductors are located between the first linear conductors, and a second region in which the first conductors are located between the second linear conductors.

Owner:MURATA MFG CO LTD

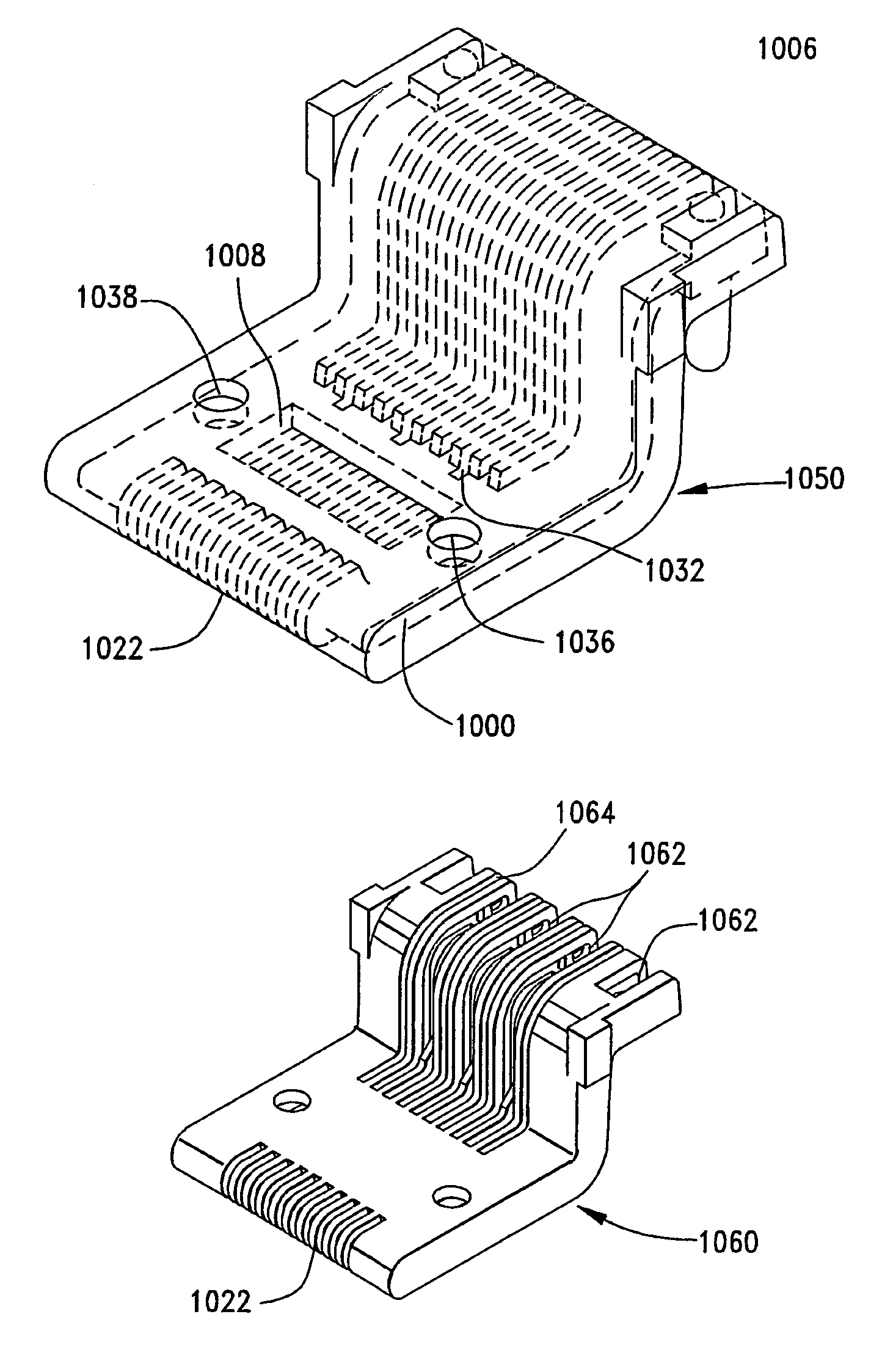

Grouped element transmission channel link with pedestal aspects

ActiveUS7273401B2Easy to controlSimple transmission structurePrinted circuit assemblingElectrically conductive connectionsTransmission channelGroup element

A pedestal connector that incorporates one or more grouped element channel link transmission lines is seen to have a dielectric body and two opposing contact ends that are intended to contact opposing contacts or traces. The dielectric body has an S-shaped configuration such that the transmission lines supported thereon make at least one change in direction, thereby permitting the use of such connector to interconnect elements lying in two different planes. The transmission lines include slots that extend within the frame and which define opposing, conductive surfaces formed on the dielectric body which are separated by an intervening air gap.

Owner:MOLEX INC

Multi-layer capacitive coupling in phased array antennas

InactiveCN1720641AEnhancing Capacitive CouplingAntenna arrays manufactureIndividually energised antenna arraysCapacitanceCurrent sheet

A phased array antenna(10) includes a current sheet array (20) on a substrate (23), at least one dielectric layer (24) between the current sheet array and a ground plane (30), and at least one conductive plane (25) adjacent to the substrate for providing additional coupling between adjacent dipole antenna elements of the current sheet array.

Owner:HARRIS CORP

Very Dense NVM Bitcell

ActiveUS20120205734A1Reduce sizeEnhanced capacitive couplingTransistorSolid-state devicesGate capacitanceEngineering

An asymmetric non-volatile memory bitcell is described. The bitcell comprises source and drain regions comprising carriers of the same conductivity type. A floating gate rests on top of the well, and extends over a channel region, and at least a portion of the source and drain regions. The drain region comprises additional carriers of a second conductivity type, allowing band to band tunneling. The source region comprises additional carriers of a first conductivity type, thereby increasing source-gate capacitance. Thus, the bitcell incorporates a select device, thereby decreasing the overall size of the bitcell. The bitcell may be created without any additional CMOS process steps, or through the addition of a single extra mask step.

Owner:SYNOPSYS INC

Phased array antenna with edge elements and associated methods

InactiveUS20050030245A1Enhancing Capacitive CouplingEnhanced couplingSimultaneous aerial operationsRadiating elements structural formsCapacitanceCapacitive coupling

A phased array antenna includes a substrate having a first surface, and a second surface adjacent thereto and defining an edge therebetween. A plurality of dipole antenna elements are on the first surface, and at least a portion of at least one dipole antenna element is on the second surface. Each dipole antenna element includes a medial feed portion and a pair of legs extending outwardly therefrom. Adjacent legs of adjacent dipole antenna elements on the first and second surfaces include respective spaced apart end portions having predetermined shapes and relative positioning for providing increased capacitive coupling between the adjacent dipole antenna elements.

Owner:HARRIS CORP

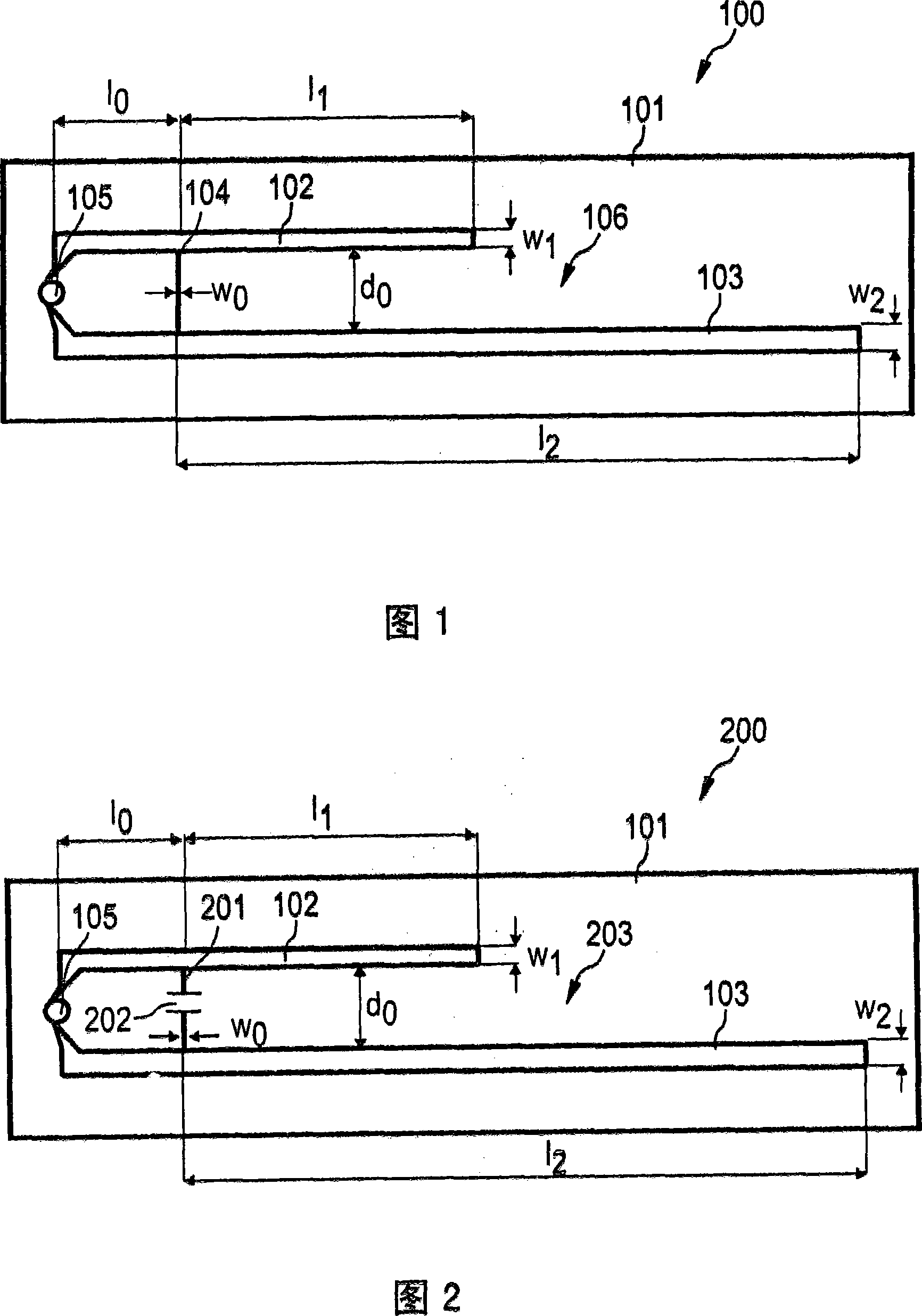

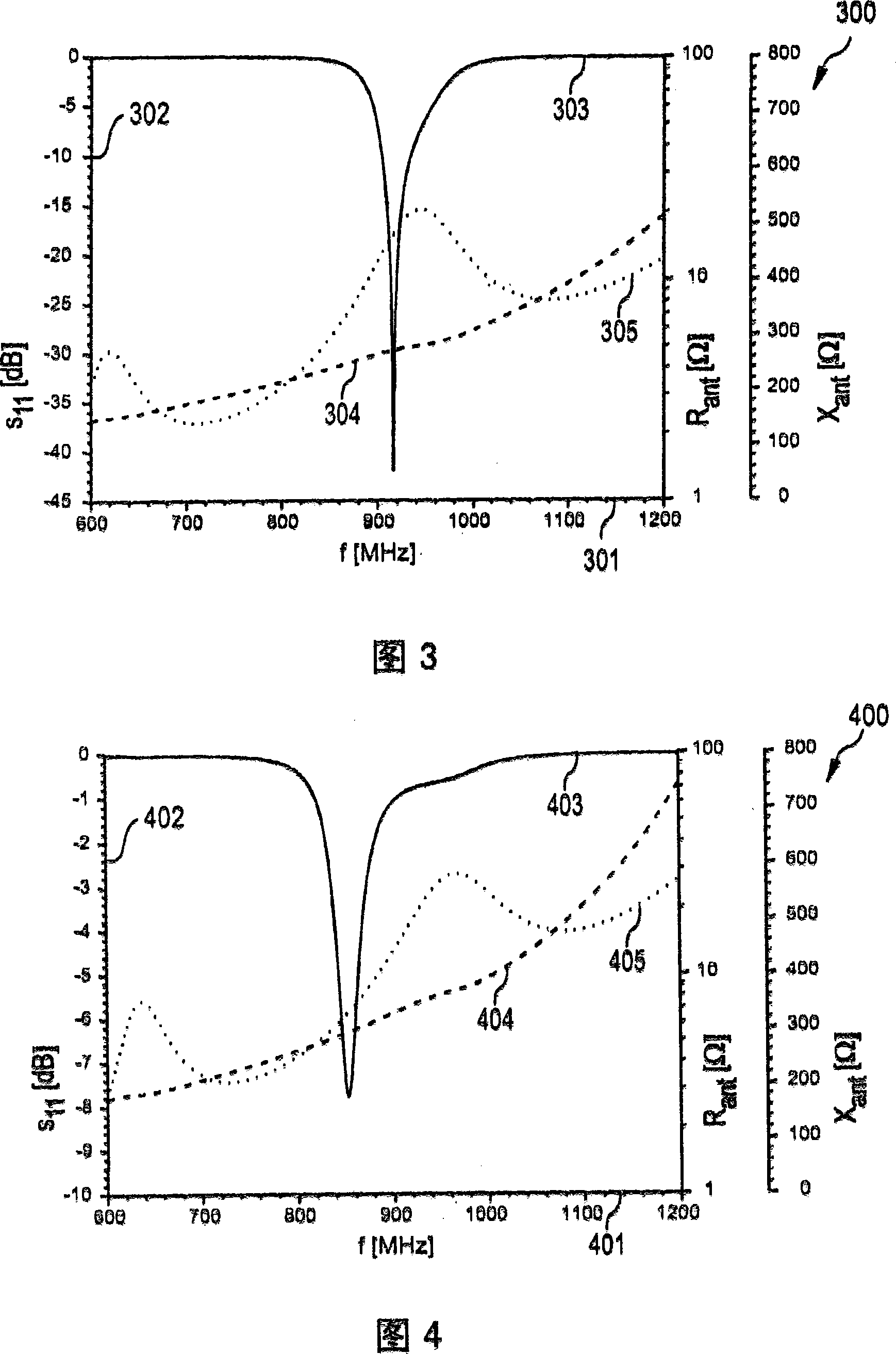

Antenna structure, transponder and method of manufacturing an antenna structure

ActiveCN101233532AFlexible operationGet Broadband CapabilitiesAntenna supports/mountingsAntenna feed intermediatesElectrically conductiveIntegrated circuit

An antenna structure (106) comprising a first electrically conductive element (102) having a first end and a second end, a second electrically conductive element (103) having a first end and a second end, and a coupling structure (104) short- circuiting the first electrically conductive element (102) with the second electrically conductive element (103) by means of electrically connecting the electrically conductive elements (102, 103) at positions between the first and the second ends, wherein an integrated circuit (105) is connectable between the first end of the first electrically conductive element (102) and the first end of the second electrically conductive element (103).

Owner:NXP BV

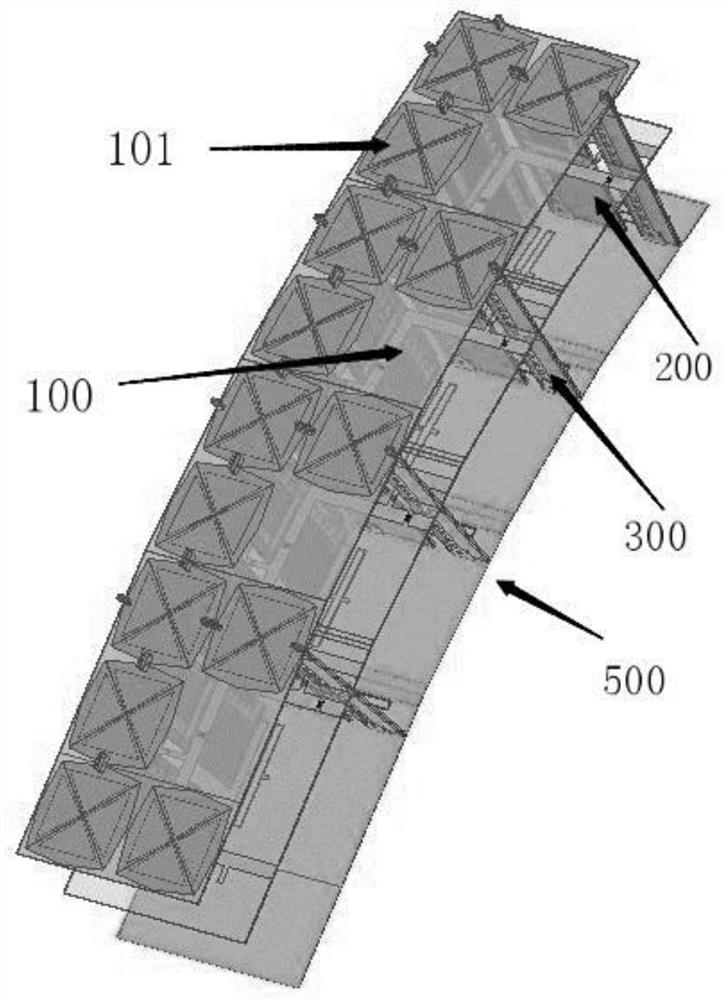

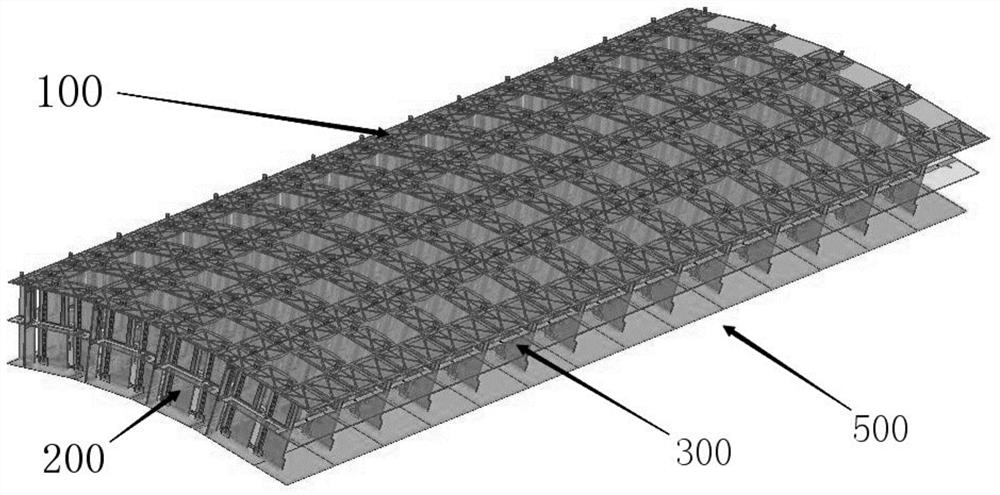

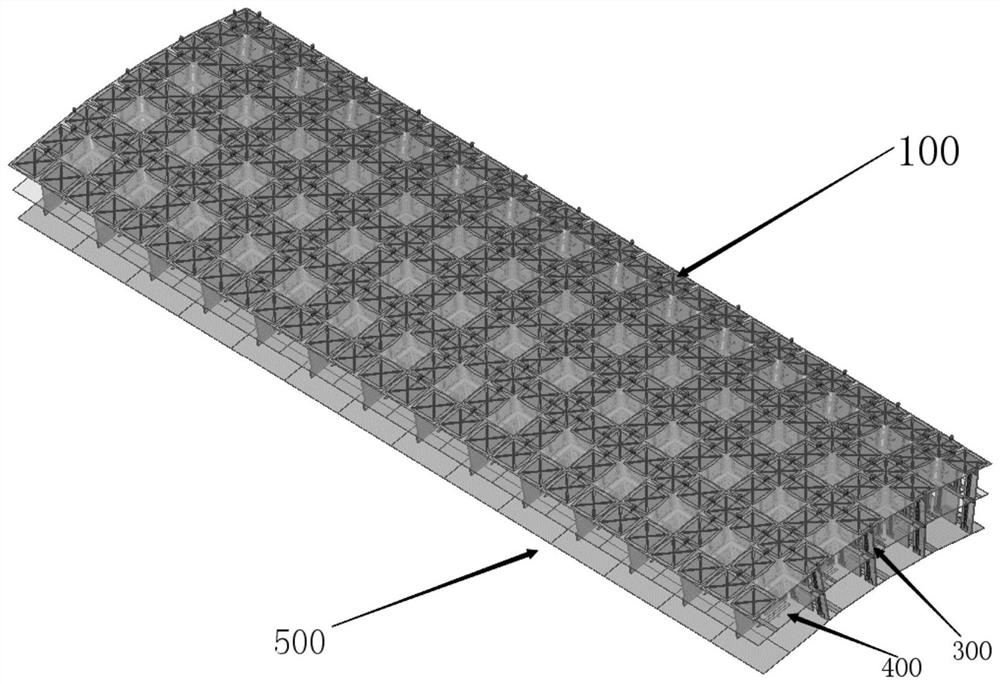

Tightly-coupled ultra-wideband low-profile conformal phased array based on resistance ring loading

ActiveCN113517553AExpand low frequency bandwidthImprove Broadband MatchingParticular array feeding systemsSimultaneous aerial operationsUltra-widebandCapacitance

The invention discloses a tightly-coupled ultra-wideband low-profile conformal phased array based on resistance ring loading and a development method thereof. A method for enhancing capacitive coupling is provided, a traditional cross-shaped dipole is improved, a resistive frequency selection surface composed of a micro-strip line and a lumped resistor is loaded between an antenna radiation patch and a floor, and the working bandwidth of the antenna is expanded. A feed structure of a power divider and double-balun is applied, so that better matching can be realized, and the profile height of the antenna is reduced. The whole antenna array is subjected to conformal processing, a light and thin dielectric substrate is applied, a thick and heavy wide-angle impedance matching layer is omitted, the antenna array is lighter, and the metal floor is bent at a certain radian so that the antenna array can be conveniently installed on a working platform. In the fL-8fL frequency band, 45-degree scanning active standing waves can be smaller than 3, and the overall height of the antenna is smaller than 0.53 high-frequency wavelengths.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

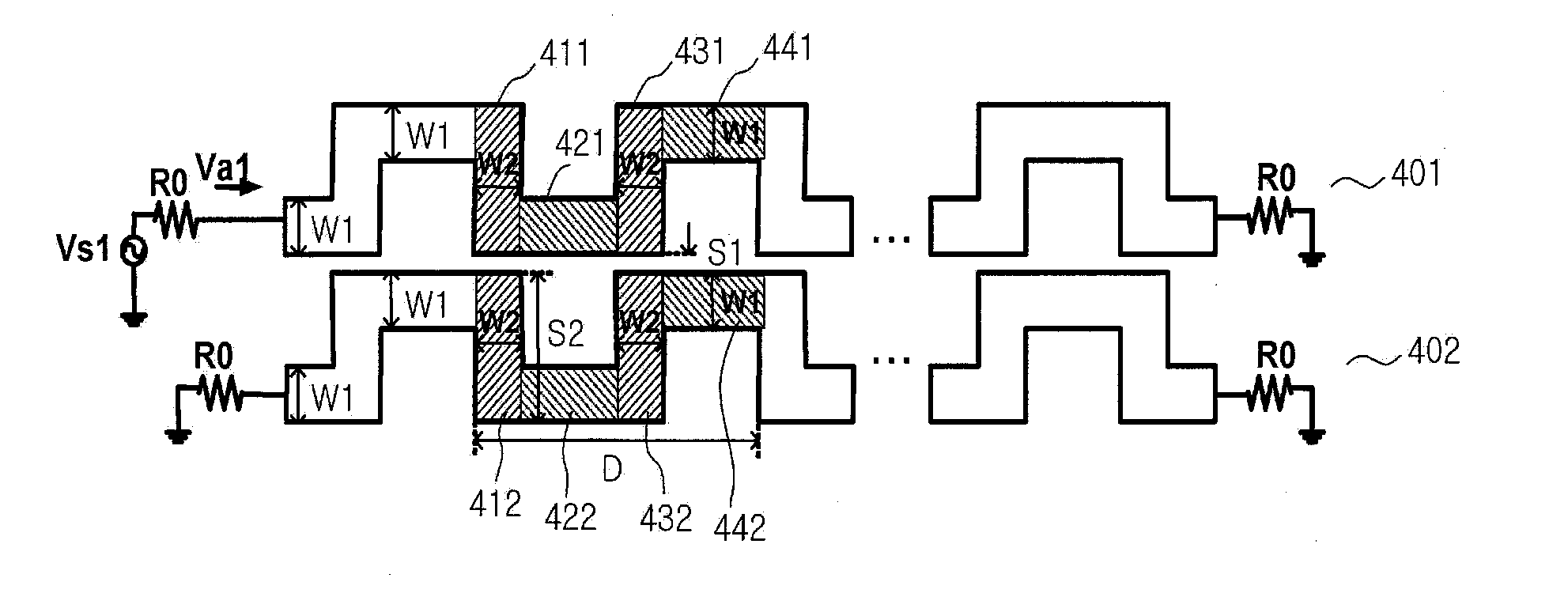

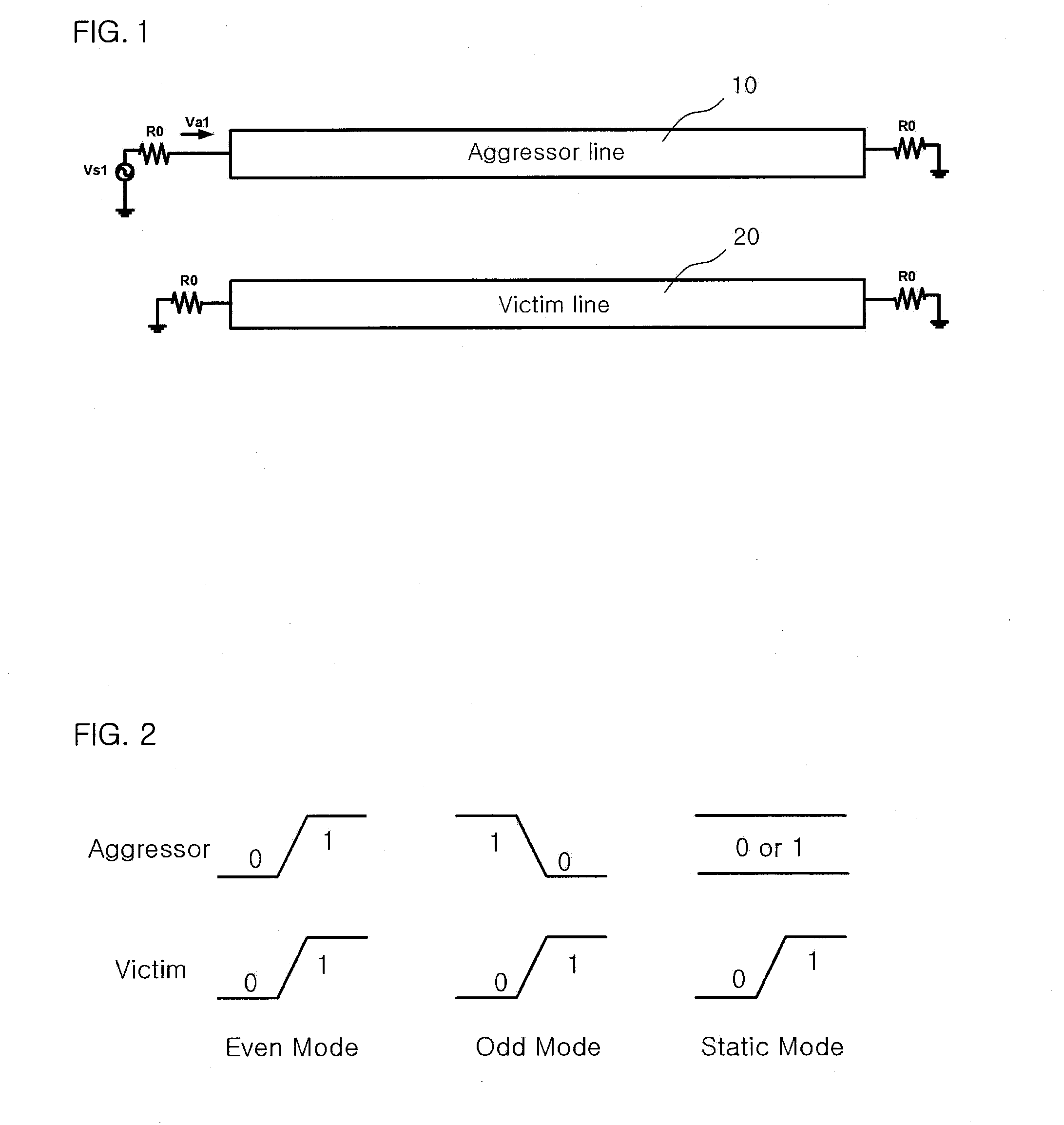

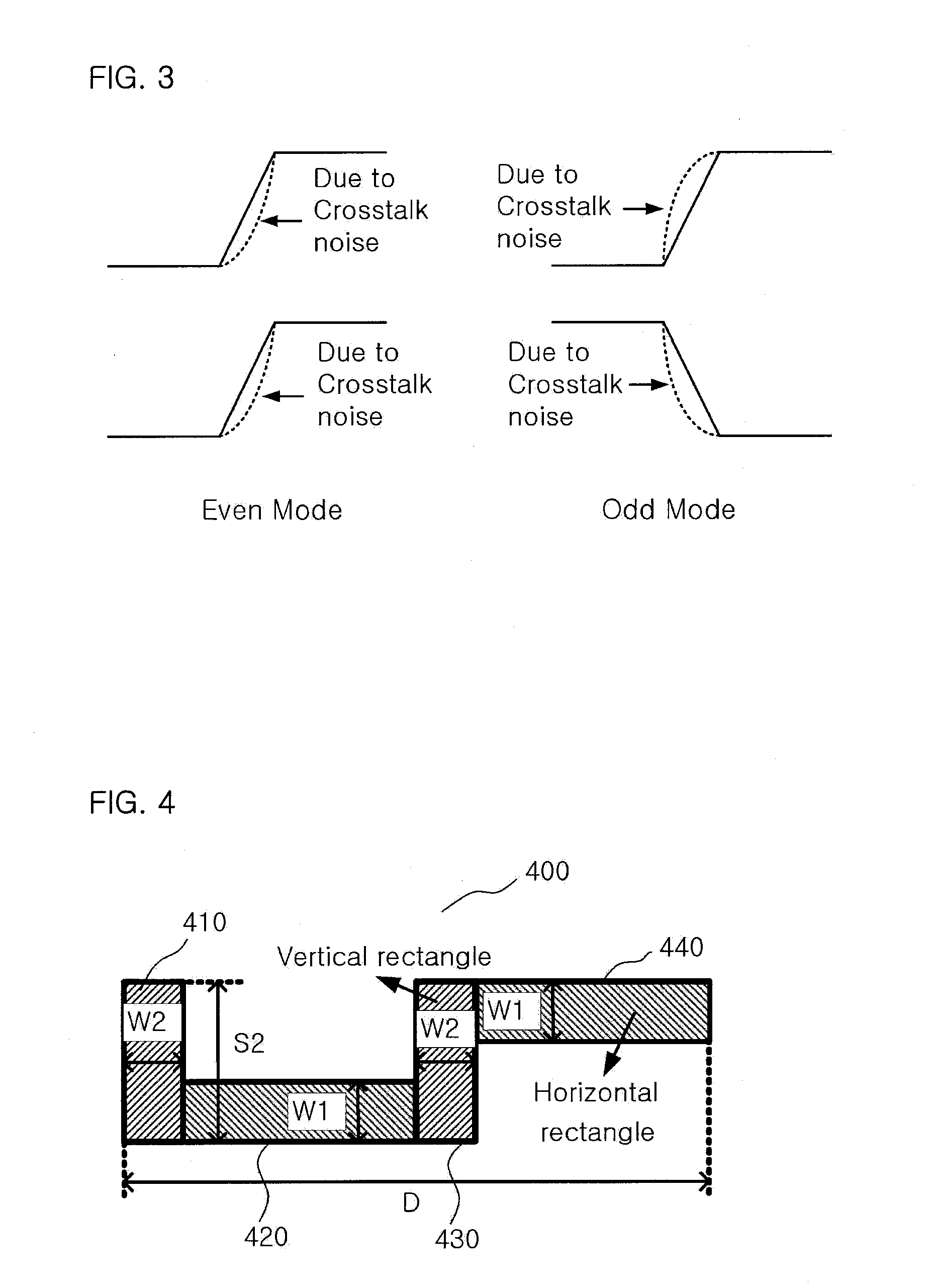

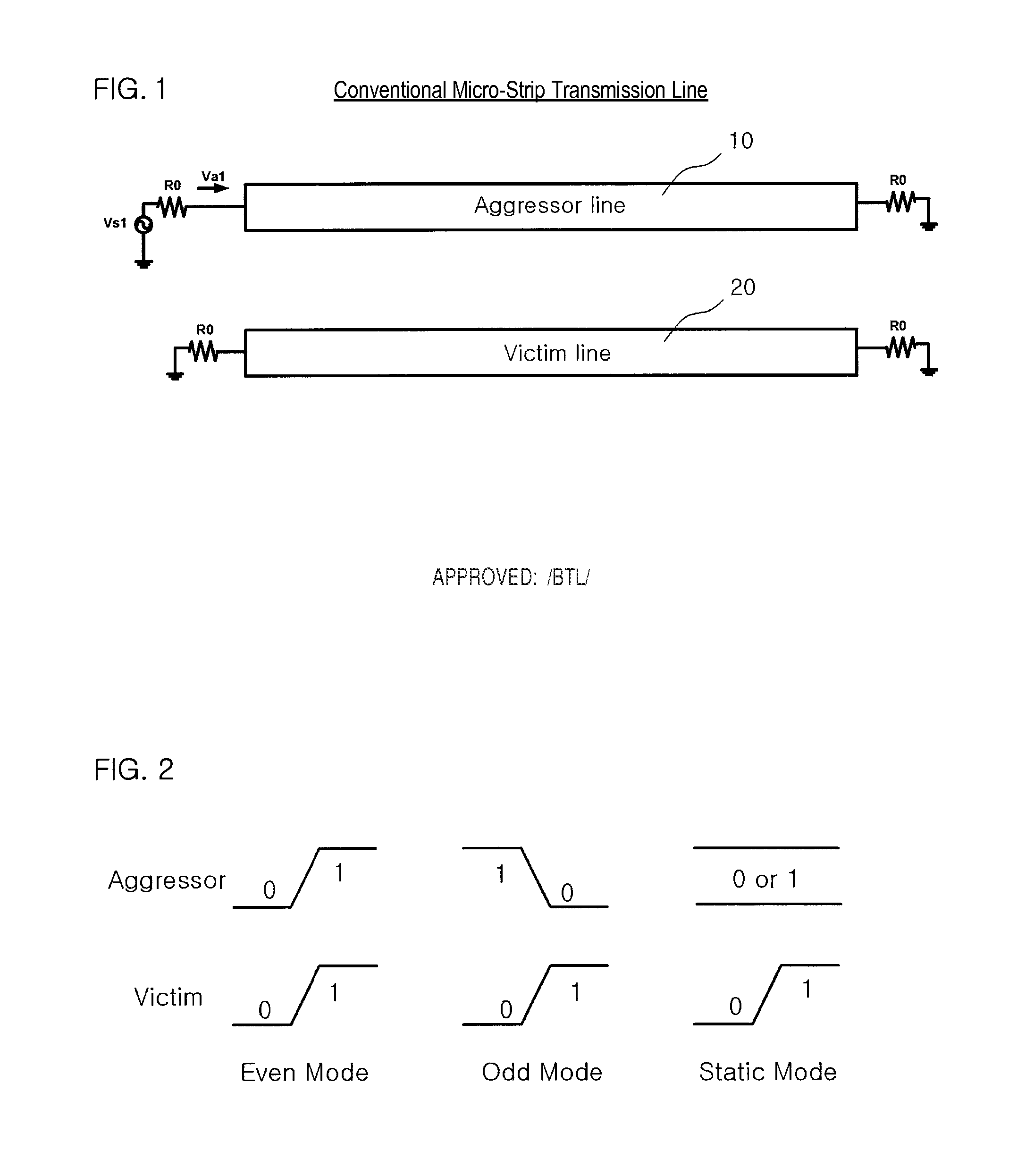

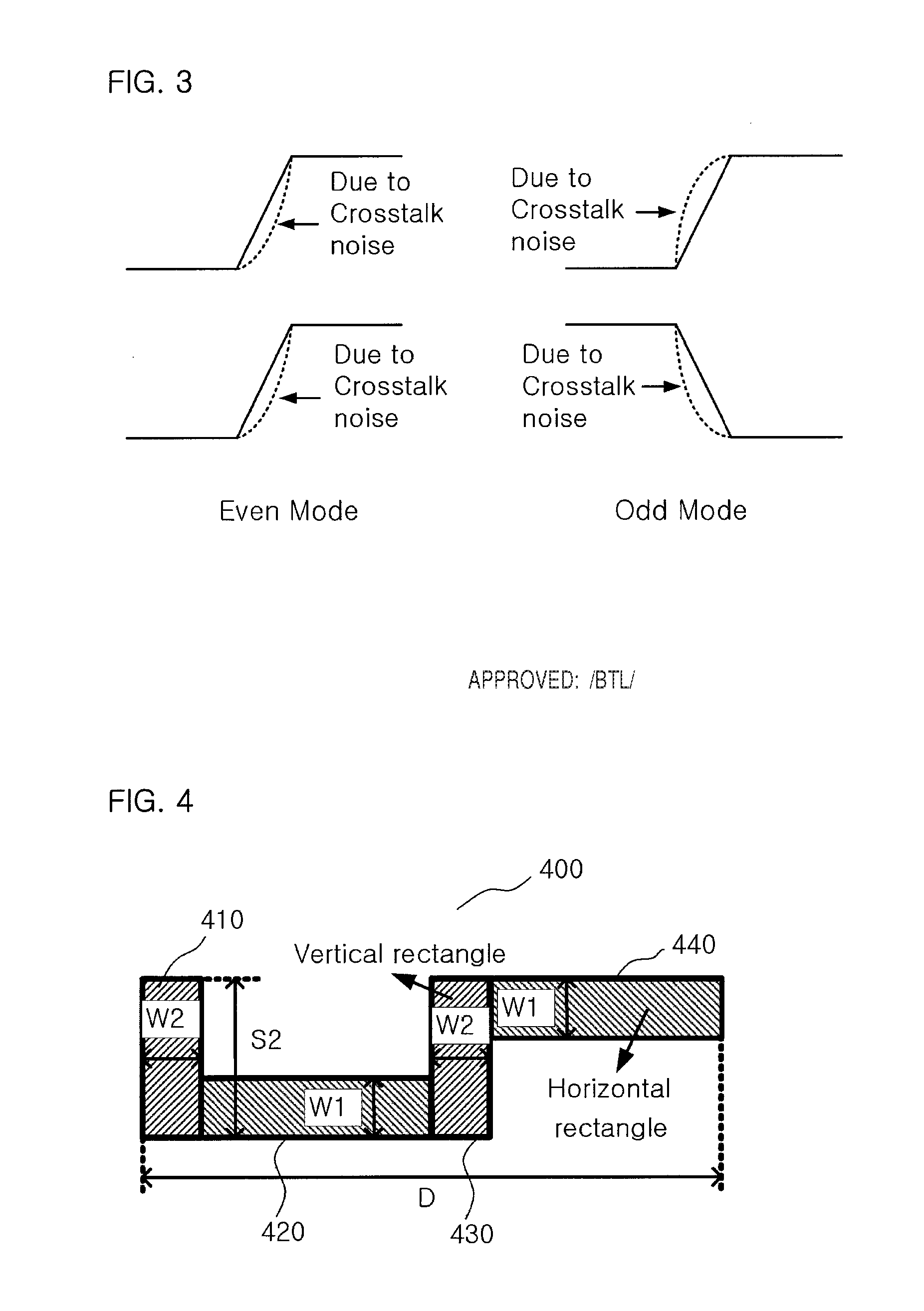

Micro-strip transmission line structure of a serpentine type

InactiveUS20100207700A1Reduce far end crosstalkIncrease couplingMultiple-port networksCross-talk/noise/interference reductionCapacitive couplingCapacitance

A micro-strip transmission line capable of reducing far-end crosstalk is provided. The micro-strip transmission line having a serpentine shape is capable of reducing the far-end crosstalk of the transmission line by increasing capacitive coupling between neighboring transmission lines by allowing parallel micro-strip transmission lines to have serpentine shapes. In the structure of the micro-strip transmission line having the serpentine shape, it is possible to reduce the far-end crosstalk of the transmission line by increasing capacitive coupling between neighboring transmission lines by allowing parallel micro-strip transmission lines to have serpentine shapes.

Owner:POSTECH ACAD IND FOUND

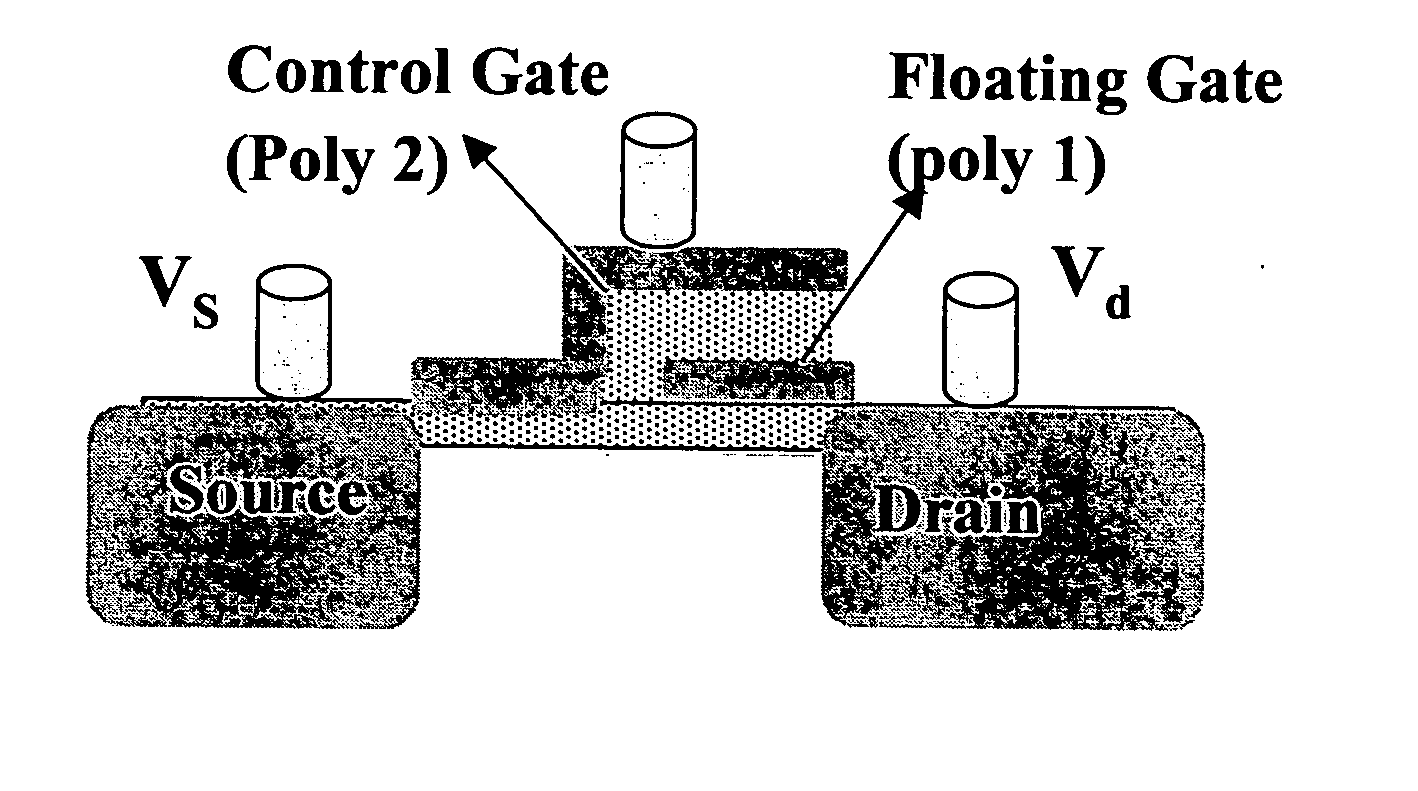

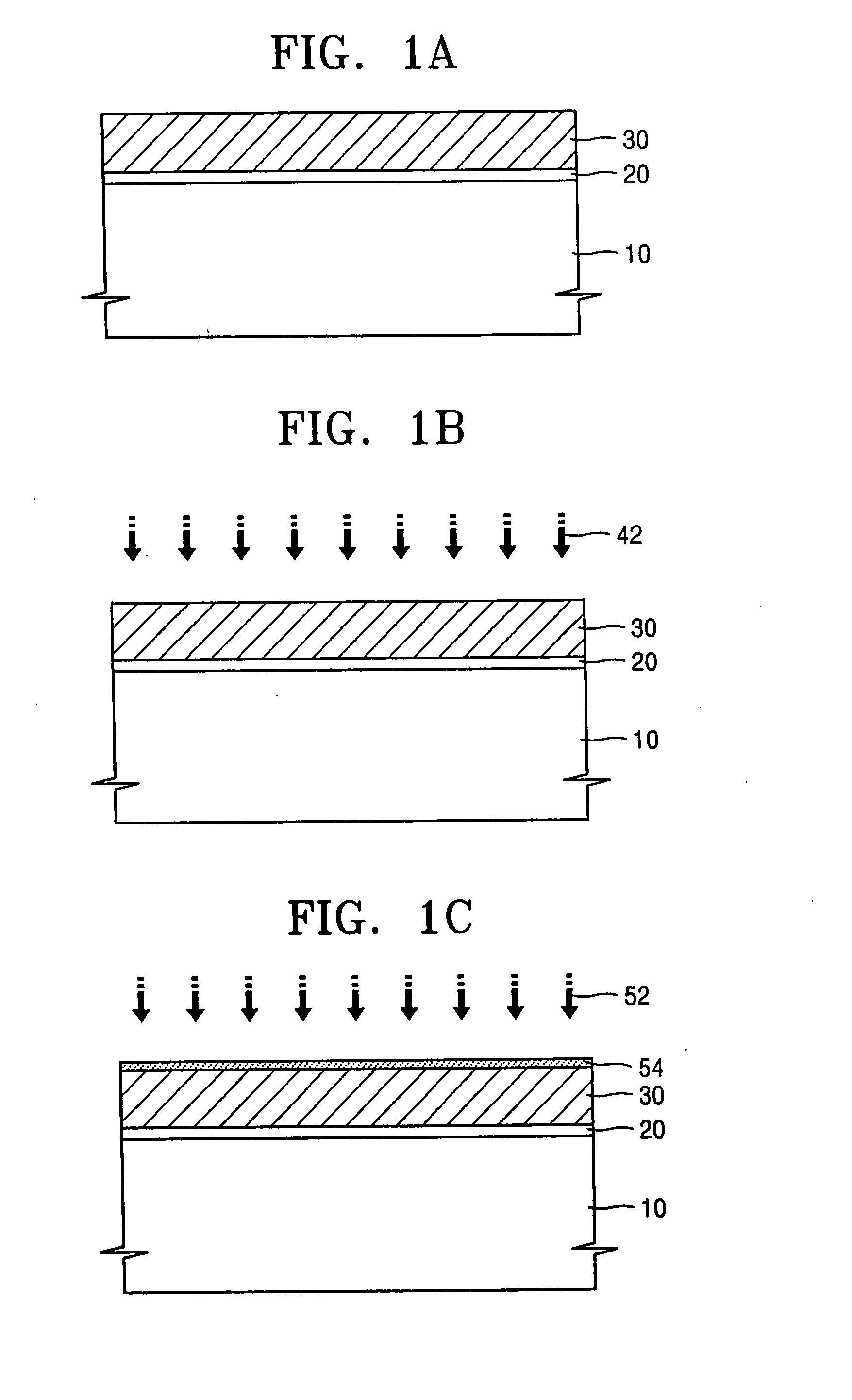

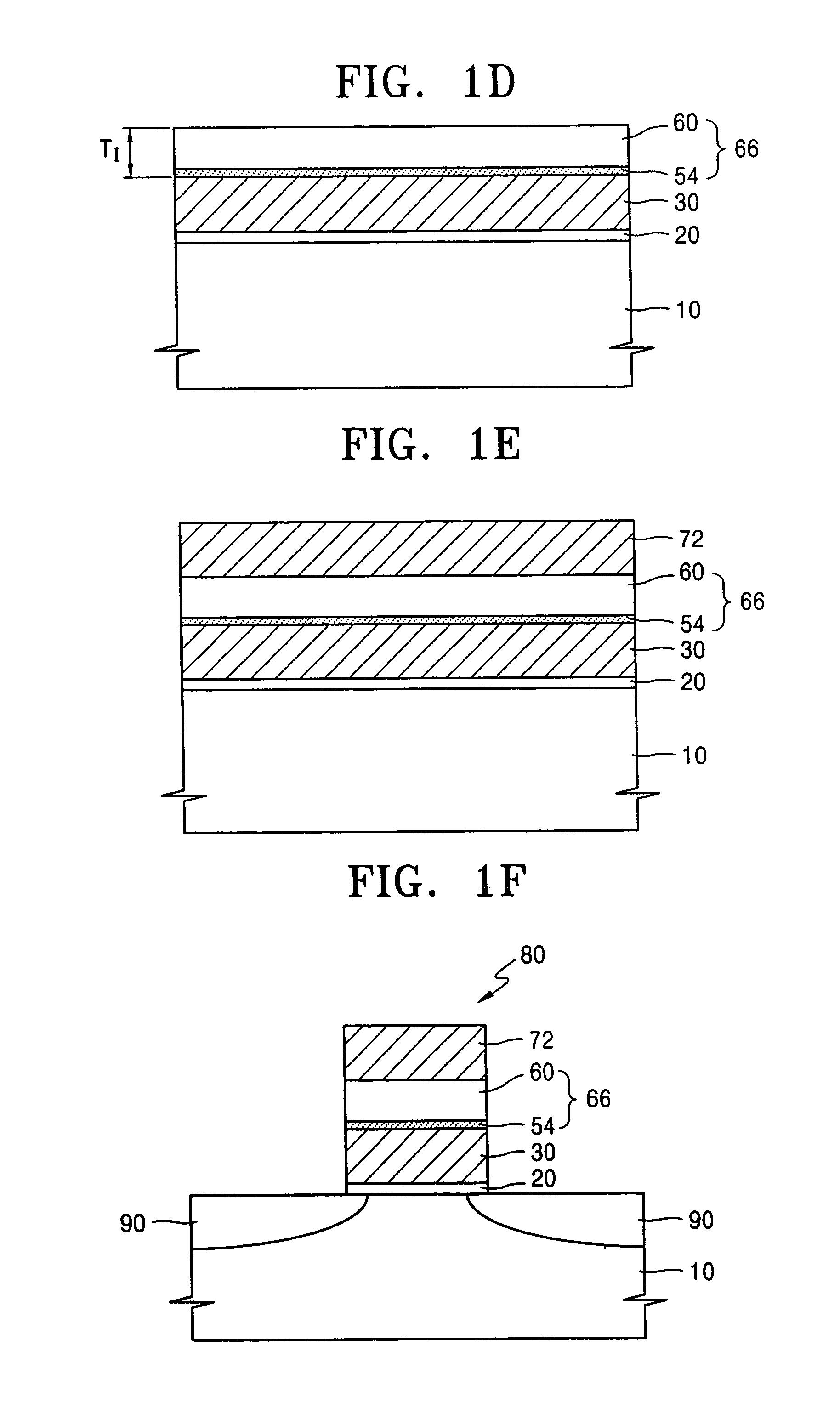

Method of manufacturing a thin dielectric layer using a heat treatment and a semiconductor device formed using the method

ActiveUS20050106897A1Enhancing Capacitive CouplingLower programming voltageSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceGate dielectric

In a method for forming a semiconductor device and a semiconductor device formed in accordance with the method, a thin dielectric layer is provided between a lower conductive layer and an upper conductive layer. In one embodiment, the thin dielectric layer comprises an inter-gate dielectric layer, the lower conductive layer comprises a floating gate and the upper dielectric layer comprises a control gate of a transistor, for example, a non-volatile memory cell transistor. The thin dielectric layer is formed using a heat treating process that results in reduction of surface roughness of the underlying floating gate, and results in a thin silicon oxy-nitride layer being formed on the floating gate. In this manner, the thin dielectric layer provides for increased capacitive coupling between the lower floating gate and the upper control gate. This also leads to a lowered programming voltage, erasing voltage and read voltage for the transistor, while maintaining the threshold voltage in a desired range. In addition, the size of the transistor and resulting storage cell can be minimized and the need for a high-voltage region in the circuit is mitigated, since, assuming a lowered programming voltage, pumping circuitry is not required.

Owner:SAMSUNG ELECTRONICS CO LTD

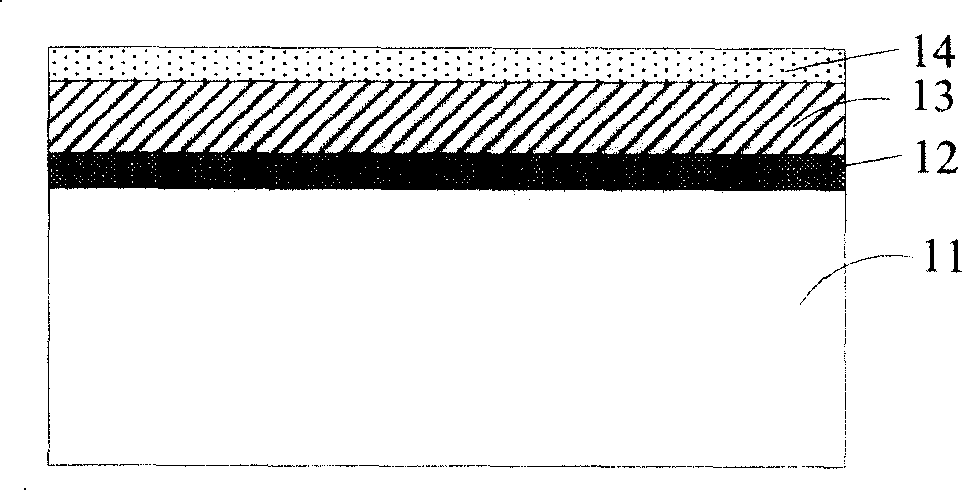

Semiconductor memory and forming method thereof

ActiveCN101207024AStop the leakEnhanced electron tunnelingSolid-state devicesSemiconductor/solid-state device manufacturingDielectricCoupling ratio

The invention relates to a grid formation method. The invention comprises a tunneling insulating layer, a first polysilicon layer, a first interlayer insulating layer, a second interlayer insulating layer and a second polysilicon layer,which are formed on a semiconductor substrate in sequence, wherein, the first interlayer insulating layer adopts oxygen-rich silicon nitride, and the second interlayer insulating layer adopts high-K dielectrics. The invention provides a gate structure correspondingly, and also provides a semi-conductor memory and the manufacturing method thereof. Because the invention adopts high-K dielectric material as the second interlayer insulating layer to replace silicon nitride and silicon oxide of the ONO in the prior art, and the dielectric constant of the high-K dielectric material is higher than that of the silicon oxide, the thickness of the high K-dielectric material can be reduced, and therefore the area of a storage unit is reduced, simultaneously the higher coupling ratio is kept between the first interlayer insulating layer and the floating gate, and the higher coupling ratio ensures the programmable voltage to be decreased. Thereby the operating voltage of the flash memory is reduced, and the shorter programming / erasing time can be realized.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

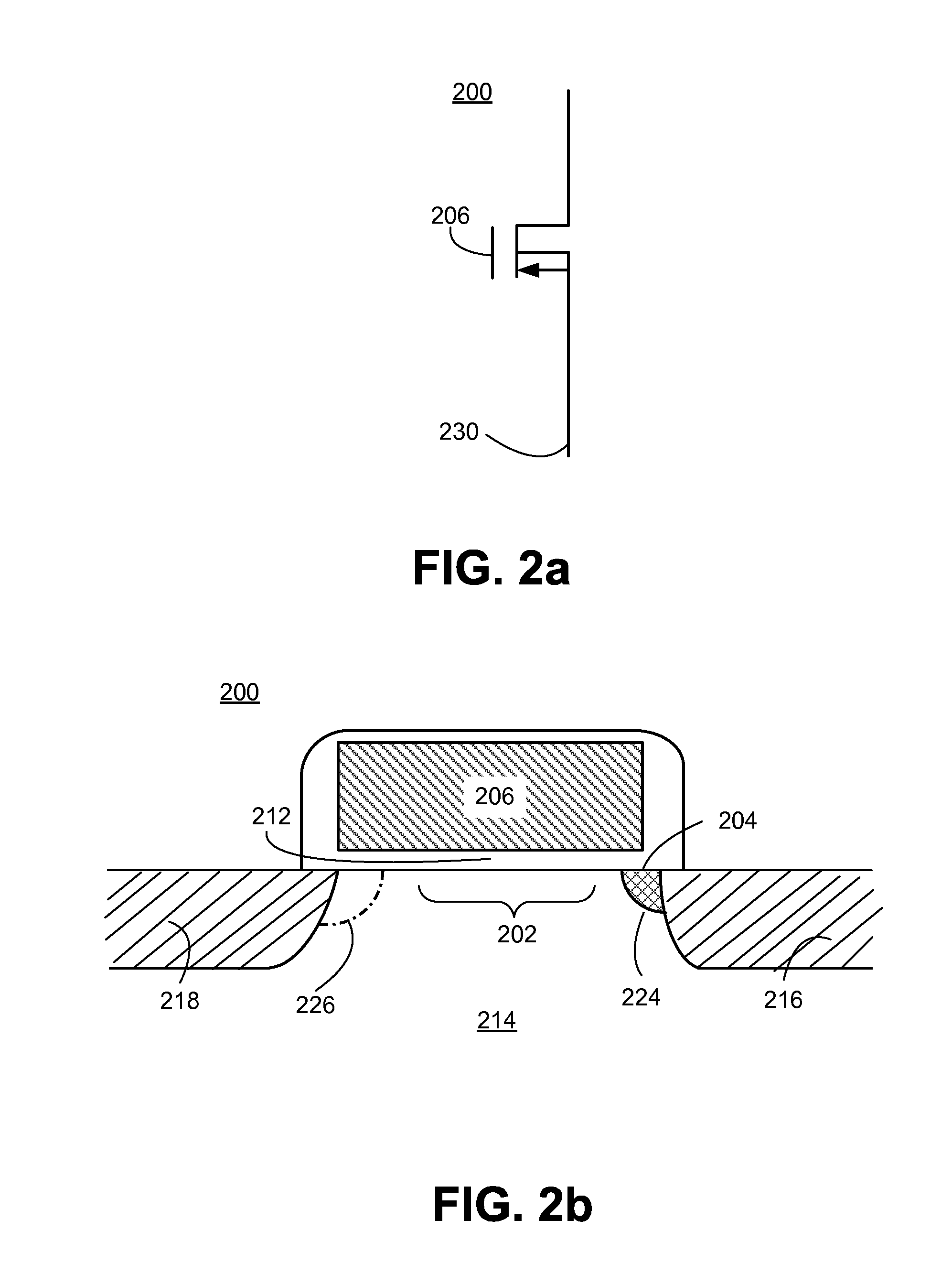

Fingerprint sensing device with interposer structure

ActiveUS20160358008A1Enhancing Capacitive CouplingHigh dielectric constantPhotomechanical coating apparatusPrint image acquisitionCapacitanceCapacitive coupling

The invention relates to a fingerprint sensing device comprising: a sensing chip comprising an array of sensing elements being configured to be connected to readout circuitry for detecting a capacitive coupling between each of the sensing elements and a finger placed on a sensing surface of the sensing device, wherein a surface of the sensing elements define a sensing plane; a plurality of interposer structures arranged on the sensing chip extending above sensing plane, wherein the plurality of interposer structures have substantially the same height above the sensing plane; and a protective plate attached to the sensing chip by means of an adhesive arranged on the sensing chip, wherein the protective plate rests on the interposer structures such that a distance between the protective plate and the sensing plane is defined by the height of the interposer structures.

Owner:FINGERPRINT CARDS ANACATUM IP AB

Stacked gate region of a memory cell in a memory device

InactiveUS6949792B2Enhancing Capacitive CouplingReducing scaling sizeTransistorSolid-state devicesCapacitanceVertical edge

Semiconductor devices are disclosed utilizing at least one polysilicon structure in a stacked gate region according to the present invention. The stacked gate region includes a substrate, at least one trench, an oxide layer, at least one floating gate layer and the at least one polysilicon structure. The at least one polysilicon structure is formed adjacent to vertical edges of the at least one floating gate layer and above the oxide layer. The polysilicon structure, which includes polysilicon wings and ears, is used to increase the capacitive coupling of memory cells in memory devices, thereby allowing for further reduction or scaling in the size of memory cells and devices.

Owner:MICRON TECH INC

Very dense NVM bitcell

ActiveUS8598642B2Small sizeEnhancing Capacitive CouplingTransistorSolid-state devicesEngineeringCmos process

An asymmetric non-volatile memory bitcell is described. The bitcell comprises source and drain regions comprising carriers of the same conductivity type. A floating gate rests on top of the well, and extends over a channel region, and at least a portion of the source and drain regions. The drain region comprises additional carriers of a second conductivity type, allowing band to band tunneling. The source region comprises additional carriers of a first conductivity type, thereby increasing source-gate capacitance. Thus, the bitcell incorporates a select device, thereby decreasing the overall size of the bitcell. The bitcell may be created without any additional CMOS process steps, or through the addition of a single extra mask step.

Owner:SYNOPSYS INC

Multifunctional GNSS antenna

PendingCN111864382AMiniaturizationReduce signal interferenceSimultaneous aerial operationsRadiating elements structural formsTelecommunicationsDielectric plate

The invention discloses a multifunctional GNSS antenna, and belongs to the technical field of communication. The multifunctional GNSS antenna comprises a PCB, a first dielectric plate and a first radiation part which are arranged in sequence, and the PCB is connected with the first radiation part through a first feed part. And the first dielectric plate is also provided with a second radiation part and a plurality of metallized via holes, the second radiation part is connected with the PCB through a second feed part, the plurality of metallized via holes are arranged around the first radiationpart, and the second radiation part is arranged at the outer sides of the plurality of metallized via holes. According to the multifunctional GNSS antenna, signal interference and coupling of the second radiation part to the first radiation part are effectively reduced, and miniaturization of the antenna is facilitated.

Owner:HARXON CORP

Compact ultra-wideband omnidirectional antenna

ActiveCN112886233ASuppression of reactance characteristicsEnhancing Capacitive CouplingSimultaneous aerial operationsRadiating elements structural formsUltra-widebandCapacitance

The invention relates to a compact ultra-wideband omnidirectional antenna comprising a first metal layer, a second metal layer and a dielectric substrate. The first metal layer and the second metal layer are printed on the upper layer and the lower layer of the dielectric substrate respectively, and each metal layer is composed of a double-branch flag-shaped radiator, double parasitic bands, a curved groove, a short open-circuit branch knot and a center metal disc. A short branch is loaded on a conical feed structure, the reactance characteristic of the antenna at high frequency is effectively suppressed, a high-frequency resonance point is introduced, and when double parasitic bands are added, a new resonance point is added between two existing resonance points, so that the bandwidth is improved, the 1.8-3.85 GHz passband characteristic is formed. A short open-circuit branch knot is added to the tail end of the first branch knot, a curve-shaped groove is etched, capacitive coupling and a current path are increased, and the low-frequency cut-off frequency is reduced. Finally, the impedance bandwidth of the antenna can reach 78% (1.69-3.85 GHz), in the impedance bandwidth, the cross polarization level on the horizontal plane is smaller than-20 dB, and the efficiency in the working frequency band is 80%-91%.

Owner:CHONGQING UNIV

Semiconductor structure and manufacturing method thereof

InactiveCN103794564AReduce Capacitive CouplingReduce parasitic coupling effectsTransistorSolid-state devicesCapacitanceSemiconductor structure

The invention provides a manufacturing method of a semiconductor structure. The method comprises the following steps: a) a substrate is provided, and the substrate comprises a first direction and a second direction; b) a gate stack is formed on the substrate, and the grid stack comprises a first insulating layer and a floating gate in turn; c) the floating gate is etched in the first direction so that at least two recesses are formed on the side wall of the floating gate in the first direction; d) a second insulating layer and a control gate are formed on the floating gate via deposition, and the second insulating layer and the control gate cover the side surface of the floating gate in the first direction; e) the floating gate is etched in the second direction so that at least two recesses are formed on the side wall of the floating gate in the second direction; and f) source / drain regions are formed on the two sides of the stack gate. Correspondingly, the invention also provides the semiconductor structure. Capacitive coupling between two adjacent lists of units can be reduced and the capacitive coupling between the control gate and the floating gate can be enhanced.

Owner:李迪

Serpentine micro-strip lines configured in an aggressor/victim type transmission line structure

InactiveUS8384489B2Reduce transmissionEnhancing Capacitive CouplingMultiple-port networksCross-talk/noise/interference reductionCapacitanceCapacitive coupling

A micro-strip transmission line capable of reducing far-end crosstalk is provided. The micro-strip transmission line having a serpentine shape is capable of reducing the far-end crosstalk of the transmission line by increasing capacitive coupling between neighboring transmission lines by allowing parallel micro-strip transmission lines to have serpentine shapes. In the structure of the micro-strip transmission line having the serpentine shape, it is possible to reduce the far-end crosstalk of the transmission line by increasing capacitive coupling between neighboring transmission lines by allowing parallel micro-strip transmission lines to have serpentine shapes.

Owner:POSTECH ACAD IND FOUND

Common mode choke coil

ActiveUS9312062B2Improve abilitiesSignals is relatively smallTransformers/inductances coils/windings/connectionsTransformers/inductances magnetic coresElectrical conductorInput/output

Owner:MURATA MFG CO LTD

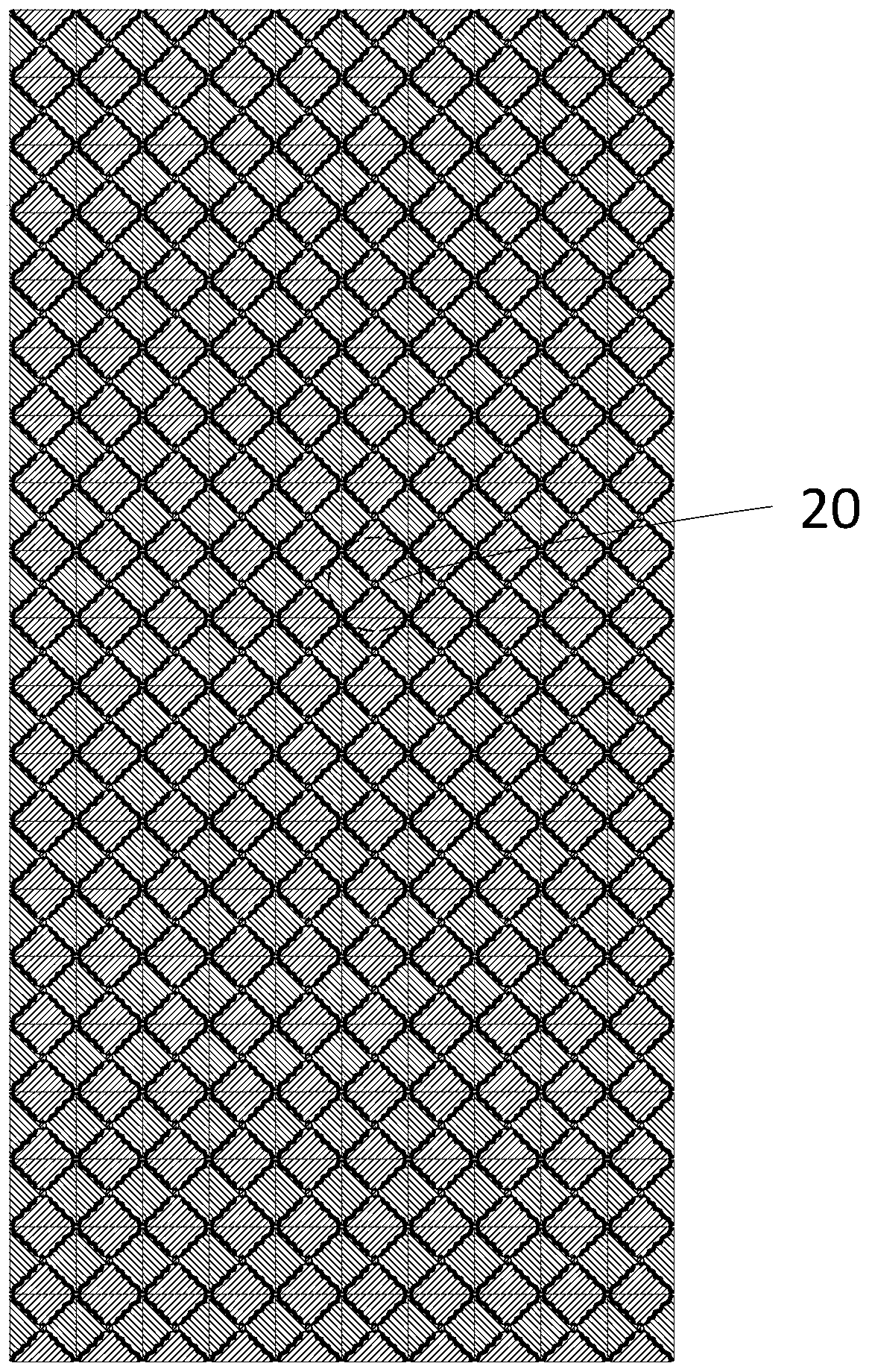

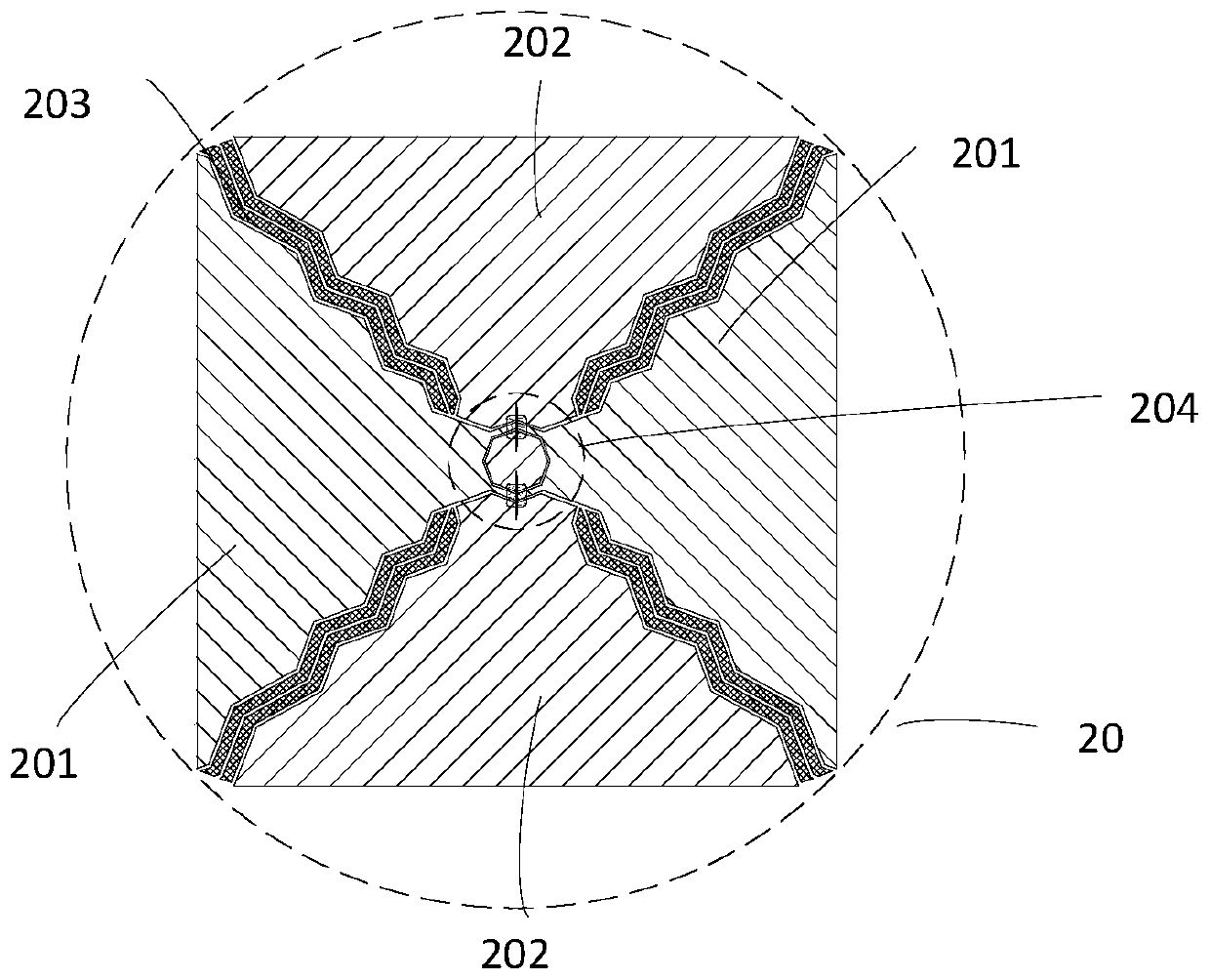

Touch sensor pattern, touch sensor, touch control device, and electronic terminal

PendingCN111065994AIncrease capacitive couplingIncrease the amount of capacitance changeInput/output processes for data processingPhysicsEngineering

The invention discloses a touch sensor pattern, a touch sensor, a touch device and an electronic terminal. The touch sensor pattern includes: at least two sensing units, each of the two sensing unitsincluding a first sensing electrode arranged in a first direction, a second sensing electrode arranged in a second direction, a first driving electrode arranged in a third direction, and a second driving electrode arranged in a fourth direction; wherein the first induction electrode is connected with the second induction electrode; the first driving electrode is connected with the second driving electrode; the first induction electrode and the first driving electrode are perpendicular to each other; and the second induction electrodes and the second driving electrodes are parallel to each other and are alternately arranged. According to the touch sensor pattern provided by the invention, under the condition of the same pattern area, the coupling of the driving electrode and the sensing electrode is increased, so that the touch variation is increased, and the suspension performance is improved.

Owner:SHENZHEN GOODIX TECH CO LTD

Process for making plane floating grid and nonvolatile memory element containing same

InactiveCN1505104AImprove flatnessEnhancing Capacitive CouplingSemiconductor/solid-state device manufacturingSemiconductor devicesMechanical engineeringPolycrystalline silicon

The invention relates to a plane floating grid making method, mainly including: deposit oxide between polycrystal silicon layers to cover the wafer surface; open the floating grid region (except extension part) and etching oxide between partial polycrystal silicon layers; open all the floating regions (except extension part) and all the active regions. It can make an approximate 'T' floating grid with flat and wide surface and coupled area with the control grid. It also relates to a construction of involatile memory component with the plane floating grid by the making method.

Owner:WINBOND ELECTRONICS CORP

Method of manufacturing a thin dielectric layer using a heat treatment and a semiconductor device formed using the method

ActiveUS7190024B2Enhancing Capacitive CouplingLower programming voltageTransistorSolid-state devicesCapacitanceGate dielectric

In a method for forming a semiconductor device and a semiconductor device formed in accordance with the method, a thin dielectric layer is provided between a lower conductive layer and an upper conductive layer. In one embodiment, the thin dielectric layer comprises an inter-gate dielectric layer, the lower conductive layer comprises a floating gate and the upper dielectric layer comprises a control gate of a transistor, for example, a non-volatile memory cell transistor. The thin dielectric layer is formed using a heat treating process that results in reduction of surface roughness of the underlying floating gate, and results in a thin silicon oxy-nitride layer being formed on the floating gate. In this manner, the thin dielectric layer provides for increased capacitive coupling between the lower floating gate and the upper control gate. This also leads to a lowered programming voltage, erasing voltage and read voltage for the transistor, while maintaining the threshold voltage in a desired range. In addition, the size of the transistor and resulting storage cell can be minimized and the need for a high-voltage region in the circuit is mitigated, since, assuming a lowered programming voltage, pumping circuitry is not required.

Owner:SAMSUNG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com