Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

340 results about "Coupling ratio" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Coupling Ratio. The percentage of Light transferred to a receiving output Port with respect to the total power of all output ports.

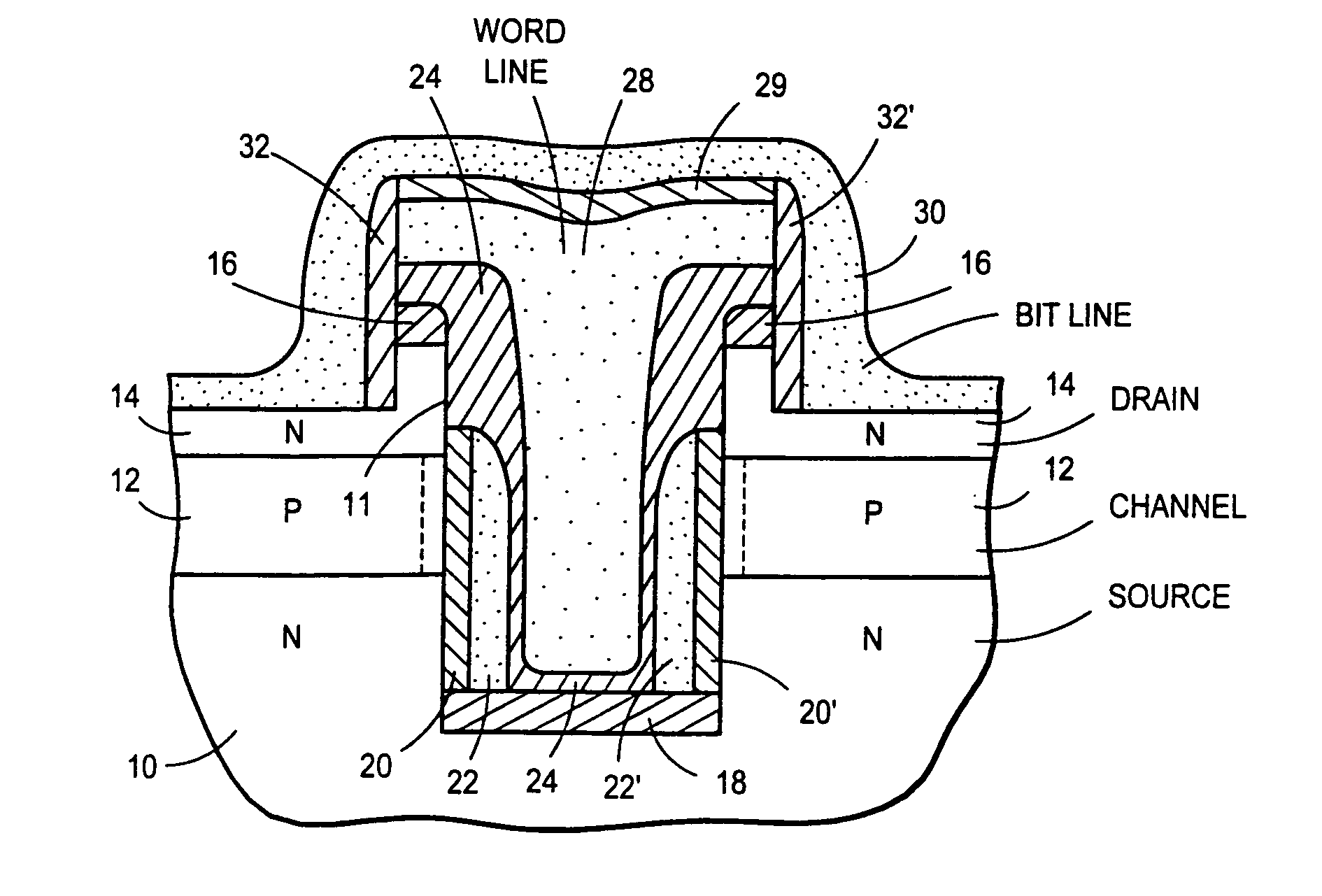

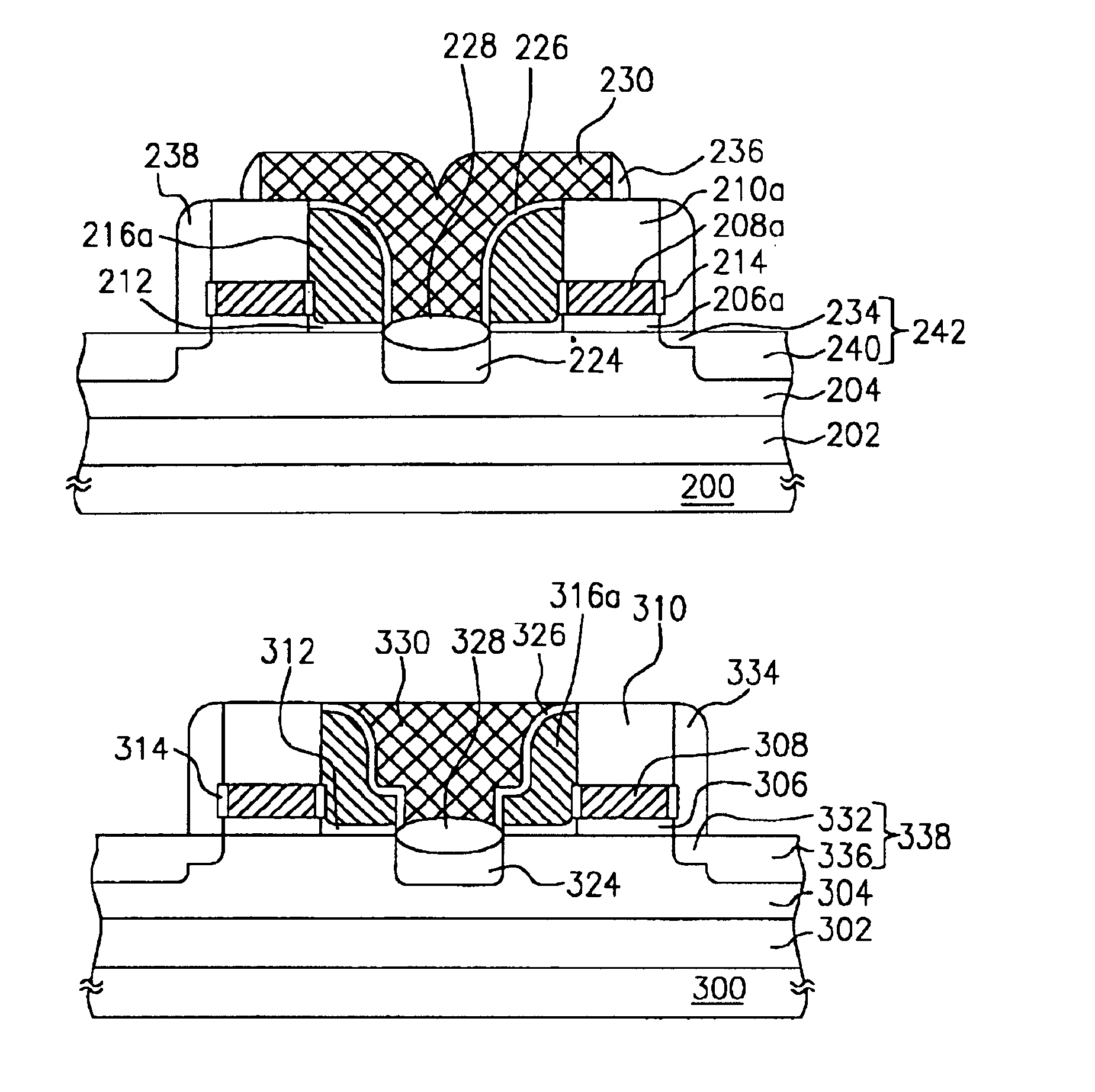

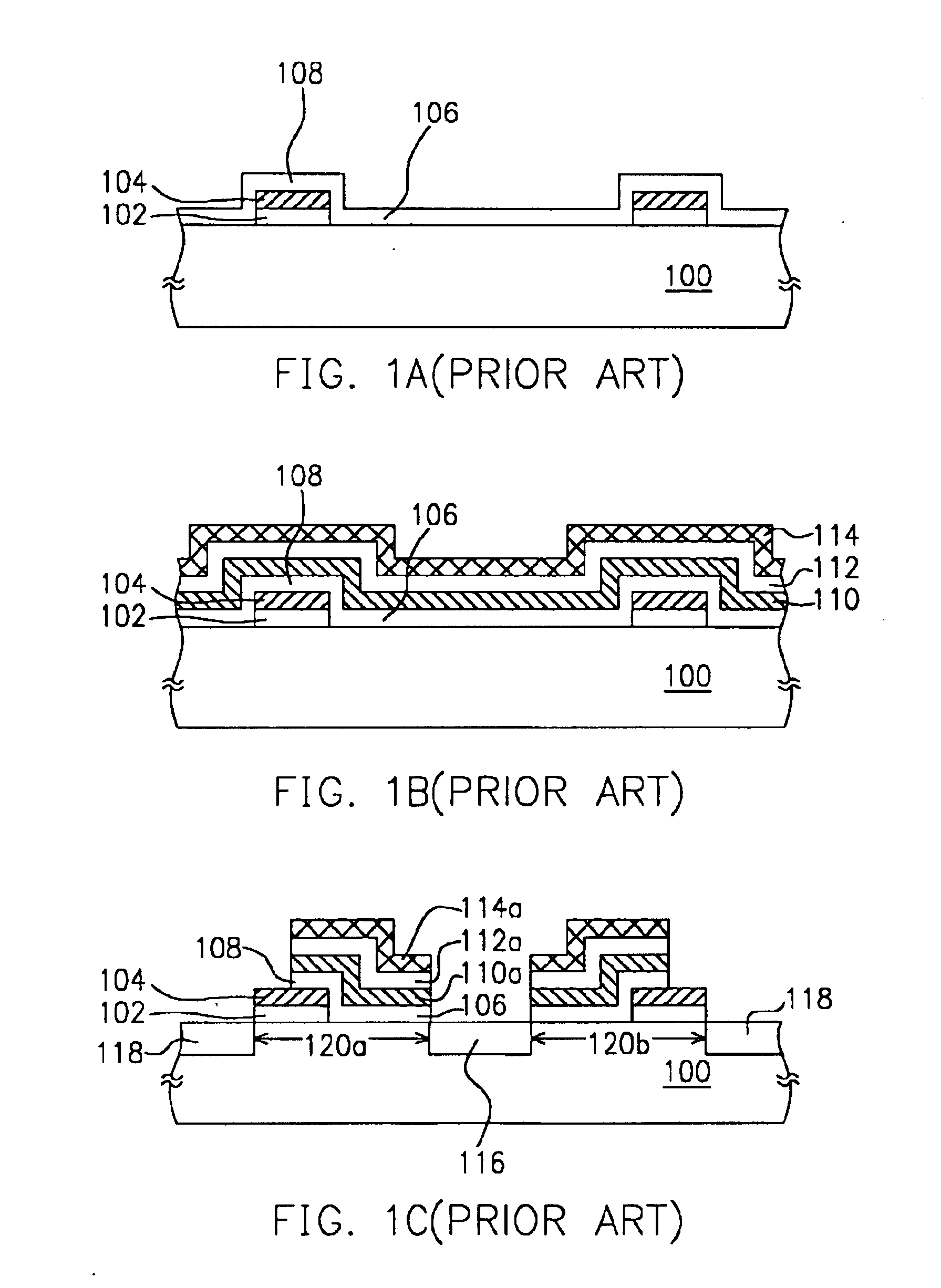

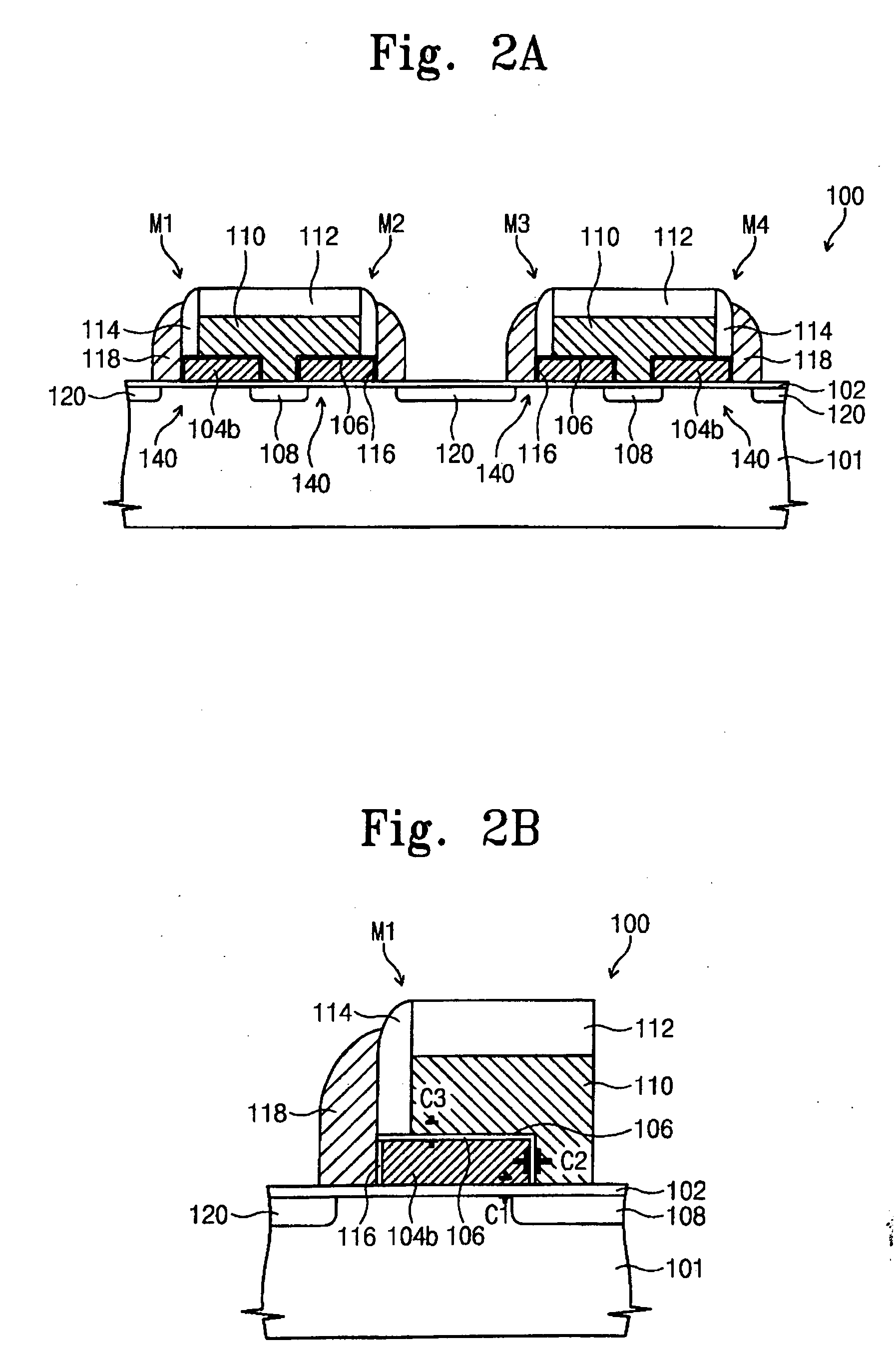

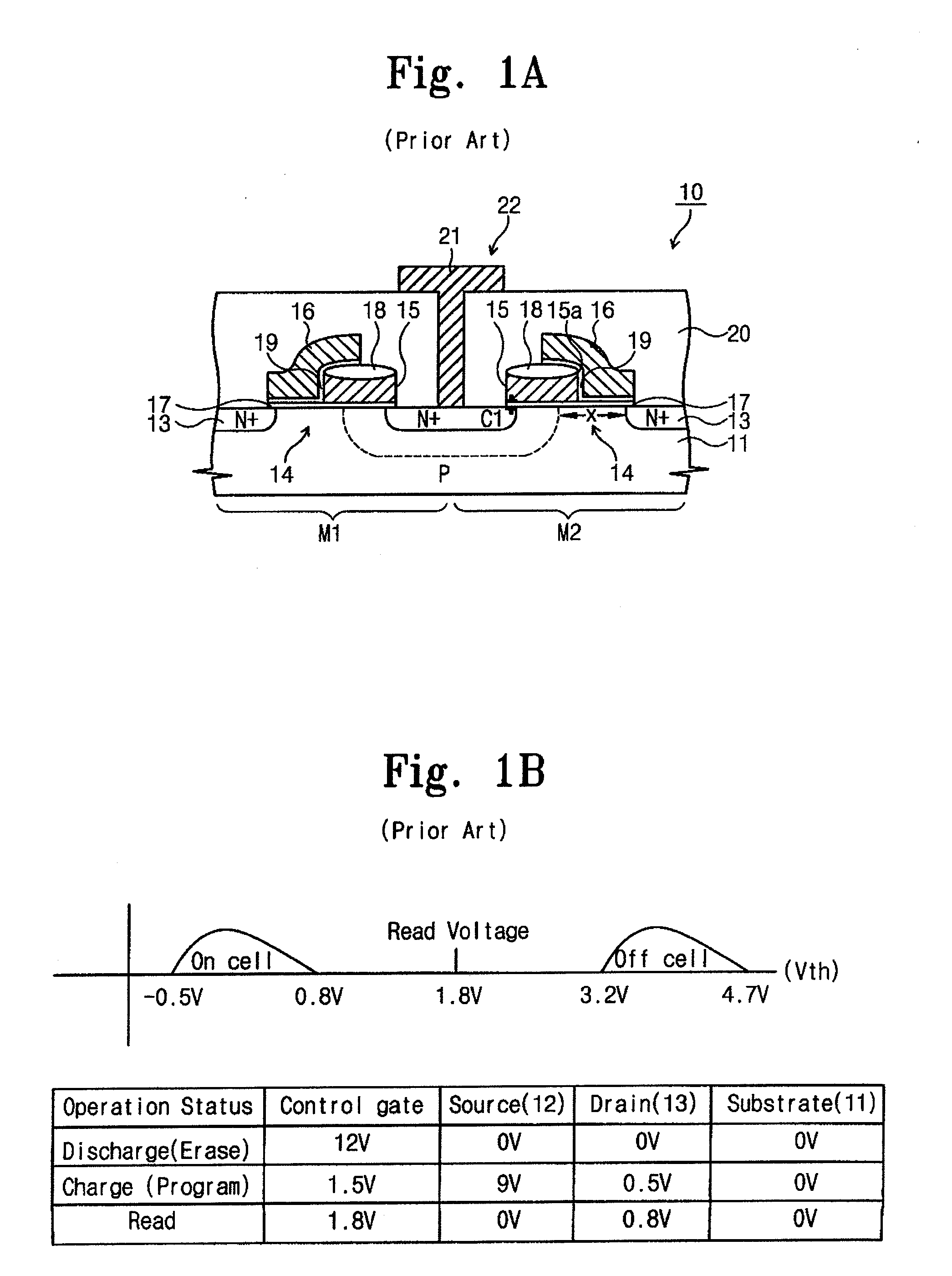

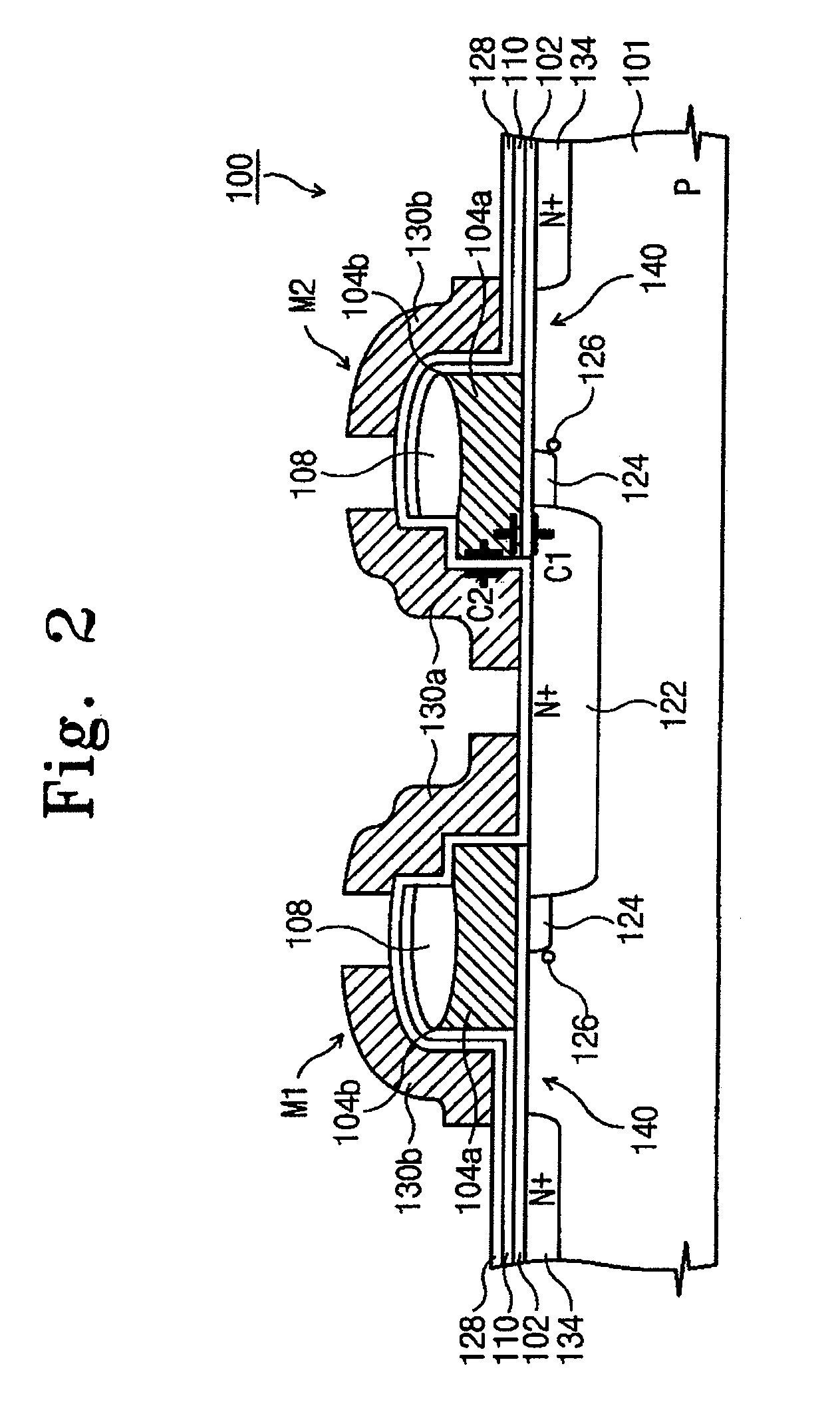

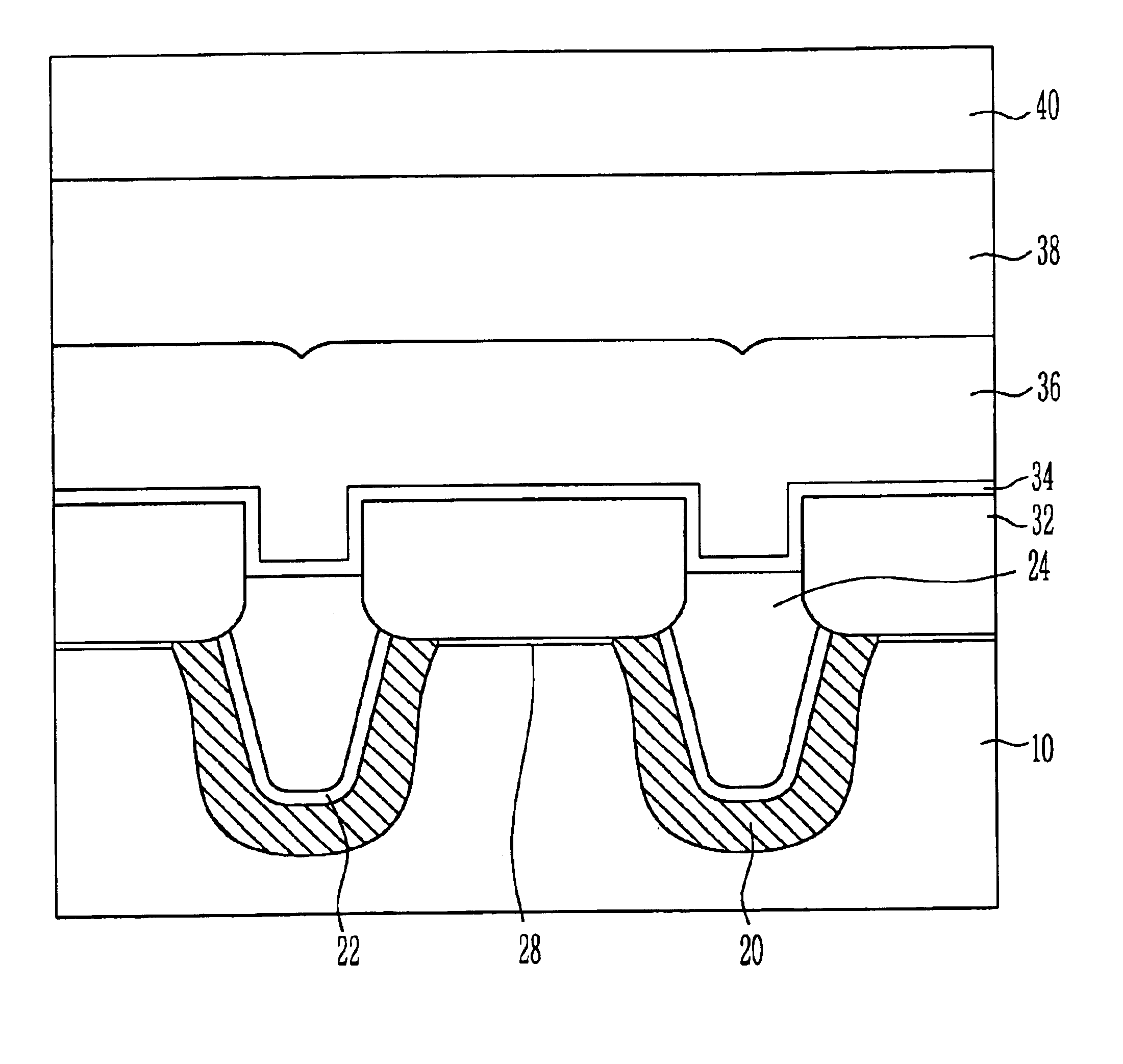

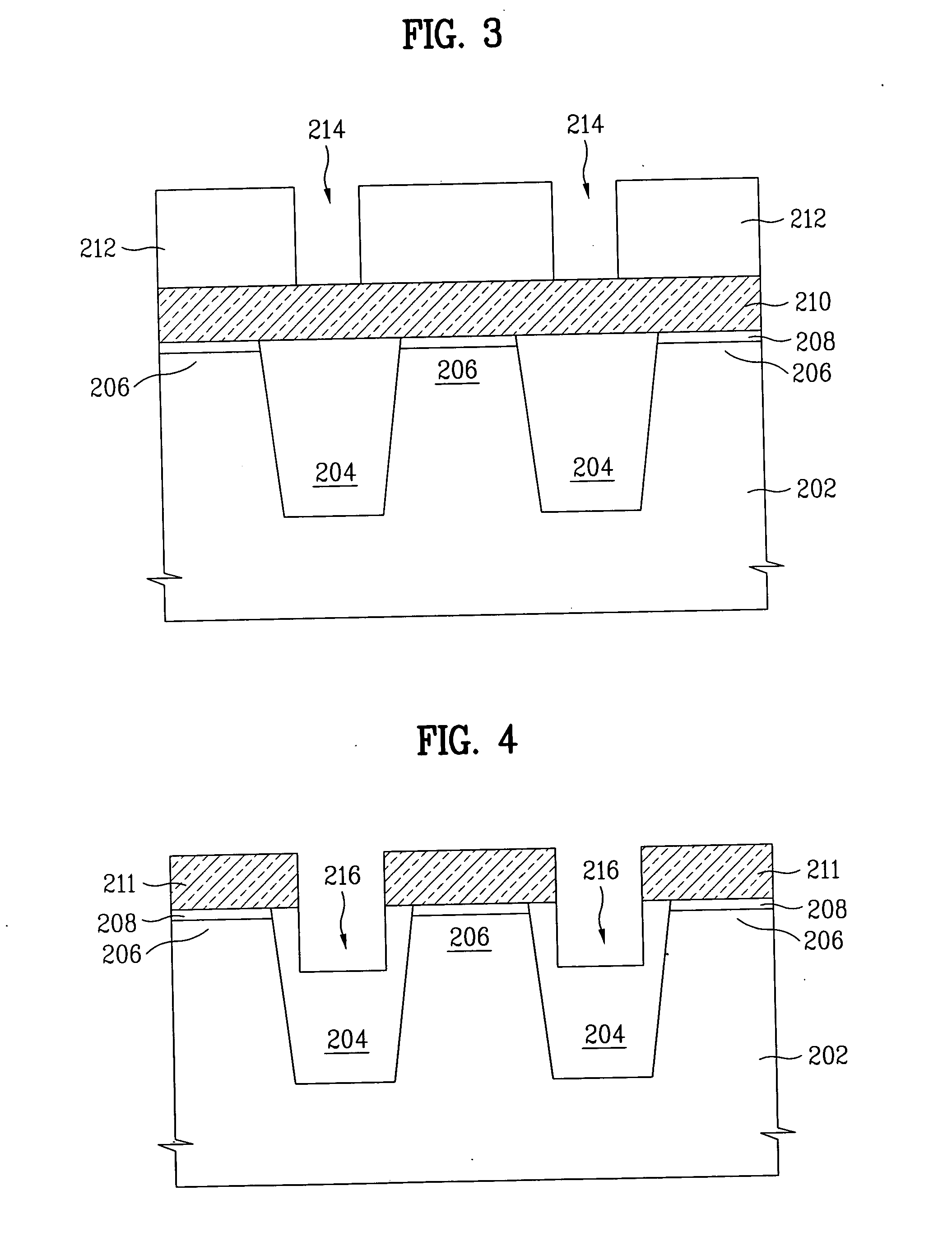

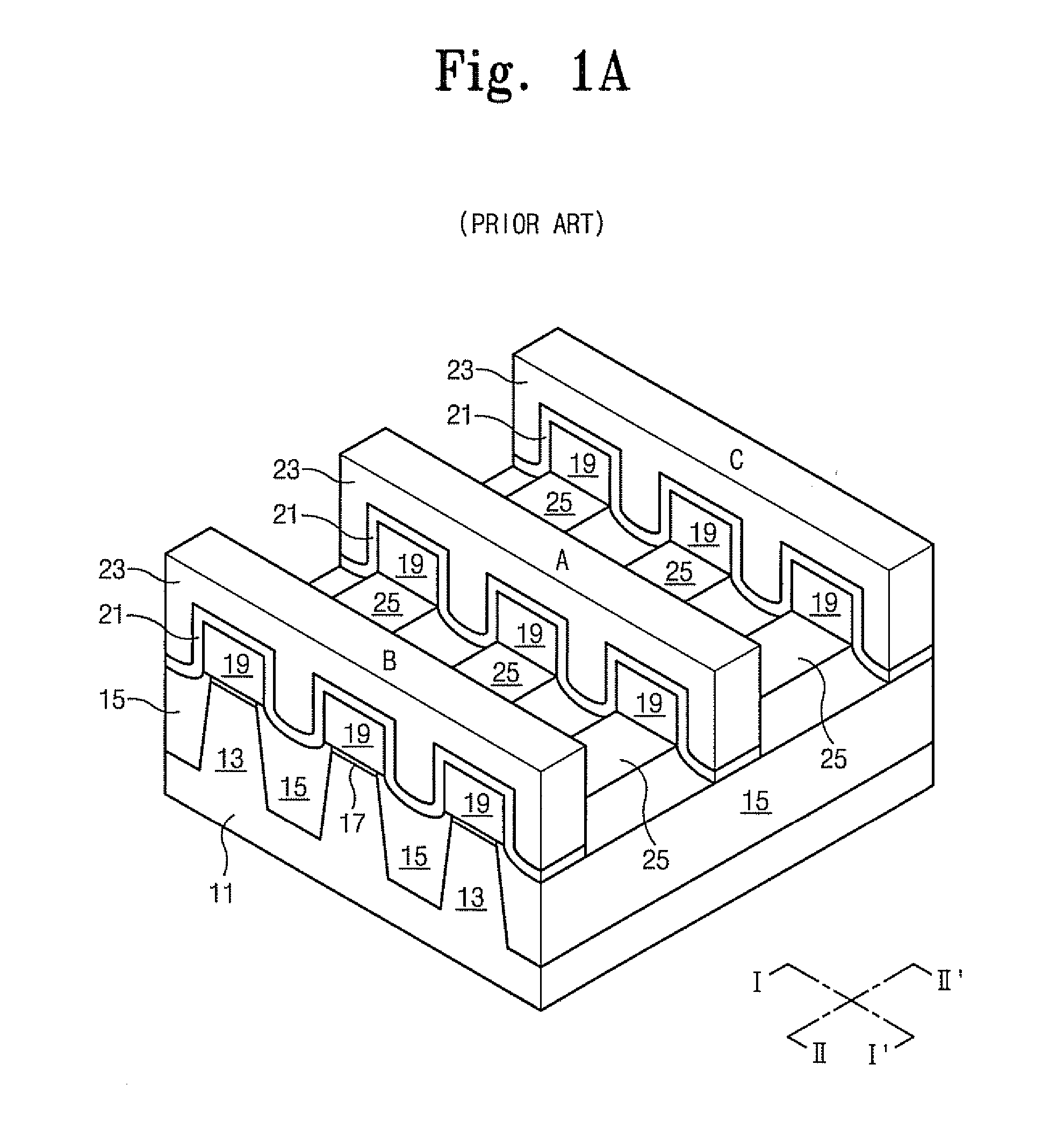

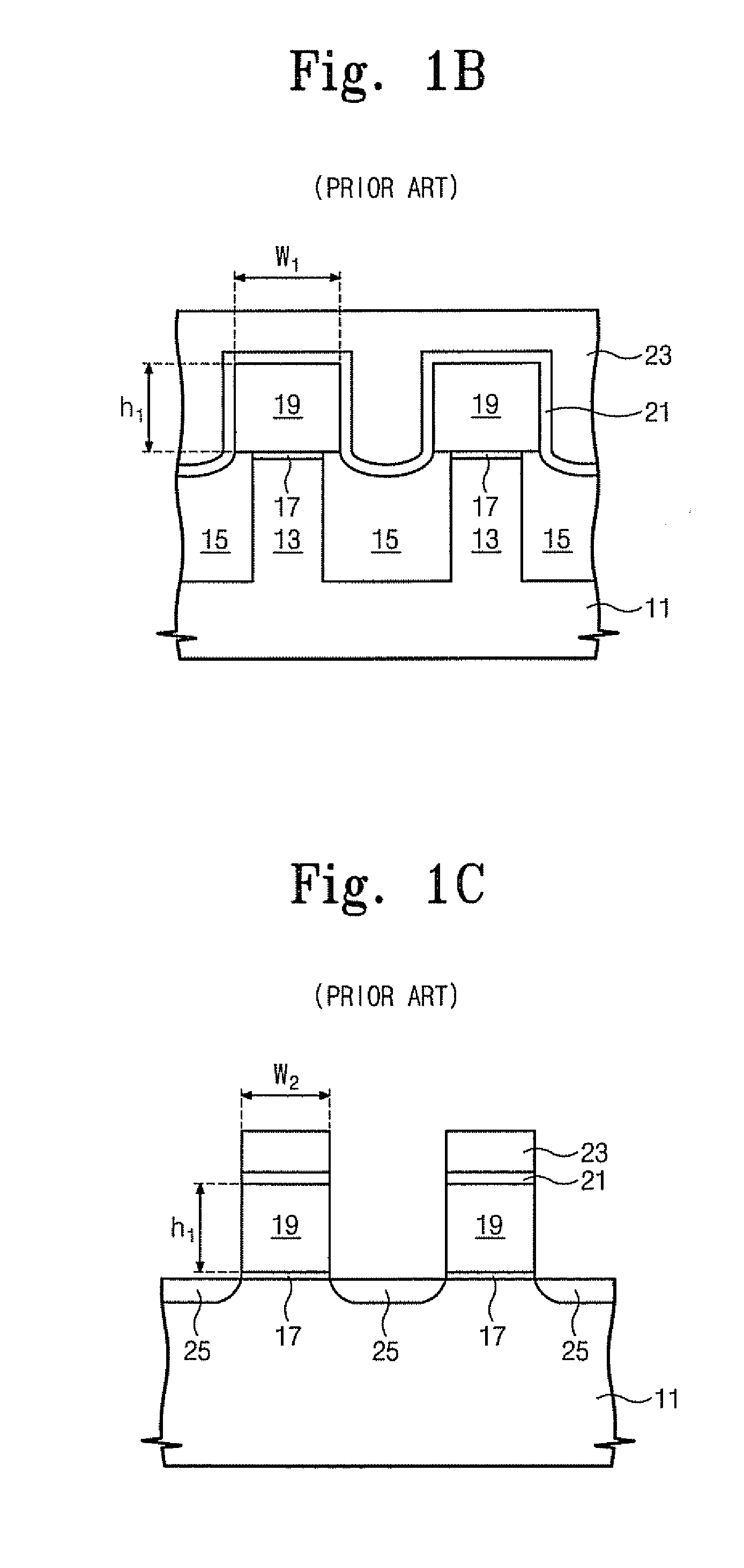

Flash memory device using semiconductor fin and method thereof

ActiveUS20060044915A1Improve scalabilityProgramming and erasing efficiencySolid-state devicesSemiconductor/solid-state device manufacturingCoupling ratioEngineering

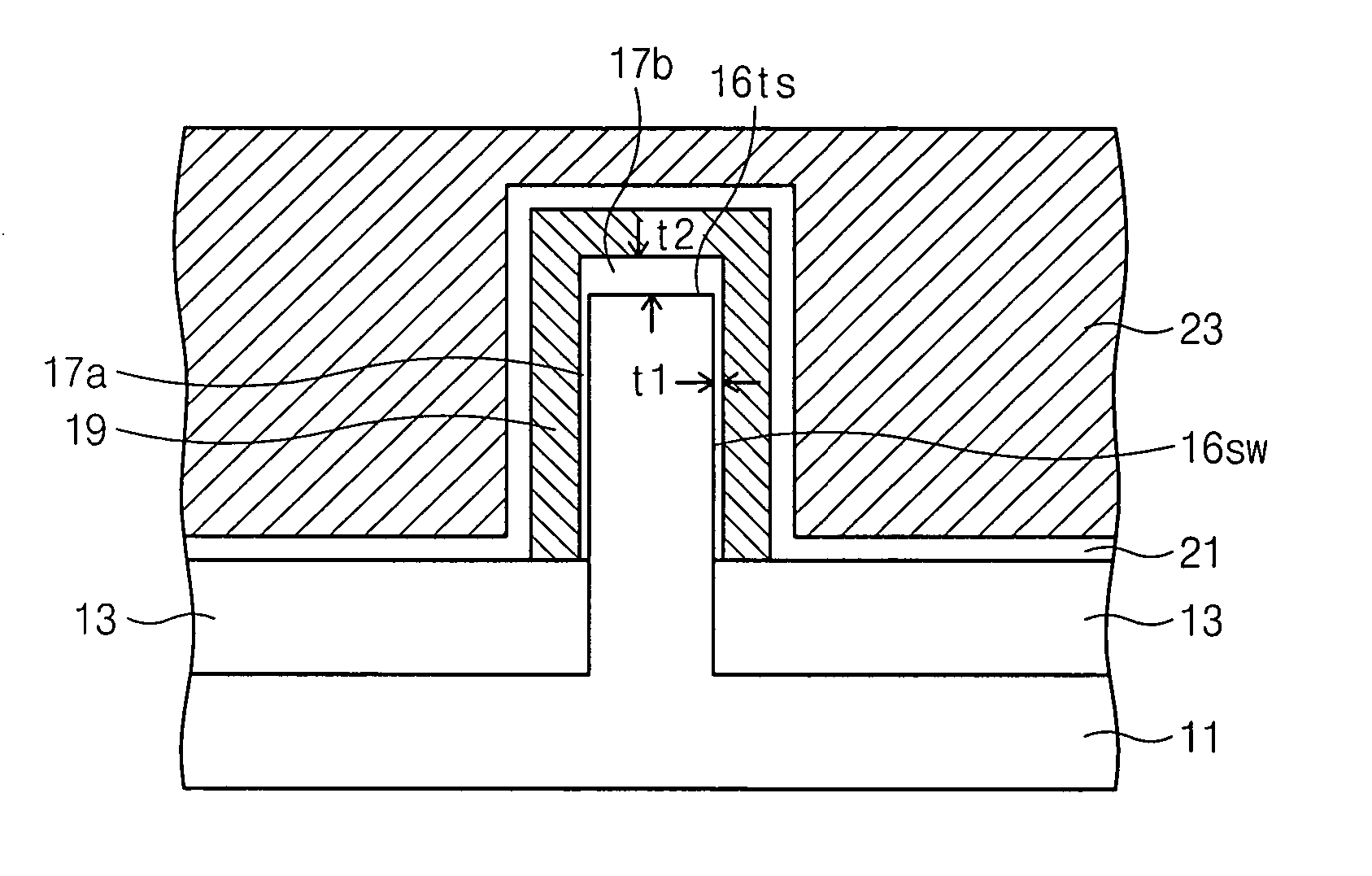

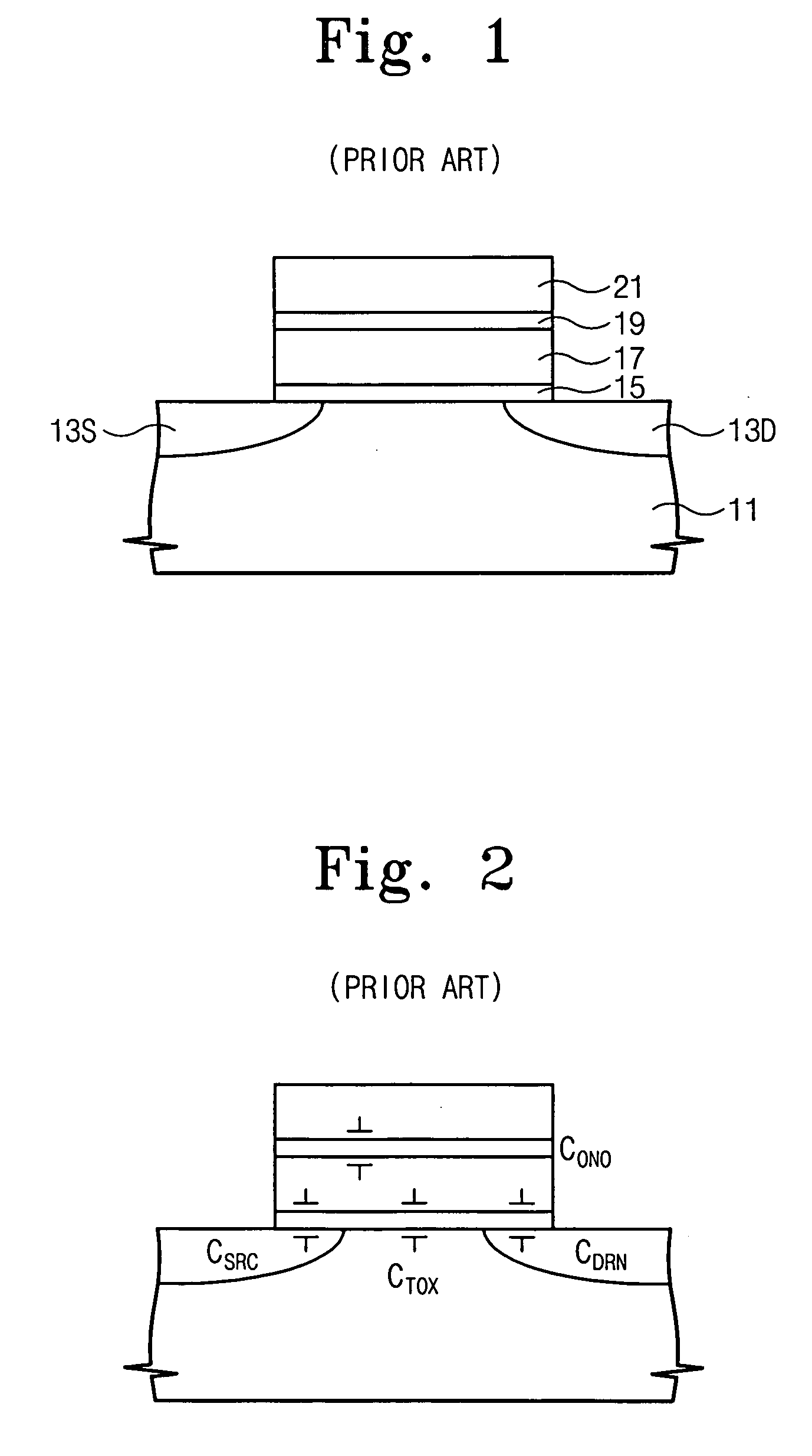

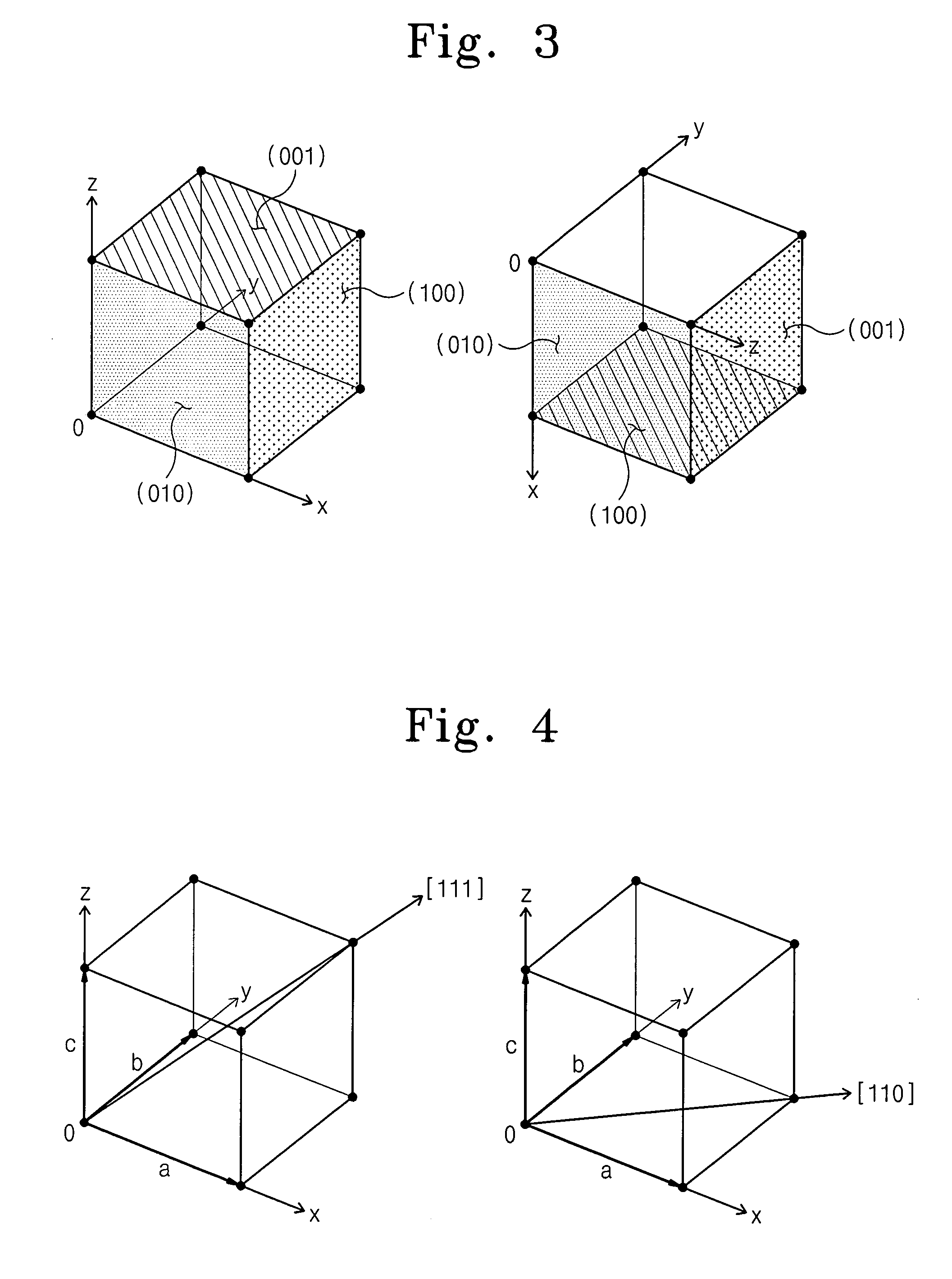

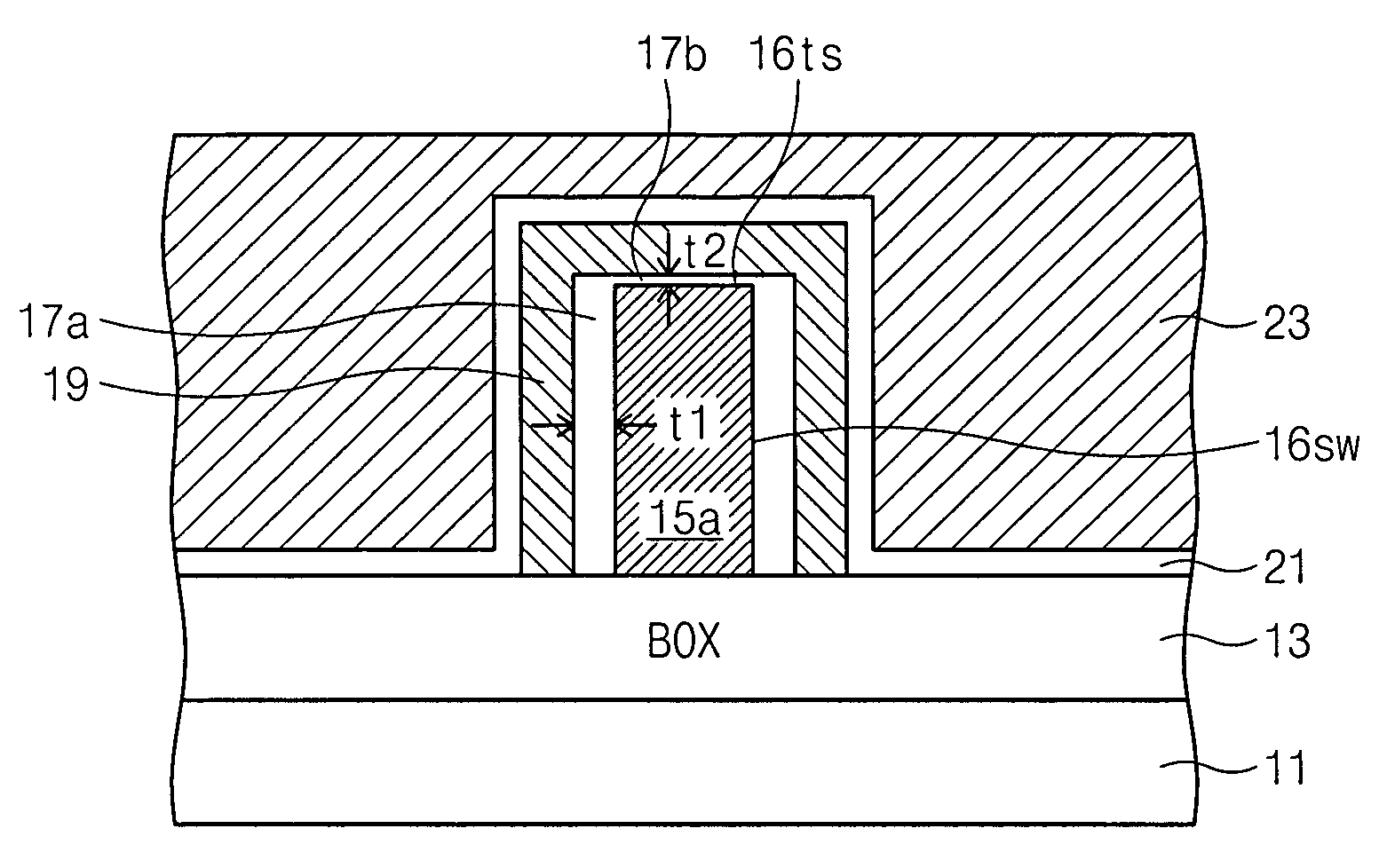

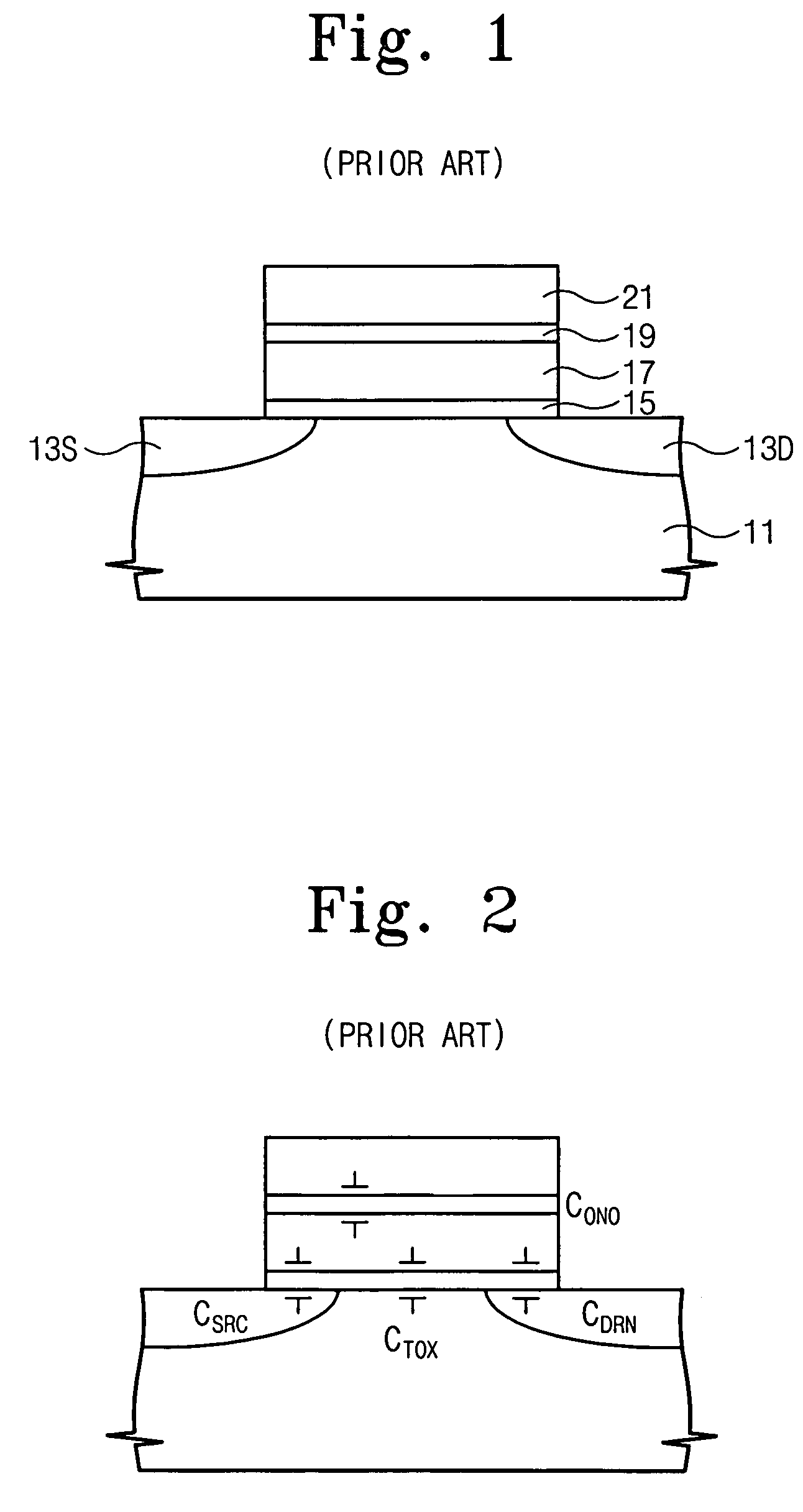

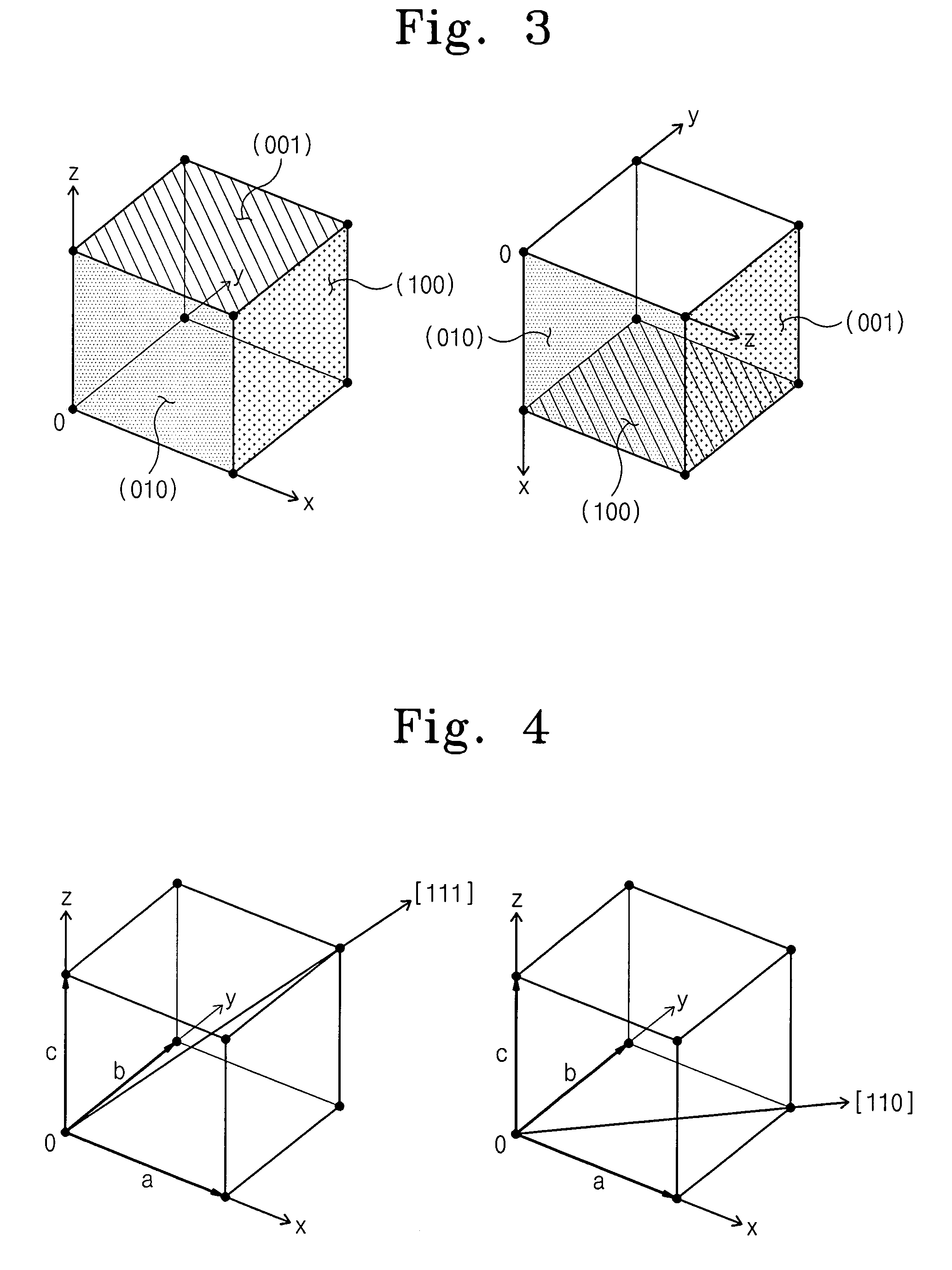

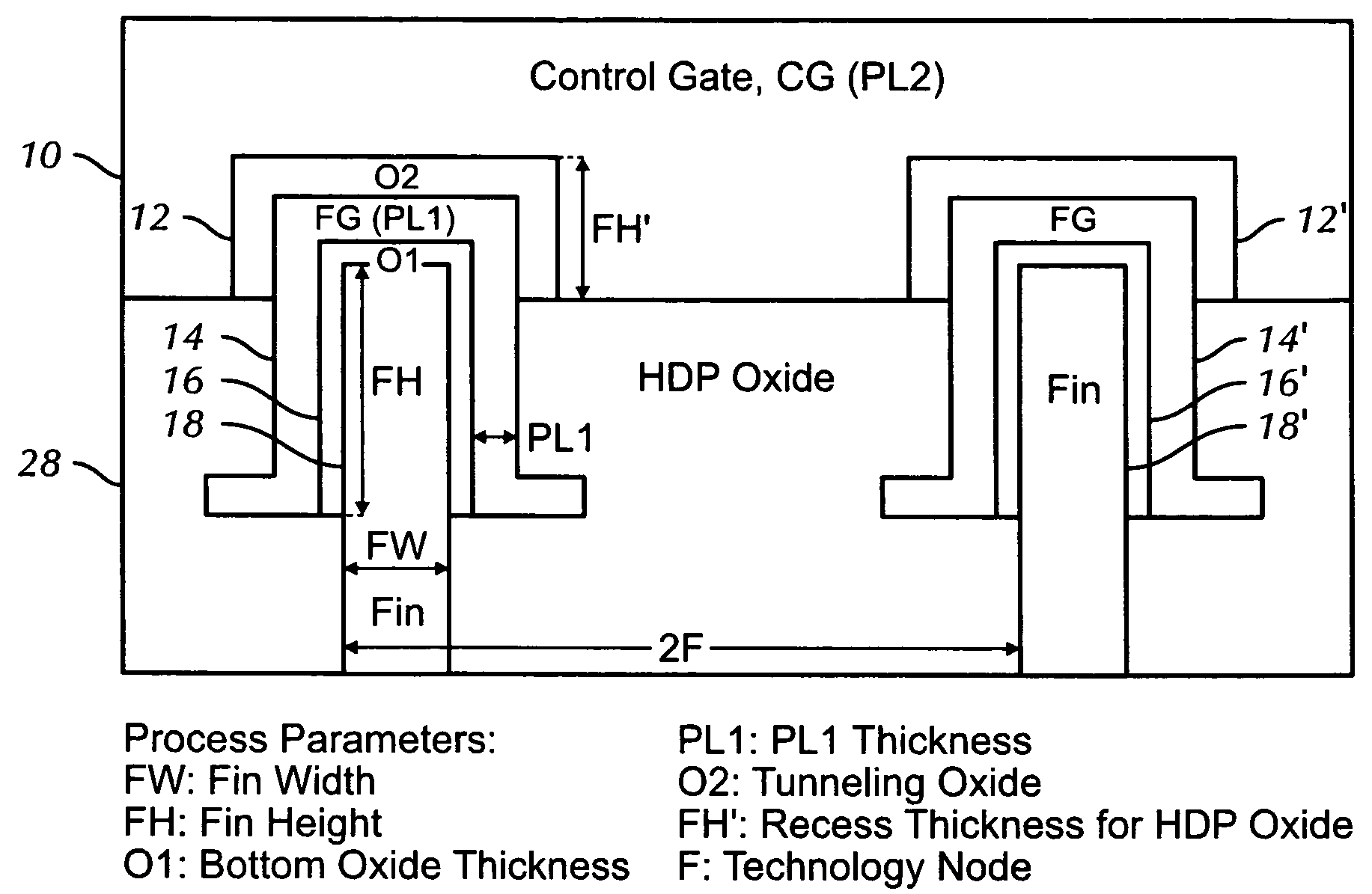

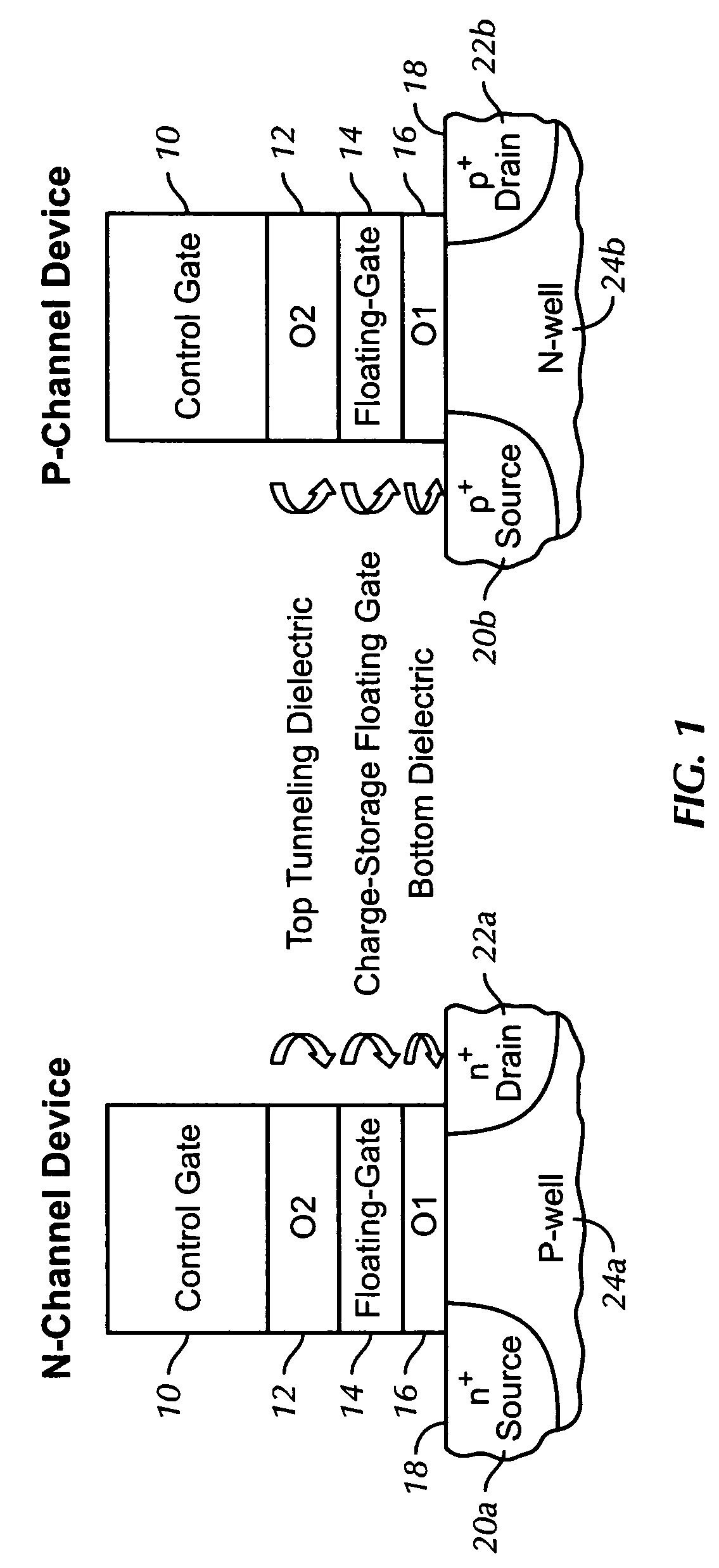

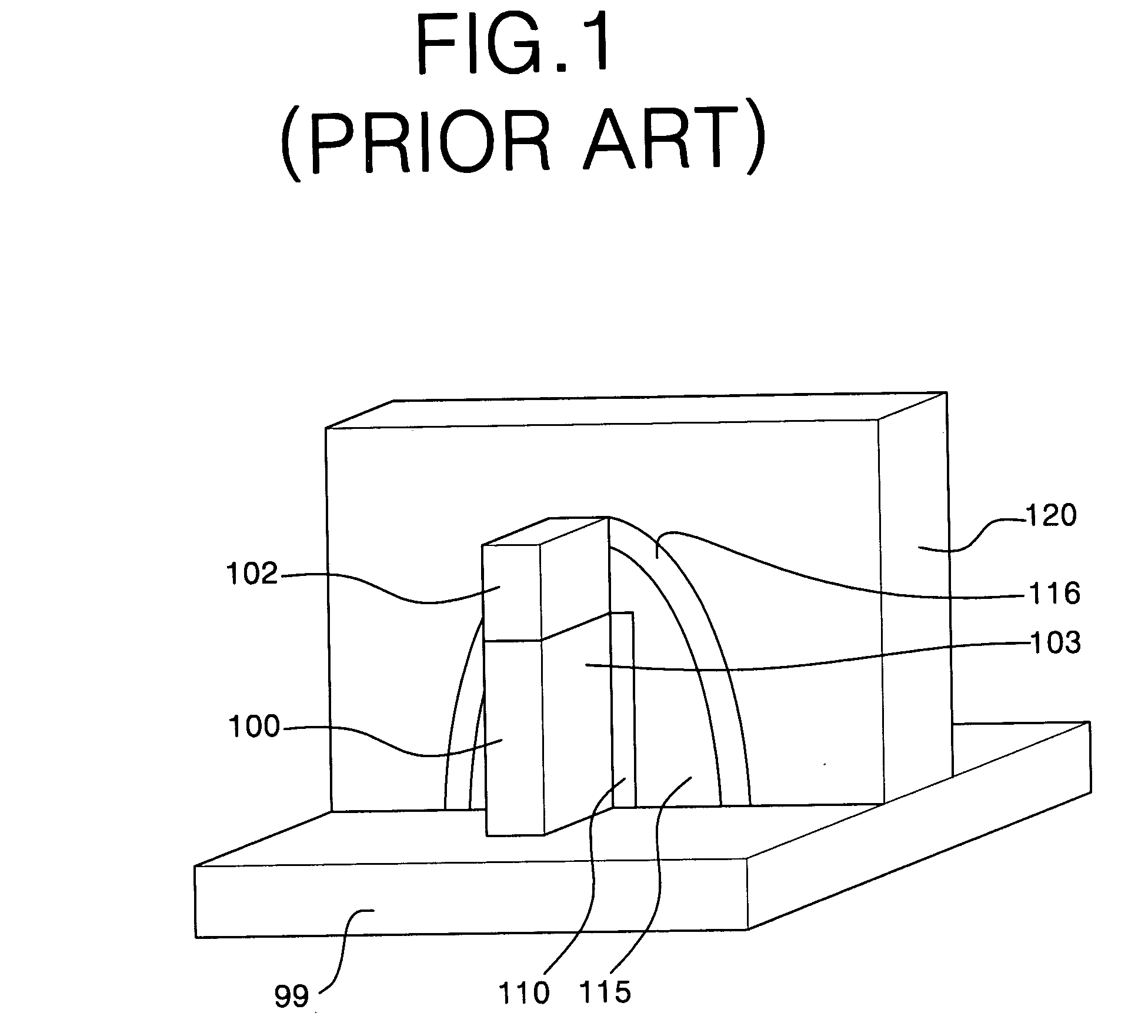

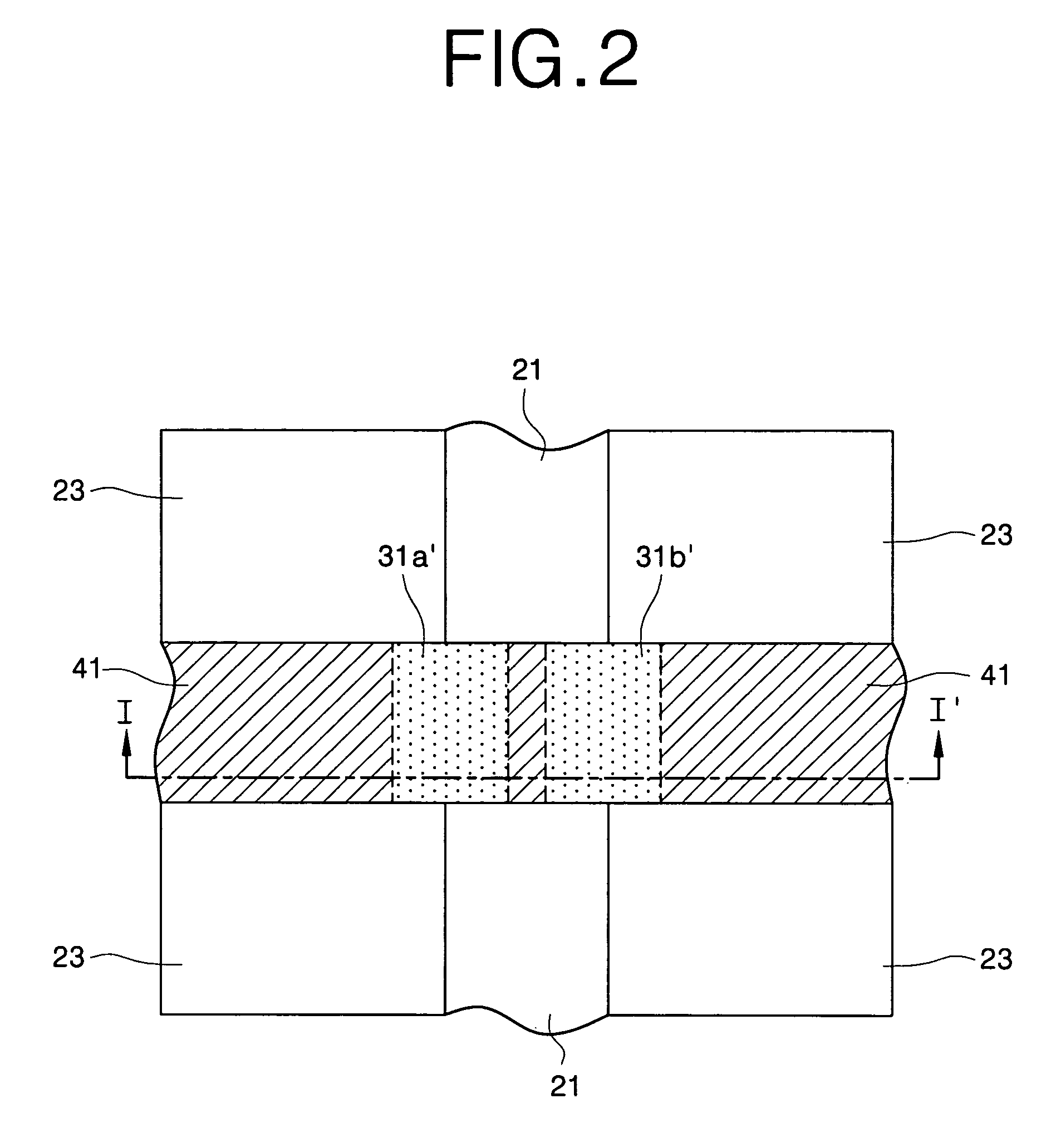

A flash memory device according to the present invention includes a semiconductor fin including a top surface and a side surface originated from different crystal planes. The flash memory device comprises: insulating layers having different thicknesses formed on a side surface and a top surface of the semiconductor fin, a storage electrode, a gate insulating layer and a control gate electrode sequentially formed on the insulating layers. A thin insulating layer enables charges to be injected or emitted through it, and a thick insulating layer increases a coupling ratio. Accordingly, it is possible to increase an efficiency of a programming or an erase operation of a flash memory device.

Owner:SAMSUNG ELECTRONICS CO LTD

Flash memory device using semiconductor fin and method thereof

ActiveUS7285820B2Improve scalabilityProgramming and erasing efficiencyTransistorSolid-state devicesCoupling ratioCrystal plane

A flash memory device according to the present invention includes a semiconductor fin including a top surface and a side surface originated from different crystal planes. The flash memory device comprises: insulating layers having different thicknesses formed on a side surface and a top surface of the semiconductor fin, a storage electrode, a gate insulating layer and a control gate electrode sequentially formed on the insulating layers. A thin insulating layer enables charges to be injected or emitted through it, and a thick insulating layer increases a coupling ratio. Accordingly, it is possible to increase an efficiency of a programming or an erase operation of a flash memory device.

Owner:SAMSUNG ELECTRONICS CO LTD

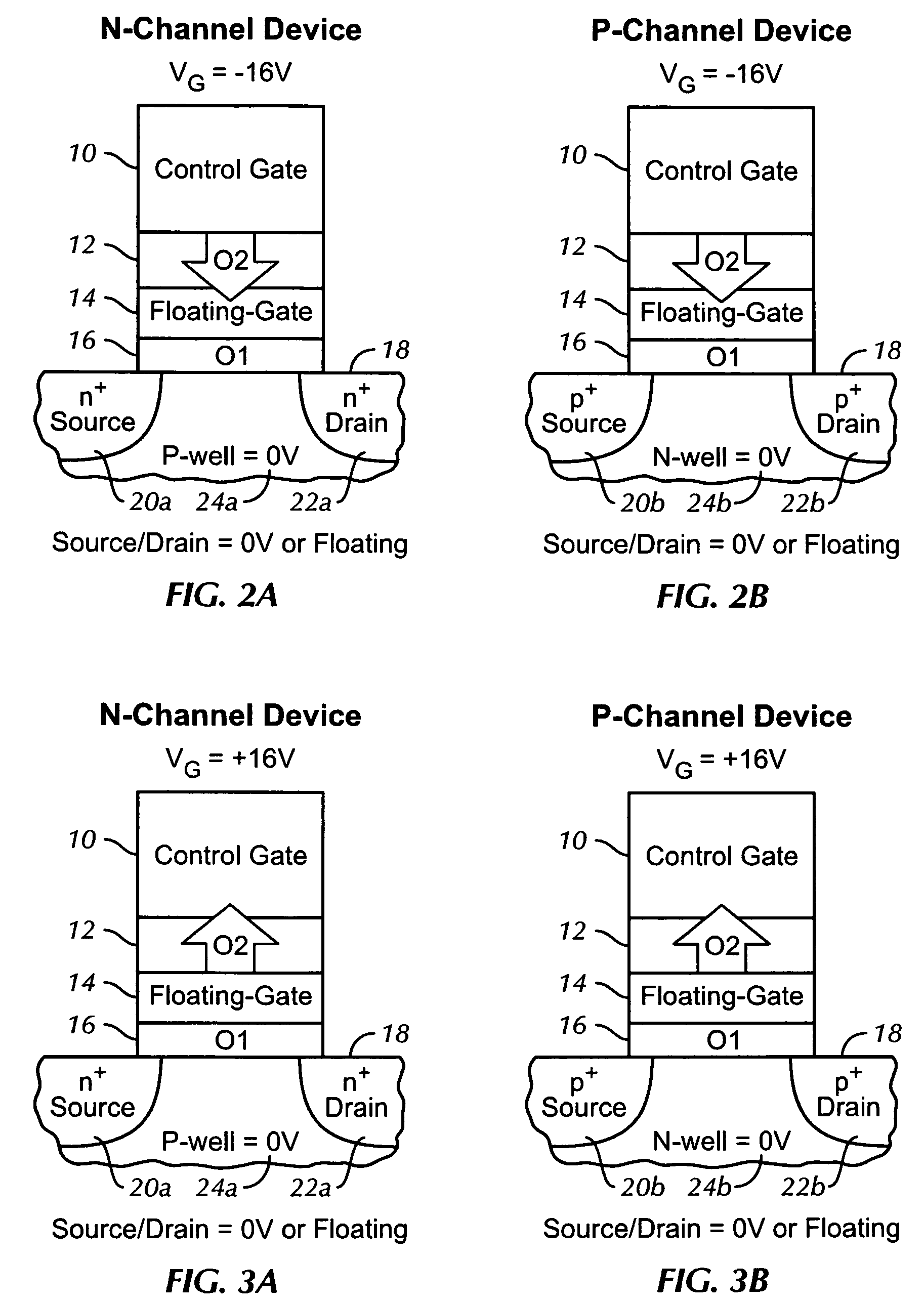

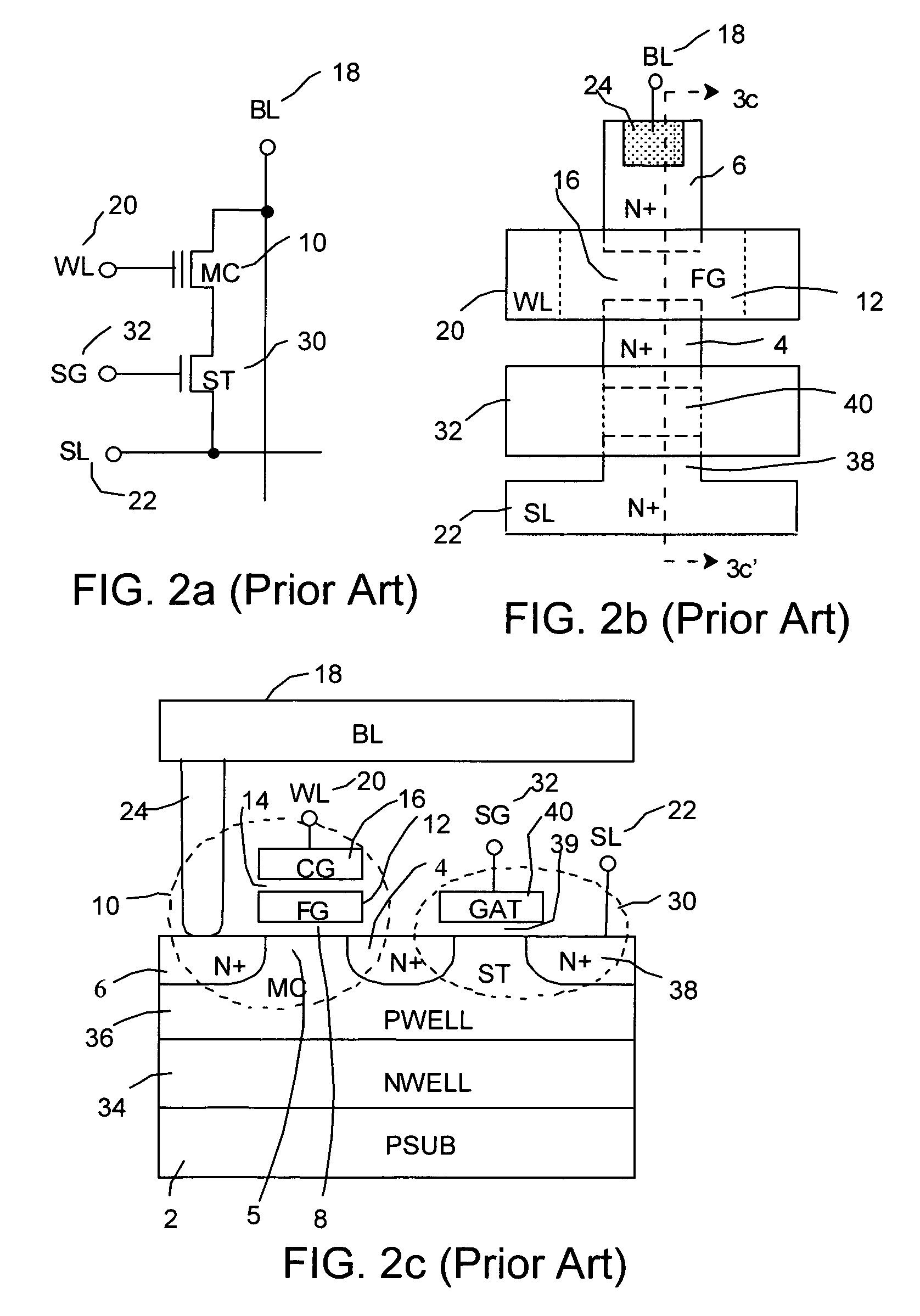

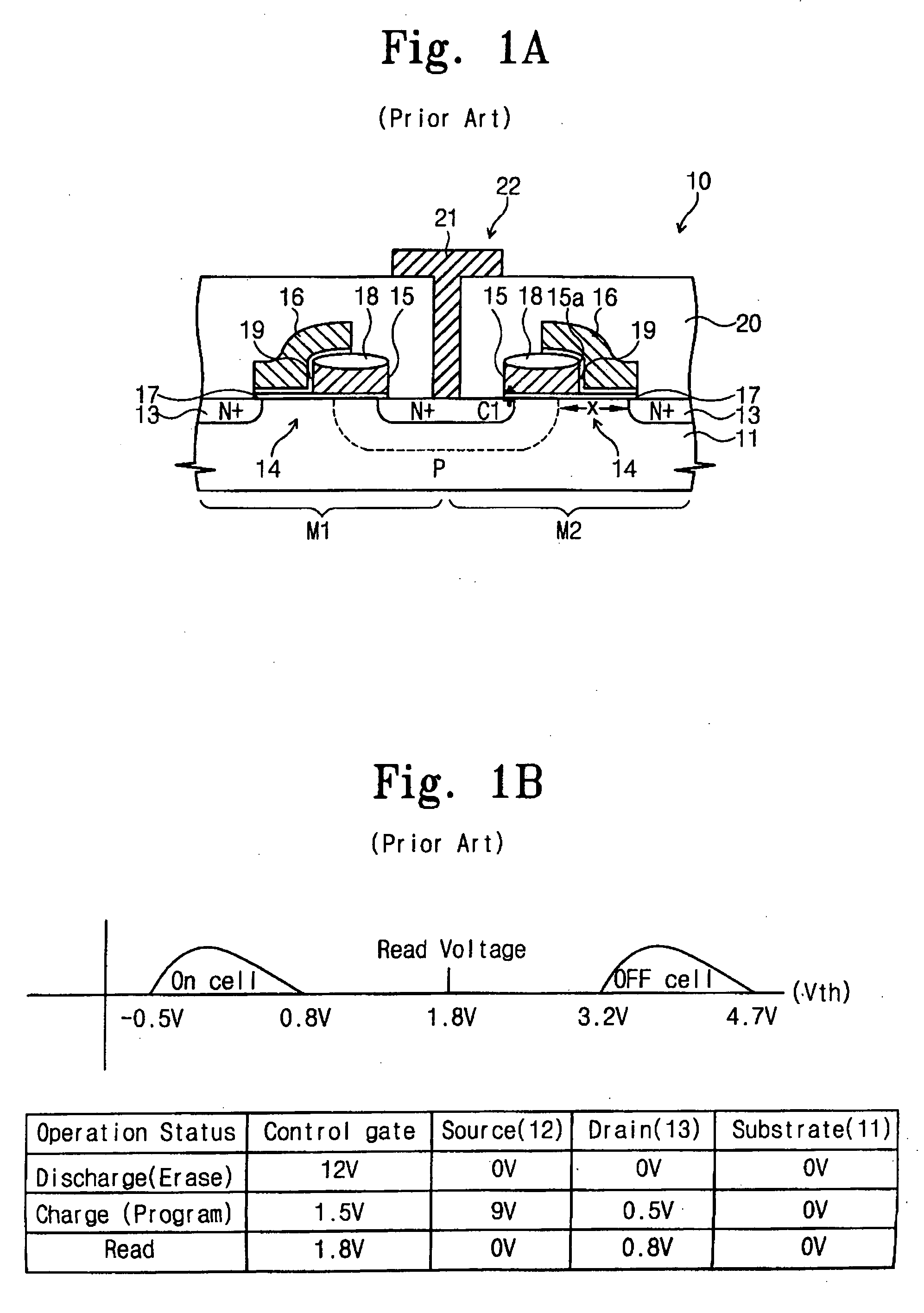

Cell operation methods using gate-injection for floating gate nand flash memory

ActiveUS20080080248A1Low gate coupling ratioLower ratioSolid-state devicesRead-only memoriesOn cellsCoupling ratio

A method of performing an operation on a flash memory cell device, used when a gate coupling ratio between a floating gate and a control gate of less than 0.4. A potential is required to be applied across the control gate. Electrons are either injected to the floating gate from the control gate or ejected from the floating gate to the control gate. The operation associated with the injection or the ejection is determined by the nature of a silicon channel provided in the device. Devices using a bulk-tied FinFET-like structure are particularly suited to this method. The method is also particularly suited for use on cells in a NAND array.

Owner:MACRONIX INT CO LTD

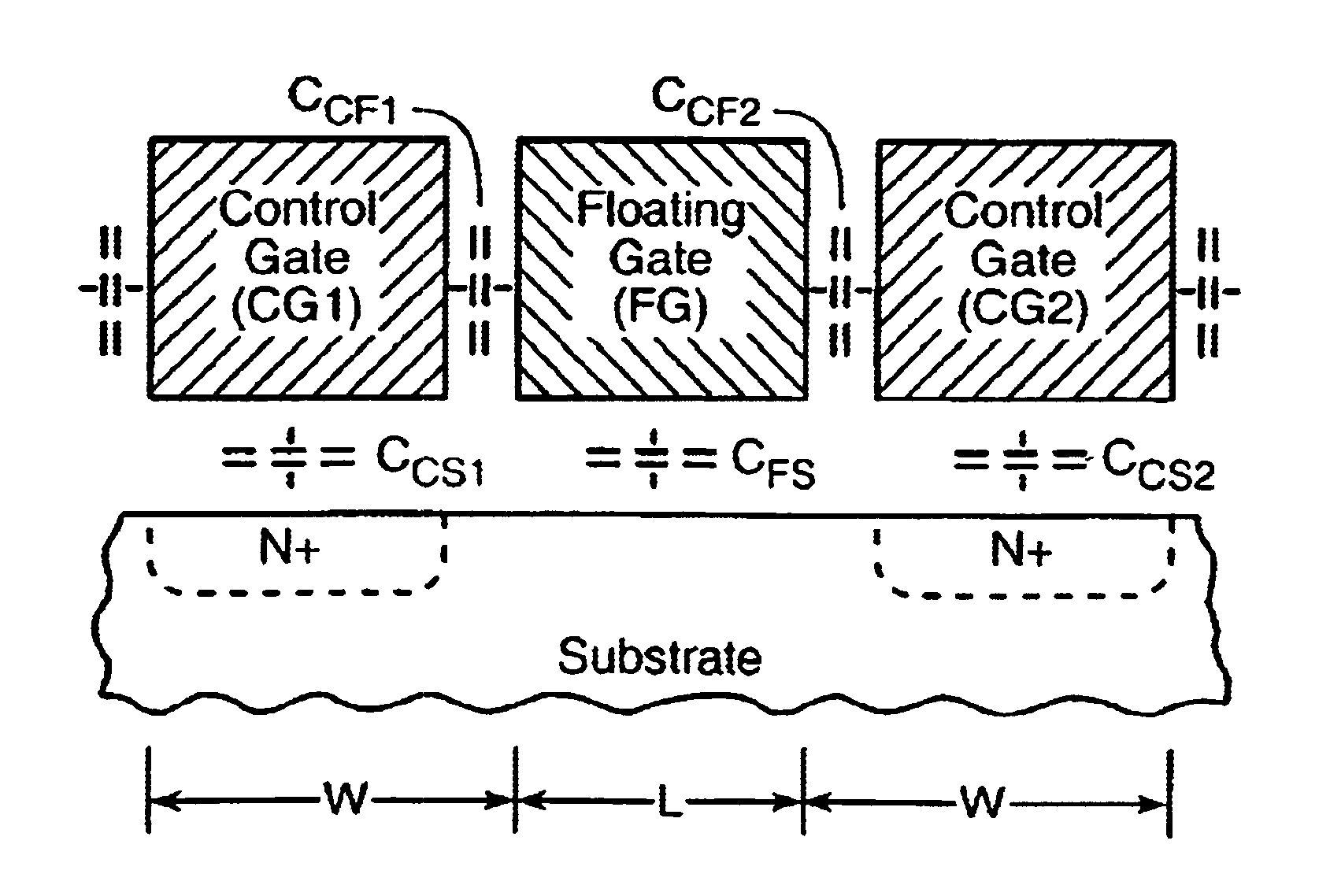

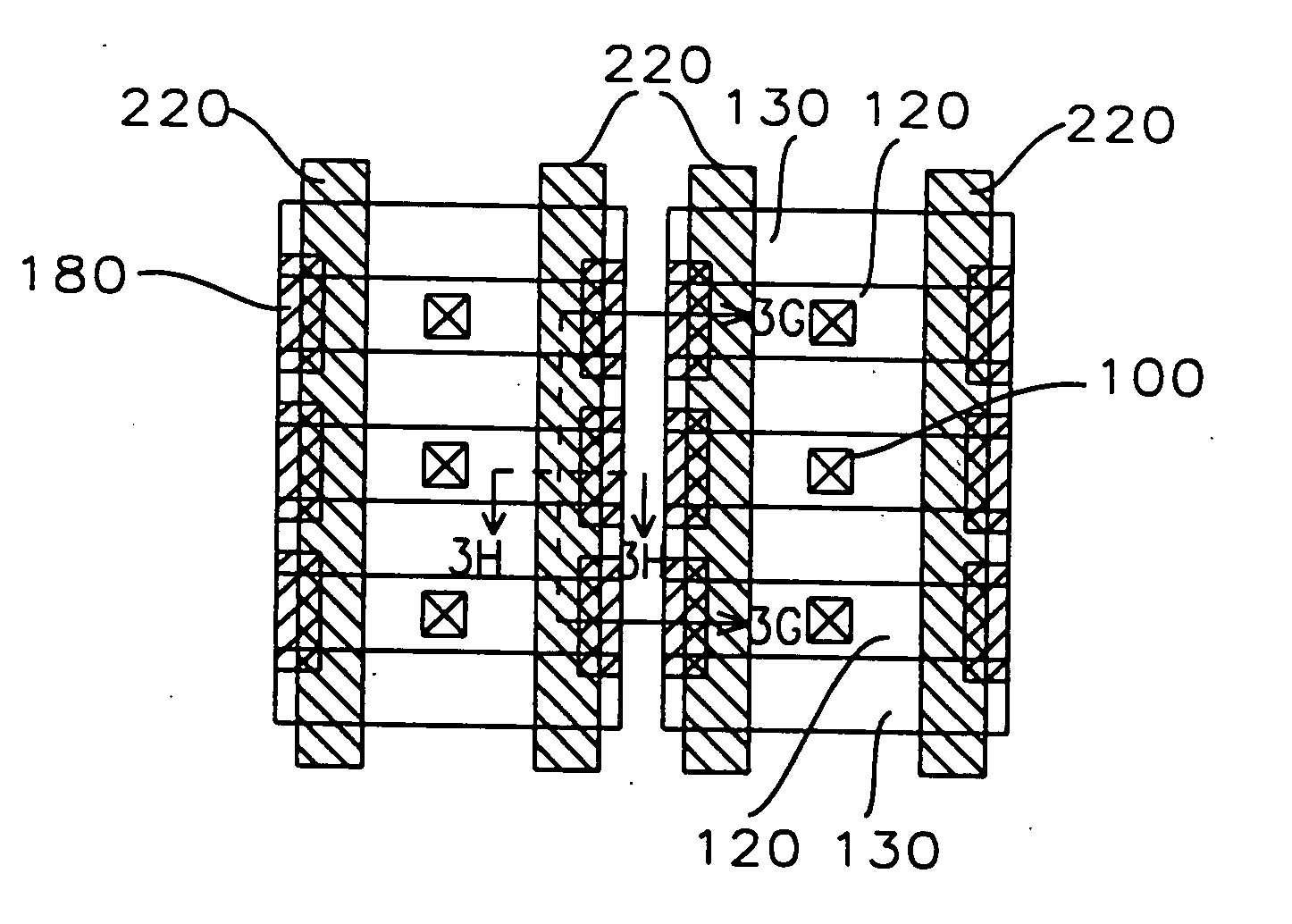

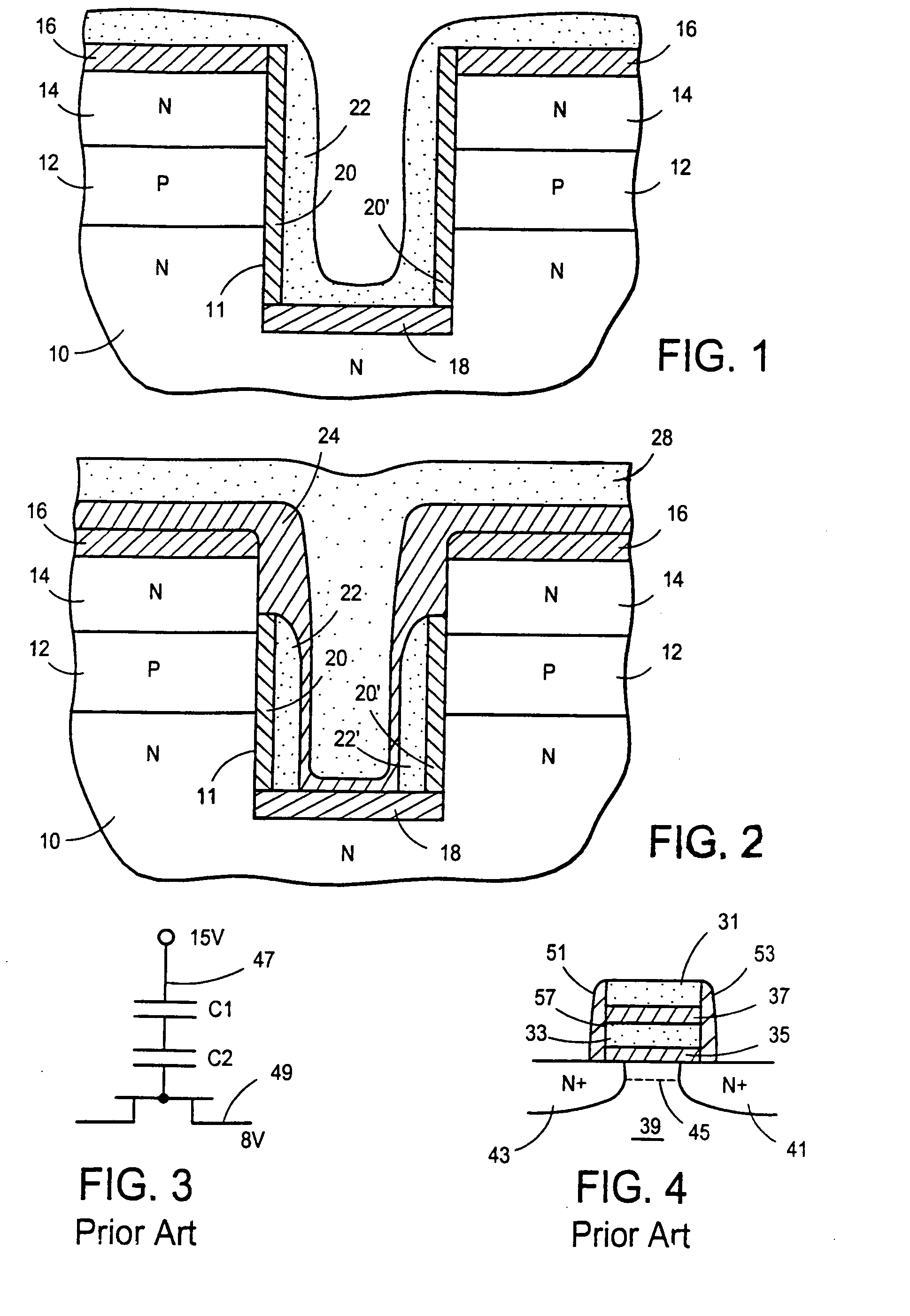

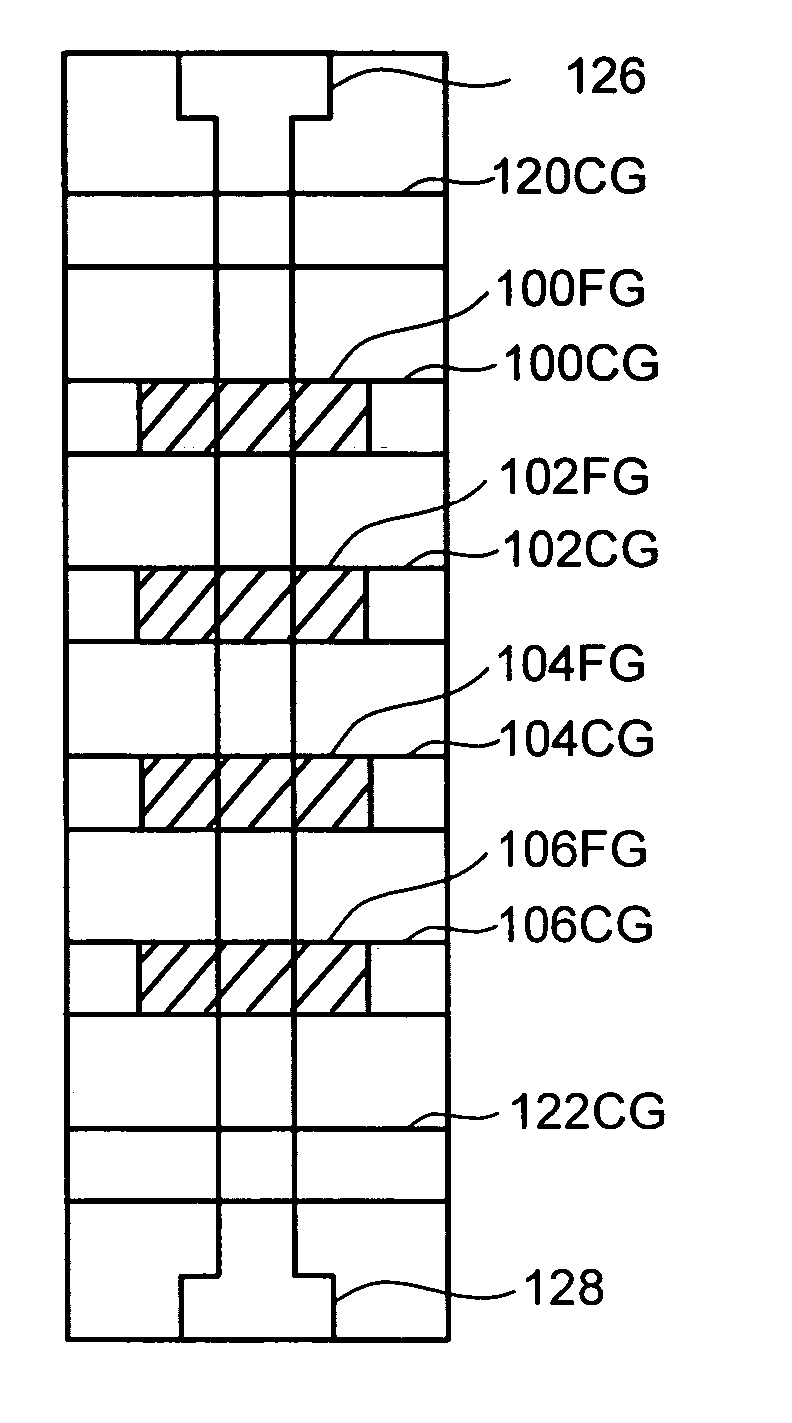

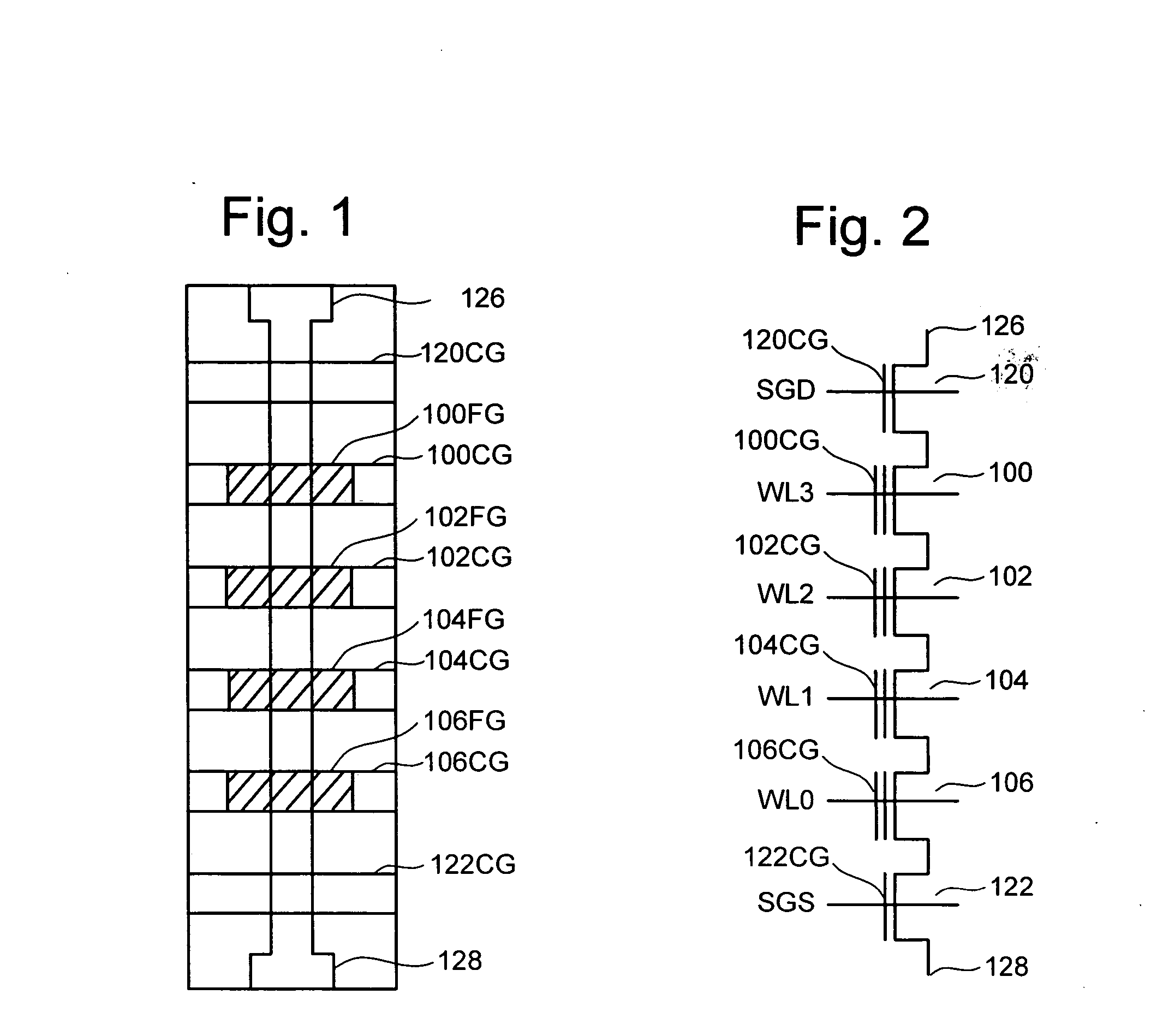

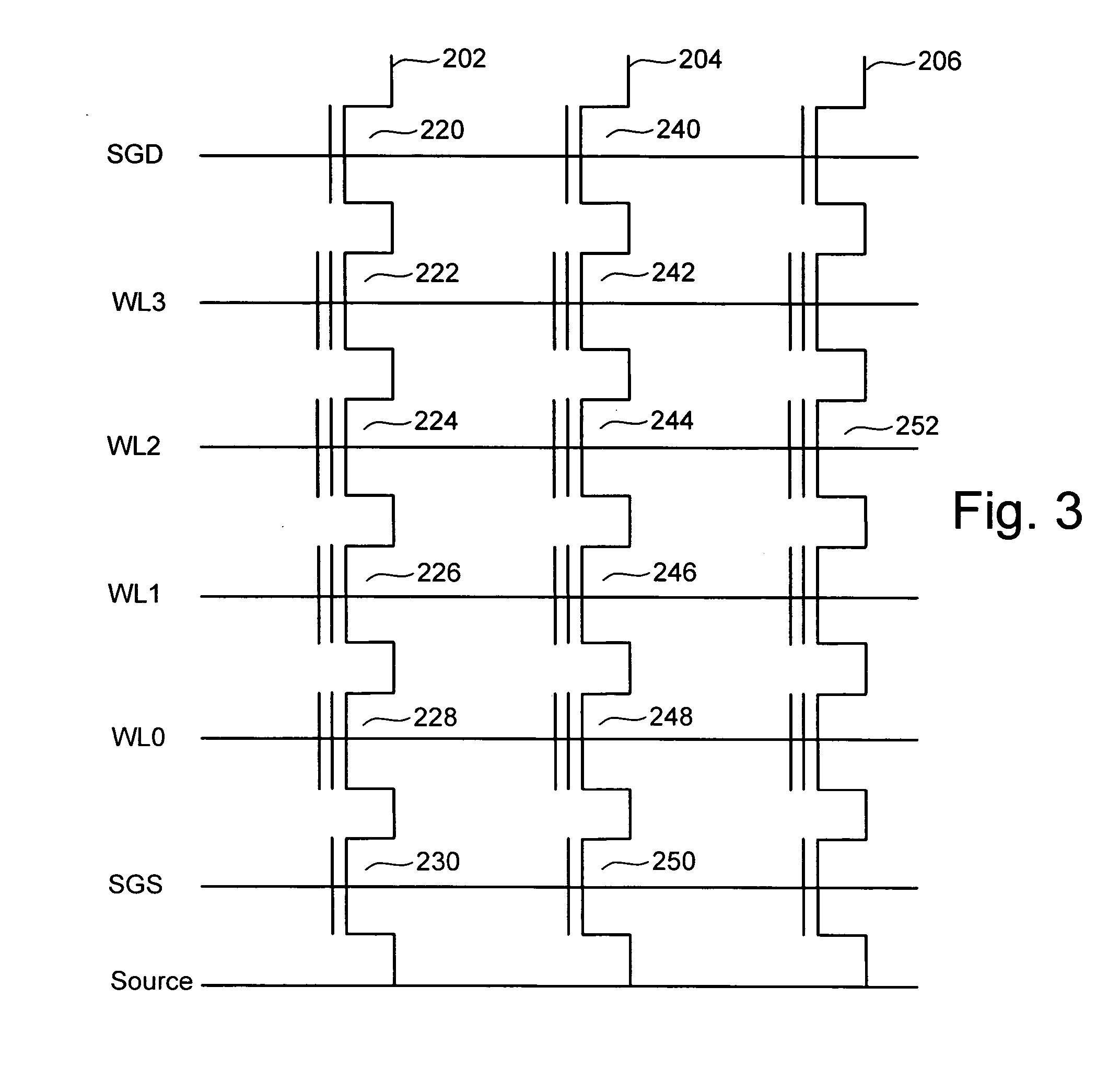

Flash memory cell arrays having dual control gates per memory cell charge storage element

InactiveUS6888755B2Increase coupling areaImprove the coupling ratioTransistorSolid-state devicesCapacitanceImage resolution

A flash NAND type EEPROM system with individual ones of an array of charge storage elements, such as floating gates, being capacitively coupled with at least two control gate lines. The control gate lines are preferably positioned between floating gates to be coupled with sidewalls of floating gates. The memory cell coupling ratio is desirably increased, as a result. Both control gate lines on opposite sides of a selected row of floating gates are usually raised to the same voltage while the second control gate lines coupled to unselected rows of floating gates immediately adjacent and on opposite sides of the selected row are kept low. The control gate lines can also be capacitively coupled with the substrate in order to selectively raise its voltage in the region of selected floating gates. The length of the floating gates and the thicknesses of the control gate lines can be made less than the minimum resolution element of the process by forming an etch mask of spacers.

Owner:SANDISK TECH LLC

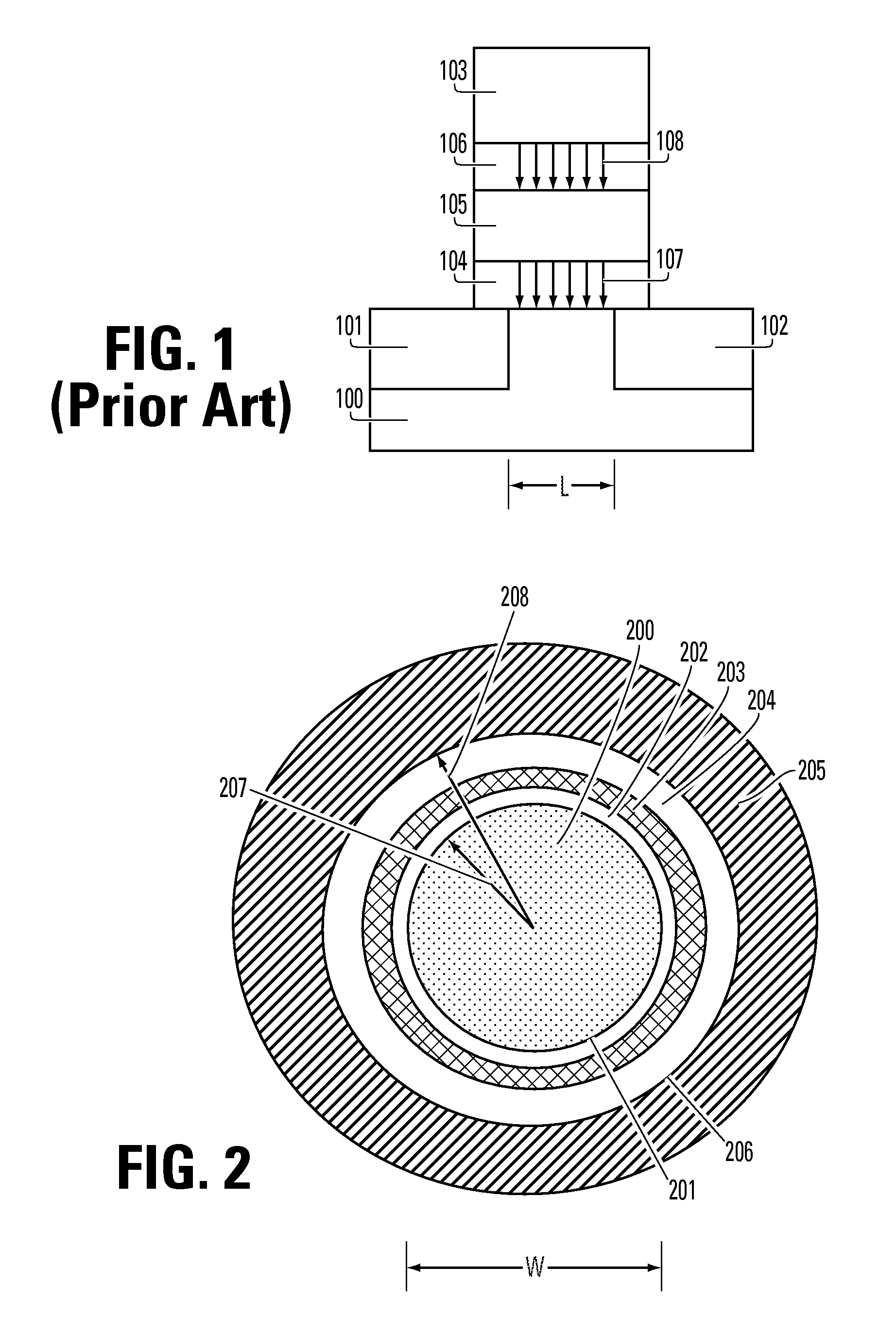

Cylindrical channel charge trapping devices with effectively high coupling ratios

ActiveUS20080099830A1Read-only memoriesSemiconductor/solid-state device manufacturingCylindrical channelElectrical conductor

A memory cell comprising: a source region and a drain region separated by a semiconductor channel region, the channel region having a channel surface having an area A1 including a first cylindrical region, a first dielectric structure on the channel surface, a dielectric charge trapping structure on the first dielectric structure, a second dielectric structure on the dielectric charge trapping structure, a conductive layer having a conductor surface having an area A2 including a second cylindrical region on the second dielectric structure, the conductor surface overlying the dielectric charge trapping structure and the channel surface of the channel region, and the ratio of the area A2 to the area A1 being greater than or equal to 1.2 are described along with devices thereof and methods for manufacturing.

Owner:MACRONIX INT CO LTD

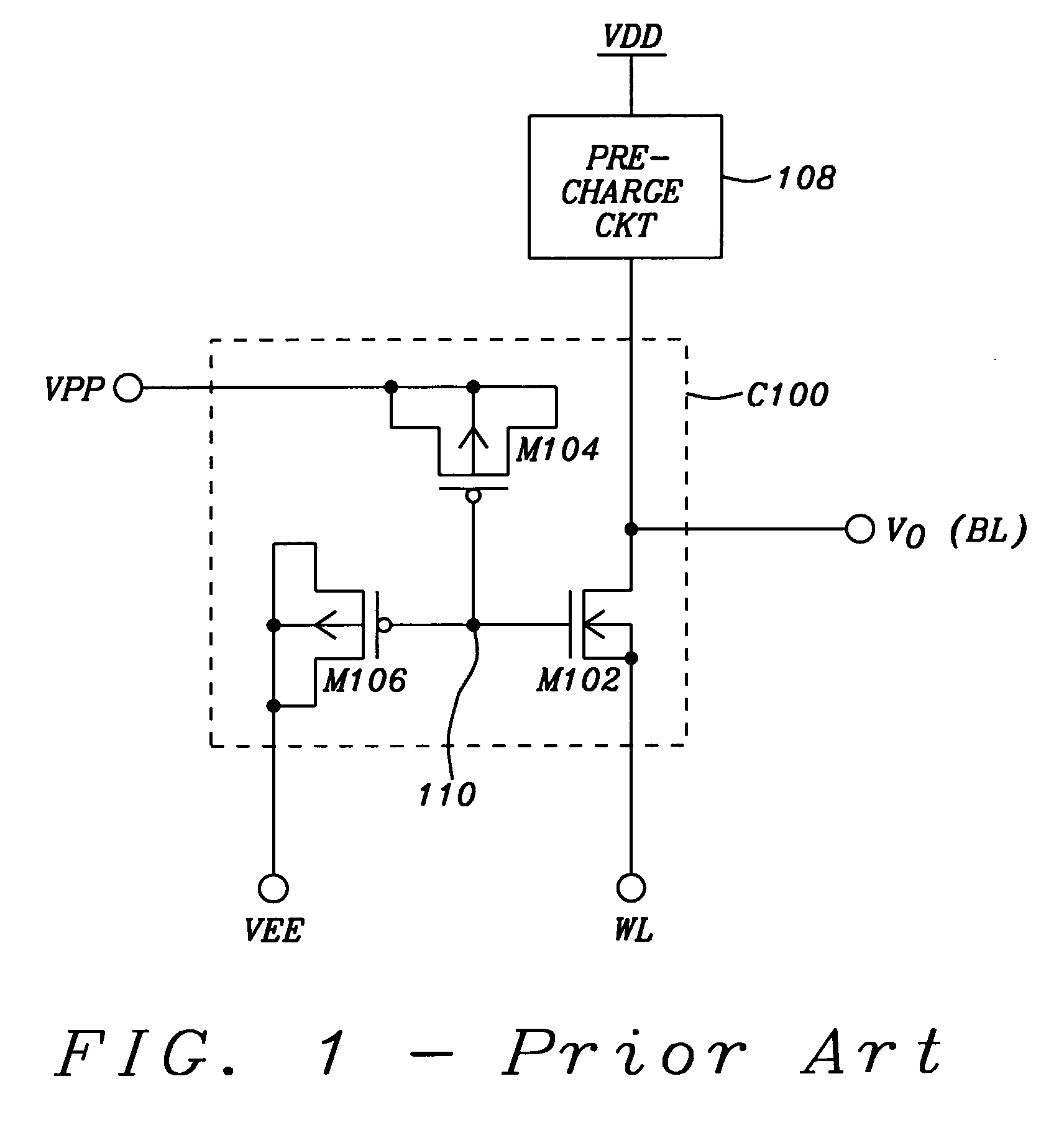

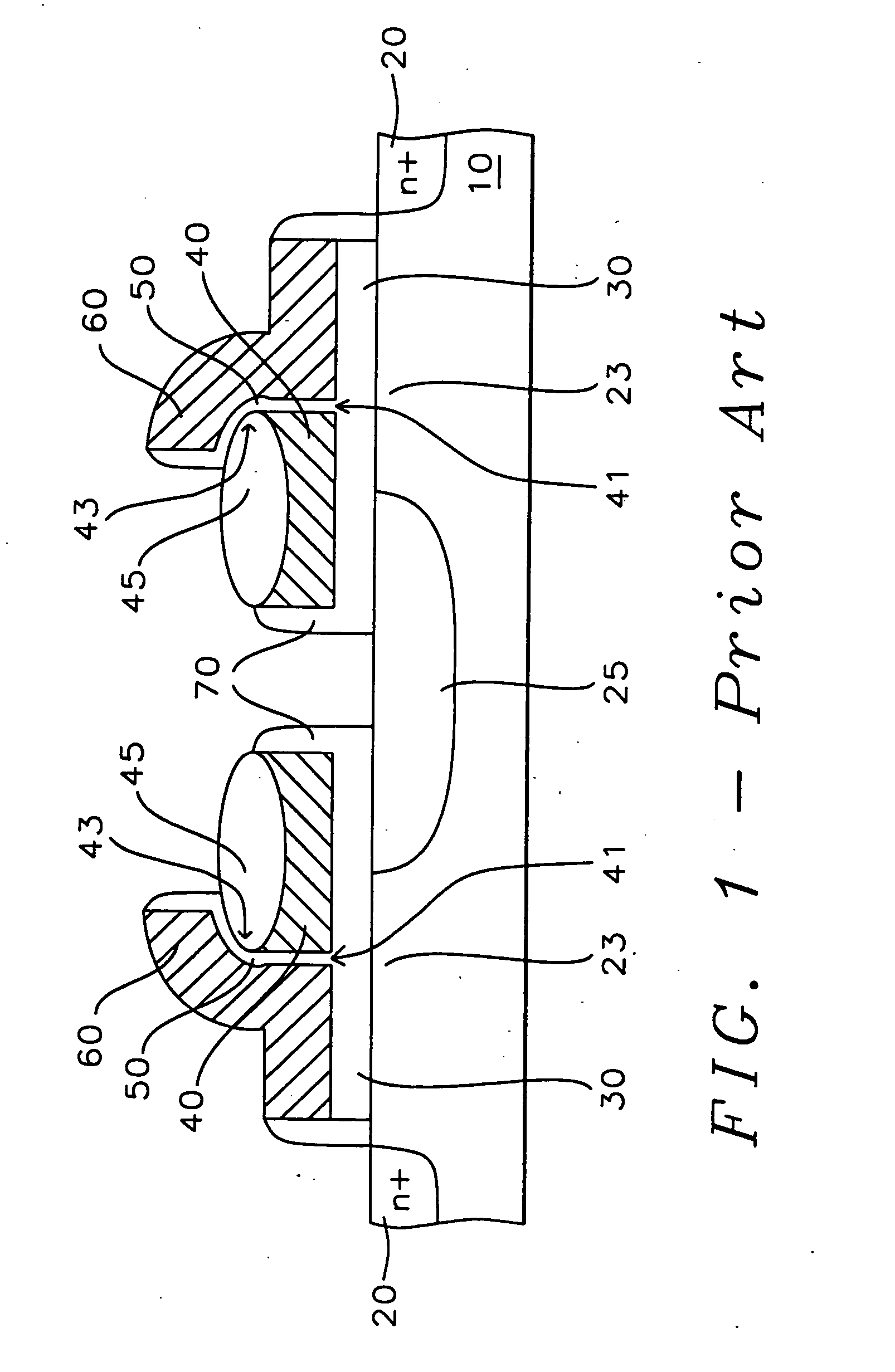

Single-polycrystalline silicon electrically erasable and programmable nonvolatile memory device

A single polycrystalline silicon floating gate nonvolatile memory cell has a MOS capacitor and a storage MOS transistor fabricated with dimensions that allow fabrication using current low voltage logic integrated circuit process. The MOS capacitor has a first plate connected to a gate of the storage MOS transistor to form a floating gate node. The physical size of the MOS capacitor is relatively large (approximately 10 time greater) when compared to a physical size of the storage MOS transistor to establish a large coupling ratio (approximately 90% between the second plate of the MOS capacitor and the floating gate node. When a voltage is applied to the second plate of the MOS capacitor and a voltage applied to the source region or drain region of the MOS transistor establishes a voltage field within the gate oxide of the MOS transistor such that Fowler-Nordheim edge tunnel is initiated.

Owner:APLUS FLASH TECH

Method to increase coupling ratio of source to floating gate in split-gate flash

InactiveUS20050207264A1Improve the coupling ratioIncrease lateral couplingTransistorSolid-state devicesFirst FillCoupling ratio

A split-gate flash memory cell having a three-dimensional source capable of three-dimensional coupling with the floating gate of the cell, as well as a method of forming the same are provided. This is accomplished by first forming an isolation trench, lining it with a conformal oxide, then filling with an isolation oxide and then etching the latter to form a three-dimensional coupling region in the upper portion of the trench. A floating gate is next formed by first filling the three-dimensional region of the trench with polysilicon and etching it. The control gate is formed over the floating gate with an intervening inter-poly oxide. The floating gate forms legs extending into the three-dimensional coupling region of the trench thereby providing a three-dimensional coupling with the source which also assumes a three-dimensional region. The leg or the side-wall of the floating gate forming the third dimension provides the extra area through which coupling between the source and the floating gate is increased. In this manner, a higher coupling ratio is achieved without an increase in the cell size while at the same time alleviating the punchthrough and junction break-down of source region by sharing gate voltage along the side-wall.

Owner:TAIWAN SEMICON MFG CO LTD

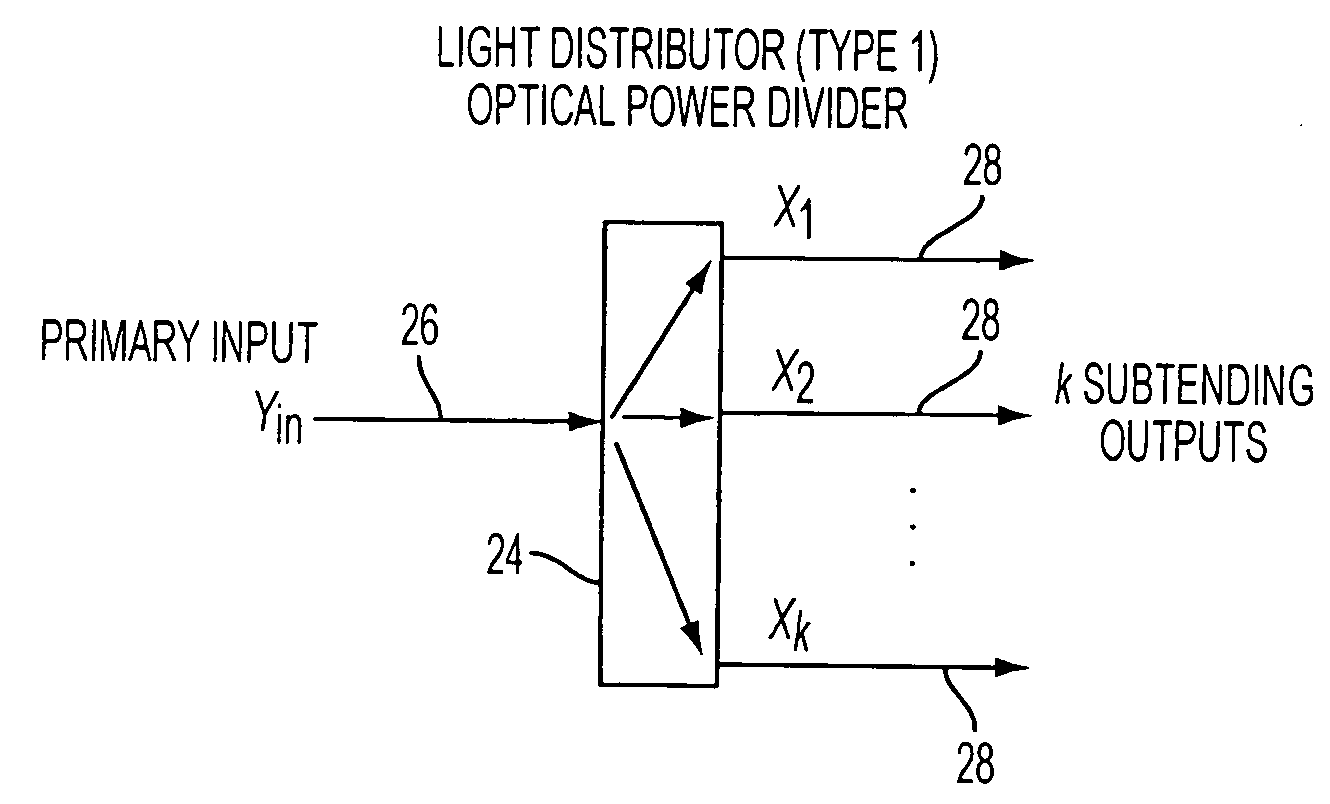

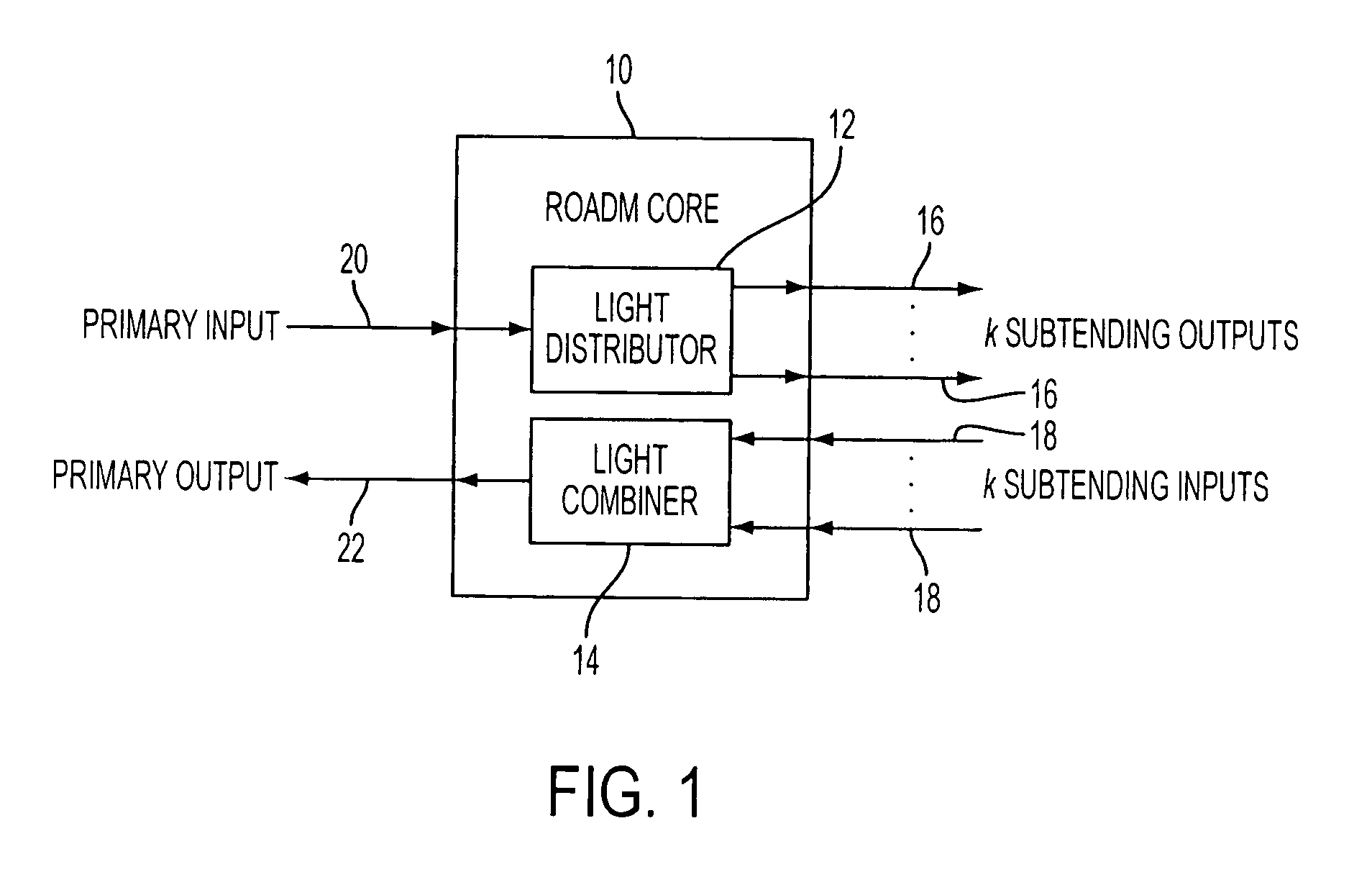

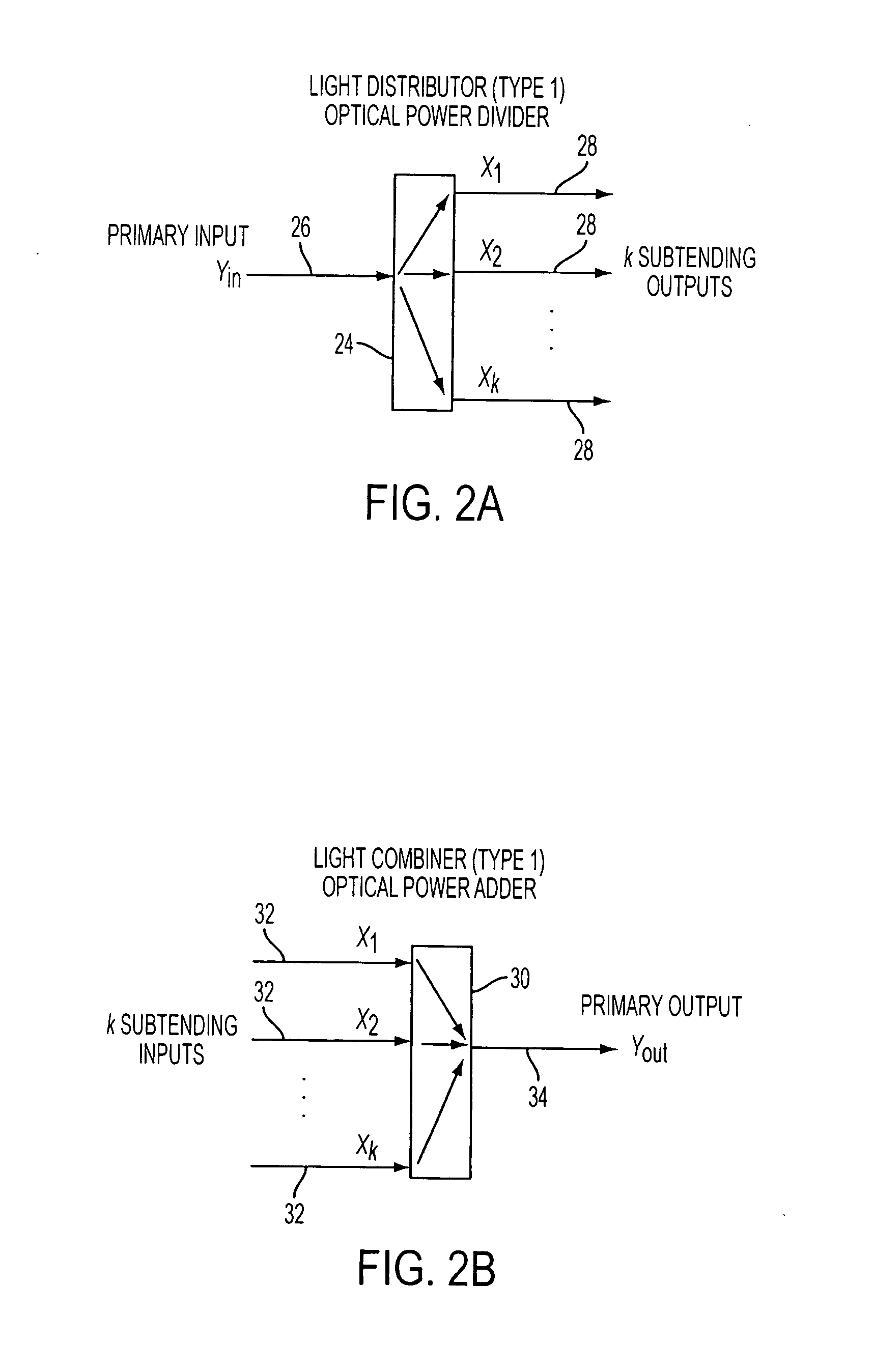

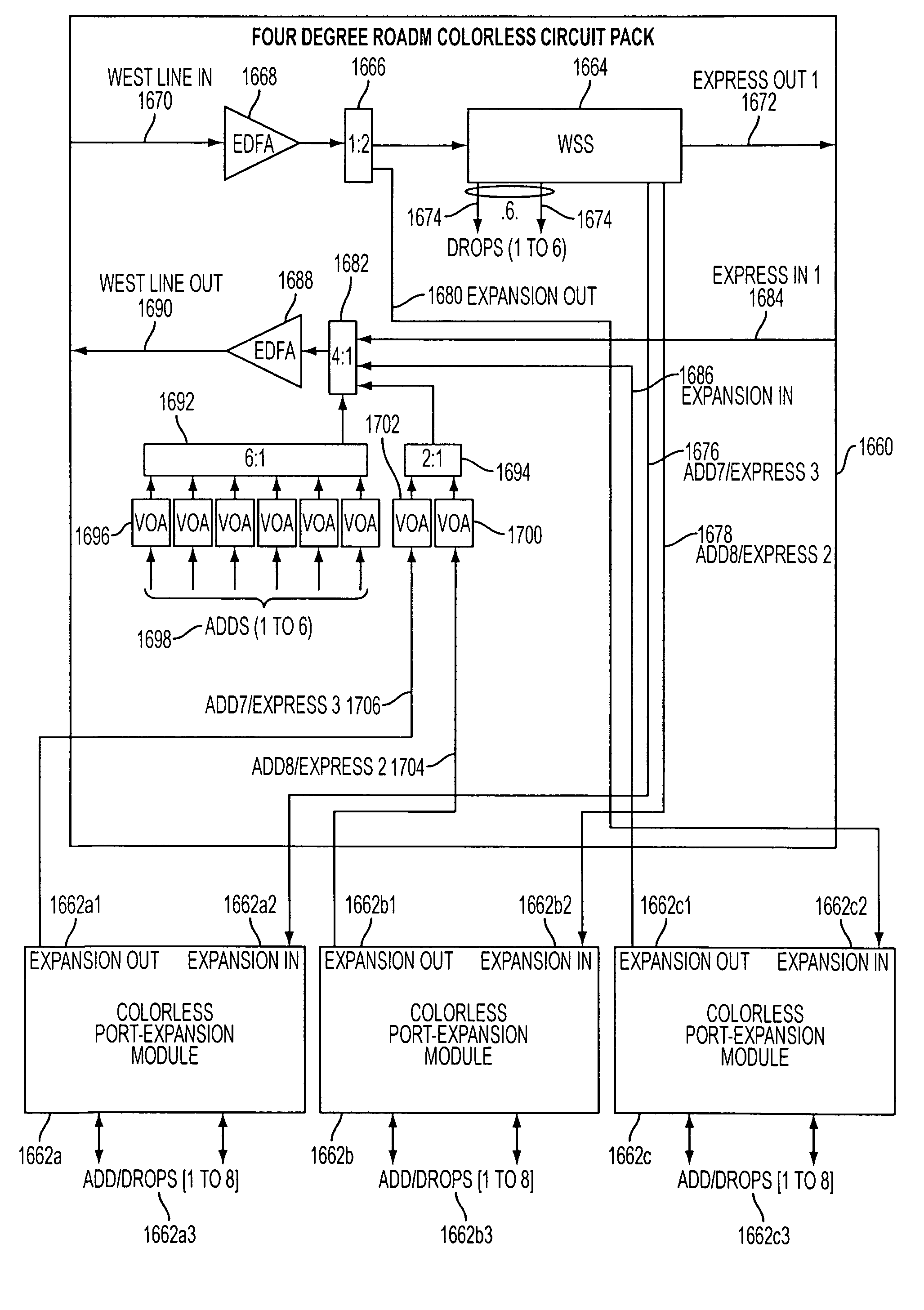

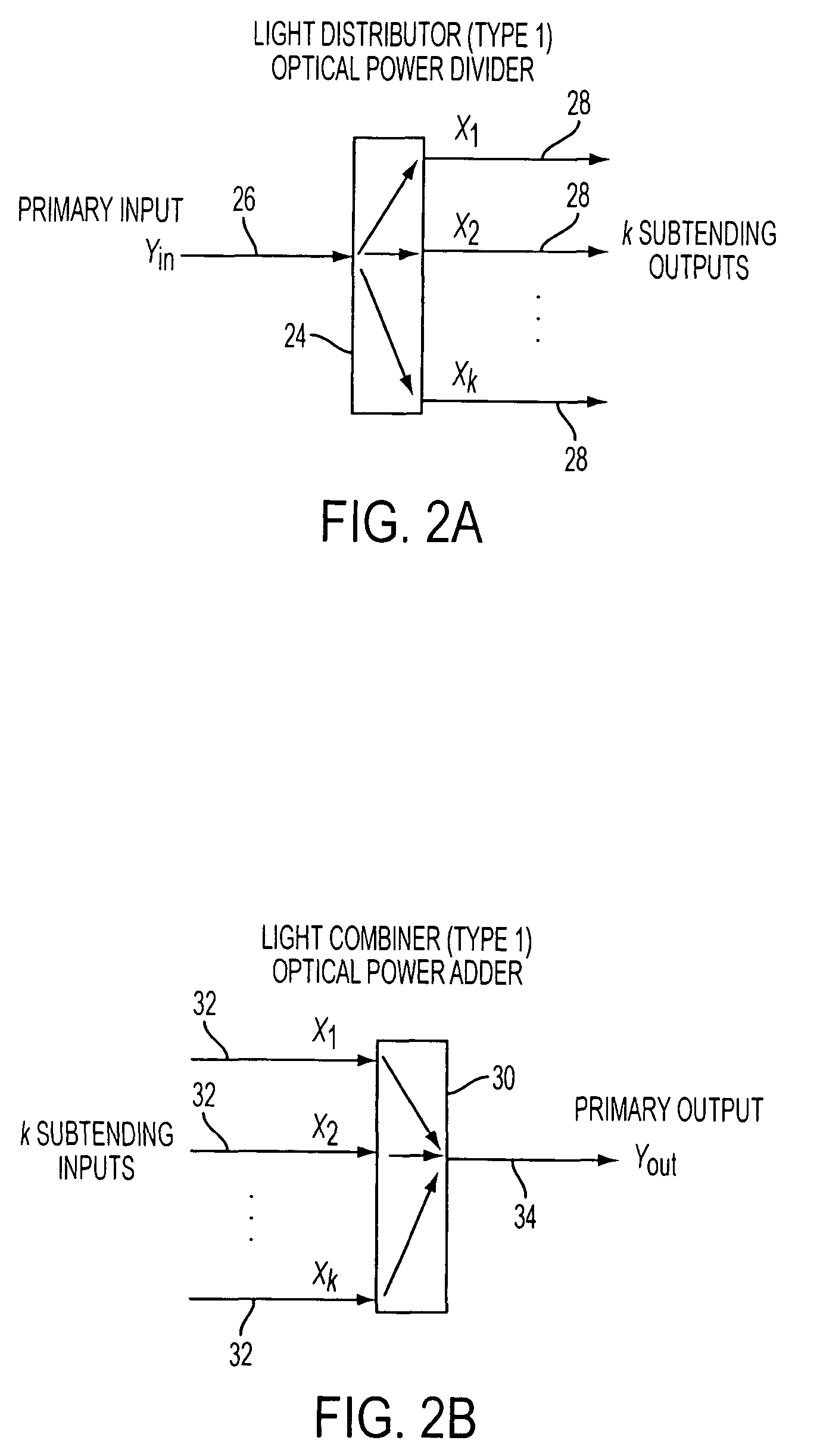

Reconfigurable optical add drop multiplexer core device, procedure and system using such device, optical light distributor, and coupling-ratio assigning procedure

ActiveUS20080260386A1Maximize power levelPower maximizationWavelength-division multiplex systemsOptical add-drop multiplexerCoupling ratio

A reconfigurable optical add drop multiplexer core device includes a light distributor, a light combiner, and first and second sets of add and drop ports. The light distributor is configured to receive an optical signal along a primary input of the reconfigurable optical add drop multiplexer core device and to distribute the received optical signal along a plurality of subtending outputs. The light combiner is configured to receive optical signals along a plurality of subtending inputs, to combine the received optical signals into a combined signal, and to output the combined signal. The add and drop ports in the first set function as add and drop ports, respectively, and the add and drop ports in the second set function as both add and drop ports, respectively, and as express ports connectable to another reconfigurable optical add drop multiplexer core device.

Owner:TELLABS OPERATIONS

Vertically integrated flash EPROM for greater density and lower cost

InactiveUS20070004134A1Increase cell areaImprove the coupling ratioSolid-state devicesSemiconductor/solid-state device manufacturingIon implantationPhotolithography

Owner:VORA MADHUKAR B

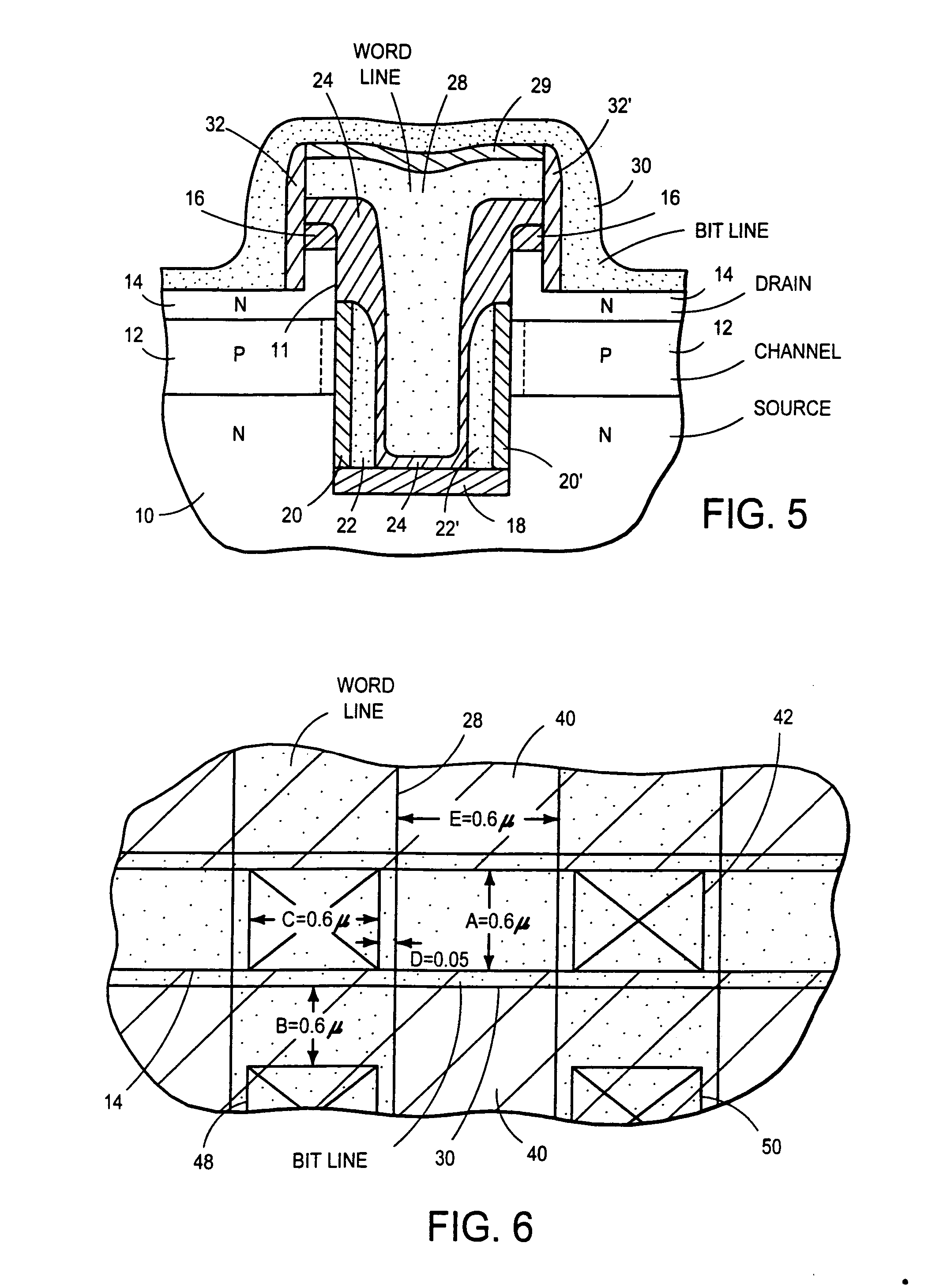

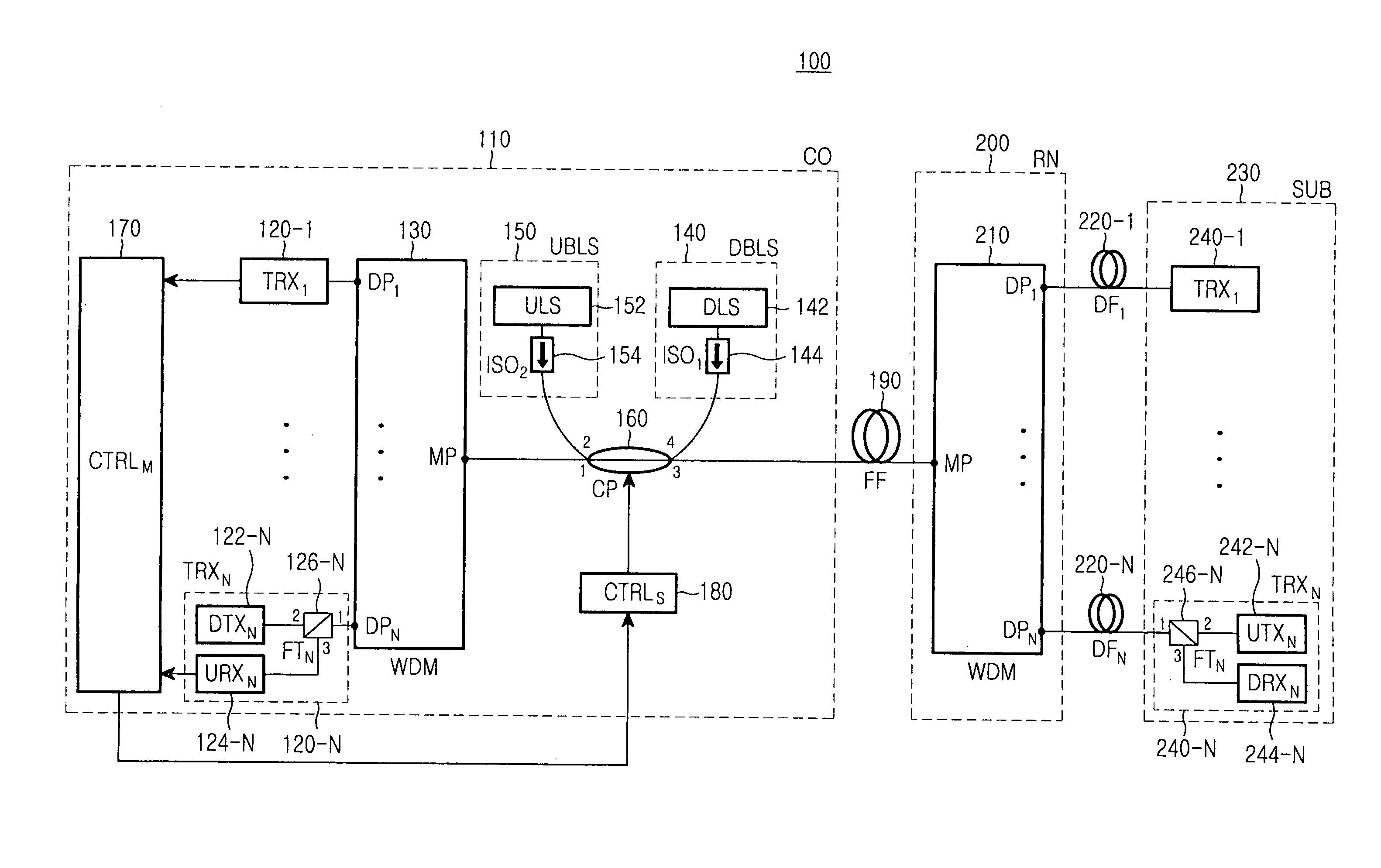

Wavelength-division-multiplexed light source and wavelength-division-multiplexed passive optical network using the same

InactiveUS20070036483A1Effective maintenanceWavelength-division multiplex systemsCoupling light guidesFiberCoupling ratio

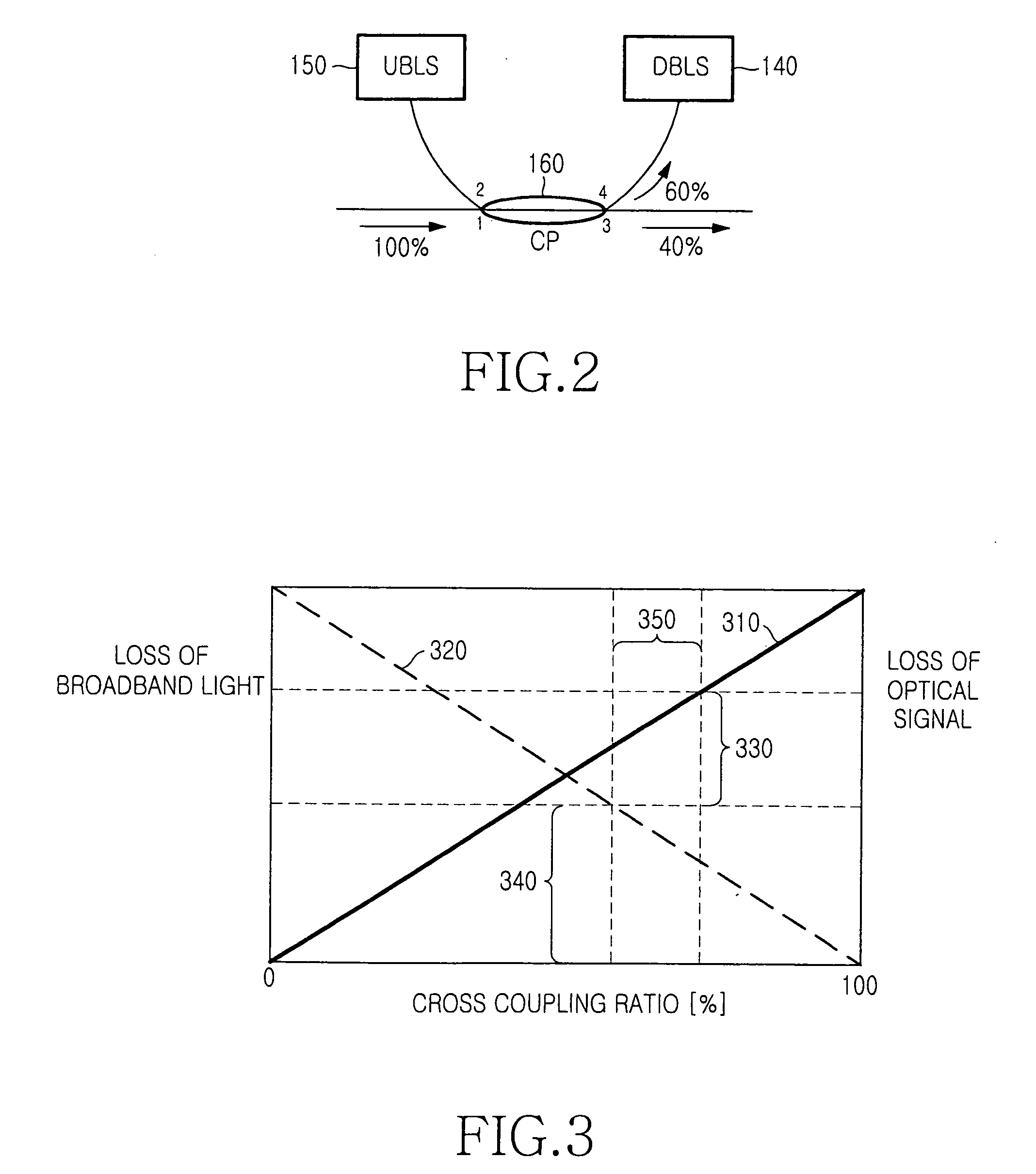

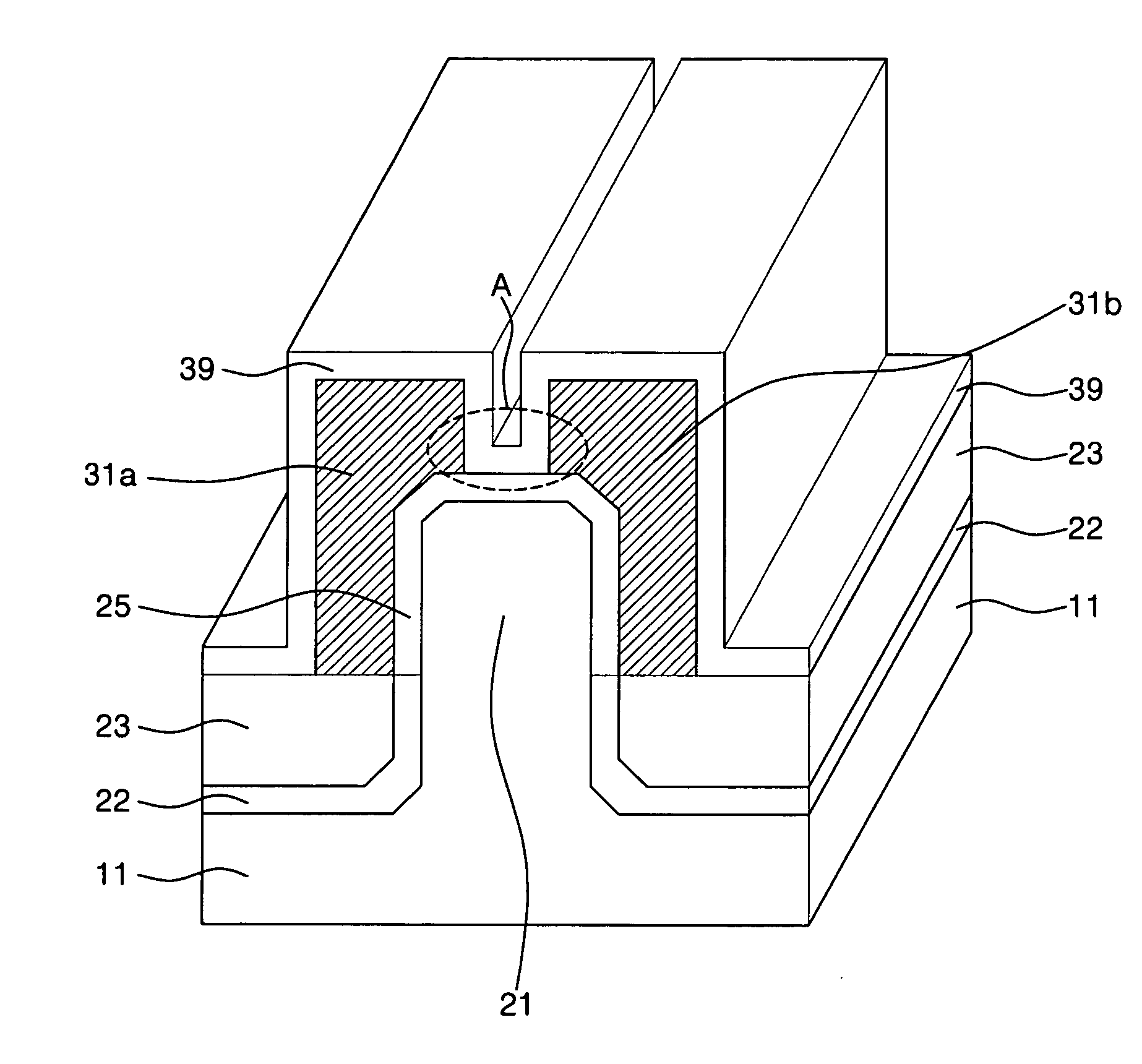

A wavelength-division-multiplexed light source for transmitting broadband light through a fiber and receiving an optical signal through the fiber is disclosed. The wavelength-division-multiplexed light source includes: a light source for outputting broadband light; and a coupler for outputting the broadband light, which has been input from the light source, to the fiber through cross coupling, and outputting an optical signal, which has been input from the fiber, through bar coupling, based on a predetermined cross coupling ratio, wherein the cross coupling ratio of the coupler is adjusted depending on a power of the optical signal.

Owner:SAMSUNG ELECTRONICS CO LTD

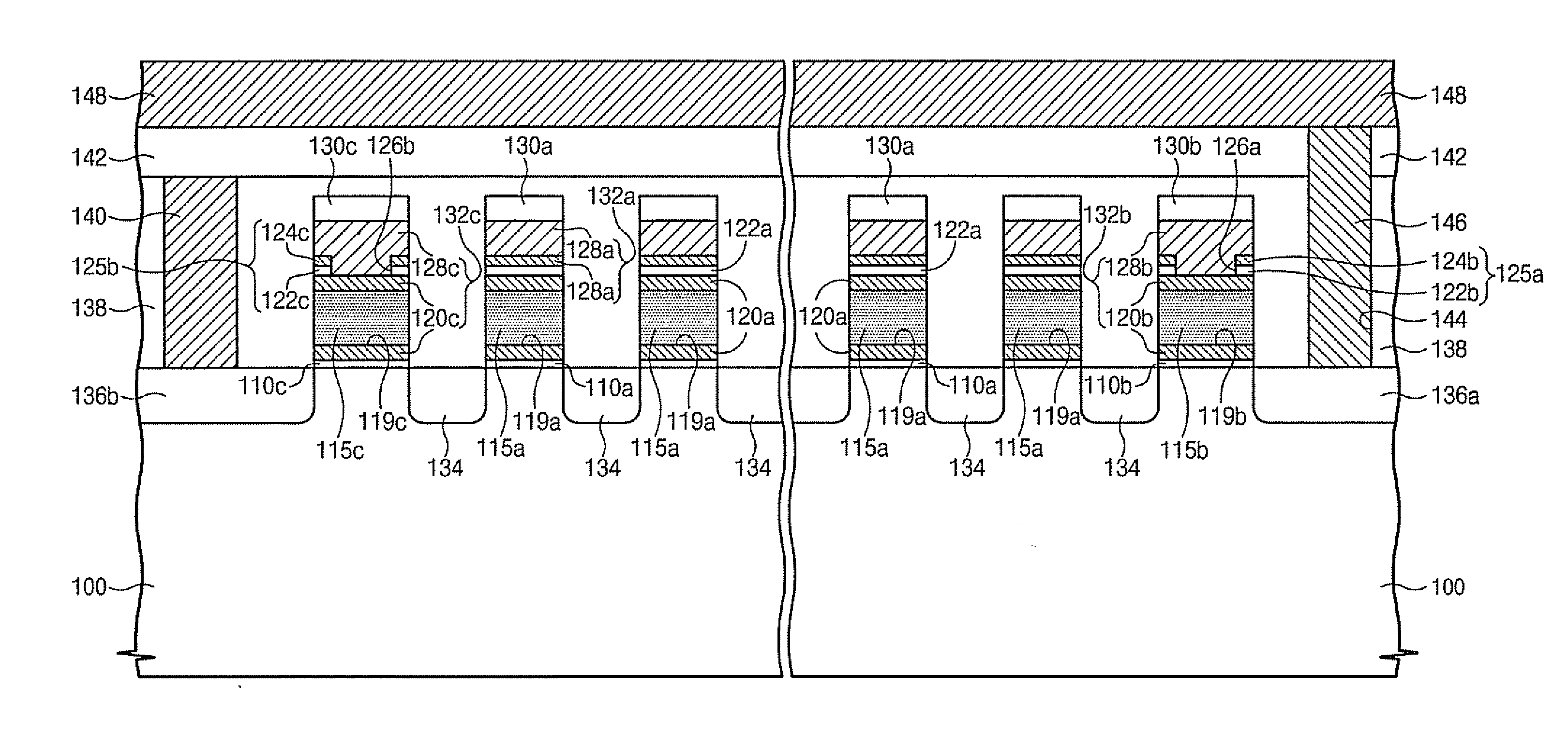

Nonvolatile memory cells having high control gate coupling ratios using grooved floating gates and methods of forming same

InactiveUS20050260814A1TransistorSemiconductor/solid-state device manufacturingGate dielectricCoupling ratio

A non-volatile memory cell includes a semiconductor substrate having a fin-shaped active region extending therefrom. A tunnel dielectric layer is provided, which extends on opposing sidewalls and an upper surface of the fin-shaped active region. A floating gate electrode is provided on the tunnel dielectric layer. This floating gate electrode has at least a partial groove therein. An inter-gate dielectric layer is also provided. This inter-gate dielectric layer extends on the floating gate electrode and into the at least a partial groove. A control gate electrode is provided, which extends on the inter-gate dielectric layer and into the at least a partial groove.

Owner:SAMSUNG ELECTRONICS CO LTD

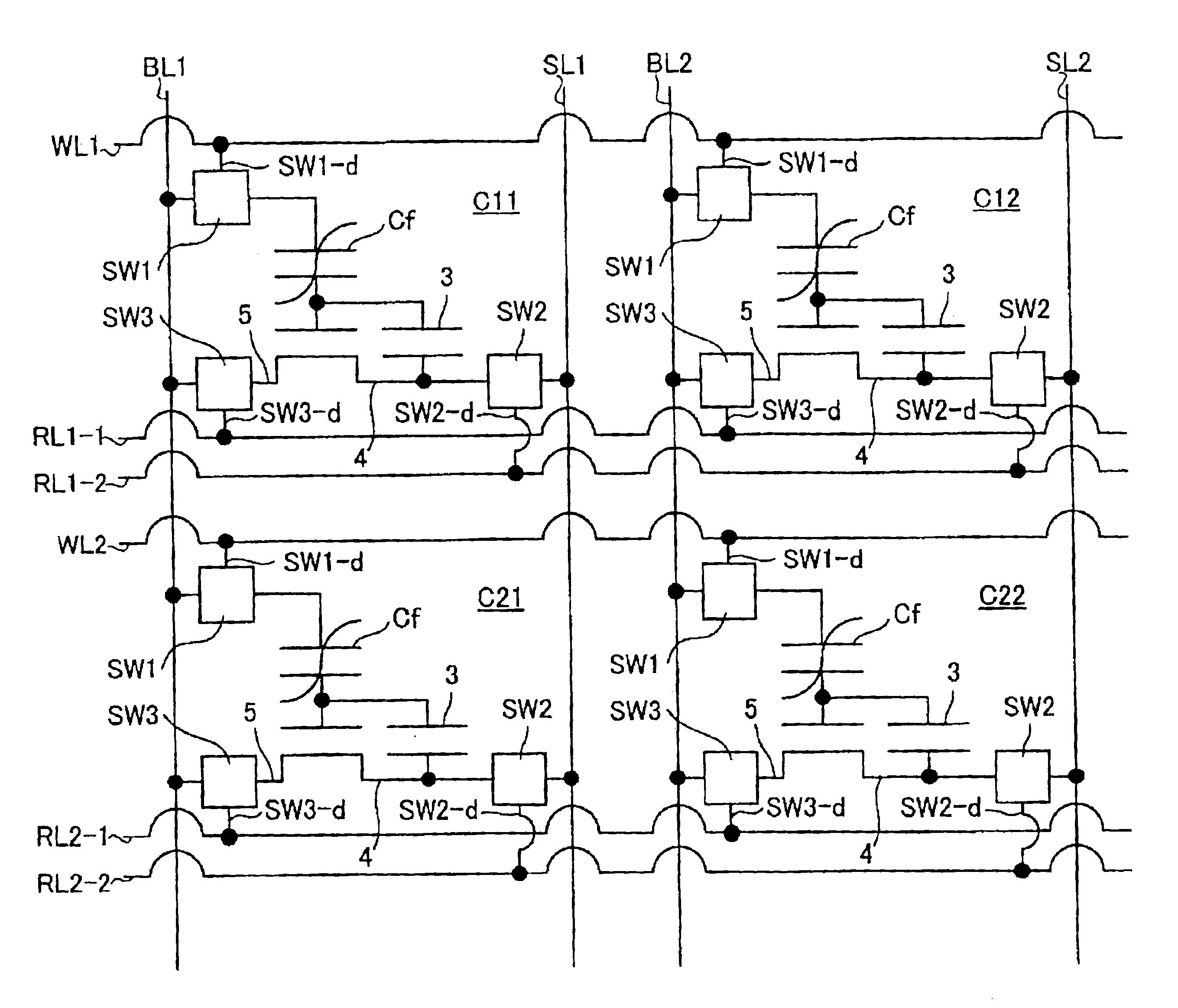

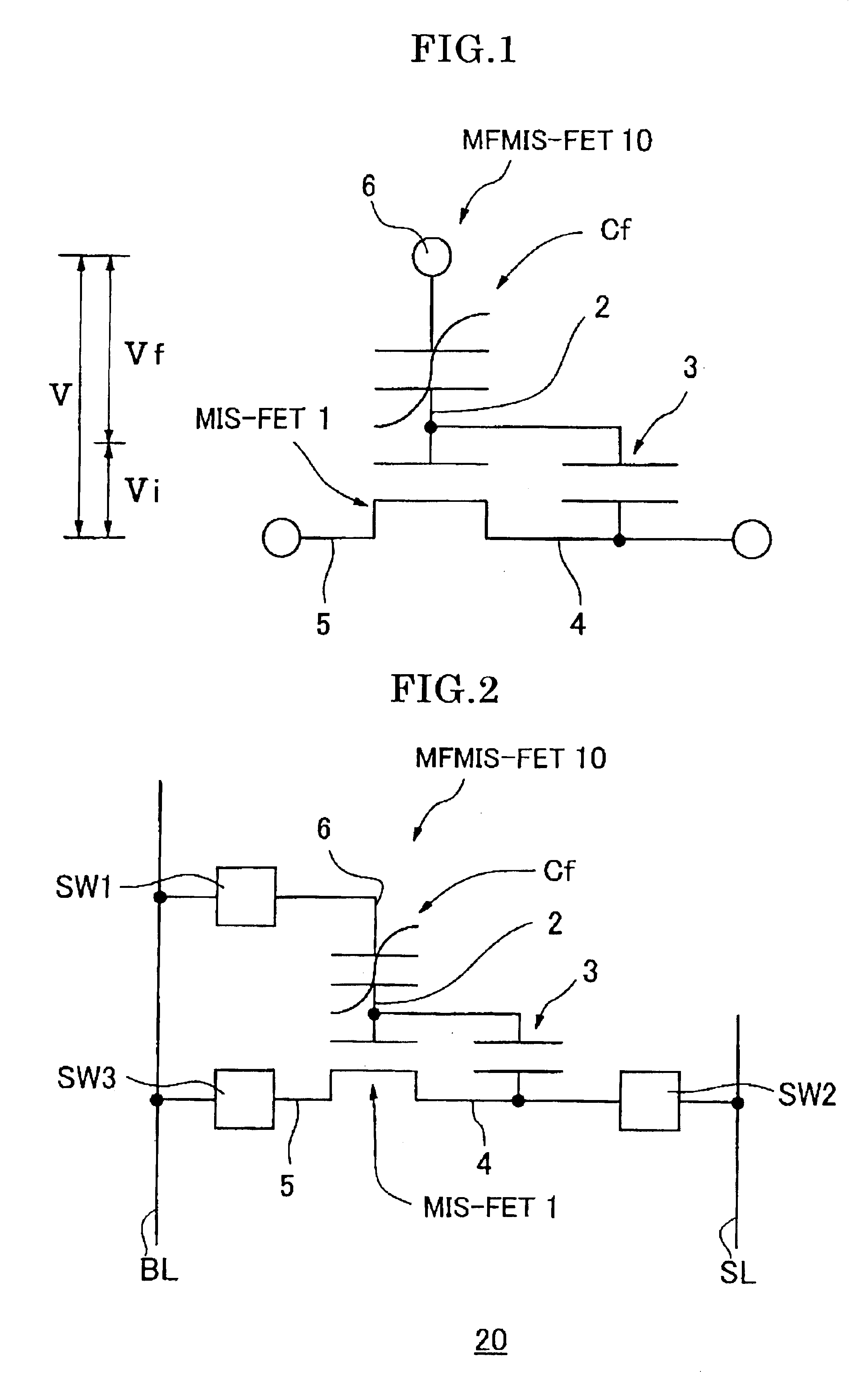

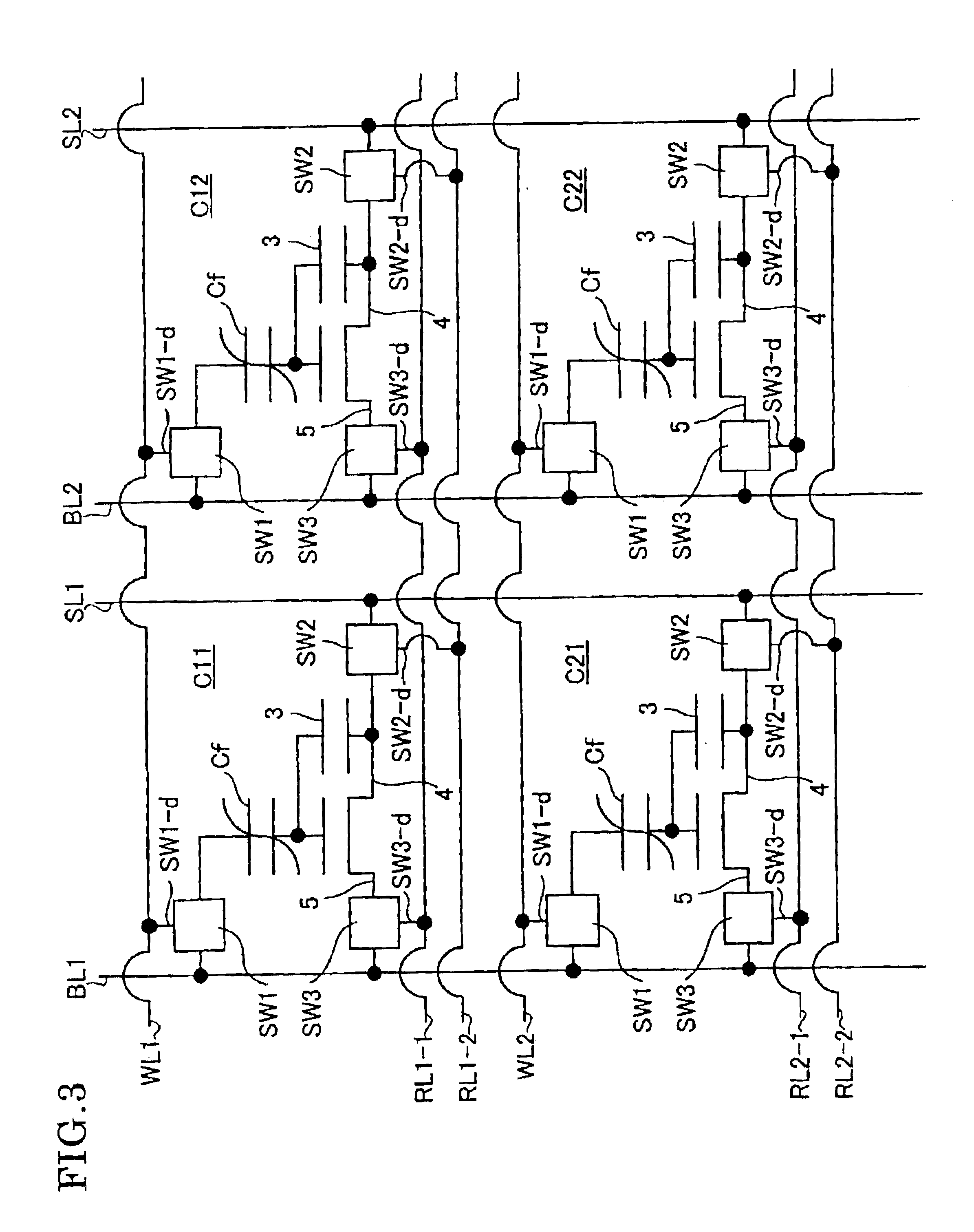

Ferroelectric non-volatile memory device having integral capacitor and gate electrode, and driving method of a ferroelectric non-volatile memory device

InactiveUS6898105B2Increase the areaImprove the coupling ratioTransistorSolid-state devicesElectrical conductorCoupling ratio

A ferroelectric non-volatile memory device that allows the coupling ratio to be increased and the effect of voltage distribution to the ferroelectric capacitor to be improved without increasing the area of the gate electrode of a detection MIS field effect transistor is provided. In a memory cell structure, a semiconductor including regions for a source, a channel, and a drain, a gate insulator on the channel region, a floating gate conductor, a ferroelectrics, and an upper electrode conductor are layered in this order. The structure includes a paraelectric capacitor having one end connected to the floating gate conductor and the other end connected to the source region.

Owner:SEIKO NPC +1

Reconfigurable optical add drop multiplexer core device, procedure and system using such device, optical light distributor, and coupling-ratio assigning procedure

ActiveUS8116629B2Power maximizationWavelength-division multiplex systemsCoupling light guidesOptical add-drop multiplexerCoupling ratio

A reconfigurable optical add drop multiplexer core device includes a light distributor, a light combiner, and first and second sets of add and drop ports. The light distributor is configured to receive an optical signal along a primary input of the reconfigurable optical add drop multiplexer core device and to distribute the received optical signal along a plurality of subtending outputs. The light combiner is configured to receive optical signals along a plurality of subtending inputs, to combine the received optical signals into a combined signal, and to output the combined signal. The add and drop ports in the first set function as add and drop ports, respectively, and the add and drop ports in the second set function as both add and drop ports, respectively, and as express ports connectable to another reconfigurable optical add drop multiplexer core device.

Owner:TELLABS OPERATIONS

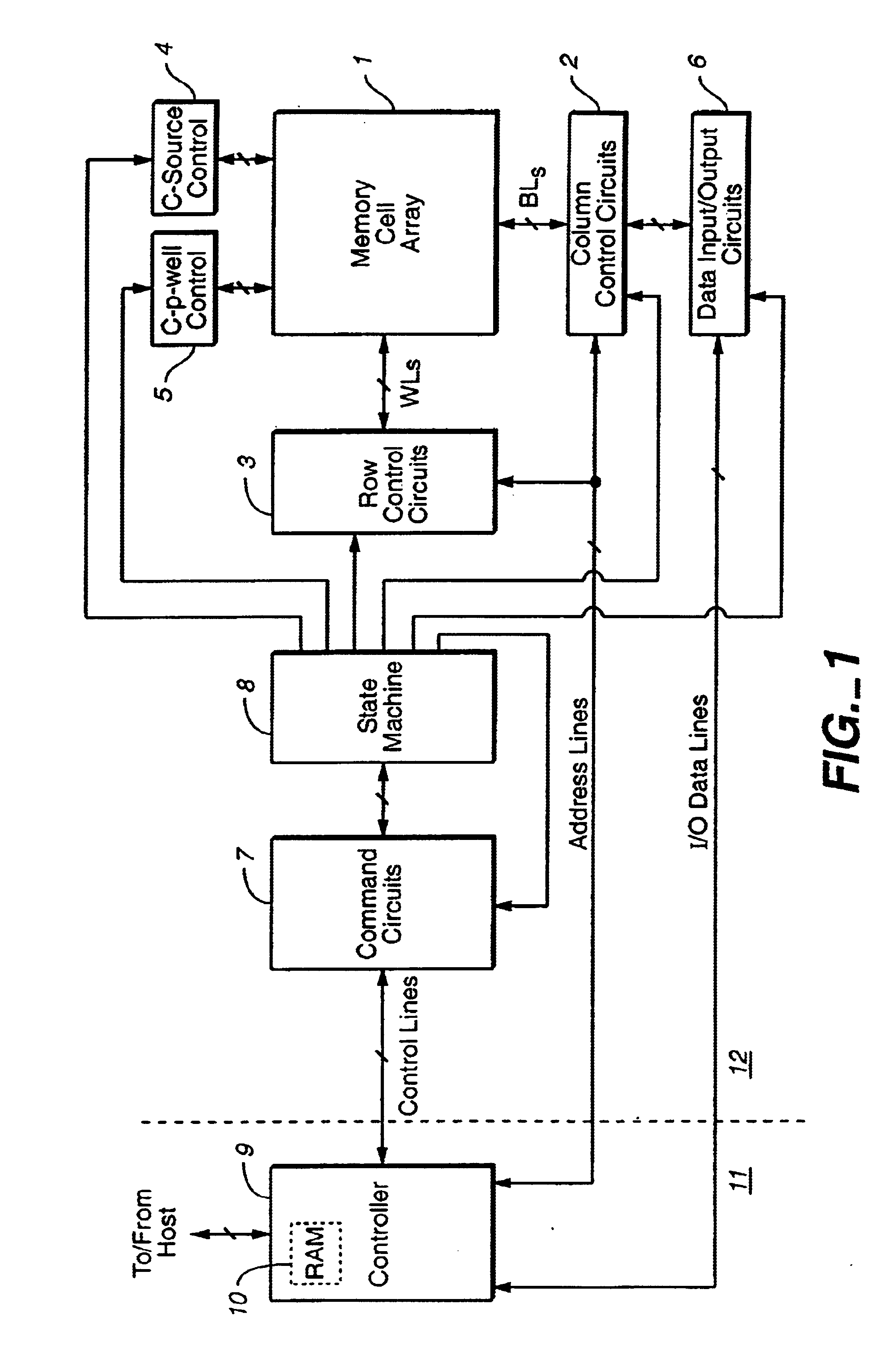

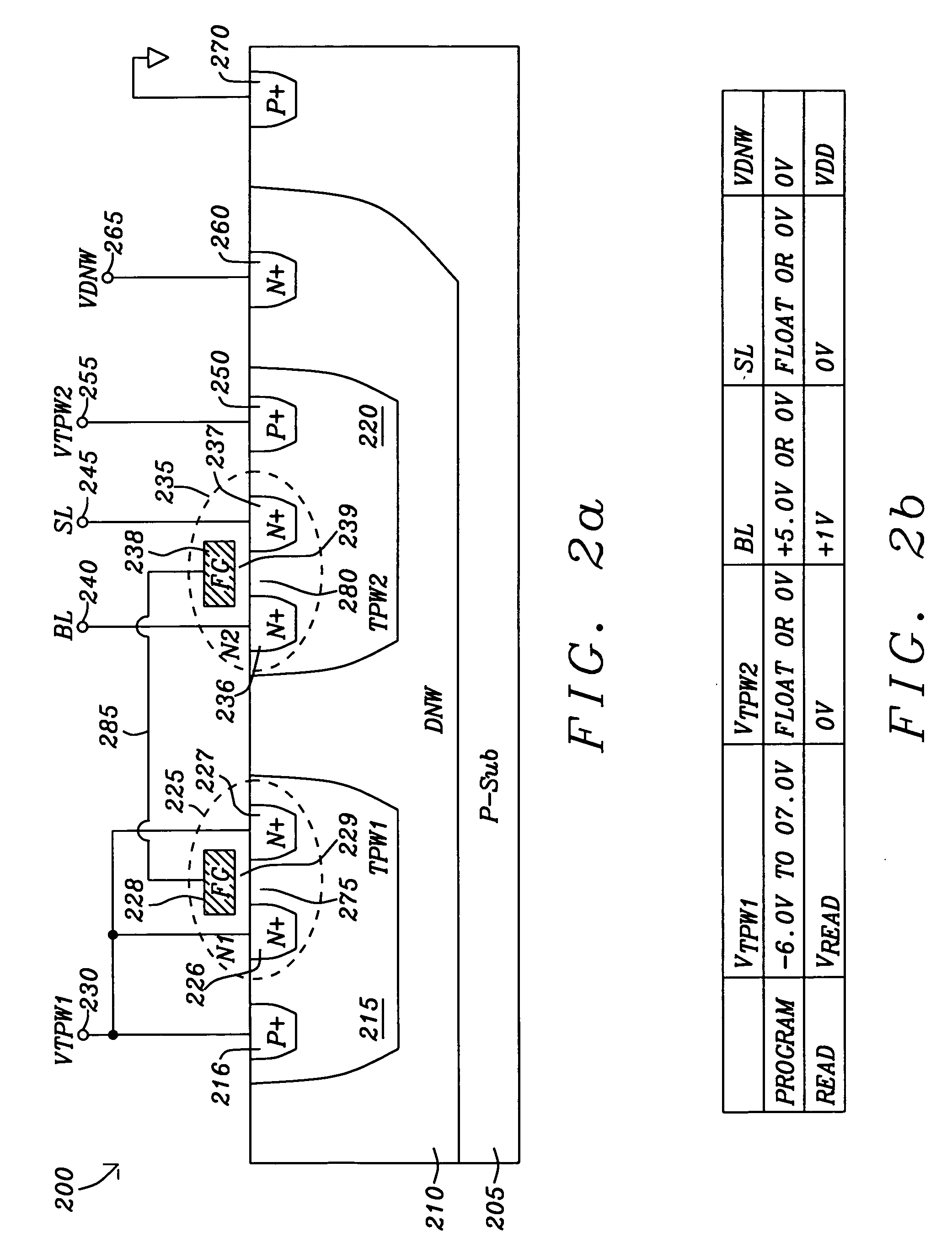

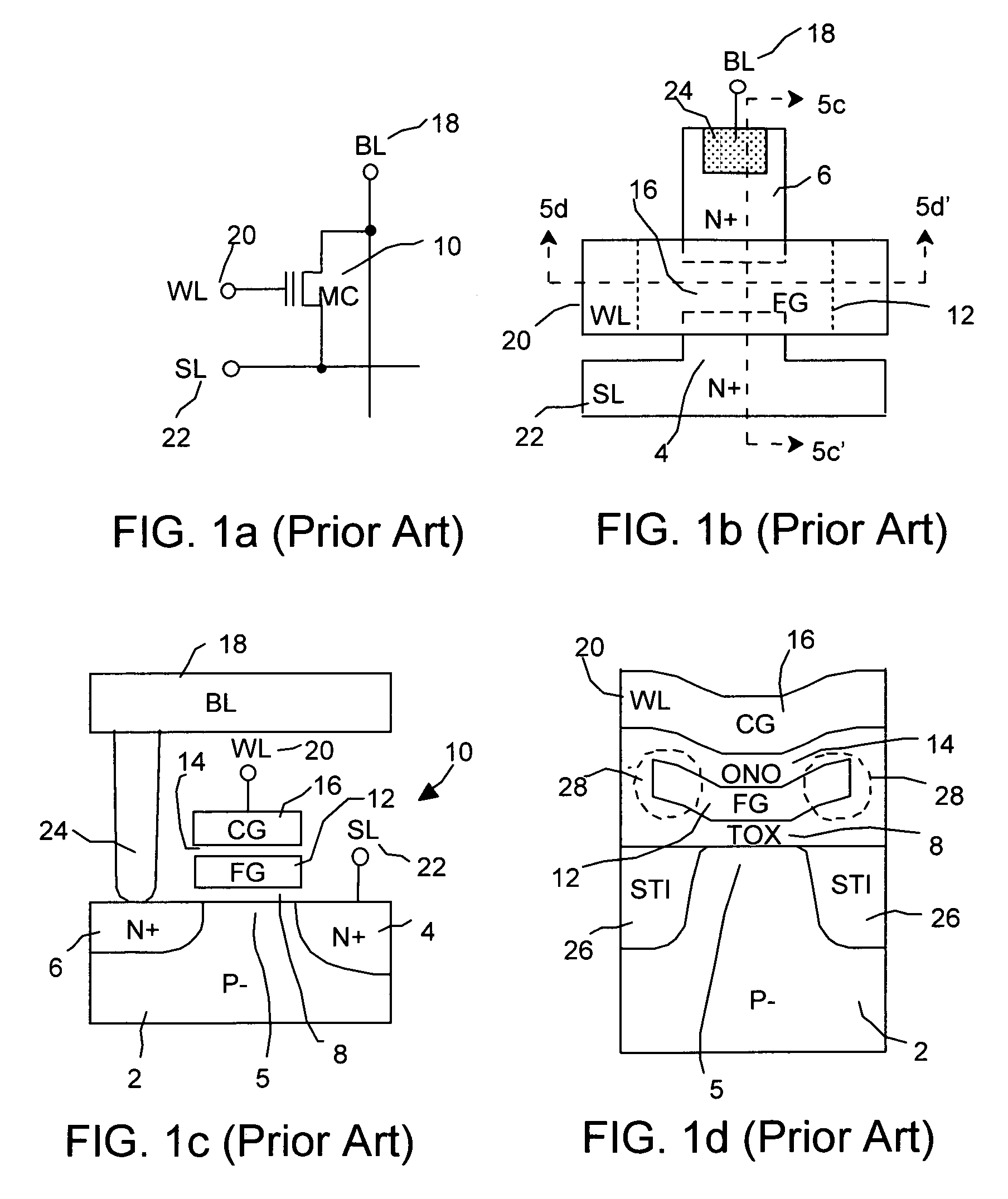

Monolithic, combo nonvolatile memory allowing byte, page and block write with no disturb and divided-well in the cell array using a unified cell structure and technology with a new scheme of decoder and layout

InactiveUS7064978B2Large positive voltageSmaller memory cell.Semiconductor/solid-state device detailsSolid-state devicesInsulation layerFowler nordheim

A nonvolatile memory array has a single transistor flash memory cell and a two transistor EEPROM memory cell which maybe integrated on the same substrate. The nonvolatile memory cell has a floating gate with a low coupling coefficient to permit a smaller memory cell. The floating gate placed over a tunneling insulation layer, the floating gate is aligned with edges of the source region and the drain region and having a width defined by a width of the edges of the source the drain. The floating gate and control gate have a relatively small coupling ratio of less than 50% to allow scaling of the nonvolatile memory cells. The nonvolatile memory cells are programmed with channel hot electron programming and erased with Fowler Nordheim tunneling at relatively high voltages.

Owner:CALLAHAN CELLULAR L L C

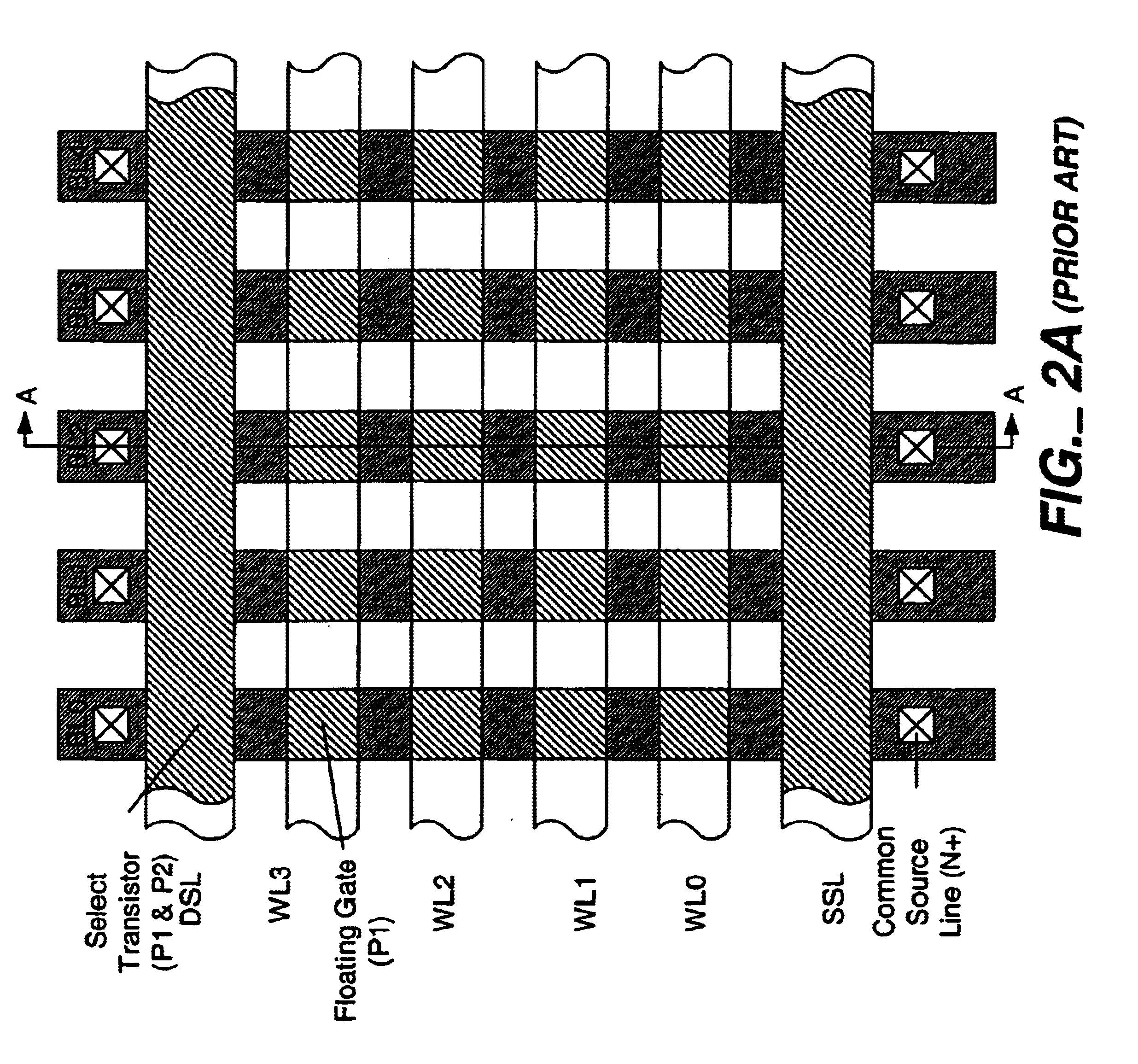

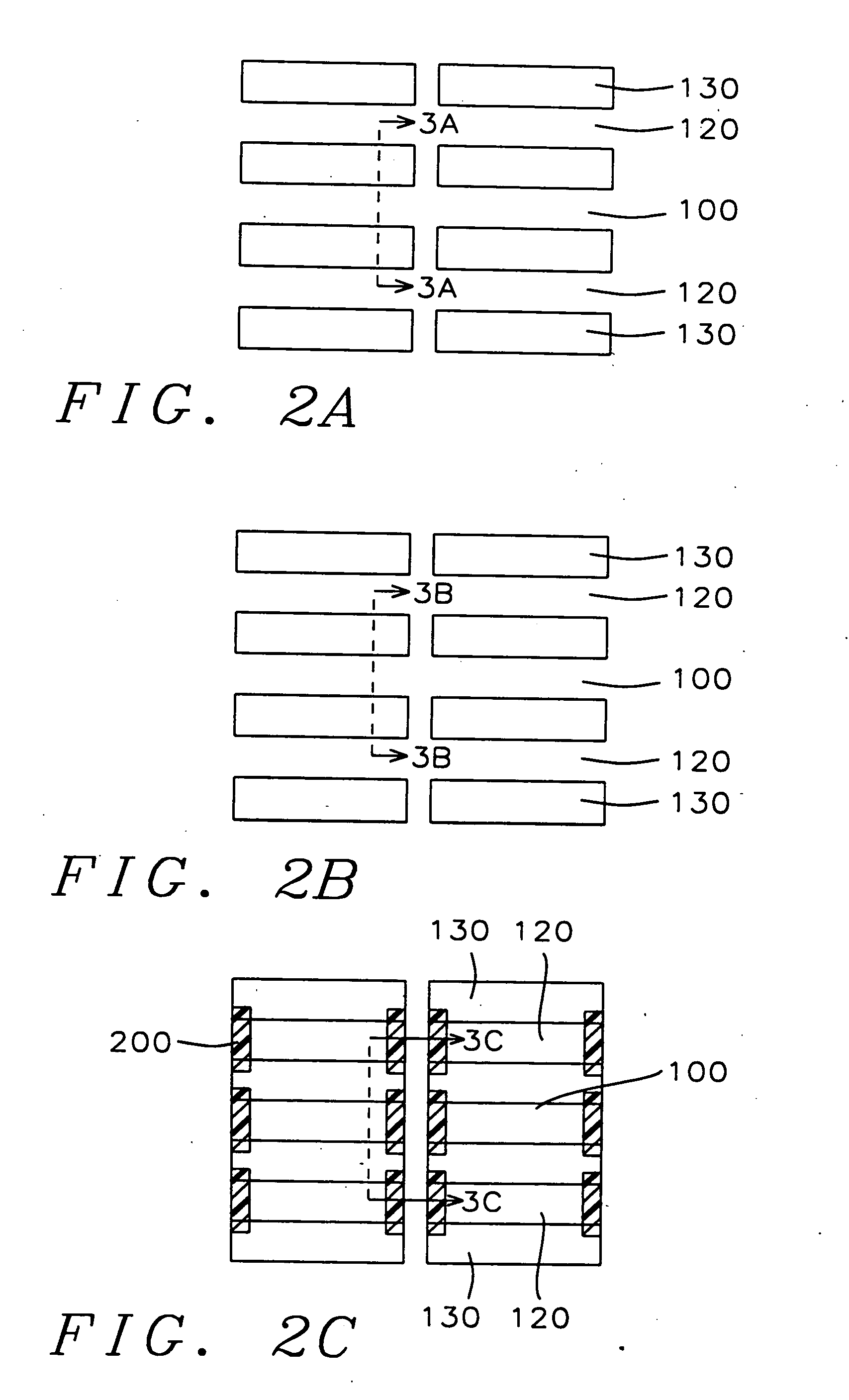

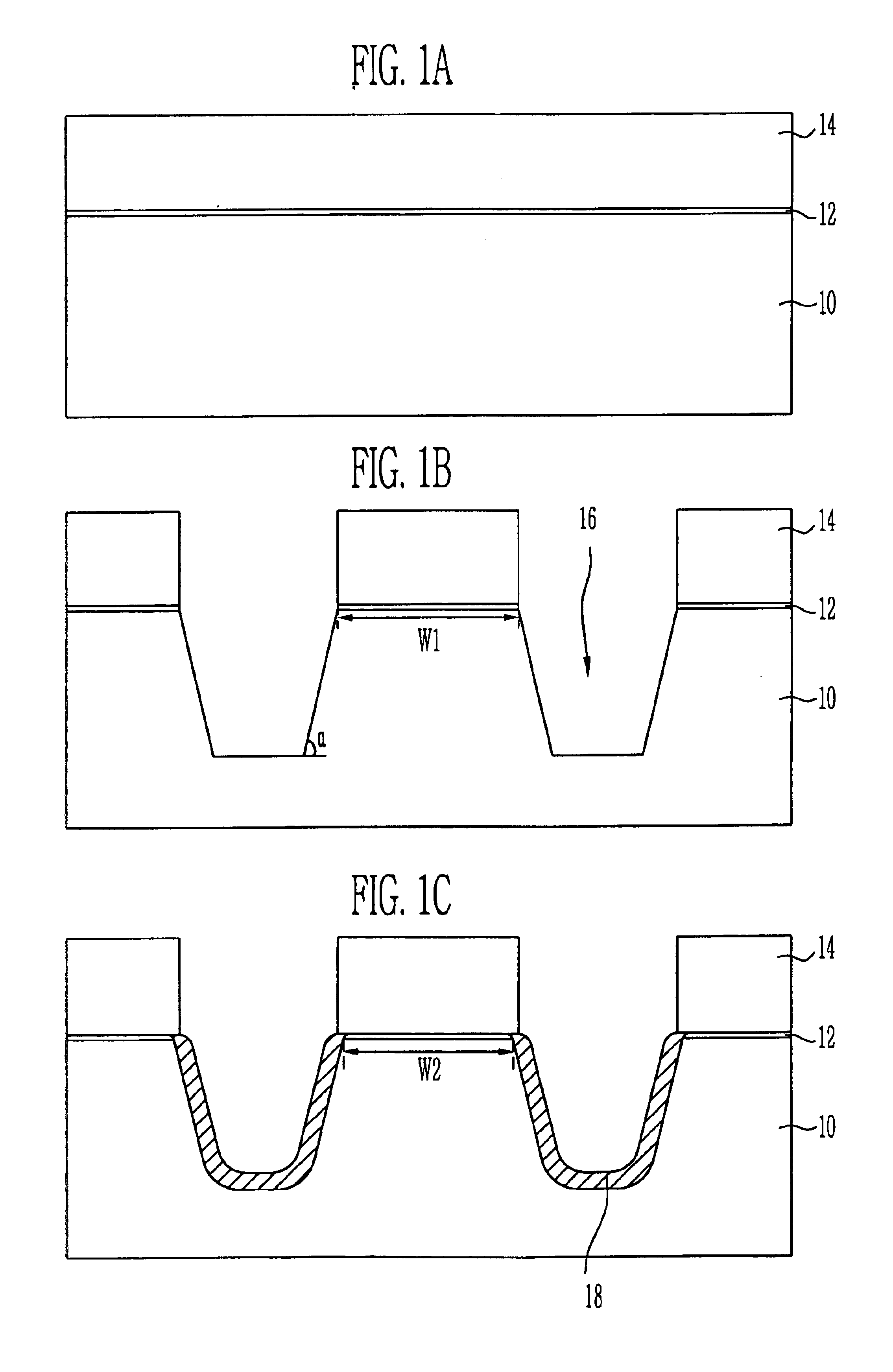

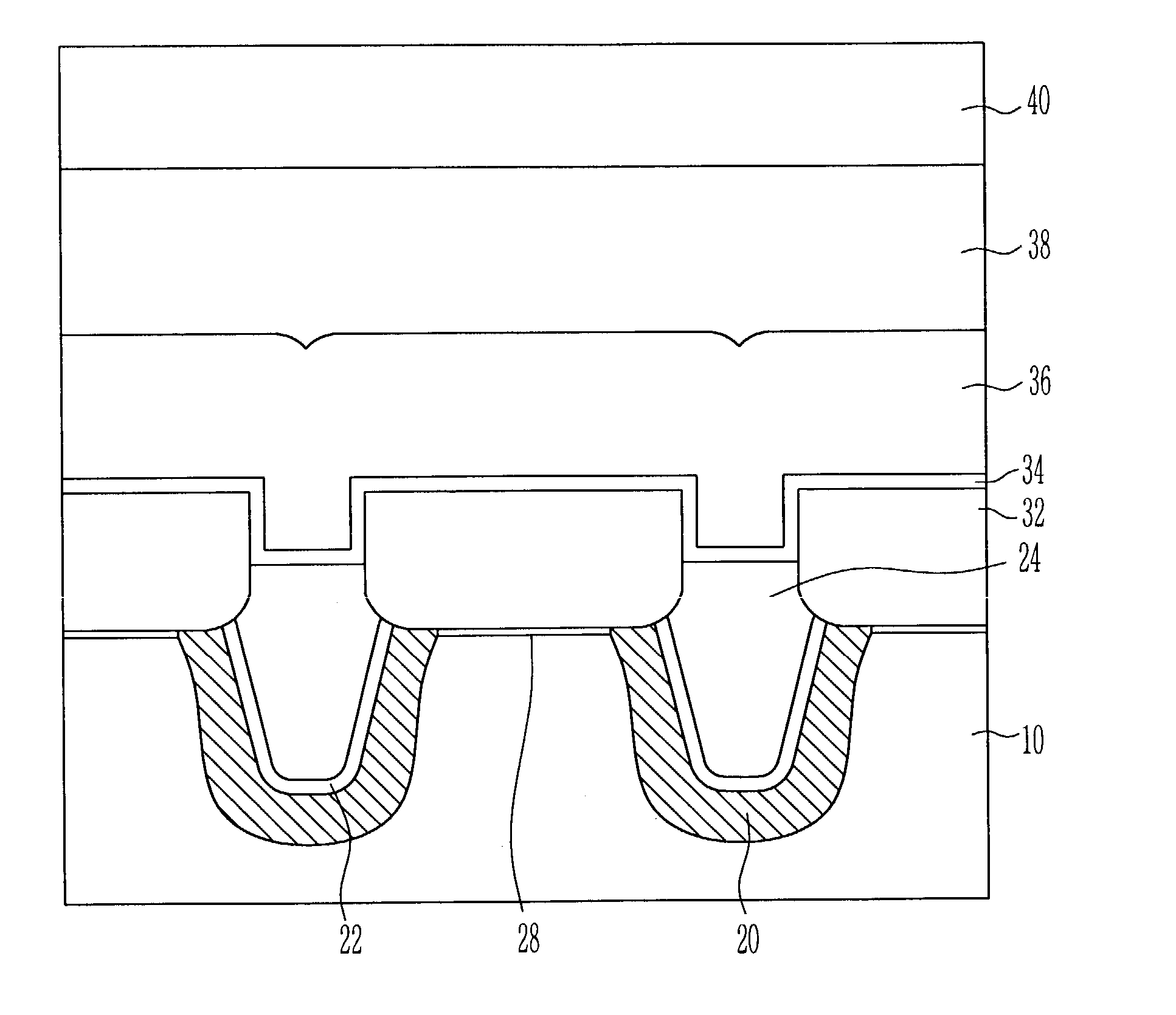

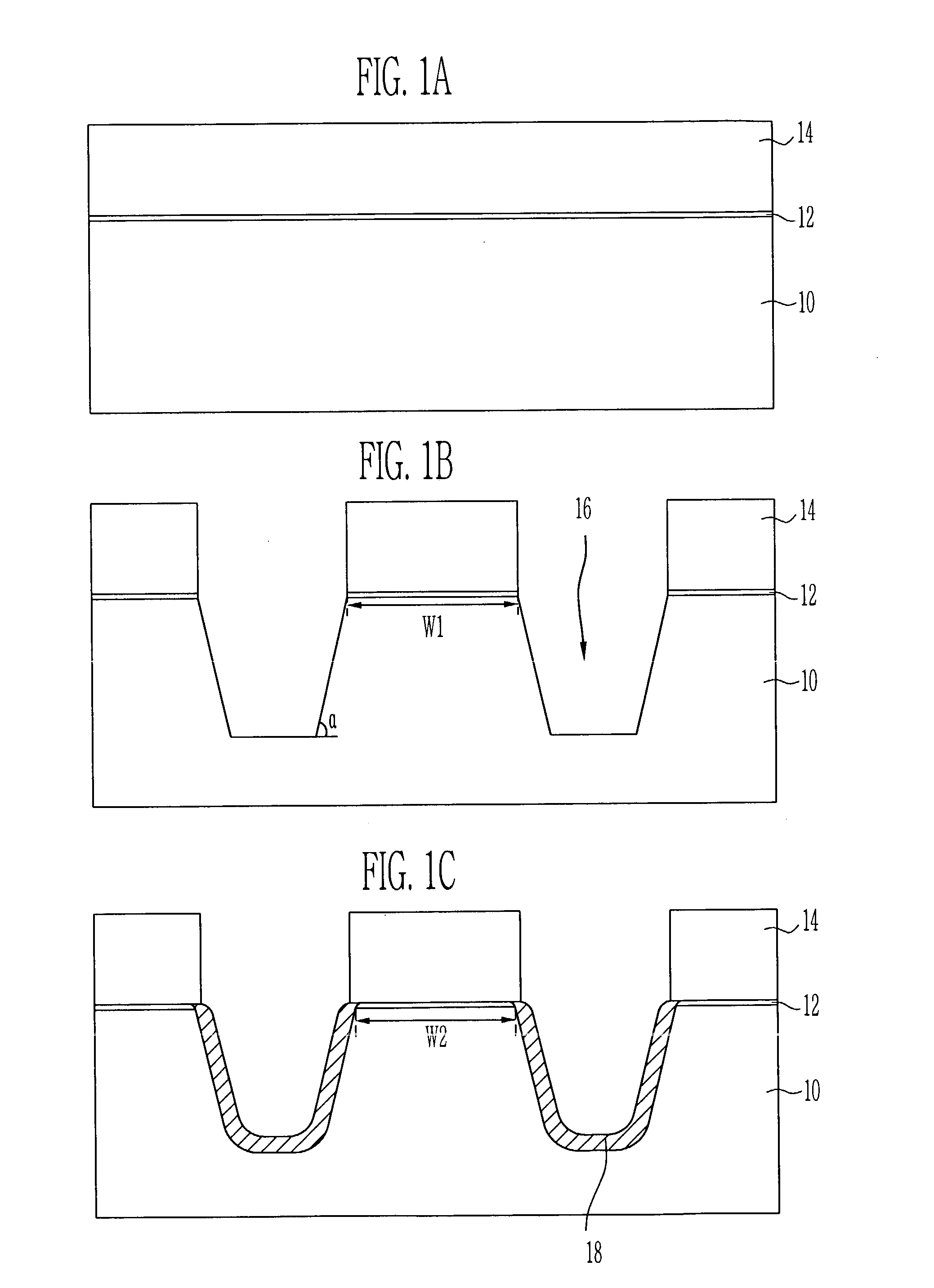

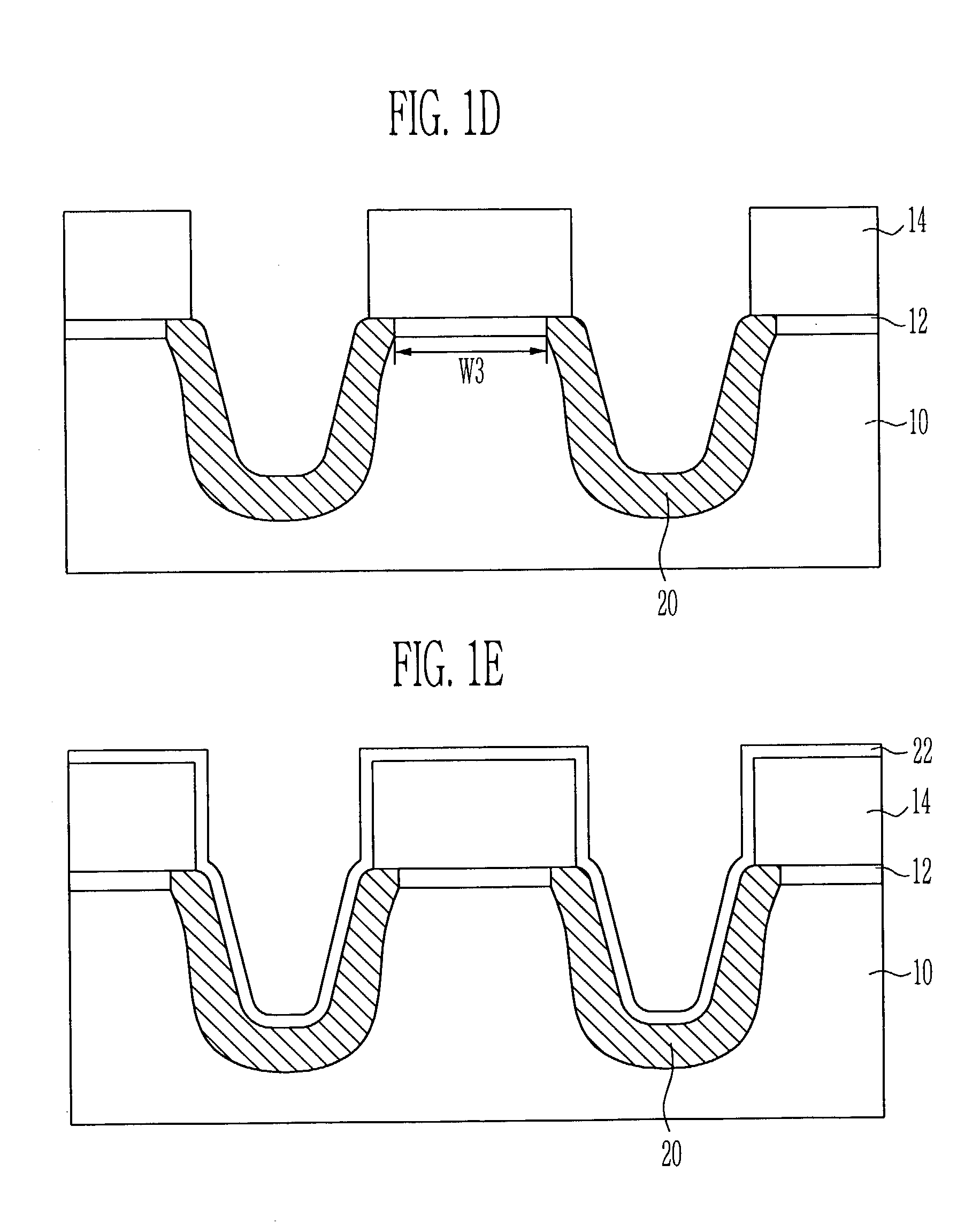

Self-aligned trench filling with high coupling ratio

ActiveUS20060110880A1Increase widthAdd depthSolid-state devicesSemiconductor/solid-state device manufacturingSelf limitingDielectric

Self-aligned trench filling to isolate active regions in high-density integrated circuits is provided. A deep, narrow trench is etched into a substrate between active regions. The trench is filled by growing a suitable dielectric such as silicon dioxide. The oxide grows from the substrate to fill the trench and into the substrate to provide an oxide of greater width and depth than the trench. Storage elements for a NAND type flash memory system, for example, can be fabricated by etching the substrate to form the trench after or as part of etching to form NAND string active areas. This can ensure alignment of the NAND string active areas between isolation trenches. Because the dielectric growth process is self-limiting, an open area resulting from the etching process can be maintained between the active areas. A subsequently formed inter-gate dielectric layer and control gate layer can fill the open area to provide sidewall coupling between control gates and floating gates.

Owner:SANDISK TECH LLC

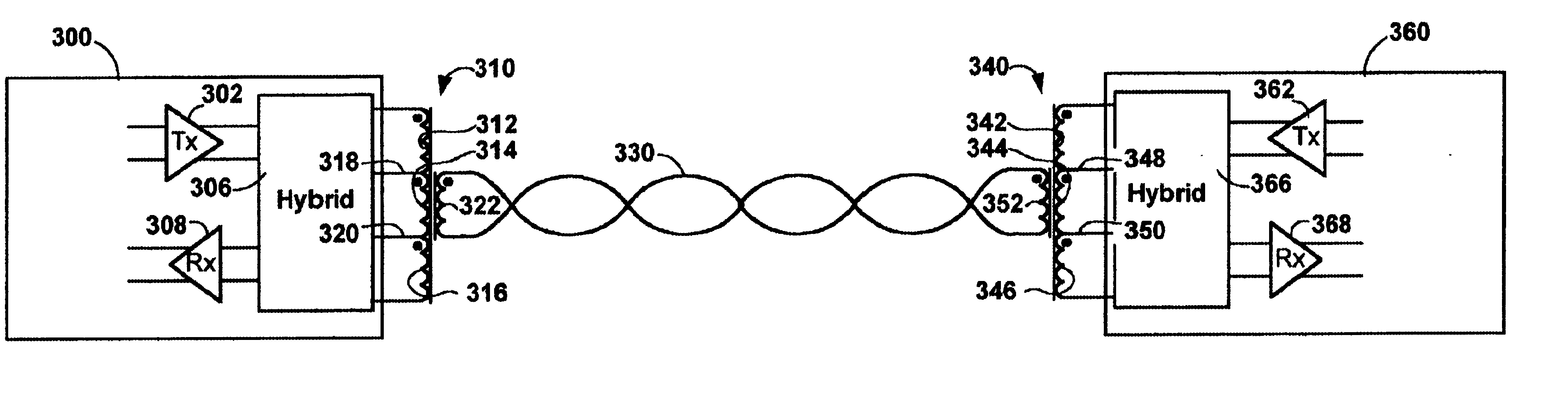

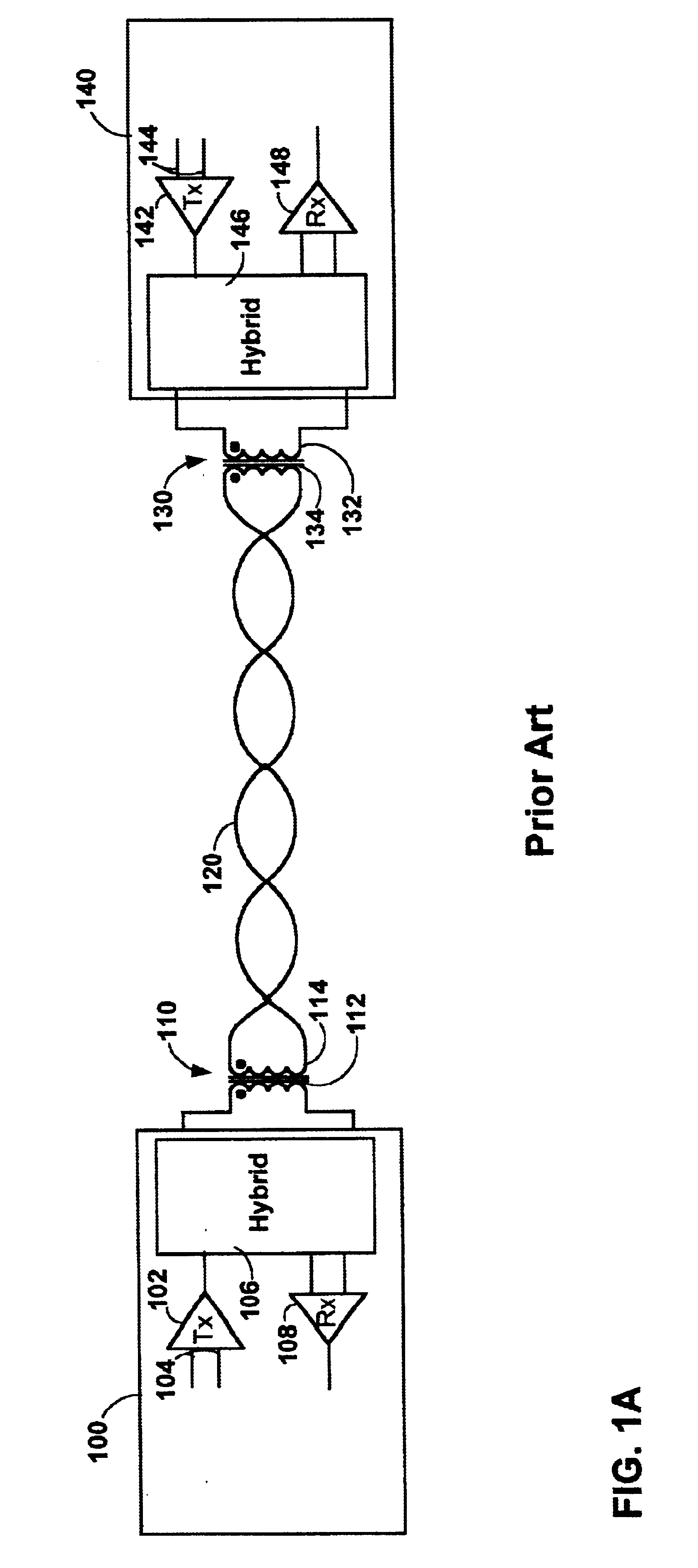

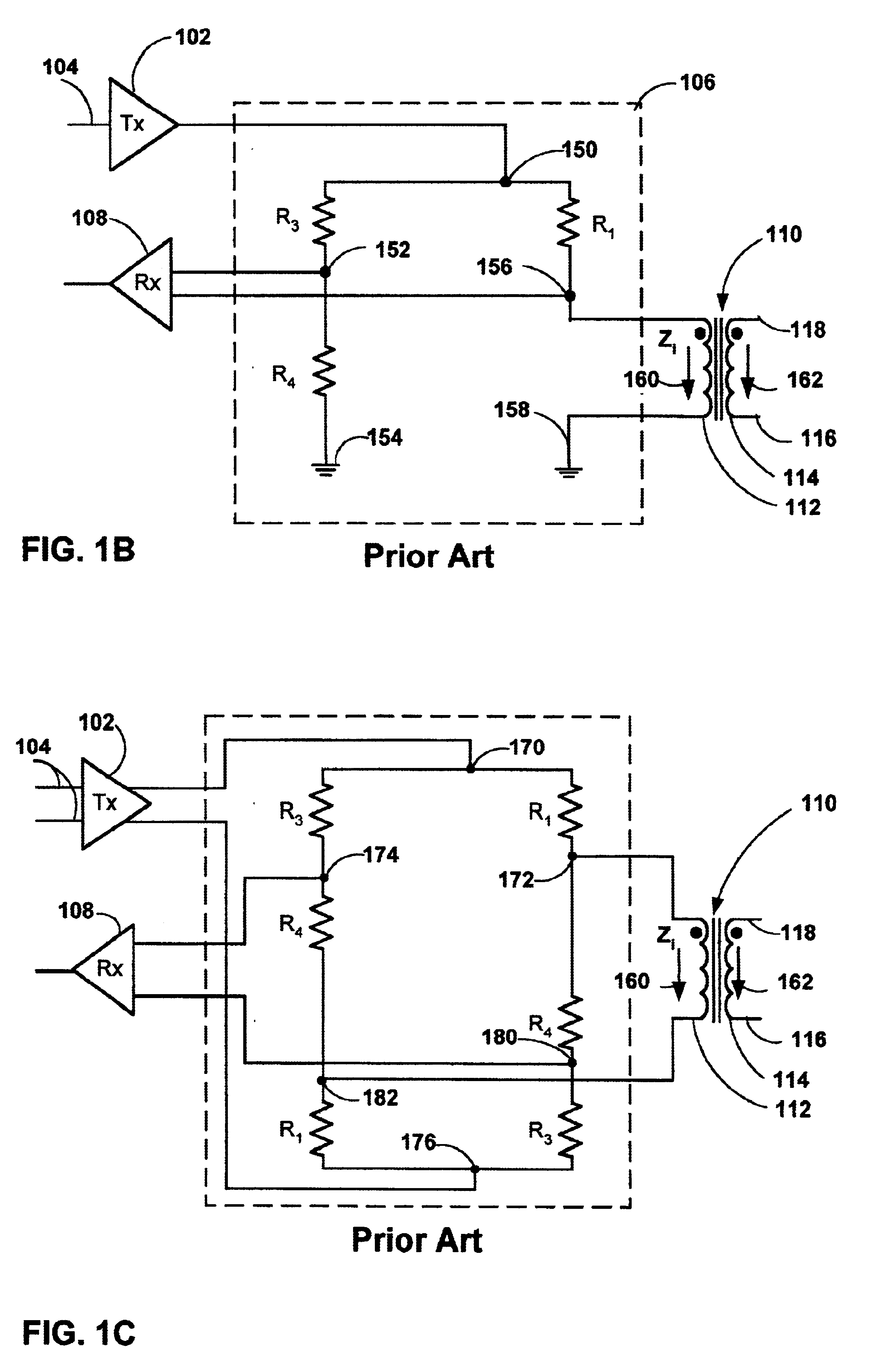

Dual impedance hybrid

InactiveUS6760434B1Two-way loud-speaking telephone systemsTransmission path divisionRelative magnitudeDual impedance

A method and apparatus for coupling an xDSL transceiver with a subscriber line is disclosed. A hybrid circuit is disclosed which exhibits a different relative gain factor for transmitted signals and received signals. The difference in gain factors results in part from a combined balance circuit and transformer which exhibit a different coupling ratio between the primary and secondary coils on the receive path and the transmit path. The hybrid circuit may be used to isolate the receive signal from the transmit signal in the full duplex mode of operation. The gain from the transmit port to the receive port is minimum and most of the energy is transmitted to the subscriber line.In an embodiment of the invention a hybrid circuit for communicating a transmit signal and a receive signal across a subscriber line is disclosed. The hybrid circuit includes: a transformer and a balance circuit. The transformer includes a primary inductor and a secondary inductor and the secondary inductor for coupling to the subscriber line and the primary inductor including at least two inductive portions. The balance circuit includes a transmit interface to input the transmit signal and a receive interface to output the receive signal, and the balance circuit coupling both the transmit interface and the receive interface with the at least two inductive portions of the primary to change the relative magnitude of an induced emf between the primary and the secondary for the transmit signal and the receive signal. In an alternate embodiment of the invention a method for communicating a transmit signal and a receive signal across a subscriber line is disclosed.

Owner:IKANOS COMMUNICATIONS

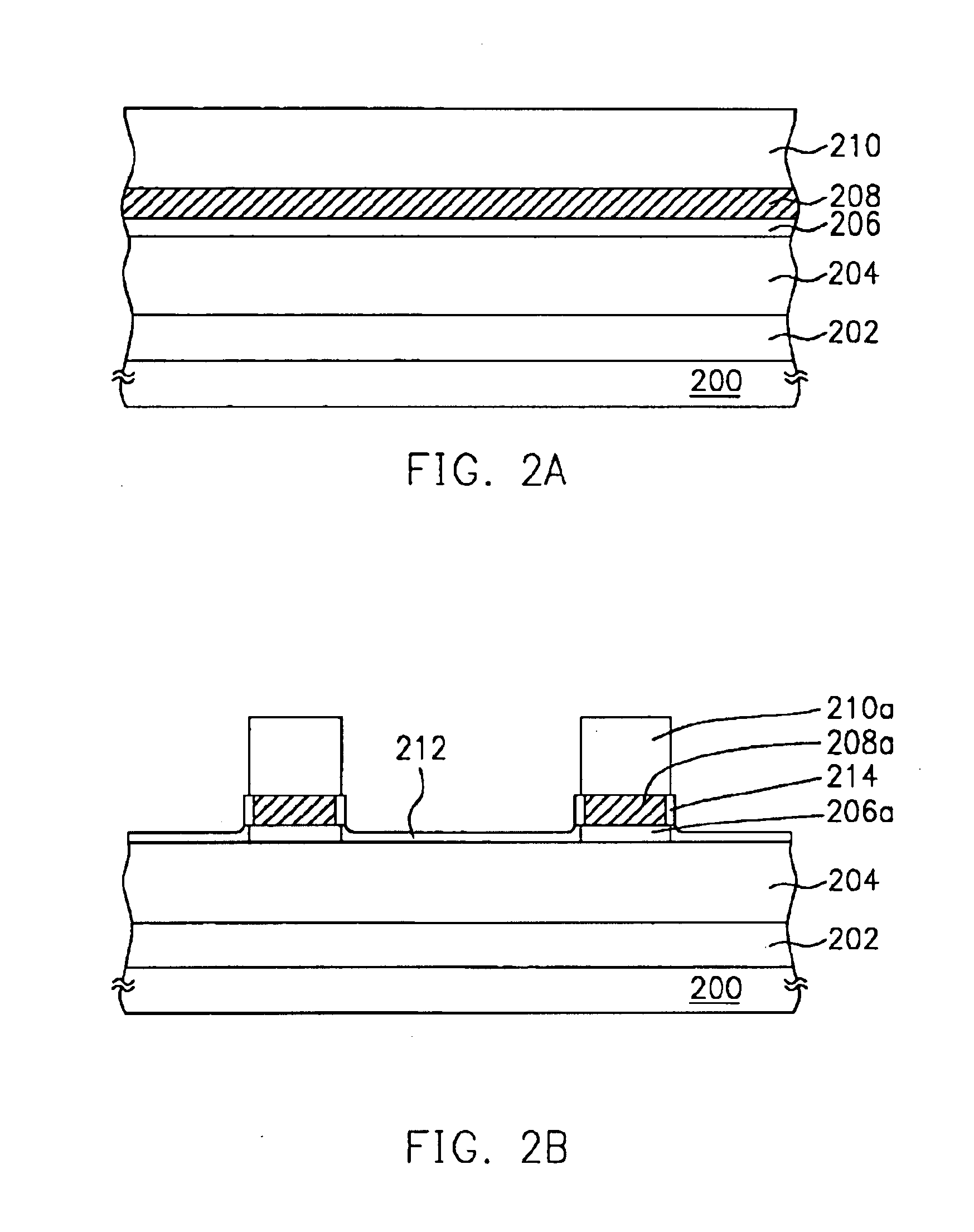

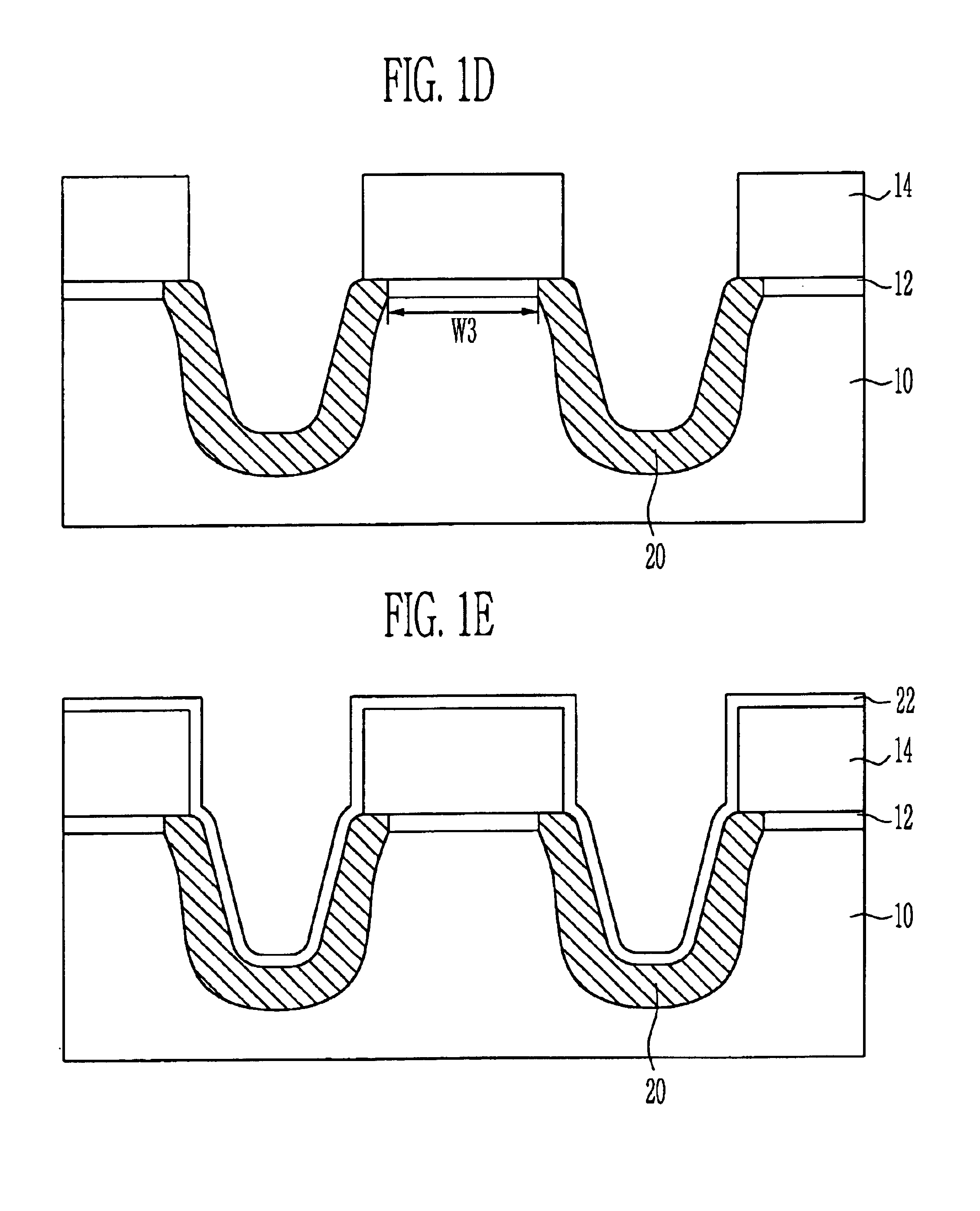

Method of manufacturing high coupling ratio flash memory having sidewall spacer floating gate electrode

InactiveUS6875660B2Reduce operating speedImprove memory performanceSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricCoupling ratio

A method of manufacturing a flash memory is provided. First, a substrate with a first gate structure and a second gate structure thereon is provided. The first gate structure and the second gate structure each comprises of a dielectric layer, a first conductive layer and a cap layer. A tunneling oxide layer is formed over the substrate and then a first spacer is formed on the sidewall of the first conductive layer. Thereafter, a second conductive layer is formed on one side designated for forming a source region of the sidewalls of the first gate structure and the second gate structure. Then, the source region is formed in the substrate in the designated area. Next, an inter-gate dielectric layer is formed over the second conductive layer and then an insulating layer is formed over the source region. After forming a third conductive layer over the area between the first gate structure and the second gate structure, a drain region is formed in the substrate.

Owner:POWERCHIP SEMICON MFG CORP

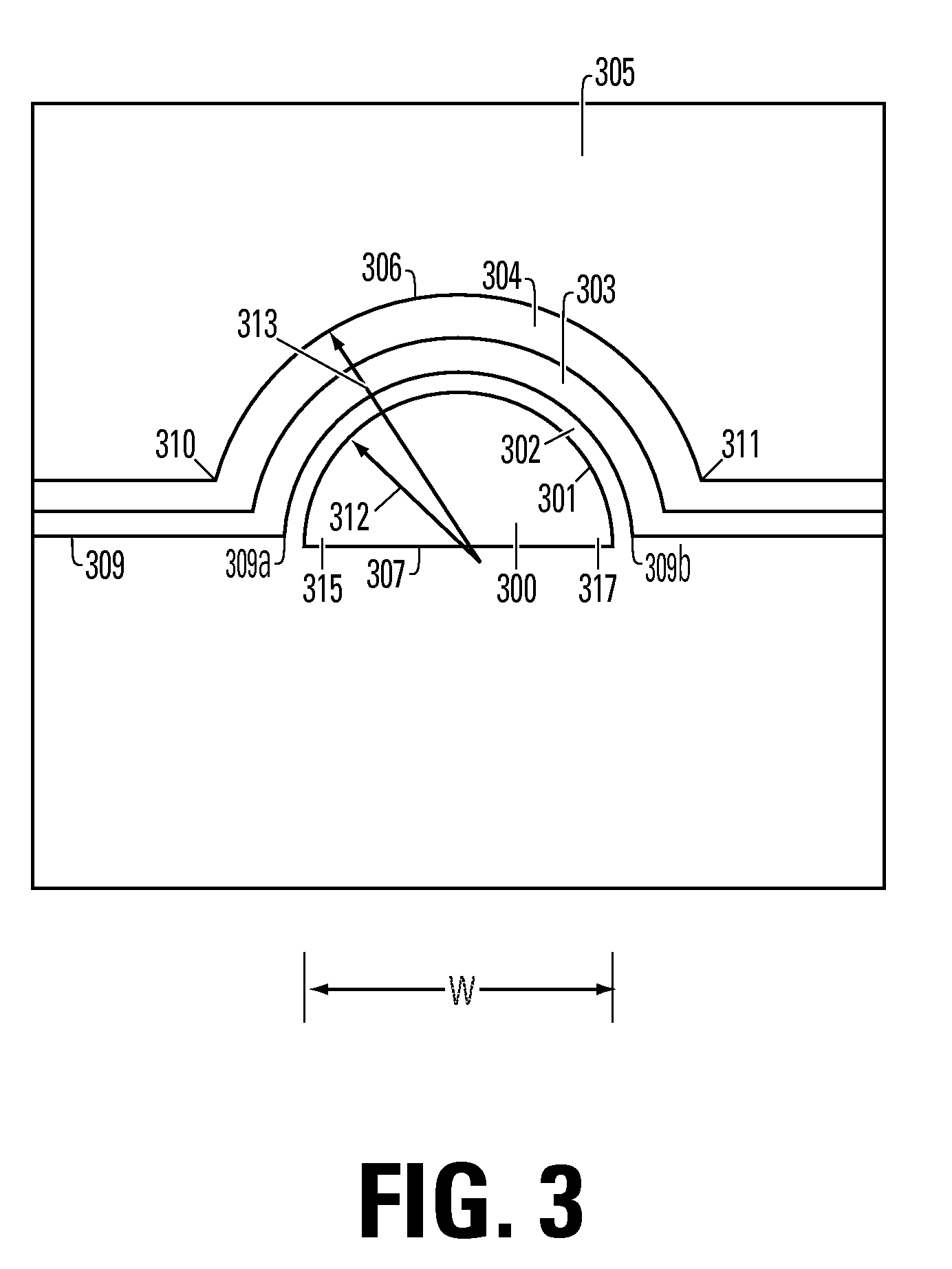

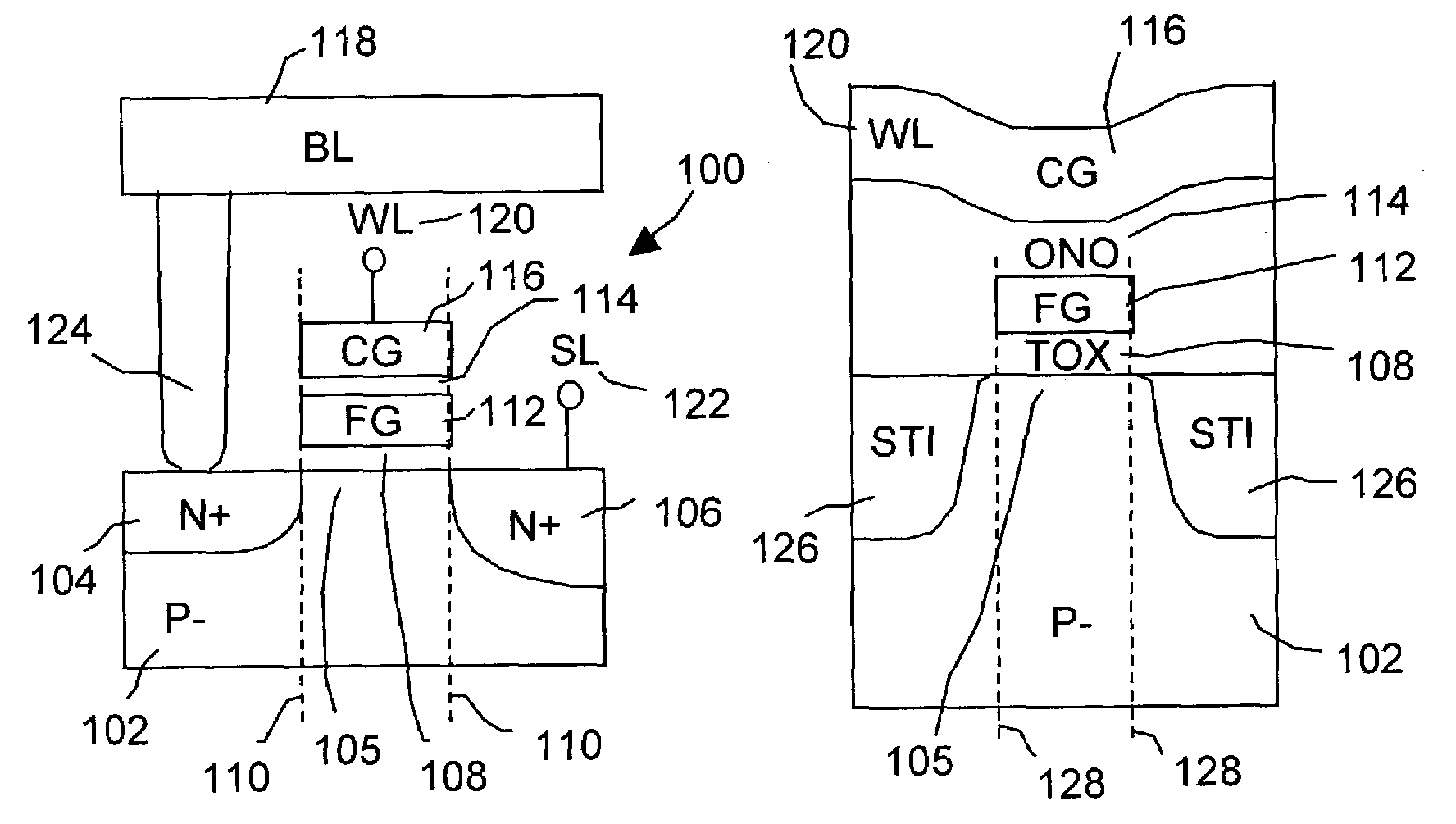

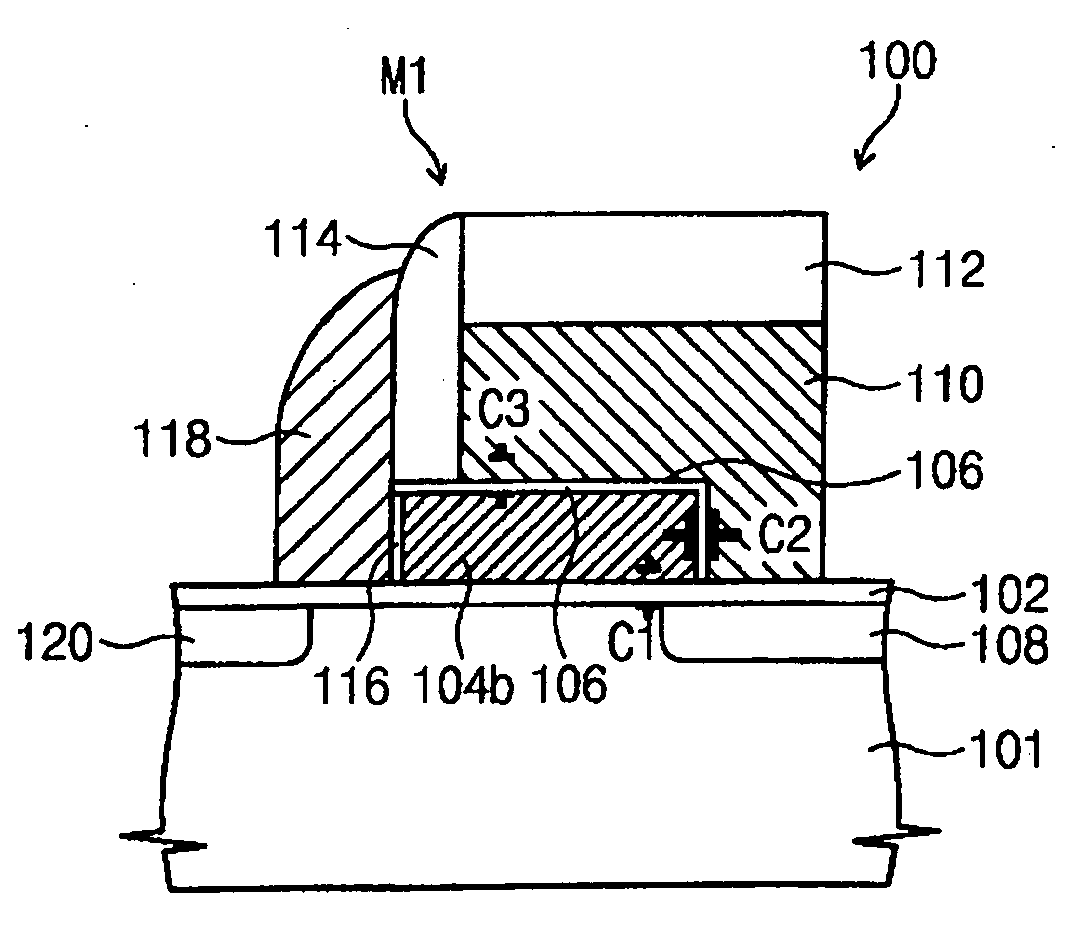

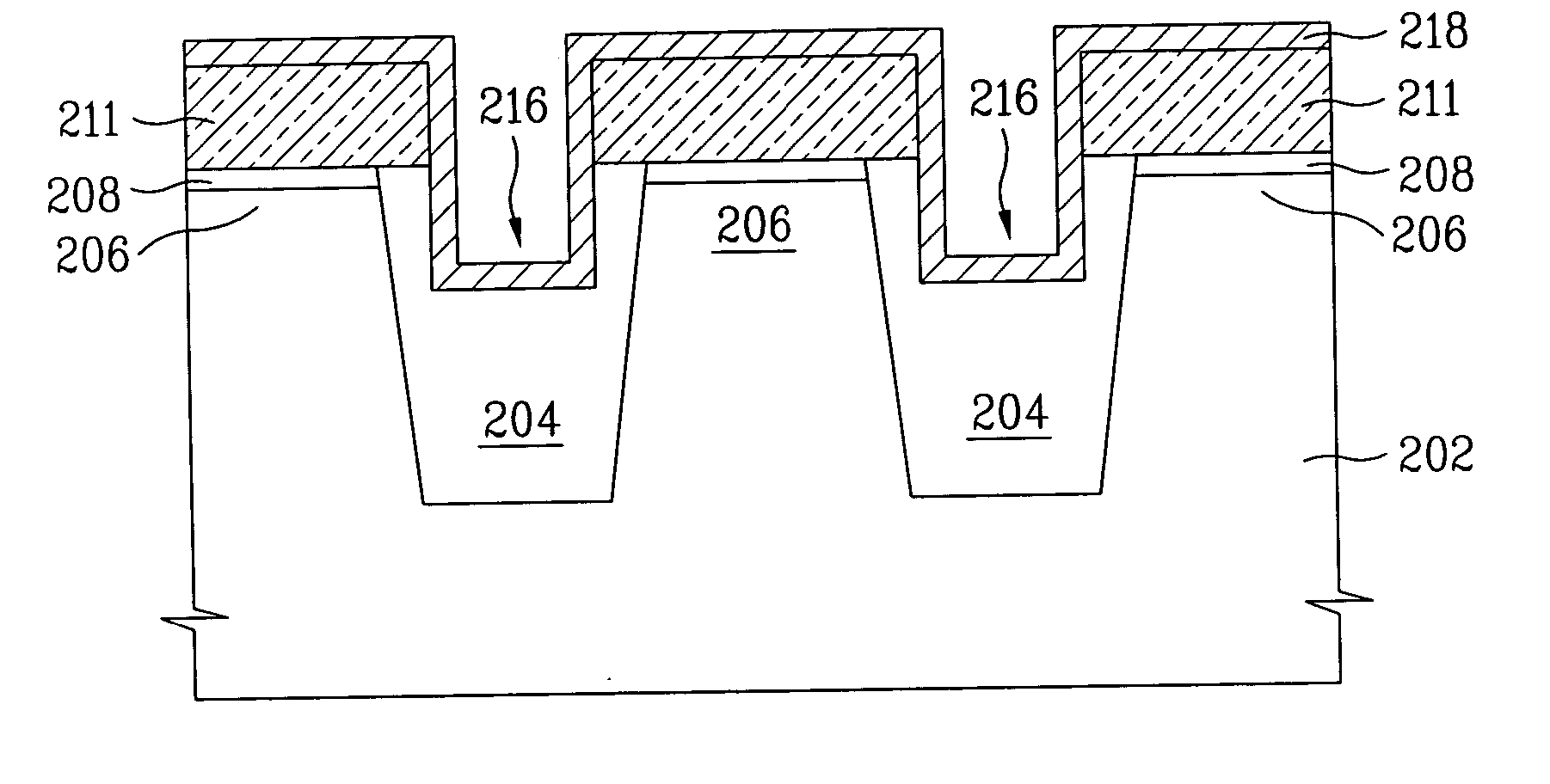

Split gate non-volatile memory devices and methods of forming same

InactiveUS20060202255A1Increased floating gate coupling ratioAccelerated programTransistorSolid-state devicesCoupling ratioEngineering

Non-volatile memory devices and methods for fabricating non-volatile memory devices are disclosed. More specifically, split gate memory devices are provided having frameworks that provide increased floating gate coupling ratios, thereby enabling enhanced programming and erasing efficiency and performance.

Owner:SAMSUNG ELECTRONICS CO LTD

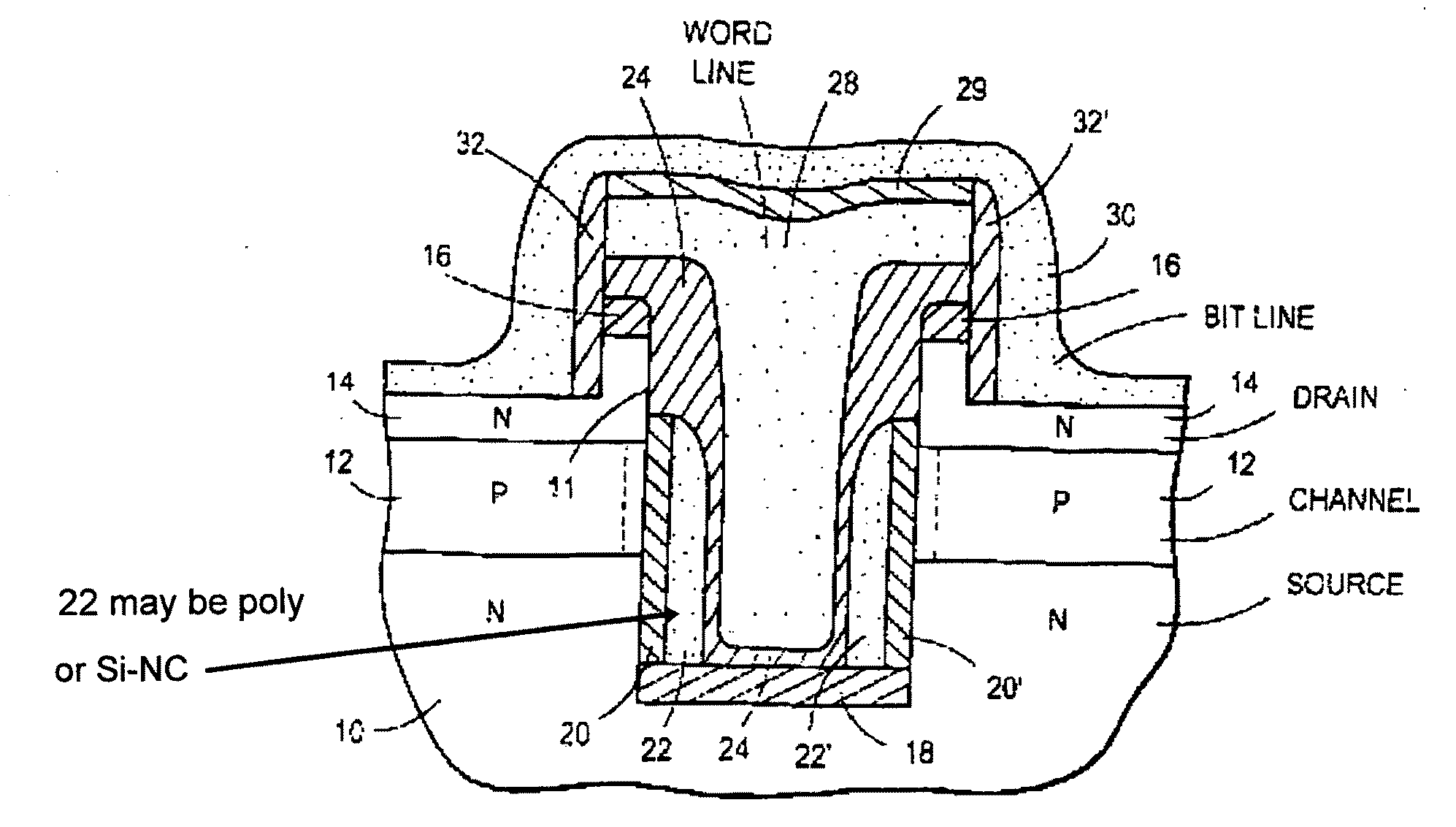

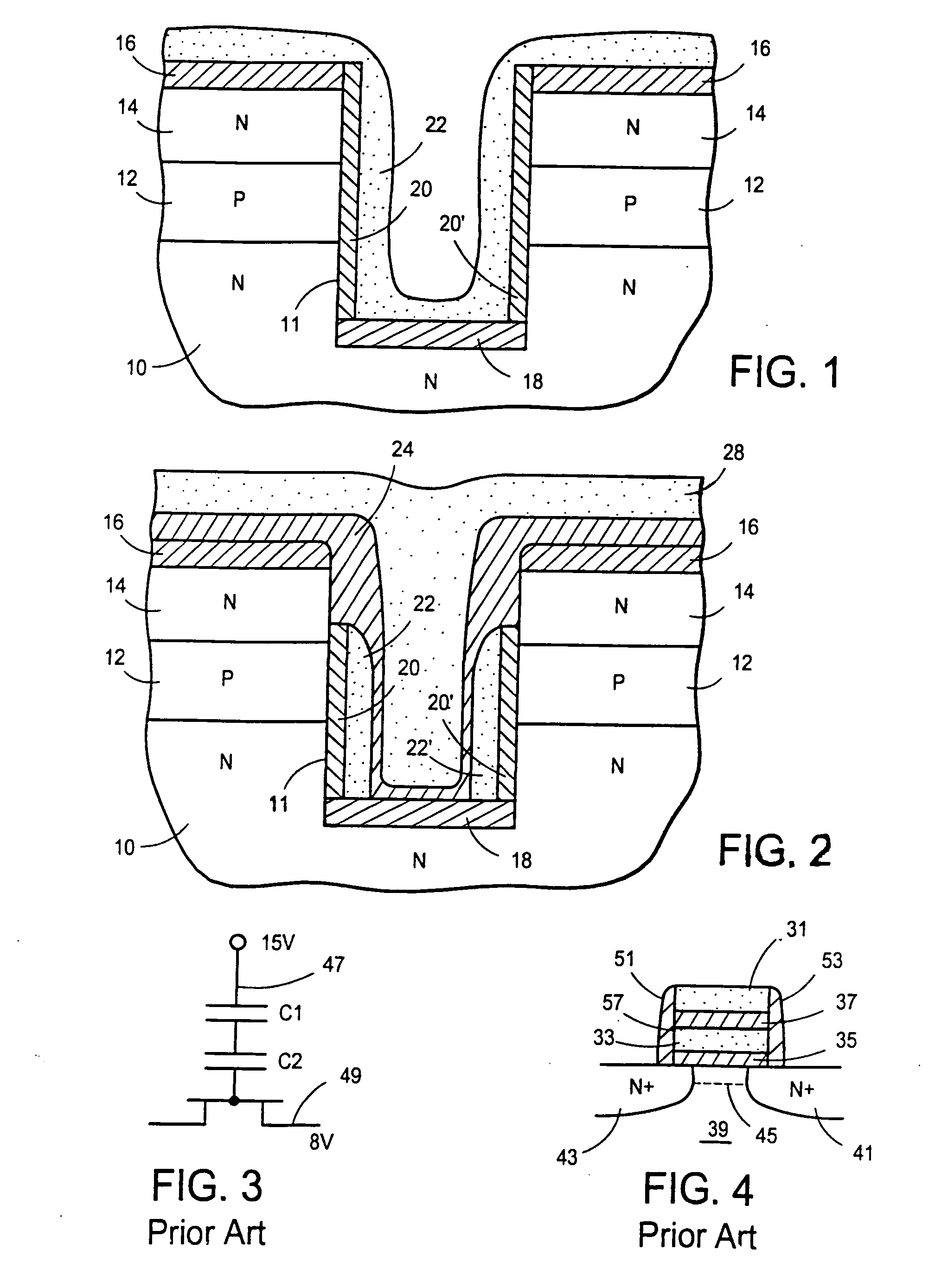

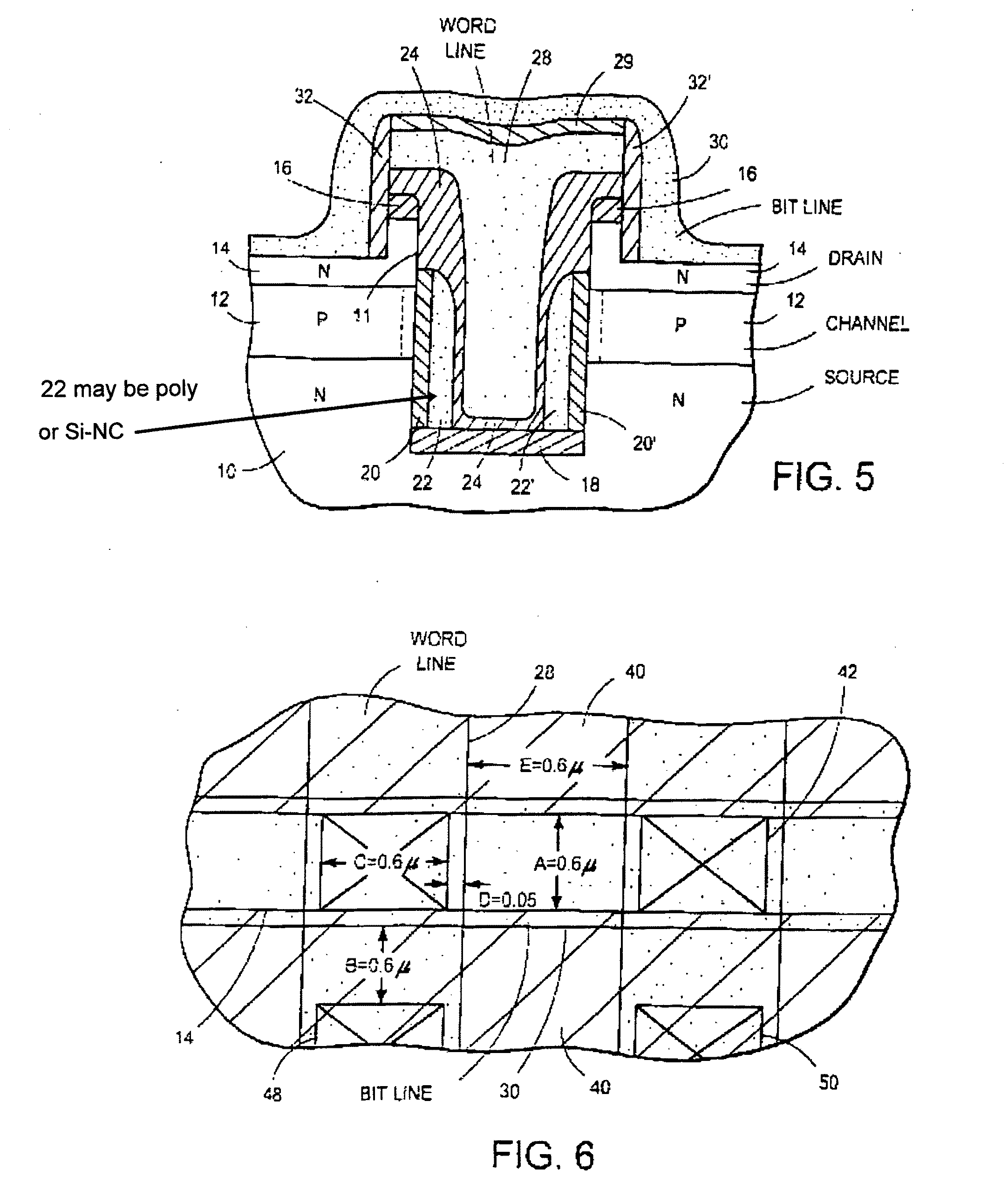

Vertically integrated flash EPROM for greater density and lower cost

InactiveUS20090039407A1Increase cell areaImprove the coupling ratioTransistorSolid-state devicesIon implantationPolycrystalline silicon

A nonvolative memory in the form of a vertical flash EPROM with high density and low cost. A vertical MOS transistor is formed in well etched into a semiconductor substrate, the substrate having source, body and drain regions formed by ion implantation. A thin gate oxide or oxide-nitride-oxide (ONO) layer is formed in the well and a self-aligned floating gate of polysilicon is formed over the gate oxide in the well to overlie the body region. An anisotropic etch is used to form the self aligned floating gate so as to remove all horizontal components and leave no portion of said floating gate extending beyond the perimeter of said well such that its lateral extents are determined by the anisotropic etch and not photolithography. Leff is determined by the energy of the implants used for form the source and drain regions and not by lithography. A deep field oxide bounding parts of said well keeps the coupling ratio good at all feature sizes. A vertically oriented NMOS and PMOS transistor are also disclosed.

Owner:VORA MADHUKAR B

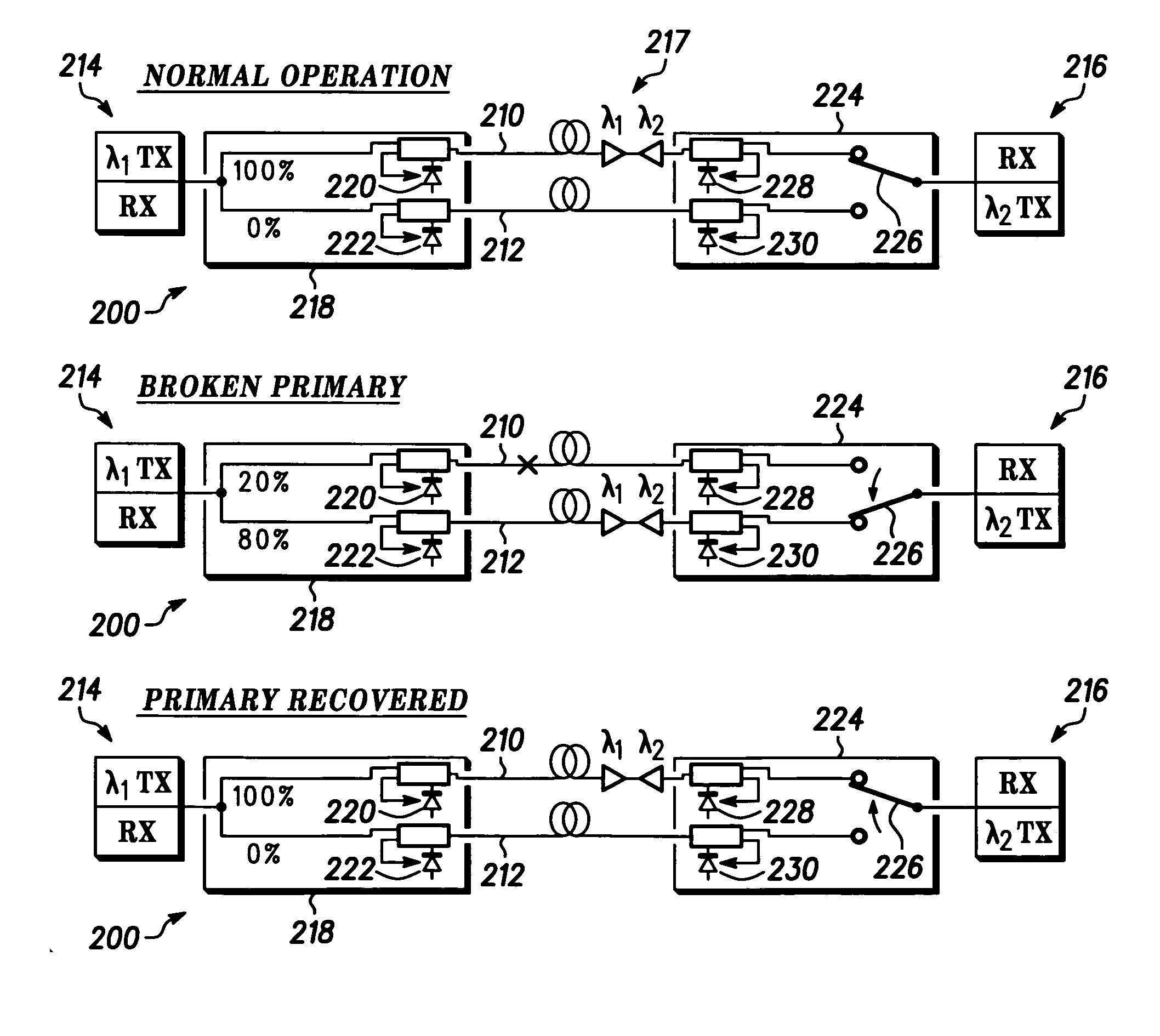

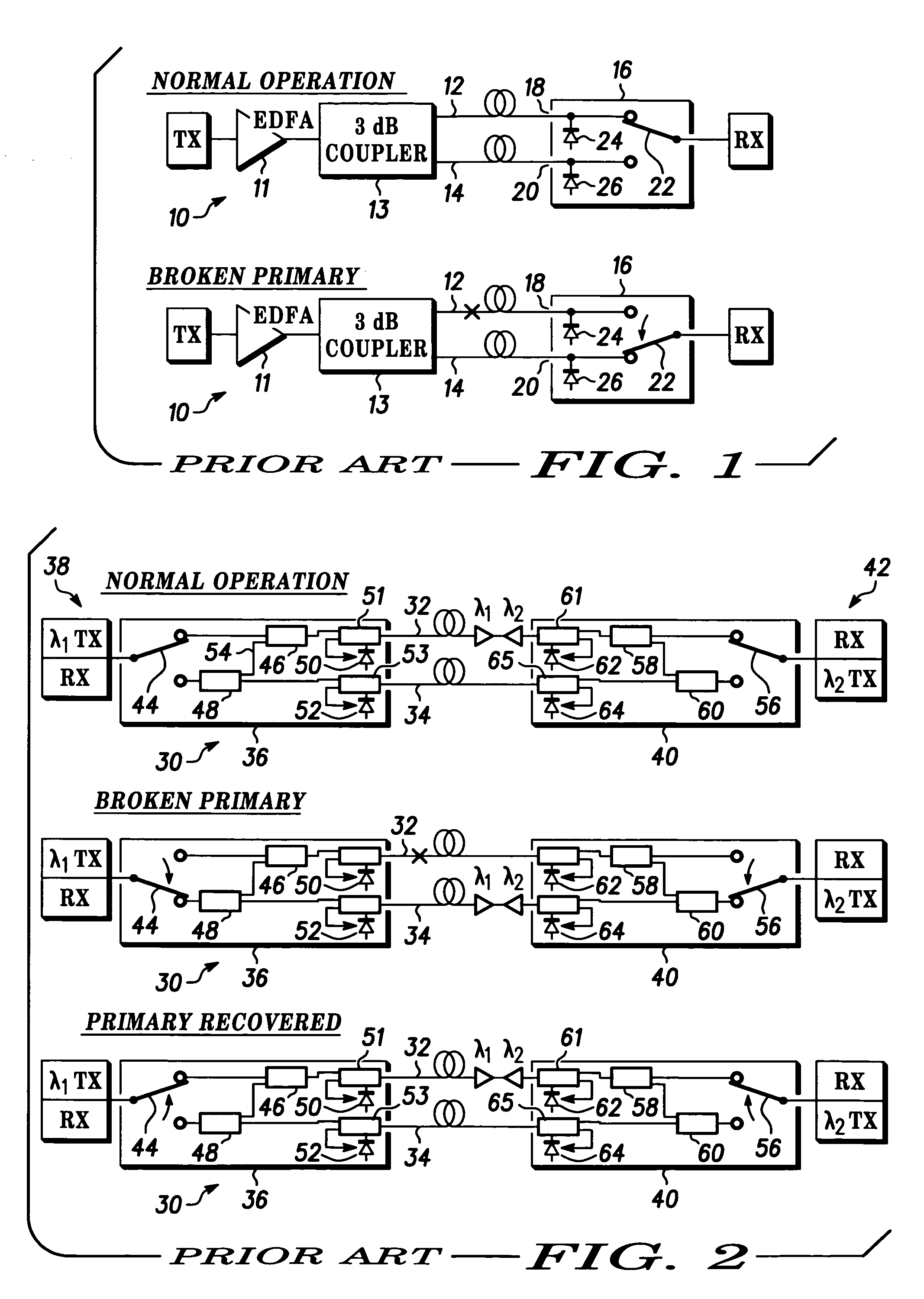

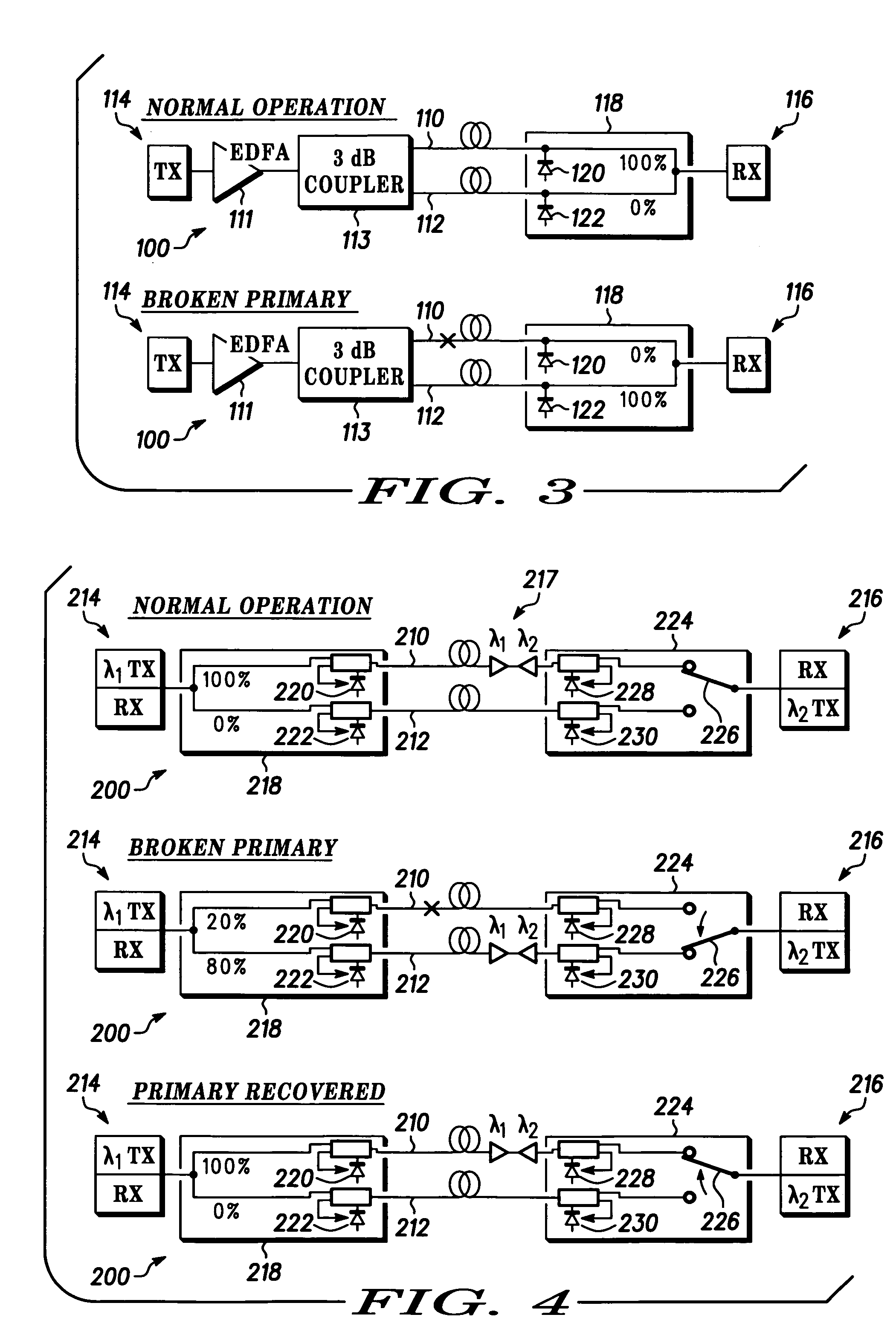

Use of variable ratio couplers for network protection and recovery

The disclosure is directed toward an optical transmission system comprising a primary path disposed between a first end and a second end. The primary path is configured to transmit optical signals between the first end and the second end. A secondary path is disposed between the first end and the second end. The secondary path is configured to transmit optical signals between the first end and the second end, e.g., in the event of a break in the primary path. A first variable ratio coupler is coupled to the primary path and the secondary path between the first end and the second end. The first variable ratio coupler is configured to adjust a coupling ratio between the primary path and the secondary path.

Owner:GOOGLE TECH HLDG LLC

Split gate non-volatile memory devices and methods of forming the same

InactiveUS20080093647A1Increased floating gate coupling ratioAccelerated programTransistorCoupling ratioEngineering

Non-volatile memory devices and methods for fabricating non-volatile memory devices are disclosed. More specifically, split gate memory devices are provided having frameworks that provide increased floating gate coupling ratios, thereby enabling enhanced programming and erasing efficiency and performance.

Owner:SAMSUNG ELECTRONICS CO LTD

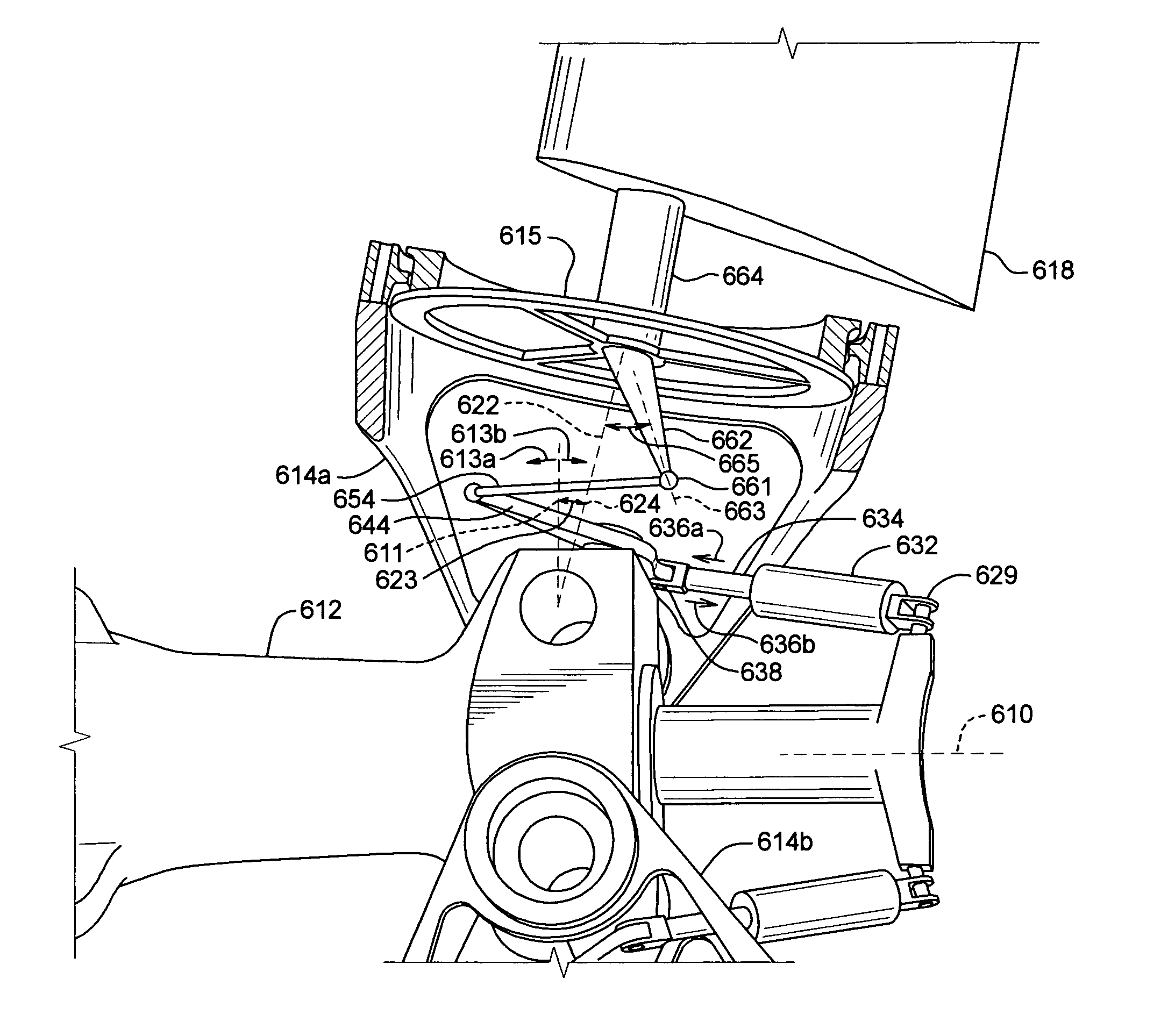

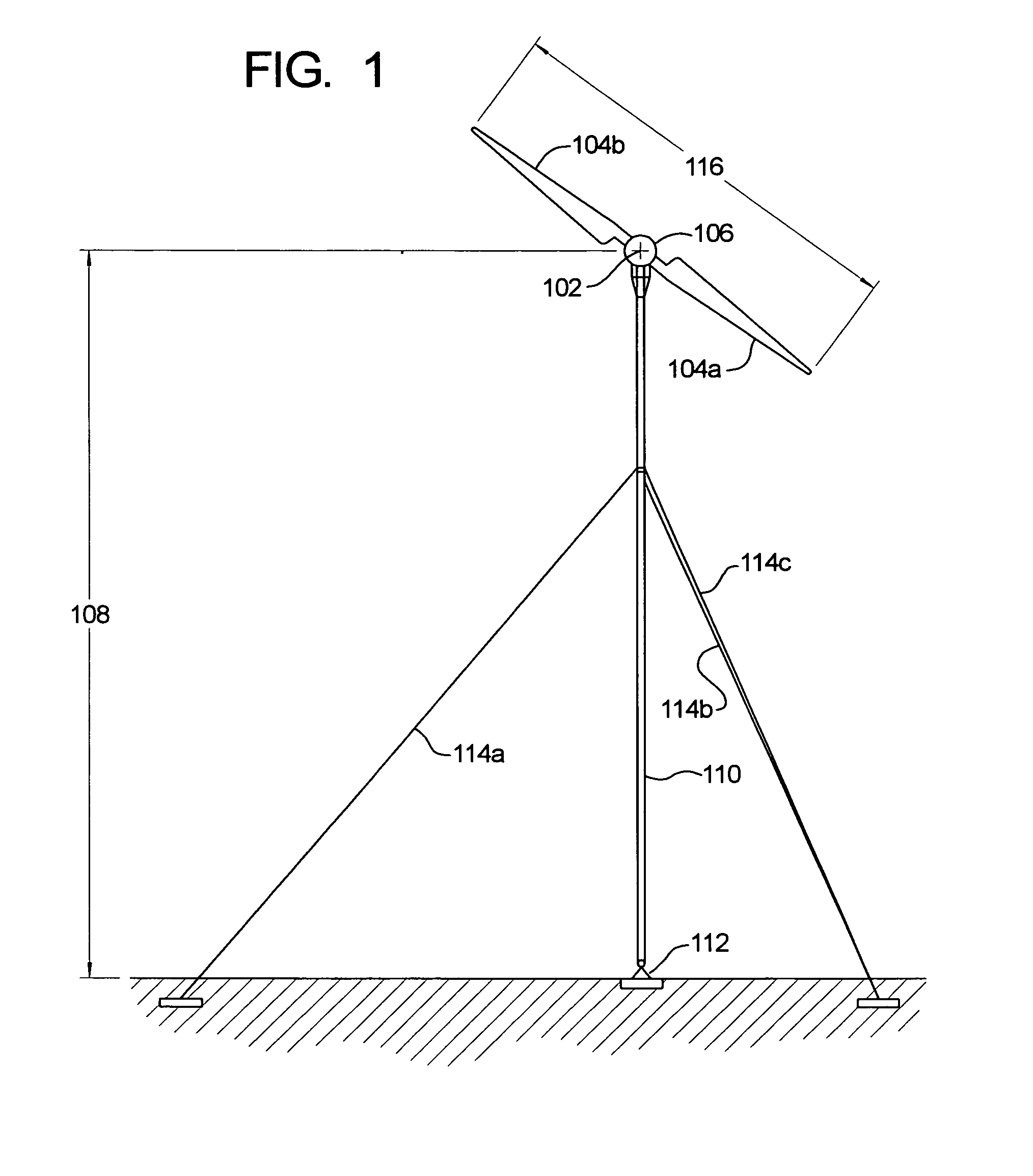

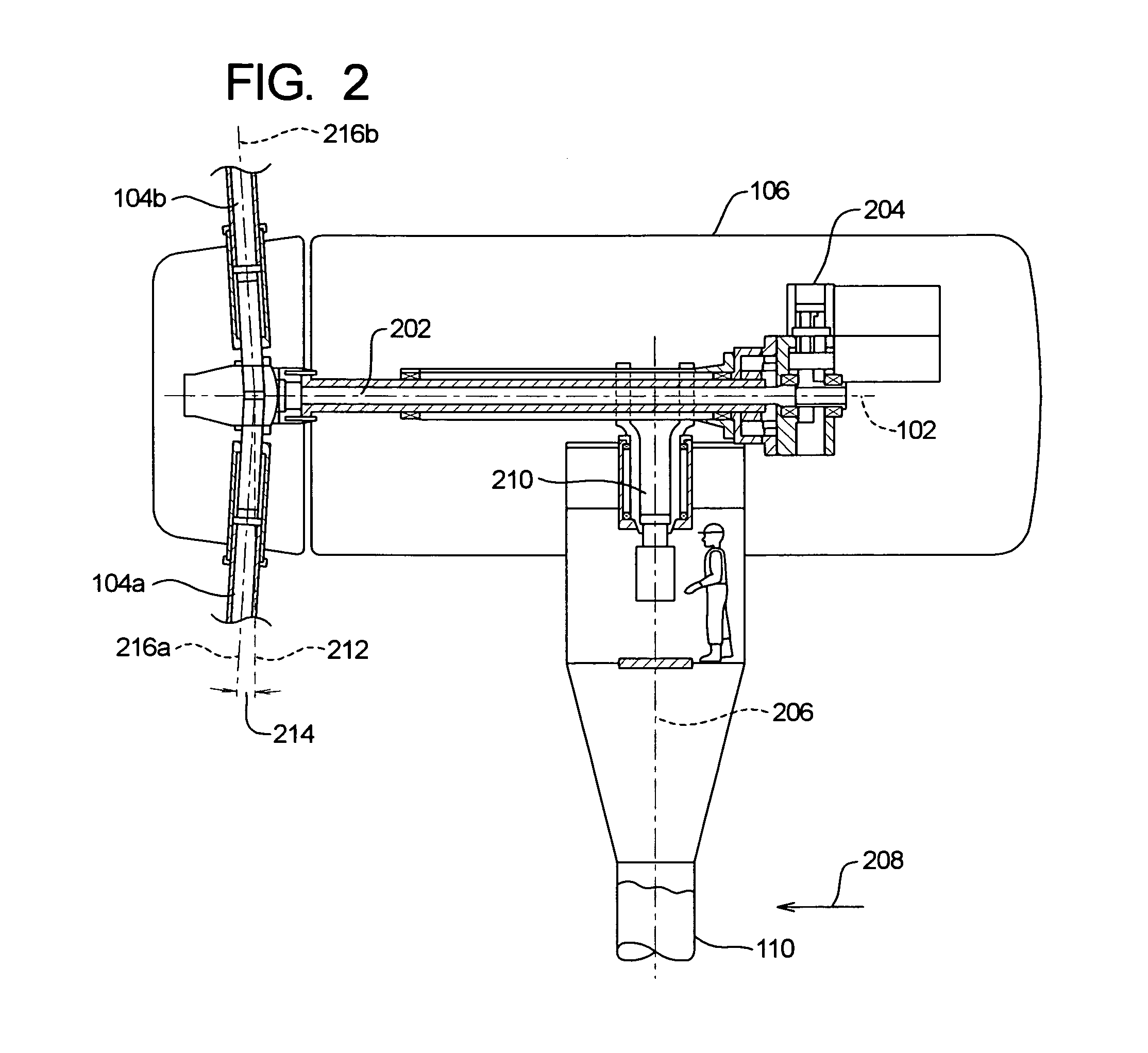

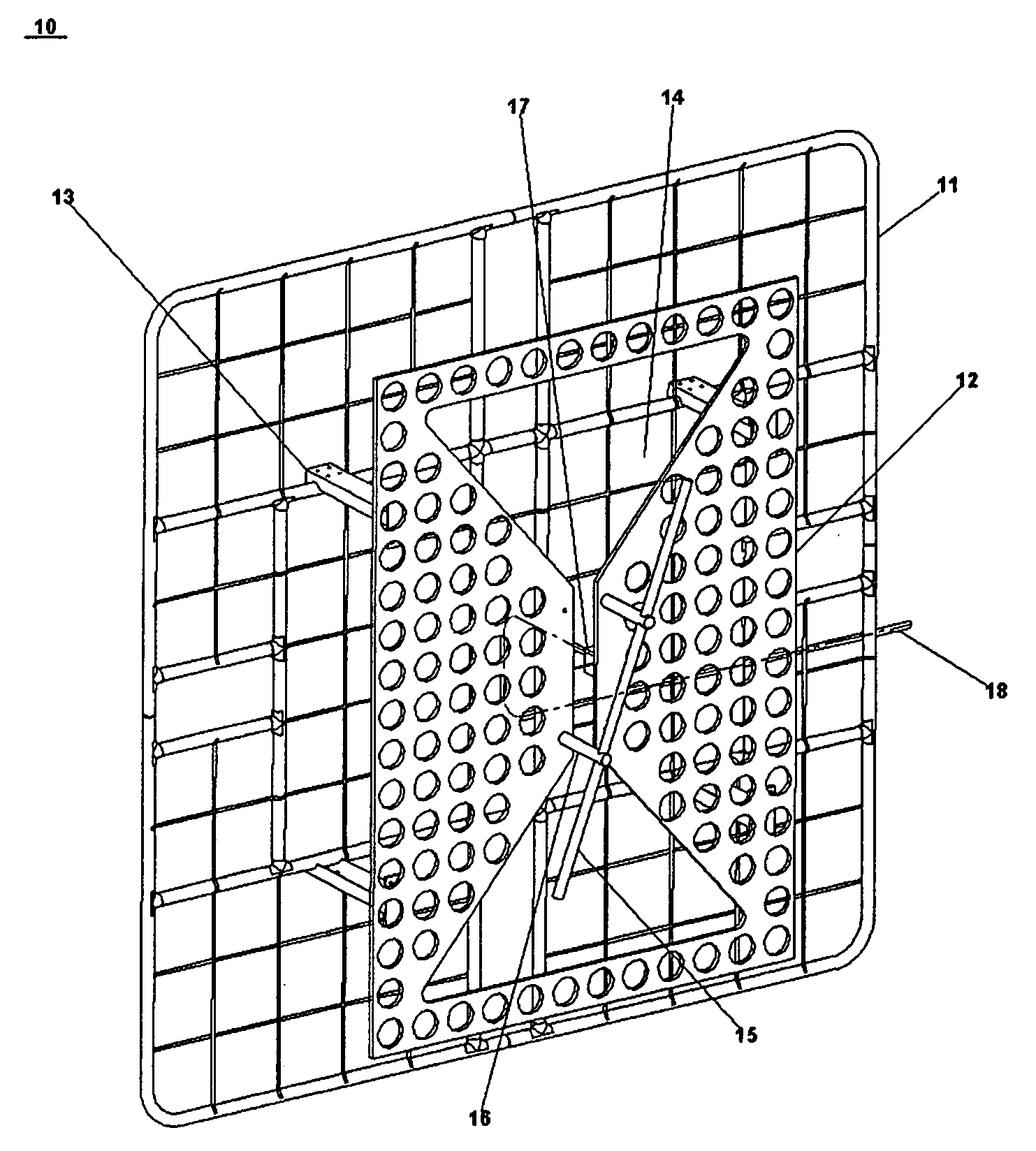

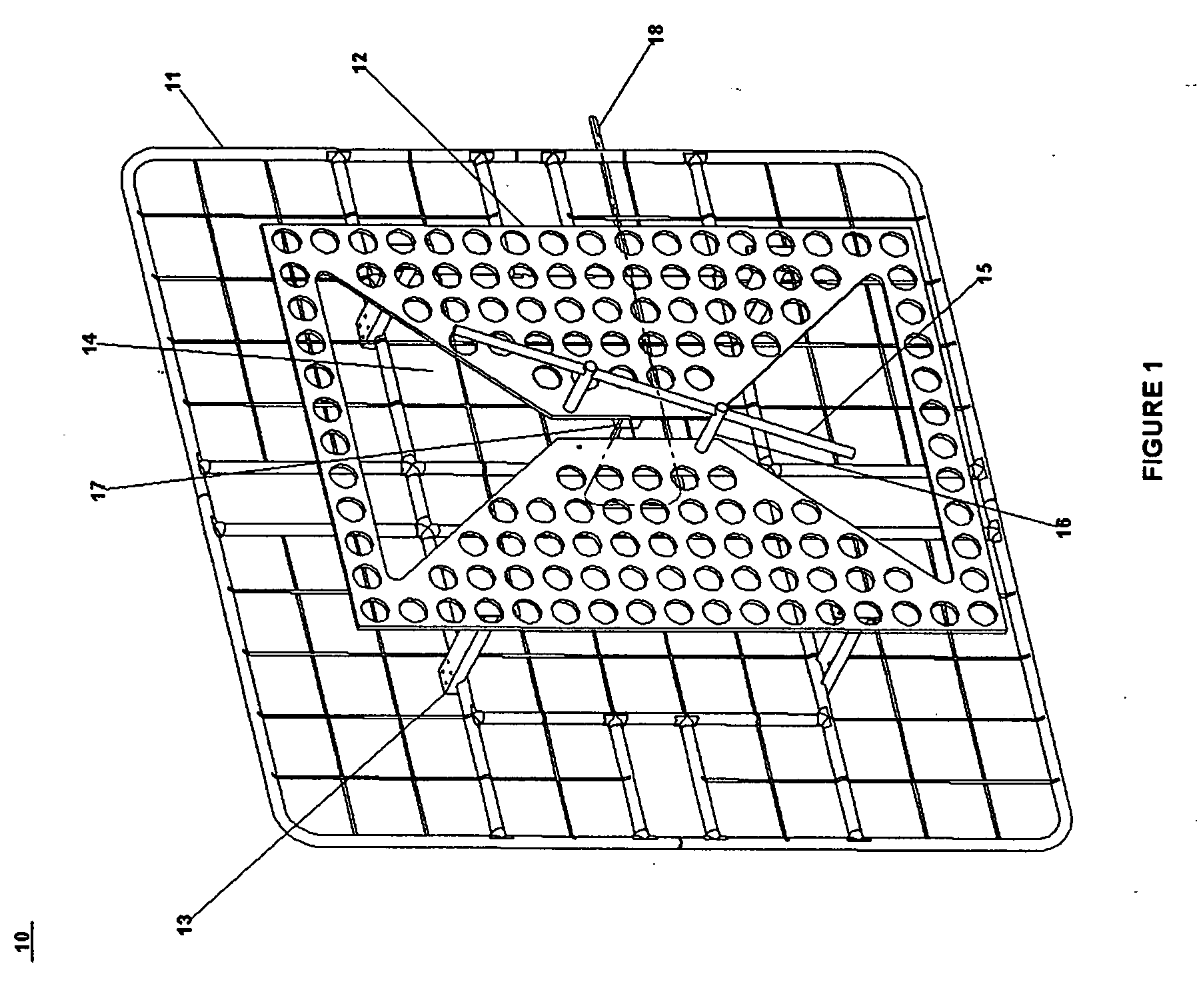

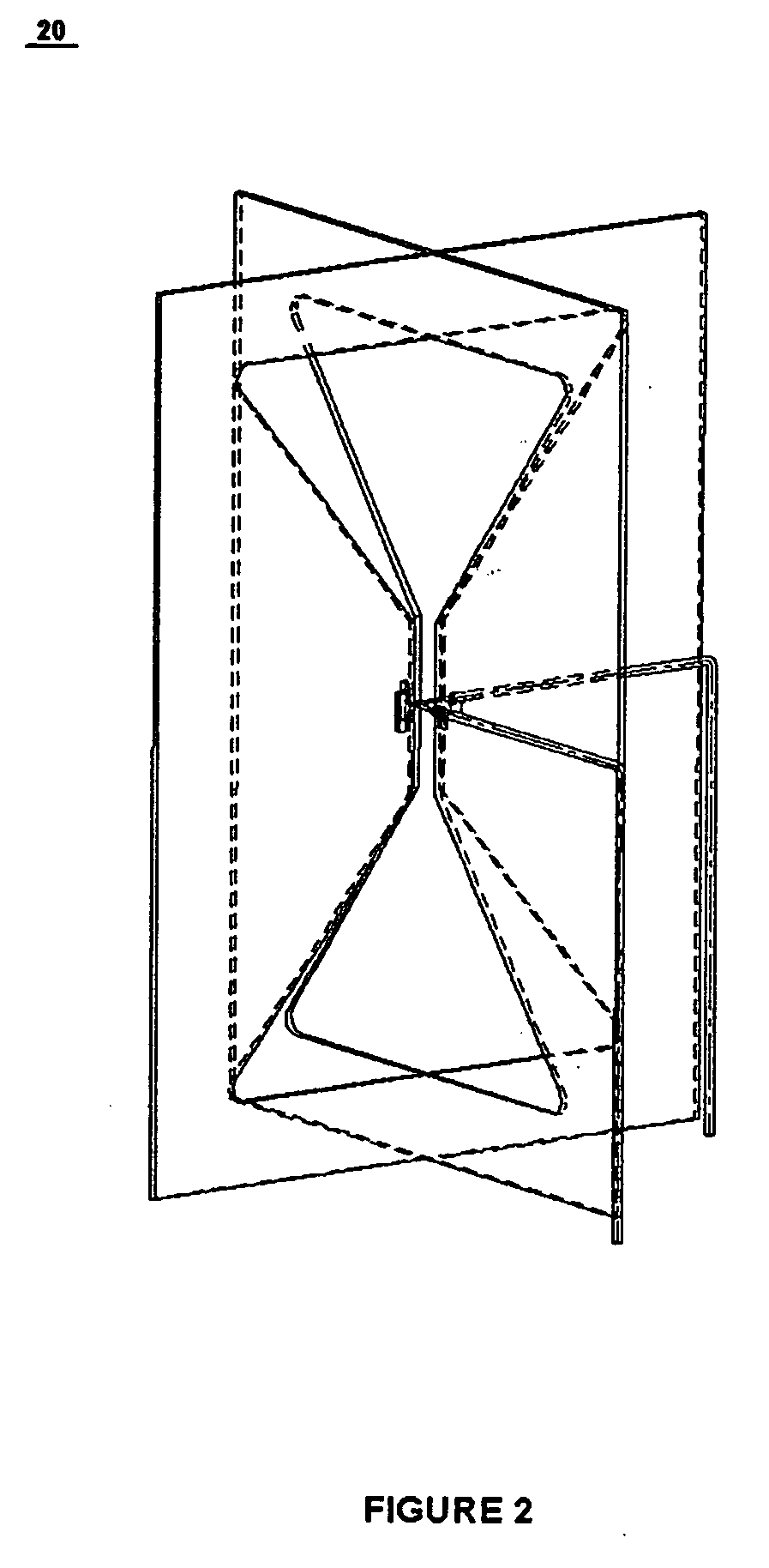

Method and apparatus for controlling pitch and flap angles of a wind turbine

InactiveUS7530785B1Large coupling ratioReduce eliminatePropellersWind motor controlControl systemCoupling ratio

A wind turbine with improved response to wind conditions is provided. Blade flap angle motion is accompanied by a change in pitch angle by an amount defining a pitch / flap coupling ratio. The coupling ratio is non-constant as a function of a flap angle and is preferably a substantially continuous, non-linear function of flap angle. The non-constant coupling ratio can be provided by mechanical systems such as a series of linkages or by configuring electronic or other control systems and / or angle sensors. A link with a movable proximal end advantageously is part of the mechanical system. The system can provide relatively large coupling ratios and relatively large rates of coupling ratio changes especially for near-feather pitches and low flap angles.

Owner:THE WIND TURBINE

Method of manufacturing a flash memory cell using a self-aligned floating gate

A method of manufacturing a flash memory cell. The method includes controlling a wall sacrificial oxidization process, a wall oxidization process and a cleaning process of a trench insulating film that are performed before / after a process of forming the trench insulating film for burying a trench to etch the trench insulating film to a desired space. Therefore, it is possible to secure the coupling ratio of a floating gate by maximum and implement a device of a smaller size.

Owner:SK HYNIX INC

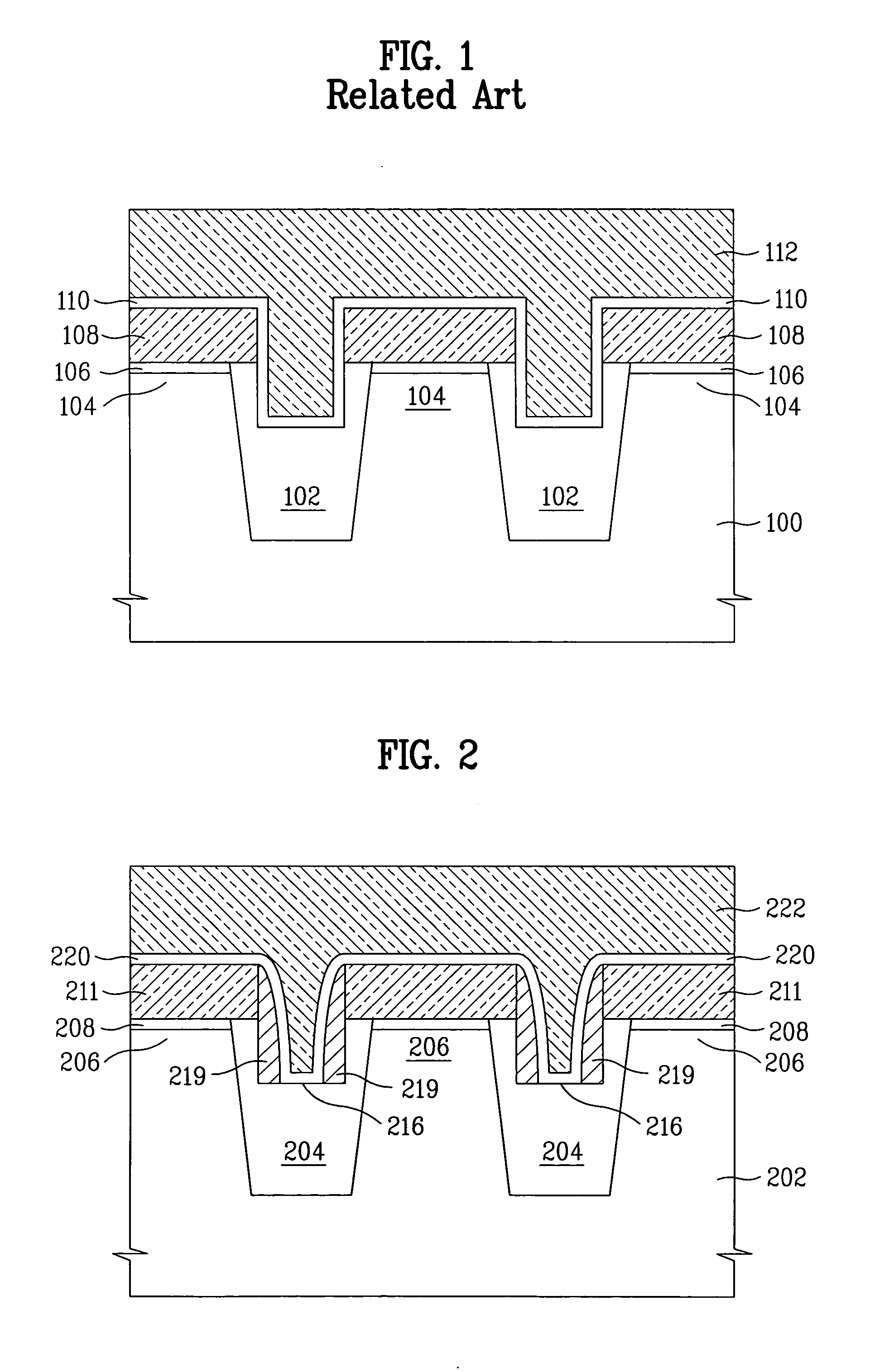

Non-volatile memory device and fabricating method thereof

InactiveUS20050139900A1Low integrationImprove the coupling ratioTransistorSolid-state devicesElectrical conductorIsolation layer

The present invention provides a non-volatile memory device and fabricating method thereof, in which a height of a floating gate conductor layer pattern is sustained without lowering a degree of integration and by which a coupling ratio is raised. The present invention includes a trench type device isolation layer defining an active area within a semiconductor substrate, a recess in an upper part of the device isolation layer to have a prescribed depth, a tunnel oxide layer on the active area of the semiconductor substrate, a floating gate conductor layer pattern on the tunnel oxide layer, a conductive floating spacer layer provided to a sidewall of the floating gate conductor layer pattern and a sidewall of the recess, a gate-to-gate insulating layer on the floating fate conductor layer pattern and the conductive floating spacer layer, and a control gate conductor layer on the gate-to-gate insulating layer.

Owner:DONGBU ELECTRONICS CO LTD

Large value piezoelectric quartz multi-component force sensor

ActiveCN101149301ASimple structureEasy to operateForce measurement using piezo-electric devicesPiezoelectric quartzCoupling ratio

The invention relates to a big-force piezoelectric quartz multi-component force sensor. It is made up of the sensor body composed by the up cover, the pedestal, the force sensing component, the pretightening bolt, the hollow bolt, the lock ring and the sleeve with two apertures. The force sensing component in sensor is the quartz wafer. The four groups of quartz crystal are set in the form of square relative to the coordinate, which are installed between the up cover and pedestal buckle slot and were pretightened by the shrink range. The sensor has the simple structure, good character, low cost, high rigidity, high sensitivity, high natural frequency, good linearity, small coupling ratio and small cross distribution. So it can get the static, dynamic and instantaneous forces of six dimensions. It is mainly for measuring the six dimension big force in the heavy load operation device and the other axes. So it has widely use.

Owner:DALIAN UNIV OF TECH

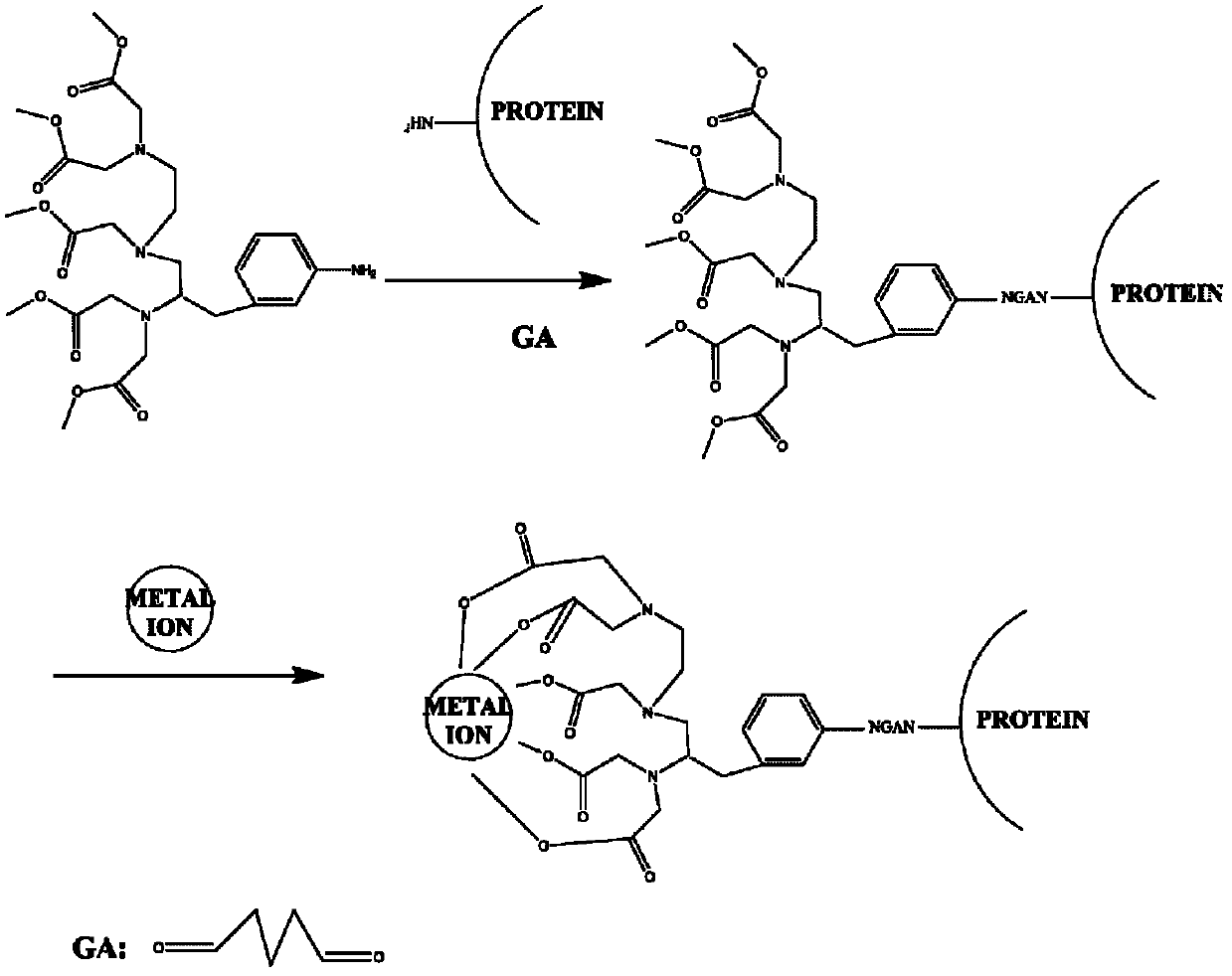

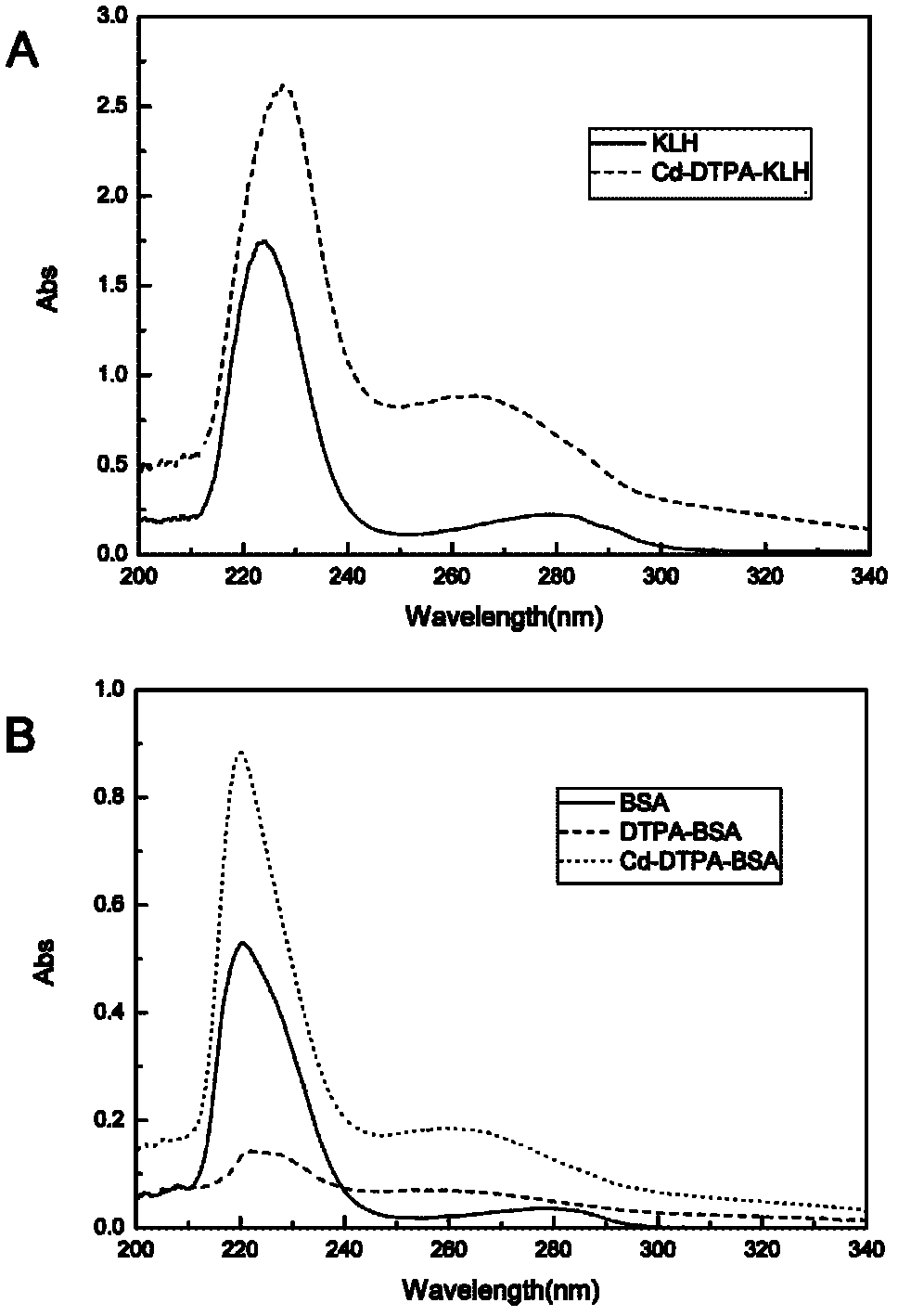

Synthesis and application method of antigens for various heavy metals

ActiveCN102260347ATroubleshoot compositingEnsure safetyOvalbuminSerum albuminAntigenSynthesis methods

The invention provides a synthesis and application method of an antigen for multiple heavy metals in the technical field of environment pollution detection. The molecular structure of the antigen is as follows: according to the invention, complete antigens of multiple heavy metals including cadmium, lead, mercury, zinc and the like can be synthesized; and the complete antigens are purified and represented to identify key parameters of the structures and coupling ratio so that a simple, rapid and effective heavy metal antigen synthesis method is established.

Owner:SHANGHAI JIAO TONG UNIV

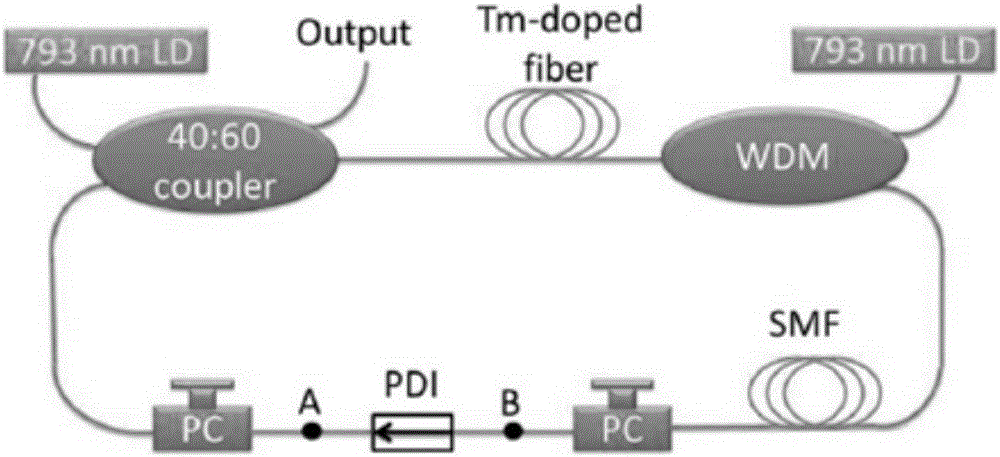

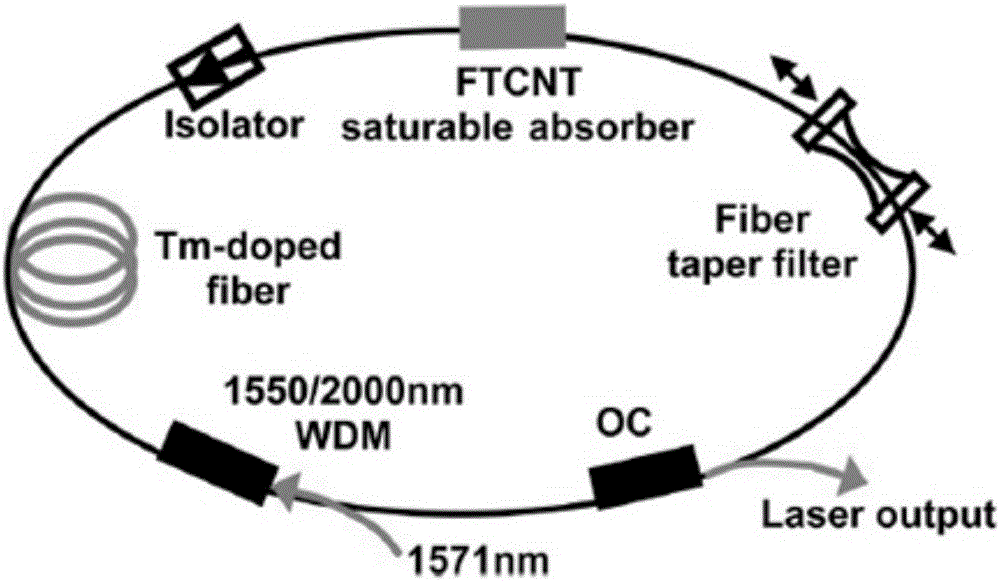

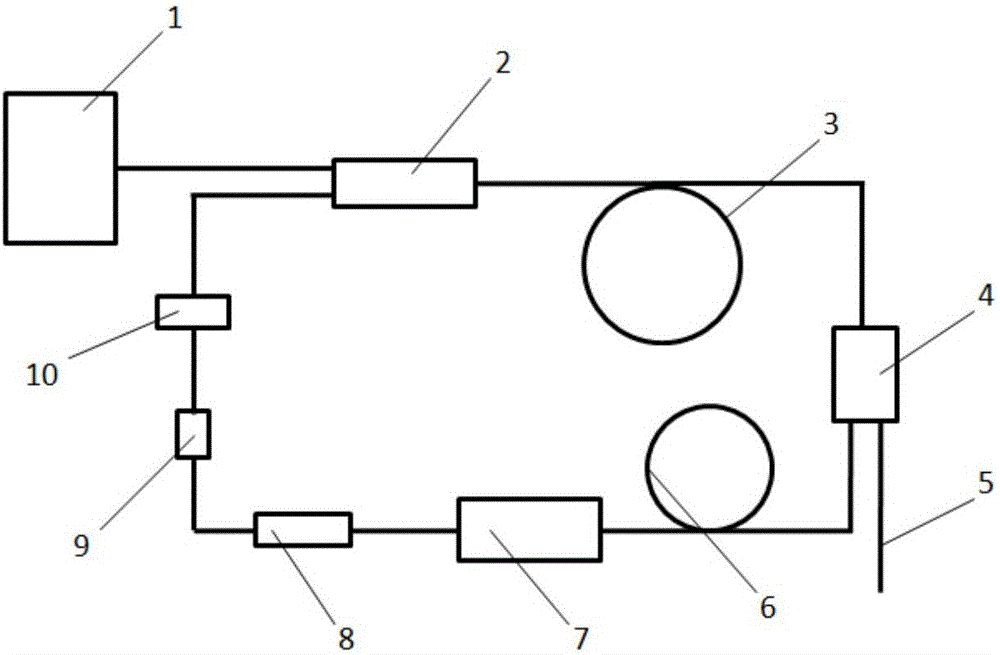

Tapered fiber-based tunable dual-wavelength mode-locked fiber laser

InactiveCN106129786AAchieve laser outputGood effectActive medium shape and constructionMode locked fiber laserCarbon nanotube

The invention discloses a tapered fiber-based tunable dual-wavelength mode-locked fiber laser, which comprises a (2+1)*1 beam combiner, a thulium-doped fiber, a coupler, a polarization controller, a polarization independent isolator, a tapered fiber and a single-walled carbon nanotube which are sequentially connected end to end, wherein the (2+1)*1 beam combiner is also connected with a pump light source; the coupling ratio of the coupler is 10 to 90; the coupler comprises a 10% output port and a 90% output port in all; the 10% output port is connected to an output fiber; the 90% output port is connected to the polarization controller; the modulation period of the tapered fiber is 6.8-7.2nm; and the taper twist of the tapered fiber is 7.0-7.5microns. Through the tapered fiber with specific modulation period and modulation depth, the problem of laser mode competition is successfully solved by the tapered fiber; and output of tapered fiber-based tunable dual-wavelength mode-locked fiber laser light with a 2micron waveband is achieved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

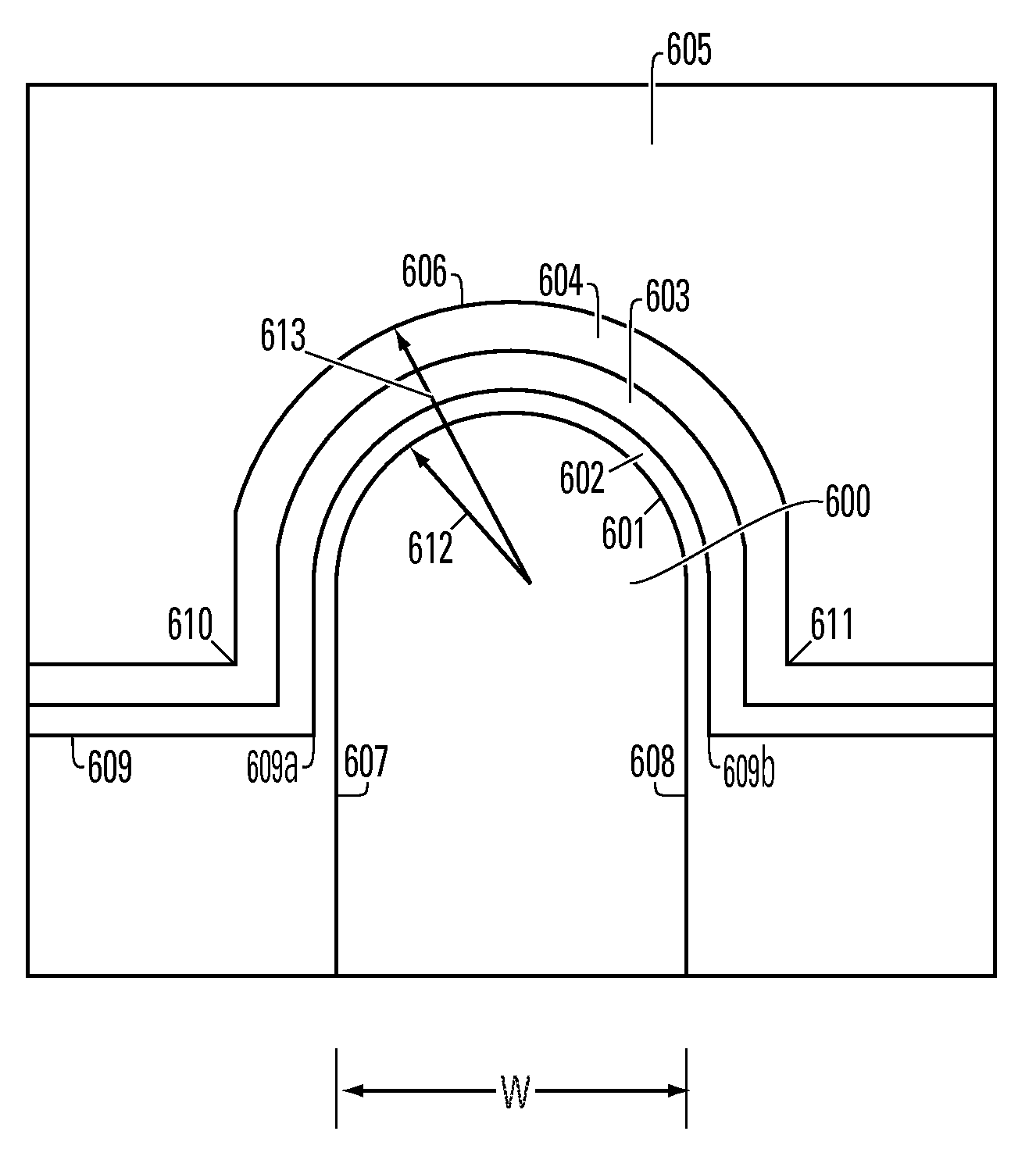

Non-Volatile Memory Devices with Wraparound-Shaped Floating Gate Electrodes and Methods of Forming Same

Non-volatile memory devices include memory cells therein with reduced cell-to-cell coupling capacitance. These memory cells include floating gate electrodes with open-ended wraparound shapes that operate to reduce the cell-to-cell coupling capacitance in a bit line direction, while still maintaining a high coupling ratio between control and floating gate electrodes within each memory cell.

Owner:SAMSUNG ELECTRONICS CO LTD

Circularly polarized broadcast panel system and method using a parasitic dipole

A bow-tie slot panel antenna is described, having a parasitic element positioned at an orientation from the slot to generate orthogonal fields. By adjusting the coupling ratios, dimensions and angle of orientation of the parasitic element, circularly polarized fields can be effectively produced, using the panel antenna as the primary radiator.

Owner:SPX CORP

Method of manufacturing a flash memory cell

InactiveUS20030119260A1Small sizeBig ratioTransistorSolid-state devicesCoupling ratioElectrical and Electronics engineering

A method of manufacturing a flash memory cell. The method includes controlling a wall sacrificial oxidization process, a wall oxidization process and a cleaning process of a trench insulating film that are performed before / after a process of forming the trench insulating film for burying a trench to etch the trench insulating film to a desired space. Therefore, it is possible to secure the coupling ratio of a floating gate by maximum and implement a device of a smaller size.

Owner:SK HYNIX INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com