Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

135 results about "Fowler nordheim" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Fowler–Nordheim tunneling is the wave-mechanical tunneling of electrons through a rounded triangular barrier created at the surface of an electron conductor by applying a very high electric field. Individual electrons can escape by Fowler-Nordheim tunneling from many materials in various different circumstances.

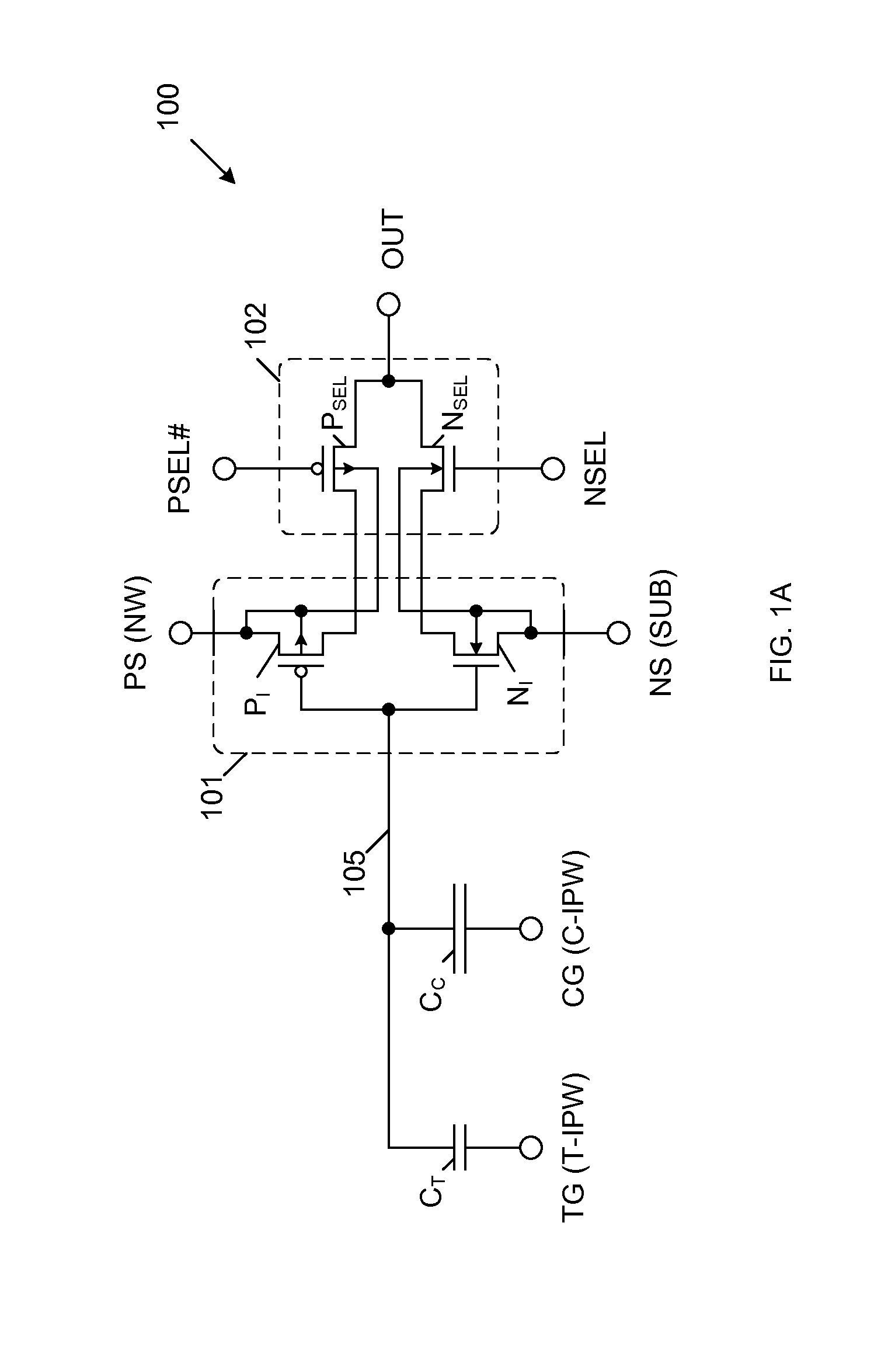

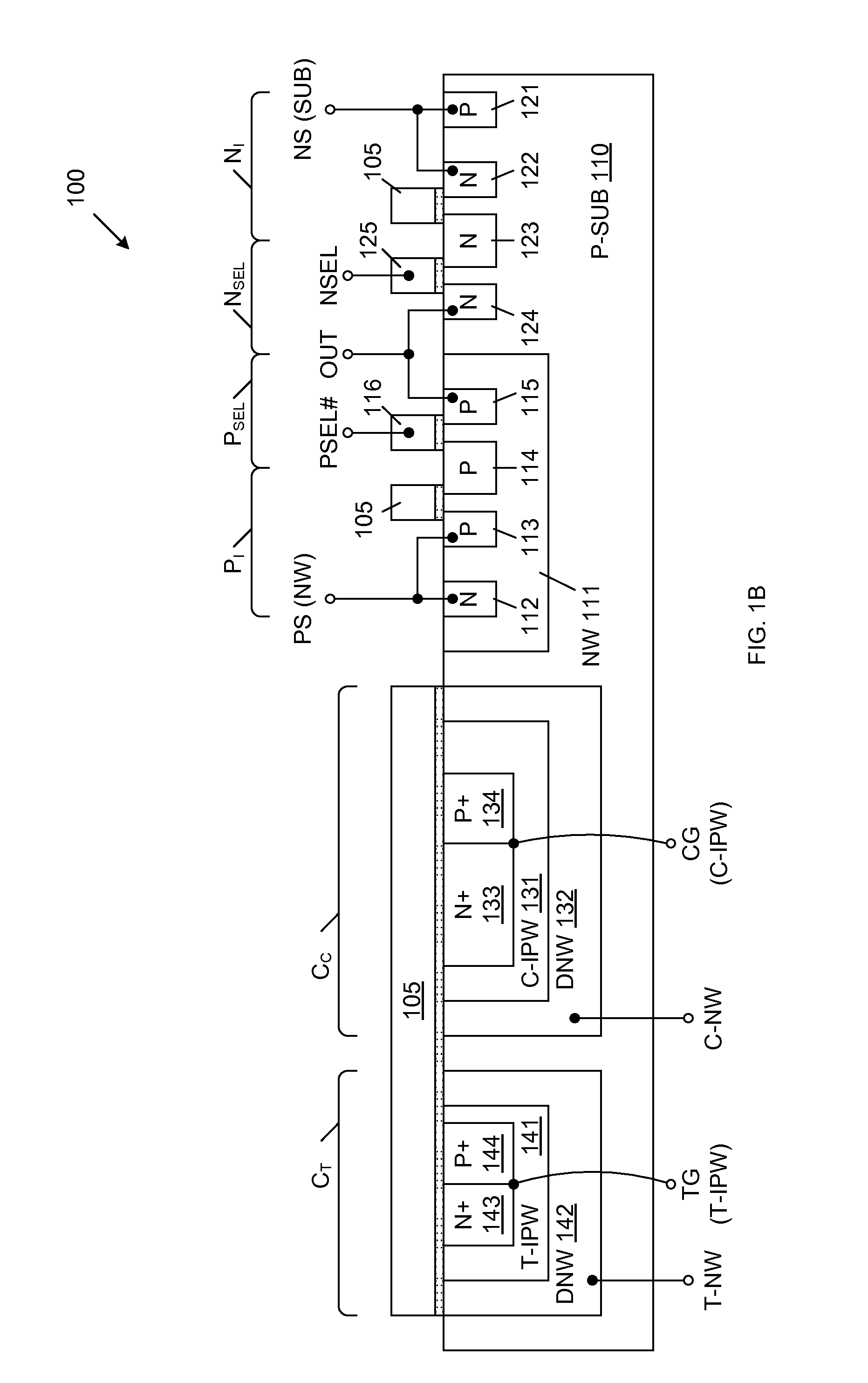

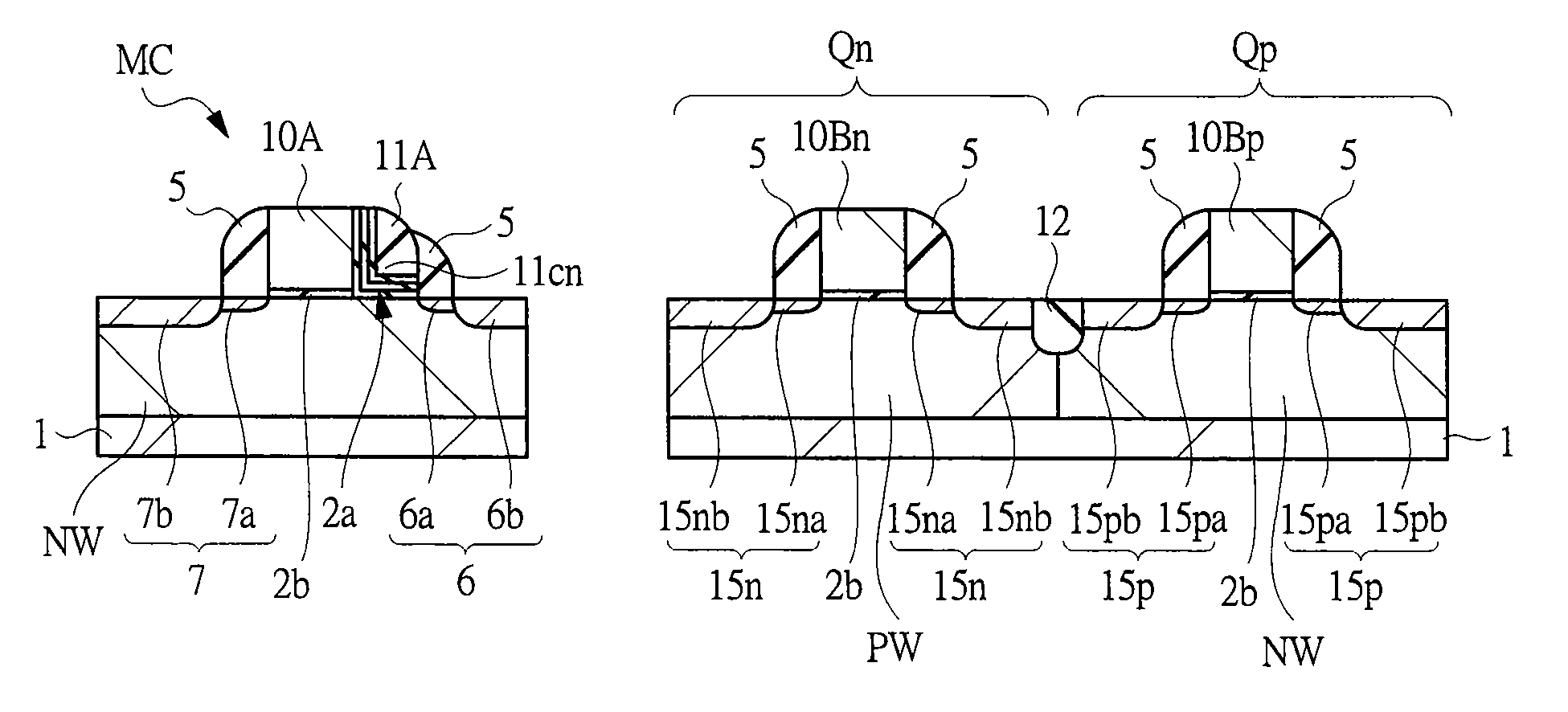

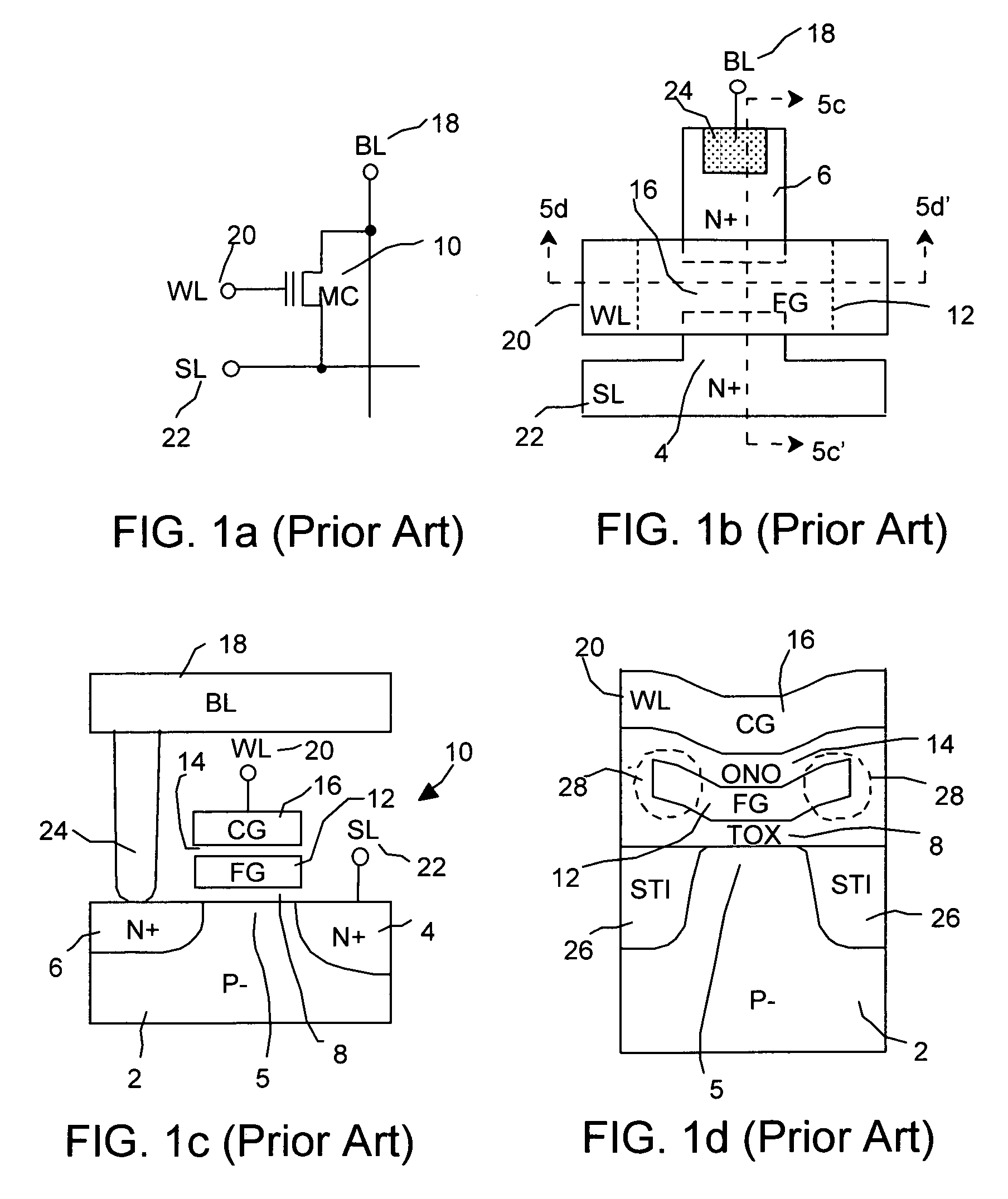

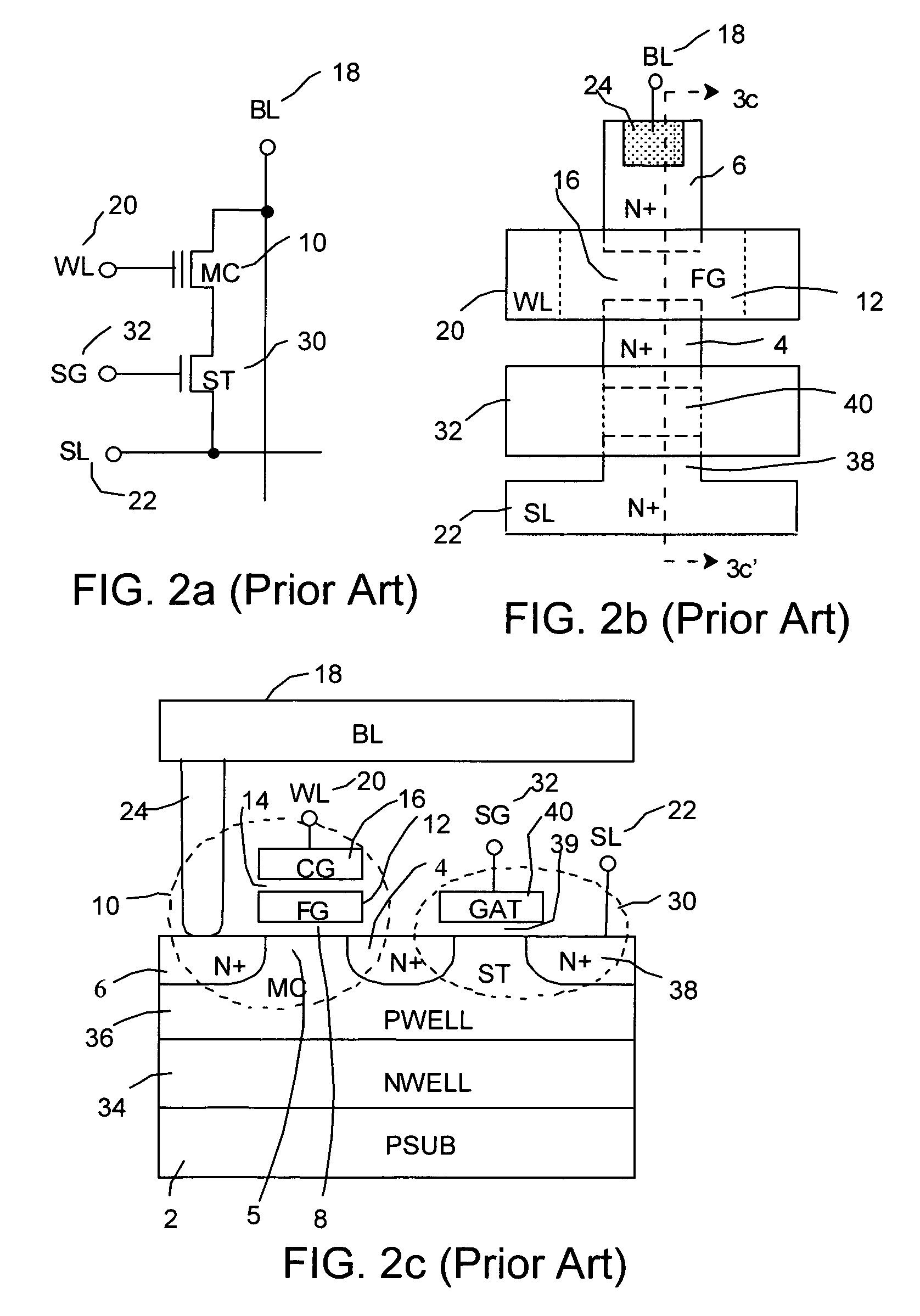

Floating gate inverter type memory cell and array

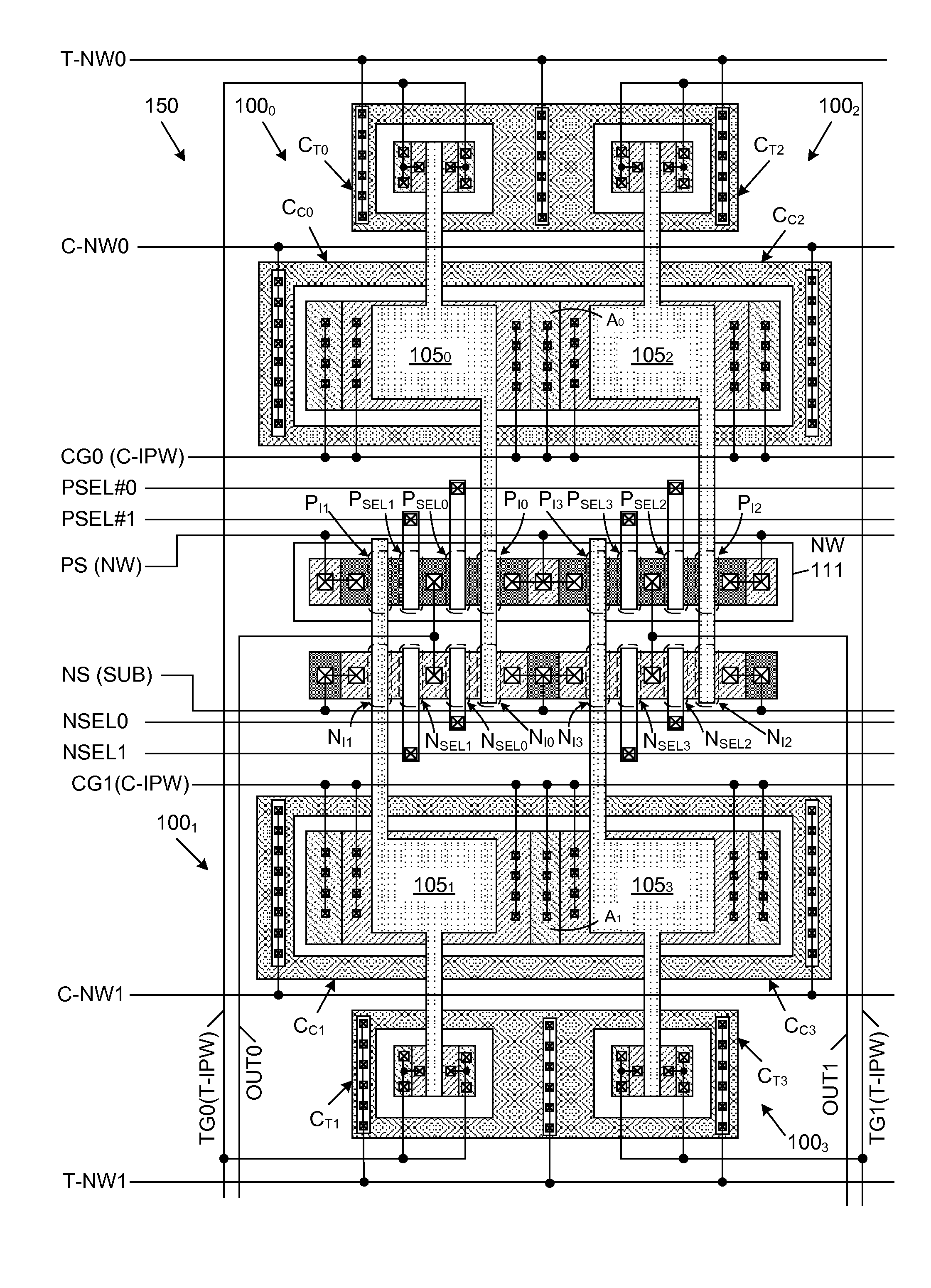

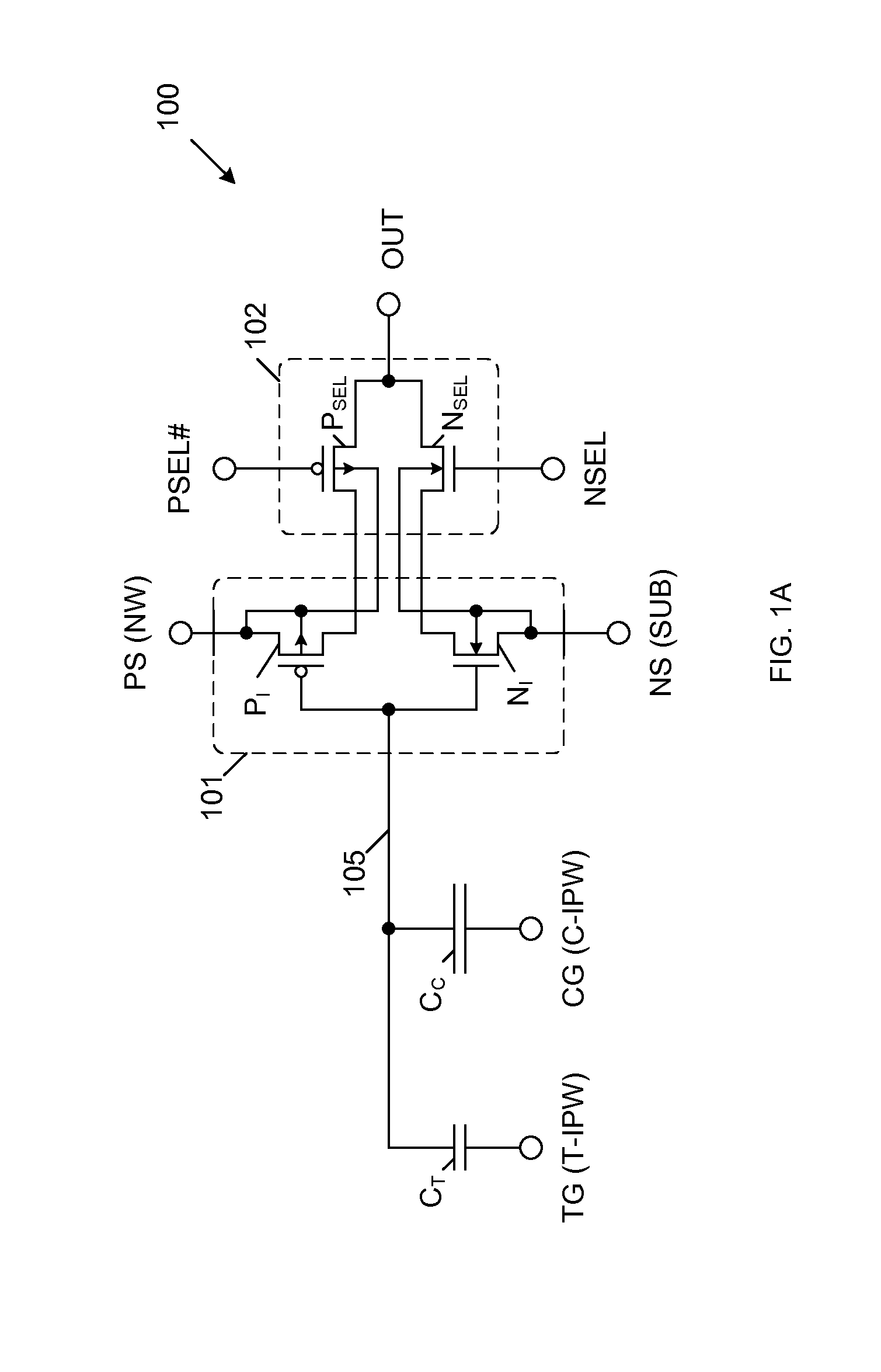

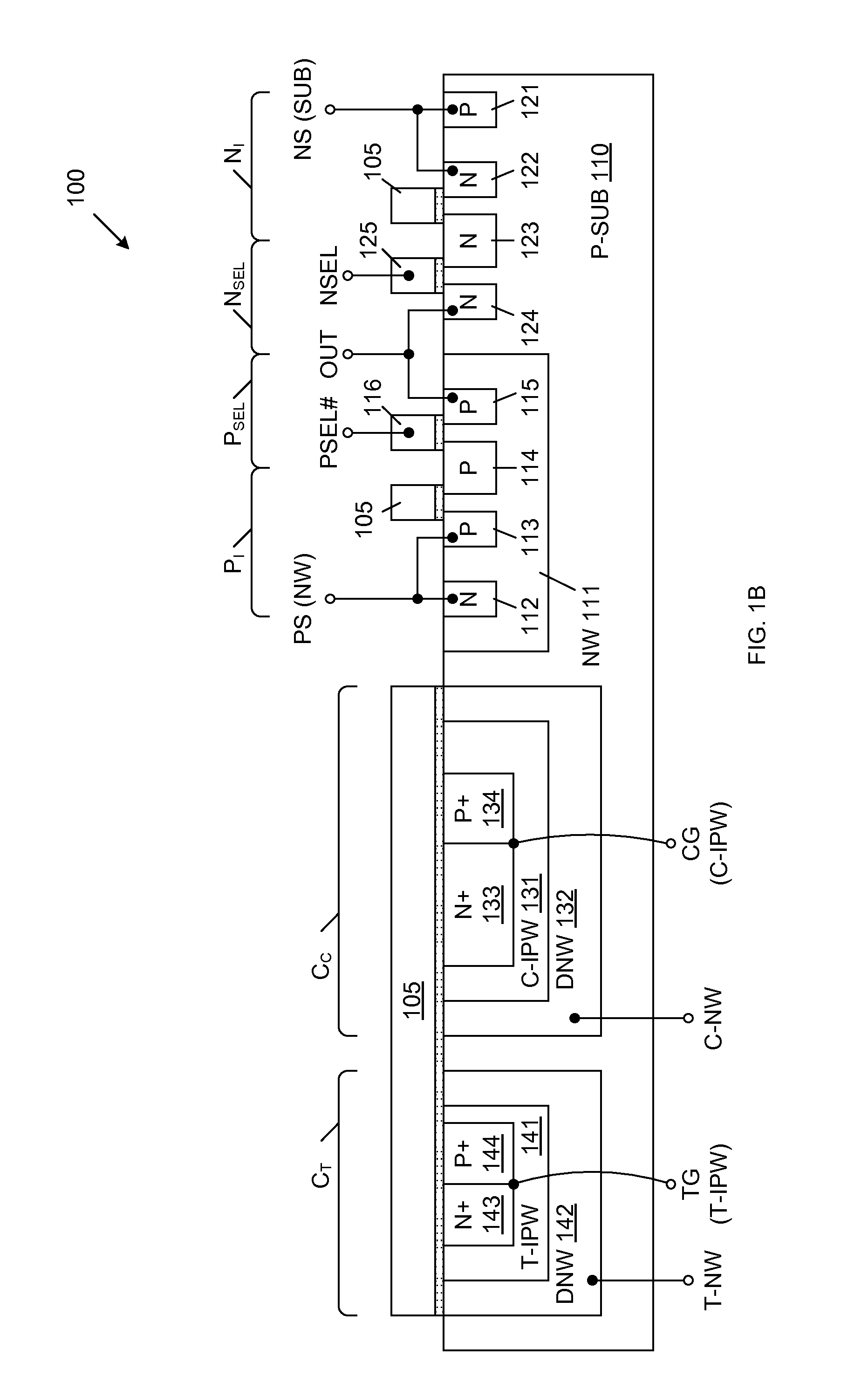

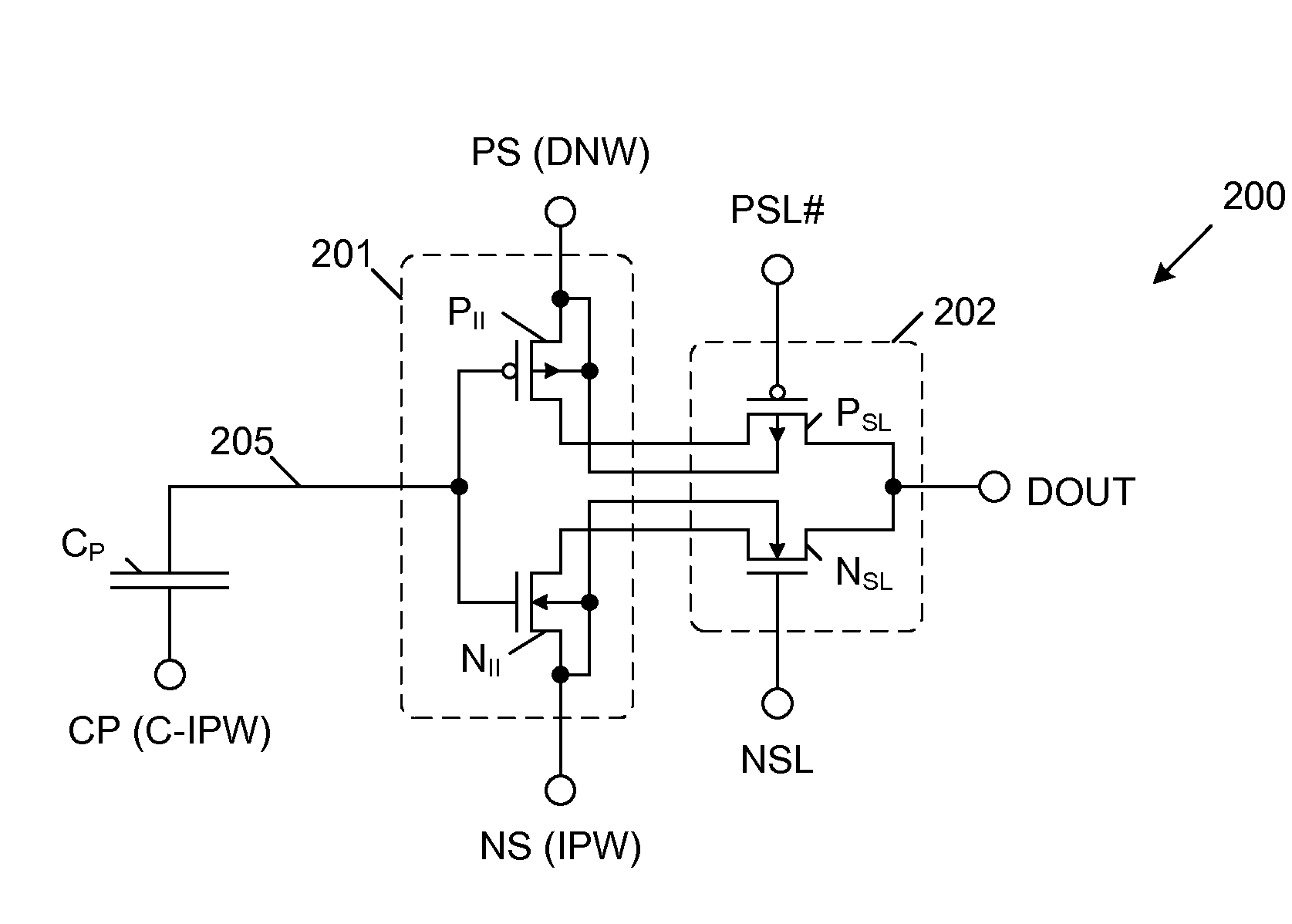

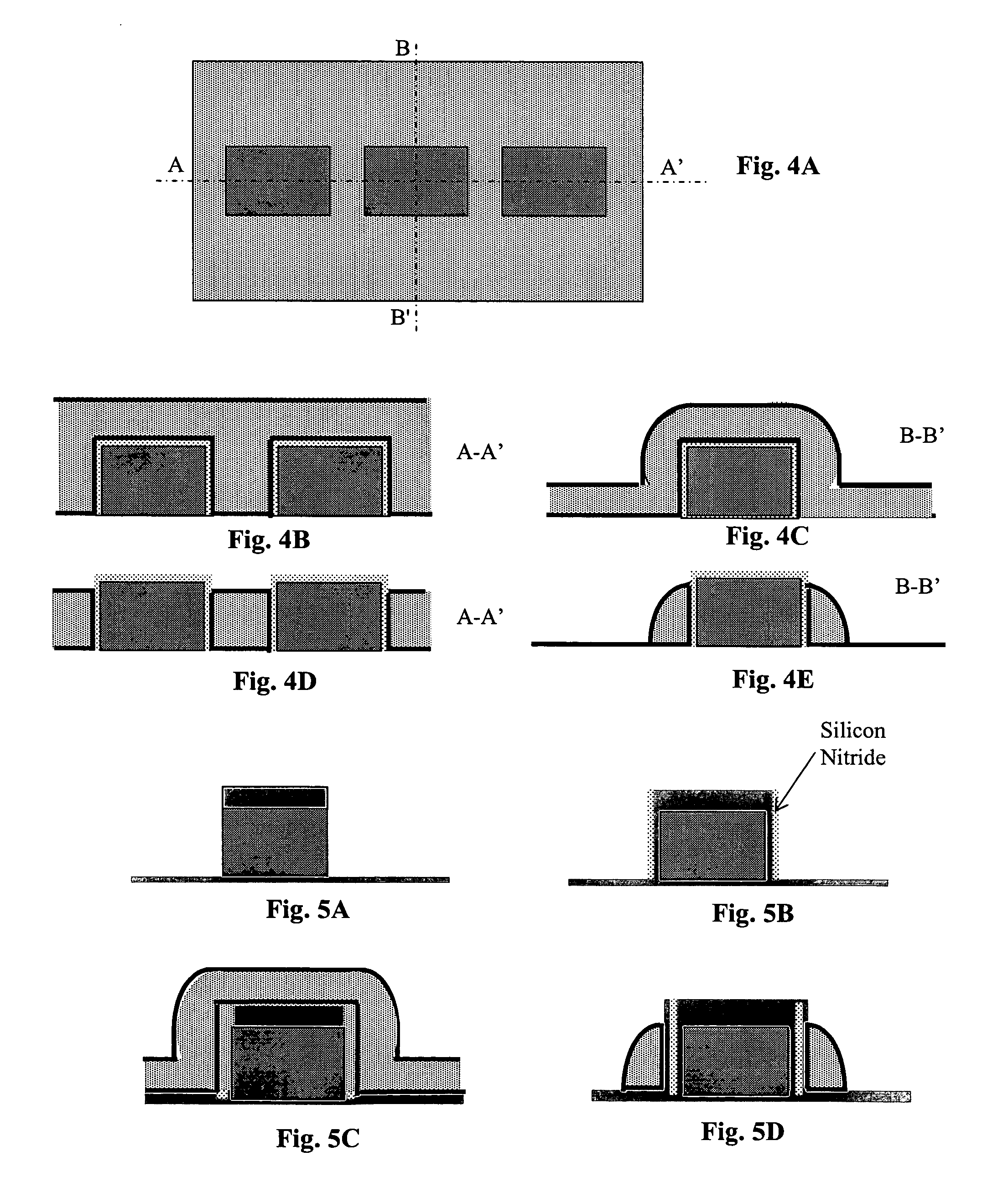

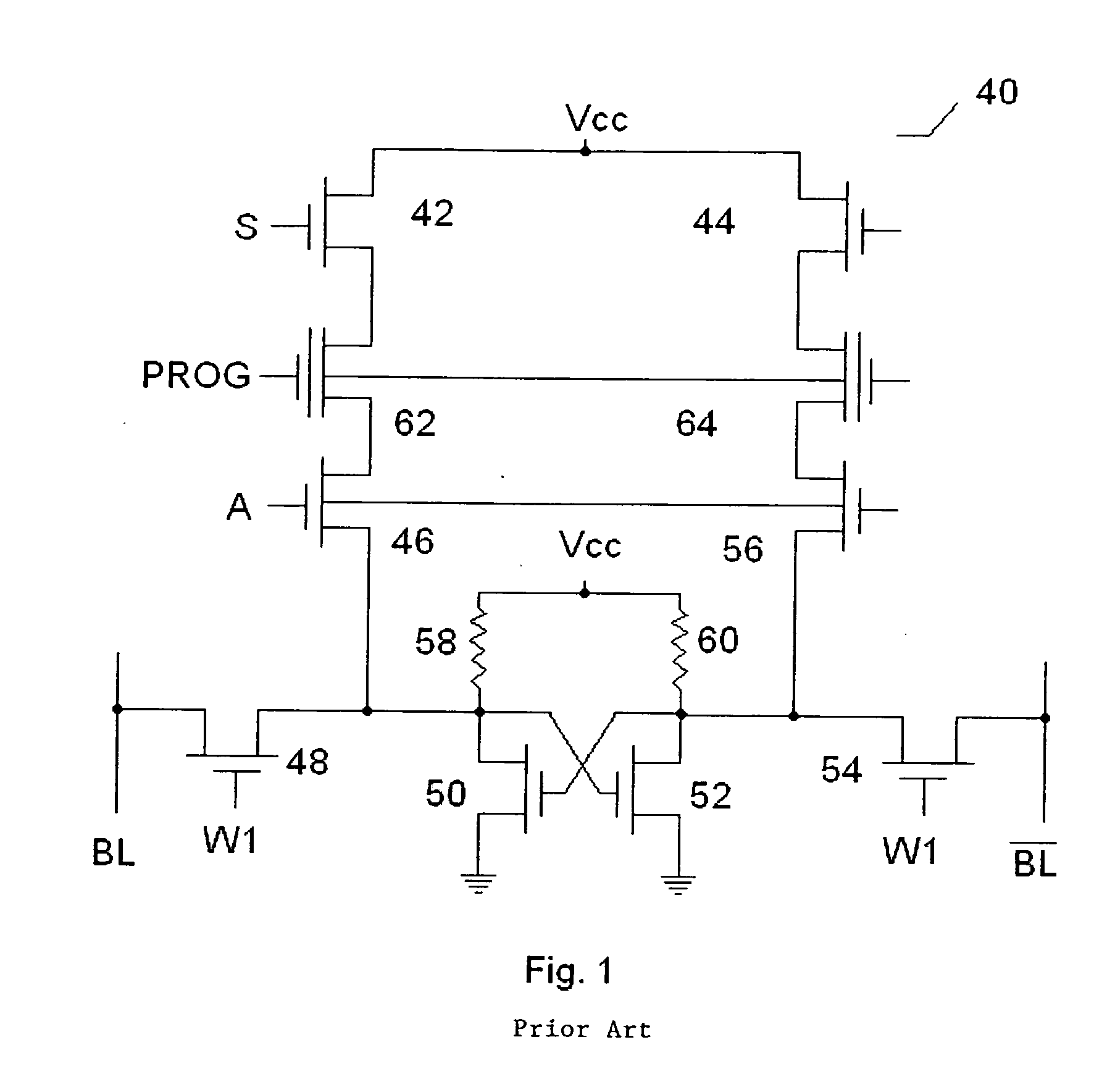

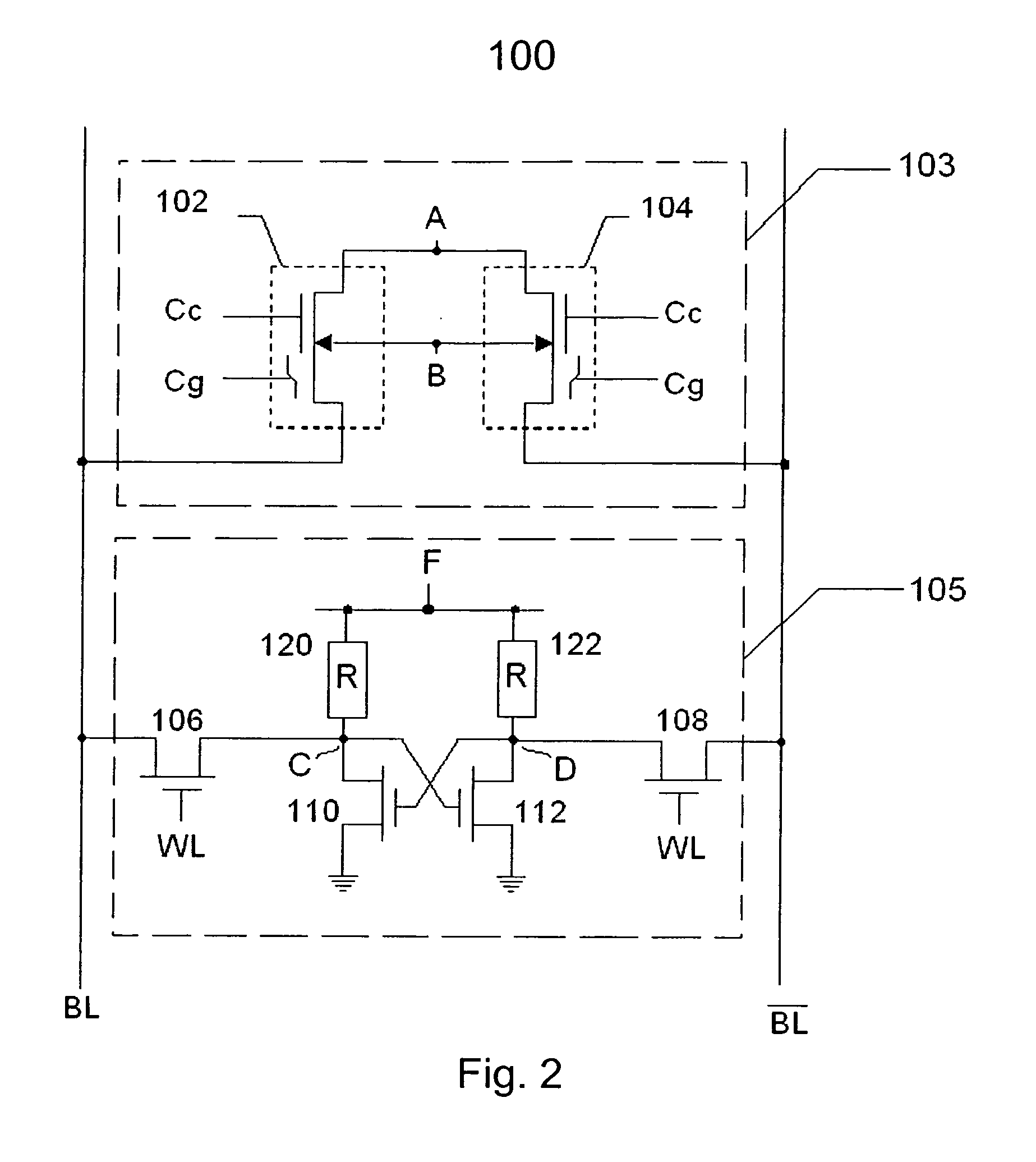

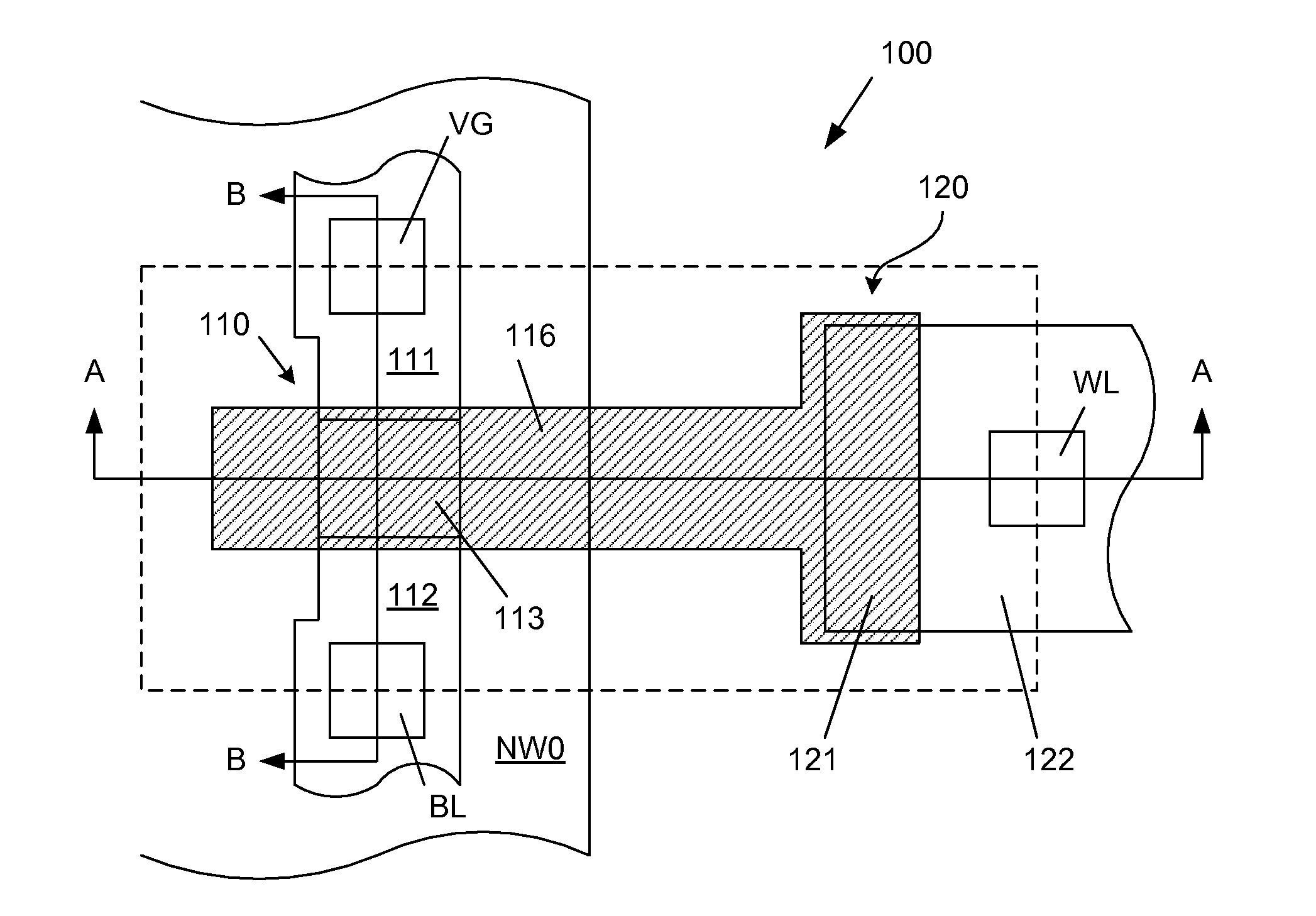

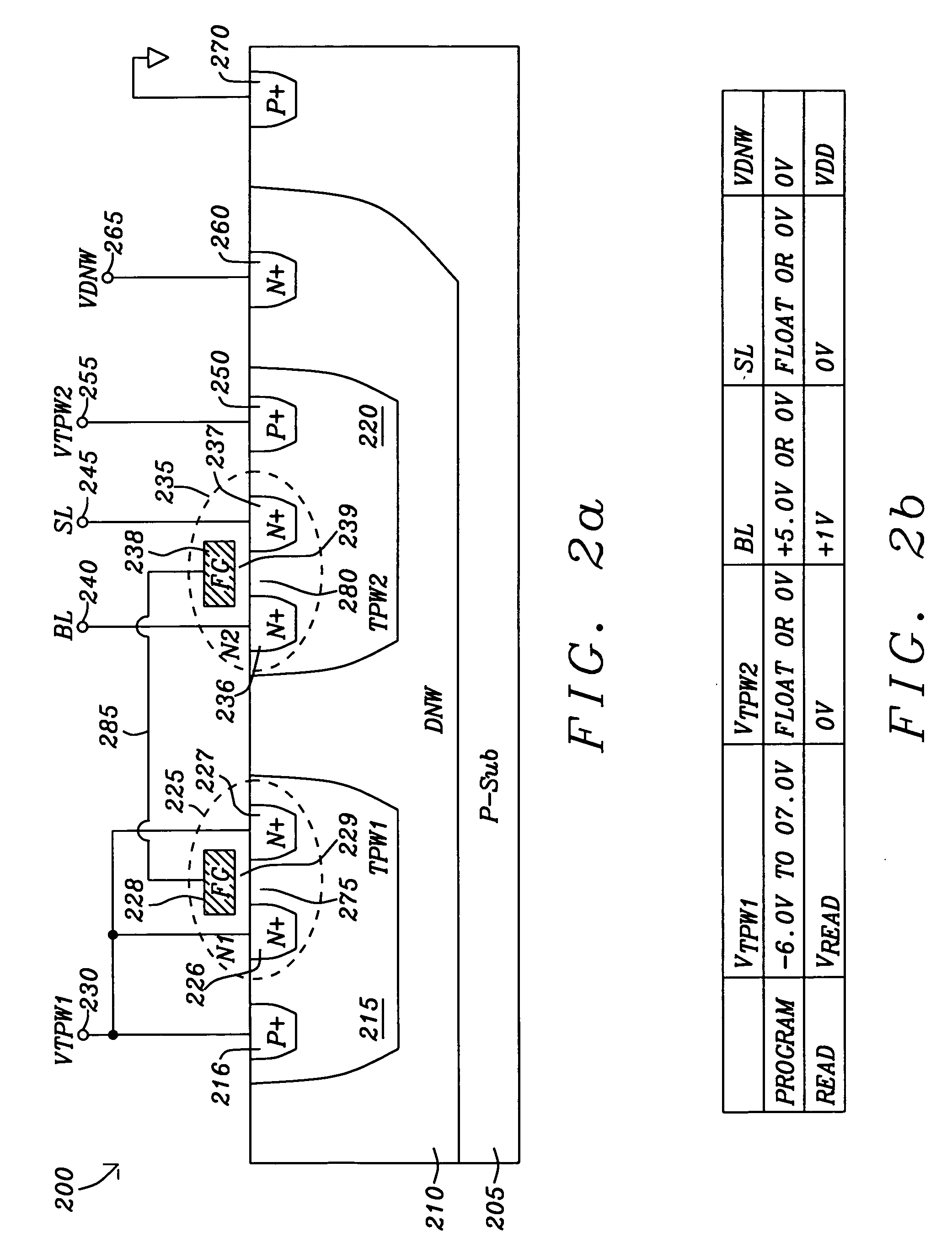

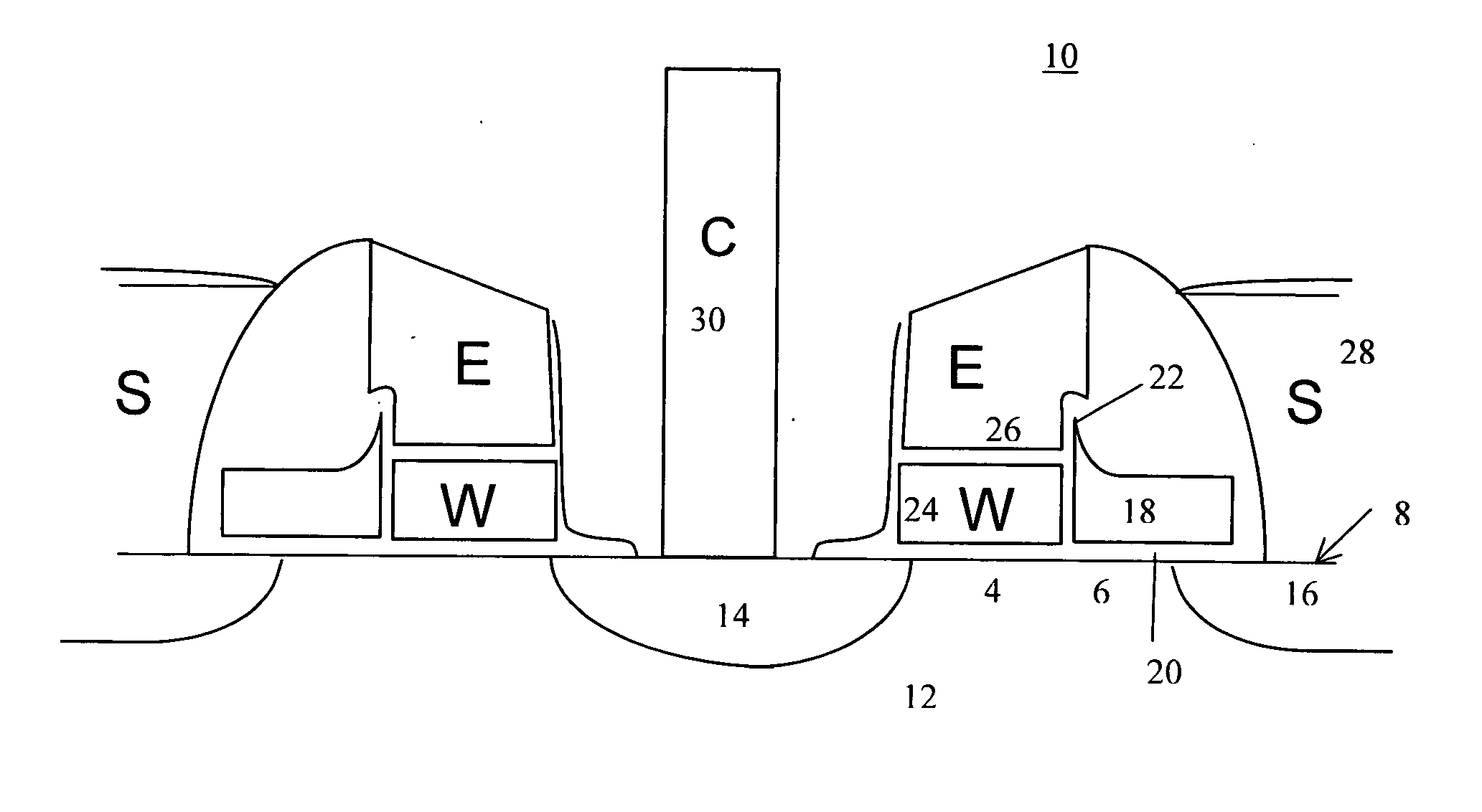

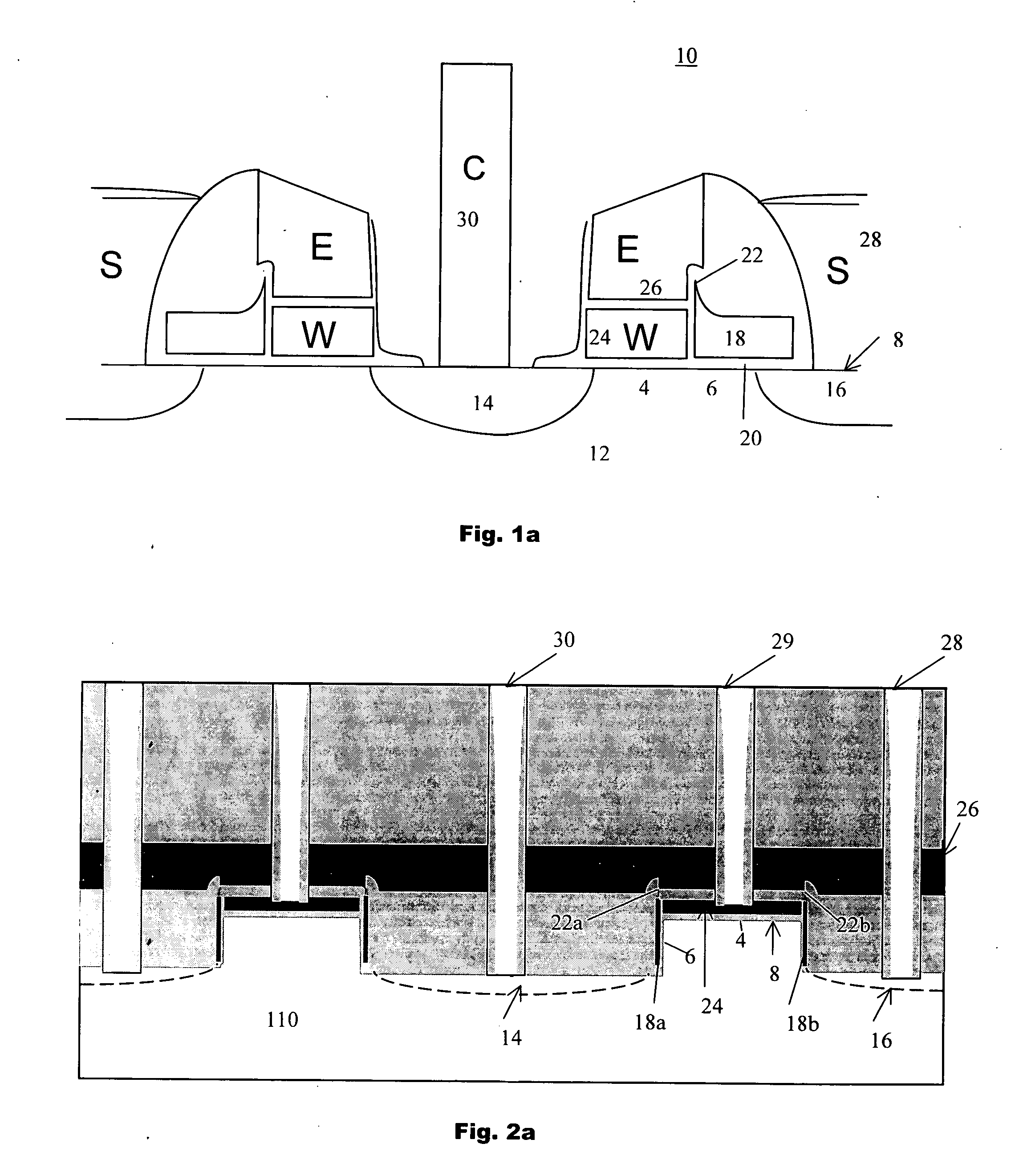

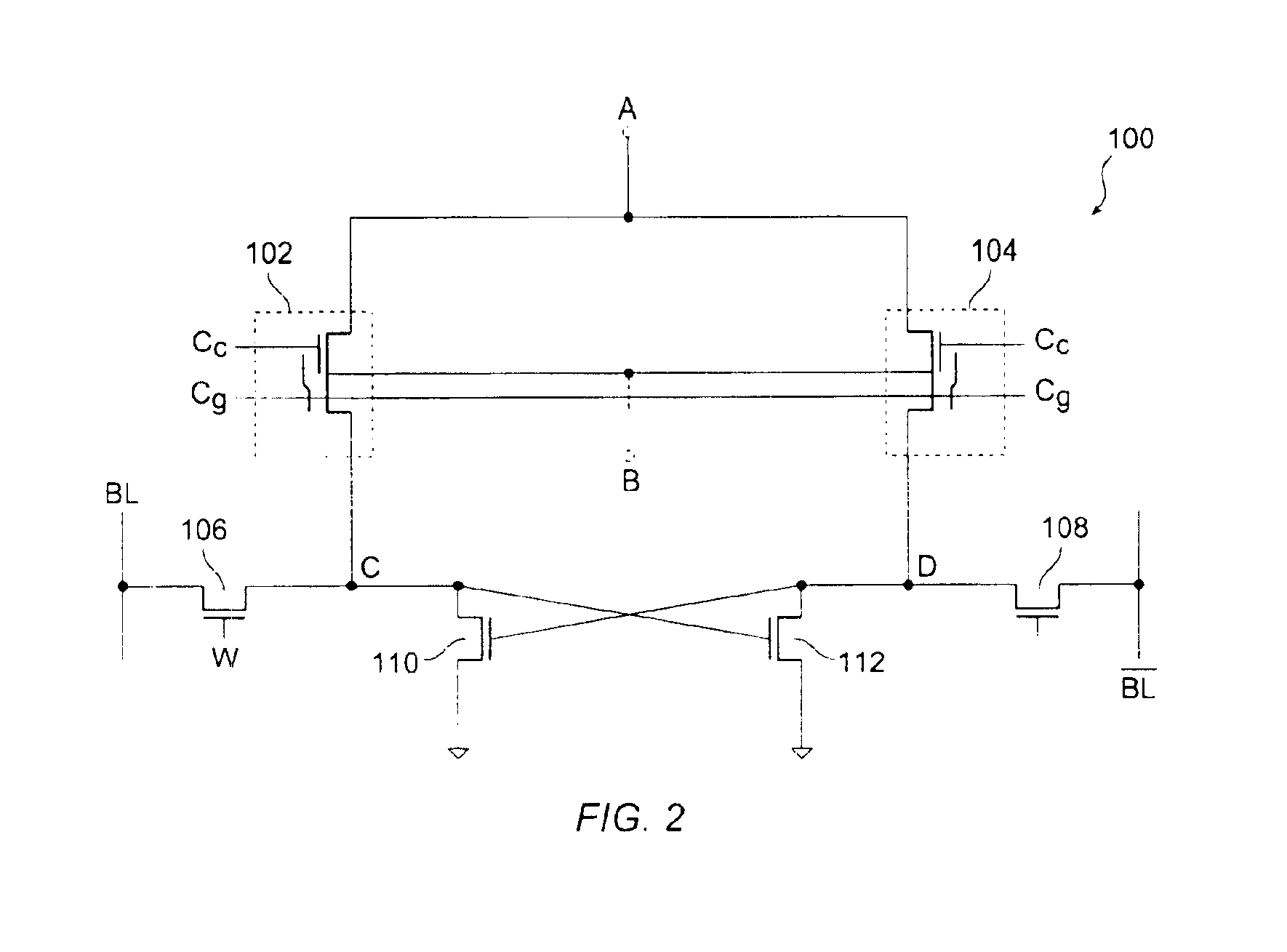

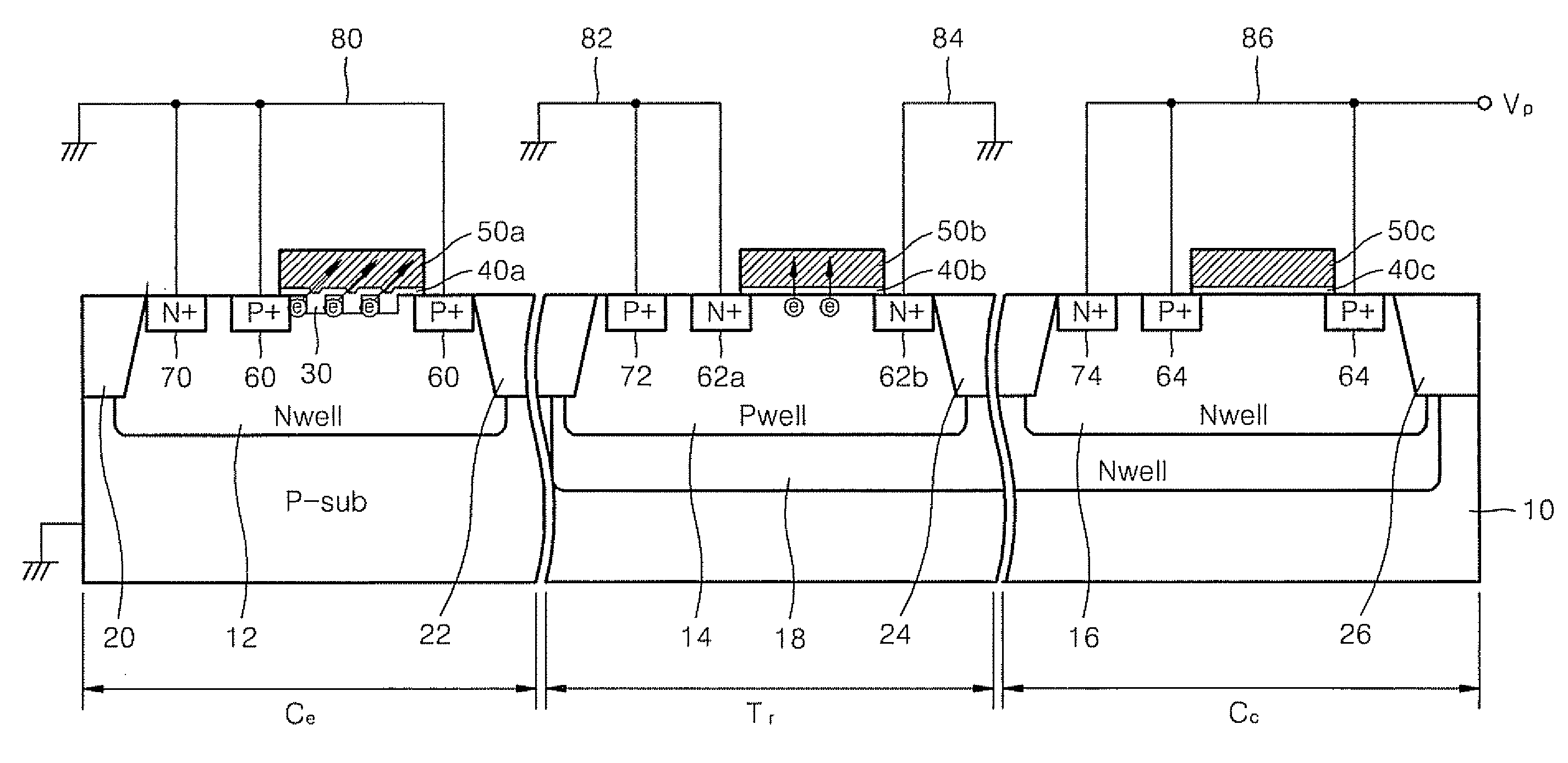

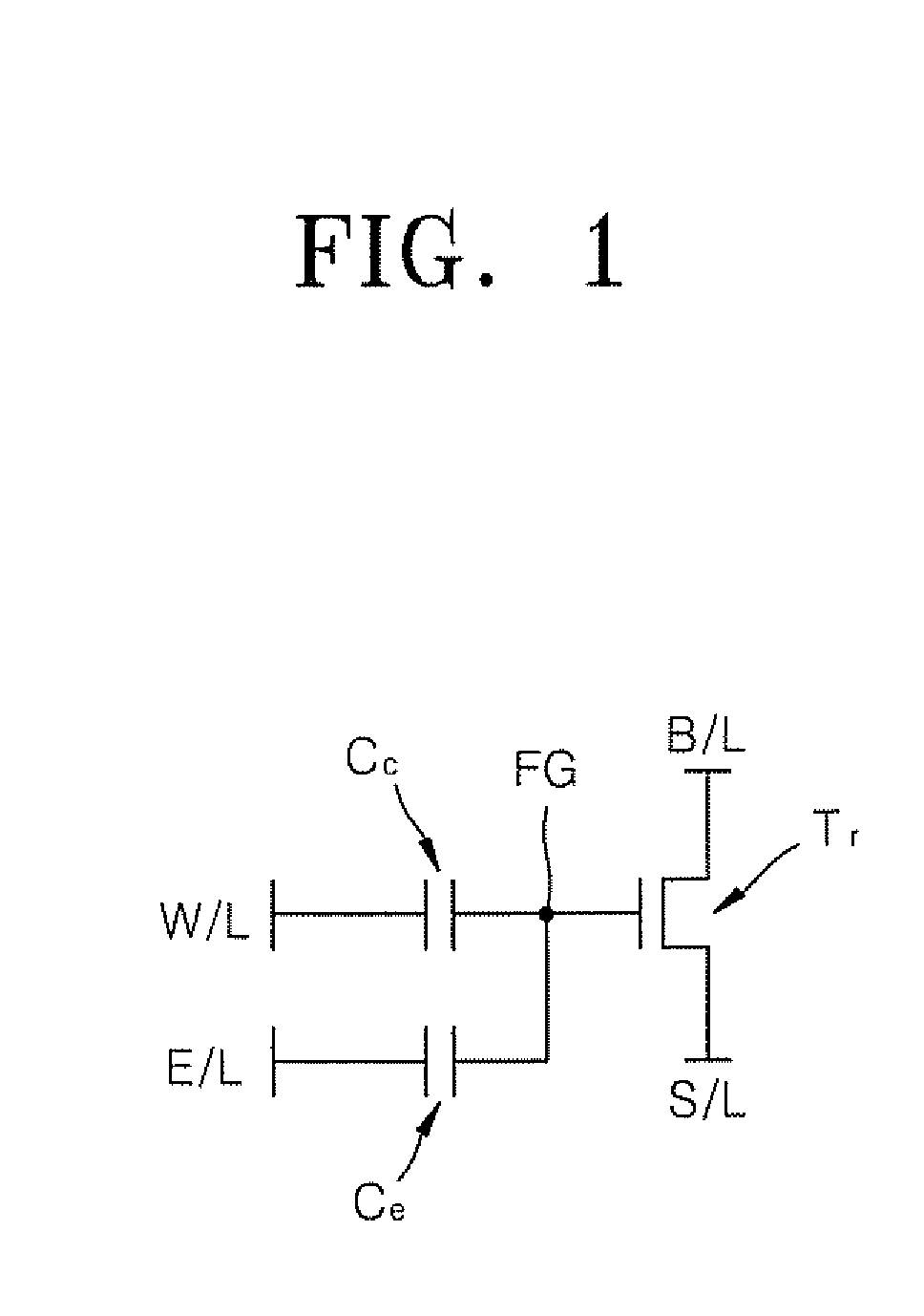

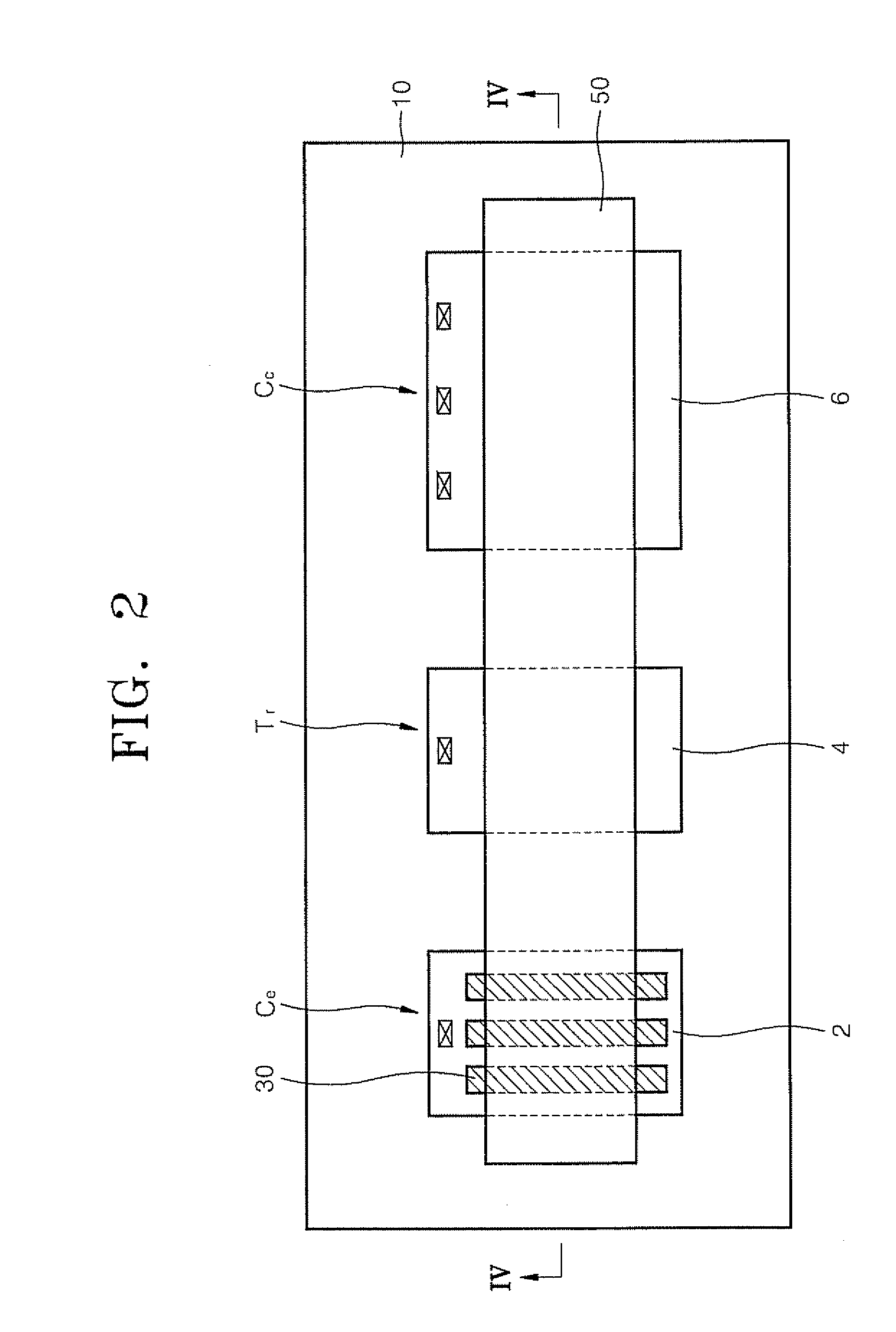

A non-volatile memory (NVM) cell and array includes a control capacitor, tunneling capacitor, CMOS inverter and output circuit. The CMOS inverter includes PMOS and NMOS inverter transistors. The control capacitor, tunneling capacitor and PMOS and NMOS inverter transistors share a common floating gate, which is programmed / erased by Fowler-Nordheim tunneling. The output circuit includes PMOS and NMOS select transistors. The PMOS inverter and select transistors share a common source / drain region. Similarly, the NMOS inverter and select transistors share a common source / drain region. This configuration minimizes the required layout area of the non-volatile memory cell and allows design of arrays with smaller footprints. Alternately, the tunneling capacitor may be excluded, further reducing the required layout area of the NVM cell. In this case, the NMOS inverter transistor functions as a tunneling capacitor for programming and erasing the cell, and the PMOS inverter transistor functions as a tunneling capacitor for erasing the cell.

Owner:TOWER SEMICONDUCTOR

Floating Gate Inverter Type Memory Cell And Array

ActiveUS20100157669A1Optimize layoutReduce layout areaTransistorSolid-state devicesCMOSFowler nordheim

A non-volatile memory (NVM) cell and array includes a control capacitor, tunneling capacitor, CMOS inverter and output circuit. The CMOS inverter includes PMOS and NMOS inverter transistors. The control capacitor, tunneling capacitor and PMOS and NMOS inverter transistors share a common floating gate, which is programmed / erased by Fowler-Nordheim tunneling. The output circuit includes PMOS and NMOS select transistors. The PMOS inverter and select transistors share a common source / drain region. Similarly, the NMOS inverter and select transistors share a common source / drain region. This configuration minimizes the required layout area of the non-volatile memory cell and allows design of arrays with smaller footprints. Alternately, the tunneling capacitor may be excluded, further reducing the required layout area of the NVM cell. In this case, the NMOS inverter transistor functions as a tunneling capacitor for programming and erasing the cell, and the PMOS inverter transistor functions as a tunneling capacitor for erasing the cell.

Owner:TOWER SEMICONDUCTOR

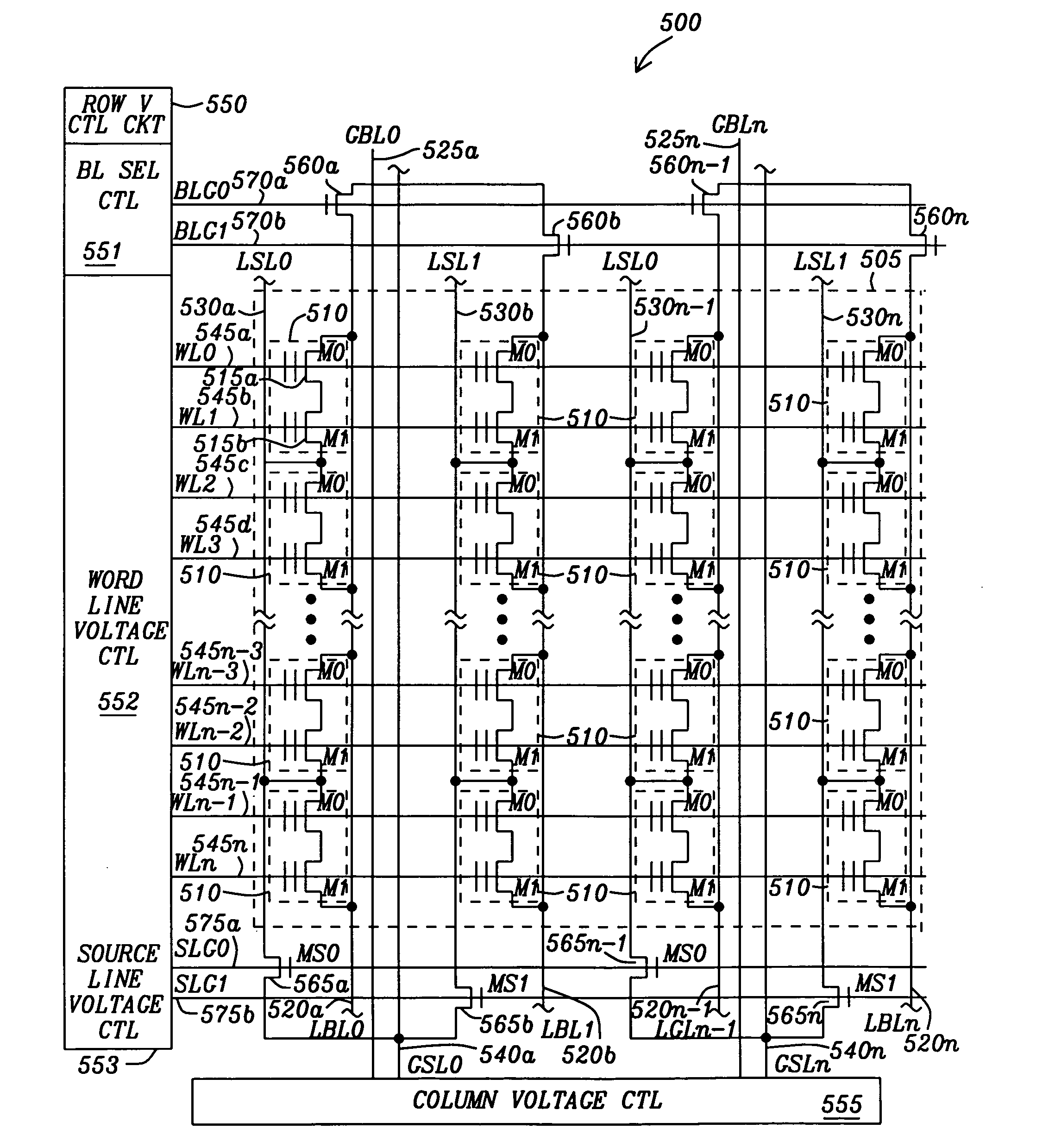

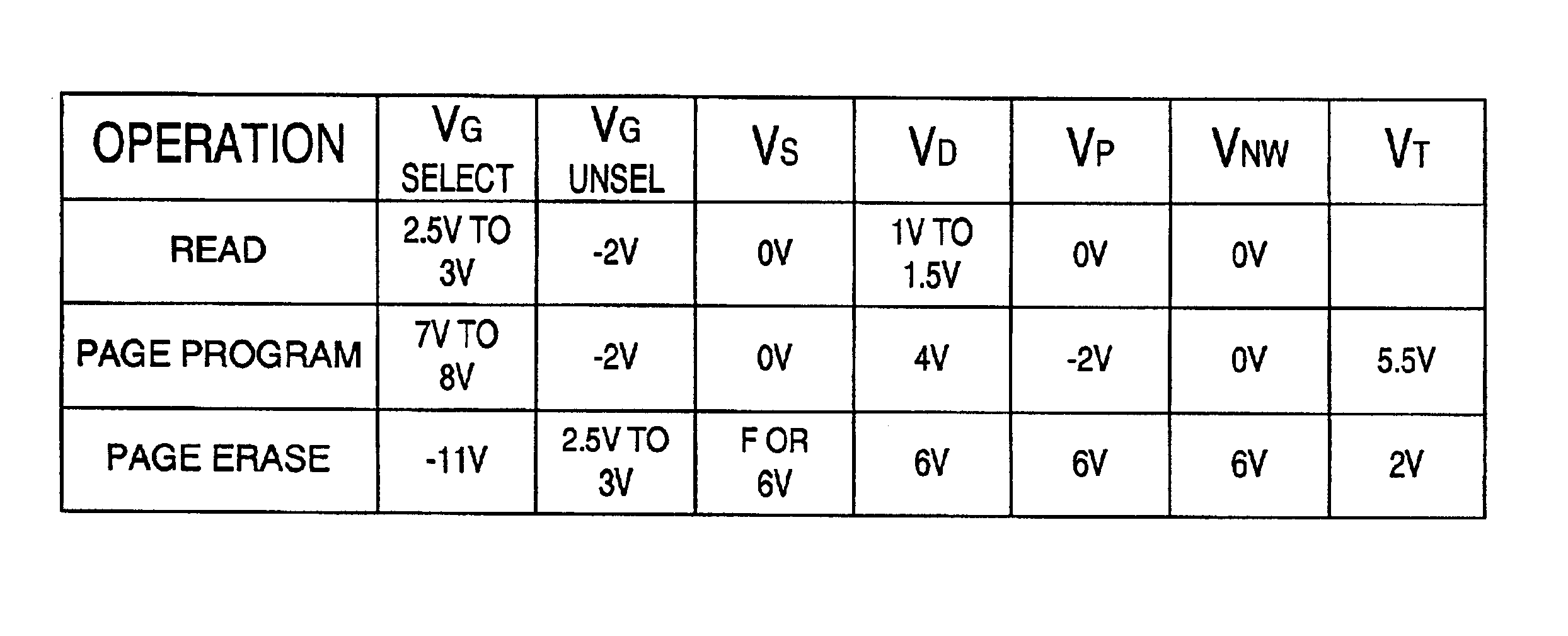

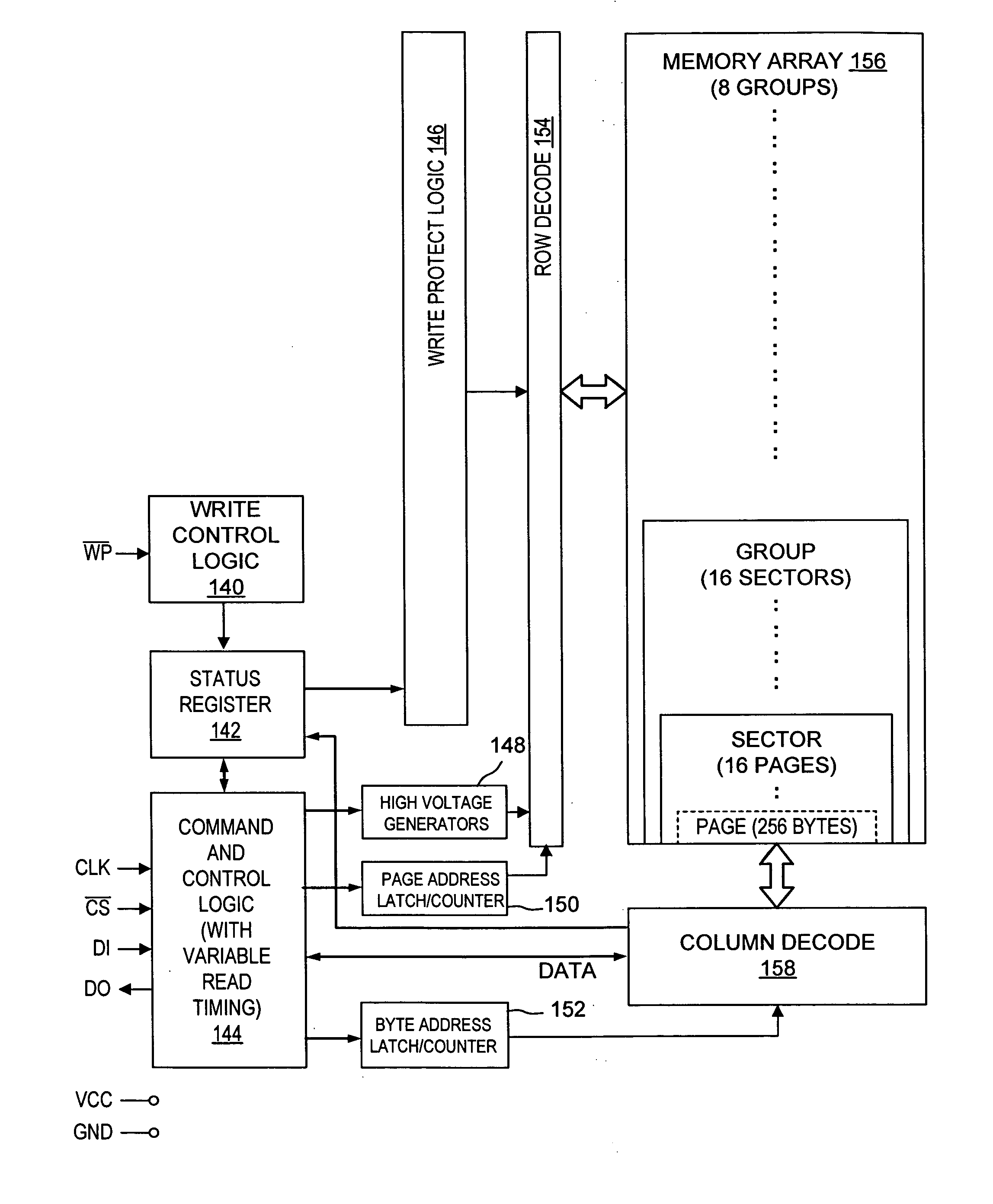

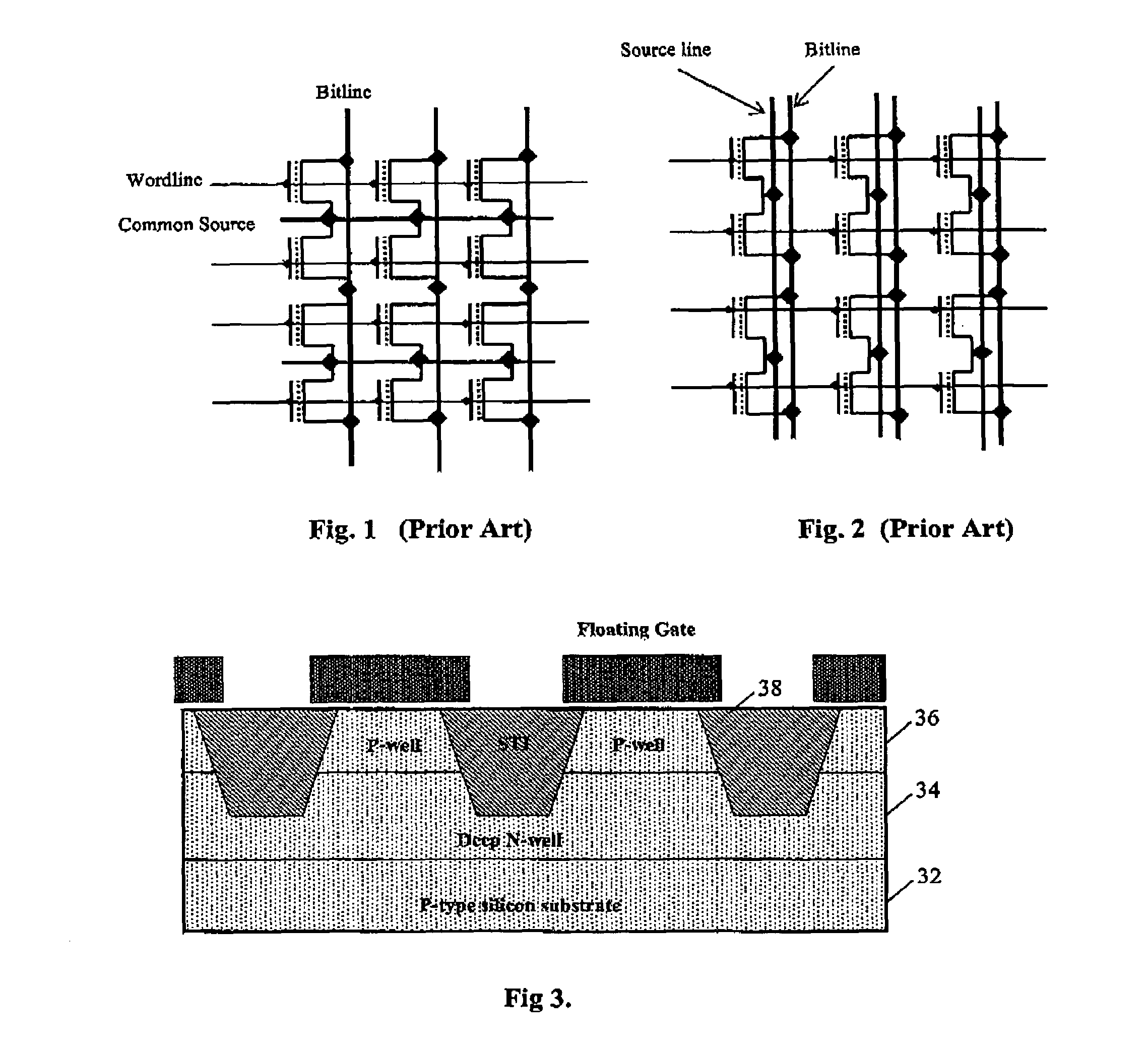

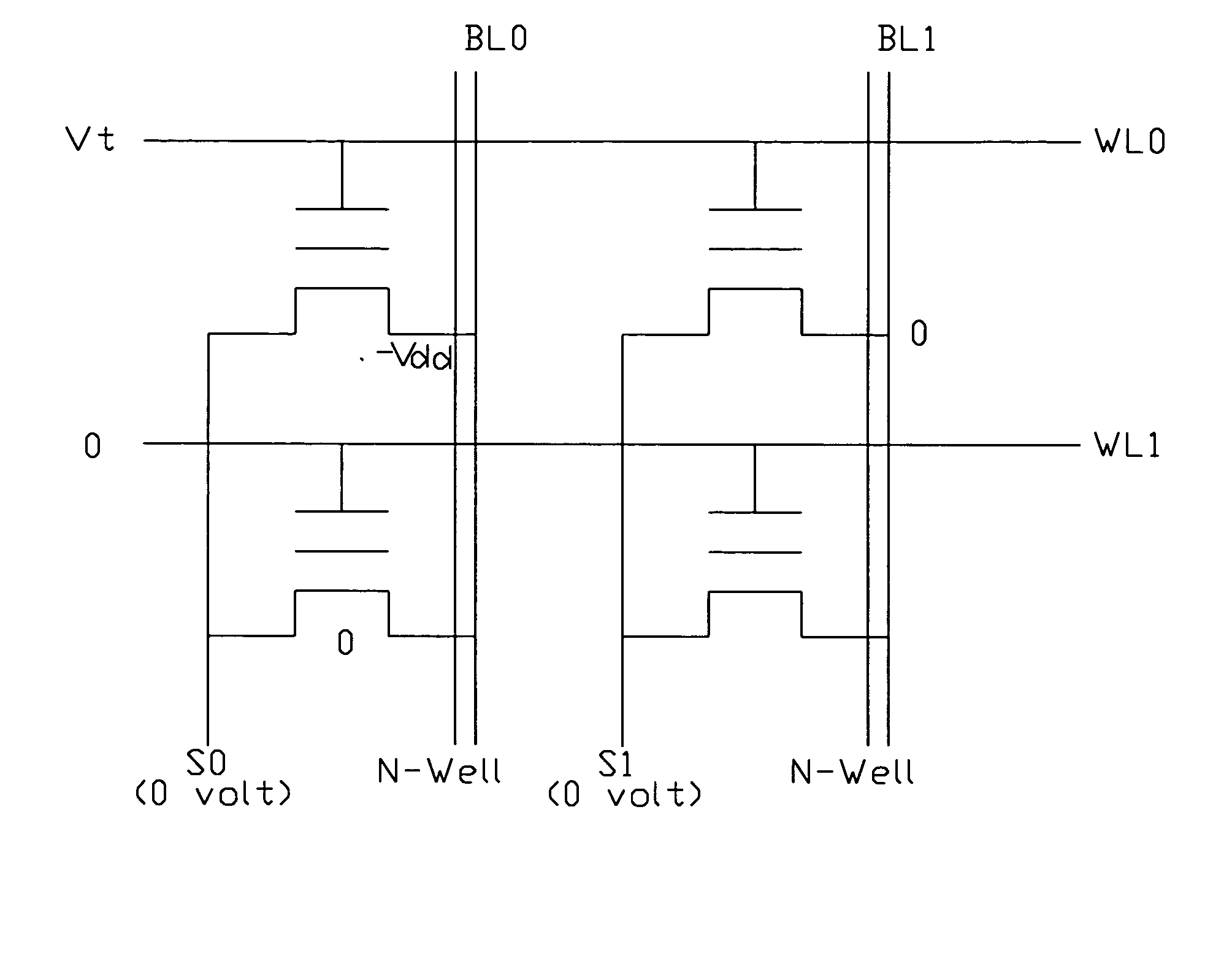

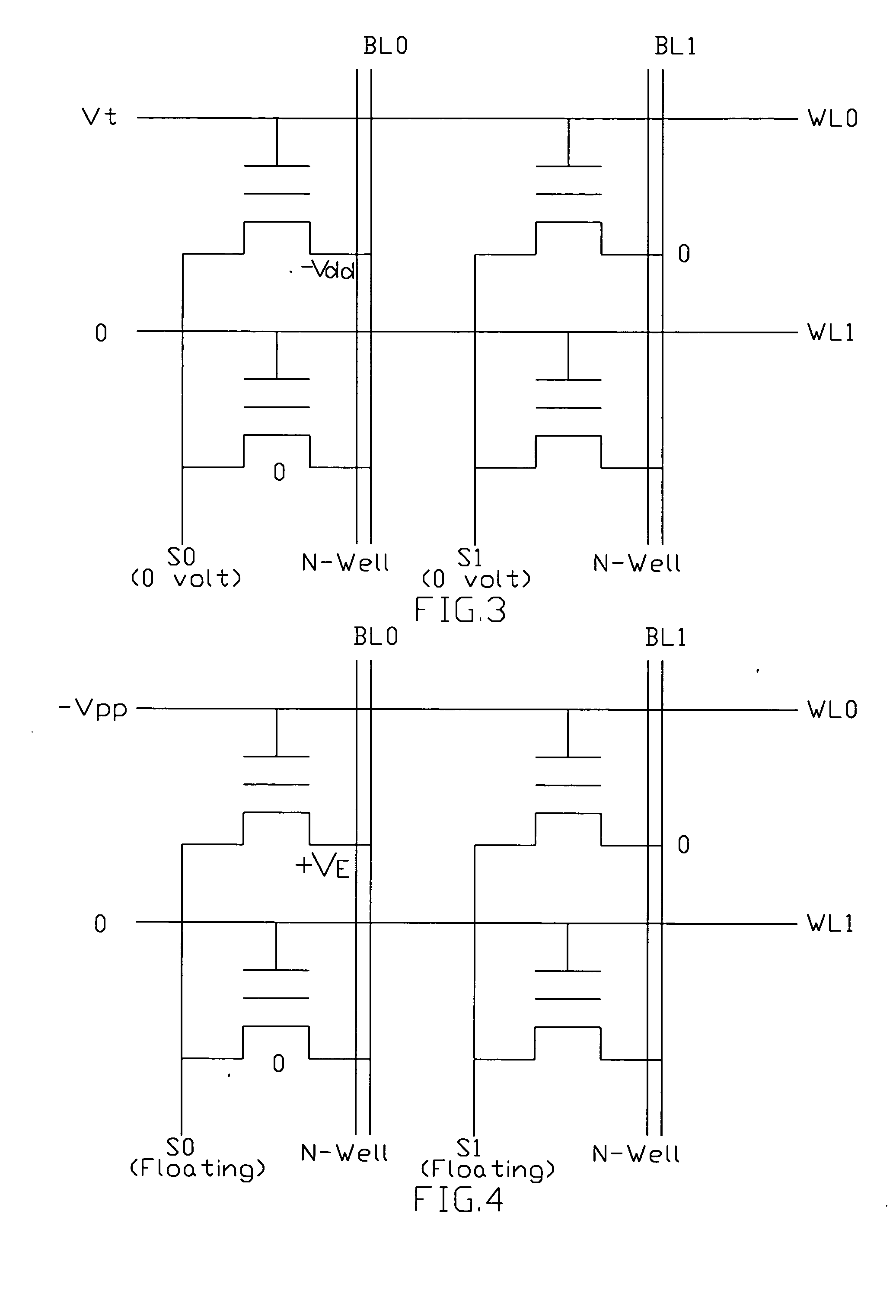

Method and apparatus for multiple byte or page mode programming and reading and for erasing of a flash memory array

A memory array contains memory cells designed to be erased using Fowler-Nordheim ("FN") tunneling through the channel area, and programmed using either channel hot electron injection ("CHE") or channel-initiated secondary electron injection ("CISEI"). To reduce disturbance of the floating gate potential of unselected memory cells during programming operations and read operations, the unselected word lines are brought to a negative potential rather than ground potential. To reduce disturbance of the floating gate potential of unselected memory cells during FN erase operations, the unselected word lines are brought to a positive potential rather than ground potential.

Owner:WINBOND ELECTRONICS CORP

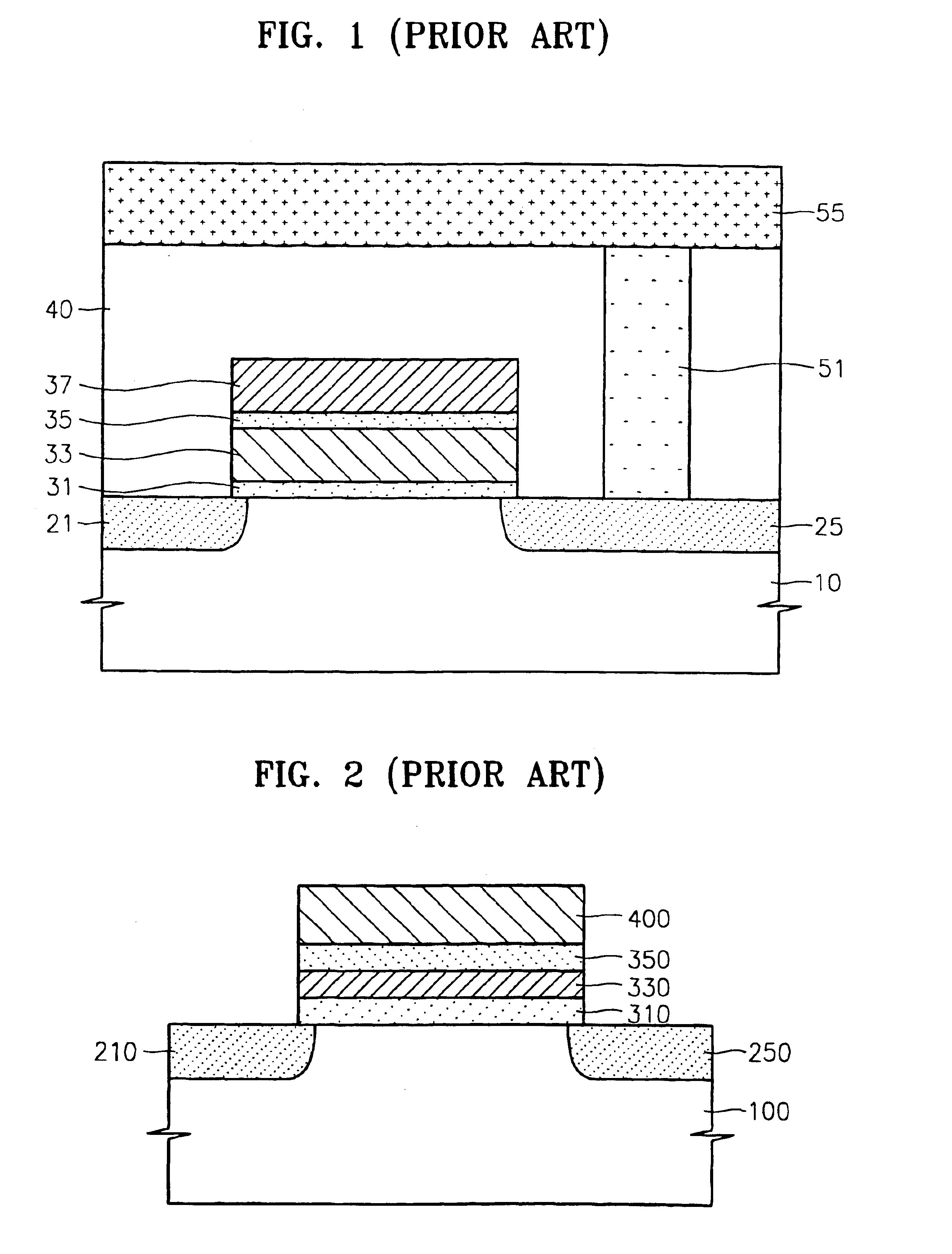

Memory cell having enhanced high-K dielectric

ActiveUS7365389B1Reduce leakage currentSolve the lack of heightSemiconductor/solid-state device manufacturingSemiconductor devicesFowler nordheimDielectric layer

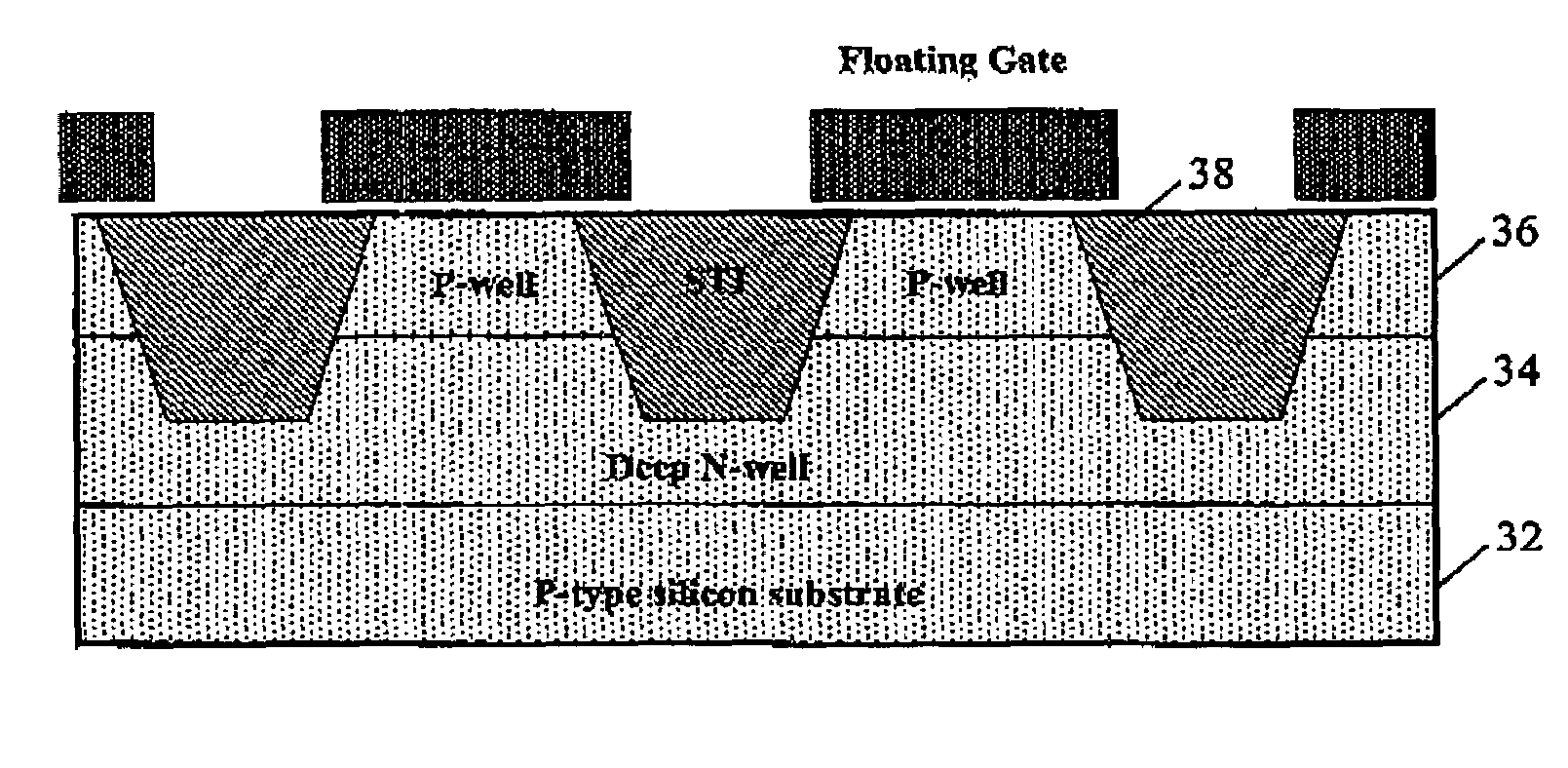

A semiconductor memory device may include an intergate dielectric layer of a high-K, high barrier height dielectric material interposed between a charge storage layer and a control gate. With this intergate high-K, high barrier height dielectric in place, the memory device may be efficiently erased using Fowler-Nordheim tunneling.

Owner:SPANSION LLC

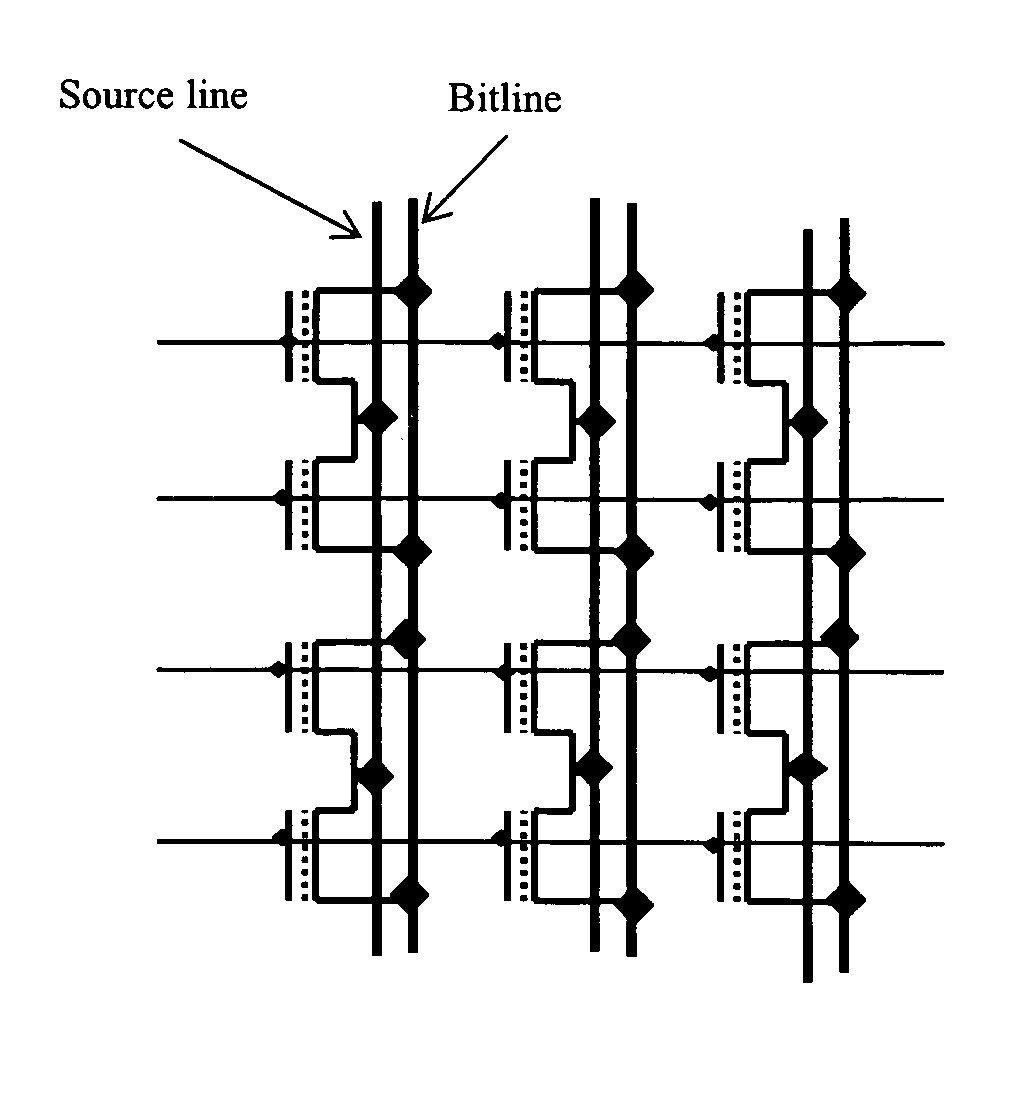

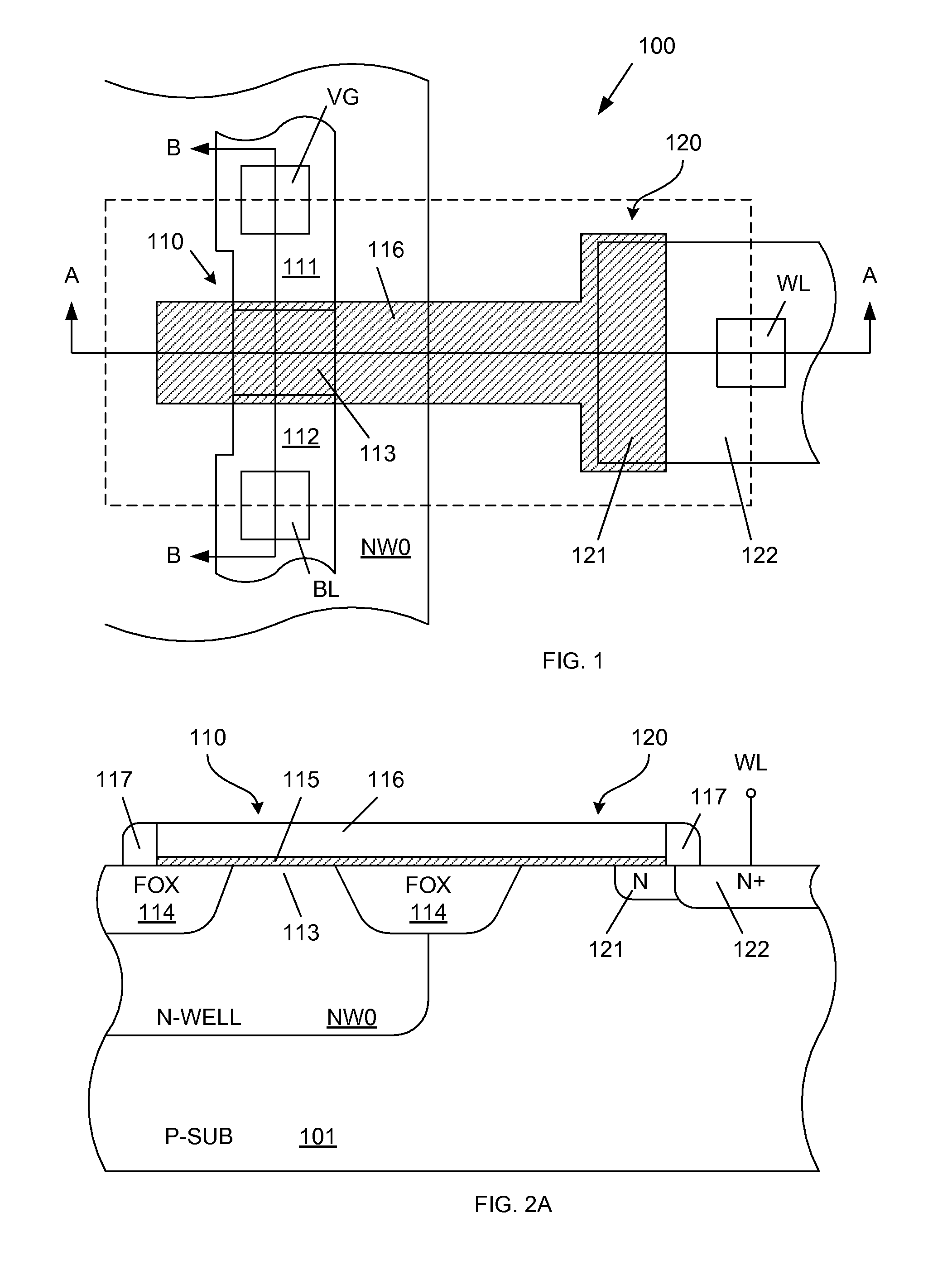

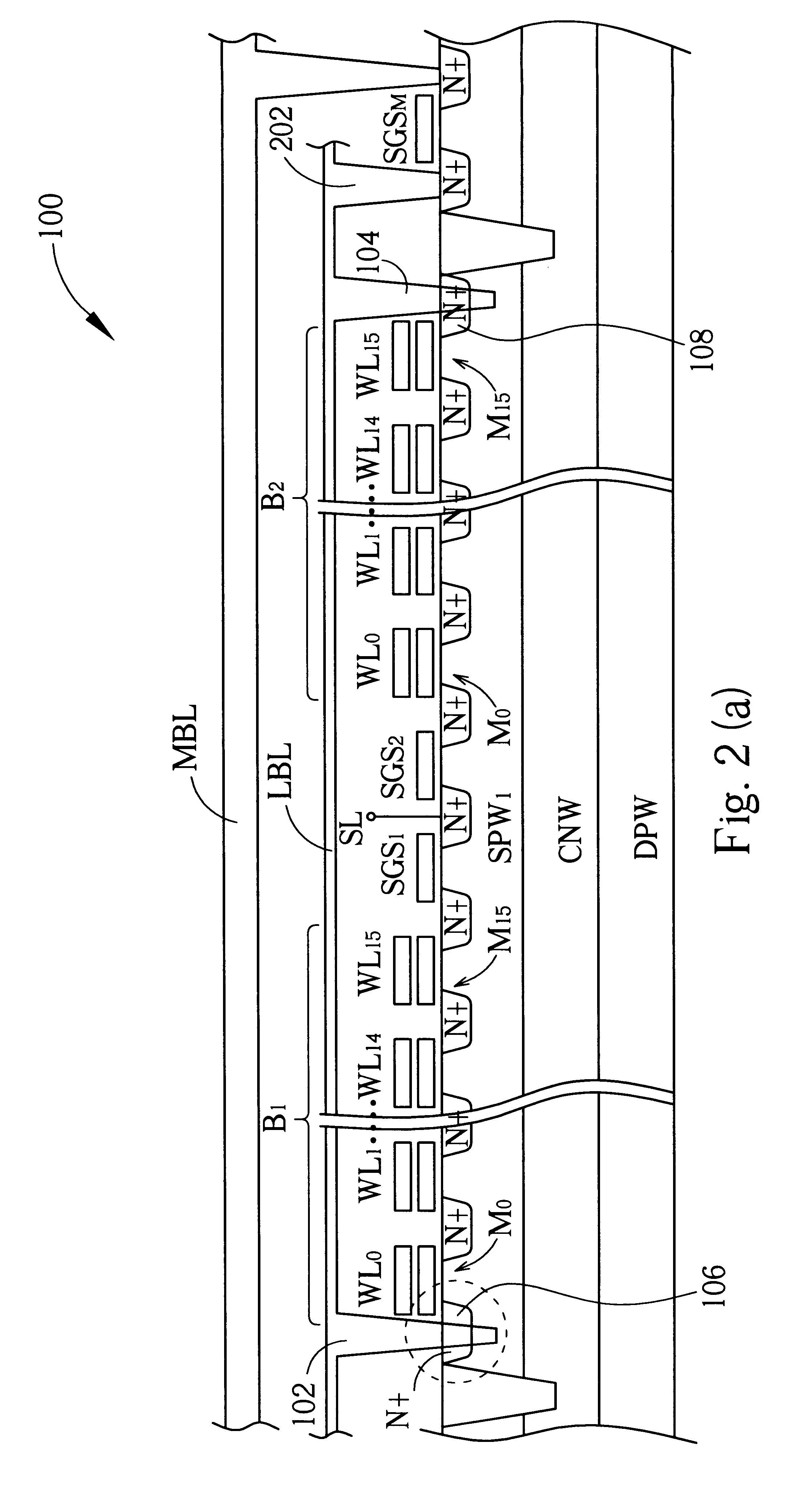

NAND based NMOS NOR flash memory cell, a NAND based NMOS nor flash memory array, and a method of forming a NAND based NMOS NOR flash memory array

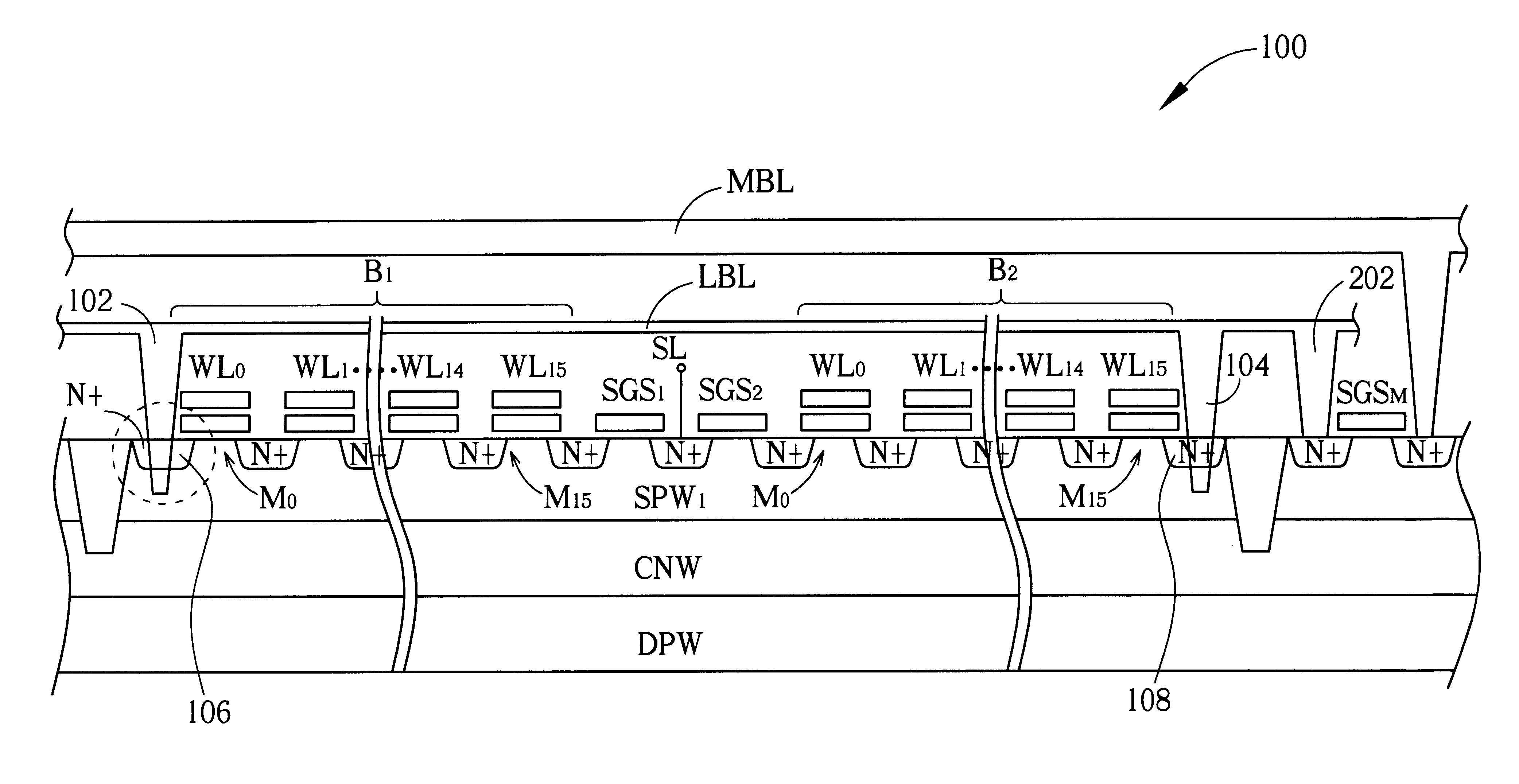

InactiveUS20090279360A1Fast and asynchronous random accessReduce processingSolid-state devicesRead-only memoriesBit lineCharge retention

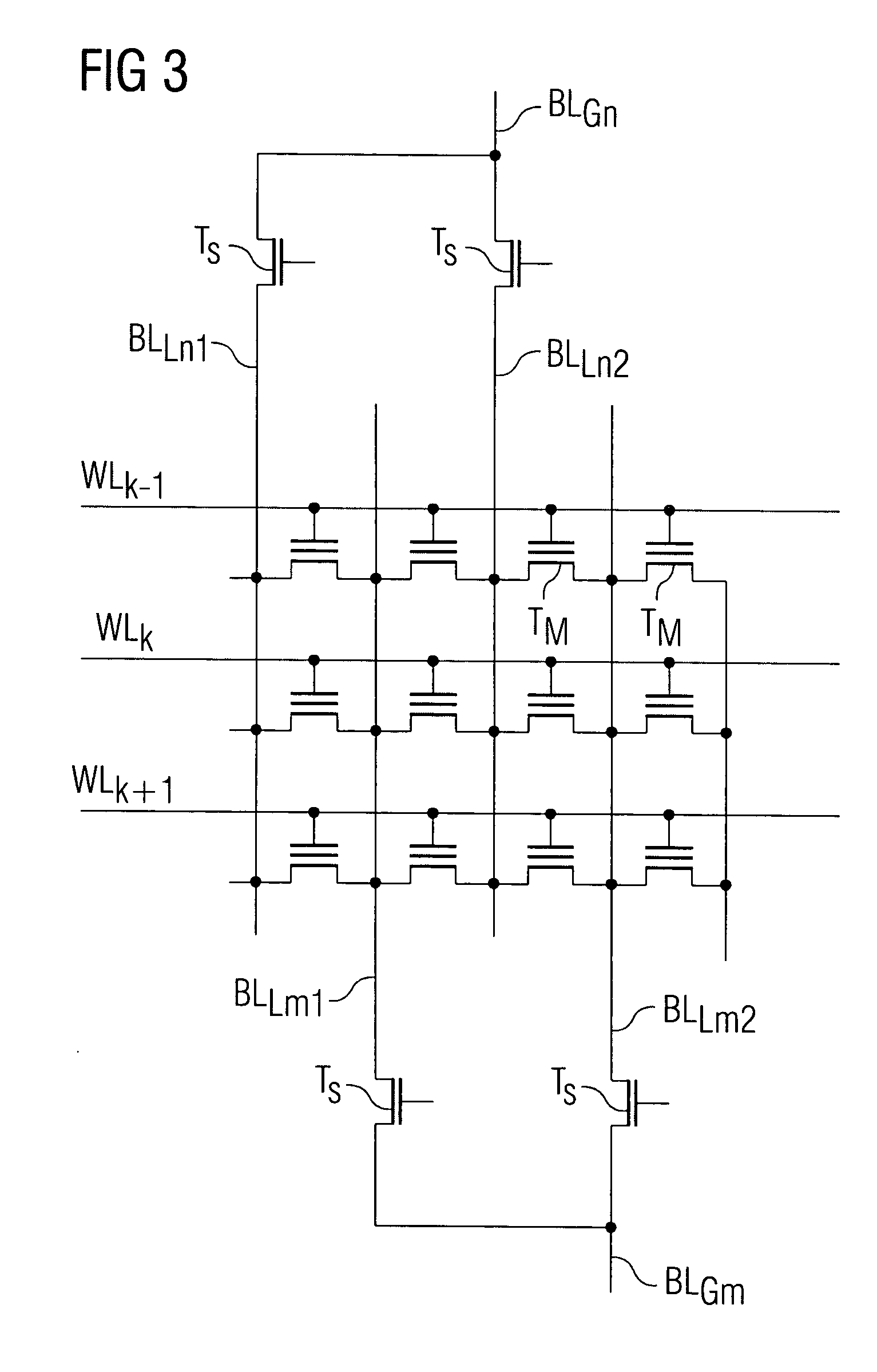

A NOR flash nonvolatile memory device provides the memory cell size and a low current program process of a NAND flash nonvolatile memory device and the fast, asynchronous random access of a NOR flash nonvolatile memory device. The NOR flash nonvolatile memory device has an array of NOR flash nonvolatile memory circuits. Each NOR flash nonvolatile memory circuit includes a plurality of charge retaining transistors serially connected in a NAND string. A drain of a topmost charge retaining transistor is connected to a bit line associated with the serially connected charge retaining transistors and a source of a bottommost charge retaining transistor is connected to a source line associated with the charge retaining transistors. Each control gate of the charge retaining transistors on each row is commonly connected to a word line. The charge retaining transistors are programmed and erased with a Fowler-Nordheim tunneling process.

Owner:APLUS FLASH TECH

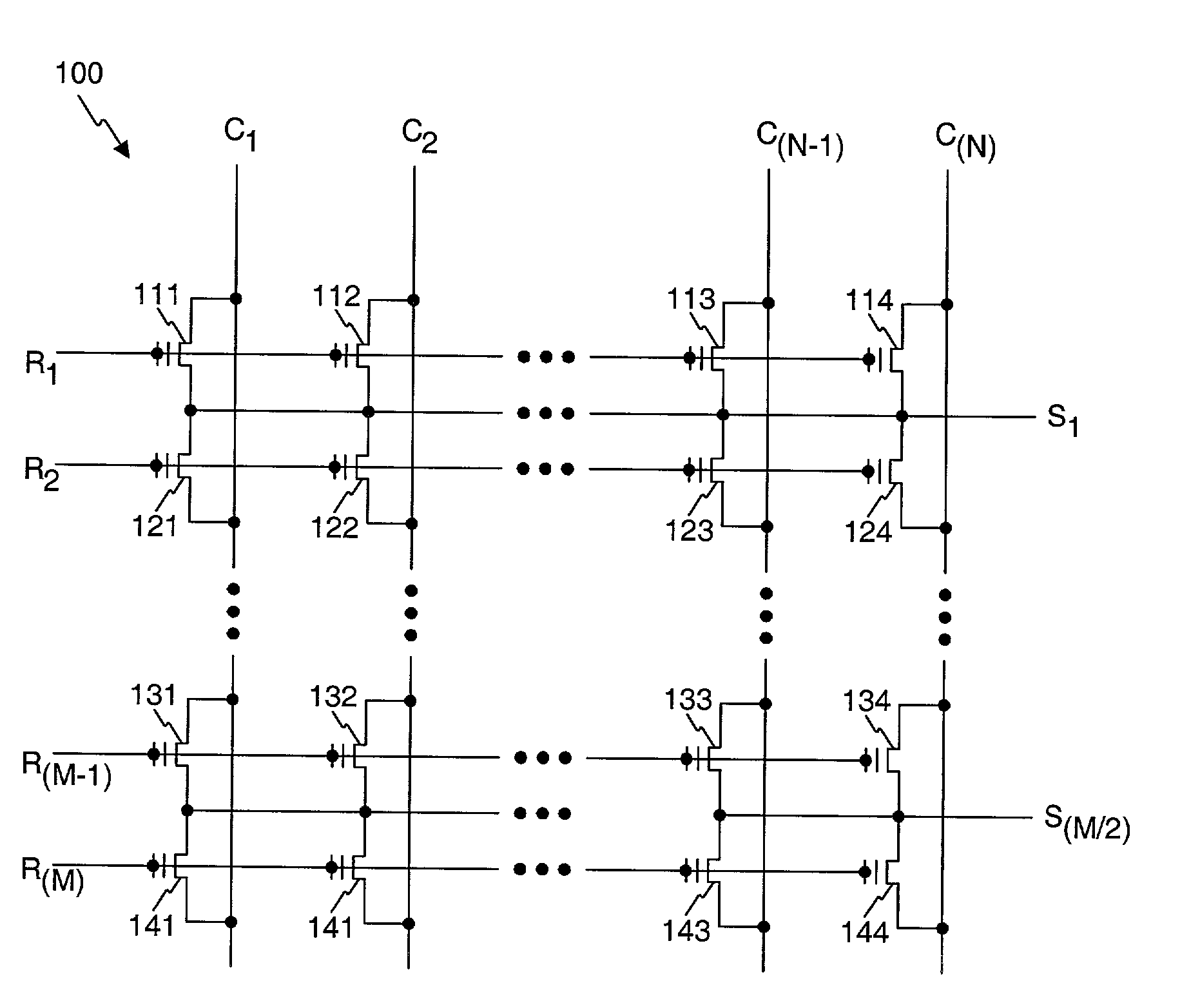

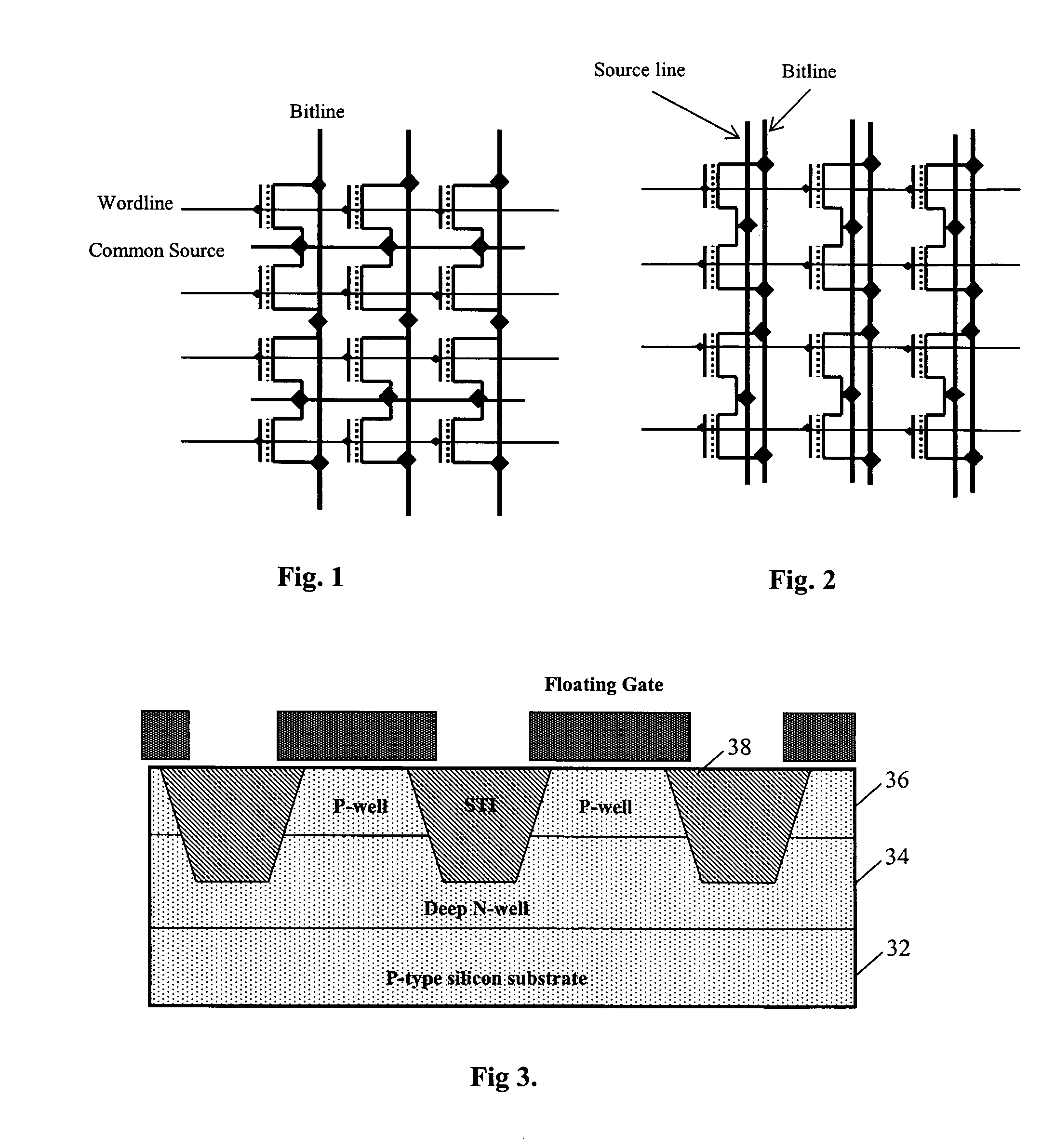

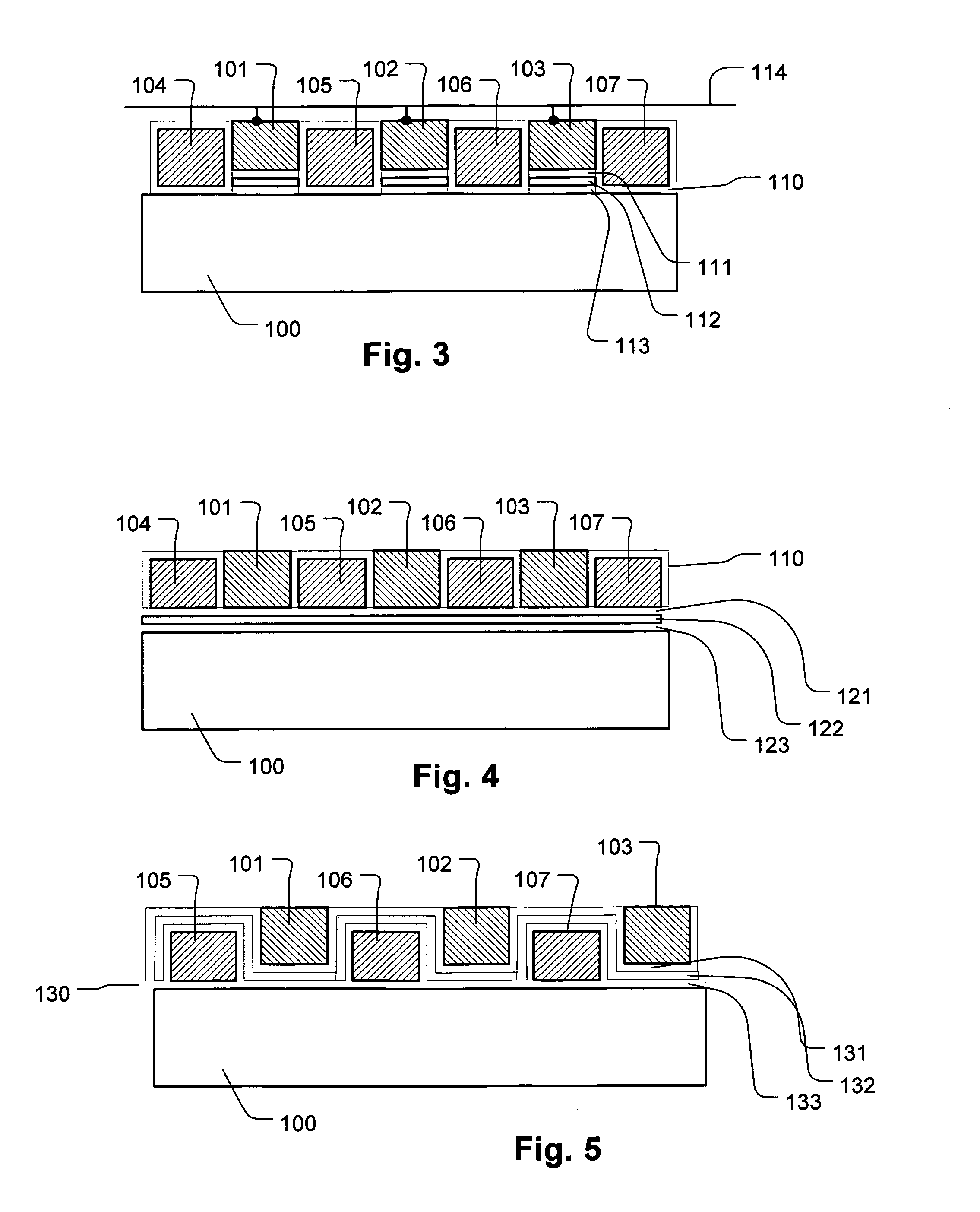

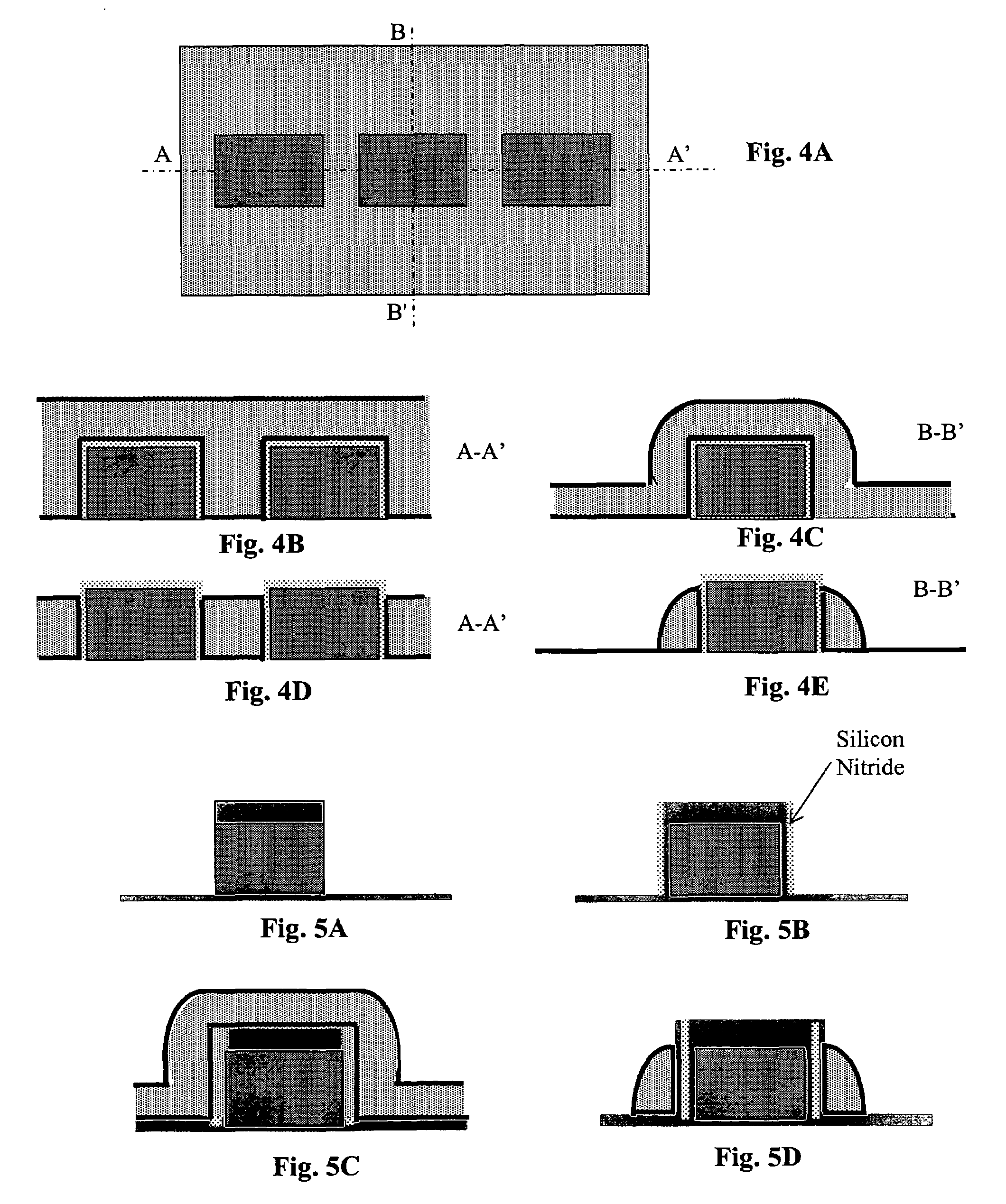

Low voltage EEPROM memory arrays

InactiveUS20050110073A1Increase cell read currentReduce voltageTransistorSolid-state devicesLow voltageFowler nordheim

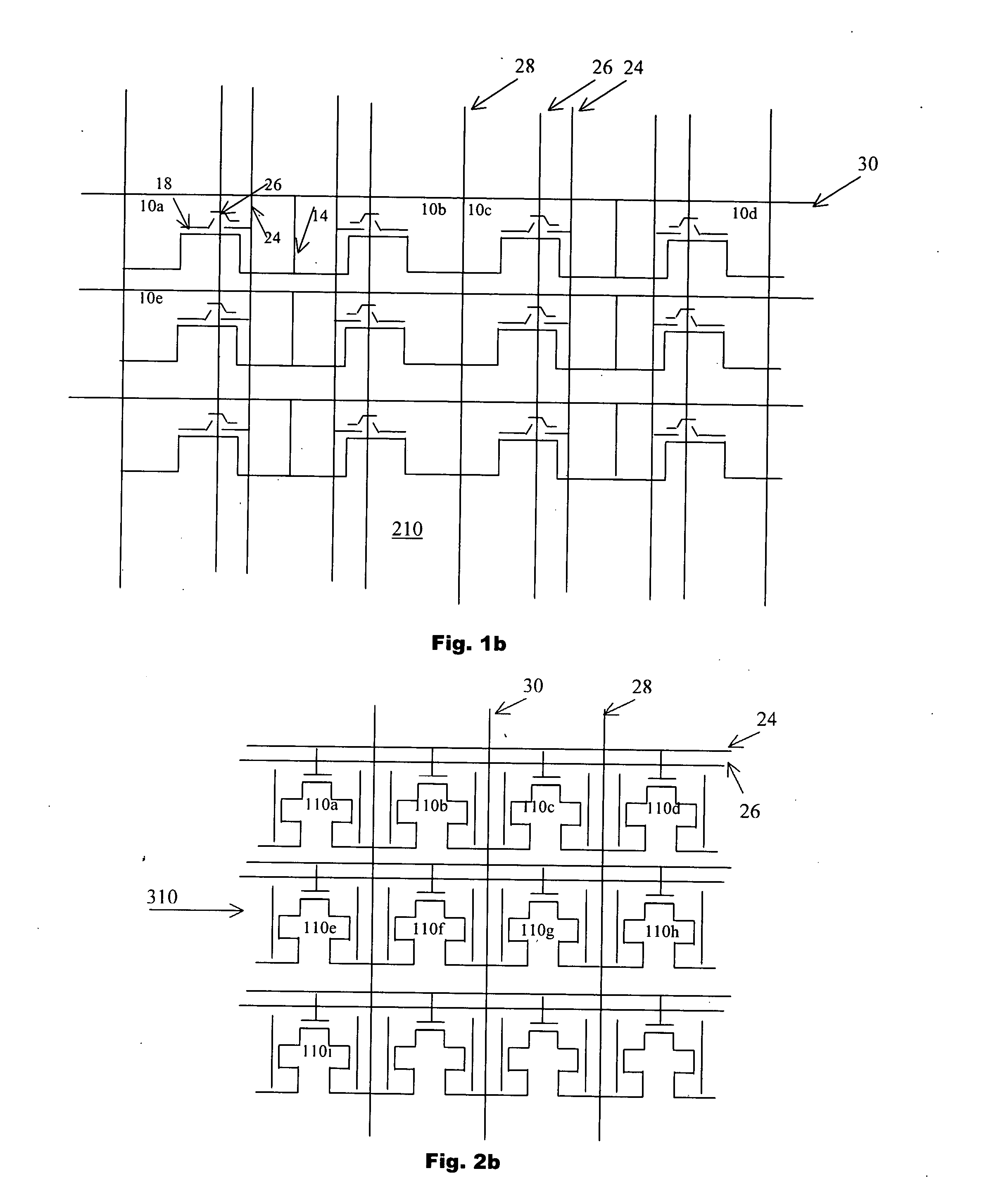

A non-volatile memory array includes memory cells connected in a common source arrangement and formed in columns of isolated well regions so that Fowler-Nordheim tunneling is used for both write and erase operations of the memory cells. The memory arrays can be formed as NOR arrays or NAND arrays. In one embodiment, the memory array of the present invention is formed as a byte alterable EEPROM with parallel access. In another embodiment, an insulated gate bipolar transistor (IGBT) is coupled to the memory cells to increase the cell read current of the memory array. When the memory array incorporates IGBTs on the bitlines, the cell read current becomes independent of the wordline voltages. Thus, the memory array of the present invention can be operated at low voltages. The use of IGBTs in the memory array of the present invention enables formation of embedded non-volatile memories in low-voltage digital integrated circuits.

Owner:SPADEA GREGORIO

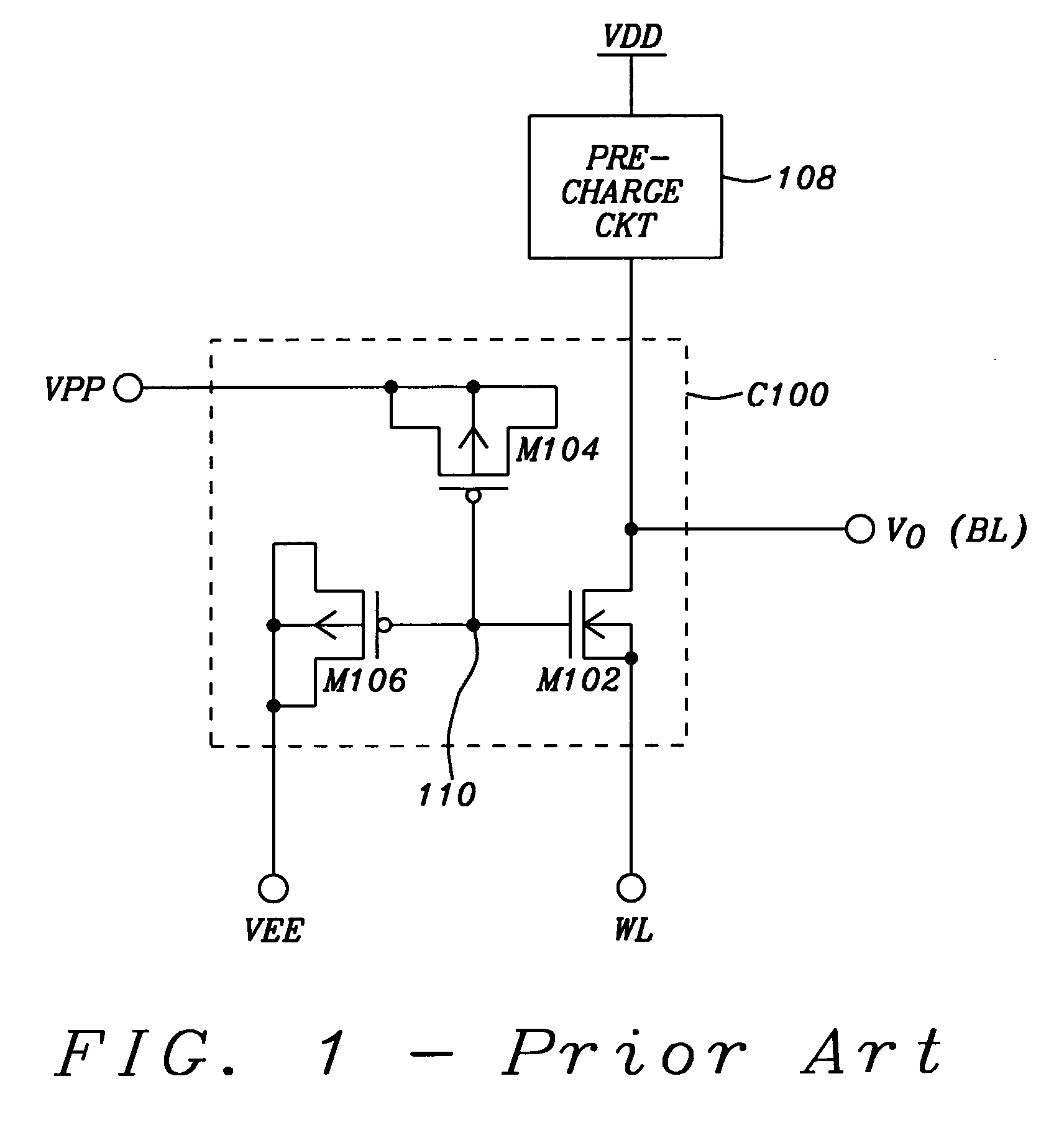

Non-volatile and static random access memory cells sharing the same bitlines

A memory cell structure includes non-volatile as well as SRAM memory cells that share the same bitline and operate differentially. The SRAM cell includes first and second MOS transistors that are coupled to the same true and complementary bit lines that the non-volatile memory cells are coupled to. The non-volatile memory cells are erased prior to being programmed. Programming of the non-volatile memory cells may be carried out via hot-electron injection or Fowler-Nordheim tunneling. Data stored in the non-volatile memory cells may be transferred to the SRAM cell. The differential reading and writing of data reduces over-erase of the non-volatile devices.

Owner:O2IC

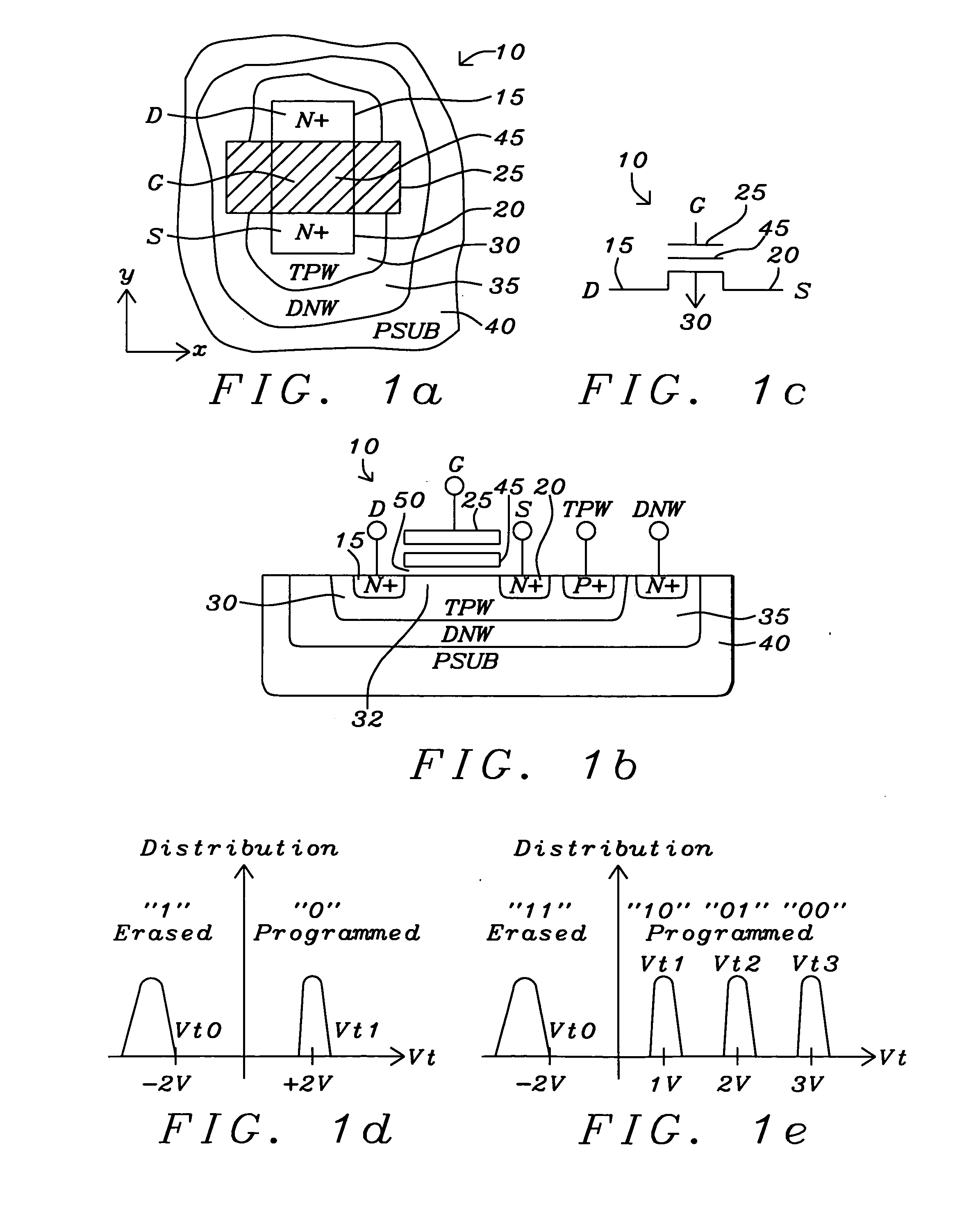

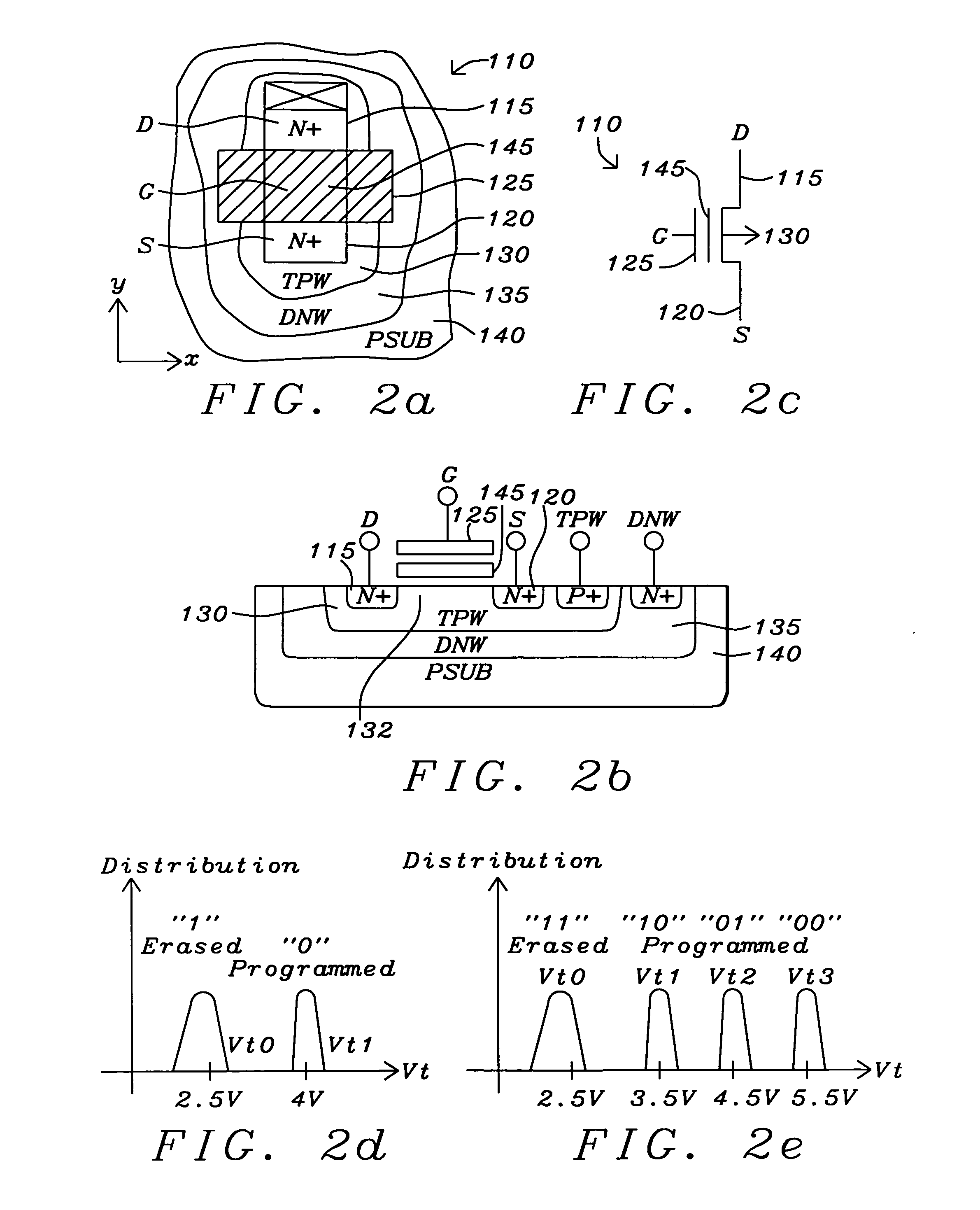

Non-Volatile Memory Embedded In A Conventional Logic Process And Methods For Operating Same

InactiveUS20070279987A1Minimizes probabilityHighly optimized SoCSolid-state devicesRead-only memoriesBit lineFowler nordheim

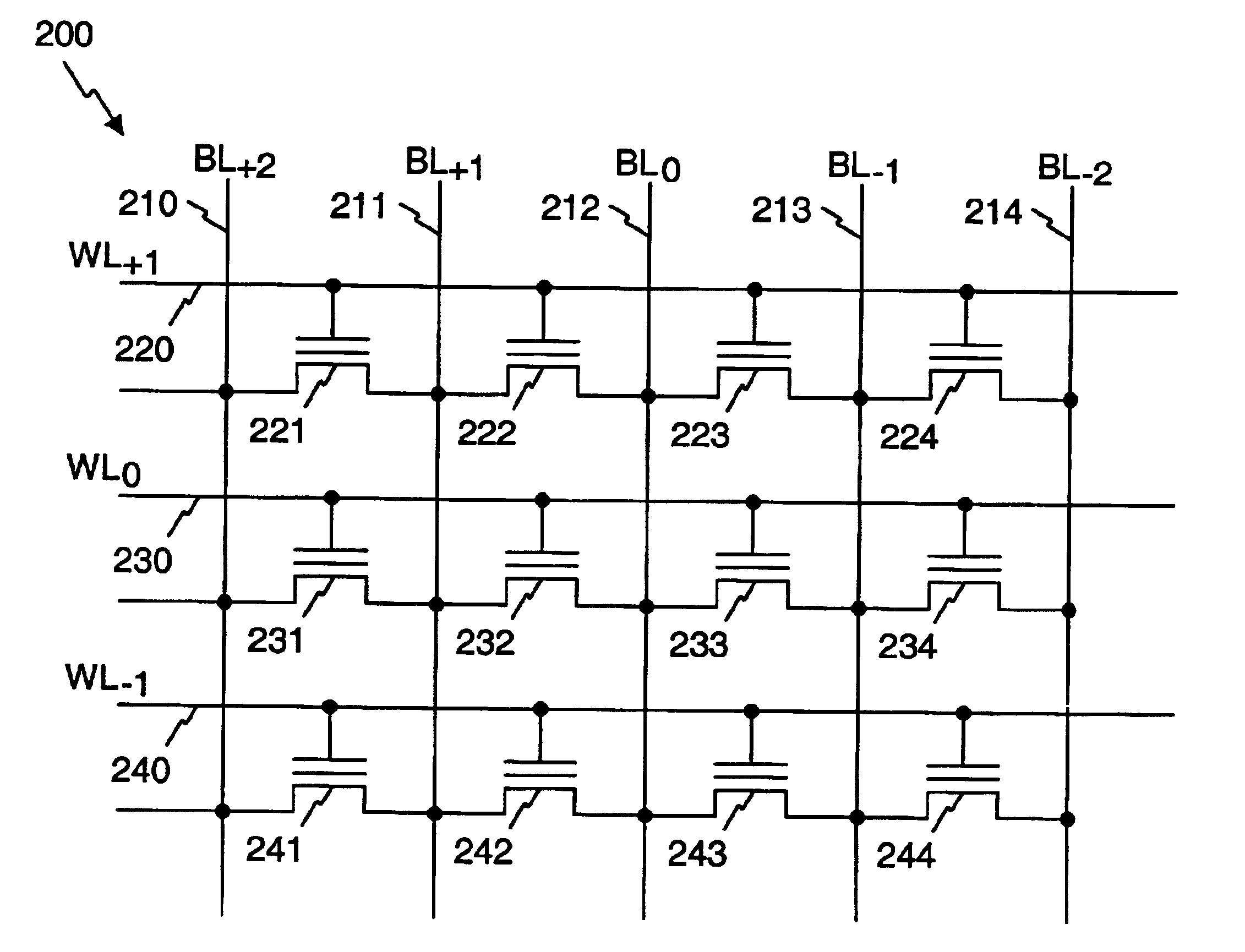

A non-volatile memory system including an array of cells, each having an access transistor and a capacitor sharing a floating gate. The access transistors in each row are fabricated in separate well regions, which are independently biased. Within each row, the source of each access transistor is coupled to a corresponding virtual ground line, and each capacitor structure is coupled to a corresponding word line. Alternately, the source of each access transistor in a column is coupled to a corresponding virtual ground line. Within each column, the drain of each access transistor is coupled to a corresponding bit line. Select memory cells in each row are programmed by band-to-band tunneling. Bit line biasing prevents programming of non-selected cells of the row. Programming is prevented in non-selected rows by controlling the well region voltages of these rows. Sector erase operations are implemented by Fowler-Nordheim tunneling.

Owner:MOSYS INC

Method and apparatus for multiple byte or page mode programming of a flash memory array

Owner:WINBOND ELECTRONICS CORP

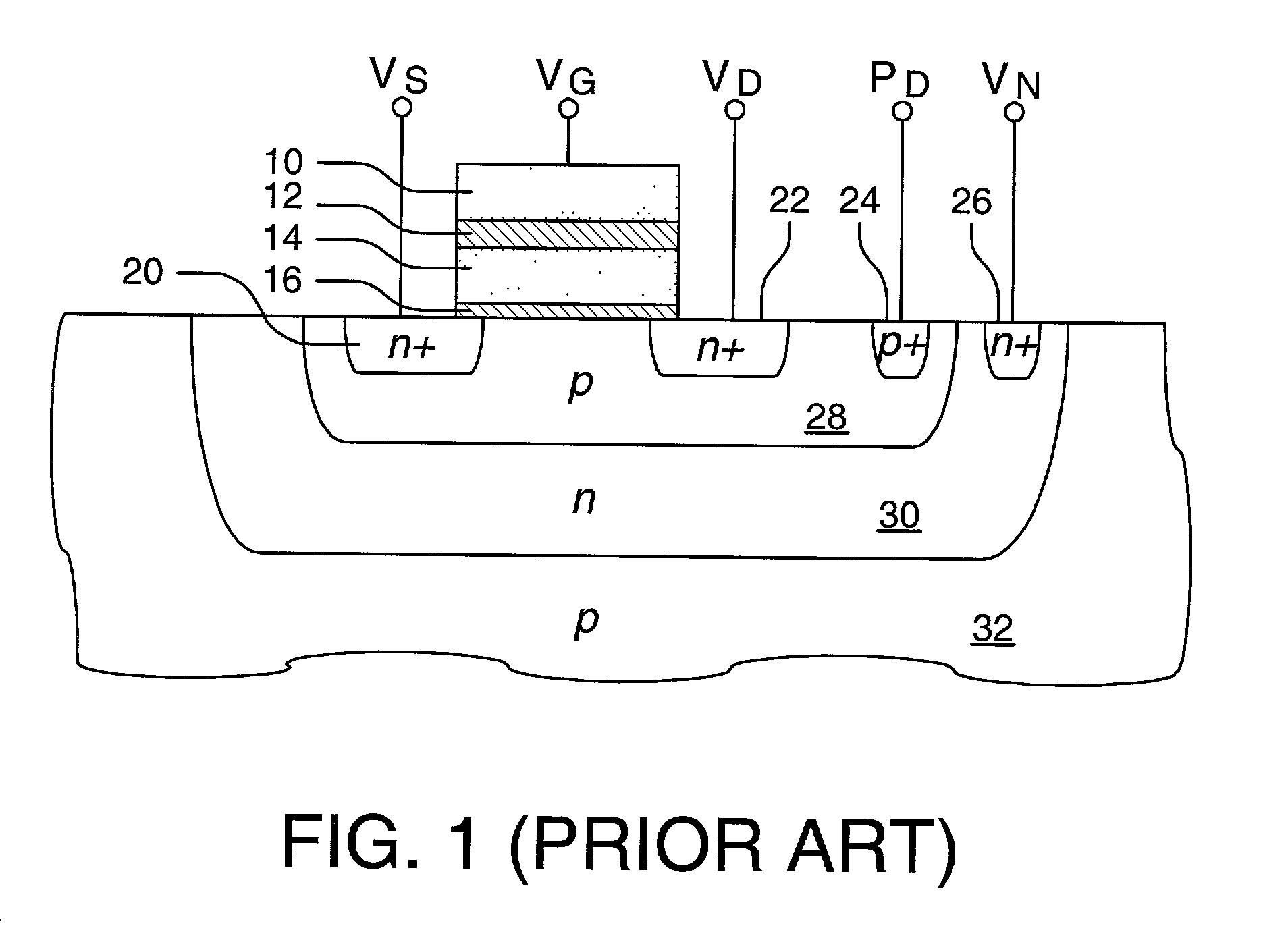

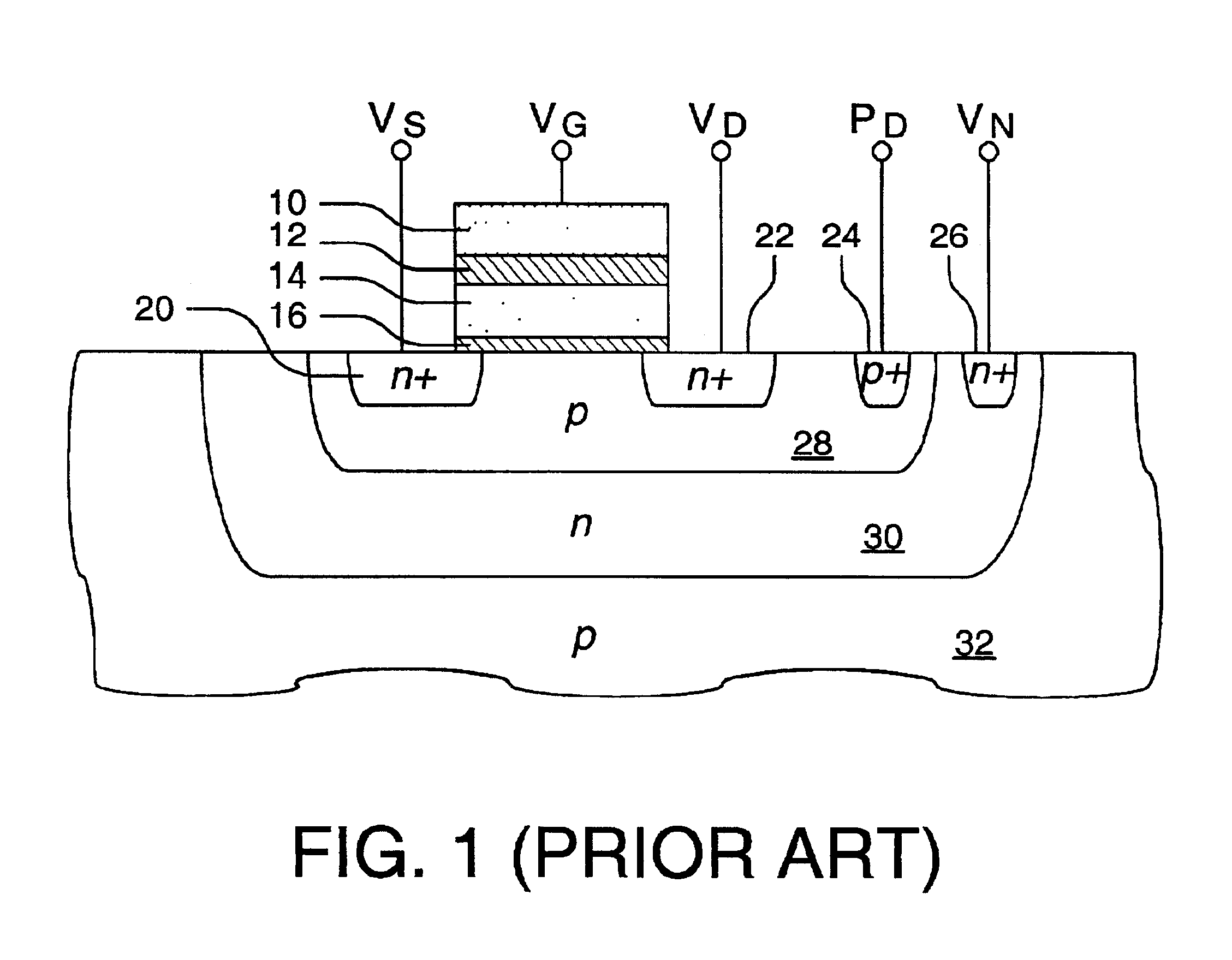

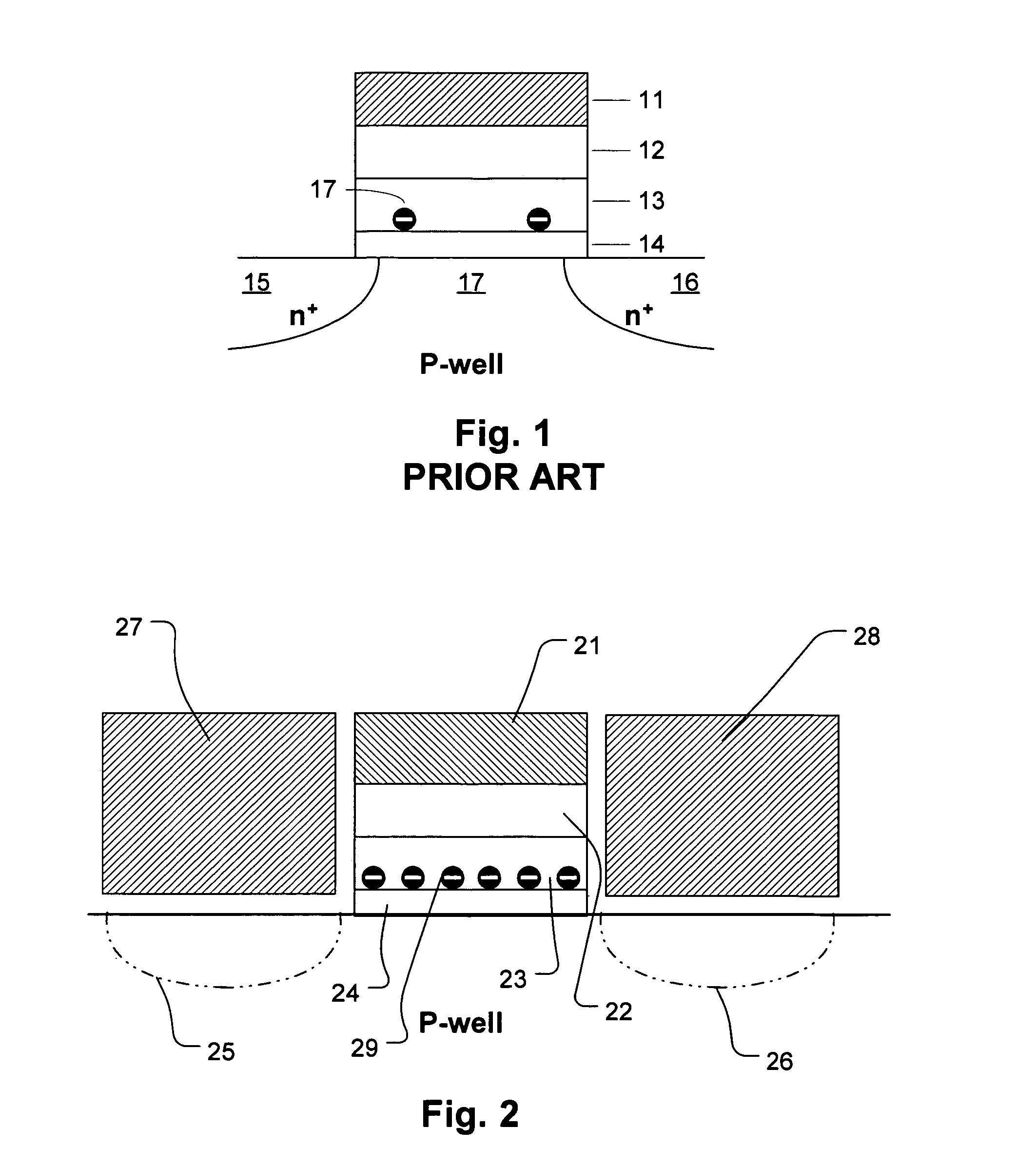

Single-polycrystalline silicon electrically erasable and programmable nonvolatile memory device

A single polycrystalline silicon floating gate nonvolatile memory cell has a MOS capacitor and a storage MOS transistor fabricated with dimensions that allow fabrication using current low voltage logic integrated circuit process. The MOS capacitor has a first plate connected to a gate of the storage MOS transistor to form a floating gate node. The physical size of the MOS capacitor is relatively large (approximately 10 time greater) when compared to a physical size of the storage MOS transistor to establish a large coupling ratio (approximately 90% between the second plate of the MOS capacitor and the floating gate node. When a voltage is applied to the second plate of the MOS capacitor and a voltage applied to the source region or drain region of the MOS transistor establishes a voltage field within the gate oxide of the MOS transistor such that Fowler-Nordheim edge tunnel is initiated.

Owner:APLUS FLASH TECH

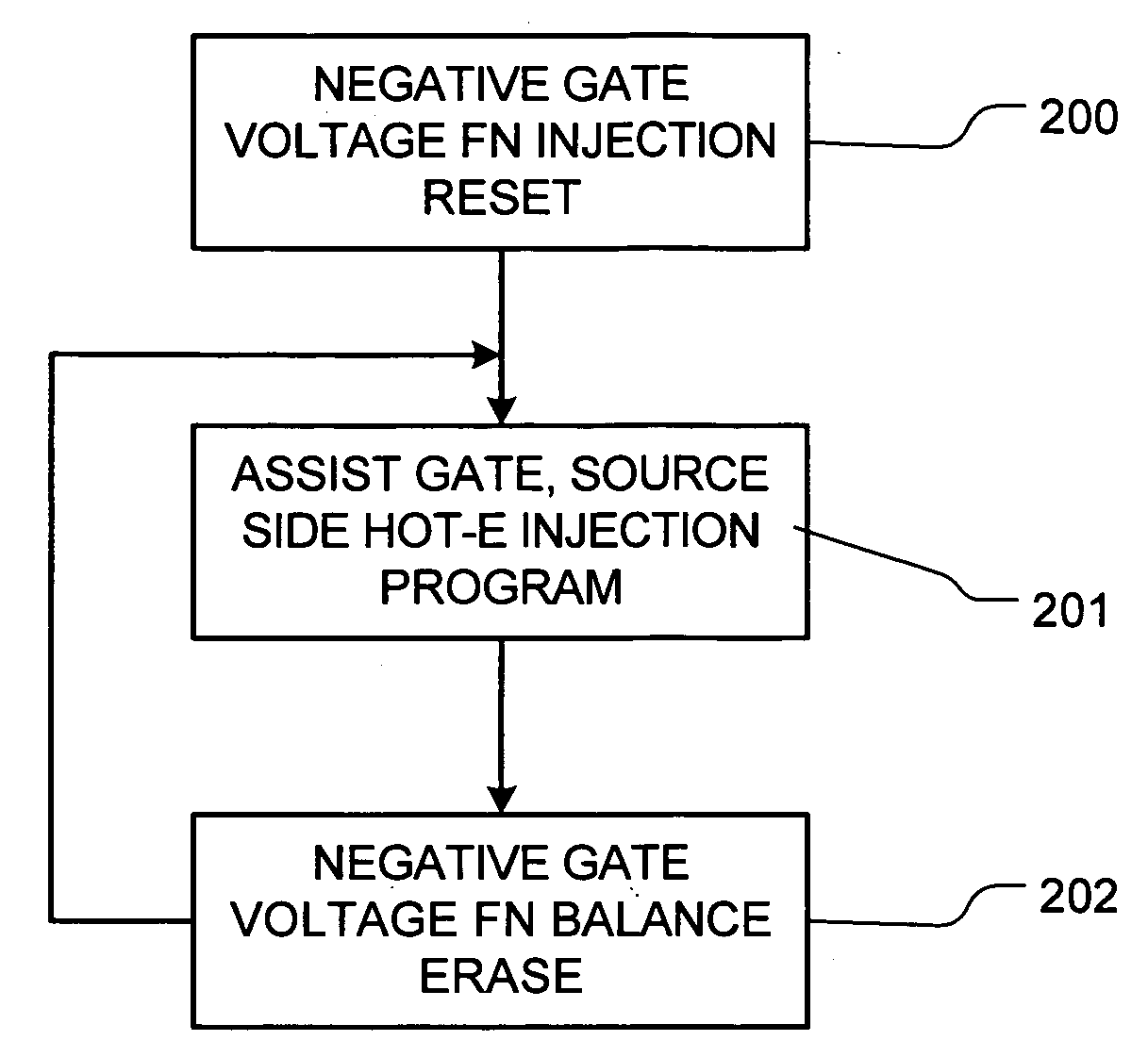

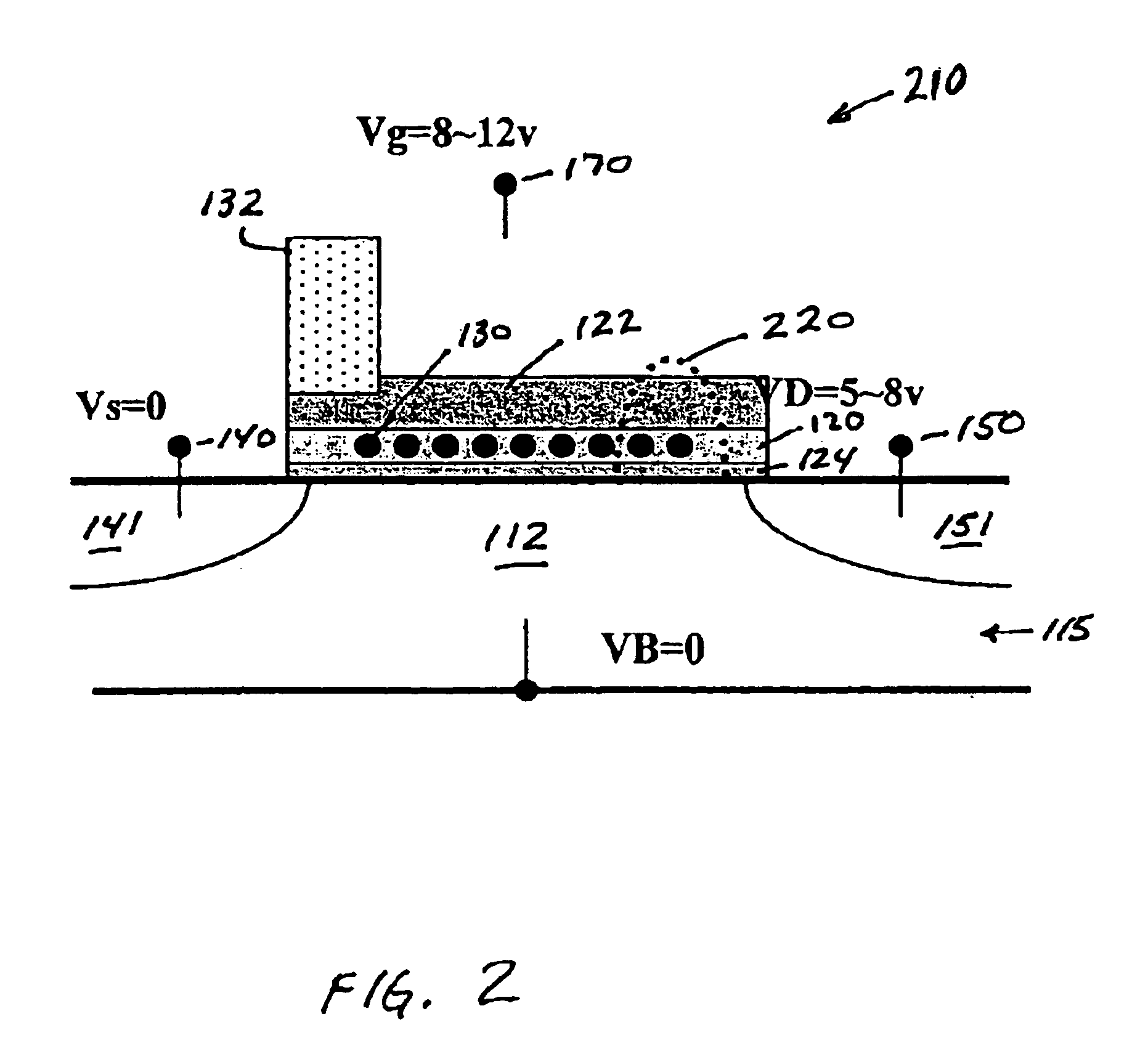

Inversion bit line, charge trapping non-volatile memory and method of operating same

ActiveUS7158420B2Easy to scaleLower average currentRead-only memoriesDigital storageBit lineFowler nordheim

A charge trapping memory device in which a field induced inversion layer is used to replace the source and drain implants. The memory cell are adapted to store two bits, one on the left side and one on the right side of the charge trapping structure. A positive threshold voltage erase state is induced using negative gate voltage Fowler Nordheim FN tunneling which establishes a charge balance condition at a positive voltage. A low current, source side, hot electron injection programming method is used.

Owner:MACRONIX INT CO LTD

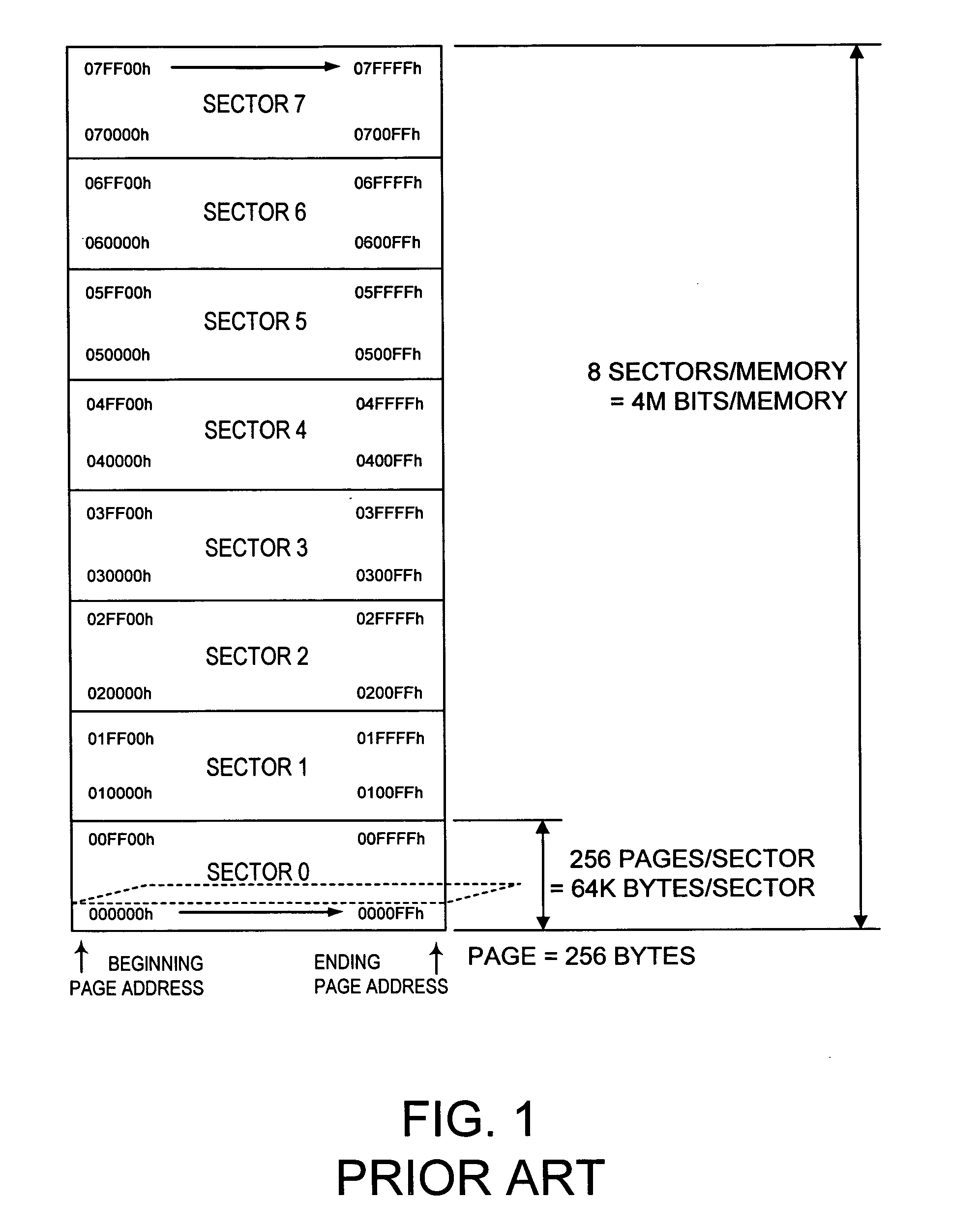

Small sector floating gate flash memory

ActiveUS20060256606A1Small sector sizeSacrificing original benefitRead-only memoriesDigital storageFowler nordheimMemory array

To control the problem of program and erase disturb in flash memory arrays having multiple sectors of cells grouped in each isolation wells of the flash memory array, a refresh procedure is used that involves two readings of each of the cells in a “refresh area” of a group under different read timing conditions, with other read conditions being constant or varied as desired. Cells that yield the same result in both reads are not excessively disturbed and need not be reprogrammed. However, cells that read differently may be excessively disturbed and should be reprogrammed. The refresh procedure is particularly suitable for memory arrays with small sector size and many sectors per group. The memory arrays preferably incorporate memory cells that use hot electron programming and Fowler-Nordheim erase.

Owner:WINBOND ELECTRONICS CORP

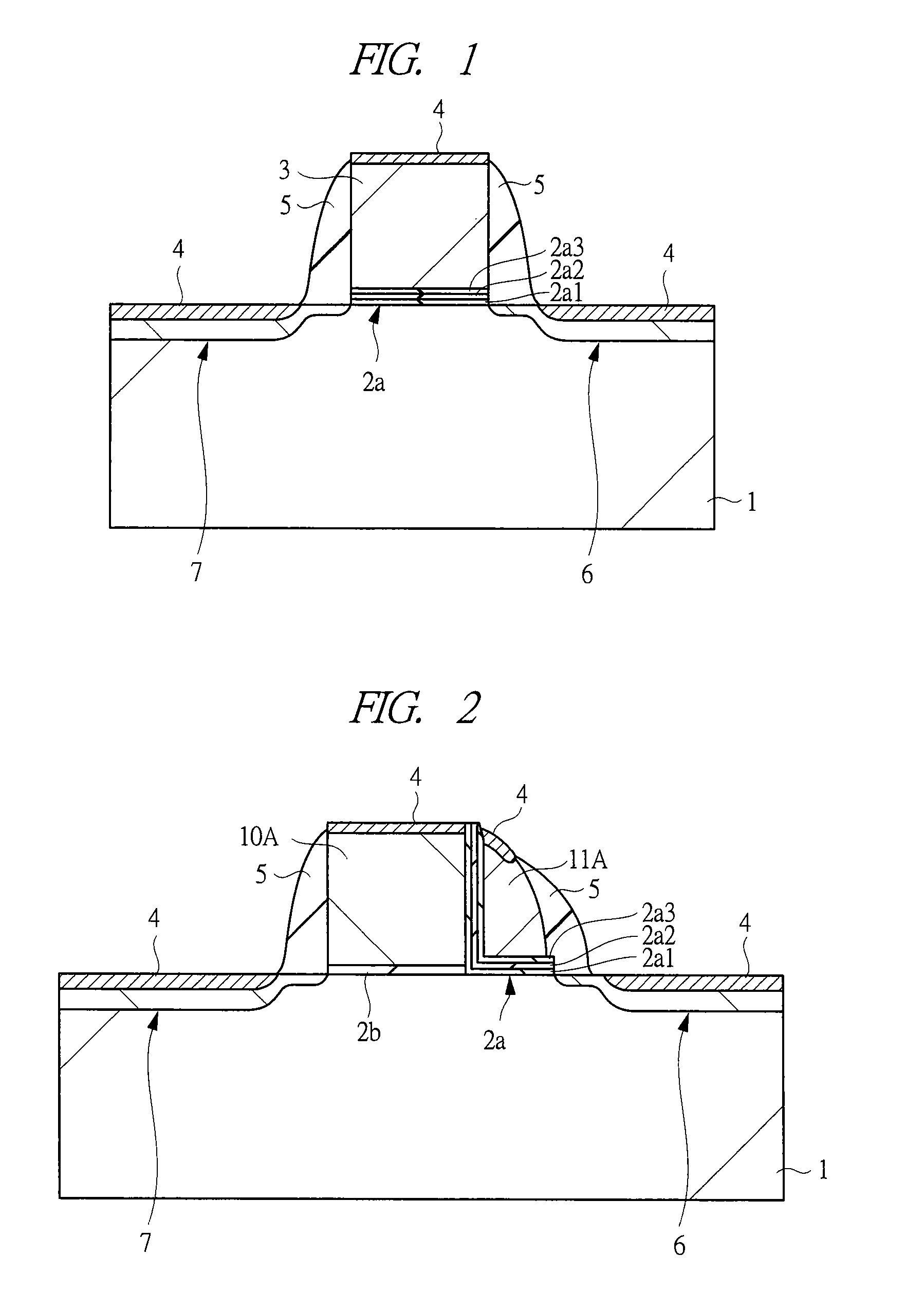

Nonvolatile semiconductor memory devices with charge injection corner

ActiveUS20080290401A1The formation process is simpleImprove injection efficiencySolid-state devicesRead-only memoriesManufacturing cost reductionCharge injection

An erase method where a corner portion on which an electric field concentrates locally is provided on the memory gate electrode, and charges in the memory gate electrode are injected into a charge trap film in a gate dielectric with Fowler-Nordheim tunneling operation is used. Since current consumption at the time of erase can be reduced by the Fowler-Nordheim tunneling, a power supply circuit area of a memory module can be reduced. Since write disturb resistance can be improved, a memory array area can be reduced by adopting a simpler memory array configuration. Owing to both the effects, an area of the memory module can be largely reduced, so that manufacturing cost can be reduced. Further, since charge injection centers of write and erase coincide with each other, so that (program and erase) endurance is improved.

Owner:RENESAS ELECTRONICS CORP

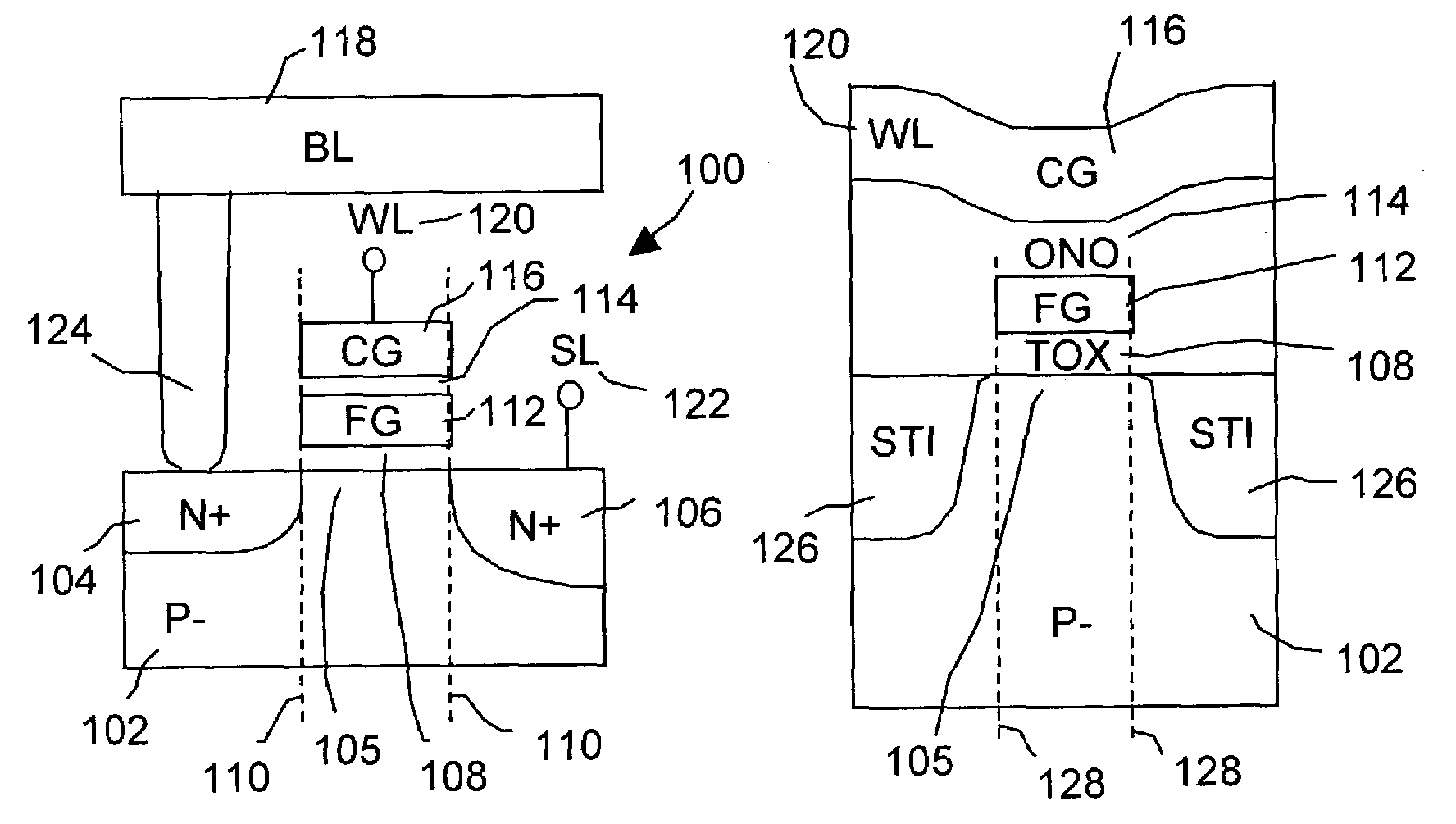

Nonvolatile memory cell having floating gate, control gate and separate erase gate, an array of such memory cells, and method of manufacturing

A nonvolatile memory cell having a floating gate for the storage of charges thereon has a control gate and a separate erase gate. The cell is programmed by hot channel electron injection and is erased by poly to poly Fowler-Nordheim tunneling. A method for making an array of unidirectional cells in a planar substrate, as well as an array of bidirectional cells in a substrate having a trench, is disclosed. An array of such cells and a method of making such an array is also disclosed.

Owner:SILICON STORAGE TECHNOLOGY

Low voltage EEPROM memory arrays

InactiveUS7075140B2Increase cell read currentReduce voltageTransistorSemiconductor/solid-state device testing/measurementLow voltageFowler nordheim

A non-volatile memory array includes memory cells connected in a common source arrangement and formed in columns of isolated well regions so that Fowler-Nordheim tunneling is used for both write and erase operations of the memory cells. The memory arrays can be formed as NOR arrays or NAND arrays. In one embodiment, the memory array of the present invention is formed as a byte alterable EEPROM with parallel access. In another embodiment, an insulated gate bipolar transistor (IGBT) is coupled to the memory cells to increase the cell read current of the memory array. When the memory array incorporates IGBTs on the bitlines, the cell read current becomes independent of the wordline voltages. Thus, the memory array of the present invention can be operated at low voltages. The use of IGBTs in the memory array of the present invention enables formation of embedded non-volatile memories in low-voltage digital integrated circuits.

Owner:SPADEA GREGORIO

Method and apparatus for multiple byte or page mode programming of a flash memory array

A memory array contains memory cells designed to be erased using Fowler-Nordheim ("FN") tunneling through the channel area, and programmed using either channel hot electron injection ("CHE") or channel-initiated secondary electron injection ("CISEI"). To reduce disturbance of the floating gate potential of unselected memory cells during programming operations and read operations, the unselected word lines are brought to a negative potential rather than ground potential. To reduce disturbance of the floating gate potential of unselected memory cells during FN erase operations, the unselected word lines are brought to a positive potential rather than ground potential.

Owner:WINBOND ELECTRONICS CORP

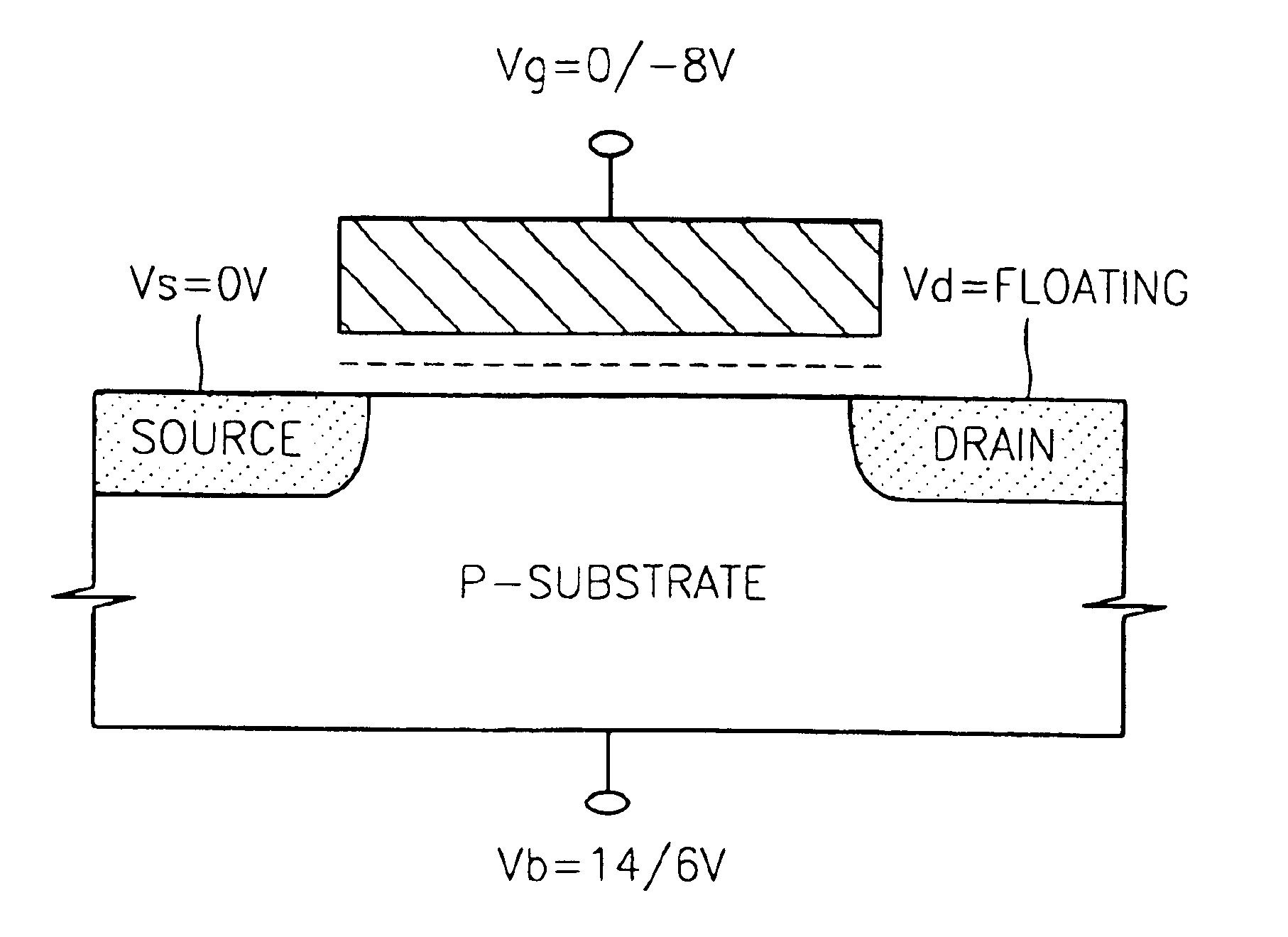

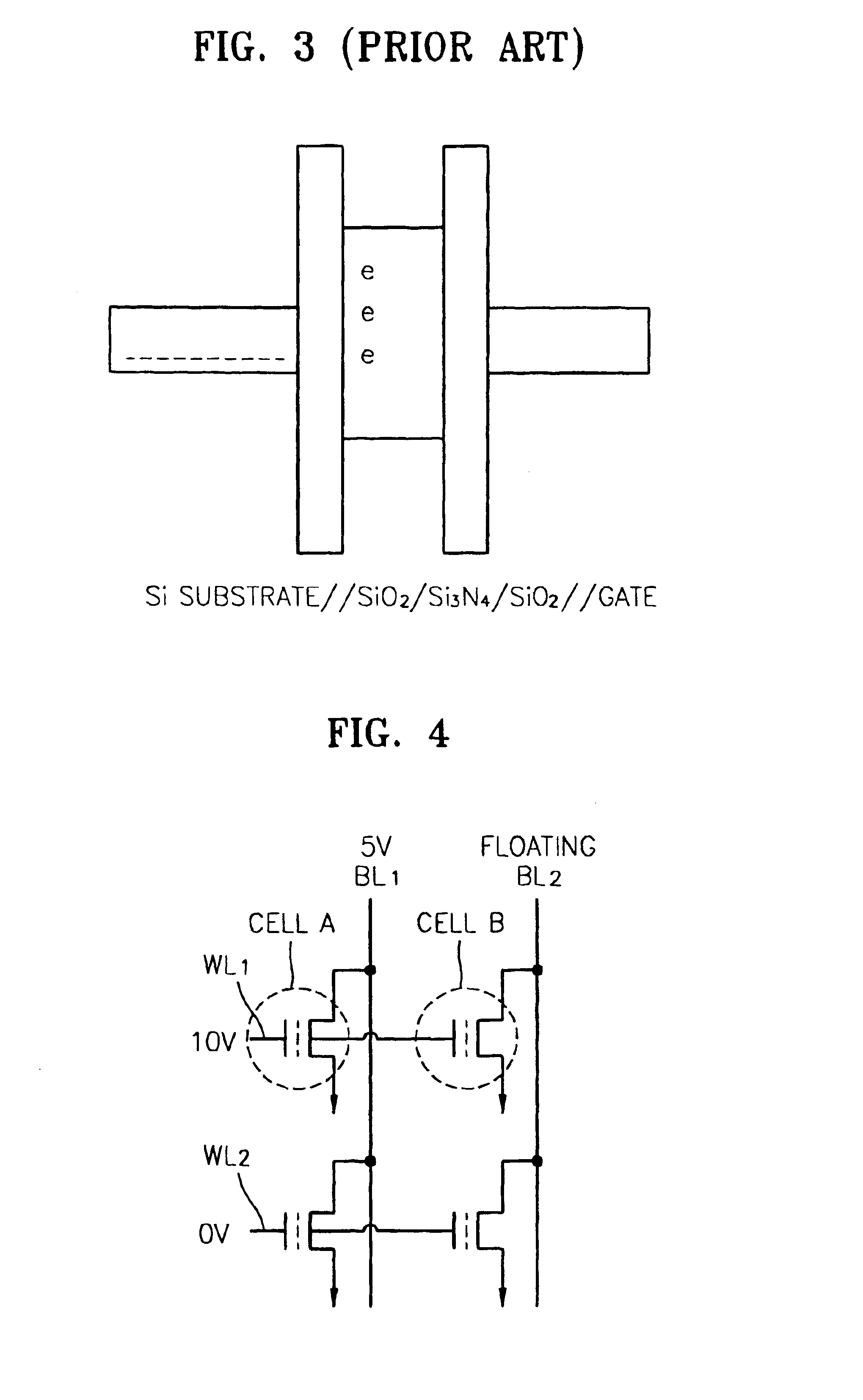

Method for operating NOR type flash memory device including SONOS cells

InactiveUS6847556B2Easy to integrateSimple processTransistorSolid-state devicesBit lineFowler nordheim

Provided is a method for operating a NOR-type flash memory device using SONOS cells. The SONOS cells are selectively programmed using channel hot electron injection and erased using Fowler-Nordheim tunneling and hot hole injection. When the SONOS cells are programmed, a voltage within a range of 8V-12V is applied to a selected word line and a voltage within a range of 3V-6V is applied to a selected bit line. When the SONOS cells are erased, the selected word line is ground and a voltage within a range of 13V-18V is applied to a substrate. Alternatively, a voltage of about −8V is applied to the selected word line, a voltage of about 6V is applied to the substrate, and a bit line and a source line float.

Owner:SAMSUNG ELECTRONICS CO LTD

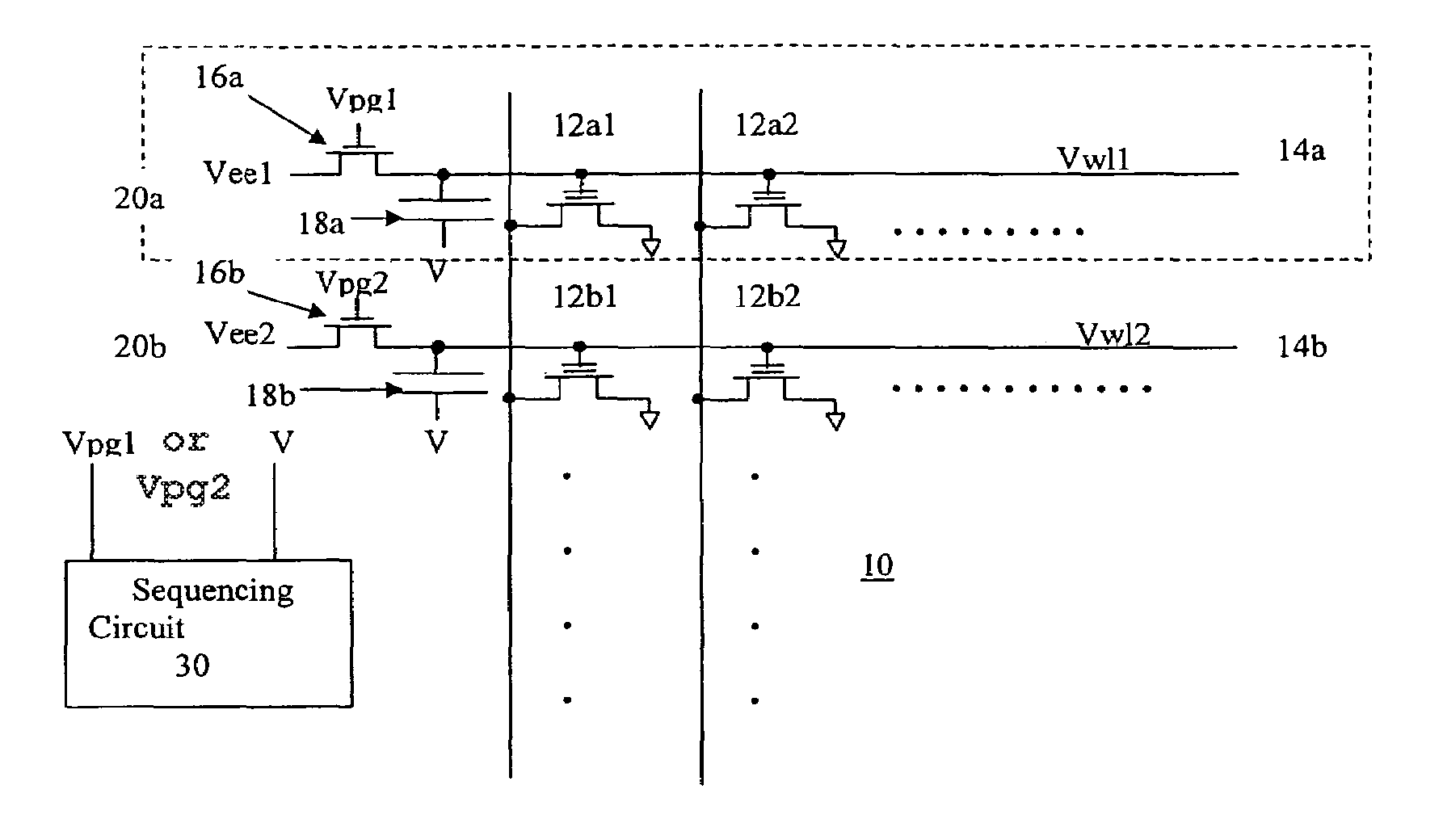

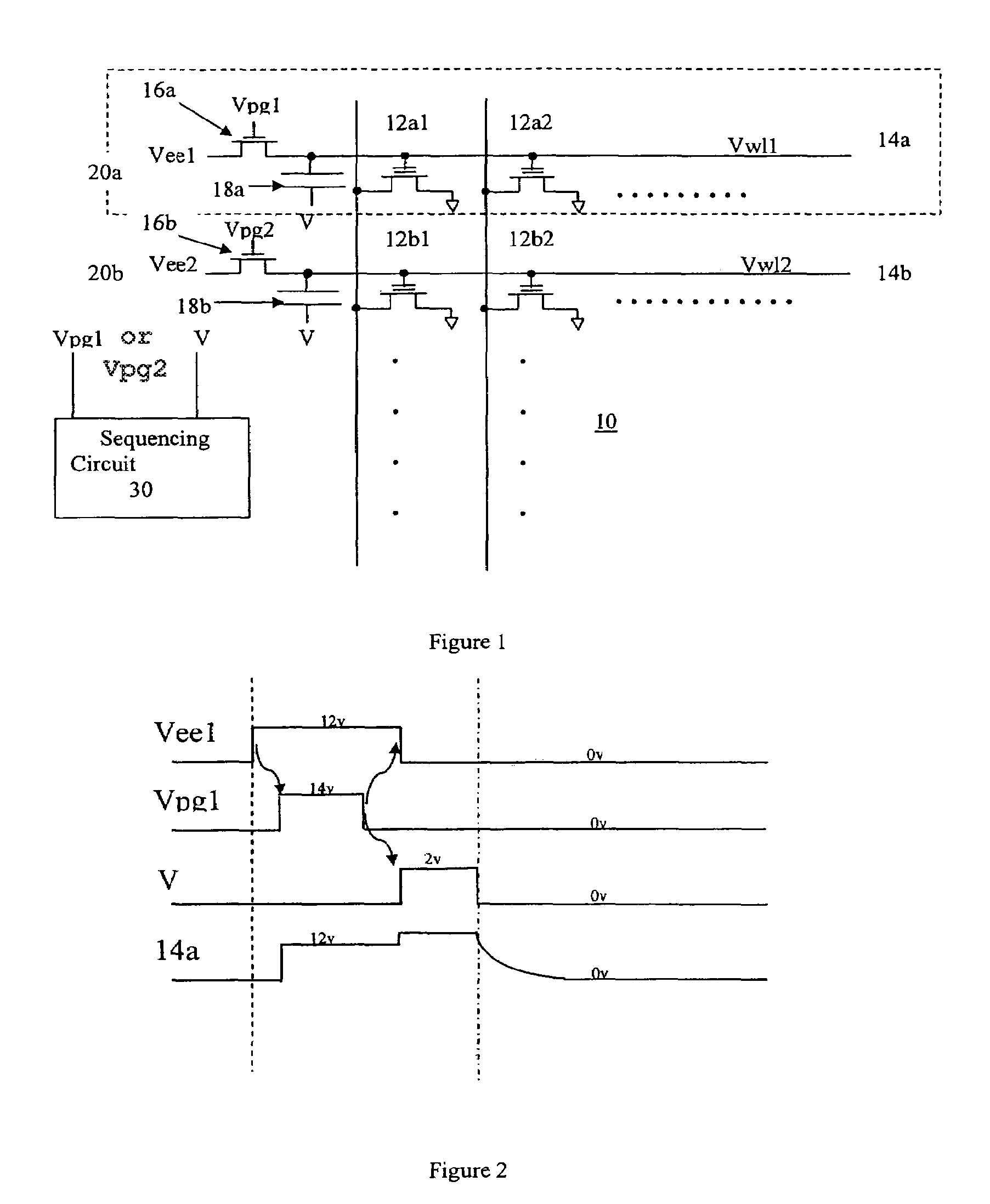

Word line voltage boosting circuit and a memory array incorporating same

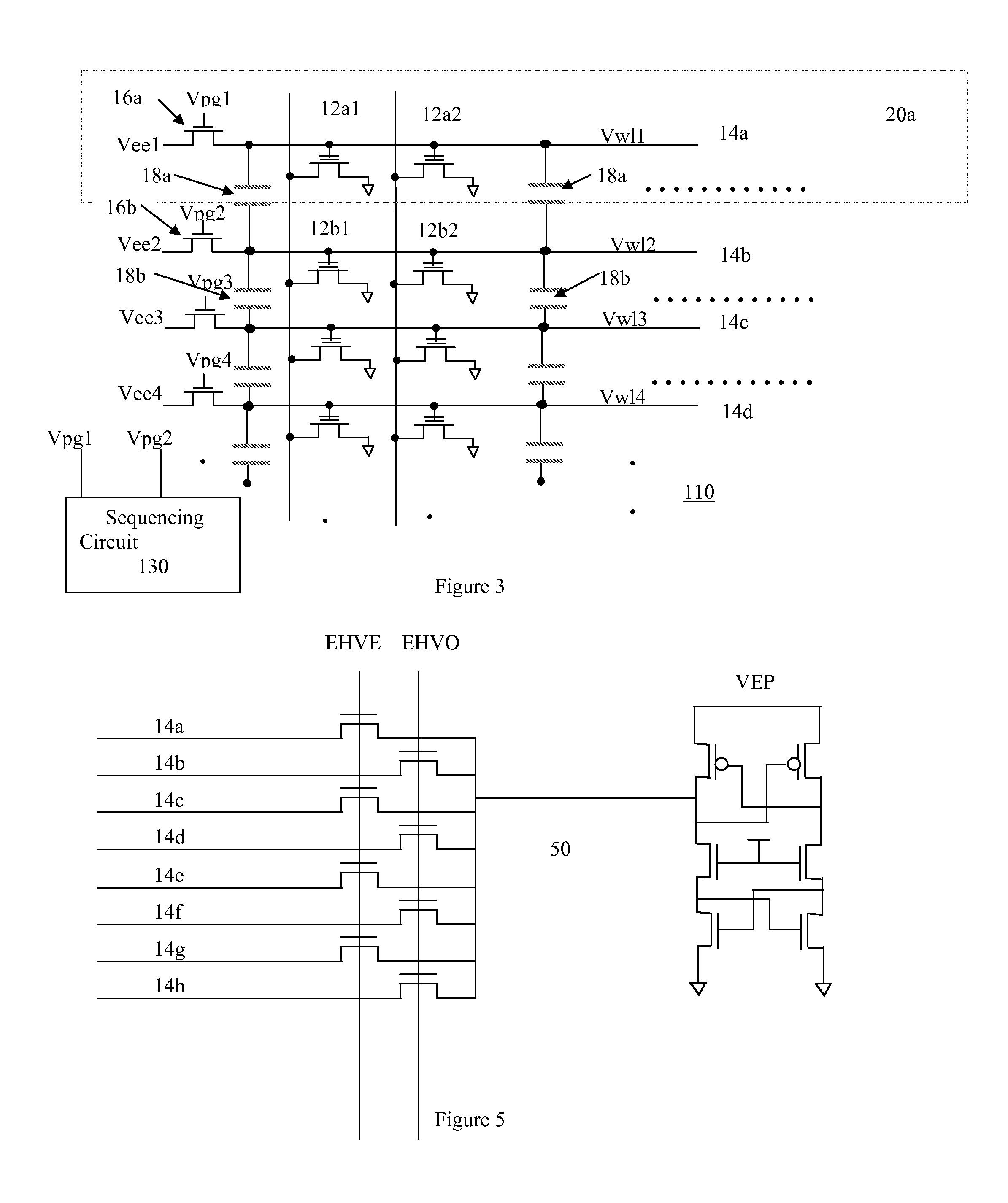

A first embodiment of a word line voltage boosting circuit for use with an array of non-volatile memory cells has a capacitor, having two ends, connected to the word line. One end of the capacitor is electrically connected to the word line. The other end of the capacitor is electrically connected to a first voltage source. The word line is also connected through a switch to a second source voltage source. A sequencing circuit activates the switch such that the word line is connected to the second voltage source, and the other end of the capacitor is not connected to the first voltage source. Then the sequencing circuit causes the switch to disconnect the word line from the second voltage source, and connect the second end of the capacitor to the first voltage source. The alternate switching of the connection boosts the voltage on the word line. In a second embodiment, a first word line is electrically connected to a first switch to a first voltage source. An adjacent word line, capacitively coupled to the first word line, is electrically connected to a second switch to a second voltage source. A sequencing circuit activates the first switch and the second switch such that the first word line is connected to the first voltage source, and the second word line is disconnected from the second voltage source. Then the sequencing circuit causes the first switch to disconnect the first word line from the first voltage source, and causes the second word line to be electrically connected to the second voltage source. The alternate switching of the connection boosts the voltage on the first word line, caused by its capacitive coupling to the second word line. A boosted voltage on the word line may be used to improve cycling and yield, where the memory cells of the array are of the floating gate type and erase through the mechanism of Fowler-Nordheim tunneling from the floating gate to a control gate which is connected to the word line.

Owner:SILICON STORAGE TECHNOLOGY

Charge-trapping memory device and methods for operating and manufacturing the cell

InactiveUS20050104117A1Reduce the total amount of chargingReduce degradationTransistorSolid-state devicesGate dielectricFowler nordheim

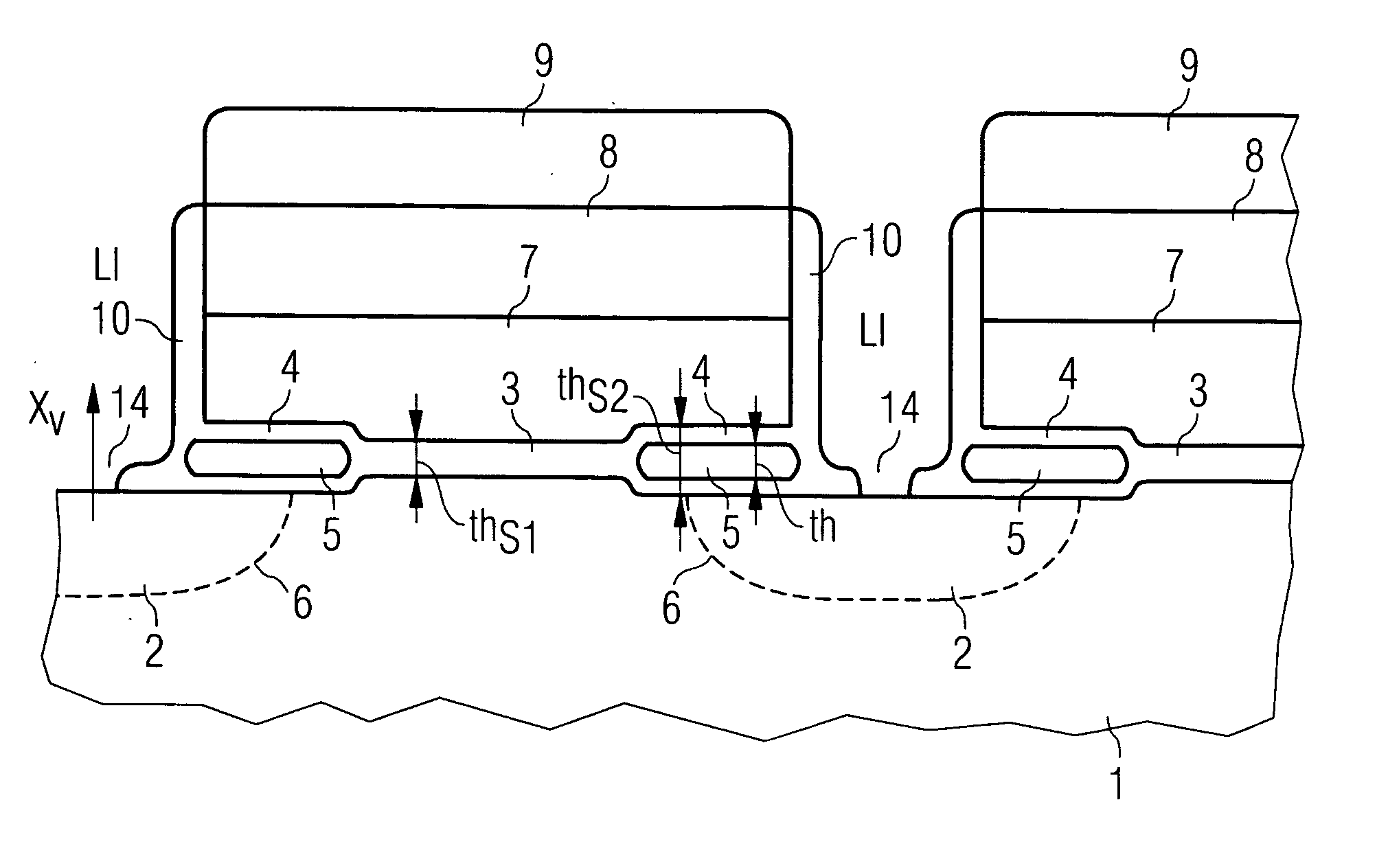

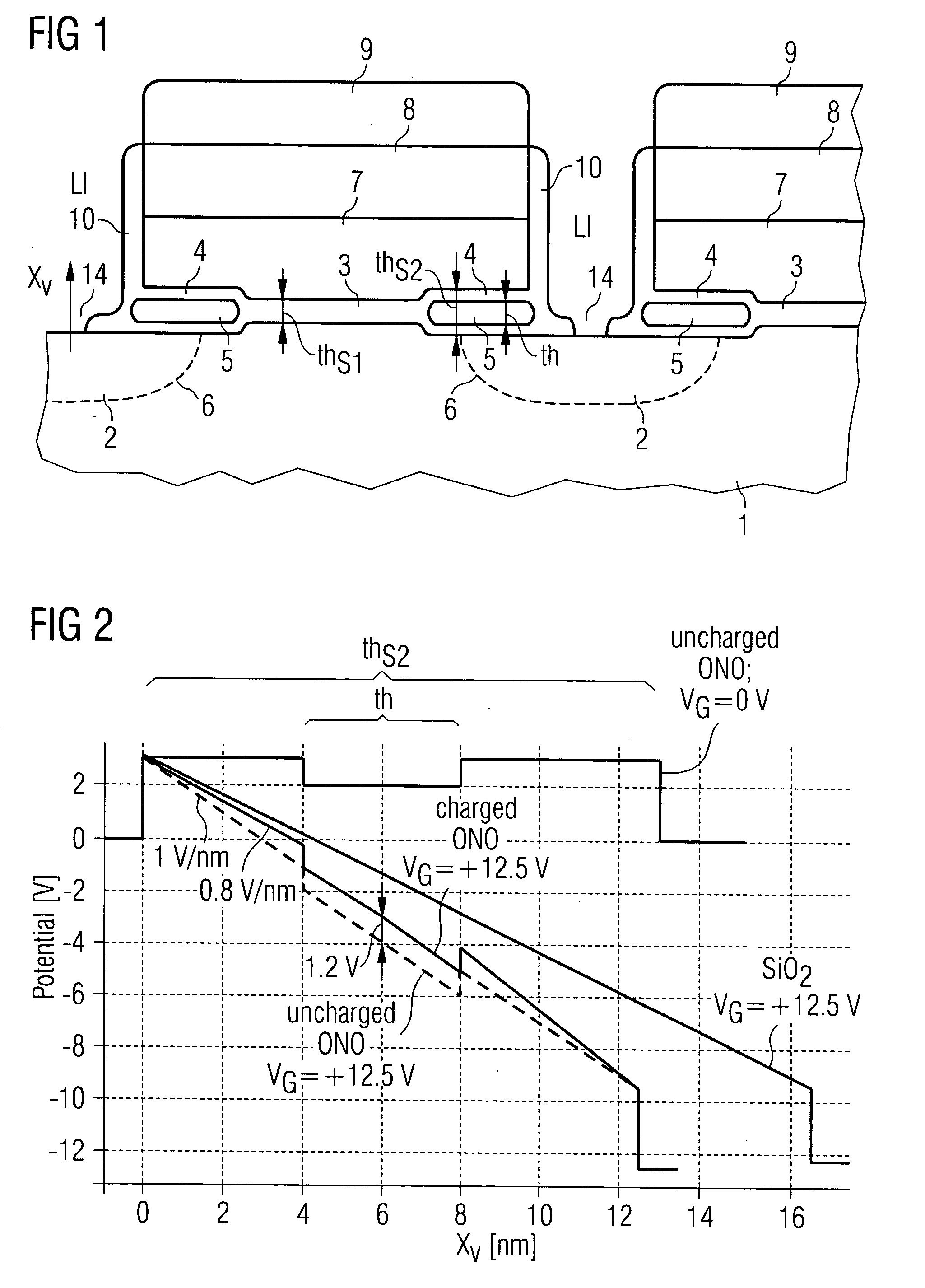

The charge-trapping layer comprises two strips above the source and drain junctions. The thicknesses of the charge-trapping layer and the gate dielectric are chosen to facilitate Fowler-Nordheim-tunnelling of electrons into the strips during an erasure process. Programming is performed by injection of hot holes into the strips individually for two-bit storage.

Owner:POLARIS INNOVATIONS

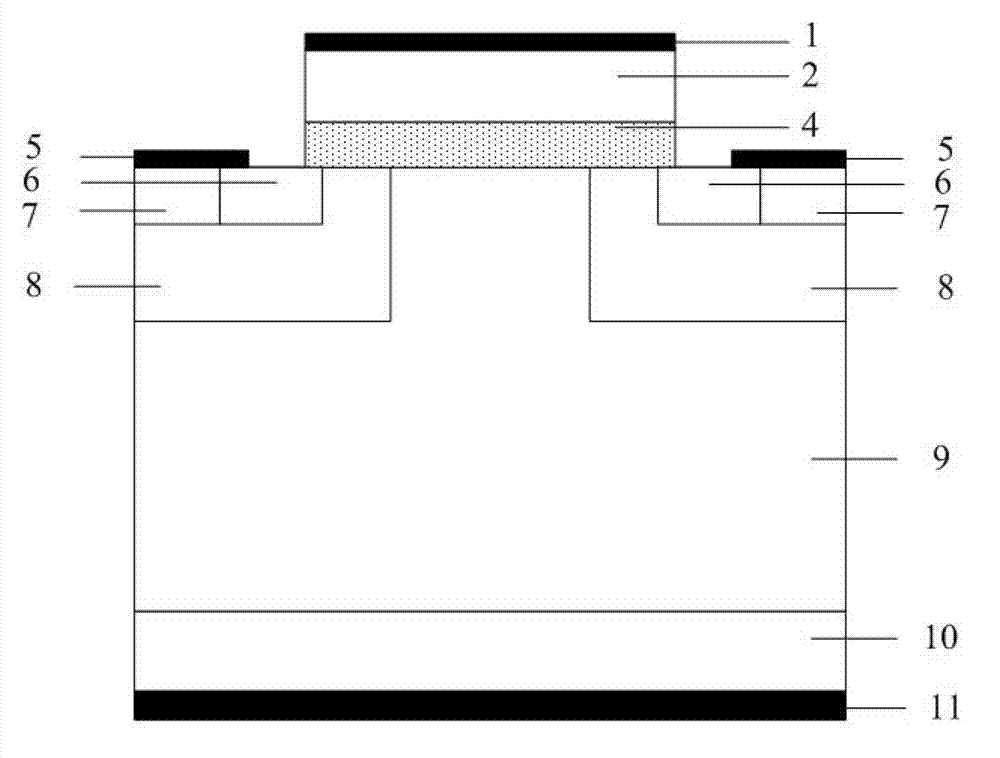

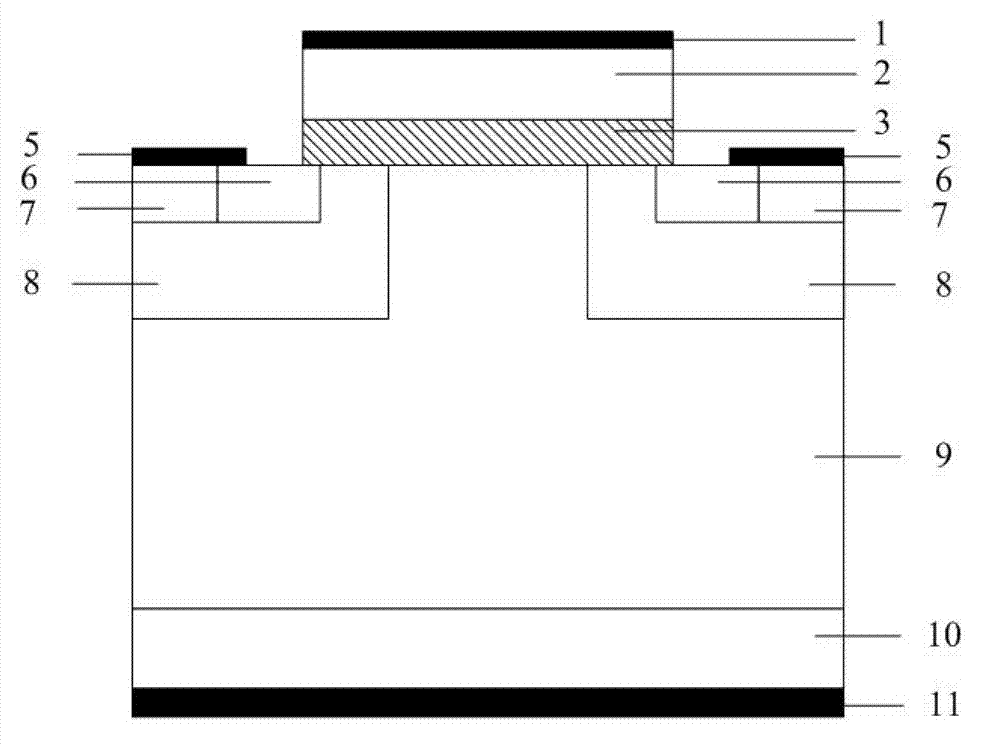

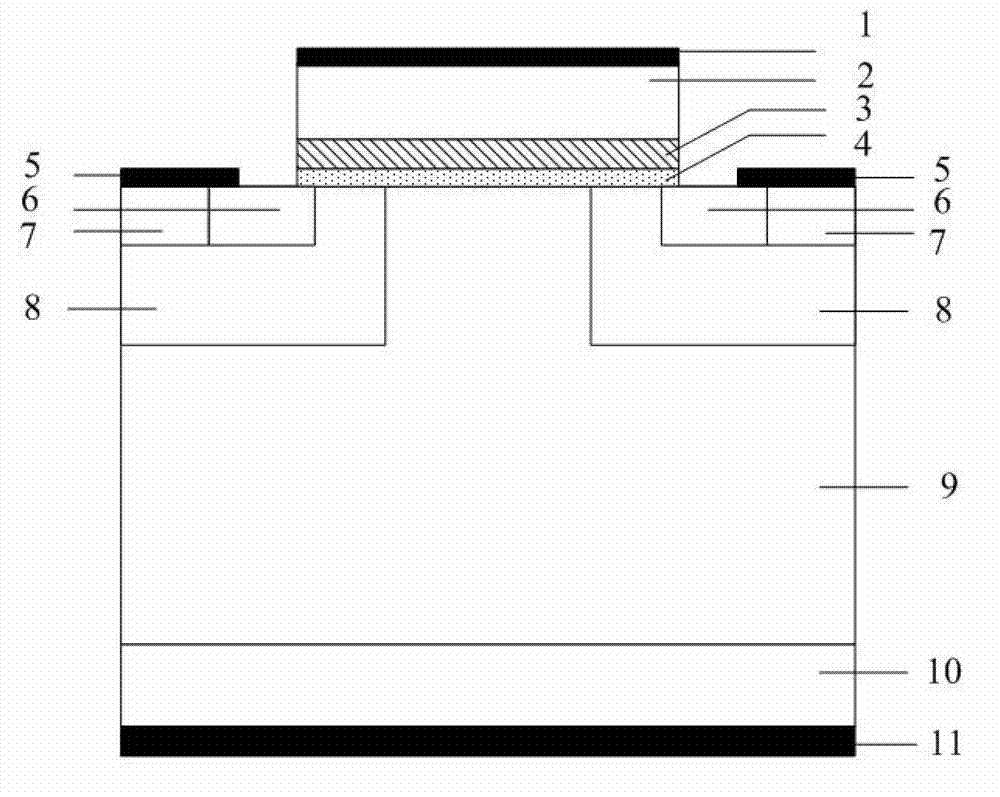

SiC vertical double diffusion metal oxide semiconductor structure (VDMOS) device with composite gate dielectric structure

InactiveCN102779852ALower breakdown voltageAvoid premature breakdownSemiconductor devicesDielectricGate dielectric

The invention discloses a SiC vertical double diffusion metal oxide semiconductor structure (VDMOS) device with a composite gate dielectric structure, and belongs to the technical field of power semiconductor devices. A thought of differentiating modulation of electric fields is adopted according to difference of intensities of electric fields and difference of defect concentrations of gate dielectrics in different areas, namely, high-k gate dielectrics are adopted in channel regions with high-defect concentration and a low electric field, so that a large quantity of trap states caused by using a SiO2 / SiC interface is avoided; the influence on Fowler-Nordheim (FN) tunneling current is obviously reduced; and meanwhile, because the electric field intensity in a channel injection area is small, the reduction on gate dielectric breakdown voltage caused by small offset of conduction band / valence band is weakened; and moreover, a SiO2 gate dielectric (a junction field-effect transistor (JFET) area is formed in a way of extension and is not subjected to ion injection, the surface quality of the JFET area is good, and the SiO2 / SiC interface state is low) is adopted by the JFET area with low defect concentration and a high electric field, and enough high conduction band offset is supplied by the SiO2 dielectric, so that the ahead breakdown of the gate dielectric is avoided.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

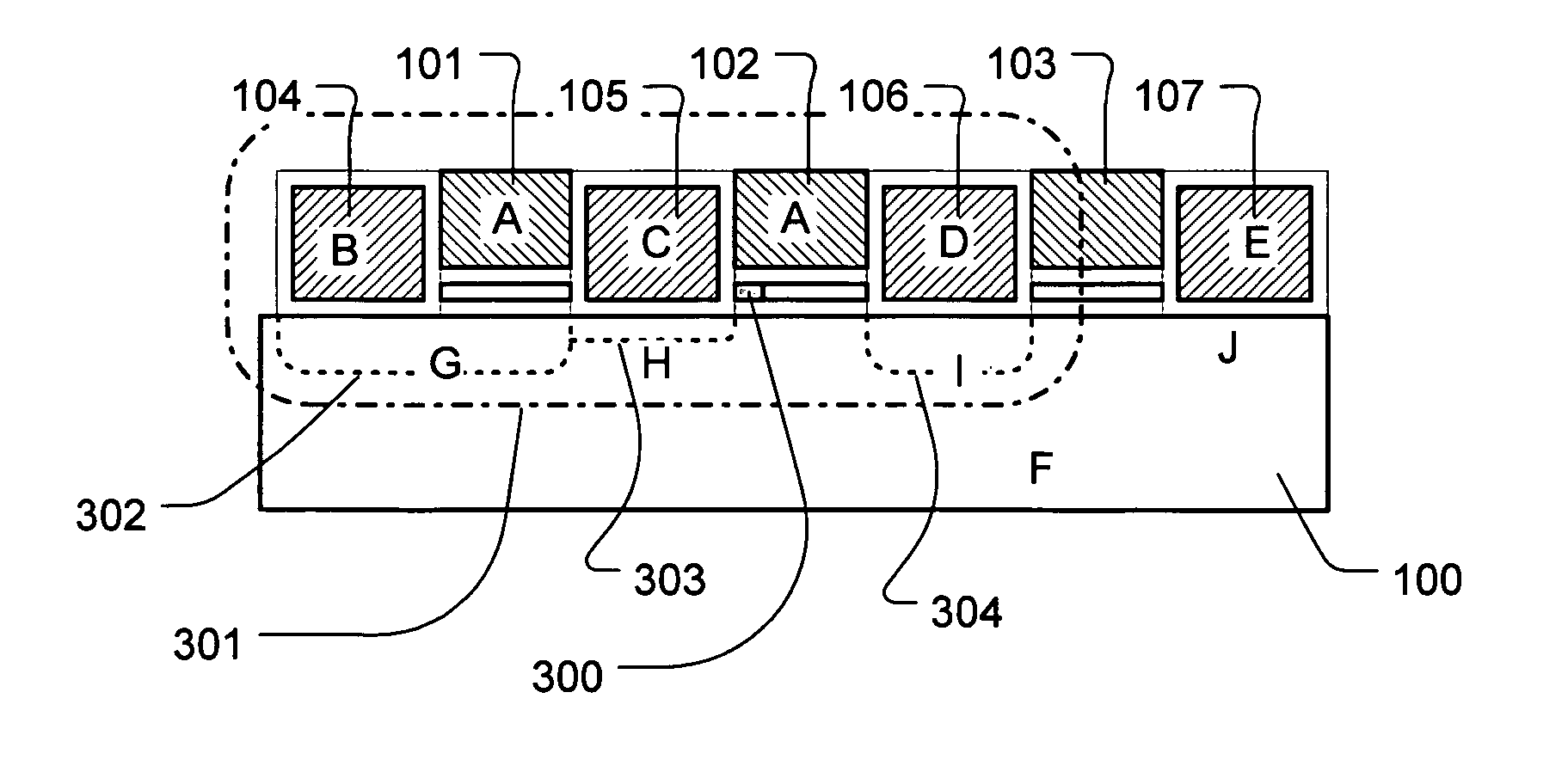

Monolithic, combo nonvolatile memory allowing byte, page and block write with no disturb and divided-well in the cell array using a unified cell structure and technology with a new scheme of decoder and layout

InactiveUS7064978B2Large positive voltageSmaller memory cell.Semiconductor/solid-state device detailsSolid-state devicesInsulation layerFowler nordheim

A nonvolatile memory array has a single transistor flash memory cell and a two transistor EEPROM memory cell which maybe integrated on the same substrate. The nonvolatile memory cell has a floating gate with a low coupling coefficient to permit a smaller memory cell. The floating gate placed over a tunneling insulation layer, the floating gate is aligned with edges of the source region and the drain region and having a width defined by a width of the edges of the source the drain. The floating gate and control gate have a relatively small coupling ratio of less than 50% to allow scaling of the nonvolatile memory cells. The nonvolatile memory cells are programmed with channel hot electron programming and erased with Fowler Nordheim tunneling at relatively high voltages.

Owner:CALLAHAN CELLULAR L L C

Non-volatile static random access memory

InactiveUS6965524B2Easy to optimizeRead-only memoriesDigital storageStatic random-access memoryFowler nordheim

In accordance with the present invention, a memory cell includes a non-volatile device and a SRAM cell. The SRAM cell includes first and second MOS transistors. The non-volatile device is a load to the SRAM cell. The memory cell may be adapted to operate differentially if a second SRAM cell and a second non-volatile device is disposed therein. If so adapted, the SRAM cells and / or the non-volatile devices when programmed store and supply complementary data. The non-volatile devices are erased prior to being programmed. Programming of the non-volatile devices may be done via hot-electron injection or Fowler-Nordheim tunneling. When a power failure occurs, the data stored in the SRAM are loaded in the non-volatile devices. After the power is restored, the data stored in the non-volatile devices are restored in the SRAM cells. The differential reading and wring of data reduces over-erase of the non-volatile devices.

Owner:O2IC

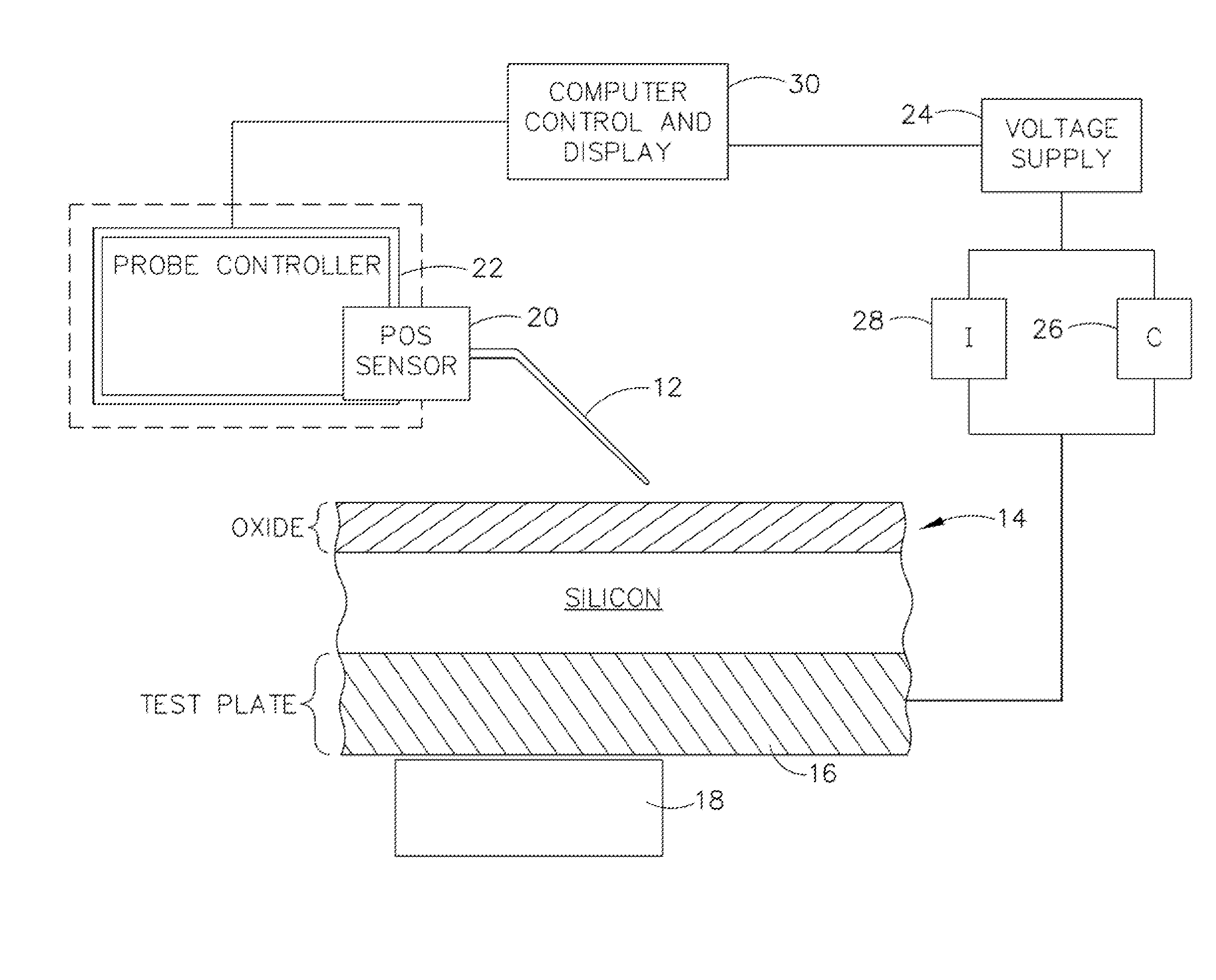

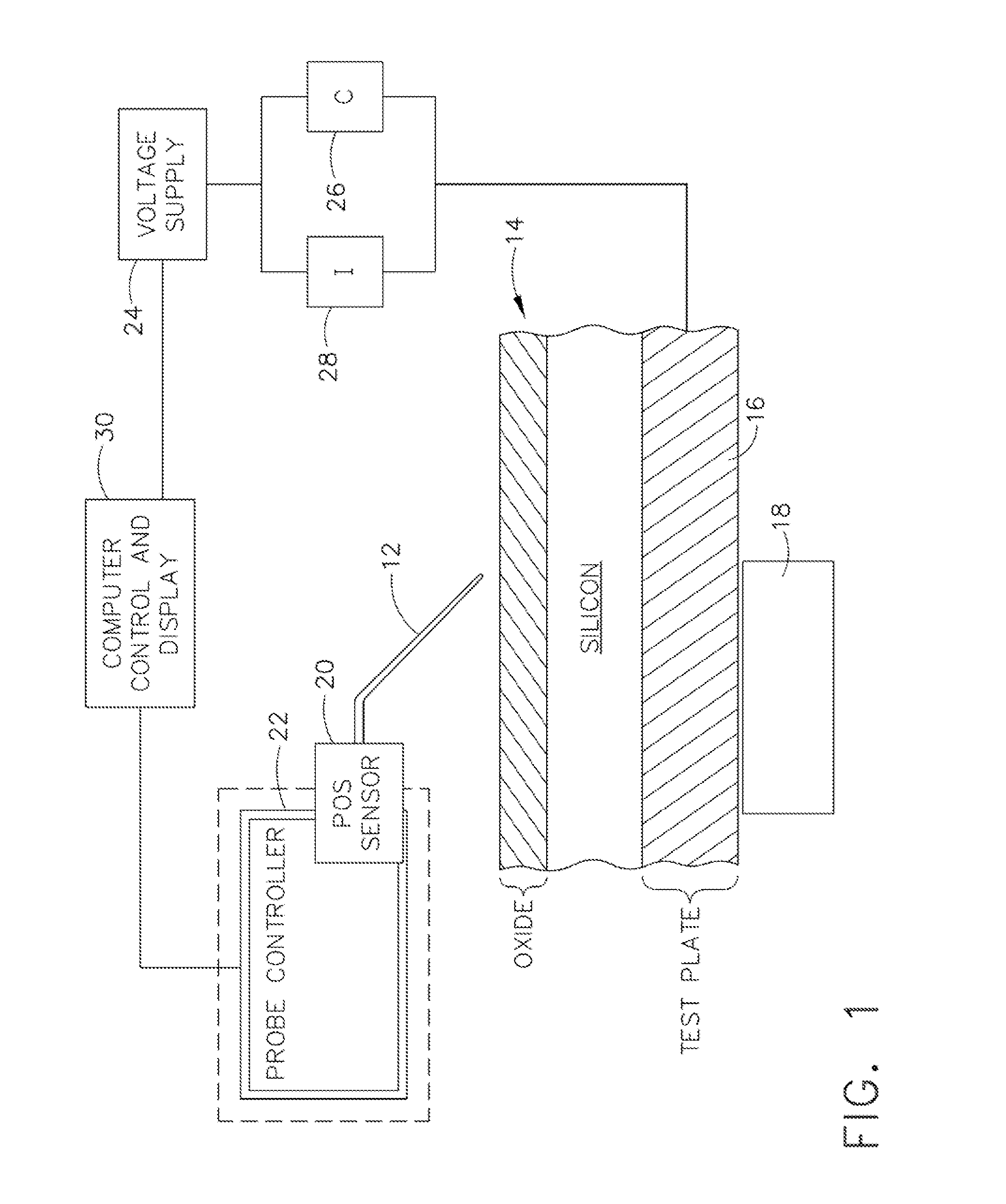

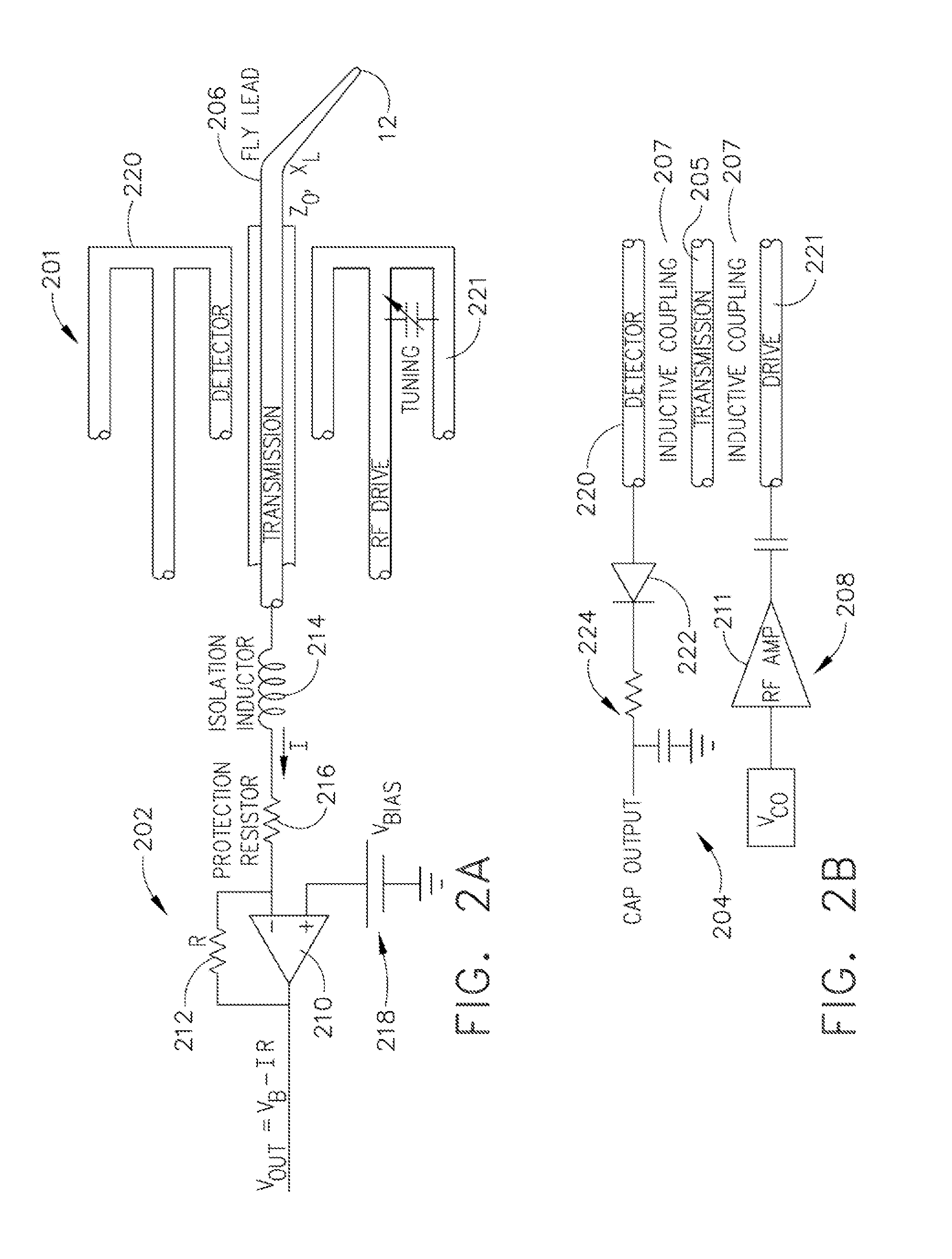

Apparatus and method for combined micro-scale and nano-scale c-v, q-v, and i-v testing of semiconductor materials

InactiveUS20100148813A1Small capacitance variationReduced measurement areaCapacitance measurementsSemiconductor characterisationSemiconductor materialsFowler nordheim

Current Voltage and Capacitance Voltage (IV and CV) measurements are critical in measurement of properties of electronic materials especially semiconductors. A semiconductor testing device to accomplish IV and CV measurement supports a semiconductor wafer and provides a probe for contacting a surface on the wafer under control of an atomic Force Microscope or similar probing device for positioning the probe to a desired measurement point on the wafer surface. Detection of contact by the probe on the surface is accomplished and test voltage is supplied to the semiconductor wafer. A first circuit for measuring capacitance sensed by the probe based on the test voltage and a complimentary circuit for measuring Fowler Nordheim current sensed by the probe based on the test voltage are employed with the probe allowing the calculation of characteristics of the semiconductor wafer based on the measured capacitance and Fowler Nordheim current.

Owner:MULTIPROBE

Non-volatile memory technology suitable for flash and byte operation application

ActiveUS20050083738A1Reduce mold sizeReduce process complexityRead-only memoriesDigital storageProgrammable read-only memoryFowler nordheim

The present invention provides a non-volatile memory cell structure suitable for the flash memory cell and EEPROM cell (electrically erasable programmable read only memory cell) to perform the byte programming and byte erase operations. In the programming operation, a higher negative voltage applied to the drain region, such that the hot hole is generated to induce the hot electron into the floating gate through the tunneling oxide layer in the lateral electrical field. In addition, the gate voltage is around the threshold voltage, which dependent on the integration circuit device design. Furthermore, the non-volatile memory cell utilized the channel Fowler-Nordheim tunneling for erasing operation. In order to perform the byte erasing operation, the drain junction used as an inhibition switch. Thus, the unselected cell in the same word line is inhibited by biasing the drain to ground. Therefore, the word lines of unselected cells are ground.

Owner:MARLIN SEMICON LTD

SONOS memory cell having high-K dielectric

ActiveUS20070029601A1TransistorSemiconductor/solid-state device manufacturingFowler nordheimDielectric layer

A semiconductor memory device may include an intergate dielectric layer of a high-K dielectric material interposed between a floating gate and a control gate. With this intergate high-K dielectric in place, the memory device may be erased using Fowler-Nordheim tunneling.

Owner:LONGITUDE FLASH MEMORY SOLUTIONS LTD

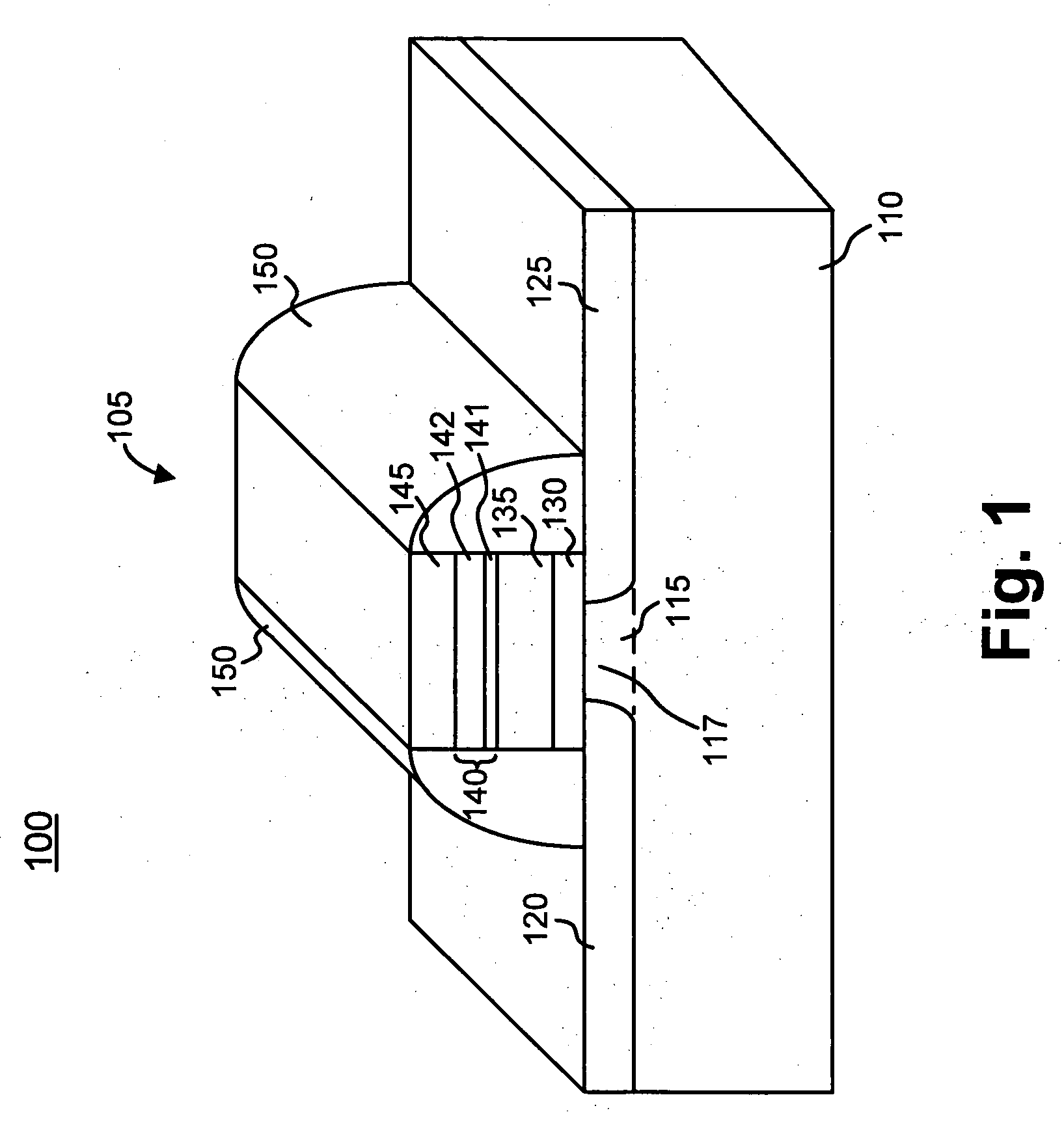

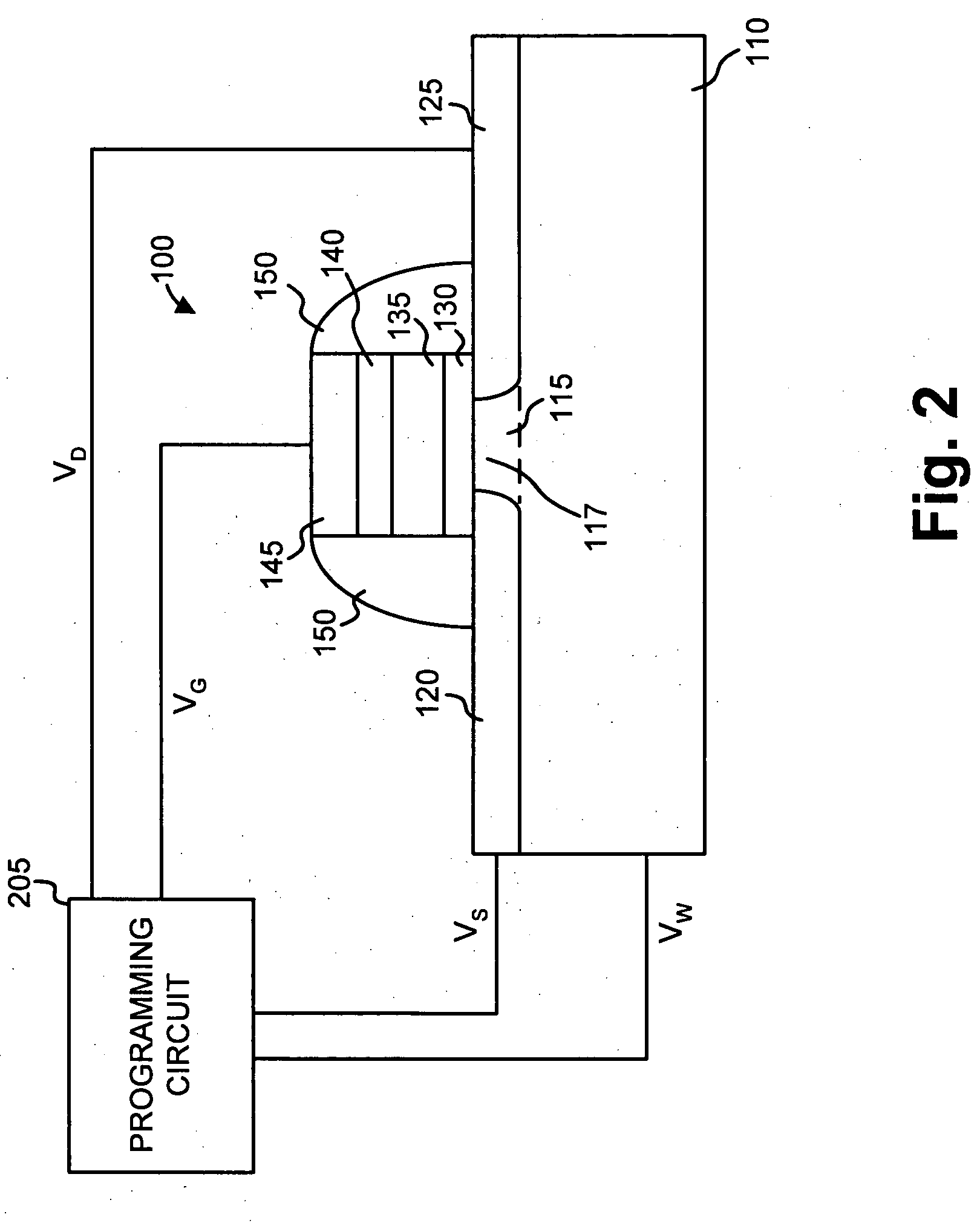

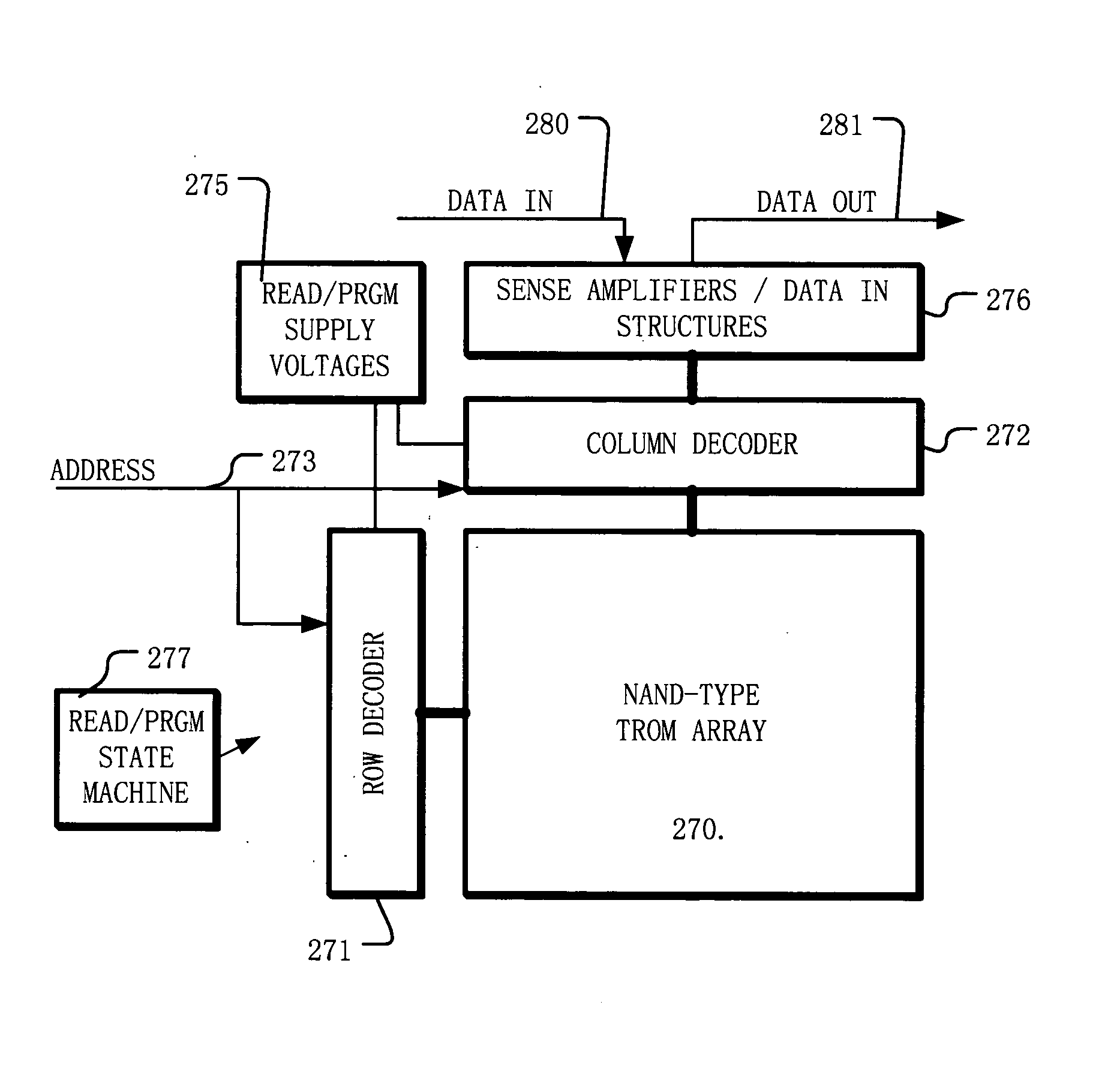

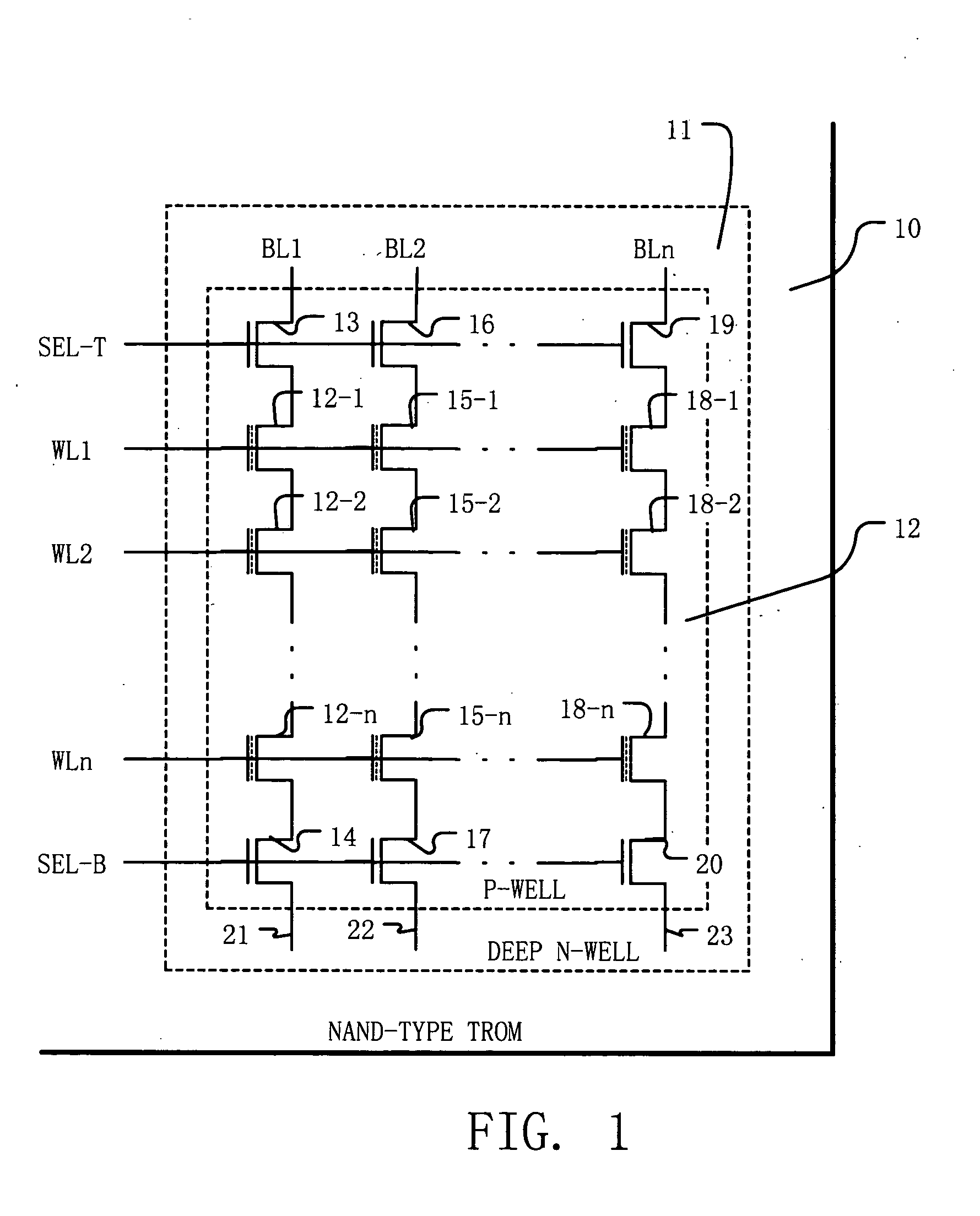

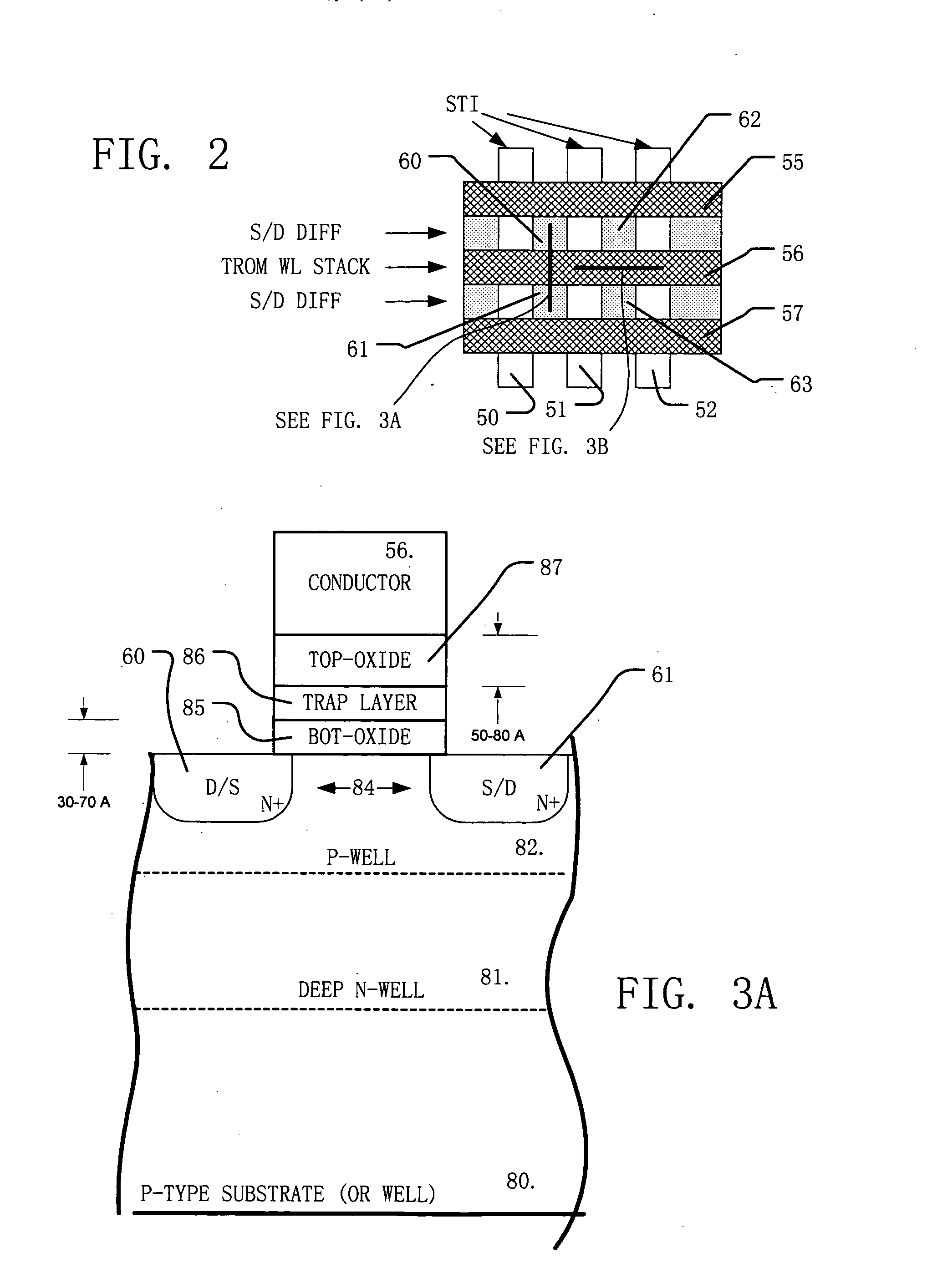

Trap read only non-volatile memory (TROM)

ActiveUS20050169055A1Small small design ruleSmall scaleLogic circuits characterised by logic functionSolid-state devicesDielectricTrapping

A Trap Read Only Memory (TROM) architecture employs a NAND-type array structure configured as a read-only memory that is programmed only one time. The memory cells in the array comprise a gate terminal, a first channel terminal (source / drain), a second channel terminal (drain / source) and a channel region between the first and second channel terminals. A charge trapping structure, such as a layer of silicon nitride, is formed over the channel region. A tunneling dielectric is placed between the channel region and the charge trapping structure, and a blocking dielectric is placed between the charge trapping structure and the gate terminal. An E-field assisted (Fowler-Nordheim FN) tunneling program algorithm is applied.

Owner:MACRONIX INT CO LTD

Inversion bit line, charge trapping non-volatile memory and method of operating same

ActiveUS20060245246A1Easy to scaleLower average currentRead-only memoriesDigital storageBit lineTrapping

A charge trapping memory device in which a field induced inversion layer is used to replace the source and drain implants. The memory cell are adapted to store two bits, one on the left side and one on the right side of the charge trapping structure. A positive threshold voltage erase state is induced using negative gate voltage Fowler Nordheim FN tunneling which establishes a charge balance condition at a positive voltage. A low current, source side, hot electron injection programming method is used.

Owner:MACRONIX INT CO LTD

Method of over-erase prevention in a non-volatile memory device and related structure

InactiveUS6930928B2Raise the threshold voltageParticular applicabilityRead-only memoriesDigital storageFowler nordheimDevice form

A method for enhancing erase of a non-volatile memory device in which the method prevents the over-erase of the memory device is disclosed. The disclosed method includes steps which are performed to precondition the memory device before a program or erase cycle is initiated. The method includes performing a step which includes a tunneling program, such as a Fowler-Nordheim (F-N) tunneling program, to increase the threshold voltage of the non-volatile memory device prior to performing the program / erase cycle. The disclosed method has particular applicability to a non-volatile memory device formed with an NROM device. The disclosed method attenuates or eliminates an over-erase condition in the non-volatile memory device. The related structure that is present in the preconditioning step is also disclosed.

Owner:MACRONIX INT CO LTD

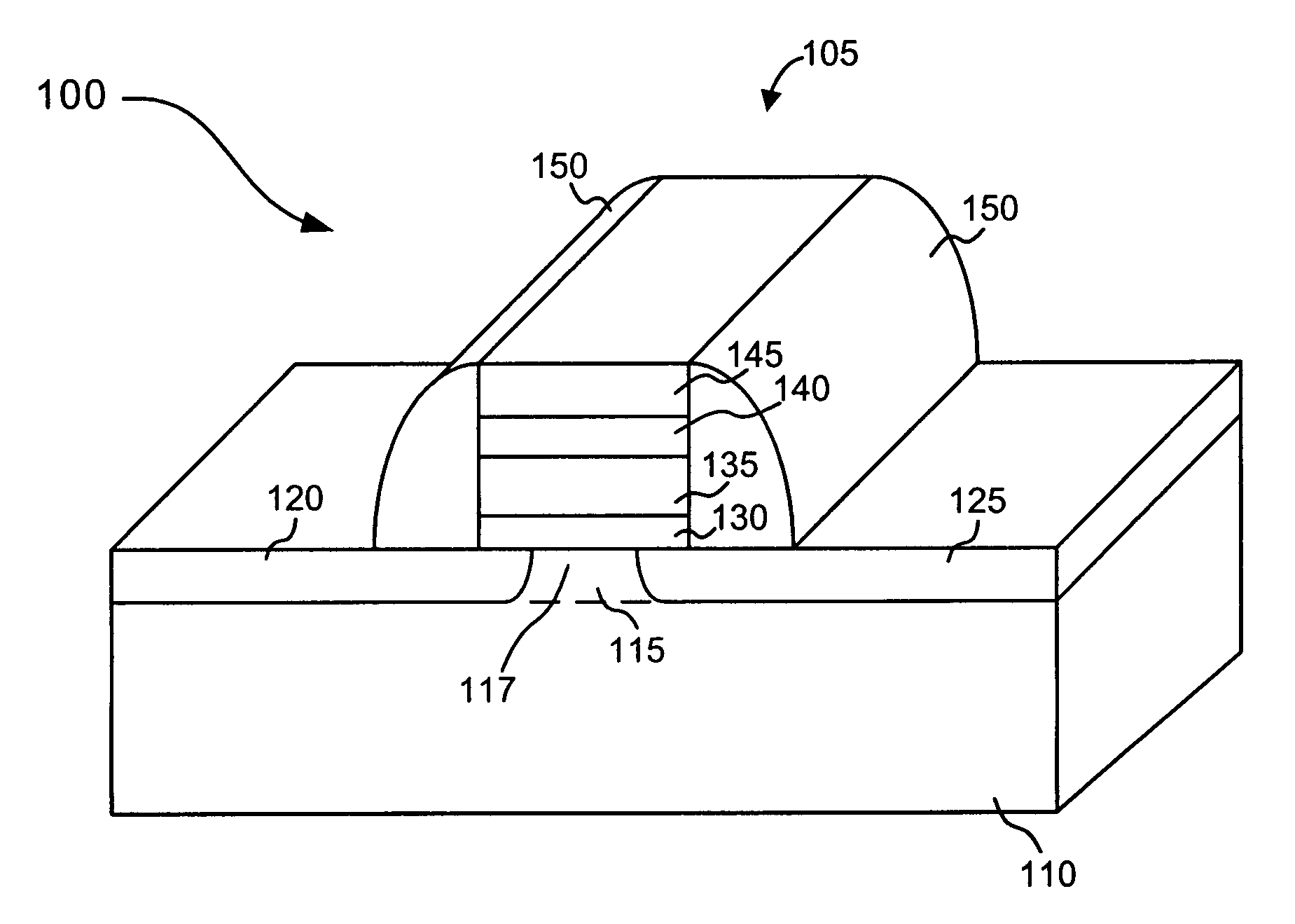

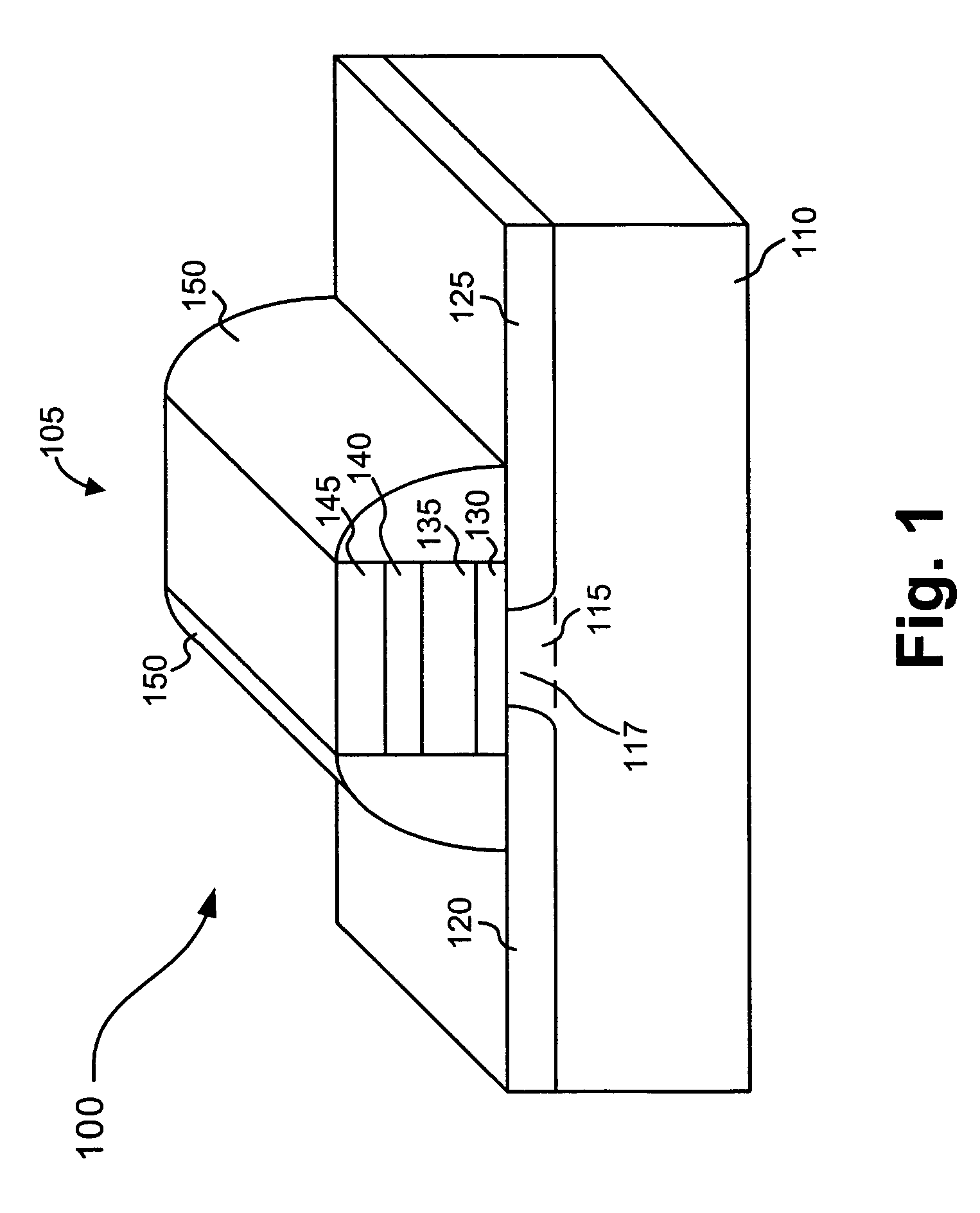

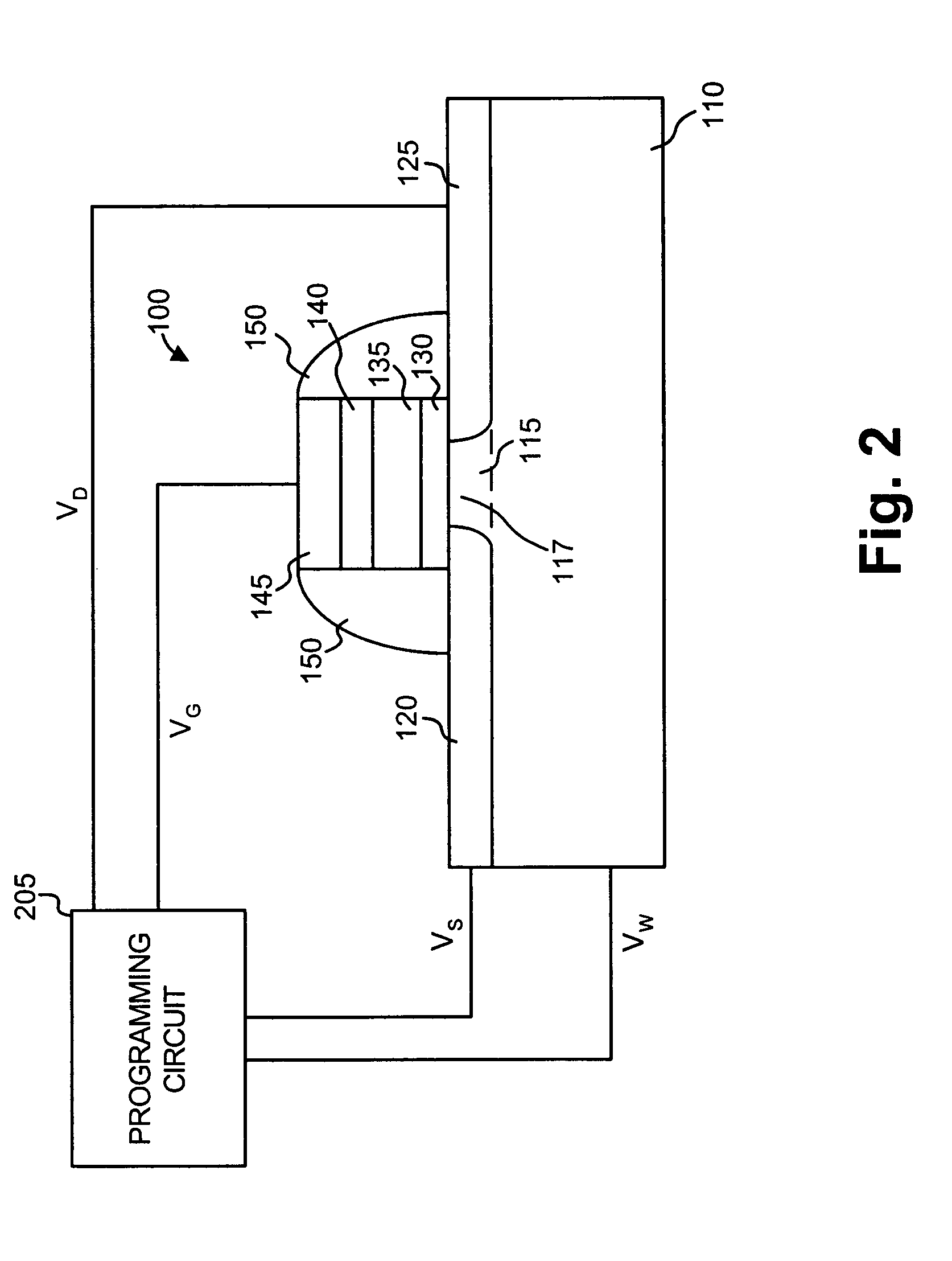

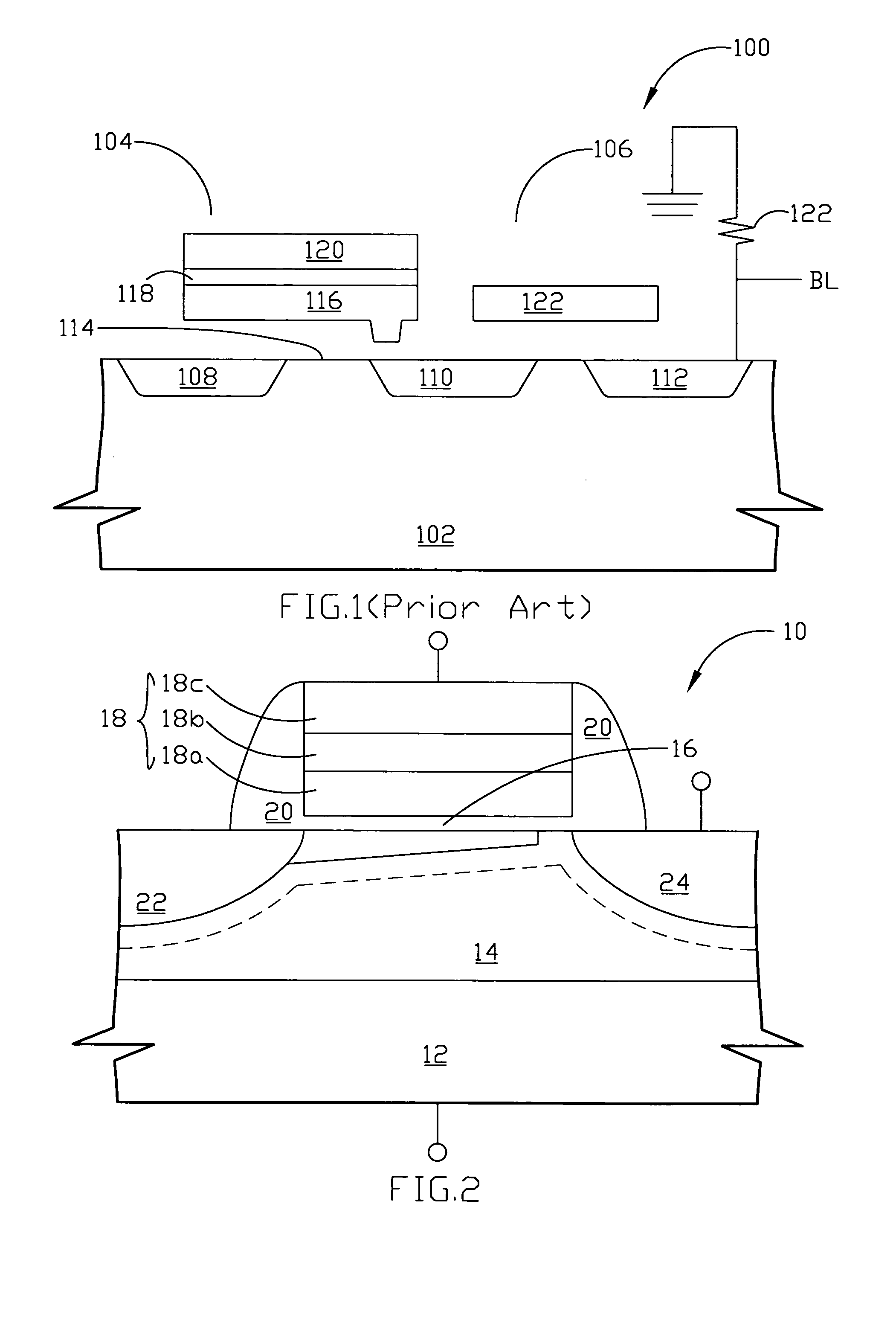

EEPROMs with Trenched Active Region Structures and Methods of Fabricating and Operating Same

An EEPROM includes a semiconductor substrate and a device isolation region defining first, second and third active regions in the semiconductor substrate. The EEPROM also includes at least one first insulation region in at least one first trench in the first active region. A floating gate insulation layer is disposed on the at least one first insulation region and the first, second and third active regions and a floating gate conduction layer is disposed on the floating gate insulation layer. Impurity-containing regions may be disposed in each of the first, second and third active regions at respective sides of the floating gate conduction layer. The floating gate insulation layer may include at least one thinned portion proximate the at least one first insulation region, which may aid Fowler-Nordheim tunneling at this site.

Owner:SAMSUNG ELECTRONICS CO LTD

Bi-directional Fowler-Nordheim tunneling flash memory

A low-voltage nonvolatile memory array includes a cell well of a first conductivity type formed in a substrate; columns of buried bit lines of a second conductivity type formed within the cell well, wherein columns of the buried bit lines are isolated from each other and each is further divided into of sub-bit line segments with deeply doped source wells of the first conductivity type connected to the cell well; a plurality of memory cell blocks serially arranged over one of the columns of buried bit lines, wherein a memory cell block corresponds to a sub-bit line segment, and each memory cell block includes at least one memory transistor having a stacked gate, source, and drain; and a local bit line overlying the memory cell blocks and electrically connected to the drain of the memory transistor via a contact plug short-circuiting the drain and the subjacent buried bit line.

Owner:POWERCHIP SEMICON CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com