Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

6190results about How to "Reduce leakage current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

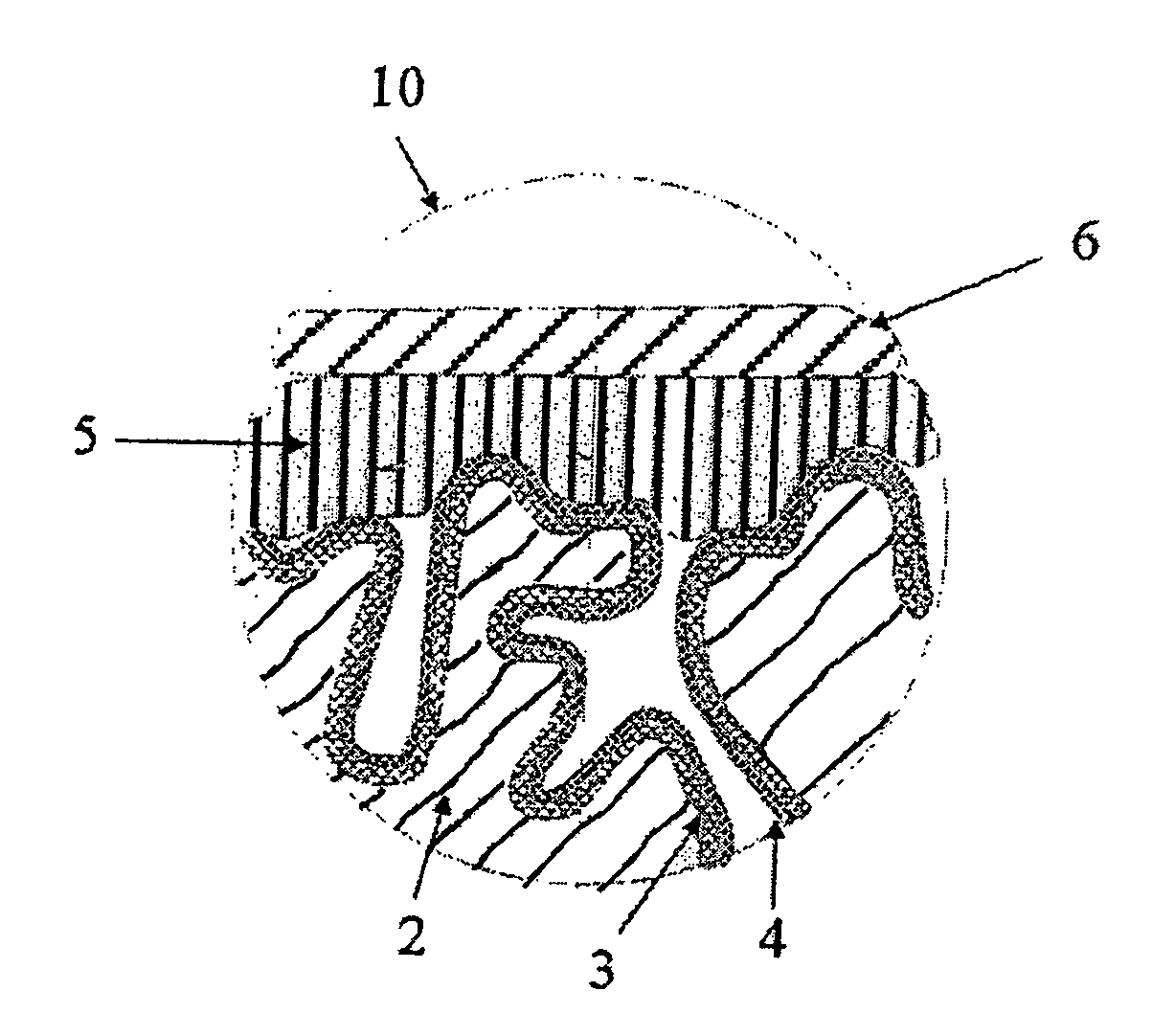

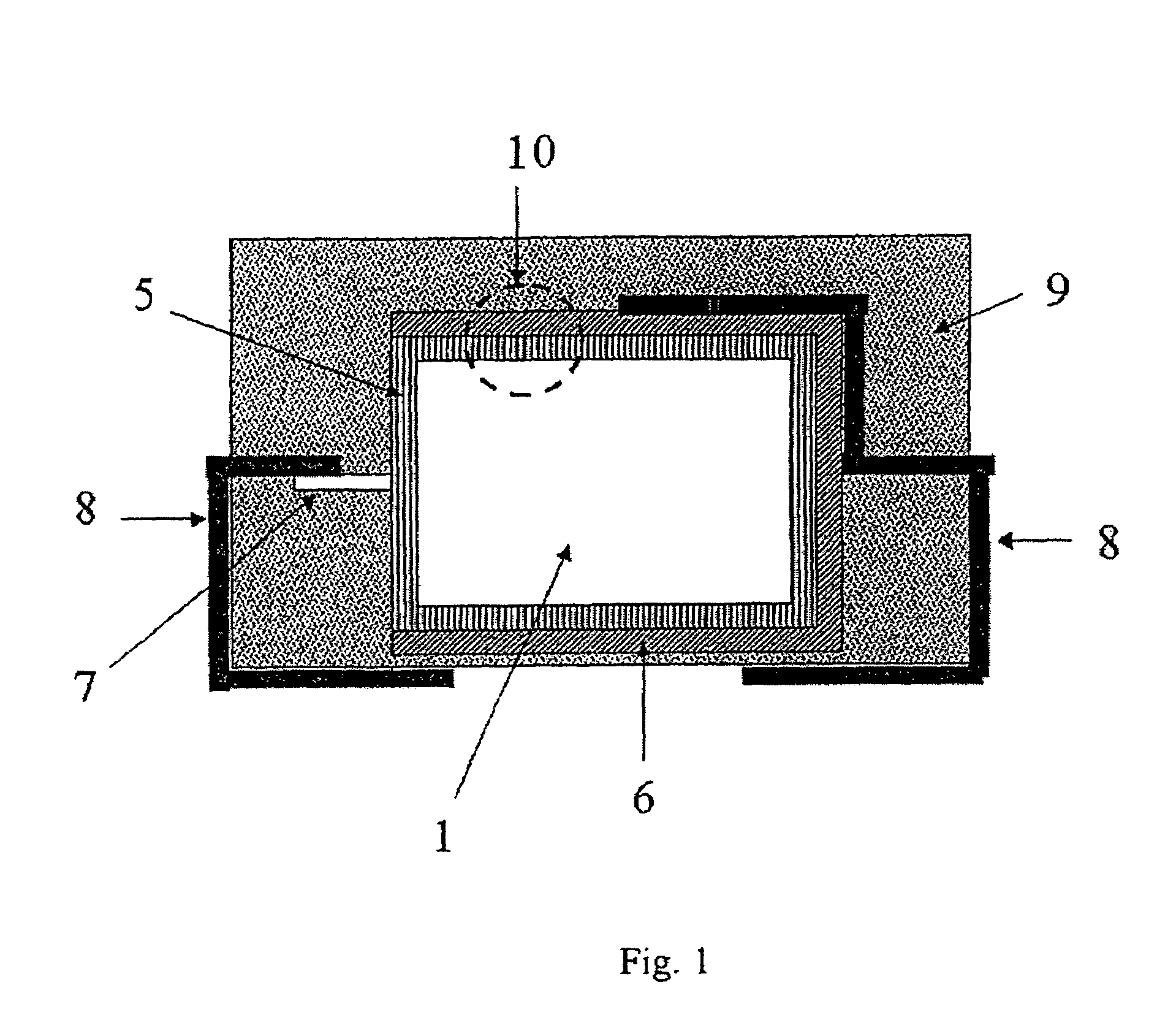

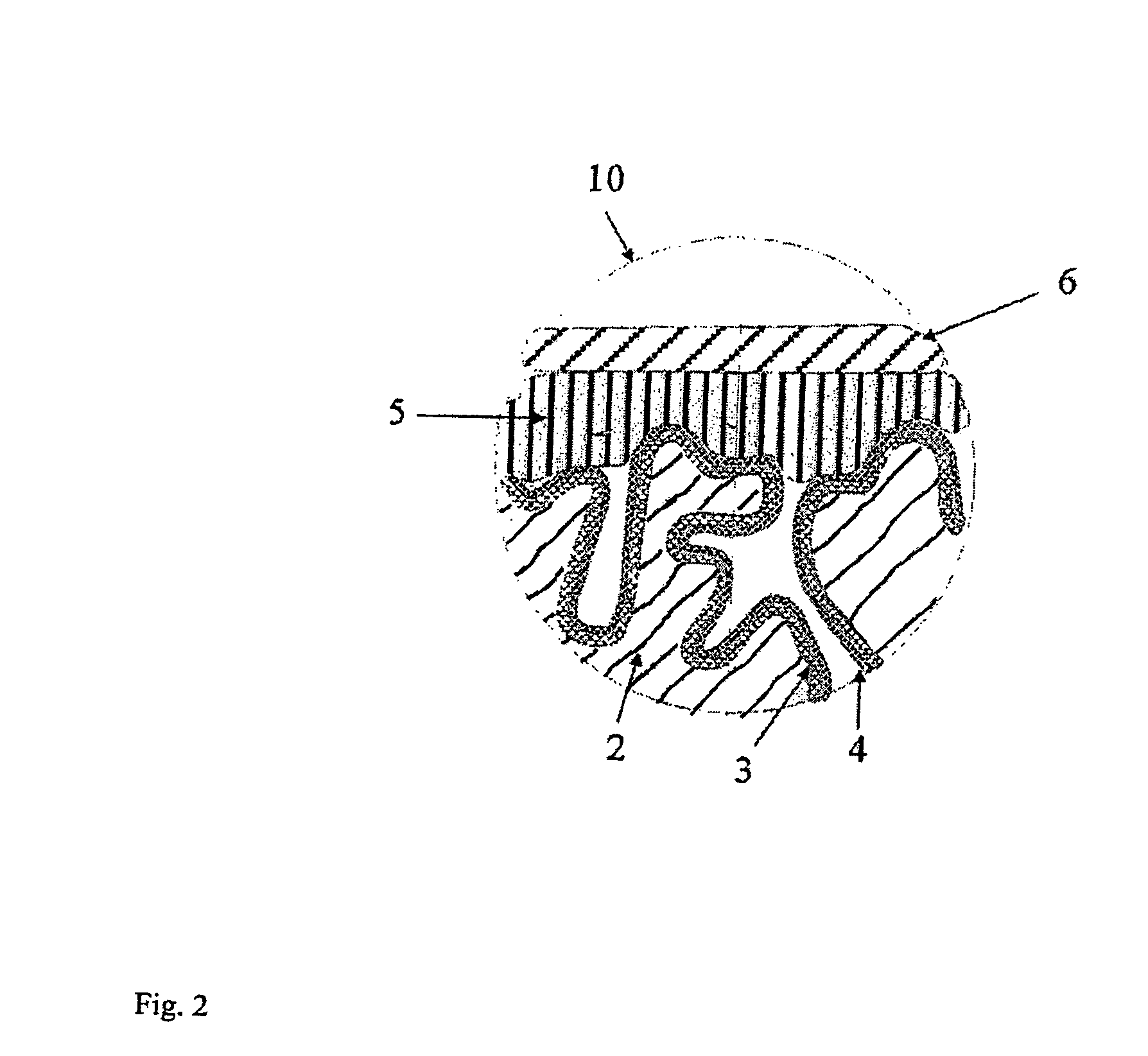

Electrolytic capacitors with a polymeric outer layer

ActiveUS6987663B2Reduce leakage currentLow ESRHybrid capacitor electrolytesSolid electrolytic capacitorsPolymer scienceElectrolysis

Electrolytic capacitors having low equivalent series resistance and low leakage current are described. The electrolytic capacitors include a solid electrolyte layer of a conductive material in particular a conductive polymer, and an outer layer that includes binders, polymeric anions and conductive polymers (e.g., polythiophenes). Also described is a method of preparing electrolytic capacitors that involves forming the conductive polymer of the solid electrolyte layer in situ by means of chemical oxidative polymerization or electrochemical polymerization. Electronic circuits that include the electrolytic capacitors are also described.

Owner:HERAEUS PRECIOUS METALS GMBH & CO KG

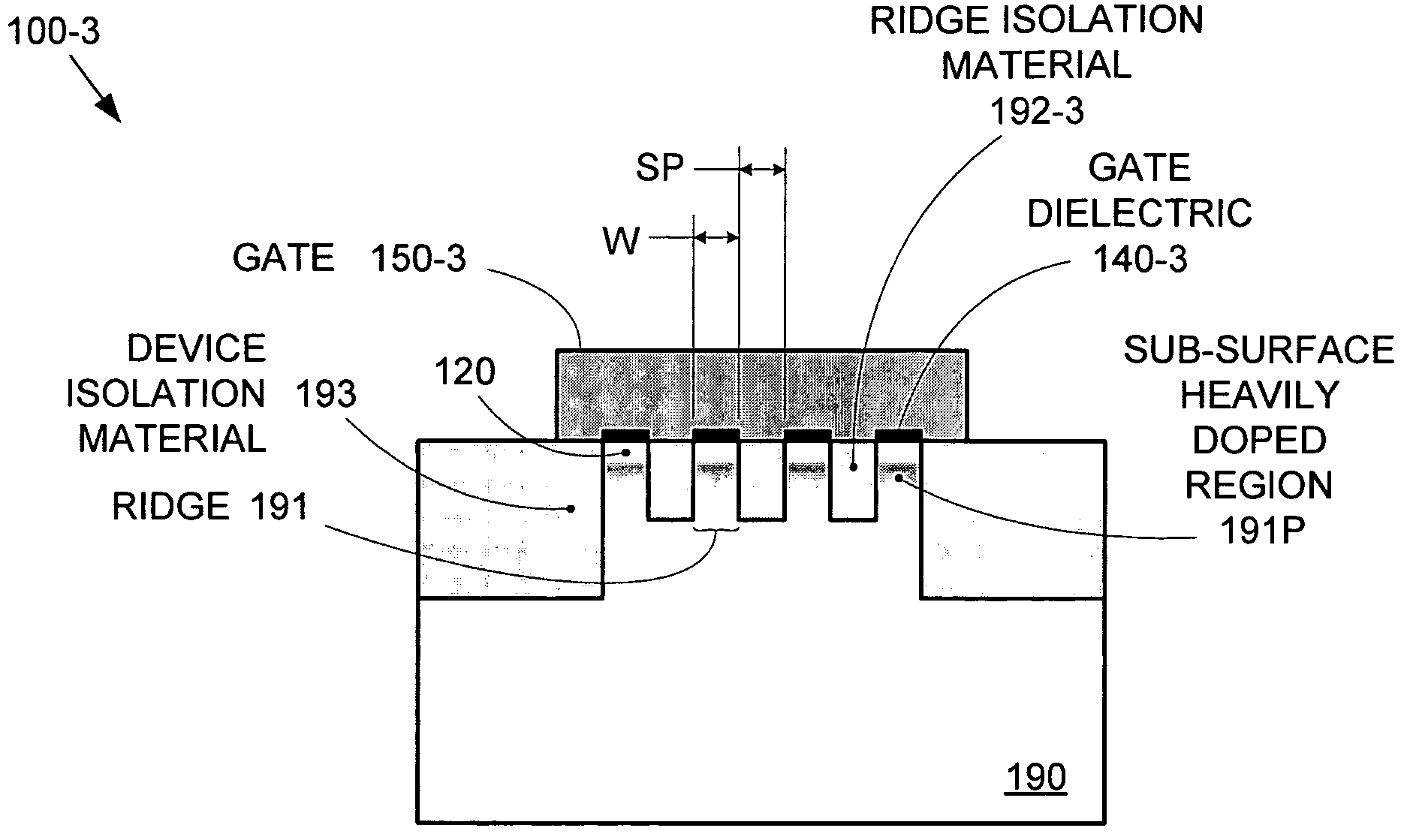

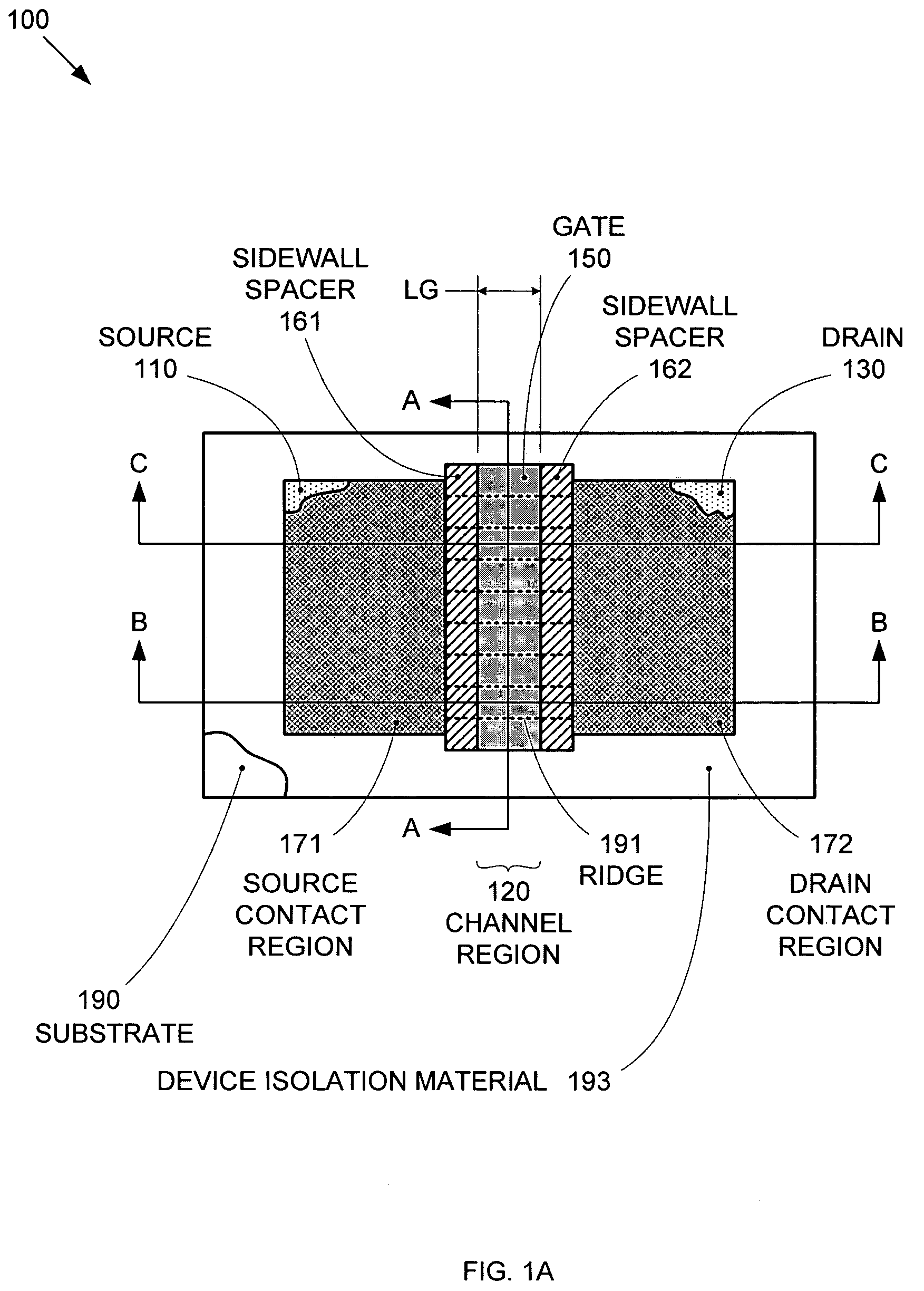

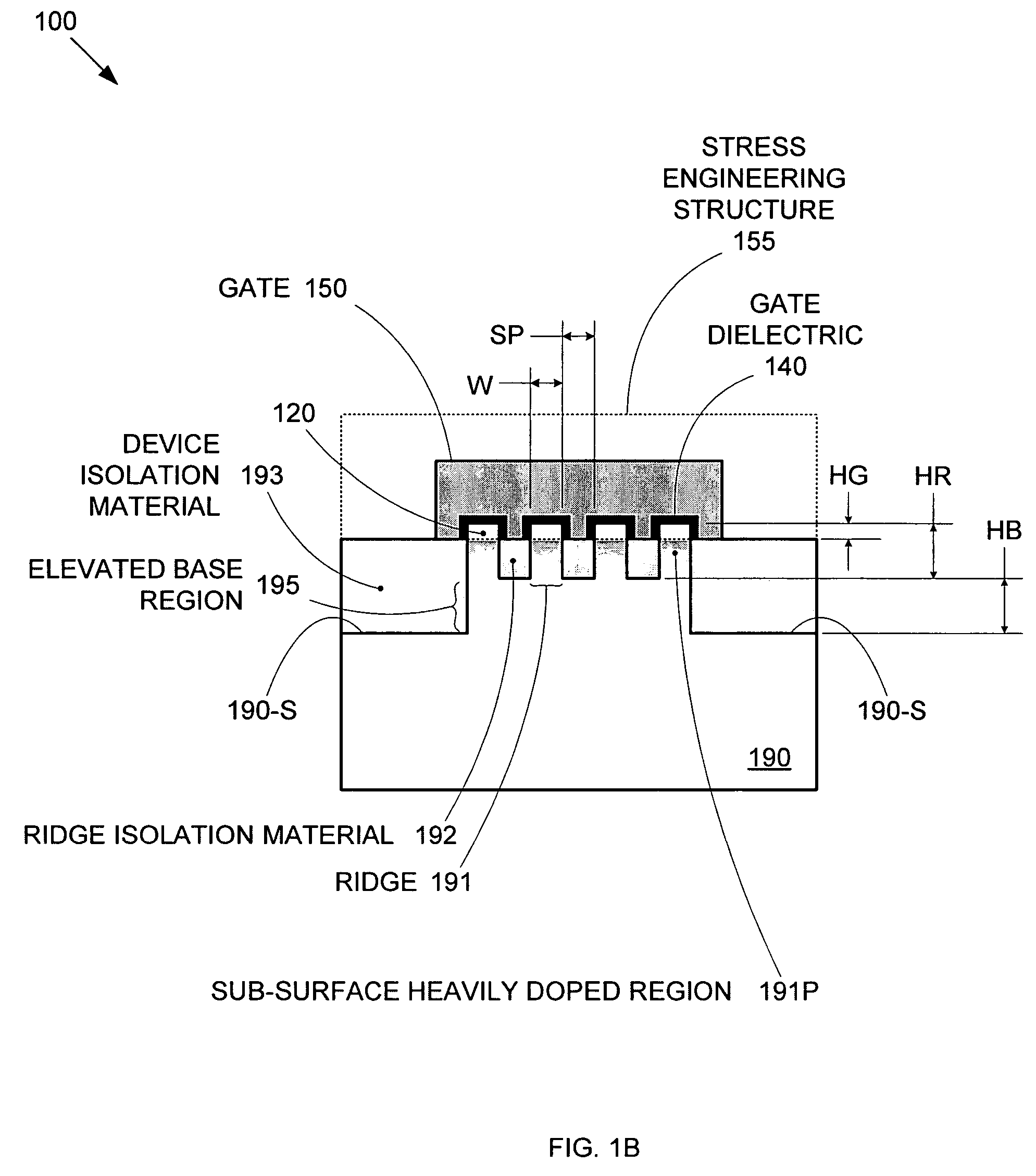

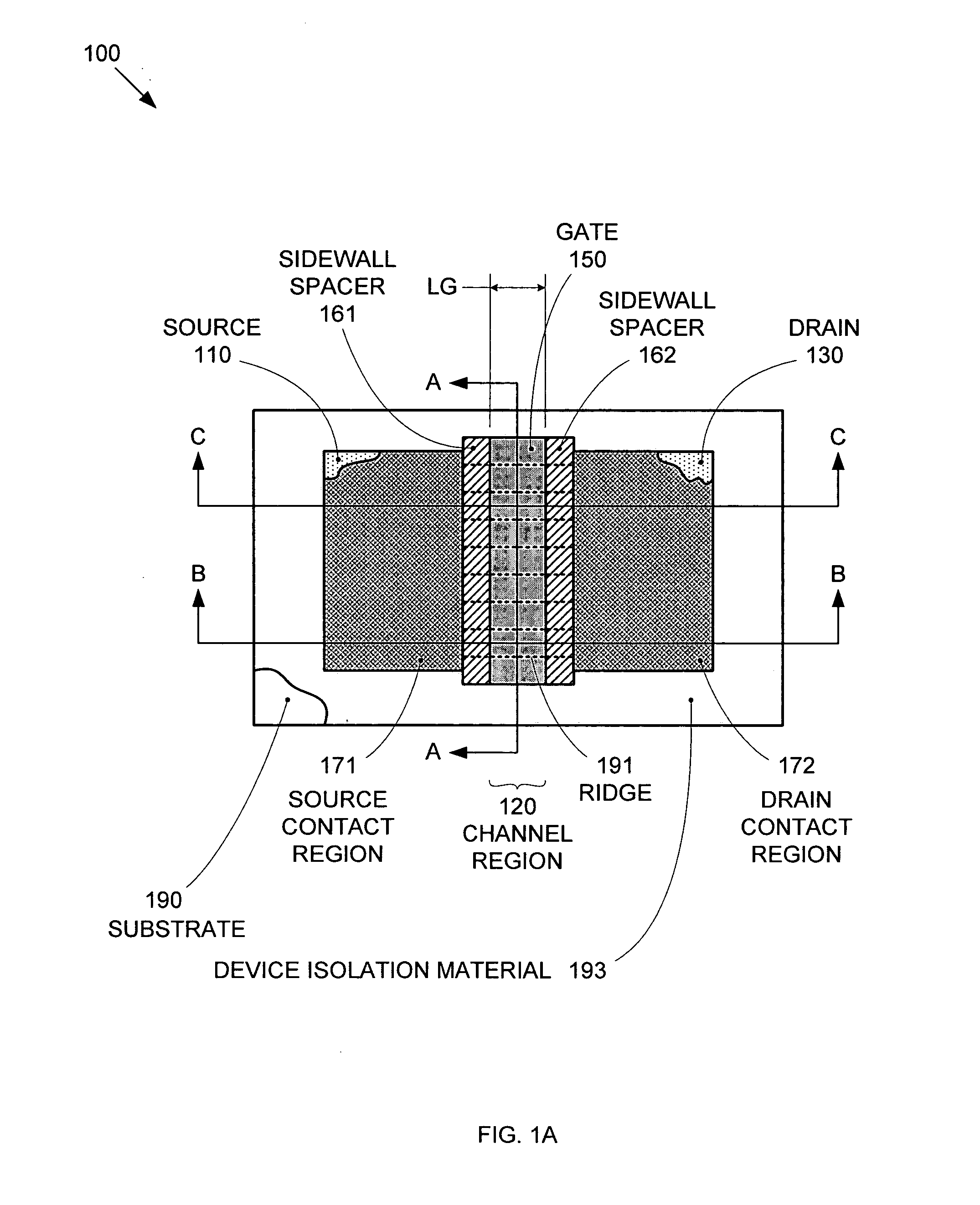

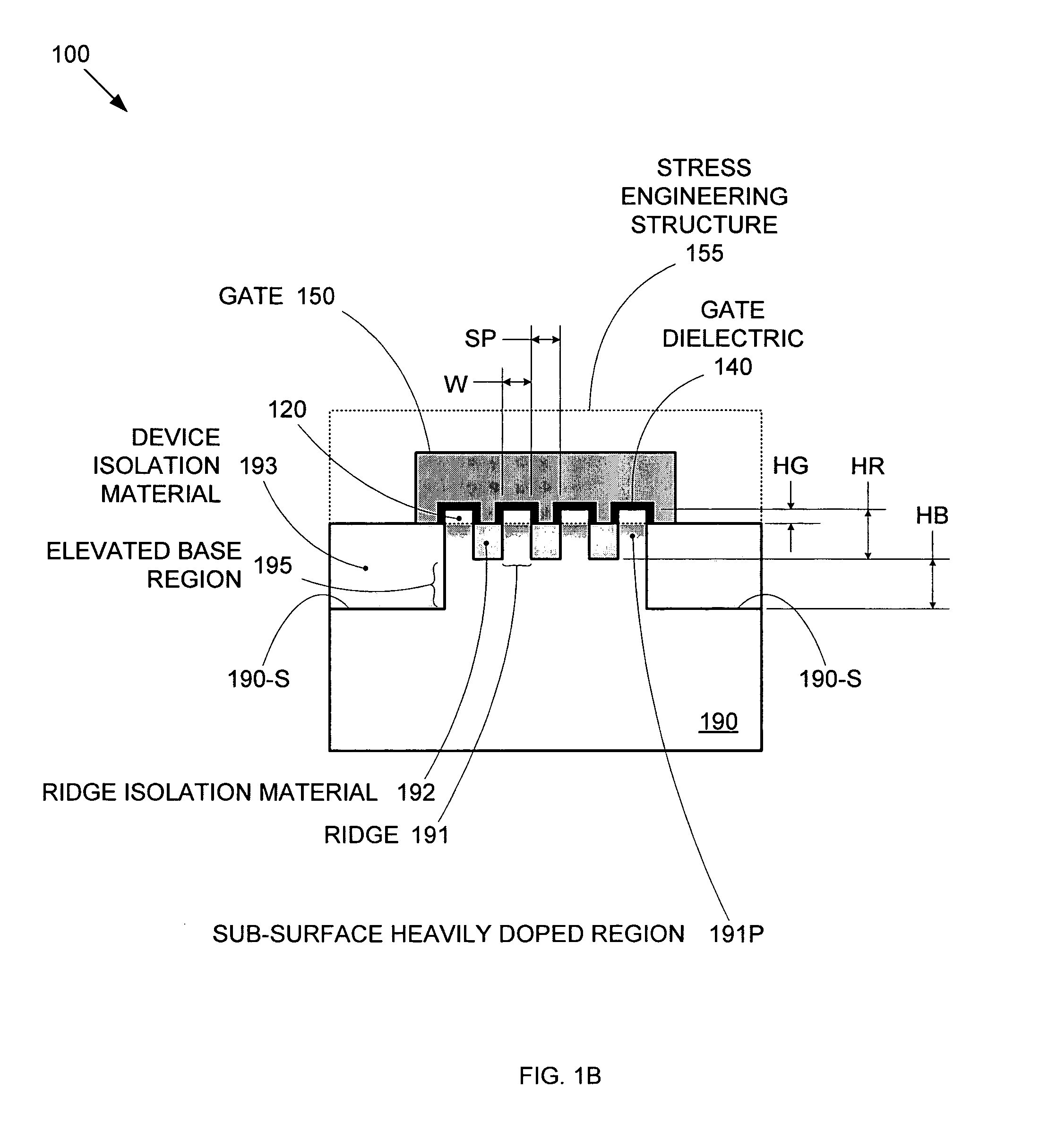

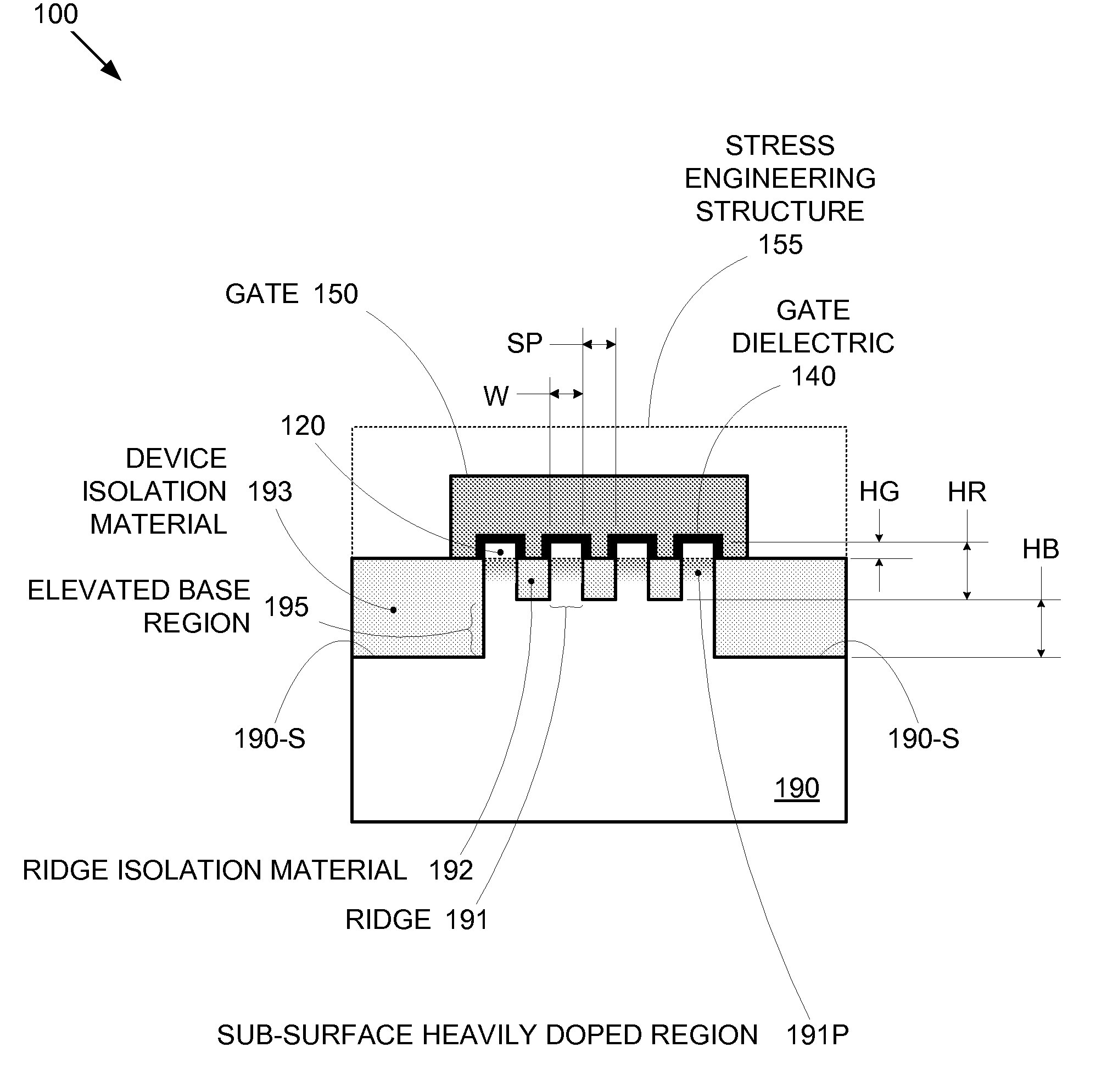

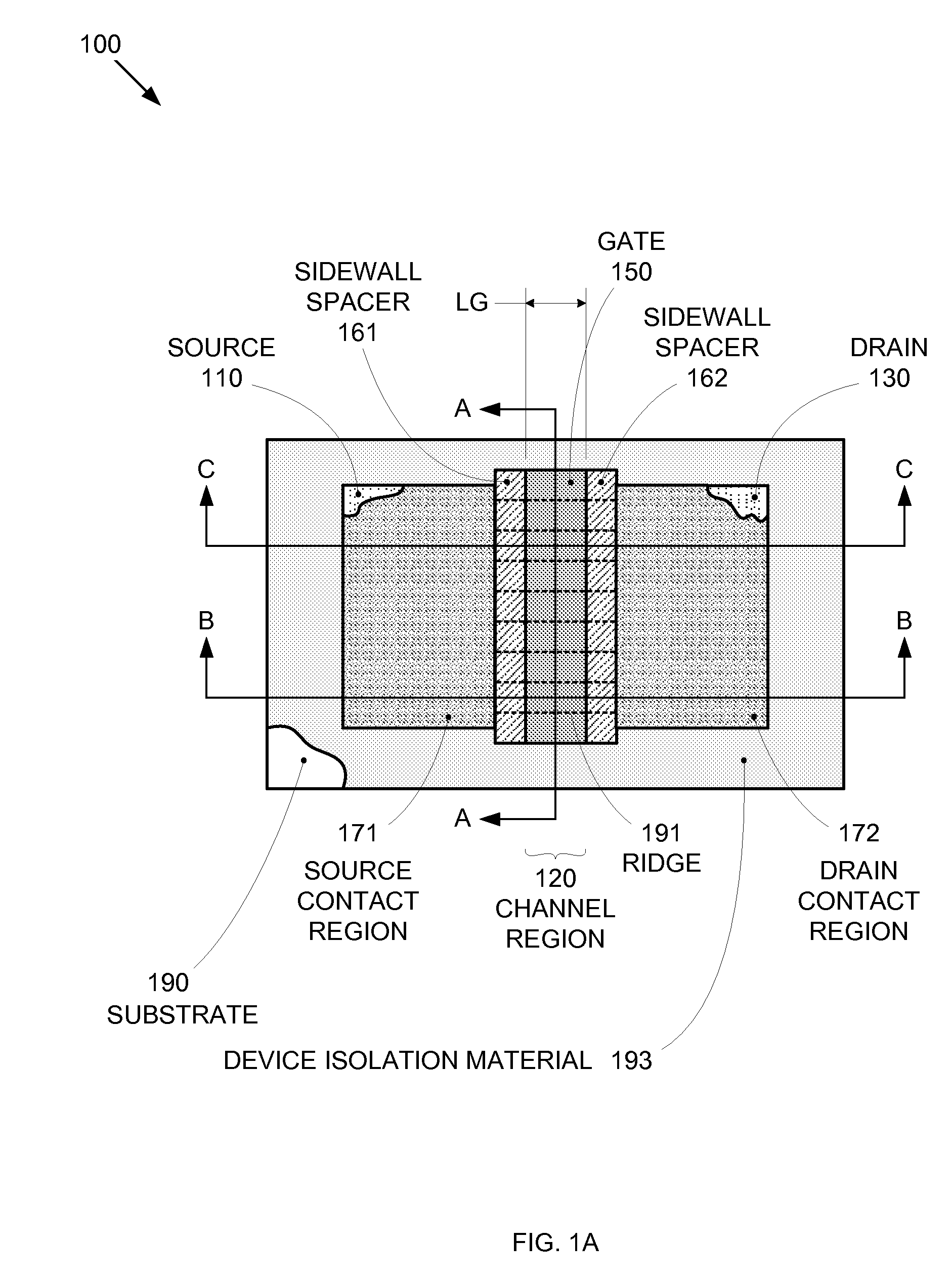

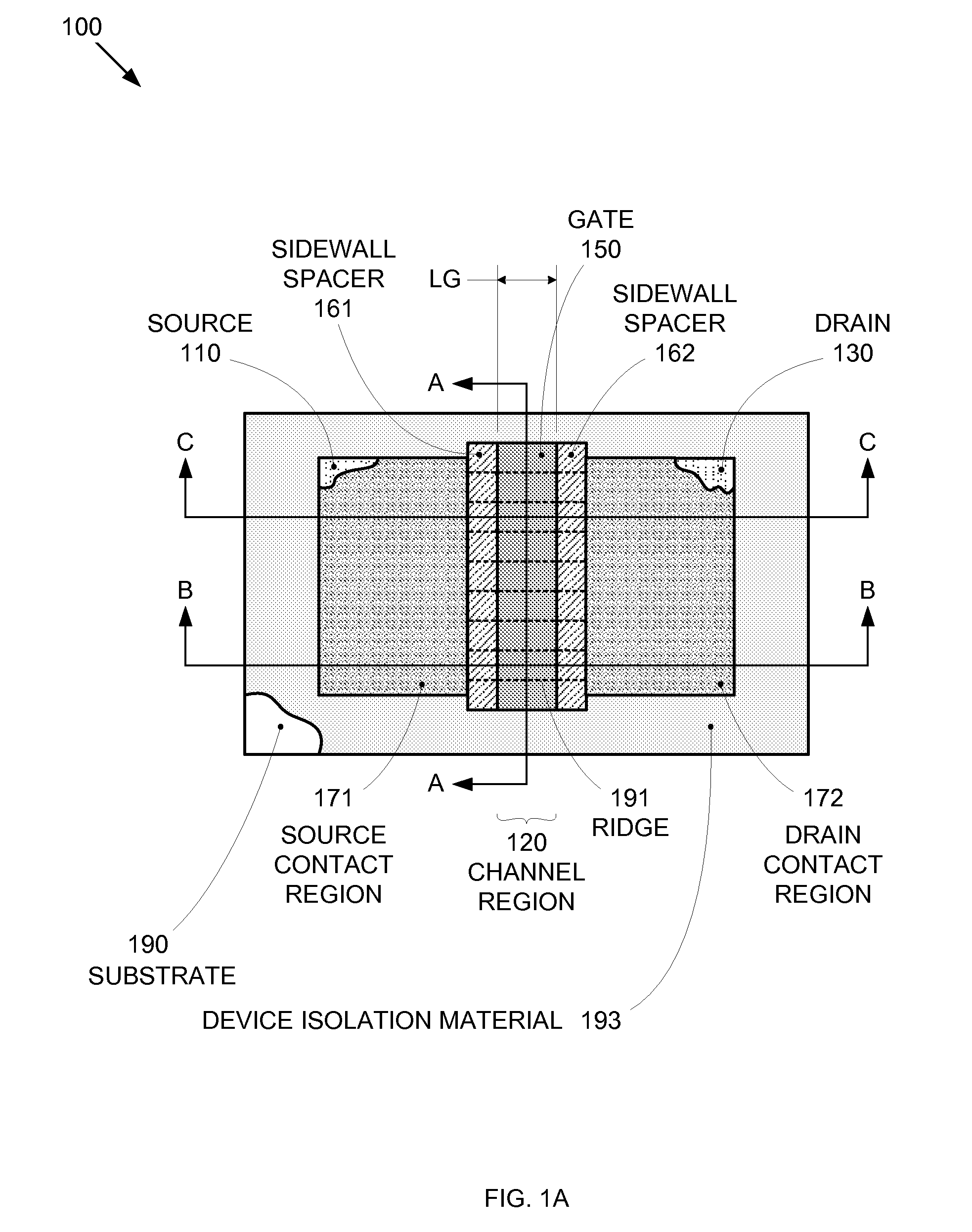

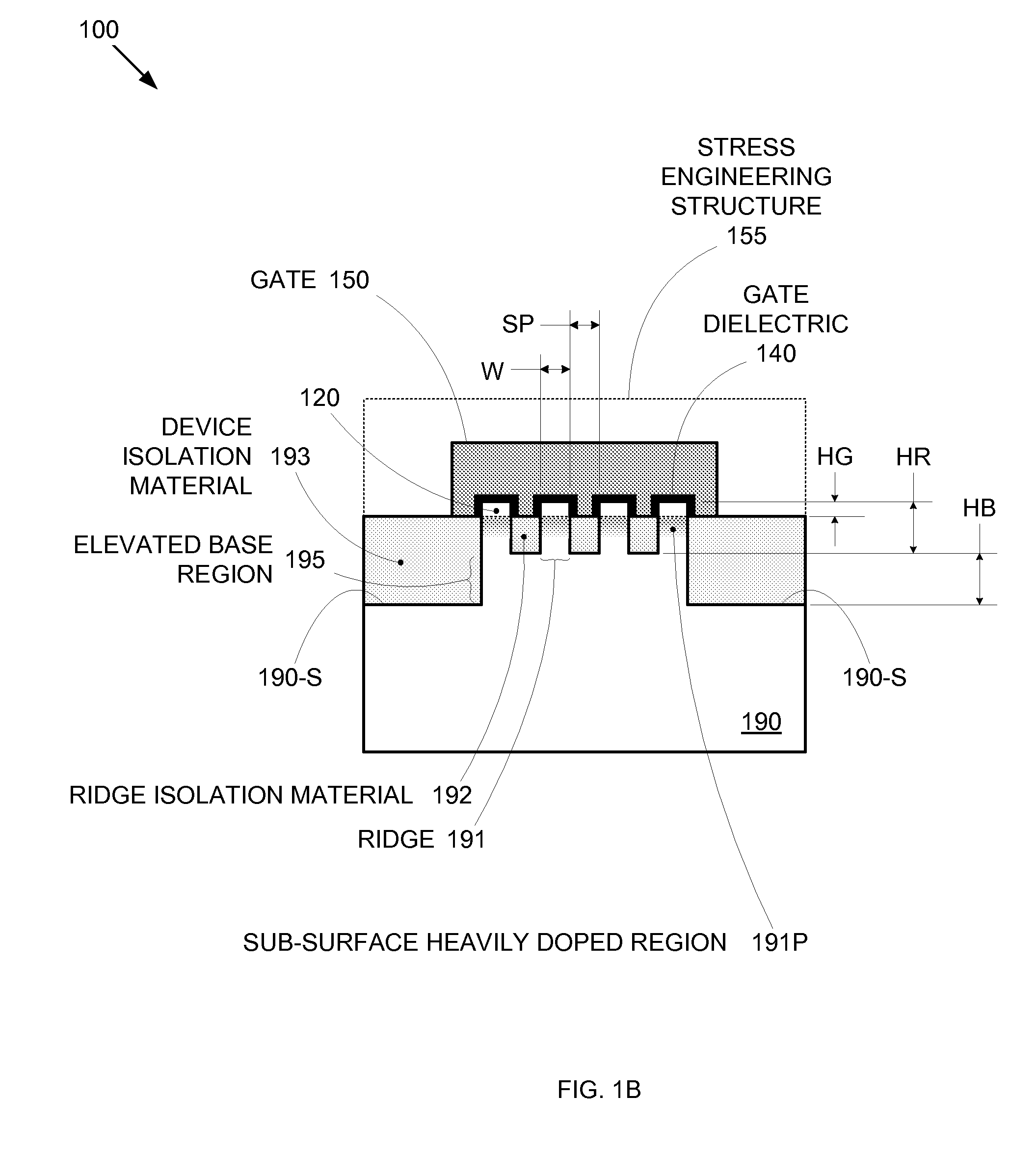

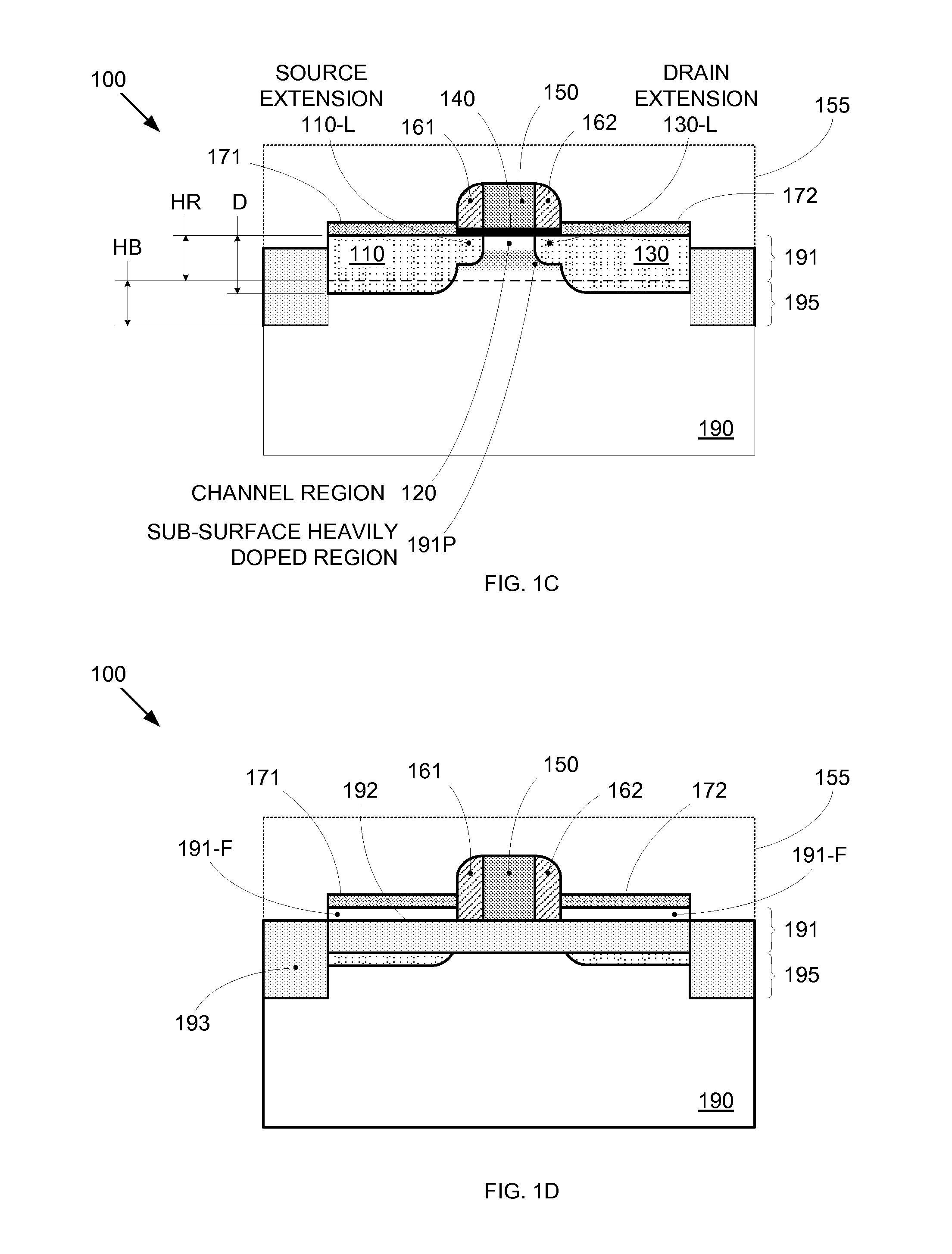

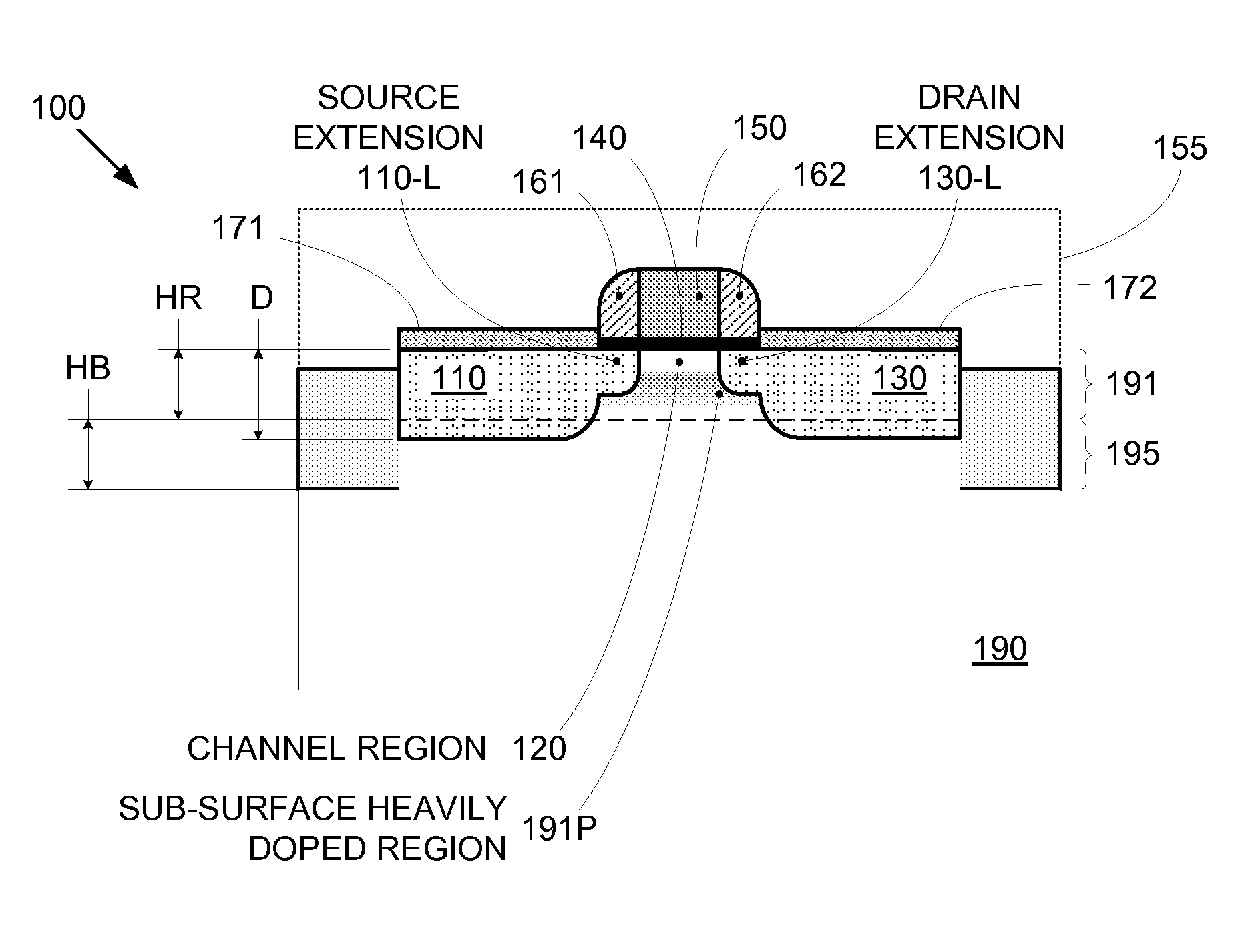

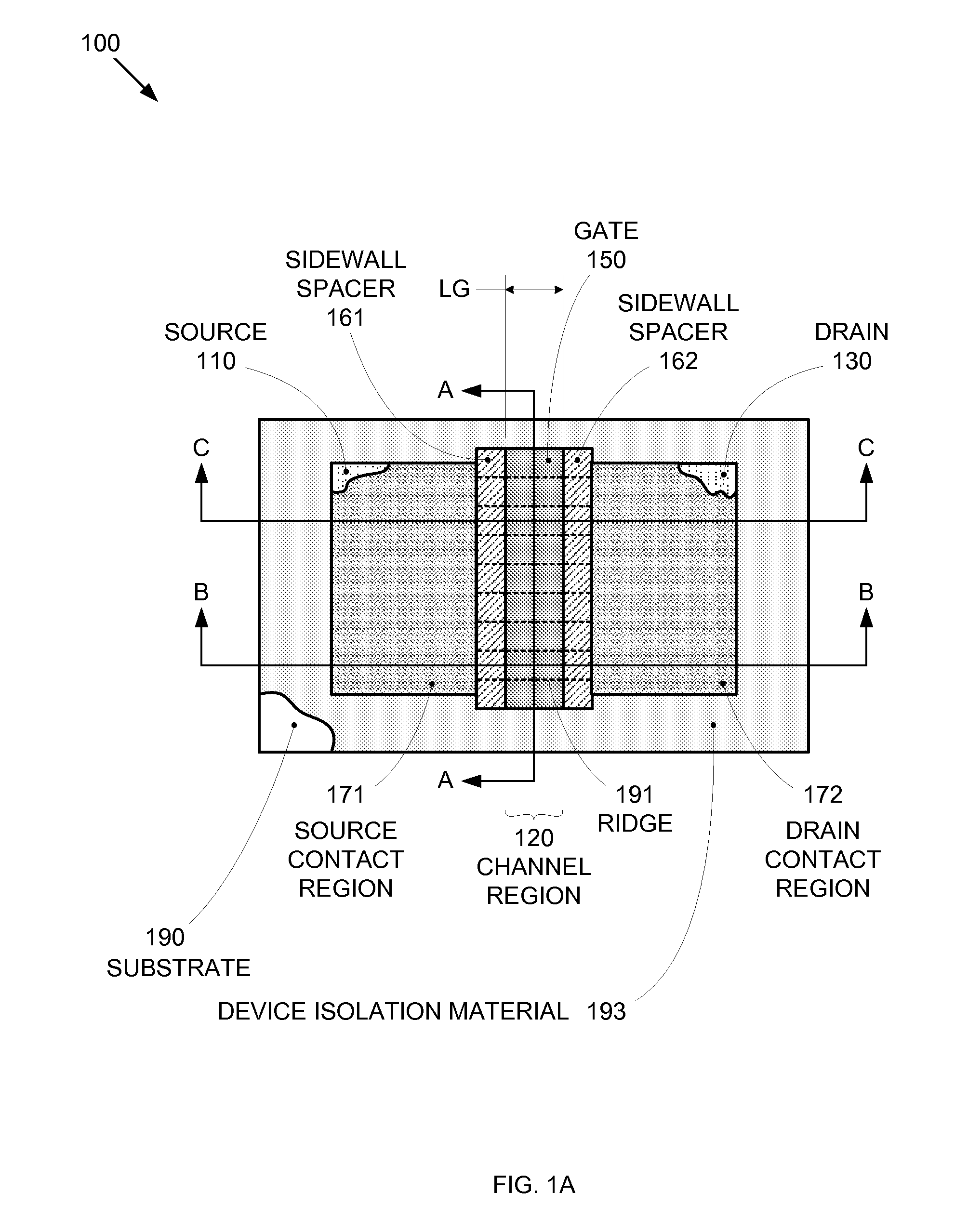

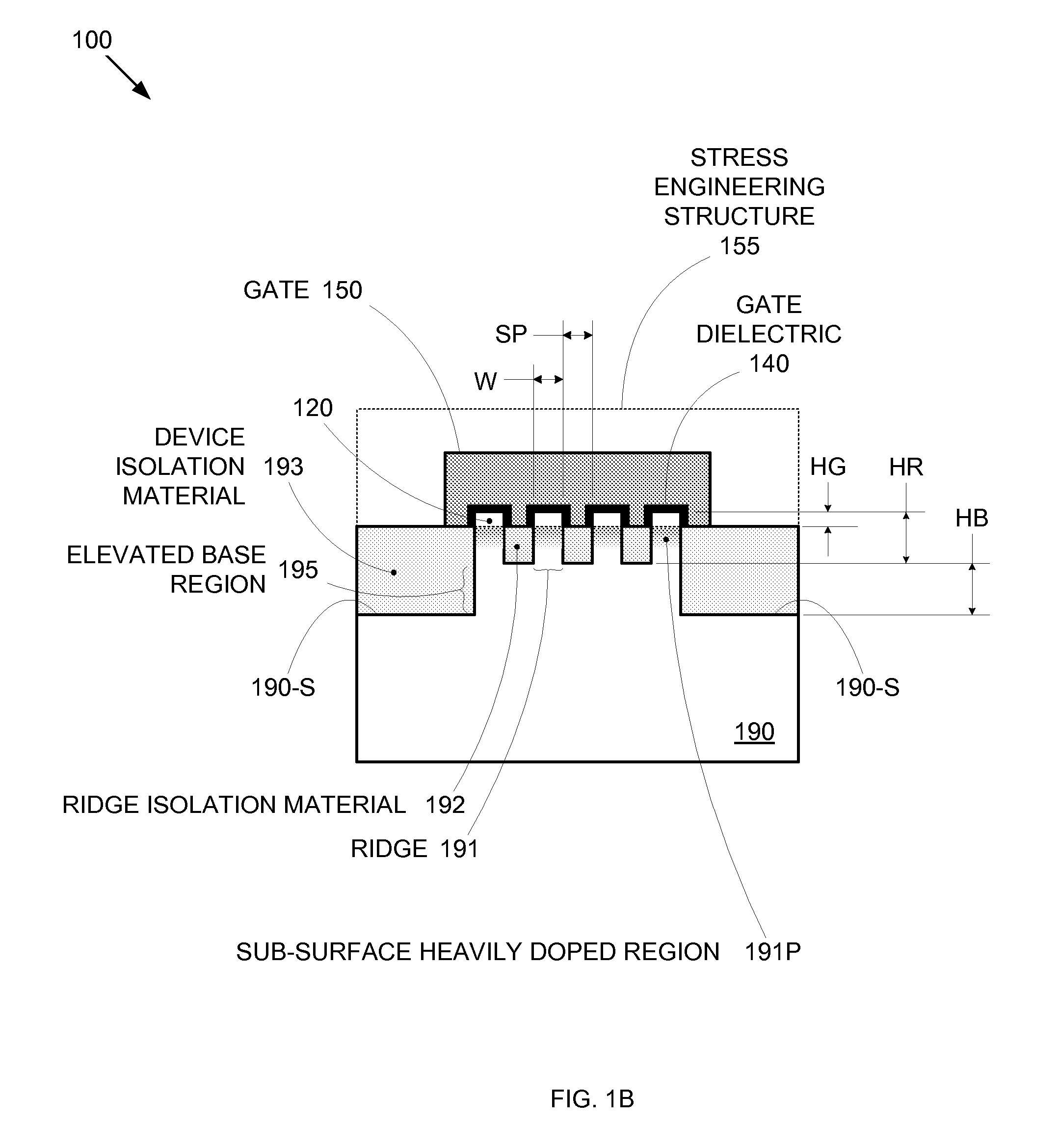

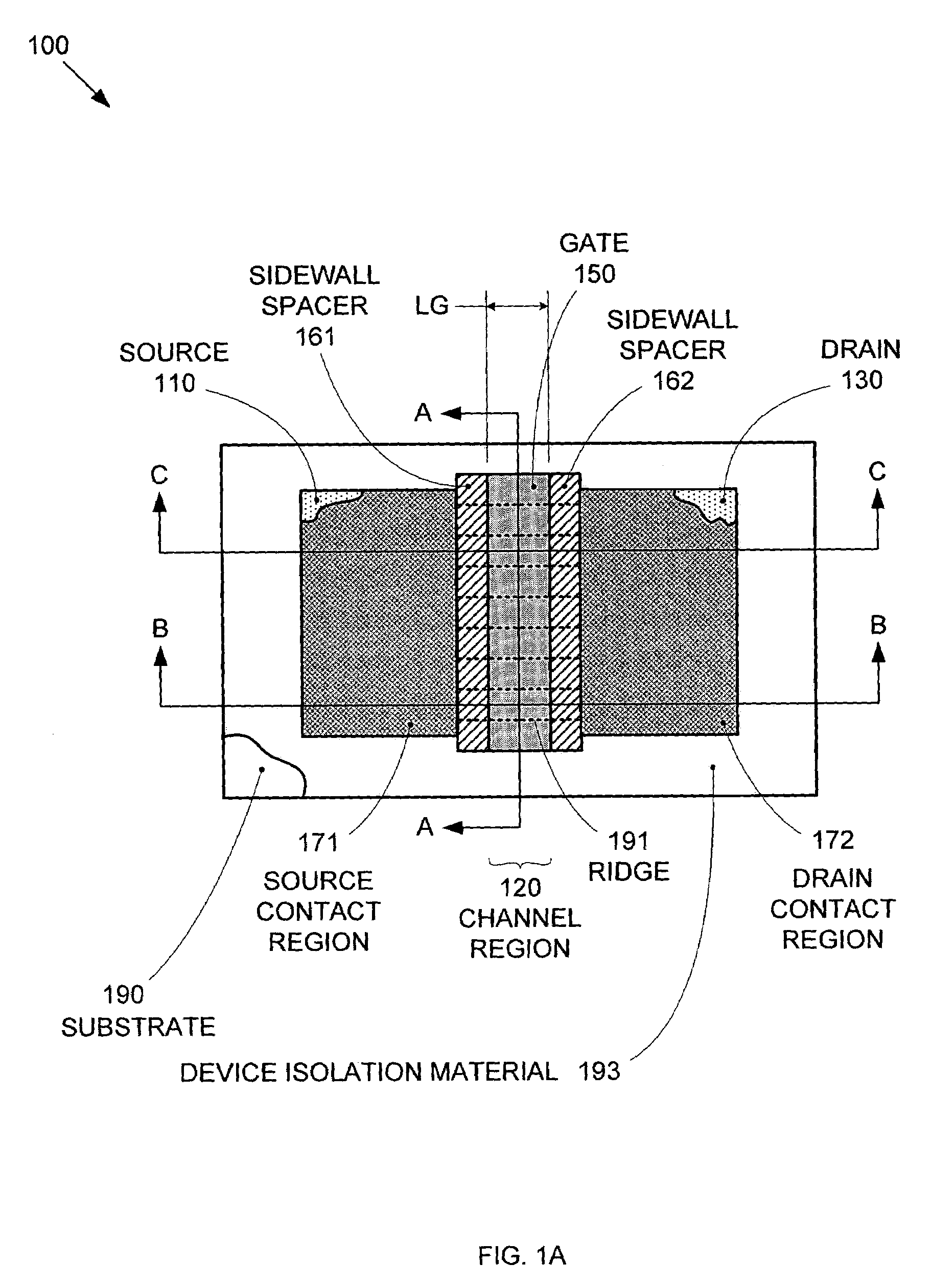

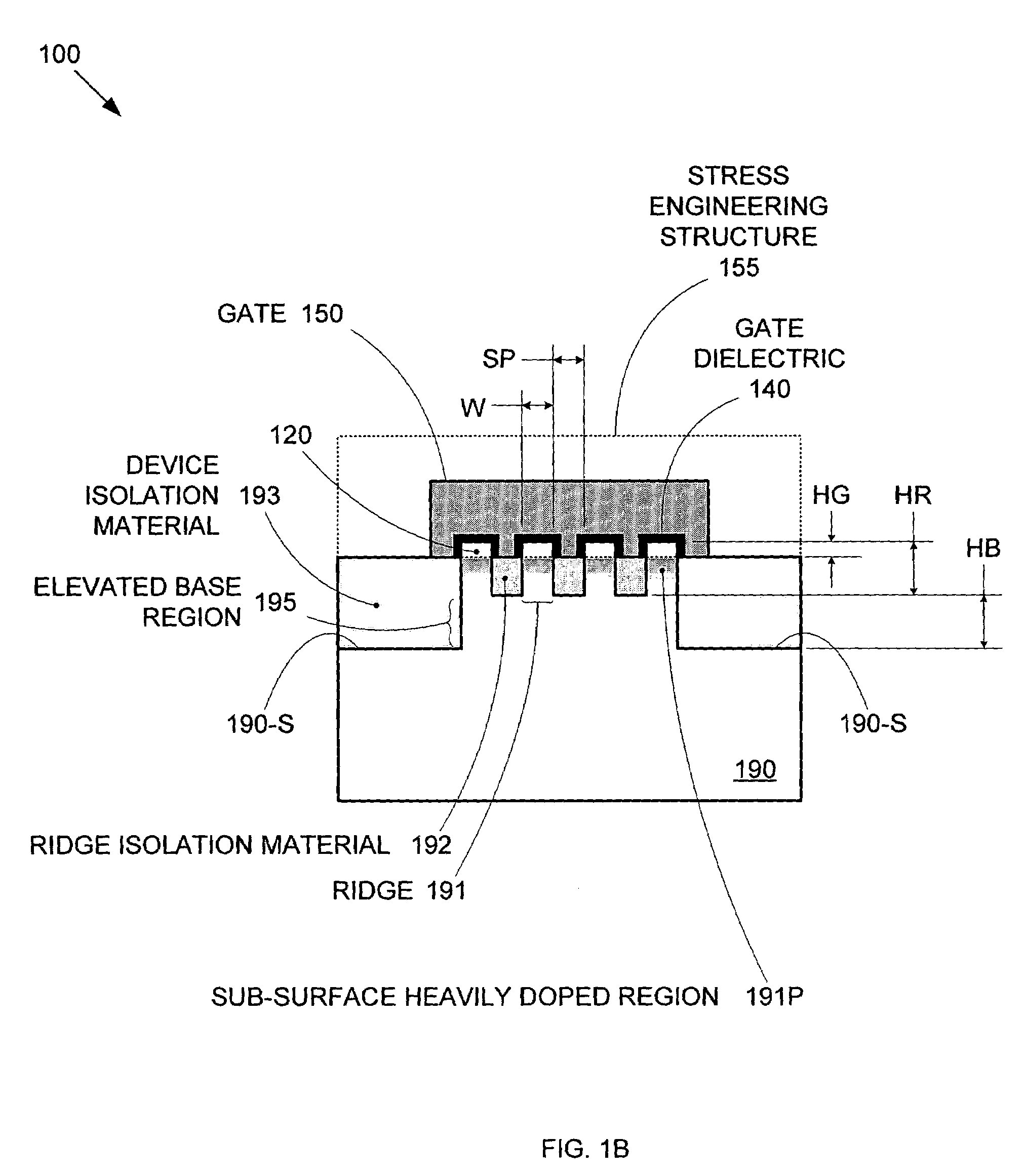

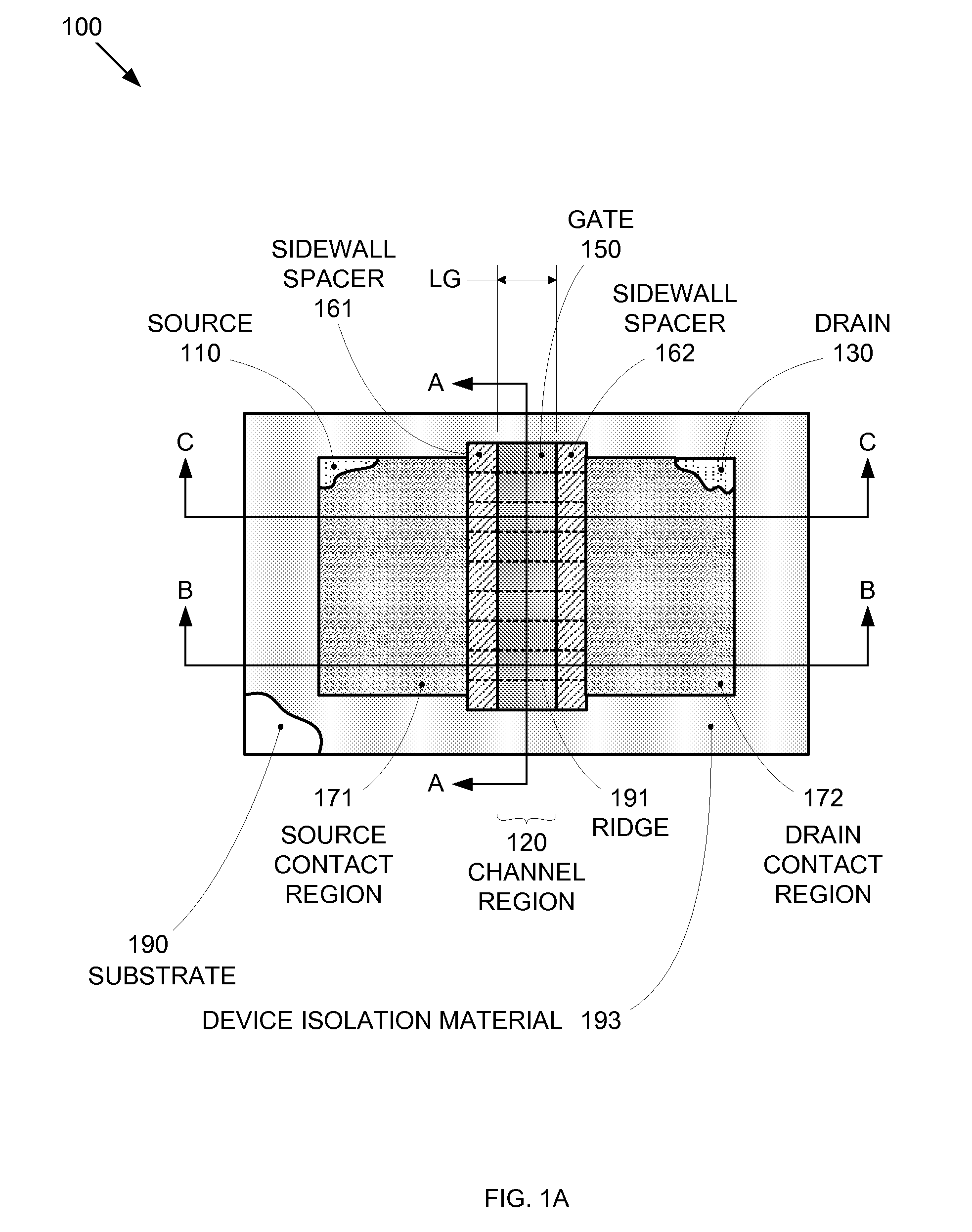

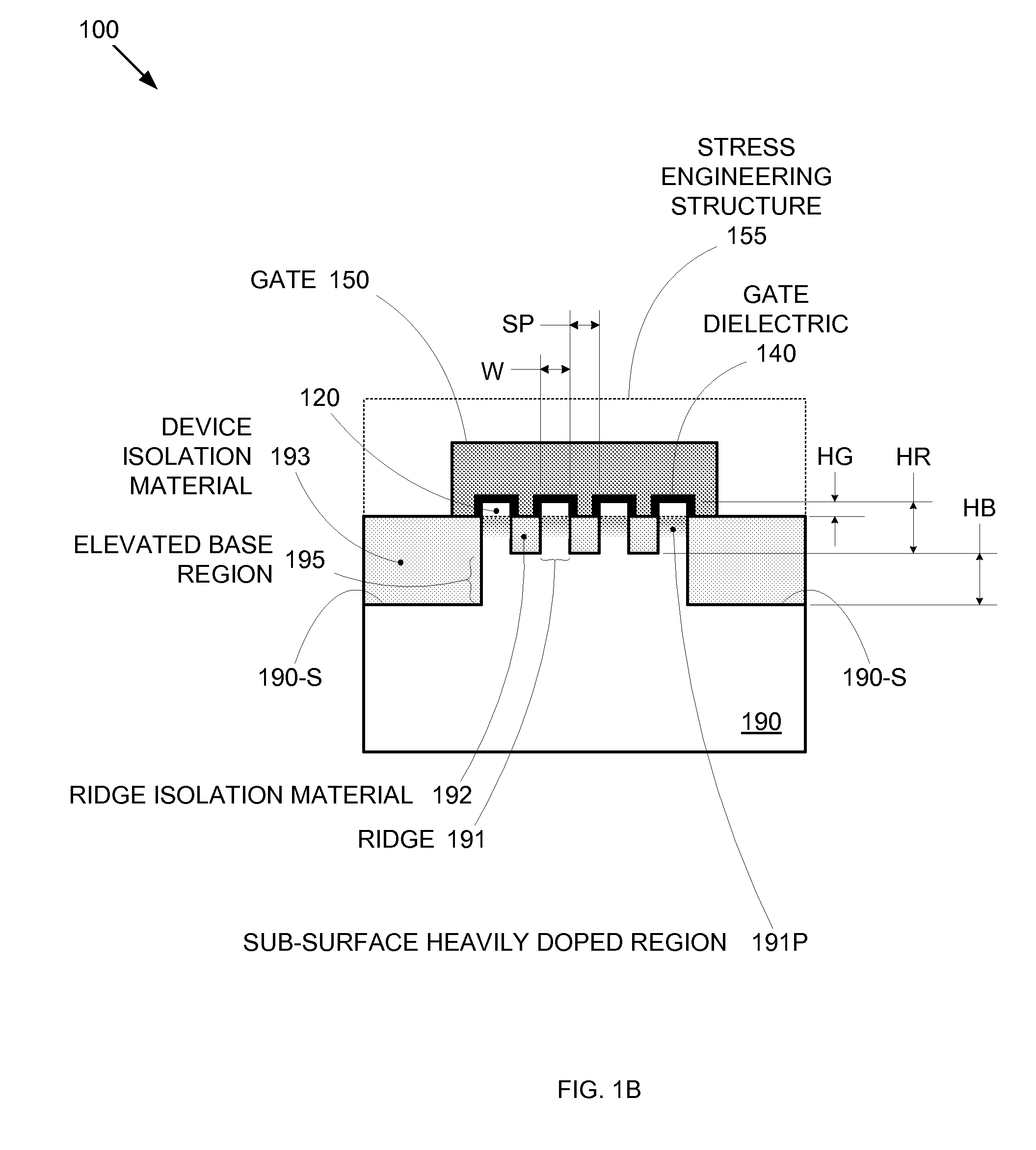

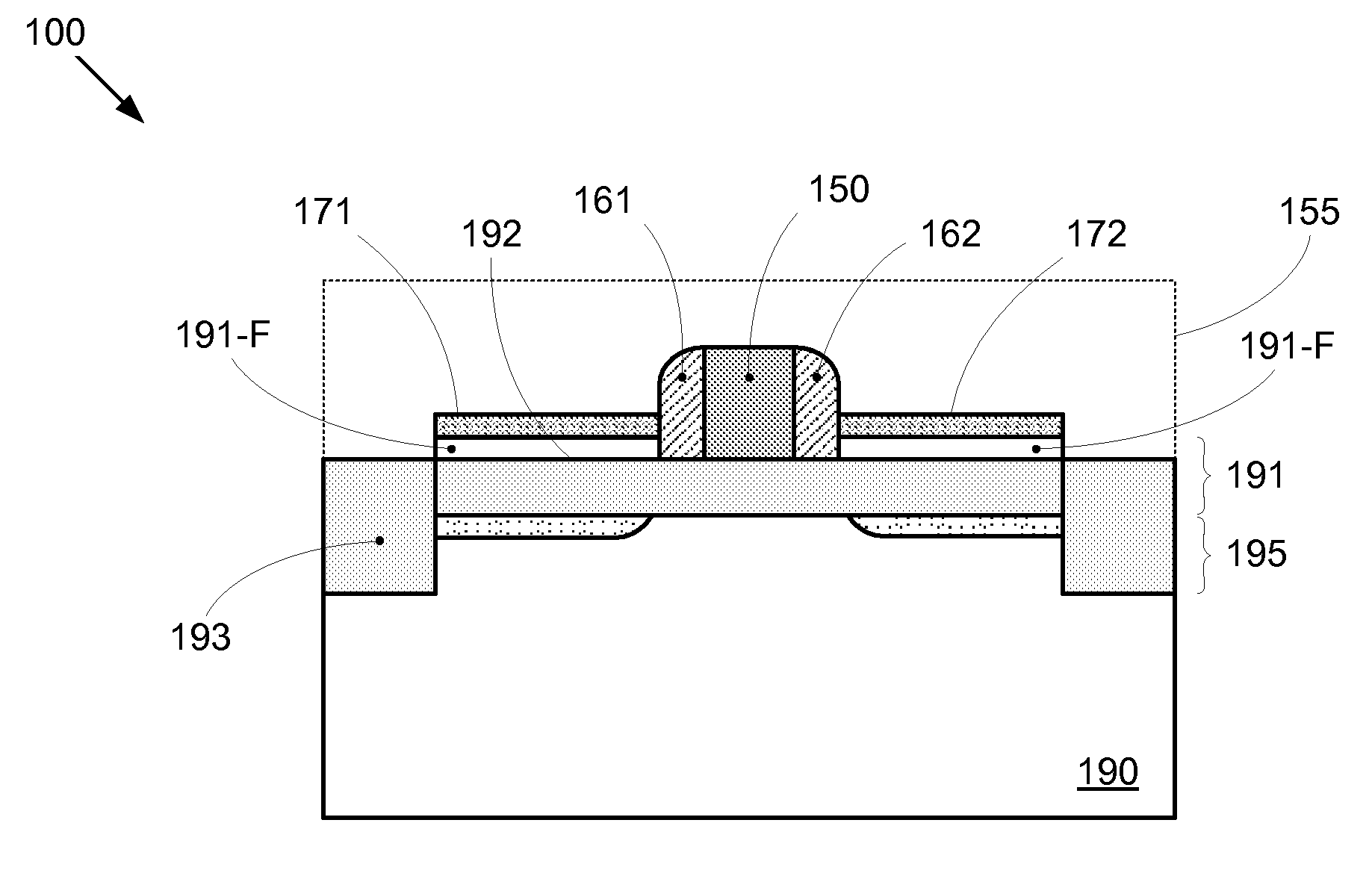

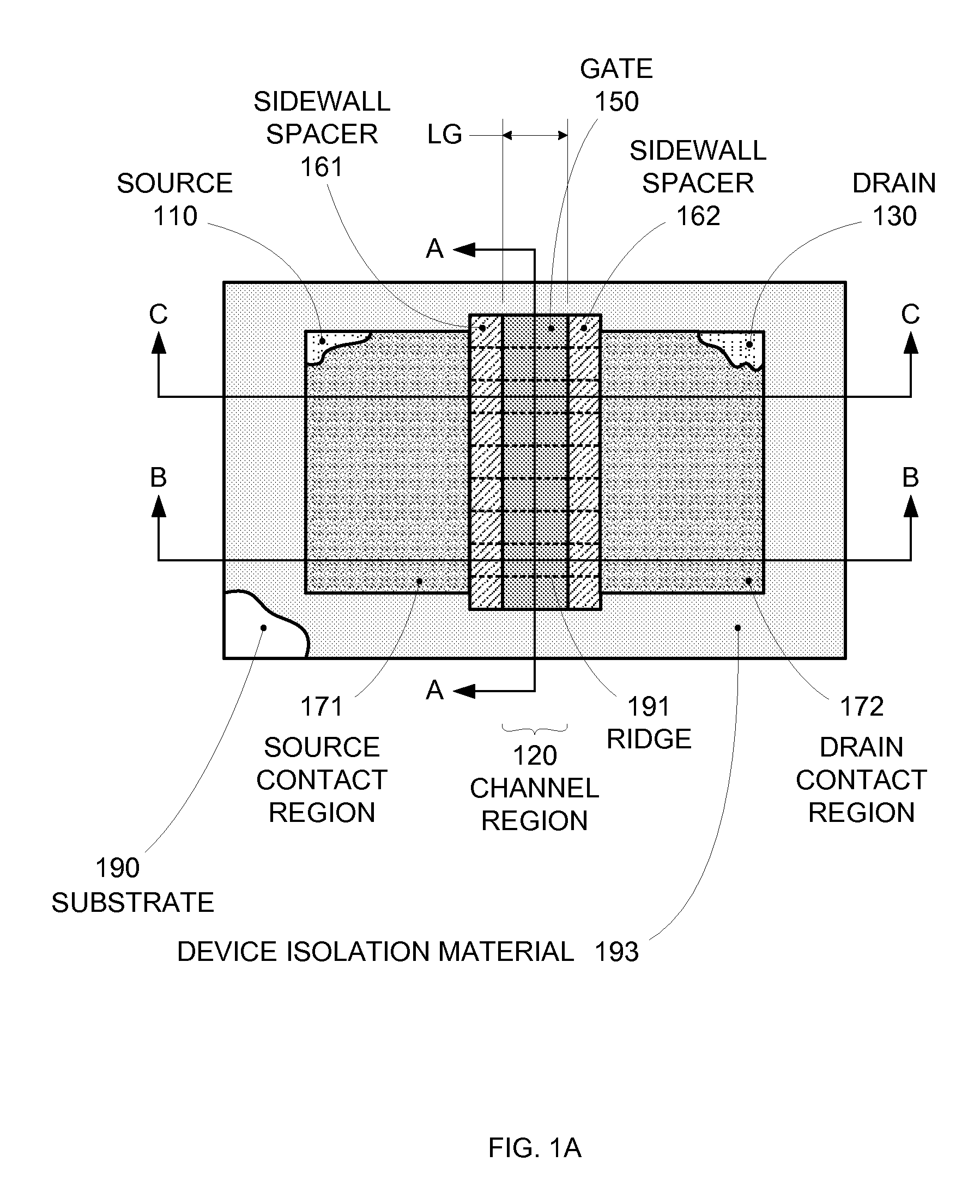

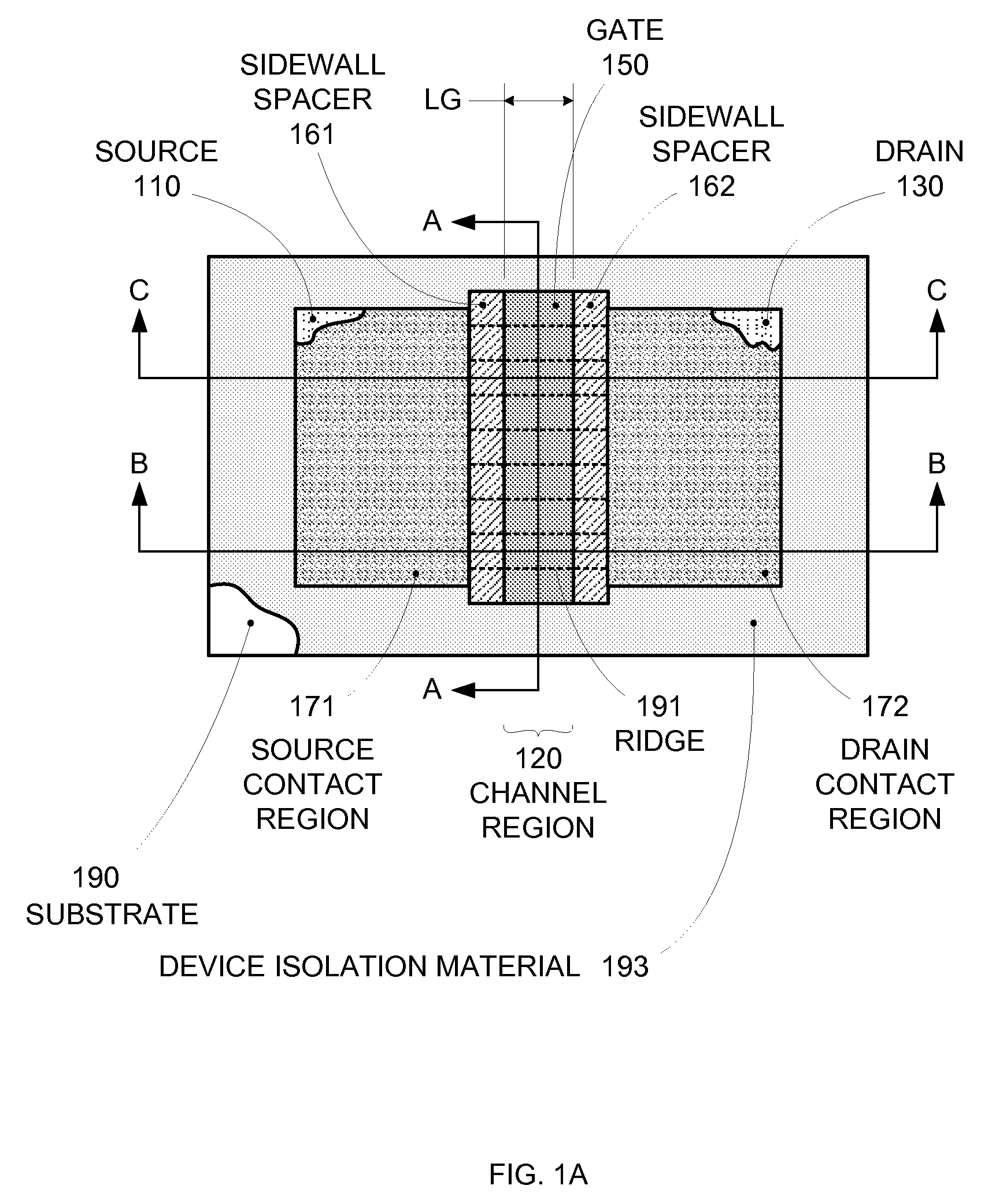

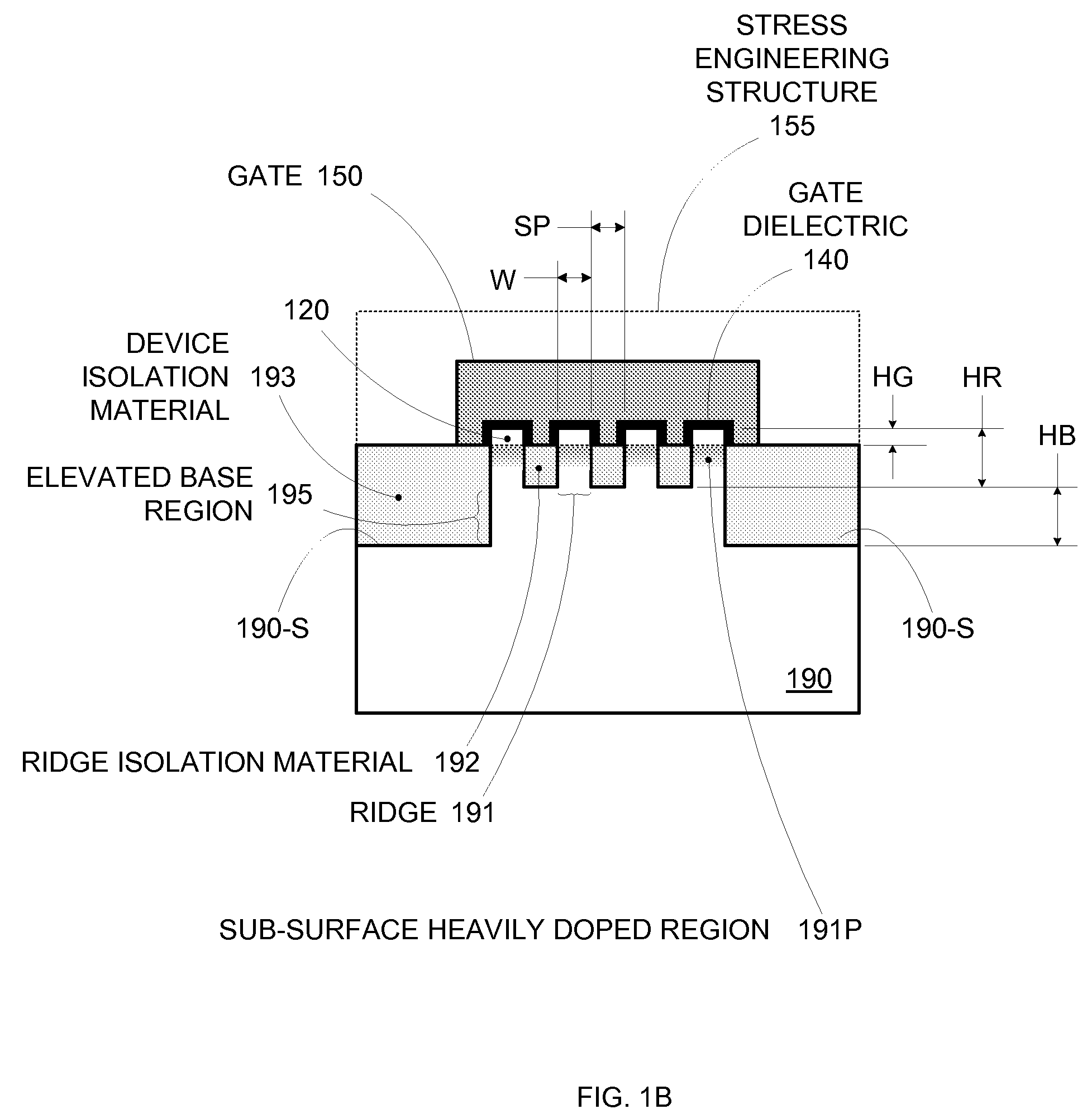

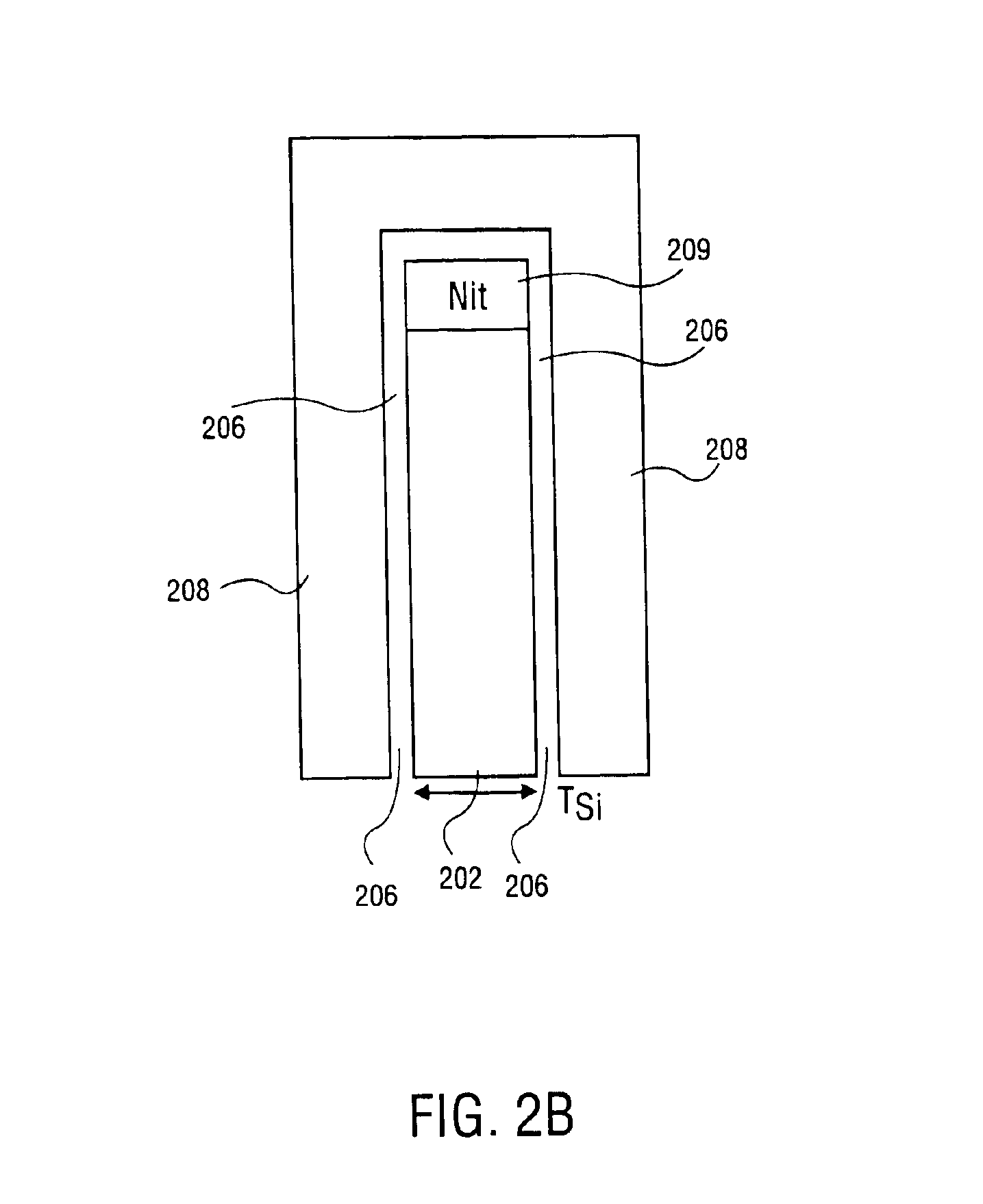

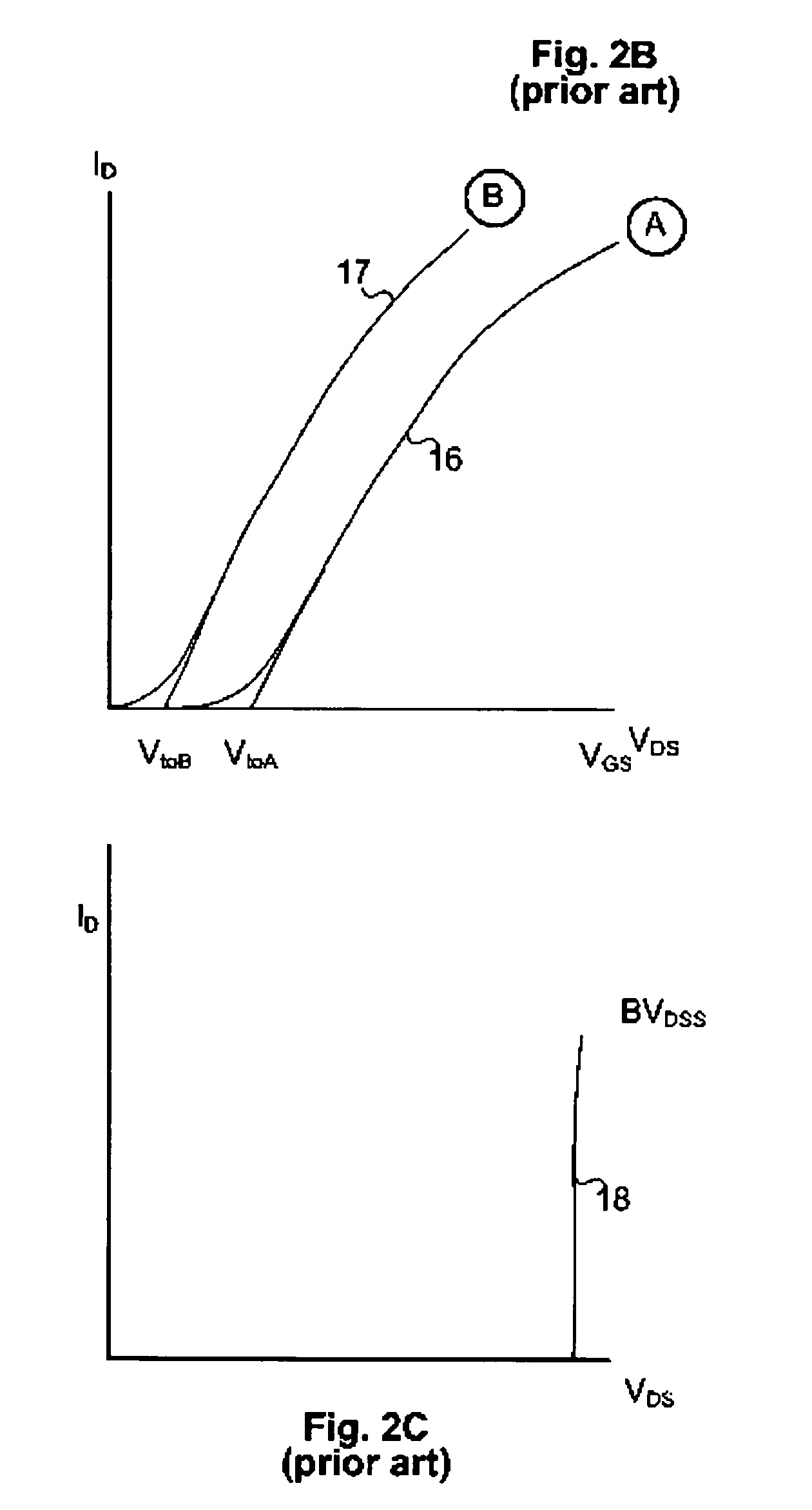

Segmented channel MOS transistor

ActiveUS7247887B2Improve performance consistencyImprove performanceTransistorSolid-state devicesMOSFETLithographic artist

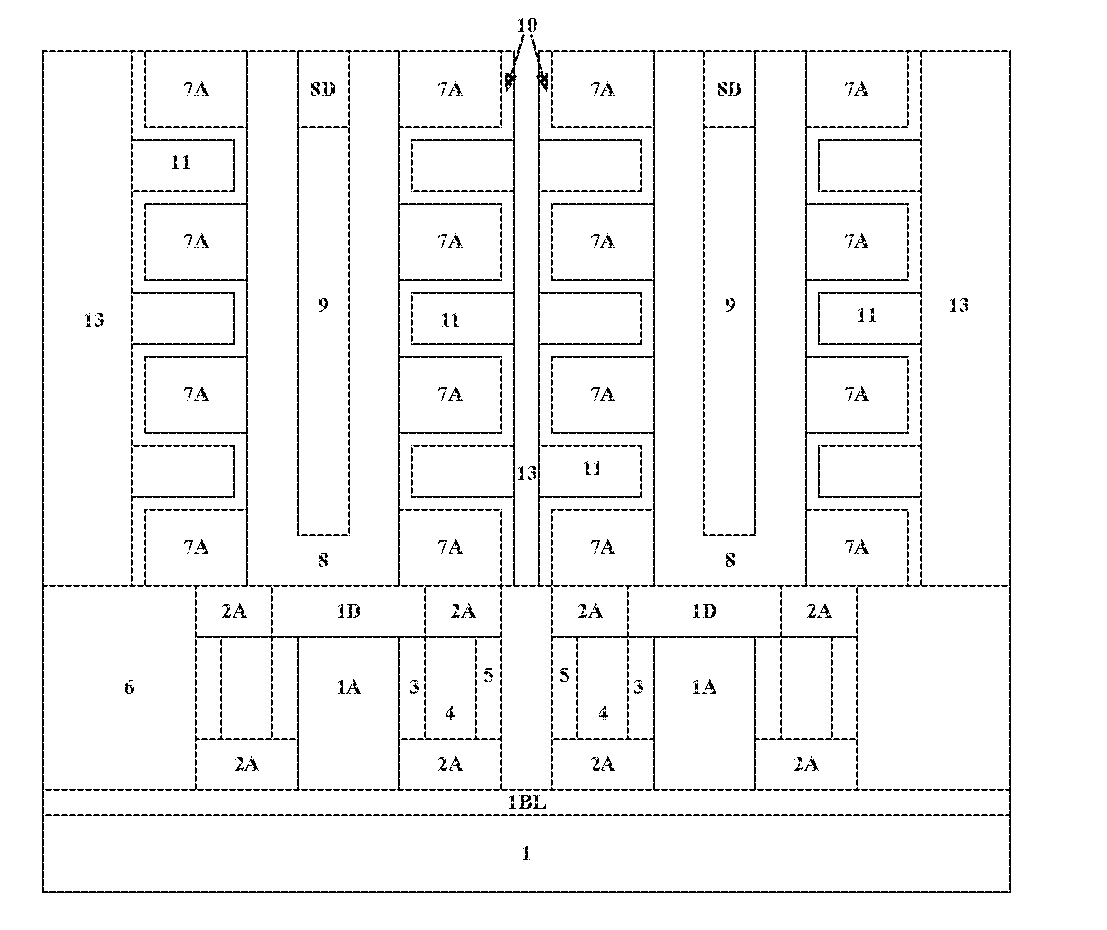

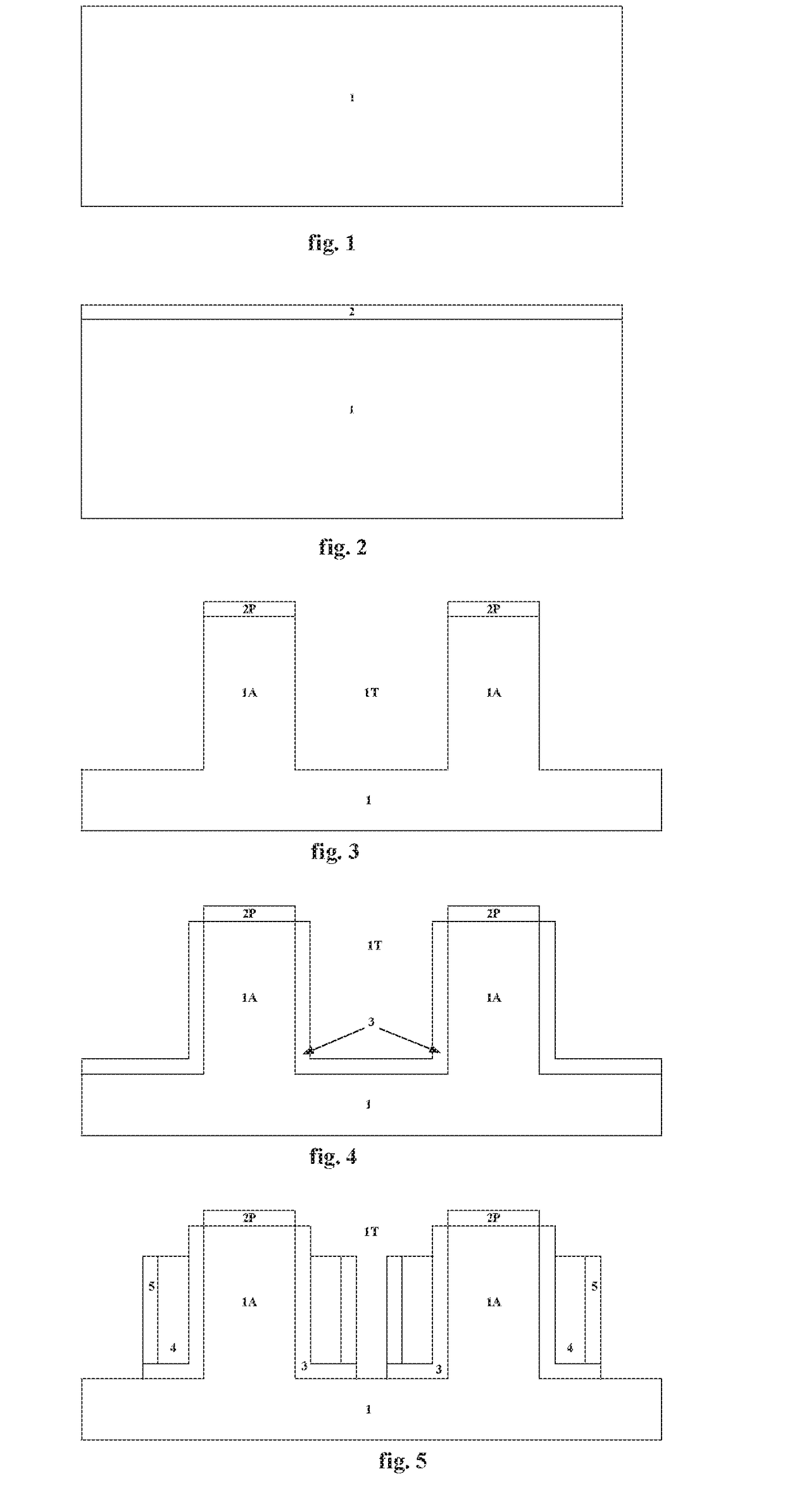

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

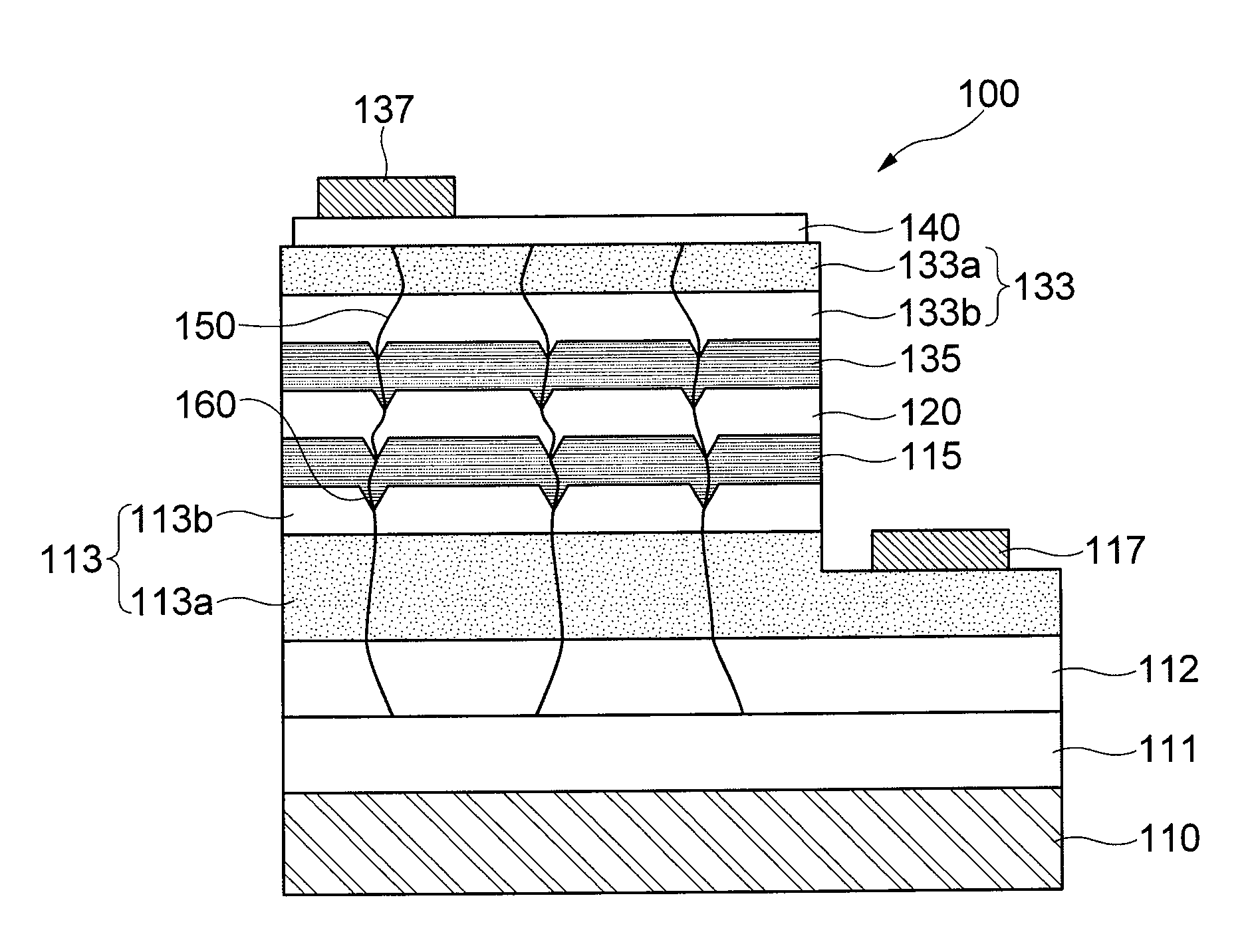

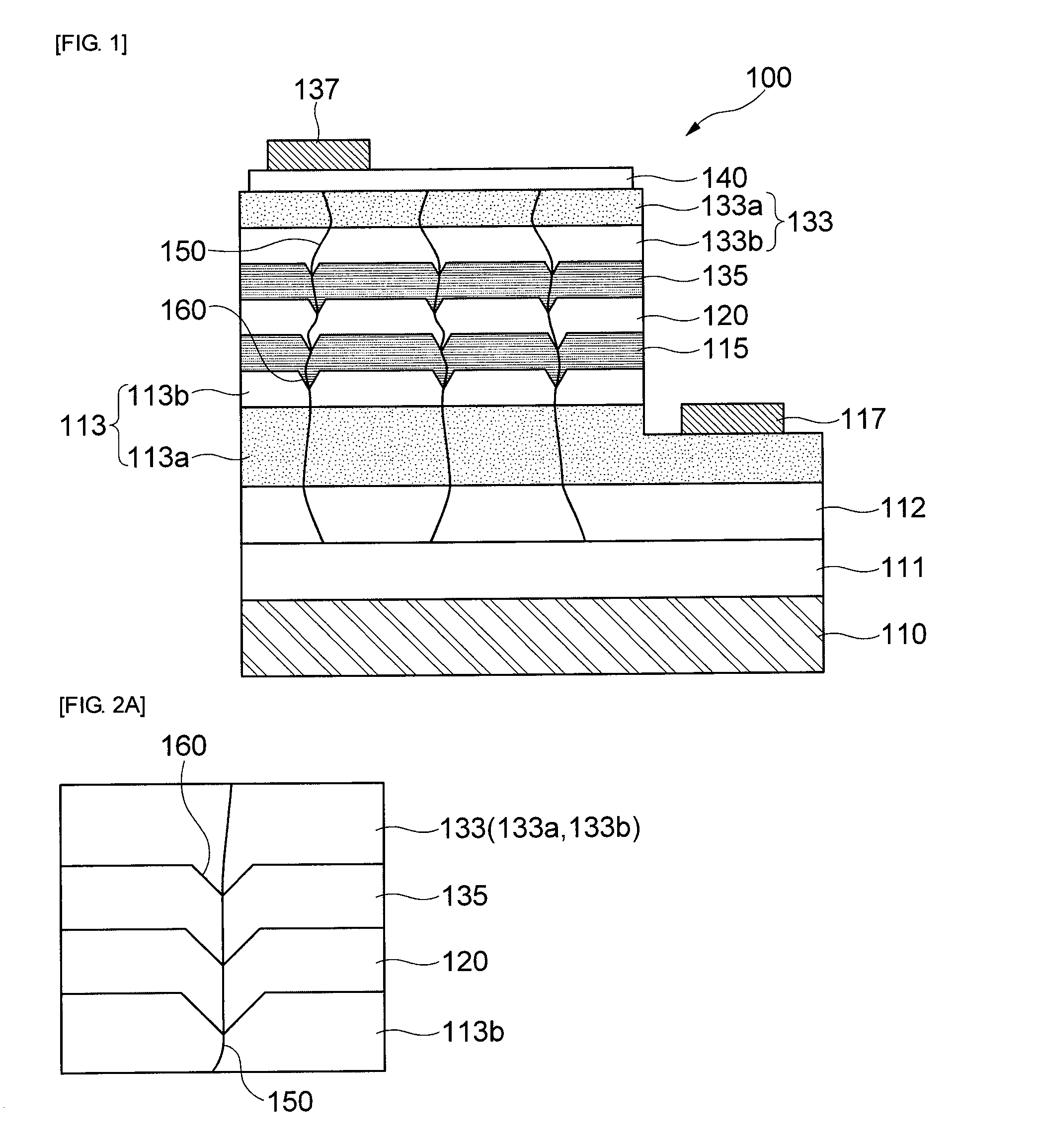

Nitride semiconductor light emitting device and fabrication method thereof

ActiveUS8129711B2Good effectReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesActive layerLight emitting device

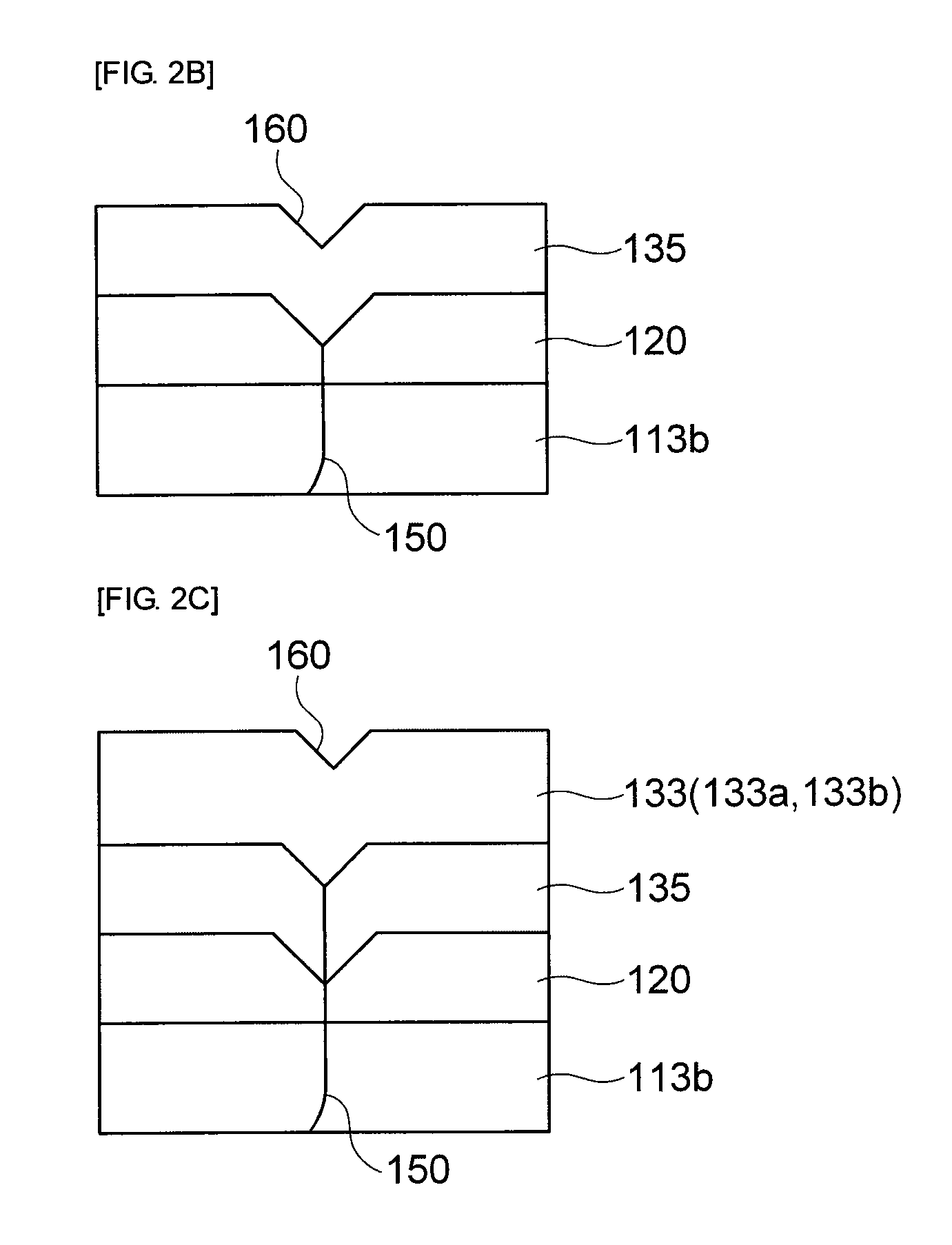

The present invention relates to a GaN based nitride based light emitting device improved in Electrostatic Discharge (ESD) tolerance (withstanding property) and a method for fabricating the same including a substrate and a V-shaped distortion structure made of an n-type nitride semiconductor layer, an active layer and a p-type nitride semiconductor layer on the substrate and formed with reference to the n-type nitride semiconductor layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor light emitting element, and its manufacturing method

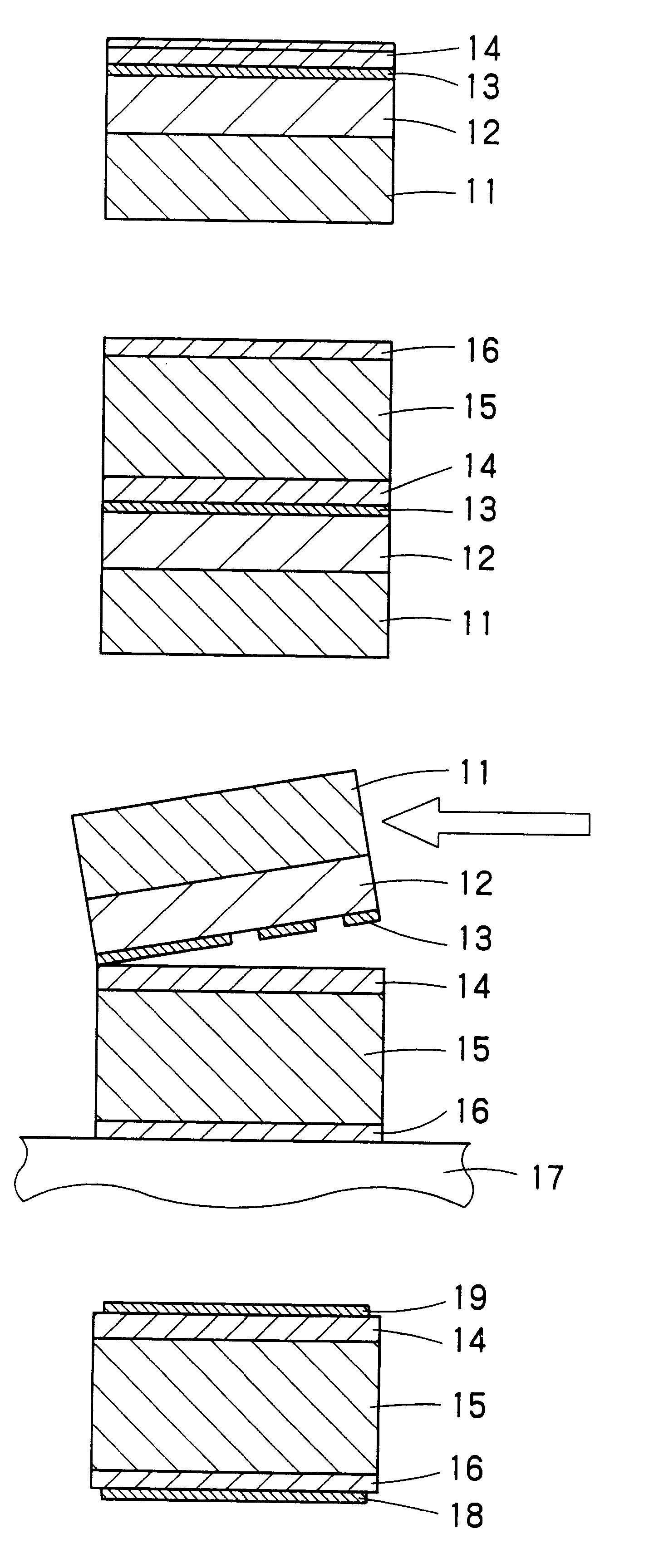

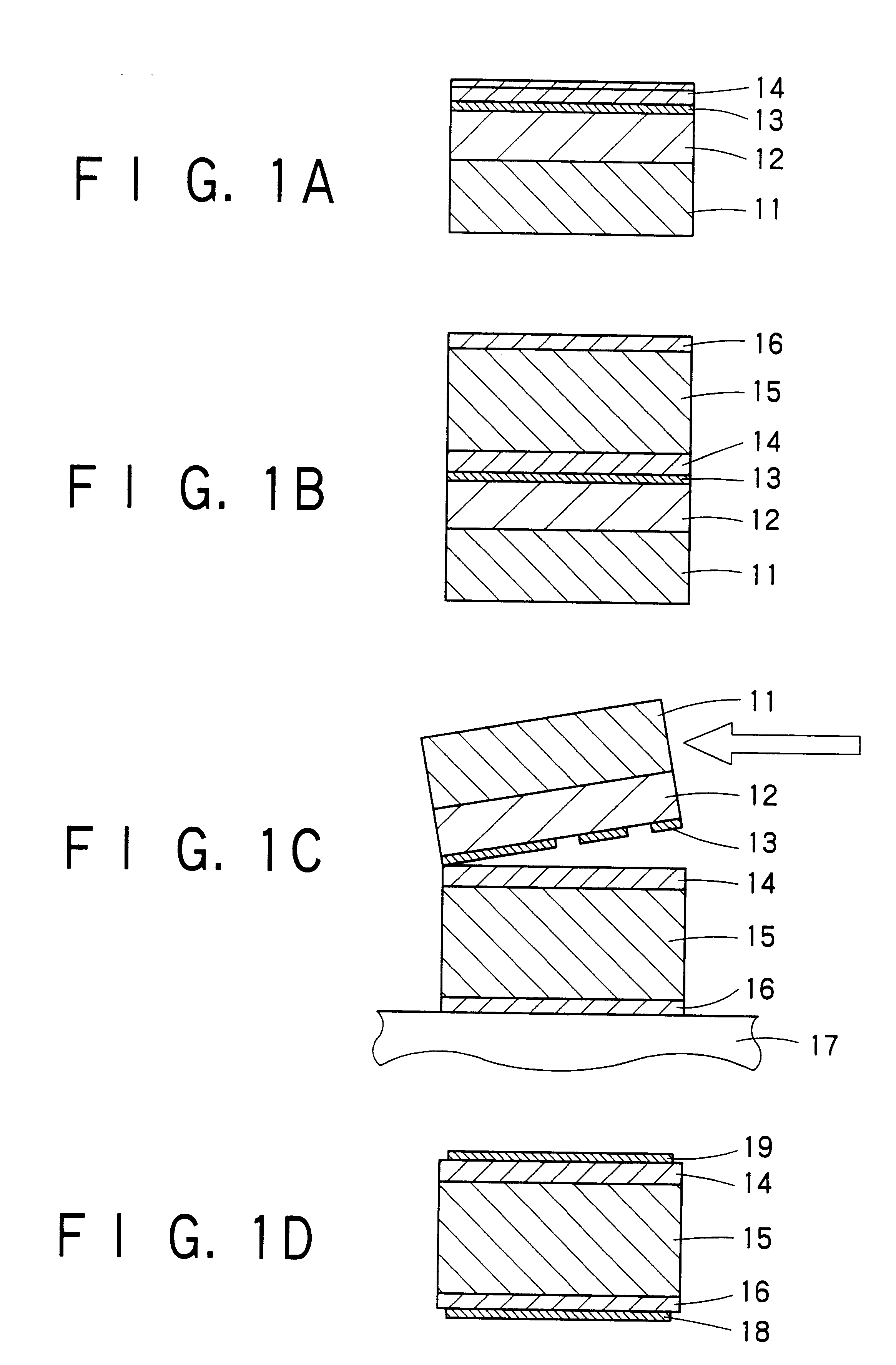

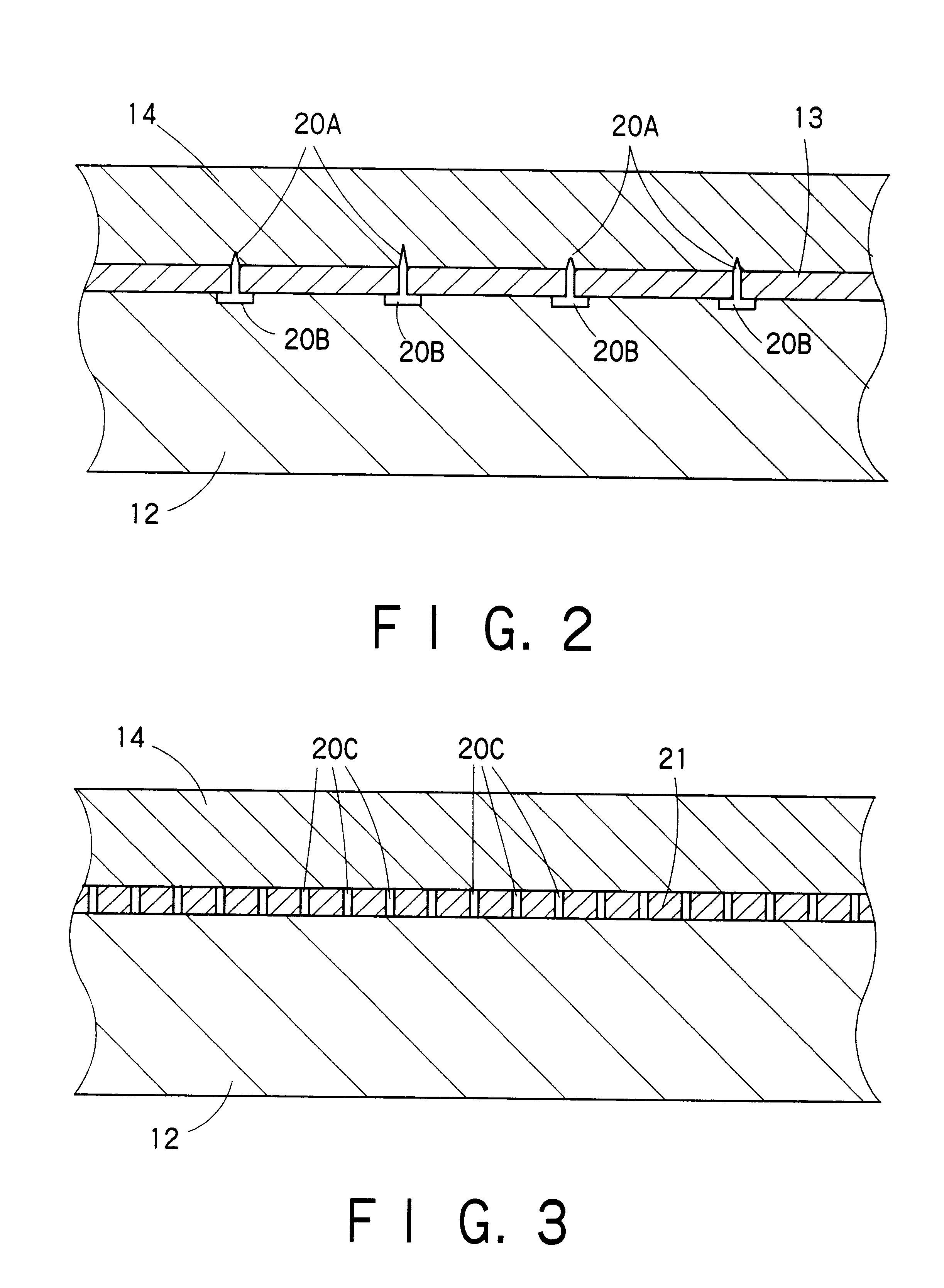

InactiveUS6303405B1Quality improvementImprove electricitySolid-state devicesSemiconductor/solid-state device manufacturingLaser lightHeat stress

A semiconductor light emitting element of nitride compound semiconductors excellent in cleavability, heat radiation and resistance to leakage is made by epitaxially grow a nitride compound semiconductor layers on a substrate of sapphire, for example, and thereafter separating the substrate. For separating the substrate, there are a technique using a abruption mechanism susceptible to a stress such as a "lift-off layer" and a recesses on a substrate. A technique using laser light to cause a local dense heat stress at the abruption mechanism is effective. A nitride compound semiconductor obtained by separating the substrate may be used as a new substrate to epitaxially grow high-quality nitride compound semiconductors thereon.

Owner:ALPAD CORP

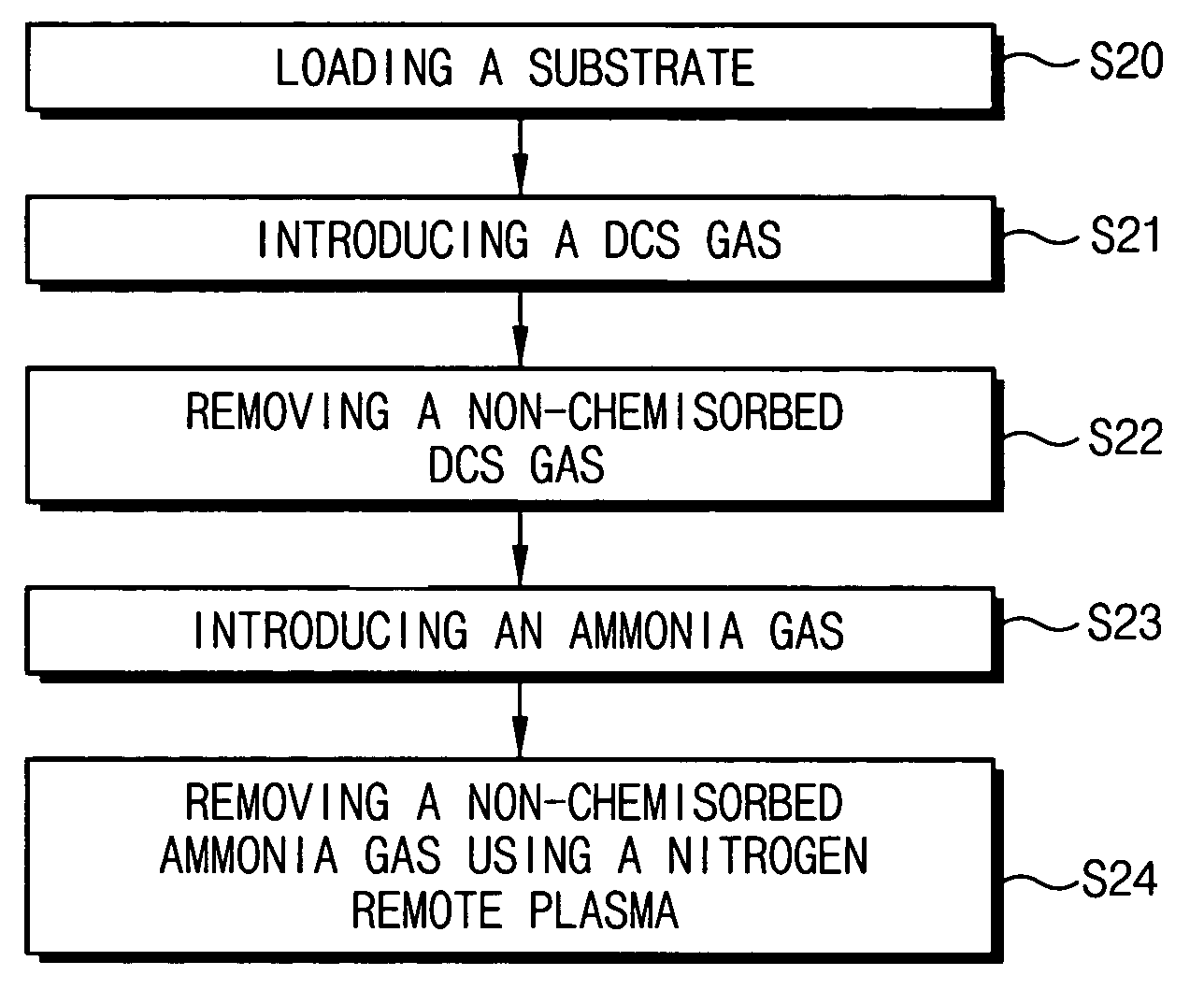

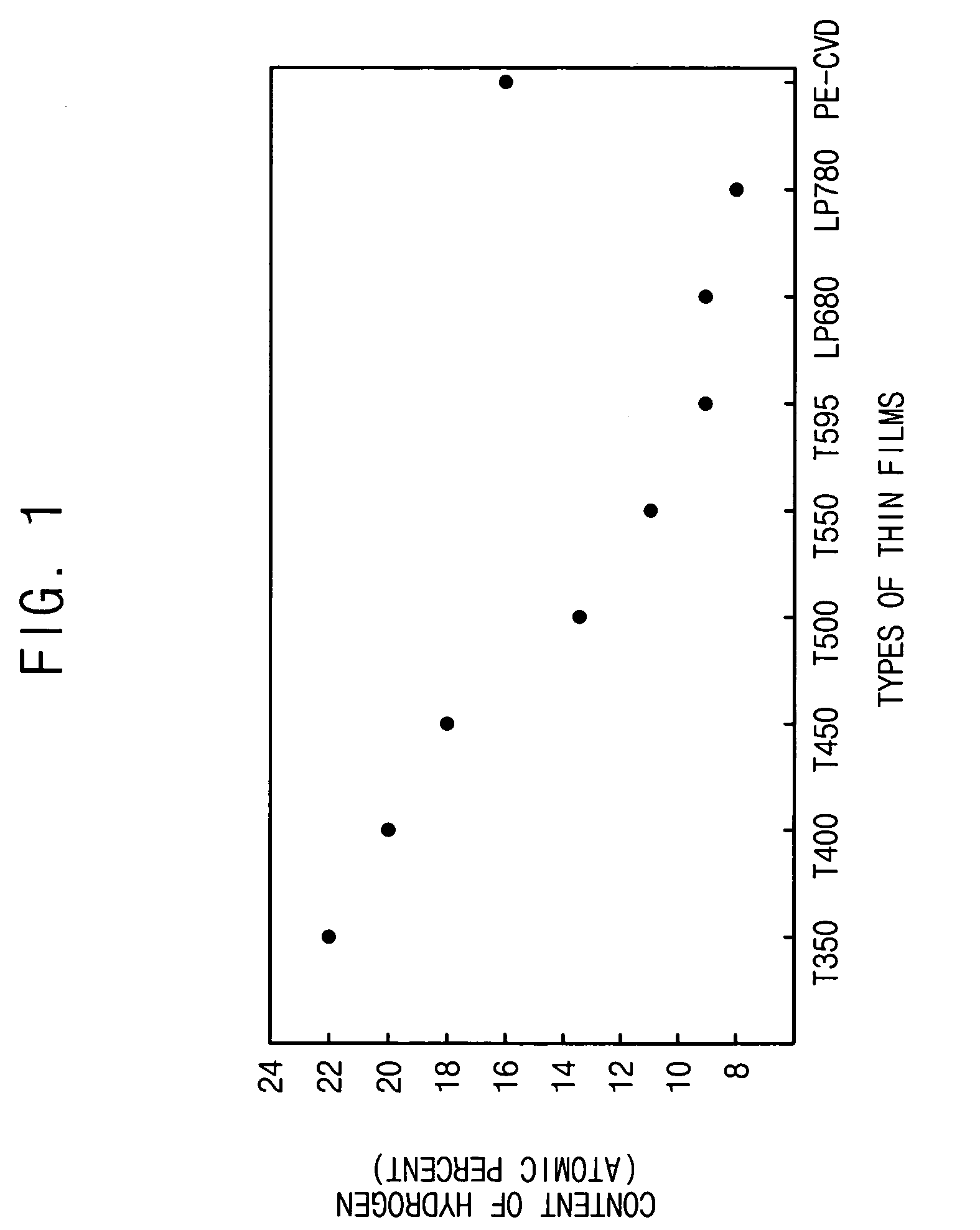

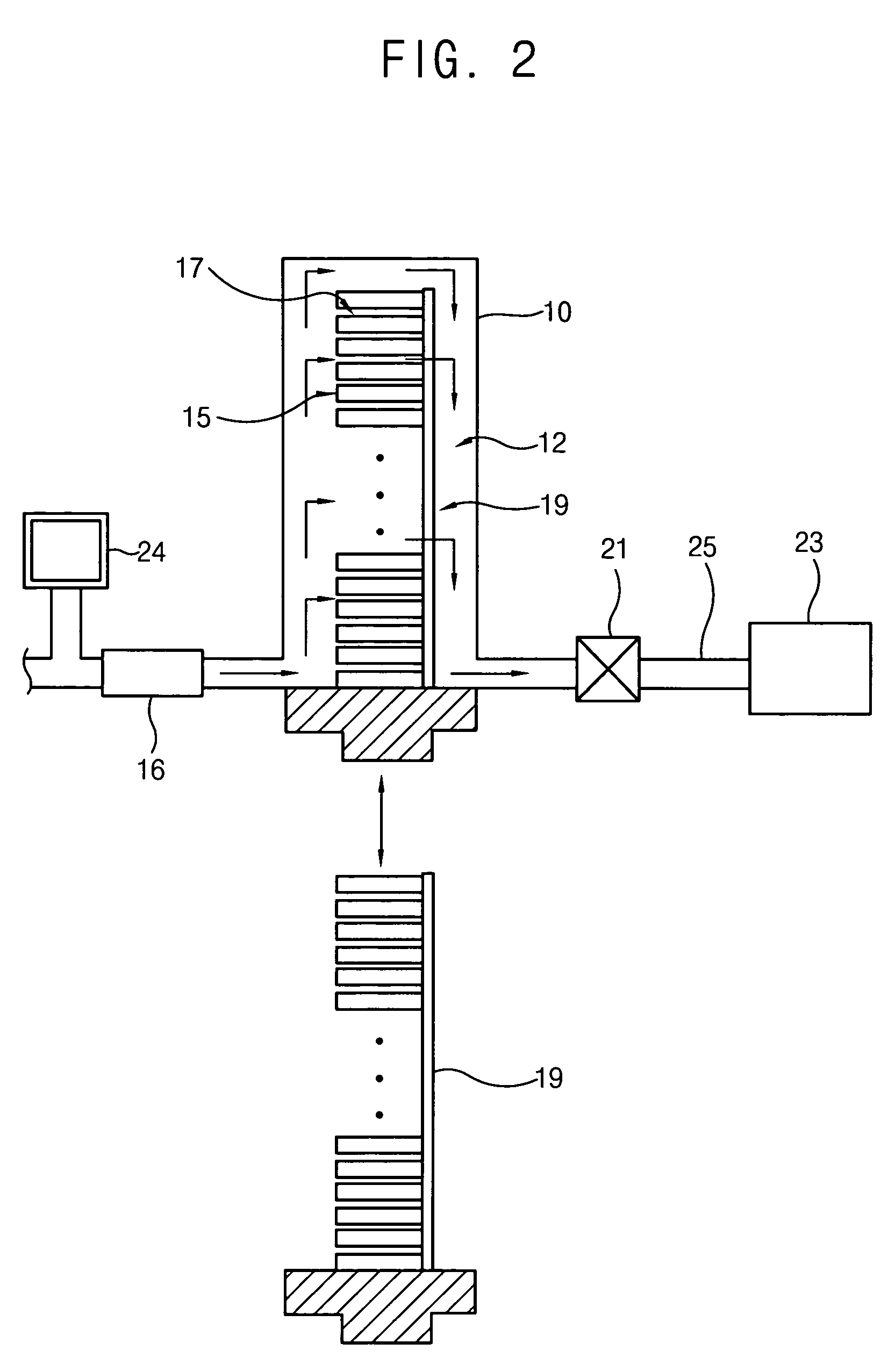

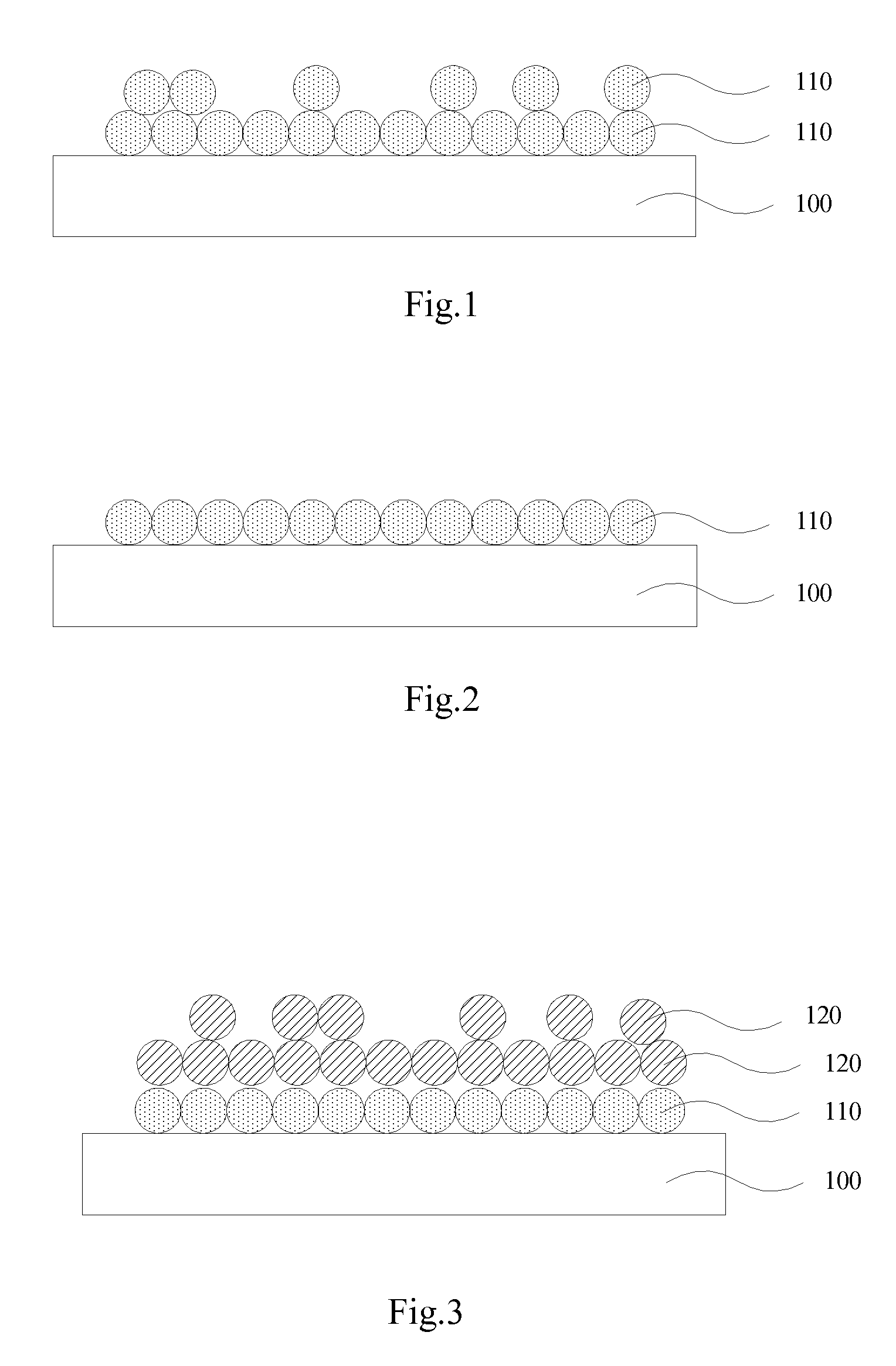

Method of forming a layer and forming a capacitor of a semiconductor device having the same layer

InactiveUS20060014384A1Low hydrogen contentReduce leakage currentSemiconductor/solid-state device manufacturingCapacitorsChemical reactionDevice material

In a method of forming a layer using an atomic layer deposition process, after a substrate is loaded into a chamber, a first reactant is provided onto the substrate. The first reactant is partially chemisorbed on the substrate. A second reactant is introduced into the chamber to form a preliminary layer on the substrate by chemically reacting the second reactant with the chemisorbed first reactant. Impurities in the preliminary layer and unreacted reactants are simultaneously removed using a plasma for removing impurities to thereby form the layer on the substrate. The impurities in the layer may be effectively removed so that the layer may have reduced leakage current.

Owner:SAMSUNG ELECTRONICS CO LTD

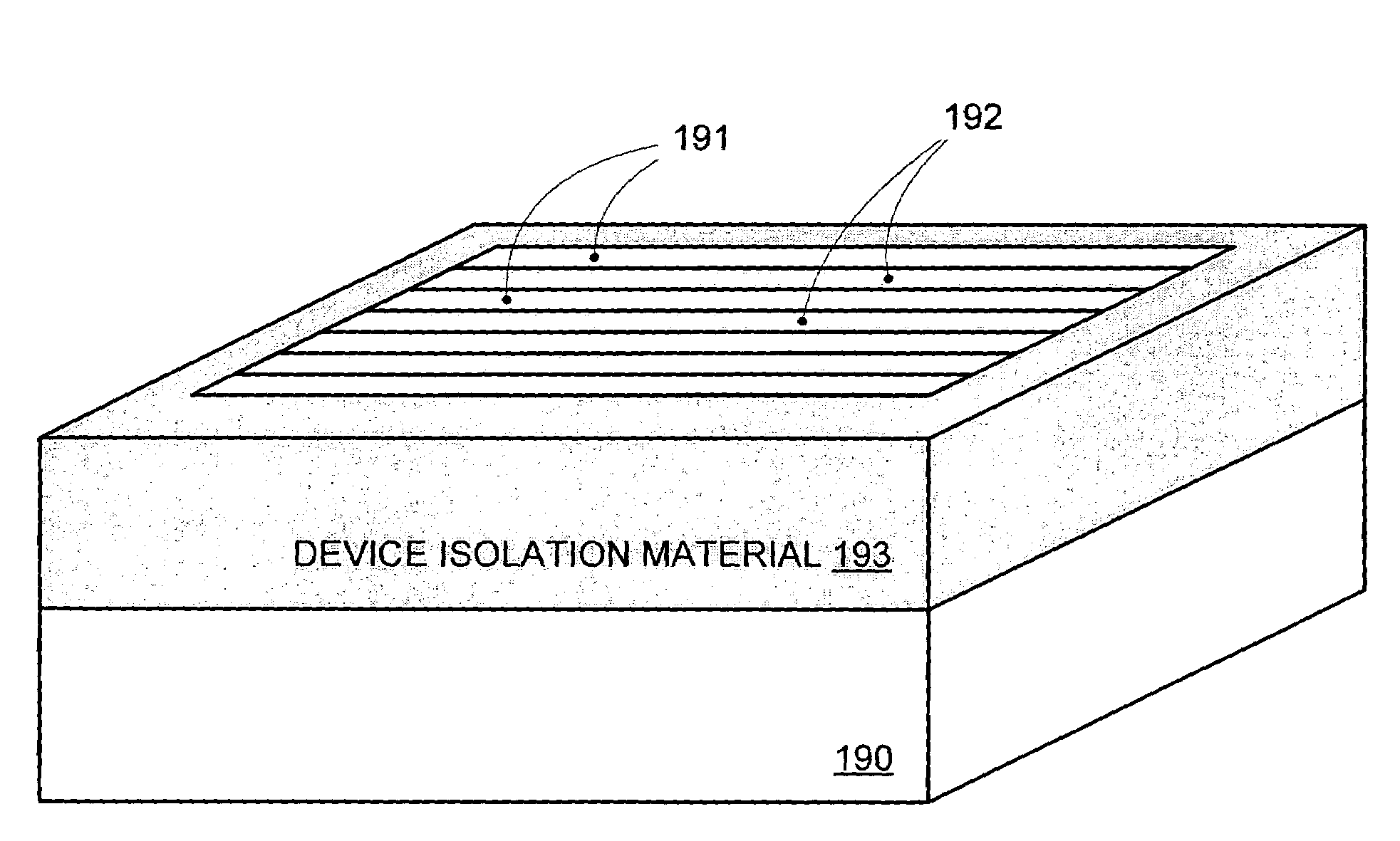

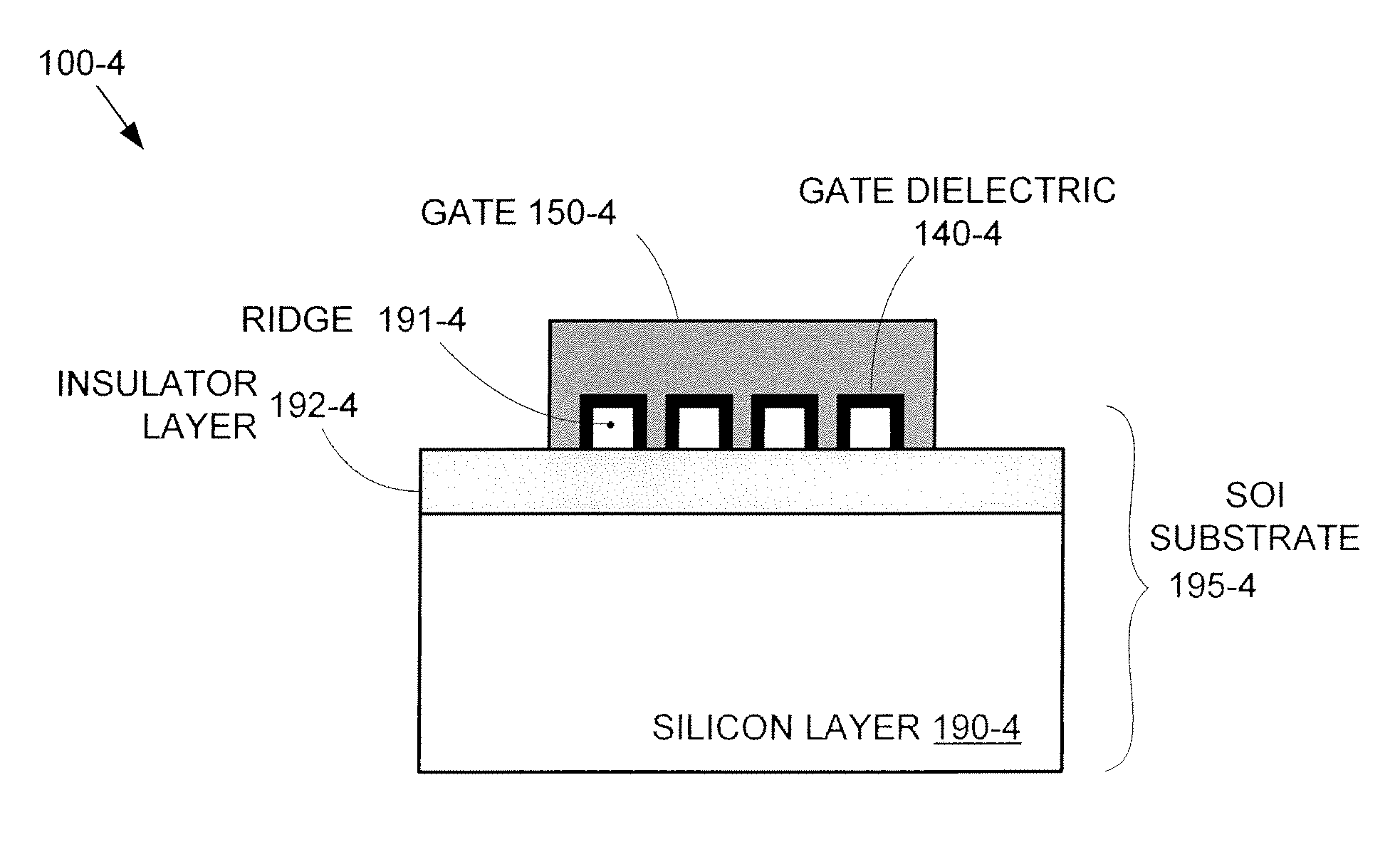

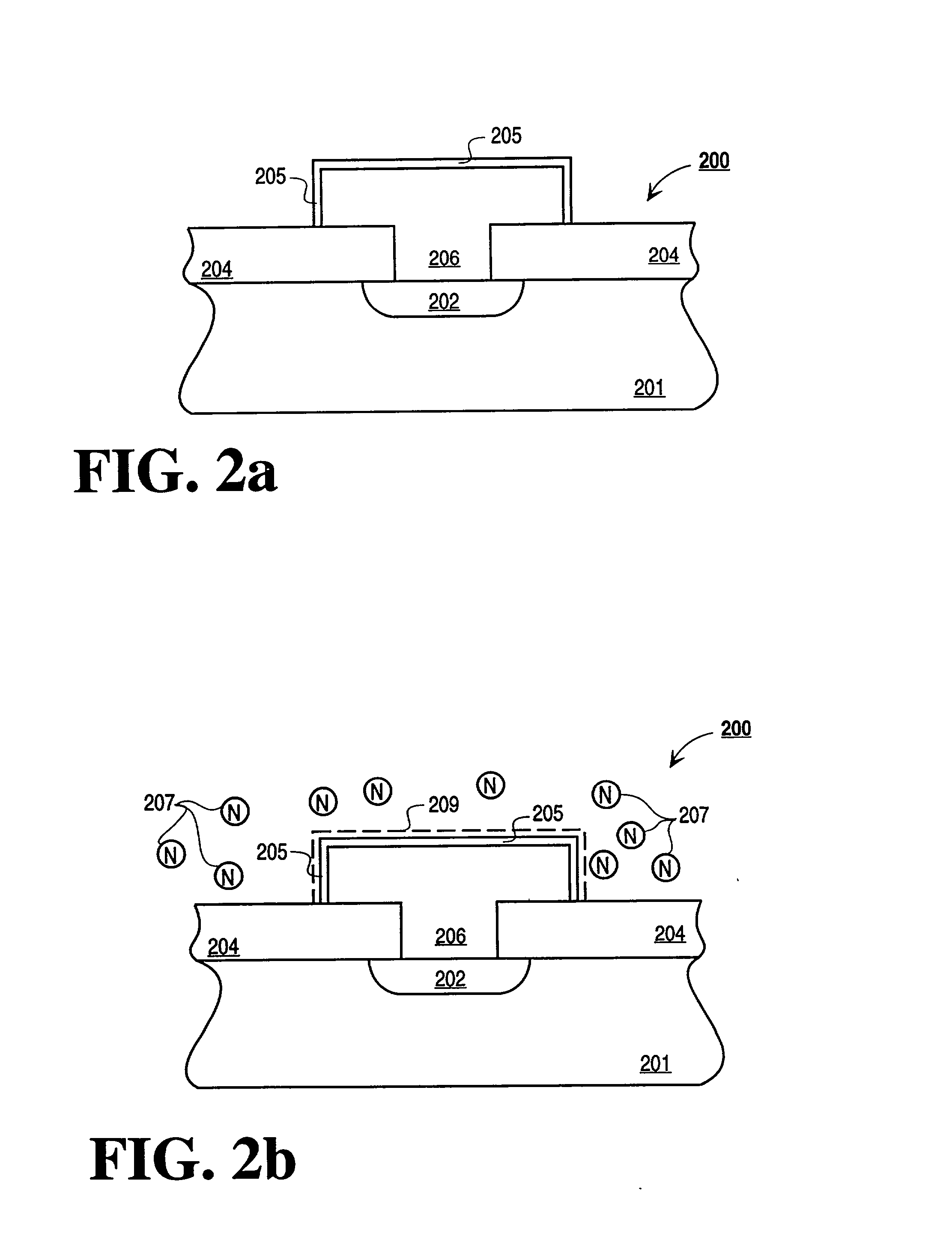

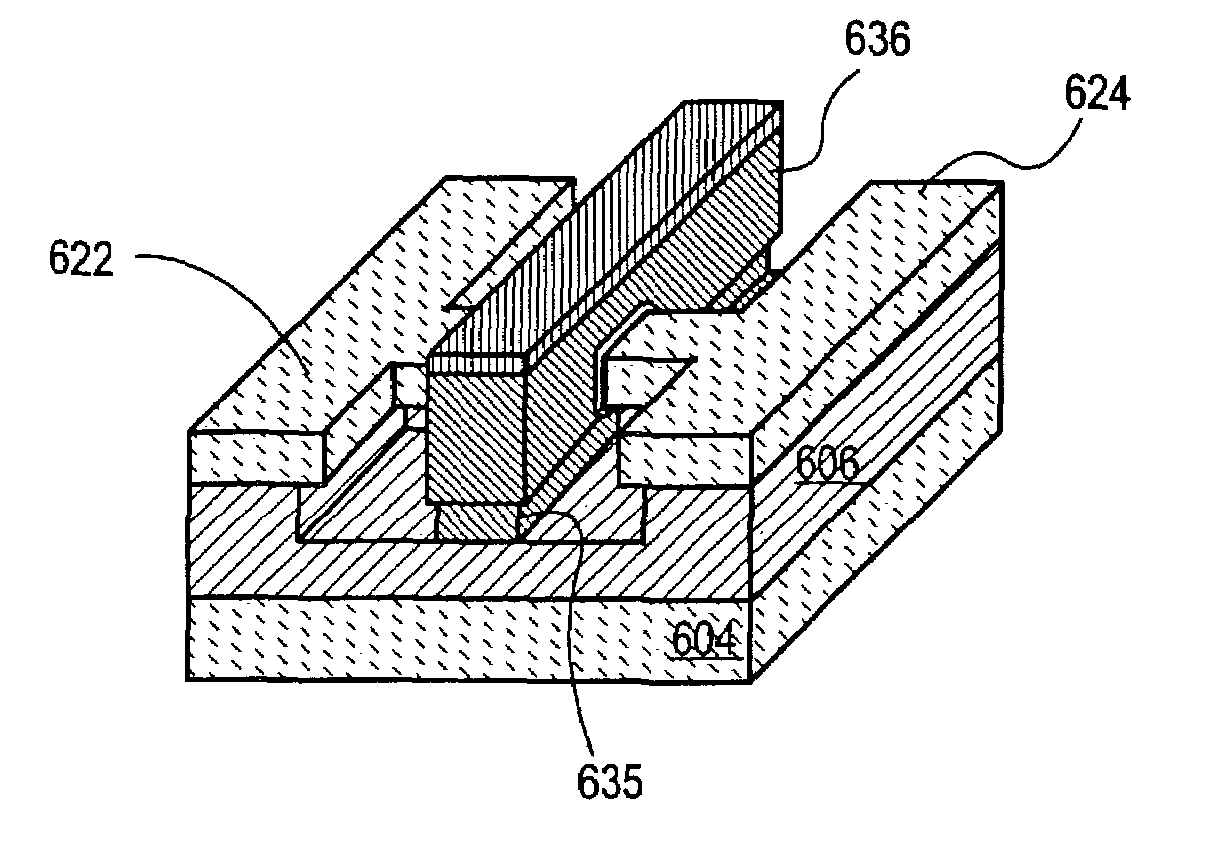

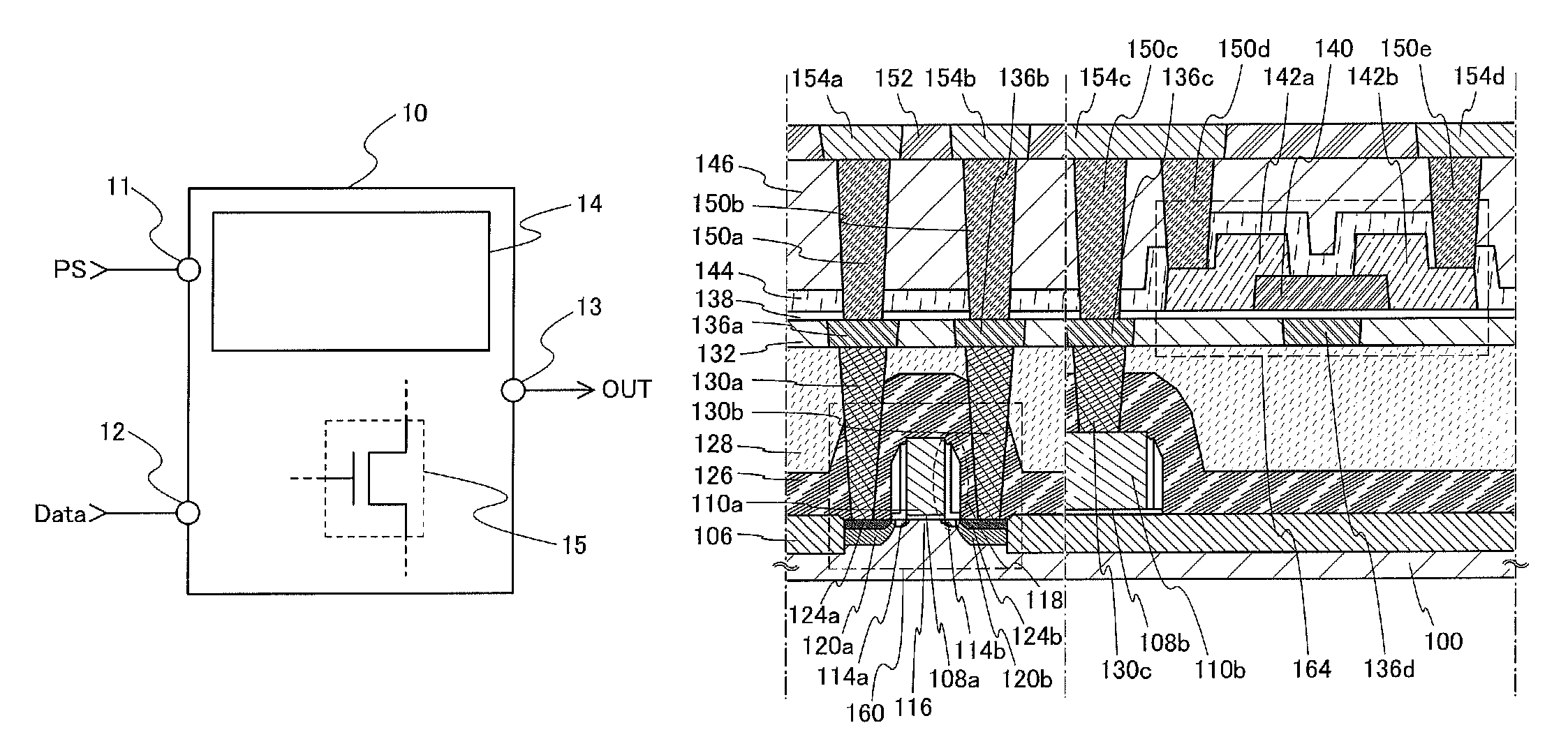

Integrated circuit on corrugated substrate

ActiveUS7190050B2Improve performance consistencyImprove performanceTransistorSemiconductor/solid-state device detailsMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

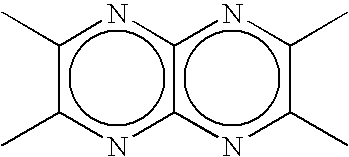

Organic electroluminescent device and material for organic electroluminescent device

ActiveUS20090167167A1Improve performanceHigh electron-accepting propertyOrganic chemistryDischarge tube luminescnet screensOrganic electroluminescenceMolecular physics

Disclosed is a novel compound useful as a constituent of an organic EL device. Also disclosed is a practical organic EL device using this compound. This organic EL device has low driving voltage, long life, and reduced leakage current. Specifically disclosed is a compound characterized by having at least one structure (1) shown below in a molecule. Structure (1)

Owner:IDEMITSU KOSAN CO LTD +1

Dielectric film and formation method thereof, semiconductor device, non-volatile semiconductor memory device, and fabrication method for a semiconductor device

InactiveUS20080277715A1Improve wiring speedLow working voltageTransistorSemiconductor/solid-state device detailsDielectricHydrogen

Owner:FOUND FOR ADVANCEMENT OF INT SCI

Atomic Layer Deposition Method and Semiconductor Device Formed by the Same

ActiveUS20080315292A1Improve storage capability capabilityImprove capability memory isolation capabilitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingAtomic layer depositionDielectric layer

There is provided a method of manufacturing a semiconductor device, including the following steps: flowing a first precursor gas to the semiconductor substrate within a ALD chamber to form a first discrete monolayer on the semiconductor substrate; flowing an inert purge gas to the semiconductor substrate within the ALD chamber; flowing a second precursor gas to the ALD chamber to react with the first precursor gas which has formed the first monolayer, thereby forming a first discrete compound monolayer; and flowing an inert purge gas; forming a first dielectric layer to cover the discrete compound monolayer; forming a second third monolayer above first dielectric layer; and forming a second discrete compound monolayer; and forming a second dielectric layer to cover the second discrete compound monolayer above the first dielectric layer. There is also provided a semiconductor device formed by the ALD method.

Owner:SEMICON MFG INT (SHANGHAI) CORP

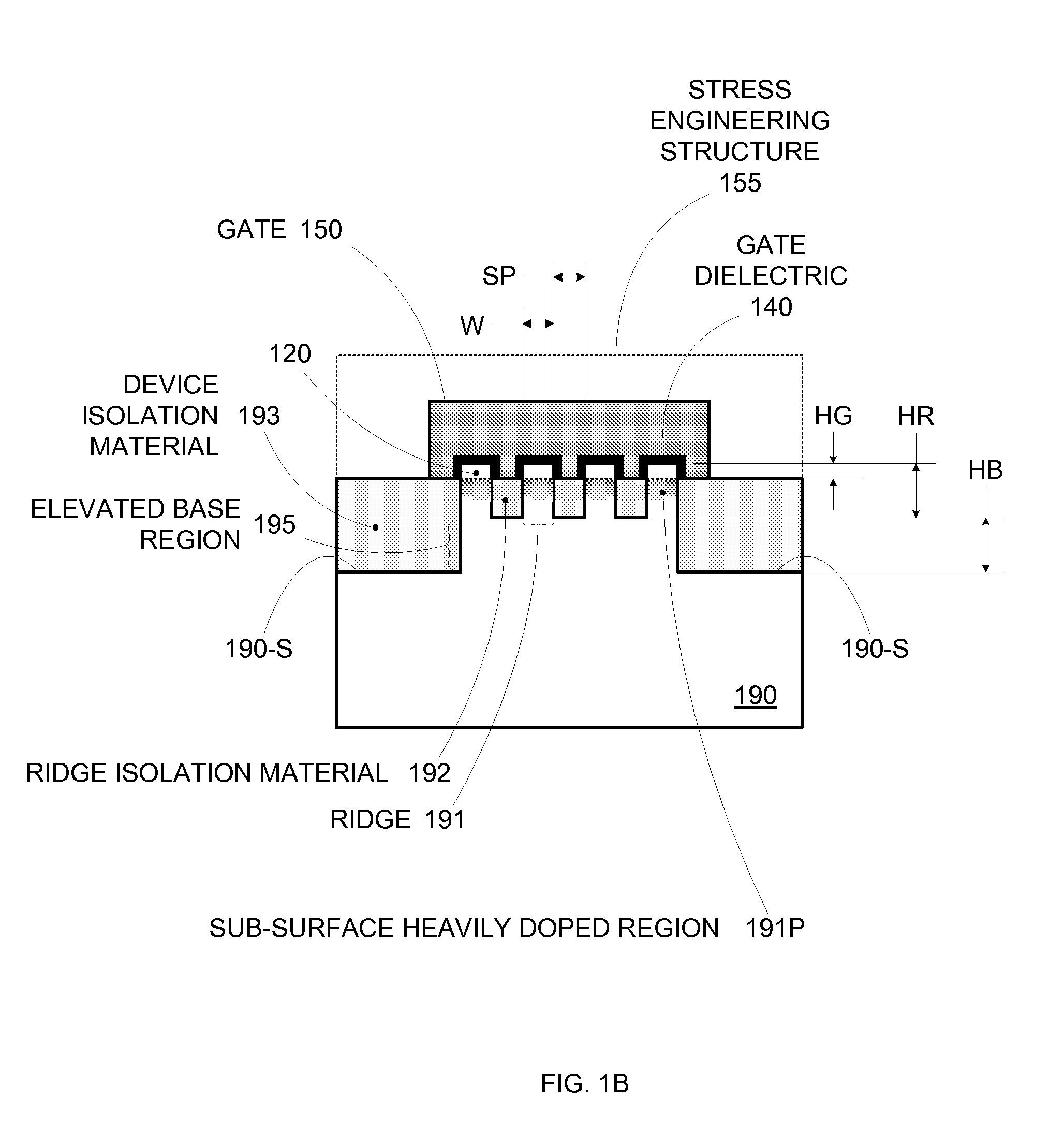

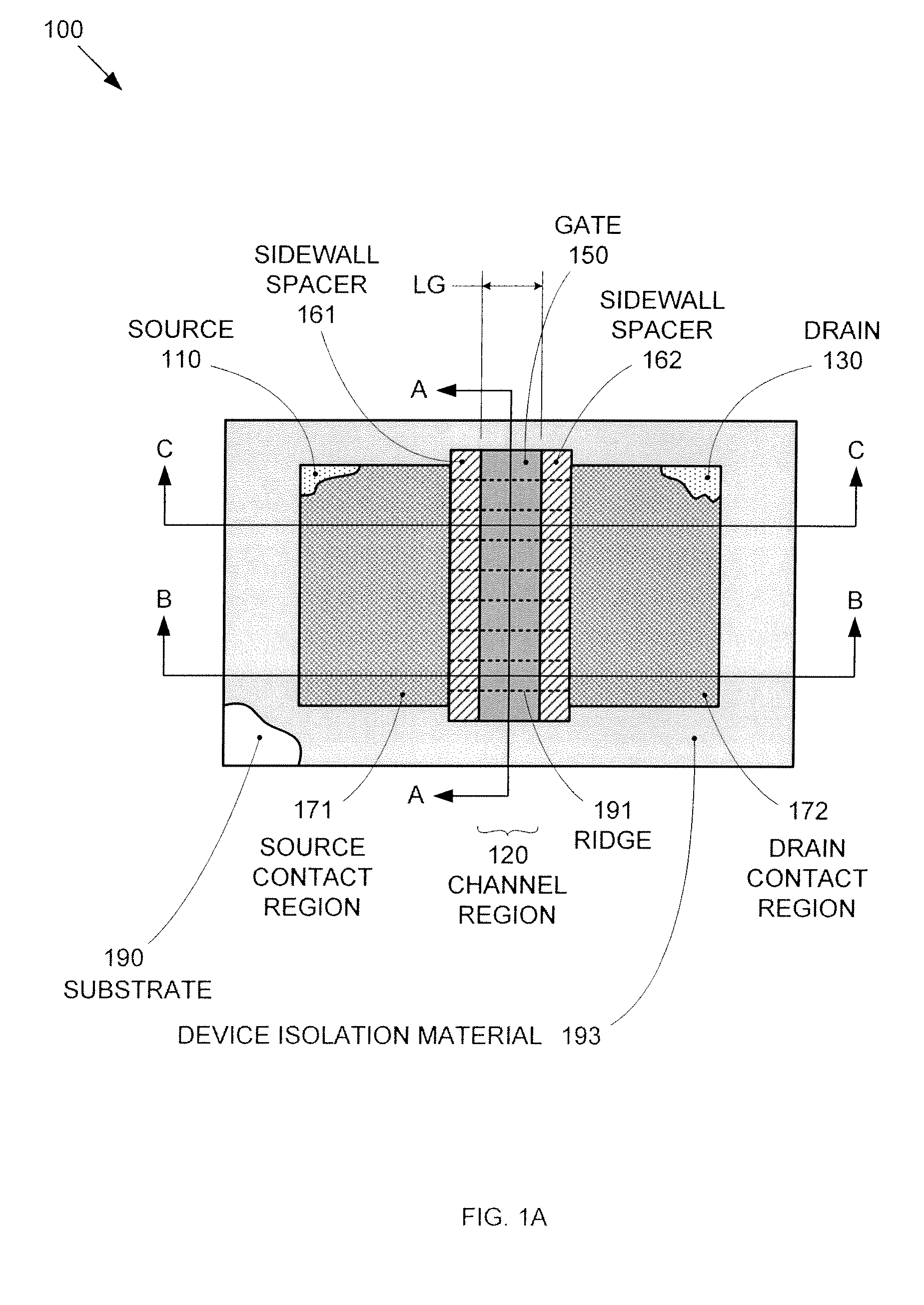

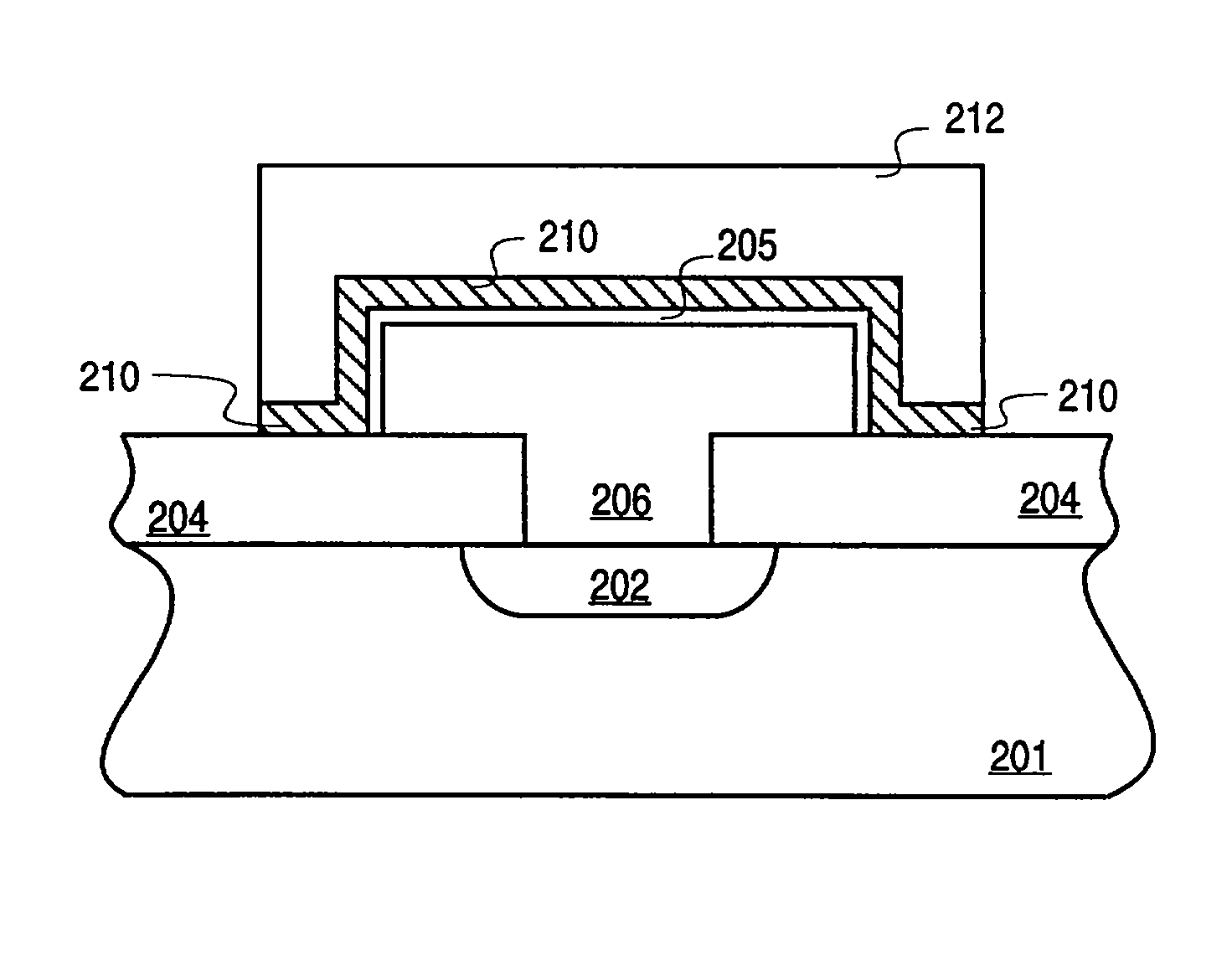

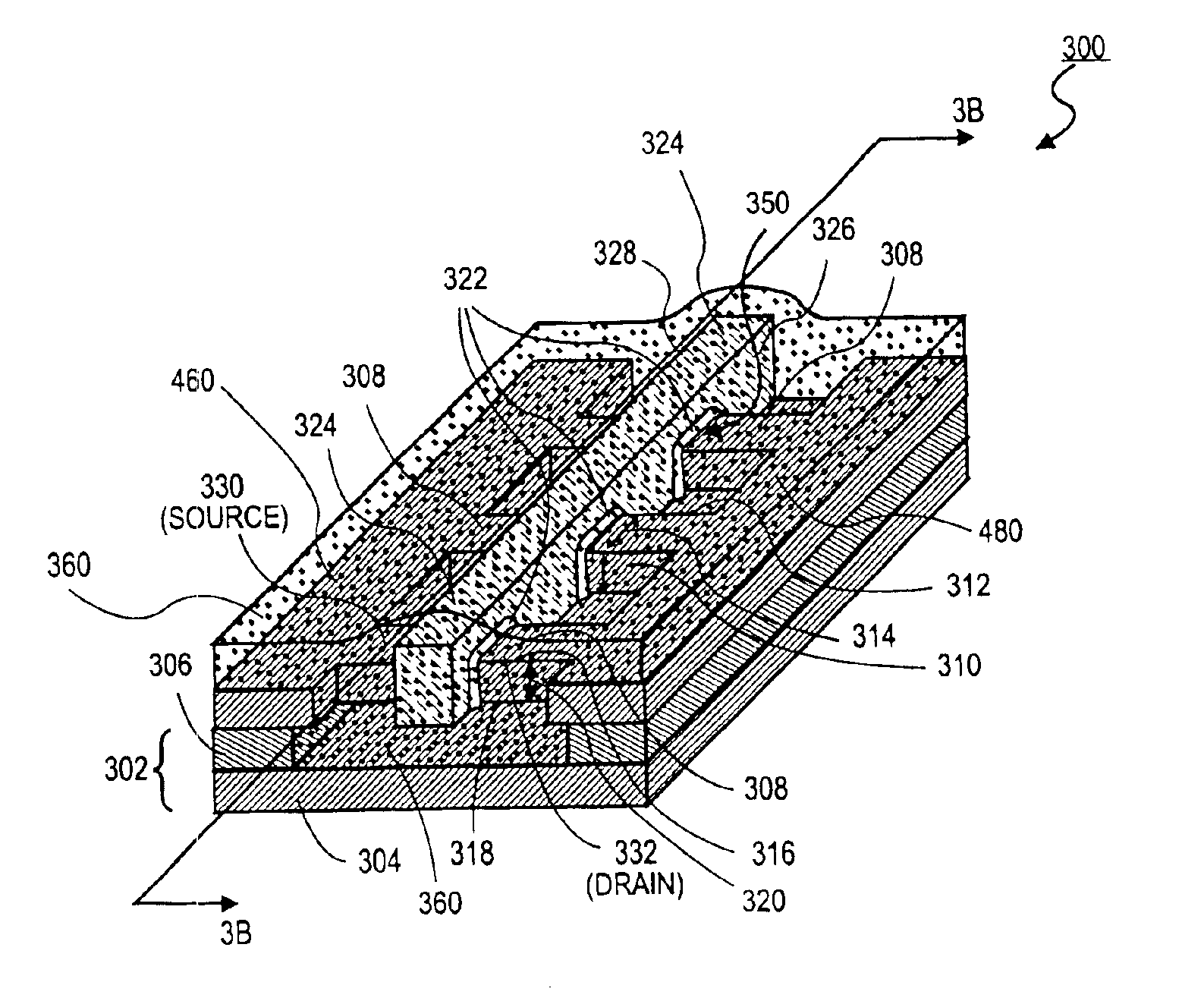

Enhanced Segmented Channel MOS Transistor with Multi Layer Regions

ActiveUS20070120156A1Increase costImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

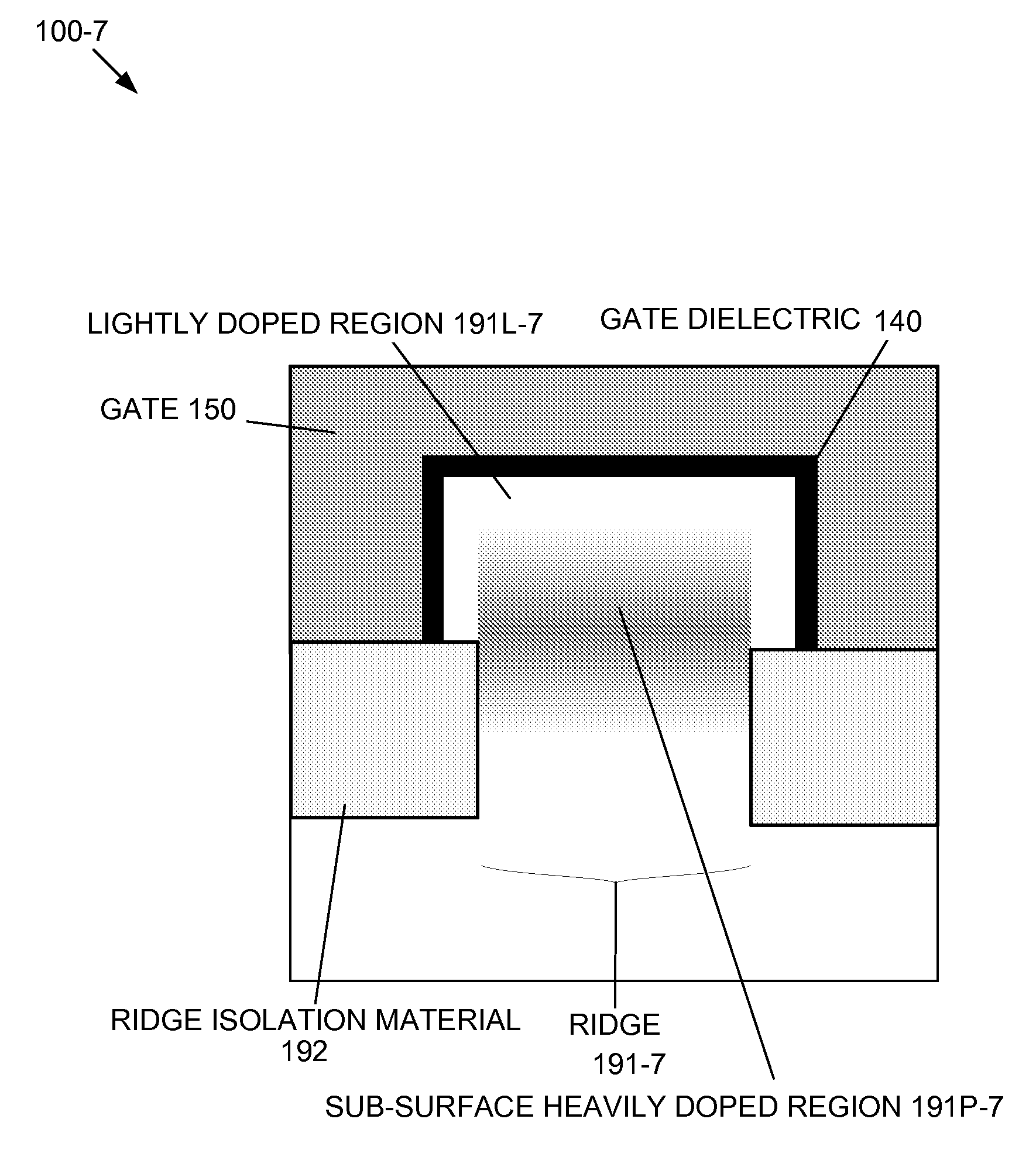

Enhanced Segmented Channel MOS Transistor with Narrowed Base Regions

ActiveUS20070128782A1Increase costImprove performanceThyristorSolid-state devicesPre-existingImage resolution

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

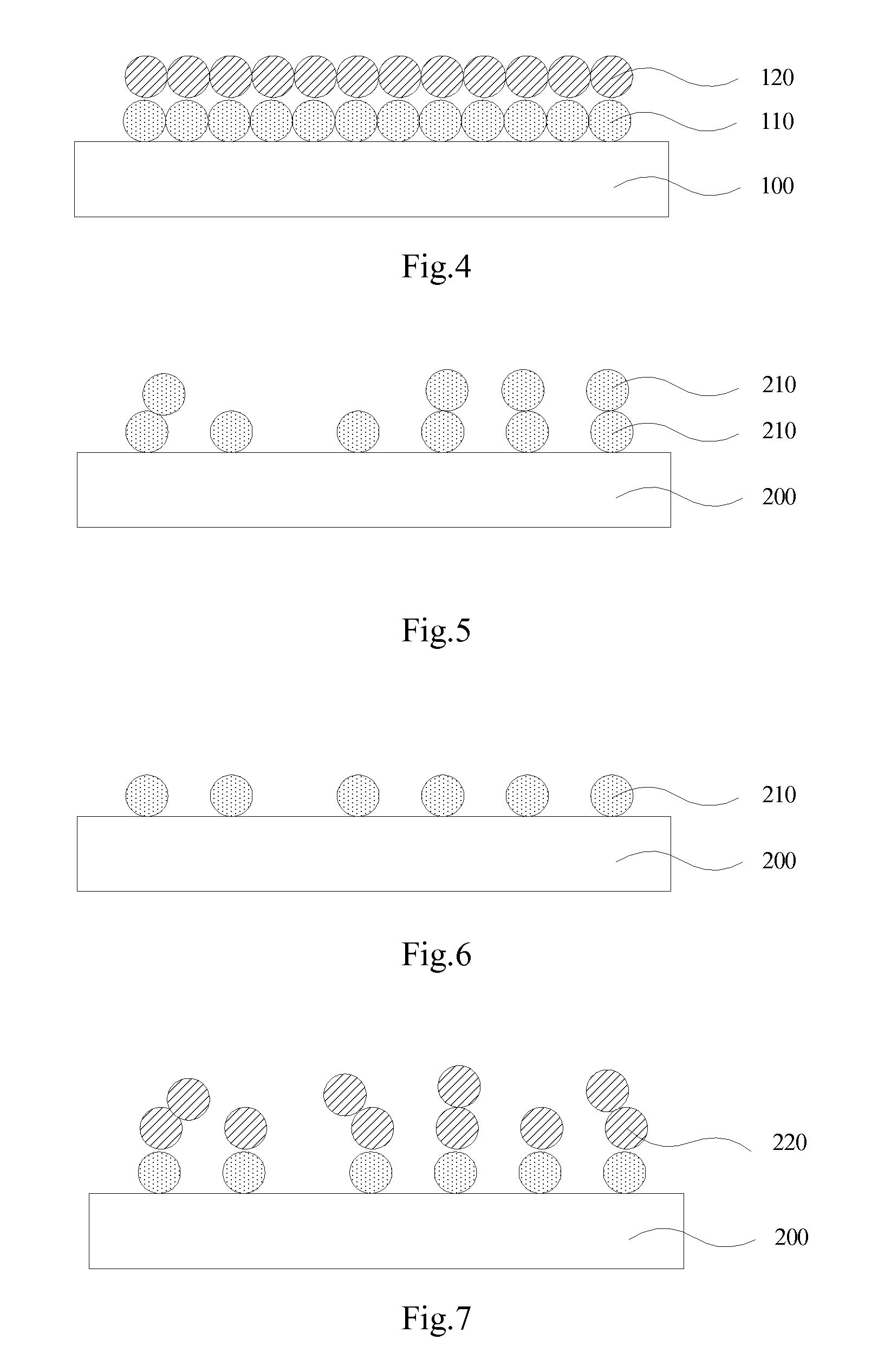

Sequential Selective Epitaxial Growth

ActiveUS20070122954A1Increase costImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETCMOS

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. A multi step epitaxial process can be used to extend the ridges with different dopant types, high mobility semiconductor, and or advanced multi-layer strutures. For CMOS integrated circuits a capping layer is formed over the a first region. Epitaxial layers are formed in a second region. Then the capping layer is removed from the first region and a capping layer is formed over the second region. Epitaxial layers can than be formed in the first region.

Owner:SYNOPSYS INC

Method of IC production using corrugated substrate

ActiveUS7265008B2Improve performance consistencyImprove performanceLaser detailsSolid-state devicesMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Enhanced segmented channel MOS transistor with narrowed base regions

ActiveUS7508031B2Improve performance consistencyImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably produced. Ridges on the corrugated substrate can be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials, high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

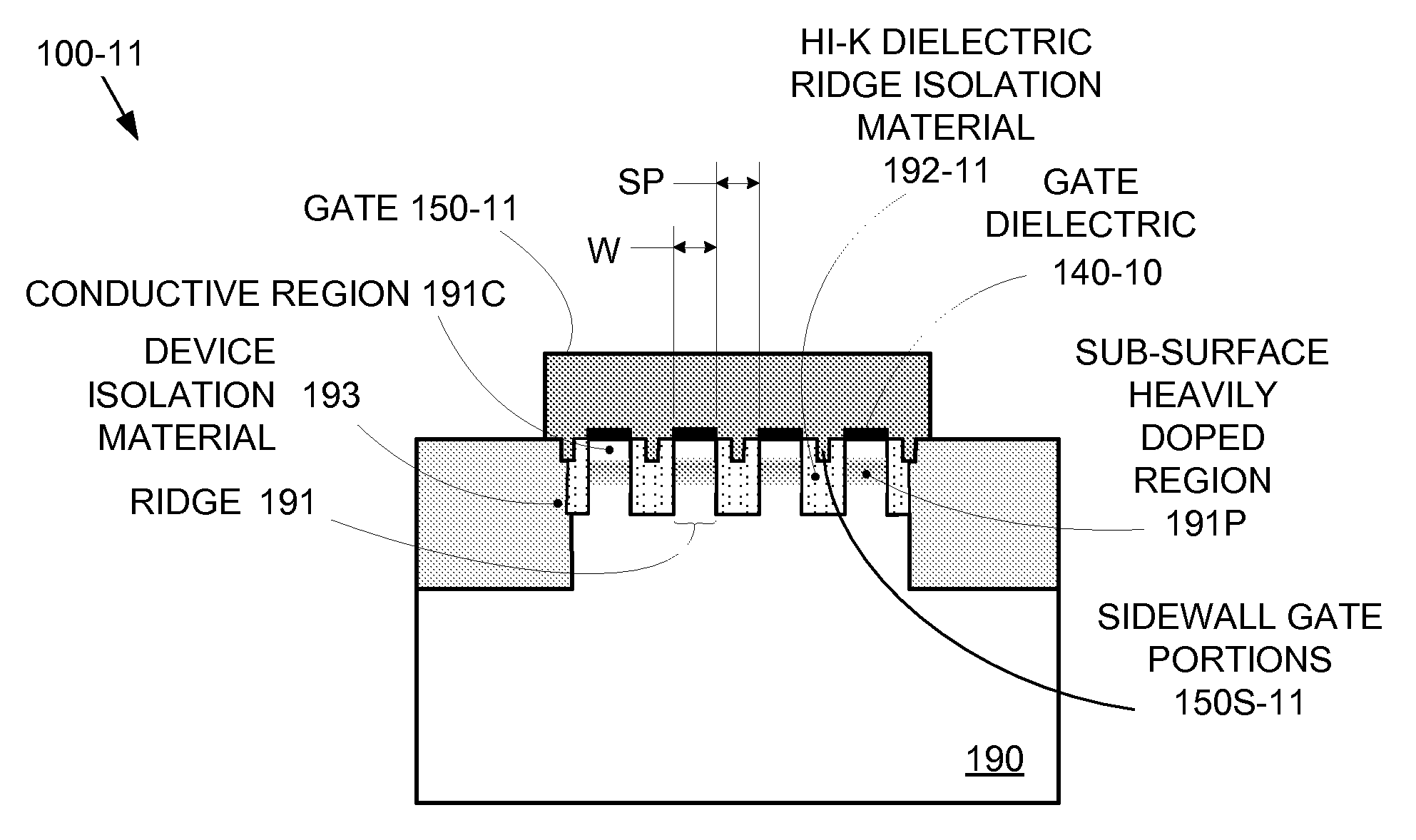

Enhanced Segmented Channel MOS Transistor with High-Permittivity Dielectric Isolation Material

ActiveUS20070122953A1Increase costImprove performanceTransistorSolid-state devicesMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Enhanced segmented channel MOS transistor with high-permittivity dielectric isolation material

ActiveUS7605449B2Improve performance consistencyImprove performanceTransistorSolid-state devicesMOSFETPerformance enhancement

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping, “wrapped” gates, epitaxially grown conductive regions, epitaxially grown high mobility semiconductor materials (e.g. silicon-germanium, germanium, gallium arsenide, etc.), high-permittivity ridge isolation material, and narrowed base regions can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

Integrated Circuit On Corrugated Substrate

ActiveUS20070132053A1Improve performance consistencyImprove performanceTransistorSemiconductor/solid-state device detailsMOSFETSemiconductor materials

By forming MOSFETs on a substrate having pre-existing ridges of semiconductor material (i.e., a “corrugated substrate”), the resolution limitations associated with conventional semiconductor manufacturing processes can be overcome, and high-performance, low-power transistors can be reliably and repeatably produced. Forming a corrugated substrate prior to actual device formation allows the ridges on the corrugated substrate to be created using high precision techniques that are not ordinarily suitable for device production. MOSFETs that subsequently incorporate the high-precision ridges into their channel regions will typically exhibit much more precise and less variable performance than similar MOSFETs formed using optical lithography-based techniques that cannot provide the same degree of patterning accuracy. Additional performance enhancement techniques such as pulse-shaped doping and “wrapped” gates can be used in conjunction with the segmented channel regions to further enhance device performance.

Owner:SYNOPSYS INC

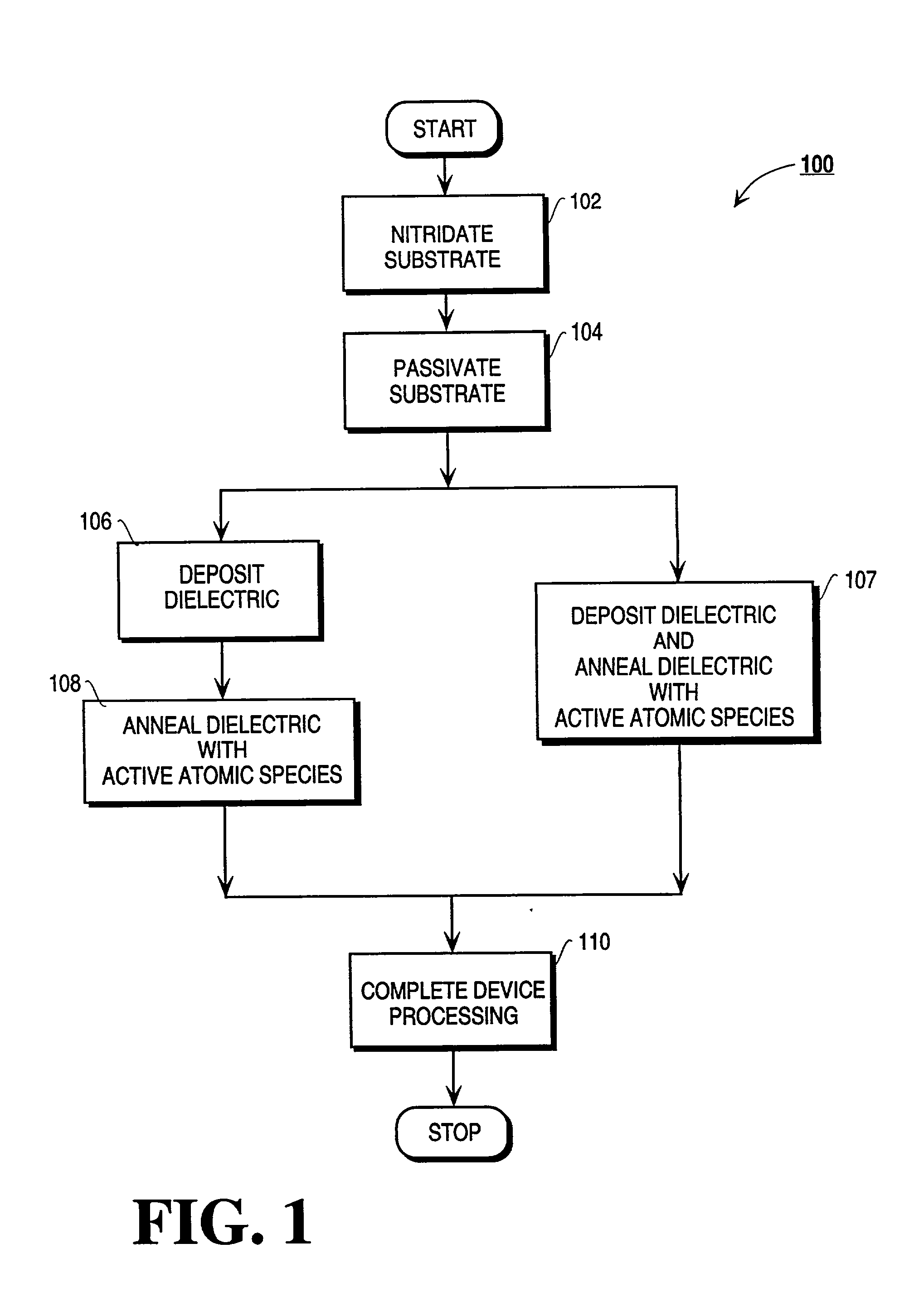

Method and apparatus for the formation of dielectric layers

InactiveUS20020009861A1Simple interfaceImprove performanceTransistorVacuum evaporation coatingAtomic speciesDielectric layer

A method and apparatus for forming and annealing a dielectric layer. According to the present invention an active atomic species is generated in a first chamber. A dielectric layer formed on a substrate is then exposed to the active atomic species in a second chamber, wherein the second chamber is remote from the first chamber.

Owner:APPLIED MATERIALS INC

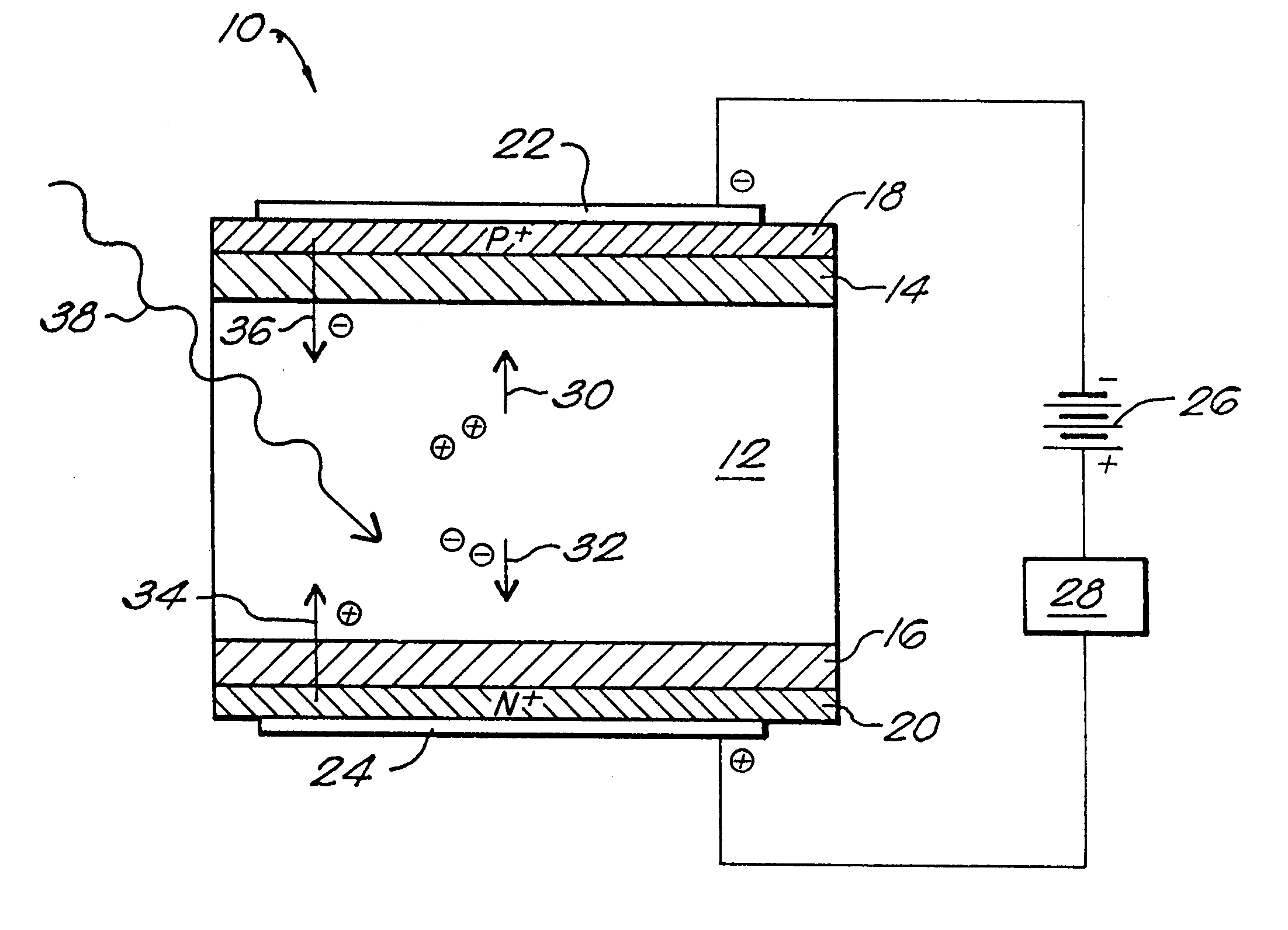

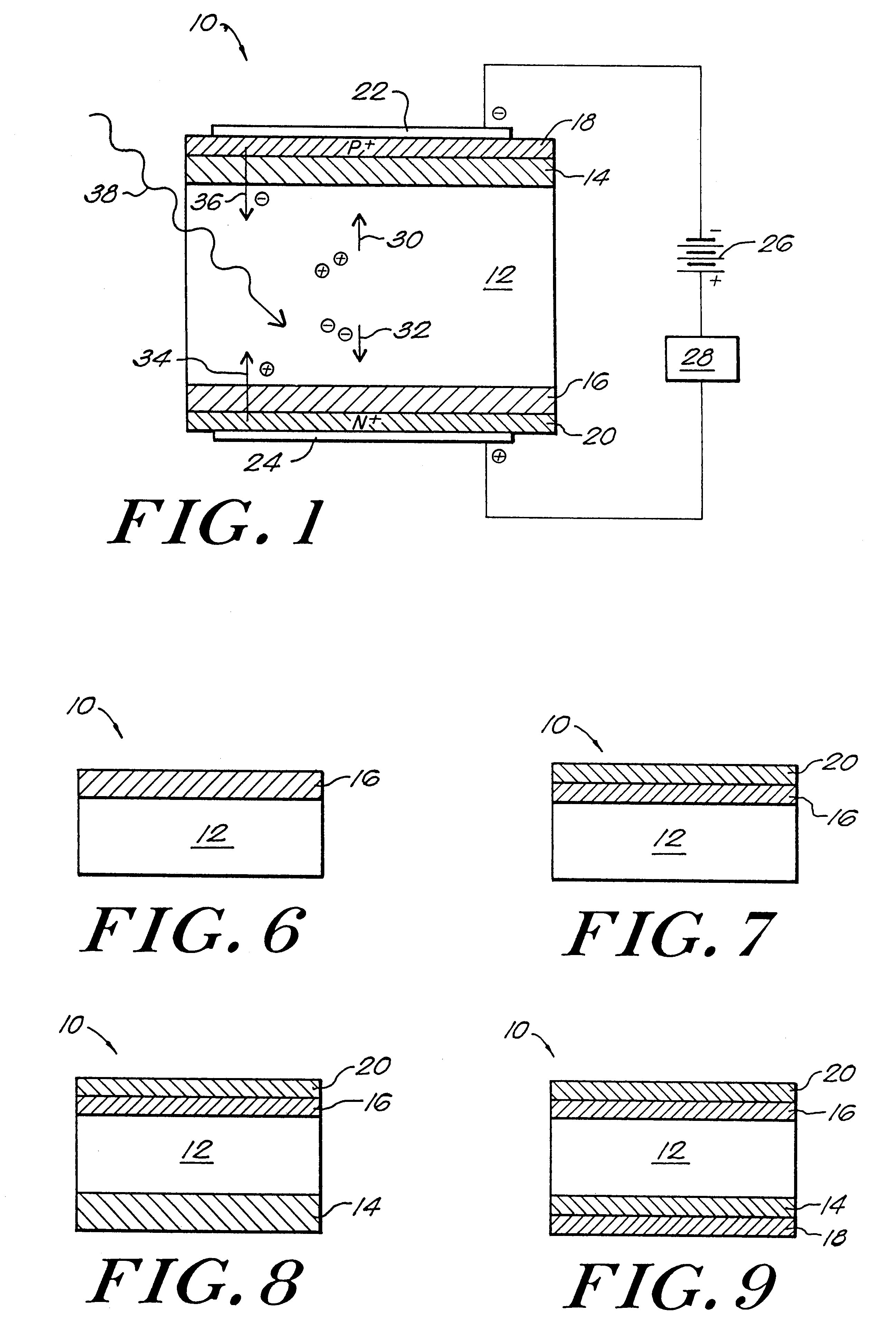

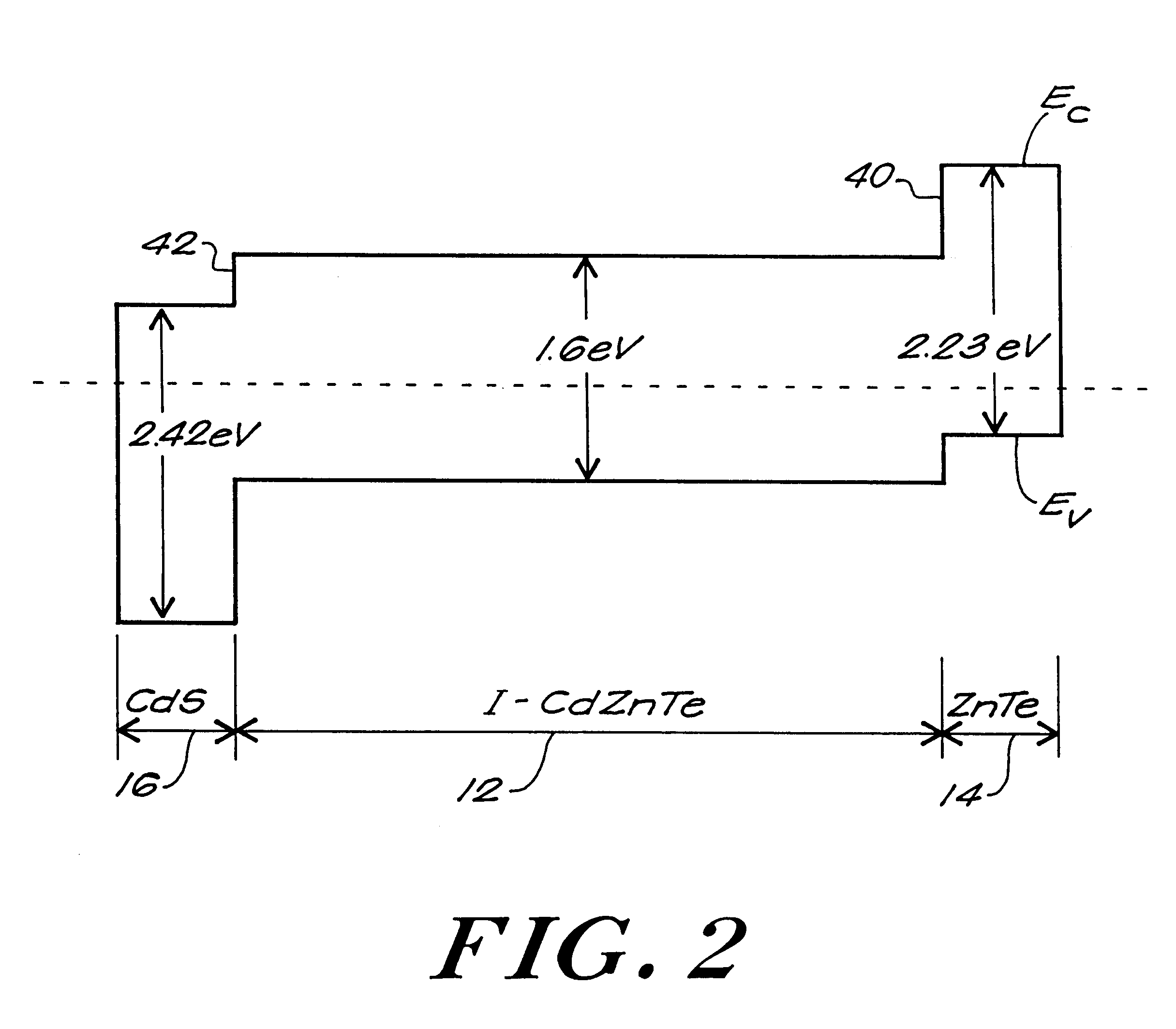

Semiconductor P-I-N detector

InactiveUS6255708B1Reduce leakage currentMitigating dopant diffusionSolid-state devicesSemiconductor/solid-state device manufacturingDopantIndium

A semiconductor P-I-N detector including an intrinsic wafer, a P-doped layer, an N-doped layer, and a boundary layer for reducing the diffusion of dopants into the intrinsic wafer. The boundary layer is positioned between one of the doped regions and the intrinsic wafer. The intrinsic wafer can be composed of CdZnTe or CdTe, the P-doped layer can be composed of ZnTe doped with copper, and the N-doped layer can be composed of CdS doped with indium. The boundary layers is formed of an undoped semiconductor material. The boundary layer can be deposited onto the underlying intrinsic wafer. The doped regions are then typically formed by a deposition process or by doping a section of the deposited boundary layer.

Owner:MASIMO SEMICON +2

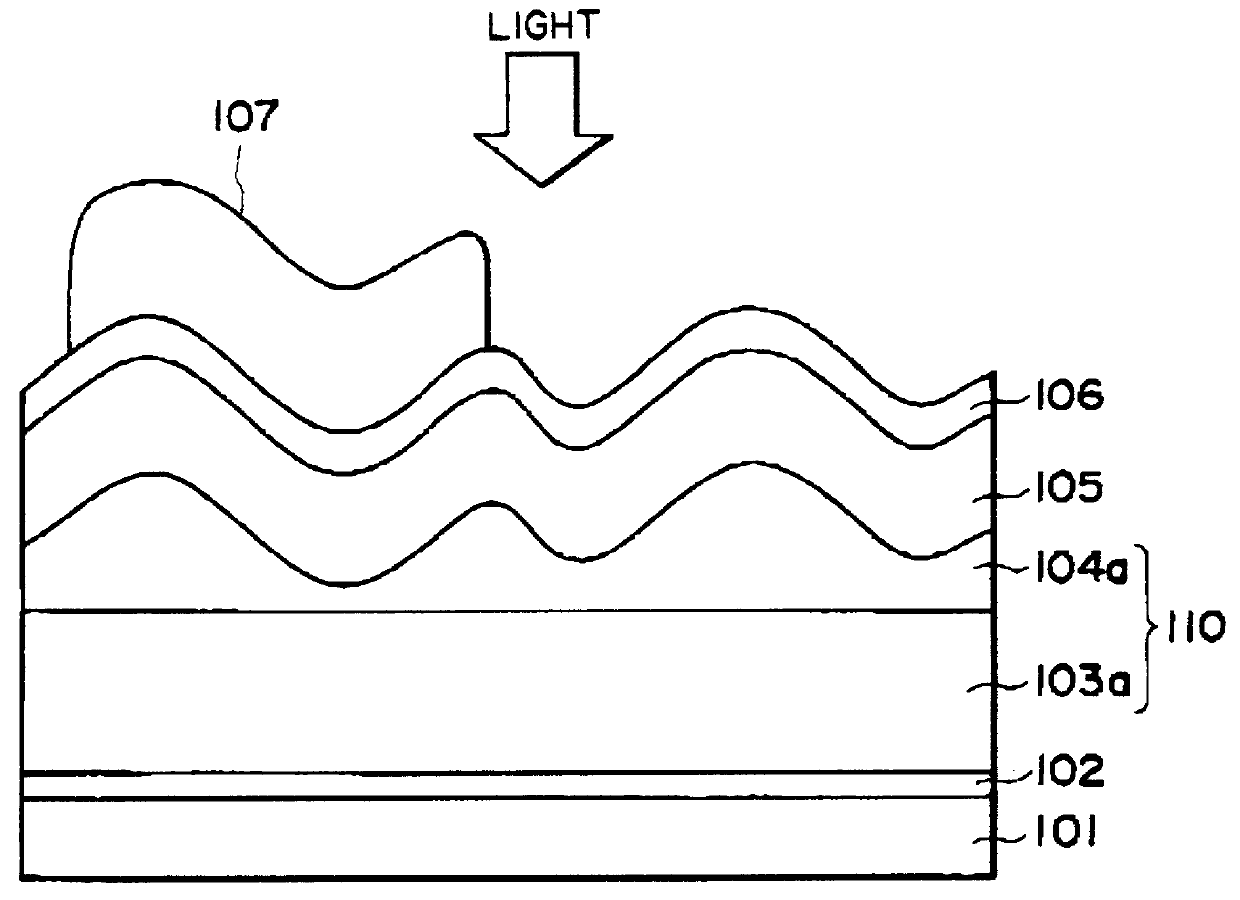

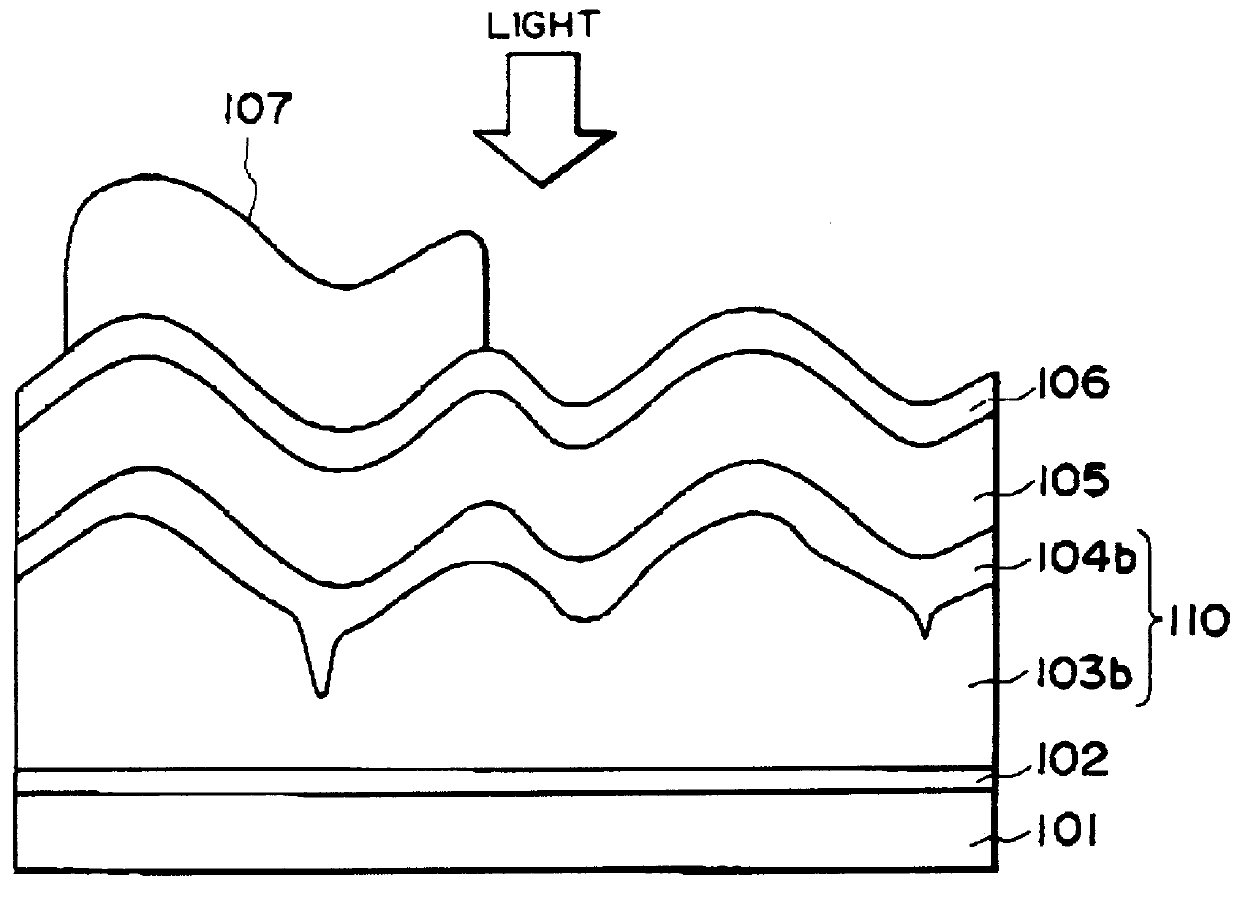

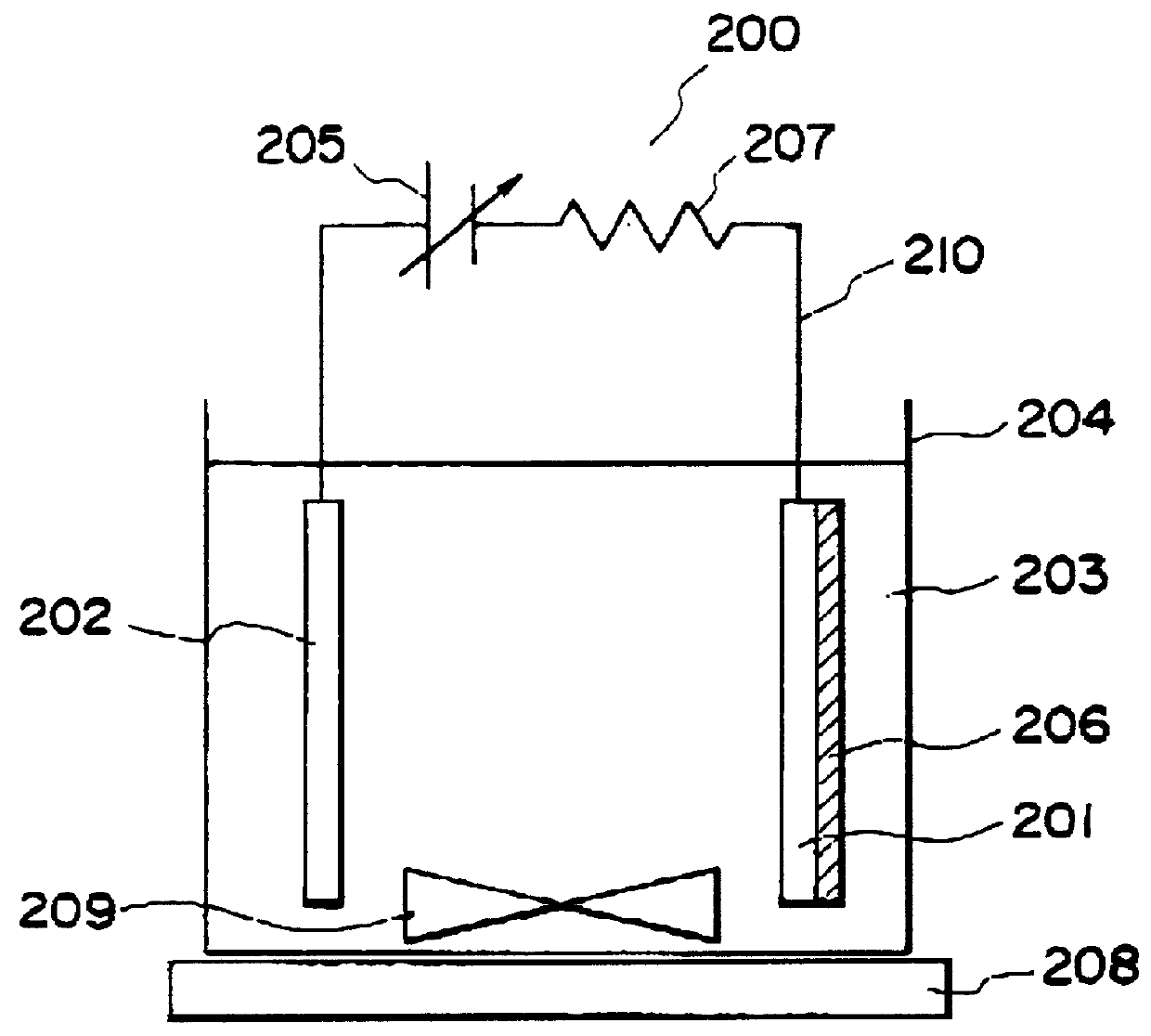

Process for producing photo-electricity generating device

InactiveUS6123824AInhibition of abnormal growthReduce leakage currentElectrolytic inorganic material coatingSurface reaction electrolytic coatingElectricityPower flow

A photo-electricity generating device is produced through the steps of: immersing an electrode and an electroconductive substrate in an aqueous solution comprising nitrate ions and zinc ions, supplying a current passing through a gap between the electrode and the electroconductive substrate to form a first zinc oxide layer on the electroconductive substrate, etching the first zinc oxide layer, and forming a semiconductor layer on the zinc oxide layer. The zinc oxide layer may preferably be formed in two zinc oxide layers under different electrudeposition conditions. In this case, the etching step may preferably be performed between steps for forming these zinc oxide layers. The zinc oxide layer is provided with an unevenness at its surface suitable for constituting a light-confining layer of a resultant photo-electricity generating device.

Owner:CANON KK

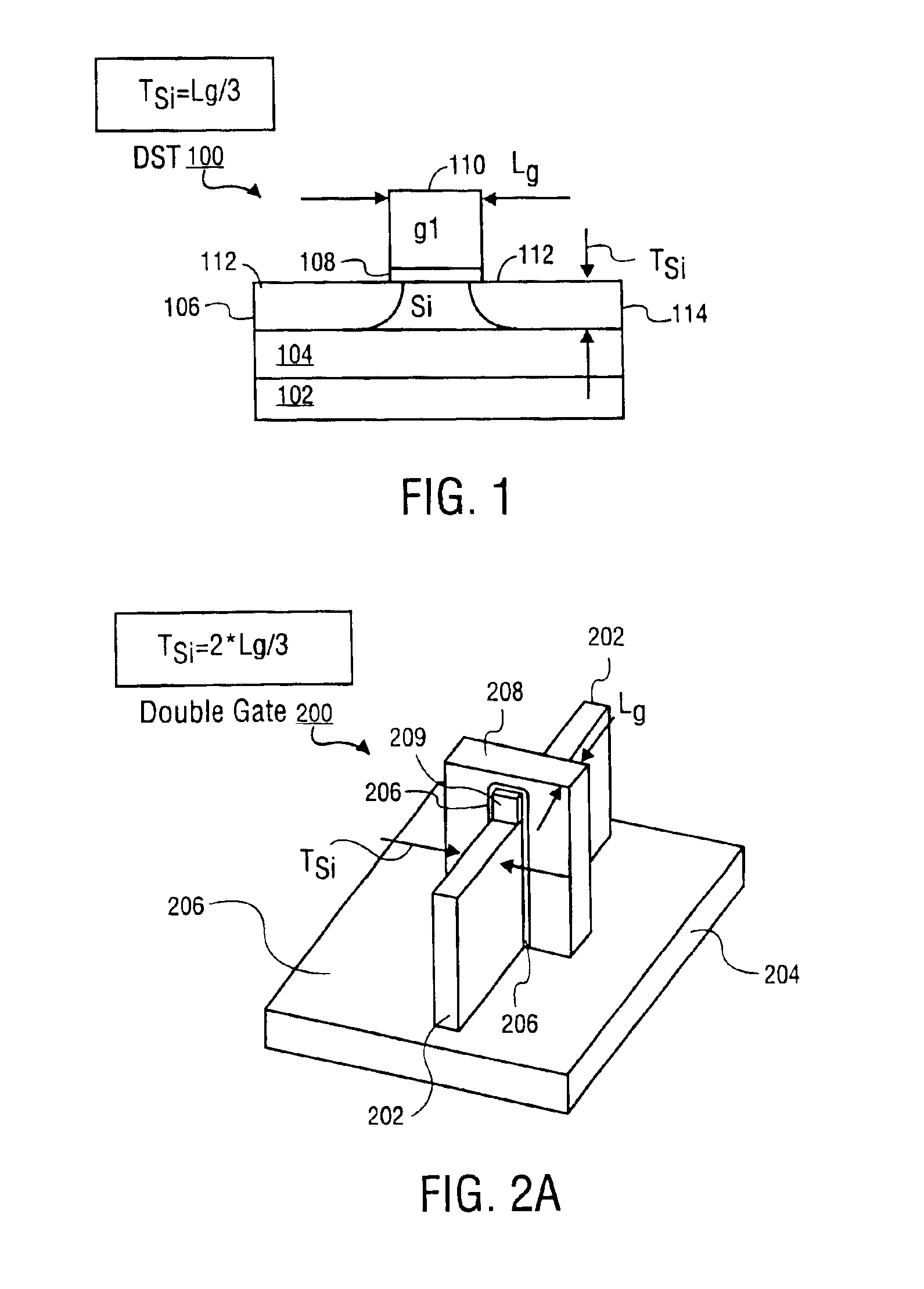

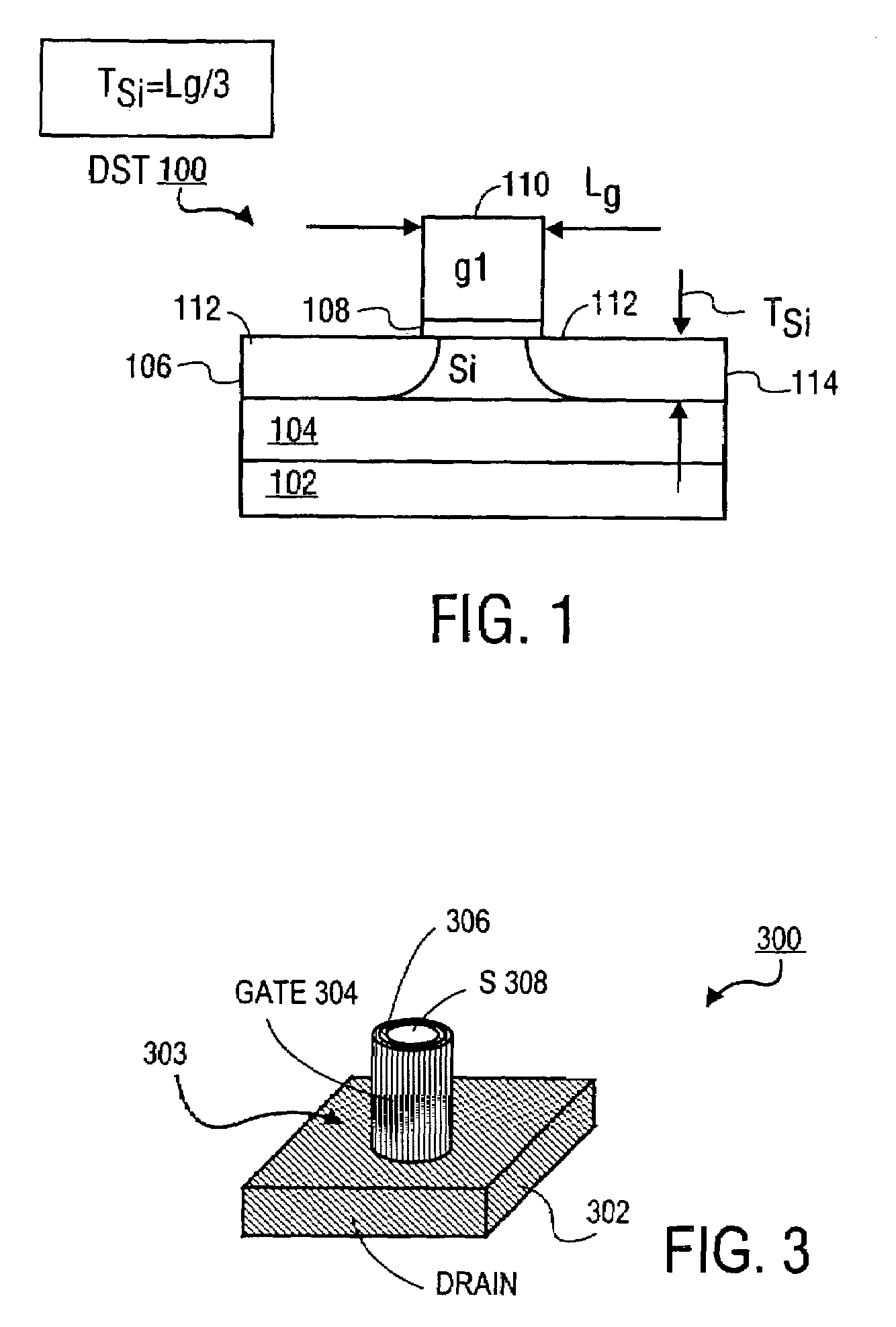

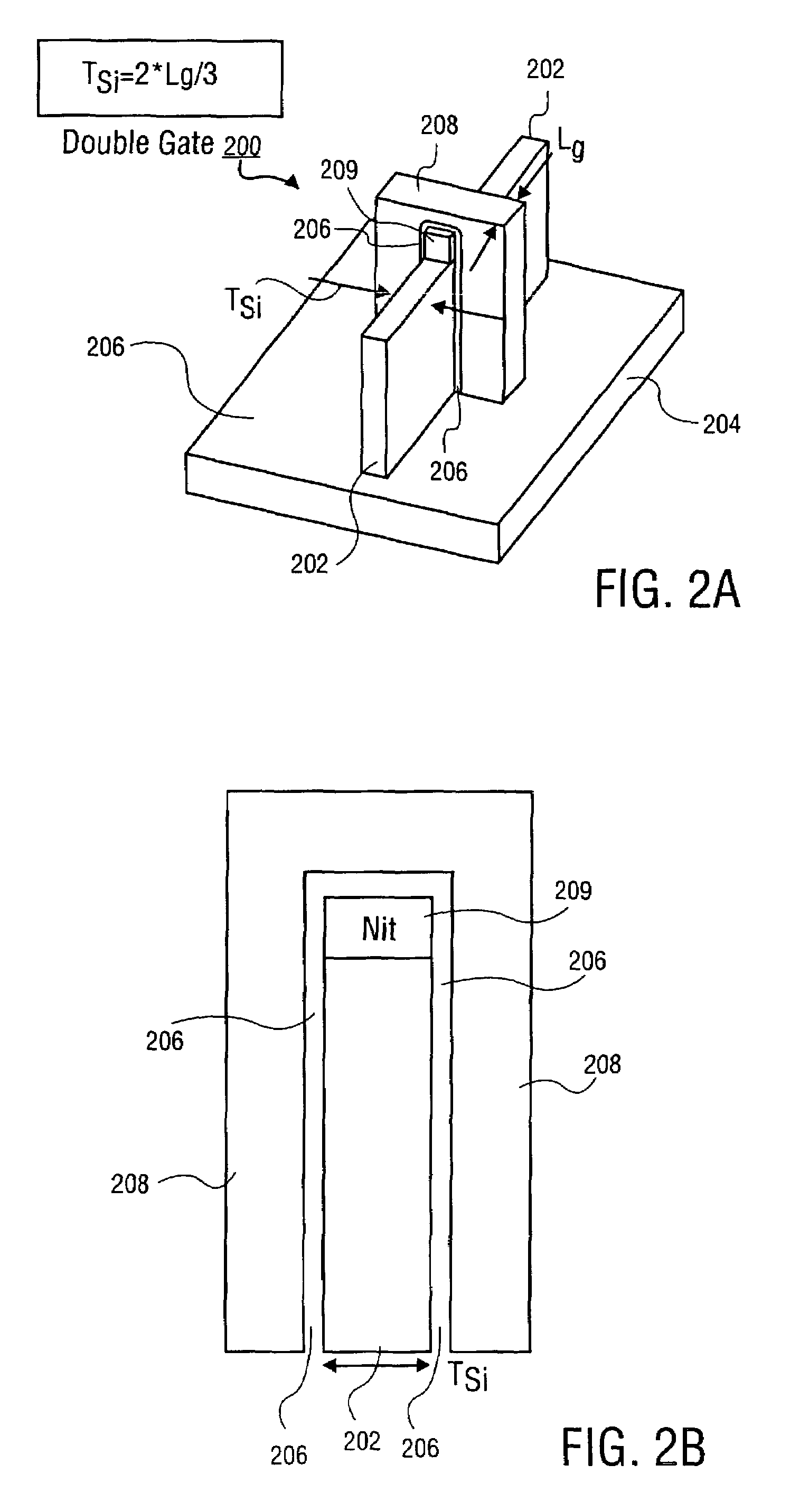

Nonplanar device with stress incorporation layer and method of fabrication

InactiveUS6909151B2Improve performanceHigh carrier mobilityTransistorSolid-state devicesGate dielectricSemiconductor

A semiconductor device comprising a semiconductor body having a top surface and laterally opposite sidewalls is formed on an insulating substrate. A gate dielectric layer is formed on the top surface of the semiconductor body and on the laterally opposite sidewalls of the semiconductor body. A gate electrode is formed on the gate dielectric on the top surface of the semiconductor body and is formed adjacent to the gate dielectric on the laterally opposite sidewalls of the semiconductor body. A thin film is then formed adjacent to the semiconductor body wherein the thin film produces a stress in the semiconductor body.

Owner:INTEL CORP

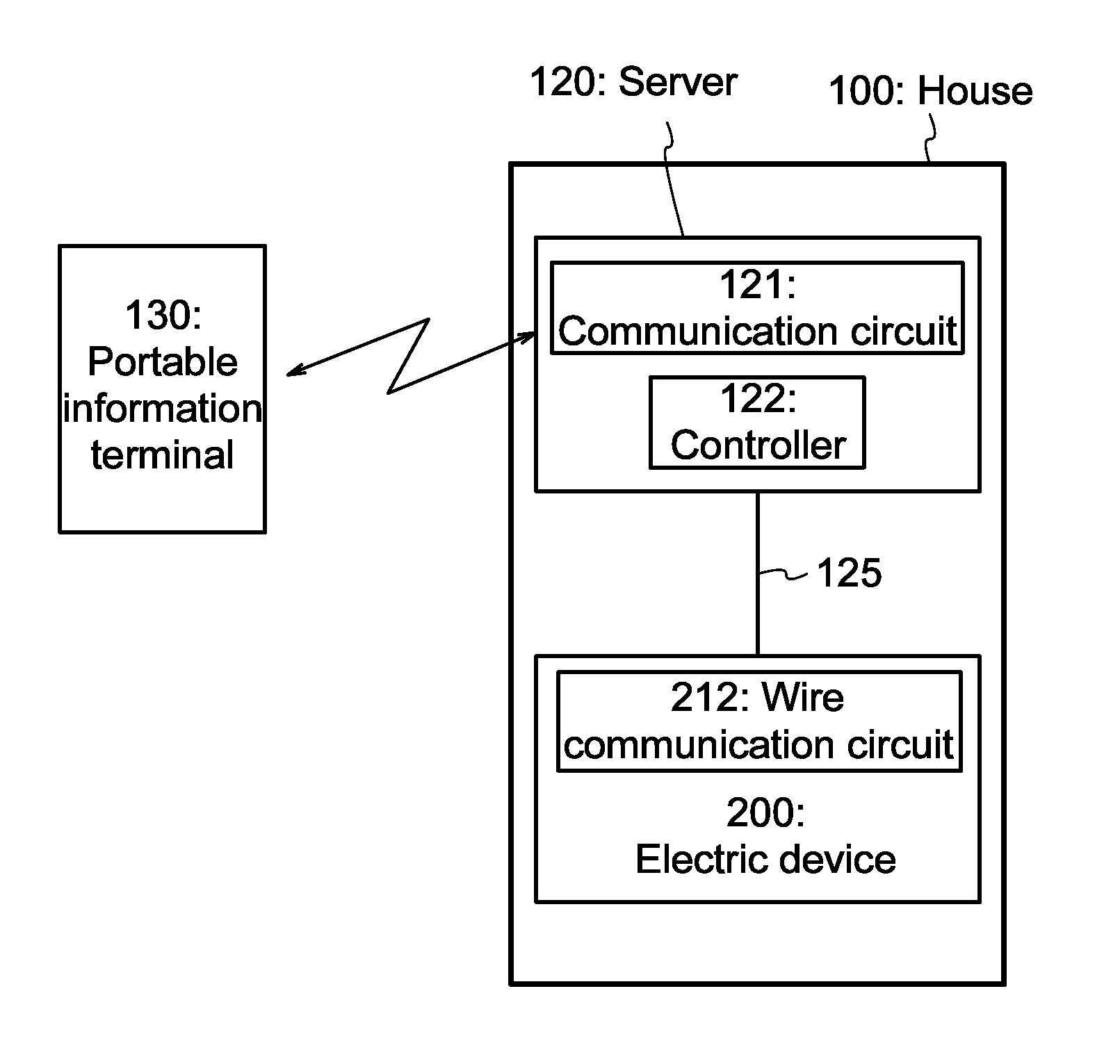

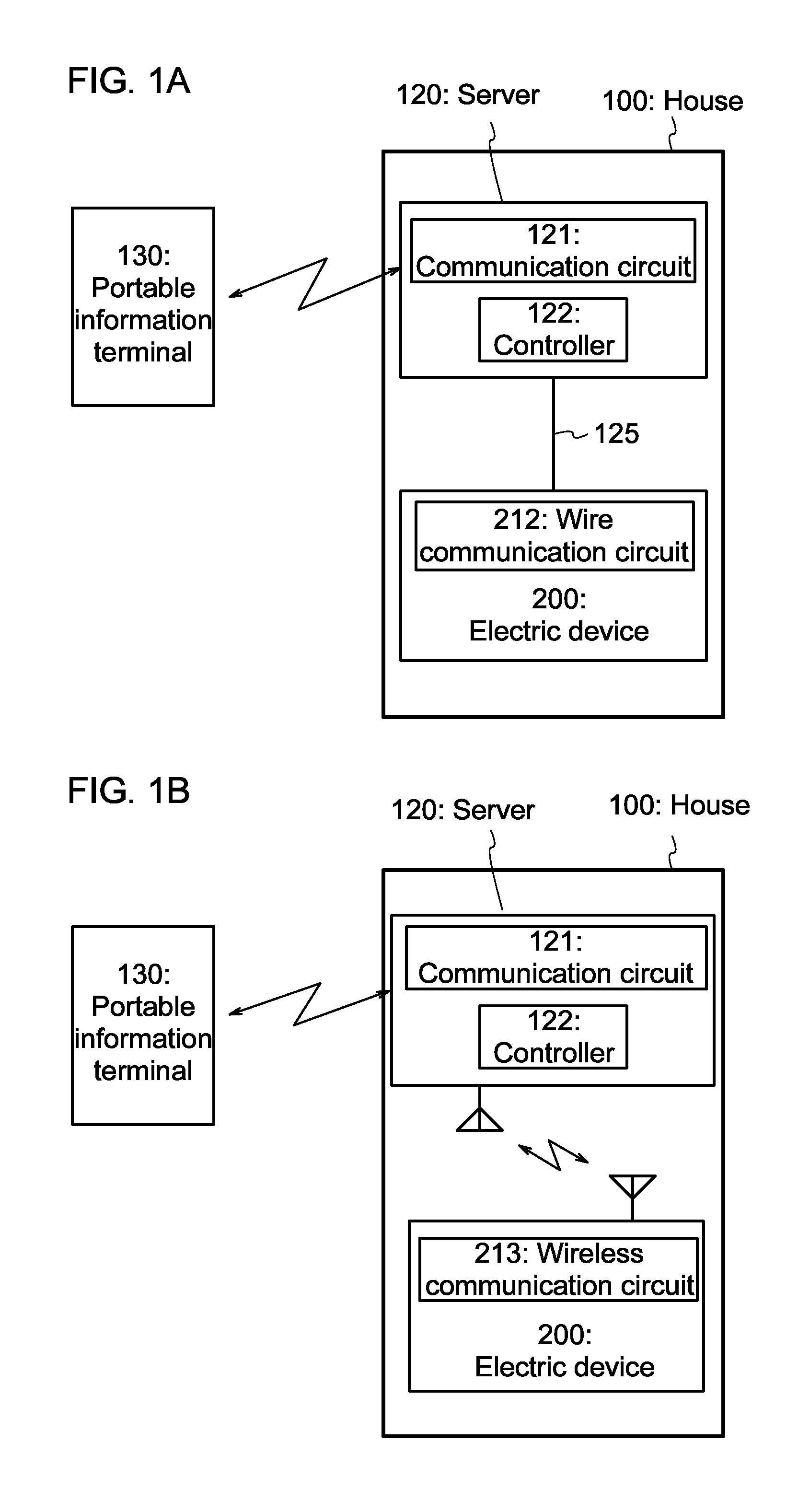

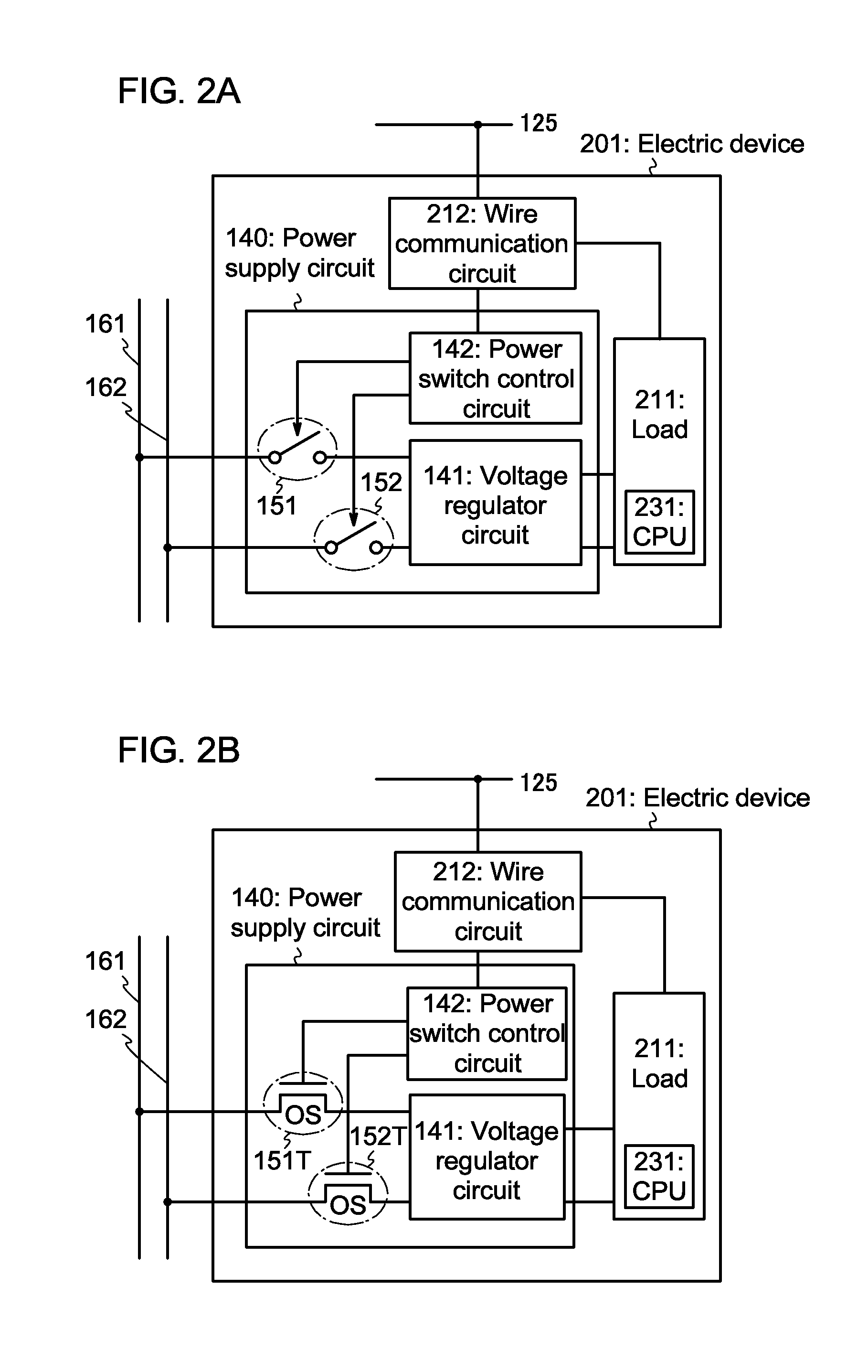

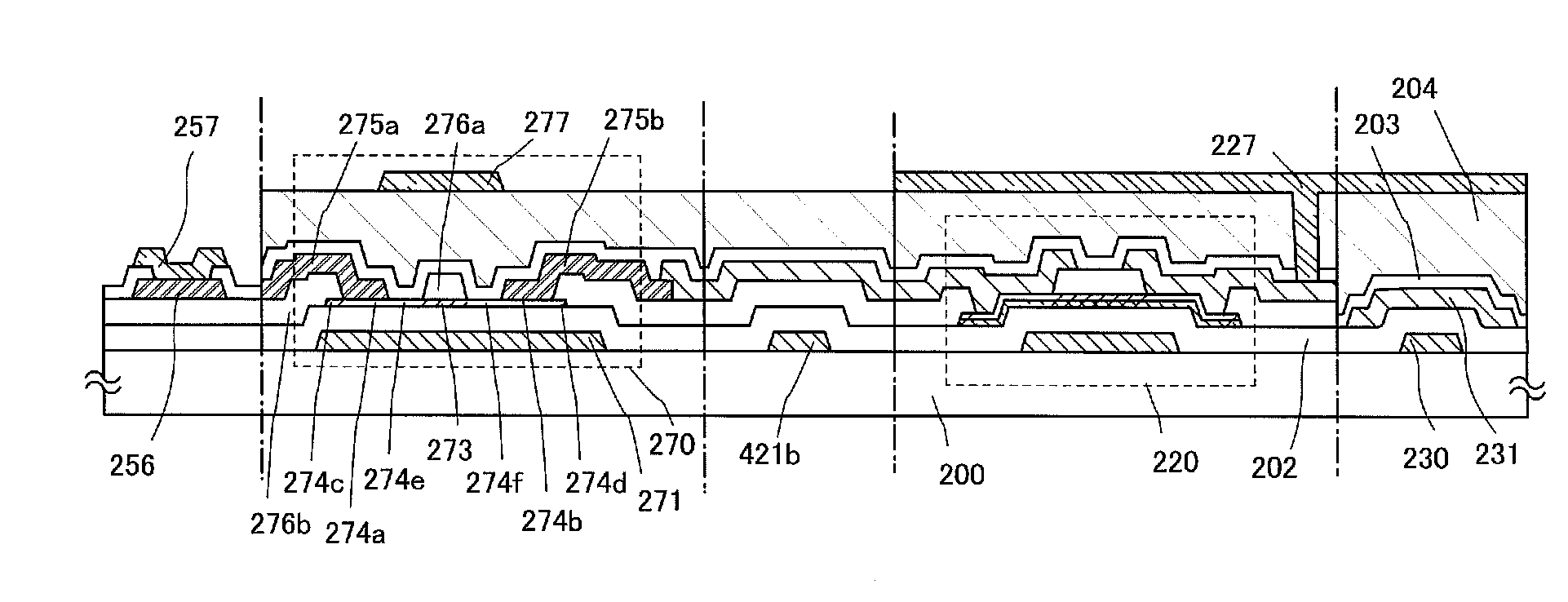

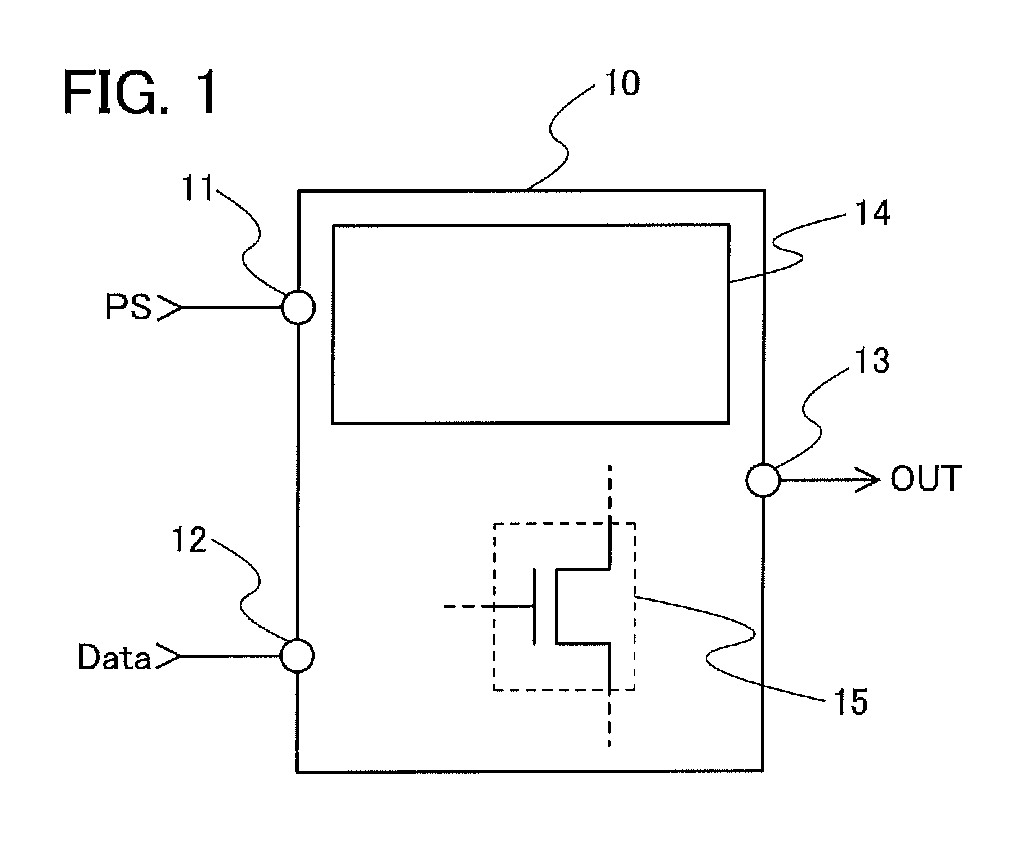

Remote control system

ActiveUS20140009270A1Total current dropReduce power consumptionTransistorElectric signal transmission systemsRemote controlComputer terminal

Provided is a remote control system with which leakage current flowing in a switch can be reduced so that power consumption can be reduced. The remote control system includes a portable information terminal, a server, and an electric device. The on / off of the switch included in the electric device is controlled using information transmitted from the portable information terminal to the server. The switch includes a transistor formed using a semiconductor whose band gap is larger than that of single crystal silicon in a channel formation region.

Owner:SEMICON ENERGY LAB CO LTD

Nonplanar semiconductor device with partially or fully wrapped around gate electrode and methods of fabrication

InactiveUS7456476B2Easily fully depletedReduced drain induced barrier (DIBL)TransistorSemiconductor/solid-state device manufacturingGate dielectricEngineering

A nonplanar semiconductor device and its method of fabrication is described. The nonplanar semiconductor device includes a semiconductor body having a top surface opposite a bottom surface formed above an insulating substrate wherein the semiconductor body has a pair laterally opposite sidewalls. A gate dielectric is formed on the top surface of the semiconductor body on the laterally opposite sidewalls of the semiconductor body and on at least a portion of the bottom surface of semiconductor body. A gate electrode is formed on the gate dielectric, on the top surface of the semiconductor body and adjacent to the gate dielectric on the laterally opposite sidewalls of semiconductor body and beneath the gate dielectric on the bottom surface of the semiconductor body. A pair source / drain regions are formed in the semiconductor body on opposite sides of the gate electrode.

Owner:TAHOE RES LTD

Three-Dimensional Semiconductor Device and Manufacturing Method Therefor

InactiveUS20170154895A1Improve control characteristicsReduce off-state leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETEtching

A three-dimensional semiconductor device, comprising a plurality of memory cell transistors and a plurality of select transistors at least partially overlapped in the vertical direction, wherein each select transistor comprises a first drain, an active region and a common source formed in the substrate, distributed along the vertical direction, as well as a metal gate distributed around the active region; wherein each memory cell transistor comprises a channel layer distributed perpendicularly to the substrate surface, a plurality of inter-layer insulating layers and a plurality of gate stack structures alternately stacked along the sidewalls of said channel layer, a second drain located on top of said channel layer; wherein said channel layer and said the first drain are electrically connected. In accordance with the three-dimensional semiconductor memory device and manufacturing method of the present invention, the multi-gate MOSFET is formed beneath the stack structure of the memory cell string including vertical channel to serve as the select transistor, this can improve the control characteristics of the gate threshold voltage, reduce the off-state leakage current, prevent the substrate from over-etching, and effectively improve the reliability of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

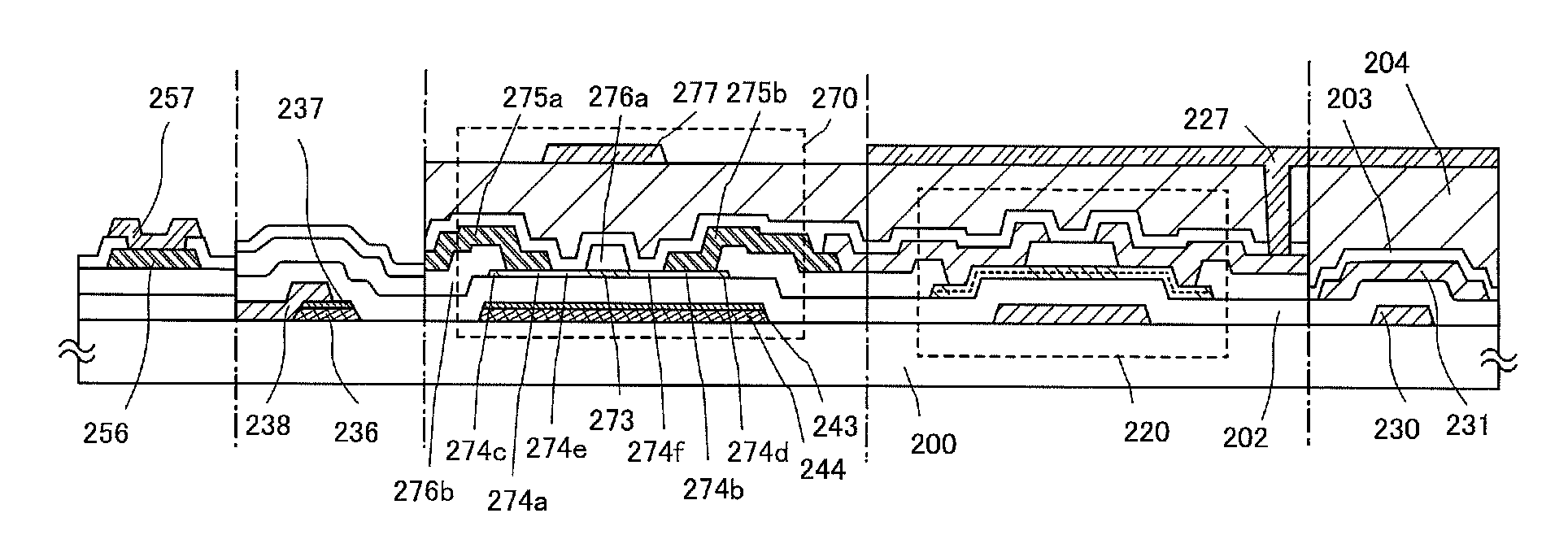

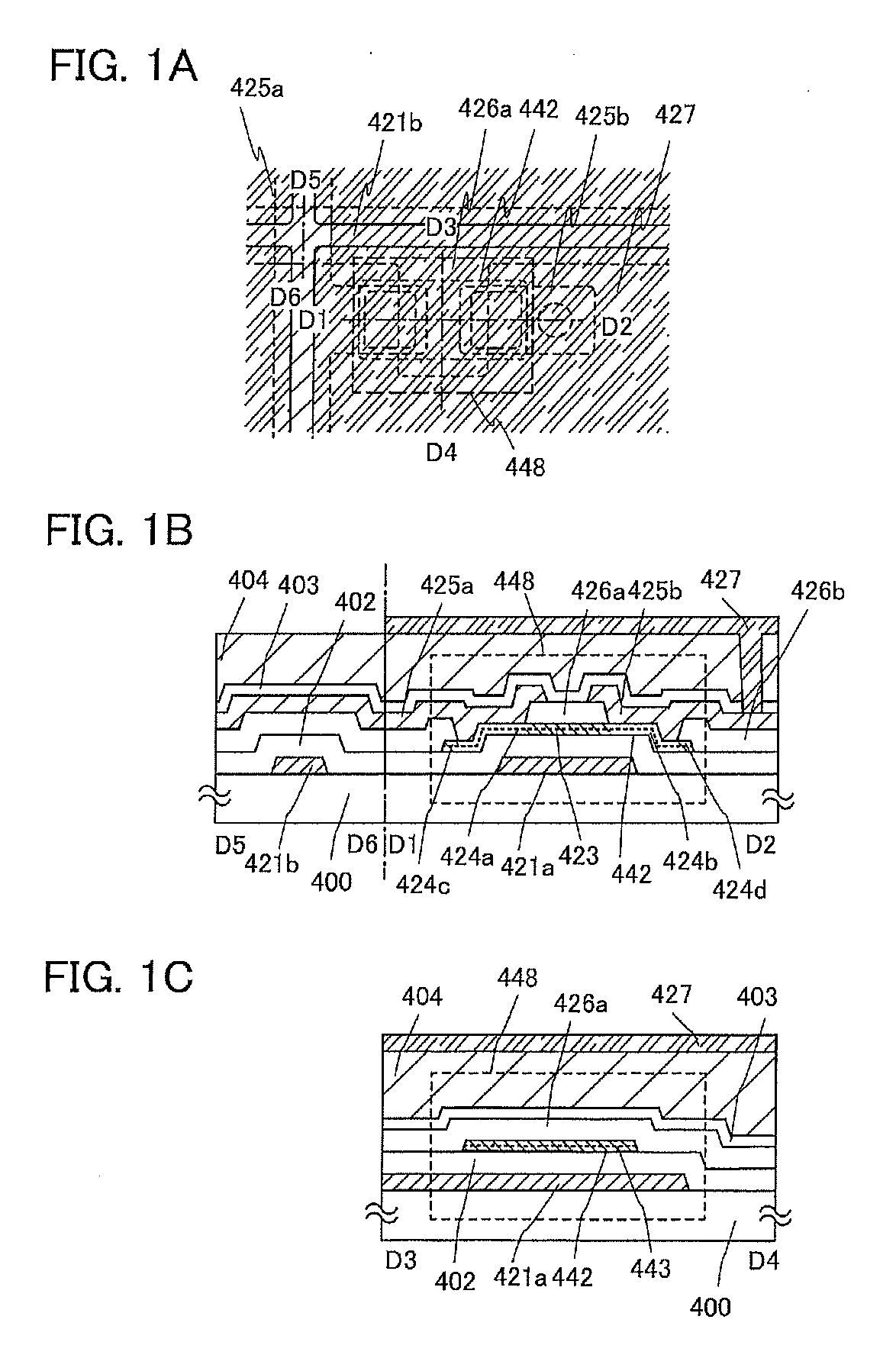

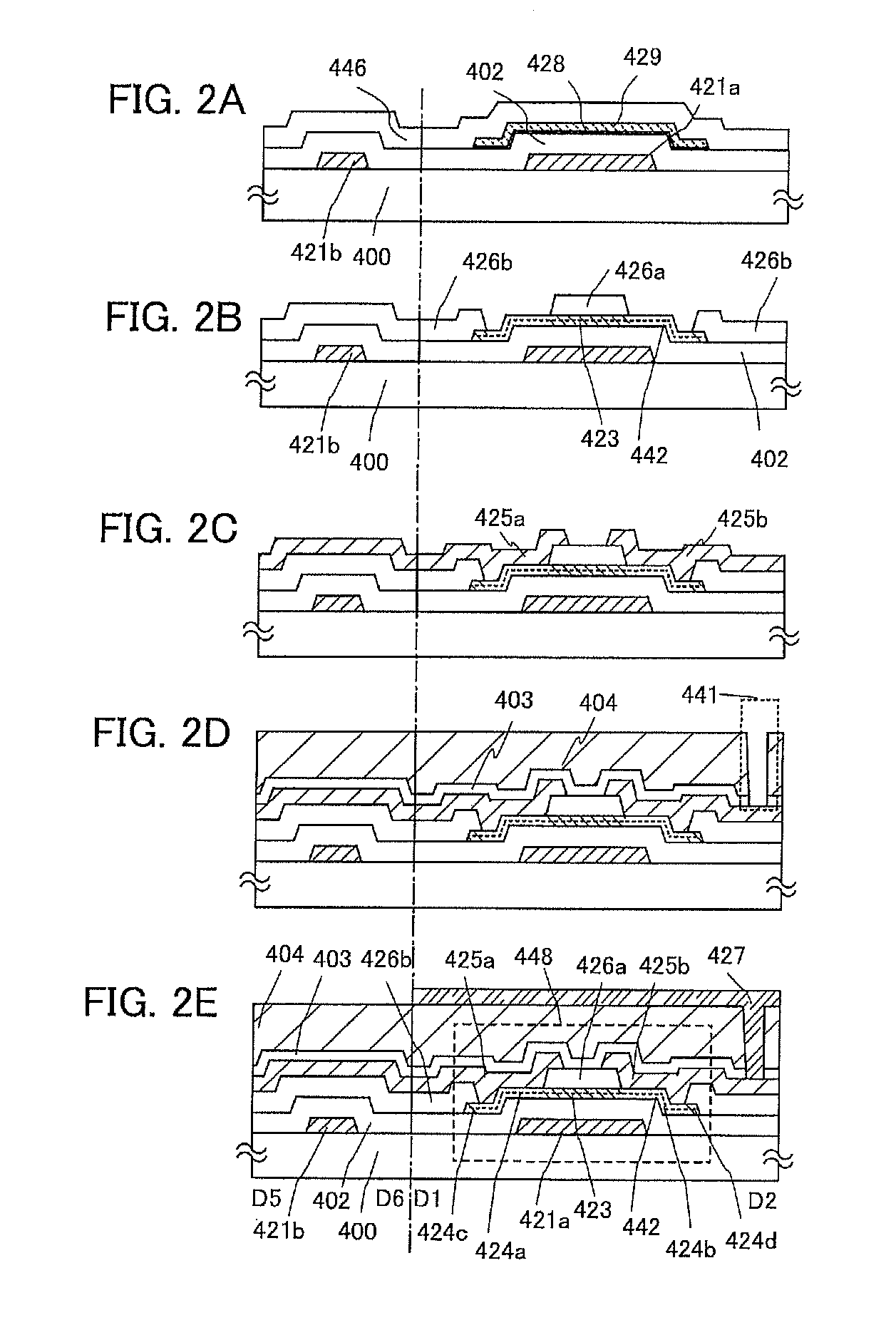

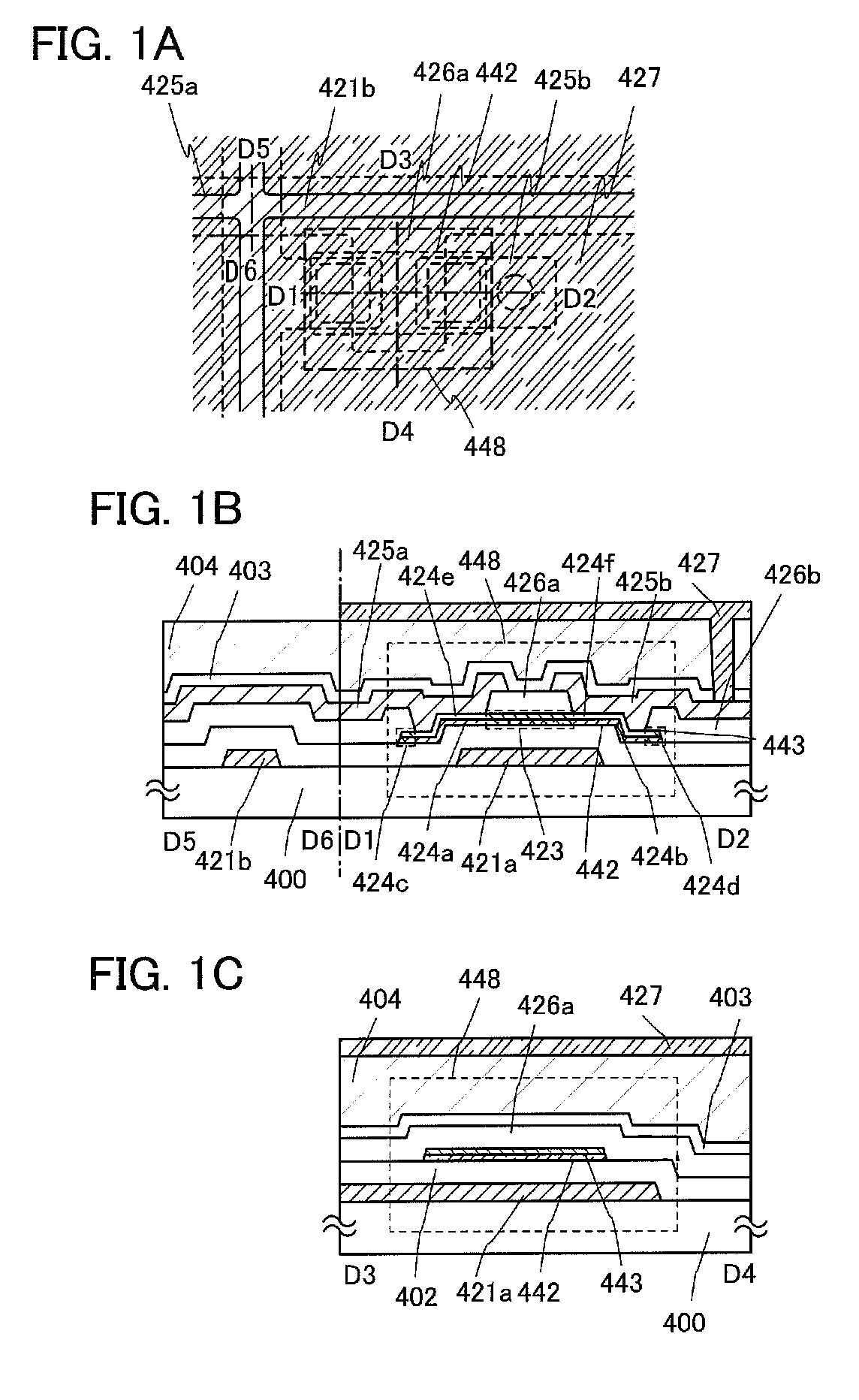

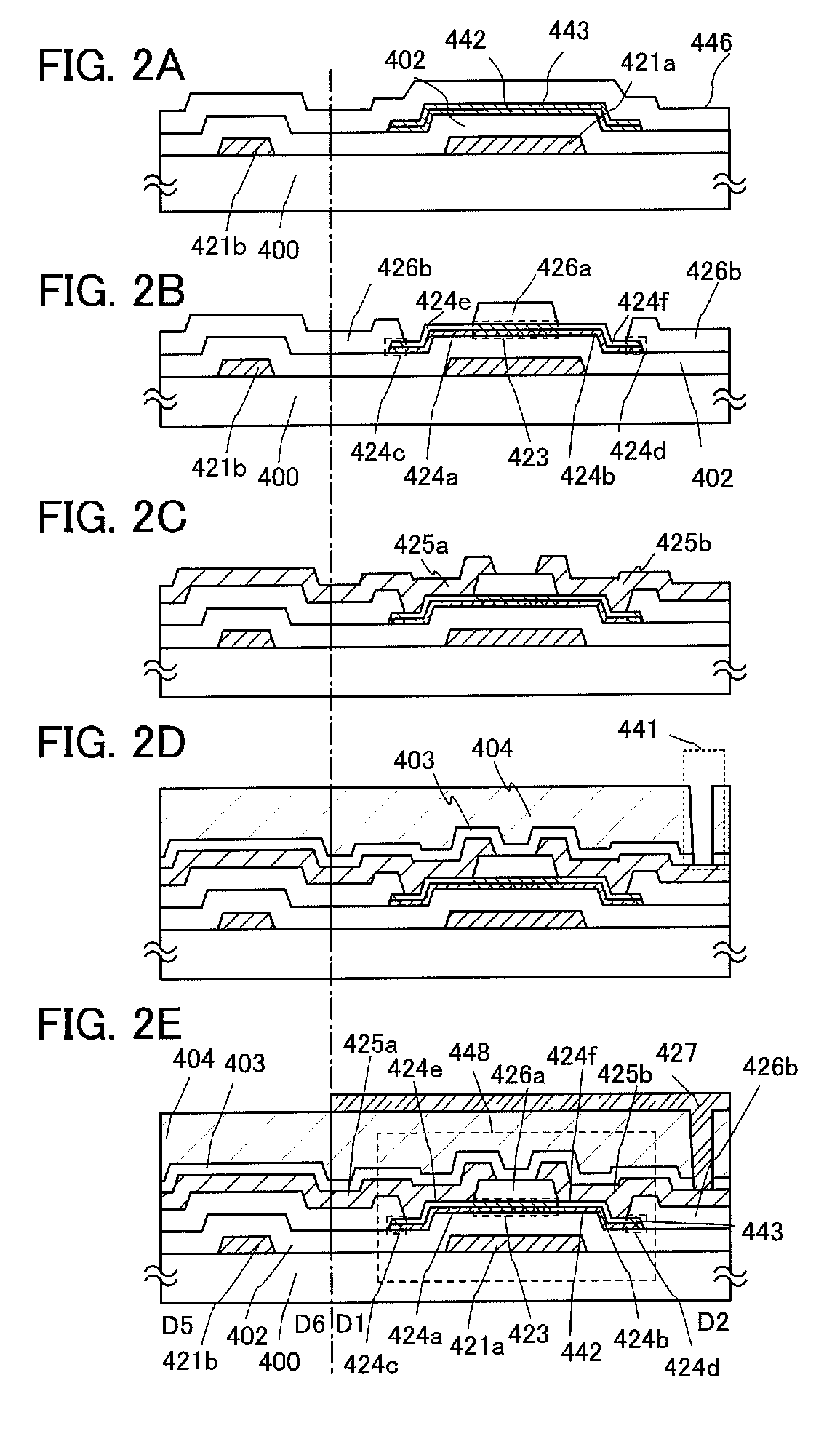

Semiconductor device and method for manufacturing the same

ActiveUS20110037068A1Manufacturing cost be reduceEasily breakTransistorSolid-state devicesOxide semiconductorOxide

One object is to provide a semiconductor device with a structure which enables reduction in parasitic capacitance sufficiently between wirings. In a bottom-gate type thin film transistor including a stacked layer of a first layer which is a metal thin film oxidized partly or entirely and an oxide semiconductor layer, the following oxide insulating layers are formed together: an oxide insulating layer serving as a channel protective layer which is over and in contact with a part of the oxide semiconductor layer overlapping with a gate electrode layer; and an oxide insulating layer which covers a peripheral portion and a side surface of the stacked oxide semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and manufacturing method thereof

ActiveUS20110024751A1Reduce manufacturing costEasily brokenTransistorSolid-state devicesBottom gateSemiconductor

In a bottom-gate thin film transistor using the stack of the first oxide semiconductor layer and the second oxide semiconductor layer, an oxide insulating layer serving as a channel protective layer is formed over and in contact with part of the oxide semiconductor layer overlapping with a gate electrode layer. In the same step as formation of the insulating layer, an oxide insulating layer covering a peripheral portion (including a side surface) of the stack of the oxide semiconductor layers is formed.

Owner:SEMICON ENERGY LAB CO LTD

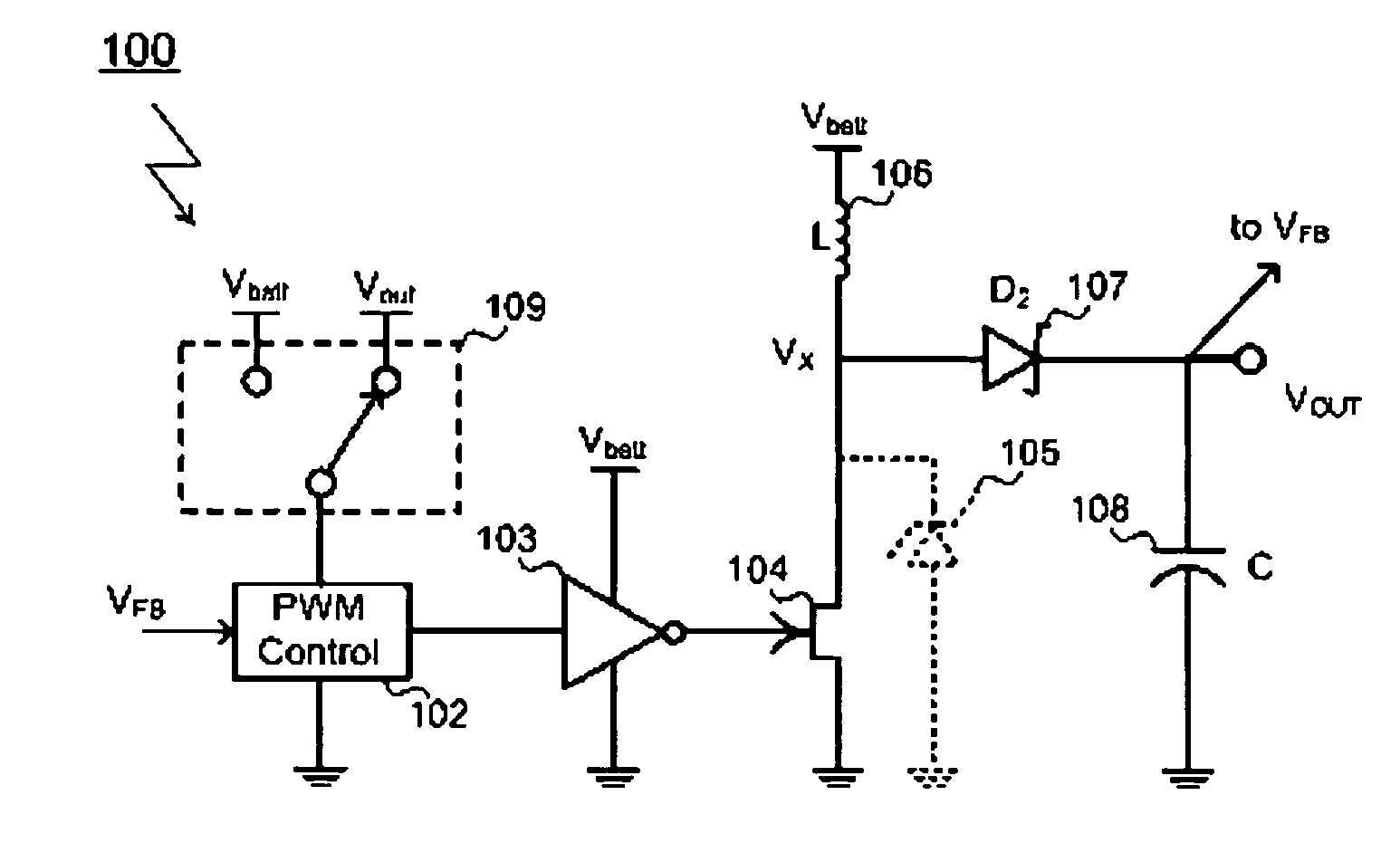

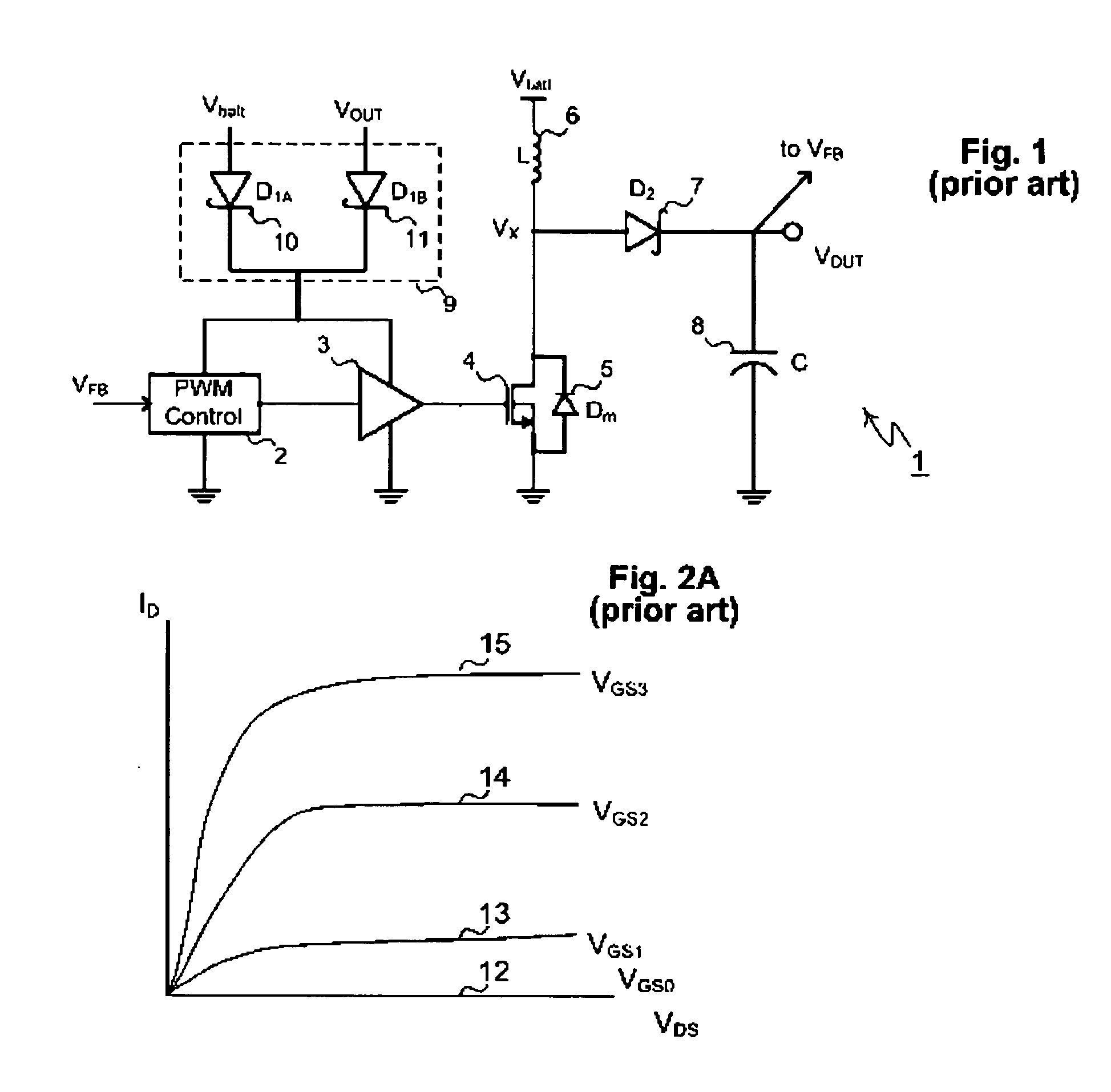

High-Frequency Power MESFET Boost Switching Power Supply

InactiveUS20080186004A1Lower on-resistanceLow off-state drain leakageTransistorDc-dc conversionMOSFETHigh frequency power

A MESFET based boost converter includes an N-channel MESFET connected to a node Vx. An inductor connects the node Vx to a battery or other power source. The node Vx is also connected to an output node via a Schottky diode or a second MESFET or both. A control circuit drives the MESFET (and the second MESFET) so that the inductor is alternately connected to ground and to the output node. The maximum voltage impressed across the low side MESFET is optionally clamped by a Zener diode. In some implementations, the MESFET is connected in series with a MOSFET. The MOSFET is switched off during sleep or standby modes to minimize leakage current through the MESFET. The MOSFET is therefore switched at a low frequency compared to the MESFET and does not contribute significantly to switching losses in the converter. In other implementations, more than one MESFET is connected in series with a MOSFET, the MOSFETs being switched off during periods of inactivity to suppress leakage currents.

Owner:ADVANCED ANALOGIC TECHNOLOGIES INCORPORATED

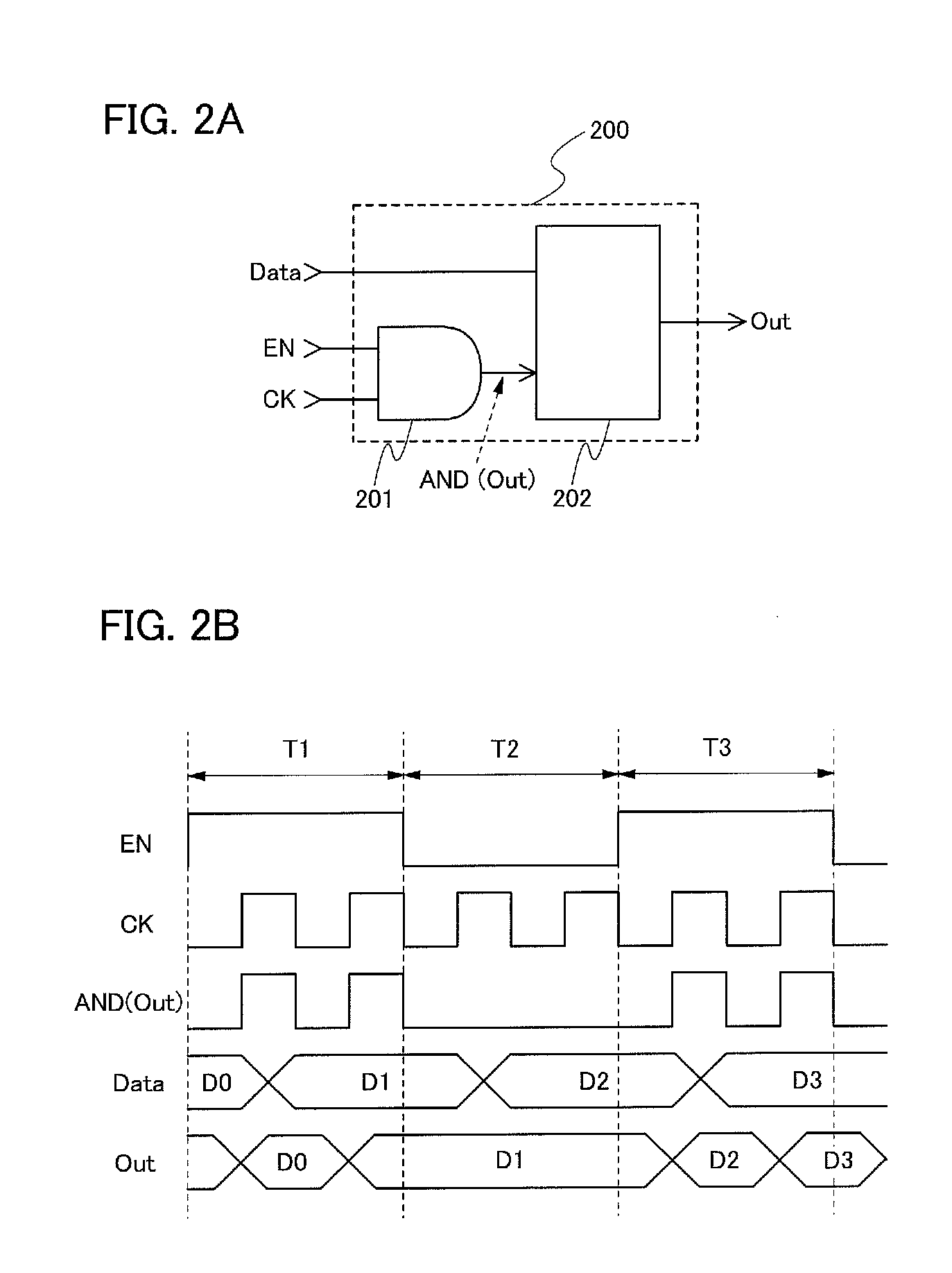

Logic circuit and semiconductor device

ActiveUS8207756B2Reduce dynamic power consumptionLeakage of highTransistorPower reduction by control/clock signalHydrogen concentrationPower semiconductor device

In a logic circuit where clock gating is performed, the standby power is reduced or malfunction is suppressed. The logic circuit includes a transistor which is in an off state where a potential difference exists between a source terminal and a drain terminal over a period during which a clock signal is not supplied. A channel formation region of the transistor is formed using an oxide semiconductor in which the hydrogen concentration is reduced. Specifically, the hydrogen concentration of the oxide semiconductor is 5×1019 (atoms / cm3) or lower. Thus, leakage current of the transistor can be reduced. As a result, in the logic circuit, reduction in standby power and suppression of malfunction can be achieved.

Owner:SEMICON ENERGY LAB CO LTD

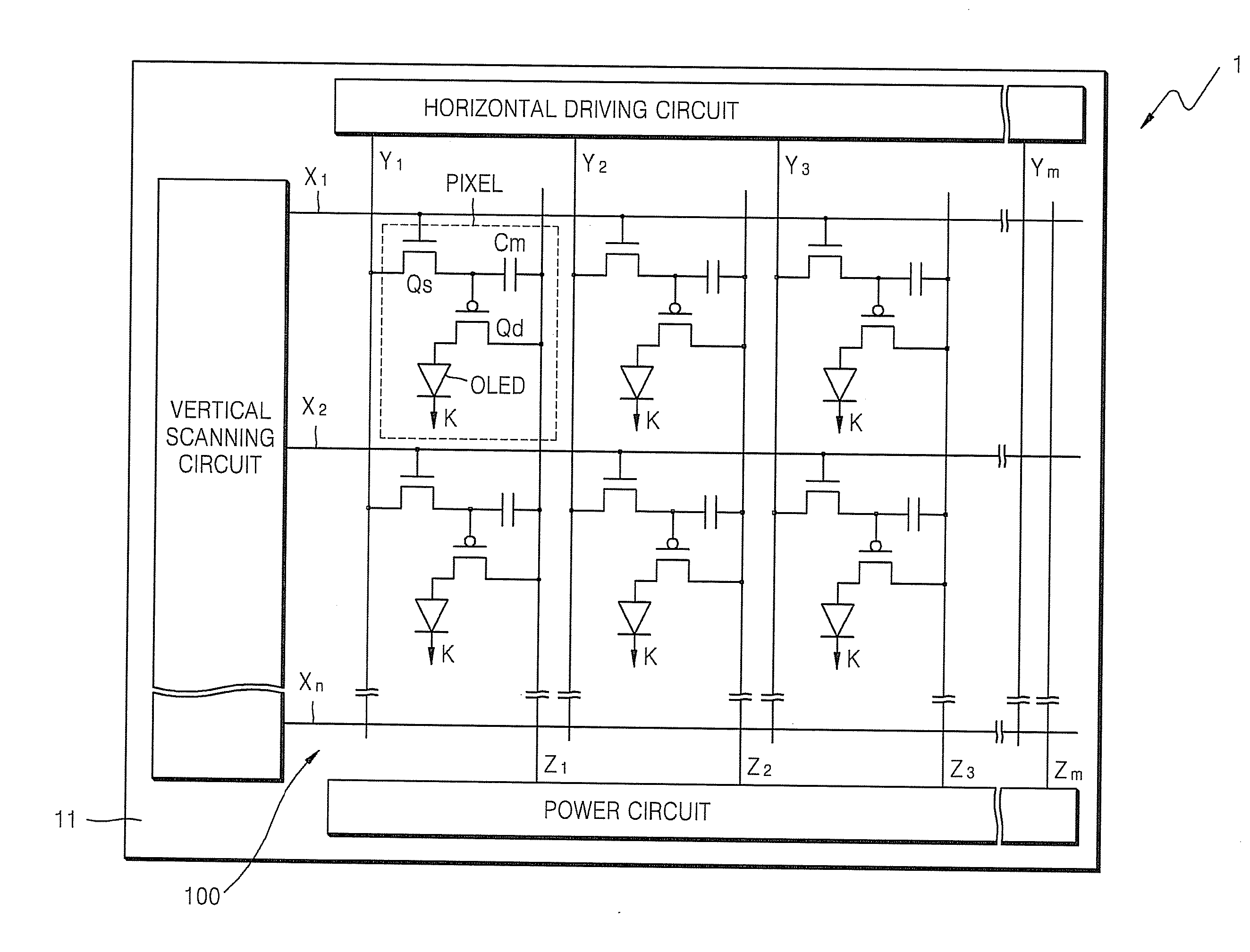

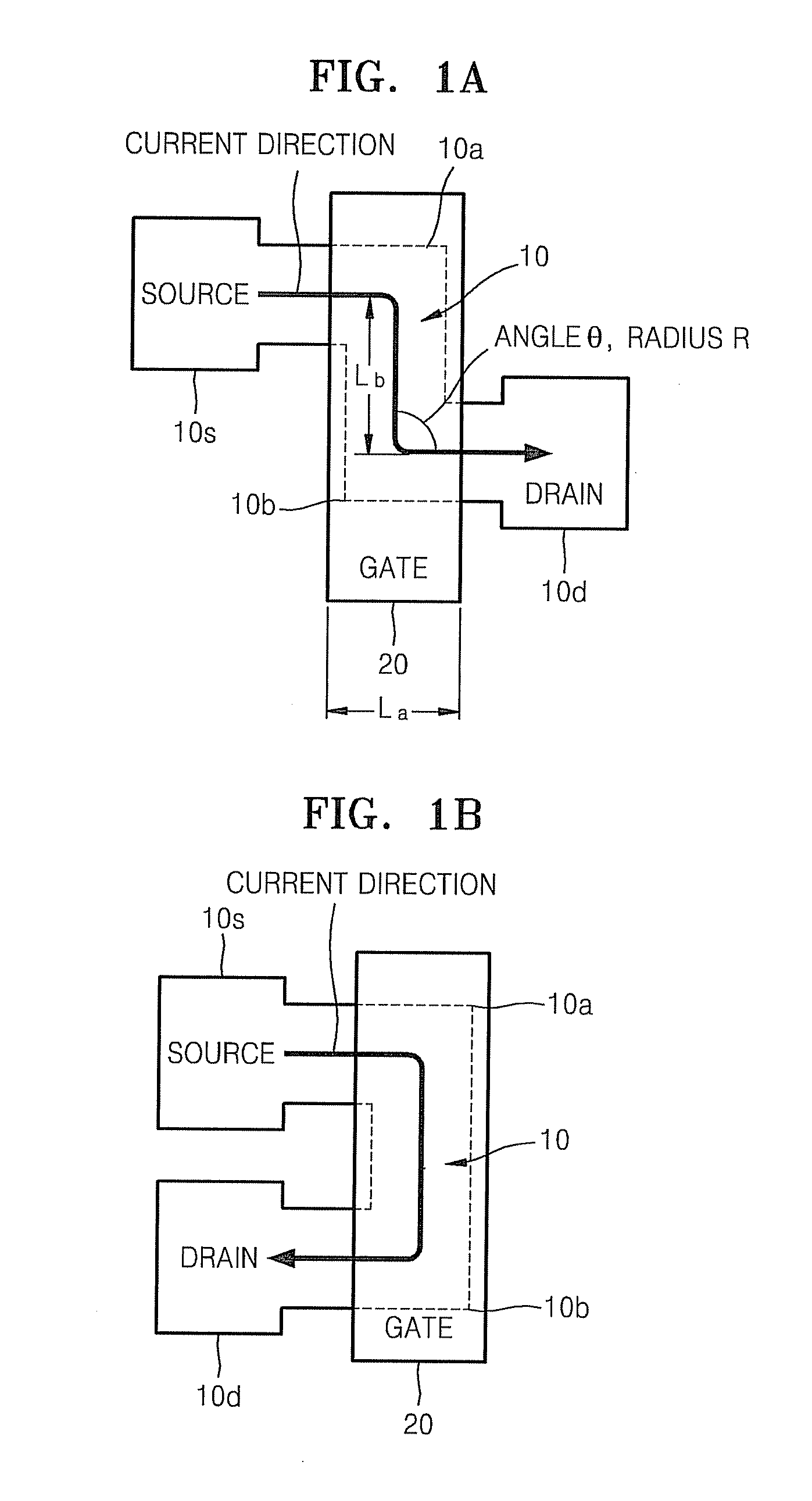

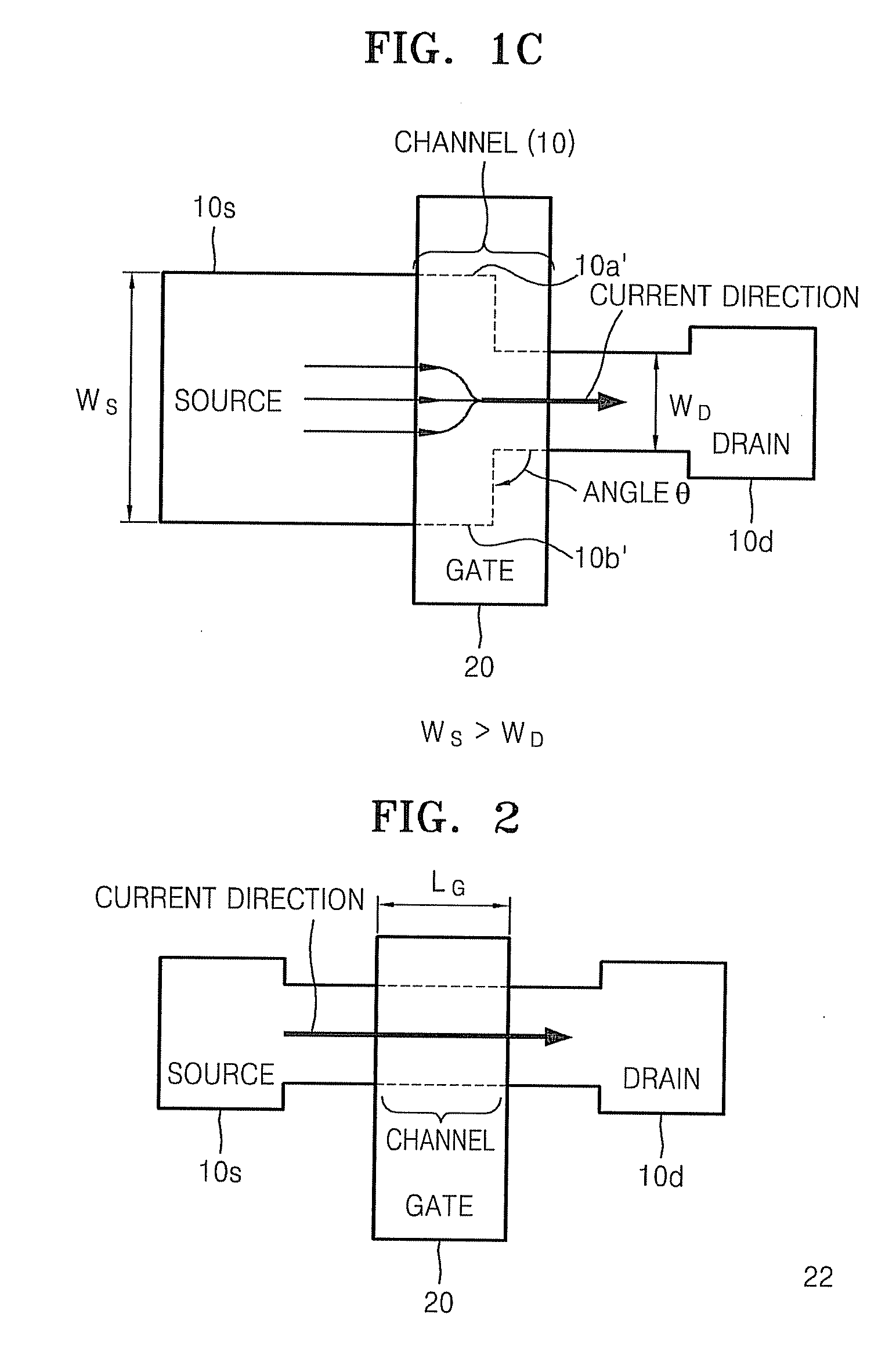

POLY-Si THIN FILM TRANSISTOR AND ORGANIC LIGHT-EMITTING DISPLAY HAVING THE SAME

ActiveUS20070128777A1Reduce leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingElectronTransistor

A thin film transistor comprises an Si-based channel having a nonlinear electron-moving path, a source and a drain disposed at both sides of the channel, a gate disposed above the channel, an insulator interposed between the channel and the gate, and a substrate supporting the channel and the source and the drain disposed at either side of the channel respectively.

Owner:SAMSUNG ELECTRONICS CO LTD

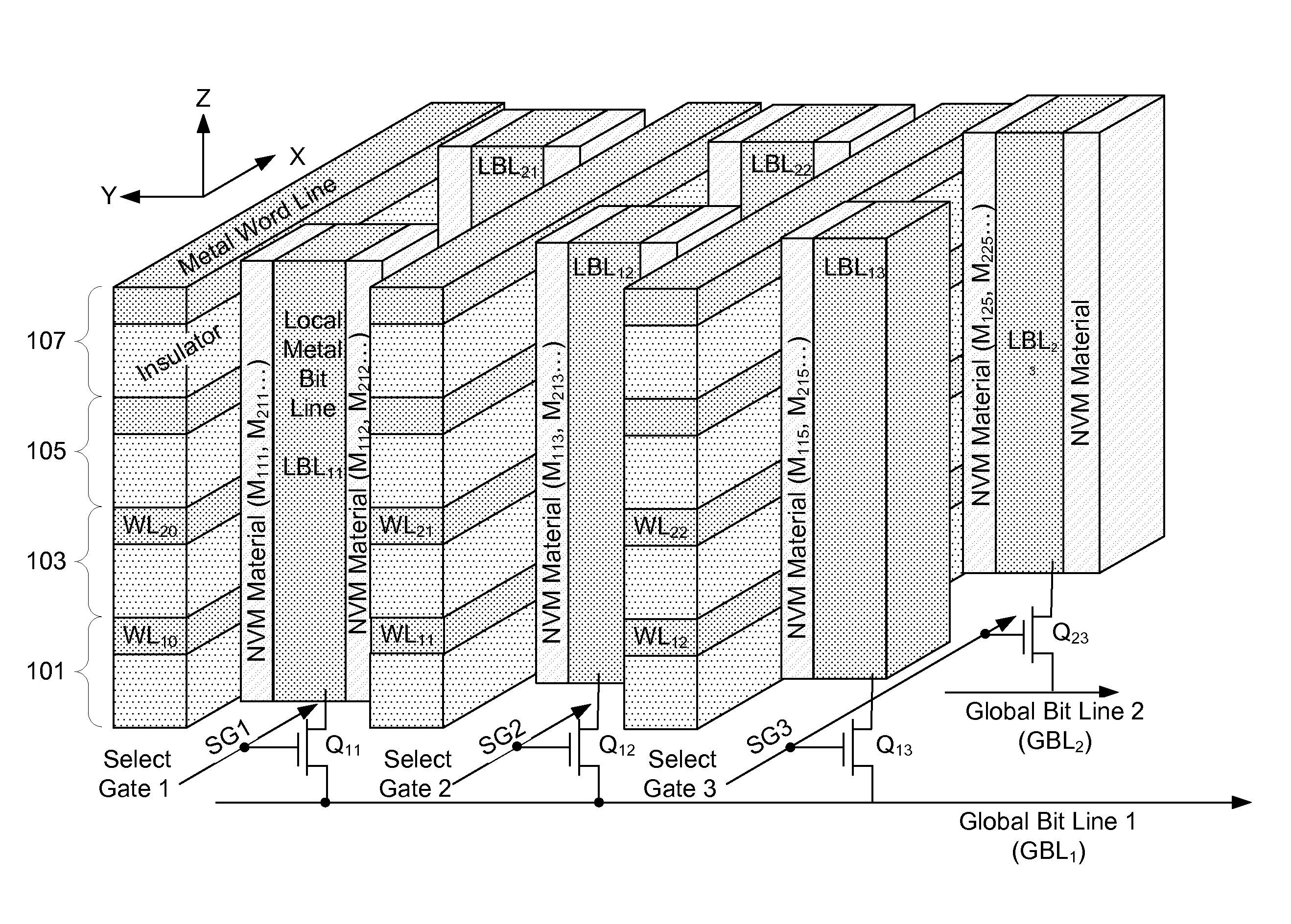

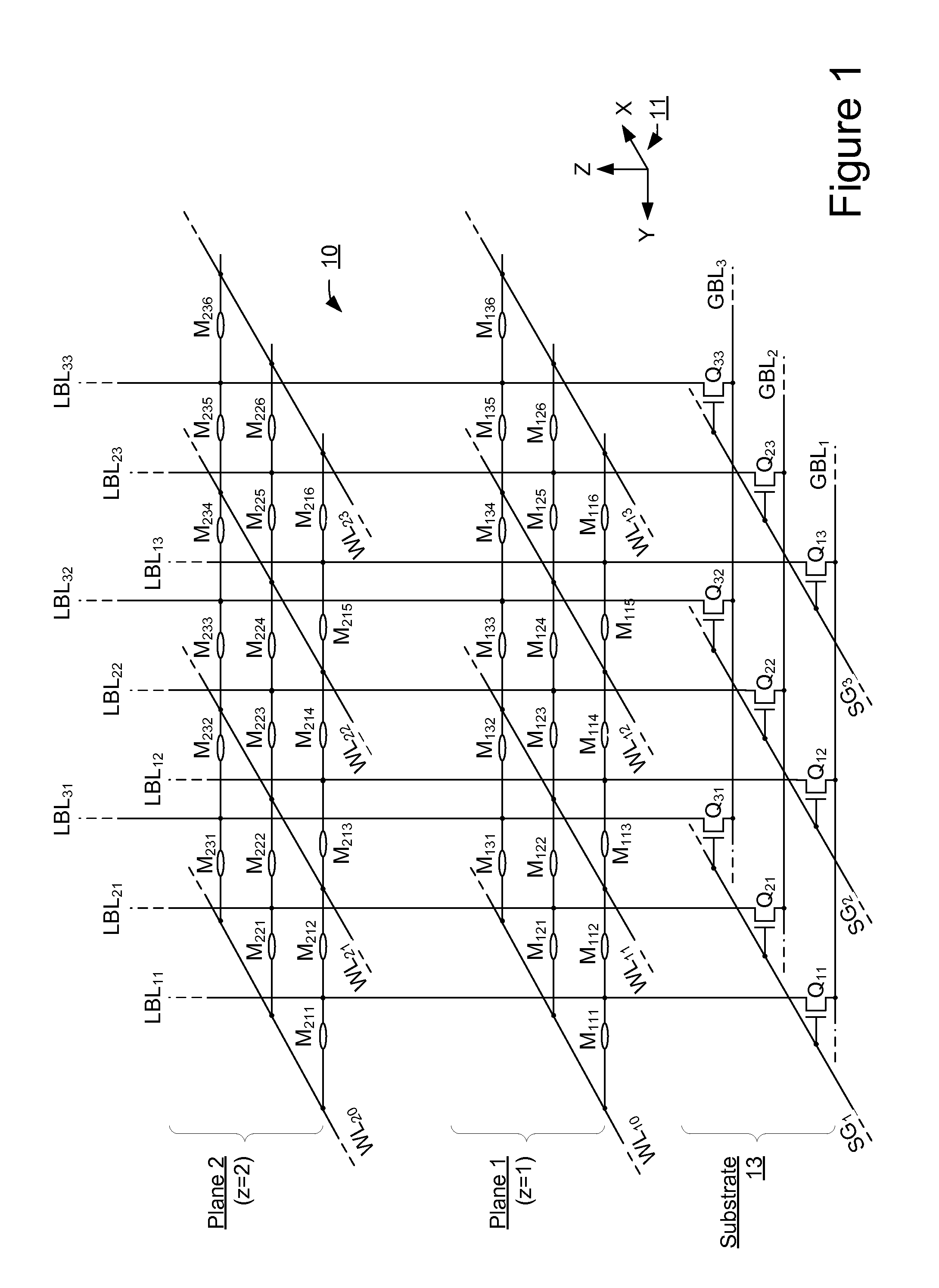

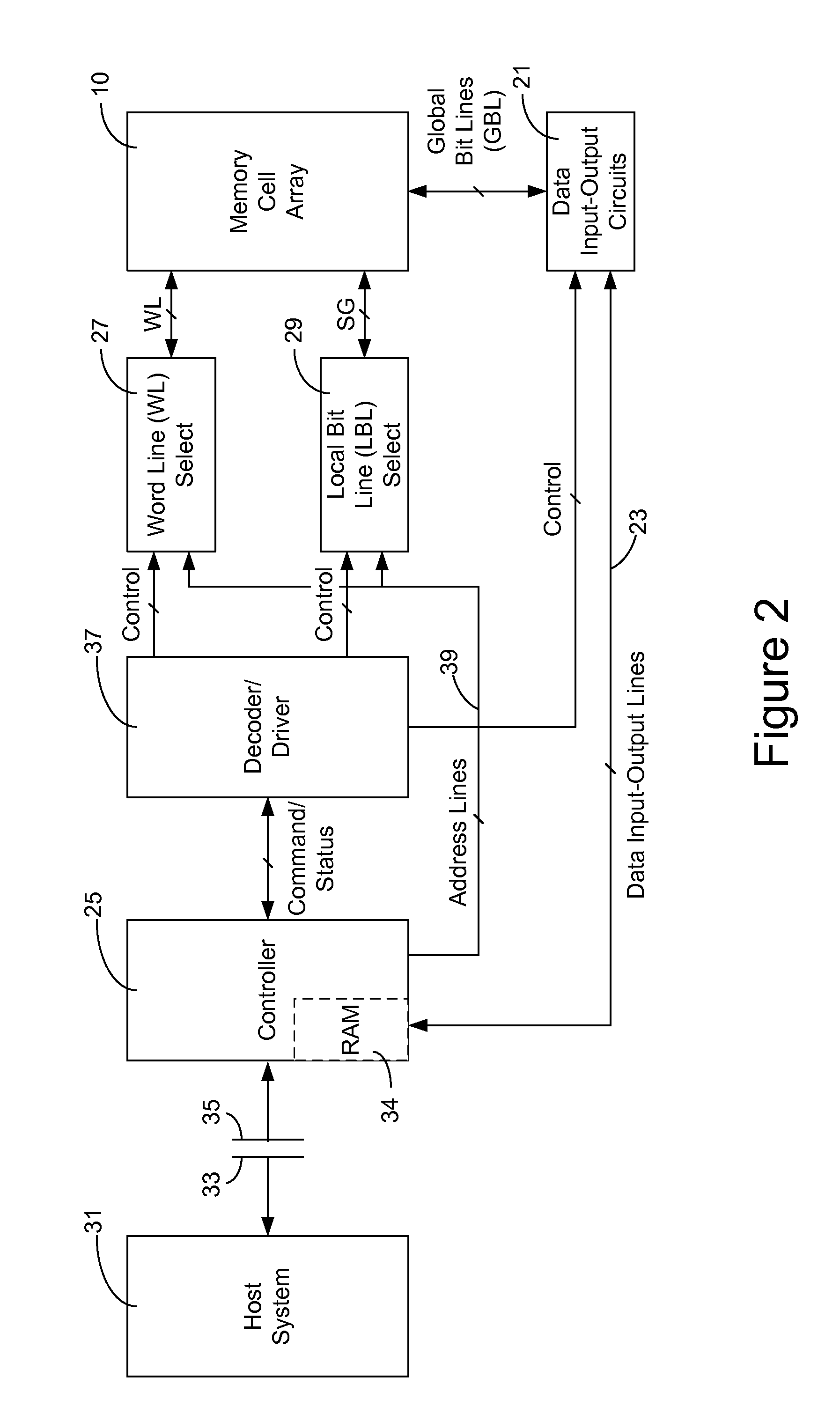

Three dimensional non-volatile storage with dual gate selection of vertical bit lines

ActiveUS20120147648A1Reduce leakage currentSolid-state devicesRead-only memoriesBit lineSemiconductor

A three-dimensional array adapted for memory elements that reversibly change a level of electrical conductance in response to a voltage difference being applied across them. Memory elements are formed across a plurality of planes positioned different distances above a semiconductor substrate. Bit lines to which the memory elements of all planes are connected are oriented vertically from the substrate and through the plurality of planes.

Owner:SANDISK TECH LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com