Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

905results about How to "Avoid leakage current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

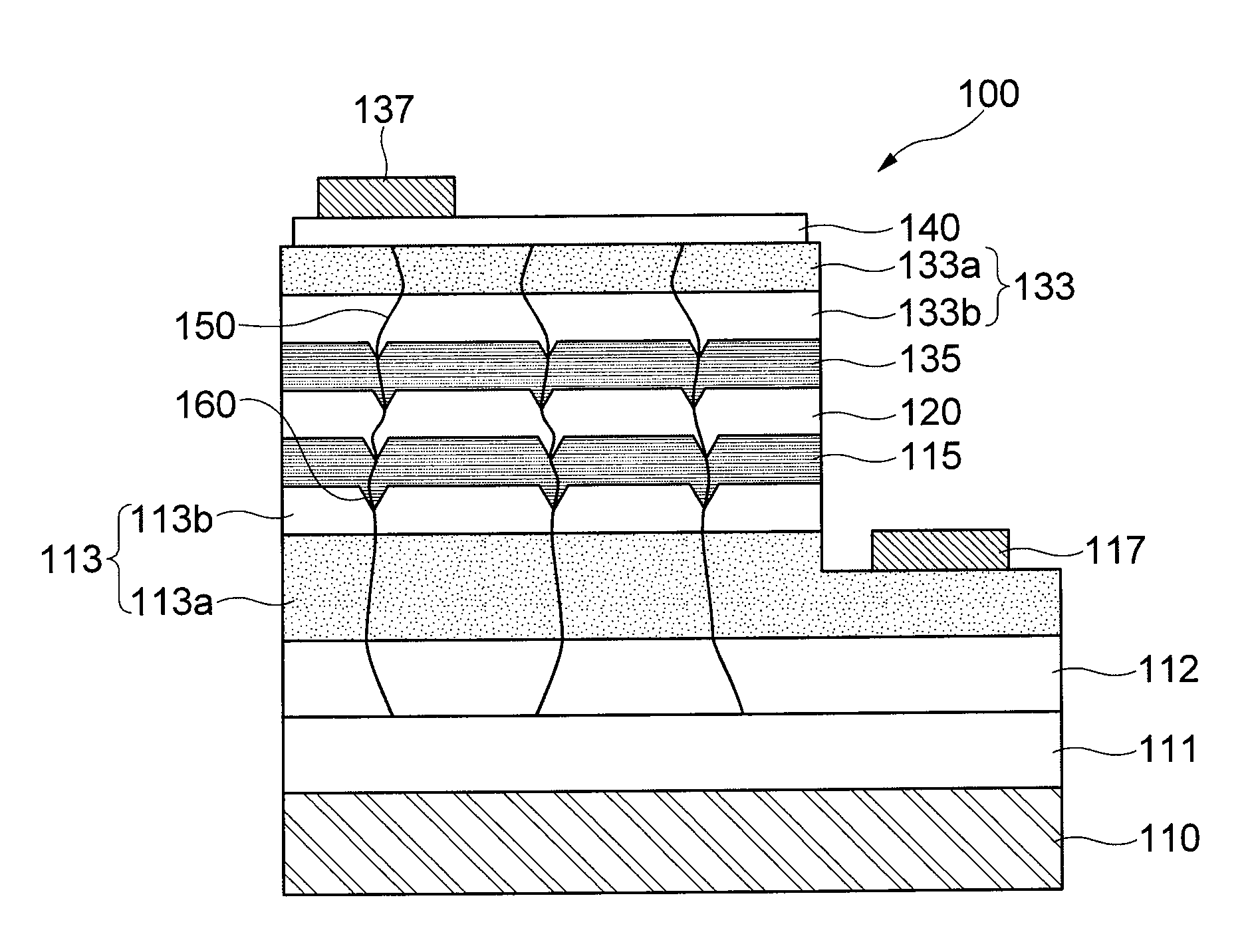

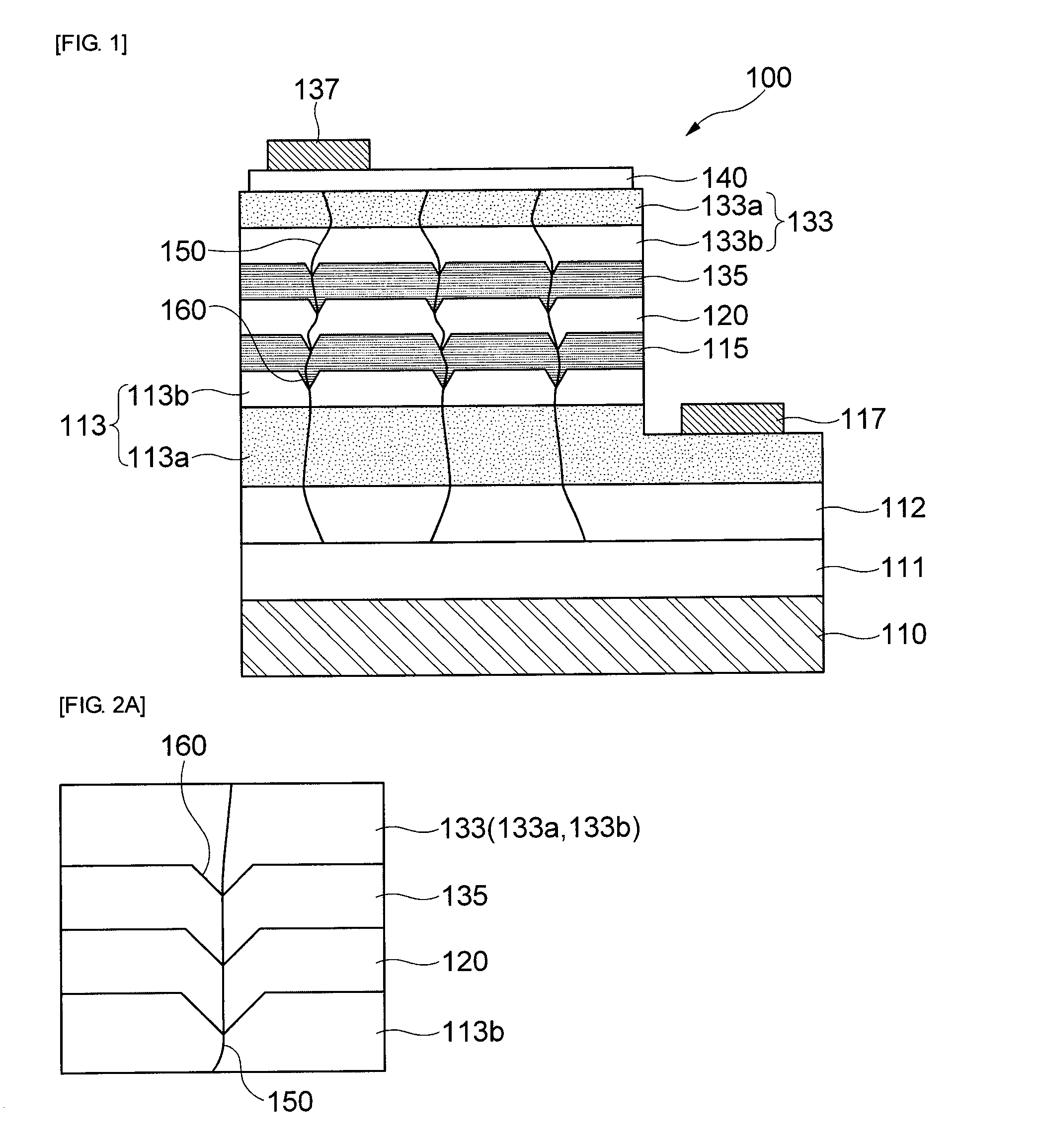

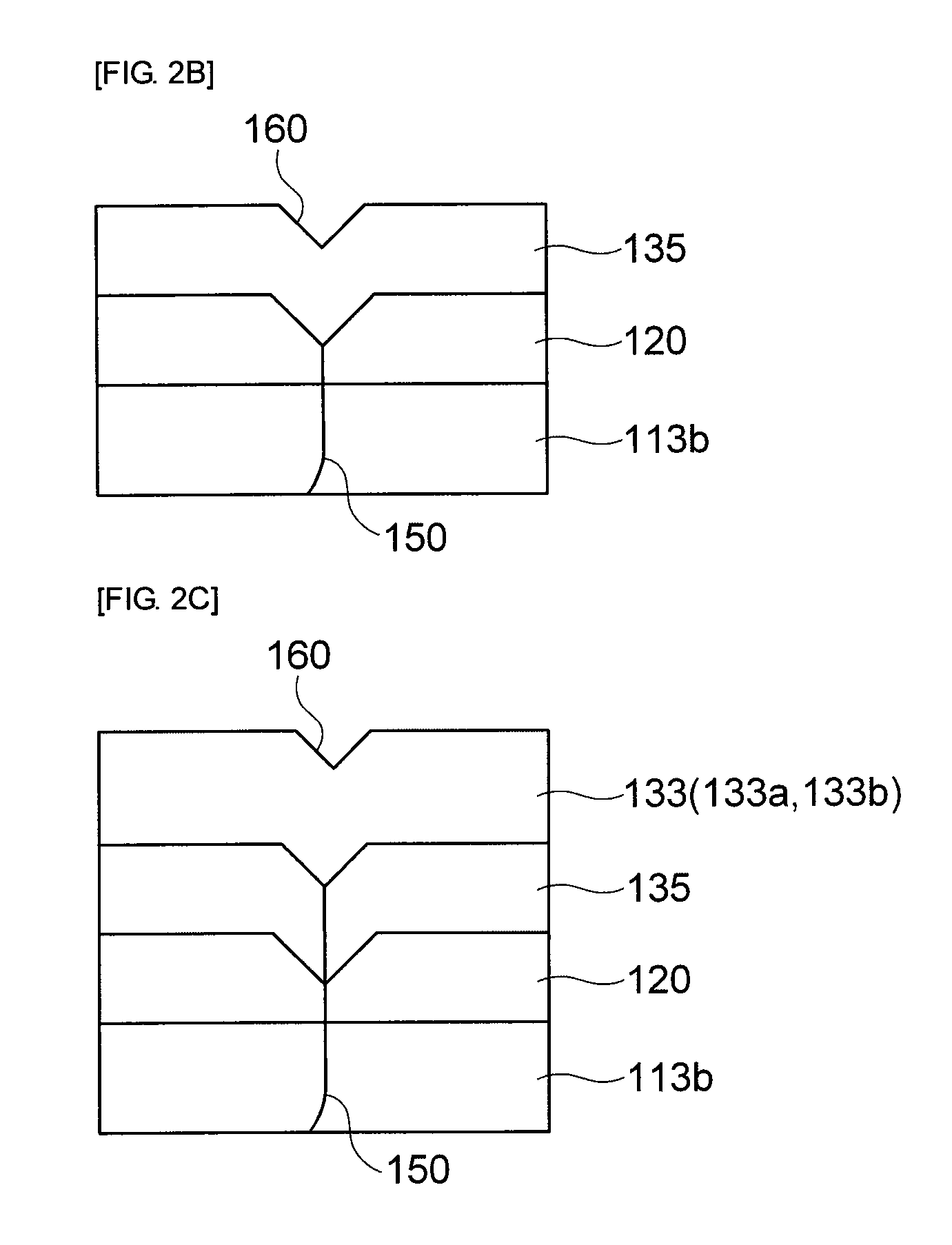

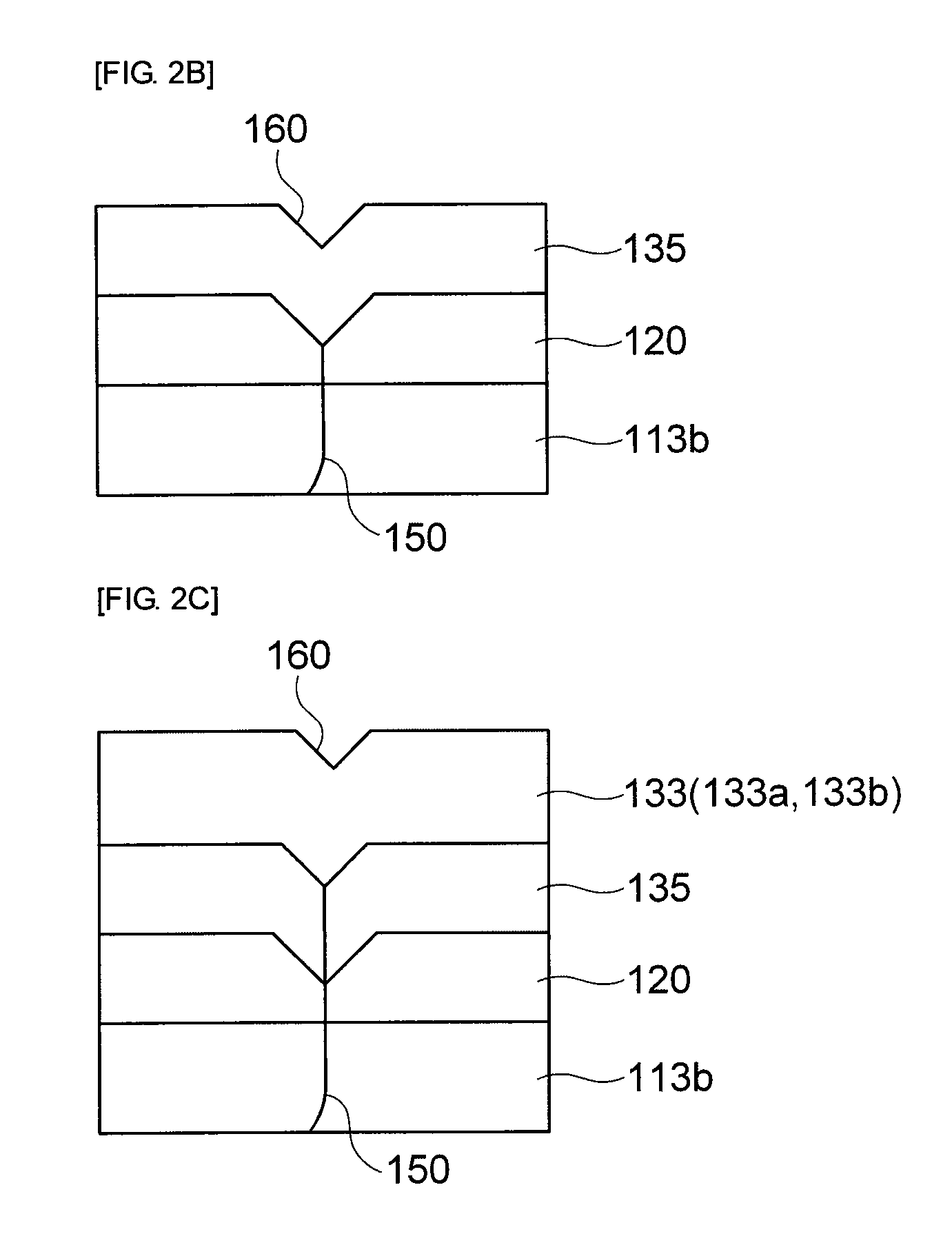

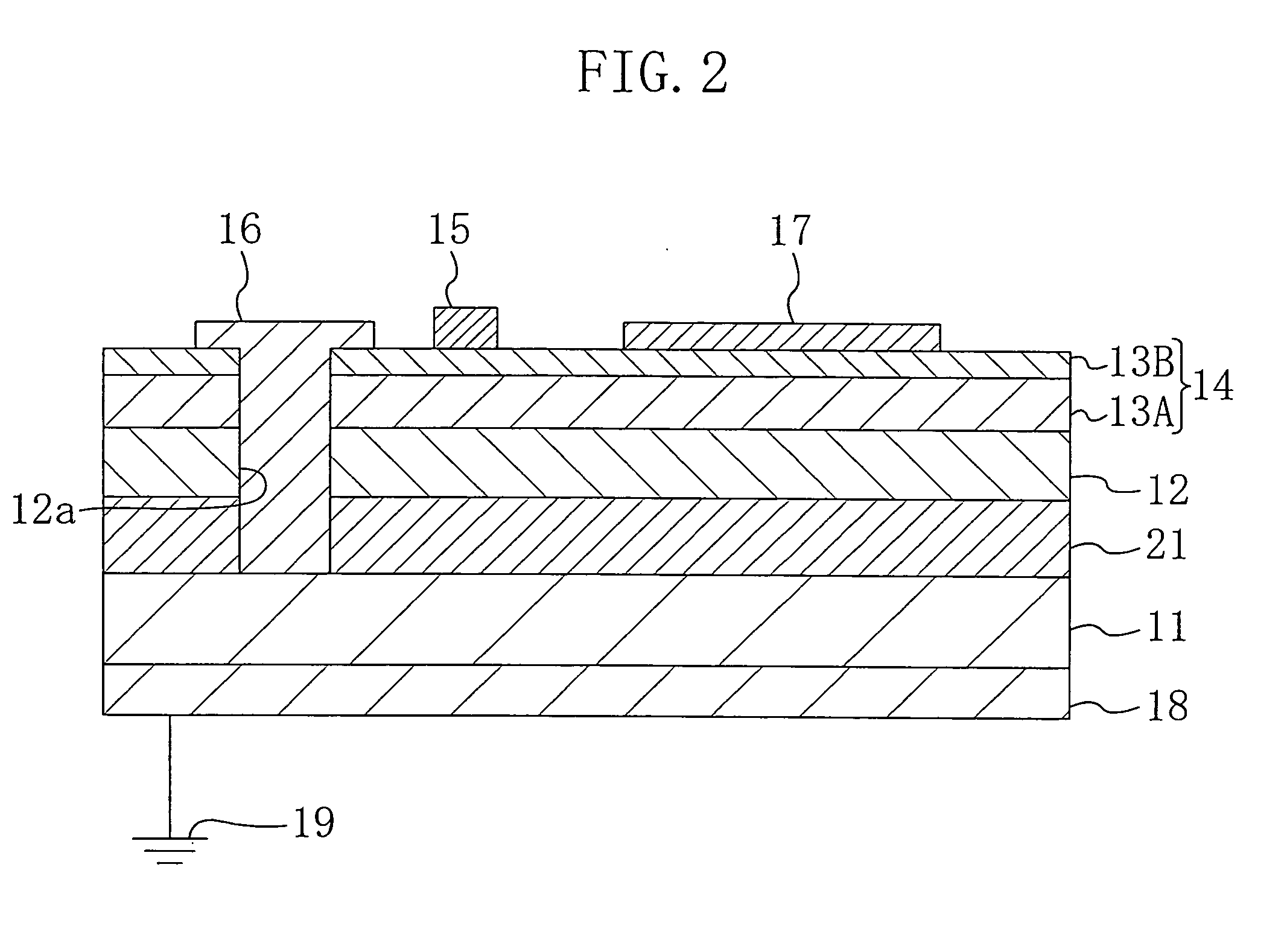

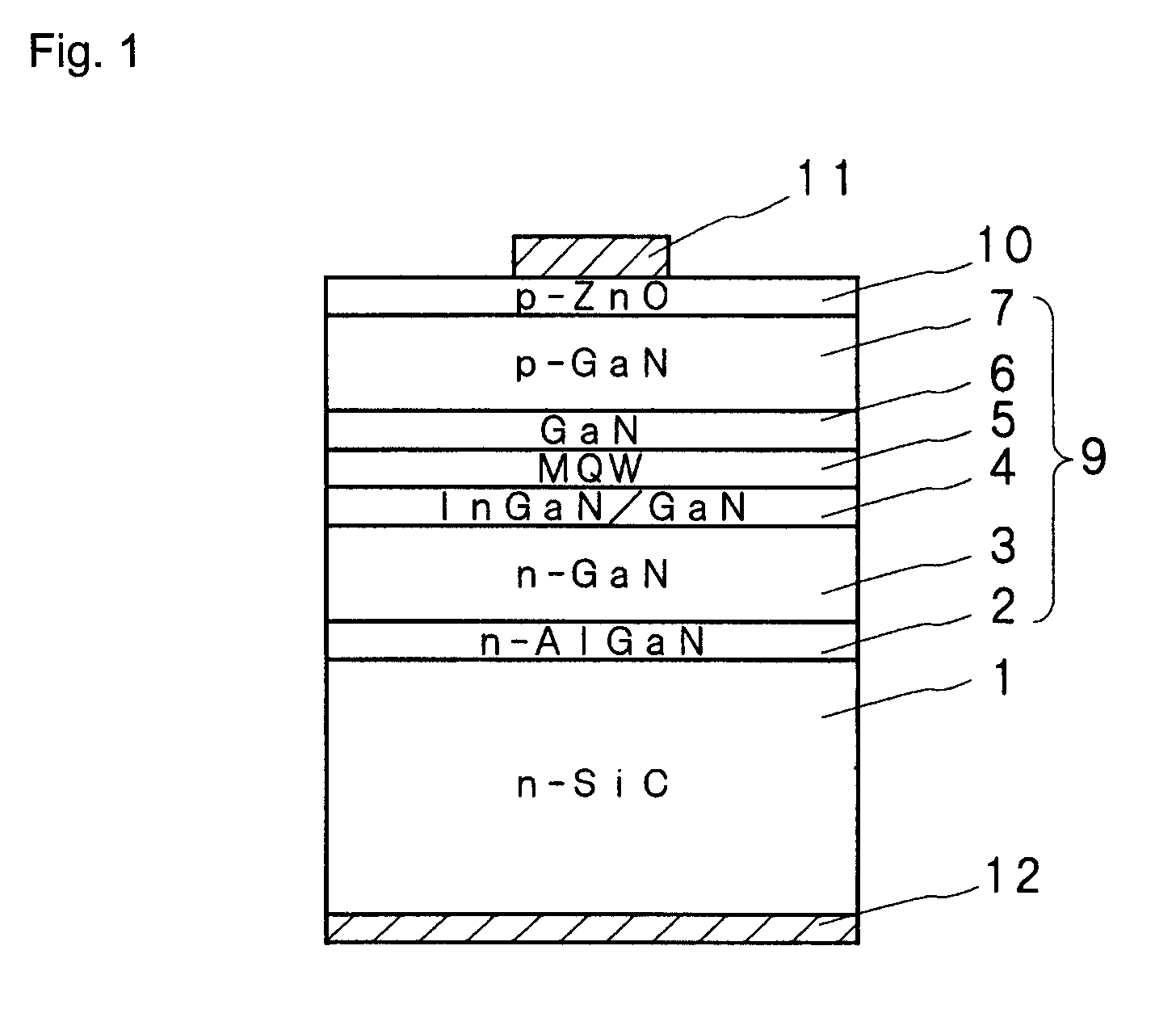

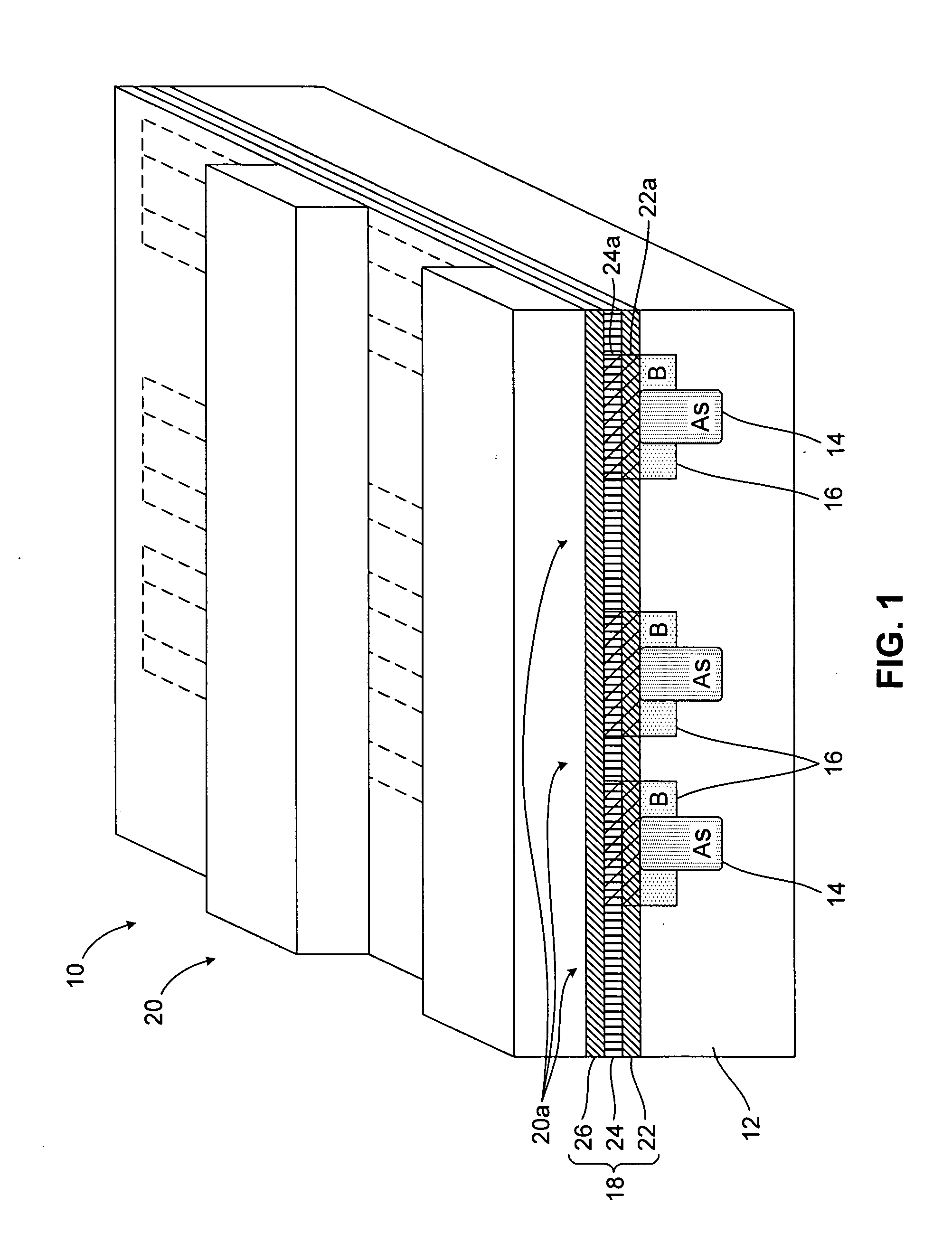

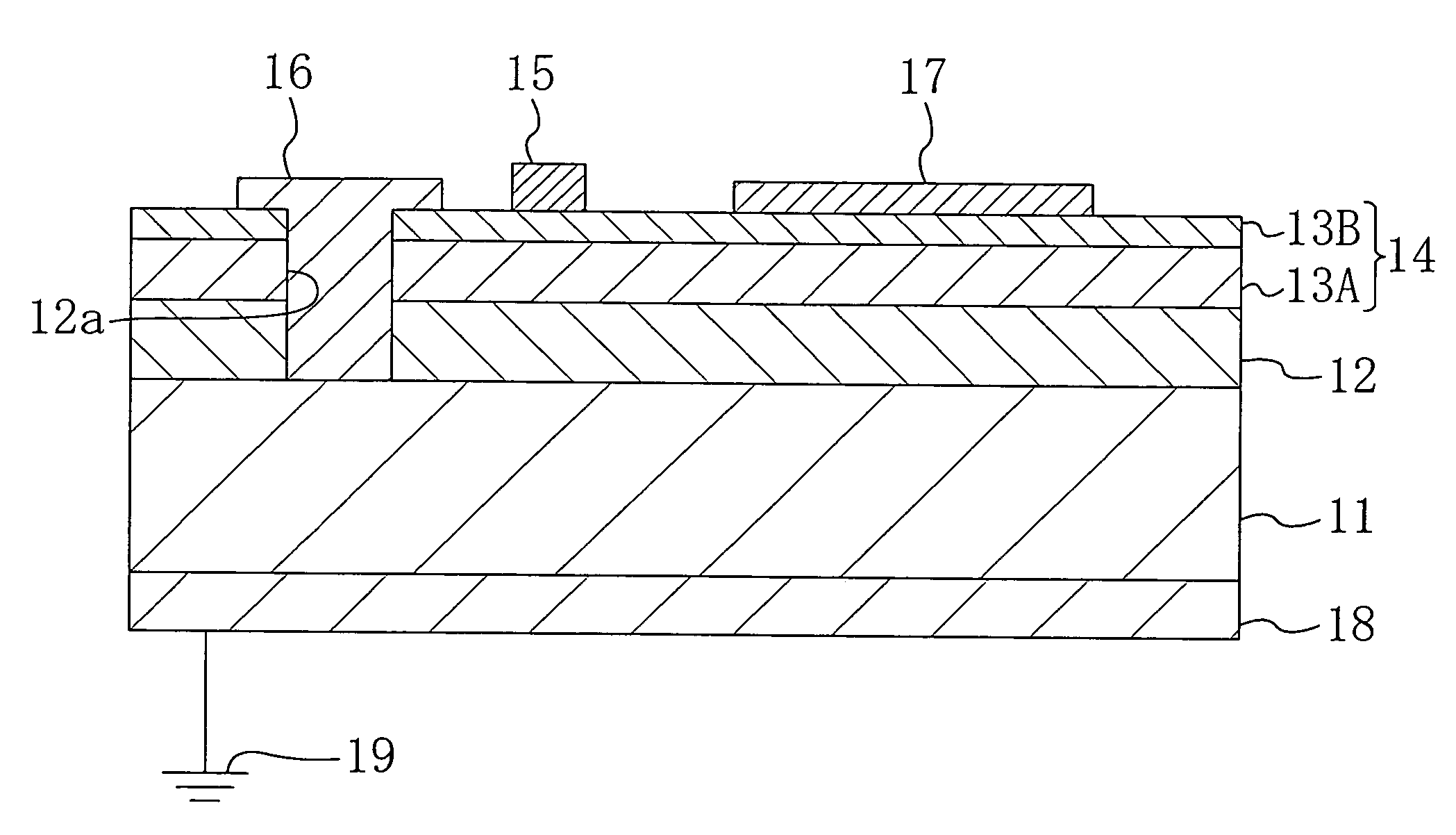

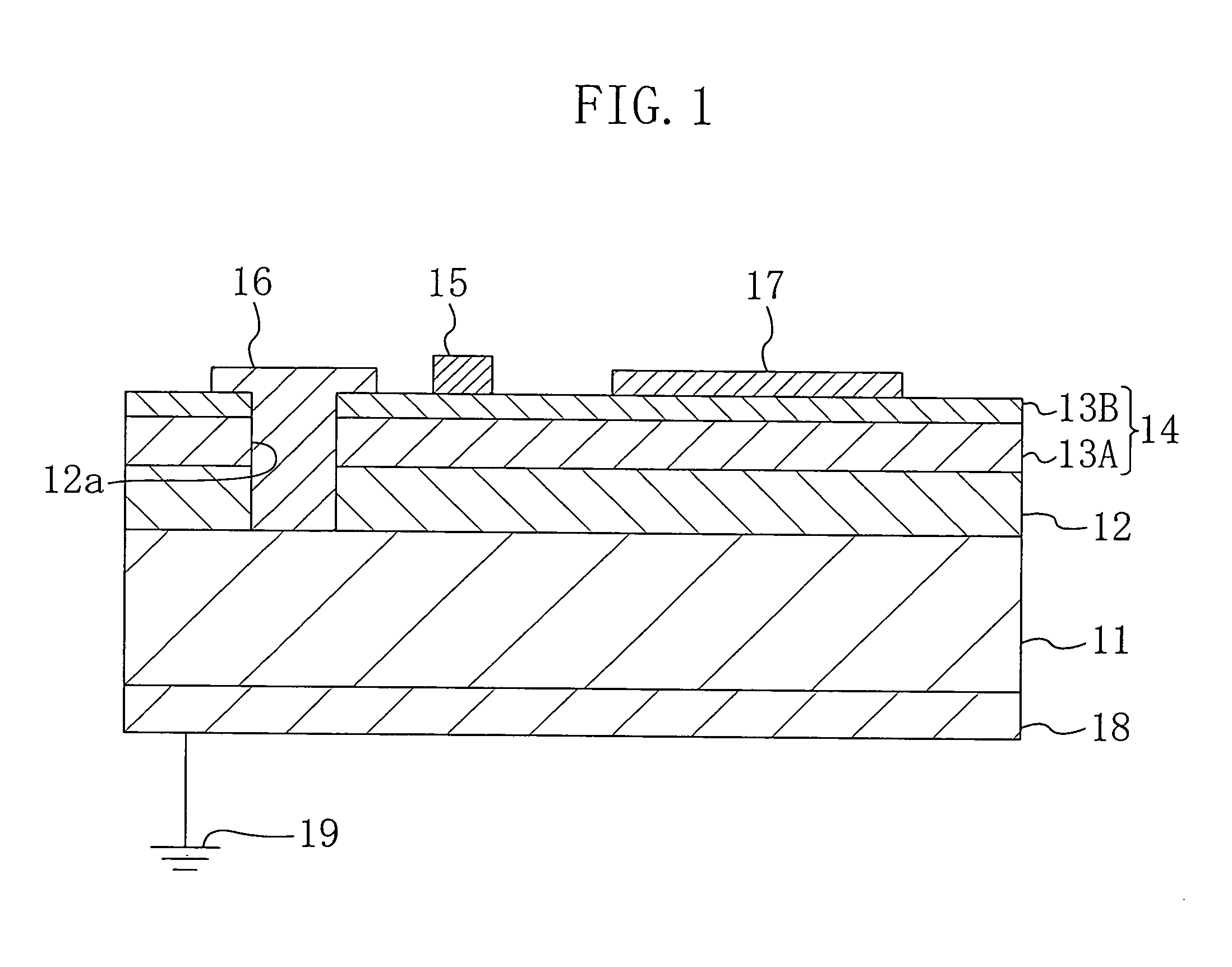

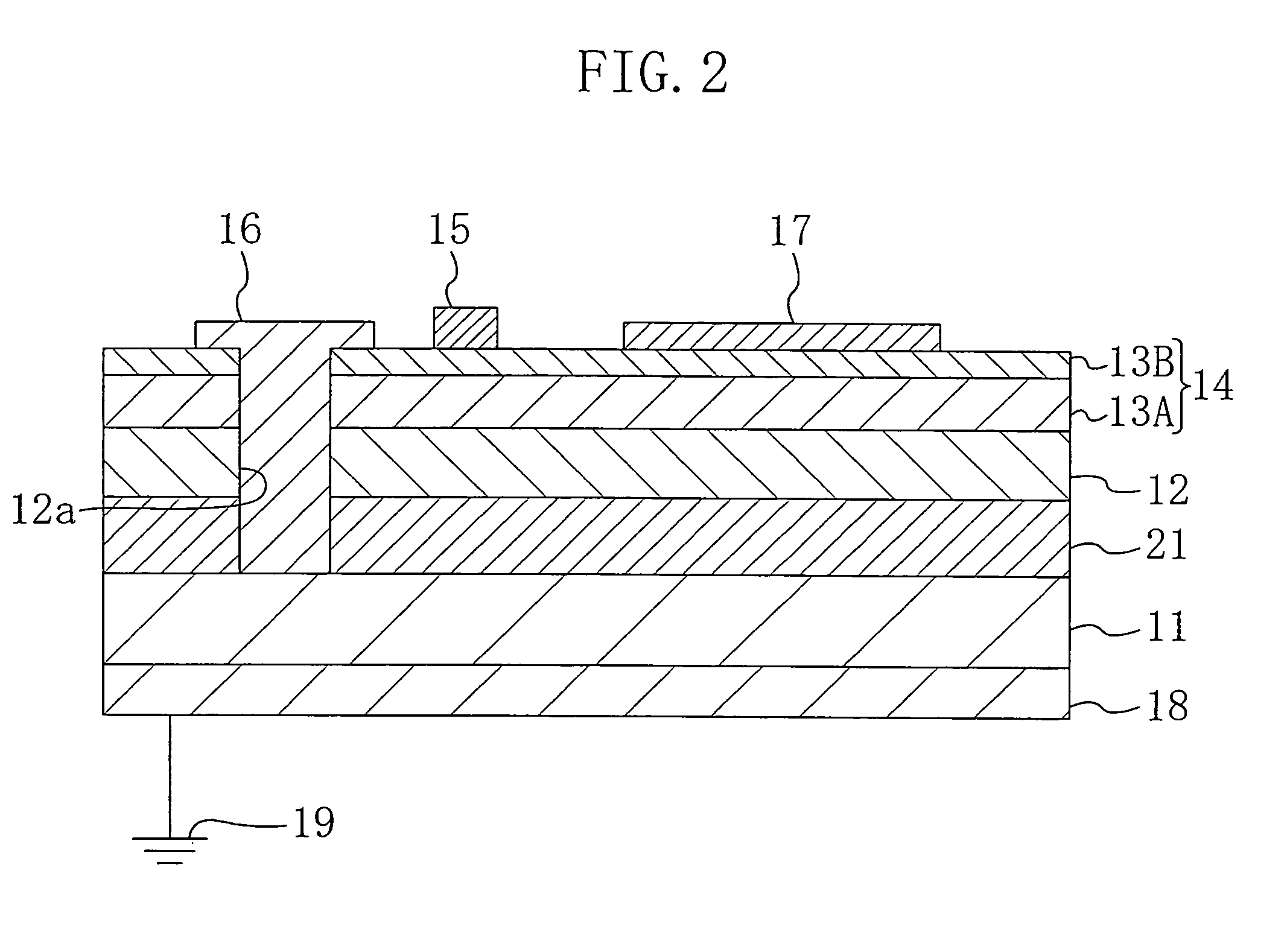

Nitride semiconductor light emitting device and fabrication method thereof

ActiveUS8129711B2Good effectReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesActive layerLight emitting device

The present invention relates to a GaN based nitride based light emitting device improved in Electrostatic Discharge (ESD) tolerance (withstanding property) and a method for fabricating the same including a substrate and a V-shaped distortion structure made of an n-type nitride semiconductor layer, an active layer and a p-type nitride semiconductor layer on the substrate and formed with reference to the n-type nitride semiconductor layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Nitride semiconductor light emitting device and fabrication method thereof

ActiveUS20090014713A1Good effectReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesActive layerLight emitting device

The present invention relates to a GaN based nitride based light emitting device improved in Electrostatic Discharge (ESD) tolerance (withstanding property) and a method for fabricating the same including a substrate and a V-shaped distortion structure made of an n-type nitride semiconductor layer, an active layer and a p-type nitride semiconductor layer on the substrate and formed with reference to the n-type nitride semiconductor layer.

Owner:SAMSUNG ELECTRONICS CO LTD

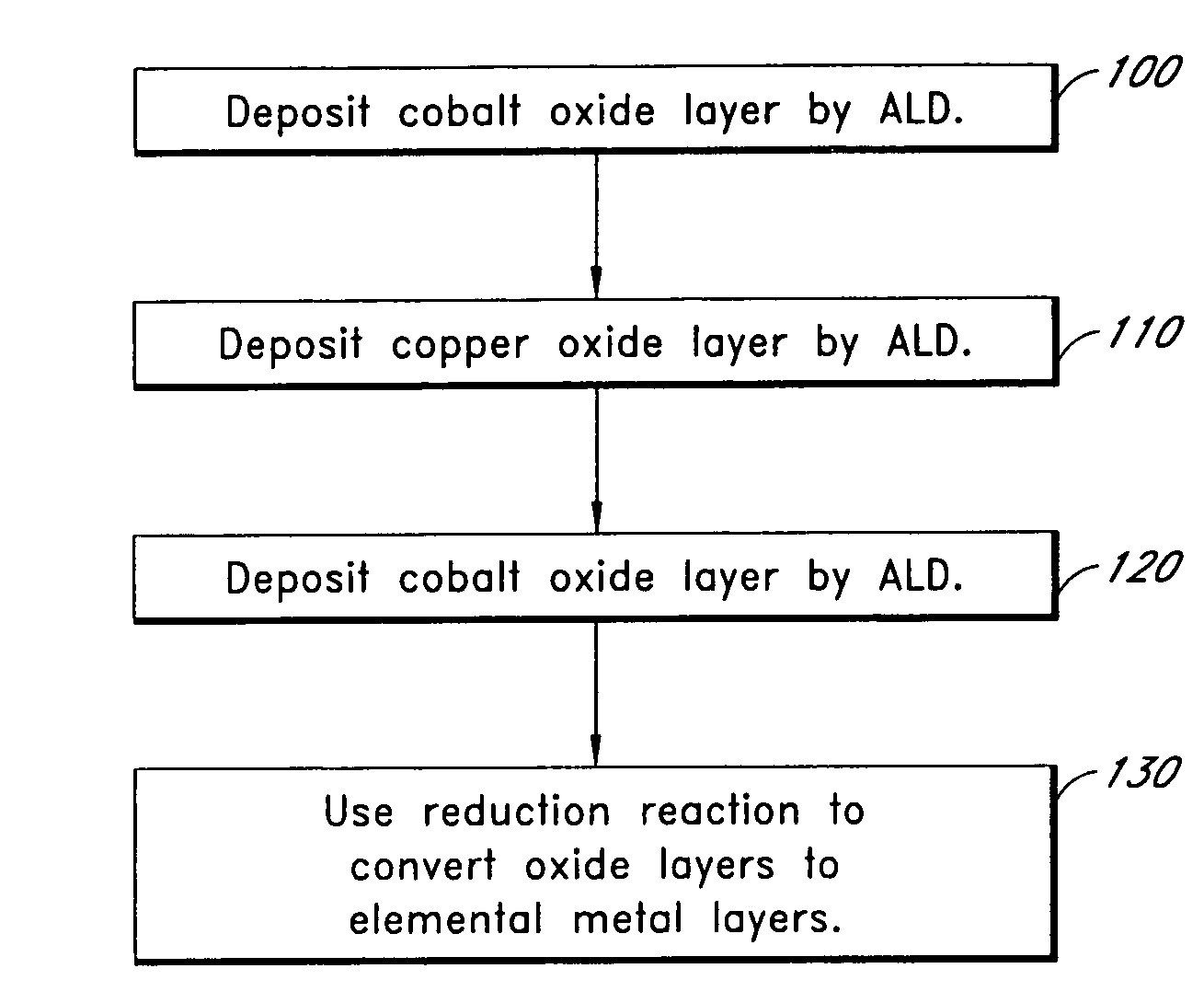

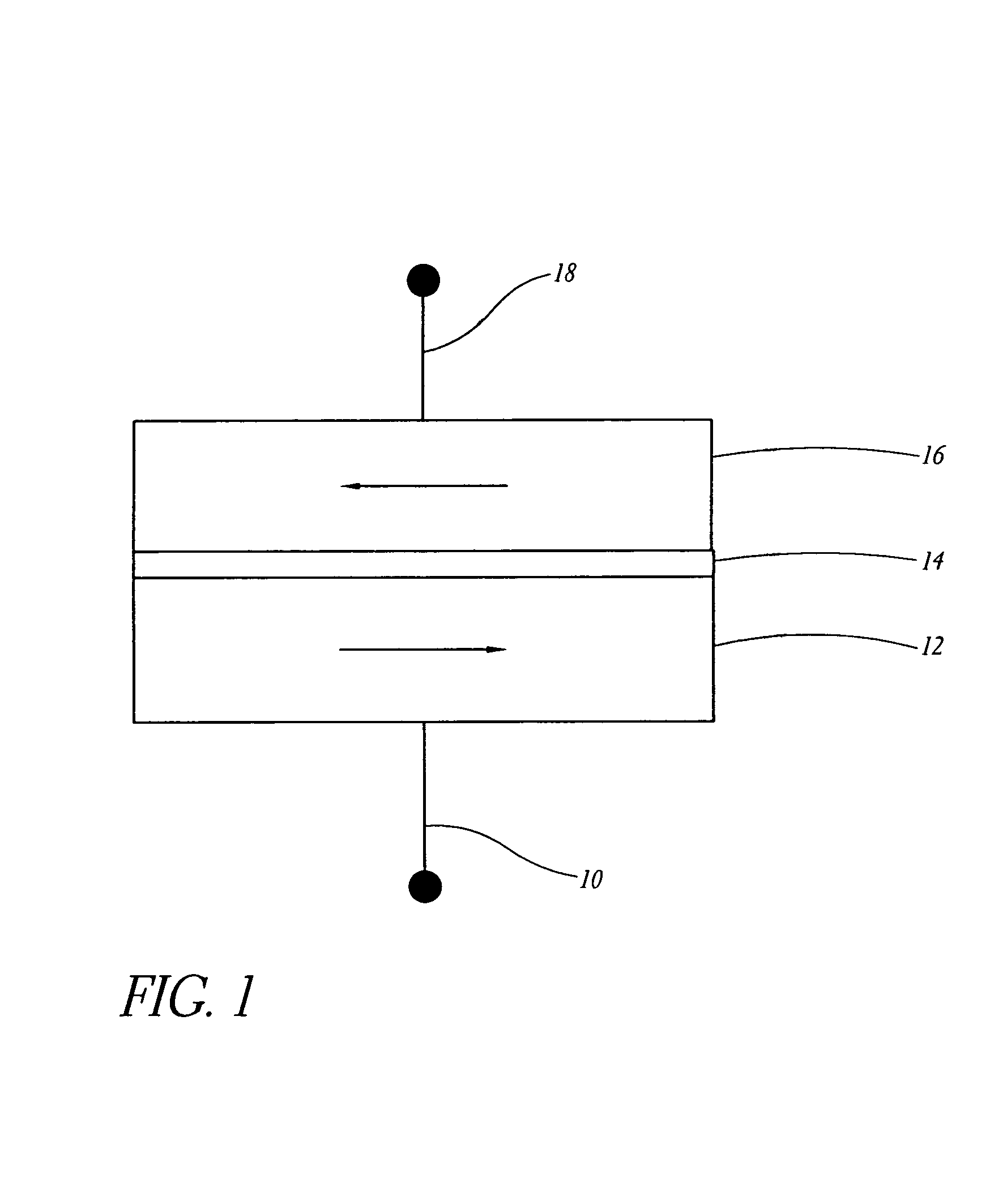

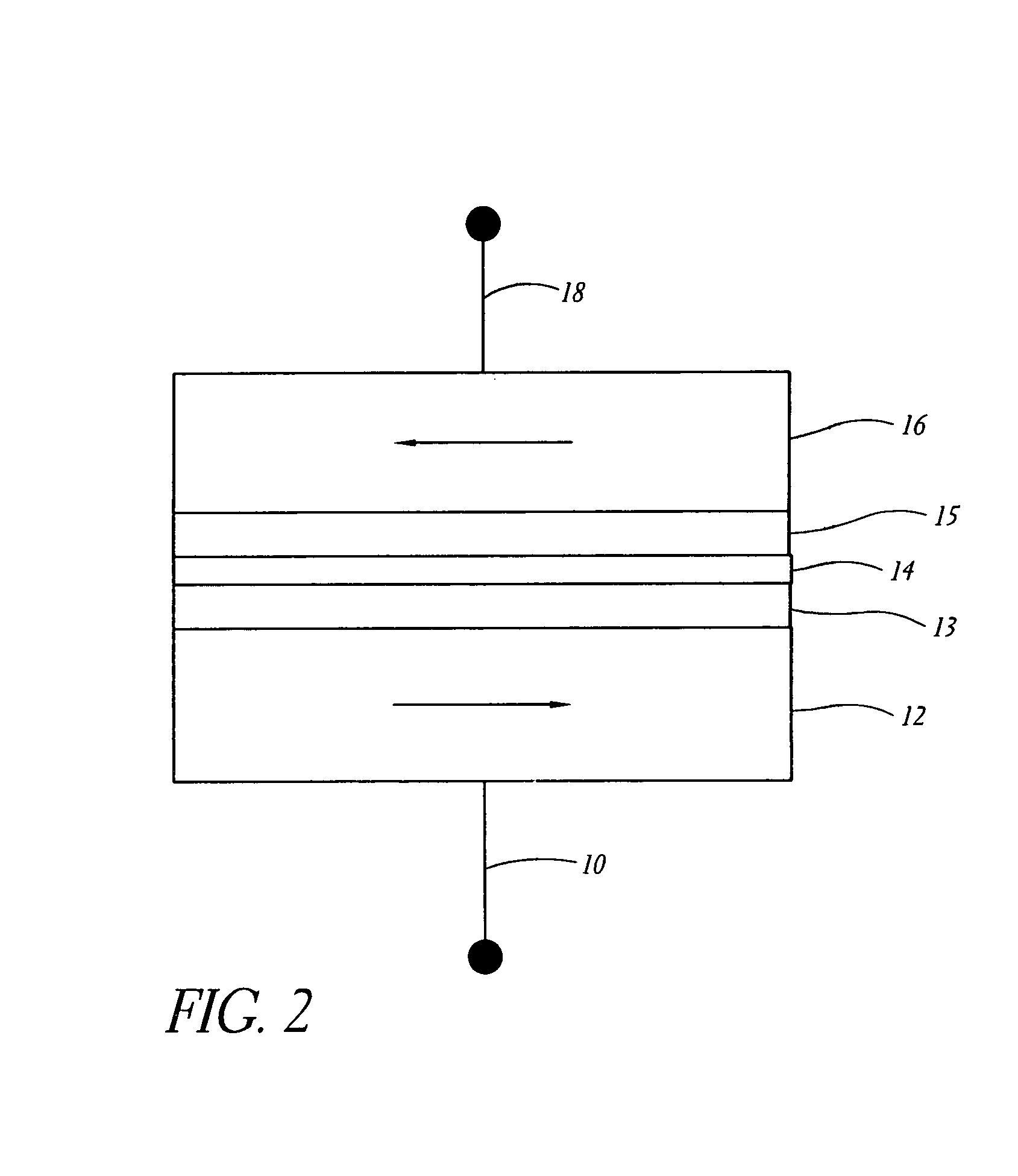

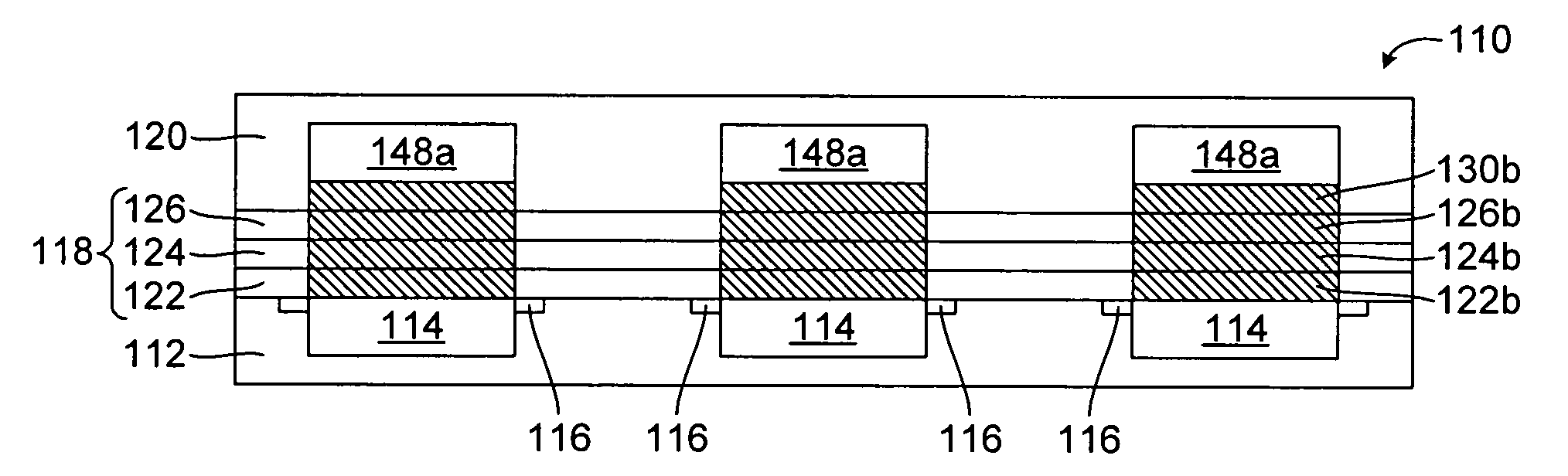

Thin films for magnetic device

InactiveUS7220669B2Inhibit migrationIncreasing the thicknessNanostructure applicationNanomagnetismDielectricThin layer

Methods are provided for forming uniformly thin layers in magnetic devices. Atomic layer deposition (ALD) can produce layers that are uniformly thick on an atomic scale. Magnetic tunnel junction dielectrics, for example, can be provided with perfect uniformity in thickness of 4 monolayers or less. Furthermore, conductive layers, including magnetic and non-magnetic layers, can be provided by ALD without spiking and other non-uniformity problems. The disclosed methods include forming metal oxide layers by multiple cycles of ALD and subsequently reducing the oxides to metal. The oxides tend to maintain more stable interfaces during formation.

Owner:ASM INTERNATIONAL

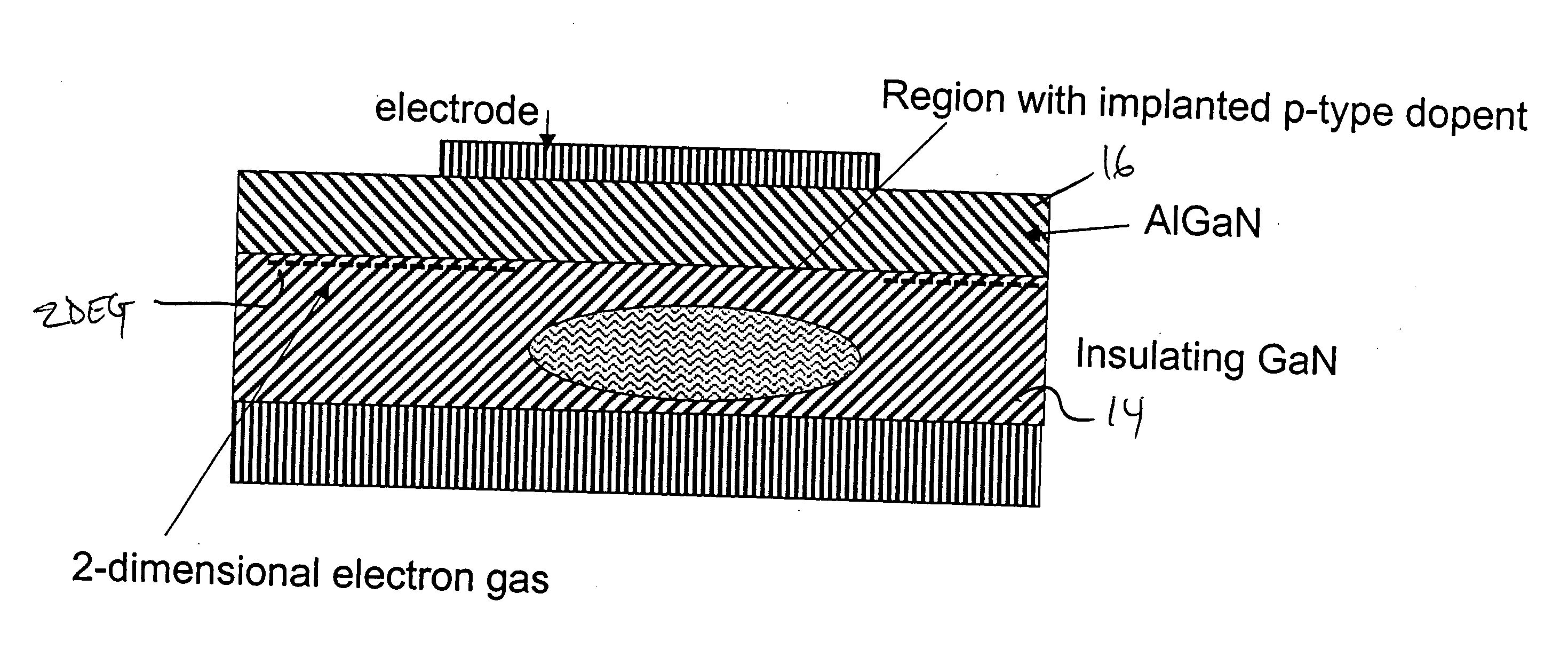

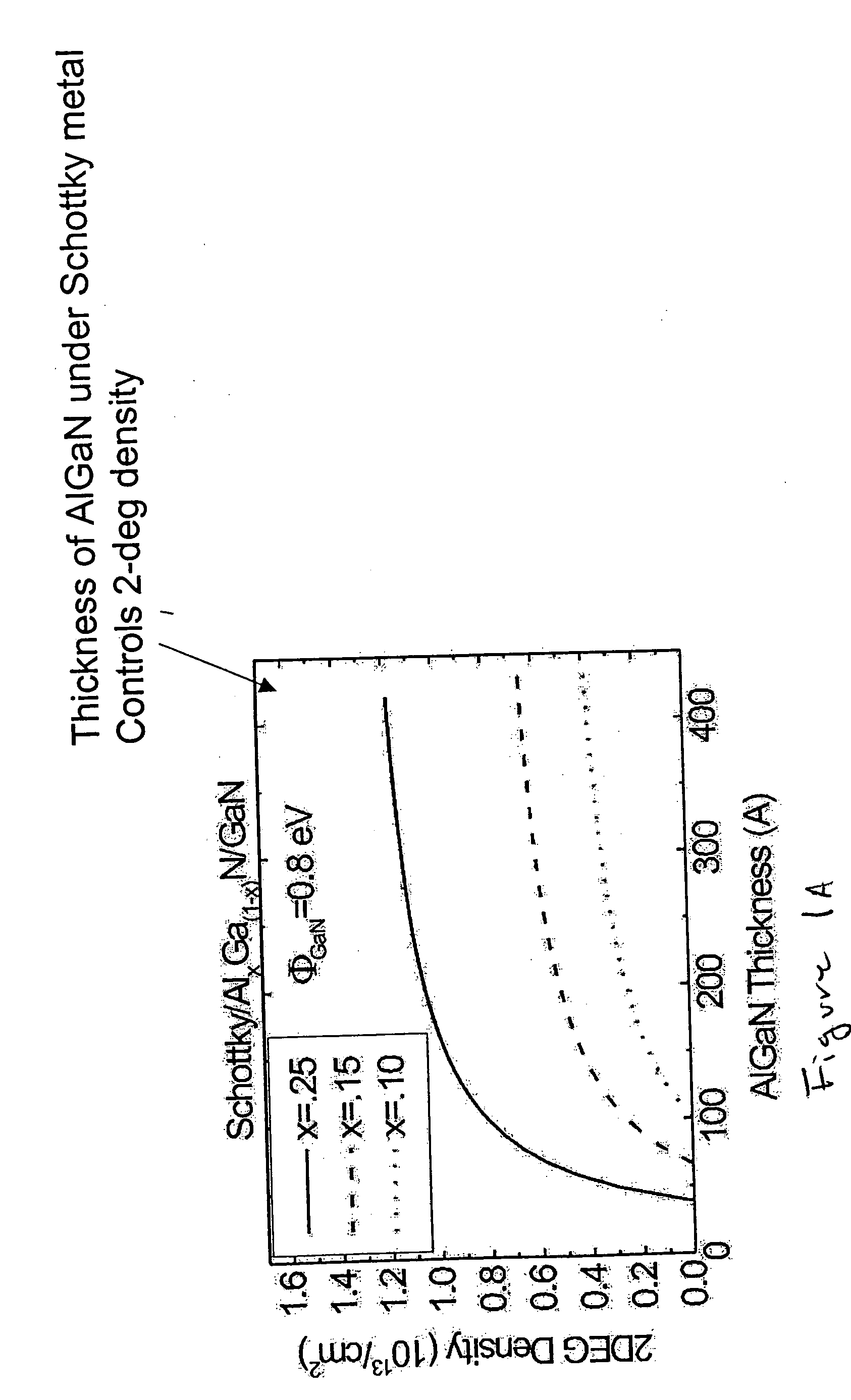

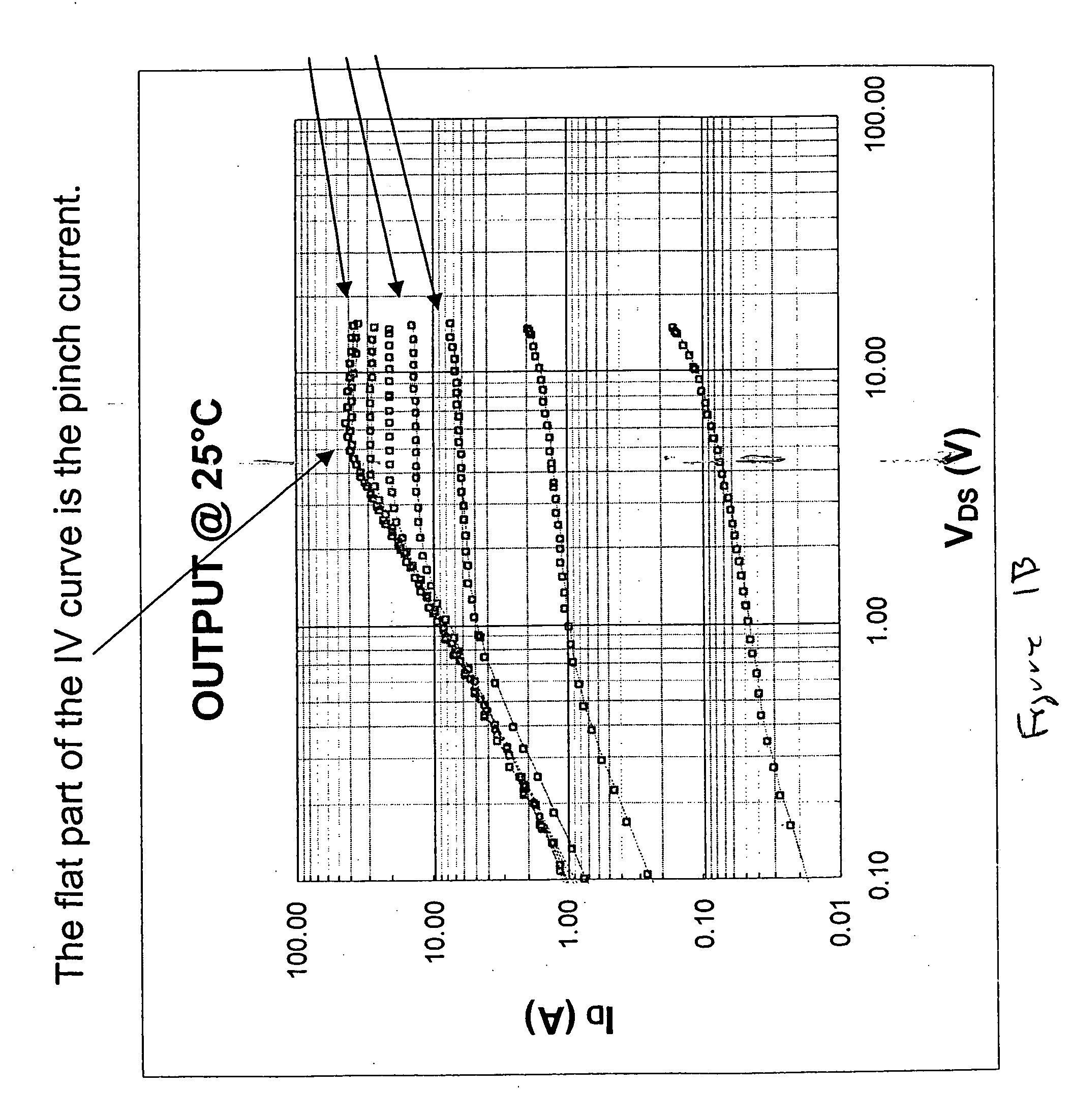

III-Nitride current control device and method of manufacture

ActiveUS20050194612A1Without sacrificing wafer areaReduce leakageSemiconductor/solid-state device detailsSolid-state devicesOhmic contactEngineering

A III-nitride device includes a recessed electrode to produce a nominally off, or an enhancement mode, device. By providing a recessed electrode, a conduction channel formed at the interface of two III-nitride materials is interrupted when the electrode contact is inactive to prevent current flow in the device. The electrode can be a schottky contact or an insulated metal contact. Two ohmic contacts can be provided to form a rectifier device with nominally off characteristics. The recesses formed with the electrode can have sloped sides. The electrode can be formed in a number of geometries in conjunction with current carrying electrodes of the device. A nominally on device, or pinch resistor, is formed when the electrode is not recessed. A diode is also formed by providing non-recessed ohmic and schottky contacts through an insulator to an AlGaN layer.

Owner:INFINEON TECH AMERICAS CORP

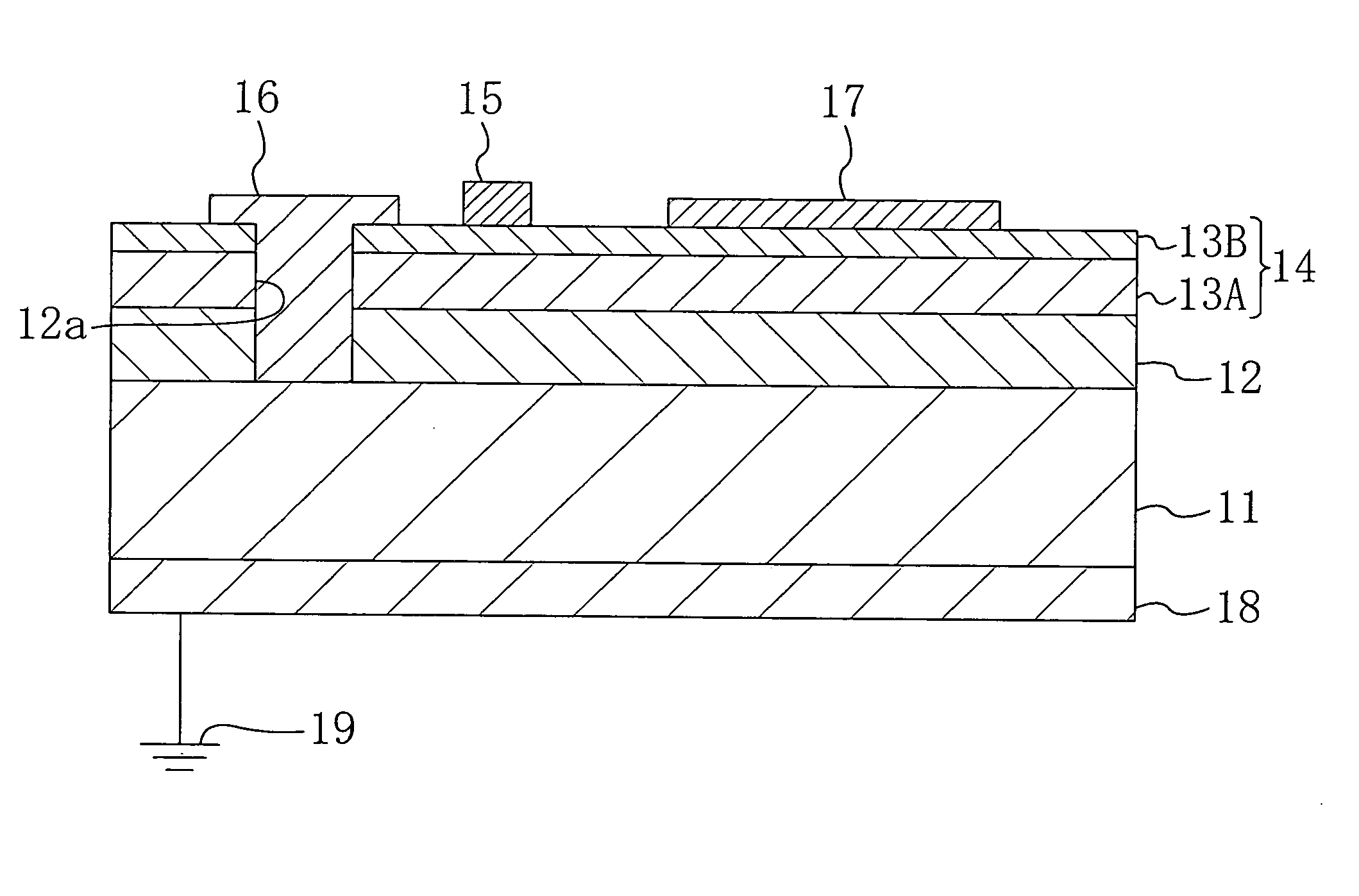

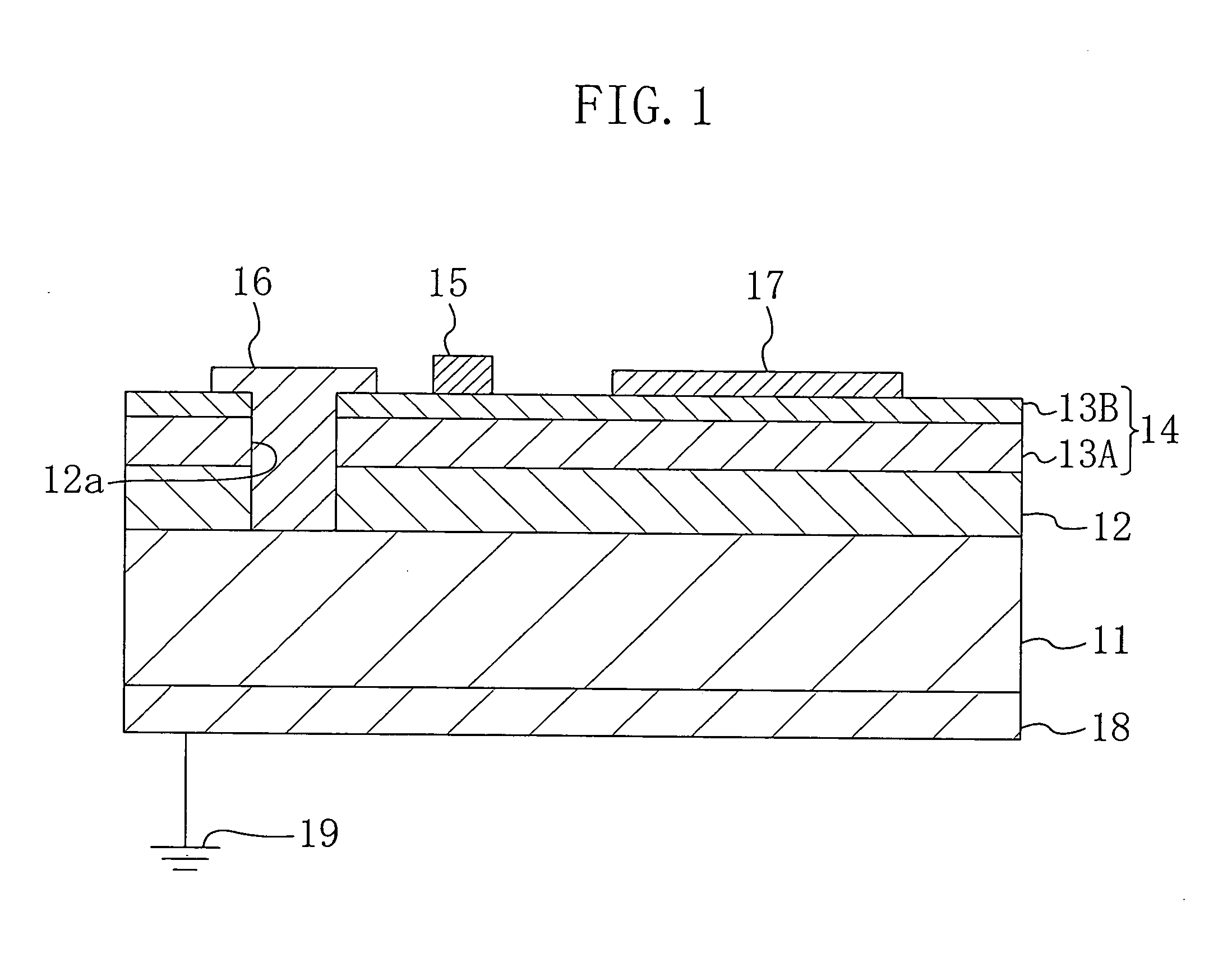

Semiconductor device

ActiveUS20050001235A1Promote formationObstruction is producedLaser active region structureSemiconductor/solid-state device manufacturingHigh resistanceDevice material

A semiconductor device has: a buffer layer formed on a conductive substrate and made of AlxGa1-xN with a high resistance; an element-forming layer formed on the buffer layer, having a channel layer, and made of undoped GaN and N-type AlyGa1-yN; and a source electrode, a drain electrode and a gate electrode which are selectively formed on the element-forming layer. The source electrode is filled in a through hole provided in the buffer layer and the element-forming layer, and is thus electrically connected to the conductive substrate.

Owner:PANASONIC CORP

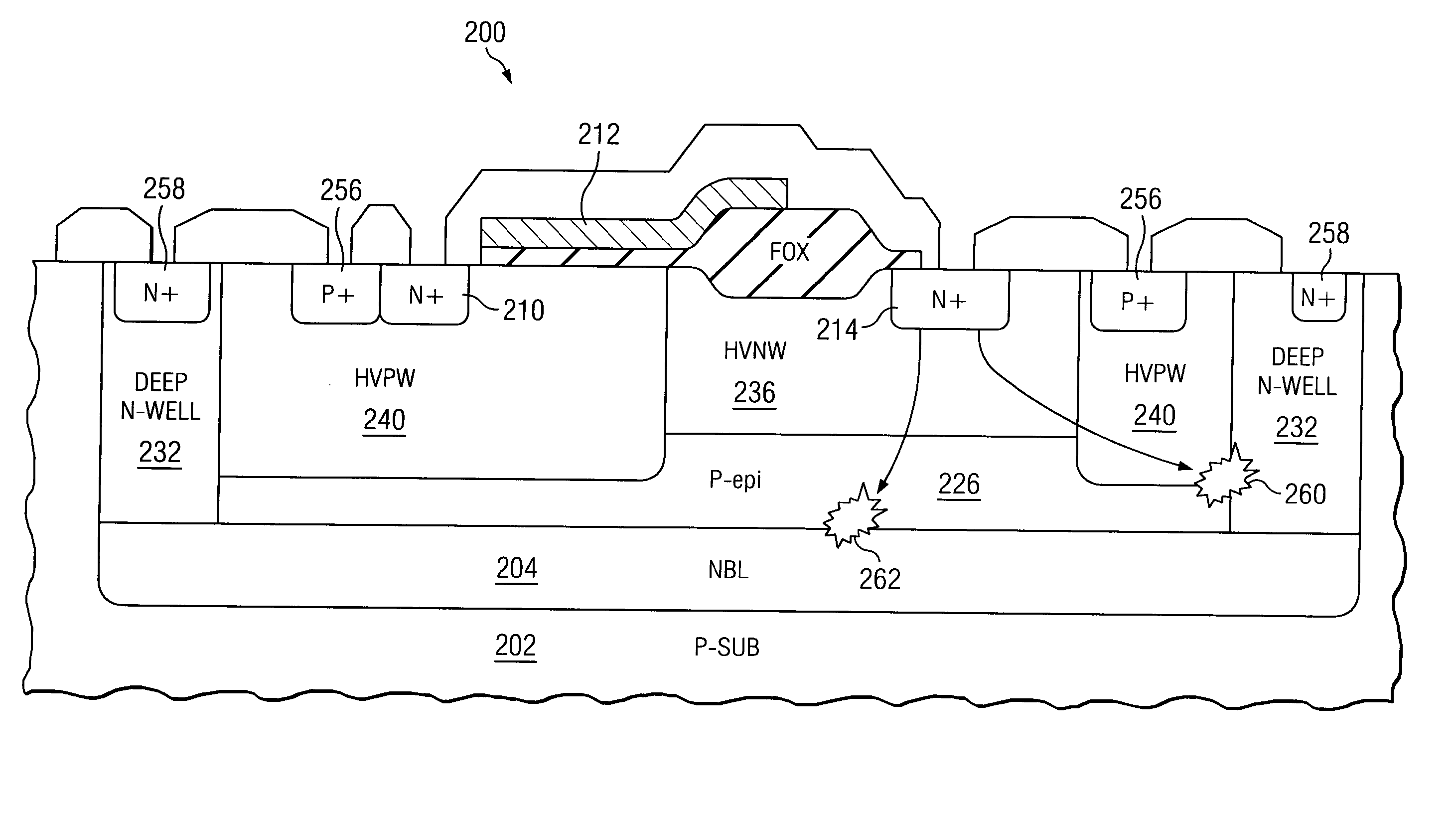

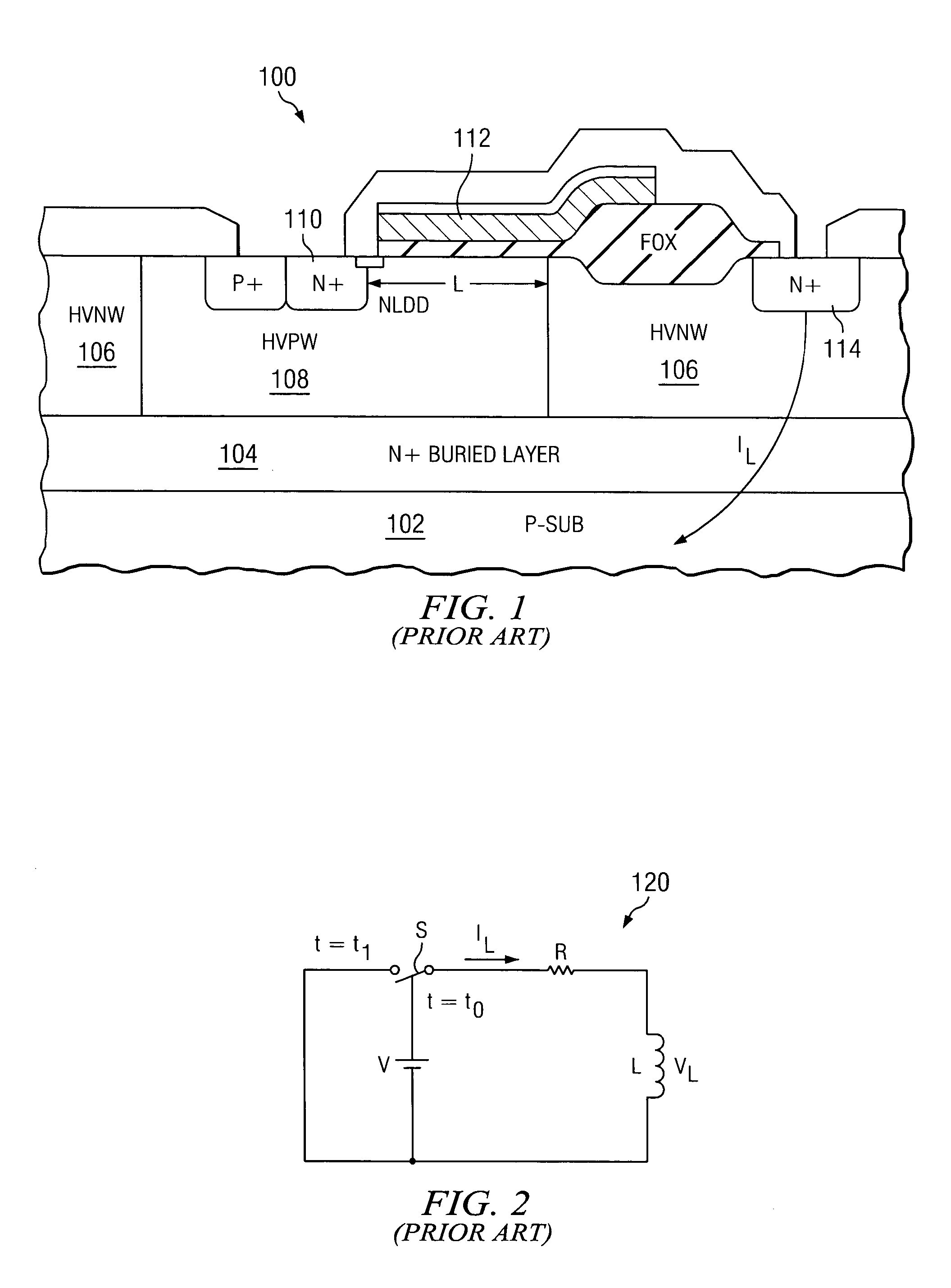

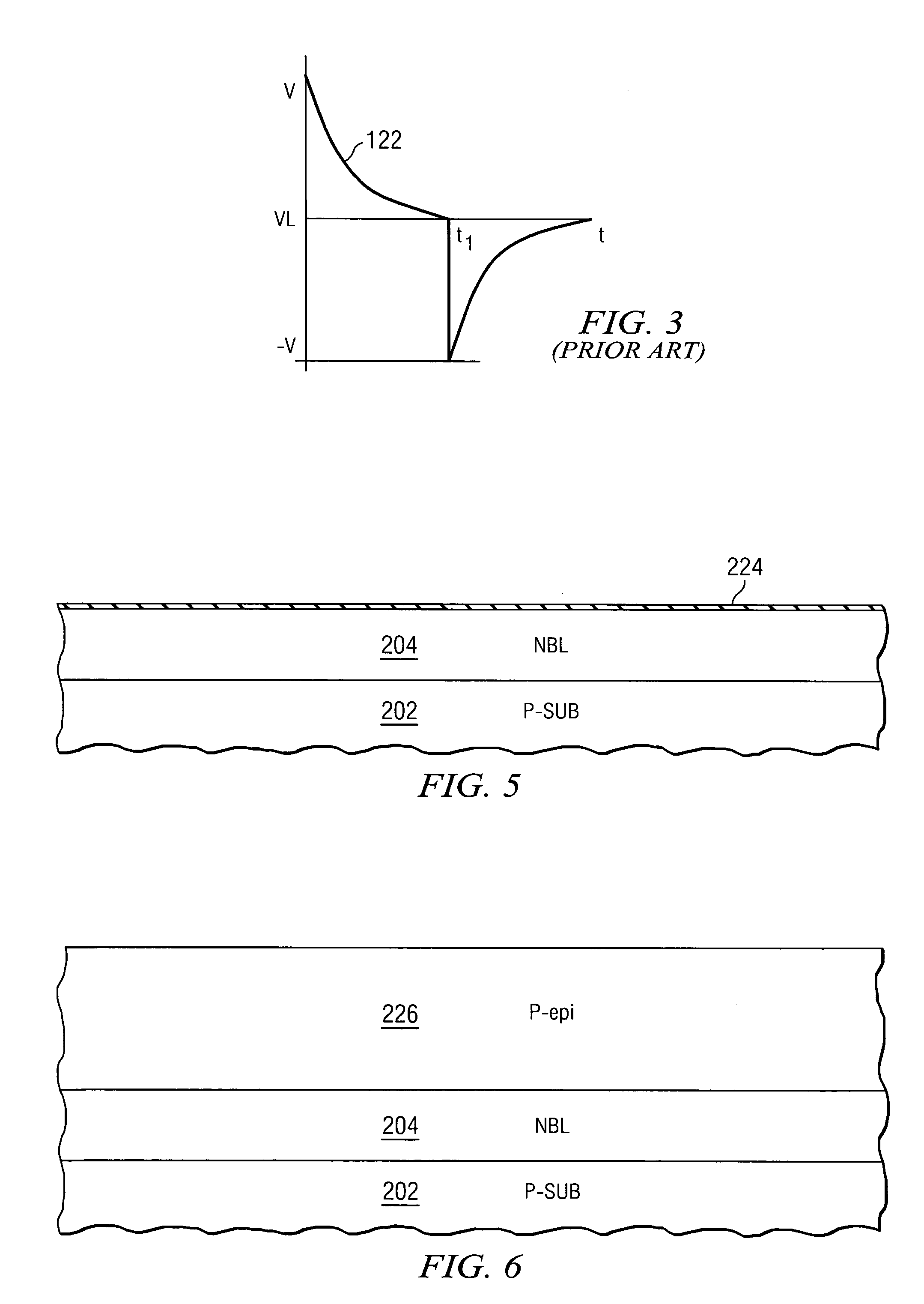

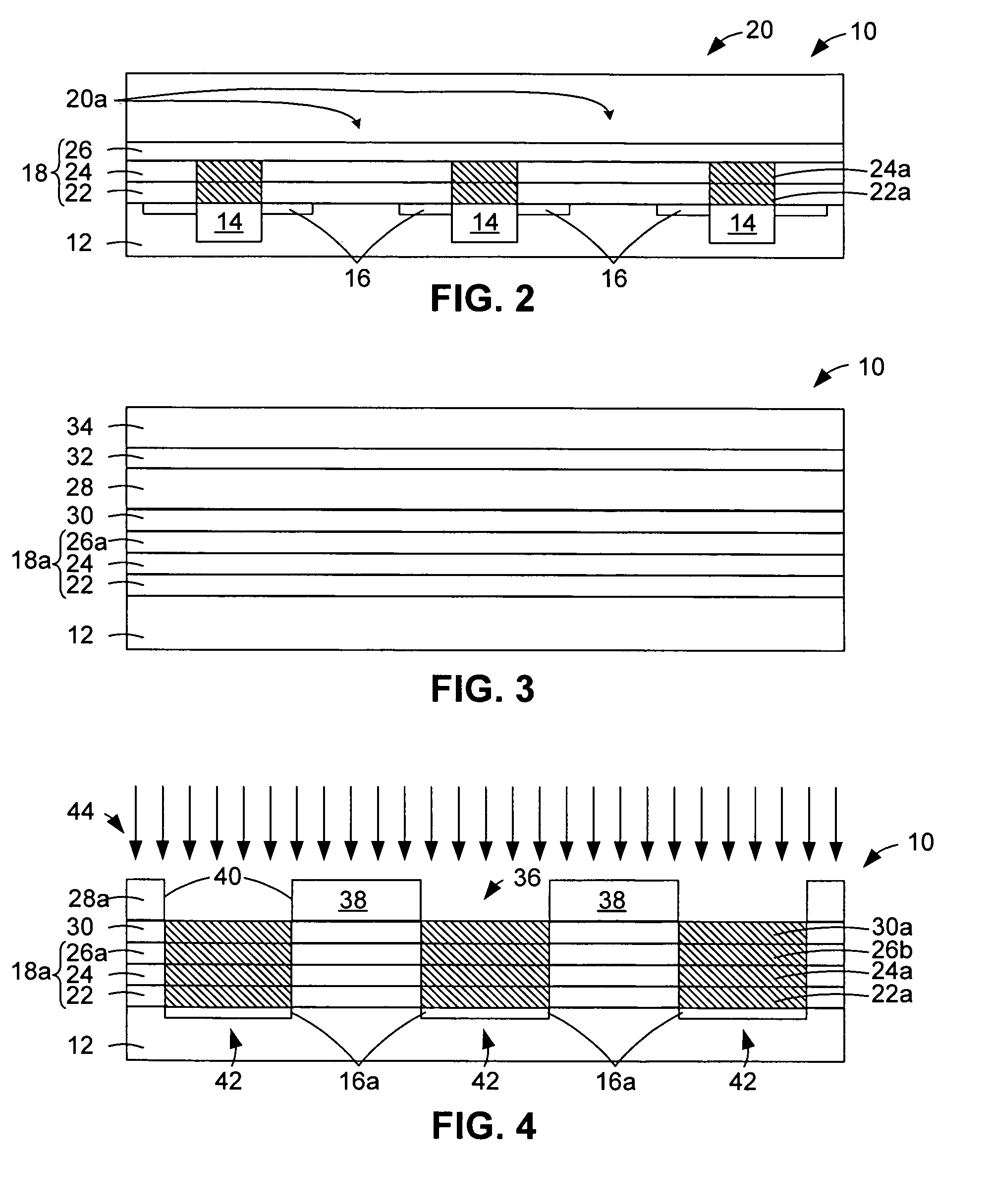

Ldmos device with isolation guard rings

InactiveUS20050073007A1Avoid leakage currentLatch-up, early breakdown and reliability issues are preventedSemiconductor/solid-state device detailsSolid-state devicesLDMOSDevice material

A method of forming a LDMOS semiconductor device and structure for same. A preferred embodiment comprises forming a first guard ring around and proximate the drain of a LDMOS device, and forming a second guard ring around the first guard ring. The first guard ring comprises a P+ base guard ring, and the second guard ring comprises an N+ collector guard ring formed in a deep N-well, in one embodiment. The first guard ring and second guard ring prevent leakage current from flowing from the drain of the LDMOS device to the substrate.

Owner:TAIWAN SEMICON MFG CO LTD

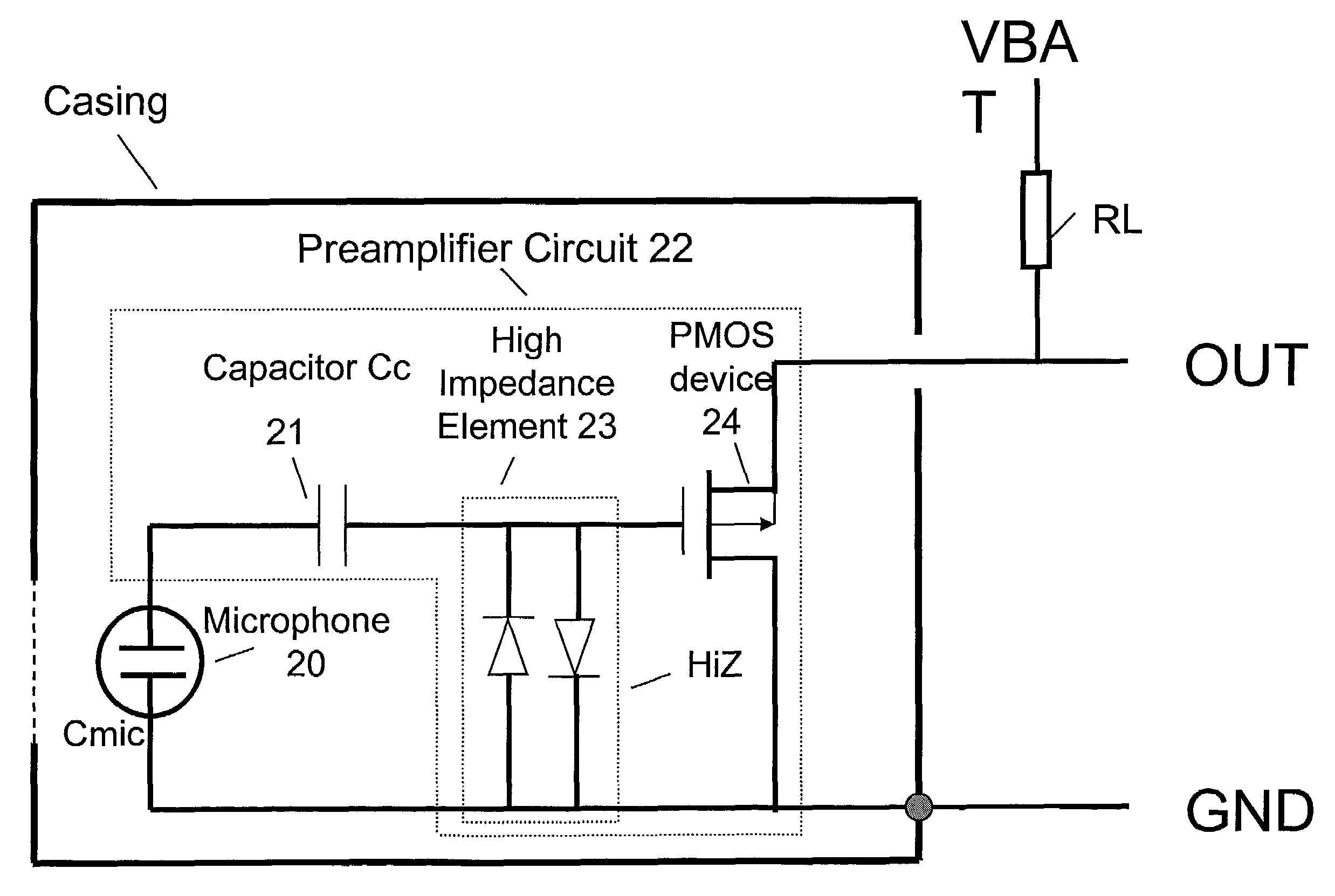

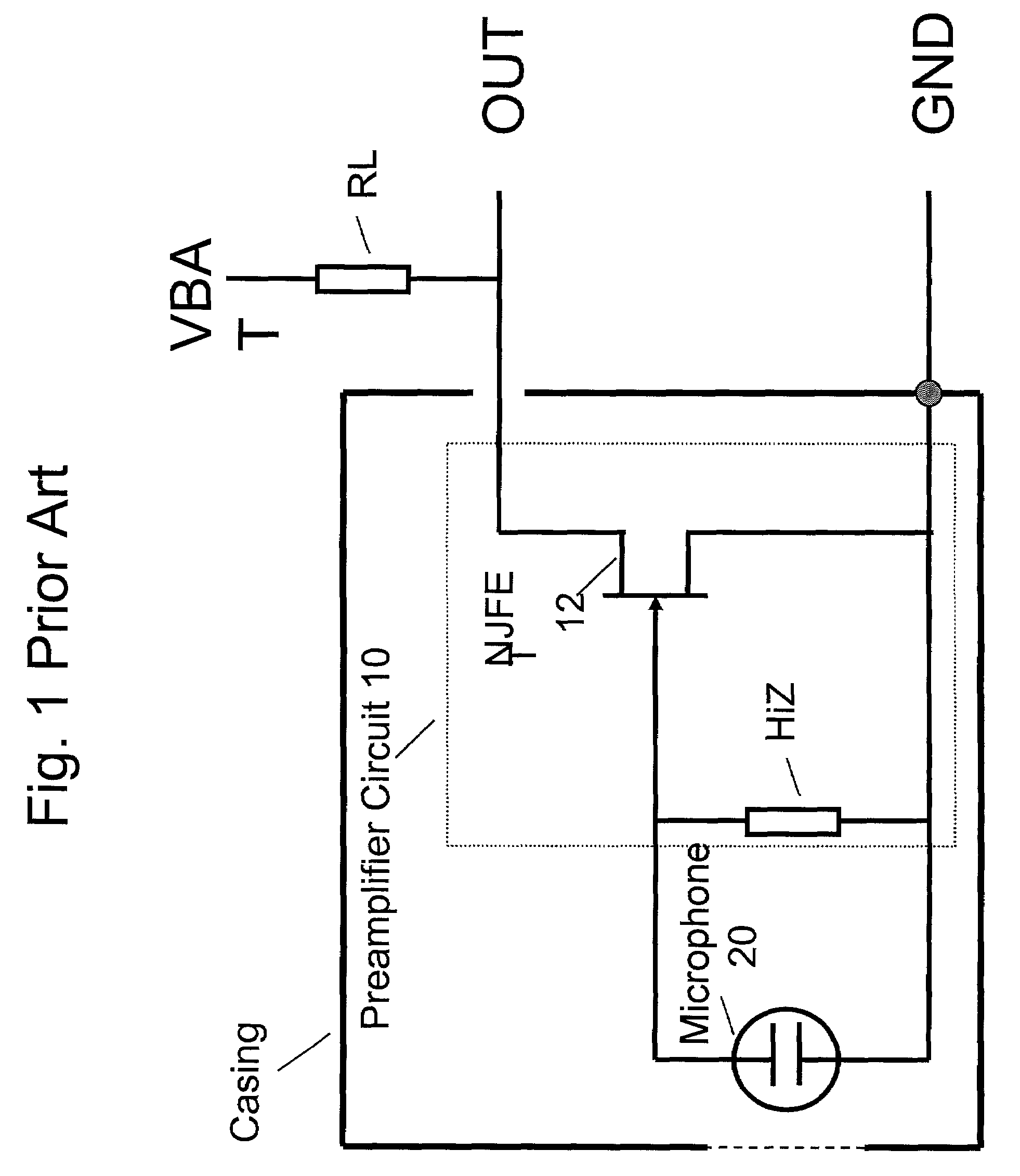

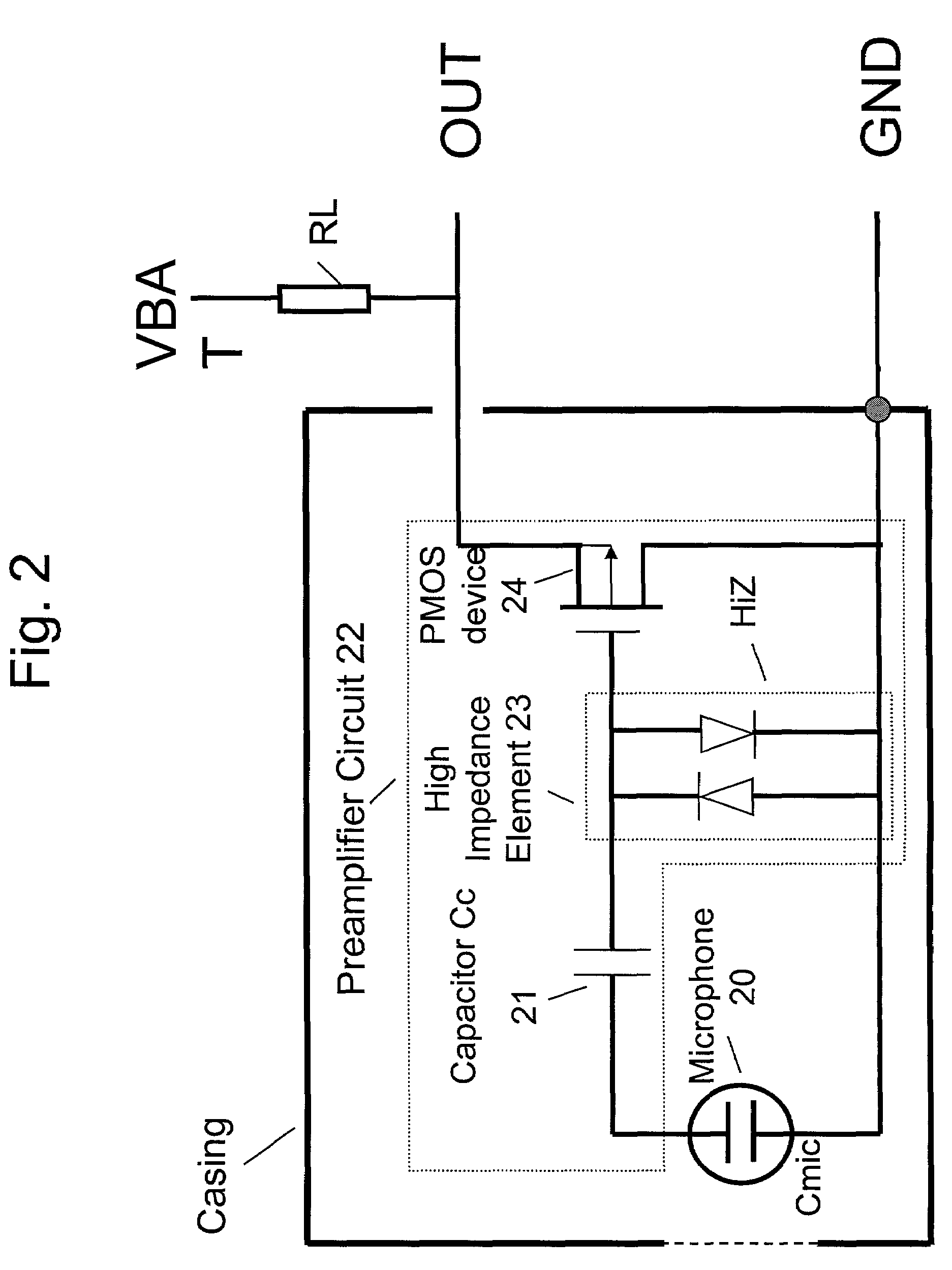

Electret condensor microphone preamplifier that is insensitive to leakage currents at the input

InactiveUS7110560B2Reduce input leakage currentAvoid leakage currentLow frequency amplifiersTransducer casings/cabinets/supportsCapacitanceOperating point

A preamplifier having extremely high input impedance amplifies the electrical signal output from an electret condenser microphone (ECM) without suffering from the effects of a DC leakage current at the input. The preamplifier circuit includes a pair of cross-coupled PN junction diodes setting the input impedance, a PMOS device, and a load resistor configured similarly to a conventional preamplifier. A capacitor is placed between the input and the cross-coupled diodes such that a DC path no longer exists to bias the cross-coupled diodes. Therefore, leakage currents are prevented from upsetting the DC operating point of the preamplifier and biasing the cross-coupled diodes. Consequently, small signal gain distortion, excessive demodulation products and increased noise can be avoided.

Owner:SONION

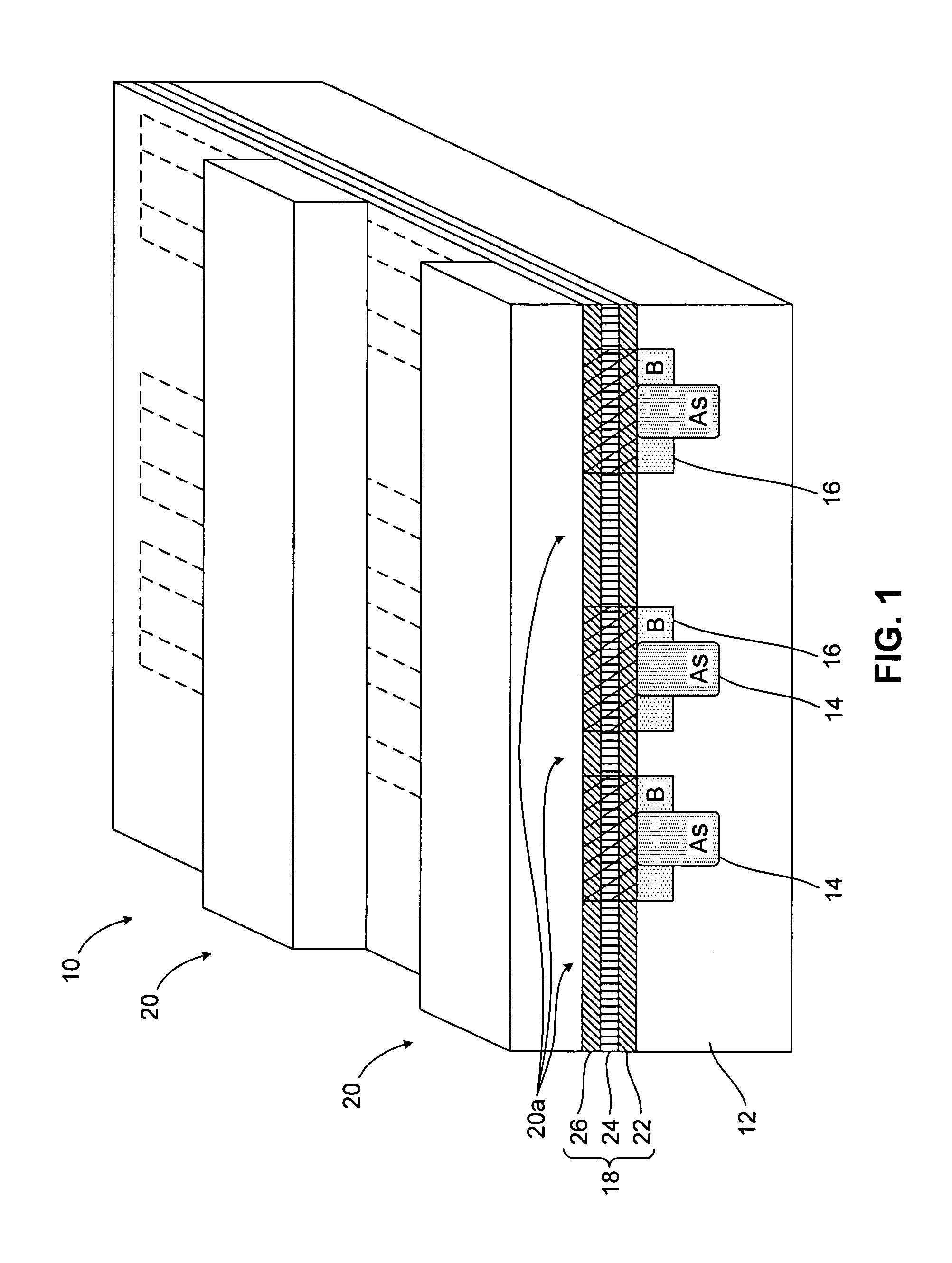

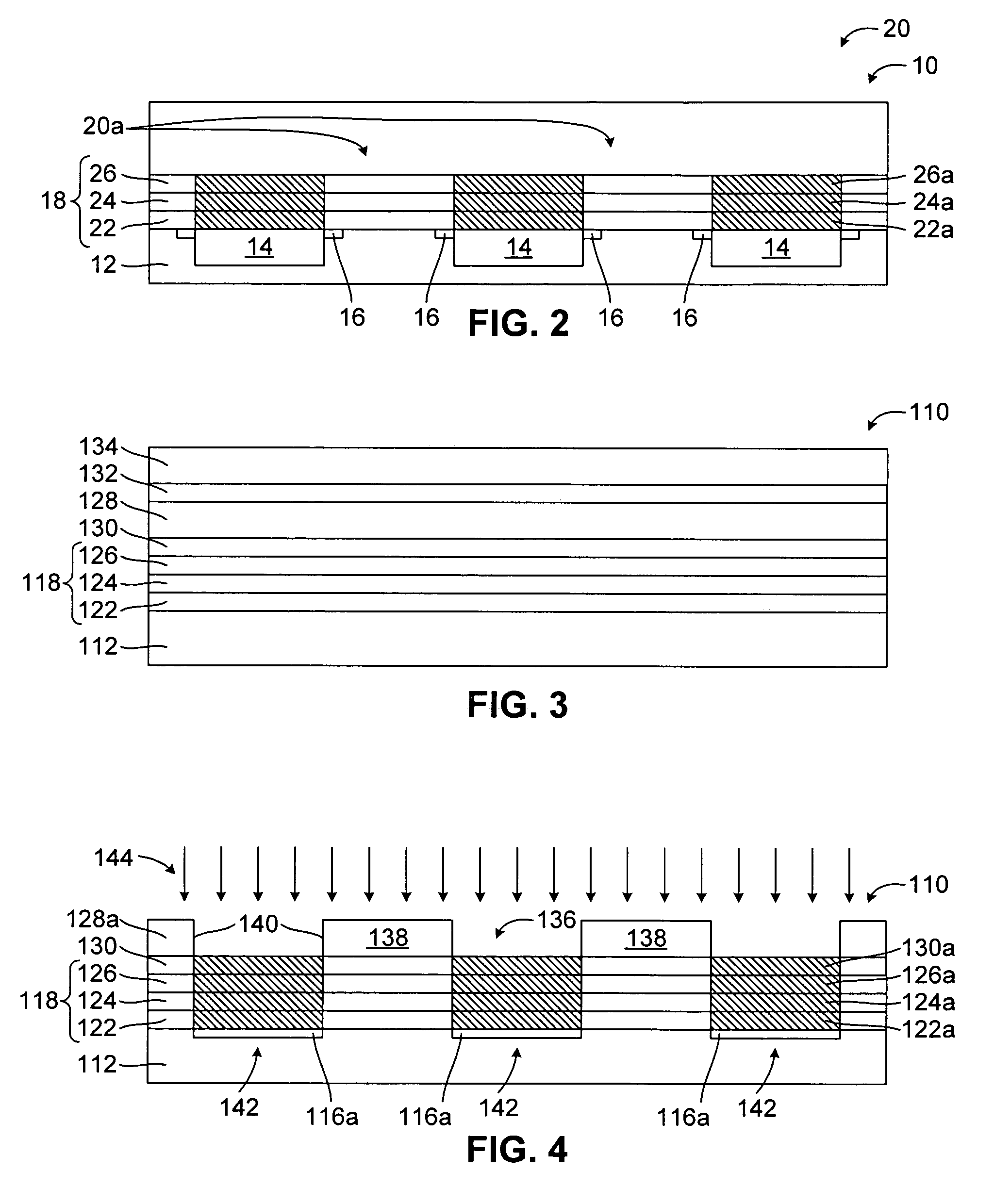

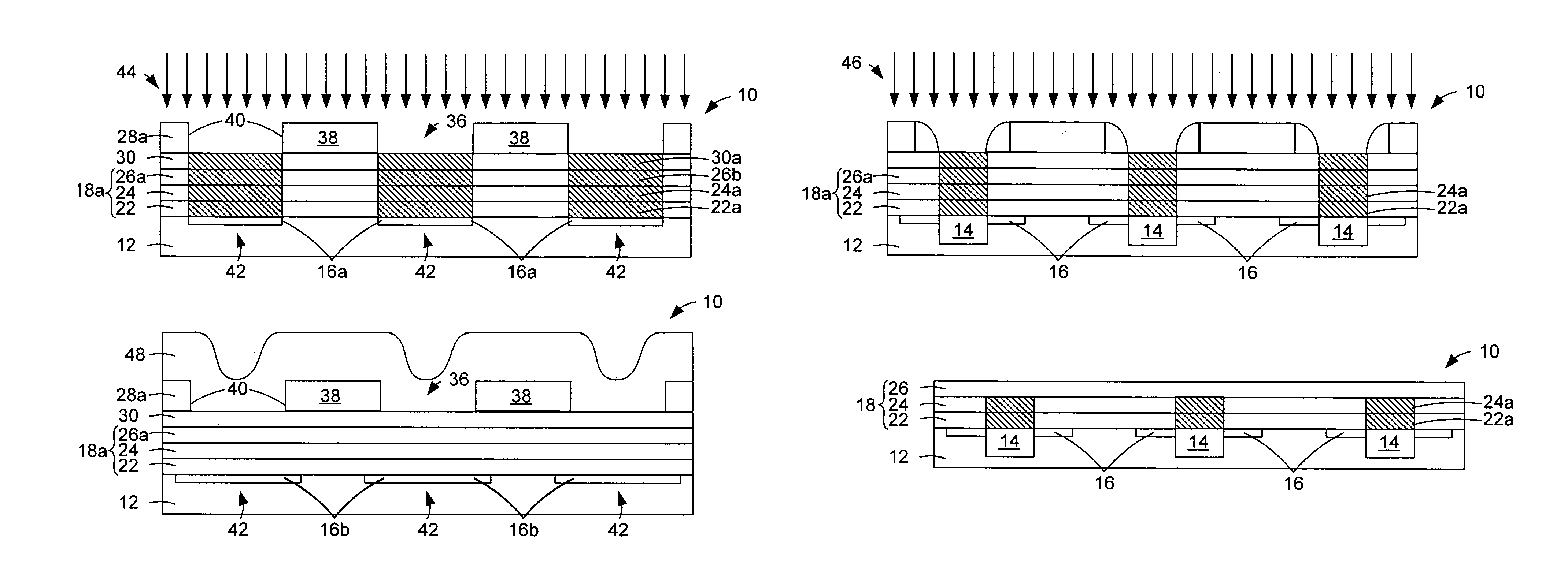

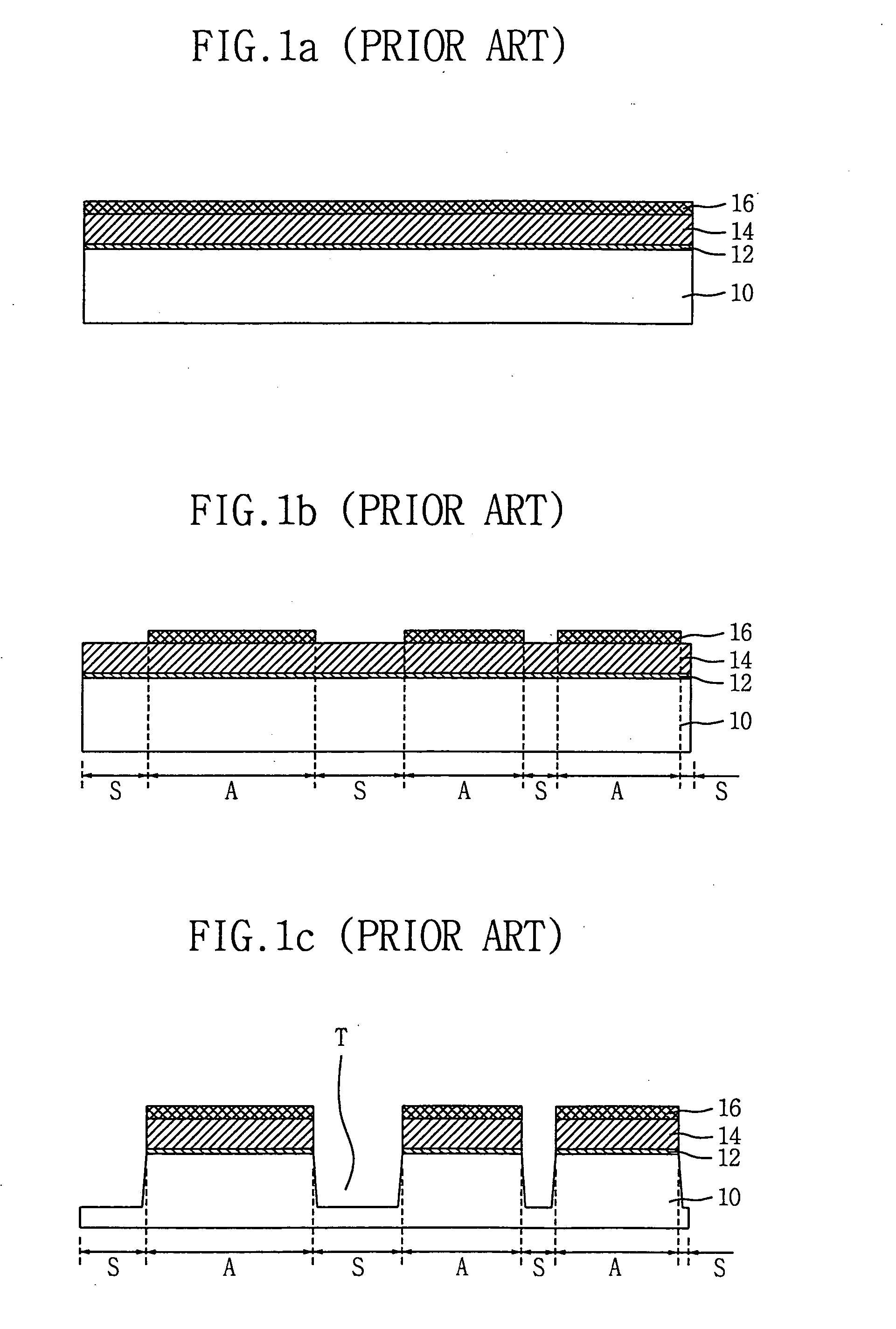

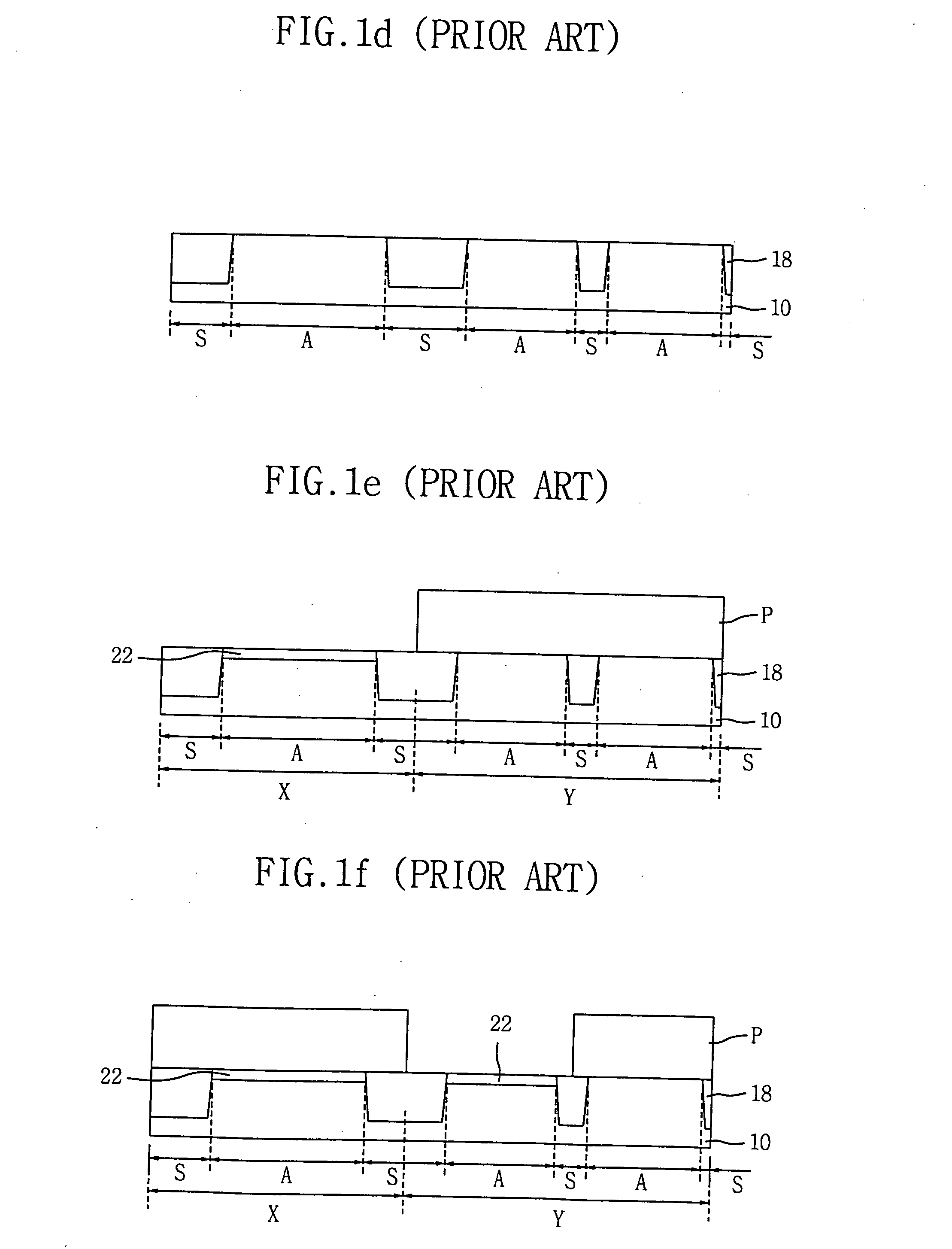

Disposable hard mask for memory bitline scaling

ActiveUS7018868B1Avoid leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorHard mask

The invention is a semiconductor device and a method of manufacturing the semiconductor device. The semiconductor device includes buried bitlines in a semiconductor substrate. Additionally, doped regions are formed adjacent the buried bitlines. The doped regions adjacent the buried bitlines inhibit a leakage current between the buried bitlines.

Owner:INFINEON TECH LLC

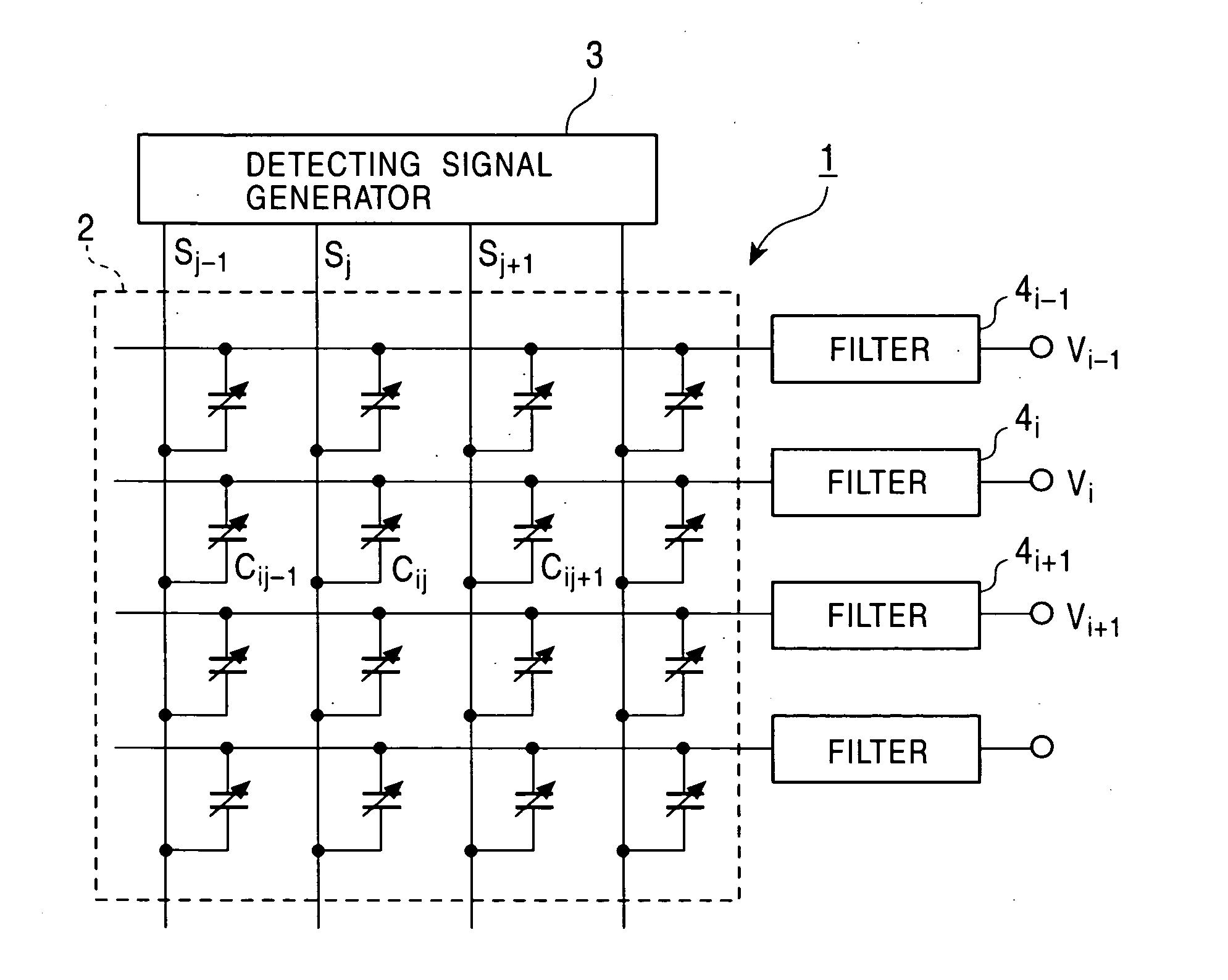

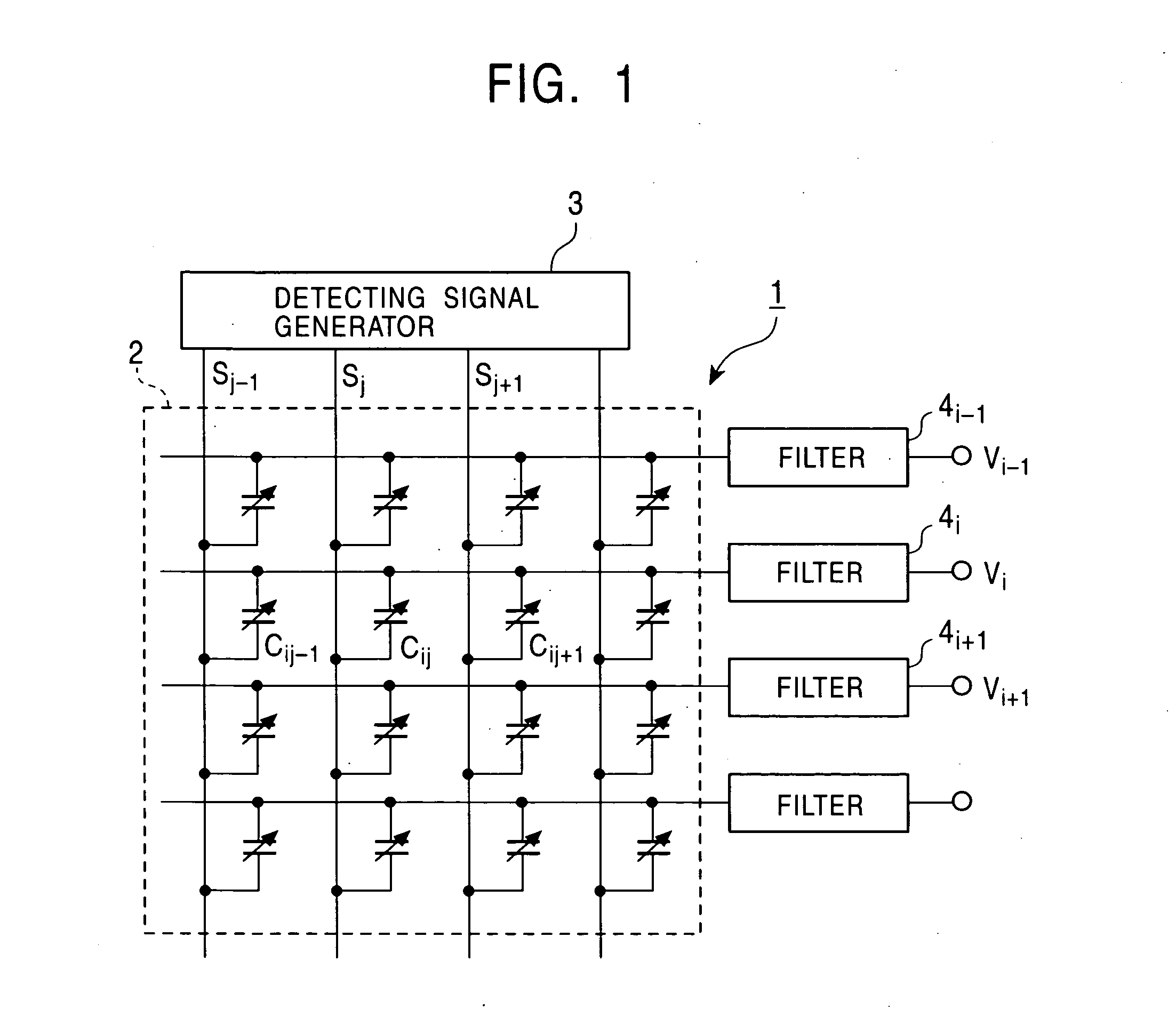

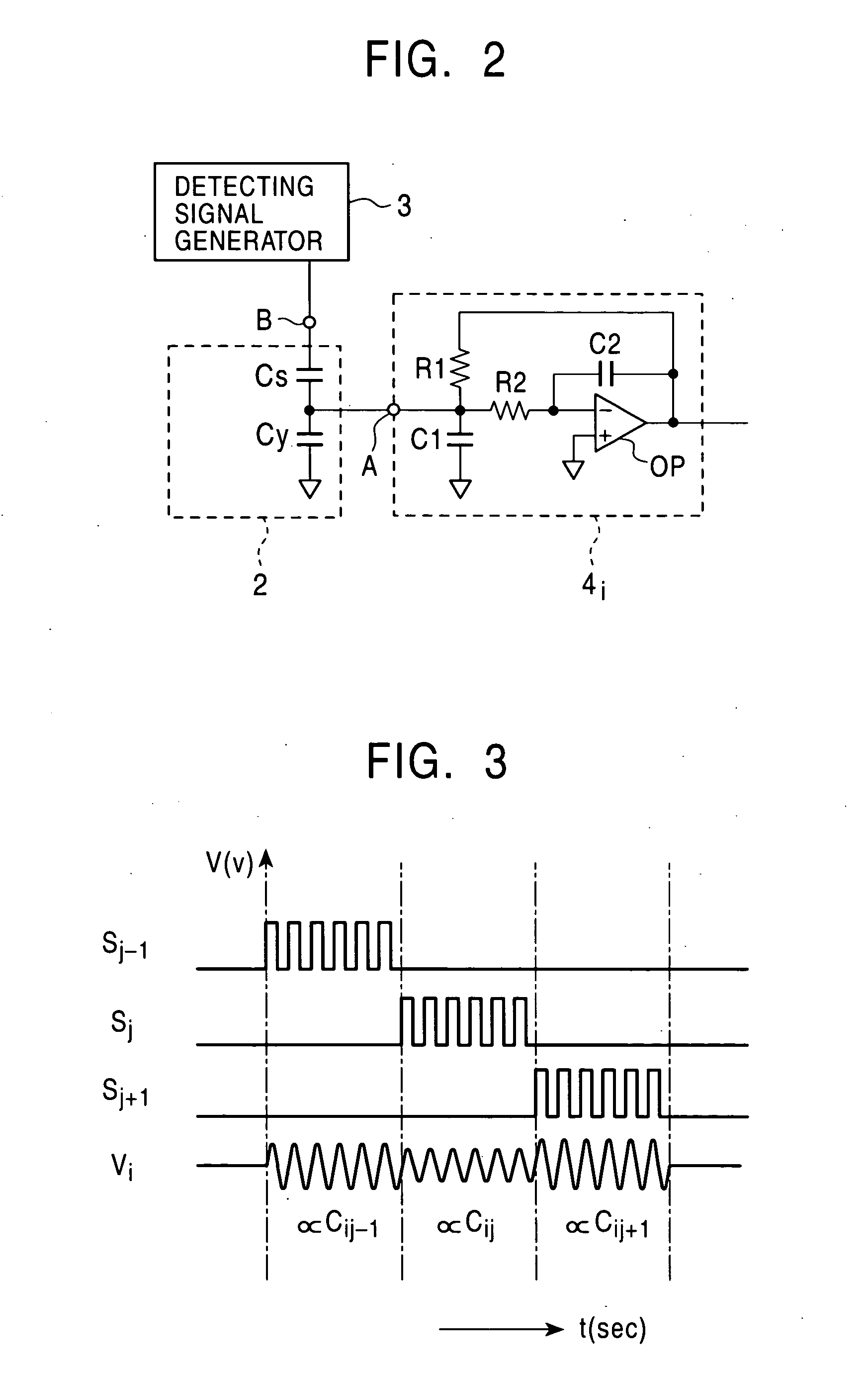

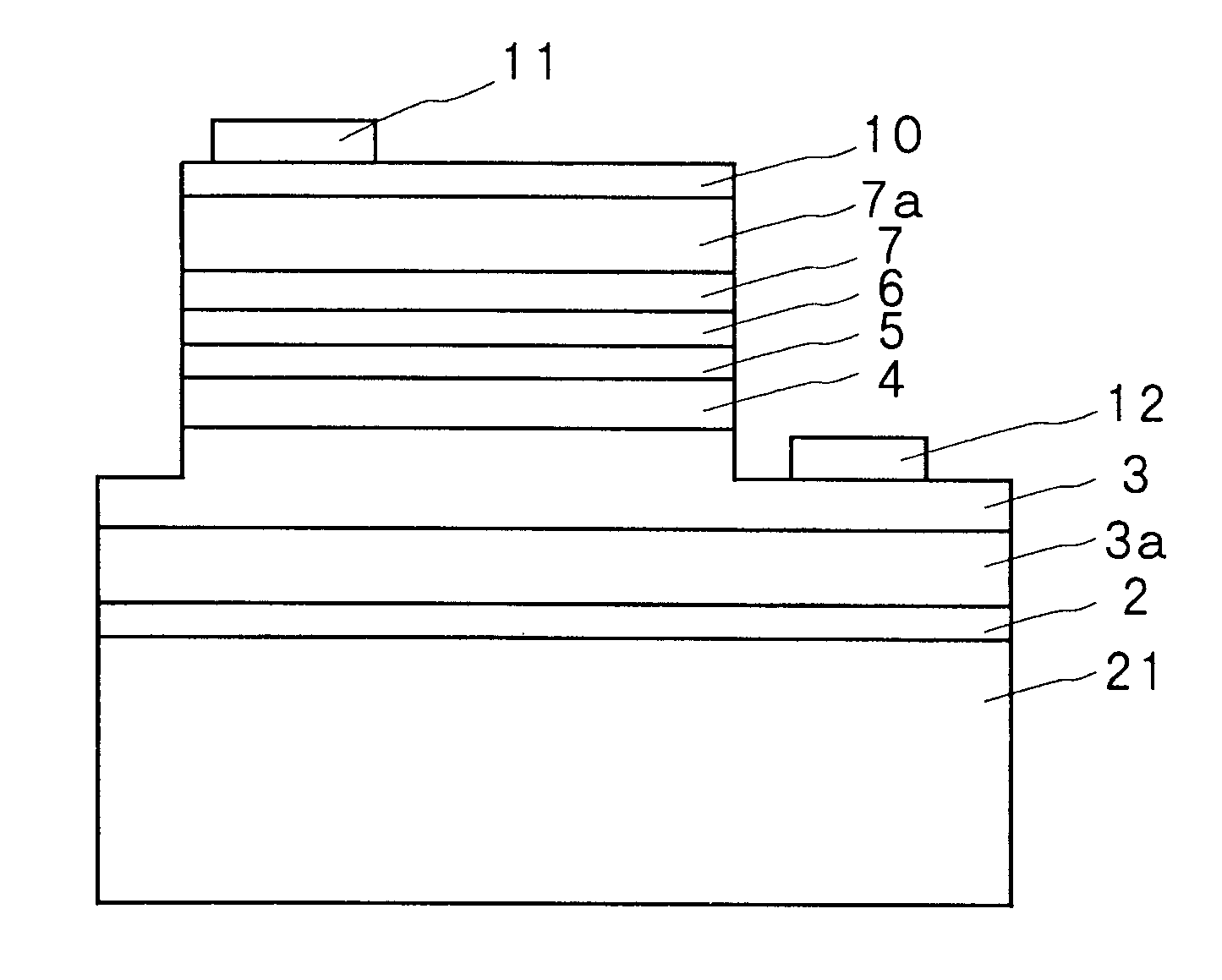

Capacitive sensor

InactiveUS20050005703A1Low frequency noiseReduce low frequency noisePerson identificationForce measurementCapacitive sensingSignal generator

A pressure-sensitive capacitive sensor includes a sensing unit in which a plurality of column wires and a plurality of row wires are formed in a matrix, a detecting signal generator, and filters. Capacitances at intersections between the column wires and the row wires change in accordance with externally applied pressure. The detecting signal generator sequentially outputs pulse signals of a predetermined frequency to the column wires of the sensing unit. The filters are connected to the respective row wires of the sensing unit and extract amplitudes of signals of the predetermined frequency. The amplitude is proportional to the capacitance at the intersection.

Owner:ALPS ALPINE CO LTD

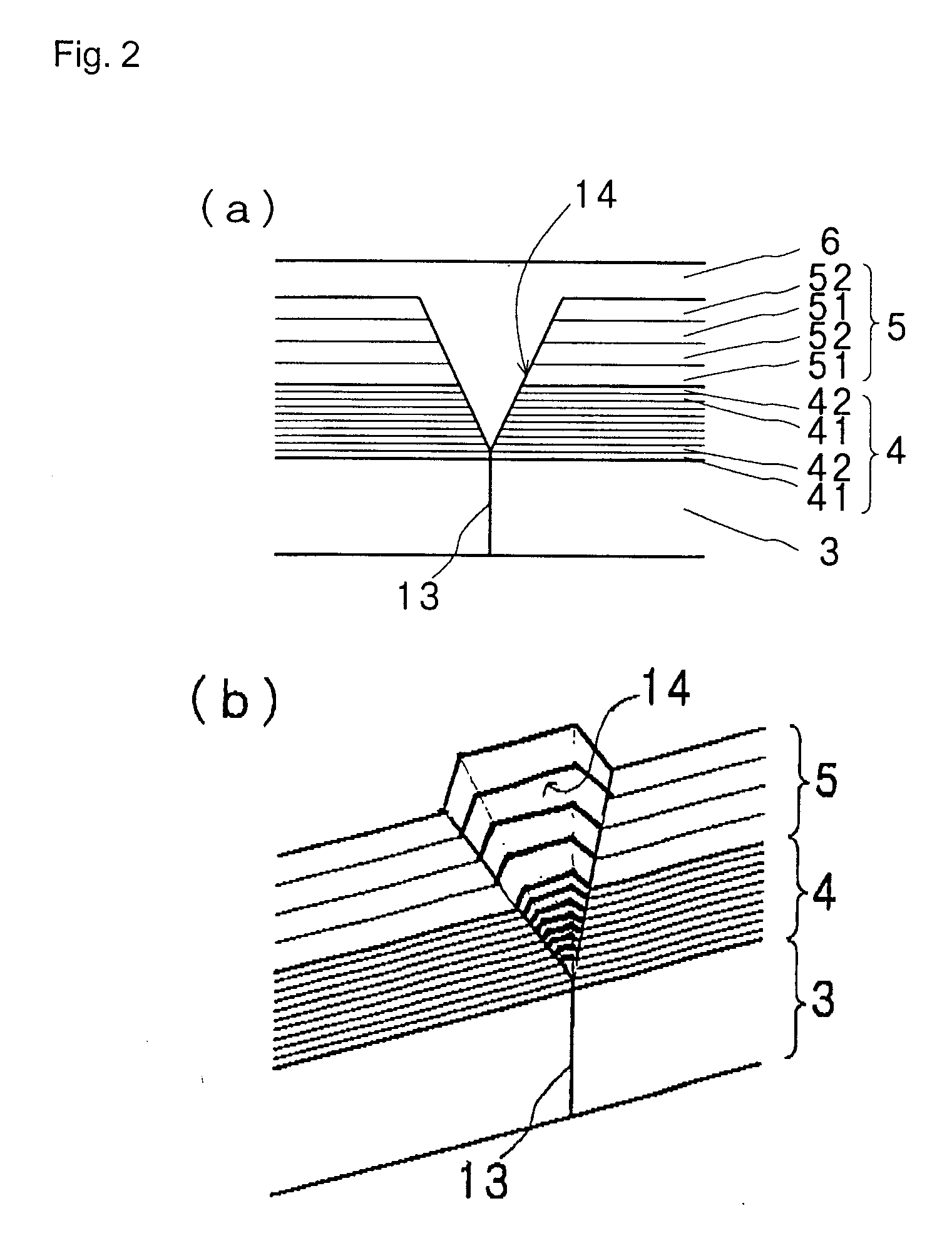

Nitride semiconductor light emitting element

InactiveUS20070122994A1Suppresses minimizesImprove film qualityLaser detailsSolid-state devicesThreading dislocationsQuantum efficiency

A nitride semiconductor light-emitting element suppresses leakage currents and non-radiative recombination centers by providing, as an underlying layer of the active layer, a pit formation layer that reliably generates pits, while maintaining a good film quality, so that the internal quantum efficiency is improved, and the light-emitting characteristics are also improved. A nitride semiconductor lamination portion including at least an active layer for forming a light-emitting portion is present on a substrate, and a pit formation layer is formed as a superlattice layer of nitride semiconductor on the side of the substrate of the active layer. The pit formation layer generates pits in the end portions of threading dislocations that are generated in the nitride semiconductor layer on the side of the substrate.

Owner:ROHM CO LTD

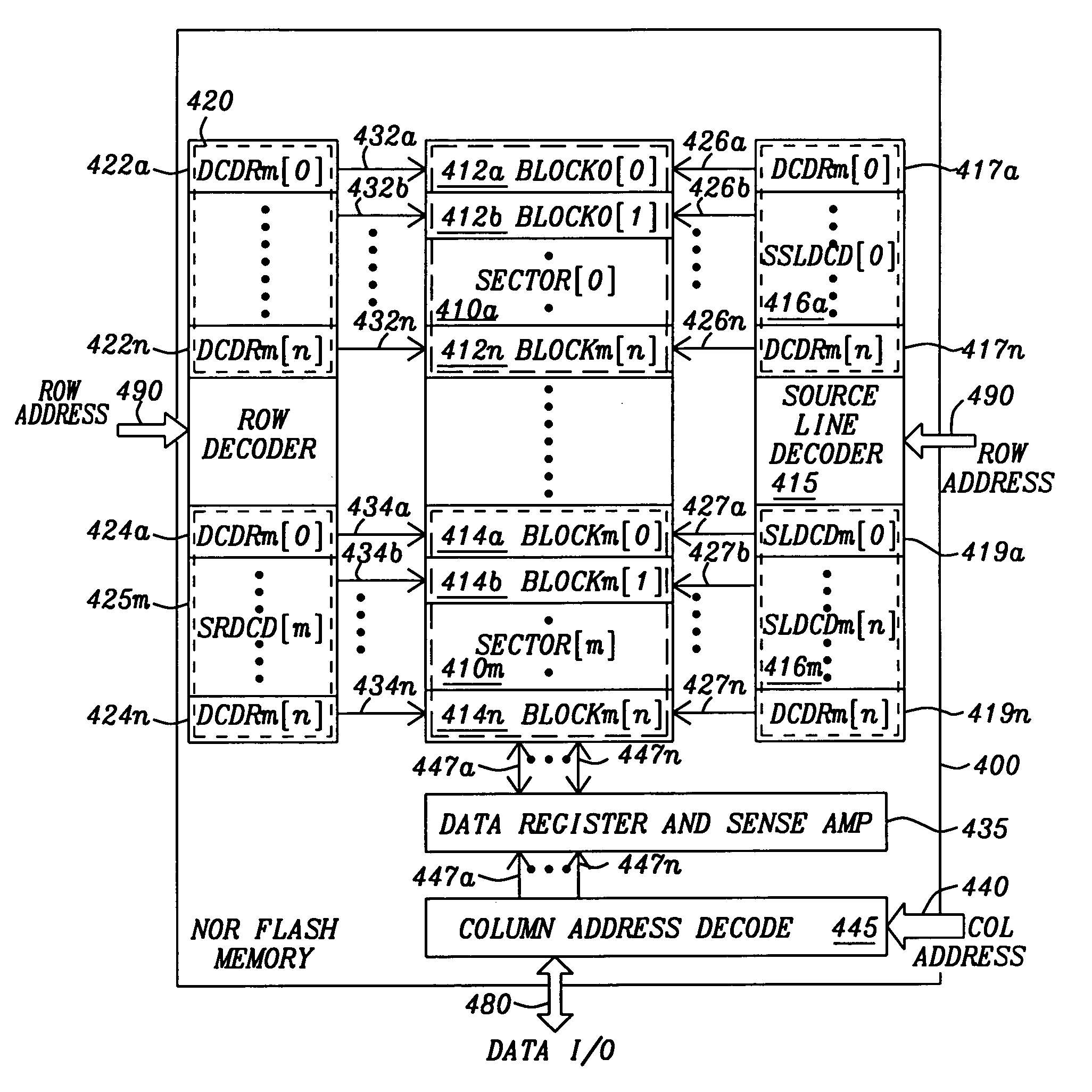

Apparatus and method for inhibiting excess leakage current in unselected nonvolatile memory cells in an array

InactiveUS20090316487A1Reduce leakage currentAvoid leakage currentRead-only memoriesDigital storageSub thresholdSubthreshold leakage current

An apparatus and method for operating an array of NOR connected flash nonvolatile memory cells erases the array in increments of a page, block, sector, or the entire array while minimizing sub-threshold leakage current through unselected nonvolatile memory cells. The apparatus has a row decoder circuit and a source decoder circuit for selecting the nonvolatile memory cells for providing biasing conditions for reading, programming, verifying, and erasing the selected nonvolatile memory cells while minimizing sub-threshold leakage current through unselected nonvolatile memory cells.

Owner:APLUS FLASH TECH

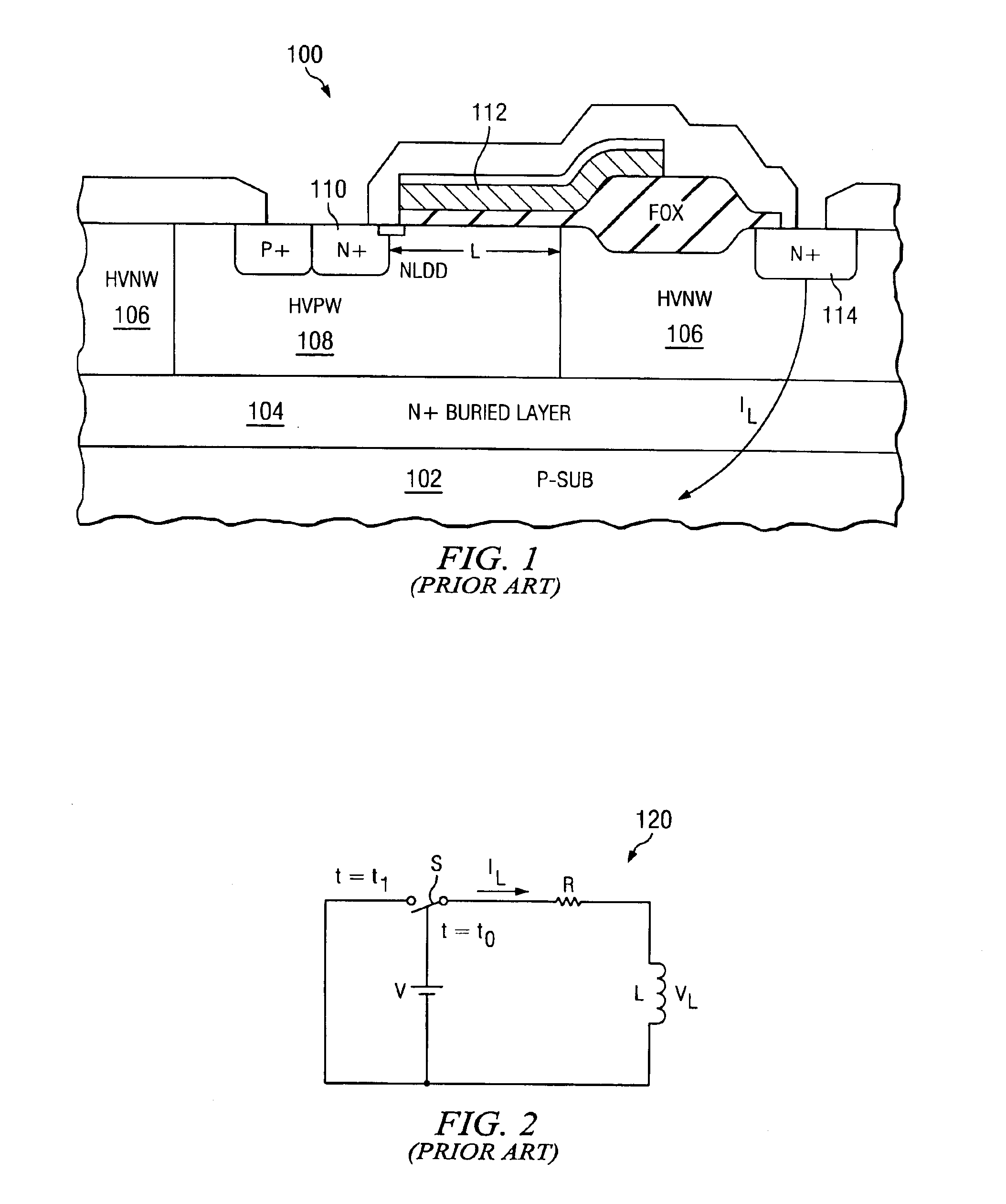

LDMOS device with isolation guard rings

InactiveUS6924531B2Avoid leakage currentLatch-up, early breakdown and reliability issues are preventedSemiconductor/solid-state device detailsSolid-state devicesLDMOSEngineering

A method of forming a LDMOS semiconductor device and structure for same. A preferred embodiment comprises forming a first guard ring around and proximate the drain of a LDMOS device, and forming a second guard ring around the first guard ring. The first guard ring comprises a P+ base guard ring, and the second guard ring comprises an N+ collector guard ring formed in a deep N-well, in one embodiment. The first guard ring and second guard ring prevent leakage current from flowing from the drain of the LDMOS device to the substrate.

Owner:TAIWAN SEMICON MFG CO LTD

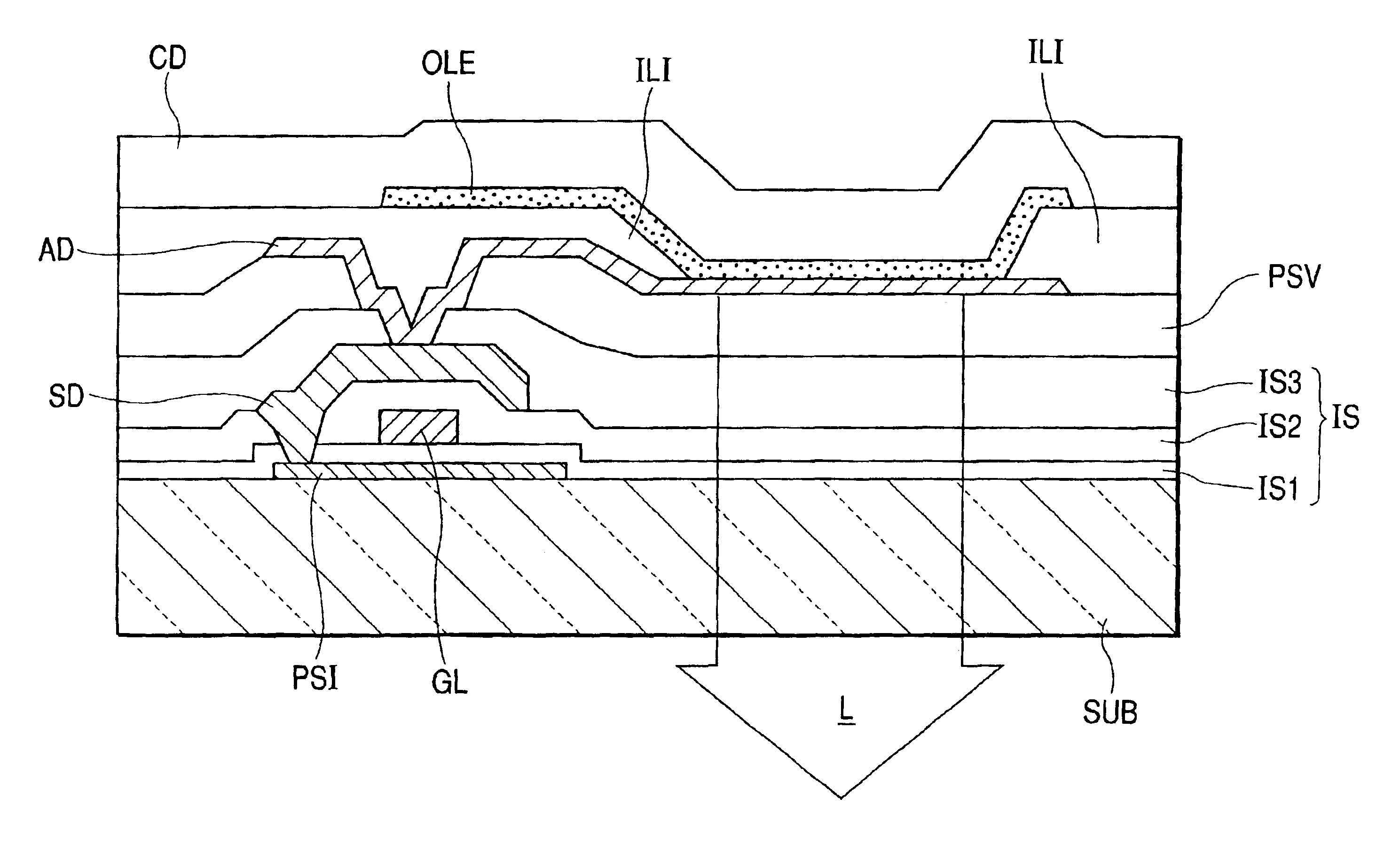

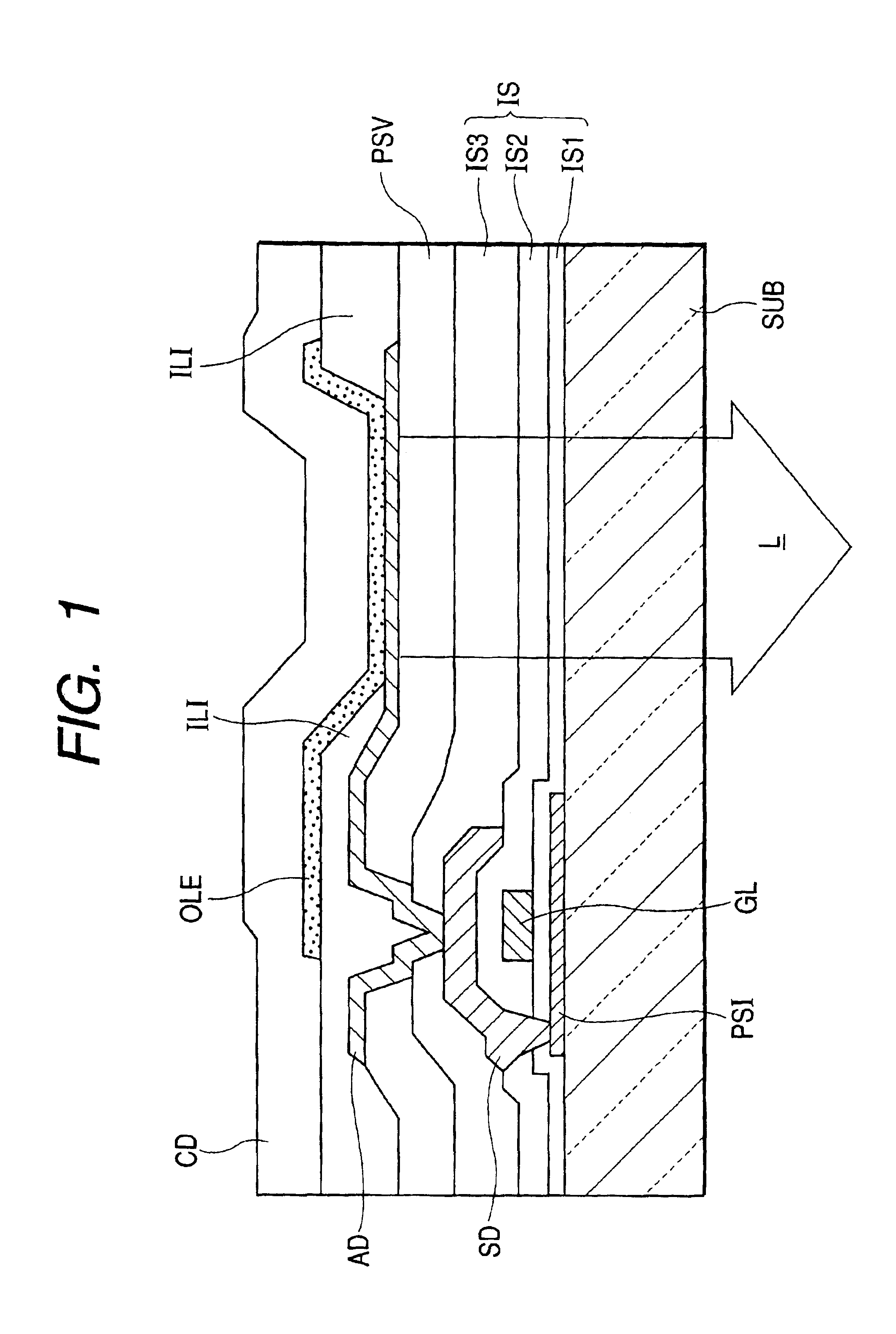

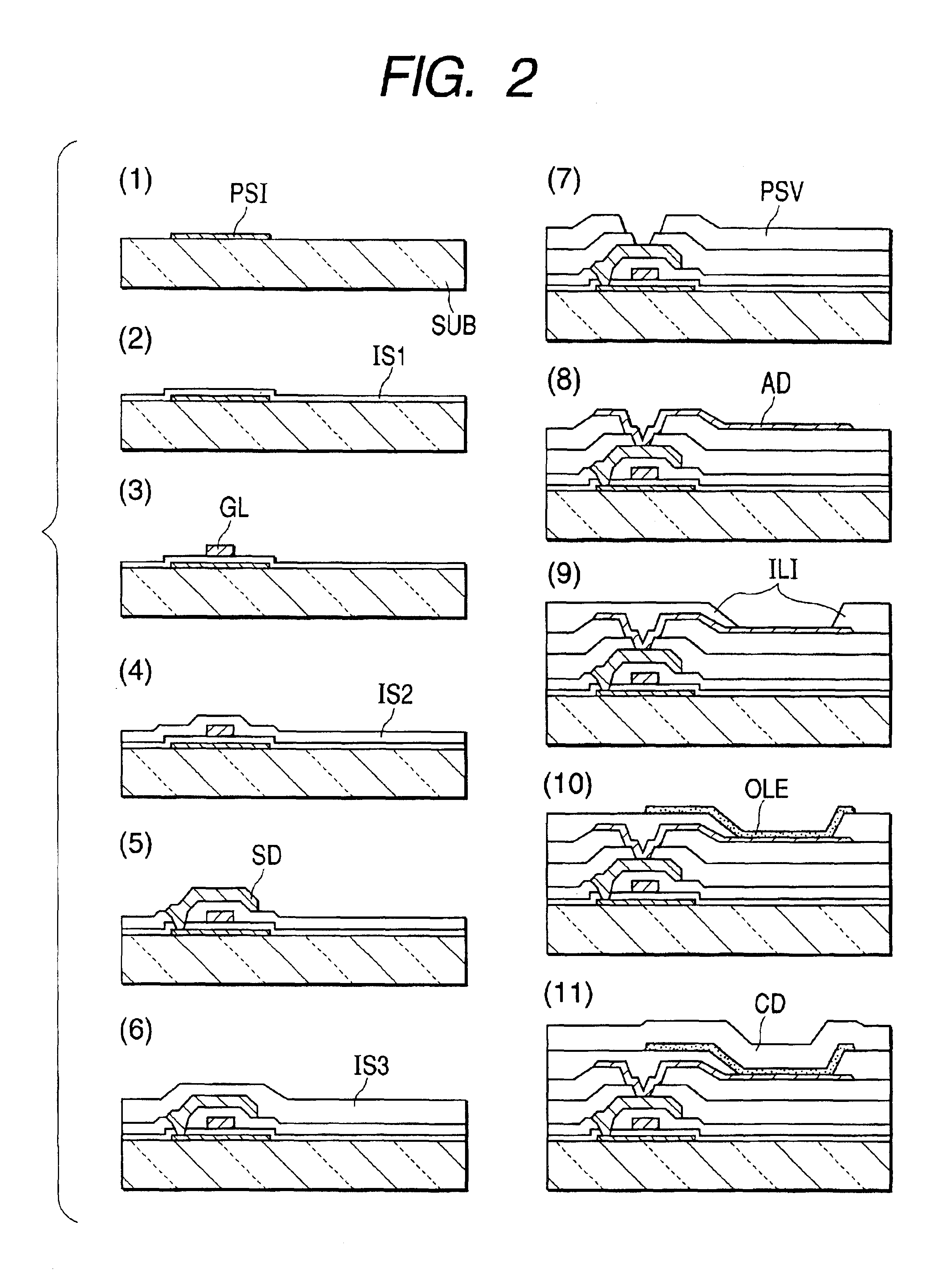

Display module

ActiveUS6888304B2High qualityImprove flatnessDischarge tube luminescnet screensStatic indicating devicesOptoelectronicsInsulation layer

This display module prevents the leakage current generated between a first electrode layer and a second electrode layer that constitute a pixel via an organic light emitting layer and obtains uniform luminance. An interlayer insulation layer ILI is provided between an edge of a first electrode layer AD and an organic light emitting layer OLE that constitute the pixel and the distance between the edge and a second electrode layer CD is secured sufficiently. Further, the interlayer insulation layer ILI is coated with a resin material having fluidity and flatness is improved as a whole. An aperture that accommodates the organic light emitting layer OLE is formed in this interlayer insulation layer ILI and the coated organic light emitting layer OLE is formed in uniform thickness and through a necessary and sufficient spread.

Owner:SAMSUNG DISPLAY CO LTD

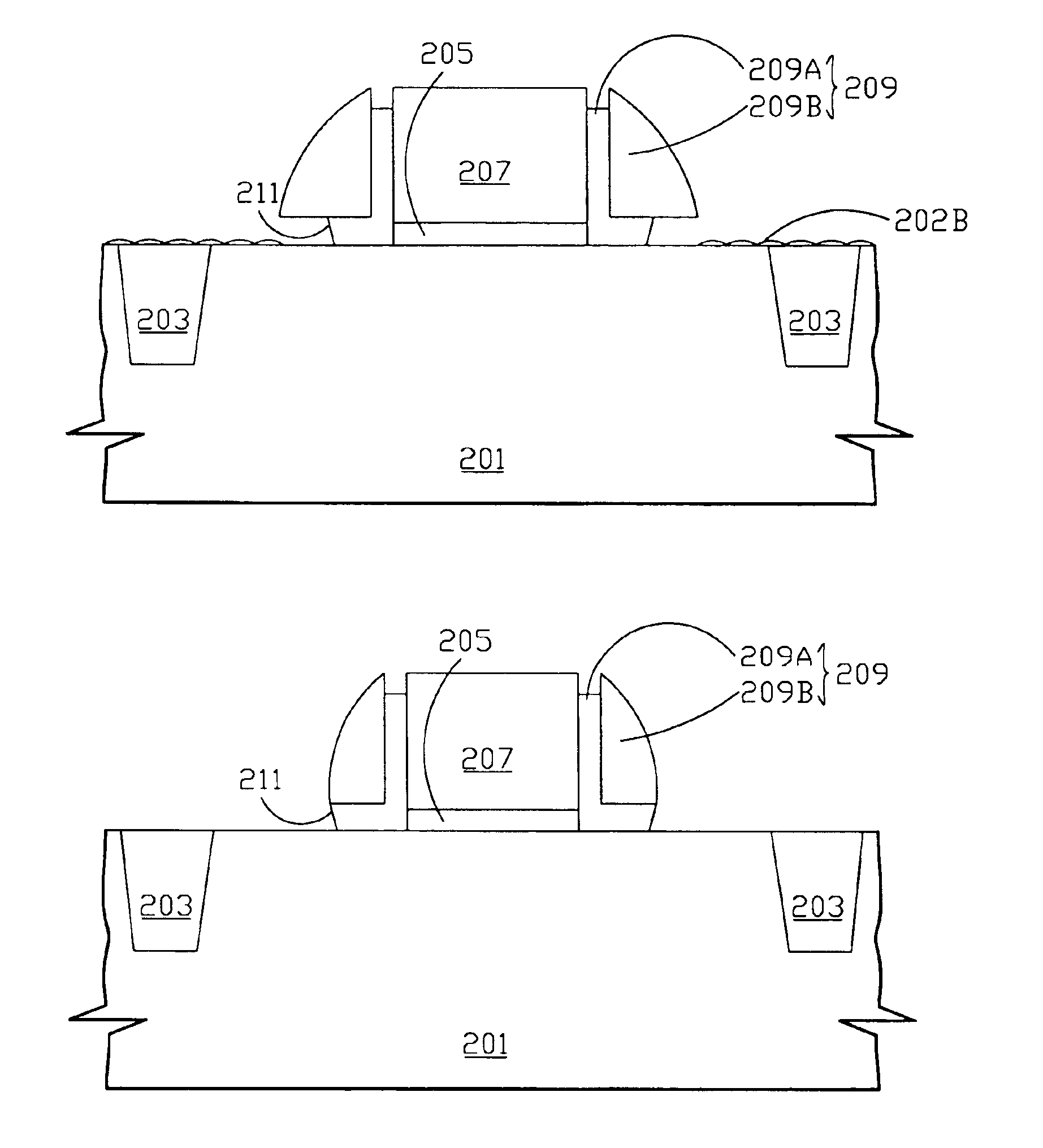

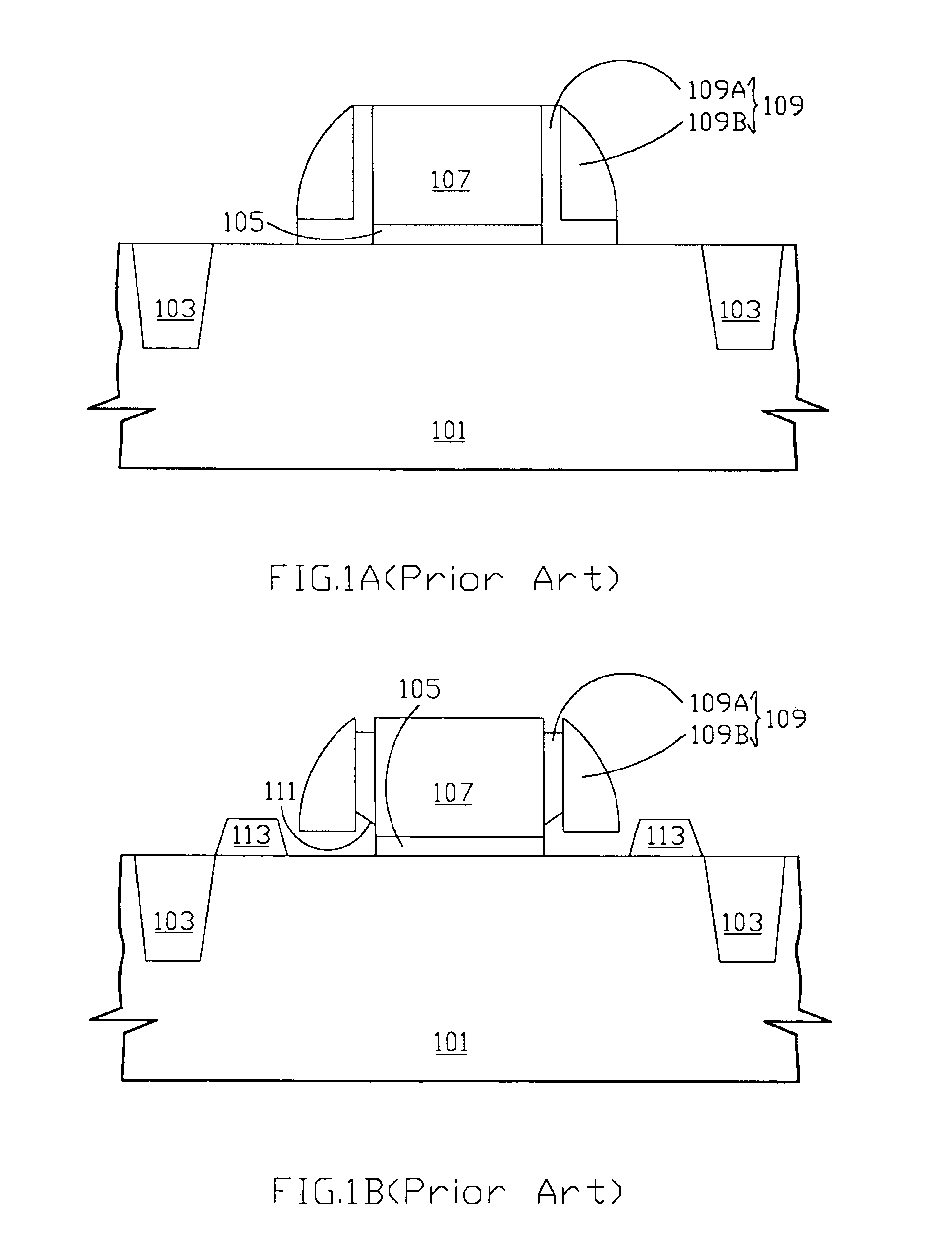

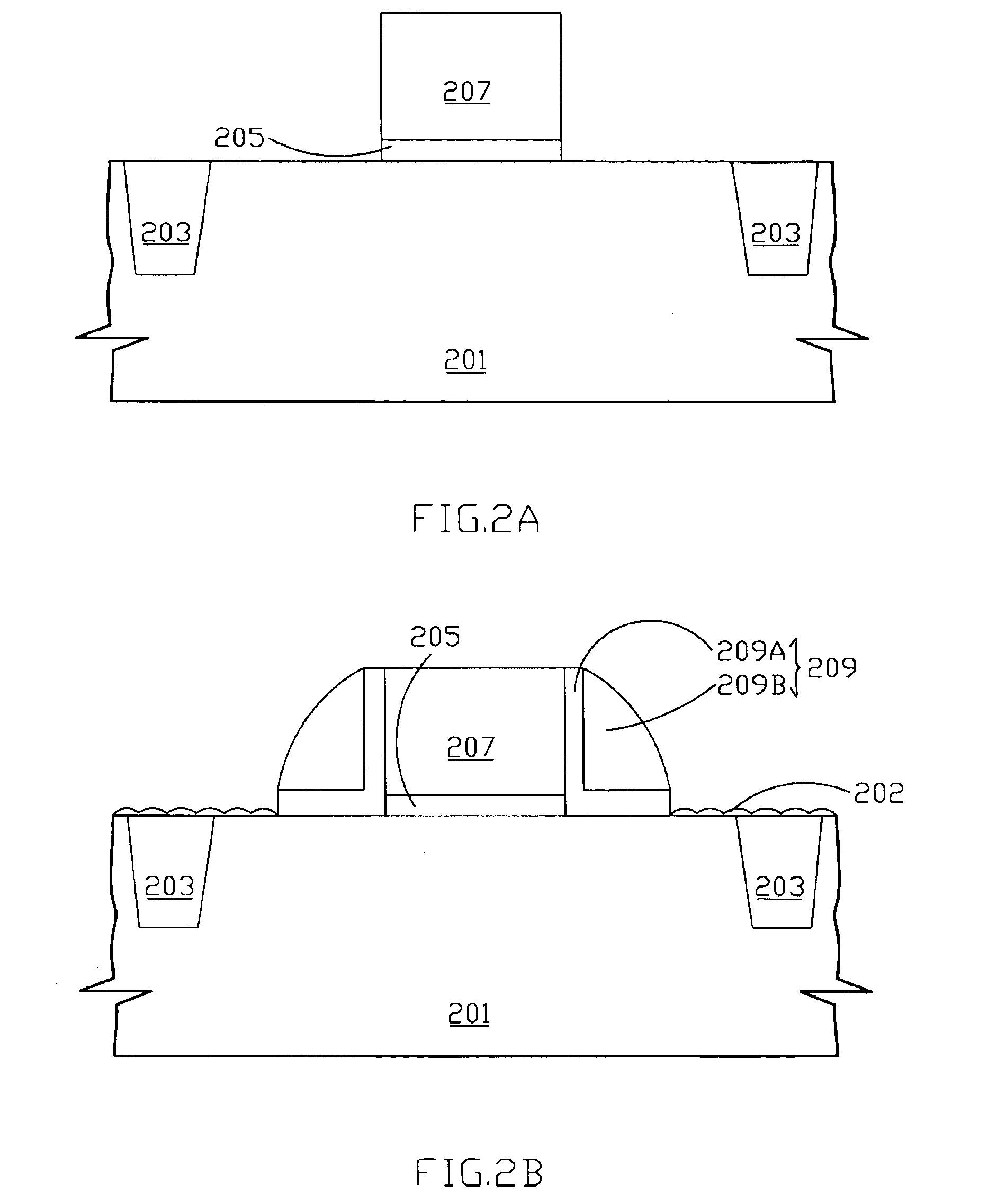

Method for preventing to form a spacer undercut in SEG pre-clean process

InactiveUS6991991B2Avoid leakage currentFast etchSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

A method for preventing to form a spacer undercut in SEG preclean process is provided. This present invention utilizes HFEG solution to etch the first spacer and the second spacer simultaneously, which can prevent from producing a spacer undercut, meanwhile; a native oxide layer upon a surface of a semiconductor substrate is removed. Hence, the clean surface on the semiconductor substrate is obtained. This method includes the steps as follows: Firstly, the native oxide layer upon the surface of the semiconductor substrate is removed by DHF (HF in deionized water) solution. Then, etching the first spacer and the second spacer at the same time by HFEG (HF diluted by ethylene glycol) solution. Also, the native oxide upon the semiconductor substrate is removed. Therefore, it obtains the clean semiconductor surface without a serious spacer undercut.

Owner:MARLIN SEMICON LTD

Bitline hard mask spacer flow for memory cell scaling

ActiveUS6927145B1Avoid leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingLithographic artistImage resolution

The invention is a semiconductor device and a method of forming the semiconductor device. The semiconductor device comprises a substrate; buried bitlines formed in the substrate narrower than achievable at a resolution limit of lithography; a doped region formed adjacent at least one of the buried bitlines; a charge trapping layer disposed over the substrate; and a conductive layer disposed over the charge trapping layer, wherein the doped region adjacent the least one of the buried bitlines inhibits a leakage current between the buried bitlines.

Owner:INFINEON TECH LLC

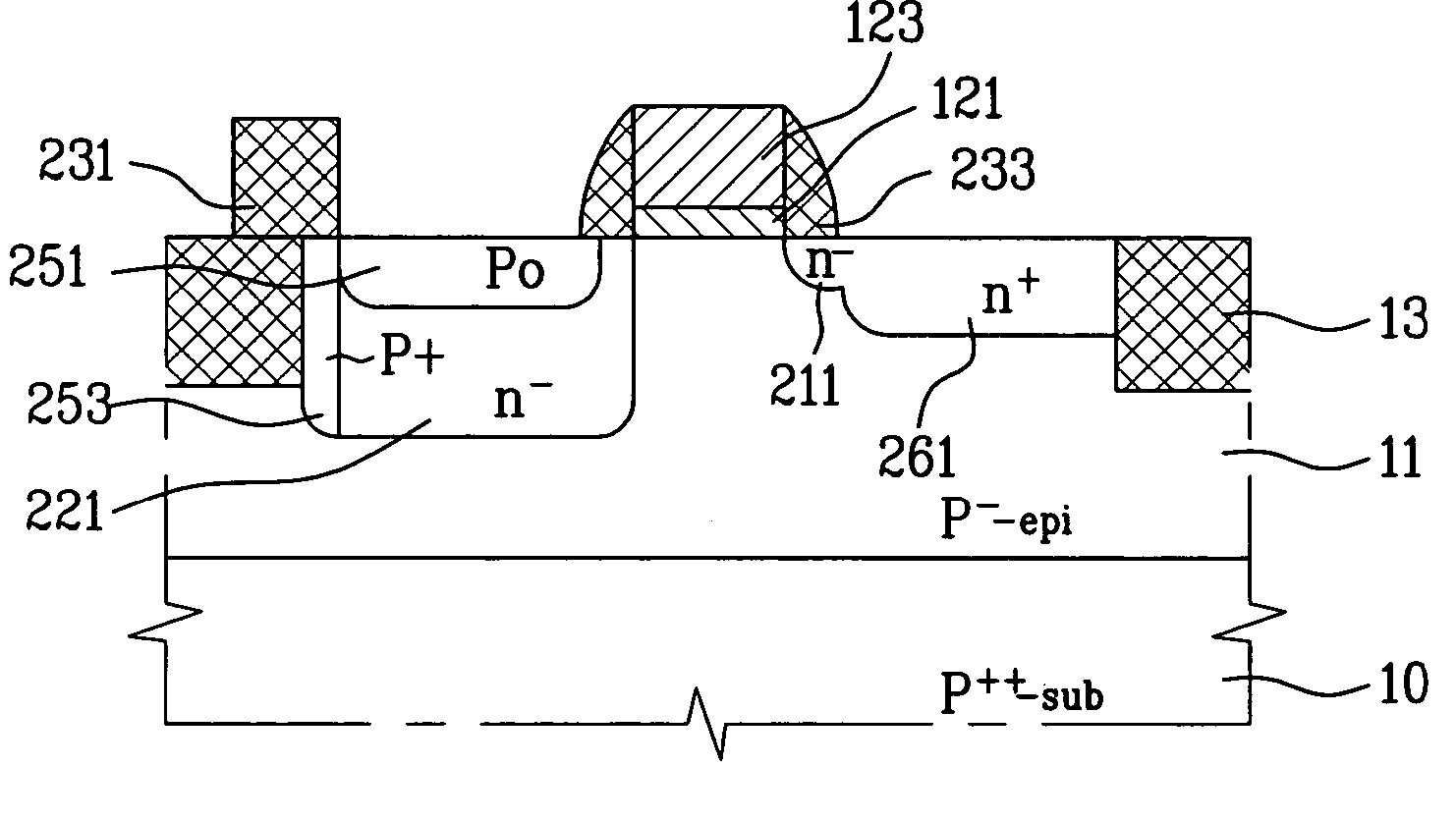

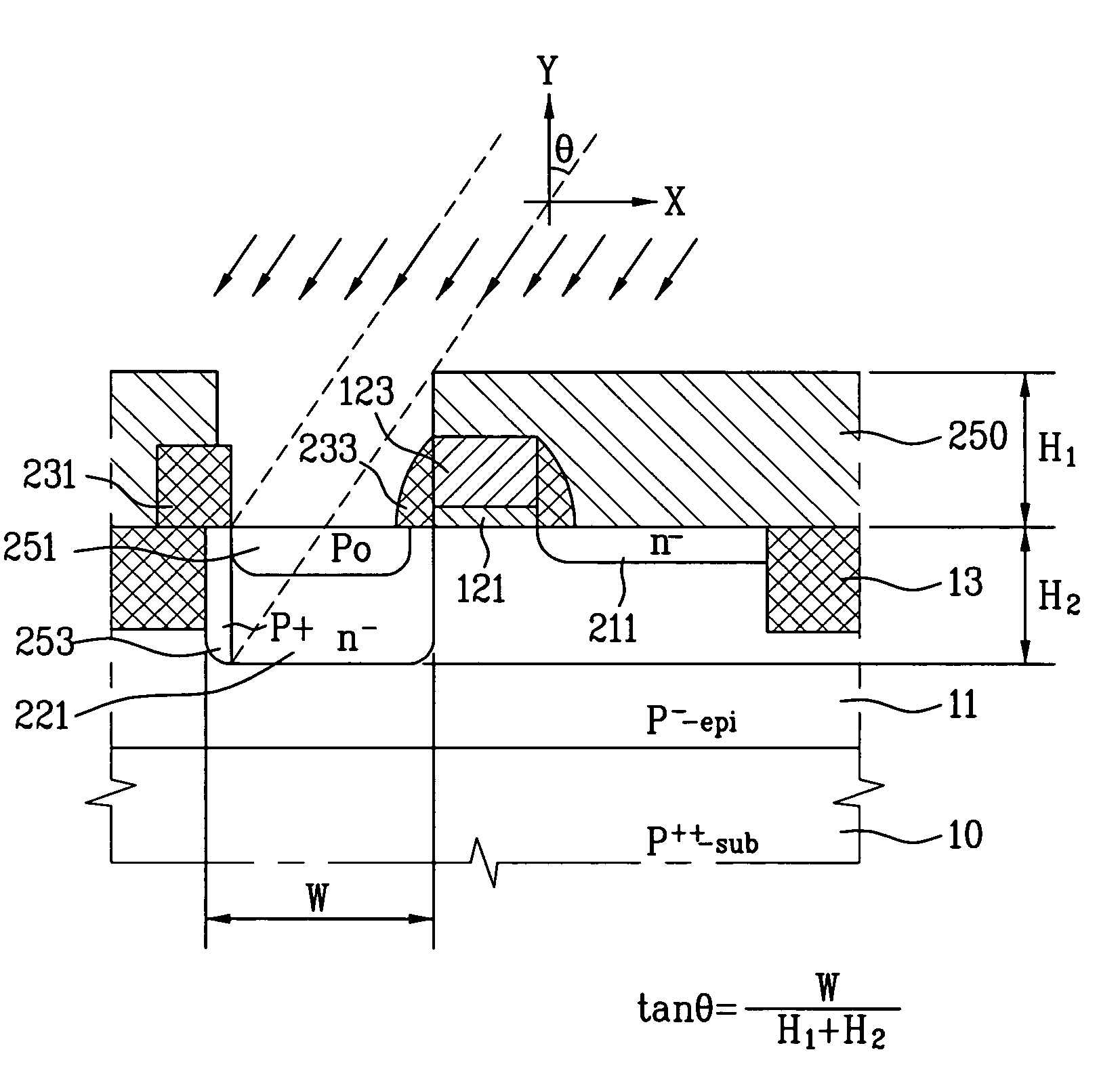

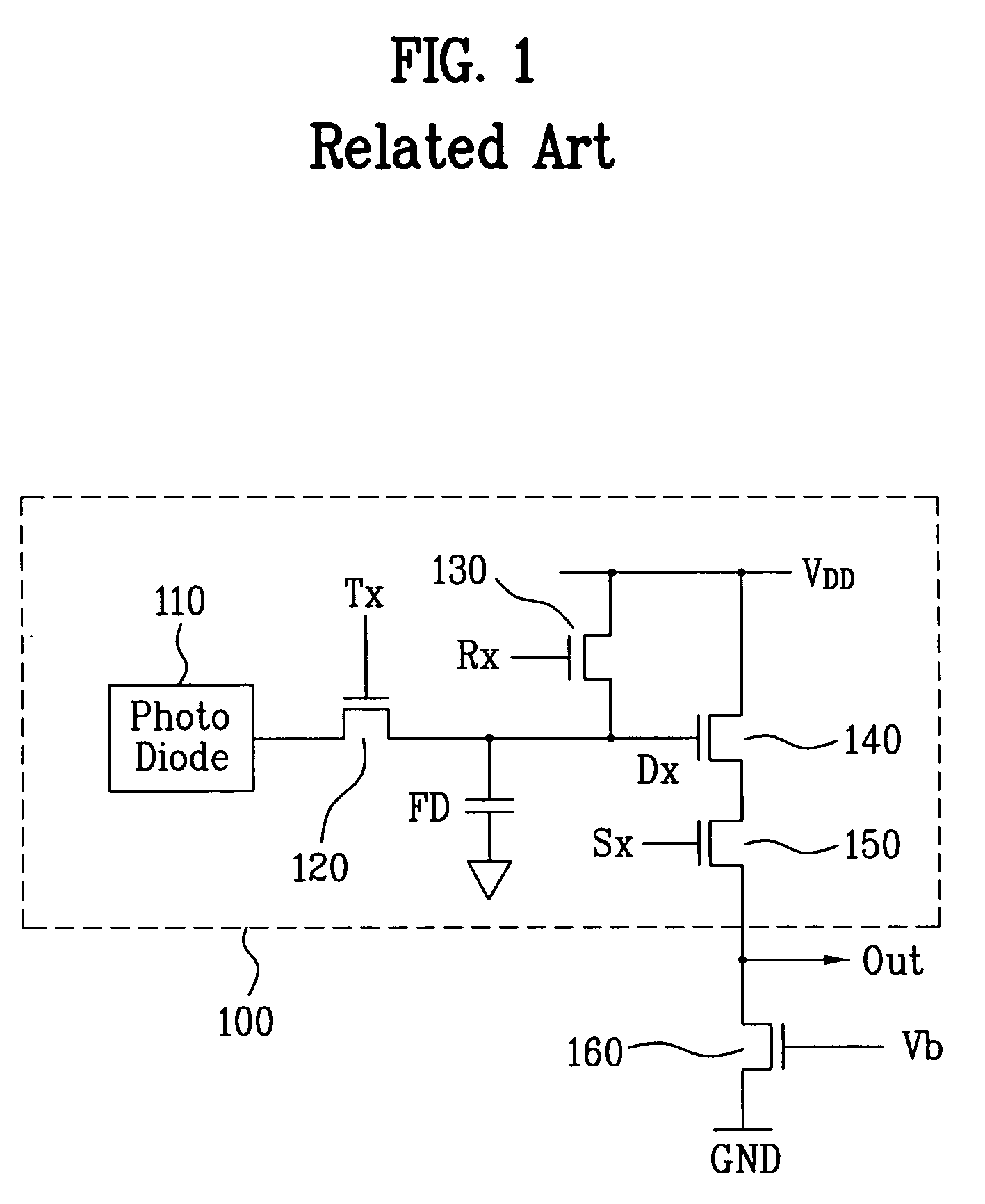

CMOS image sensor and method for fabricating the same

ActiveUS20050088556A1Reduce dark currentAvoid leakage currentTelevision system detailsTelevision system scanning detailsCMOSIsolation layer

A CMOS image sensor and a method for fabricating the same is disclosed, to decrease a darkcurrent generated in the boundary between a diffusion area of a photodiode and a device isolation layer, which includes a first conductive type semiconductor substrate having an active area and a device isolation area, the active area including a photodiode and a transistor; a device isolation layer formed in the device isolation area of the semiconductor substrate; a second conductive type diffusion area formed in the photodiode of the semiconductor substrate at a predetermined interval from the device isolation layer; a gate insulating layer and a gate electrode formed in the transistor of the semiconductor substrate; and a first conductive type first diffusion area formed in the semiconductor substrate of the boundary between the second conductive type diffusion area and the device isolation layer.

Owner:III HLDG 4

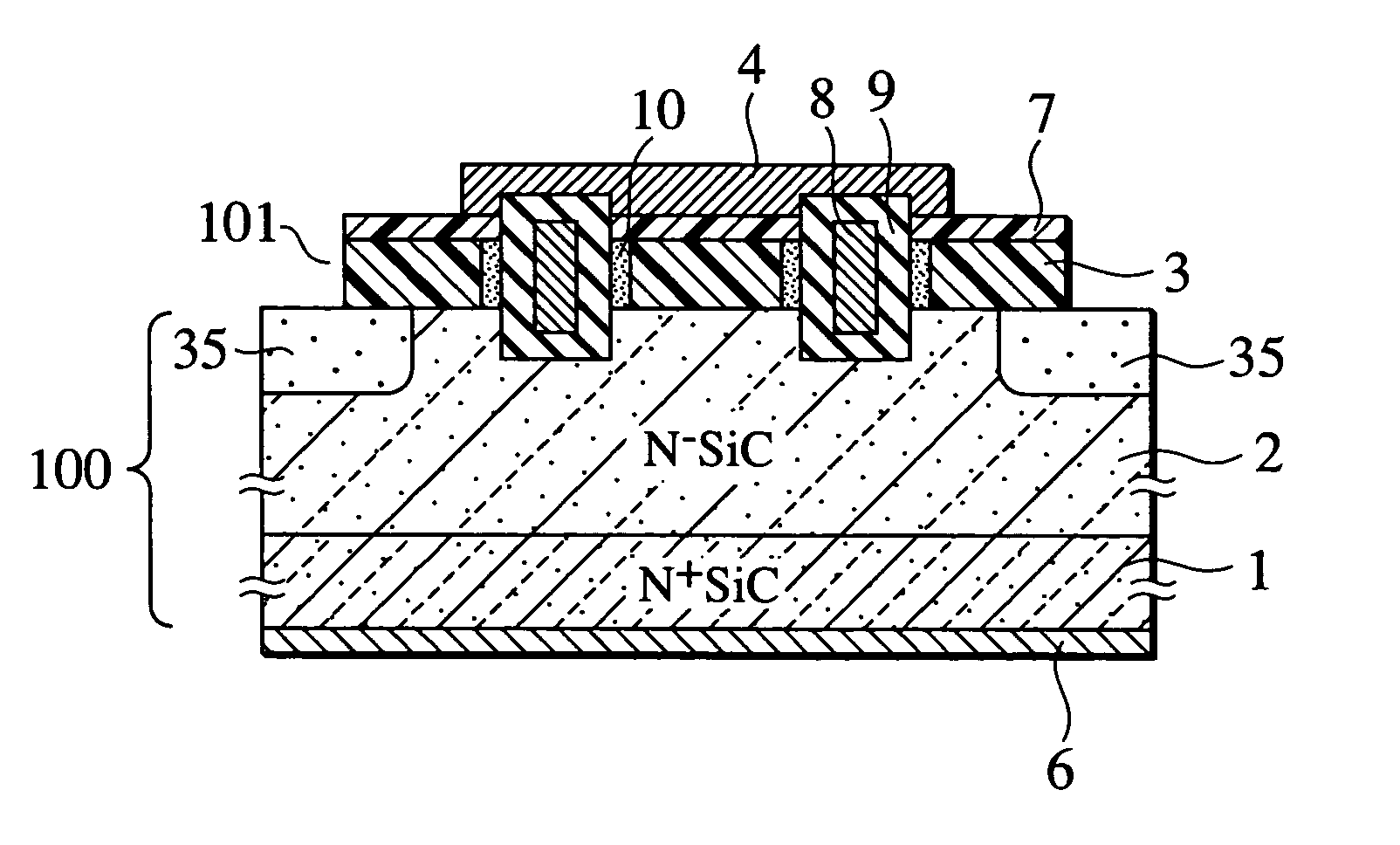

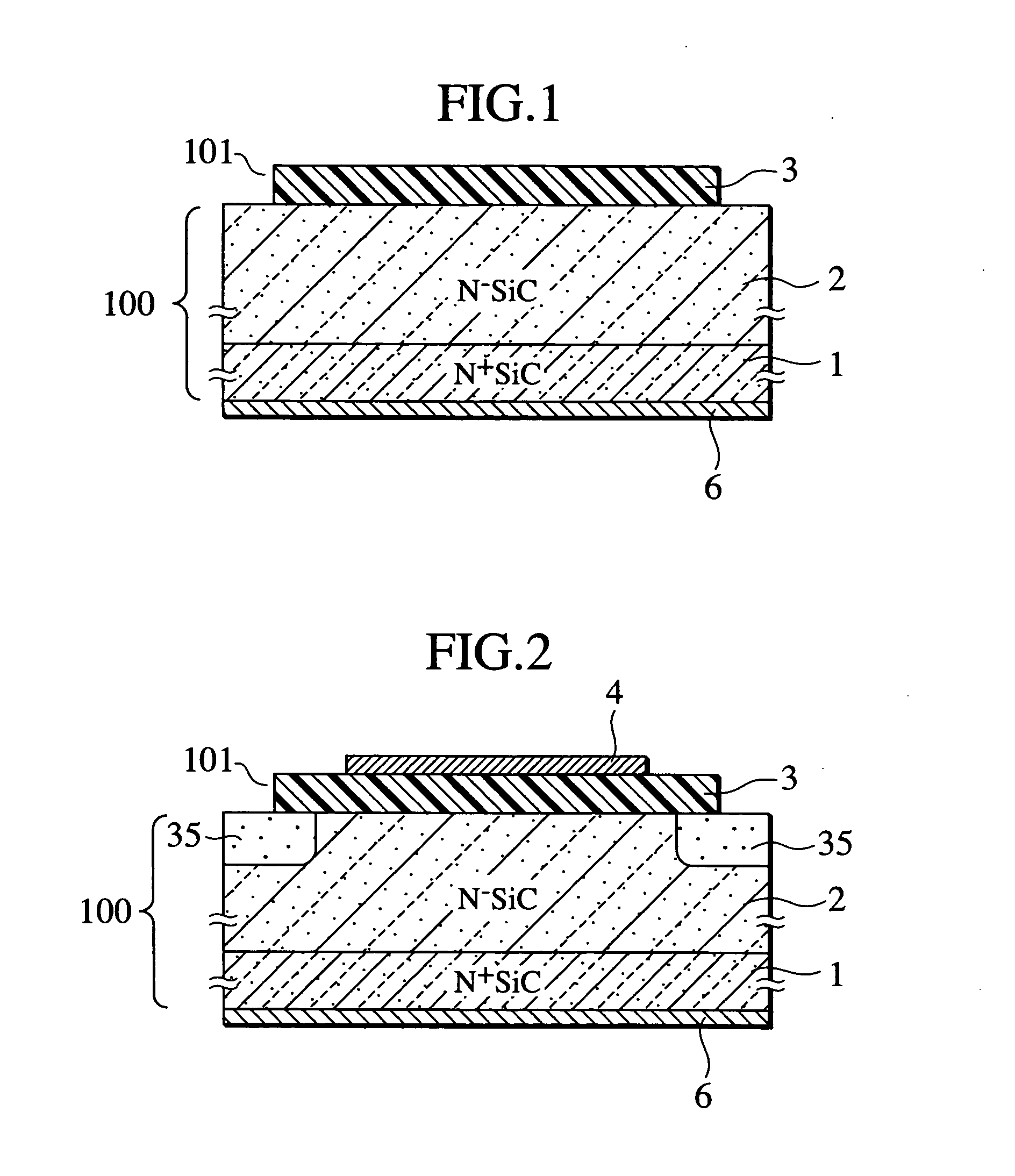

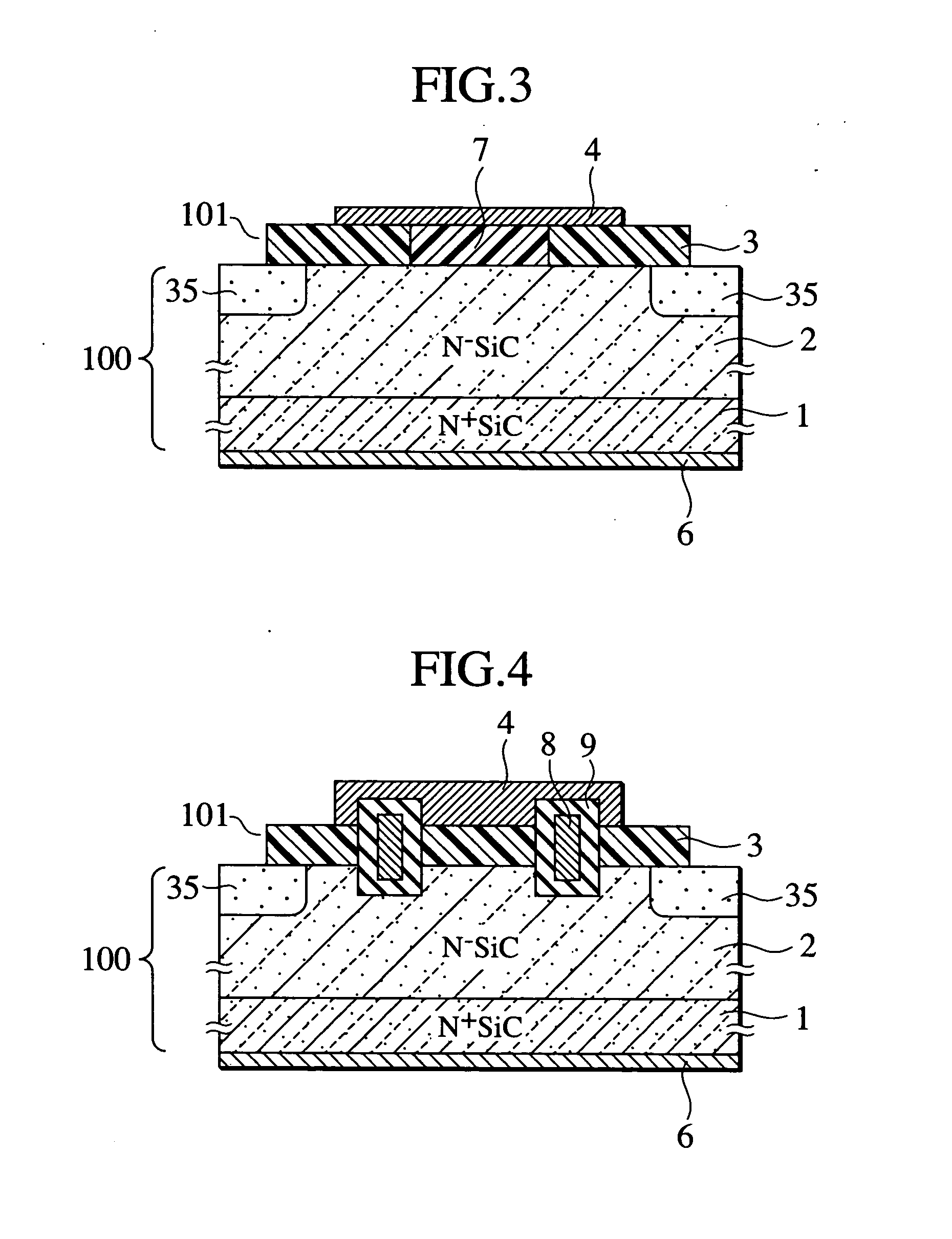

Semiconductor device and method of manufacturing the same

ActiveUS20050045892A1Reduce impurity concentrationImprove pressure resistanceSemiconductor/solid-state device manufacturingDiodeHeterojunctionDevice material

An aspect of the present invention provides a semiconductor device that includes a first semiconductor region of a first conductivity type and a second semiconductor region of a second conductivity type, having a different band gap from the first semiconductor region and forming a heterojunction with the first semiconductor region.

Owner:NISSAN MOTOR CO LTD

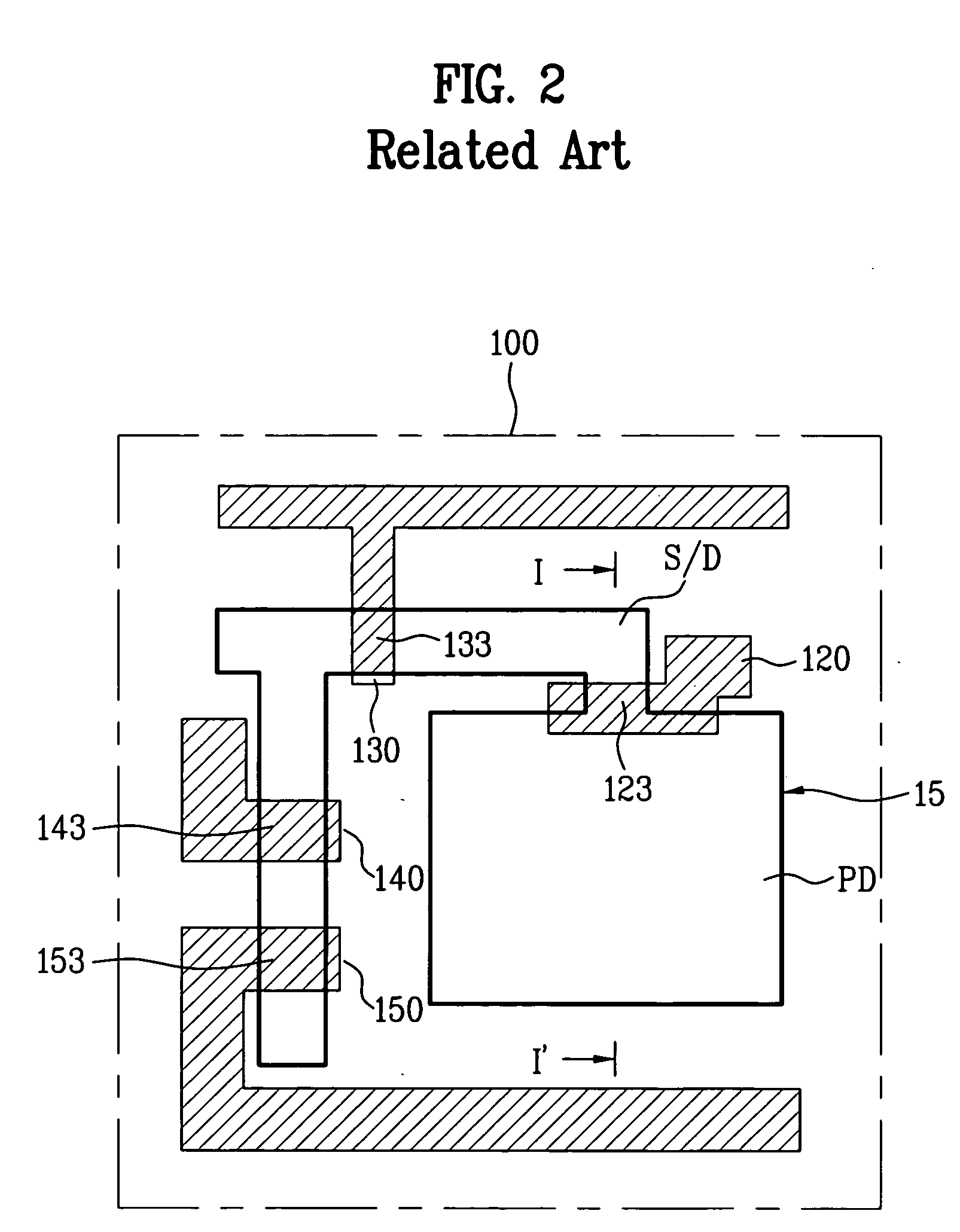

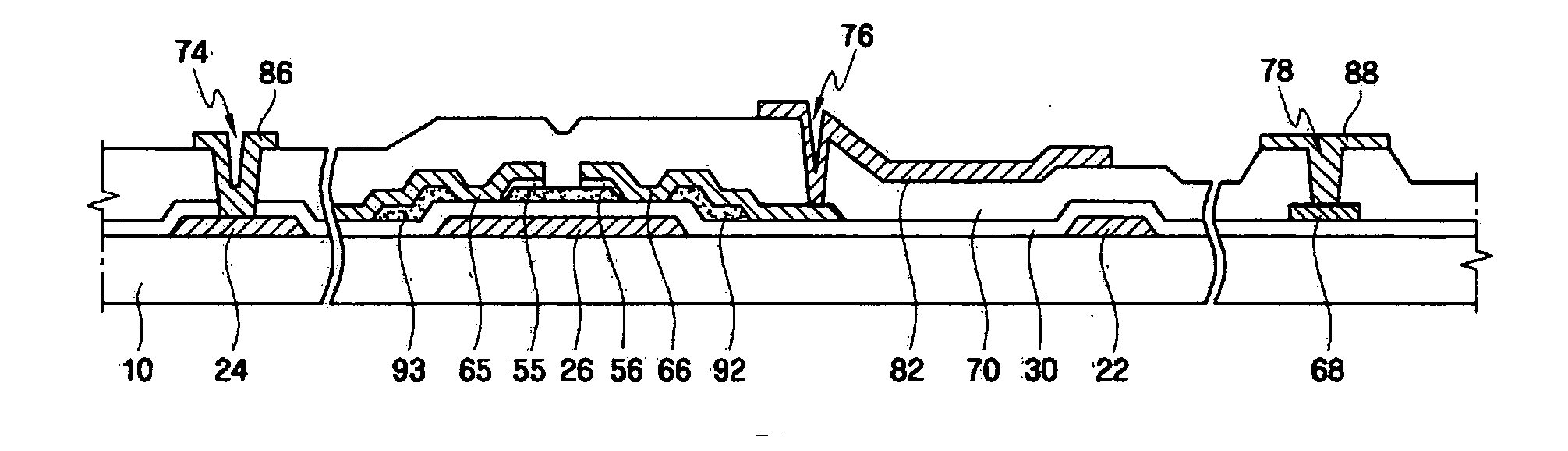

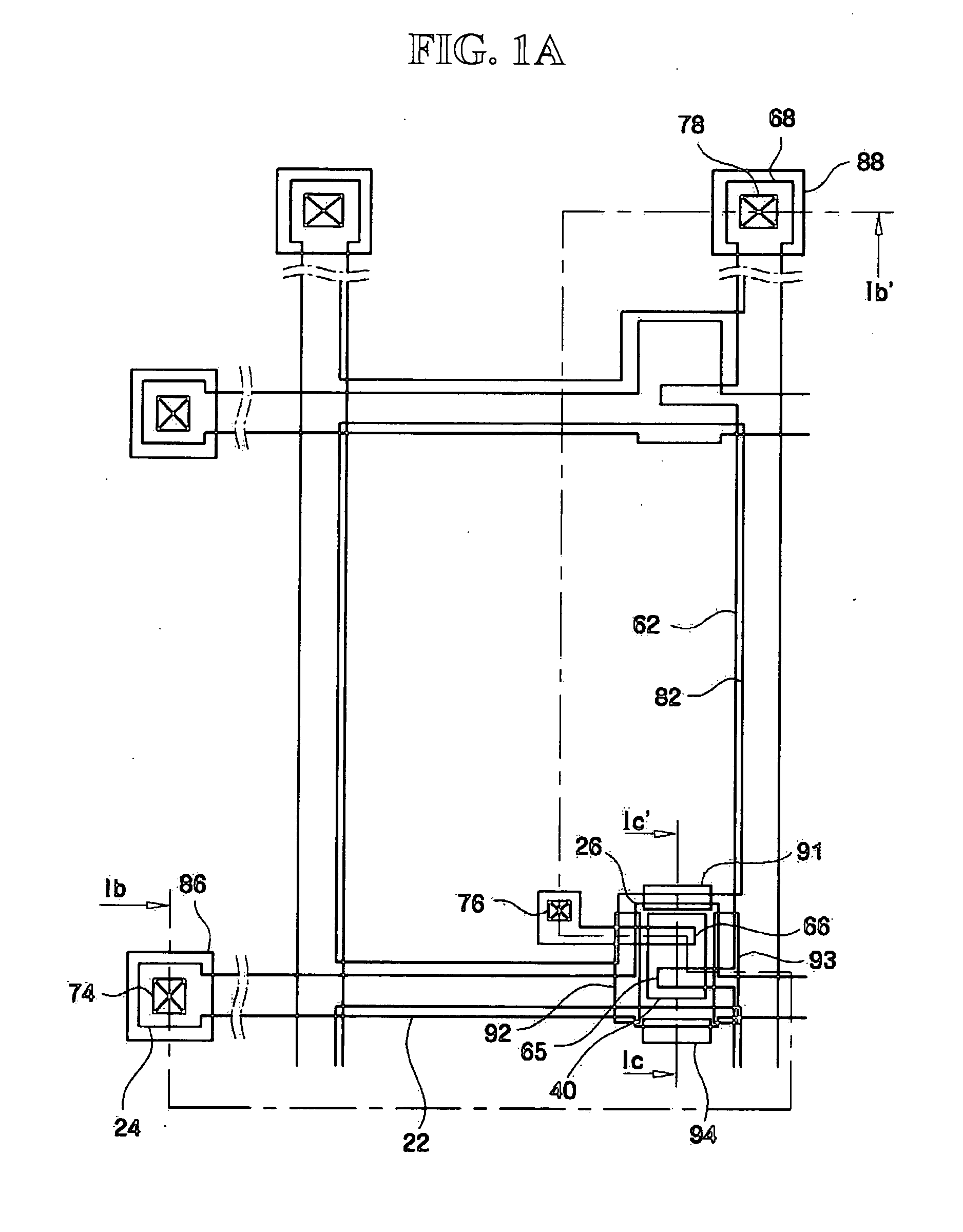

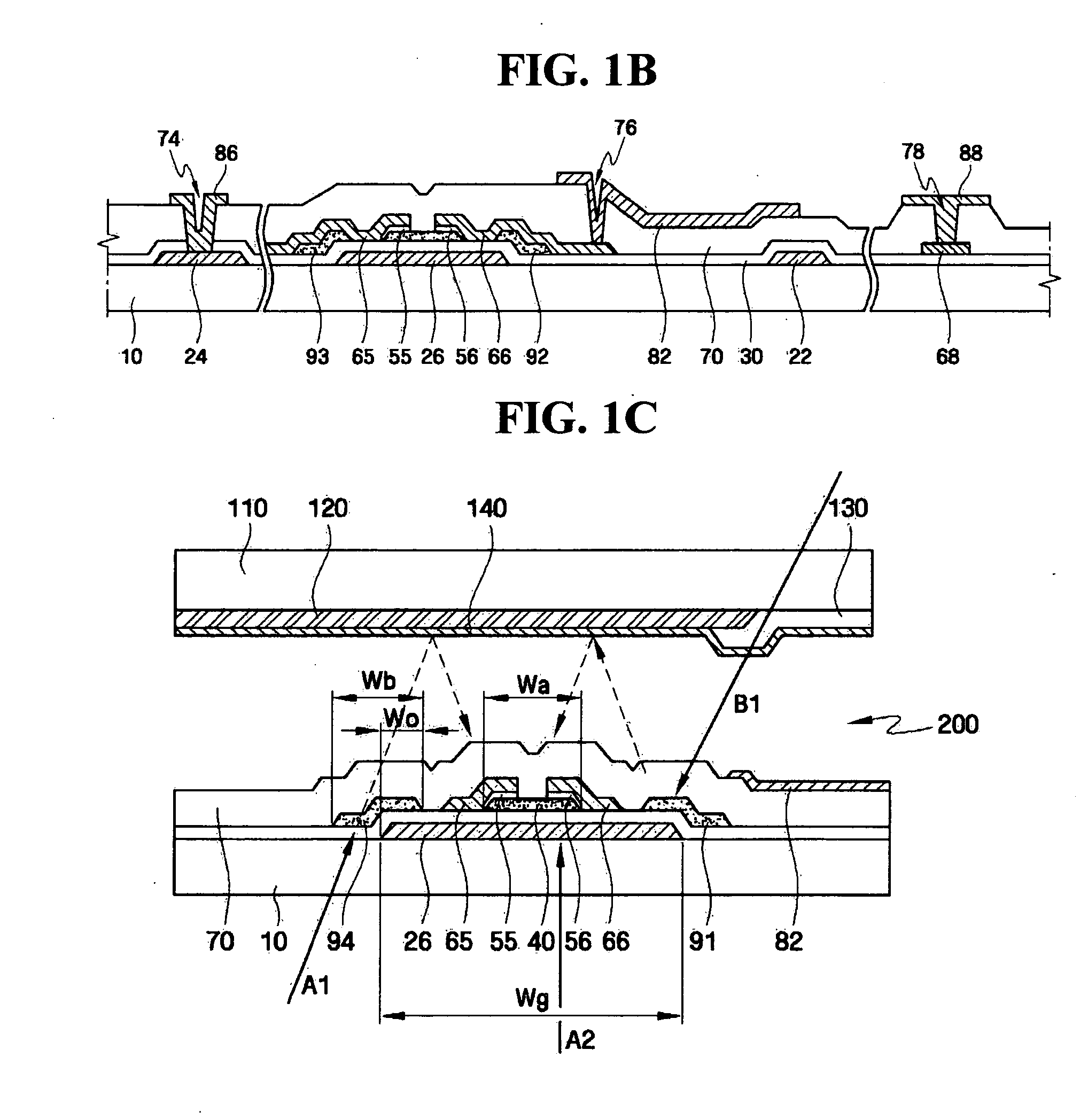

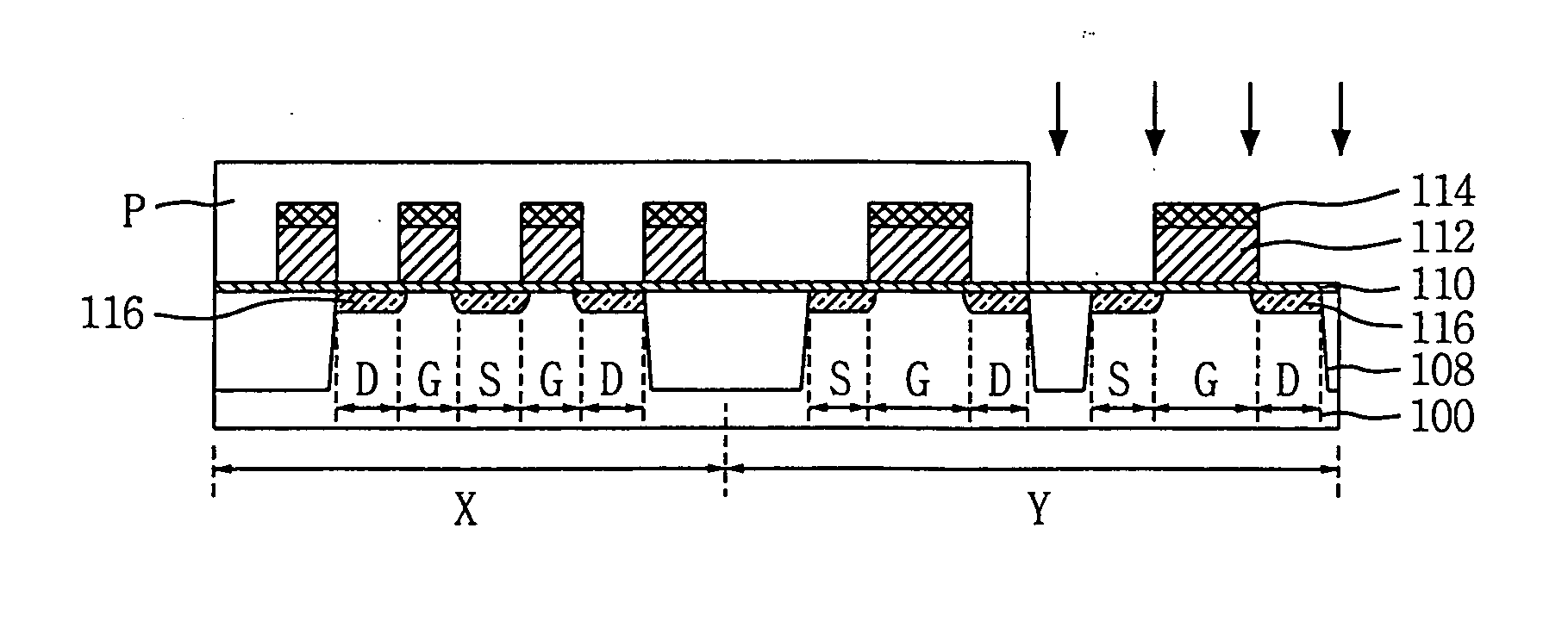

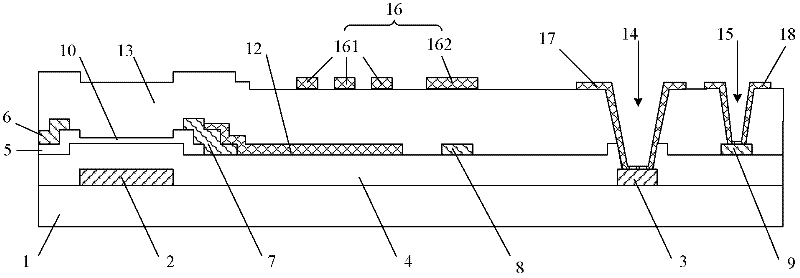

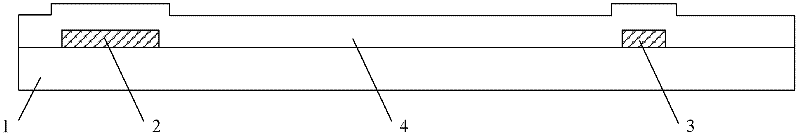

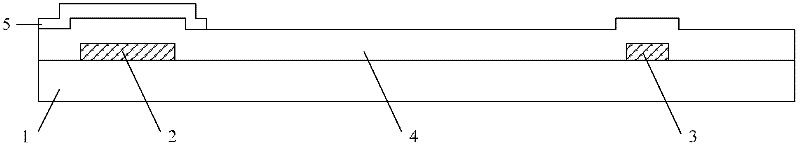

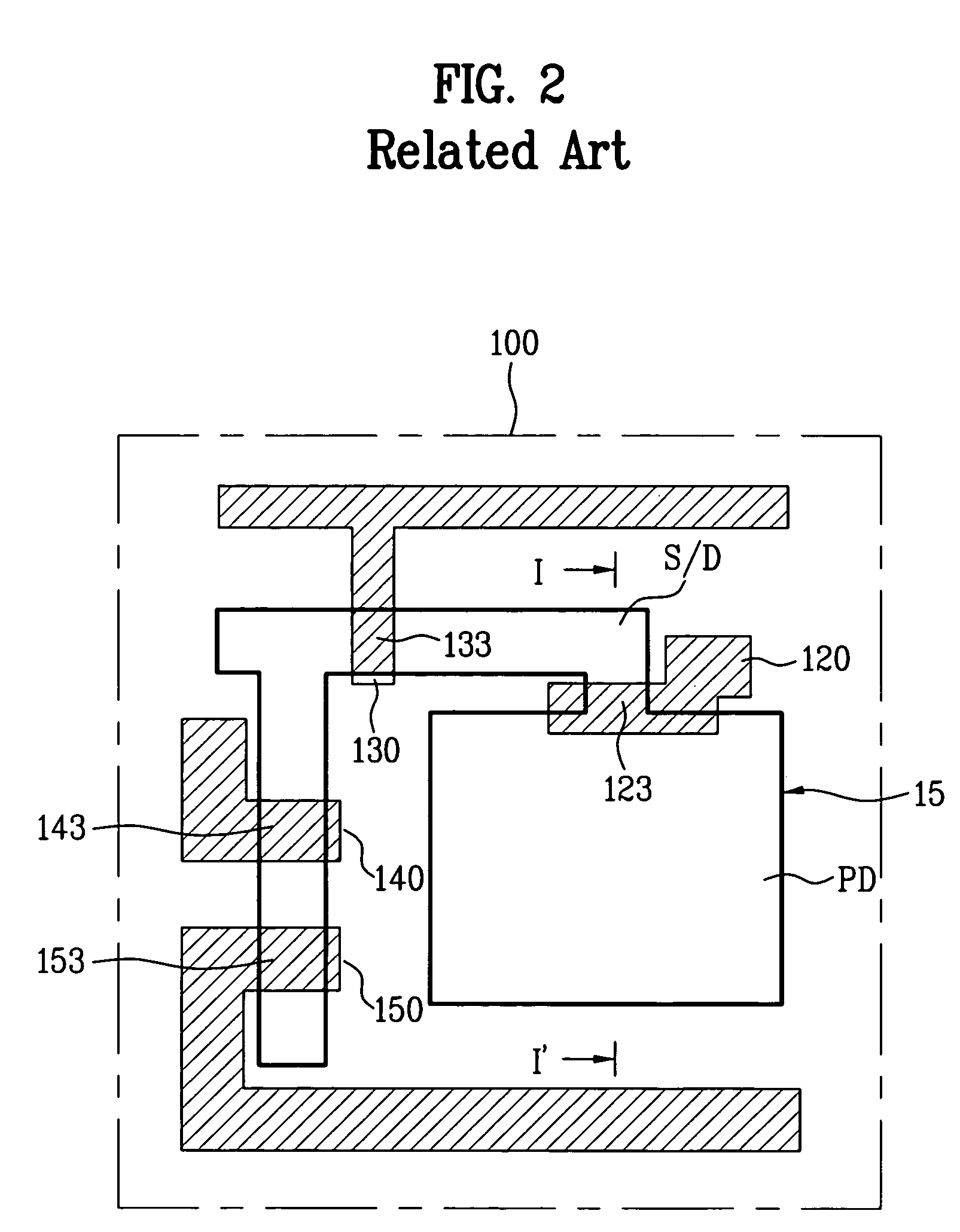

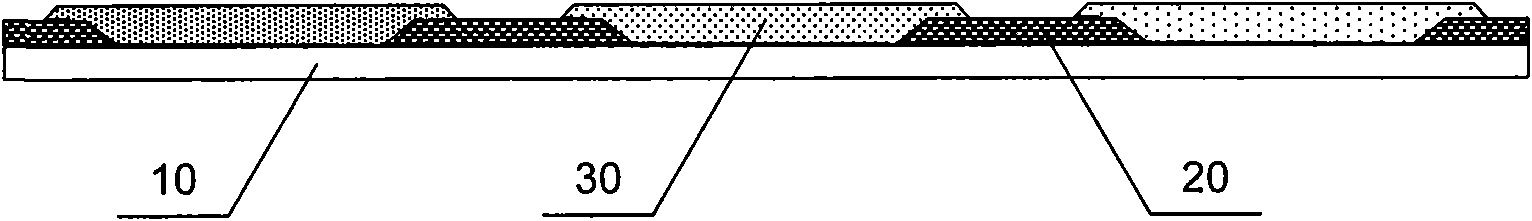

TFT array panel, liquid crystal display including same, and method of manufacturing TFT array panel

InactiveUS20060243979A1Avoid leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayDisplay device

A thin film transistor (TFT) array panel effectively minimizing light leakage current and a liquid crystal display including the same. The panel includes a transistor structure having a gate electrode formed on an insulating substrate; a semiconductor layer formed on and insulated from the gate electrode; a light blocking layer formed around and overlapping a portion of the gate electrode; a data line intersecting the gate line to form a source electrode, which overlaps a portion of the semiconductor layer; a drain electrode opposing to the source electrode and overlapping a portion of the semiconductor layer, and a pixel electrode formed on and insulated from the transistor structure and electrically connected to the drain electrode.

Owner:SAMSUNG DISPLAY CO LTD

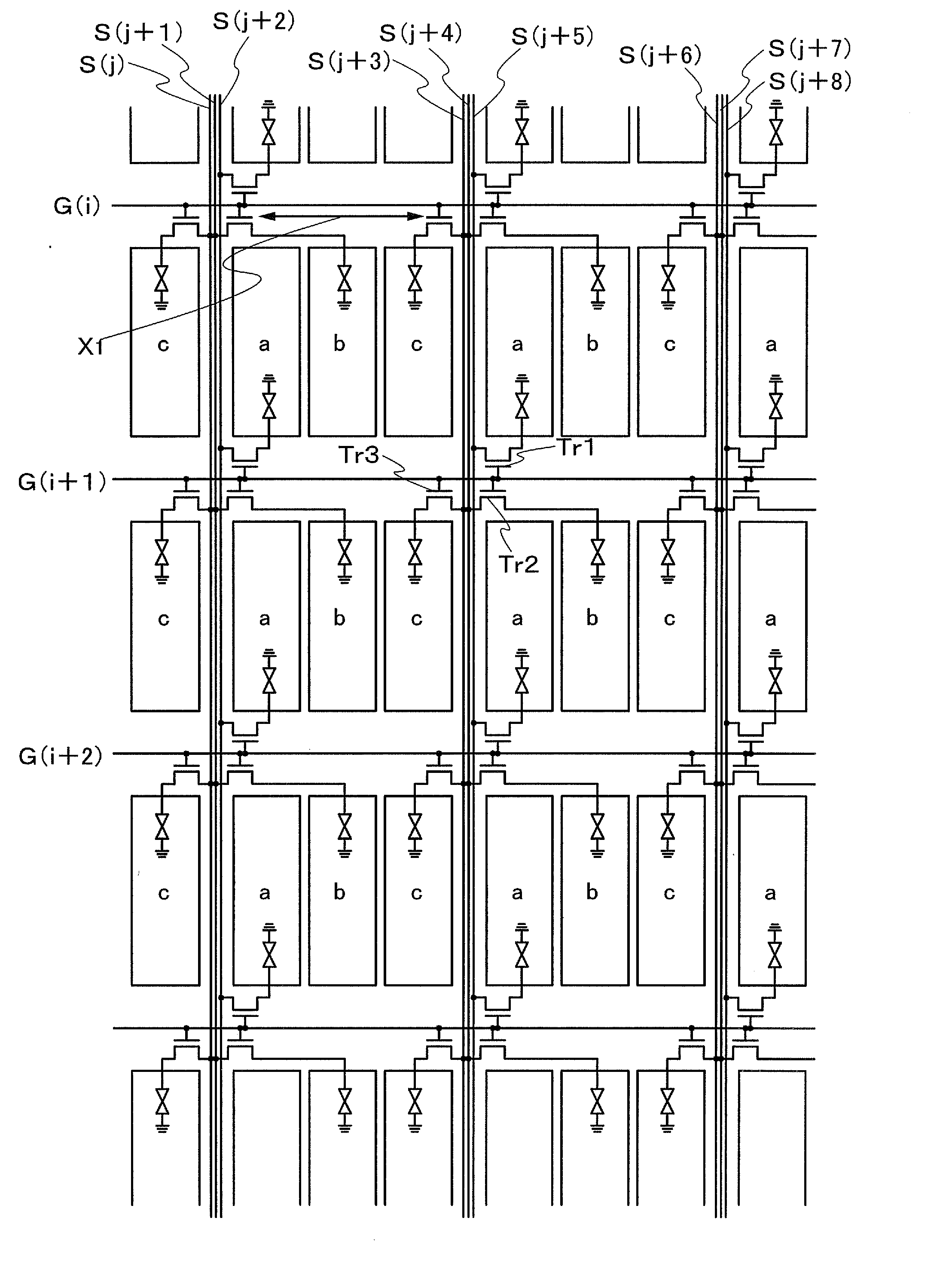

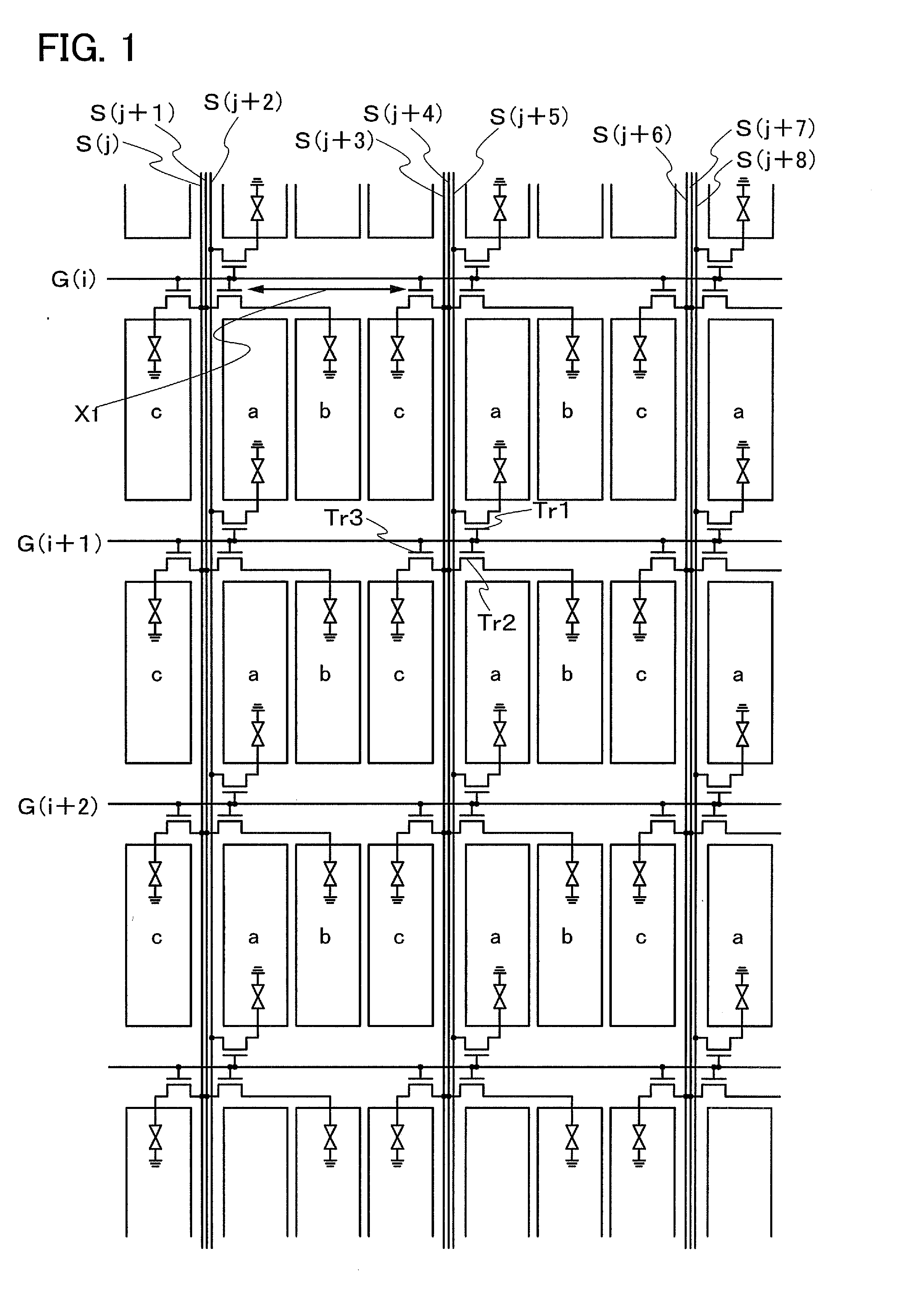

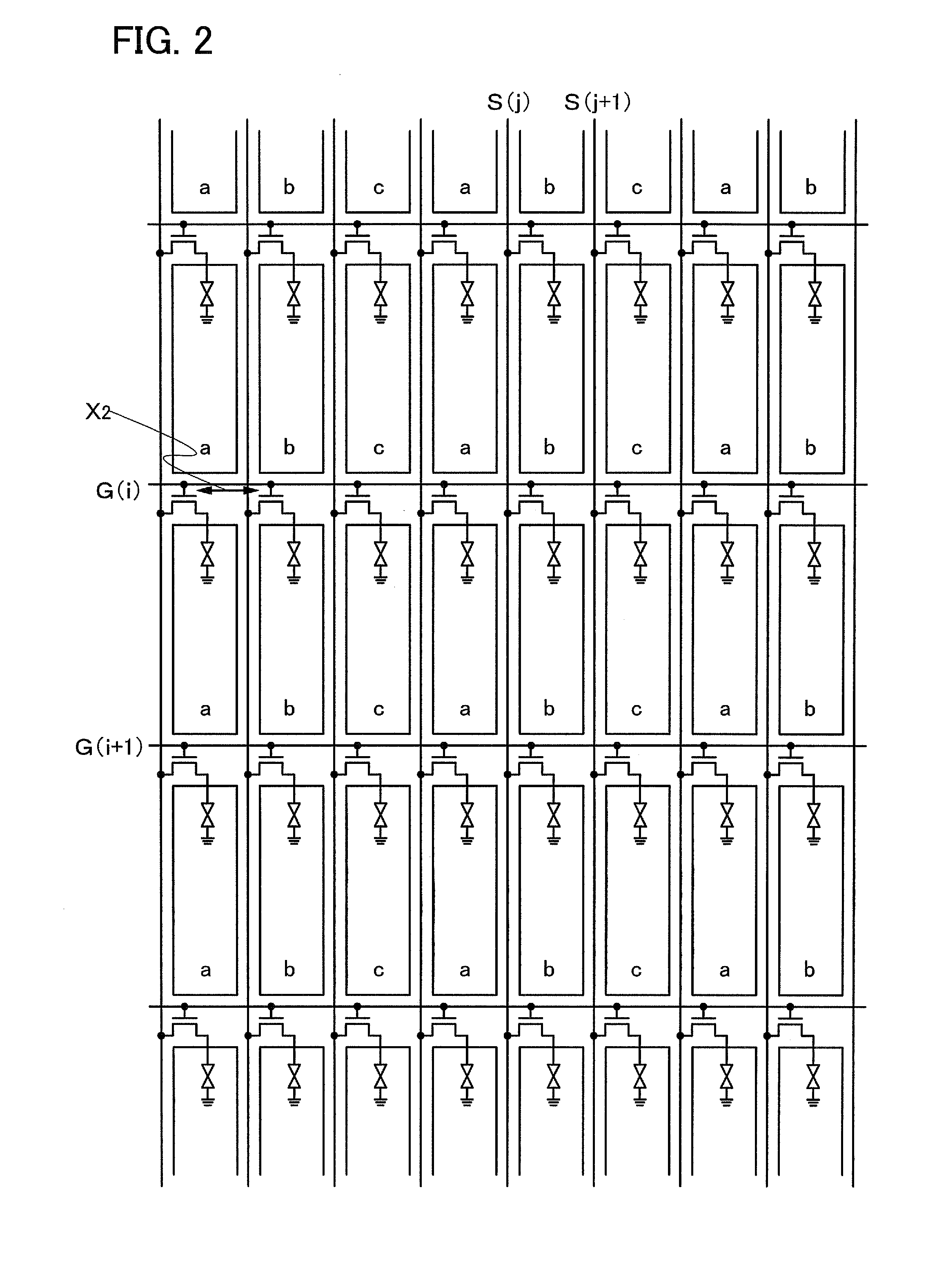

TFT arrangement for display device

ActiveUS20090140253A1Increase distanceReduce aperture ratioStatic indicating devicesElectroluminescent light sourcesDisplay deviceSingle crystal

A new TFT arrangement is demonstrated, which enables prevention of TFT to be formed over a joint portion between the adjacent SOI layers prepared by the process including the separation of a thin single crystal semiconductor layer from a semiconductor wafer. The TFT arrangement is characterized by the structure where a plurality of TFTs each belonging to different pixels is gathered and arranged close to an intersection portion of a scanning line and a signal line. This structure allows the distance between regions, which are provided with the plurality of TFTs, to be extremely large compared with the distance between adjacent TFTs in the conventional TFT arrangement in which all TFTs are arranged in at a regular interval. The formation of a TFT over the joint portion can be avoided by the present arrangement, which leads to the formation of a display device with a negligible amount of display defects.

Owner:SEMICON ENERGY LAB CO LTD

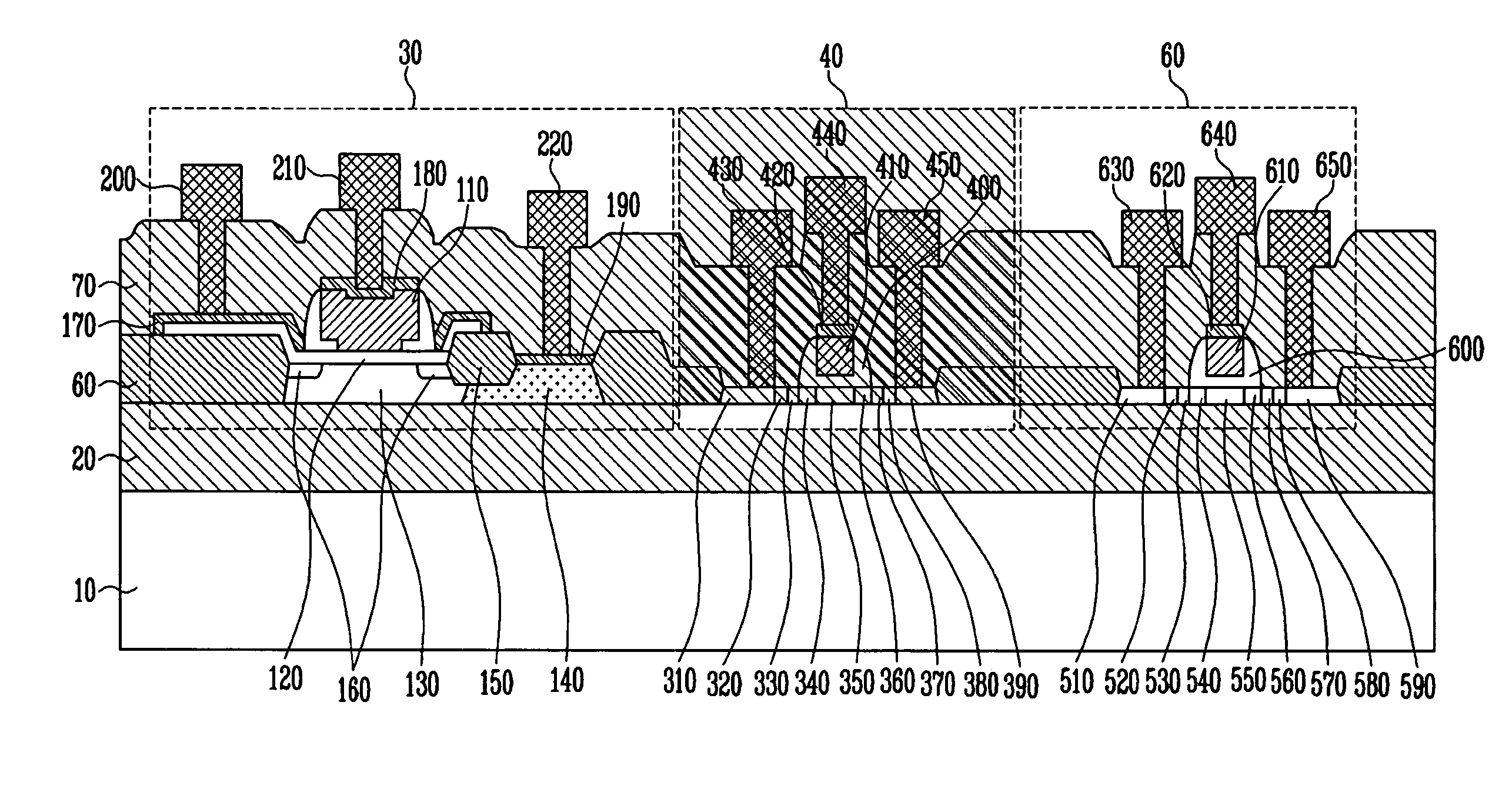

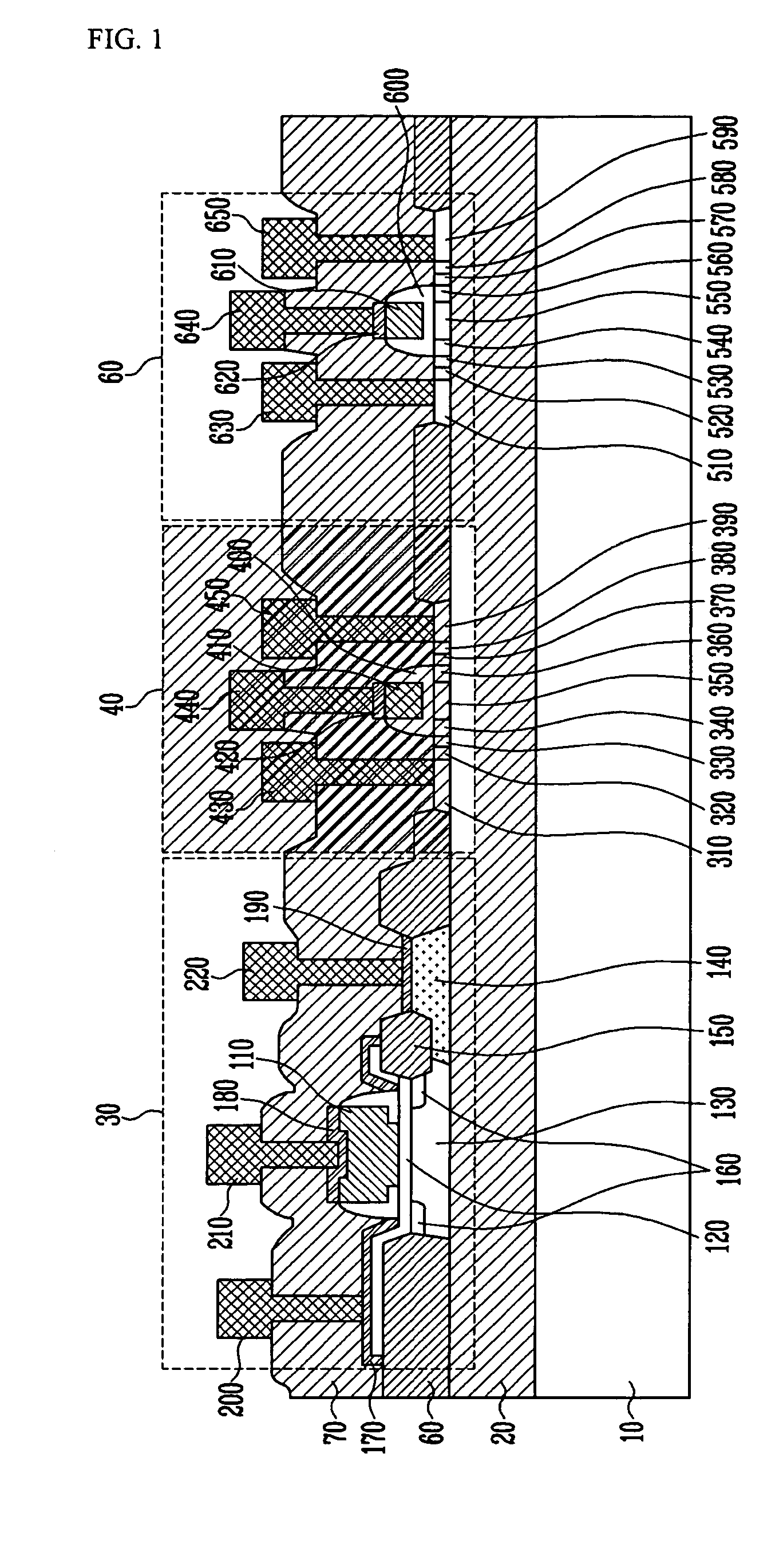

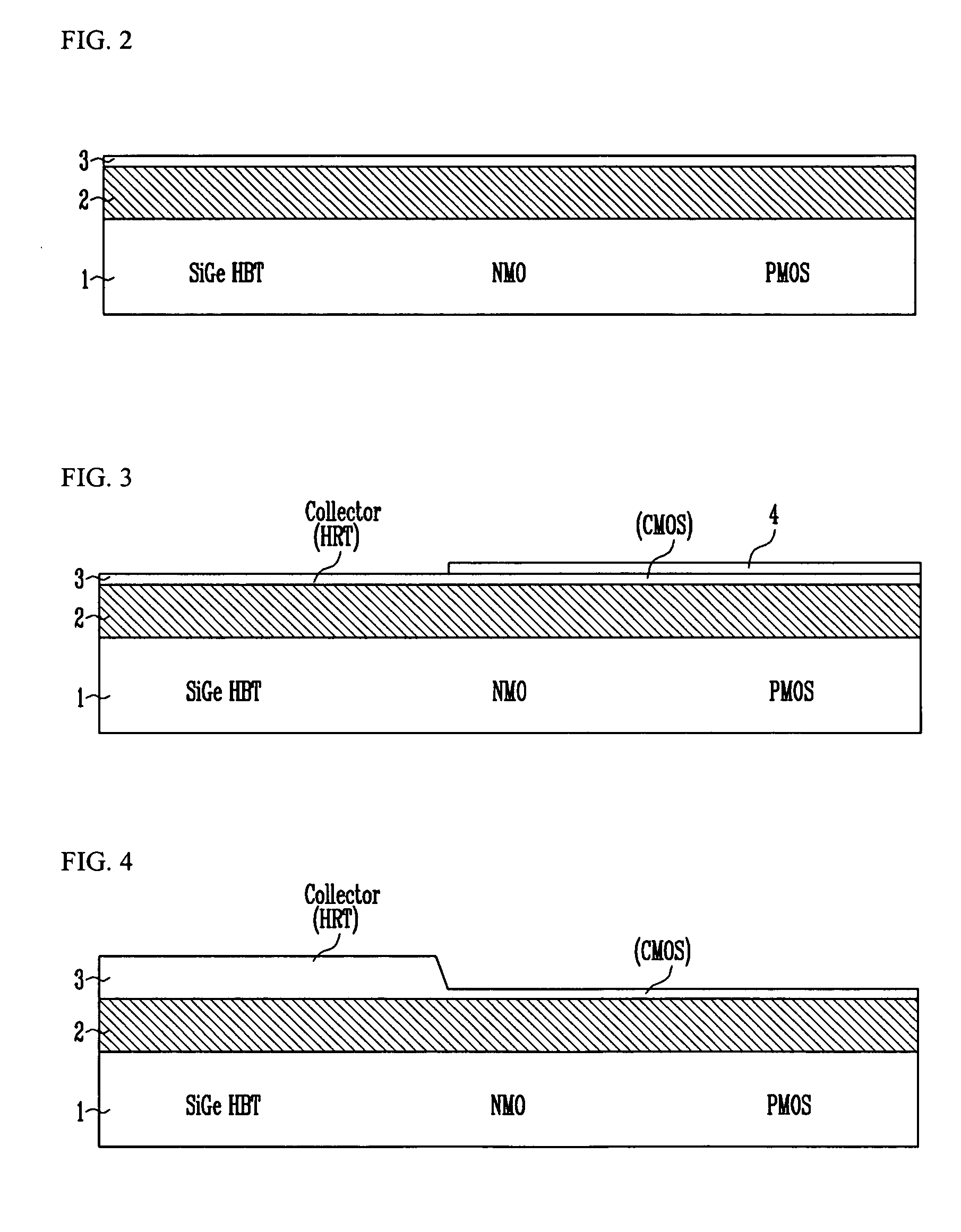

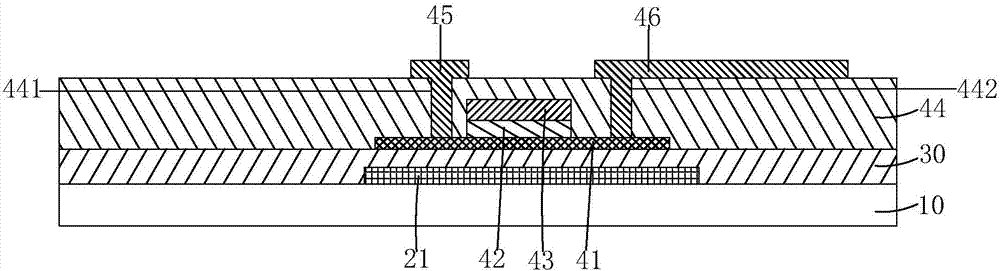

NMOS device, PMOS device, and SiGe HBT device formed on SOI substrate and method of fabricating the same

Provided are an NMOS device, a PMOS device and a SiGe HBT device which are implemented on an SOI substrate and a method of fabricating the same. In manufacturing a Si-based high speed device, a SiGe HBT and a CMOS are mounted on a single SOI substrate. In particular, a source and a drain of the CMOS are formed of SiGe and metal, and thus leakage current is prevented and low power consumption is achieved. Also, heat generation in a chip is suppressed, and a wide operation range may be obtained even at a low voltage.

Owner:ELECTRONICS & TELECOMM RES INST

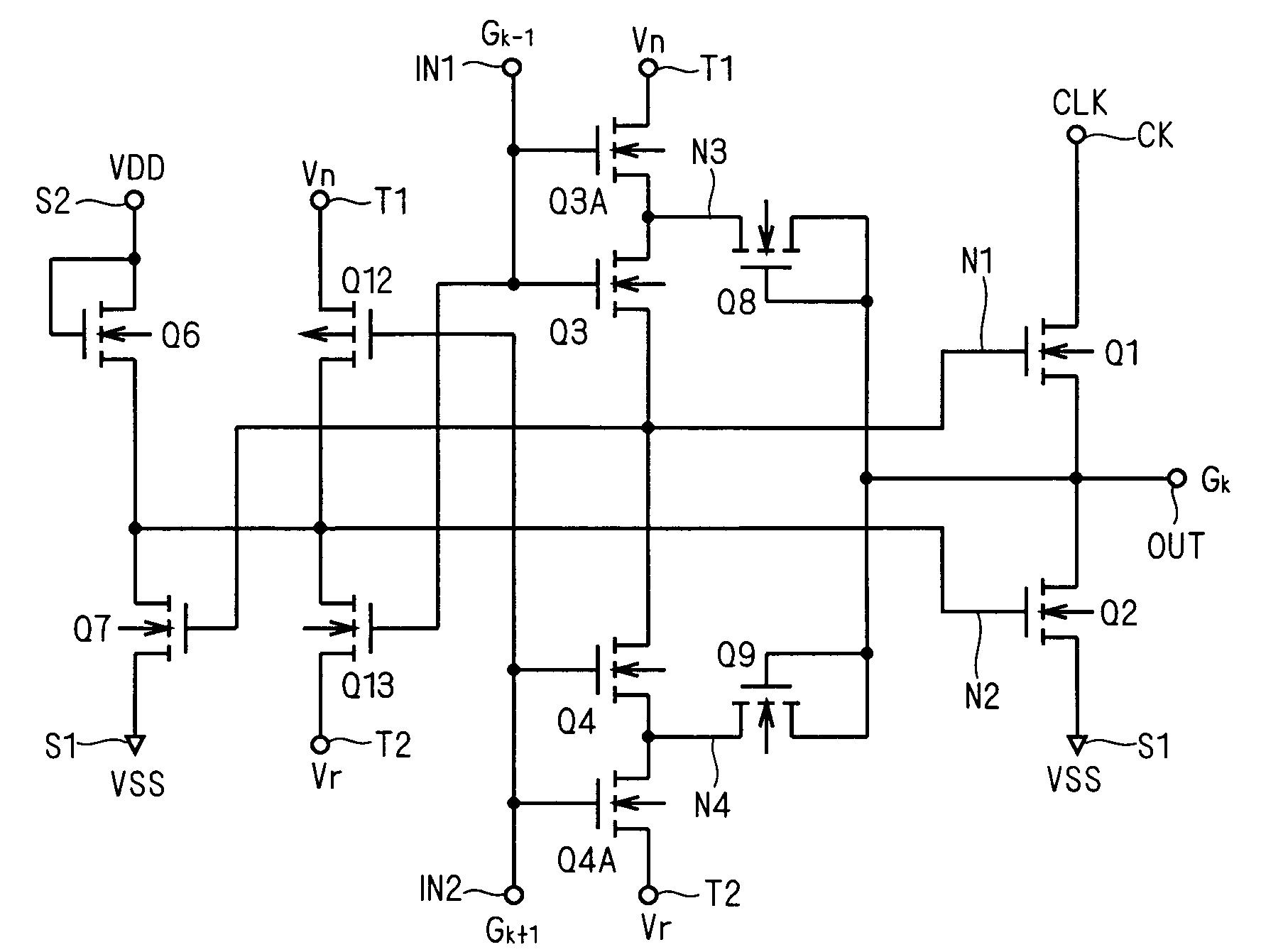

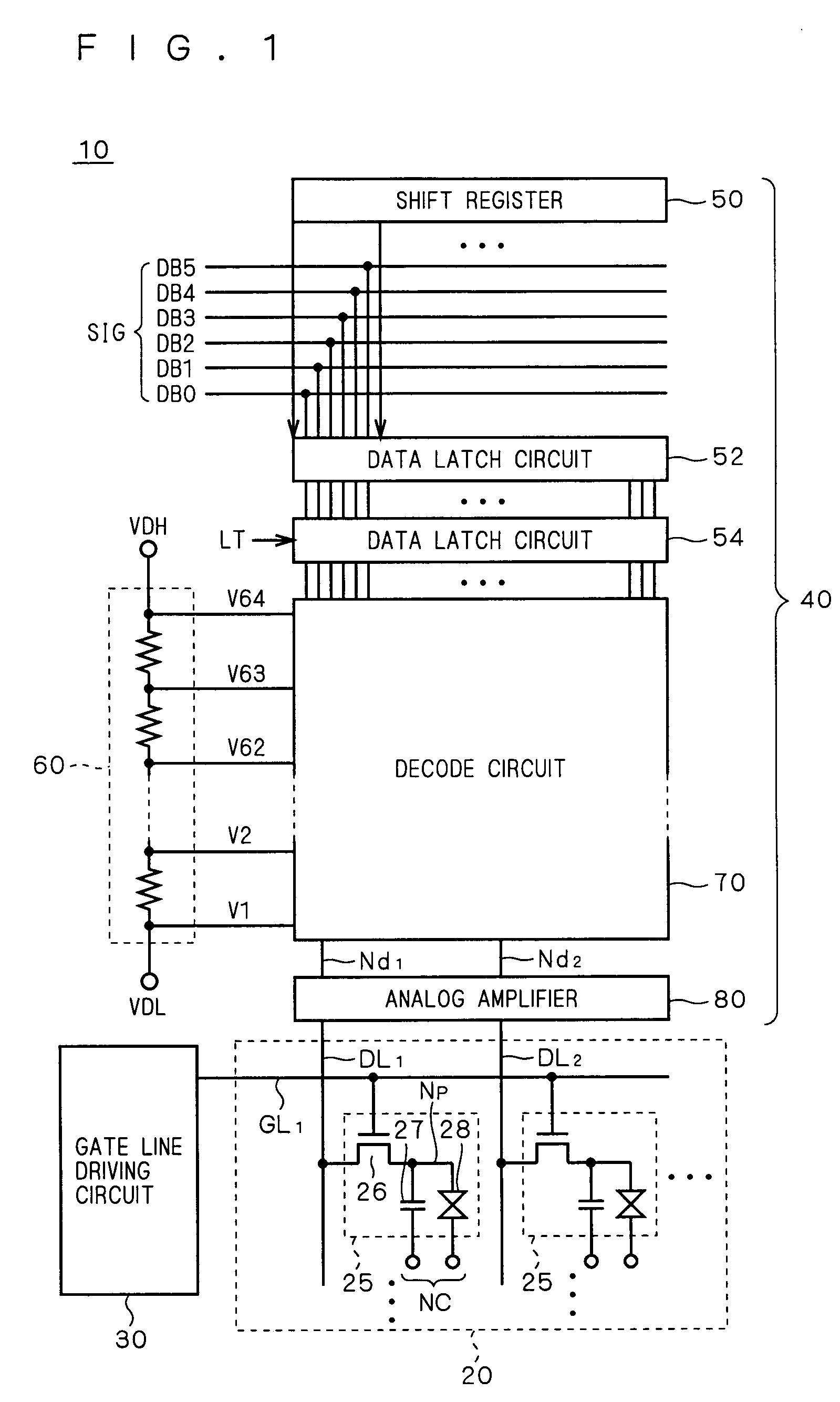

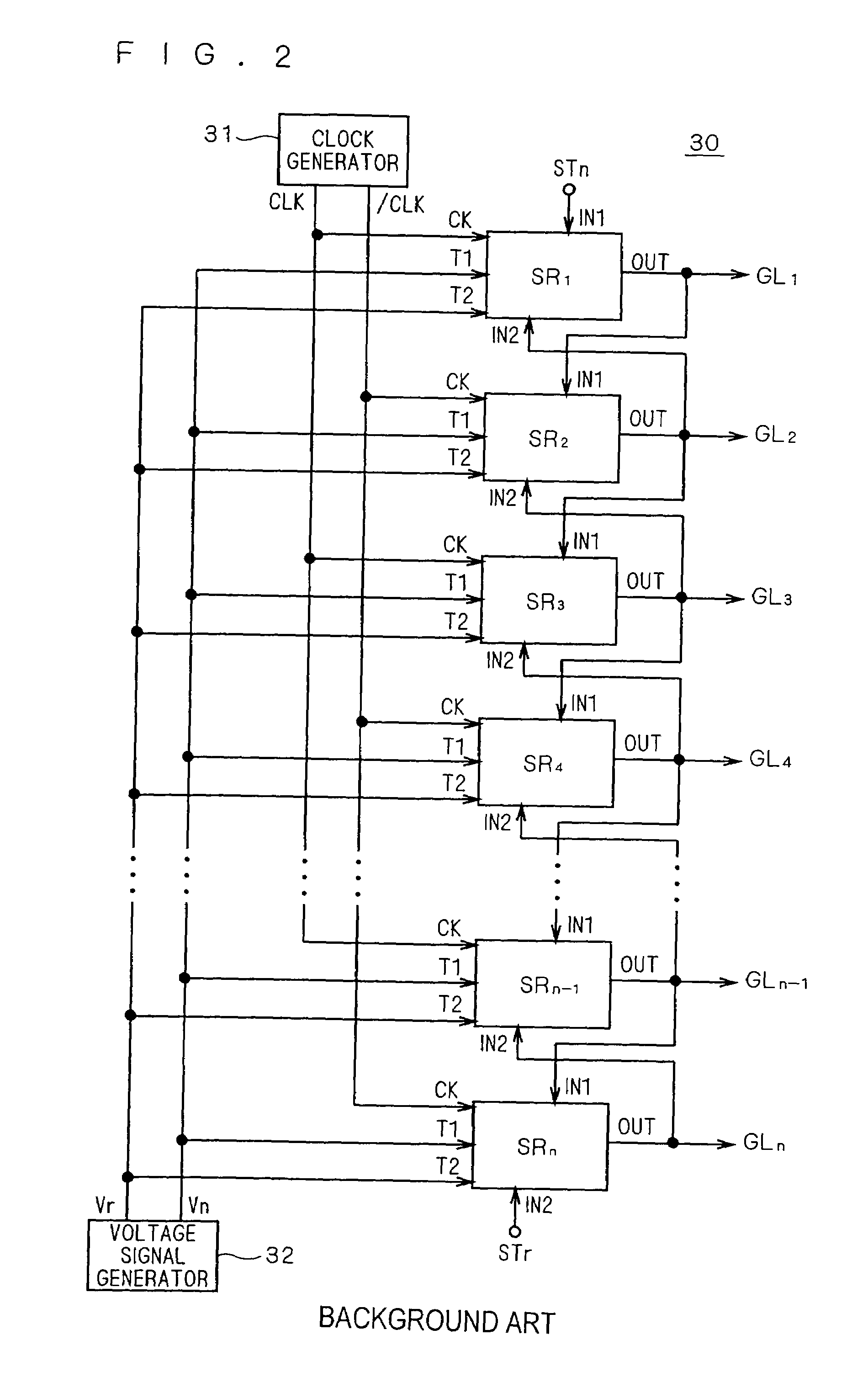

Shift register circuit and image display apparatus equipped with the same

ActiveUS7636412B2Reduce impactSuppress failureStatic indicating devicesDigital storageShift registerProcessor register

Malfunction caused by leakage current of the transistor is prevented in the shift register in which the signal can be shifted bi-directionally. The bi-directional unit shift register includes a transistor Q1 between a clock terminal CK and an output terminal OUT, a transistor Q2 for discharging the output terminal OUT, and transistors Q3, Q4 for providing first and second voltage signals Vn, Vr, which are complementary to each other, to the first node or a gate node of the transistor Q1. Furthermore, a transistor Q5, having a gate connected to a second node or a gate node of the transistor Q2, for discharging the first node is arranged.

Owner:TRIVALE TECH

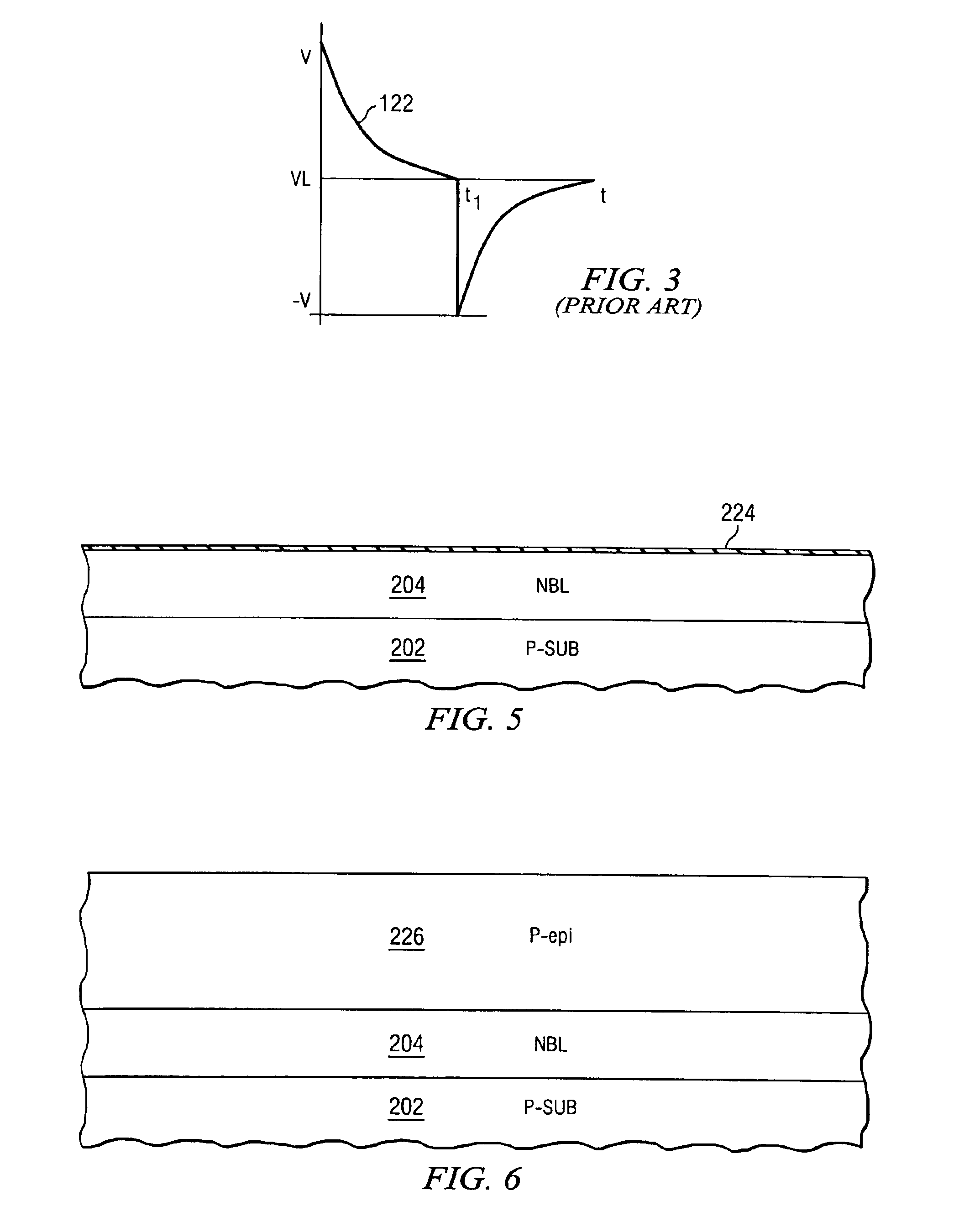

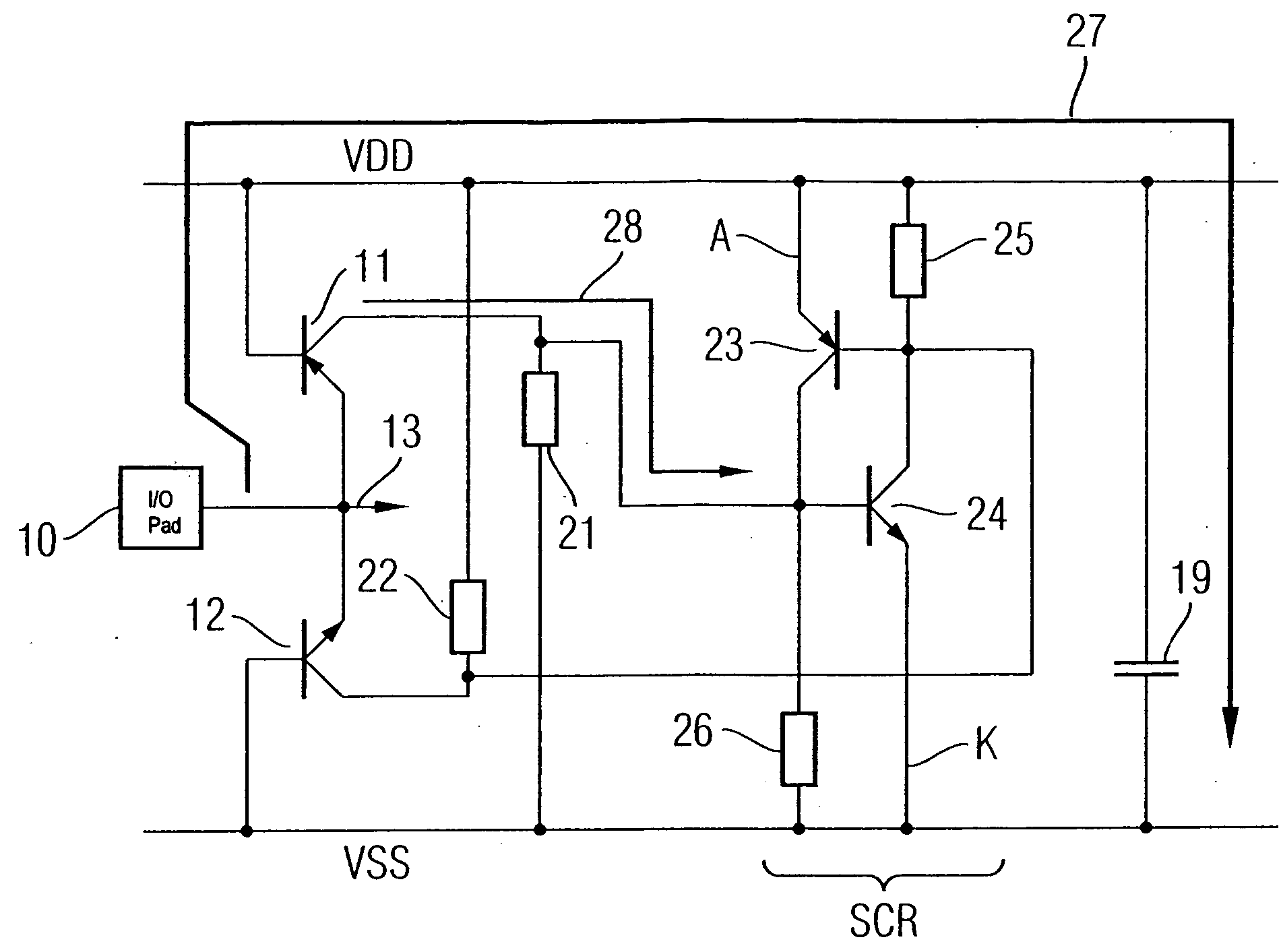

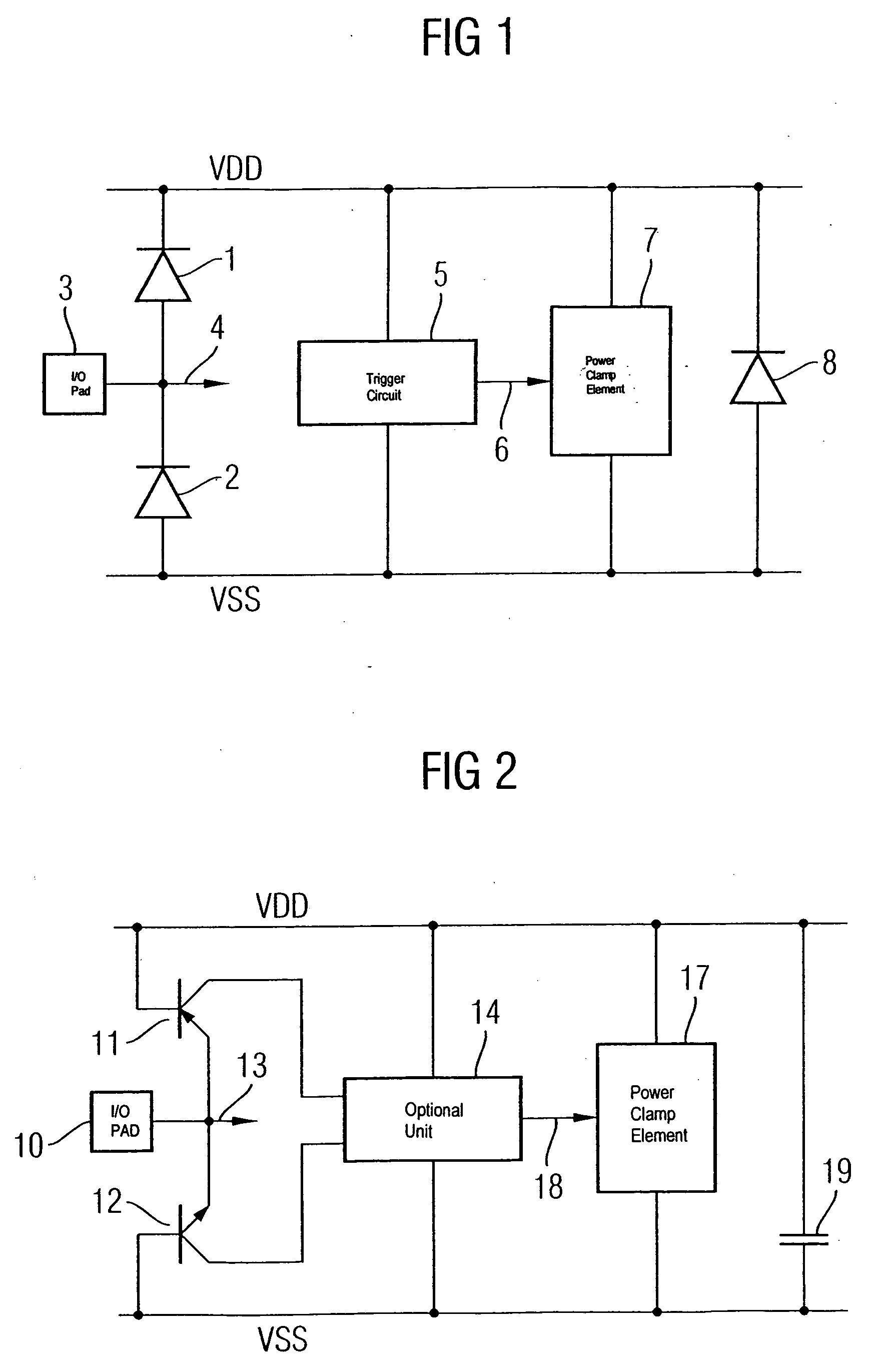

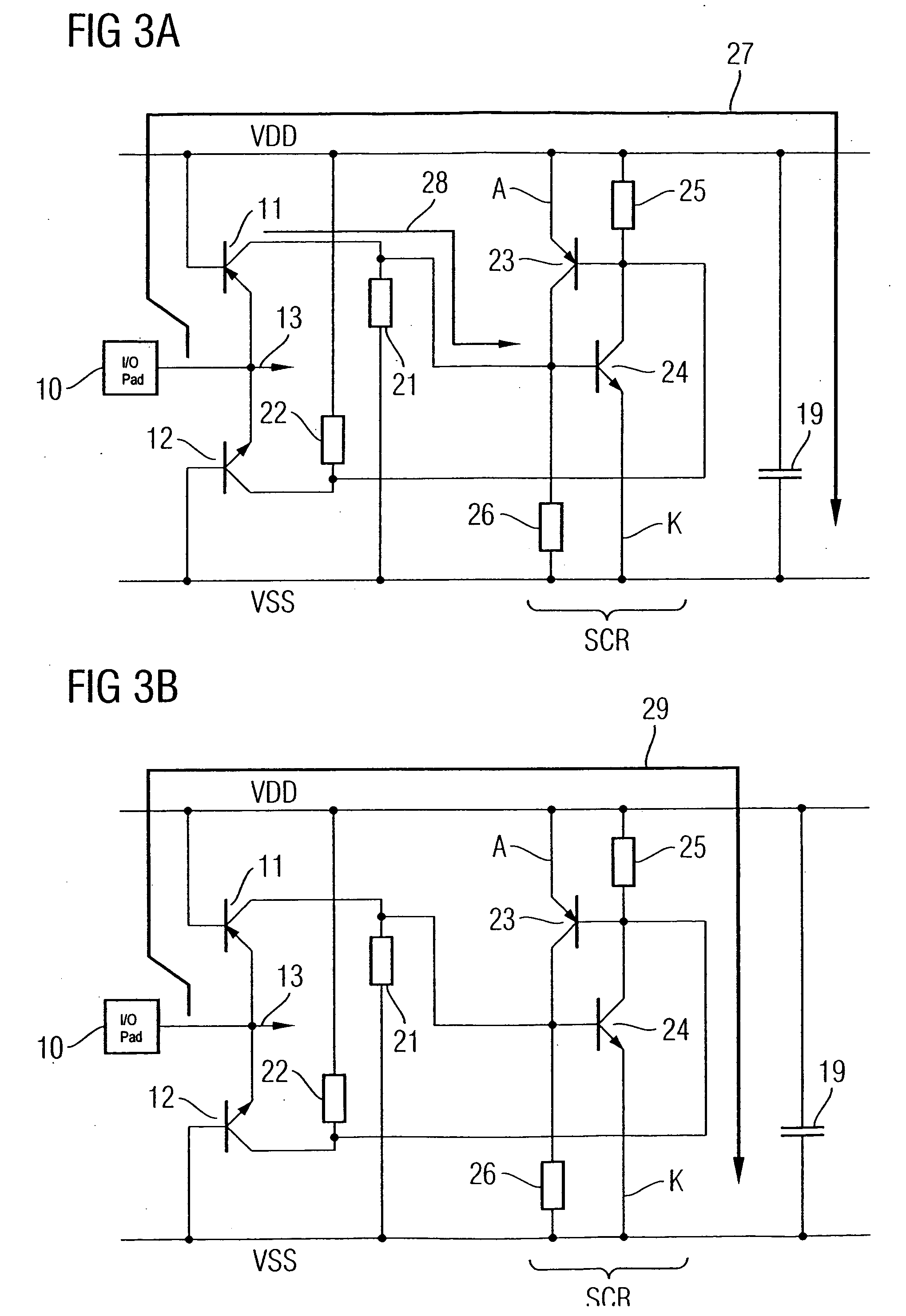

ESD protective circuit with collector-current-controlled triggering for a monolithically integrated circuit

ActiveUS20050195540A1Avoid damageAvoid leakage currentTransistorSemiconductor/solid-state device detailsEngineeringIntegrated circuit

An ESD protective circuit protects an input or output of a monolithically integrated circuit. The ESD protective circuit has at least one bipolar transistor structure and one ESD protective element between two supply networks. The emitter of the bipolar transistor structure is electrically connected to the input or output, while the base is electrically connected to one of the two supply networks. The collector produces a current signal, which is used for triggering of the ESD protective element, when an ESD load occurs at the input or output.

Owner:INFINEON TECH AG

Method of manufacturing a transistor

InactiveUS20050048729A1Avoid leakage currentReduce the annealing processSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerGate oxide

A method of manufacturing a transistor according to some embodiments includes sequentially forming a dummy gate oxide layer and a dummy gate electrode on an active region of a semiconductor substrate, ion-implanting a first conductive impurity into source / drain regions to form first impurity regions, and ion-implanting the first conductive impurity to form second impurity regions that are overlapped by the first impurity regions. The method includes forming a pad polysilicon layer on the source / drain regions, sequentially removing the pad polysilicon layer and the dummy gate electrode from a gate region of the semiconductor substrate, annealing the semiconductor substrate, and ion-implanting a second conductive impurity to form a third impurity region in the gate region. The method includes removing the dummy gate oxide layer, forming a gate insulation layer, and forming a gate electrode on the gate region.

Owner:SAMSUNG ELECTRONICS CO LTD

Field effect transistor semiconductor device

ActiveUS7078743B2Avoid leakage currentPromote formationLaser active region structureSemiconductor/solid-state device manufacturingHigh resistanceField-effect transistor

A semiconductor device has: a buffer layer formed on a conductive substrate and made of AlxGa1-xN with a high resistance; an element-forming layer formed on the buffer layer, having a channel layer, and made of undoped GaN and N-type AlyGa1-yN; and a source electrode, a drain electrode and a gate electrode which are selectively formed on the element-forming layer. The source electrode is filled in a through hole provided in the buffer layer and the element-forming layer, and is thus electrically connected to the conductive substrate.

Owner:PANASONIC CORP

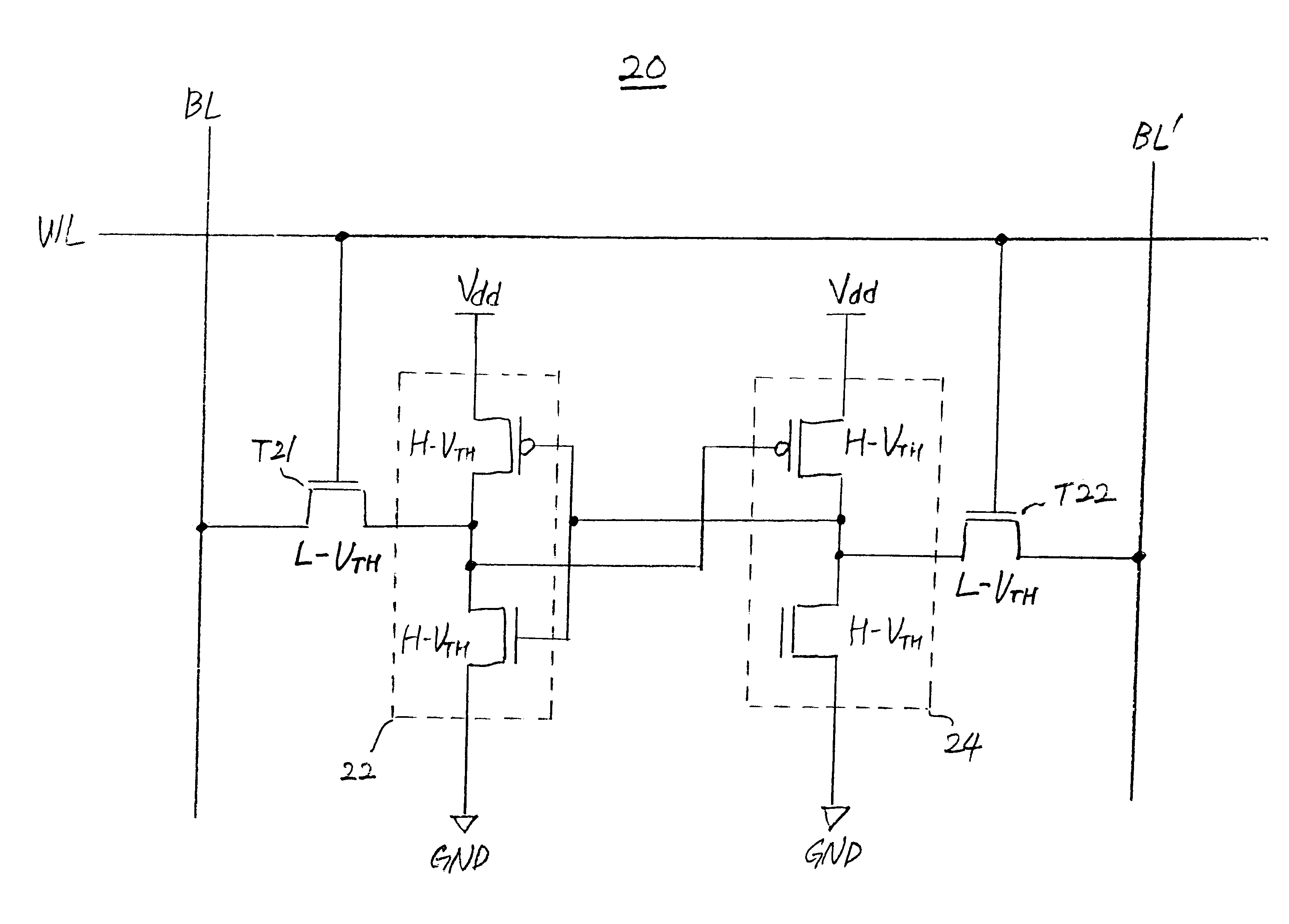

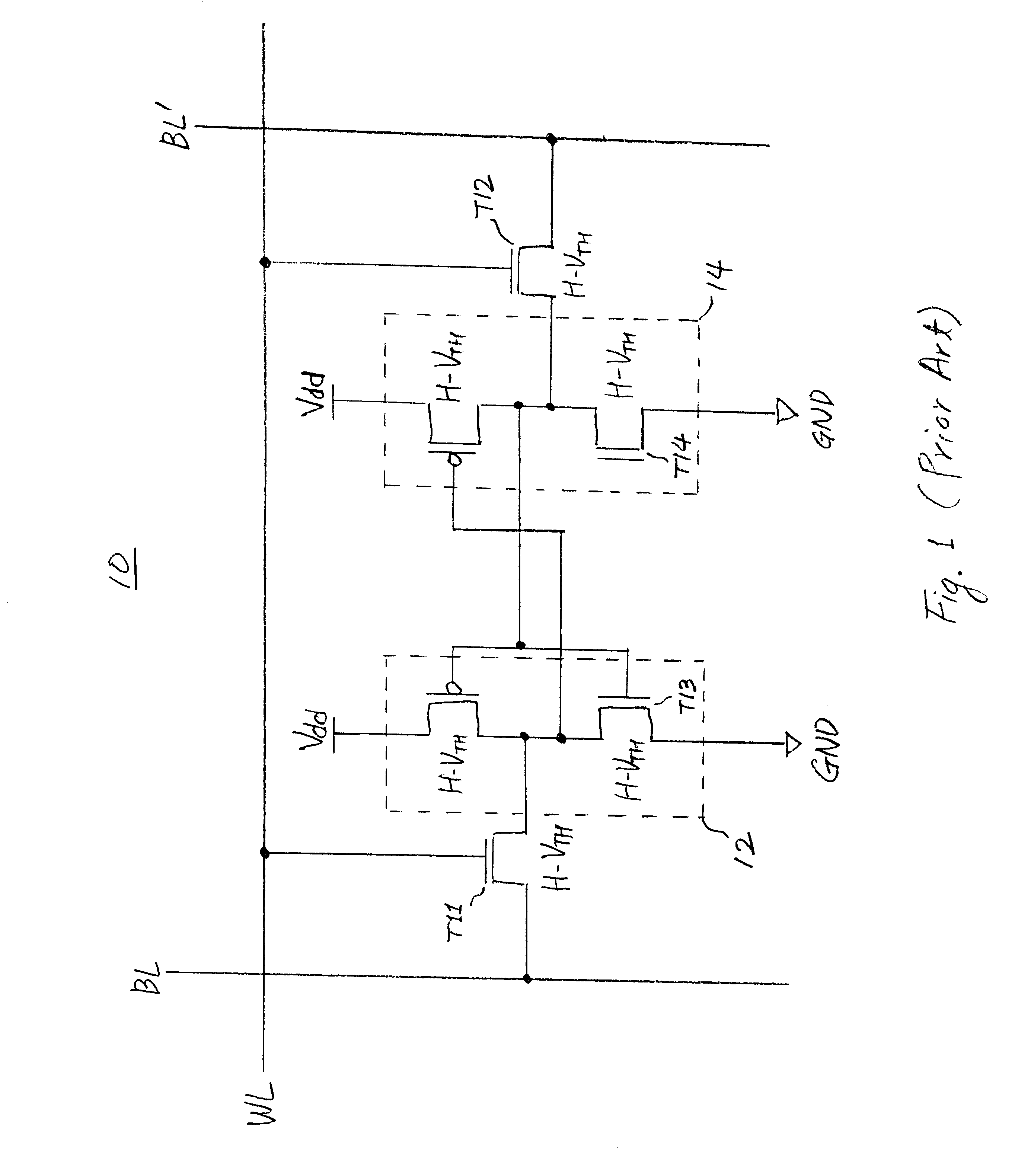

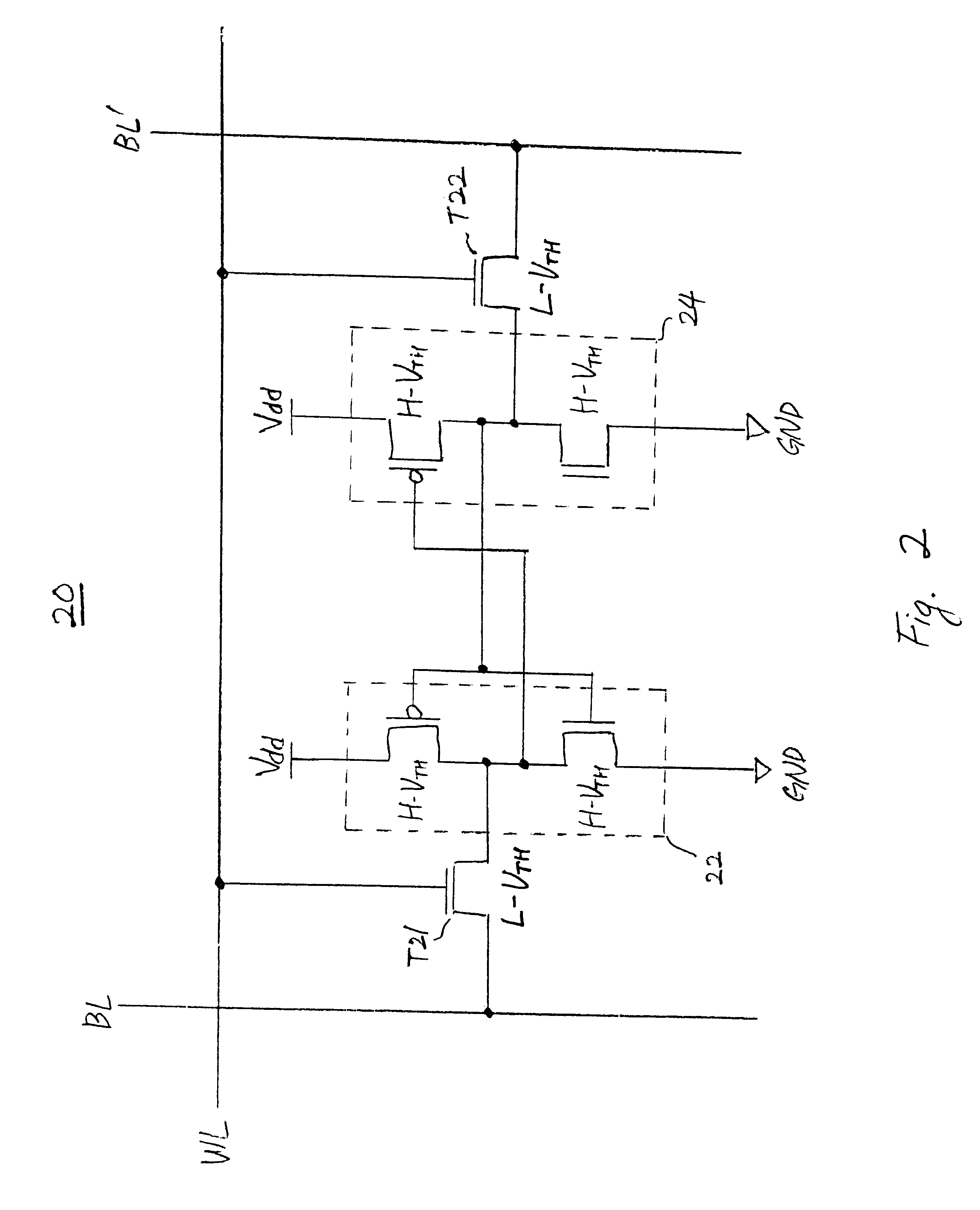

High performance semiconductor memory device with low power consumption

InactiveUS6307805B1Improve performanceIncrease speedSolid-state devicesDigital storageHigh densityEngineering

A semiconductor memory device accessed with wordlines and bitlines has memory cells which operate at high performance with lower power consumption and have a high density. Each of the memory cells has pass transistors connected to a corresponding wordline and a corresponding pair of bitlines, and the pass transistors are gated by a signal of the corresponding wordline. The semiconductor memory device includes a wordline drive unit for selectively driving the wordlines in response to a row address. A wordline driver in the wordline drive unit boosts a corresponding wordline in a positive direction when the corresponding wordline is activated to access the memory cell and boosts the corresponding wordline in a negative direction when the corresponding wordline is inactive. By boosting the wordline in the positive direction, the performance of the memory cells is enhanced, and by boosting the wordline in the negative direction, a leakage current in the pass transistors with a low-threshold voltage is prevented.

Owner:IBM CORP

Manufacture method of array substrate, array substrate and display device

InactiveCN102645808AReduce parasitic capacitanceReduce signal delaySemiconductor/solid-state device manufacturingNon-linear opticsEngineeringData lines

The invention provides a manufacture method of an array substrate, the array substrate and a display device. A display region of the array substrate comprises a gate line, a data line and a plurality of pixel units. A non-display region comprises a gate bonding pad and a data bonding pad. Each of the pixel units comprises a thin film transistor, a pixel electrode and a common electrode. The pixel electrode is connected to a drain electrode of the thin film transistor. The common electrode comprises a first common electrode arranged above the pixel electrode and a second common electrode arranged above the data line. A protective film is arranged between a common electrode layer and a pixel electrode layer. An inorganic insulating film and an organic insulating film are arranged between the pixel electrode and the data line and between the thin film transistor and the protective film, respectively. The inorganic insulating film is formed above the data line, a source and the drain of the thin film transistor, and a semiconductor layer of a channel region, and the organic insulating film is arranged above the inorganic insulating film. The invention can reduce signal delay on the data line, and prevent generation of leakage current in the thin film transistor at a high temperature.

Owner:BOE TECH GRP CO LTD +1

OLED display panel and manufacturing method thereof

ActiveCN107170762AMaintain propertiesGuaranteed to workSolid-state devicesSemiconductor/solid-state device manufacturingHigh energyEngineering

The invention provides an OLED display panel and a manufacturing method thereof. Through arranging a red light-shielding color block which totally covers an active layer above an IGZO TFT, influence of high-energy blue light which is incident from top of the IGZO TFT to the active layer of IGZO can be reduced, thereby preventing generation of photogenerated leakage current, ensuring characteristics of the IGZO TFT, and sustaining normal operation of the IGZO TFT. Furthermore because the red light-shielding color block which covers the active layer only blocks the high-energy shortwave blue light which affects the active layer of the IGZO TFT, the light in other wave bands can penetrate through normally, aperture rate of the light emitting area of the OLED display panel is not affected.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

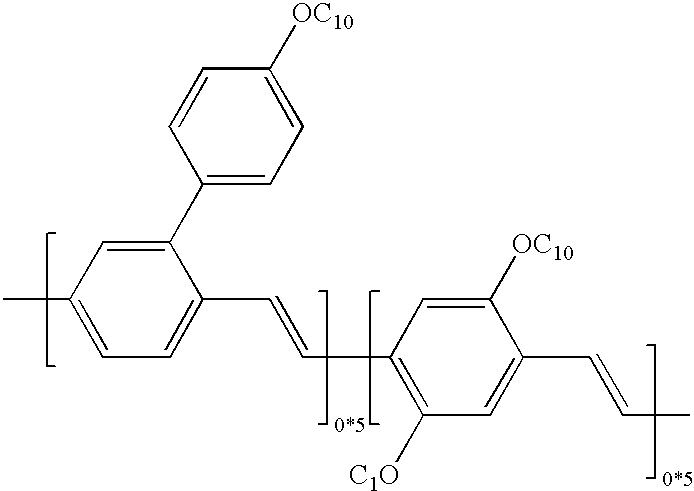

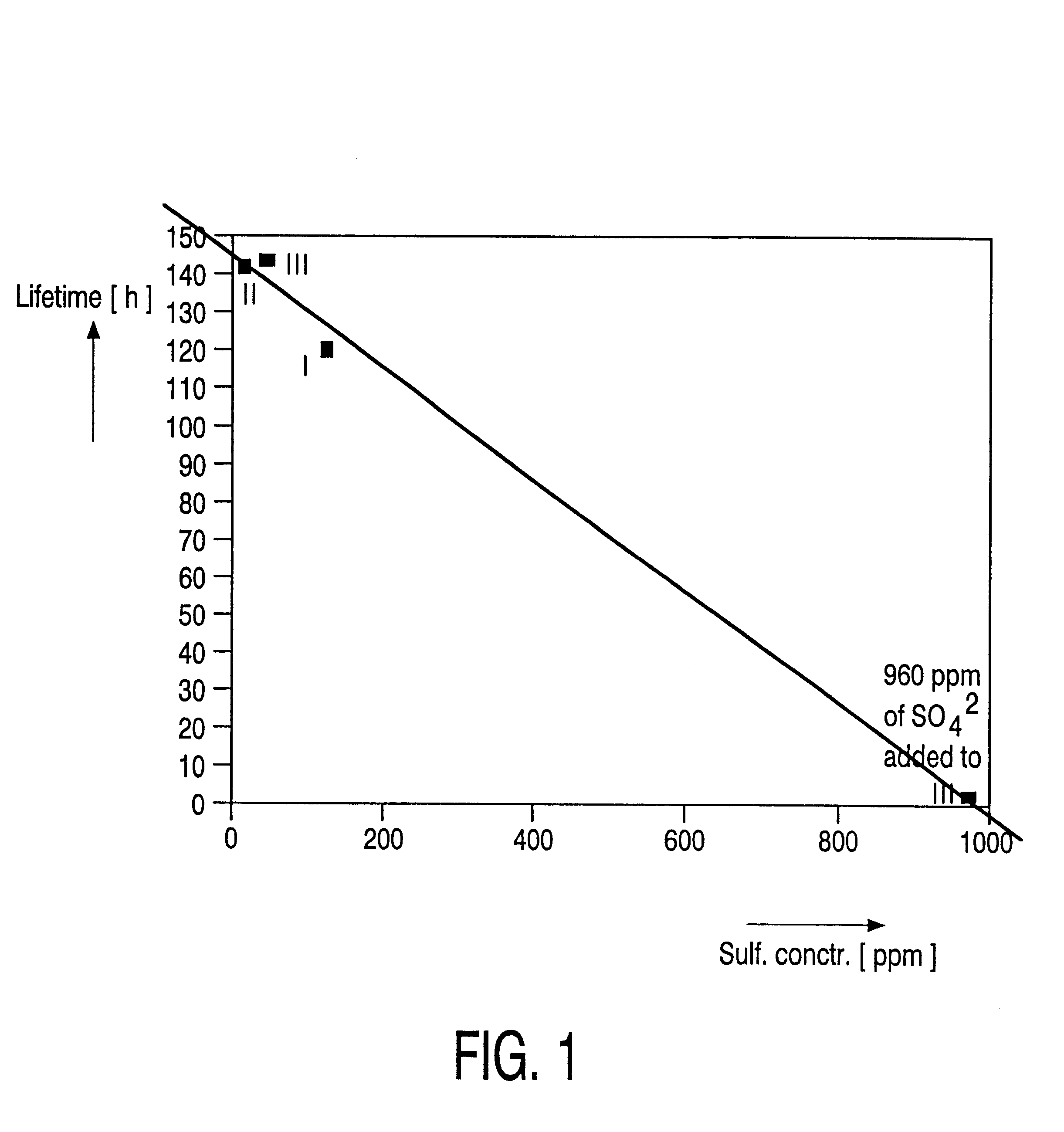

Led comprising a conductive transparent polymer layer with low sulfate and high metal ion content

InactiveUS6586764B2Extended service lifePrevent substantial absorption of visible lightElectroluminescent light sourcesConductive materialIon contentOligomer

The invention pertains to an organic light emitting diode (LED) comprising a transparent electrode, superposed by a layer of a conductive transparent polymer (CTP), superposed by a layer of a light emitting polymer, oligomer, or low molecular weight compound superposed by a metal cathode, characterized in that the CTP layer has a sulfate ion content of less than 7,500 ppm, and a metal ion content of more than 0.04 mmoles / g.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

CMOS image sensor and method for fabricating the same

ActiveUS7232712B2Reduce dark currentAvoid leakage currentTelevision system detailsTelevision system scanning detailsCMOSIsolation layer

A CMOS image sensor and a method for fabricating the same is disclosed, to decrease a darkcurrent generated in the boundary between a diffusion area of a photodiode and a device isolation layer, which includes a first conductive type semiconductor substrate having an active area and a device isolation area, the active area including a photodiode and a transistor; a device isolation layer formed in the device isolation area of the semiconductor substrate; a second conductive type diffusion area formed in the photodiode of the semiconductor substrate at a predetermined interval from the device isolation layer; a gate insulating layer and a gate electrode formed in the transistor of the semiconductor substrate; and a first conductive type first diffusion area formed in the semiconductor substrate of the boundary between the second conductive type diffusion area and the device isolation layer.

Owner:III HLDG 4

Color film base plate and manufacturing method thereof

ActiveCN101825802AAvoid leakage currentImprove voltage retention and contrastNon-linear opticsLiquid-crystal displayEngineering

The invention relates to a color film base plate and a manufacturing method thereof. The color film base plate comprises a first black matrix, color resin, a protecting layer and a common electrode which are formed on a base plate, wherein a second black matrix for preventing the reflecting light of the first black matrix from projecting into an array base plate TFT (Thin Film Transistor) channel region is formed on the protecting layer. The manufacturing method of the color film base plate comprises the following steps of: forming a pattern comprising the first black matrix and the color resin on the base plate; forming a pattern comprising the protecting layer and the second black matrix; and forming a pattern comprising the common electrode. By mounting two layers of black matrix patterns, the second black matrix can effectively block the reflecting light reflected from the surface of the first black matrix, which enables the reflecting light reflected from the surface of the first black matrix not to project into the TFT channel region, thereby effectively avoiding the generation of leakage current, improving the retention rate and contrast ratio of voltage at maximum, and enhancing the quality of a liquid crystal display.

Owner:BOE TECH GRP CO LTD +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com