Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2975 results about "Tunnel junction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

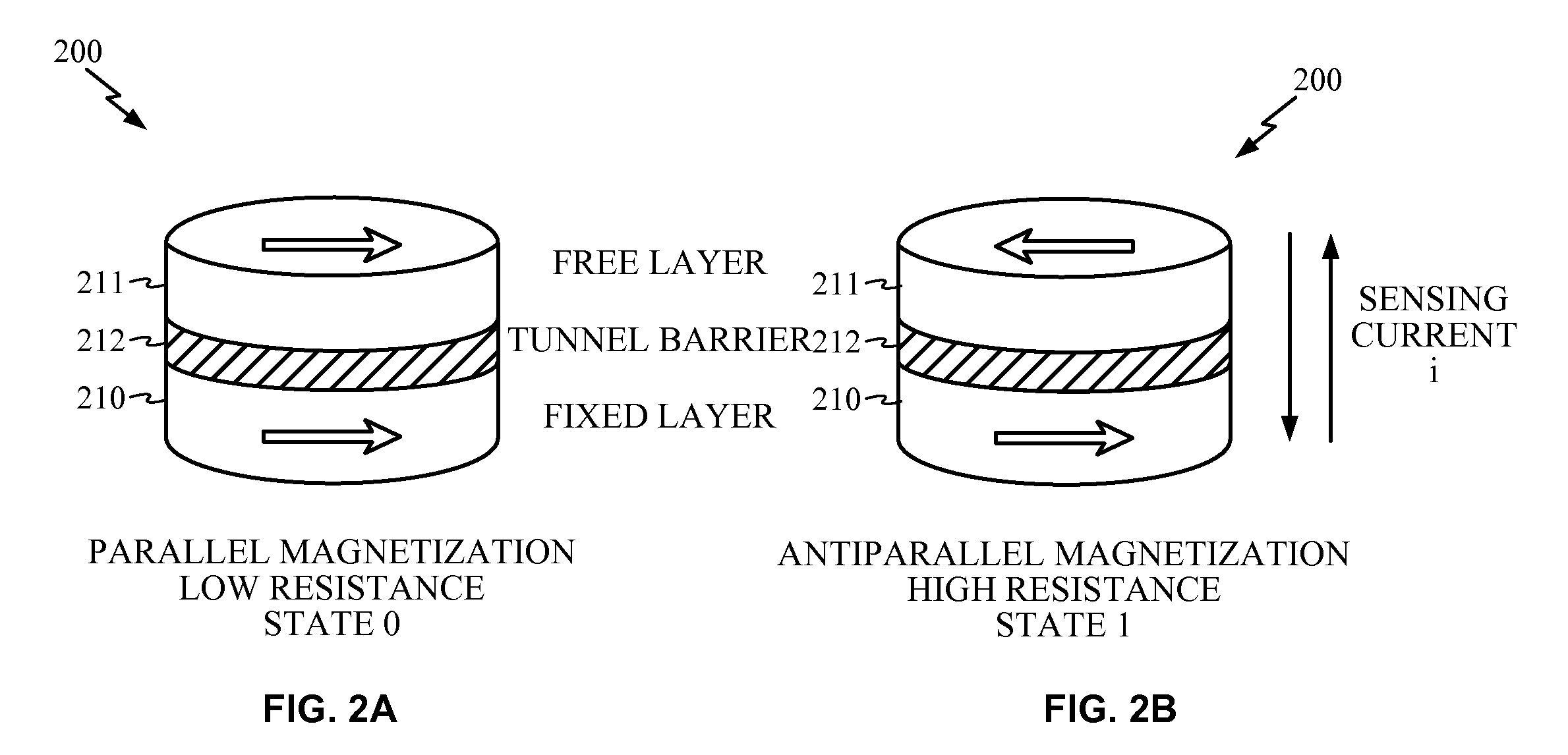

In electronics/spintronics, a tunnel junction is a barrier, such as a thin insulating layer or electric potential, between two electrically conducting materials. Electrons (or quasiparticles) pass through the barrier by the process of quantum tunnelling. Classically, the electron has zero probability of passing through the barrier. However, according to quantum mechanics, the electron has a non-zero wave amplitude in the barrier, and hence it has some probability of passing through the barrier. Tunnel junctions serve a variety of different purposes.

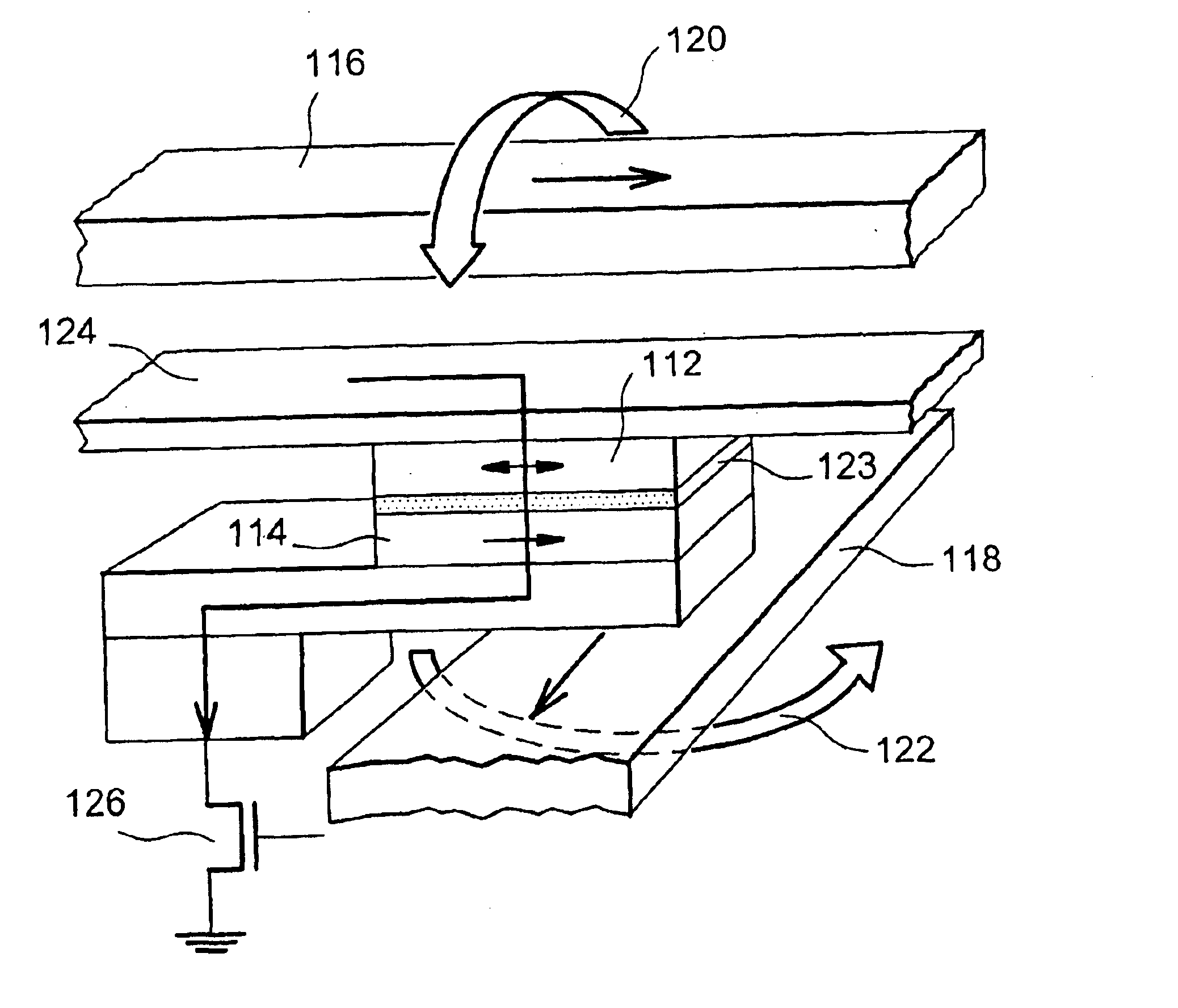

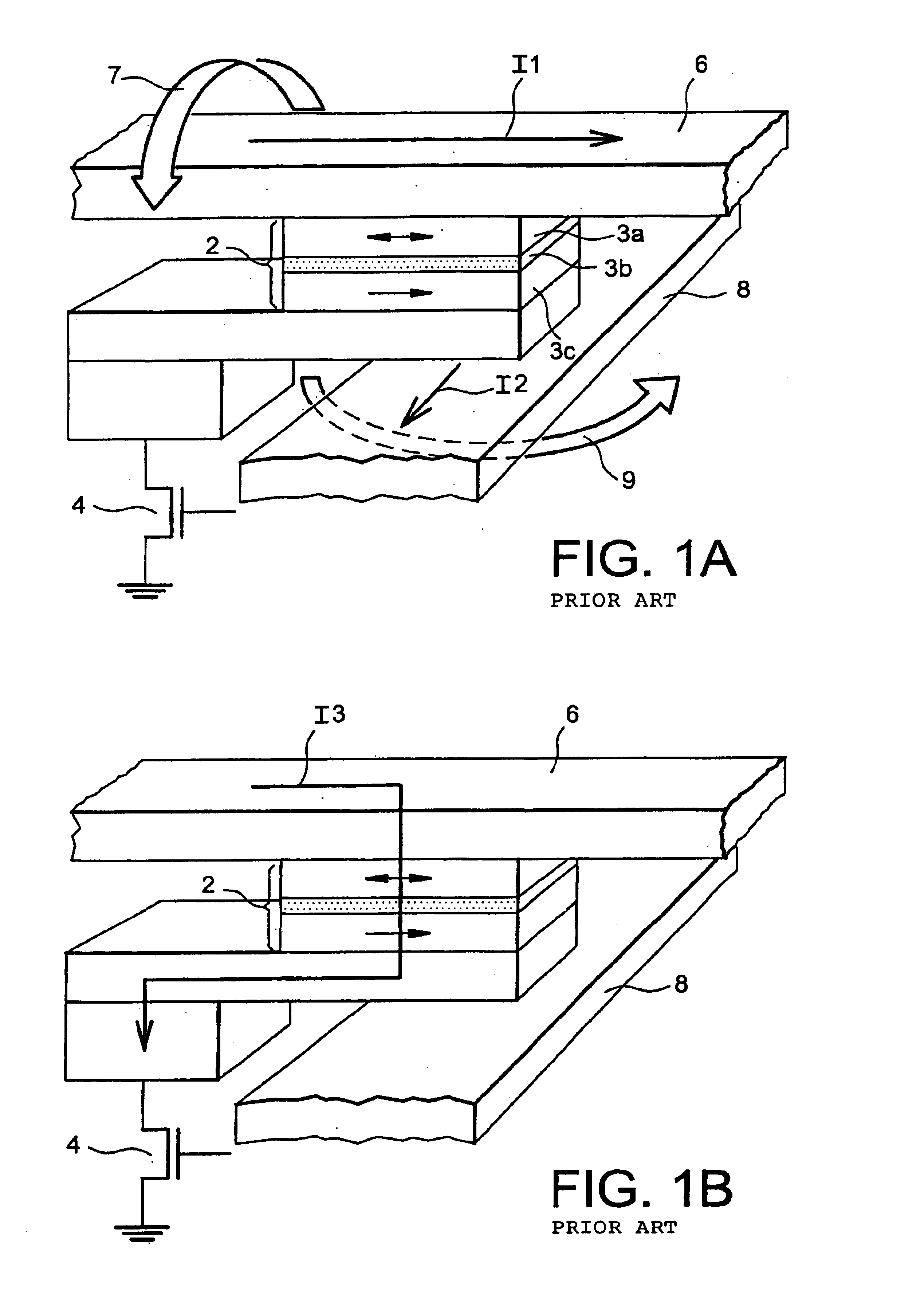

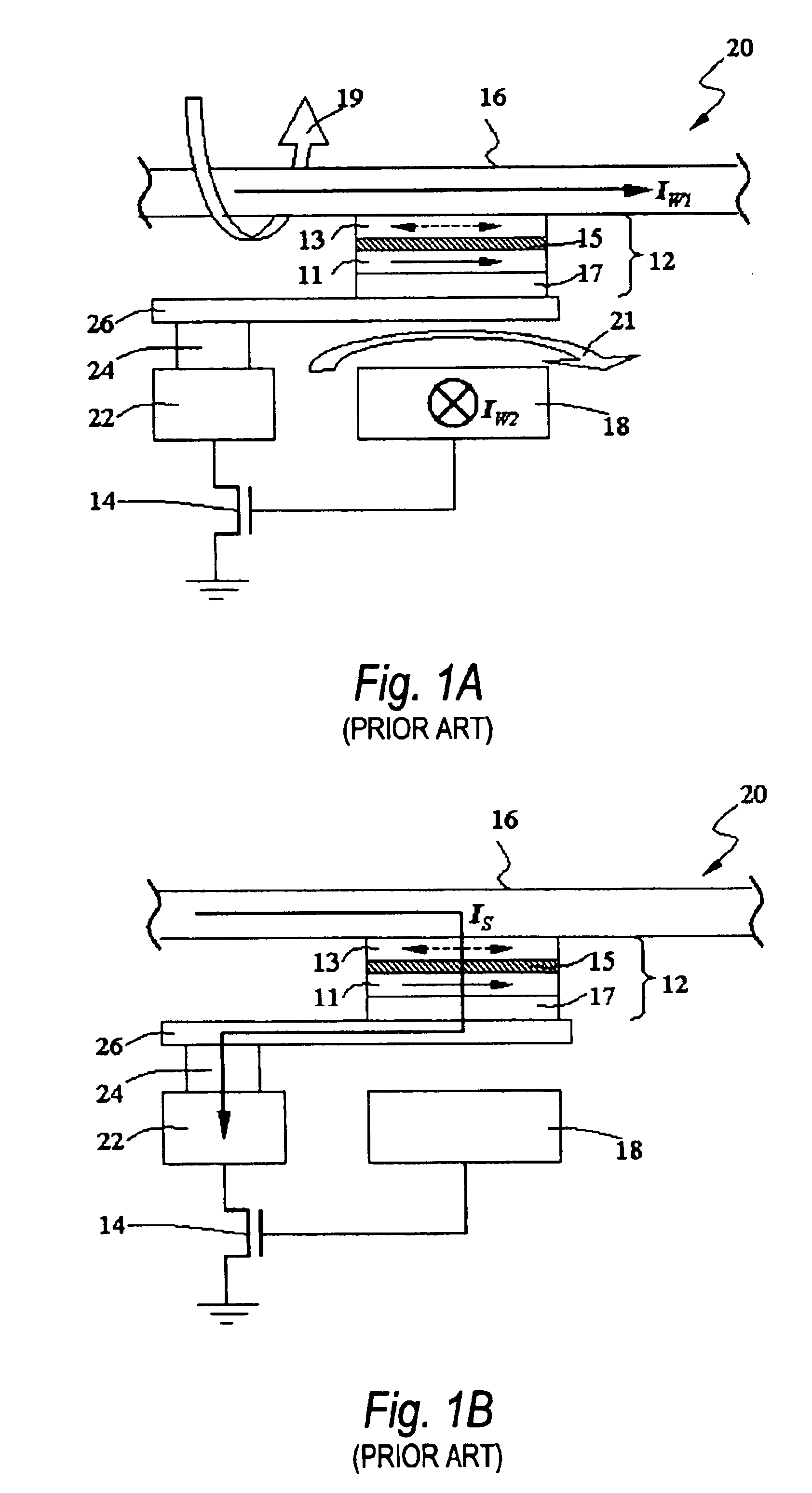

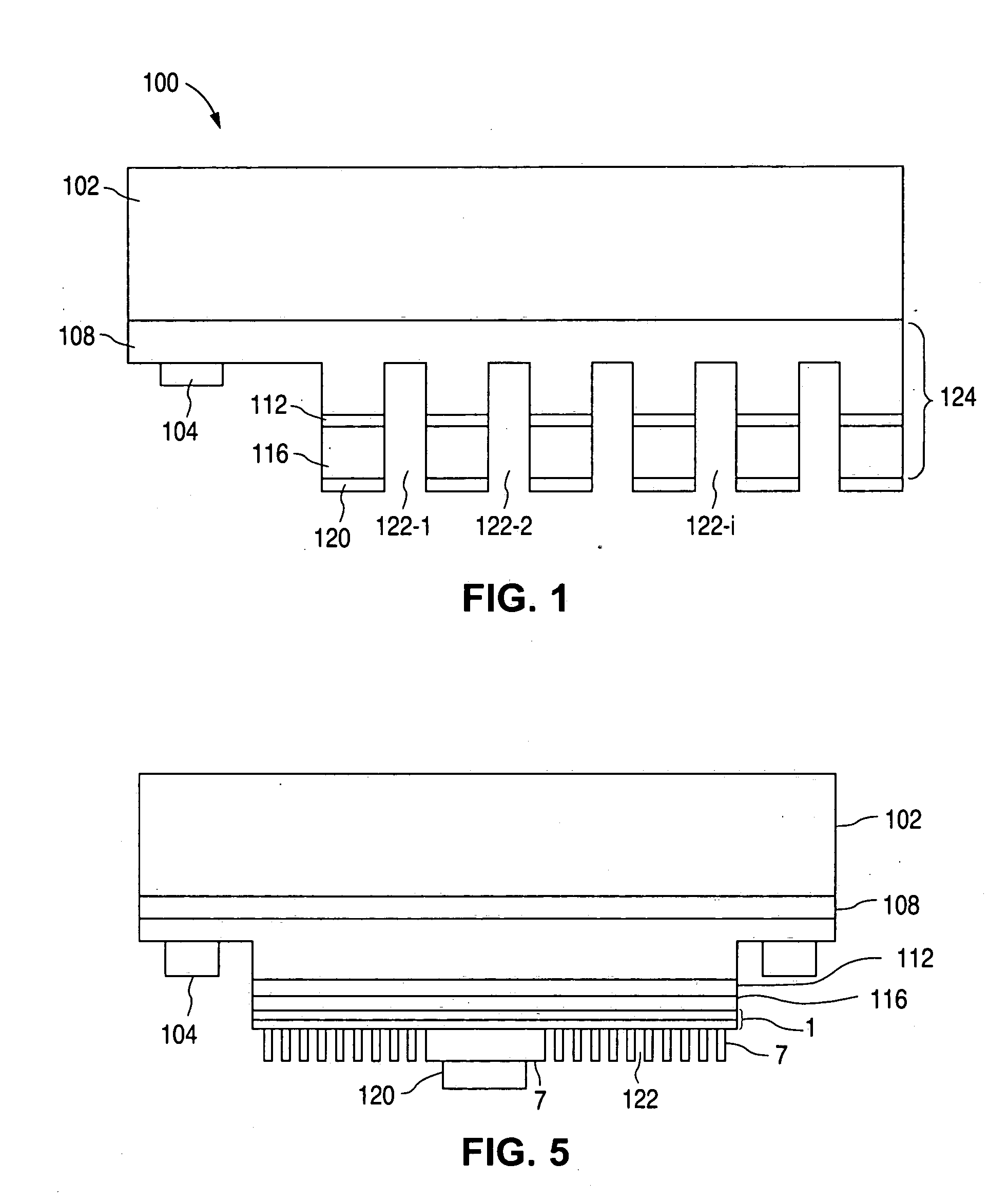

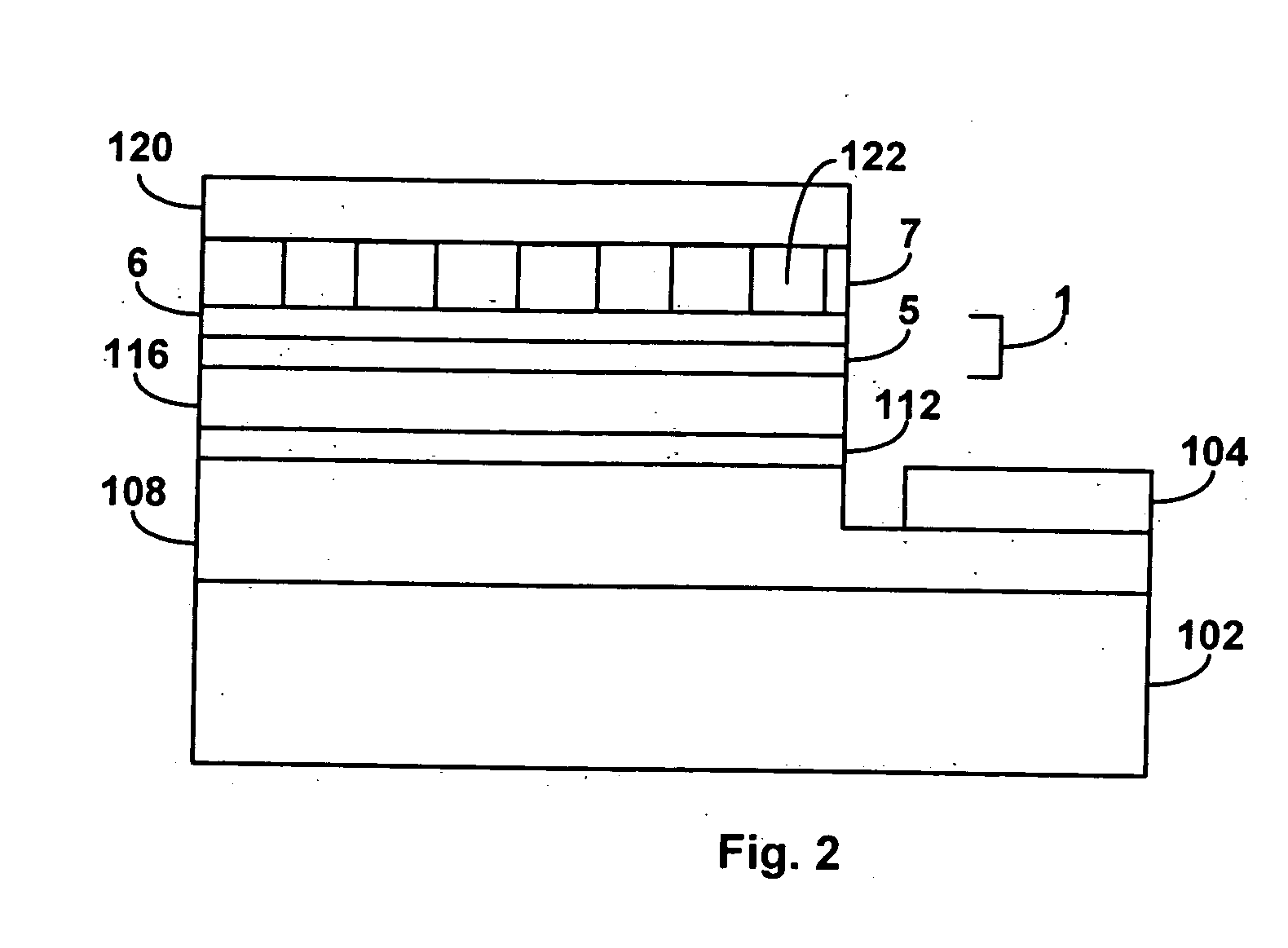

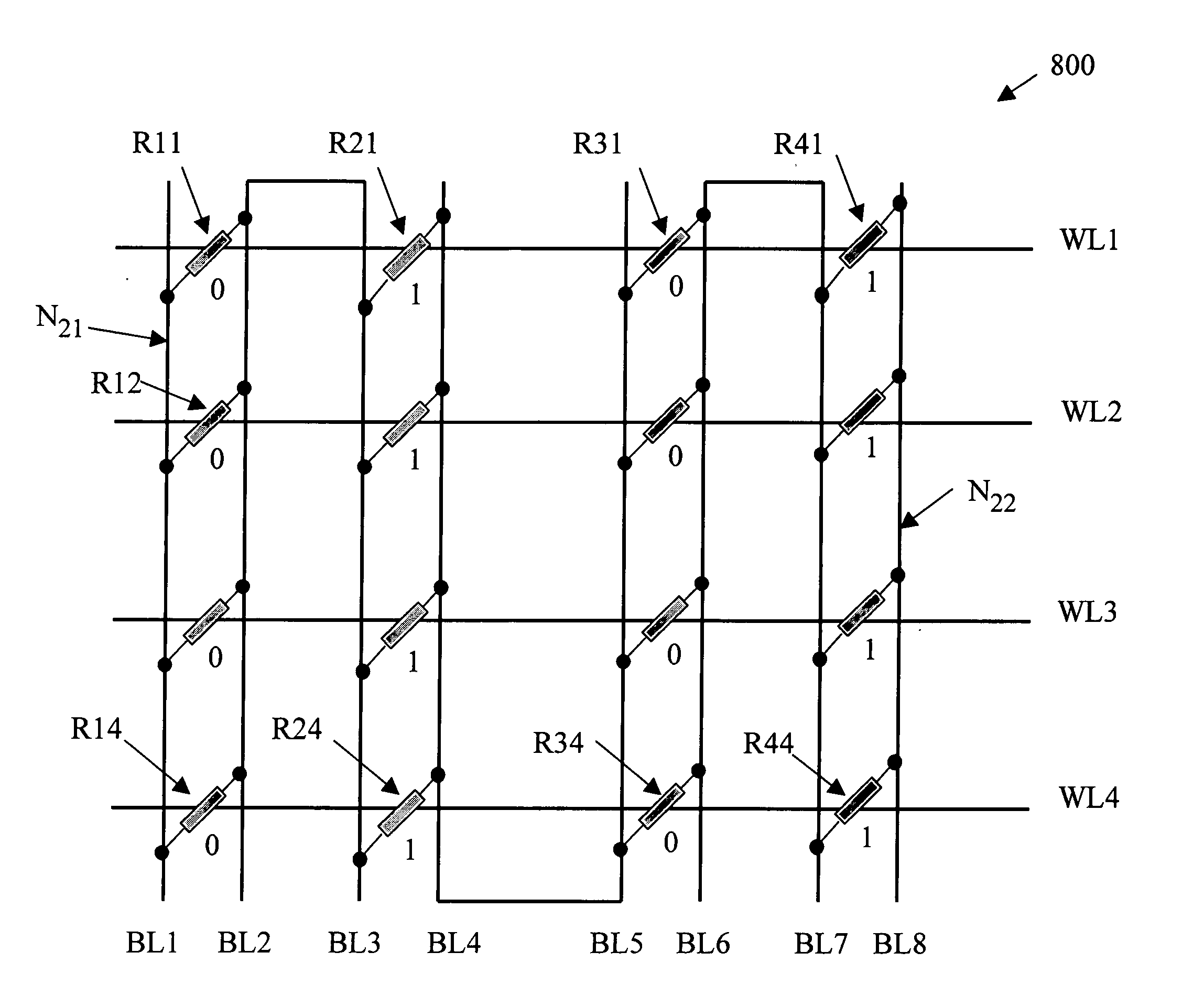

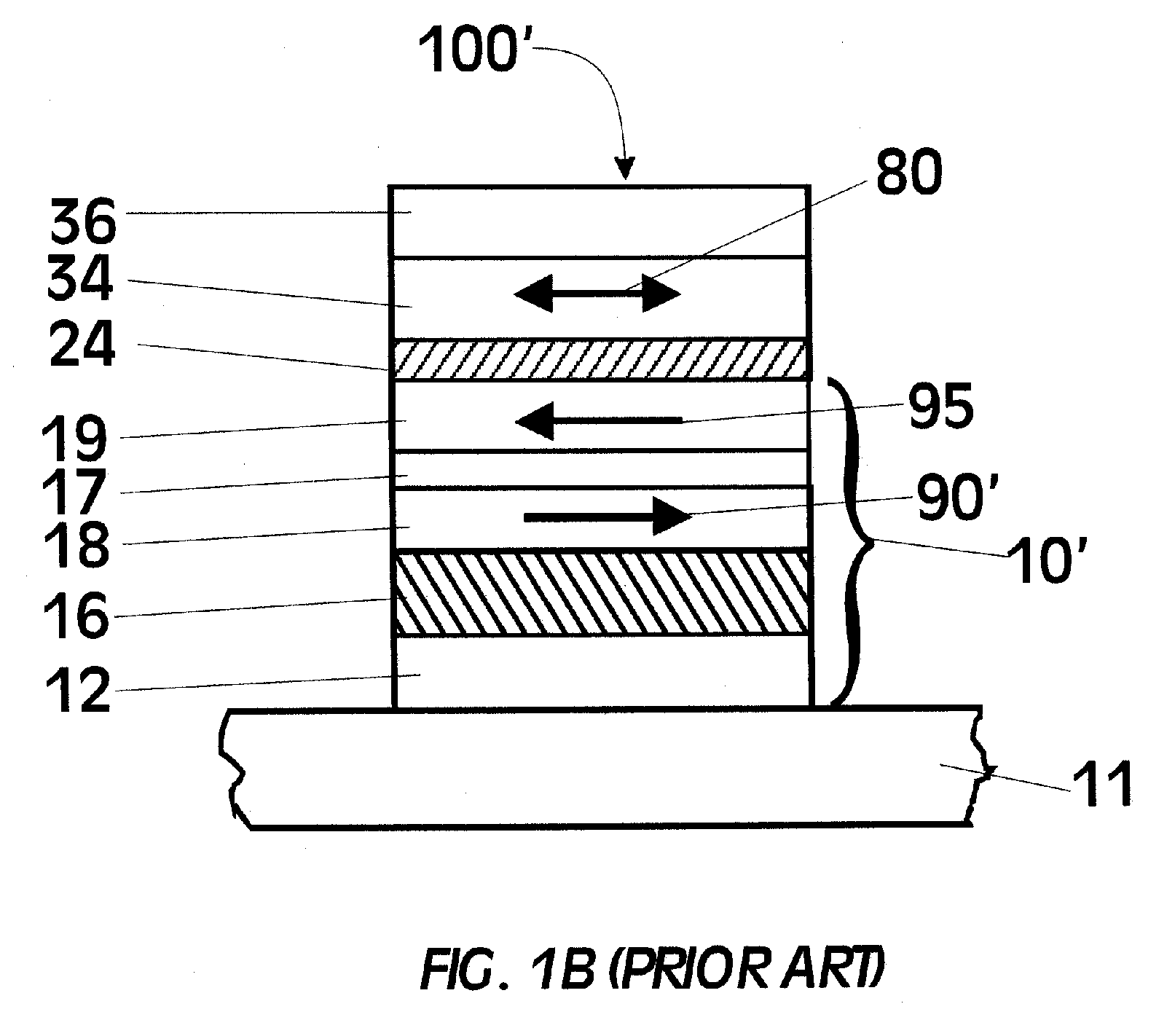

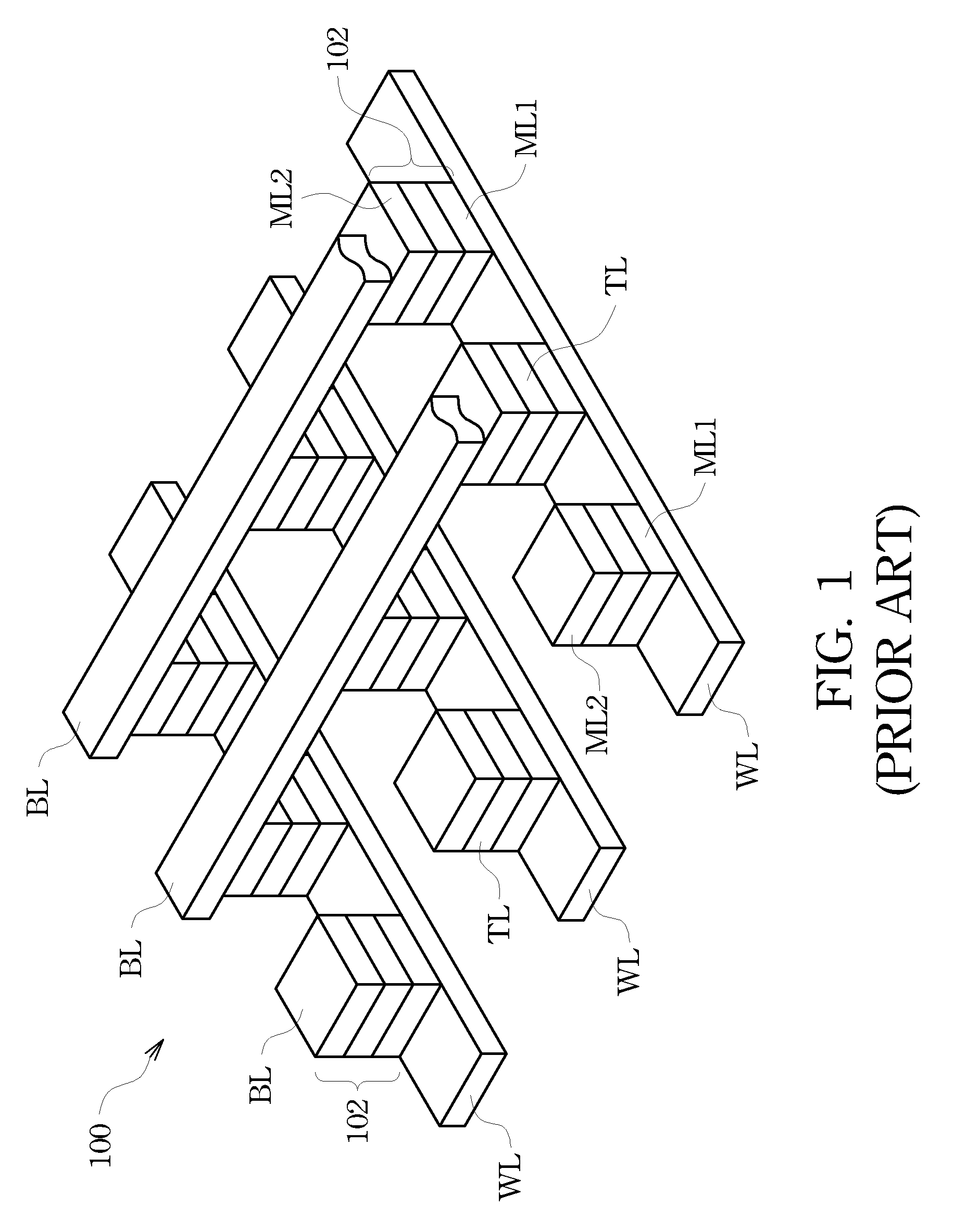

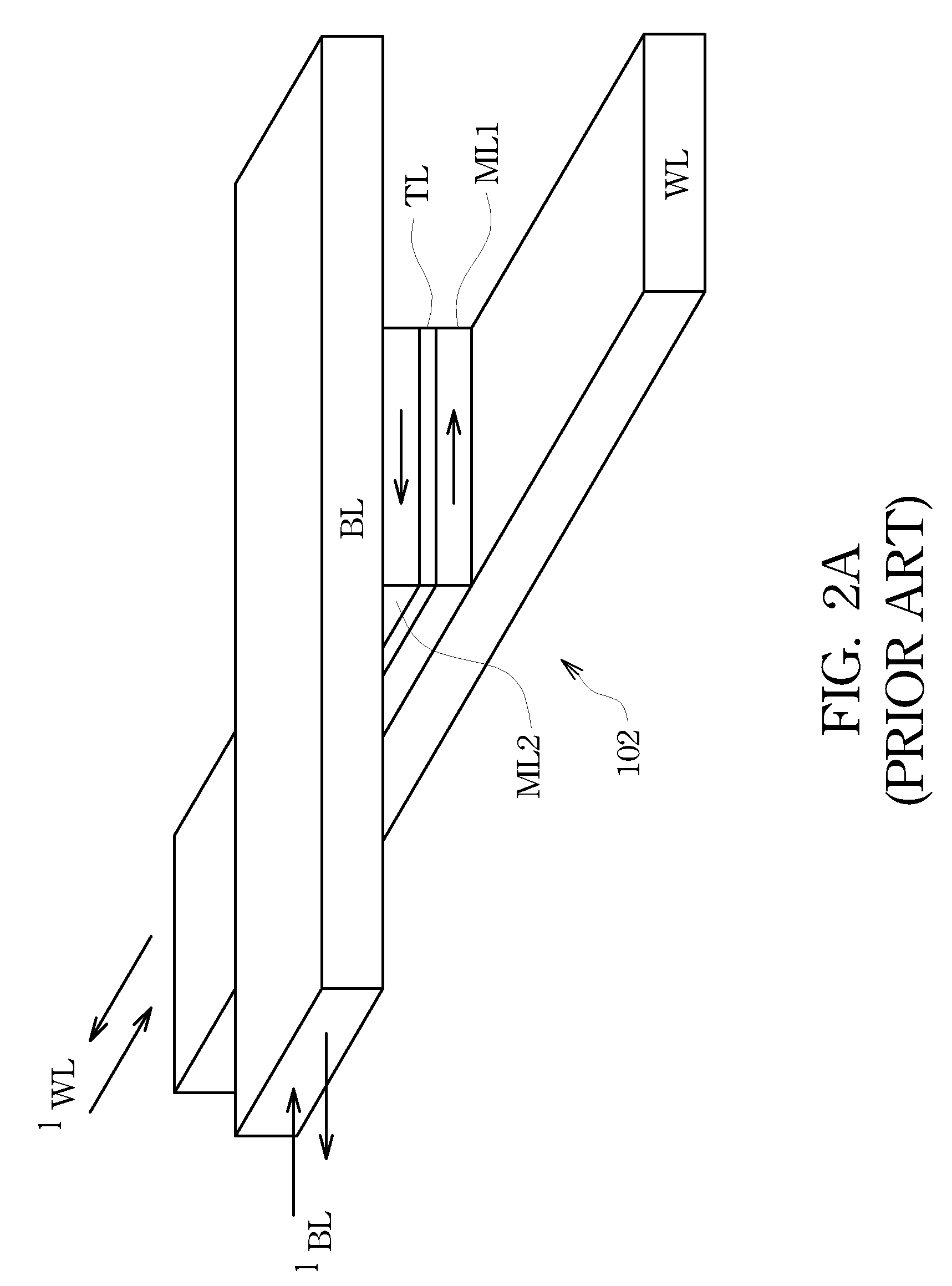

Thermally-assisted magnetic random access memory (MRAM)

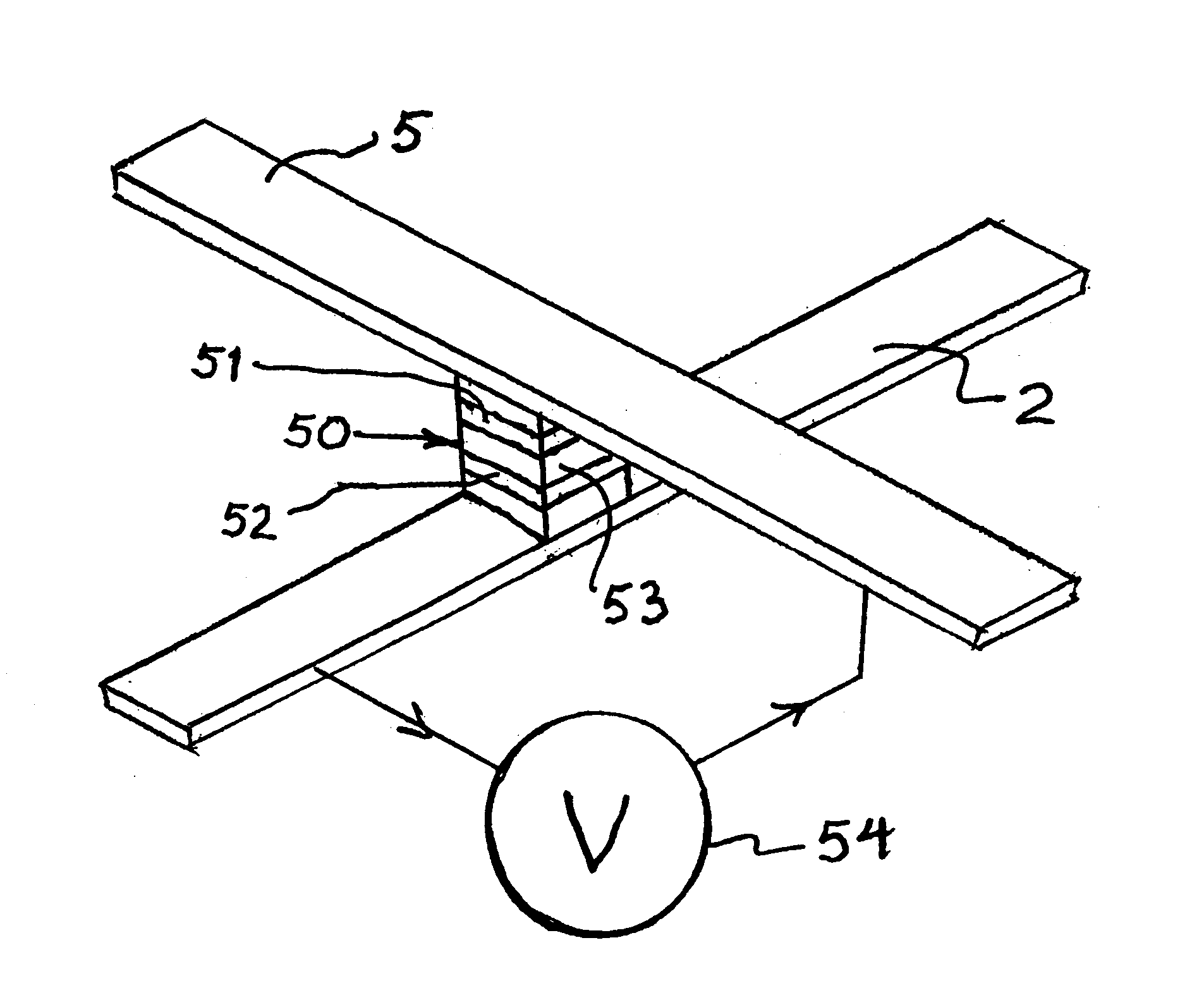

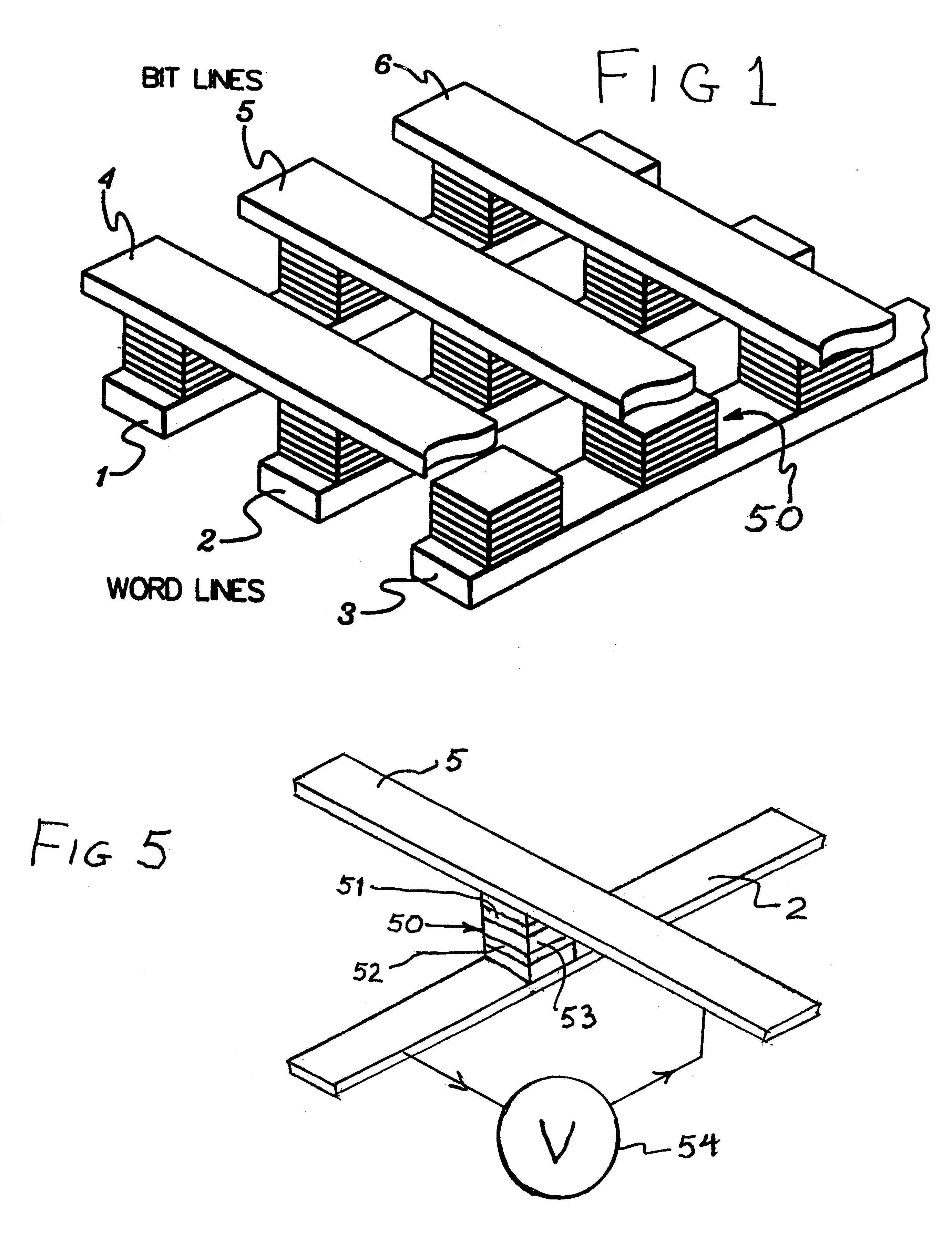

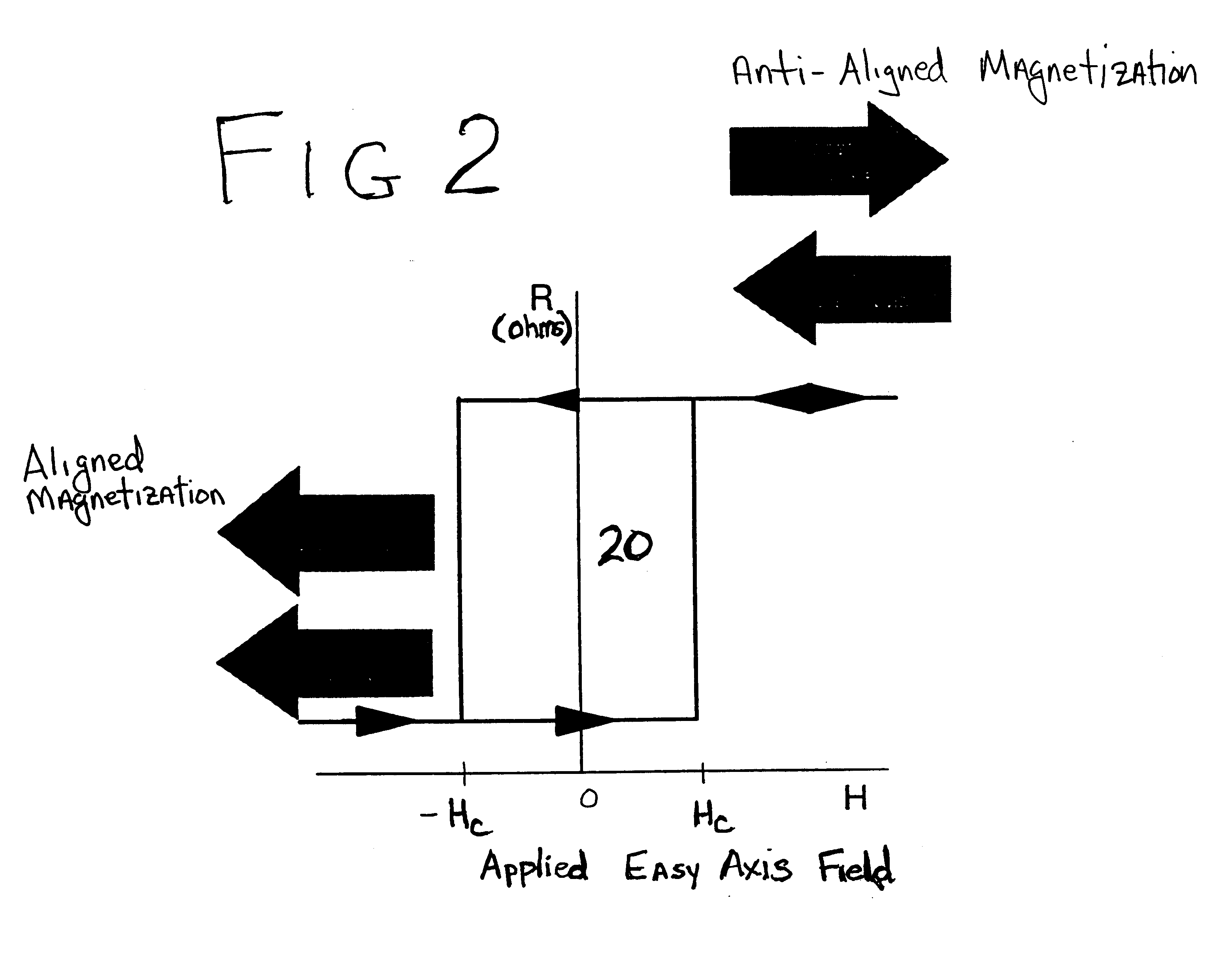

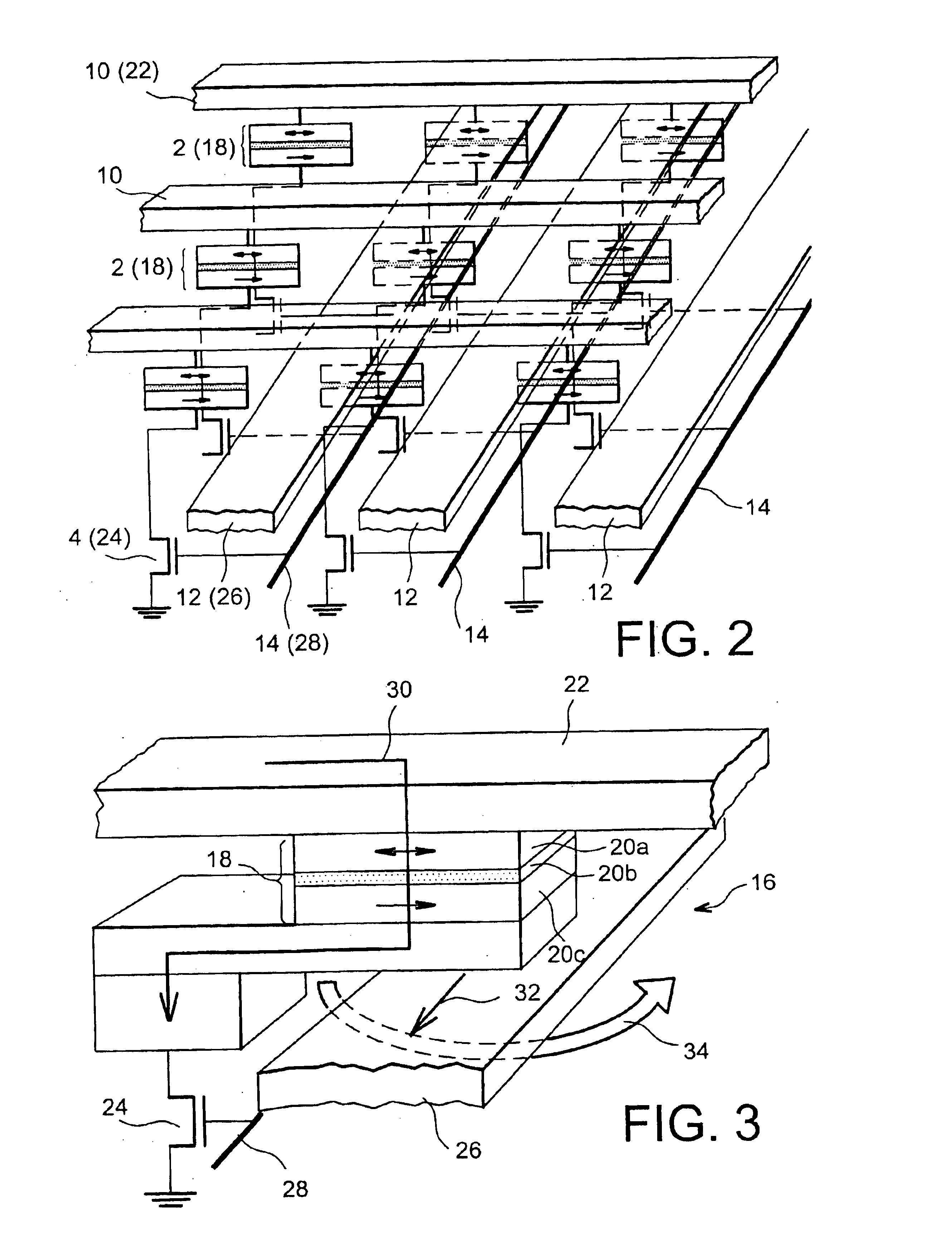

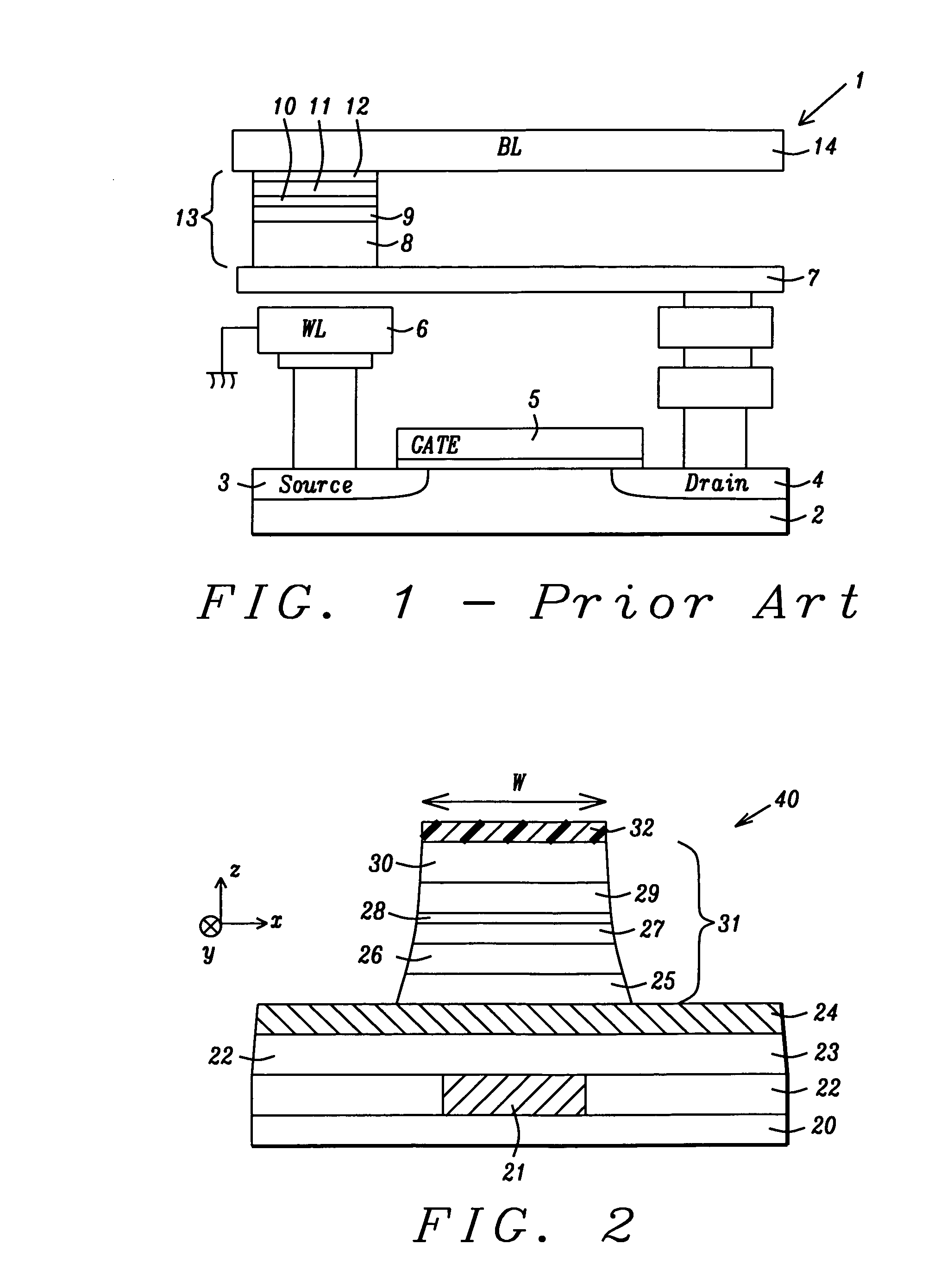

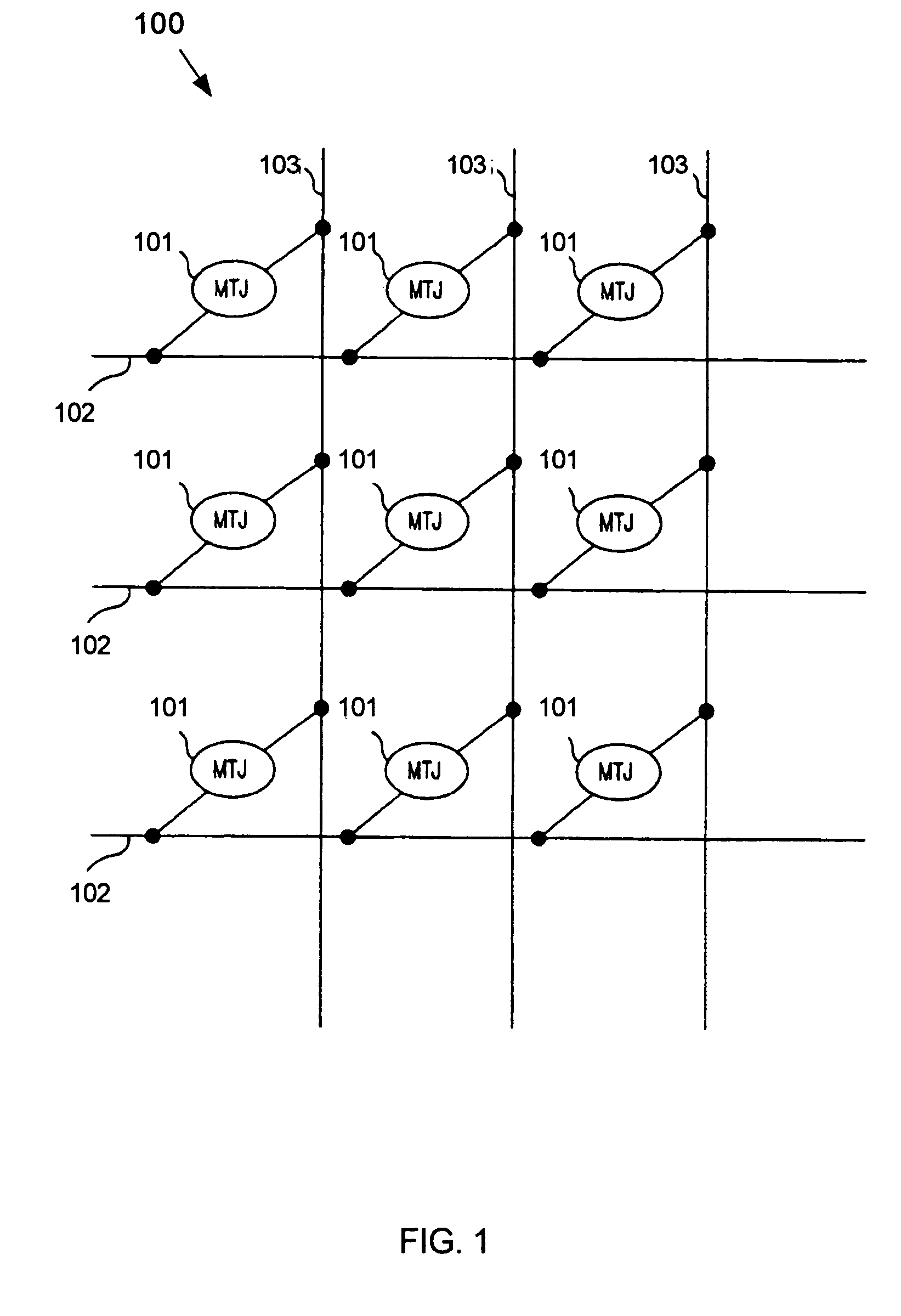

It is important to ensure good selectivity of a single magnetic tunnel junction storage cell within a memory array without affecting nearby storage cells. For this purpose, this memory array of storage cells preferably comprises a) an array of electrically conducting bit lines and electrically conducting word lines which form intersections therebetween, b) a storage cell disposed at each of said intersections, each storage cell comprising at least one reversible magnetic region or layer characterized by a magnetization state which can be reversed by applying thereto a selected external magnetic field, said reversible magnetic layer comprising a material whose magnetization state is more easily reversed upon a change in the temperature thereof, and c) a temperature change generator for changing the temperature of said reversible magnetic layer of only a selected one of said array of storage cells at any moment. To select a cell, it is preferable to select a cell by using a brief pulse of tunnelling current between the intersecting bit and word lines at that cell in order to provide sufficient Joule heating to facilitate a change in the magnetization state of its reversible magnetic layer, which preferably comprises a ferrimagnetic material.

Owner:IBM CORP

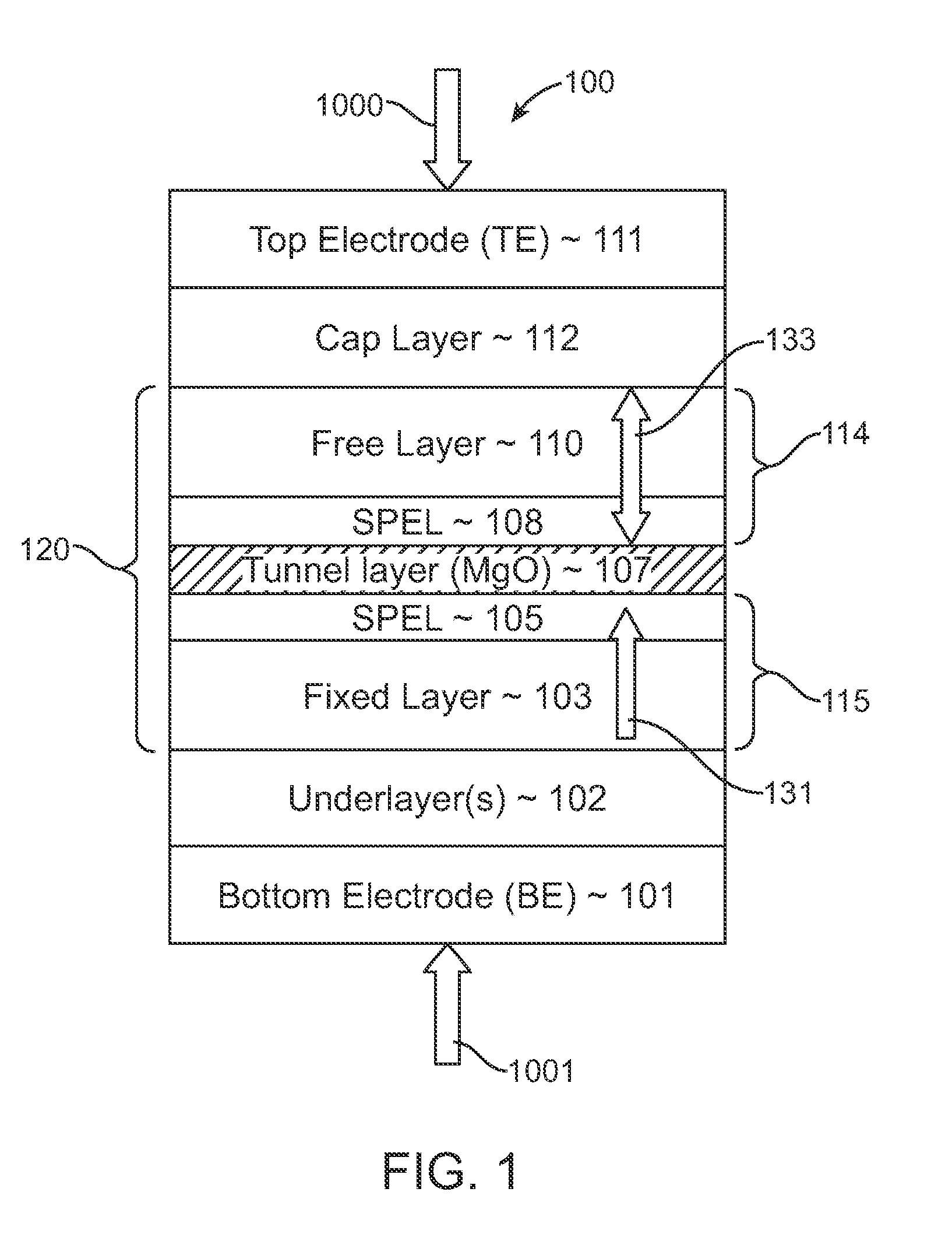

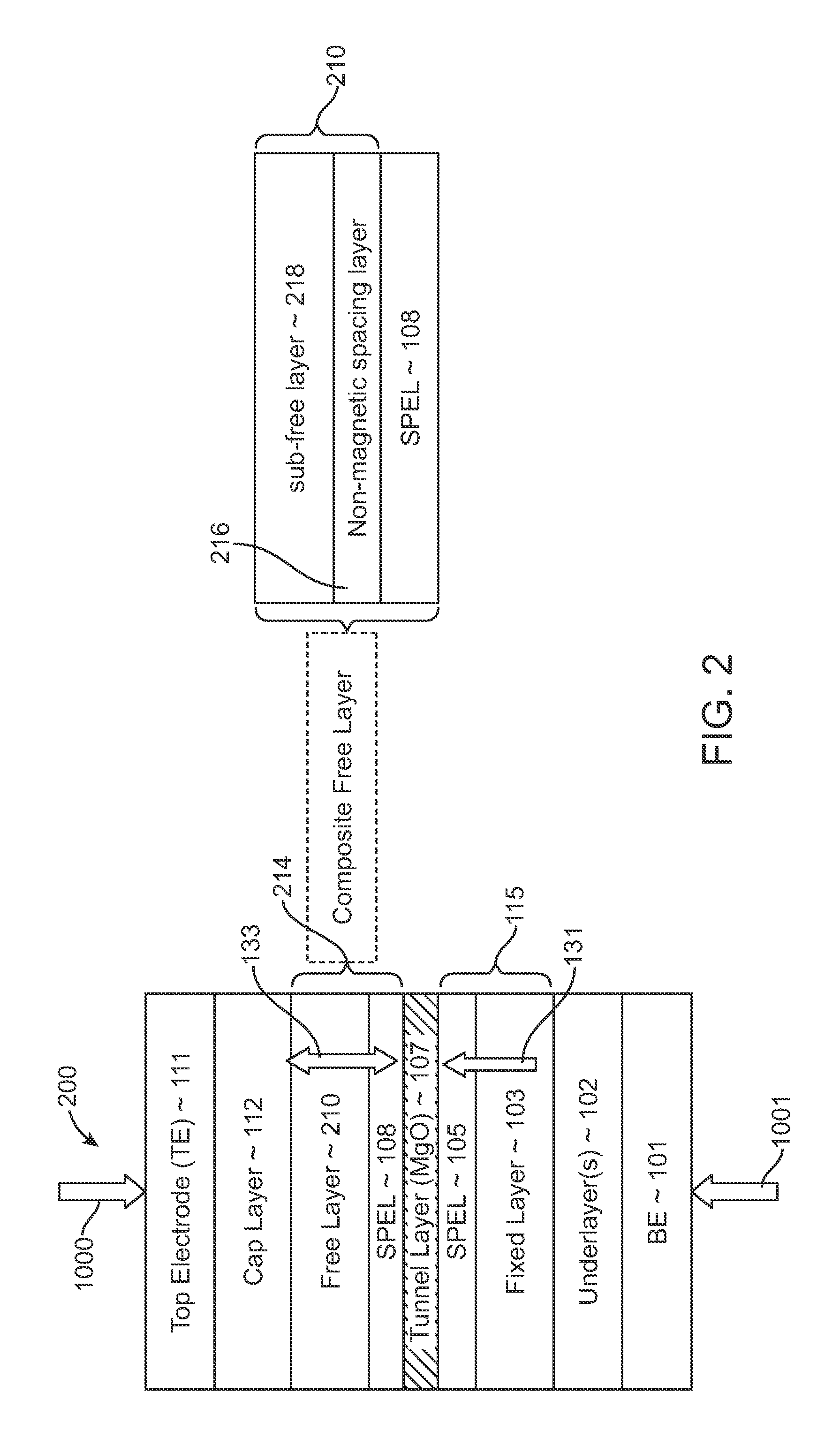

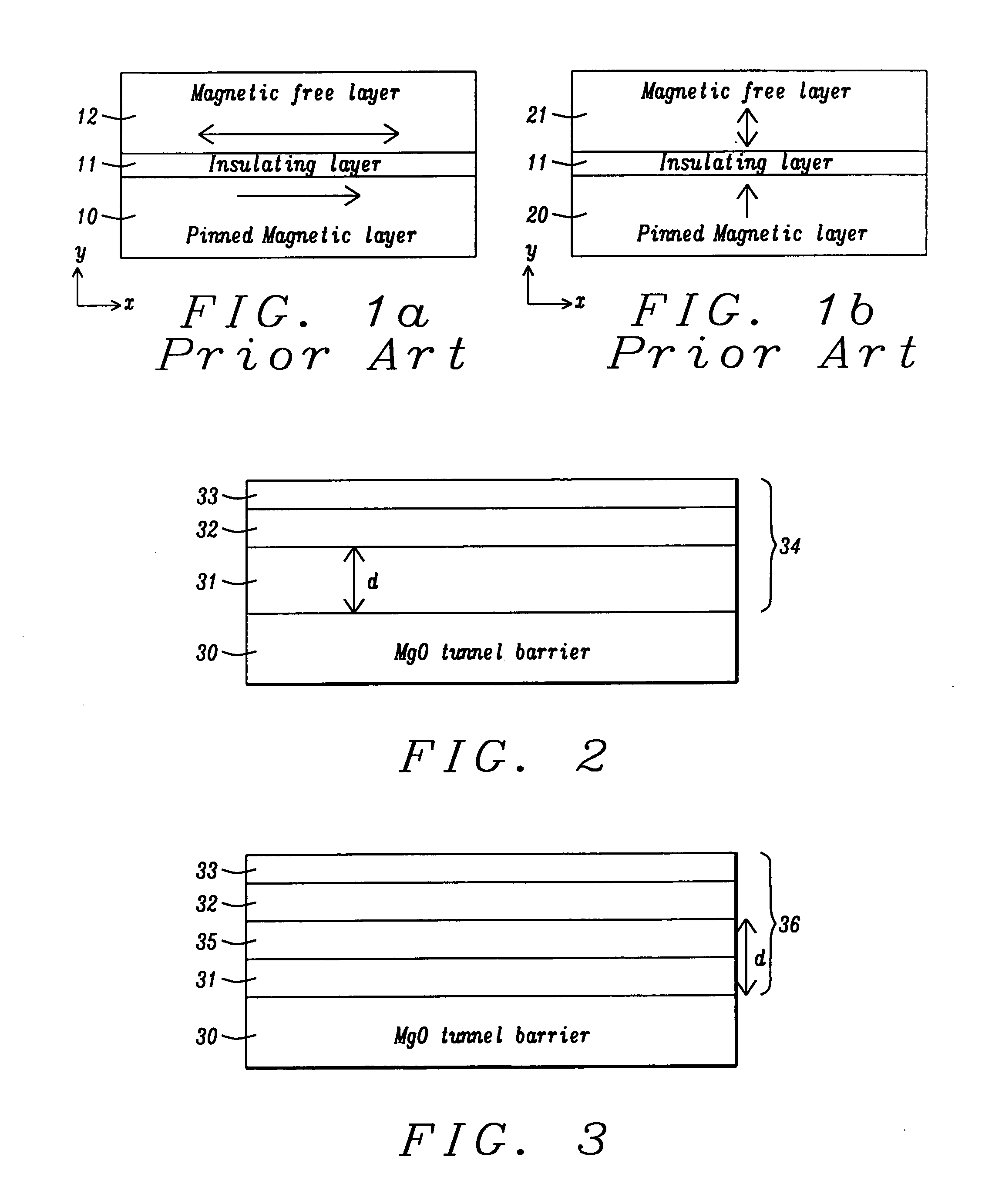

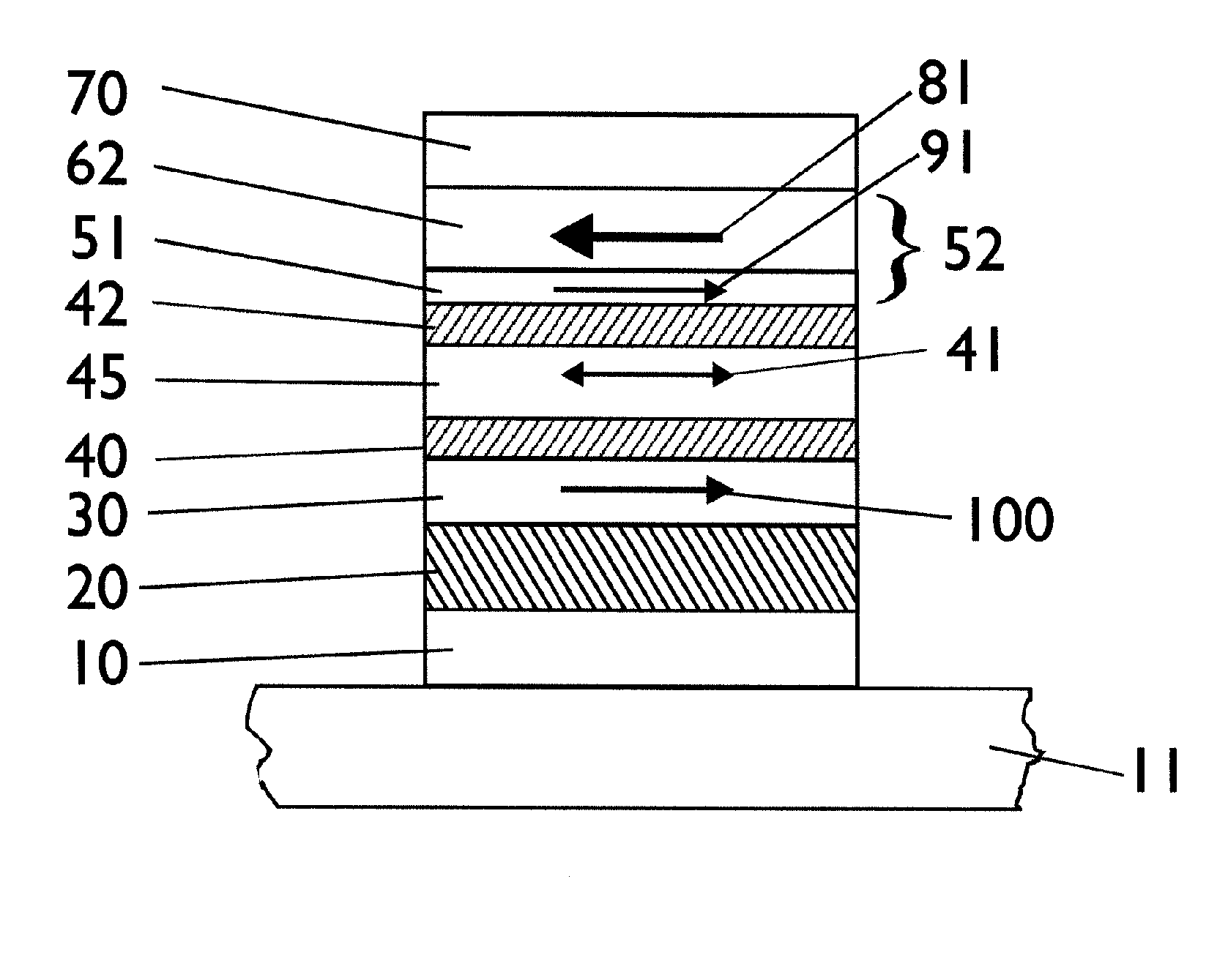

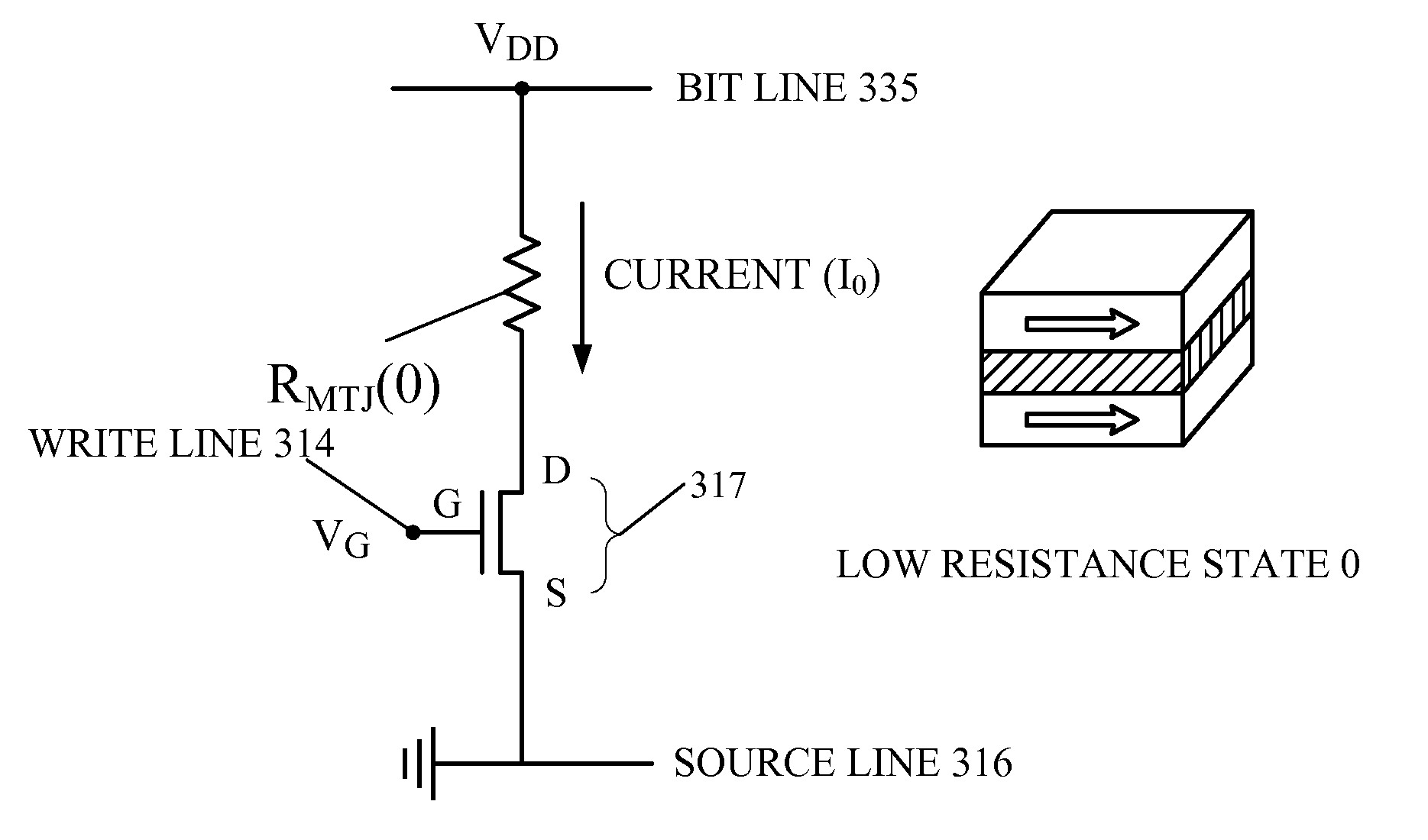

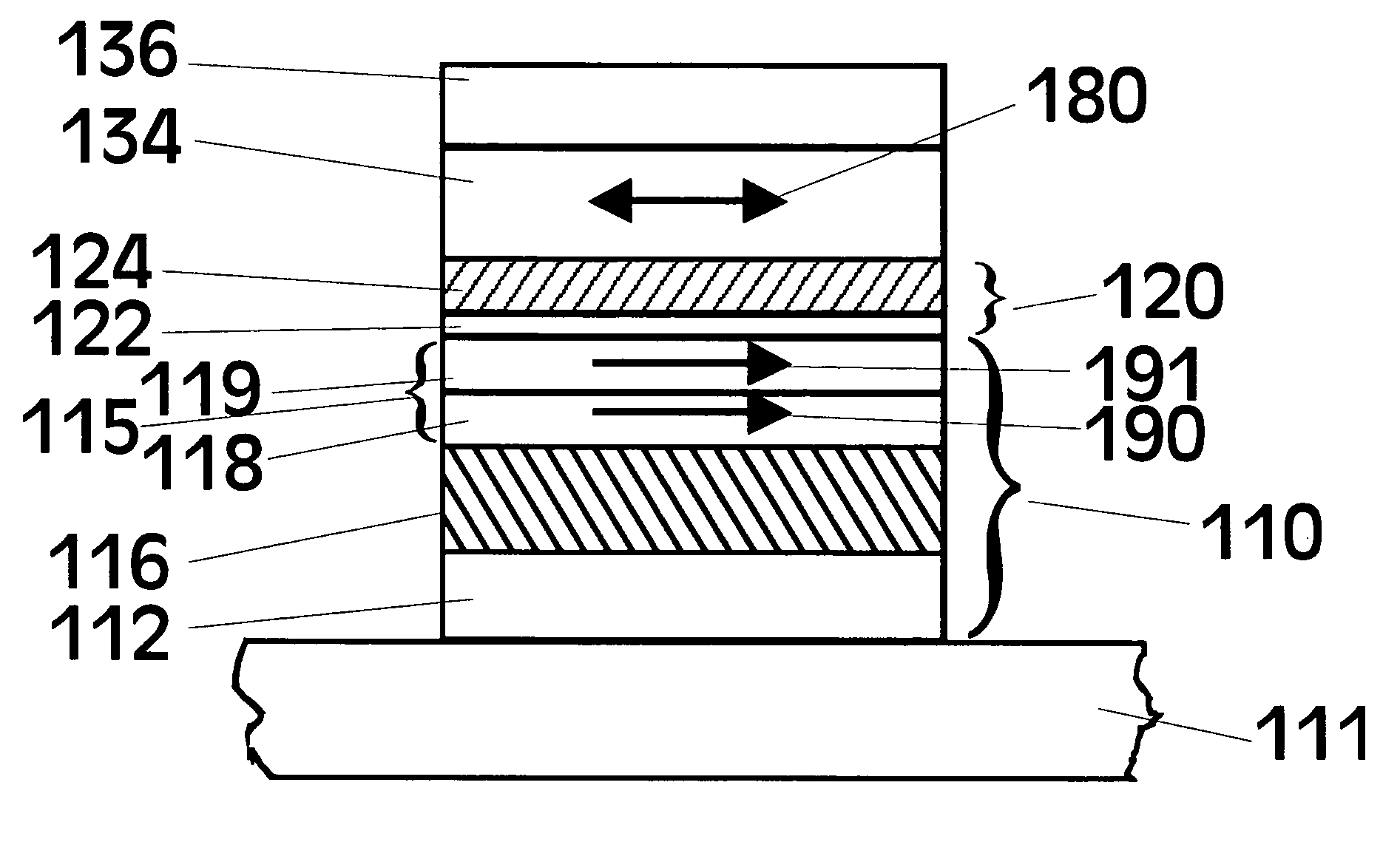

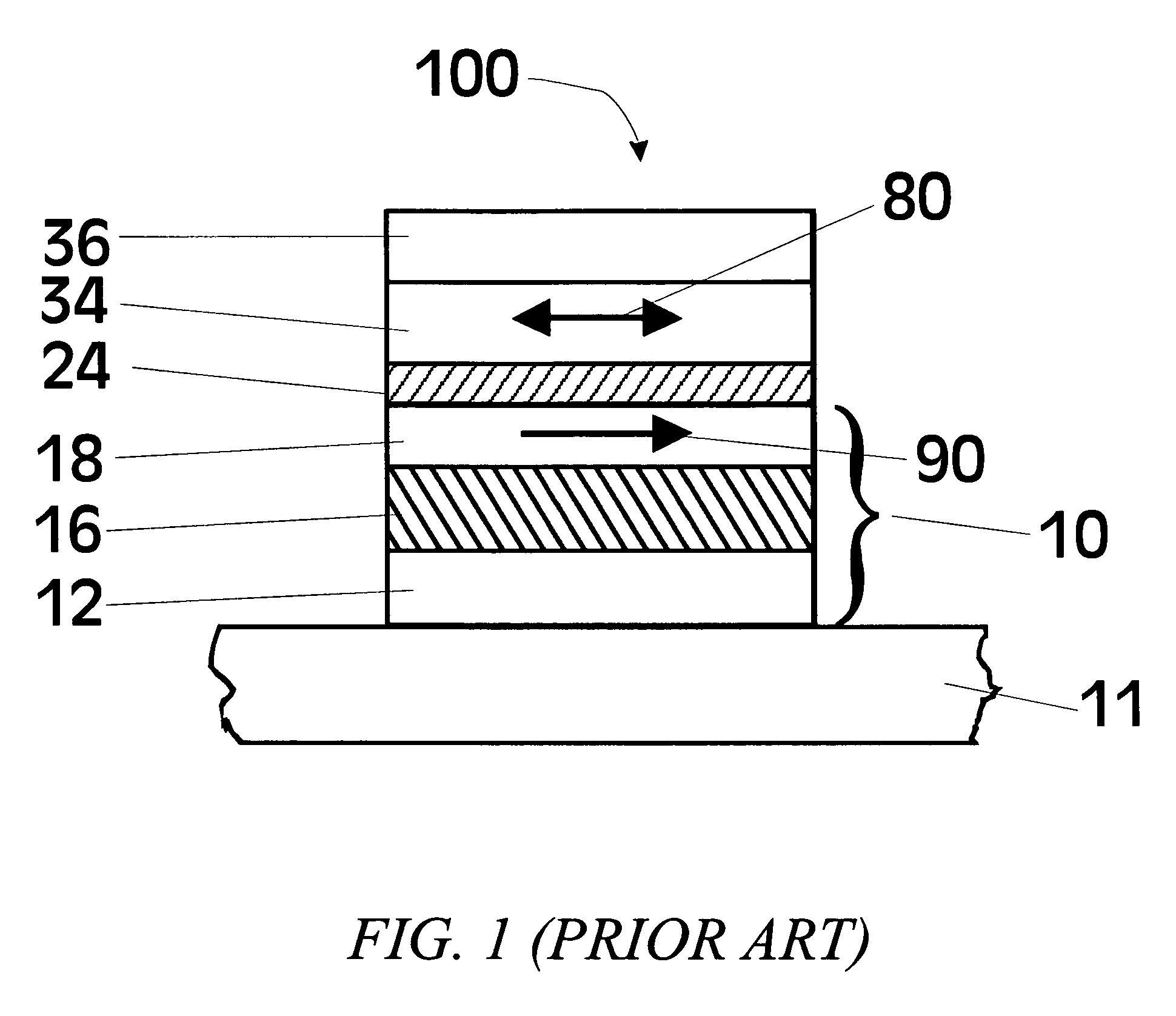

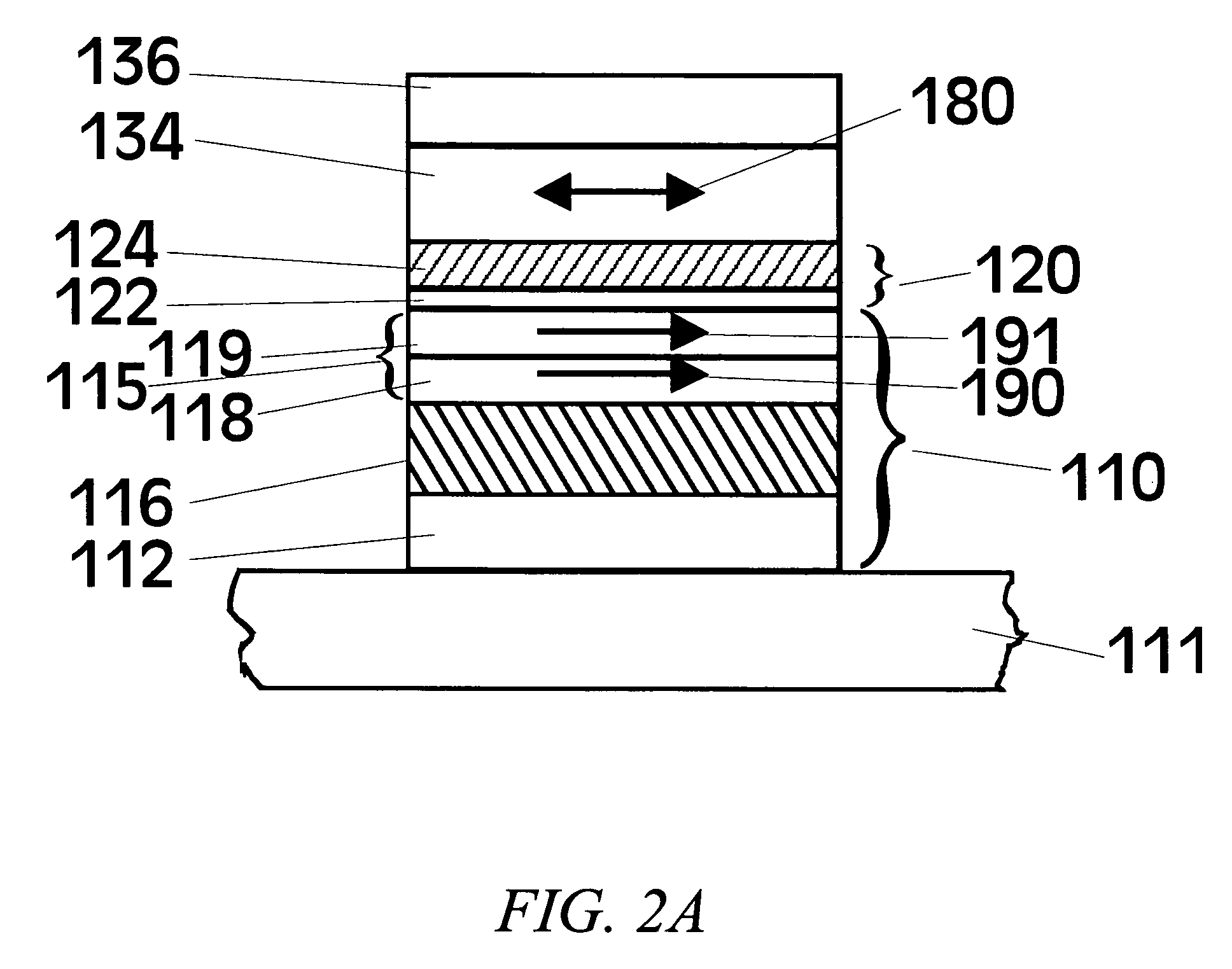

Spin-transfer torque magnetic random access memory having magnetic tunnel junction with perpendicular magnetic anisotropy

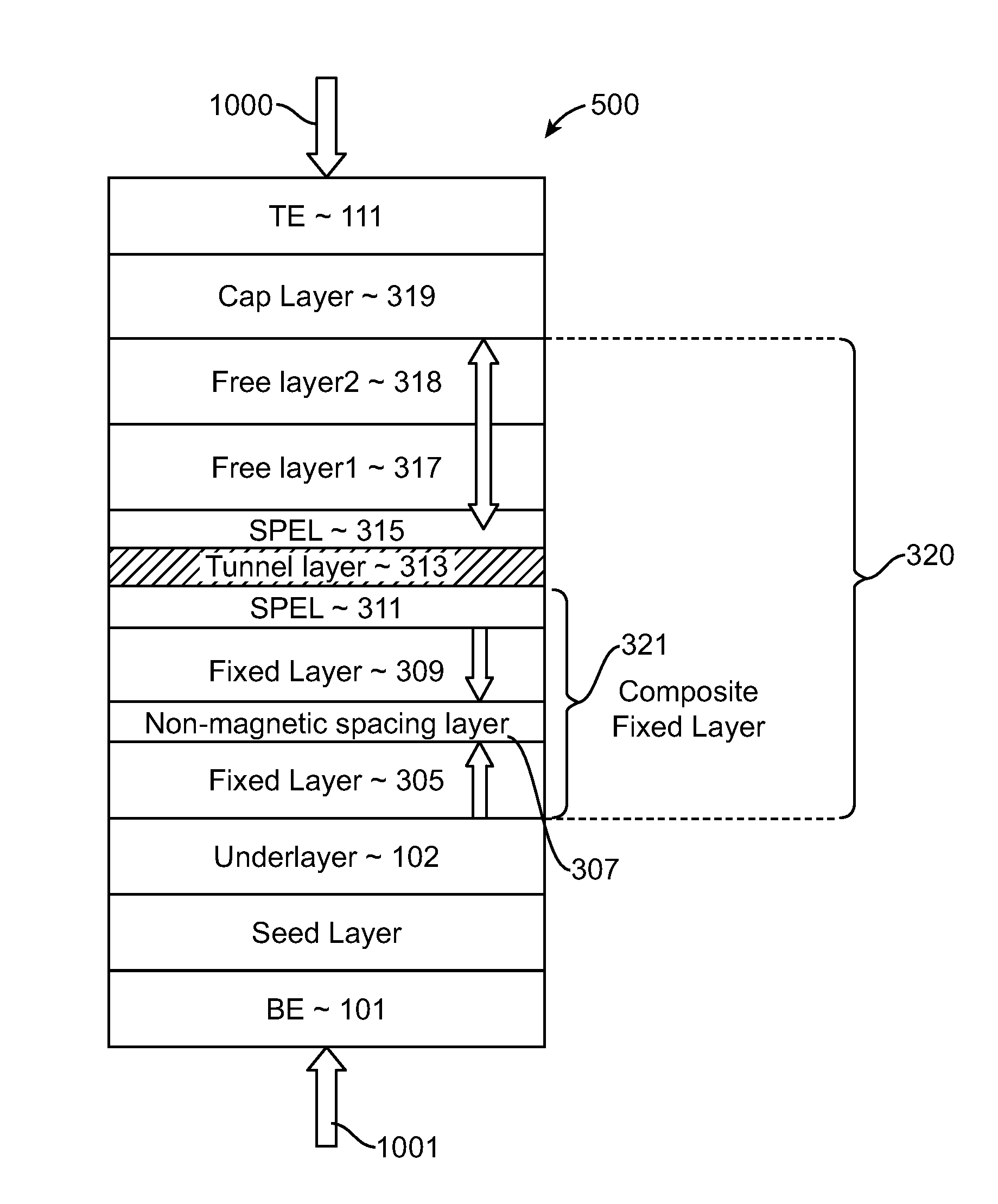

A spin-torque transfer memory random access memory (STTMRAM) element includes a fixed layer formed on top of a substrate and a a tunnel layer formed upon the fixed layer and a composite free layer formed upon the tunnel barrier layer and made of an iron platinum alloy with at least one of X or Y material, X being from a group consisting of: boron (B), phosphorous (P), carbon (C), and nitride (N) and Y being from a group consisting of: tantalum (Ta), titanium (Ti), niobium (Nb), zirconium (Zr), tungsten (W), silicon (Si), copper (Cu), silver (Ag), aluminum (Al), chromium (Cr), tin (Sn), lead (Pb), antimony (Sb), hafnium (Hf) and bismuth (Bi), molybdenum (Mo) or rhodium (Ru), the magnetization direction of each of the composite free layer and fixed layer being substantially perpendicular to the plane of the substrate.

Owner:AVALANCHE TECH

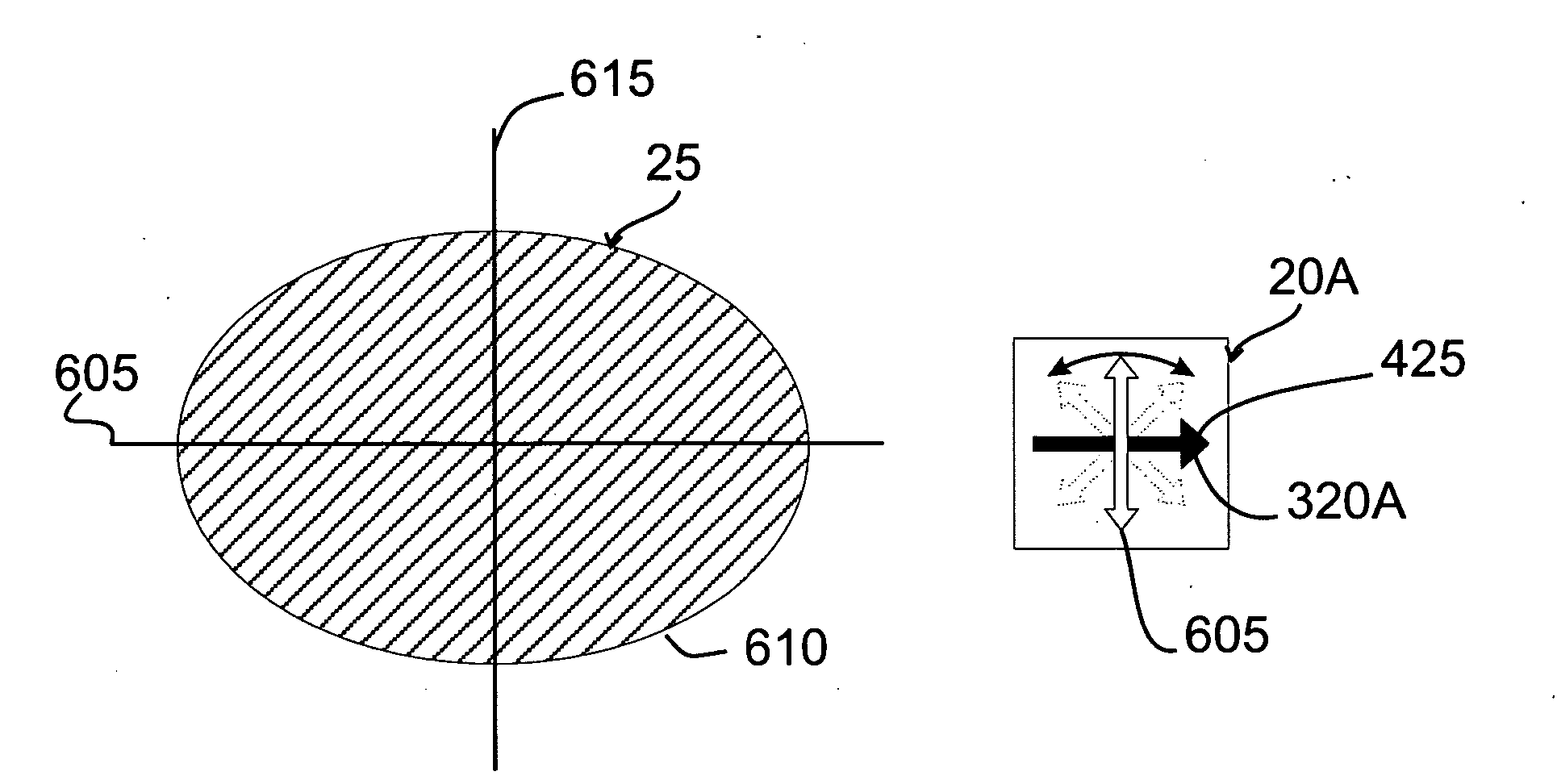

Magnetic tunnel junction magnetic device, memory and writing and reading methods using said device

InactiveUS6950335B2Good reproducibilityEliminate errorsNanomagnetismMagnetic-field-controlled resistorsMagnetizationSemiconductor

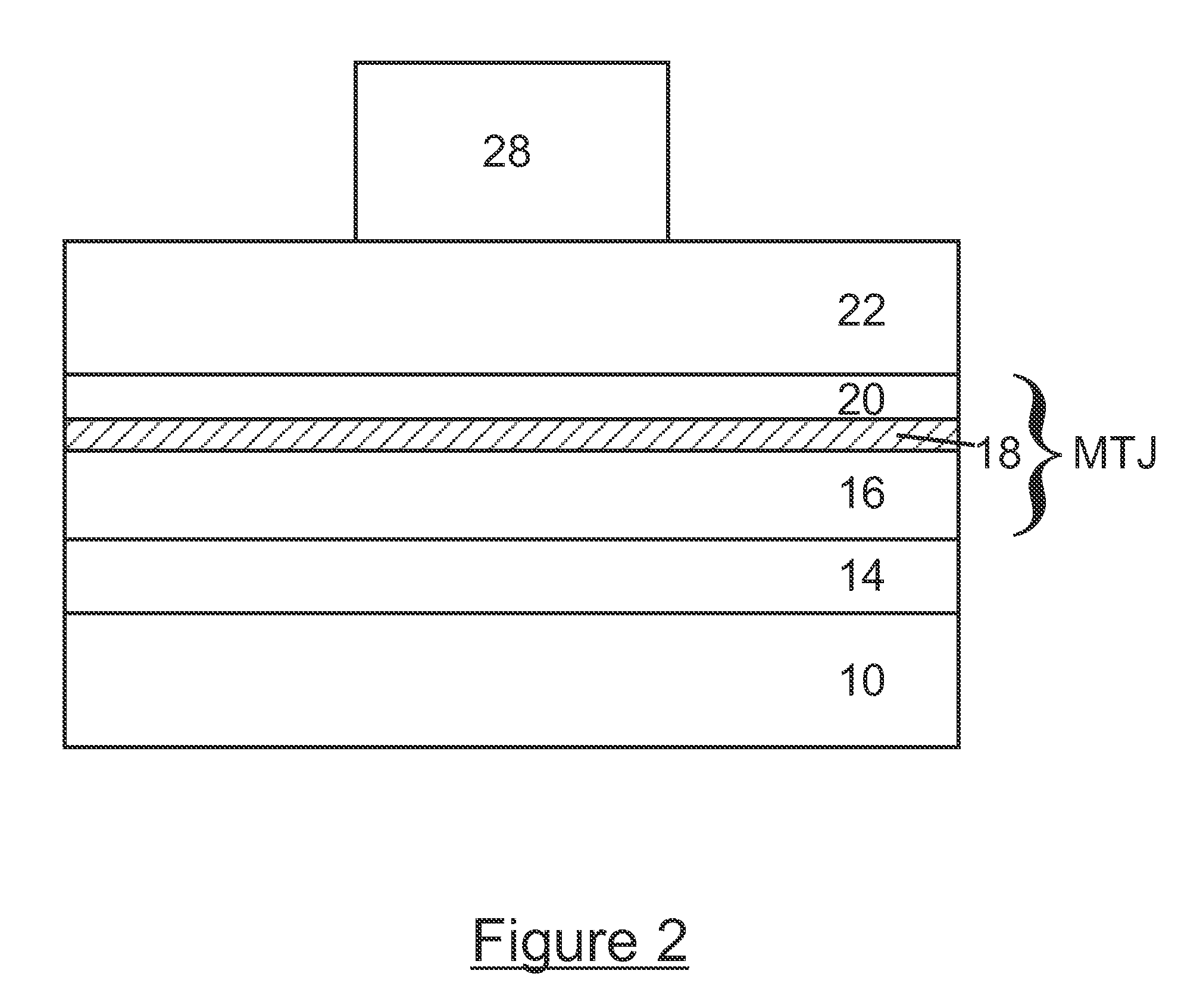

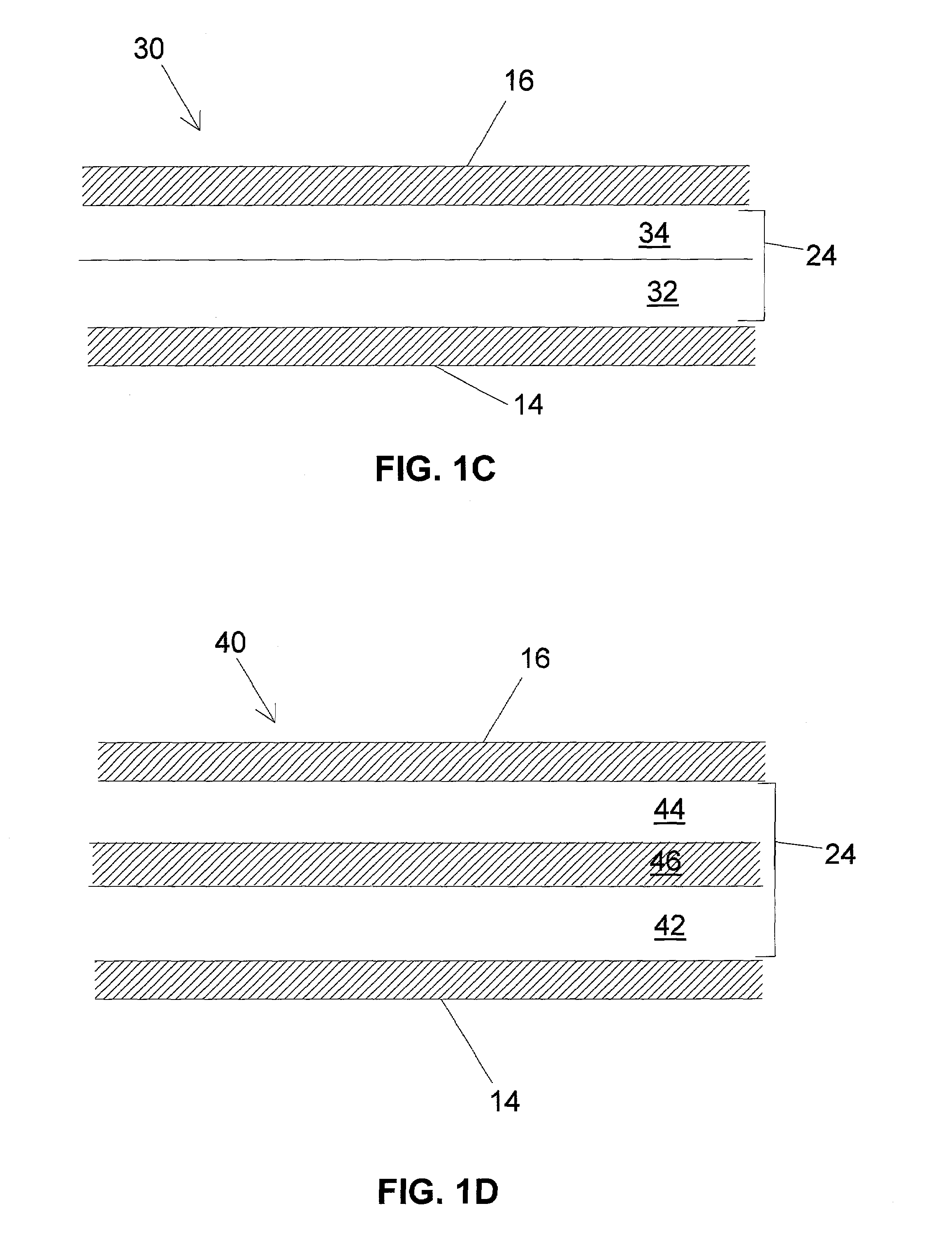

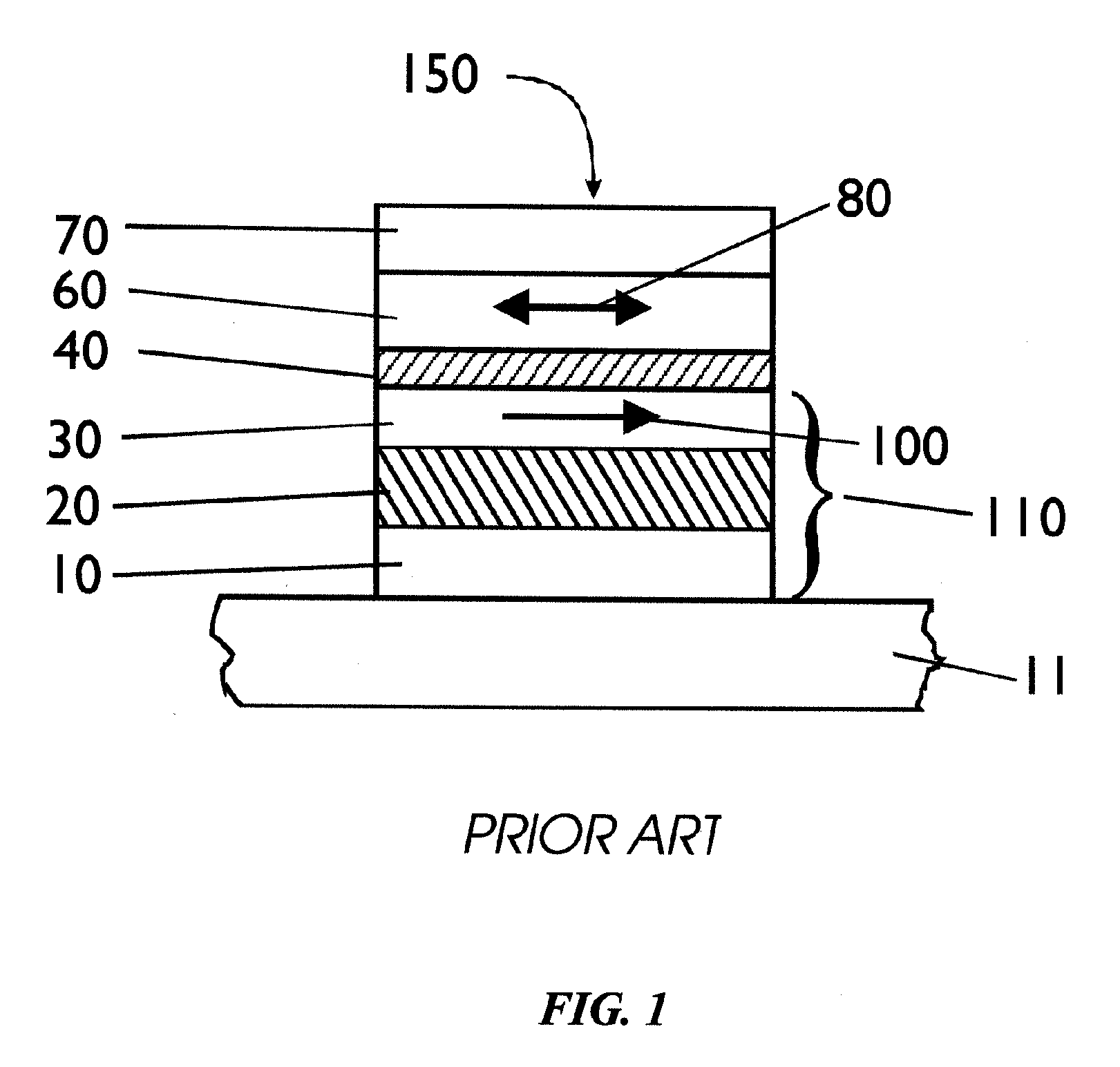

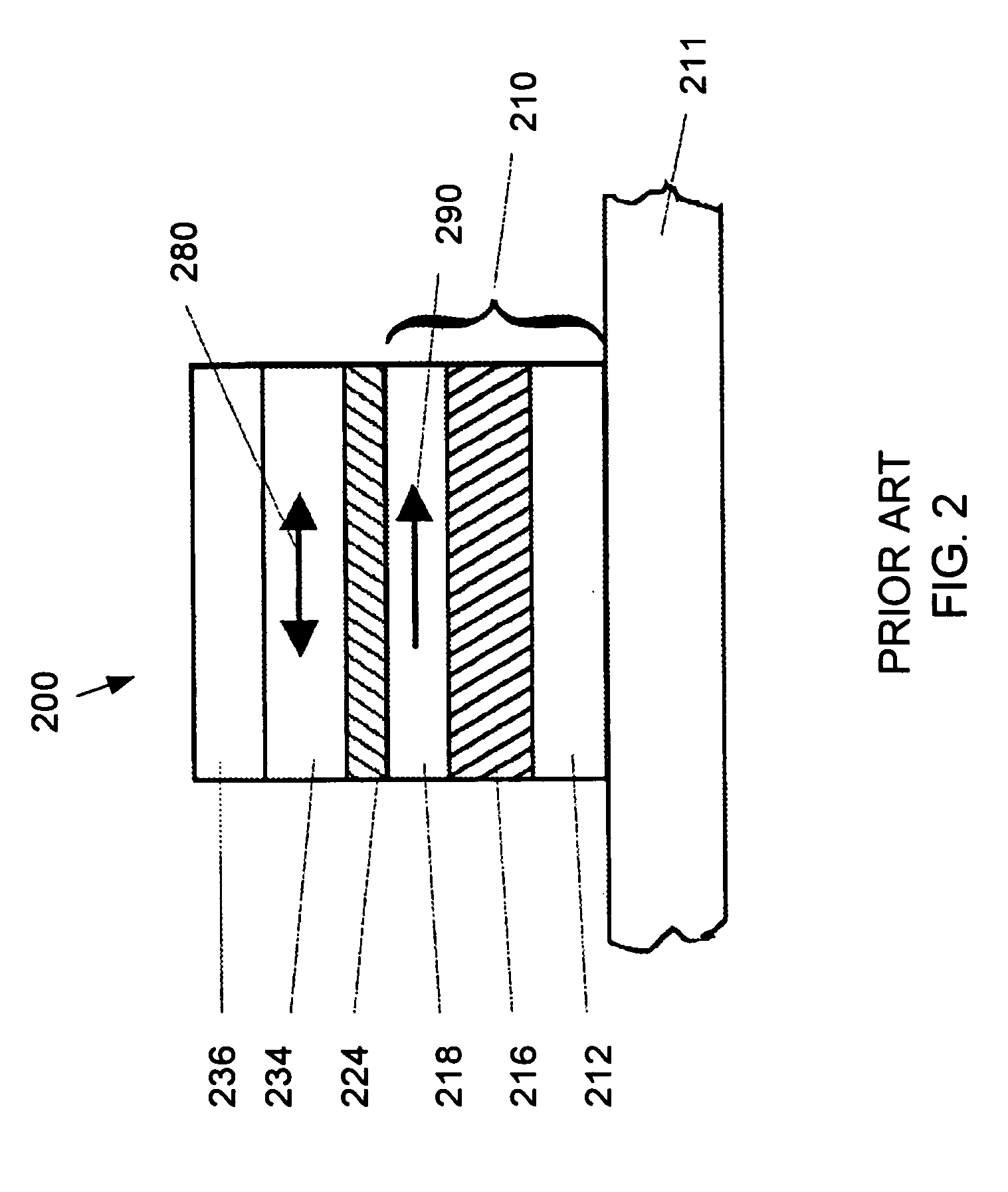

Magnetic tunnel junction magnetic device (16) for writing and reading uses a reference layer (20c) and a storage layer (20a) separated by a semiconductor or insulating layer (20b). The blocking temperature of the magnetisation of the storage layer is less than that of the reference layer. The storage layer is heated (22, 24) above the blocking temperature of its magnetisation. A magnetic field (34) is applied (26) to it orientating its magnetization with respect to that of the reference layer without modifying the orientation of the reference layer.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

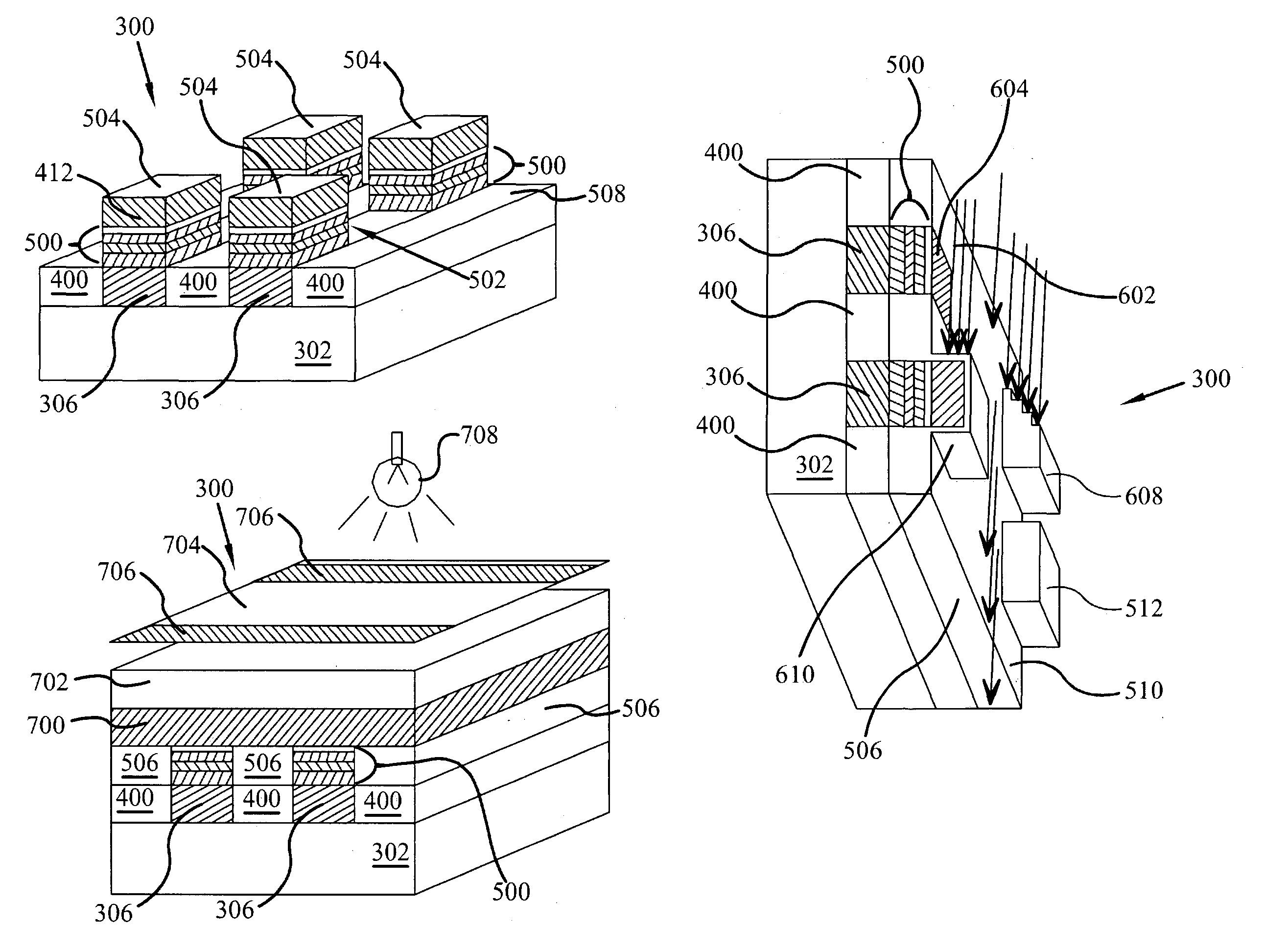

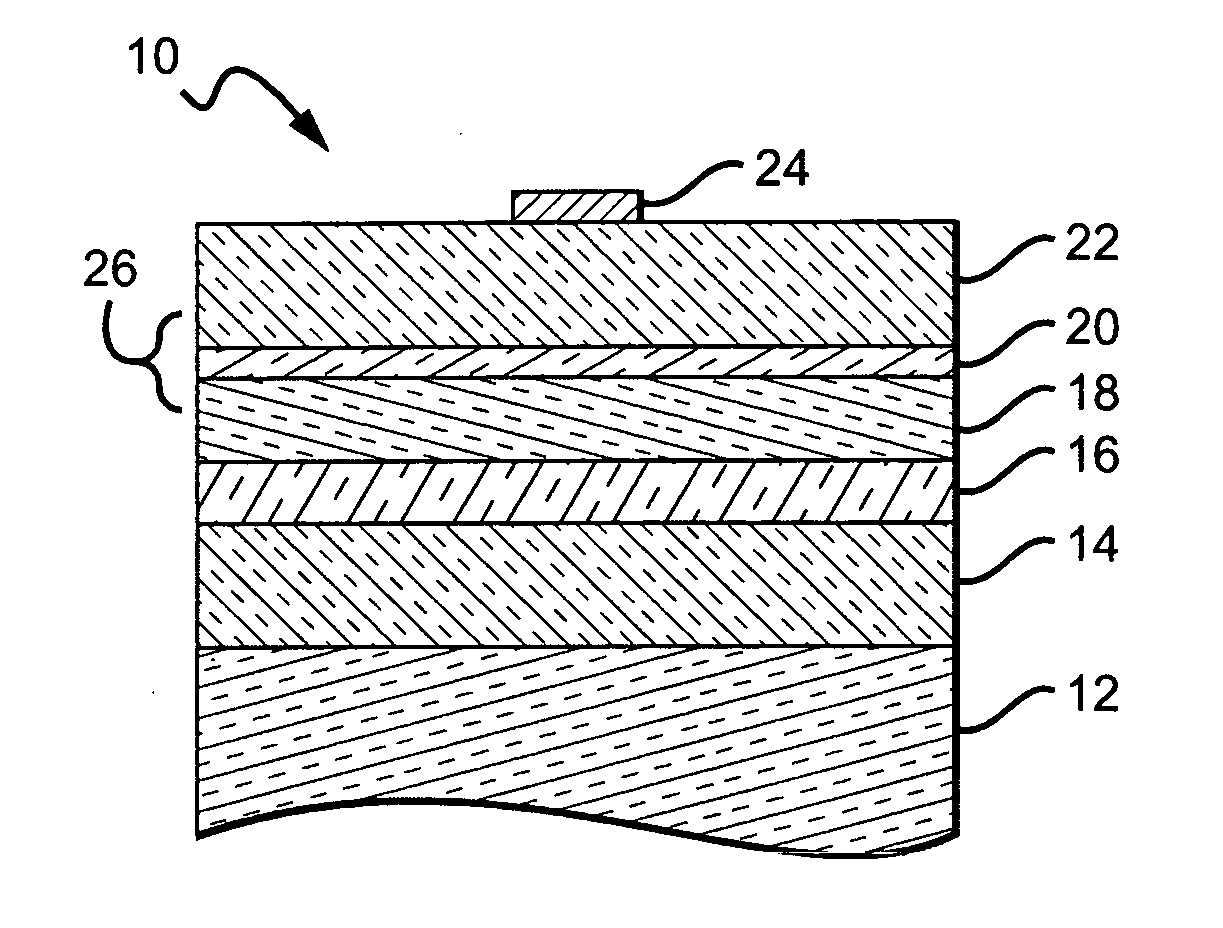

Solar cell with epitaxially grown quantum dot material

ActiveUS20050155641A1Improve conversion efficiencyImprove efficiencyPV power plantsNanoinformaticsQuantum dotTunnel junction

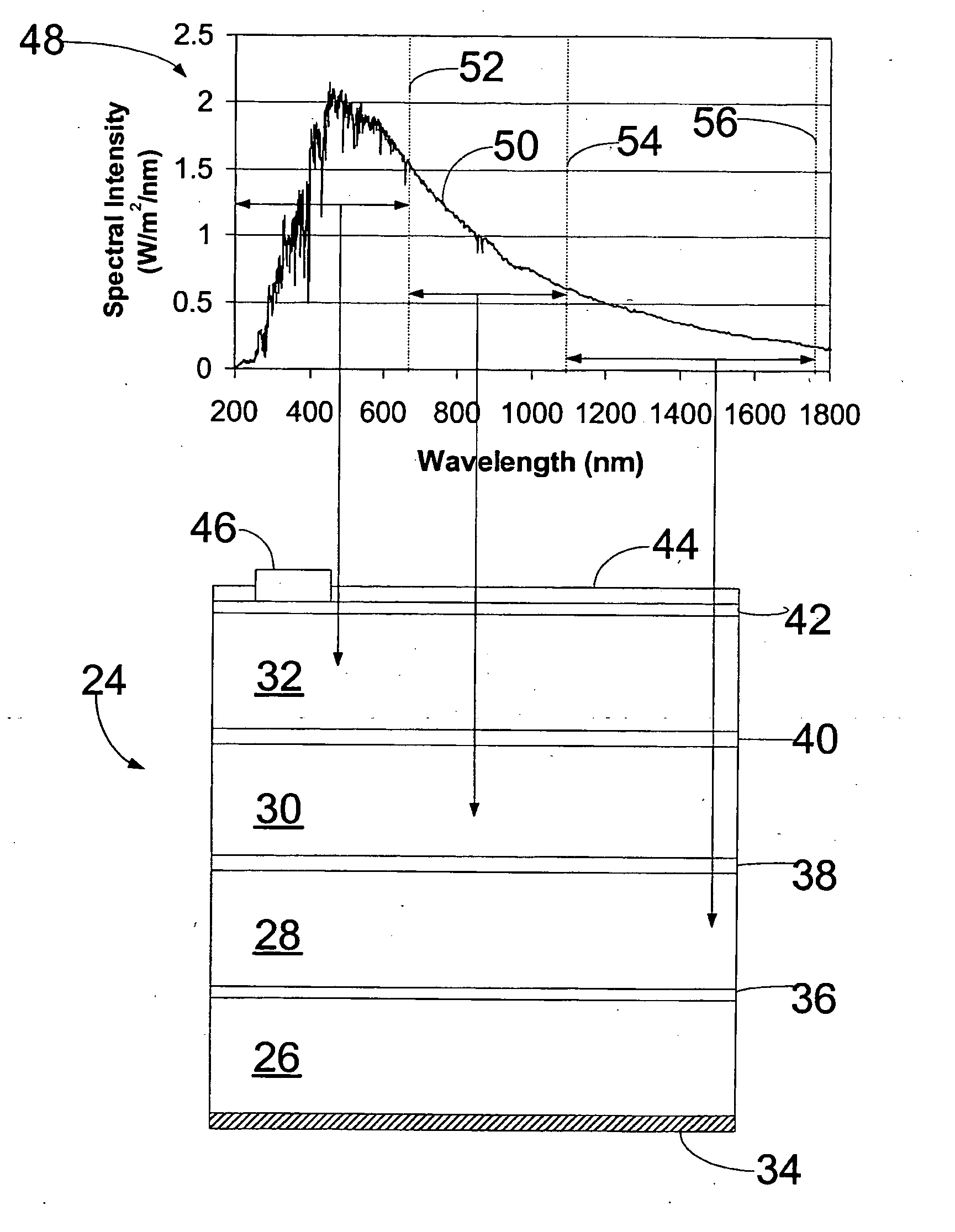

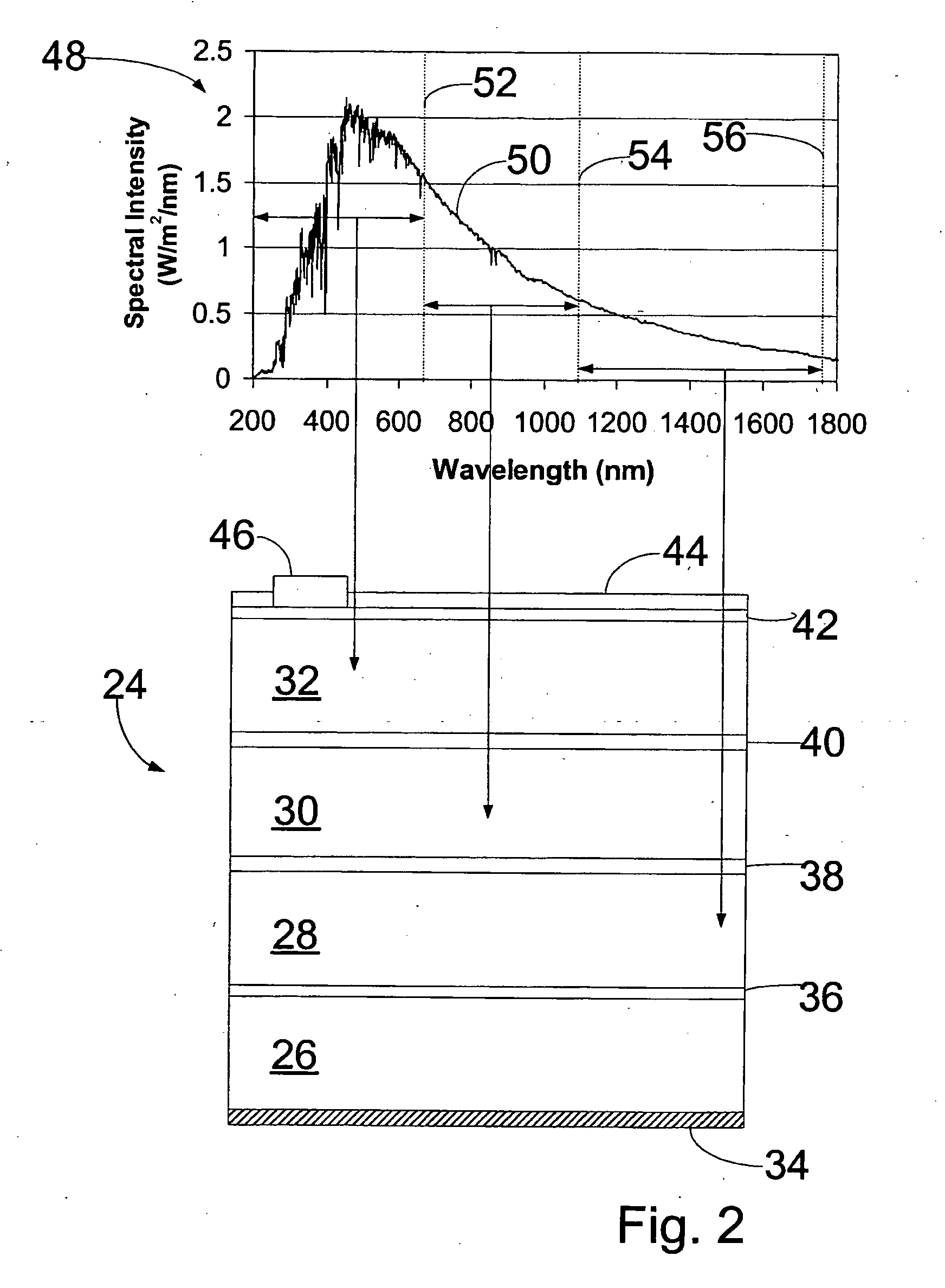

A monolithic semiconductor photovoltaic solar cell comprising a plurality of subcells disposed in series on an electrically conductive substrate. At least one subcell of the plurality of subcells includes an epitaxially grown self-assembled quantum dot material. The subcells are electrically connected via tunnel junctions. Each of the subcells has an effective bandgap energy. The subcells are disposed in order of increasing effective bangap energy, with the subcell having the lowest effective bandgap energy being closest to the substrate. In certain cases, each subcell is designed to absorb a substantially same amount of solar photons.

Owner:CYRIUM TECH INC +1

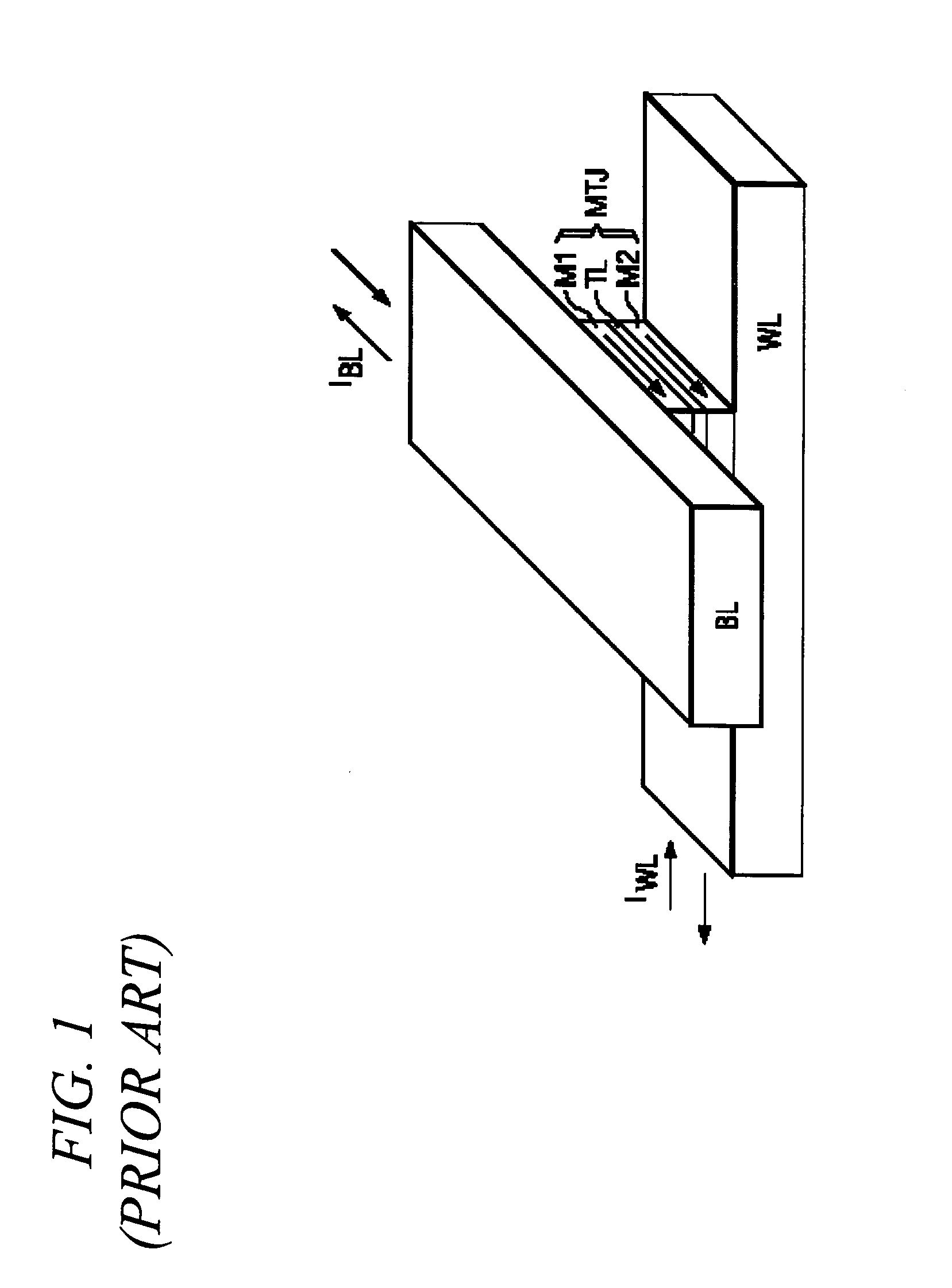

Magnetic tunnel junction memory device

InactiveUS6845038B1Improve permeabilityLow resistivityDigital storageBit linePerpendicular magnetization

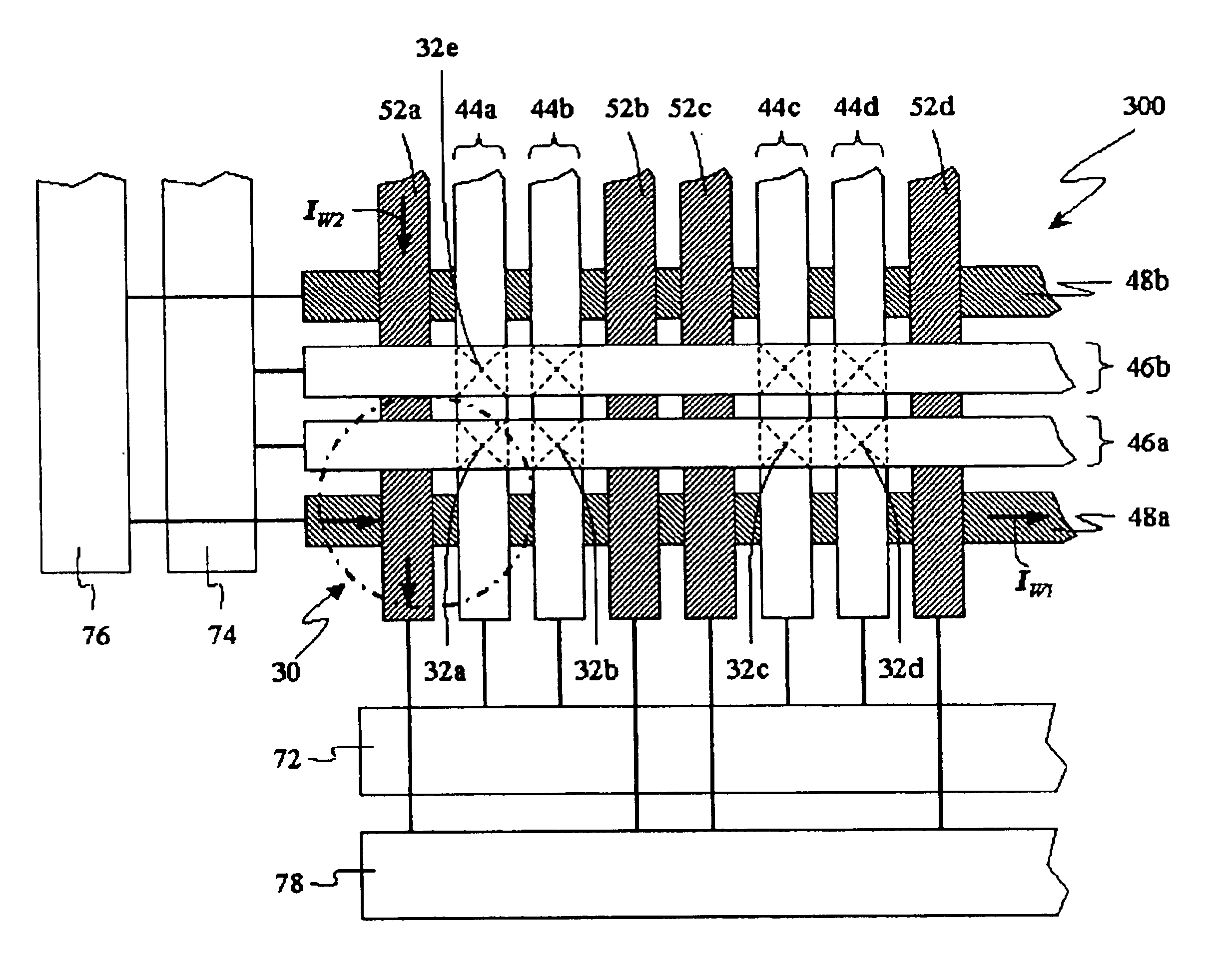

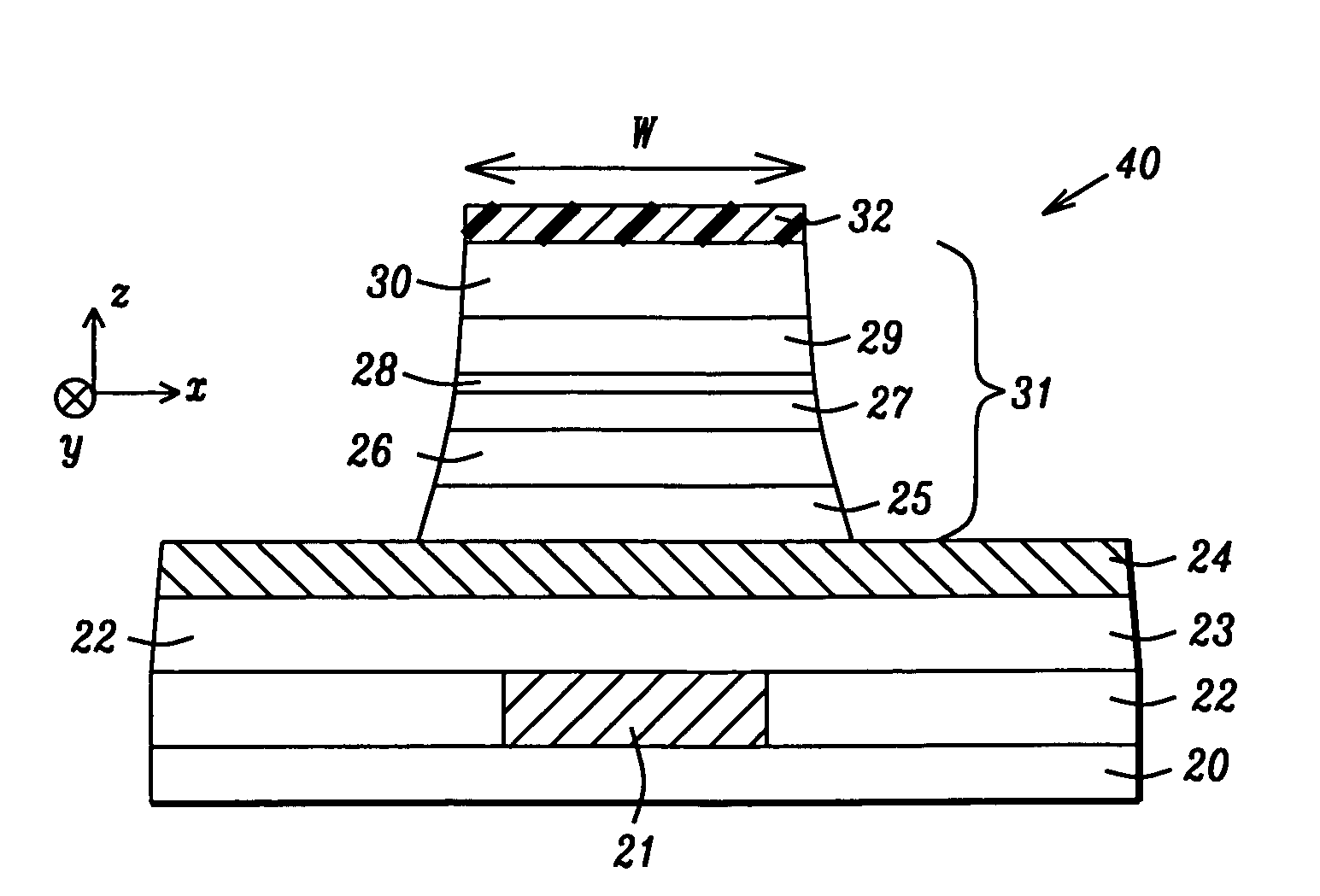

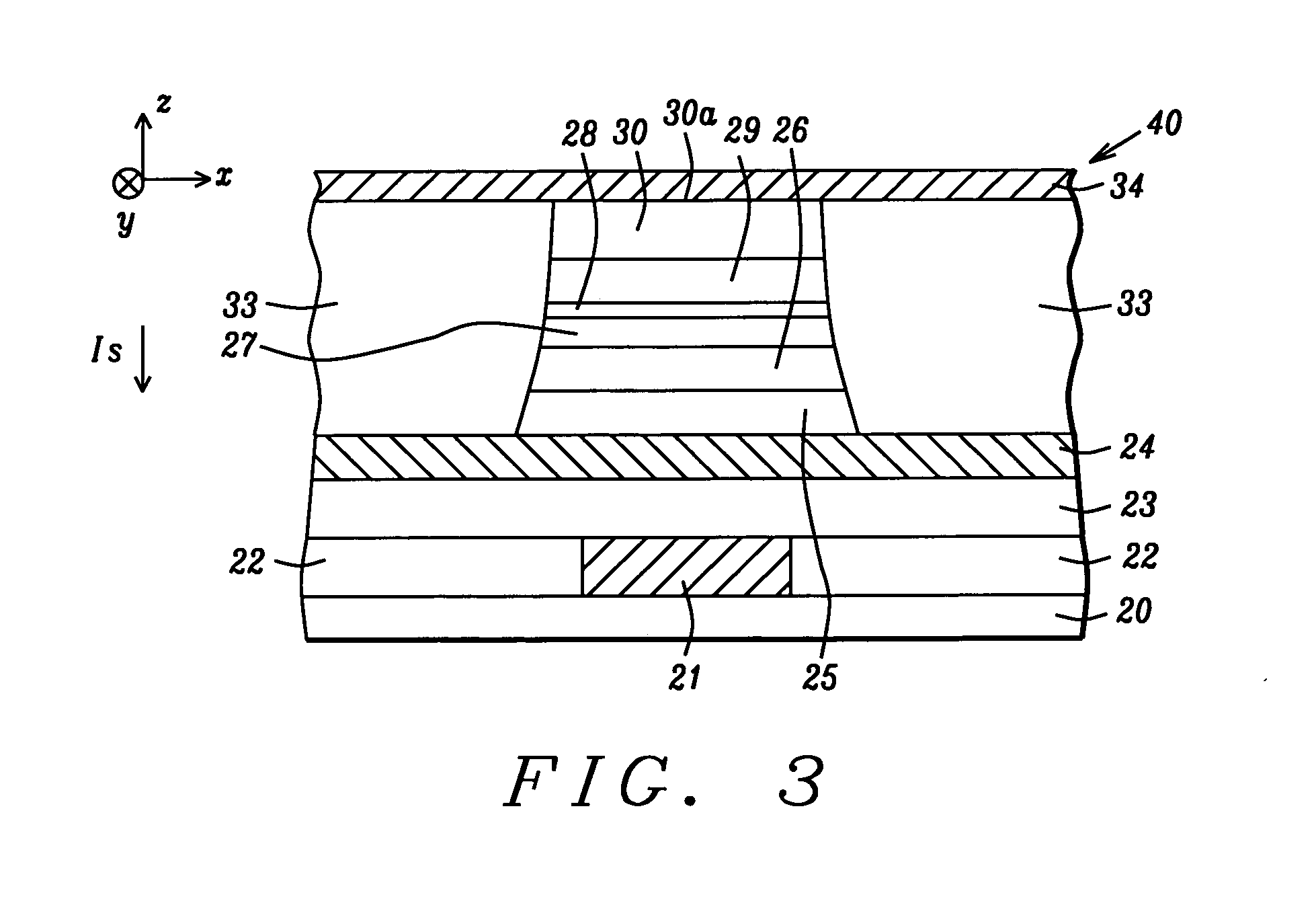

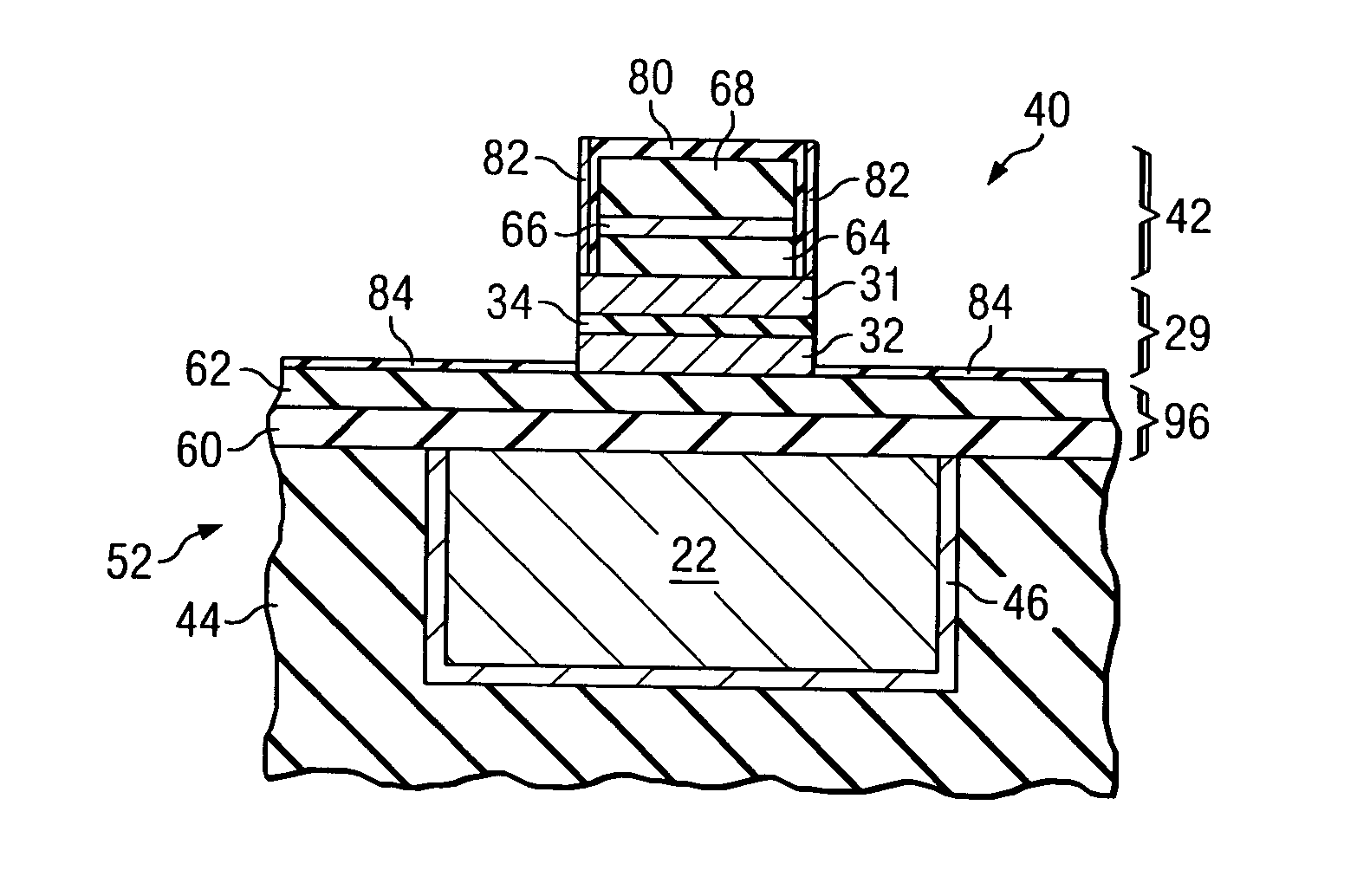

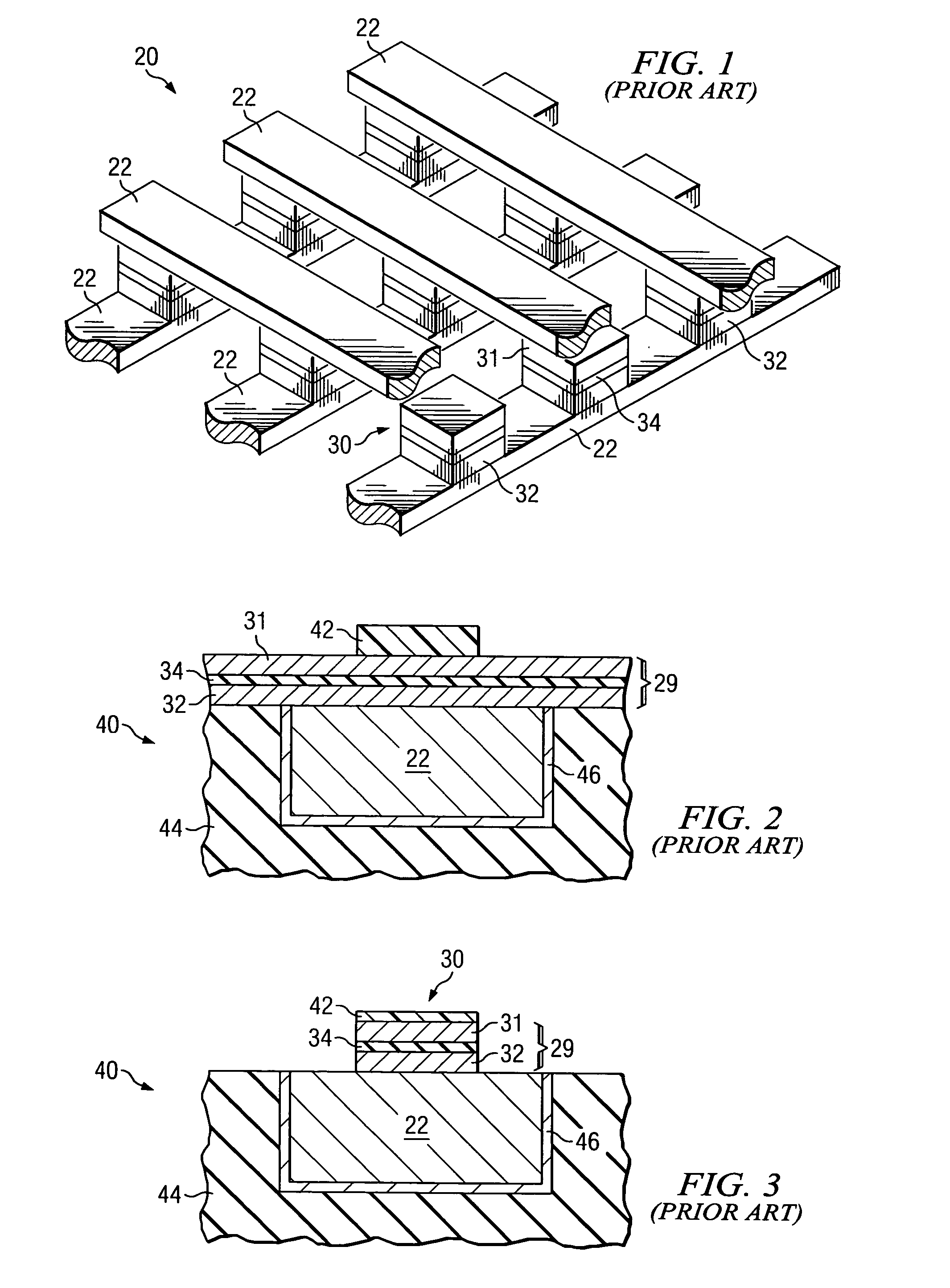

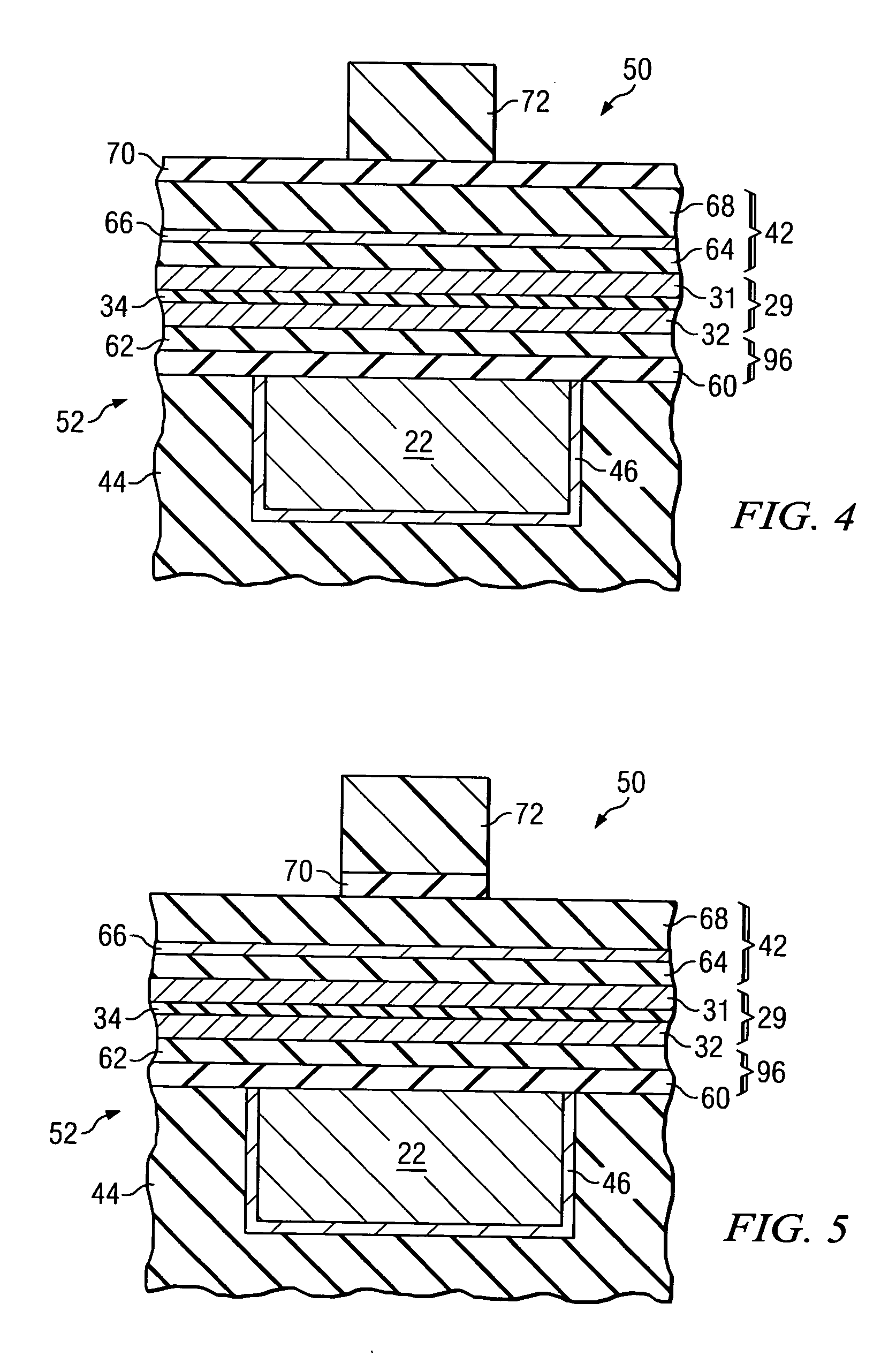

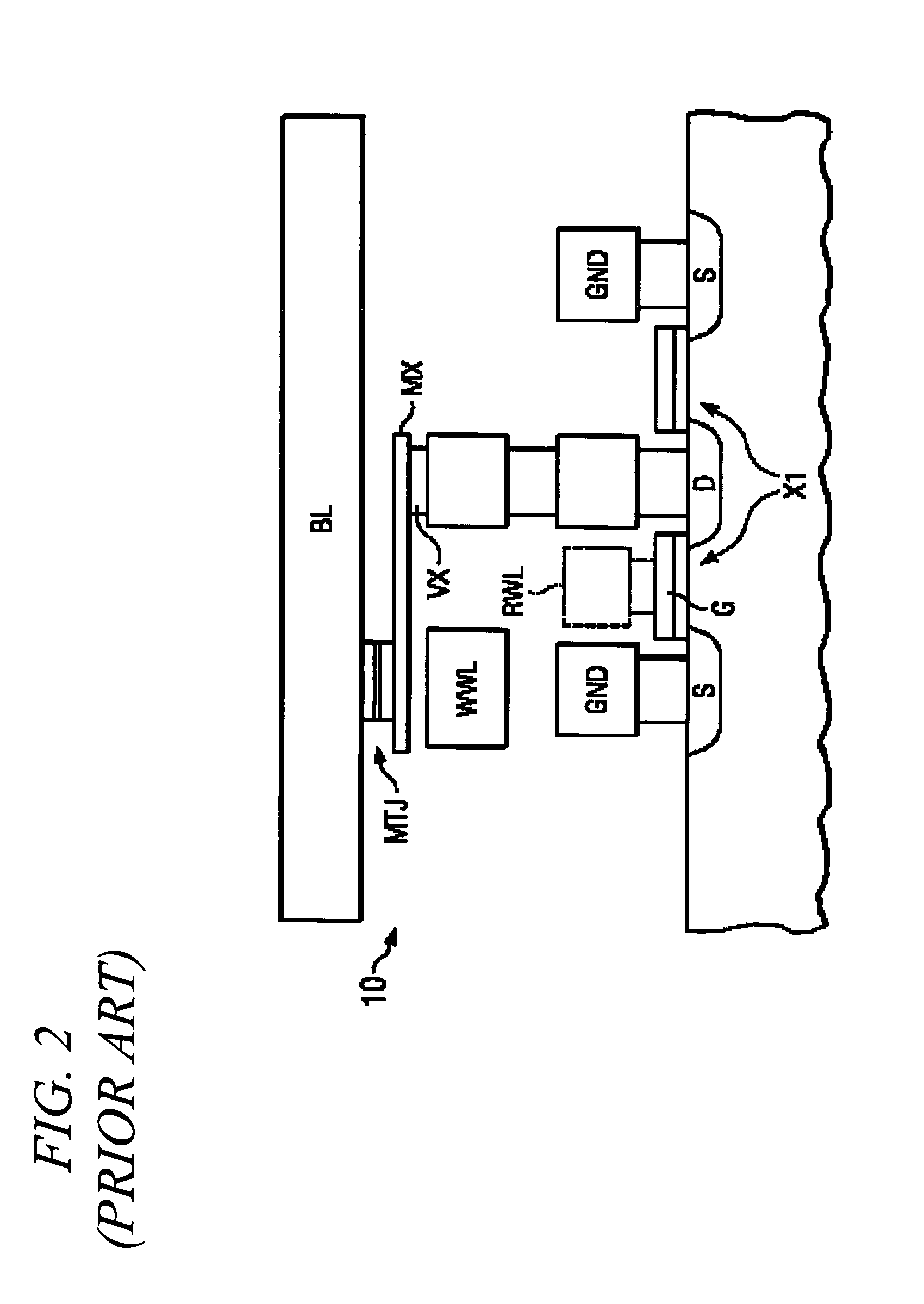

A memory cell for magnetic random access memory devices based on a magnetic tunnel junction (MTJ) memory element with a perpendicular orientation of magnetization in pinned and free magnetic layers, and a tunnel barrier layer sandwiched between the pinned and free layers. The memory cell can include the MTJ memory element, a magnetic flux guide in series with selection devices, such as a bit line, a word line, and a transistor. The magnetic flux guide can have two electrically conductive magnetic portions with the MTJ memory element positioned between the magnetic portions. The MTJ memory element is magnetically isolated from the magnetic flux guide by thin non-magnetic conductive spacers. The MTJ memory element is arranged in a vertical space between the intersecting bit and word lines at their intersection region. The memory cell also includes write and excitation lines. The write line is parallel to the bit line and the excitation line is parallel to the word line. The write and excitation lines also intersect each other and define a corner. The MTJ memory element is positioned in the corner of the intercepting write and excitation lines.

Owner:SHUKH ALLA MIKHAILOVNA

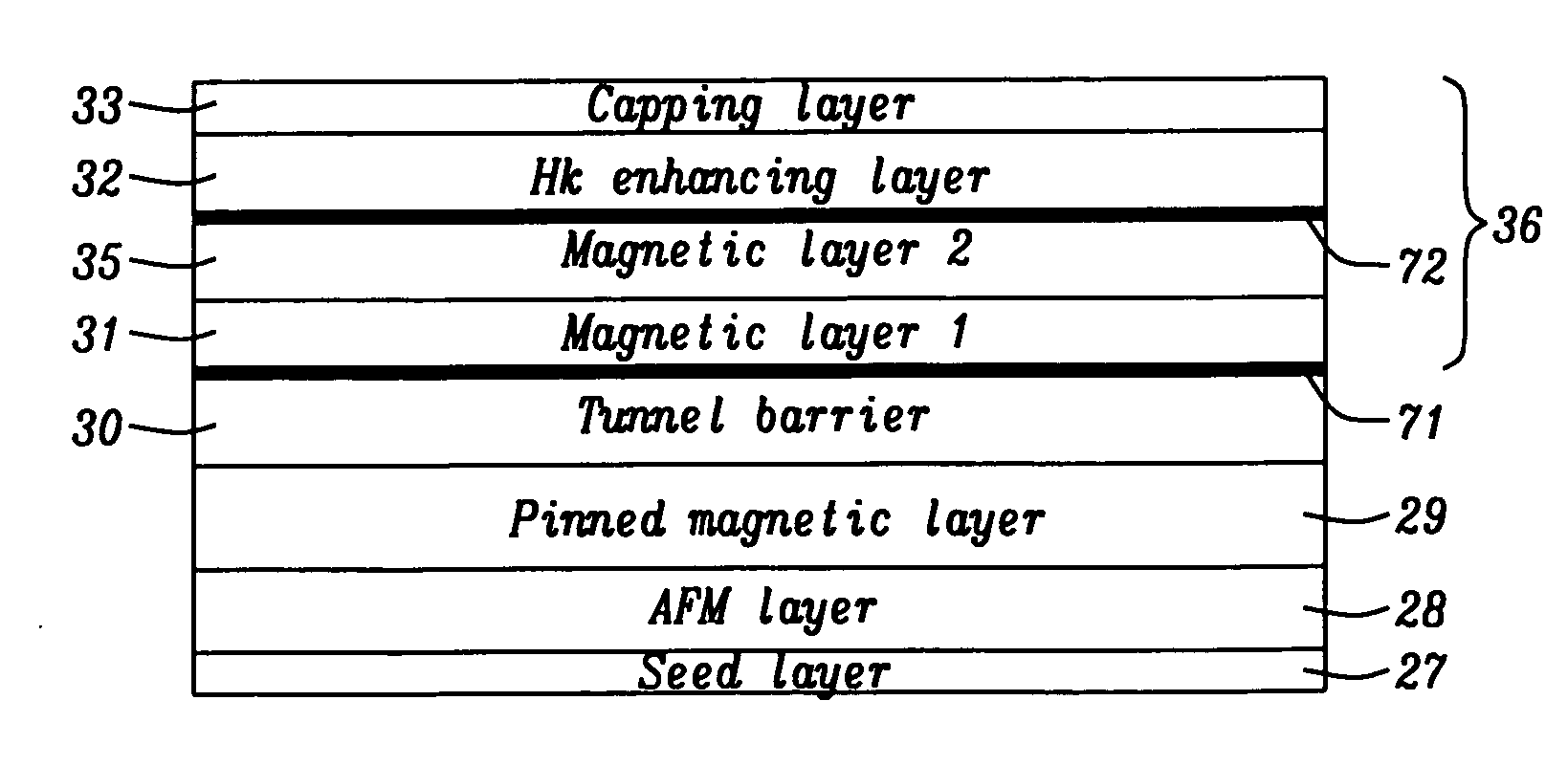

Magnetic element with improved out-of-plane anisotropy for spintronic applications

ActiveUS20120205758A1Without degrading thermal stability and MR ratioEnhanced interfacial perpendicular anisotropyMagnetic-field-controlled resistorsGalvano-magnetic material selectionPerpendicular anisotropyAlloy

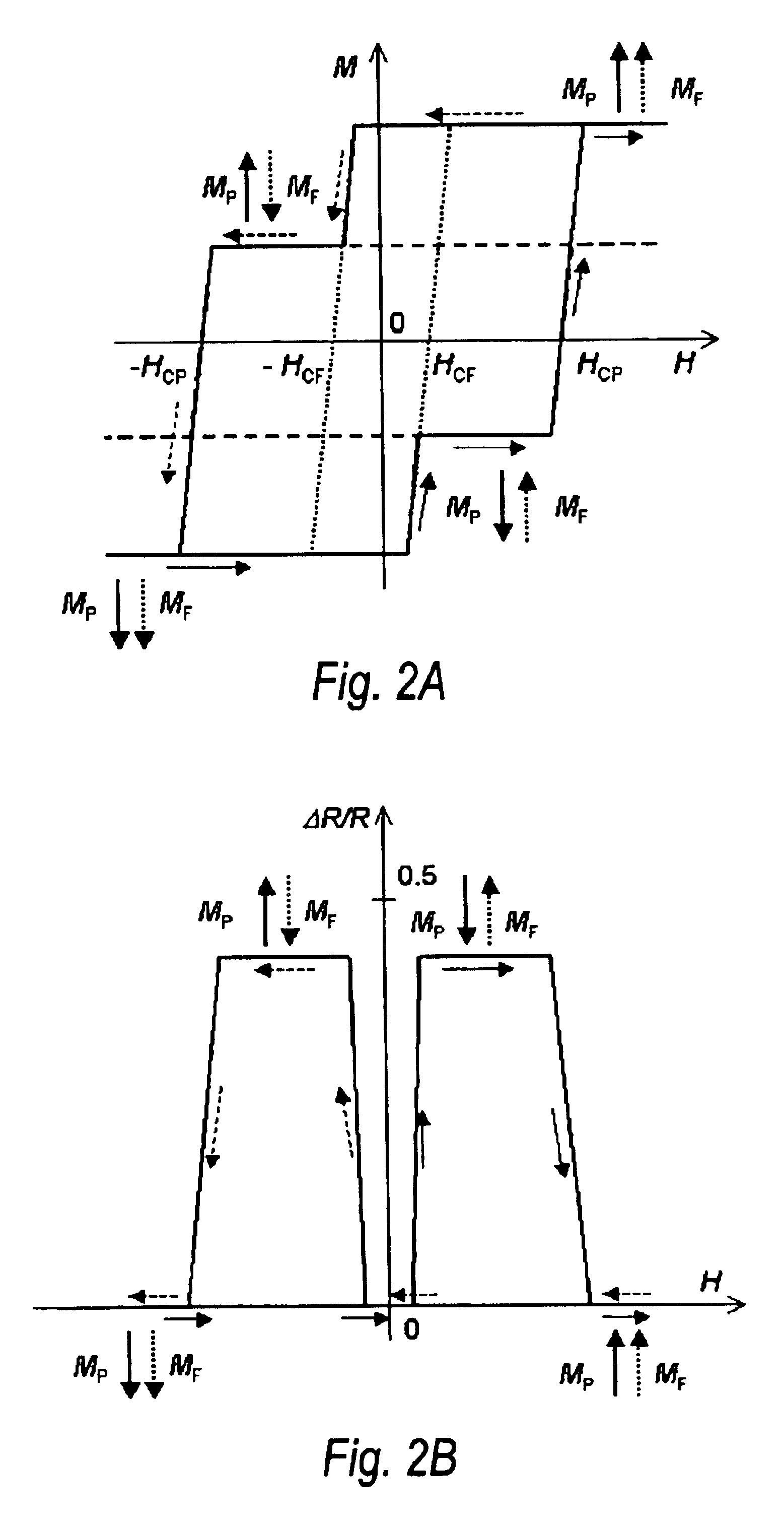

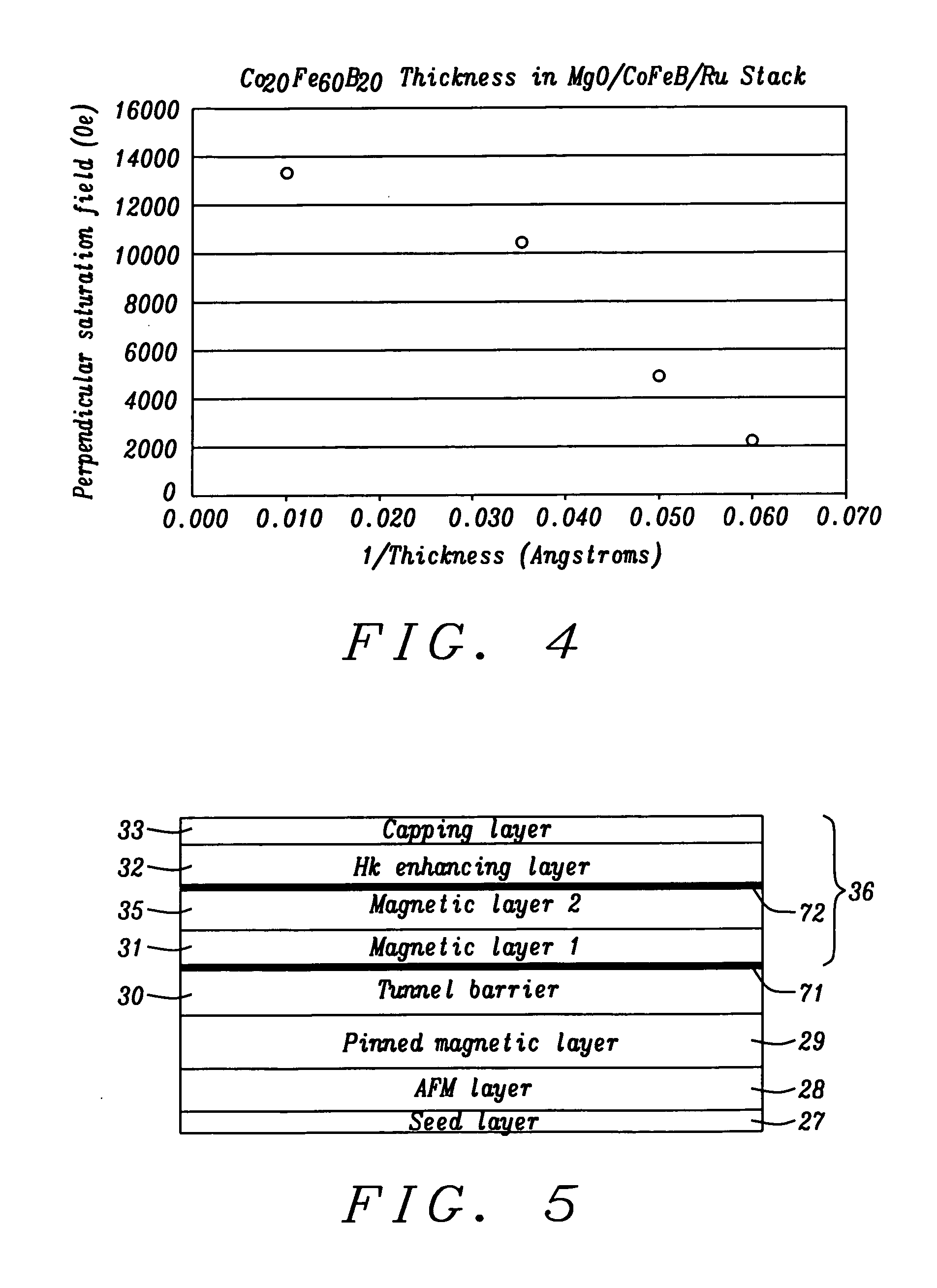

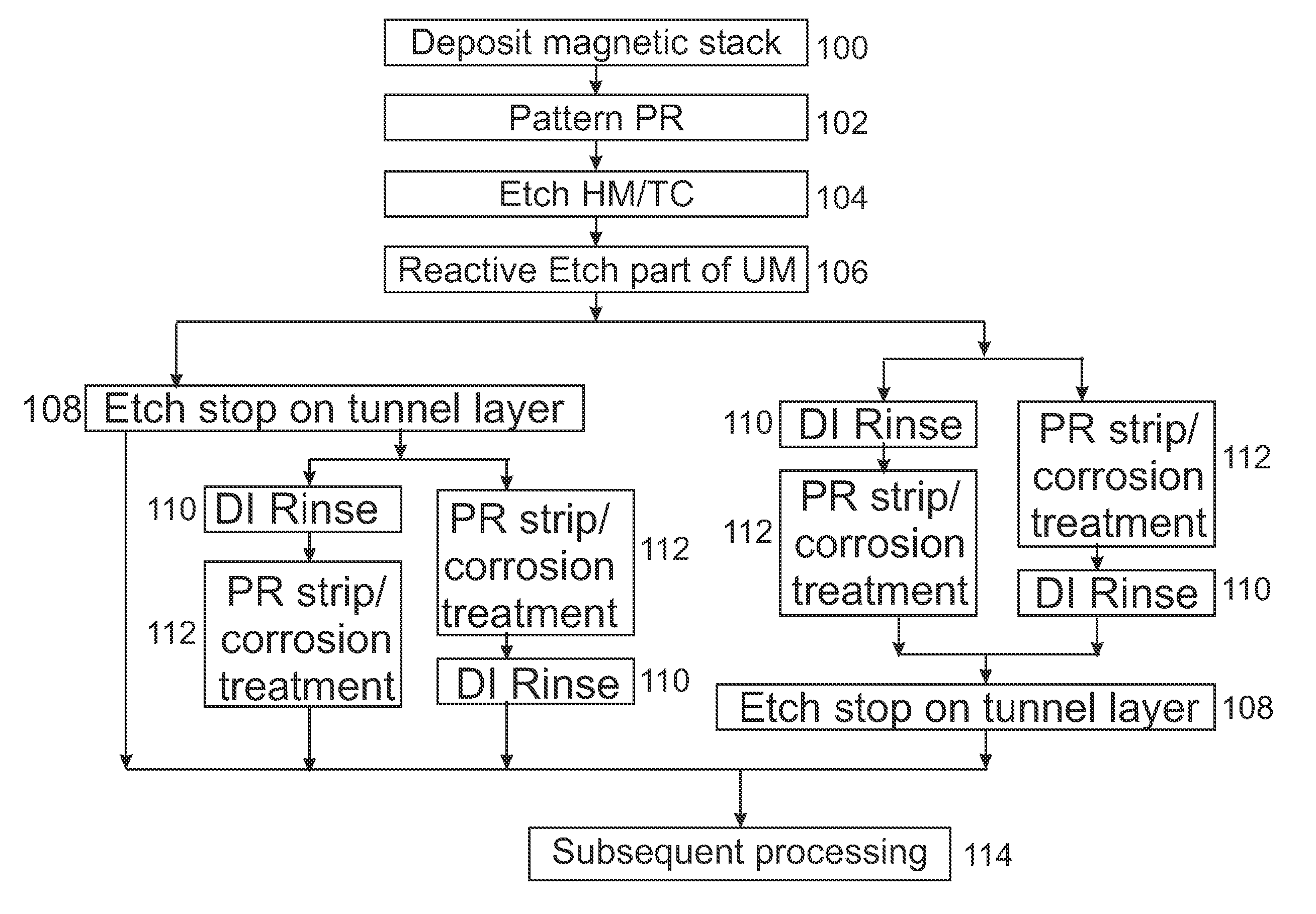

A magnetic element is disclosed wherein first and second interfaces of a free layer with a Hk enhancing layer and tunnel barrier, respectively, produce enhanced surface perpendicular anisotropy to lower switching current or increase thermal stability in a magnetic tunnel junction (MTJ). In a MTJ with a bottom spin valve configuration where the Hk enhancing layer is an oxide, the capping layer contacting the Hk enhancing layer is selected to have a free energy of oxide formation substantially greater than that of the oxide. The free layer may be a single layer or composite comprised of an Fe rich alloy such as Co20Fe60B20. With a thin free layer, the interfacial perpendicular anisotropy may dominate the shape anisotropy to generate a magnetization perpendicular to the planes of the layers. The magnetic element may be part of a spintronic device or serve as a propagation medium in a domain wall motion device.

Owner:TAIWAN SEMICON MFG CO LTD

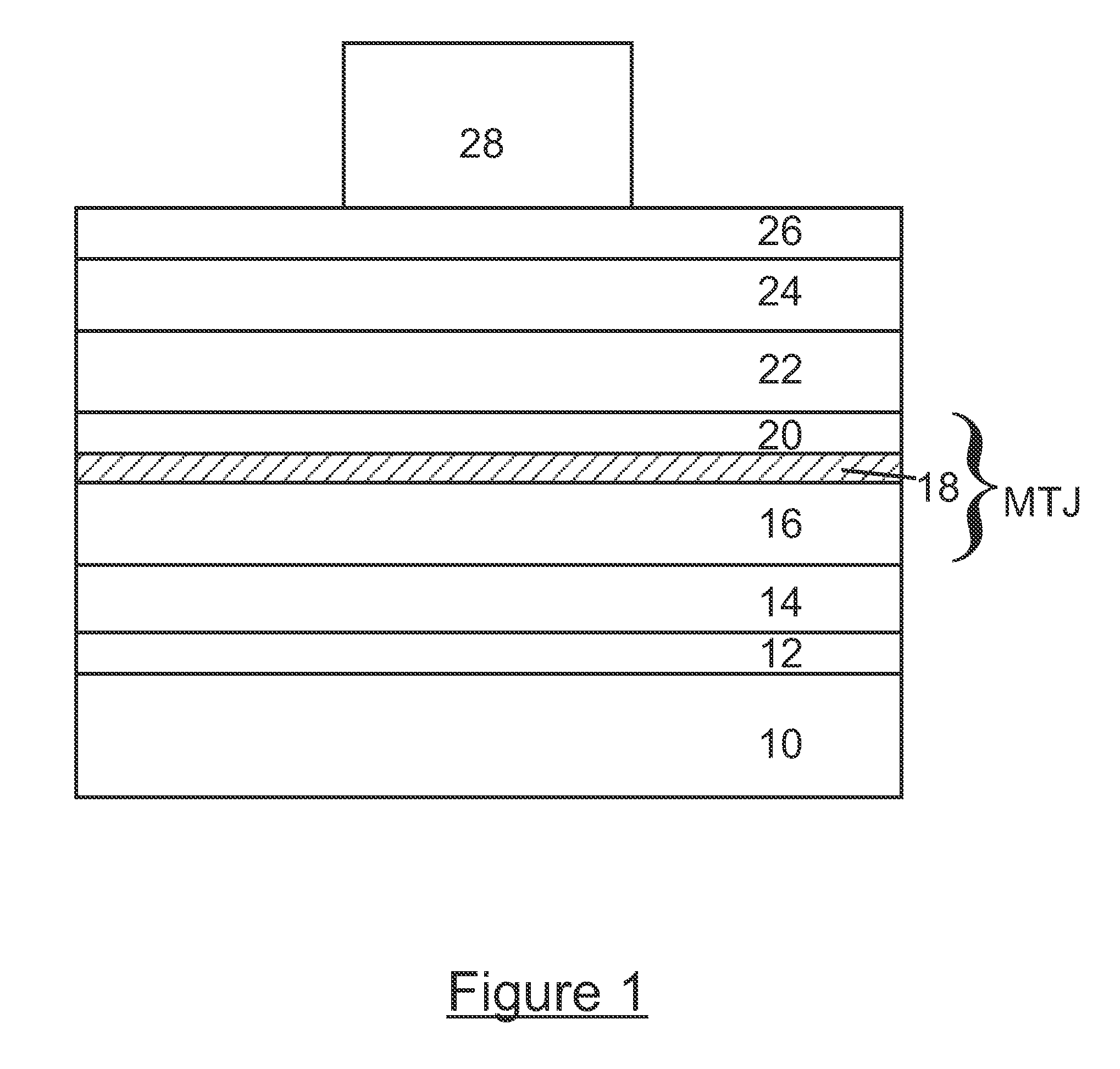

Dry etch stop process for eliminating electrical shorting in MRAM device structures

ActiveUS20100022030A1Improve electrical isolationGood repeatabilityOrganic active ingredientsSenses disorderElectricityEngineering

The present invention relates generally to semiconductor fabrication and particularly to fabricating magnetic tunnel junction devices. In particular, this invention relates to a method for using the dielectric layer in tunnel junctions as an etch stop layer to eliminate electrical shorting that can result from the patterning process.

Owner:OEM GRP LLC

Novel magnetic tunnel junction (MTJ) to reduce spin transfer magnetization switching current

ActiveUS20080179699A1Reduce magnetic “ dead layer ”Magnetic-field-controlled resistorsSolid-state devicesLayer interfaceSpins

Owner:TAIWAN SEMICON MFG CO LTD

Magnetoresistive memory device

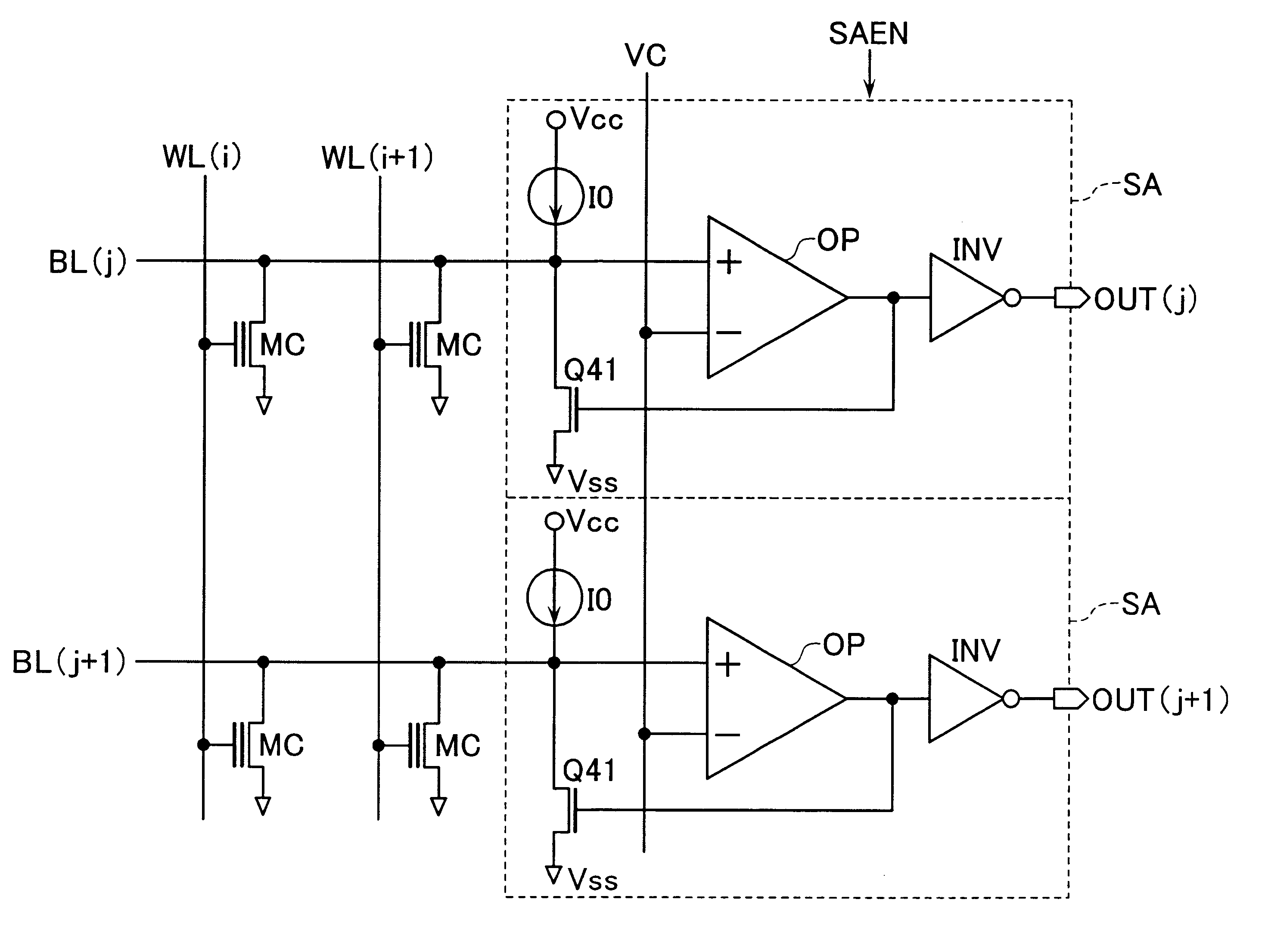

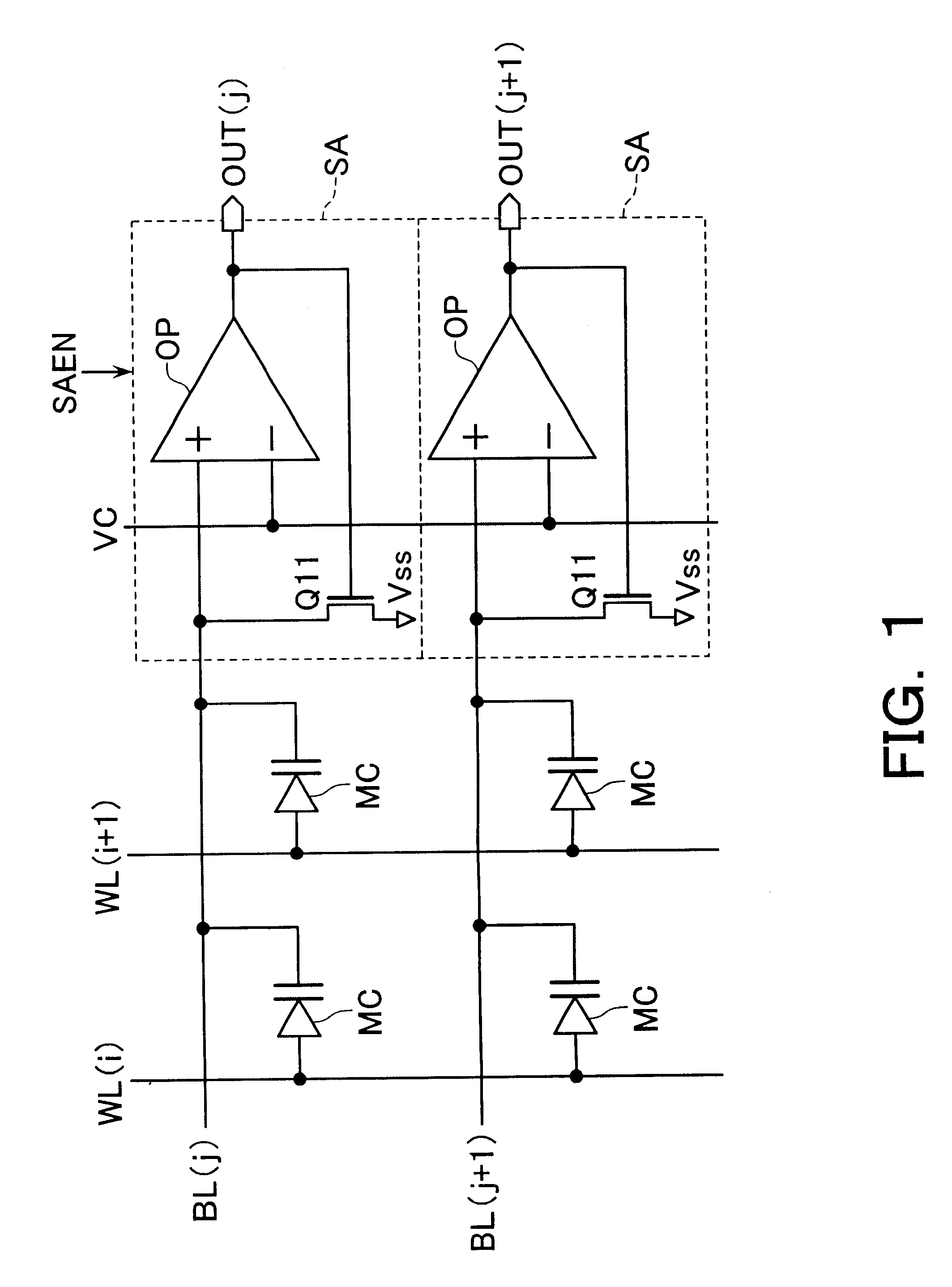

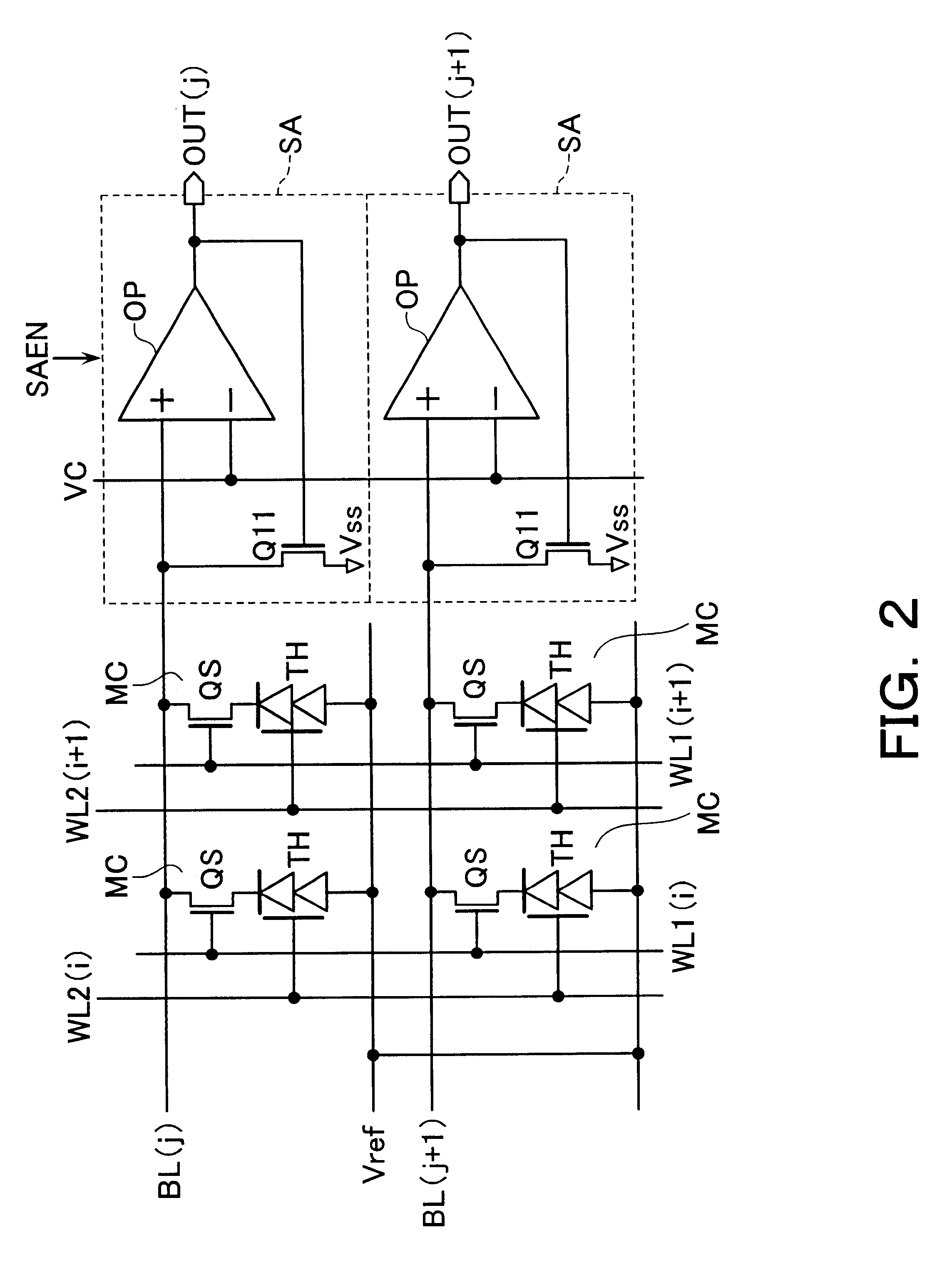

An integrated semiconductor memory device with an array of memory cells MC using magnetic tunnel junction (MTJ) cells is disclosed. A sense amplifier SA that is connected to a bit line BL for data readout of a selected memory cell MC is arranged using an operational amplifier OP. The operational amplifier OP has an inverting input terminal which is connected to the bit line BL and a non-inverting input terminal, to which a potentially fixed constant voltage VC is given. A PMOS transistor Q31 is provided, which can also do double-duty as a current source load. This PMOS transistor has its drain and gate that are connected to the inverting input terminal, and a source as connected to an output terminal of the operational amplifier OP whereby the transistor is under feedback control in response to an output of the operational amplifier OP so that a clamped voltage potential of the bit lime BL is fixed to the voltage VC.

Owner:KK TOSHIBA

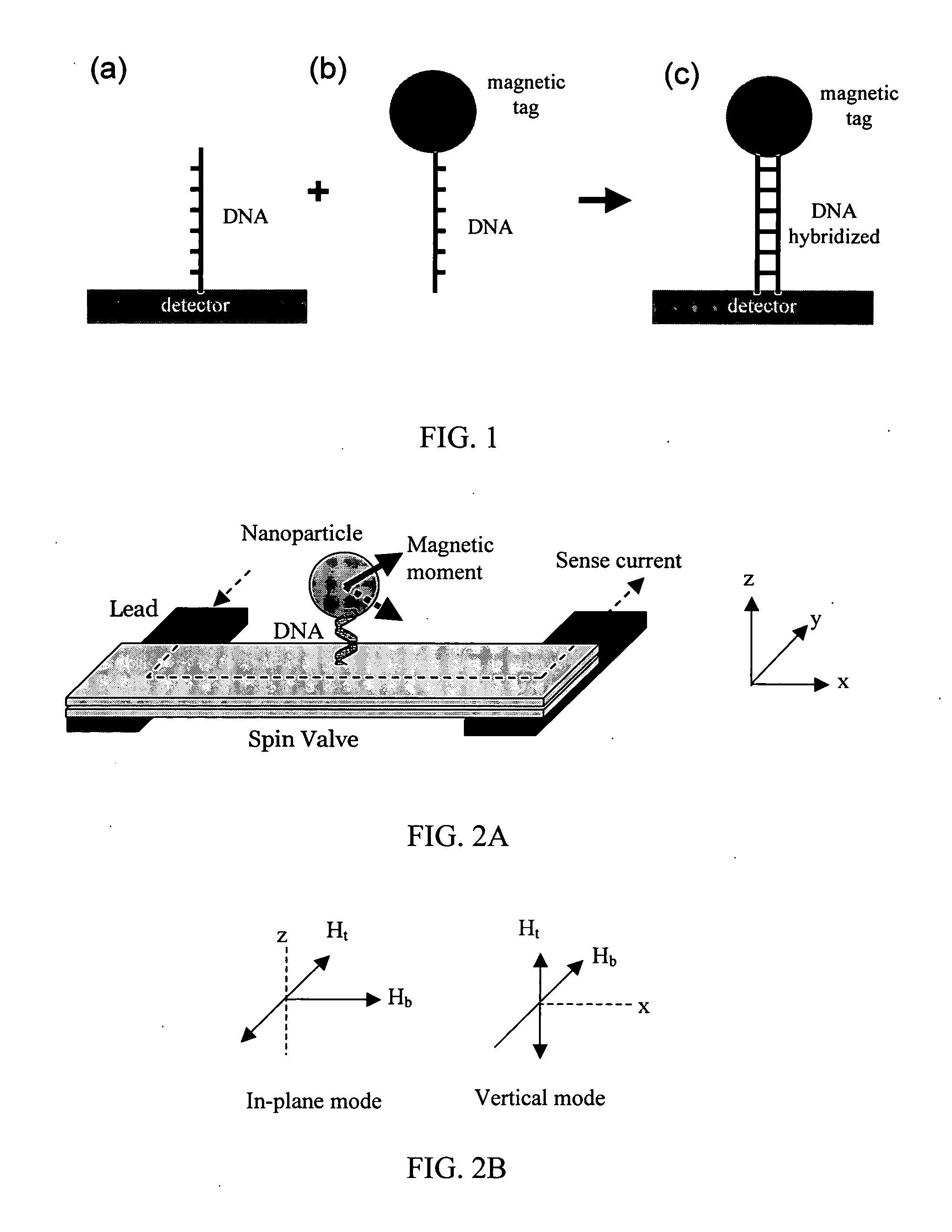

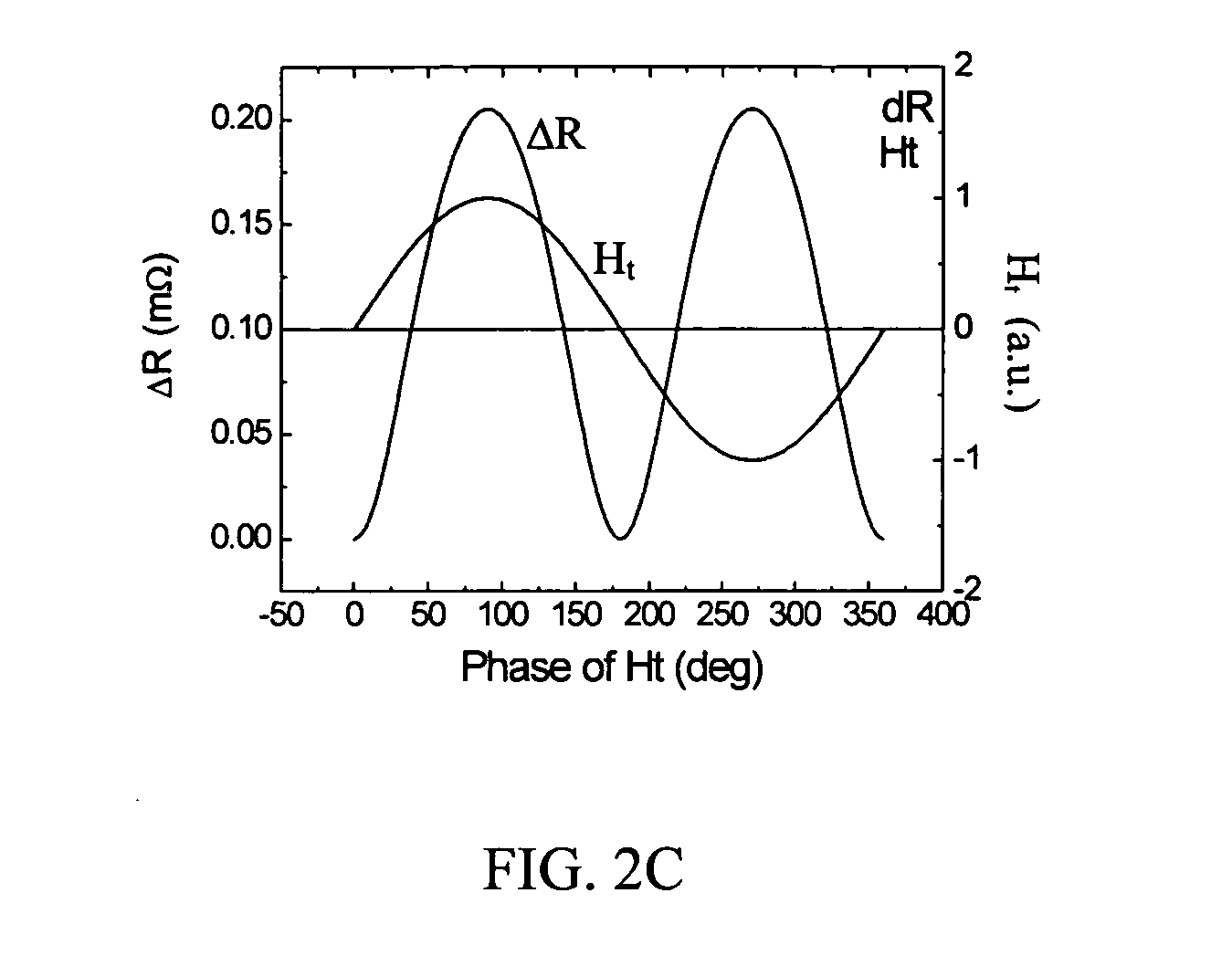

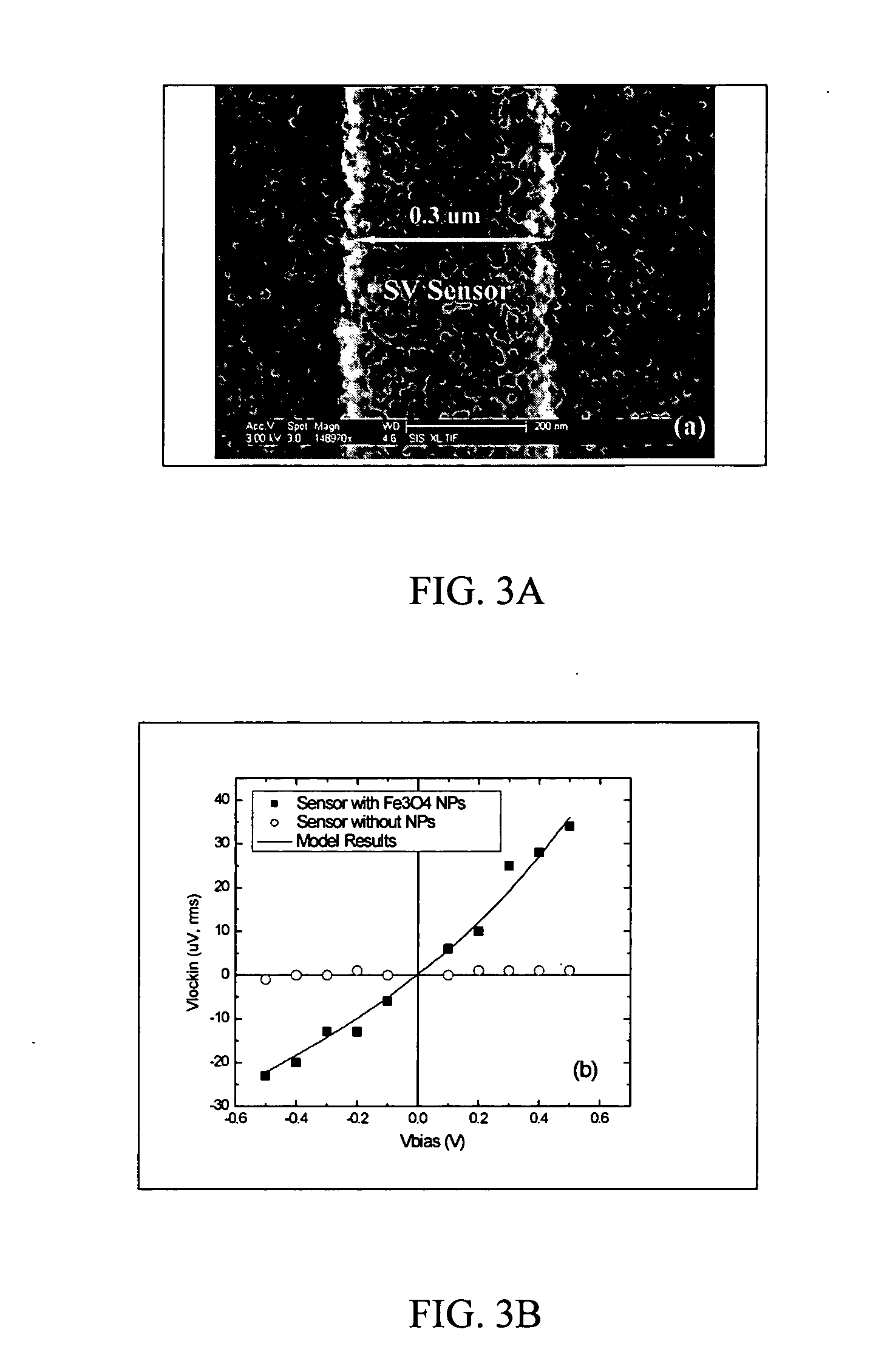

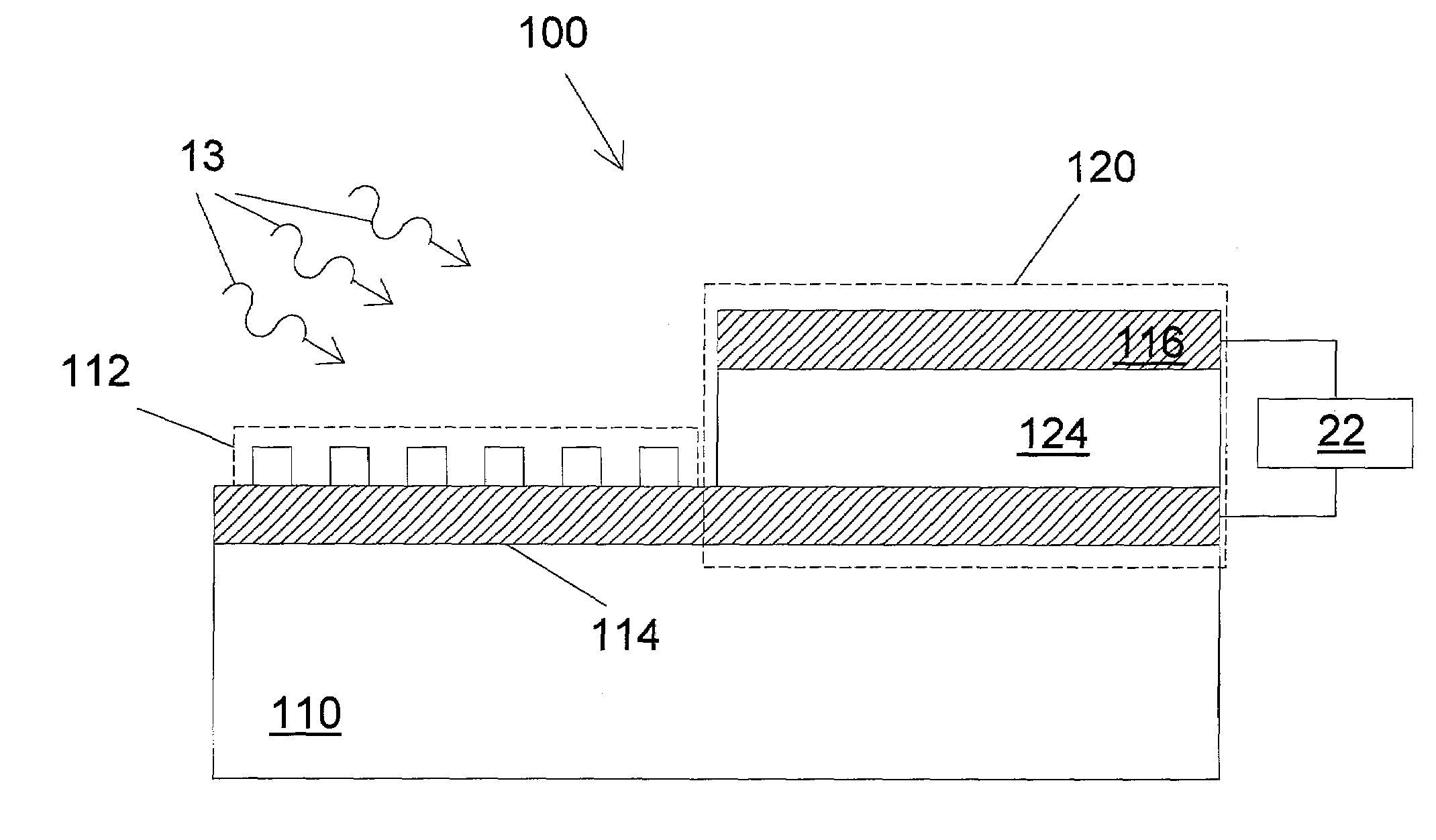

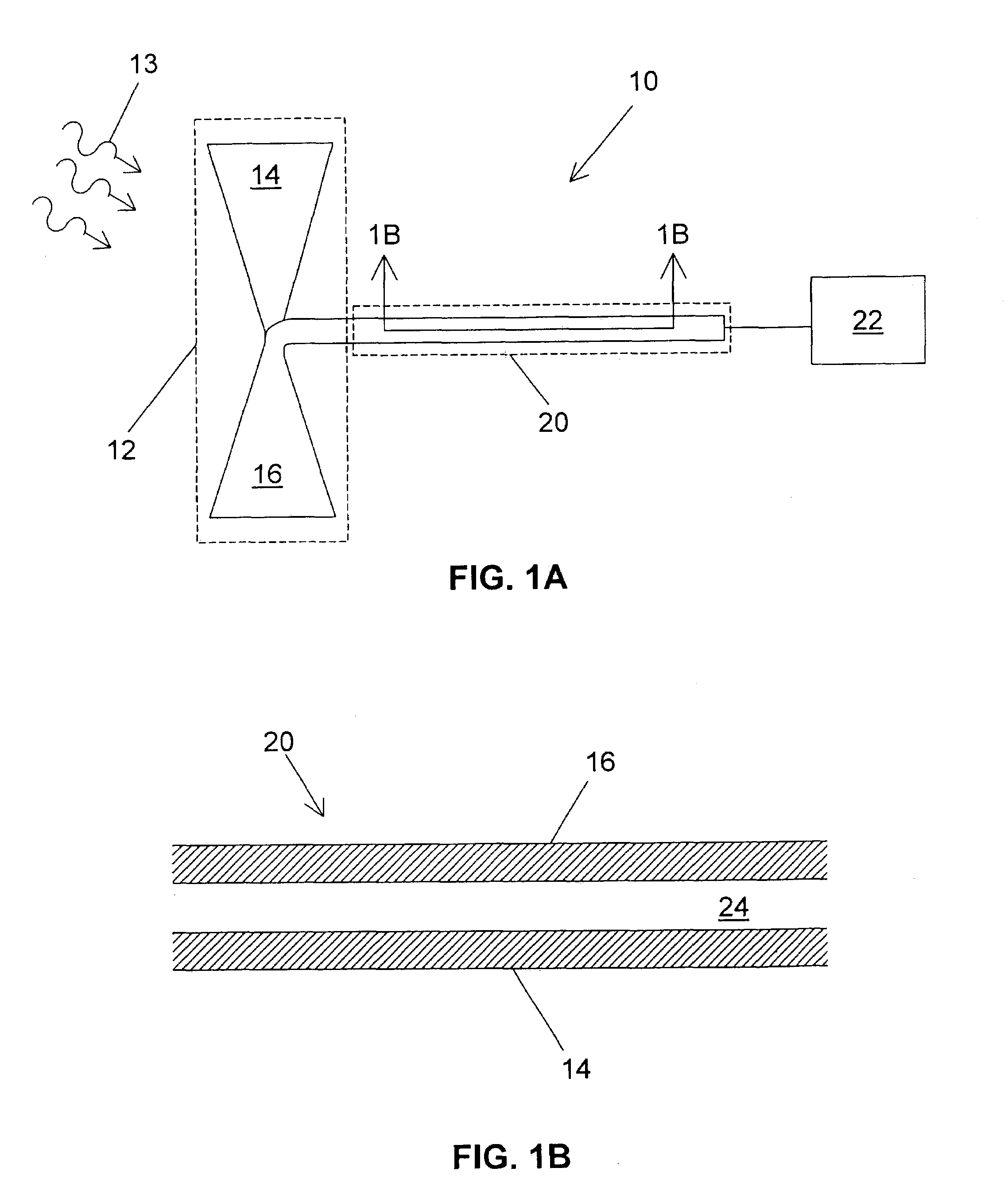

Magnetic nanoparticles, magnetic detector arrays, and methods for their use in detecting biological molecules

Magnetic nanoparticles and methods for their use in detecting biological molecules are disclosed. The magnetic nanoparticles can be attached to nucleic acid molecules, which are then captured by a complementary sequence attached to a detector, such as a spin valve detector or a magnetic tunnel junction detector. The detection of the bound magnetic nanoparticle can be achieved with high specificity and sensitivity.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

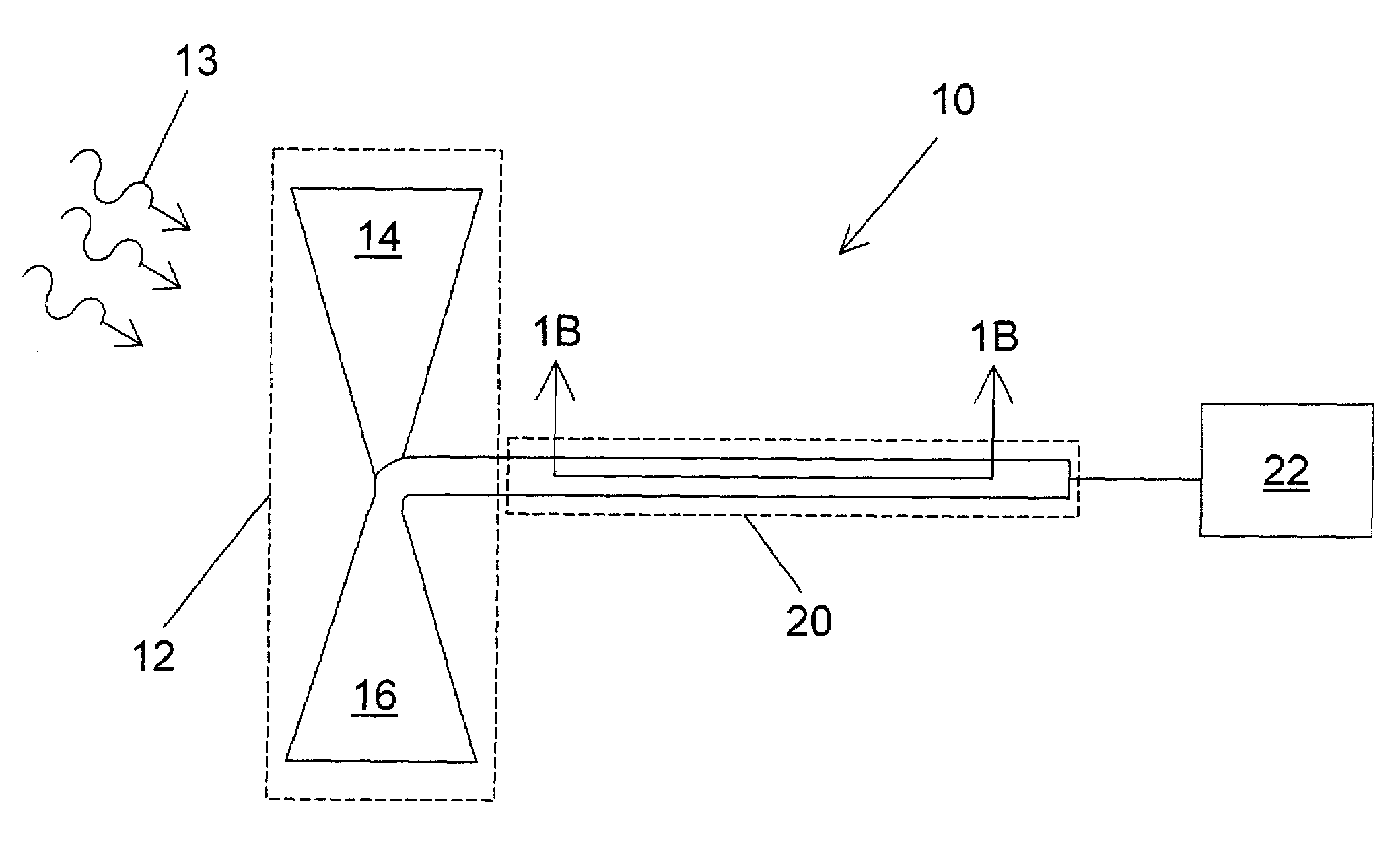

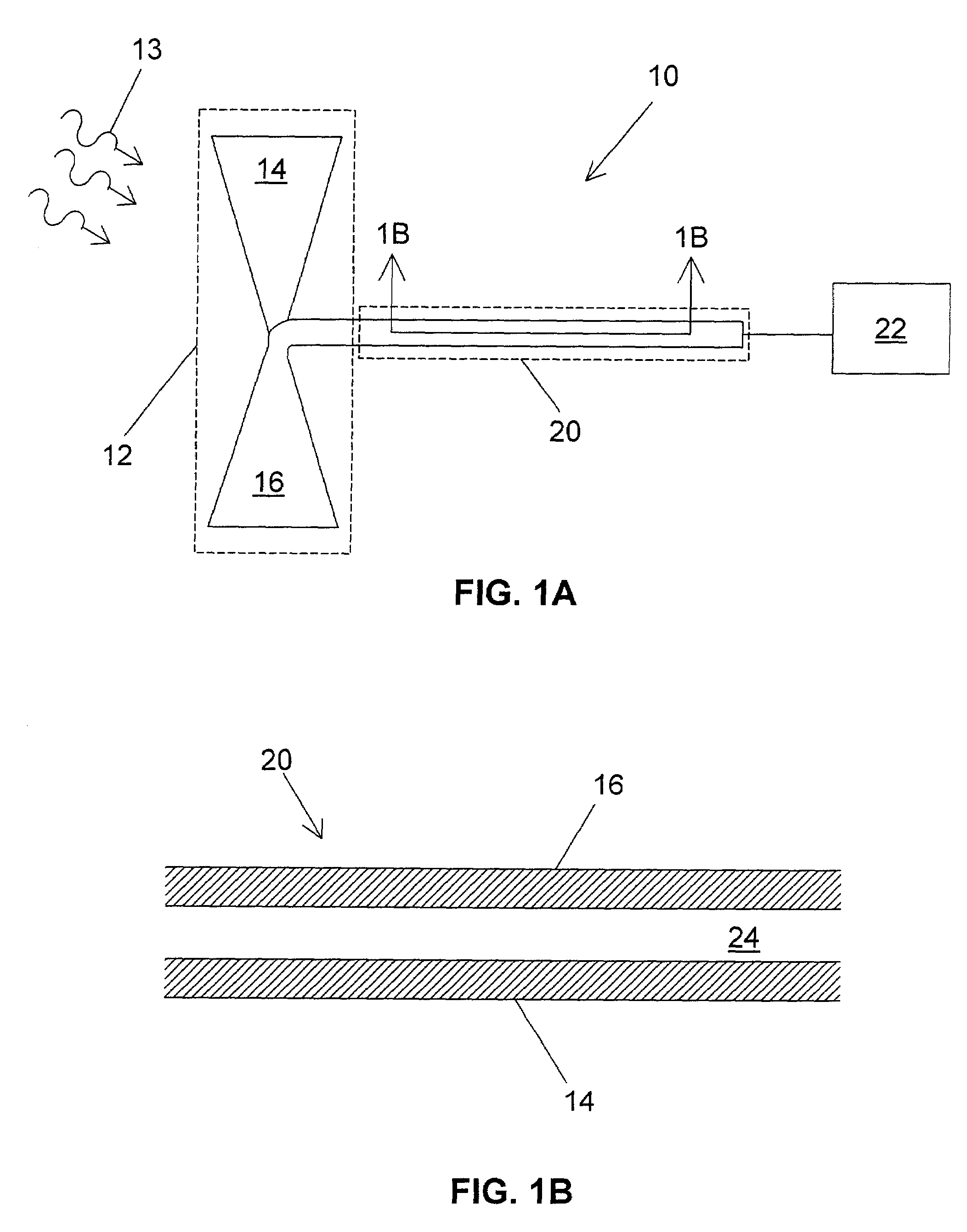

Surface plasmon devices

InactiveUS7010183B2Laser optical resonator constructionOptical resonator shape and constructionSoftware engineeringEngineering

A device including an input port configured to receive an input signal is described. The device also includes an output port and a structure, which structure includes a tunneling junction connected with the input port and the output port. The tunneling junction is configured in a way (i) which provides electrons in a particular energy state within the structure, (ii) which produces surface plasmons in response to the input signal, (iii) which causes the structure to act as a waveguide for directing at least a portion of the surface plasmons along a predetermined path toward the output port such that the surface plasmons so directed interact with the electrons in a particular way, and (iv) which produces at the output port an output signal resulting from the particular interaction between the electrons and the surface plasmons.

Owner:UNIV OF COLORADO THE REGENTS OF

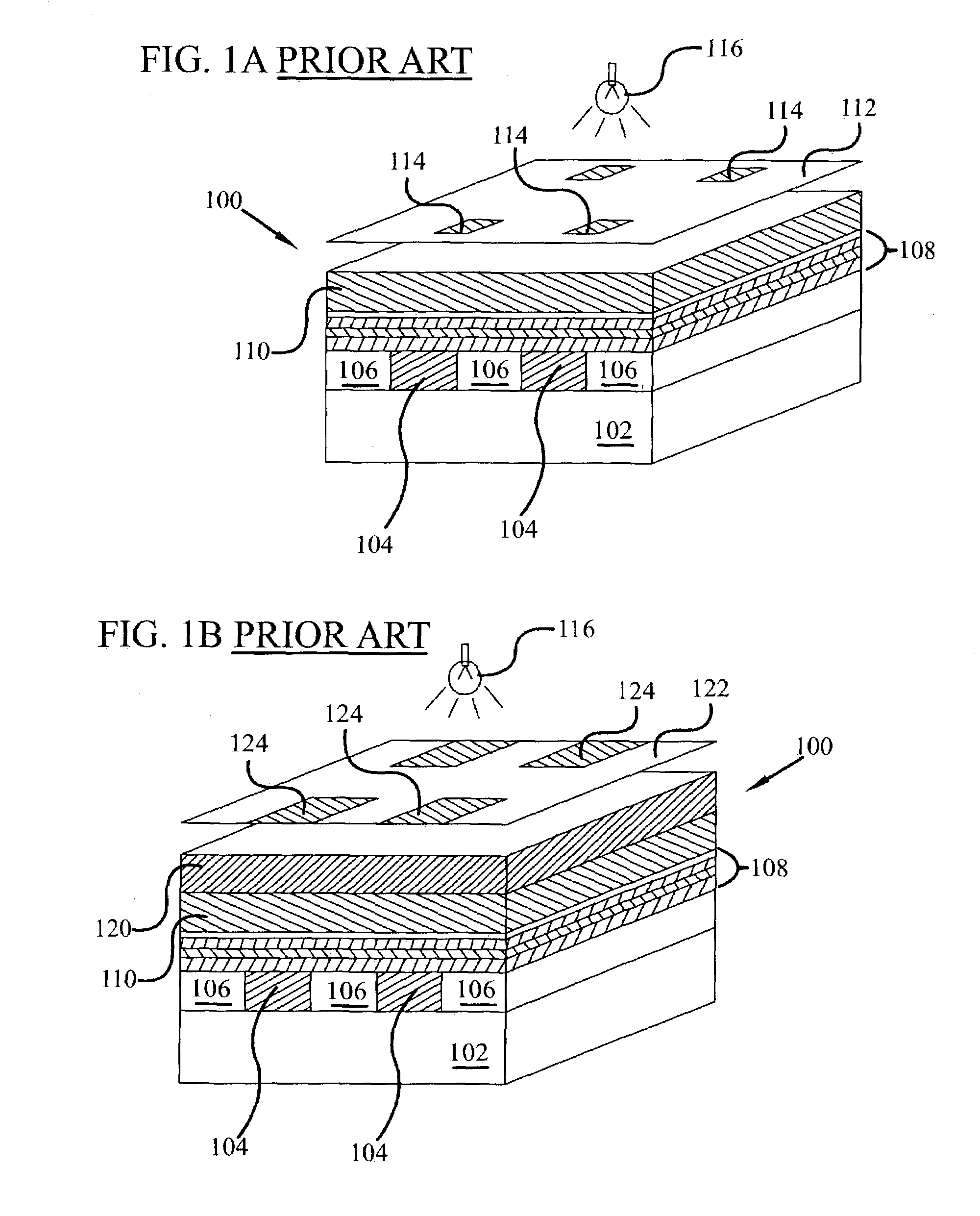

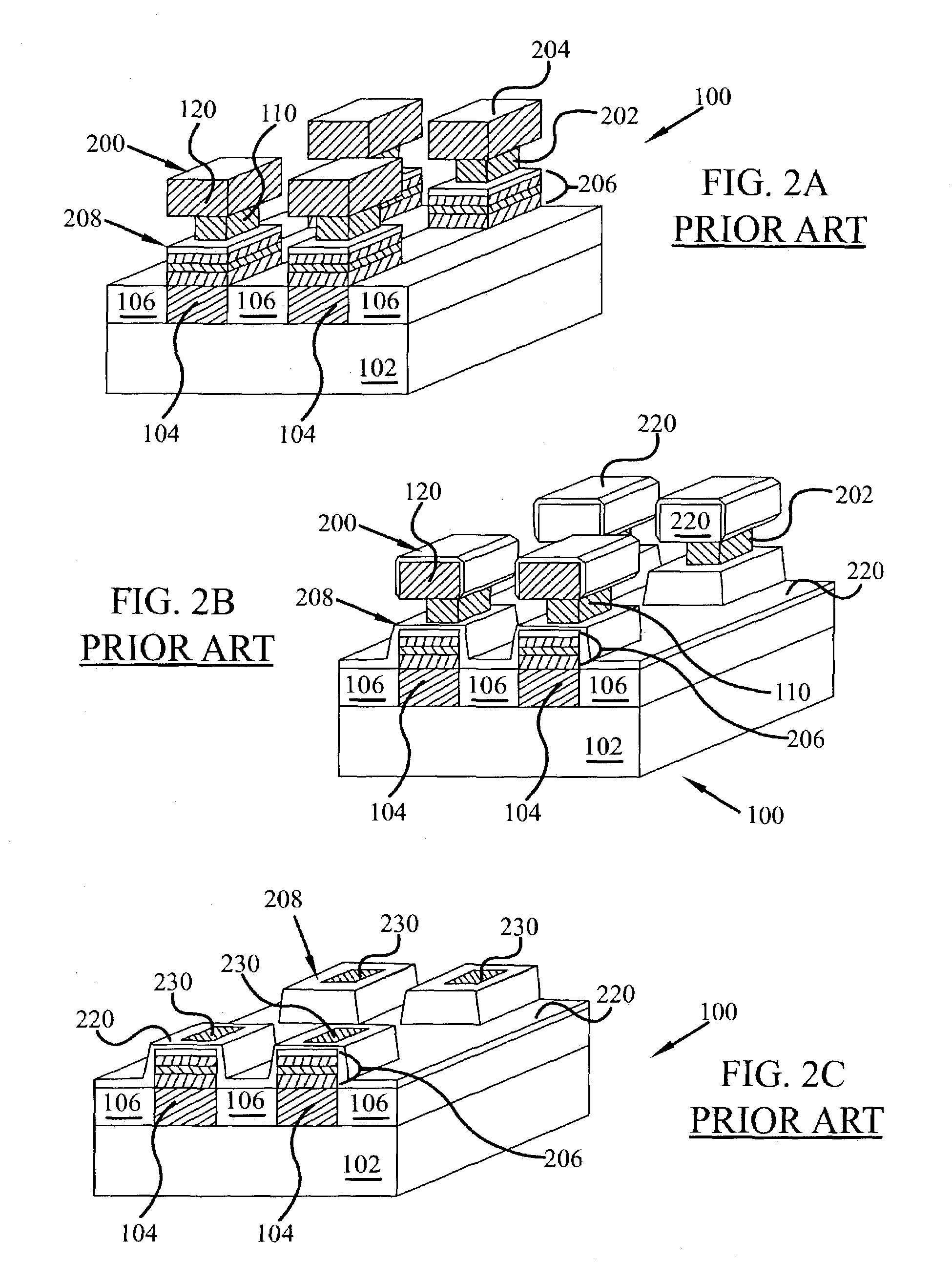

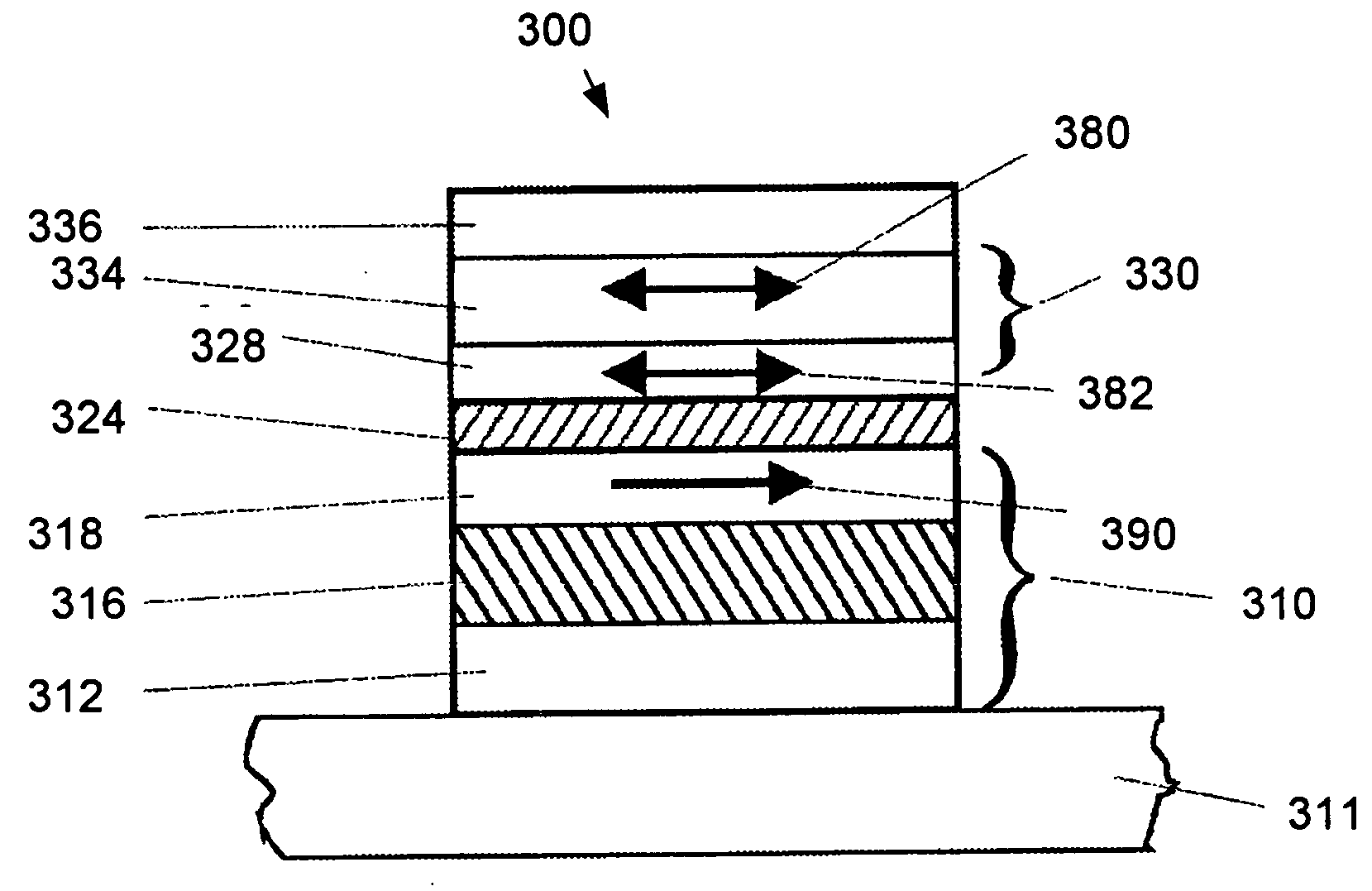

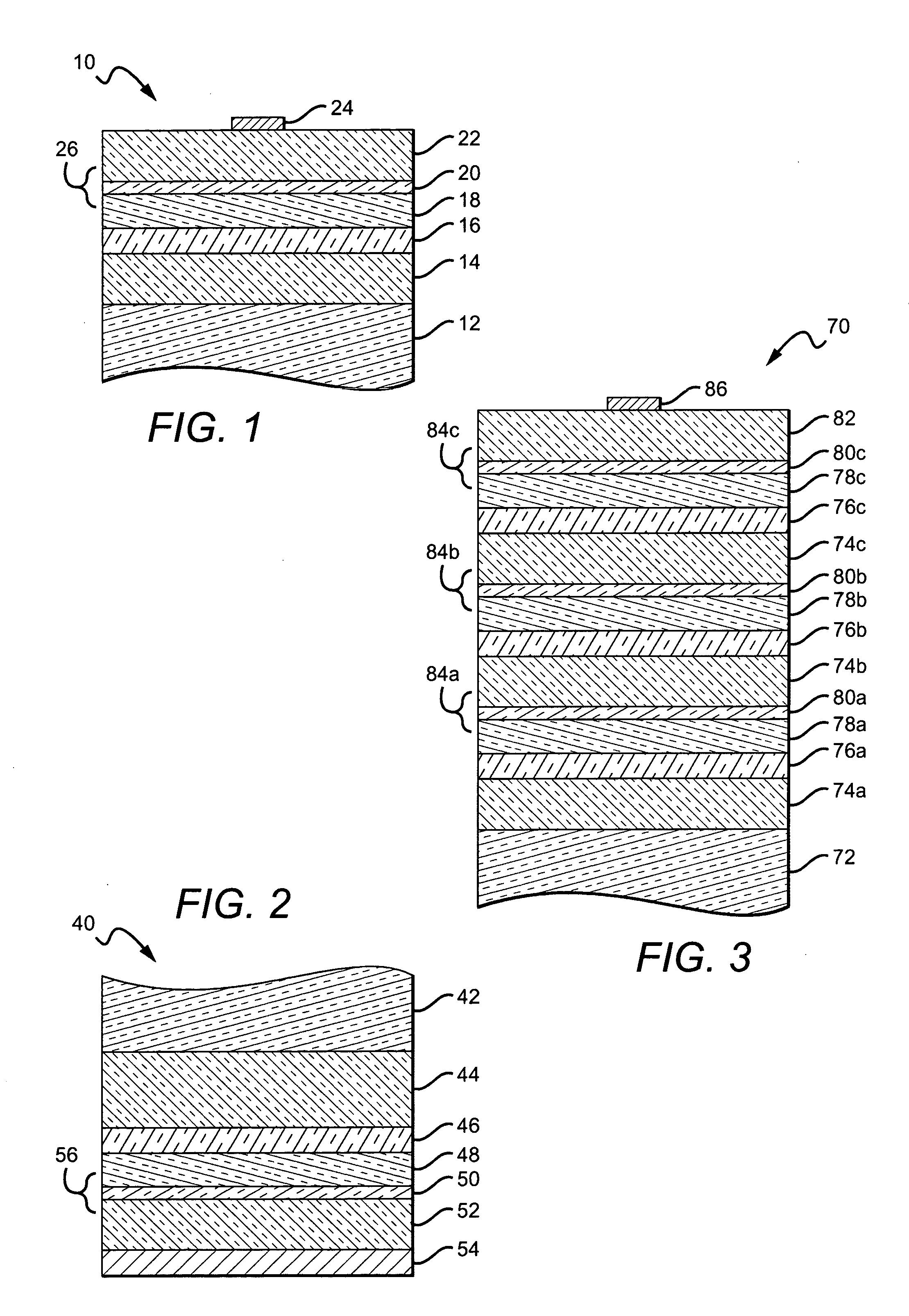

Photonic crystal light emitting device

ActiveUS7012279B2Solid-state devicesSemiconductor/solid-state device manufacturingCrystal structurePhotonic crystal structure

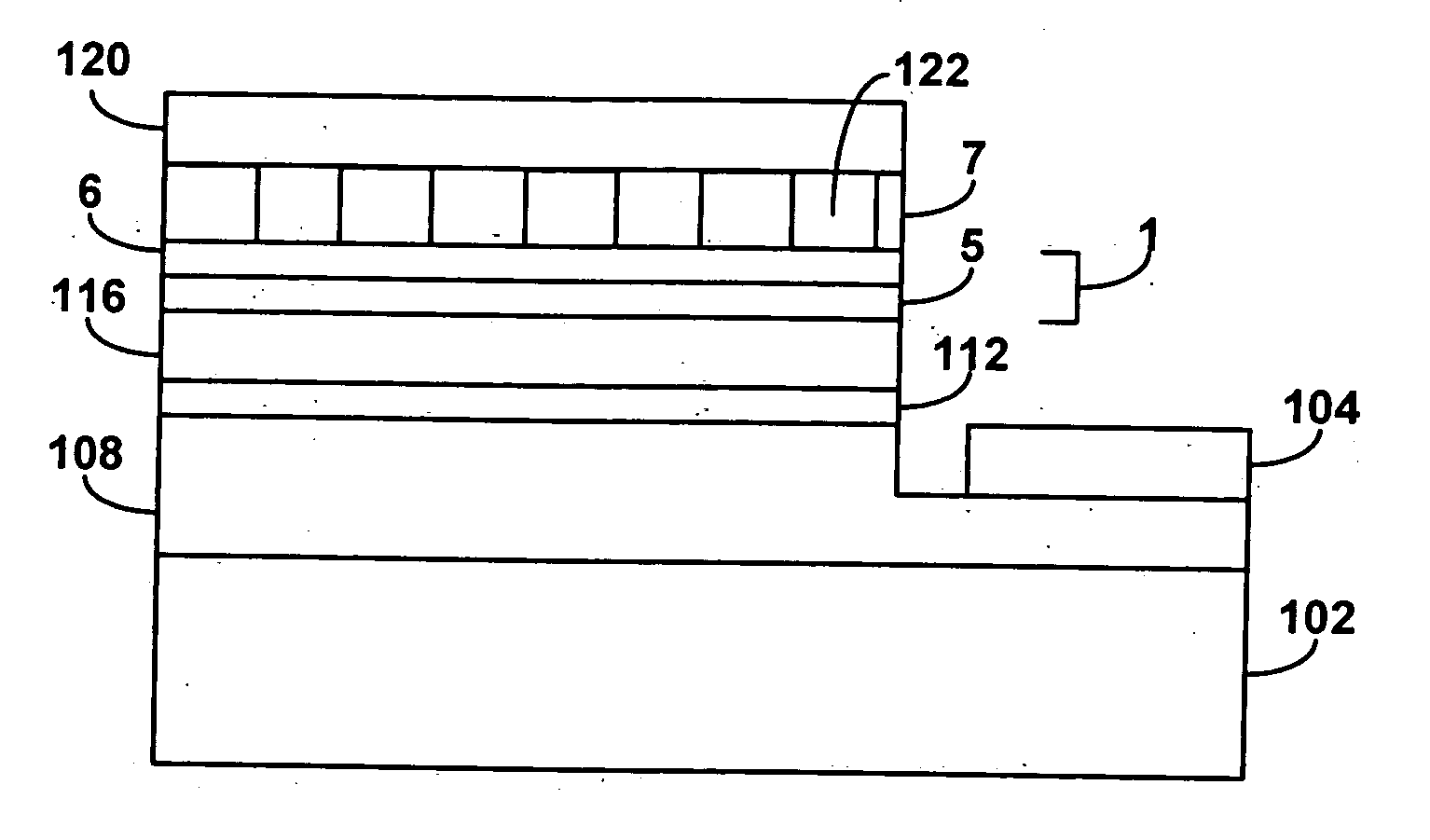

A photonic crystal structure is formed in an n-type layer of a III-nitride light emitting device. In some embodiments, the photonic crystal n-type layer is formed on a tunnel junction. The device includes a first layer of first conductivity type, a first layer of second conductivity type, and an active region separating the first layer of first conductivity type from the first layer of second conductivity type. The tunnel junction includes a second layer of first conductivity type and a second layer of second conductivity type and separates the first layer of first conductivity type from a third layer of first conductivity type. A photonic crystal structure is formed in the third layer of first conductivity type.

Owner:AVAGO TECH INT SALES PTE LTD +1

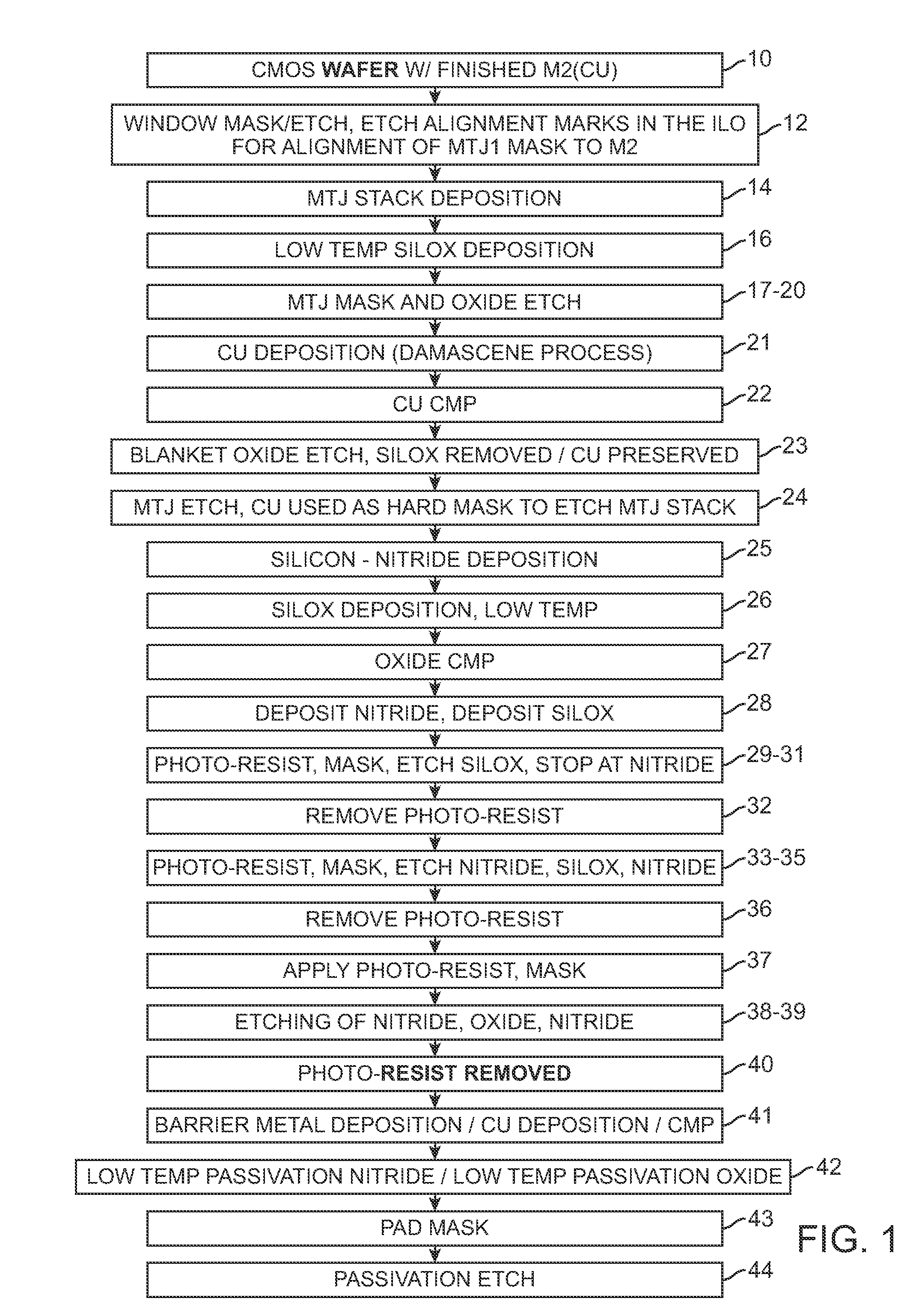

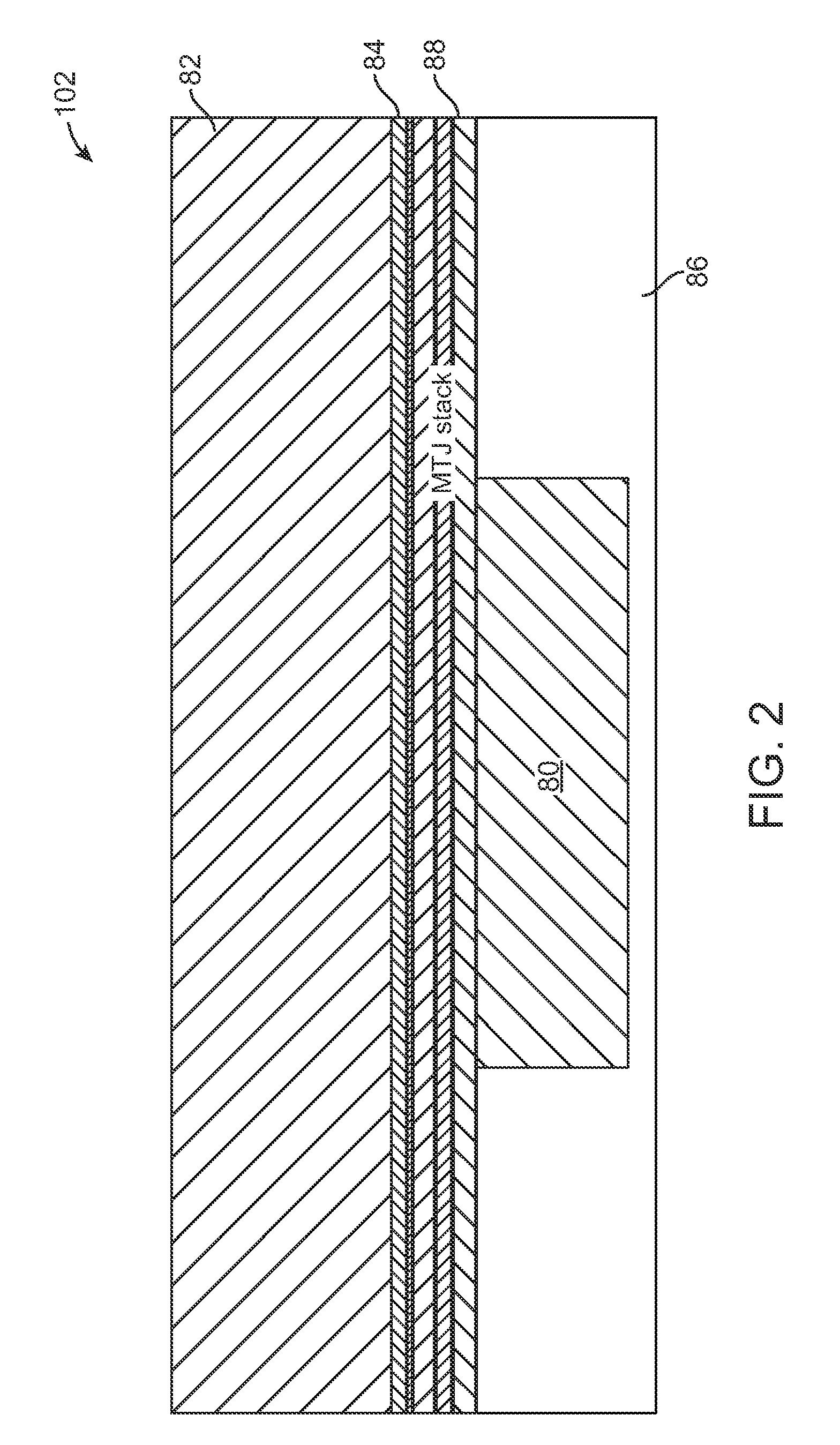

Fabrication process for a magnetic tunnel junction device

InactiveUS20050051820A1Avoid shortingMagnetic-field-controlled resistorsSolid-state devicesEngineeringOxygen

A method of fabricating a magnetic tunnel junction (MTJ) device is provided. A patterned hard mask is oxidized to form a surface oxide thereon. An MTJ stack is etched in alignment with the patterned hard mask after the oxidizing of the patterned hard mask. Preferably, the MTJ stack etch recipe includes chlorine and oxygen. Etch selectivity between the hard mask and the MTJ stack is improved.

Owner:INFINEON TECH AG +1

Photonic crystal light emitting device

ActiveUS20050082545A1Solid-state devicesSemiconductor/solid-state device manufacturingCrystal structurePhotonic crystal structure

A photonic crystal structure is formed in an n-type layer of a III-nitride light emitting device. In some embodiments, the photonic crystal n-type layer is formed on a tunnel junction. The device includes a first layer of first conductivity type, a first layer of second conductivity type, and an active region separating the first layer of first conductivity type from the first layer of second conductivity type. The tunnel junction includes a second layer of first conductivity type and a second layer of second conductivity type and separates the first layer of first conductivity type from a third layer of first conductivity type. A photonic crystal structure is formed in the third layer of first conductivity type.

Owner:AVAGO TECH INT SALES PTE LTD +1

Reference current source for current sense amplifier and programmable resistor configured with magnetic tunnel junction cells

InactiveUS20060092689A1Improve reliabilityWithout compromising device design marginDigital storageAudio power amplifierReference current

A reference current source for a magnetic memory device is preferably configured with magnetic tunnel junction cells and includes more than four reference magnetic memory cells to improve reliability of the magnetic memory device and to reduce sensitivity at a device level to individual cell failures. The reference current source includes a large number of magnetic memory cells coupled in an array, and a current source provides a reference current dependent on the array resistance. In another embodiment a large number of magnetic memory cells are coupled to current sources that are summed and scaled to produce a reference current source. A current comparator senses the unknown state of a magnetic memory cell. In a further embodiment, an array of magnetic memory cells is configured to provide a non-volatile, adjustable resistance. In a further embodiment, the array of magnetic memory cells is configured with a tap to provide a non-volatile, adjustable potentiometer.

Owner:INFINEON TECH AG

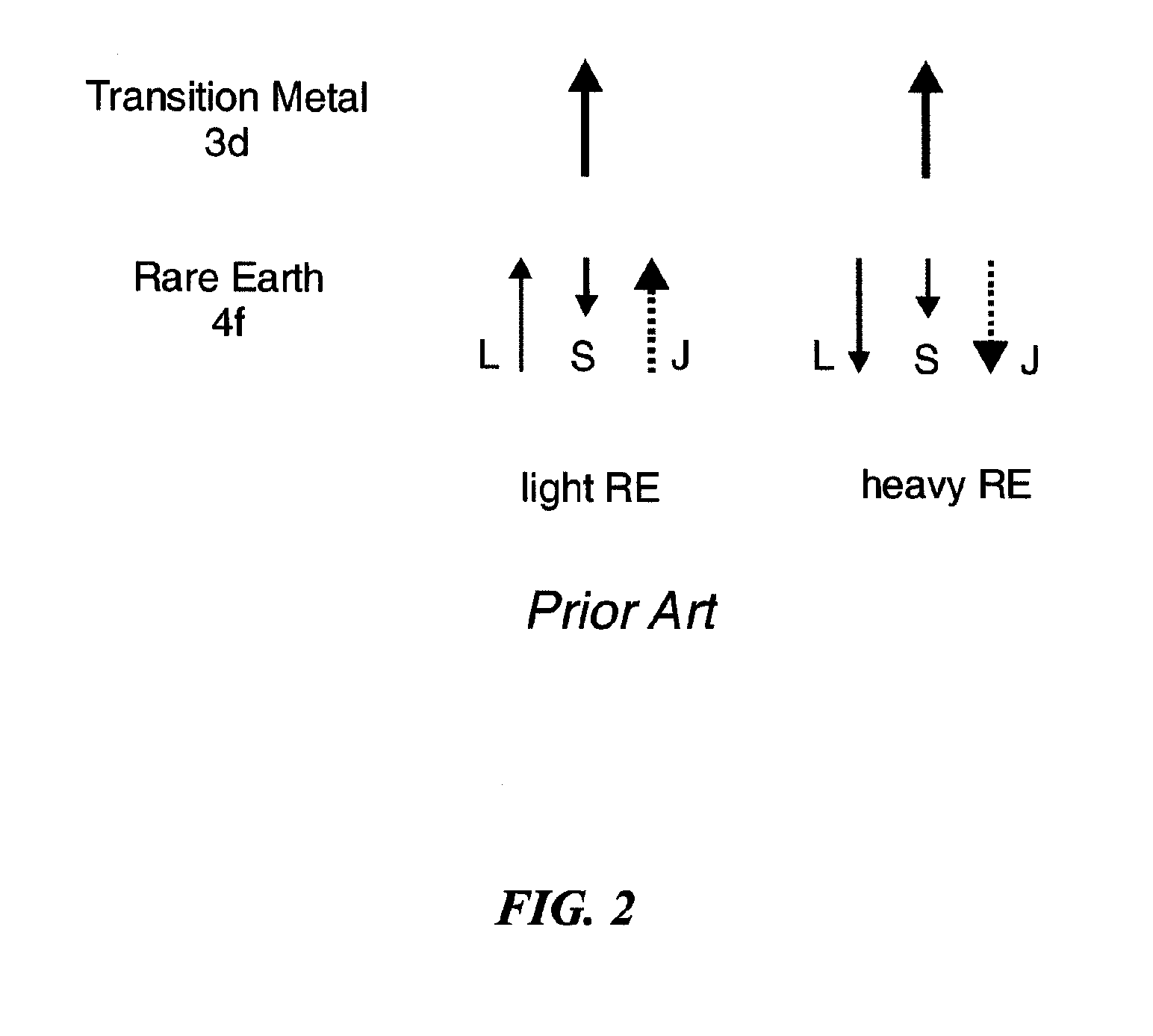

Spin-polarization devices using rare earth-transition metal alloys

ActiveUS7230265B2Magnetic-field-controlled resistorsGalvano-magnetic material selectionRare-earth elementMetal alloy

A tunnel barrier in proximity with a layer of a rare earth element-transition metal (RE—TM) alloy forms a device that passes negatively spin-polarized current. The rare earth element includes at least one element selected from the group consisting of Gd, Tb, Dy, Ho, Er, Tm, and Yb. The RE and TM have respective sub-network moments such that the absolute magnitude of the RE sub-network moment is greater than the absolute magnitude of the TM sub-network moment. An additional layer of magnetic material may be used in combination with the tunnel barrier and the RE—TM alloy layer to form a magnetic tunnel junction. Still other layers of tunnel barrier and magnetic material may be used in combination with the foregoing to form a flux-closed double tunnel junction device.

Owner:IBM CORP

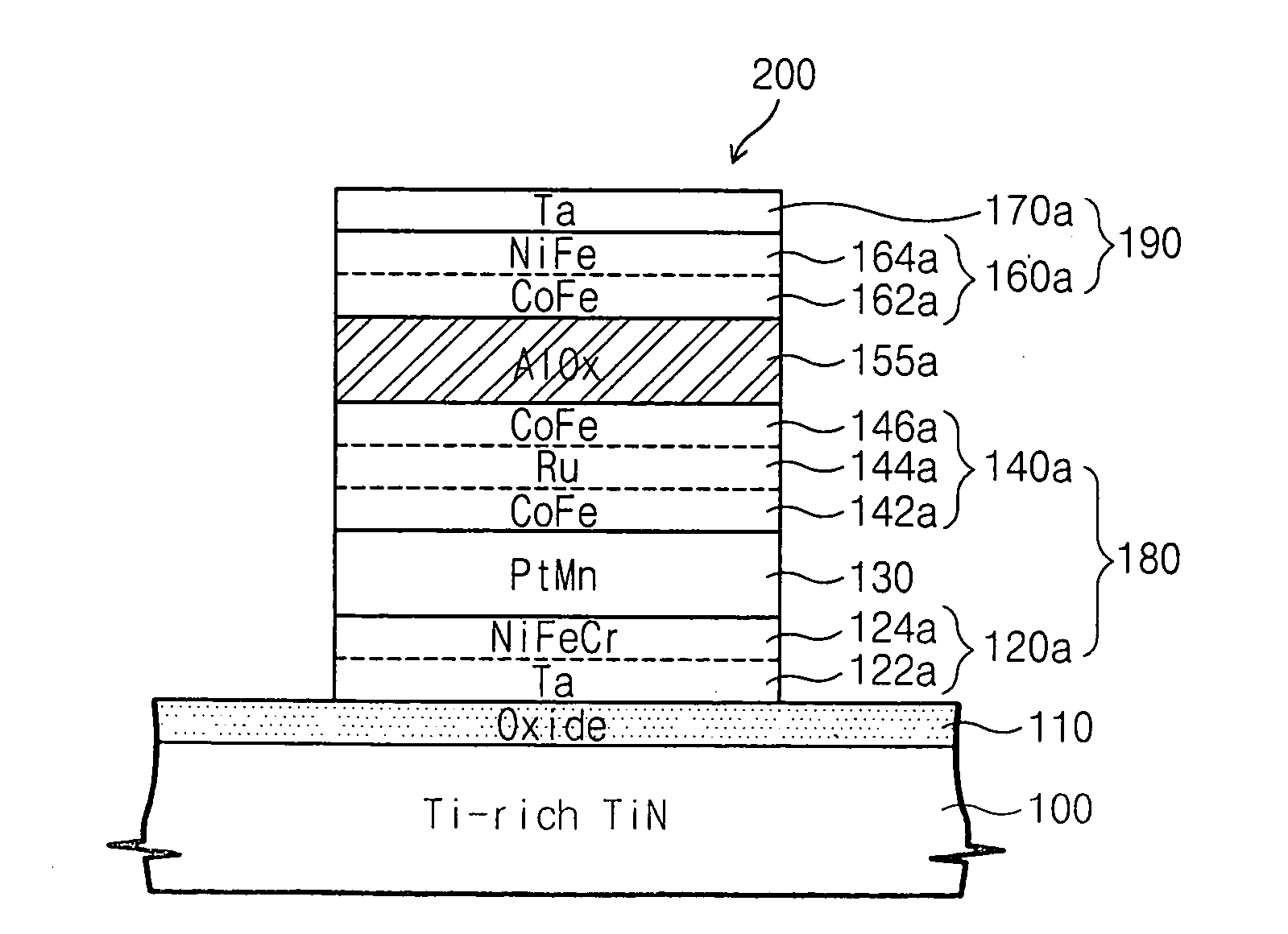

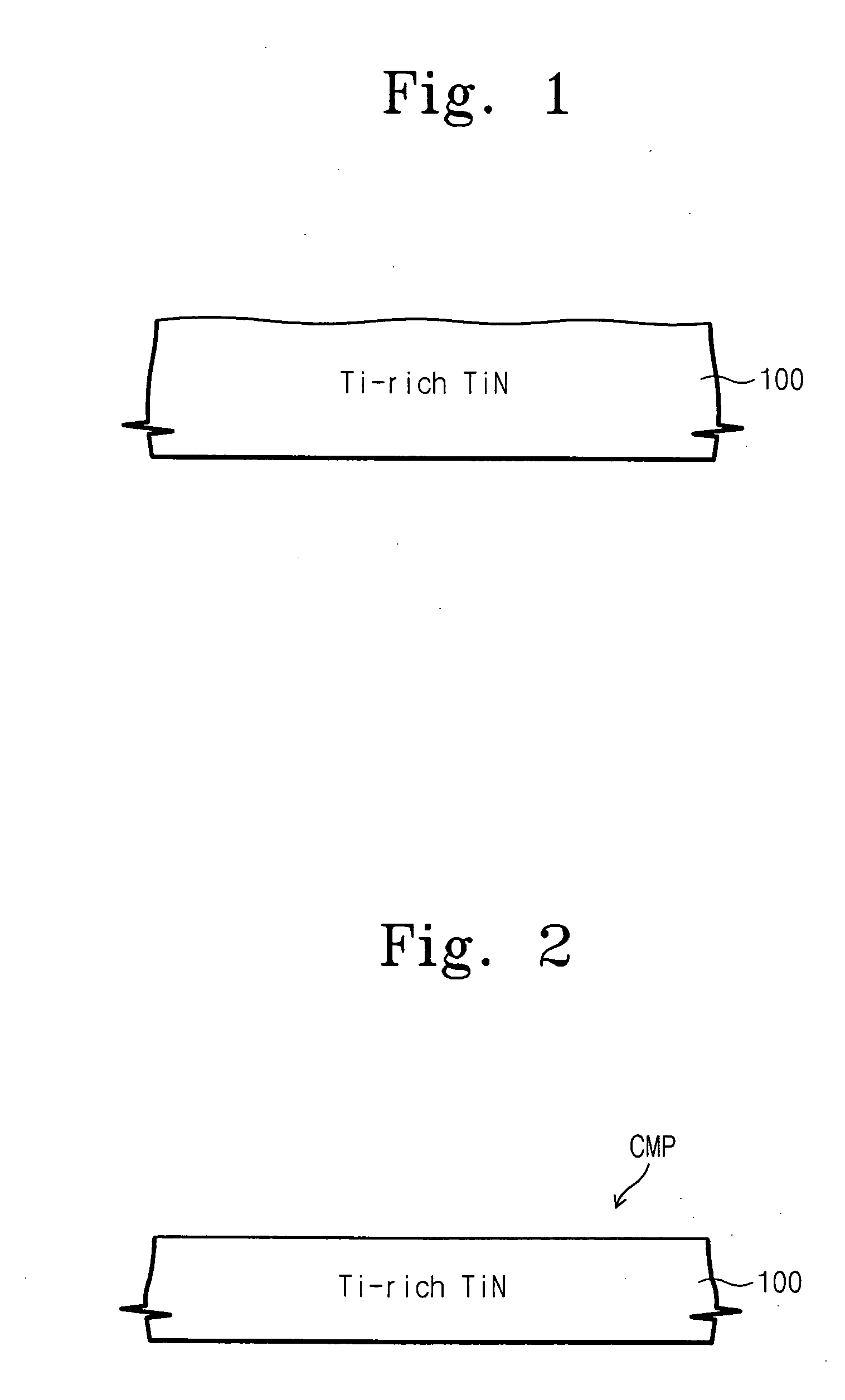

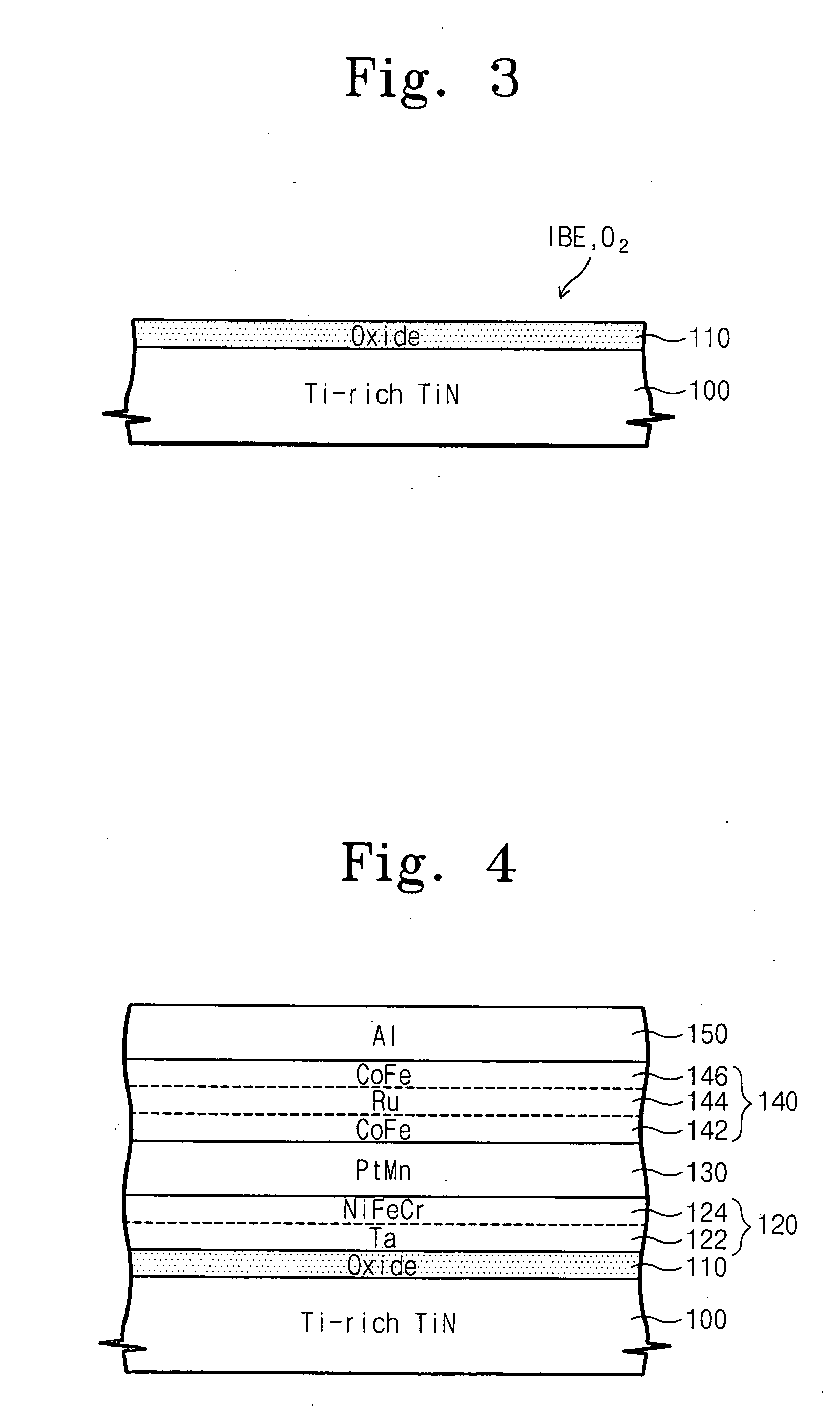

Magnetic random access memory devices having titanium-rich lower electrodes with oxide layer and oriented tunneling barrier, and methods for forming the same

ActiveUS20050006682A1Addressing Insufficient ControlLow polishing rateNanostructure applicationNanomagnetismRandom access memoryTitanium

Magnetic Random Access Memory (MRAM) devices include a lower electrode and a magnetic tunnel junction on the lower electrode. The magnetic tunnel junction includes a seed layer and a tunneling barrier that is oriented in a same direction as the most closely packed plane direction of the seed layer. An oxide layer may be provided between the lower electrode and the magnetic tunnel junction. The lower electrode may be a titanium-rich TiN layer having more than 50 atomic percent titanium content. Analogous fabrication methods are also described.

Owner:SAMSUNG ELECTRONICS CO LTD

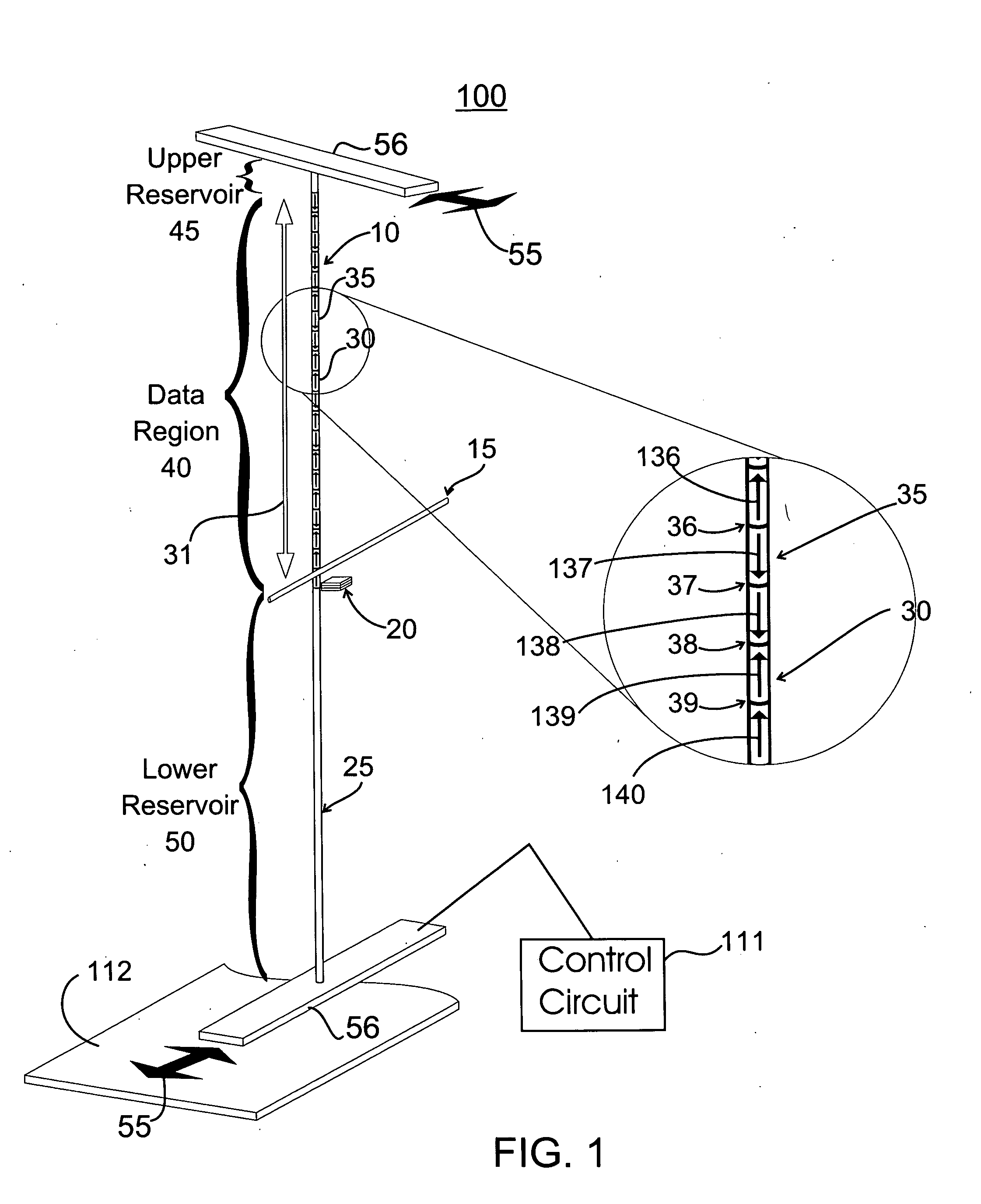

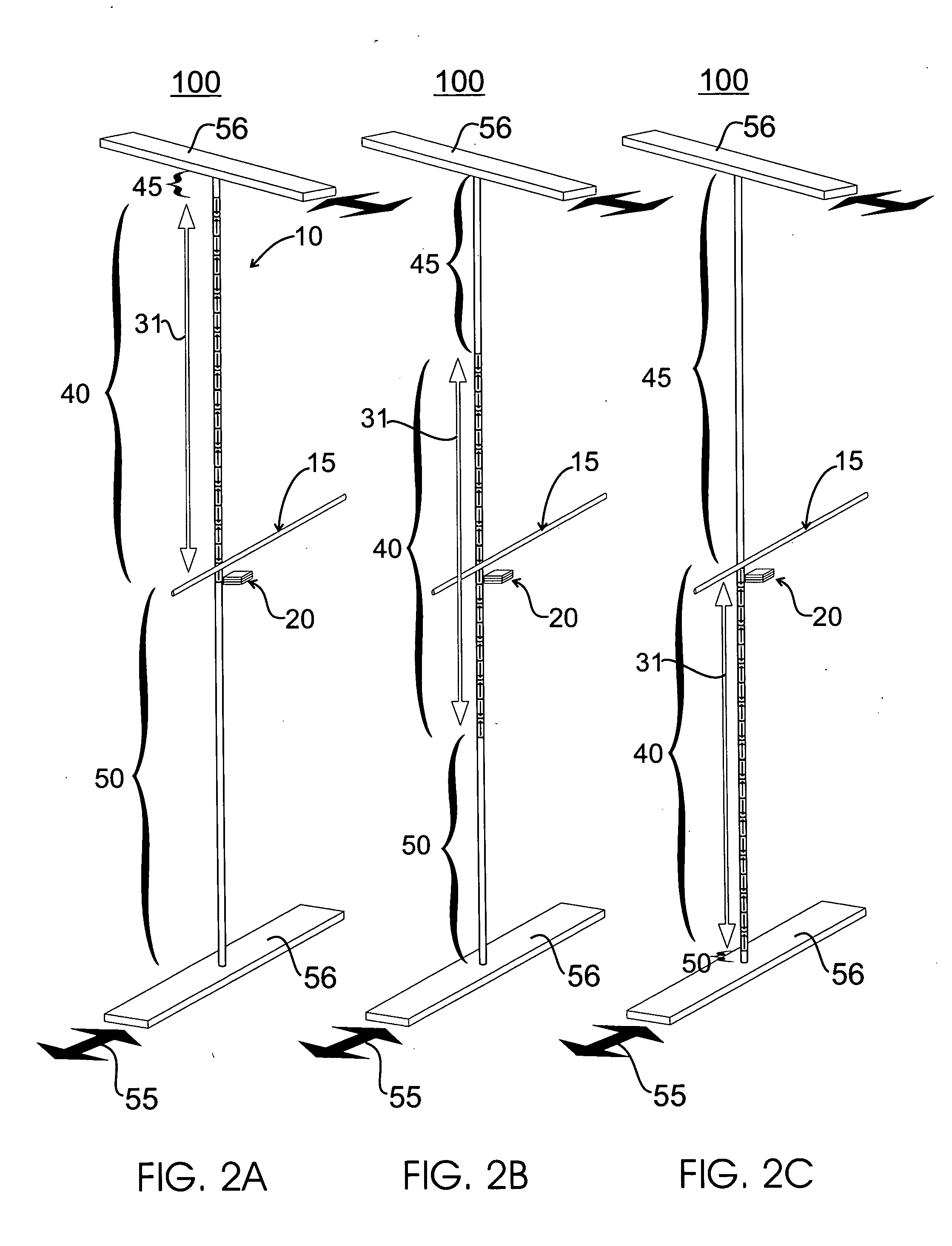

System and method for transferring data to and from a magnetic shift register with a shiftable data column

InactiveUS20060120132A1Magnitude fringing fieldEasy to operateDigital storageShift registerData storing

A magnetic shift register utilizes a data column comprising a thin wire of magnetic material. A writing element selectively changes the direction of the magnetic moment in the magnetic domains to write the data to the data column. Associated with each domain wall are large magnetic fringing fields concentrated in a very small space. These magnetic fringing fields write to and read from the magnetic shift register. When the domain wall is moved close to another magnetic material, the fringing fields change the direction of the magnetic moment in the magnetic material, effectively “writing” to the magnetic material. A reading element similar to a tunneling junction comprises a free layer and a pinned layer of magnetic material. Fringing fields change the direction of the magnetic moment in the free layer with respect to the pinned layer, changing electrical resistance of the reading element and “reading” data stored in the magnetic shift register.

Owner:GLOBALFOUNDRIES US INC

Surface plasmon devices

A device including an input port configured to receive an input signal is described. The device also includes an output port and a structure, which structure includes a tunneling junction connected with the input port and the output port. The tunneling junction is configured in a way (i) which provides electrons in a particular energy state within the structure, (ii) which produces surface plasmons in response to the input signal, (iii) which causes the structure to act as a waveguide for directing at least a portion of the surface plasmons along a predetermined path toward the output port such that the surface plasmons so directed interact with the electrons in a particular way, and (iv) which produces at the output port an output signal resulting from the particular interaction between the electrons and the surface plasmons.

Owner:UNIV OF COLORADO THE REGENTS OF

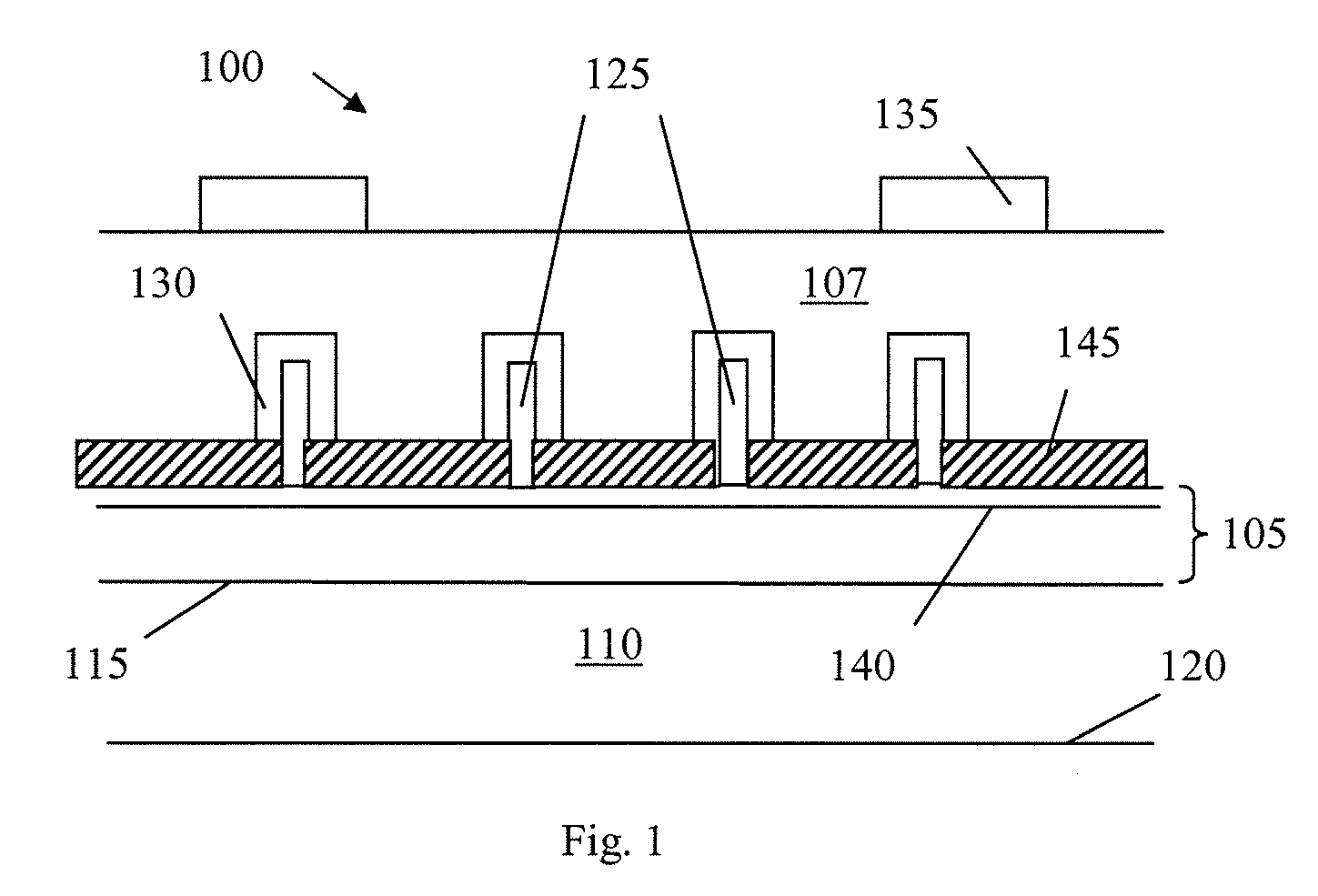

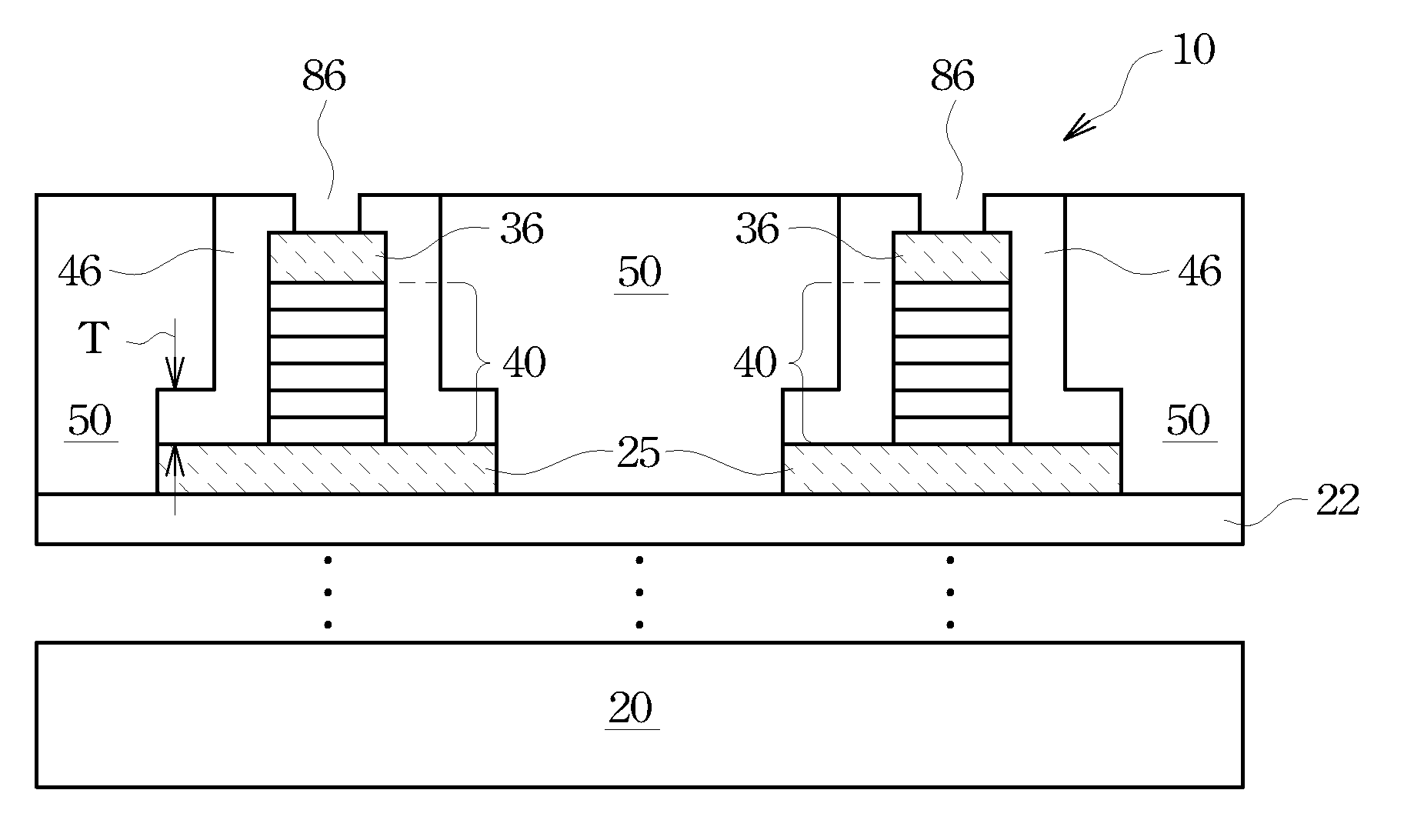

Directional ion etching process for patterning self-aligned via contacts

The invention provides a directional ion etching process to pattern self-aligned via contacts in the manufacture of semiconductor devices such as high density magnetic random access memory (MRAM). In a particular embodiment, a semiconductor wafer is prepared with vertically arranged layers, including a patterned layer in electrical contact with a conductive row layer. The patterned layer may be a magnetic tunnel junction layer. A photoresist is deposited on the junction layer, masked, exposed and developed. The non-protected junction layer is etched to provide appropriate junction stacks. The remaining photoresist caps are not dissolved, rather they and the surface of the wafer are coated with a dielectric. Directional ion etching at a low angle relative to the junction stack layer removes the coated photoresist caps and thereby provides at least one patterned self-aligned via contact.

Owner:SAMSUNG ELECTRONICS CO LTD

Magnetic tunnel junction with improved tunneling magneto-resistance

InactiveUS20050110004A1Improve featuresNanostructure applicationNanomagnetismInterface layerMagnetic memory

A magnetic tunnel element that can be used, for example, as part of a read head or a magnetic memory cell, includes a first layer formed from an amorphous material, an amorphous tunnel barrier layer, and an interface layer between the first layer and the tunnel barrier layer. The interface layer is formed from a material that is crystalline when the material is in isolation from both the first layer and the tunnel barrier layer. Alternatively, the thickness of the interface layer is selected so that the interface layer is not crystalline. The first layer is formed from at least one material selected from the group consisting of amorphous ferromagnetic material, amorphous ferrimagnetic materials, and amorphous non-magnetic materials. The interface layer is formed from a material selected from the group consisting of a ferromagnetic material and a ferrimagnetic material.

Owner:GLOBALFOUNDRIES INC

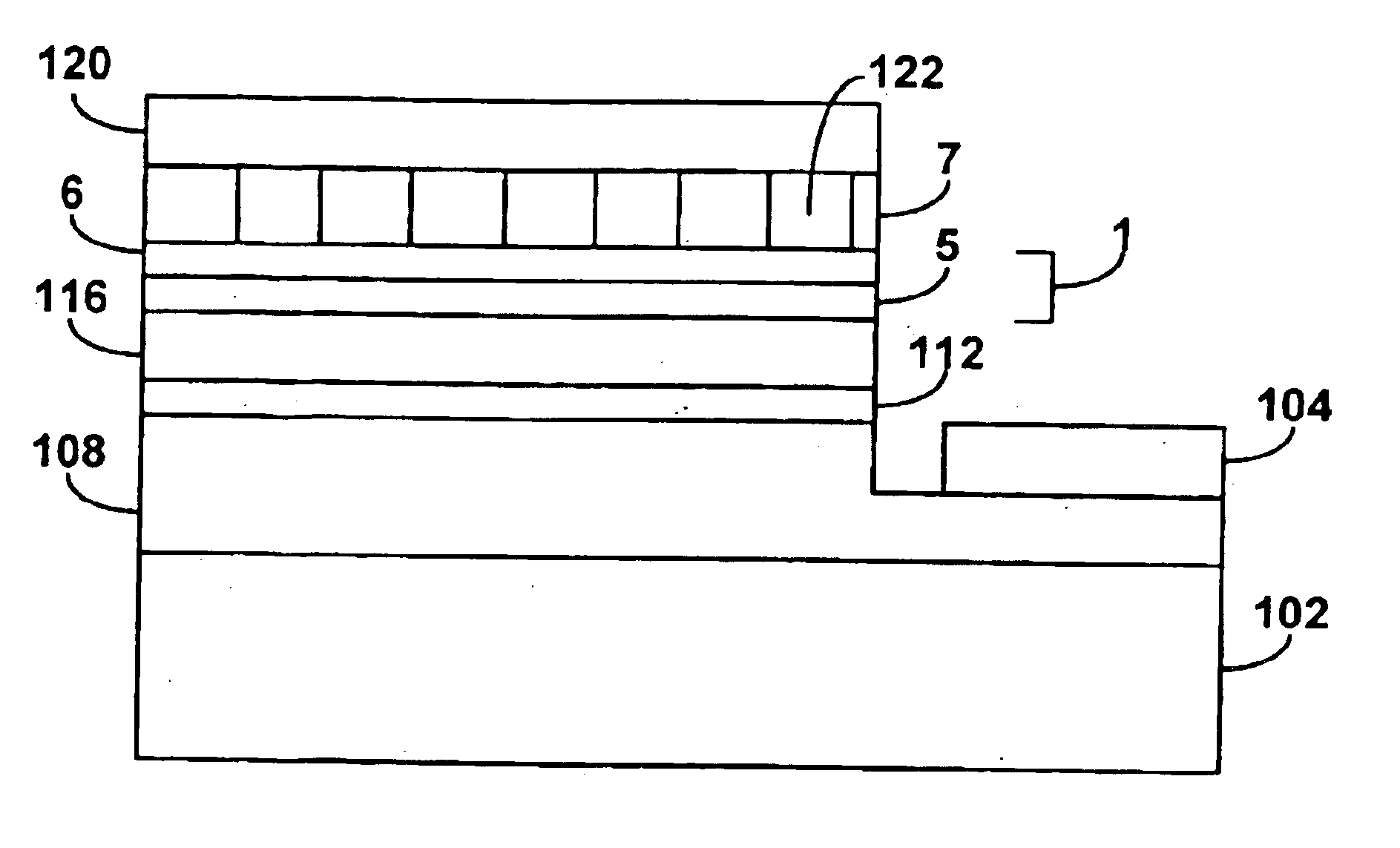

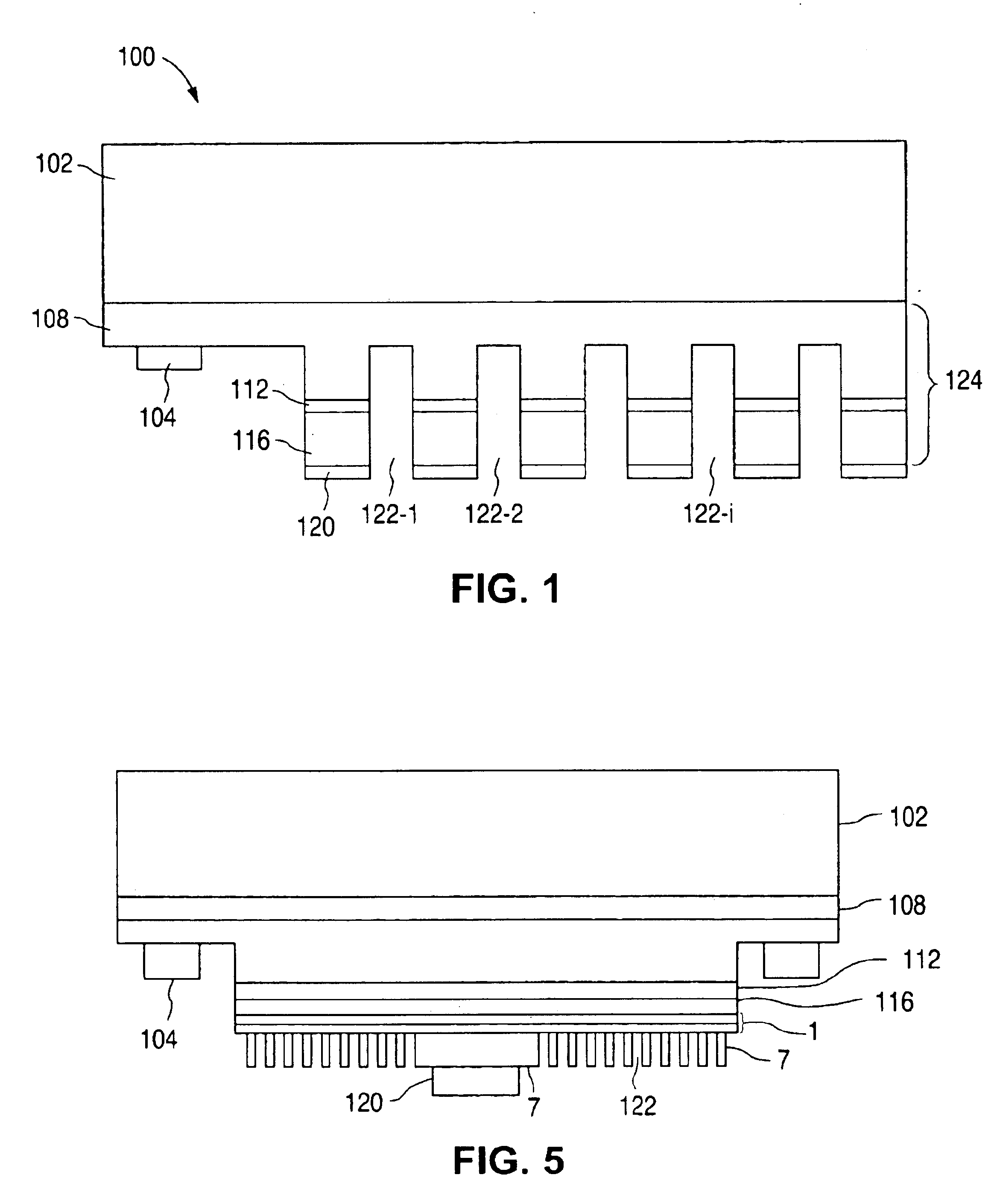

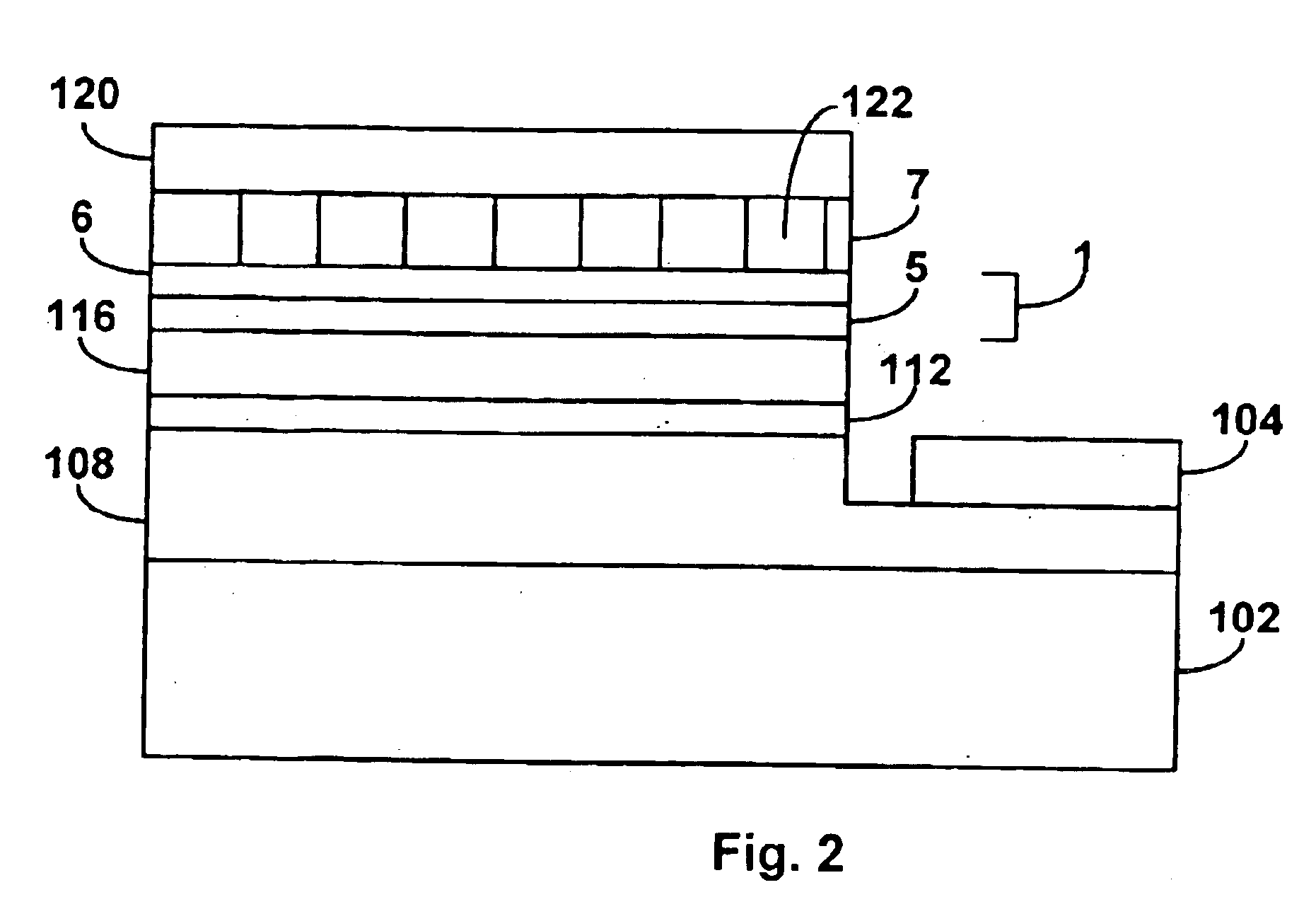

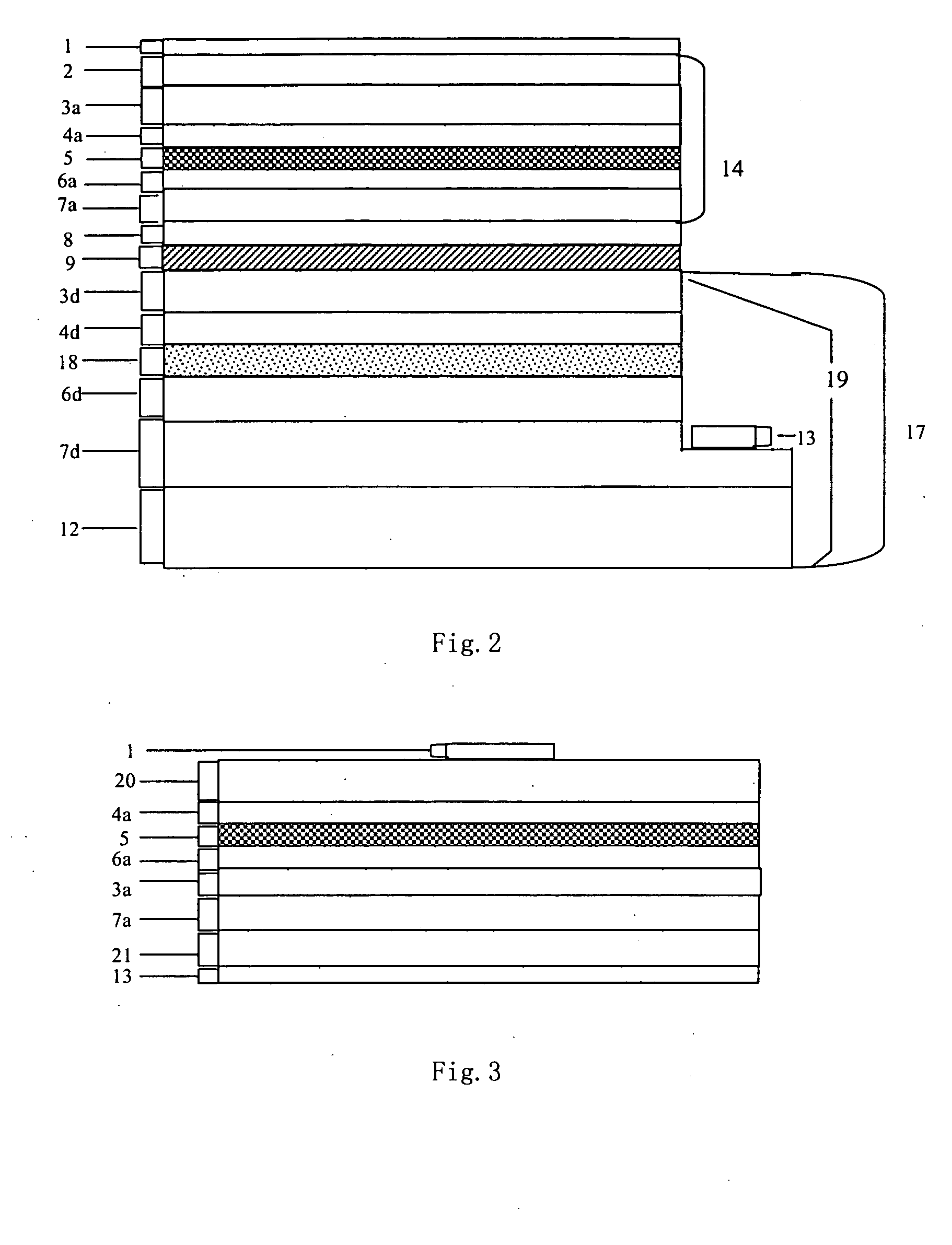

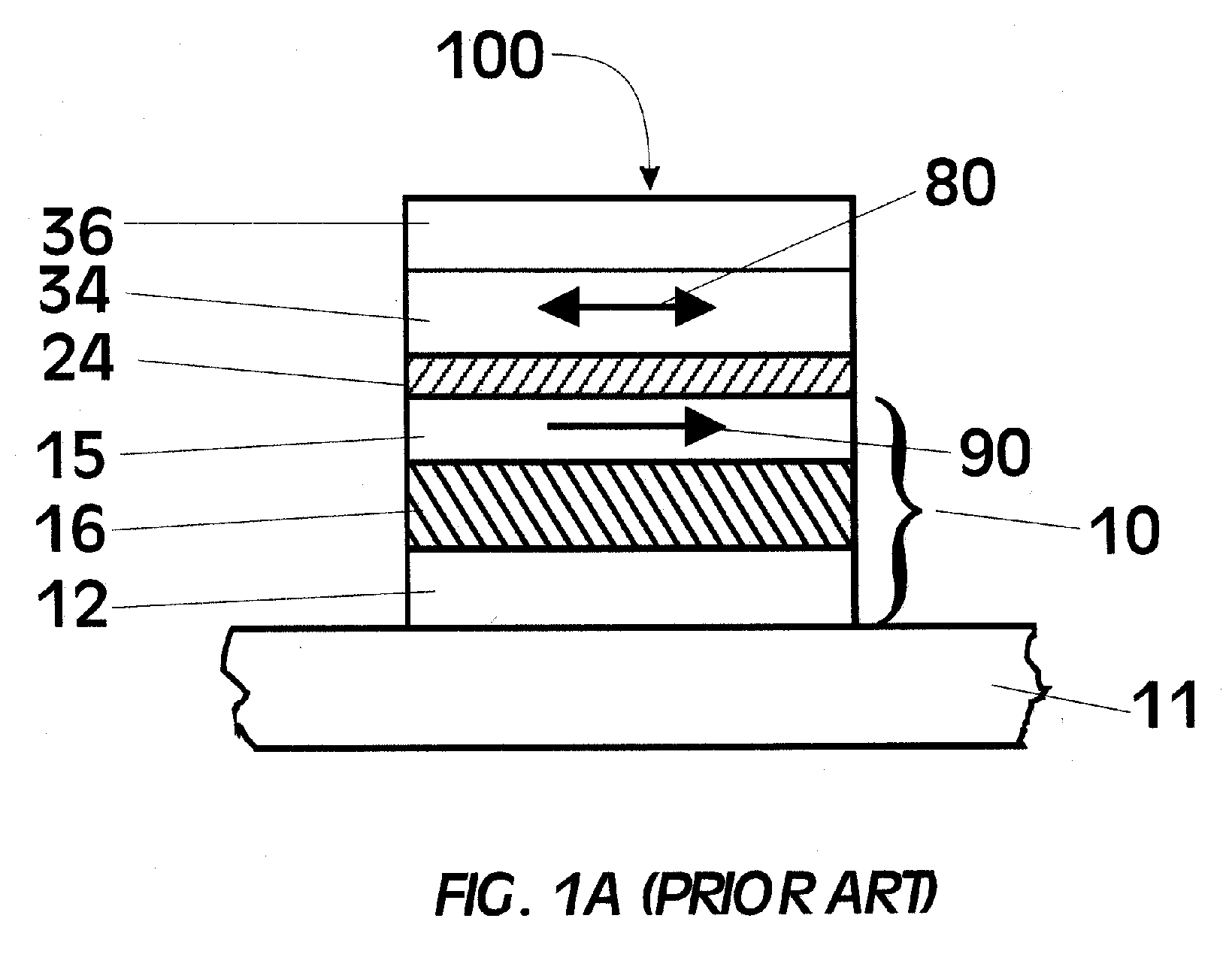

High efficiency multi-active layer tunnel regenerated white light emitting diode

InactiveUS20050067627A1Improved current spreadingEasy to spreadSemiconductor devicesGreen cellSemiconductor materials

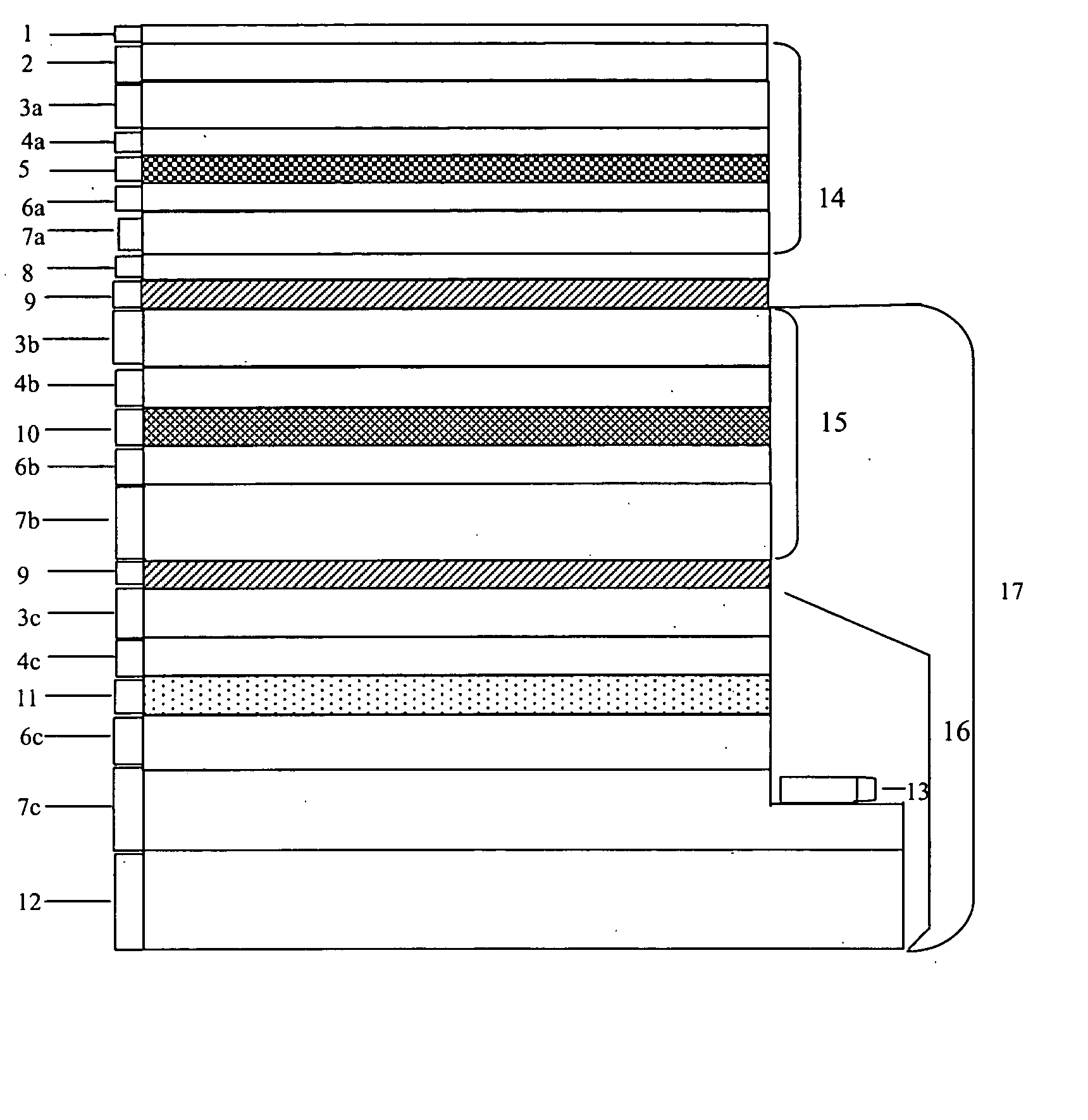

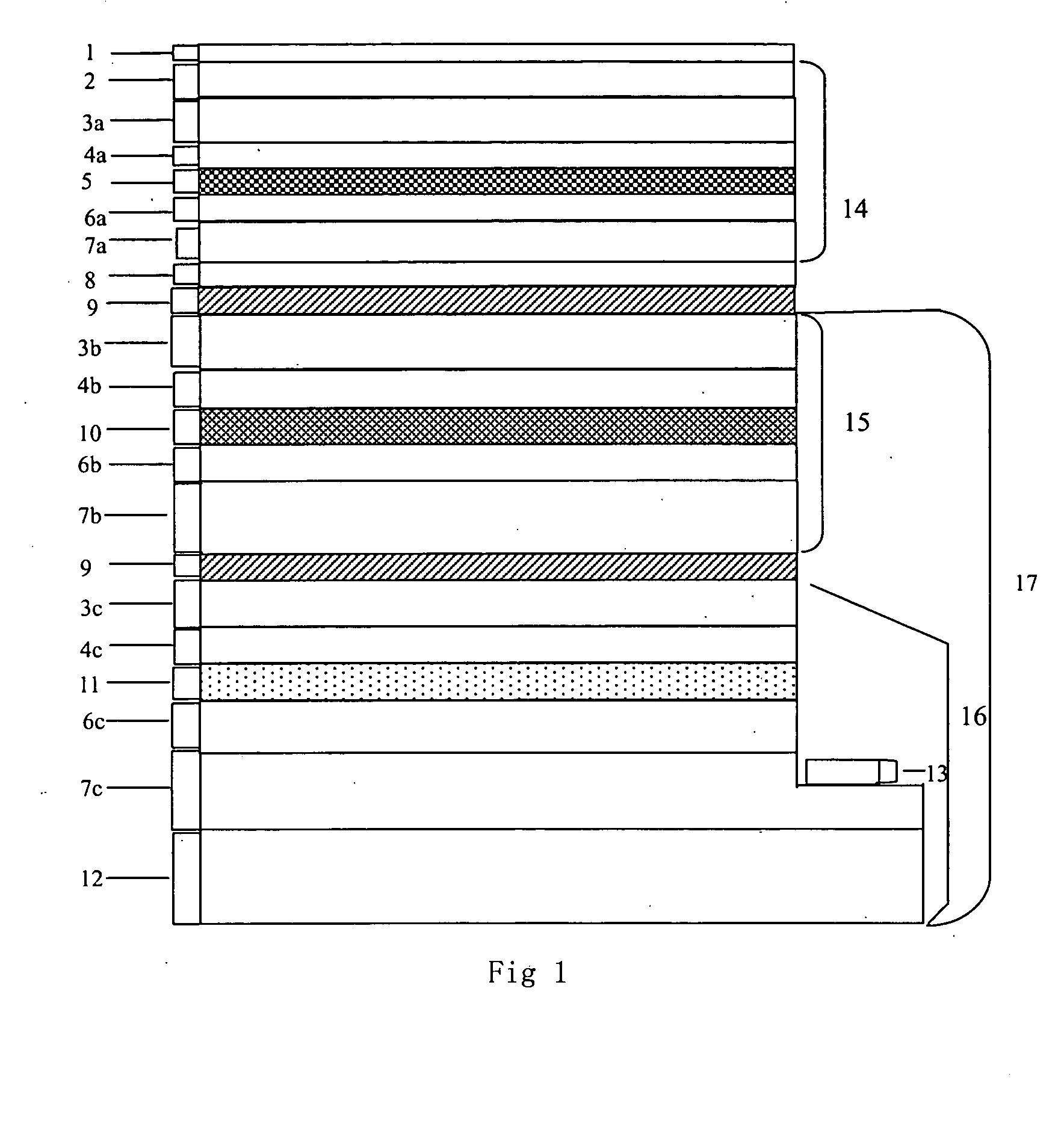

A high efficiency and high brightness multi-active layer tunneling regenerated white color semiconductor light emitting diode having a p type electrode 1, a monolithic red light cell 14, a tunnel junction 9, a monolithic green light 15 and blue light cell 16 (or a monolithic cyan light cell 19), wherein each of said cells are electrically connected by tunnel junctions 9, and the red cell physically connected with blue and green cell (or cyan cell) by wafer bonding layer 8. The lights from each cell synthesize white color light. The white light emitting diode only has one time optical-electrical conversion, so the quantum efficiency is high. Moreover, the white LED totally made from semiconductor materials, the lifetime of the white LED lamp is not limited by the relatively short lifetime of fluorescent material.

Owner:BEIJING UNIV OF TECH

Magnetic Tunnel Junctions Using Amorphous Materials as Reference and Free Layers

ActiveUS20060098354A1Improve barrier propertiesImprove performanceNanomagnetismNanoinformaticsBoronTunnel junction

Magnetic tunnel junctions are constructed from a MgO or Mg—ZnO tunnel barrier and amorphous magnetic layers in proximity with, and on respective sides of, the tunnel barrier. The amorphous magnetic layer preferably includes Co and at least one additional element selected to make the layer amorphous, such as boron. Magnetic tunnel junctions formed from the amorphous magnetic layers and the tunnel barrier have tunneling magnetoresistance values of up to 200% or more.

Owner:IBM CORP

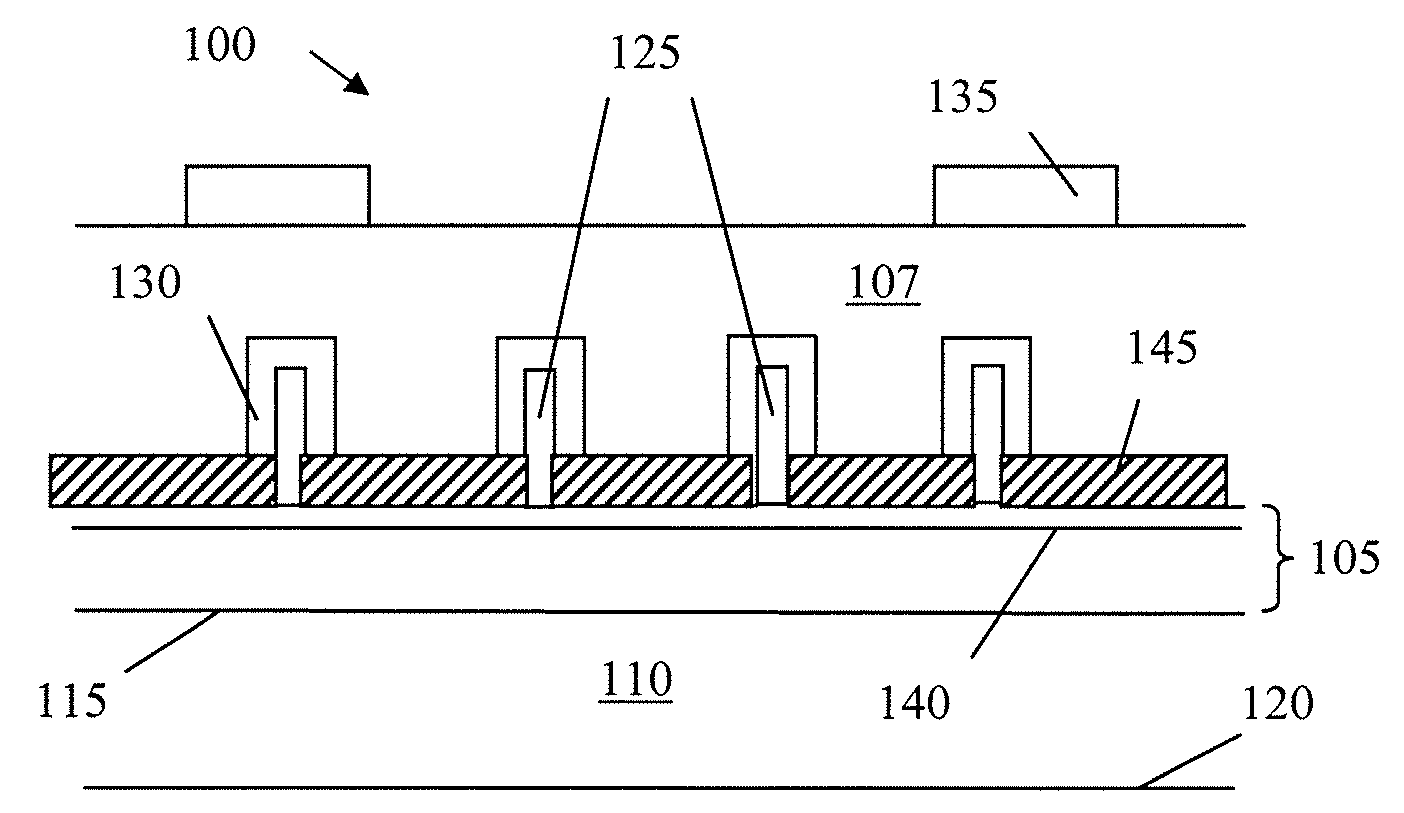

Multilayered Film-Nanowire Composite, Bifacial, and Tandem Solar Cells

A photovoltaic device includes a substrate having at least two surfaces and a multilayered film disposed on at least a portion of at least one surface of the substrate. Elongated nanostructures are disposed on the multilayered film. The device incorporates a top layer of the multilayered film contacting the elongated nanostructures that is a tunnel junction. The device has at least one layer deposited over the elongated nanostructures defining a portion of a photoactive junction. A solar panel includes at least one photovoltaic device. The solar panel isolates each such devices from its surrounding atmospheric environment and permits the generation of electrical power.

Owner:GENERAL ELECTRIC CO

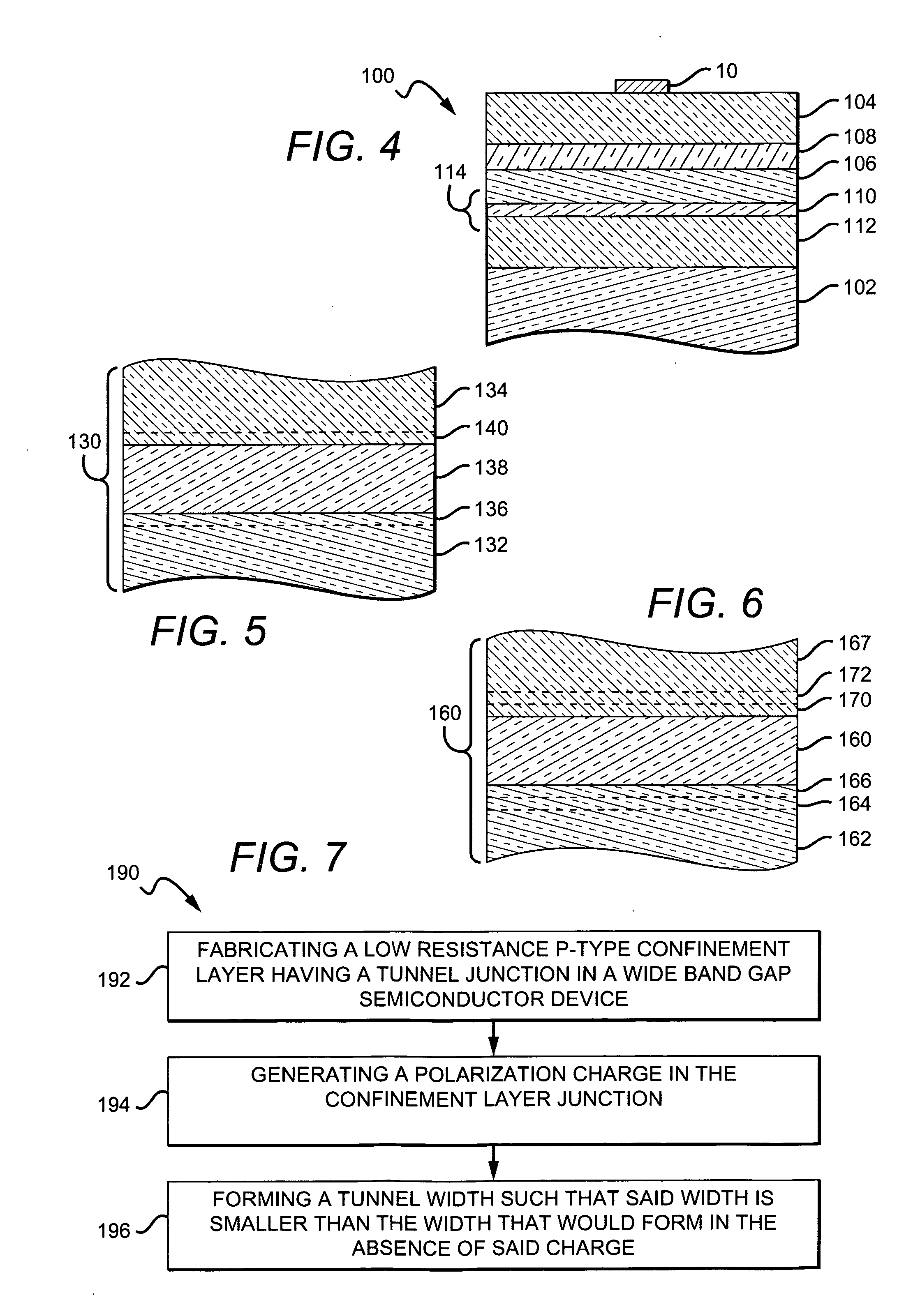

High efficiency LEDs with tunnel junctions

An LED made from a wide band gap semiconductor material and having a low resistance p-type confinement layer with a tunnel junction in a wide band gap semiconductor device is disclosed. A dissimilar material is placed at the tunnel junction where the material generates a natural dipole. This natural dipole is used to form a junction having a tunnel width that is smaller than such a width would be without the dissimilar material. A low resistance p-type confinement layer having a tunnel junction in a wide band gap semiconductor device may be fabricated by generating a polarization charge in the junction of the confinement layer, and forming a tunnel width in the junction that is smaller than the width would be without the polarization charge. Tunneling through the tunnel junction in the confinement layer may be enhanced by the addition of impurities within the junction. These impurities may form band gap states in the junction.

Owner:CREELED INC

Gate Level Reconfigurable Magnetic Logic

ActiveUS20100039136A1Write currentIncrease current densitySolid-state devicesDigital storageSignal onRandom access memory

A re-programmable gate logic includes a plurality of non-volatile re-configurable resistance state-based memory circuits in parallel, wherein the circuits are re-configurable to implement or change a selected gate logic, and the plurality of non-volatile re-configurable resistance state-based memory circuits are each adapted to receive a logical input signal. An evaluation switch in series with the plurality of parallel non-volatile re-configurable resistance state-based memory circuits is configured to provide an output signal based on the programmed states of the memory circuits. A sensor is configured to receive the output signal and provide a logical output signal on the basis of the output signal and a reference signal provided to the sensor. The reconfigurable logic may be implemented based on using spin torque transfer (STT) magnetic tunnel junction (MTJ) magnetoresistance random access memory (MRAM) as the re-programmable memory elements. The logic configuration is retained without power.

Owner:QUALCOMM INC

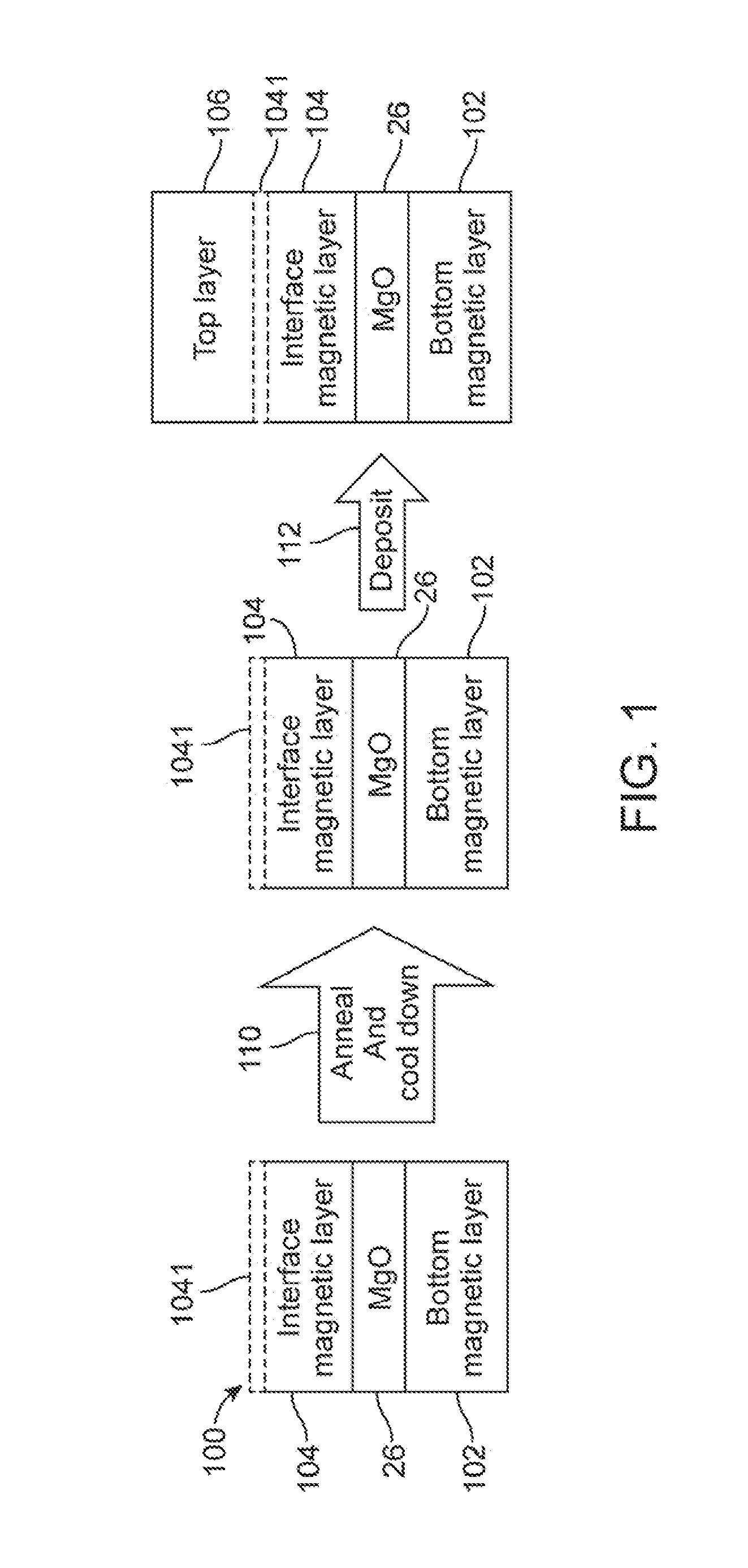

In-Situ Formed Capping Layer in MTJ Devices

InactiveUS20090209050A1Eliminate oxidationSolid-state devicesSemiconductor/solid-state device manufacturingTunnel junctionIntegrated circuit

A method of forming an integrated circuit includes forming magnetic tunnel junction (MTJ) layers; etching the MTJ layers to form a MTJ cell; and forming a dielectric capping layer on sidewalls of the MTJ cell, wherein the step of forming the dielectric capping layer is in-situ performed with the step of etching the MTJ layers.

Owner:TAIWAN SEMICON MFG CO LTD

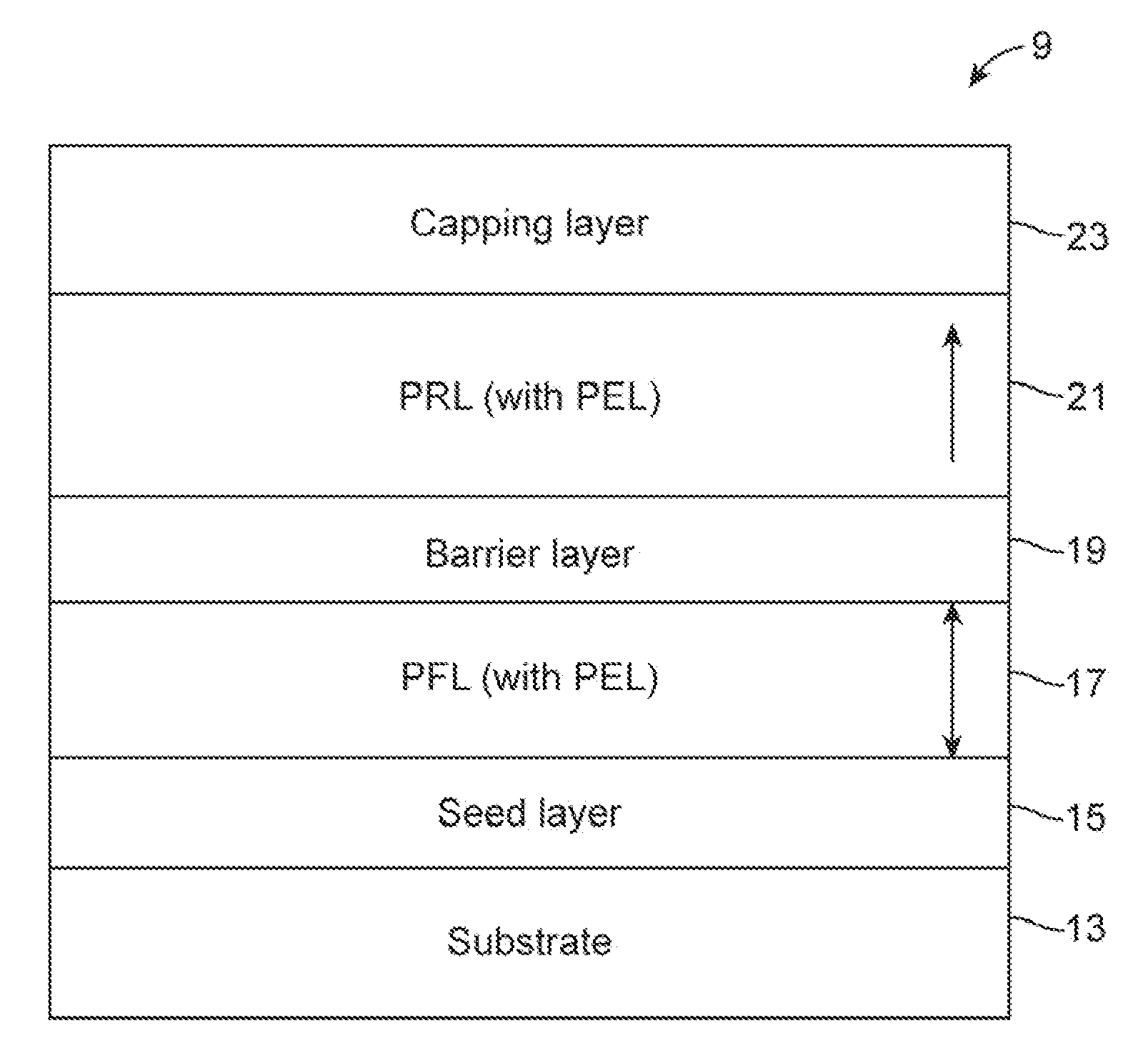

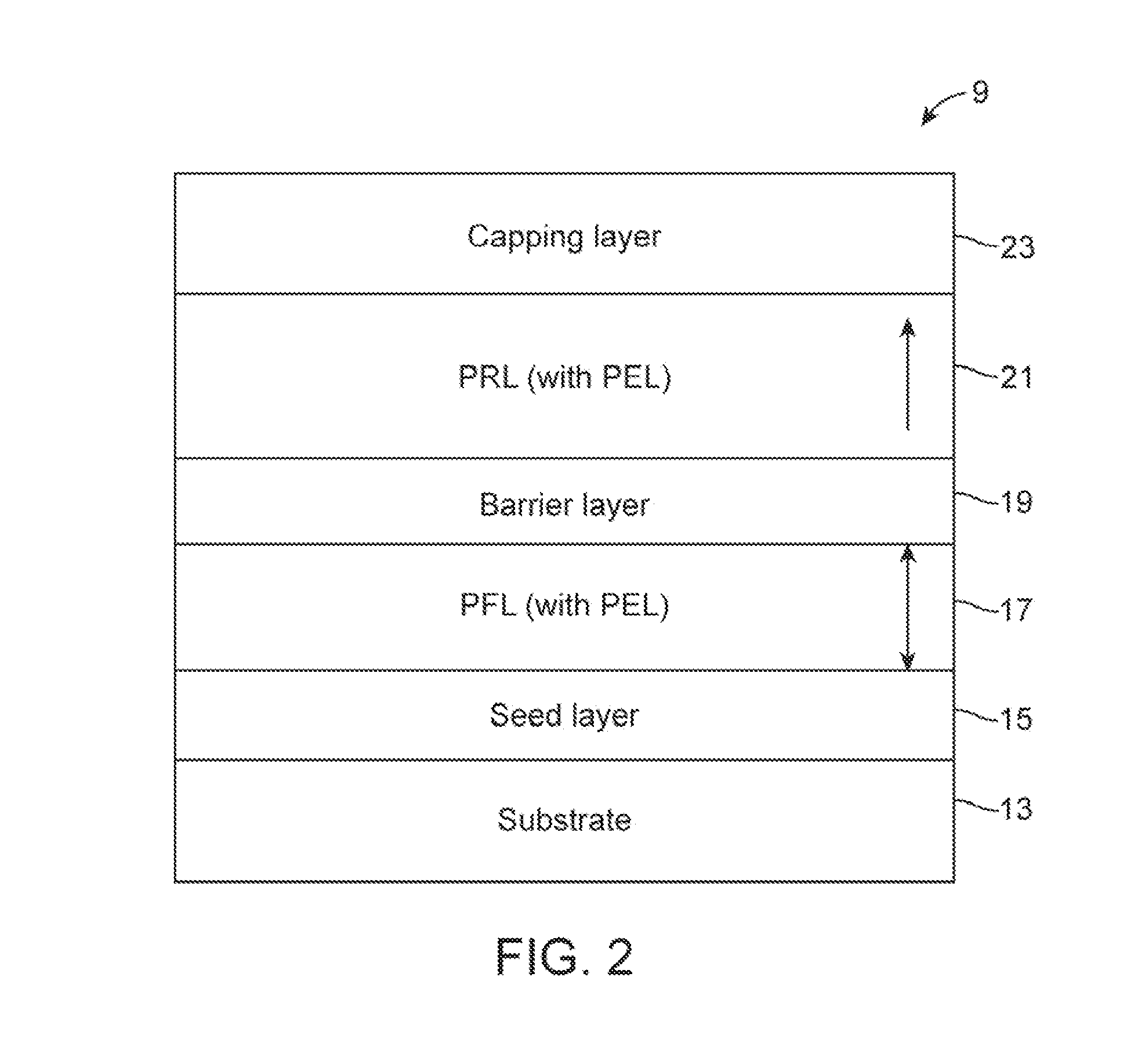

Memory system having thermally stable perpendicular magneto tunnel junction (MTJ) and a method of manufacturing same

InactiveUS20120146167A1Increase stiffnessReduced dampingMagnetic-field-controlled resistorsGalvano-magnetic device detailsRandom access memoryMagneto

A spin-torque transfer magnetic random access memory (STTMRAM) element employed to store a state based on the magnetic orientation of a free layer, the STTMRAM element is made of a first perpendicular free layer (PFL) including a first perpendicular enhancement layer (PEL). The first PFL is formed on top of a seed layer. The STTMRAM element further includes a barrier layer formed on top of the first PFL and a second perpendicular reference layer (PRL) that has a second PEL, the second PRL is formed on top of the barrier layer. The STTMRAM element further includes a capping layer that is formed on top of the second PRL.

Owner:AVALANCHE TECH

Mg-Zn oxide tunnel barriers and method of formation

ActiveUS7252852B1Not diminishing spin polarizationImprove performanceNanomagnetismMagnetic measurementsOxygenZinc

ZnMg oxide tunnel barriers are grown which, when sandwiched between ferri- or ferromagnetic layers, form magnetic tunnel junctions exhibiting high tunneling magnetoresistance (TMR). The TMR may be increased by annealing the magnetic tunnel junctions. The zinc-magnesium oxide tunnel barriers may be incorporated into a variety of other devices, such as magnetic tunneling transistors and spin injector devices. The ZnMg oxide tunnel barriers are grown by first depositing a zinc and / or magnesium layer onto an underlying substrate in oxygen-poor (or oxygen-free) conditions, and subsequently depositing zinc and / or magnesium onto this layer in the presence of reactive oxygen.

Owner:IBM CORP

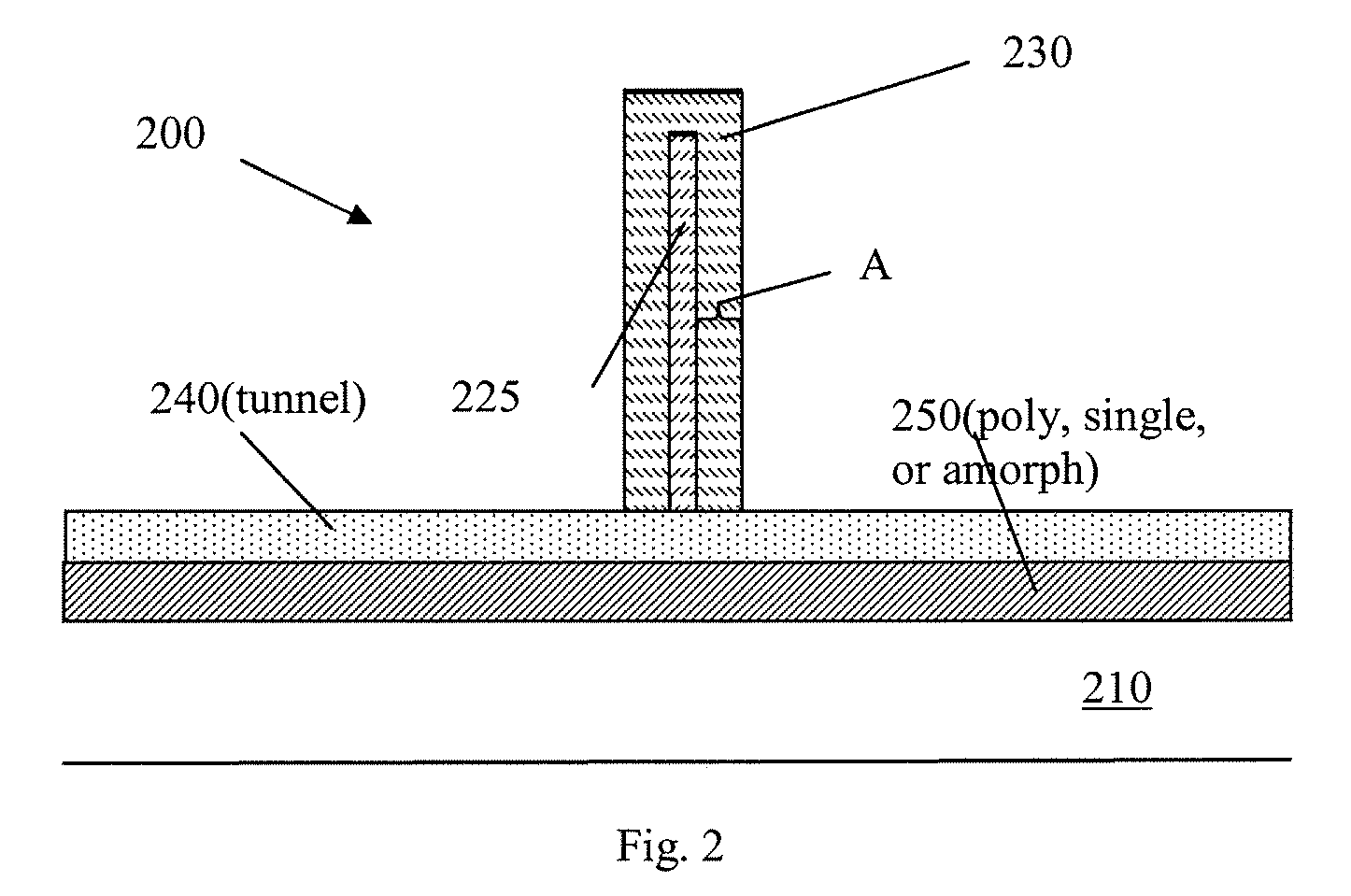

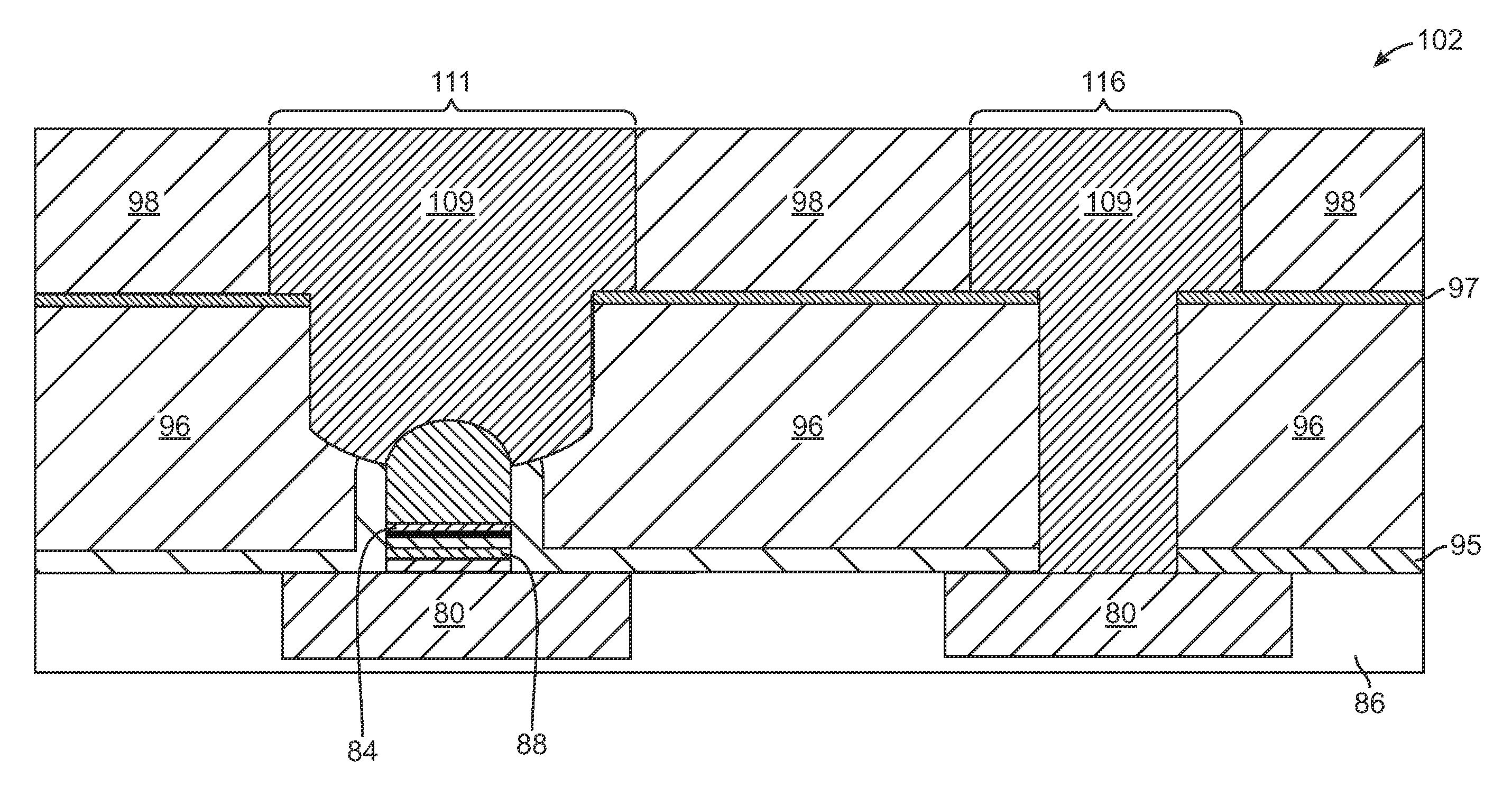

Magnetic Random Access Memory (MRAM) Manufacturing Process for a Small Magnetic Tunnel Junction (MTJ) Design with a Low Programming Current Requirement

A method of making a magnetic random access memory cell includes forming a magnetic tunnel junction (MTJ) on top of a wafer, depositing oxide on top of the MTJ, depositing a photo-resist layer on top of the oxide layer, forming a trench in the photo-resist layer and oxide layer where the trench has a width that is substantially the same as that of the MTJ. Then, the photo-resist layer is removed and a hard mask layer is deposited on top of the oxide layer in the trench and the wafer is planarized to remove the portion of the hard mask layer that is not in the trench to substantially level the top of oxide layer and the hard layer on the wafer. The remaining oxide layer is etched and the the MTJ is etched to remove the portion of the MTJ which is not covered by the hard mask layer.

Owner:AVALANCHE TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com