Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

134 results about "Atomic species" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

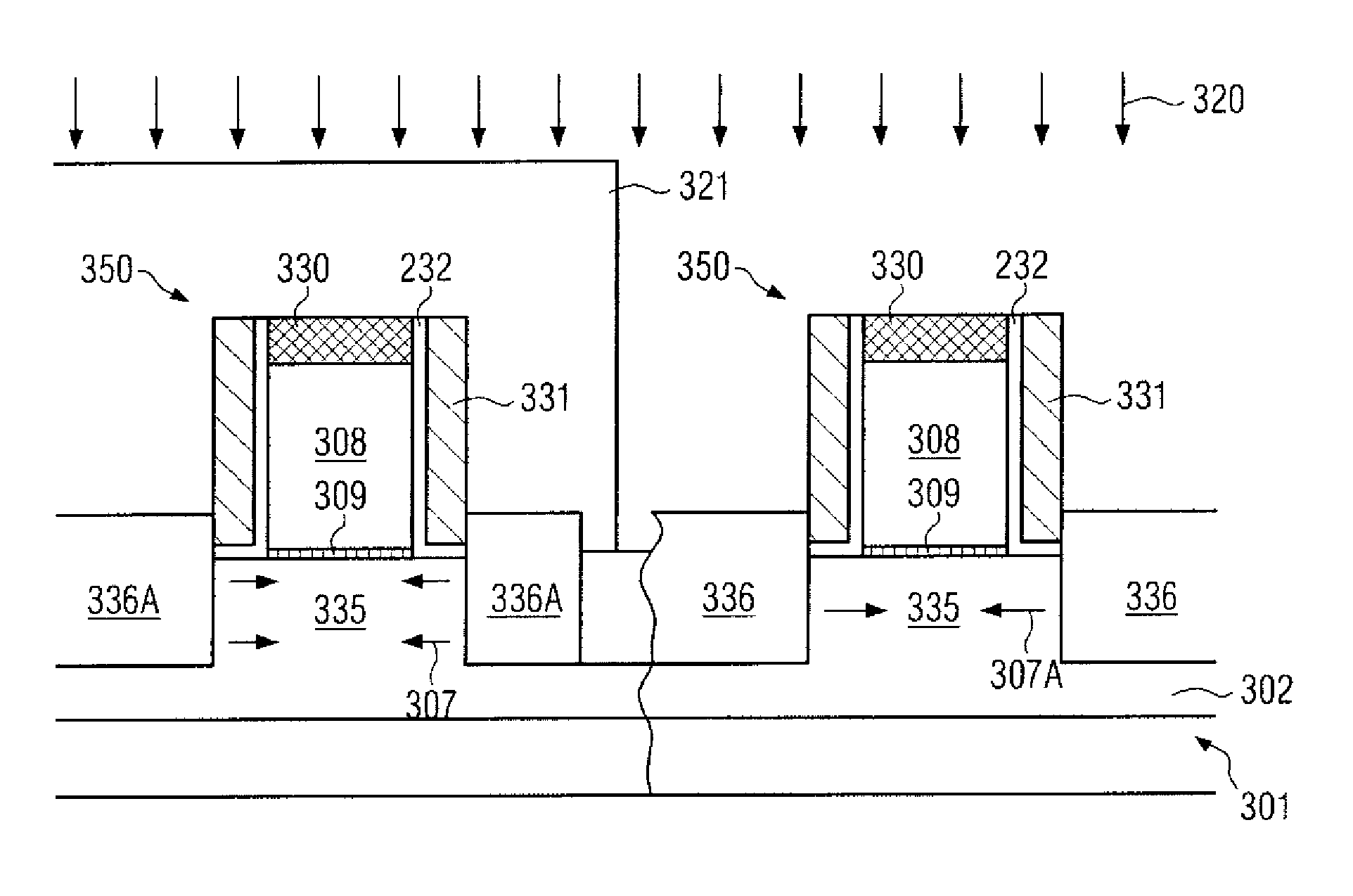

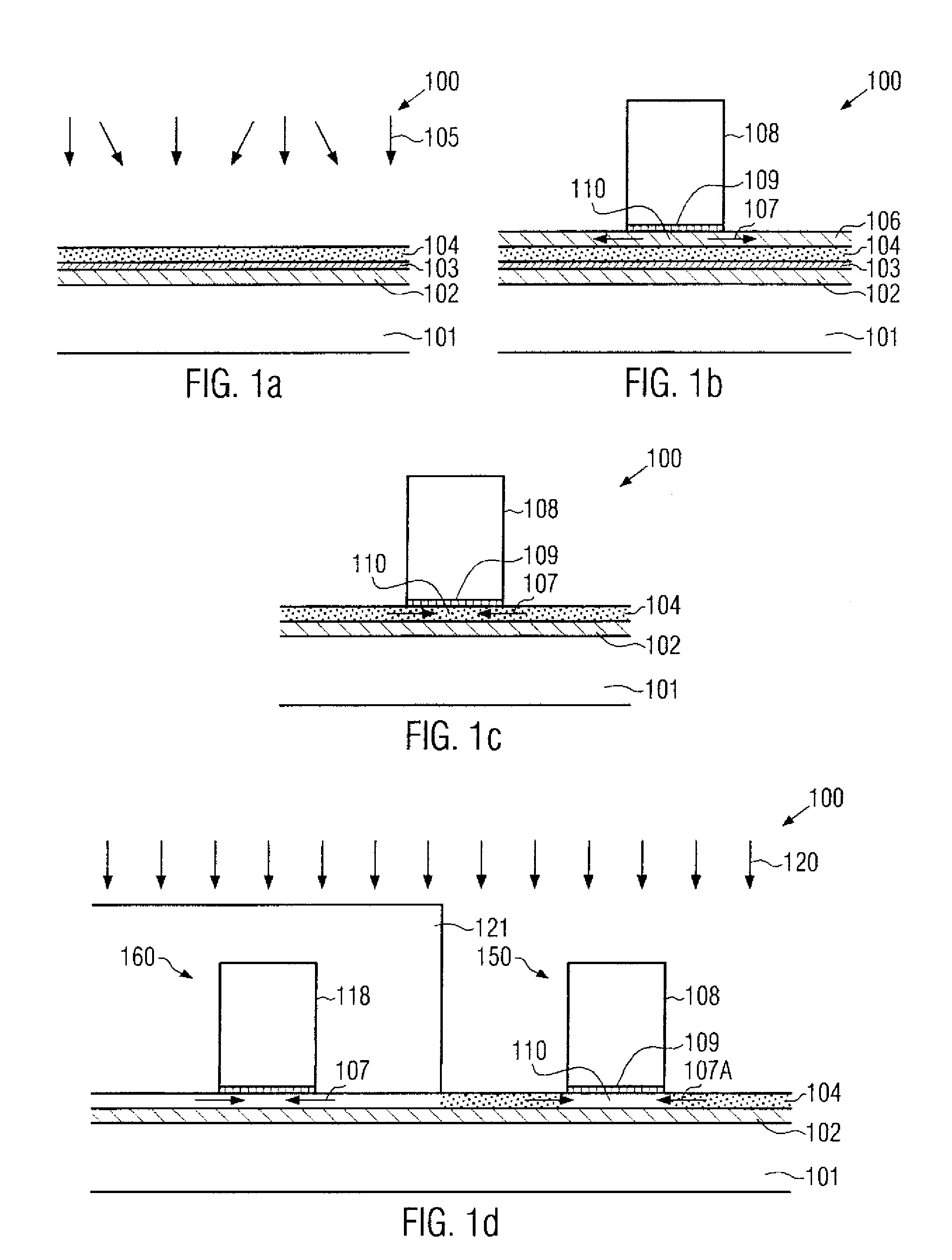

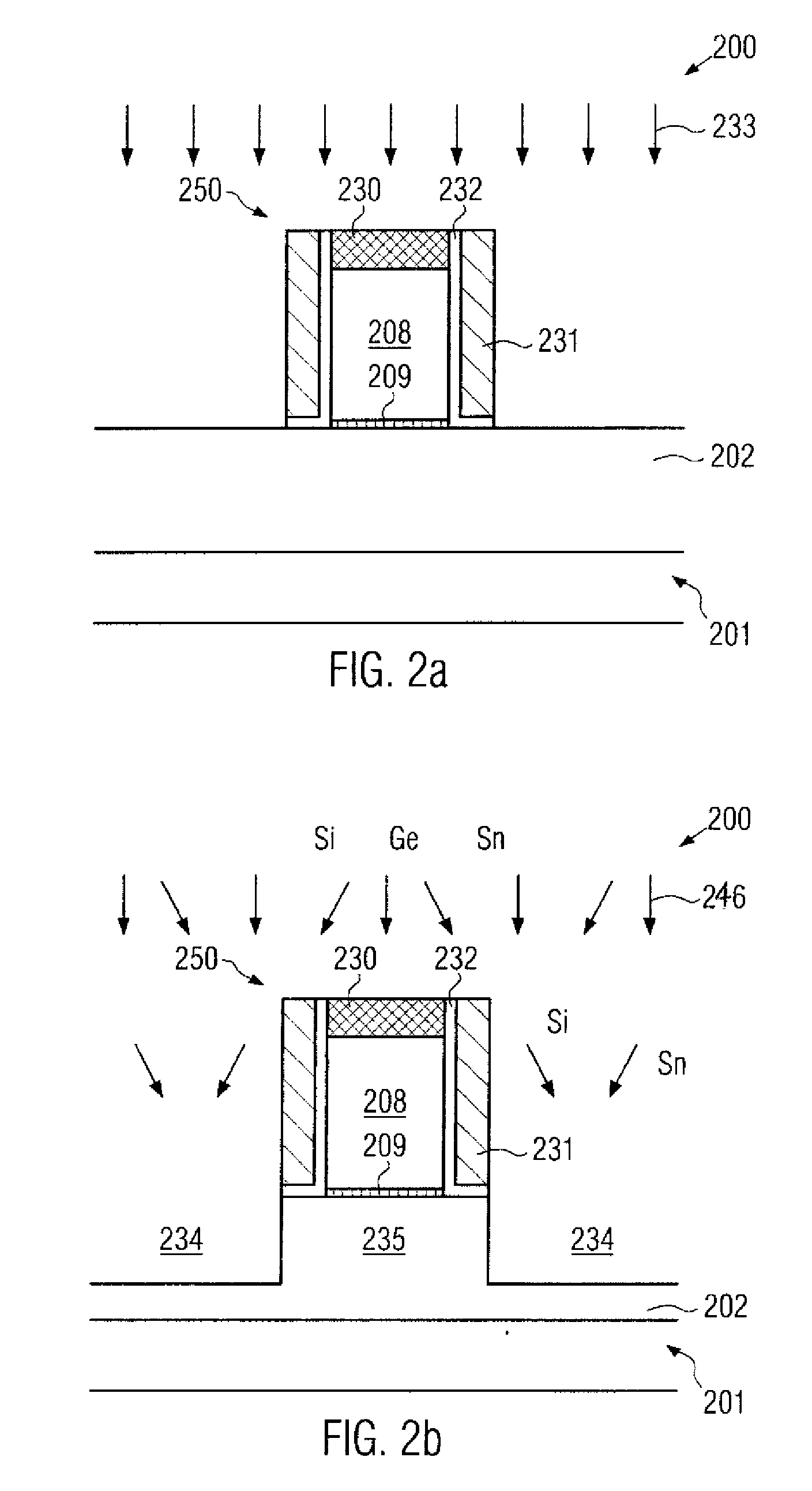

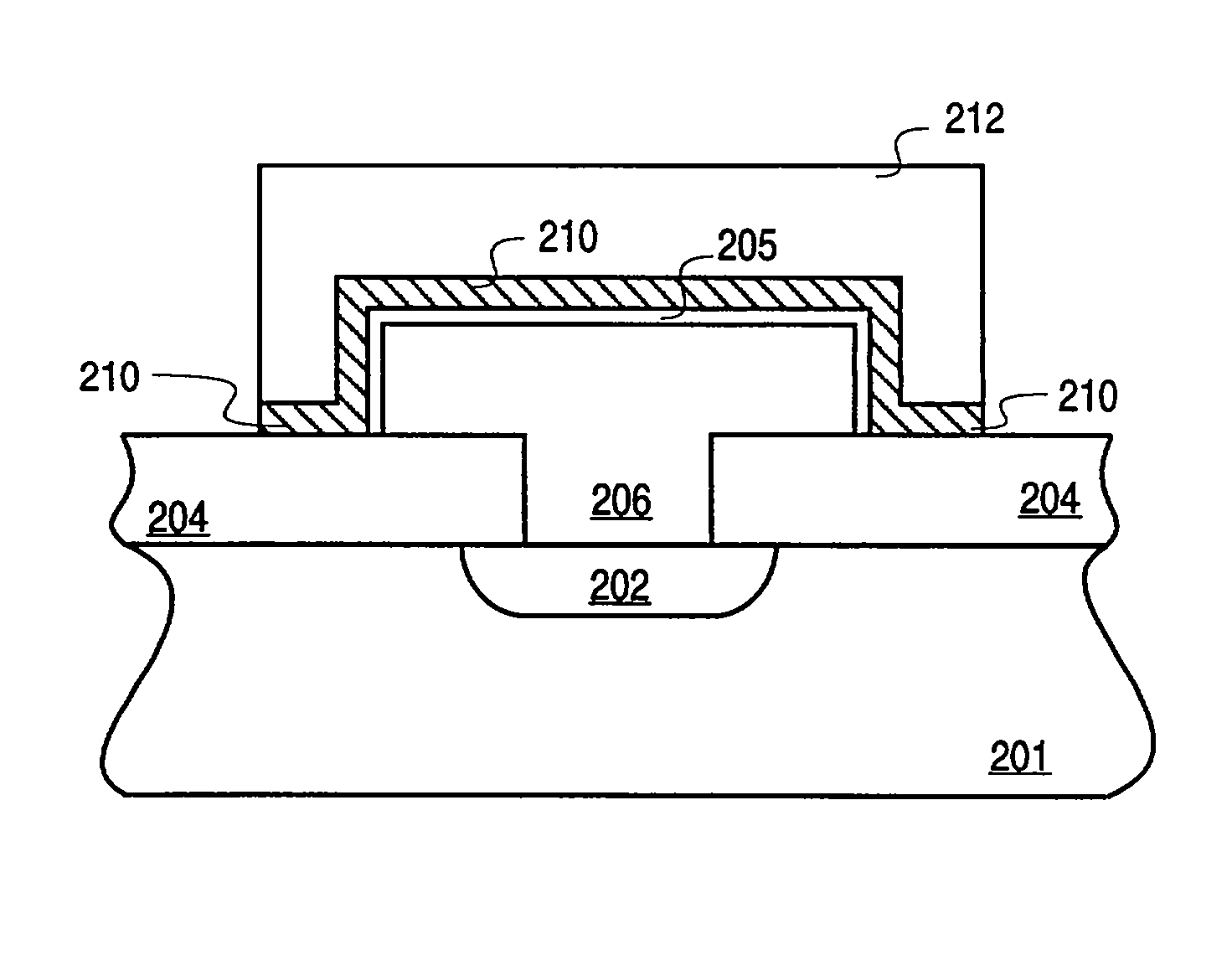

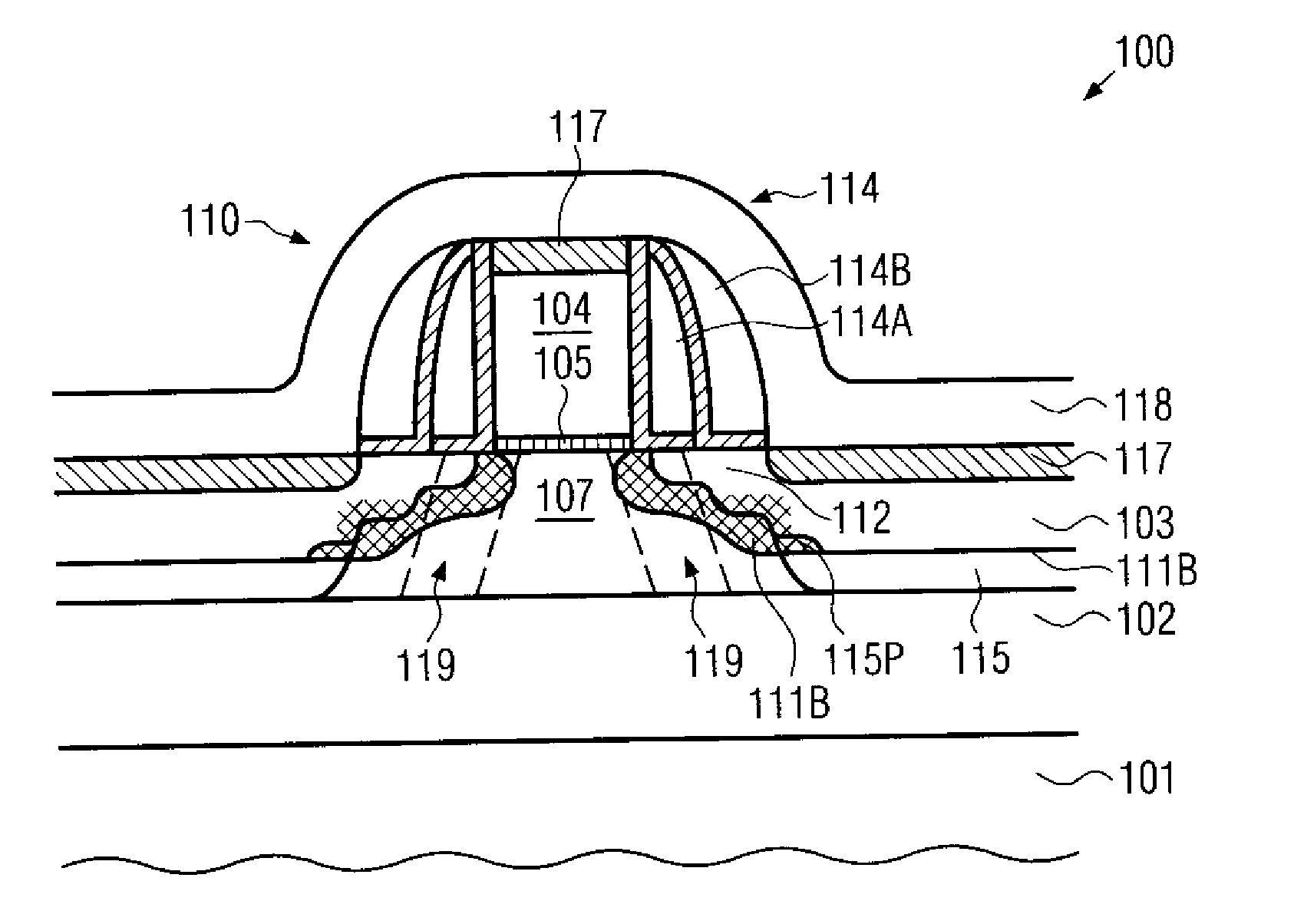

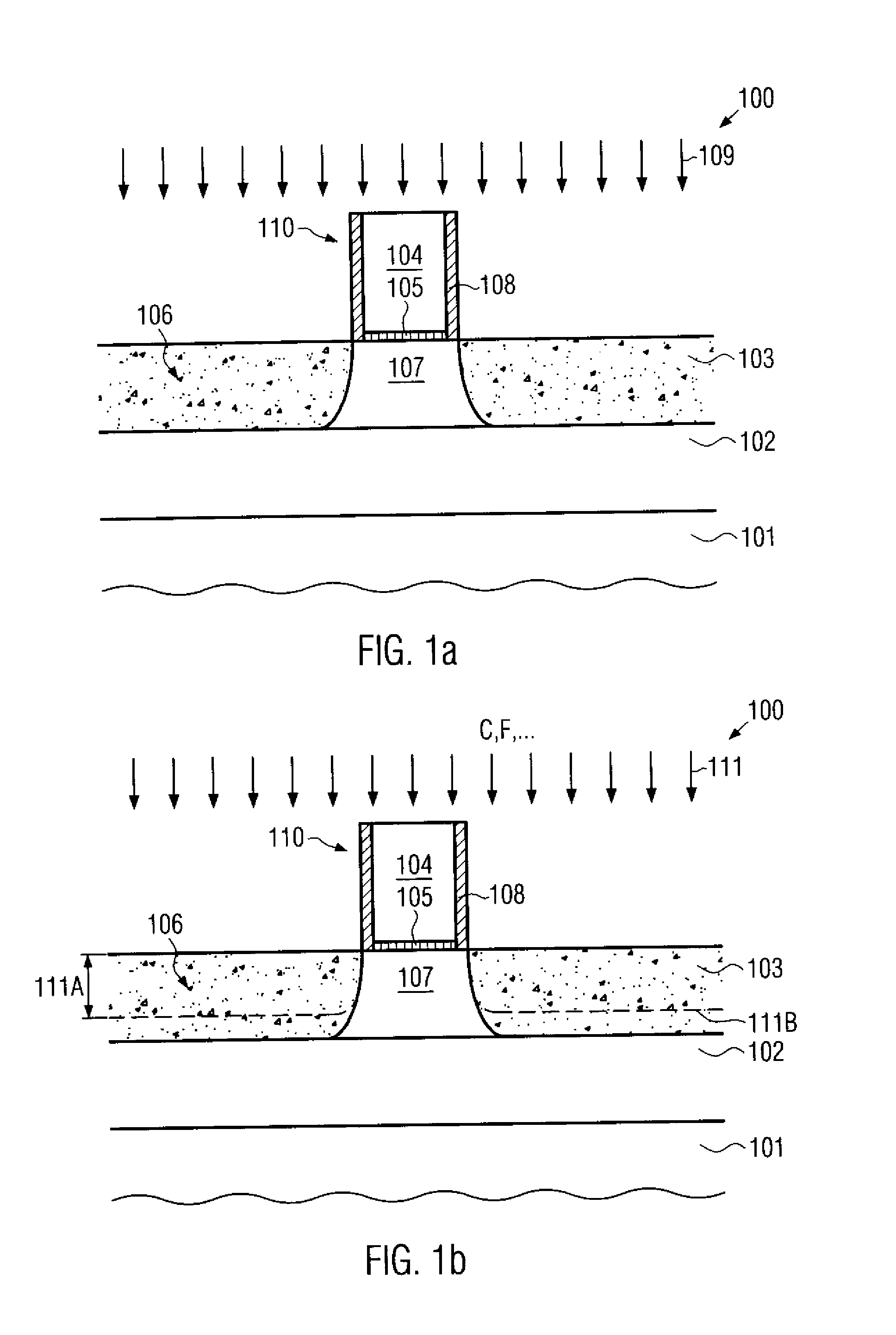

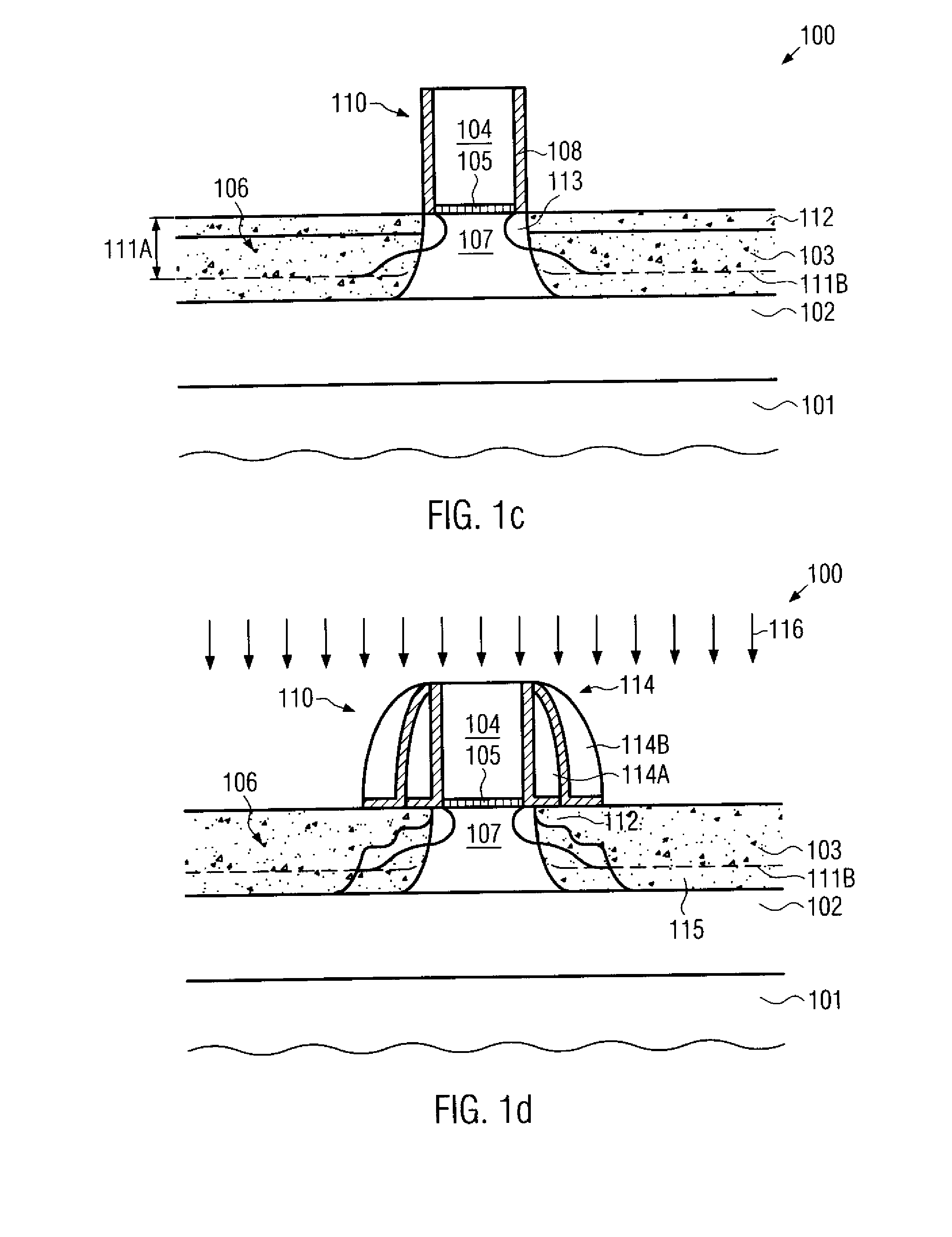

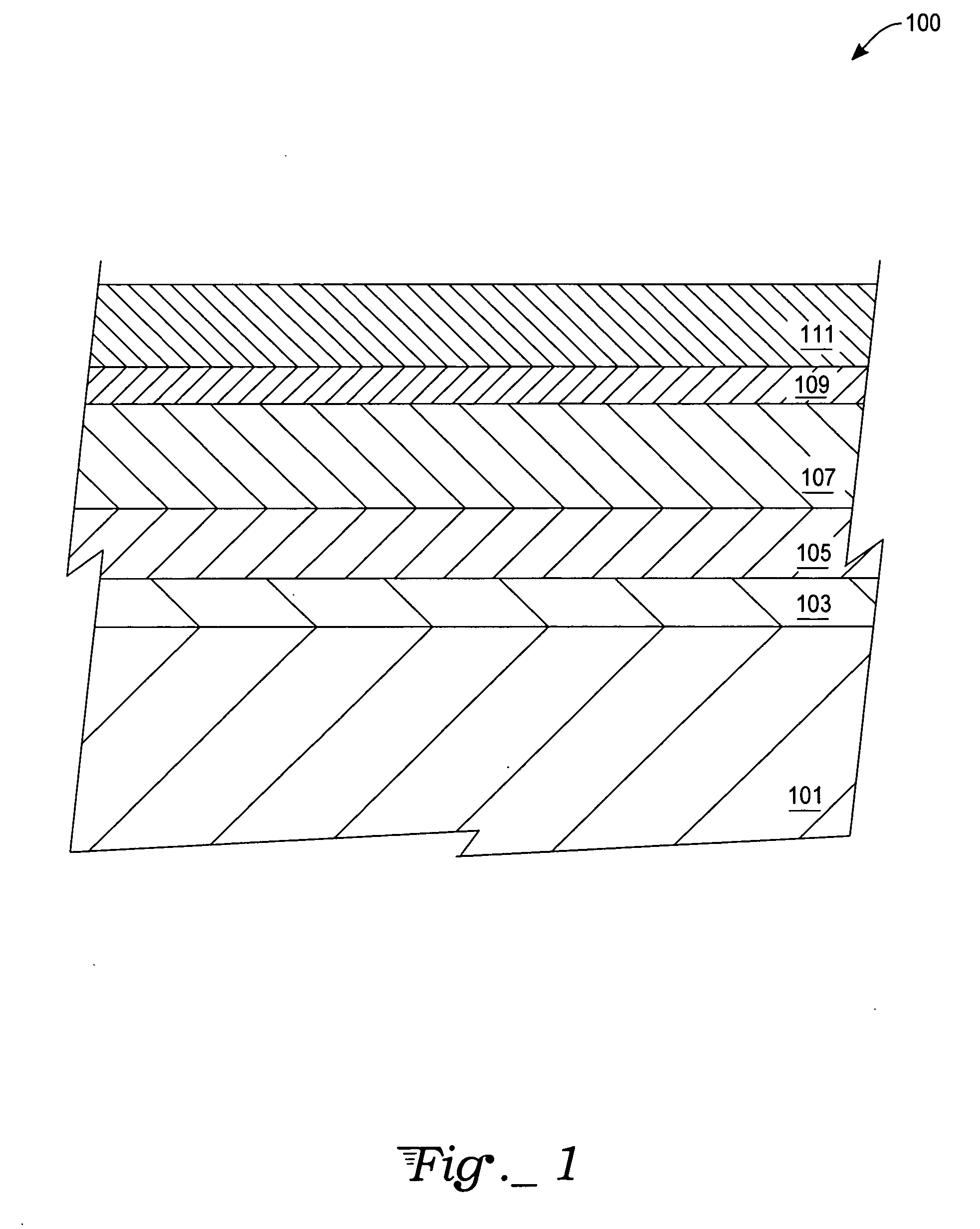

Technique for strain engineering in si-based transistors by using embedded semiconductor layers including atoms with high covalent radius

By incorporating an atomic species of increased covalent radius, which may at least partially substitute germanium, a highly efficient strain mechanism may be provided, in which the risk of stress relief due to germanium conglomeration and lattice defects may be reduced. The atomic species of increased radius, such as tin, may be readily incorporated by epitaxial growth techniques on the basis of tin hydride.

Owner:GLOBALFOUNDRIES INC

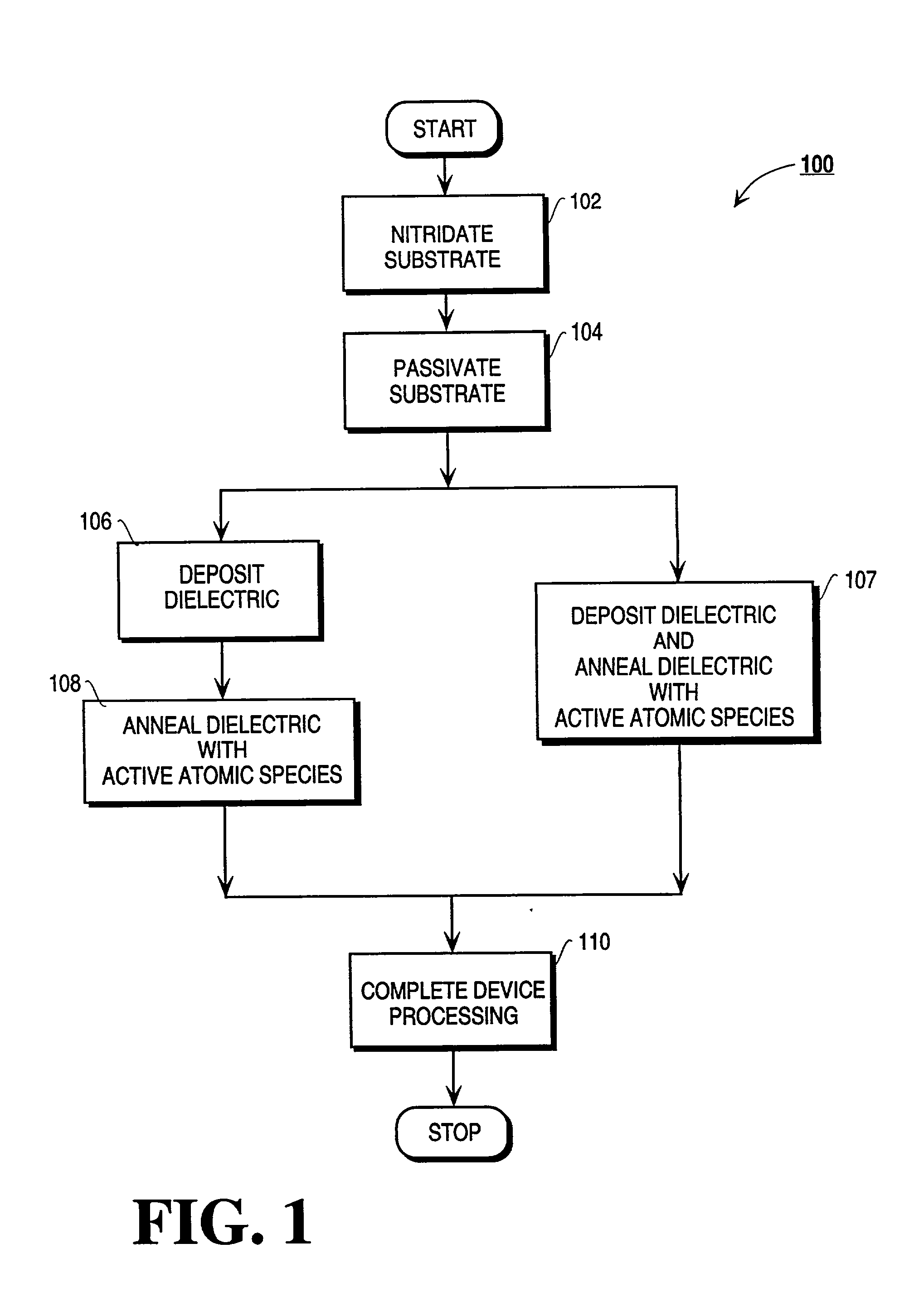

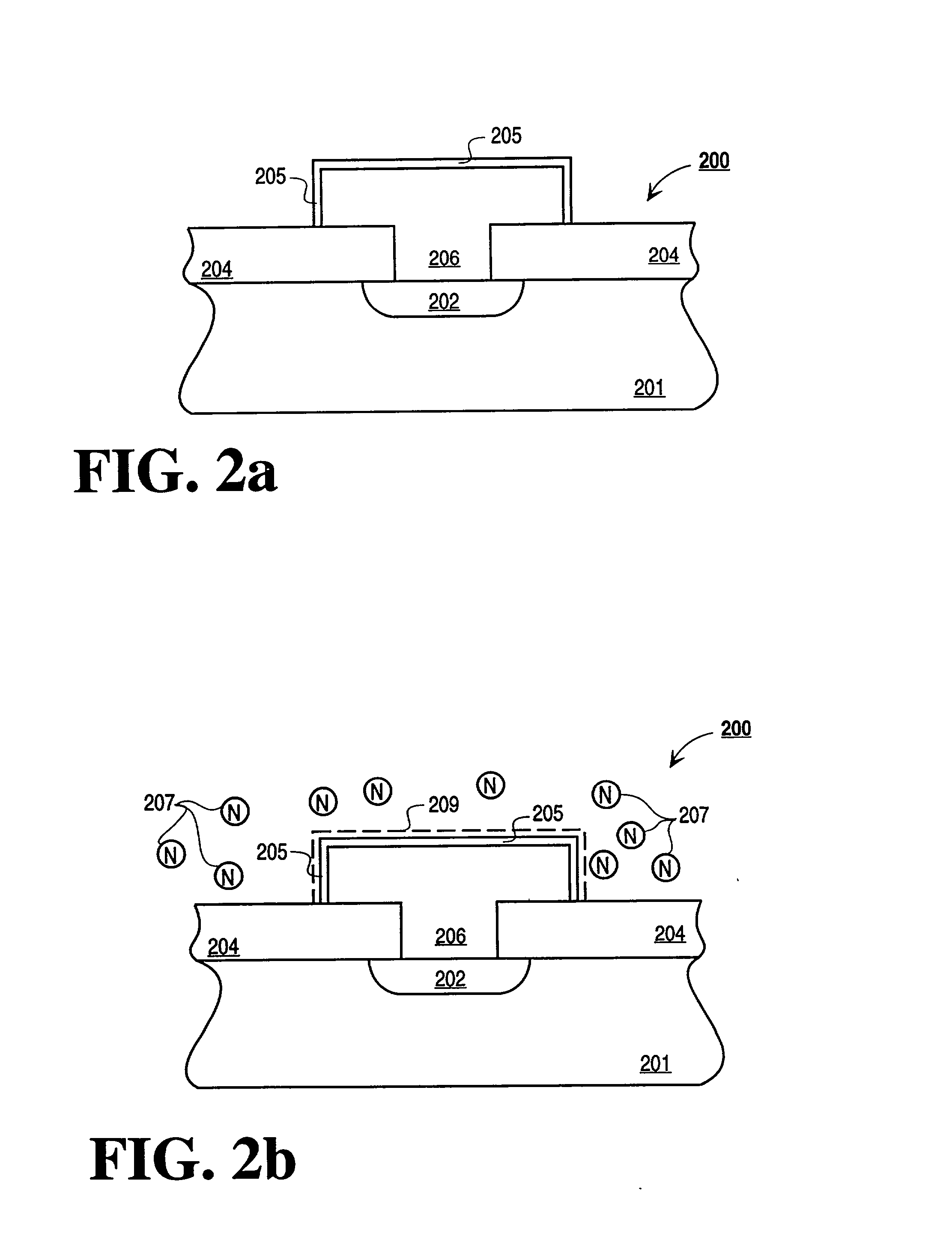

Method and apparatus for the formation of dielectric layers

InactiveUS20020009861A1Simple interfaceImprove performanceTransistorVacuum evaporation coatingAtomic speciesDielectric layer

A method and apparatus for forming and annealing a dielectric layer. According to the present invention an active atomic species is generated in a first chamber. A dielectric layer formed on a substrate is then exposed to the active atomic species in a second chamber, wherein the second chamber is remote from the first chamber.

Owner:APPLIED MATERIALS INC

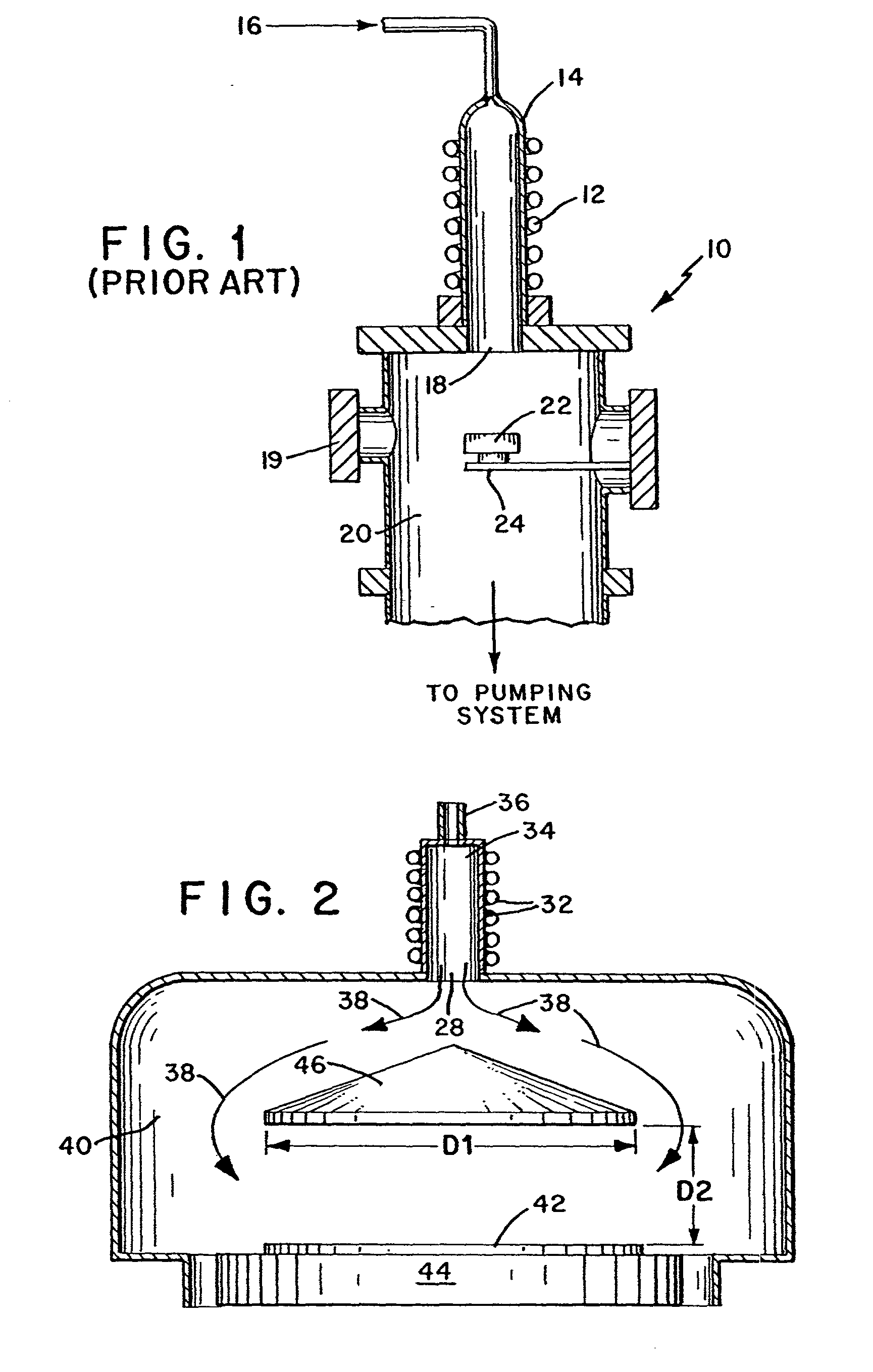

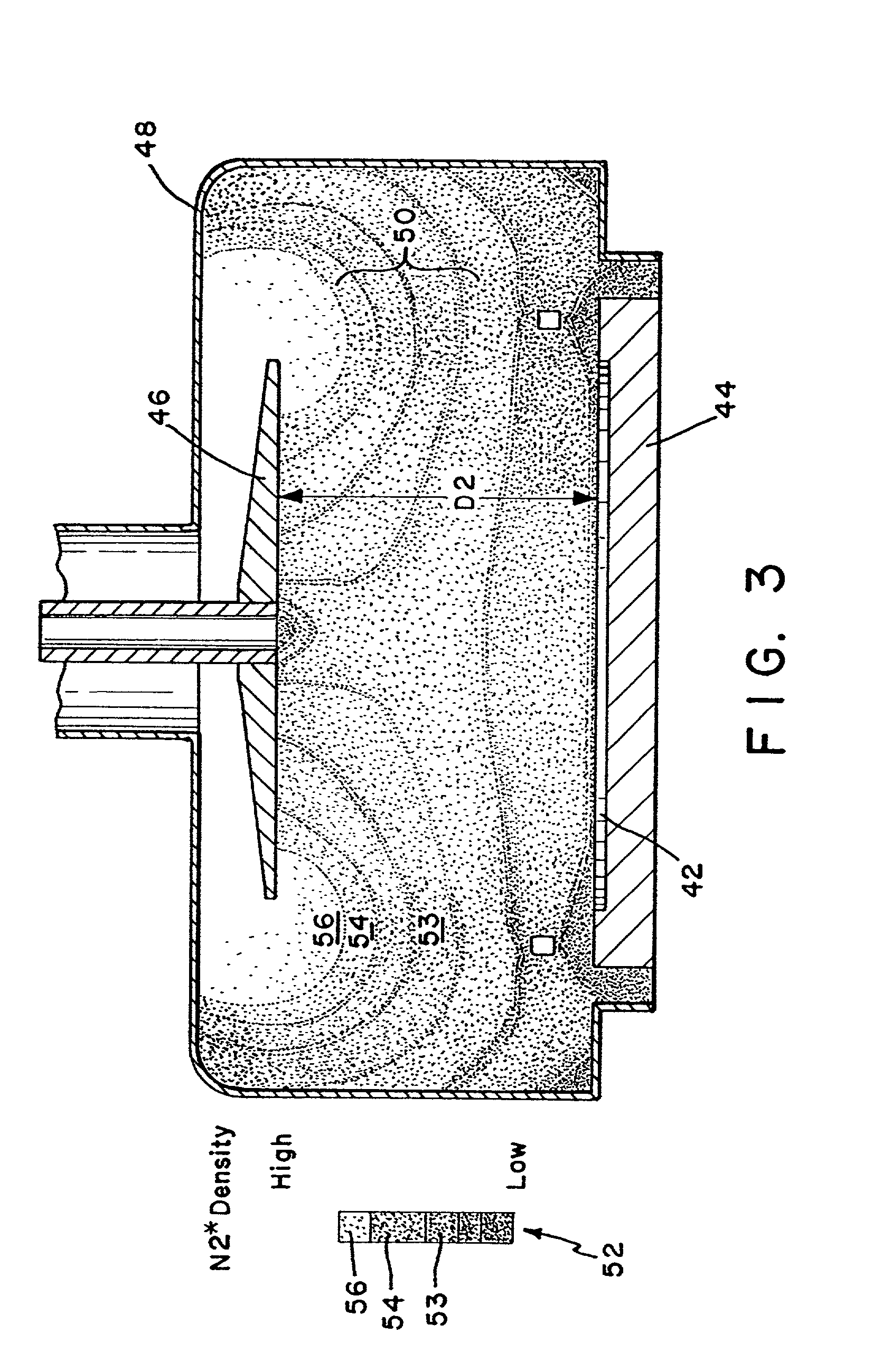

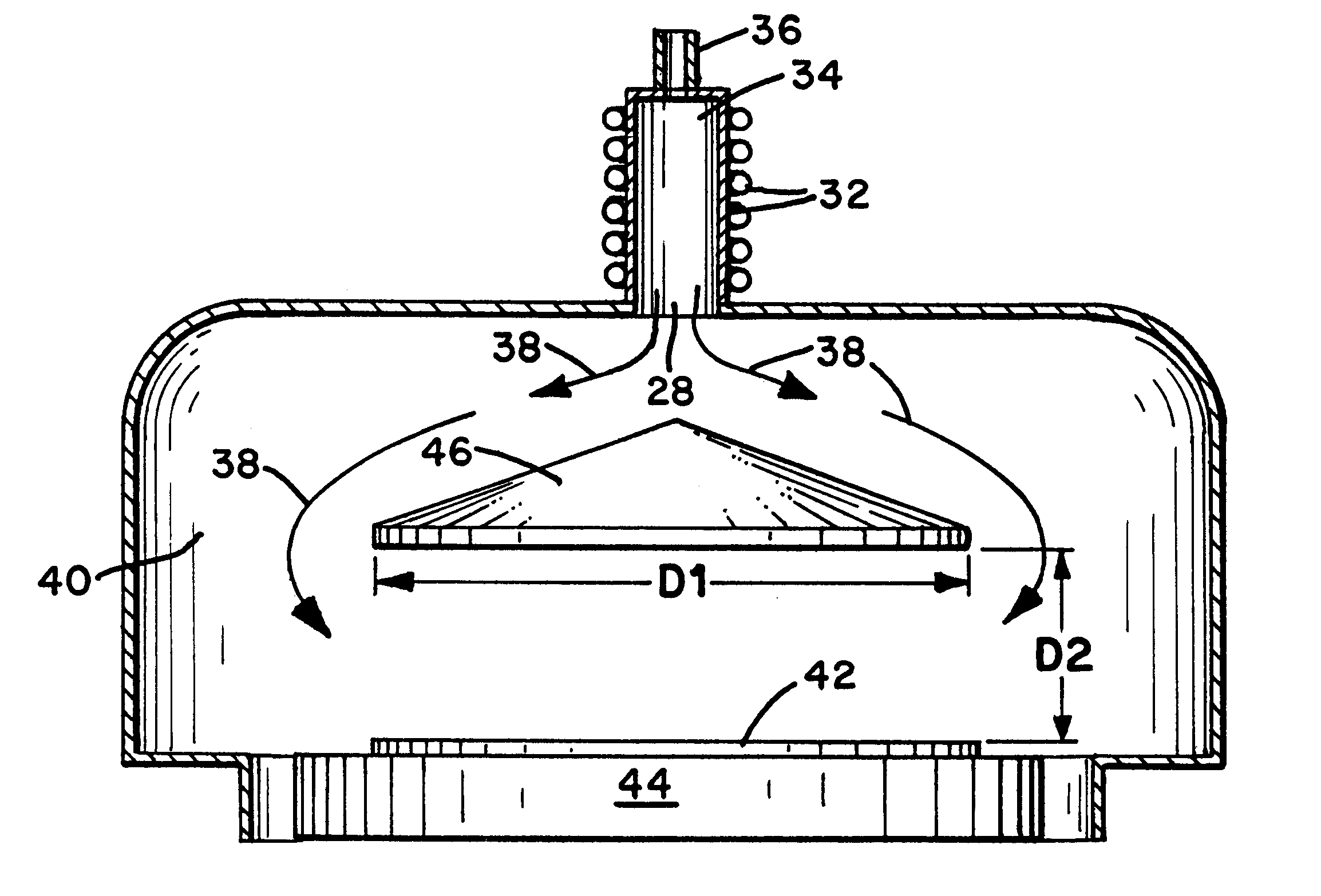

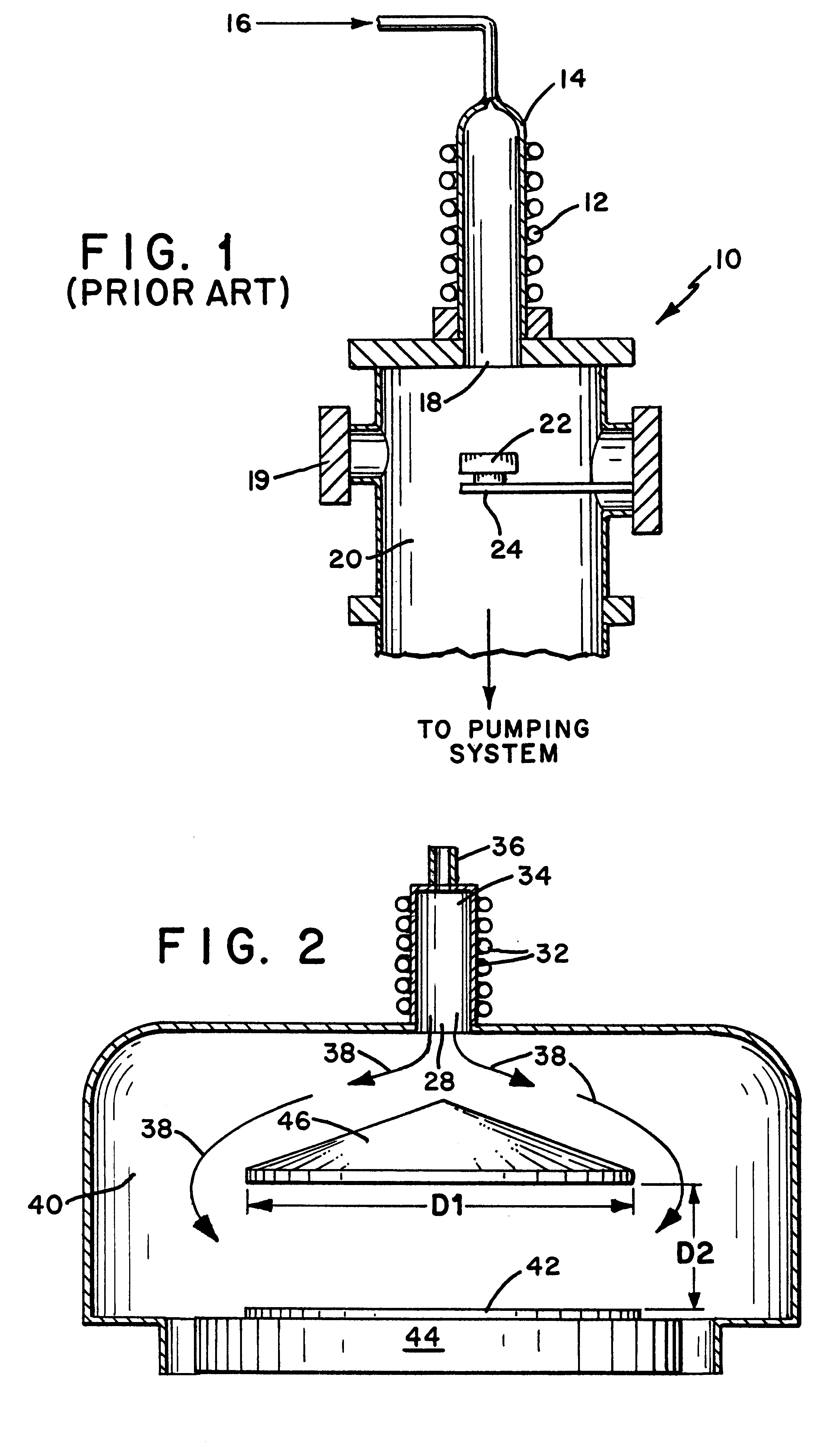

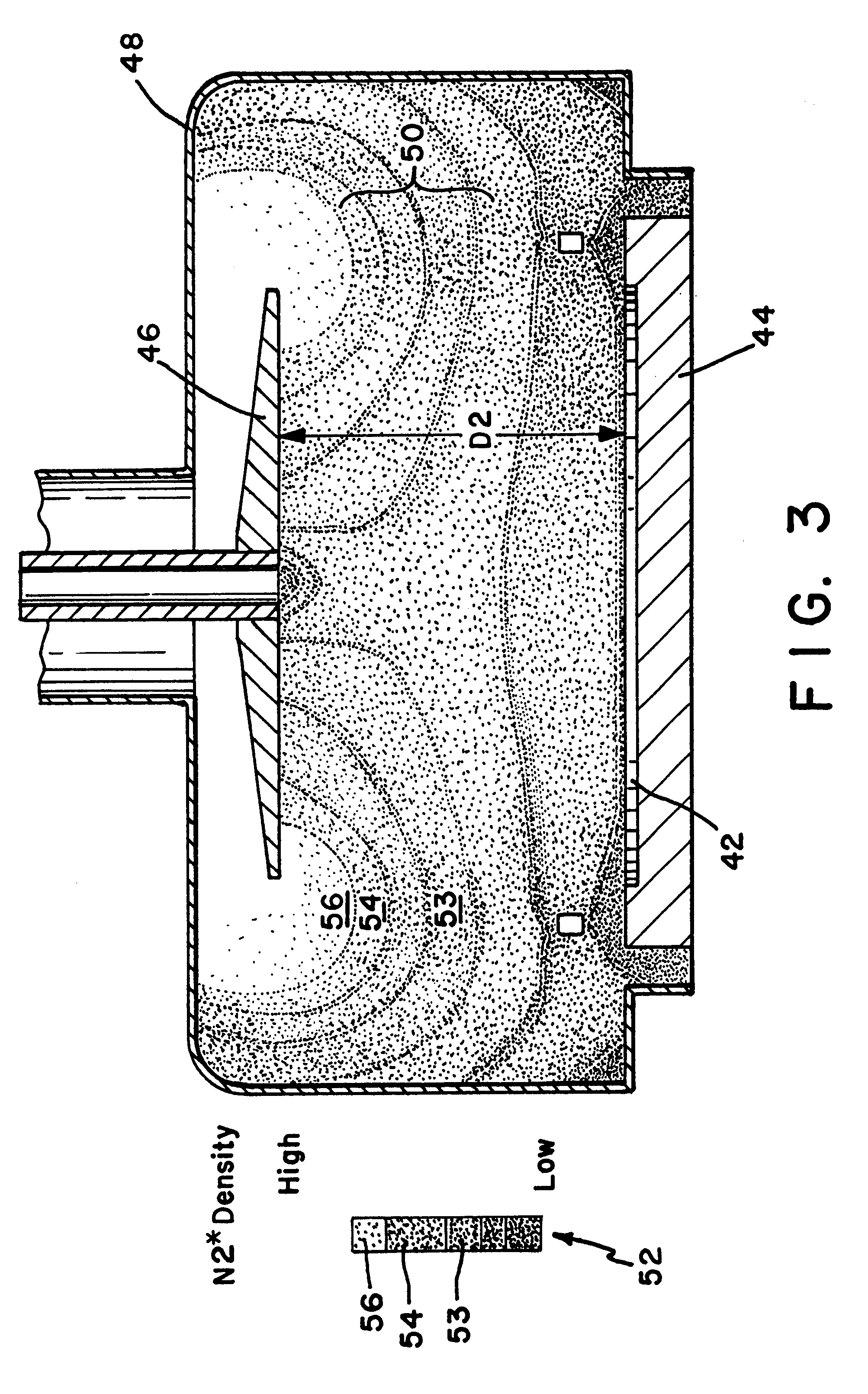

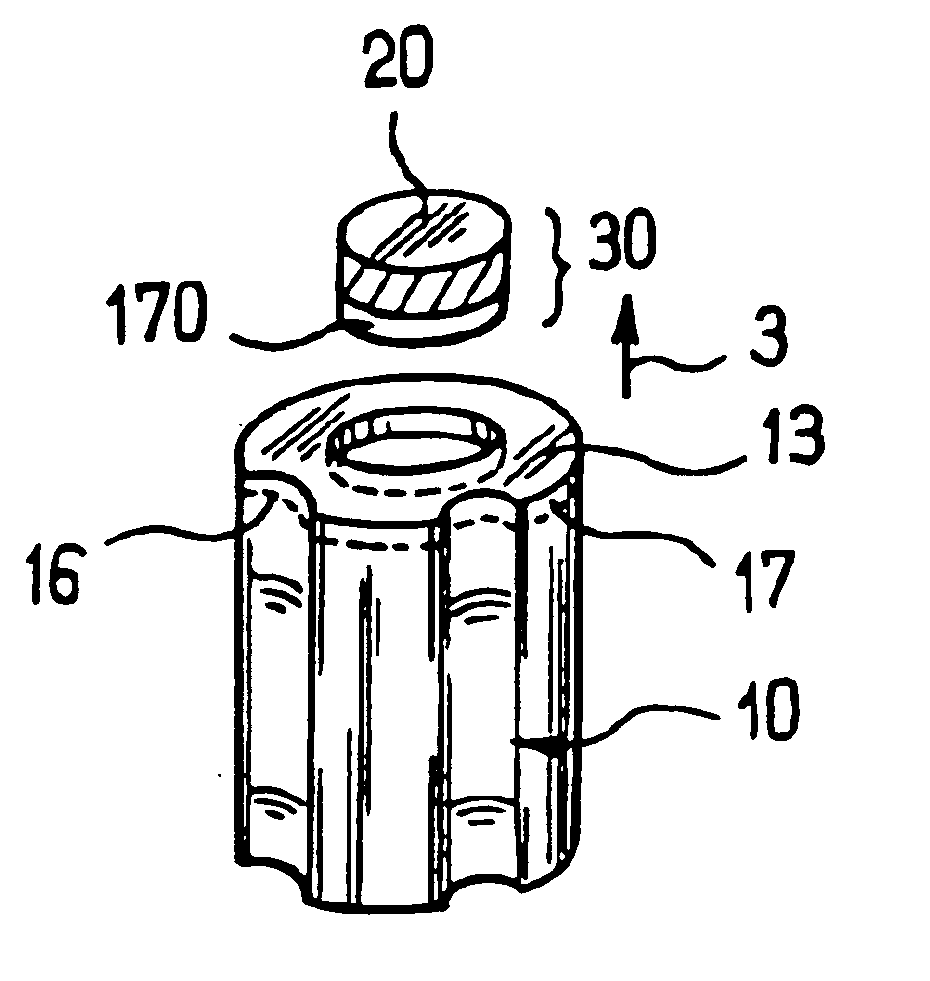

Apparatus and method for injecting and modifying gas concentration of a meta-stable or atomic species in a downstream plasma reactor

InactiveUS20020029747A1Reduce lossesElectric discharge tubesChemical vapor deposition coatingGas passingActive matter

This invention provides an apparatus and method for injecting gas within a plasma reactor and tailoring the distribution of an active species generated by the remote plasma source over the substrate or wafer. The distribution may be made more or less uniform, wafer-edge concentrated, or wafer-center concentrated. A contoured plate or profiler is provided for modifying the distribution. The profiler is an axially symmetric plate, having a narrow top end and a wider bottom end, shaped to redistribute the gas flow incident upon it. The profiler is situated below an input port within the plasma reactor chamber and above the wafer. The method for tailoring the distribution of the active species over the substrate includes predetermining the profiler diameter and adjusting the profiler height over the substrate. A coaxial injector tube, for the concurrent injection of activated and non-activated gas species, allows gases (or gas mixtures) to be delivered in an axially symmetric manner whereby one gas can be excited in a high density RF plasma, while the other gas can be prevented from excitation and / or dissociation caused by exposure to the plasma or heated surfaces in the source apparatus. The gas admixture that is not to be excited or dissociated prior to contact with the wafer surface is shielded from direct exposure to the RF field surrounding the plasma confinement tube. The tube walls are also shielded from the infrared energy emitted from the plasma. The profiler is used in conjunction with the coaxial injector tube for redistributing the excited gases emerging from the injector tube, while allowing the non-excited gases to pass through its center.

Owner:NOVELLUS SYSTEMS

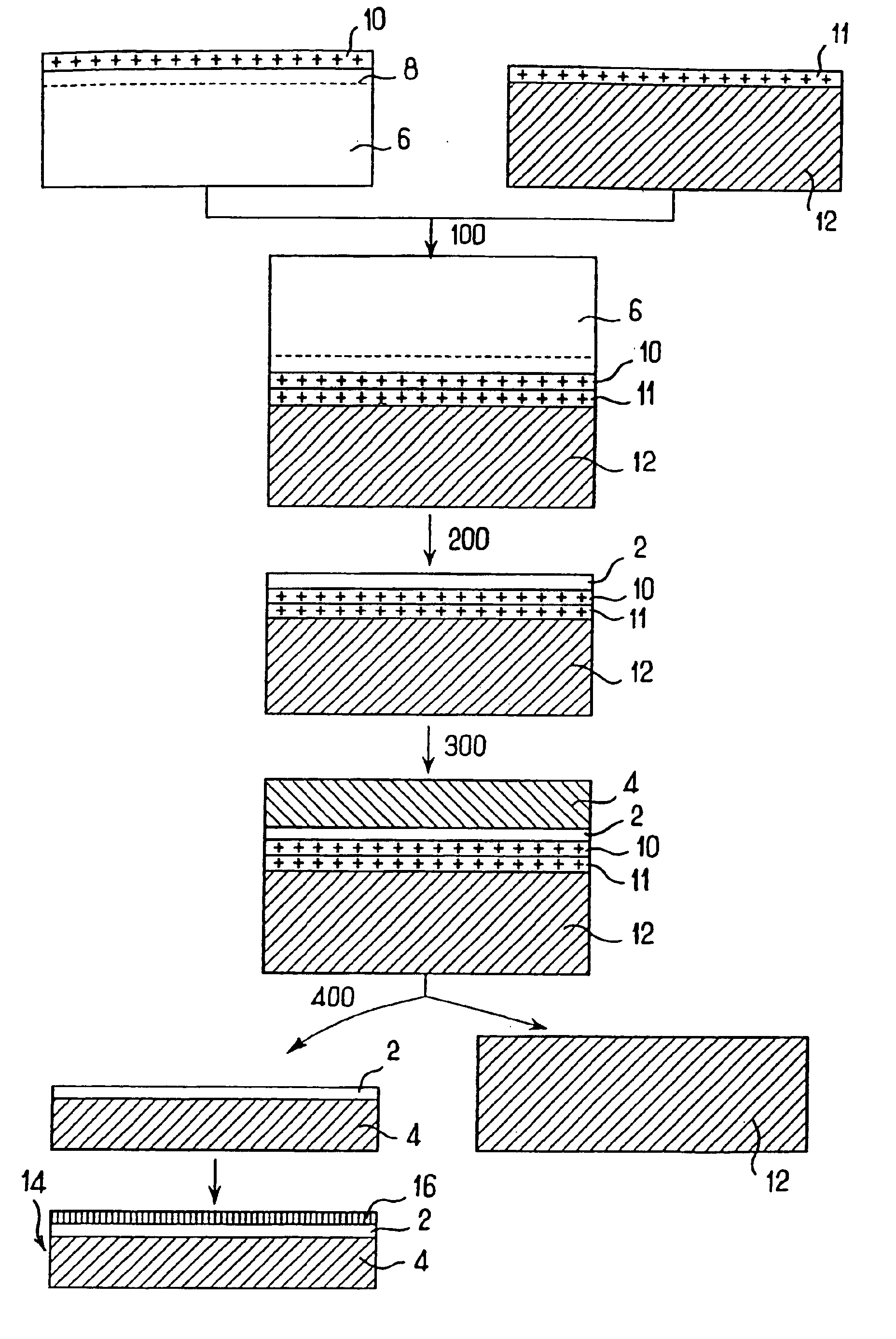

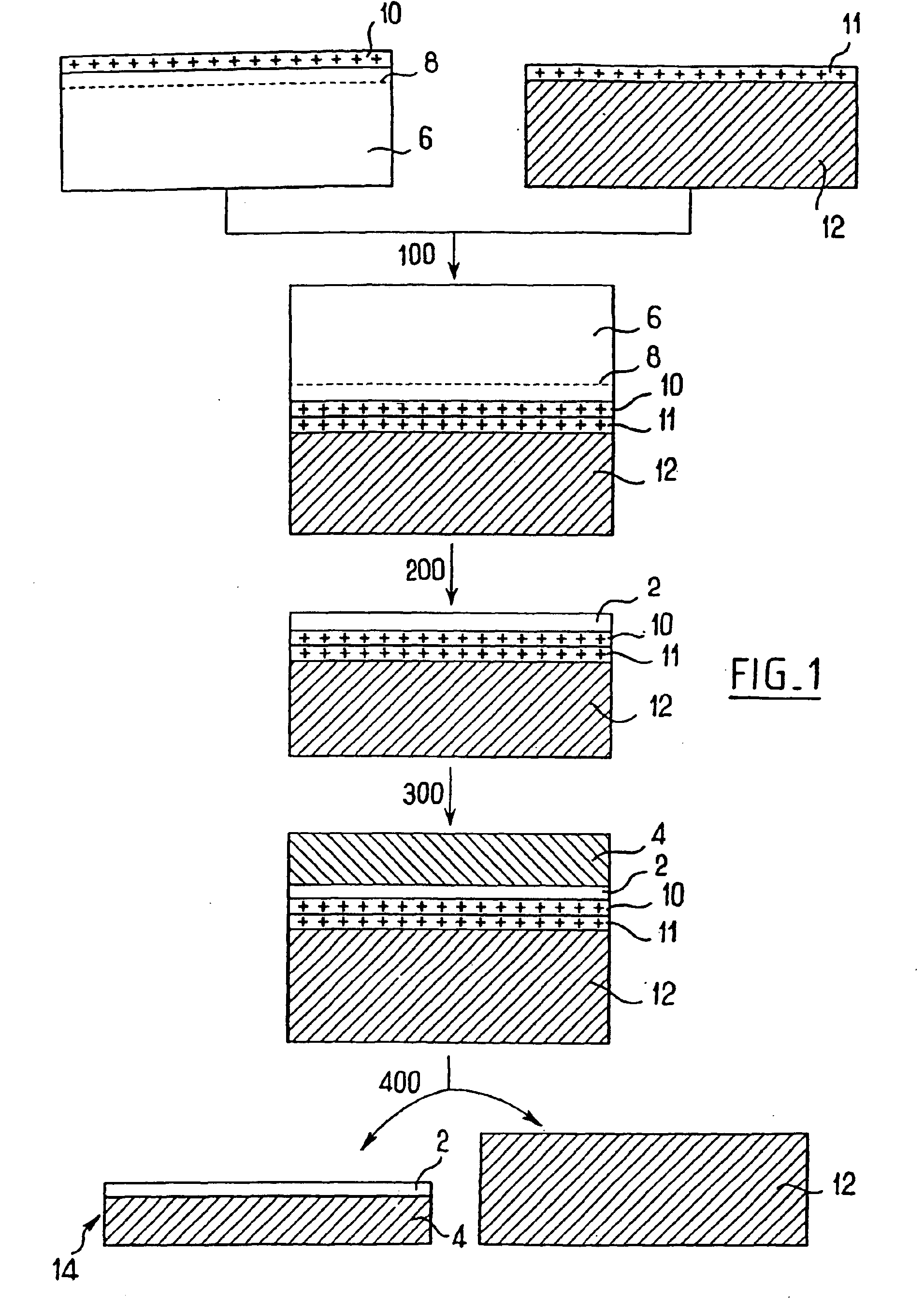

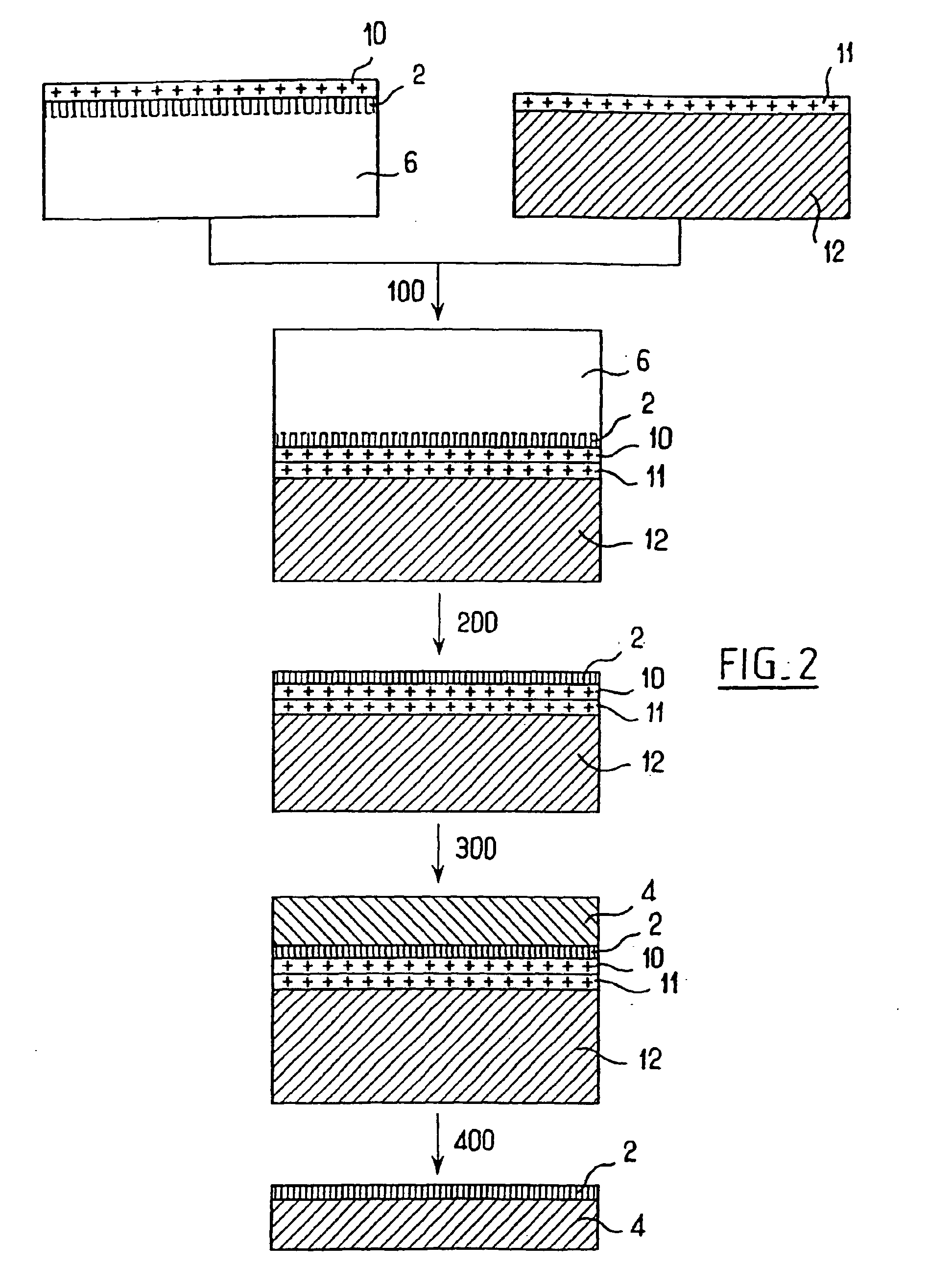

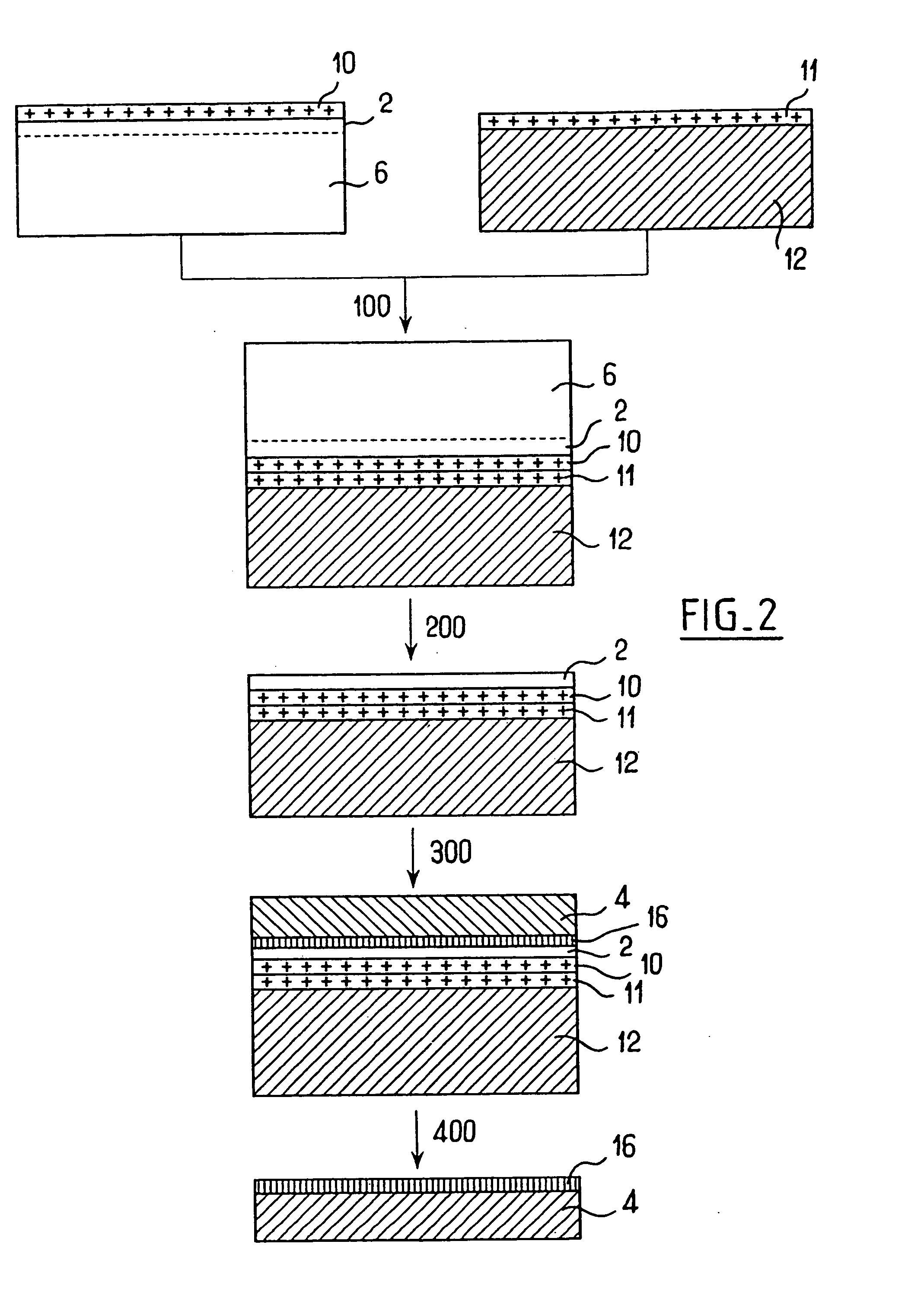

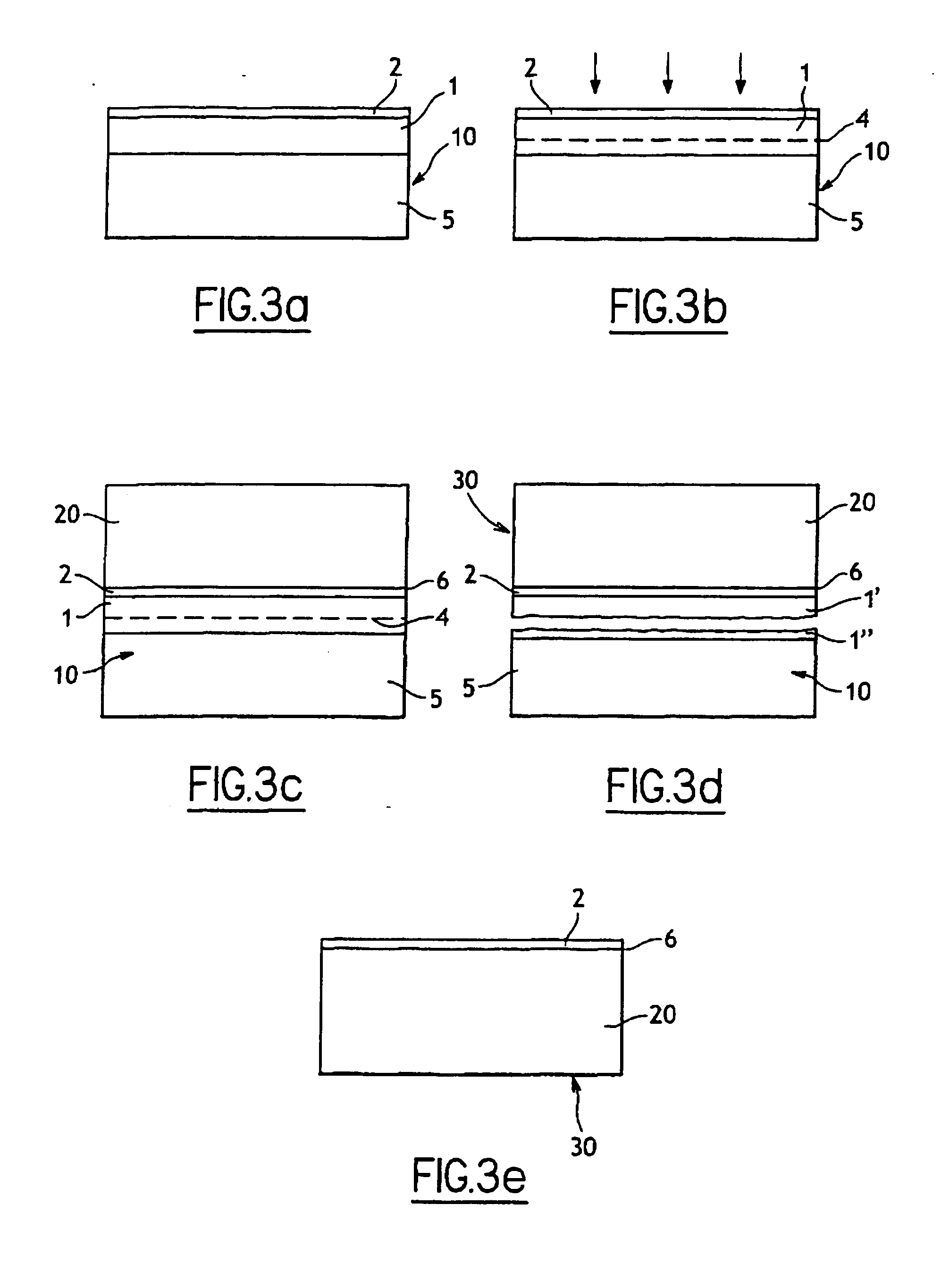

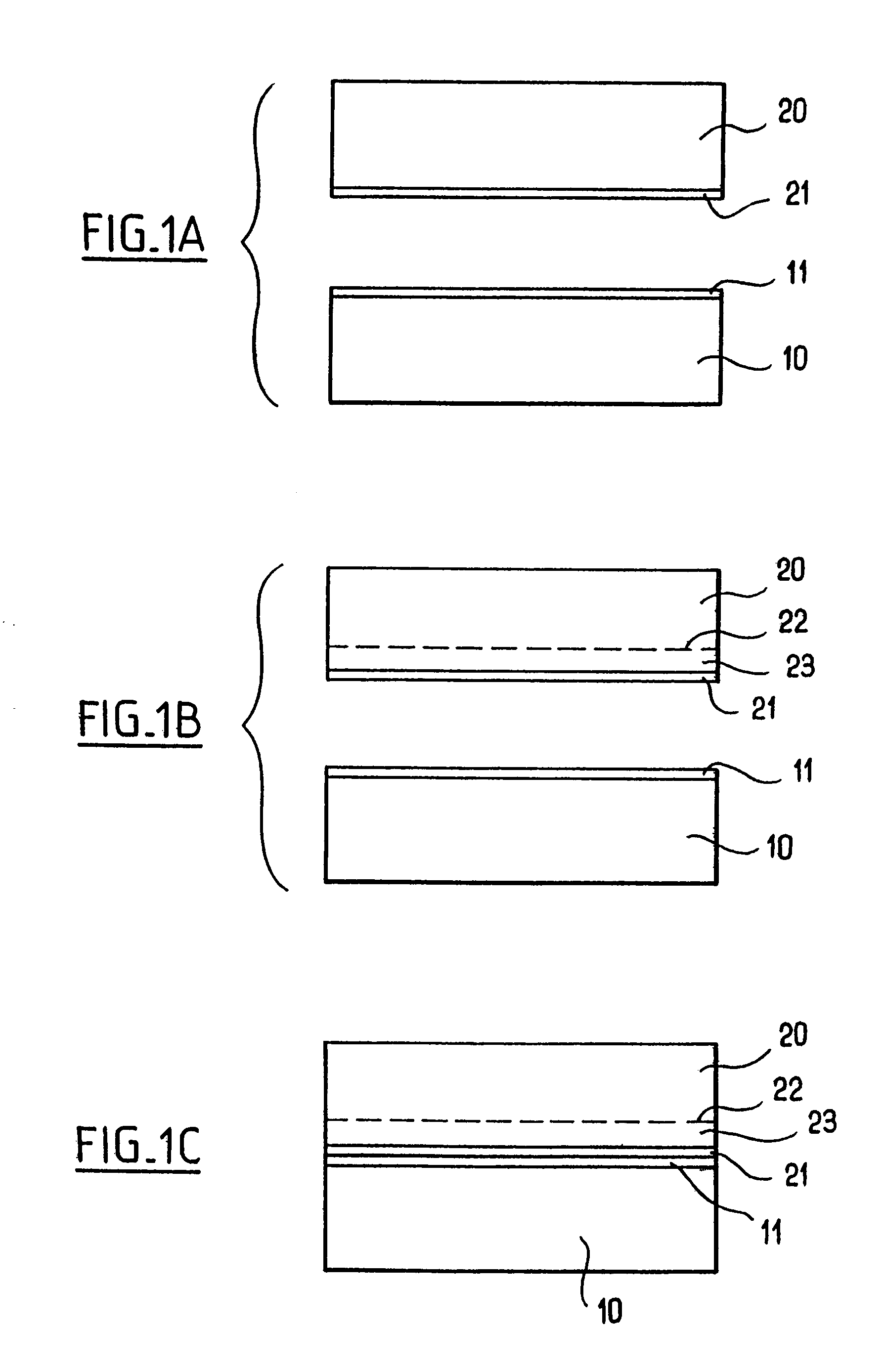

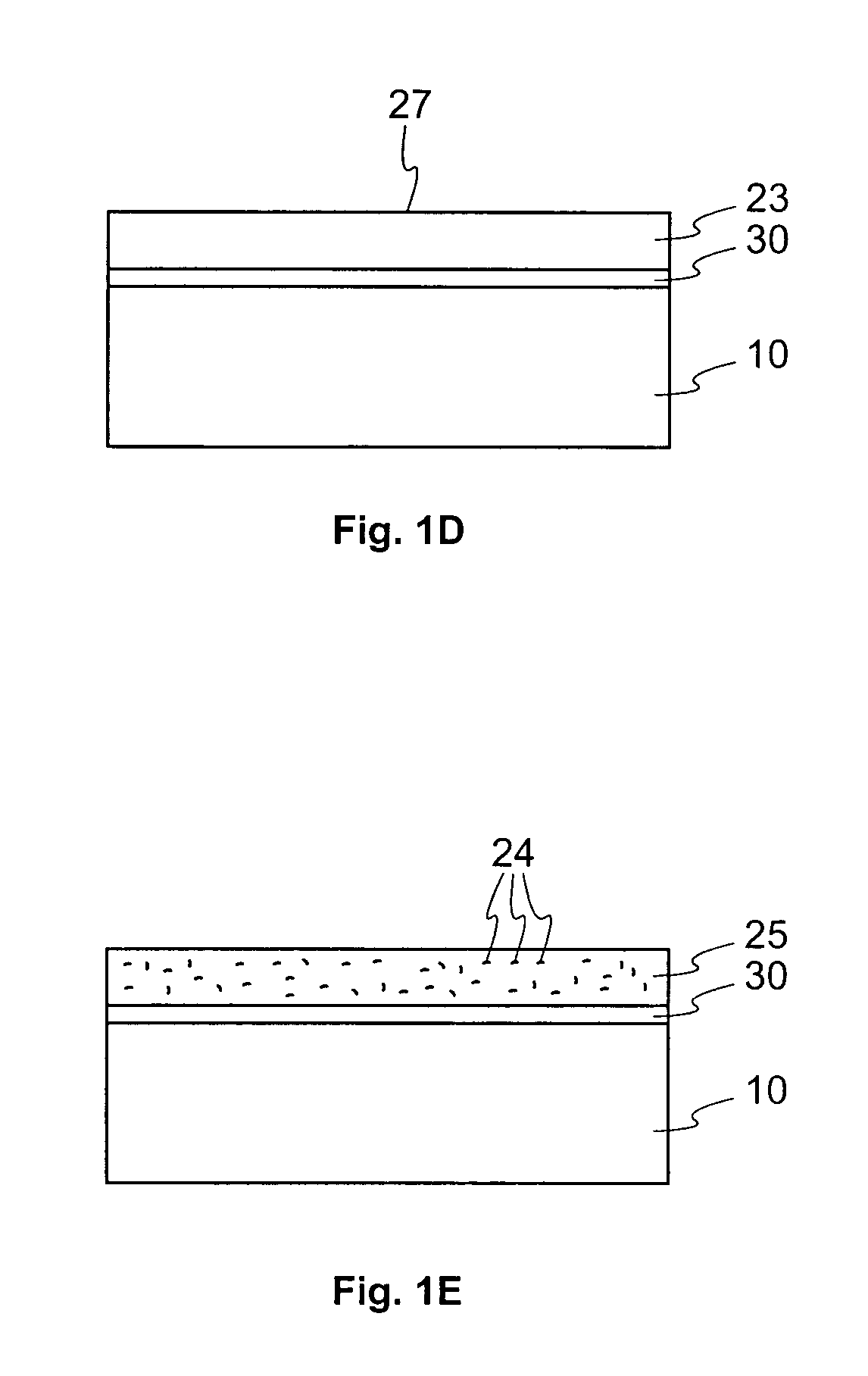

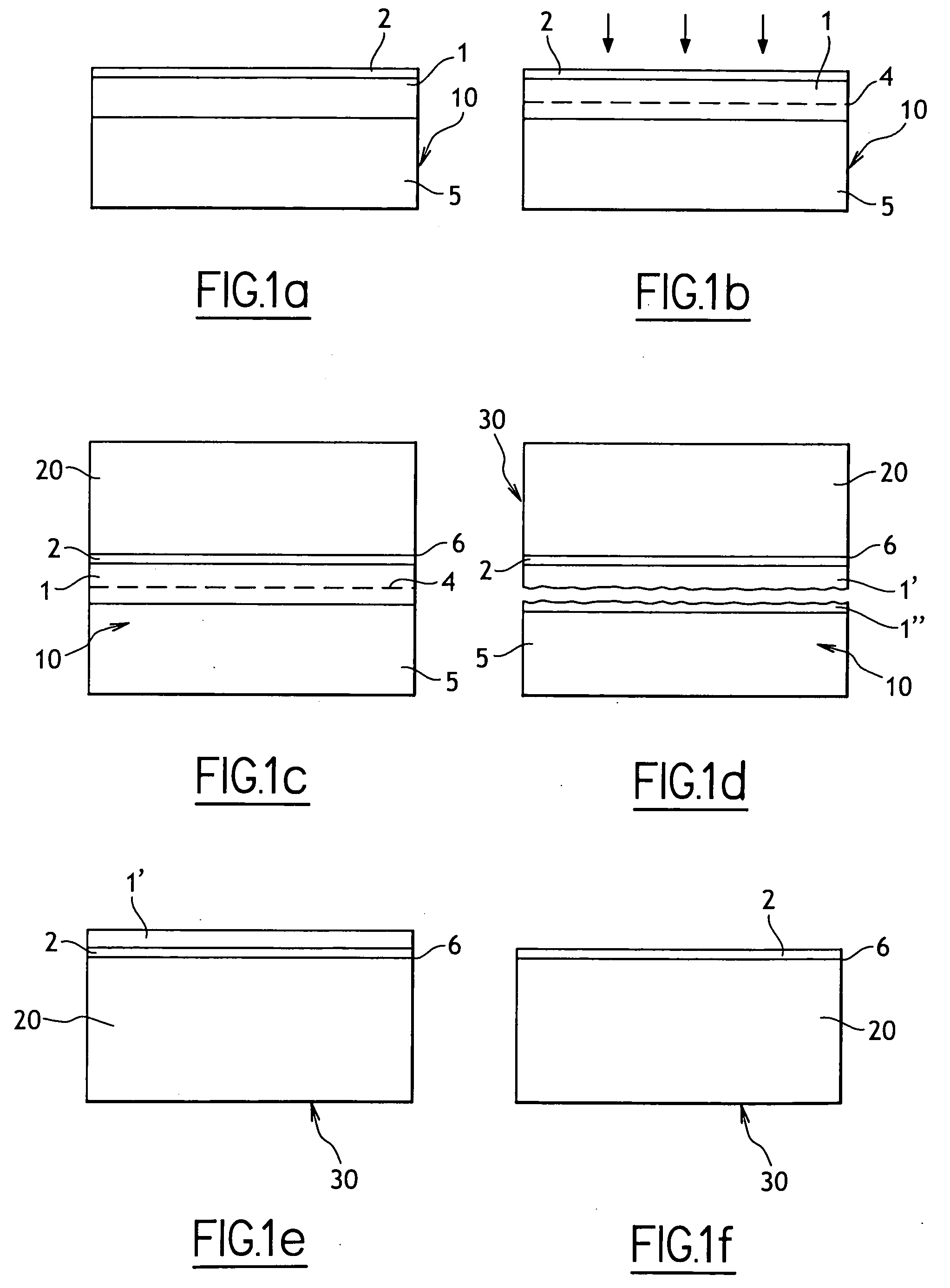

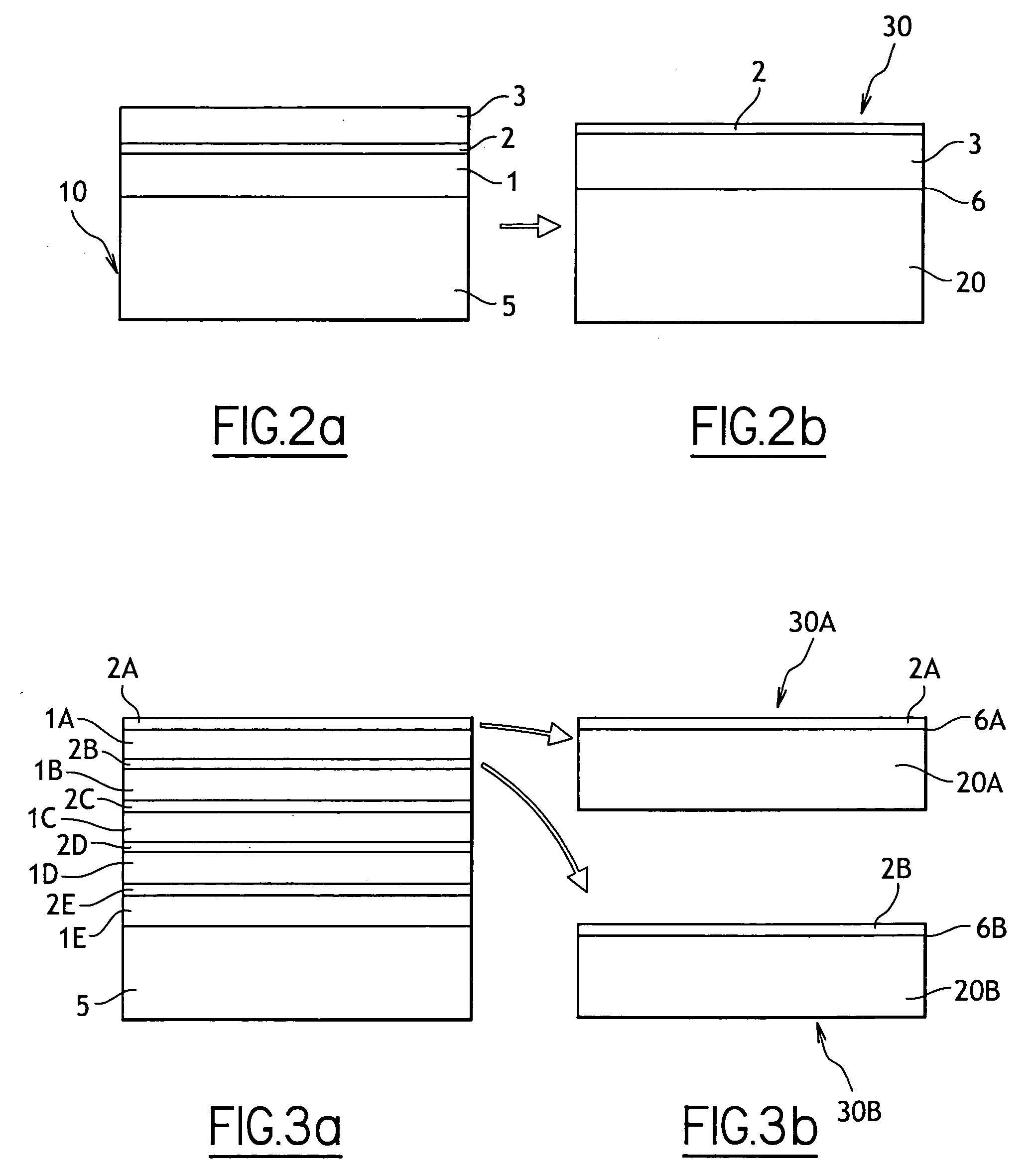

Methods for fabricating final substrates

InactiveUS6867067B2Solid-state devicesSemiconductor/solid-state device manufacturingComposite substrateOptoelectronics

Methods for fabricating final substrates for use in optics, electronics, or optoelectronics are described. In an embodiment, the method includes forming a zone of weakness beneath a surface of a source substrate to define a transfer layer, and forming a first bonding layer on the source substrate surface. A second bonding layer may be formed on a surface of an intermediate support, and the exposed surfaces of the first and second bonding layers joined to form a composite substrate. Next, the source substrate is detached from the composite substrate along the zone of weakness to expose a surface of the transfer layer, and a support material is deposited onto the exposed surface of the transfer layer. The transfer layer and support material are then separated from the composite substrate by elimination of at least the first bonding layer to form the final substrate. The zone of weakness may advantageously be formed by implanting atomic species into the source substrate.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

Soi transistor having a reduced body potential and a method of forming the same

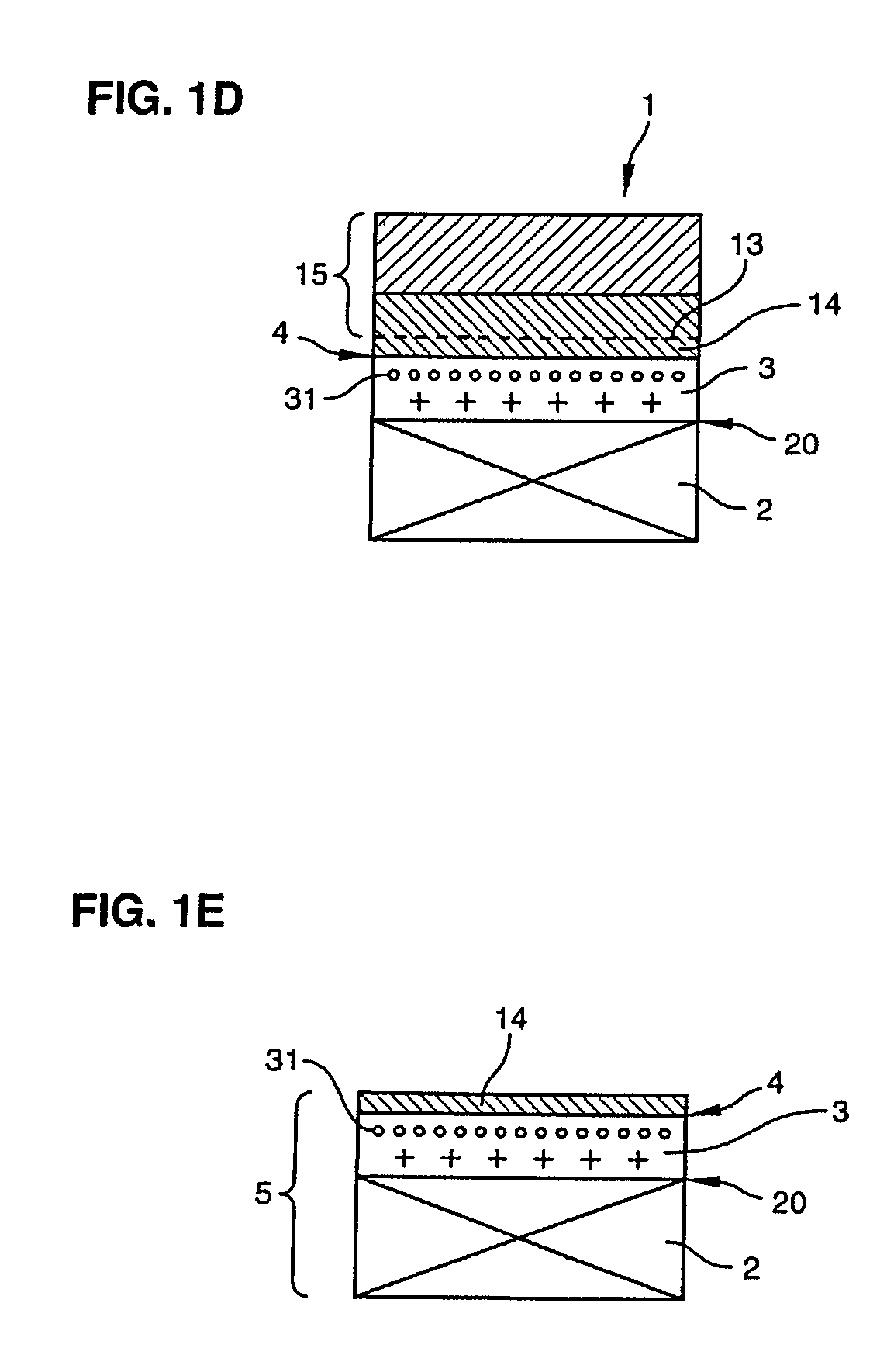

ActiveUS20070252205A1Reduce hysteresis effectsImprove compatibilitySolid-state devicesSemiconductor/solid-state device manufacturingJunction leakageCharge carrier

By introducing a atomic species, such as carbon, fluorine and the like, into the drain and source regions, as well as in the body region, the junction leakage of SOI transistors may be significantly increased, thereby providing an enhanced leakage path for accumulated minority charge carriers. Consequently, fluctuations of the body potential may be significantly reduced, thereby improving the overall performance of advanced SOI devices. In particular embodiments, the mechanism may be selectively applied to threshold voltage sensitive device areas, such as static RAM areas.

Owner:ADVANCED MICRO DEVICES INC

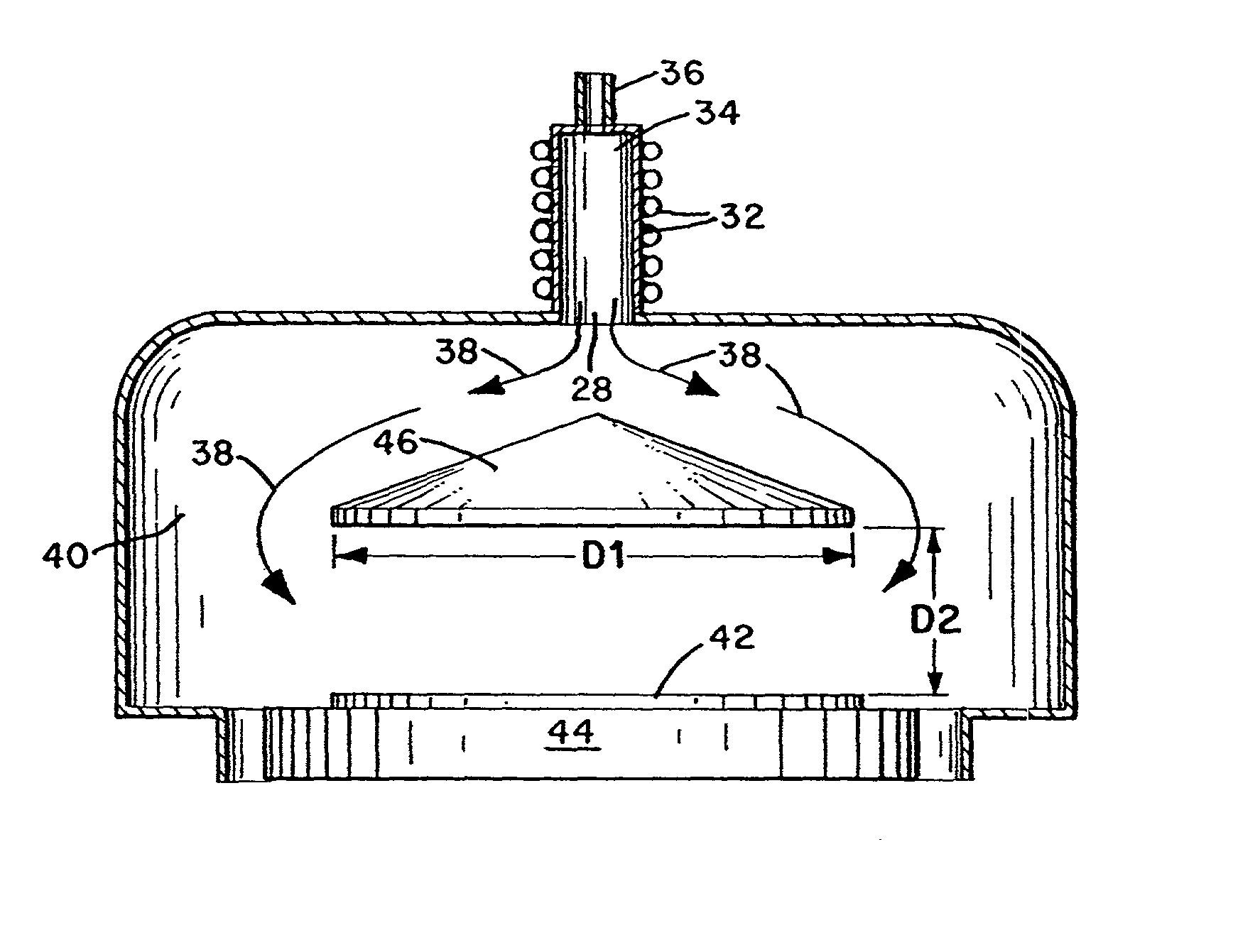

Apparatus and method for injecting and modifying gas concentration of a meta-stable or atomic species in a downstream plasma reactor

InactiveUS6287643B1Reduce lossesElectric discharge tubesPretreated surfacesRemote plasmaHigh density

An apparatus and method for injecting gas within a plasma reactor and tailoring the distribution of an active species generated by the remote plasma source over the substrate or wafer. The distribution may be uniform, wafer-edge concentrated, or wafer-center concentrated. A contoured plate or profiler modifies the distribution. The profiler is an axially symmetric plate, having a narrow top end and a wider bottom end, shaped to redistribute the gas flow incident upon it. The method for tailoring the distribution of the active species over the substrate includes predetermining the profiler diameter and adjusting the profiler height over the substrate. A coaxial injector tube, for the concurrent injection of activated and non-activated gas species, allows gases to be delivered in an axially symmetric manner whereby one gas can be excited in a high density RF plasma, while the other gas can be prevented from excitation and / or dissociation caused by exposure to the plasma or heated surfaces in the source apparatus. The profiler is used in conjunction with the coaxial injector tube for redistributing the excited gases emerging from the injector tube, while allowing the non-excited gases to pass through its center.

Owner:NOVELLUS SYSTEMS

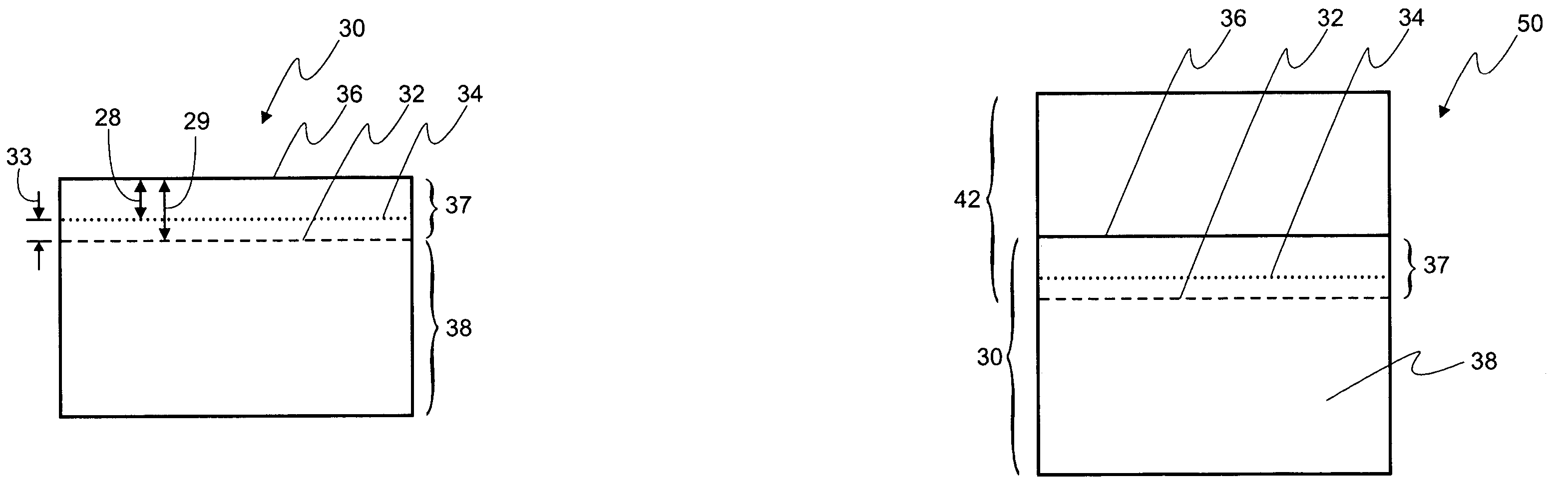

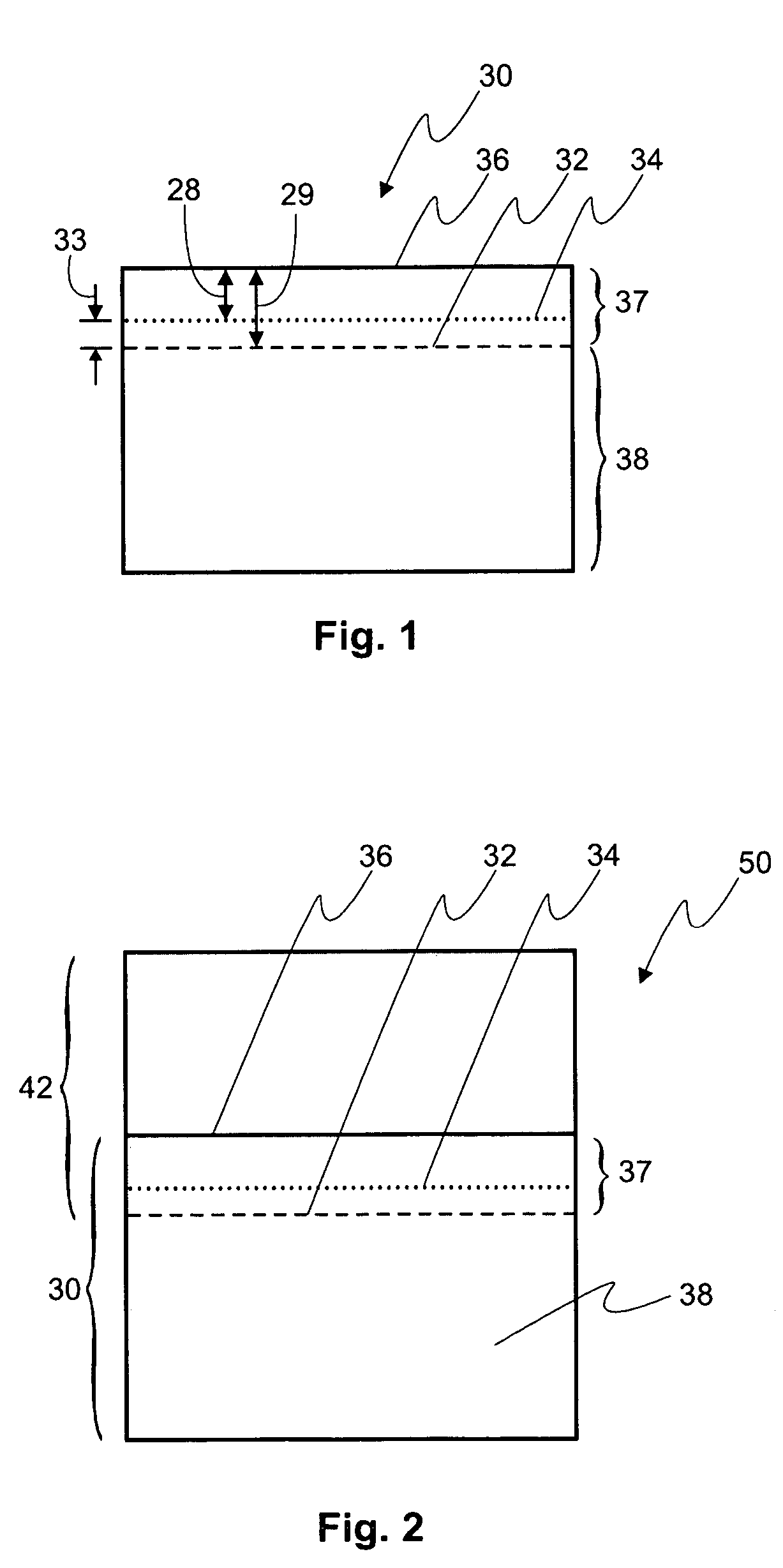

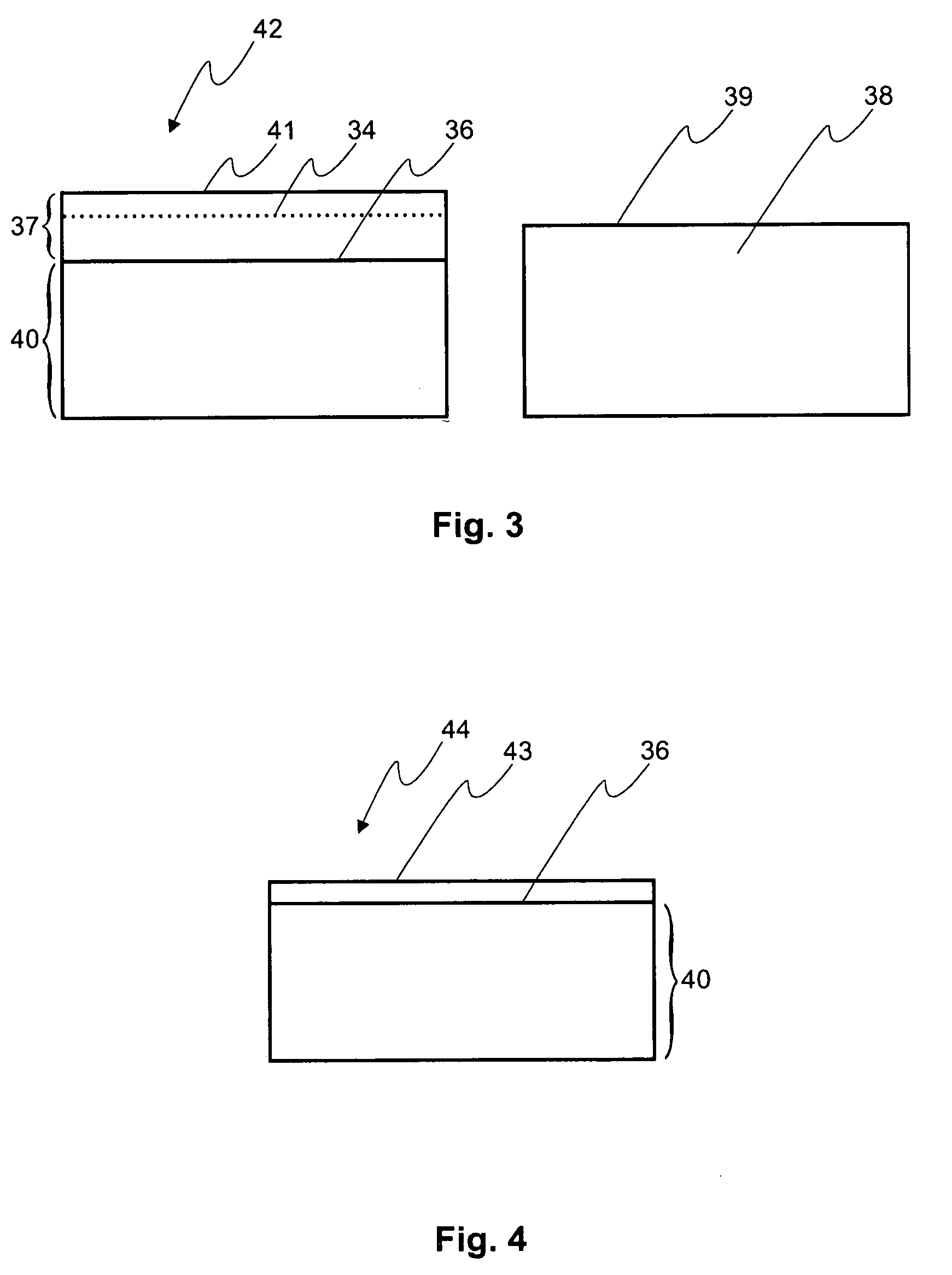

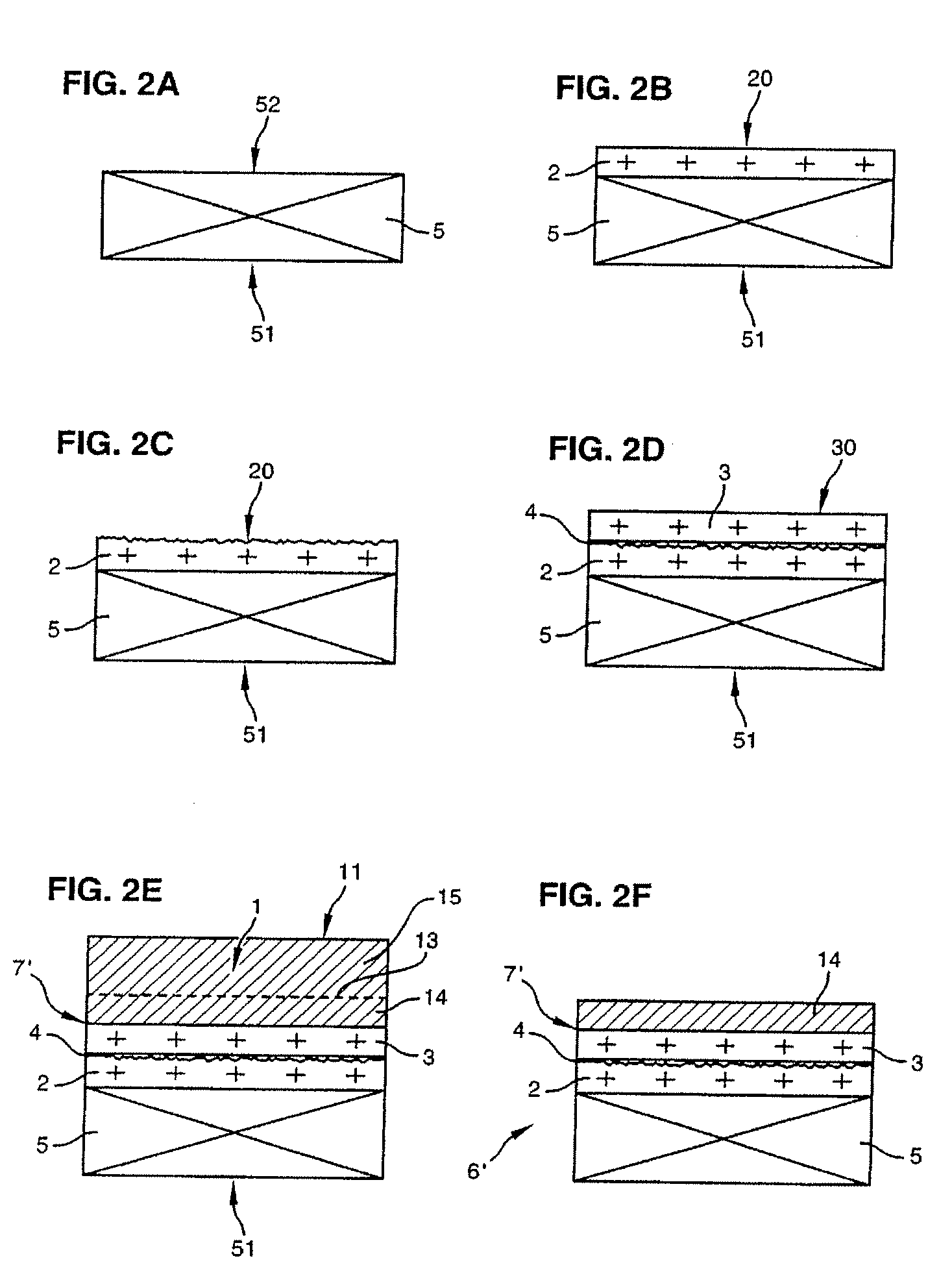

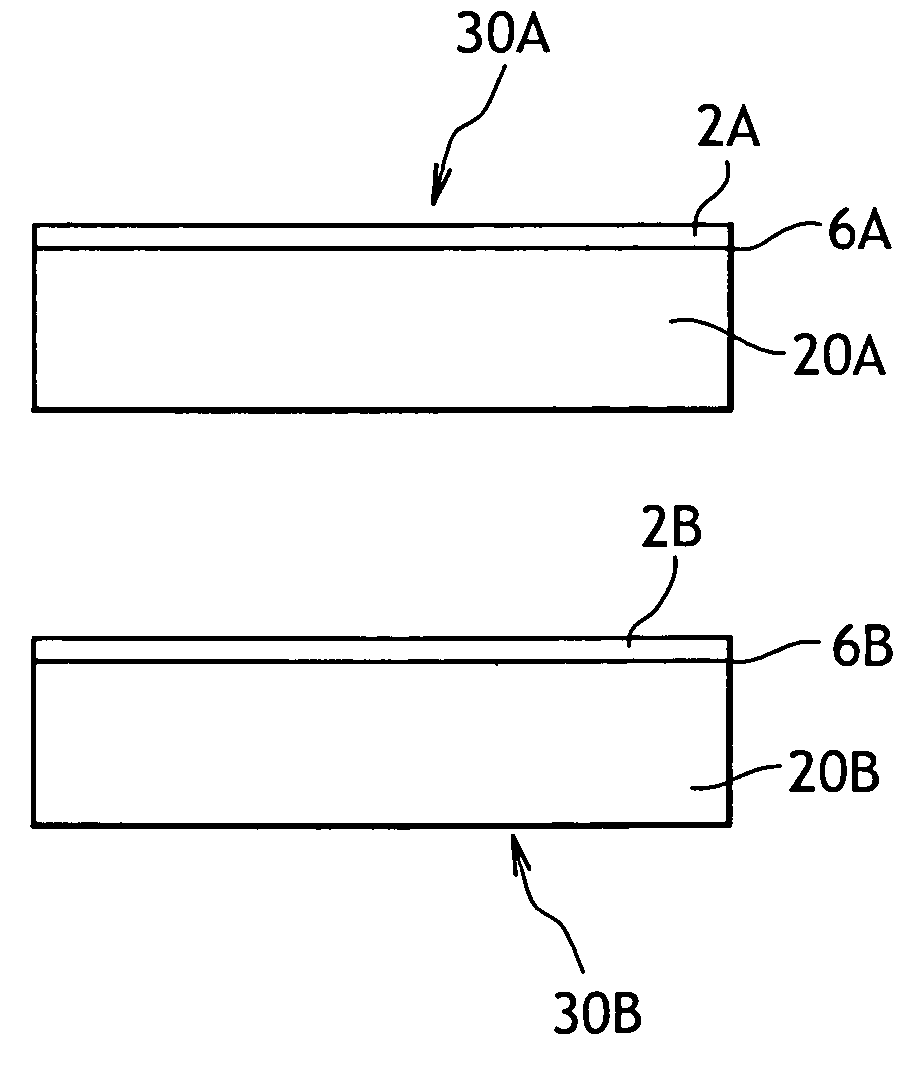

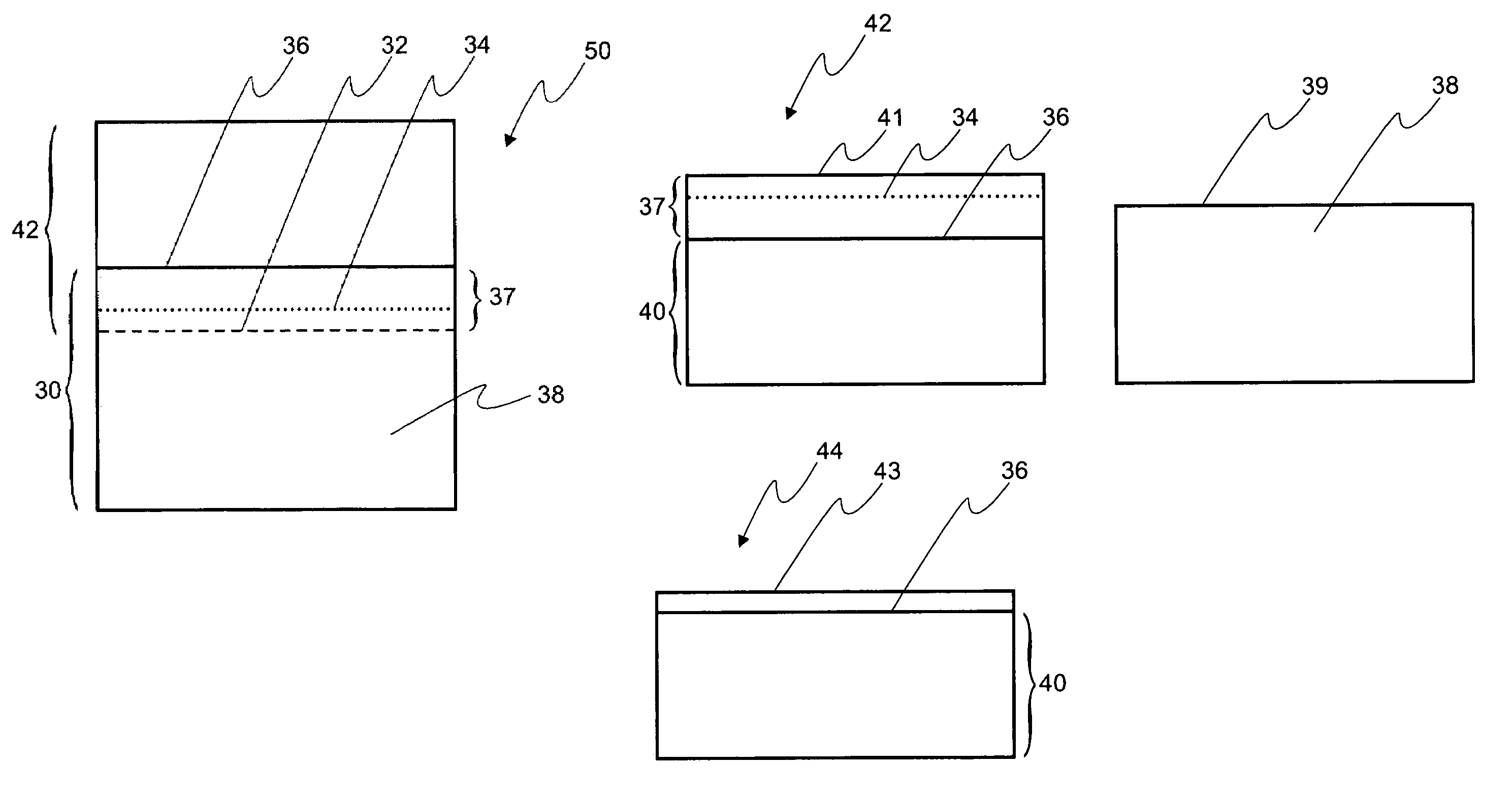

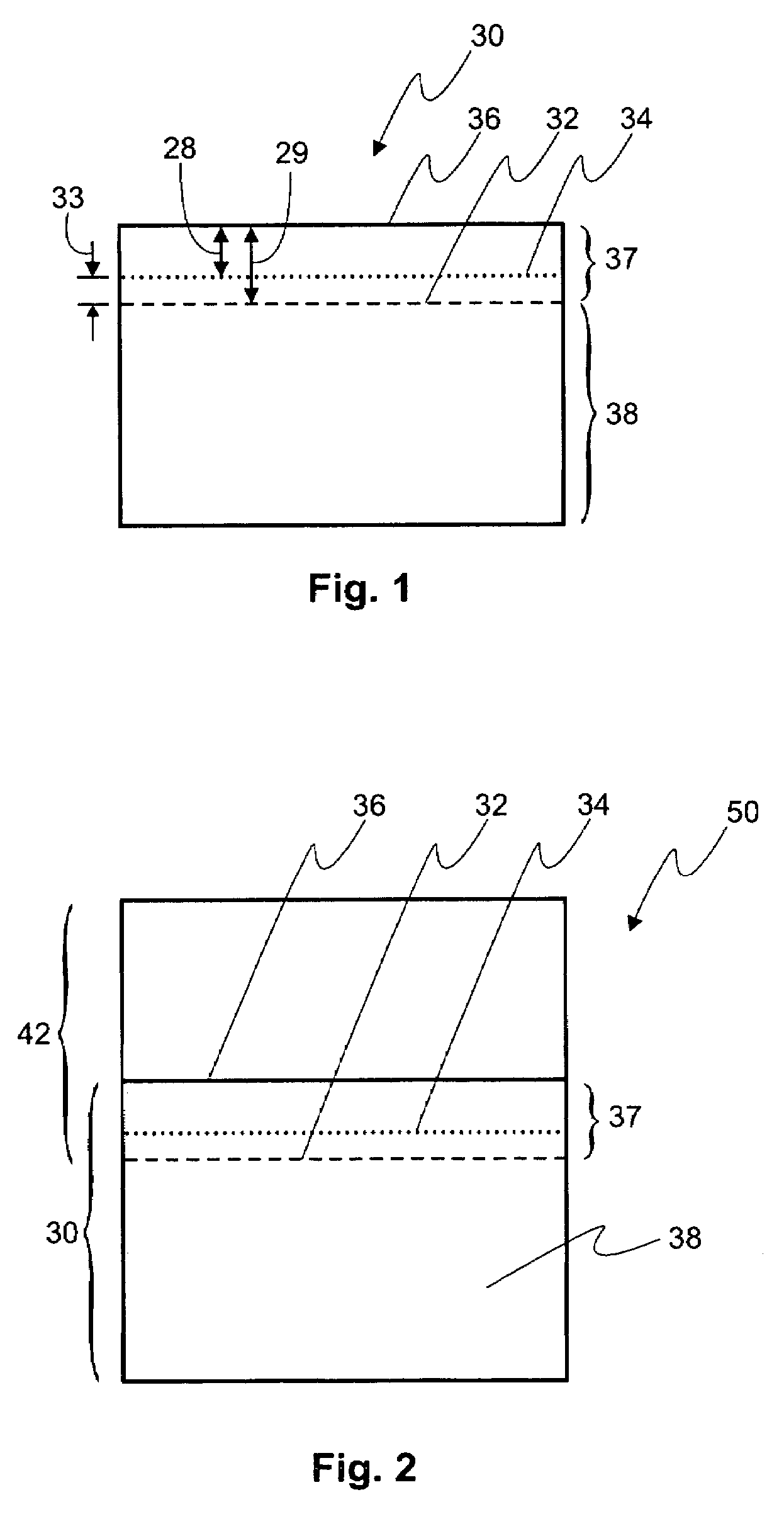

Methods for fabricating a substrate

InactiveUS20050026394A1Simple methodOvercome difficultiesPolycrystalline material growthSemiconductor/solid-state device manufacturingComposite substrateEngineering

A method is provided for fabricating a substrate for optics, electronics, or opto-electronics. This method includes the steps of implanting atomic species into a face of a source substrate to form a weakened zone therein corresponding to the depth of penetration of the atomic species; transferring the seed layer on to a support substrate by bonding a face of the support substrate to the face of the source substrate and detaching the seed layer from the source substrate; depositing a working layer on the seed layer to form a composite substrate comprising the support substrate, seed layer and working layer; and detaching the seed layer and the working layer from the support substrate to form a substrate. Advantageously, the support substrate comprises a material having a thermal expansion value of about 0.7 to 3 times the coefficient value of the working layer, and the seed layer includes a crystal lattice parameter sufficient for the epitaxial growth of the working layer onto the seed layer such that the working layer has a dislocation concentration of less than about 107 / cm2.

Owner:SOITEC SA

Multi-layered wiring layer and method of fabricating the same

InactiveUS6538324B1Semiconductor/solid-state device detailsSolid-state devicesDevice materialNitrogen

There is provided a barrier film preventing diffusion of copper from a copper wiring layer formed on a semiconductor substrate. The barrier film has a multi-layered structure of first and second films wherein the first film is composed of crystalline metal containing nitrogen therein, and the second film is composed of amorphous metal nitride. The barrier film is constituted of common metal atomic species. The barrier film prevents copper diffusion from a copper wiring layer into a semiconductor device, and has sufficient adhesion characteristic to both a copper film and an interlayer insulating film.

Owner:GK BRIDGE 1

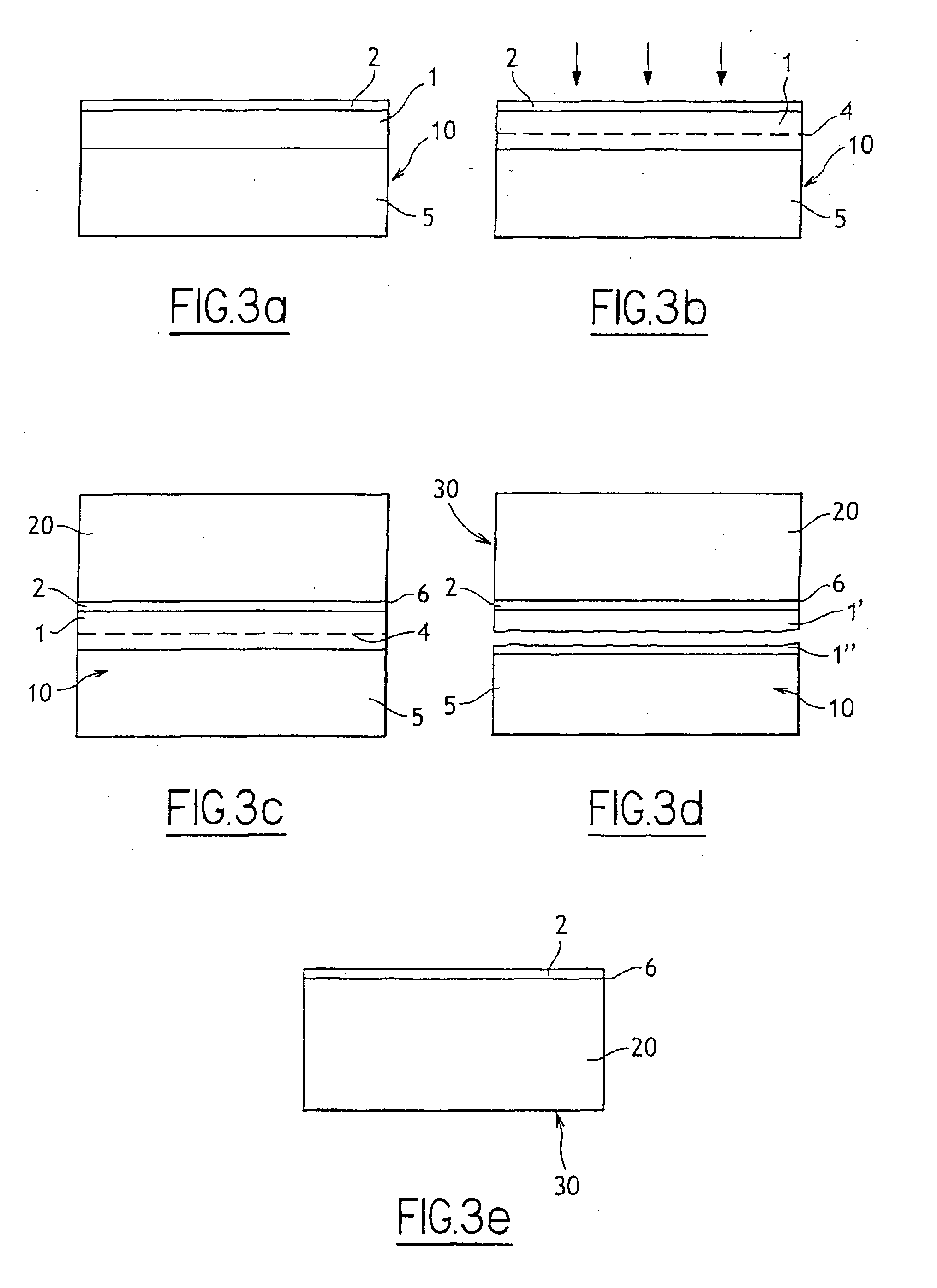

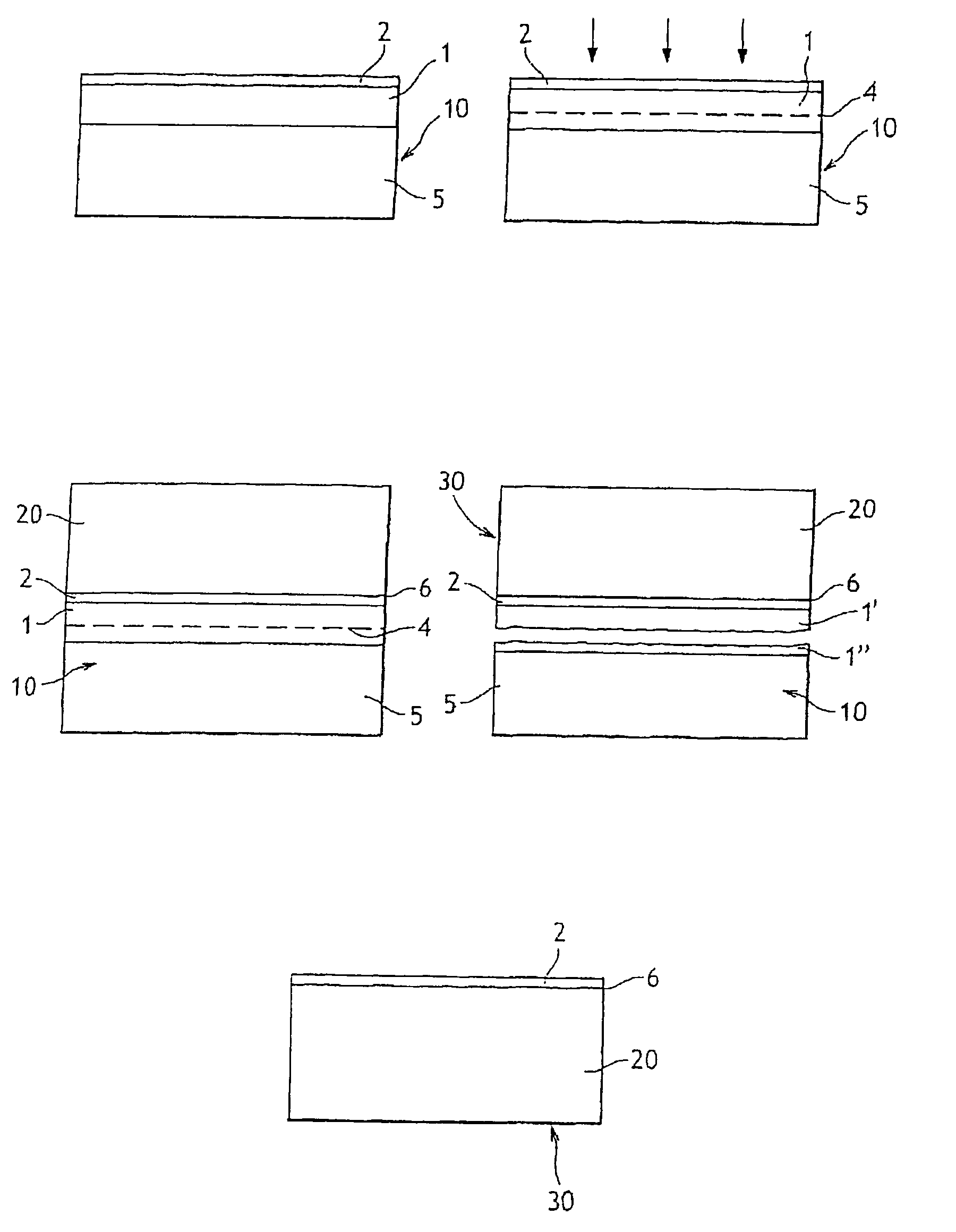

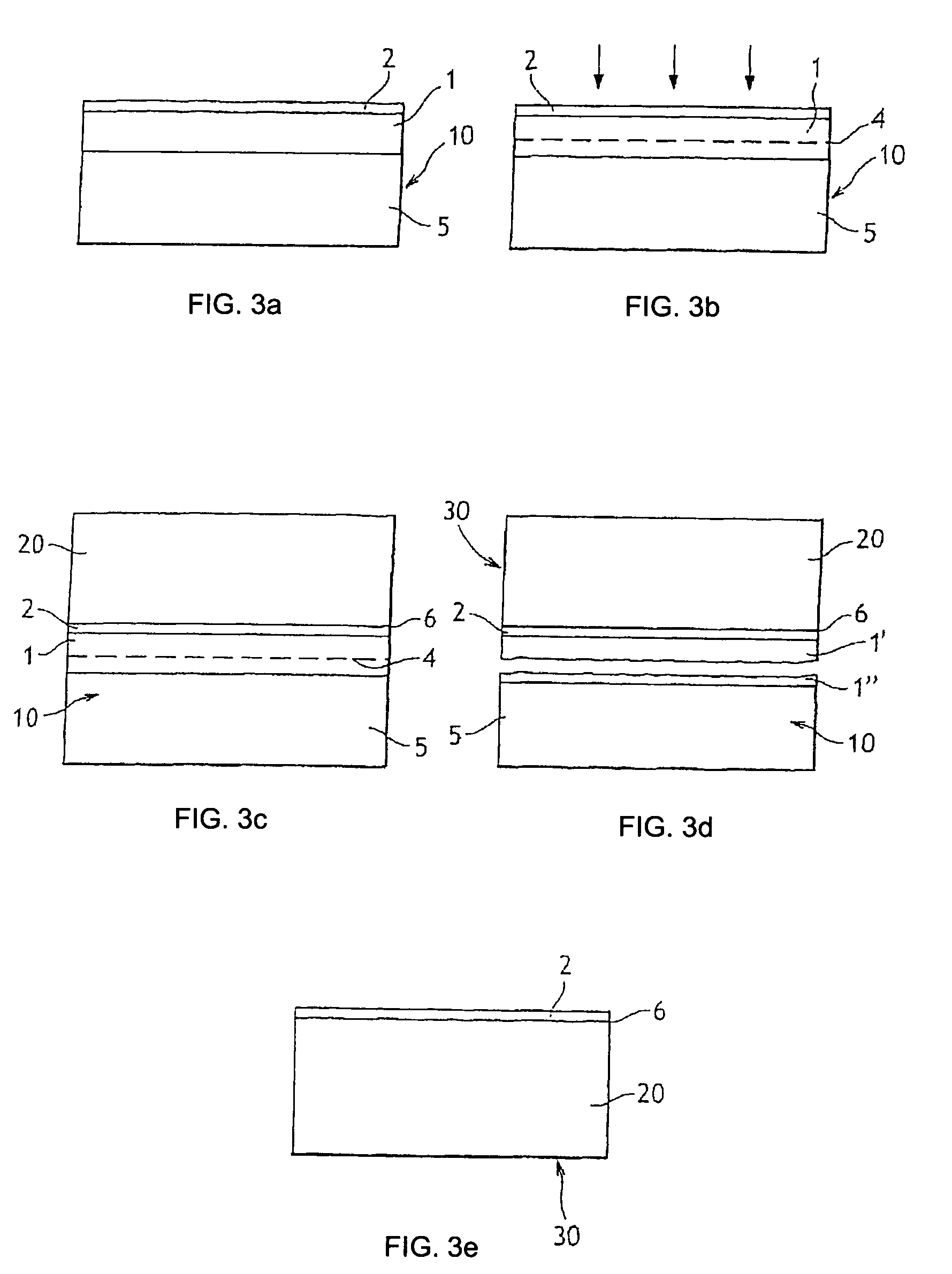

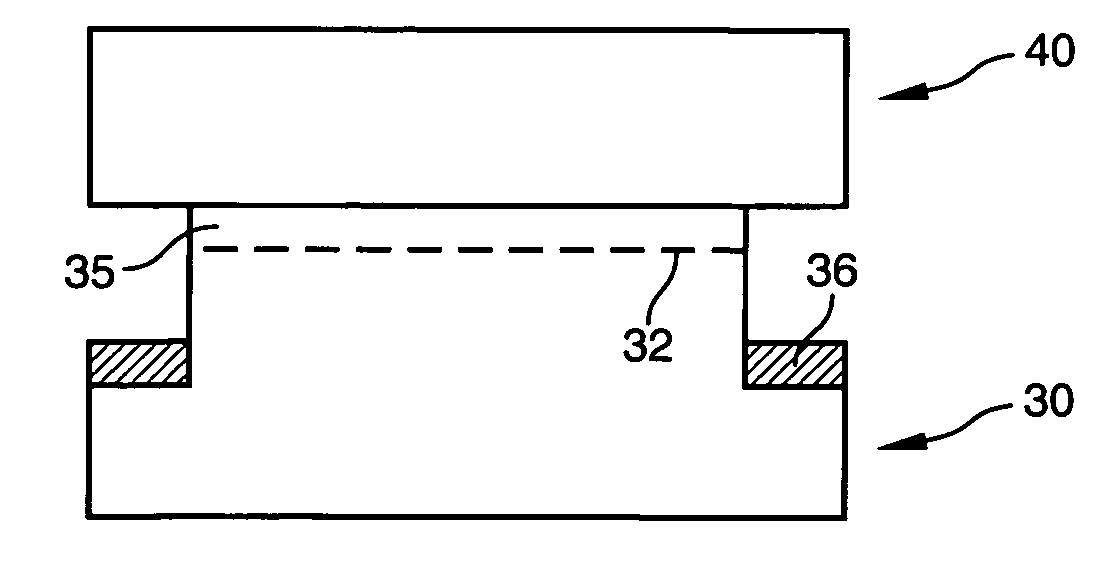

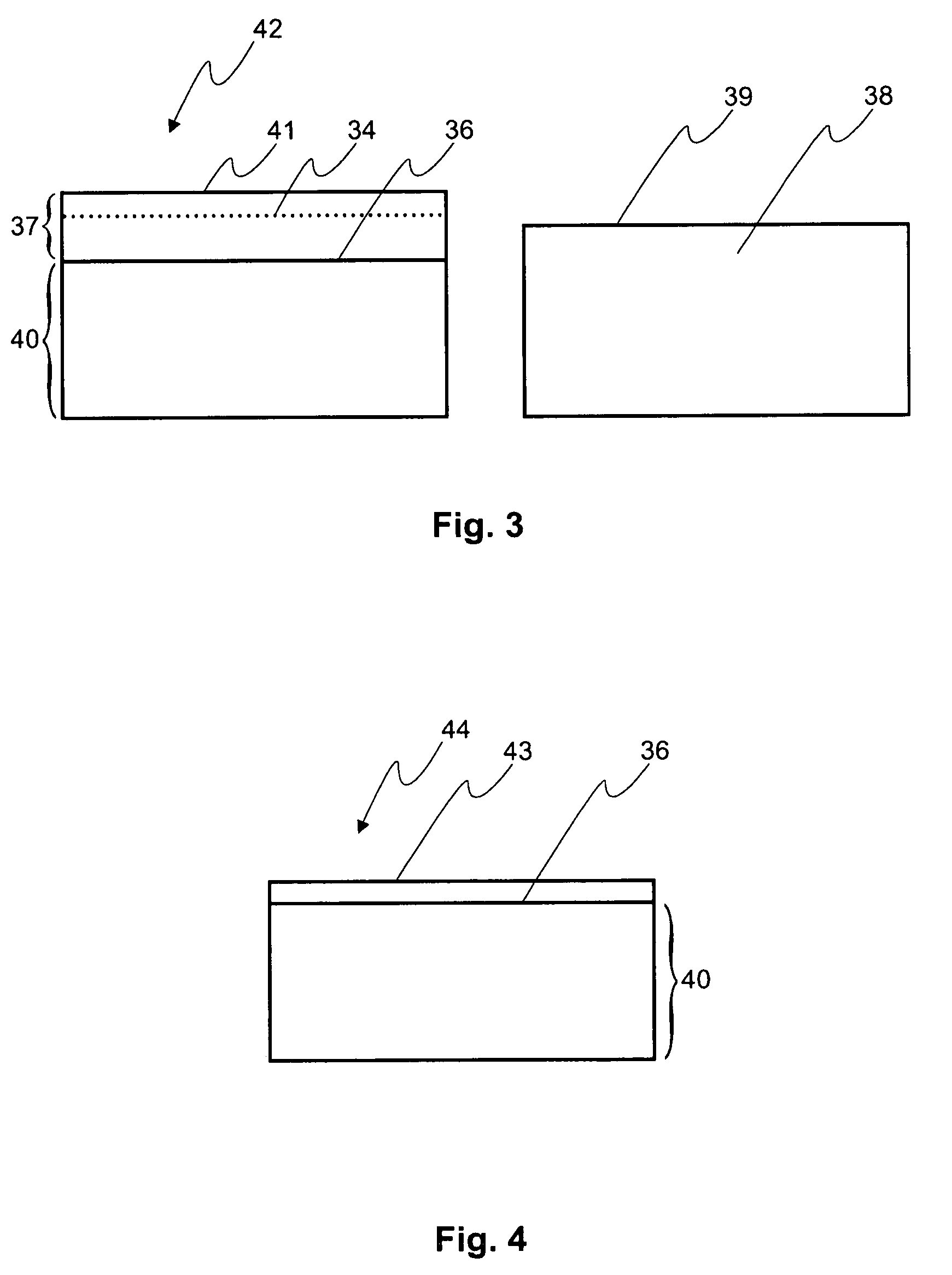

Method of fabricating substrates, in particular for optics, electronics or optoelectronics

ActiveUS6858107B2Reduce lossesDecorative surface effectsSemiconductor/solid-state device manufacturingOptoelectronicsIngot

A method of fabricating substrates while minimizing loss of starting material of an ingot, wherein a layer is transferred onto a support. The technique includes forming a flat front face on a raw ingot of material, implanting atomic species through the front face to a controlled mean implantation depth to create a zone of weakness that defines a top layer of the ingot, bonding a support to the front face of the ingot, wherein the support has a surface area that is smaller than a surface area of the front face of the ingot, and detaching from the ingot at the zone of weakness that portion of the top layer that is bonded to the support to form the substrate.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

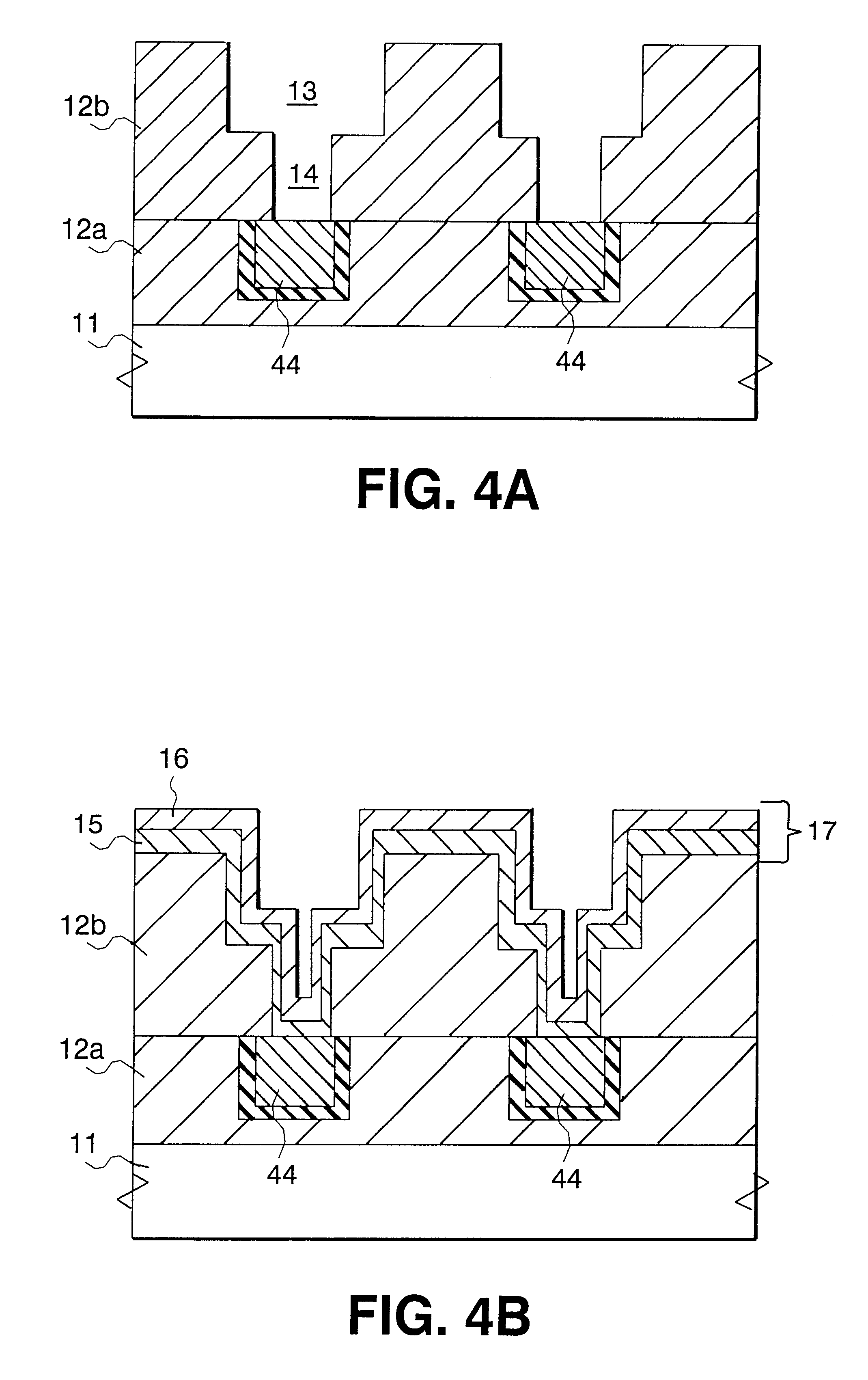

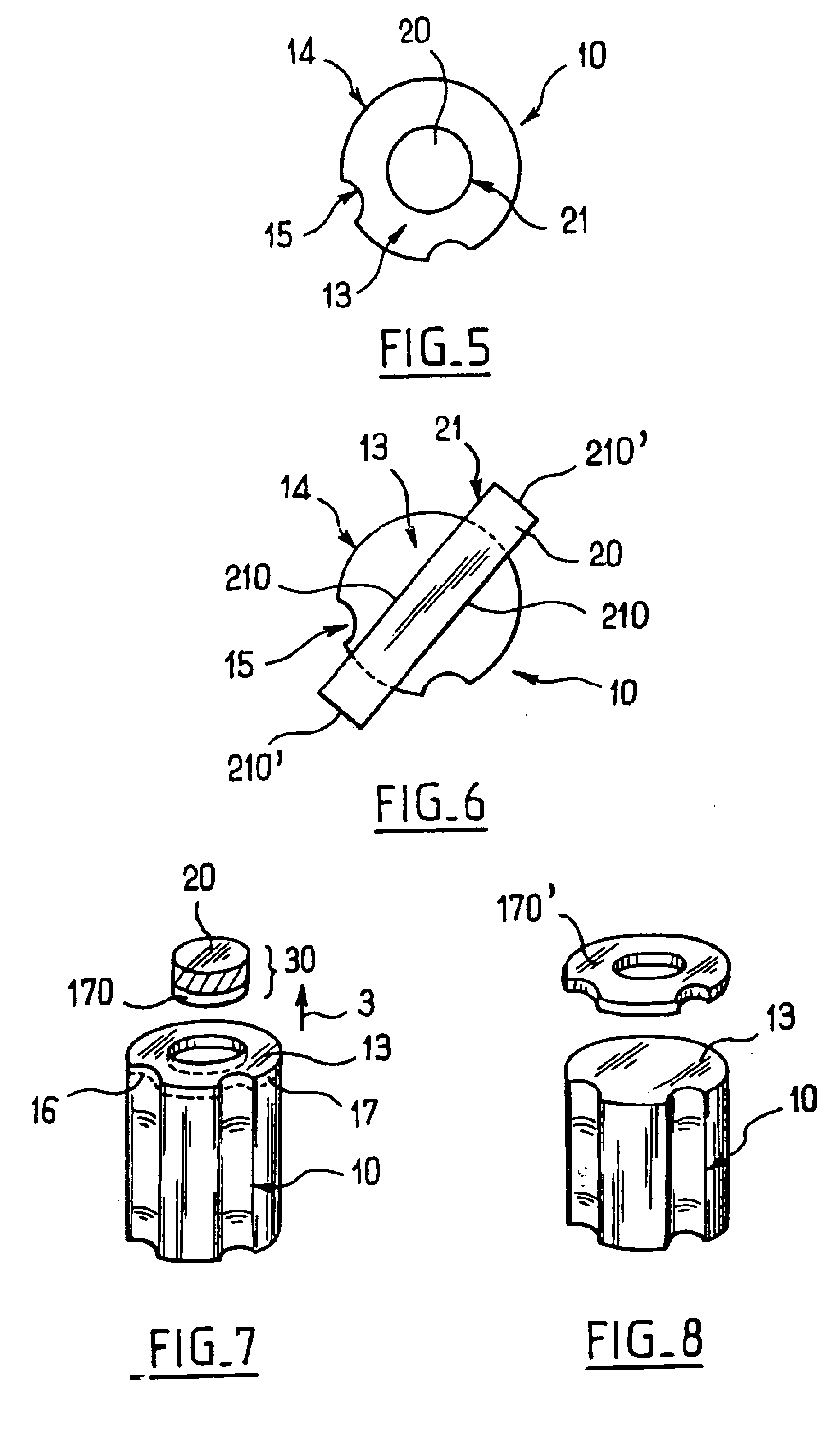

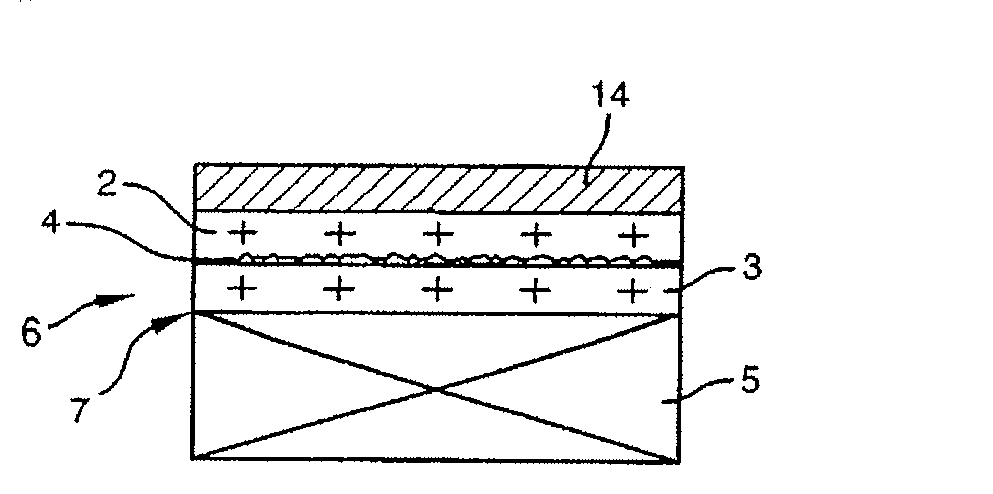

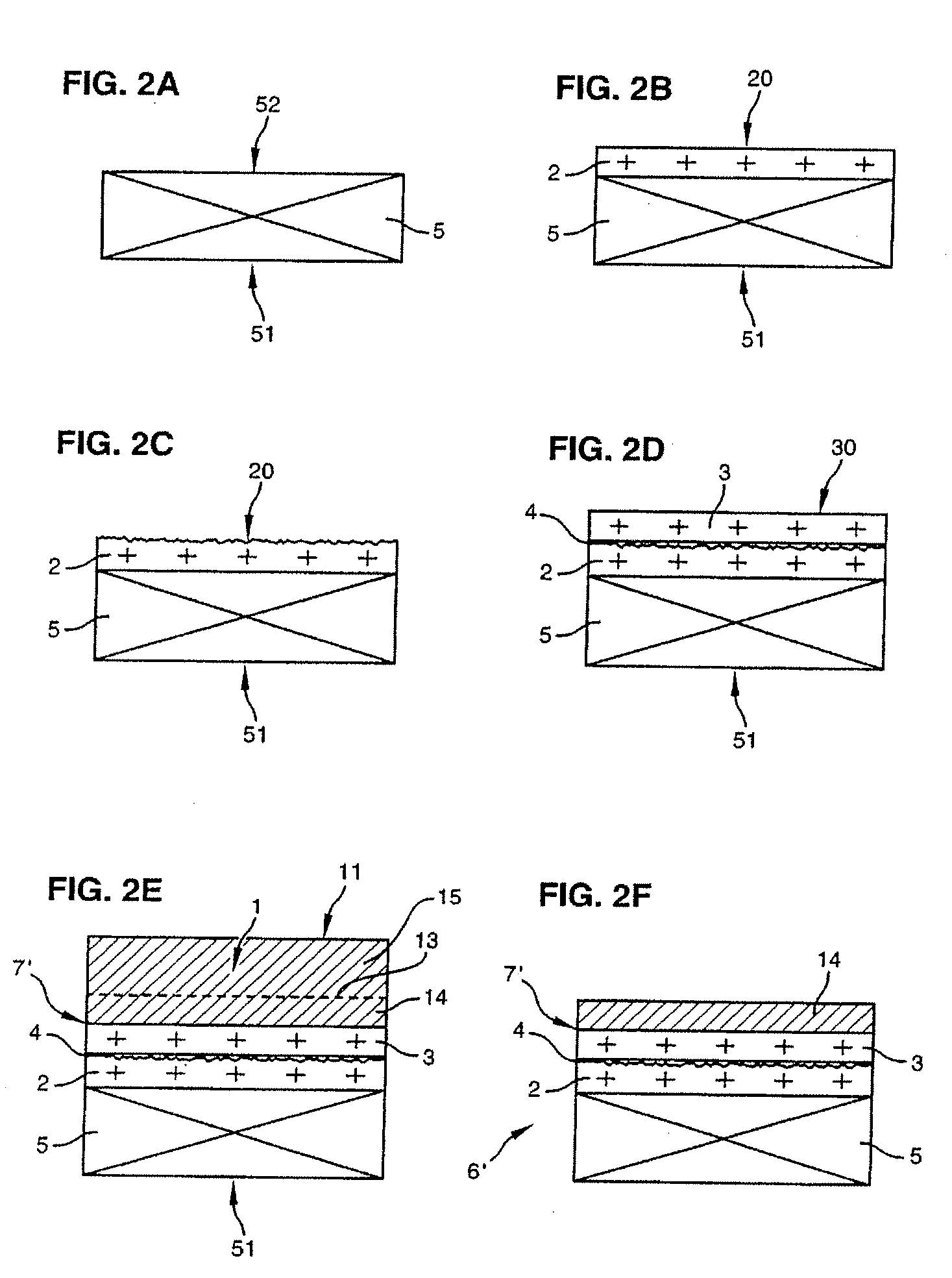

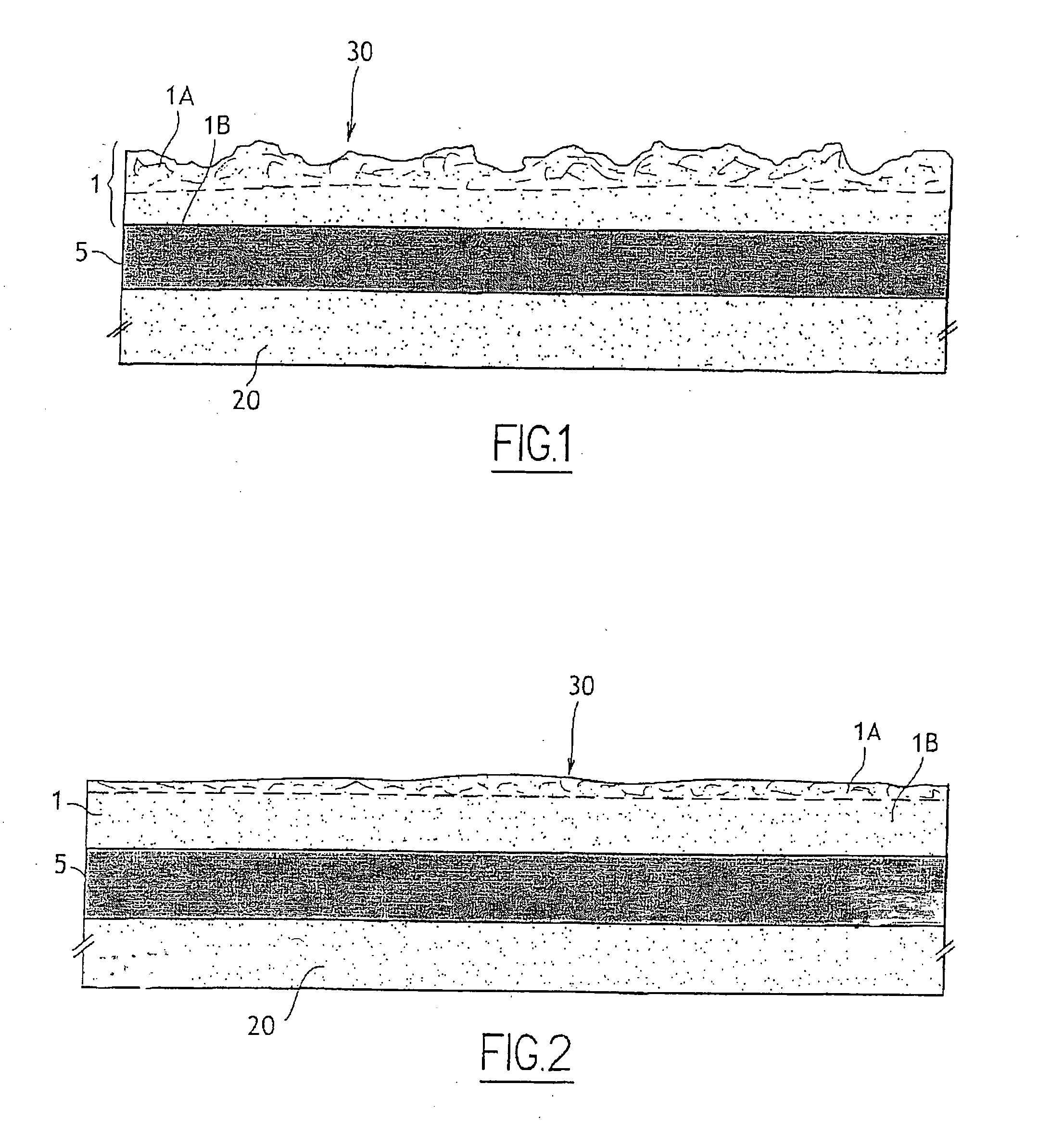

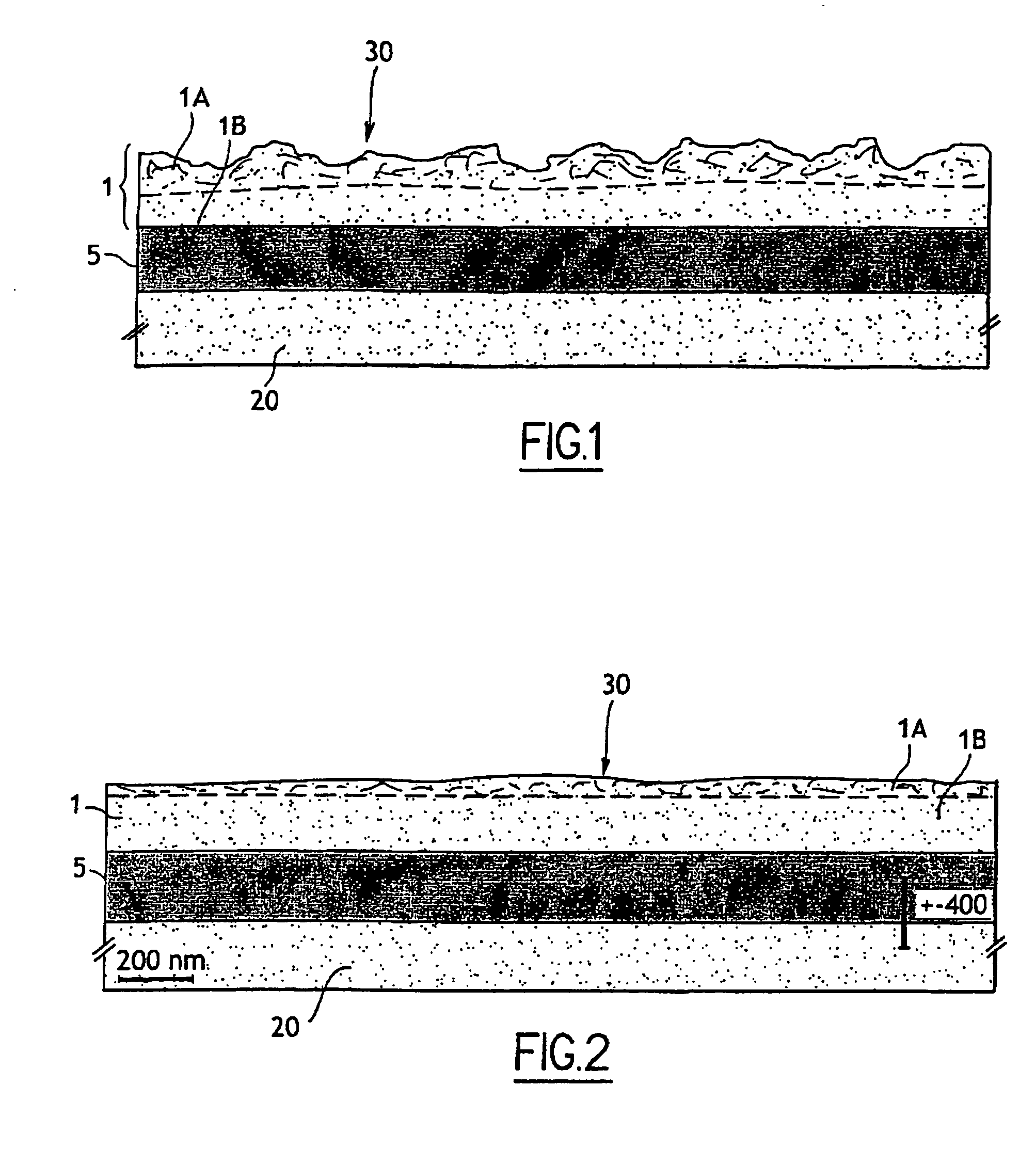

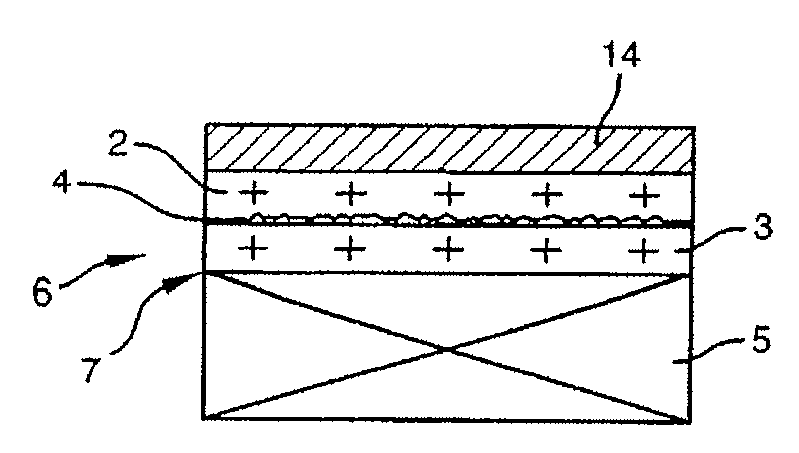

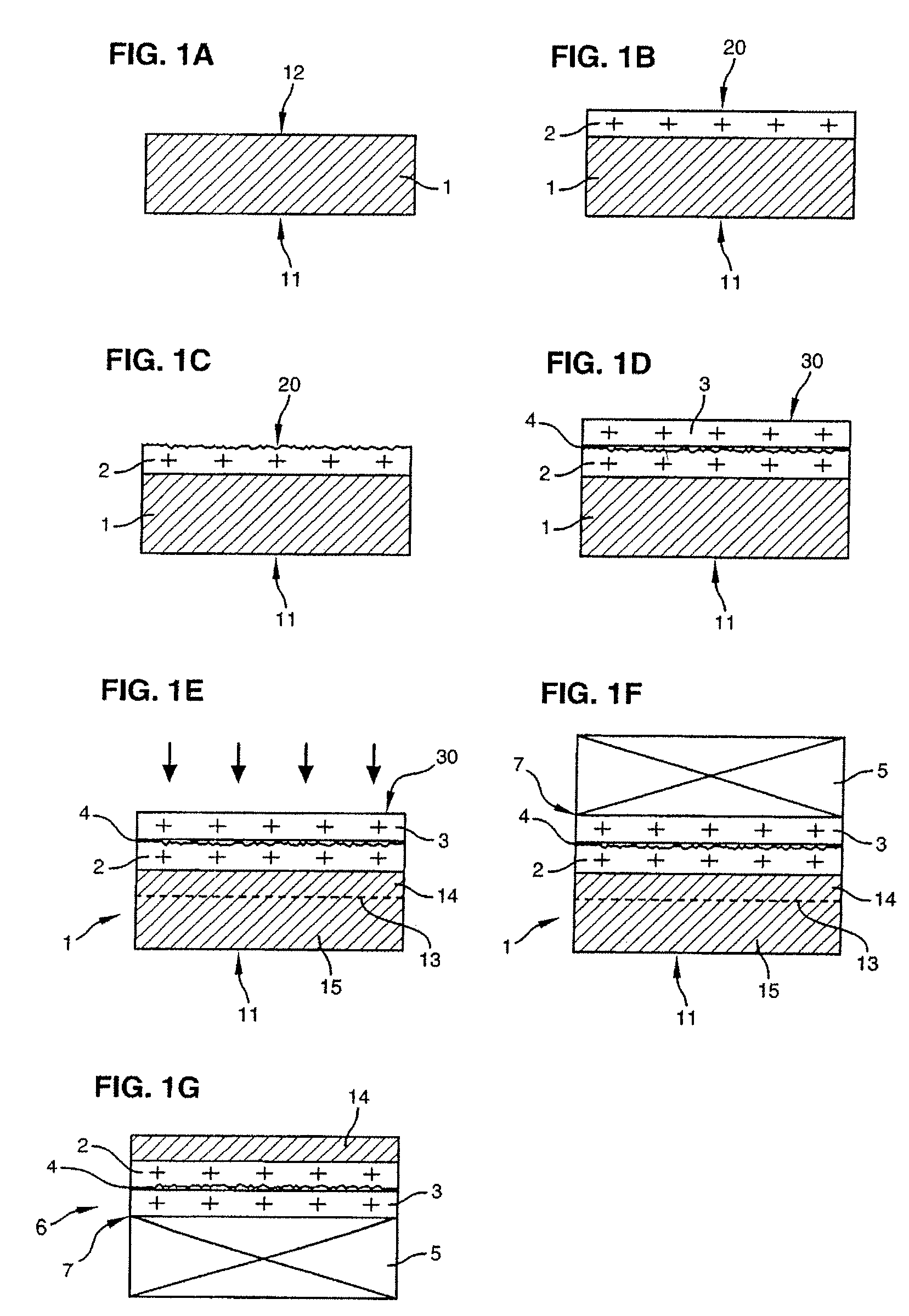

Fabrication of hybrid substrate with defect trapping zone

ActiveUS20080171443A1Inhibition formationReduce defect formationSemiconductor/solid-state device manufacturingSemiconductor materialsTrapping

A process for fabricating a hybrid substrate that has a defect trapping zone. The process includes the steps of forming or depositing a first insulator layer on a first substrate of semiconductor material; increasing roughness of the first insulator layer surface; depositing a second insulator layer on the roughened surface of the first insulator to form a trapping zone between the layers; bonding a second substrate onto the second insulator layer by molecular adhesion; and transferring an active layer formed by the implantation of atomic species into one of the substrates. The trapping zone is able to retain gaseous species present at the various interfaces of the hybrid substrate to limit the formation of defects on the surface of the active layer that is transferred.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

Method for fabricating novel semiconductor and optoelectronic devices

Owner:MONOLITHIC 3D

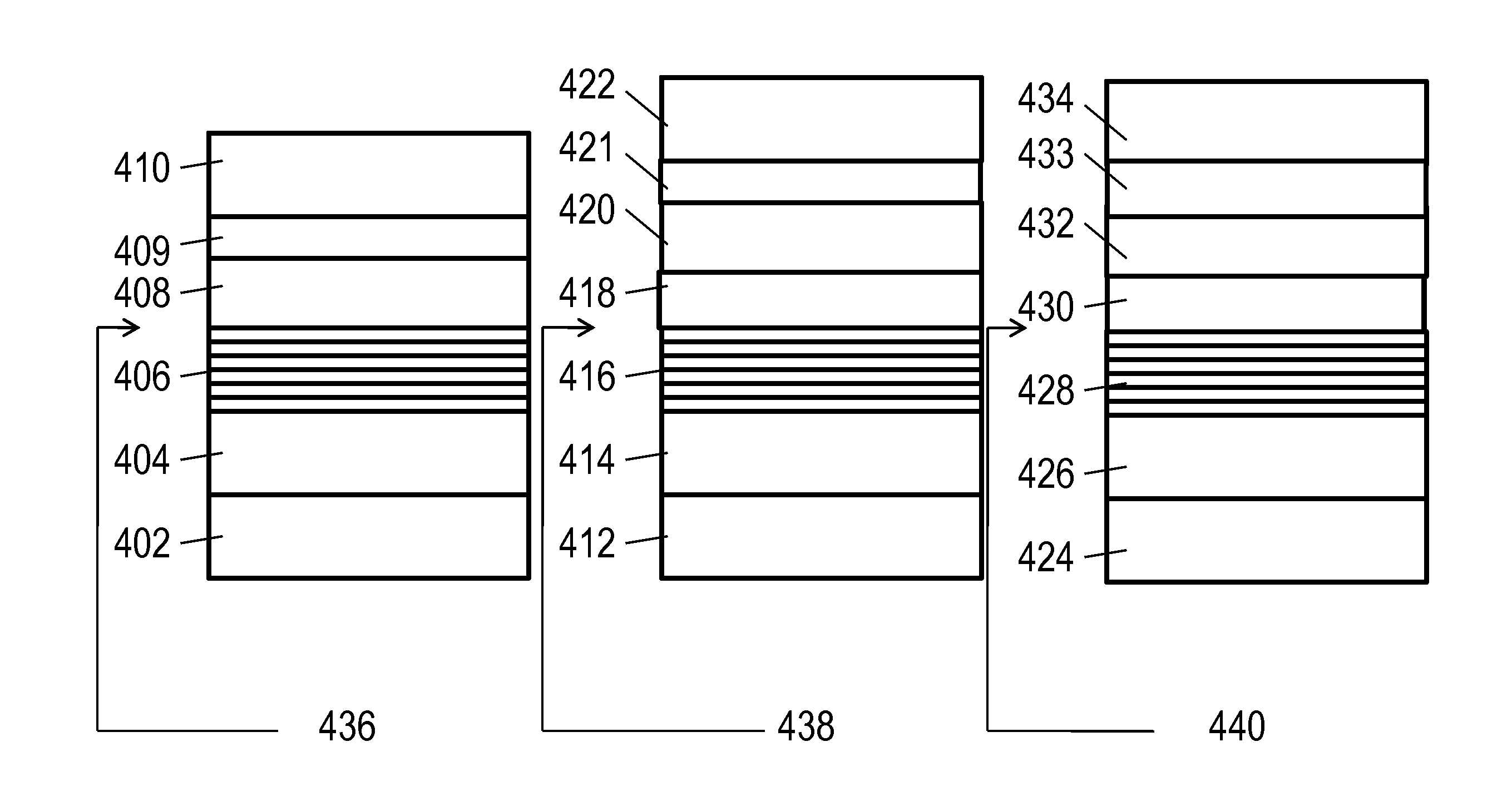

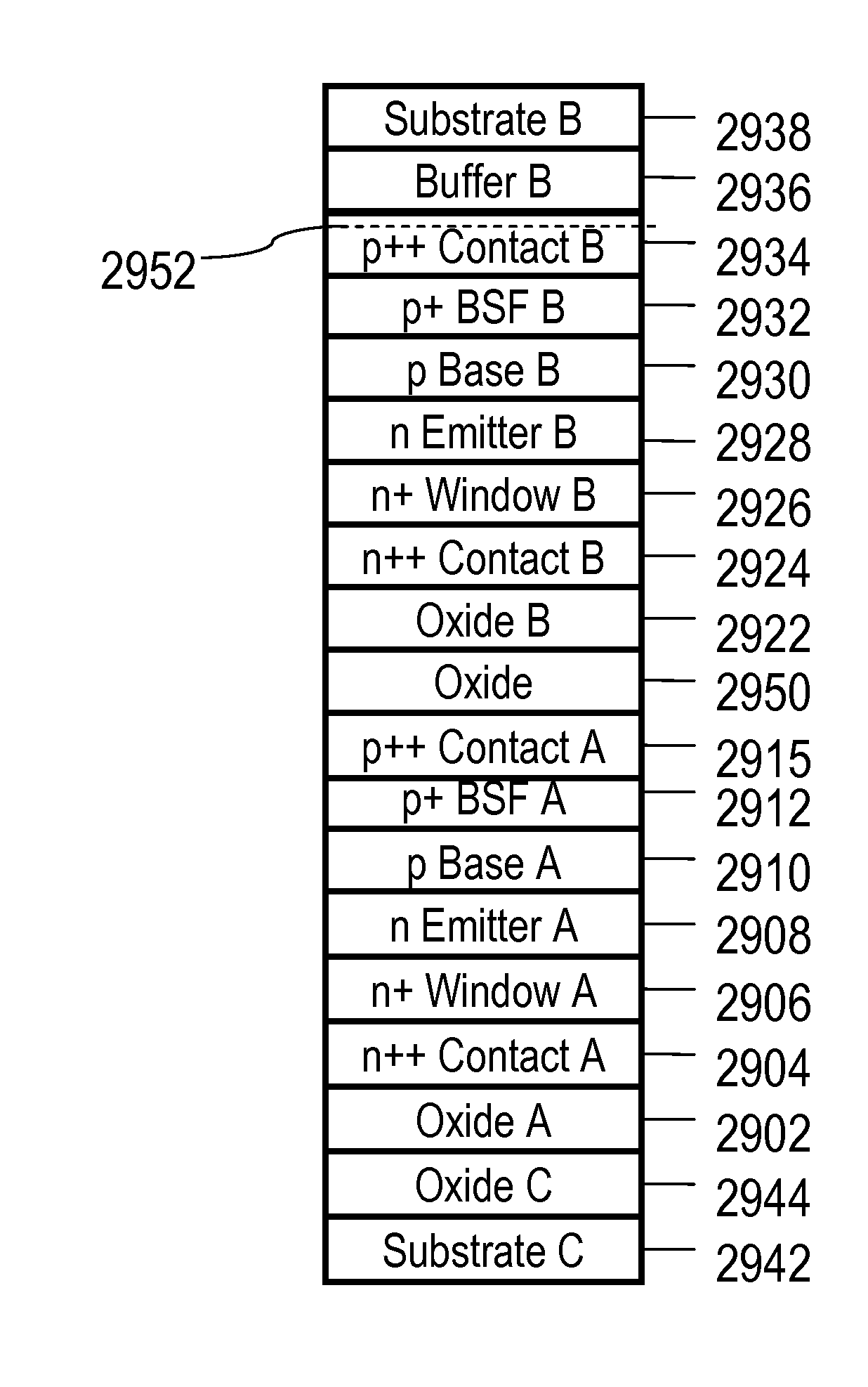

Novel semiconductor and optoelectronic devices

ActiveUS20120094414A1Solid-state devicesSemiconductor/solid-state device manufacturingLength waveAtomic species

A method for fabricating a light-emitting integrated device, comprises overlying three layers, wherein each of the three layers emits light at a different wavelength, and wherein the overlying comprises one of: performing an atomic species implantation, performing a laser lift-off, performing an etch-back, or chemical-mechanical polishing (CMP).

Owner:MONOLITHIC 3D

Atomic implantation and thermal treatment of a semiconductor layer

ActiveUS20050245049A1Minimize surface roughnessOvercome problemsSemiconductor/solid-state device manufacturingElectrical conductorSemiconductor structure

Methods for forming a semiconductor structure are described. In an embodiment, the technique includes providing a donor wafer having a first semiconductor layer and a second semiconductor layer on the first layer and having a free surface; coimplanting two different atomic species through the free surface of the second layer to form a zone of weakness zone in the first layer; bonding the free surface of the second layer to a host wafer; and supplying energy to detach at the zone of weakness a semiconductor structure comprising the host wafer, the second layer and a portion of the first layer. Advantageously, the donor wafer includes a SiGe layer, and the co-implantation of atomic species is conducted according to implantation parameters adapted to enable a first species to form the zone of weakness in the SiGe layer, and to enable a second species to provide a concentration peak located beneath the zone of weakness in the donor wafer to thus minimize surface roughness resulting from detachment at the zone of weakness.

Owner:SOITEC SA

Thermal treatment of a semiconductor layer

InactiveUS20060014363A1Shorten the durationReduce economic costsSemiconductor/solid-state device manufacturingSemiconductor materialsSemiconductor package

A method for forming a structure that includes a layer that is removed from a donor wafer that has a first layer made of a semiconductor material containing germanium. The method includes the steps of forming a weakness zone in the thickness of the first layer; bonding the donor wafer to a host wafer; and supplying energy so as to weaken the donor wafer at the level of the zone of weakness. The zone of weakness is formed by subjecting the donor wafer to a co-implantation of at least two different atomic species, while the bonding is carried out by performing a thermal treatment at a temperature between 300° C. and 400° C. for a duration of from 30 minutes to four hours.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

Method for producing a high quality useful layer on a substrate

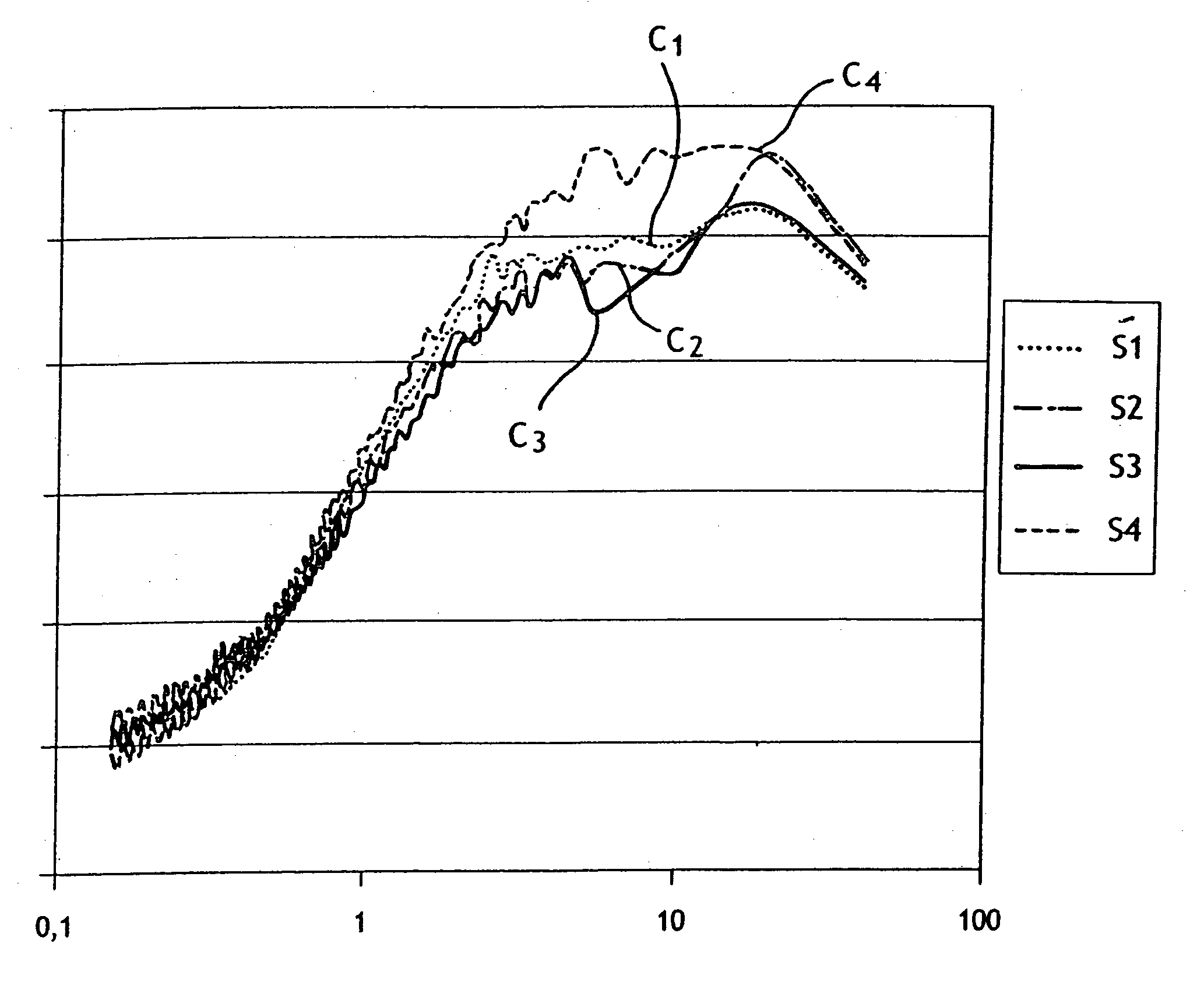

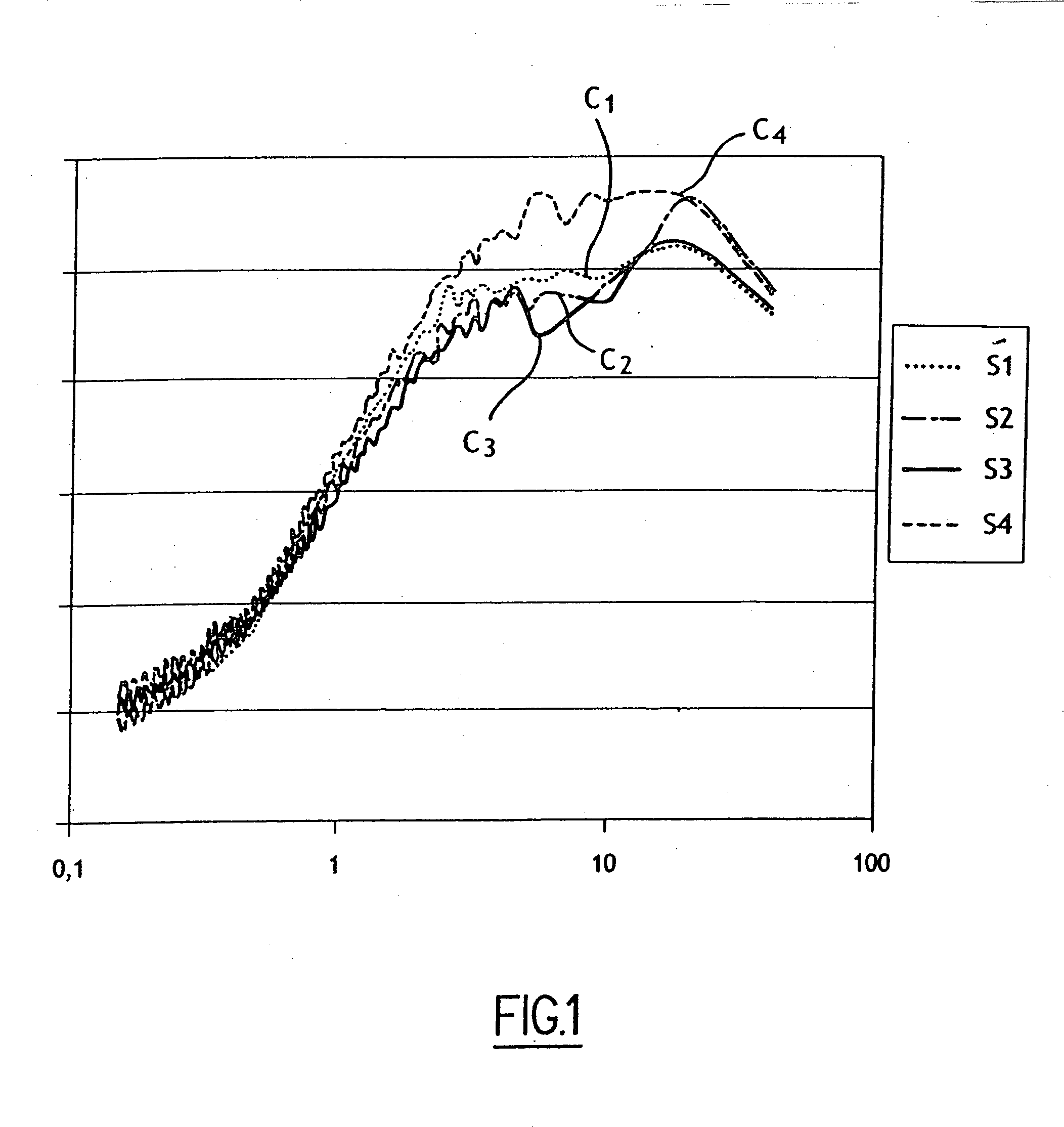

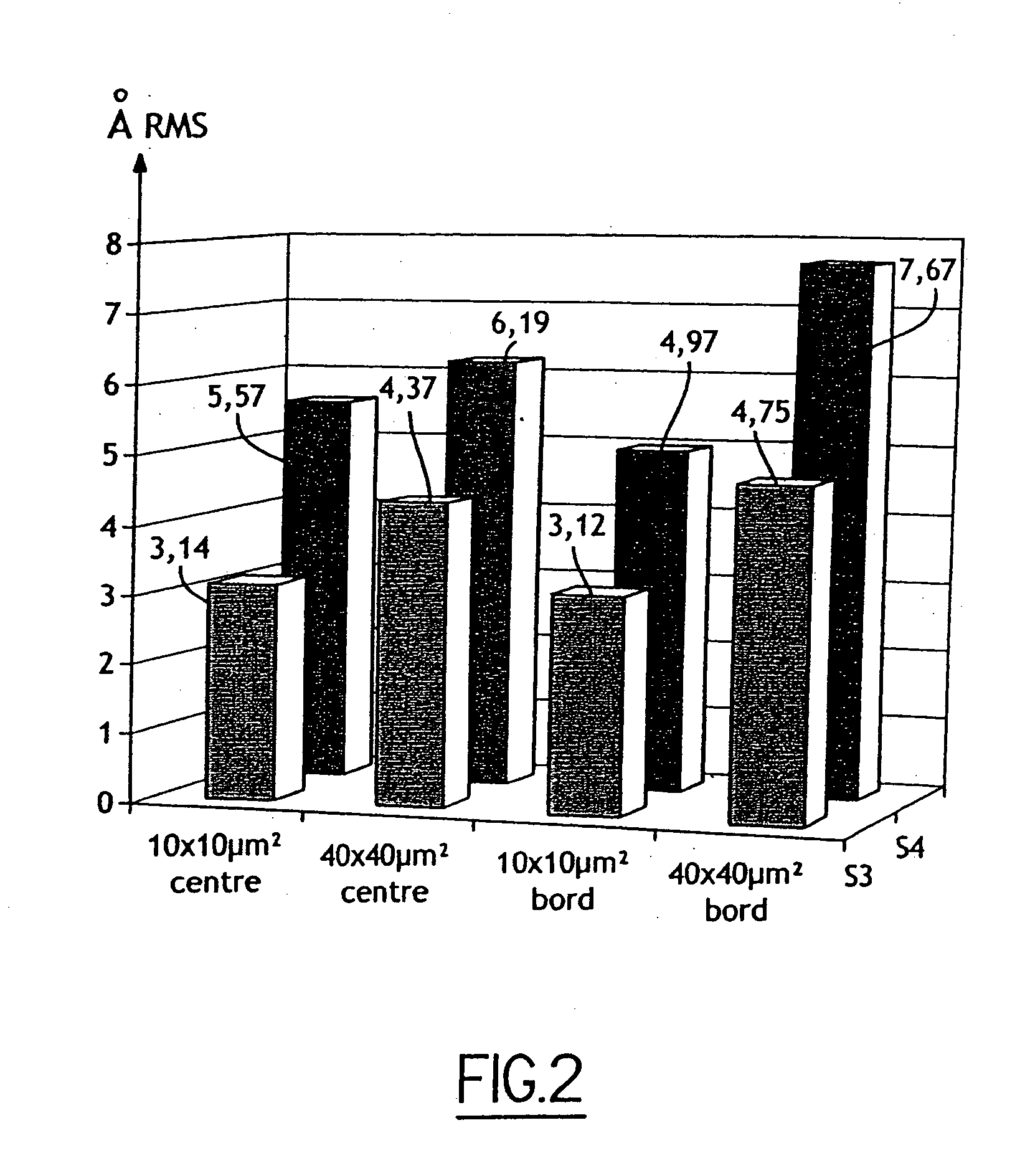

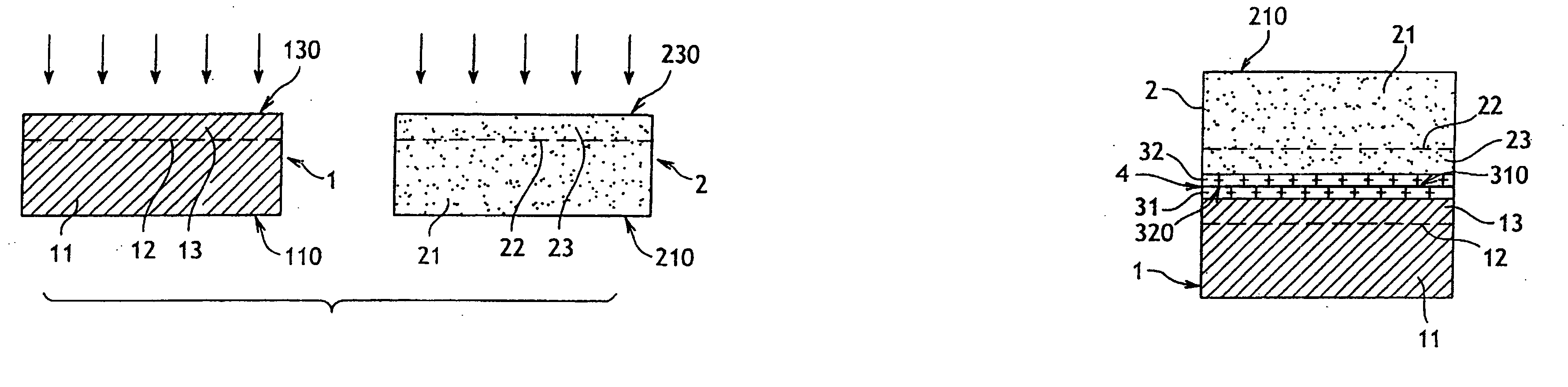

ActiveUS20050026426A1Minimize low-frequency roughnessSufficient smoothnessSemiconductor/solid-state device manufacturingSemiconductor materialsAtomic species

A method for producing a high quality useful layer of semiconductor material on a substrate. The method includes implanting at least two different atomic species into a face of a donor substrate to a controlled mean implantation depth to form a weakened zone therein and to define a useful layer. The implanting step is conducted to minimize low-frequency roughness at the weakened zone. Next, the method includes bonding a support substrate to the face of the donor substrate, and detaching the useful layer from the donor substrate along the weakened zone. A structure is thus formed that includes the useful layer on the support substrate with the useful layer presenting a surface for further processing. The technique also includes thermally treating the structure to minimize high-frequency roughness of the surface of the useful layer. The result is a surface having sufficient smoothness so that chemical mechanical polishing (CMP) is not needed.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

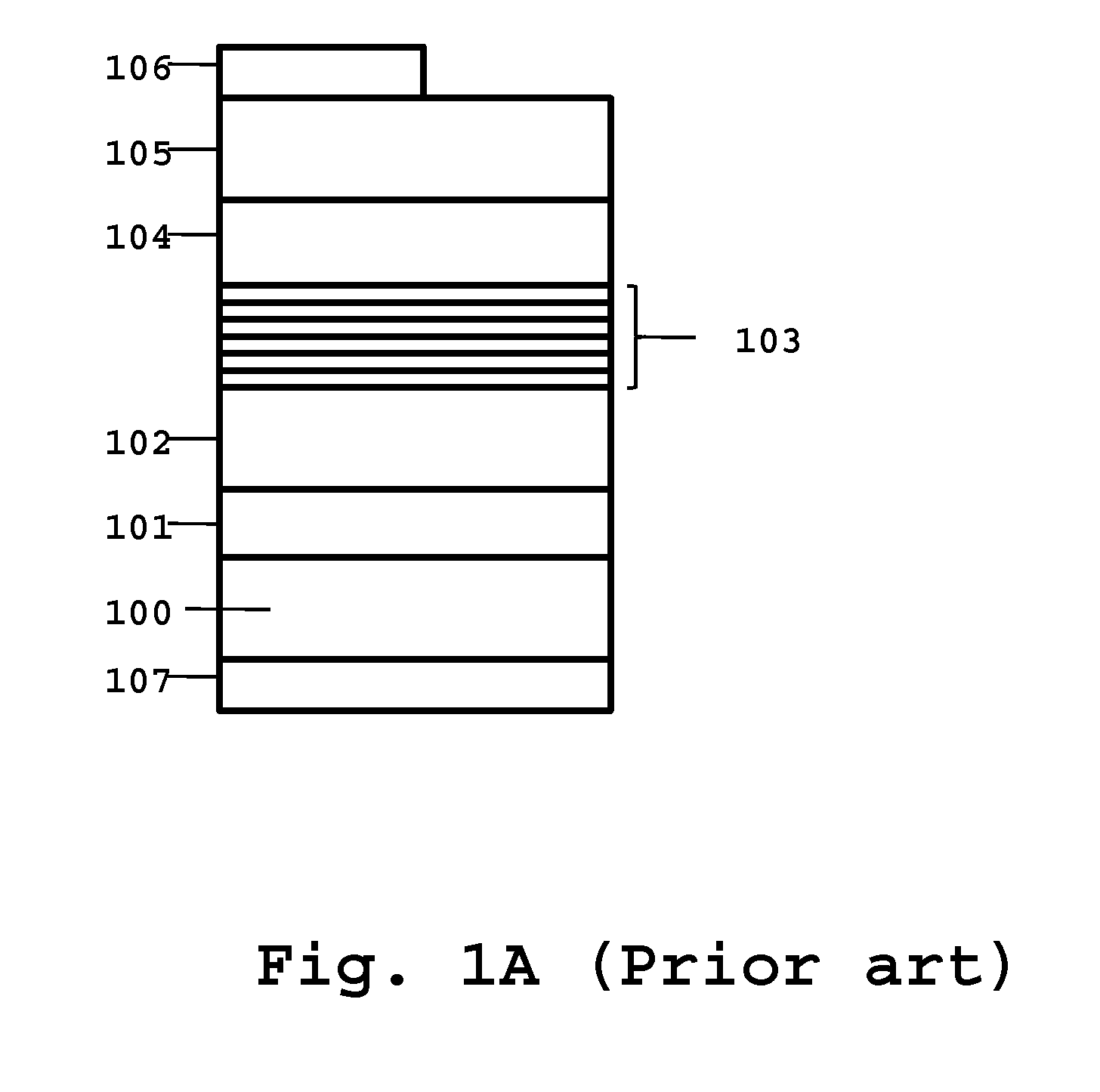

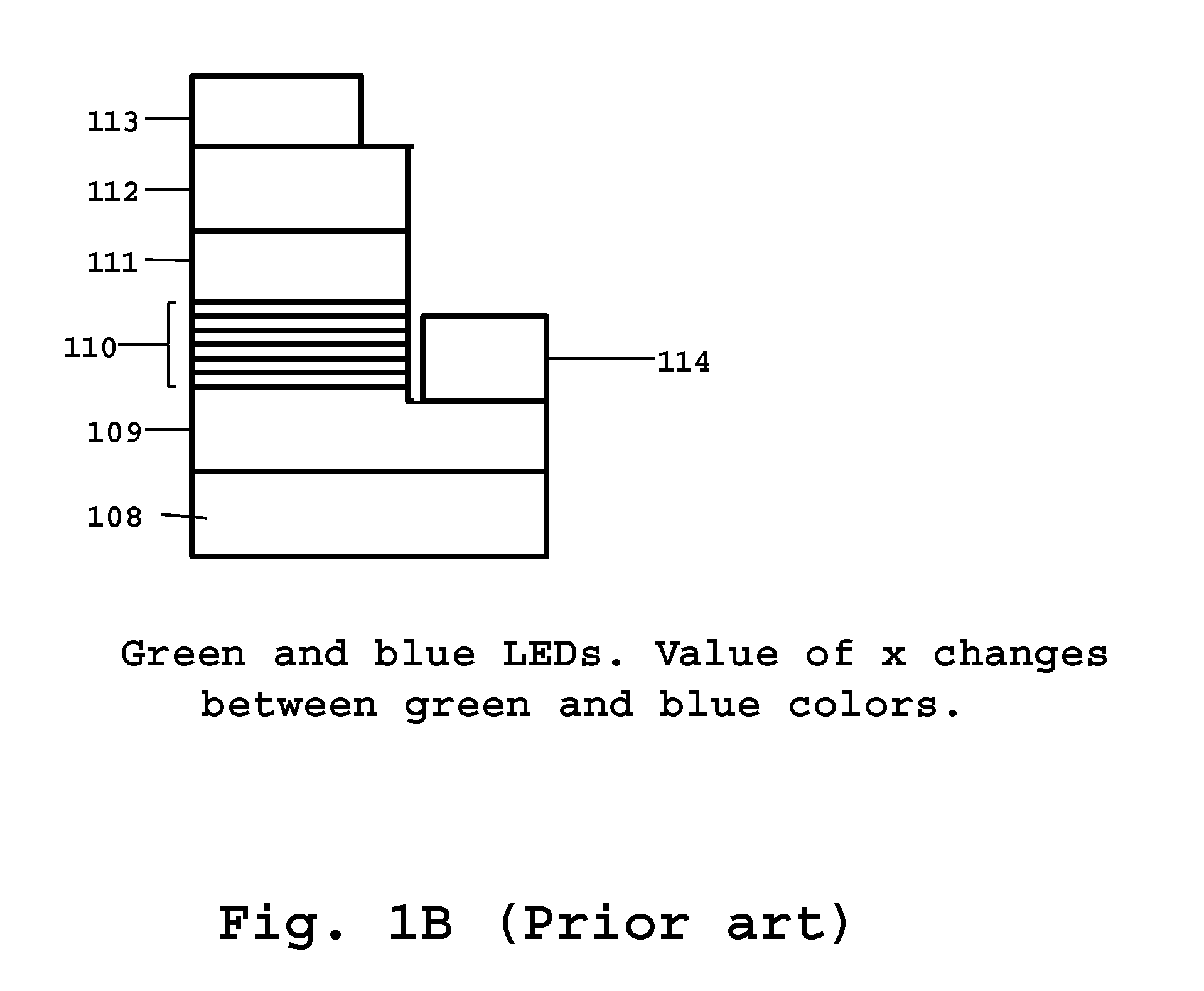

Method of fabricating an epitaxially grown layer

ActiveUS20060118513A1Easy to separatePolycrystalline material growthLight-sensitive devicesAtomic speciesBiology

A method of forming an epitaxially grown layer by providing a support substrate that includes a region of weakness therein to define a support portion and a remainder portion on opposite sides of the region of weakness. The region of weakness comprises atomic species implanted in the support substrate to facilitate detachment of the support portion from the remainder portion. The method also includes epitaxially growing an epitaxially grown layer in association with the support portion.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

Methods for fabricating a substrate

InactiveUS7235462B2Simple methodOvercome difficultiesPolycrystalline material growthSemiconductor/solid-state device manufacturingComposite substrateEngineering

A method is provided for fabricating a substrate for optics, electronics, or opto-electronics. This method includes the steps of implanting atomic species into a face of a source substrate to form a weakened zone therein corresponding to the depth of penetration of the atomic species; transferring the seed layer on to a support substrate by bonding a face of the support substrate to the face of the source substrate and detaching the seed layer from the source substrate; depositing a working layer on the seed layer to form a composite substrate comprising the support substrate, seed layer and working layer; and detaching the seed layer and the working layer from the support substrate to form a substrate. Advantageously, the support substrate comprises a material having a thermal expansion value of about 0.7 to 3 times the coefficient value of the working layer, and the seed layer includes a crystal lattice parameter sufficient for the epitaxial growth of the working layer onto the seed layer such that the working layer has a dislocation concentration of less than about 107 / cm2.

Owner:SOITEC SA

Method of layer transfer comprising sequential implantations of atomic species

InactiveUS20060063353A1Limited blister formationReduce surface roughnessSemiconductor/solid-state device manufacturingOptoelectronicsAtomic species

A method of manufacturing a crystalline wafer that includes implanting first atomic species in a donor substrate to form a region of weakness at a first depth therein and configured to facilitate detachment of a first layer of the donor substrate from a remaining portion of the donor substrate. The first layer and remaining portion are disposed on opposite sides of the region of weakness. The method also includes implanting second atomic species in the donor substrate to form a gettering region at a second depth therein that is different than the first depth to reduce or minimize migration of the implanted first atomic species past the gettering region. This reduces or minimizes an increase in roughness of a surface produced on the first layer after detachment thereof from the remaining portion at the region of weakness.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

Methods for forming a semiconductor structure

ActiveUS20050196937A1High strengthMinimize surface roughnessSemiconductor/solid-state device manufacturingElectrical conductorSemiconductor structure

Methods for forming a semiconductor structure are described. In an embodiment, the technique includes providing a donor wafer having a first semiconductor layer and a second semiconductor layer on the first layer and having a free surface, implanting atomic species through the free surface of the second layer to form a zone of weakness zone in the first layer, and bonding the free surface of the second layer to a host wafer. The method also includes supplying energy to detach at the zone of weakness a semiconductor structure comprising the host wafer, the second layer and a portion of the first layer, conducting a bond strengthening step on the structure after detachment at a temperature of less than about 800° C. to improve the strength of the bond between the second layer and the host wafer, and selectively etching the first layer portion to remove it from the structure and to expose a surface of the second layer. The implanting step includes implantation parameters chosen to minimize surface roughness resulting from detachment at the zone of weakness.

Owner:SOITEC SA

Wafer and method of producing a substrate by transfer of a layer that includes foreign species

ActiveUS7008859B2Improve uniformityImprove controllabilitySolid-state devicesSemiconductor/solid-state device manufacturingOptical propertyAtomic species

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES +1

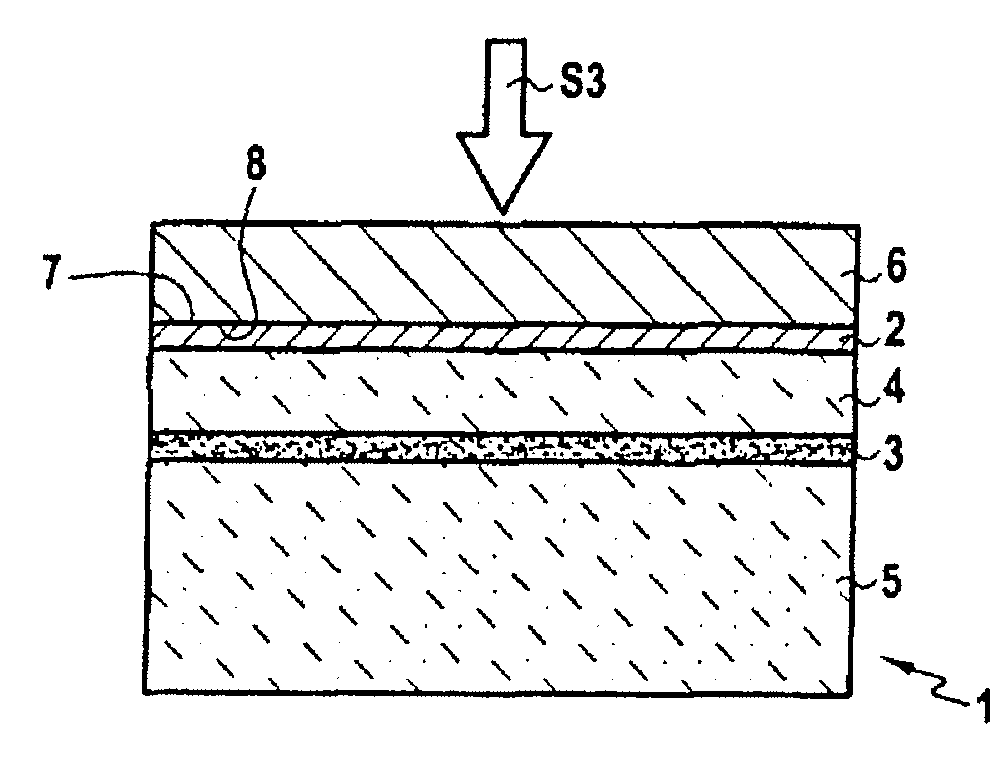

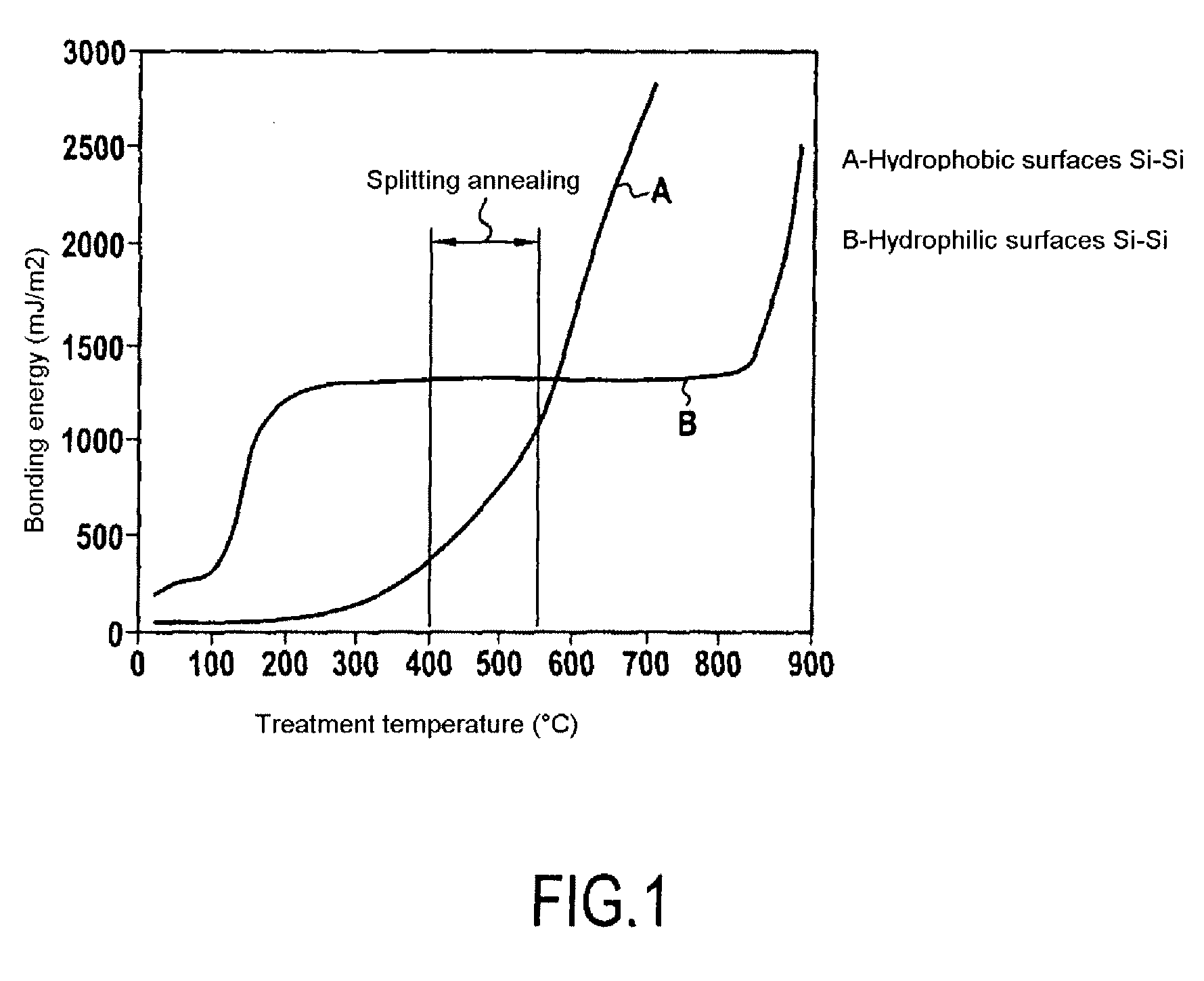

Process for high temperature layer transfer

InactiveUS20080064182A1Inhibition defectImproved bonding energySemiconductor/solid-state device manufacturingBond energyThin layer

The invention concerns a method for transferring a thin layer from a donor wafer onto a receiving wafer by implanting at least one atomic species into the donor wafer to form a weakened zone therein, with the weakened zone being including microcavities or platelets therein, and the thin layer being defined between the weakened zone and a surface of the donor wafer; molecular bonding of the surface of the donor wafer onto a surface of the receiving wafer; splitting the thin layer at the zone of weakness by heating to a high temperature to transfer the thin layer to the receiving substrate; and treating the donor wafer to block or limit the formation of microcavities or platelets by trapping the atoms of at least one of the implanted atomic species at least until a certain release temperature is reached during the splitting. This method enables bonding energy to be reinforced adjacent the layer to be transferred and hence limits defects in the resulting heterostructure.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

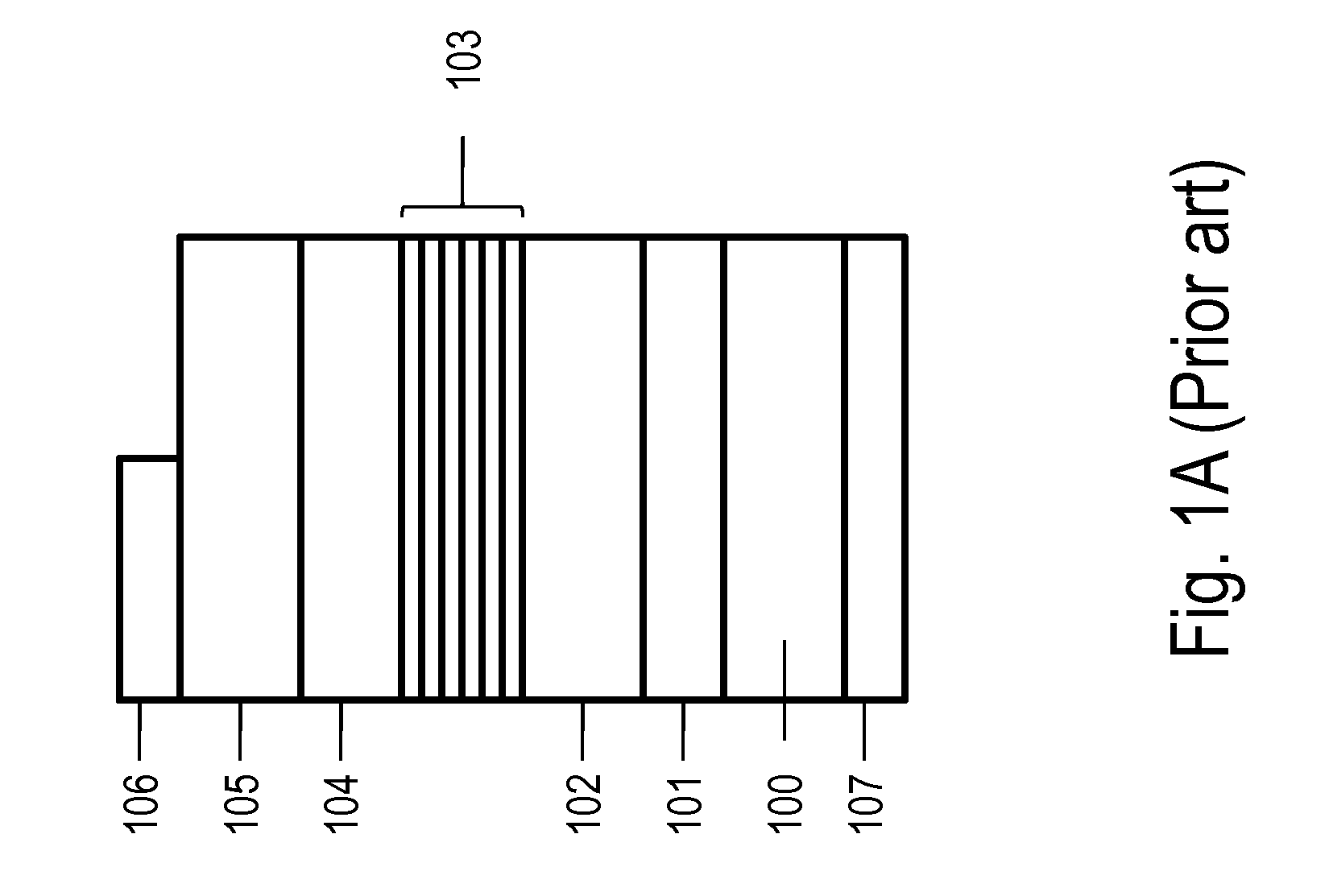

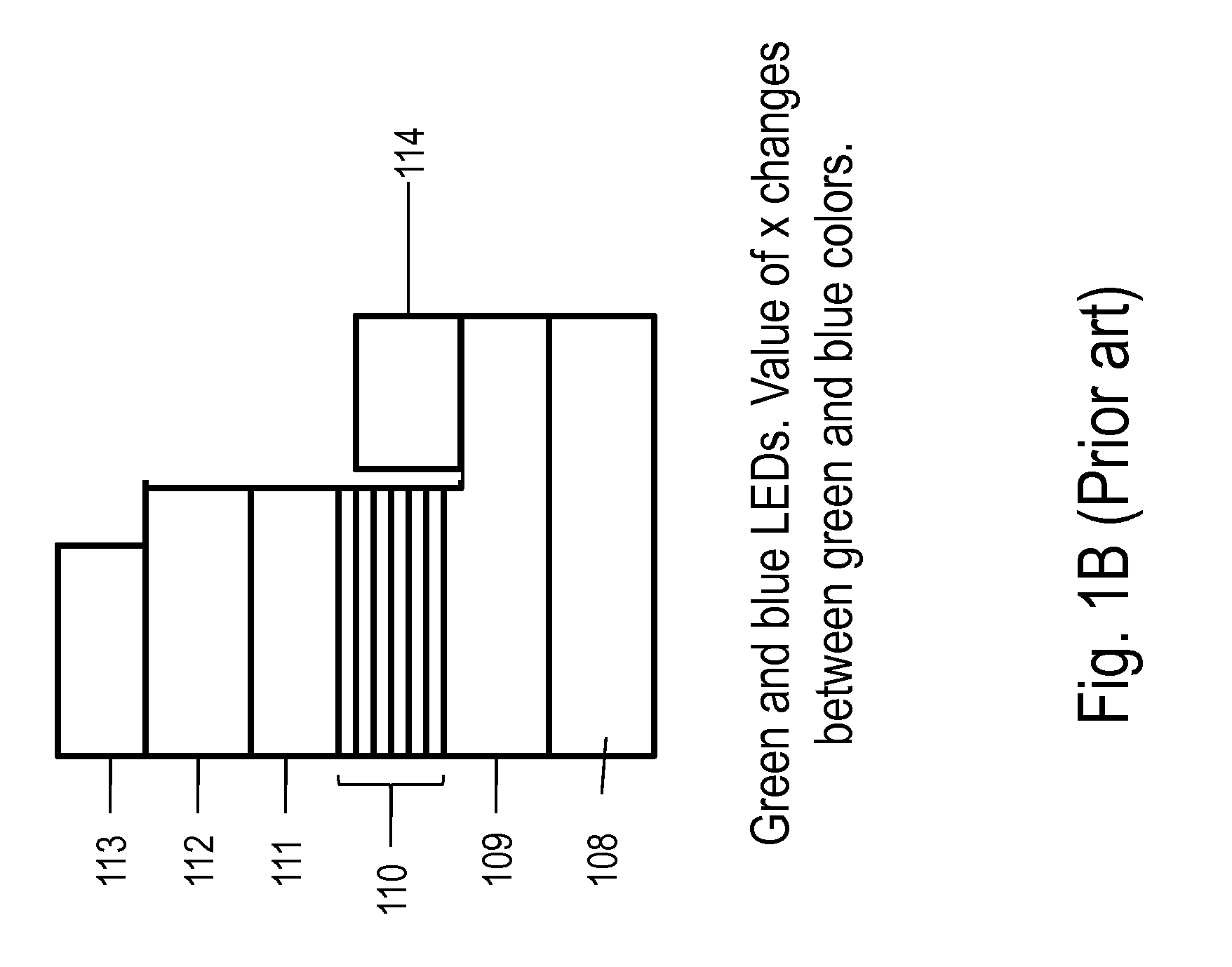

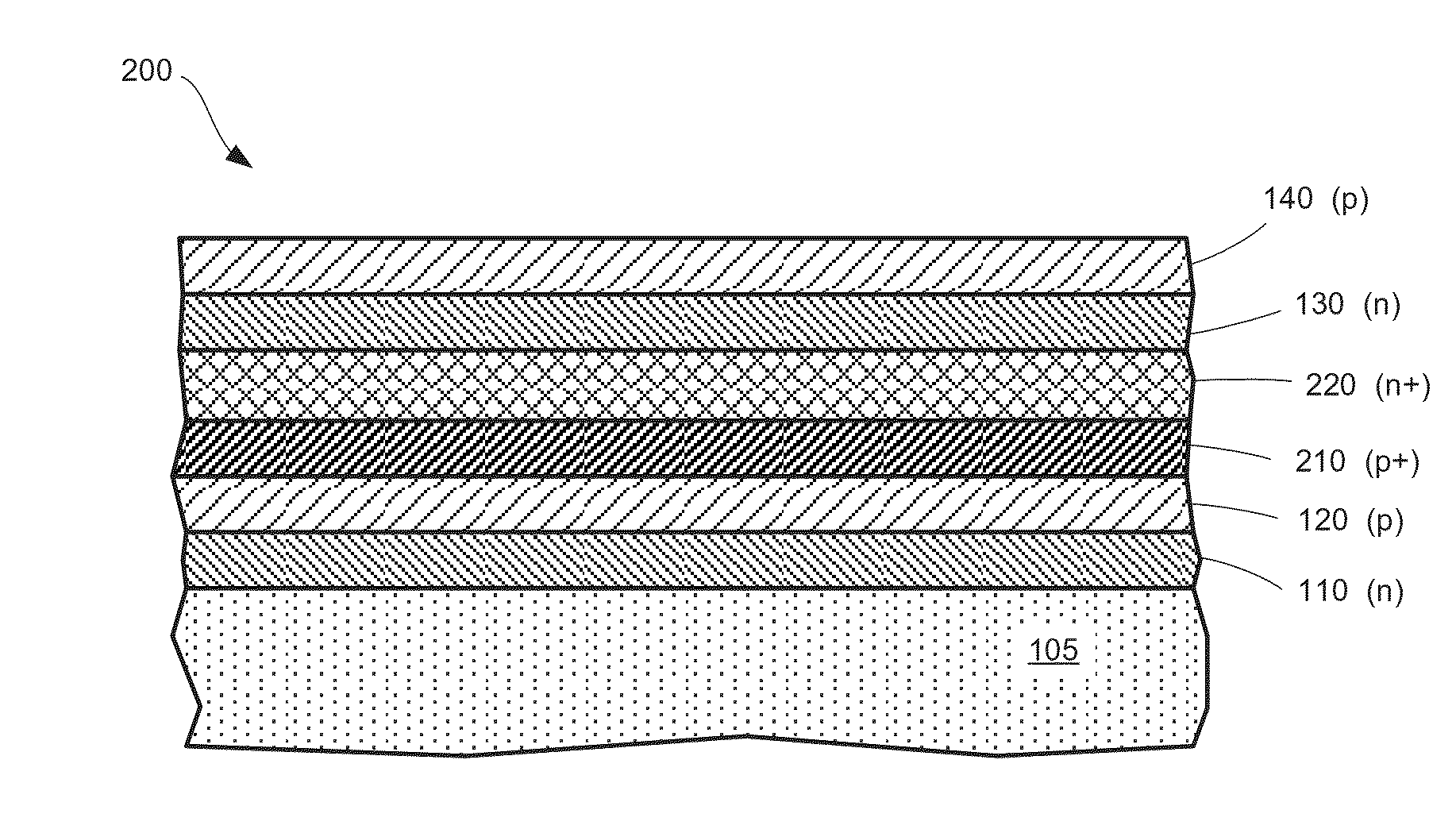

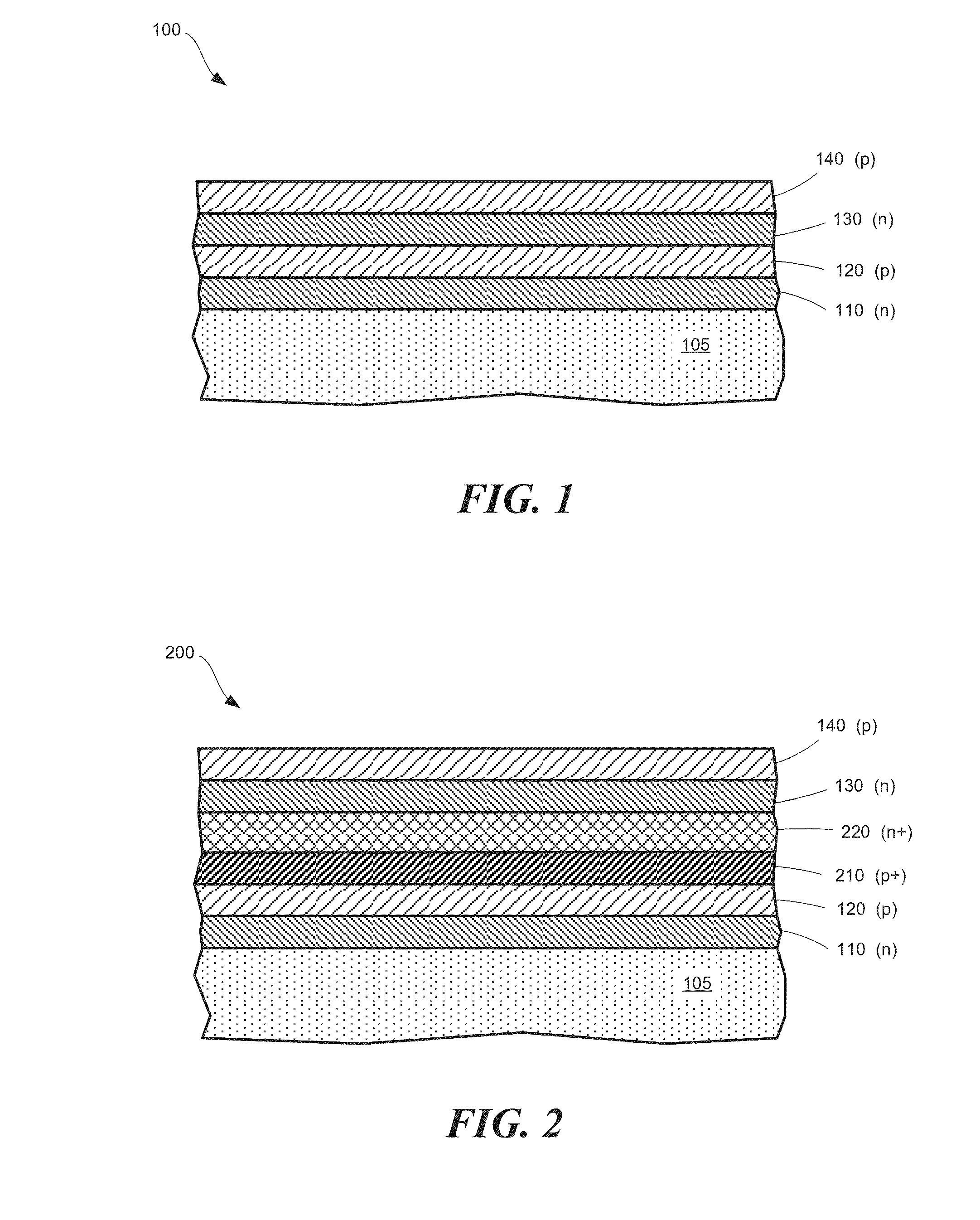

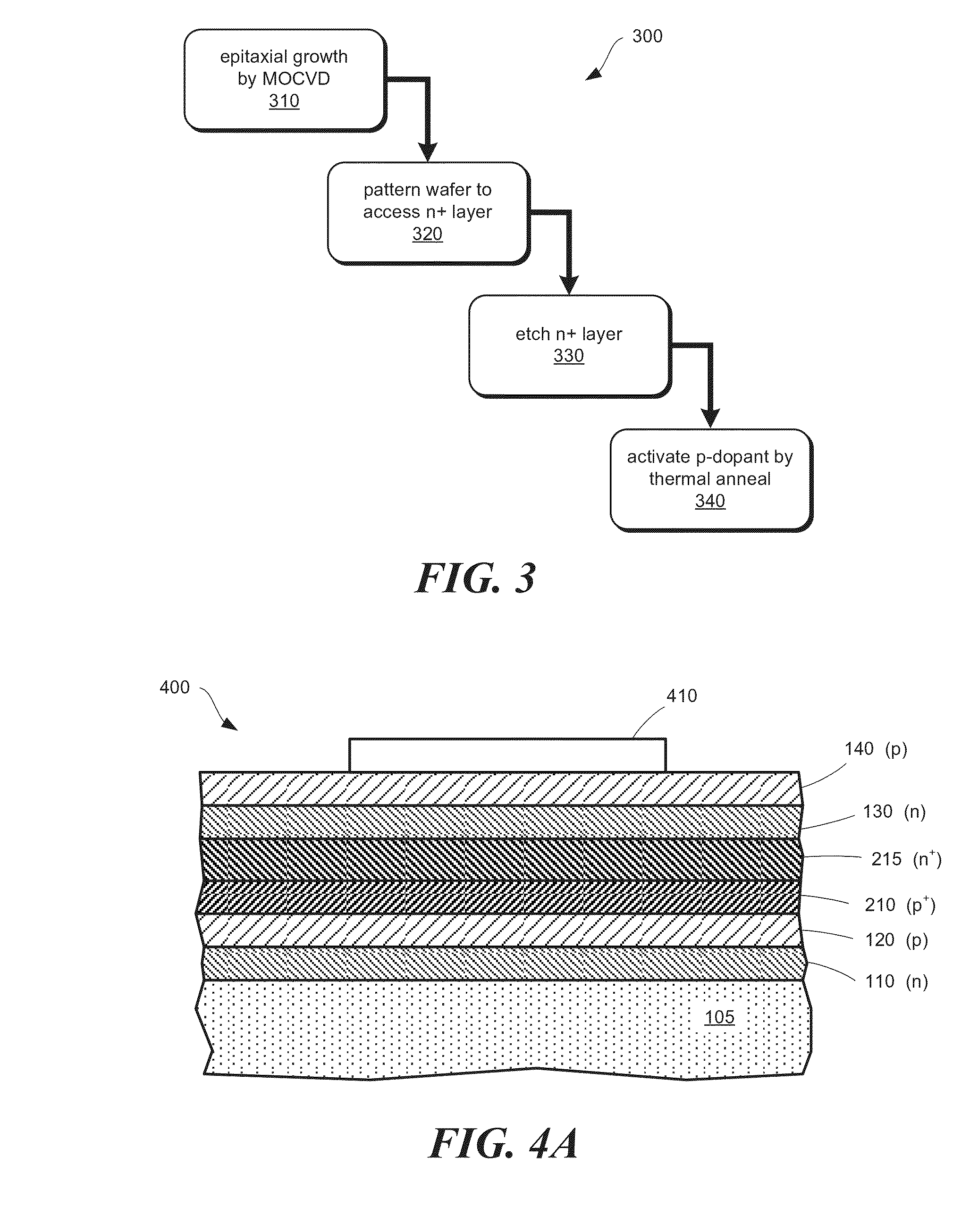

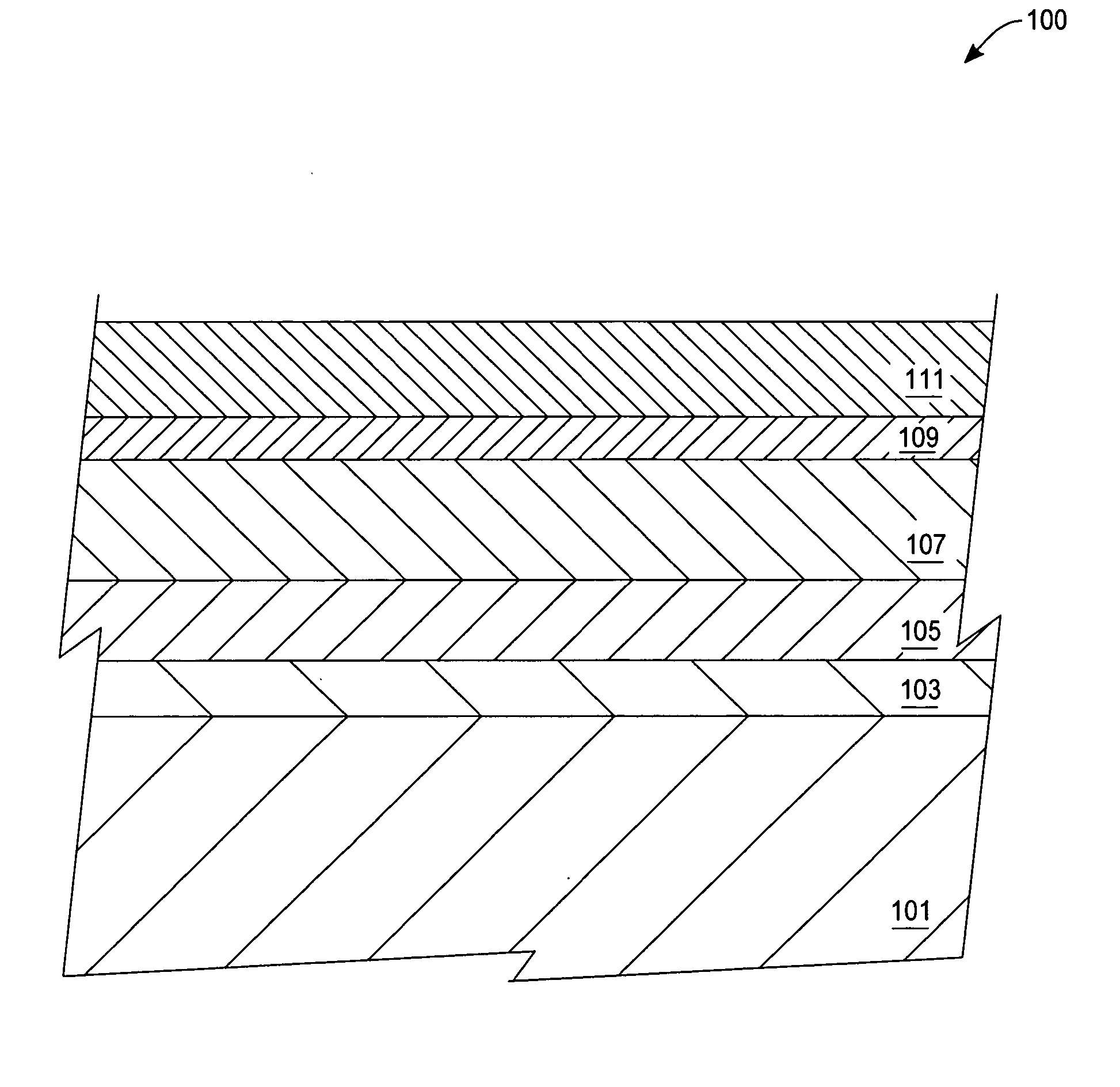

Method to make buried, highly conductive p-type iii-nitride layers

ActiveUS20160197151A1Reduce resistanceImprove conductivitySemiconductor/solid-state device manufacturingDiodeDopantPorous layer

A conductive, porous gallium-nitride layer can be formed as an active layer in a multilayer structure adjacent to one or more p-type III-nitride layers, which may be buried in a multilayer stack of an integrated device. During an annealing process, dopant-bound atomic species in the p-type layers that might otherwise neutralize the dopants may dissociate and out-diffuse from the device through the porous layer. The release and removal of the neutralizing species may reduce layer resistance and improve device performance.

Owner:YALE UNIV

Fabrication of hybrid substrate with defect trapping zone

ActiveUS7632739B2Inhibition formationReduce defect formationSemiconductor/solid-state device manufacturingSemiconductor materialsTrapping

A process for fabricating a hybrid substrate that has a defect trapping zone. The process includes the steps of forming or depositing a first insulator layer on a first substrate of semiconductor material; increasing roughness of the first insulator layer surface; depositing a second insulator layer on the roughened surface of the first insulator to form a trapping zone between the layers; bonding a second substrate onto the second insulator layer by molecular adhesion; and transferring an active layer formed by the implantation of atomic species into one of the substrates. The trapping zone is able to retain gaseous species present at the various interfaces of the hybrid substrate to limit the formation of defects on the surface of the active layer that is transferred.

Owner:SOITEC SA

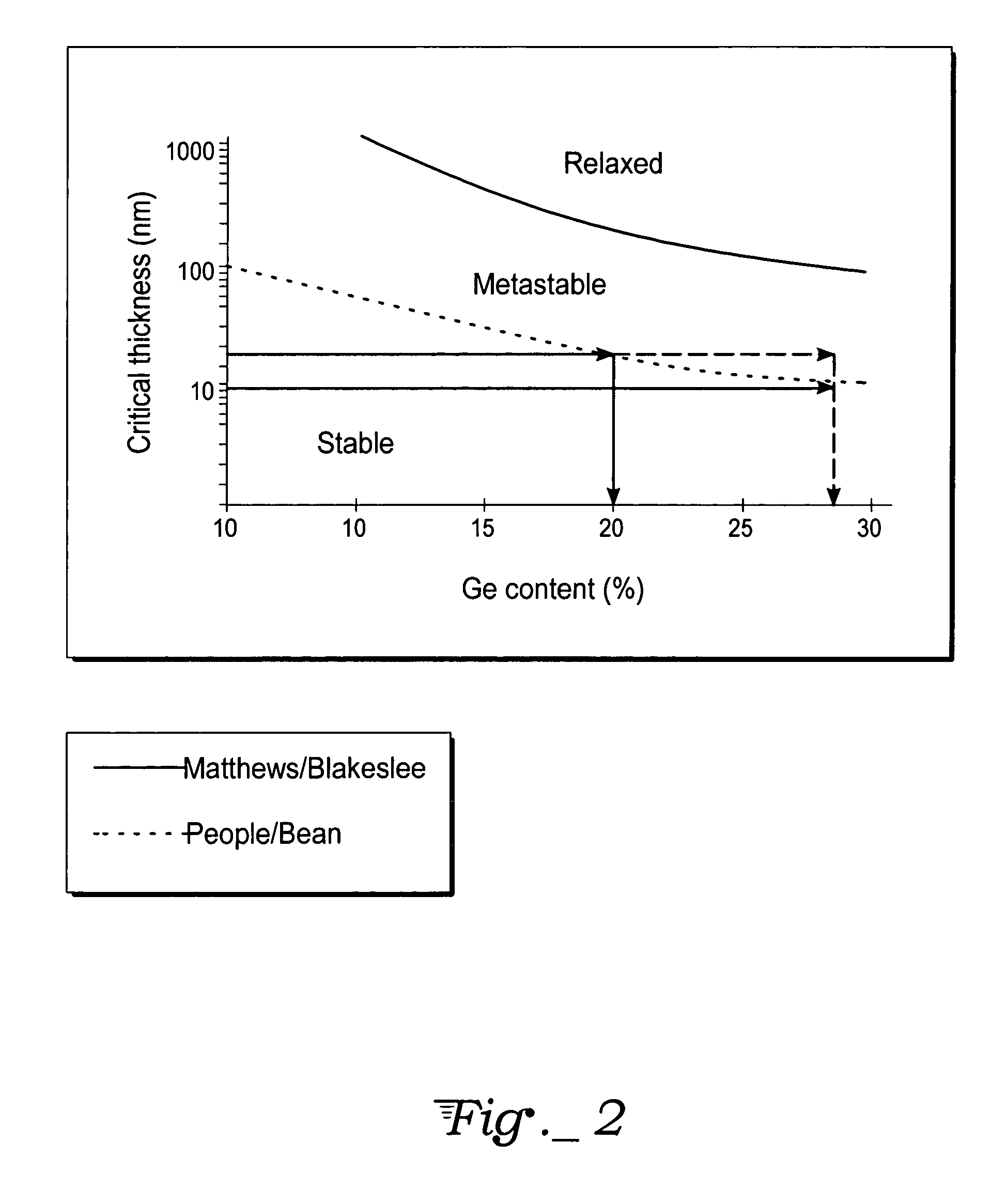

Strain-compensated metastable compound base heterojunction bipolar transistor

InactiveUS20070102834A1High densityGreat energy bandSemiconductor/solid-state device manufacturingSemiconductor devicesDevice typeDevice form

A method for pseudomorphic growth and integration of an in-situ doped, strain-compensated metastable compound base into an electronic device, such as, for example, a SiGe NPN HBT, by substitutional placement of strain-compensating atomic species. The invention also applies to strained layers in other electronic devices such as strained SiGe, Si in MOS applications, vertical thin film transistors (VTFT), and a variety of other electronic device types. Devices formed from compound semiconductors other than SiGe, such as, for example, GaAs, InP, and AlGaAs are also amenable to beneficial processes described herein.

Owner:ATMEL CORP

Treatment of a removed layer of silicon-germanium

InactiveUS20060160328A1Reduce in quantityLow costSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingSemiconductor structure

The invention relates to a method of forming a structure comprising a removed layer taken from a donor wafer, the donor wafer including a first layer formed of Si1-xGex and a second layer of Si1-yGey on the first layer, where x and y, respectively, are in the range of 0 to 1, with x being different from y. The method includes the steps of providing a donor wafer that includes a first layer of Si1-xGex and a second layer of Si1-yGey located on the first layer, with x and y respectively, being in the range of 0 to 1, and x being different than y; implanting atomic species into the donor wafer to form a zone of weakness in the first layer; bonding the donor wafer to a receiver wafer; detaching the second layer and a portion of the first layer from the donor wafer by supplying energy to bonded wafers sufficient to cause cleavage at the zone of weakness to form an intermediate structure thereof; conducting a rapid thermal anneal of the intermediate structure at a temperature of about 1000° C. or more for a period of time not exceeding 5 minutes; and removing any remaining portions of the first layer of the intermediate structure to provide a semiconductor structure comprising the second layer on the receiving wafer. Preferably, the remaining portions of the first layer are removed from the intermediate structure by selective etching.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

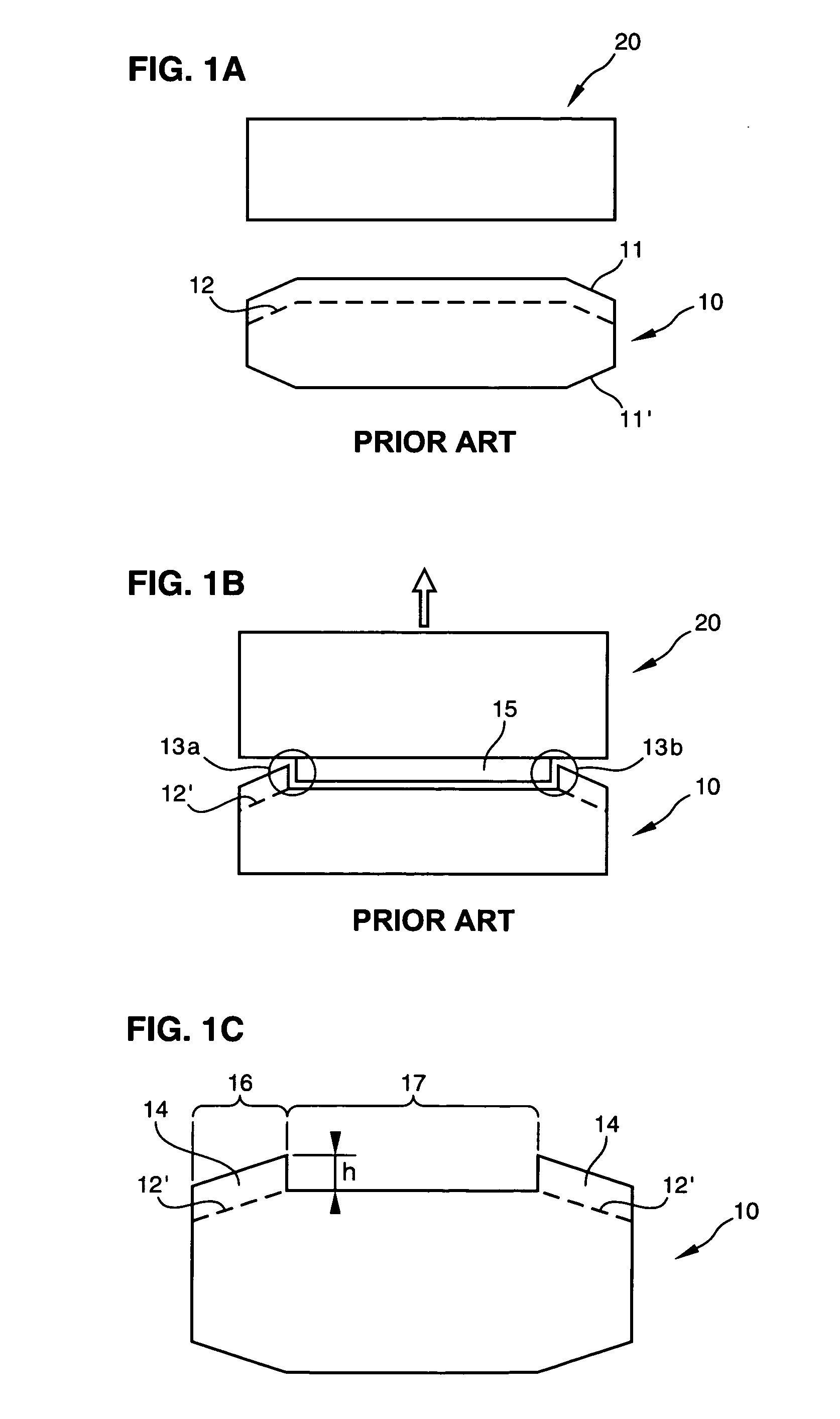

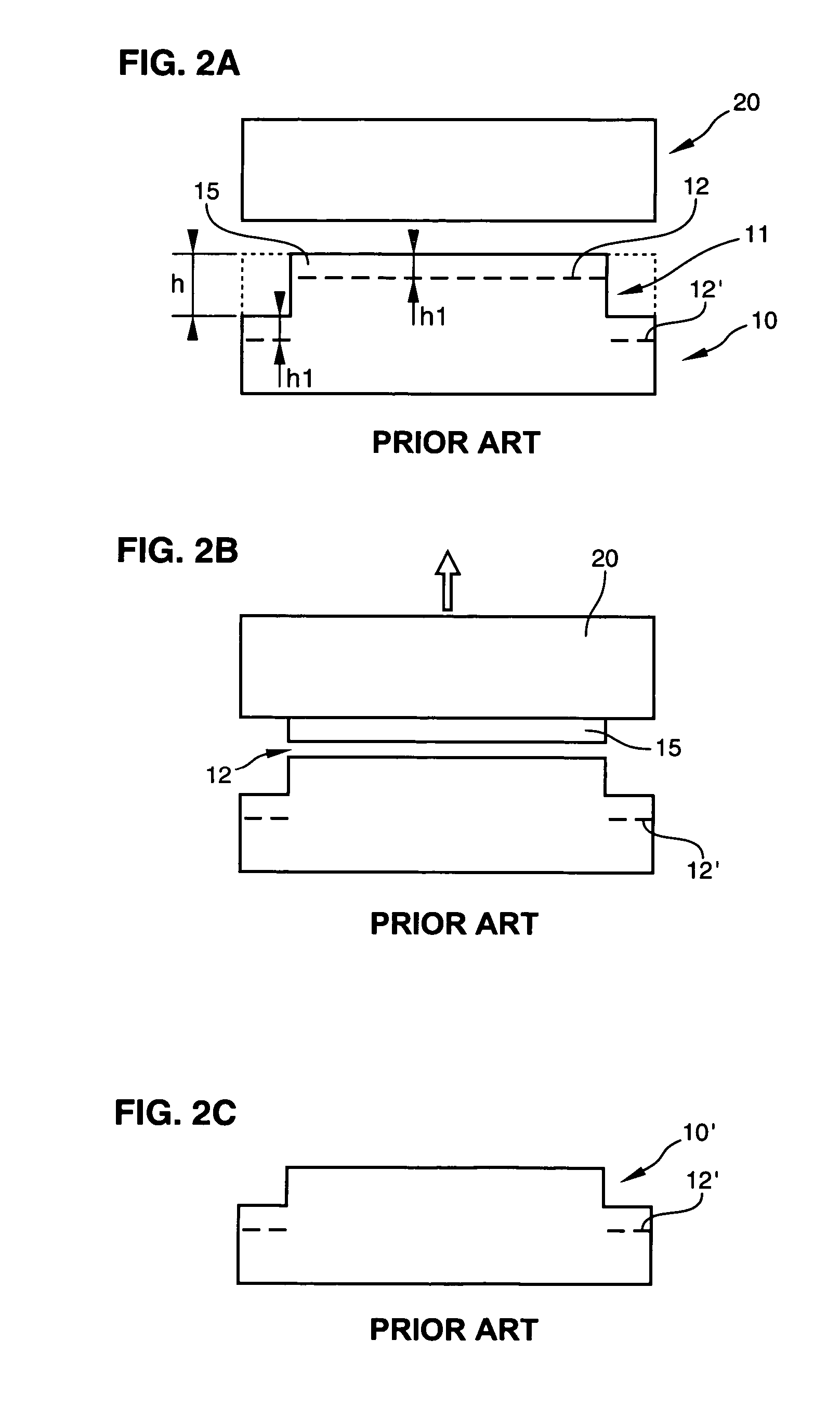

Film taking-off method

ActiveUS20070023867A1Improve crystal qualityRegular borderSemiconductor/solid-state device detailsSolid-state devicesAtomic speciesElectron

The invention relates to a method of producing a film intended for applications in electronics, optics or optronics starting from an initial wafer, which includes a step of implanting atomic species through one of the faces of the wafer. This method includes forming a step of defined height around the periphery of the wafer, with the step having a mean thickness that is less than that of the wafer; and selectively implanting atomic species through a face of the wafer but not through the step to form an implanted zone at a defined implant depth with the film being defined between the face of the wafer and the implanted zone. The implantation of atomic species into the step can be prevented by forming a protective layer at least over the step or by masking the step. The invention also relates to a wafer obtainable by the method.

Owner:SOITEC SA

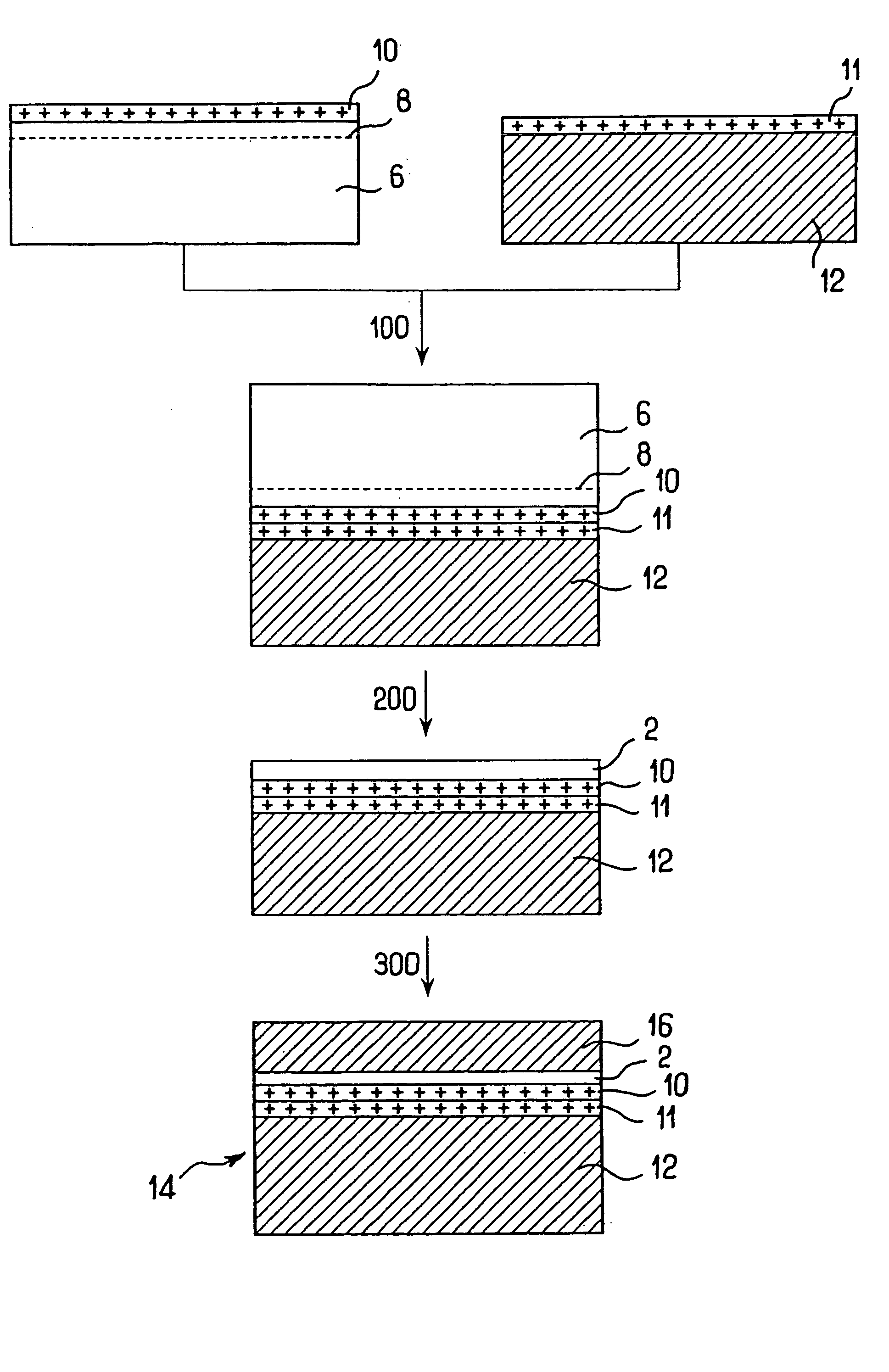

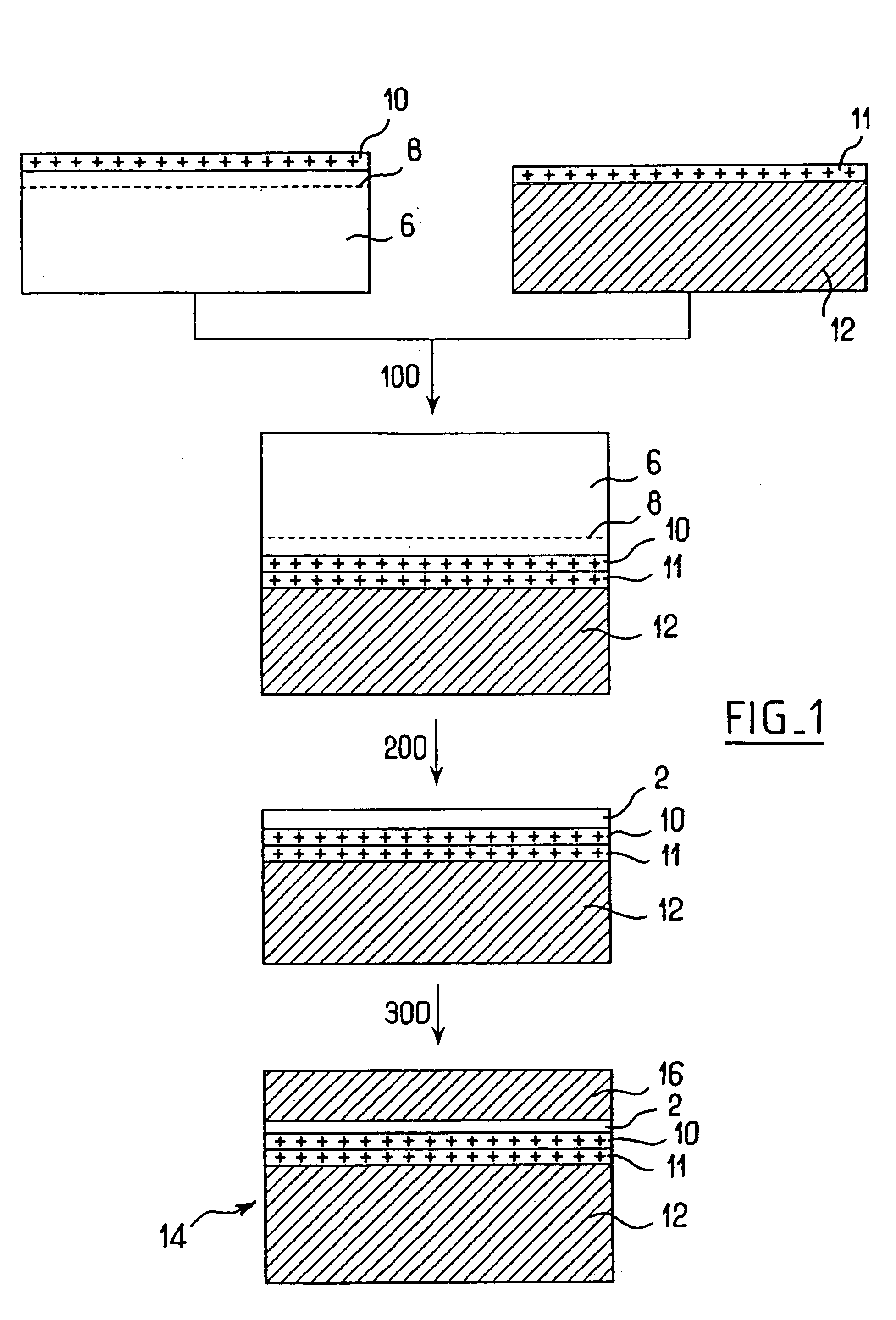

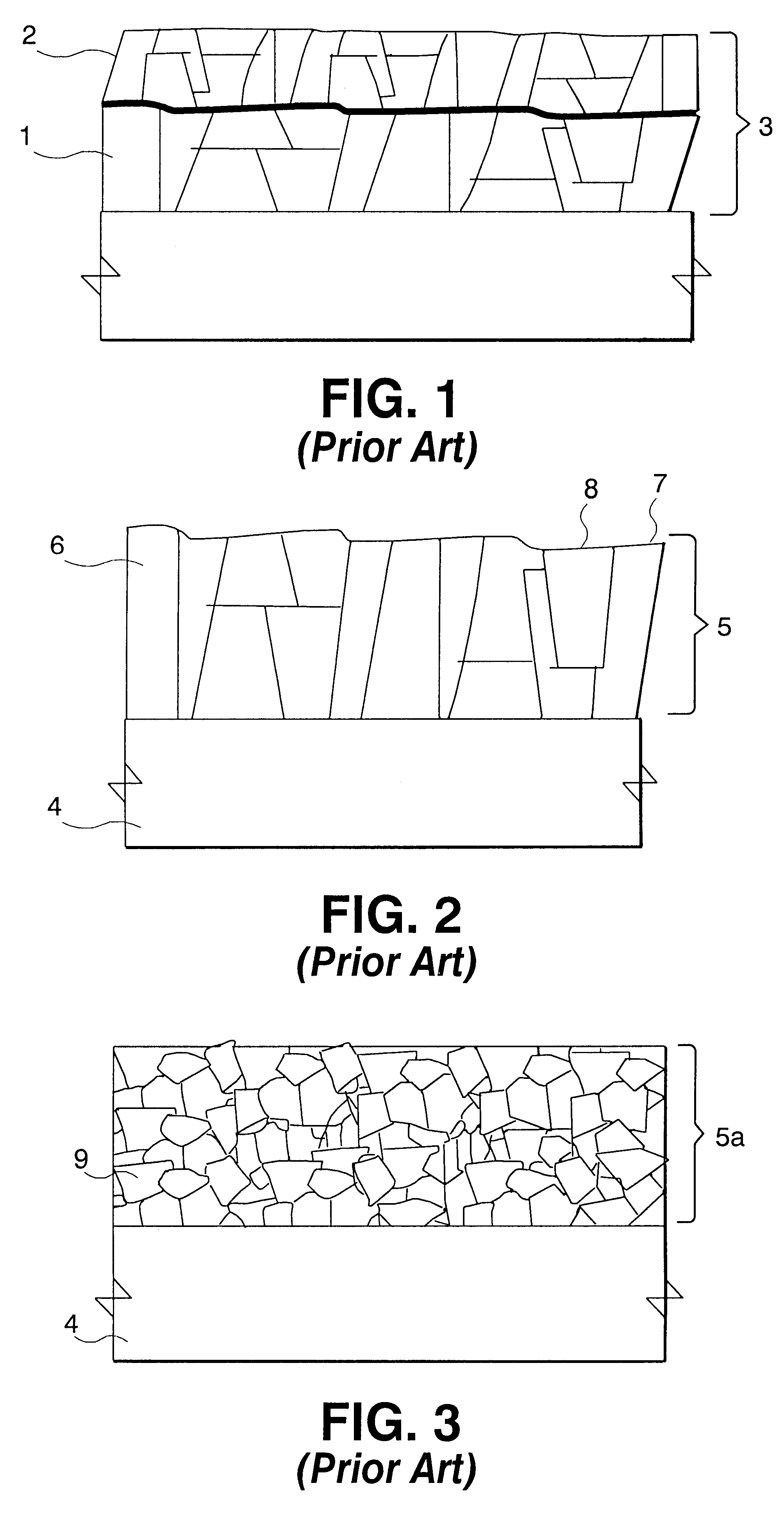

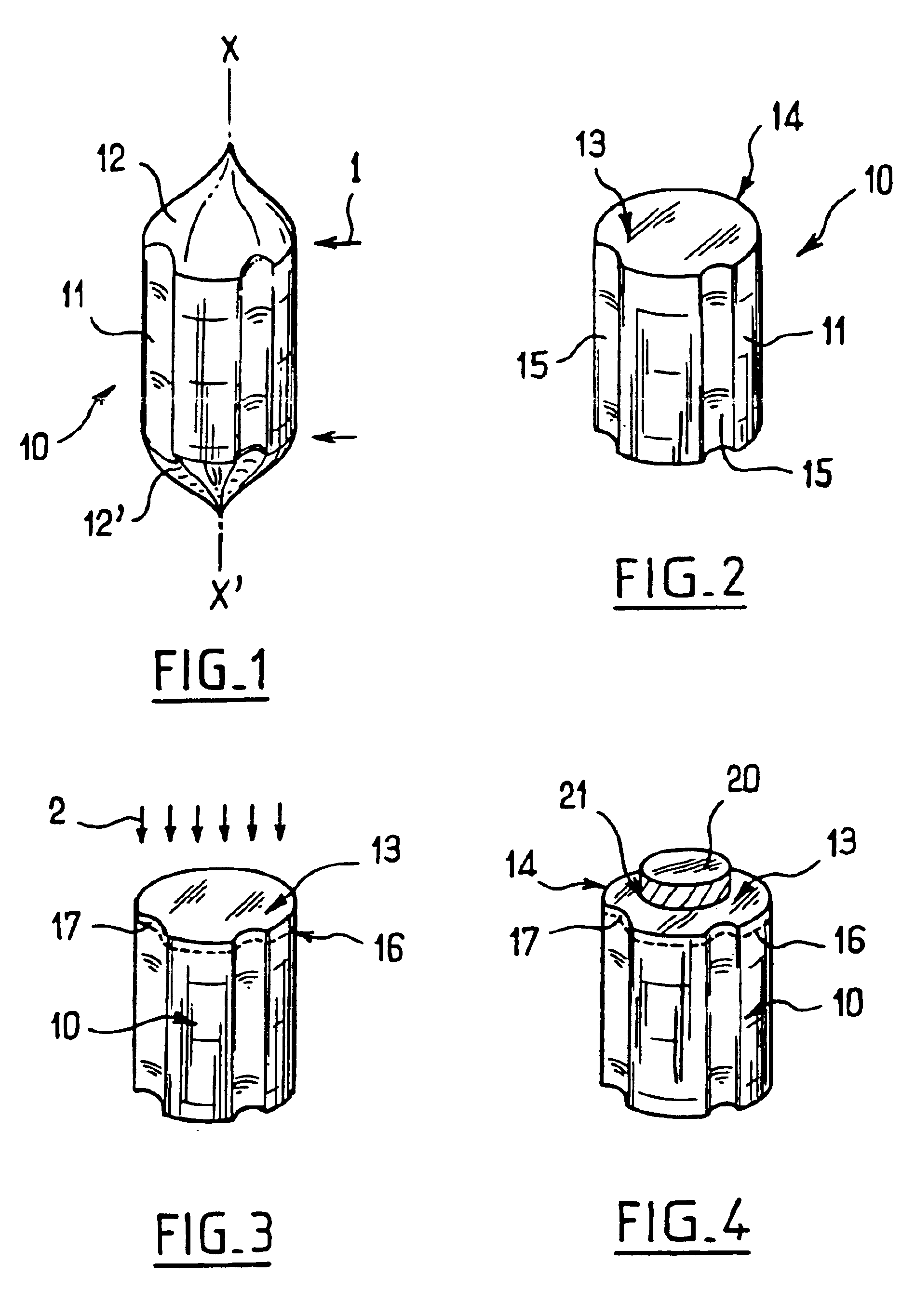

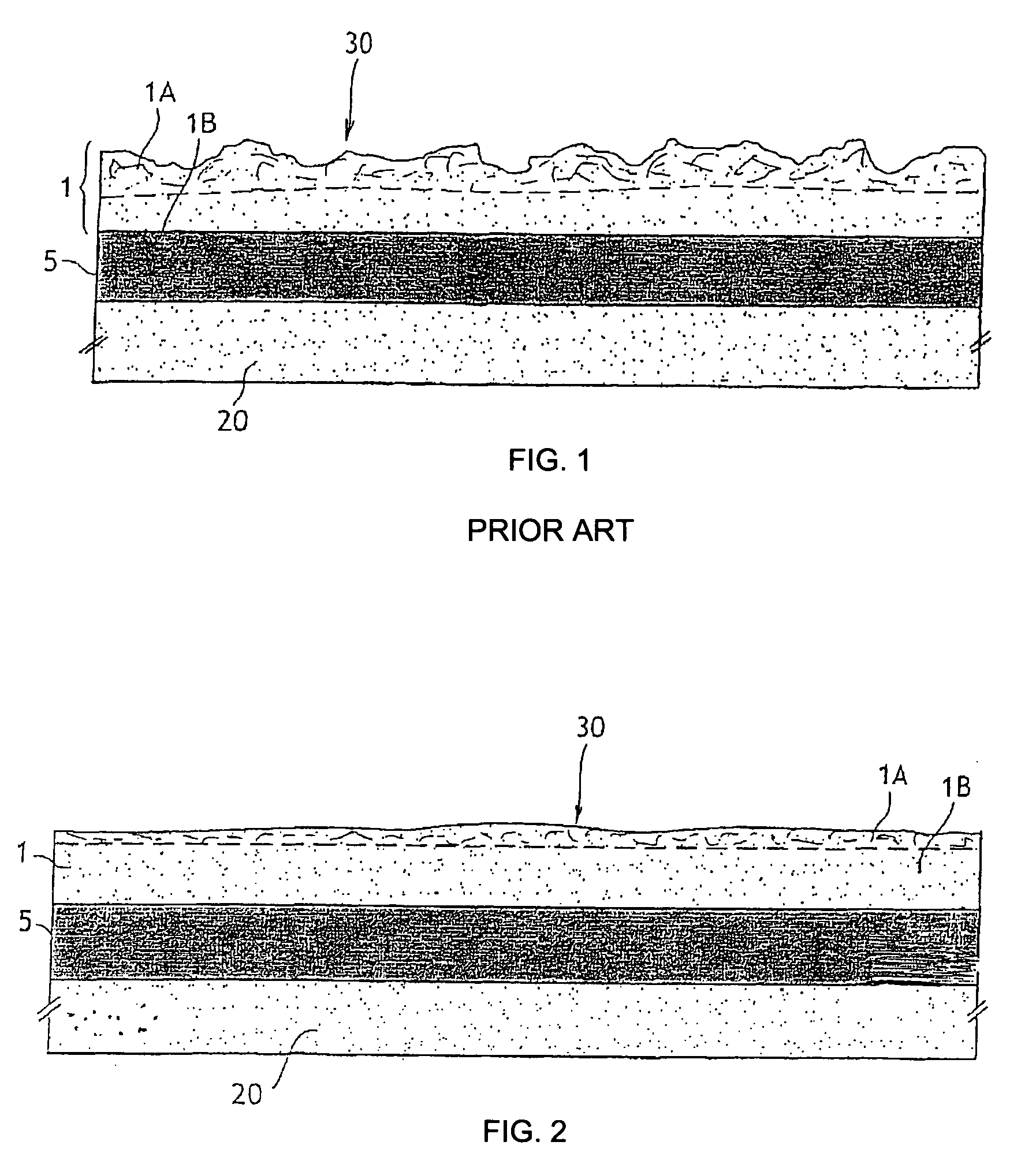

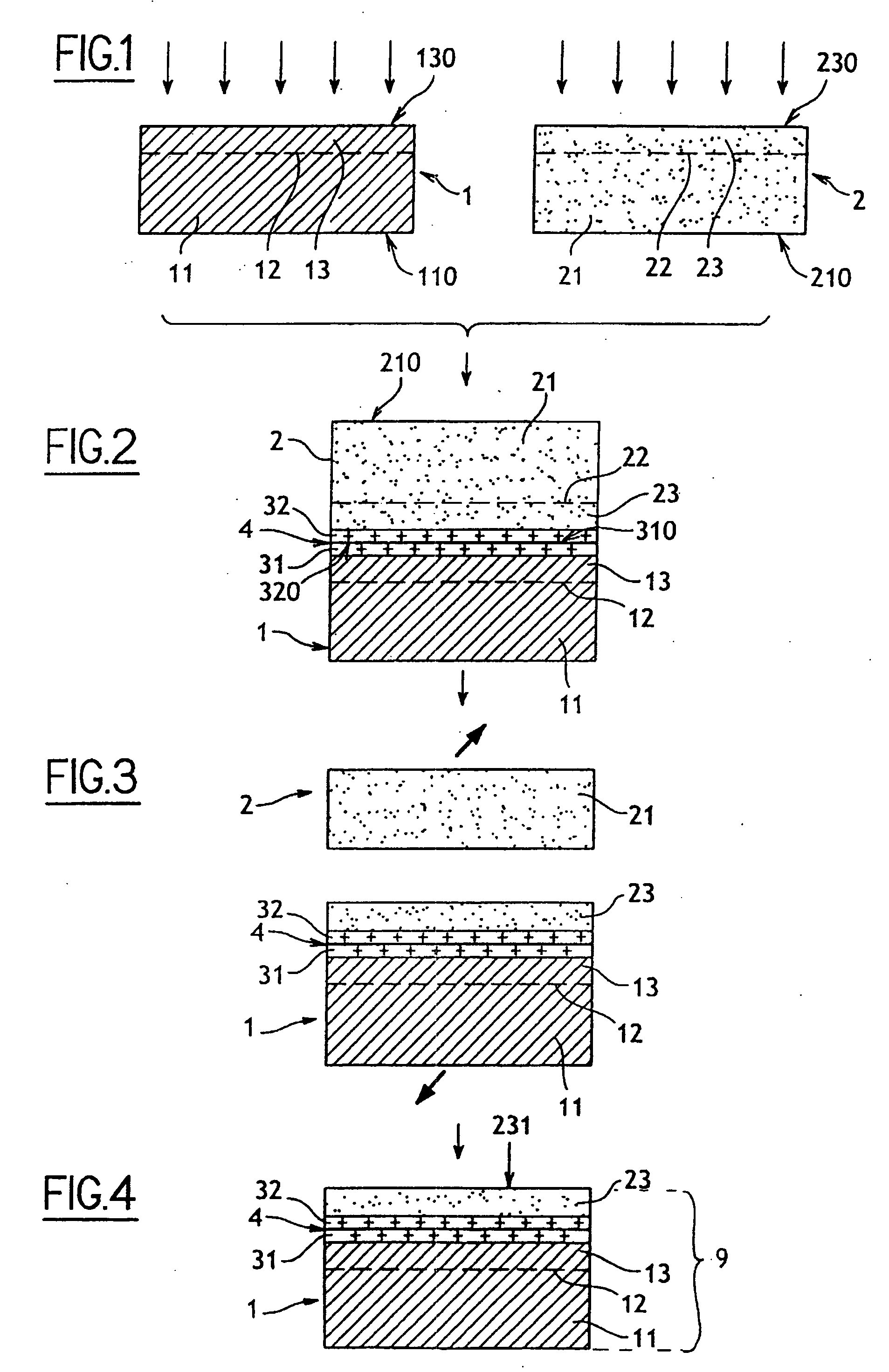

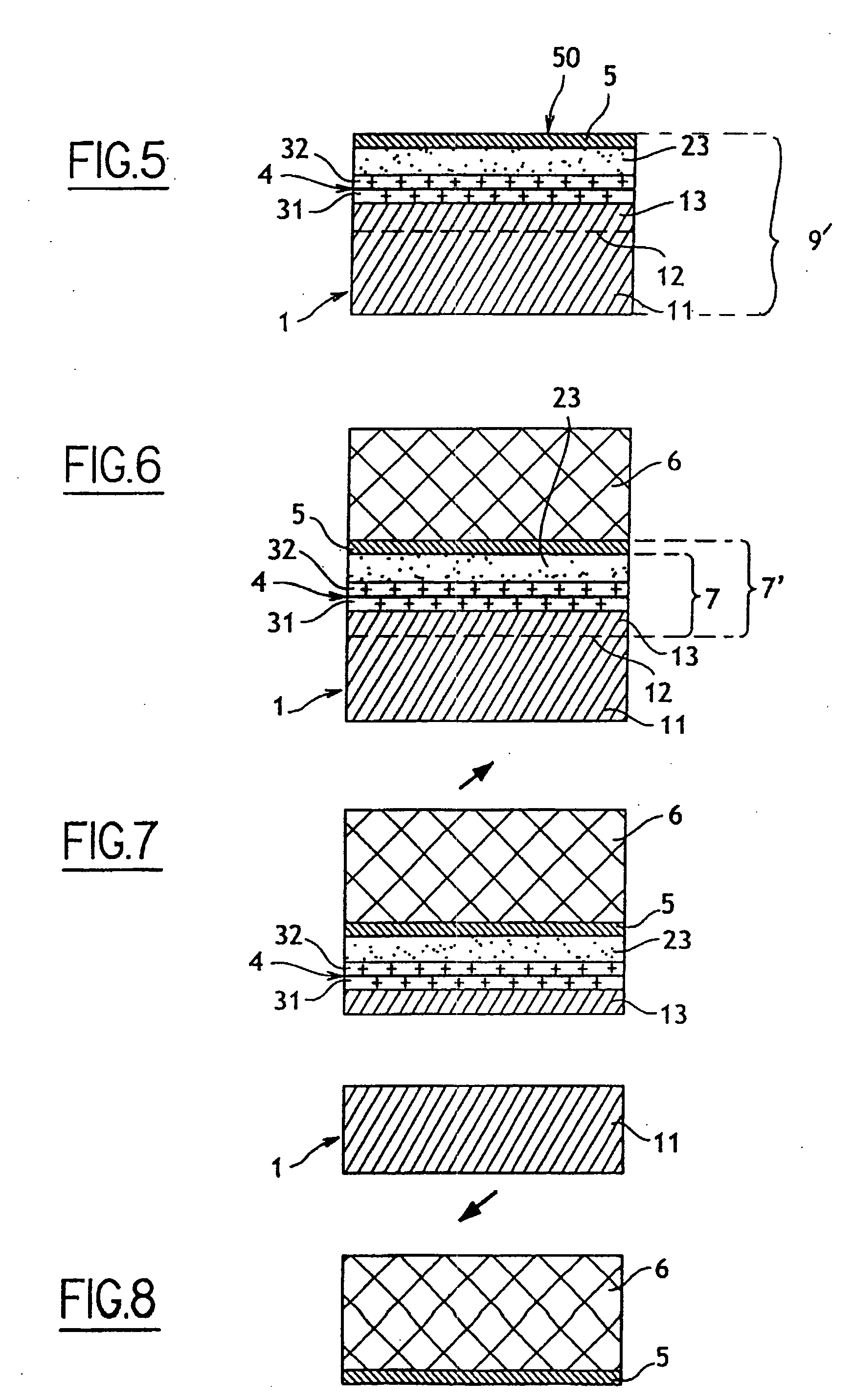

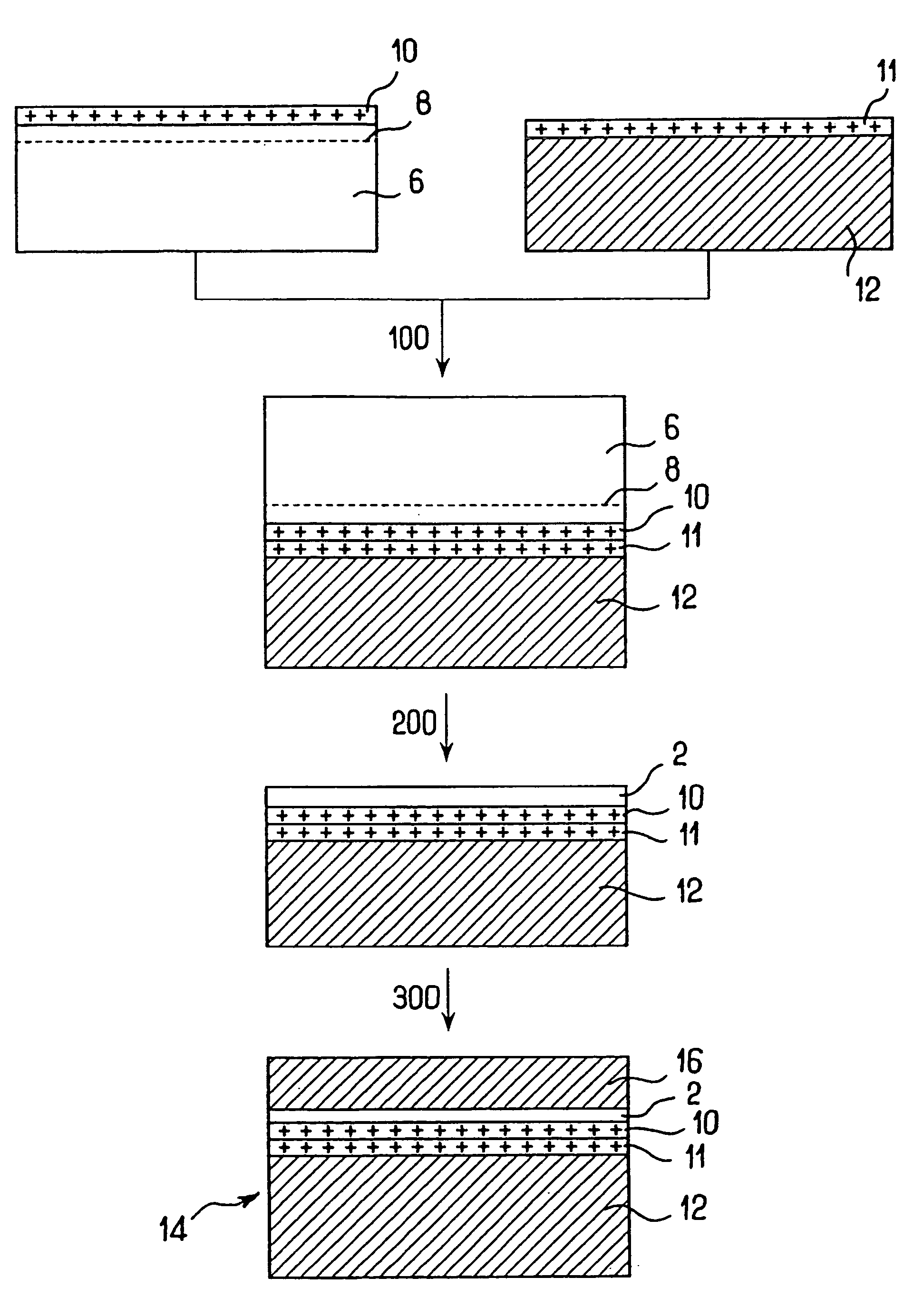

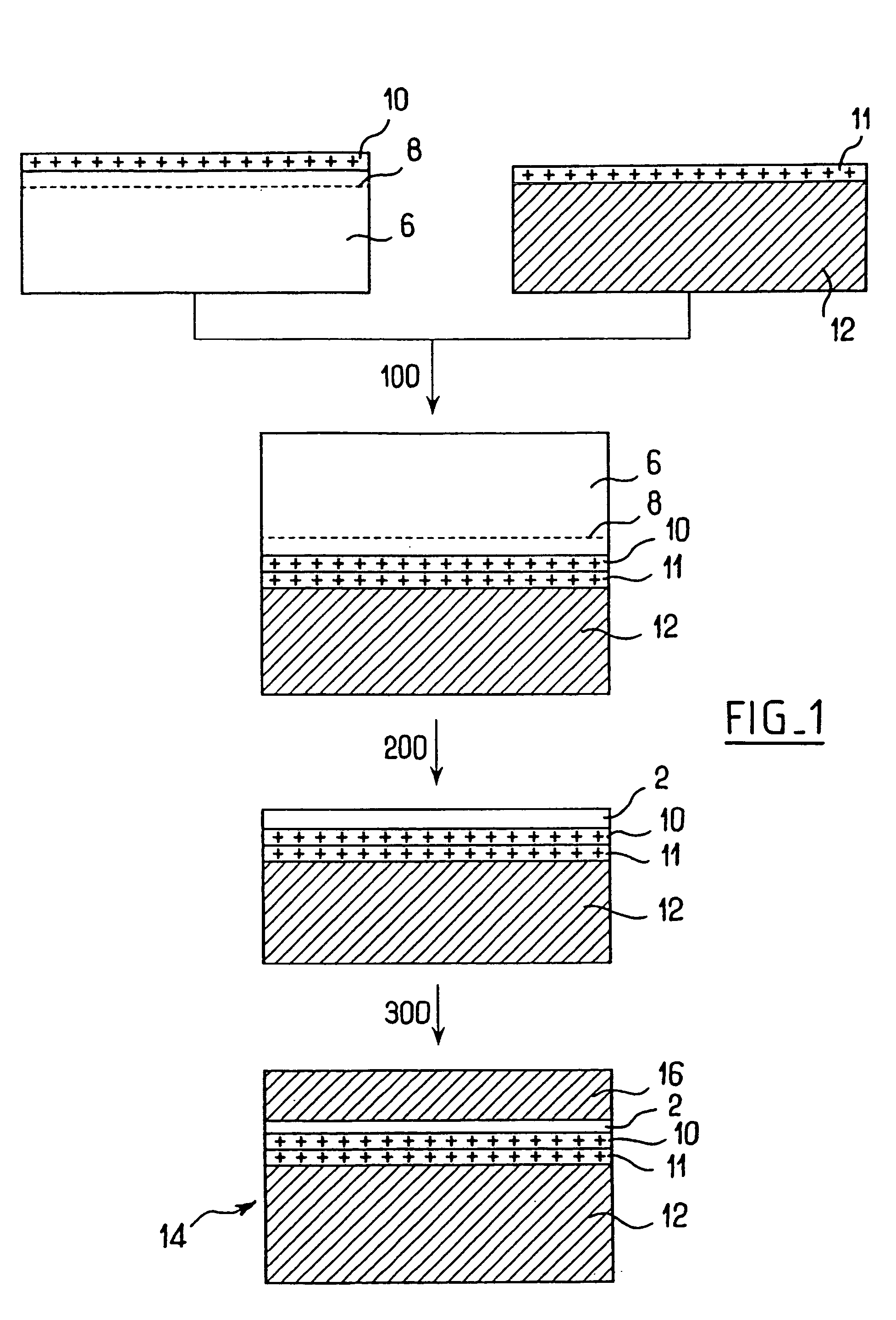

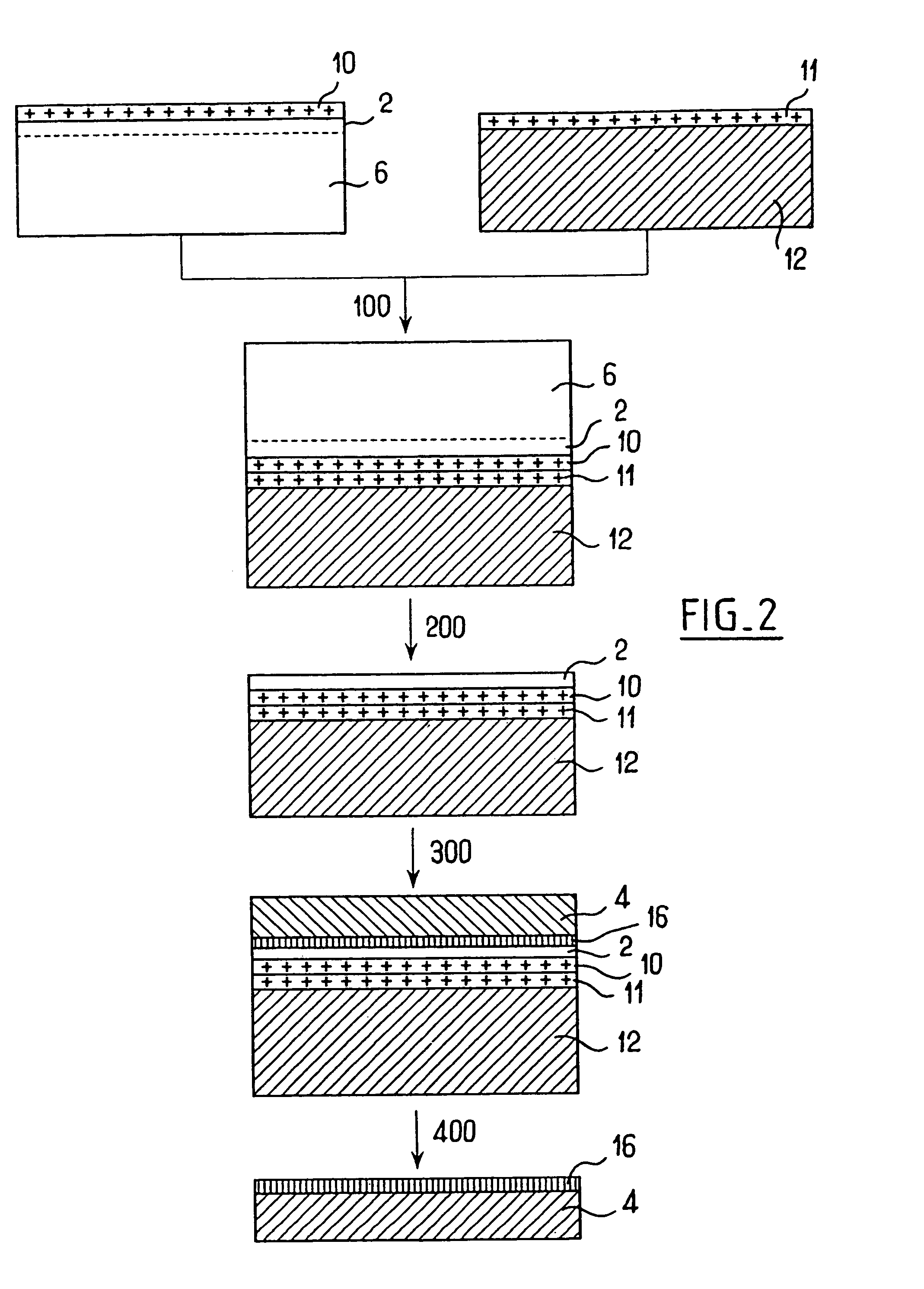

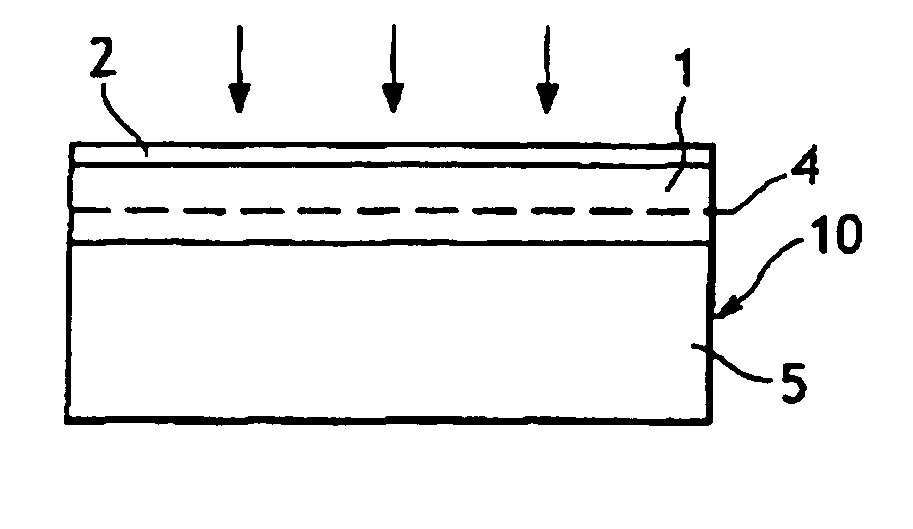

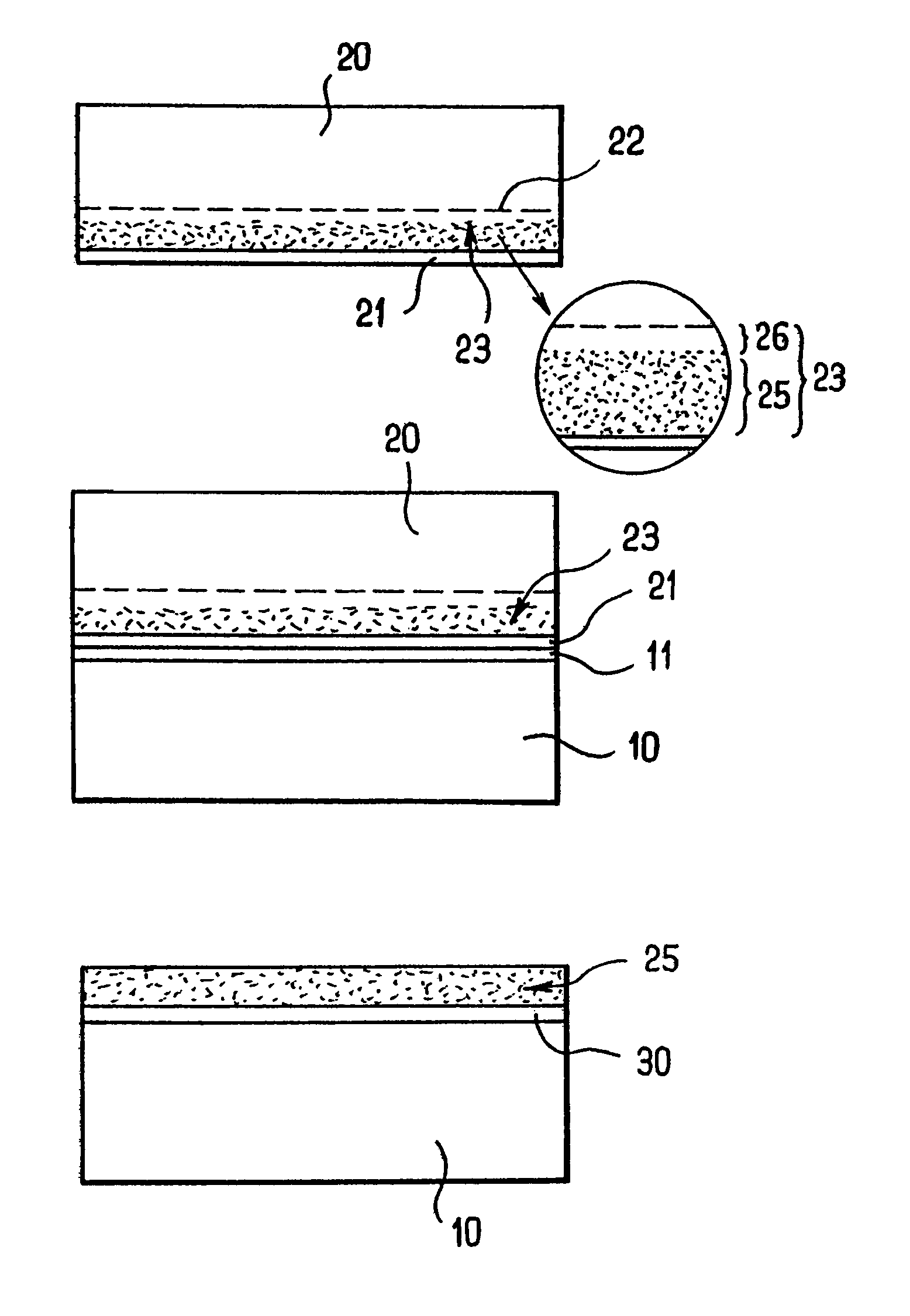

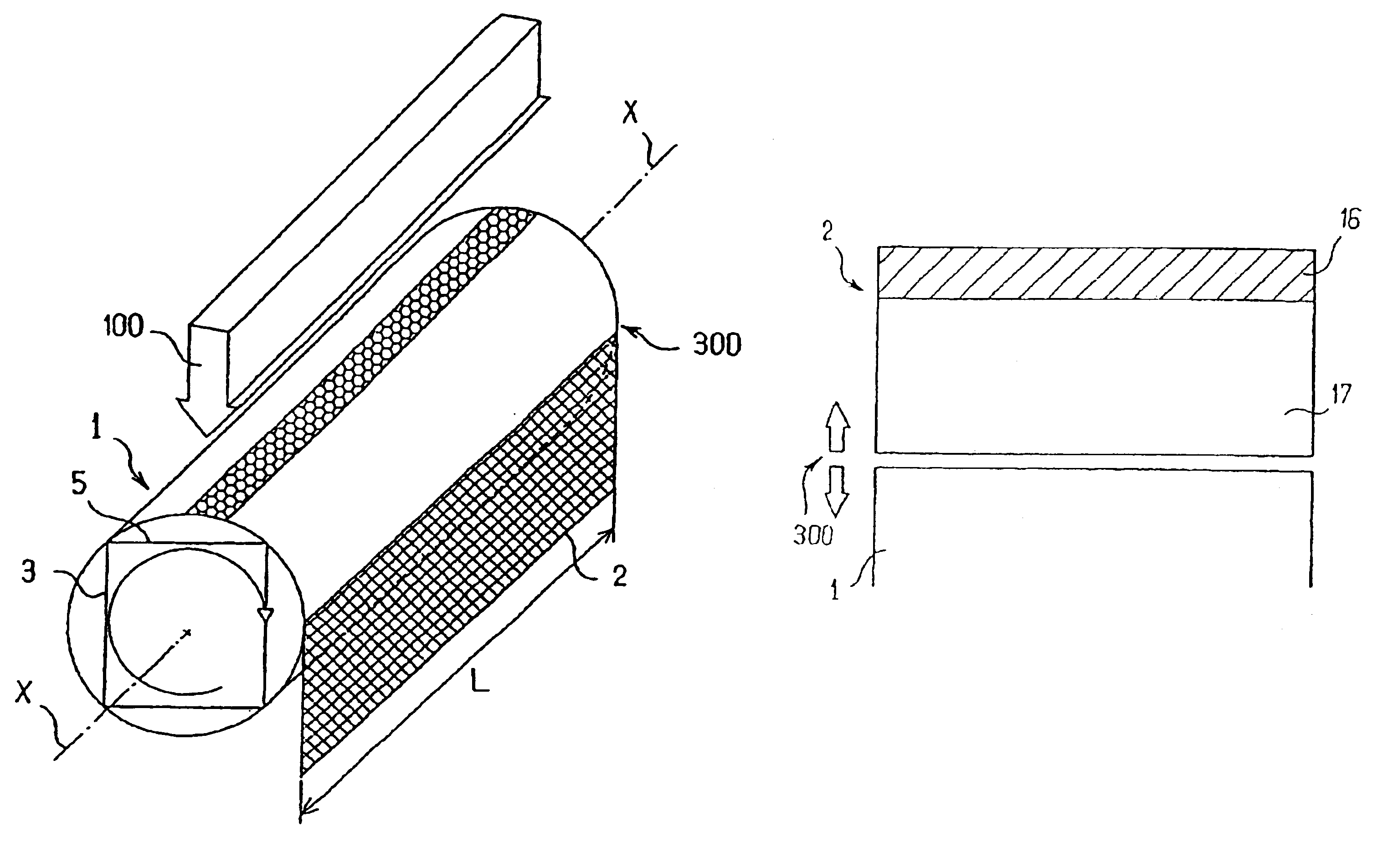

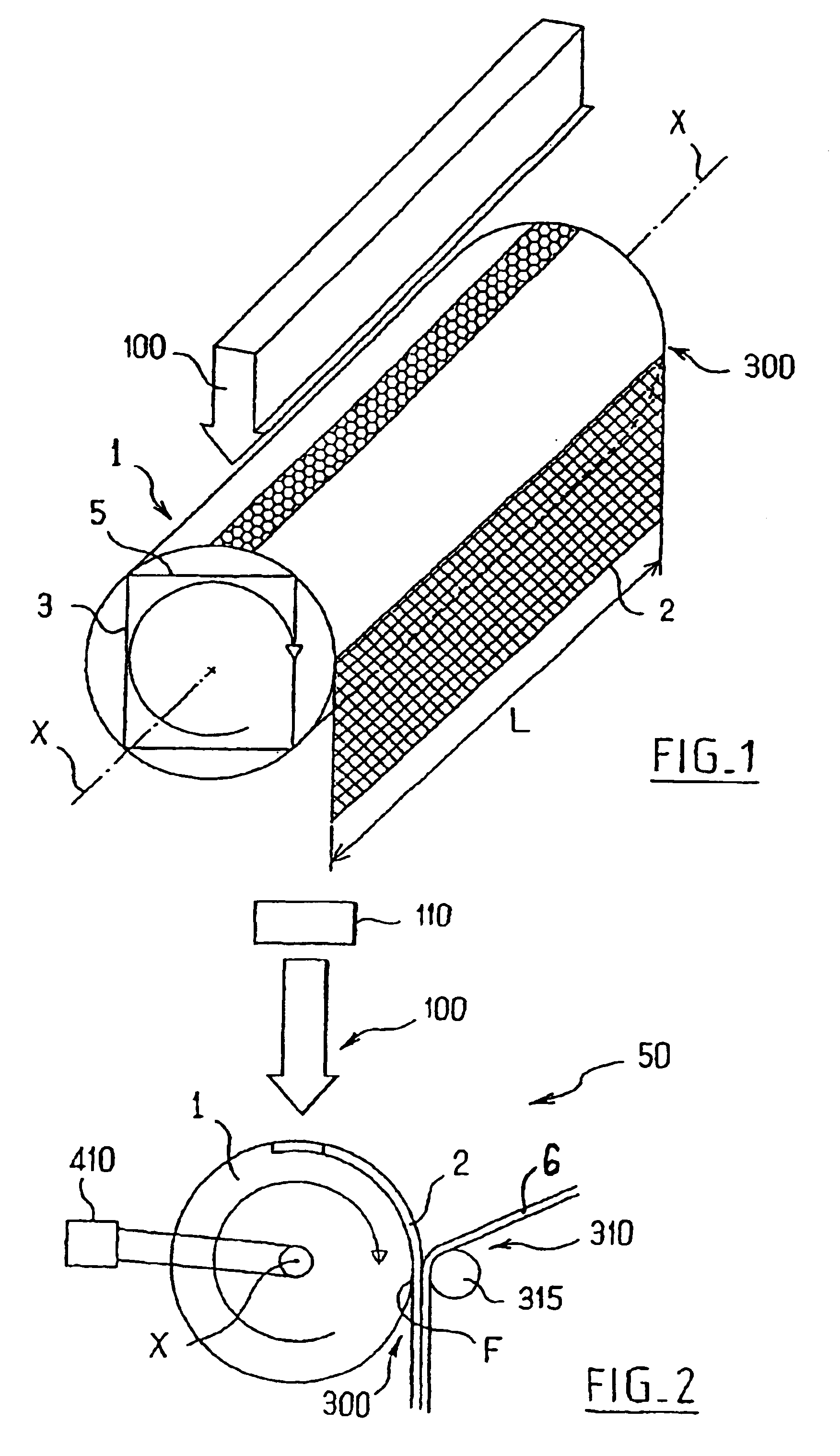

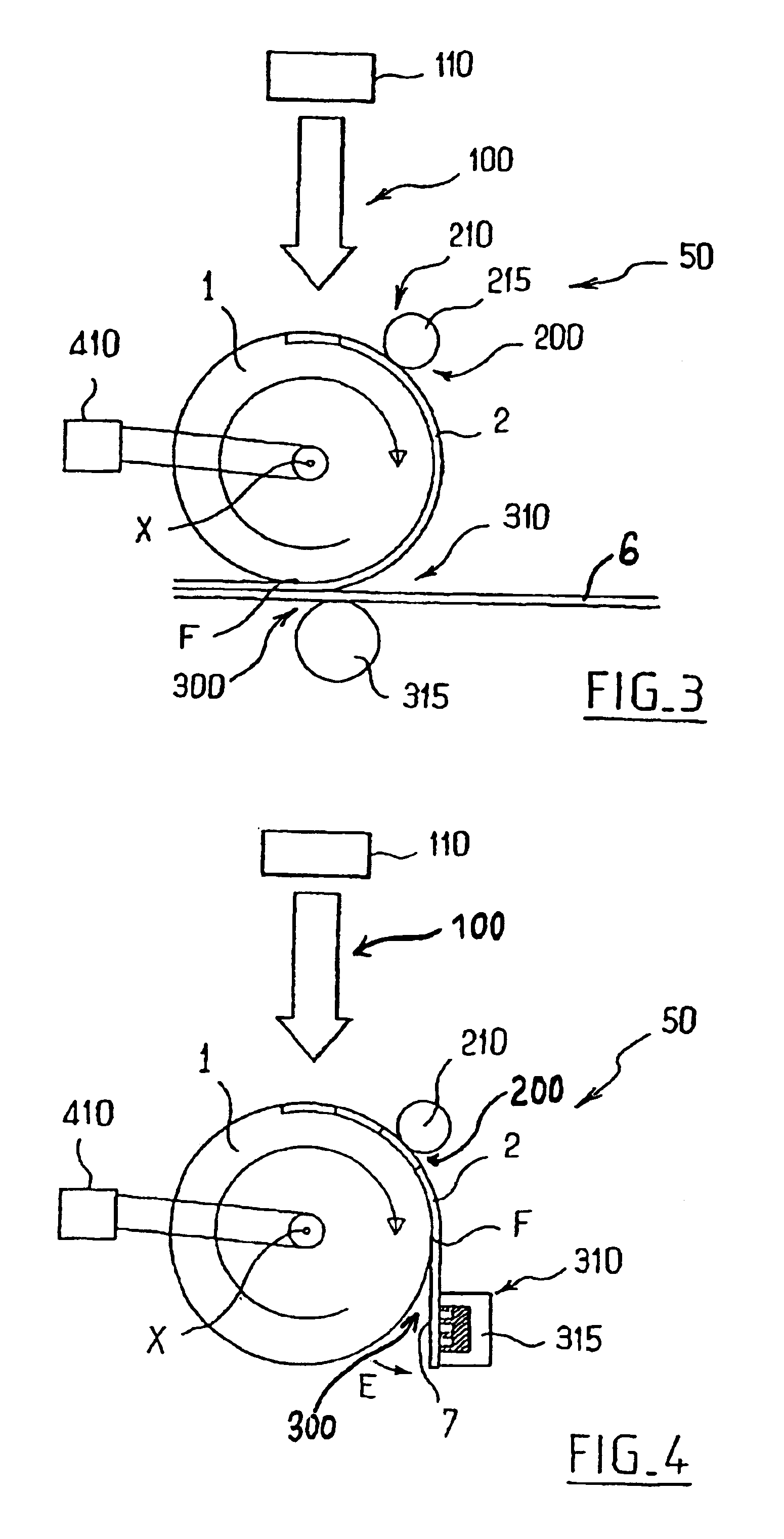

Method and device for making substrates

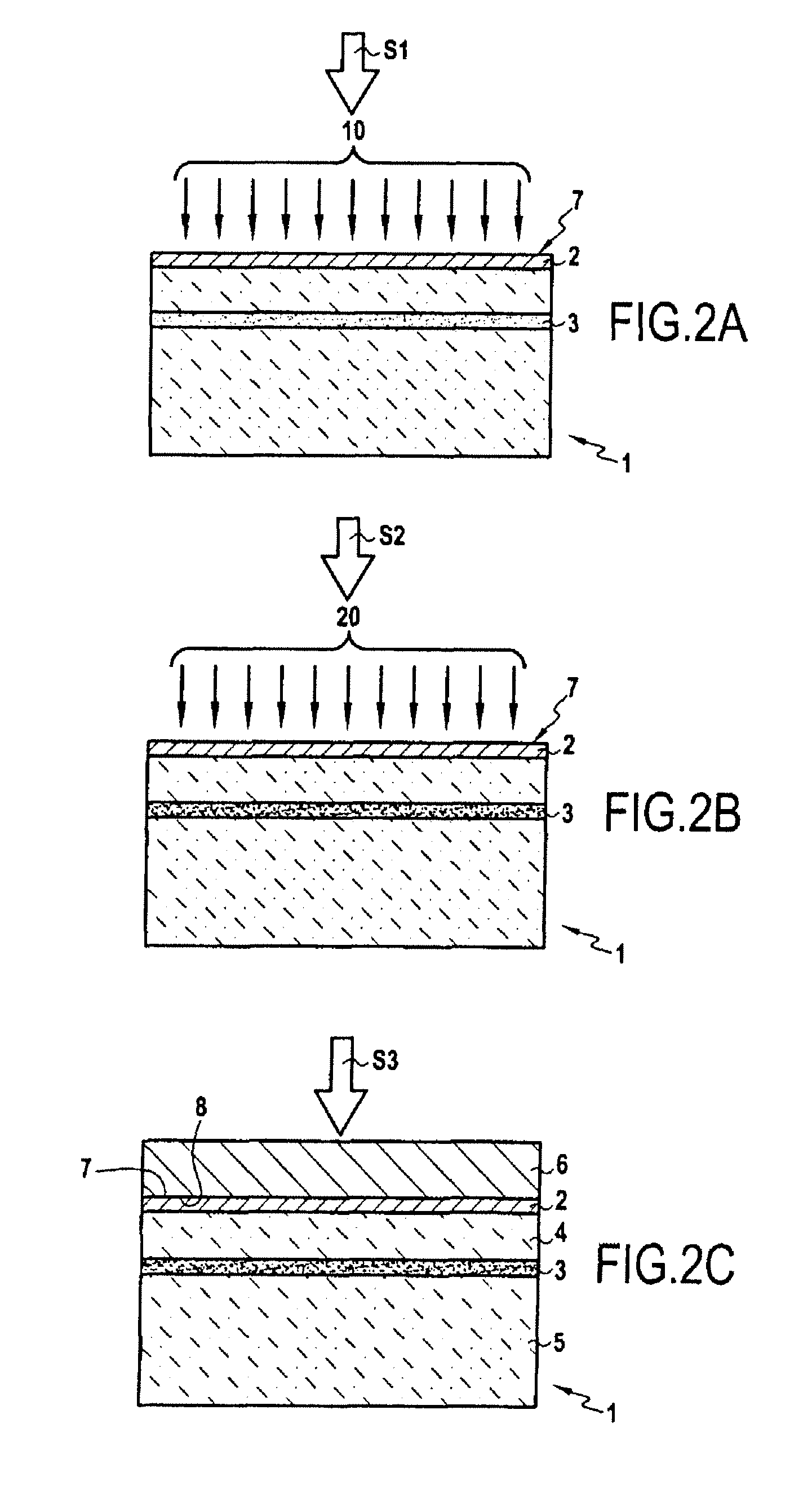

InactiveUS6855619B2Low production costPrevent deformabilityPolycrystalline material growthAfter-treatment detailsIngotAtomic species

The invention concerns a method for making substrates, in particular for optics, electronics or optoelectronics. The method includes an operation which consists in implanting (100) atomic species beneath the surface of a material in the form of a cylindrical ingot (1), at a depth of implantation distributed about a certain value by bombardment of the atomic species on a zone of the ingot (1) cylindrical surface, and an operation which consists in removing (300), at a separation depth located proximate to the depth of implantation, the layer (2) of material located between the surface and the separation depth, to remove the layer (2) from the rest of the cylindrical ingot (1).

Owner:SOITEC SA

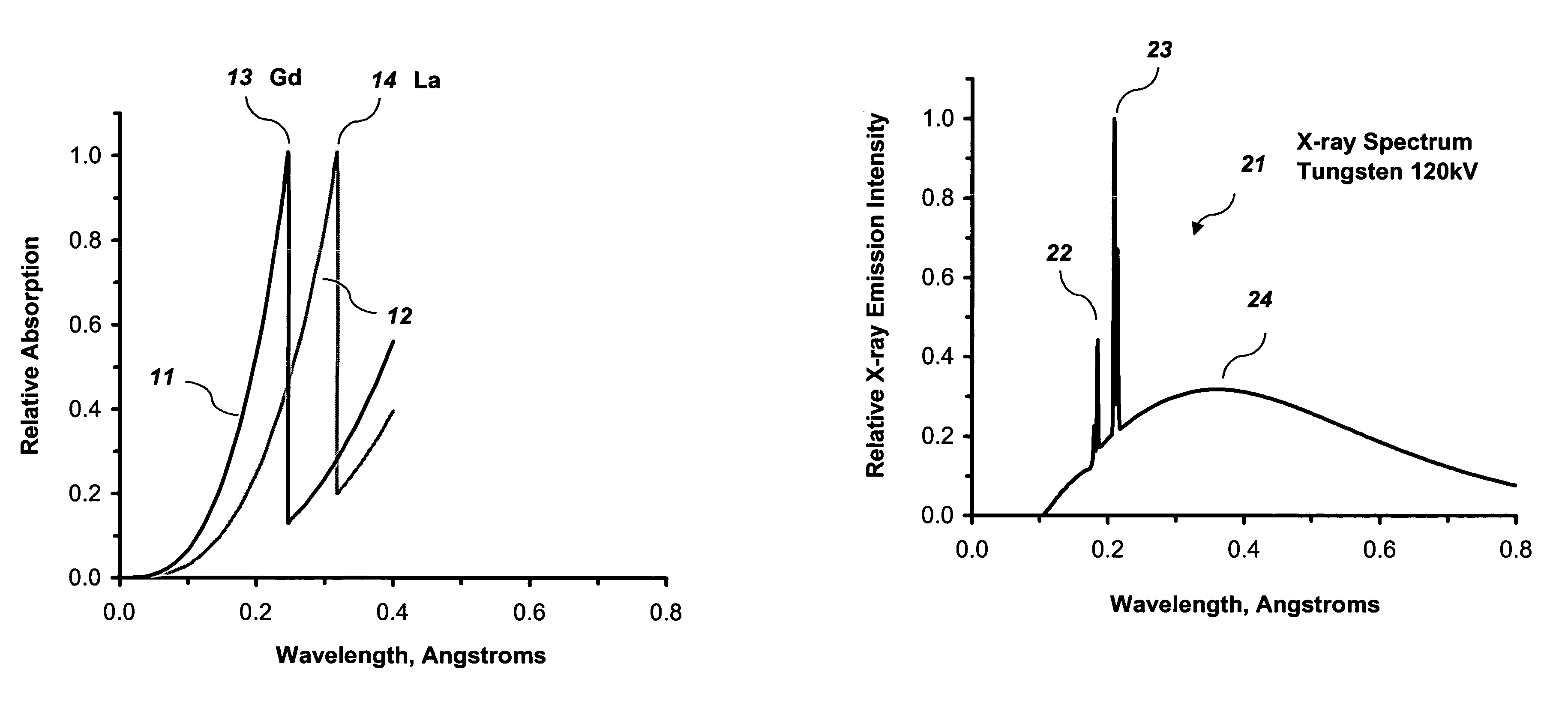

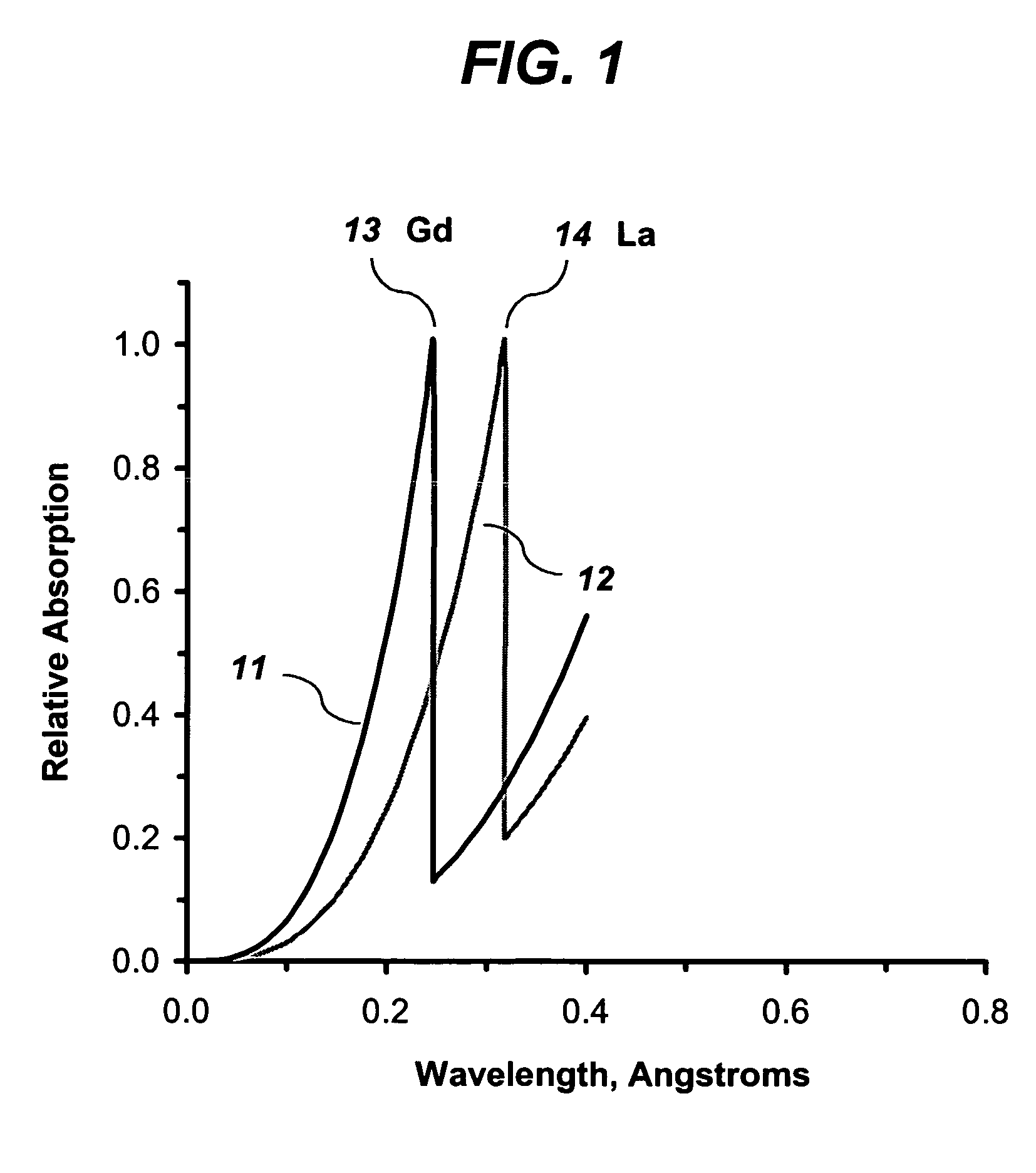

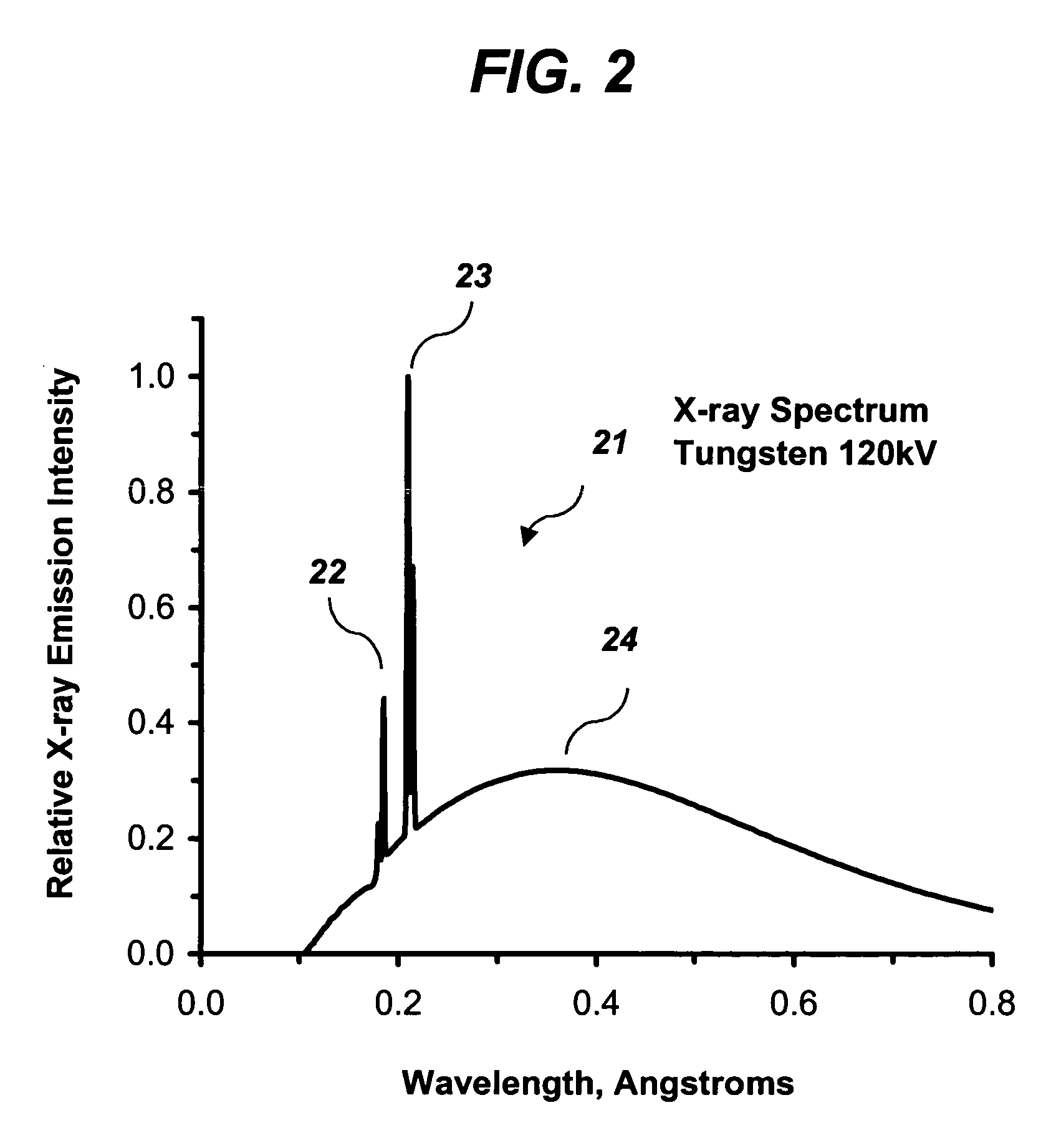

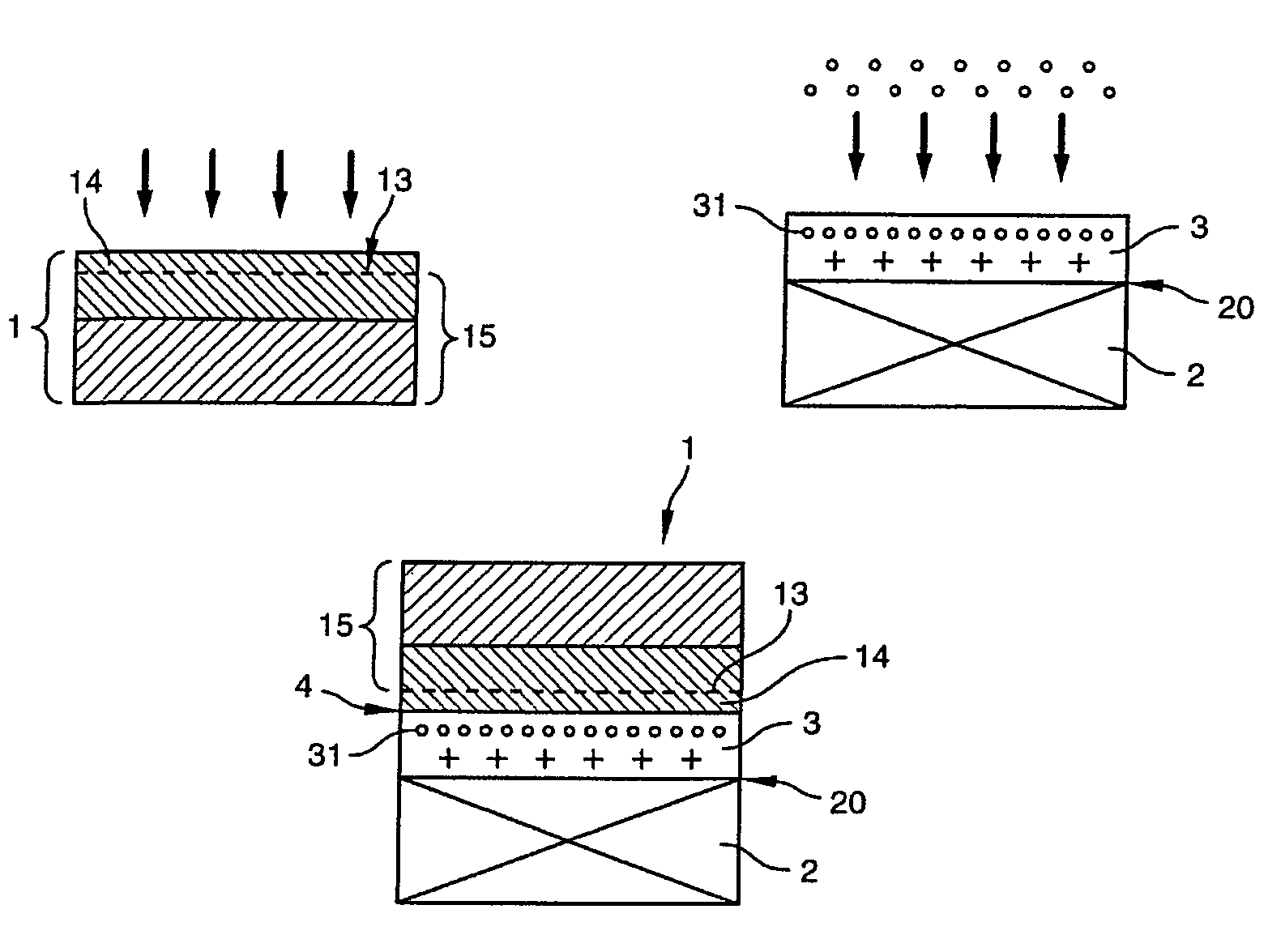

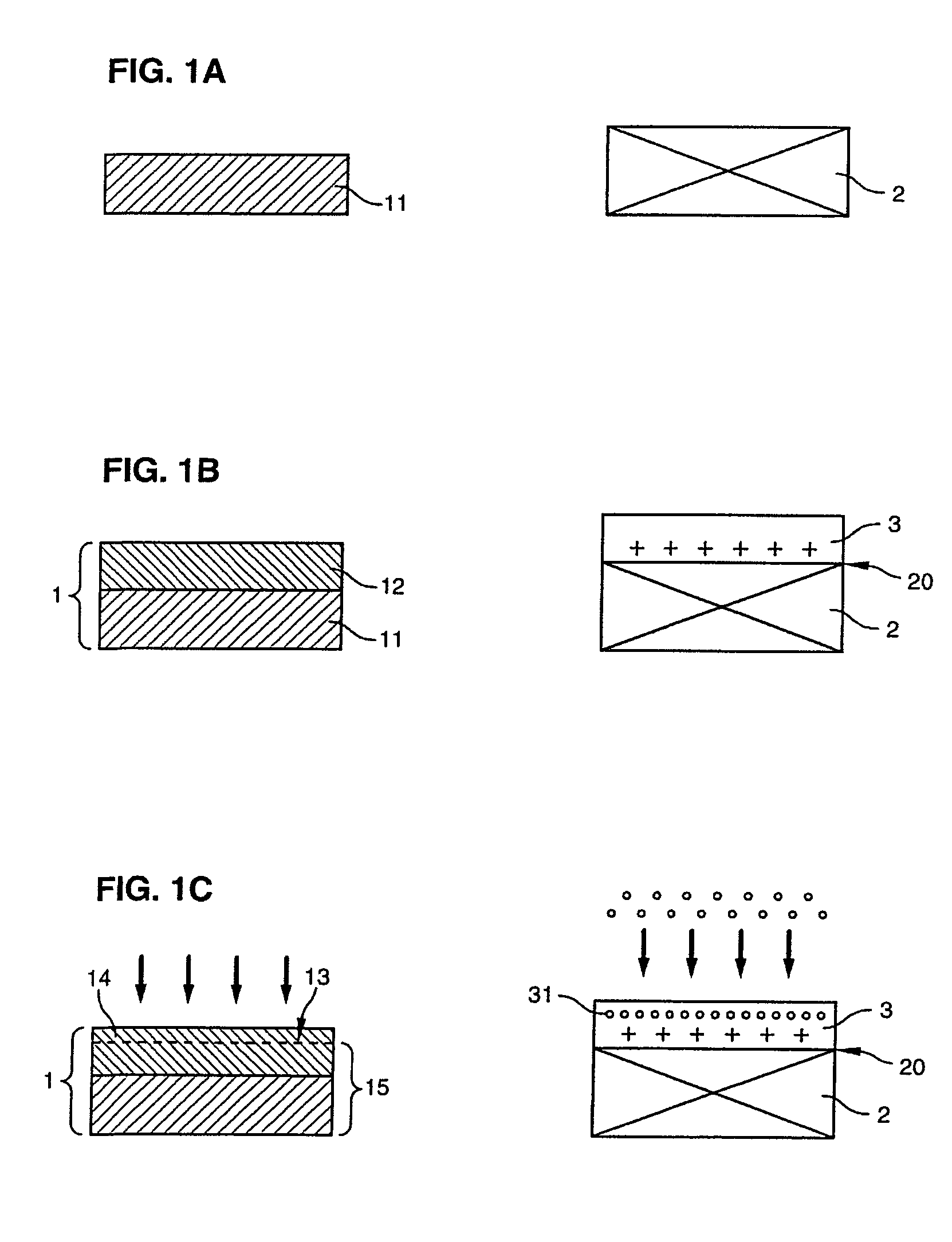

Ionizing radiation imaging system and method with decreased radiation dose

Owner:PEDIATRIC IMAGING TECH

Semiconductor-on-insulator type heterostructure and method of fabrication

InactiveUS7485551B2Reduce limit formationLimit and eliminates defectSemiconductor/solid-state device manufacturingNanotechnologySemiconductor materialsTrapping

Owner:SOITEC SA

Method of layer transfer comprising sequential implantations of atomic species

InactiveUS7323398B2Easy to disengageReduce and minimize migrationSemiconductor/solid-state device manufacturingOptoelectronicsAtomic species

A method of manufacturing a crystalline wafer that includes implanting first atomic species in a donor substrate to form a region of weakness at a first depth therein and configured to facilitate detachment of a first layer of the donor substrate from a remaining portion of the donor substrate. The first layer and remaining portion are disposed on opposite sides of the region of weakness. The method also includes implanting second atomic species in the donor substrate to form a gettering region at a second depth therein that is different than the first depth to reduce or minimize migration of the implanted first atomic species past the gettering region. This reduces or minimizes an increase in roughness of a surface produced on the first layer after detachment thereof from the remaining portion at the region of weakness.

Owner:SOITEC SA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com