Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

319results about How to "Inhibition defect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

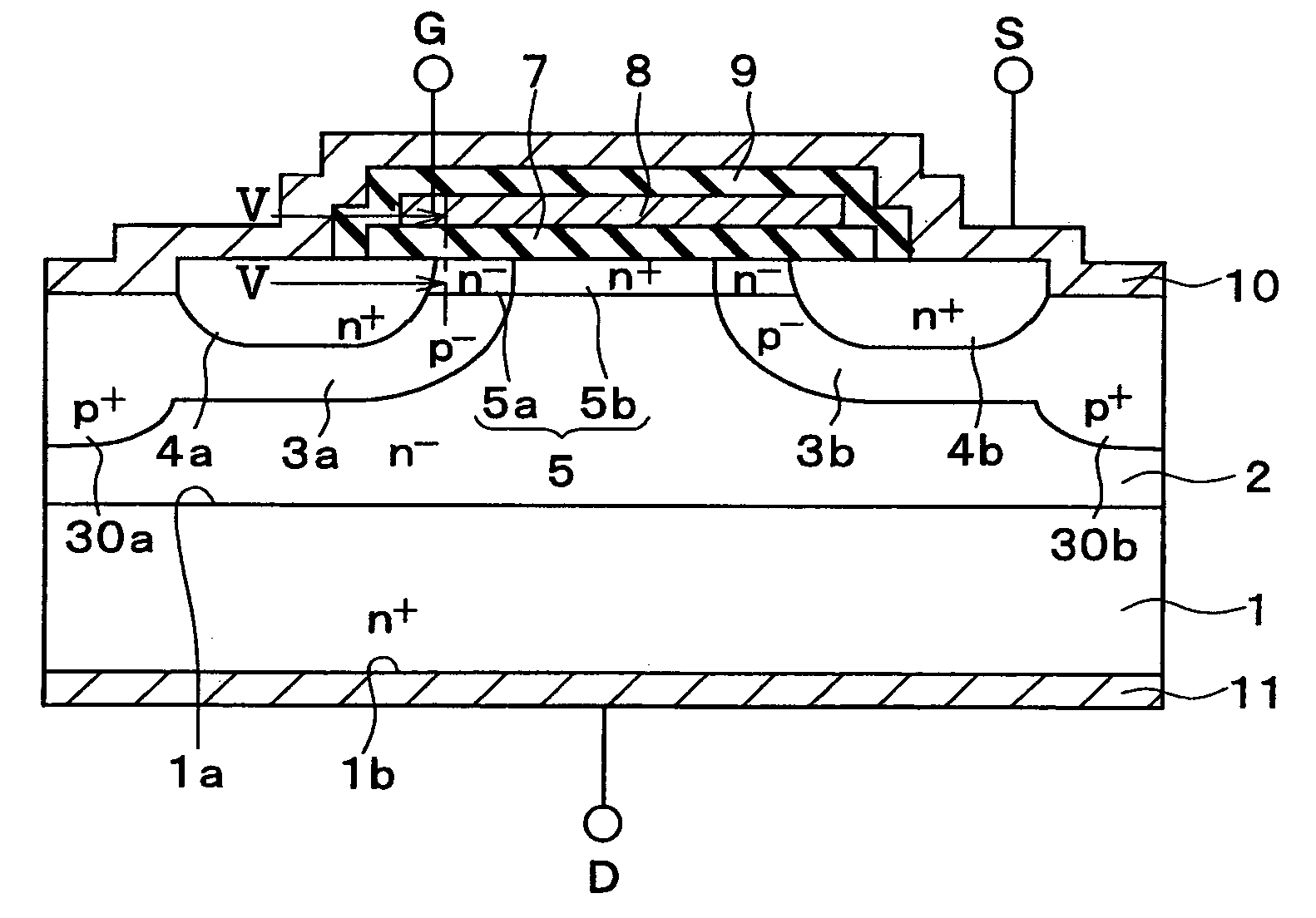

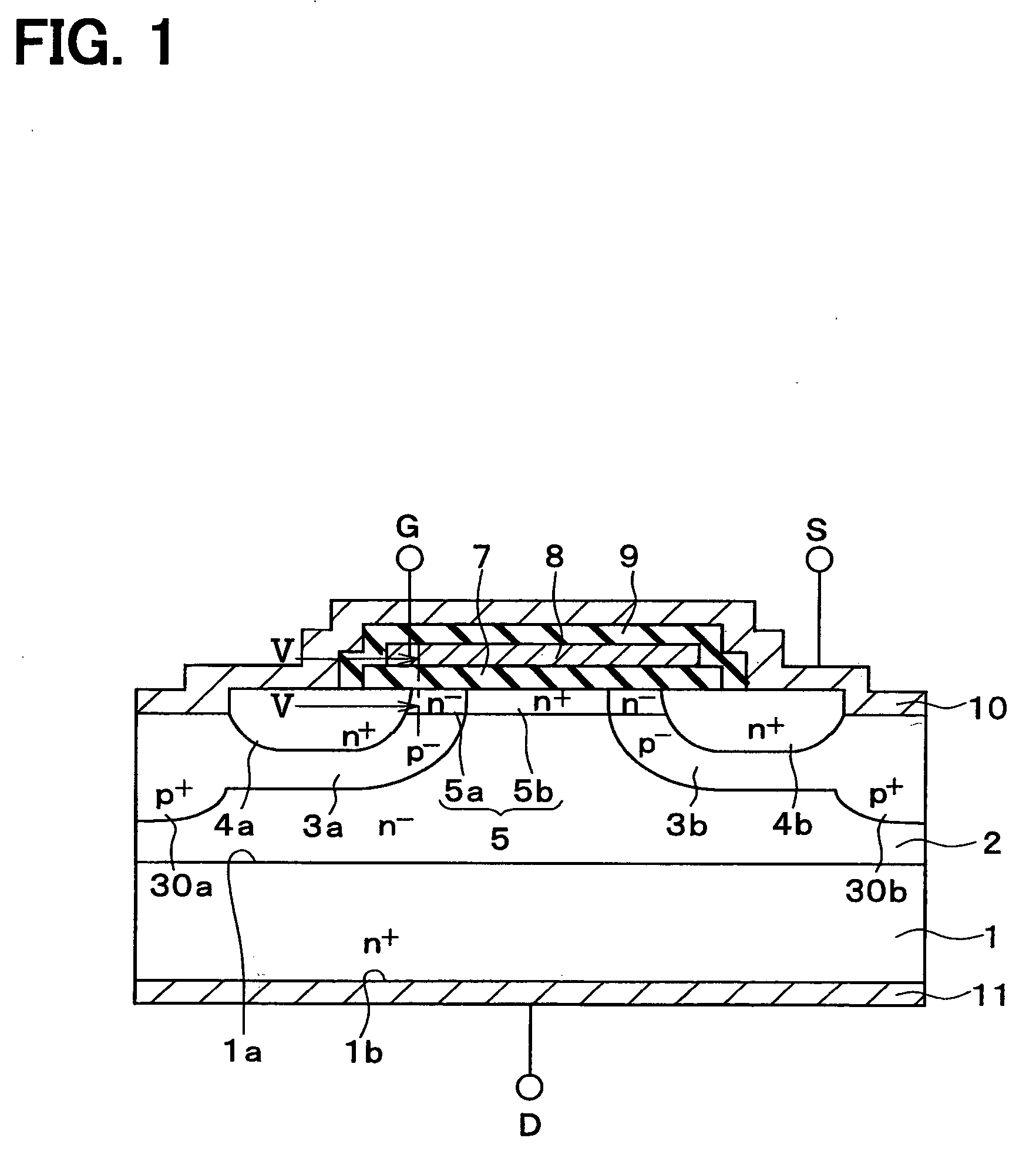

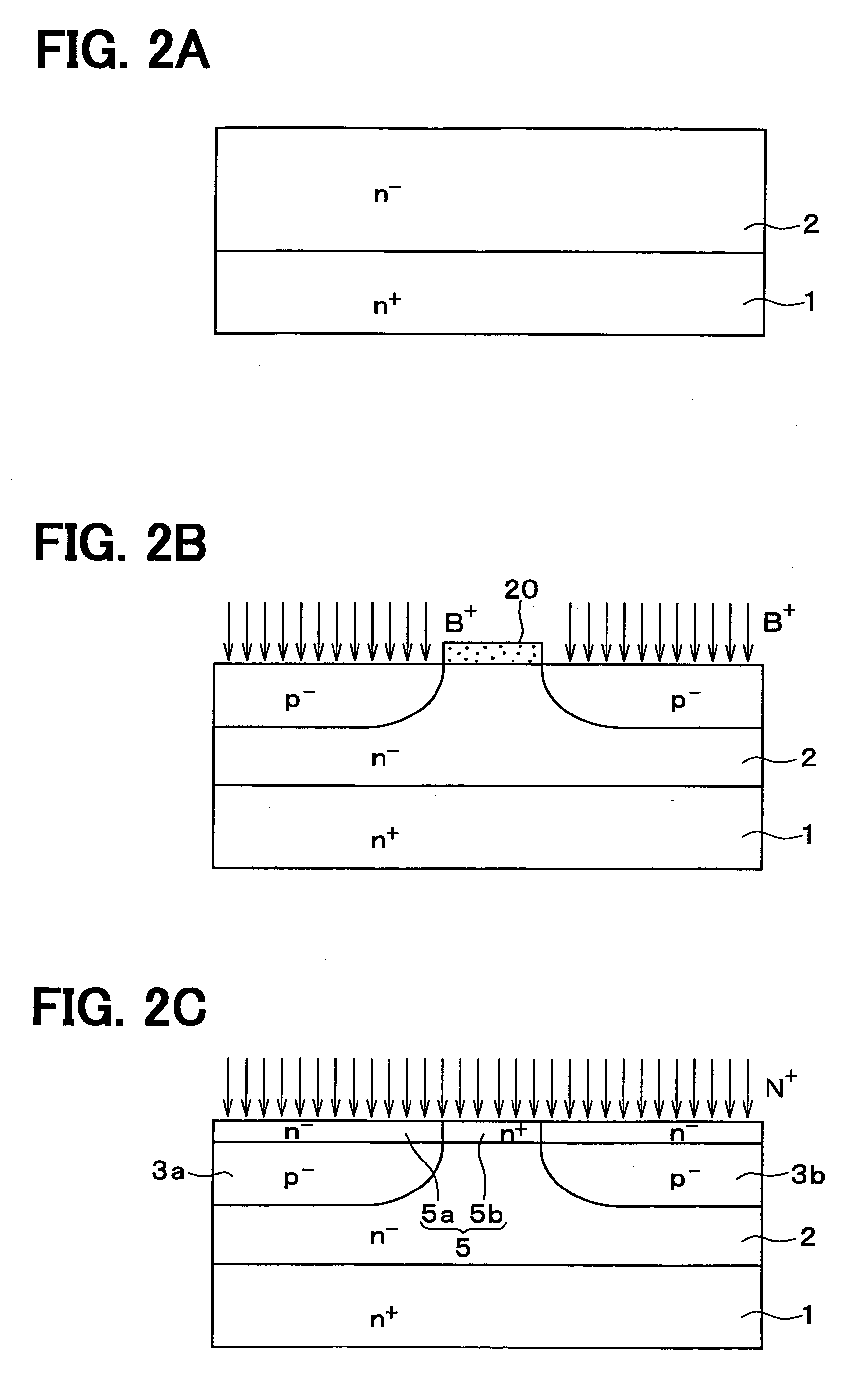

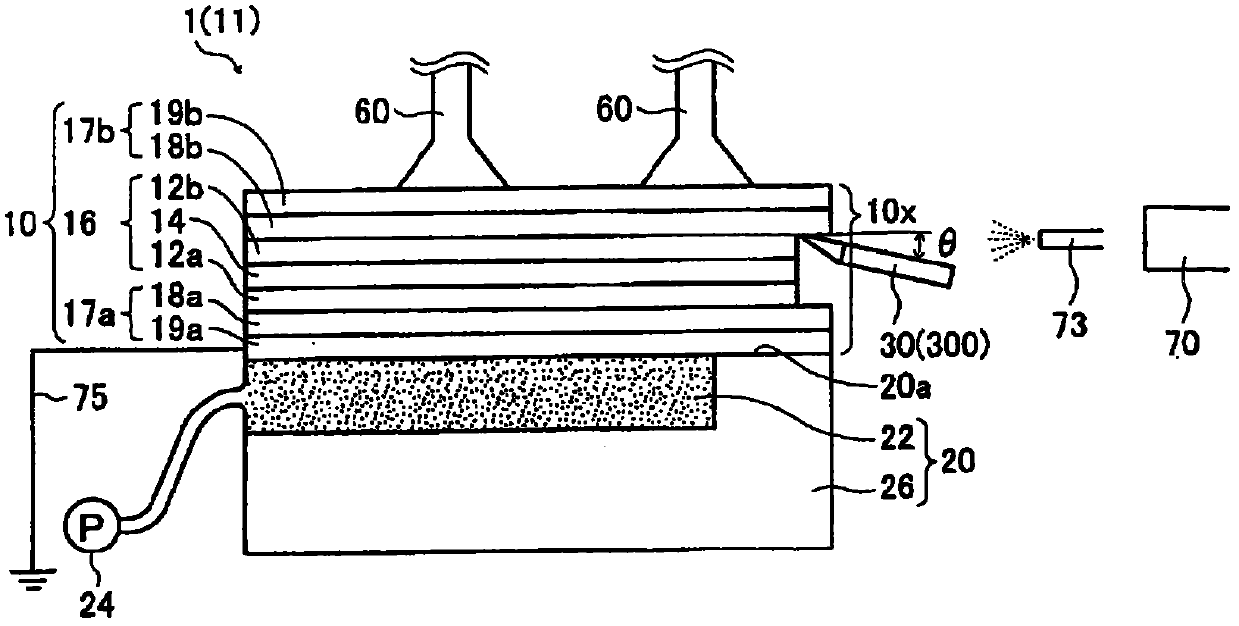

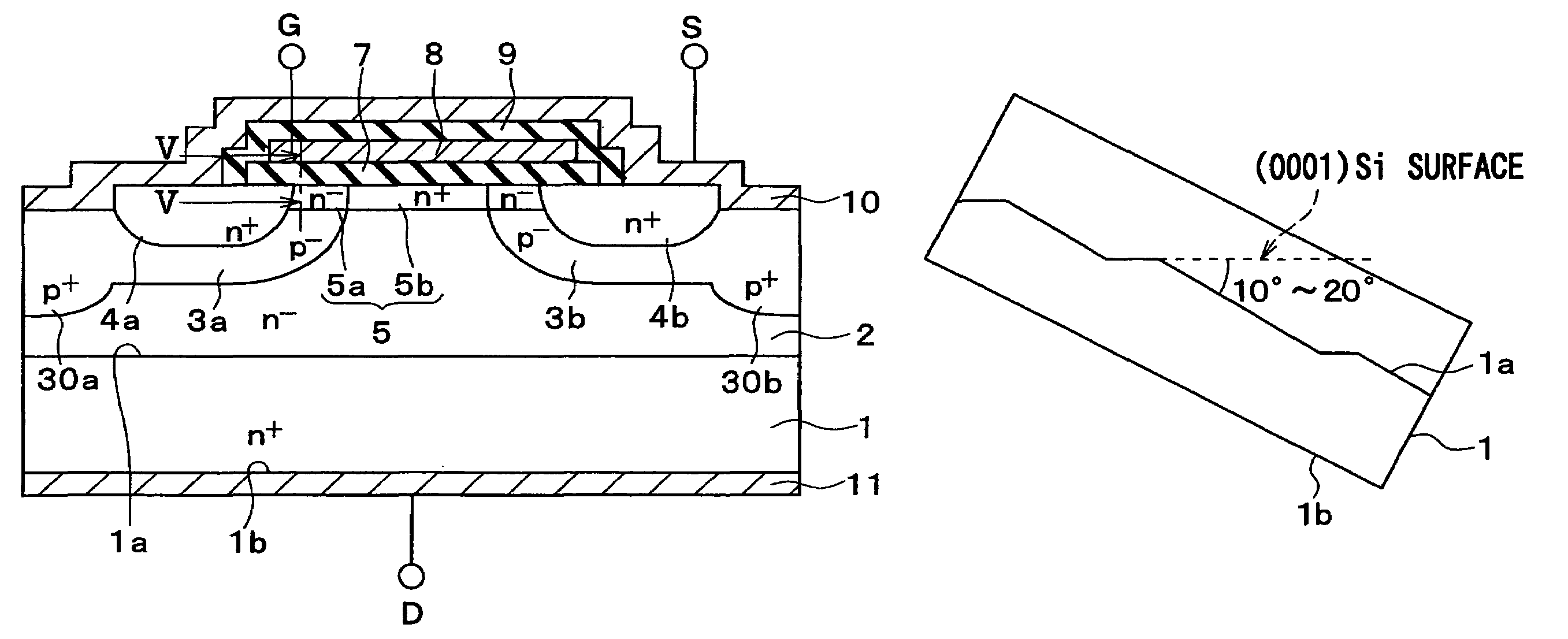

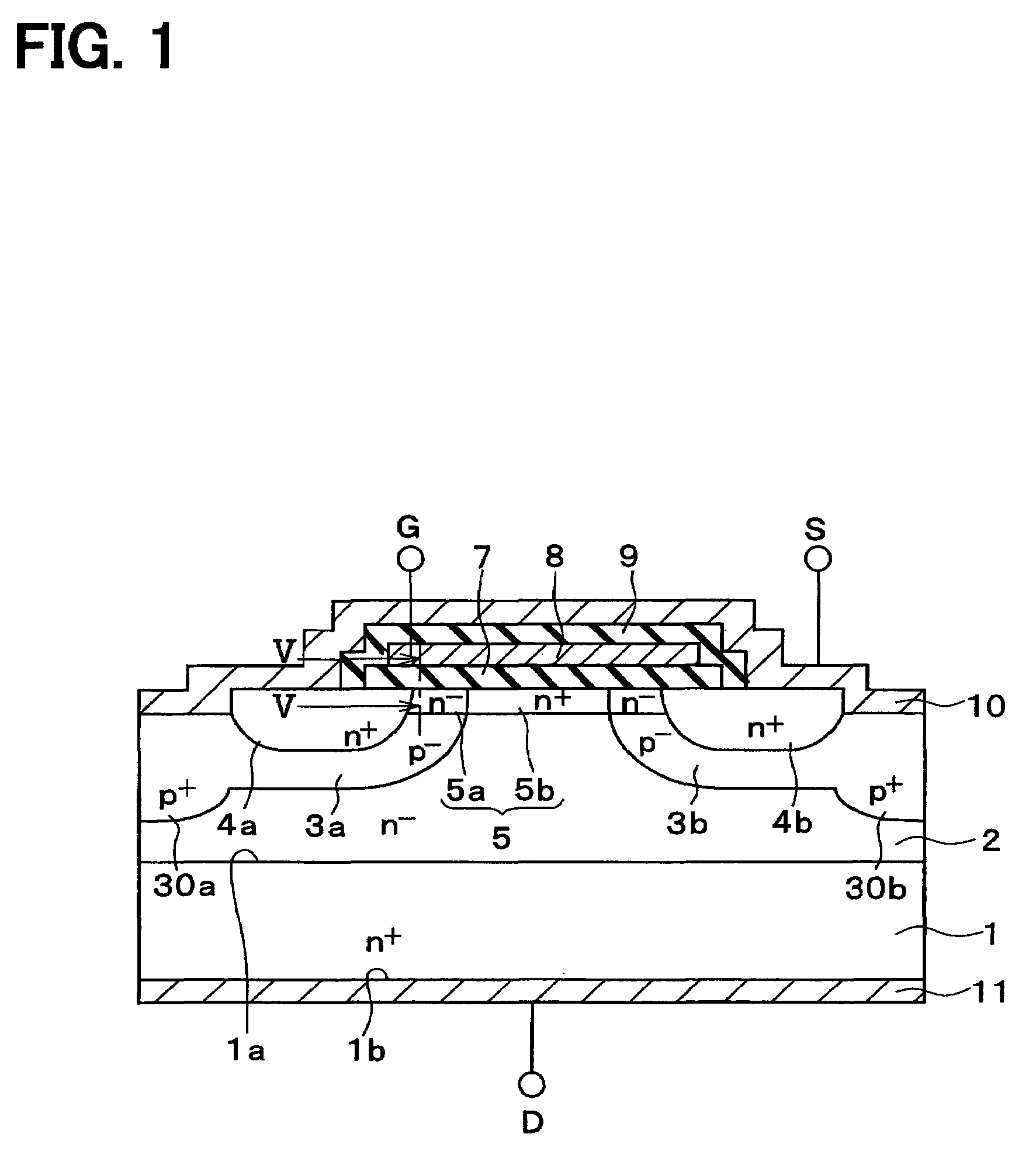

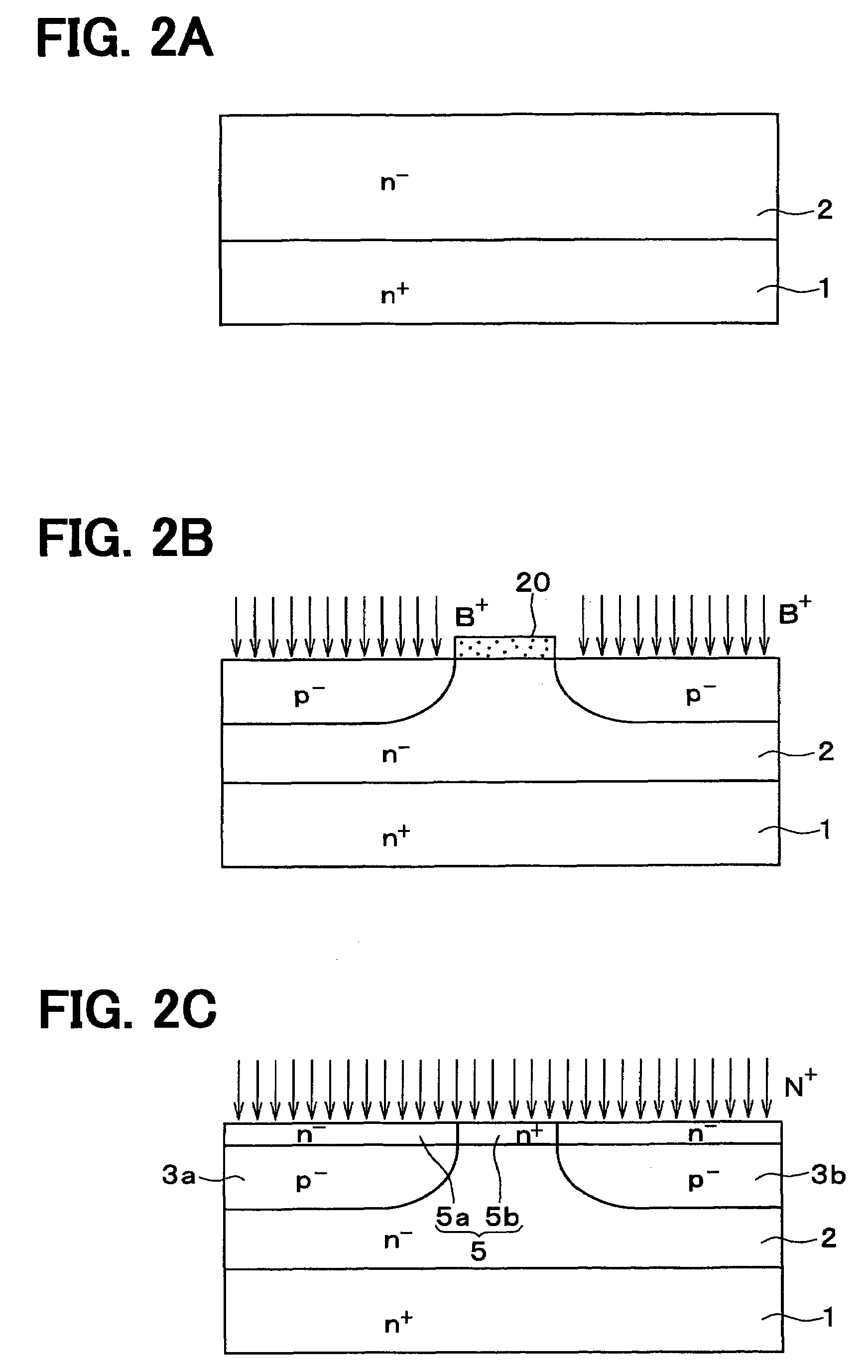

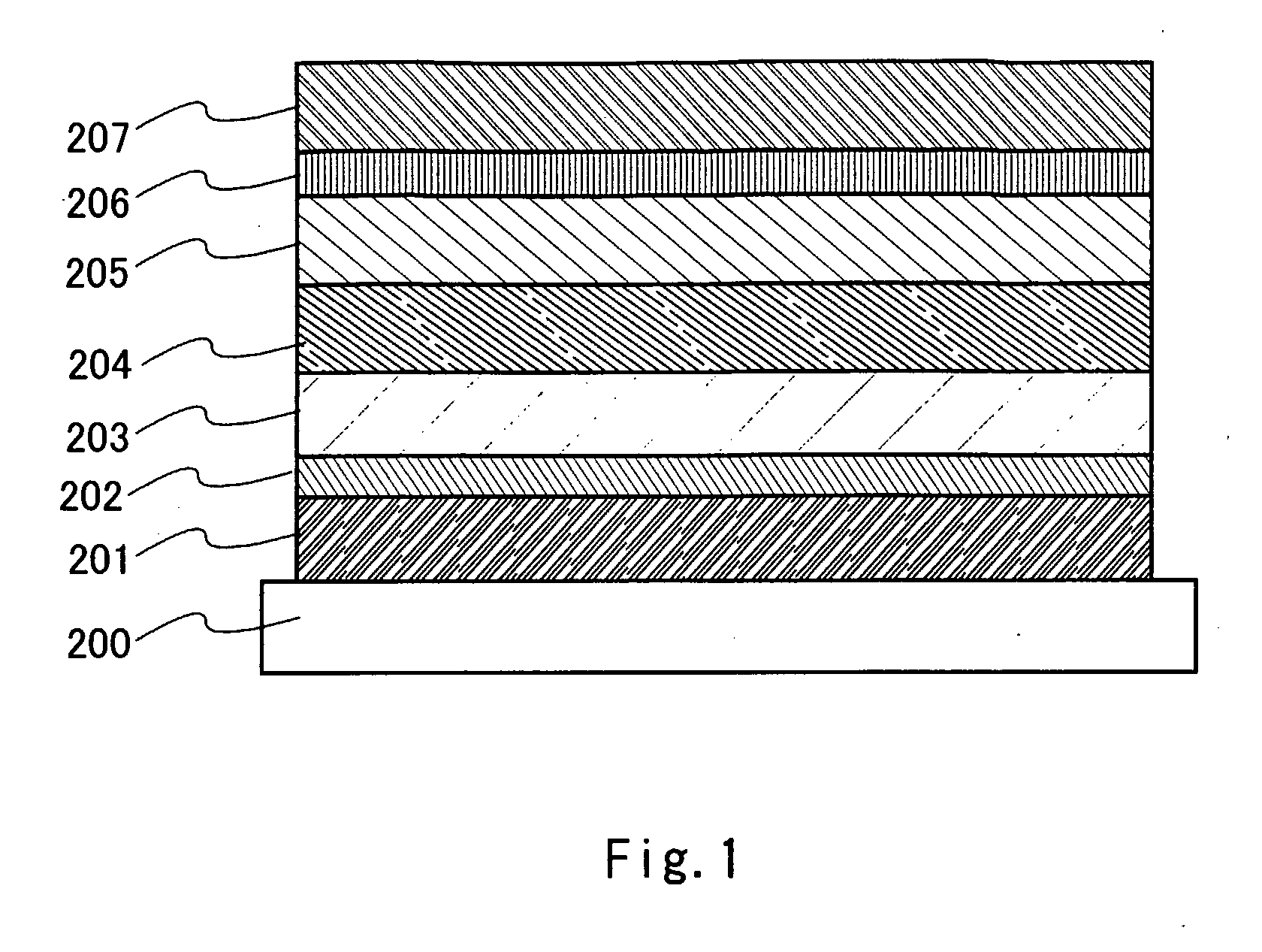

Silicon carbide semiconductor device and method for manufacturing the same

ActiveUS20050230686A1Improve surface conditionImprove regularitySemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialSemiconductor

A silicon carbide semiconductor device includes: a semiconductor substrate having a principal surface and a backside surface; a drift layer disposed on the principal surface; a base region disposed on the drift layer; a source region disposed on the base region; a surface channel layer disposed on both of the drift layer and the base region for connecting between the source region and the drift layer; a gate insulation film disposed on the surface channel layer and including a high dielectric constant film; a gate electrode disposed on the gate insulation film; a source electrode disposed on the source region; and a backside electrode disposed on the backside surface.

Owner:DENSO CORP

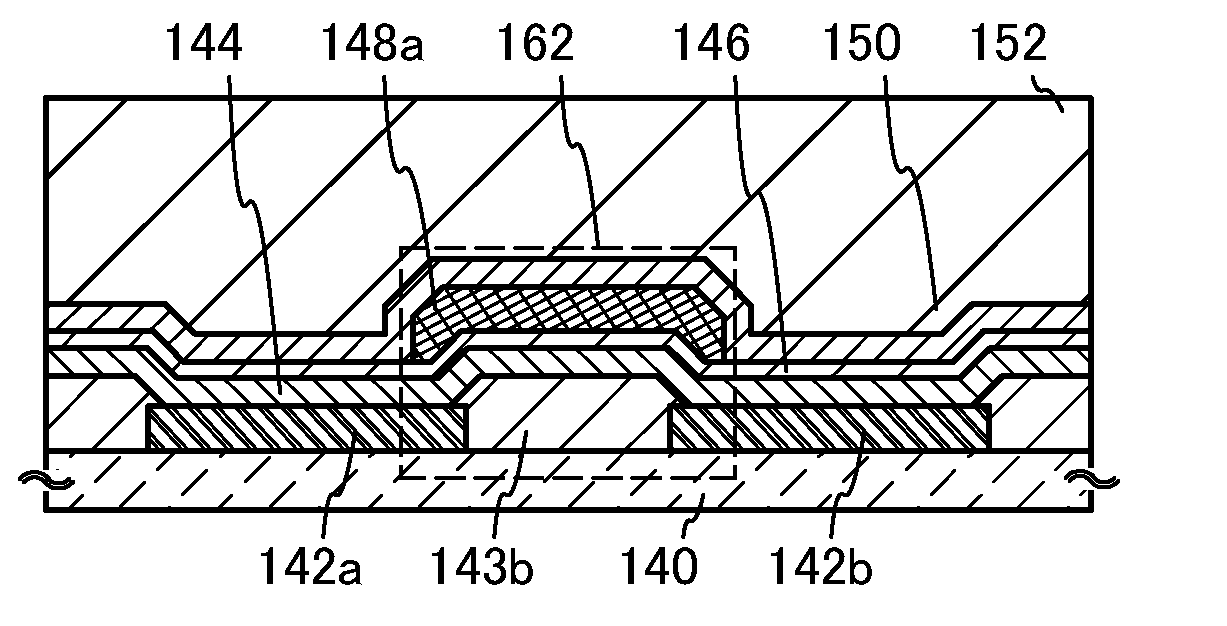

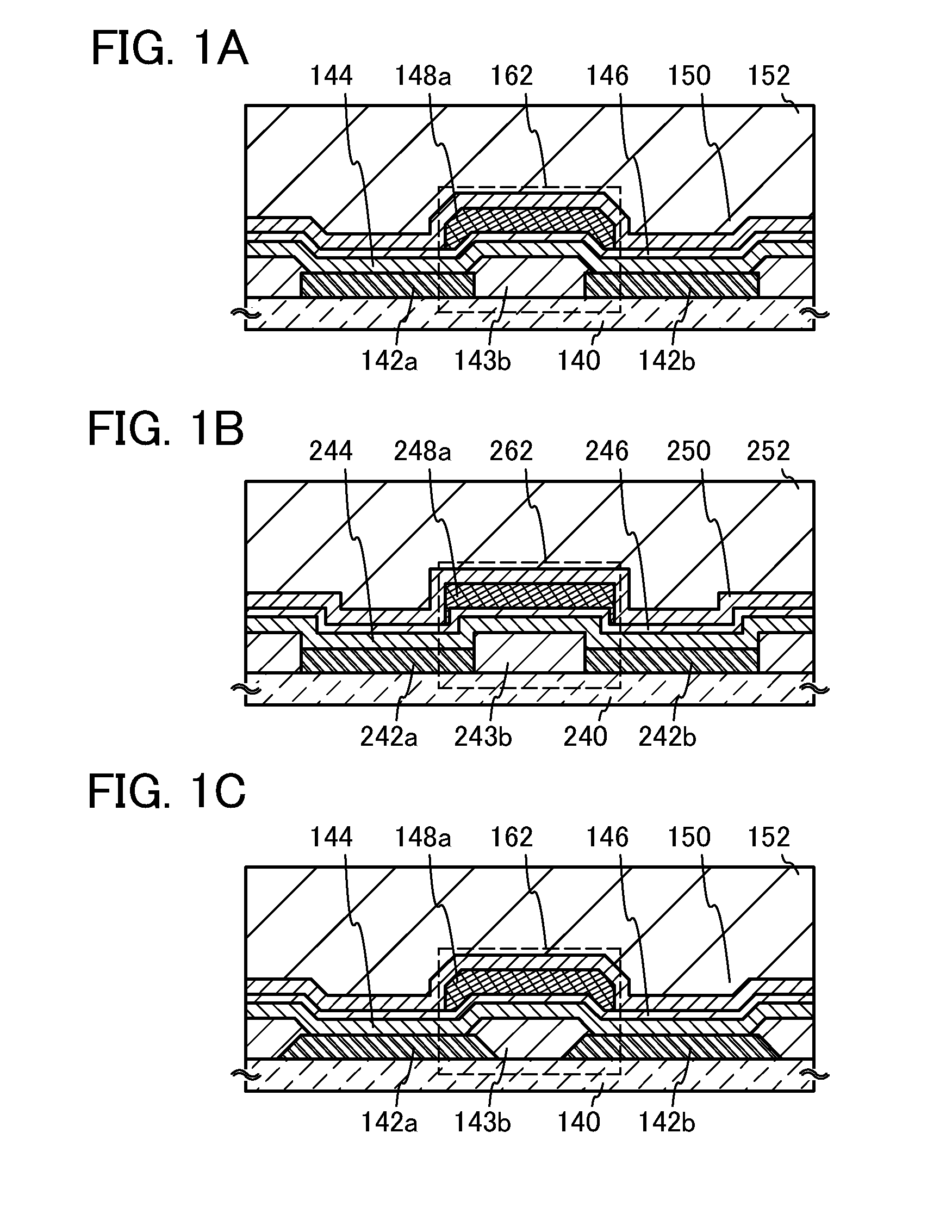

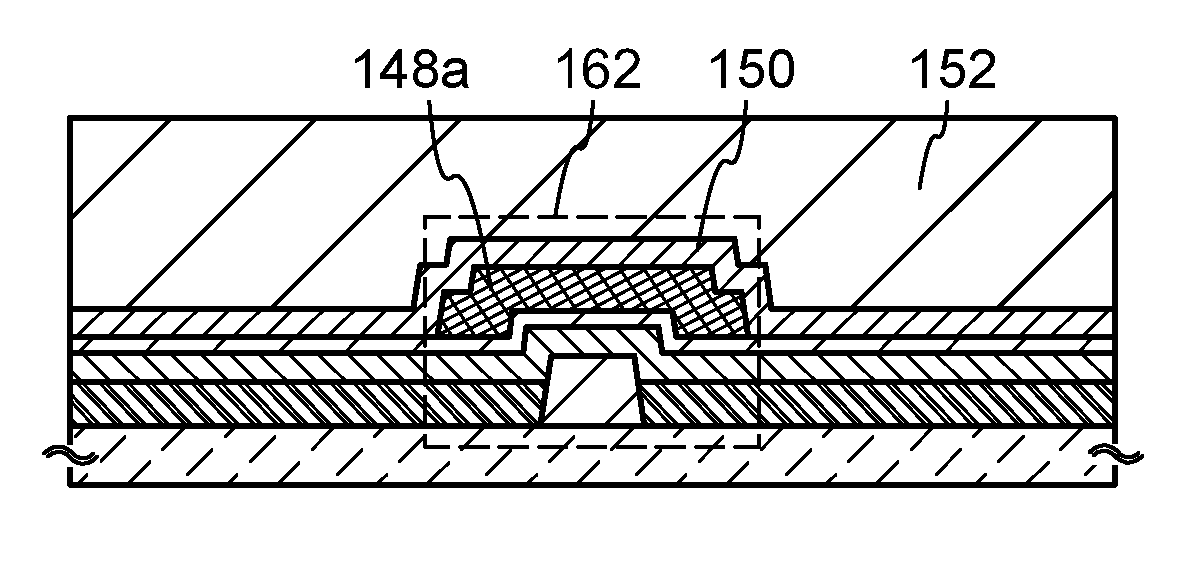

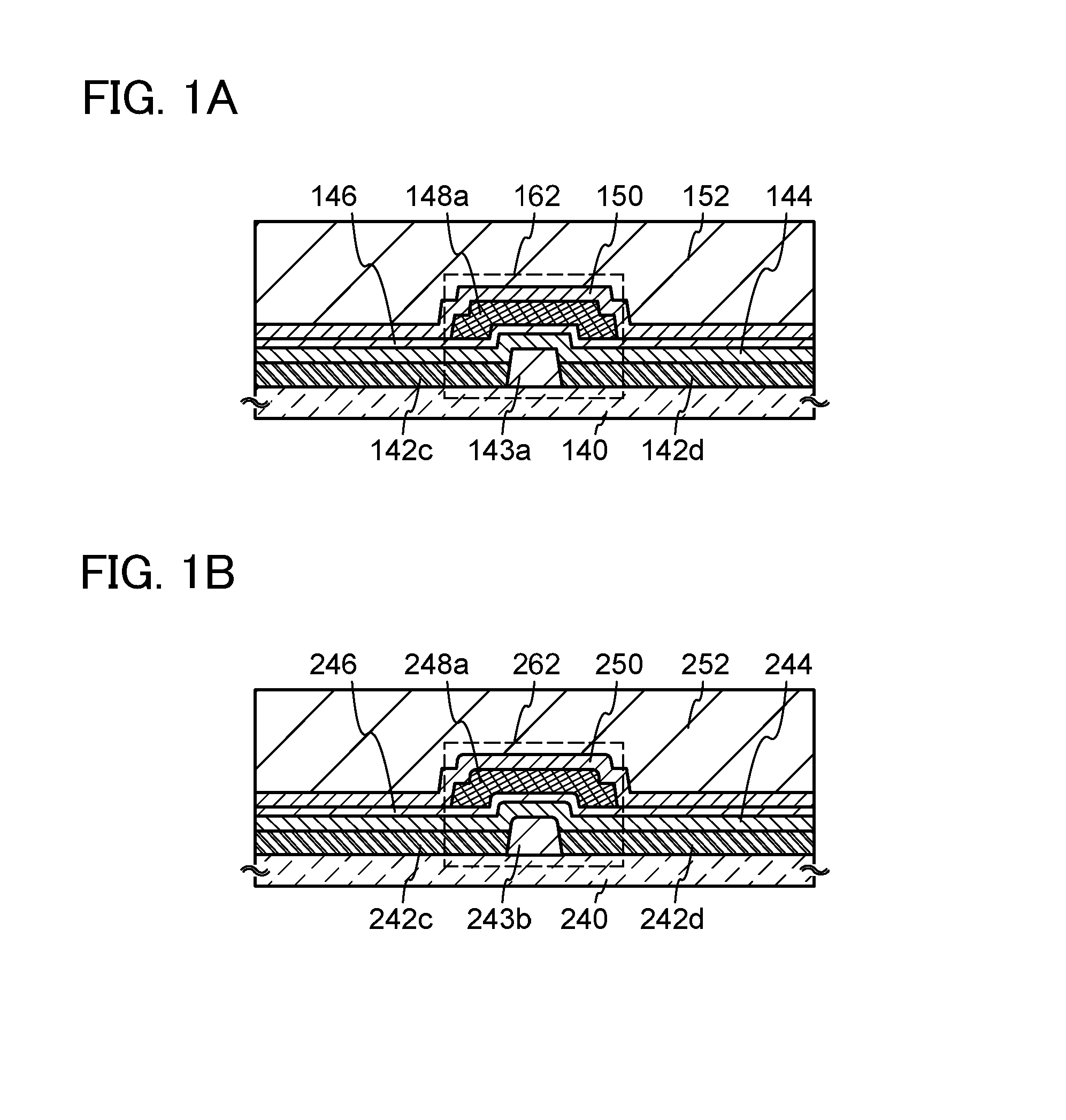

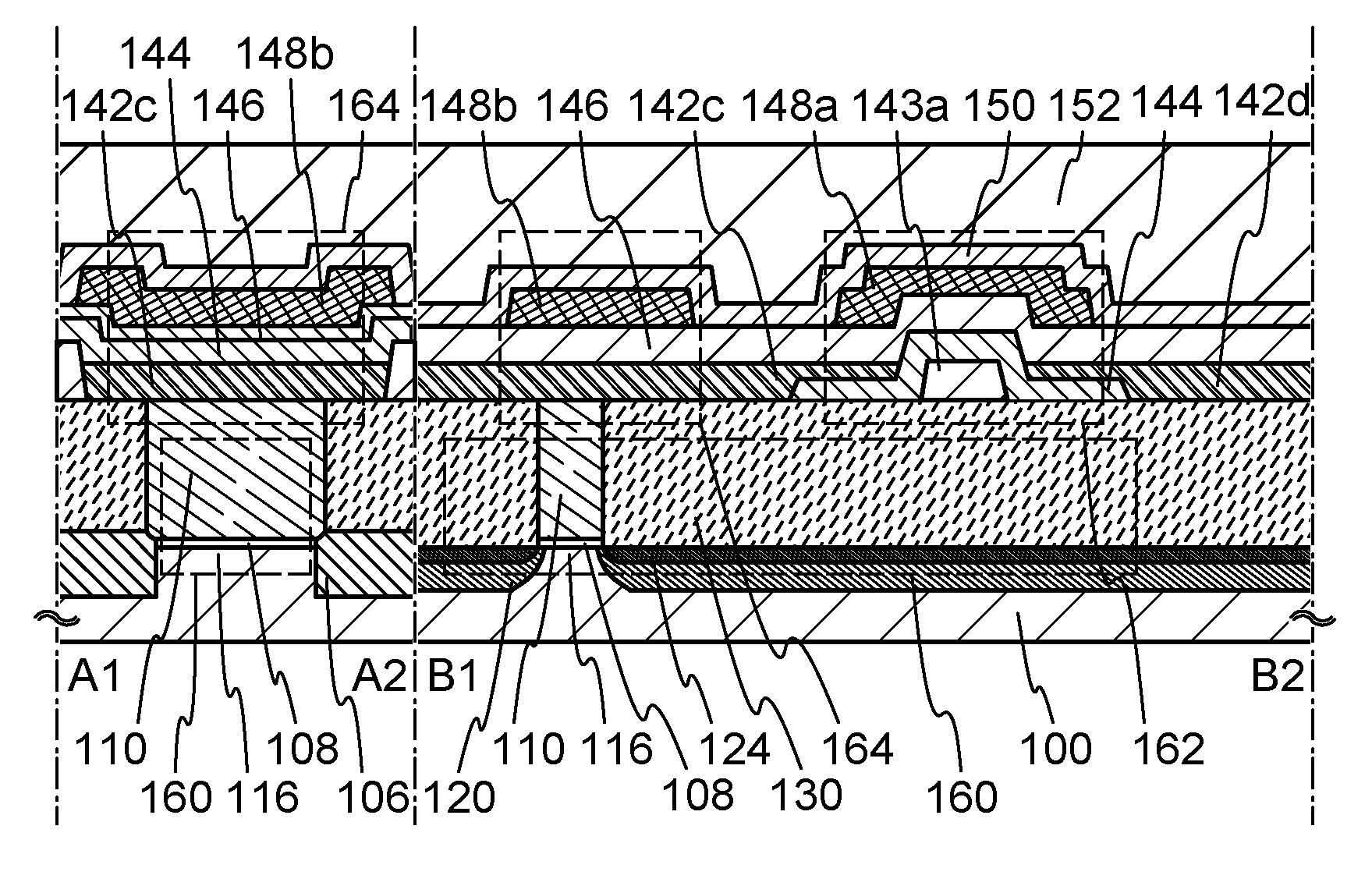

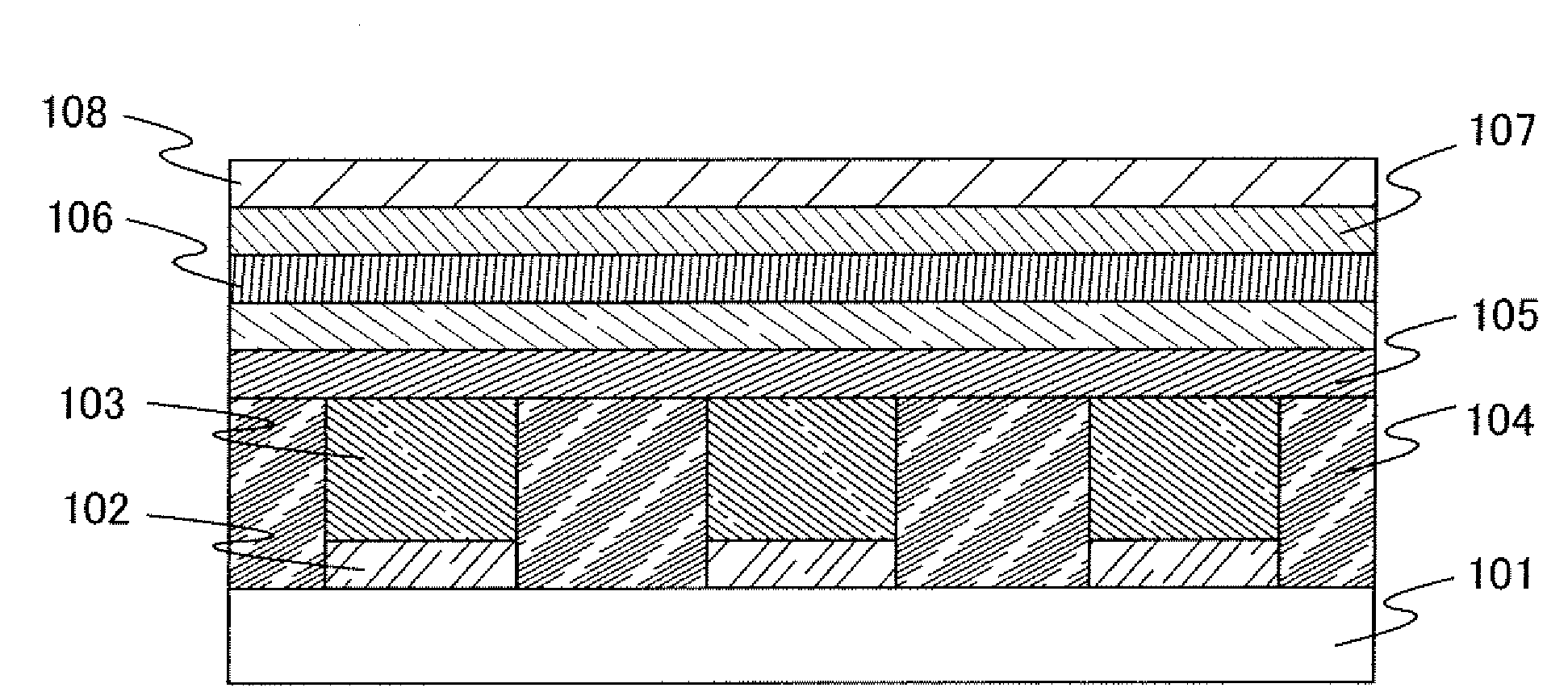

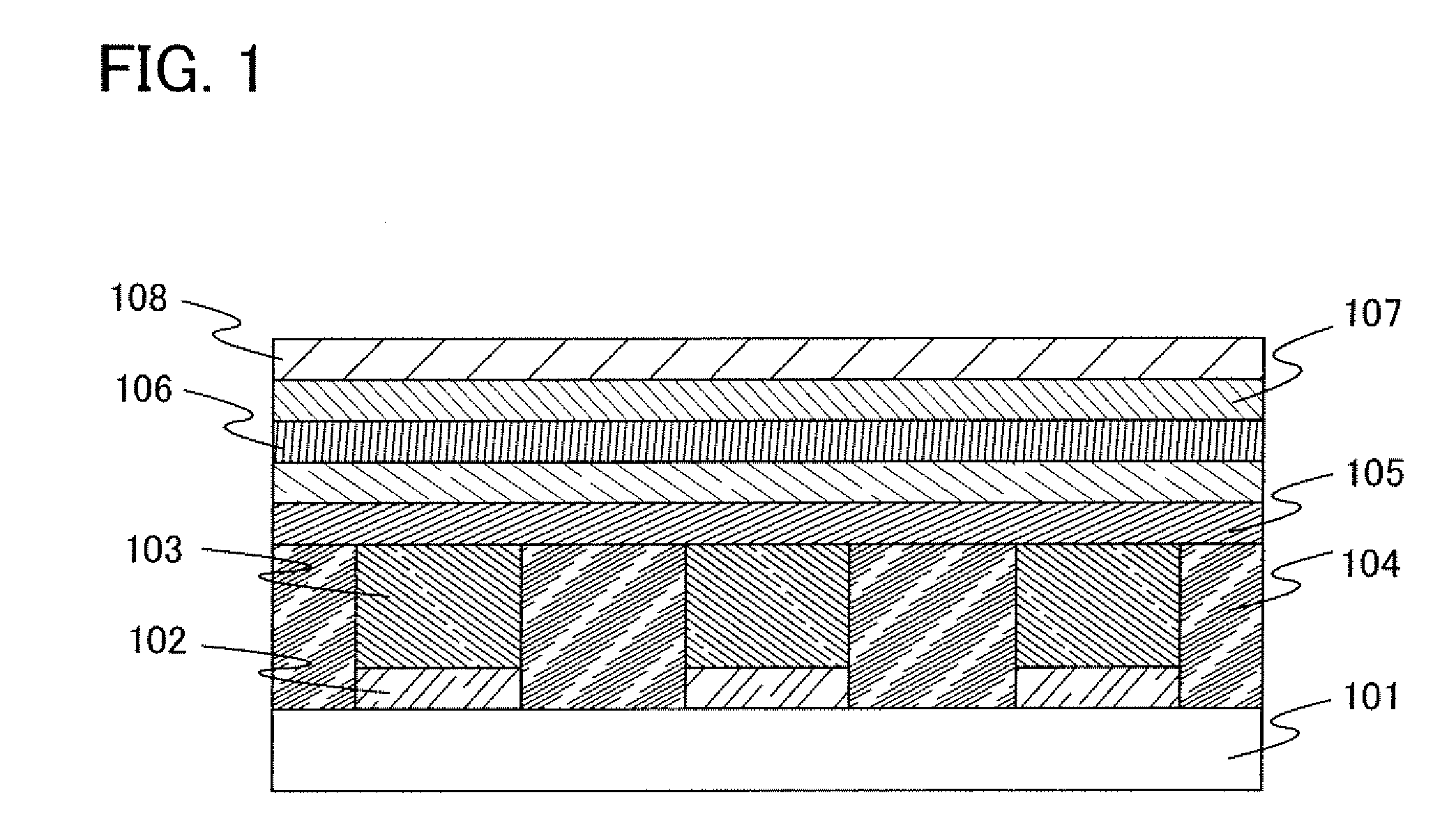

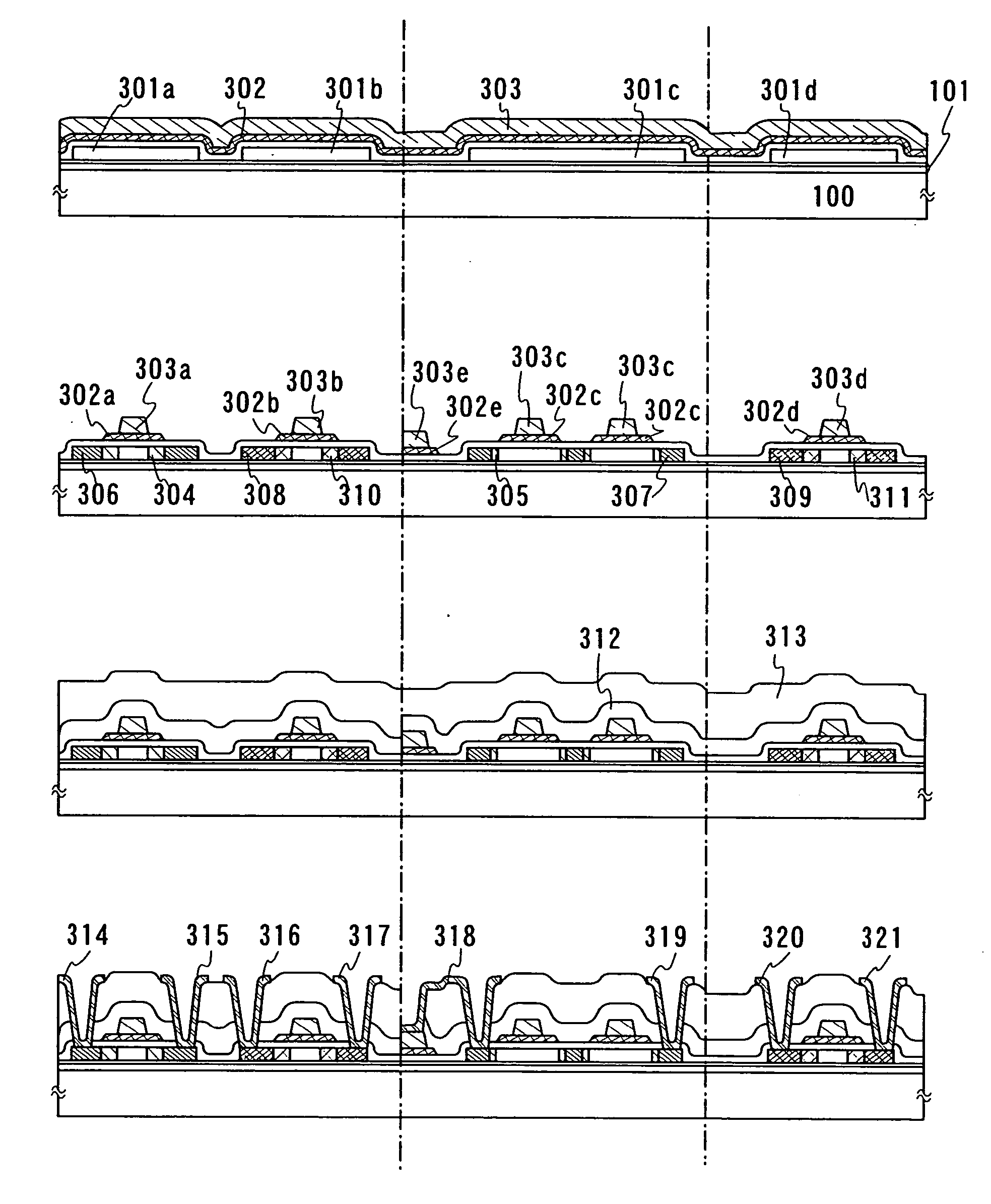

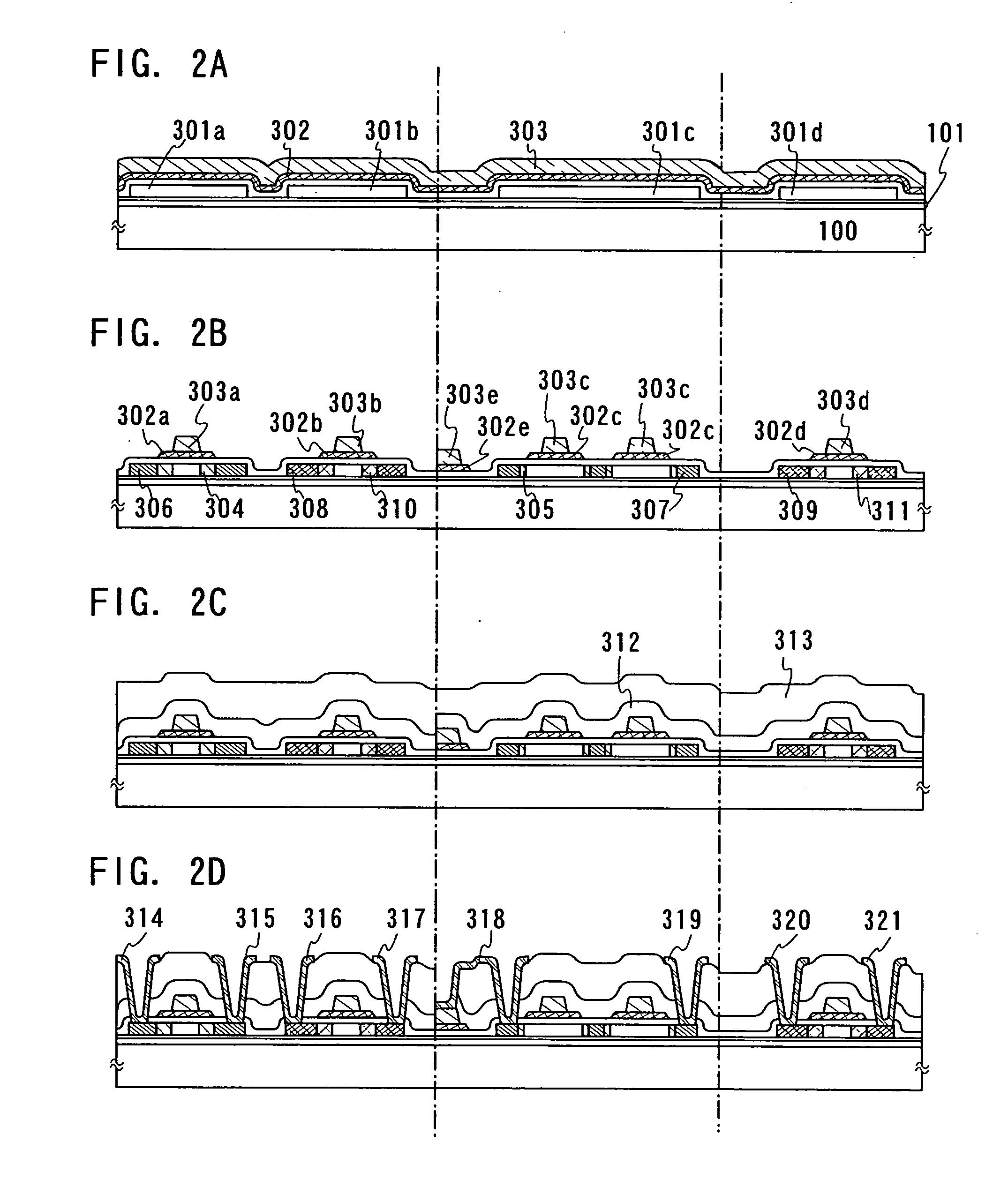

Semiconductor device and method for manufacturing semiconductor device

InactiveUS20110215317A1Inhibition defectMaintaining favorable characteristicTransistorSolid-state devicesPhysicsOxide semiconductor

Disclosed is a semiconductor device including an insulating layer, a source electrode and a drain electrode embedded in the insulating layer, an oxide semiconductor layer in contact with the insulating layer, the source electrode, and the drain electrode, a gate insulating layer covering the oxide semiconductor layer, and a gate electrode over the gate insulating layer. The upper surface of the surface of the insulating layer, which is in contact with the oxide semiconductor layer, has a root-mean-square (RMS) roughness of 1 nm or less. There is a difference in height between an upper surface of the insulating layer and each of an upper surface of the source electrode and an upper surface of the drain electrode. The difference in height is preferably 5 nm or more. This structure contributes to the suppression of defects of the semiconductor device and enables their miniaturization.

Owner:SEMICON ENERGY LAB CO LTD

Method for manufacturing electronic device and separation apparatus used therefor

InactiveCN102171745ASuppression of substrate defectsInhibition defectSolid-state devicesSemiconductor/solid-state device manufacturingEngineering

Owner:ASAHI GLASS CO LTD

Silicon carbide semiconductor device and method for manufacturing the same

ActiveUS7365363B2Improve surface conditionImprove regularitySemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialSemiconductor

A silicon carbide semiconductor device includes: a semiconductor substrate having a principal surface and a backside surface; a drift layer disposed on the principal surface; a base region disposed on the drift layer; a source region disposed on the base region; a surface channel layer disposed on both of the drift layer and the base region for connecting between the source region and the drift layer; a gate insulation film disposed on the surface channel layer and including a high dielectric constant film; a gate electrode disposed on the gate insulation film; a source electrode disposed on the source region; and a backside electrode disposed on the backside surface.

Owner:DENSO CORP

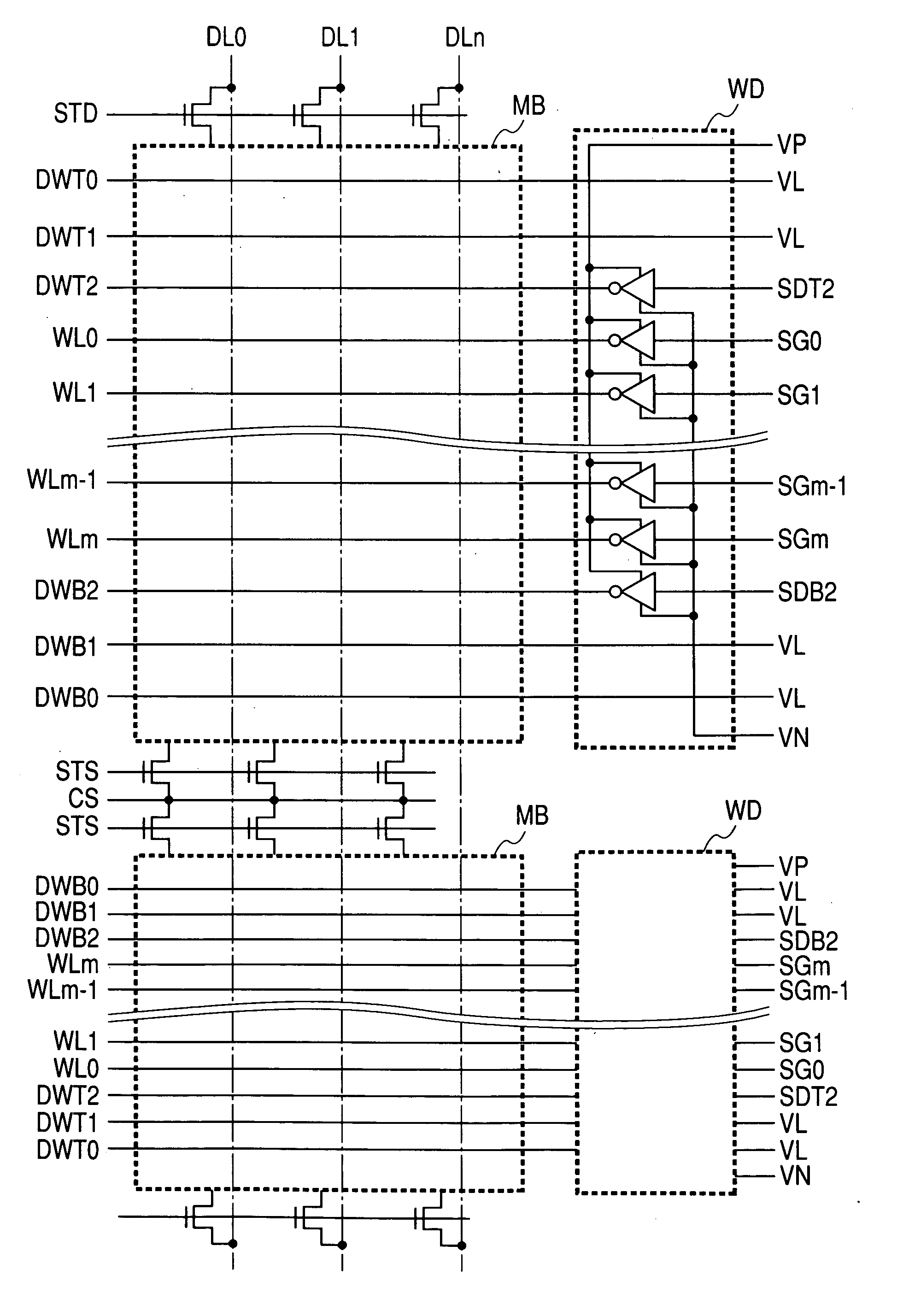

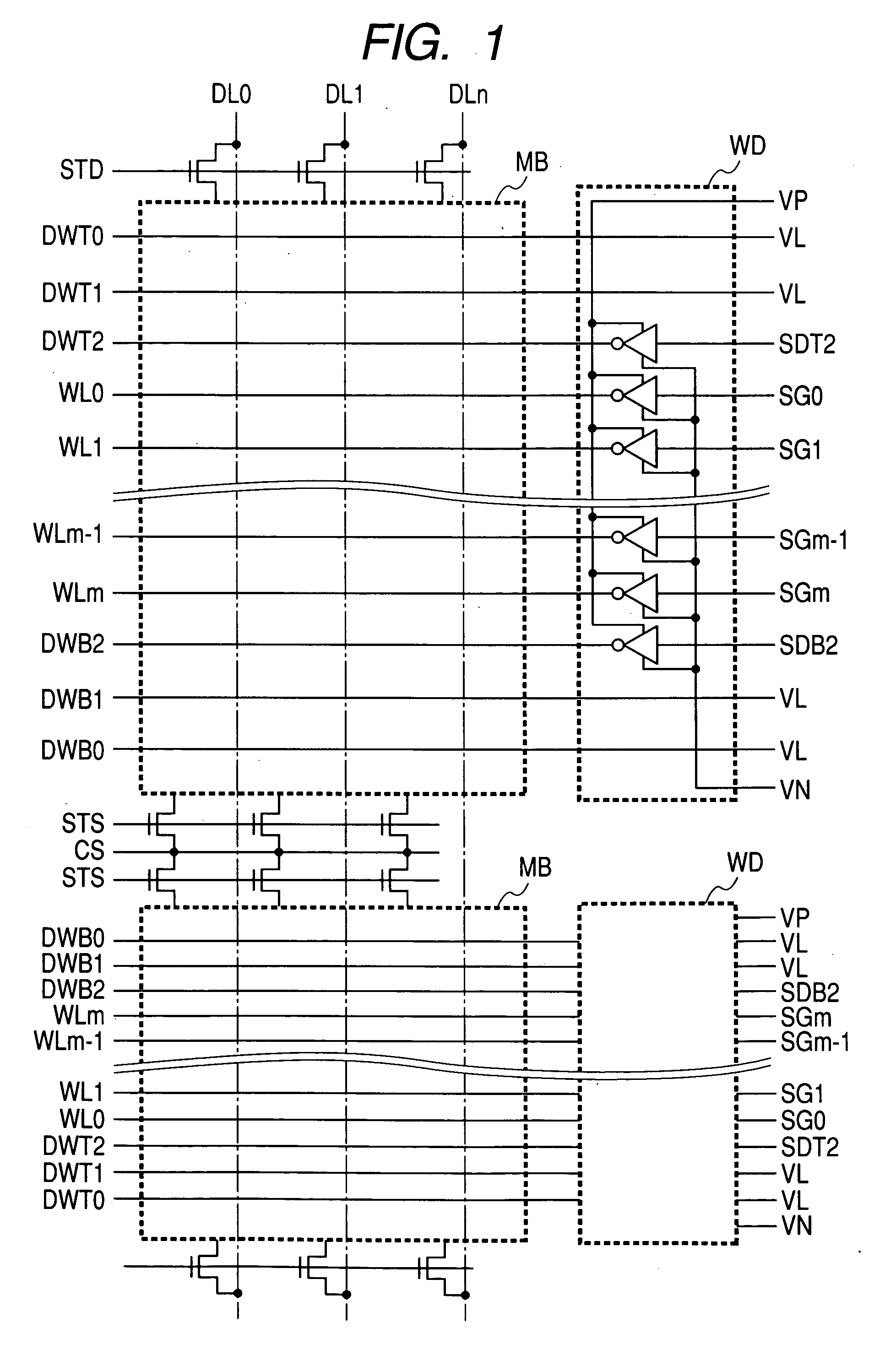

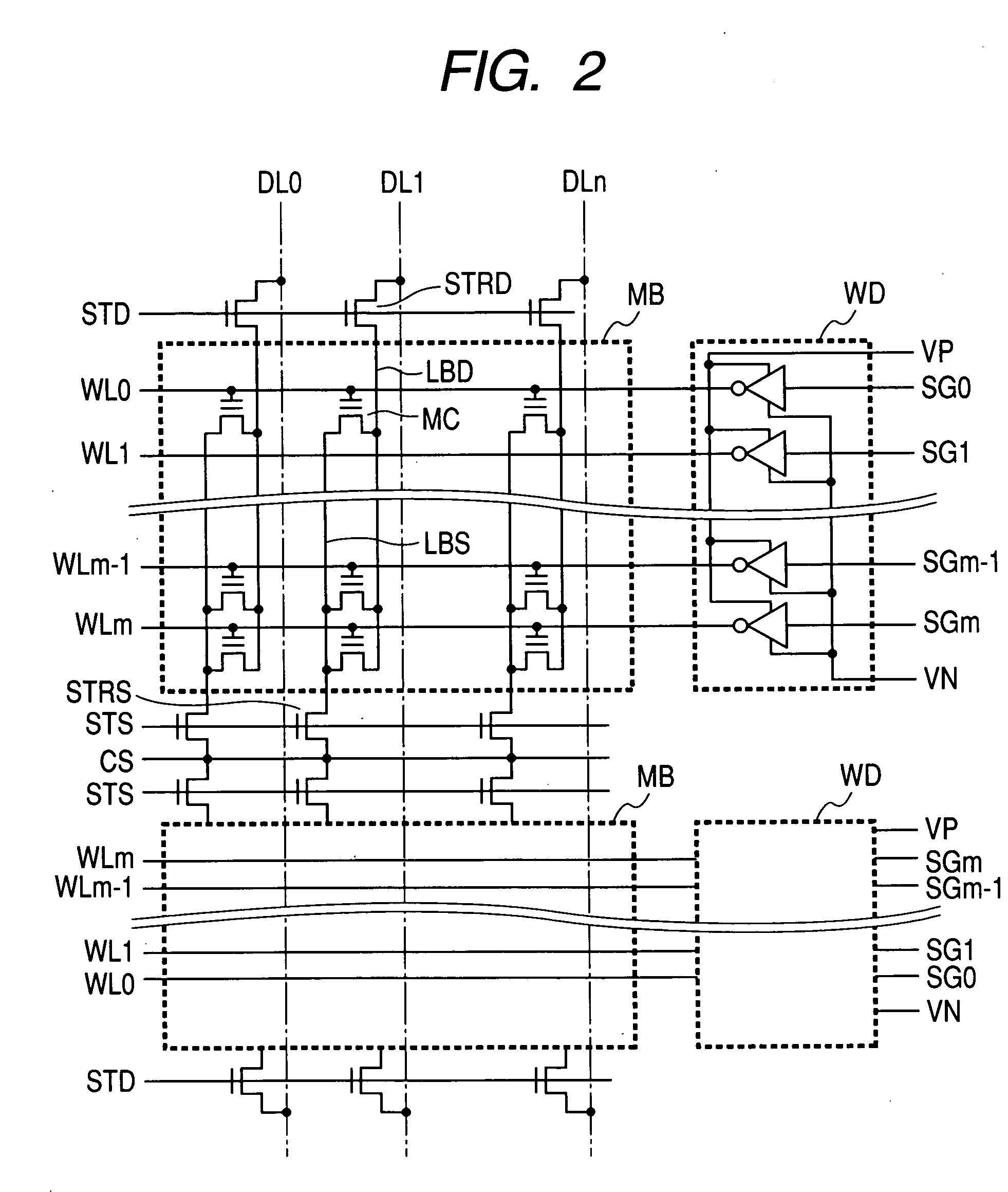

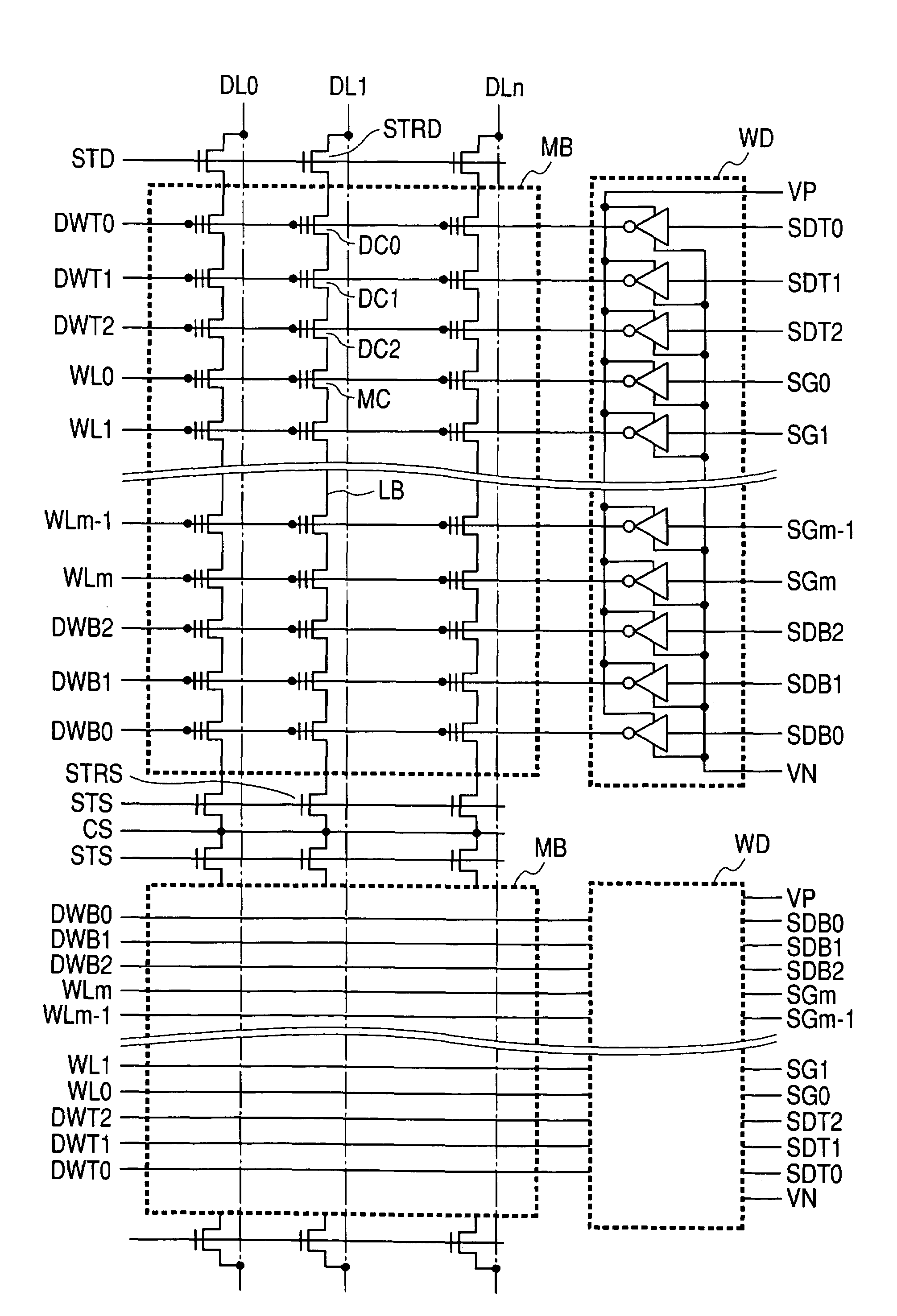

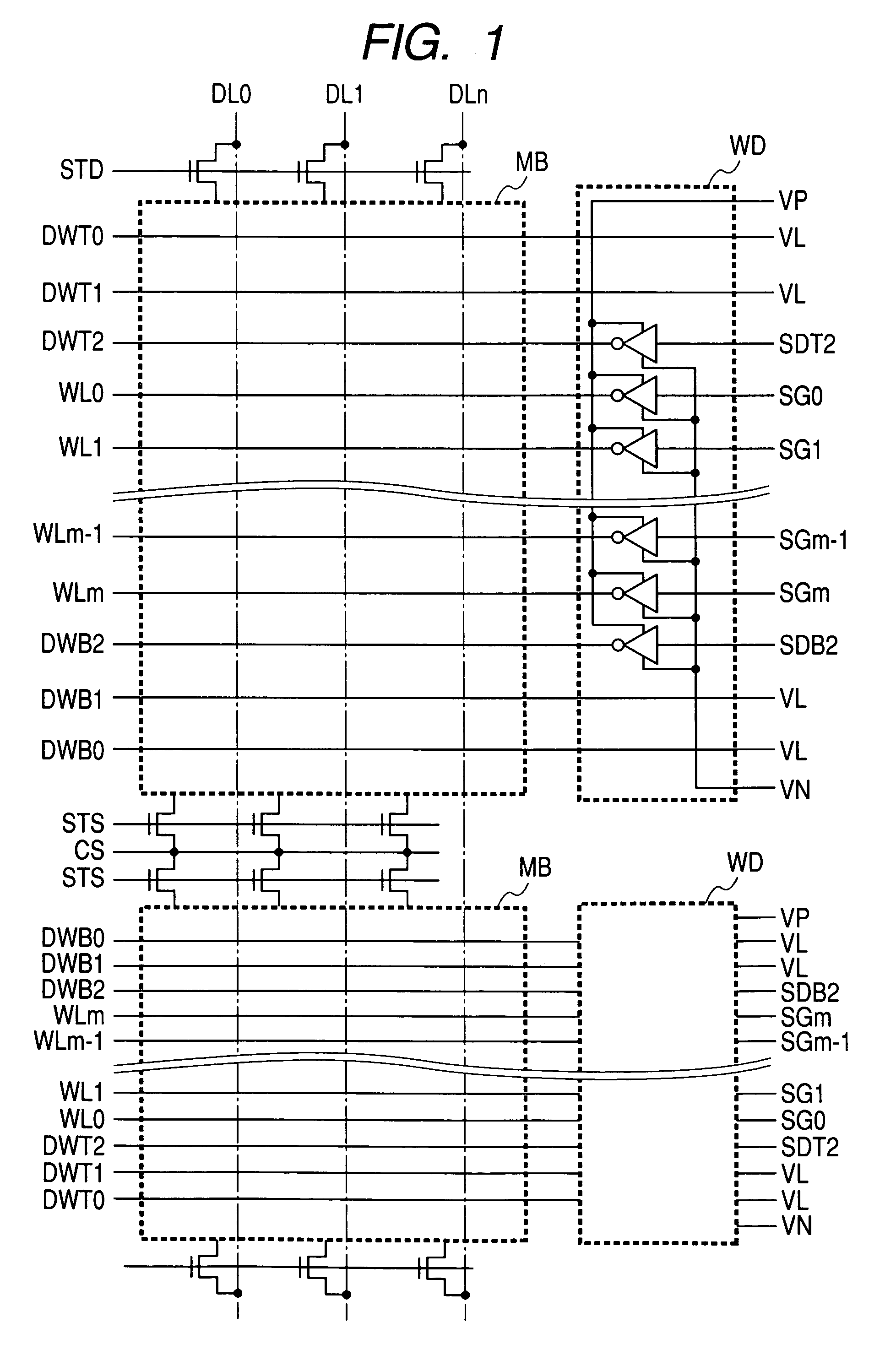

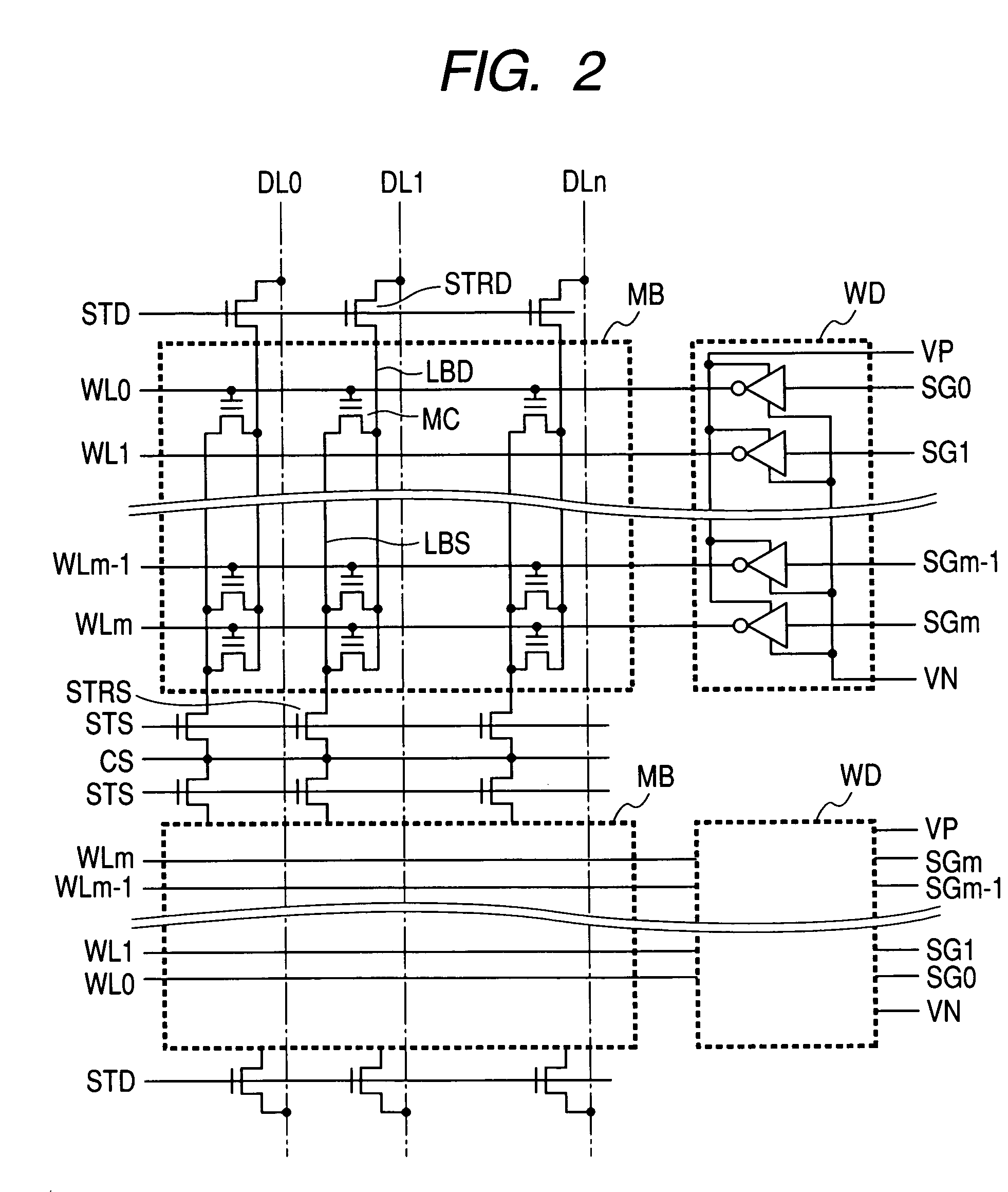

Semiconductor memory device

InactiveUS20060039230A1Increase productionImprove reliabilityRead-only memoriesDigital storageComputer scienceSemiconductor

An object of the present invention is to provide a semiconductor memory device capable of preventing a defect caused by falling of a word line and deterioration in patterning precision due to disturbance of the pitch of word lines at an end of a memory block. Plural dummy word lines are disposed at an end of a memory block, a word driver is mounted for the dummy word line to control the threshold voltage of a dummy memory cell formed below the dummy word line. Also at the time of operating a memory area for storing data from the outside, a bias is applied to the dummy word line. The invention can prevent a defect caused by falling of a word line and deterioration in patterning precision due to disturbance of the pitches of word lines at an end of a memory block, and realize high yield and reliably operation.

Owner:RENESAS ELECTRONICS CORP

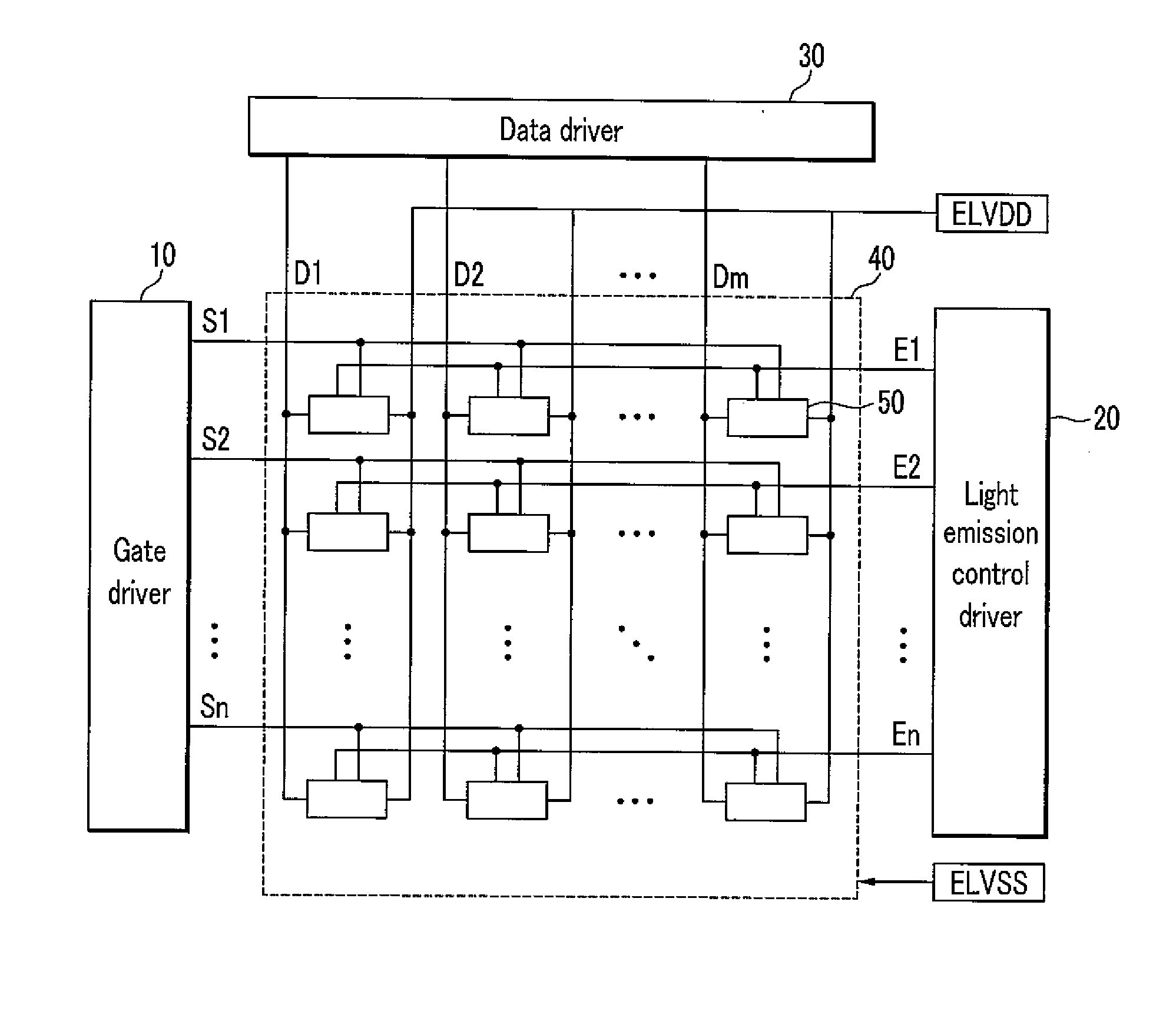

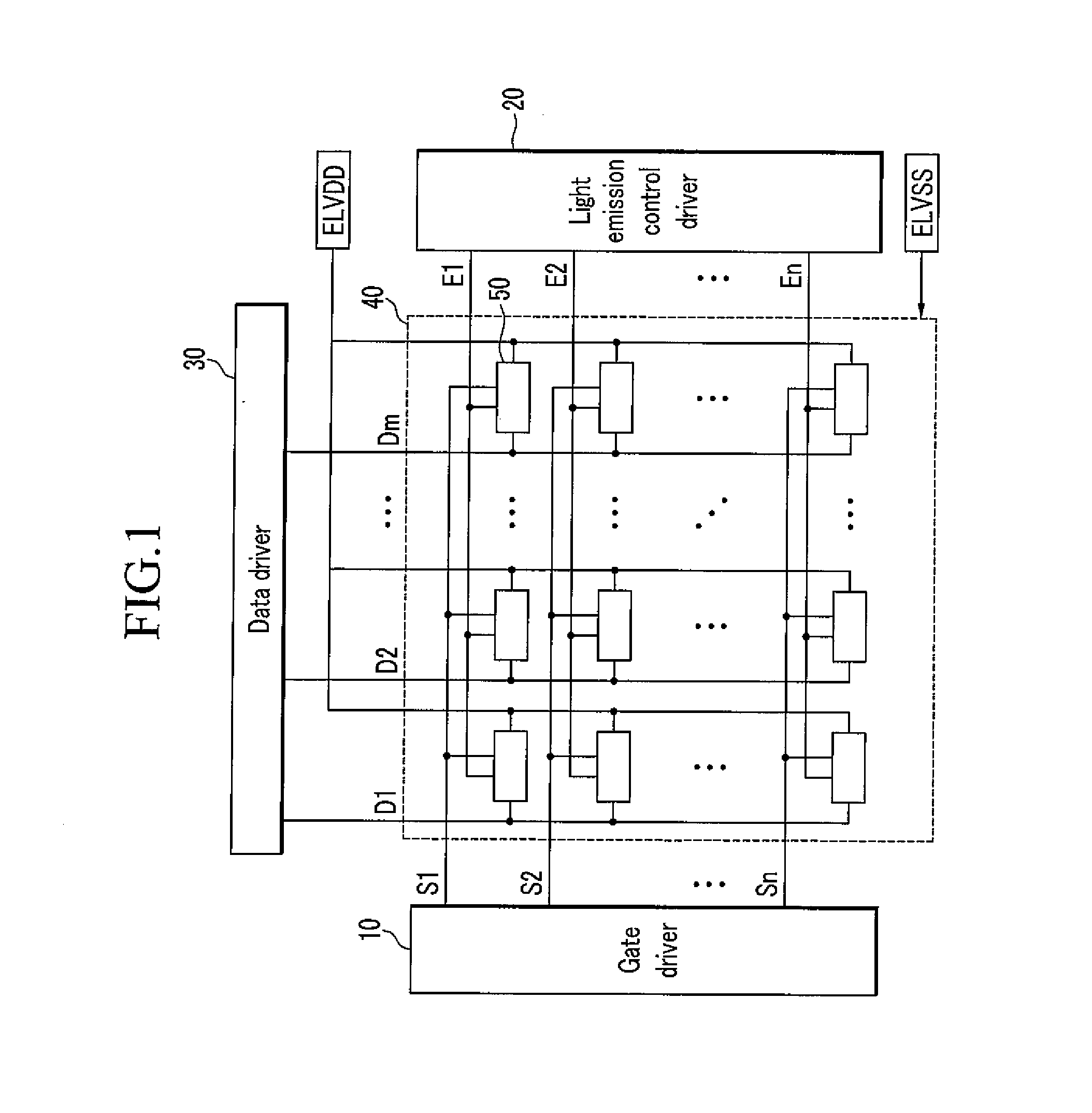

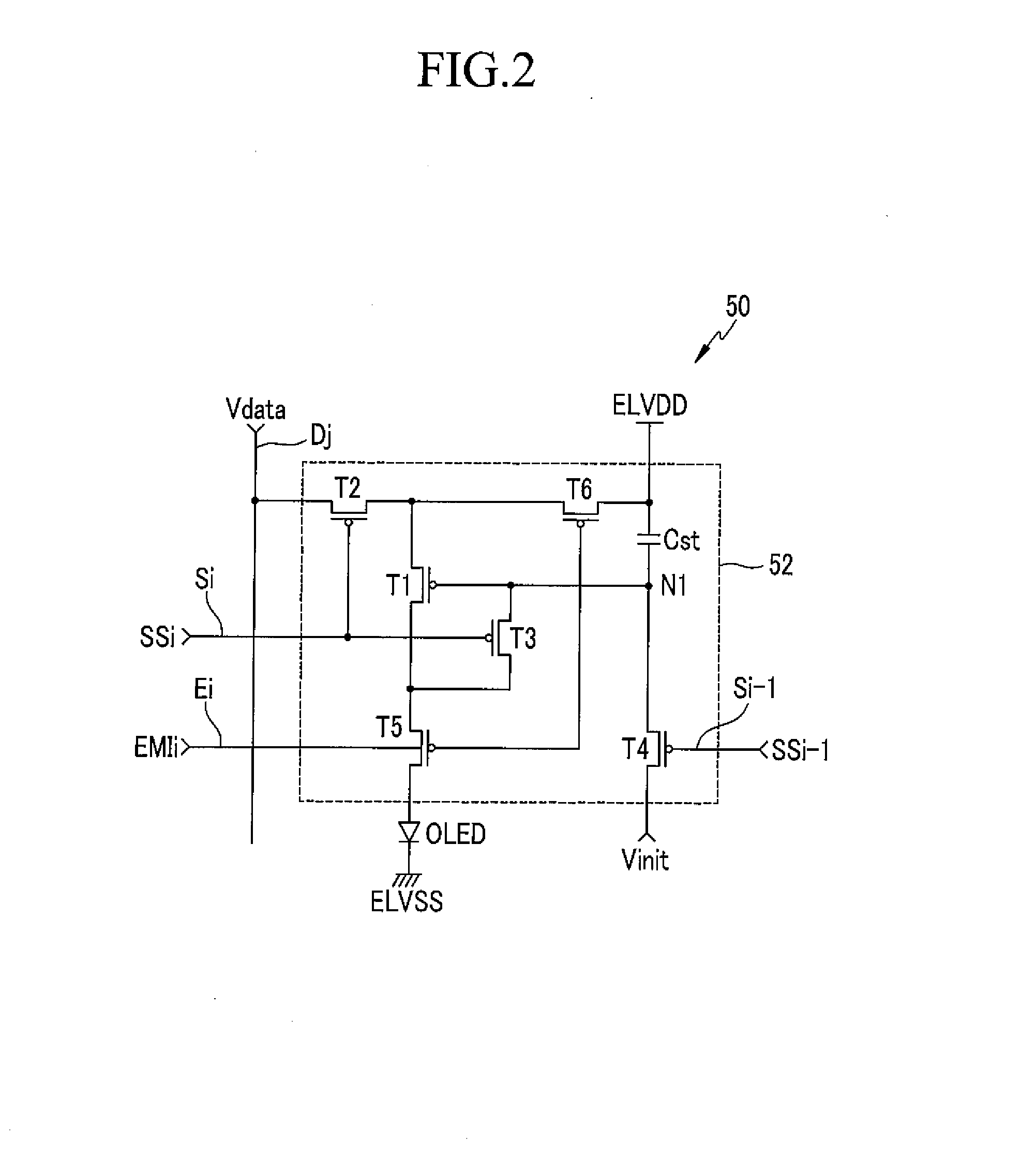

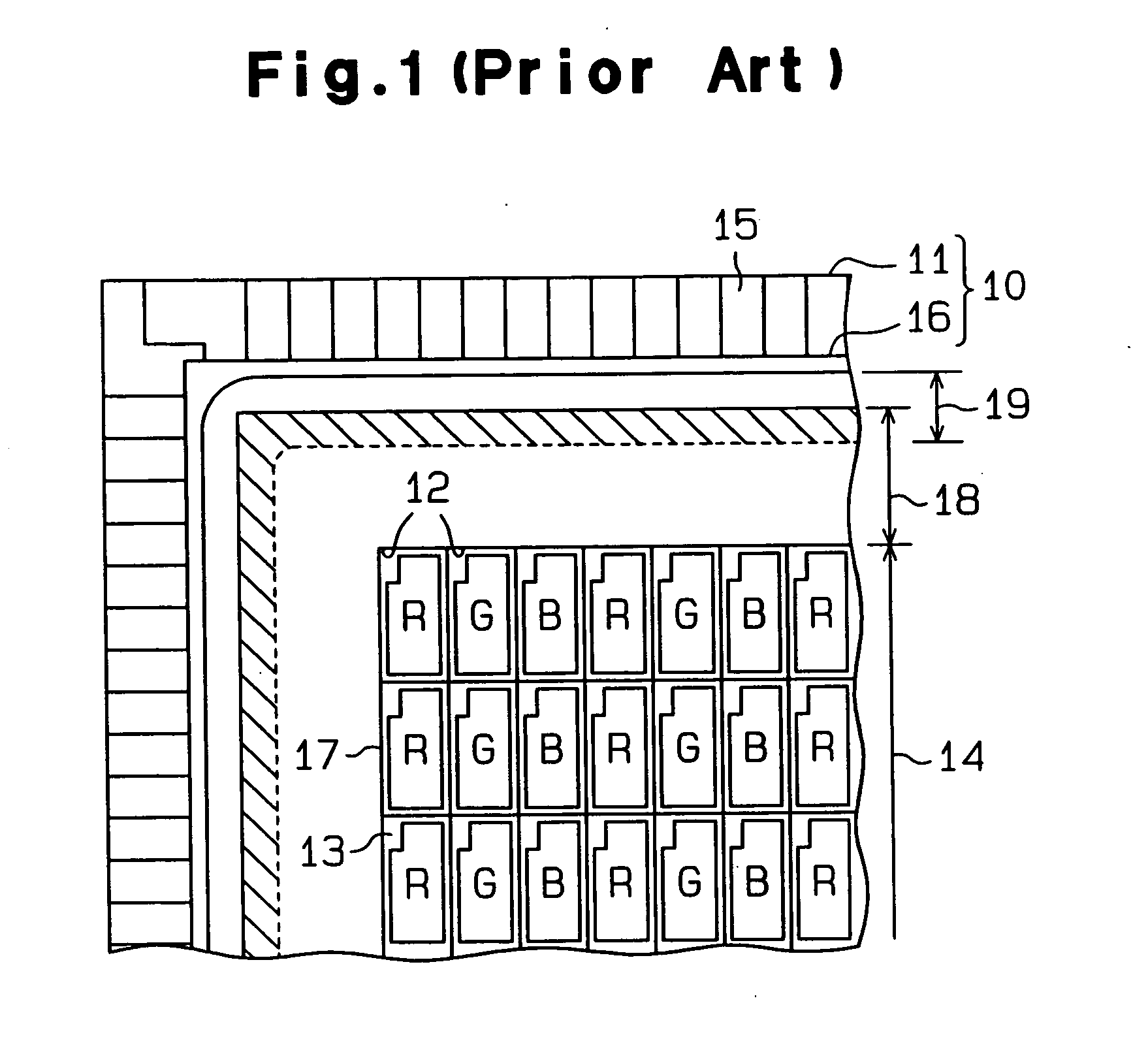

Organic light emitting diode display

ActiveUS20130335397A1Inhibition defectCathode-ray tube indicatorsInput/output processes for data processingControl signalDisplay device

A display including: pixels; a gate driver for supplying a gate signal to gate lines; a lighting test circuit coupled to a first input line (for transmitting a lighting test signal), and a second input line (for transmitting a test control signal), the light test circuit being for supplying the lighting test signal to data lines according to the test control signal; a first power supply line for supplying a gate high level voltage to the gate driver and at a periphery of the gate driver and the lighting test circuit; and a second power supply line for supplying a gate low level voltage to the gate driver and at a periphery of the gate driver and the lighting test circuit. The second input line is coupled to the first power supply line or the second power supply line through a resistor.

Owner:SAMSUNG DISPLAY CO LTD

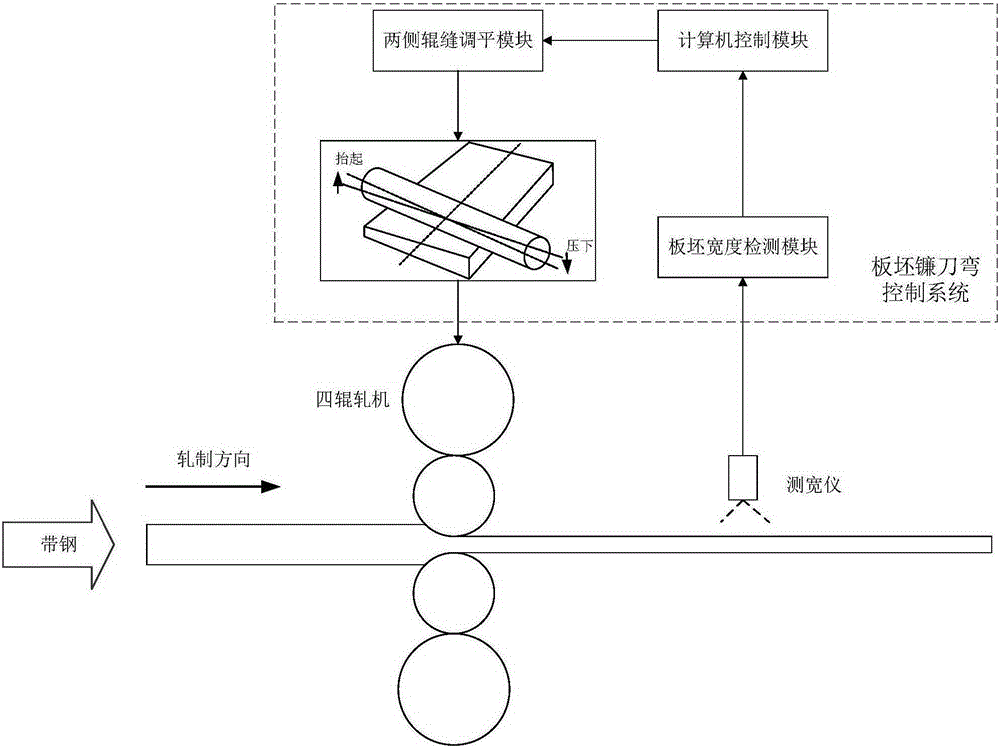

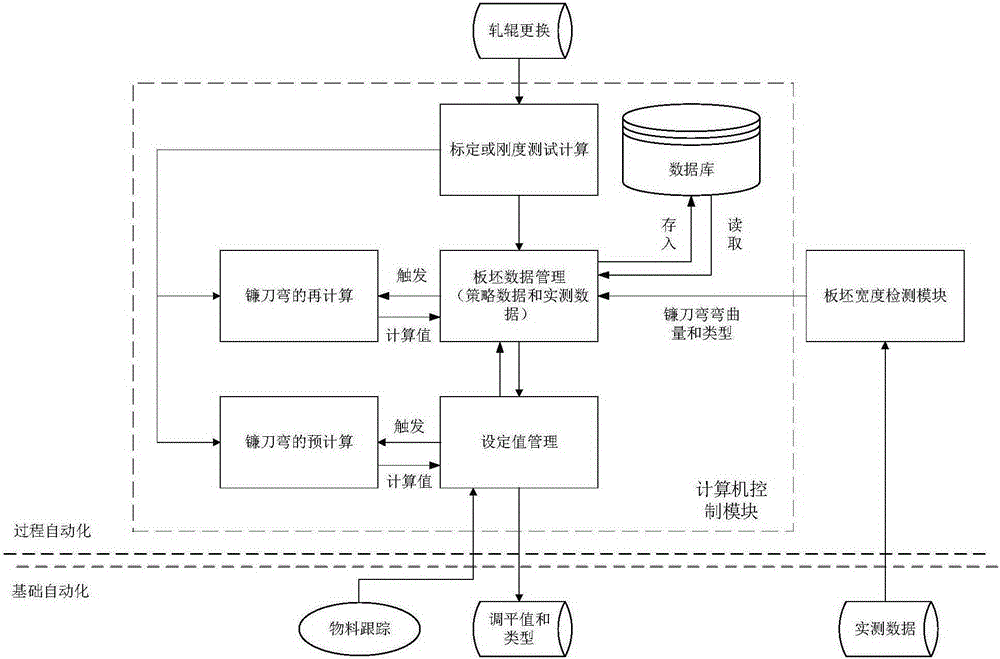

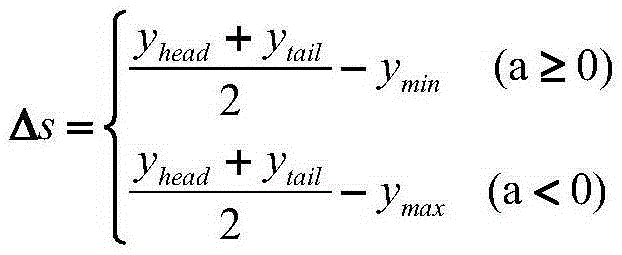

Slab sickle bending control system and method used for roughing mill

InactiveCN105234189AIncreased level of controlInhibition defectRoll force/gap control deviceAutomatic controlStrip mill

The invention discloses a slab sickle bending control system and a slag sickle bending control method used for a roughing mill, and belongs to the field of mechanical automatic control. The control system comprises a slab width detecting module, two side roller beam leveling modules, a computer control module and a storage unit. The slag width detecting module is used for processing centre line offset data detected by a width detector and sending the processed centre line offset data to the computer control module; the computer control module is used for calculating a leveling value of each gate by collecting a set value of slag and practically measured value data, and sending the leveling value to the two side roller beam leveling modules; and the two side roller beam leveling modules are used for regulating two side roller beams of the roughing mill according to the leveling value, and controlling the slab sickle bending. The control system is applicable on the roughing mill, capable of calculating the leveling value of each gate more accurately, and capable of effectively controlling slag sickle bending and guaranteeing stability of finishing rolling unit production, thereby relieving steel scrap caused by off-tracking, shifting and the like, increasing yield and bringing direct economic benefits for enterprises.

Owner:BEIJING SHOUGANG AUTOMATION INFORMATION TECH

Semiconductor memory device comprising controllable threshould voltage dummy memory cells

InactiveUS7301815B2Increase productionImprove reliabilityRead-only memoriesDigital storageEngineeringSemiconductor

The present invention provides a semiconductor memory device capable of preventing a defect caused by falling of a word line and deterioration in patterning precision due to disturbance of the pitch of word lines at an end of a memory block. Plural dummy word lines are disposed at an end of a memory block and a word driver is mounted for the dummy word line to control the threshold voltage of a dummy memory cell formed below the dummy word line. Also at the time of operating a memory area for storing data from the outside, a bias is applied to the dummy word line. The invention can prevent a defect caused by falling of a word line and deterioration in patterning precision due to disturbance of the pitches of word lines at an end of a memory block, and realize high yield and reliable operation.

Owner:RENESAS ELECTRONICS CORP

Method of preparing high-performance powder metallurgy product by coating alloy powder with organic matter

ActiveCN108465806AIncrease oxygen contentImprove mechanical propertiesTransportation and packagingMetal-working apparatusChemical reactionAlloy

The invention provides a method of preparing a high-performance powder metallurgy product by coating alloy powder with an organic matter, and belongs to the field of powder metallurgy. The method comprises the following steps that the surface of the alloy powder is coated with a layer of an organic matter film by a solution coating method, the organic matter is dissolved in a solvent, a layer of aliquid film is formed on the surface of the alloy powder, after the solvent is removed, the alloy powder can be uniformly coated with the organic matter, any chemical reactions are not required, thesurface of the alloy powder is coated with the layer of the organic matter film, and the purpose that the easy-to-oxidize alloy powder is isolated from oxygen is achieved. The possibility that the surface of the easy-to-oxidize alloy powder can react with the oxygen is very high, the mechanical performance of a formed alloy component is relatively poor due to the increase of the oxygen content inthe forming process, and the organic matter is used for coating, so that the oxygen control effect in the forming process can be achieved effectively; and the oxidation resistance of the alloy powdercan be improved through the coating treatment in the forming process, so that the relatively low oxygen content and the good mechanical performance are advantageously kept after the forming is carriedout.

Owner:UNIV OF SCI & TECH BEIJING

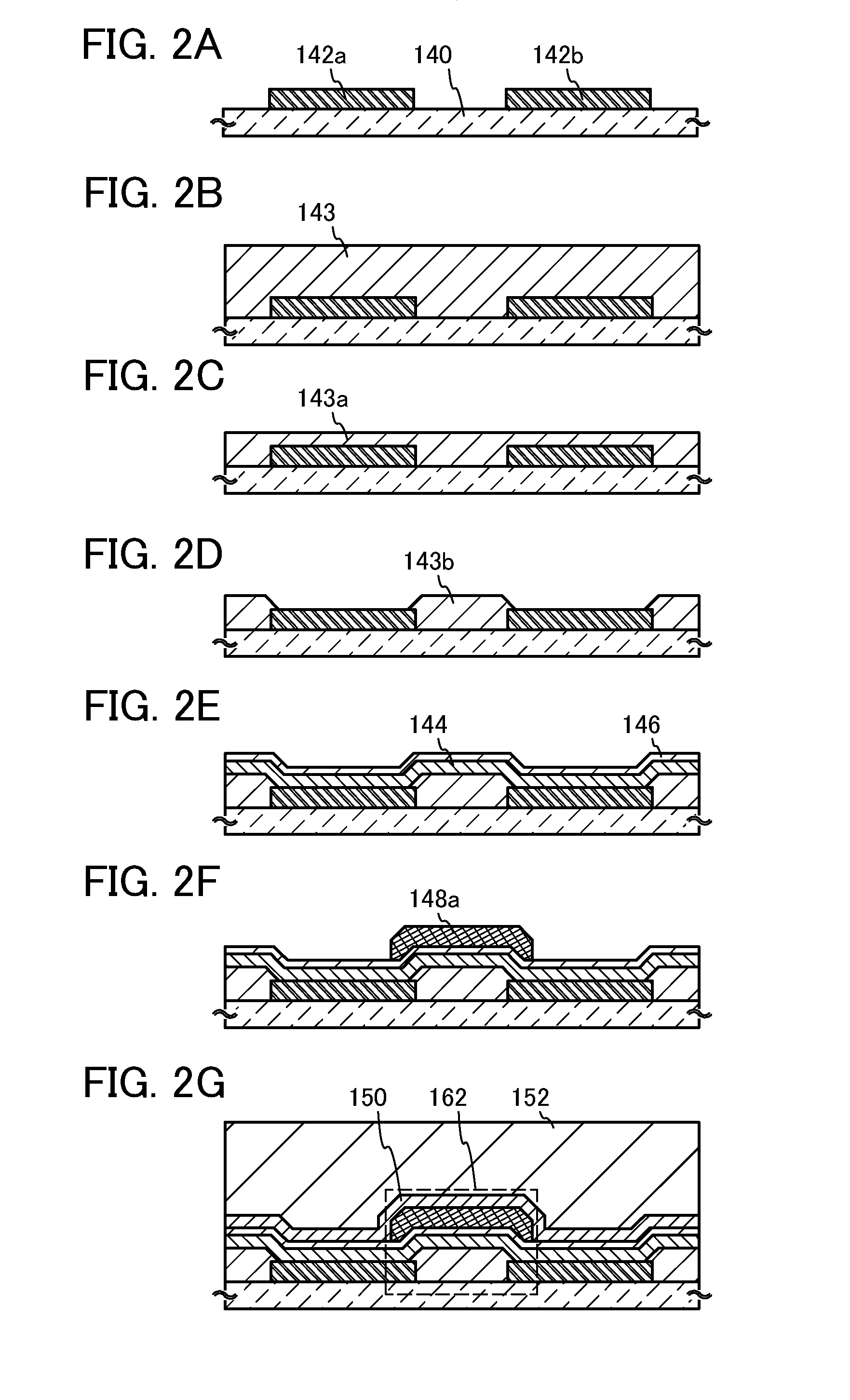

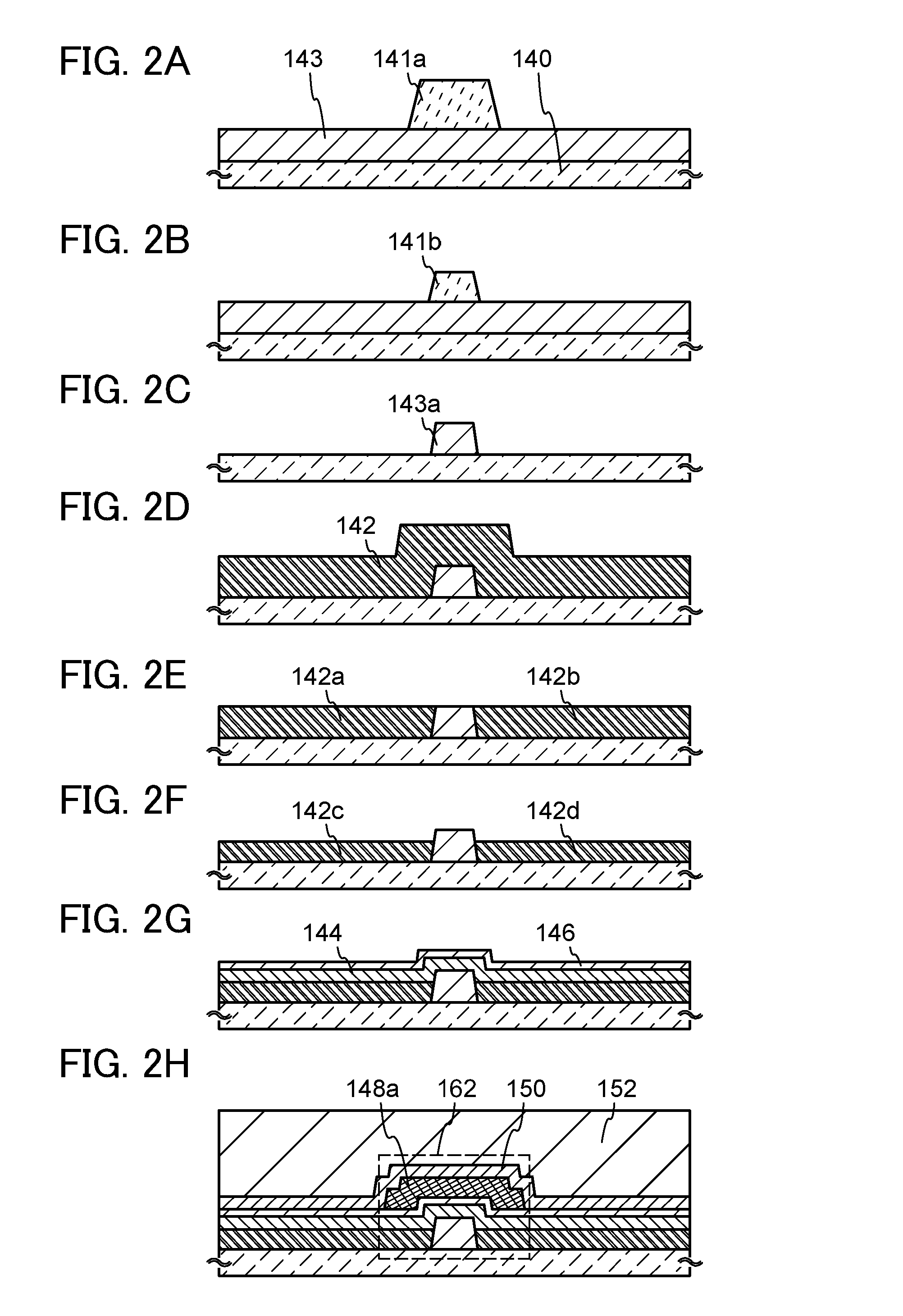

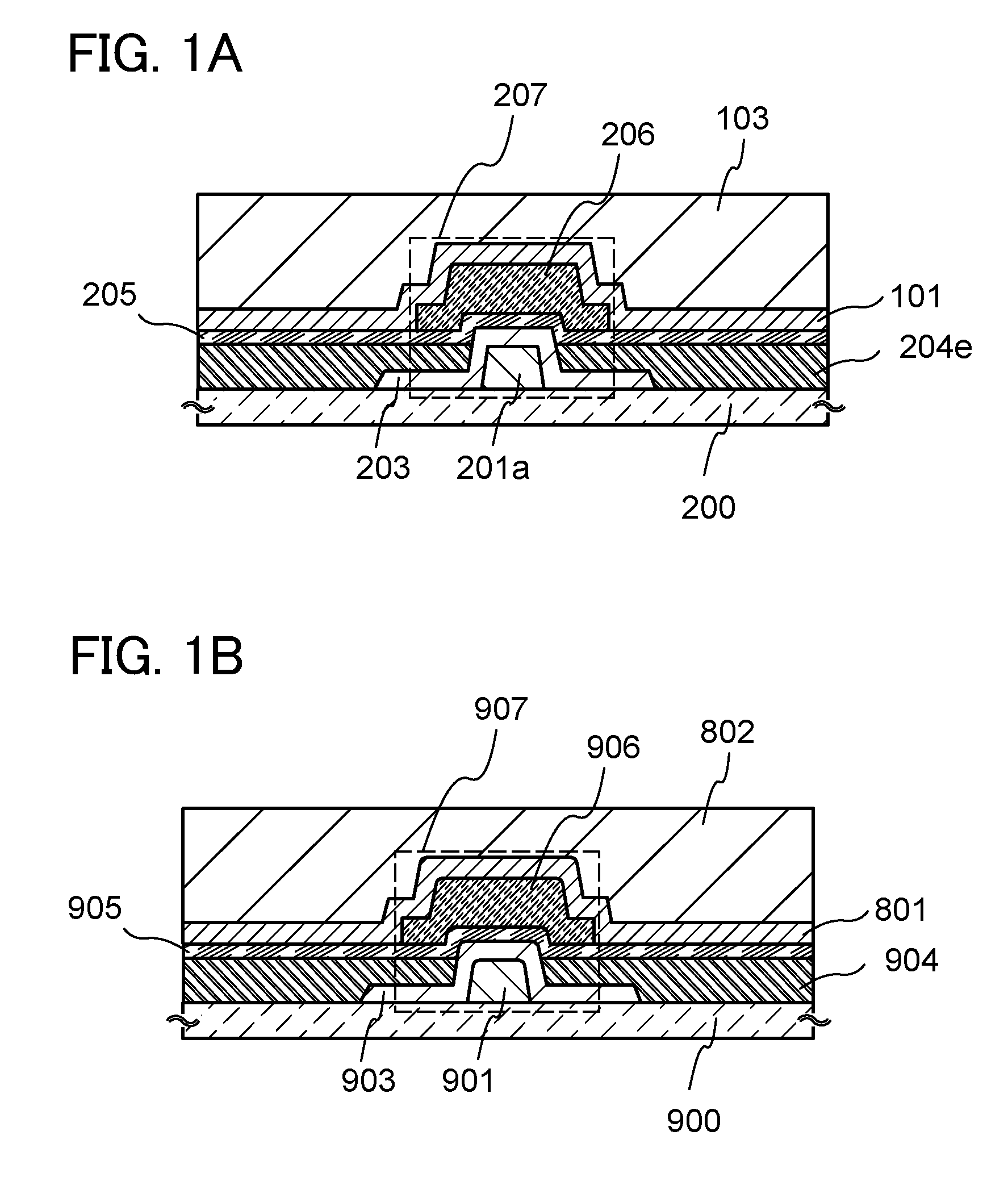

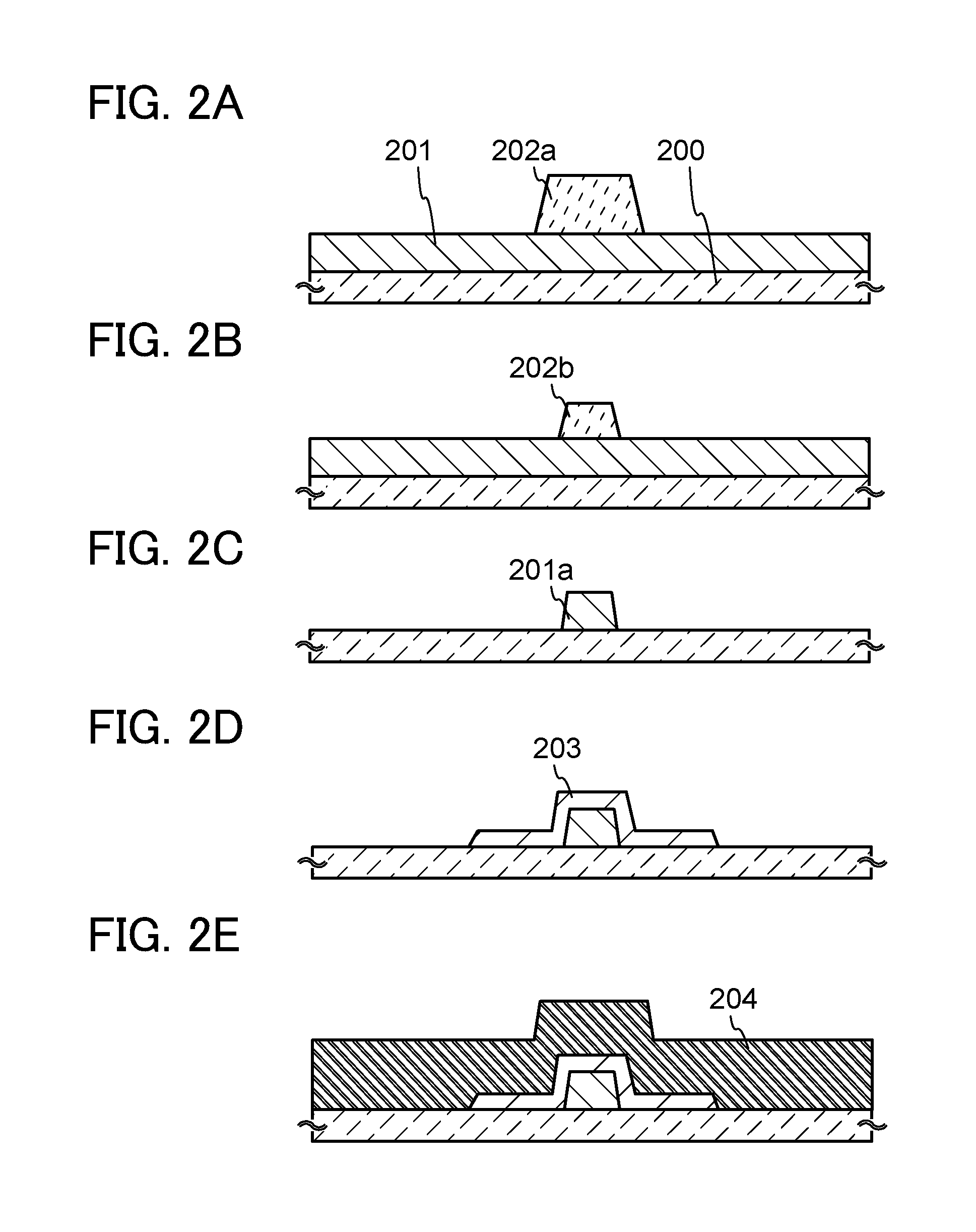

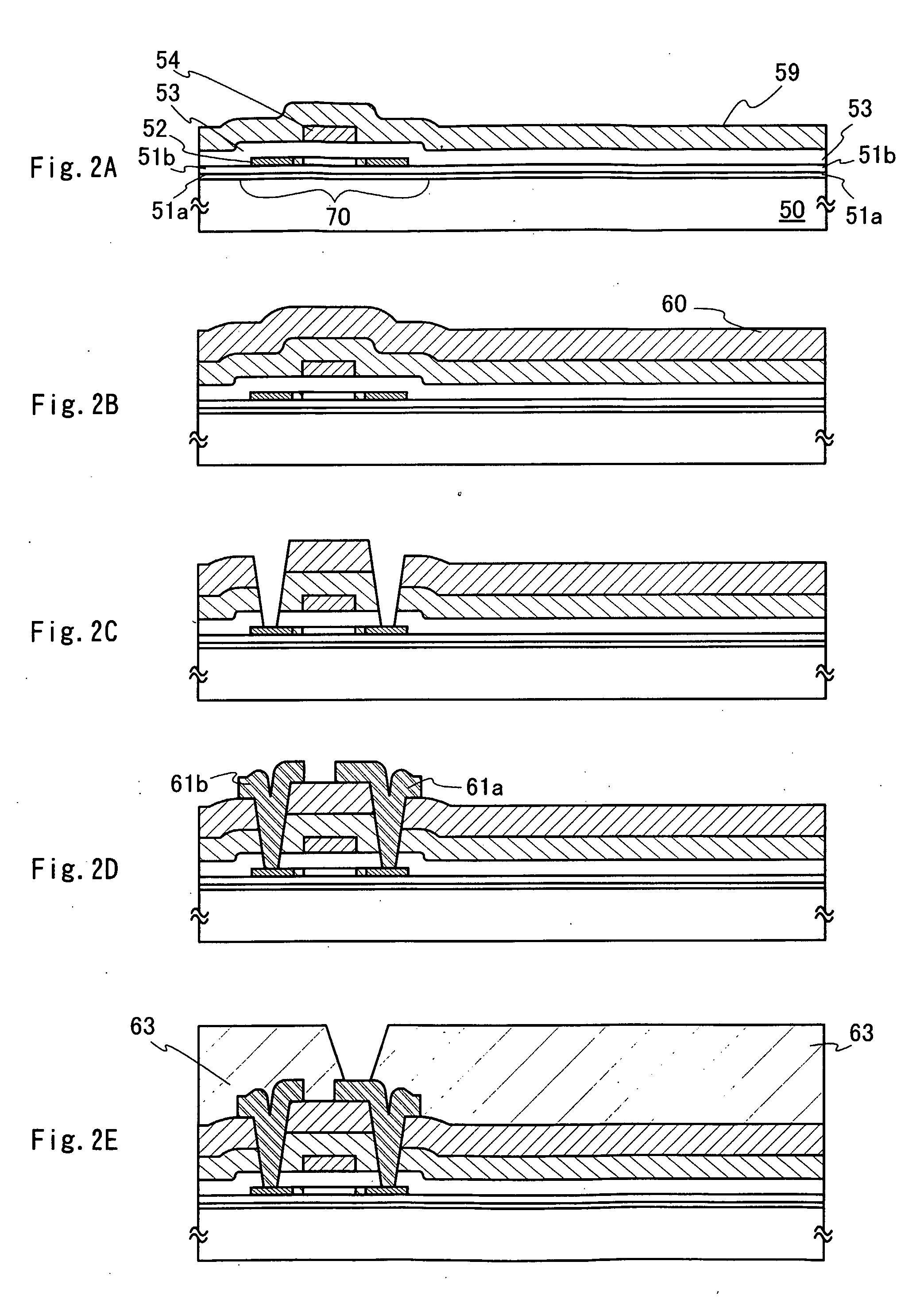

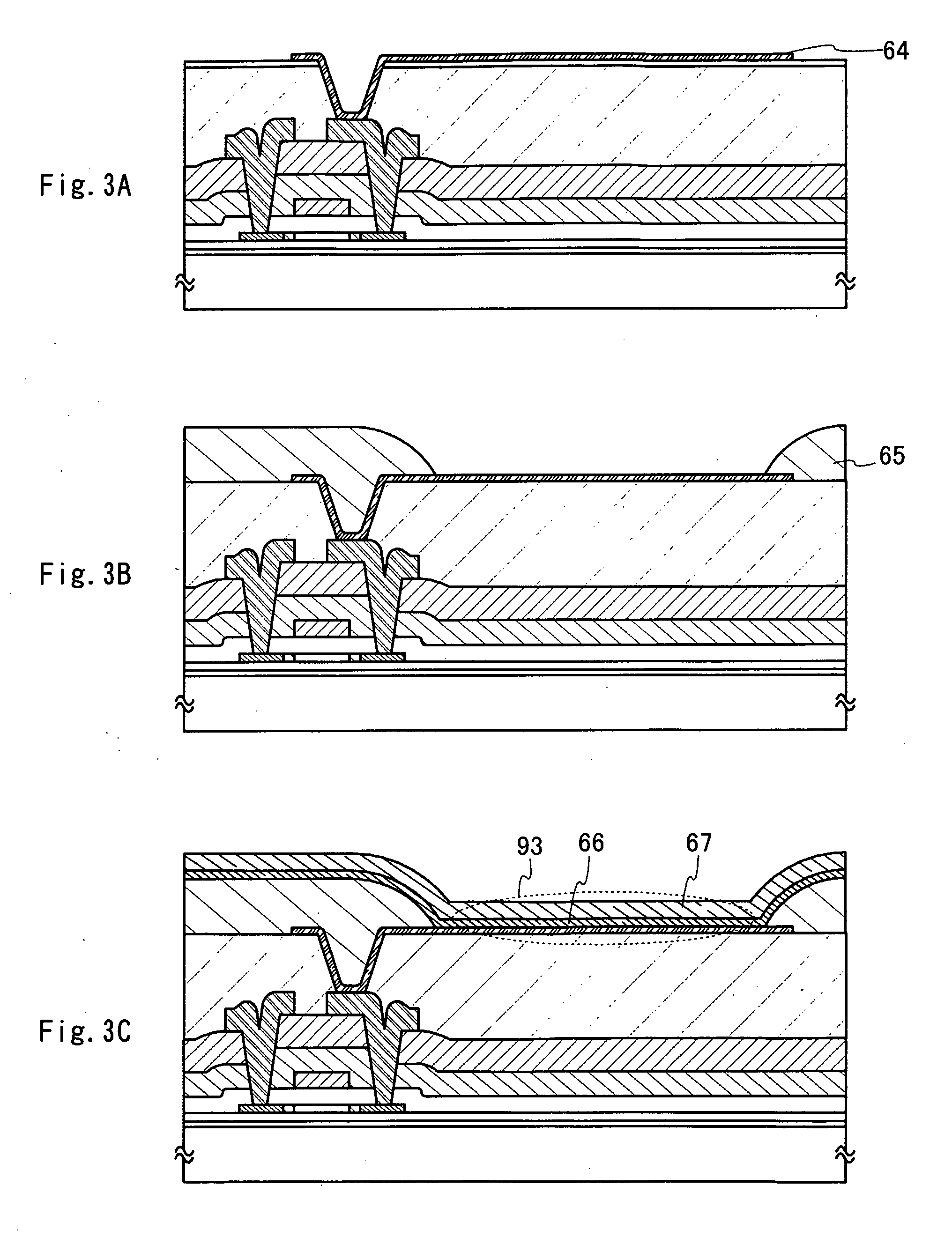

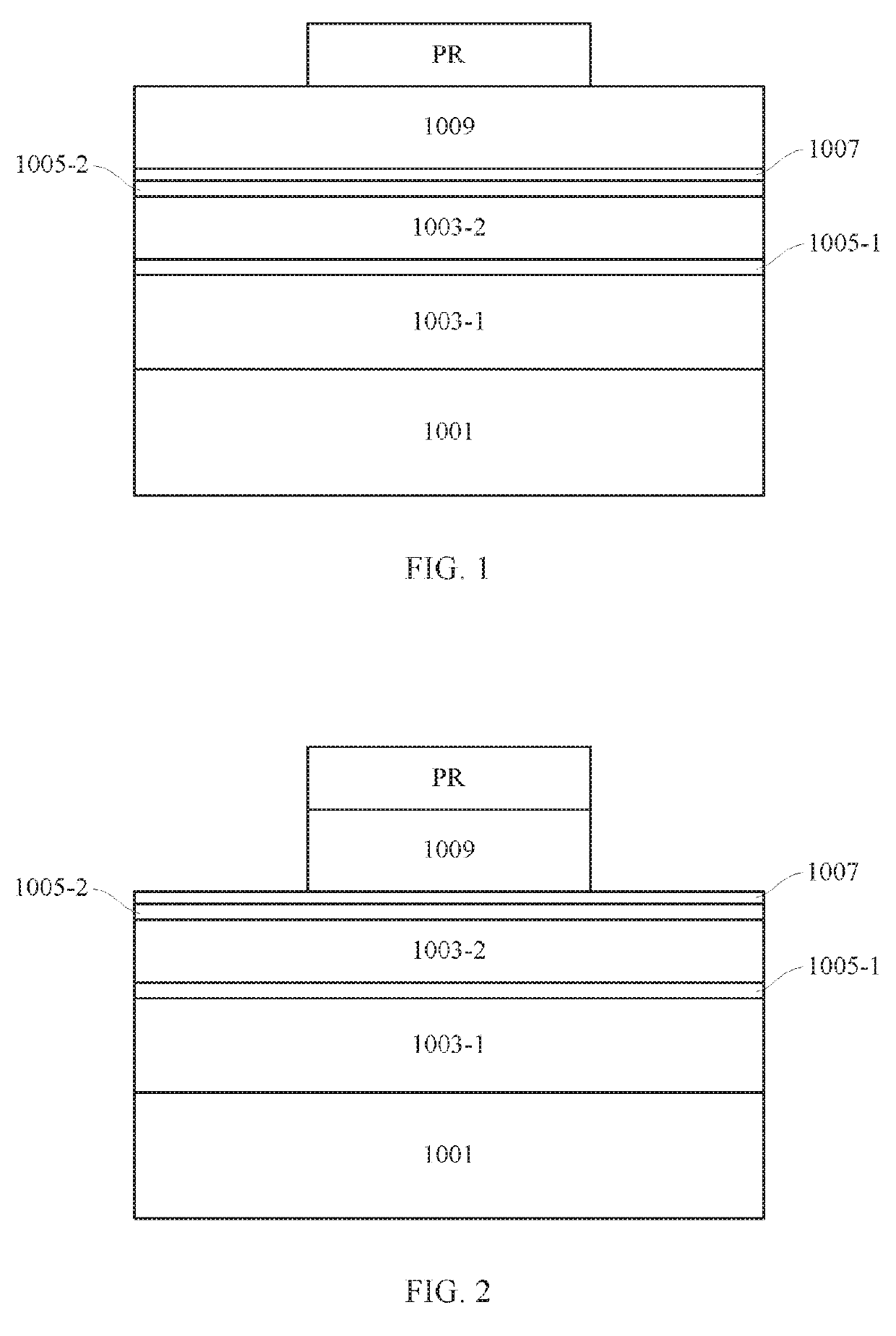

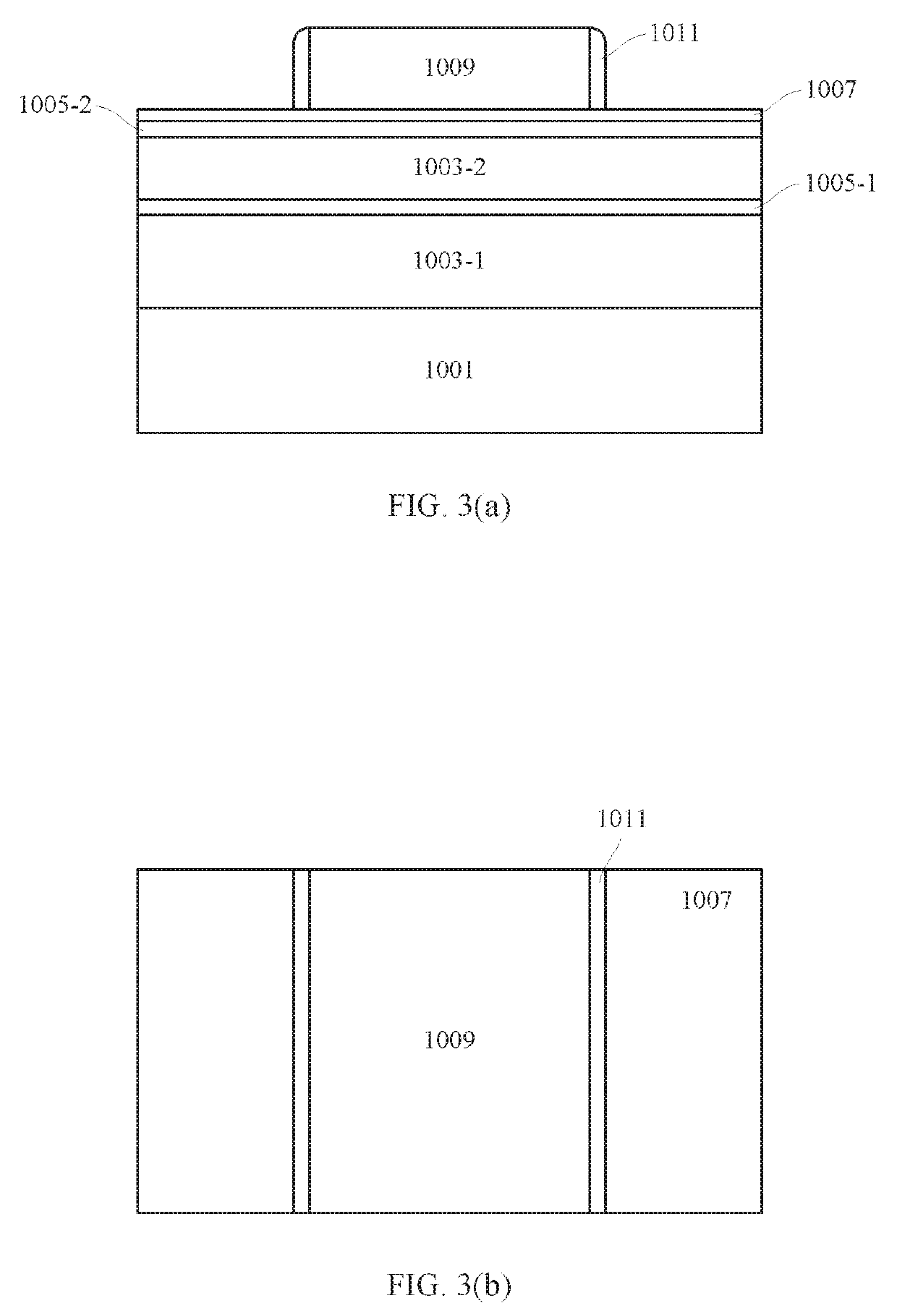

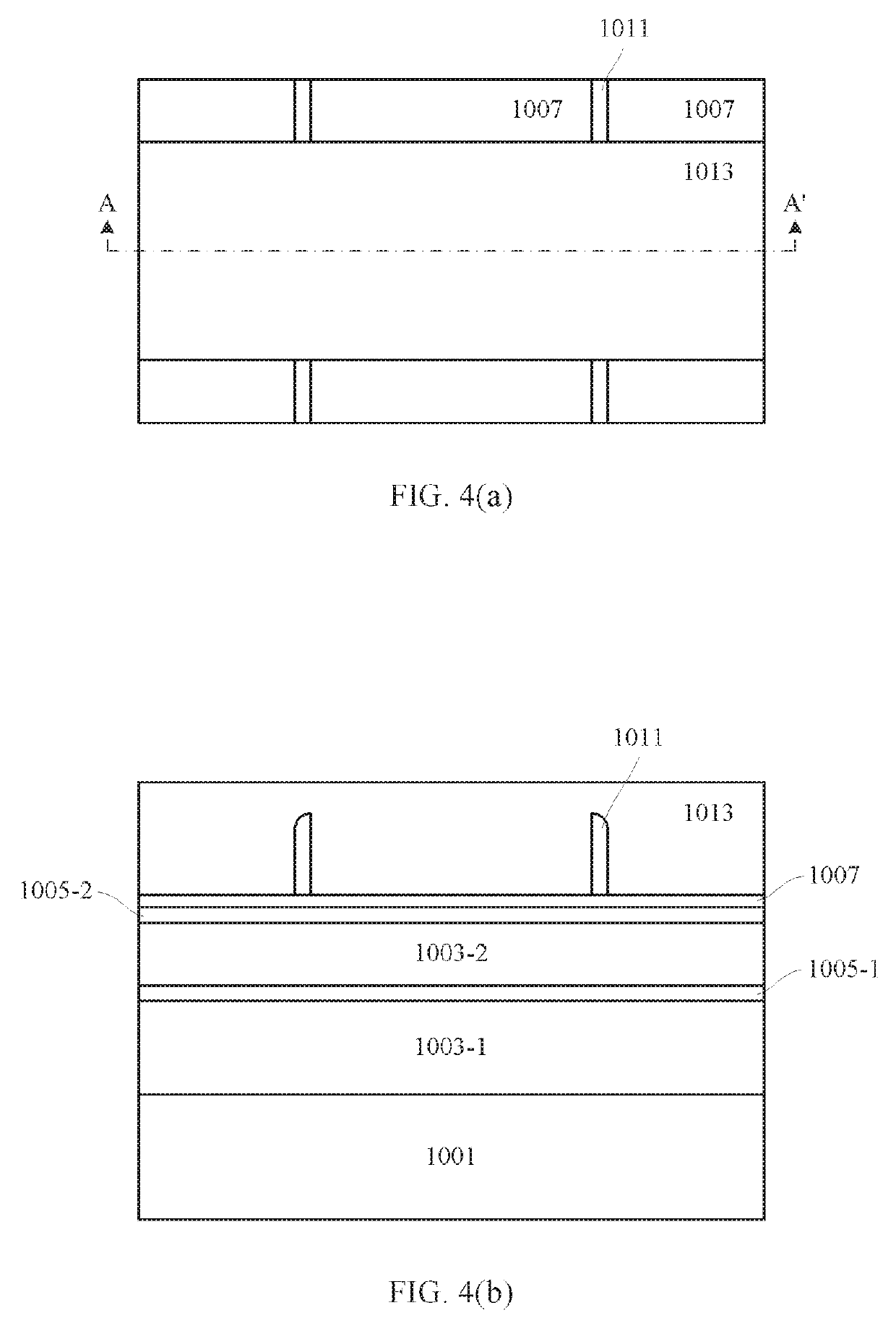

Manufacturing method of semiconductor device

ActiveUS8207025B2FunctionalSmall sizeSolid-state devicesRead-only memoriesPower semiconductor deviceEngineering

In an embodiment, an insulating film is formed over a flat surface; a mask is formed over the insulating film; a slimming process is performed on the mask; an etching process is performed on the insulating film using the mask; a conductive film covering the insulating film is formed; a polishing process is performed on the conductive film and the insulating film, so that the conductive film and the insulating film have equal thicknesses; the conductive film is etched, so that a source electrode and a drain electrode which are thinner than the conductive film are formed; an oxide semiconductor film is formed in contact with the insulating film, the source electrode, and the drain electrode; a gate insulating film covering the oxide semiconductor film is formed; and a gate electrode is formed in a region which is over the gate insulating film and overlaps with the insulating film.

Owner:SEMICON ENERGY LAB CO LTD

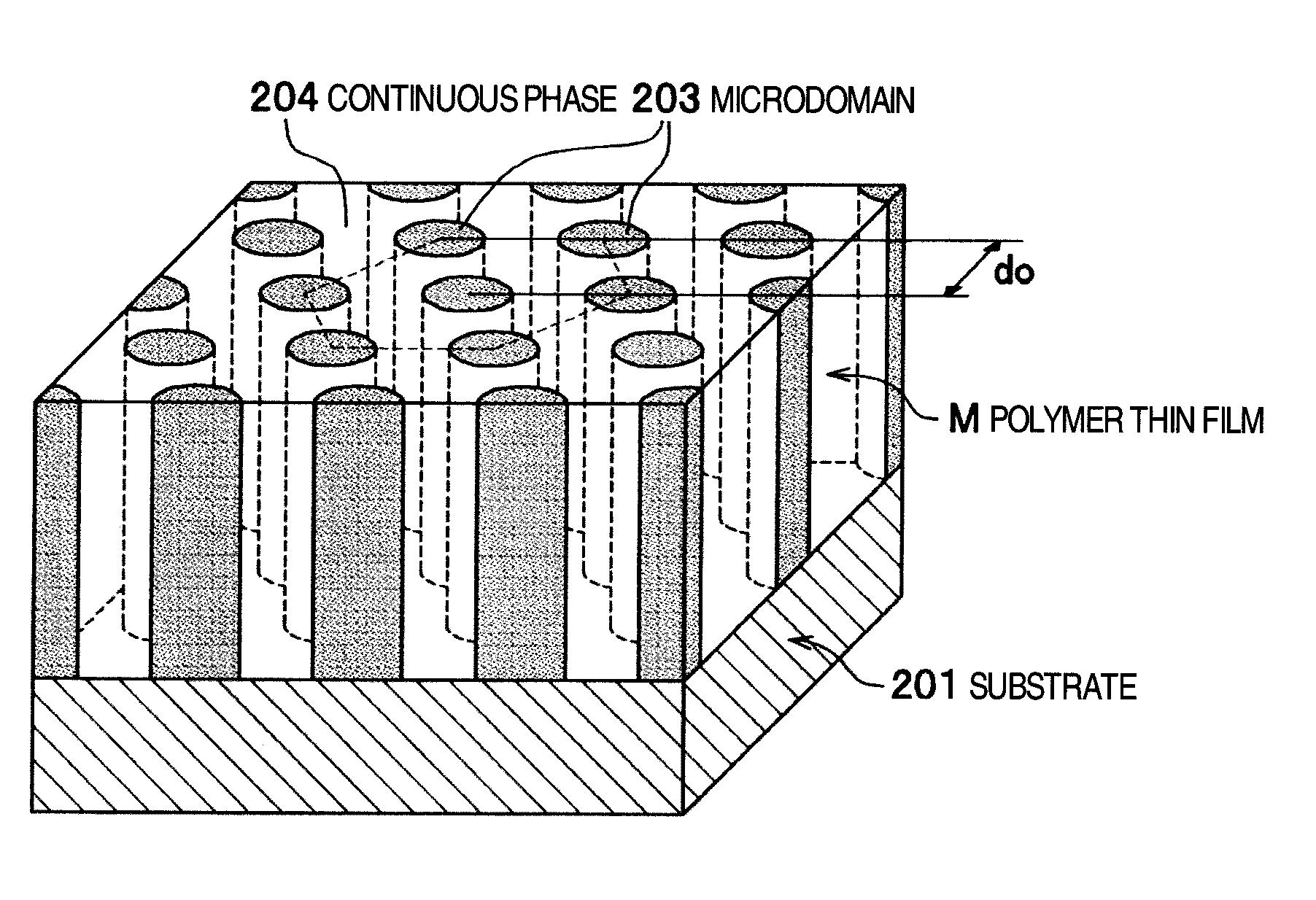

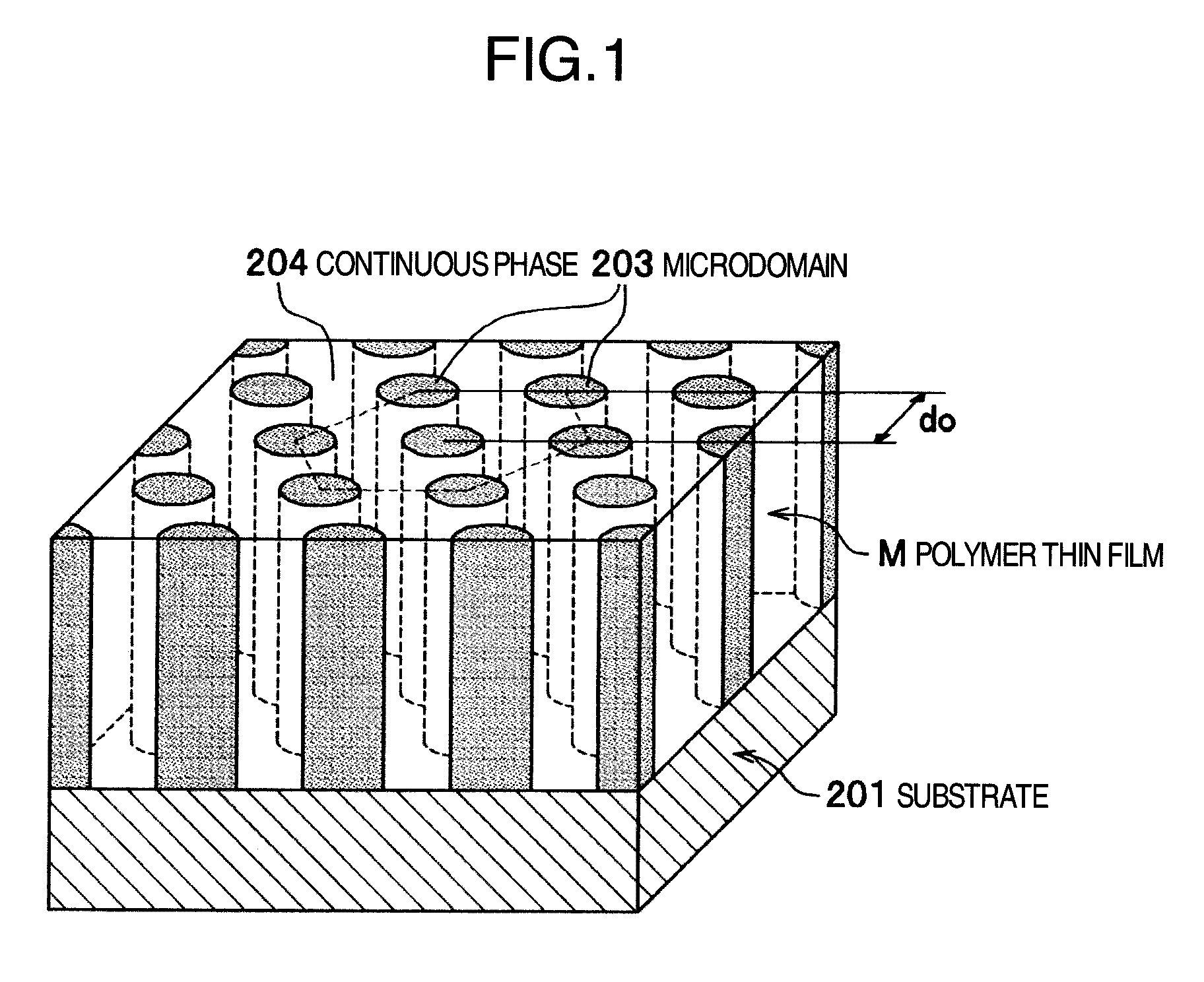

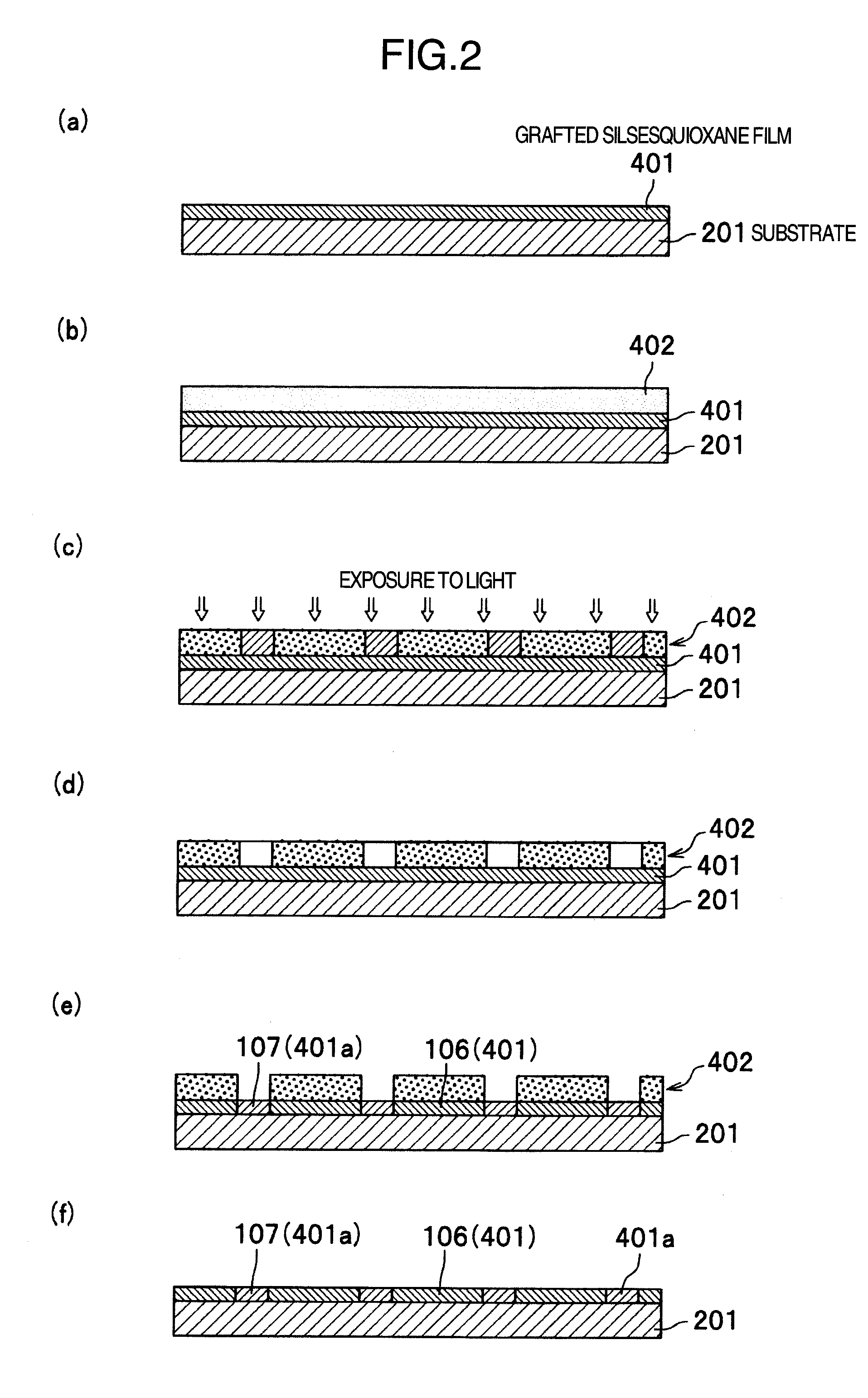

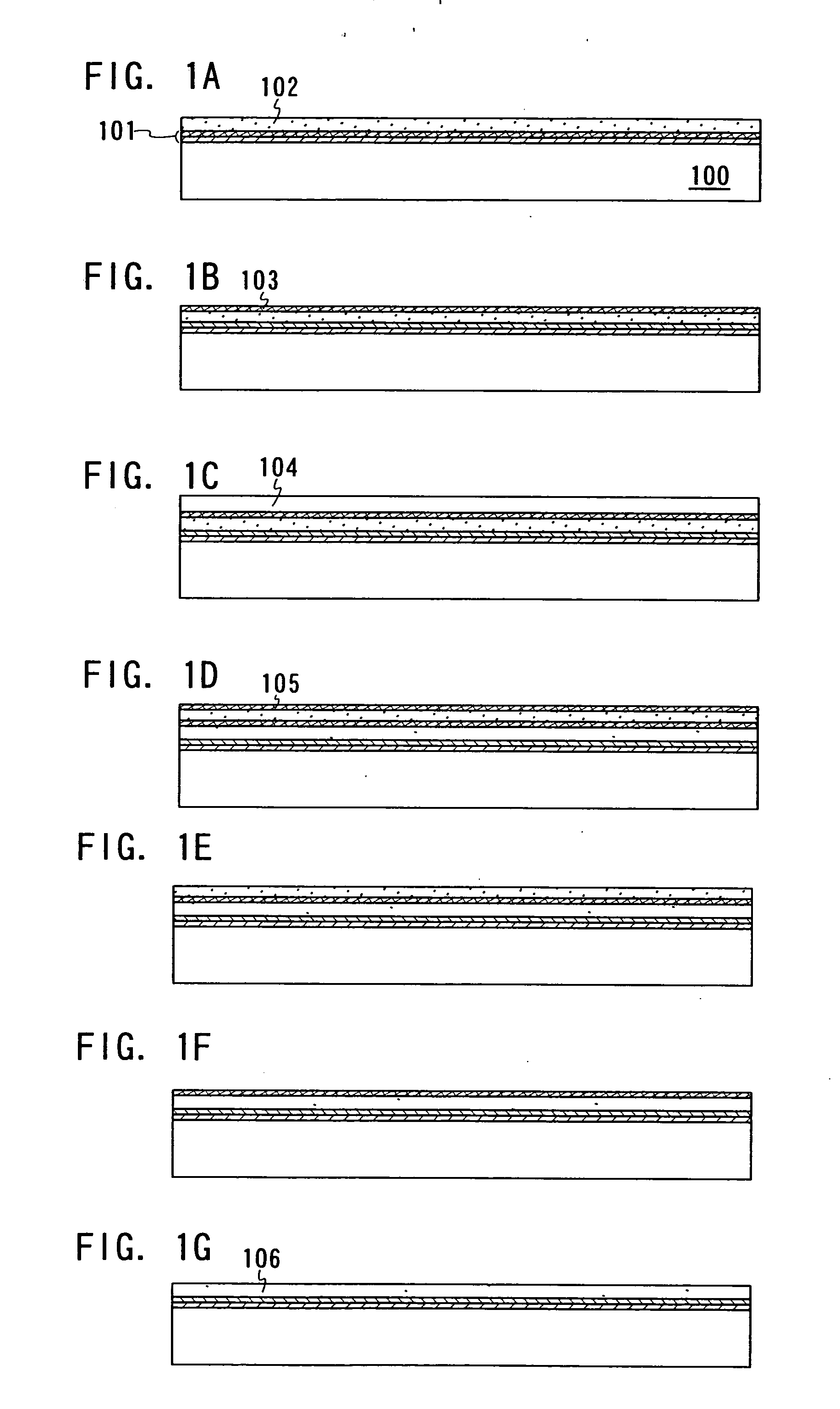

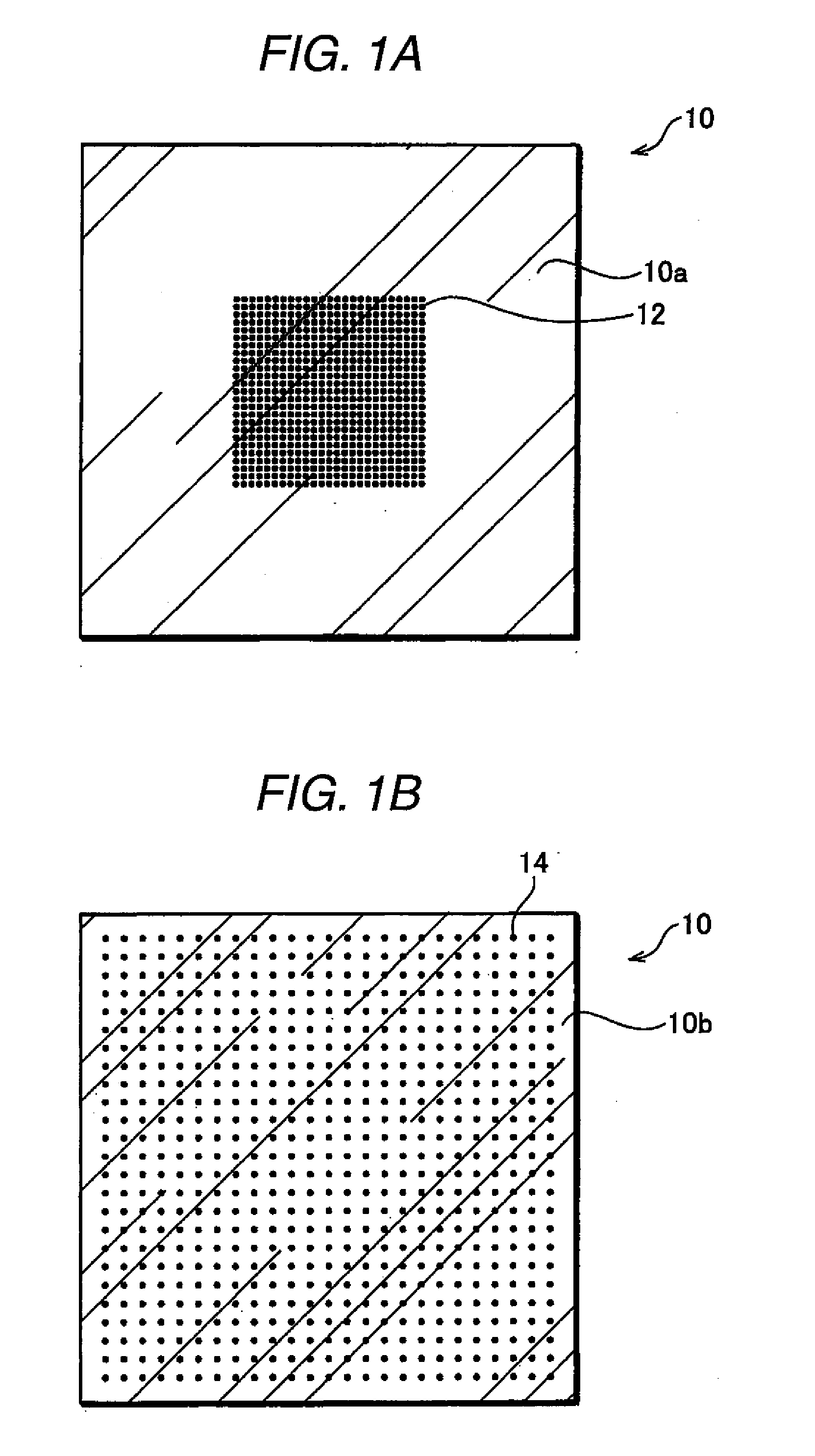

Polymer thin film, patterned media, production methods thereof, and surface modifying agents

InactiveUS20110281085A1Simple structureImprove regularityLayered productsDecorative surface effectsFine structurePolymer science

The objects of the present invention are to provide a polymer thin film having finer structure than the conventional product, excellent regularity over a wide range and only limited defects, patterned media, methods for producing the thin film and patterned media, and surface modifying agent used in these production methods.The method of the present invention is for producing a polymer thin film with a plurality of microdomains regularly arranged in a continuous phase by microphase separation on a substrate, comprising steps for forming a grafted silsesquioxane film on the substrate, and for forming a pattern different in chemical properties from the grafted silsesquioxane film in such a way that the pattern corresponds to the microdomain arrangement.

Owner:HITACHI LTD

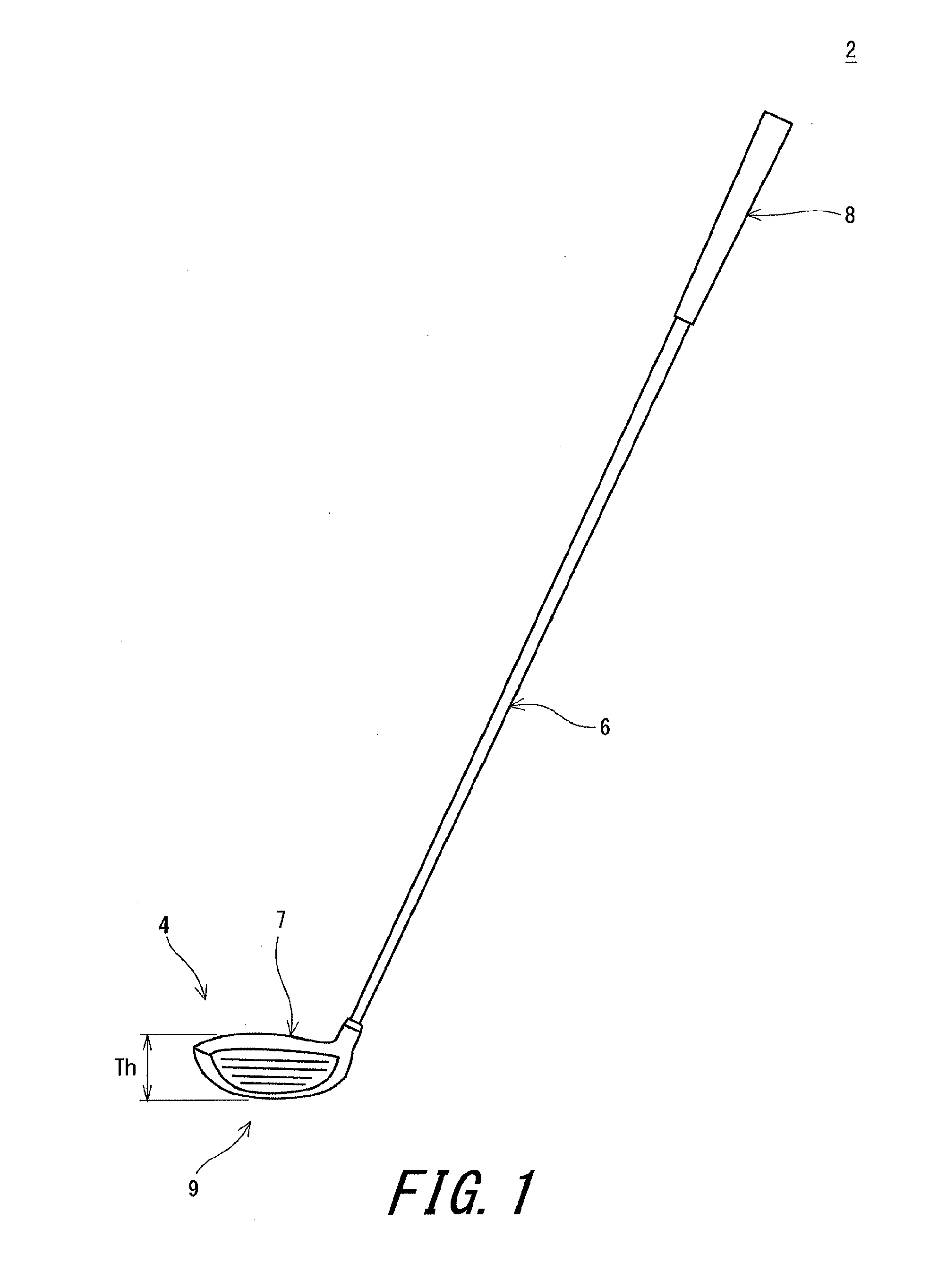

Golf club head

Owner:SUMITOMO RUBBER IND LTD

Manufacturing method of semiconductor device

InactiveUS20120034743A1FunctionalSmall sizeSolid-state devicesSemiconductor/solid-state device manufacturingMiniaturizationEngineering

A semiconductor device in which a defect is suppressed and miniaturization is achieved is provided. An insulating film is formed over a flat surface; a first mask is formed over the insulating film; a second mask is formed by performing a slimming process on the first mask; an insulating layer is formed by performing an etching process on the insulating film using the second mask; an oxide semiconductor layer covering the insulating layer is formed; a conductive film covering the oxide semiconductor layer is formed; a surface of the conductive film is flattened by performing a polishing process on the conductive film; an etching process is performed on the conductive film, so that a conductive layer is formed and a surface of the conductive layer is lower than a surface of an uppermost part of the oxide semiconductor layer; a gate insulating film in contact with the conductive layer and the oxide semiconductor layer is formed; and a gate electrode is formed in a region which is over the gate insulating film and overlaps with the insulating layer.

Owner:SEMICON ENERGY LAB CO LTD

Apparatus for manufacturing bonded substrate

The present invention provide an apparatus for manufacturing a bonded substrate that suppresses a defect in the bonded substrate. When the pressure in a vacuum chamber is at the atmospheric level, upper and lower chuck units respectively attract substrates through vacuum. When the vacuum chamber is depressurized, each chuck unit electrostatically attracts the associated substrate. During the depressurization of the vacuum chamber, the pressure for attracting each substrate to the associated chuck unit is controlled to be equal to the pressure in the vacuum chamber. This prevents each substrate from falling from or moving relative to the associated chuck unit. The first and second substrates are thus bonded together as accurately aligned.

Owner:FUJITSU LTD

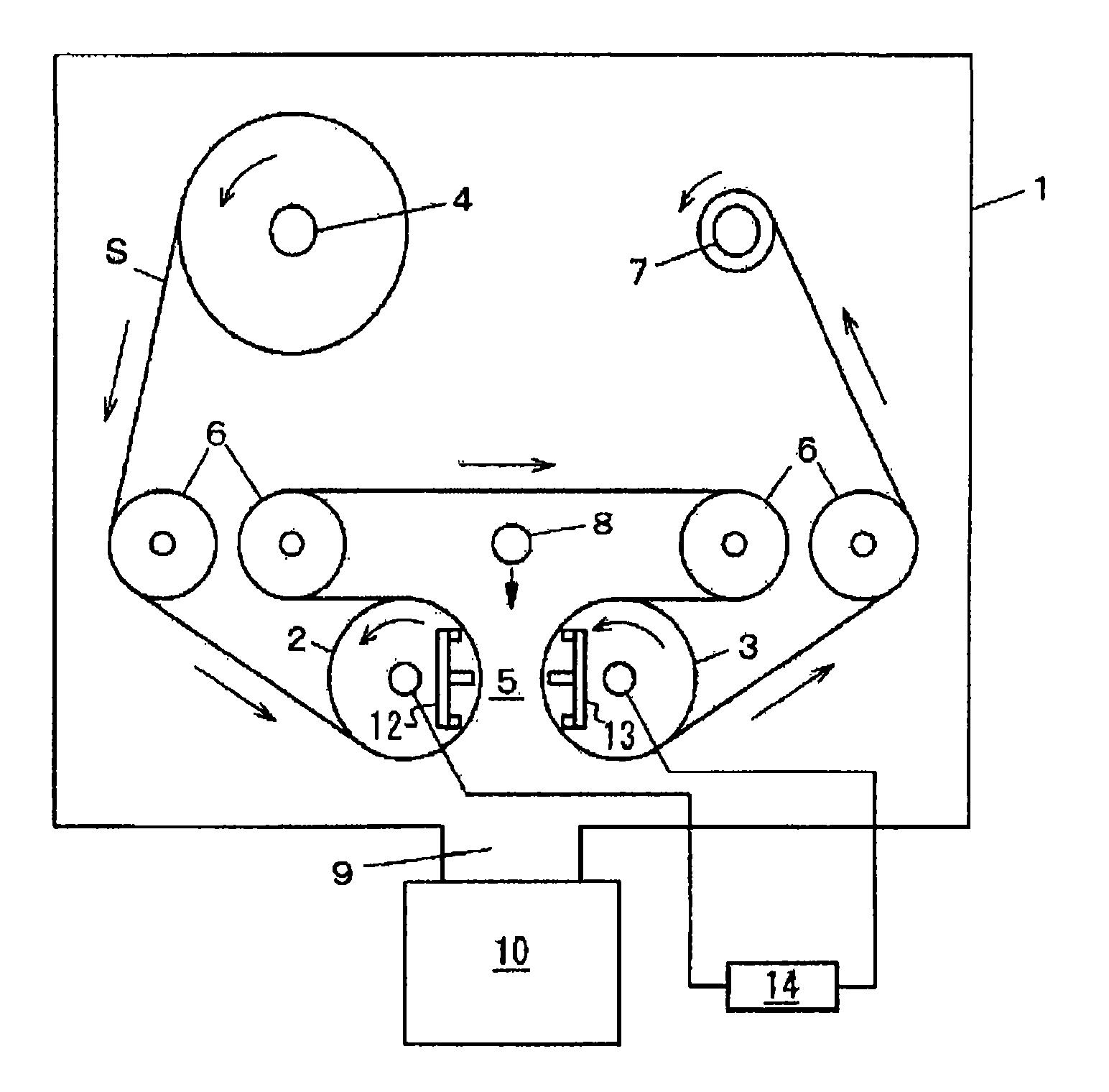

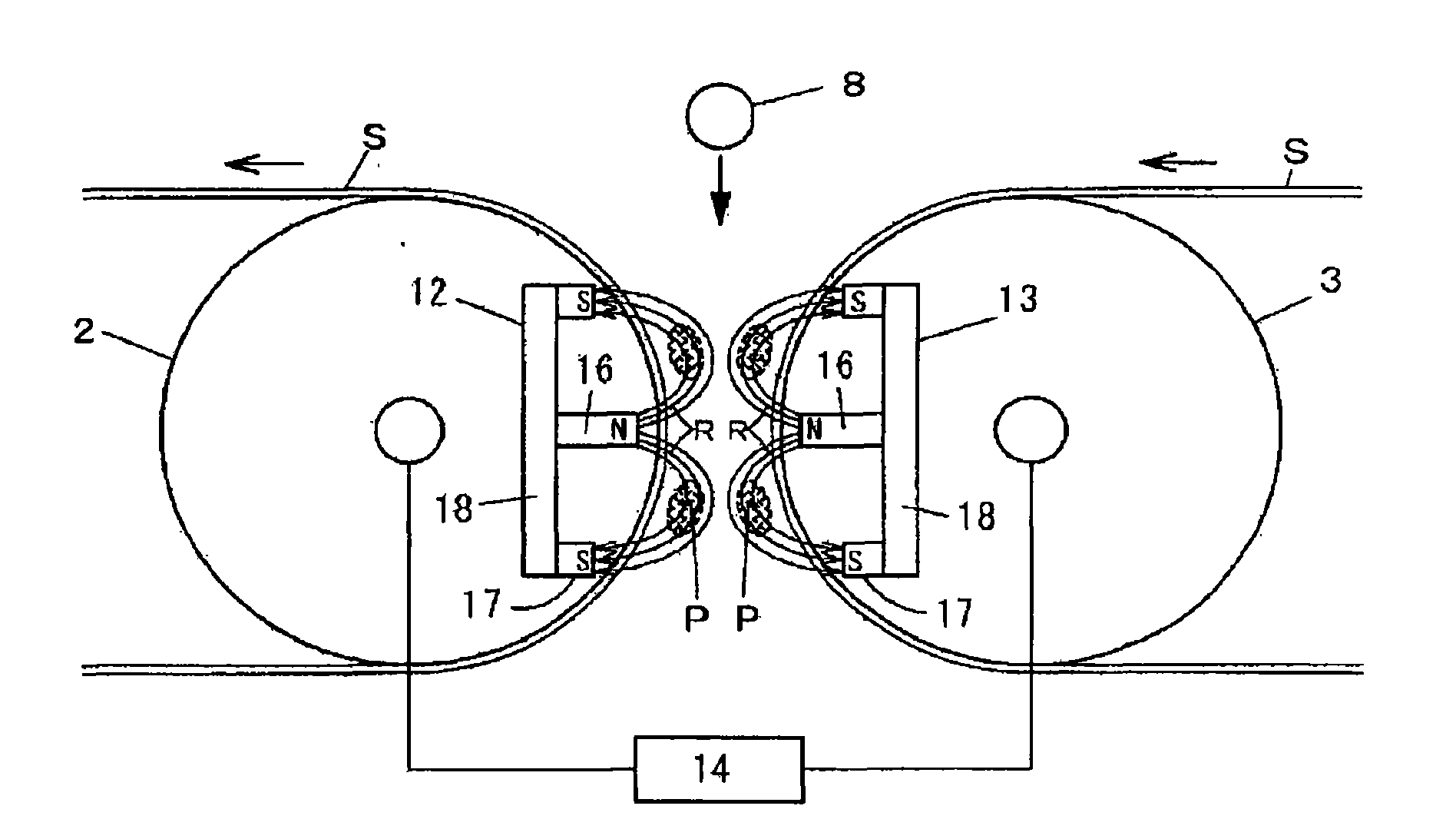

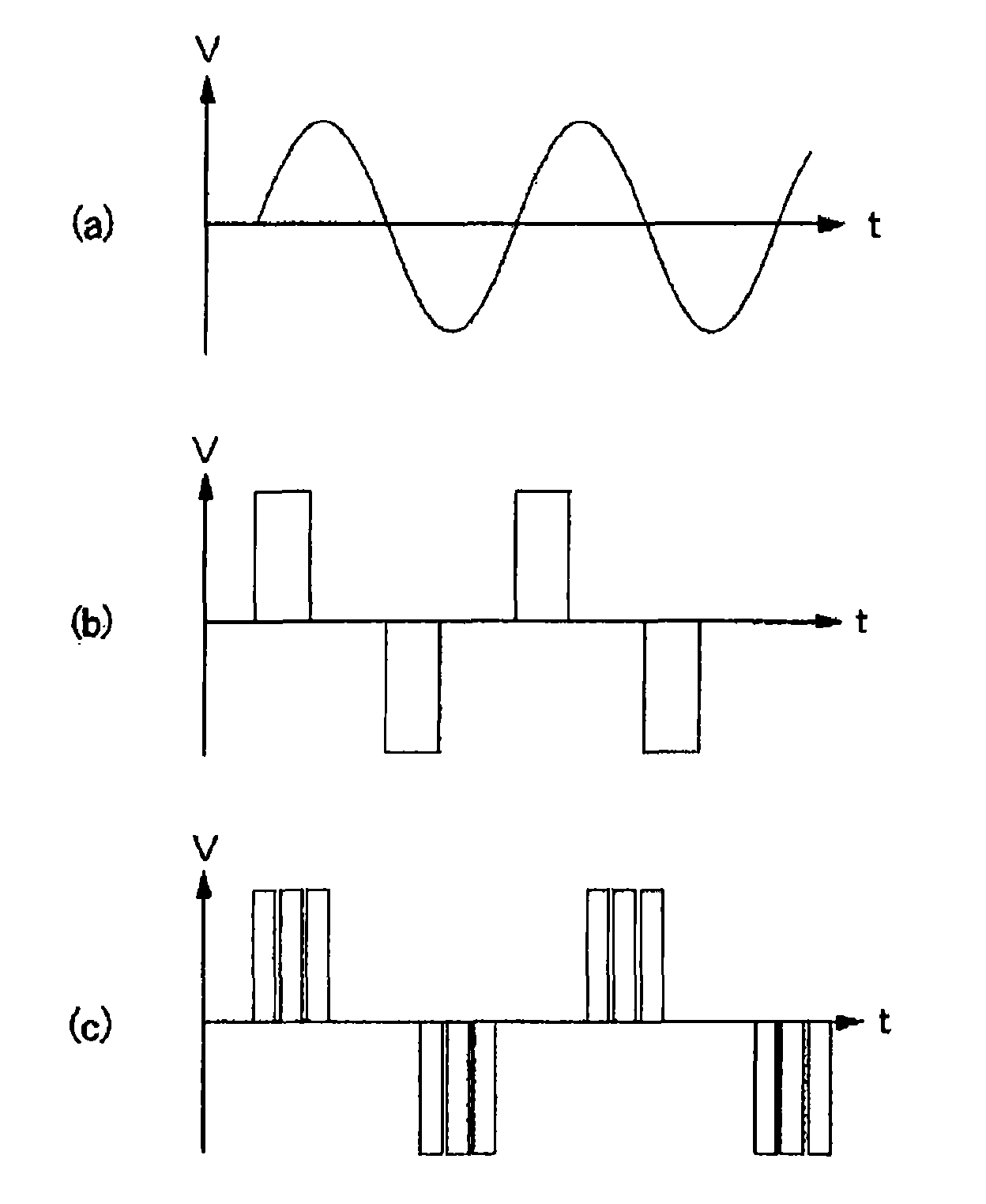

Continuous film forming apparatus

ActiveCN101611168AEfficient formationInhibition defectElectric discharge tubesChemical vapor deposition coatingVacuum pumpingGas supply

A continuous film forming apparatus comprises a pair of film forming rolls (2, 3) where winding substrates (S) are arranged opposite to each other in parallel, magnetic field generation members (12, 13) provided in respective film forming rolls (2, 3) and generating a magnetic field for converging plasma to the vicinity of the roll surface facing the opposing space (5) between the film forming rolls, a plasma power supply (14) where the polarity of one and the other electrodes is inverted alternately, a gas supply pipe (8) for supplying a film froming gas to the opposing space (5), and a means for vacuum pumping the opposing space (5). The plasma power supply (14) has one electrode connected with one film forming roll (2), and the other electrode connected with the other film forming roll (3).

Owner:KOBE STEEL LTD

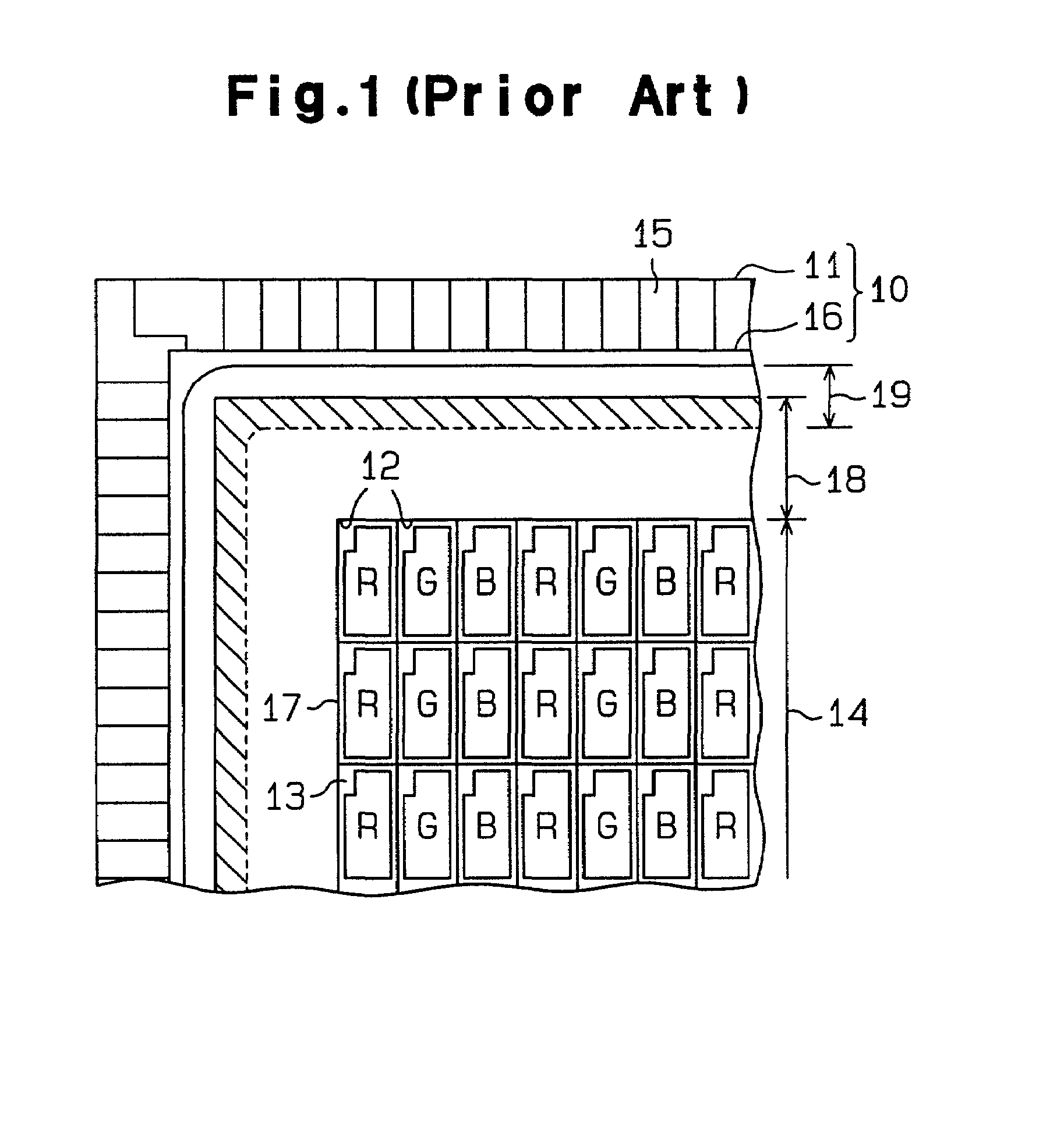

Light-emitting device, method for manufacturing the same, and electronic apparatus

InactiveUS20090001879A1Improve reliabilityFew defectDischarge tube luminescnet screensLamp detailsInorganic compoundOrganic compound

The present invention provides a light-emitting device including a light-emitting element over a substrate, the light-emitting element is partitioned from an adjacent light-emitting element by a partition wall, the light-emitting element comprising a first electrode, a layer formed over the first electrode, a light-emitting layer formed over the layer and a second electrode formed over the light-emitting layer, the layer contains an inorganic compound, an organic compound and a halogen atom, the partition wall contains the inorganic compound and the organic compound, and the layer. The light-emitting device provides higher reliability and fewer defects.

Owner:SEMICON ENERGY LAB CO LTD

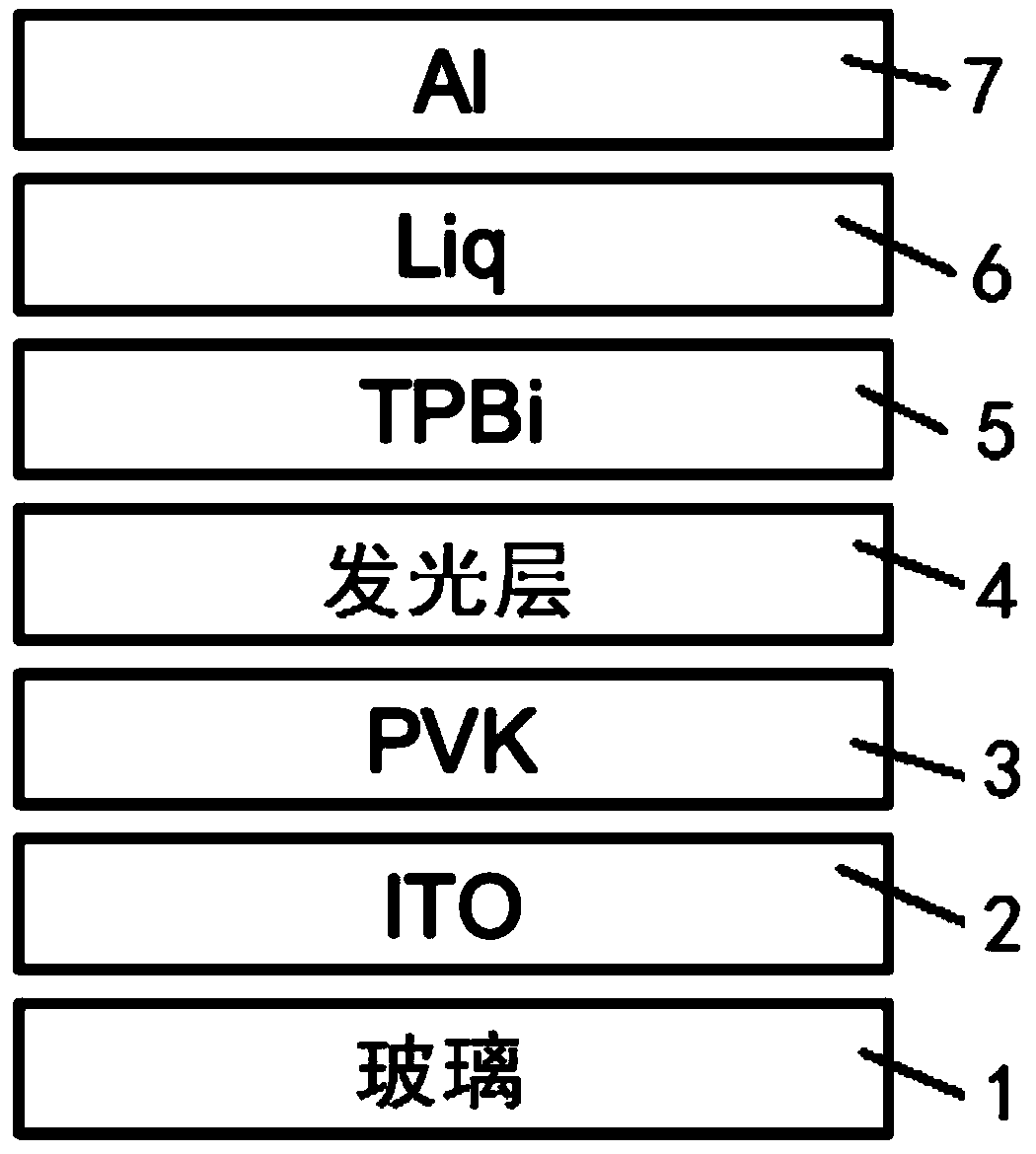

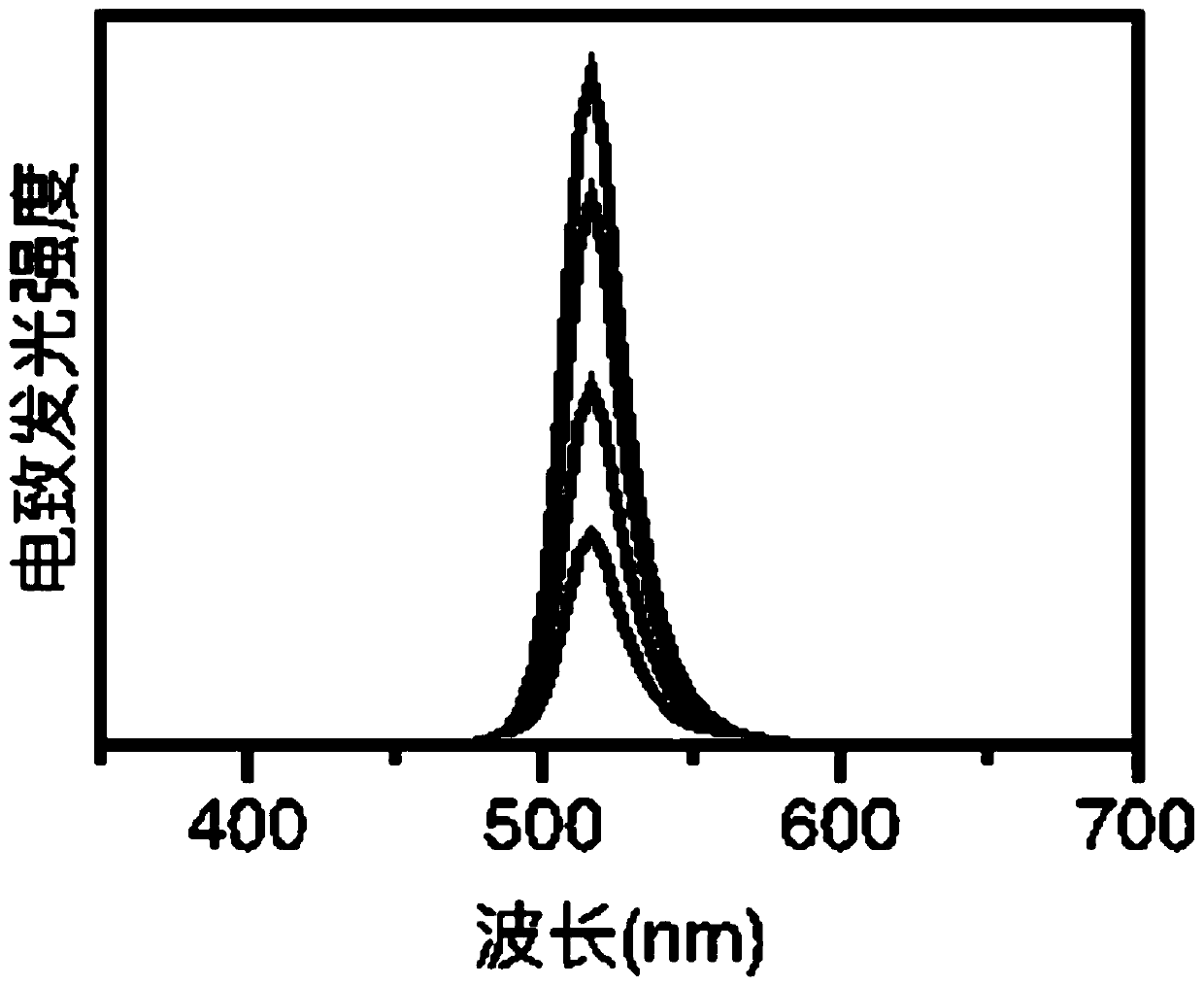

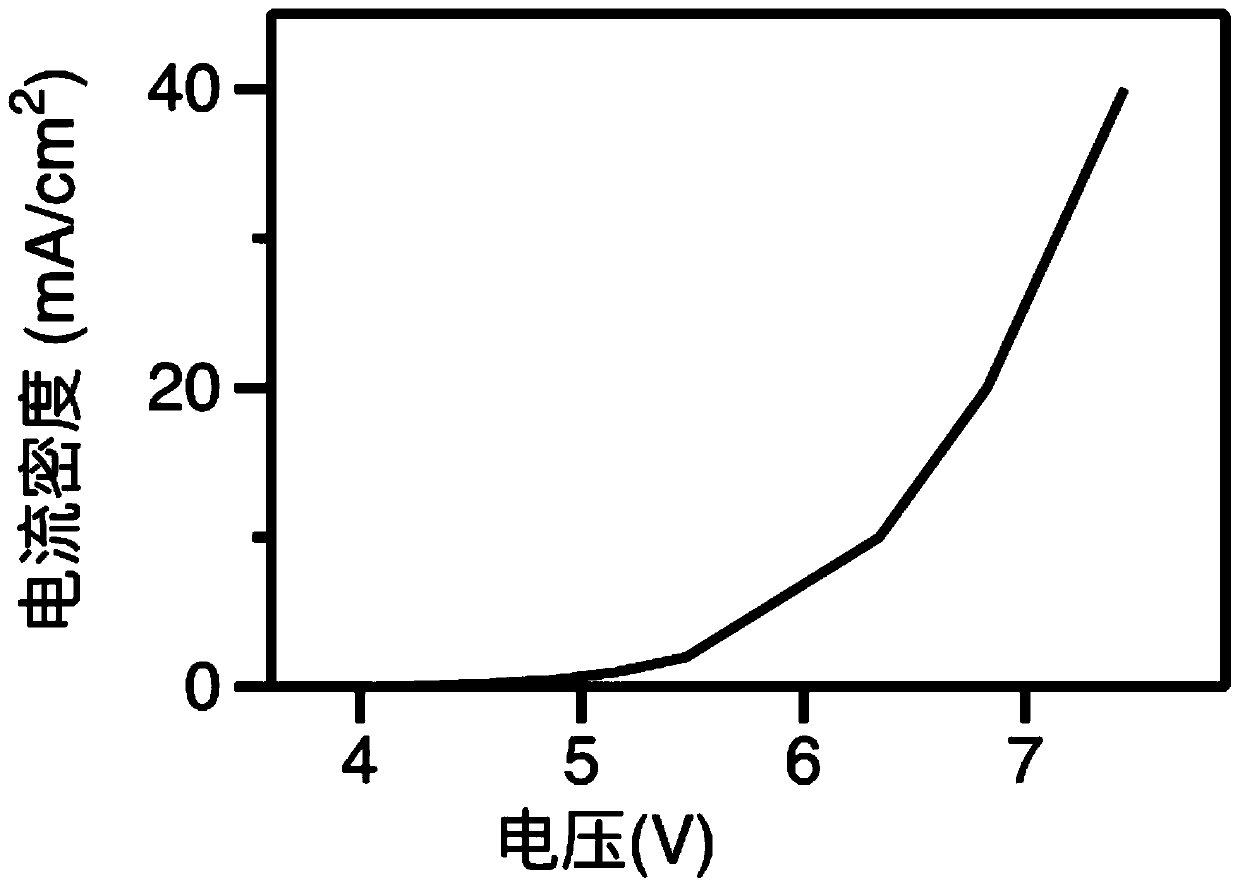

Perovskite LED device based on surface ligand control and preparation method thereof

InactiveCN110867532ALong luminous lifeImprove luminous efficiencySolid-state devicesSemiconductor/solid-state device manufacturingActive agentSurface-active agents

The invention relates to a method for preparing a perovskite LED device based on surface ligand control, including the following steps: applying an organic solution of a hole injection layer materialto the surface of a conductive substrate, and forming a hole injection layer after annealing; dissolving cesium bromide, lead bromide and phenethylamine bromide in an organic solvent under the effectof a 3-(decyl dimethyl ammonium) propane-1-sulfonic acid inner salt surfactant to obtain a perovskite precursor solution, applying the perovskite precursor solution to the surface of the hole injection layer and obtaining a perovskite film after annealing; treating the surface of the perovskite film with an alkylamine organic solution to form a light-emitting layer; and successively preparing an electron transport layer, an electron injection layer and a metal cathode electrode on the surface of the light-emitting layer. The method of the invention is simple and convenient, has a wide range ofmaterials and good repeatability, and can achieve the device performance. Through surface ligand exchange, the flatness and uniformity of the perovskite film are improved, the formation of defects iseffectively suppressed, and the overall performance of the device is significantly improved.

Owner:SUZHOU UNIV

Method for manufacturing semiconductor device

InactiveUS20060134891A1Yield and reliability be improveHigh reliableSolid-state devicesSemiconductor/solid-state device manufacturingSilicon oxideCrystalline semiconductor

An object of the present invention is to provide a method for manufacturing a semiconductor device in which, after crystallizing by using an element that promotes crystallization, holes are prevented from being generated in a crystalline semiconductor film with a concentration of the element in the crystalline semiconductor film decreased by performing gettering. To solve the problem, as a feature of the structure of the invention, in the case of removing a silicon oxide film formed over the semiconductor film, an etchant made of a solution containing fluorine and a substance having surface activity is used.

Owner:SEMICON ENERGY LAB CO LTD

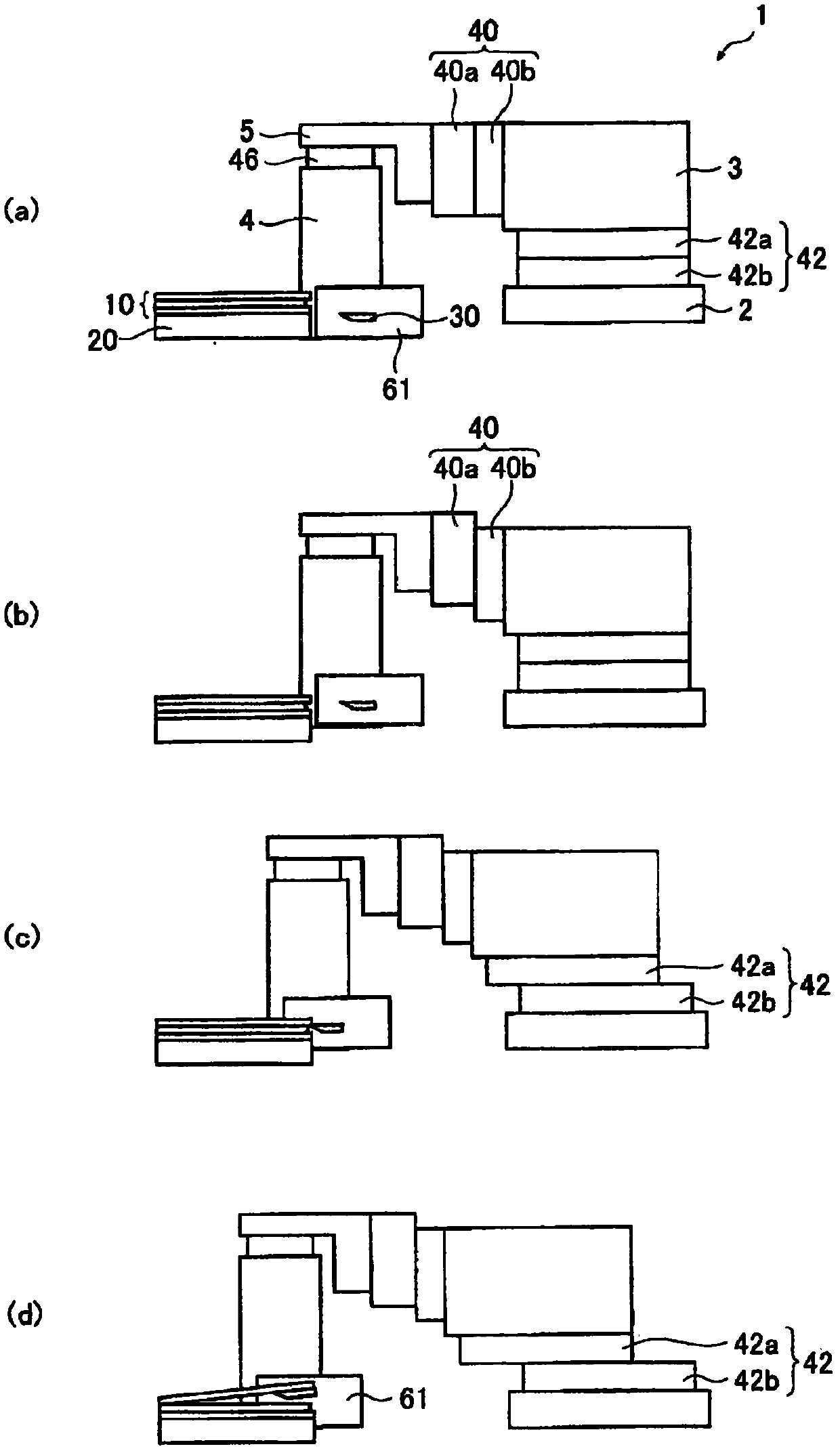

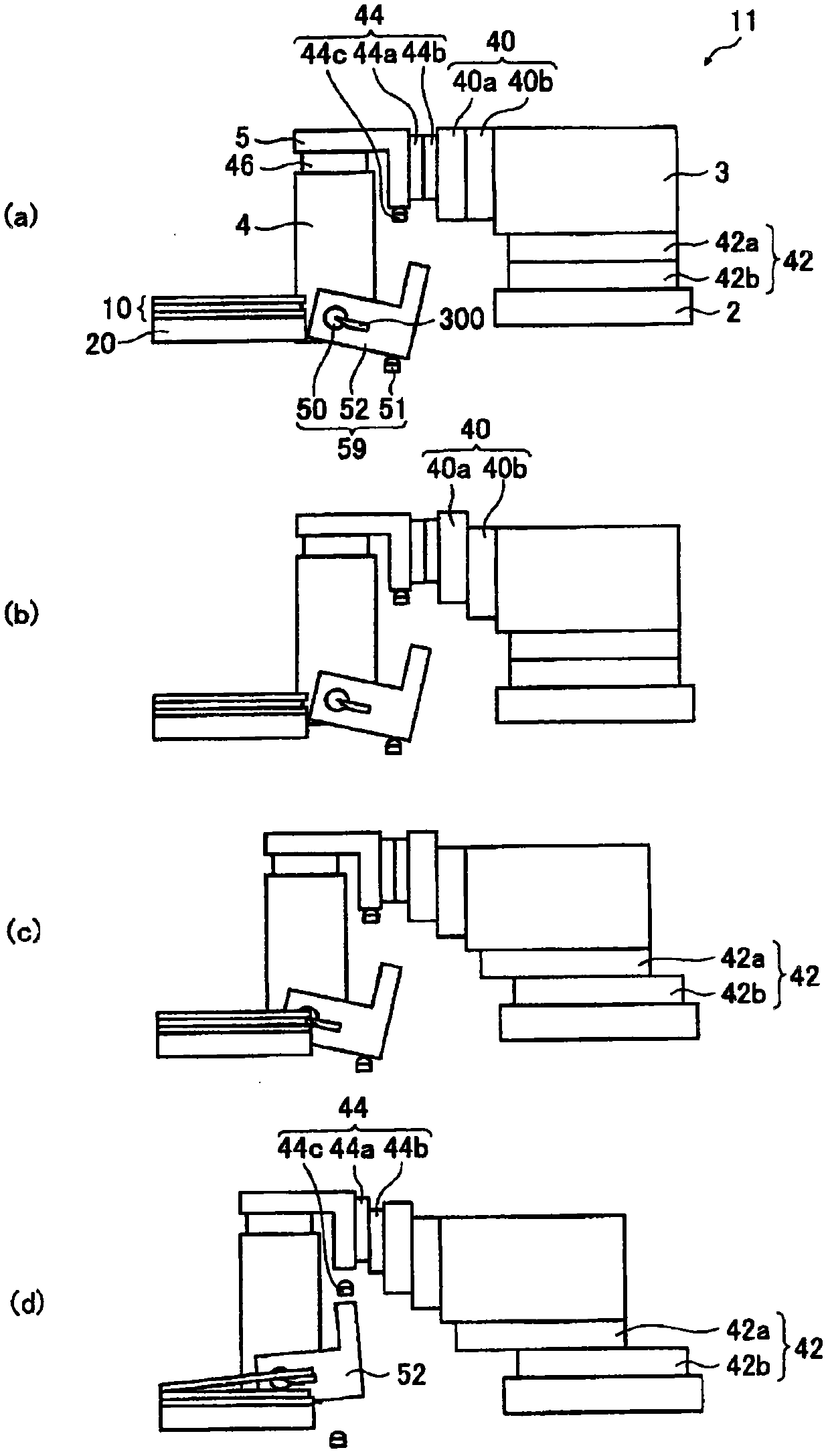

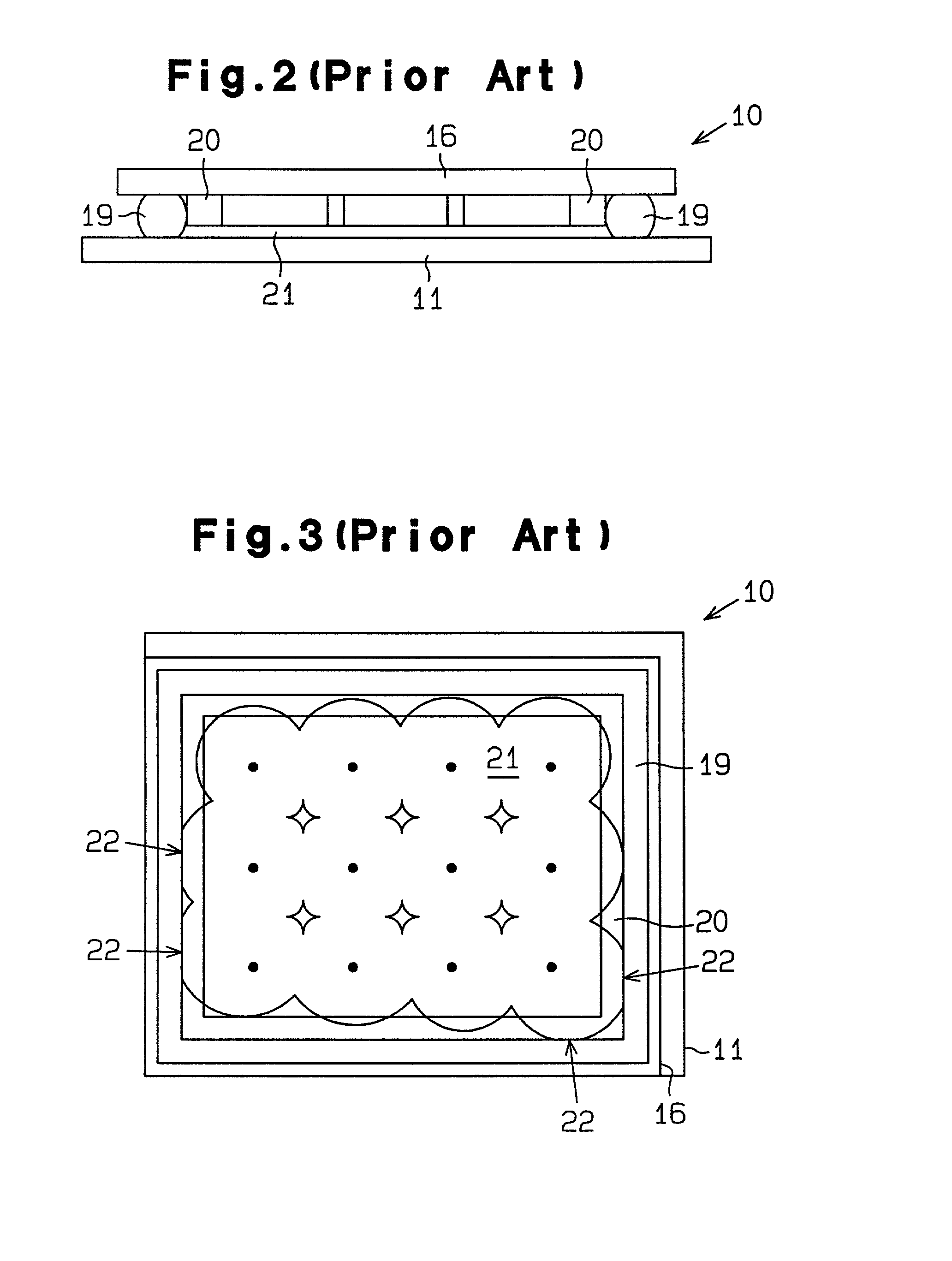

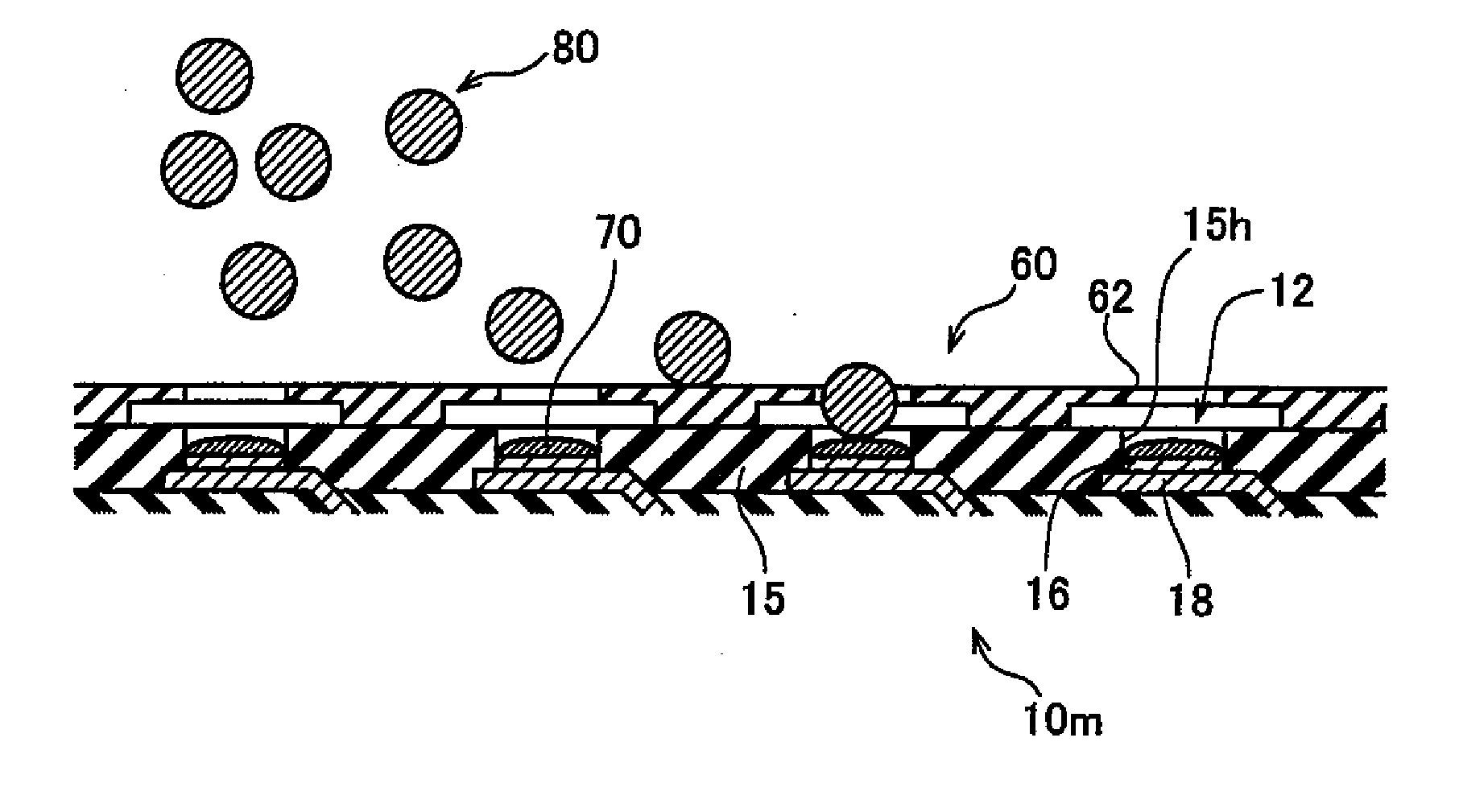

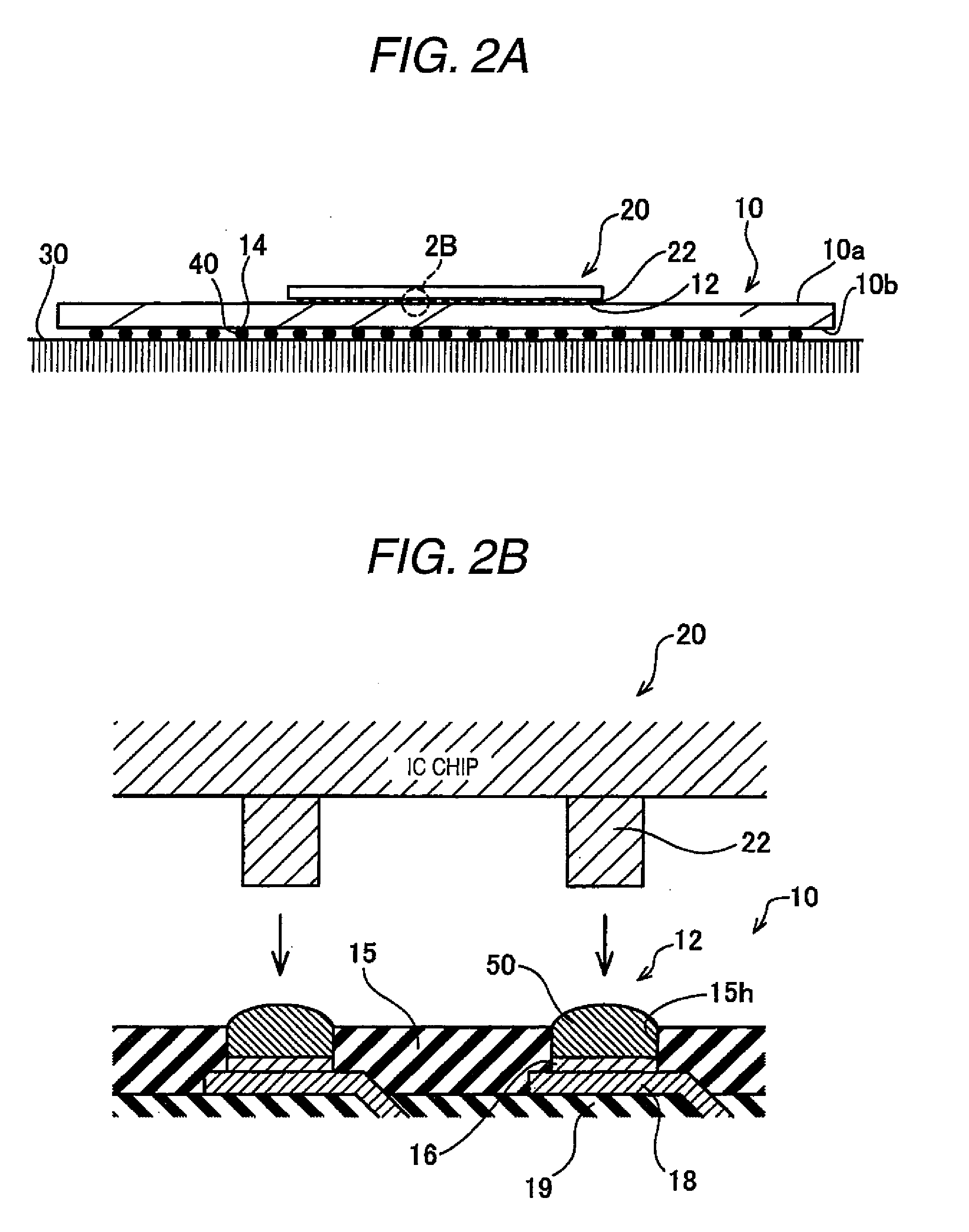

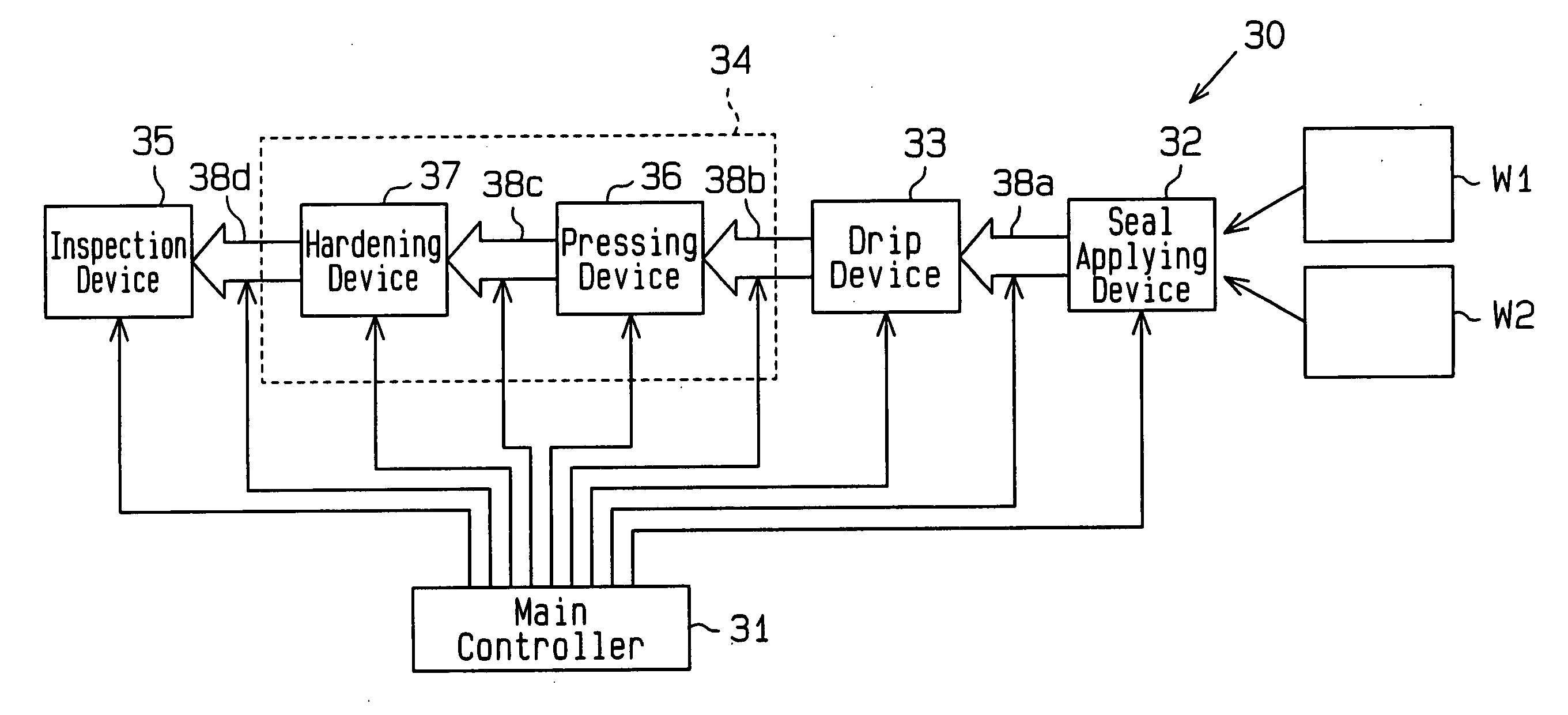

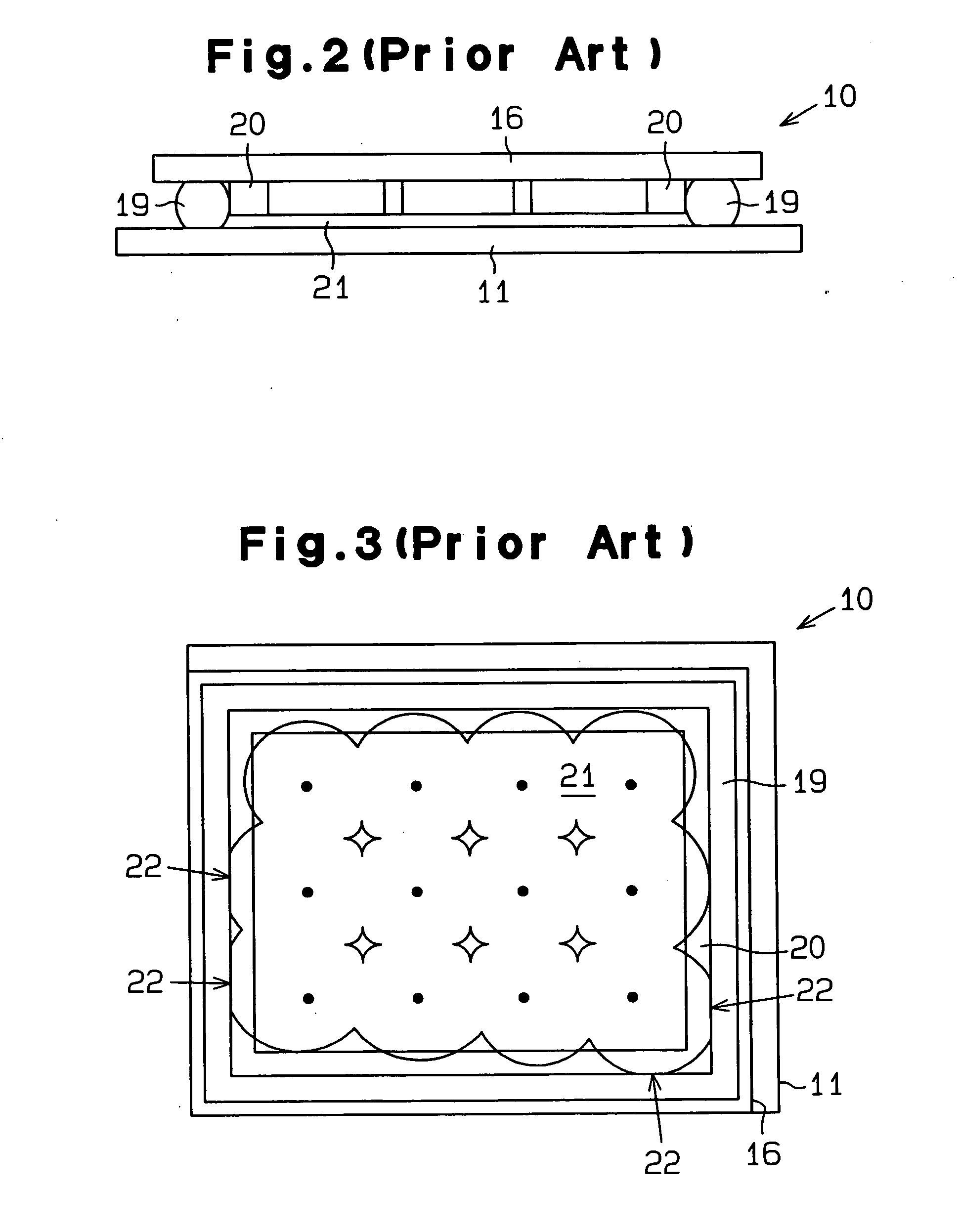

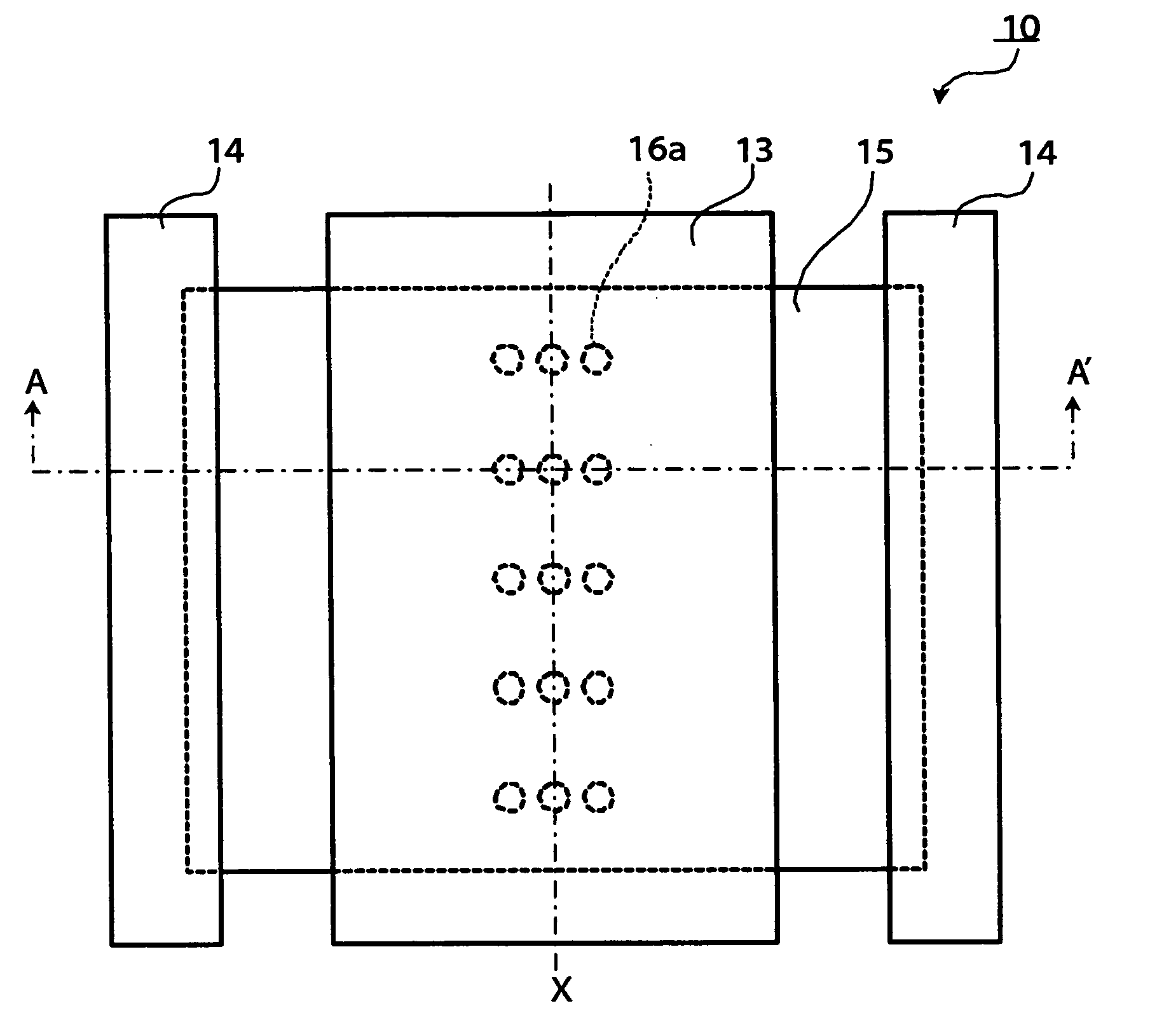

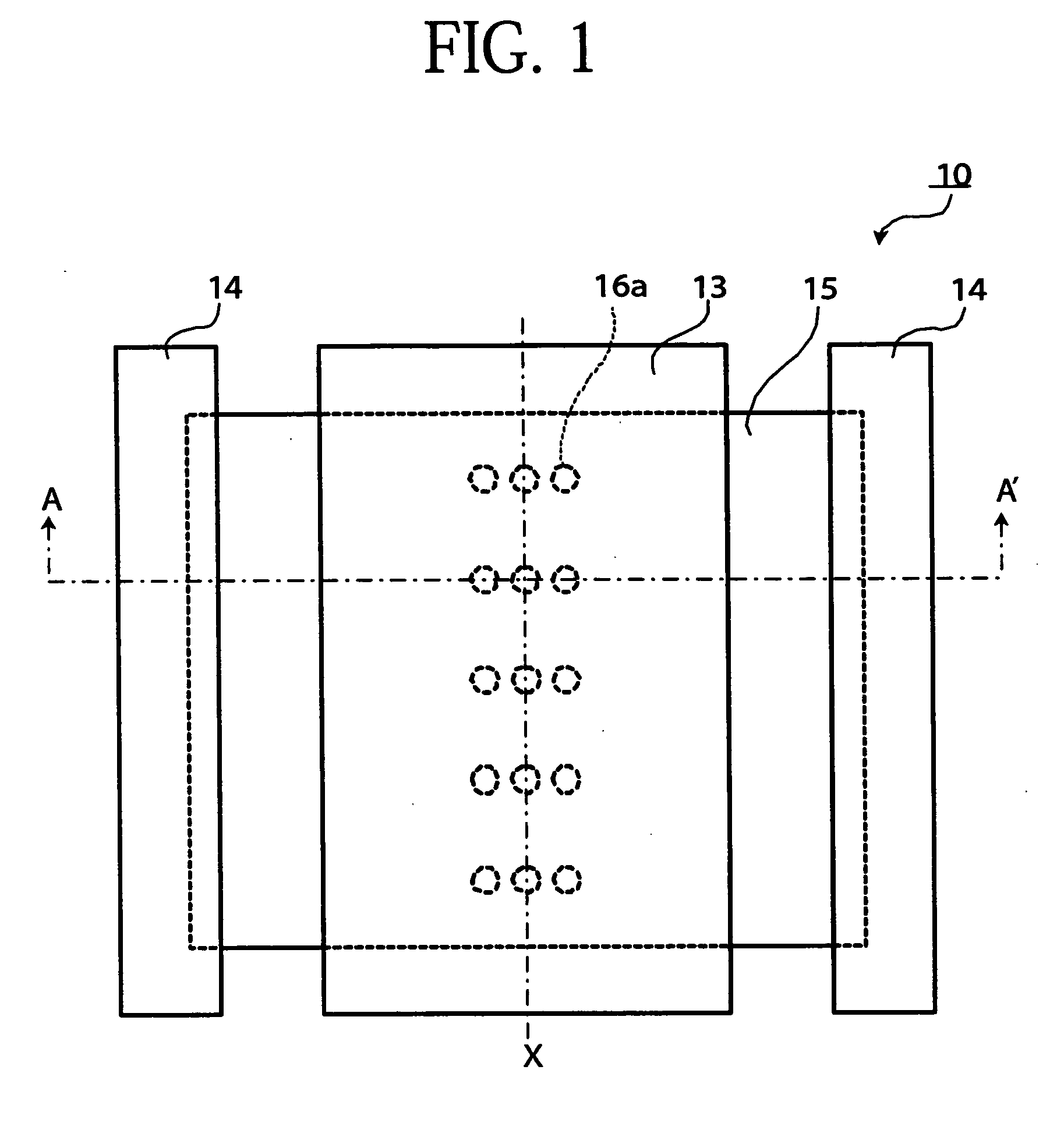

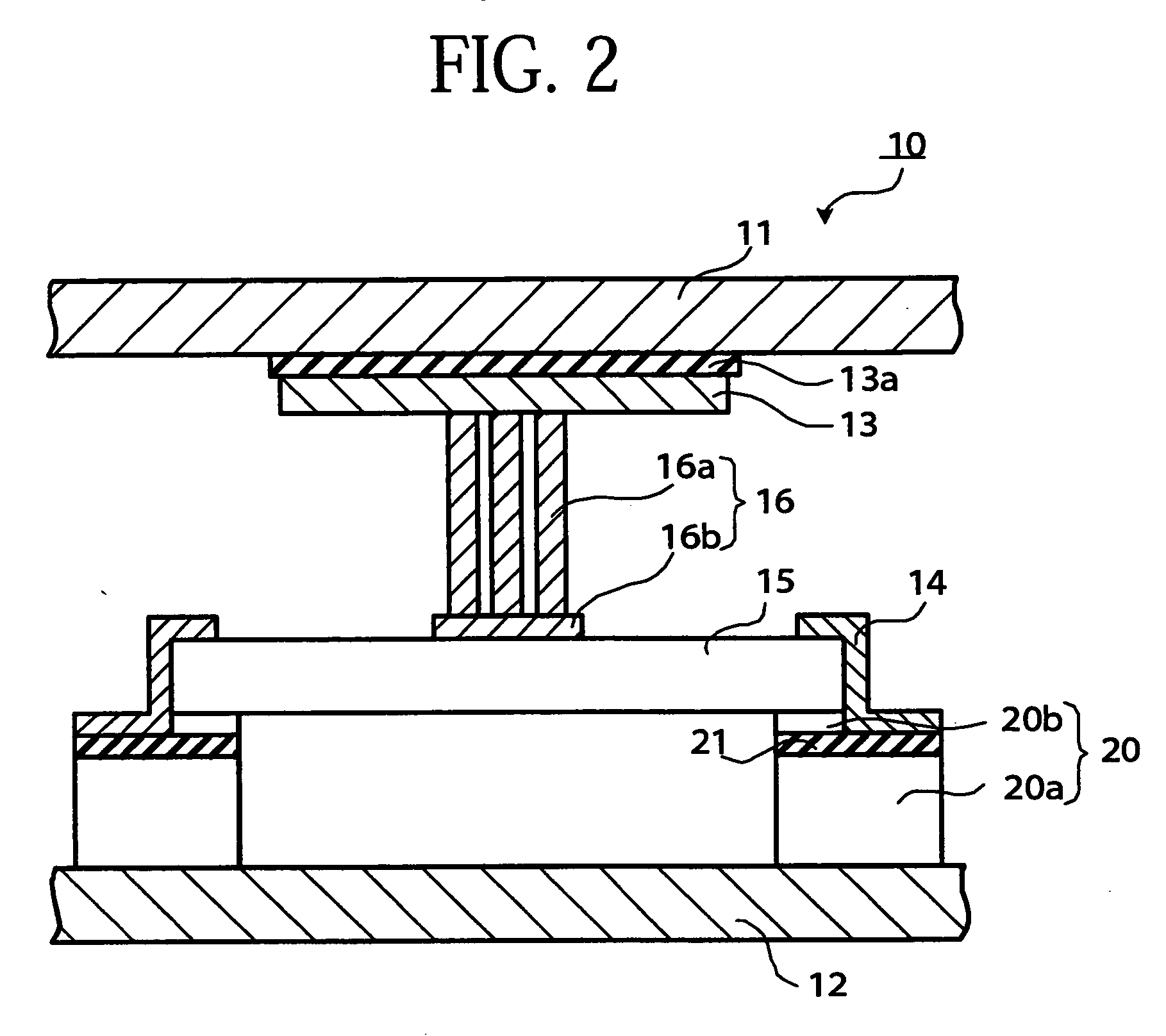

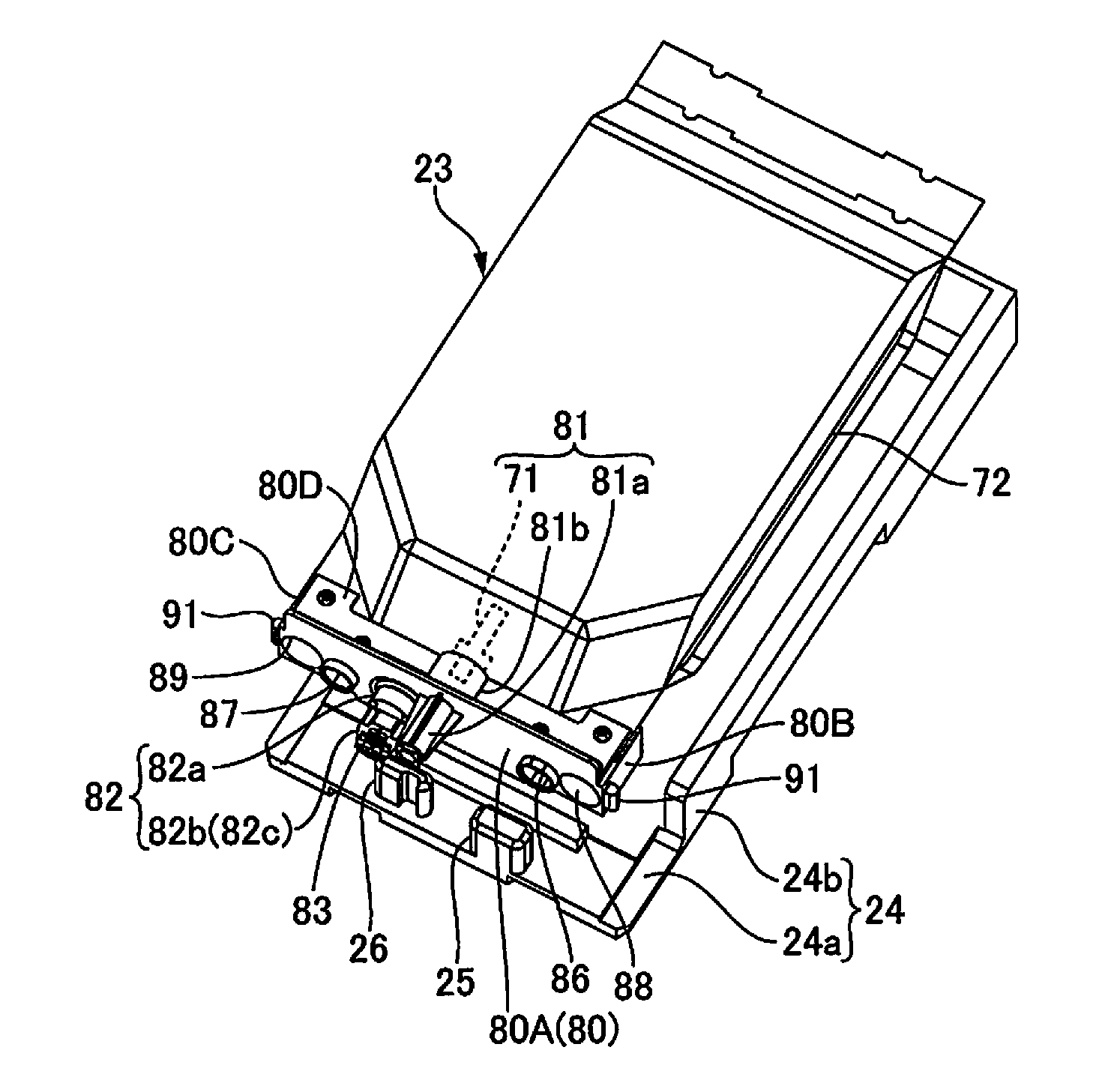

Solder ball mounting apparatus and wiring board manufacturing method

InactiveUS20090283574A1Inhibition defectReduce connection failuresSemiconductor/solid-state device detailsSolid-state devicesSolder ballEngineering

A wiring board includes an insulating layer having a plurality of through holes formed therein, a base substrate layer positioned below the insulating layer, and a plurality of electrodes disposed on the base substrate layer, each electrode having an exposed surface exposed from a respective through hole, each exposed surfaces being coated with a flux. A plurality of solder balls are disposed on the fluxes in the through holes, respectively. An apparatus for mounting the solder balls on the plurality of electrodes includes: a solder ball removing unit configured to remove a first plurality of solder balls located other than in the through holes; and a solder ball pressing unit configured to press a second plurality of solder balls individually disposed in the through holes towards respective electrodes and into respective flux.

Owner:NGK SPARK PLUG CO LTD

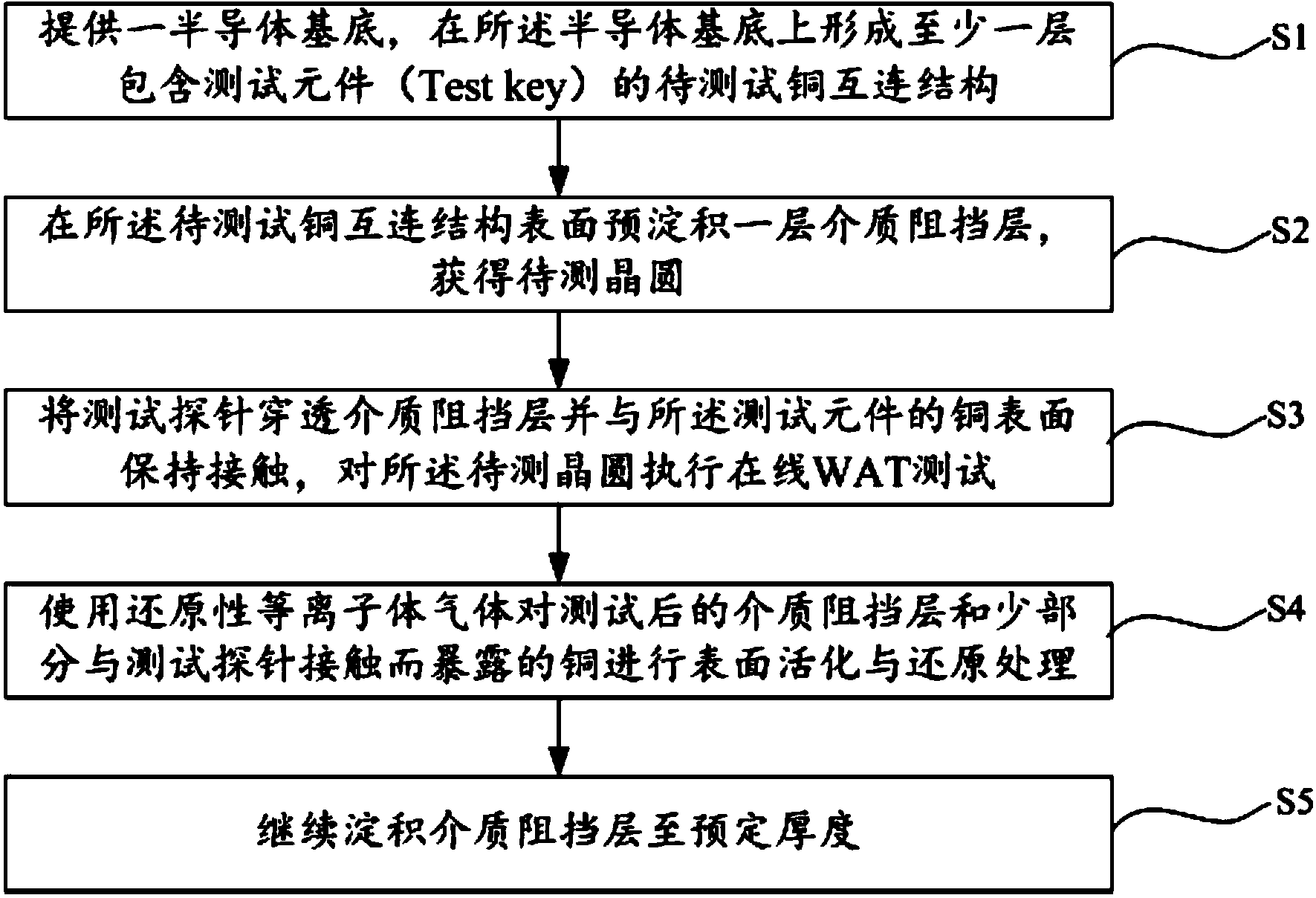

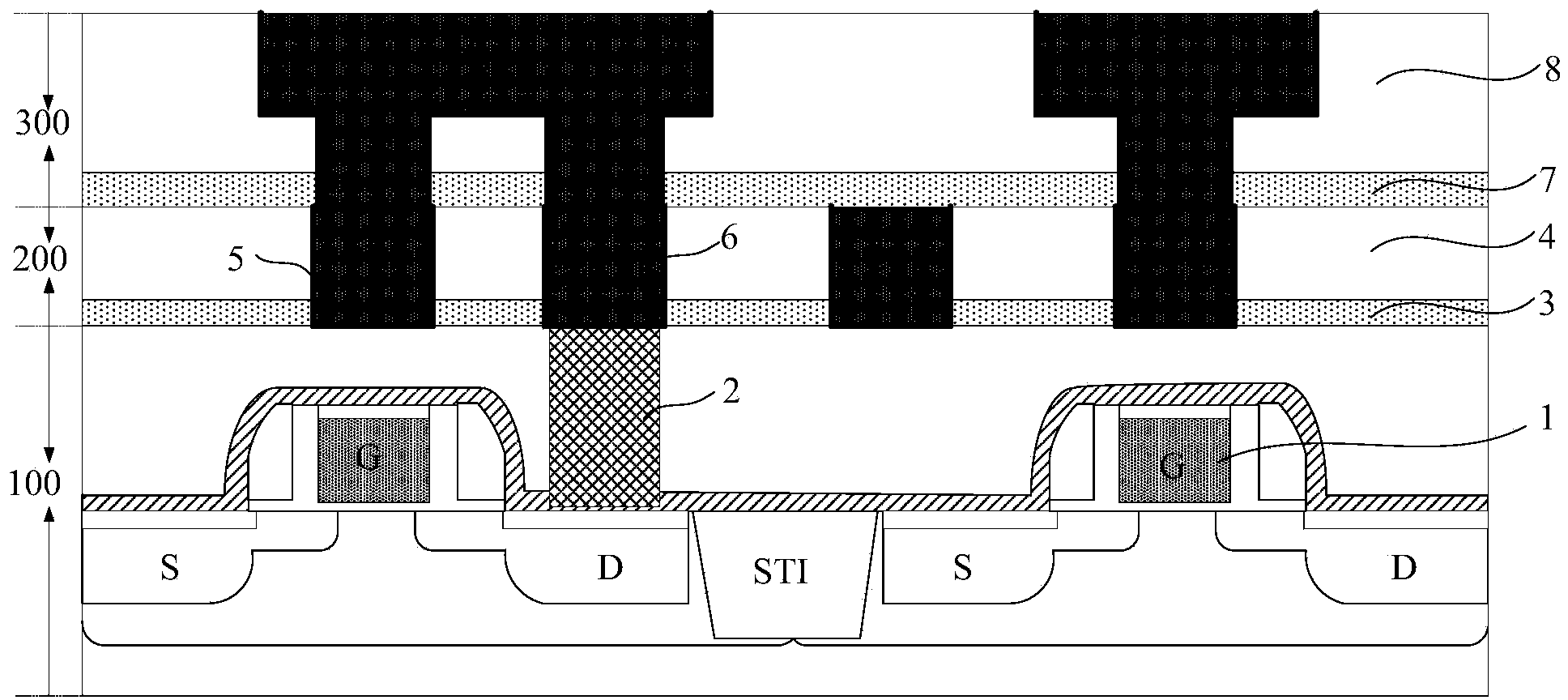

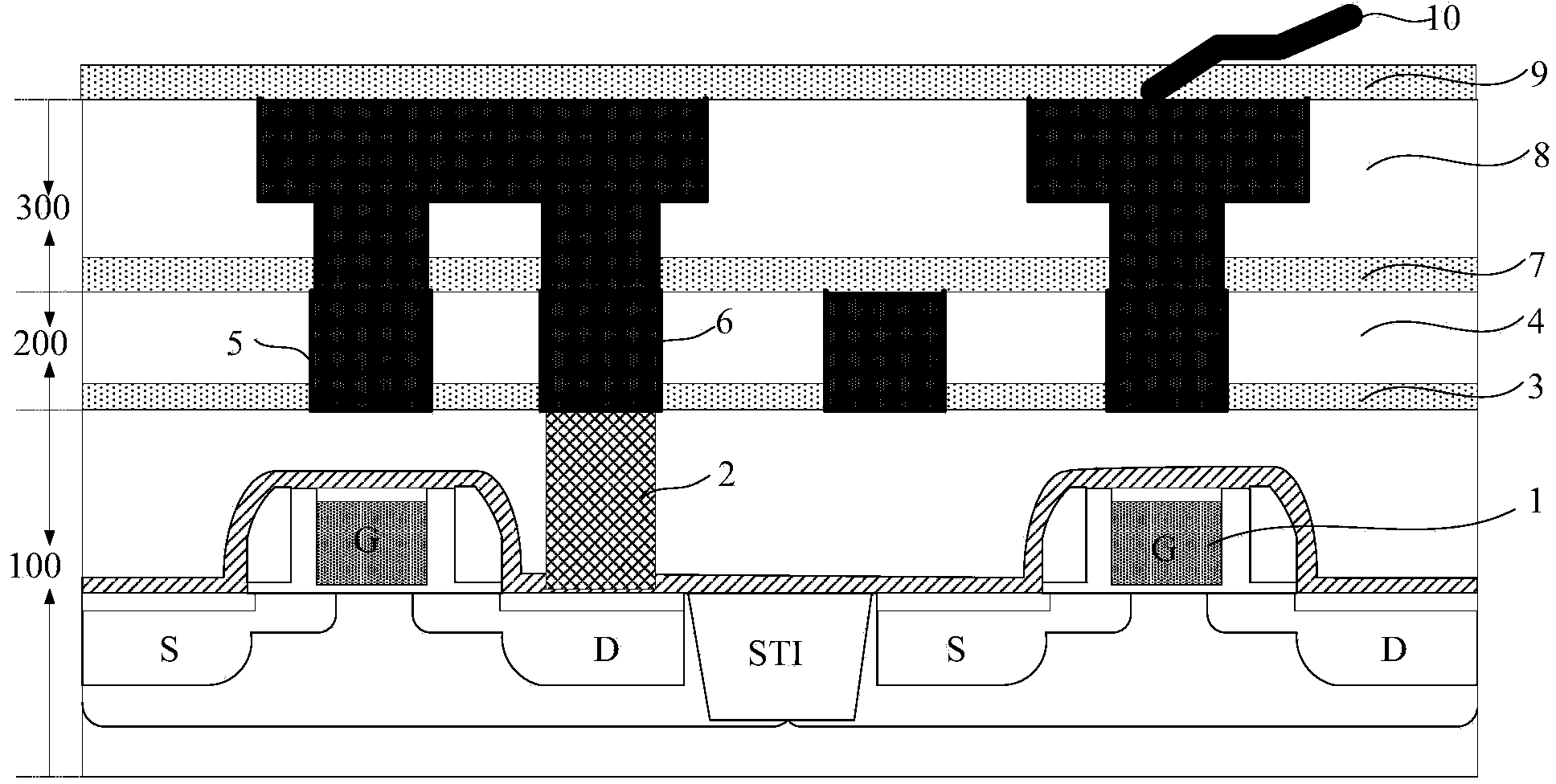

Method for lowering influence on copper interconnection reliability from online WAT testing

ActiveCN103972160AConvenient thermal protectionEfficient removalSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingReduction treatmentSurface plasmon

The invention provides a method for lowering the influence on the copper interconnection reliability from the online WAT testing. The method comprises the steps that at least one layer of to-be-tested copper interconnection structure comprising a testing component is formed on a semiconductor substrate; a dielectric barrier layer is deposited on the surface of the to-be-tested copper interconnection structure in advance, and a wafer to be tested is obtained; a testing probe penetrates through the dielectric barrier layer and keeps contact with the copper surface of the testing component, and online WAT testing is carried out on the wafer to be tested; surface activation and reduction treatment are carried out on the tested dielectric barrier layer and a small part of copper exposed after making contact with the testing probe through reducing plasma gas; the dielectric barrier layer continues to be deposited to be at the preset thickness. Through the method for combining the pre-deposited dielectric barrier layer serving as an isolation protection layer before the testing with the surface plasma activation and reduction treatment after the testing, defects in copper and dielectric materials are effectively restrained from being generated in the online WAT testing process, and the influence on the copper interconnection reliability from the online WAT testing is lowered significantly.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

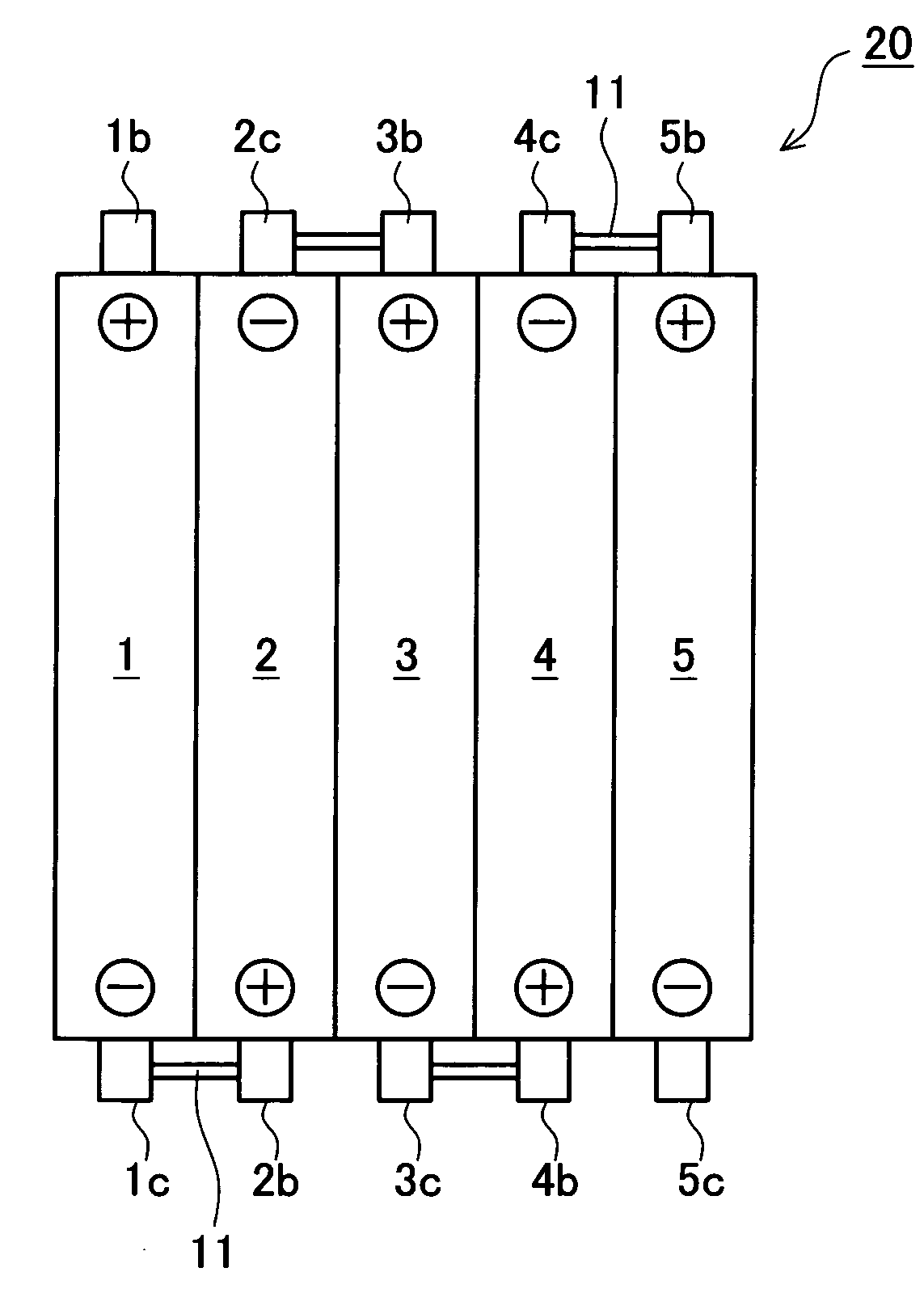

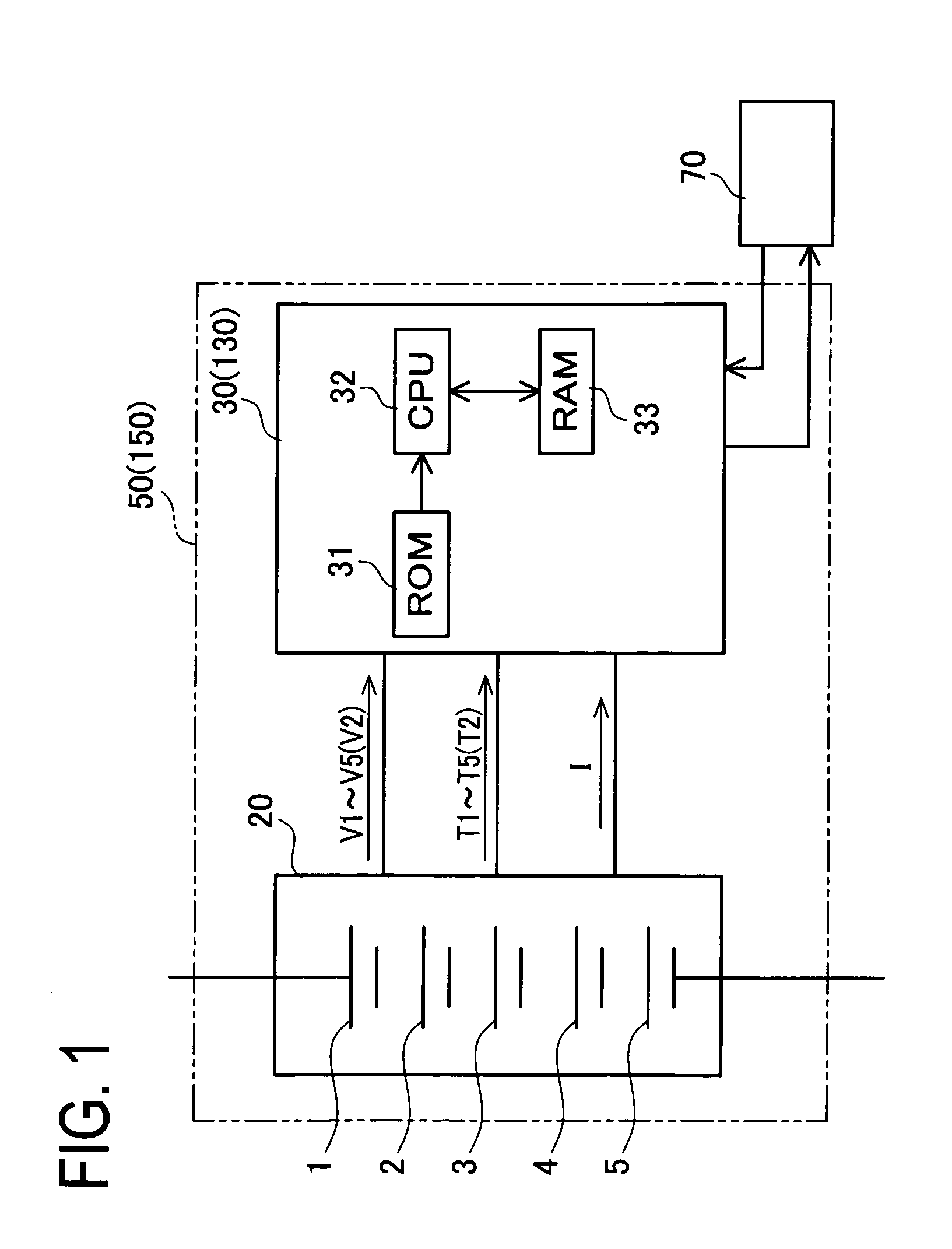

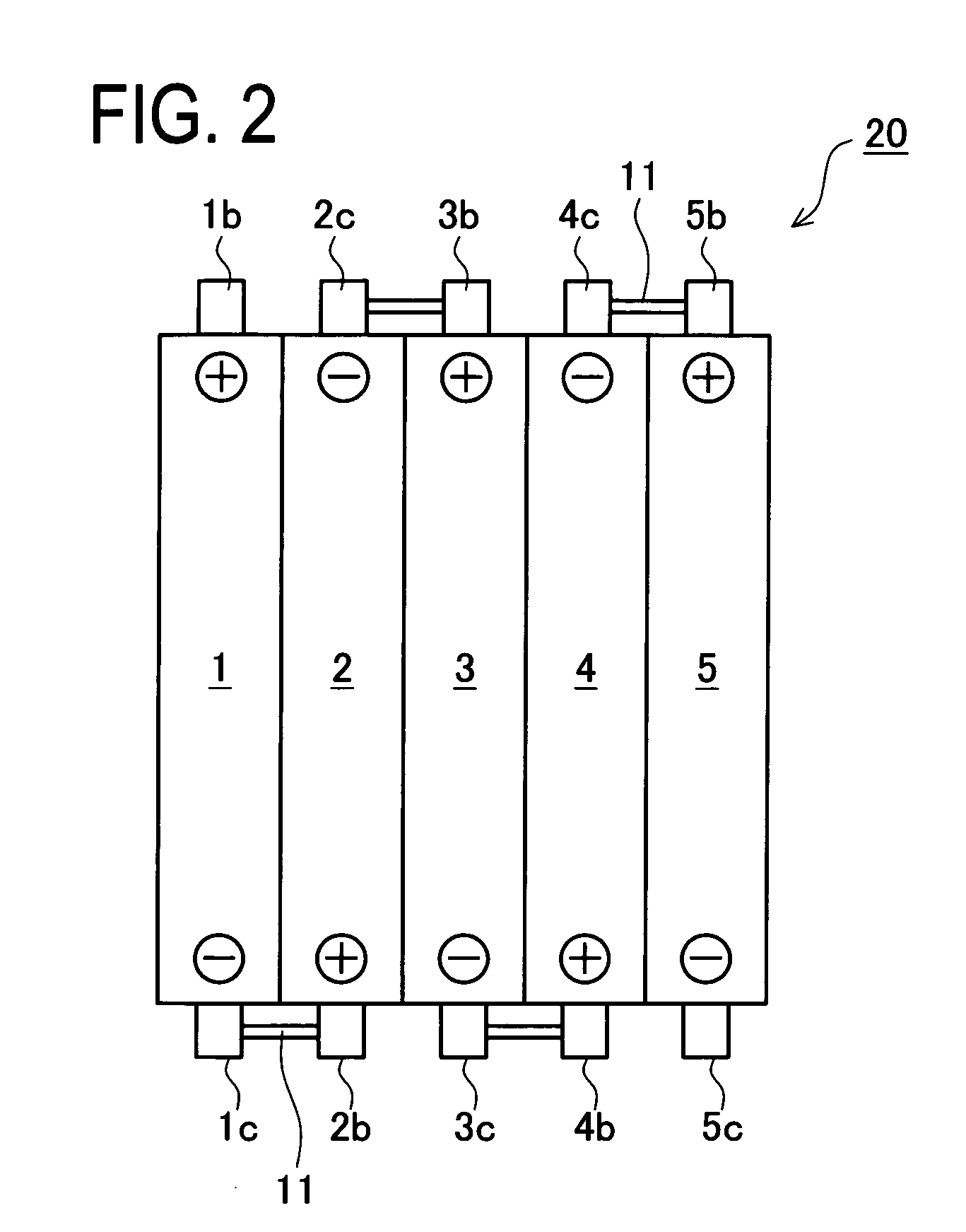

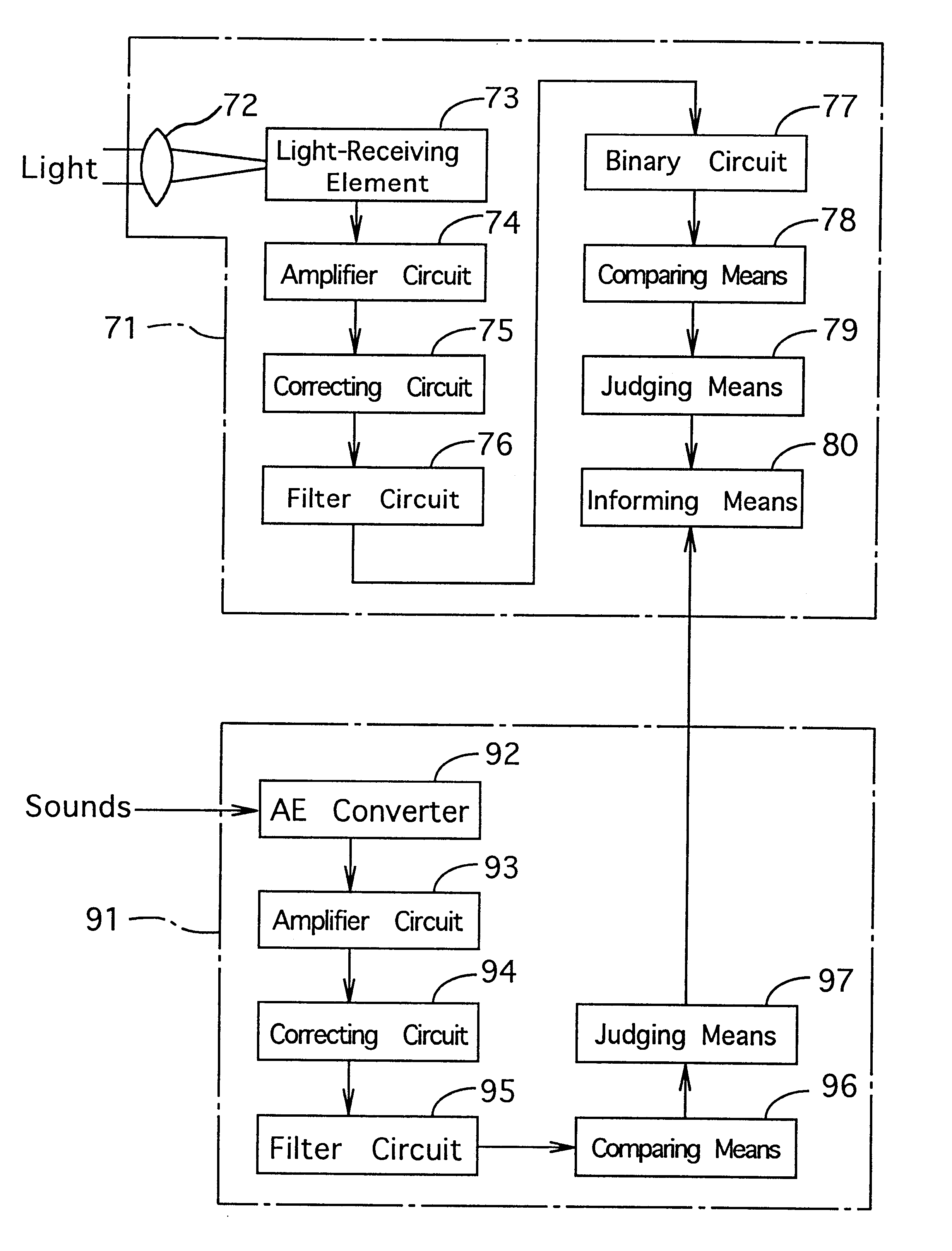

Battery pack producing method and battery pack

ActiveUS20080315835A1Inhibition defectSufficient performanceBatteries circuit arrangementsElectrical testingEngineeringBattery pack

Provided is a battery pack producing method and a battery pack capable of suppressing defects such as overcharging or overdischarging in one or more of the used secondary batteries constituting a battery pack, and sufficiently exhibiting the performance of the used secondary batteries of the battery pack. This method includes an obtaining process for obtaining each full charge capacity of the used secondary batteries, a selecting process for selecting one or more used secondary batteries having similar full charge capacities from the used secondary batteries whose full charge capacities have been obtained, and an assembling process for assembling the selected secondary batteries.

Owner:PANASONIC EV ENERGY CO LTD

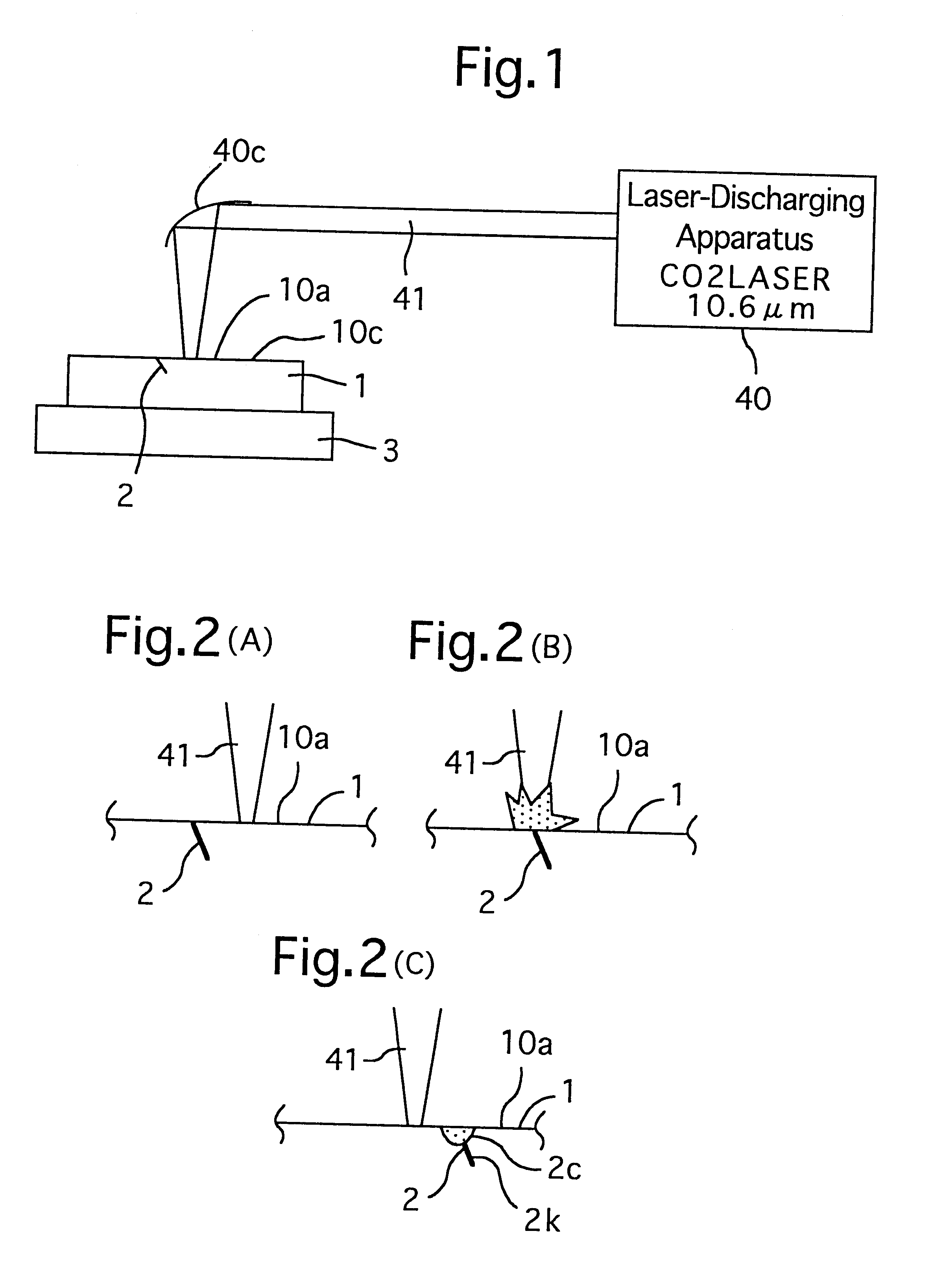

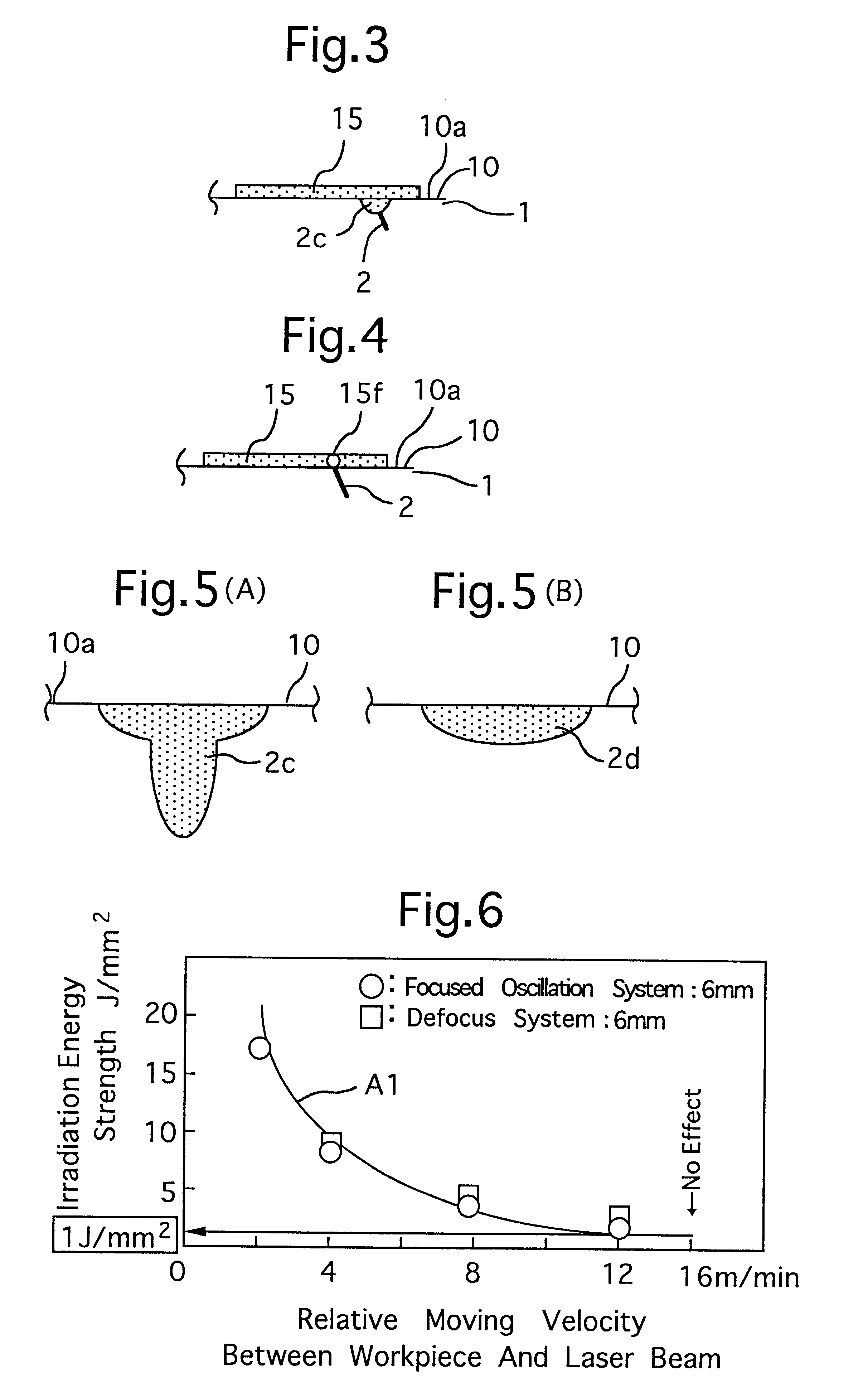

Process of cladding by welding

InactiveUS6329630B1Inhibition defectGuaranteed StrengthElectrostatic cleaningWelding/cutting media/materialsForeign matterHigh density

A process of cladding by welding includes the steps of: (1) preparing a workpiece having a cladding-scheduled portion including an exposed normal region, the exposed normal region having a normal surface including a possibility that a foreign substance portion exists, and the foreign substance portion to form a defect of cladding; (2) irradiating the exposed region of the cladding-scheduled portion of the workpiece with an high-density energy beam, the high-density energy beam capable of eliminating or decreasing the foreign substance portion, substantially without melting the exposed normal region of the cladding-scheduled portion; and (3) covering the exposed normal region of the cladding-scheduled portion of the workpiece with a clad layer.

Owner:TOYOTA JIDOSHA KK

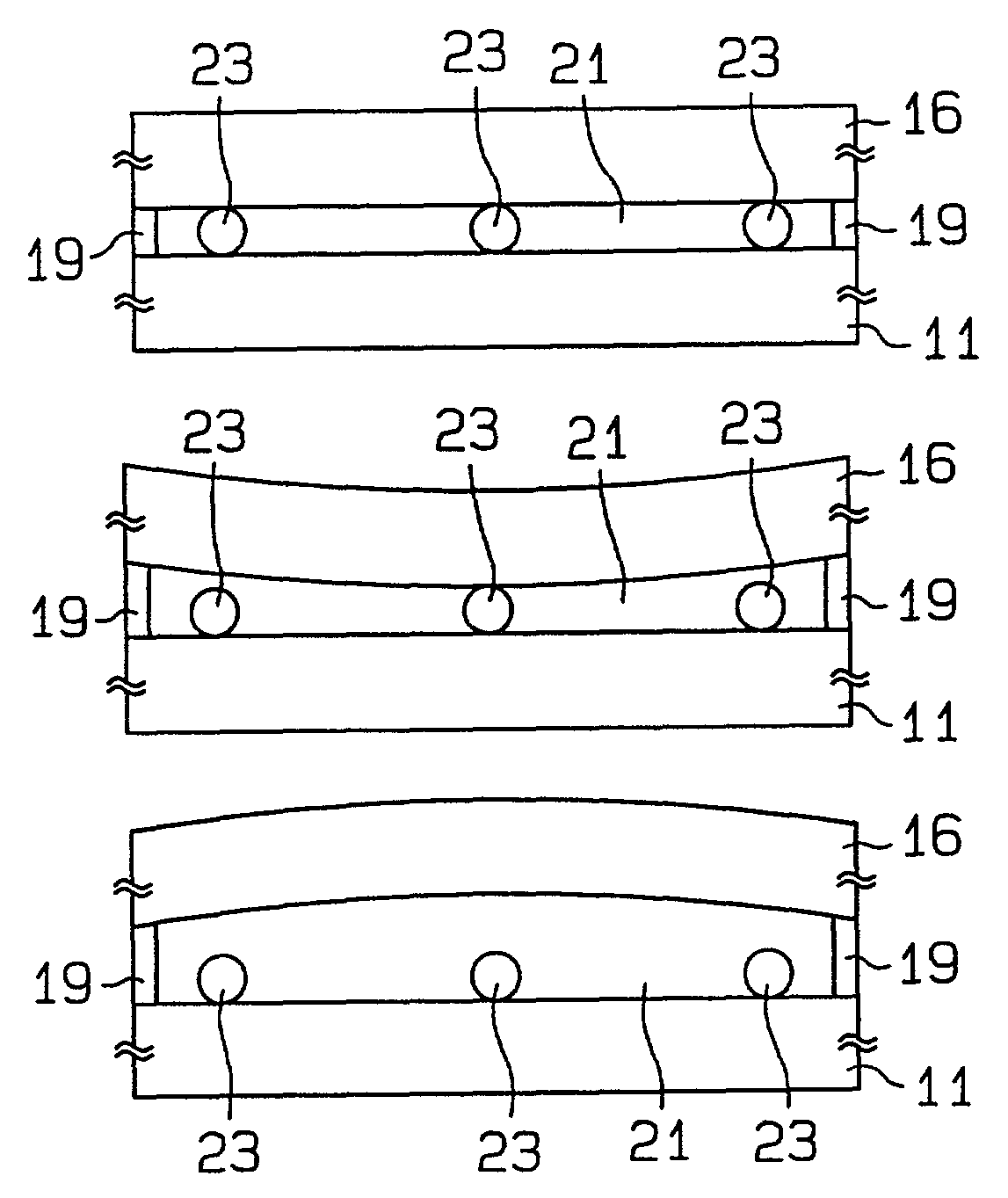

Apparatus for manufacturing bonded substrate

InactiveUS20060201629A1Inhibition defectLamination ancillary operationsLayered product treatmentEngineeringVacuum chamber

The present invention provide an apparatus for manufacturing a bonded substrate that suppresses a defect in the bonded substrate. When the pressure in a vacuum chamber is at the atmospheric level, upper and lower chuck units respectively attract substrates through vacuum. When the vacuum chamber is depressurized, each chuck unit electrostatically attracts the associated substrate. During the depressurization of the vacuum chamber, the pressure for attracting each substrate to the associated chuck unit is controlled to be equal to the pressure in the vacuum chamber. This prevents each substrate from falling from or moving relative to the associated chuck unit. The first and second substrates are thus bonded together as accurately aligned.

Owner:FUJITSU LTD

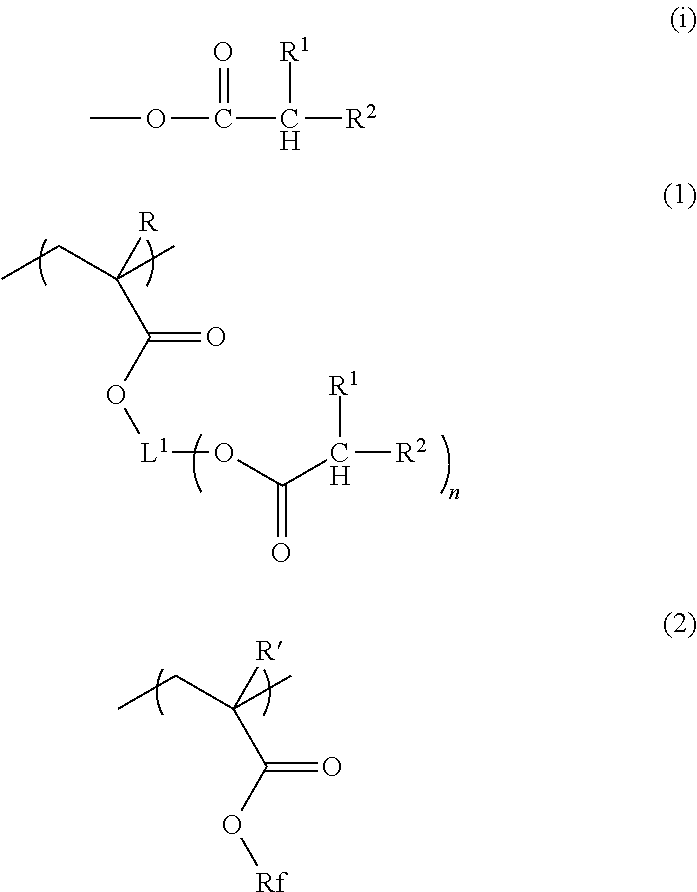

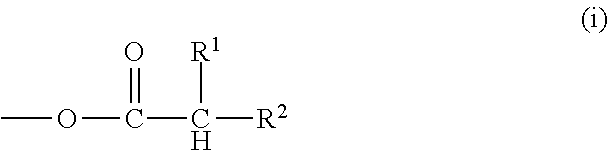

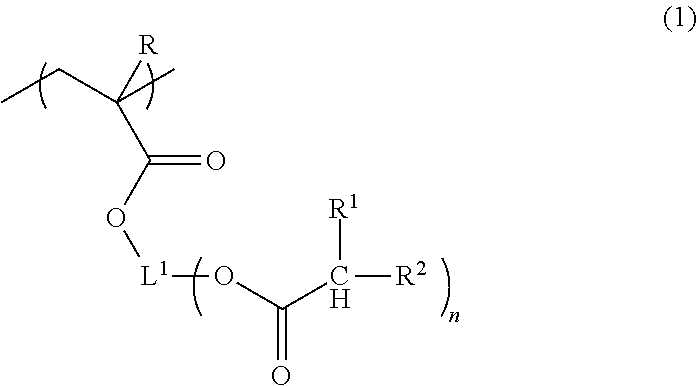

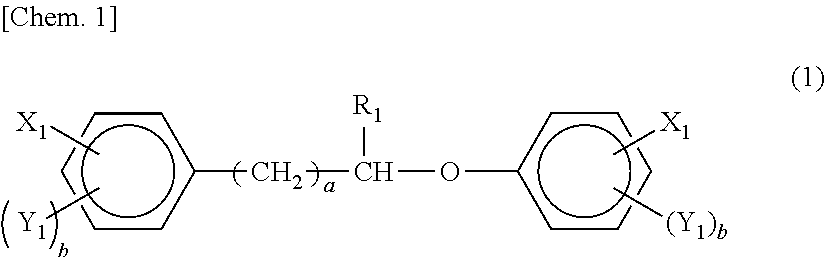

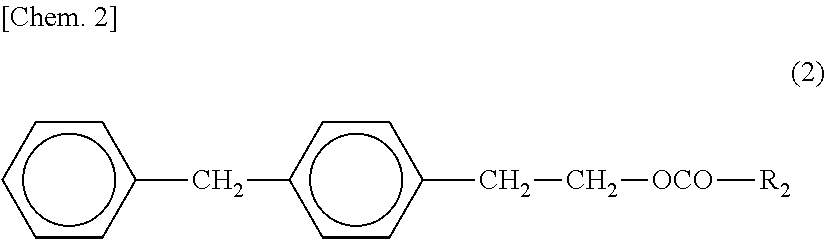

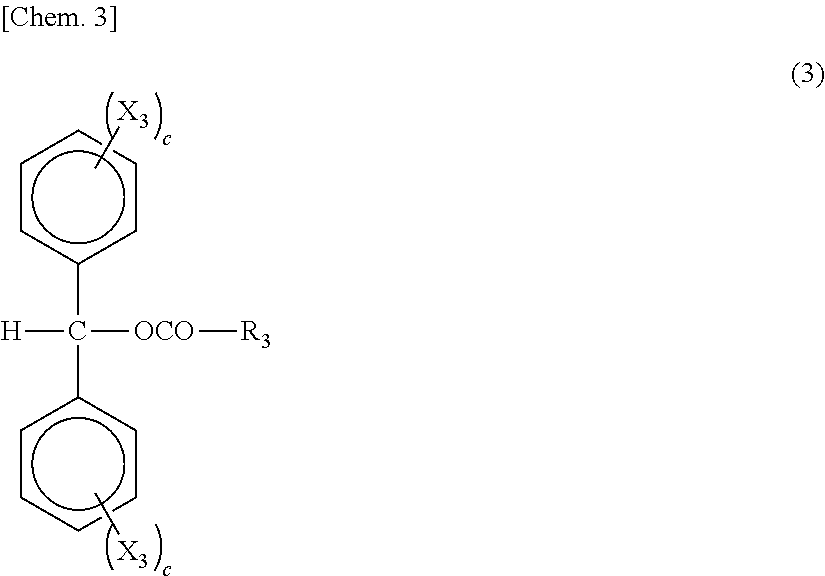

Hole-Injecting Material, Material for Light-Emitting Element, Light-Emitting Element, Organic Compound, Monomer, and Monomer Mixture

InactiveUS20080154005A1Sufficient hole injecting propertyInhibition defectLiquid crystal compositionsOrganic chemistryDopantAryl

An object of the present invention to provide a material for a light-emitting element or a hole injecting high molecular weight material which has a sufficient hole injecting property, without using a dopant having an electron accepting property. One of materials of the present invention which can achieve the object, has a repeating unit represented by the following formula (1), In the formula (1), R1 represents hydrogen, an alkyl group, a cyano group, or an alkoxy group, and R2 represents an aryl group. The material has an ionization potential of 4.9 eV or more and 5.4 eV or less.

Owner:SEMICON ENERGY LAB CO LTD

Thermoelectric element

ActiveUS20070068566A1Inhibition defectThermoelectric device with peltier/seeback effectThermoelectric device detailsThermoelectric materialsThermoelectric element

A thermoelectric element has a first substrate at a high temperature side, a second substrate at a low temperature side facing the first substrate, a thermoelectric material placed on the second substrate via a silicon layer, a first electrode formed on the first substrate, and a second electrode formed on the silicon layer. The thermoelectric element has a stress releasing section which is formed between the first electrode and the thermoelectric material, and which includes a plurality of columnar portions. The stress releasing section suppresses defects such as cracks that might be produced in the thermoelectric element due to a stress generated in the thermoelectric element.

Owner:TDK CORPARATION

Composition for forming liquid immersion upper layer film, and polymer

ActiveUS20130217850A1Increase contentEasy to synthesizeSemiconductor/solid-state device manufacturingEmulsion paintsPolymer scienceSolvent

An immersion upper layer film-forming composition includes [A] a polymer component that includes a polymer (A1), and [B] a solvent, the polymer (A1) including a structural unit (I) that includes a group represented by the following formula (i). The structural unit (I) is preferably a structural unit (I-1) represented by the following formula (1). The polymer component [A] preferably further includes a structural unit (II-1) represented by the following formula (2), the structural unit (II-1) being included in the polymer (A1) or a polymer other than the polymer (A1). The polymer component [A] preferably further includes a structural unit (III) that includes a carboxyl group, the structural unit (III) being included in the polymer (A1) or a polymer other than the polymer (A1).

Owner:JSR CORPORATIOON

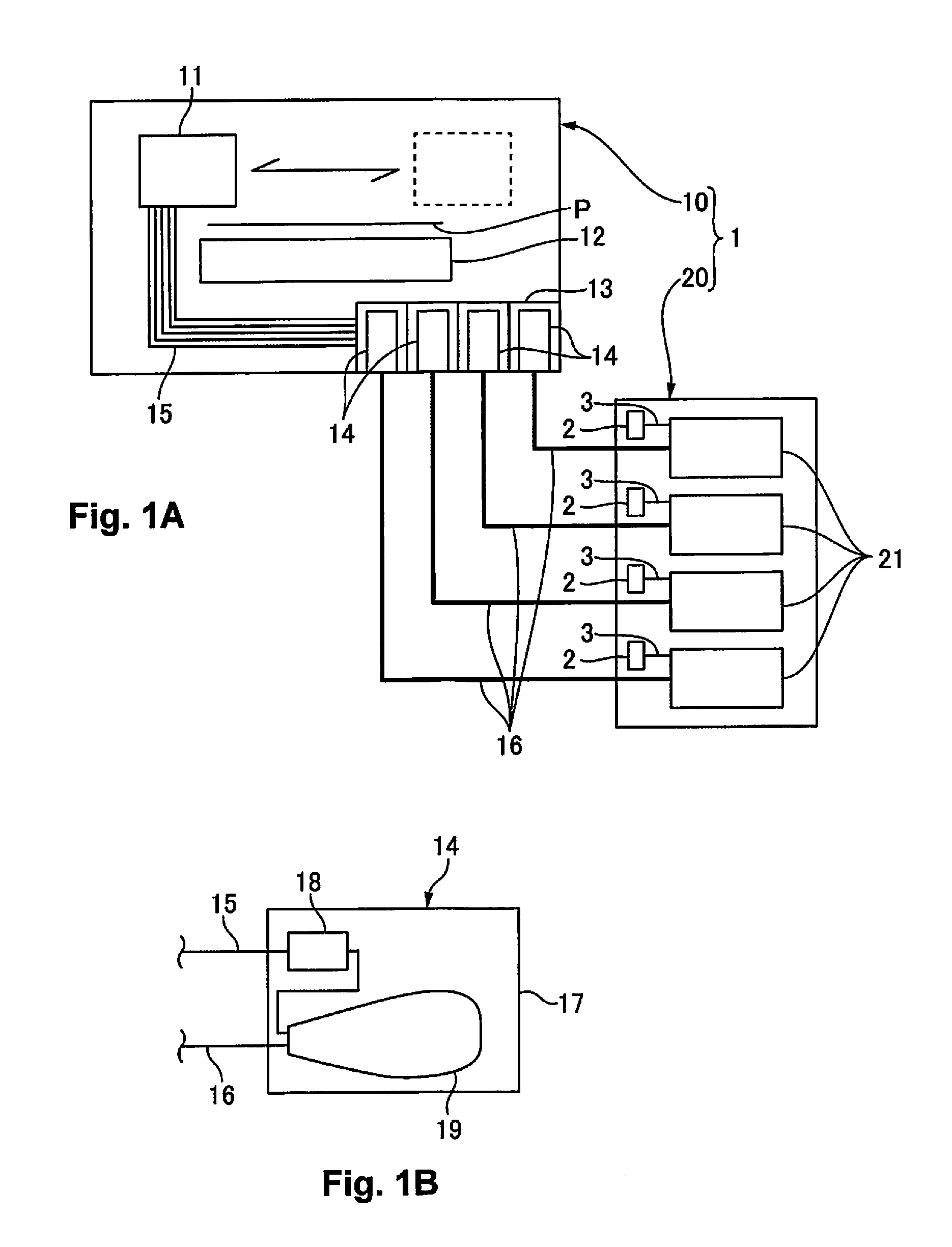

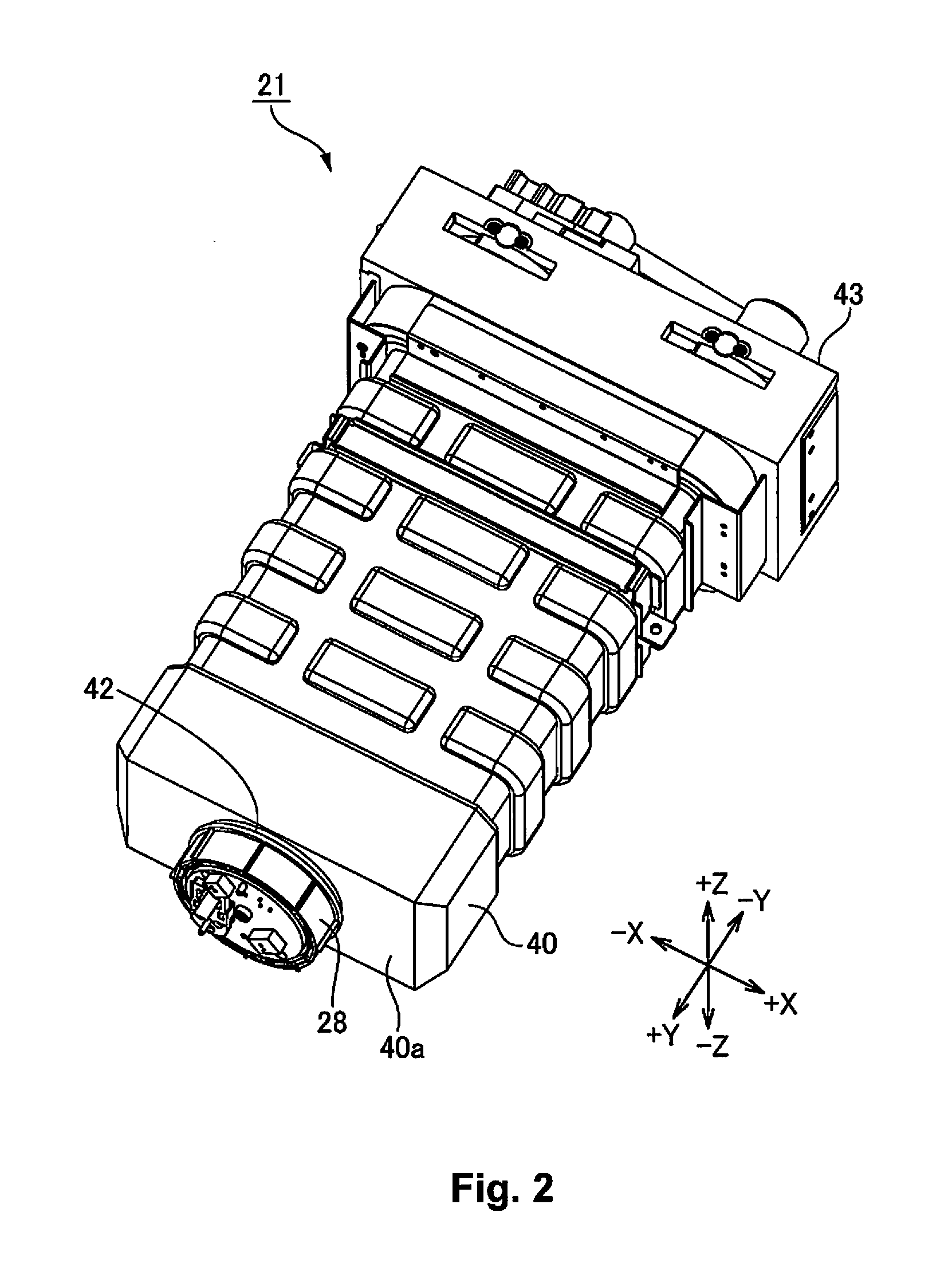

Liquid ejecting apparatus

ActiveUS20150273501A1Suppress positional deviation of coverResistance be doubleLiquid spraying apparatusMedical atomisersEngineeringMechanical engineering

Owner:SEIKO EPSON CORP

Solid writing material

InactiveUS20150376433A1Improve light resistanceGood molding effectPencil leadsNon-propelling pencilsElectron transfer reactionsColor changes

The invention aims at providing a solid writing material having a good color changing property or color extinguishing property, and having an excellent light resistance, moldability and strength. The solid writing material includes an inner core usable for writing and an outer shell covering an outer peripheral surface of the inner core; the inner core including a reversible thermochromic microcapsuled pigment encapsulating a temperature-sensitive color-changeable color-memorizing composition and an excipient; the temperature-sensitive color-changeable color-memorizing composition including at least (a) an electron-donating coloring organic compound, (b) an electron accepting compound and (c) a reaction medium effecting reversibly an electron transfer reaction between the (a) and (b) components in a specific temperature range; the outer shell including a filler.

Owner:PILOT PEN CO LTD

Nanometer semiconductor devices having high-quality epitaxial layer

ActiveUS10475935B2Improve mobilityInhibition defectTransistorNanoinformaticsElectrical conductorNanowire

There are provided a nanometer semiconductor device with a high-quality epitaxial layer and a method of manufacturing the same. According to an embodiment, the semiconductor device may include: a substrate; at least one nanowire spaced apart from the substrate; at least one semiconductor layer, each formed around a periphery of respective one of the at least one nanowire to at least partially surround the corresponding nanowire, wherein the semiconductor layer(s) formed around the respective nanowire(s) are separated from each other; an isolation layer formed on the substrate, exposing the at least one semiconductor layer; and a gate stack formed on the isolation layer and intersecting the at least one semiconductor layer, wherein the gate stack includes a gate dielectric layer at least partially surrounding a periphery of respective one of the at least one semiconductor layer and a gate conductor layer.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

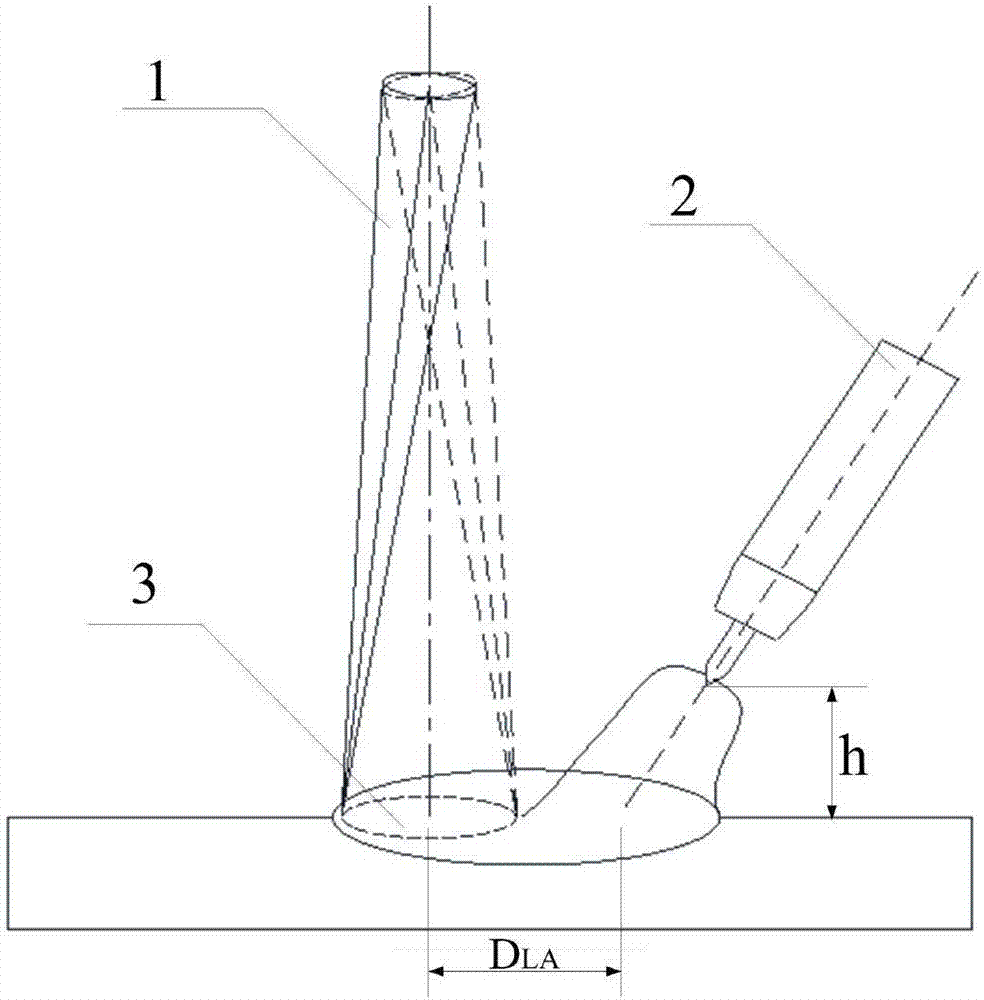

Vibrating welding method of laser scanning-TIG compound molten bath

InactiveCN107498182AAchieve stirring effectInhibition defectLaser beam welding apparatusLaser scanningMolten bath

The invention discloses a vibrating welding method of a laser scanning-TIG compound molten bath. The method is implemented by compounding laser scanning and TIG welding. According to the method, during welding, two compound welding modes of performing laser scanning of a groove first and performing welding by a TIG weld gun then or performing welding by the TIG weld gun first and performing laser scanning of the groove then are selected; as a result of different materials and welding demands, the track of the laser scanning molten bath has different modes. As the ranges on two sides of the laser scanning groove are same or different or only one side of the groove is scanned by laser, the scanning track can be round, sinusoidal and triangular or special regions are selectively scanned. By means of mutual enhancement and coupling action of laser and arc, the depth of fusion is increased and the efficiency is increased; the molten bath is stirred by scanning the welding molten bath by laser, so that the temperature gradient is reduced, the solidification and crystallization processes are improved, and the welding joint performance is improved.

Owner:SHANGHAI JIAO TONG UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com