Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

103641 results about "Hemt circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Color el display and method for producing the same

ActiveUS20080129195A1Quality improvementHigh color purityDischarge tube luminescnet screensLamp detailsDisplay deviceEngineering

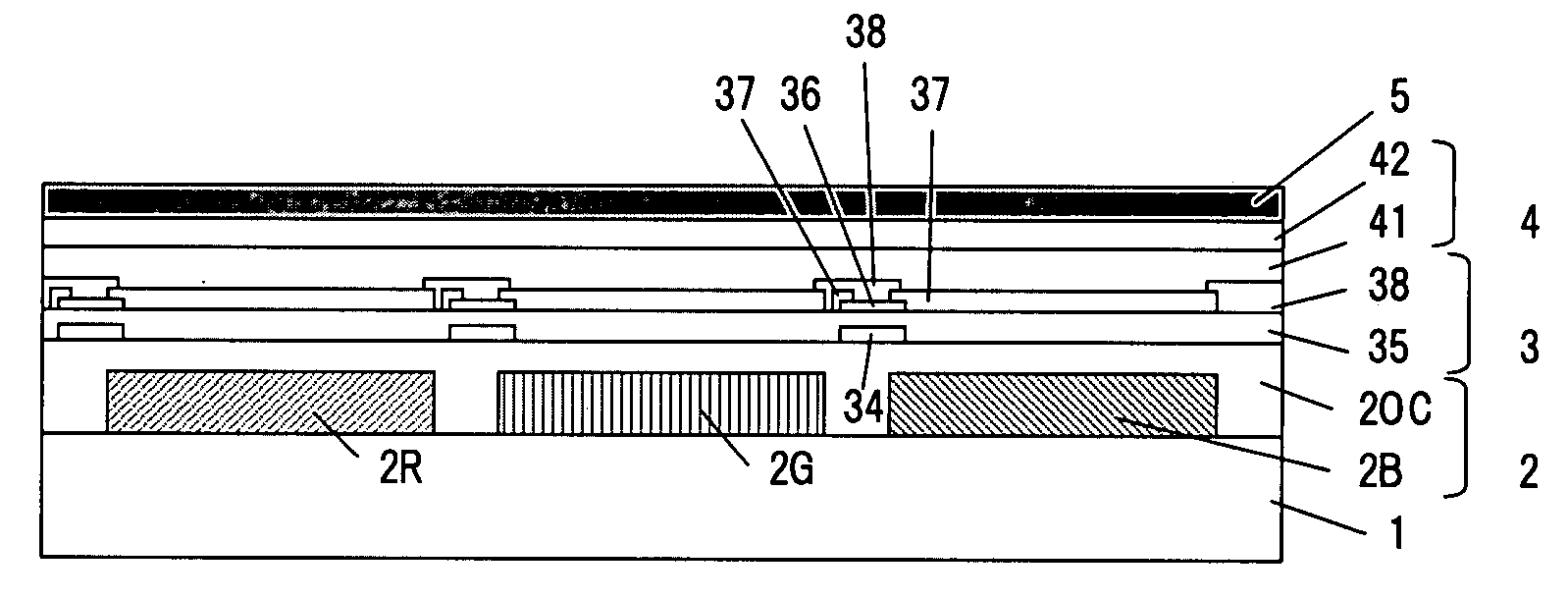

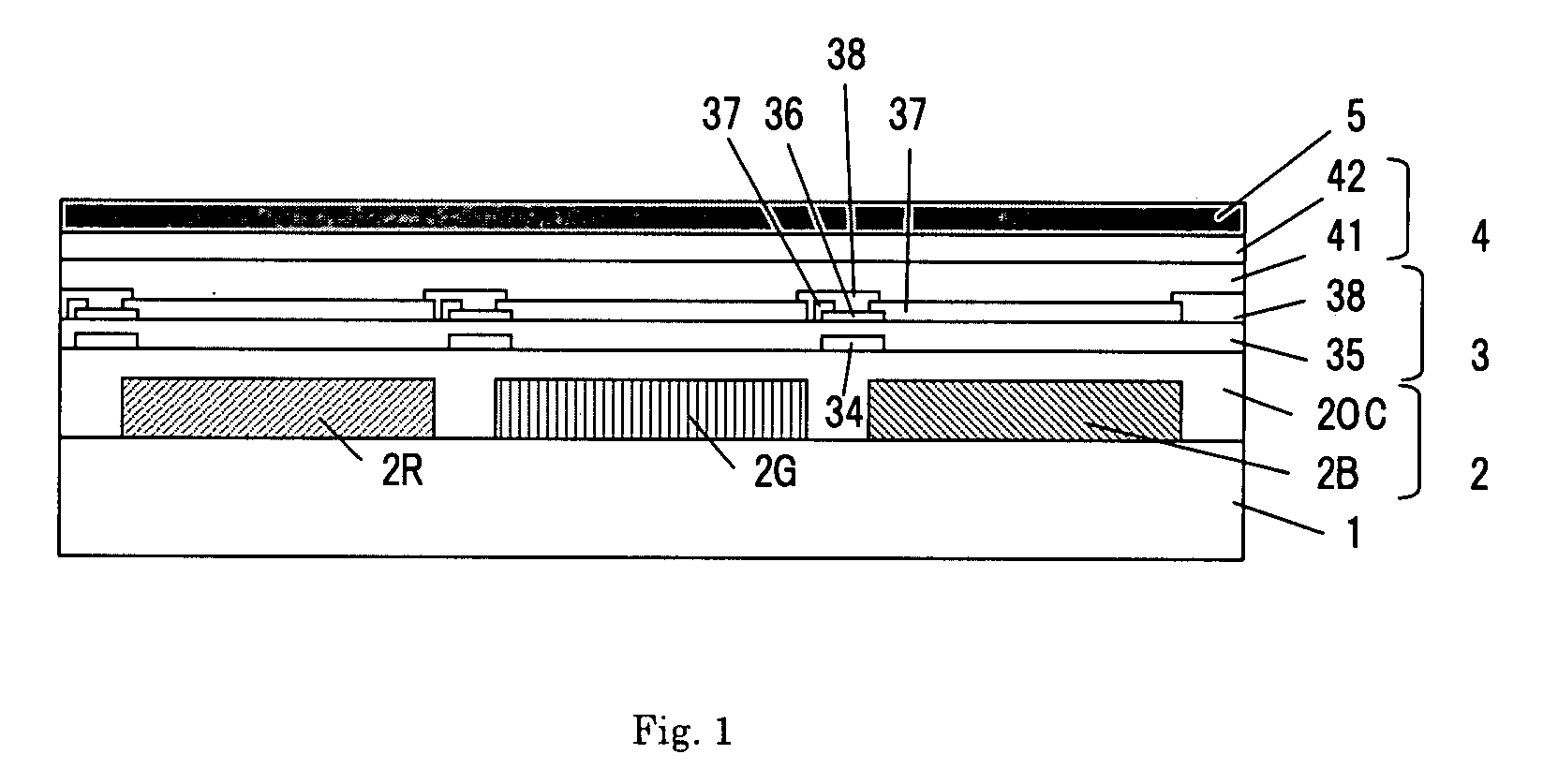

One embodiment of the present invention is a color EL display characterized in that at least color filters, a thin film transistor circuit, an organic EL layer, and a common electrode are laminated in this order on a transparent substrate. Another embodiment of the invention is a method for producing a color EL display comprising the steps of forming color filters or a transparent substrate; forming a thin film transistor circuit; forming an organic EL layer; and forming a common electrode, wherein process temperatures of the steps of forming the thin film transistor circuit and subsequent steps are 200° C. or less.

Owner:TOPPAN PRINTING CO LTD

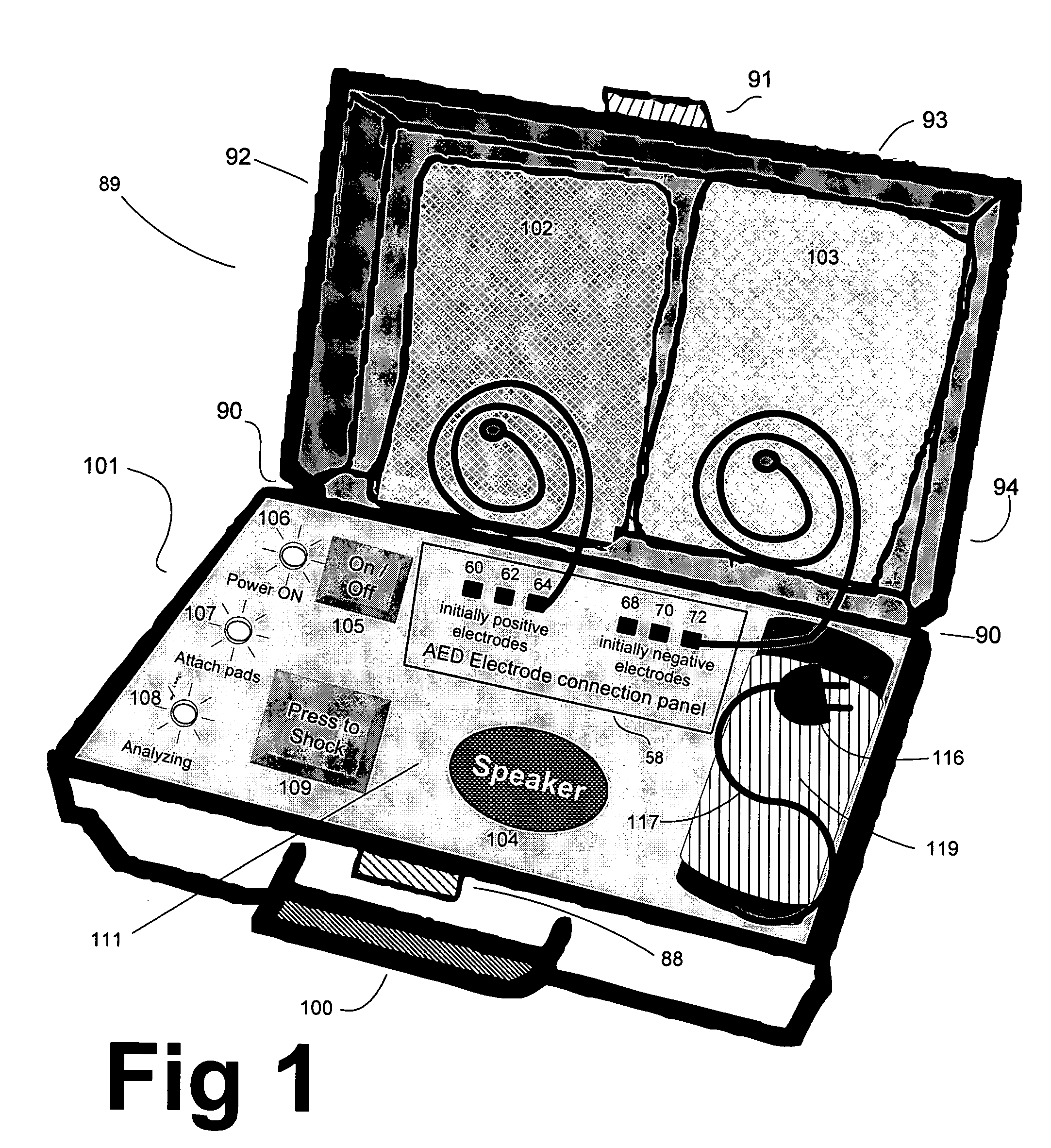

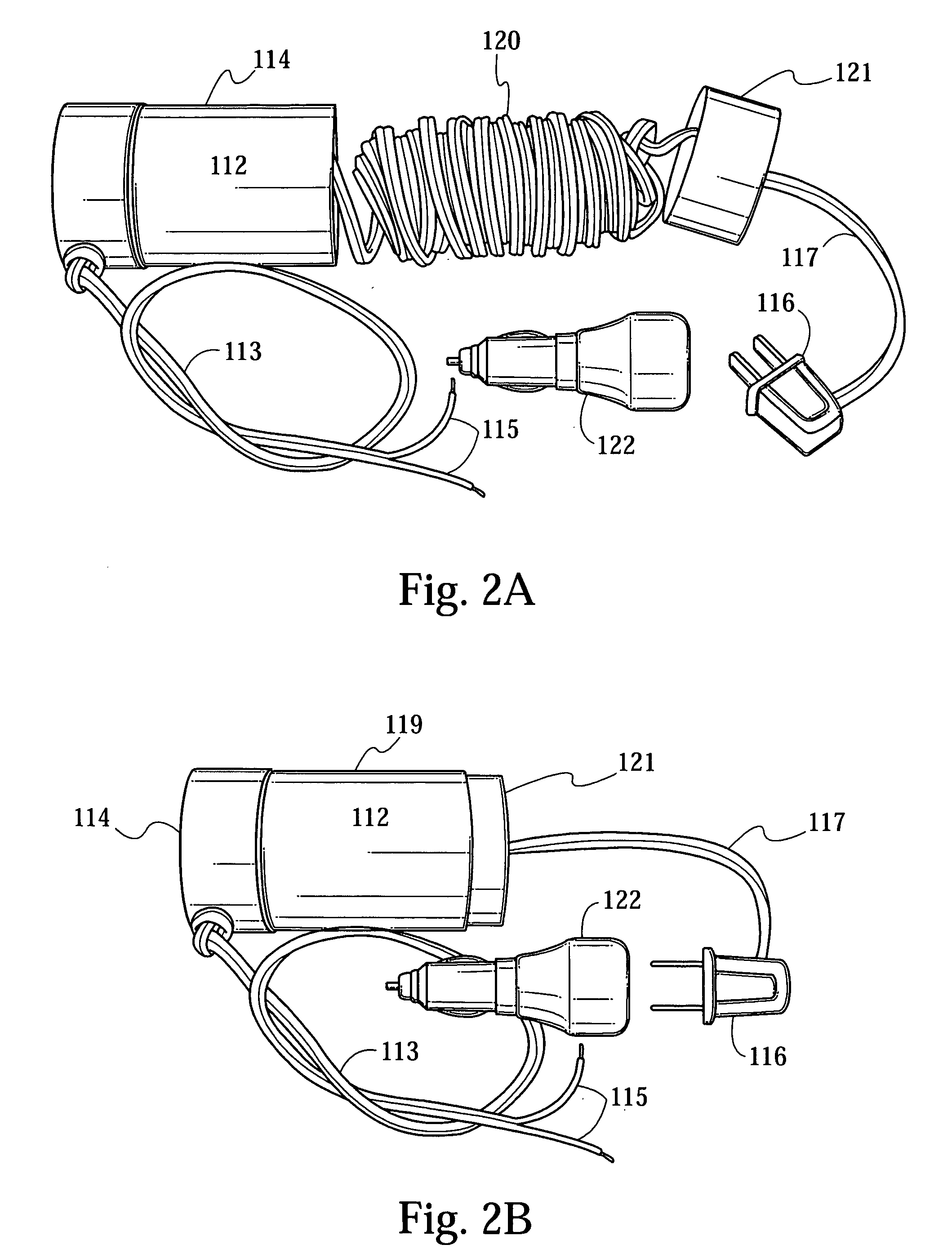

Advanced automatic external defibrillator powered by alternative and optionally multiple electrical power sources and a new business method for single use AED distribution and refurbishment

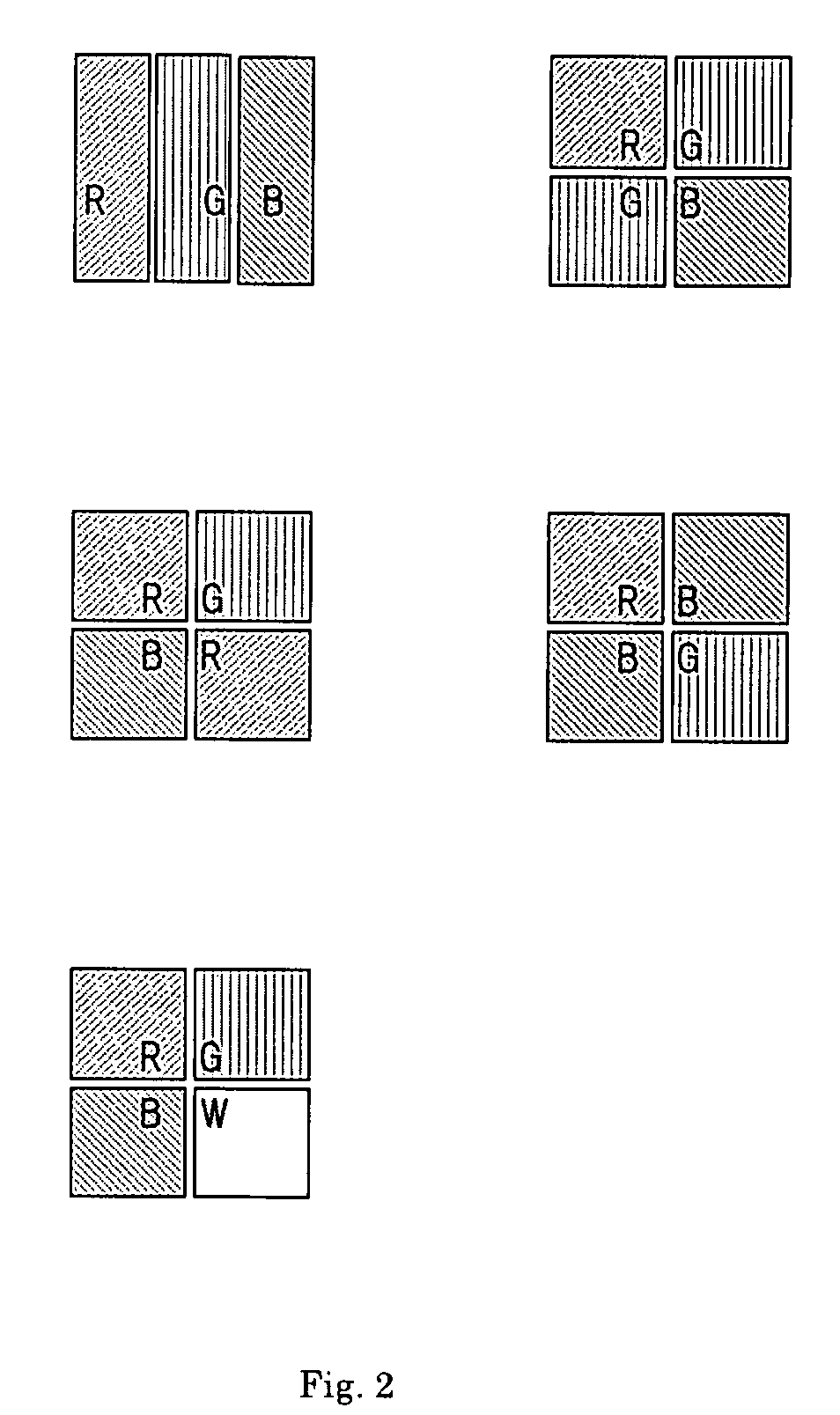

InactiveUS20040143297A1Improve reliabilityRapid and easy deploymentData processing applicationsHeart defibrillatorsEngineeringAutomatic external defibrillator

An AED being powered by 120 / 240 VAC electrical power alone, being powered by external DC power alone, or any in combination with or without internal-integral battery power, and further an AED access service business method for sales of access to AEDs. The inventive AED, in addition to the defibrillator circuitry comprises a long, tangle free power access cord to be plugged into an external source of AC or DC power and optionally, additional sets of body surface and alternative electrodes positioned in the esophagus and / or heart. The AED has additional advanced capabilities including the ability to deliver rapid sequential shocks through one or more sets of patient electrodes, and the optional mode of shock delivery whereby the shock is delayed while the AED continues to analyze the patients ECG waveform and delays the defibrillation shock or sequence of shocks until the ECG analysis indicates conditions are optimum for successful defibrillation.

Owner:RAMSEY MAYNARD III

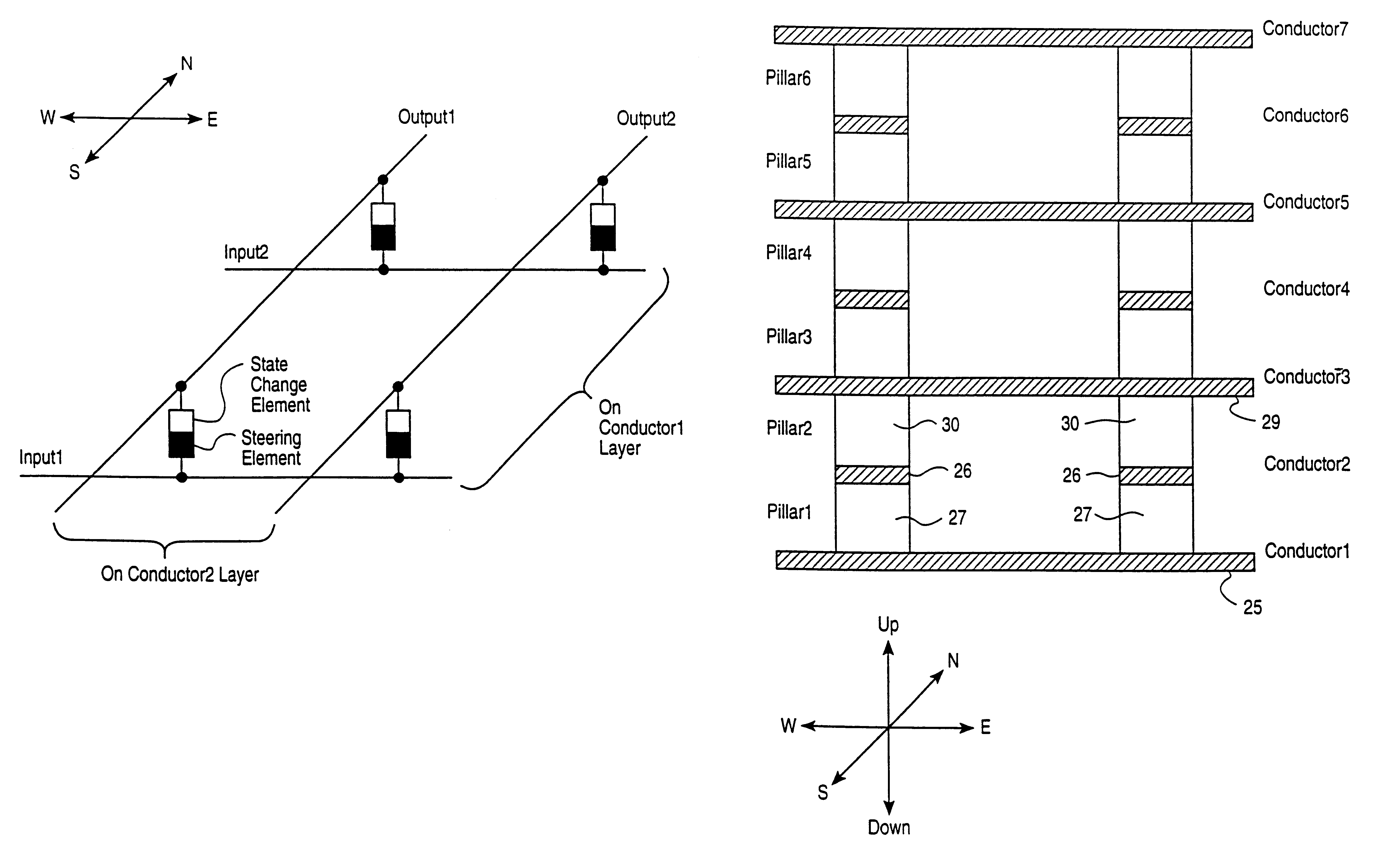

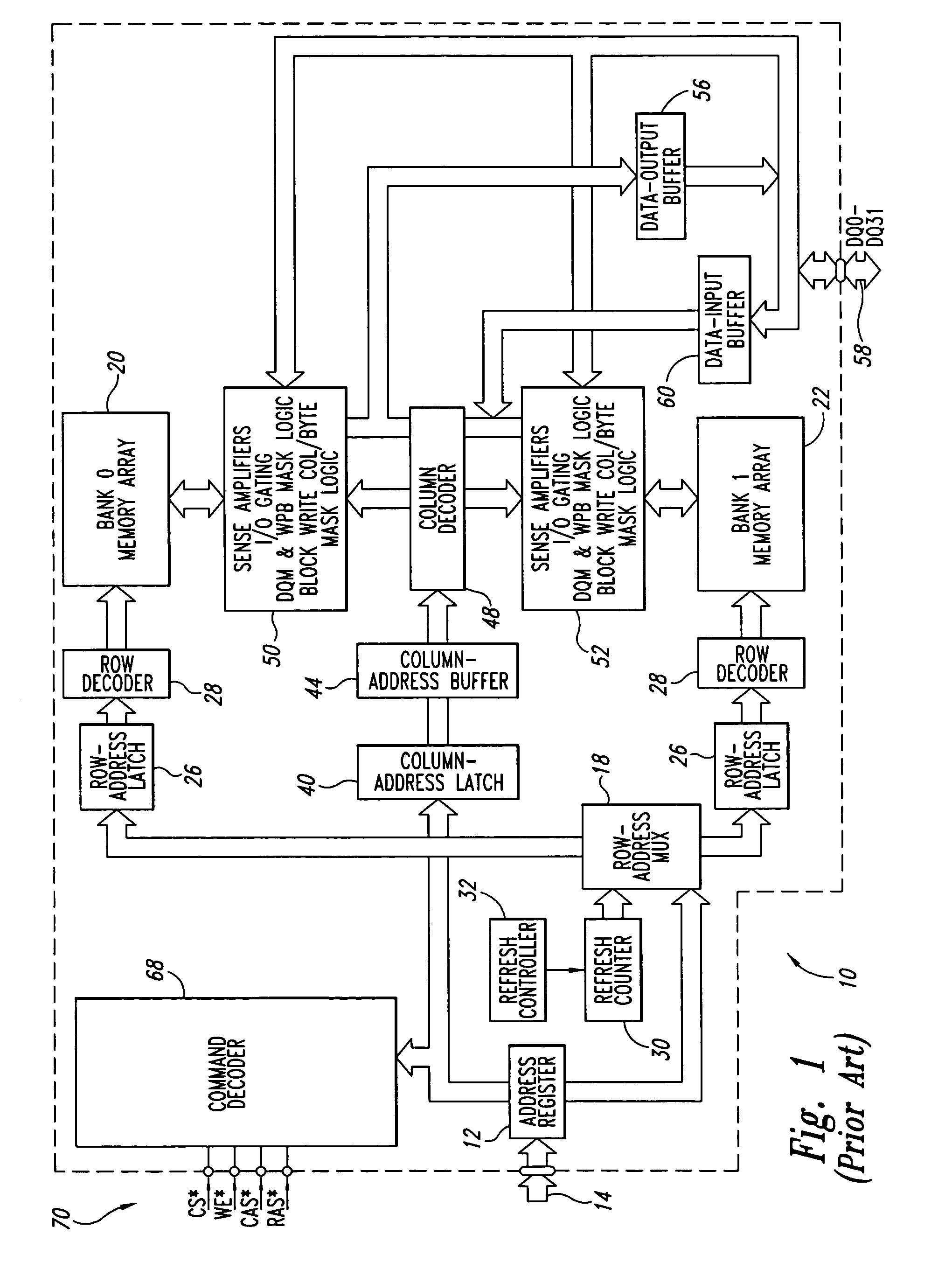

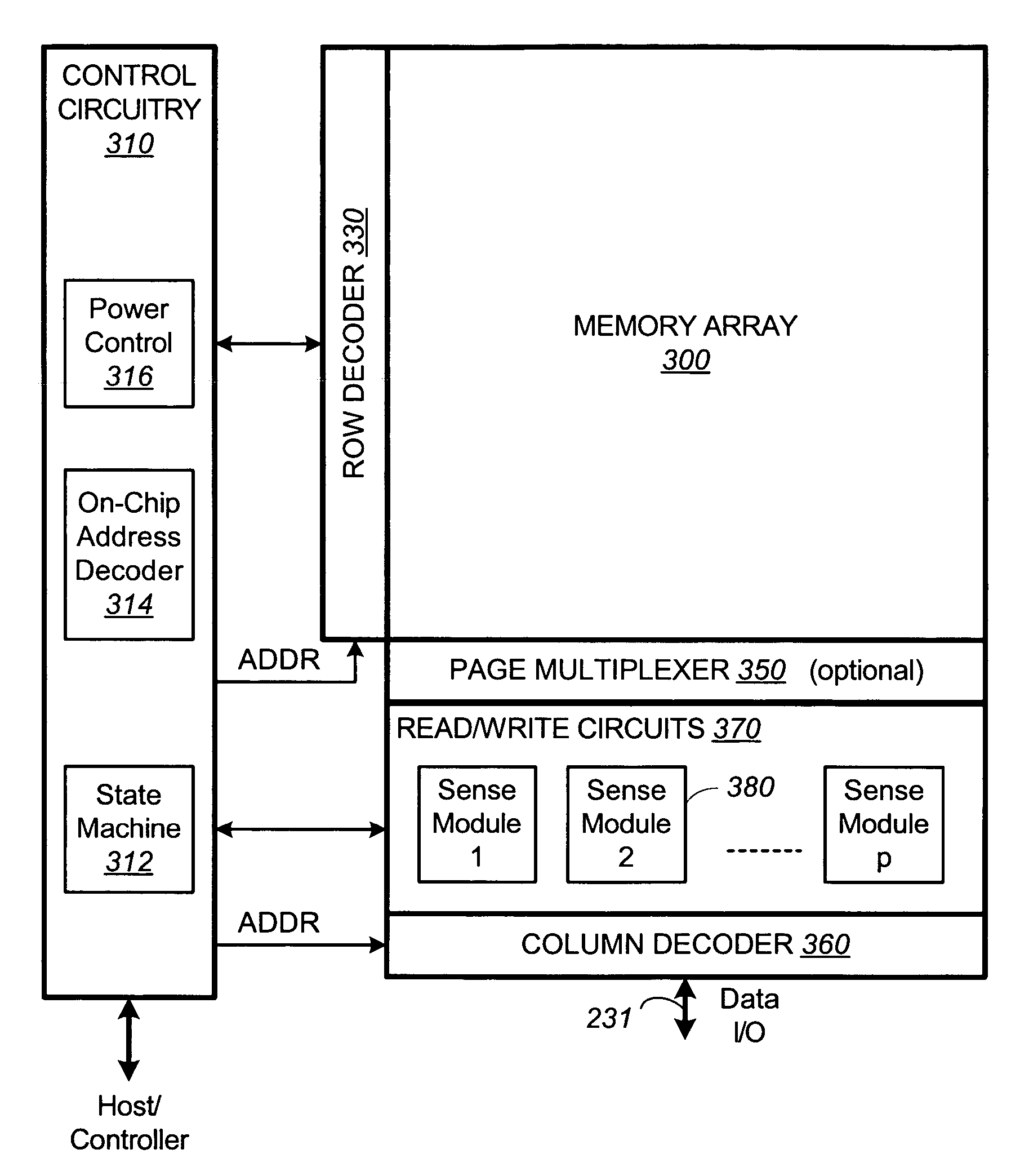

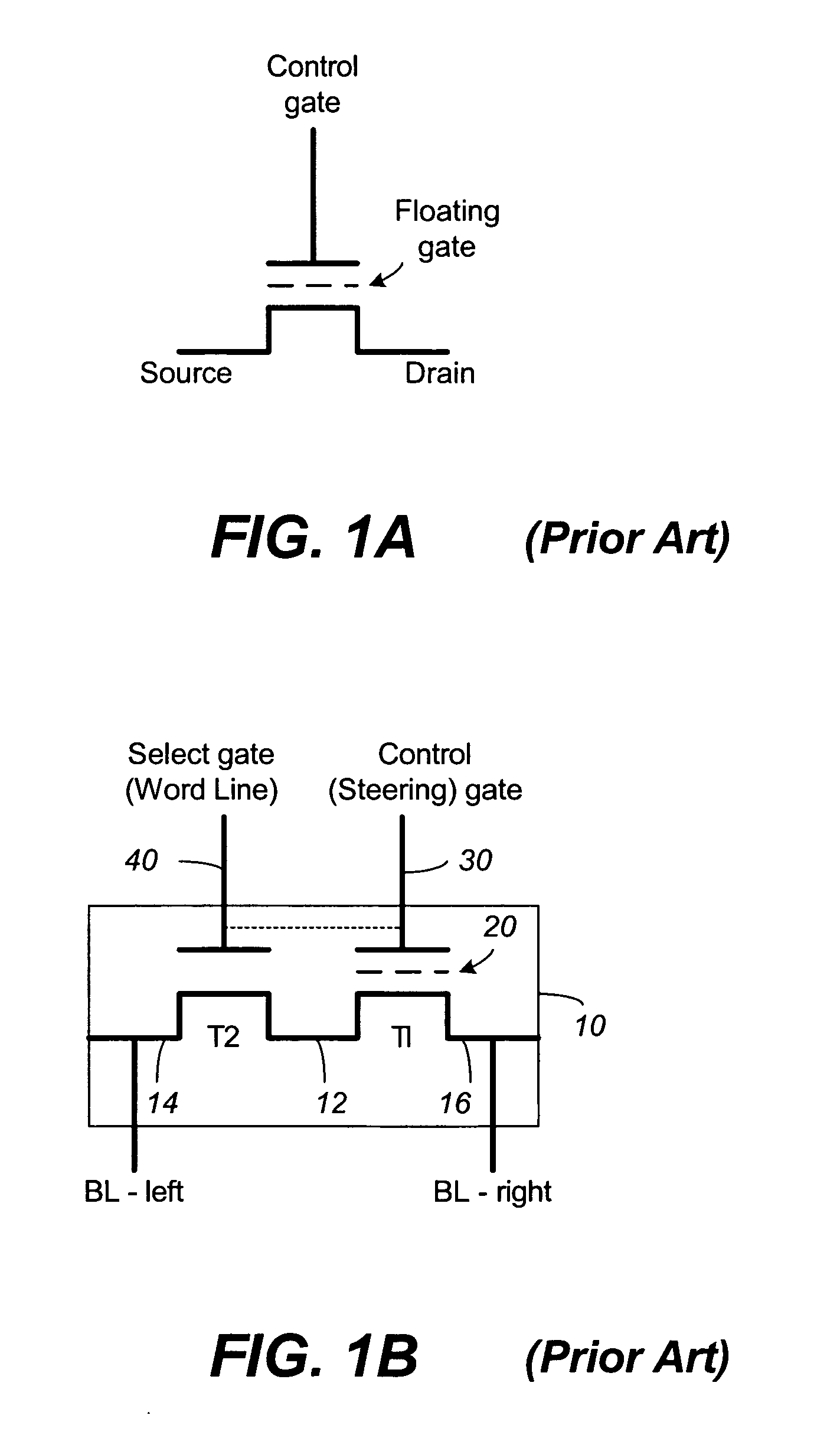

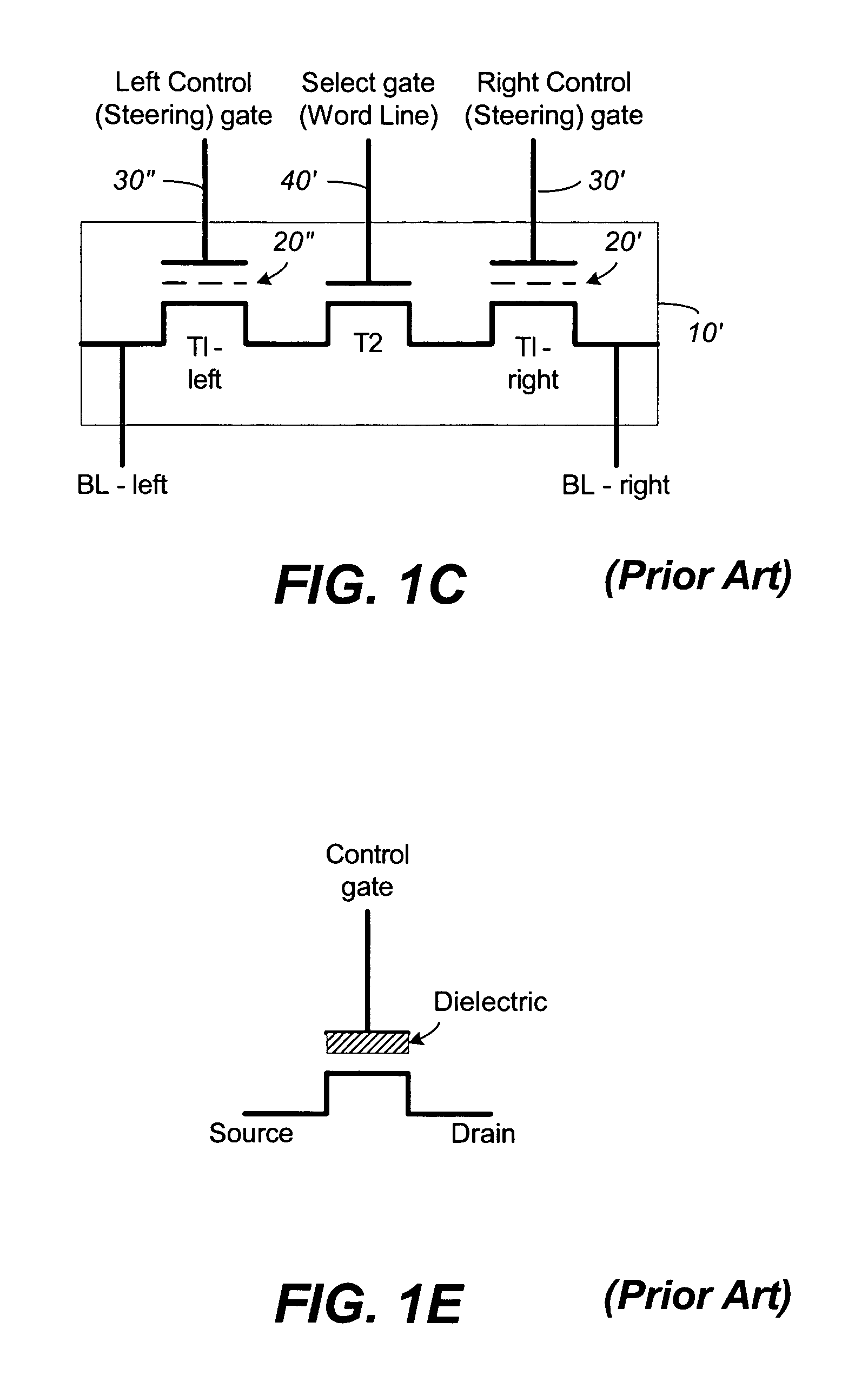

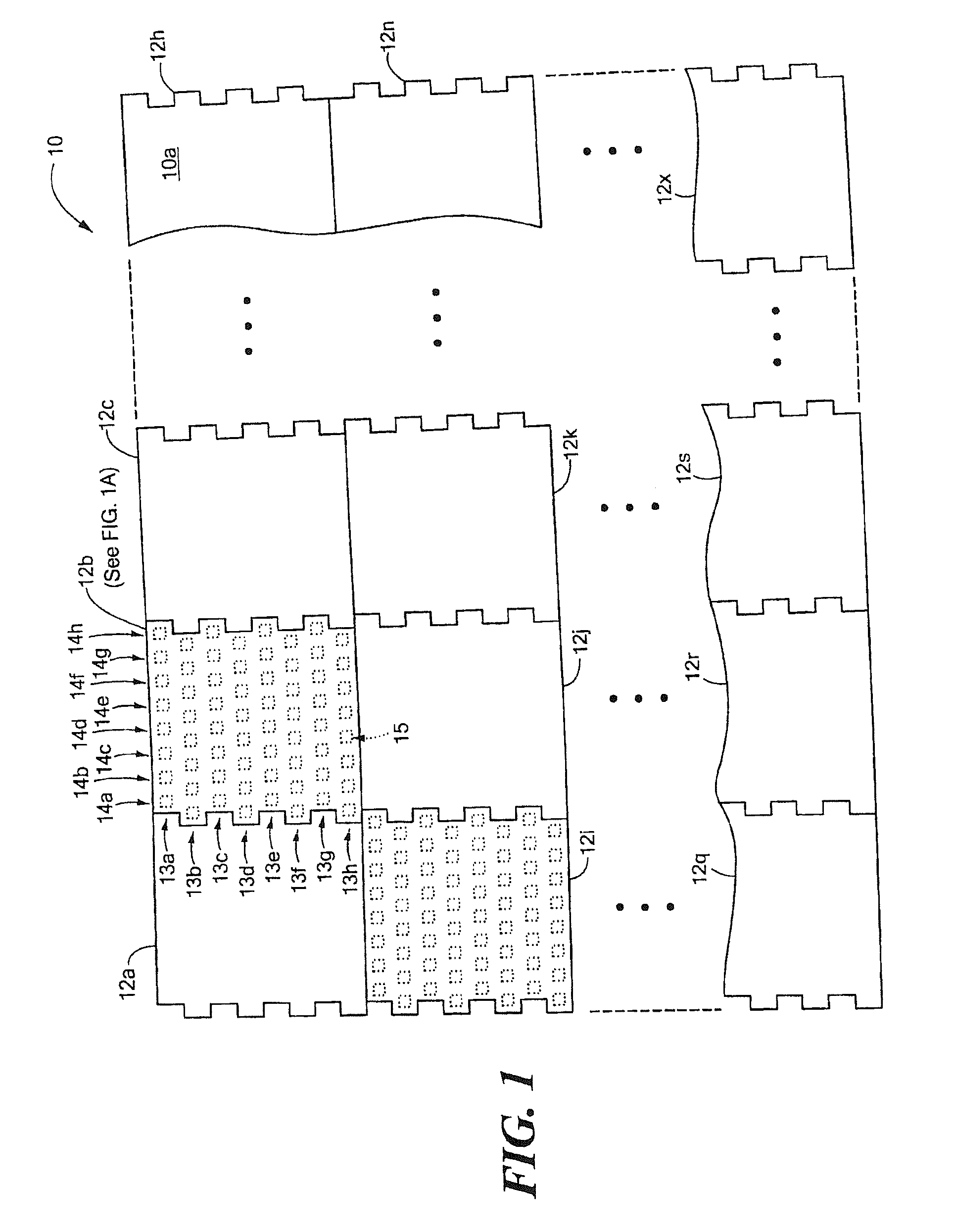

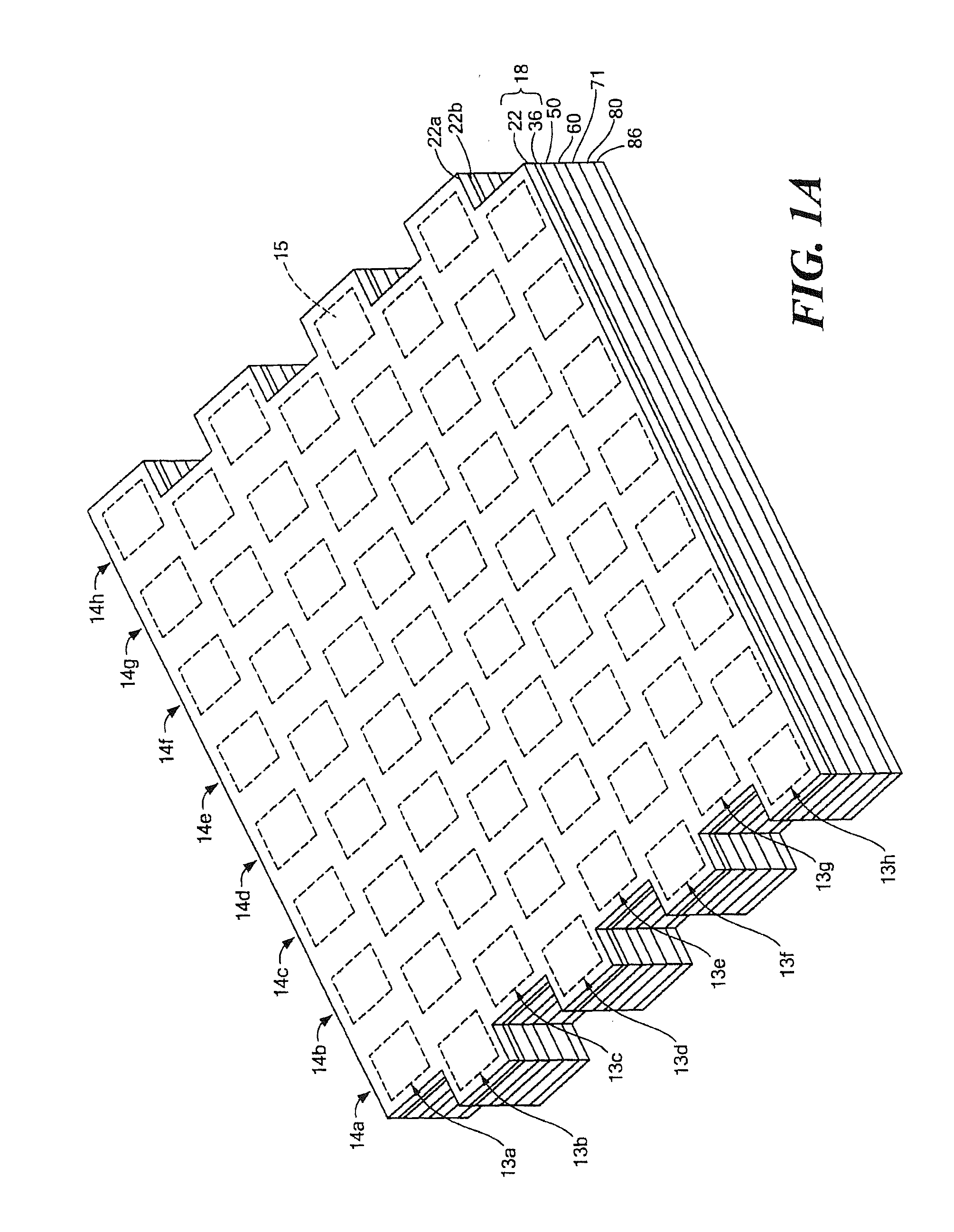

Vertically stacked field programmable nonvolatile memory and method of fabrication

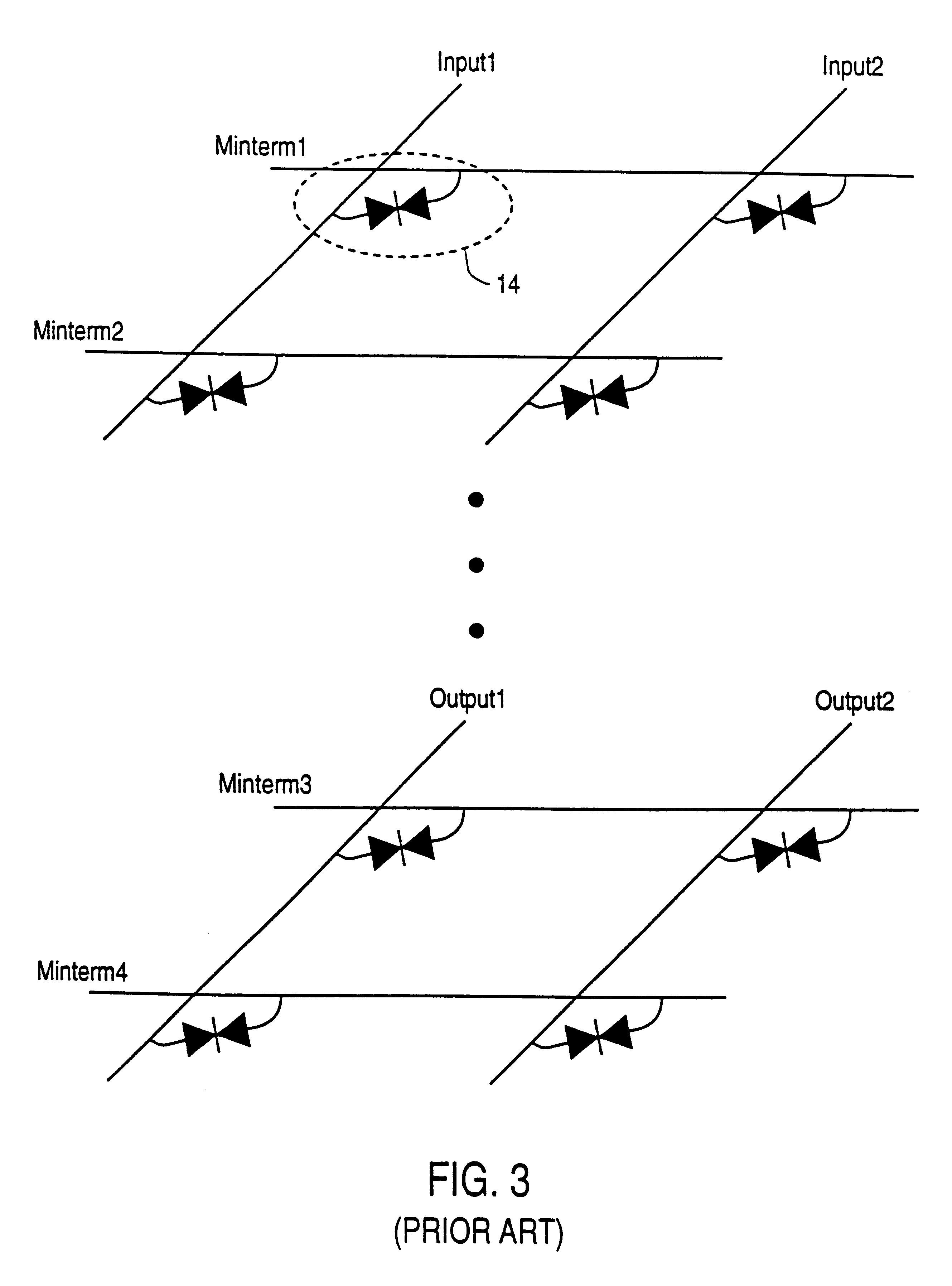

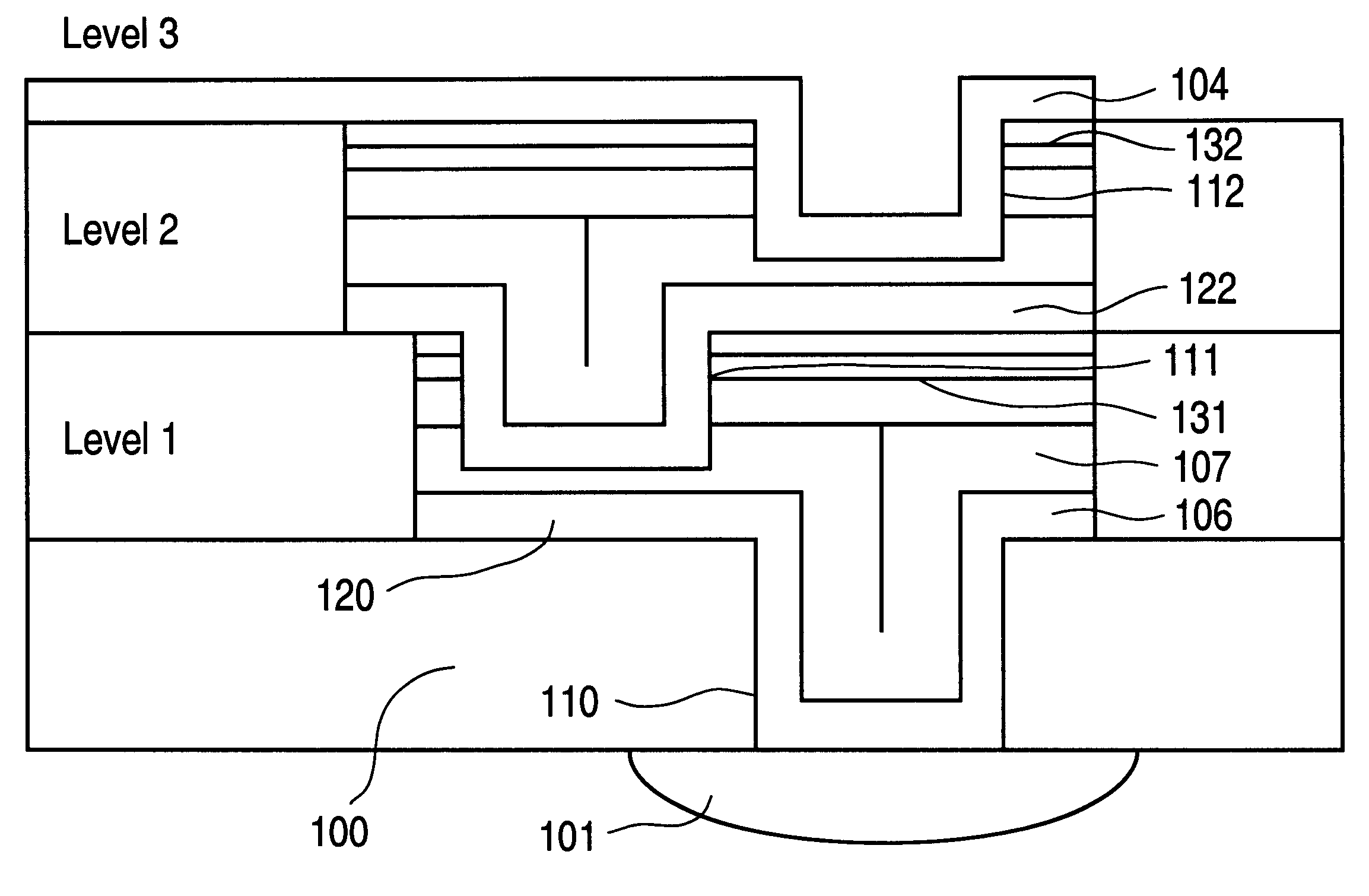

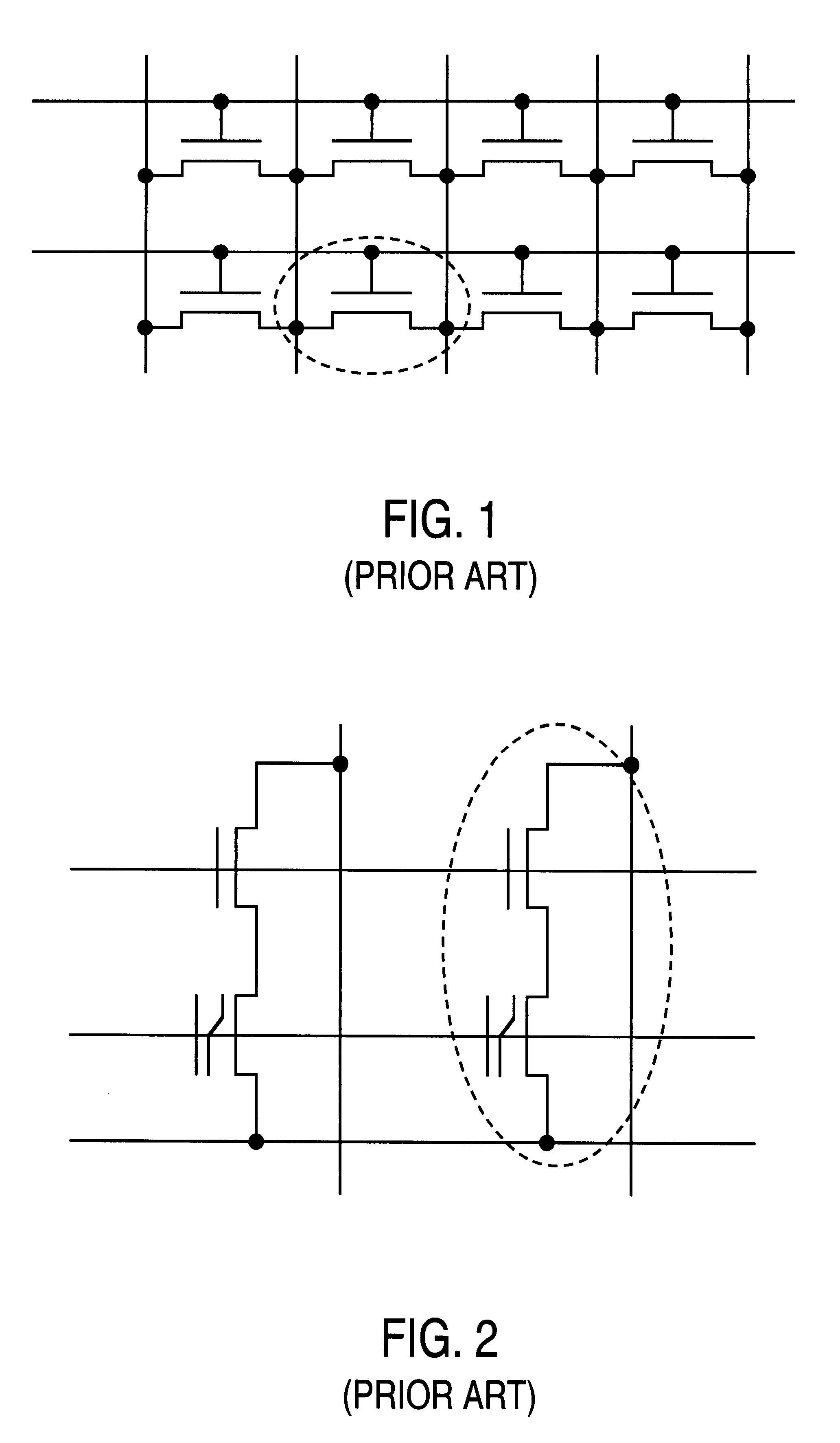

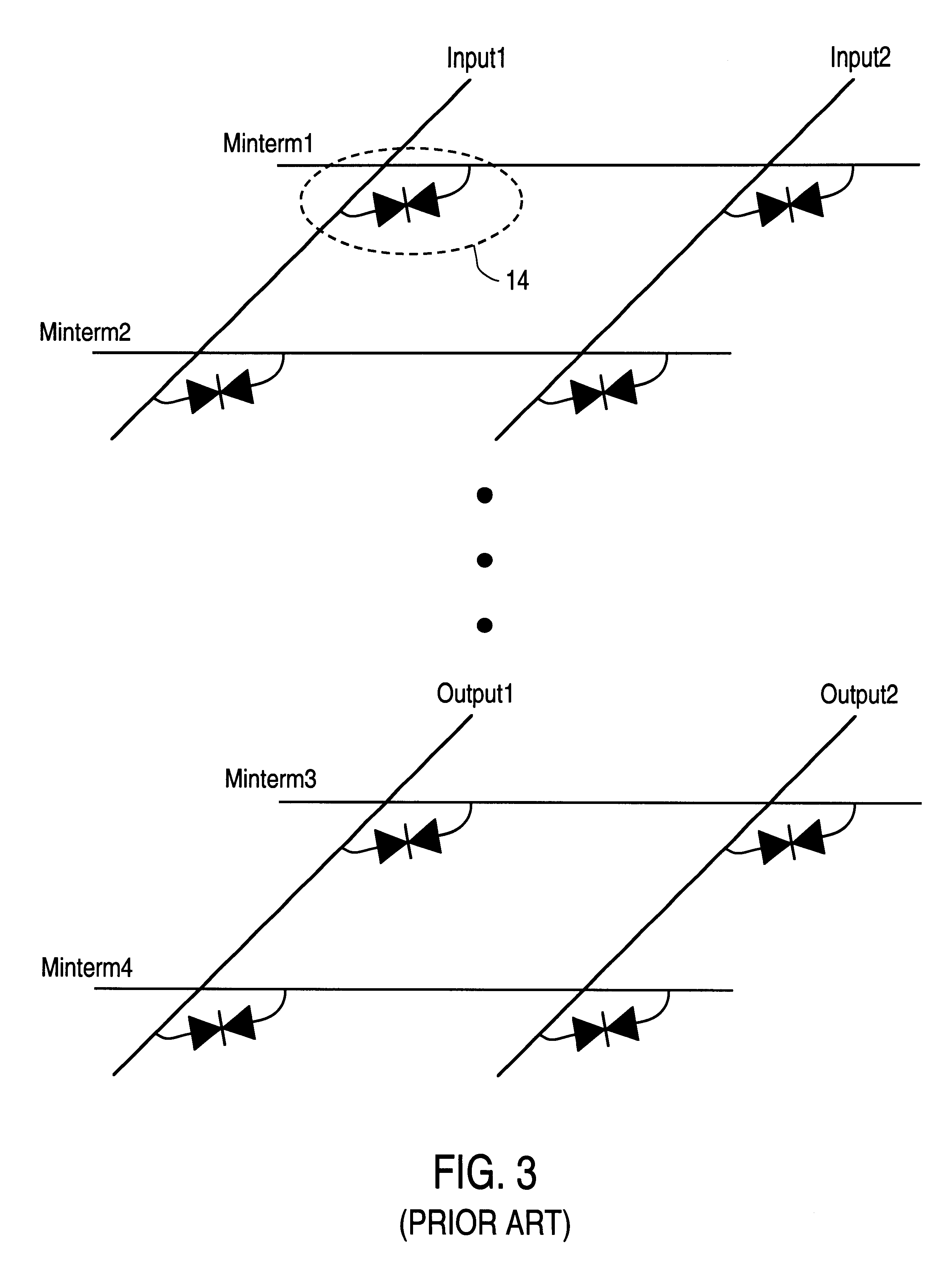

A very high density field programmable memory is disclosed. An array is formed vertically above a substrate using several layers, each layer of which includes vertically fabricated memory cells. The cell in an N level array may be formed with N+1 masking steps plus masking steps needed for contacts. Maximum use of self alignment techniques minimizes photolithographic limitations. In one embodiment the peripheral circuits are formed in a silicon substrate and an N level array is fabricated above the substrate.

Owner:SANDISK TECH LLC

Vertically stacked field programmable nonvolatile memory and method of fabrication

A very high density field programmable memory is disclosed. An array is formed vertically above a substrate using several layers, each layer of which includes vertically fabricated memory cells. The cell in an N level array may be formed with N+1 masking steps plus masking steps needed for contacts. Maximum use of self alignment techniques minimizes photolithographic limitations. In one embodiment the peripheral circuits are formed in a silicon substrate and an N level array is fabricated above the substrate.

Owner:SANDISK TECH LLC

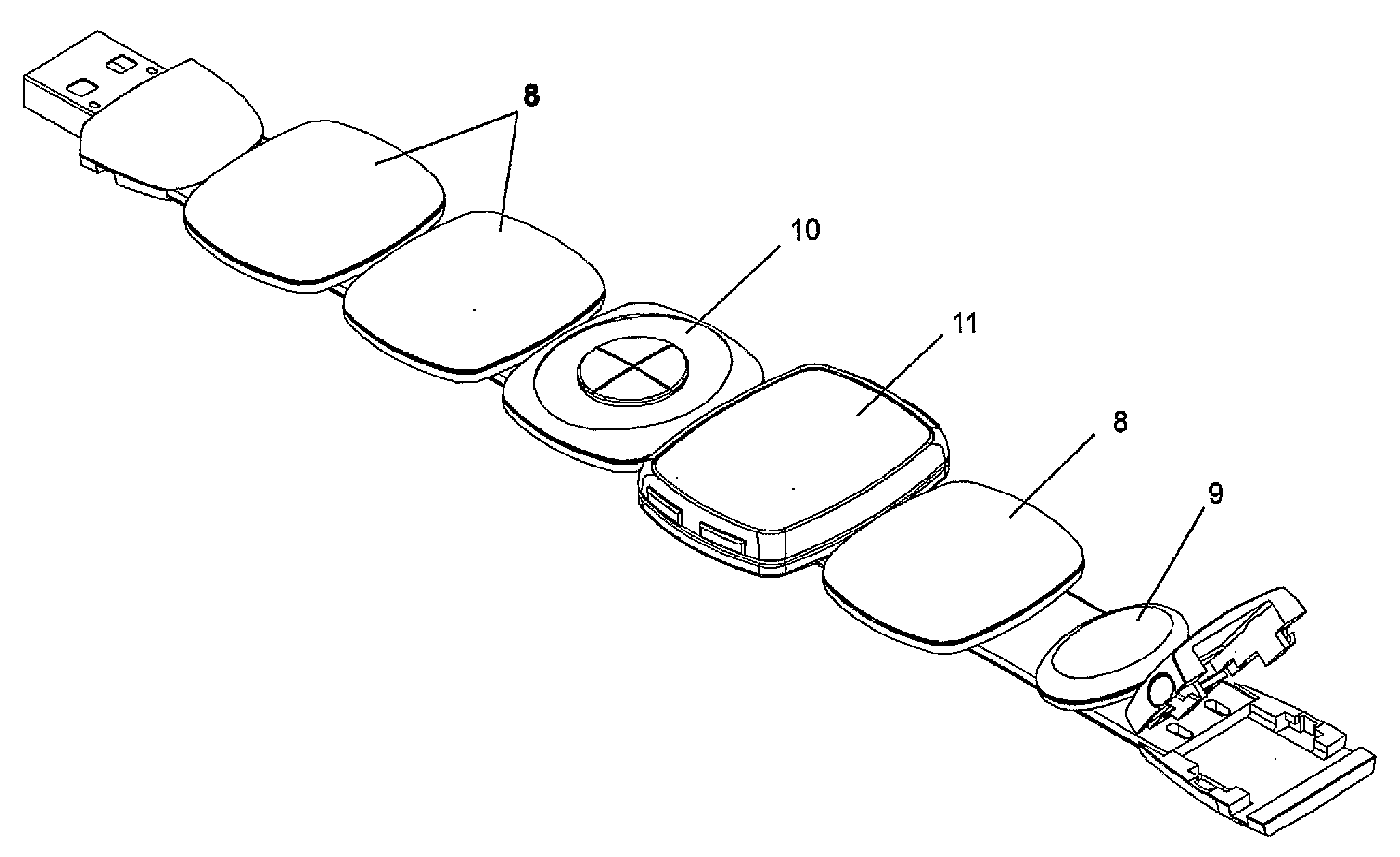

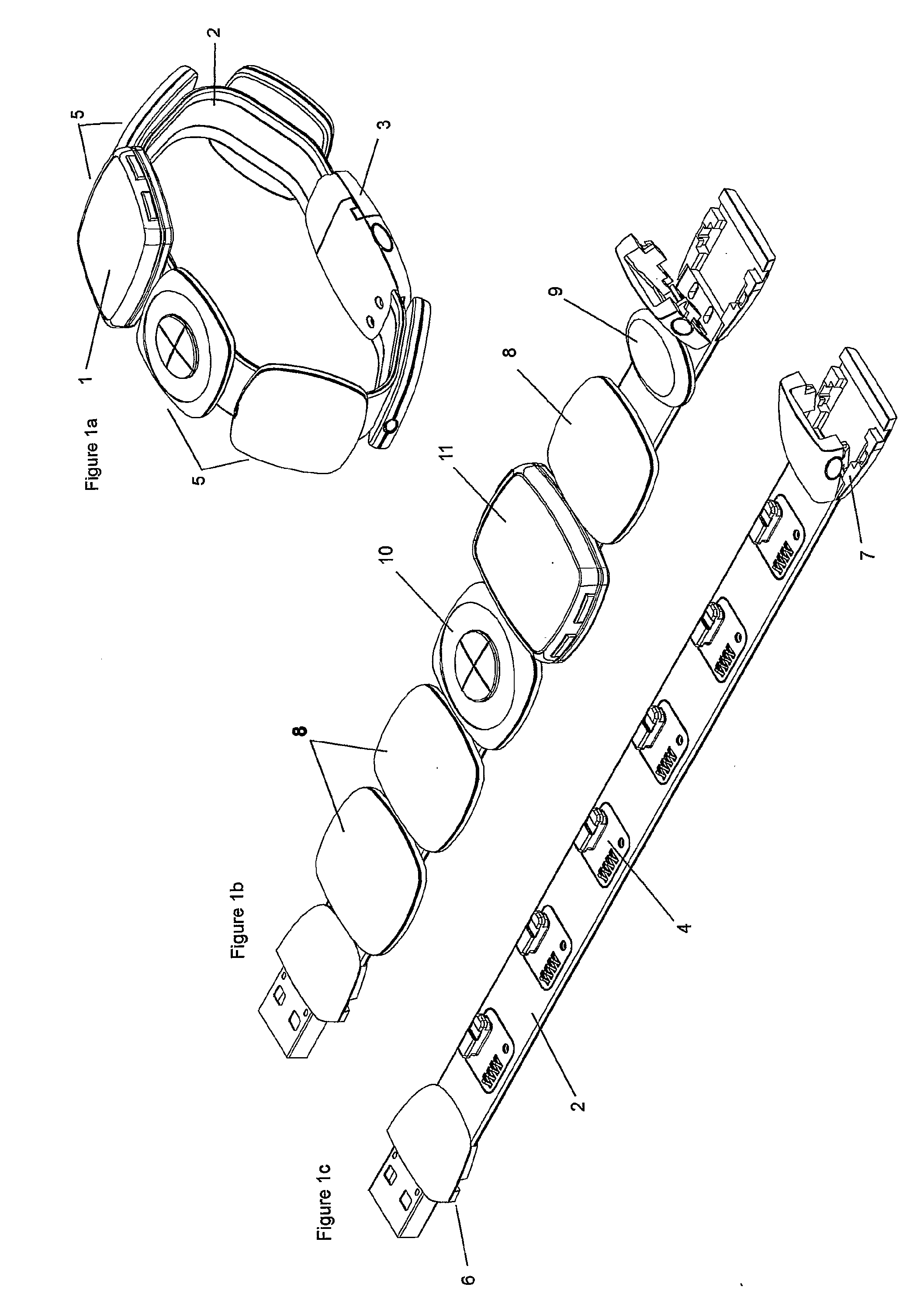

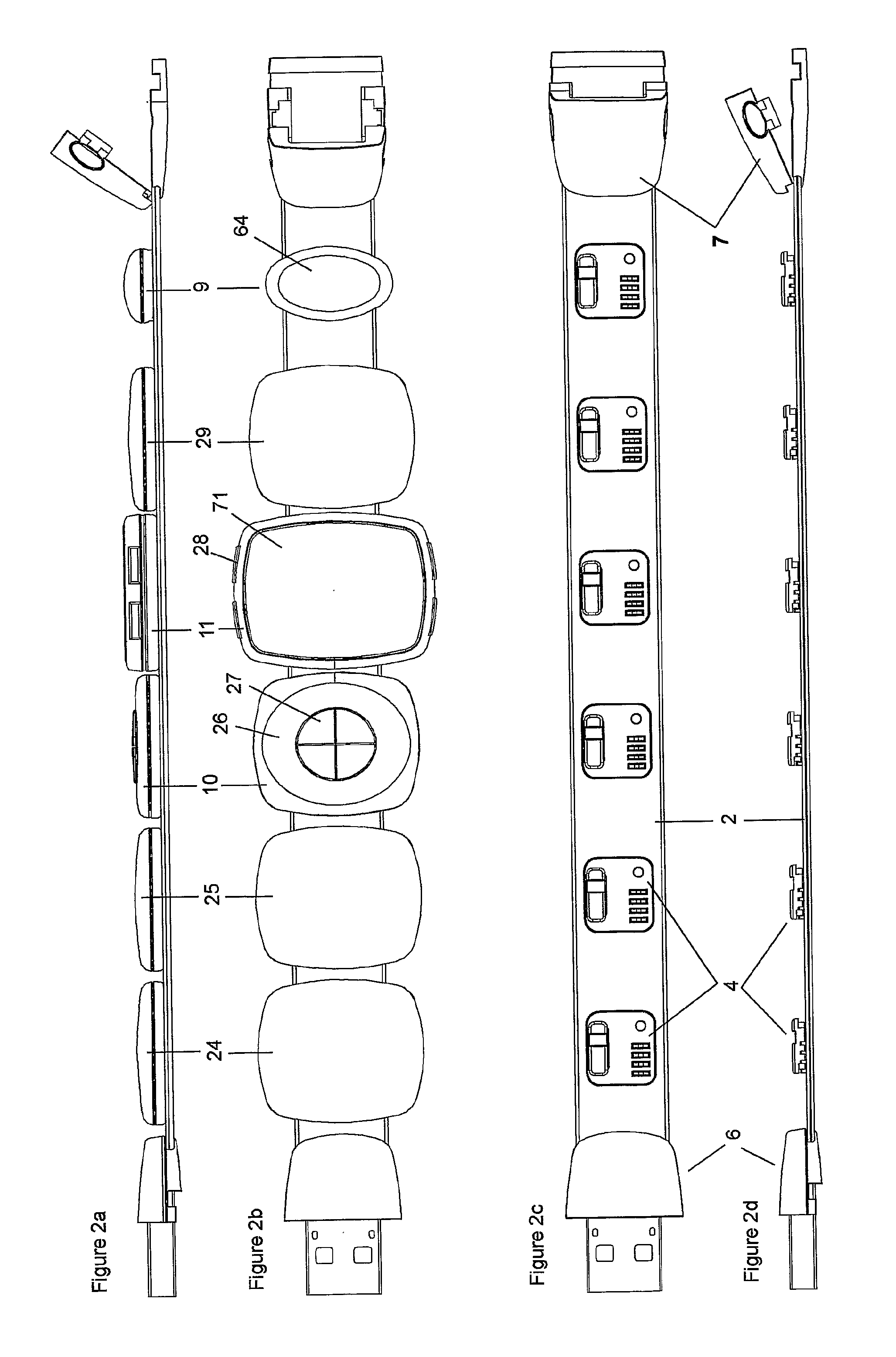

Wearable Modular Interface Strap

A wearable modular interface strap device for supporting multiple module units comprising a flexible strap with a plurality of electrically connected nodes acting as docking points to serial bus interface and mechanically connect removable modules, with the strap being 10 mechanically lockable in a loop by a clasp containing hub and host circuitry to enable network communication between modules and to a universal connector plug for recharging and data-exchange. Said strap containing a plurality of electrical wires between control circuitry and nodes and arranged to be wearable as a wristband, alternatively as a wrist device that when opened forms a curved handset with audio input and outputs at alternate ends, or arranged in a necklace configuration. Said device capable of supporting interchangeable modules such as displays, control devices, rechargeable batteries, a module with removable earpiece units, and a plurality of functional modules suitable for communication, data storage, location and environment sensing.

Owner:DANIEL SIMON R +1

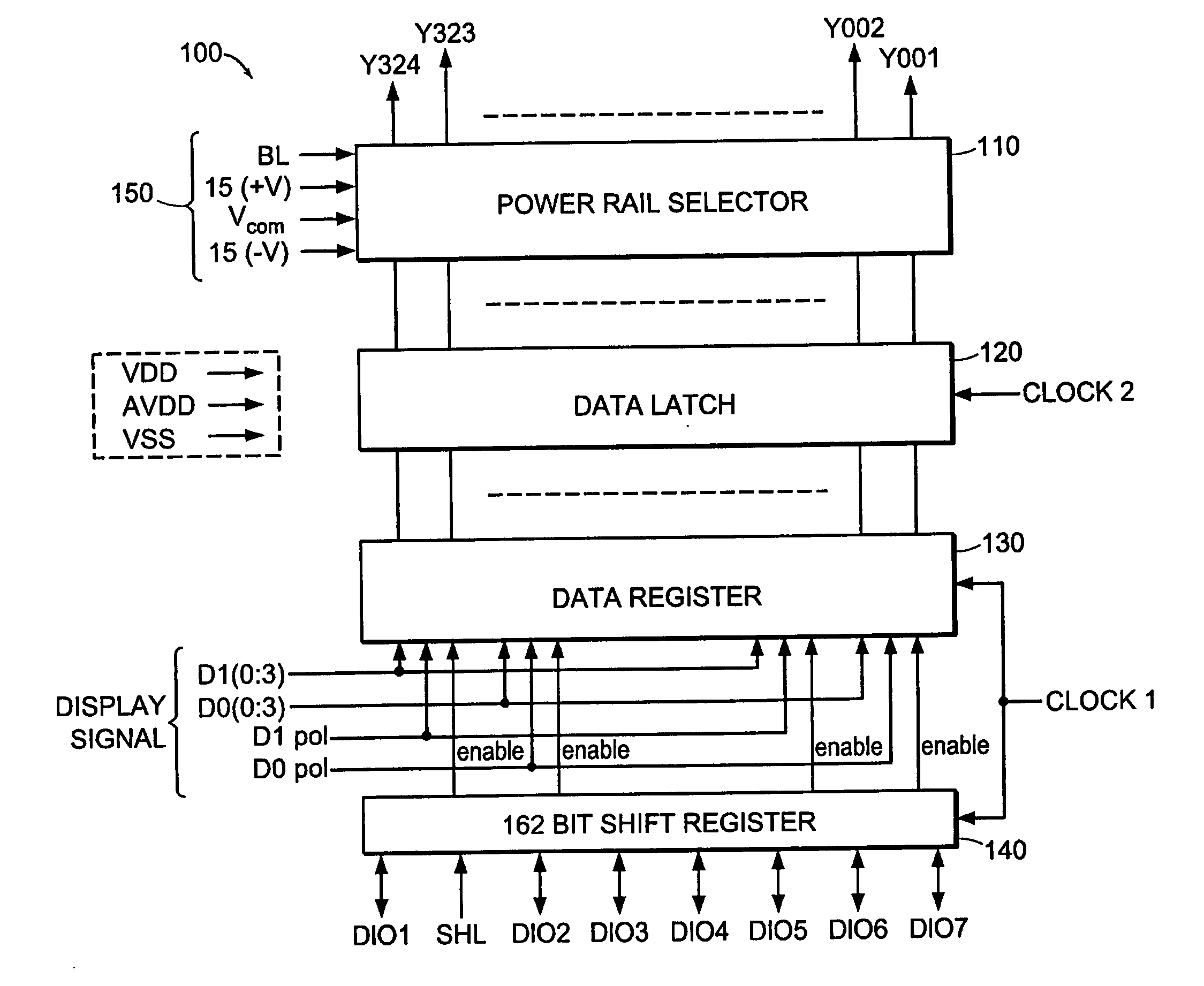

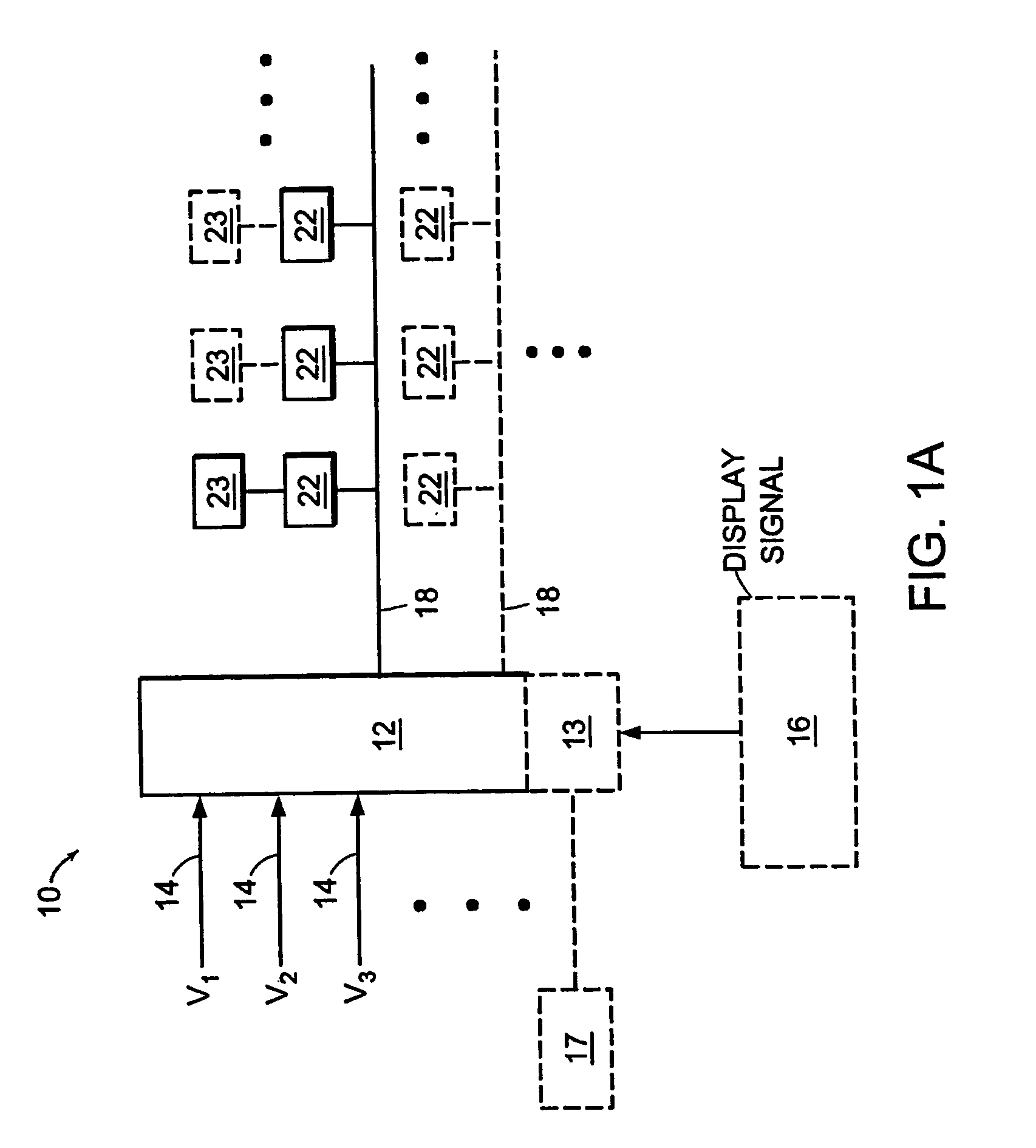

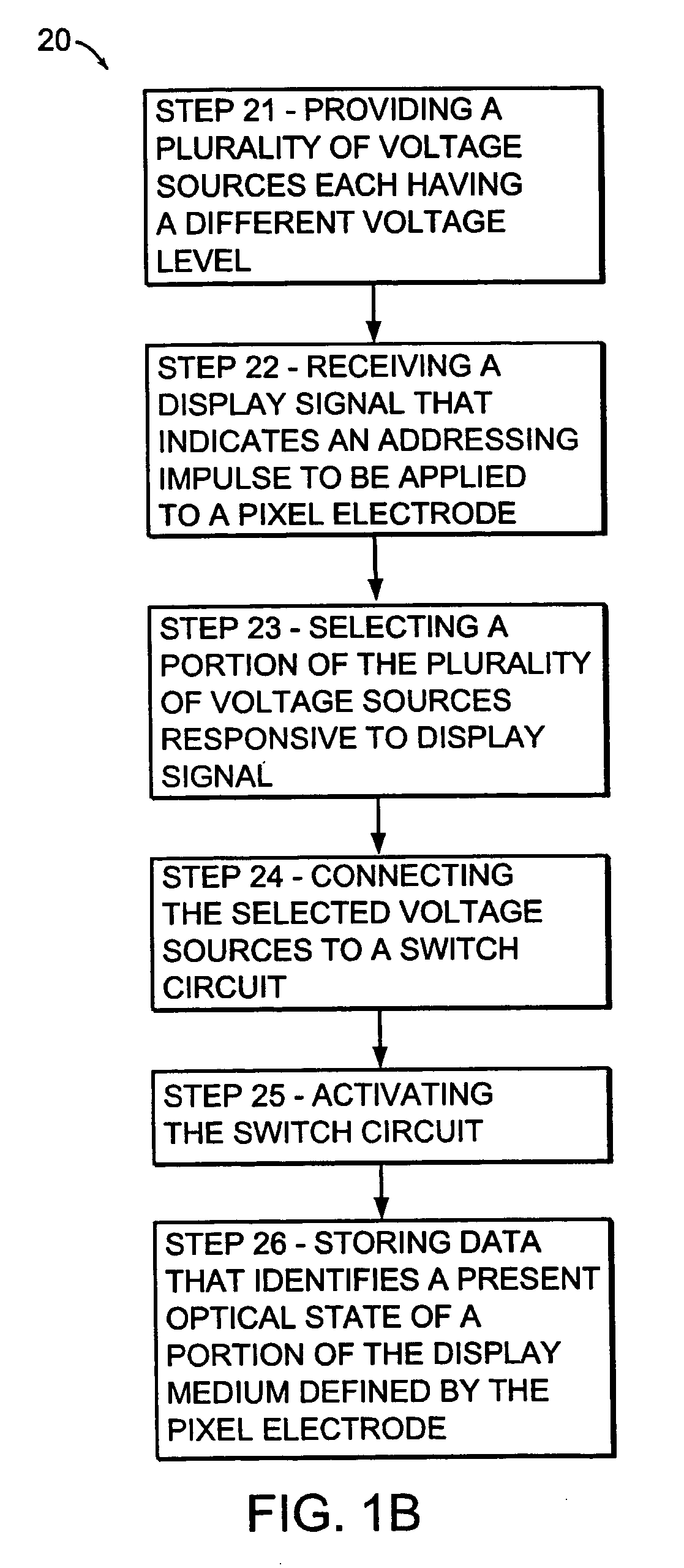

Voltage modulated driver circuits for electro-optic displays

ActiveUS7202847B2Low implementation costFaster design timeCathode-ray tube indicatorsNon-linear opticsDriver circuitElectricity

A method and system for applying addressing voltages to pixels of a display involves receiving input data. The input data includes an indication of an addressing voltage impulse to be applied to a pixel via an electrode. One or more voltage sources are selected, to provide the addressing voltage impulse. The one or more voltage sources each have a pre-selected voltage. The selected one or more voltage sources are electrically connected to an electrode to apply the addressing voltage impulse to the pixel.

Owner:E INK CORPORATION

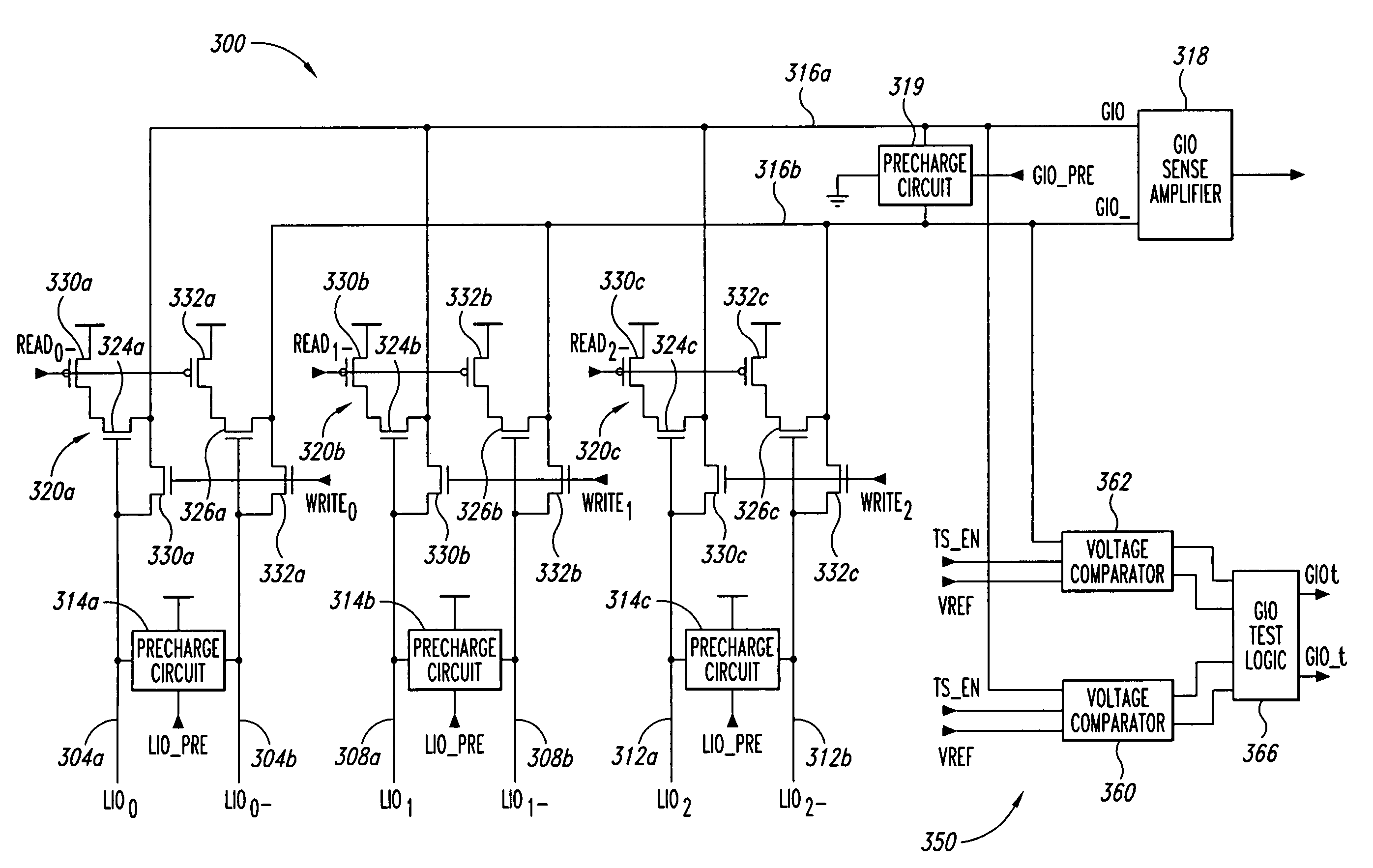

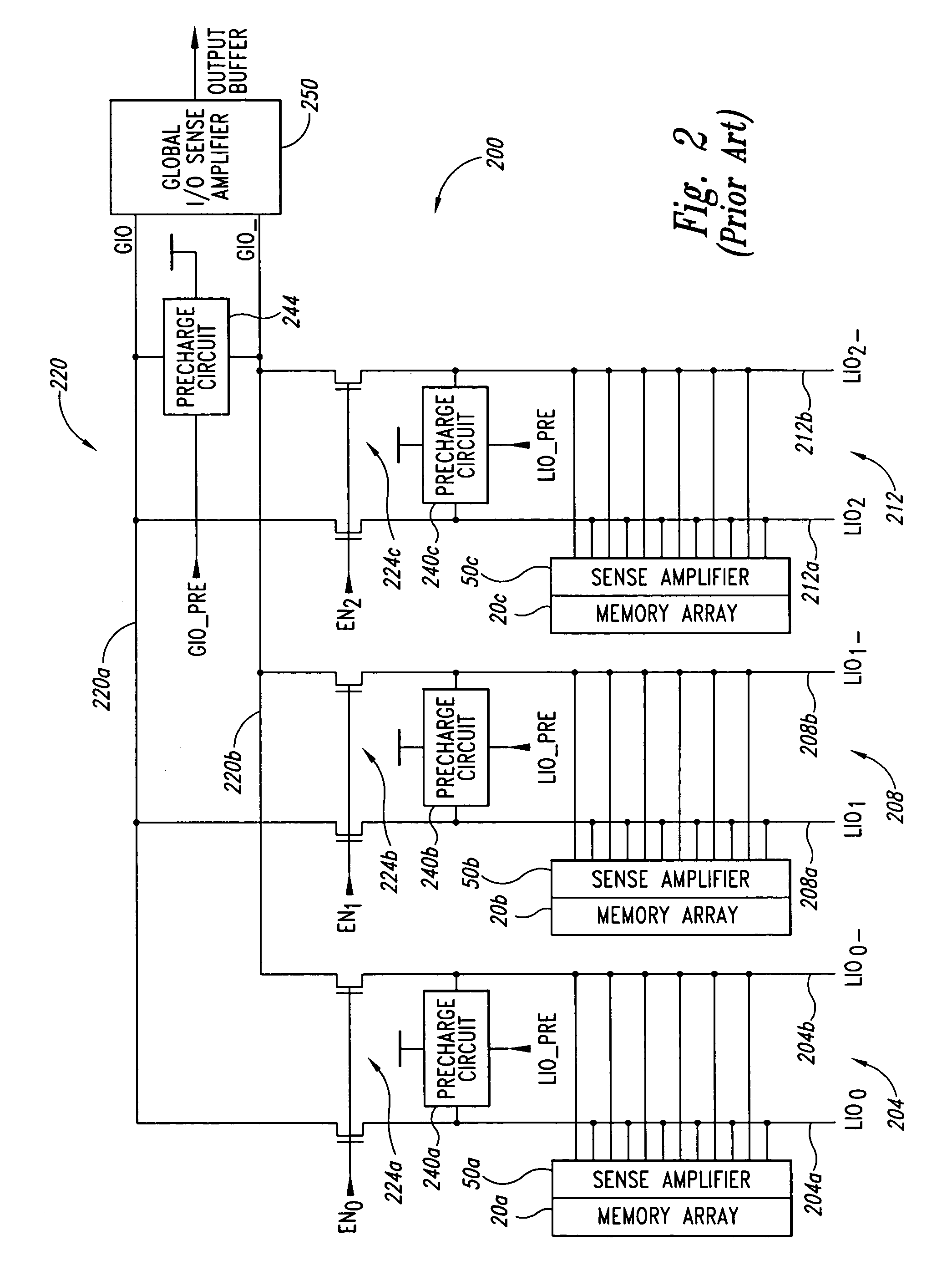

Data path having grounded precharge operation and test compression capability

A data path for coupling data between a memory cell and an input / output (IO) line sense amplifier. An IO line coupling circuit is coupled to a pair of global data lines and a pair of local data lines to couple and decouple each of the global data lines to and from a voltage supply based on the voltage levels of the local data lines for the memory read operation. For the memory write operation, the IO line coupling circuit couples and decouples each of the global data lines to and from a respective one of the local data lines. The data path also includes a first precharge circuit coupled to the global data lines to couple the global data lines to ground to precharge the signal lines prior to a memory read or write operation, and can further include a test compression circuit coupled to the global data lines.

Owner:MOSAID TECH

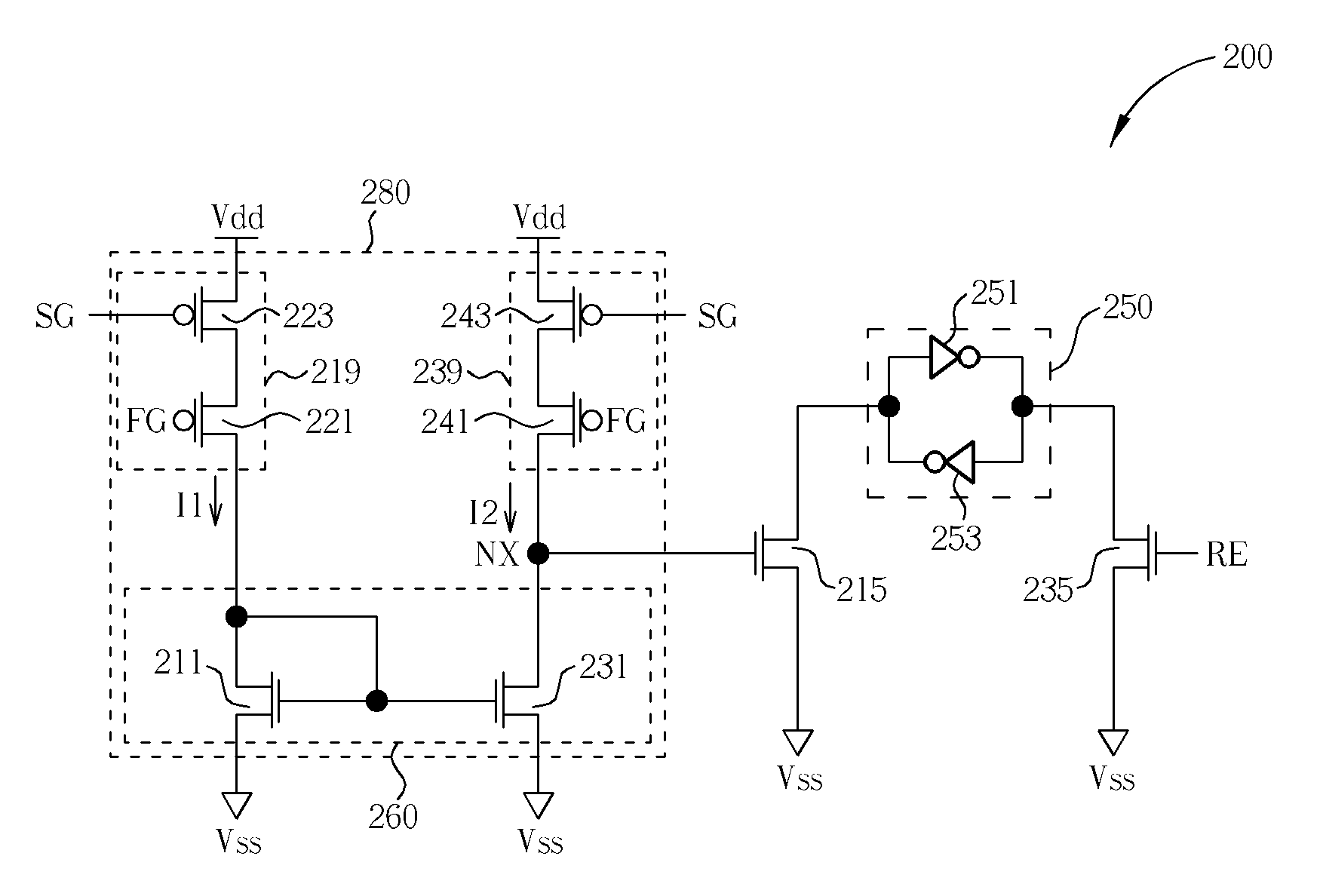

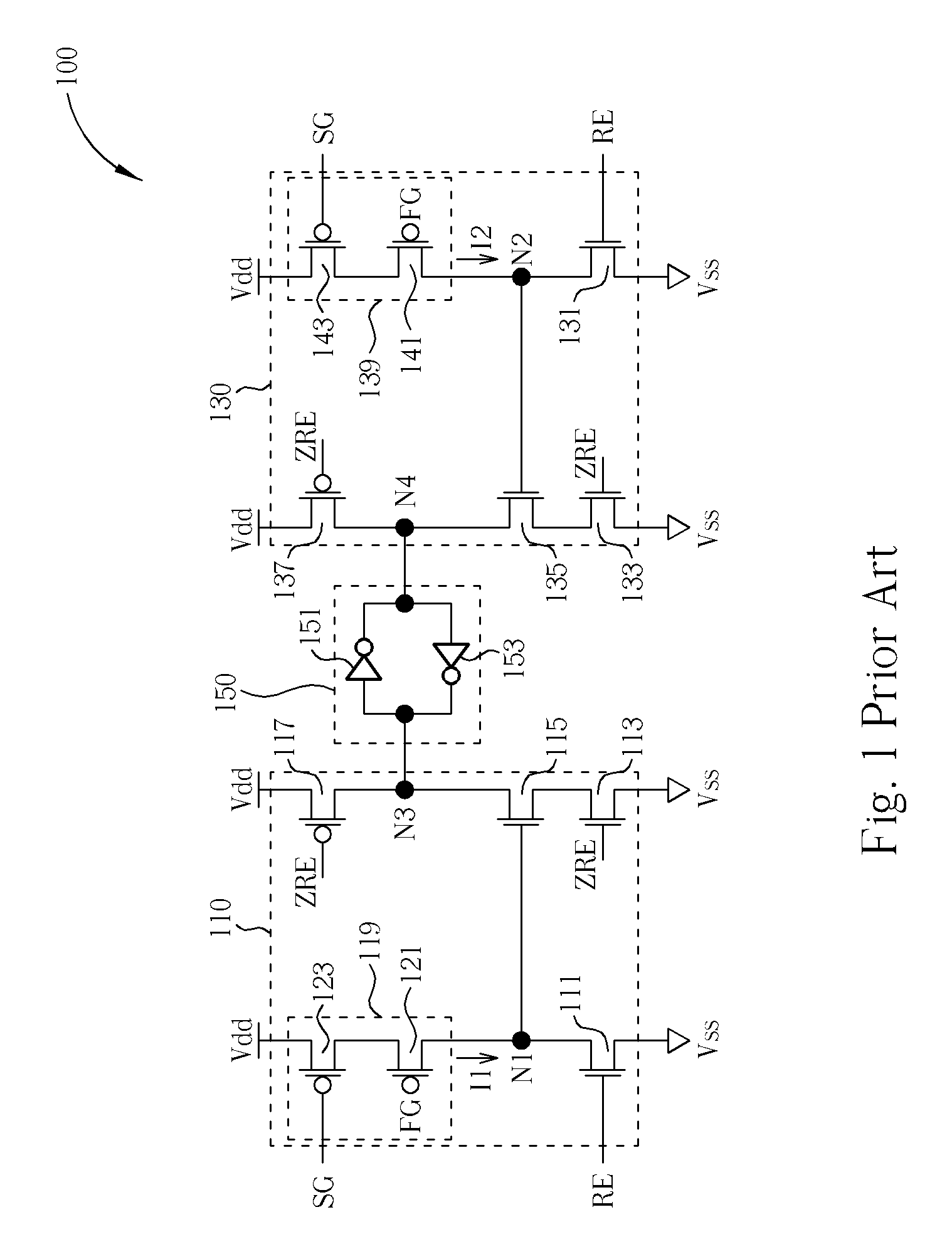

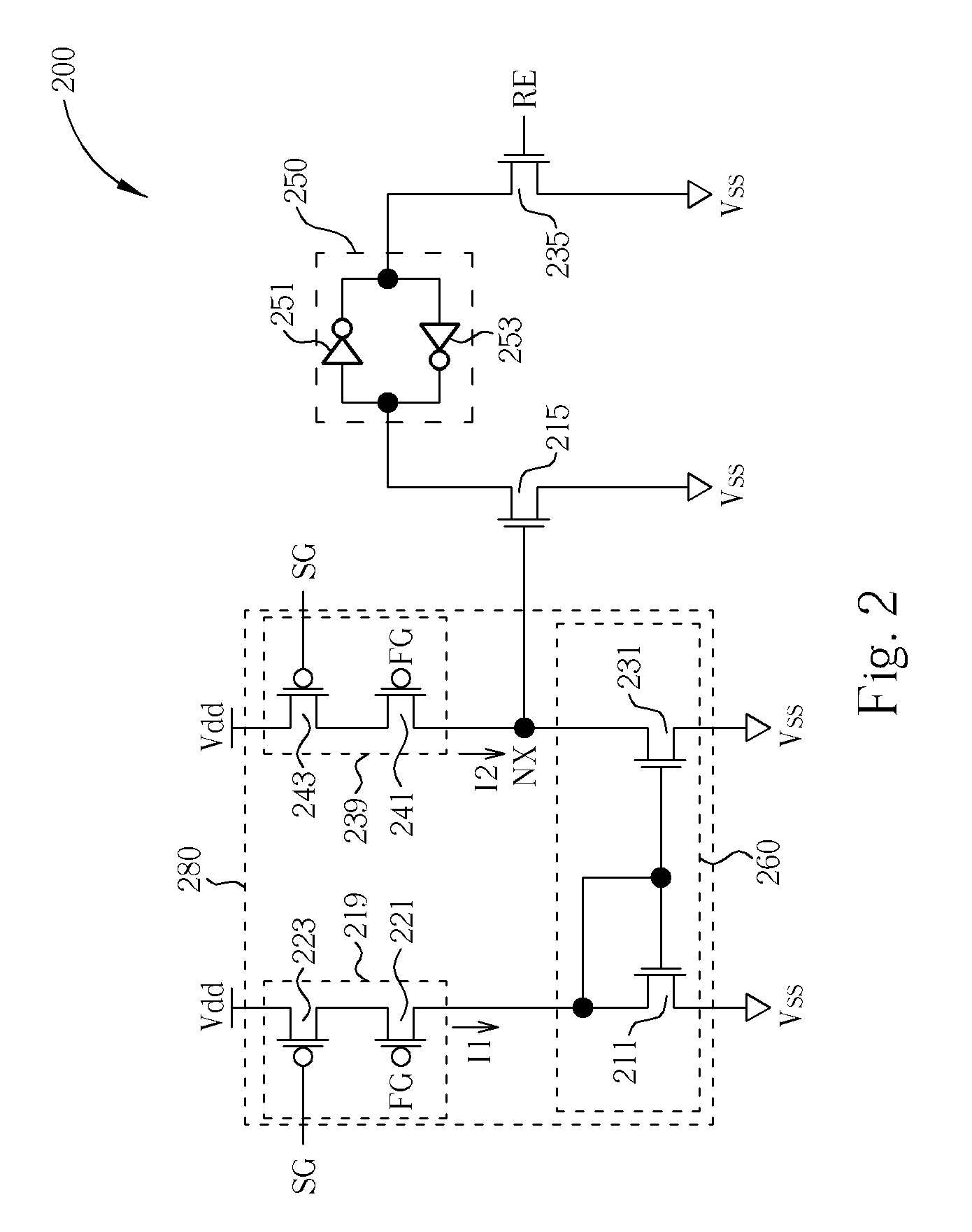

Sense amplifier circuit having current mirror architecture

A sense amplifier circuit for use in a semiconductor memory device has complemented logic states at opposite sides of the latch circuit in the sense amplifier circuit determinate all the time in operation. The sense amplifier circuit takes advantage of a current mirror circuit for ascending or descending a voltage level at the gate of a transistor by charge accumulation or charge dissipation, which turns on or off the transistor so as to control the logic states at opposite sides of the latch circuit in the sense amplifier circuit.

Owner:EMEMORY TECH INC

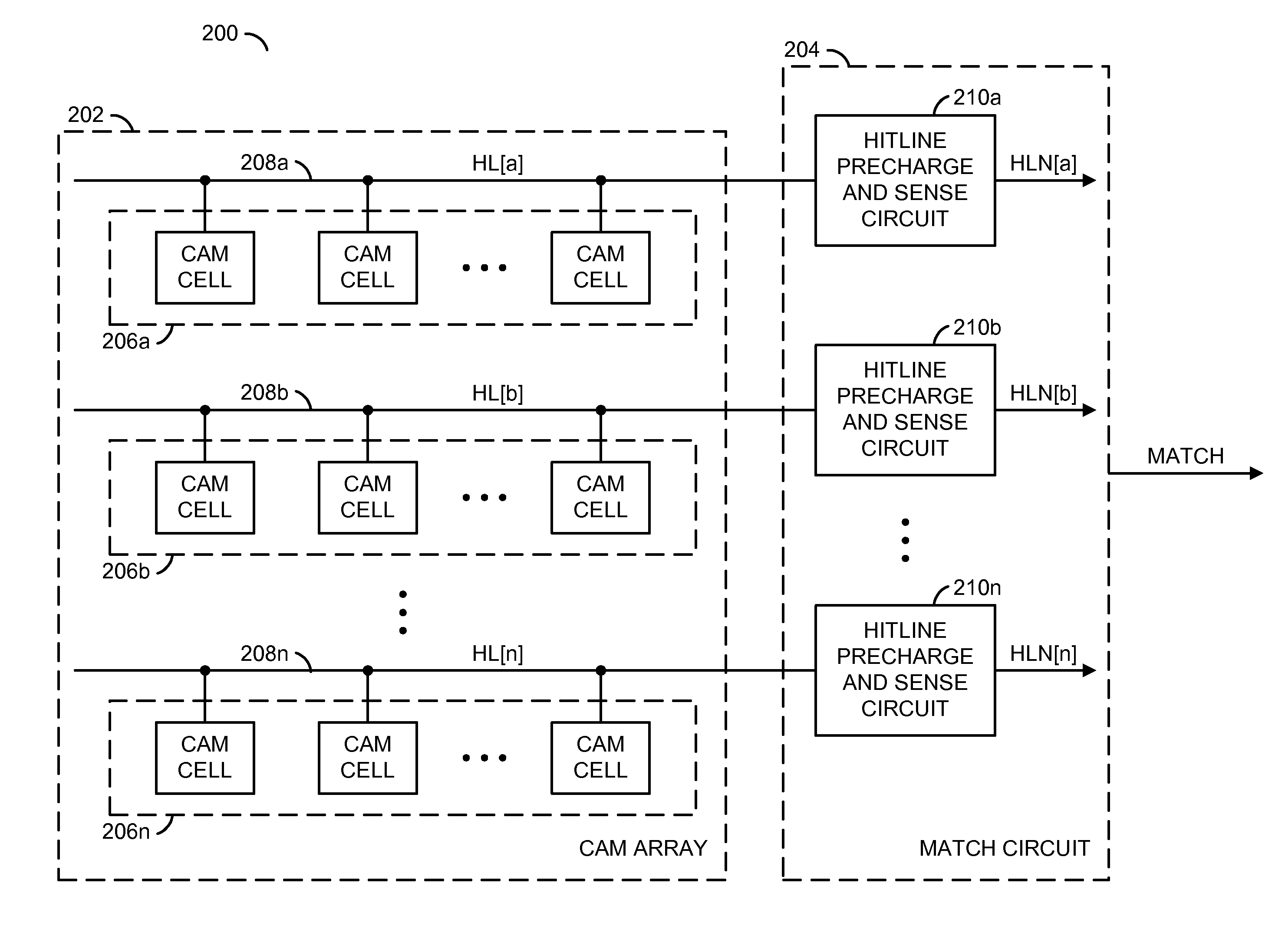

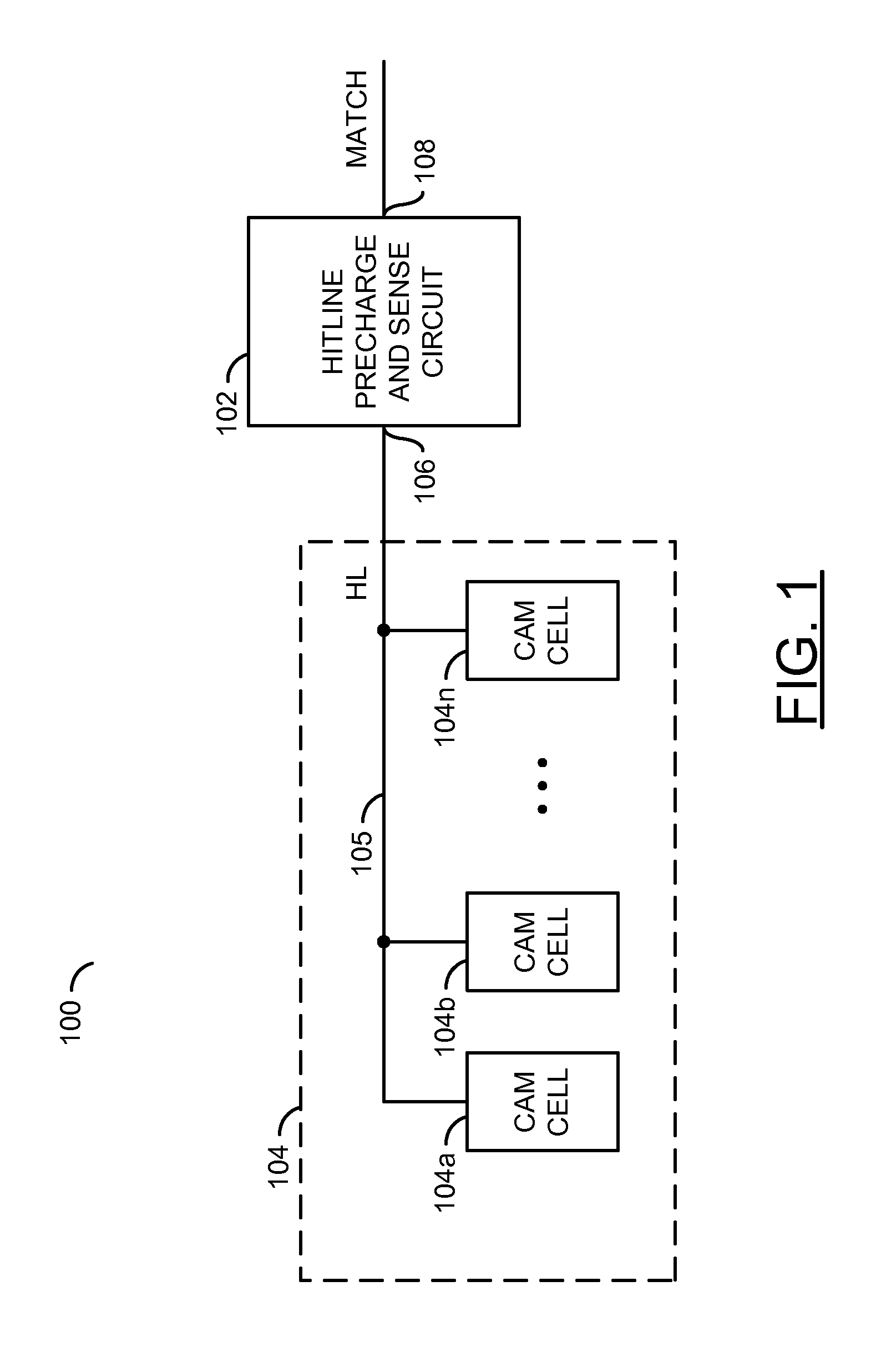

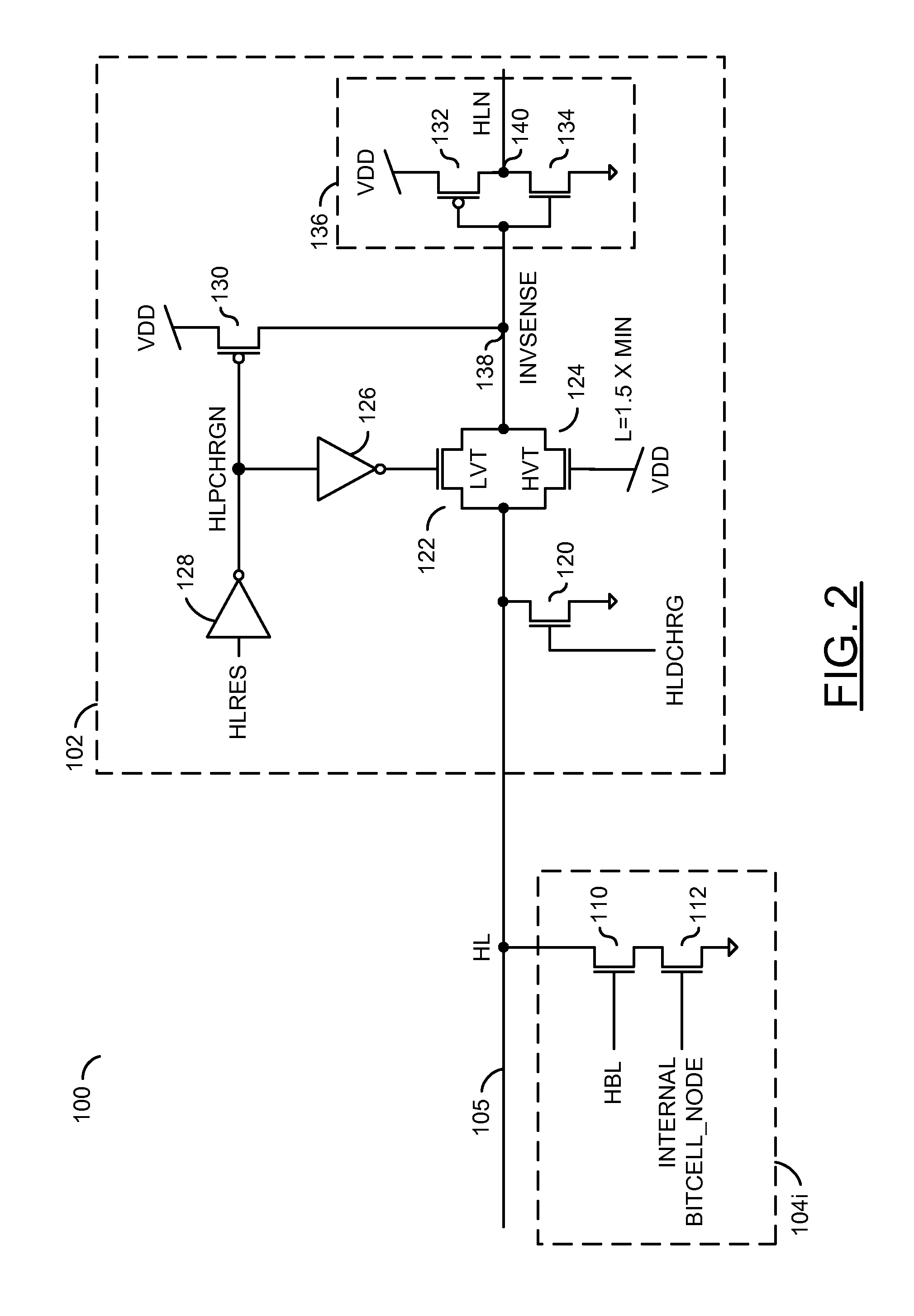

Low power content addressable memory hitline precharge and sensing circuit

An apparatus and a method of operating the apparatus. The apparatus includes a driver circuit and a memory circuit. The driver circuit may be configured to precharge a hitline in response to a predetermined voltage level and a control signal and sense a result of a compare operation based upon a hitline signal on the hitline. The driver circuit generally precharges the hitline to a voltage level lower than the predetermined voltage level and senses the result of the compare operation using the full predetermined voltage level. The memory circuit may be configured to perform the compare operation using the hitline.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

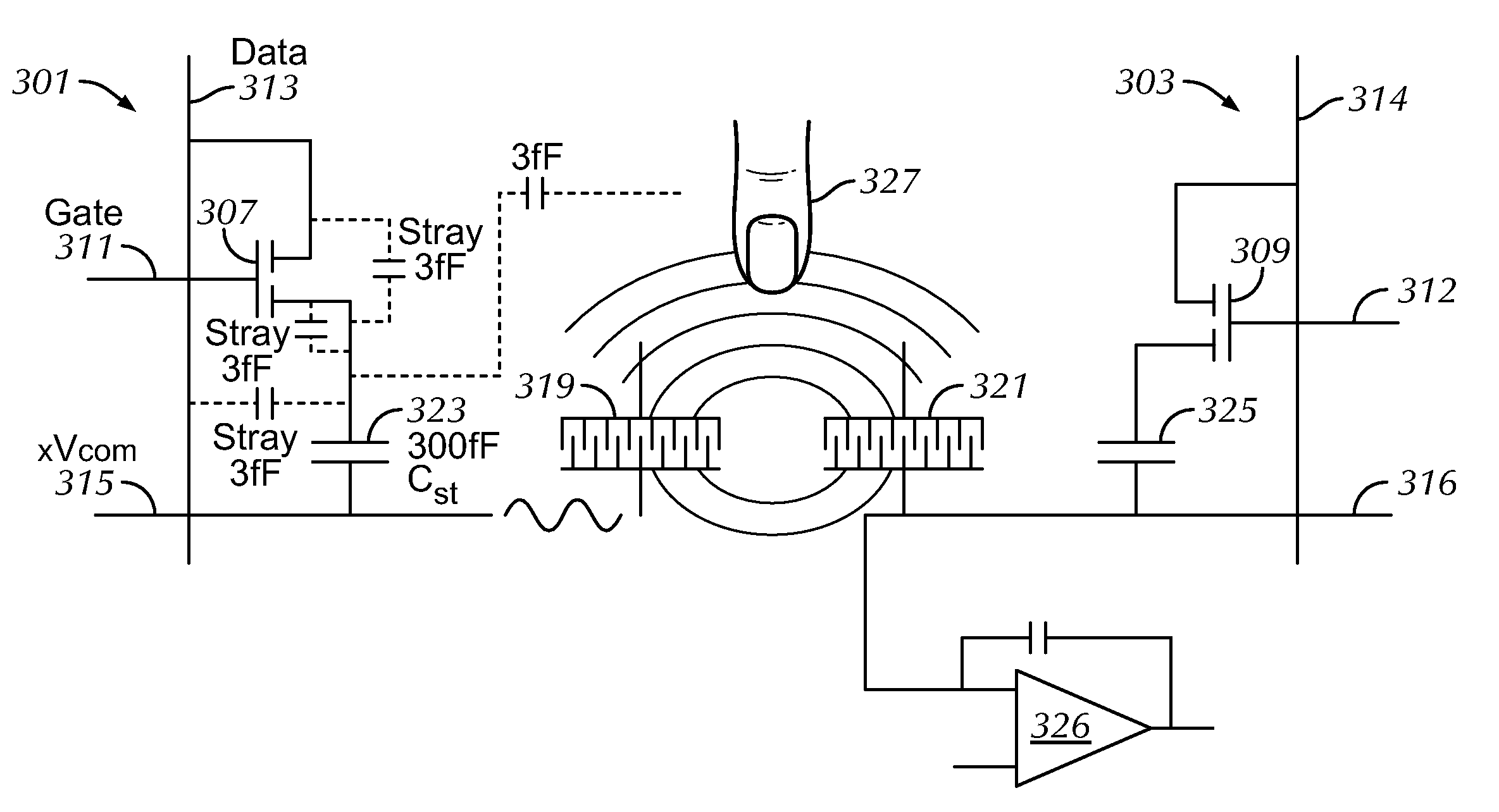

Display with dual-function capacitive elements

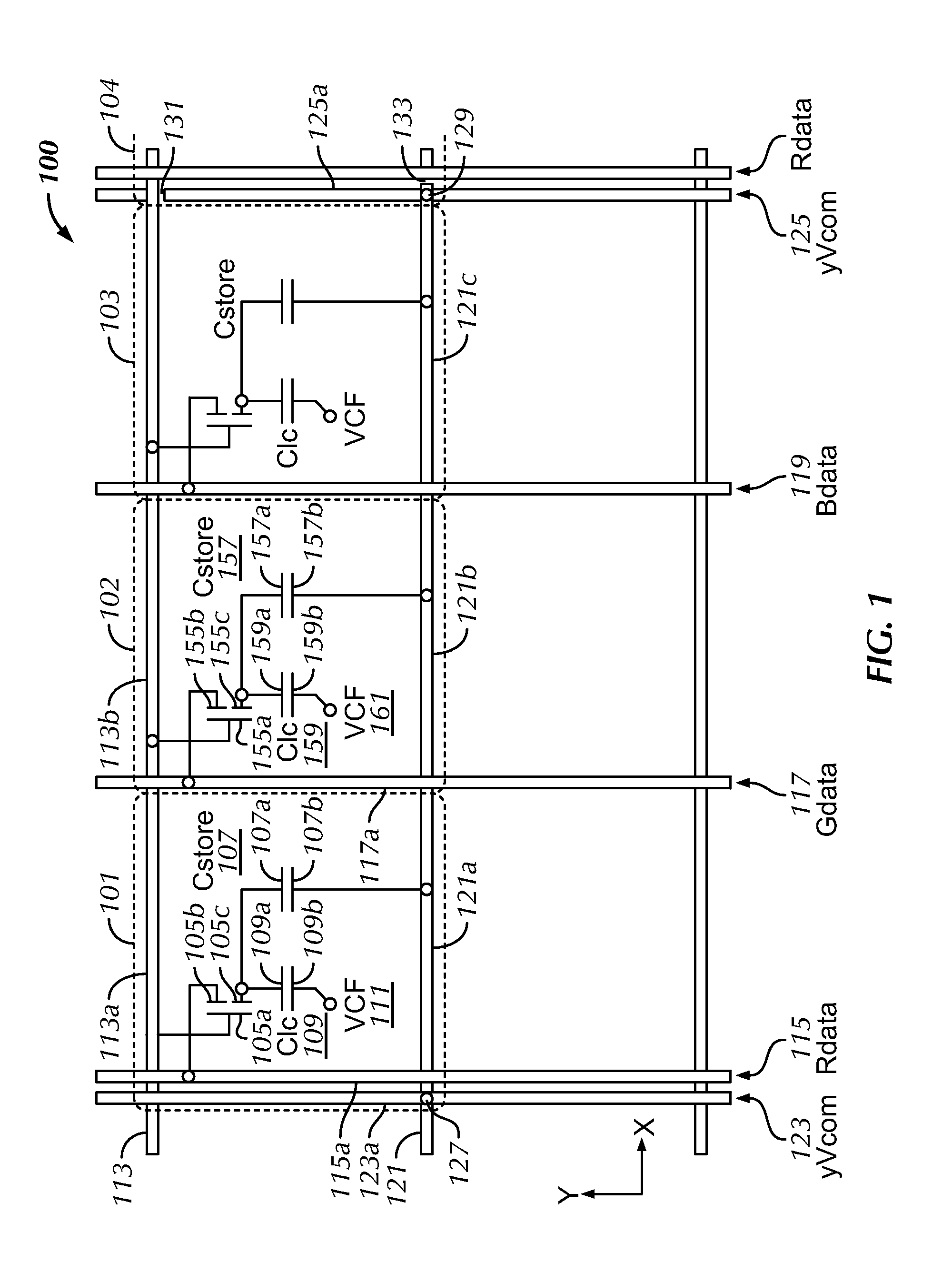

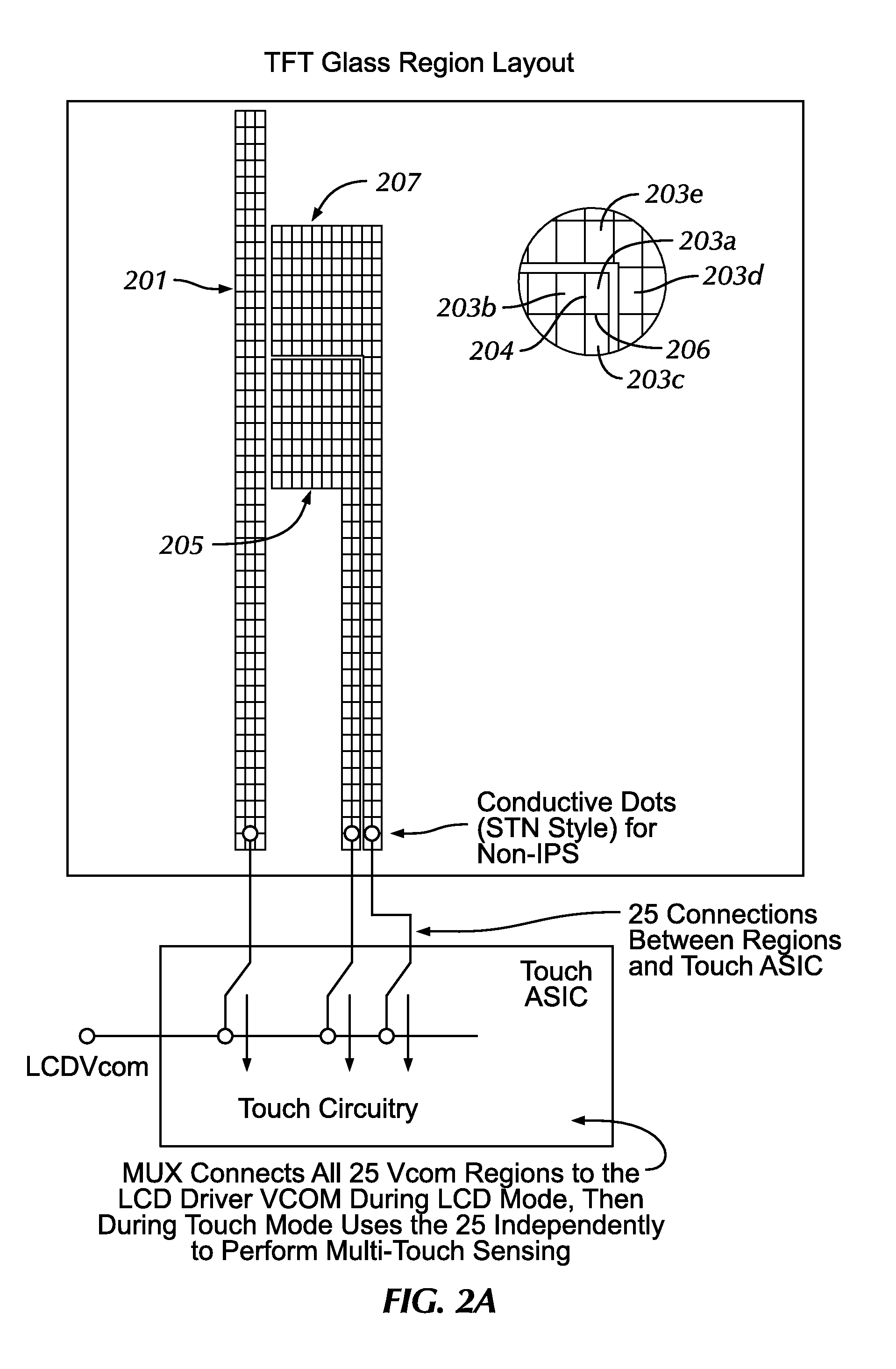

A touch screen including display pixels with capacitive elements is provided. The touch screen includes first common voltage lines connecting capacitive elements in adjacent display pixels, and a second common voltage line connecting first common voltage lines. The pixels can be formed as electrically separated regions by including breaks in the common voltage lines. The regions can include a drive region that is stimulated by stimulation signals, a sense region that receives sense signals corresponding to the stimulation signals. A grounded region can also be included, for example, between a sense region and a drive region. A shield layer can be formed of a substantially high resistance material and disposed to shield a sense region. A black mask line and conductive line under the black mask line can be included, for example, to provide low-resistance paths between a region of pixels and touch circuitry outside the touch screen borders.

Owner:APPLE INC

OLED display with aging compensation

Owner:GLOBAL OLED TECH

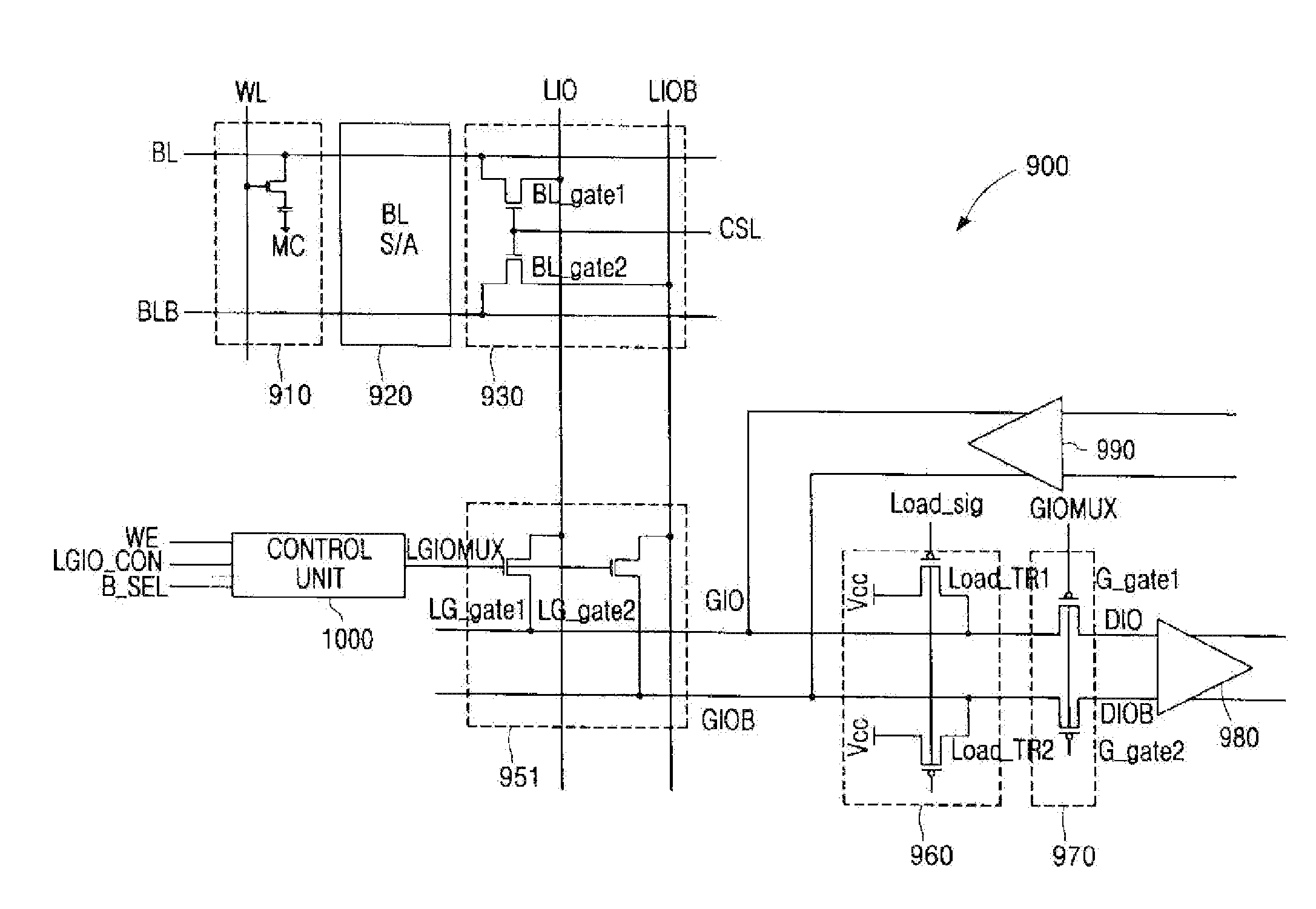

Memory device with separate read and write gate voltage controls

A circuit and method are provided for controlling the gate voltage of a transistor acting between local and global input / output lines of a memory device, the circuit including a local input / output line, a local from / to global input / output multiplexer in signal communication with the local input / output line, a global input / output line in signal communication with the local from / to global input / output multiplexer, and a local from / to global input / output controller having an input node and an output node, the input node disposed for receiving a signal indicative of an input or output operation, and the output node in signal communication with a gate of the local from / to global input / output multiplexer for providing a gate signal of a first or second level in the presence of the output operation, and a gate signal of a third level in the presence of the input operation.

Owner:SAMSUNG ELECTRONICS CO LTD

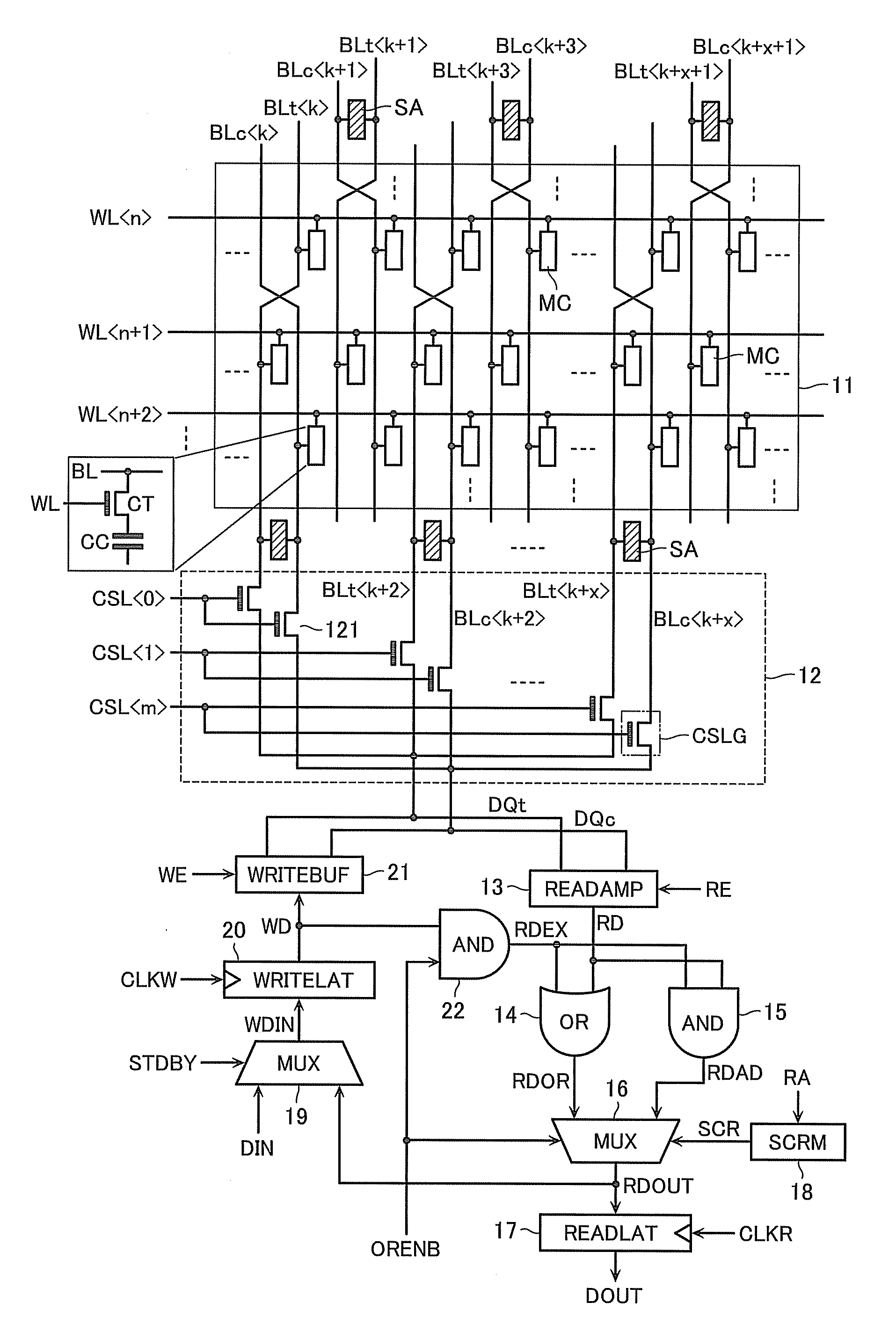

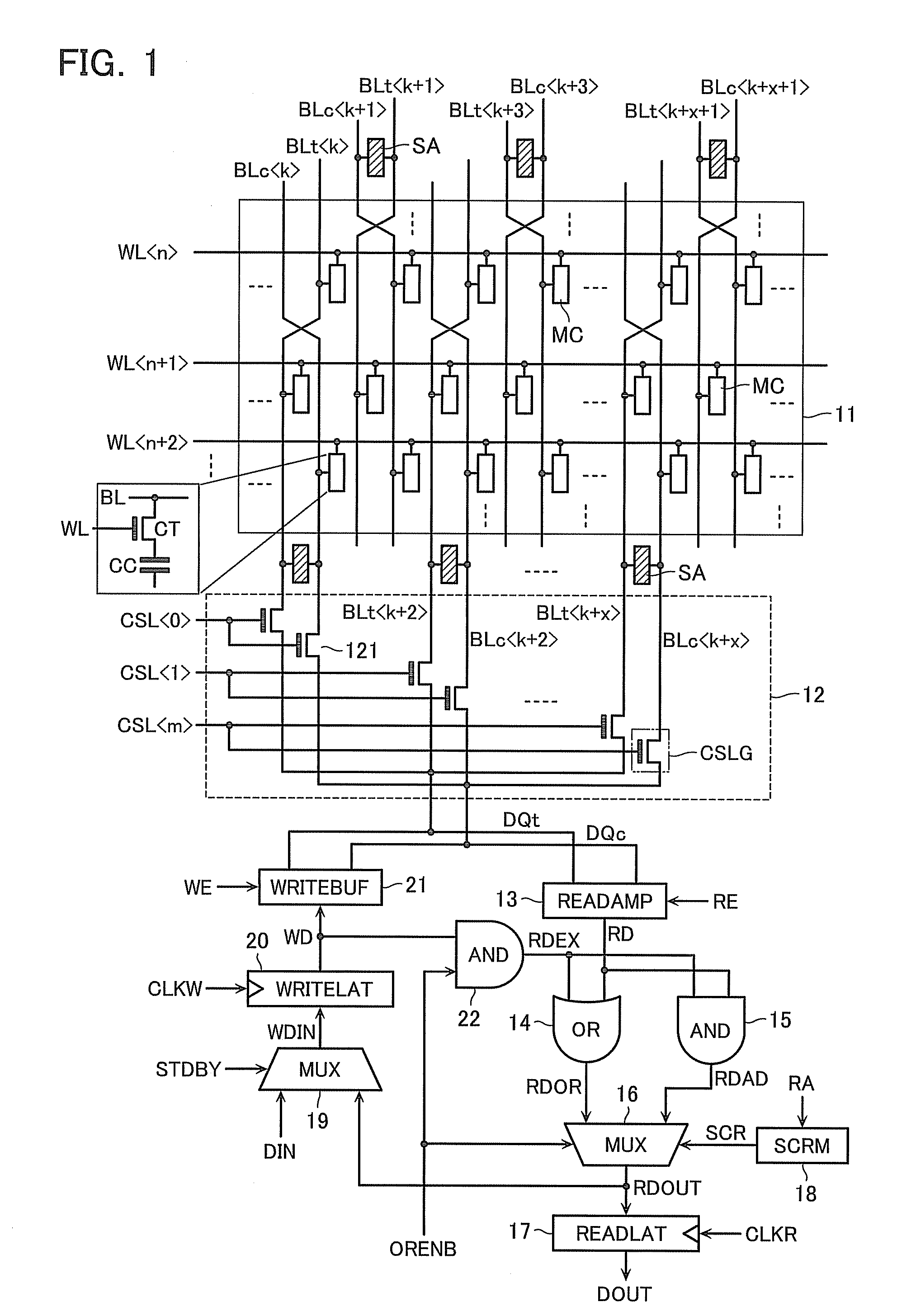

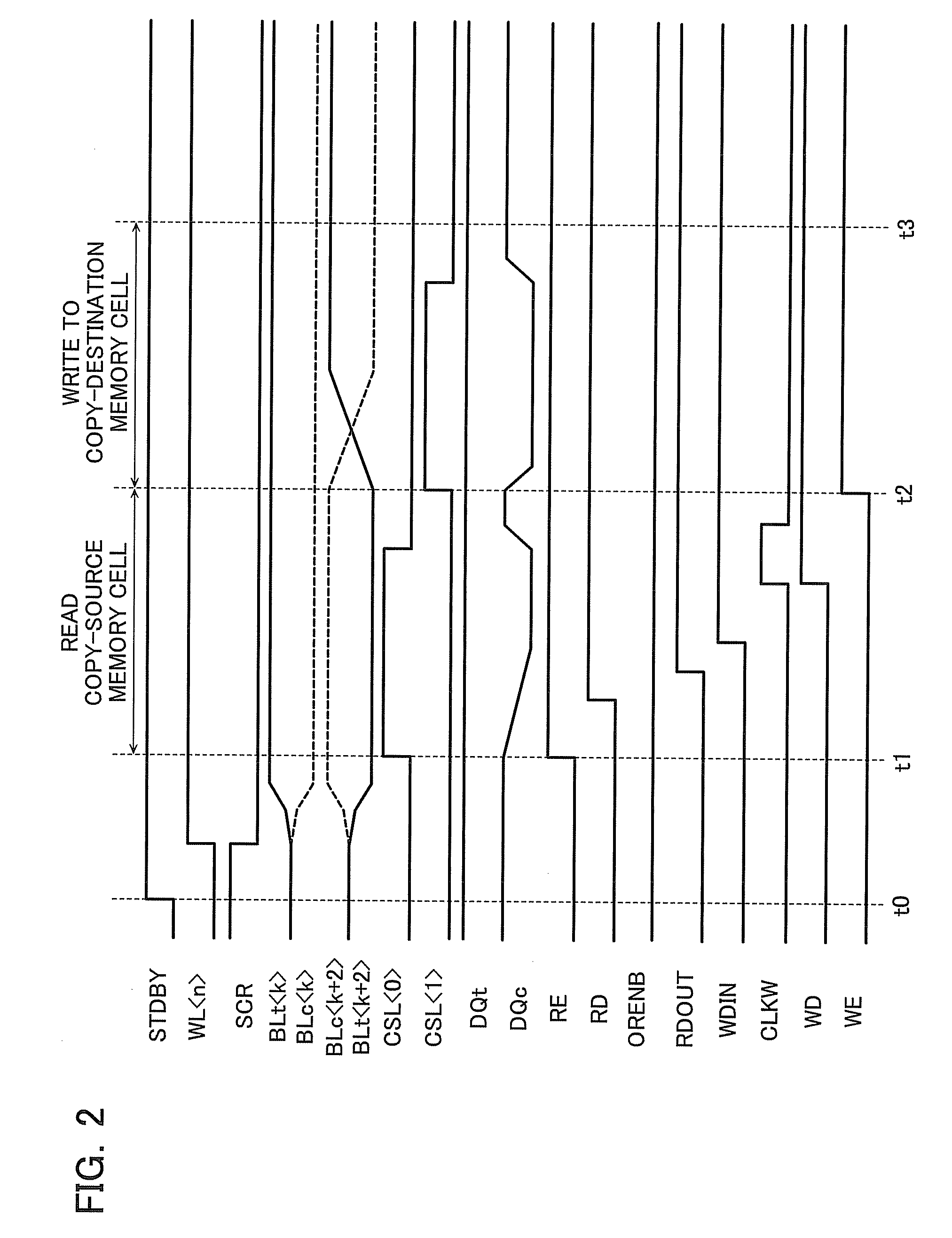

Semiconductor memory device

A sense amplifier circuit senses and amplifies a signal read from memory cells arranged at intersections of word-lines and bit-lines. A write circuit reads first data held in a first memory cell of the memory cells, and writes second data corresponding to the first data in a second memory cell different from the first memory cell. A data latch circuit holds data read from the first memory cell. A logic operation circuit performs a logic operation using data read from the second memory cell and data held in the data latch circuit as input values and outputs third data as an operation value. A write-back circuit writes the third data back to the first memory cell.

Owner:KIOXIA CORP

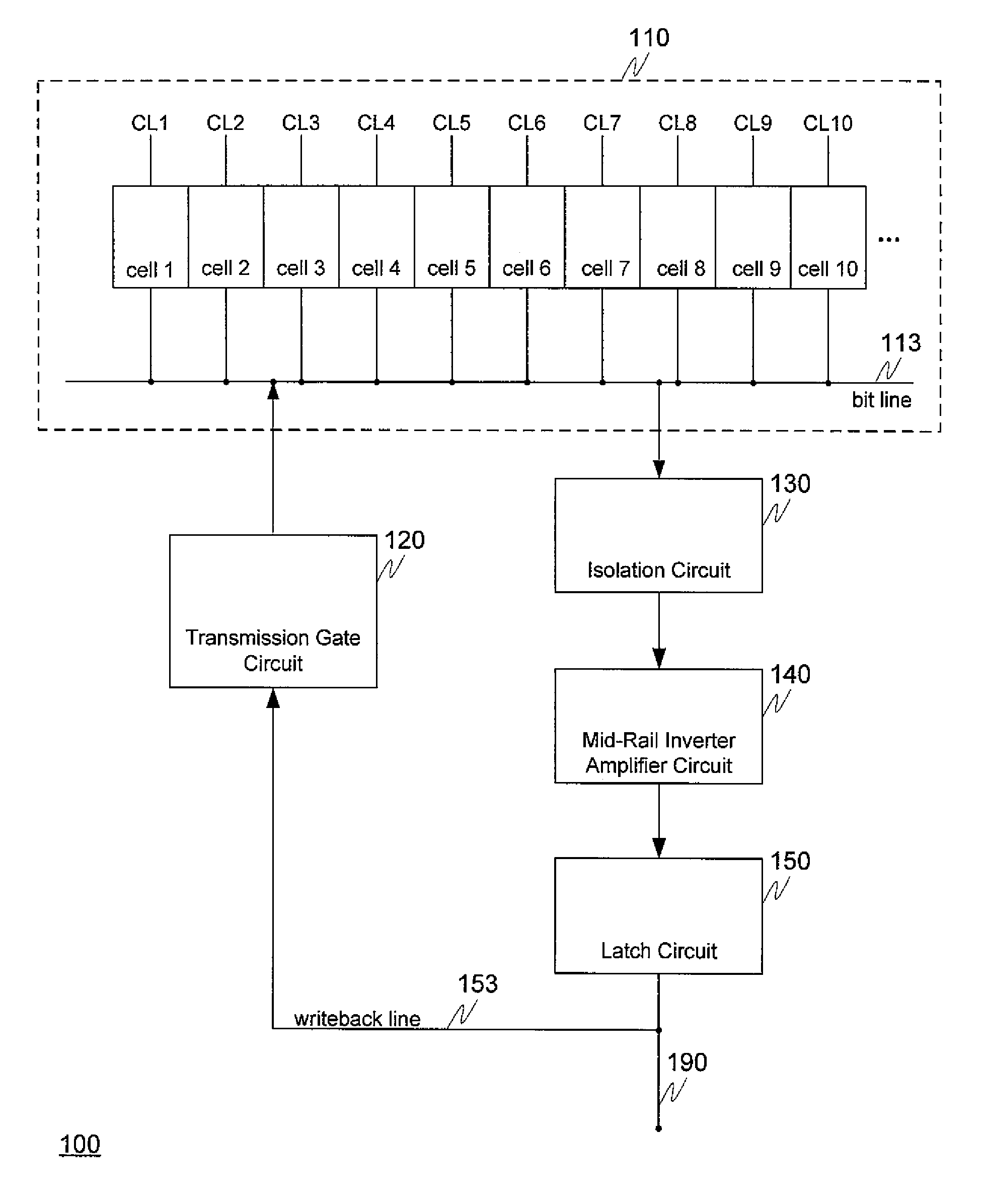

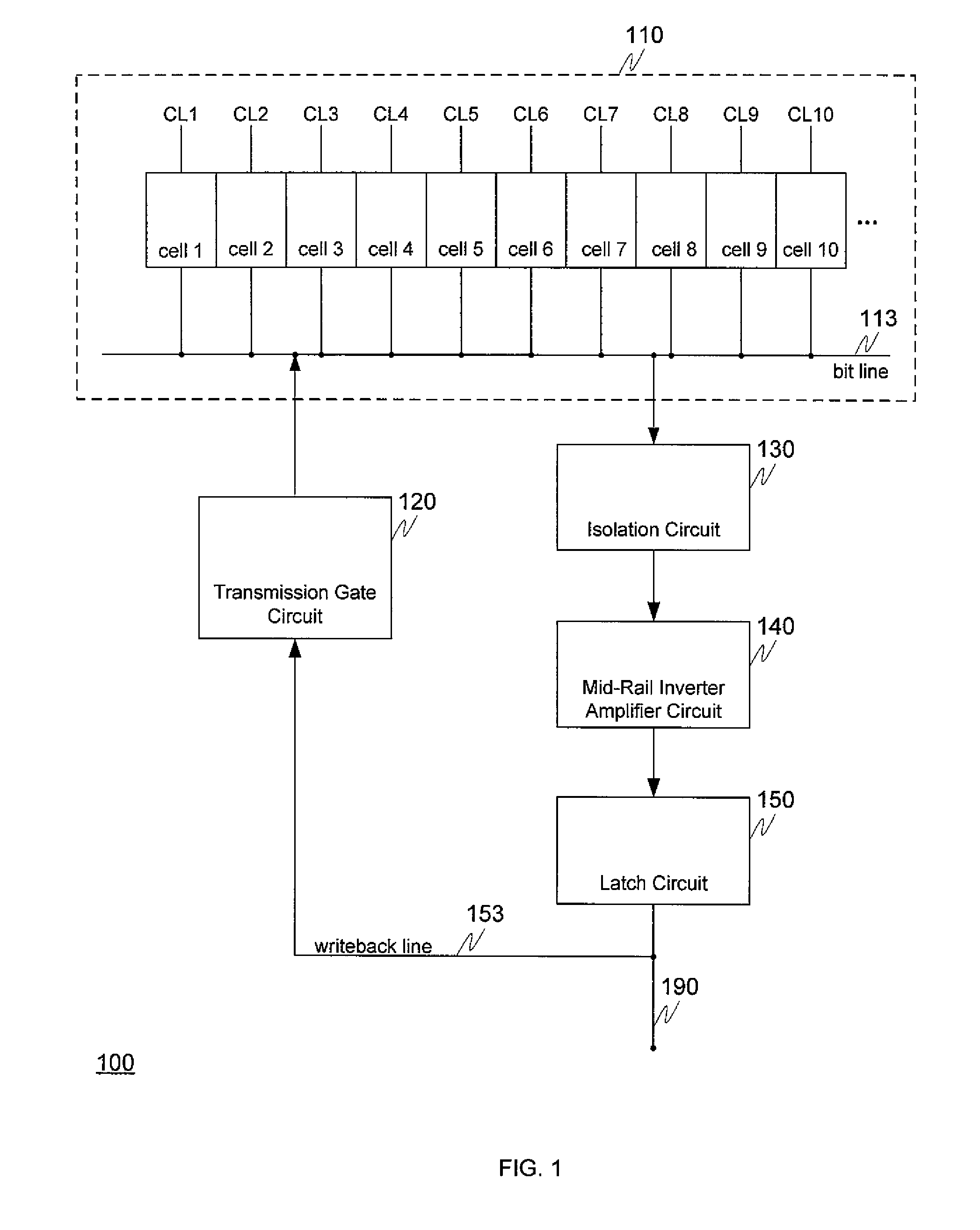

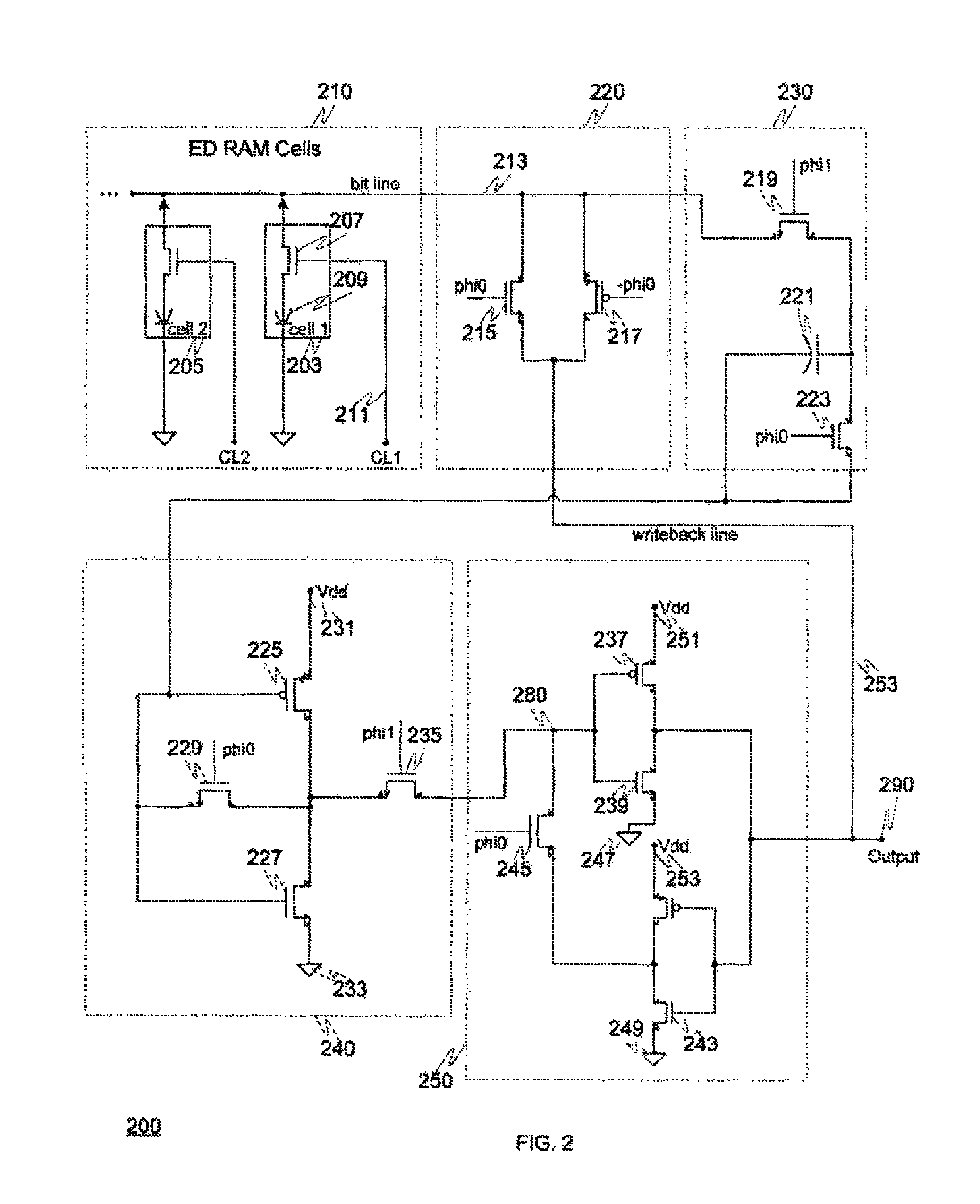

High performance eDRAM sense amplifier

Embedded dynamic random access memory (eDRAM) sense amplifier circuitry in which a bit line connected to each of a first plurality of eDRAM cells is controlled by cell control lines tied to each of the cells. During a READ operation the eDRAM cell releases its charge indicating its digital state. The digital charge propagates through the eDRAM sense amplifier circuitry to a mid-rail amplifier inverter circuit which amplifies the charge and provides it to a latch circuit. The latch circuit, in turn, inverts the charge to correctly represent at its output the logical value stored in the eDRAM cell being read, and returns the charge through the eDRAM sense amplifier circuitry to replenish the eDRAM cell.

Owner:INT BUSINESS MASCH CORP

Integrated circuit devices including input/output line pairs and precharge circuits and related memory devices

An integrated circuit device may include a pair of first and second input / output lines on a substrate and a precharge circuit connected to the first and second input / output lines. More particularly, portions of the first and second input / output lines may extend in a parallel direction along first lengths thereof, portions of the first and second input / output lines may cross one another in a twist region so that portions of the first and second input / output lines in the twist region extend in directions different than the parallel direction, and portions of the first and second input / output lines may extend in the parallel direction along second lengths. Accordingly, relative positions of the first and second input / output lines may be reversed in the first and second lengths thereof. In addition, the precharge circuit may be connected to portions of the first and second input / output lines in the twist region extending in the directions different than the parallel direction, and the precharge circuit may be configured to provide that the first and second input / output lines have a same electrical potential responsive to an enable signal. Related memory devices are also discussed.

Owner:SAMSUNG ELECTRONICS CO LTD

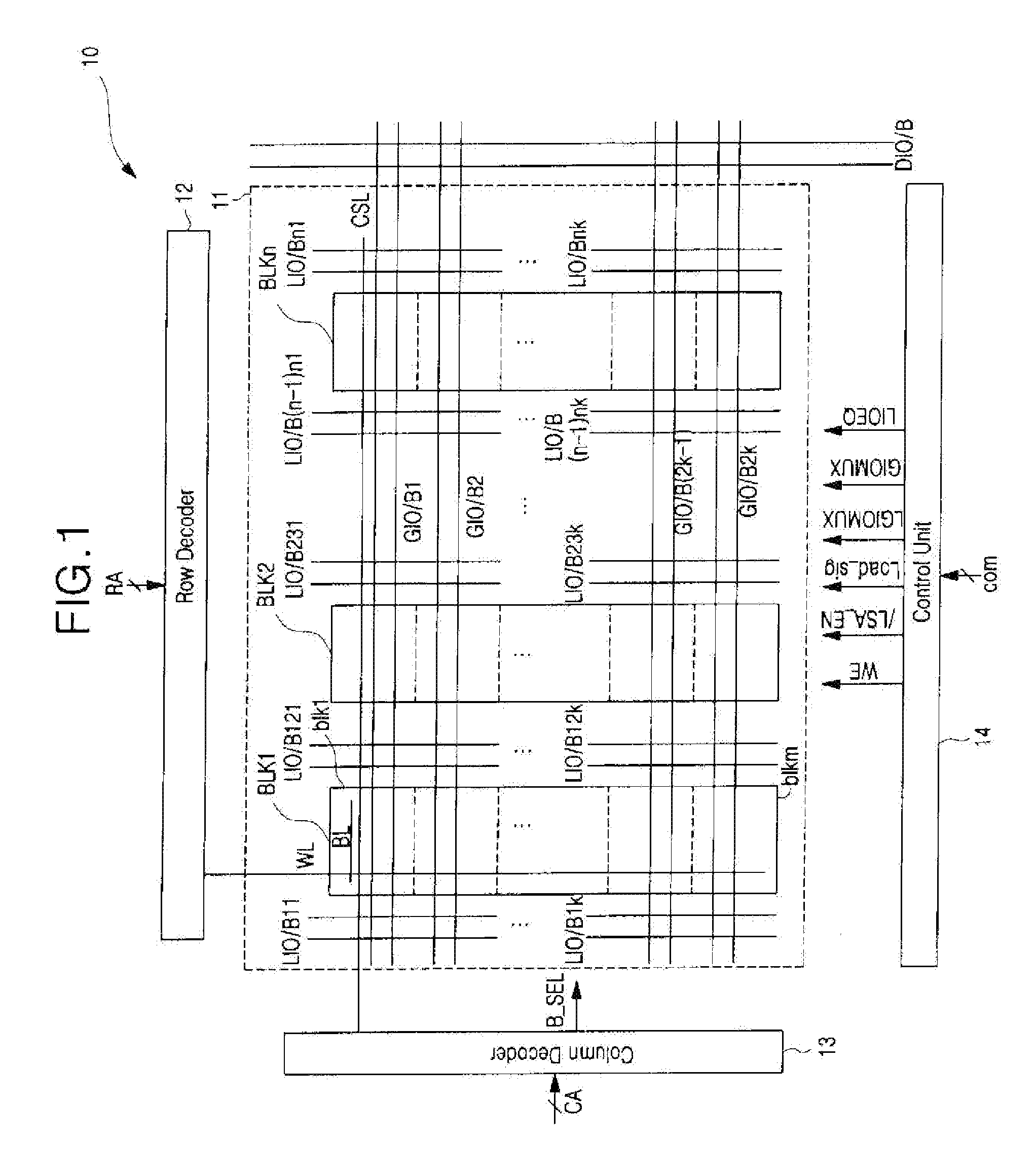

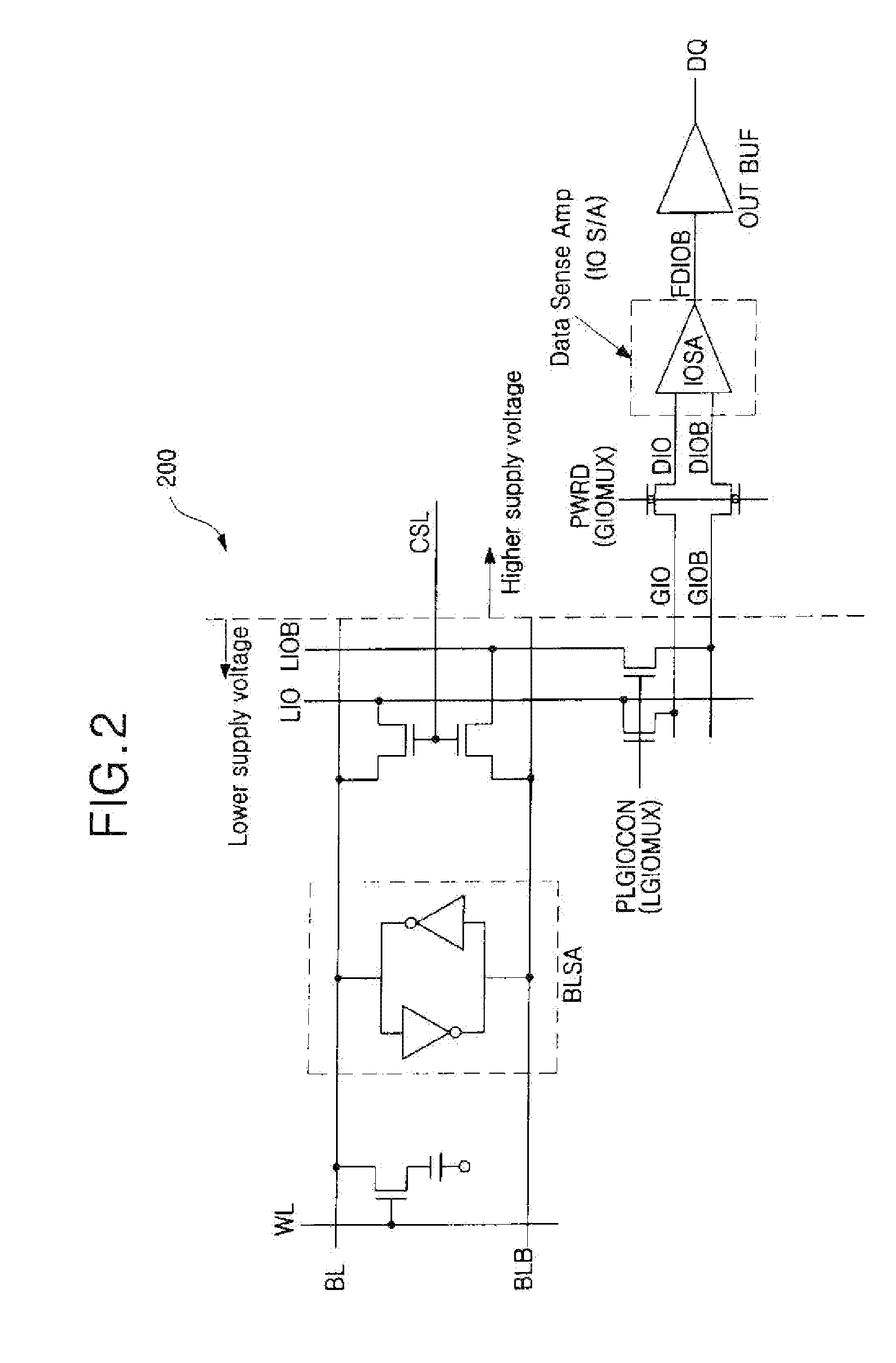

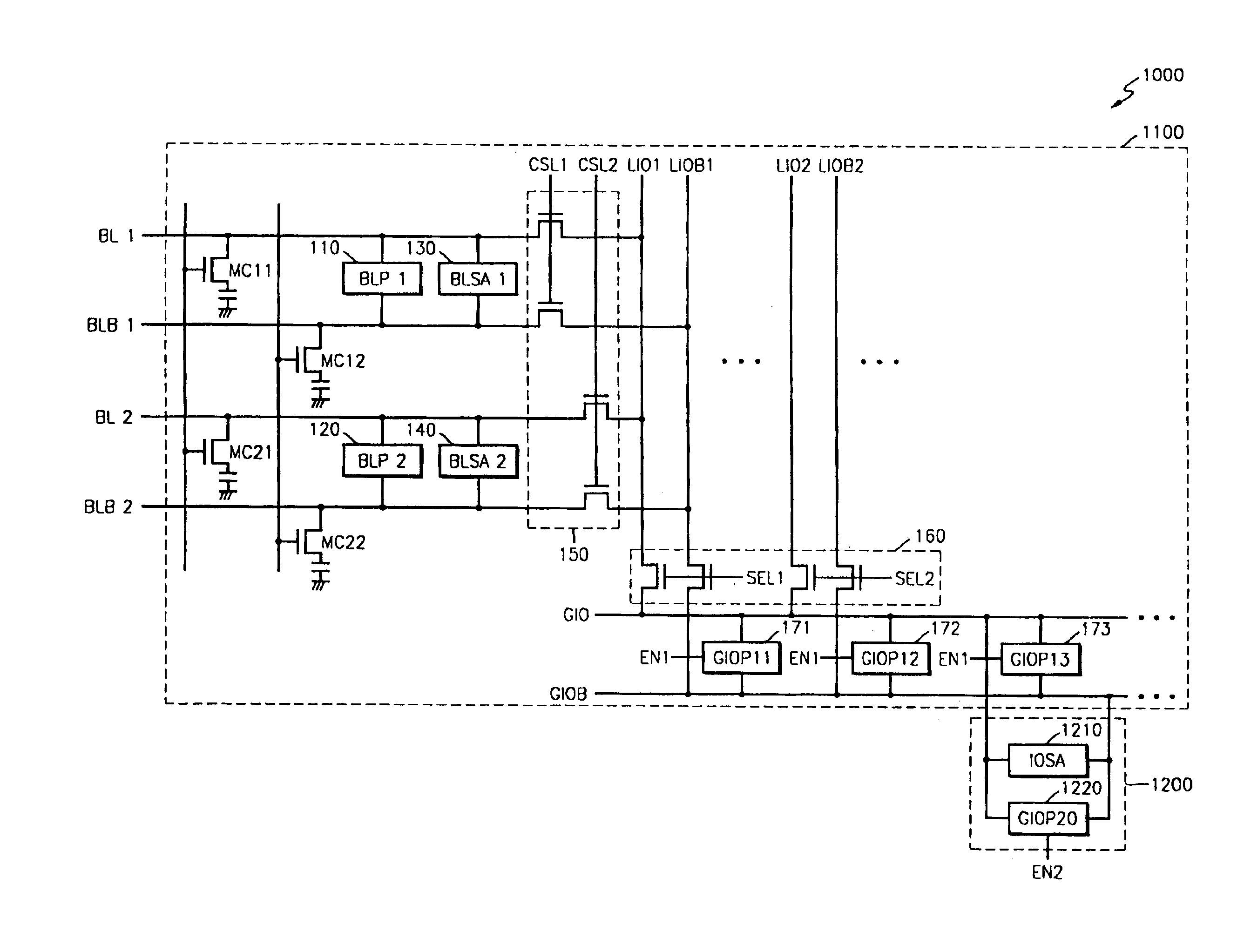

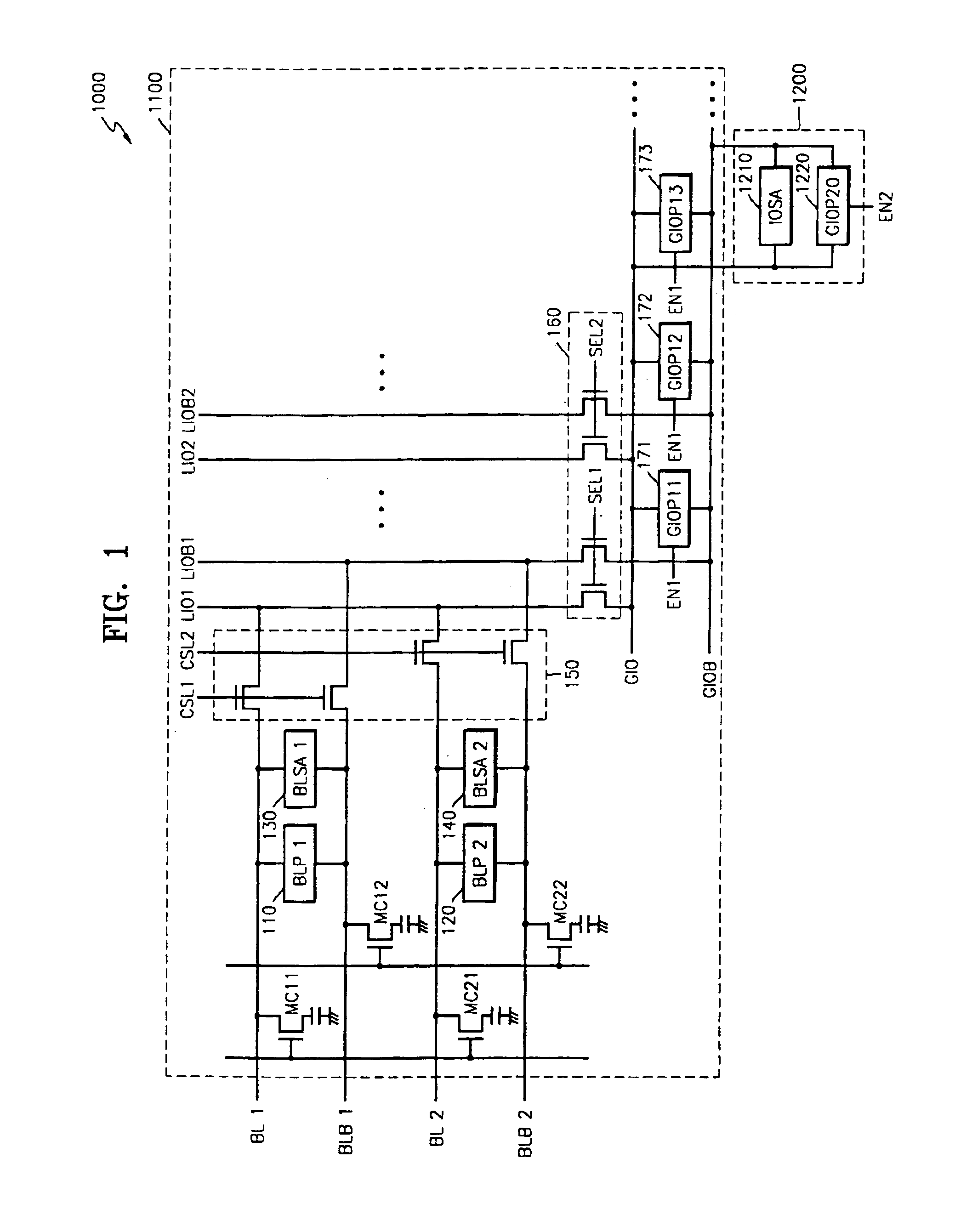

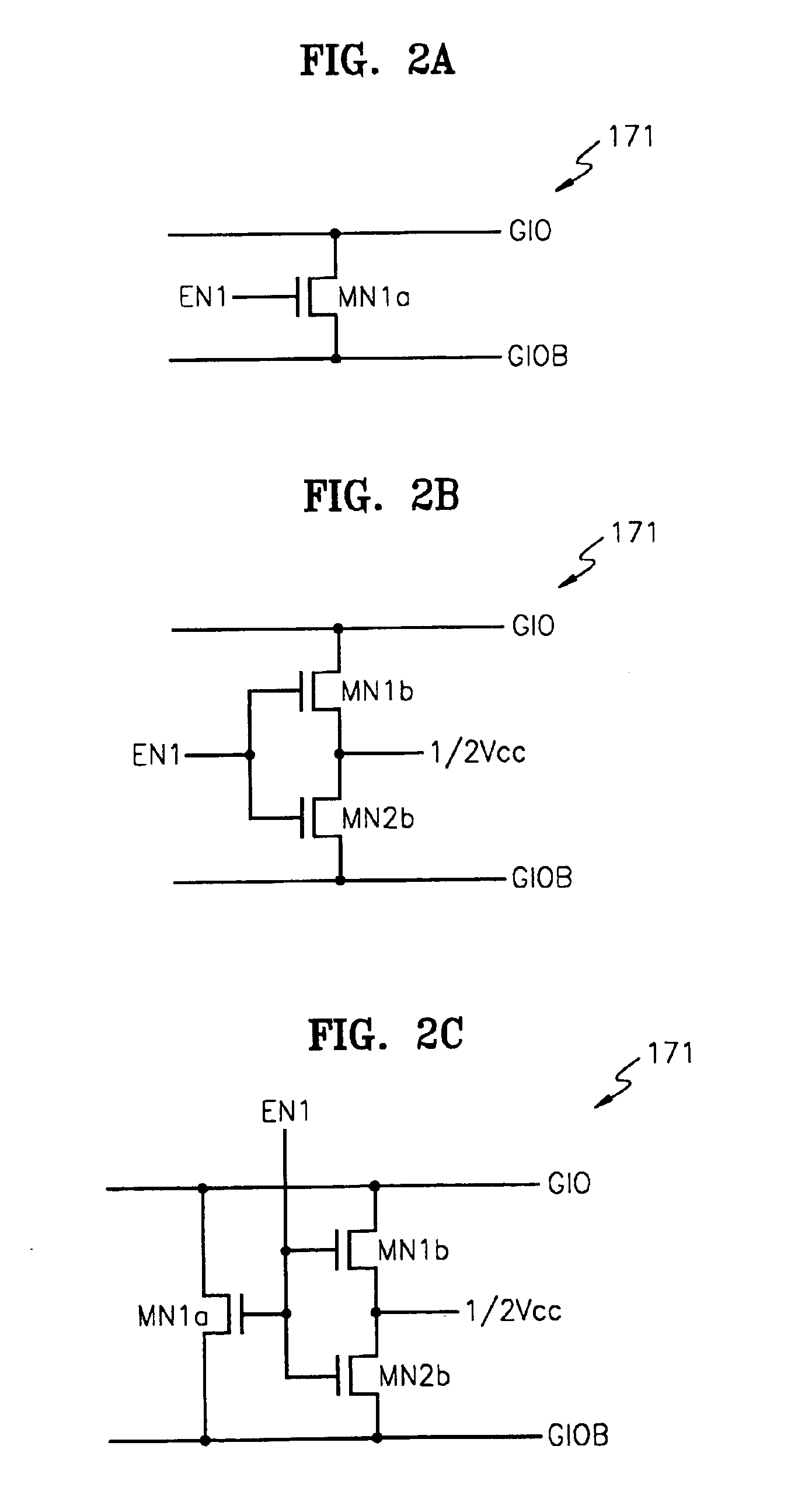

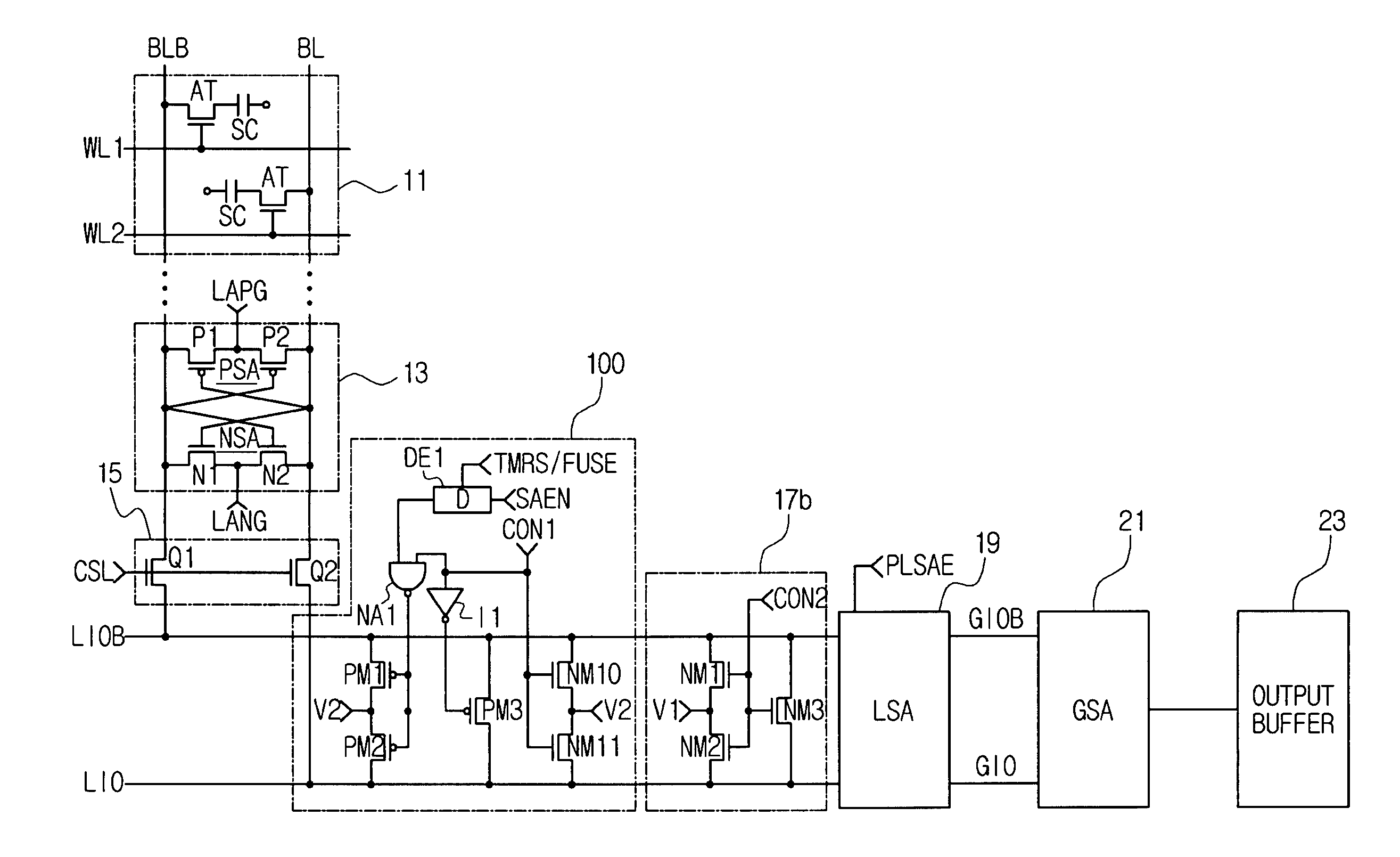

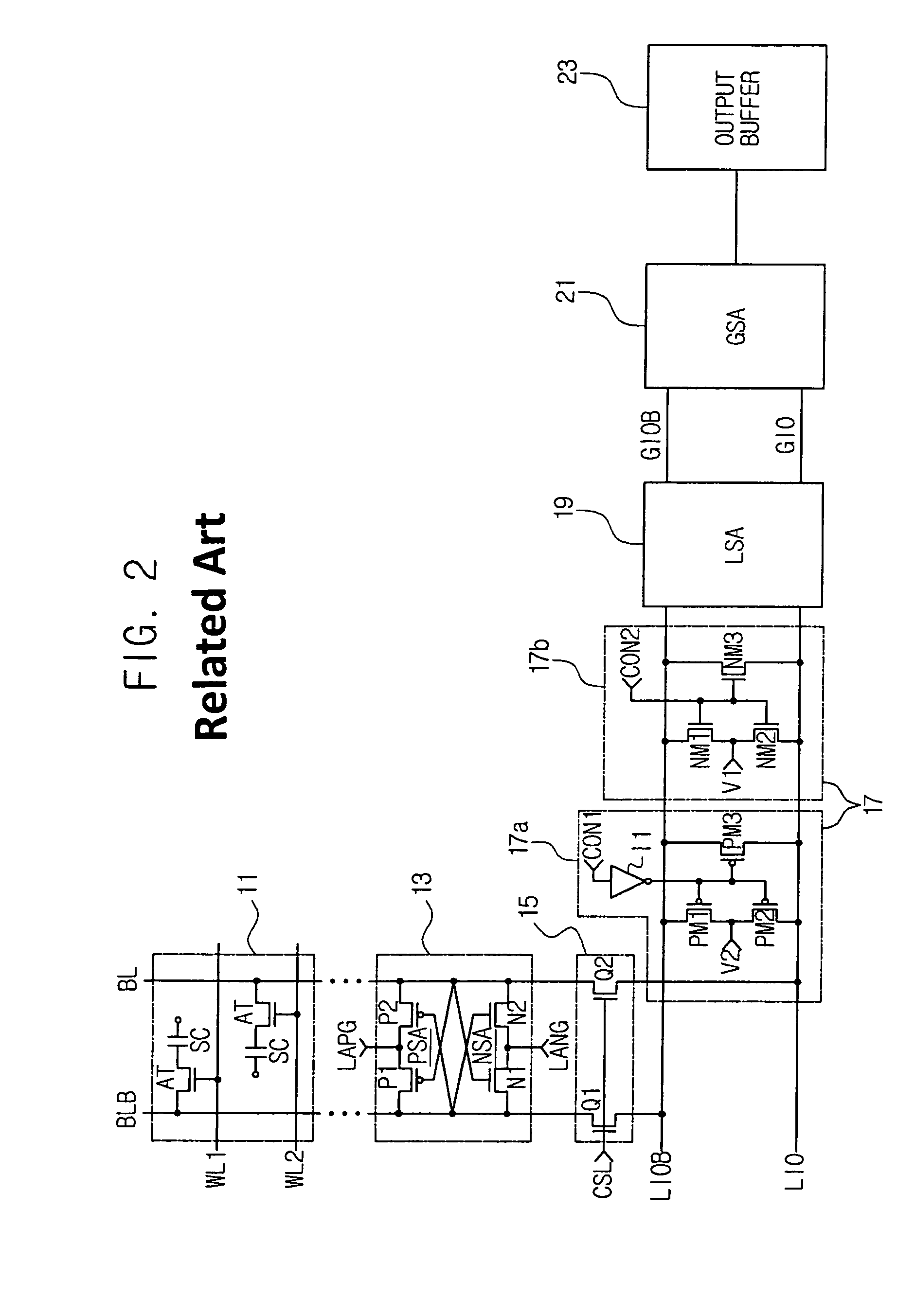

Semiconductor memory device adopting improved local input/output line precharging scheme

A semiconductor memory device capable of preventing or minimizing bit line disturbance and performing a low-voltage high-speed operation includes a read data path circuit including a bit line sense amplifier, a local input / output line sense amplifier, a column selecting unit to operationally connect bit lines connected to the bit line sense amplifier to local input / output lines connected to the local input / output line sense amplifier in response to a column selection signal, and a local input / output line precharging unit to precharge the pair of local input / output lines by a first precharging unit, equalizing the pair of local input / output lines by an equalizing unit, and to precharge the local input / output lines by a second precharging unit following an elapsed time after the bit line sense amplifier is activated, while the column selection is deactivated.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor memory apparatus and test circuit therefor

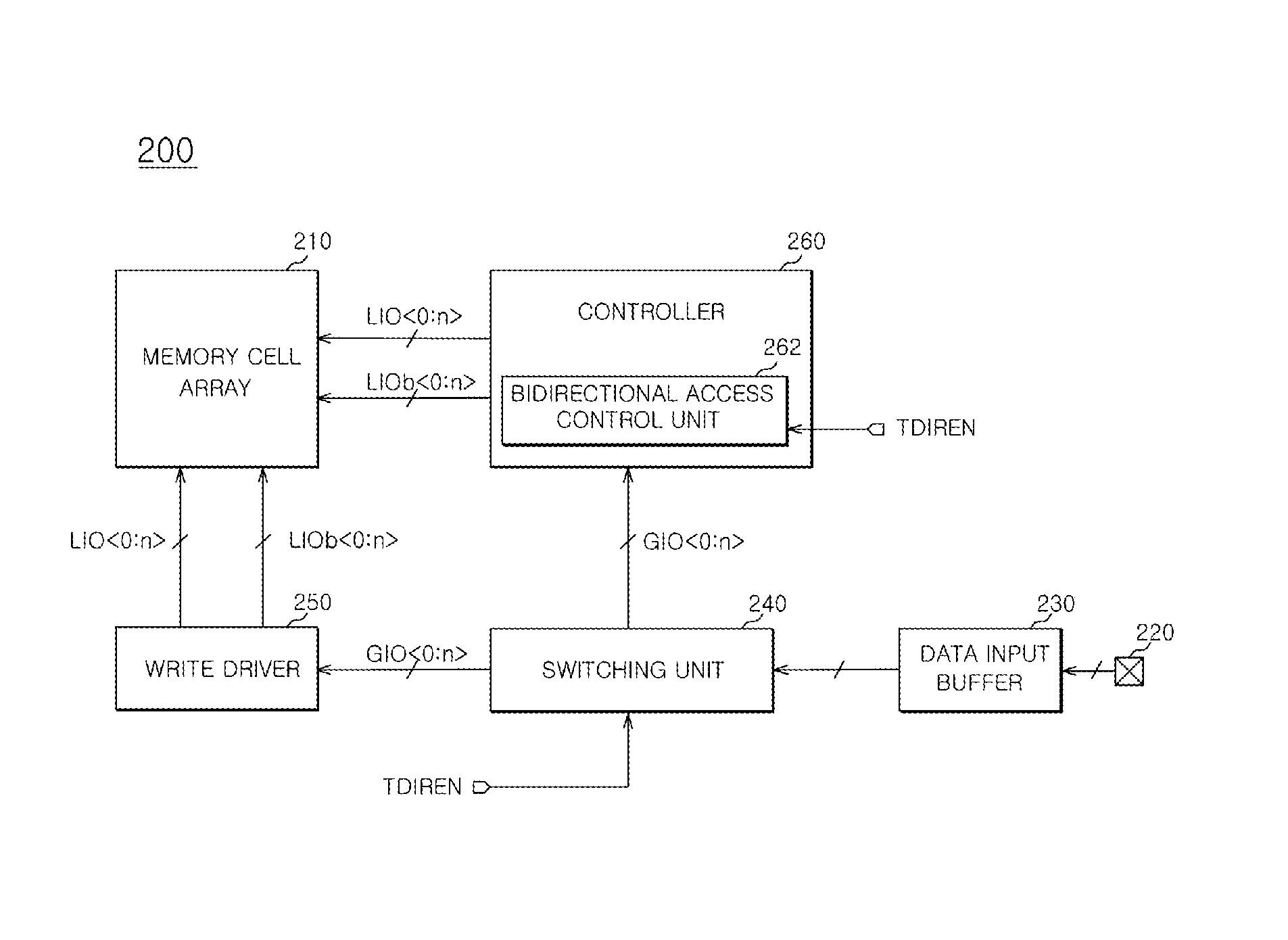

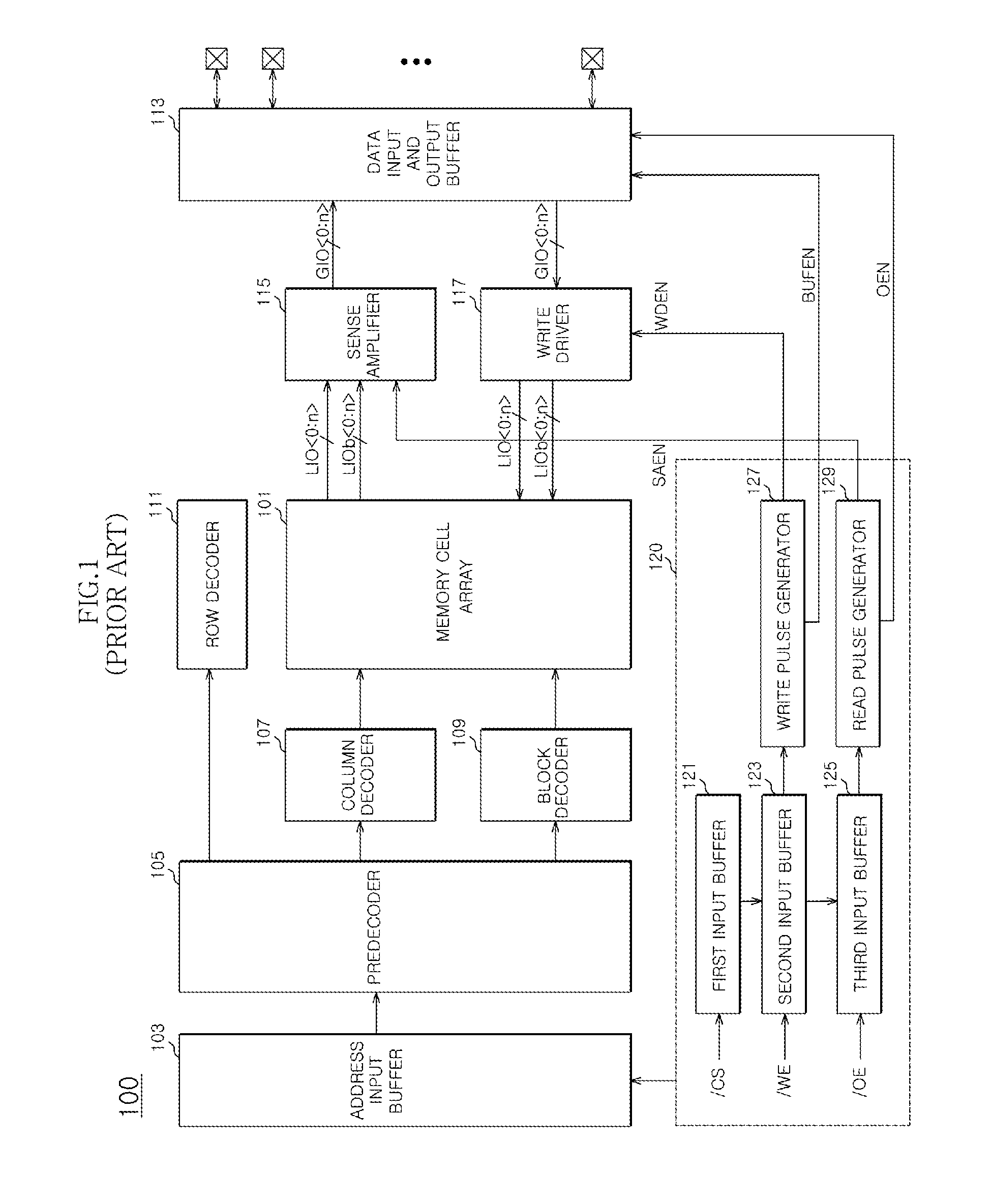

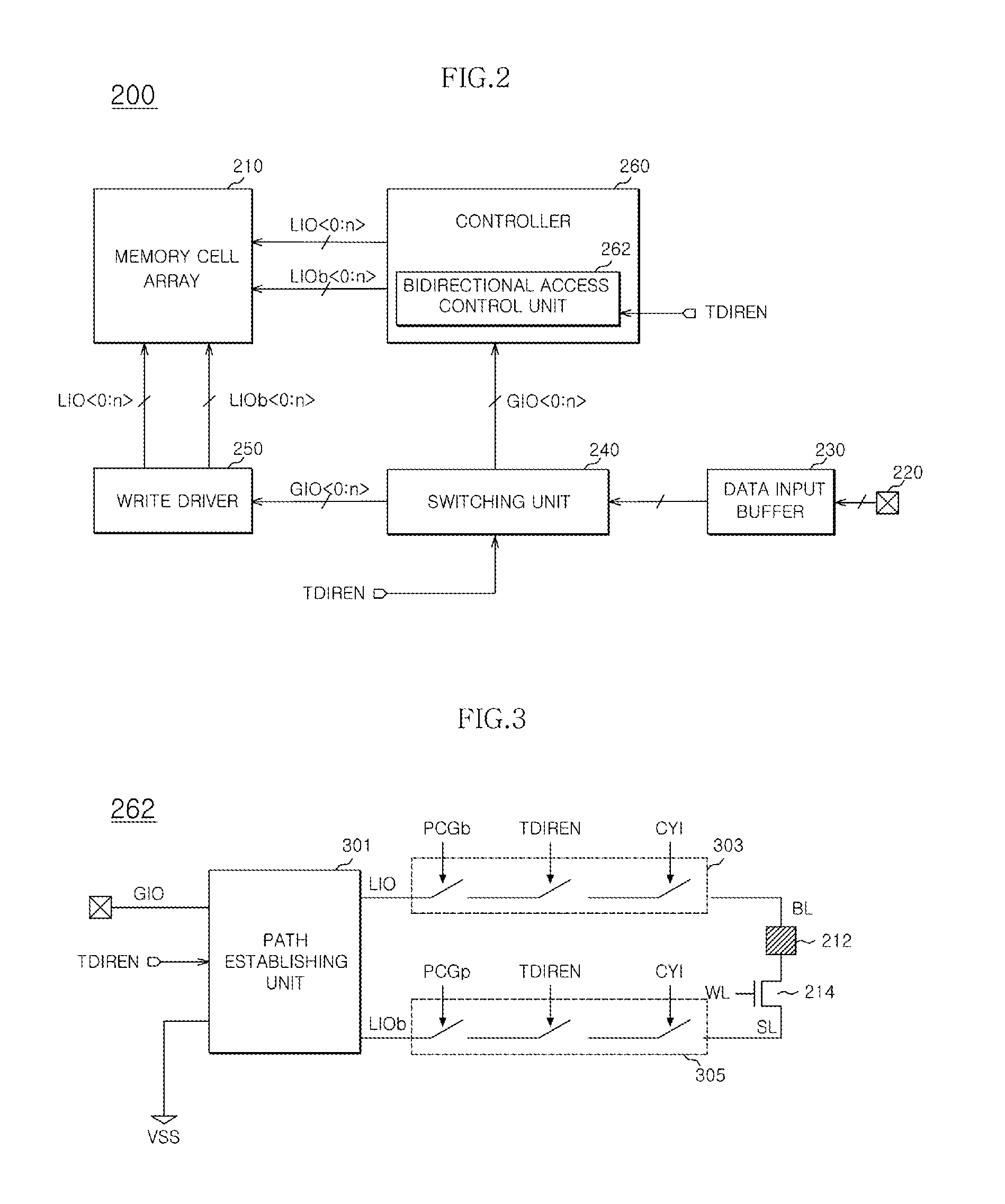

Disclosed is a semiconductor memory apparatus, including: a memory cell array configured to include a plurality of memory cells; a switching unit configured to be coupled to data input and output pads and control a data transfer path of data applied to the data input and output pads in response to a test mode signal; a write driver configured to drive data transferred from the switching unit and write the data in the memory cell array at a normal mode; and a controller configured to transfer the data from the switching unit to the memory cell at a test mode.

Owner:SK HYNIX INC

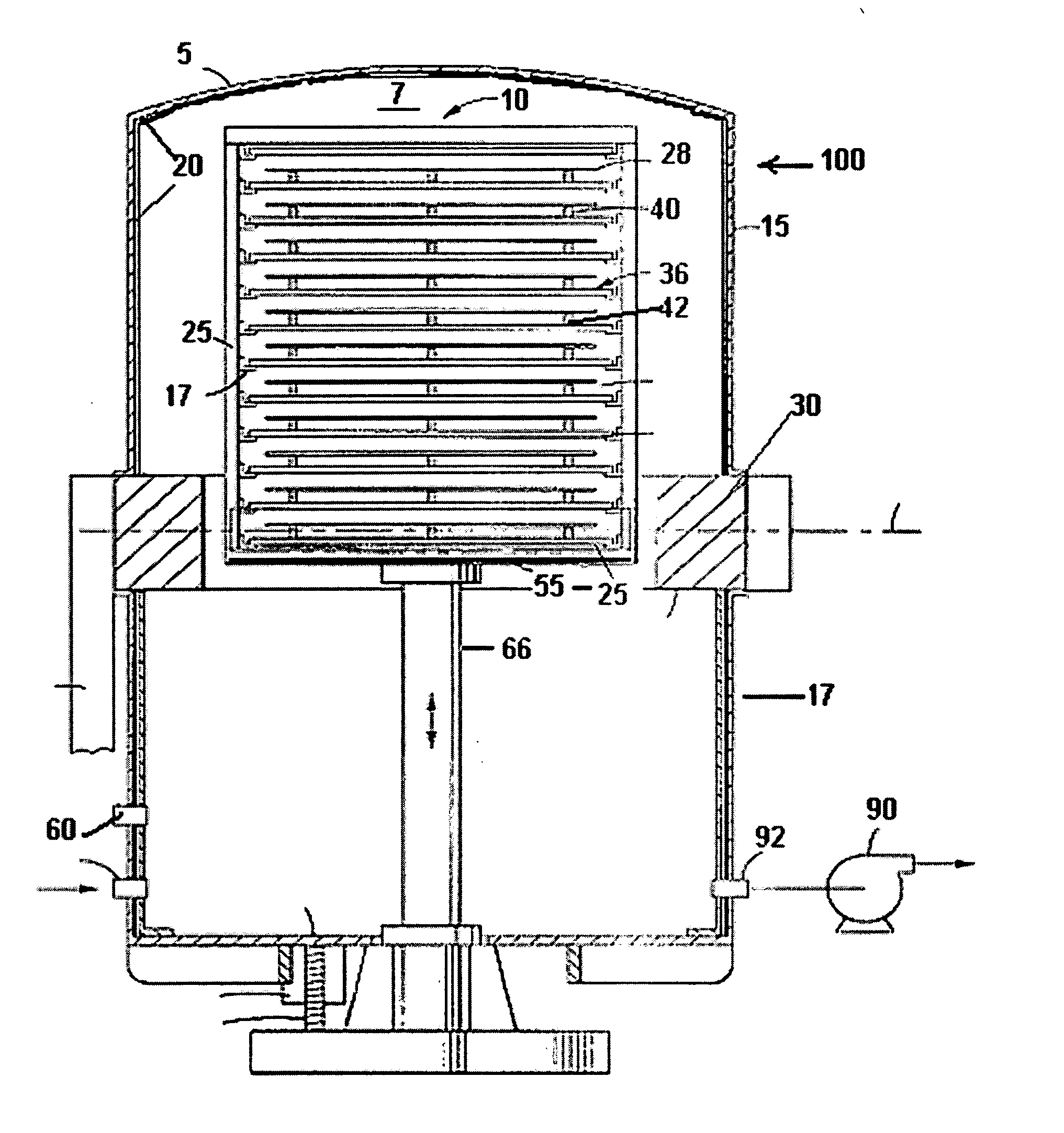

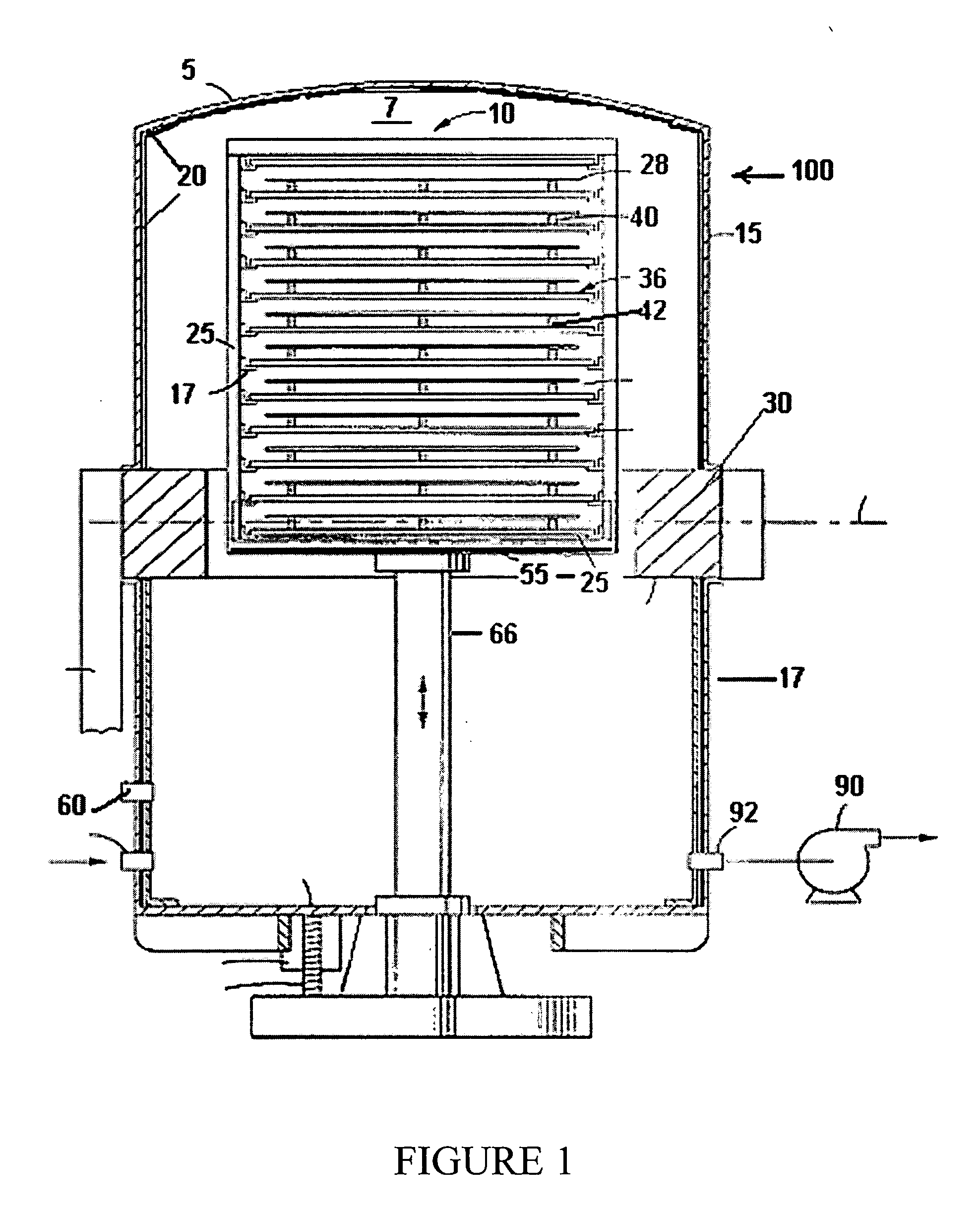

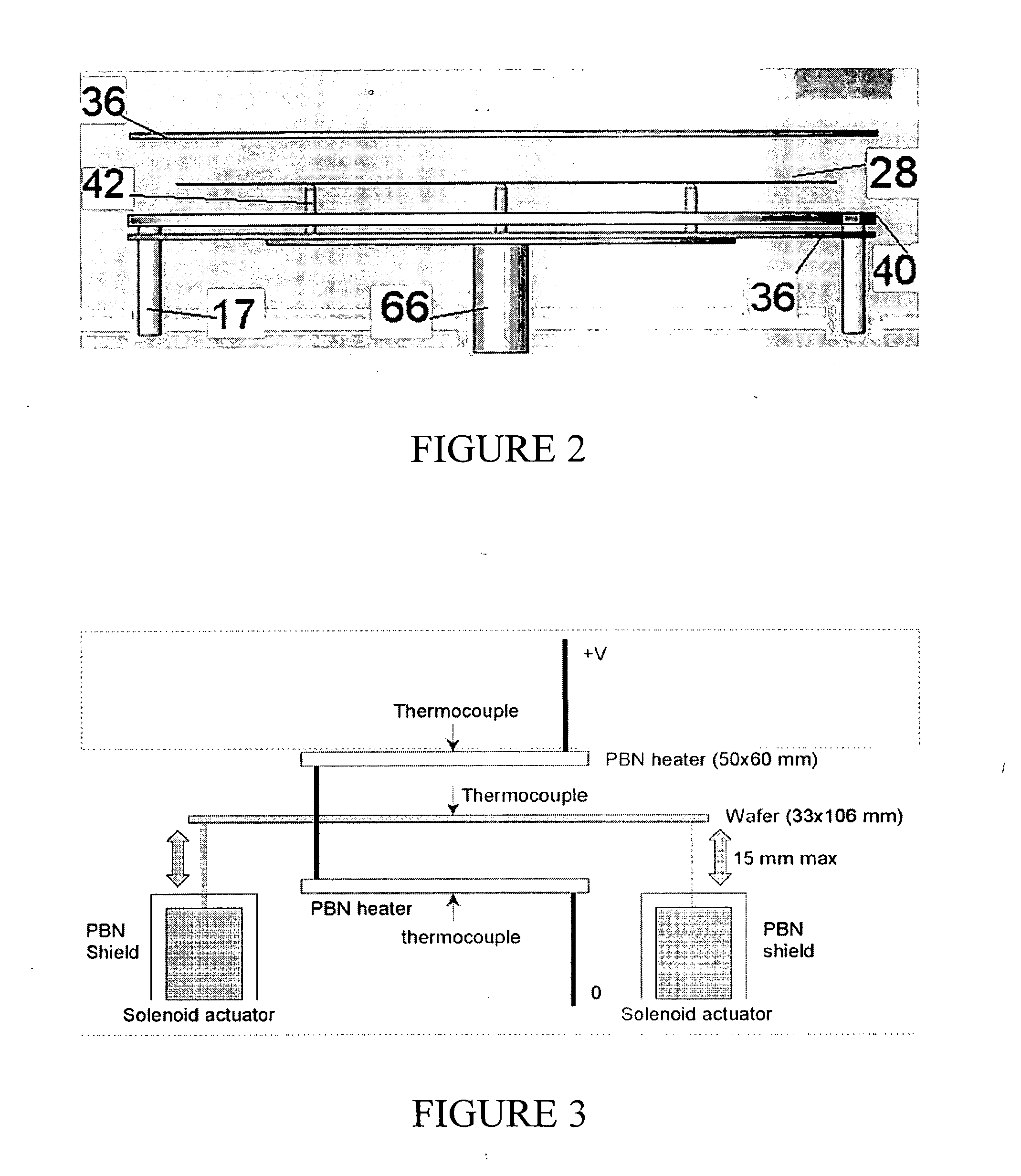

Fast heating and cooling wafer handling assembly and method of manufacturing thereof

InactiveUS20060127067A1Muffle furnacesSemiconductor/solid-state device manufacturingElectrical resistance and conductanceThermal control

A thermal control device for wafer processing which comprises a) a platform for placement of an object of various sizes to be heated, b) at least a shaft extending substantially transverse to the platform; and c) a plurality of resistance heating elements patterned in a plurality of circuits defining at least one zone for independent controlled heating of objects of varying sizes on the platform.

Owner:GENERAL ELECTRIC CO

Memory sensing circuit and method for low voltage operation

InactiveUS7046568B2Large capacityImprove performanceRead-only memoriesDigital storageBit lineAudio power amplifier

A sensing module operates with a sense amplifier sensing a conduction current of a memory cell via a coupled bit line under constant voltage condition in order to minimize bit-line to bit-line coupling. The rate of discharge of a dedicated capacitor as measured by a change in the voltage drop there across in a predetermined period is used to indicate the magnitude of the conduction current. The voltage cannot drop below a minimum level imposed by a circuit for maintaining the constant voltage condition on the bit line. A voltage shifter is used to boost the voltage during the discharge and to unboost the voltage after the discharge, so that the change in voltage drop properly reflects the rate of discharge without running into the minimum level.

Owner:SANDISK TECH LLC

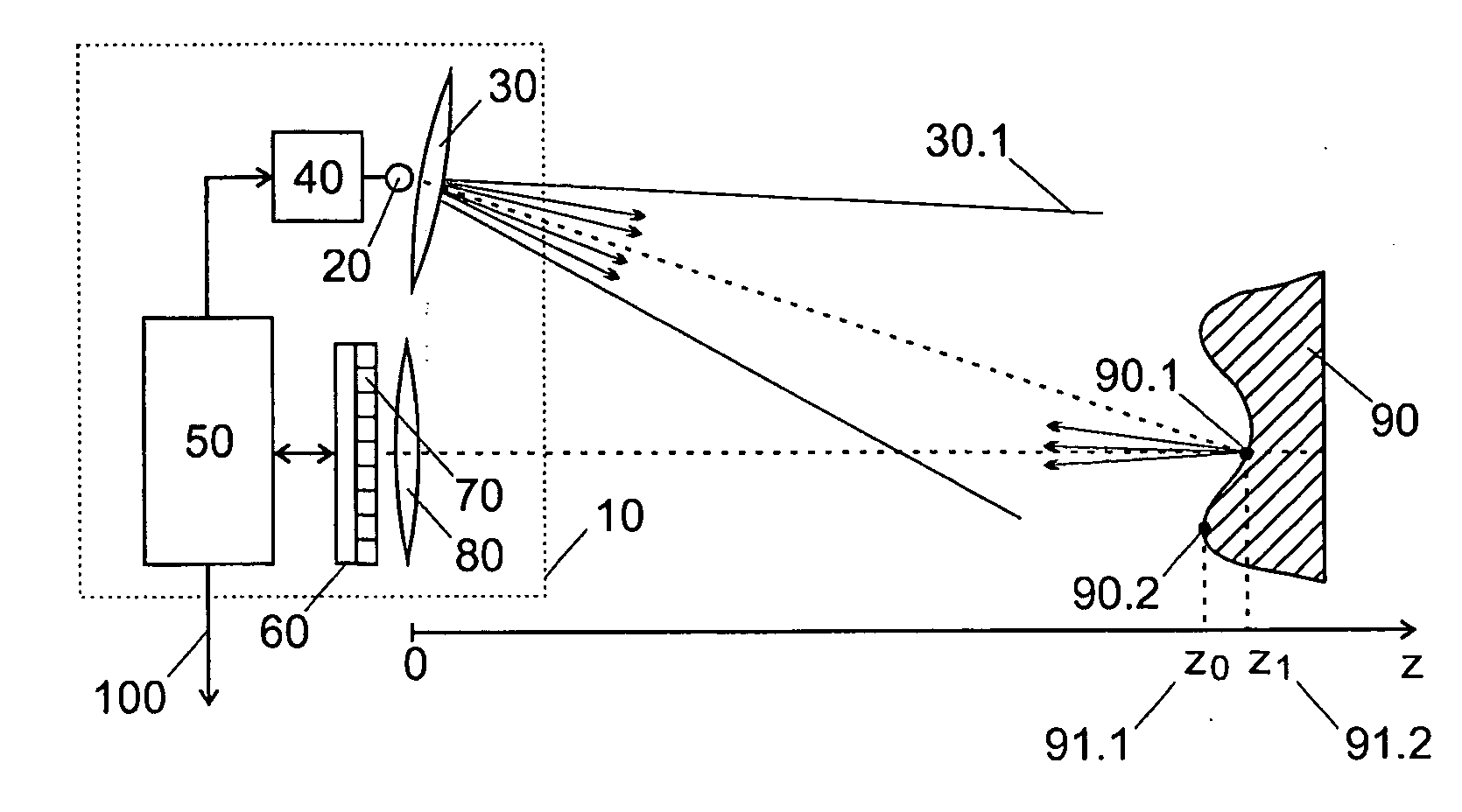

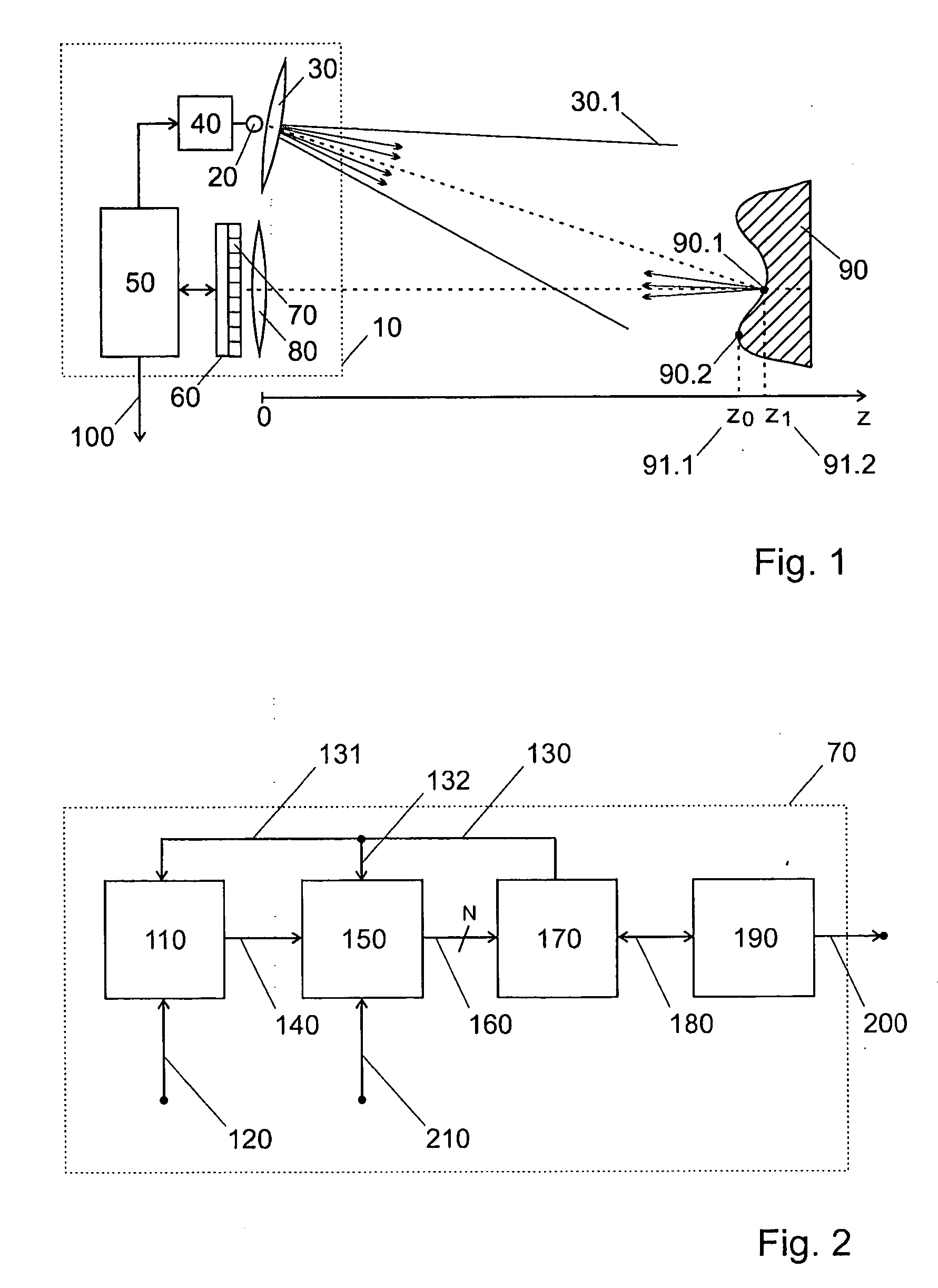

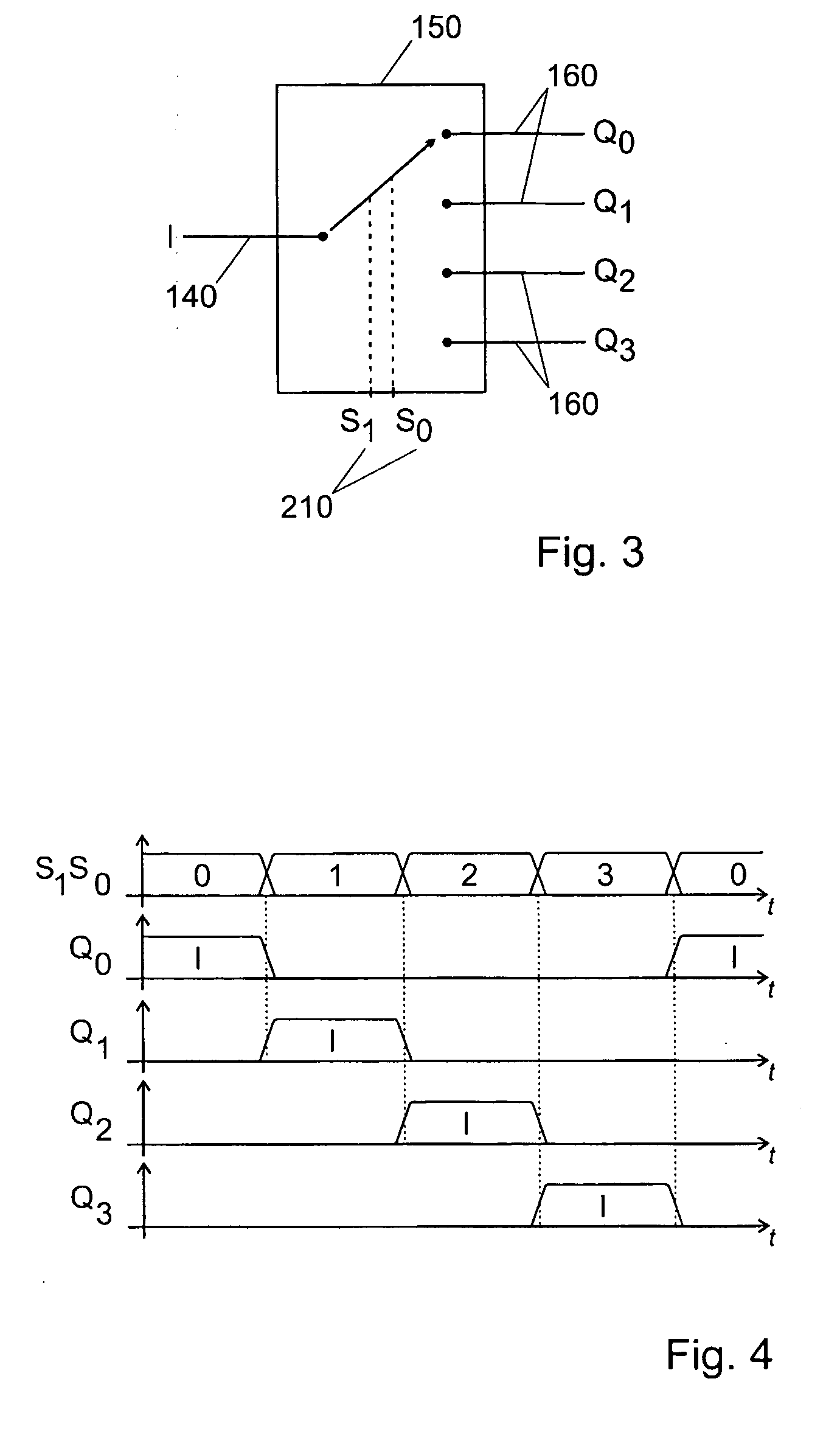

Method and arrangement for measuring the distance to an object

ActiveUS20070182949A1Low costHigh resolutionOptical rangefindersHeight/levelling measurementMultiplexerPhotonics

Arrangement (10) for measuring the distance to an object, comprising: a photonic source for illuminating said object using a continuous modulated photonic wave, a solid-state image sensor, comprising an array of avalanche photodiodes and a plurality of circuits for processing signals output by said avalanche photodiodes to yield data depending on the photonic wave reflected by said object onto said photodiodes. The circuit may comprise a multiplexer at the pixel level arranged so as to accumulate the signal output by the avalanche photodiode during different sub-periods in different storage devices.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

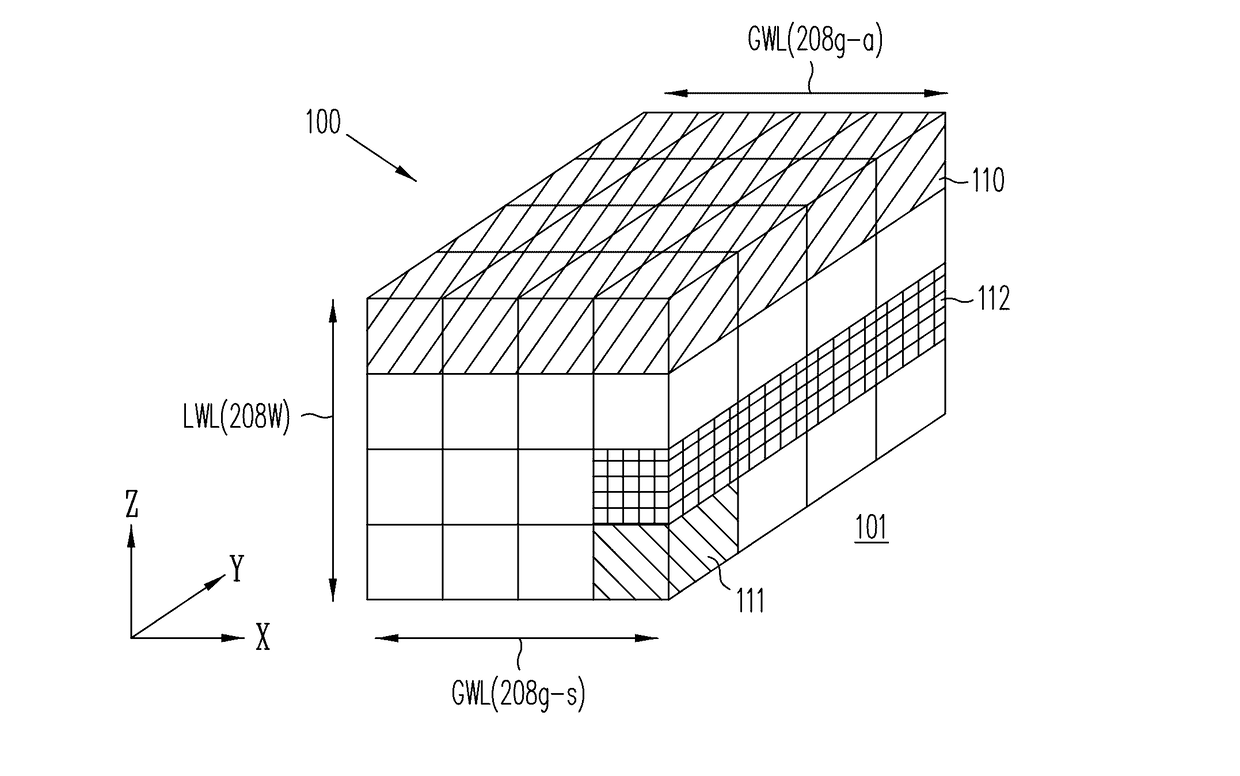

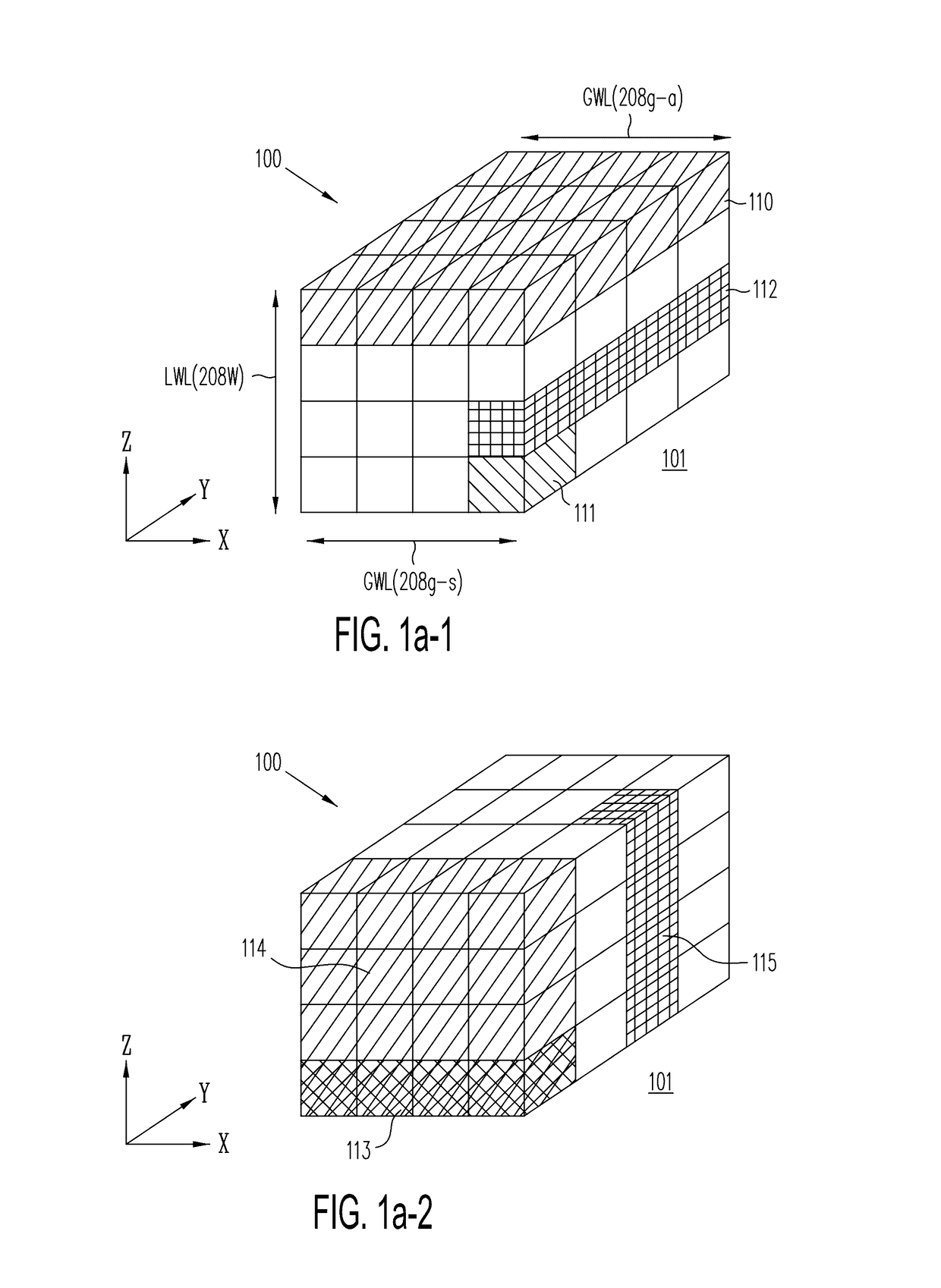

Capacitive-coupled non-volatile thin-film transistor strings in three dimensional arrays

ActiveUS20170092371A1Improve storage densityLower read latencyTransistorSolid-state devicesCapacitive couplingParasitic capacitance

Multi-gate NOR flash thin-film transistor (TFT) string arrays are organized as three dimensional stacks of active strips. Each active strip includes a shared source sublayer and a shared drain sublayer that is connected to substrate circuits. Data storage in the active strip is provided by charge-storage elements between the active strip and a multiplicity of control gates provided by adjacent local word-lines. The parasitic capacitance of each active strip is used to eliminate hard-wire ground connection to the shared source making it a semi-floating, or virtual source. Pre-charge voltages temporarily supplied from the substrate through a single port per active strip provide the appropriate voltages on the source and drain required during read, program, program-inhibit and erase operations. TFTs on multiple active strips can be pre-charged separately and then read, programmed or erased together in a massively parallel operation.

Owner:SUNRISE MEMORY CORP

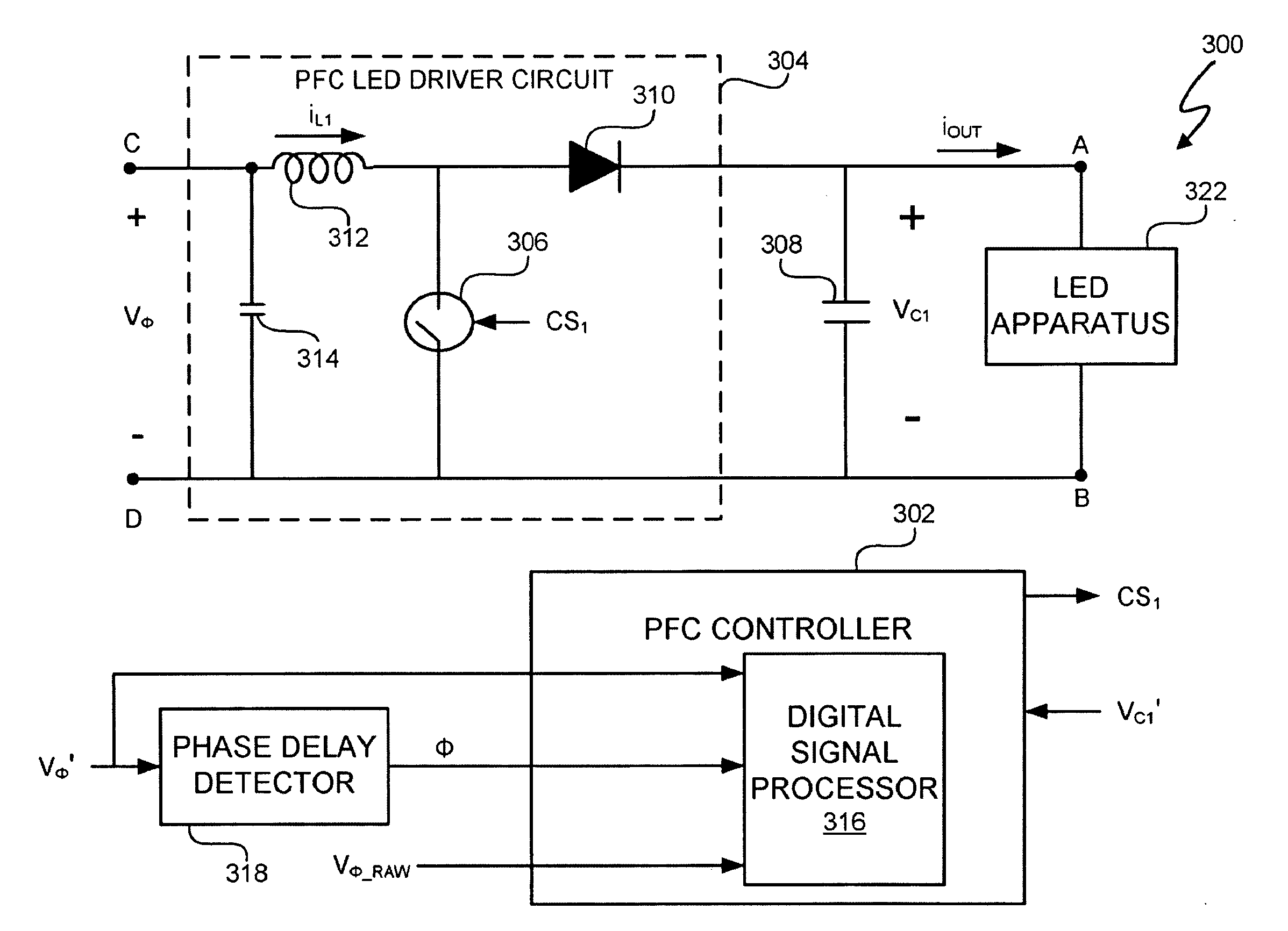

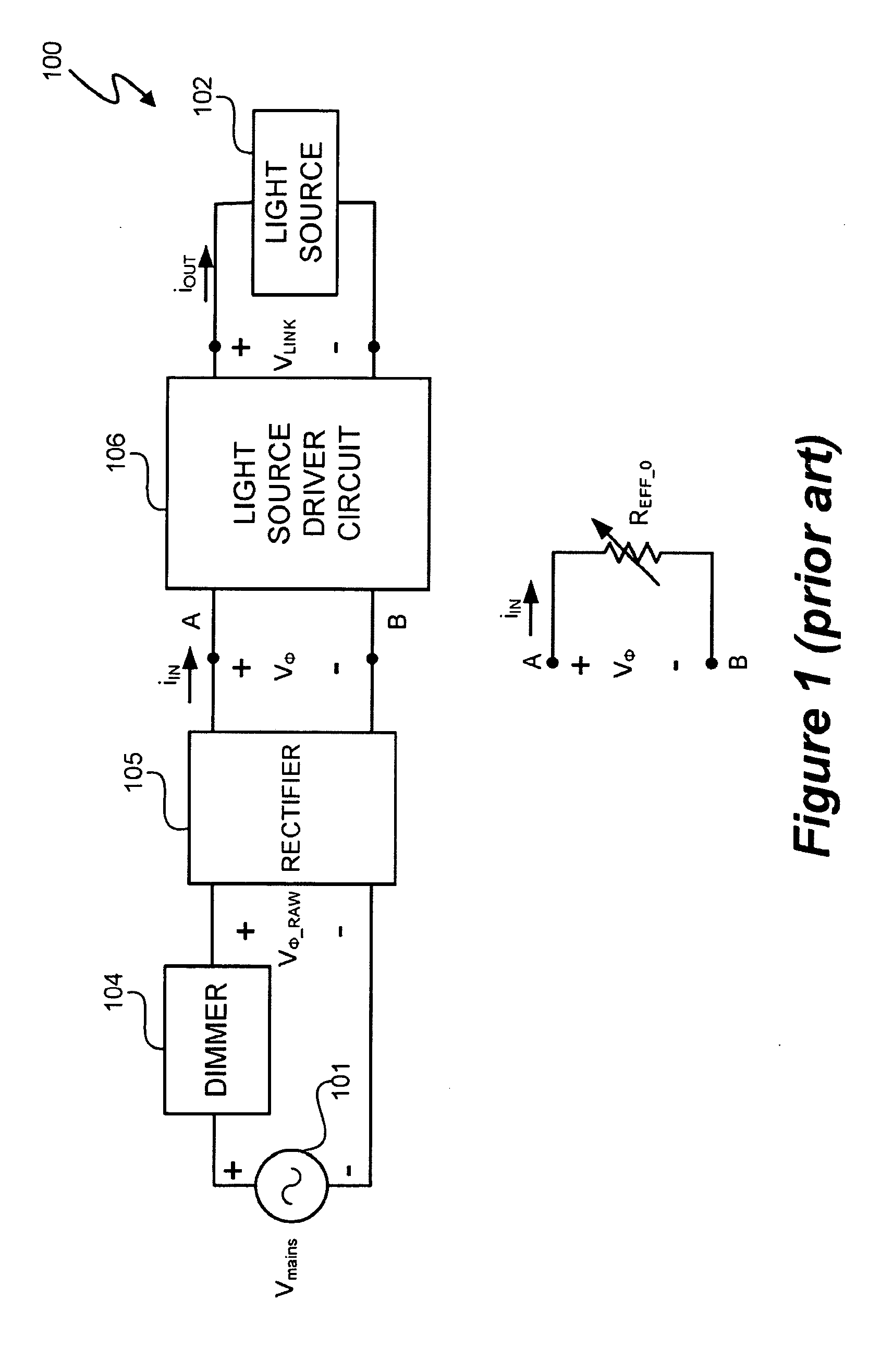

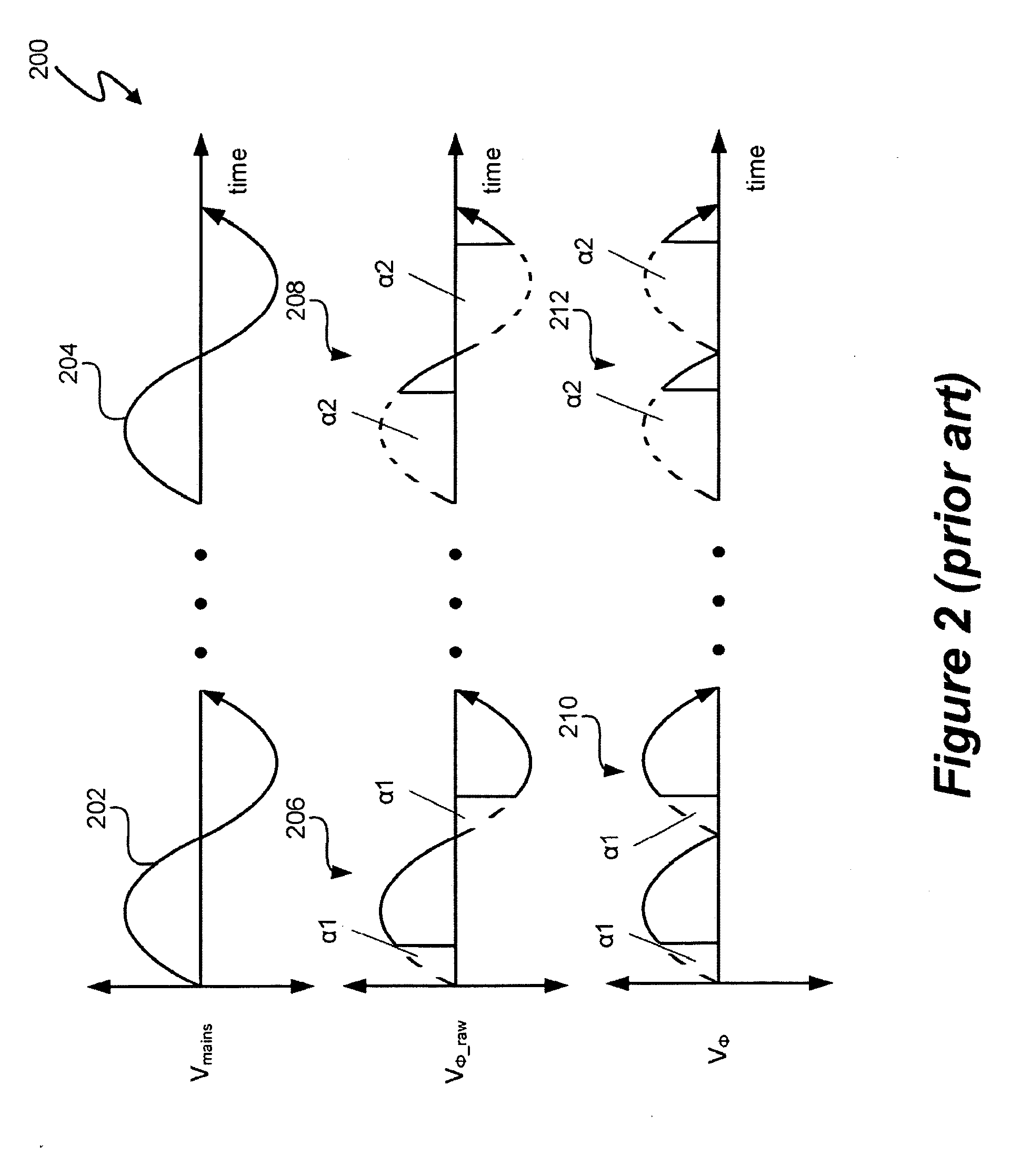

Lighting system with power factor correction control data determined from a phase modulated signal

ActiveUS20080224629A1Lower effective resistanceElectroluminescent light sourcesSemiconductor lamp usageControl powerControl data

A light emitting diode (LED) lighting system includes a power factor correction (PFC) controller that determines at least one power factor correction control parameter from phase delays of a phase modulated signal. In at least one embodiment, a peak voltage of the phase modulated signal is a PFC control parameter used bit the PFC controller to control power factor correction and generation of a link voltage by a PFC LED driver circuit. The phase delays are related to a peak voltage of the phase modulated signal. Thus, in at least one embodiment, detecting the phase delay in one or more cycles of the phase modulated signal allows the PFC controller to determine the peak voltage of the phase modulated signal.

Owner:SIGNIFY HLDG BV

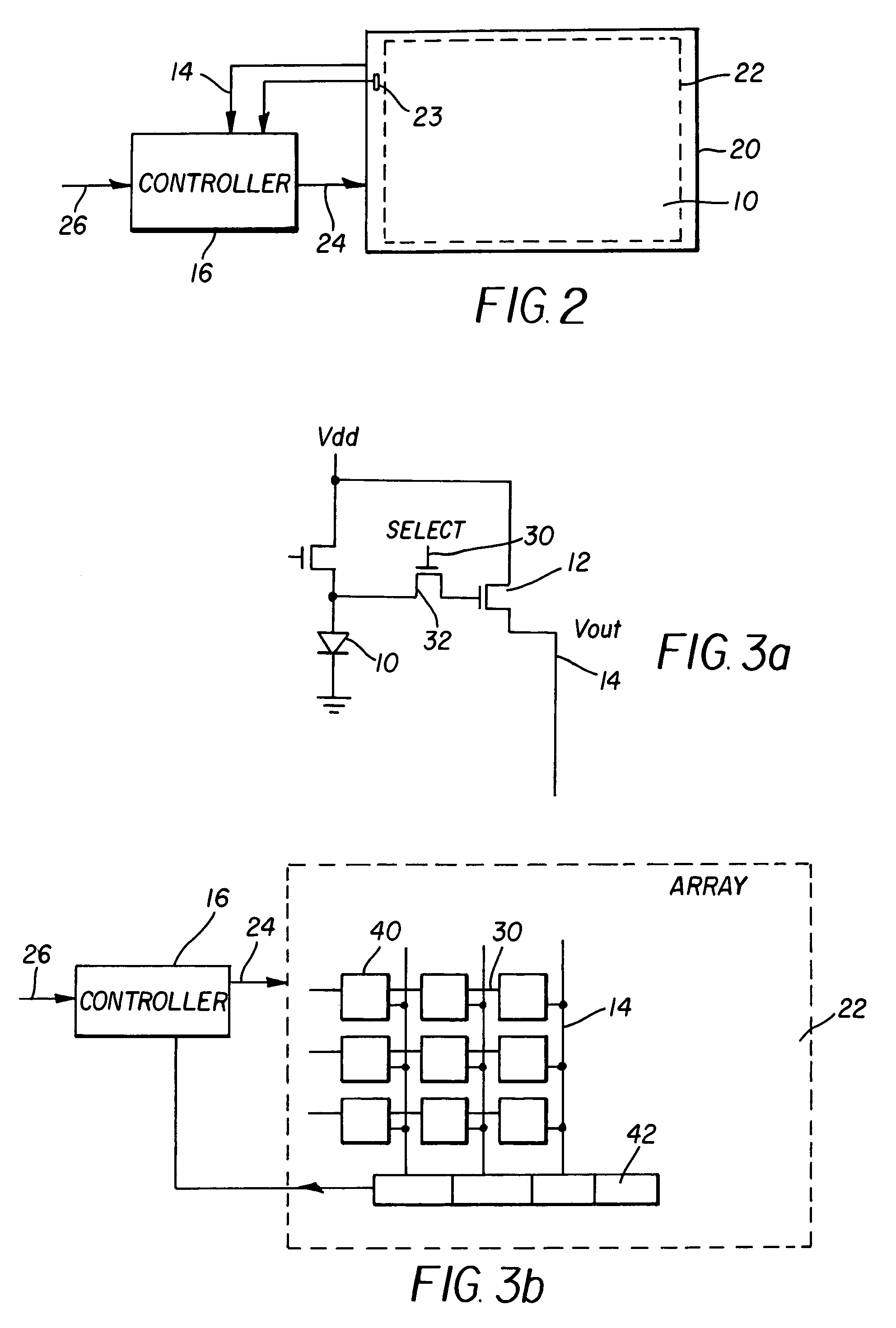

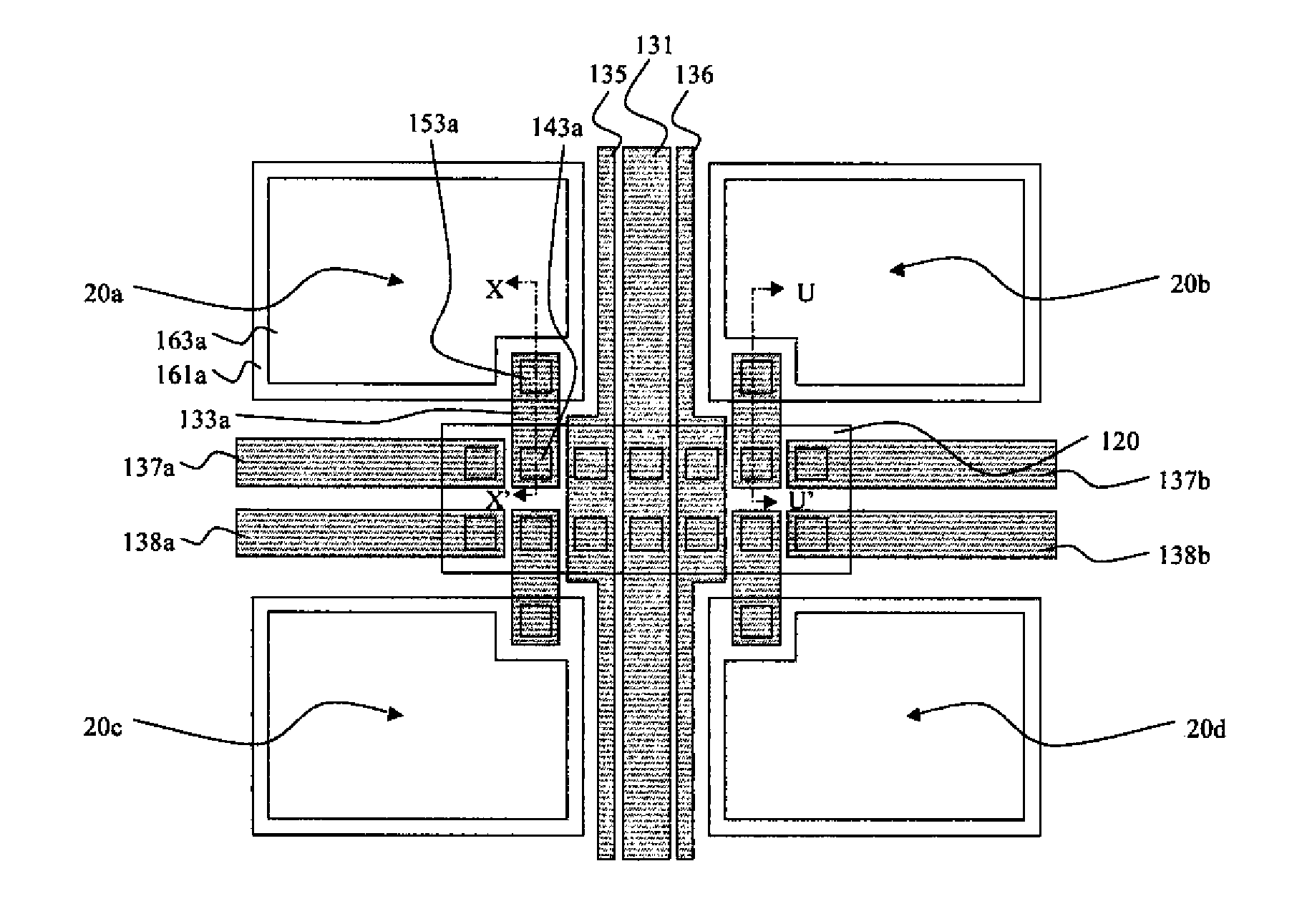

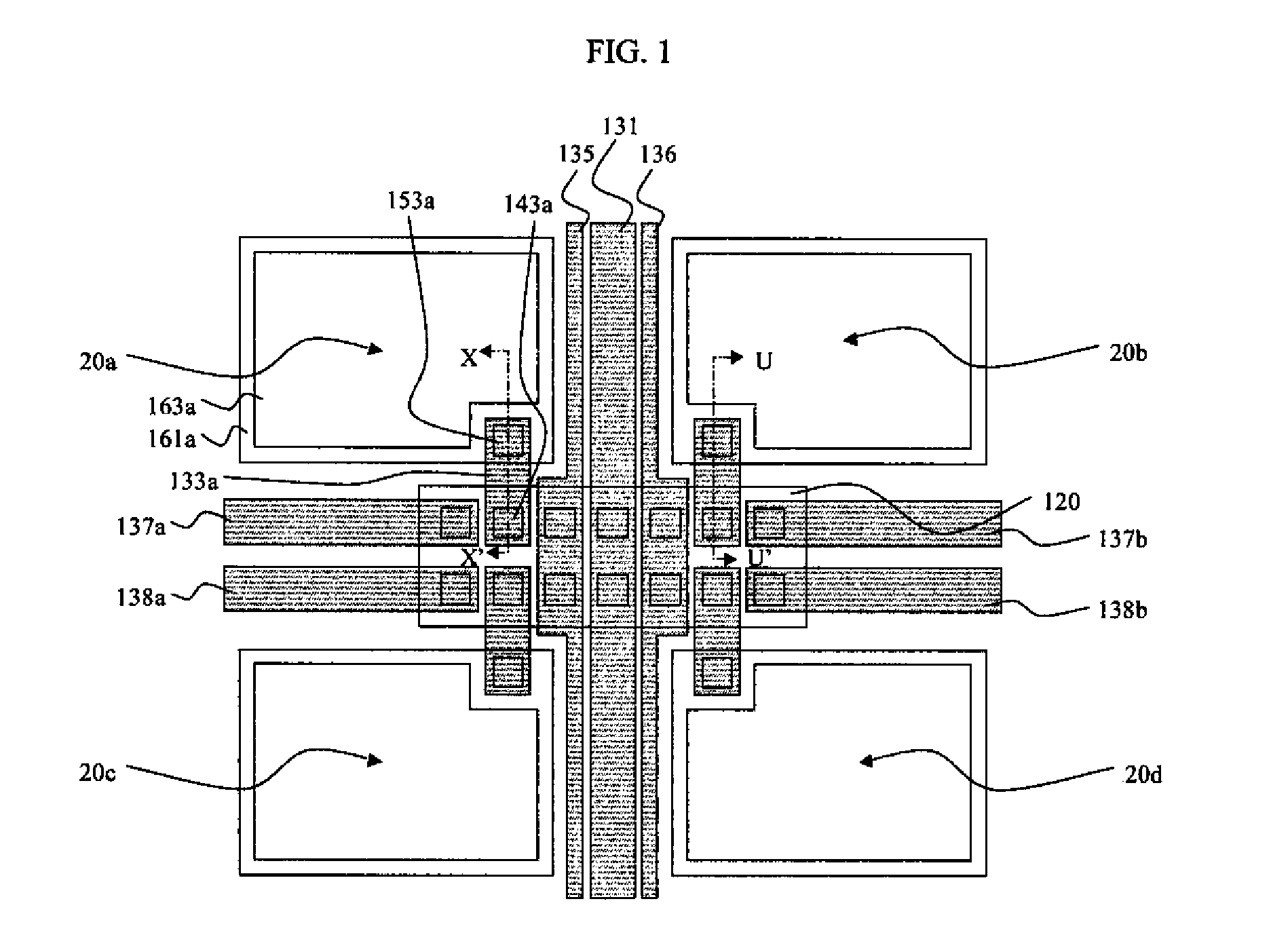

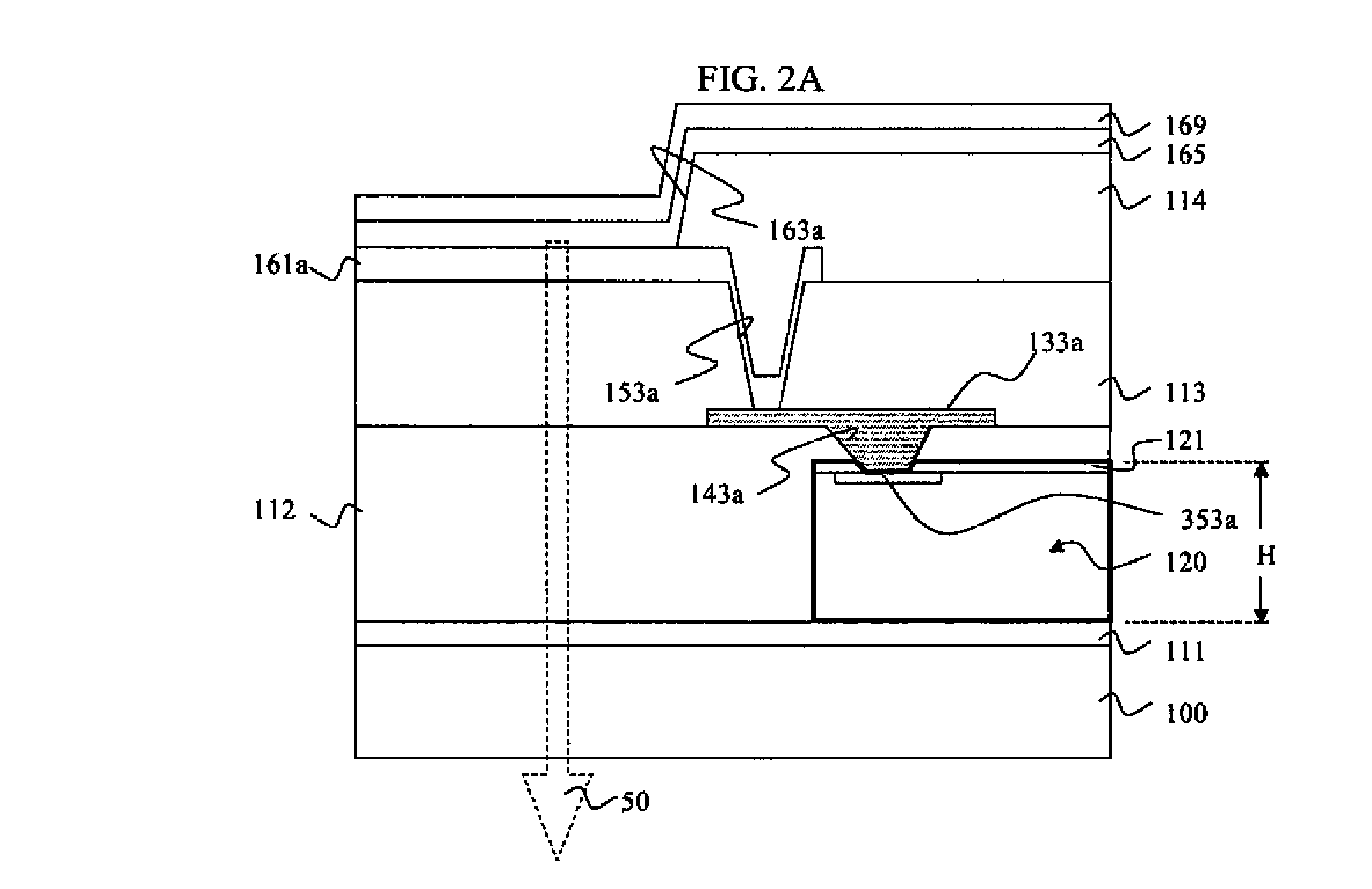

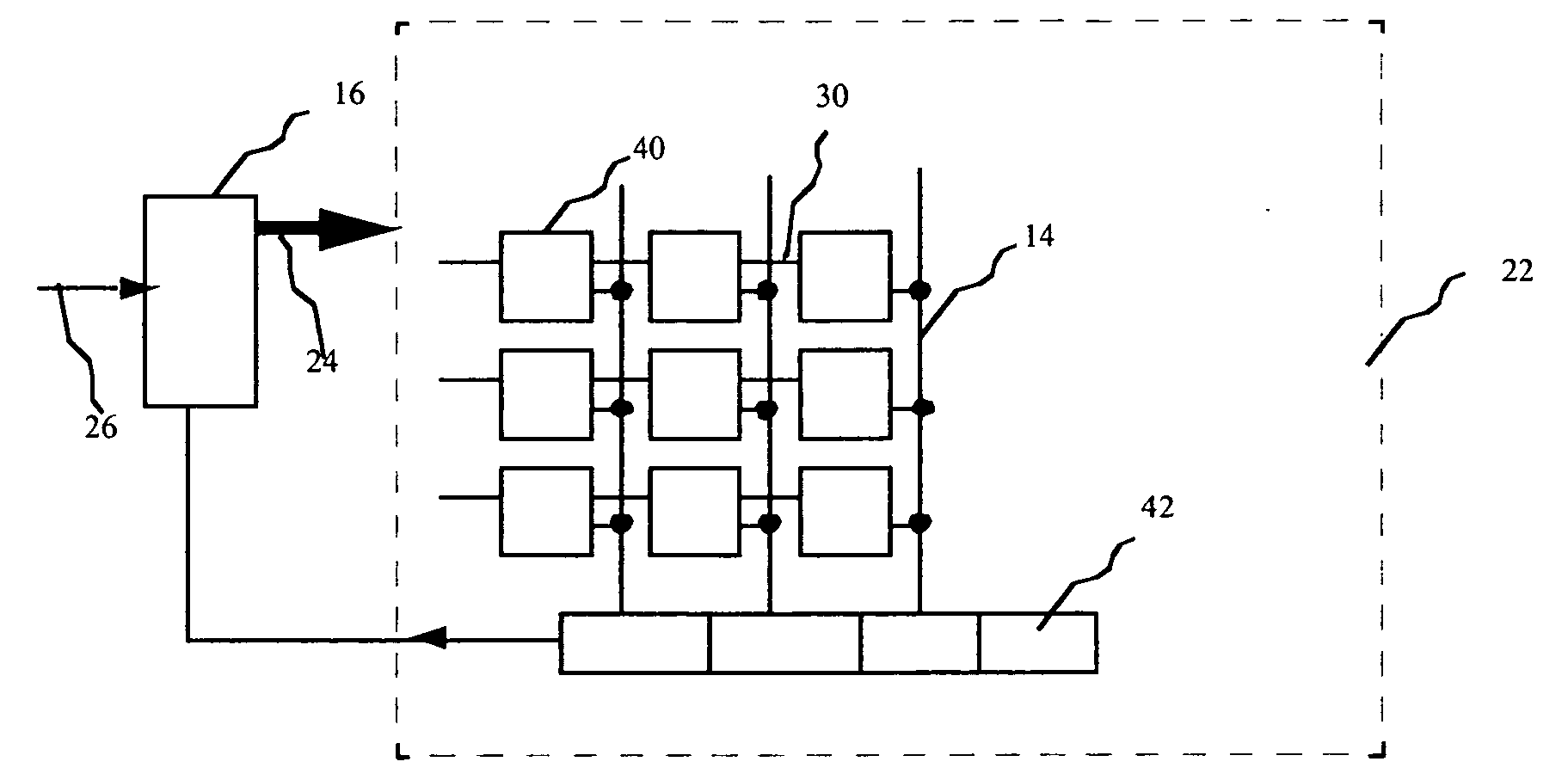

OLED device with embedded chip driving

ActiveUS7999454B2Small sizeReduce thicknessDischarge tube luminescnet screensElectroluminescent light sourcesHemt circuitsElectric current flow

An electroluminescent device having a plurality of current driven pixels arranged in rows and columns, such that when current is provided to a pixel it produces light, including each pixel having first and second electrodes and current responsive electroluminescent media disposed between the first and second electrodes; at least one chiplet having a thickness less than 20 micrometers; including transistor drive circuitry for controlling the operation of at least four pixels, the chiplet being mounted on a substrate and having connection pads; a planarization layer disposed over at least a portion of the chiplet; a first conductive layer over the planarization layer and connected to at least one of the connection pads; and a structure for providing electrical signals through the first conductive layer and at least one of the connection pads of the chiplet so that the transistor drive circuitry of the chiplet controls current to the four pixels.

Owner:X DISPLAY CO TECH LTD +1

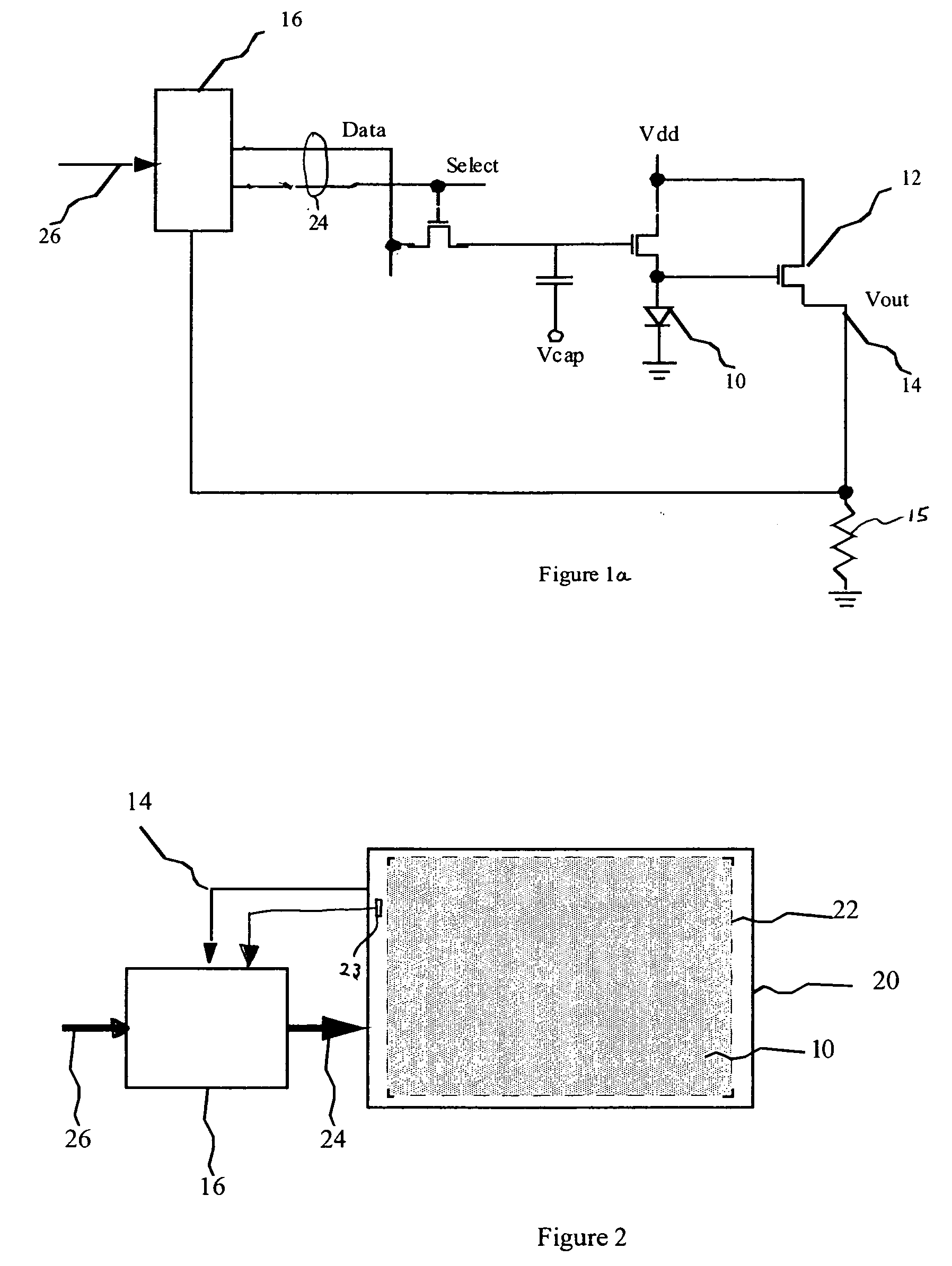

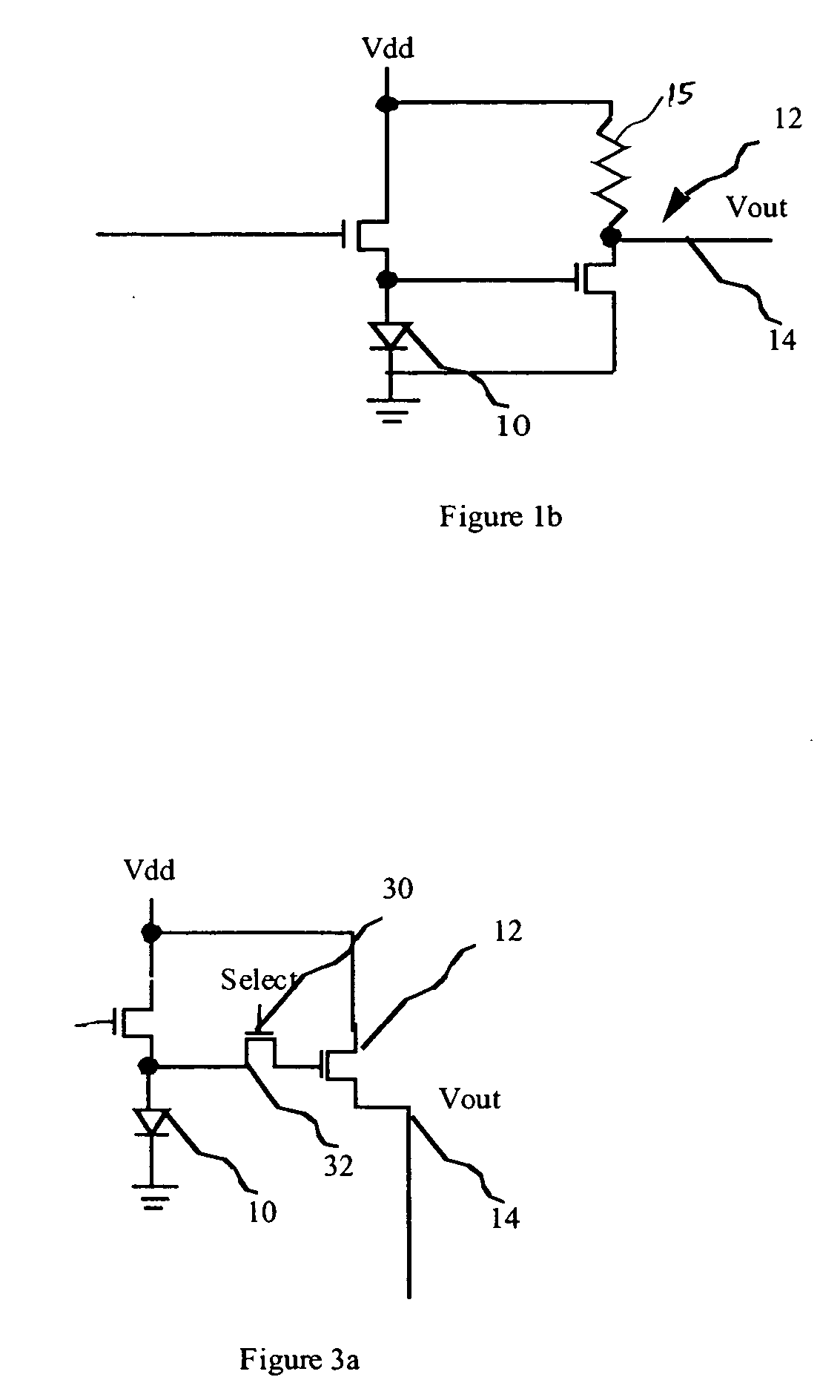

OLED display with aging compensation

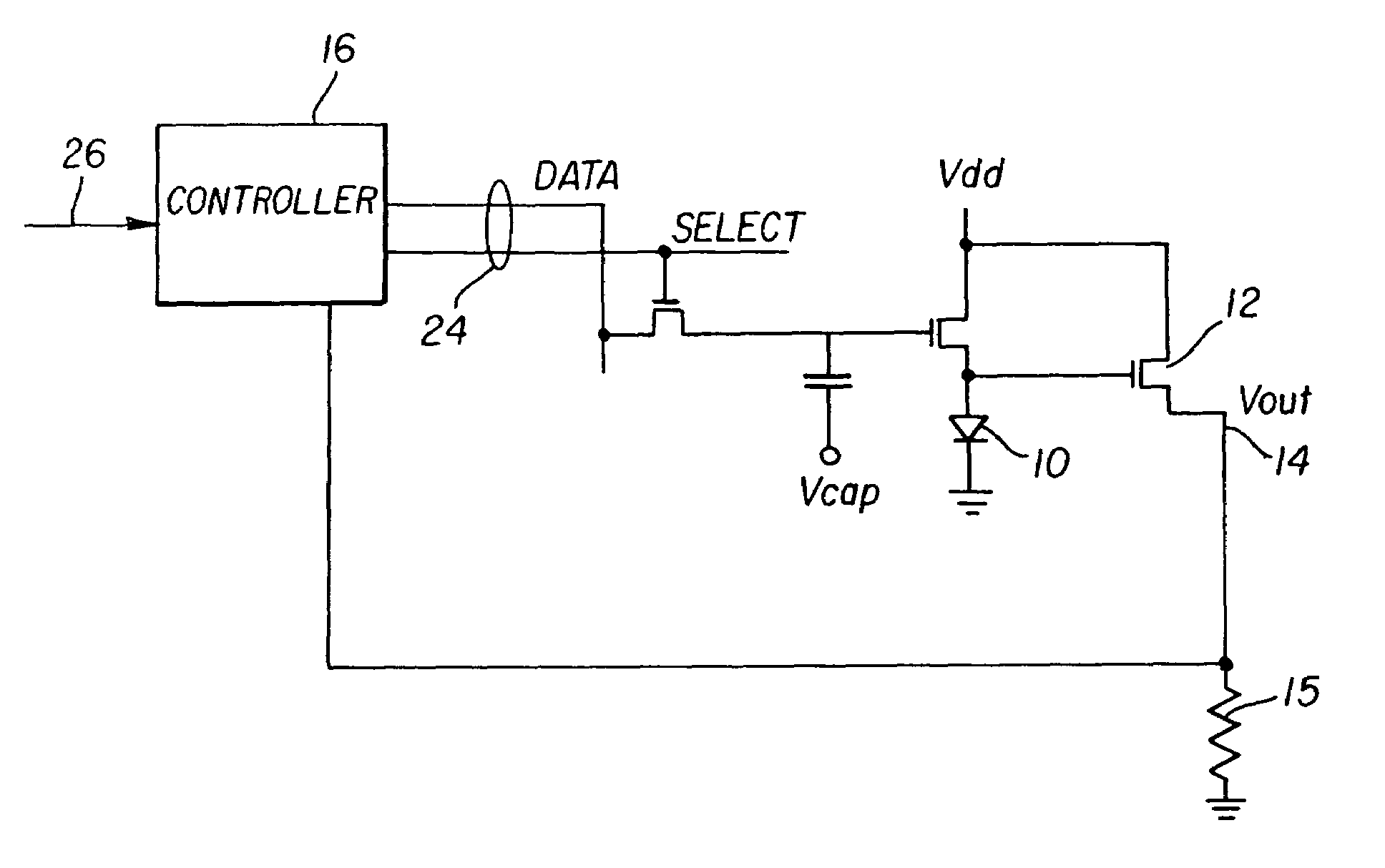

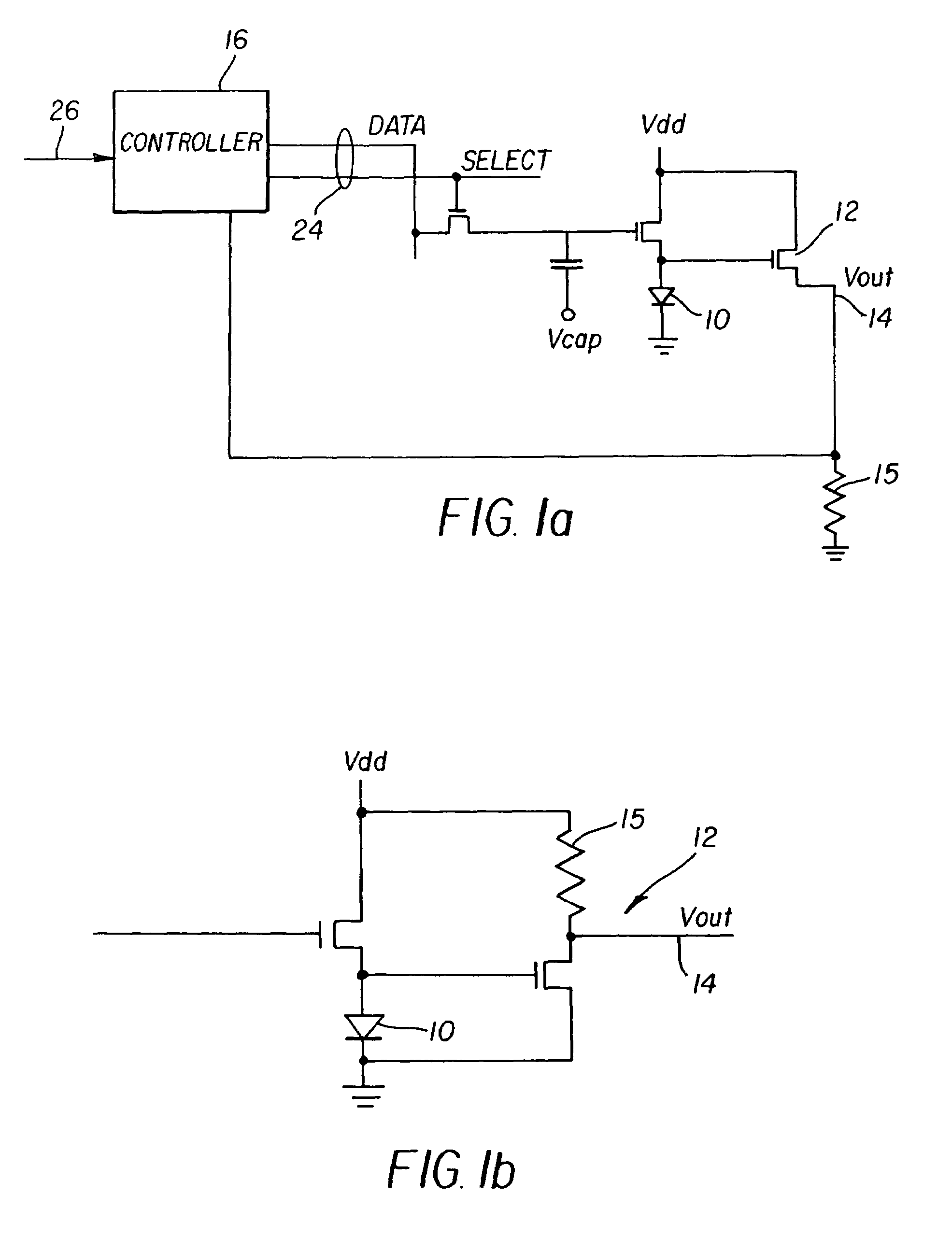

ActiveUS20050110420A1Simple voltage measurementEasy to measureHeater elementsCathode-ray tube indicatorsDisplay deviceHemt circuits

An organic light emitting diode (OLED) display includes an array of OLEDs, each OLED having two terminals; a voltage sensing circuit for each OLED including a transistor in each circuit connected to one of the terminals of a corresponding OLED for sensing the voltage across the OLED to produce feedback signals representing the voltage across the OLEDs; and a controller responsive to the feedback signals for calculating a correction signal for each OLED and applying the correction signal to data used to drive each OLED to compensate for the changes in the output of each OLED.

Owner:GLOBAL OLED TECH

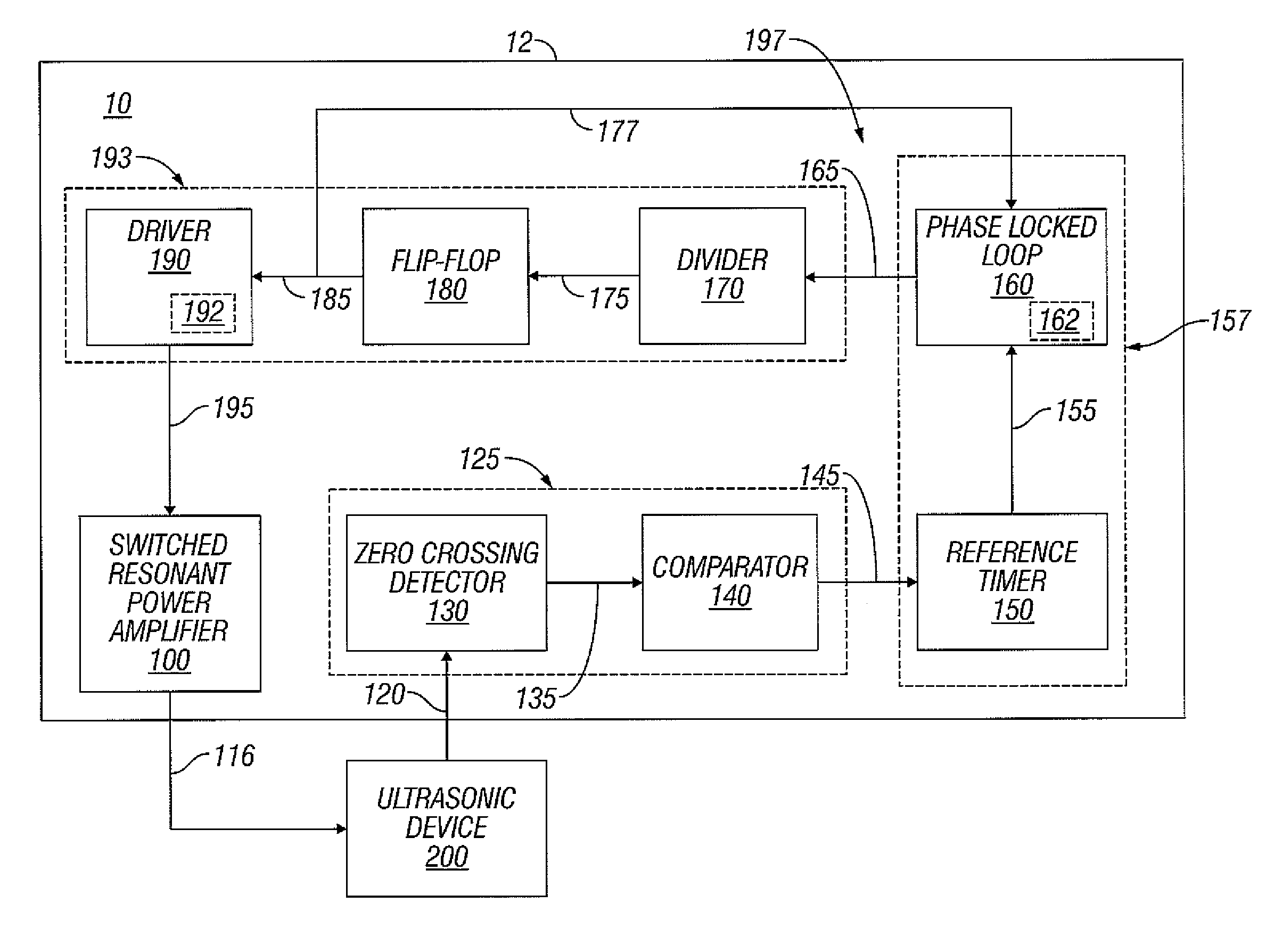

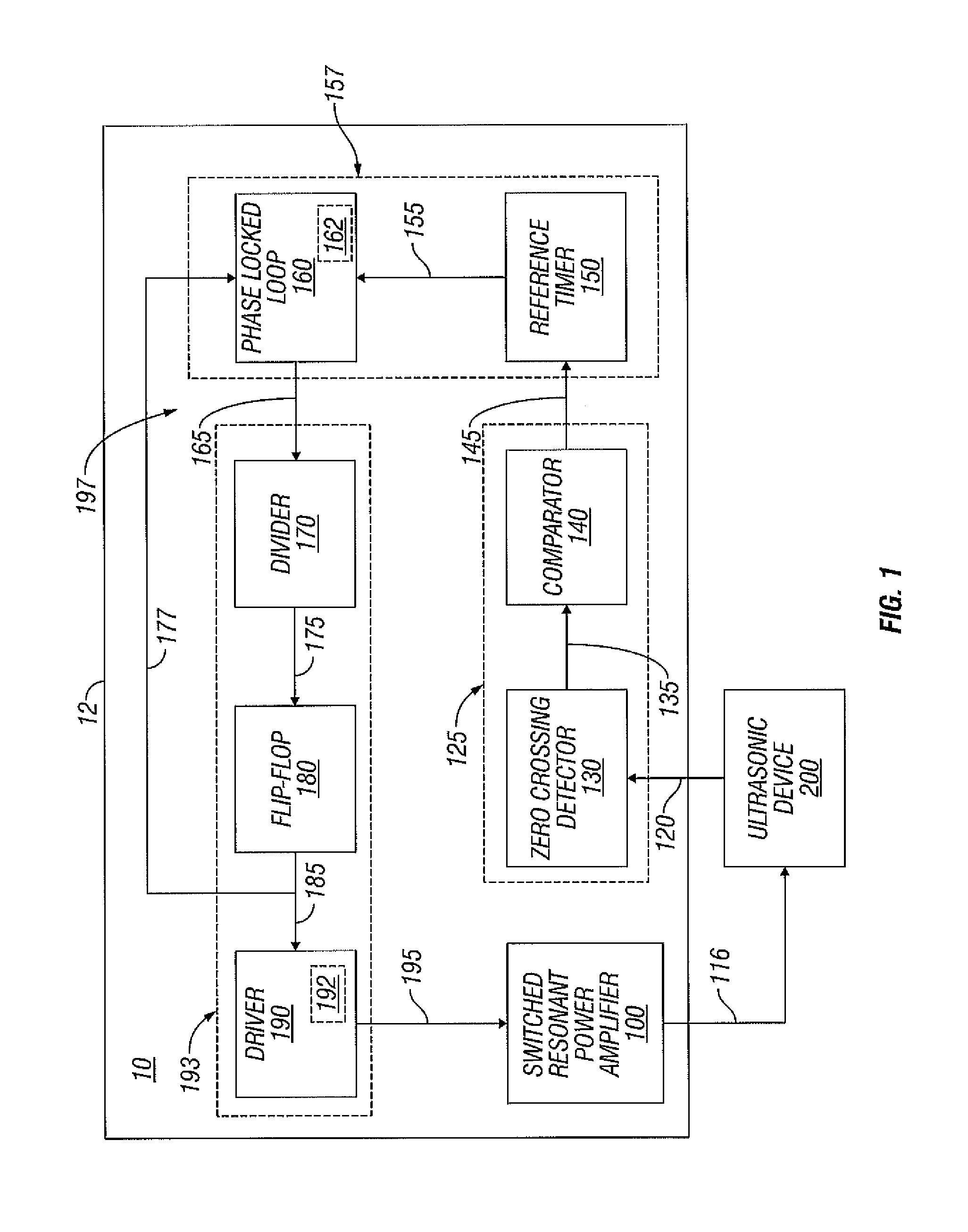

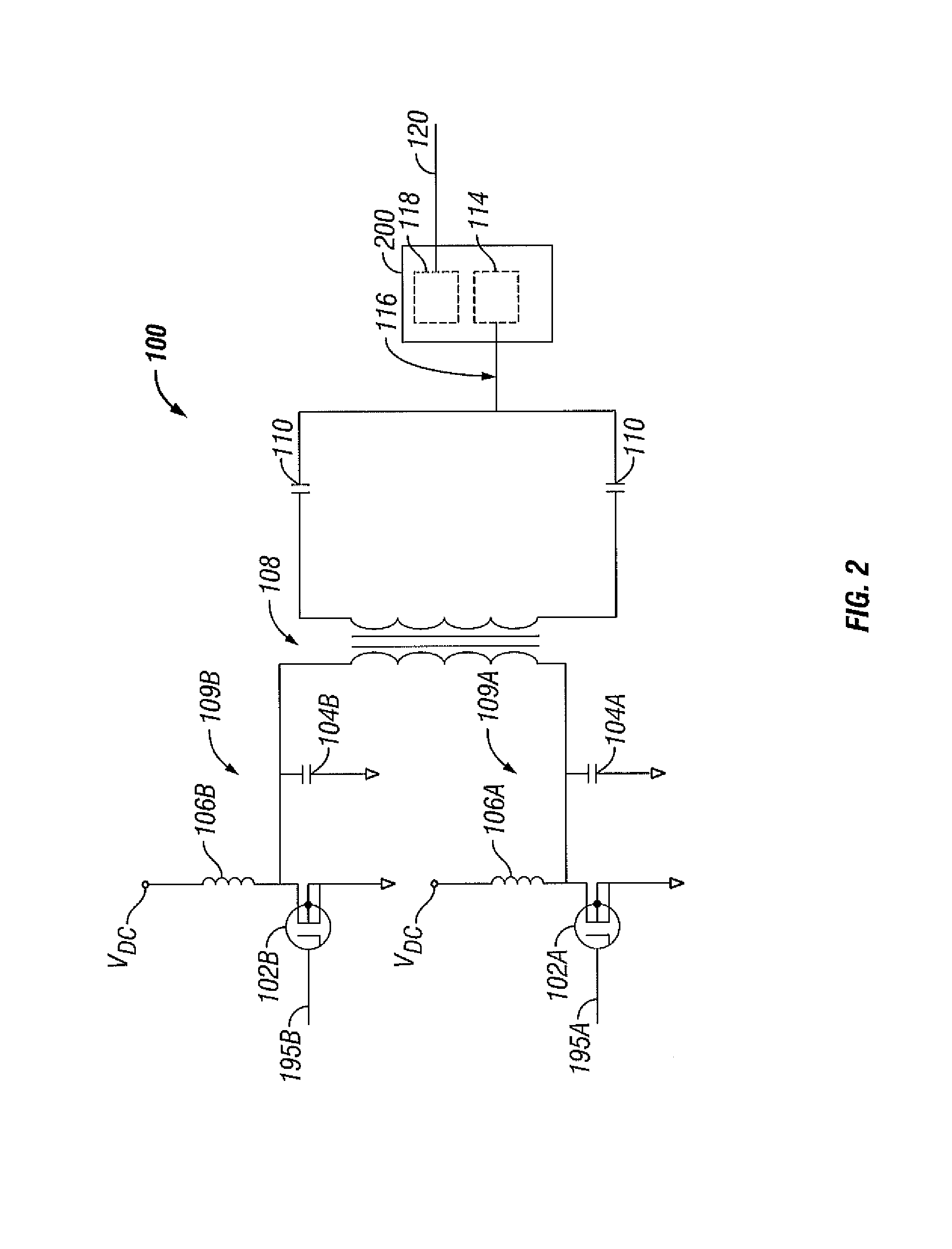

Switched resonant ultrasonic power amplifier system

ActiveUS7396336B2Operation efficiency can be improvedSmall footprintUltrasound therapyAmplifier modifications to raise efficiencyHemt circuitsControl ultrasound

Owner:COVIDIEN AG

Three dimensionally periodic structural assemblies on nanometer and longer scales

InactiveUS6261469B1Low melting pointEasily de-infiltrateSilicaPaper/cardboard articlesChromatographic separationThermoelectric materials

This invention relates to processes for the assembly of three-dimensional structures having periodicities on the scale of optical wavelengths, and at both smaller and larger dimensions, as well as compositions and applications therefore. Invention embodiments involve the self assembly of three-dimensionally periodic arrays of spherical particles, the processing of these arrays so that both infiltration and extraction processes can occur, one or more infiltration steps for these periodic arrays, and, in some instances, extraction steps. The product articles are three-dimensionally periodic on a scale where conventional processing methods cannot be used. Articles and materials made by these processes are useful as thermoelectrics and thermionics, electrochromic display elements, low dielectric constant electronic substrate materials, electron emitters (particularly for displays), piezoelectric sensors and actuators, electrostrictive actuators, piezochromic rubbers, gas storage materials, chromatographic separation materials, catalyst support materials, photonic bandgap materials for optical circuitry, and opalescent colorants for the ultraviolet, visible, and infrared regions.

Owner:ALLIEDSIGNAL INC

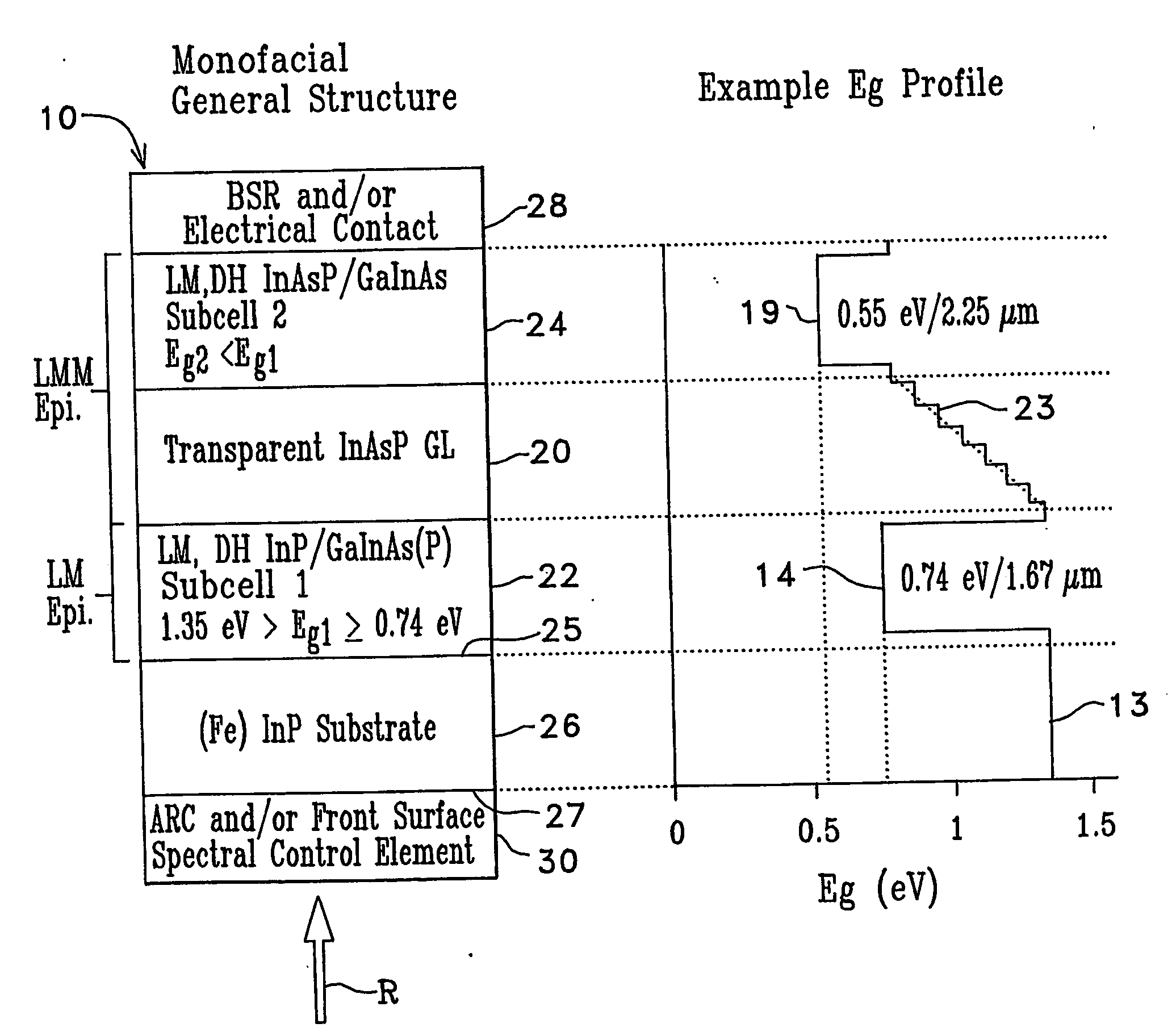

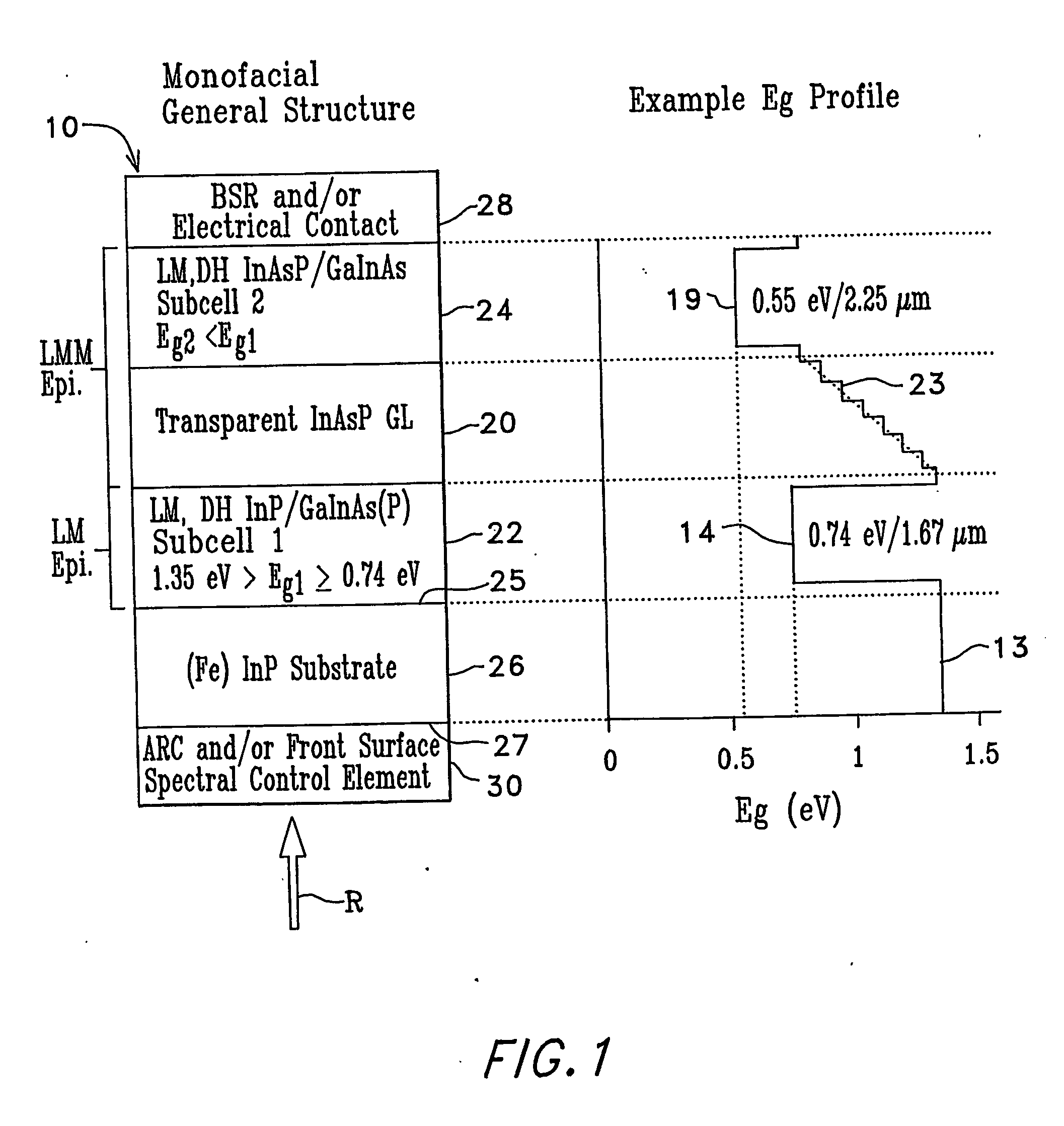

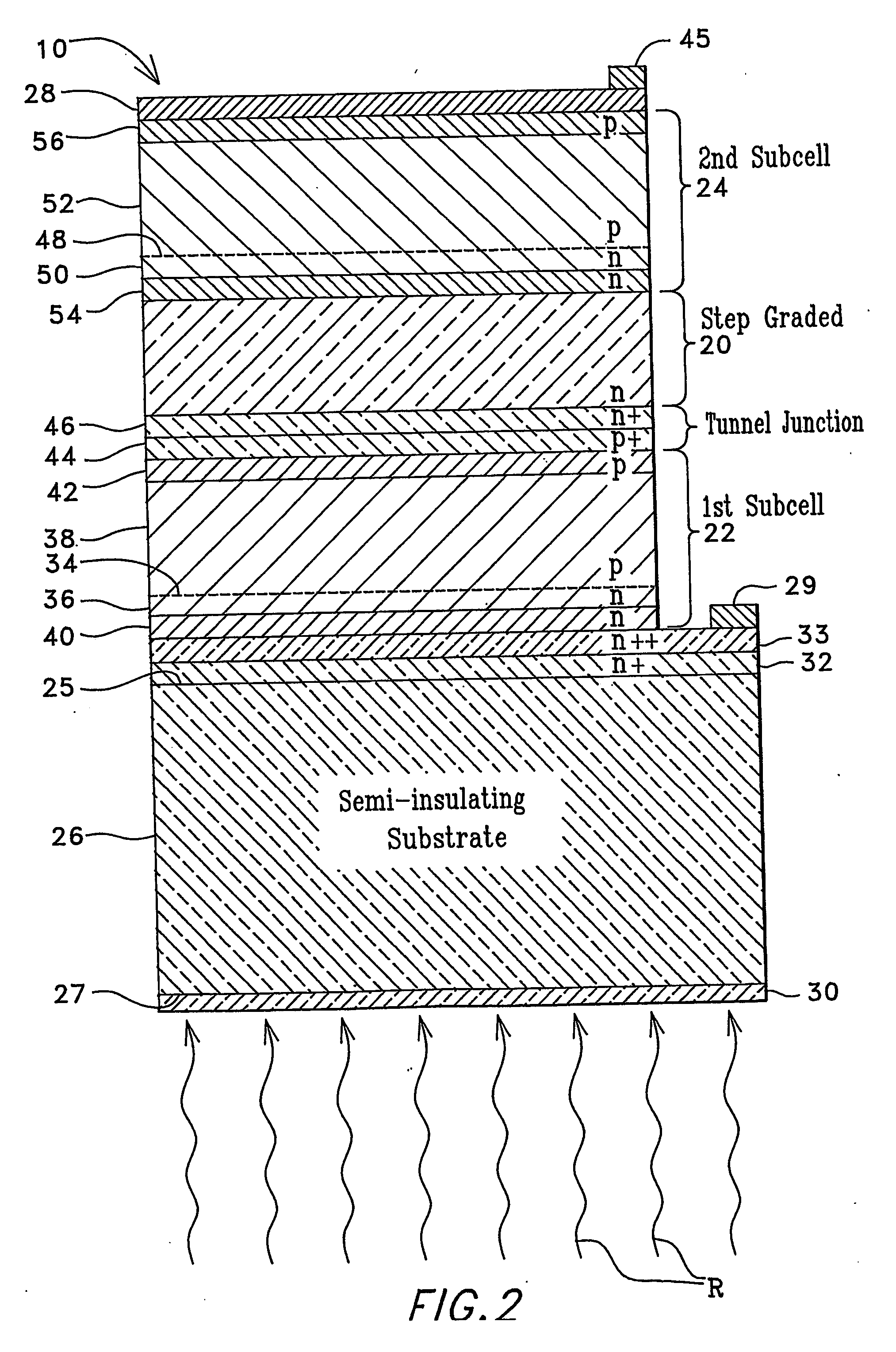

Low bandgap, monolithic, multi-bandgap, optoelectronic devices

InactiveUS20060162768A1Semiconductor/solid-state device manufacturingPhotovoltaic energy generationPhotovoltaic detectorsPhotodetector

Low-bandgap, monolithic, multi-bandgap, optoelectronic devices (10), including PV converters, photodetectors, and LED's, have lattice-matched (LM), double-heterostructure (DH), low-bandgap GaInAs(P) subcells (22, 24) including those that are lattice-mismatched (LMM) to InP, grown on an InP substrate (26) by use of at least one graded lattice constant transition layer (20) of InAsP positioned somewhere between the InP substrate (26) and the LMM subcell(s) (22, 24). These devices are monofacial (10) or bifacial (80) and include monolithic, integrated, modules (MIMs) (190) with a plurality of voltage-matched subcell circuits (262, 264, 266, 270, 272) as well as other variations and embodiments.

Owner:ALLIANCE FOR SUSTAINABLE ENERGY

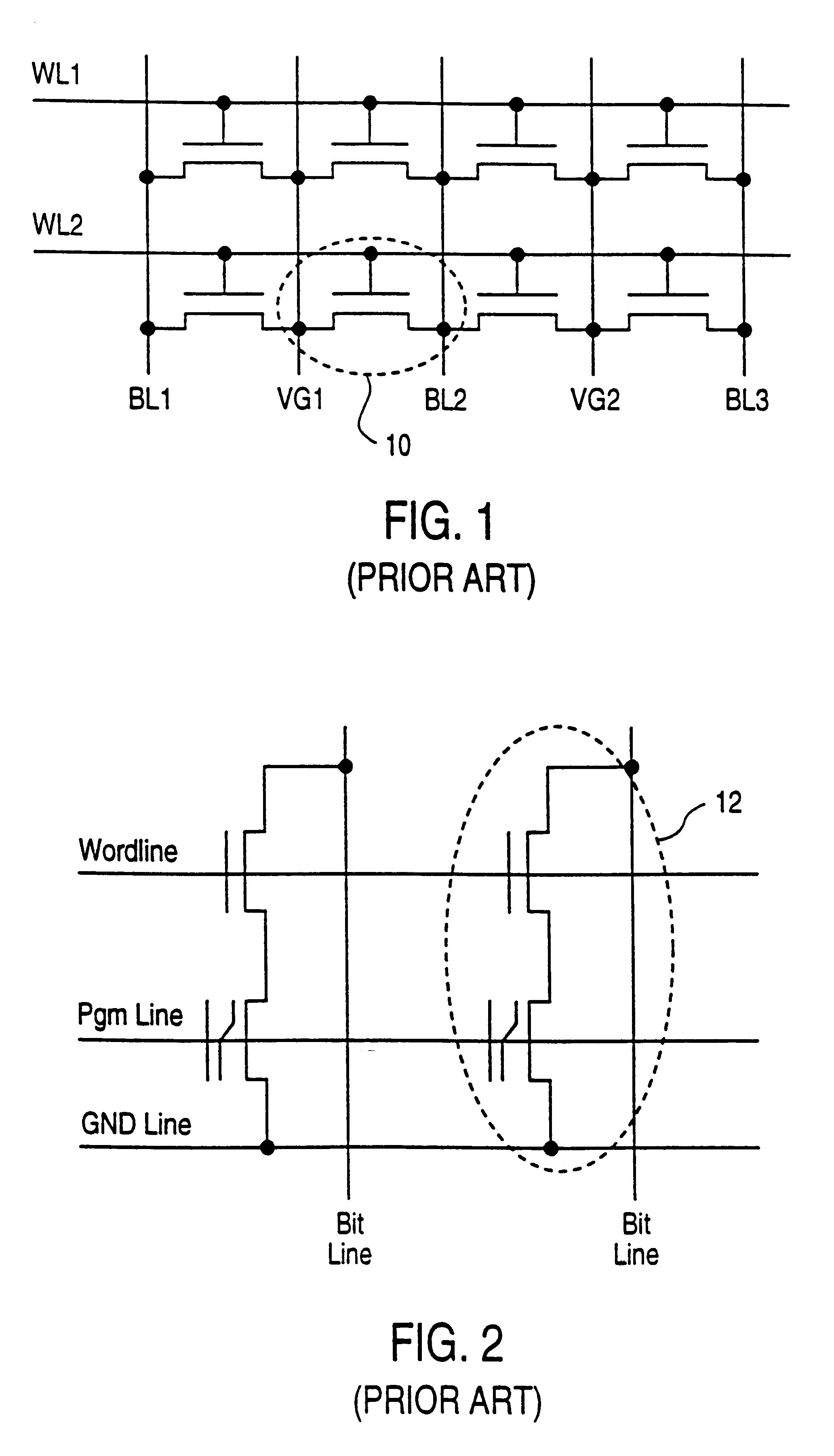

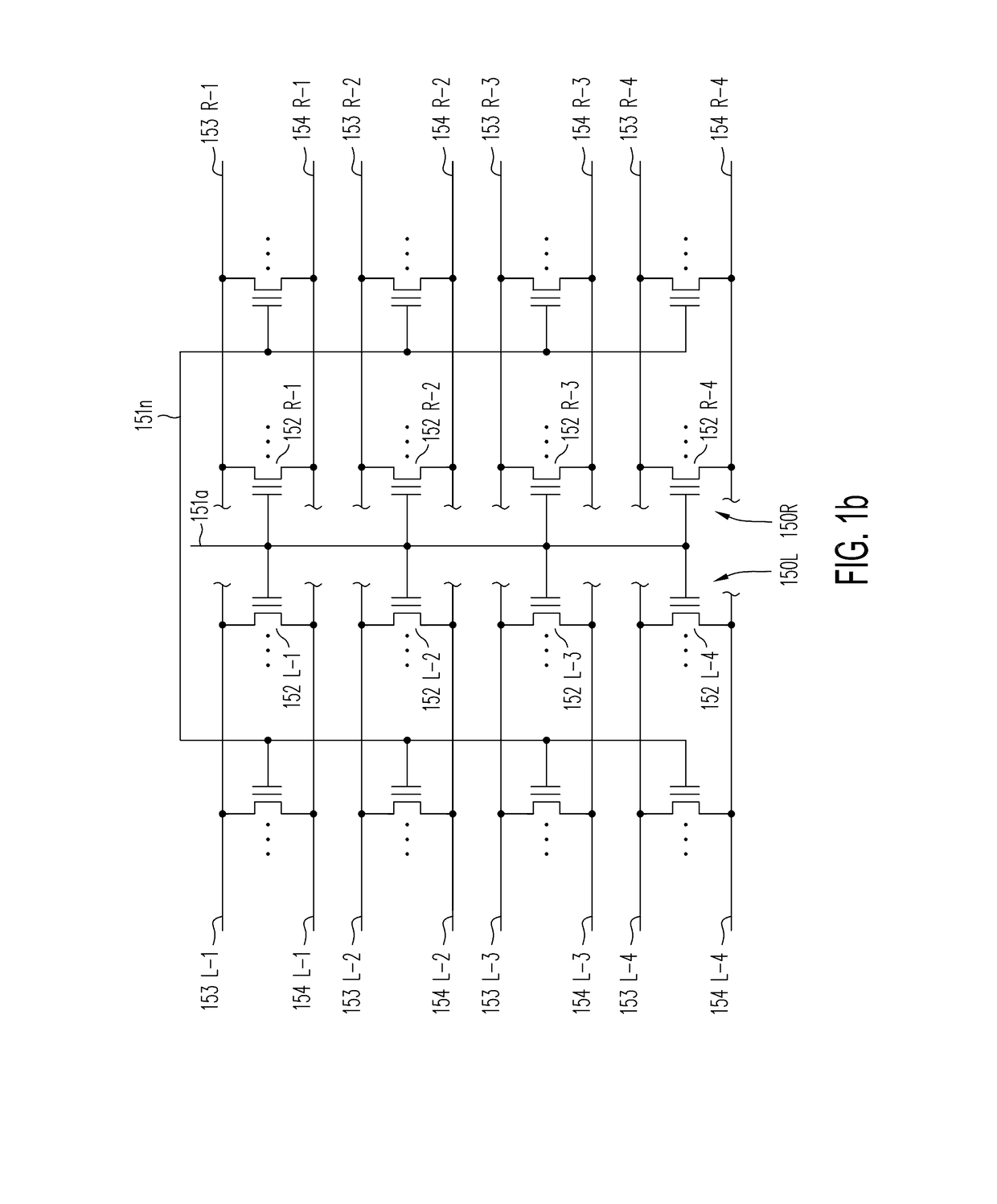

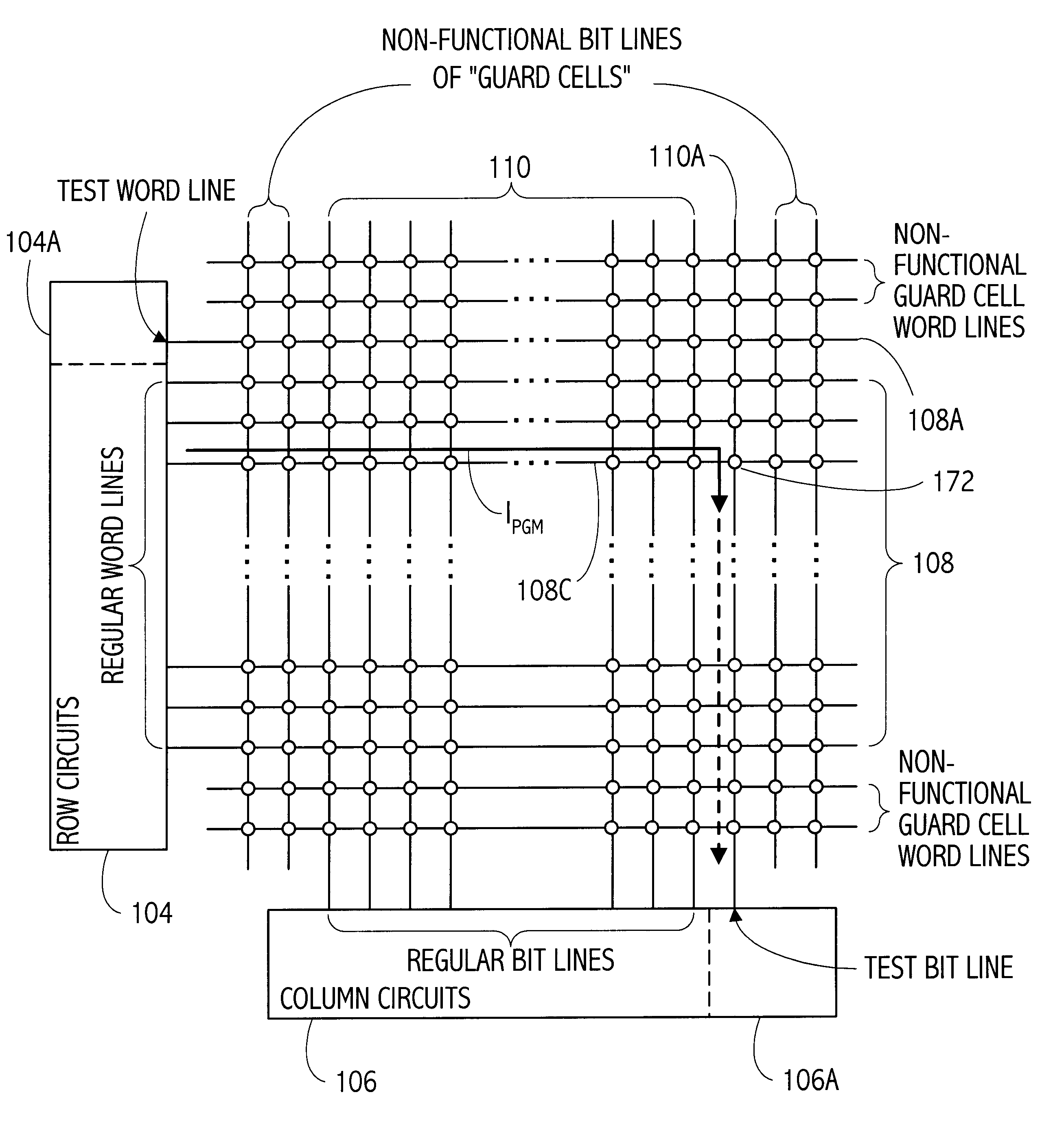

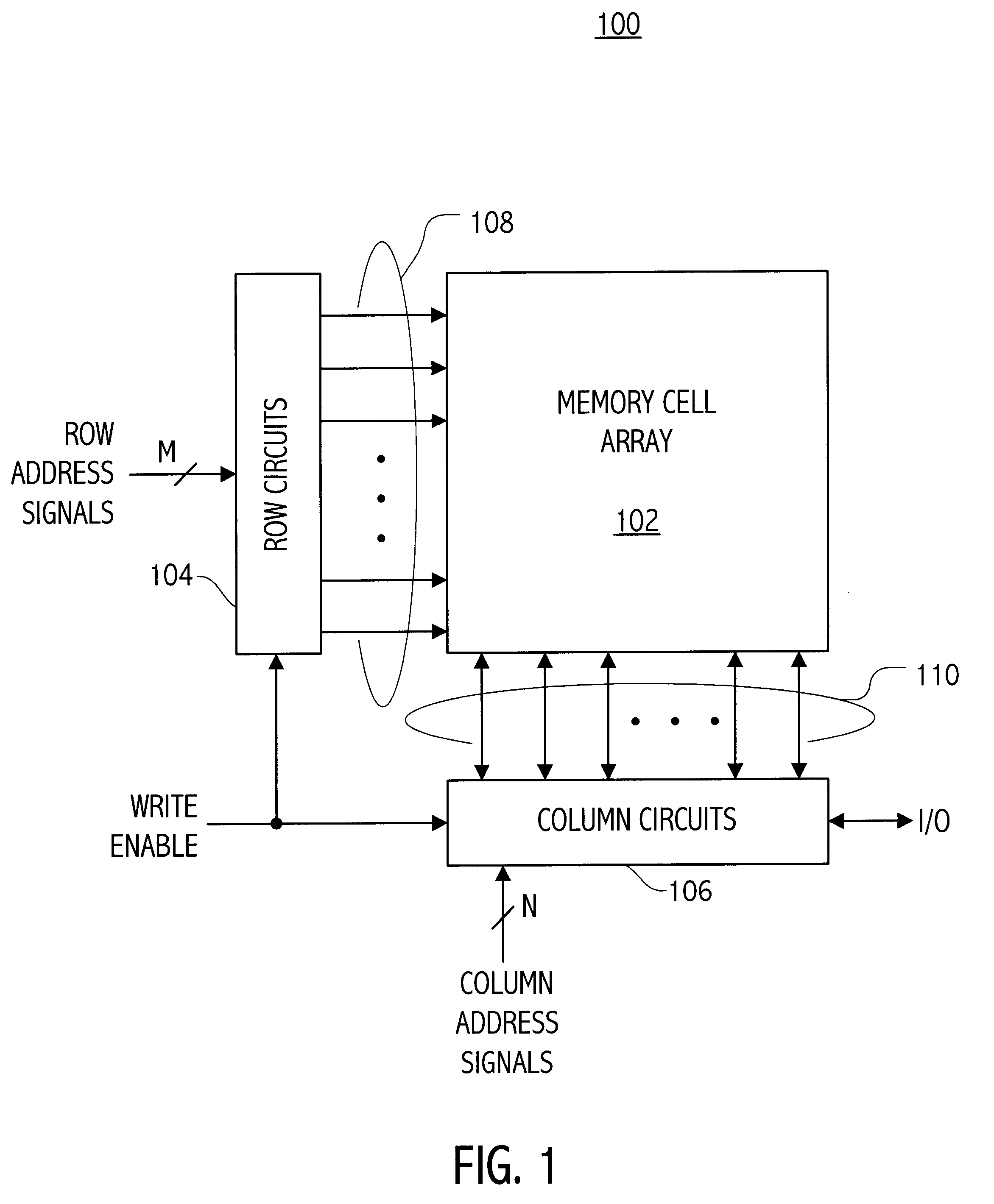

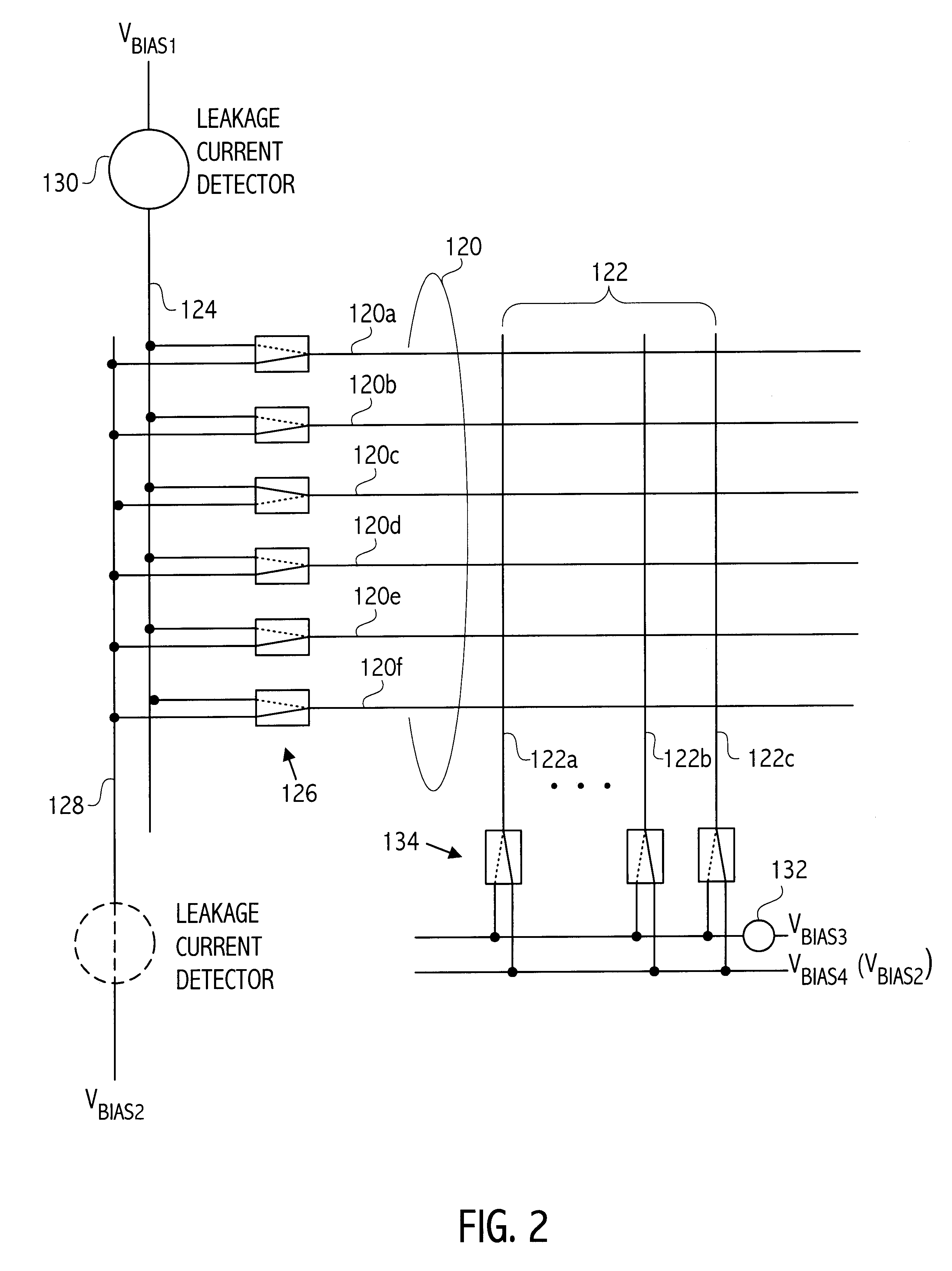

Memory array organization and related test method particularly well suited for integrated circuits having write-once memory arrays

In a preferred integrated circuit embodiment, a write-once memory array includes at least one test bit line which provides a respective test memory cell at the far end of each respective word line relative to its word line driver, and further includes at least one test word line which provides a respective test memory cell at the far end of each respective bit line relative to its bit line driver. An intra-layer short between word lines may be detected, such as during manufacturing testing, by biasing adjacent word lines to different voltages and detecting whether any leakage current flowing from one to another exceeds that normally accounted for by the memory cells and other known circuits. Intra-layer bit line shorts and inter-layer word line and bit line shorts may also be similarly detected. An "open" in a word line or bit line may be detected by trying to program the test memory cell at the far end of each such word line or bit line. If successfully programmed, the continuity of each word line and bit line is assured, and the programming circuitry for each word line and bit line is also known to be functional.

Owner:SANDISK TECH LLC

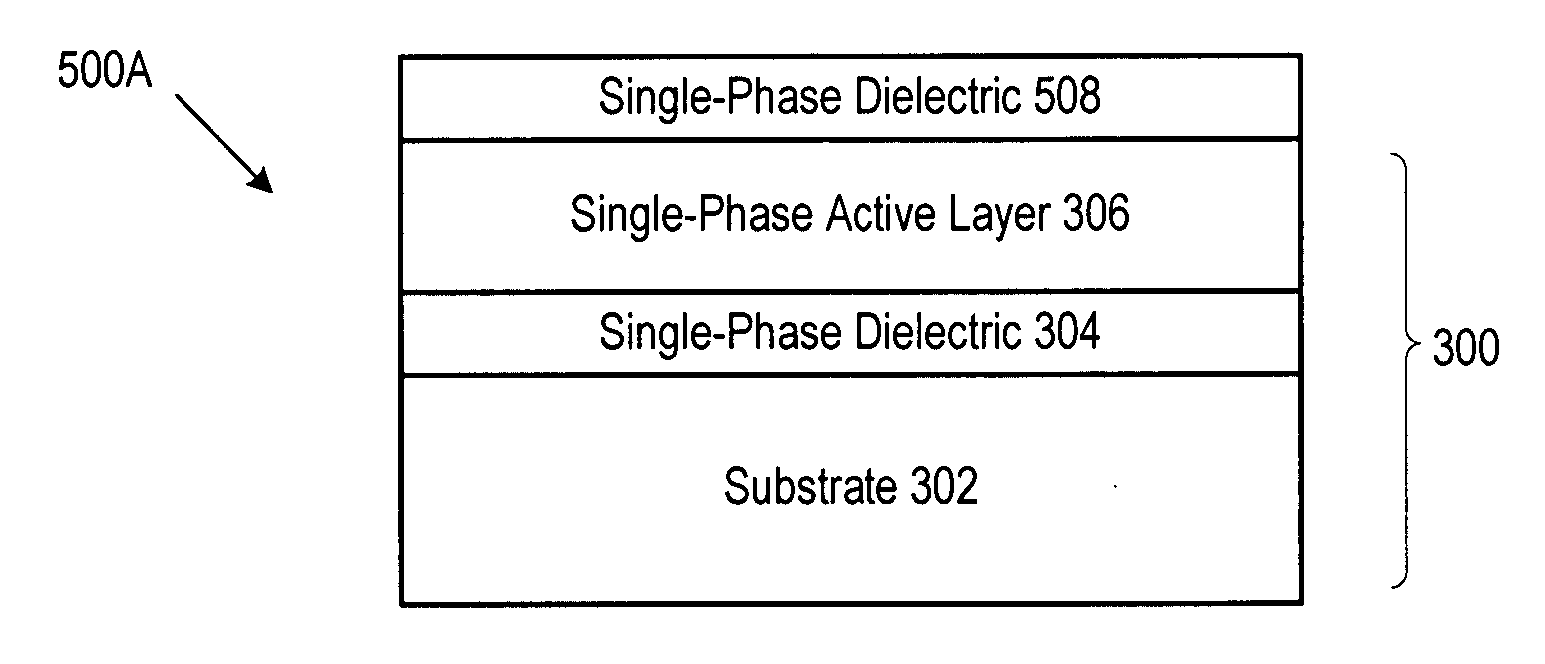

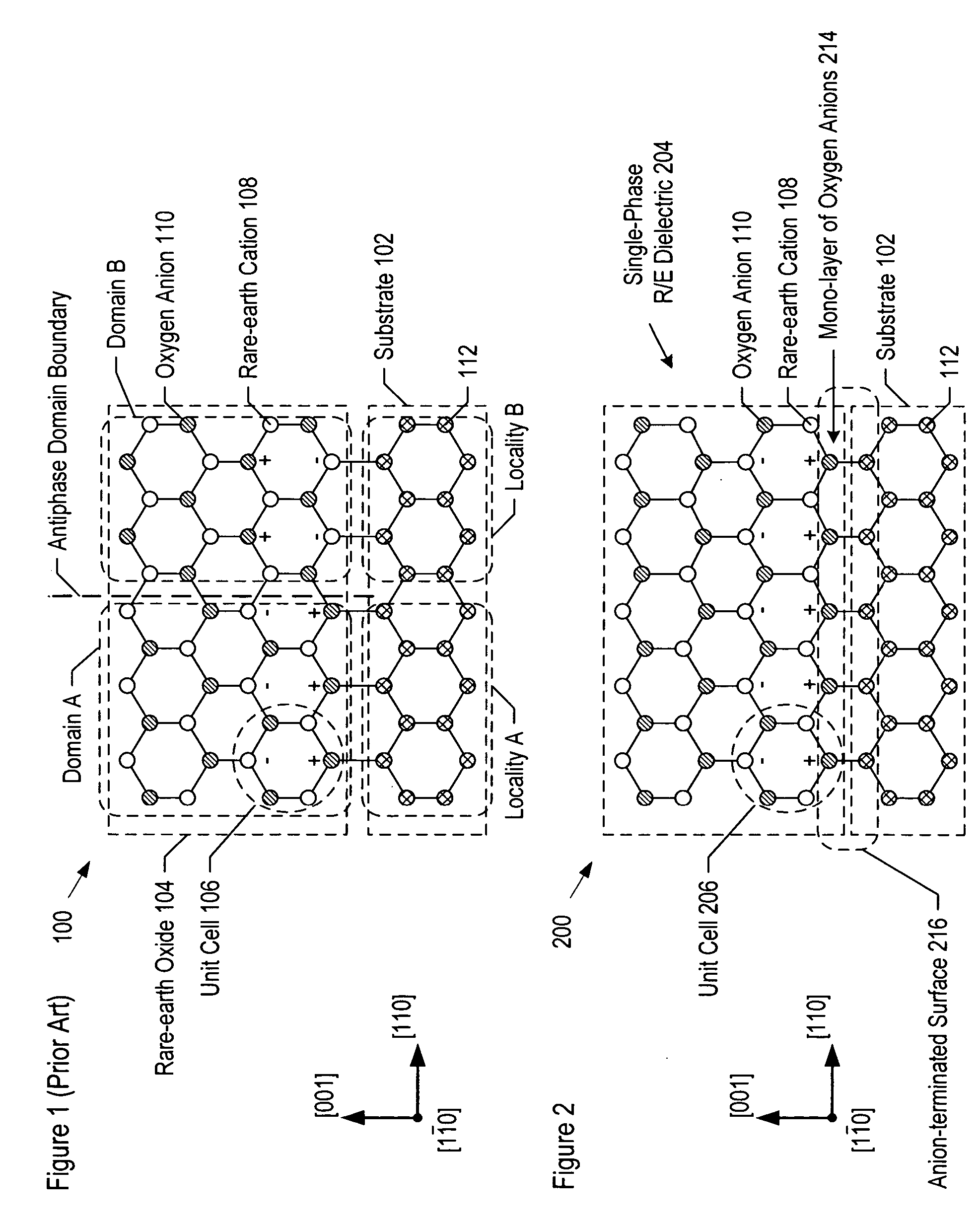

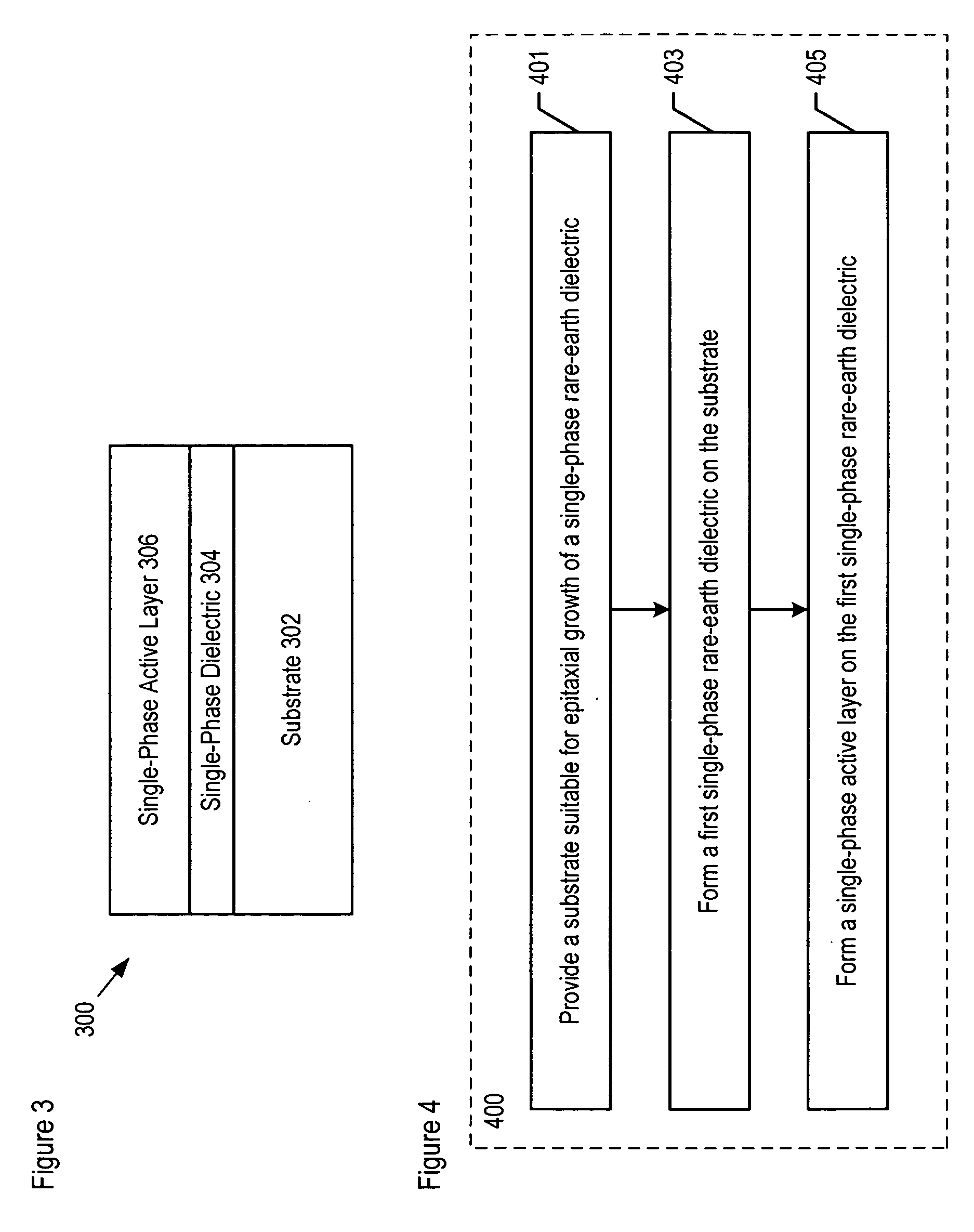

Method of forming a rare-earth dielectric layer

ActiveUS20060060131A1Quality improvementPolycrystalline material growthLaser detailsSemiconductor structureRare earth

Methods for forming compositions comprising a single-phase rare-earth dielectric disposed on a substrate are disclosed. In some embodiments, the method forms a semiconductor-on-insulator structure. Compositions and structures that are formed via the method provide the basis for forming high-performance devices and circuits.

Owner:IQE

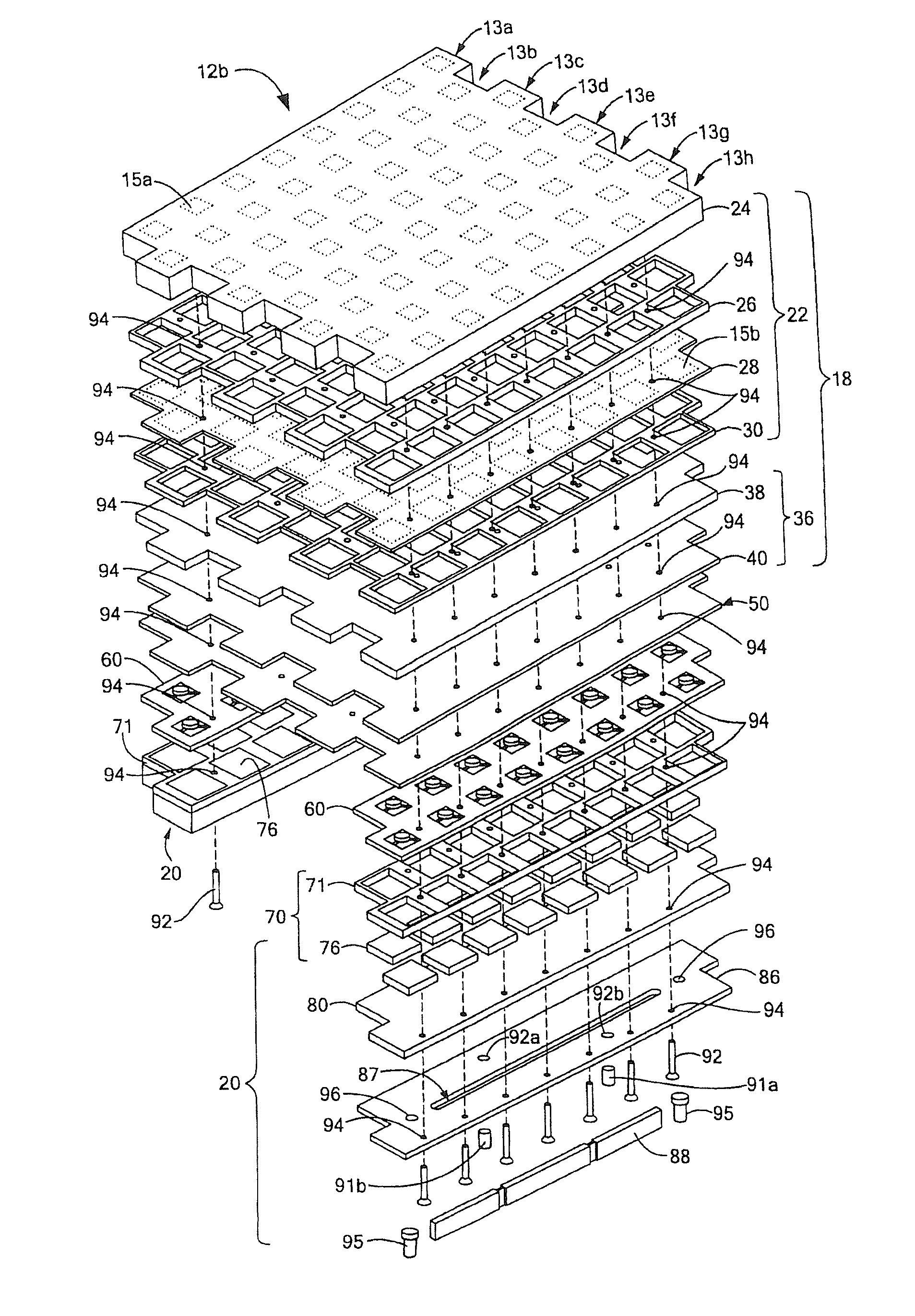

Panel Array

ActiveUS20100066631A1Low insertion lossEliminate needAntenna arrays manufactureModular arraysHemt circuitsChipset

A mixed-signal, multilayer printed wiring board fabricated in a single lamination step is described. The PWB includes one or more radio frequency (RF) interconnects between different circuit layers on different circuit boards which make up the PWB. The PWB includes a number of unit cells with radiating elements and an RF cage disposed around each unit cell to isolate the unit cell. A plurality of flip-chip circuits are disposed on an external surface of the PWB and a heat sink can be disposed over the flip chip components.

Owner:RAYTHEON CO

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com